Patents

Literature

274 results about "Cmos chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

CMOS is an onboard, battery powered semiconductor chip inside computers that stores information. This information ranges from the system time and date to system hardware settings for your computer. The picture shows an example of the most common CMOS coin cell battery (Panasonic CR 2032 3V) used to power the CMOS memory.

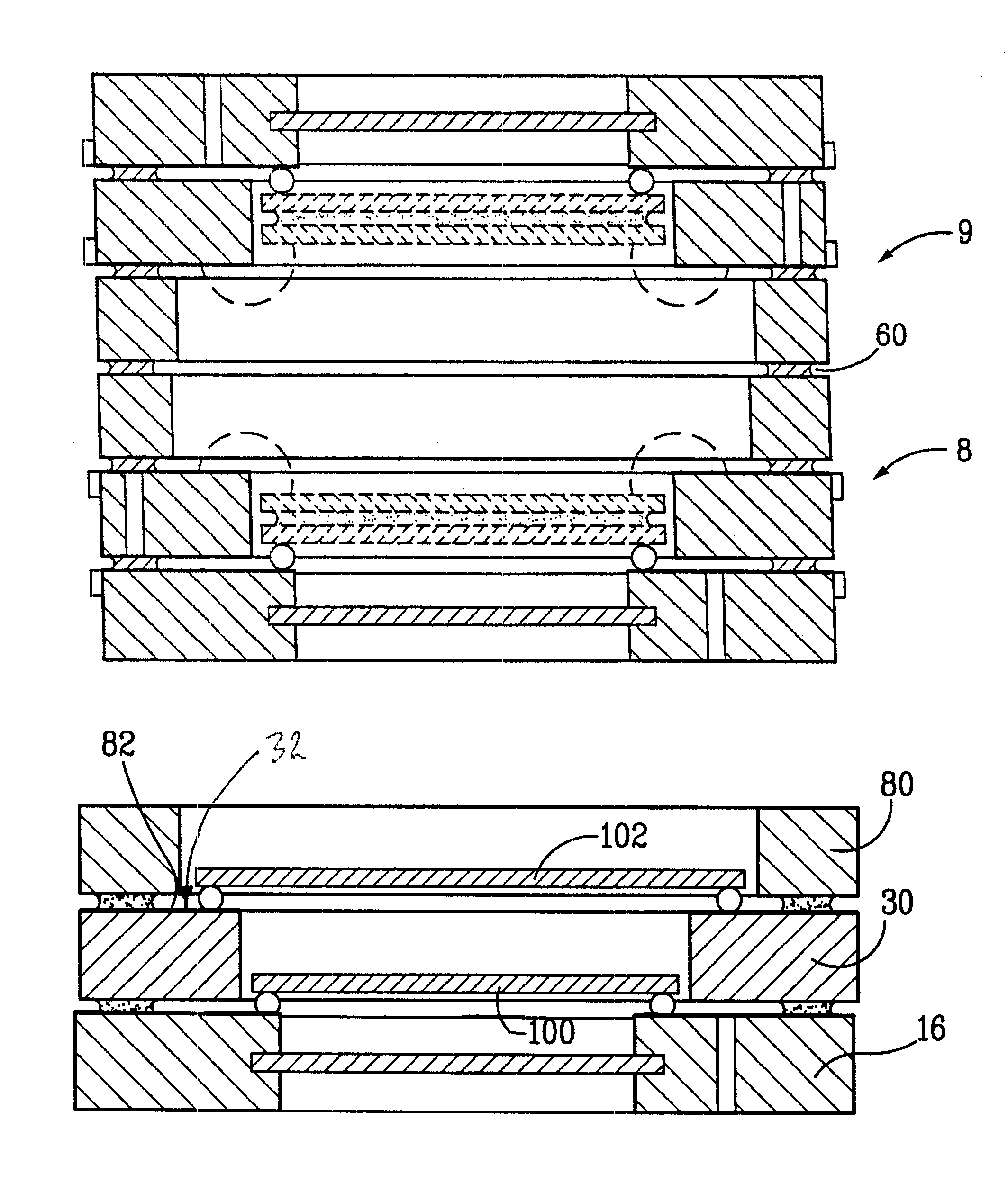

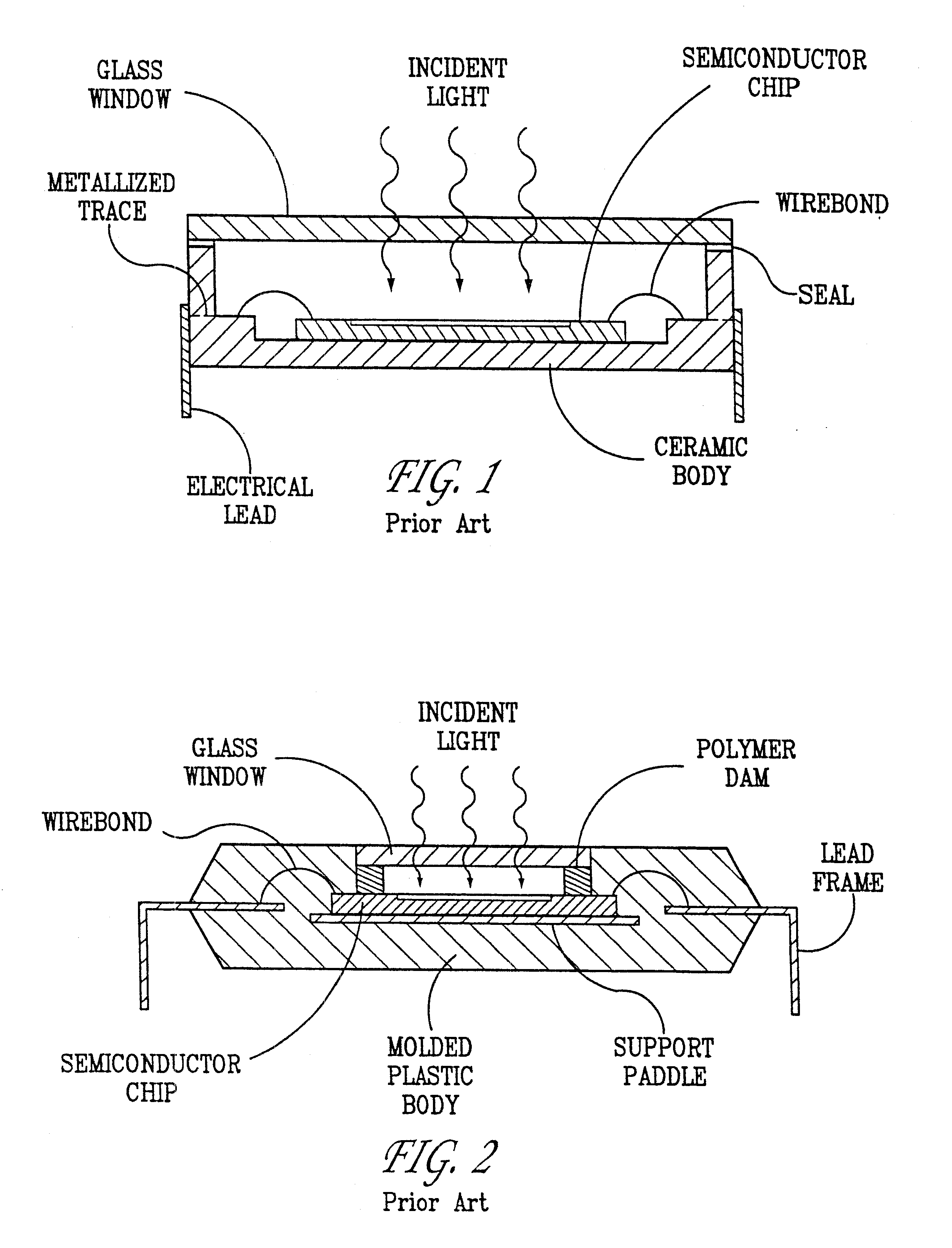

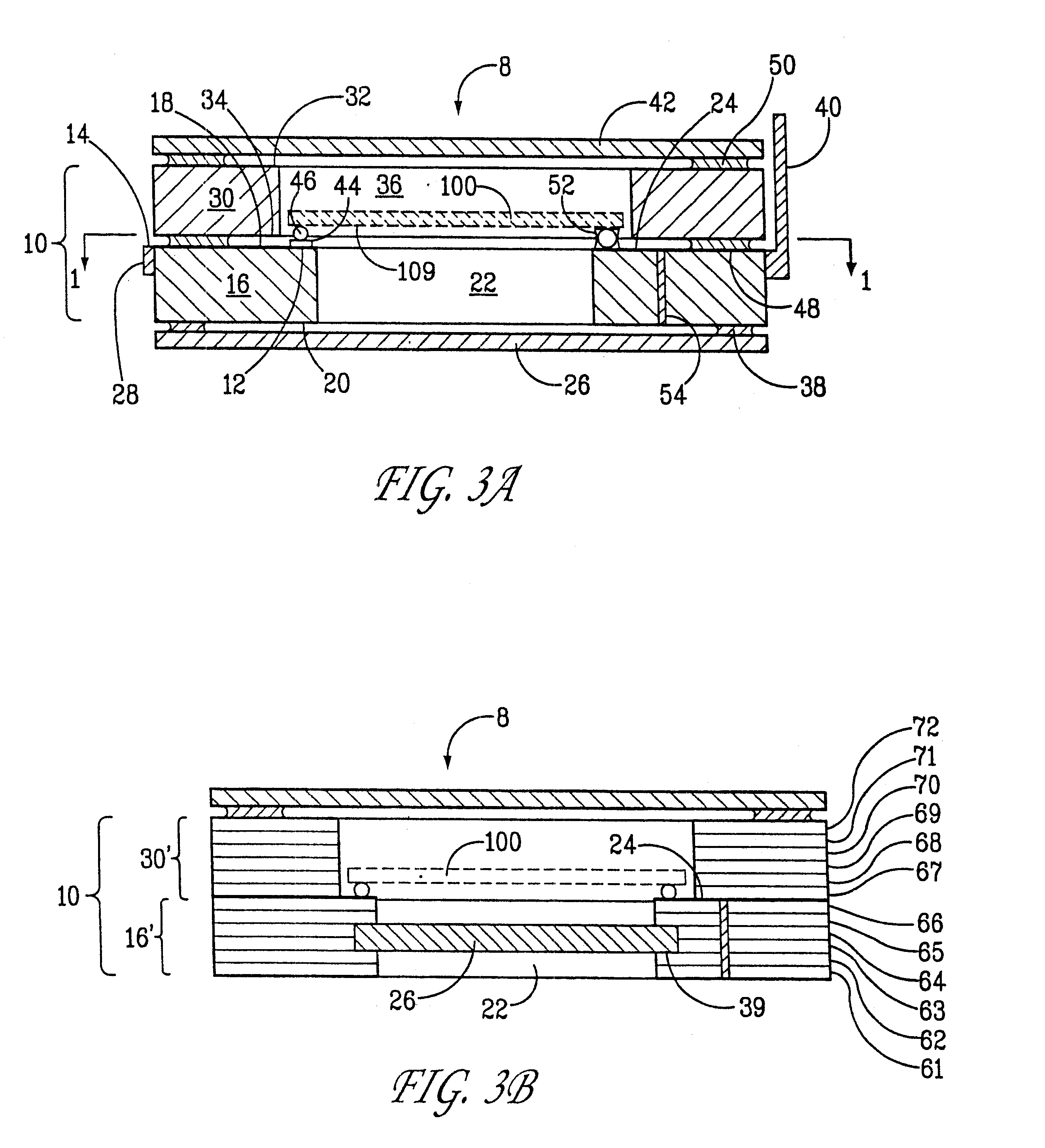

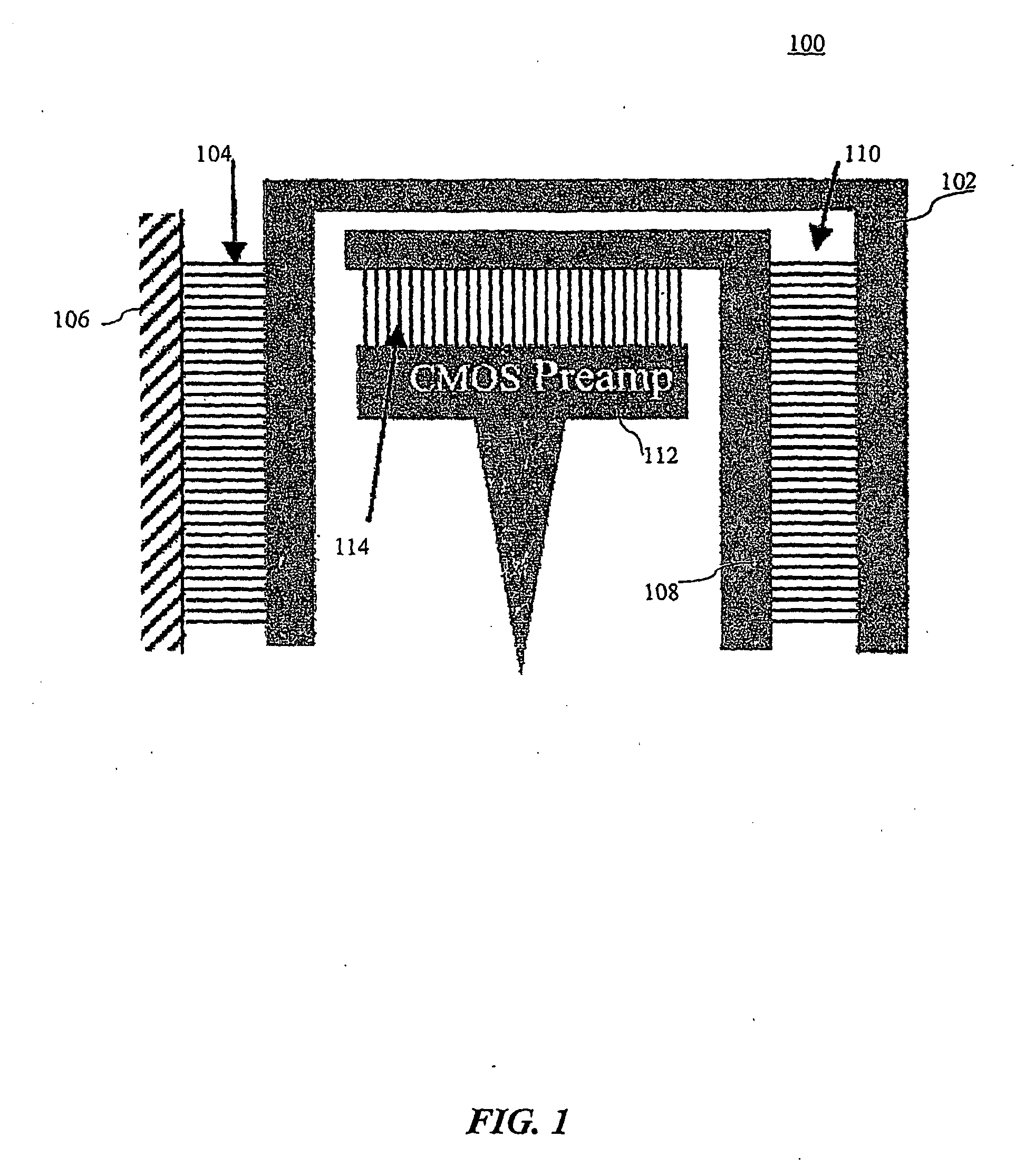

Bi-level multilayered microelectronic device package with an integral window

InactiveUS6495895B1Reduce pollutionMinimize timePrinted circuit detailsSemiconductor/solid-state device detailsHermetic sealLead bonding

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

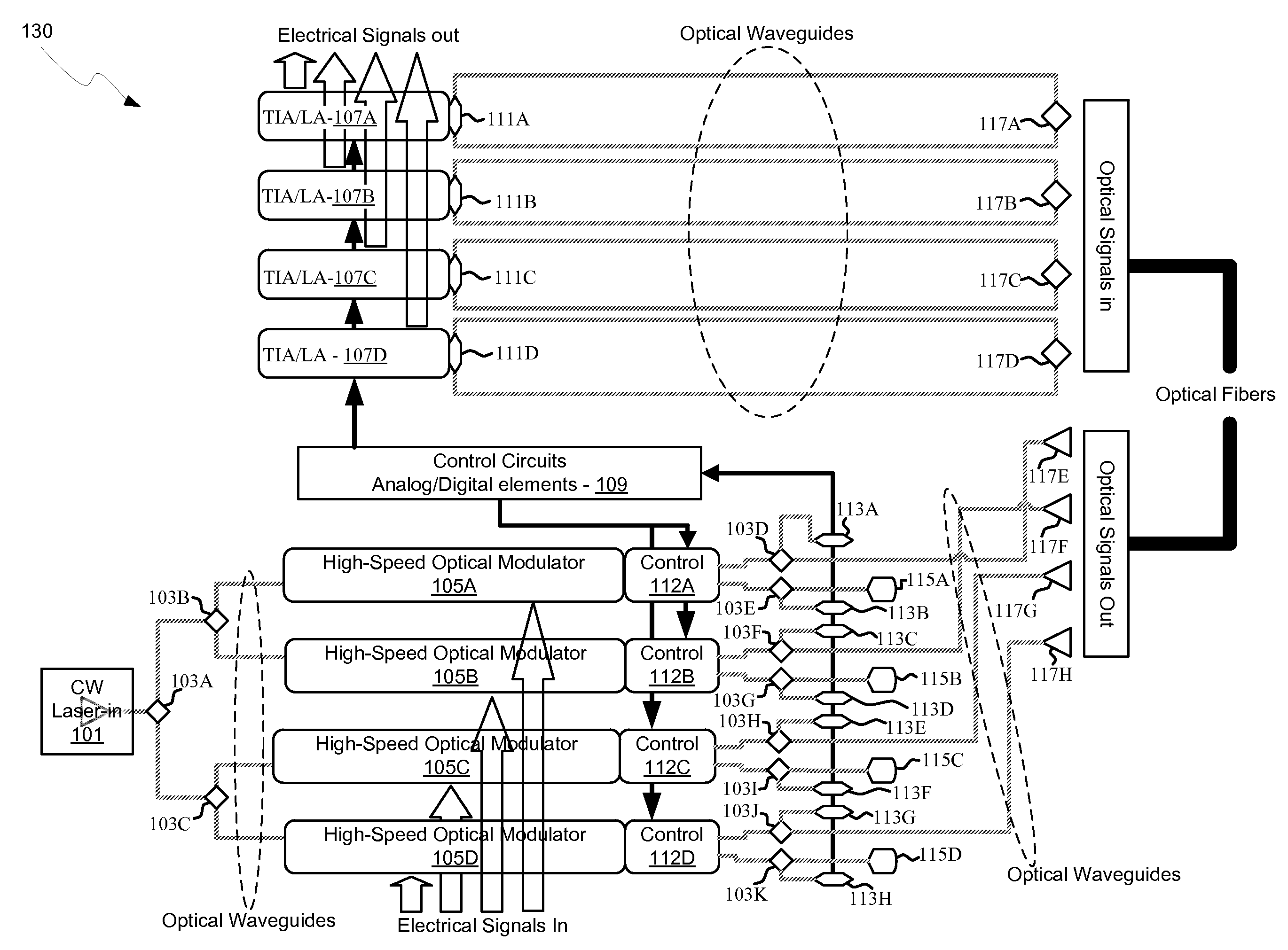

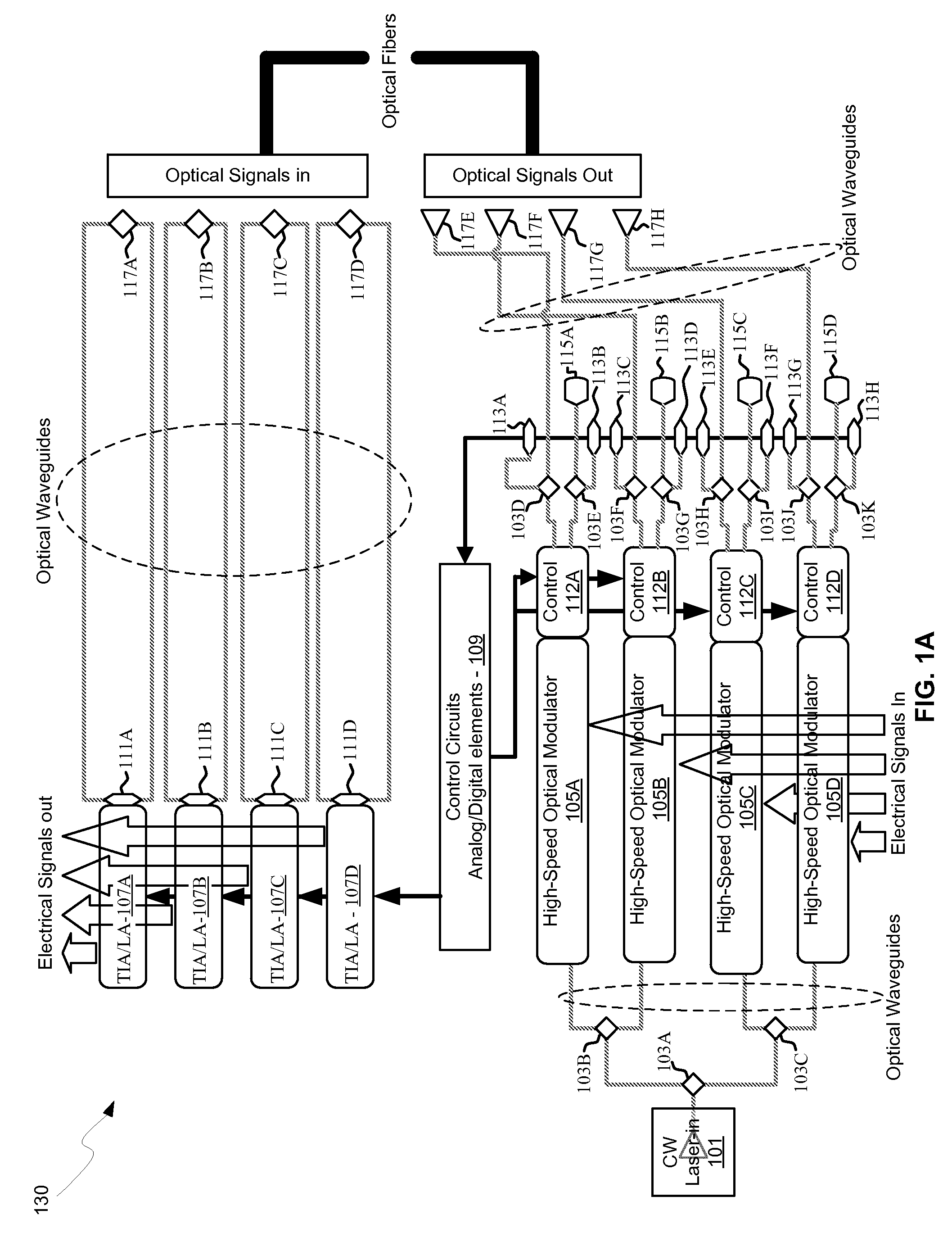

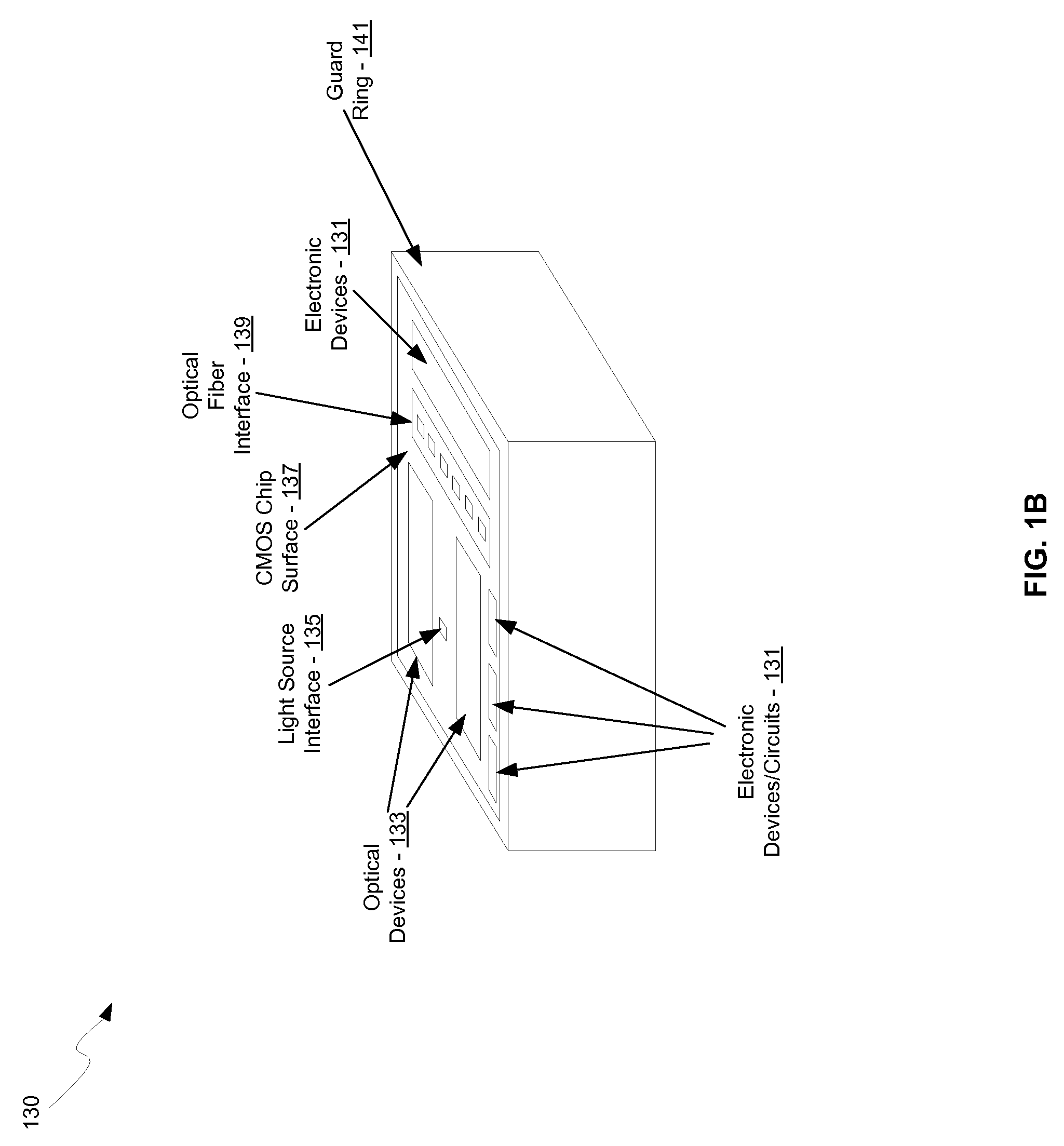

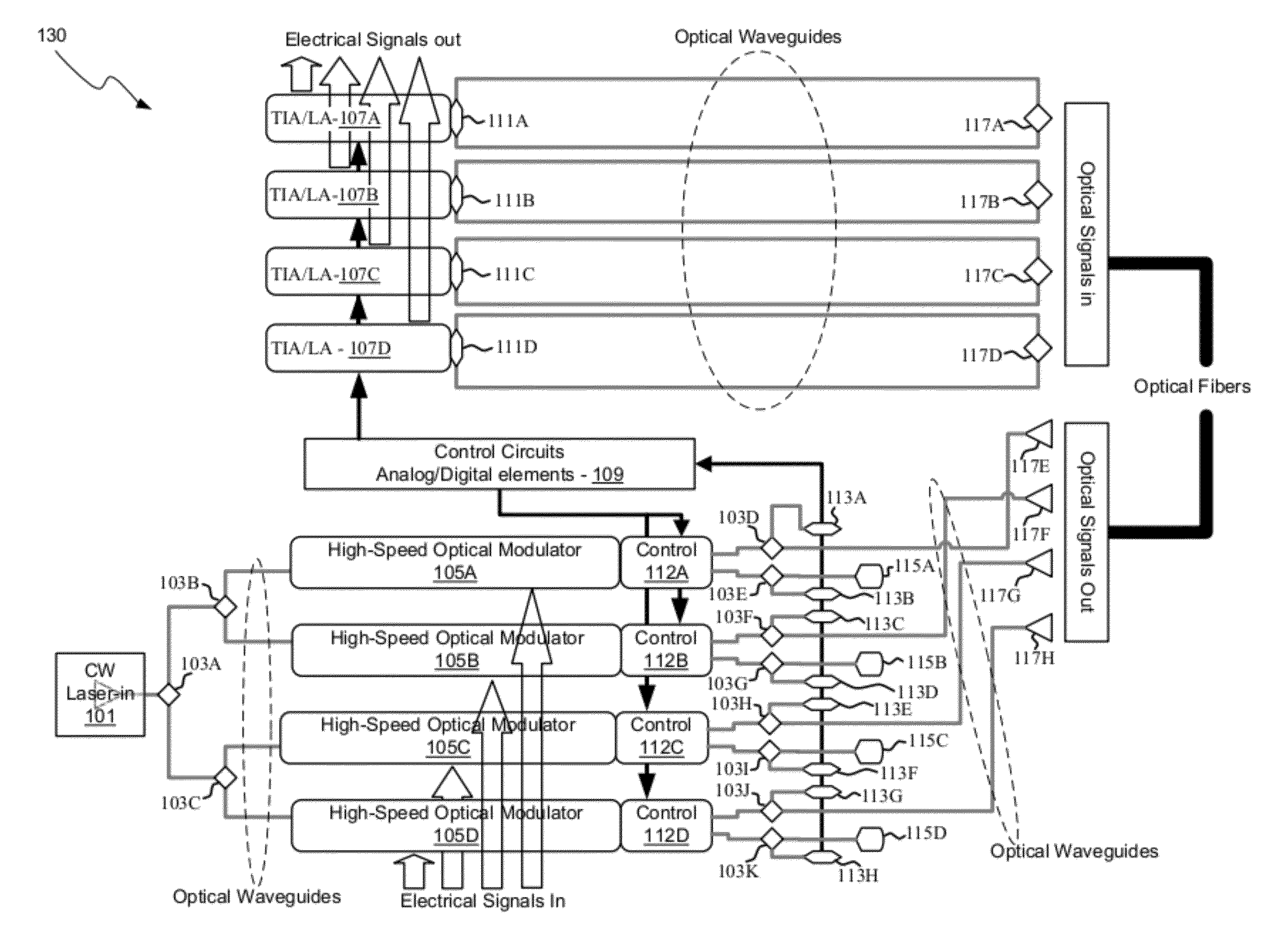

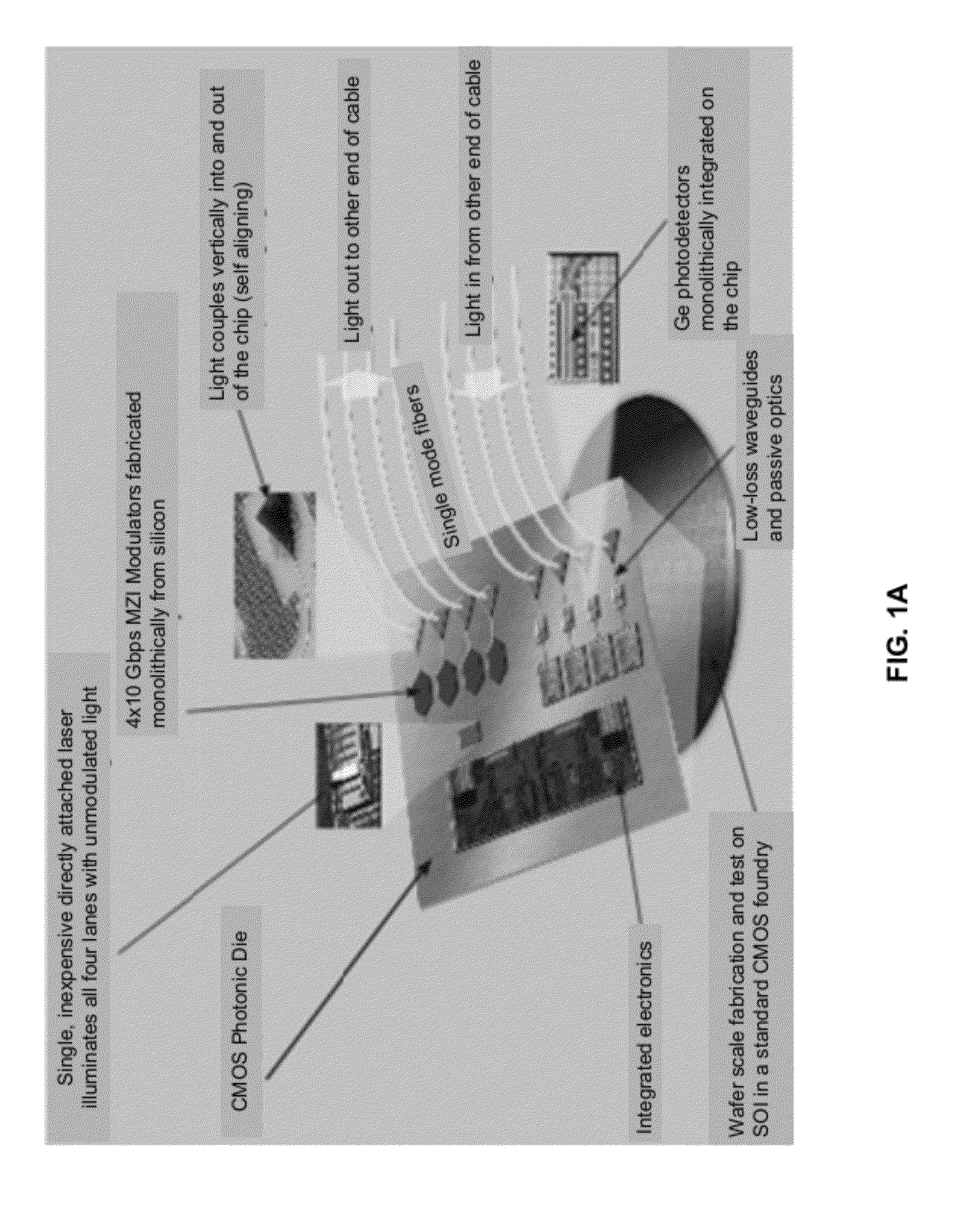

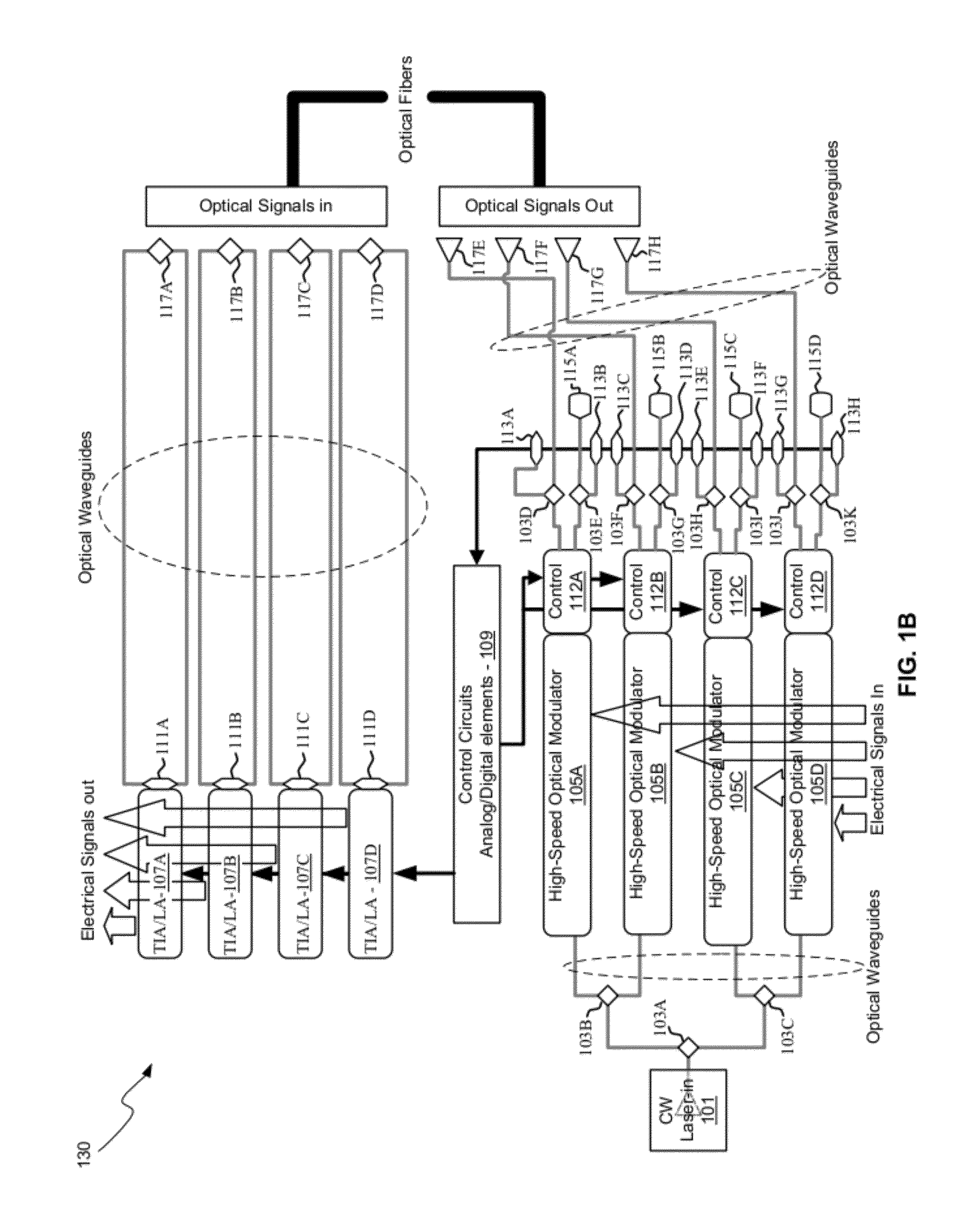

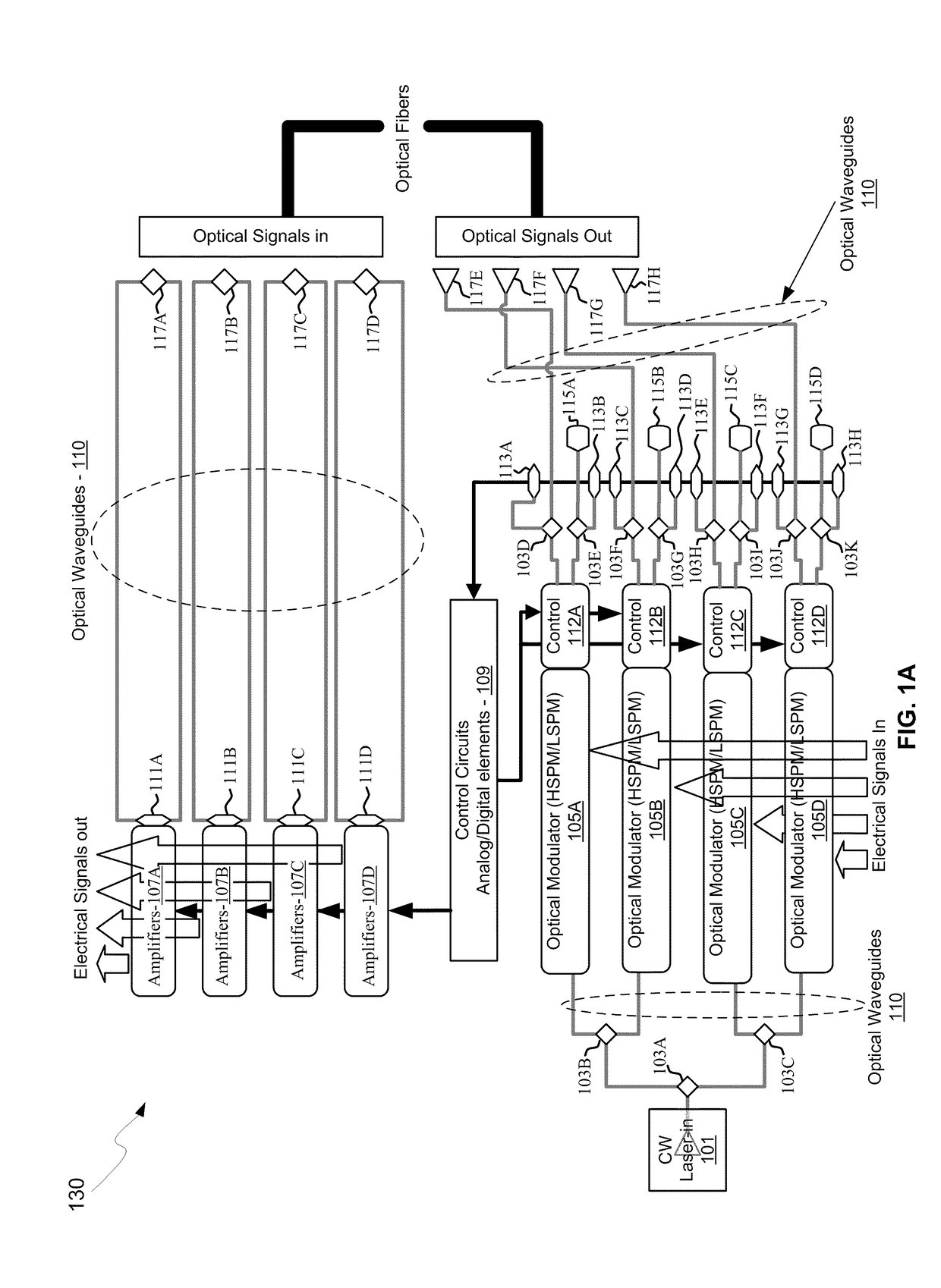

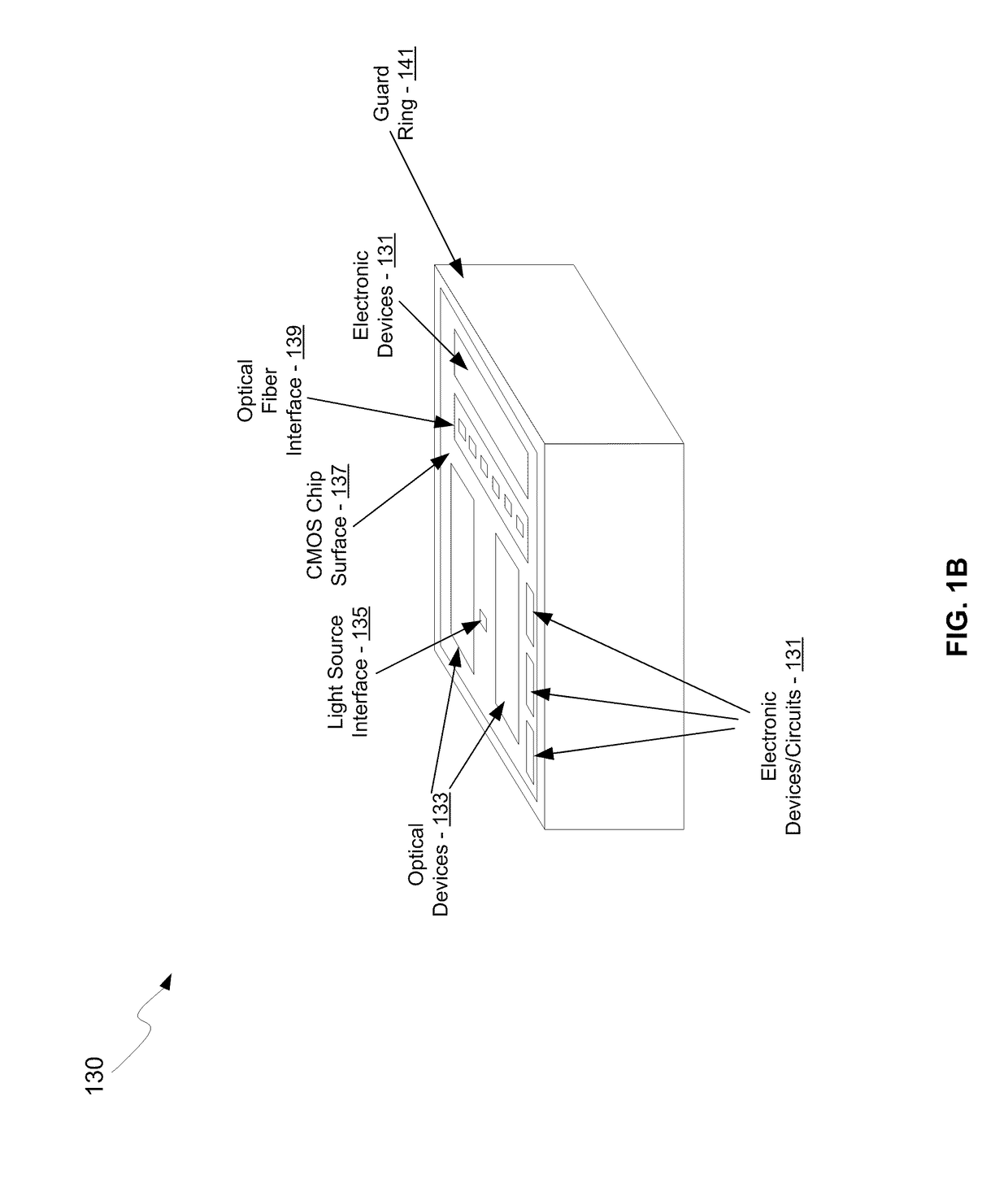

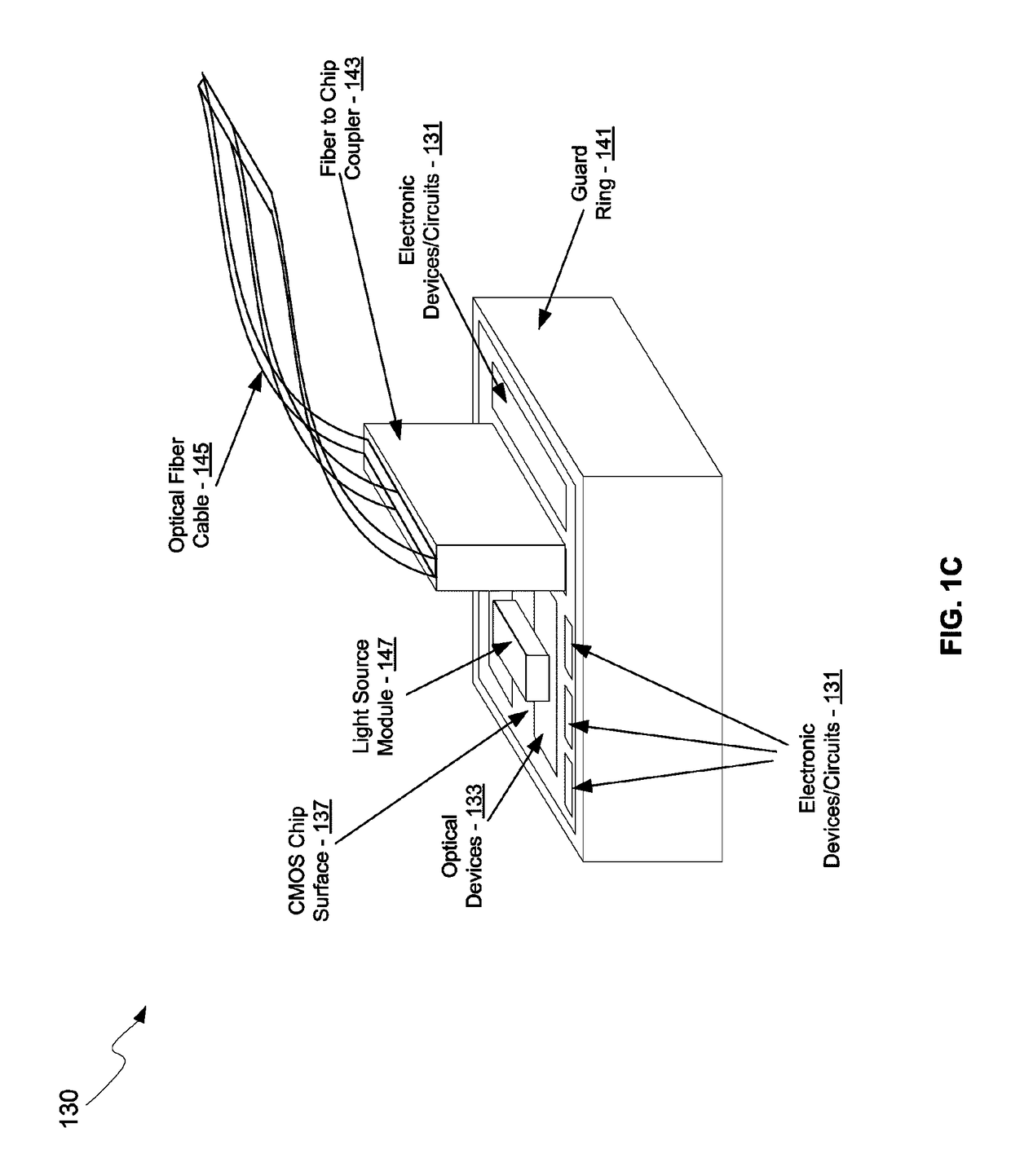

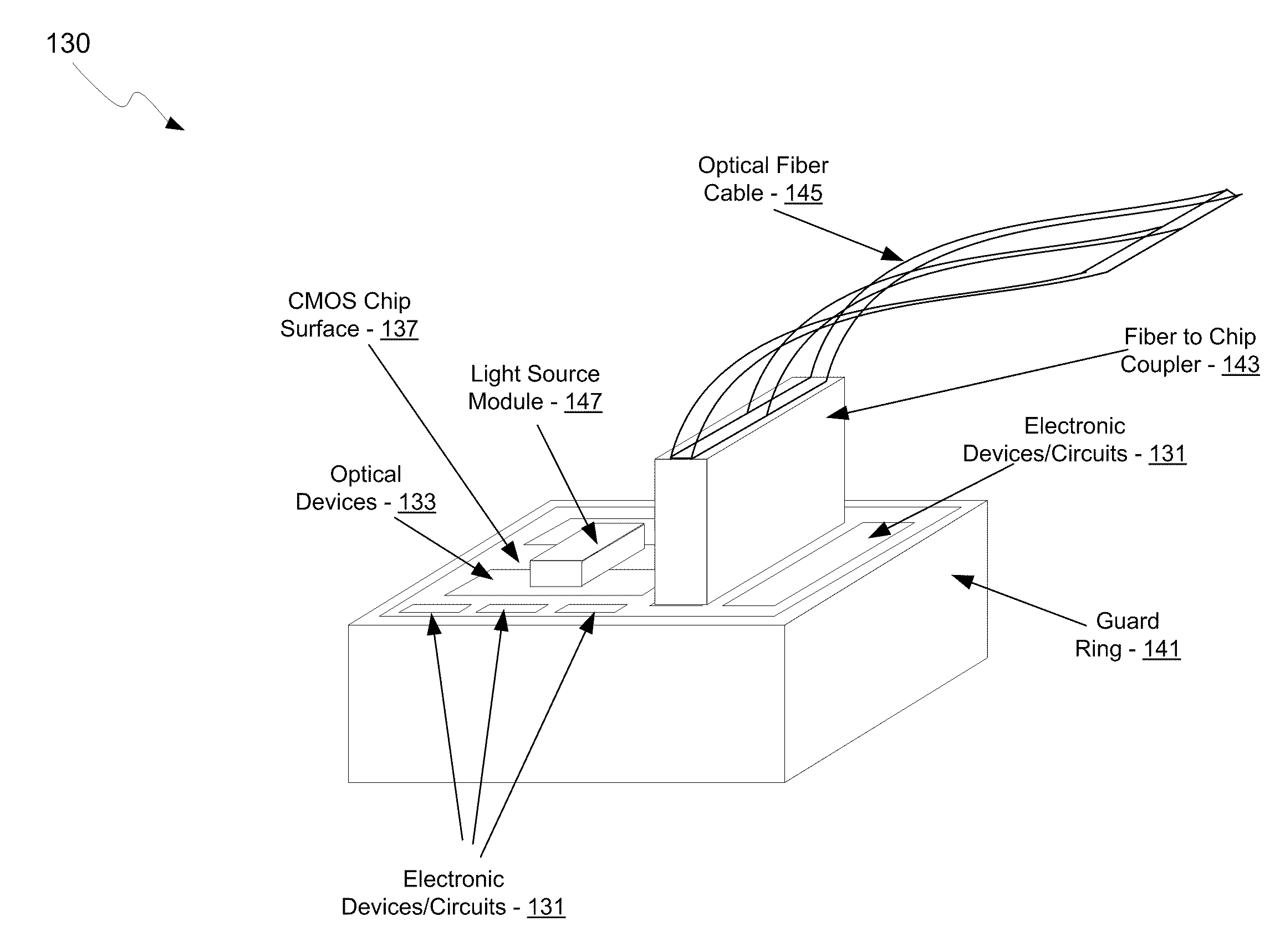

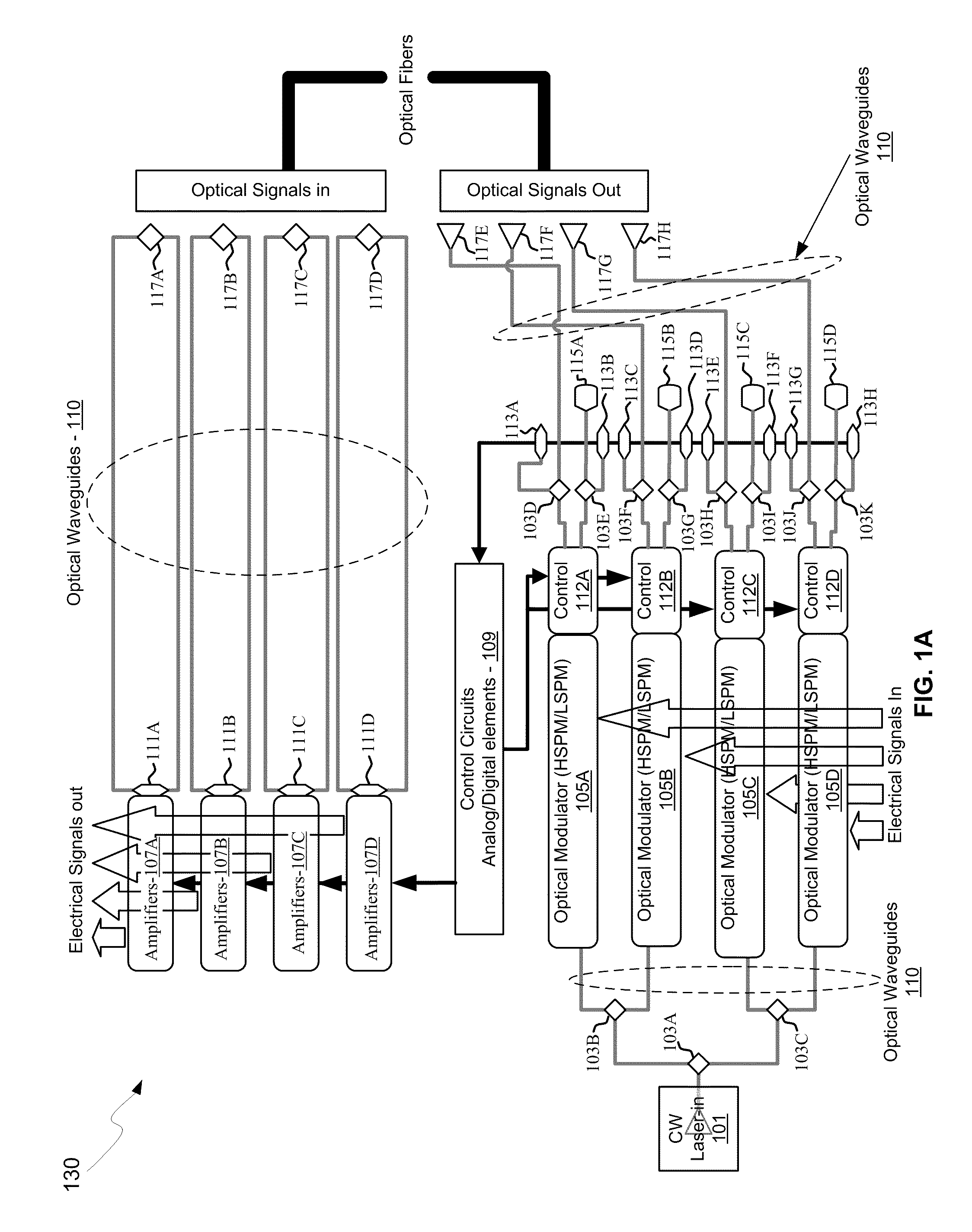

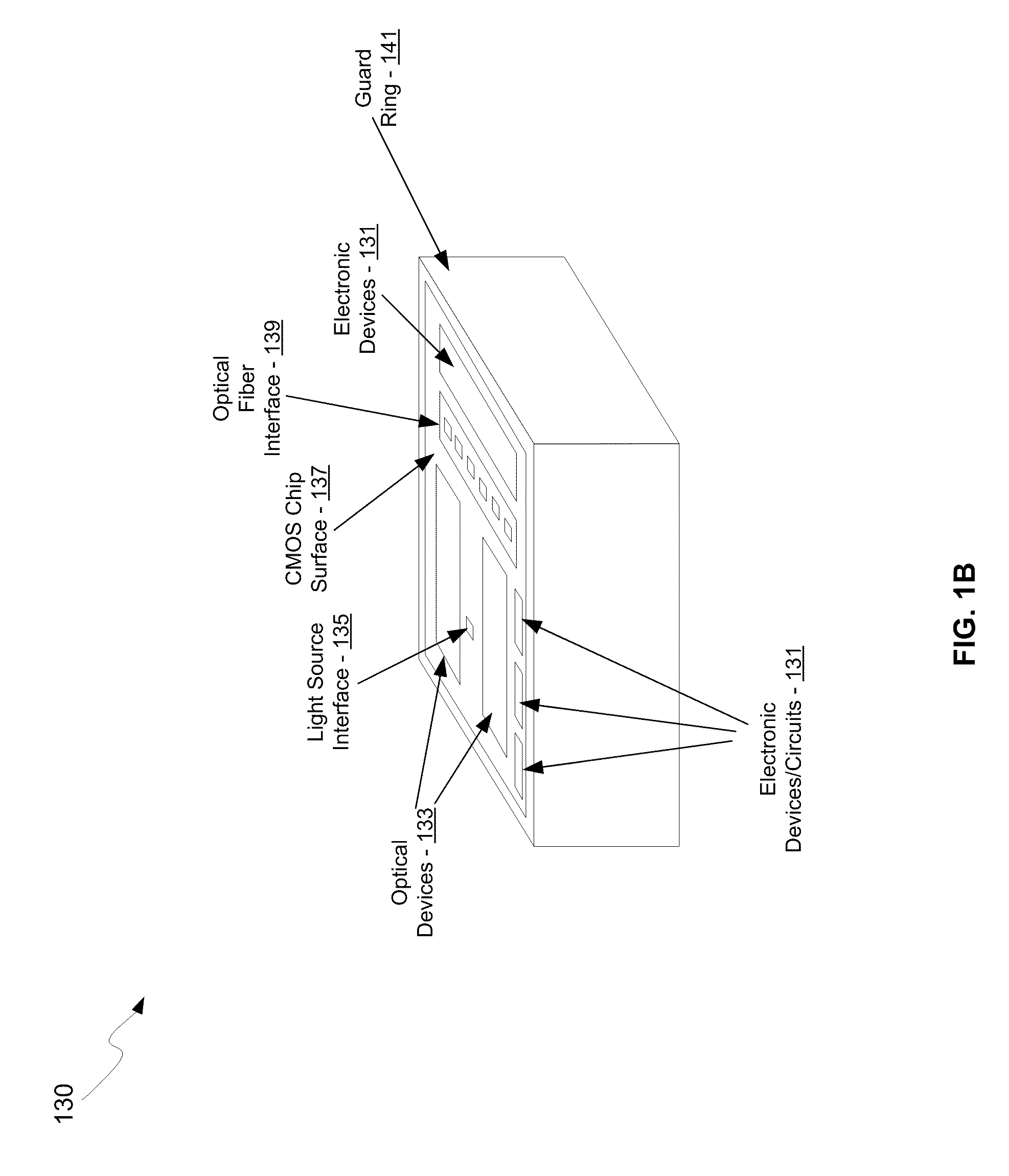

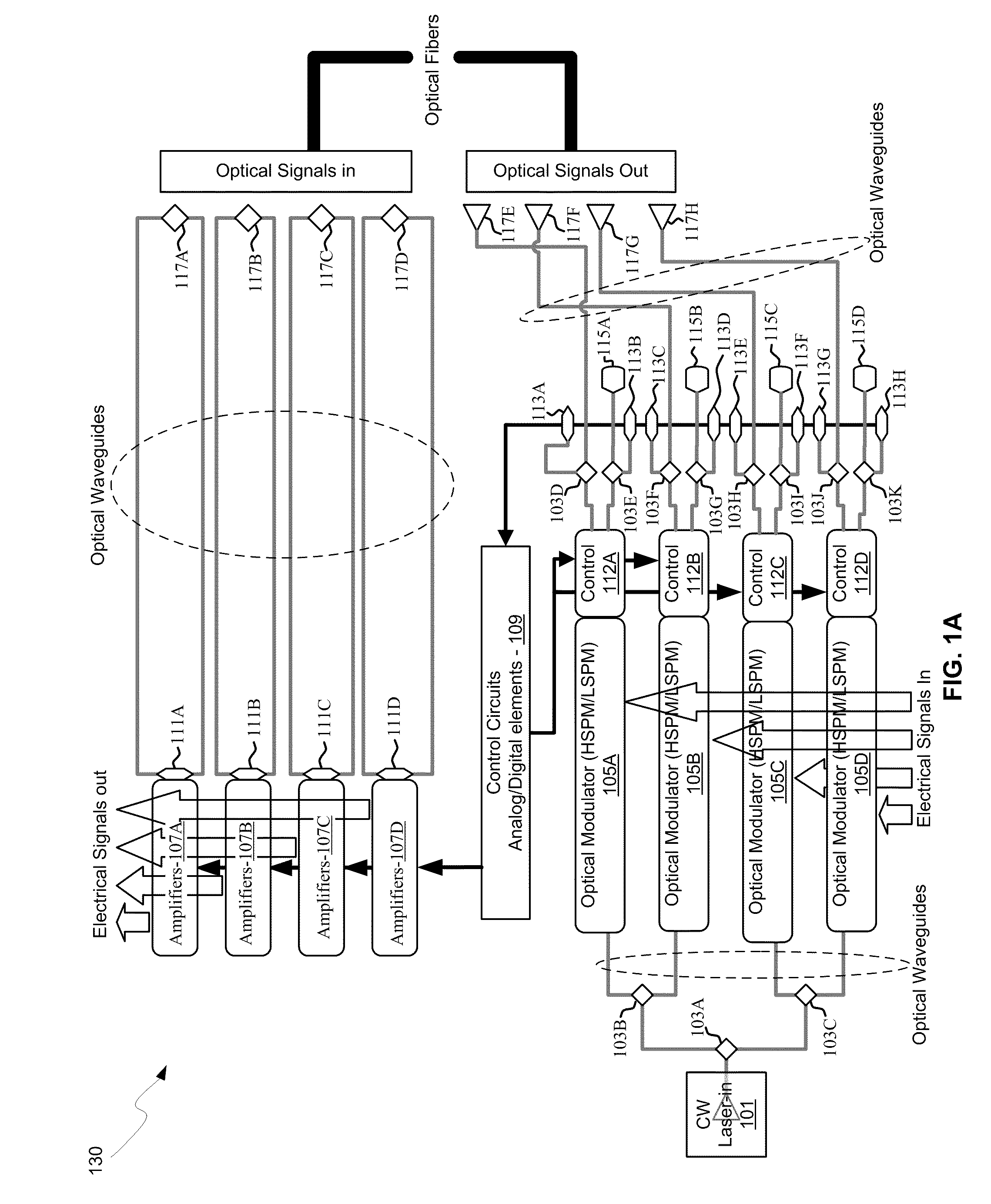

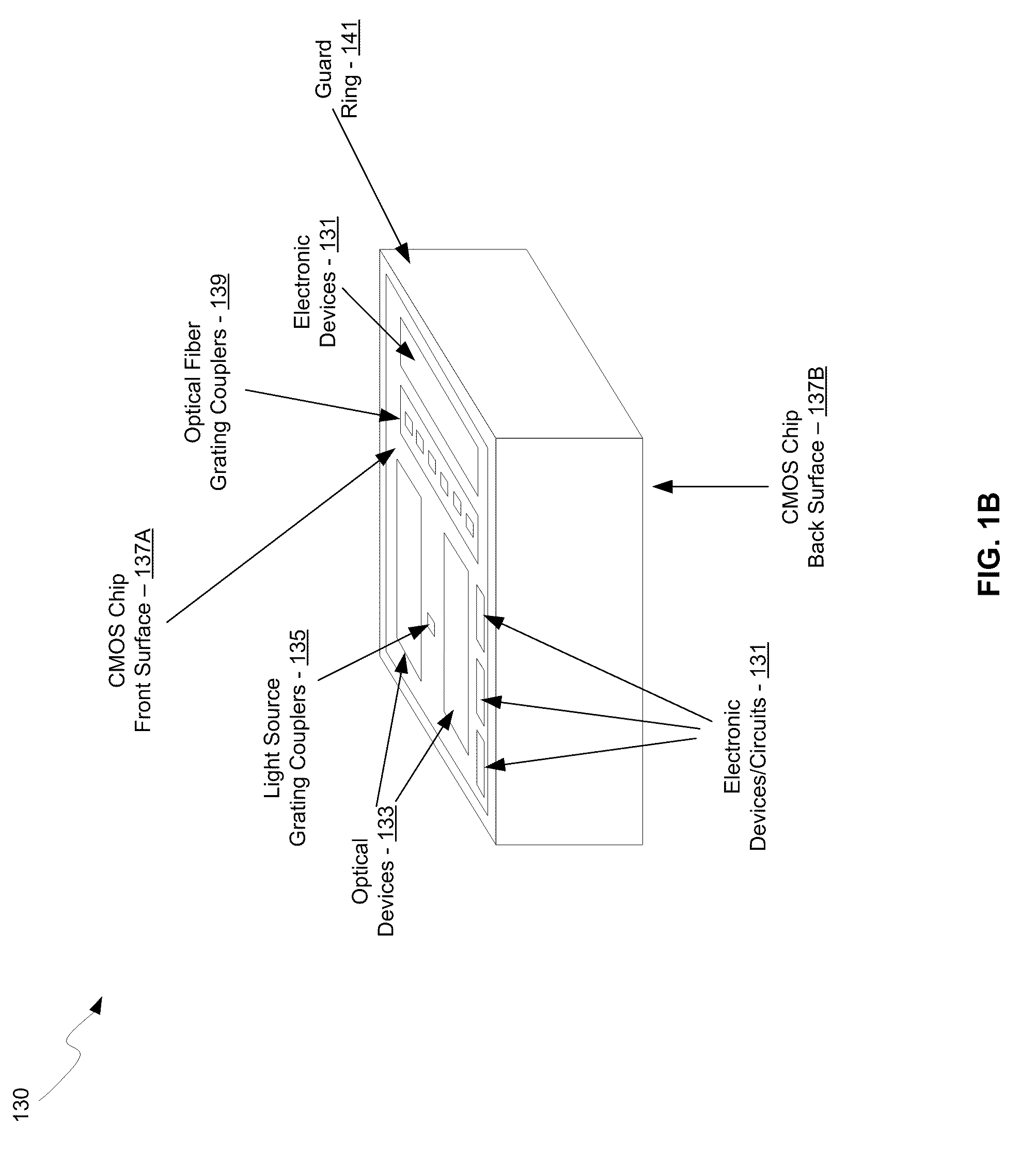

Method and system for optoelectronics transceivers integrated on a CMOS chip

Methods and systems for optoelectronics transceivers integrated on a CMOS chip are disclosed and may include receiving optical signals from optical fibers via grating couplers on a top surface of a CMOS chip, which may include a guard ring. Photodetectors may be integrated in the CMOS chip. A CW optical signal may be received from a laser source via grating couplers, and may be modulated using optical modulators, which may be Mach-Zehnder and / or ring modulators. Circuitry in the CMOS chip may drive the optical modulators. The modulated optical signal may be communicated out of the top surface of the CMOS chip into optical fibers via grating couplers. The received optical signals may be communicated between devices via waveguides. The photodetectors may include germanium waveguide photodiodes, avalanche photodiodes, and / or heterojunction diodes. The CW optical signal may be generated using an edge-emitting and / or a vertical-cavity surface emitting semiconductor laser.

Owner:CISCO TECH INC

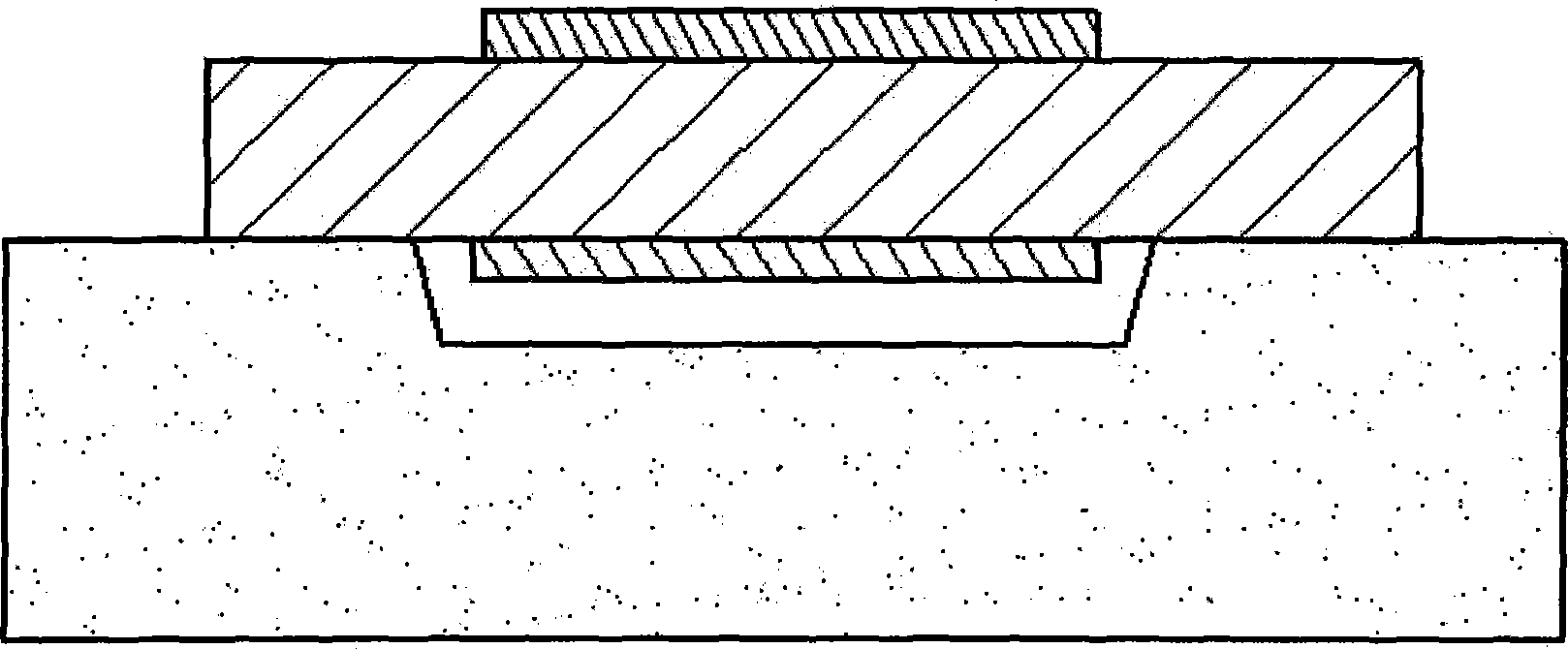

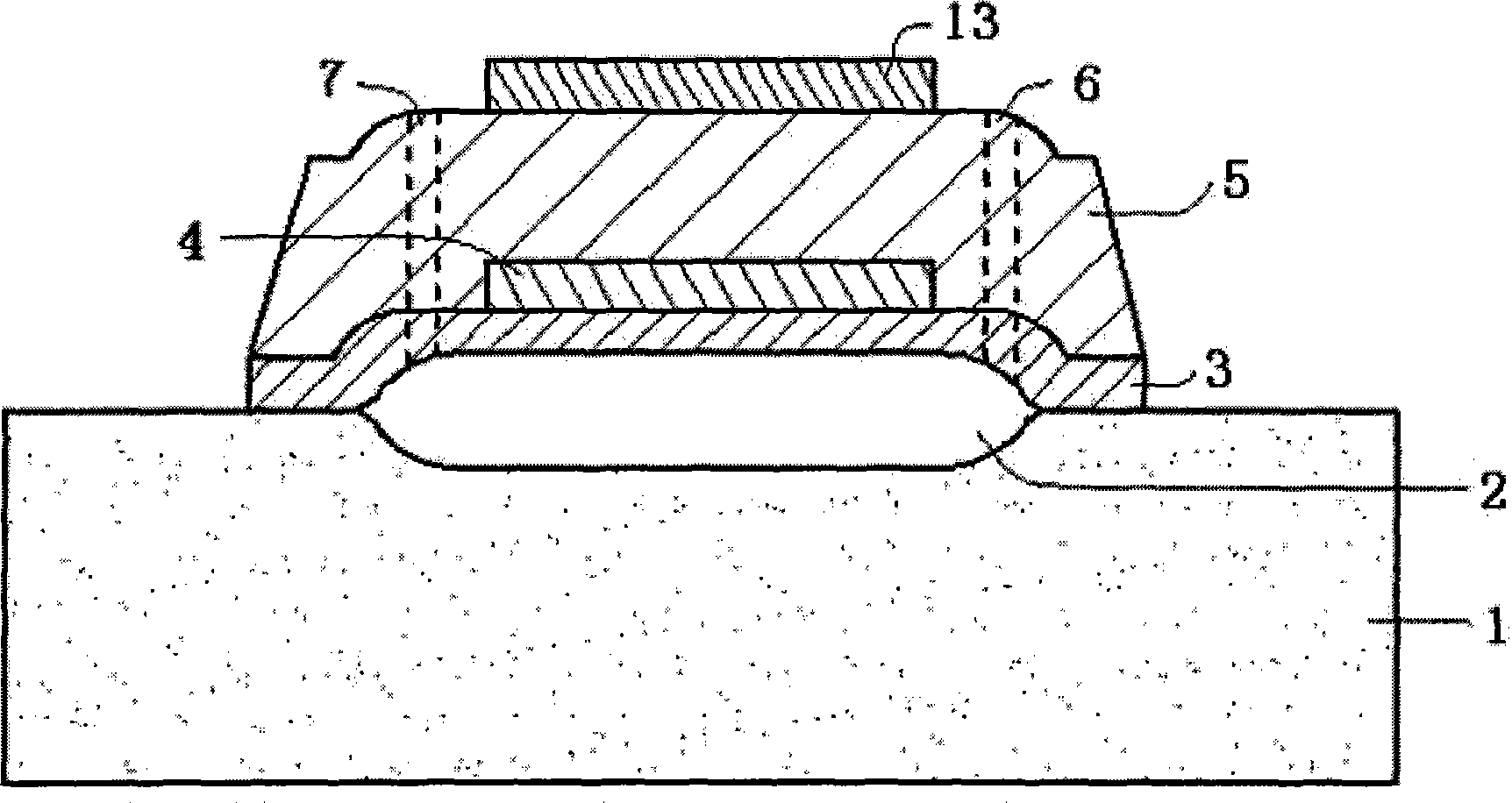

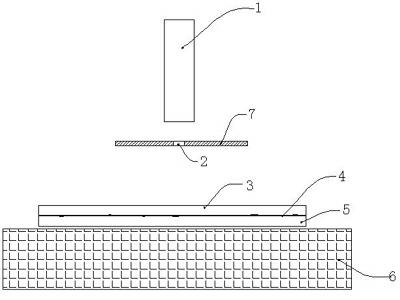

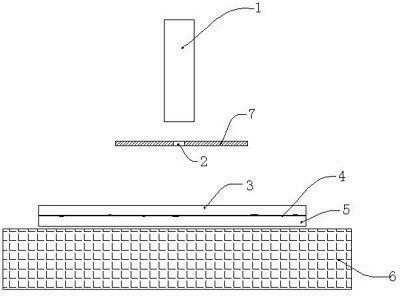

Film bulk acoustic wave resonator and preparation method thereof

InactiveCN101465628AHigh application frequencyReduce the requirements of the manufacturing process for equipmentImpedence networksThin-film bulk acoustic resonatorBulk acoustic wave

The invention discloses a thin film bulk acoustic wave resonator which comprises a substrate, a buffer layer, a piezoelectric layer and electrodes, and is characterized in that 1. A smooth concave groove and the buffer layer are arranged on the upper end surface of the substrate; the buffer layer crosses the concave groove and forms an air gap provided with a smooth upper convex edge with the substrate, and completely covers the air gap; the height of the lower top surface of the air gap is less than that of the substrate, and the air gap has flat surface and even change edge; 2. The edge of the buffer layer, which is contacted with the air gap and is close to the substrate is in smooth and outer-convex shape; the piezoelectric layer is arranged on the buffer layer; the electrodes include a bottom electrode and a top electrode; the bottom electrode is arranged in the piezoelectric layer on the buffer layer; the top electrode is arranged on the piezoelectric layer. The thin film bulk acoustic wave resonator has ingenious structure; a FBAR with stable structure and low loss can be fabricated on the substrate through the method, and the CMP process is avoided, so the thin film bulk acoustic wave resonator can be integrated into a CMOS chip conveniently.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

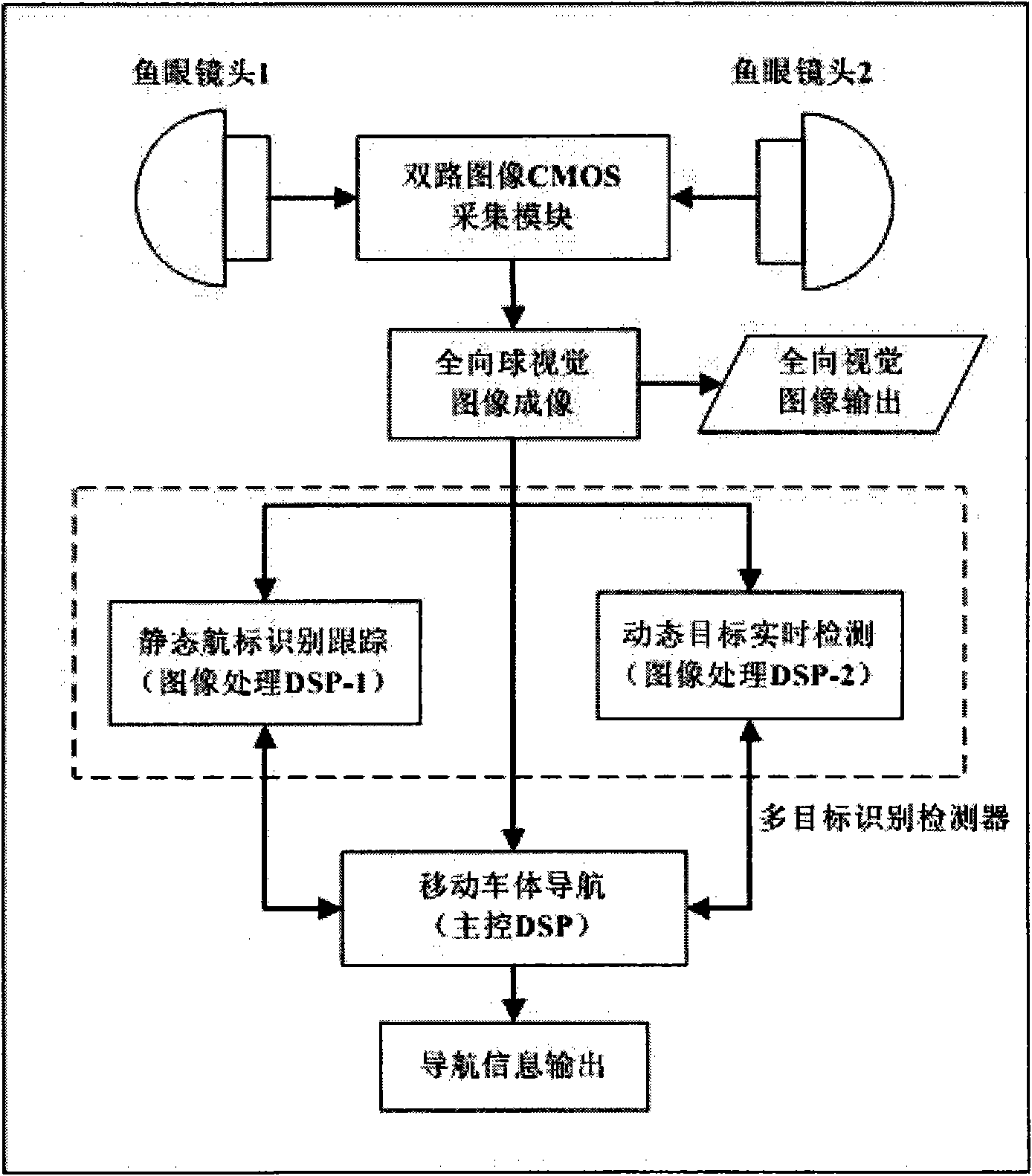

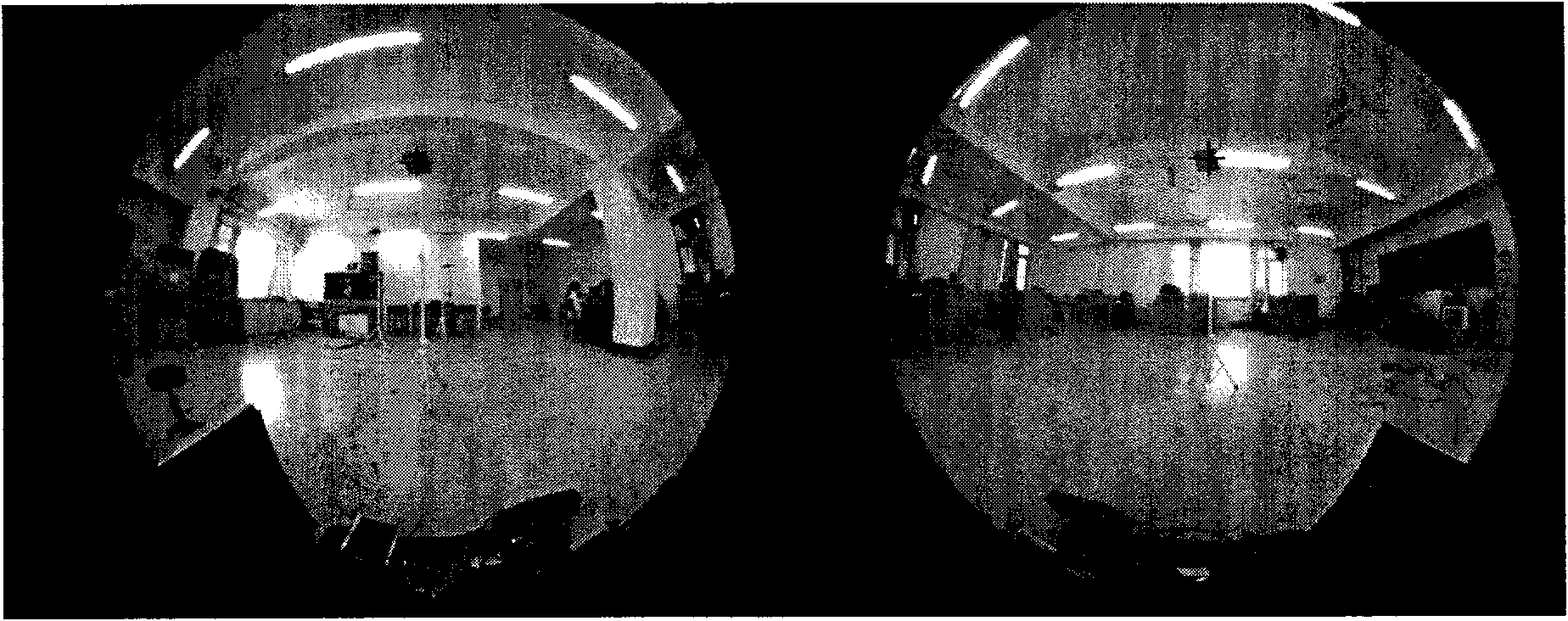

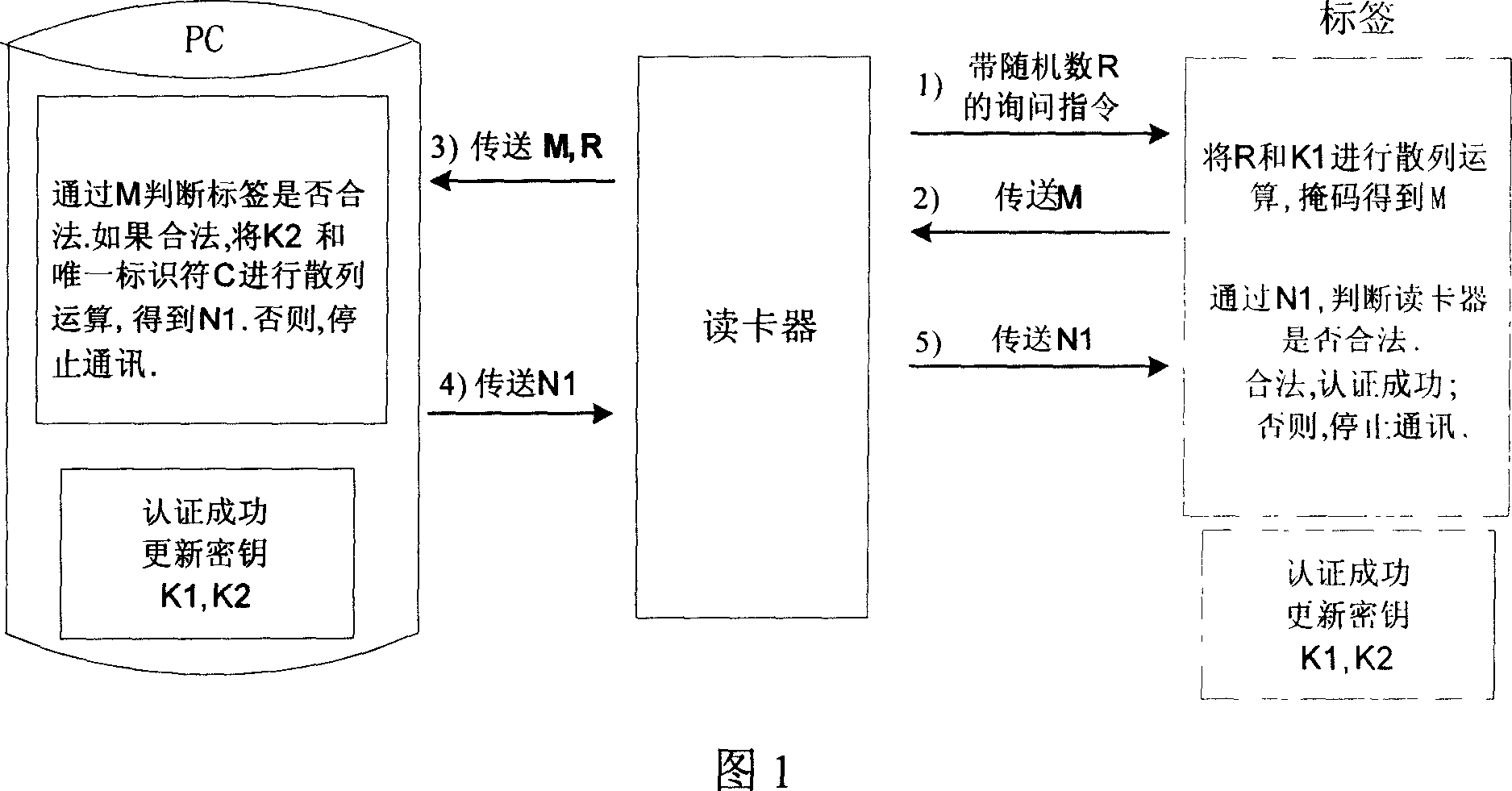

Embedded omnidirectional ball vision object detection and mobile monitoring system and embedded omnidirectional ball vision object detection and mobile monitoring method

InactiveCN101561270AGuaranteed real-timeGuaranteed reliabilityProgramme controlNavigational calculation instrumentsSafety monitoringVisual perception

The invention relates to an embedded omnidirectional ball vision object detection and mobile monitoring system and an embedded omnidirectional ball vision object detection and mobile monitoring method. Omnidirectional ball vision is a visual system with a global domain visual field and can acquire all scenes of the whole global domain at one time without the revolving and scanning of a camera. The system comprises an omnidirectional ball vision imaging system (comprising two fish-eye panoramic lens, two CMOS image acquisition chips, an FPGA controller and an SRAM memory chip), and a multi-path DSP parallel image processor (comprising a master control DSP and two paths of DSP parallel image processors). The imaging system acquires omnidirectional ball vision images by matching the two fish-eye panoramic lens and the two CMOS chips, wherein the master control DSP is responsible for data scheduling and communication, and the two paths of the parallel DSPs are independent from each other and can process the identification tracking of a static navigation mark and the real-time monitoring of a dynamic object in parallel. The method and the system have the advantages of high integrity, small volume and quick processing speed and are particularly suitable in the military or domestic field such as safety monitoring, mobile vehicle body navigation and the like.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

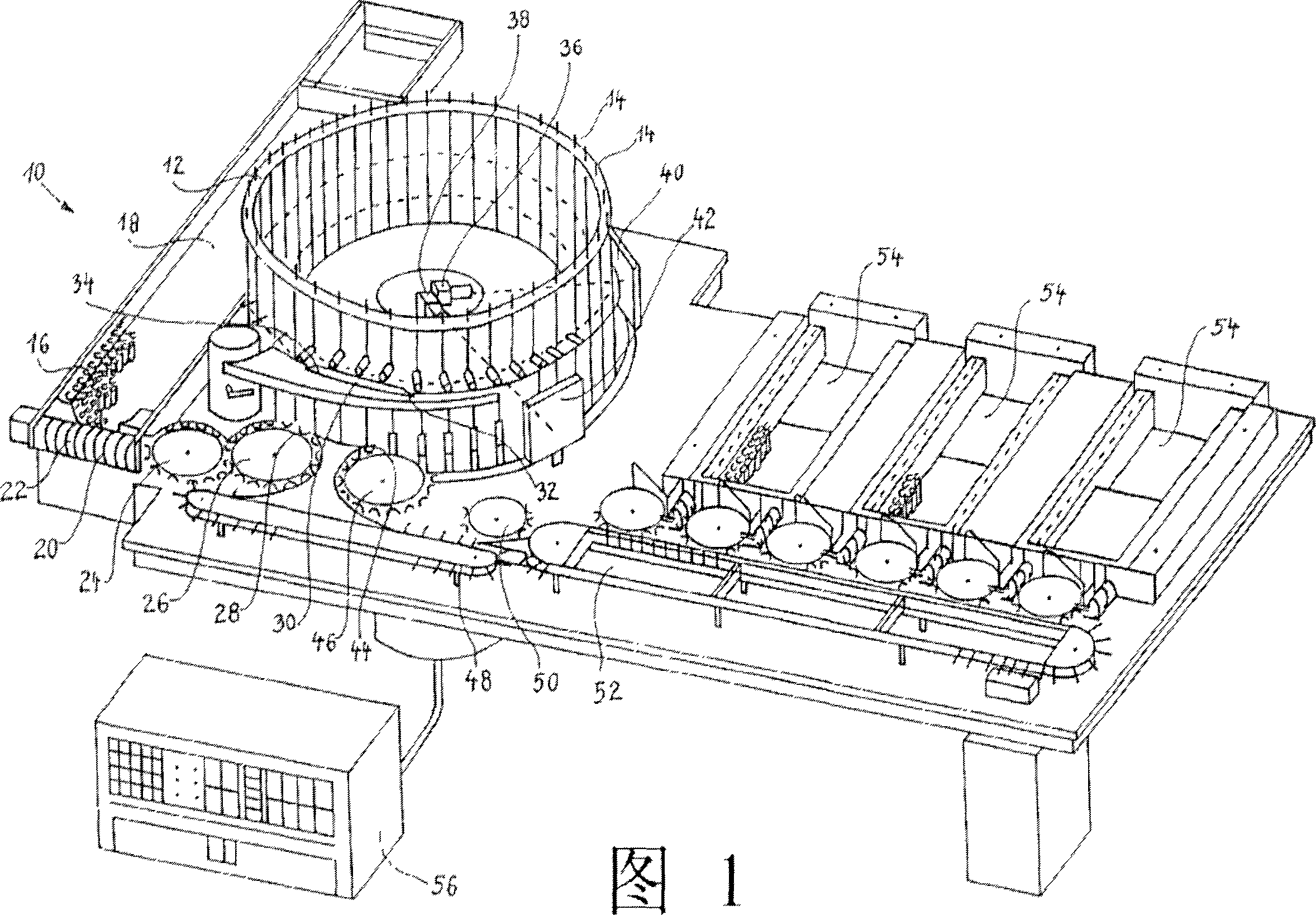

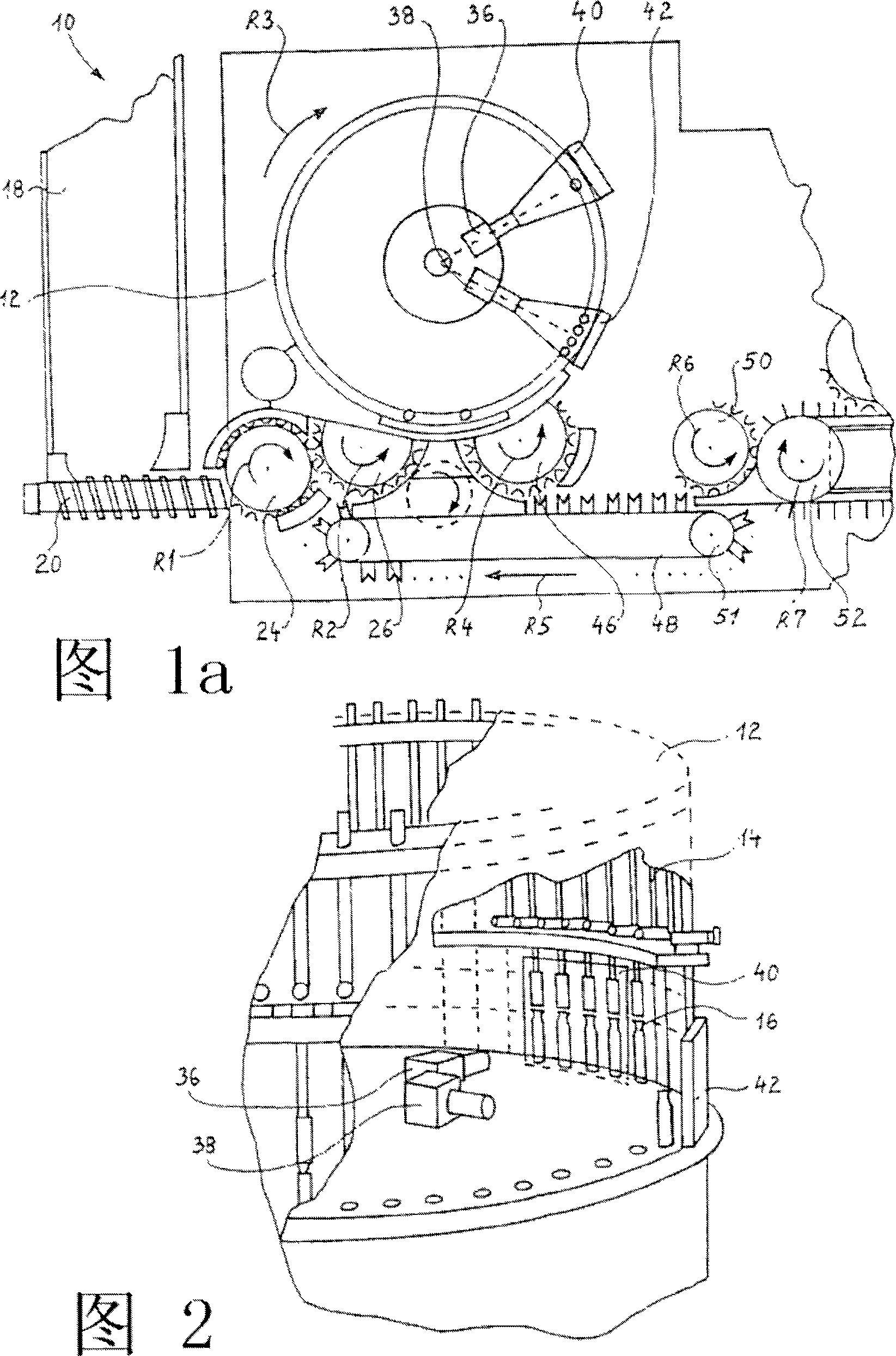

Method and device for determining foreign matter or defect of multiple filled containers

ActiveCN101061382AImage analysisOptically investigating flaws/contaminationFatigue damageForeign matter

A method for repairing a damaged portion of a combustor inner liner assembly. The method includes removing the combustor from a gas turbine engine. After inspecting the combustor to determine whether cracks exists in portions of the inner liner assembly, the method includes removing a cracked inner liner assembly from the combustor. Then the portion of the inner liner assembly, comprising a multi-hole panel region, an aft lip region, an aft seal flange region and an aft panel support leg are separated from the inner liner assembly. The multi-hole panel region and aft lip, where fatigue damage typically exists, along with the aft seal flange region, are discarded and a new aft lip region / aft seal flange region and multi-hole panel region are provided. The new parts are joined to the aft panel support leg and the inner liner assembly aft of forward bolt flange region after these parts are refurbished. The inner liner assembly is then reattached to the combustor and reassembled into the engine.

Owner:MOELLER & DEVICON

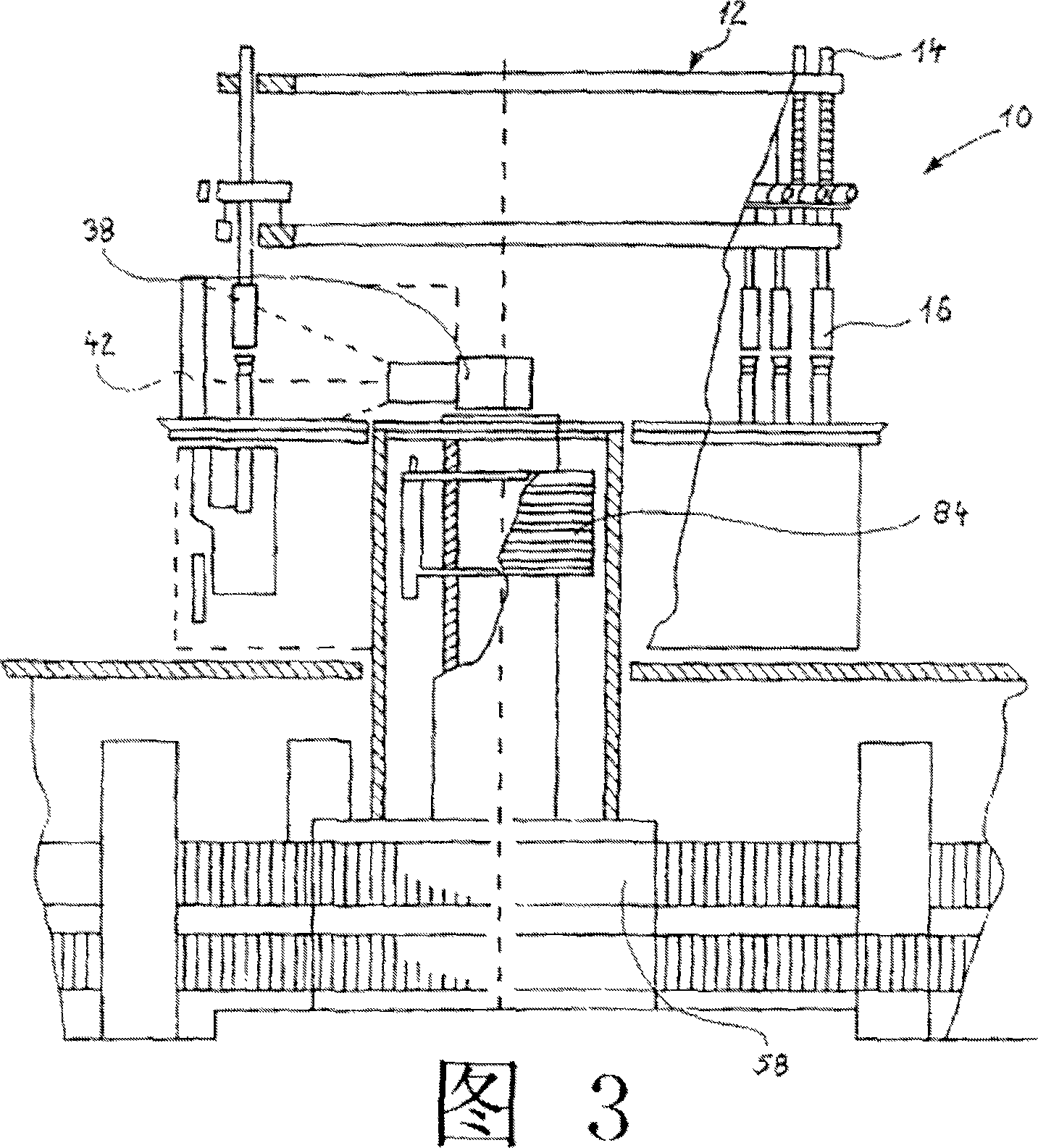

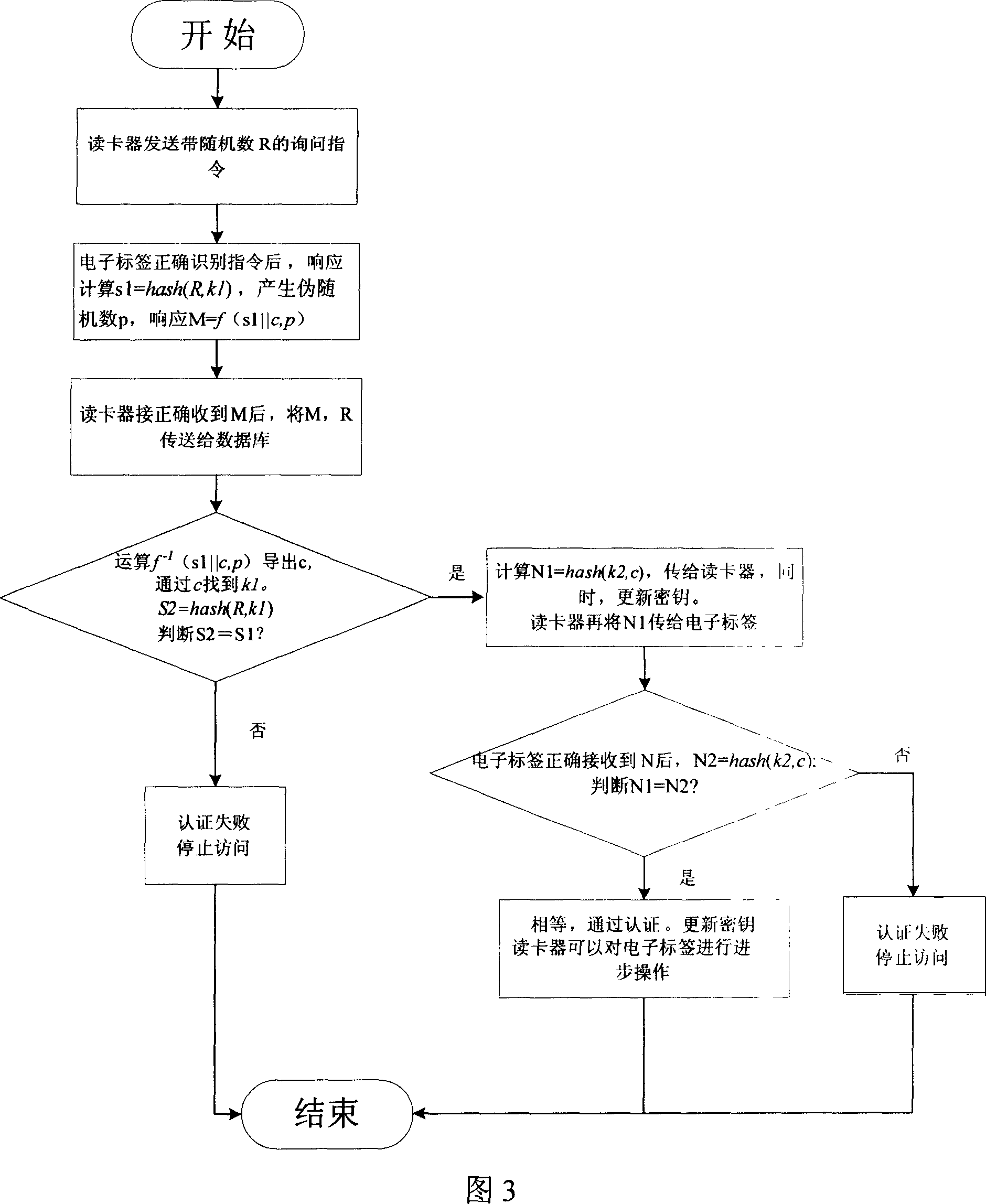

Safety identification method in radio frequency distinguishing system

InactiveCN1932835AImprove the protective effectThe certification method has obvious advantagesMultiple keys/algorithms usageSensing record carriersUltra-widebandMan-in-the-middle attack

Owner:HUAZHONG UNIV OF SCI & TECH

Method And System For A Light Source Assembly Supporting Direct Coupling To An Integrated Circuit

ActiveUS20120205524A1Radiation pyrometryBeam/ray focussing/reflecting arrangementsGratingOptical table

Owner:CISCO TECH INC

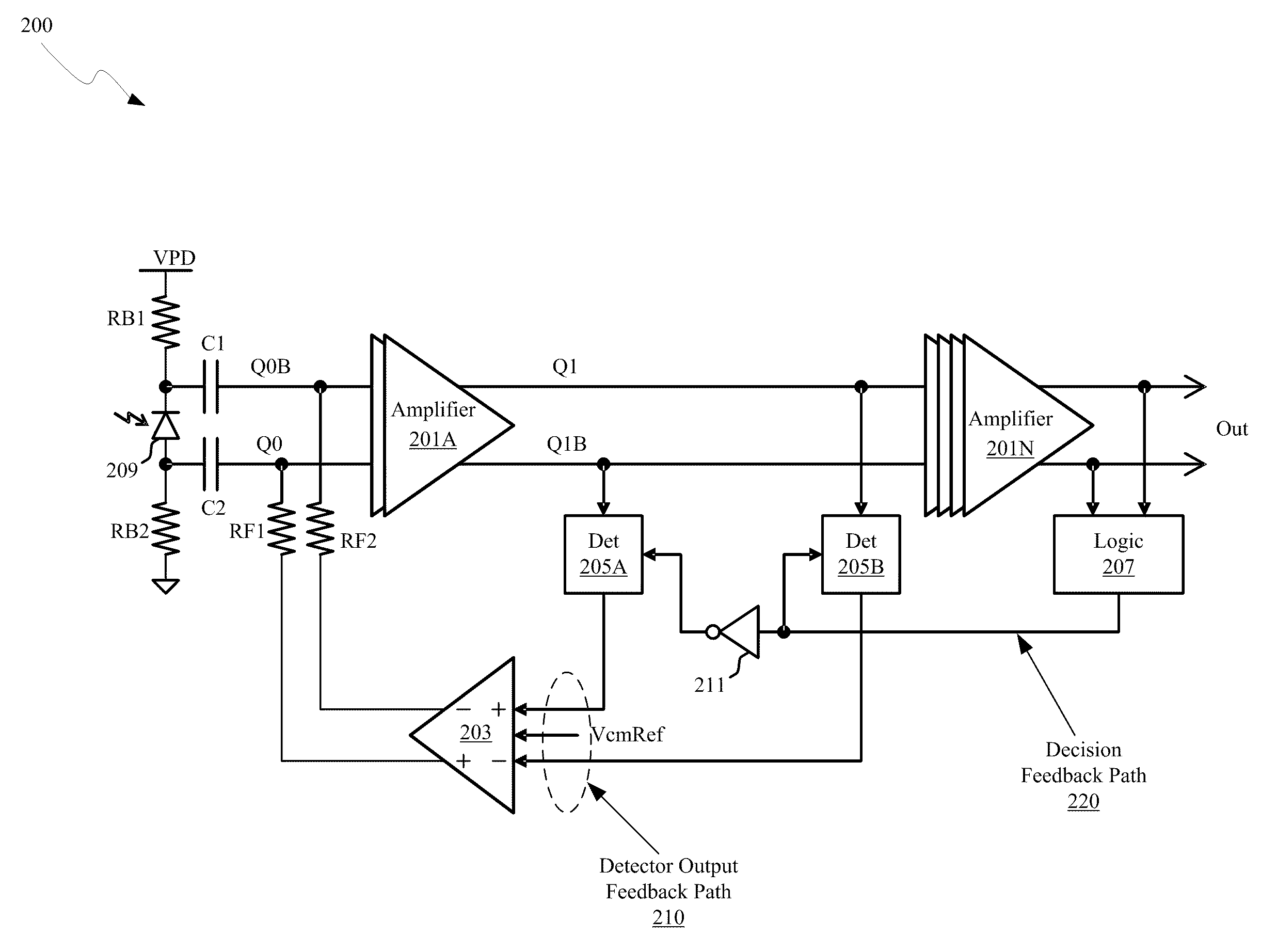

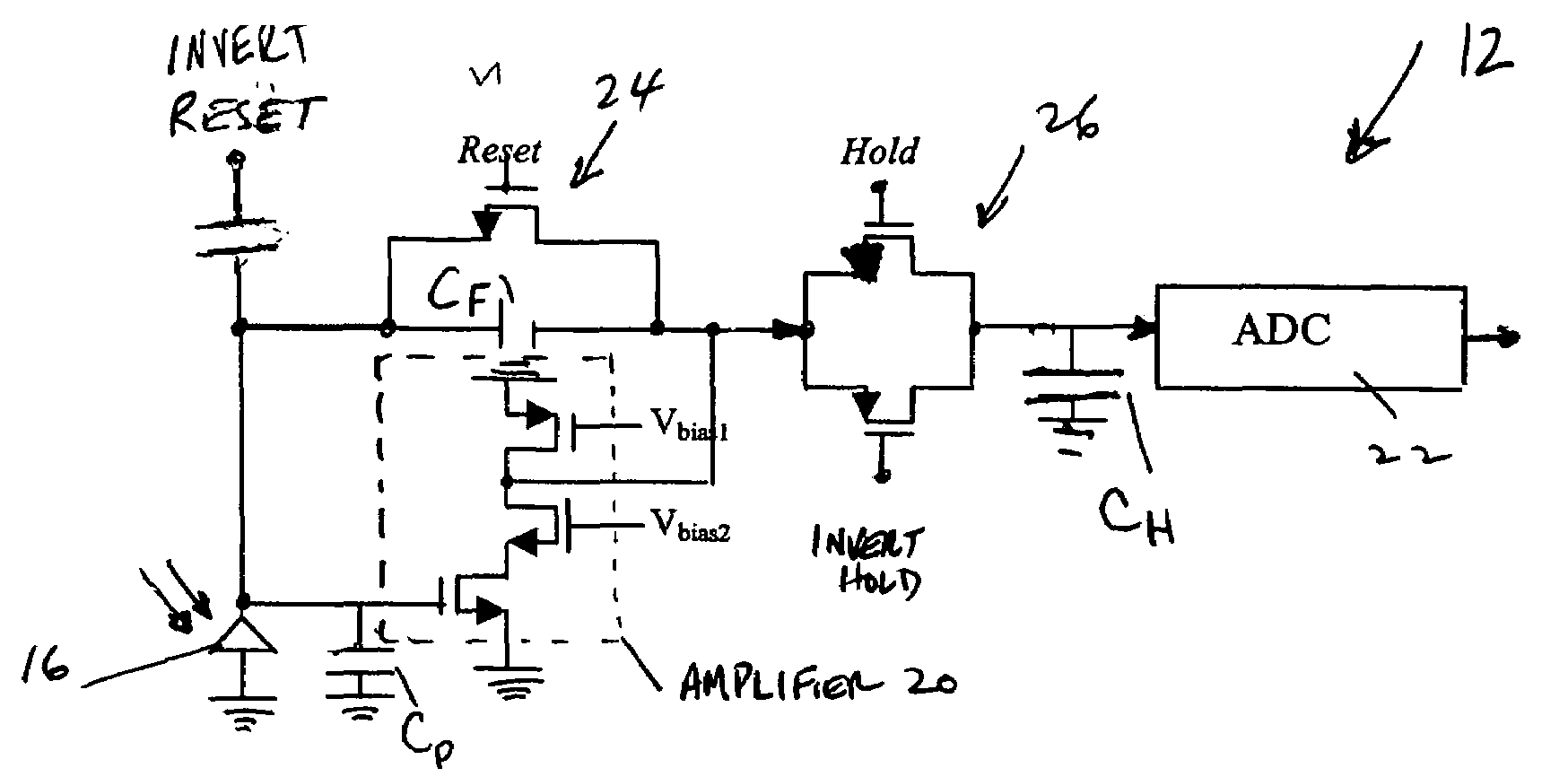

Method and system for a feedback transimpedance amplifier with sub-40khz low-frequency cutoff

ActiveUS8471639B2Negative-feedback-circuit arrangementsAmplifiers controlled by lightPhotodetectorTransimpedance amplifier

A system for a feedback transimpedance amplifier with sub-40 khz low-frequency cutoff is disclosed and may include amplifying electrical signals received via coupling capacitors utilizing a transimpedance amplifier (TIA) having feedback paths comprising source followers and feedback resistors. The feedback paths may be coupled prior to the coupling capacitors at inputs of the TIA. Voltages may be level shifted prior to the coupling capacitors to ensure stable bias conditions for the TIA. The TIA may be integrated in a CMOS chip and the source followers may comprise CMOS transistors. The TIA may receive current-mode logic or voltage signals. The electrical signals may be received from a photodetector, which may comprise a silicon germanium photodiode and may be differentially coupled to the TIA. The chip may comprise a CMOS photonics chip where optical signals for the photodetector in the CMOS photonics chip may be received via one or more optical fibers.

Owner:CISCO TECH INC

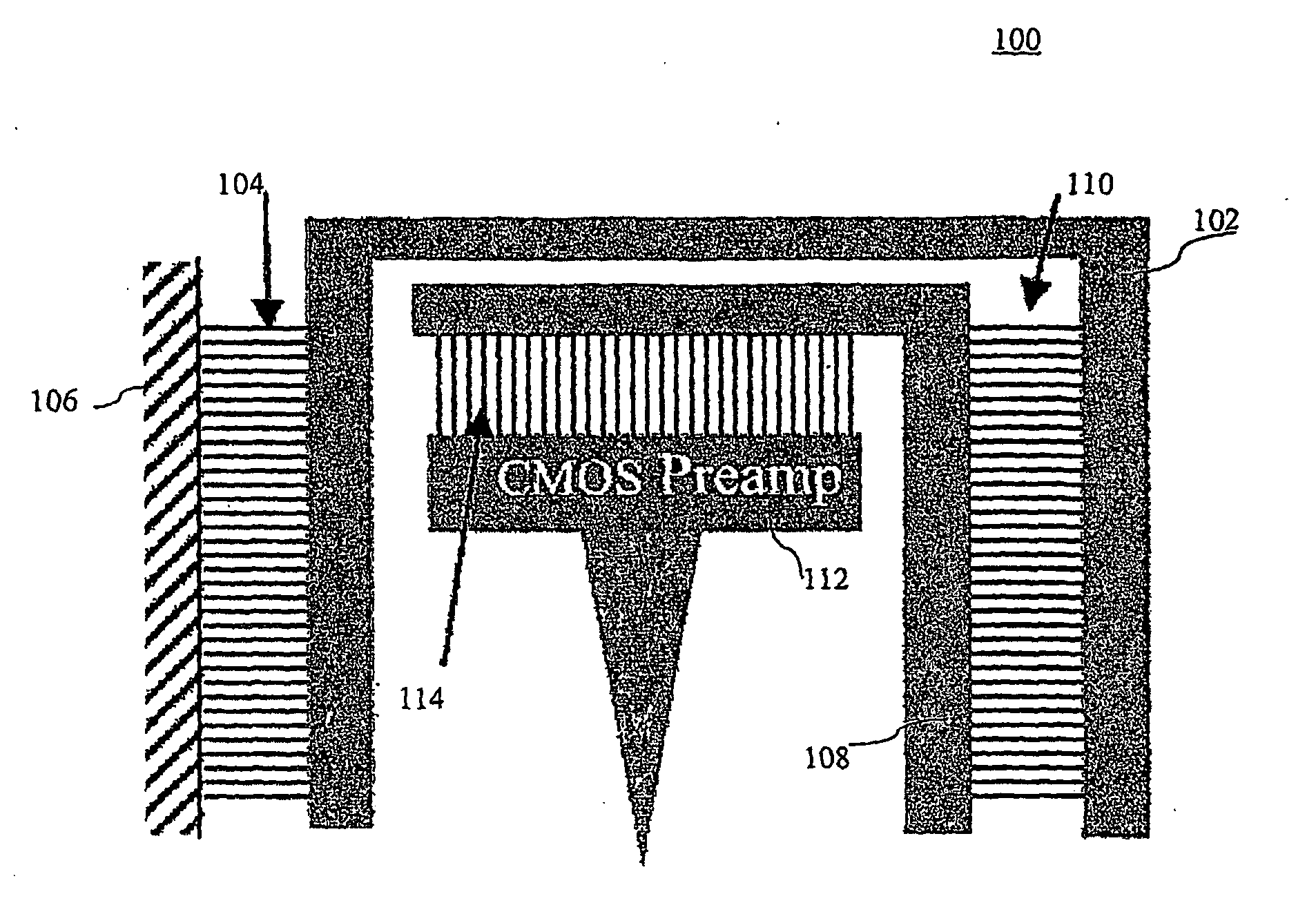

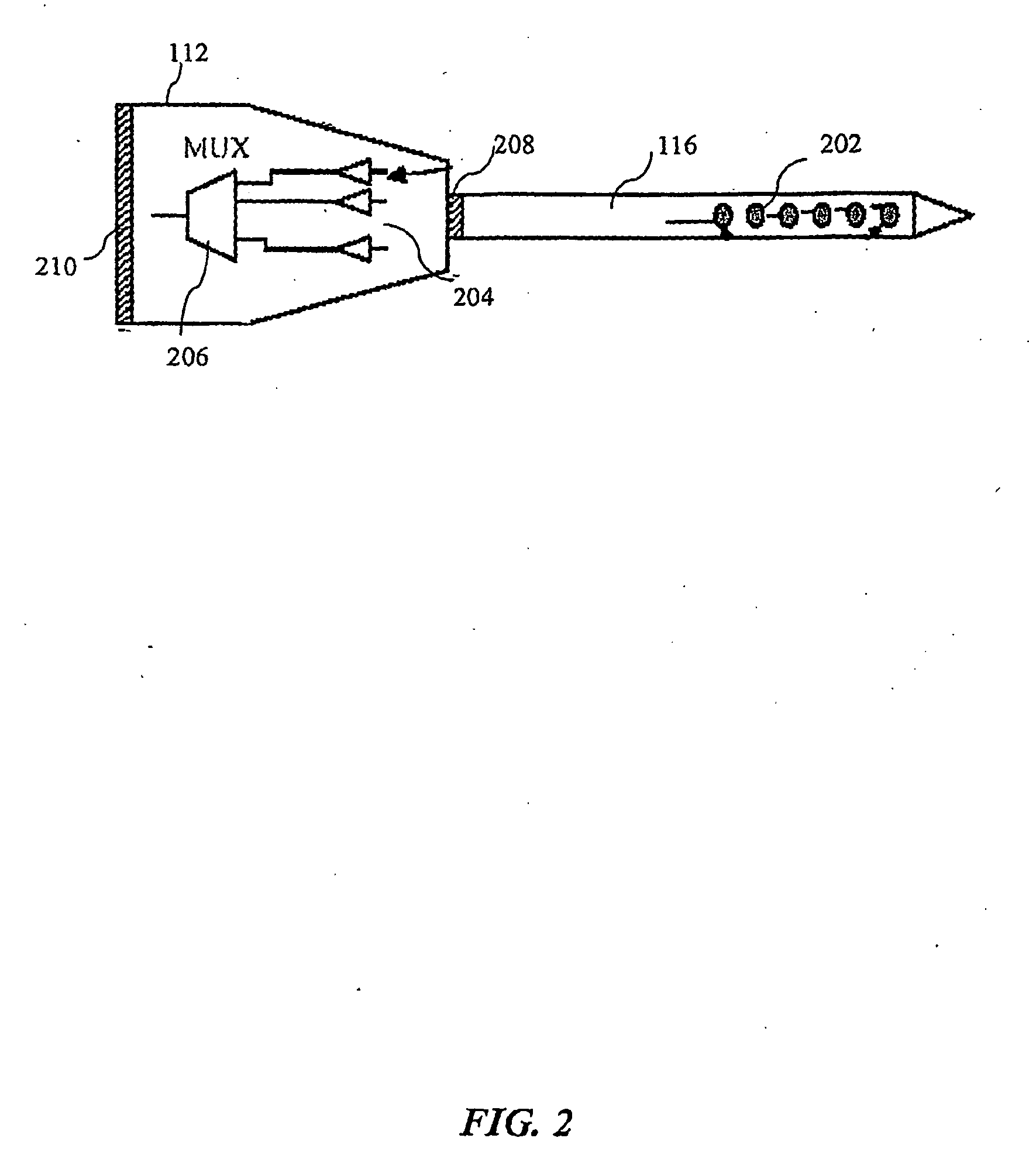

Neuralprobe and methods for manufacturing same

InactiveUS20090318824A1Eliminate needEnhanced sensing and recording of neuronal activitySemiconductor/solid-state device manufacturingMicroscale sensorsAudio power amplifierManufacturing technology

A neural probe and method of fabricating same are provided. The probe comprises a plurality of frames connected to each other and to a substrate by respective bimorphs. A probe base is connected by another bimorph to the frames. A probe tip extends from the probe base. The probe can achieve a large vertical motion and out-of-plane curling. The probe can operate according to three modes. The first mode pertains to a large-signal motion for tuning in single-unit neuronal activity. The second pertains to a small-signal motion with lock-in amplifier that increases SNR. The third pertains to burst small-signal motion for clearing tissue responses. Fabrication of a neural probe begins with a processed CMOS chip. Post-CMOS processing incorporates self-aligned selective nickel plating and sacrifices two aluminum layers. The fabrication technique produces a neural probe in which the sensing elements are in close proximity to CMOS circuitry. The fabrication technique obviates the need for post-CMOS masks, alignment, or assembly.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

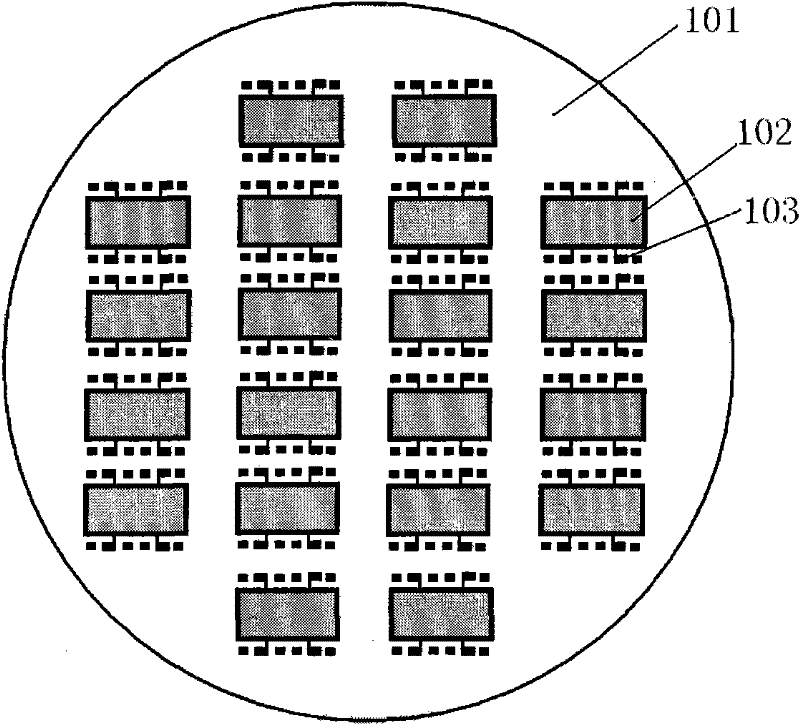

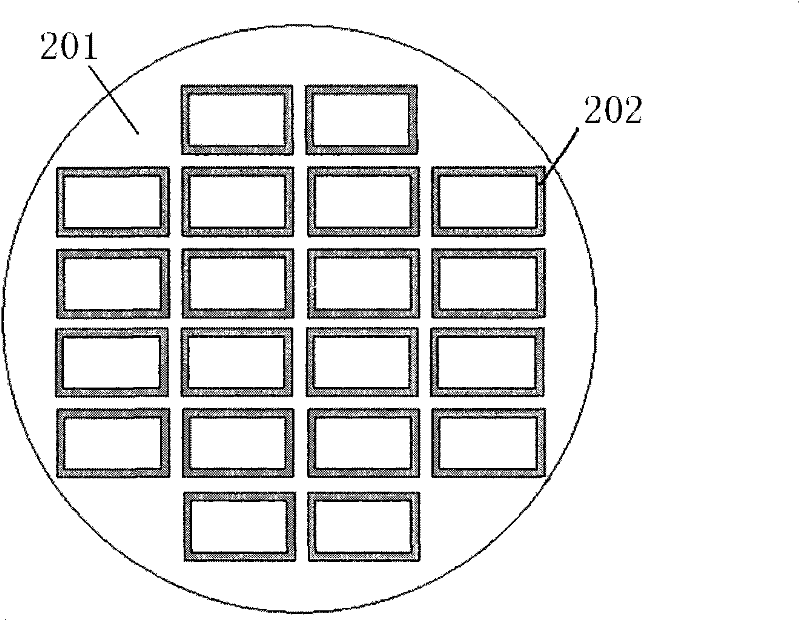

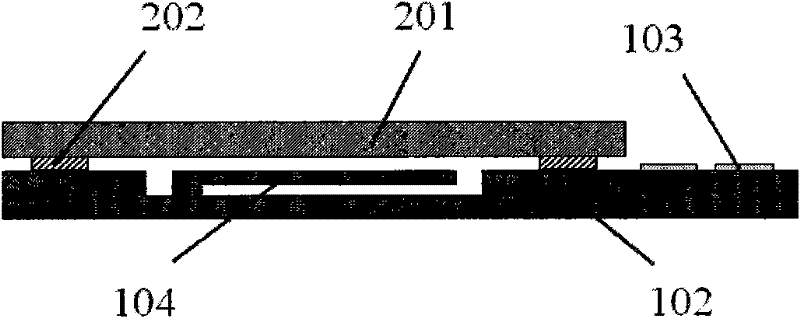

MEMS (micro electro mechanical system) wafer-level three-dimensional mixing integration packaging structure and method

ActiveCN102241388AReduce stressImprove performanceDecorative surface effectsSolid-state devicesLead bondingSlurry

The invention provides an MEMS (micro electro mechanical system) wafer-level three-dimensional mixing integration packaging structure and method based on a Chip to Wafer stacking mode. The method is characterized in that an MEMS device wafer and a silicon cover plate wafer are bonded through low-temperature bonding of glass slurry so as to realize wafer-level airtight / vacuum packaging and finish protection on movable components of the MEMS device; a CMOS (complementary metal oxide semiconductor) chip such as ASIC (application specific integrated circuit) and the like are mounted on and interconnected with the surface of the silicon cover plate wafer in a Chip to Wafer stacking mode so as to realize three-dimensional mixing integration of the CMOS chip such as ASIC and the like and the MEMS device wafer; discrete integrated micro systems are mounted on a low-cost organic substrate; multi-layer interconnection of the CMOS chip, the MEMS device and the substrate is finished through a lead bonding mode; and low-stress plastic package material is filled in a dam mode to protect the integrated micro systems and improve the environment reliability, thus forming an MEMS wafer-level three-dimensional mixing integration packaging structure which has the advantages of high density, low cost, low stress and high reliability and is easy to process.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

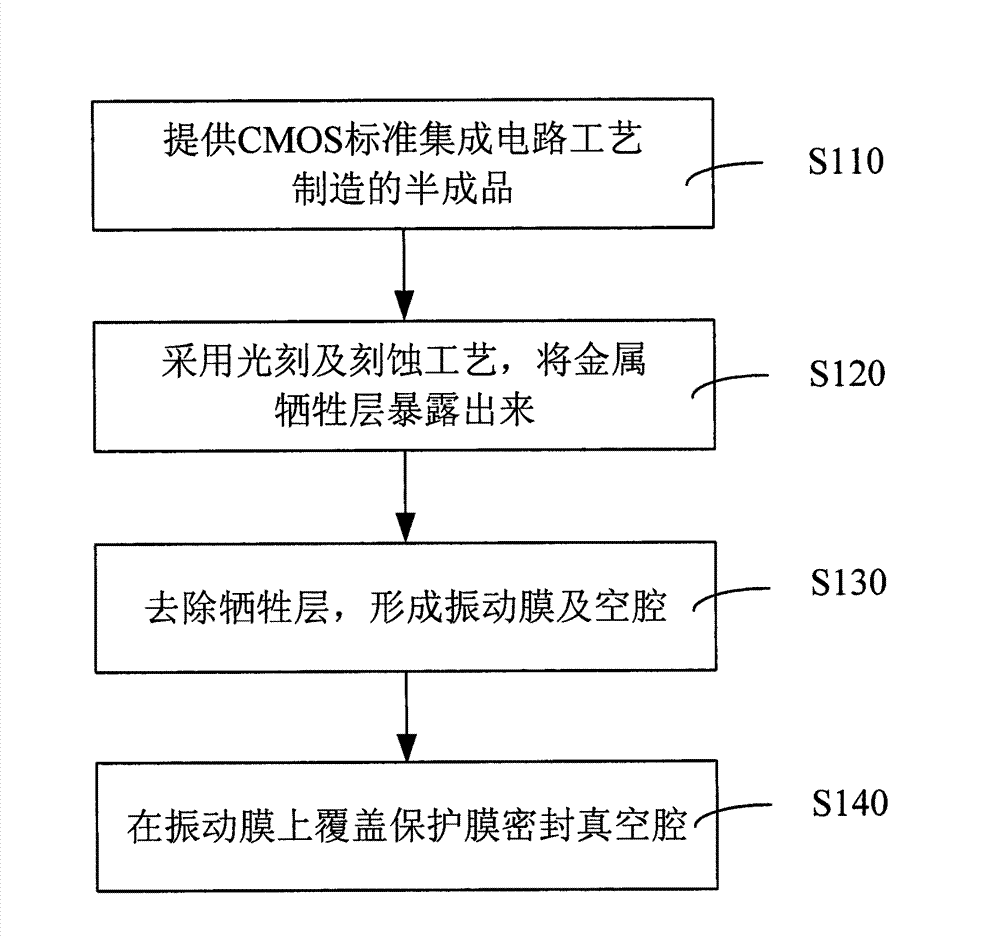

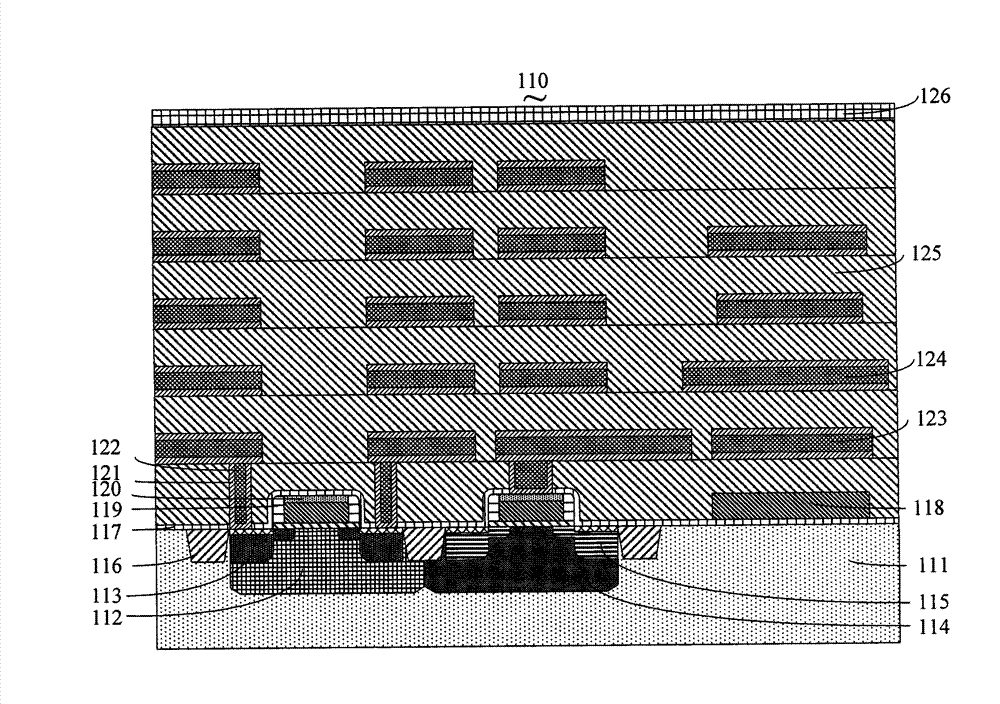

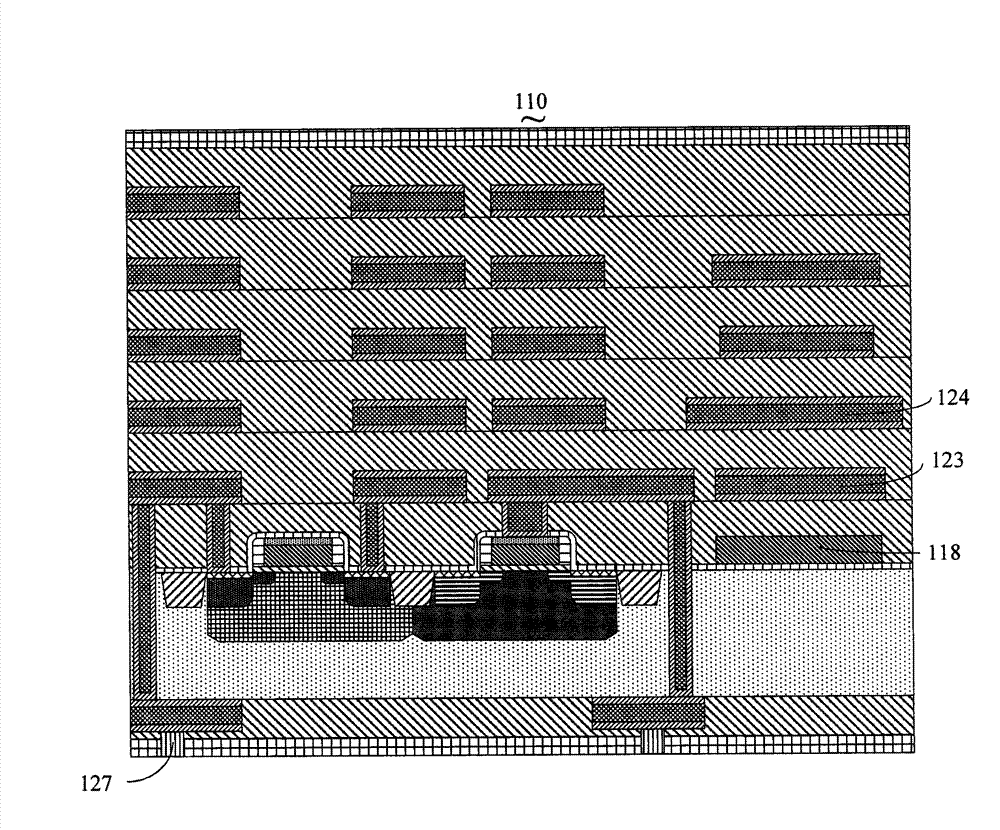

Absolute pressure transducer chip and production method thereof

ActiveCN102967407AImprove compatibilityImprove reliabilityDecorative surface effectsChemical vapor deposition coatingVibrating membraneMetallic materials

The invention relates to an absolute pressure transducer chip which comprises an absolute pressure transducer integrated on a complementary metal-oxide-semiconductor transistor (CMOS) chip. The absolute pressure transducer comprises a pressure sensitive unit, the pressure sensitive unit comprises a field-effect tube and a vibrating membrane, the field-effect tube comprises a floating gate, the vibrating membrane is provided with polycrystalline silicon or metal materials serving as grids in inserting mode and is used for inducing absolute pressure change, the floating gate is embedded in a dielectric layer of the CMOS chip, and a cavity is formed on the vibrating membrane and sealed. In the absolute pressure transducer chip, a sacrificial layer and the electric conductive vibrating membrane are manufactured on a metal electric conductive layer of an integrated circuit formed by aid of the CMOS standard manufacture process, and finally a pressure transducer micro-unit is manufactured, the existing CMOS process is not changed, and the absolute pressure transducer chip is good in compatibility. In addition, the invention further relates to a production method of the absolute pressure transducer chip.

Owner:SHENZHEN INST OF ADVANCED TECH

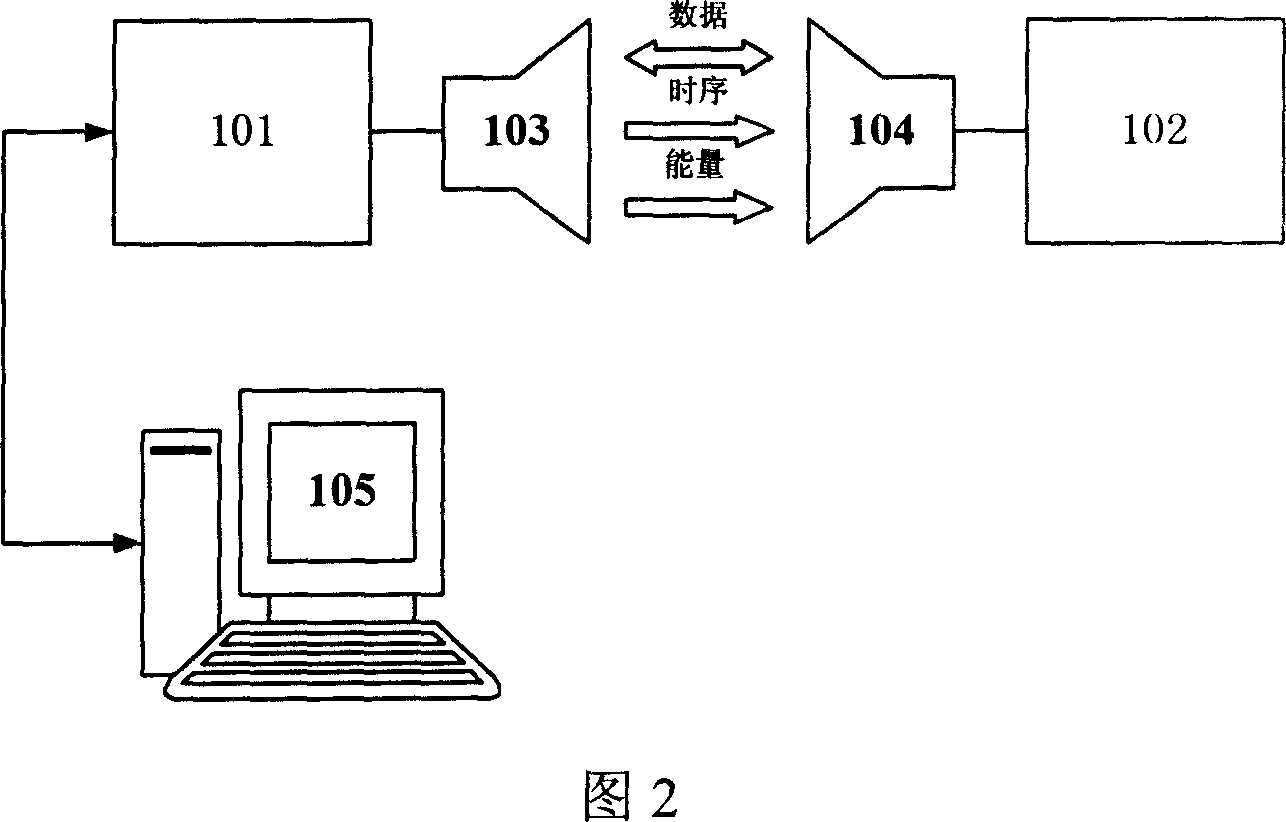

Method and system for multi-mode integrated receivers

A method and system for multi-mode integrated receivers are disclosed and may include receiving an optical signal from an optical fiber coupled to a chip comprising a photonic circuit. The photonic circuit may comprise an optical coupler, one or more multi-mode optical waveguides, and a detector. The received optical signal may be coupled to a plurality of optical modes in the one or more multi-mode optical waveguides, which are communicated to a detector to generate an electrical signal from the communicated modes. The optical coupler may comprise a grating coupler. The chip may comprise a CMOS chip, and the optical fiber may comprise a single-mode or a multi-mode fiber. The detector may comprise a germanium or silicon-germanium photodiode, and / or a waveguide detector. The optical fiber may be coupled to a top surface of the chip and the multi-mode optical waveguides may comprise rib waveguides.

Owner:CISCO TECH INC

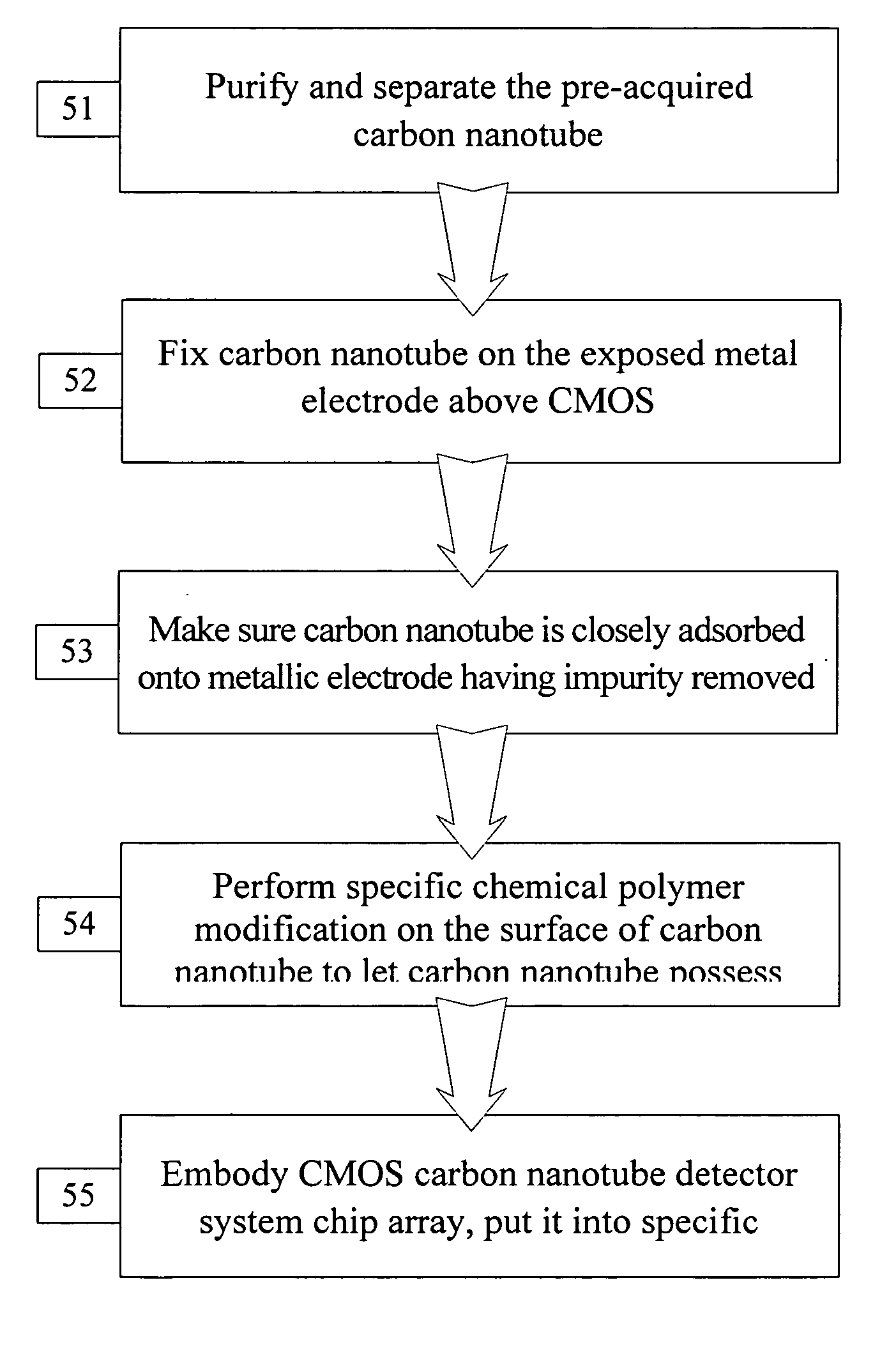

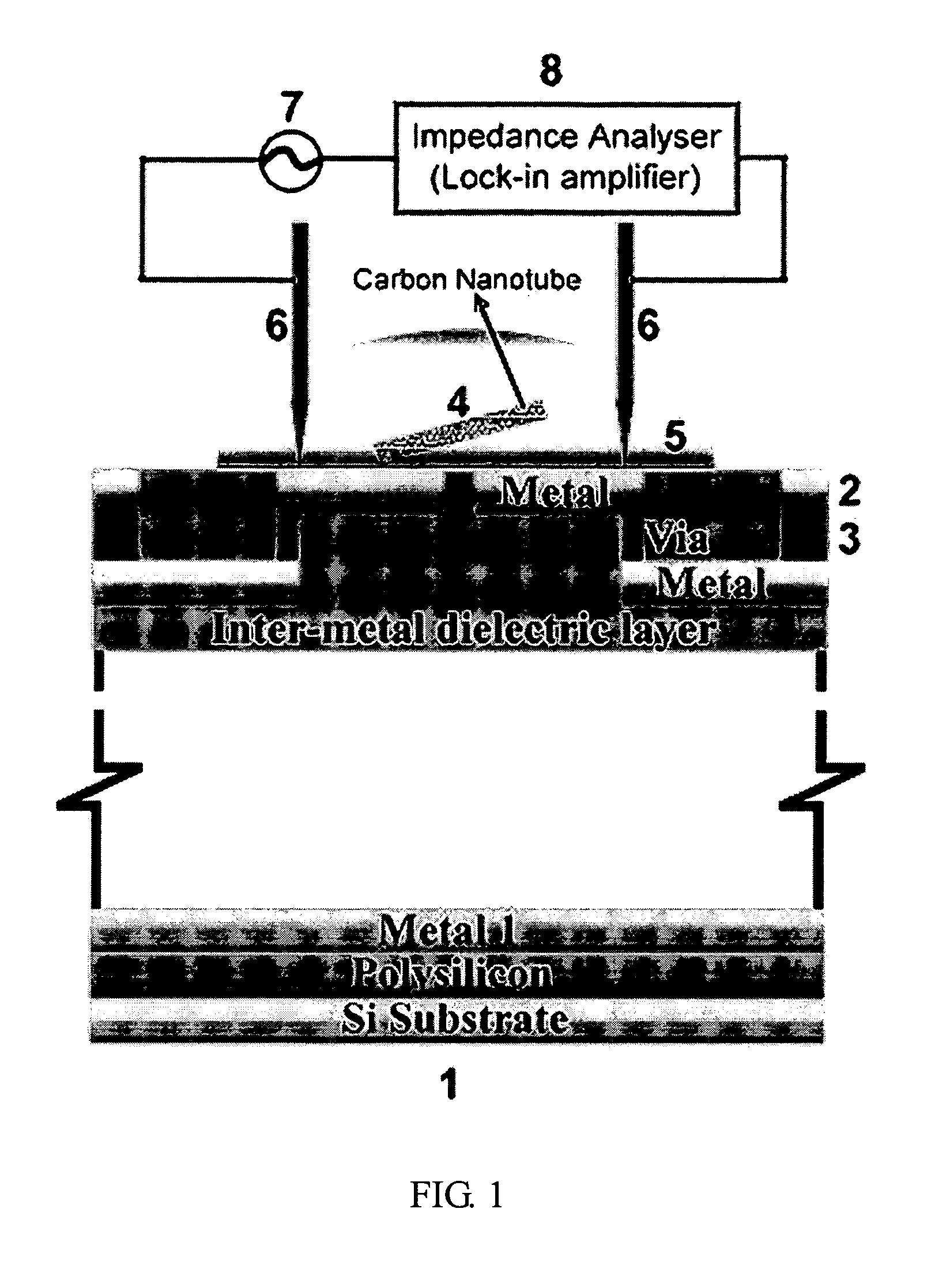

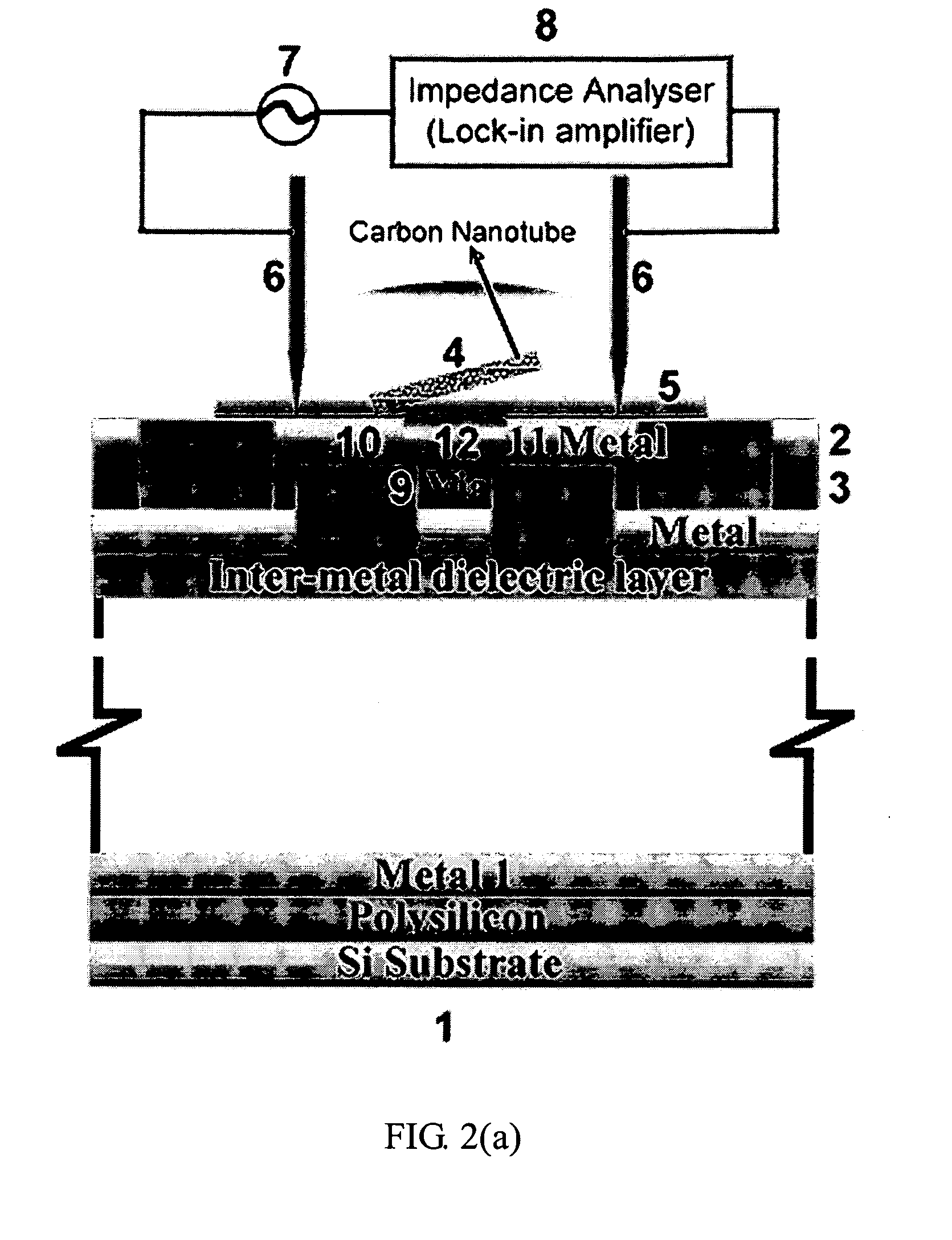

Method for integrating carbon nanotube with CMOS chip into array-type microsensor

InactiveUS20070134866A1Effectively and sequentially fixEfficient combinationNanoinformaticsSolid-state devicesProbe cardManufacturing technology

The invention disclosed a method for integrating CMOS circuit chips with carbon nanotubes (CNTs) into array-type sensors with signal processors enclosed. The method provides low-temperature and wafer-level fabrication processes including dripped a drop of dispersed CNTs solution on the top of CMOS chip, use micro probe card to contact with pairs of pads, with a function generator to generate dielectrophoresis (DEP) signal and with a lock-in amplifier to measure impedance value simultaneously. According to the impedance measurement it can detect the number of CNTs fixed on pair of pads. Only if the number of CNTs on the top of pair of pads were not expected, it would readjust the frequency of alternating current to the range of negative DEP force and repel CNTs from the top of pair of pads. Repeat positive DEP signal to attach CNTs until the number of CNTs as demand, then hold the DEP force until CNTs solution evaporated to make a well-contact between CNTs and pads. Furthermore, the surface of CNTs can be functionalized and let CNTs have high sensitivity to ambient molecules (Gas molecules, Bio molecules, et al.), then transfer the measured signal into signal processors of CMOS chips, the processors could be impedance measurement unit, current measurement unit, conductance measurement unit et. al., and it can measure, record and analyze the data of small varied signal directly.

Owner:HUANG JUNG TANG

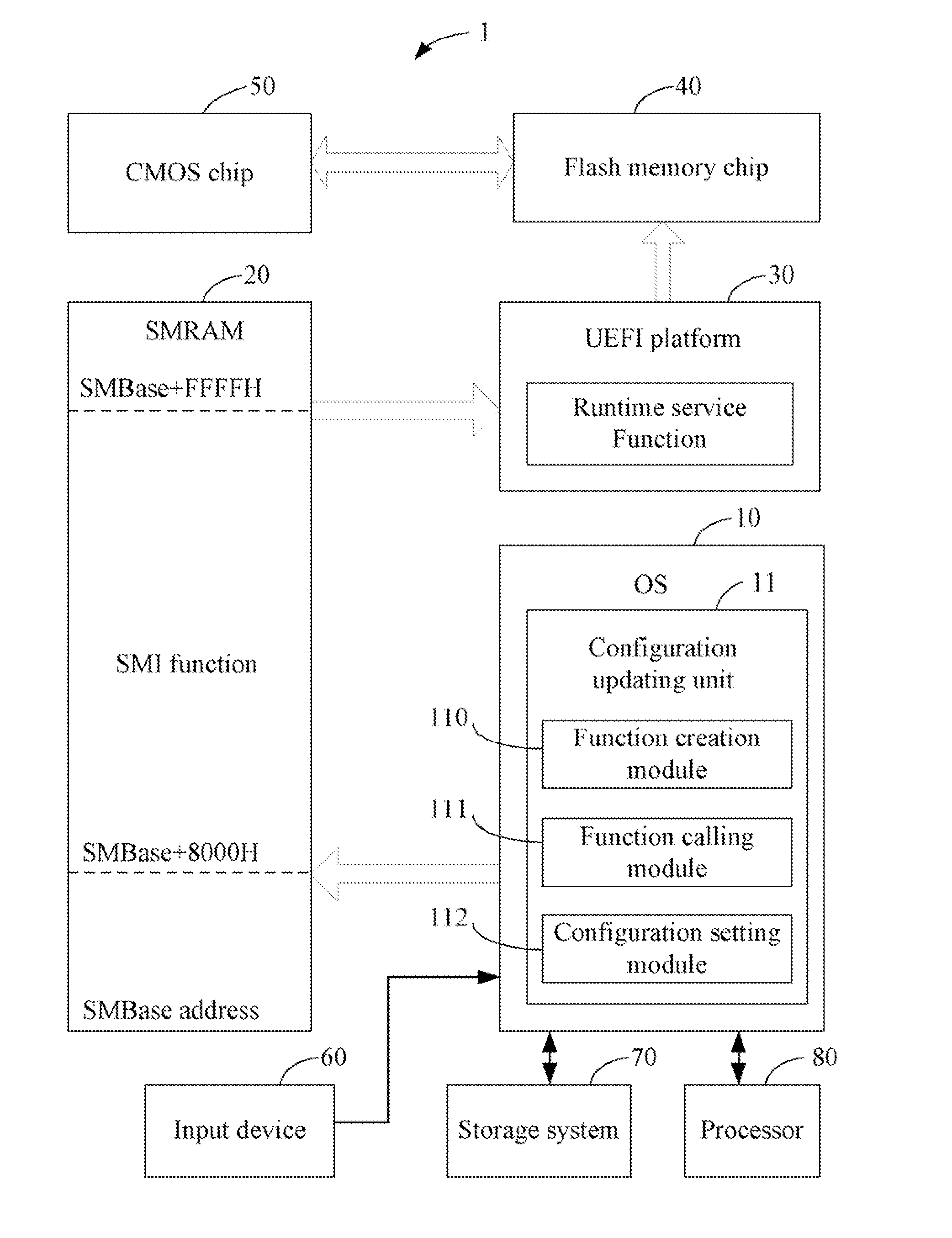

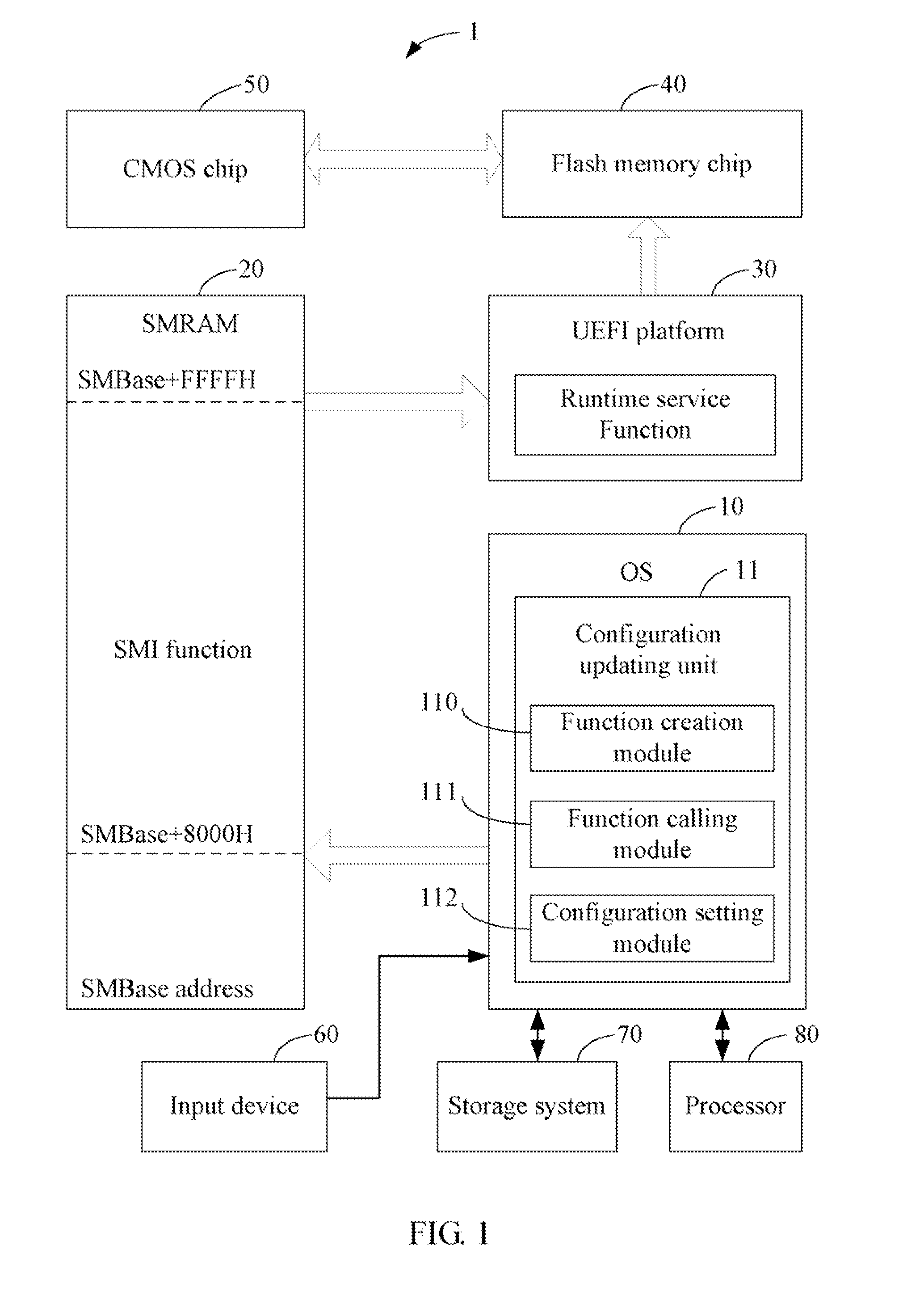

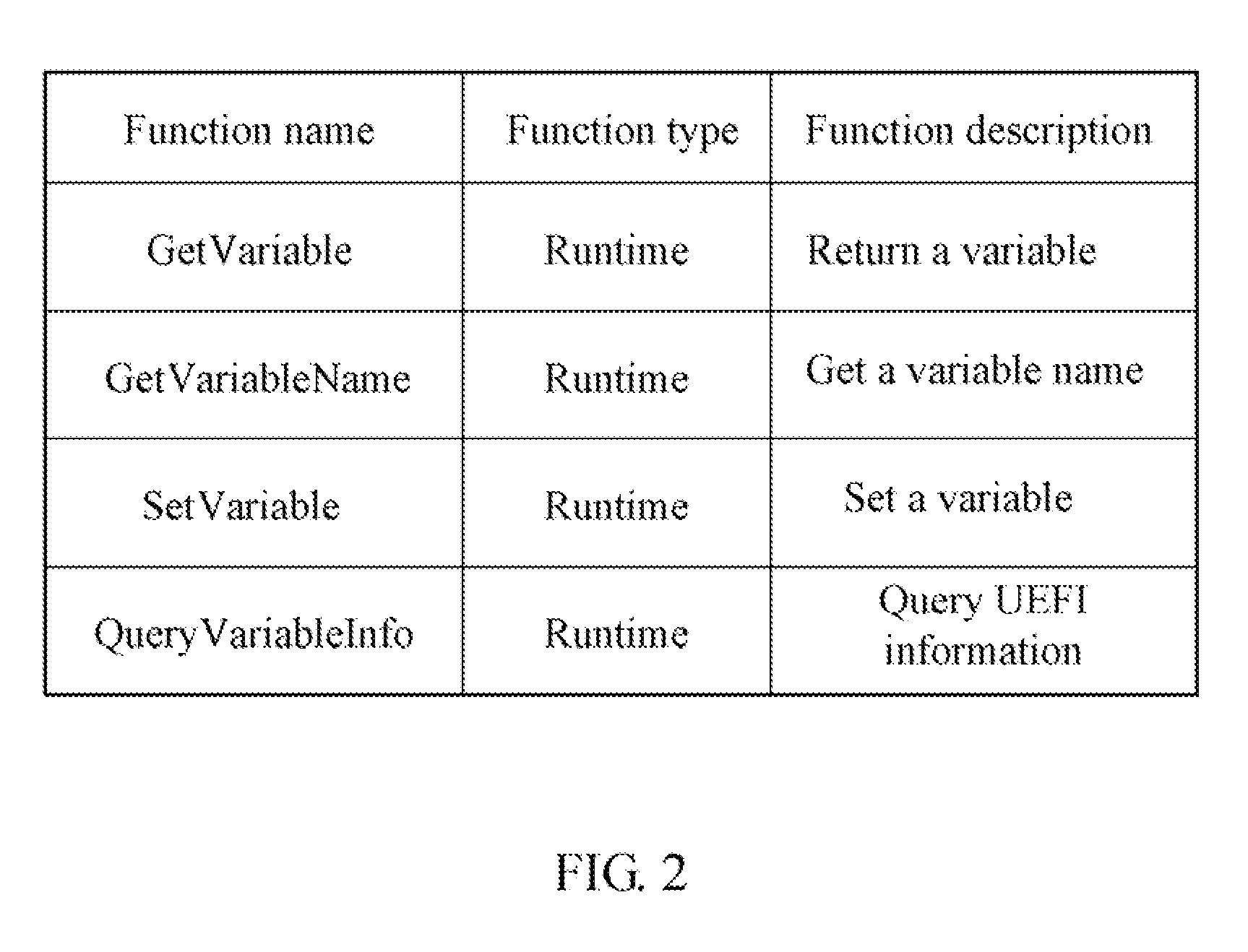

System and method for updating unified extensible firmware interface setting information

InactiveUS20110271268A1Specific program execution arrangementsMemory systemsData storingComputer science

A system and method can update unified extensible firmware interface (UEFI) setting information of a computer. The method creates a system management interrupt (SMI) function based on a UEFI platform of the computer, and stores the SMI function in a SMRAM of the computer. The method further generates an access address of the SMI function when a configuration command is input from an input device, and generate a SMI handler according to the access address. Additionally, the method calls a runtime service function of the UEFI platform by executing the SMI function through the SMI handler, and executes the runtime service function to configure UEFI setting information stored in a flash memory chip and to update BIOS data stored in a CMOS chip related to the UEFI setting information.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

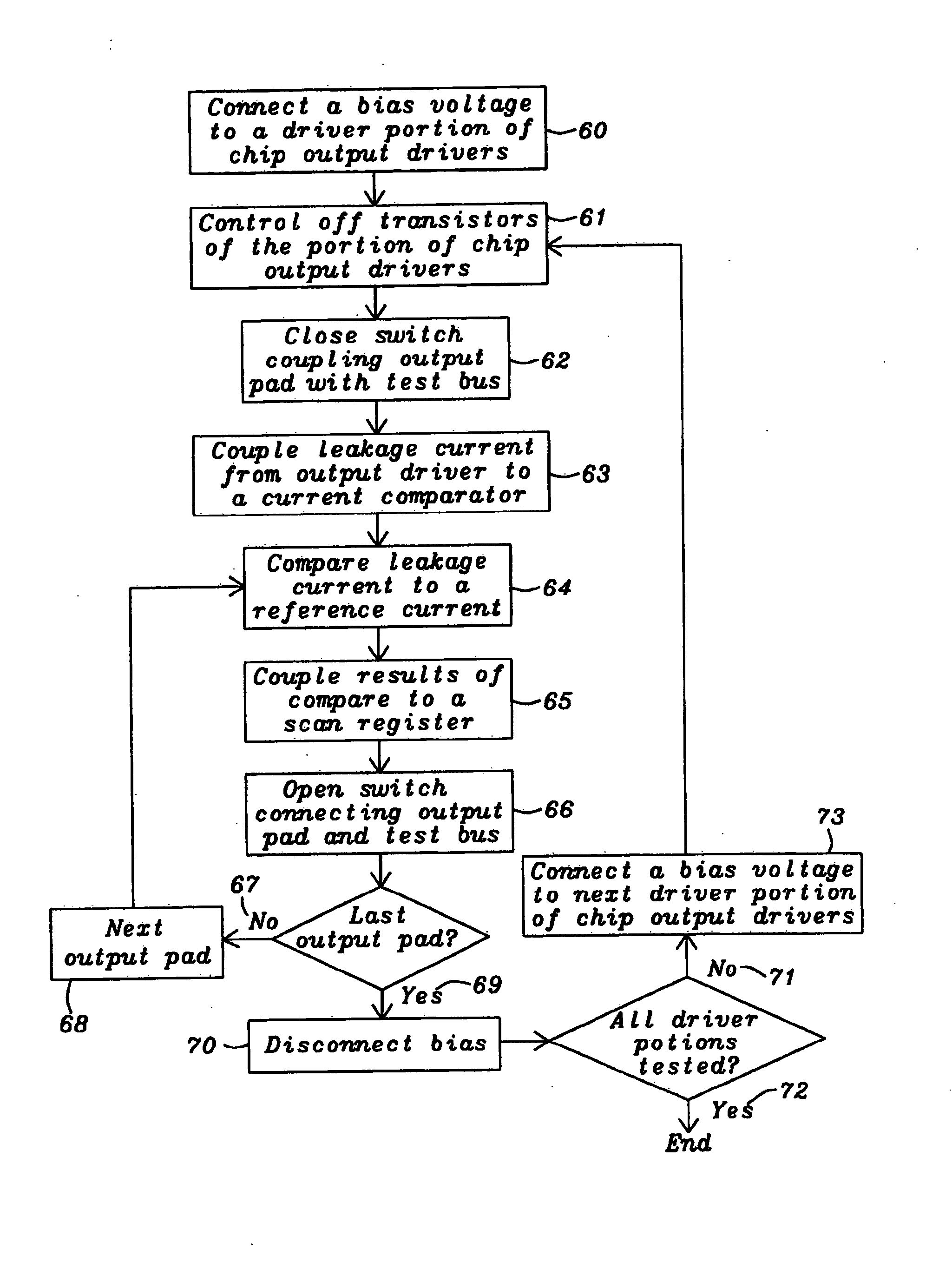

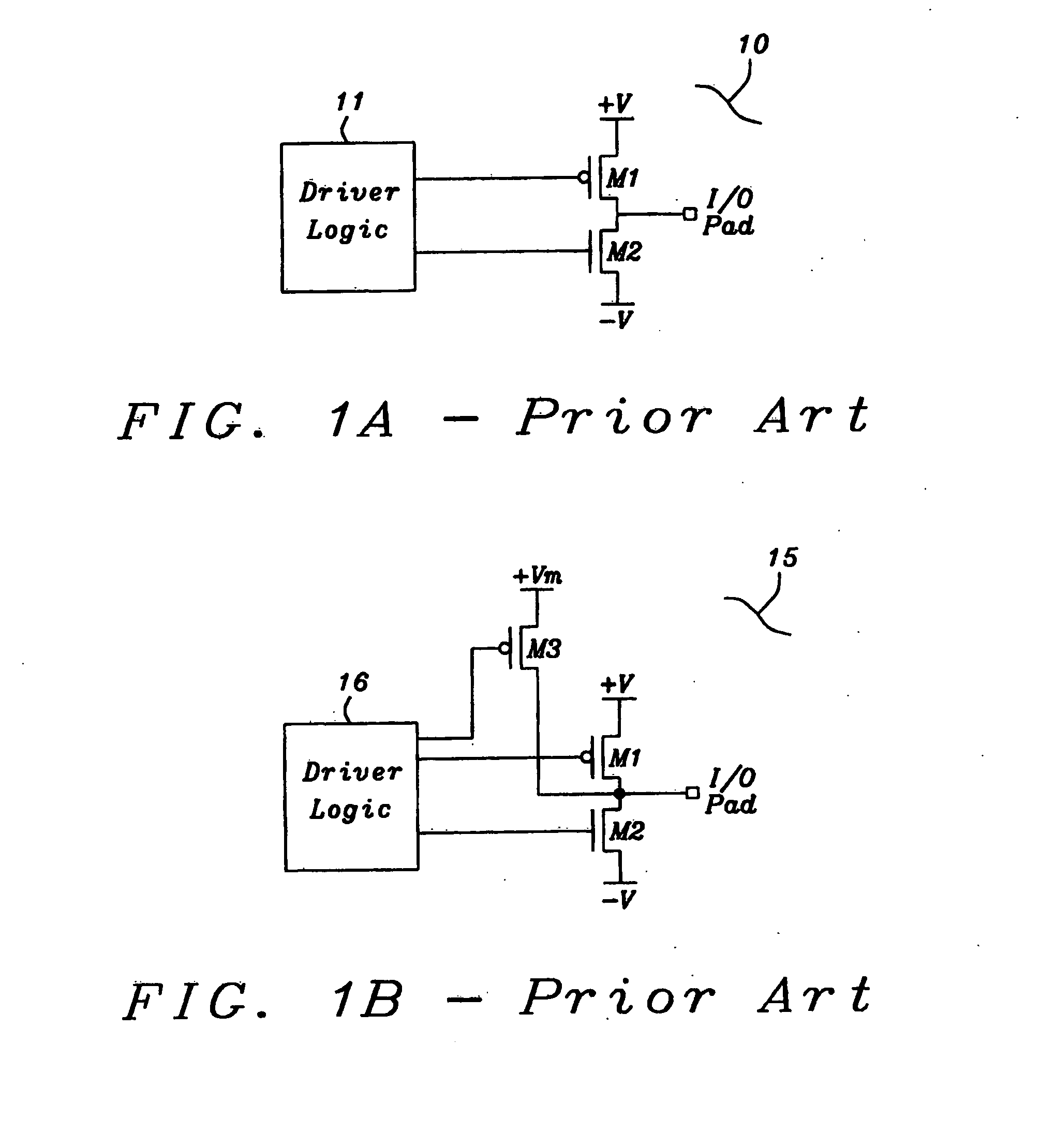

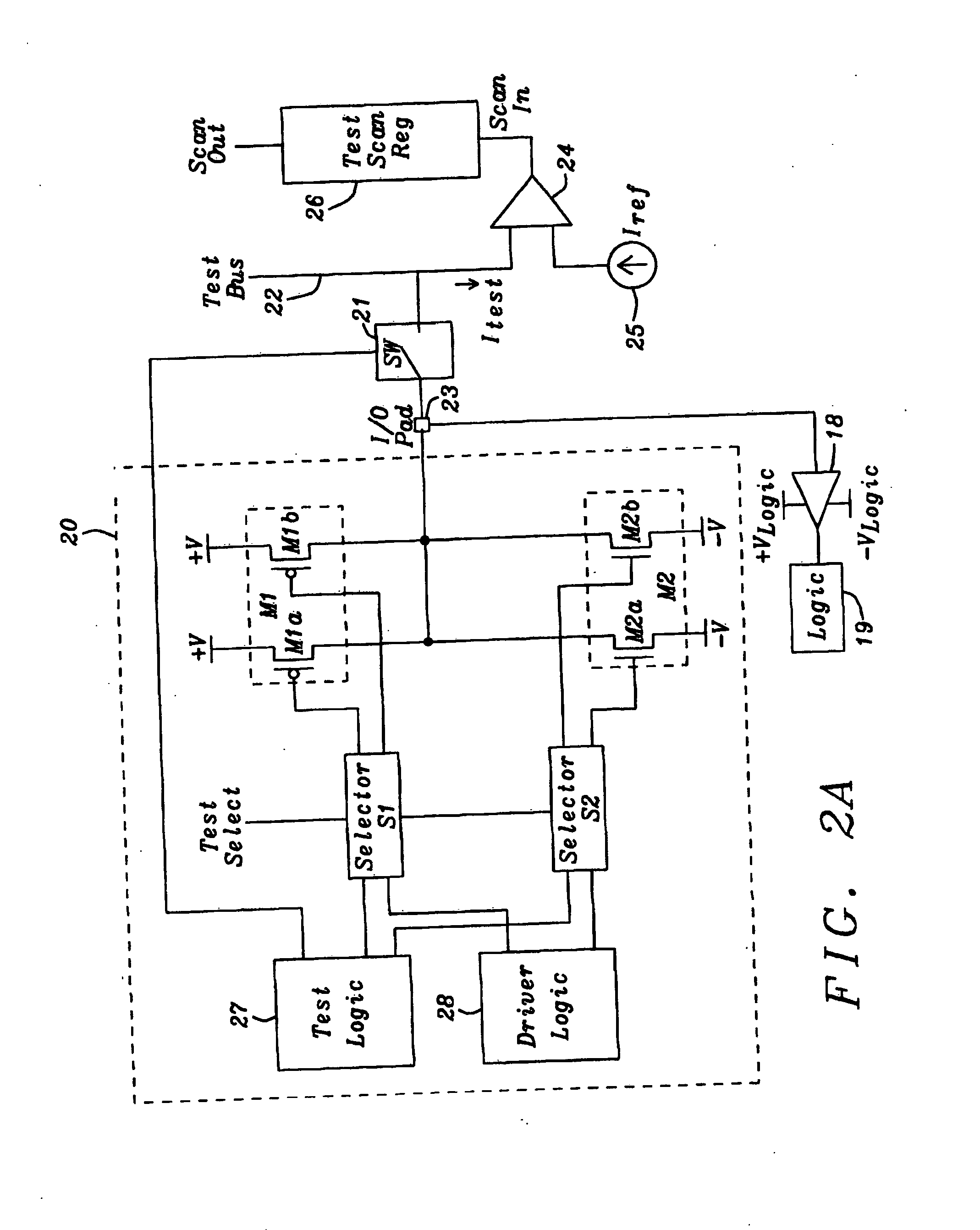

Probeless DC testing of CMOS I/O circuits

InactiveUS20070208526A1Resistance/reactance/impedenceTesting/calibration of speed/acceleration/shock measurement devicesTest inputDevice material

A method and implementation is described by which I / O input and output circuitry of a CMOS chip are measured without the need to probe the chip. Output driver transistors are used to provide marginal voltages to test input circuits, and the output driver transistors are segmented into portions where a first portion is used to provide a representative “on” current, which is coupled to a test bus that is further connected to a current comparator circuit contained within the chip. Both leakage and “on” current of the driver transistors is measured using segmented driver transistors. The output of the current comparator circuit is connected to a test scan register or to a test output from which test results are obtained digitally. The testing techniques are also applicable for other semiconductor devices.

Owner:DIALOG SEMICONDUCTOR GMBH

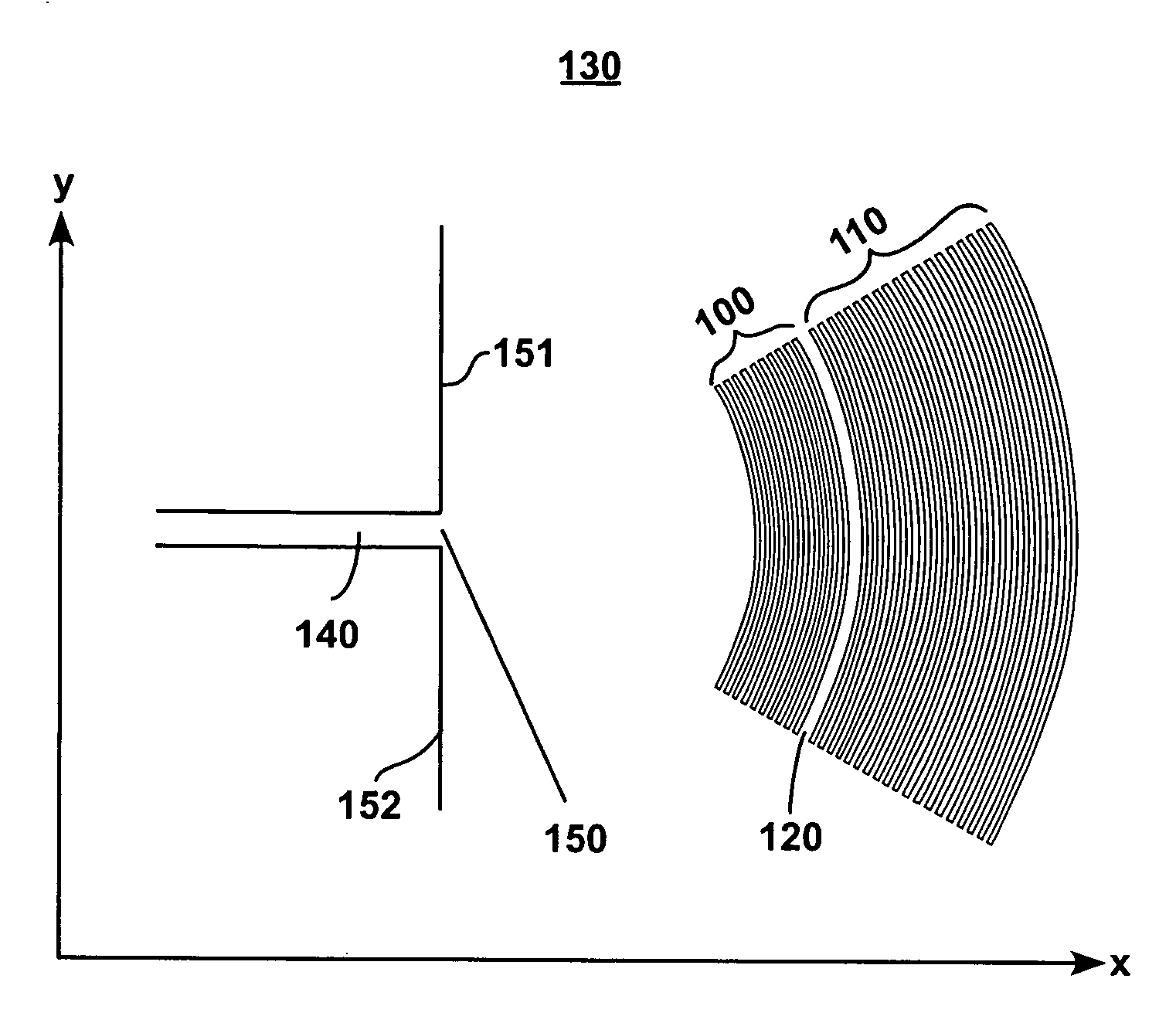

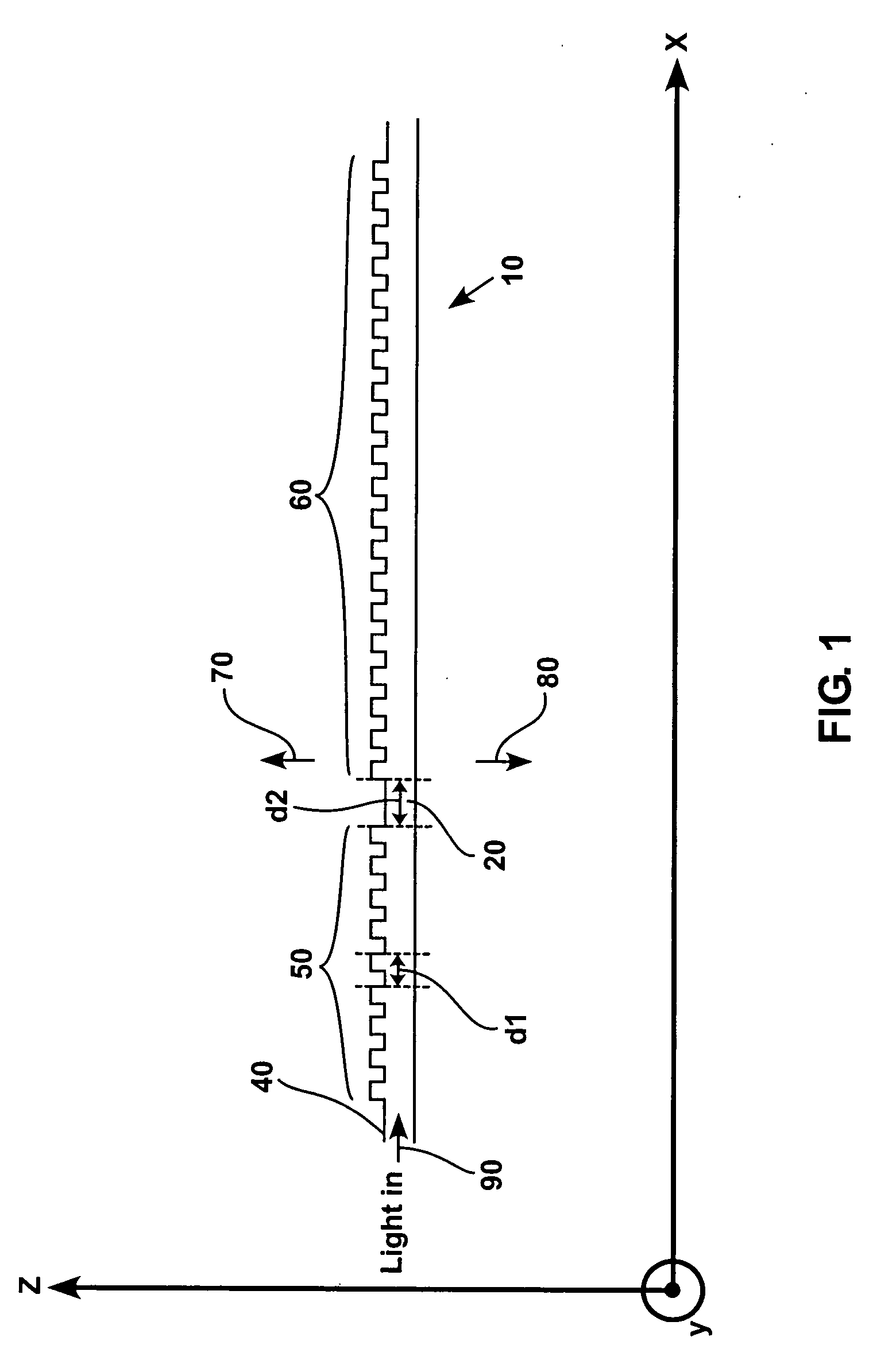

Resonantly enhanced grating coupler

InactiveUS7397987B2Improve system efficiencyImprove efficiencyCoupling light guidesOptical waveguide light guideGratingCoupling

Owner:CALIFORNIA INST OF TECH

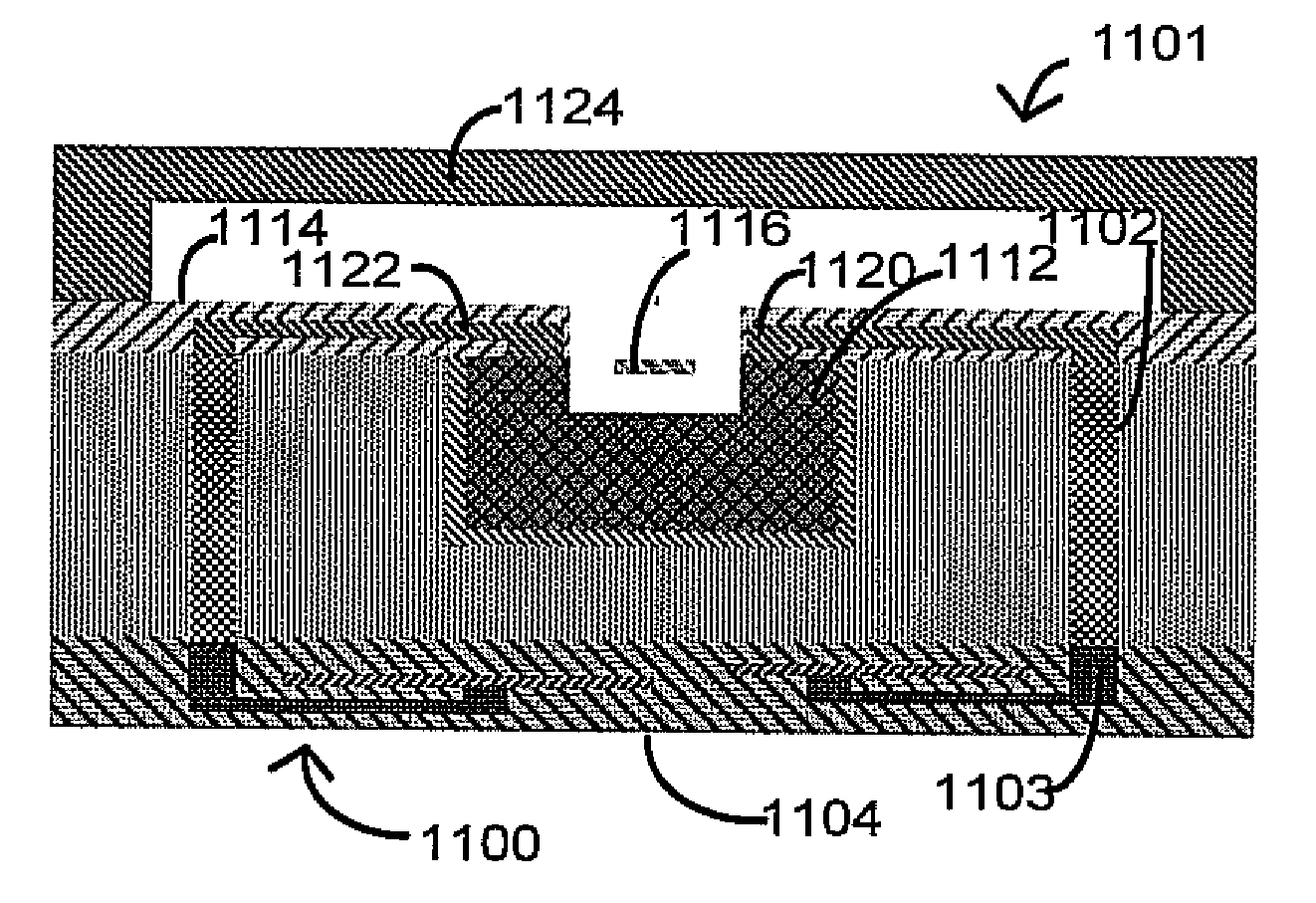

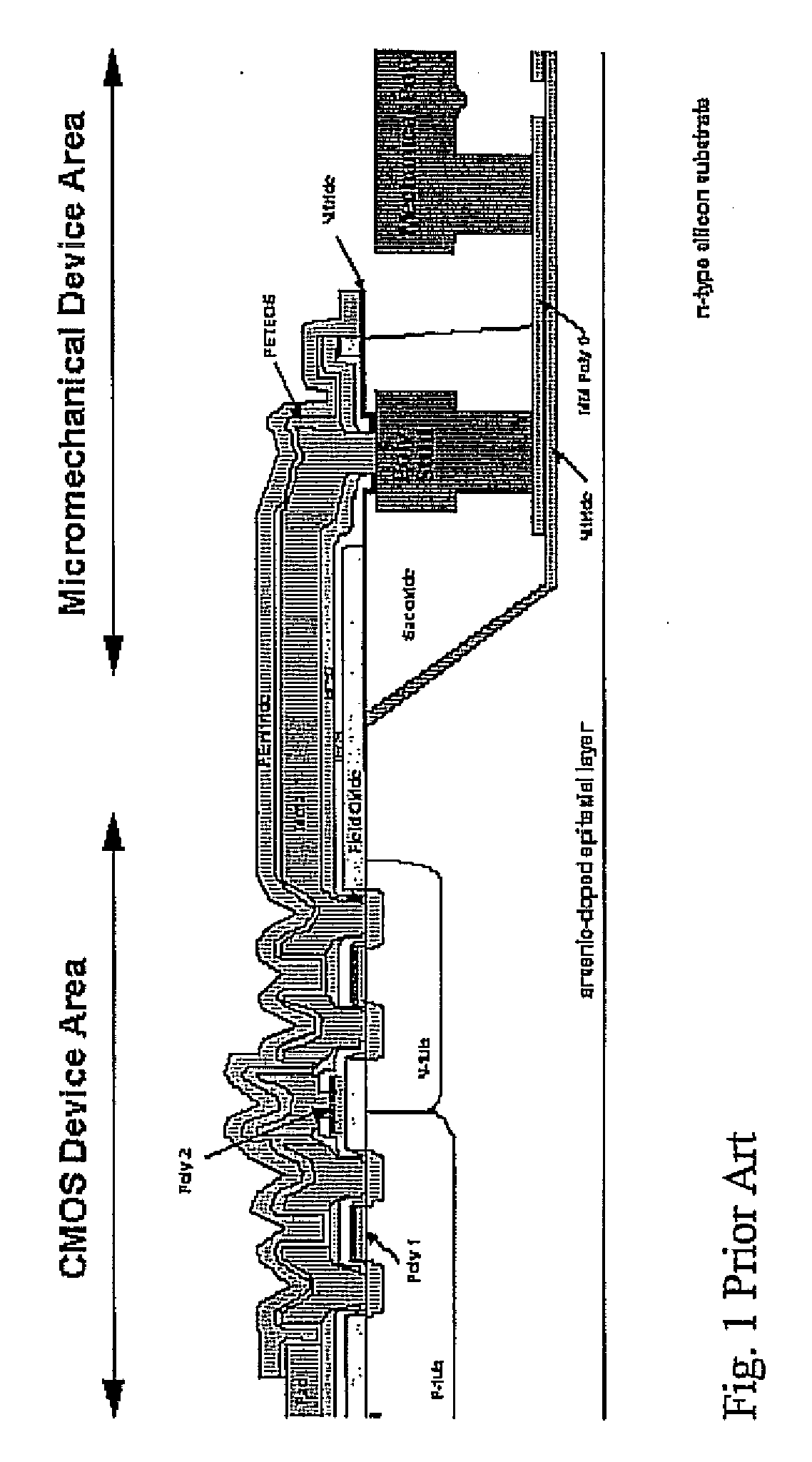

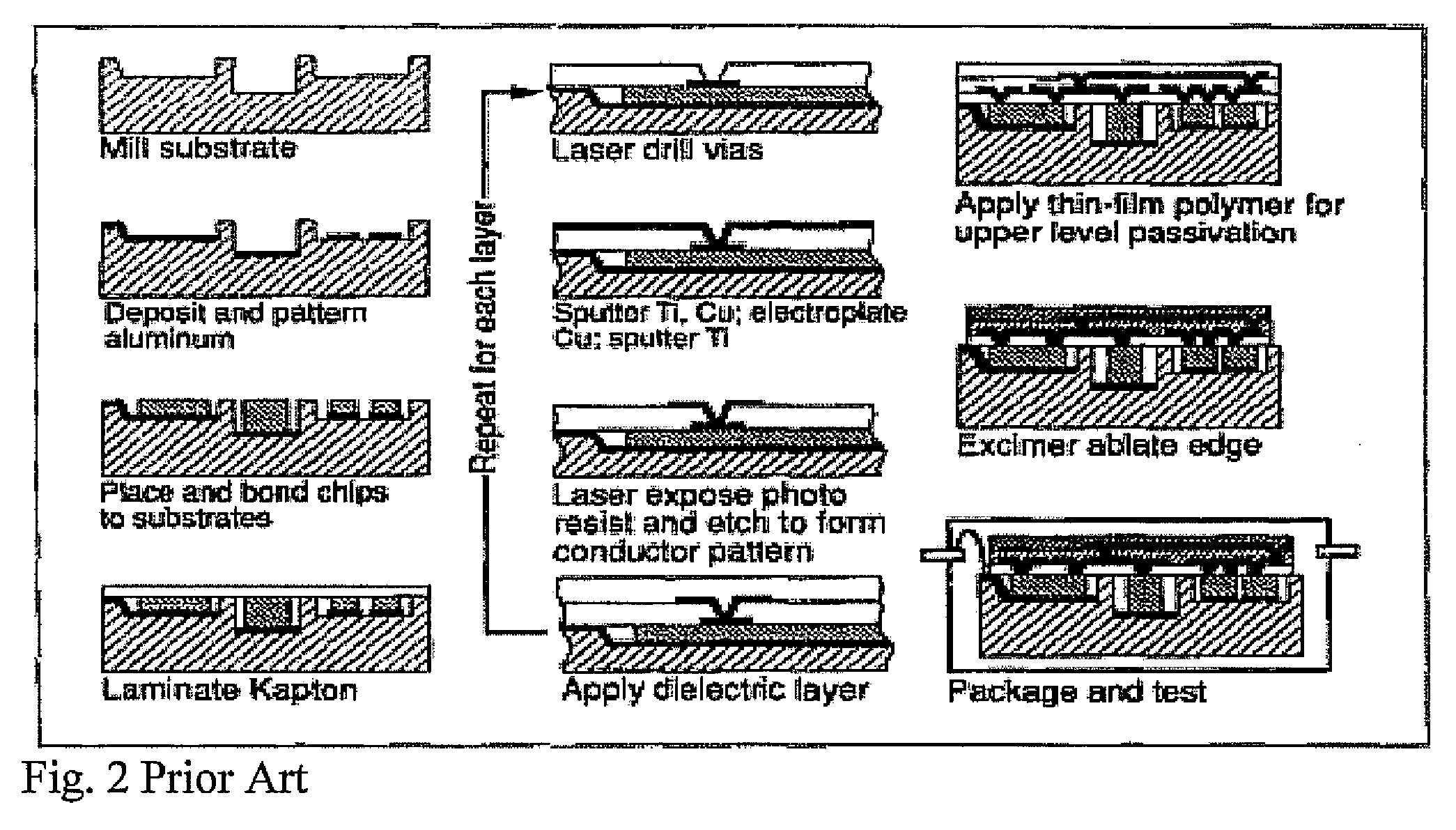

Method of forming monolithic cmos-mems hybrid integrated, packaged structures

InactiveUS20110027941A1Solid-state devicesSemiconductor/solid-state device manufacturingLayer interfaceFilling materials

A method of forming Monolithic CMOS-MEMS hybrid integrated, packaged structures includes the steps of providing: providing a semiconductor substrate with pre-fabricated cmos circuits on the front side and a polished back-side with through substrate conductive vias; forming at least one opening in the polished backside of the semiconductor substrate by appropriately protecting the front-side; applying at least one filler material in the at least one opening on the semiconductor substrate; positioning at least one prefabricated mems, nems or cmos chip on the filler material, the chip including a front face and a bare back face with the prefabricated mems / nems chips containing mechanical and dielectric layers; applying at least one planarization layer overlying the substrate, filler material and the chip; forming at least one via opening on a portion of the planarization layer interfacing pads on the chip and the through substrate conductive vias; applying at least one metallization layer overlying the planarization layer on the substrate and the chip connecting the through substrate conductive vias to the at least one chip; applying at least one second insulating layer overlying the metallization layer; performing at least one micro / nano fabrication etching step to release the mechanical layer on the prefabricated mems / nems chips; positioning protective cap to package the integrated device over the mems / nems device area on the pre-fabricated chips.

Owner:AMF NANO

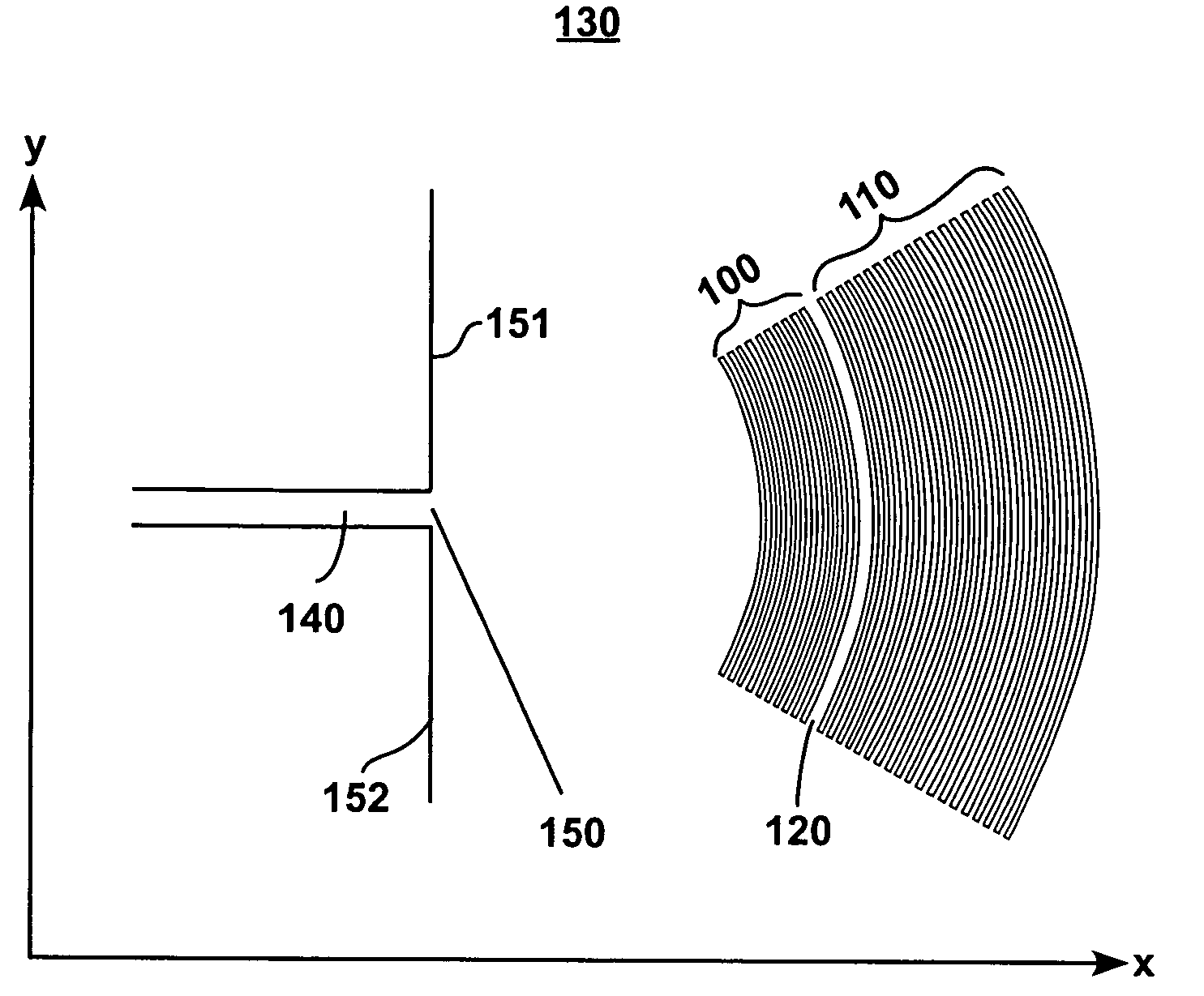

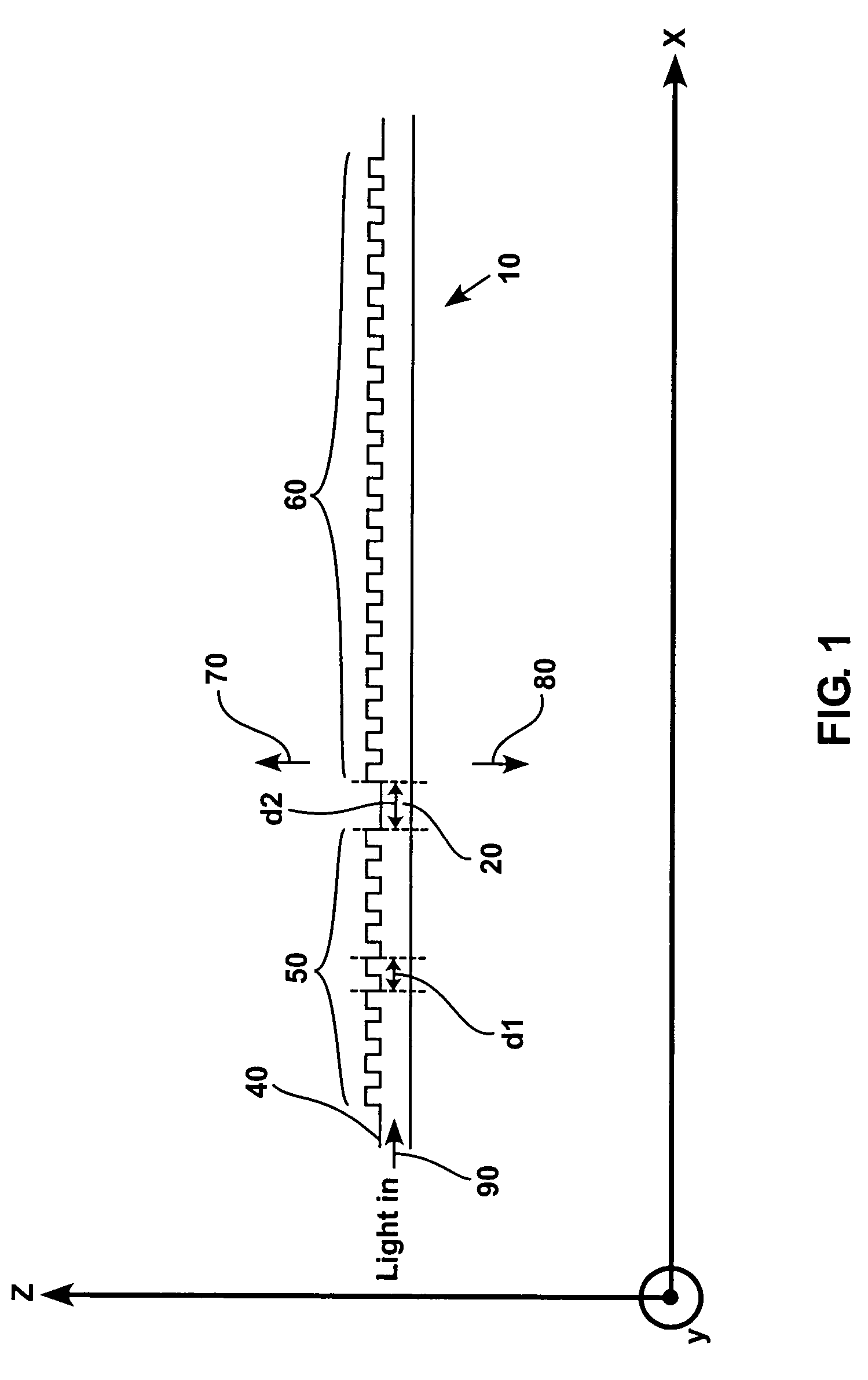

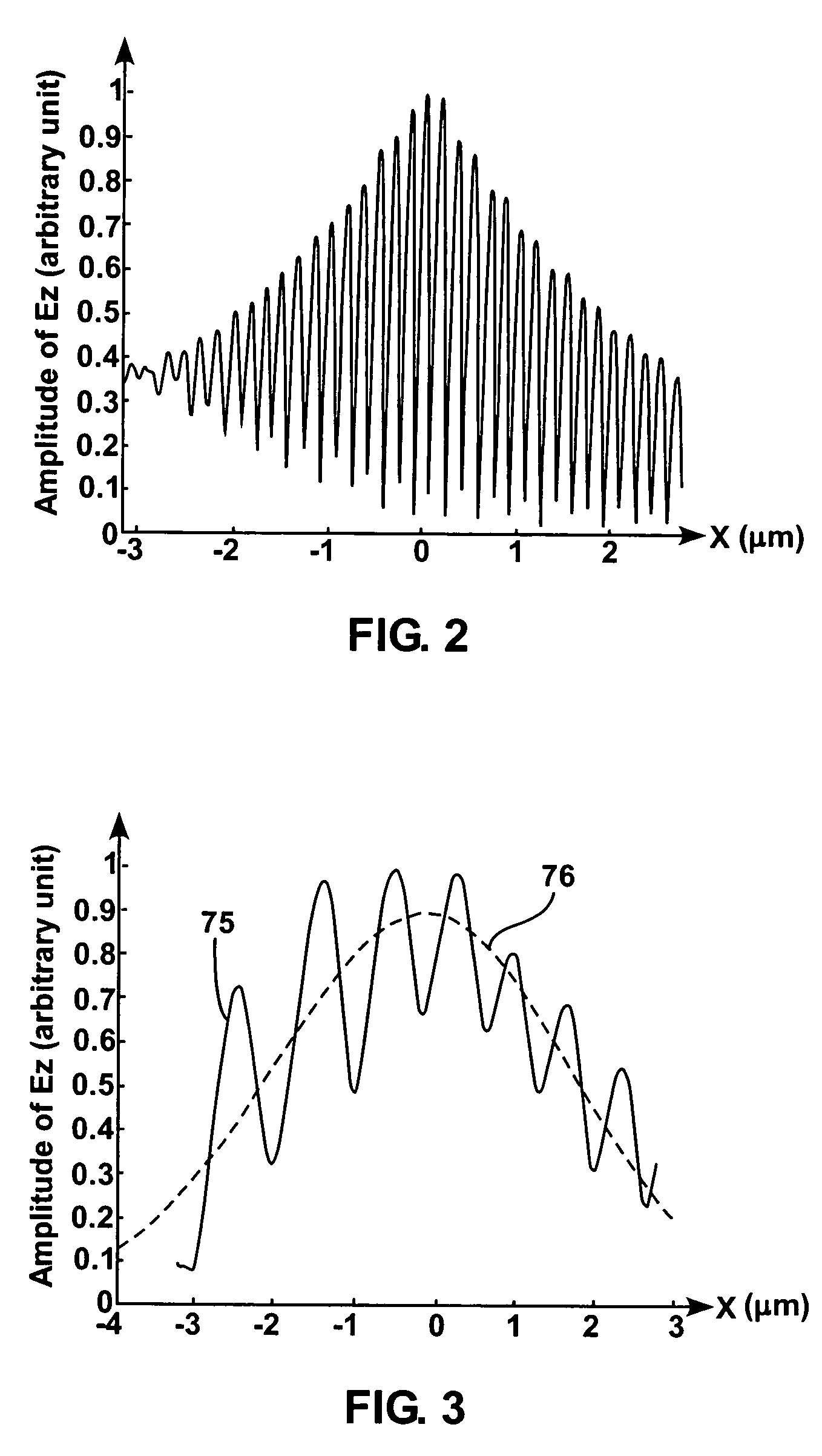

Resonantly enhanced grating coupler

InactiveUS20050286832A1Improve system efficiencyImprove efficiencyCoupling light guidesOptical waveguide light guideGratingCoupling

An apparatus and method for increasing efficiency of grating couplers are disclosed. The apparatus through the use of a defect or a reflective element allows coupling of light around a normal or nearly normal angle with a high efficiency. The method disclosed teaches how to increase the efficiency of a grating coupler through the use of a defect or a mirror. The apparatus and method can be of particular utility in the context of optical clocking implemented with a III-V chip flip-chip bonded on a CMOS chip.

Owner:CALIFORNIA INST OF TECH

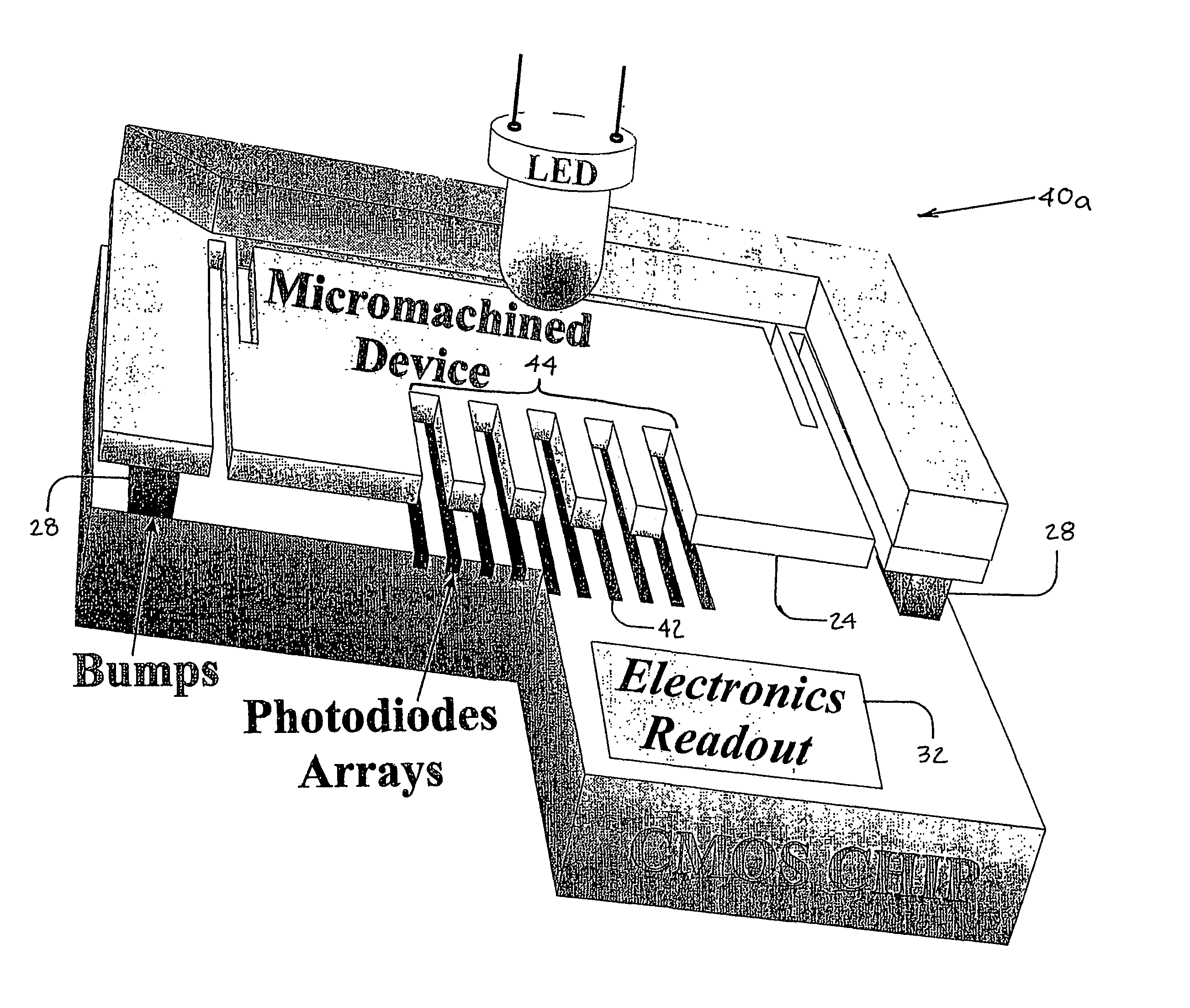

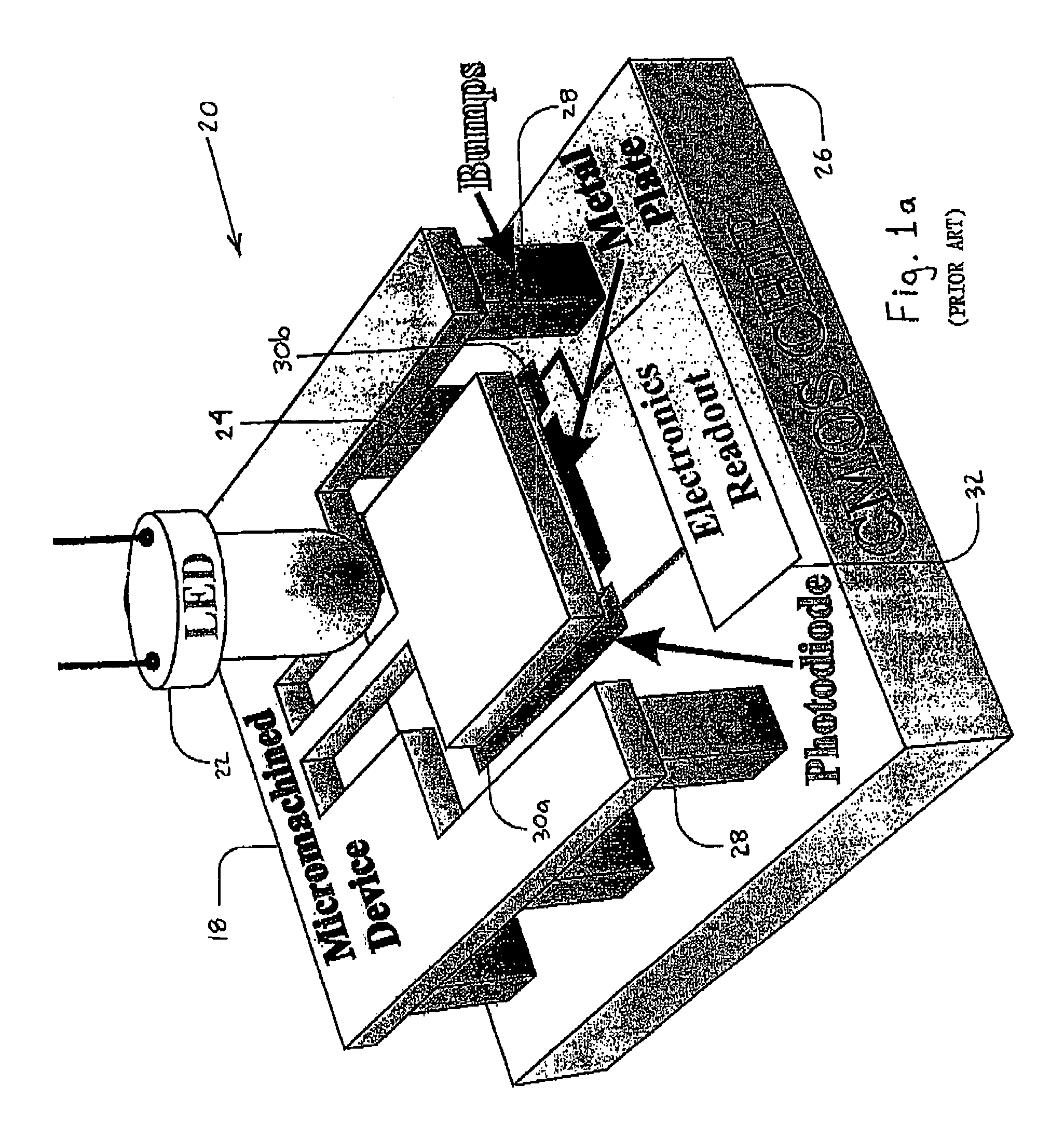

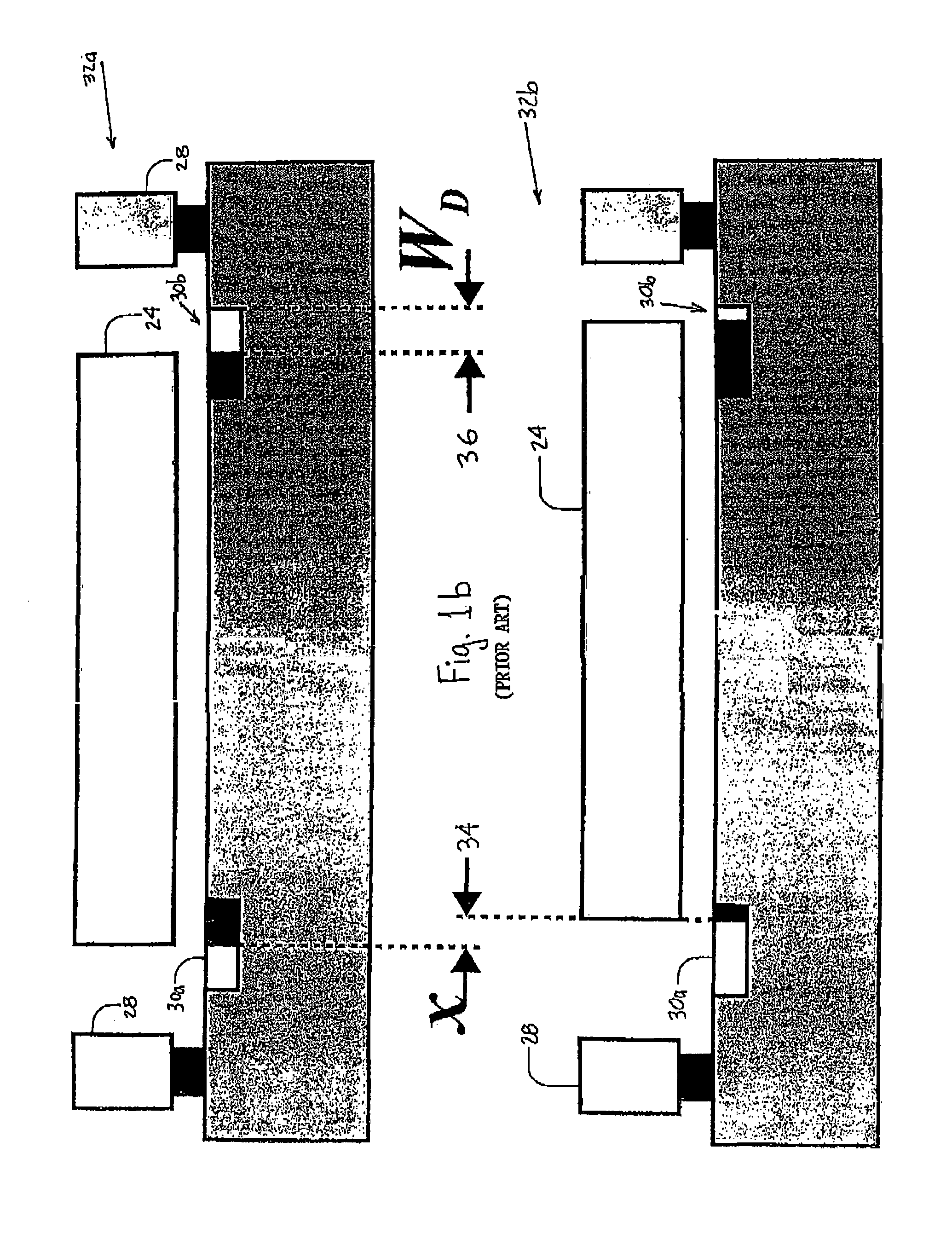

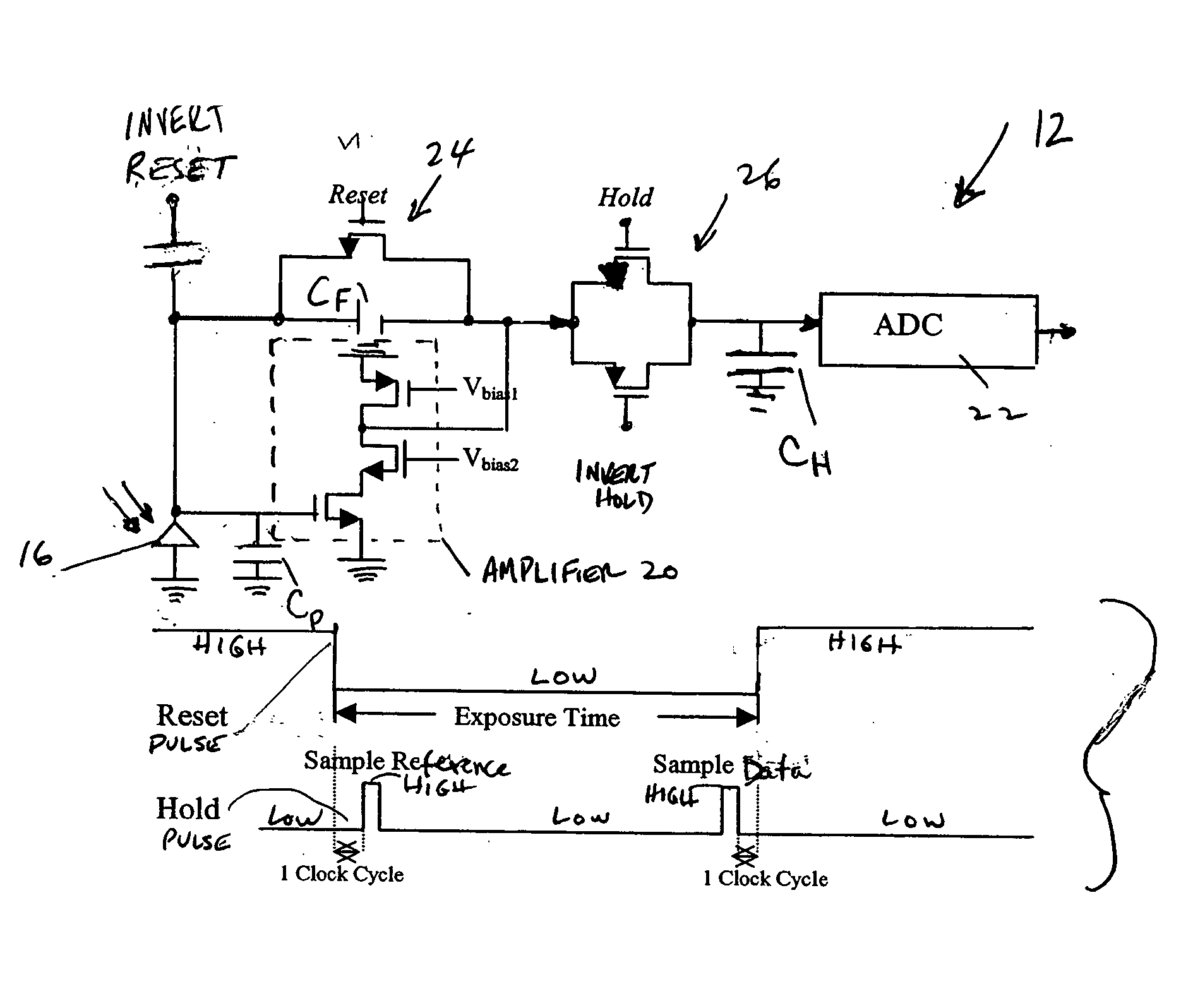

Method and apparatus for micro-machined sensors using enhanced modulated integrative differential optical sensing

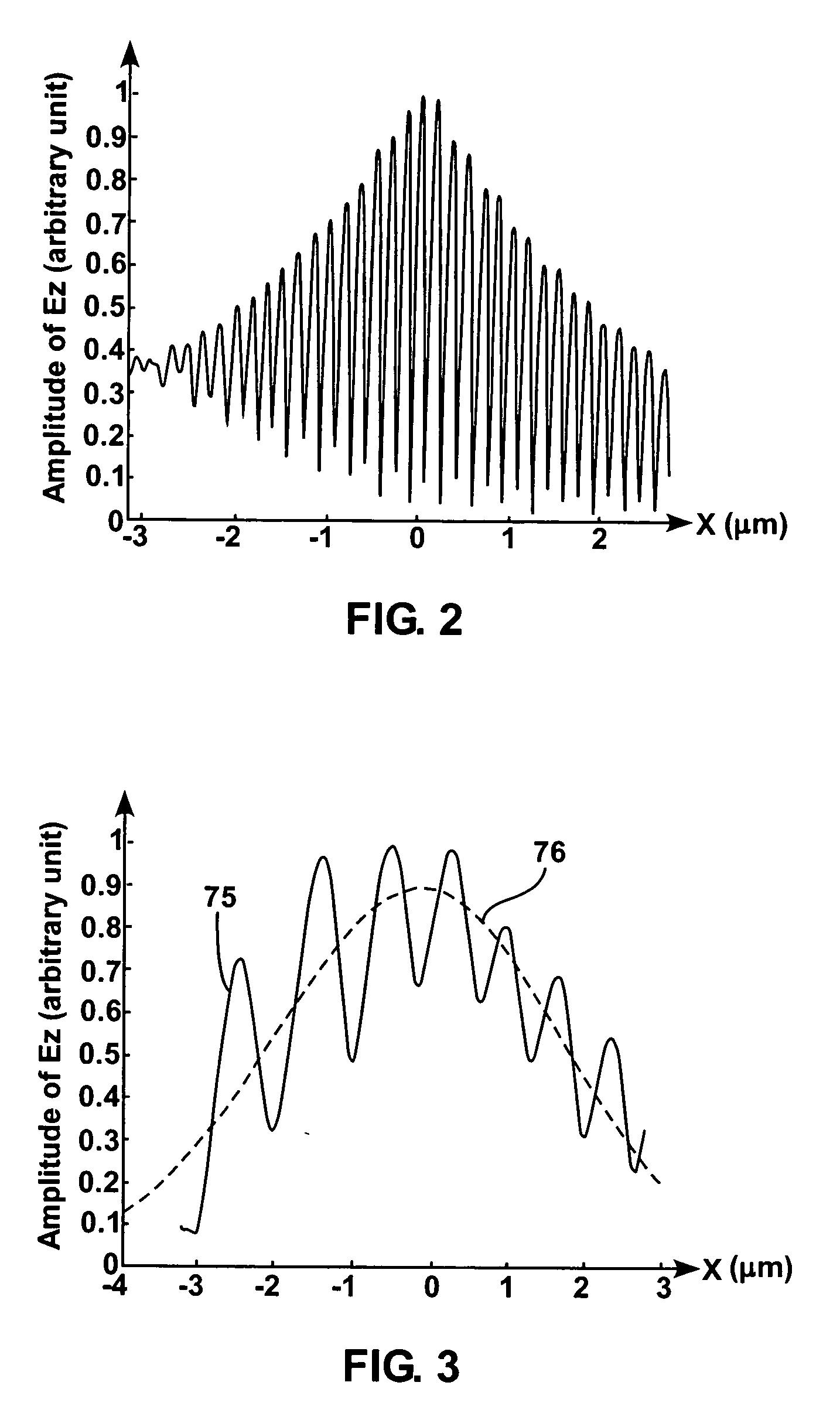

InactiveUS7091715B2Improved versionOvercome limitationsAcceleration measurement using interia forcesSemiconductor/solid-state device manufacturingOptical sensingPhotodiode

Method and apparatus for sensing the displacements of micromachined devices and sensors. The method is referred to as the enhanced modulated integrative differential optical sensing (EMIDOS). The target micromachined proof-mass, for which displacements are measured, includes a grid of slits. The micromachined device is bonded to a CMOS chip containing a matching photodiodes array and their readout electronics. The grid is aligned with the photociiodes. An illumination source, such as an LED, is then mounted above the micromachined device. A model for the noise equivalent displacement (NED), including mechanical, electrical and optical domains, as well as all noise sources is derived. The model predicts that displacements below 10−3 [√{square root over ( )}Hz] can be measured. The design comprises innovative inertial sensors, an accelerometer and a rategyroscope employing the EMIDOS. Performance models for the noise equivalent acceleration (NEA) and noise equivalent rate (NER) are also derived. The models show that an accelerometer with a very low NEA can be realized.

Owner:TECHNION RES & DEV FOUND LTD +1

Wide-angle lens-based FPGA & DSP embedded multi-valued targets threshold categorization tracking device

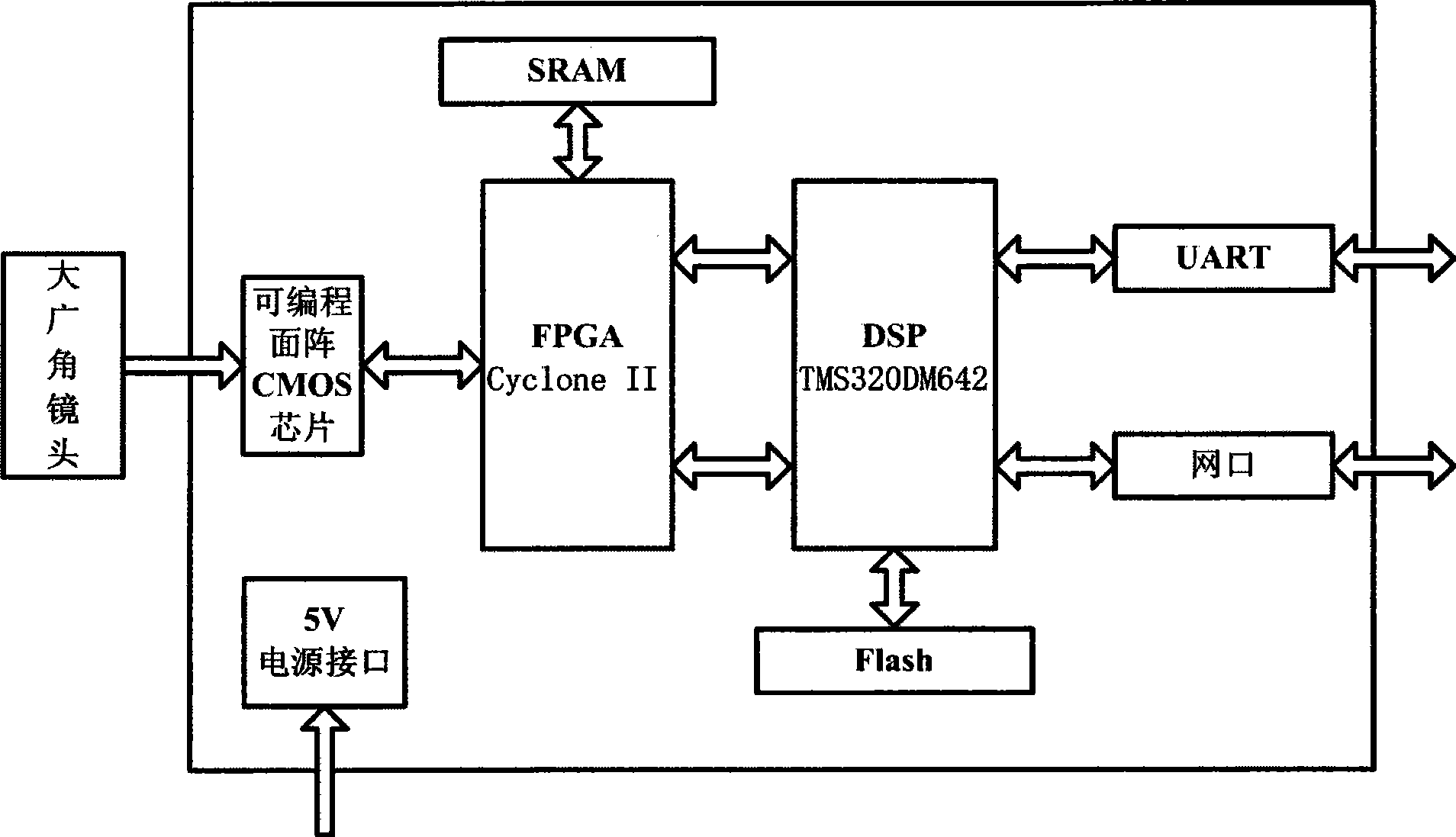

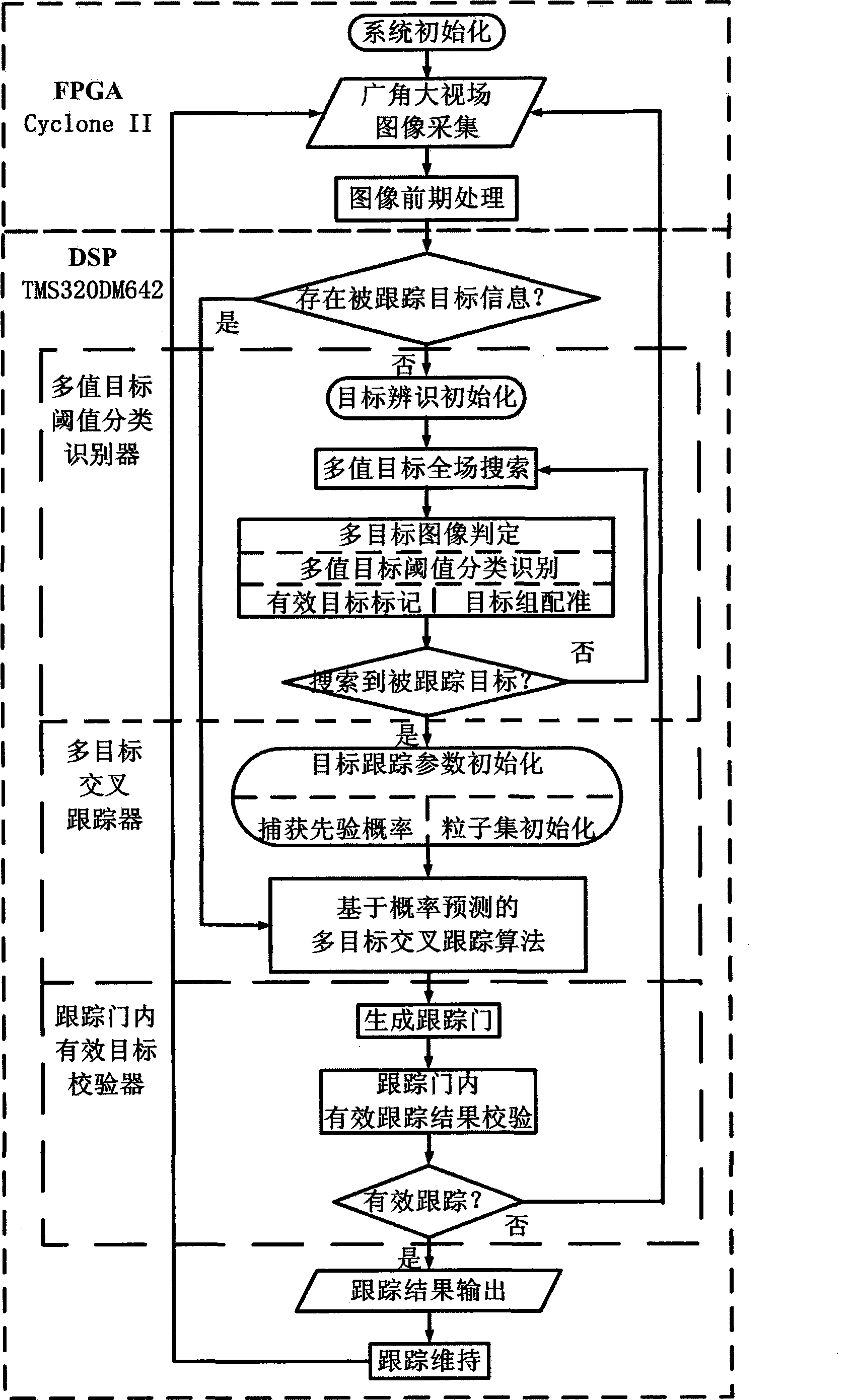

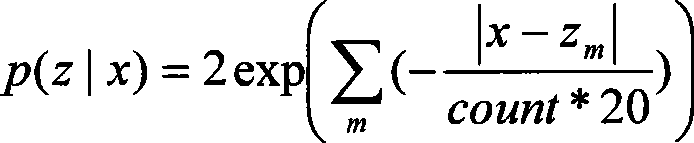

InactiveCN101447075AQuality improvementAvoid target lossTelevision system detailsImage analysisMulti target trackingEmbedded system

The invention provides a wide-angle lens-based FPGA & DSP embedded multi-valued targets threshold categorization tracking device and relates to an embedded system for identifying and tracking multi-targets in a video stream and a related algorithm. Image collection is completed by a wide-angle lens and a color area array CMOS chip; digital image pretreatment, such as digital filtering, image enhancement and the like, is carried out by the FPGA; the algorithms such as multi-valued targets threshold categorization identification, marking registration and the like are realized in a main processor with the DSP as a core; an improved image-tracking program which is based on multi-targets cross operation of a probabilistic forecasting model generates a tracking gate in real time; a target tester in the tracking gate controls and tracks a process and outputs a target value. The wide-angle lens-based multi-valued targets threshold categorization tracking device supported by an embedded hardware platform has wide application prospect in the aspects of dynamic photography, security monitoring, maneuvering target detecting, multi-targets tracking, automatic navigation of vehicles, etc. The device especially has the advantage in constructing an airborne target tracking system with small structure volume and low power consumption.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

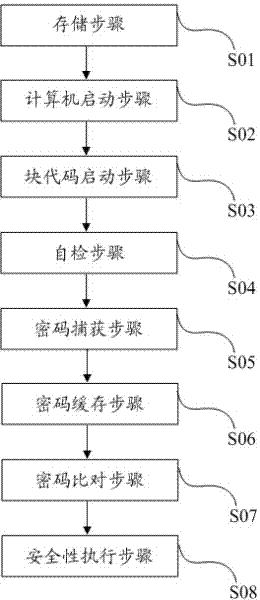

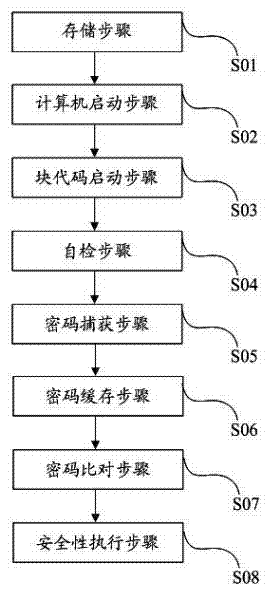

Method and computer for protecting computer security based on bios password

InactiveCN102262719AProtection securityProtection settingsDigital data authenticationCoding blockBlock code

The invention discloses a method for protecting computer security based on a BIOS password and a computer adopting the method, comprising the following steps: a storage step, writing the BIOS password in the BIOS chip in the background, setting parameters of the password checking option in the BIOS, and storing the password in the BIOS chip. The parameters are stored in the CMOS chip; the computer startup step, after the power supply voltage is stable, the CPU jumps; the block code startup step, the BIOS starts the block code; the self-test step, the device performs self-test, after the self-test passes, the control display pops up to enter the password dialog box; password capturing step, computer captures the password typed from the keyboard; password caching step, stores the captured password in the keyboard register; password comparison step, CPU reads out the input password, and compares it with the BIOS password ;Security execution steps, perform corresponding operations according to the result of password comparison. The method of the invention has high security performance, the password cannot be deciphered, and can effectively protect the setting security of the computer and the security of data in the computer.

Owner:HISENSE INTELLIGENT COMML SYST CO LTD

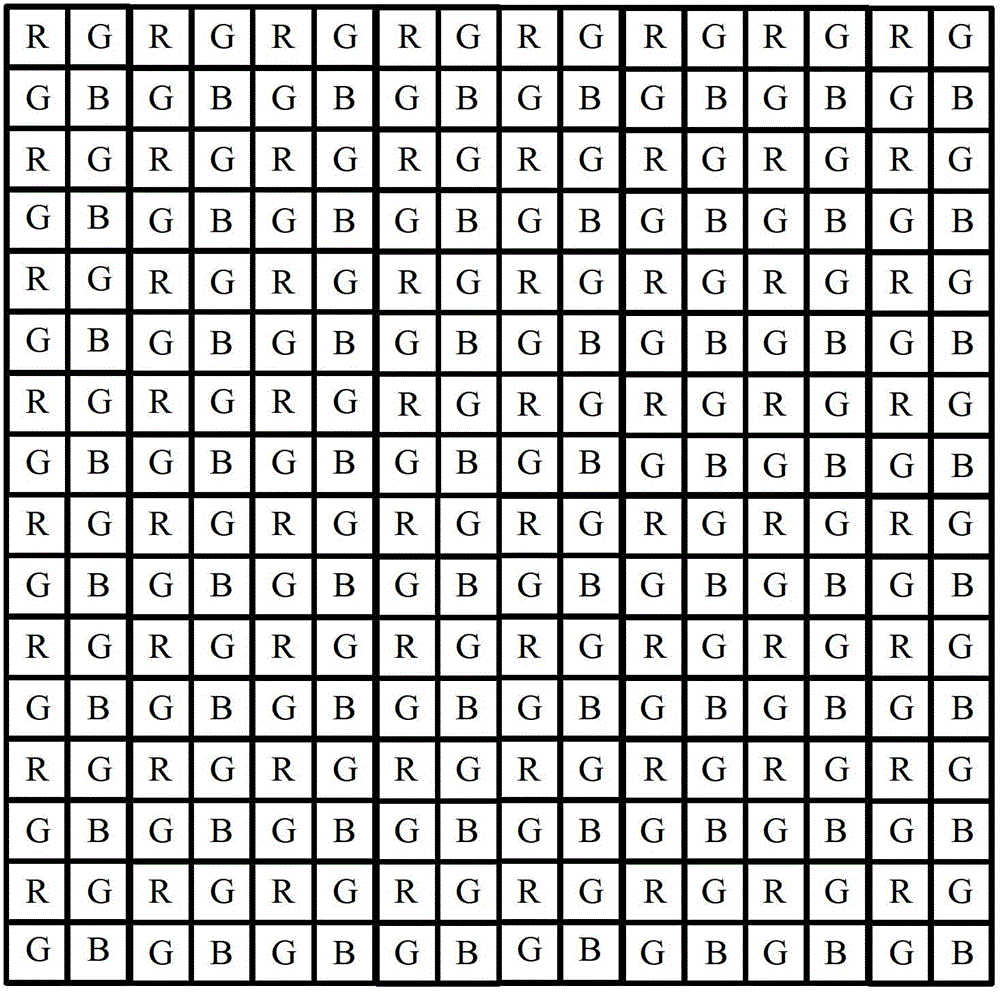

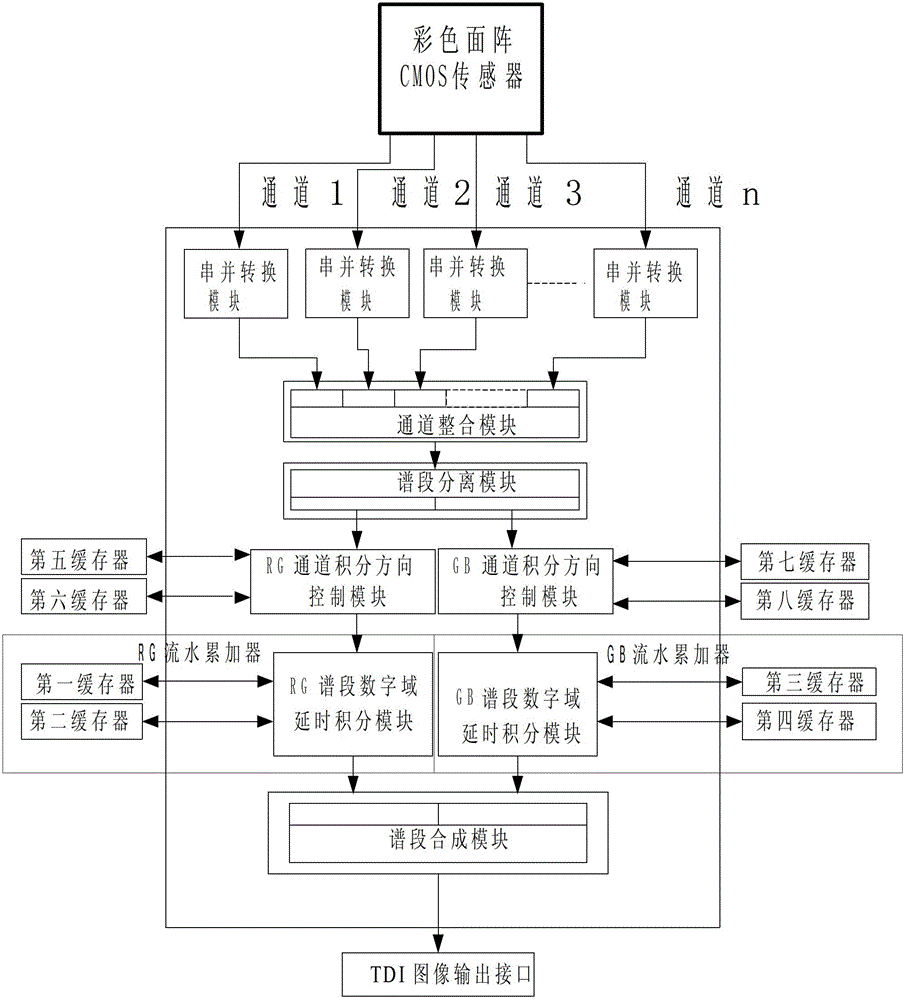

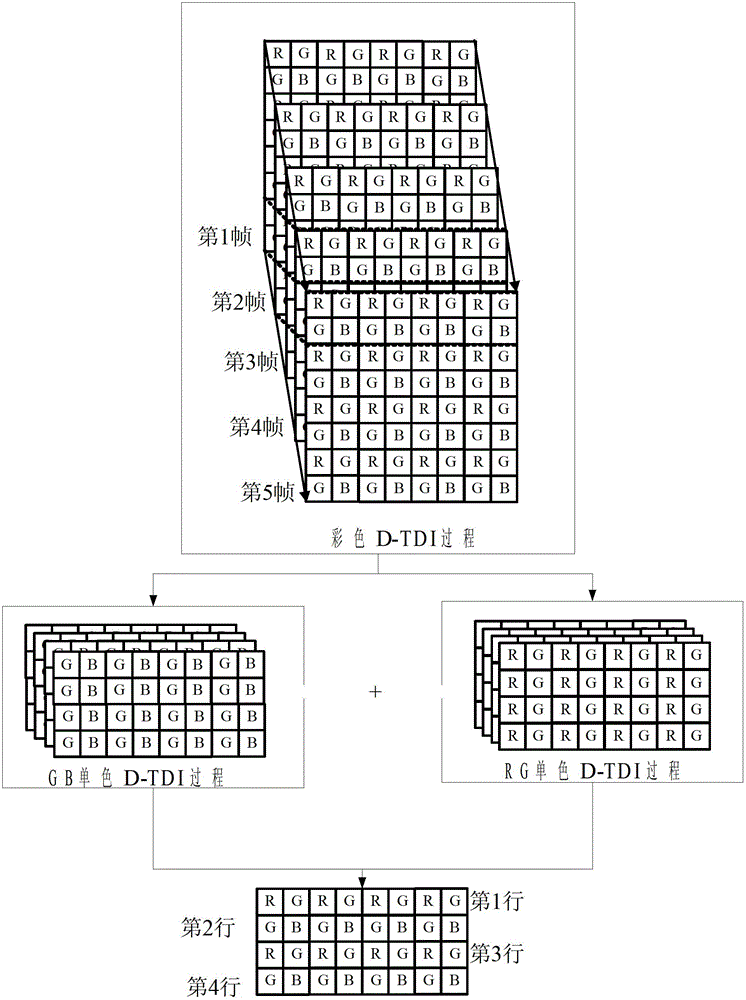

D-TDI (digital time-delay and integration) controller for color plane array CMOS (complementary metal-oxide-semiconductor transistor) sensor

ActiveCN102724447ADelayed integral implementationAchieve inversionTelevision system detailsColor television detailsCMOS sensorColor image

The invention relates to a D-TDI (digital time-delay and integration) controller for a color plane array CMOS (complementary metal-oxide-semiconductor transistor) sensor. A serial-parallel conversion module of the controller converts serial image data output by the color planar array CMOS sensor into parallel image data streams; a spectral-range separation module carries out separation on image data in odd-numbered rows and image data in even-numbered rows in parallel image data; a RG stream accumulator and a GB stream accumulator respectively carry out time delay and accumulative integration on the image data in the odd-numbered rows and the image data in the even-numbered rows, and a D-TDI integration result is output; and a spectral-range synthesis module carries out channel multiplexing on the D-TDI integration result at RG and GB spectral ranges so as to generate a Bayer-type color image. According to the invention, the odd-numbered rows and even-numbered rows of a CMOS image are processed respectively through two parallel channels so as to complete the D-TDI (digital time-delay and integration) of a RG channel and a GB channel, so that any even-numbered-level time delay and integration of a color CMOS chip can be realized.

Owner:CHANGGUANG SATELLITE TECH CO LTD

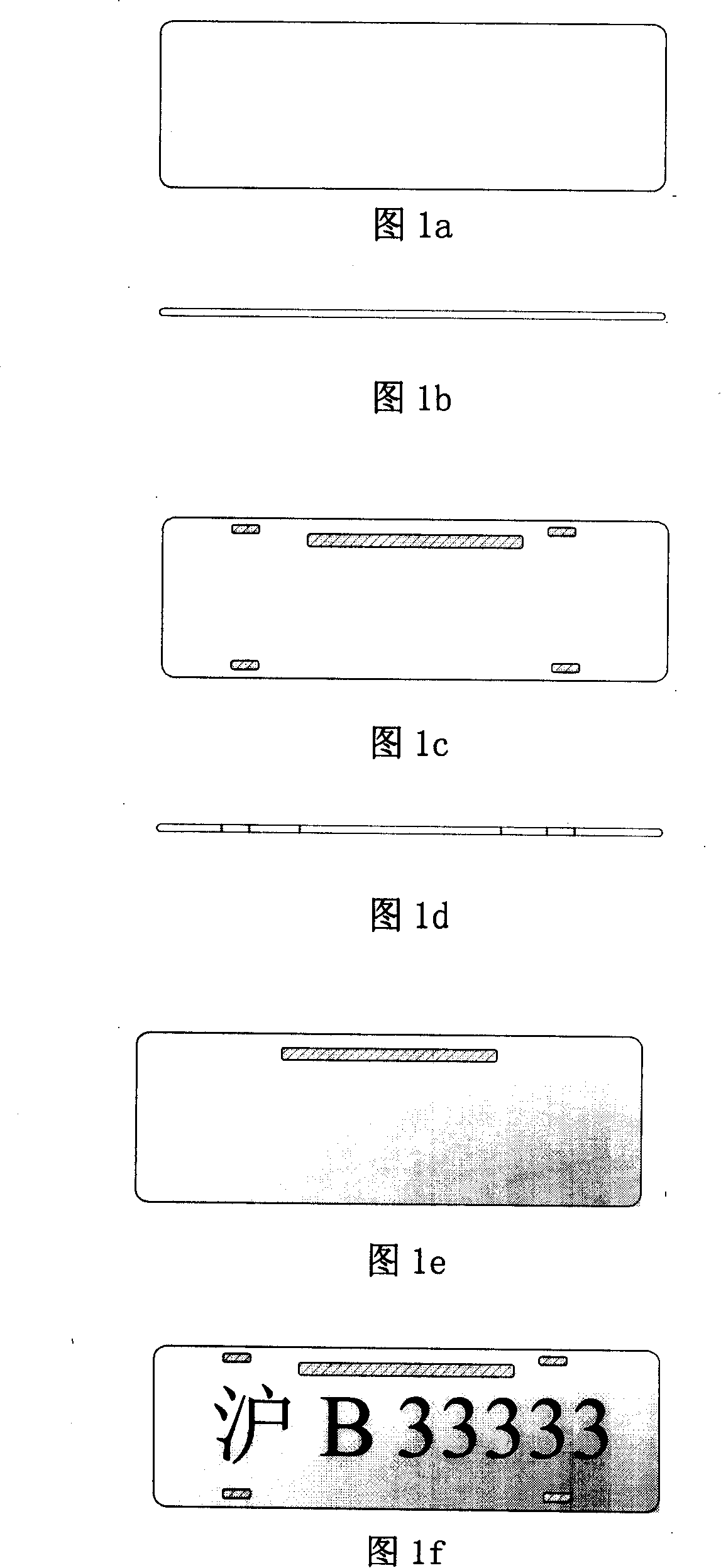

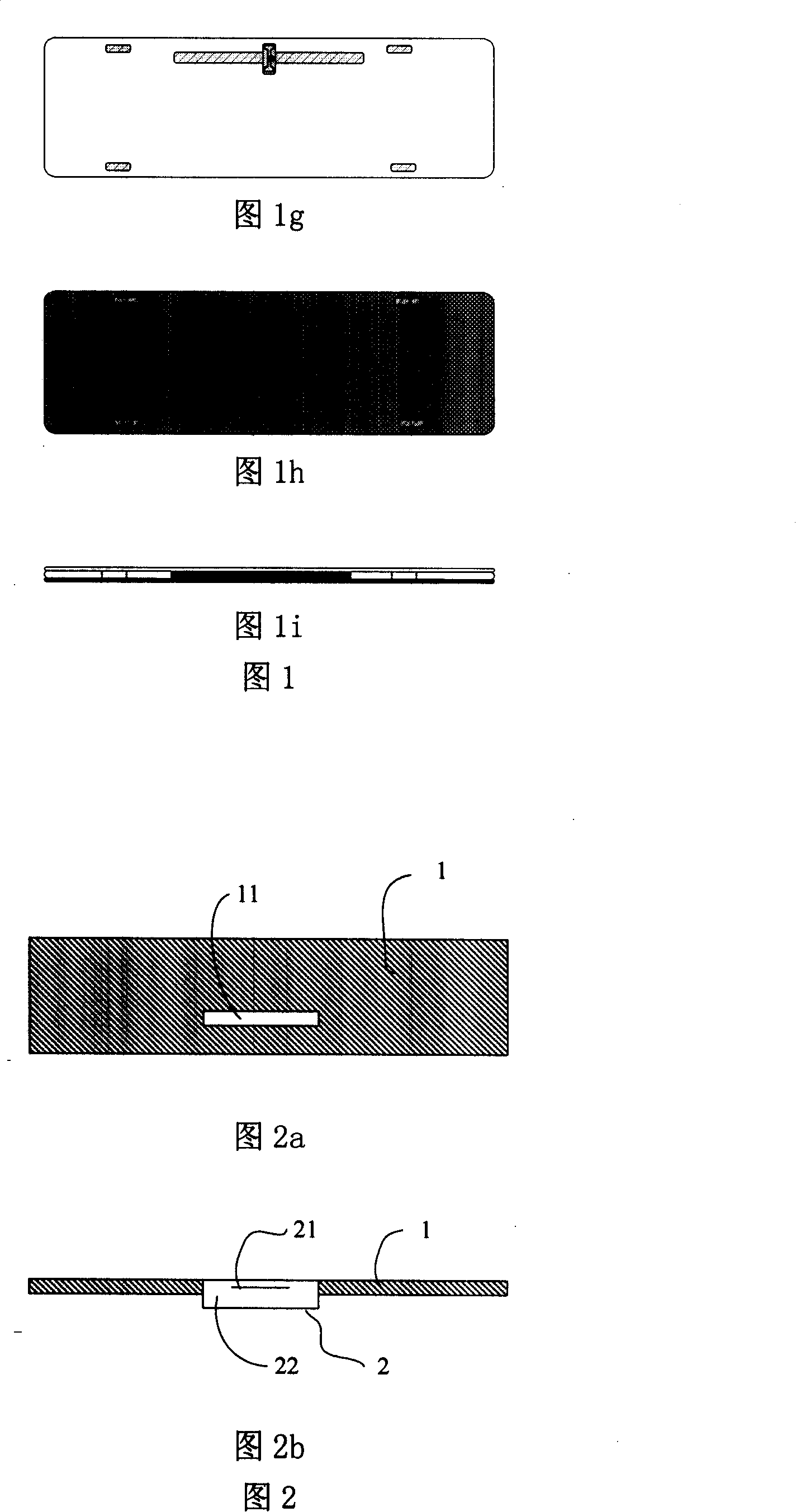

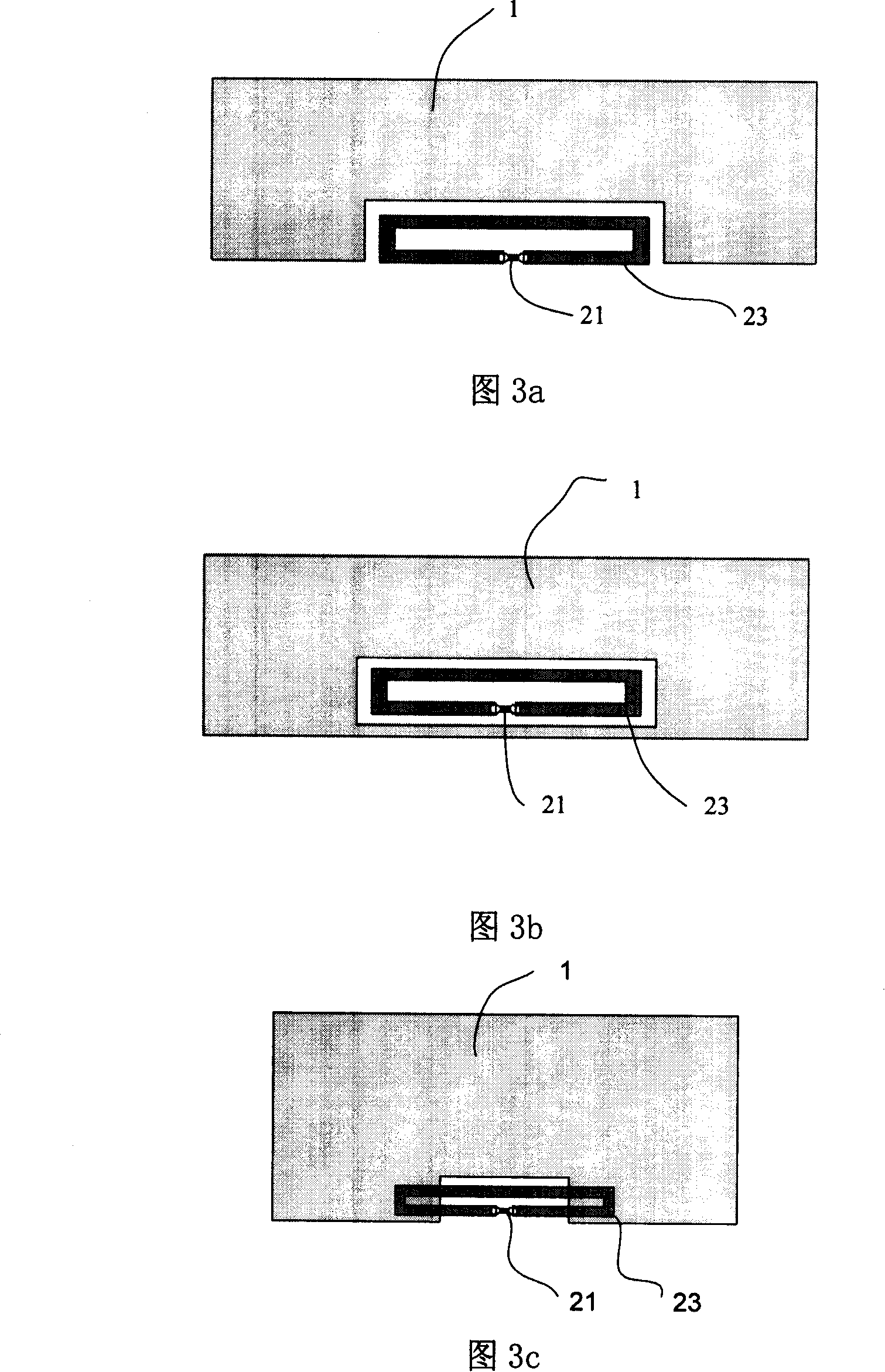

Electronic vehicle registration

InactiveCN101239604AImprove performanceMeet the needs of practical applicationsRadiating elements structural formsAntenna equipments with additional functionsResonanceRadio frequency

A kind of electronic car cards comprises a body, a radio-recognition CMOS chip set in the body, multi- frequency / single frequency resonance antenna connected with the CMOS chips. The body comprises metal structure, which constitutes the whole or local part of the antenna. The body is a metal plate with an antenna pattern. The blank area of the antenna pattern is a hole, a hatch, a notch, or the combination of them. The body is the metalloid or metal plate with antenna pattern and metal-filled film. The metal-filled film is formed using a layer of material that the radio wave can penetrate bonded with a metal-filled layer with antenna pattern. The metal-filled film is pasted onto the metalloid or metal plate. The blank area of the antenna pattern of the metal board is filled with material with low dielectric constant. The blank area of the antenna pattern of the metal board is embedded with the radio-recognition CMOS chip sealed with material with low dielectric constant. Using the car cards to construct the antenna, and the performance of the antenna is fine so that it can satisfy the demand in practical application.

Owner:NEOLOGY INC

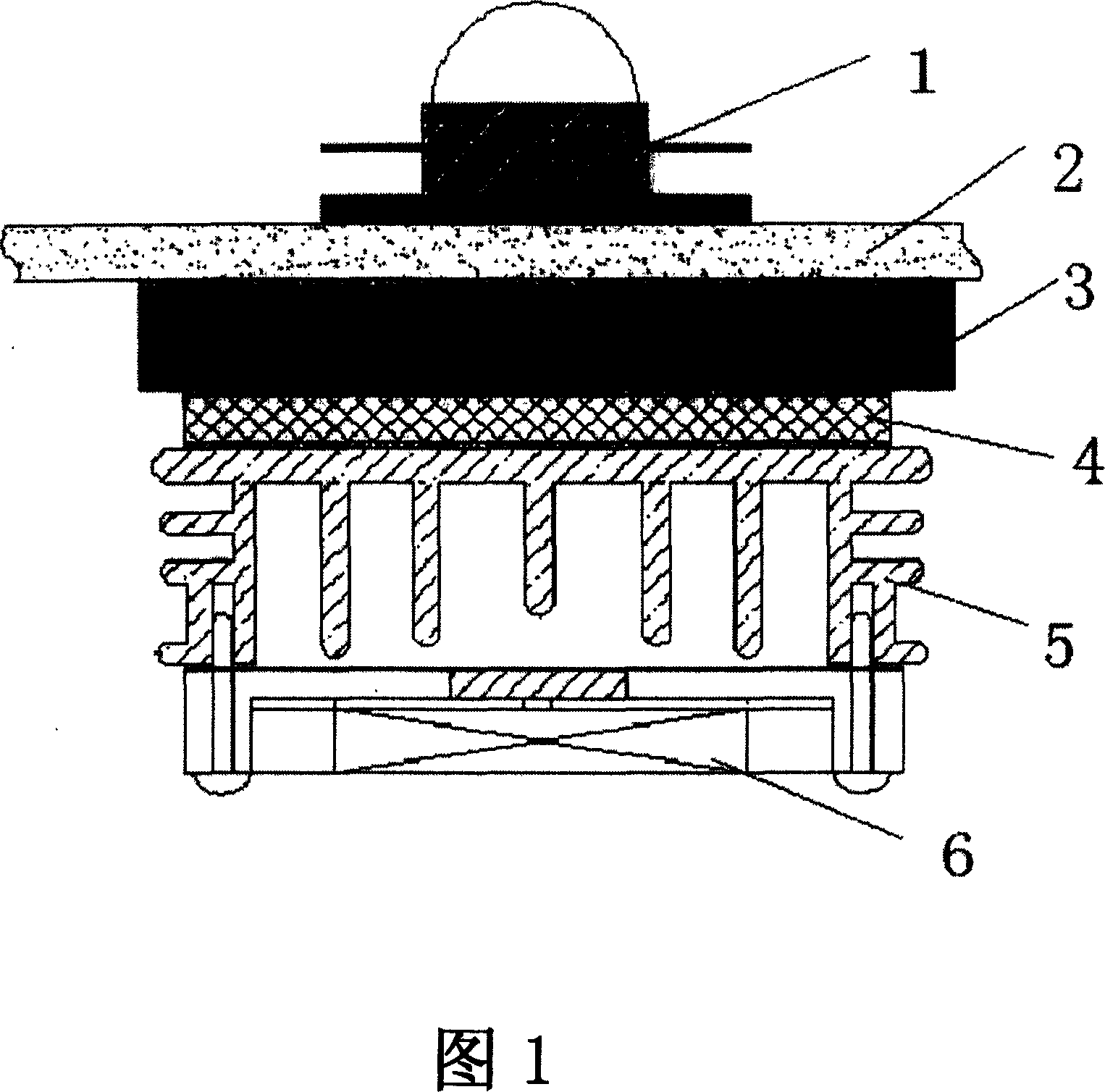

Lamp

InactiveCN101082411AReliable Optical IndexMeet the use requirements of lightingPoint-like light sourceLighting heating/cooling arrangementsEngineeringRefrigeration

The LED lamp in this invention consists of LED lamp body, metallic base plate, hot container, refrigeration slice of semiconductor, heating slice, heating fan. It resolves effectively the problem that CMOS chip can bring greatly quantity of heat immediately after high-power LED lamp is electrified, the quantity of heat introduces base plate soon and accumulates rapidly, it results in that the temperature of the COMS chip raise fleetly, so the lightness of the LED lamp attenuate hastily, even it can burn the LED lamp. It has excellence in that reasonable frame, remarkable effect, easy production, and so on.

Owner:DONGGUAN CLED OPTOELECTRONIT TECH

Method and system for optoelectronic receivers for uncoded data

A method and system for optoelectronic receivers for uncoded data are disclosed and may include amplifying received electrical signals in a signal amplifier comprising differential gain stages with signal detectors coupled to the outputs. First and second output voltages may be tracked and held utilizing the signal detectors. A difference between the tracked and held value may be amplified in a feedback path of the gain stage, which enables the dynamic configuration of a decision level. The received electrical signals may be generated from an optical signal by a PIN detector, an avalanche photodiode, or a phototransistor. The electrical signal may be received from a read channel. The feedback path may comprise digital circuitry, including an A / D converter, a state machine, and a D / A converter. The detectors may comprise envelope detectors utilized to detect maximum or minimum voltages. The signal amplifier may be integrated in a photonically-enabled CMOS chip.

Owner:CISCO TECH INC

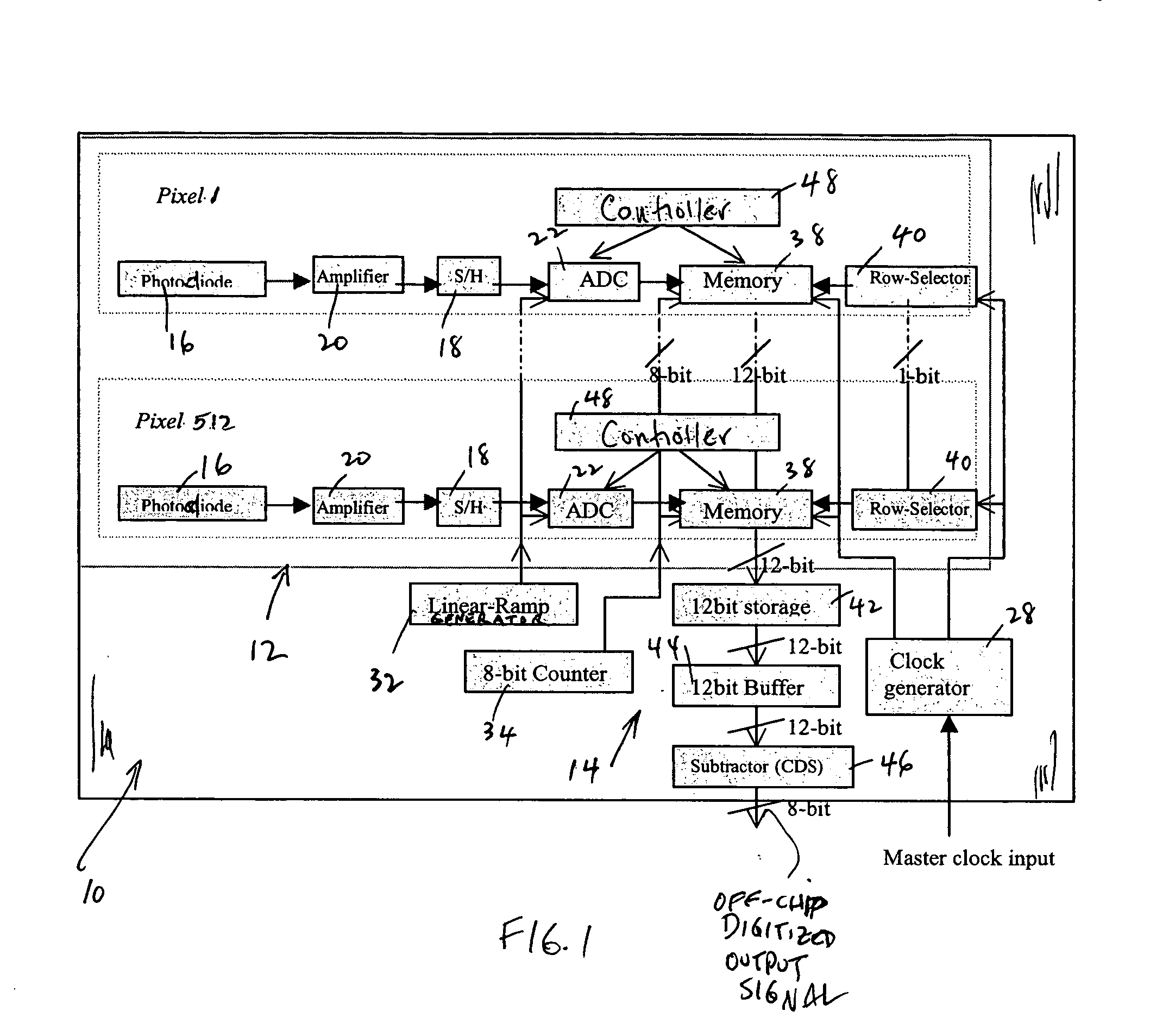

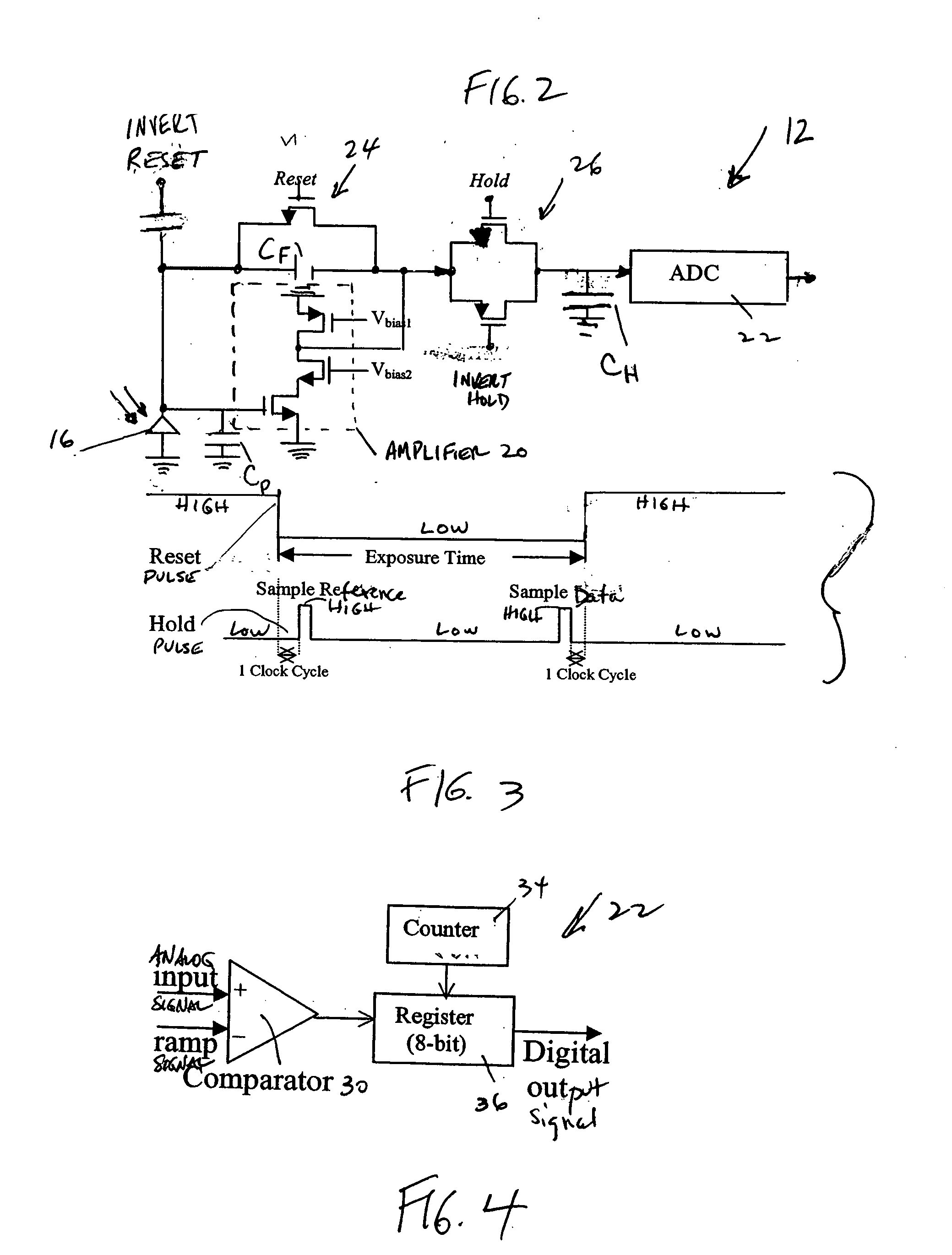

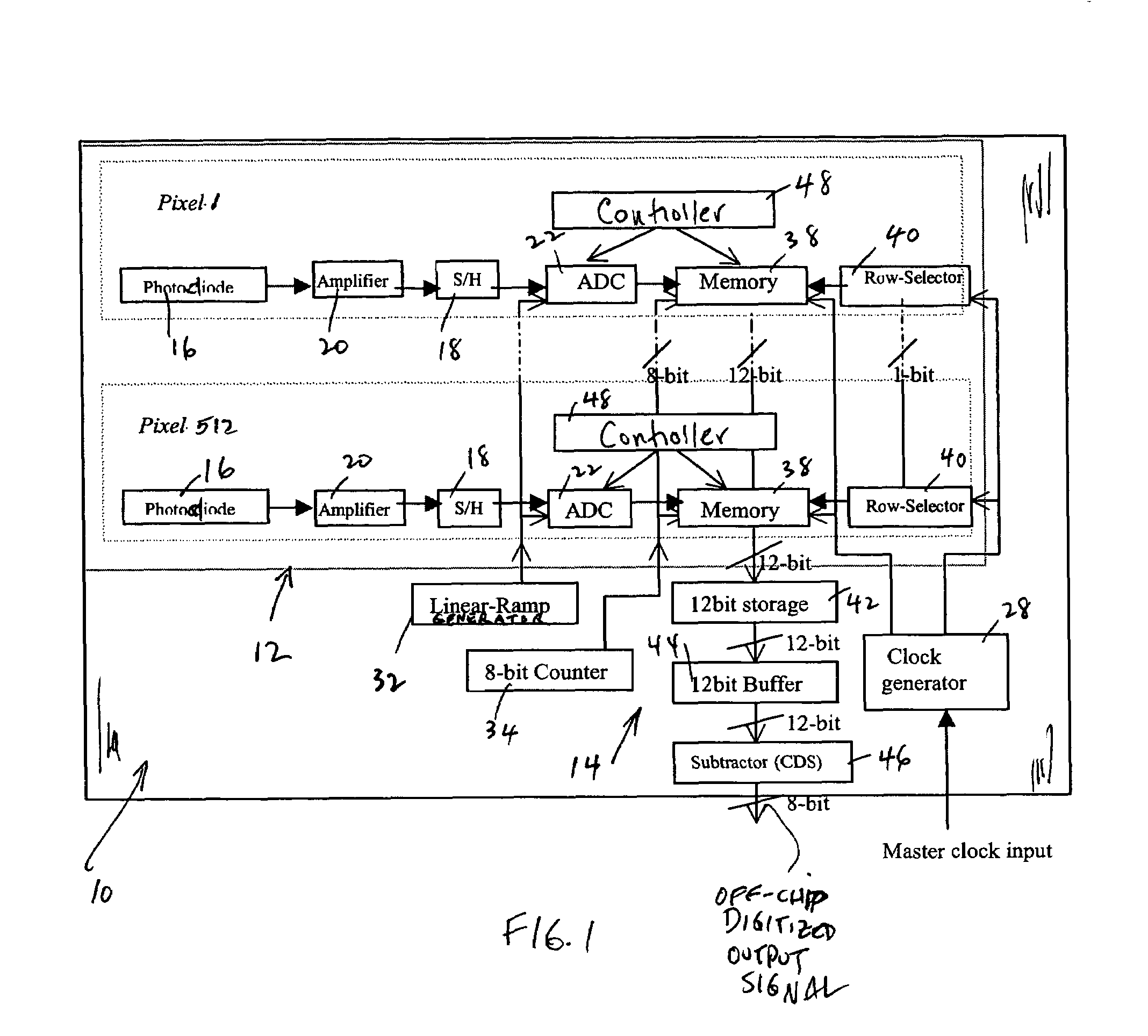

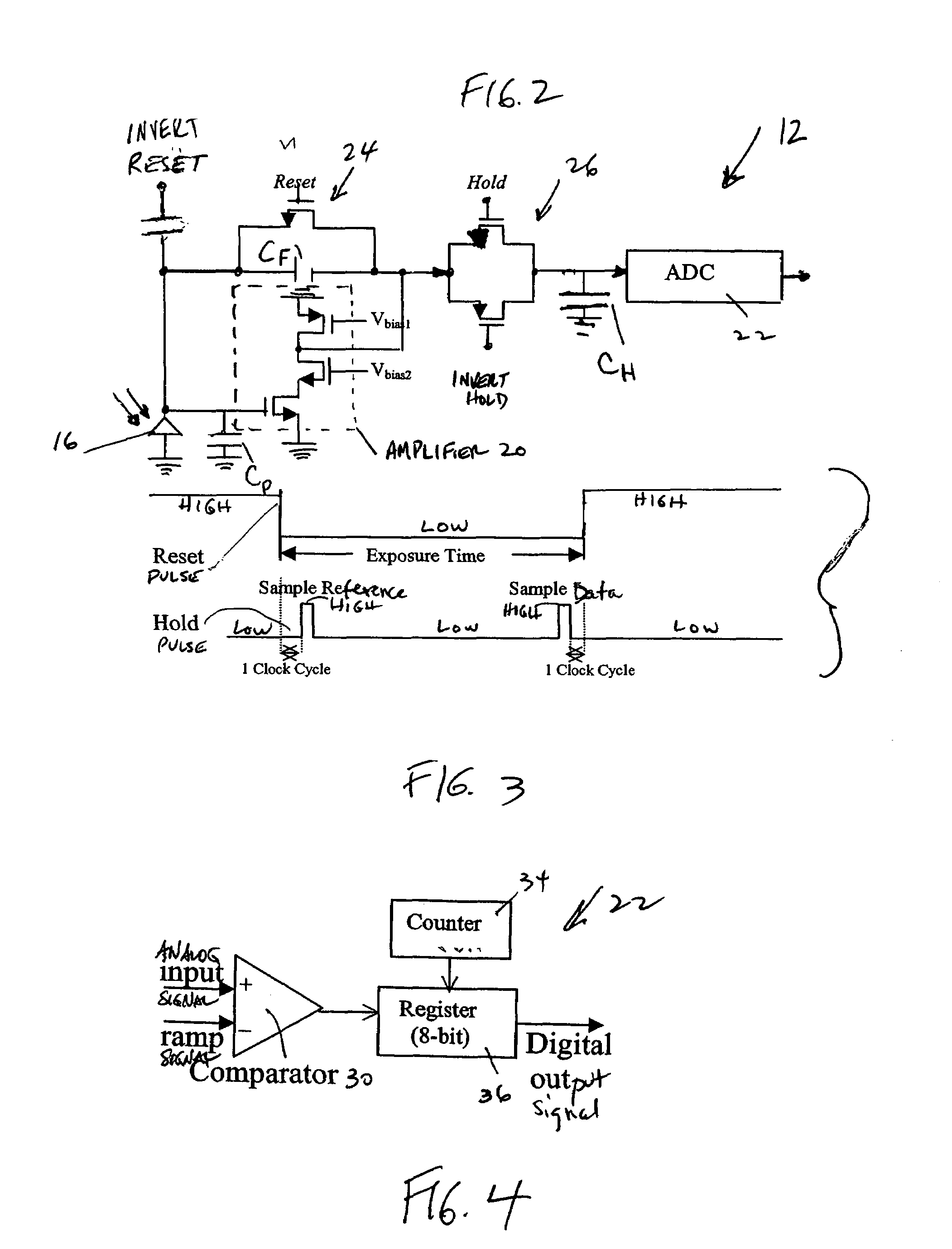

Single chip, noise-resistant, one-dimensional, CMOS sensor for target imaging

ActiveUS20050134714A1Reduce power consumptionLow costTelevision system detailsTelevision system scanning detailsSensor arrayCMOS sensor

Owner:SYMBOL TECH LLC

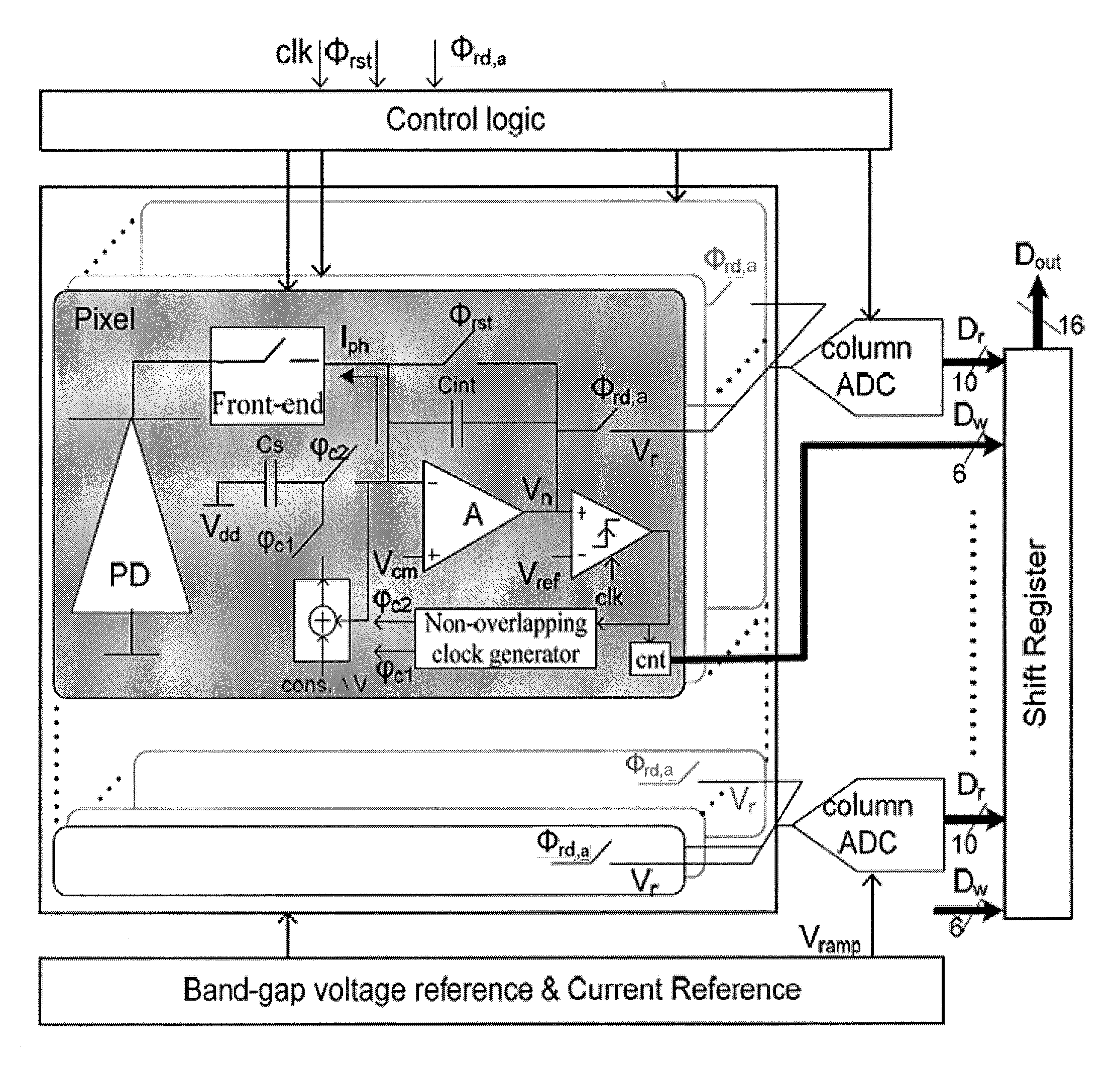

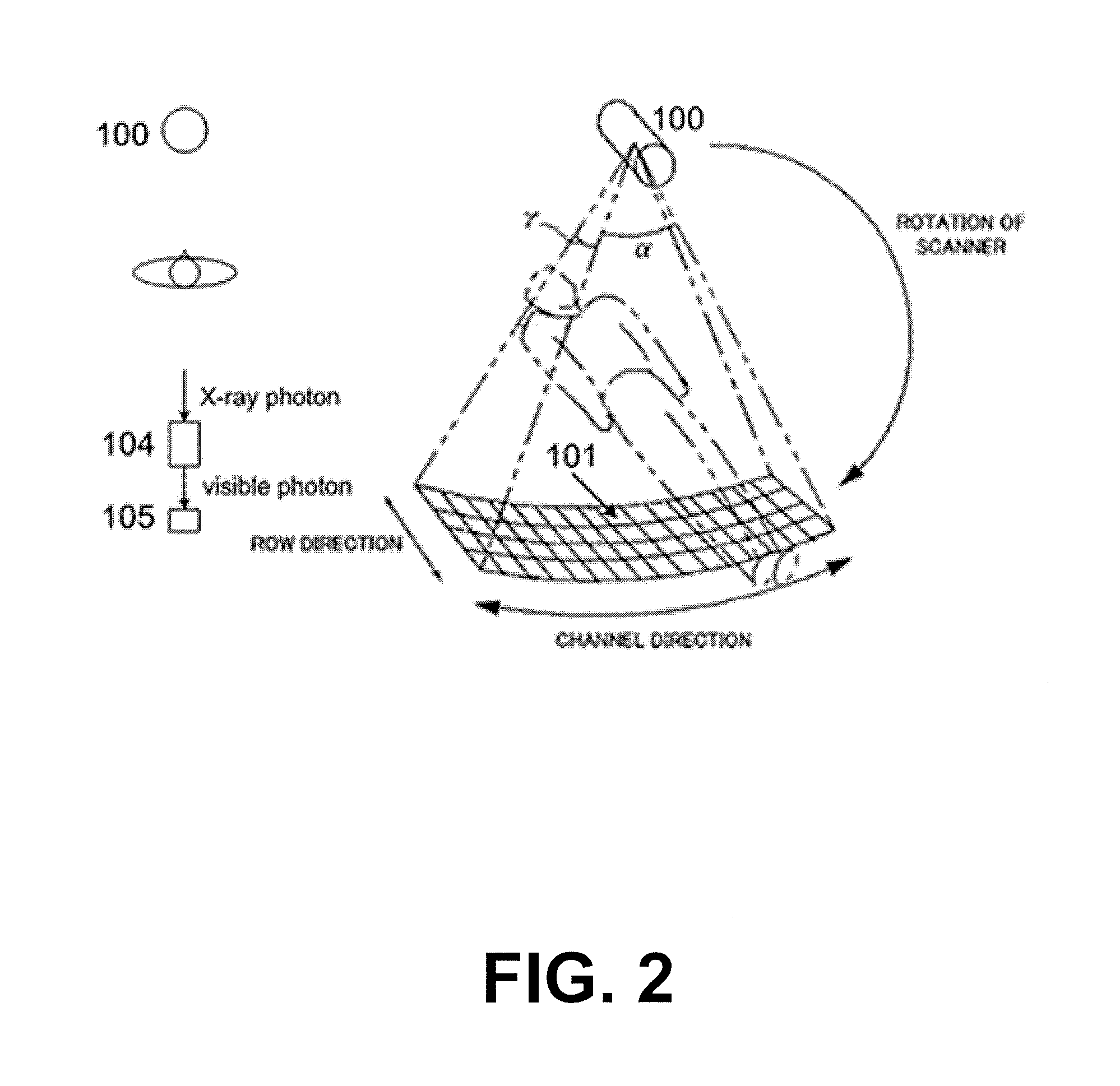

Quantum-limited highly linear CMOS detector for computer tomography

ActiveUS20110291019A1Improve linearityQuantum-limited noiseSolid-state devicesMaterial analysis by optical meansShift registerControl signal

The invention provides a CMOS CT detector design with high linearity, quantum-limited noise, good scalability, high fill factor with a single CMOS chip utilizing synchronous partial quantization. The CMOS CT detector includes a pixel array, digital column buses, analog column buses, column processing circuits, a shift register, a control signal generation circuit, and a reference generation circuit, and implements a synchronous partial quantization scheme with reset, integration and analog readout phases. Each pixel of the pixel array further includes a photodiode; an integration capacitor; an OPAMP; a reset switch; a comparator; a 1-bit dynamic random-access-memory (DRAM) cell; a circuit block for enabling subtraction of a substantially fixed amount of charge from the integrated photocharge if the integrated photovoltage increases beyond the reference voltage; an integration node; an analog buffer; and a switch coupled between the output of the DRAM cell and the digital column bus. The inclusion of a level-shifter and a current front-end improves the linearity of the detector.

Owner:THE HONG KONG UNIV OF SCI & TECH

Device and method for analyzing and counting blood cells by lensless holographic diffraction imaging

InactiveCN102660457AExpand field of viewReasonable designBioreactor/fermenter combinationsBiological substance pretreatmentsMicroscope slideMiniaturization

The invention discloses a device and method for analyzing and counting blood cells by lensless holographic diffraction imaging, relating to blood cell detection and counting technology. The invention has a lensless simple structure and wide view, can realize miniaturization, and can monitor thousands of cells with different concentrations in real time. The device comprises a glass slide for placing a sample and a cover slip arranged on the glass slide, and is characterized in that a CCD or CMOS chip is arranged below the glass slide, a light source is arranged above the glass slide, an aperture is arranged between the light source and the glass slide and is arranged on the light extraction route of the light source. The method comprises the following steps: putting a blood cell sample between the glass slide and the cover slip and with well pressing, adjusting the light source above the glass slide, and adjusting the position of the sensitive chip below the glass slide to let the light emitted from the light source pass through the aperture and be vertically incident on the cover slip, and letting the CCD or CMOS ship arranged below the glass slide record the interference images after the light passes through the blood cell sample.

Owner:NANCHANG HANGKONG UNIVERSITY

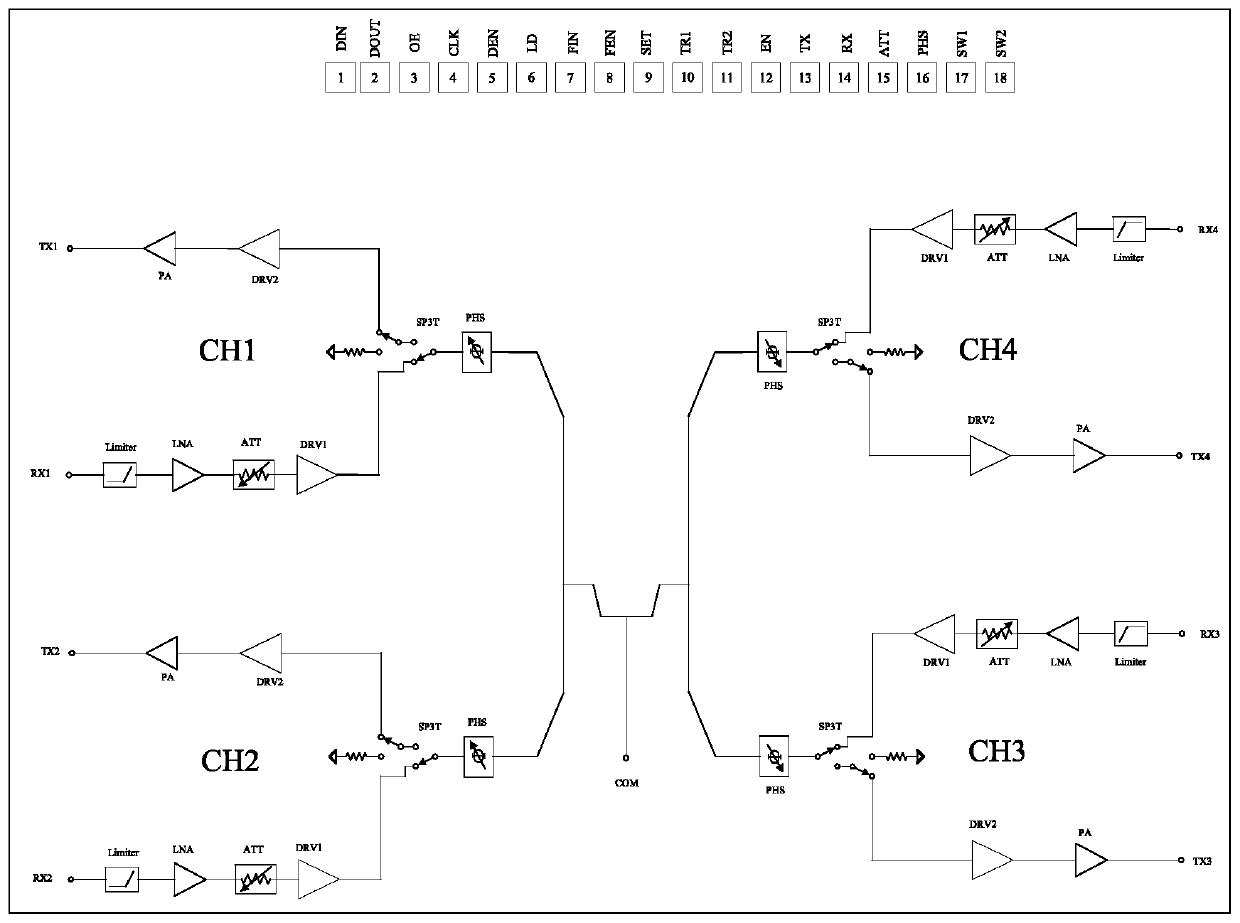

3D packaging structure based multifunctional phased array TR chip

The invention discloses a 3D packaging structure based multifunctional phased array TR chip. A chip RF part with a high-performance gallium arsenide chip comprises four identical single channels, namely, first to fourth channels CH1, CH2, CH3 and CH4, the four single channels are connected with four ports of a one-to-four power divider respectively, and each channel comprises a six-bit digital control attenuator ATT, a six-bit digital control phase shifter PHS, a low noise amplifier LNA, a driving amplifier DRV1, a driving amplifier DRV2, a power amplifier PA, a single-pole three-throw switchSP3T and a limiter Limiter; and a CMOS chip services as a control circuit of the multifunctional chip for chip logic control, and the CMOS chip and the gallium arsenide multifunctional chip are arranged in a flip way to form the integrated 3D packaging structure. The 3D packaging structure based multifunctional phased array TR chip has the advantages of small size, low cost, high consistency, highreliability and simple debugging.

Owner:ZHEJIANG CHENGCHANG TECH

Single chip, noise-resistant, one-dimensional, CMOS sensor for target imaging

ActiveUS7446806B2Reduce power consumptionLow costTelevision system detailsTelevision system scanning detailsSensor arrayCMOS sensor

A linear sensor array for imaging coded indicia includes an analog front end and a digital back end integrated on a single CMOS chip. A real-time, correlated double sampling circuit is used for noise suppression.

Owner:SYMBOL TECH LLC