Patents

Literature

2061 results about "Digital circuitry" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

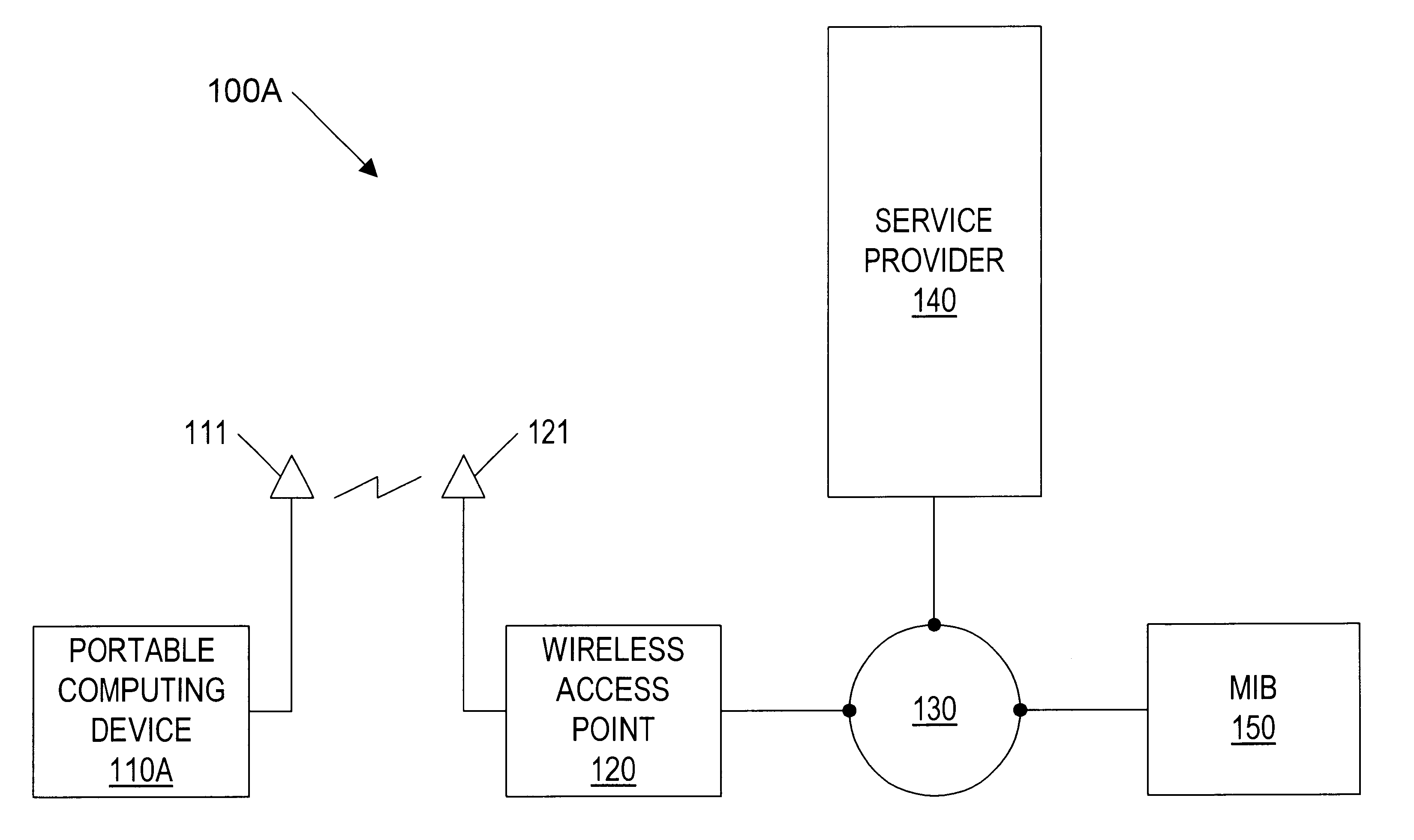

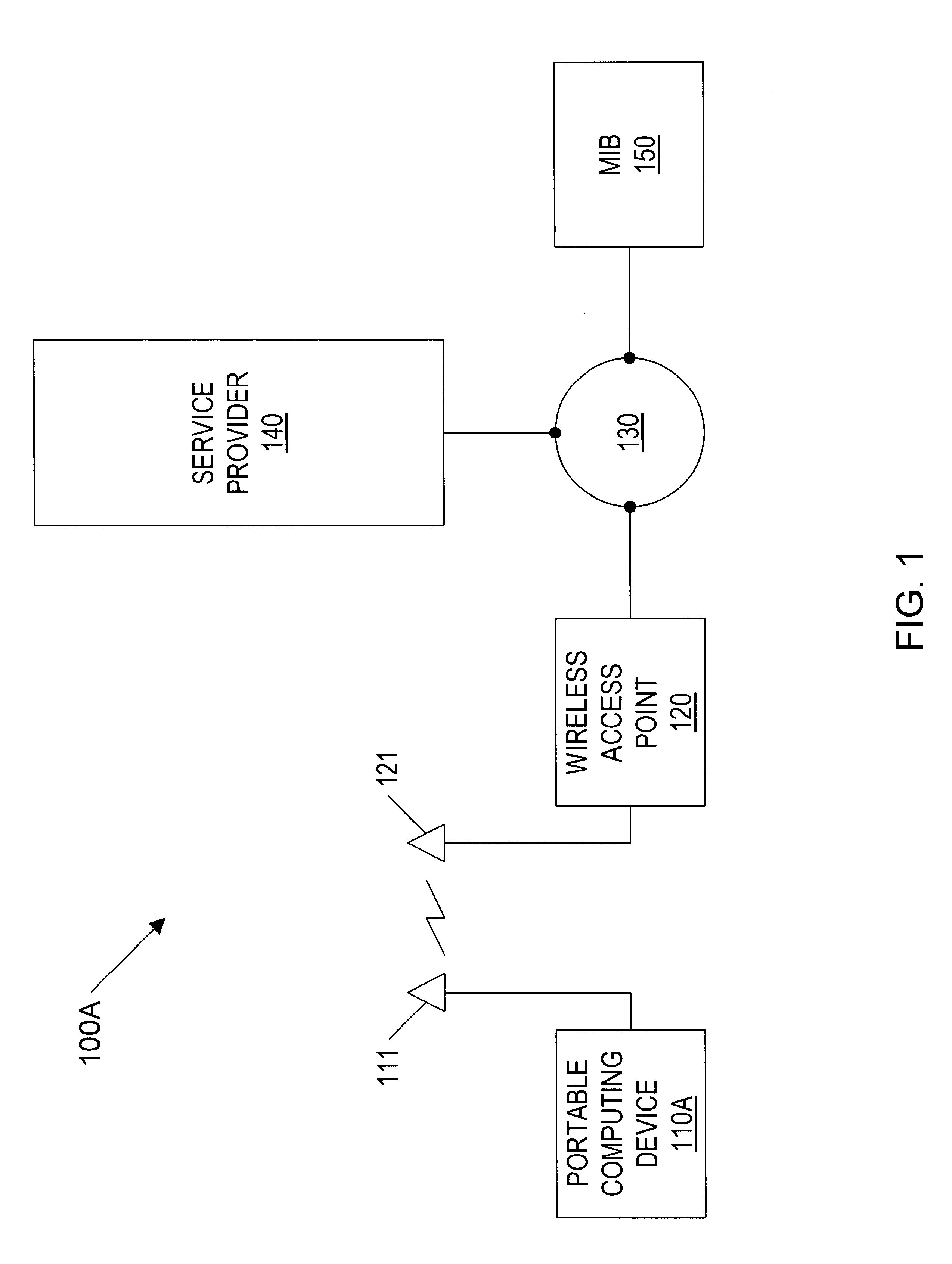

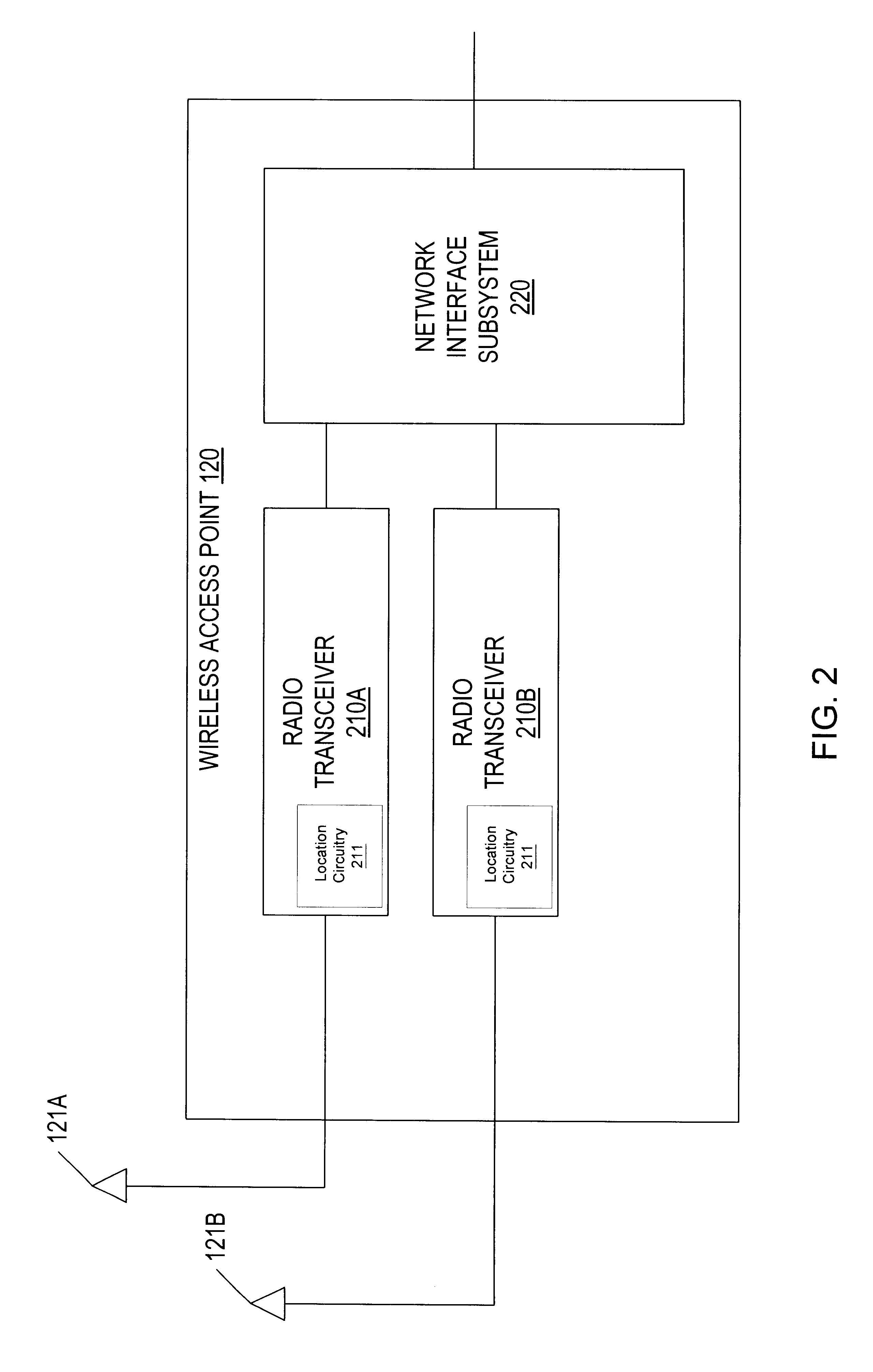

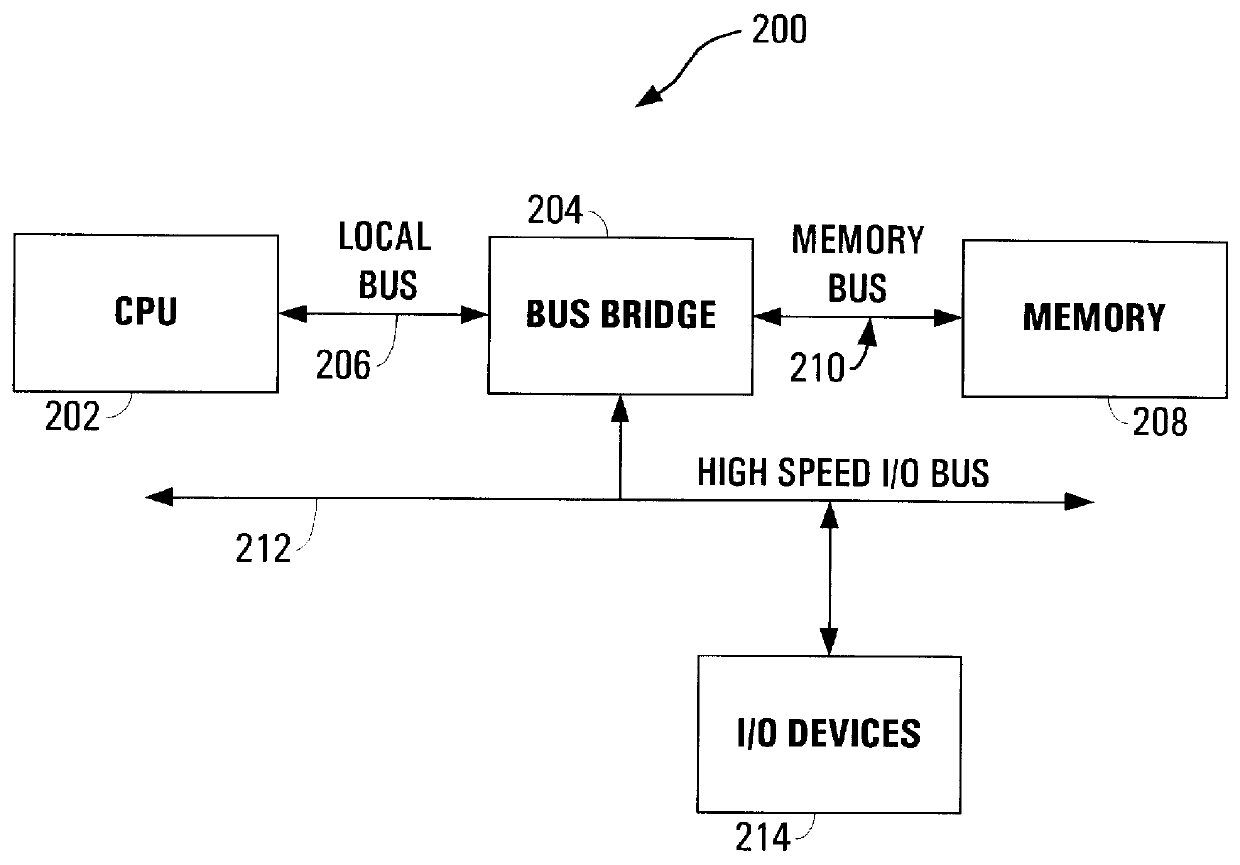

Geographic-based communication service system with more precise determination of a user's known geographic location

InactiveUS6414635B1Direction finders using radio wavesNetwork topologiesGeographic regionsGeolocation

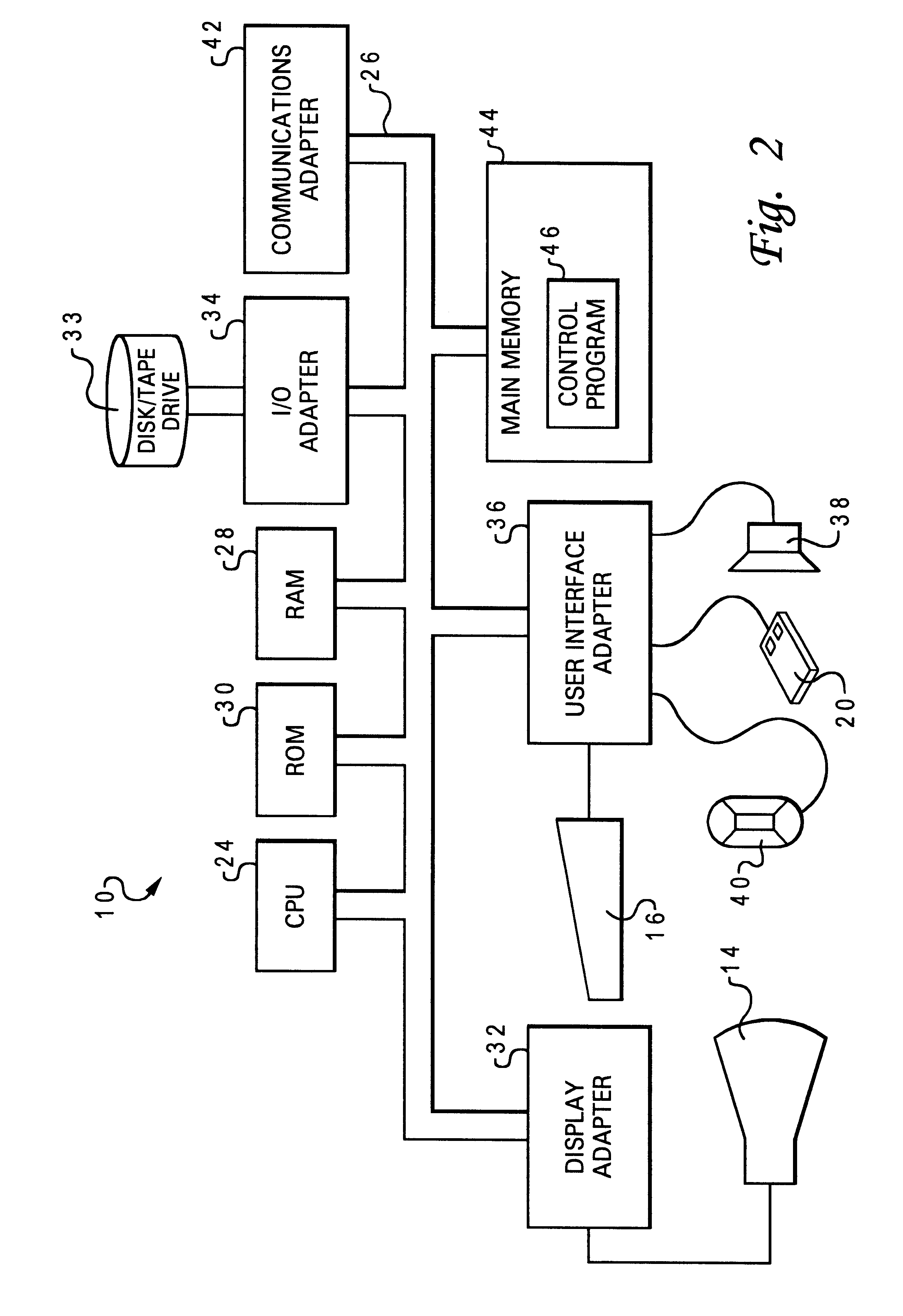

A geographic based communications service system that includes a network and a plurality of access points connected to the network and arranged at known locations in a geographic region. One or more service providers or information providers may be connected to the network to provide services or information on the network. Content provided by the service providers may be based on the known geographic location of the user of a portable computing device (PCD). The known geographic location may be determined with a high degree of precision, using one or more access points and one of several different techniques. In one embodiment, the geographic location of the PCD may be determined within a radius of ten feet. Access points may be configured to determine the bearing of a signal received from a PCD, as well as the strength of the signal transmitted by the PCD. Access points may also be configured to send and receive signals with time stamps. These time stamps may be used to calculate signal travel time, thereby allowing a determination of the distance between an access point and a PCD. Each access point may include location circuitry. The location circuitry may include both analog and digital circuitry configured to perform the various methods used to determine the precise geographic location.

Owner:META PLATFORMS INC

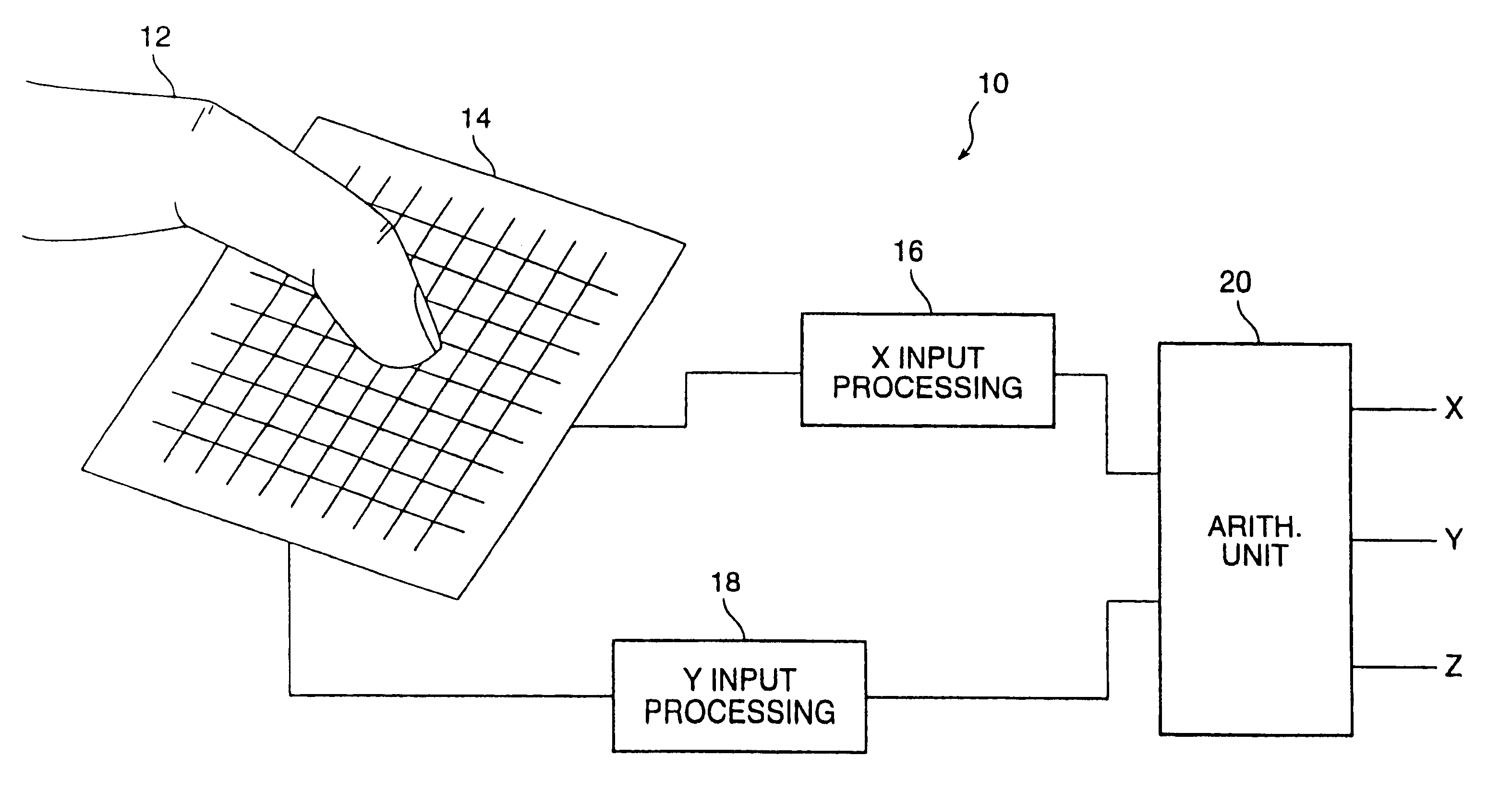

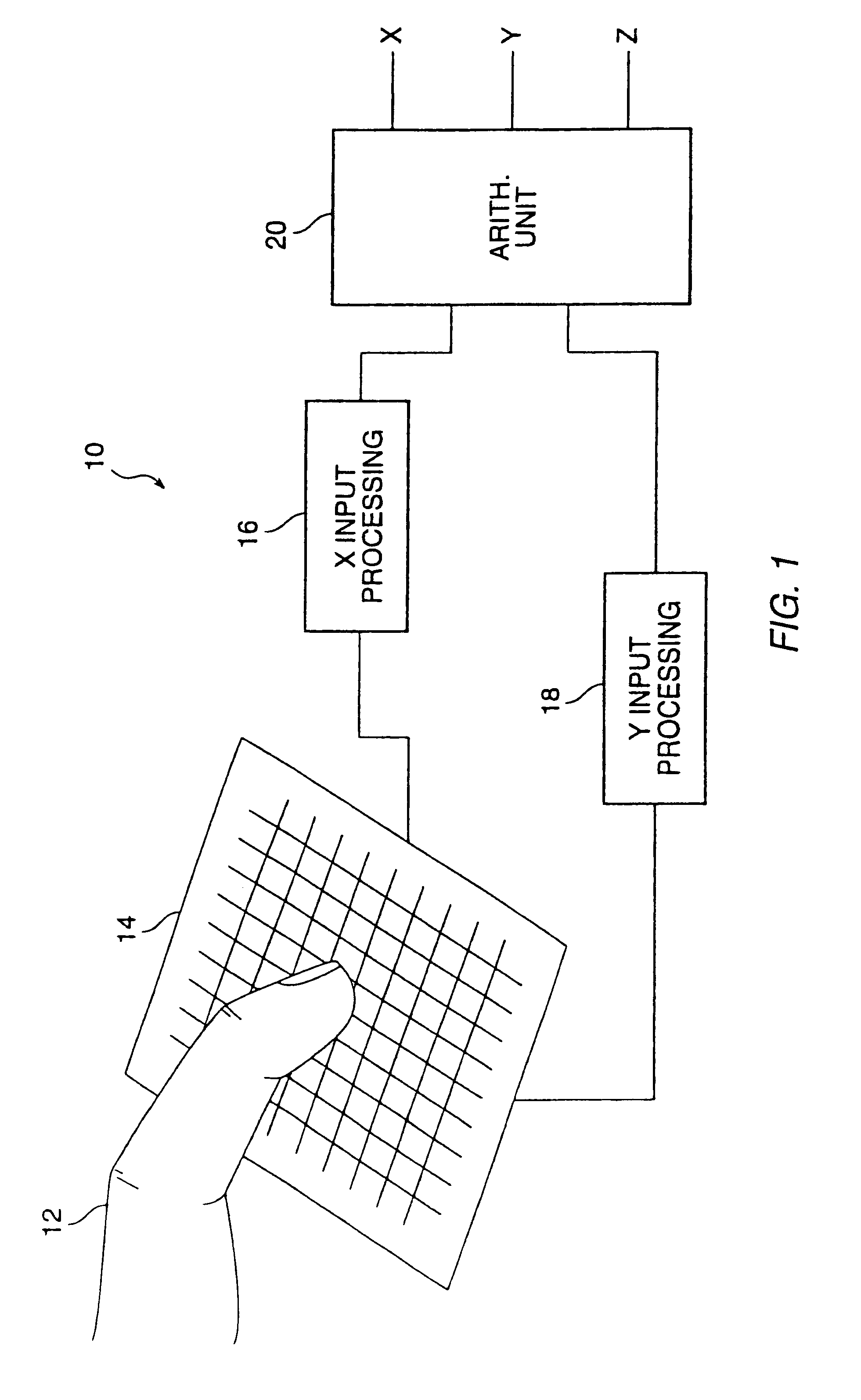

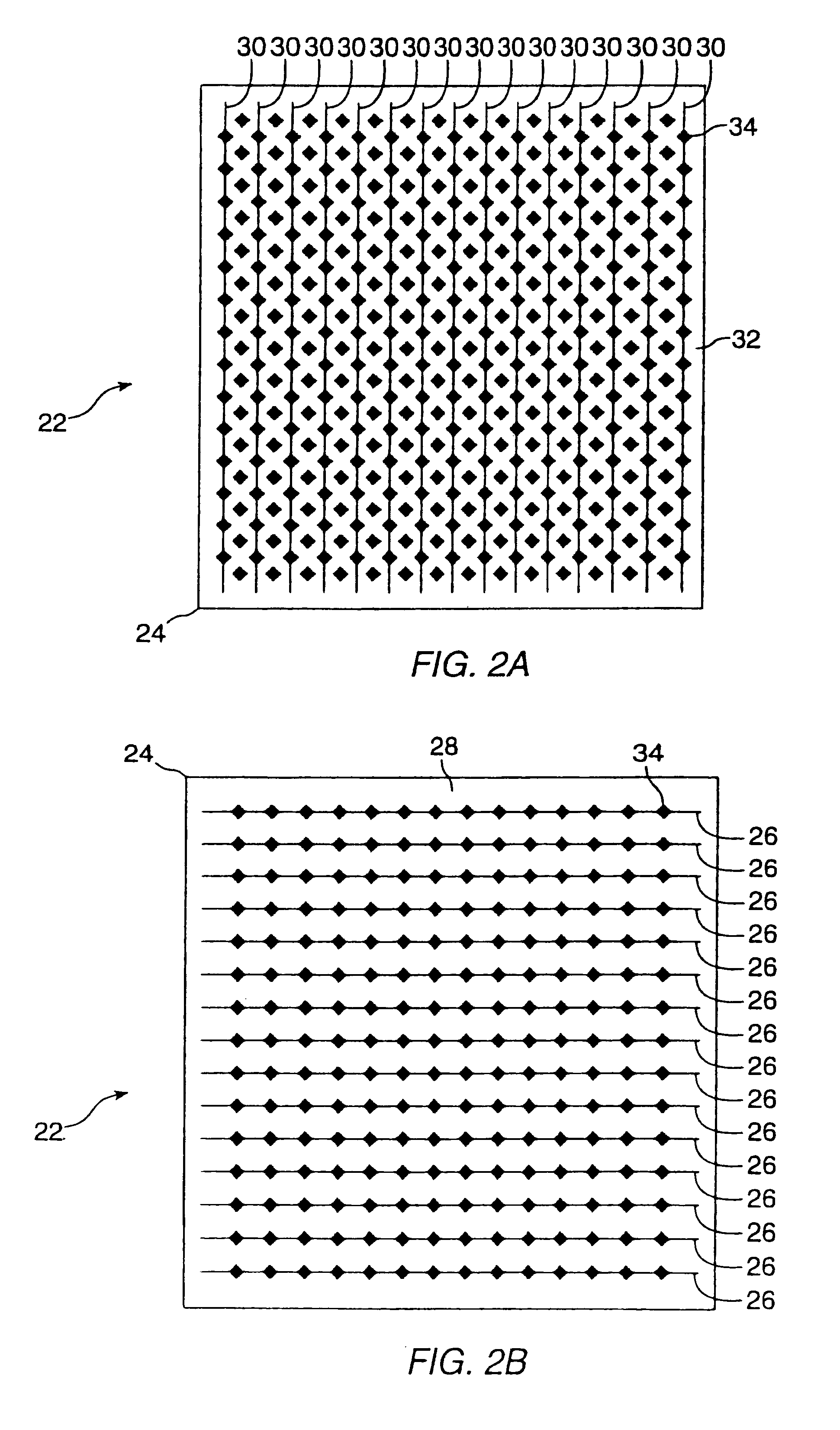

Object position detection system and method

InactiveUS6239389B1Effective positioningEasy CalibrationTransmission systemsDigital data processing detailsCapacitanceElectrical conductor

A proximity sensor system includes a sensor matrix array having a characteristic capacitance on horizontal and vertical conductors connected to sensor pads. The capacitance changes as a function of the proximity of an object or objects to the sensor matrix. The change in capacitance of each node in both the X and Y directions of the matrix due to the approach of an object is converted to a set of voltages in the X and Y directions. These voltages are processed by digital circuitry to develop electrical signals representative of the centroid of the profile of the object, i.e, its position in the X and Y dimensions. Noise reduction and background level setting techniques inherently available in the architecture are employed.

Owner:SYNAPTICS INC

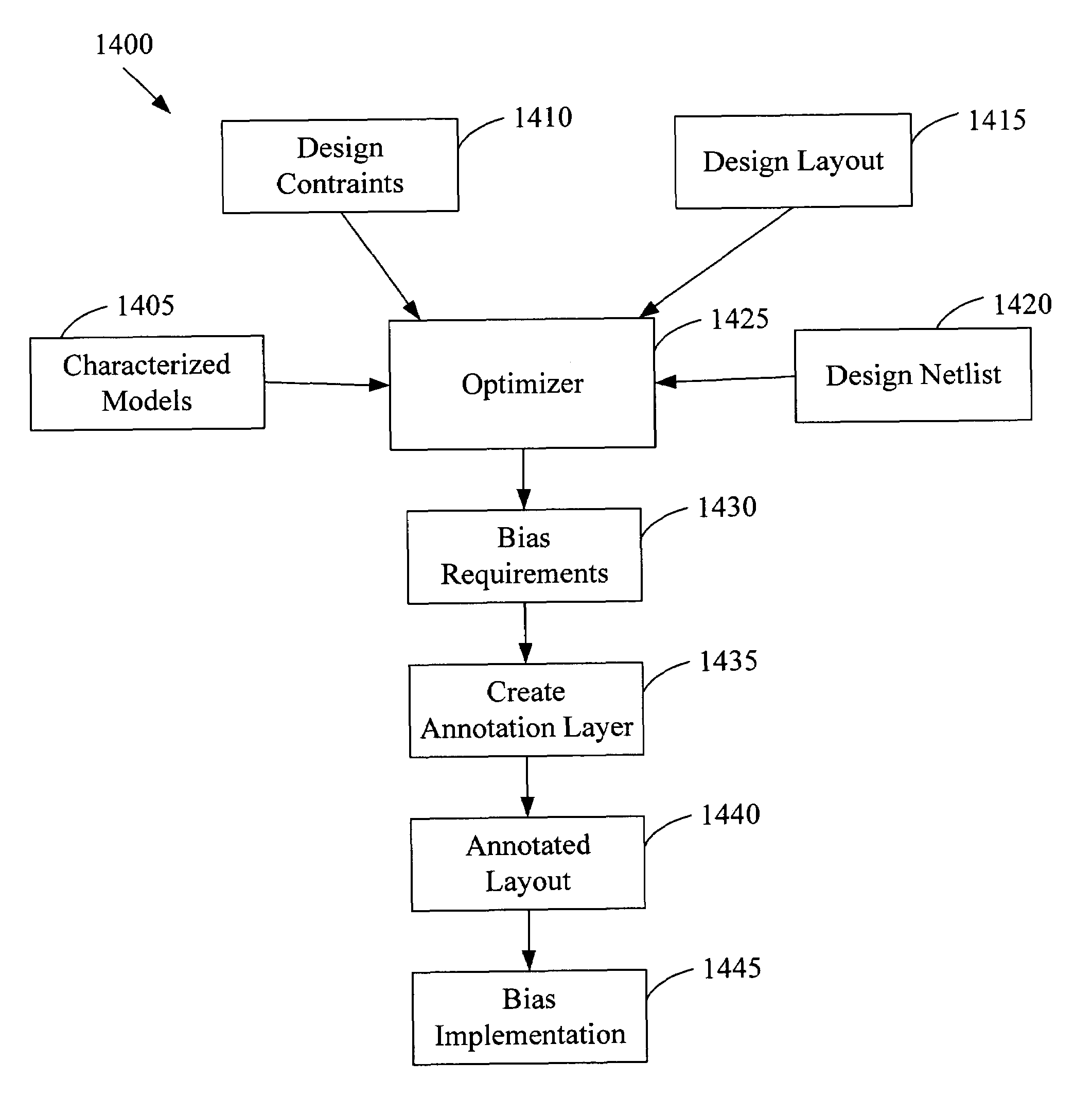

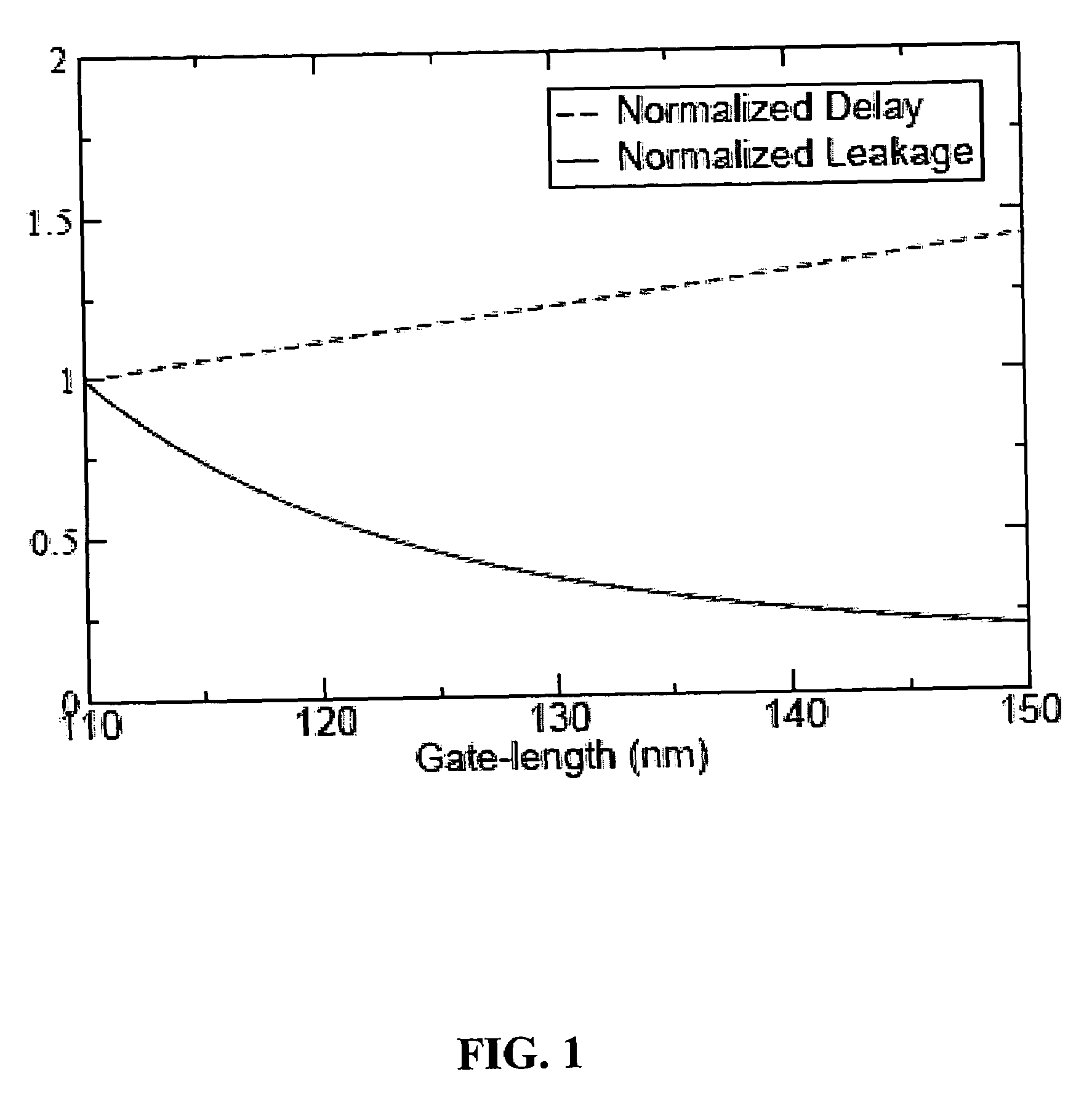

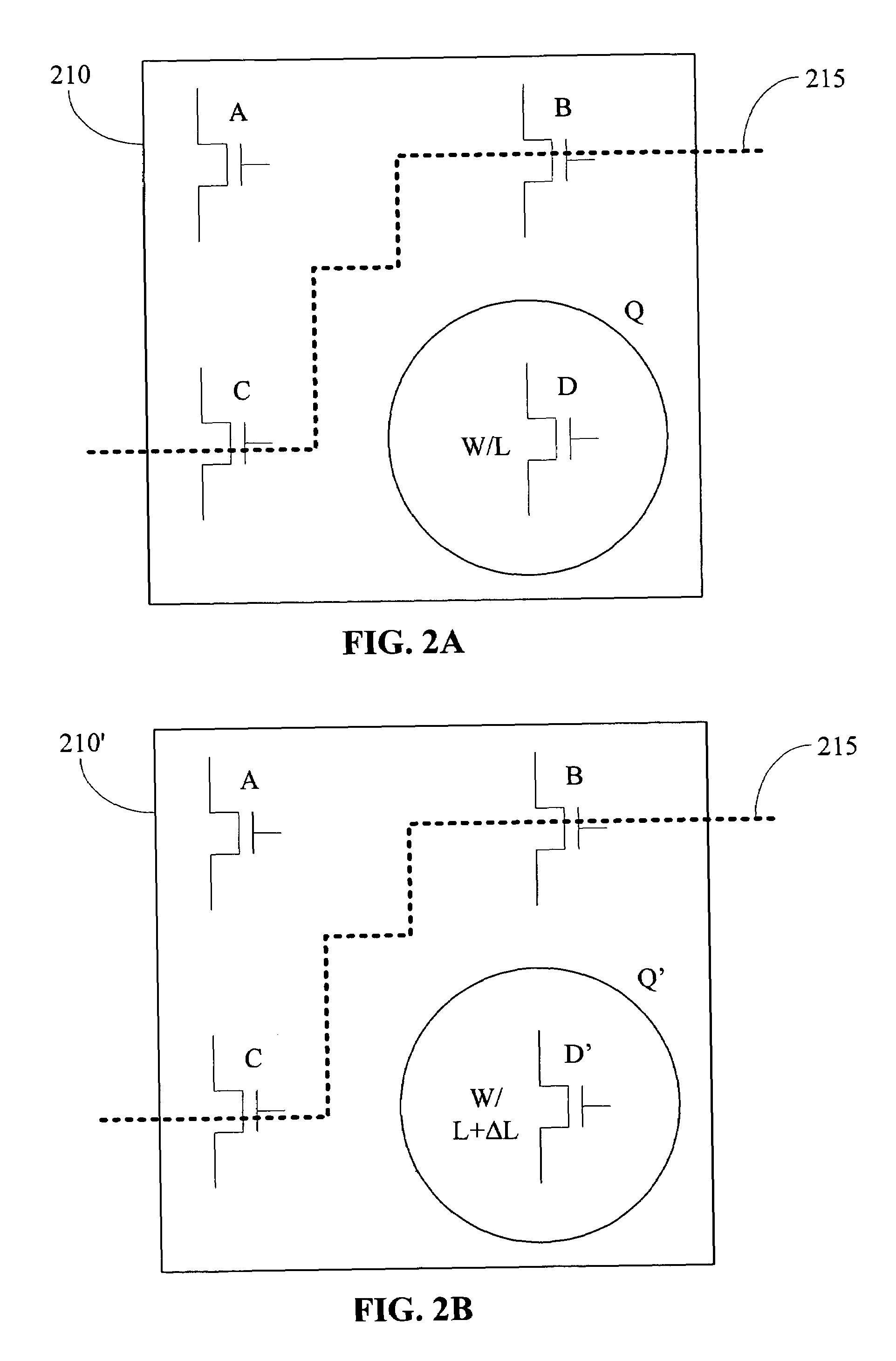

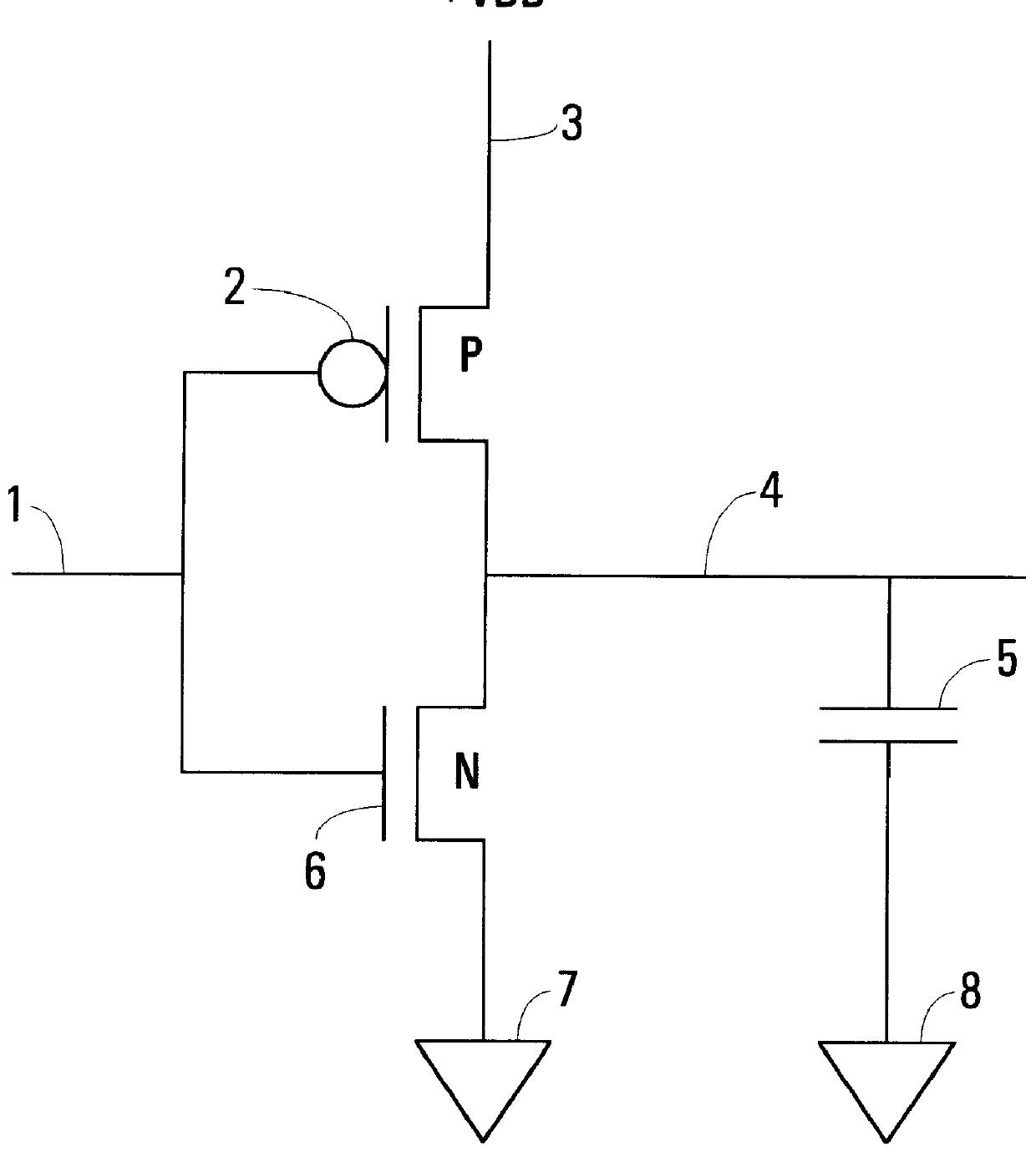

Gate-length biasing for digital circuit optimization

InactiveUS7441211B1Reduce impactImpairing time delay performance only linearlySolid-state devicesCAD circuit designEngineeringDigital electronics

Methods and apparatus for a gate-length biasing methodology for optimizing integrated digital circuits are described. The gate-length biasing methodology replaces a nominal gate-length of a transistor with a biased gate-length, where the biased gate-length includes a bias length that is small compared to the nominal gate-length. In an exemplary embodiment, the bias length is less than 10% of the nominal gate-length.

Owner:RPX CORP

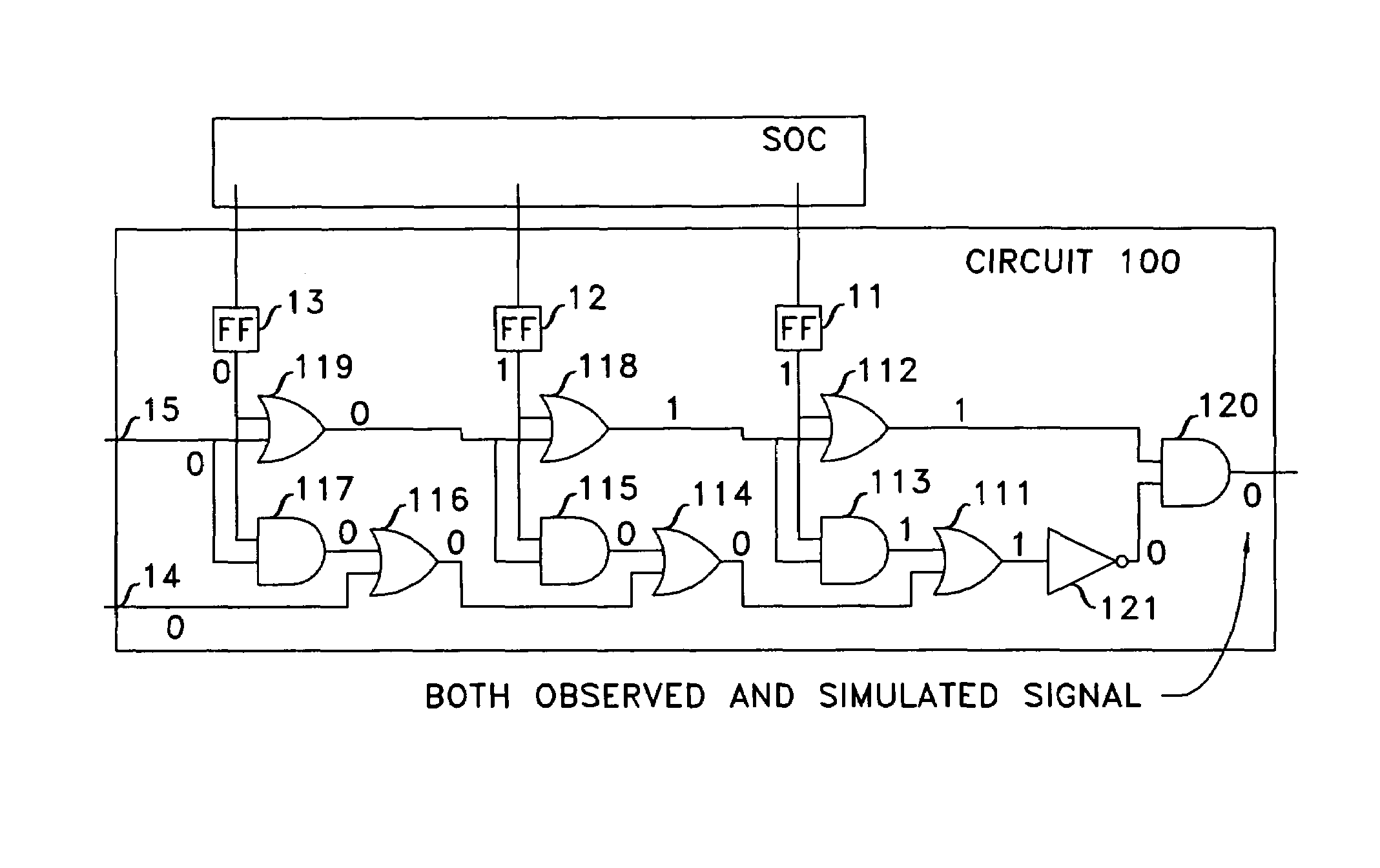

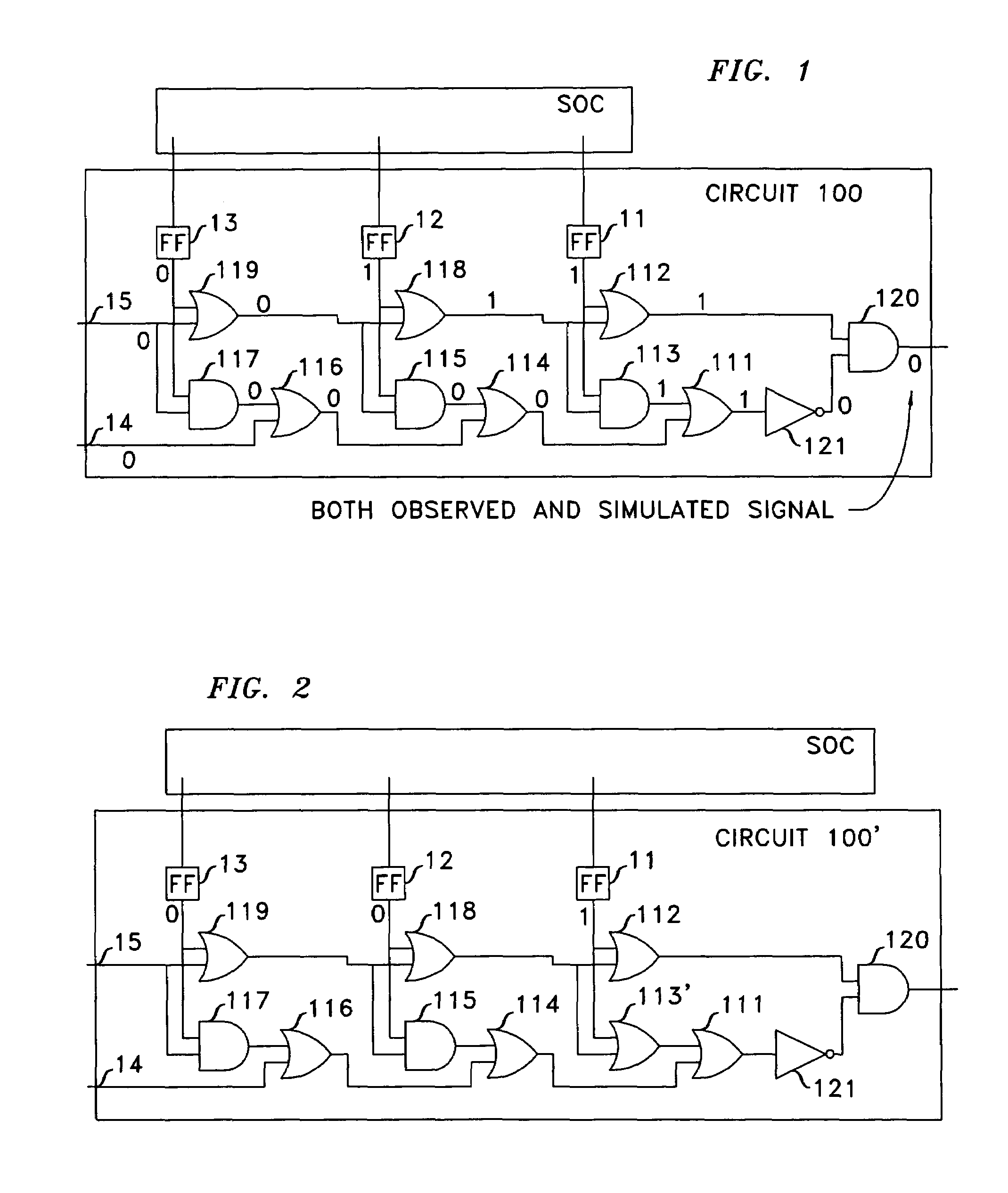

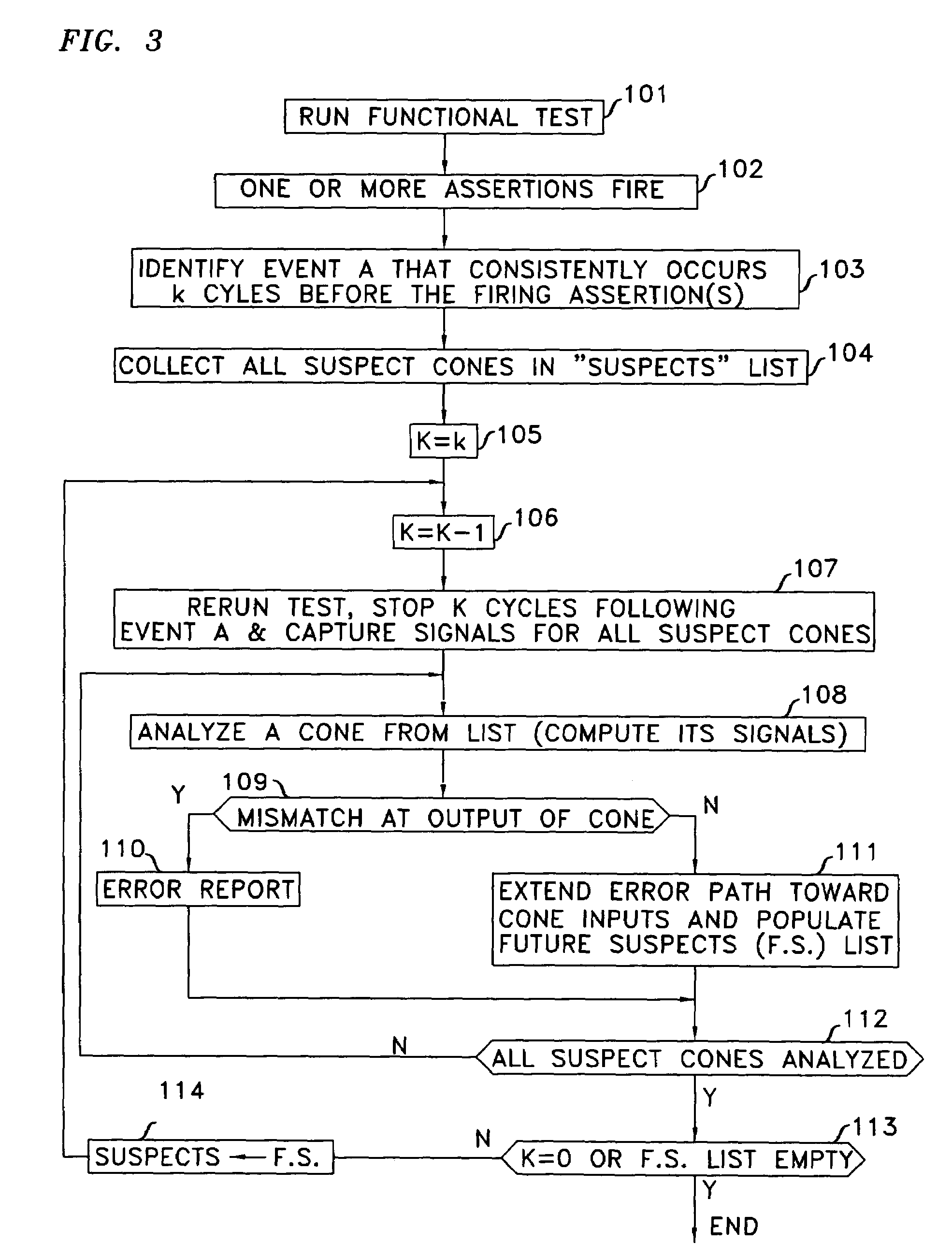

Method to locate logic errors and defects in digital circuits

When, in the course of an integrated circuit's functional test an assertion fires at clock k, the operational clock is stopped, the sequence is reapplied to capture inputs to the assertion circuit that fired, signals within the assertion circuit are computed, and the error is backtraced. Once one or more inputs of the assertion circuit are identified as potentially the source of the error, the process of backtracing is performed for each such input. When the input that is potentially the source of the error emanates from a memory circuit, the fanin cone of the memory circuit is identified and the process of backtracing through the last-identified fanin cone is undertaken for clock k−1. This is repeated iteratively until either a module of the integrated circuit is found to be the source of the error, or the error is extended to inputs of the SoC.

Owner:DAFCA

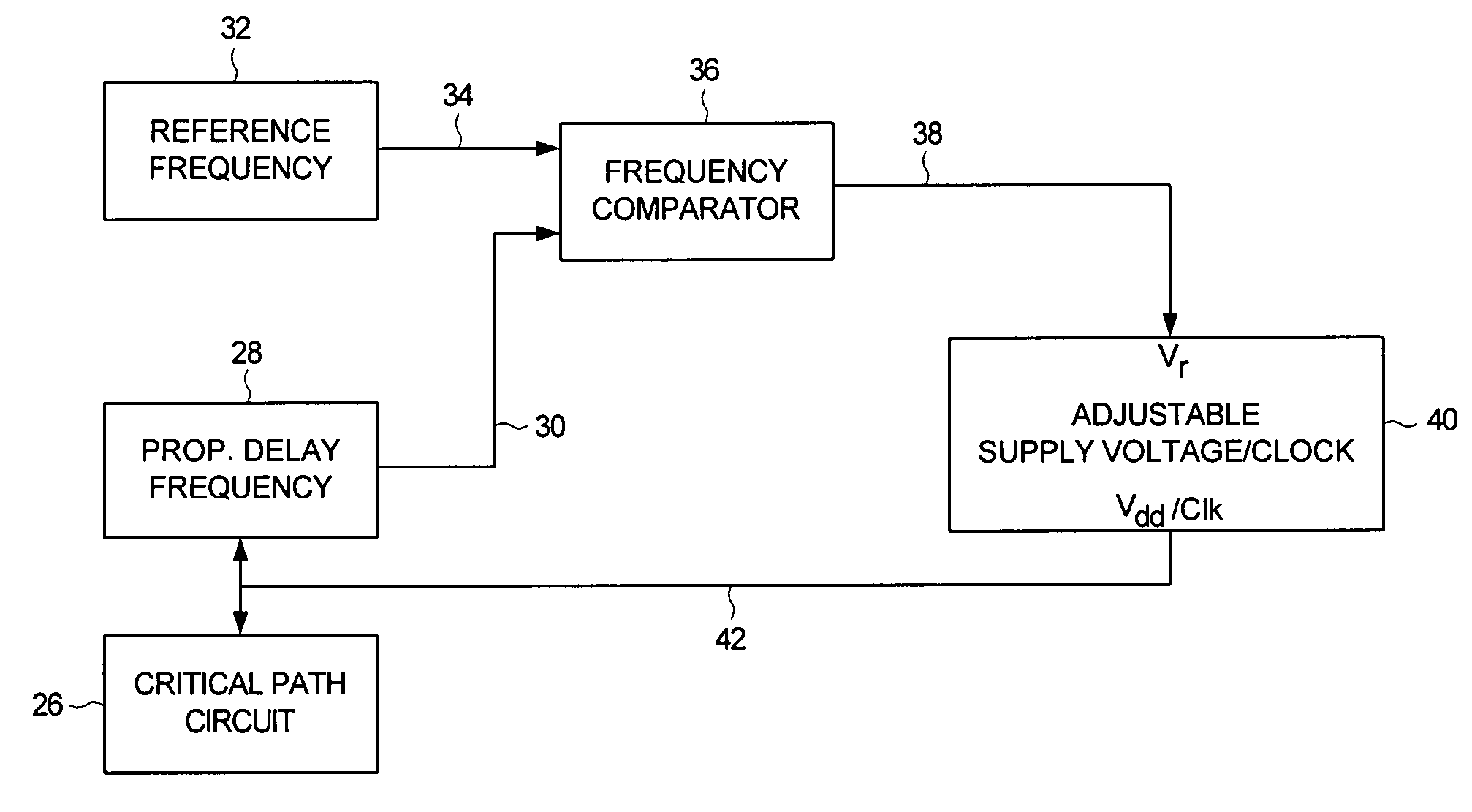

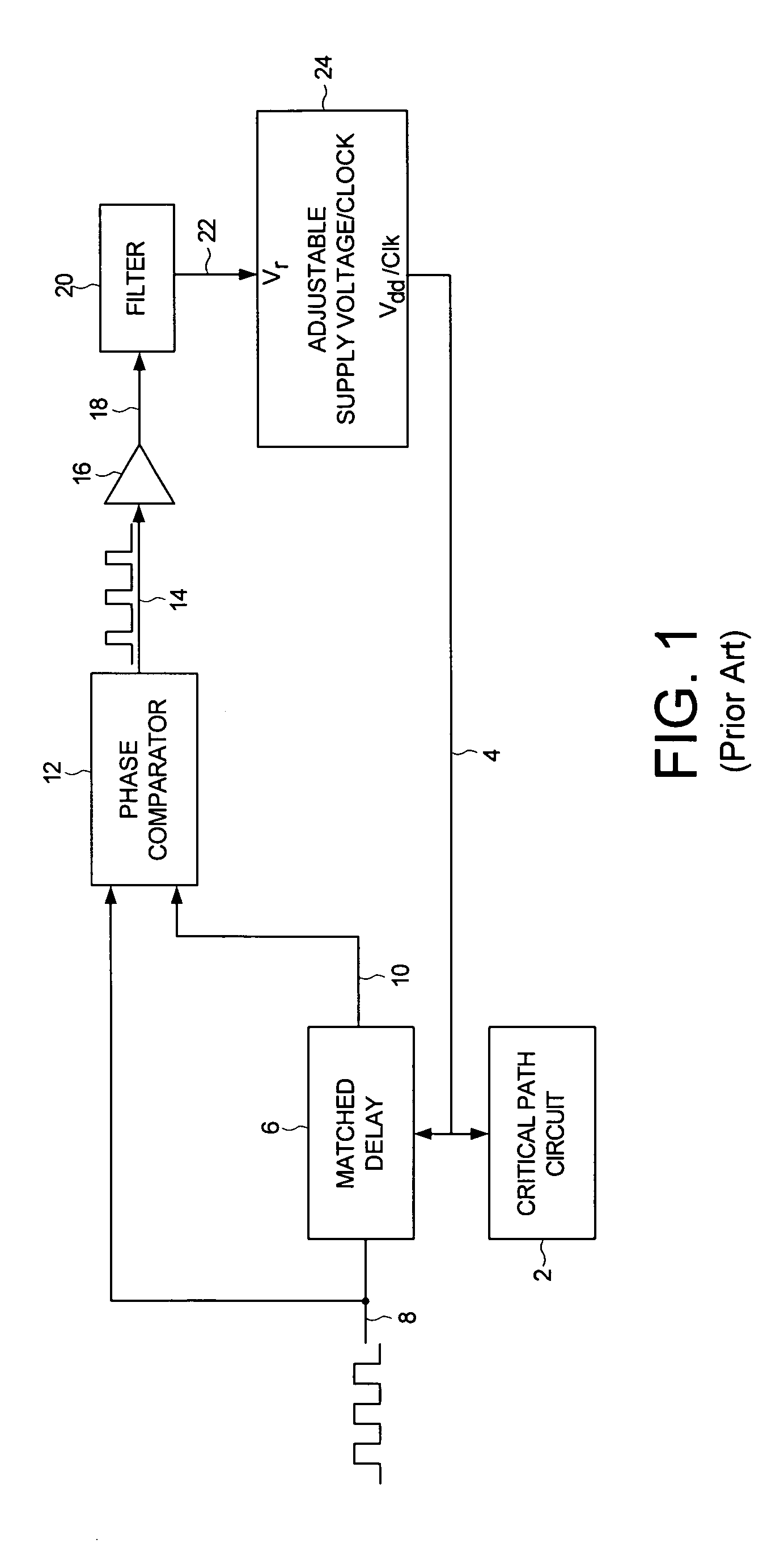

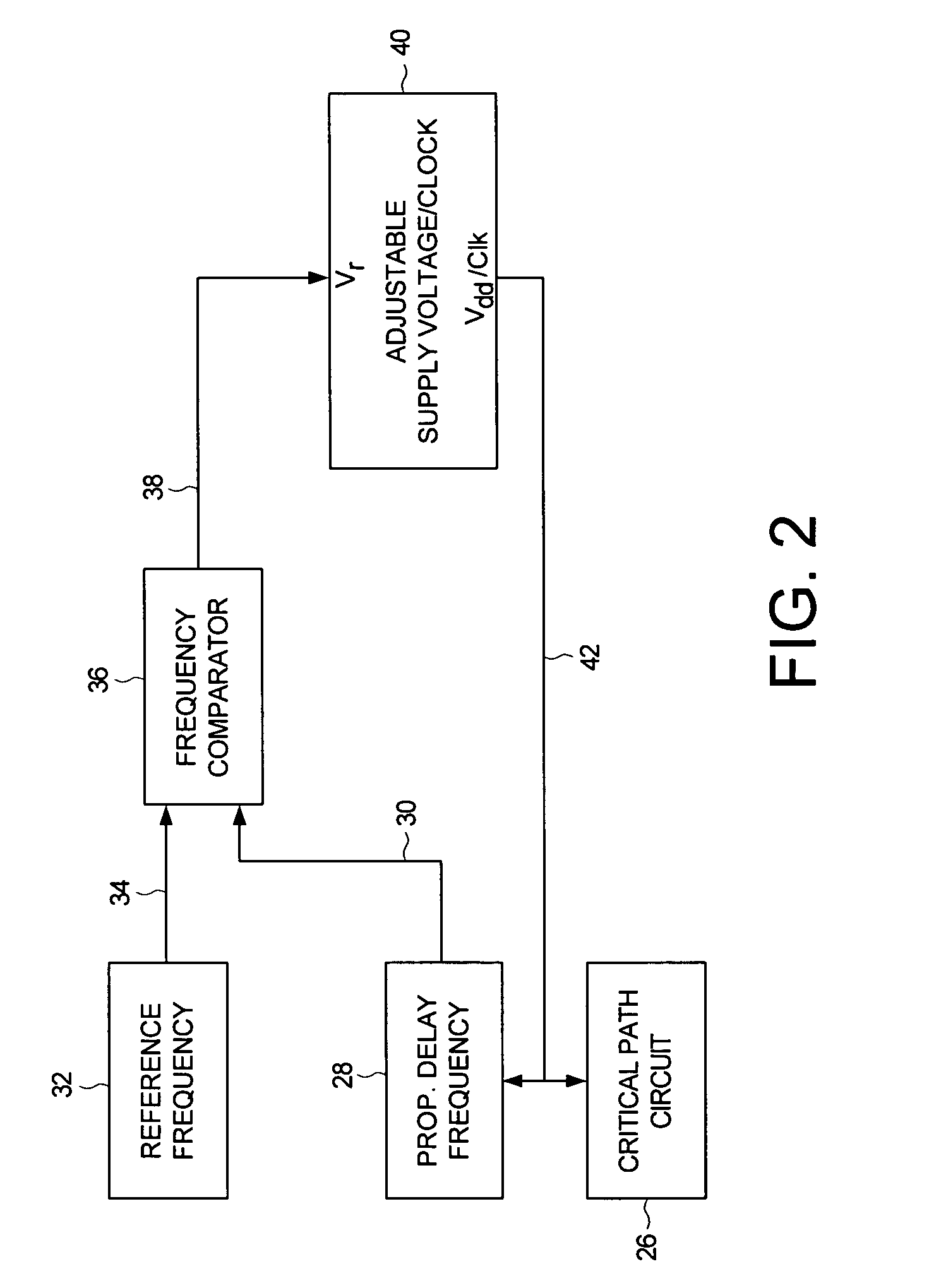

Adjusting power consumption of digital circuitry by generating frequency error representing error in propagation delay

A method and apparatus is disclosed for adjusting at least one of a supply voltage and a clocking frequency applied to digital circuitry of a computing device, wherein the digital circuitry comprises a critical path circuit. A propagation delay frequency representing a propagation delay of the critical path circuit is generated, and a frequency error signal is generated representing a difference between a reference frequency and the propagation delay frequency. At least one of the supply voltage and the clocking frequency is adjusted in response to the frequency error signal.

Owner:WESTERN DIGITAL TECH INC

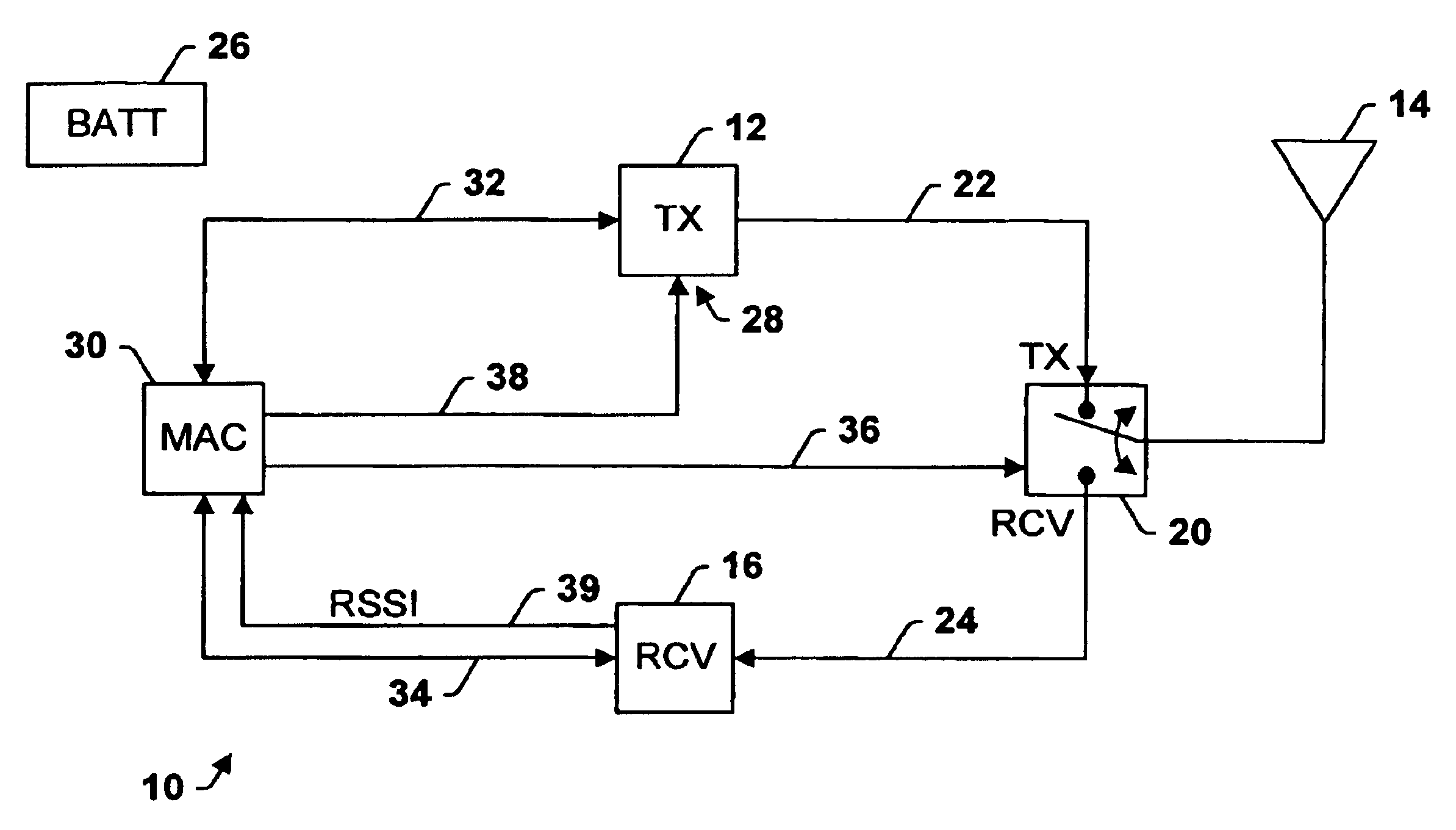

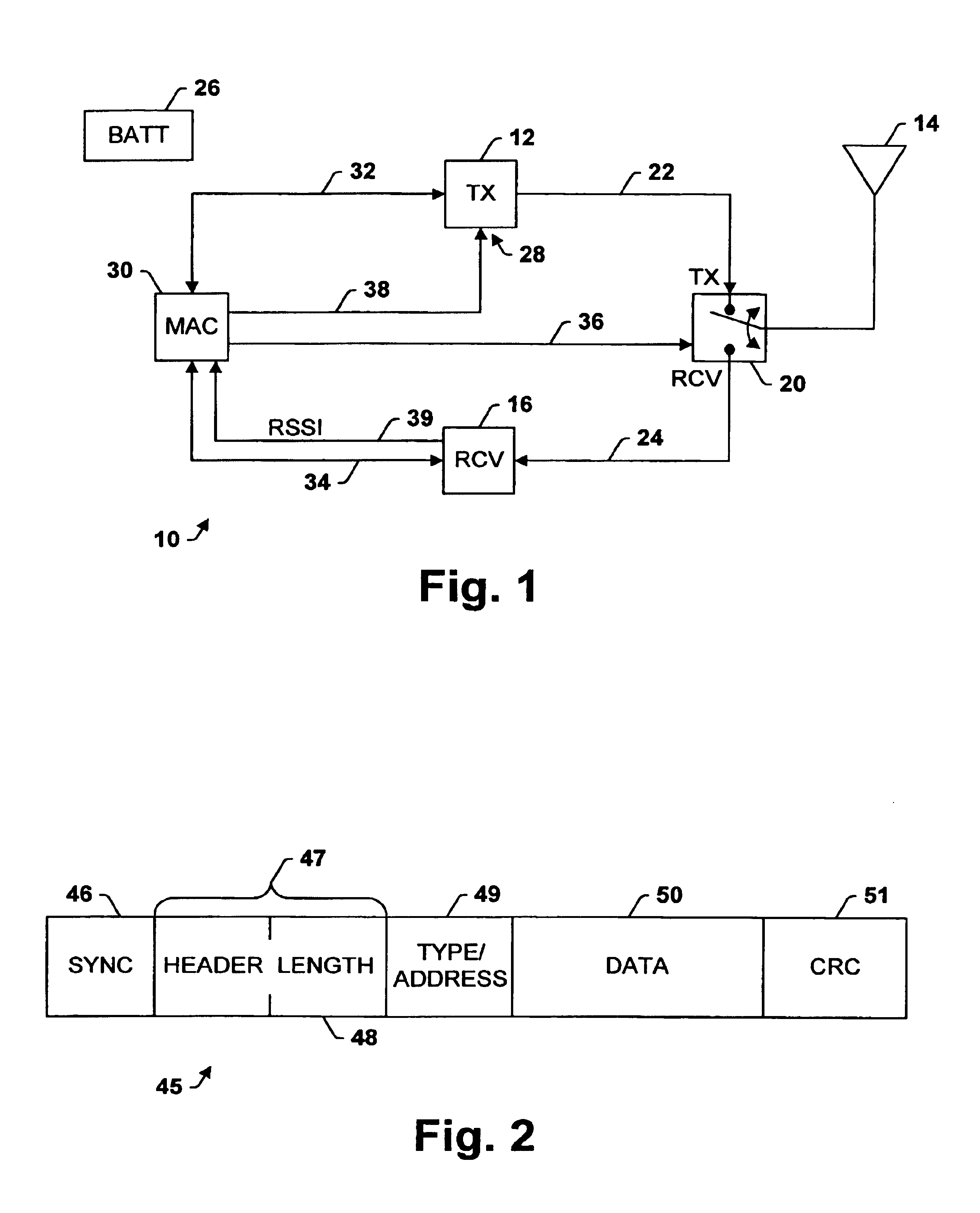

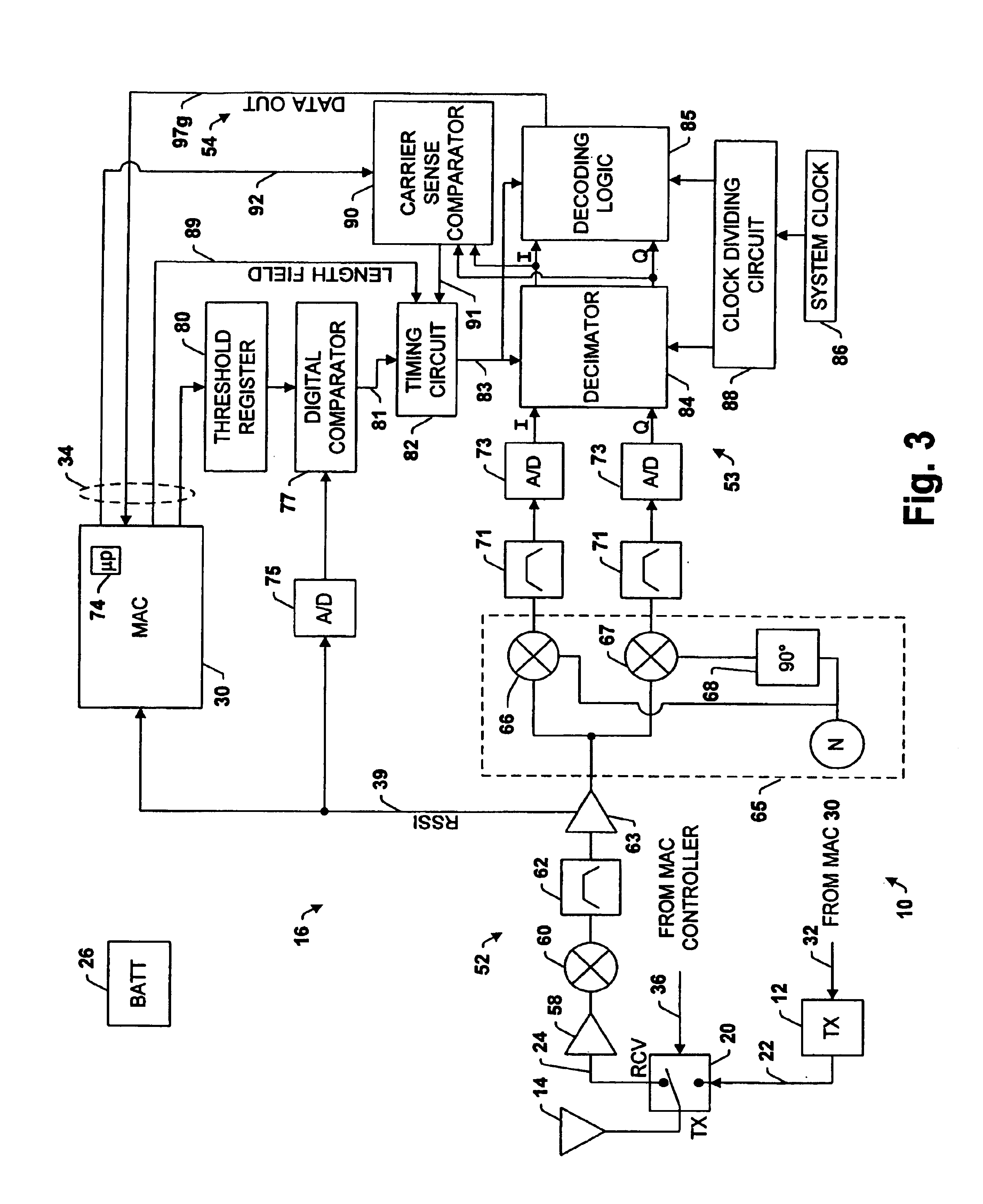

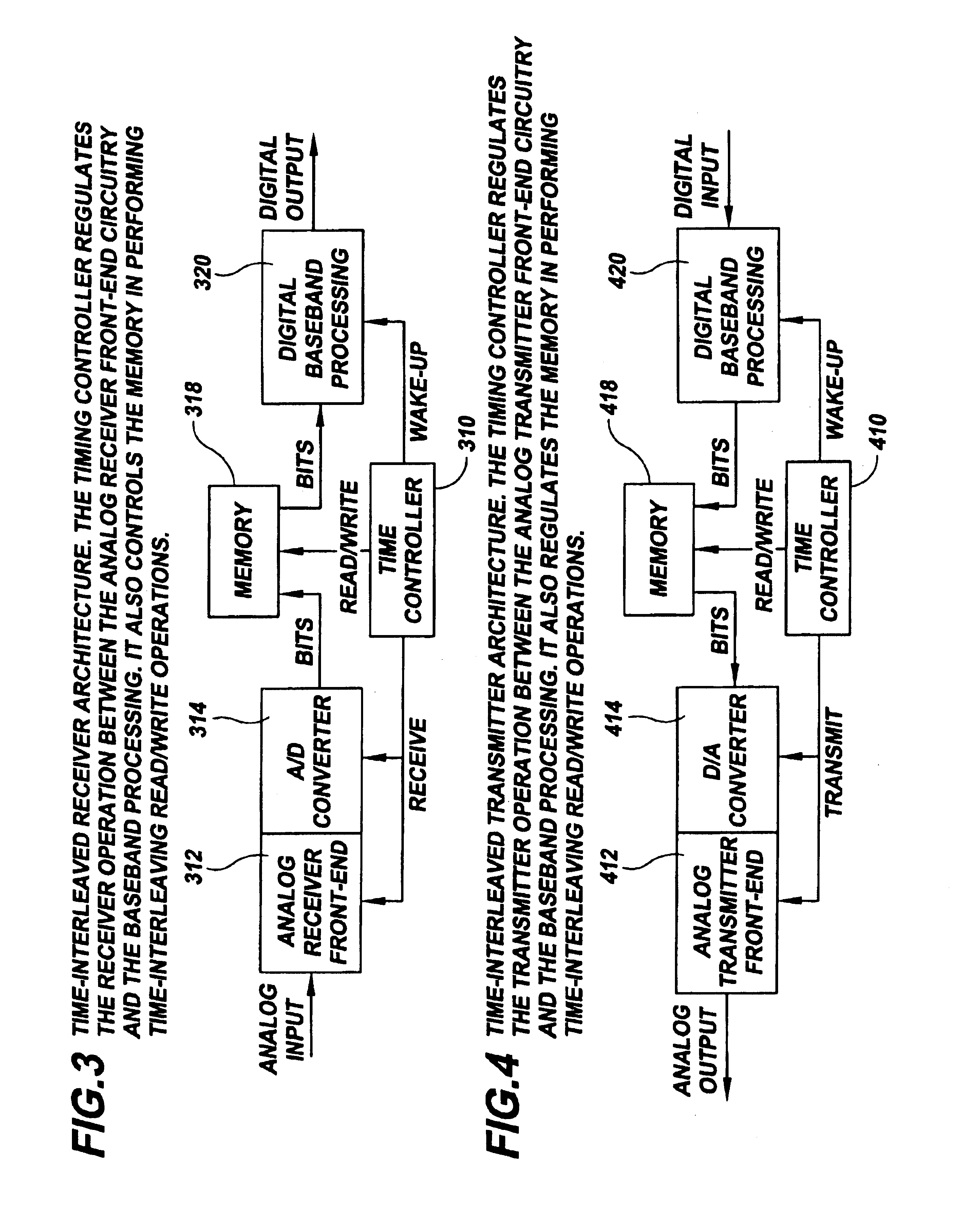

Transceiver control with sleep mode operation

InactiveUS6978149B1No delay exchangeHigh strengthEnergy efficient ICTPower managementTransceiverControl signal

A transceiver which keeps circuitry associated with a receiver in a powered down state during periods when a Received Signal Strength Indicator (RSSI) indicates that a signal being received is below a pre-determined threshold level, and which begins to power up the transmitter as soon as it is determined that a packet being received requires a response. The RSSI signal represents the strength of any signal current being received, and if the RSSI signal falls below a given threshold level, digital circuitry associated with the back-end circuitry of the receiver system is disabled. If the RSSI signal rises above the threshold level, the digital circuitry of the receiver is enabled. A control circuit within the transceiver processes the packet as it is received to determine whether the packet requires a response. If it is determined that a response is necessary, the control circuit provides a control signal to the transmitter to power up the transmitter from a sleep mode even before the entire packet has been received and processed. The control circuit then continues to process the remainder of the packet as it is received while the transmitter powers up from the sleep mode. In this manner, the transmitter will become stabilized much earlier. Accordingly, the transceiver is able to respond more quickly than conventional devices and is thus able to increase response times and overall data exchange rates. Moreover, battery power of the transceiver is utilized more efficiently compared to devices which must continuously maintain the receiver and transmitter in fully powered modes.

Owner:TELXON INC

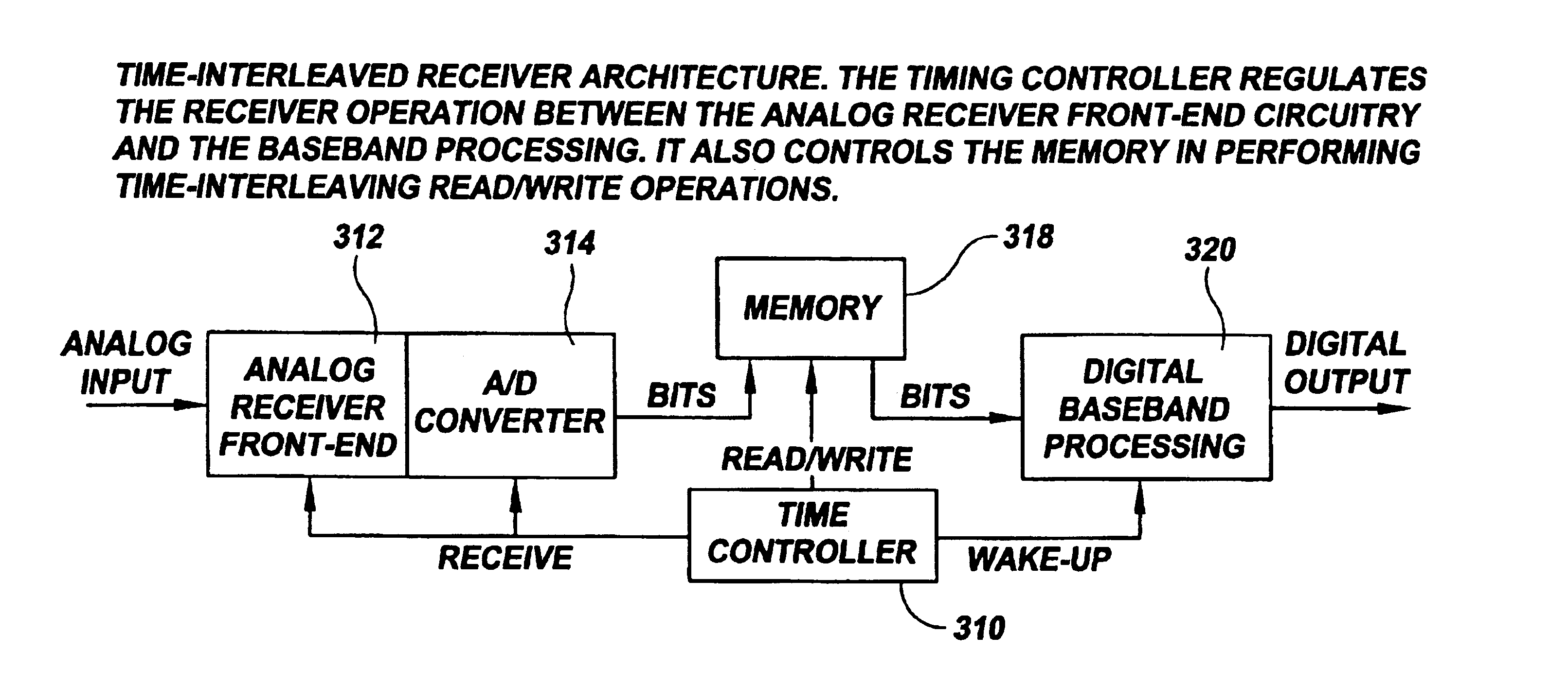

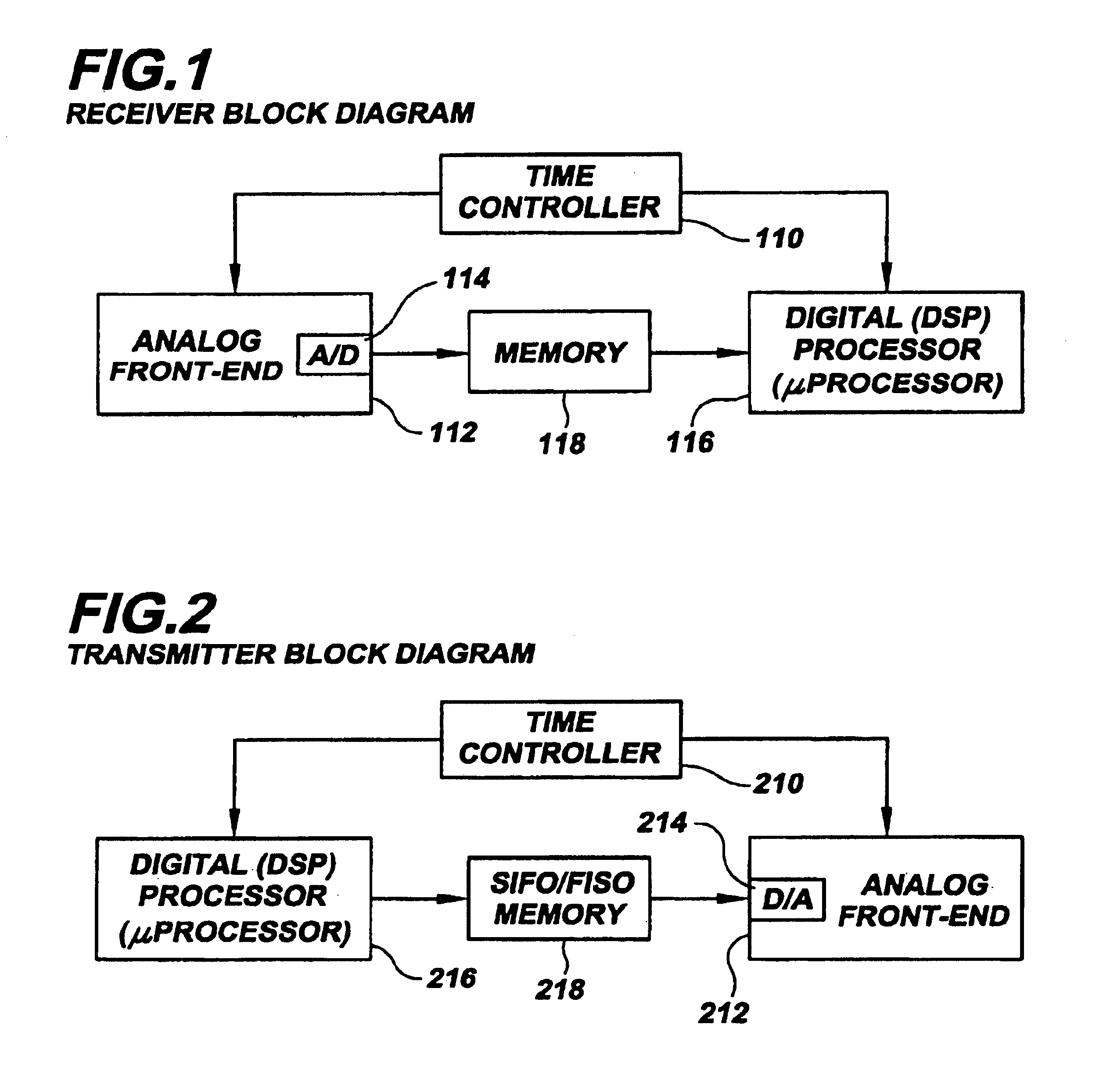

Noise-reducing arrangement and method for signal processing

InactiveUS6963626B1Effective noise reductionImprove noiseError preventionLine-faulsts/interference reductionCommunications systemDatapath

A communication system uses analog and digital circuits along the same data path in a manner that permits the analog circuitry to avoid adverse affects caused by the digital circuitry. Consistent with one embodiment directed to a signal processing system that detects faint incoming signals, the analog and digital circuits are implemented on a single piece of silicon. In such signal processing systems, noise generated by digital processing blocks can degrade the performance of sensitive analog portions. The effective noise is reduced by causing the analog and digital portions of the system to function during separate time intervals. The noise-generating portions of the system may then be turned off during a first data-communication interval while the analog block operates. The data acquired during this period is stored for subsequent processing by the digital portion during a second shorter data-communication interval. Other aspects are applicable to reception arrangements in which part of the incoming signal may be disregarded without significant degradation in performance of the rest of the system, and other aspects are directed to transmission arrangements in which the inverse of the above reception arrangement is used.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

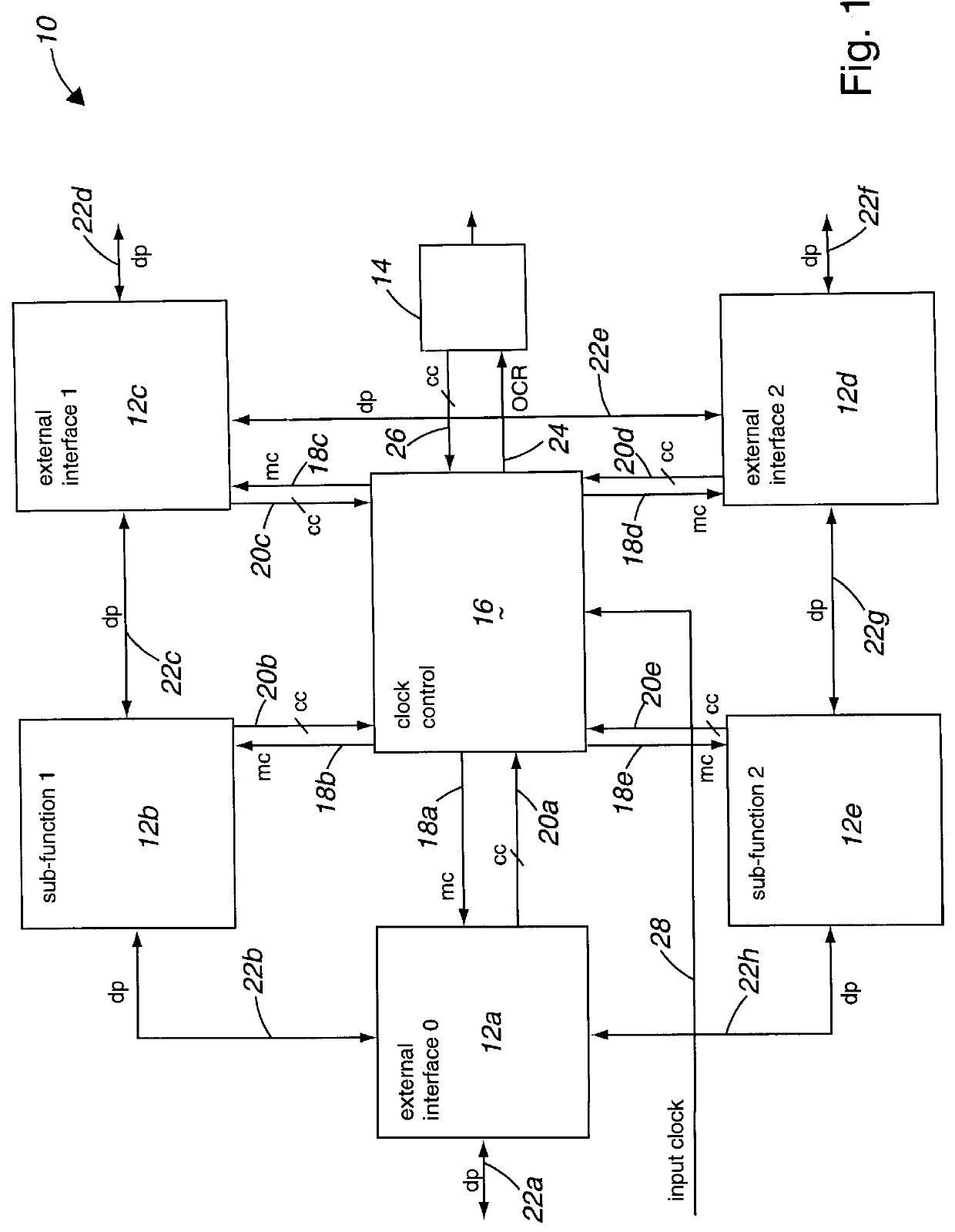

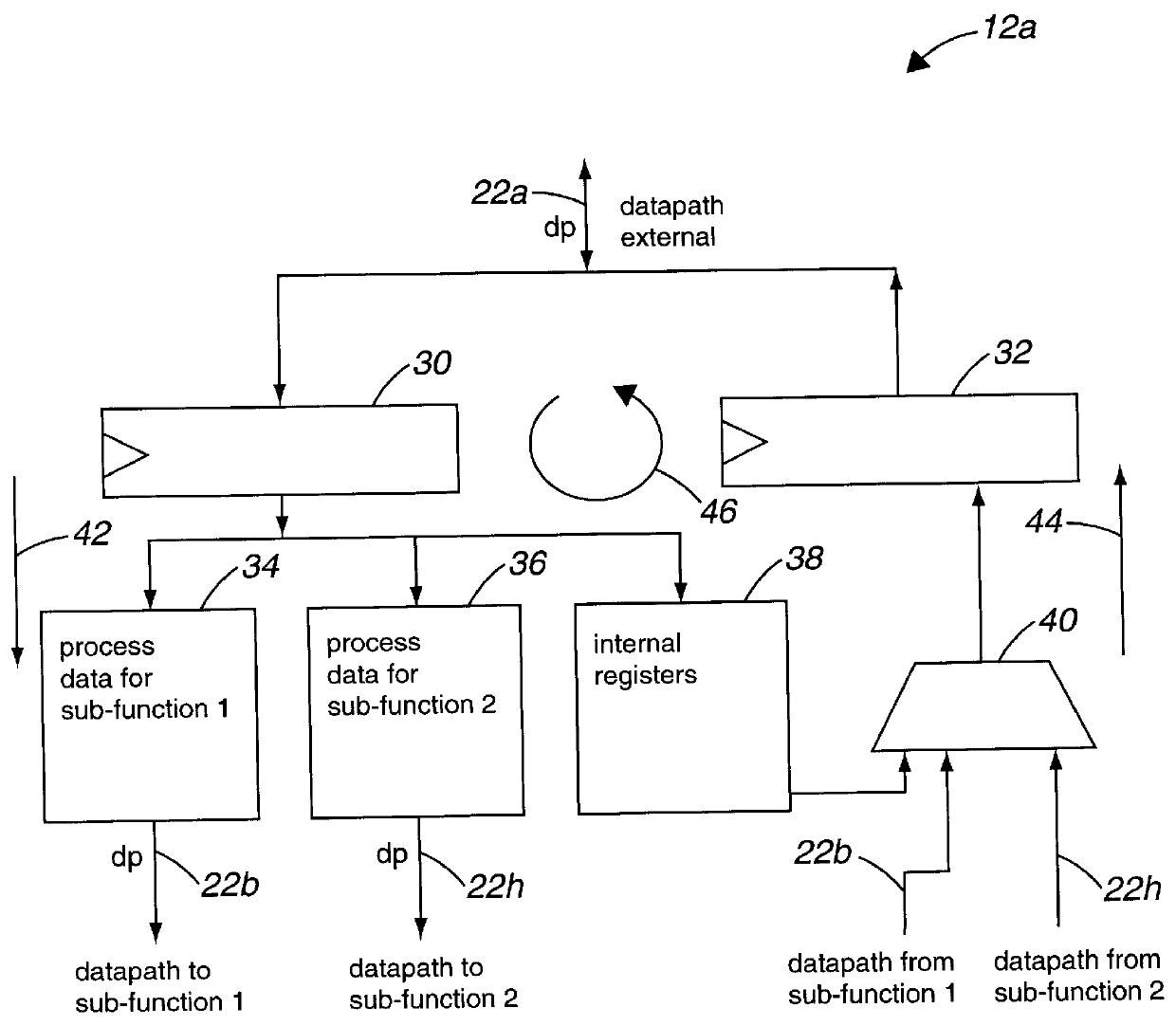

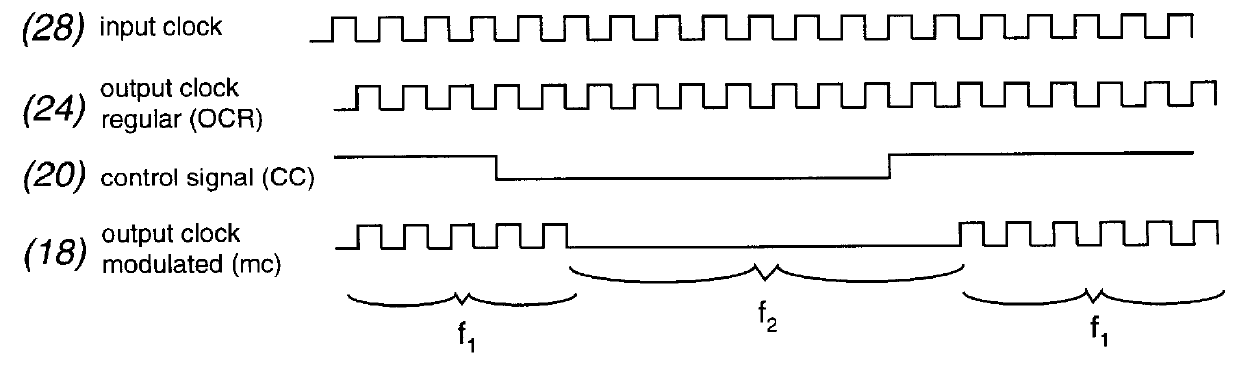

Method and apparatus for reducing power consumption in digital electronic circuits

InactiveUSRE36839E1Reduce power consumptionMinimize powerEnergy efficient ICTSolid-state devicesPower controllerData stream

An integrated circuit with power conservation includes a number of functional blocks, each of which includes a digital circuitry and at least one output control line, and a power controller coupled to the control lines. The output control lines develop clock control signals based upon a functional block's knowledge of the direction of data flow. The power controller the reduces power by deactivating functional blocks that are not needed as indicated by the clock control signals. More specifically, a system with power conservation includes a number of functional blocks capable of processing data, each of the functional blocks including a modulated clock input and N+1 clock control lines which reflect the direction of data flow, where N is a number of neighbors of a particular functional block, and a clock controller having an input clock, the clock controller being coupled to the modulated clock inputs and the clock control lines of the functional blocks. The clock controller is operative to modulate the input clock in accordance with the signals on the clock control lines to provide modulated clocks to each of the plurality of functional blocks. A method for reducing power consumption includes the steps of: a) receiving control signals from a number of functional blocks; b) selectively deactivating a particular functional block upon a request from that functional block or from another functional block; and c) activating the particular functional block upon a request from another functional block.

Owner:CONVERSANT INTPROP MANAGEMENT INC

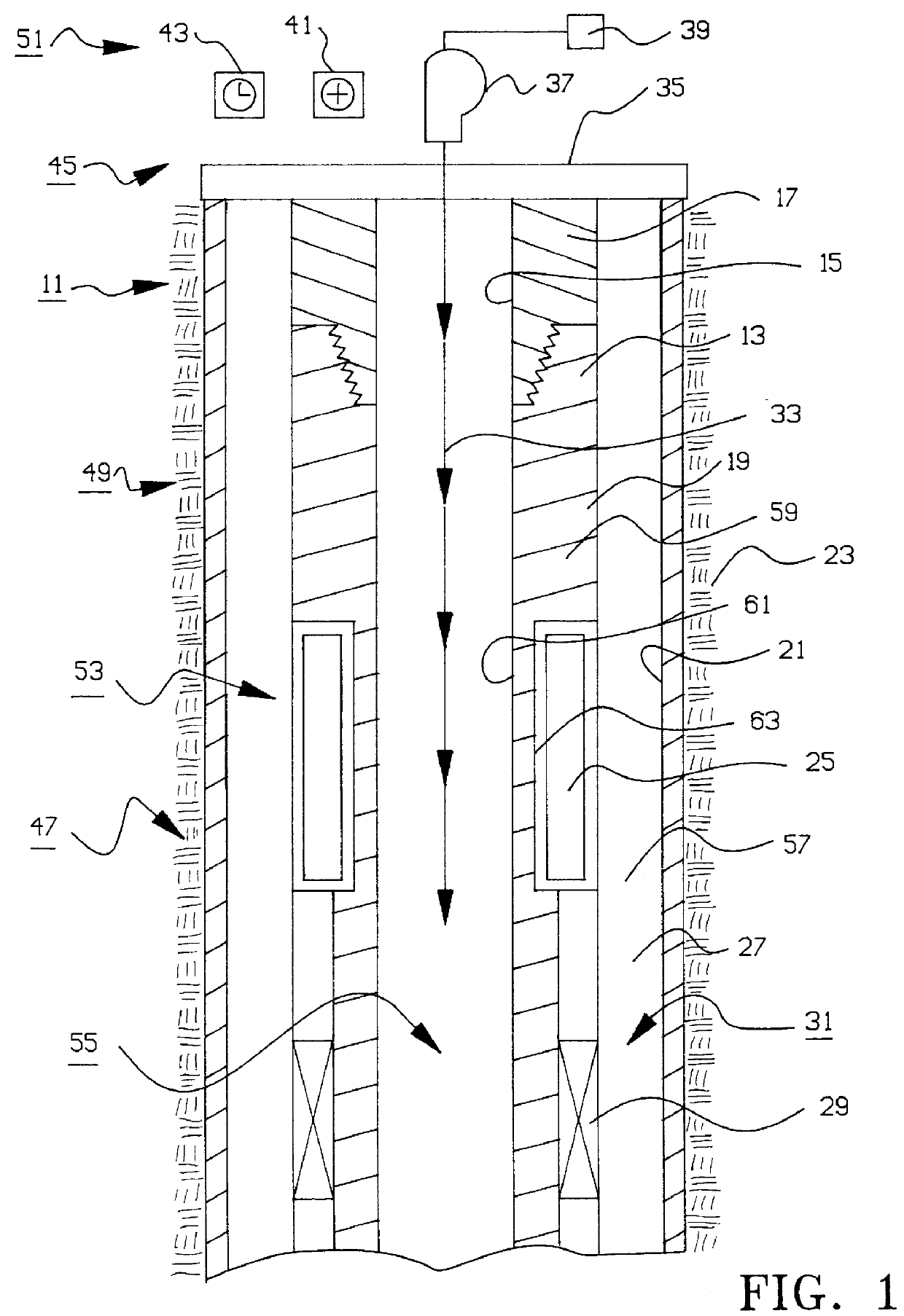

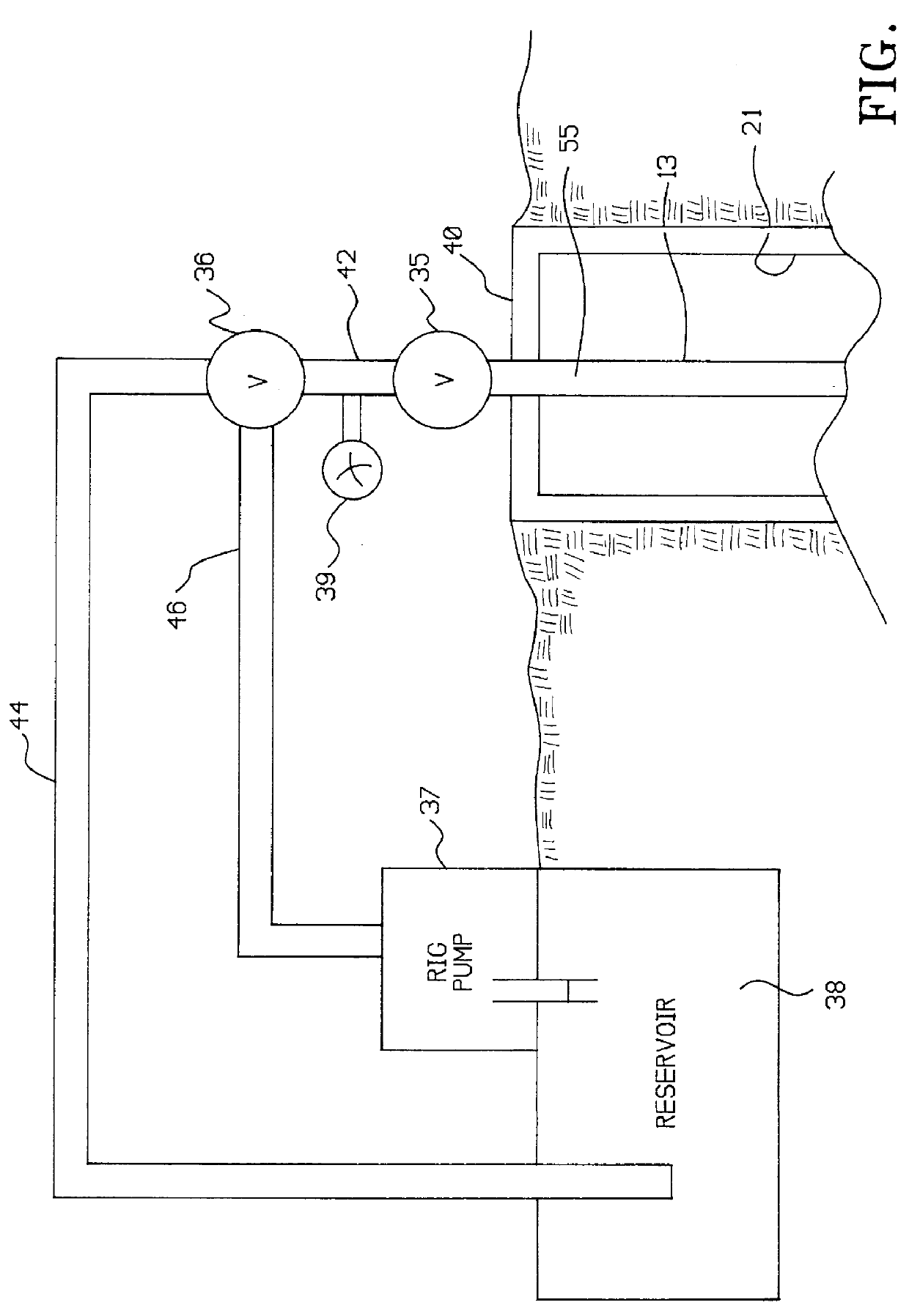

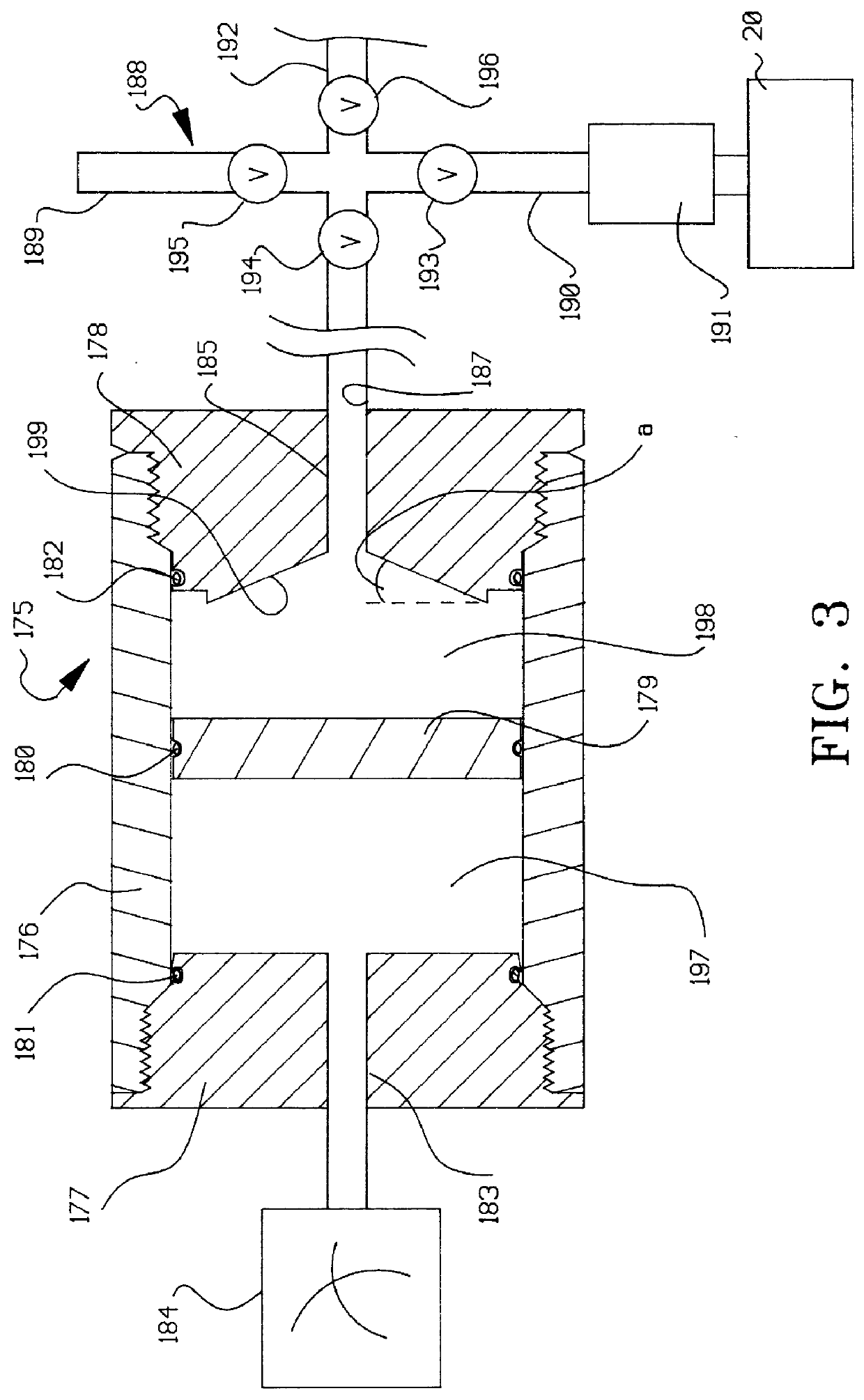

Method and apparatus for remote control of wellbore end devices

A wellbore remote control system is disclosed which includes (1) a transmission apparatus for generating at least one acoustic transmission having a particular transmission frequency, (2) a reception apparatus which includes an electronic circuit (preferably digital) which detects and identifies the acoustic transmissions, and which provides an actuation signal to an electrically-actuated wellbore tool if a match is detected.

Owner:BAKER HUGHES INC

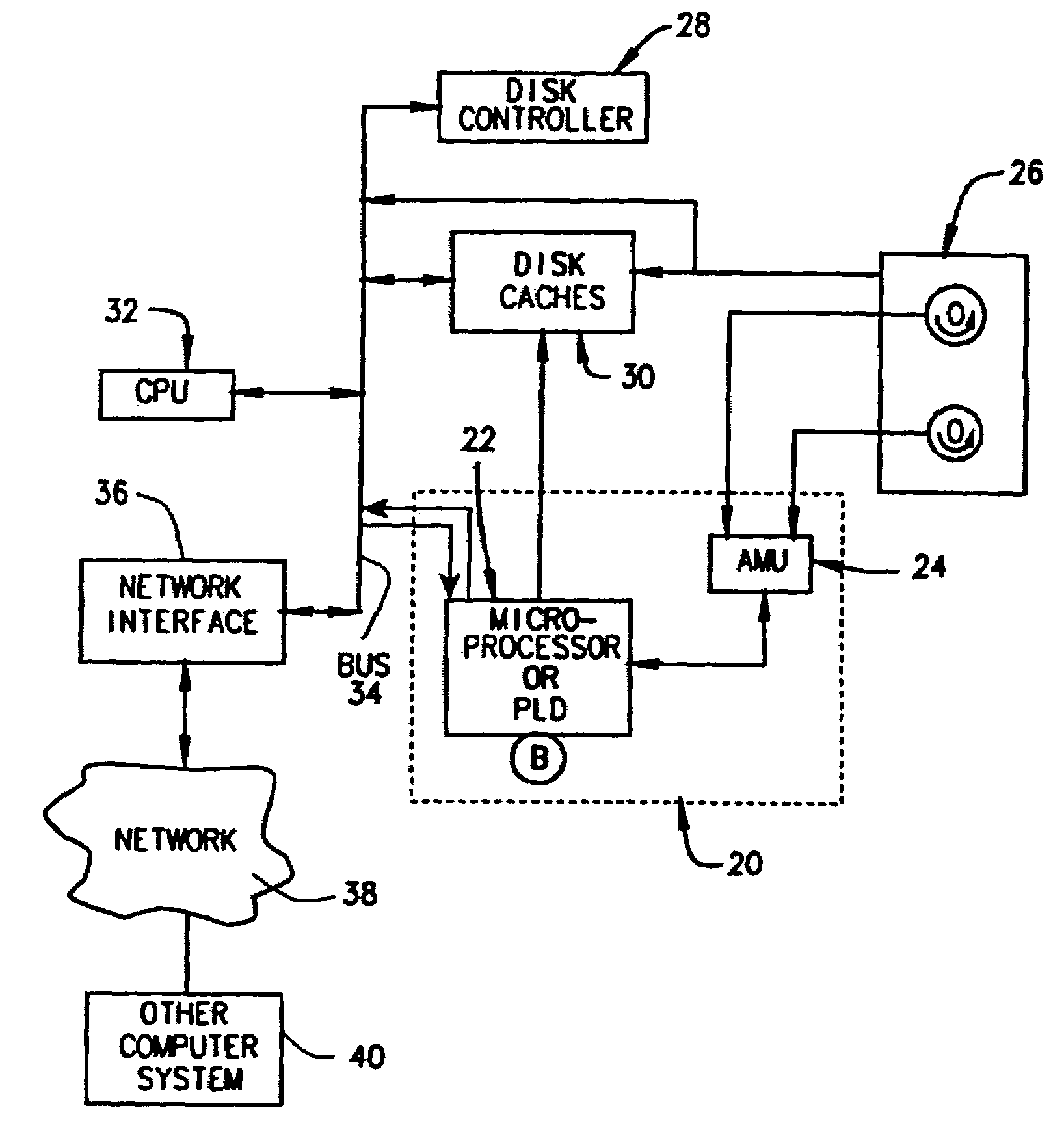

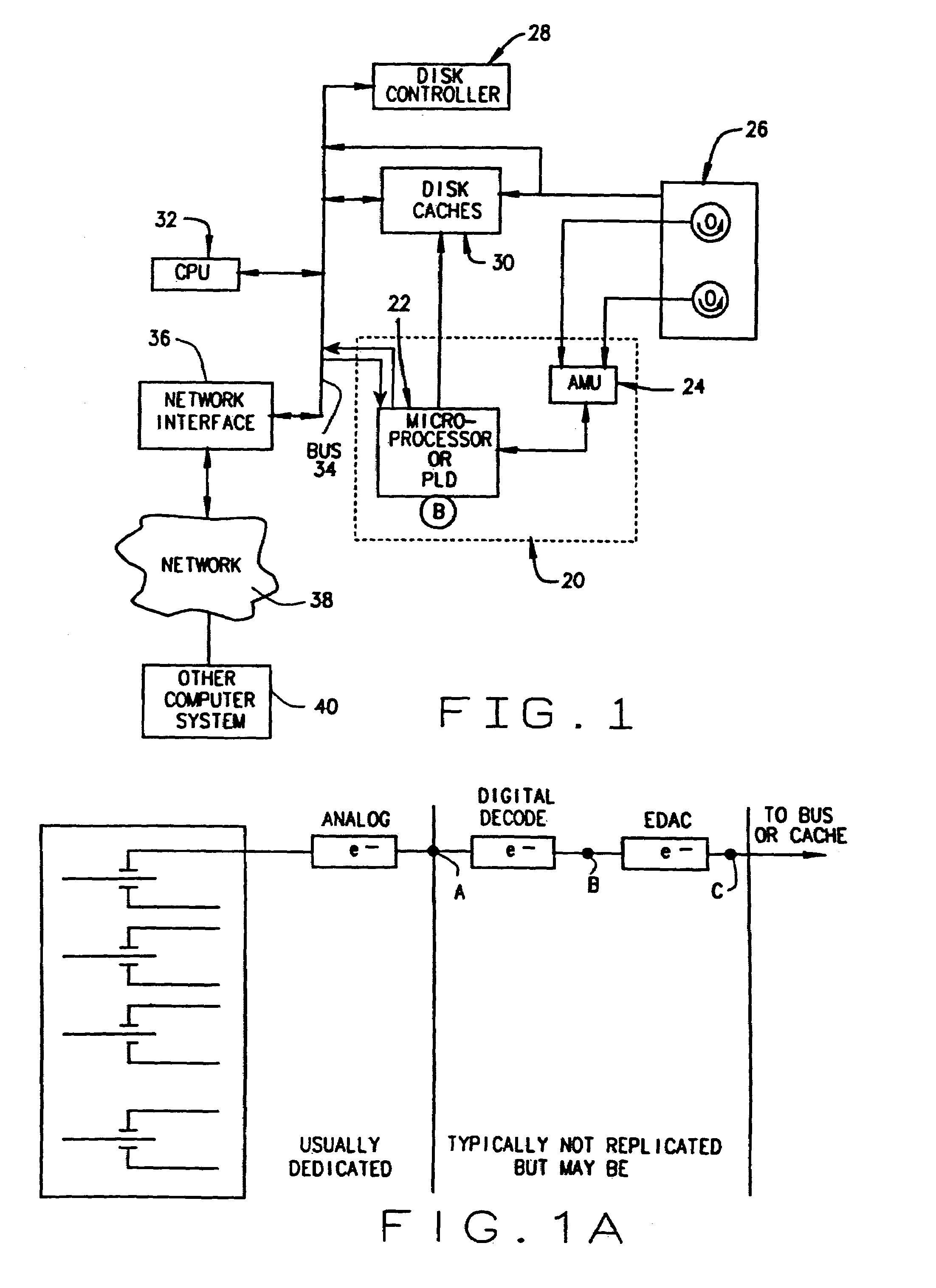

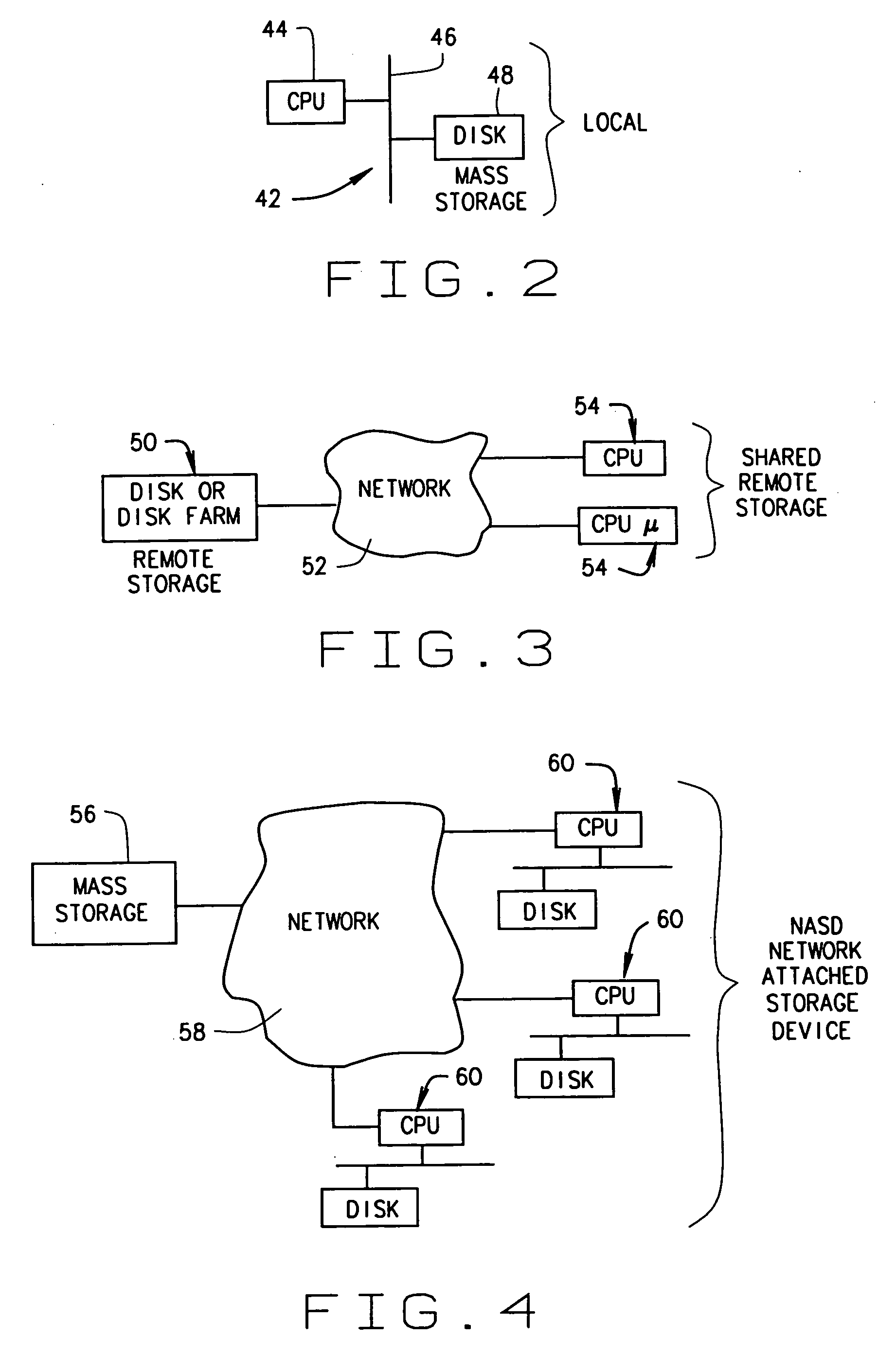

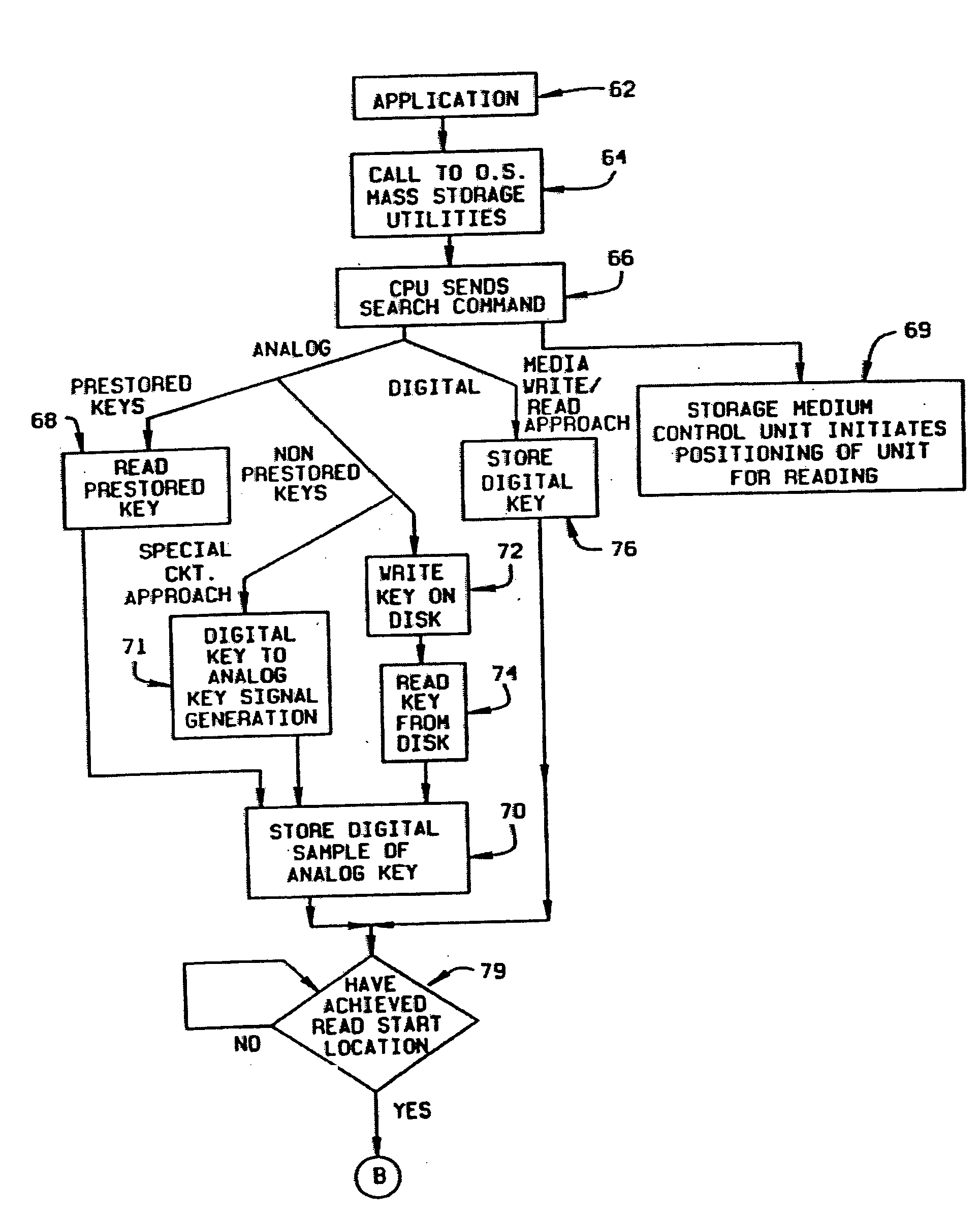

Associative database scanning and information retrieval

InactiveUS7181437B2Threshold may be loweredRaise the importanceData processing applicationsInput/output to record carriersMass storageExact match

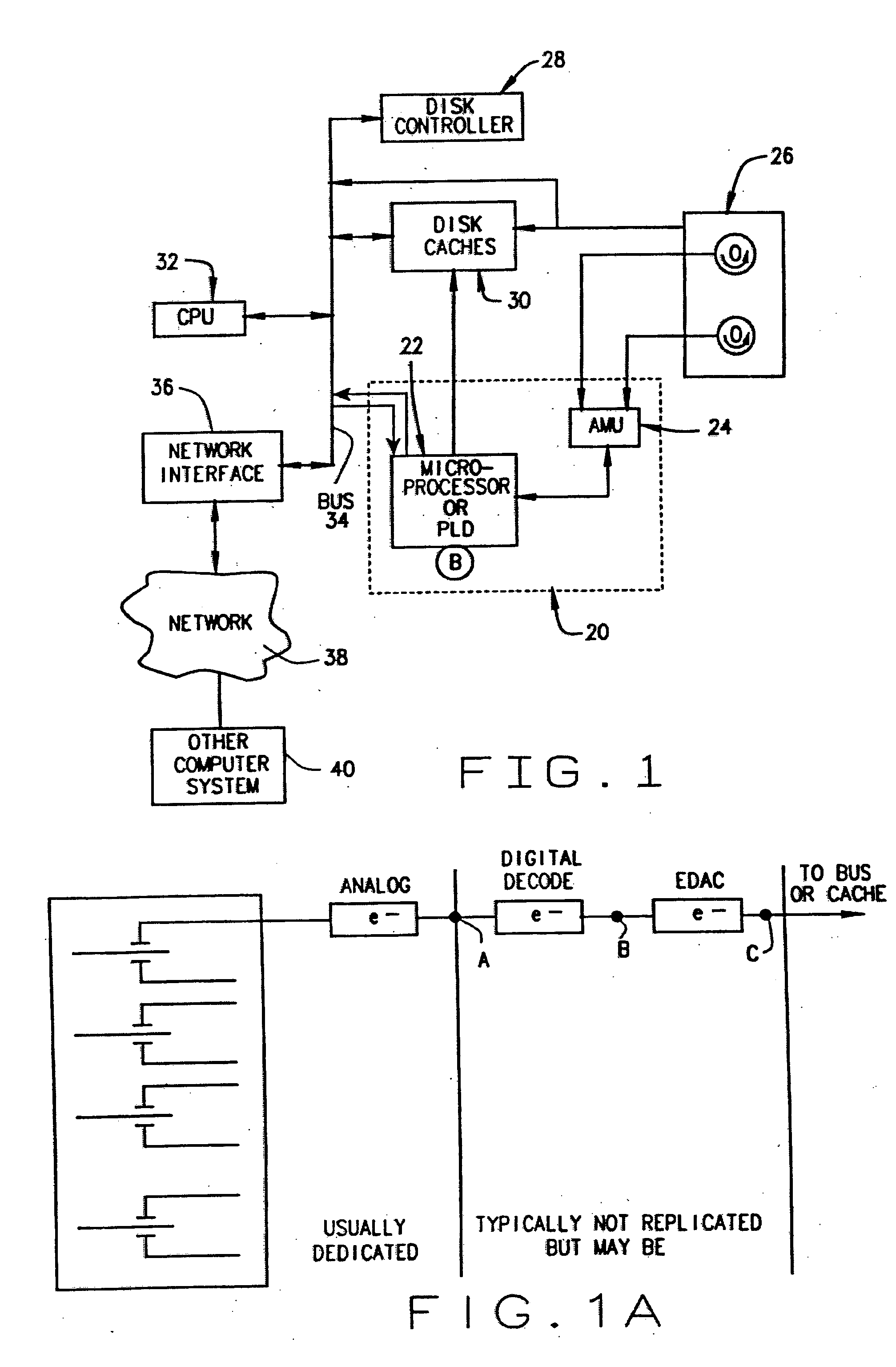

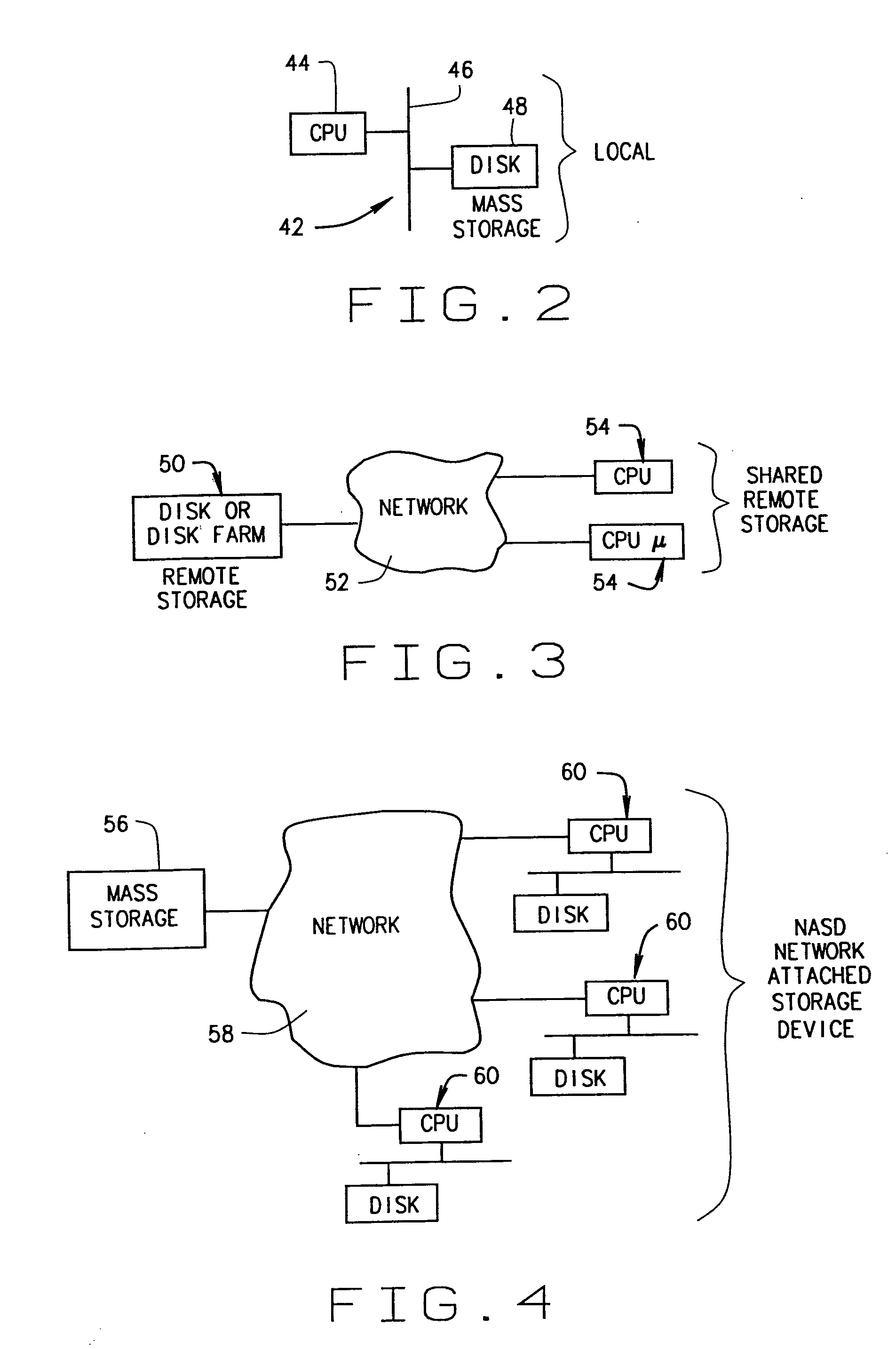

A method and device are disclosed for an associative and approximate, analog or digital scanning of databases that allows for the asynchronous accessing of data from a mass storage medium. The invention includes providing dedicated analog and digital circuitry and decision logic at the mass storage medium level for determining a key identifying the data of interest, continuously comparing the key to a signal generated from a reading of the data from the mass storage medium with an approximate or exact matching circuit to determine a pattern match, determining a correlation value between the key and the data as it is read in a continuous fashion, and determining a match based upon a preselected threshold value for the correlation value. The pattern matching technique eliminates any need to compare data based on its intrinsic structure or value, and instead is based on an analog or digital pattern. The key and data may be either analog or digital. This device and method may be provided as part of a stand-alone computer system, embodied in a network attached storage device, or can otherwise be provided as part of a computer LAN or WAN.

Owner:IP RESERVOIR

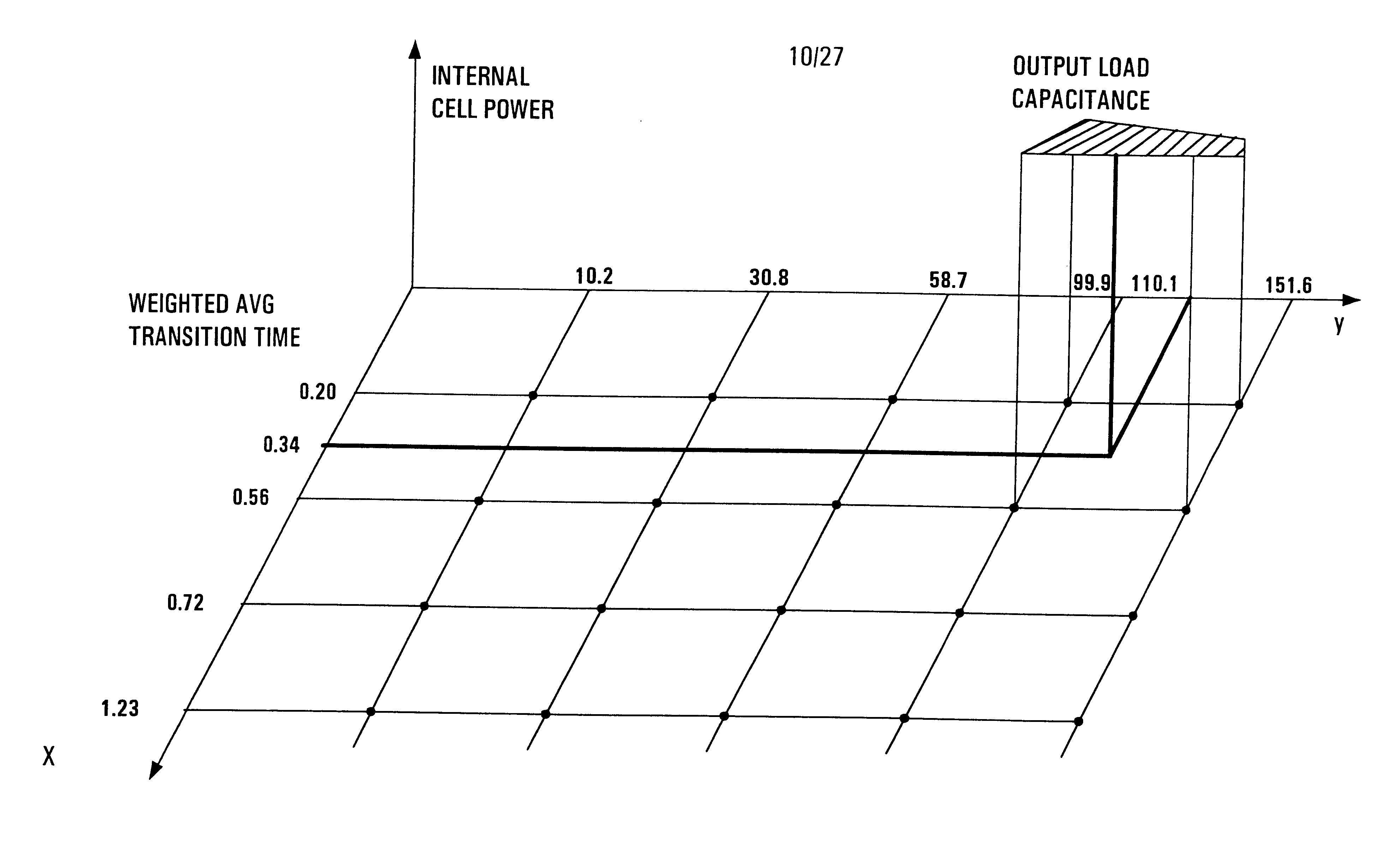

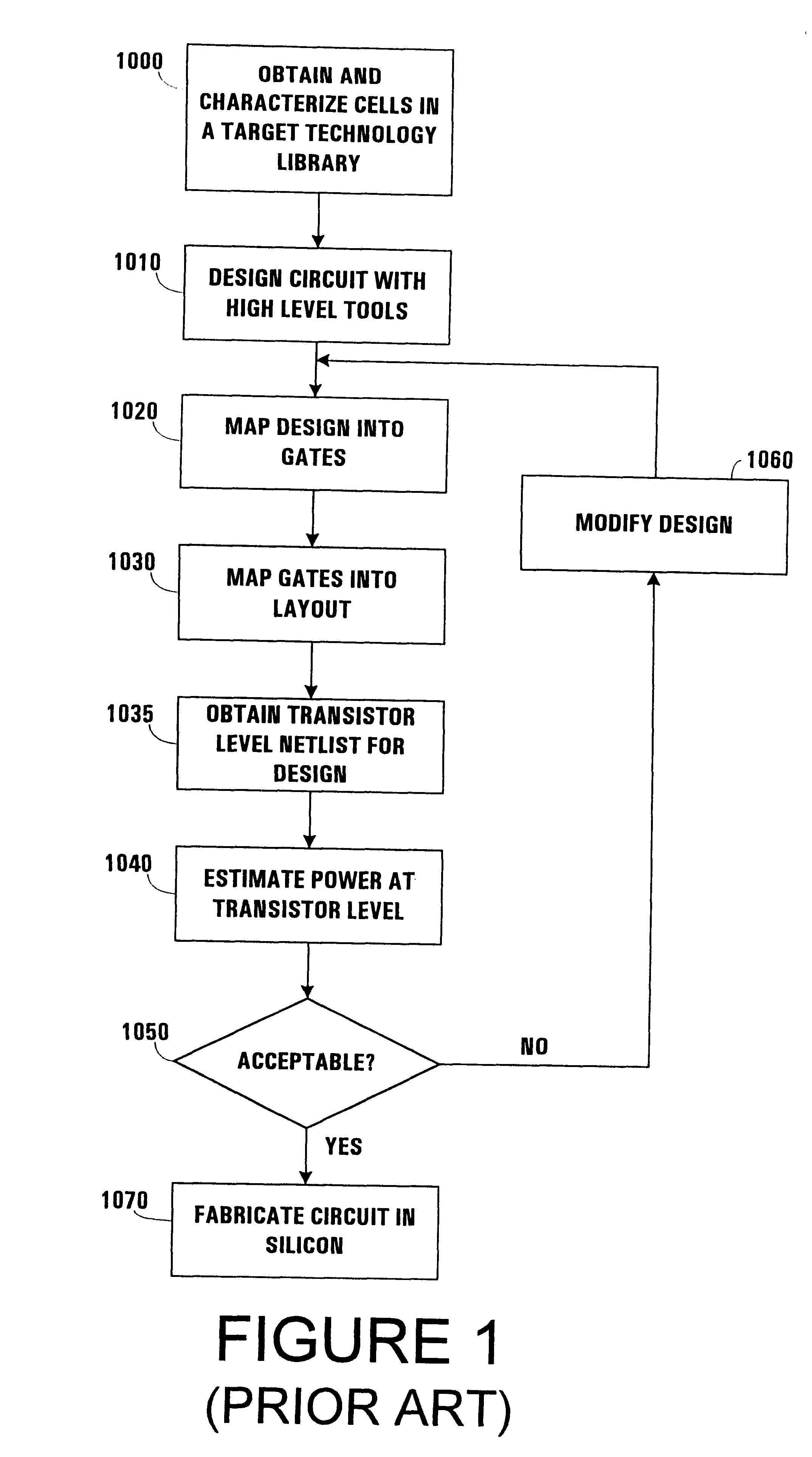

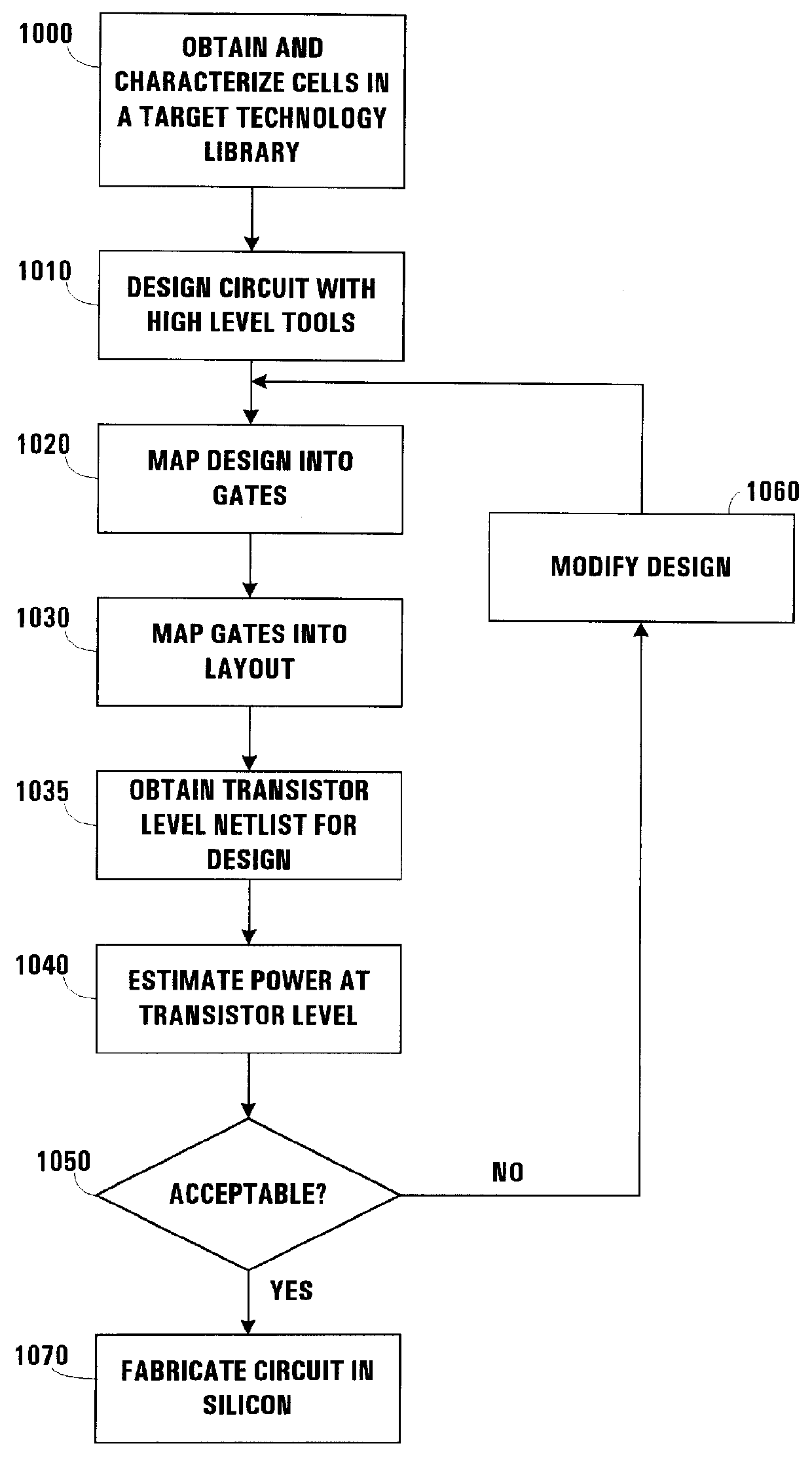

Method and apparatus for estimating internal power consumption of an electronic circuit represented as netlist

InactiveUS6345379B1Improve accuracyEasy to writeCAD circuit designSpecial data processing applicationsTransition timeNetlist

This is a method of quickly computing the power dissipated by a digital circuit using information available at the gate library level. It estimates the short-circuit power by modeling the energy dissipated by the cell per input transition as a function of the transition time or edge rate, and multiplying that value by the number of transitions per second for that input.

Owner:SYNOPSYS INC

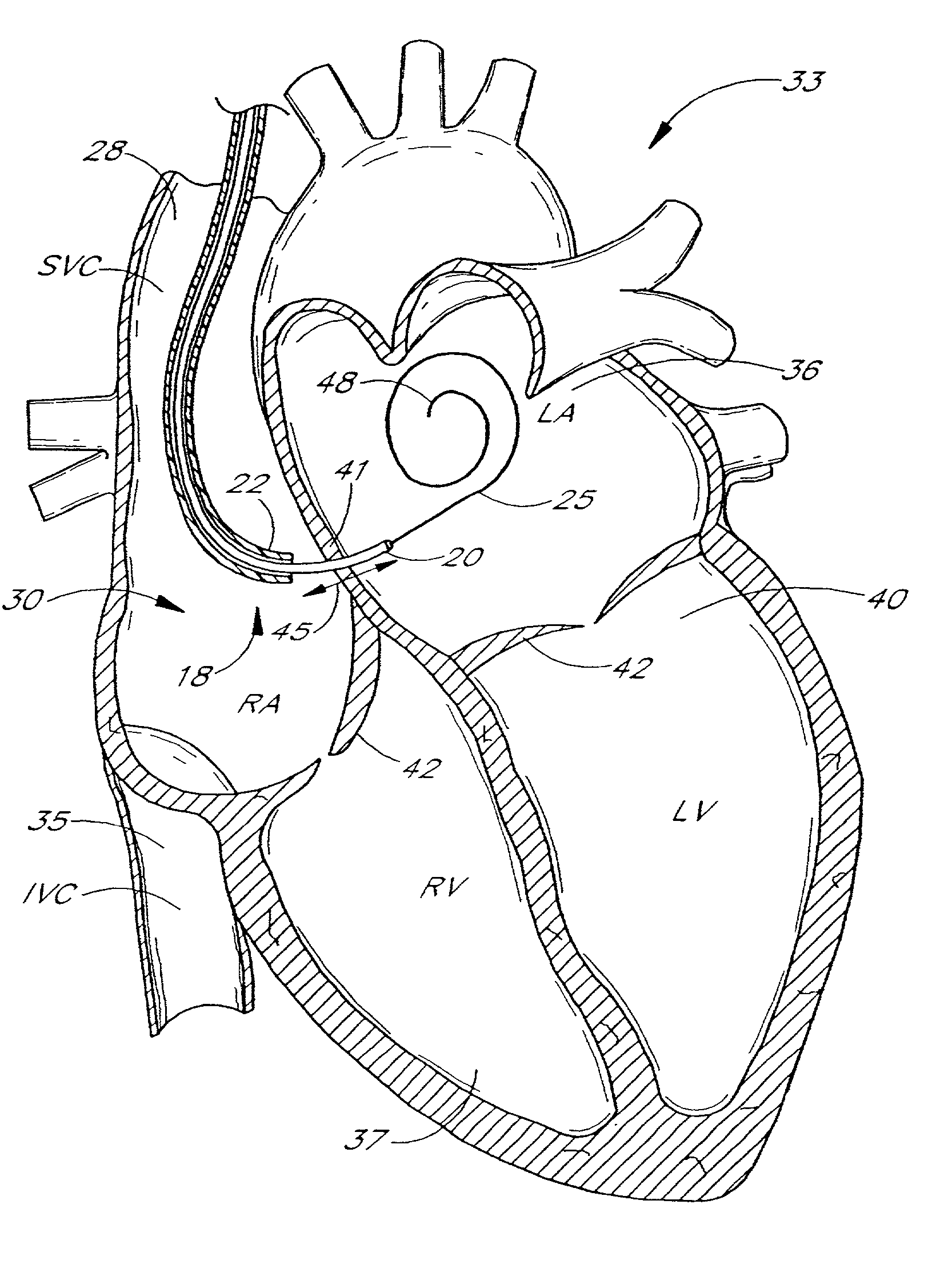

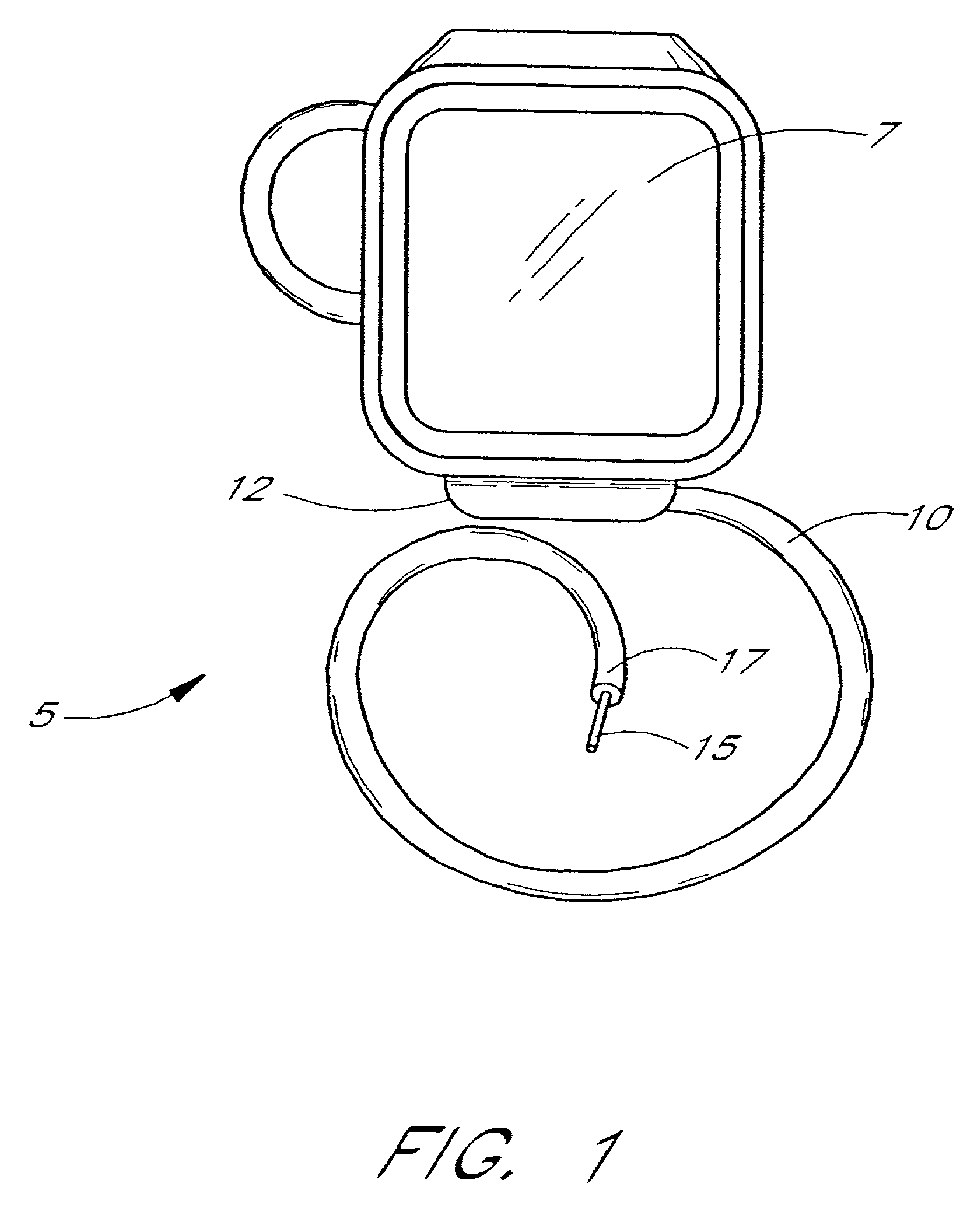

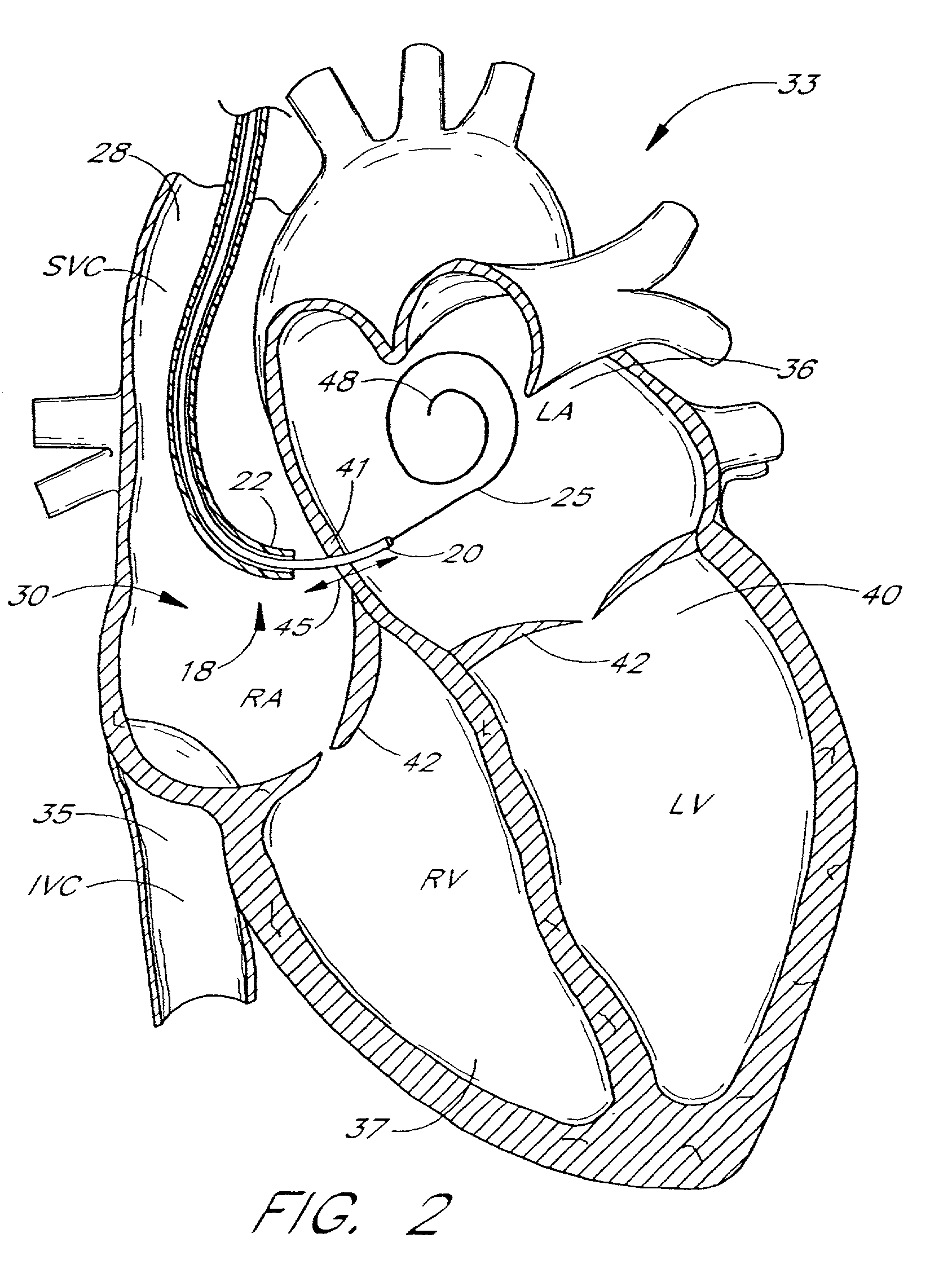

Systems and methods for detecting, diagnosing and treating congestive heart failure

The invention provides improved apparatus and methods for treating congestive heart failure in a medical patient. The apparatus includes a pressure transducer permanently implantable within the left atrium of the patient's heart and operable to generate electrical signals indicative of fluid pressures within the patient's left atrium. The pressure transducer is connected to a flexible electrical lead, which is connected in turn to electrical circuitry, which in the preferred embodiment includes digital circuitry for processing electrical signals. The electrical circuitry processes the electrical signals from the pressure transducer and, based at least in part on those signals, generates a signal that indicates a desired therapeutic treatment for treating the patient's condition. That signal is then communicated to the patient via a patient signaling device, following which the patient administers to him or herself the prescribed therapeutic treatment indicated by the signal.

Owner:CEDARS SINAI MEDICAL CENT

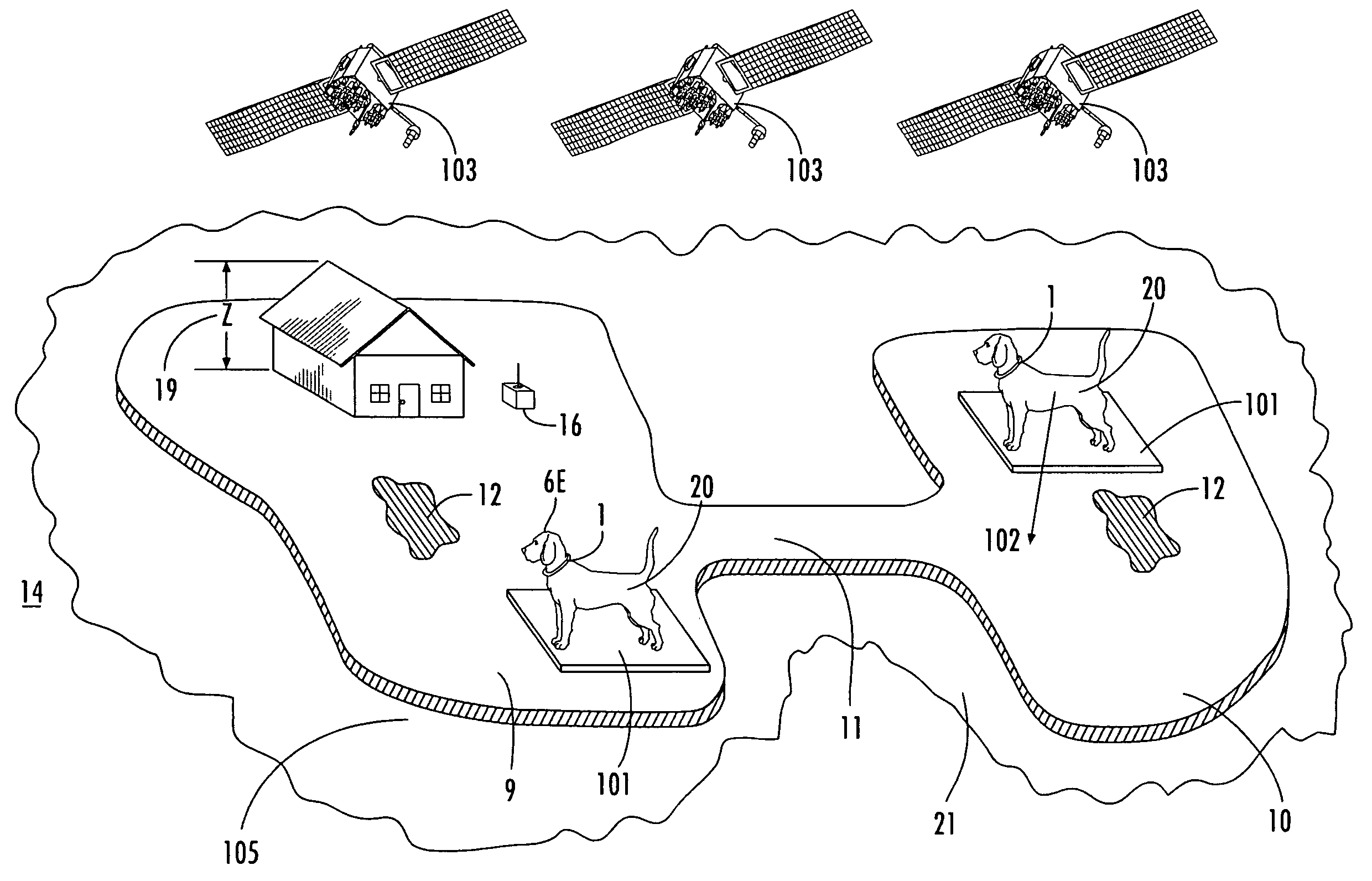

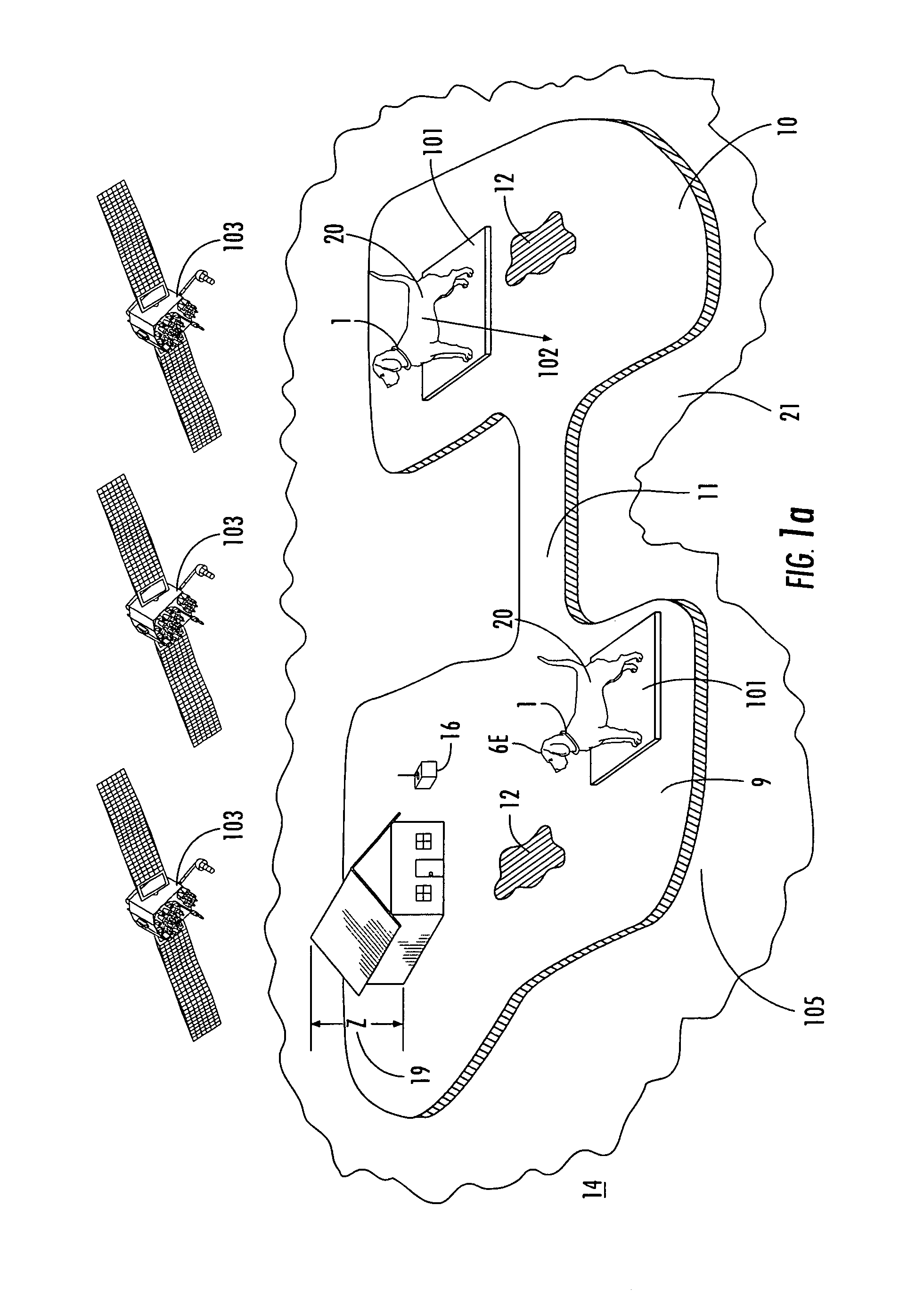

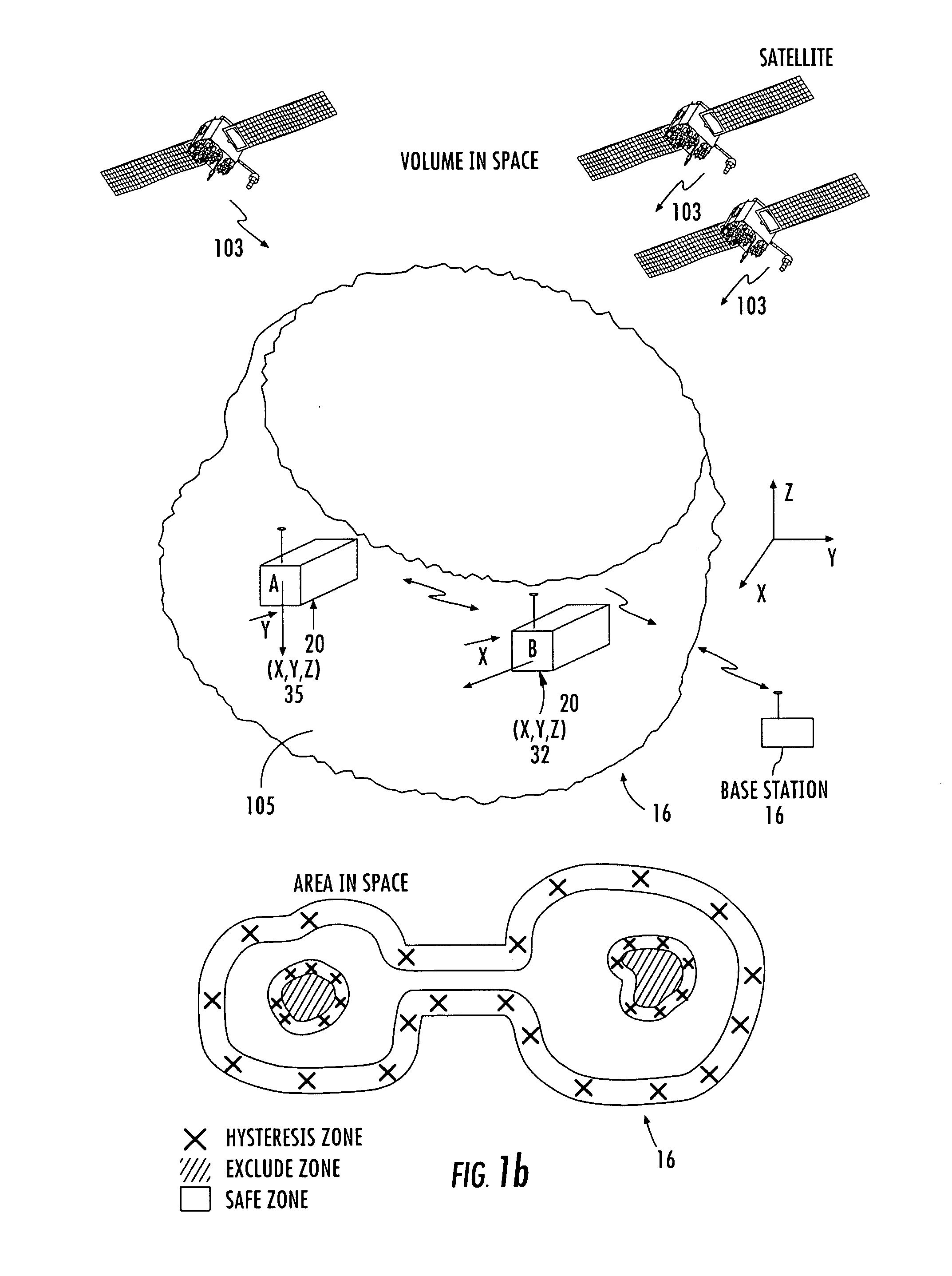

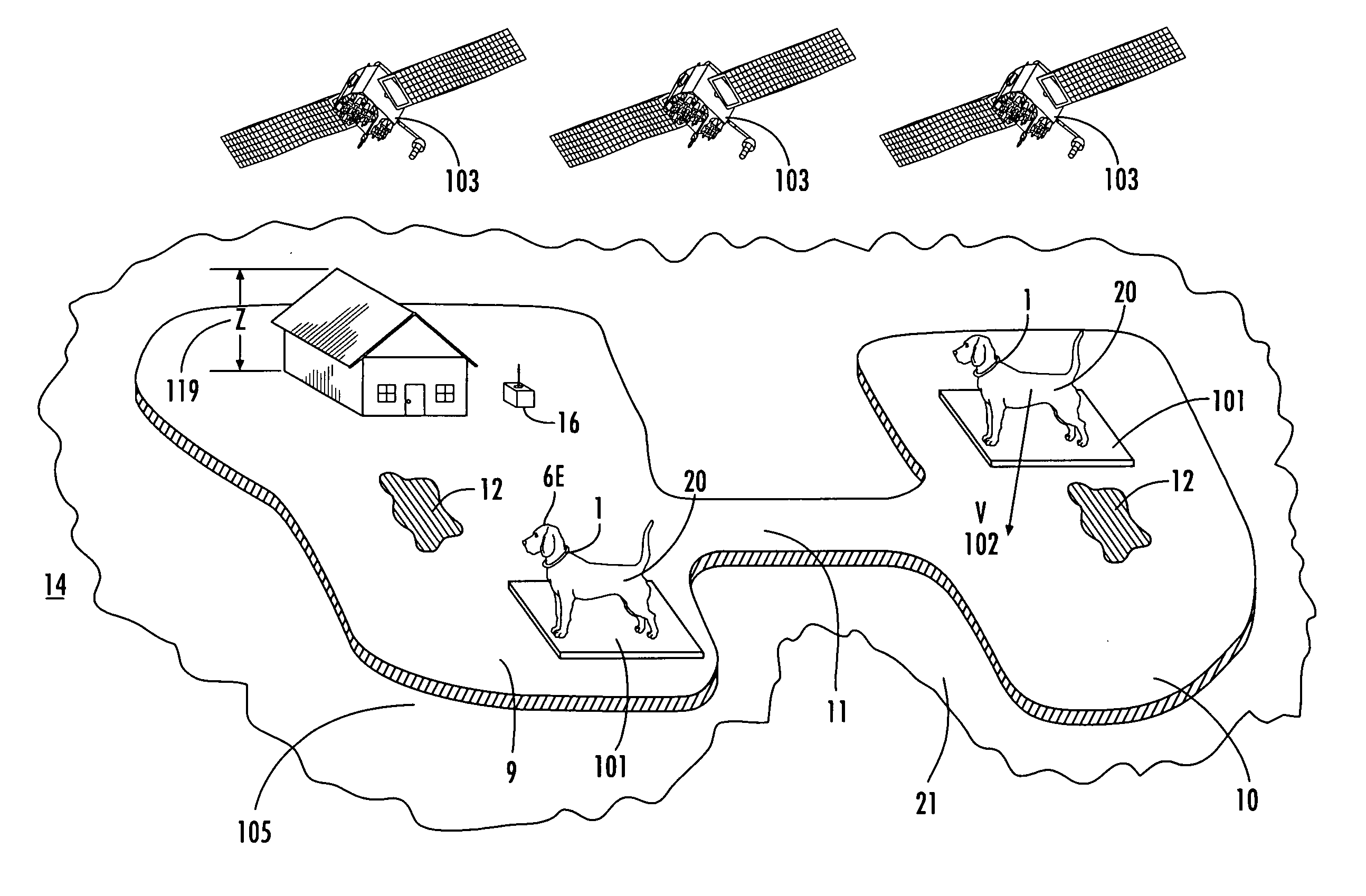

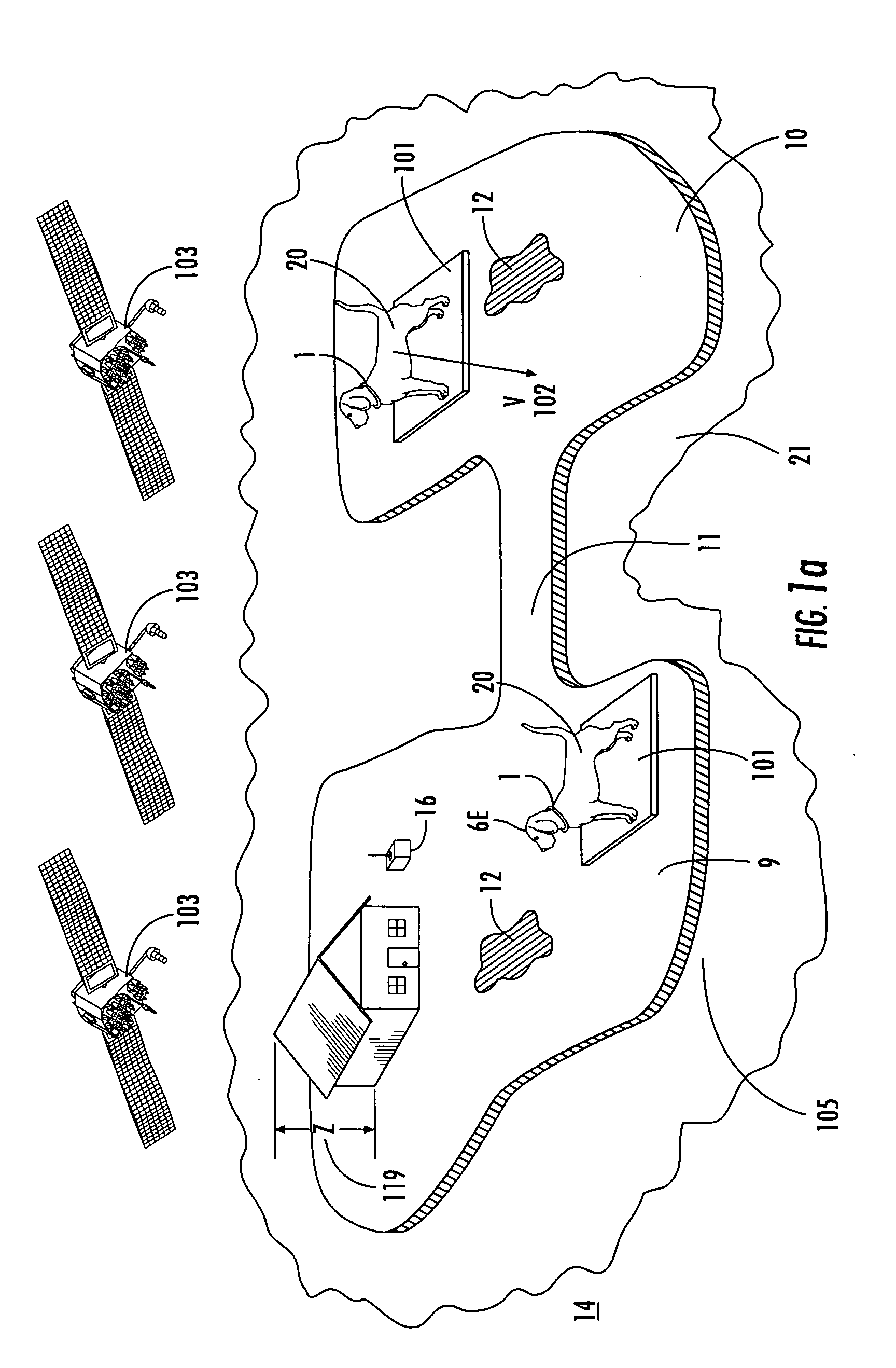

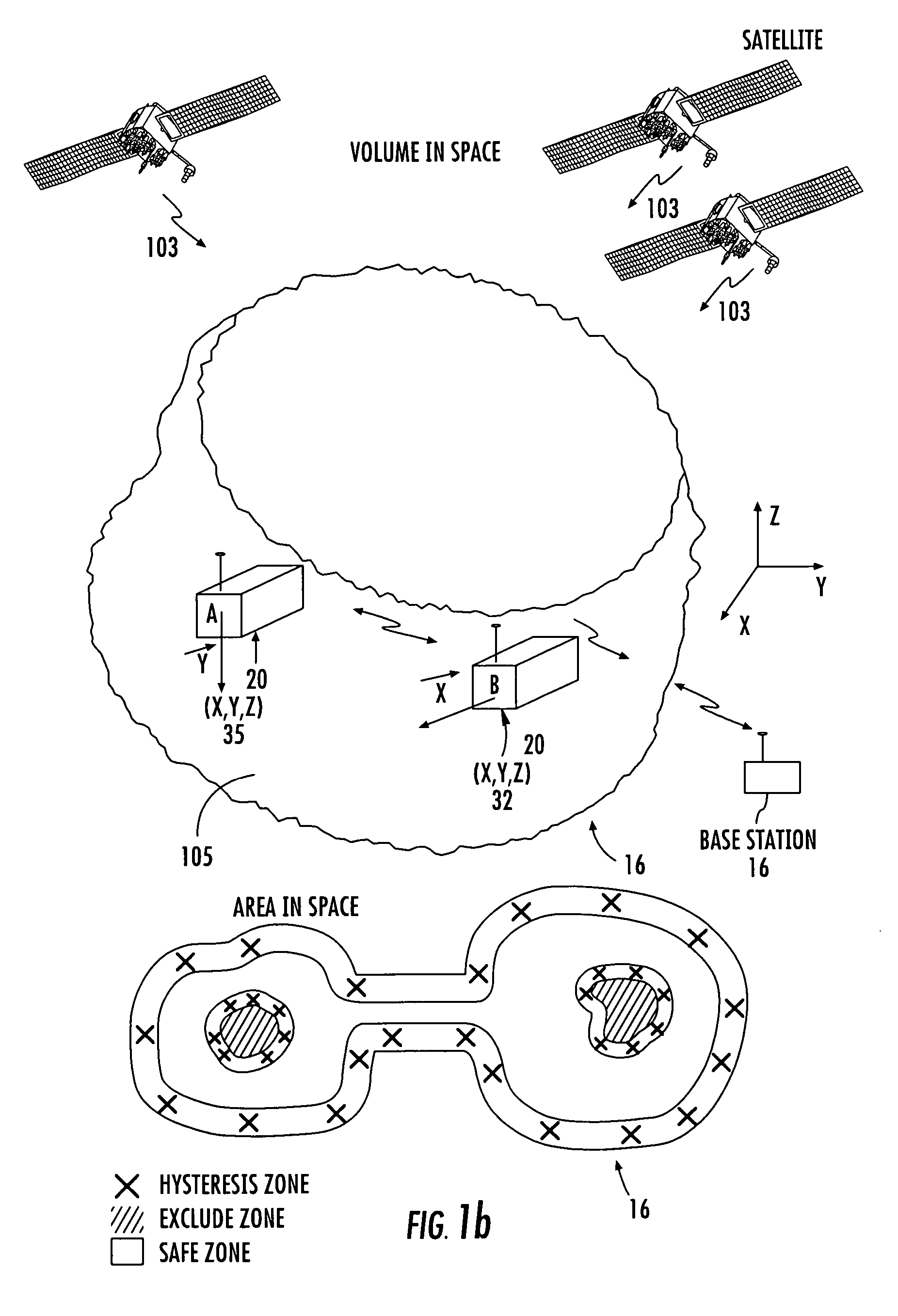

Large area position/proximity correction device with alarms using (D)GPS technology

A collar to be worn on an object or a large or small animal has been designed incorporating (D)GPS technology. The operation of the device includes programming the three dimensional boundary into the memory of the device and simply installing the collar on the animal. As the animal approaches the preprogrammed boundary, a first alarm sounds when the subject is within an arbitrary user defined distance, and a second more drastic alarm such as a shock correction is applied when the subject approaches a second position closer to the boundary. Means to easily program the device are also included in the system. The device has the capability to call or transmit important information such as location, speed, identity, and medical parameters etc to a station automatically or when polled. All necessary analog and digital circuitry, microprocessor, programming, communications hardware are integrated into the collar. The device also has applications in land, air and sea navigation, farming, construction, tracking stolen vehicles, and keeping track of children. This device could also be embedded in a specialized lawnmower that would know where your yard ended and your neighbor's began, and traverse around all obstacles in the yard. Important Military applications would include warning and directing soldiers of front line boundaries, minefield mapping and 3-D direction around MOA's for aircraft.

Owner:INT RES INST

Associative Database Scanning and Information Retrieval

InactiveUS20070118500A1Threshold may be loweredRaise the importanceData processing applicationsInput/output to record carriersMass storagePattern matching

A method and device are disclosed for an associative and approximate, analog or digital scanning of databases that allows for the asynchronous accessing of data from a mass storage medium. The invention includes providing dedicated analog and digital circuitry and decision logic at the mass storage medium level for determining a key identifying the data of interest, continuously comparing the key to a signal generated from a reading of the data from the mass storage medium with an approximate or exact matching circuit to determine a pattern match, determining a correlation value between the key and the data as it is read in a continuous fashion, and determining a match based upon a preselected threshold value for the correlation value. The pattern matching technique eliminates any need to compare data based on its intrinsic structure or value, and instead is based on an analog or digital pattern. The key and data may be either analog or digital. This device and method may be provided as part of a stand-alone computer system, embodied in a network attached storage device, or can otherwise be provided as part of a computer LAN or WAN.

Owner:IP RESERVOIR

Method and system for counting events within a simulation model

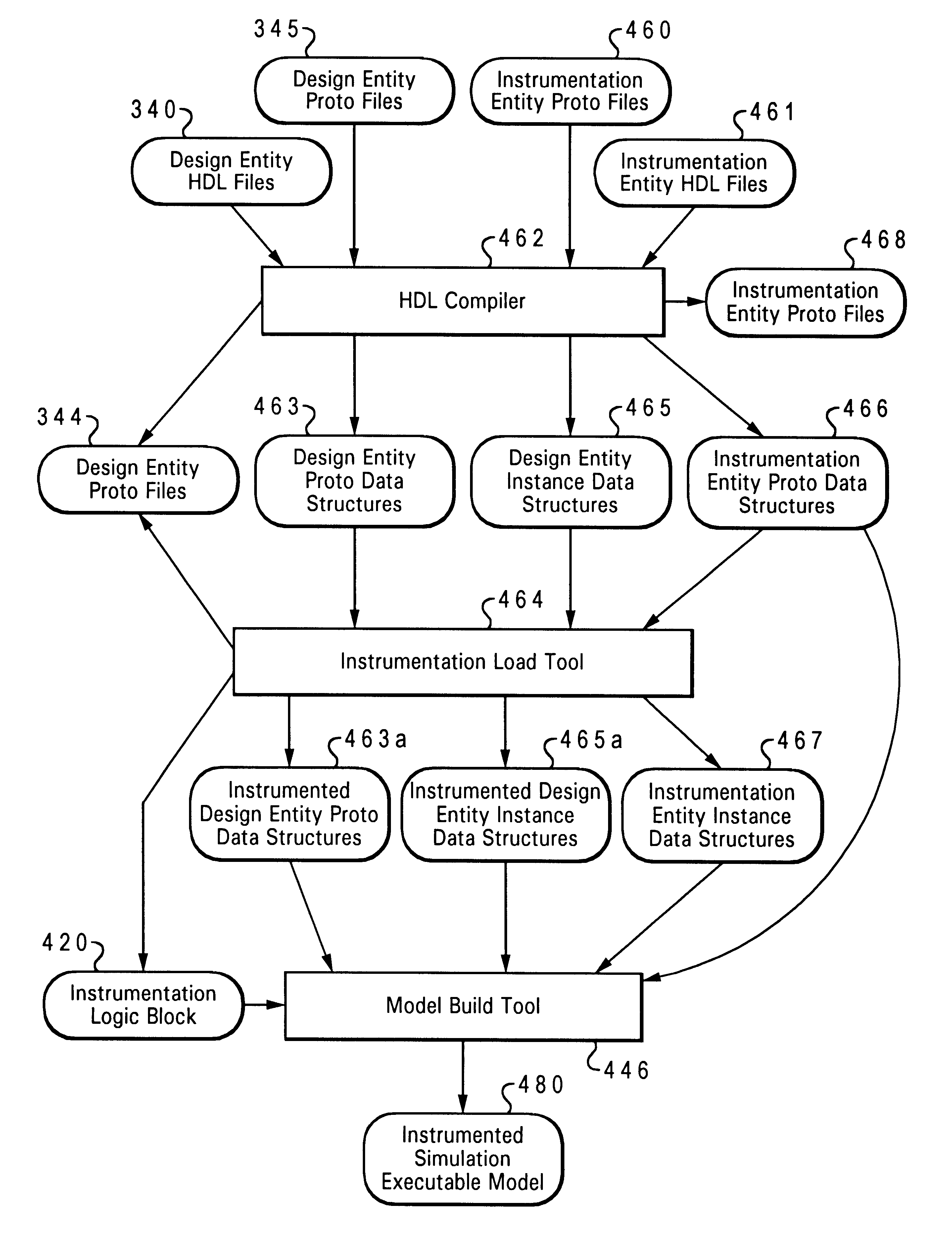

InactiveUS6470478B1Monitor performanceDigital circuit testingDetecting faulty computer hardwareTheoretical computer scienceLinear feedback shift register

A method and system that utilize the expressiveness of hardware description languages for efficiently and comprehensively monitoring performance characteristics of a digital circuit design during simulation. According to the present invention, a design entity that is part of a digital circuit design is first described utilizing a hardware description language. Next, a counting instrument is described utilizing the same hardware description language. The counting instrument is designed to detect occurrences of a count event within the design entity during simulation of the digital circuit design. The counting instrument is associated with the design entity utilizing a non-conventional call, such that the counting instrument may be utilized to monitor each instantiation of the design entity within the simulation model without the instrumentation entity becoming incorporated into the digital circuit design. In association with the counting instrument, a linear feedback shift register is automatically generated for recording the number of occurrences of the count event within the design entity.

Owner:GLOBALFOUNDRIES INC

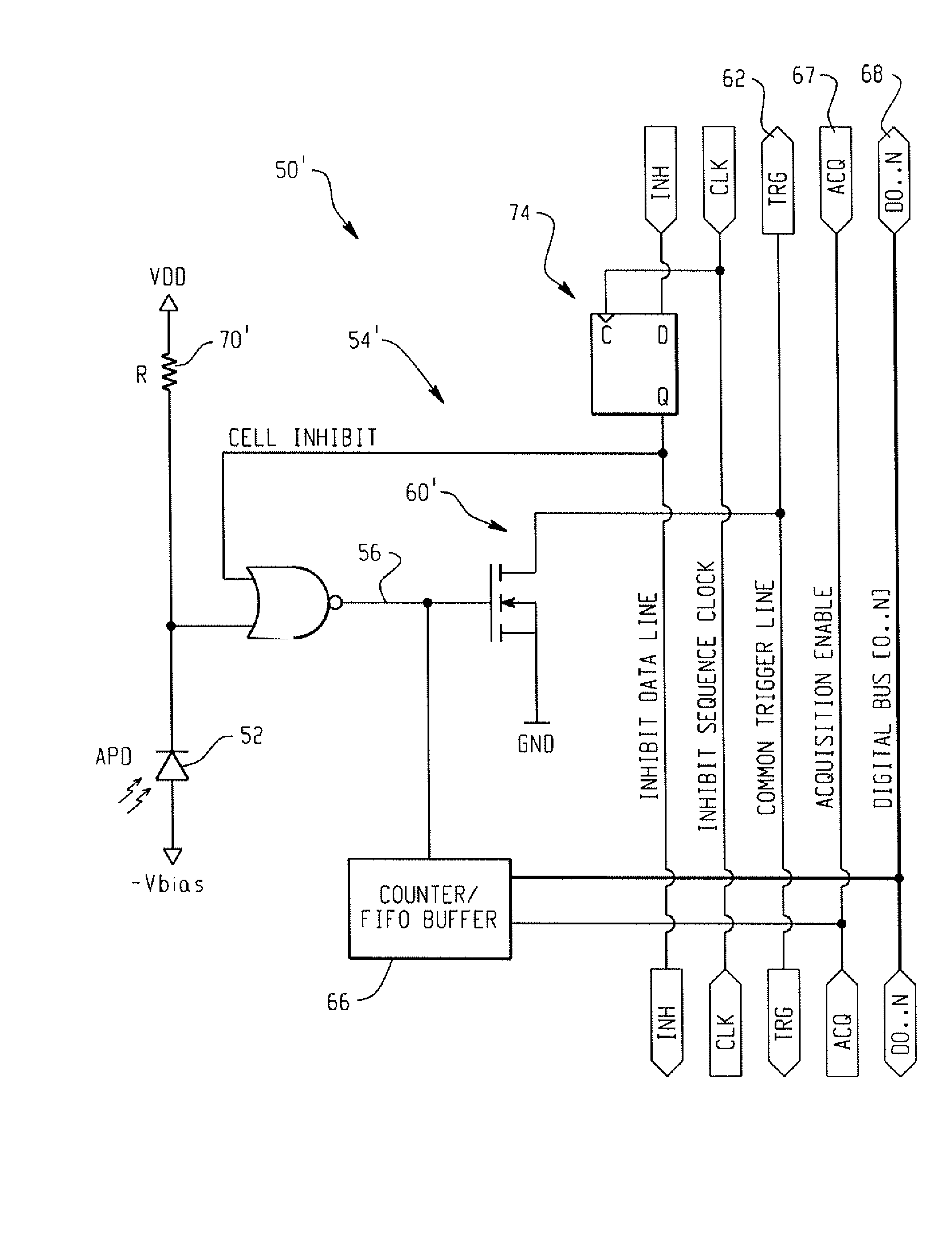

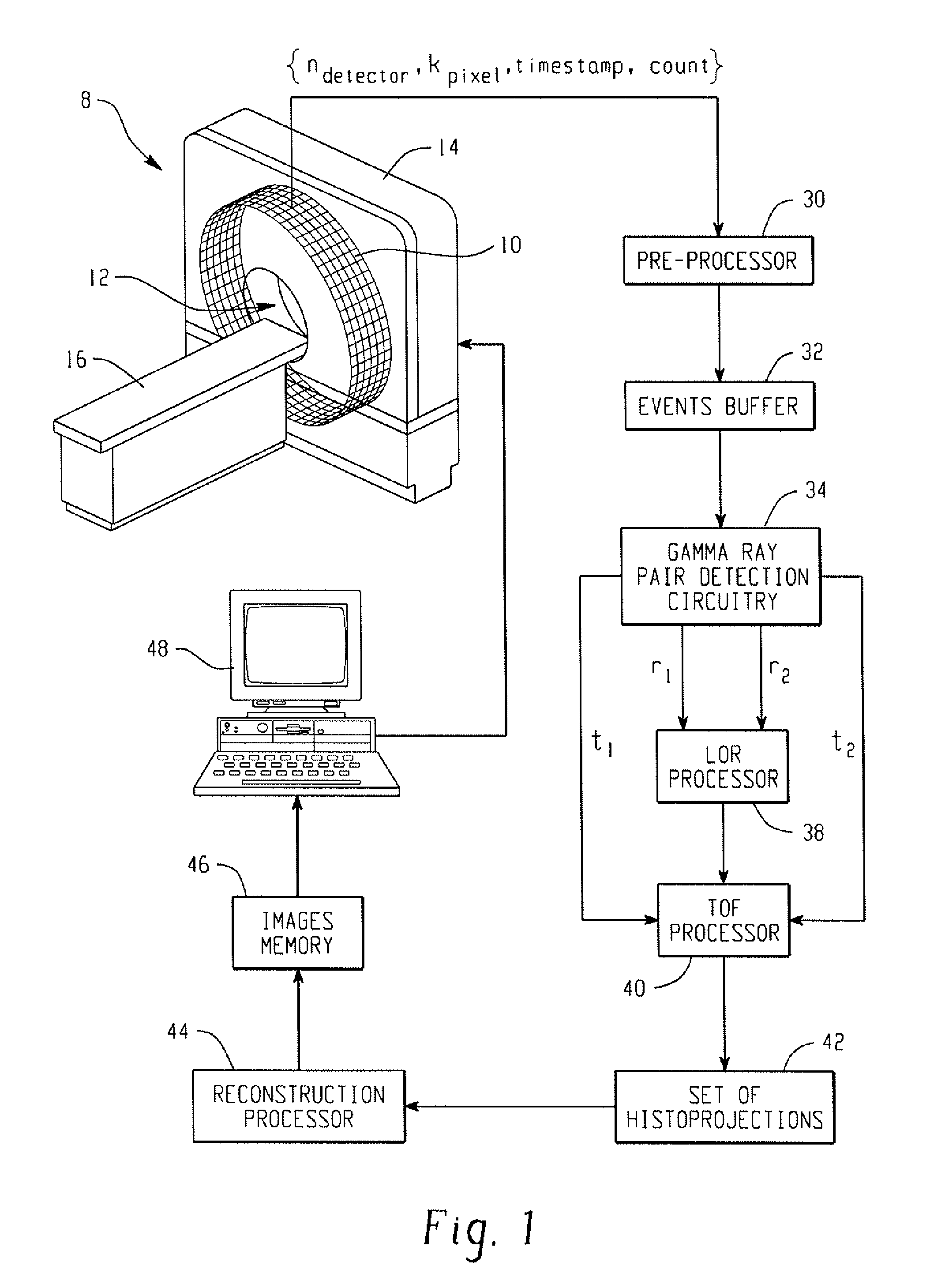

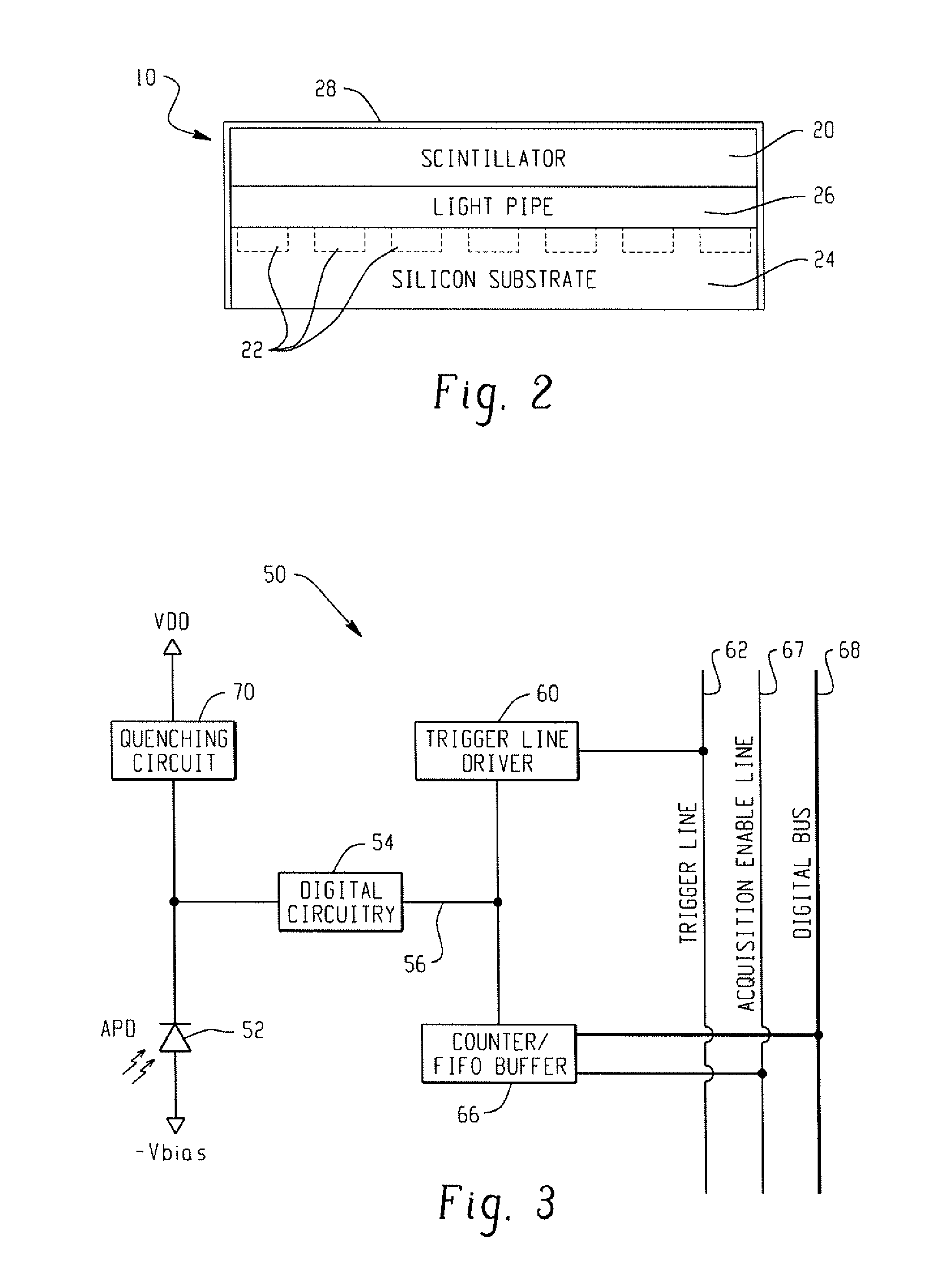

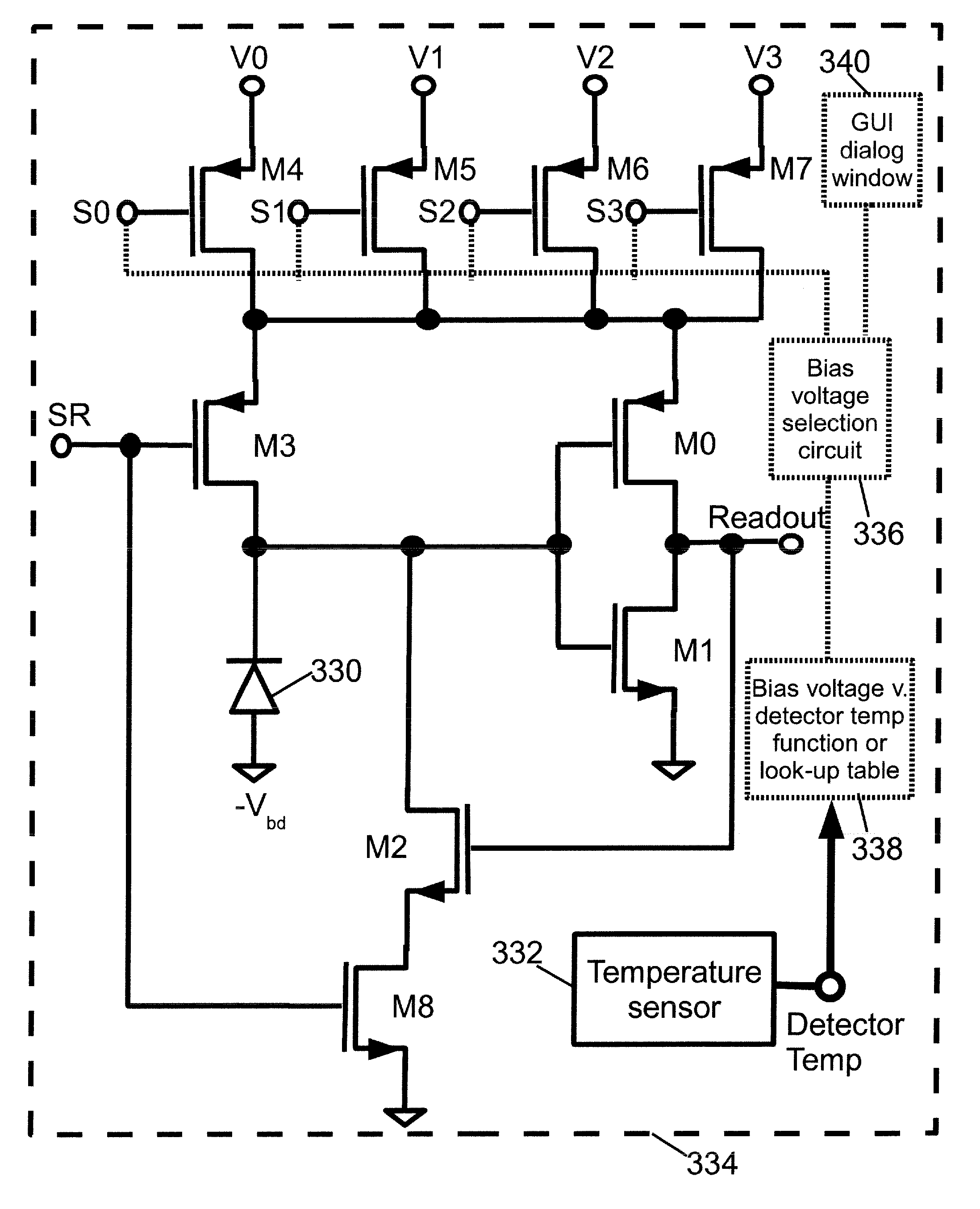

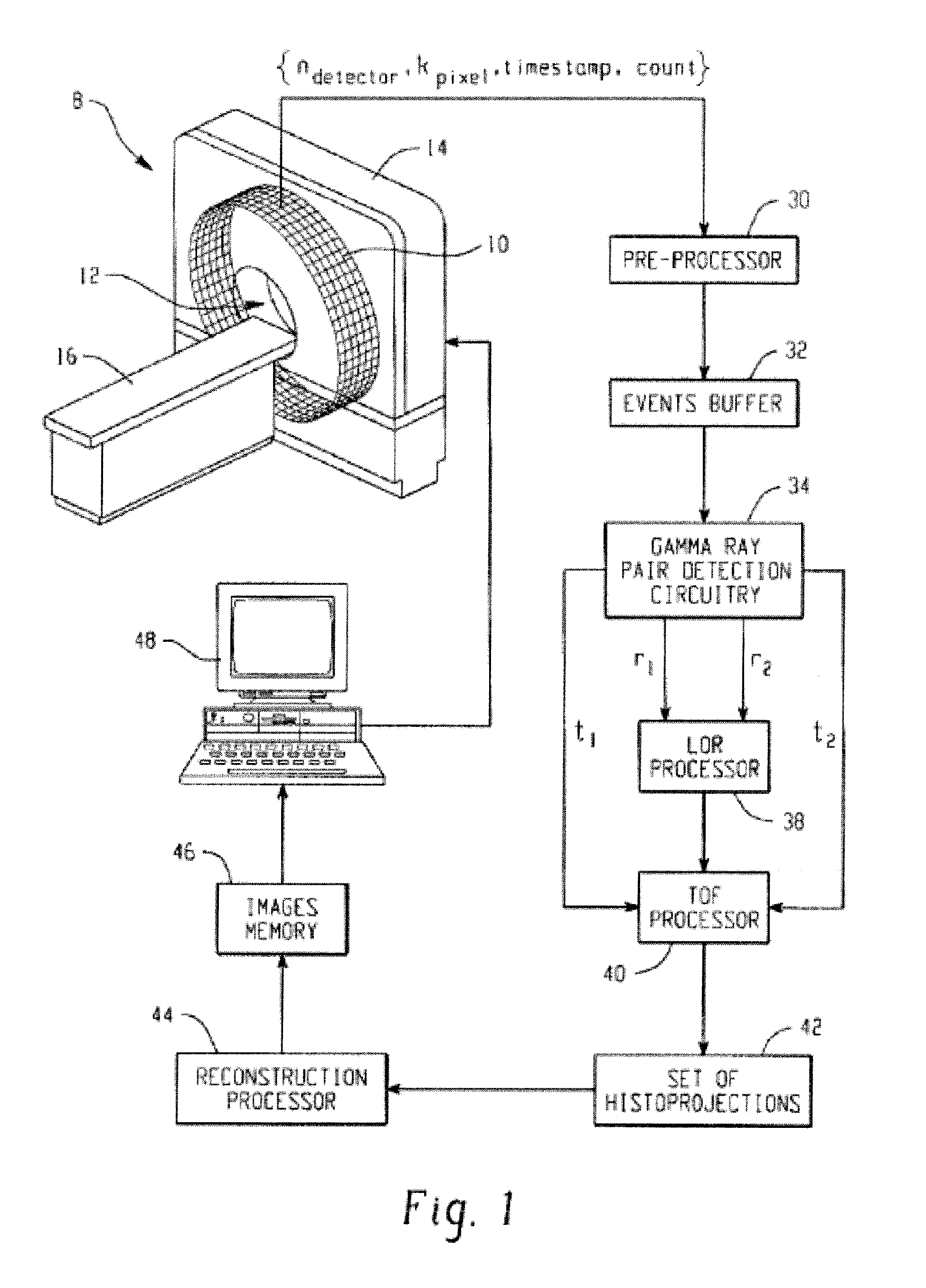

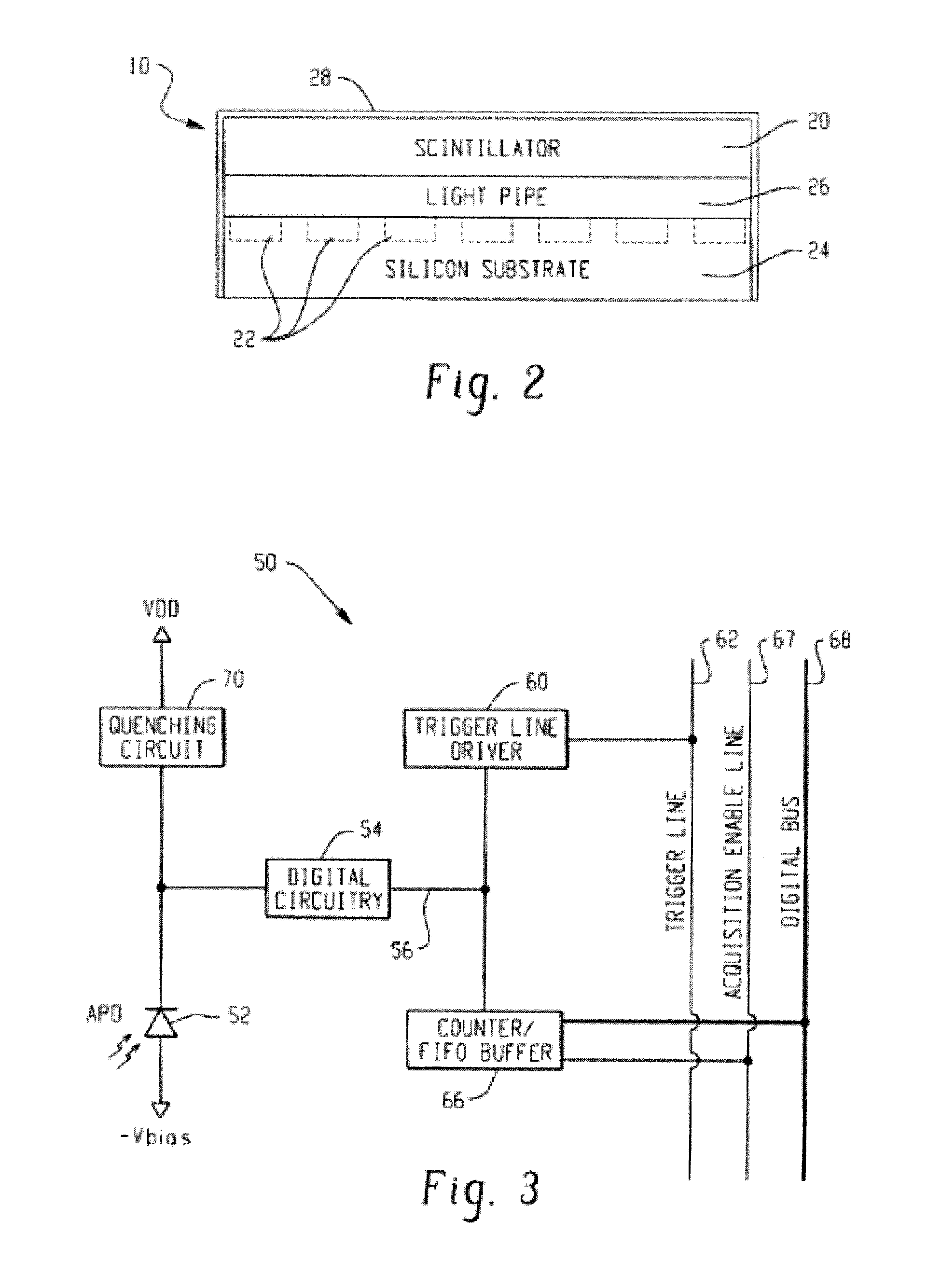

Digital silicon photomultiplier for TOF-PET

ActiveUS20080203309A1High data-rate radiation detectionImproved spatial detector resolutionMaterial analysis by optical meansTomographyQuiescent stateSilicon photomultiplier

A radiation detector includes an array of detector pixels each including an array of detector cells. Each detector cell includes a photodiode biased in a breakdown region and digital circuitry coupled with the photodiode and configured to output a first digital value in a quiescent state and a second digital value responsive to photon detection by the photodiode. Digital triggering circuitry is configured to output a trigger signal indicative of a start of an integration time period responsive to a selected number of one or more of the detector cells tranisitioning from the first digital value to the second digital value. Readout digital circuitry accumulates a count of a number of transitions of detector cells of the array of detector cells from the first digital state to the second digital state over the integration time period.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Method and apparatus for estimating internal power consumption of an electronic circuit represented as netlist

InactiveUS6075932AGreat likelihoodReduce running timeElectric devicesCAD circuit designEngineeringTransition time

This is a method of quickly computing the power dissipated by a digital circuit using information available at the gate library level. It estimates the short-circuit power by modeling the energy dissipated by the cell per input transition as a function of the transition time or edge rate, and multiplying that value by the number of transitions per second for that input.

Owner:SYNOPSYS INC

Large area position/proximity correction device with alarms using (D)GPS technology

A collar to be worn on an object or a large or small animal has been designed incorporating (D)GPS technology. The operation of the device includes programming the three dimensional boundary into the memory of the device and simply installing the collar on the animal. As the animal approaches the preprogrammed boundary, a first alarm sounds when the subject is within an arbitrary user defined distance, and a second more drastic alarm such as a shock correction is applied when the subject approaches a second position closer to the boundary. Means to easily program the device are also included in the system. The device has the capability to call or transmit important information such as location, speed, identity, and medical parameters, etc. to a station automatically or when polled. All necessary analog and digital circuitry, microprocessor, programming, communications hardware are integrated into the collar. The device also has applications in land, air and sea navigation, farming, construction, tracking stolen vehicles, and keeping track of children. This device could also be embedded in a specialized lawnmower that would know where your yard ended and your neighbor's began, and traverse around all obstacles in the yard. Important Military applications would include warning and directing soldiers of front line boundaries, minefield mapping and 3-D direction around MOA's for aircraft.

Owner:INT RES INST

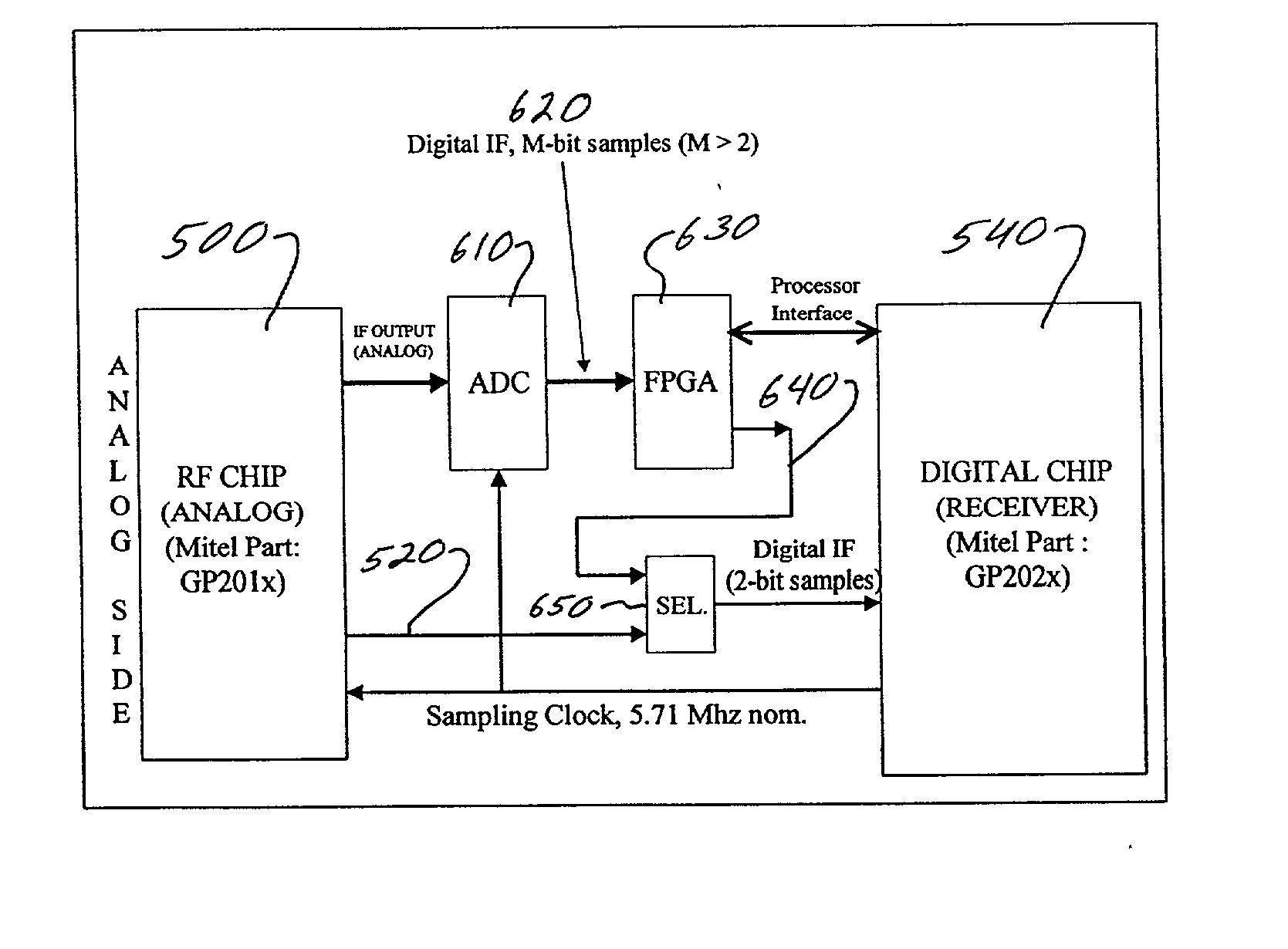

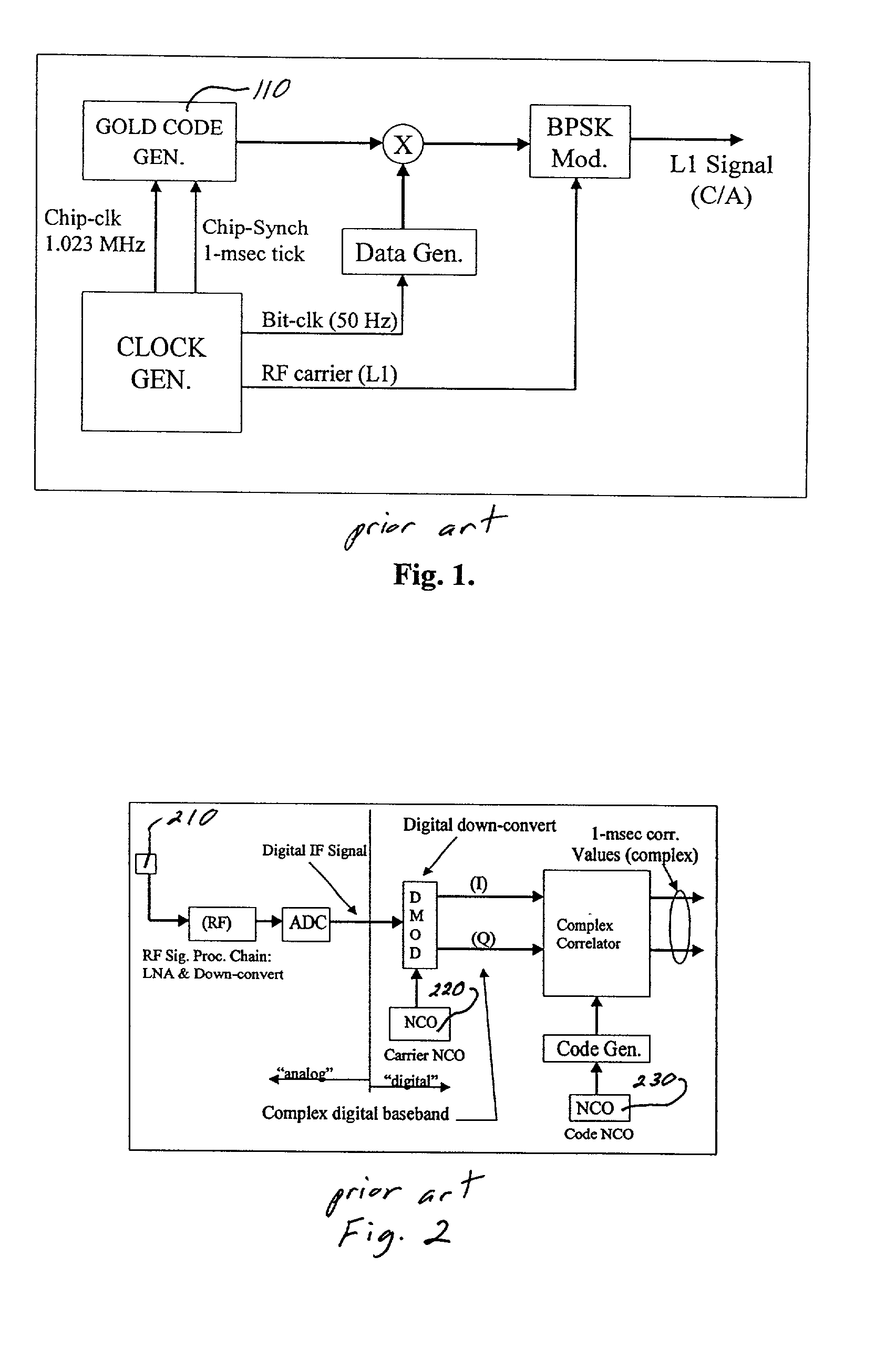

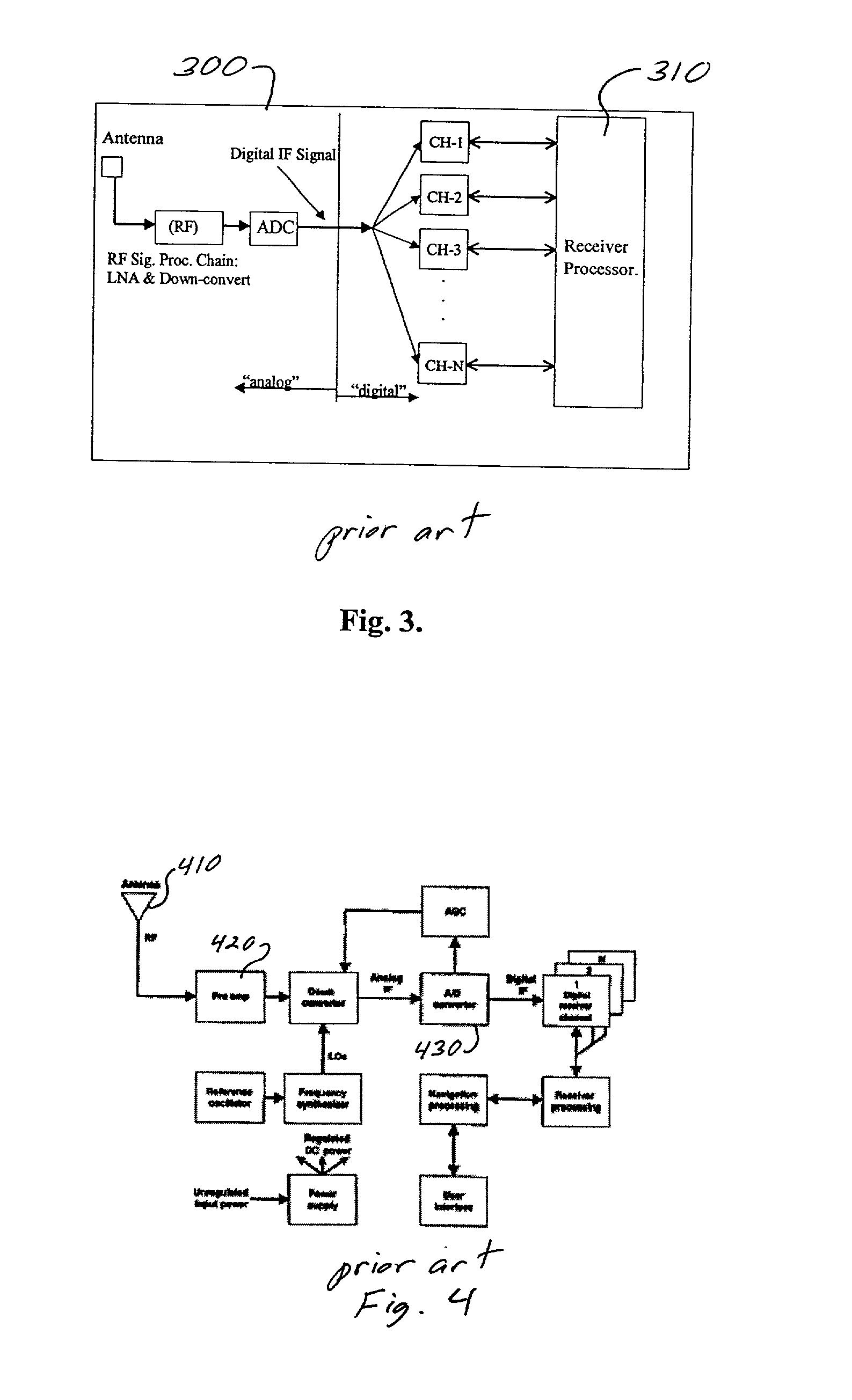

Global positioning system receiver capable of functioning in the presence of interference

Systems and methods are described for a GPS receiver capable of functioning in the presence of interference. A method includes detecting an interfering signal including: tuning a band pass filter over a frequency range; and at each of a plurality of incremental frequencies: computing a set of band pass filter coefficients; sending the set of band pass filter coefficients to a digital filter; repeatedly transforming an analog-to-digital converter output having a quantization level in excess of 2 bits into a band pass filter output with the digital filter to obtain a plurality of samples; computing an average of the plurality of samples; and comparing the average to a threshold to detect peaks that exceed a threshold. An apparatus, comprising: an analog radio frequency circuit; an analog-to-digital converter coupled to the analog radio frequency circuit, the analog-to-digital converter providing a quantization level in excess of 2 bits; a digital filter coupled to the analog-to-digital converter; and a digital circuit coupled to the digital filter.

Owner:IP GEM GRP LLC

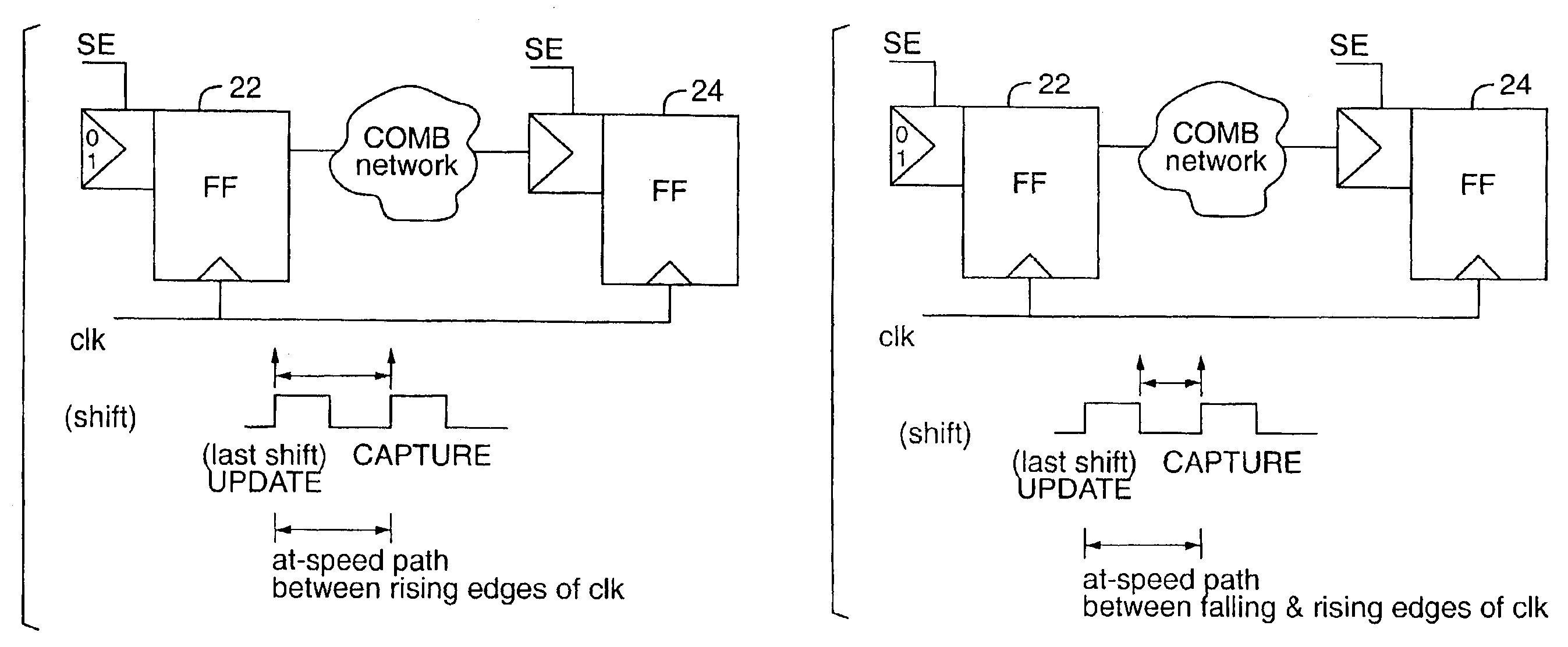

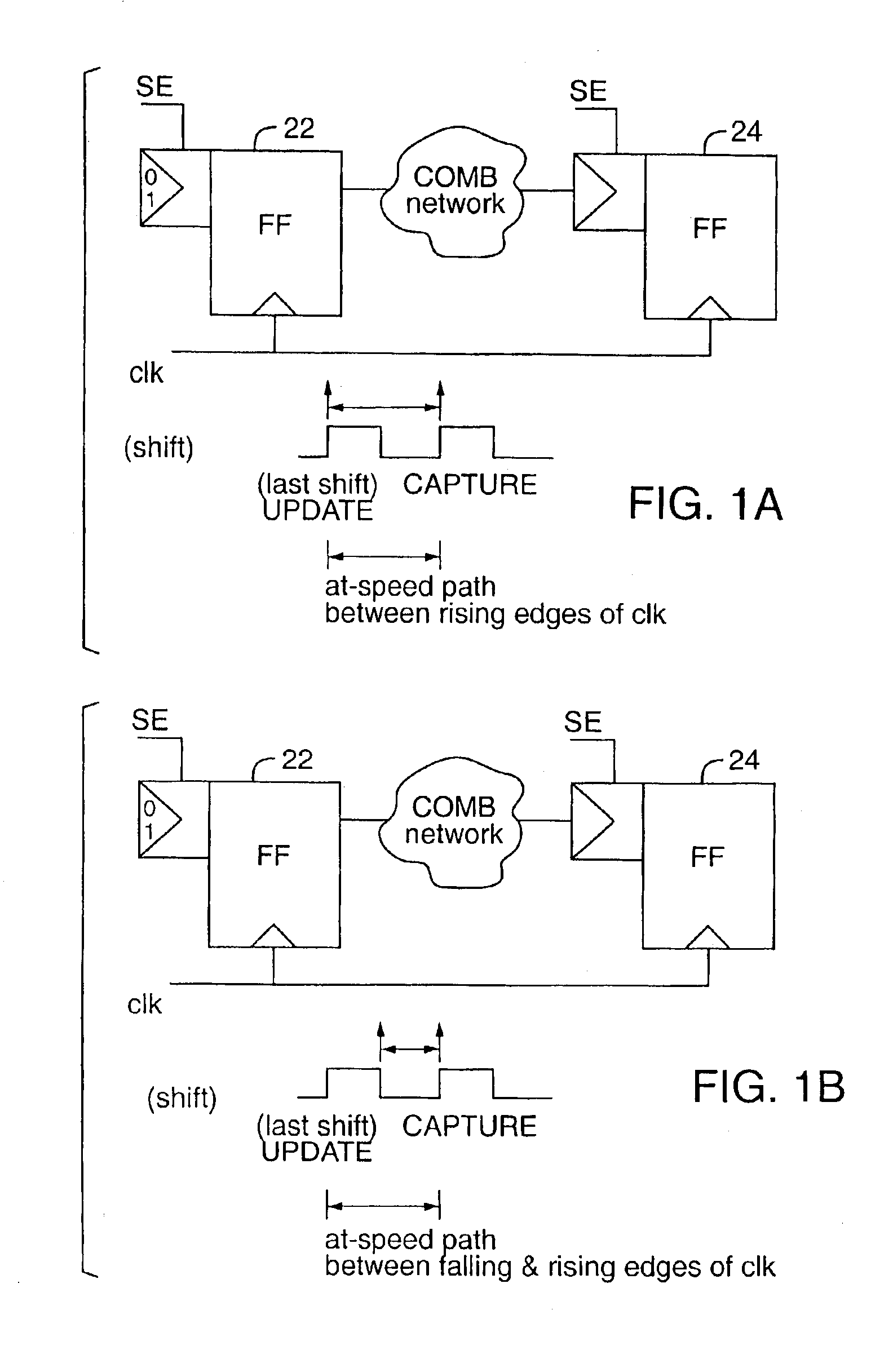

Method and apparatus for at-speed testing of digital circuits

InactiveUS6966021B2Electronic circuit testingError detection/correctionMulti inputProcessor register

A scheme for multi-frequency at-speed logic Built-In Self Test (BIST) is provided. This scheme allows at-speed testing of very high frequency integrated circuits controlled by a clock signal generated externally or on-chip. The scheme is also applicable to testing of circuits with multiple clock domains which can be either the same frequency or different frequency. Scanable memory elements of the digital circuit are connected to define plurality of scan chains. The loading and unloading of scan chains is separated from the at-speed testing of the logic between the respective domains and may be done at a faster or slower frequency than the at-speed testing. The BIST controller, Pseudo-Random Pattern Generator (PRPG) and Multi-input Signature Register (MISR) work at slower frequency than the fastest clock domain. After loading of a new test pattern, a clock suppression circuit allows a scan enable signal to propagate for more that one clock cycle before multiple capture clock is applied. This feature relaxes the speed and skew constraints on scan enable signal design. Only the capture cycle is performed at the corresponding system timing. A programmable capture window makes it possible to test every intra- and inter-domain at-speed without the negative impact of clock skew between clock domains.

Owner:MENTOR GRAPHICS CORP

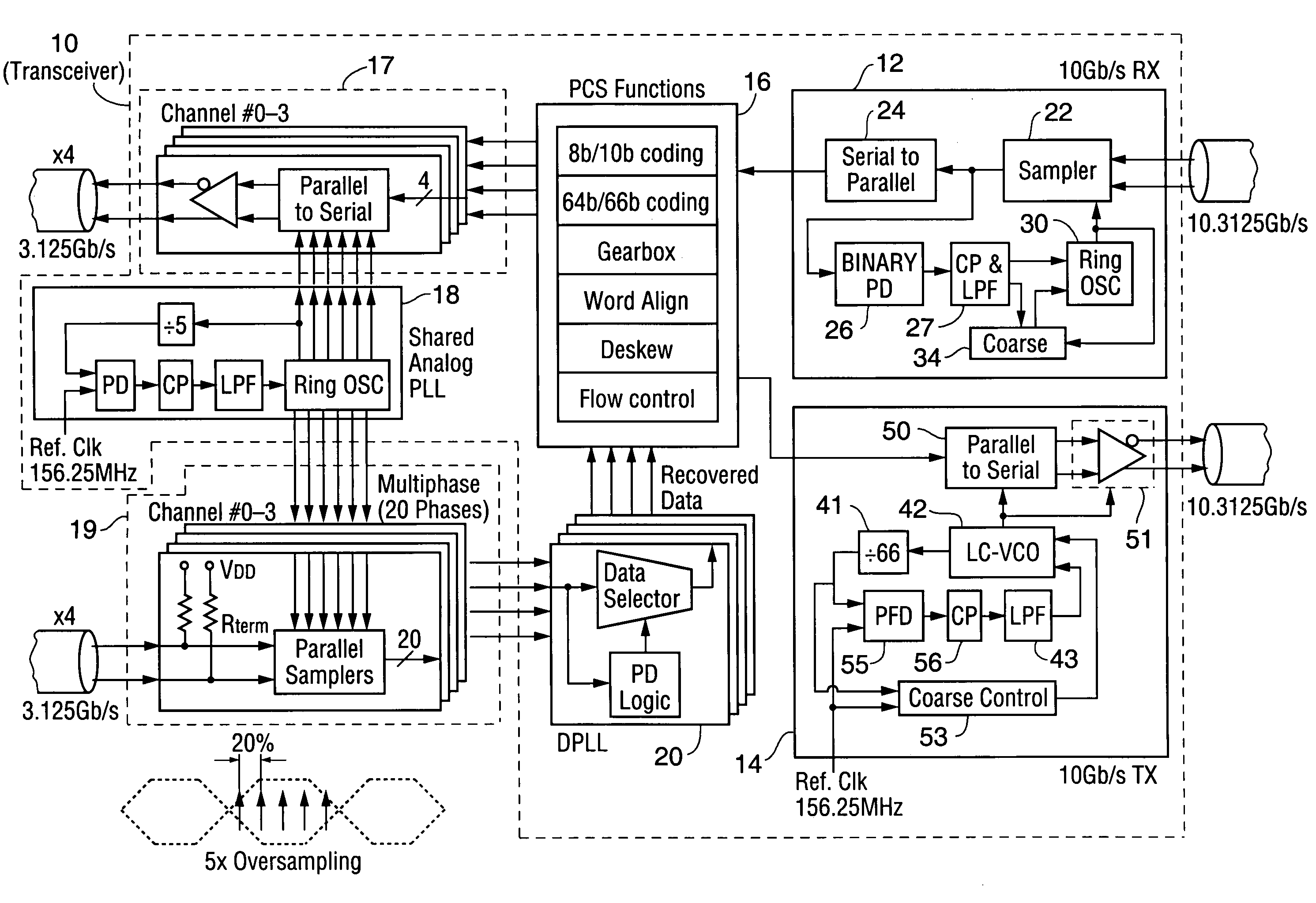

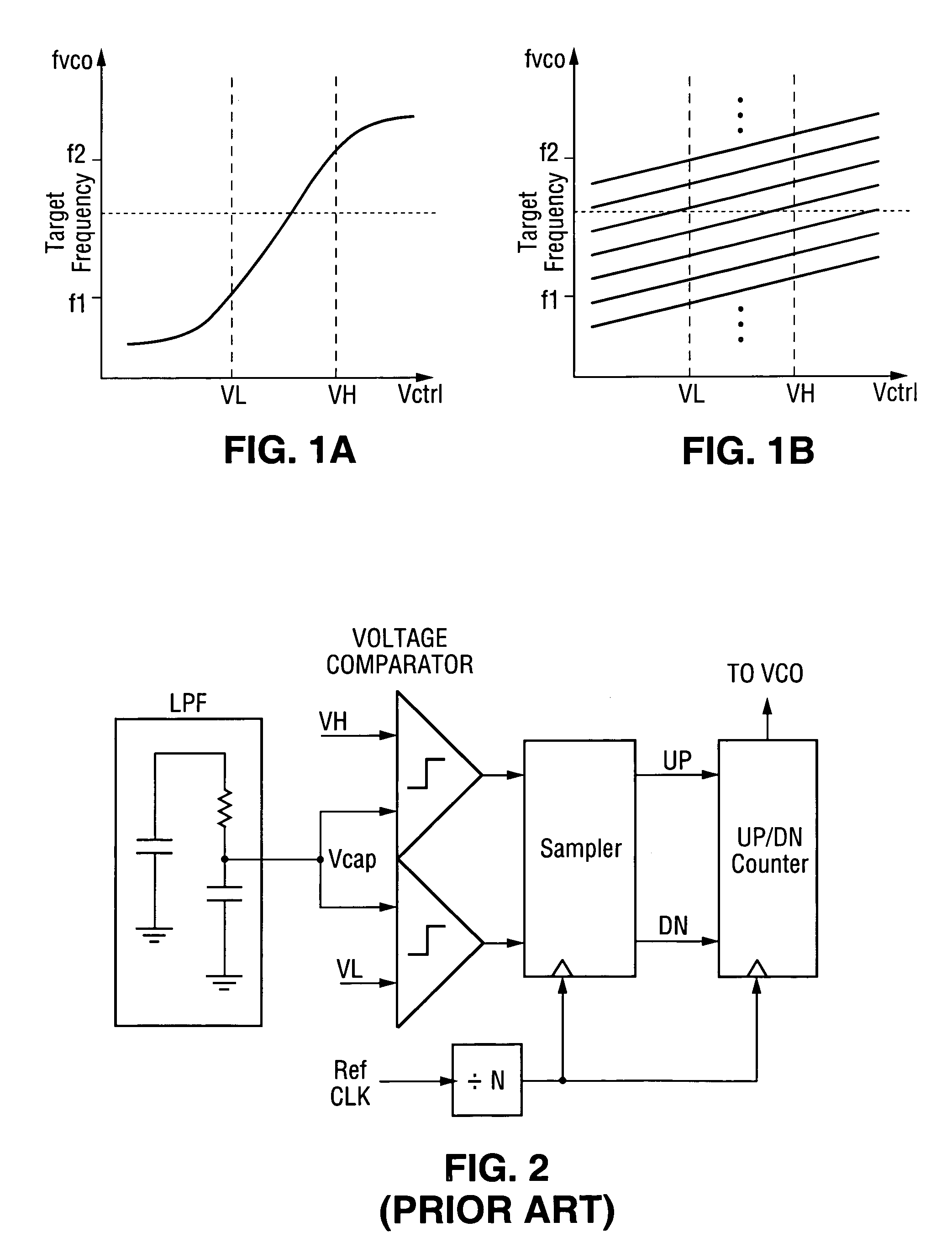

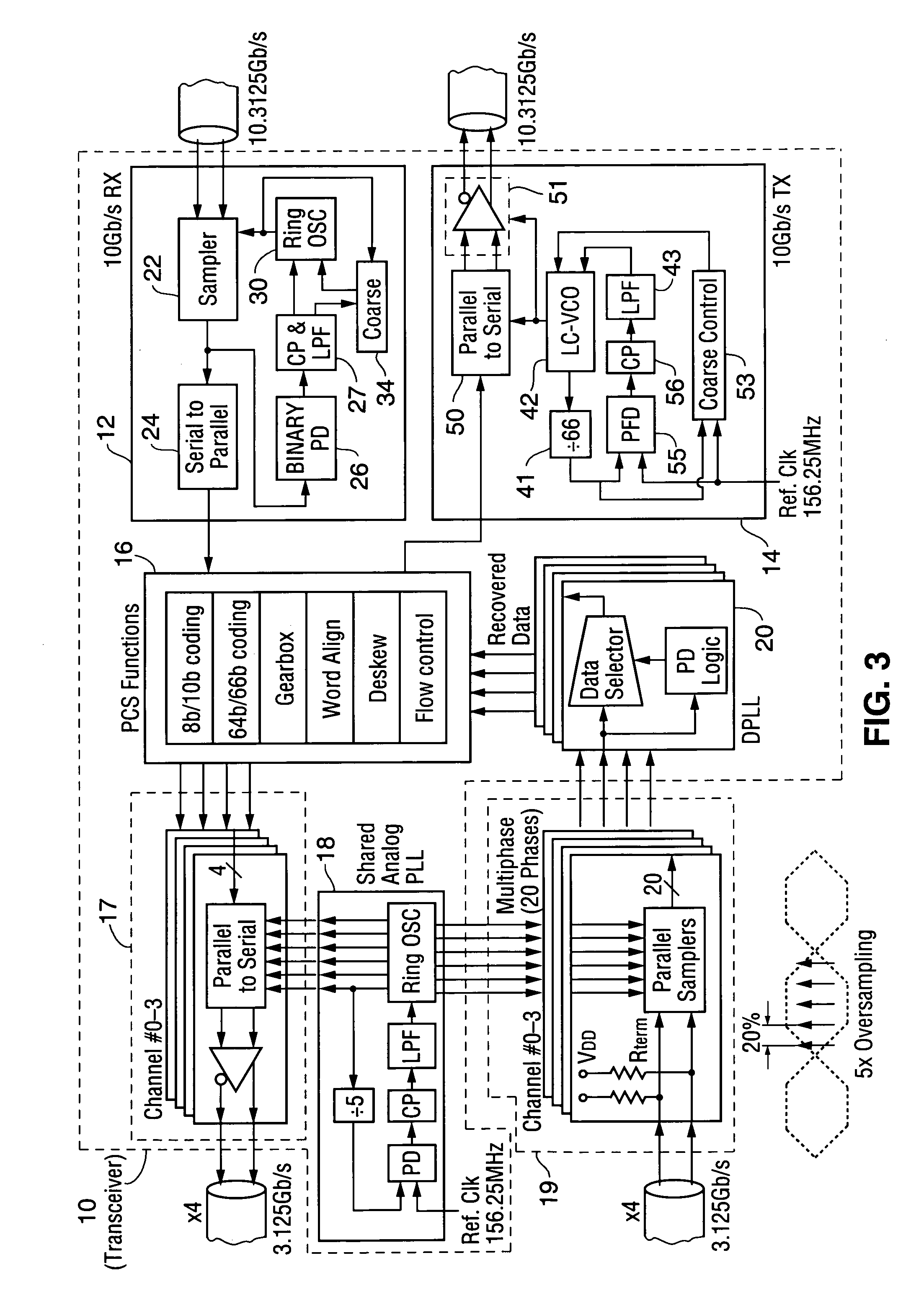

Phase lock loop with coarse control loop having frequency lock detector and device including same

ActiveUS7102446B1Improve portabilitySynchronization is simplePulse automatic controlCounting chain pulse countersTransceiverPhase locked loop circuit

A phase lock loop (PLL) for controlling a sampling clock or other clock, and a data sampling circuit, transceiver, or other device including such a PLL. The PLL includes a multi-range VCO, at least one fine control loop for controlling the VCO, and a coarse control loop for controlling the VCO by changing its frequency-voltage characteristic. The coarse control loop includes a frequency lock detector and voltage range monitoring logic. Typically, the frequency lock detector locks operation of the coarse control loop when the difference between the VCO output clock frequency and a reference frequency decreases to within a predetermined threshold, and the unlocked coarse control loop employs the voltage range monitoring logic to change the VCO frequency-voltage characteristic when the VCO's fine control voltage leaves a predetermined range. Other aspects are a transceiver (including at least two receiver interfaces and a transmitter interface) implementing a clocking scheme employing no more than three PLLs for clock generation, and a transceiver having a multi-layered receiver interface including digital circuitry and a single clock-generating PLL (an analog PLL for generating a multiphase clock to be shared by all layers of the receiver interface). Each receiver interface layer performs blind oversampling on a different received signal using the multiphase clock and the digital circuitry includes multilayered digital phase lock loop circuitry which receives the oversampled data.

Owner:LATTICE SEMICON CORP

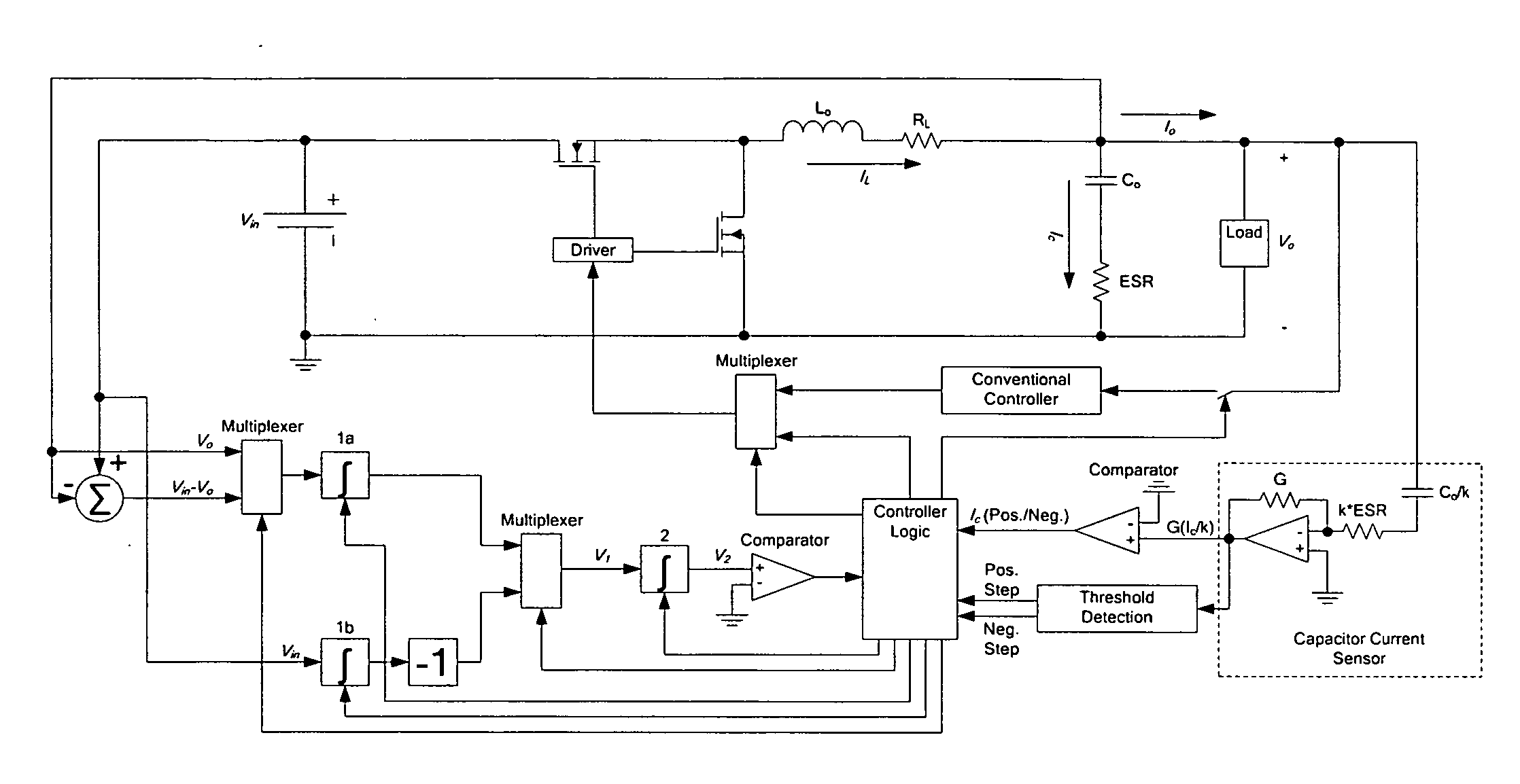

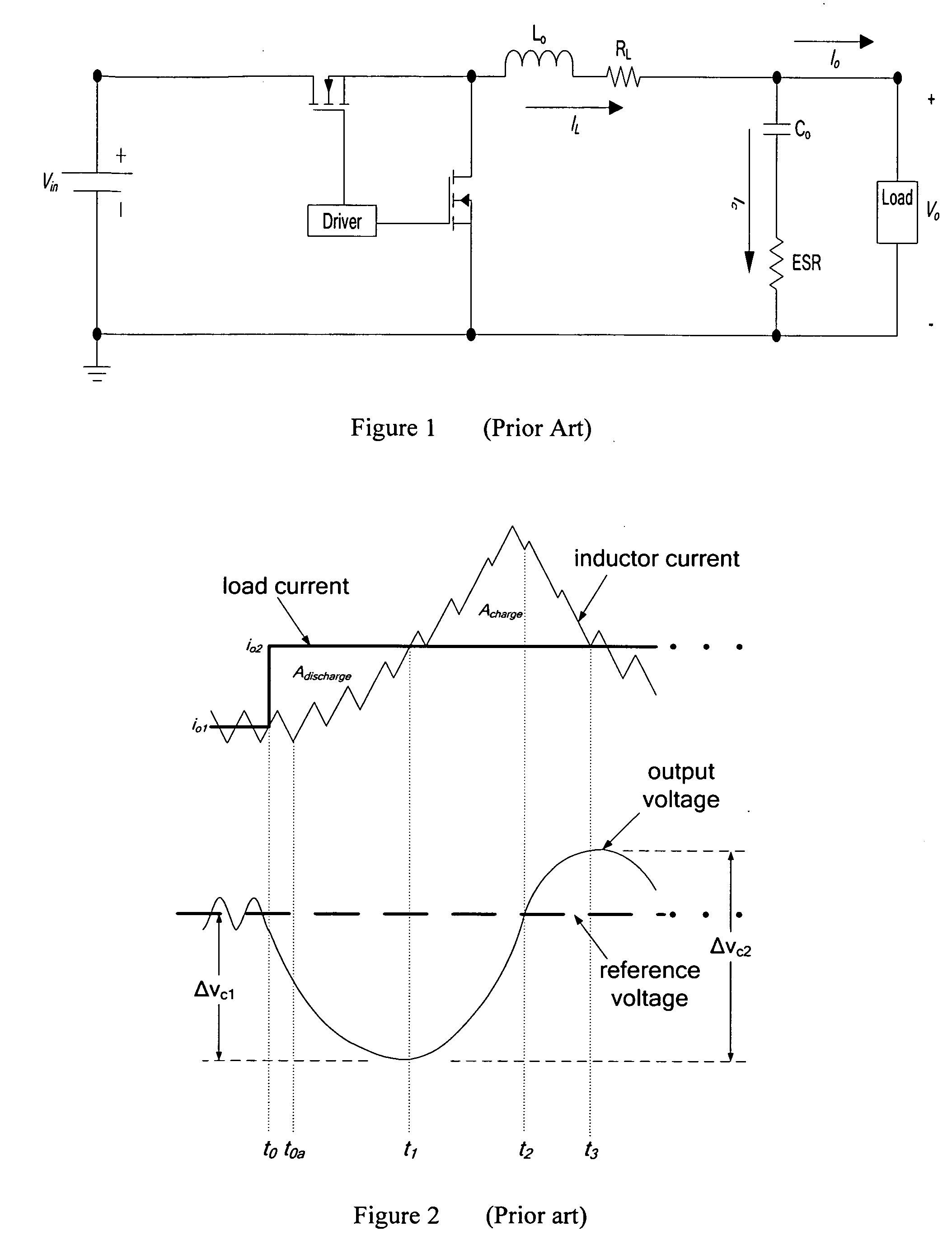

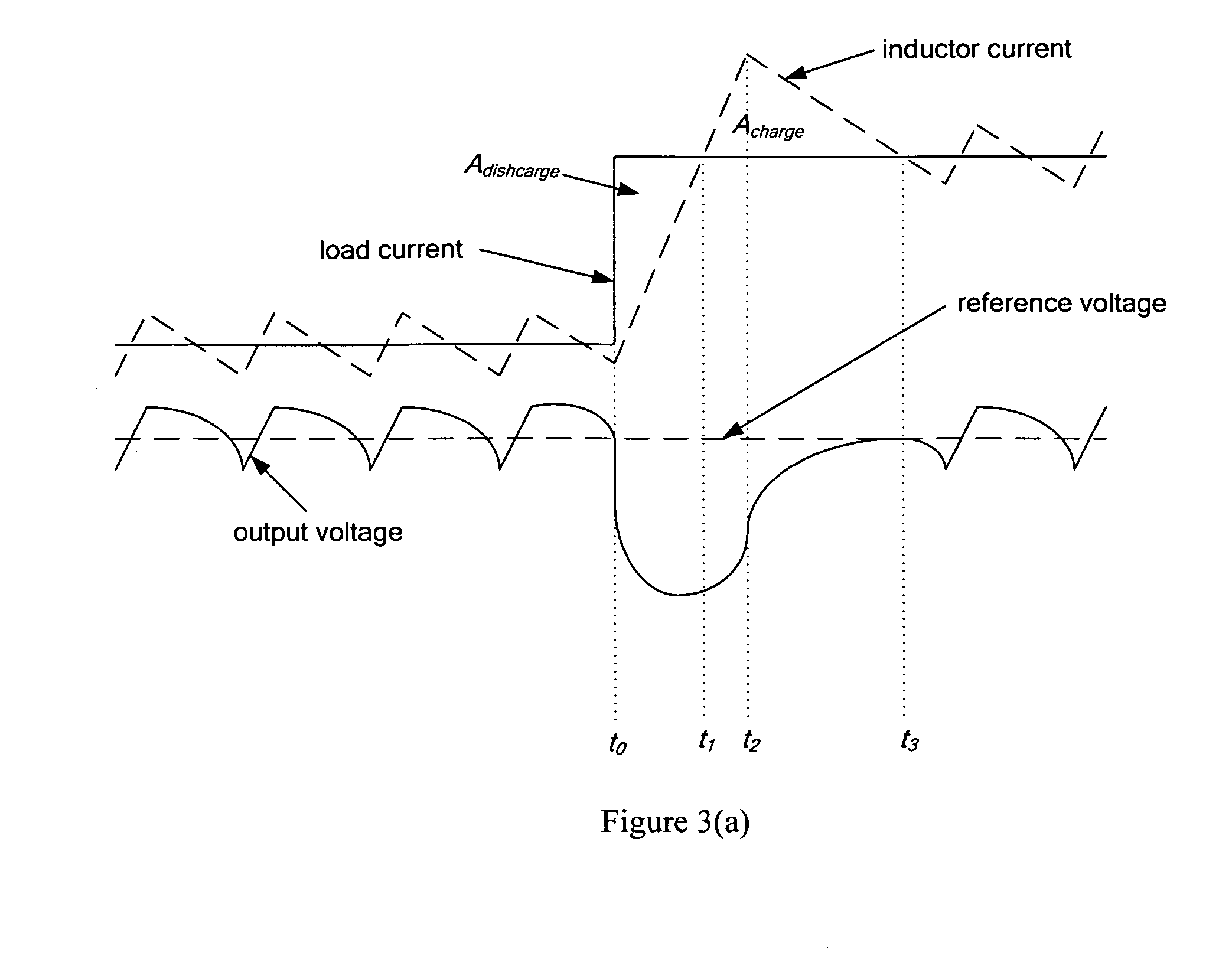

DC-DC converter with improved dynamic response

ActiveUS20080258701A1Improve dynamic performanceLow implementation costMultiple-port networksDc network circuit arrangementsFull bridgePush pull

The invention relates to a control method and a controller for a DC-DC converter, such as a synchronous Buck converter, which exploits the principle of capacitor charge balance to allow the converter to recover from a positive and / or negative load current step in the shortest achievable time, with the lowest possible voltage undershoot / overshoot. The control method may be implemented by either an analog or a digital circuit. The controller may be integrated with existing controller schemes (such as voltage-mode controllers) to provide superior dynamic performance during large-signal transient conditions while providing stable operation during steady state conditions. The invention also relates to a method and a modification of a DC-DC converter topology that comprises connecting a controlled current source between an input terminal and an output terminal of the DC-DC converter; detecting a load current step to a new load current; modifying a duty cycle of the DC-DC converter; and modifying current through a parallel output capacitor of the DC-DC converter by controlling current of the current source. The methods and circuits provided herein are applicable to Buck converters and Buck-derived converters such as forward, push-pull, half-bridge, and full-bridge converters.

Owner:GANPOWER SEMICON FOSHAN LTD

Digital silicon photomultiplier for TOF PET

ActiveUS8395127B1High data-rate radiation detectionImproved spatial detector resolutionSolid-state devicesMaterial analysis by optical meansQuiescent stateSilicon photomultiplier

A radiation detector includes an array of detector pixels each including an array of detector cells. Each detector cell includes a photodiode biased in a breakdown region and digital circuitry coupled with the photodiode and configured to output a first digital value in a quiescent state and a second digital value responsive to photon detection by the photodiode. Digital triggering circuitry is configured to output a trigger signal indicative of a start of an integration time period responsive to a selected number of one or more of the detector cells transitioning from the first digital value to the second digital value. Readout digital circuitry accumulates a count of a number of transitions of detector cells of the array of detector cells from the first digital state to the second digital state over the integration time period.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

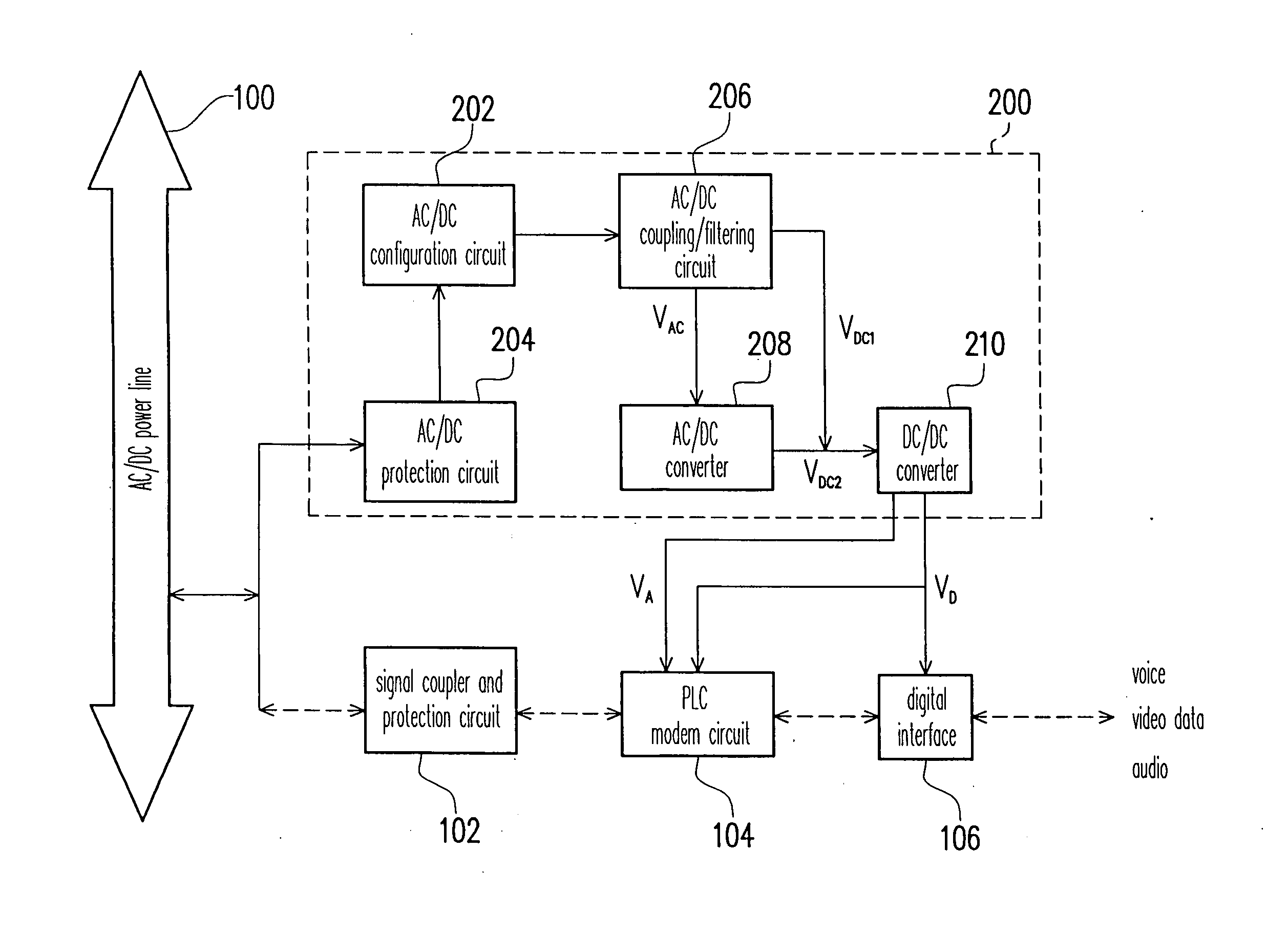

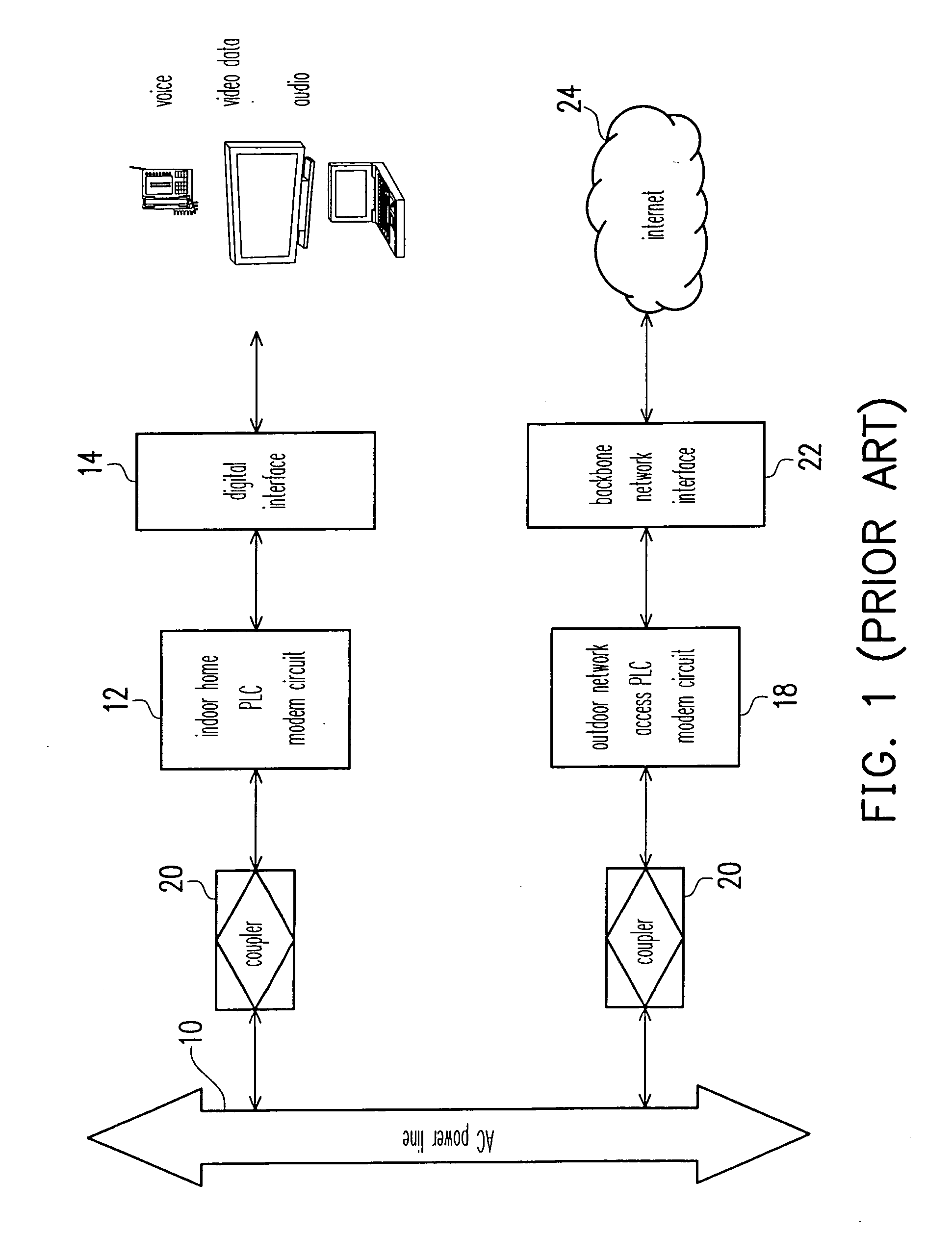

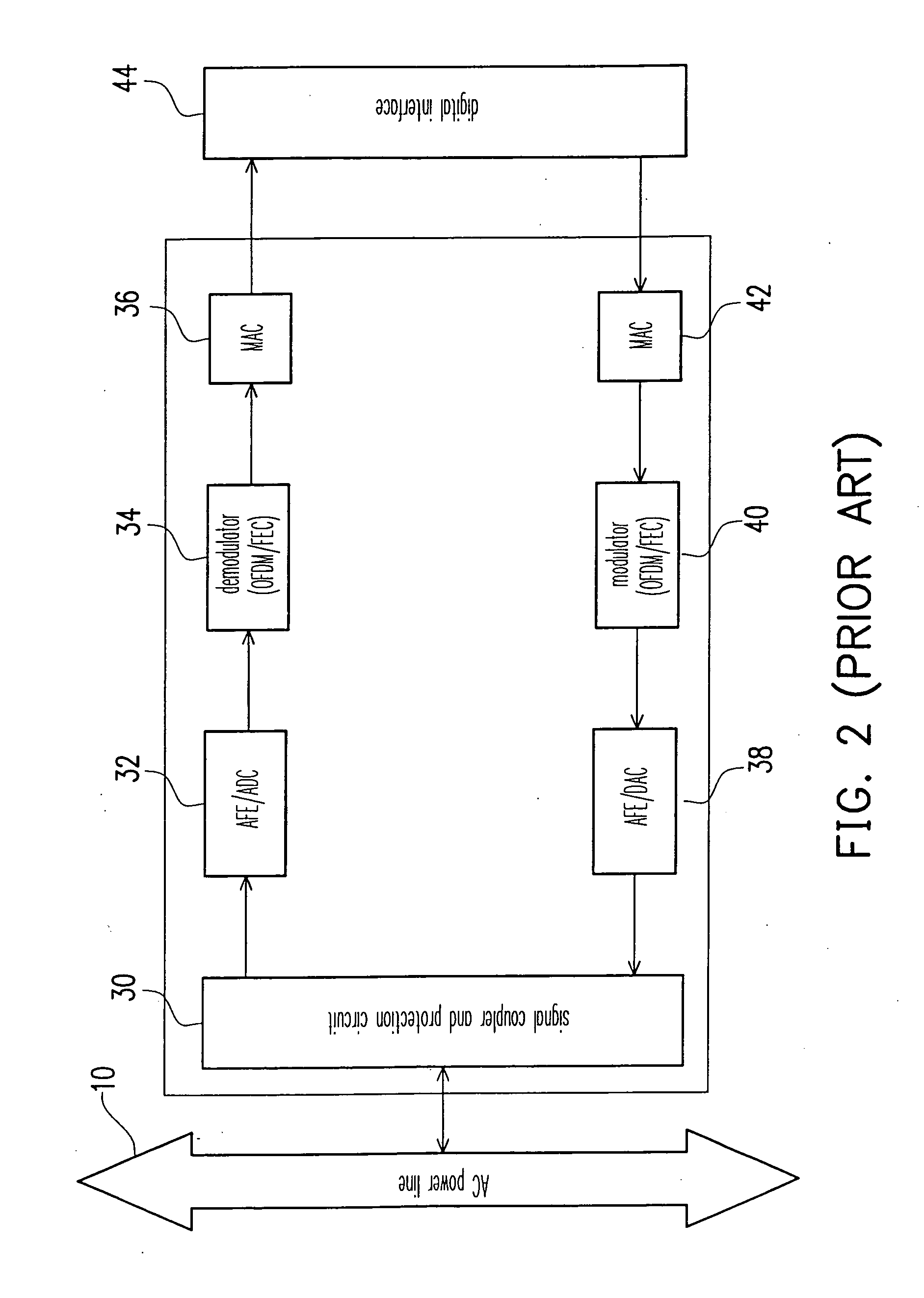

AC/DC power line communication modem

InactiveUS20070152628A1Batteries circuit arrangementsDynamo-electric motor metersVoltage converterModem device

An AC / DC power device for AC / DC power line communication is provided. An AC / DC protection circuit coupled to an AC / DC power line is able to receive an AC or DC power. An AC / DC configuration circuit coupled to the AC / DC protection circuit is used to switch between an AC mode and a DC mode PLC. An AC / DC coupling / filtering circuit coupled to the AC / DC configuration circuit is to couple and filter the received power, and then coupled an AC voltage or a first DC voltage. An AC / DC converter coupled to the AC / DC coupling / filtering circuit is used to convert the AC voltage into a second DC voltage. A DC / DC converter coupled to the AC / DC coupling / filtering circuit and the AC / DC converter is to convert the first DC voltage (DC mode) and convert the second DC voltage (AC mode), so as to output DC voltages respectively to analog and digital circuit of the PLC modem.

Owner:IND TECH RES INST

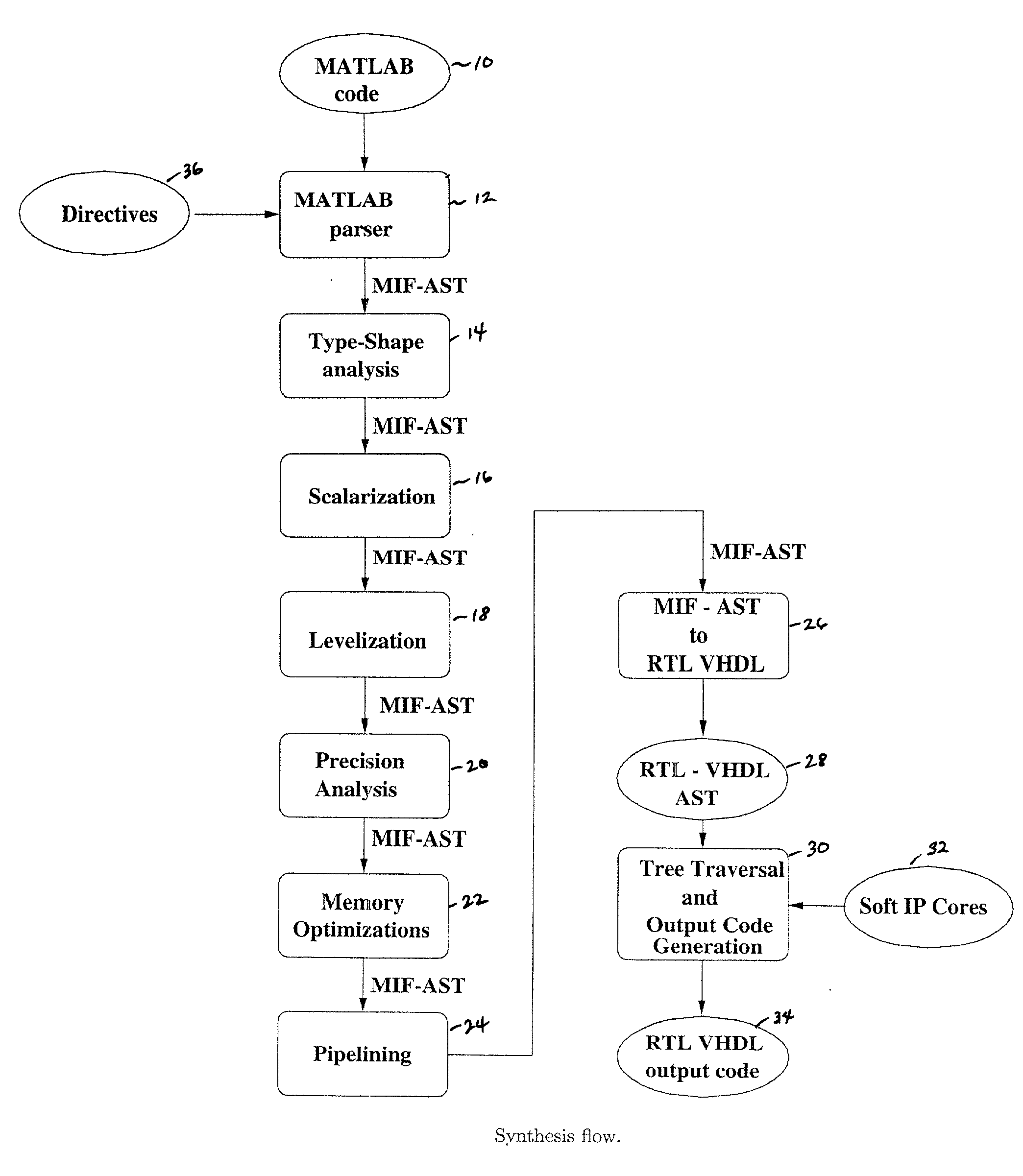

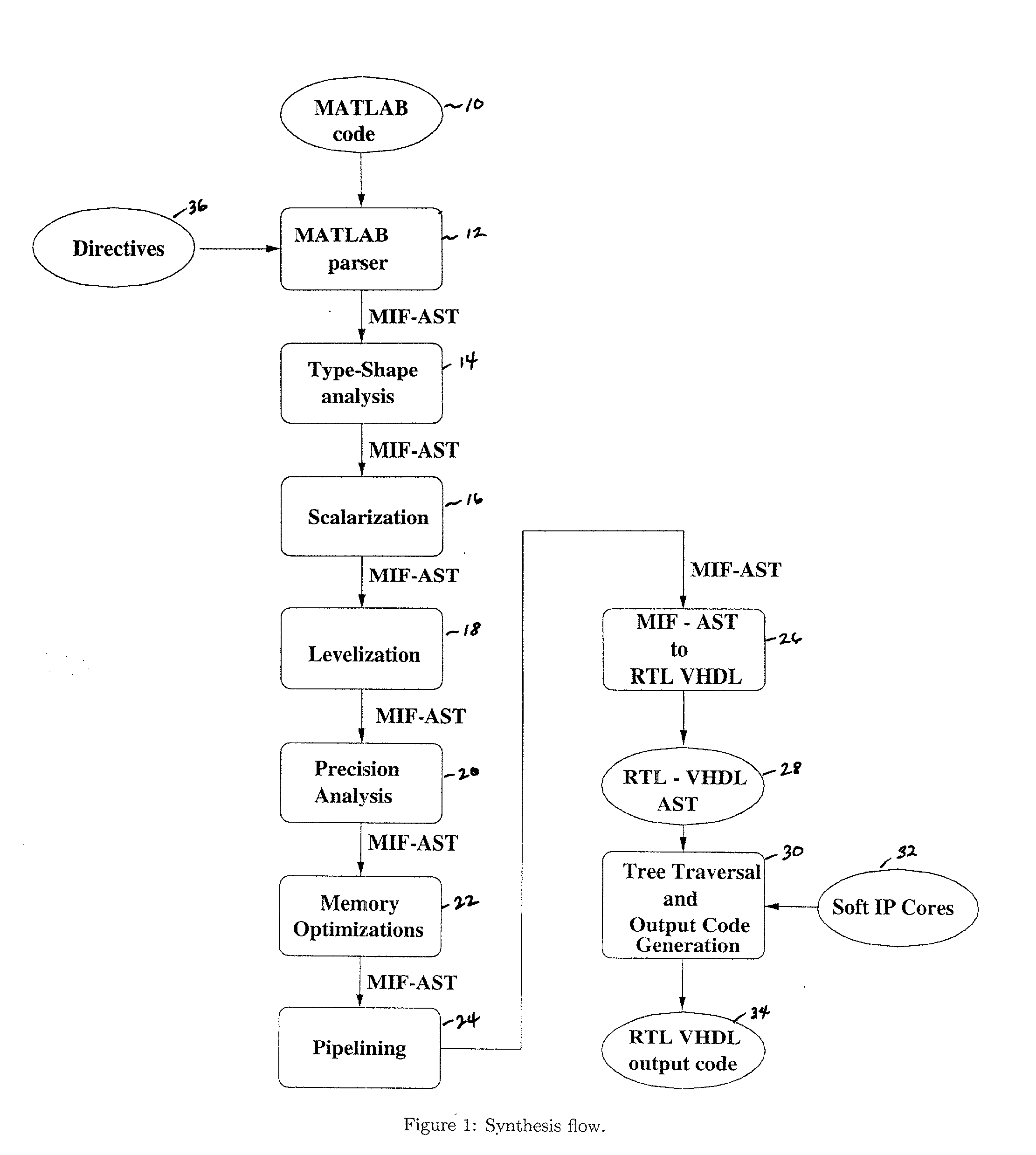

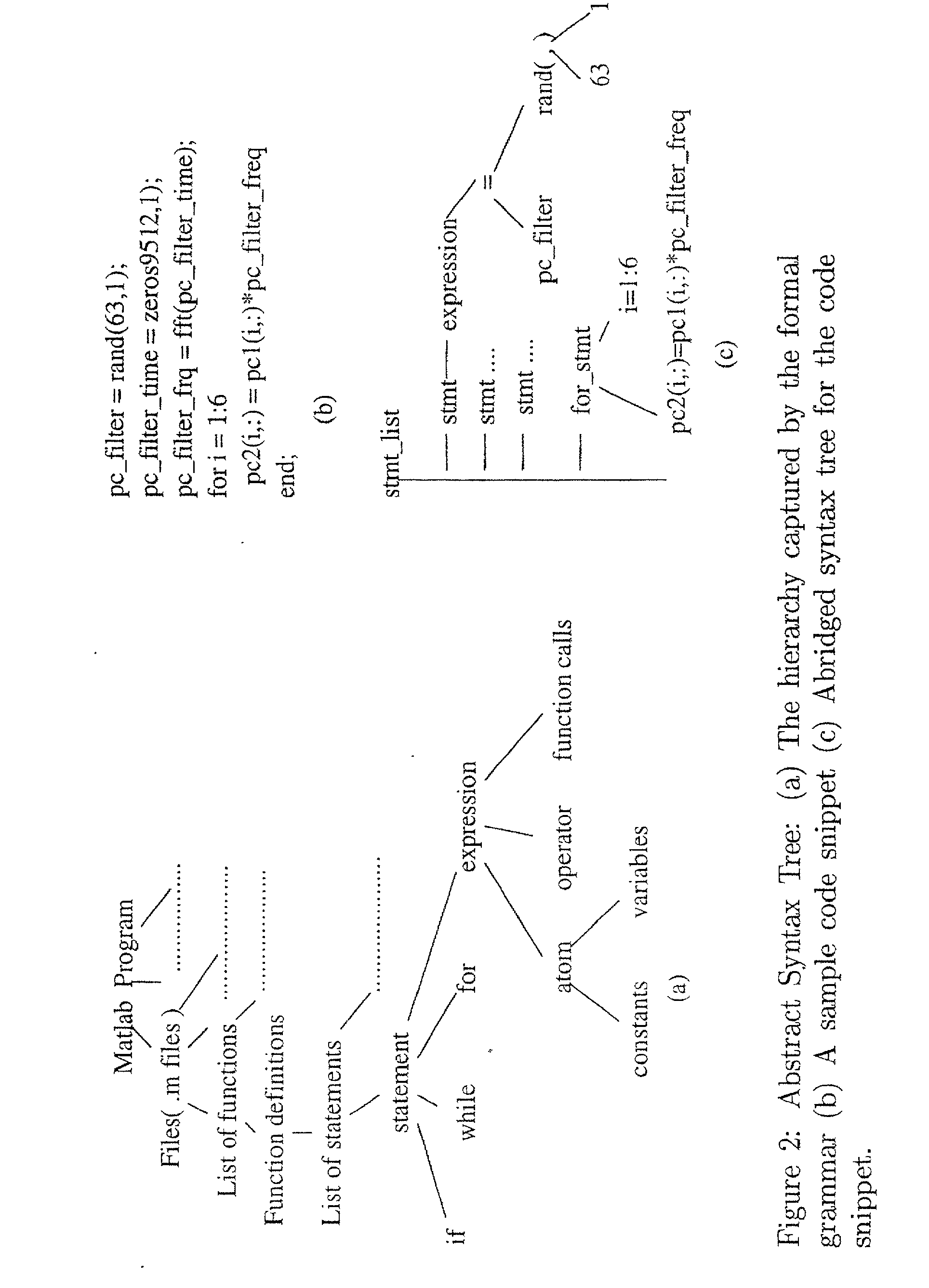

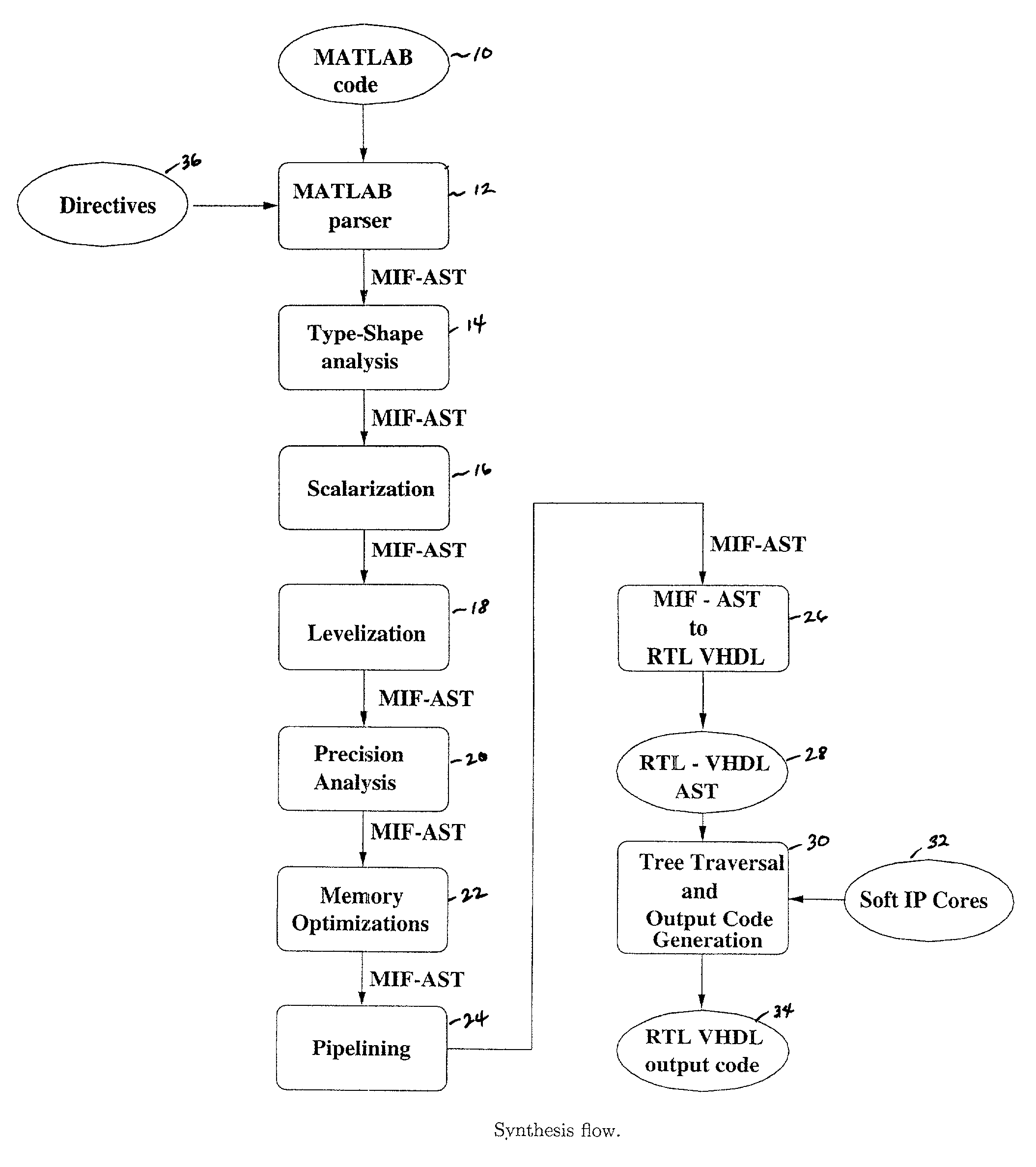

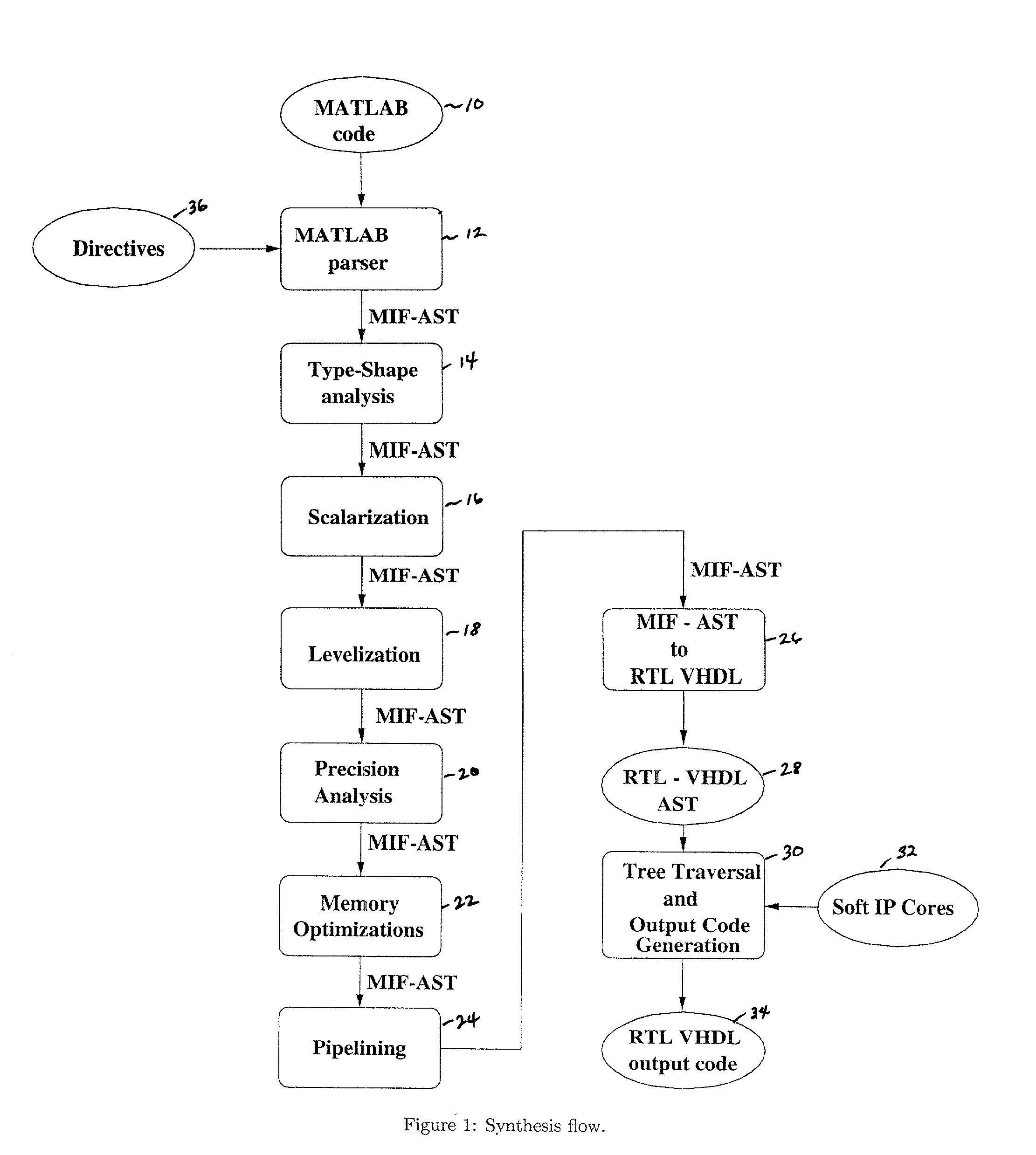

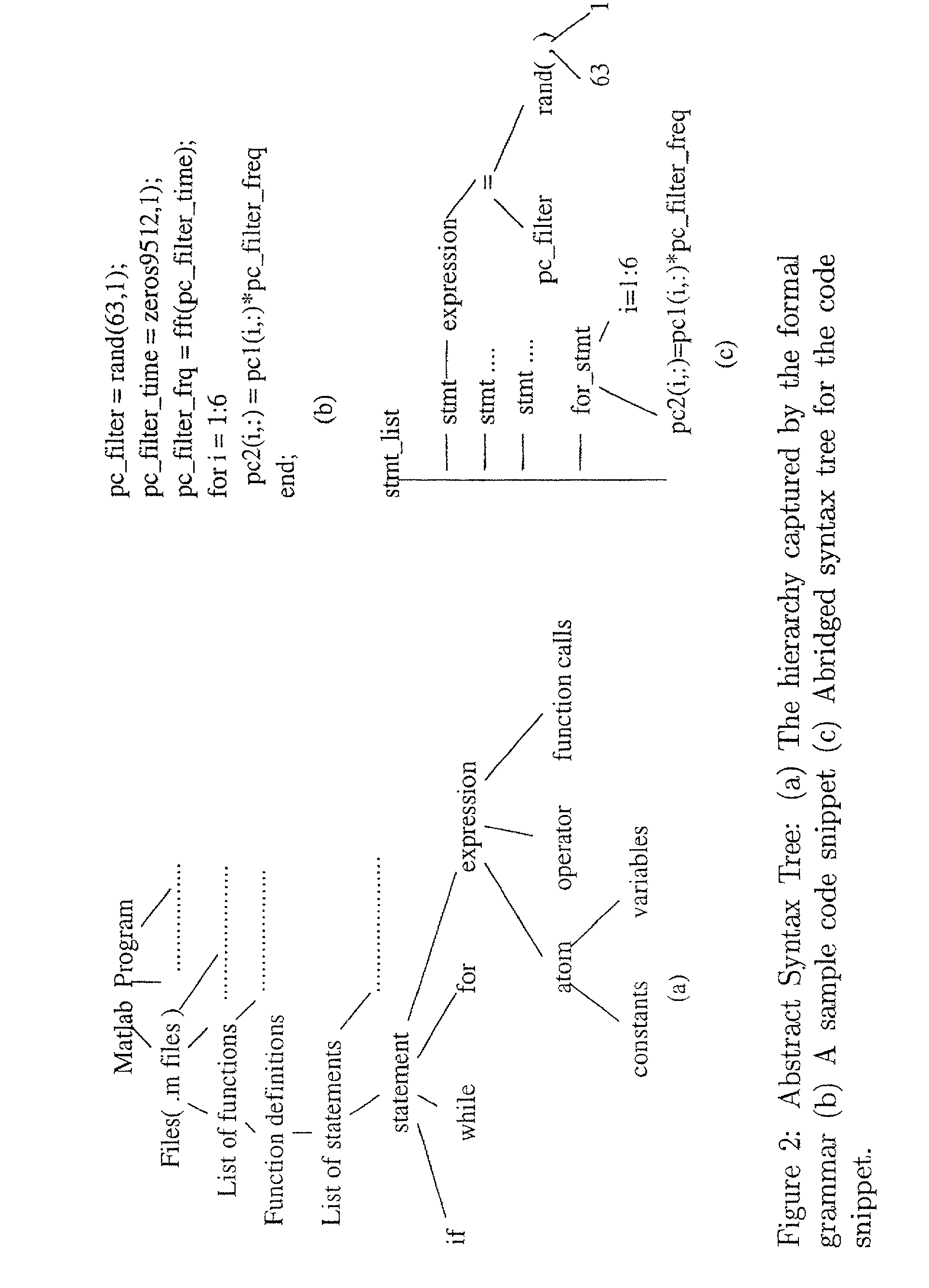

Method and apparatus for automatically generating hardware from algorithms described in matlab

Digital circuit is synthesized from algorithm described in the MATLAB programming language. A MATLAB program is compiled into RTL-VHDL, which is synthesizable using system-specific tools to develop ASIC or FPGA configuration. Intermediate transformations and optimizations are performed to obtain highly optimized description in RTL-VHDL or RTL Verilog of given MATLAB program. Optimizations include levelization, scalarization, pipelining, type-shape analysis, memory optimizations, precision analysis and scheduling.

Owner:NORTHWESTERN UNIV

Method and apparatus for automatically generating hardware from algorithms described in MATLAB

Digital circuit is synthesized from algorithm described in the MATLAB programming language. A MATLAB program is compiled into RTL-VHDL, which is synthesizable using system-specific tools to develop ASIC or FPGA configuration. Intermediate transformations and optimizations are performed to obtain highly optimized description in RTL-VHDL or RTL Verilog of given MATLAB program. Optimizations include levelization, scalarization, pipelining, type-shape analysis, memory optimizations, precision analysis and scheduling.

Owner:NORTHWESTERN UNIV

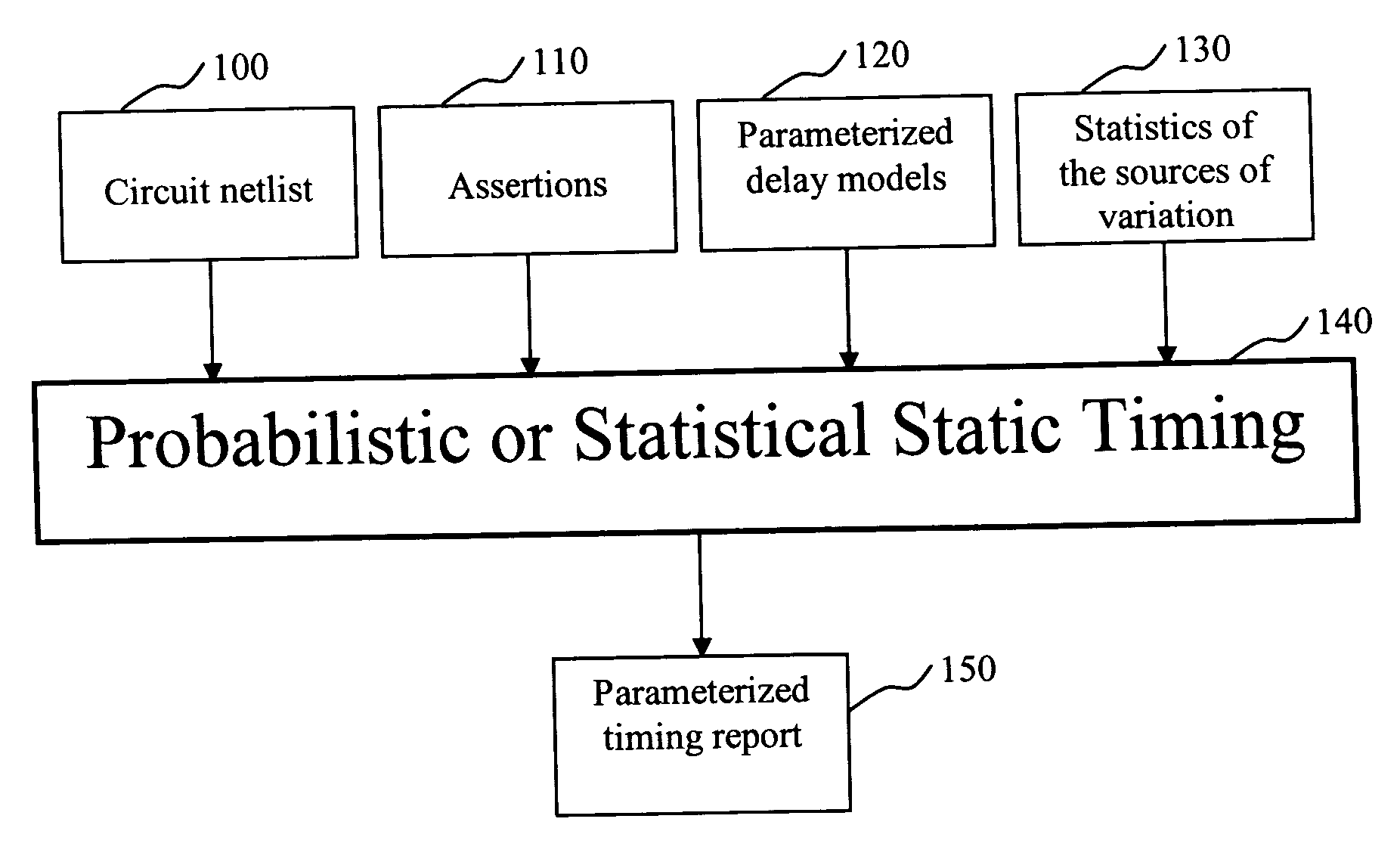

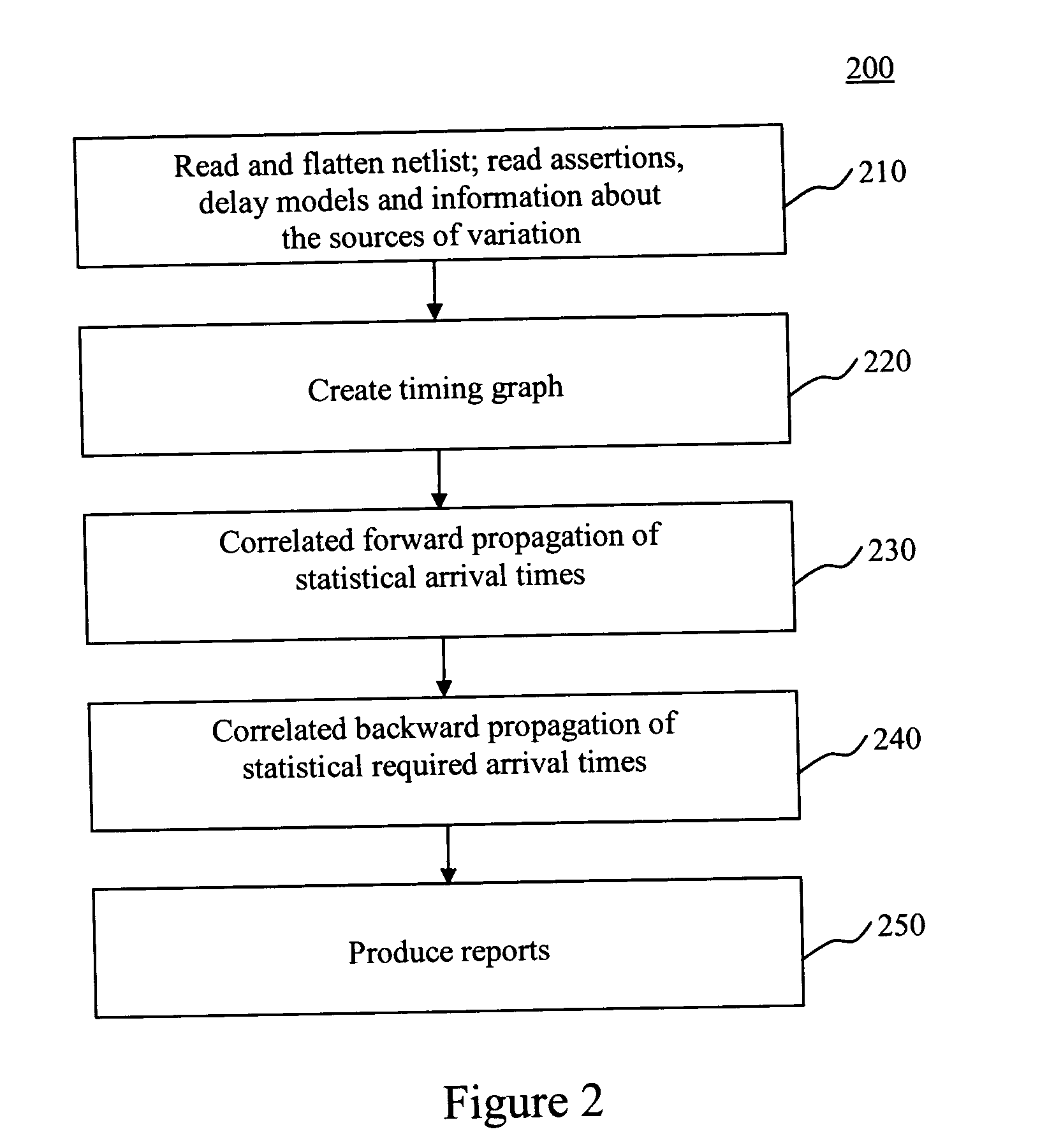

System and method for statistical timing analysis of digital circuits

ActiveUS20050065765A1Semiconductor/solid-state device manufacturingComputation using non-denominational number representationCMOSTheoretical computer science

The present invention is a system and method for statistical or probabilistic static timing analysis of digital circuits, taking into account statistical delay variations. The delay of each gate or wire is assumed to consist of a nominal portion, a correlated random portion that is parameterized by each of the sources of variation and an independent random portion. Arrival times and required arrival times are propagated as parameterized random variables while taking correlations into account. Both early mode and late mode timing are included; both combinational and sequential circuits are handled; static CMOS as well as dynamic logic families are accommodated. The timing analysis complexity is linear in the size of the graph and the number of sources of variation. The result is a timing report in which all timing quantities such as arrival times and slacks are reported as probability distributions in a parameterized form.

Owner:GLOBALFOUNDRIES US INC

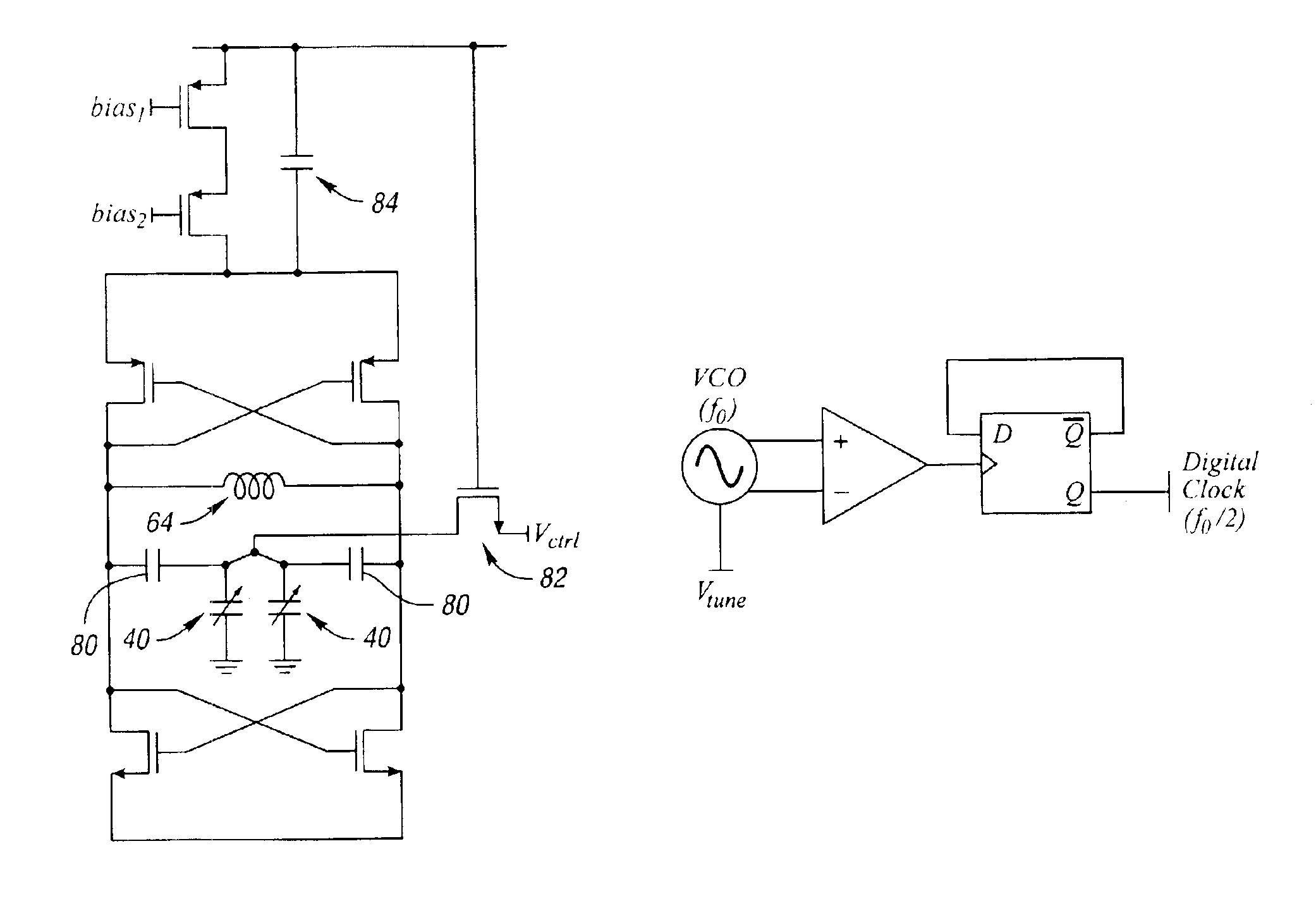

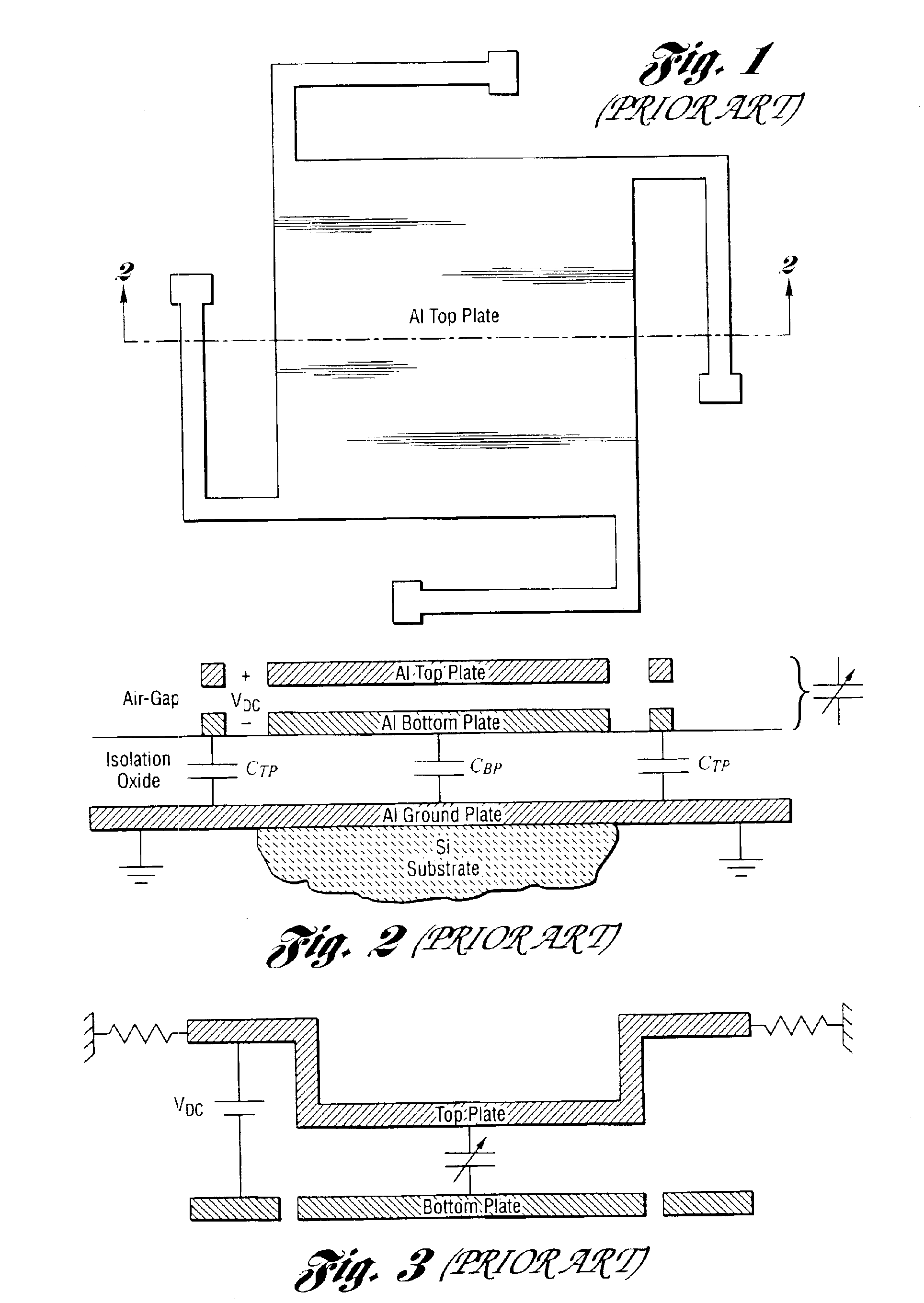

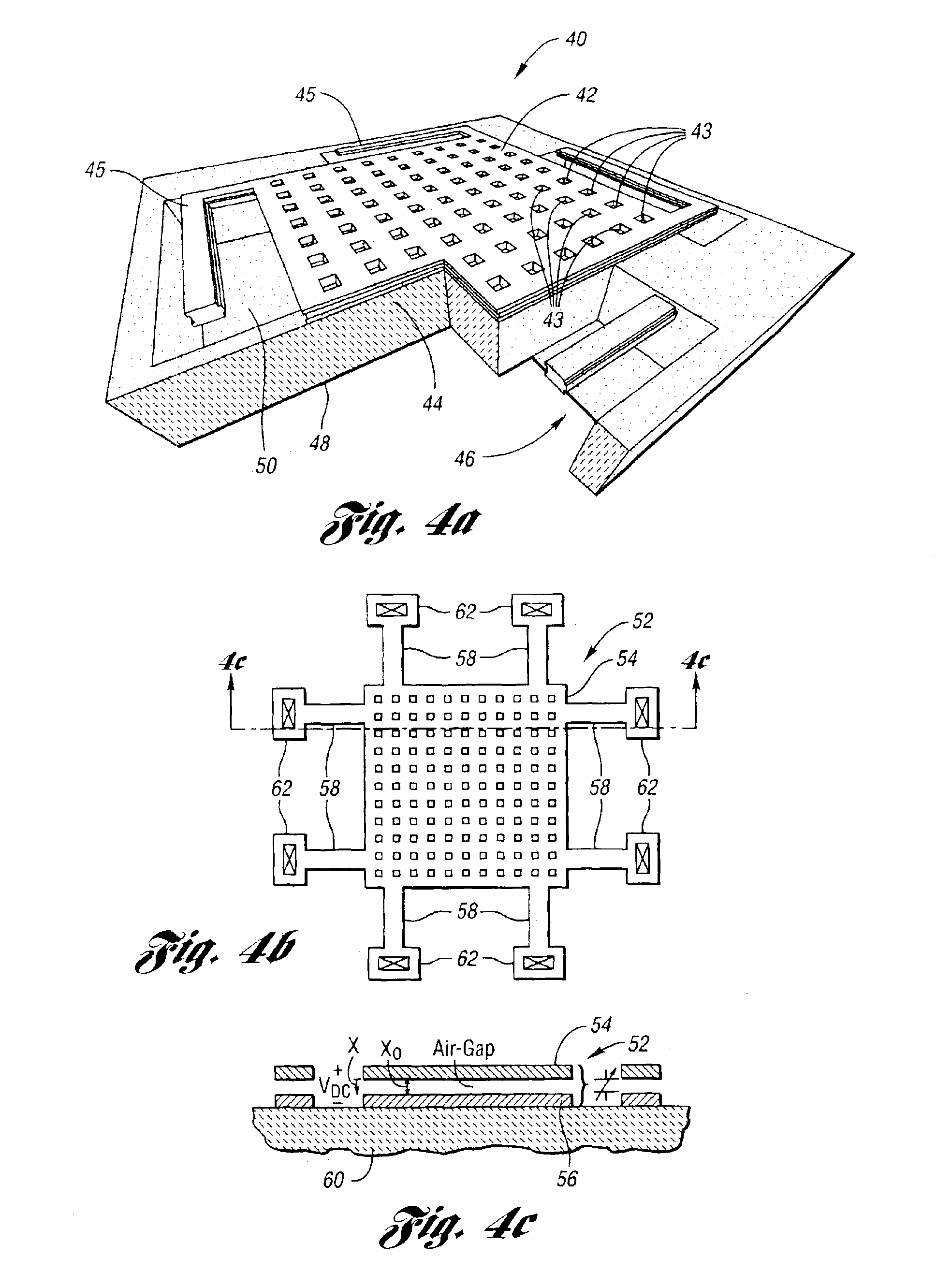

MEMS-based, computer systems, clock generation and oscillator circuits and LC-tank apparatus for use therein

InactiveUS6972635B2Reduce flicker noiseReduce phase noiseAngle modulation by variable impedenceMultiple-port networksEngineeringVaricap

MEMS-based, computer system, clock generation and oscillator circuits and LC-tank apparatus for use therein are provided and which are fabricated using a CMOS-compatible process. A micromachined inductor (L) and a pair of varactors (C) are developed in metal layers on a silicon substrate to realize the high quality factor LC-tank apparatus. This micromachined LC-tank apparatus is incorporated with CMOS transistor circuitry in order to realize a digital, tunable, low phase jitter, and low power clock, or time base, for synchronous integrated circuits. The synthesized clock signal can be divided down with digital circuitry from several GHz to tens of MHz—a systemic approach that substantially improves stability as compared to the state of the art. Advanced circuit design techniques have been utilized to minimize power consumption and mitigate transistor flicker noise upconversion, thus enhancing clock stability.

Owner:RGT UNIV OF MICHIGAN

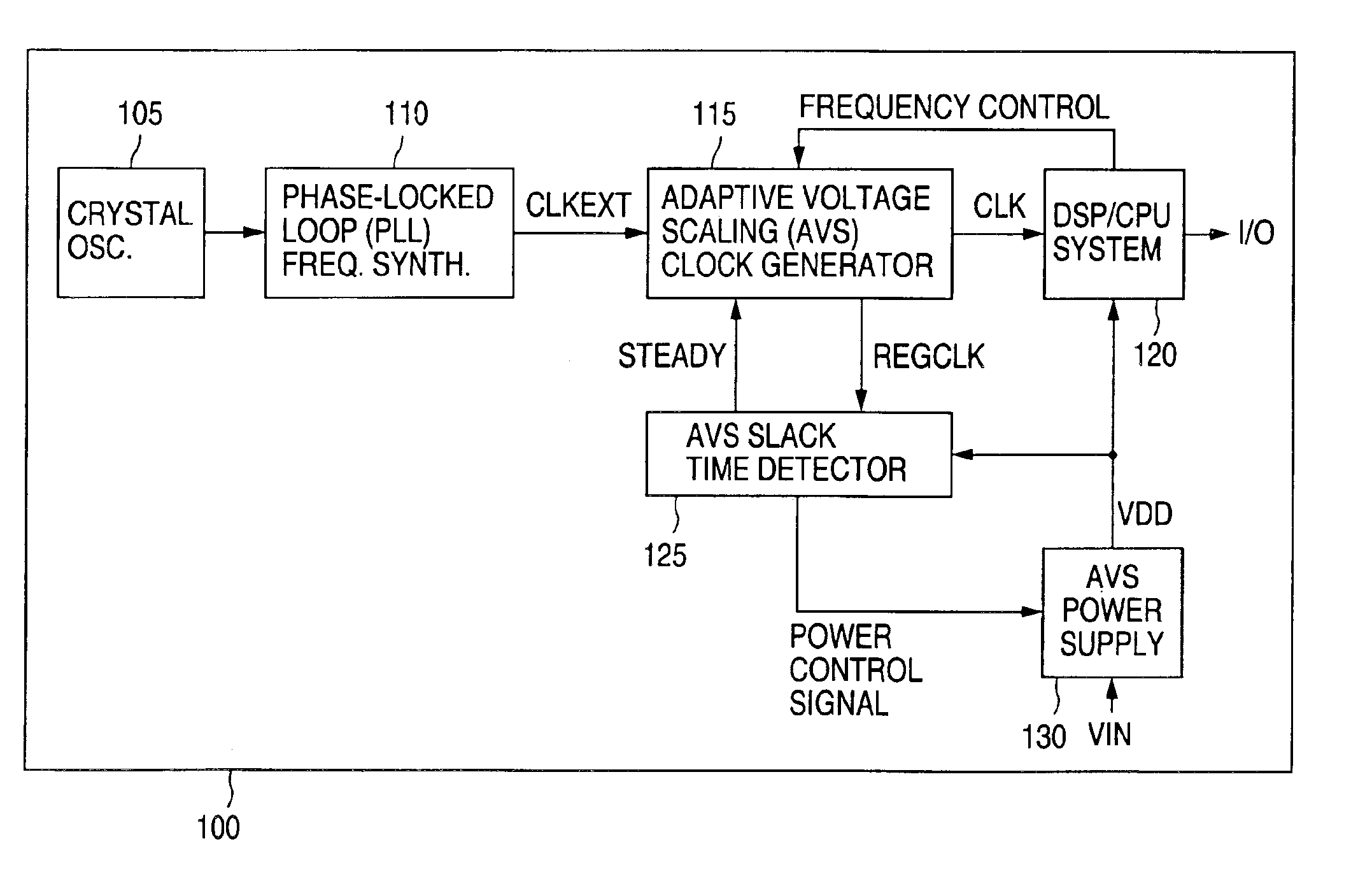

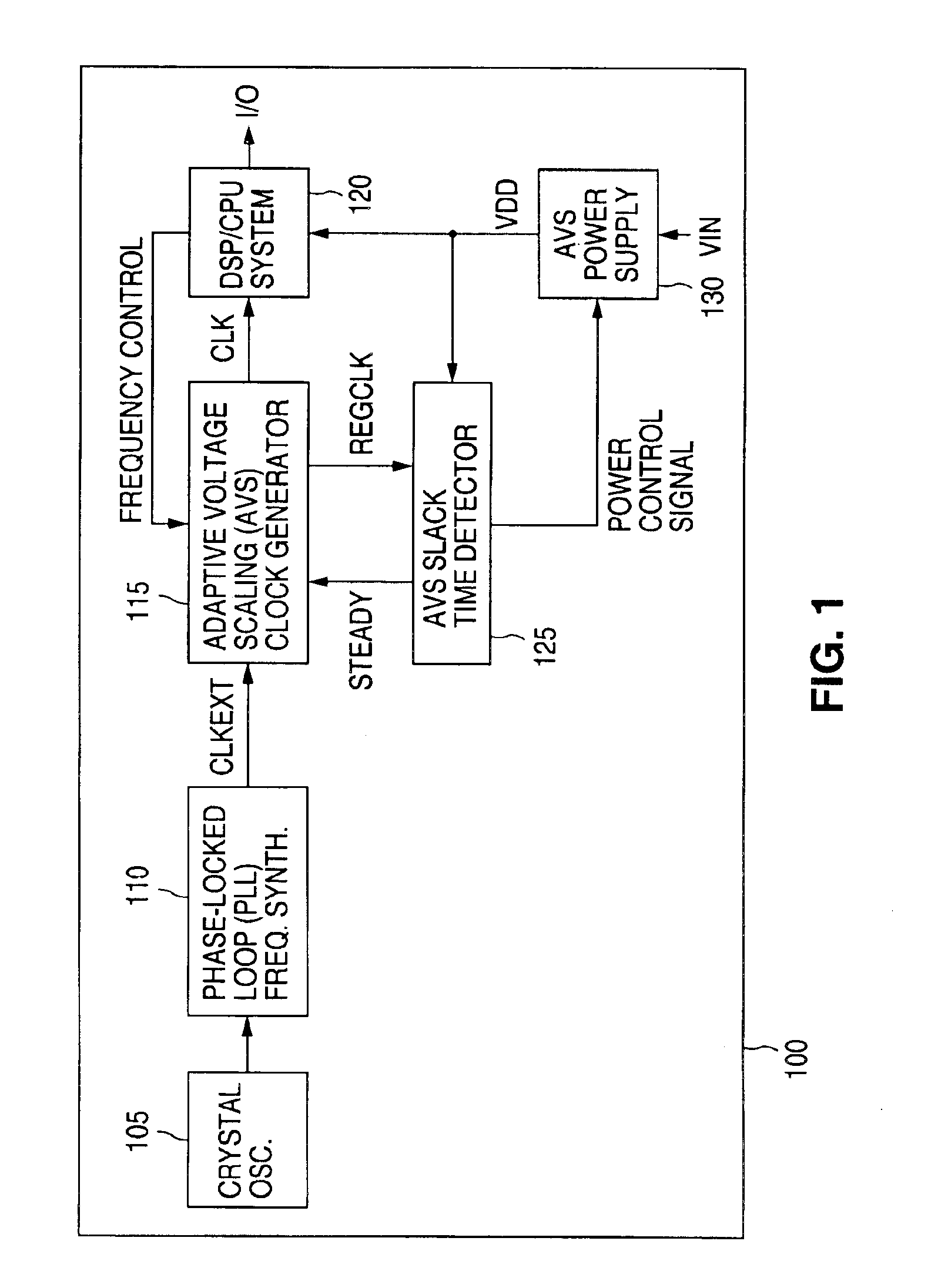

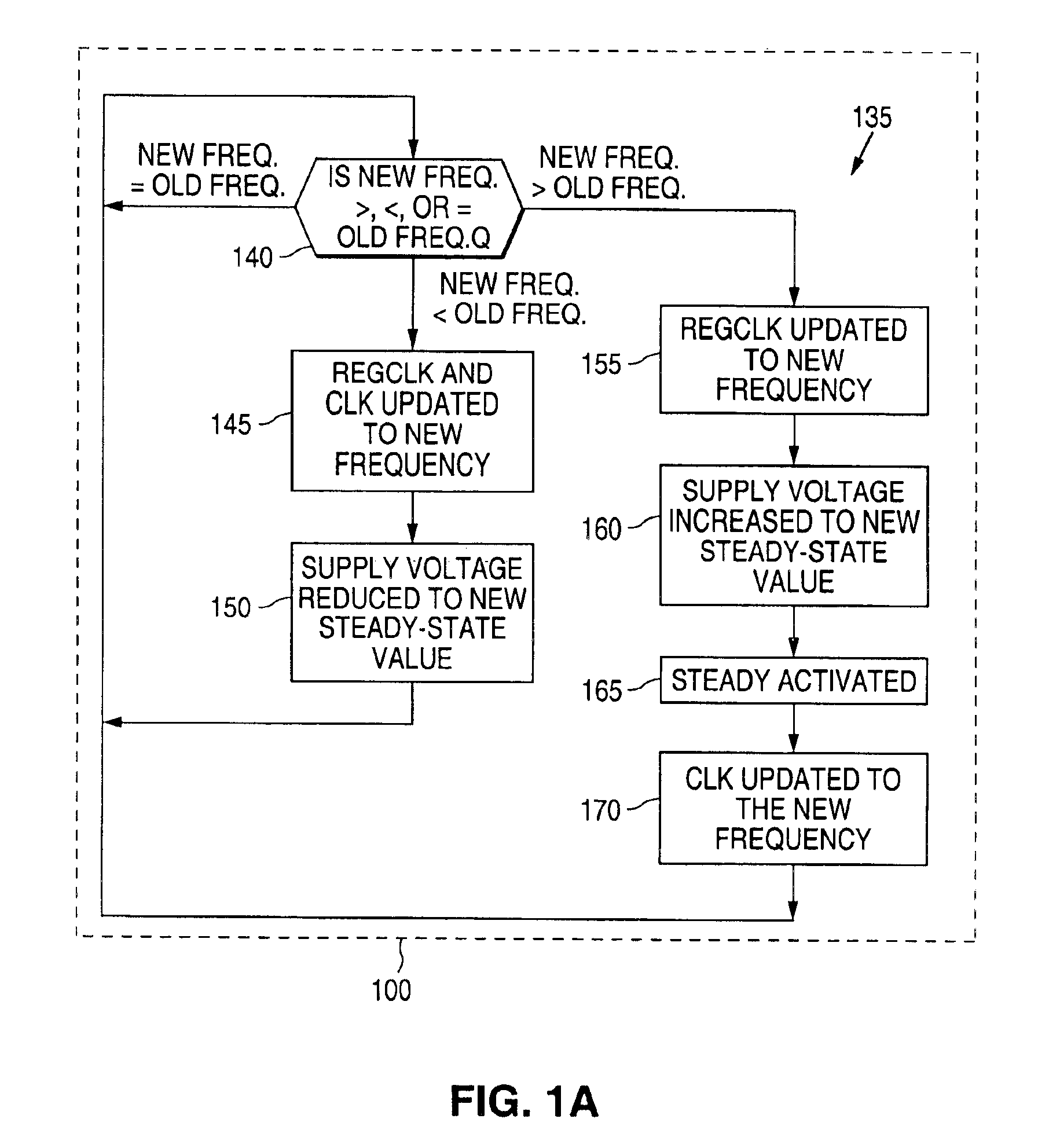

Adaptive voltage scaling digital processing component and method of operating the same

There is disclosed a digital circuit comprising a digital processing component, an adjustable power supply and power supply adjustment circuitry. The digital processing component is capable of operating at a plurality of selected clock frequencies, wherein a maximum delay time of a critical path in the digital processing component is determined by a level of a power supply, VDD, of the digital processing component. The adjustable power supply is capable of supplying VDD to the digital processing component. The power supply adjustment circuitry is operable to receive a first selected clock signal and adjusts the level of VDD such that the maximum delay time of the critical path of the digital processing component is less than a pulse-width duration between a first clock edge of the first selected clock signal and a second clock edge of the first selected clock signal immediately following the first clock edge.

Owner:NAT SEMICON CORP

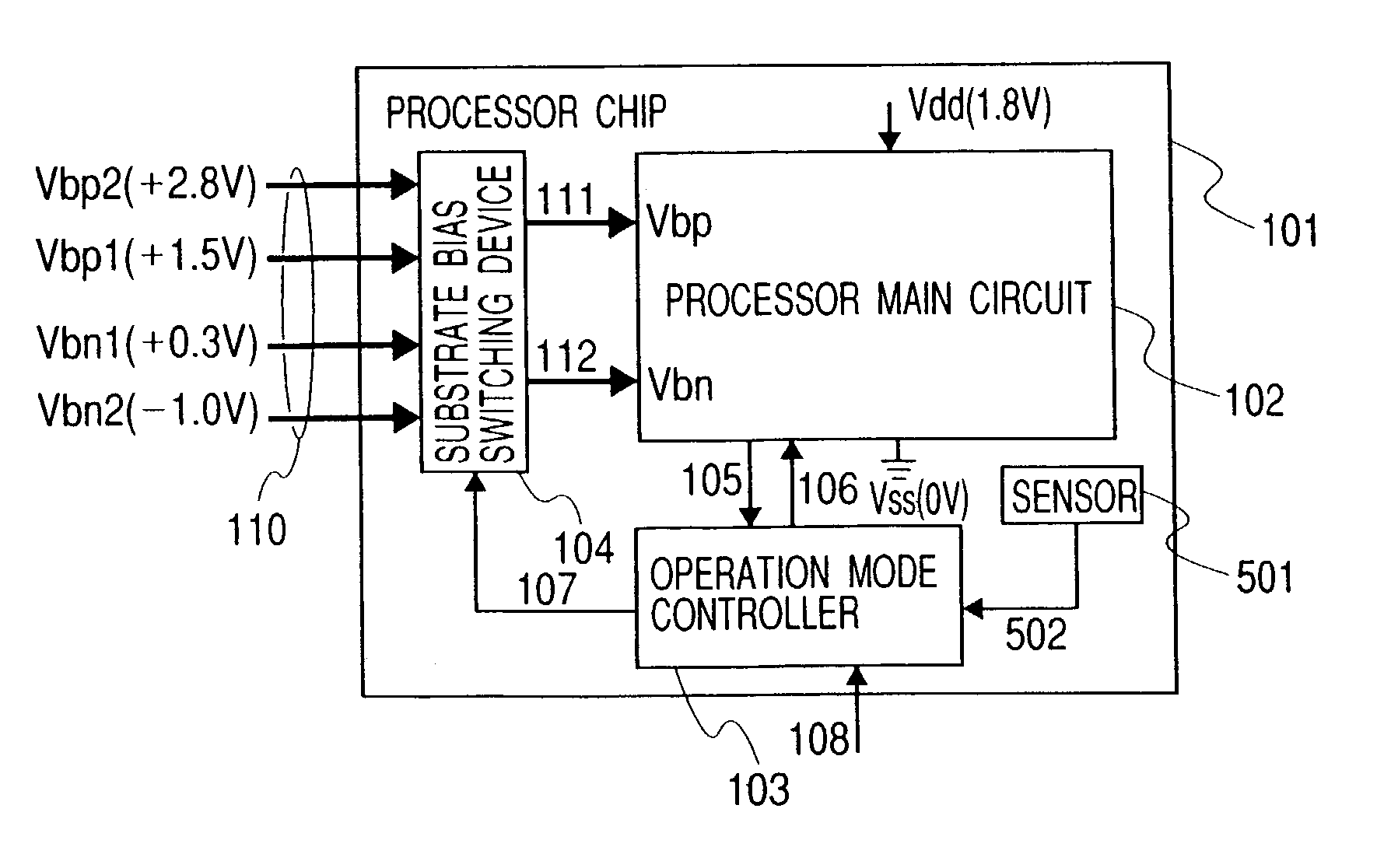

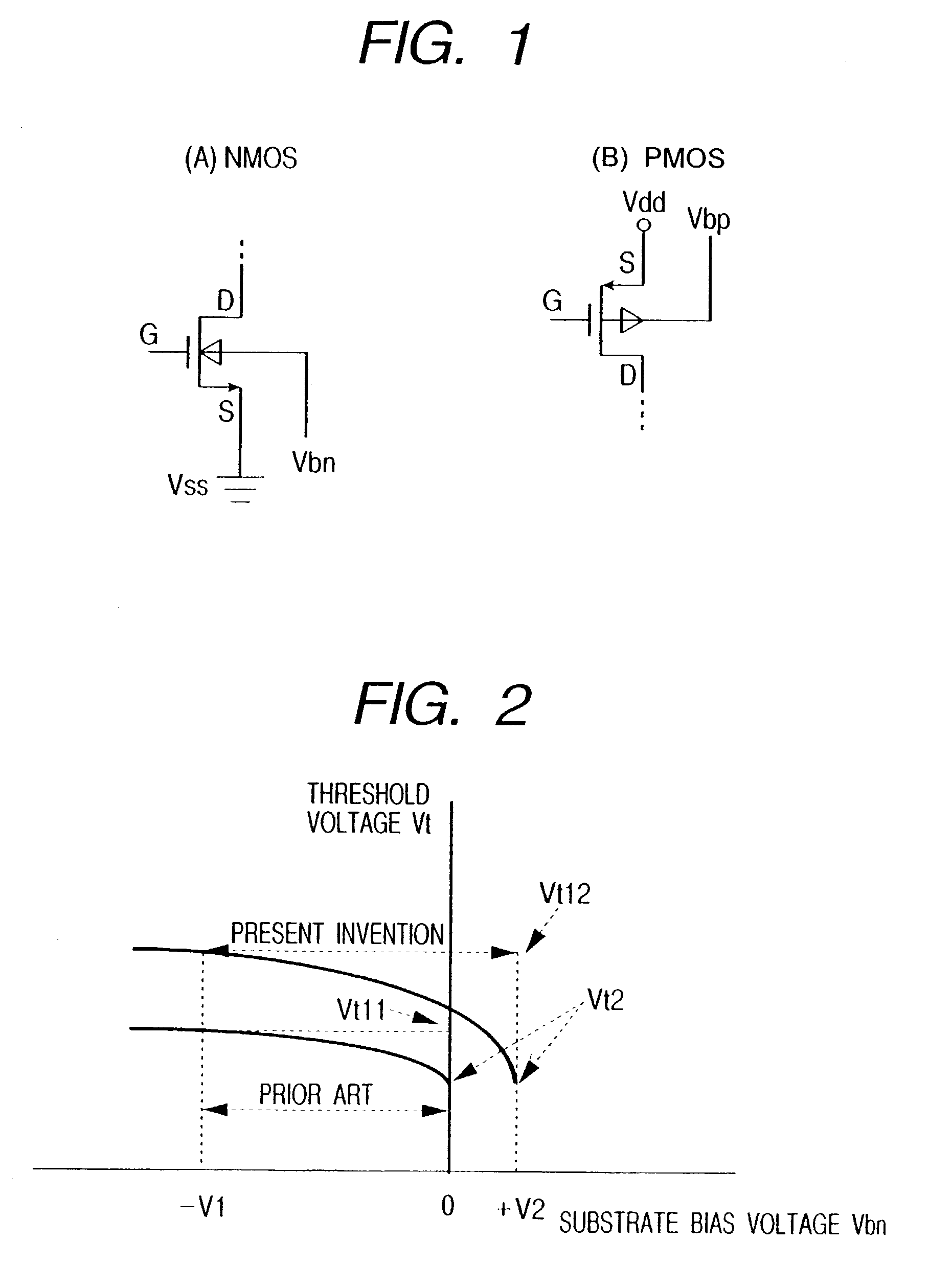

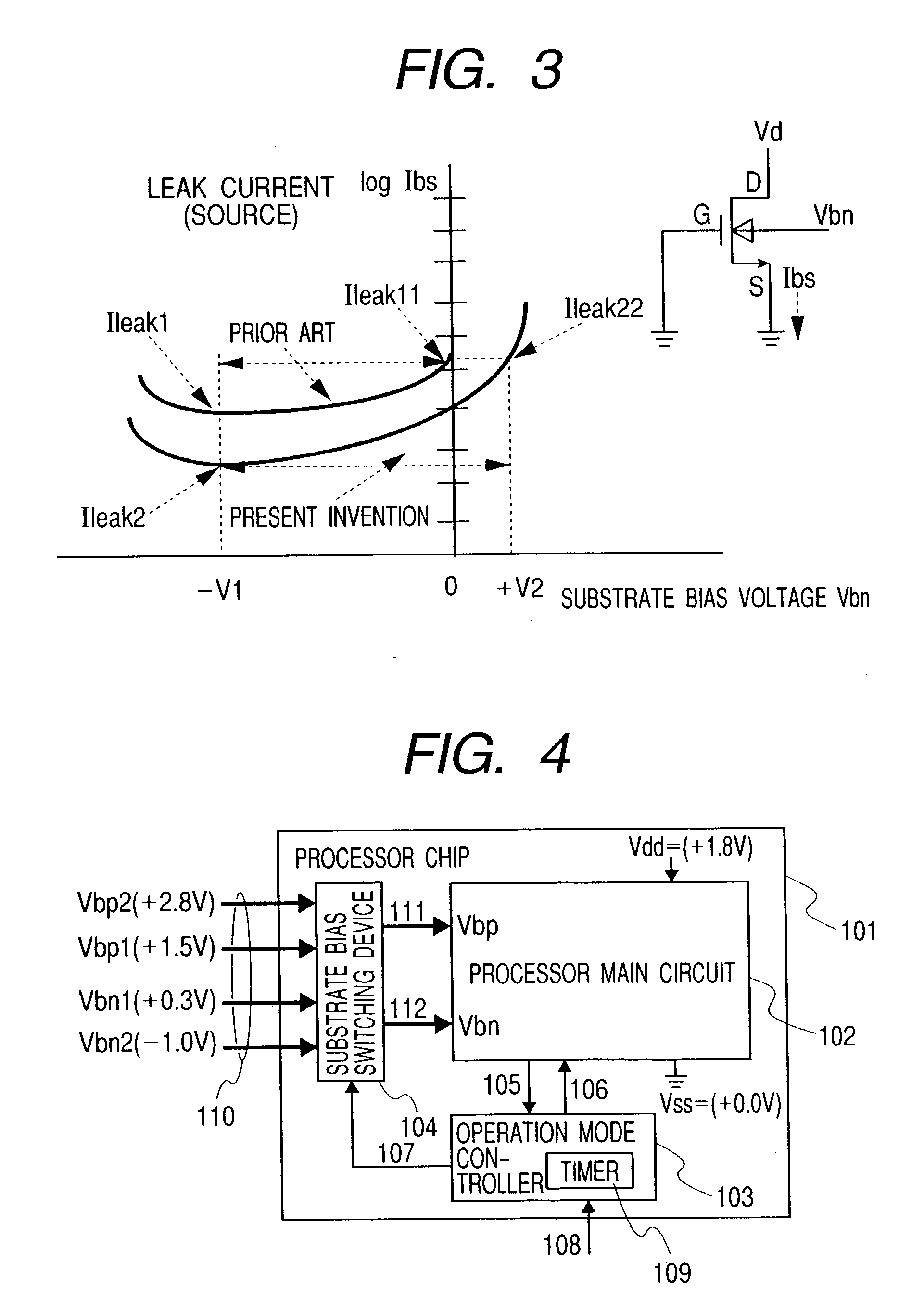

Method of setting back bias of MOS circuit, and MOS integrated circuit

In a MOS circuit comprising a plurality of MOSFETs constituting a digital circuit, an input signal is supplied to the digital circuit, and a first back bias voltage is supplied to a semiconductor substrate or a semiconductor well region in which the MOSFETs are formed, so that a pn junction between the semiconductor substrate or the semiconductor well region and a source region is brought to a forward voltage. In a non-operating state in which a circuit operation is suspended by the input signal supplied to the digital circuit as a fixed level, a second back bias voltage is applied to the semiconductor substrate or the semiconductor well region so that the pn junction between the semiconductor substrate or the semiconductor well region and the source region is brought to a reverse voltage.

Owner:RENESAS ELECTRONICS CORP