Patents

Literature

151 results about "VHDL" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

VHDL (VHSIC-HDL) (Very High Speed Integrated Circuit Hardware Description Language) is a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits. VHDL can also be used as a general purpose parallel programming language.

Polymorphic computational system and method in signals intelligence analysis

ActiveUS7386833B2Multiple digital computer combinationsComputer aided designLogic emulationSignals intelligence

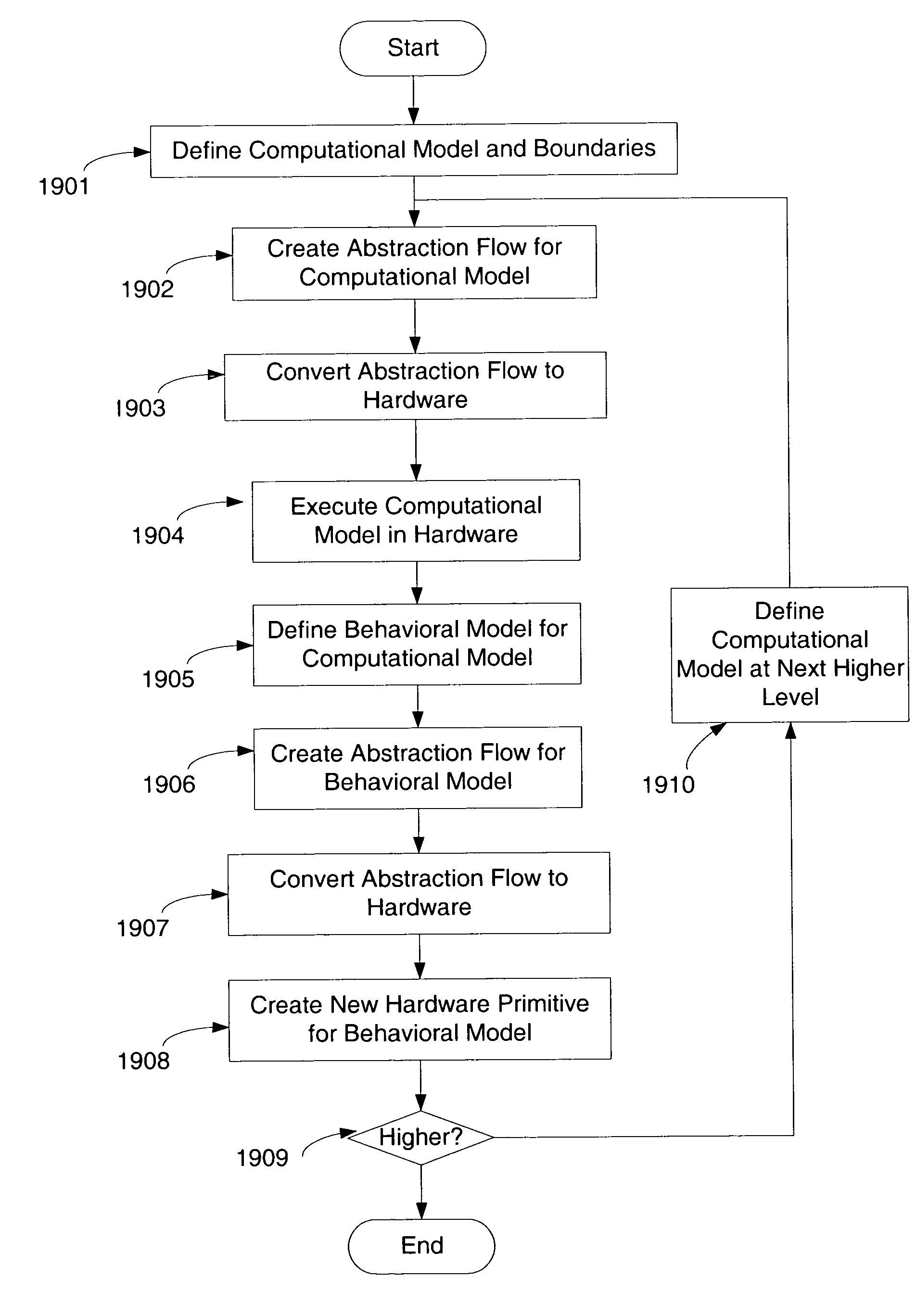

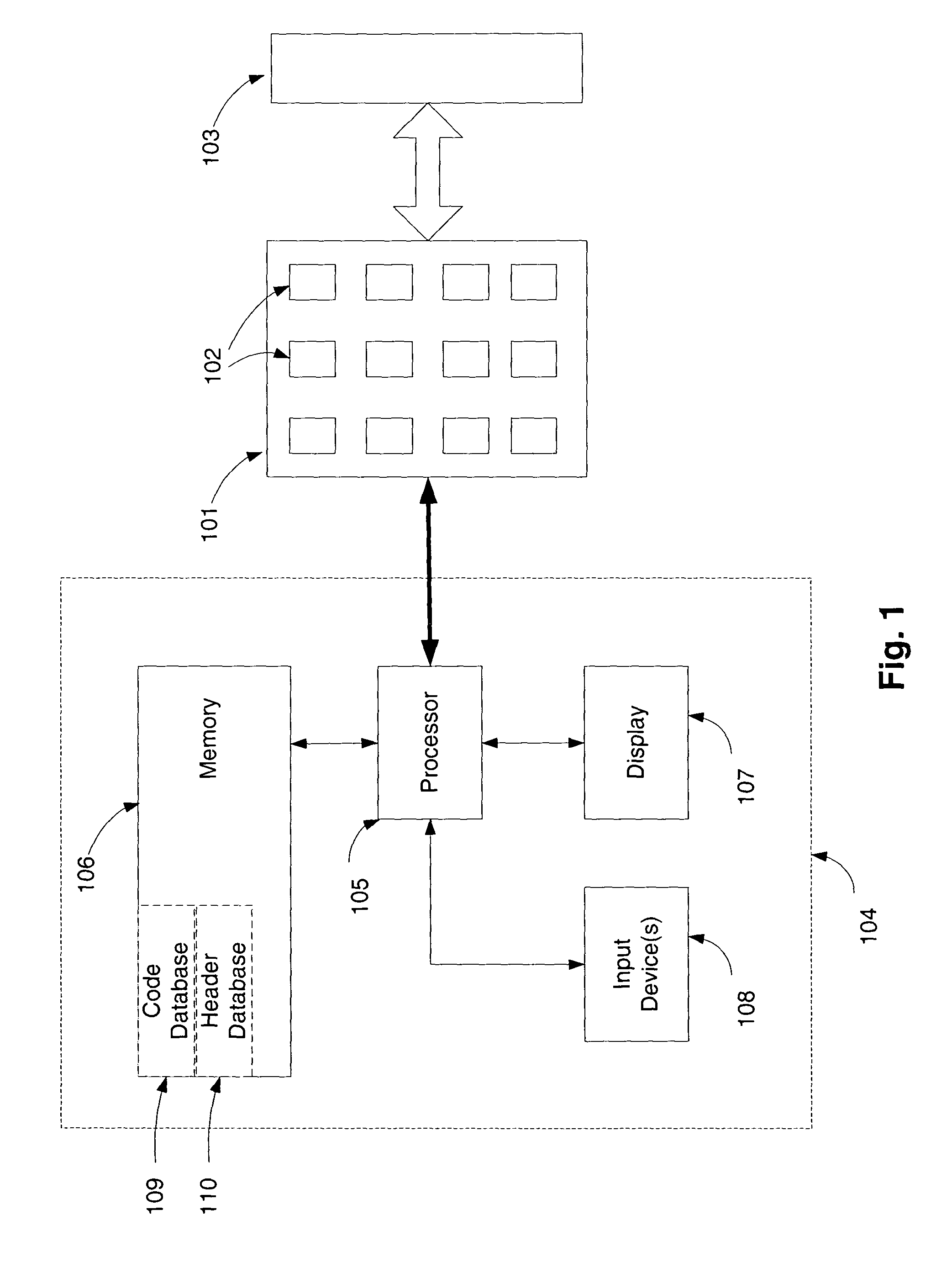

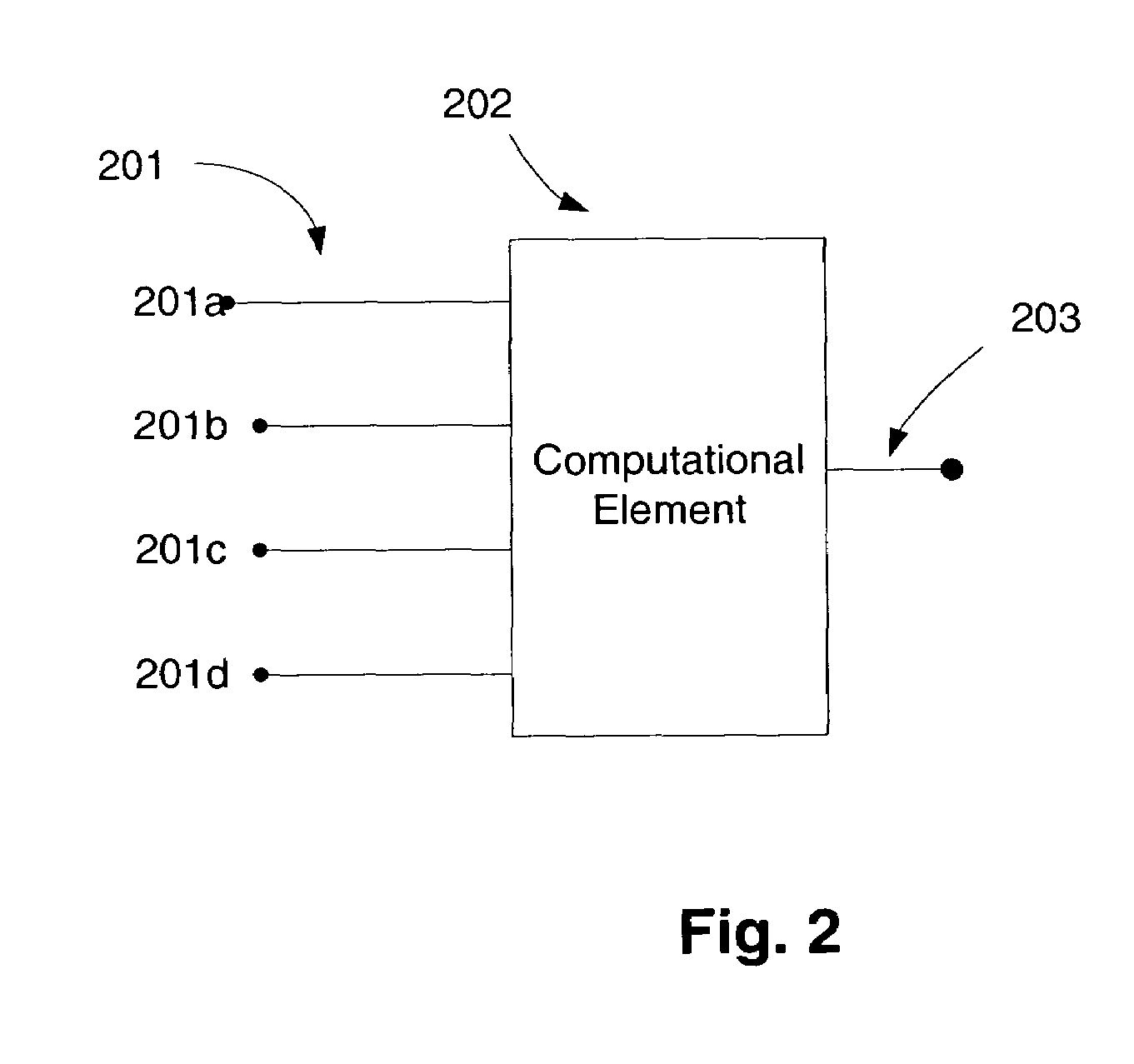

Configuration software is used for generating hardware-level code and data that may be used with reconfigurable / polymorphic computing platforms, such as logic emulators, and which may be used for conducting signals intelligence analysis, such as encryption / decryption processing, image analysis, etc. A user may use development tools to create visual representations of desired process algorithms, data structures, and interconnections, and system may generate intermediate data from this visual representation. The Intermediate data may be used to consult a database of predefined code segments, and segments may be assembled to generate monolithic block of hardware syhthesizable (RTL, VHDL, etc.) code for implementing the user's process in hardware. Efficiencies may be accounted for to minimize circuit components or processing time. Floating point calculations may be supported by a defined data structure that is readily implemented in hardware.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Method and apparatus for automatically generating hardware from algorithms described in matlab

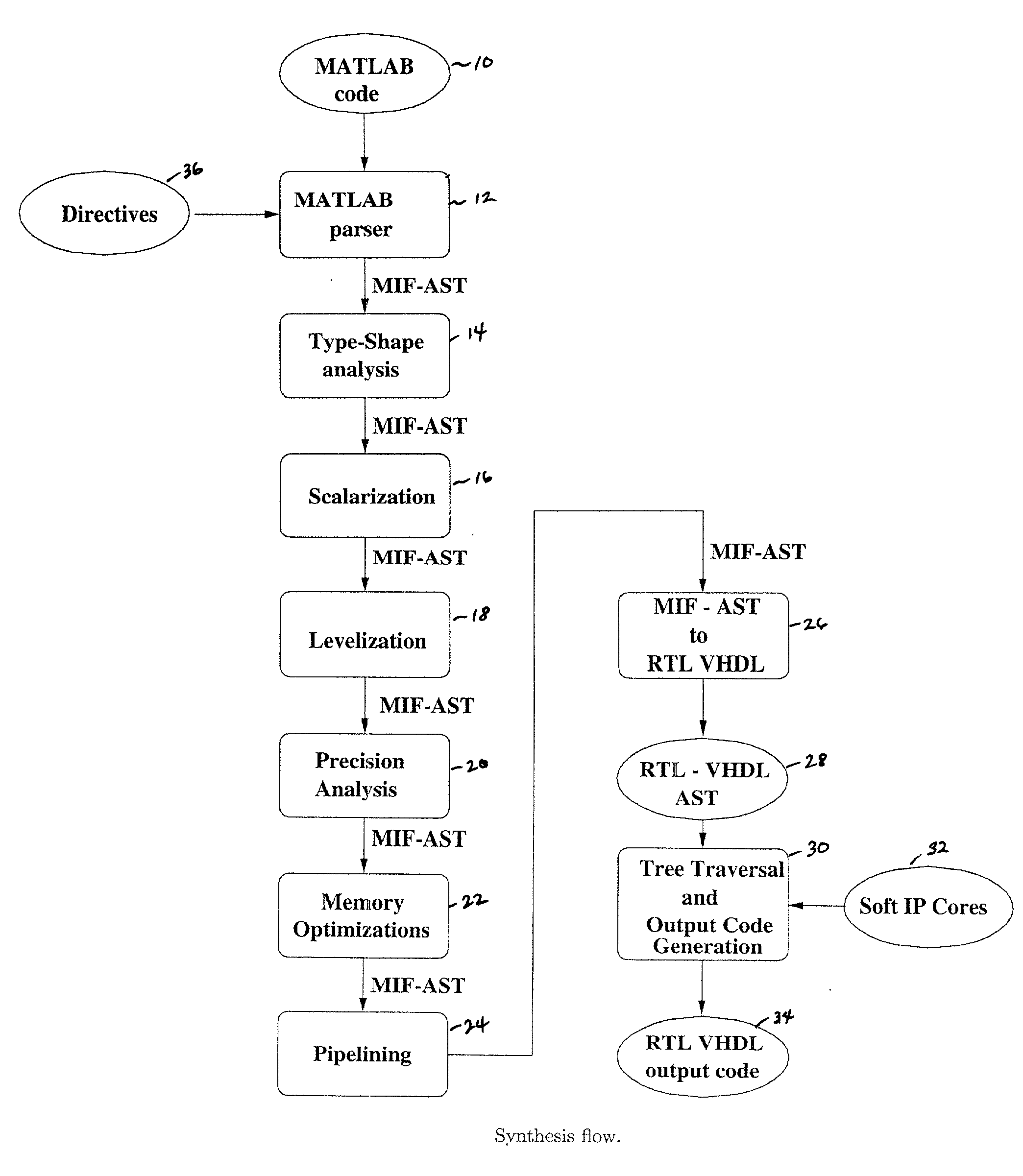

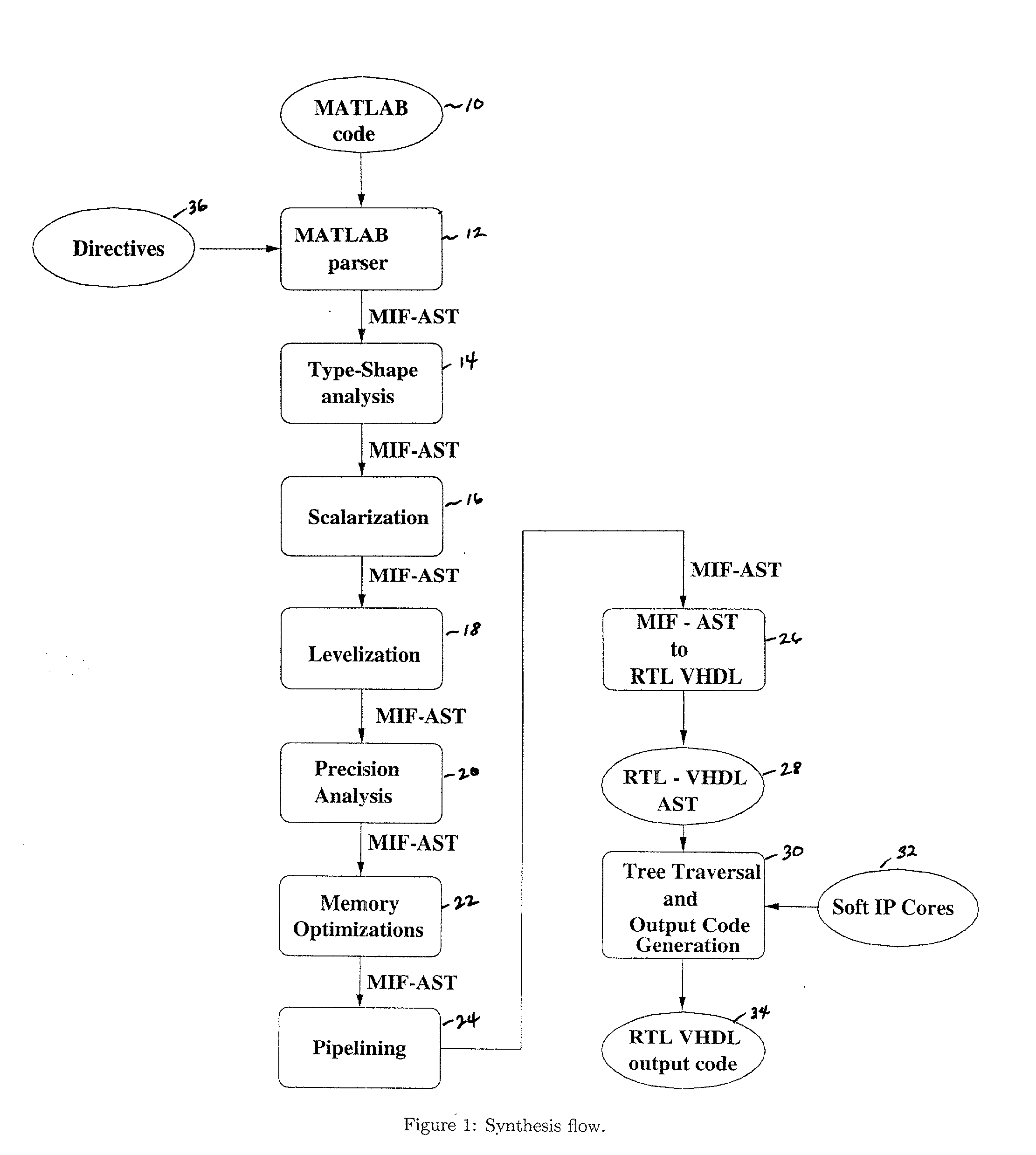

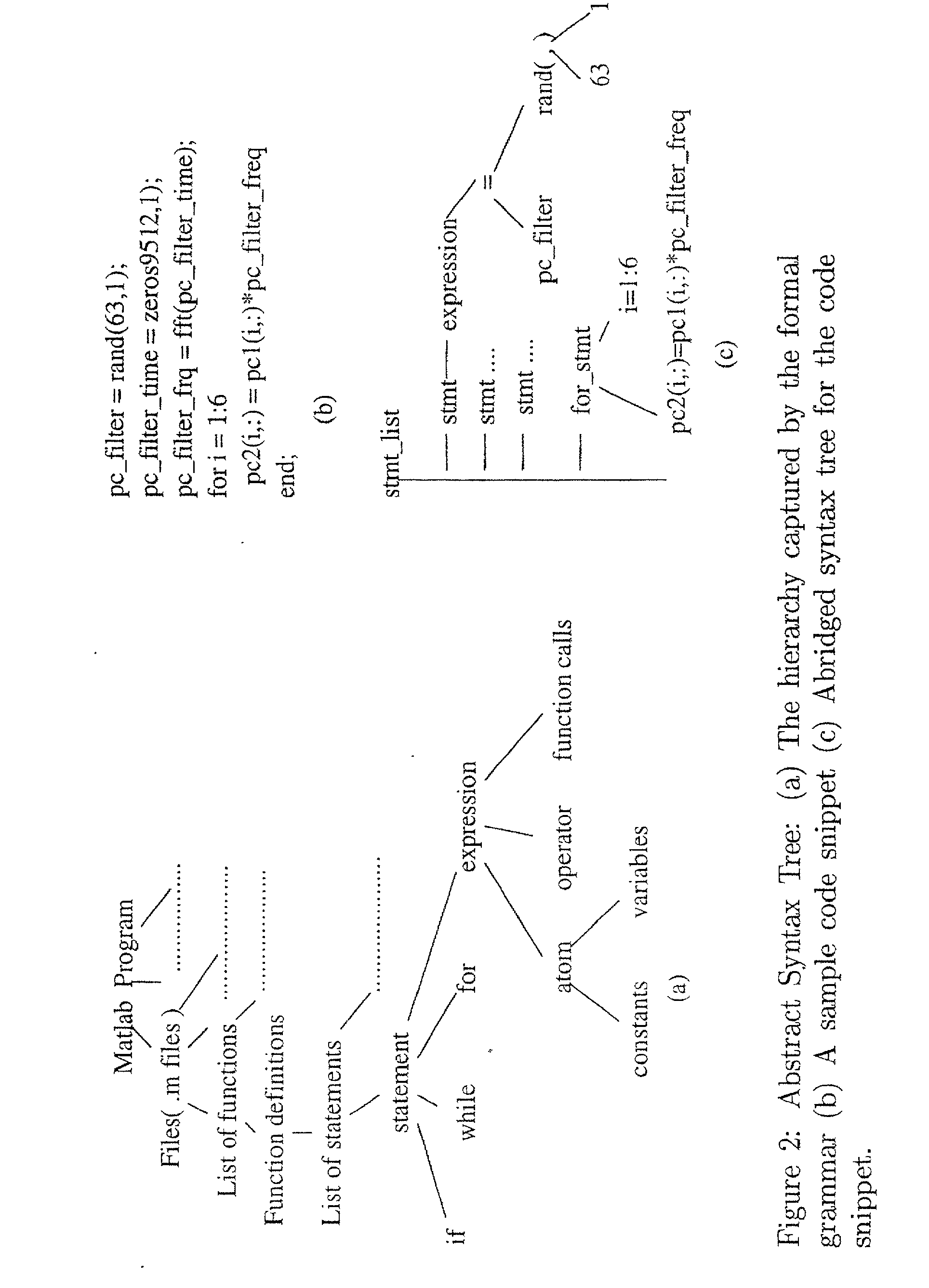

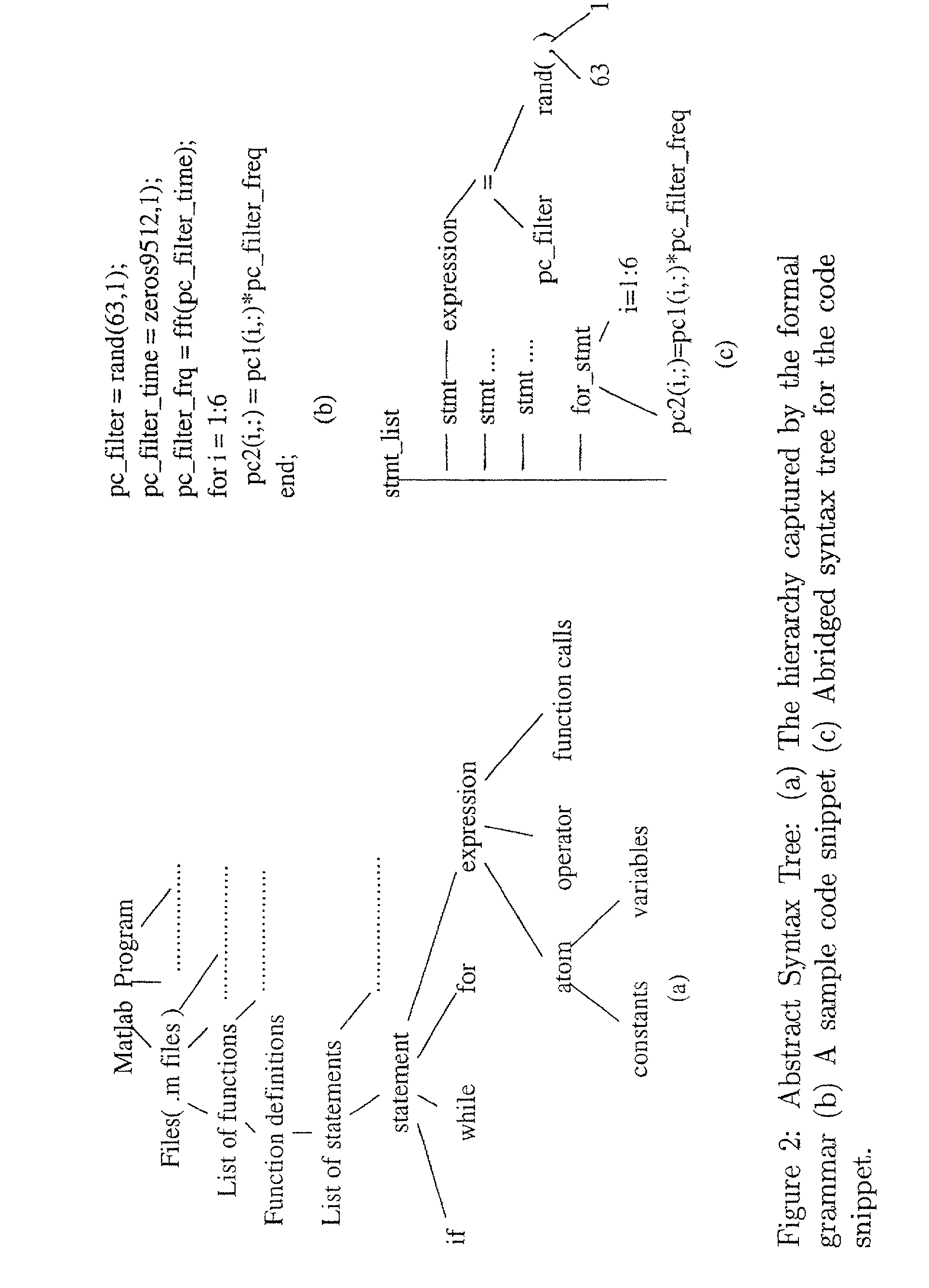

Digital circuit is synthesized from algorithm described in the MATLAB programming language. A MATLAB program is compiled into RTL-VHDL, which is synthesizable using system-specific tools to develop ASIC or FPGA configuration. Intermediate transformations and optimizations are performed to obtain highly optimized description in RTL-VHDL or RTL Verilog of given MATLAB program. Optimizations include levelization, scalarization, pipelining, type-shape analysis, memory optimizations, precision analysis and scheduling.

Owner:NORTHWESTERN UNIV

Method and apparatus for automatically generating hardware from algorithms described in MATLAB

Digital circuit is synthesized from algorithm described in the MATLAB programming language. A MATLAB program is compiled into RTL-VHDL, which is synthesizable using system-specific tools to develop ASIC or FPGA configuration. Intermediate transformations and optimizations are performed to obtain highly optimized description in RTL-VHDL or RTL Verilog of given MATLAB program. Optimizations include levelization, scalarization, pipelining, type-shape analysis, memory optimizations, precision analysis and scheduling.

Owner:NORTHWESTERN UNIV

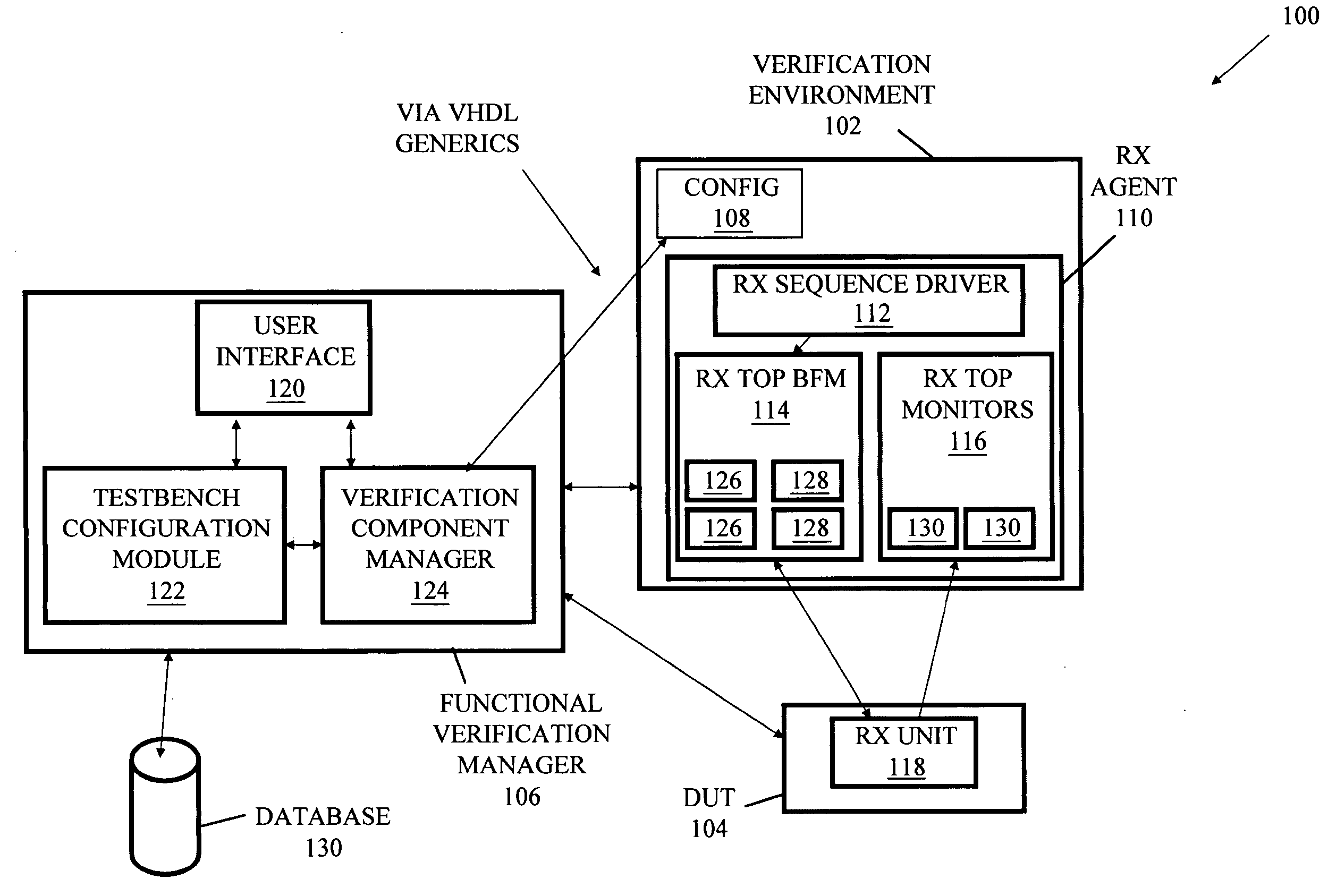

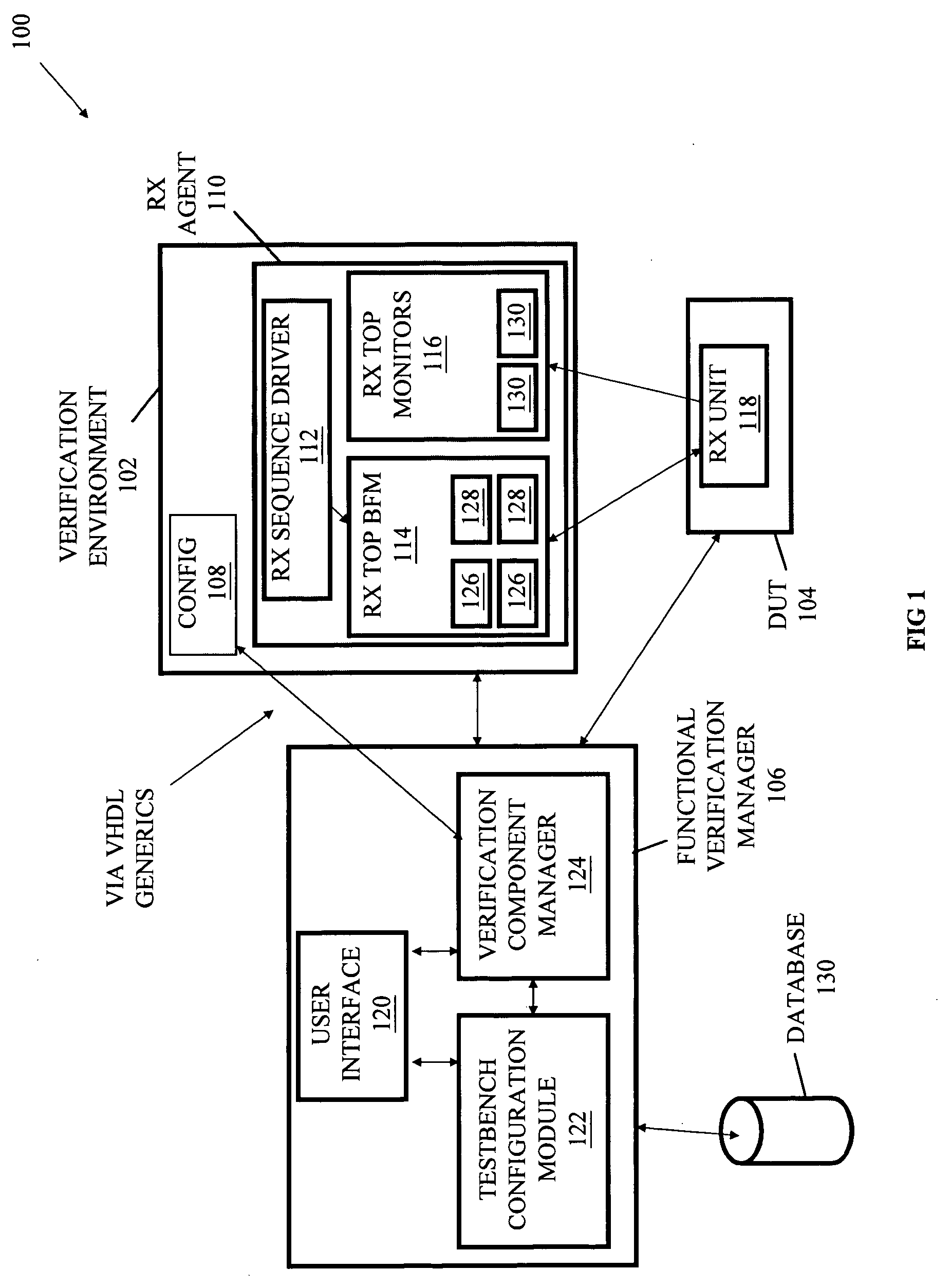

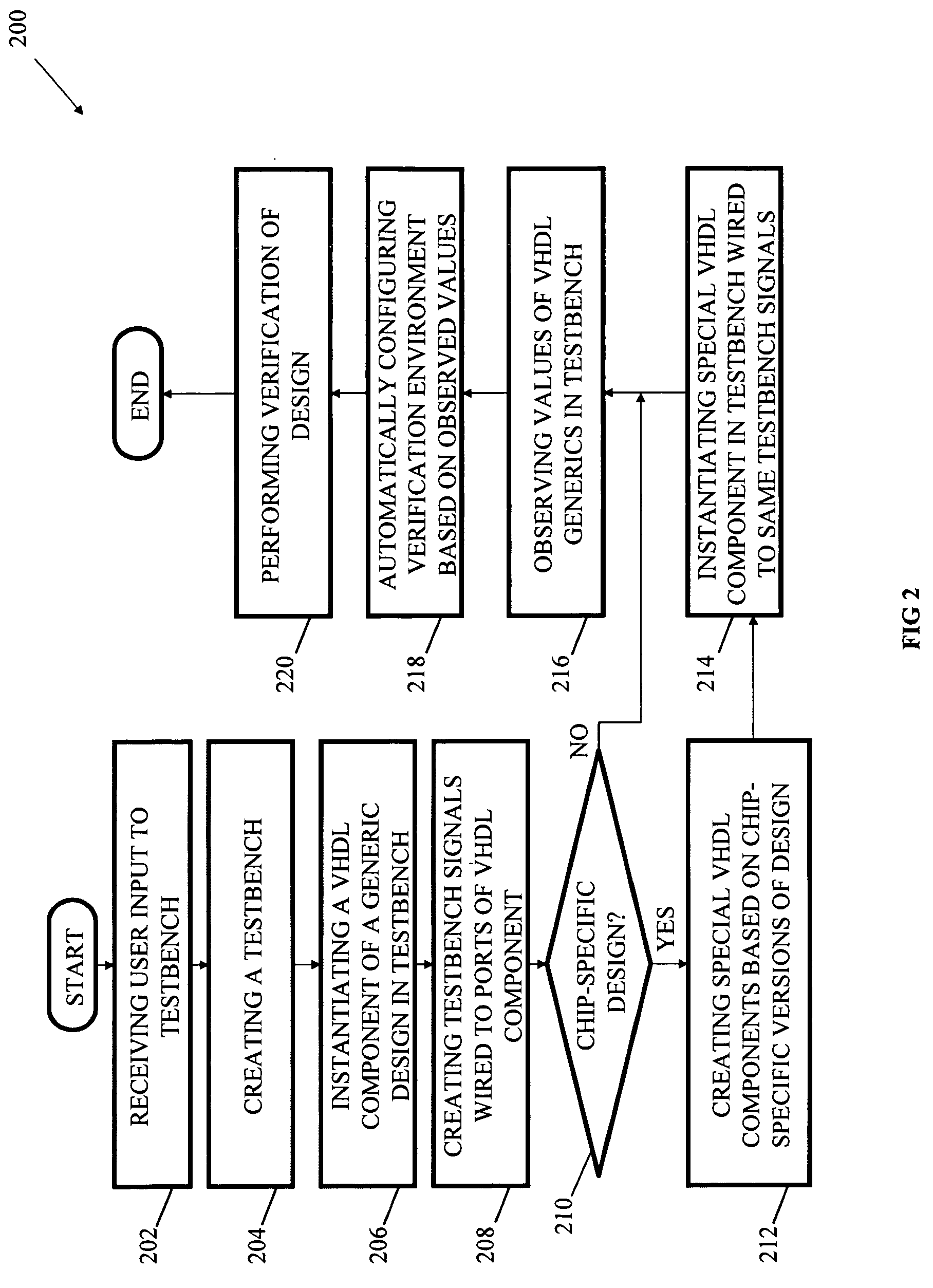

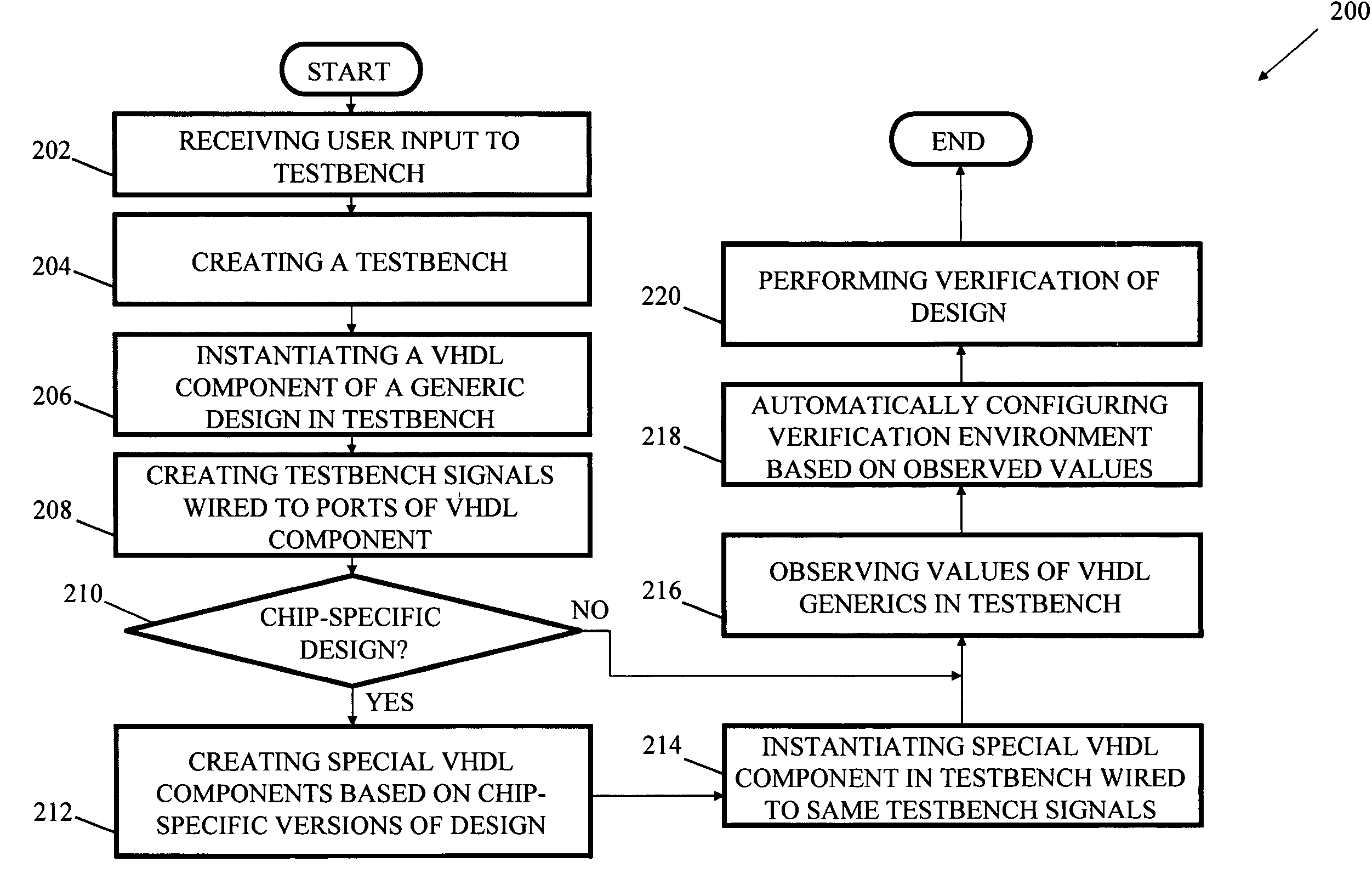

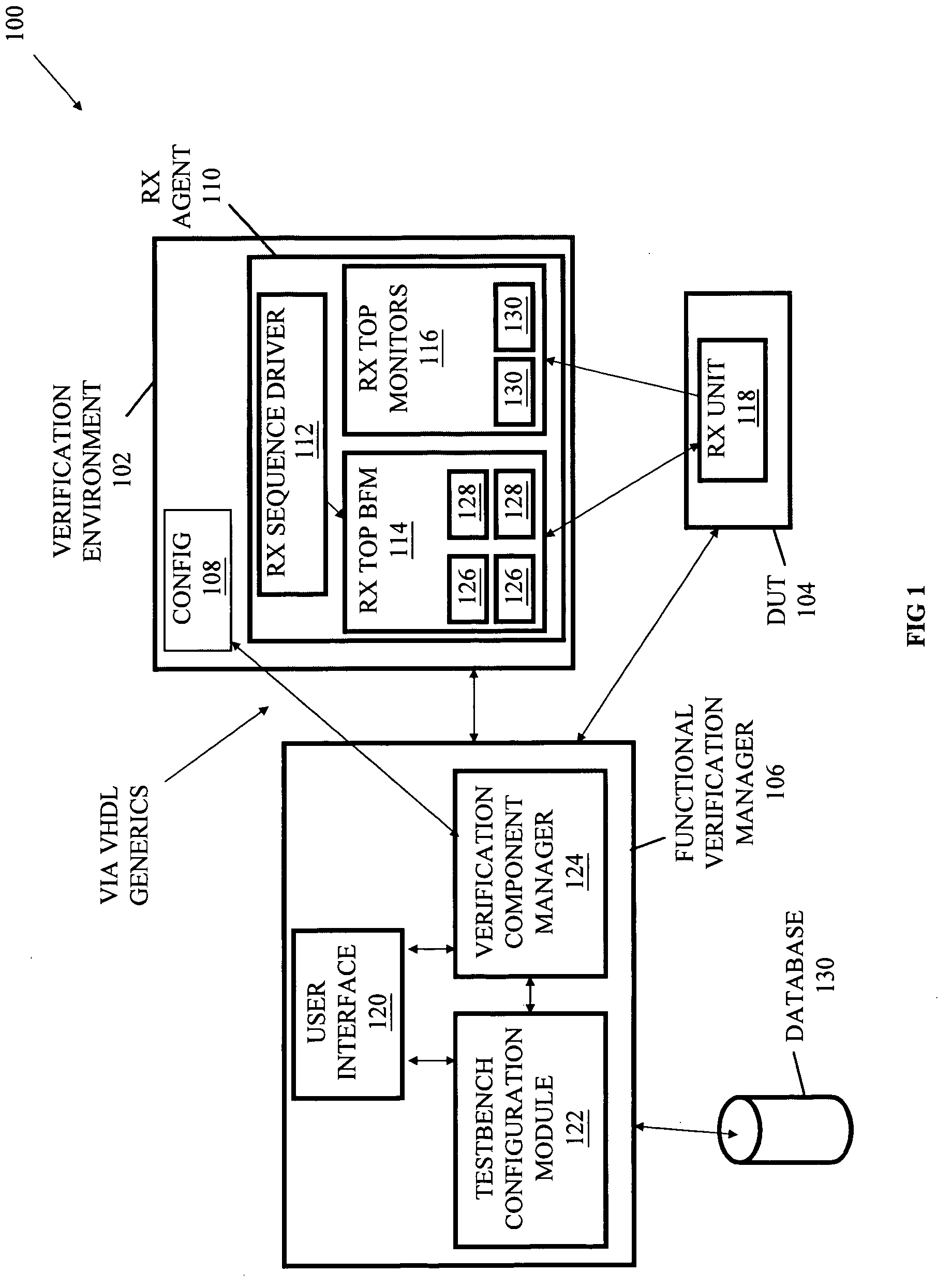

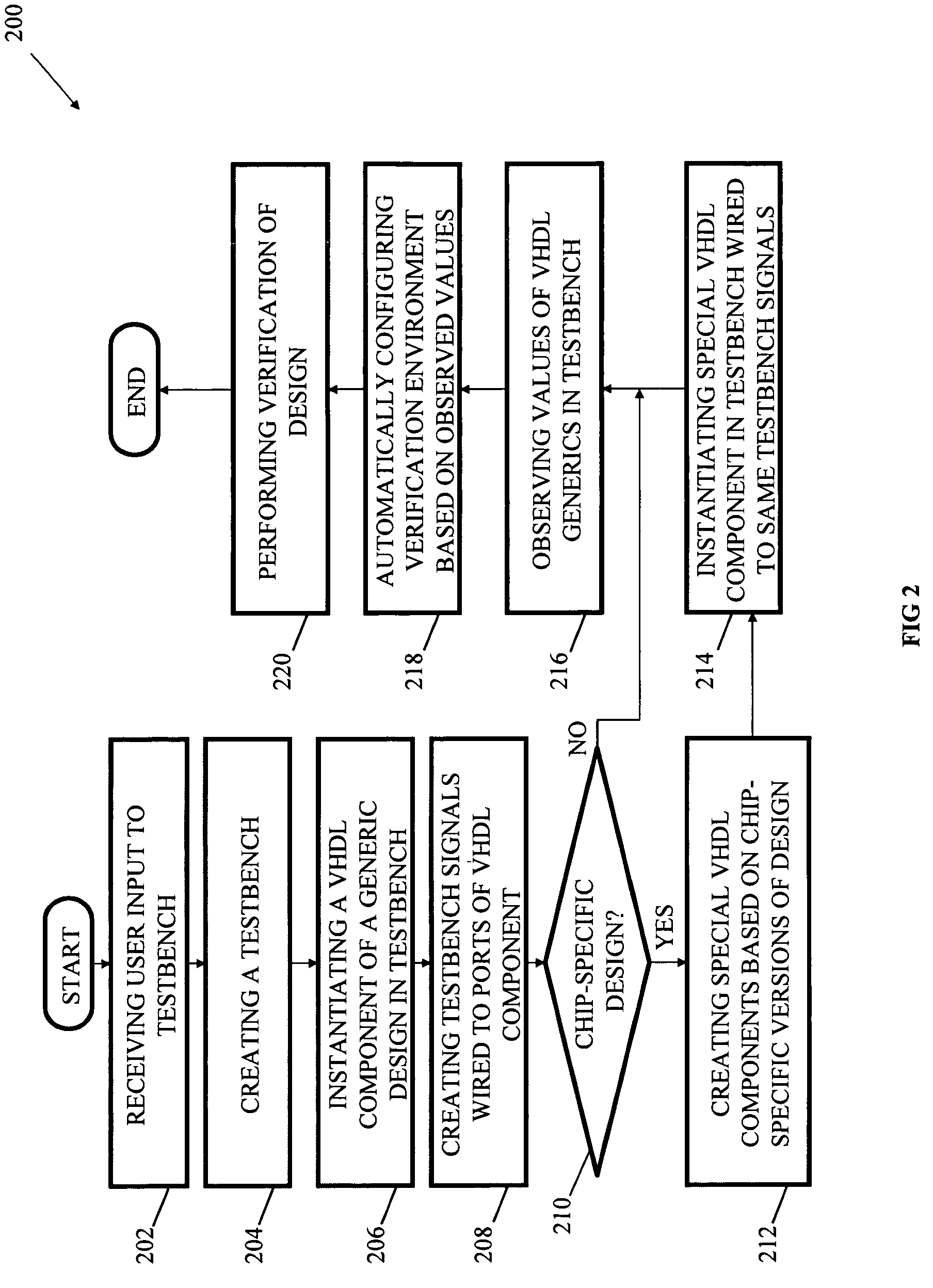

Methods, systems and media for managing functional verification of a parameterizable design

InactiveUS20060190871A1Electrical testingComputer programmed simultaneously with data introductionComputer architectureAuto-configuration

Methods, systems, and media for managing functional verification of a parameterizable design are disclosed. Embodiments include a system having a testbench configuration module adapted to configure a testbench, the testbench having testbench signals and one or more instantiated components having a plurality of ports of a generic design, where the testbench signals are wired to the plurality of ports. The testbench may also have one or more instantiated special components based on chip-specific versions of the design where the special components are wired to the same ports as the generic design. The system may also include a functional verification manager that, through a component module, observes values in the testbench and automatically configure a verification environment based on the observed values, including automatic insertion of checkers at different levels of hierarchy. The testbench may be a VHDL or Verilog testbench in some embodiments.

Owner:GLOBALFOUNDRIES INC

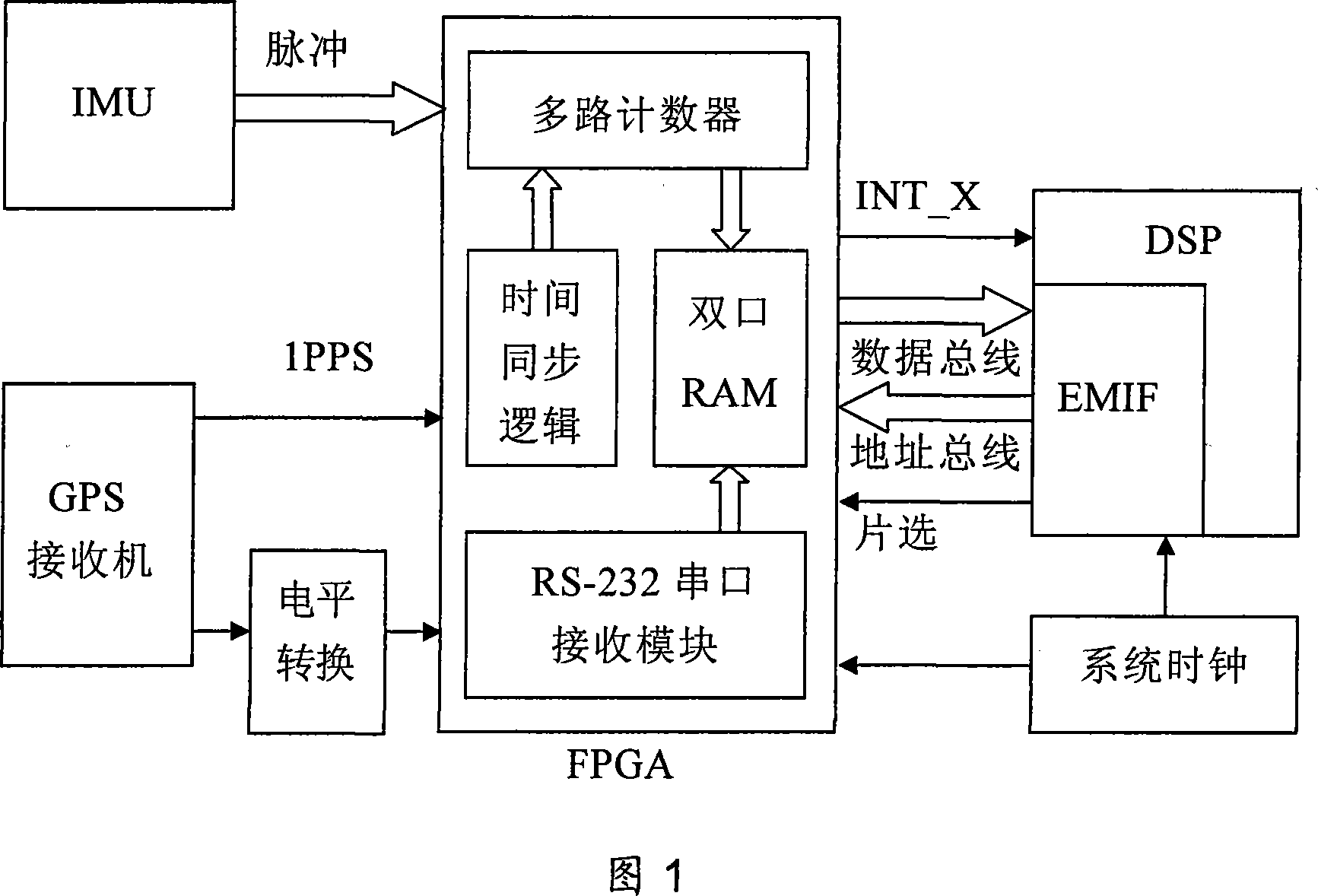

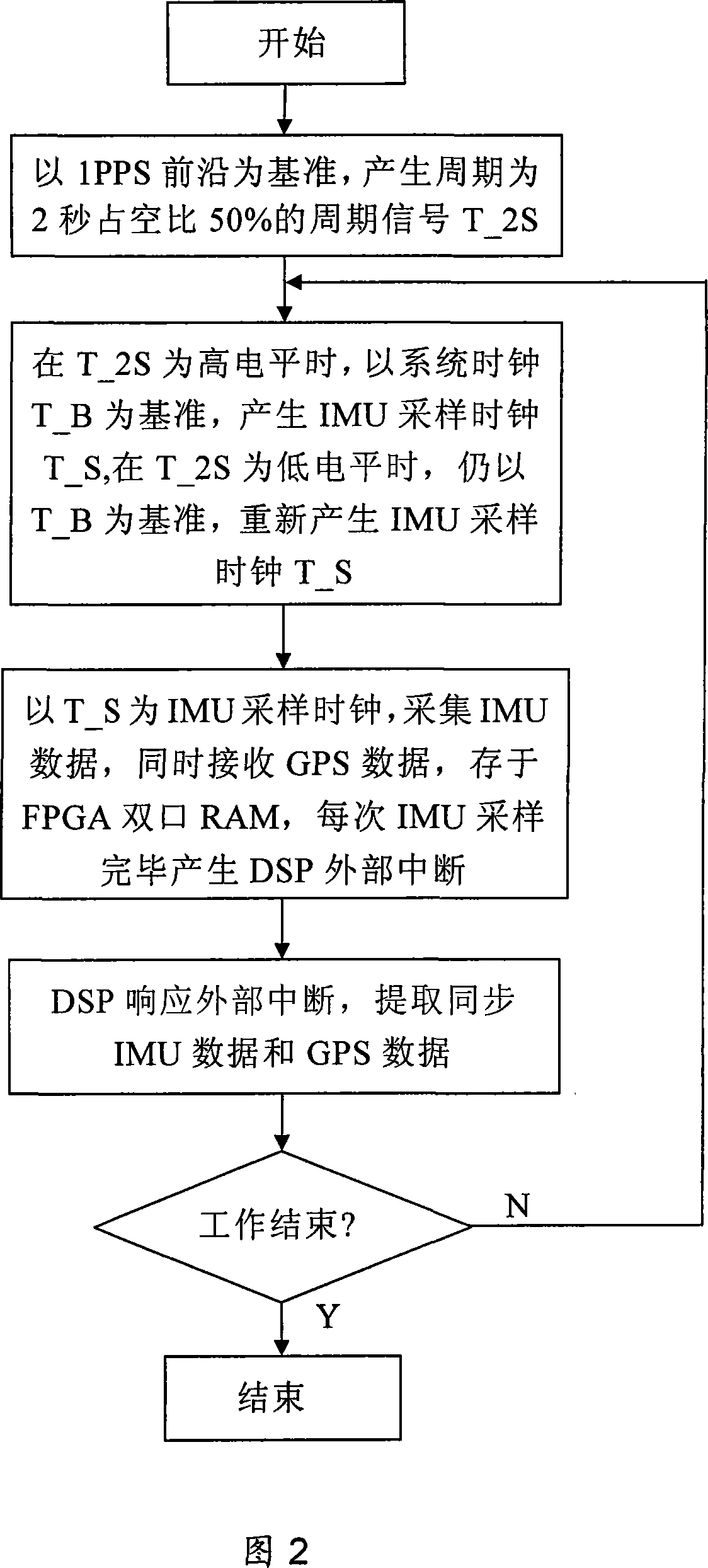

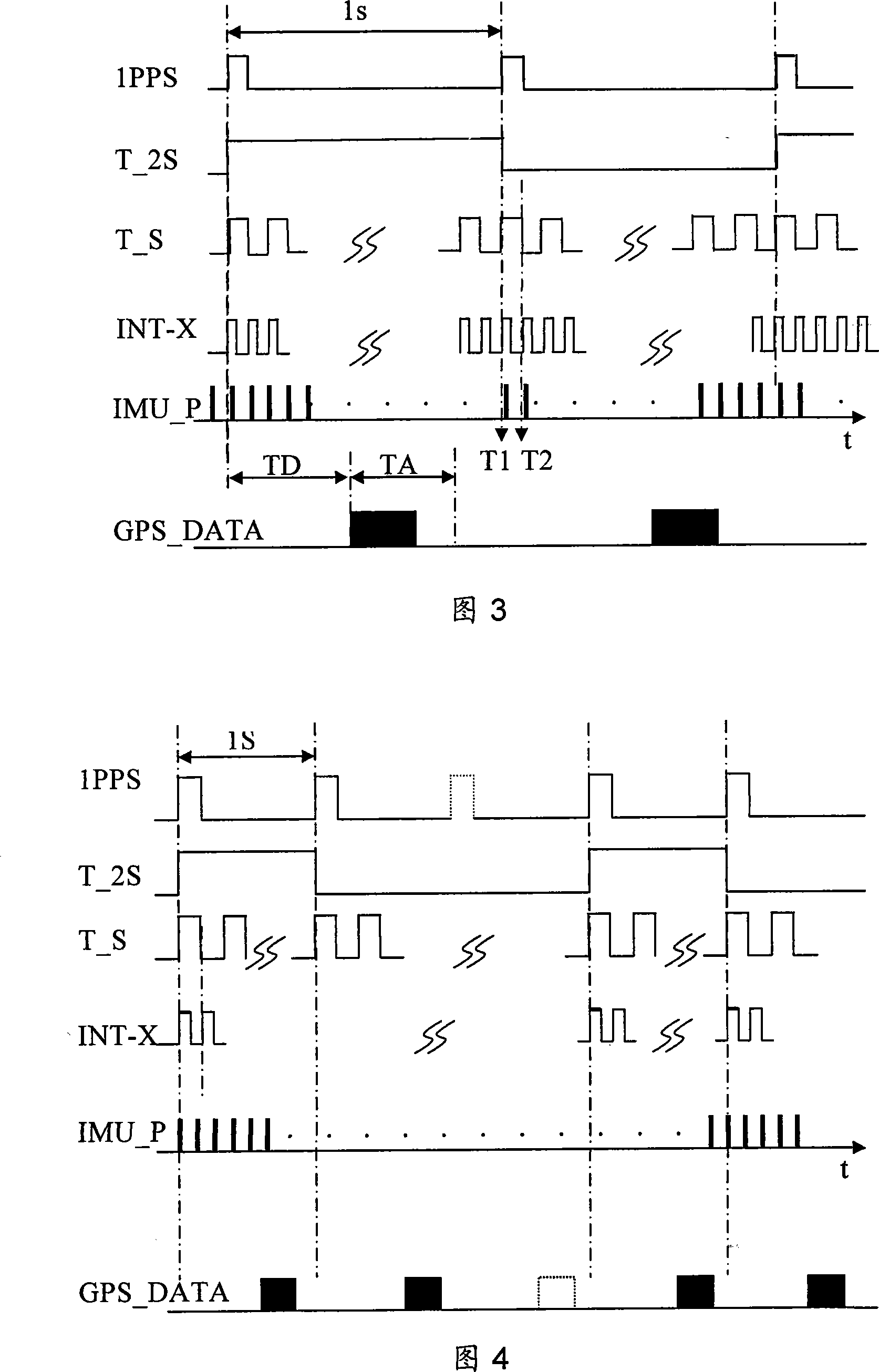

SDINS/GPS combined guidance system time synchronism and synchronous data extraction method

InactiveCN101105401AHardware time synchronizationCompact hardwareInstruments for road network navigationPulse automatic controlGuidance systemData acquisition

The invention relates to a SDINS / GPS integrated navigation system time synchronization method and synchronous data acquisition method. 1 PPS pulse of a GPS receiver is used as a reference to generate an IMU sampling clock, and the pulse signal outputted from the IMU is counted by a counter in the FPGA, so that IMP data sampling is synchronous with 1 PPS, and the synchronization of IMU data and GPS data is realized. GPS data is received through a serial port for realizing VHDL language. The floating point DSP responds the external interruption of the FPGA, reads the IMU data inside the FPGA, and acquires synchronous IMU data and reads GPS data in accordance with the IMU synchronization marks and GPS reading marks. The invention adopts hardware synchronization and time synchronization, leading to good stability. It can realize re-synchronization with 1 PPS, so as to provide high-precision synchronous data for integrated navigation computation and improve the overall performance of integrated navigation system. The DSP acquires synchronous data with interrupt mode and hardly occupies the DSP resource for computation, leading to good real-time performance.

Owner:BEIHANG UNIV

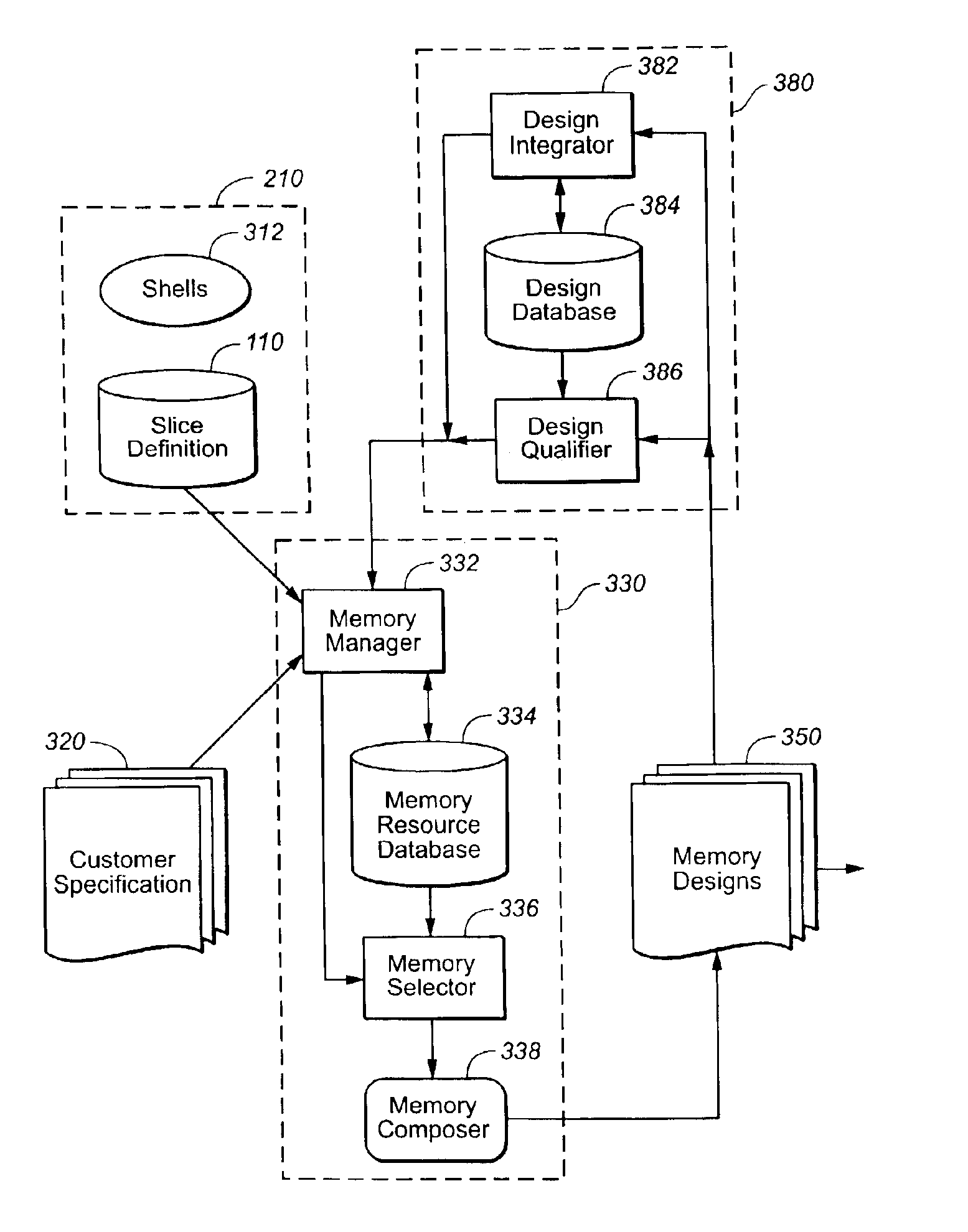

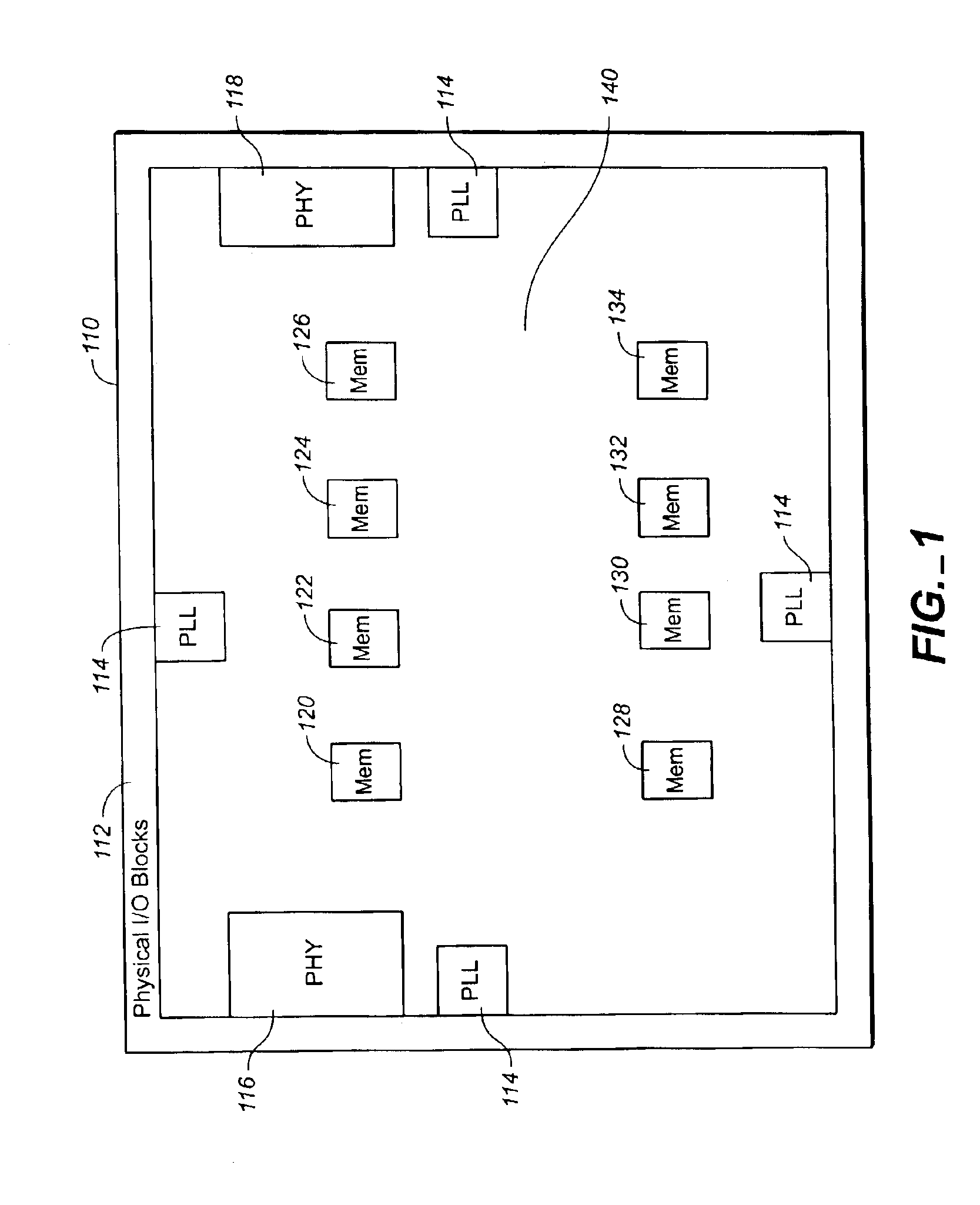

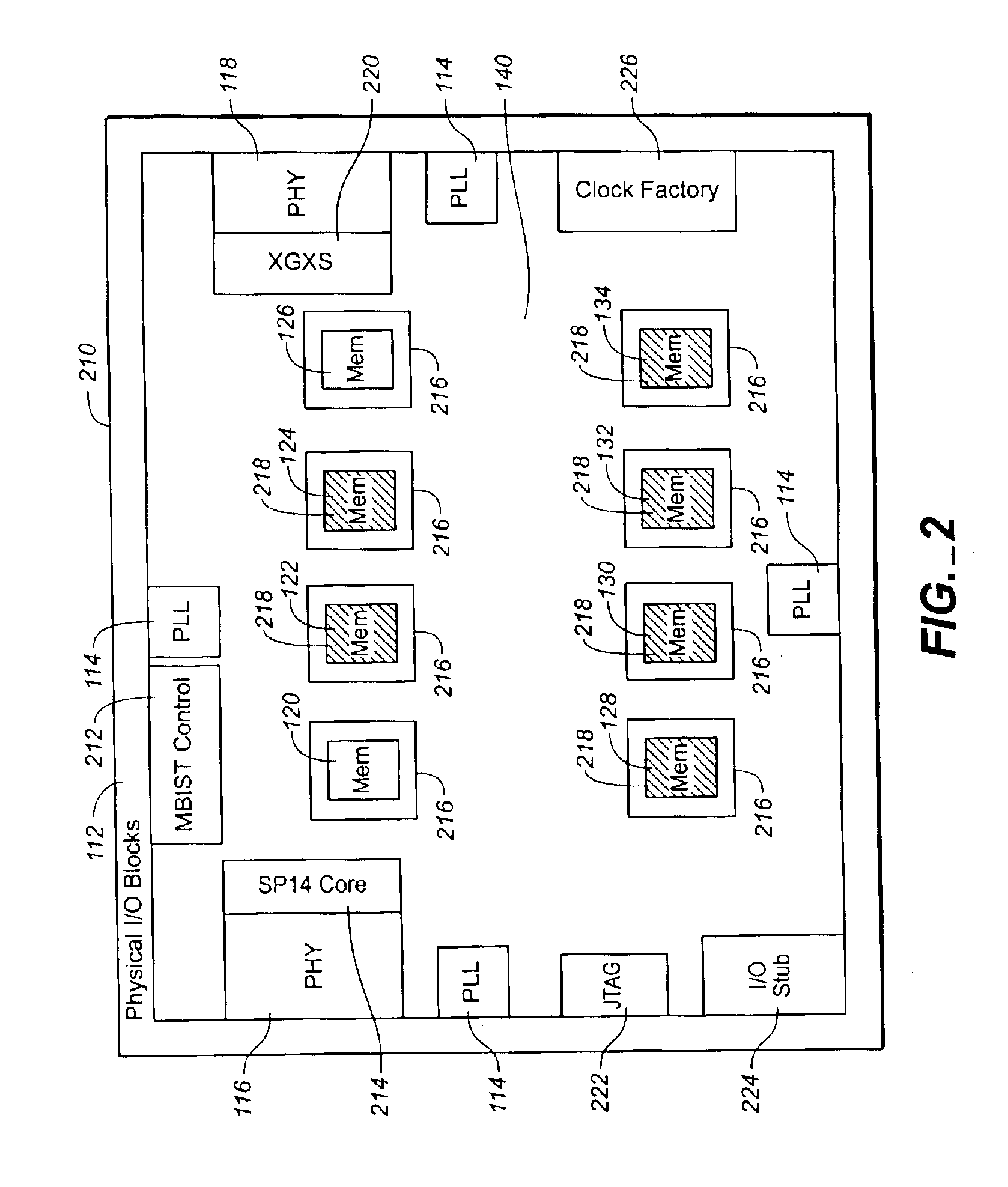

Automated selection and placement of memory during design of an integrated circuit

InactiveUS7069523B2Solid-state devicesSemiconductor/solid-state device manufacturingIntegratorComputer architecture

A tool for designing integrated circuits that optimizes the placement and timing of memory blocks within the circuit. Given a manufactured slice that has a number of blocks already diffused and logically integrated, the memory generation tool herein automatically considers the available diffused memory and the gate array of the slices to configure and optimize them into a customer's requirements for memory. The memory generation tool has a memory manager, a memory resource database, a memory resource selector, and a memory composer. Together these all interact to generate memories from the available memories within the memory resource database. The memory composer actually generates the RTL logic shells for the memories, and outputs the memory designs in Verilog, VHDL, or other tool synthesis language. Once a memory is created, it is tested. Upon successful testing, the memory manager updates the memory resource database to indicate the successfully tested memory is no longer available as a resource for the generation of further memories. A design integrator may review the memory designs output and further integrate the memory, its timing, testing, etc. with other blocks and functions of the integrated circuit.

Owner:BELL SEMICON LLC

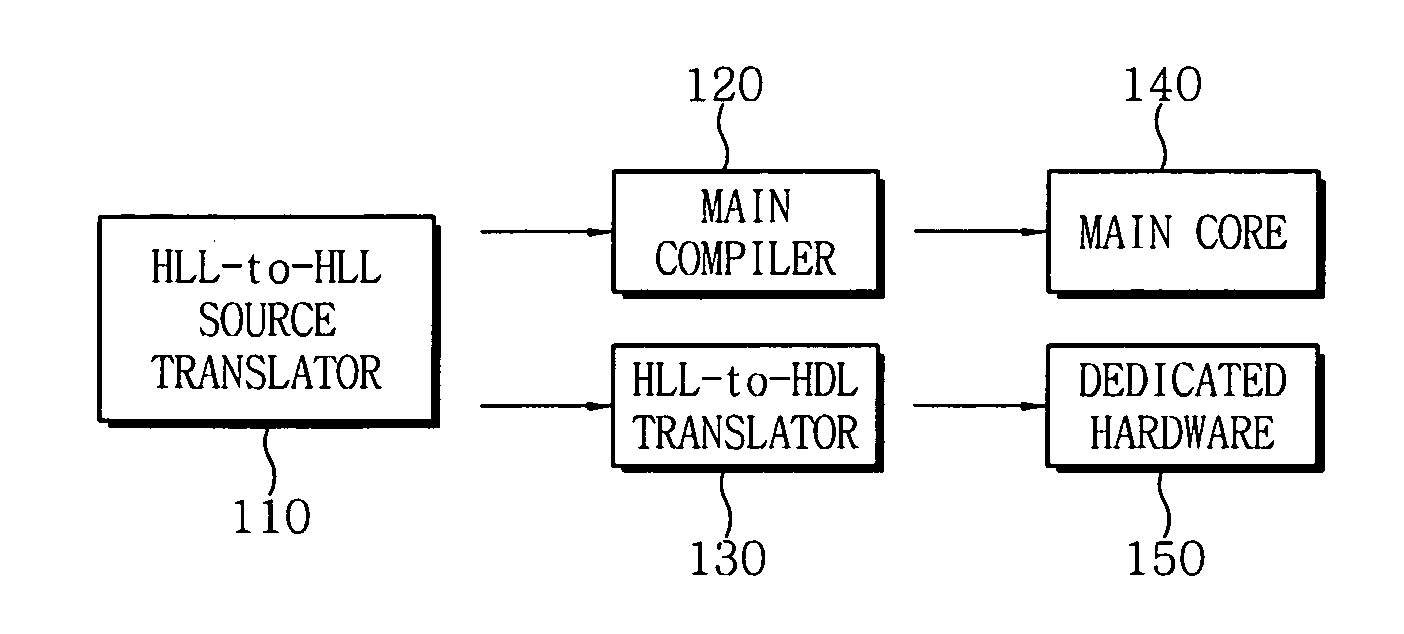

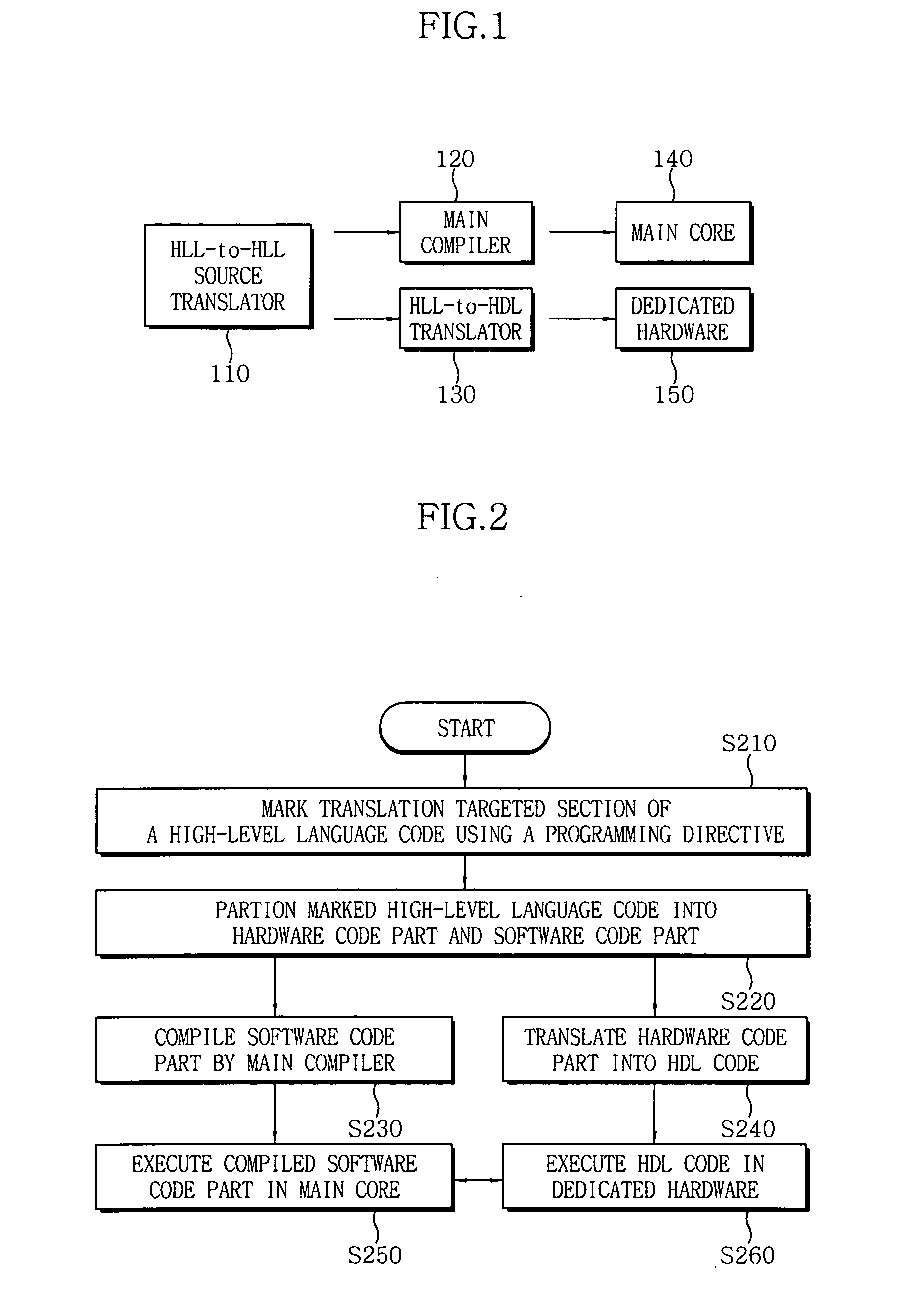

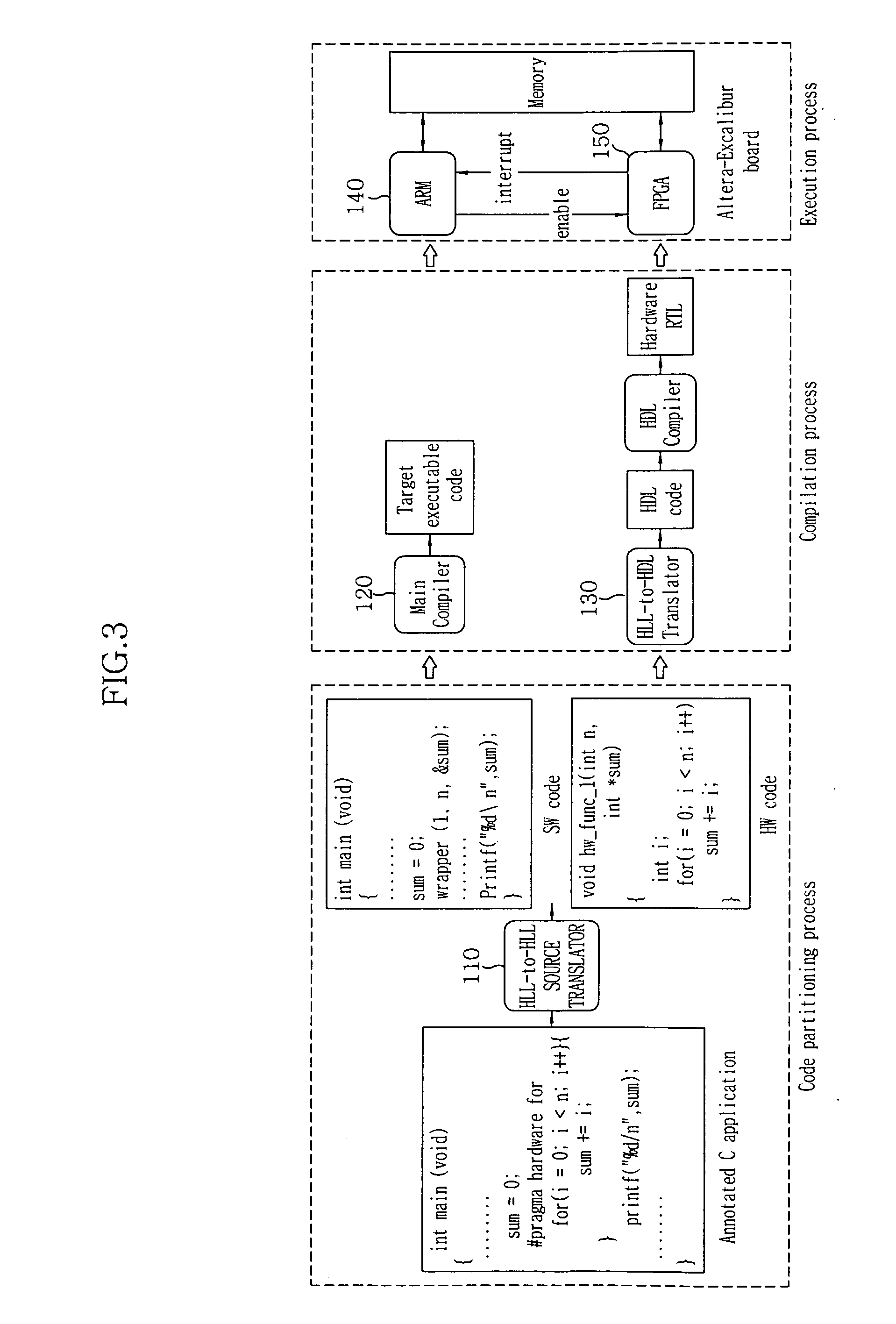

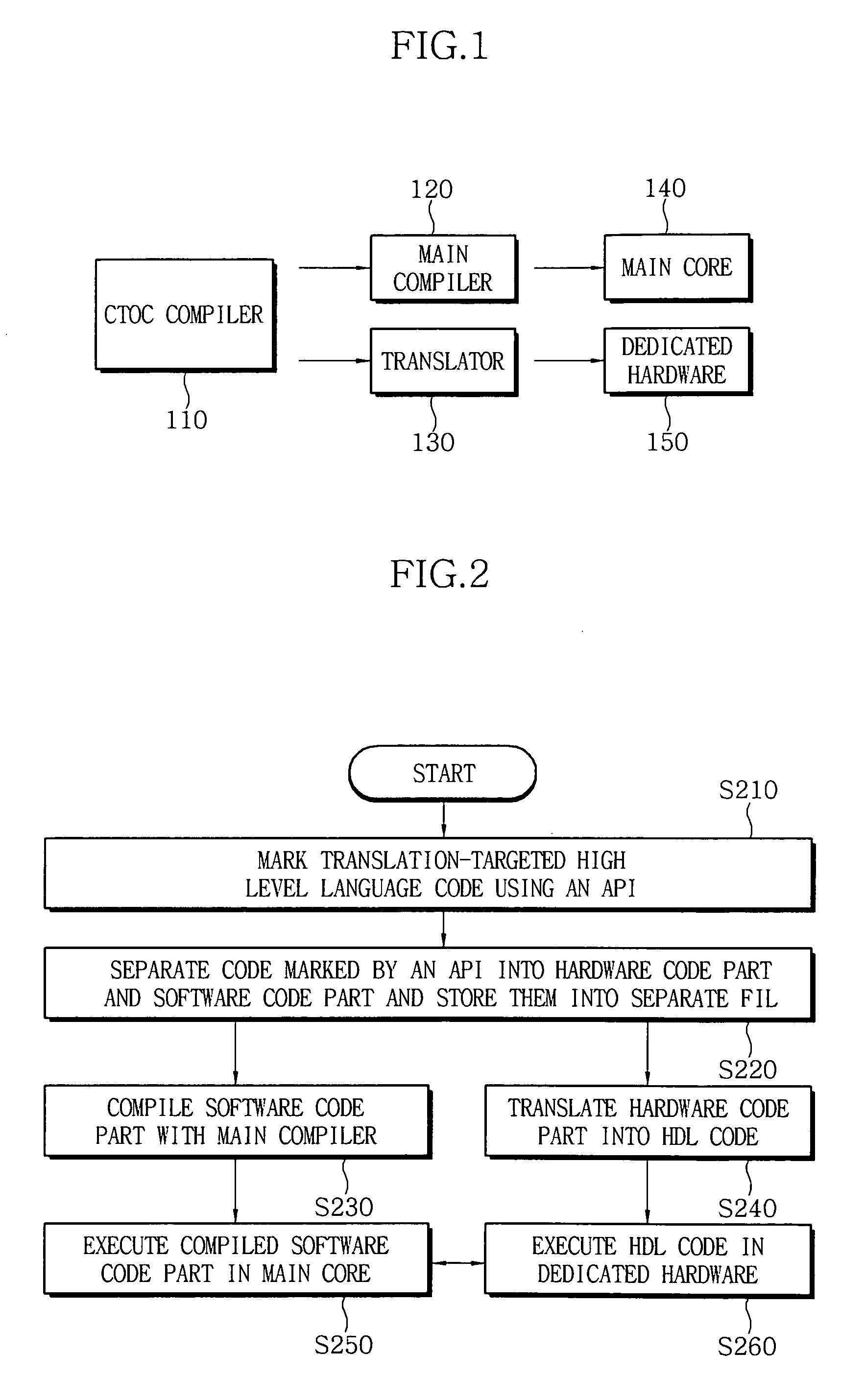

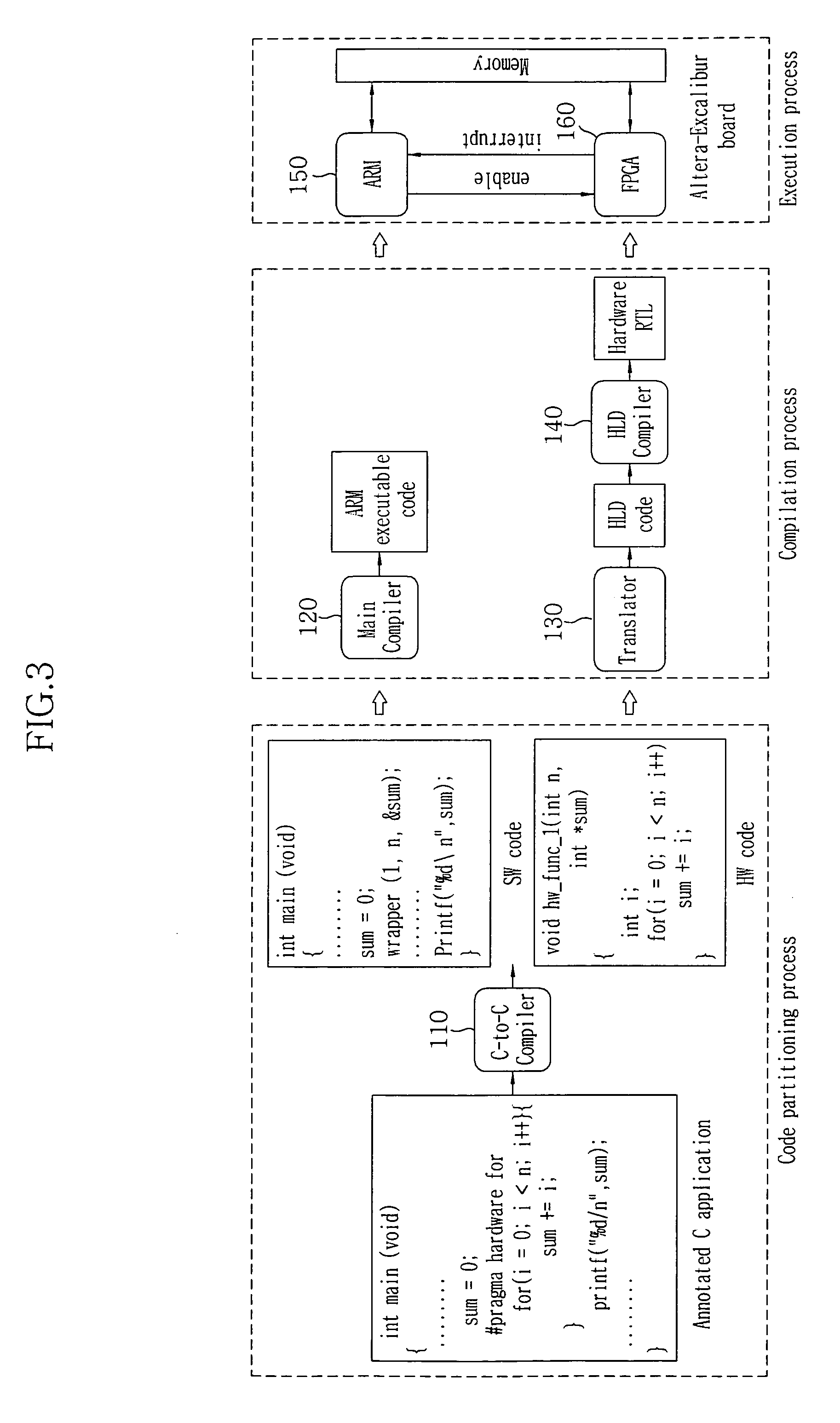

System and method for translating high-level programming language code into hardware description language code

The present invention is directed to a method and system for translating a high-level language (HLL) code such as C, C++, Fortran, Java or the like into a HDL code such as Verilog or VHDL which requires no modification in the original HLL source code, while supporting a cross call between software and hardware, and even recursive calls in hardware. The system includes: a HLL-to-HLL source translator which reads user programming directive from a translation-targeted high-level language code marked with the user directive, and separates the translation-targeted high-level language code into a hardware code part and a software code part; a main compiler which compiles the software code part; a HLL-to-HDL translator which includes the front-end and middle-end of the main compiler and a HDL backend; a main core which executes the compiled software code part; and a dedicated hardware which executes the HDL code.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

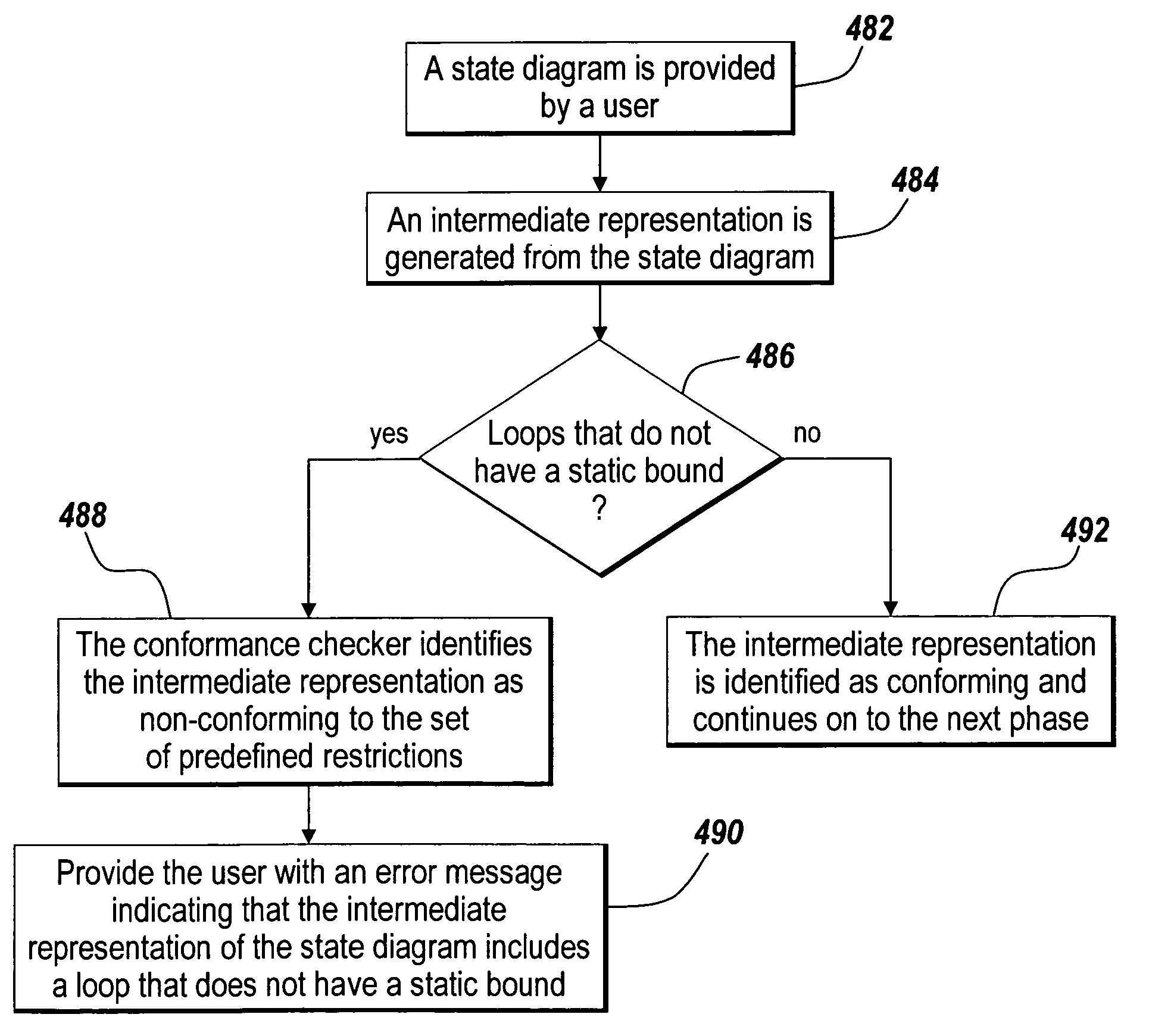

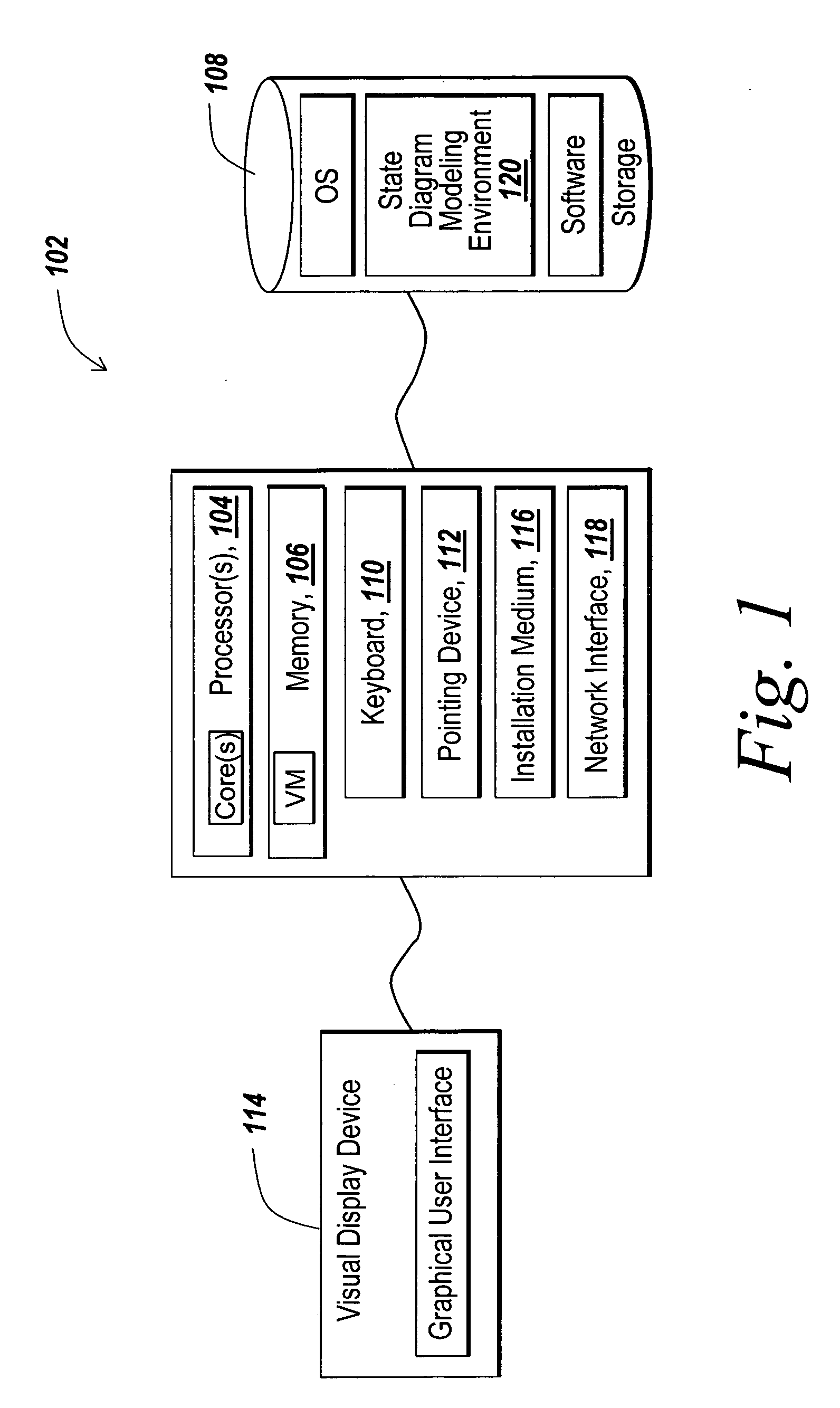

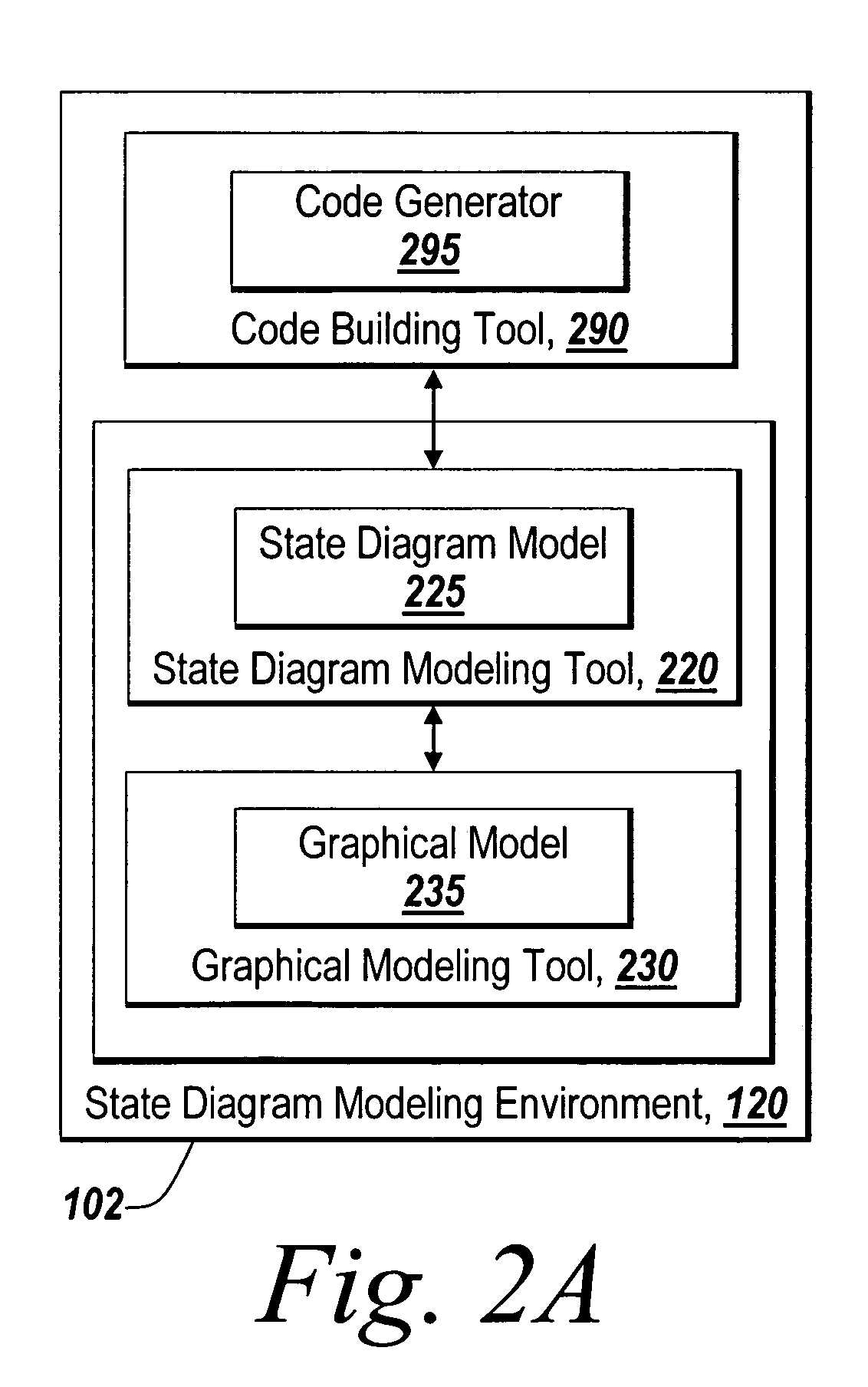

Hardware description language code generation from a state diagram

The present invention provides a state diagramming environment in a computing device that enables the conversion of a state diagram into a hardware description language. To achieve this conversion, the present invention generates an intermediate representation of the state diagram. The intermediate representation is checked against a set of predefined restrictions for compliance. The state diagramming environment converts the intermediate representation of the state diagram into a hardware description language, such as VHDL or Verilog.

Owner:THE MATHWORKS INC

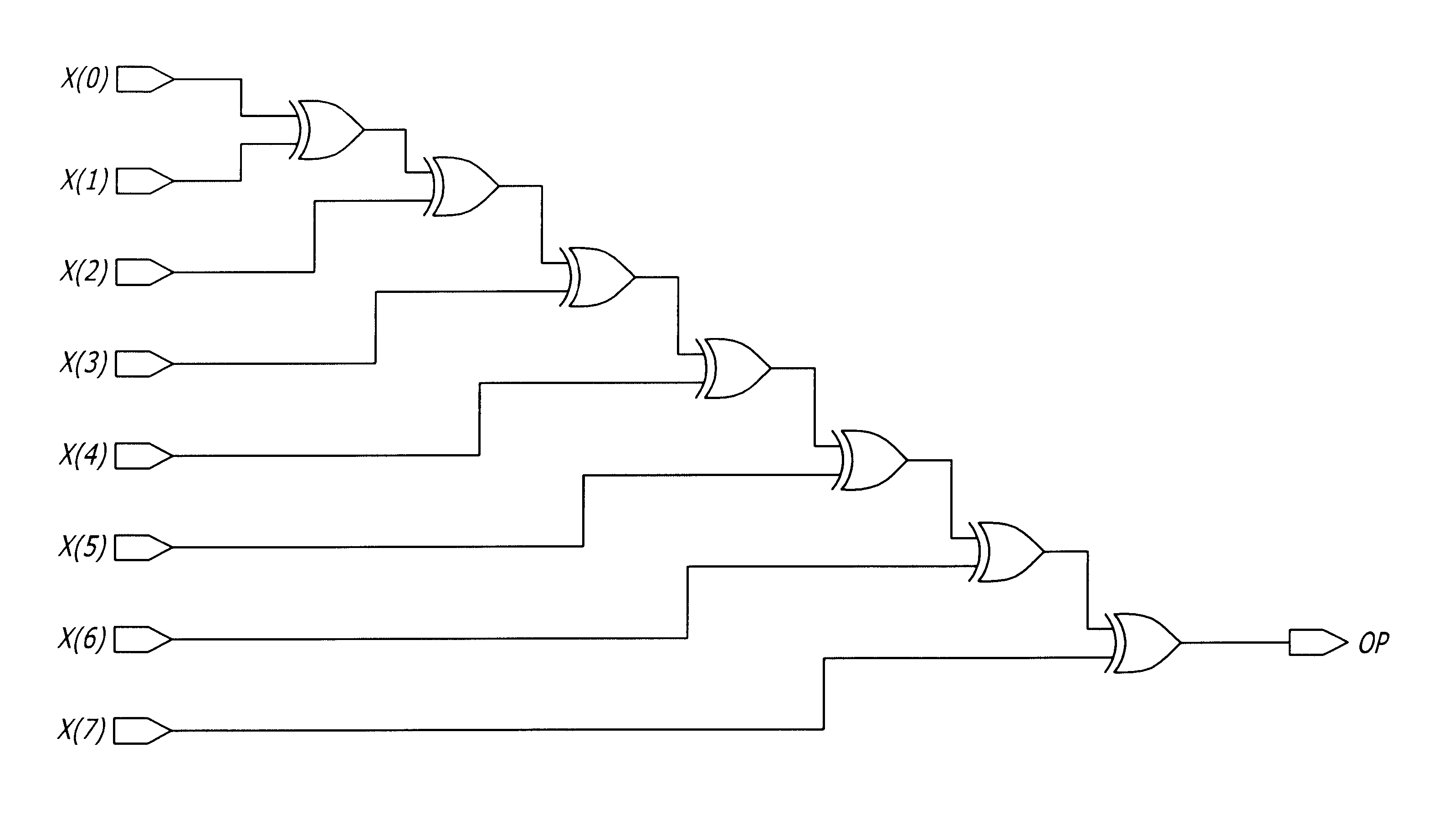

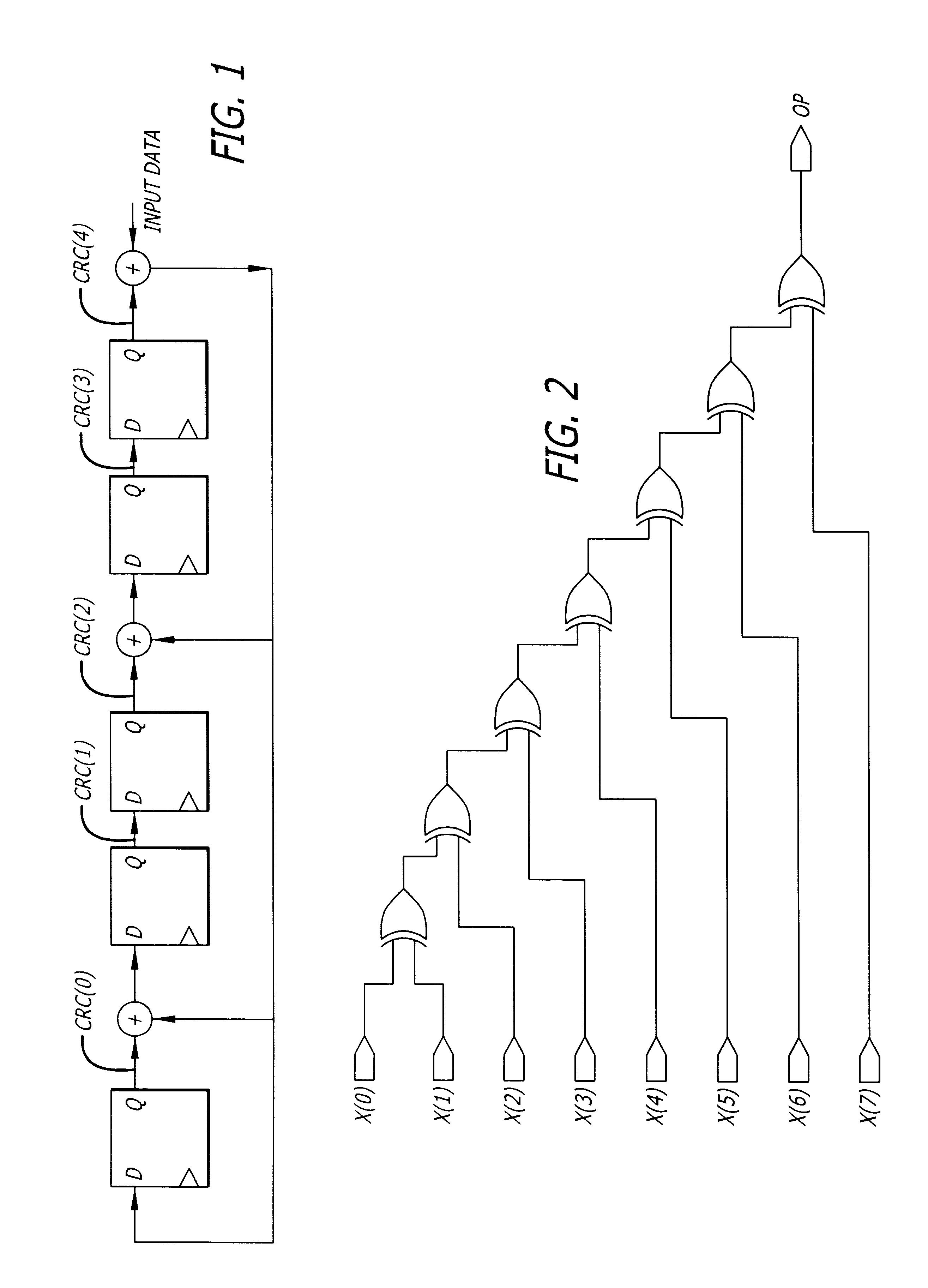

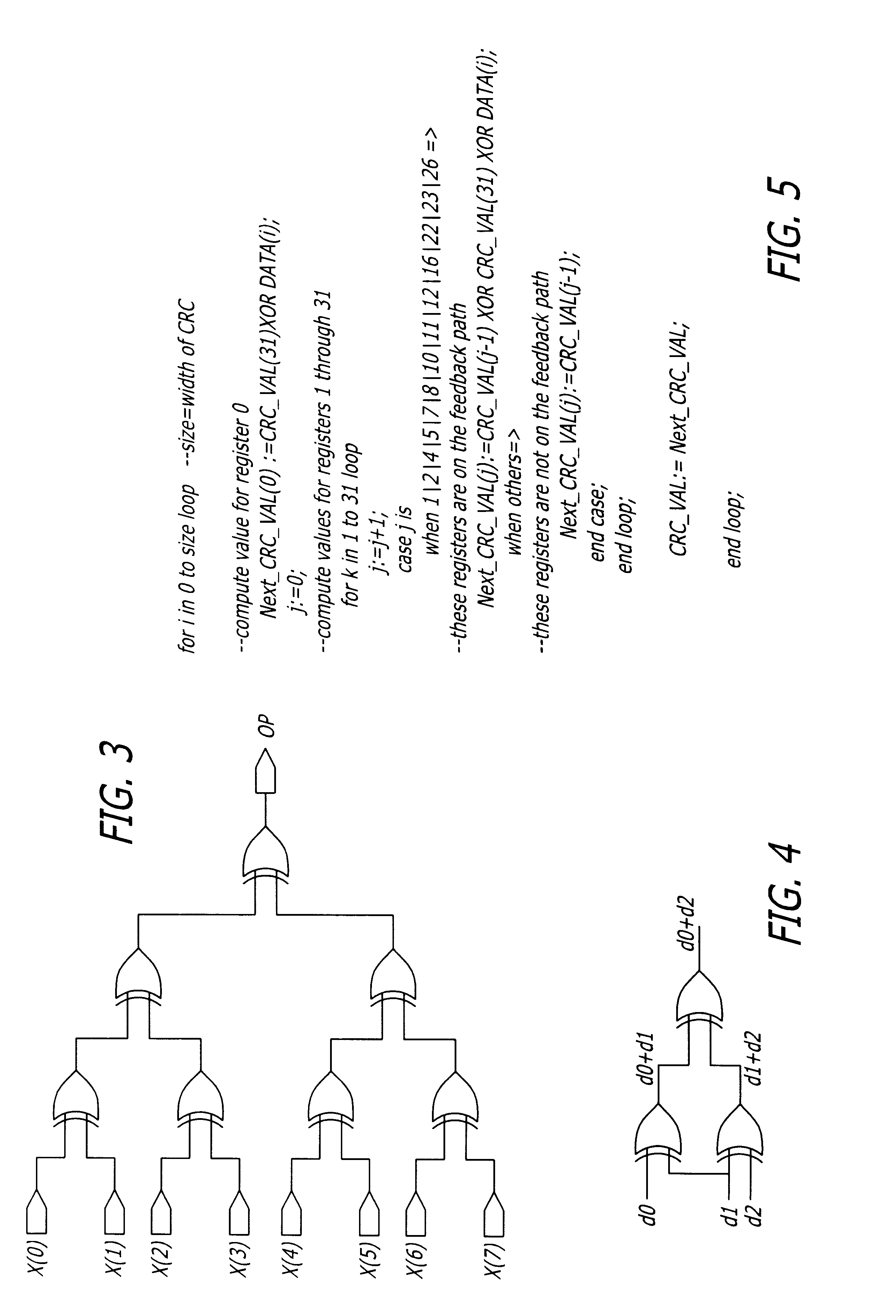

Symbol based algorithm for hardware implementation of cyclic redundancy check

A method and apparatus for generation of CRC generation / checker circuitry. A symbolic simulation-based algorithm to derive boolean equations for a parameterizable data-width CRC generator / checker is described. The equations generated are used to implement a data-flow representation of the CRC circuit in VHDL. The VHDL description is then synthesized into gates.

Owner:HANGER SOLUTIONS LLC +1

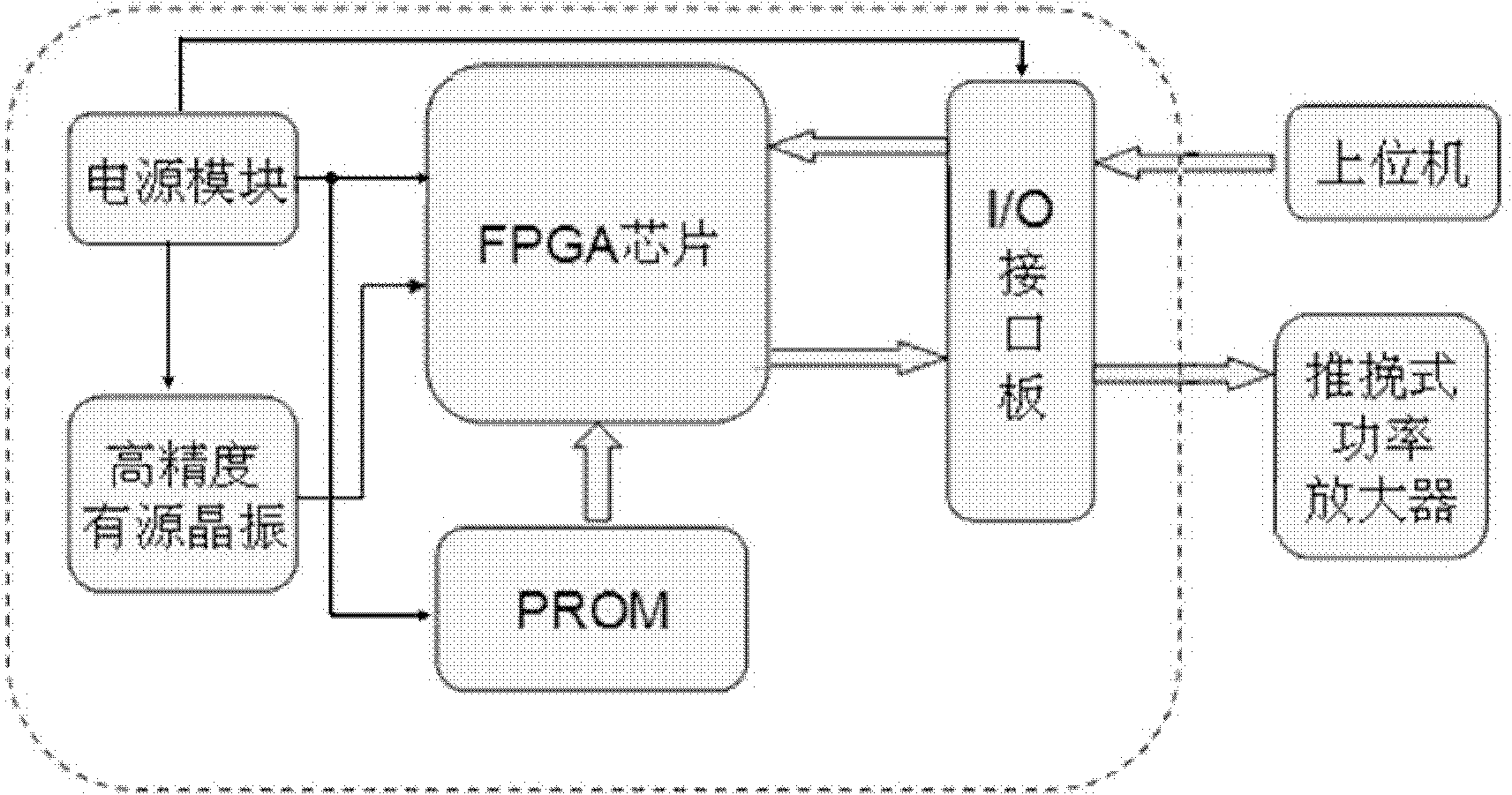

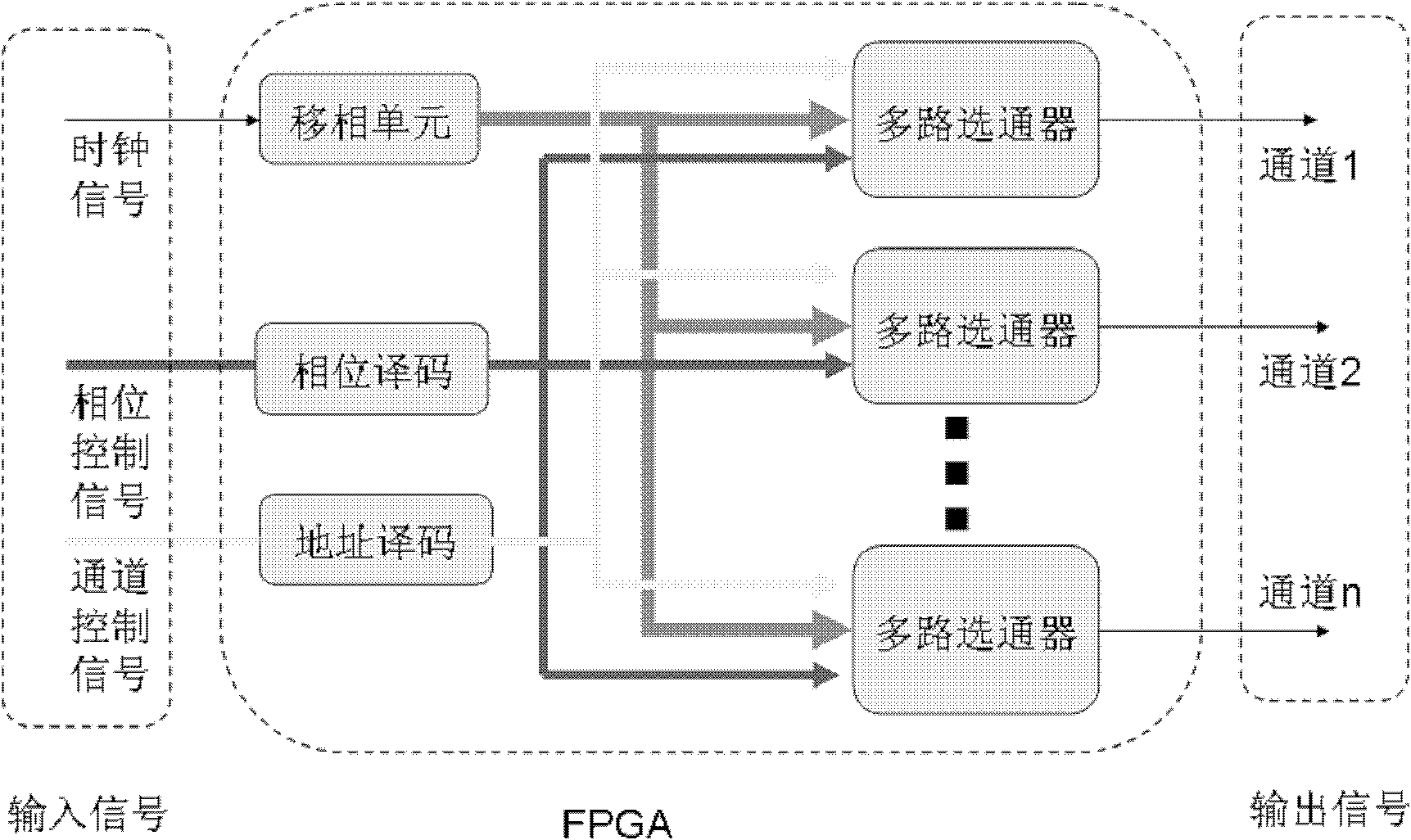

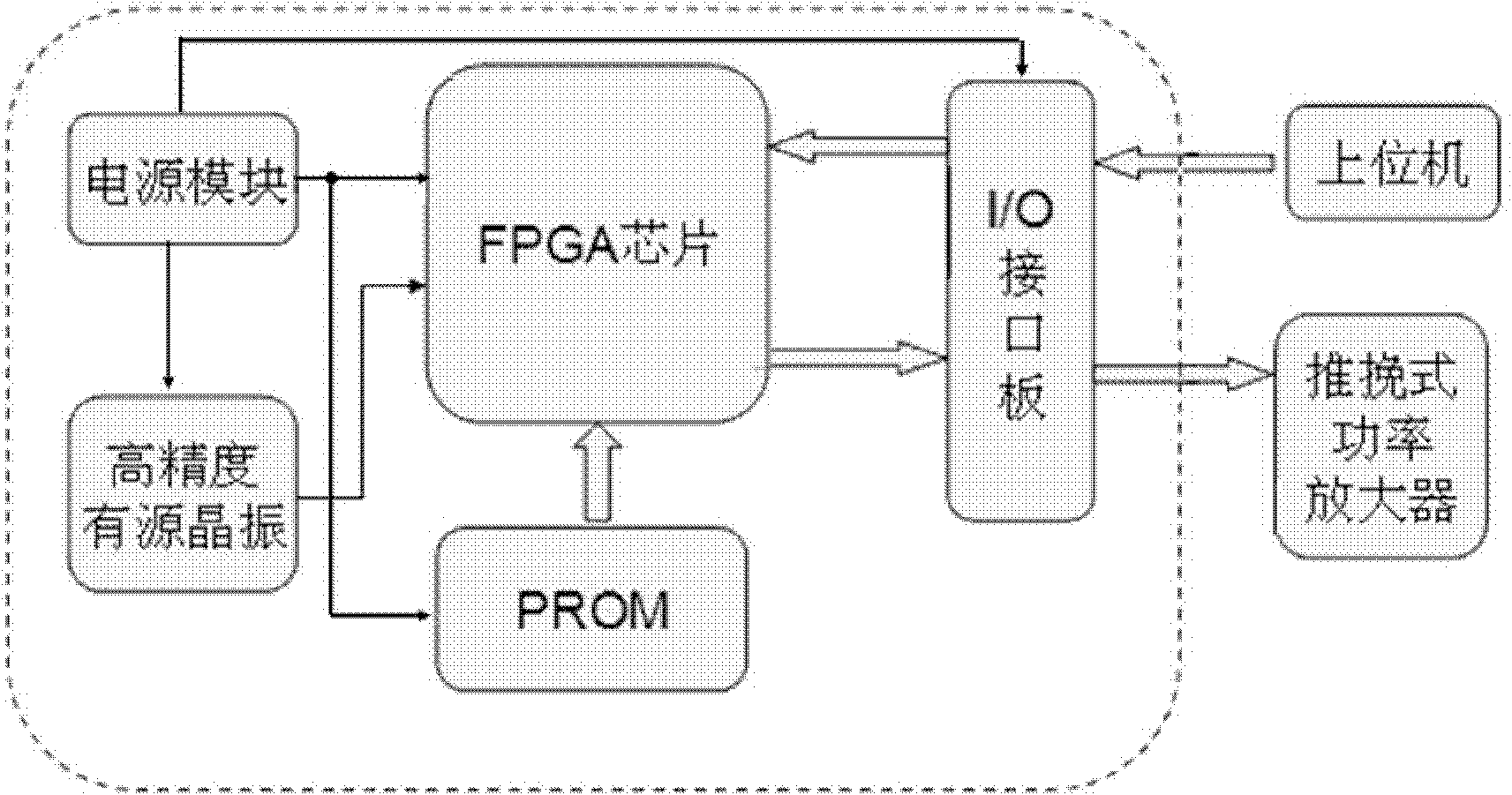

Multi-channel high precision phase control signal generation device

ActiveCN101862511AIncrease the number of channelsHigh precisionUltrasonic/sonic/infrasonic diagnosticsUltrasound therapyFpga field programmable gate arrayProgrammable read-only memory

The invention relates to a multi-channel high precision phase control signal generation device which utilizes a programmable read-only memory to generate a customized special circuit in an FPGA (Filed Programmable Gate Array) circuit through a VHDL (Very High Speed Integrated Circuit Hardware Description Language) language programming. The multi-channel high precision phase control signal generation device comprises a phase shift module, a phase coding module, an address coding module and a plurality of multi-channel gates. By taking a high precision active crystal oscillator as an information source, all multi-channel gates works in parallel to receive phase control signals of a host computer and output square wave signals of a multi-channel special phase. The output square wave signals access resonance of a power amplifier to generate sine wave signals with the same frequency and phase with the traditional output signals and the sine wave signals are used for excitation signals of an ultrasonic transducer array element in a phase control type high intensity focusing ultrasonic treatment system; and the frequency of the crystal oscillator is determined by the resonance frequency and the phase control precision requirements of the ultrasonic transducer array element. The invention dramatically increases the channel amount of the phase control signals and enhances the precision of the phase control signals, thereby satisfying the needs of the high intensity focusing ultrasonic treatment system.

Owner:SHANGHAI SHENDE MEDICAL TECH CO LTD

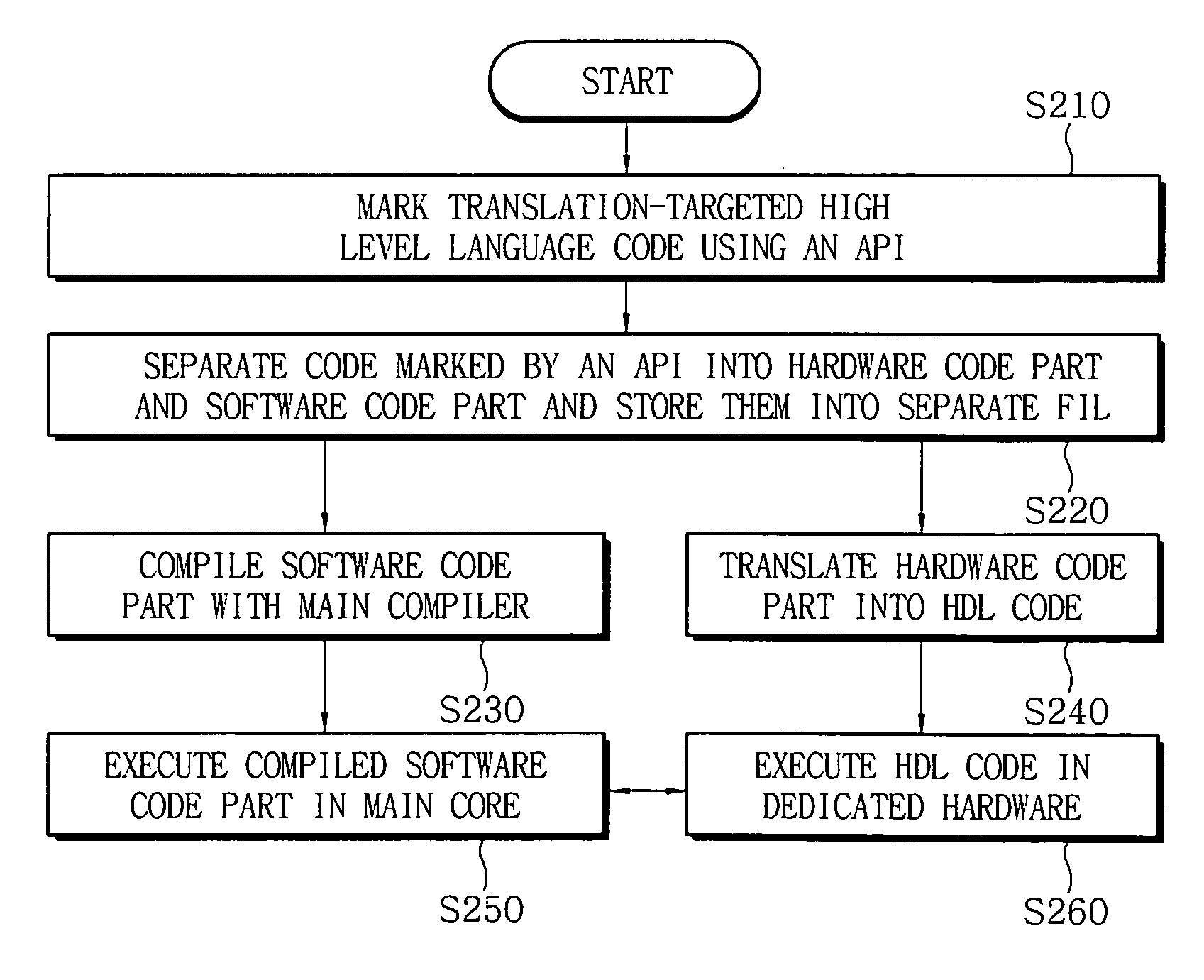

System and Method for translating high programming level languages code into Hardware Description Language code

The present invention is directed to a method and system for translating a high programming level language code such as C, C++, Fortran, Java or the like into a HDL code such as Verilog or VHDL. The system includes: a C-to-C source translator which reads user API from a translation-targeted high level language code marked with the user API, separates the translation-targeted high level language code into a hardware code part and a software code part, and stores the hardware code part and the software code part in separate files; a main compiler which compiles the stored software code part; a translator which translates the stored hardware code part into a HDL code including one or more block modules and one top module; a main core which executes the compiled software code part; and a dedicated hardware which executes the HDL code.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

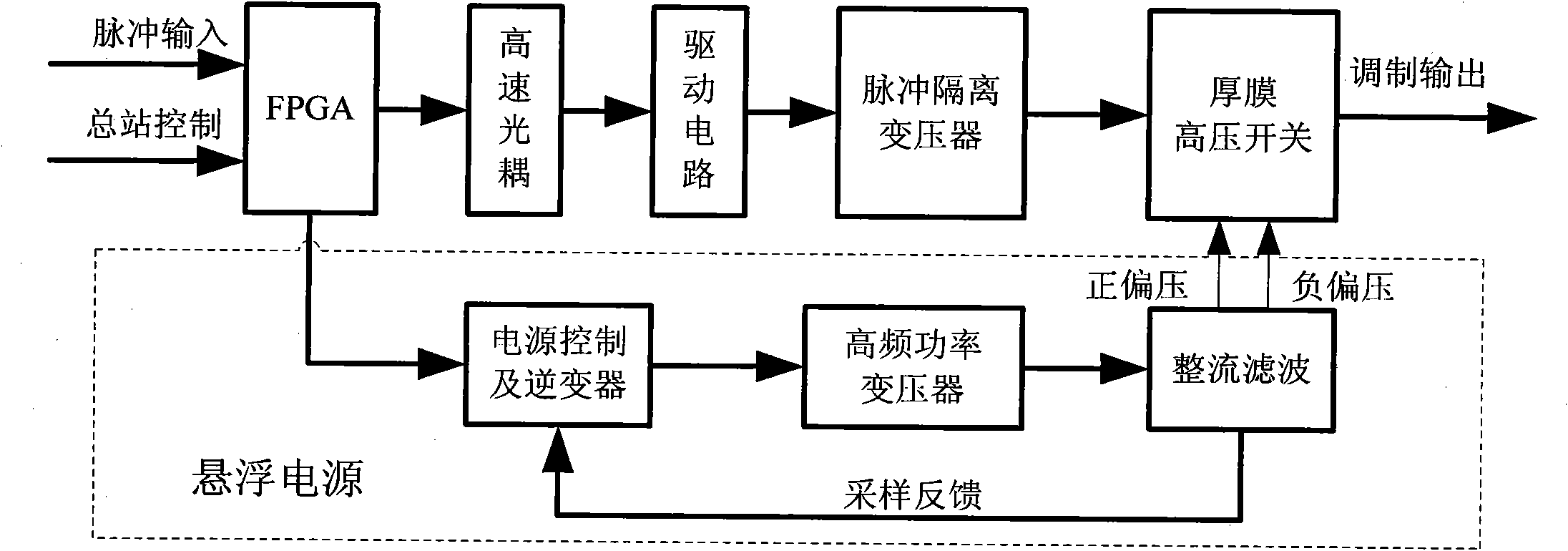

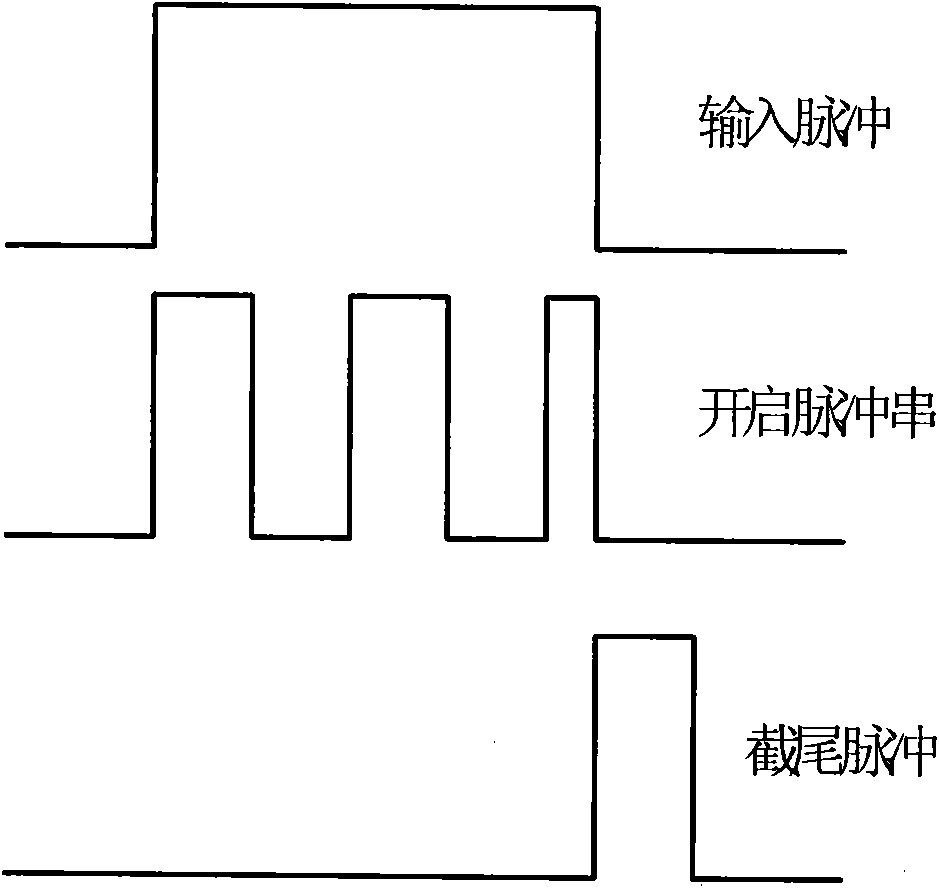

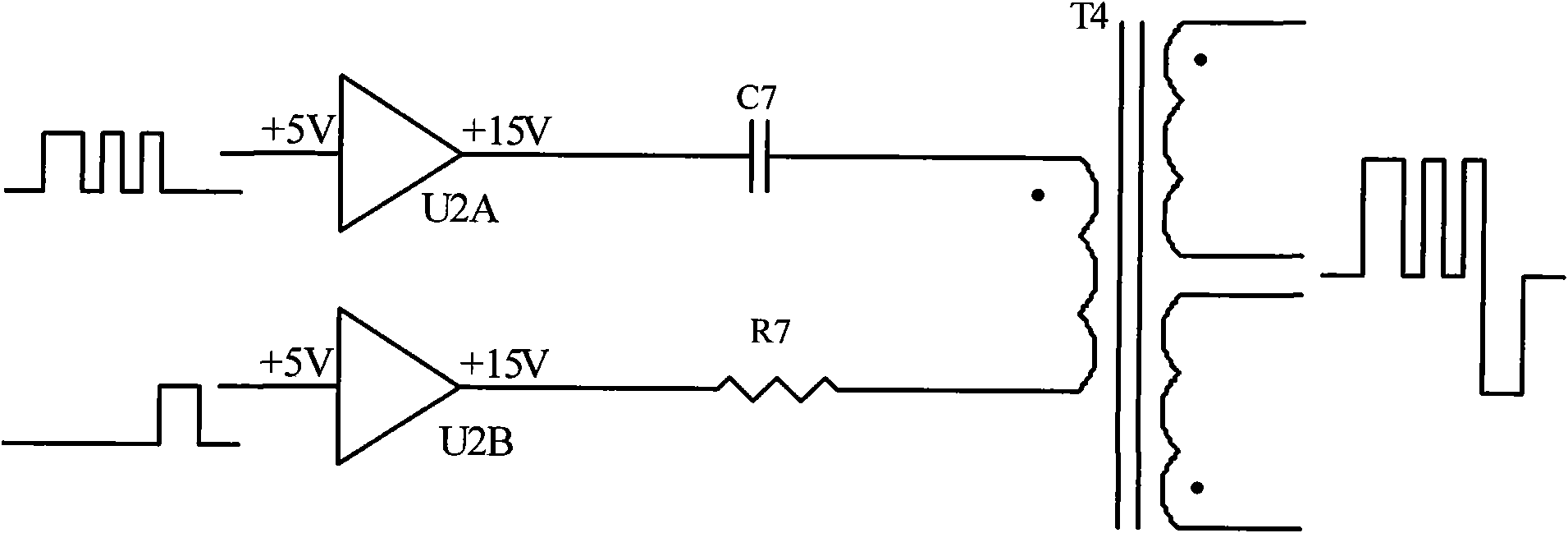

General thick film type floating plate modulator

InactiveCN101895278AAvoiding the problem of limited range-time productSimple structurePulse shapingPulse amplitude modulationSoftware languageEngineering

The invention relates to a general thick film type floating plate modulator, which comprises a control component FPGA, a high-speed logic optocoupler, a driving circuit, an impulse isolation transformer, a thick film high-pressure switching circuit and a suspension power supply, wherein the FPGA uses VHDL language to modulate ultra-wide impulse into opening impulse train and truncation impulse; an isolation strip wave duct amplifier of the high-speed logic optocoupler is used for striking a light to protect the FPGA; the driving circuit adopts a high-speed driver to amplify the opening impulse train and the truncation impulse; the impulse isolation transformer comprises a primary electrode and a dual-secondary electrode; the thick film high-pressure switching circuit is composed of an opening tube and a truncation tube auxiliary circuit; the opening impulse train and the truncation impulse are transmitted to the thick film high-pressure switching circuit through the impulse isolation transformer; and the on / off of the opening tube and the truncation tube are switched to realize compatibility of the ultra-wide impulse and a narrow impulse. The invention adopts software language to realize opening / parameters adjustment of the truncation impulse and uses reference level of a low-pressure high-efficiency inverter to adjust positive bias so as to realize generality and interchangeability.

Owner:中国兵器工业第二〇六研究所

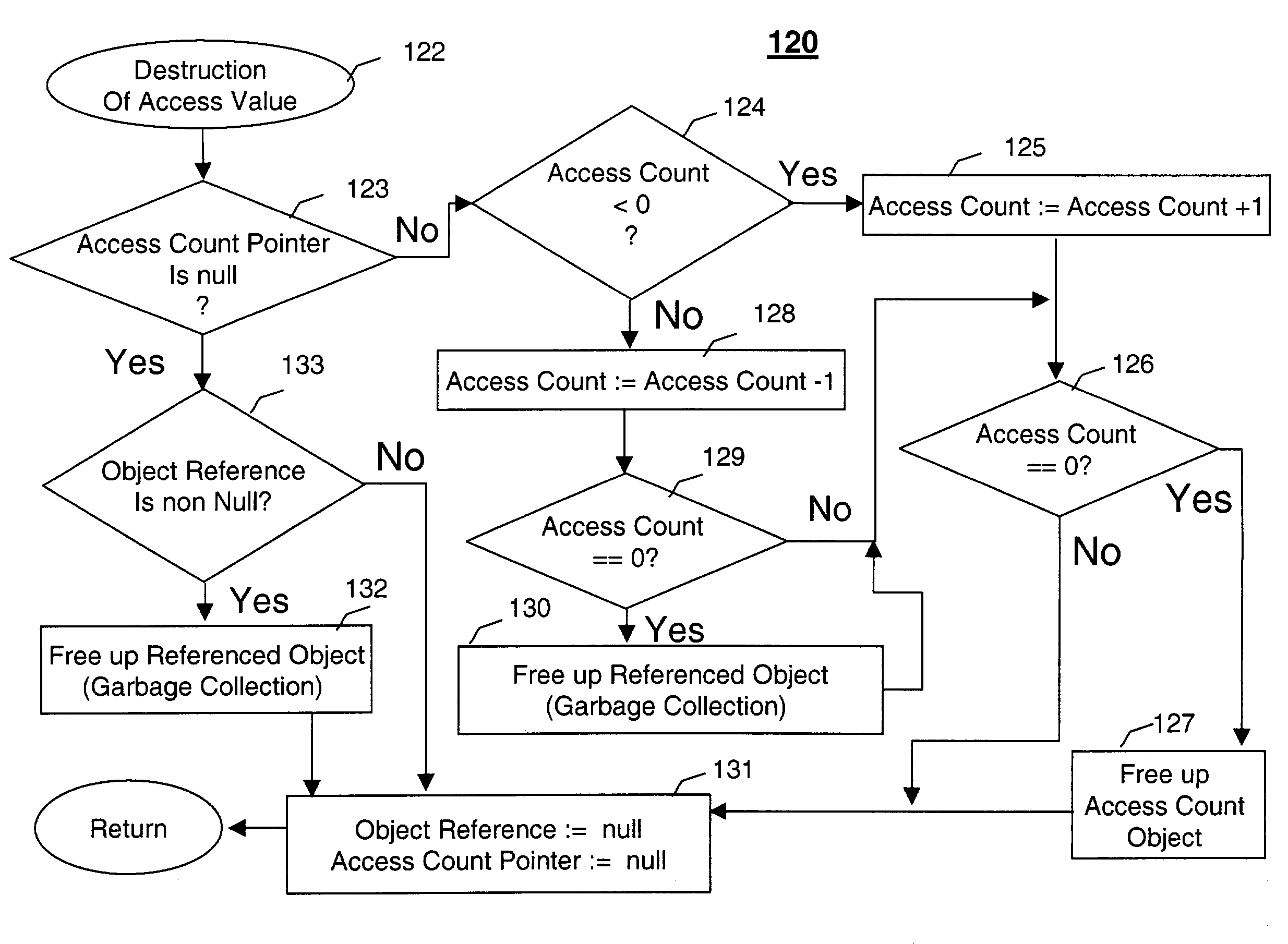

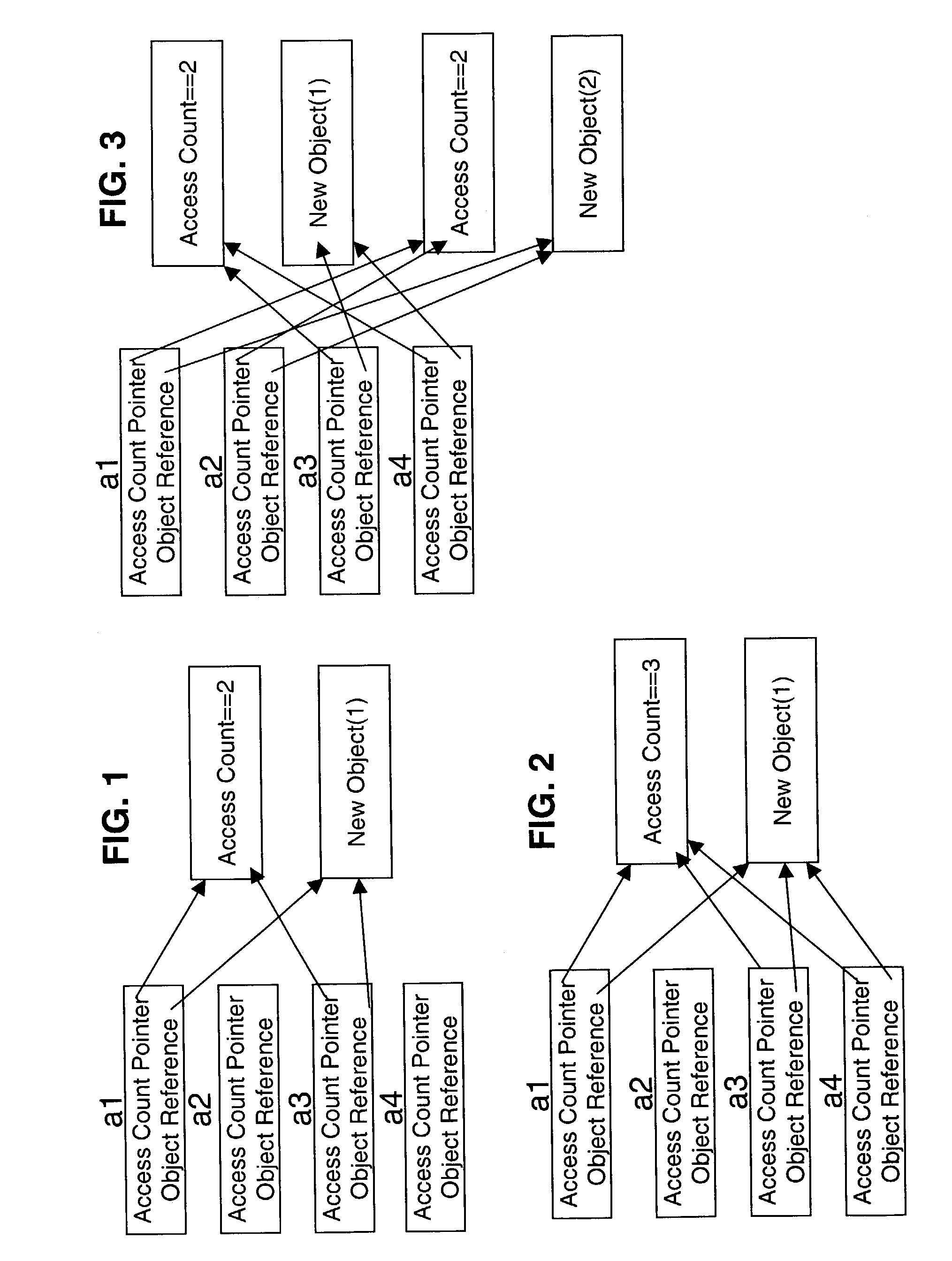

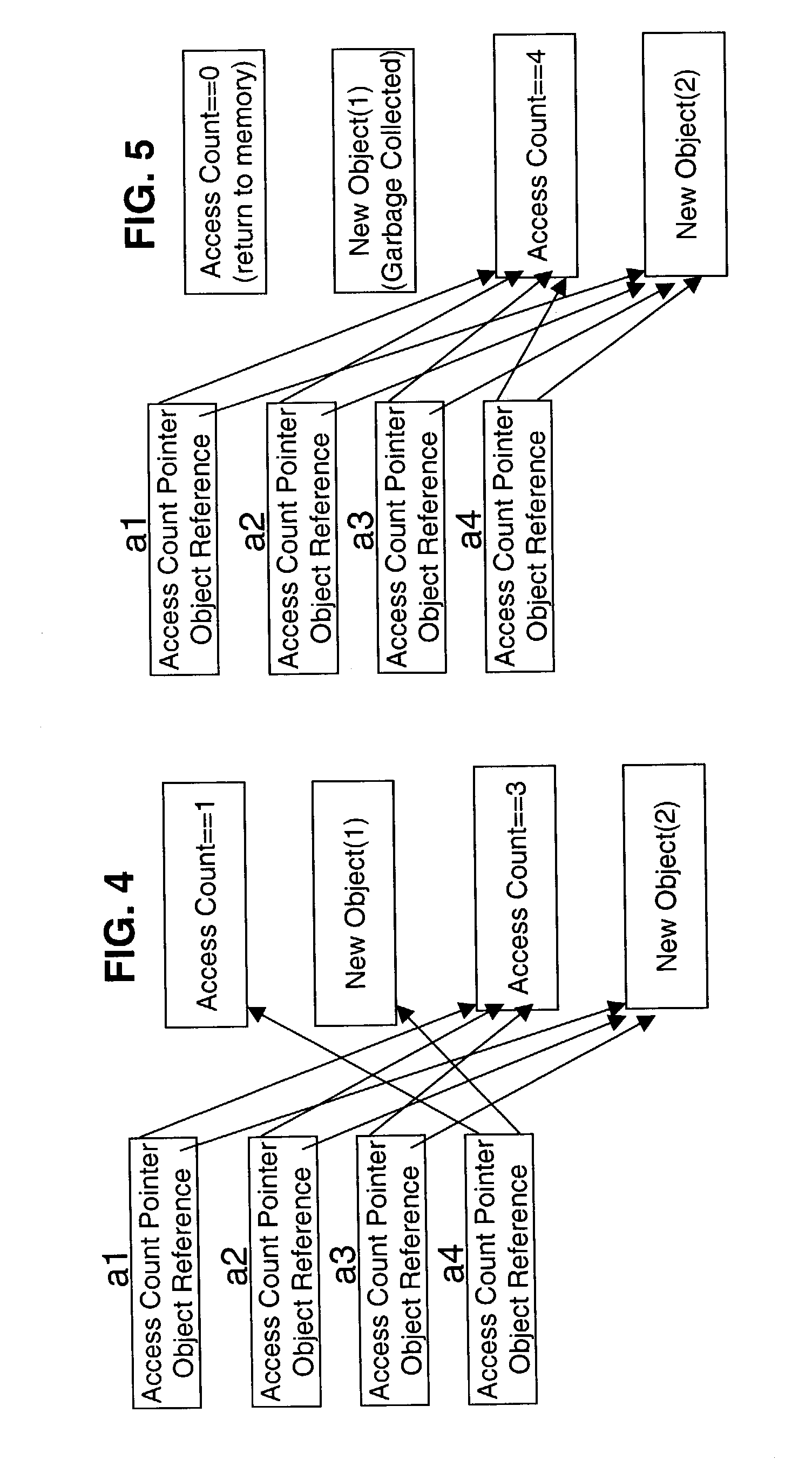

Dangling reference detection and garbage collection during hardware simulation

ActiveUS7403961B1Significant performance benefitSignificant comprehensive benefitsError detection/correctionAnalogue computers for electric apparatusWaste collectionHardware emulation

A method of dangling reference detection and garbage collection of VHDL objects within a program includes the steps of providing an Access Value having an Object Reference pointing to an Allocated Object and having and an Access Count pointer pointing to an integer object named Access Count which models a shared access count for the access values. The method sets the Object Reference and the Access Count pointer to null when constructing a new access value and enables an assignment of a negative Access Count to the shared access count when de-allocating a pointer to the Allocated Object. The method also maintains an exact count of a number of pointers pointing to the Allocated Object.

Owner:XILINX INC

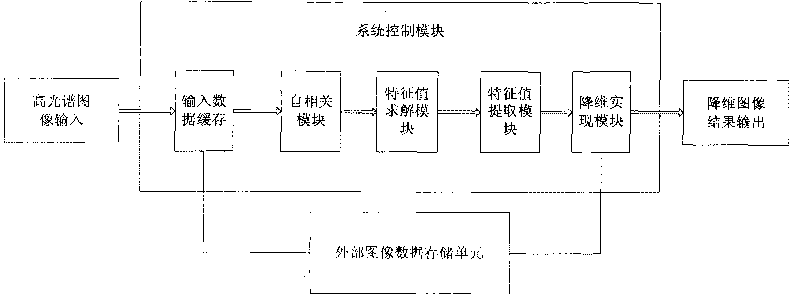

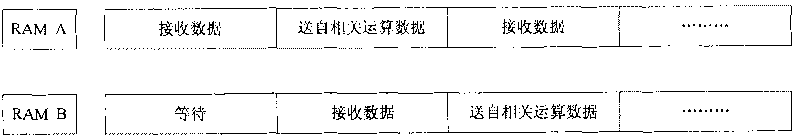

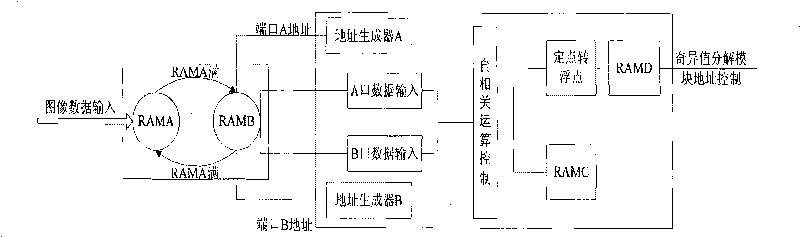

High-spectrum image dimensionality reduction chip

InactiveCN101763445AShort development cycleSave design costSpecial data processing applicationsImaging processingDimensionality reduction

The invention provides a high-spectrum image dimensionality reduction chip, which belongs to the field of image processing. The chip mainly completes the real-time dimensionality reduction processing on a large amount of high-spectrum image data. The chip is completed by adopting the VHDL speech, and is realized through being based on an in-site programmable gate array. The system chip manly comprises five parts: a system control module, a self correlation module, a feature value solving module, a feature value extracting module and a dimensionality reduction realization module. The invention can complete the real-time dimensionality reduction processing of the high-spectrum image data, and has the advantages of short development period, low design cost and low development risk.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

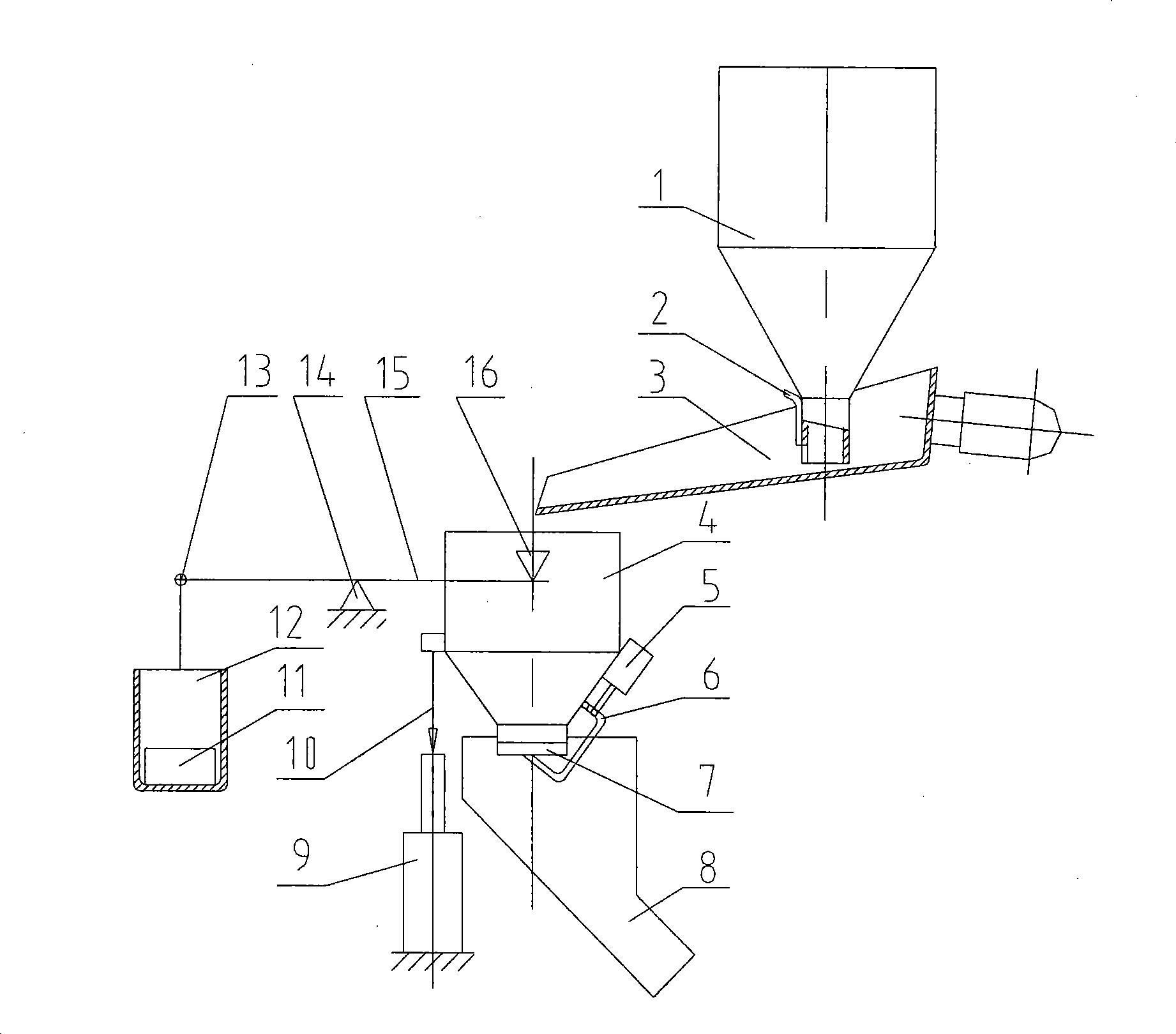

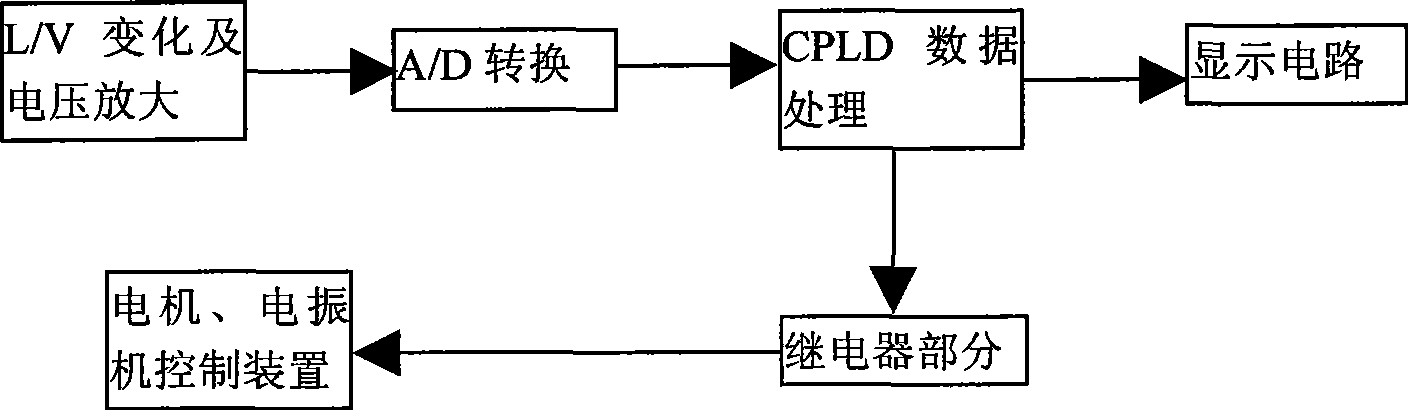

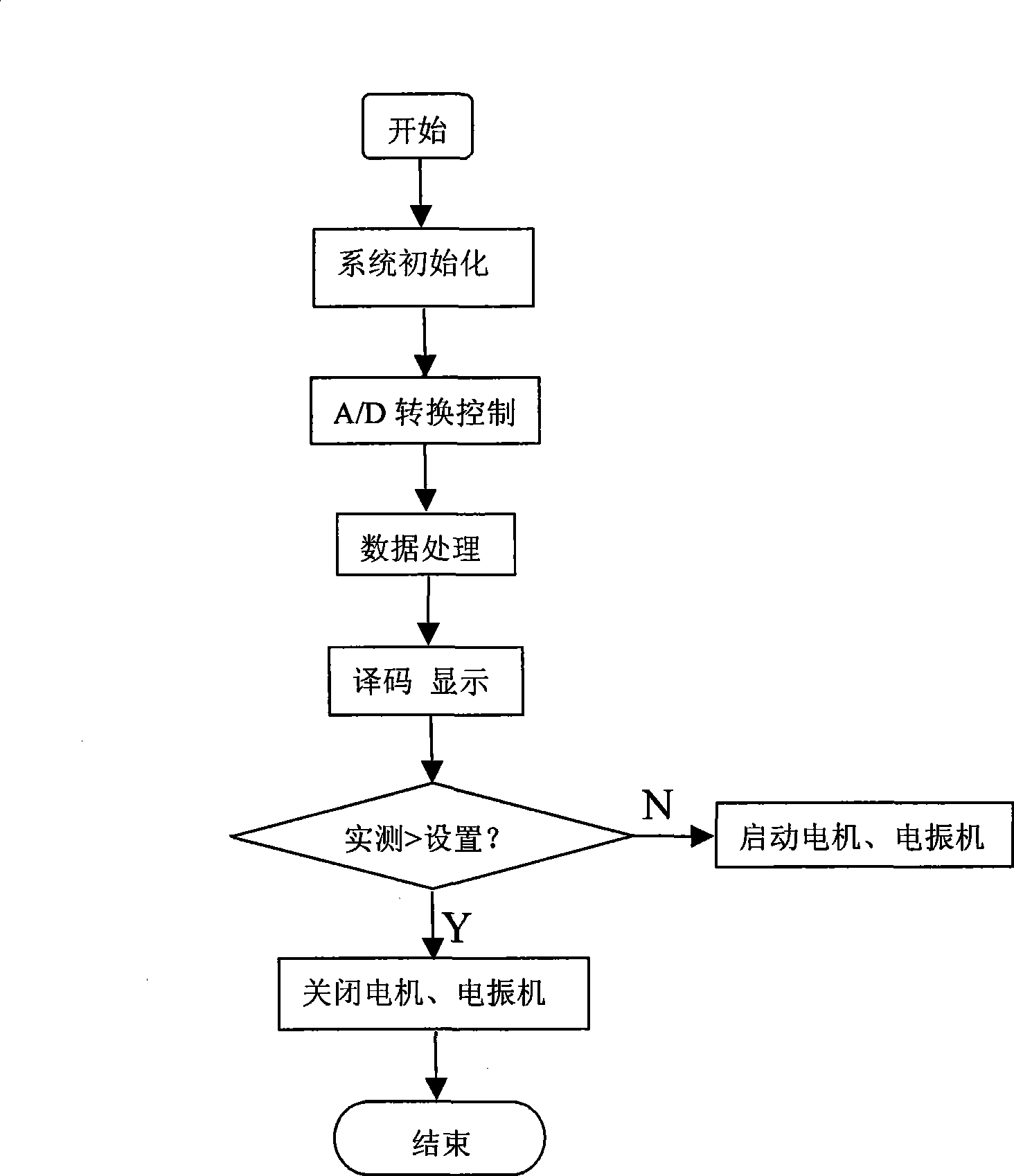

Quantitative weighing system based on buoyant force weighing sensing principle

InactiveCN101464181AIncrease flexibilityCompetitiveWeighing apparatus using counterbalanceWeighing apparatus using fluid action balancingAutomatic controlDigital control

The invention belongs to the field of detection and automatic control. A quantifying-weighing system based on the buoyancy weighing sensing principle comprises a leverage mechanism, a shedding mechanism, a buoyancy sensor and a CPLD control system. According to the liquid buoyancy principle, the buoyancy weighing sensor converts the measured gravity value in the form of linear relation into displacement value which clearly refers to the displacement, and outputs the displacement value in the form of electrical signal. The buoyancy weighing sensor is free of technical defects such as creep deformation, zero point, sensitivity drift and the like. The CPLD control system consists of an R / V change and voltage amplification module, an A / D conversion module, a CPLD data processing module, a display module, a relay part and a motor as well as an electromagnetic vibrating machine control system; and the fundamental controlling principle thereof is that the control system converts a complex digital control logical system into the SOC (design system on chip design) by employing the VHDL language and adopting the top down design method. The invention achieves the effects of reducing the size of the system, enhancing the reliability of the system, shortening the development period, reducing the development cost, and greatly improving the accuracy of the dynamic weighing.

Owner:孔令宇

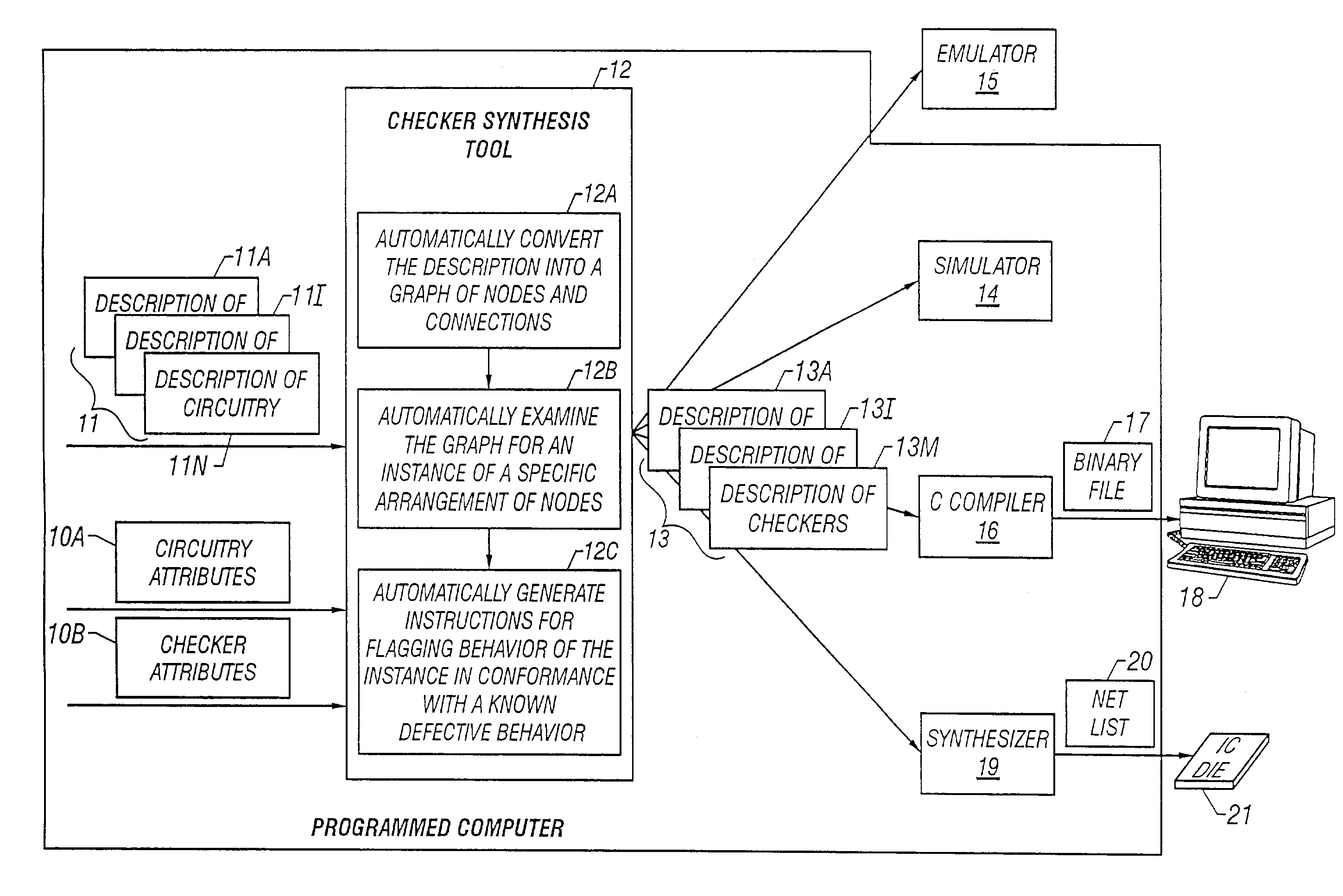

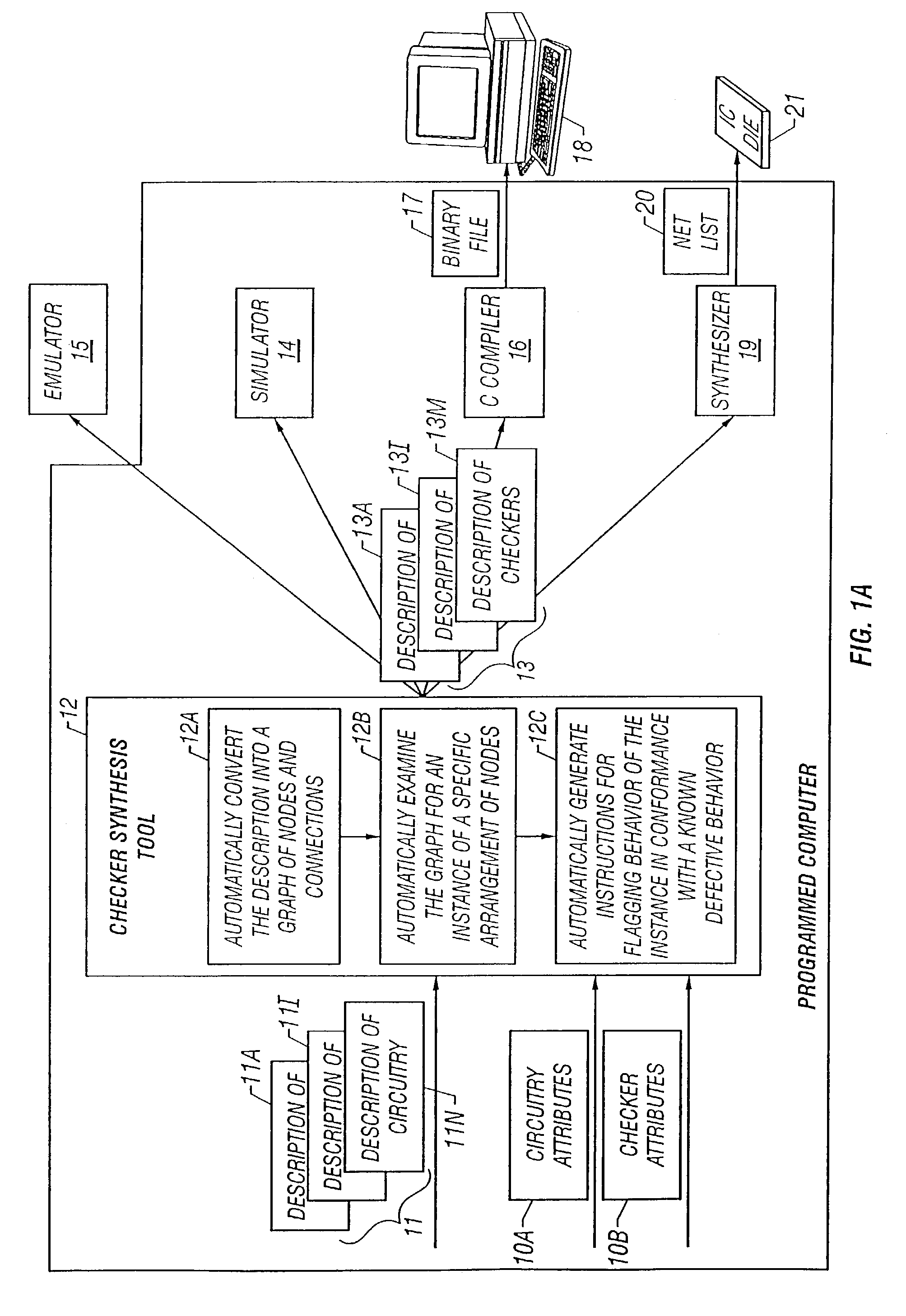

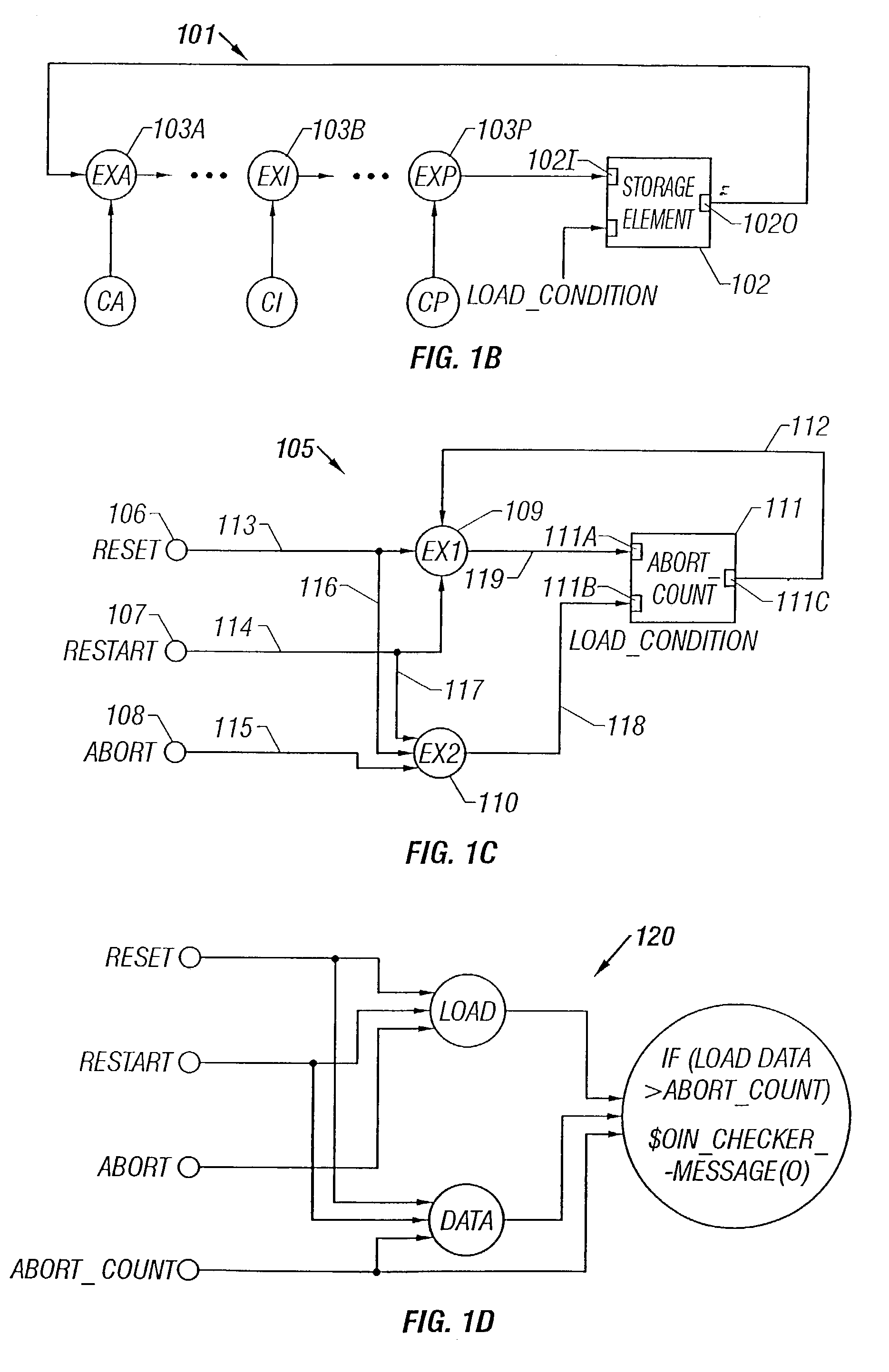

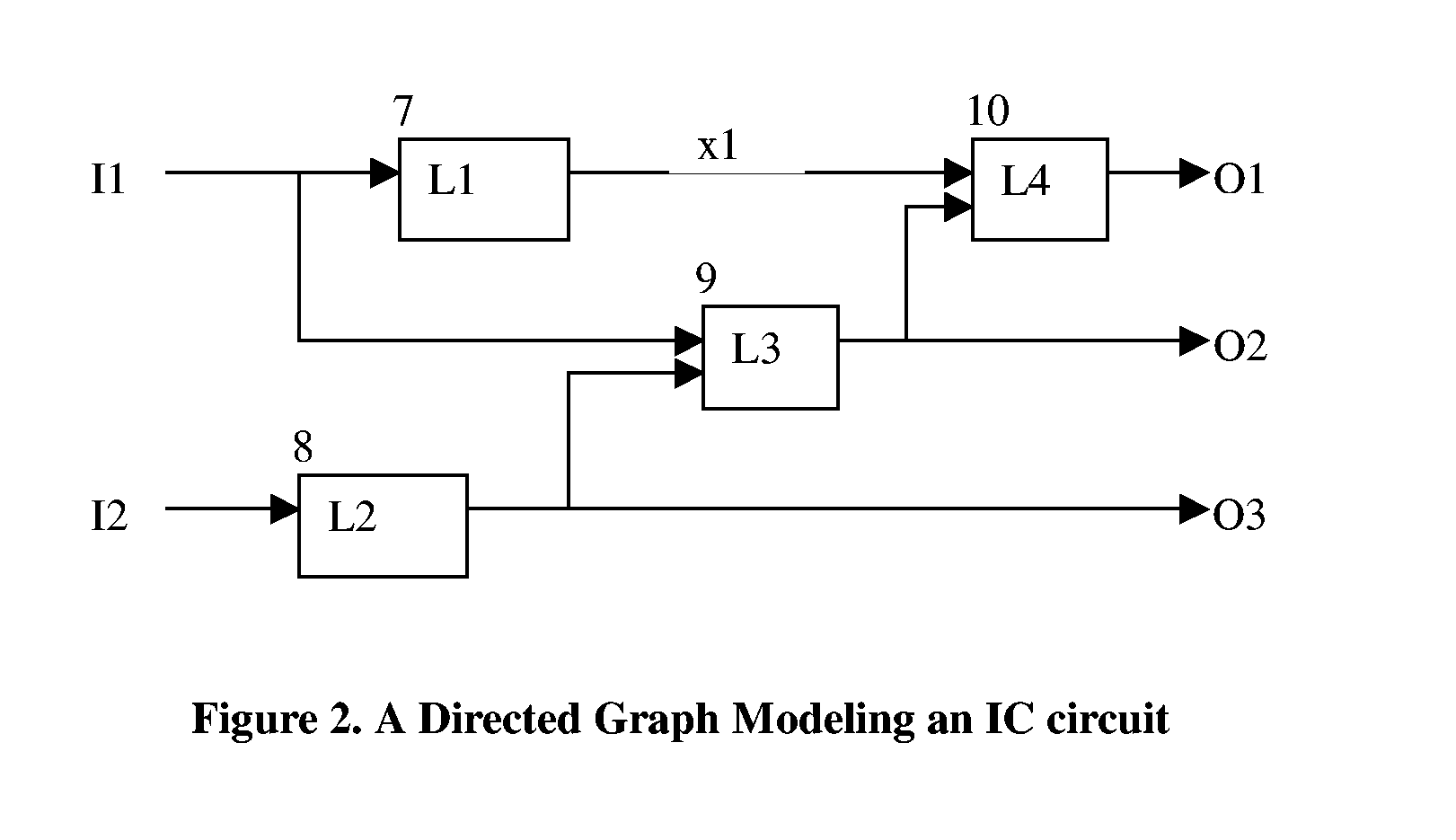

Method for automatically generating checkers for finding functional defects in a description of circuit

InactiveUS7007249B2Eliminate generationEliminating diagnosisAnalogue computers for electric apparatusCAD circuit designGraphicsProcessor register

A programmed computer generates descriptions of circuits (called “checkers”) that flag functional defects in a description of a circuit undergoing functional verification. The programmed computer automatically converts the circuit's description into a graph, automatically examines the graph for instances of a predetermined arrangement of nodes and connections, and automatically generates instructions that flag a behavior of a device represented by the instance in conformance with a known defective behavior. The checkers can be used during simulation or emulation of the circuit, or during operation of the circuit in a semiconductor die. The circuit's description can be in Verilog or VHDL and the automatically generated checkers can also be described in Verilog or VHDL. Therefore, the checkers can co-simulate with the circuit, monitoring the simulated operation of the circuit and flagging defective behavior. The programmed computer can automatically determine load conditions of registers in the circuit and automatically generate checkers to flag data loss in the registers. Some of the checkers may use signals generated by other checkers.

Owner:MENTOR GRAPHICS CORP

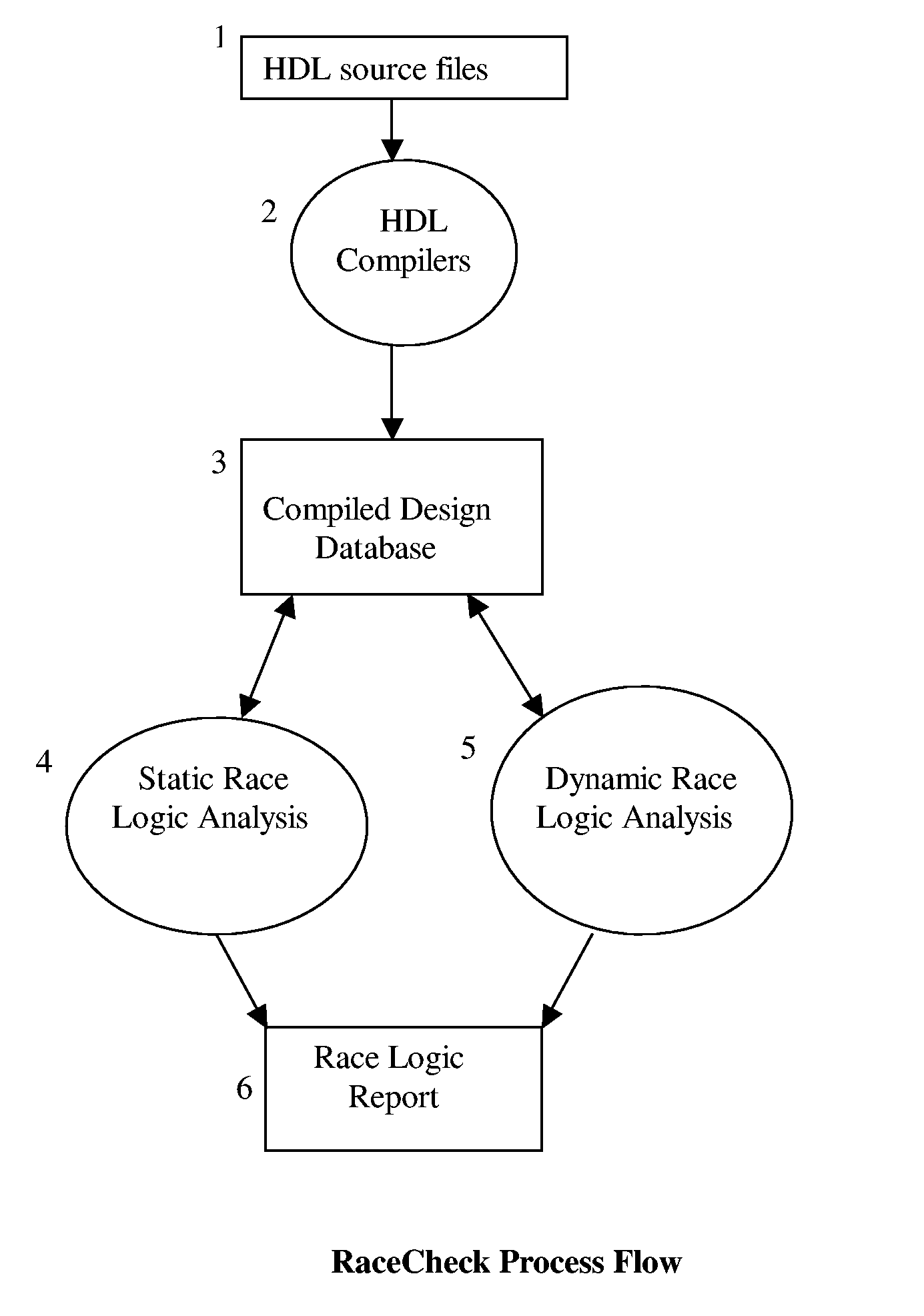

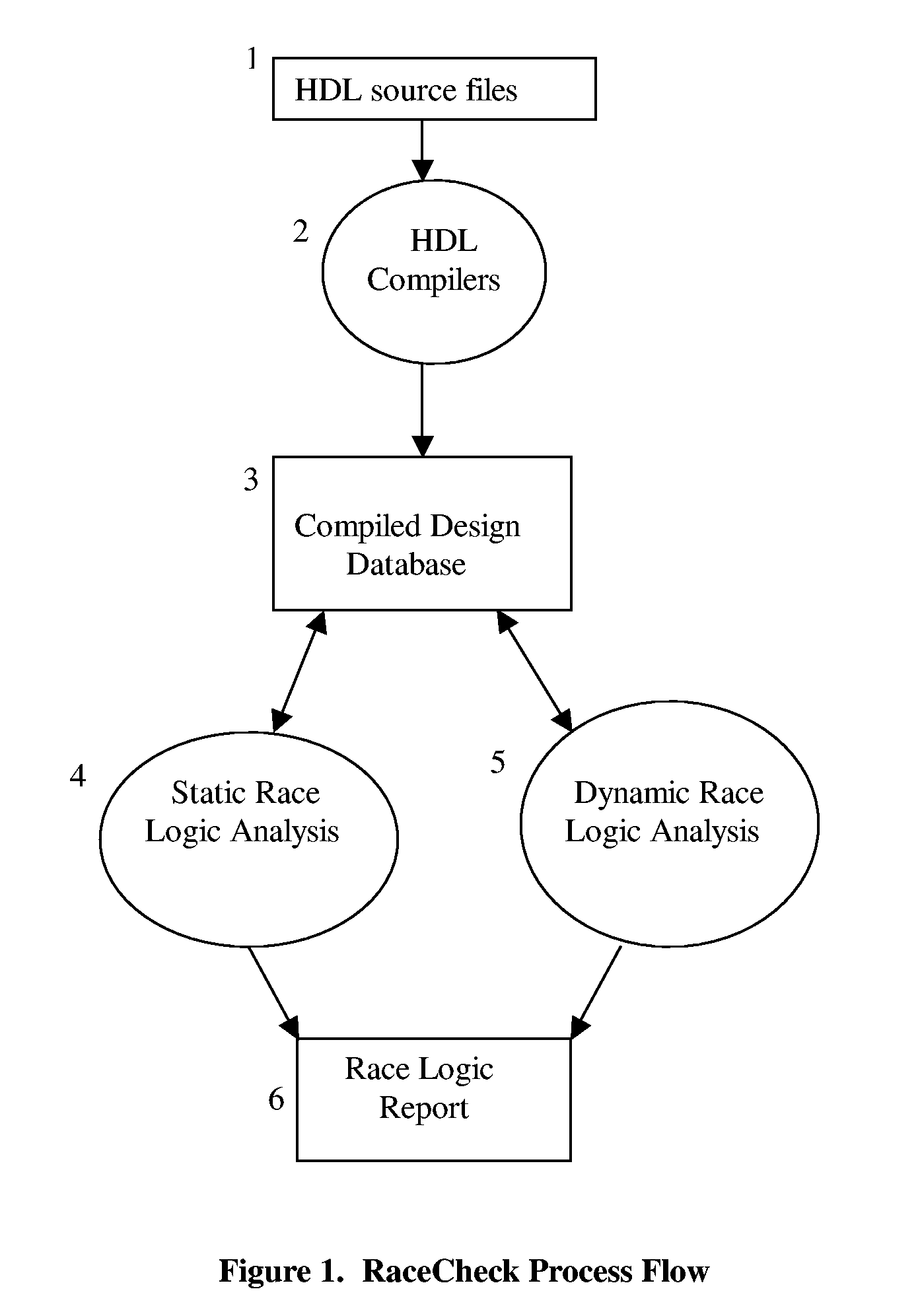

RaceCheck: A Race Logic Ana,yzer Program for Digital Integrated Circuits

ActiveUS20060075367A1Reduce effortShorten the timeElectrical testingDesign optimisation/simulationTime informationSystemC

This invention describes a race logic audit program, RaceCheck, which is unique from the prior arts. Specifically, RaceCheck can perform both static and dynamic race logic analysis, and it works with a plurality of hardware description languages (HDL), which include but not limited to: VHDL, Verilog, SystemVerilog, and SystemC. Furthermore, RaceCheck makes use of both structural and timing information of IC designs, as well as binary-decision diagram (BDD) and automatic test pattern generation (ATPG) techniques to derive accurate race logic analysis results with few false violations. Finally, RaceCheck can detect concurrent invocation races of the $random system function, concurrent invocation races of user-defined tasks and functions, zero-delay combination loops, and RaceCheck's dynamic analysis engine uses a HDL simulation kernel to perform timing-accurate race logic analysis. All these aforementioned features are unique for the invention and have not been reported in any prior arts.

Owner:DYNETIX DESIGN SOLUTIONS

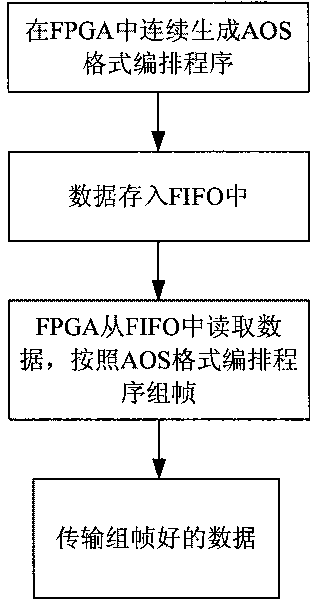

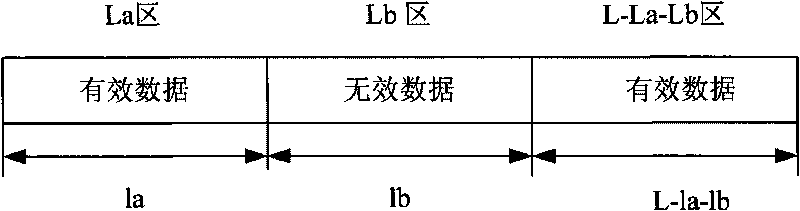

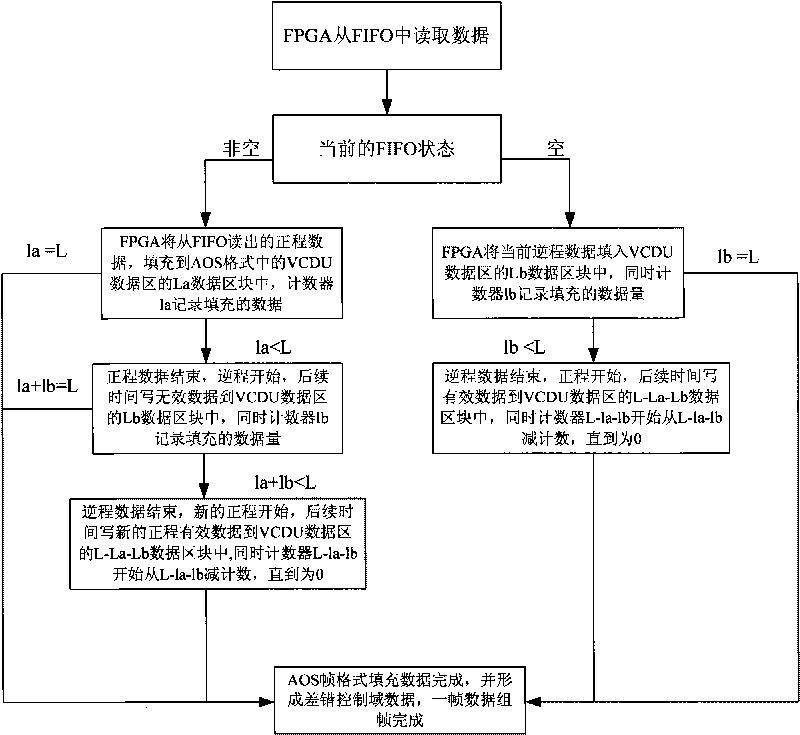

Data transmission method based on AOS encoding

ActiveCN101729088AReduce unsatisfactory frame phenomenonImprove transmission efficiencyTransmissionData streamDesign standard

The invention relates to a data transmission method based on the AOS encoding. Based on the CCSDS-suggested AOS-formatted design standard, an AOS-formatted VCDU data field is designed in a way that the data field can be divided into sections for use, compiled into a VHDL hardware logic descriptive language, and downloaded to a programmable device FPGA, and the AOS-formatted processing and output of the SAR data stream by hardware such as the FPGA, FIFO and the like is realized. By using a method of dividing the VCDU data unit into sections, when processing the current AOS-formatted frame, the valid data area at the formatted tail can continue reading in the formatted frame because new trace data appears in advance due to the short retrace time of the input data, thereby improving the transmission efficiency of the valid data of the frame, greatly reducing the frame-insufficient phenomena of the data, and being especially suitable for the situations of the trace and retrace wide-range change of the data before and after inputting. The invention effectively inhibits the formatted frame from being filled with an insufficient frame of the valid data, ensures the AOS-formatted efficiency, and enables the data processing to work at a more stable speed all the time. The invention can adapt to the random change of the trace and the retrace of the input data and prevent the formatting mistake.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

Methods, systems and media for managing functional verification of a parameterizable design

InactiveUS7237210B2Electrical testingComputer programmed simultaneously with data introductionAuto-configurationComputer architecture

Methods, systems, and media for managing functional verification of a parameterizable design are disclosed. Embodiments include a system having a testbench configuration module adapted to configure a testbench, the testbench having testbench signals and one or more instantiated components having a plurality of ports of a generic design, where the testbench signals are wired to the plurality of ports. The testbench may also have one or more instantiated special components based on chip-specific versions of the design where the special components are wired to the same ports as the generic design. The system may also include a functional verification manager that, through a component module, observes values in the testbench and automatically configure a verification environment based on the observed values, including automatic insertion of checkers at different levels of hierarchy. The testbench may be a VHDL or Verilog testbench in some embodiments.

Owner:GLOBALFOUNDRIES INC

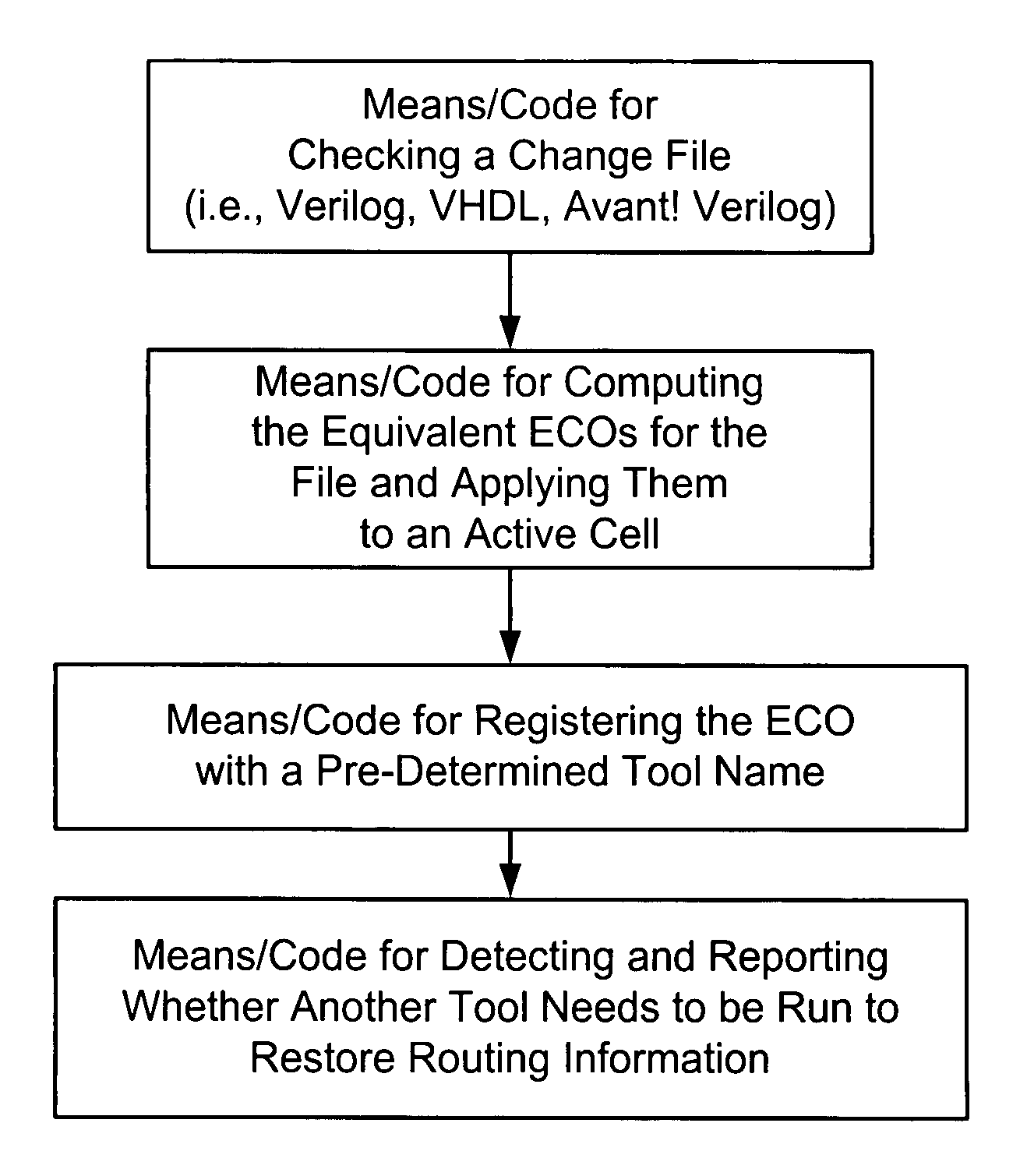

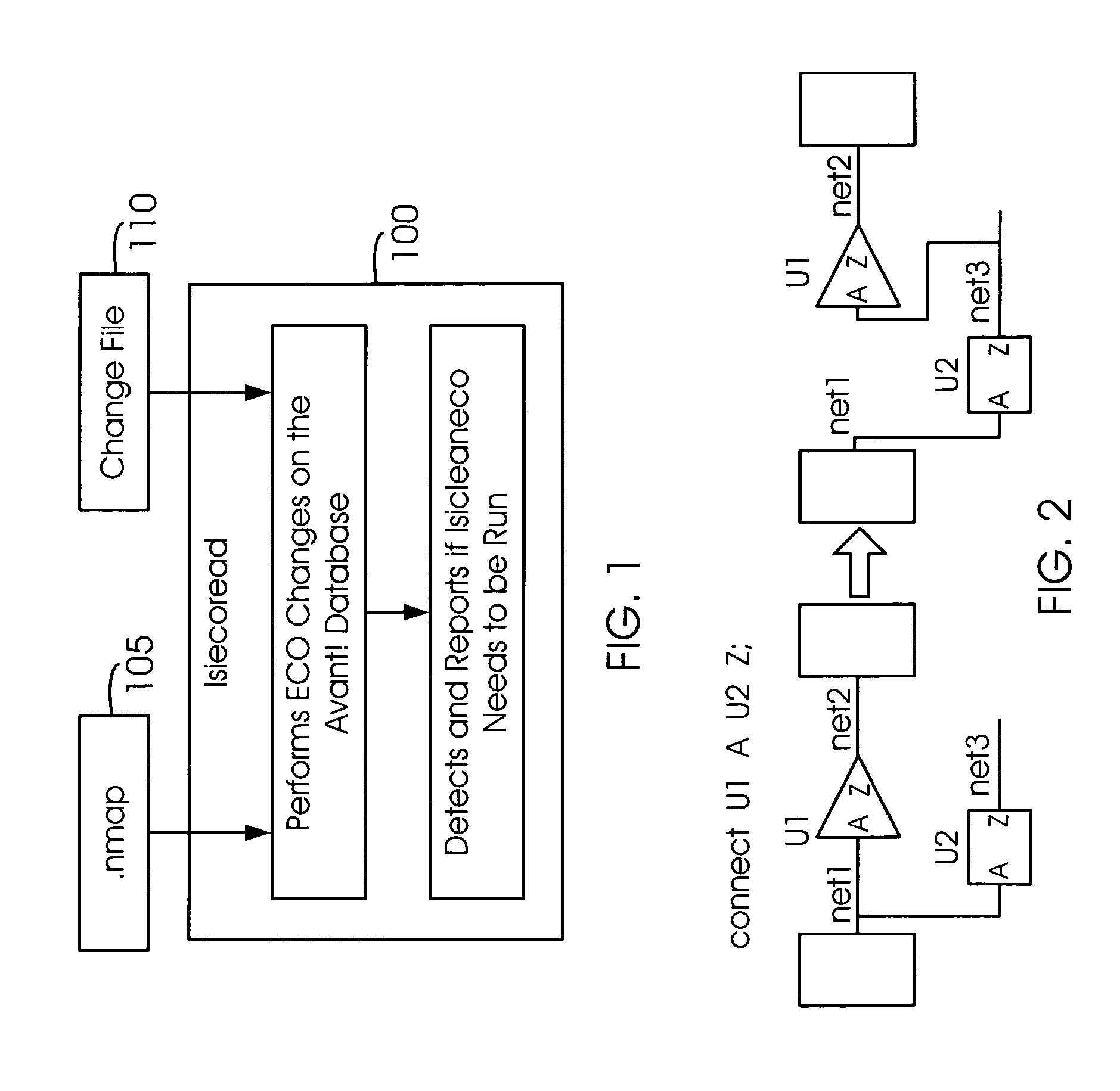

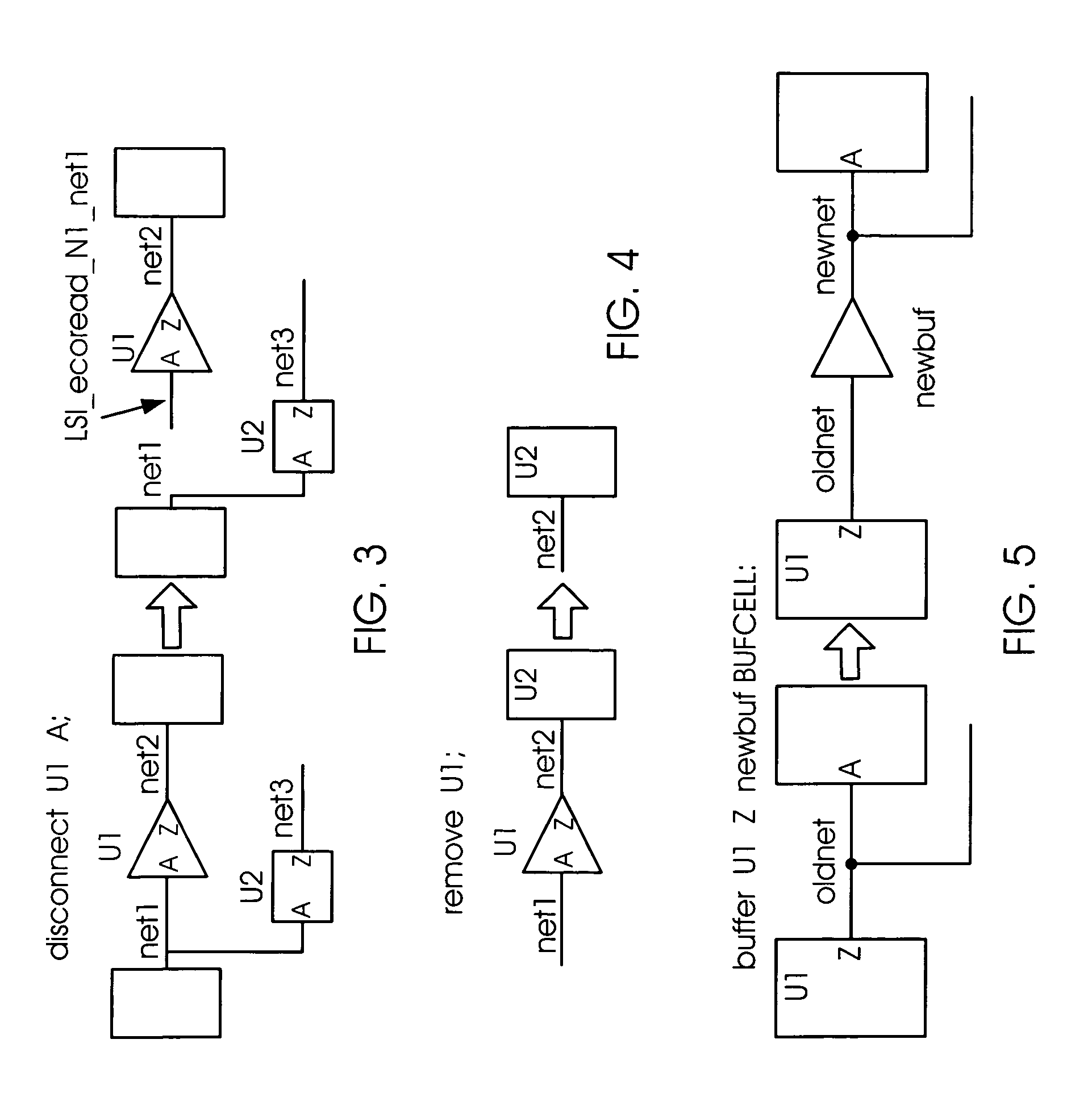

Method and apparatus for implementing engineering change orders

ActiveUS7007248B2Easy to learnEasy maintenanceData processing applicationsDigital data processing detailsApplication engineeringActive cell

Owner:BELL SEMICON LLC

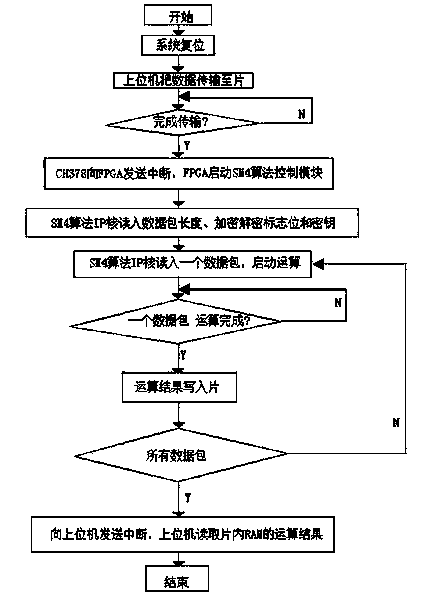

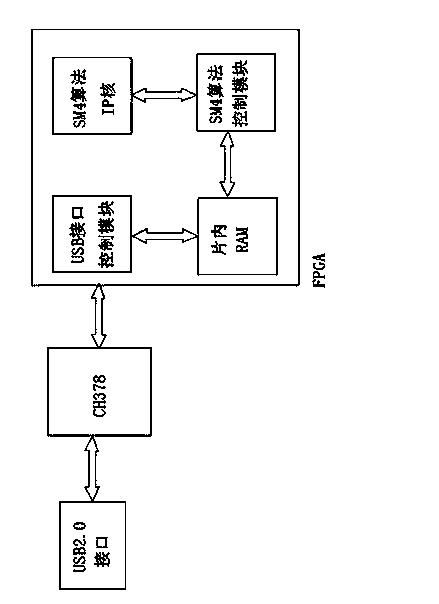

SM4 algorithm encryption unit based on FPGA chip and USB interface chip

InactiveCN103973432AFast data encryption and decryptionImprove securityEncryption apparatus with shift registers/memoriesComputer hardwareFpga implementations

The invention discloses an SM4 algorithm encryption unit based on an FPGA chip and a USB interface chip. The SM4 algorithm encryption unit based on the FPGA chip and the USB interface chip comprises the USB interface chip, the FPGA chip, a USB interface control module, an SM4 algorithm IP core, an SM4 algorithm control module and an on-chip RAM, wherein the USB interface control module, the SM4 algorithm IP core, the SM4 algorithm control module and the on-chip RAM are realized through the FPGA chip. In the SM4 algorithm encryption unit, the FPGA chip serves as a control core, and the SM4 algorithm IP core and the related control module are realized through the VHDL design; the SM4 algorithm encryption unit is connected to a user terminal through a USB interface, it is guaranteed that important data of a user are transmitted in a ciphertext mode in the network, and consequently quick operation and secure transmission of the data are achieved. The SM4 algorithm encryption unit based on the FPGA chip and the USB interface chip has the advantages of being high in data encryption and decryption speed, high in security, convenient to use and the like.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

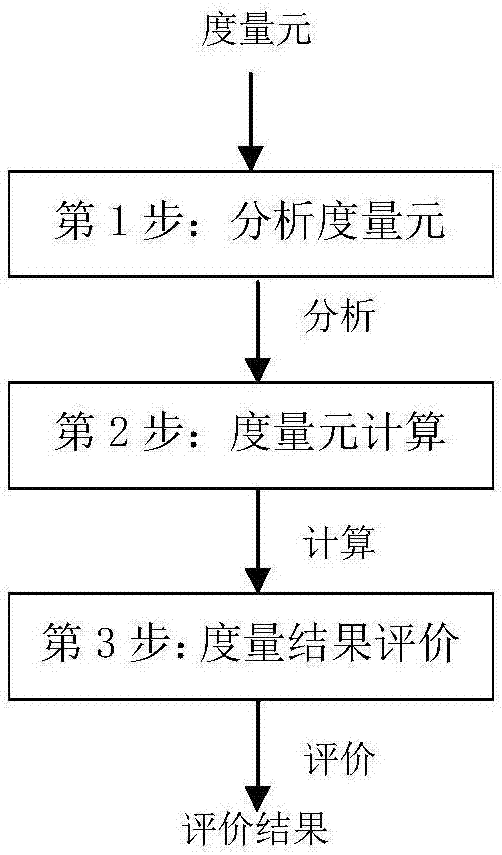

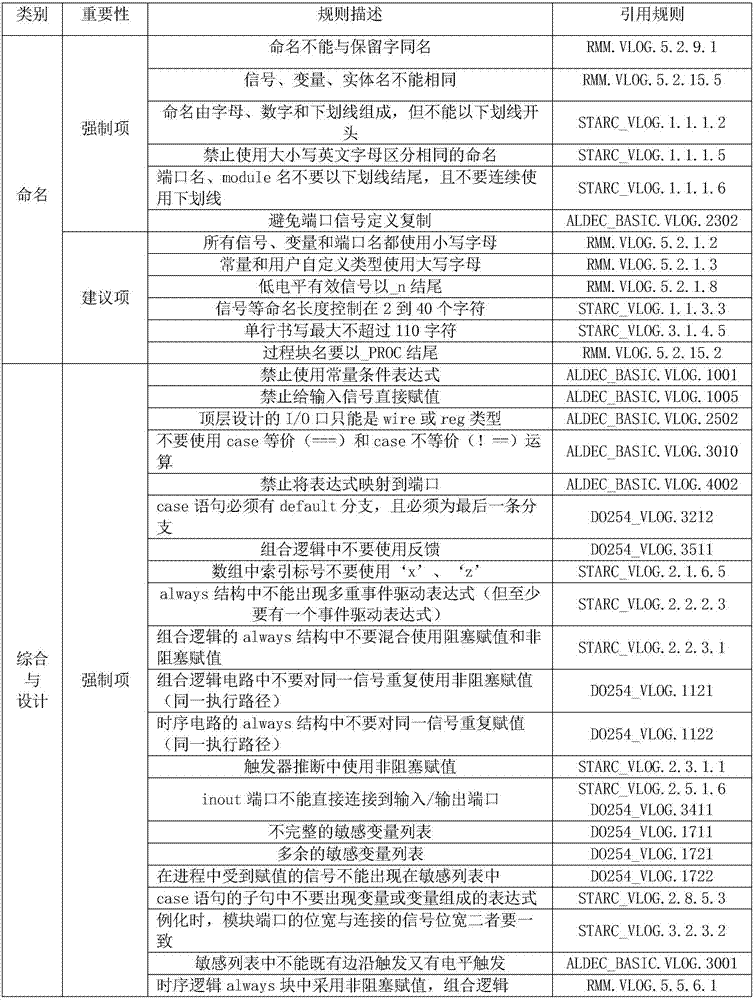

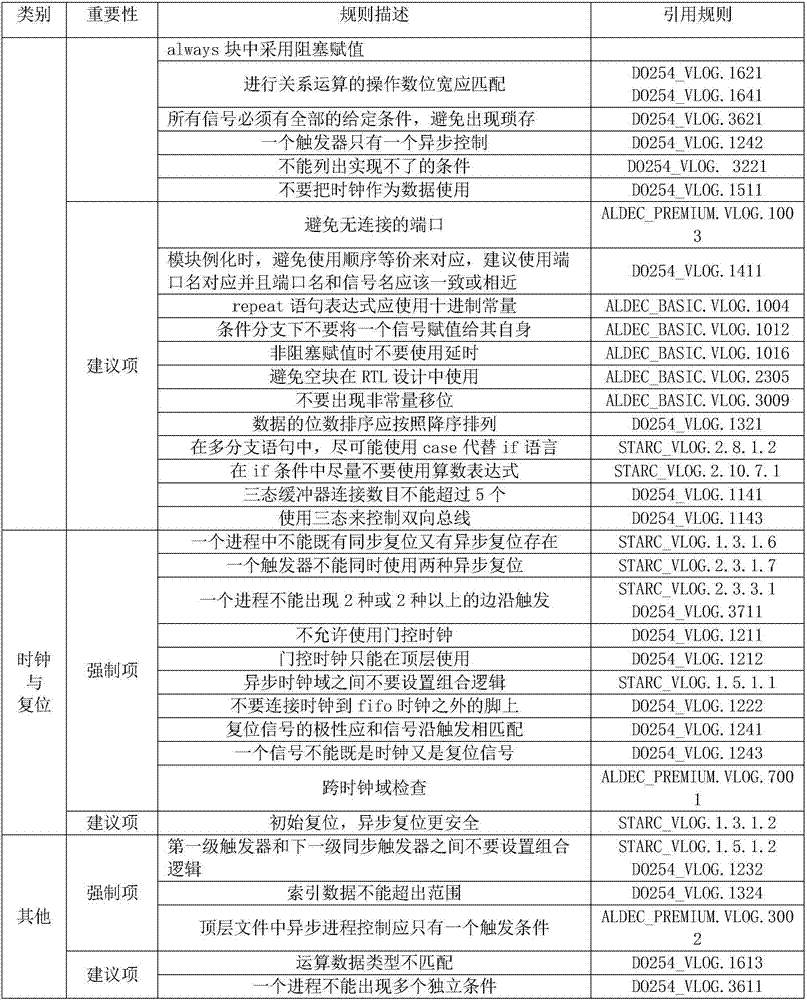

Method for measuring static quality of FPGA software

InactiveCN107341101AReduce the number of verification testsReduce subjectivitySoftware testing/debuggingEvaluation resultSoftware language

A method for measuring the static quality of FPGA software disclosed by the present invention aims to provide a method that can effectively reduce the number of verification tests and quantify the static test quality of software codes. The present invention is realized through the following technical solutions, including VHDL and Verilog In the FPGA software in different languages, the metric elements that reflect the value of software quality are screened out, and the FPGA software metric elements are classified and weighted; the evaluation rule sets that reflect a wide coverage and high degree of influence are selected, and the relevant weighting coefficients of the metric elements are extracted. Determine the severity of the impact, determine the number of evaluation metrics, and establish the analysis metrics and FPGA software quality evaluation model and rule set classification appendix table; according to the fault statistics of the reference standard GJB 2423A, calculate the total number of metrics A and the metrics and The specified metric element score is used to calculate the total number of metric element defects and the evaluation rules to give the metric evaluation result.

Owner:10TH RES INST OF CETC

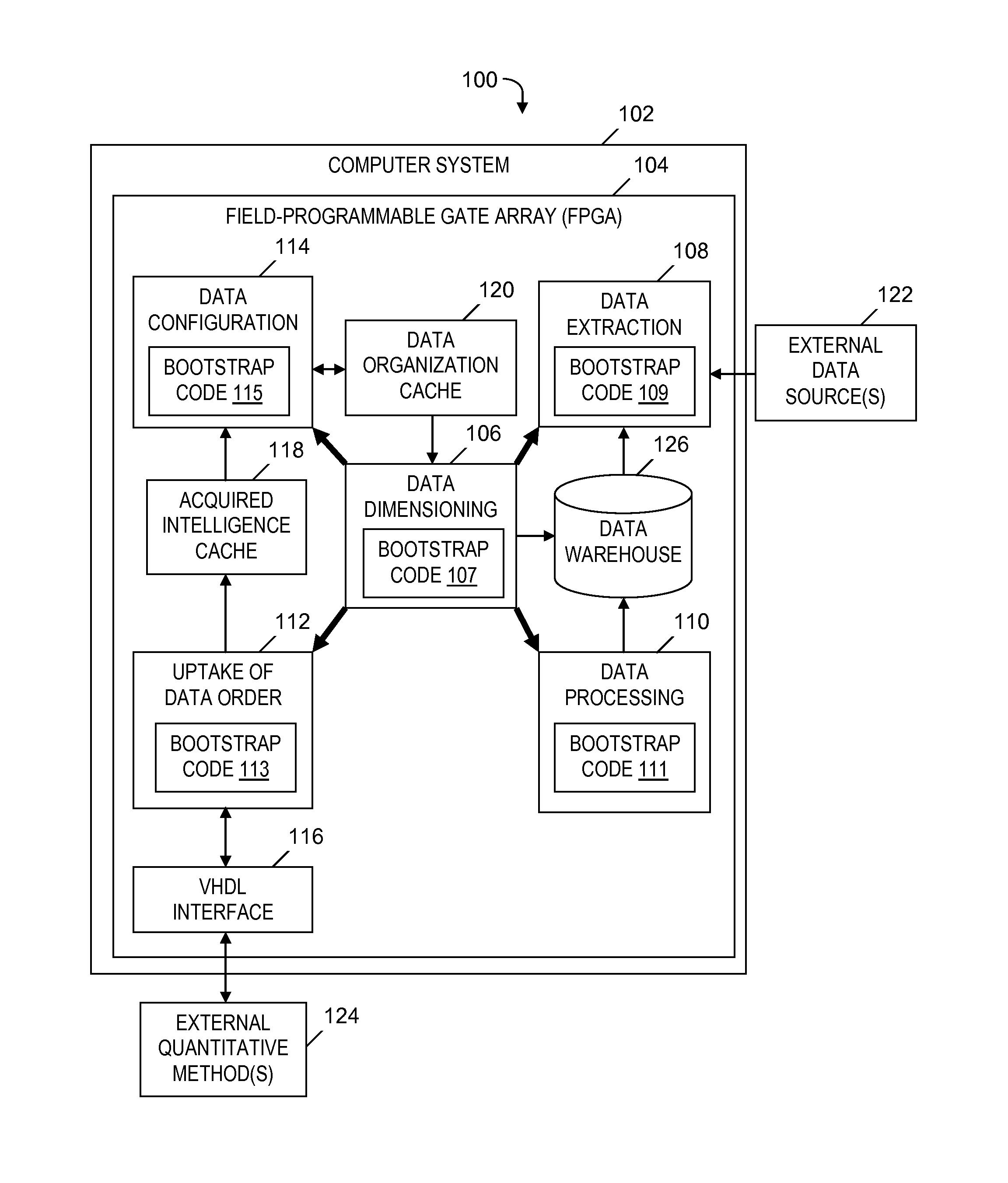

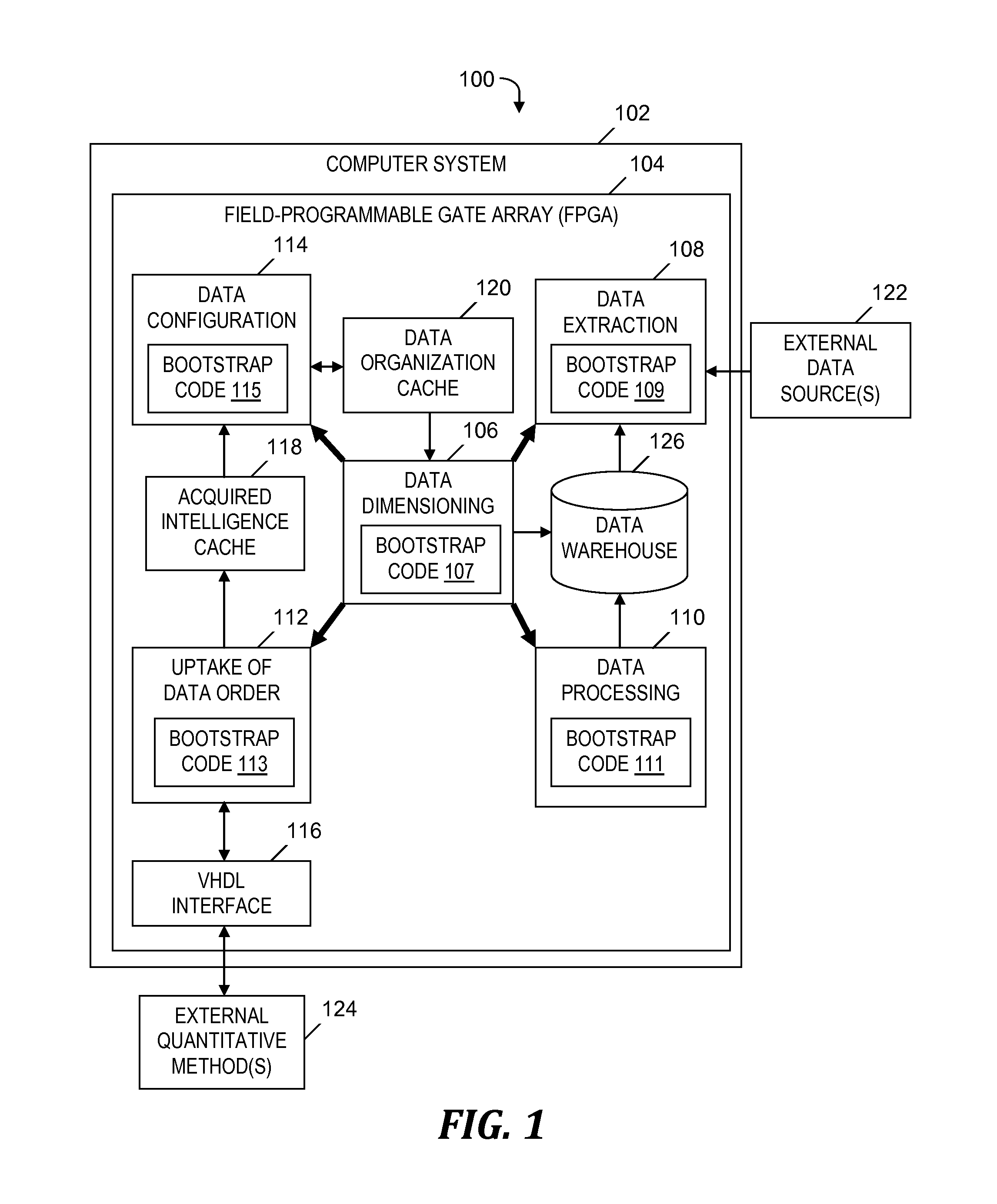

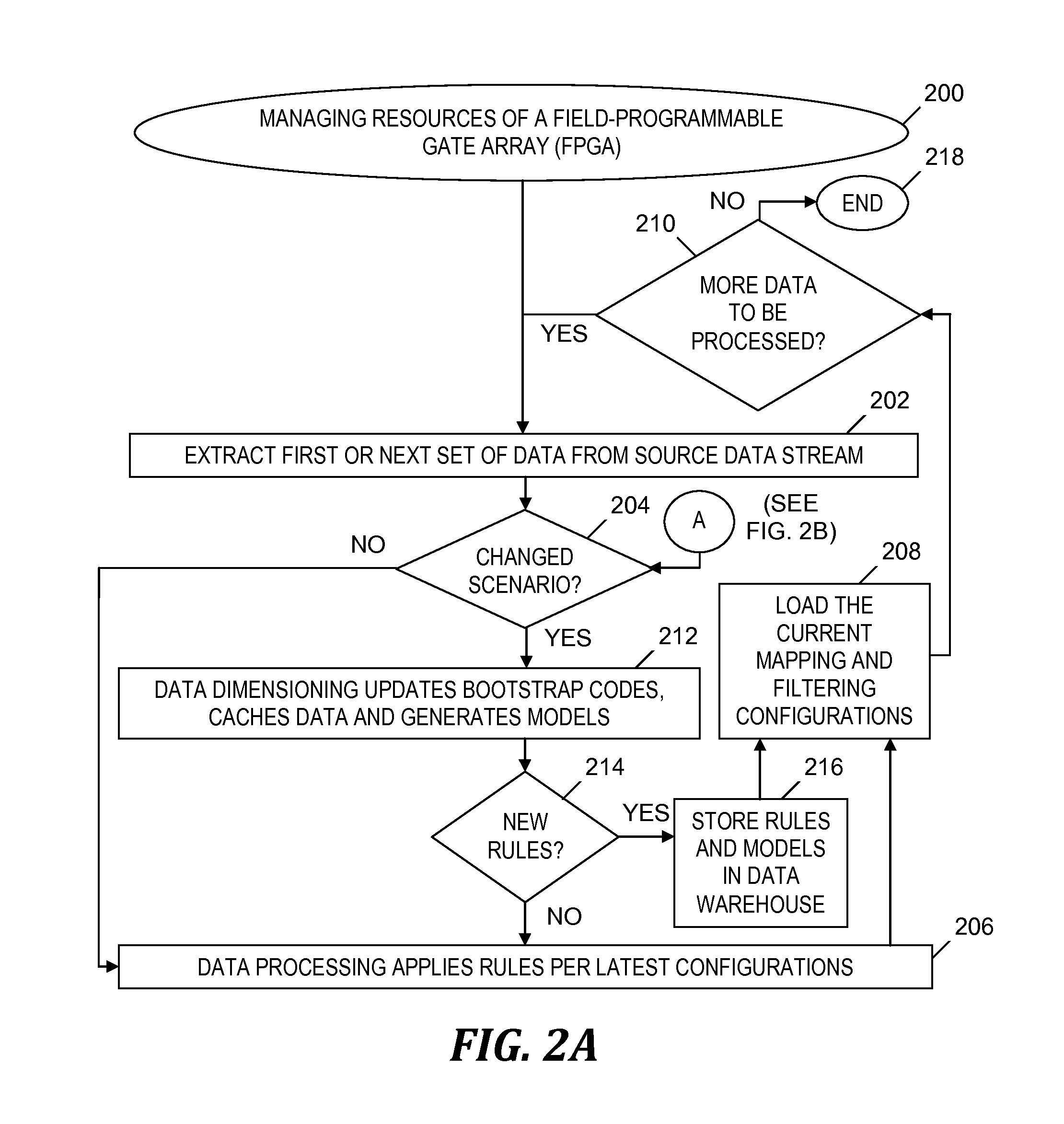

Dynamic Data Dimensioning by Partial Reconfiguration of Single or Multiple Field-Programmable Gate Arrays Using Bootstraps

An approach is presented for managing resources of a field-programmable gate array (FPGA). At runtime, first data is extracted and processed. At runtime and via a very high speed integrated circuit hardware description language (VHDL) interface, a change in a size, a structure, or a load schedule of next data is received. The change is determined by a quantitative method analyzing the first data and executing external to the FPGA. At runtime, a first bootstrap code in the FPGA executes, and in response, other bootstrap codes in the FPGA are updated. The first bootstrap code is configured to update the structure of the next data. The other bootstrap codes are configured to extract and process, and to determine an order of processing and a configuration of the next data. The next data is extracted and processed based on the updated other bootstrap codes.

Owner:GLOBALFOUNDRIES INC

Real-time simulation system oriented to space-borne electronic system

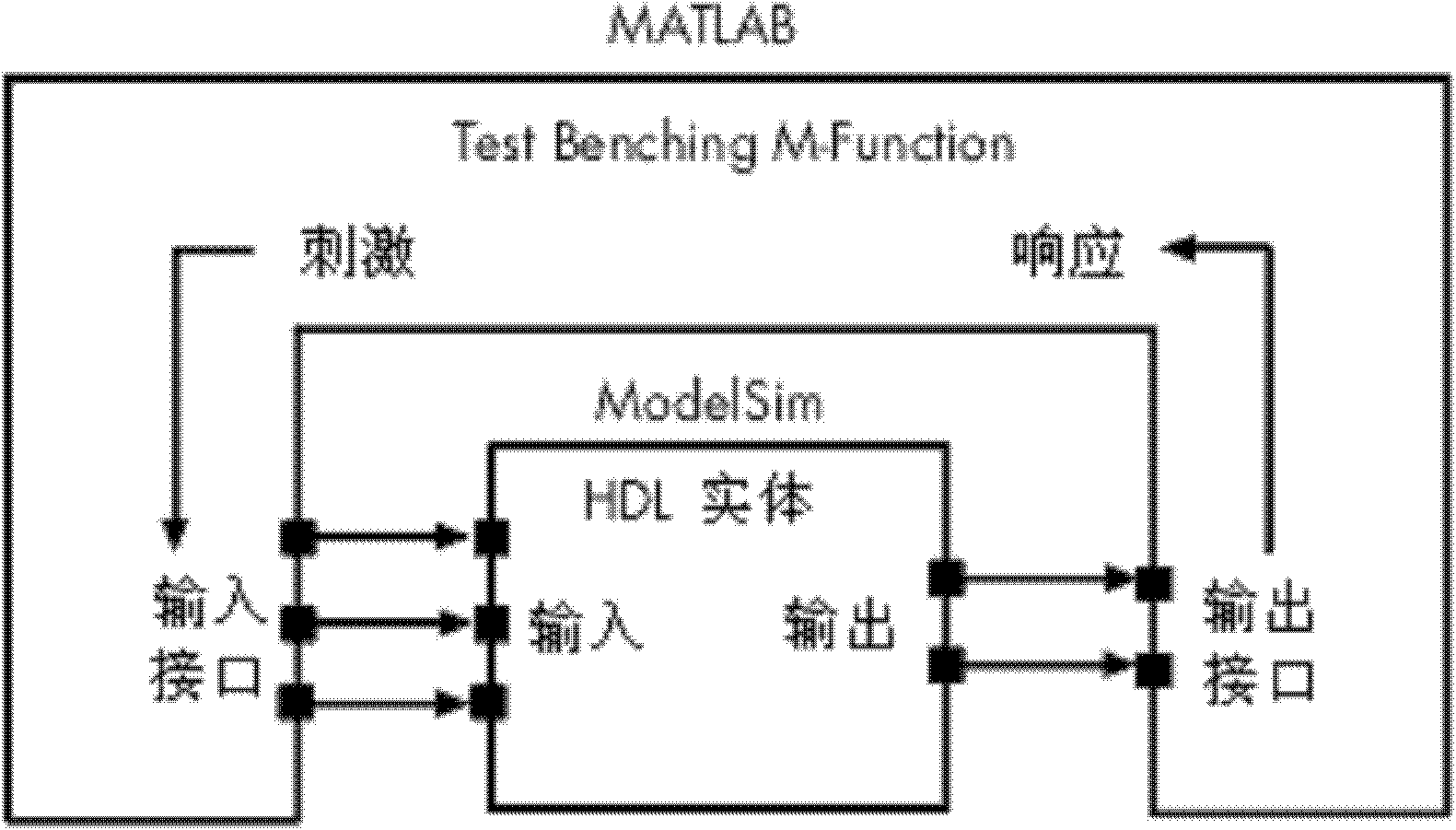

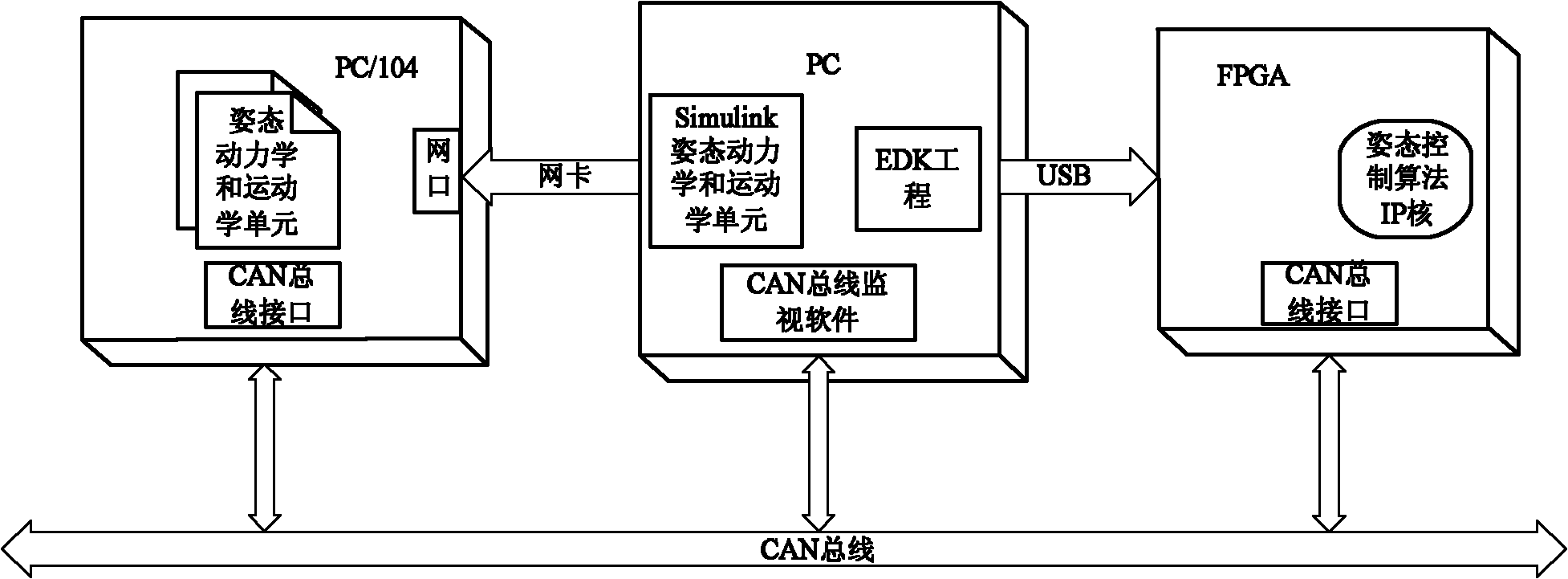

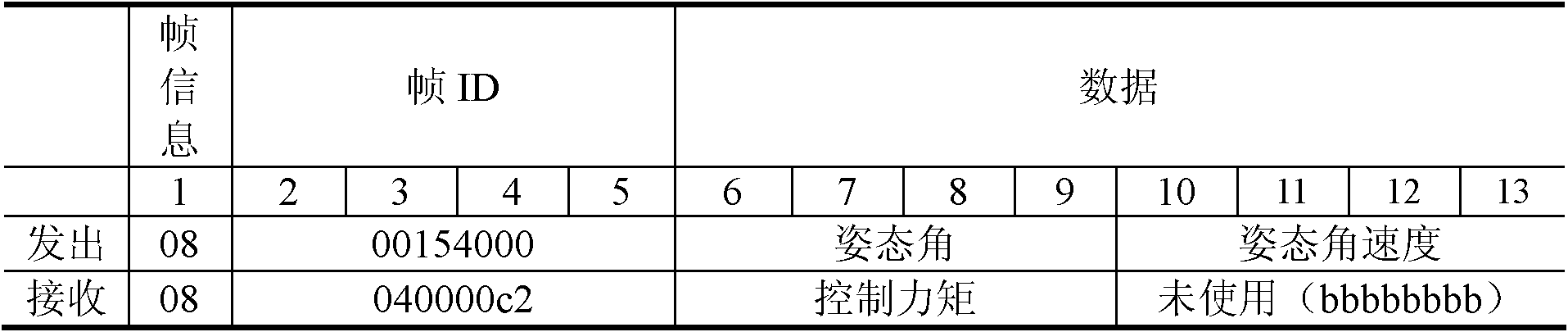

InactiveCN102495552AImprove Simulation EfficiencyImprove applicabilitySimulator controlReal-time simulationElectronic systems

The invention provides a real-time simulation system oriented to a space-borne electronic system, relates to a simulation system, and aims at solving the problems of low simulation efficiency and poor adaptability of the conventional real-time simulation system oriented to a space-borne electronic system. The system comprises a test vector unit, a design simulation verification unit and a network control unit, wherein the test vector unit is used for introducing or establishing a system vector model, and simulating and verifying test input data of a VHDL (very-high-speed integrated circuit hardware description language) entity, and calculating and verifying output data of the VHDL entity; the design simulation verification unit is used for introducing in the VHDL entity, establishing an engineering file to be simulated and verified, controlling or calculating the input data of the network control unit, and outputting the result to the test vector unit through the network control unit; and the network control unit is used for controlling the whole simulation process through a network. The real-time simulation system oriented to the space-borne electronic system is suitable for real-time simulation of the space-borne electronic system.

Owner:HARBIN INST OF TECH

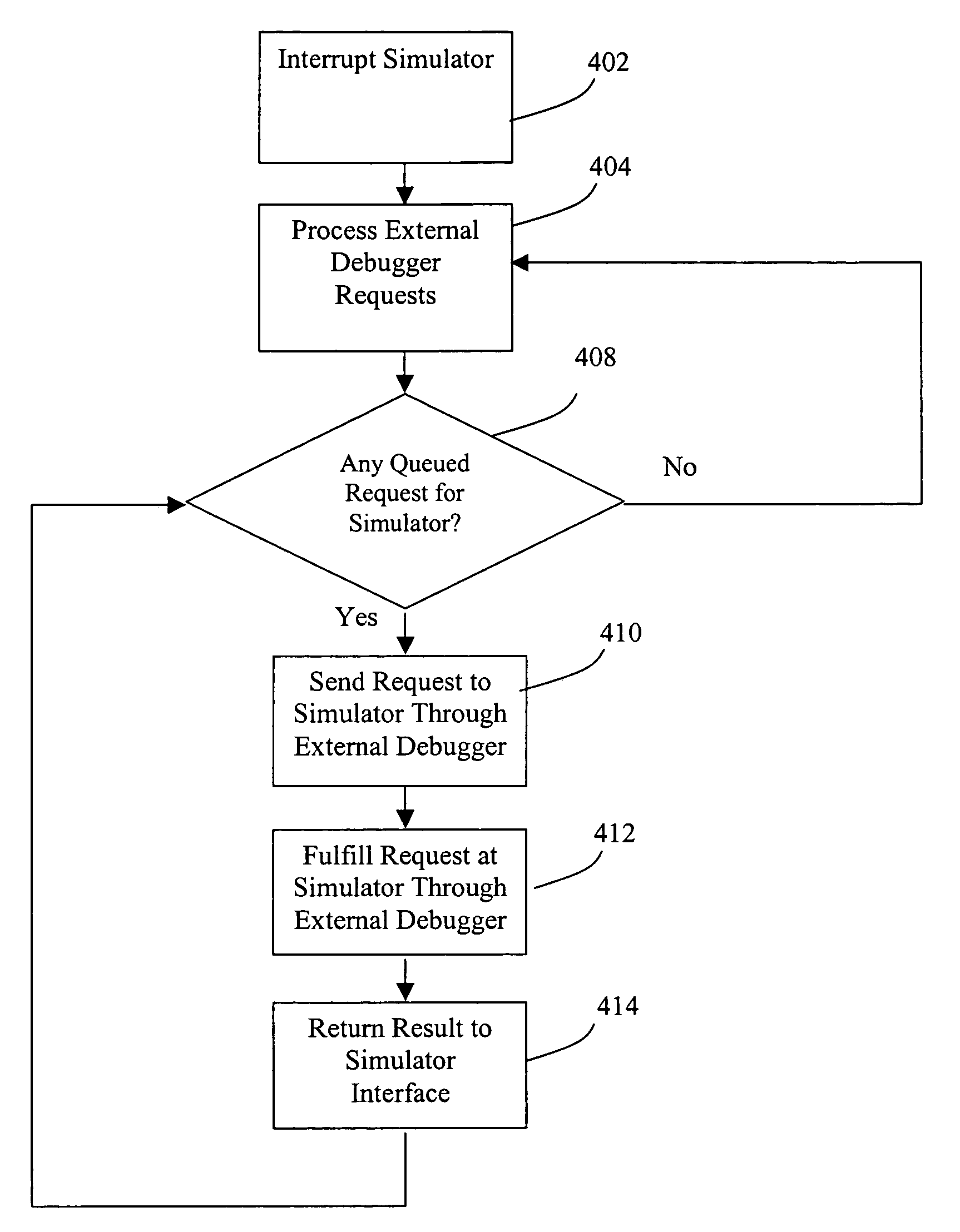

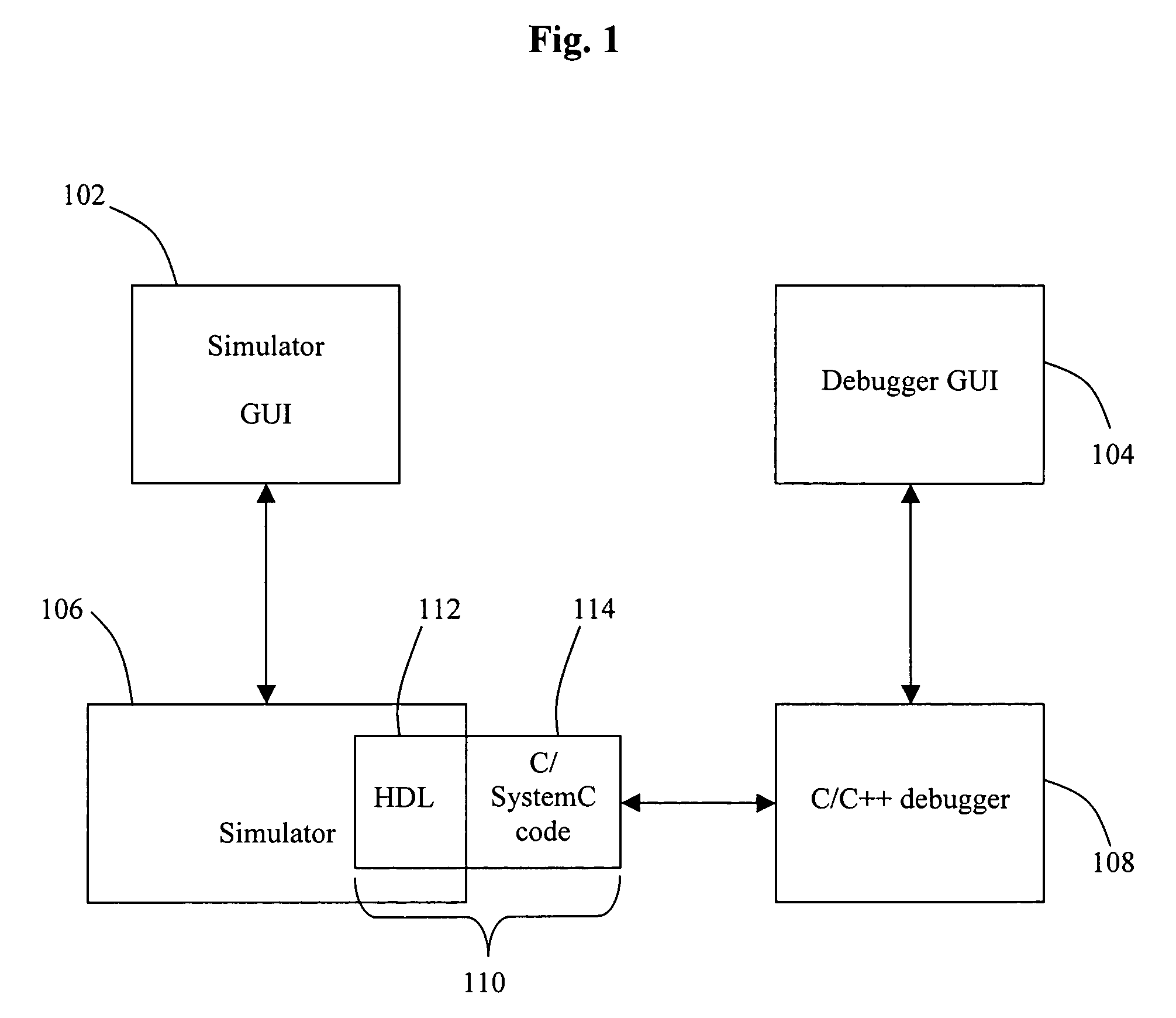

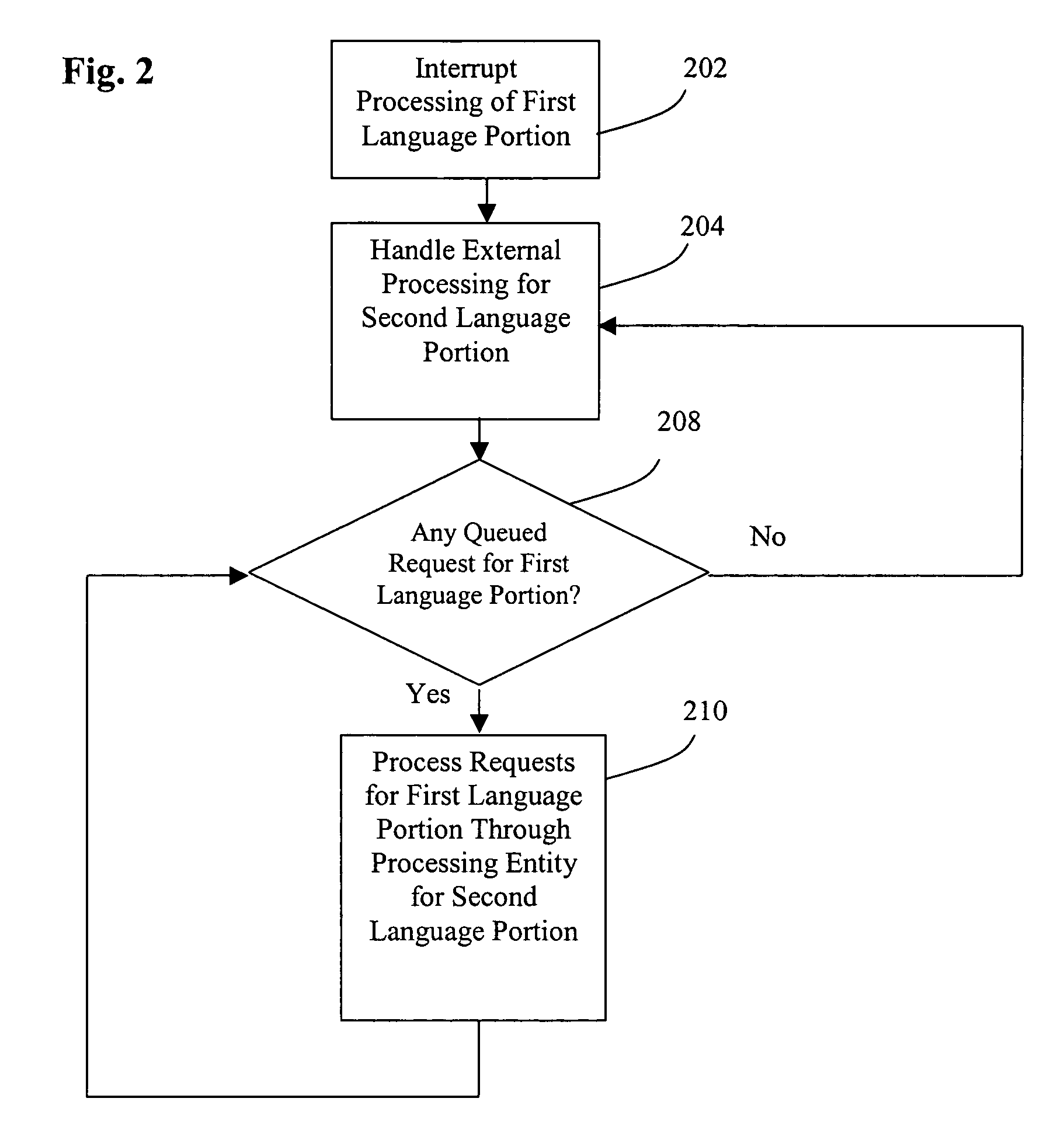

Mechanism and method for simultaneous processing and debugging of multiple programming languages

Disclosed is a method, mechanism, and computer usable medium for simultaneous processing or debugging of multiple programming languages. A particularly disclosed approach provides a method and mechanism for resolving the issue of simultaneous debugging of hardware represented by an HDL, e.g., Verilog or VHDL, and software, e.g., represented by C, C++, SystemC code. This approach overcomes the problem of the HDL portion of the design being inaccessible when C, C++ or SystemC code is debugged.

Owner:CADENCE DESIGN SYST INC

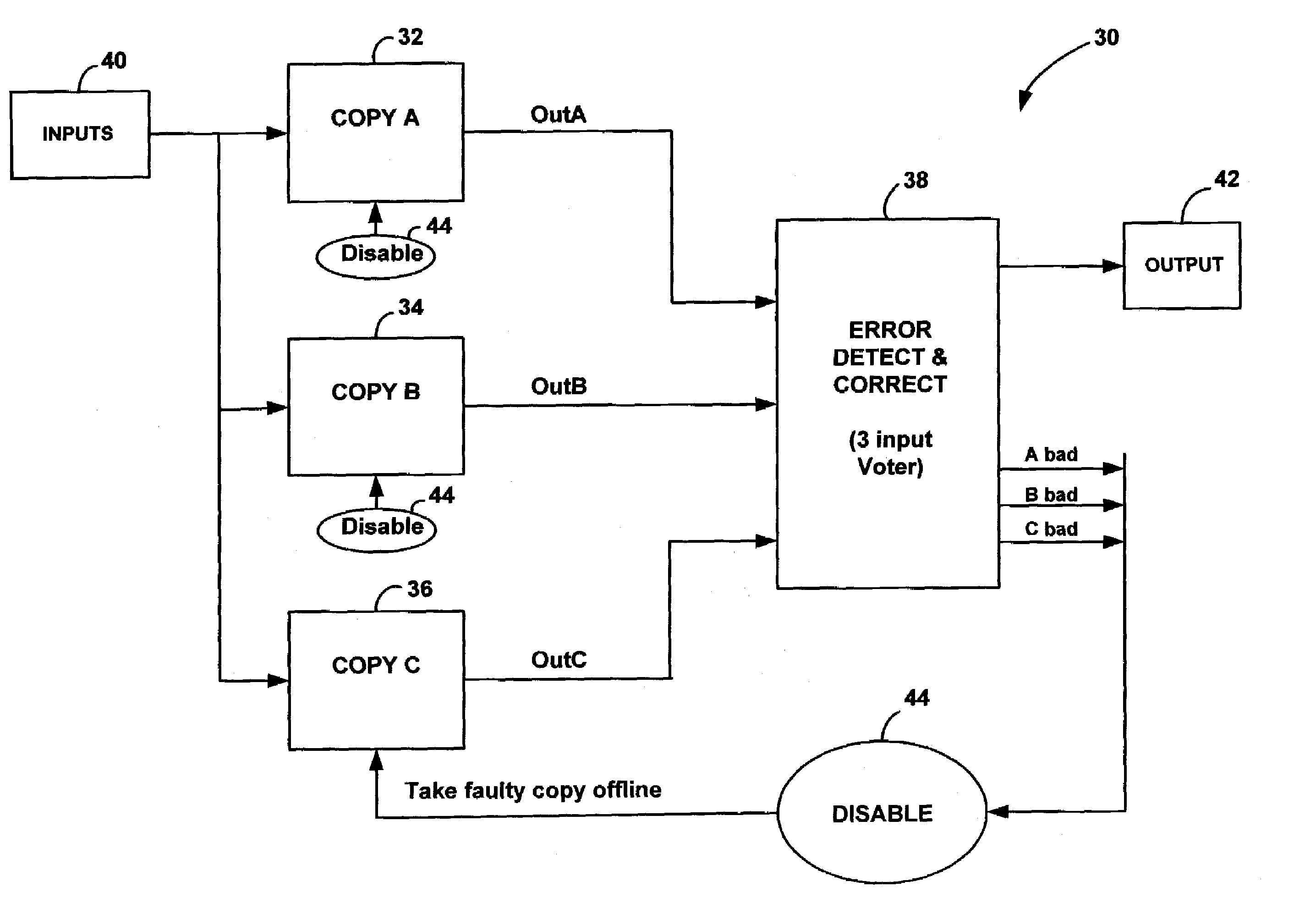

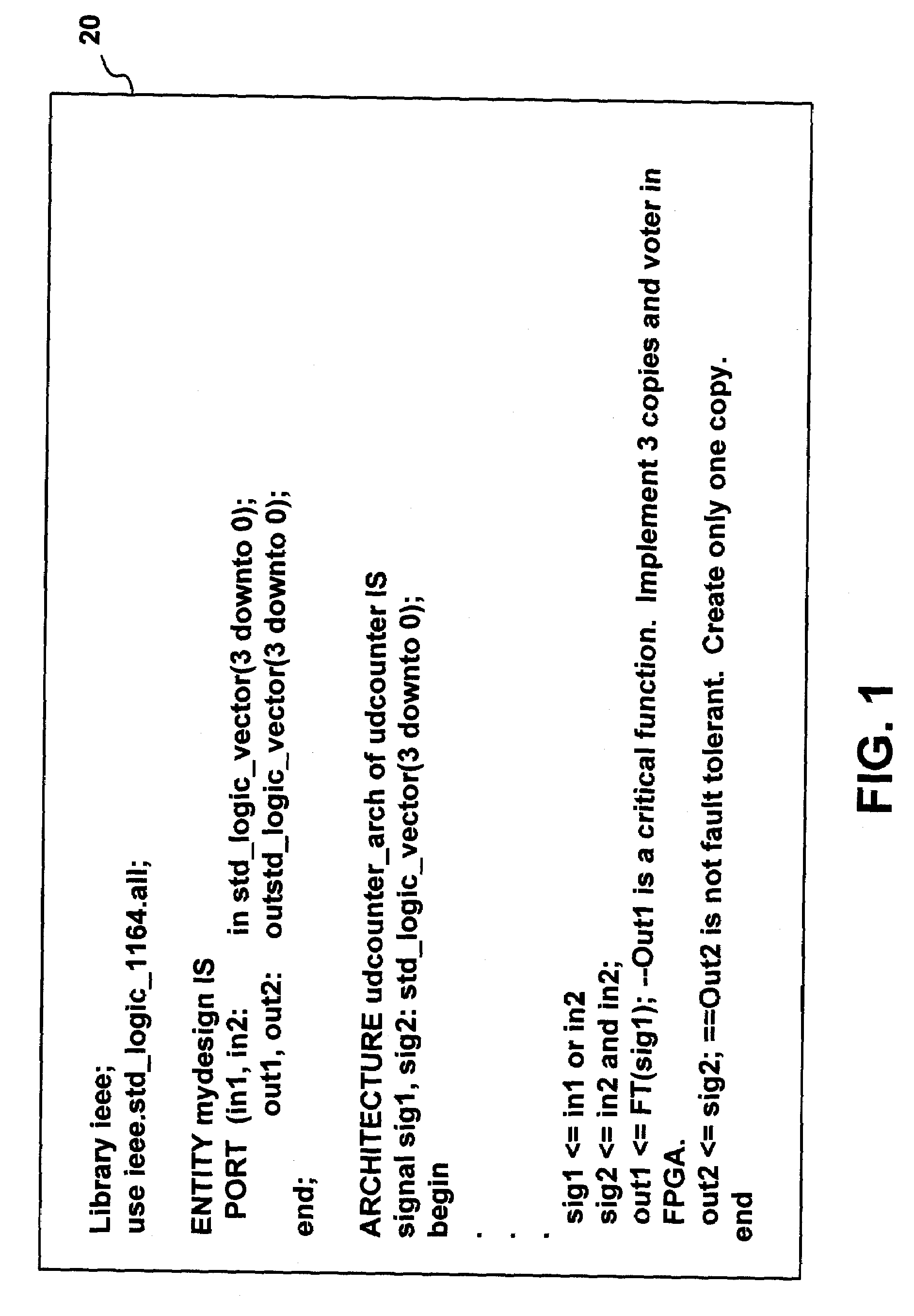

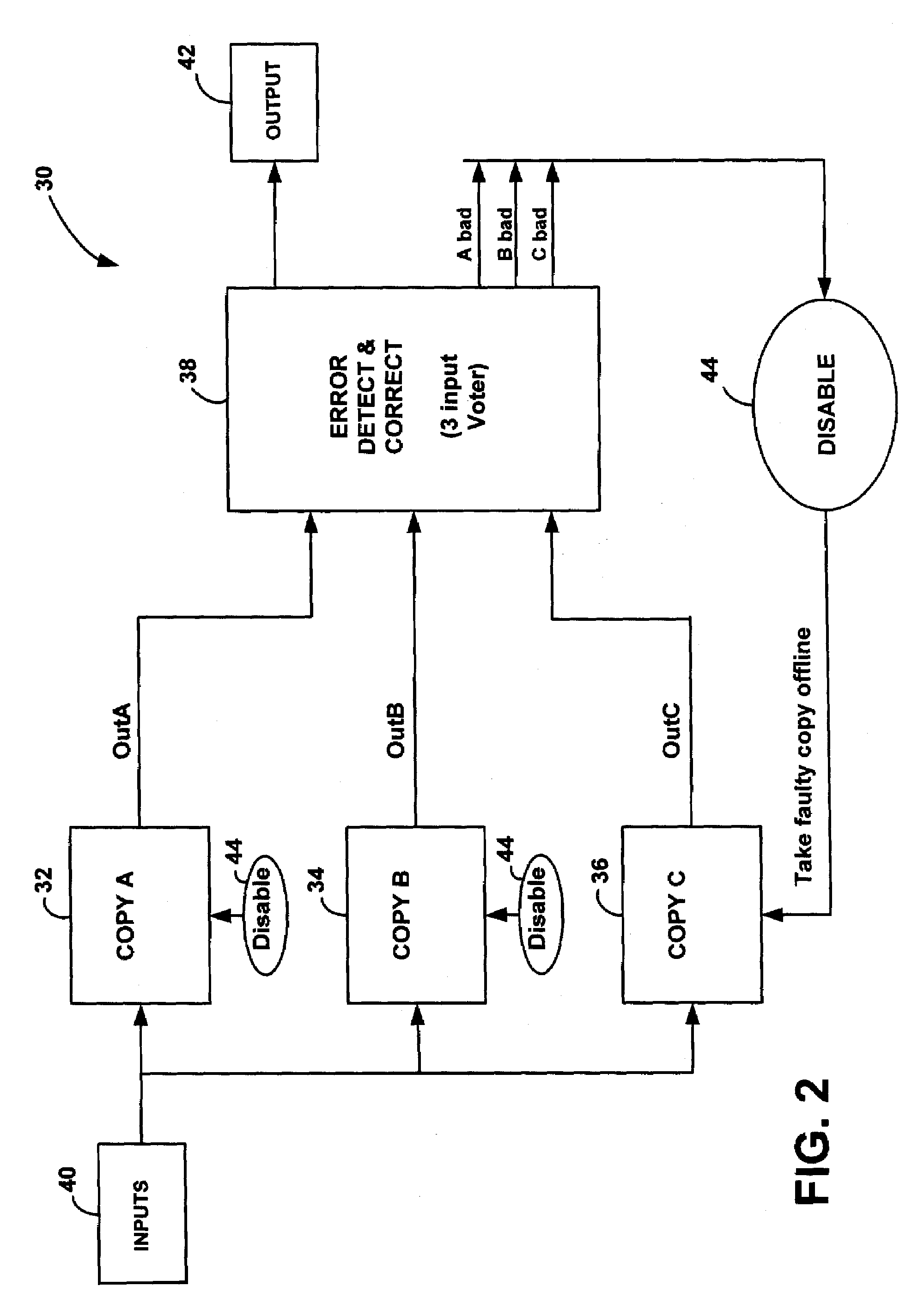

Method of selectively building redundant logic structures to improve fault tolerance

InactiveUS7134104B2CAD circuit designSoftware simulation/interpretation/emulationProcessor registerCritical function

A new hardware description language (HDL) extension at the register-transfer level (RTL) for designating particular logic functions as fault tolerant and a method of implementing a fault redundant scheme for the fault tolerant logic functions. Code (20) is written in VHDL at the RTL and includes instructions for adding the operator “FT” to certain logic functions. Logic functions that include the FT operator are considered critical functions, i.e., fault tolerant. By including the FT operator, a logic synthesis tool is alerted to the functions that have been designated as fault tolerant. As a result, the preprogrammed logic synthesis tool causes the design of the IC to include a fault redundant scheme (30) for the logic functions that include the FT operator. Fault redundant scheme (30) includes three copies of the logic function, i.e., Copy A (32), Copy B (34), and Copy C (36), as well as a majority voter 38.

Owner:IBM CORP

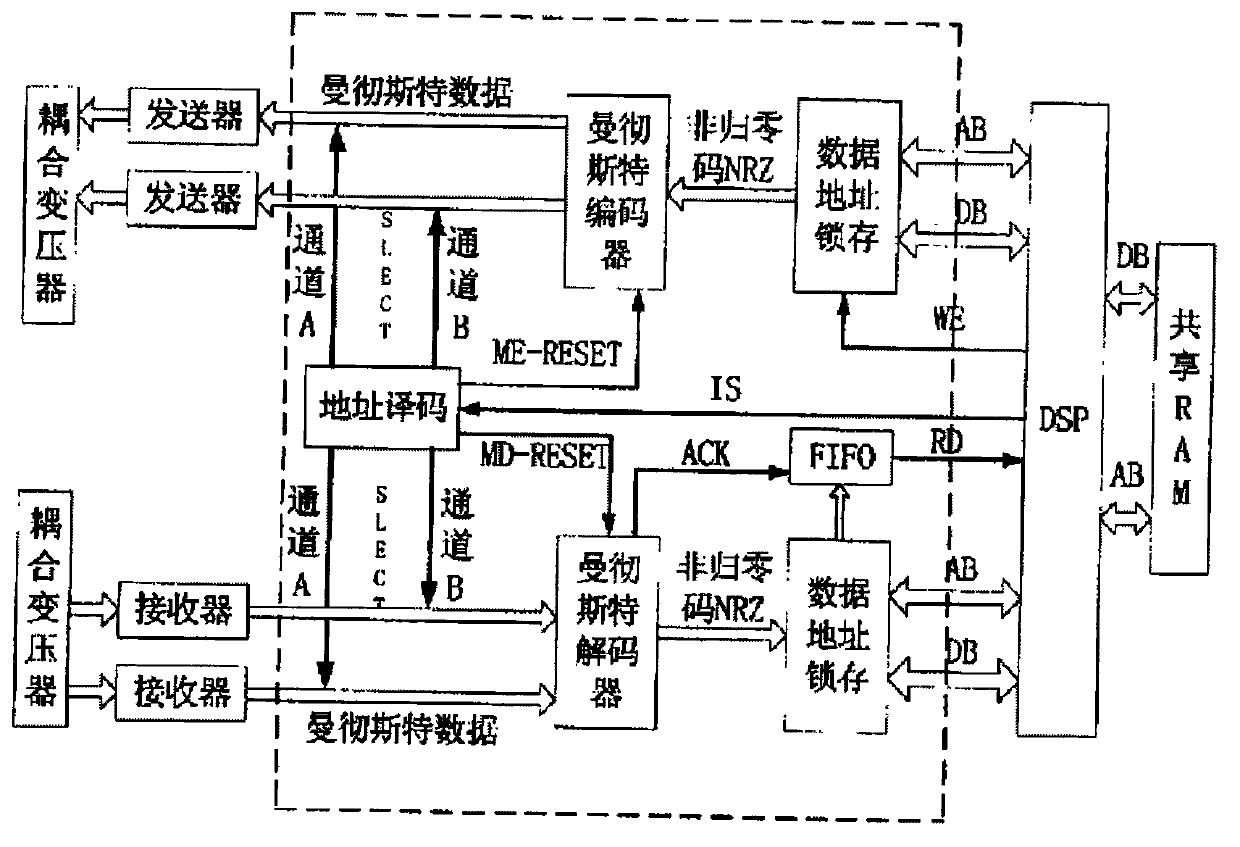

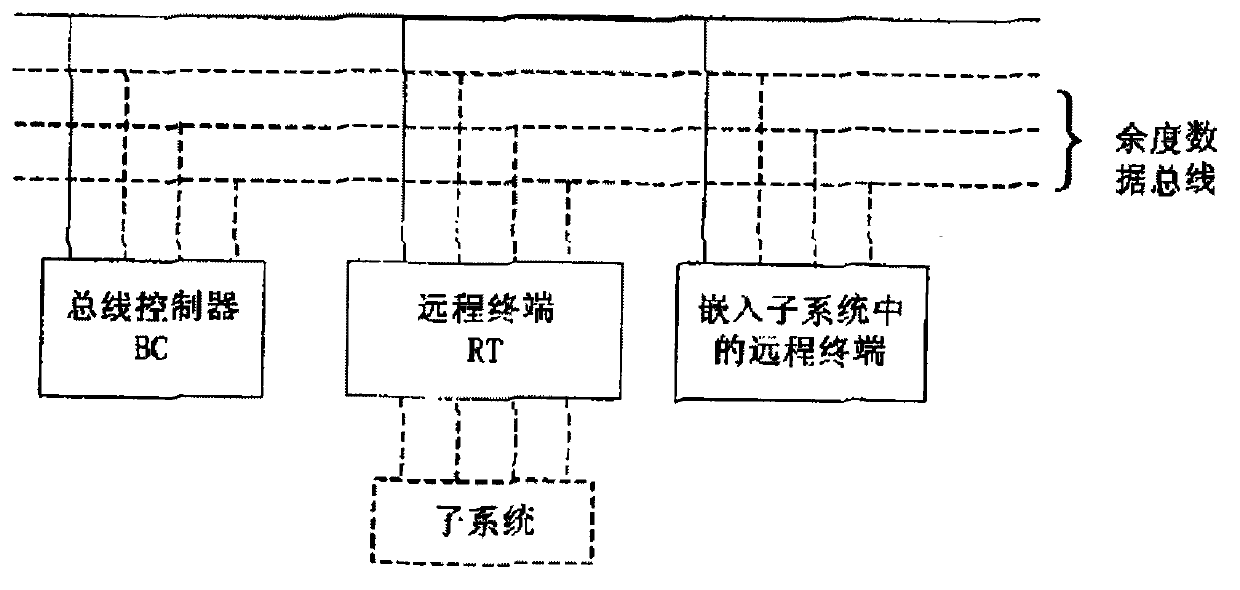

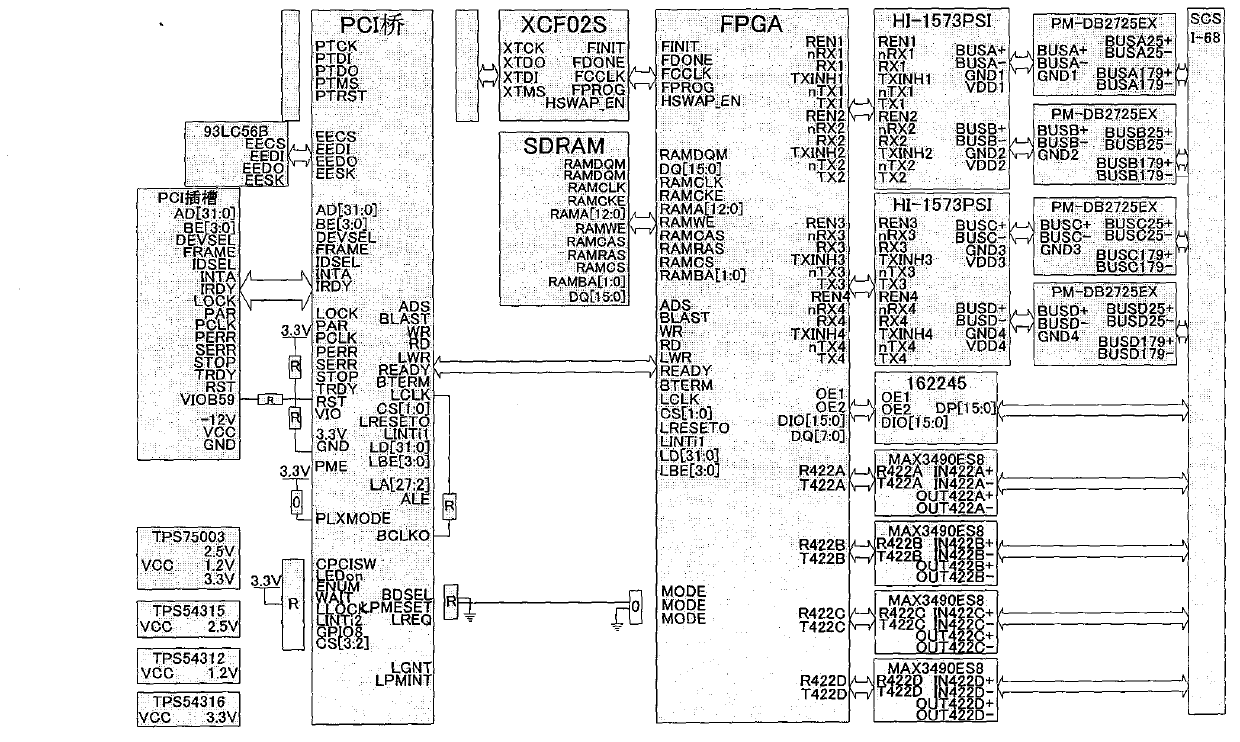

Interface board card of CPCI (Compact Peripheral Component Interconnect) framework based on MIL-STD-1553B

InactiveCN103309837AEnable simulation sharingReduce volumeElectric digital data processingFunctional expansionBus interface

The invention relates to a computer board card of a CPCI (Compact Peripheral Component Interconnect) framework, in particular to a standard bus interface module based on a MIL-STD-1553B protocol, namely, a plane internal time-division system command / response multipath transmission data bus interface module, which is widely applied to plane comprehensive avionics systems and external store management and integration systems, and gradually expands to plane control systems and the like as well as the fields of tanks, ships, spaceflight and the like. The MIL-STD-1553B protocol is realized through an FPGA (Field Programmable Gata Array); coding and decoding of a Manchester code are realized by using a VHDL (Hardware Description Language); a reasonable small-sized bus driving circuit is designed according to the MIL-STD-1553B protocol; a DSP (Digital Signal Processor) program which can support the protocol is written, and an assembled interface assembly function is realized. Due to the adoption of the interface board card, the design requirement of small size is met, functional expansion can be performed easily as required, using flexibility is realized, and the development cost of a product is much lower than that of a foreign special interface chip.

Owner:北京中航赛维奥科技有限公司 +1

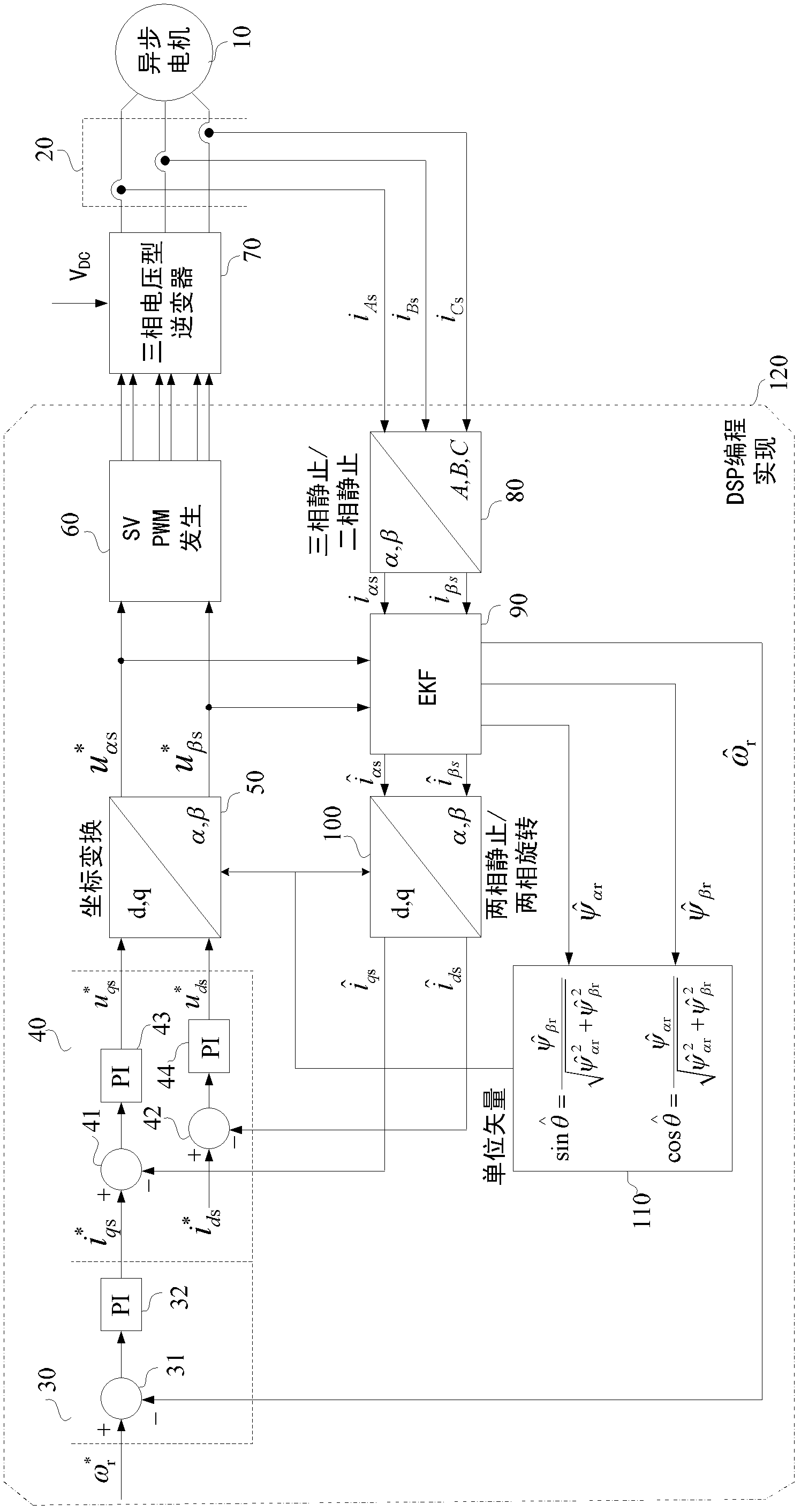

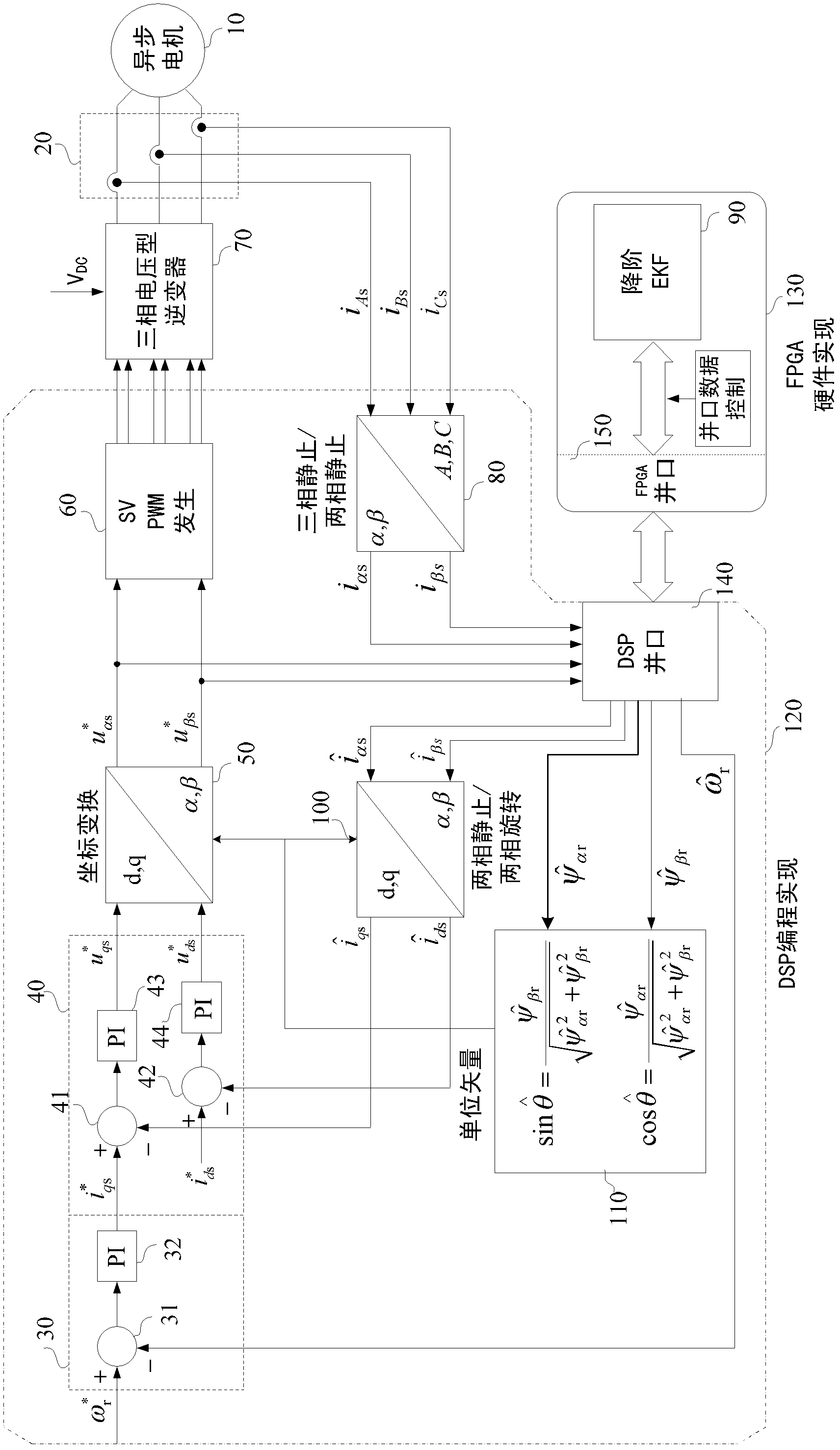

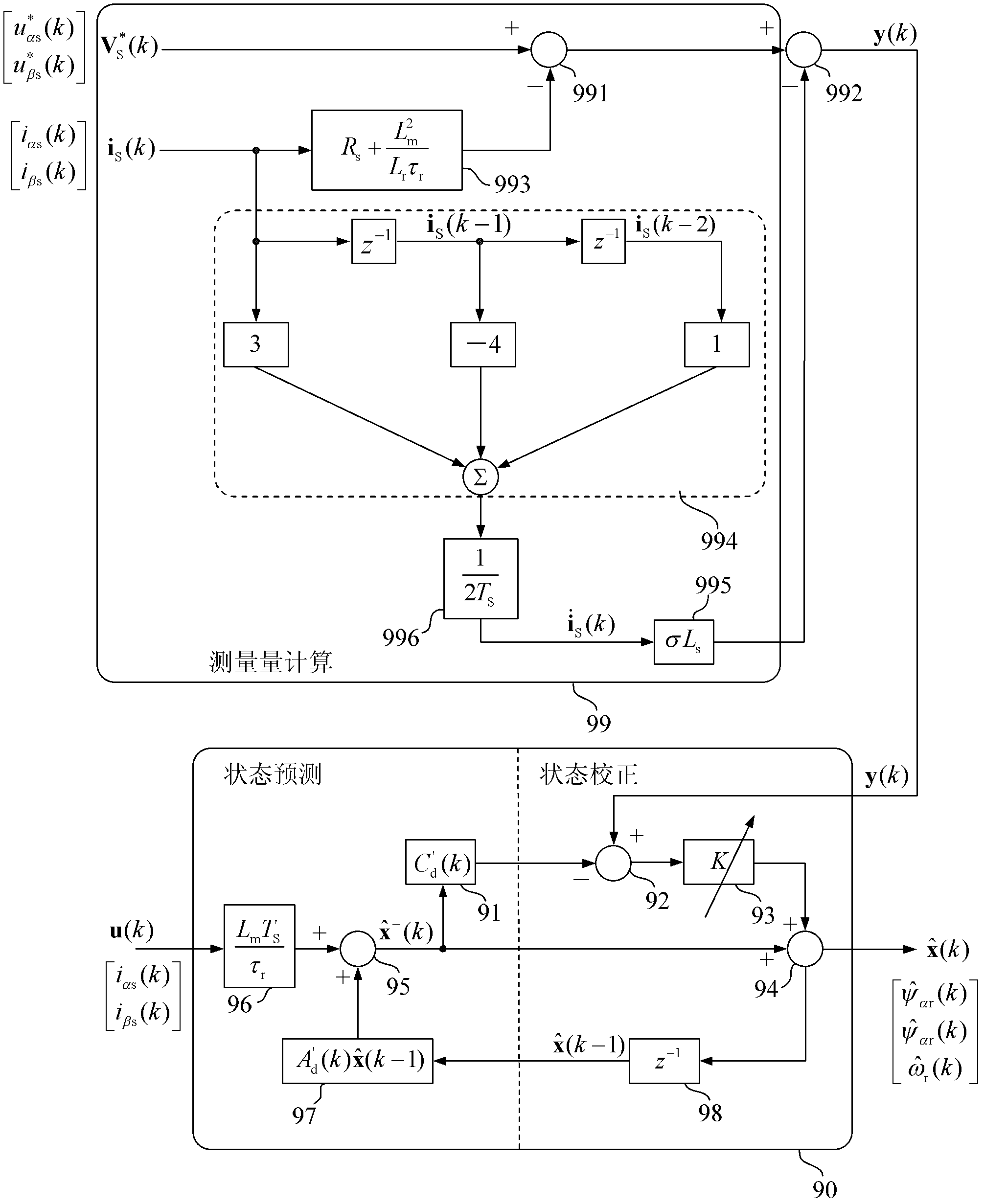

Asynchronous motor pure electronic speed feedback method

InactiveCN102629847ARelieve pressureMultiple storage spacesElectronic commutation motor controlVector control systemsMathematical modelFpga implementations

The invention provides an asynchronous motor pure electronic speed feedback method, which specifically comprises the following operation steps of: firstly obtaining a discrete time form expression of an asynchronous motor mathematical model, obtaining an asynchronous motor reduced order EKF (Extended Kalman Filter) speed estimation algorithm according to an extended Kalman filter algorithm, designing a FPGA (Field Programmable Gate Array) to realize a reduced order EKF speed estimation algorithm structure and carrying out hardware language VHDL (Verilog Hardware Description Language) description on the FPGA based on the described algorithm structure to obtain, send and transmit back state estimated values i alpha s, i beta s, Psi alpha r, Psi beta r and omega r to a main control DSP (Digital Signal Processor) through a port. The asynchronous motor pure electronic speed feedback method has the beneficial effects that the pressure of the main control DSP on real-time operation amount is greatly reduced, so that more storage spaces and more operation spaces are left for speed and current control; the EKF speed estimation algorithm realized by the FPGA in parallel is used for finishing within 1 microsecond, so that a less sampling period can be selected by using the speed estimation algorithm, therefore, the speed estimation precision is greatly improved.

Owner:XIAN UNIV OF TECH

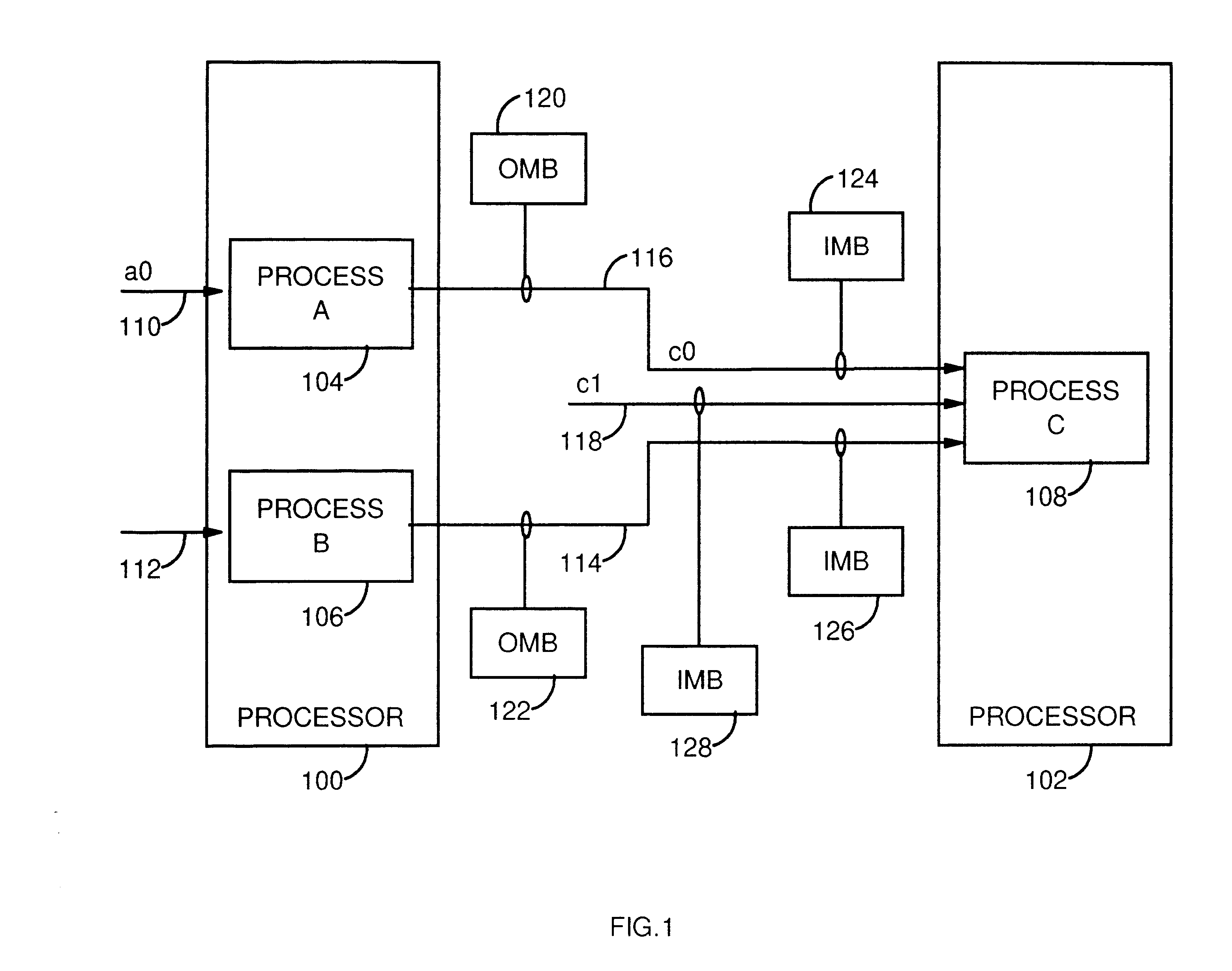

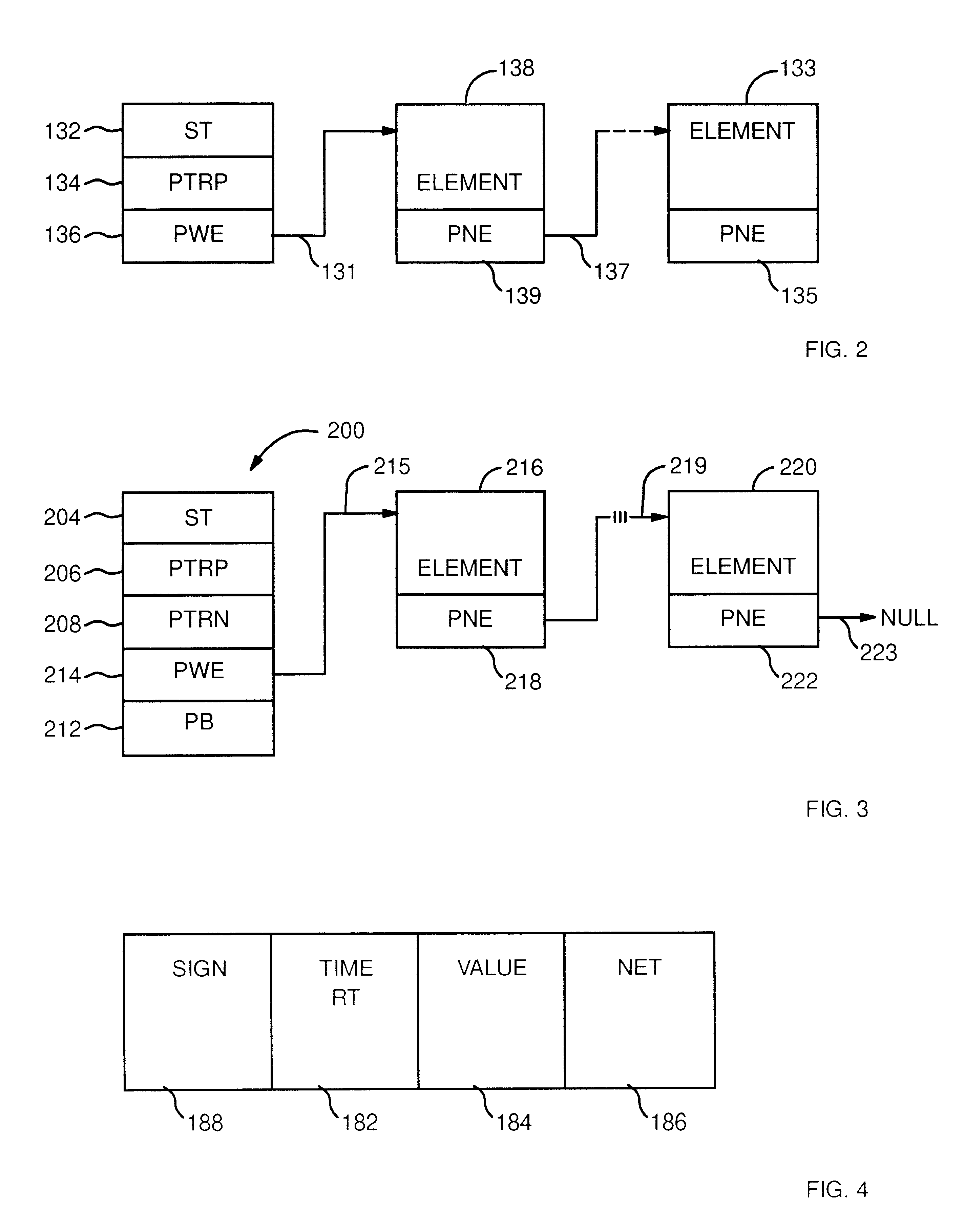

Waveform manipulation in time warp simulation

InactiveUS6195628B1Efficiently manipulatedData processing applicationsAnalogue computers for electric apparatusParallel computingChain of events

A system and method for manipulating waveforms, including transaction cancellation, in parallel time-warp simulation of circuits, such as those modeled in VHDL. Events waveforms for each output of a processor are organized by the simulation time (ST) of the events which created them and by the simulation time (RT) at which they are to be effective. A phantom buffer provides a linked list of events and associated transactions cancelled as a result of insertion of a new event in said chain of events. Rollback of a cancelled event waveform is done by restoring to the linked lists selected events and transactions from the phantom buffer.

Owner:IBM CORP

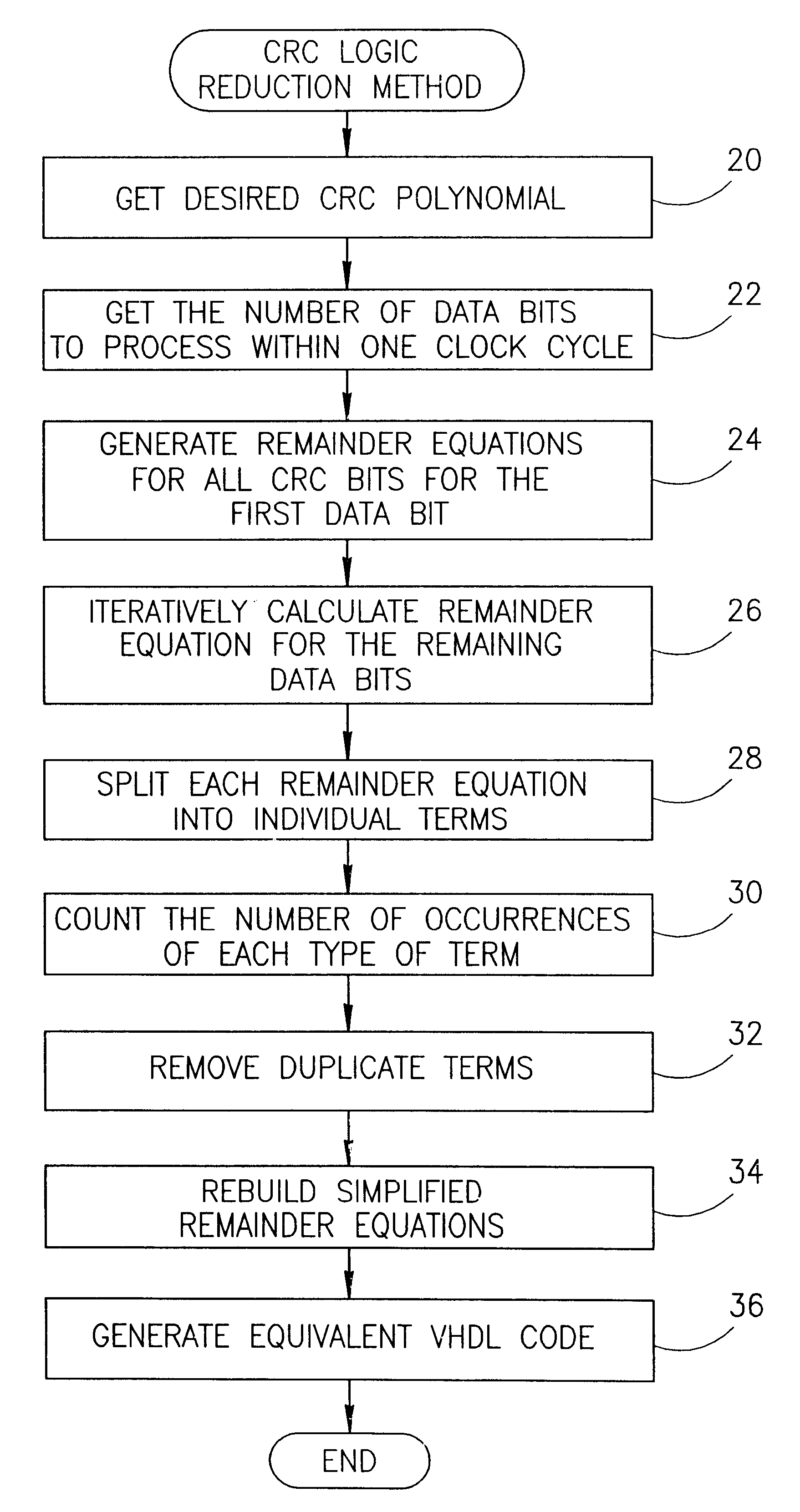

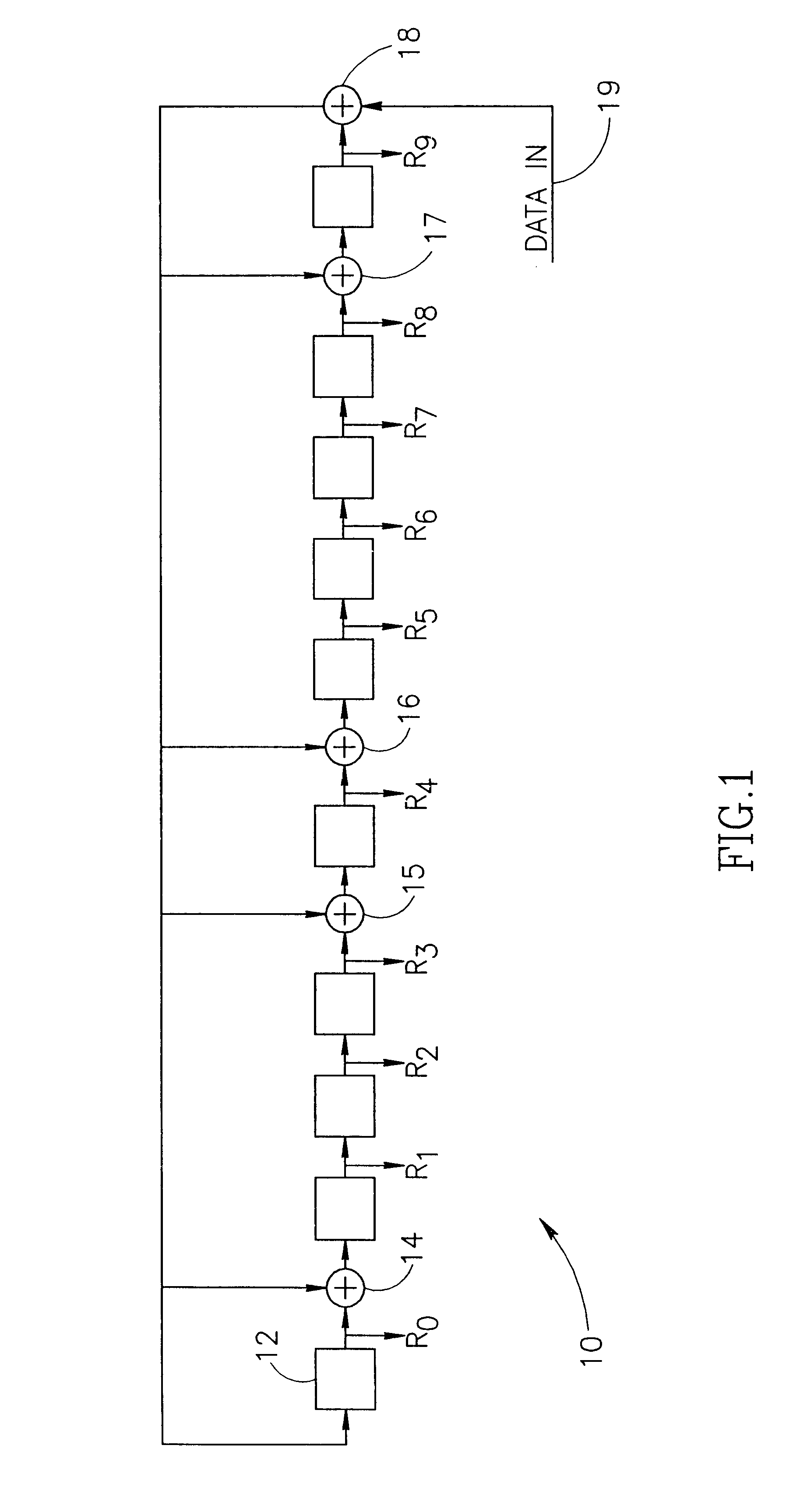

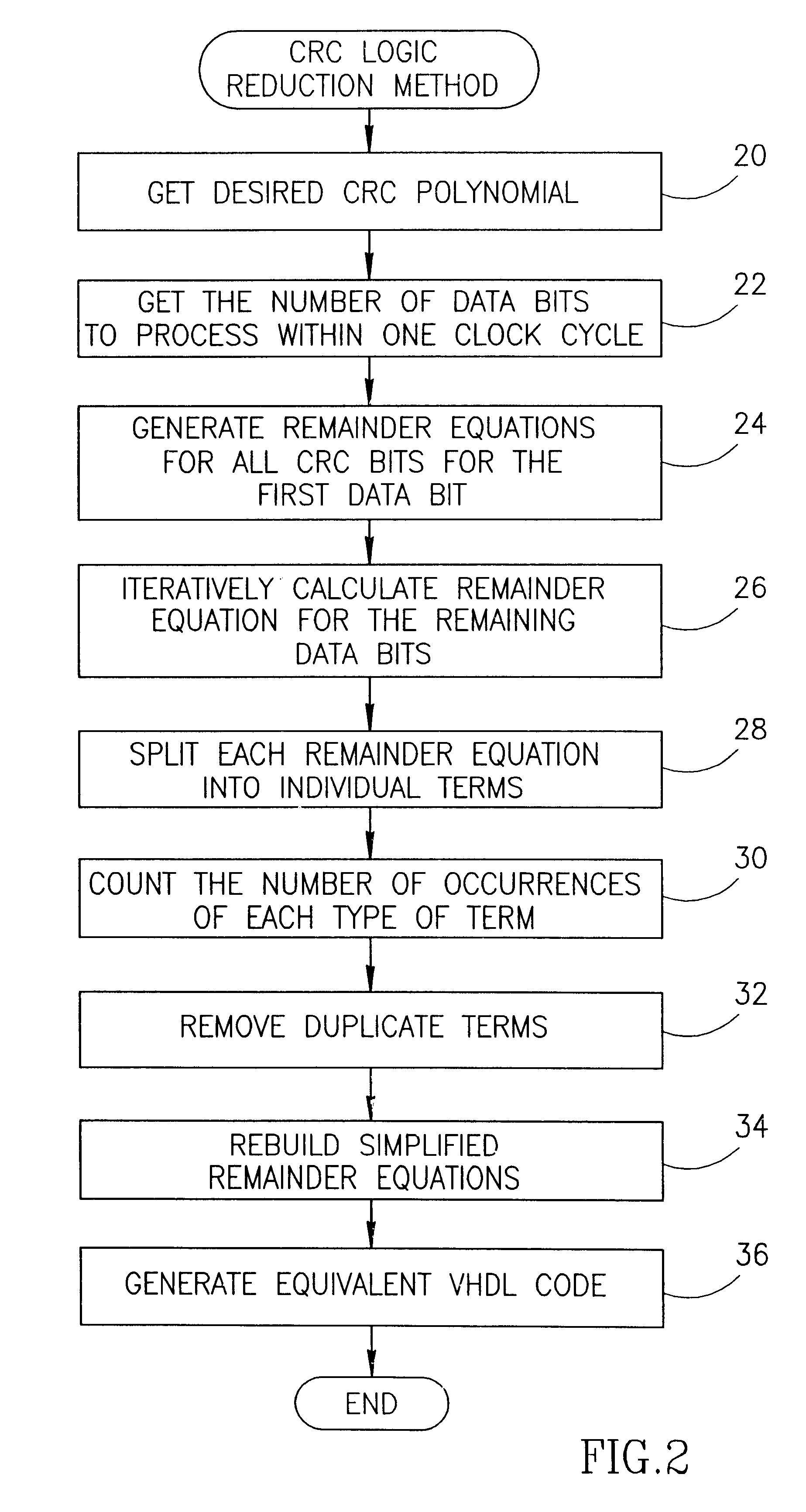

Method of synthesizing a cycle redundancy code generator circuit using hardware description language

A method of synthesizing a CRC generator circuit for generating optimized code written in a high level hardware description language such as VHDL. The hardware description language code for implementing a CRC generator circuit has significantly less delay and utilizes fewer gates than prior art CRC generator circuit synthesis techniques. The method is operative to generate VHDL code which is then used to synthesize the circuit. The method iteratively generates the remainder equations for a CRC generator given the generator polynomial. During each iteration of the software, duplicate terms in each remainder equation are eliminated. The number of iterations is equal to the number of data bits the CRC generator is to process during each clock cycle. Once all the duplicate terms in the remainder equations are removed, the equations are sorted, rebuilt and translated into hardware description language code such as VHDL. The resulting optimized code may then be synthesized.

Owner:HEWLETT PACKARD DEV CO LP