Patents

Literature

36 results about "System on chip design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

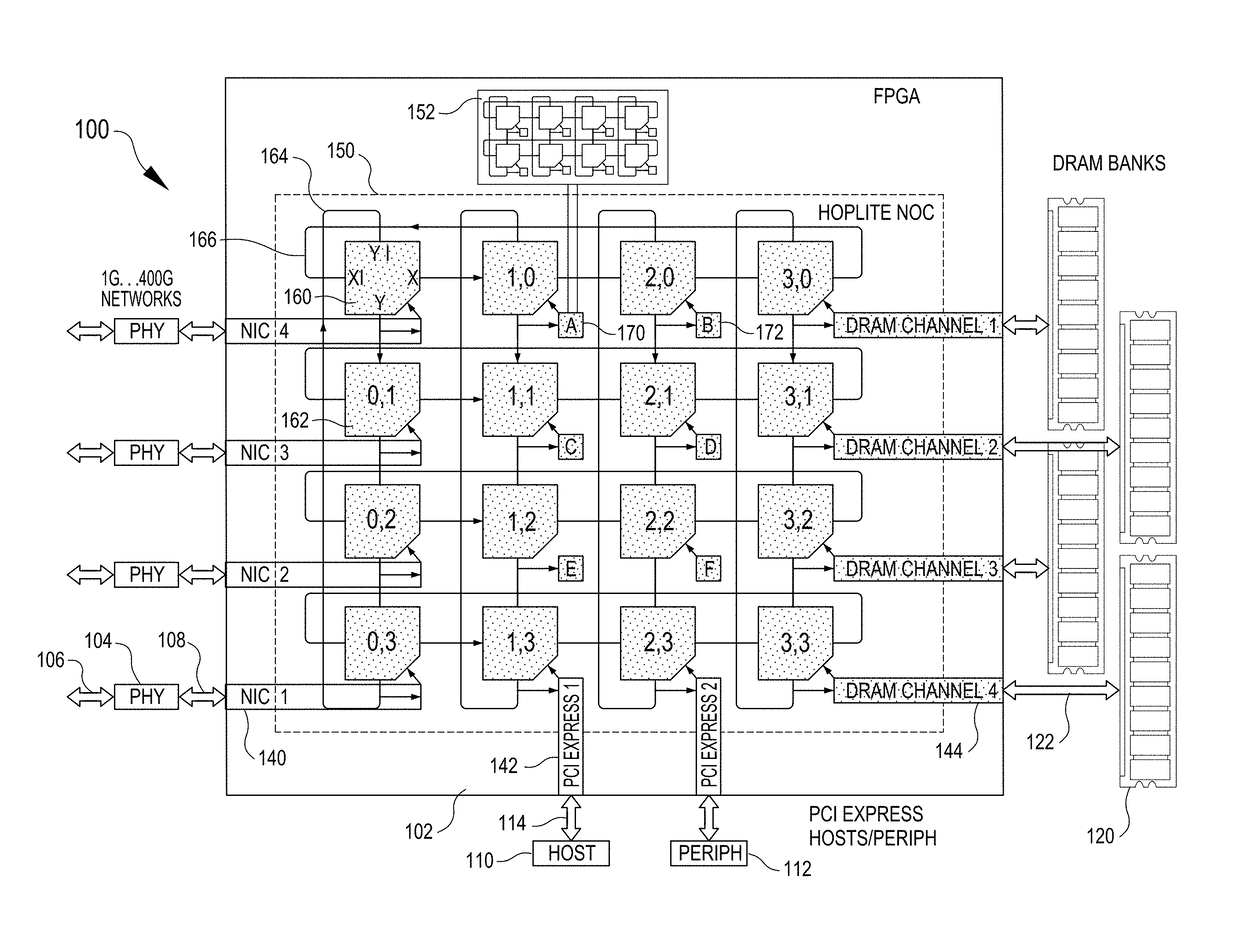

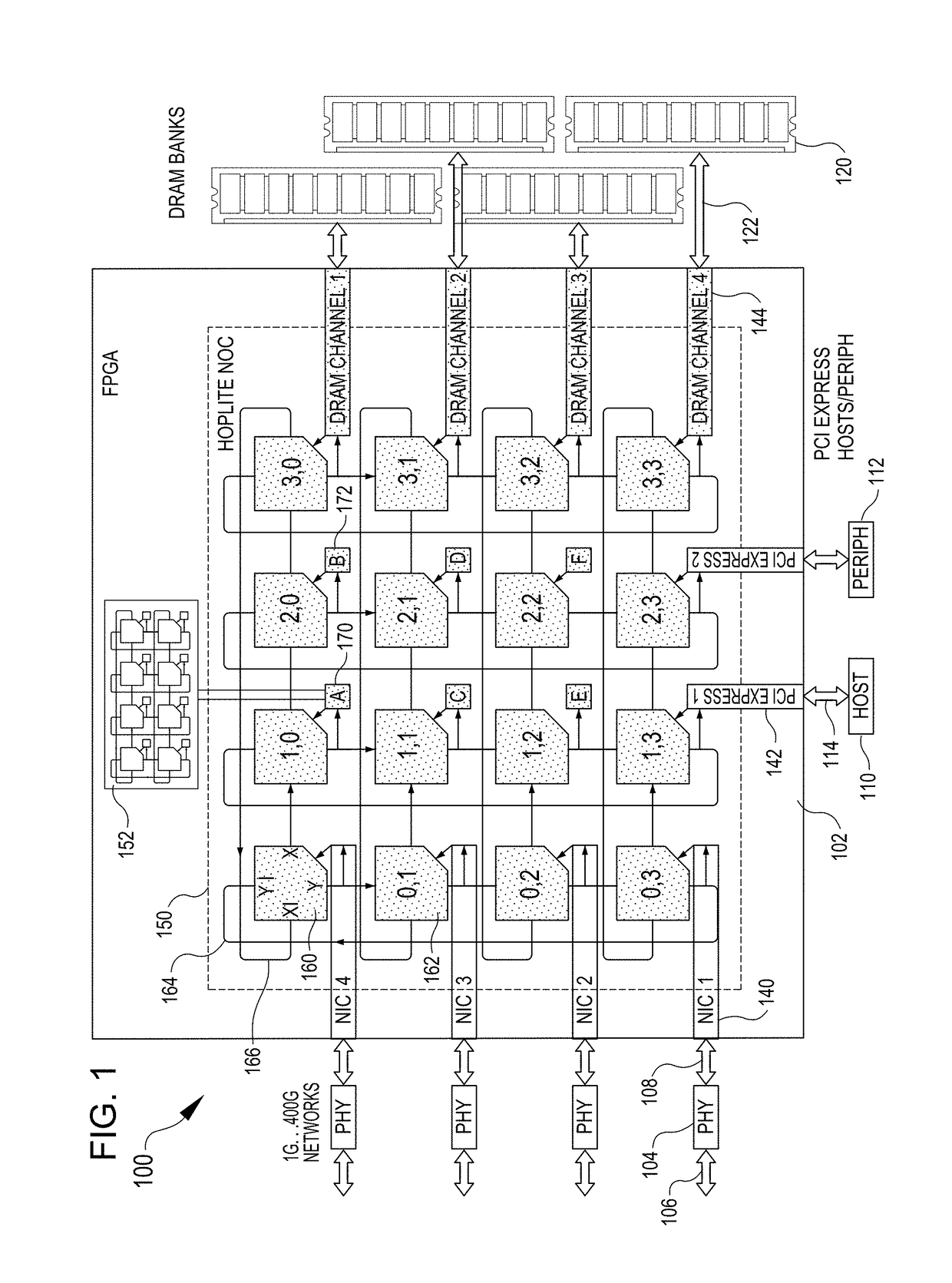

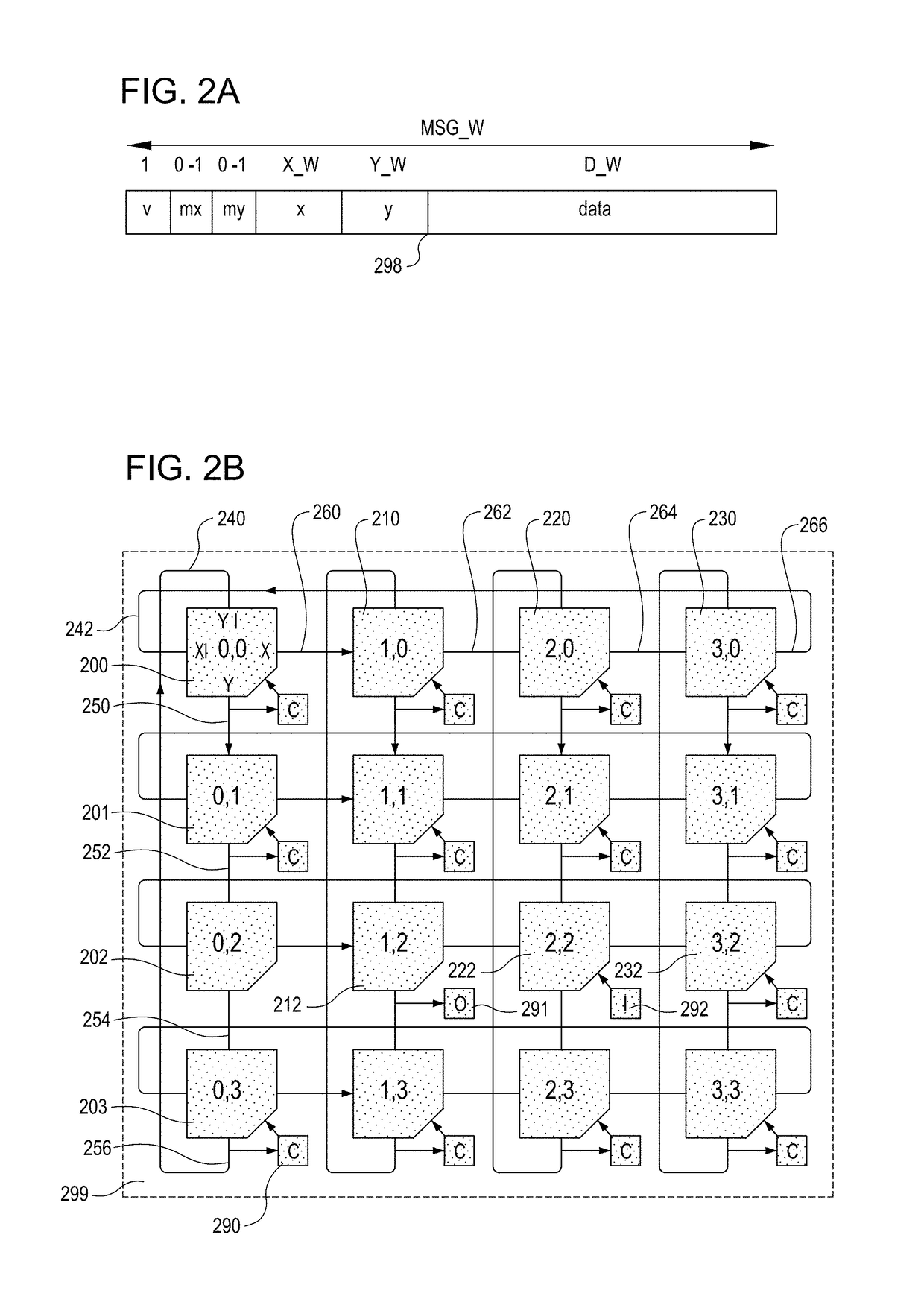

Directional two-dimensional router and interconnection network for field programmable gate arrays, and other circuits and applications of the router and network

ActiveUS20160344629A1Reduce switching delayLower latencyData switching networksNetwork sizeFpga implementations

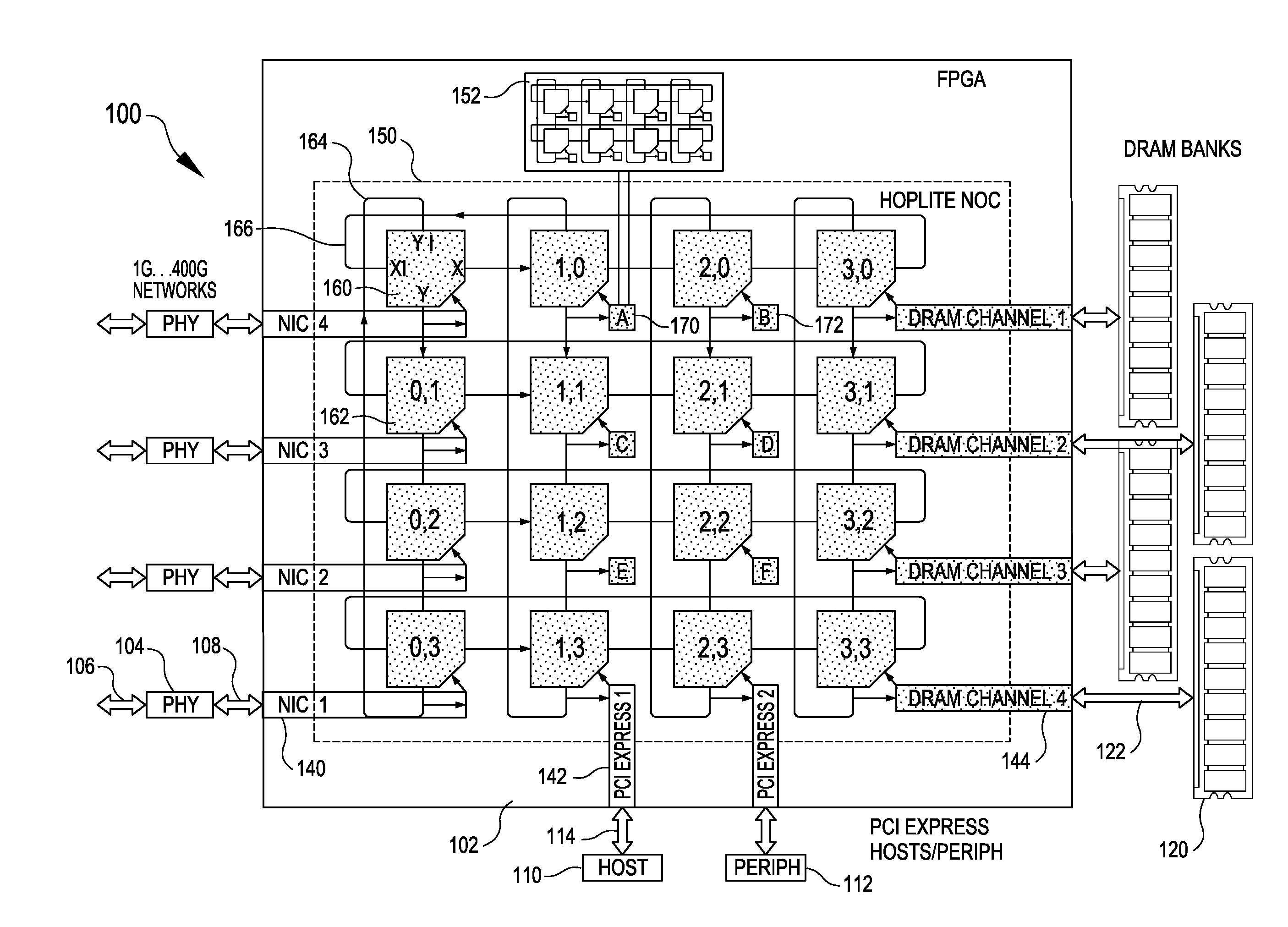

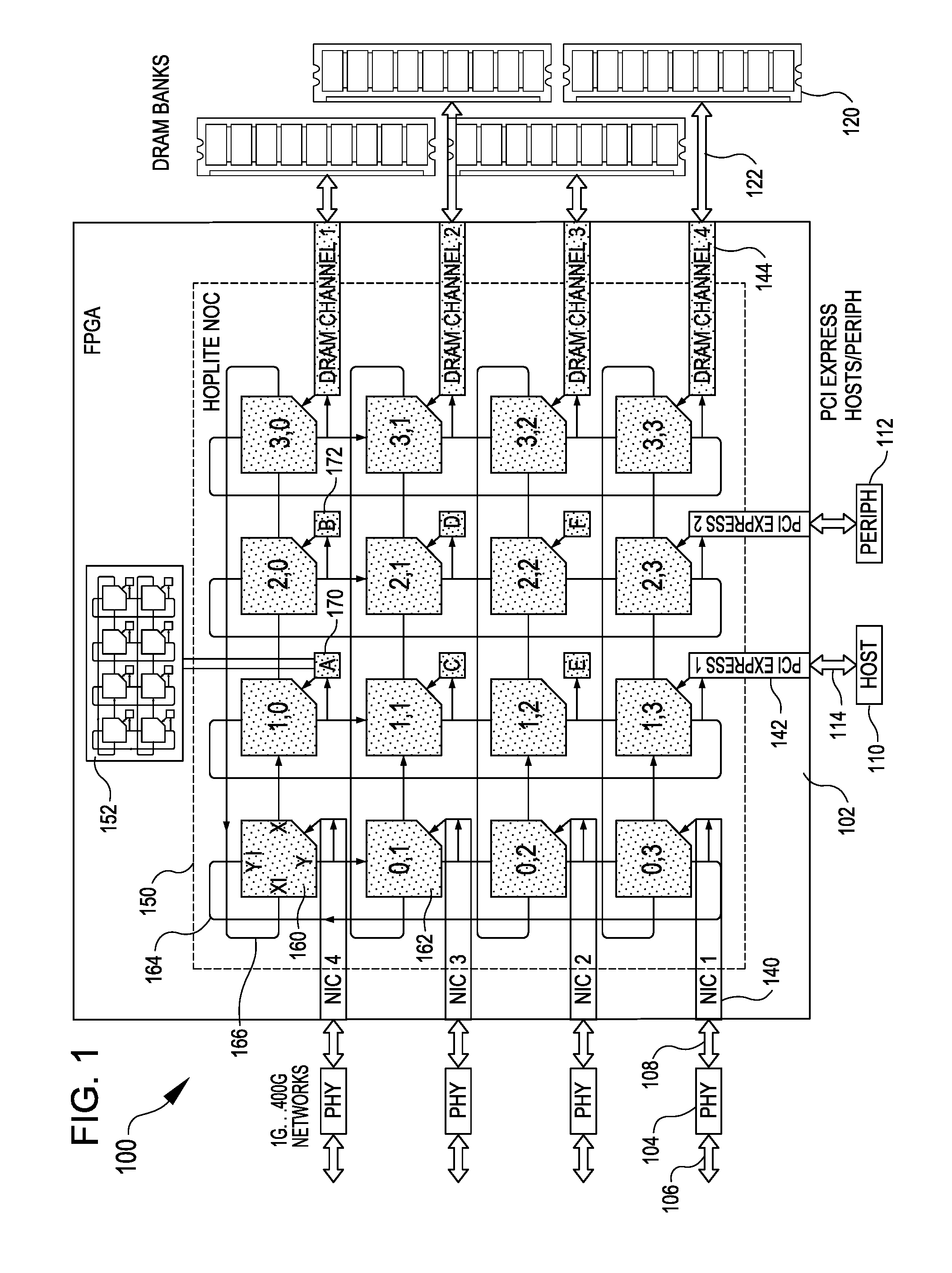

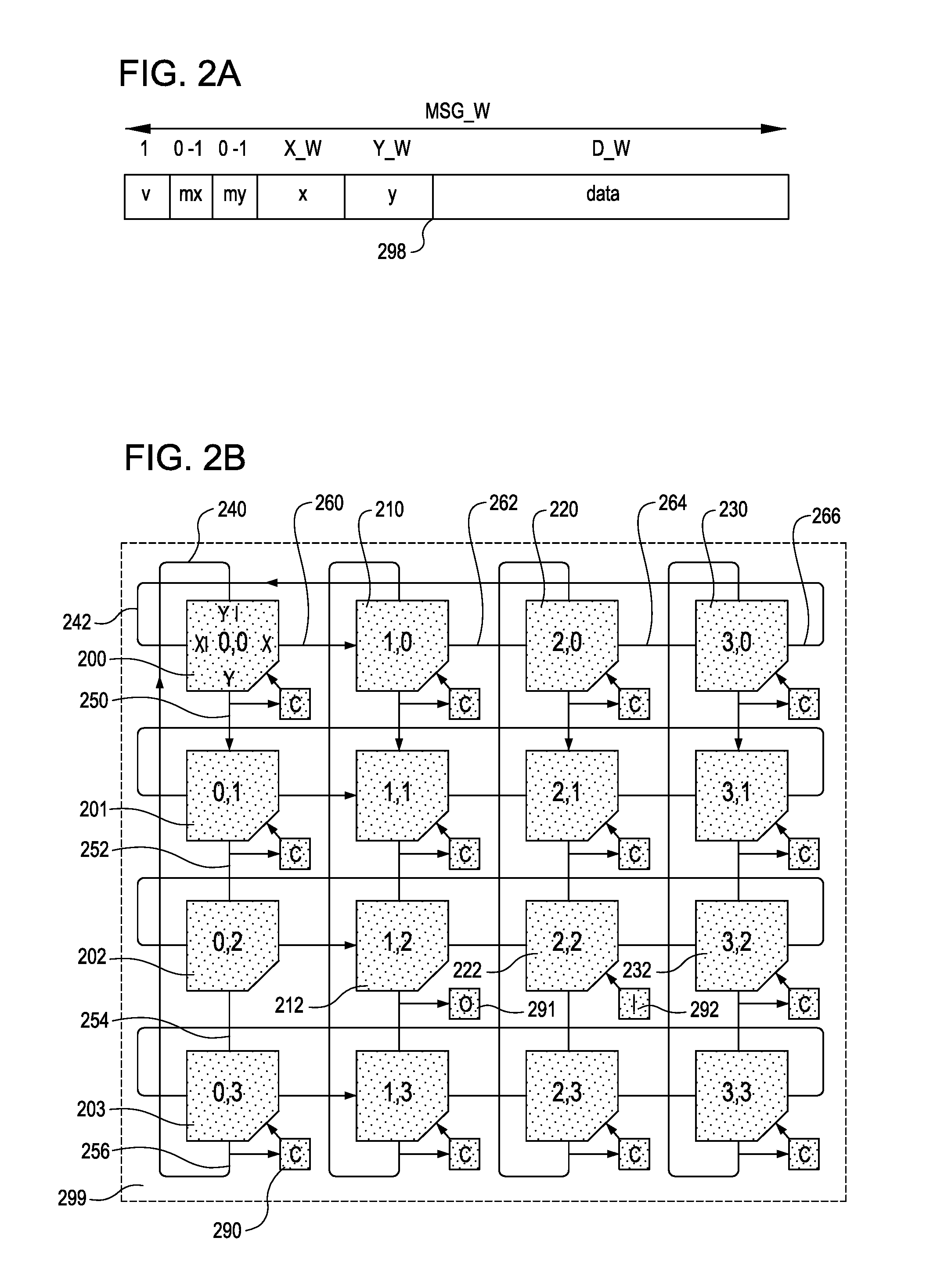

A configurable directional 2D router for Networks on Chips (NOCs) is disclosed. The router, which may be bufferless, is designed for implementation in programmable logic in FPGAs, and achieves theoretical lower bounds on FPGA resource consumption for various applications. The router employs an FPGA router switch design that consumes only one 6-LUT or 8-input ALM logic cell per router per bit of router link width. A NOC comprising a plurality of routers may be configured as a directional 2D torus, or in diverse ways, network sizes and topologies, data widths, routing functions, performance-energy tradeoffs, and other options. System on chip designs may employ a plurality of NOCs with different configuration parameters to customize the system to the application or workload characteristics. A great diversity of NOC client cores, for communication amongst various external interfaces and devices, and on-chip interfaces and resources, may be coupled to a router in order to efficiently communicate with other NOC client cores. The router and NOC enable feasible FPGA implementation of large integrated systems on chips, interconnecting hundreds of client cores over high bandwidth links, including compute and accelerator cores, industry standard IP cores, DRAM / HBM / HMC channels, PCI Express channels, and 10G / 25G / 40G / 100G / 400G networks.

Owner:GRAY RES LLC

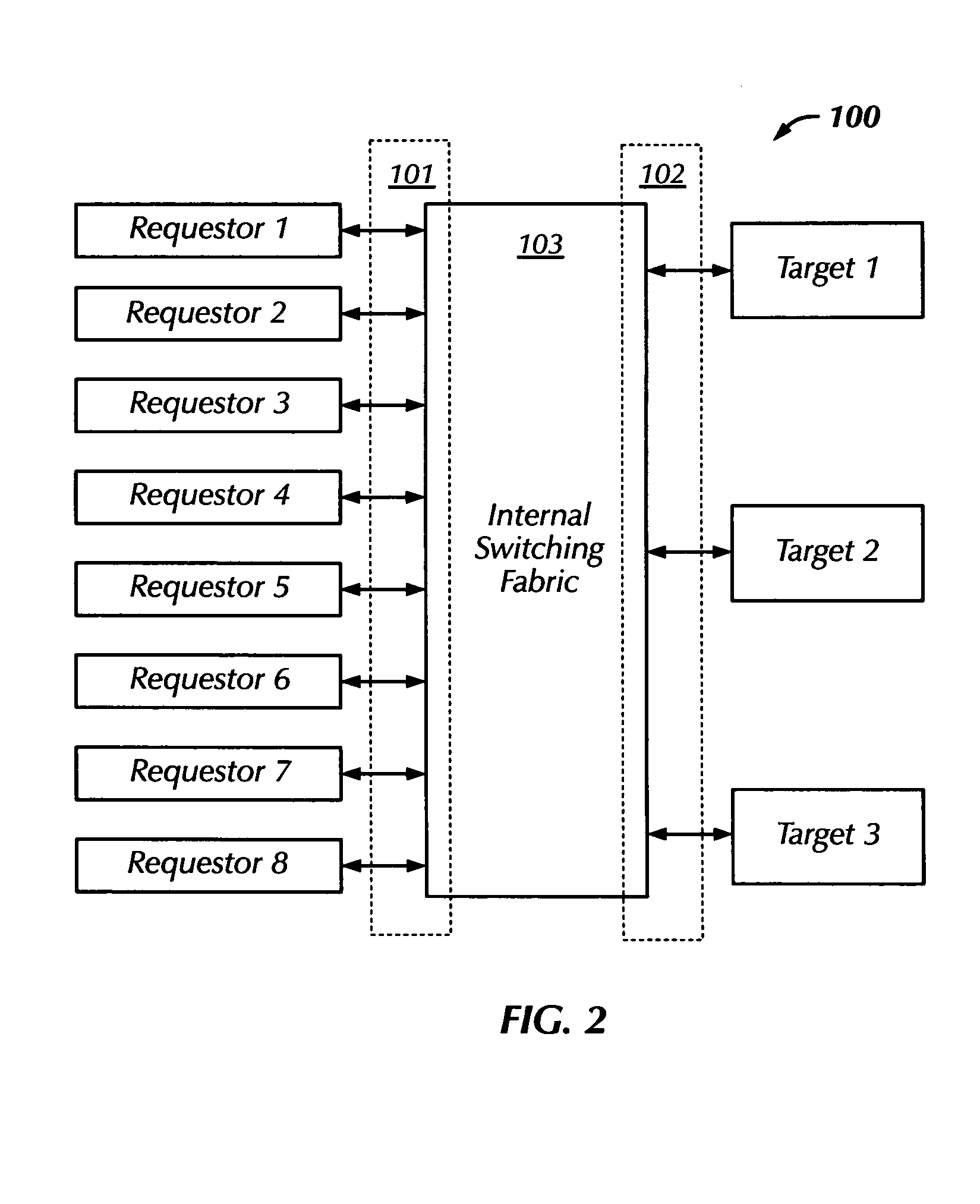

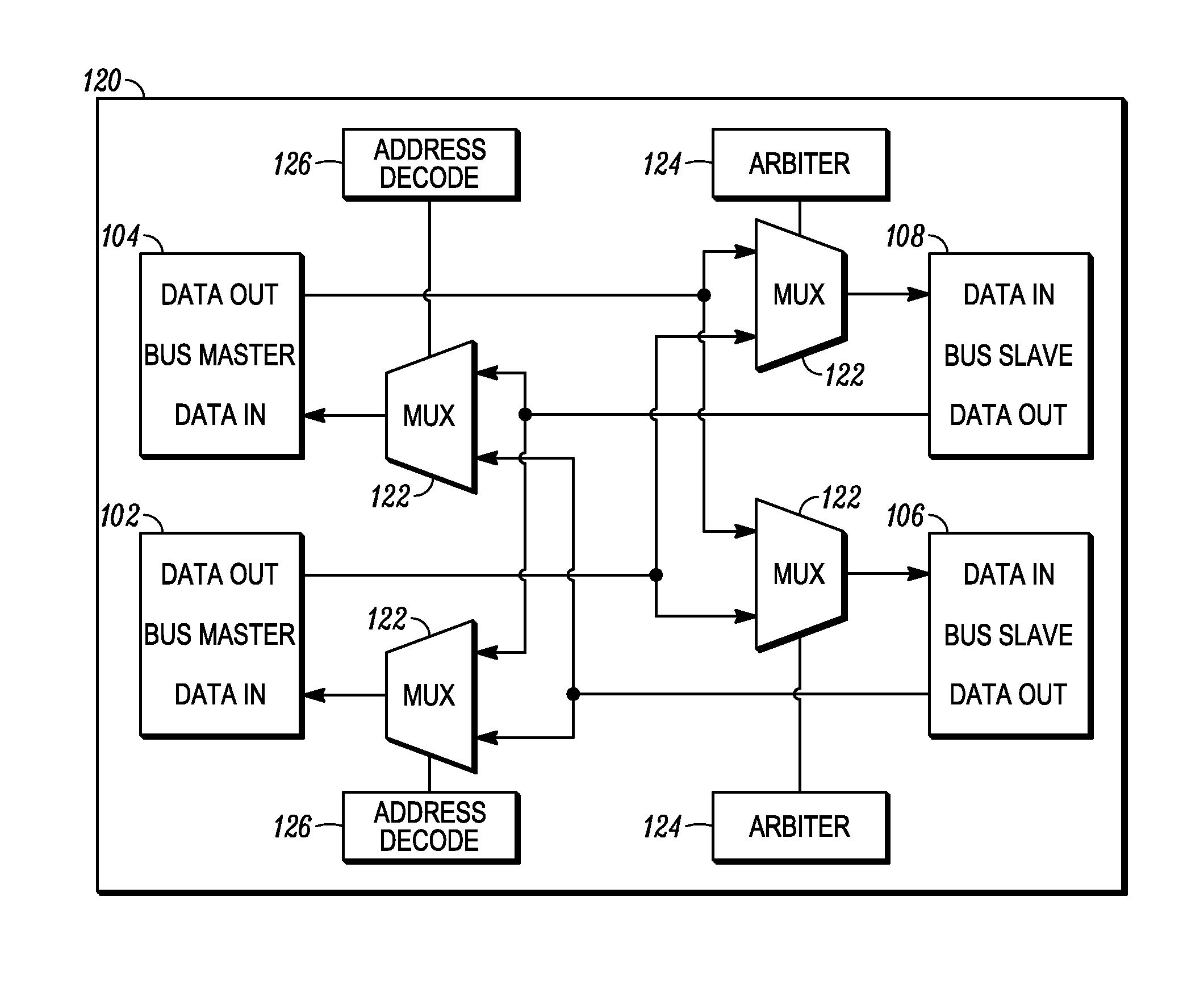

Flexible matrix fabric design framework for multiple requestors and targets in system-on-chip designs

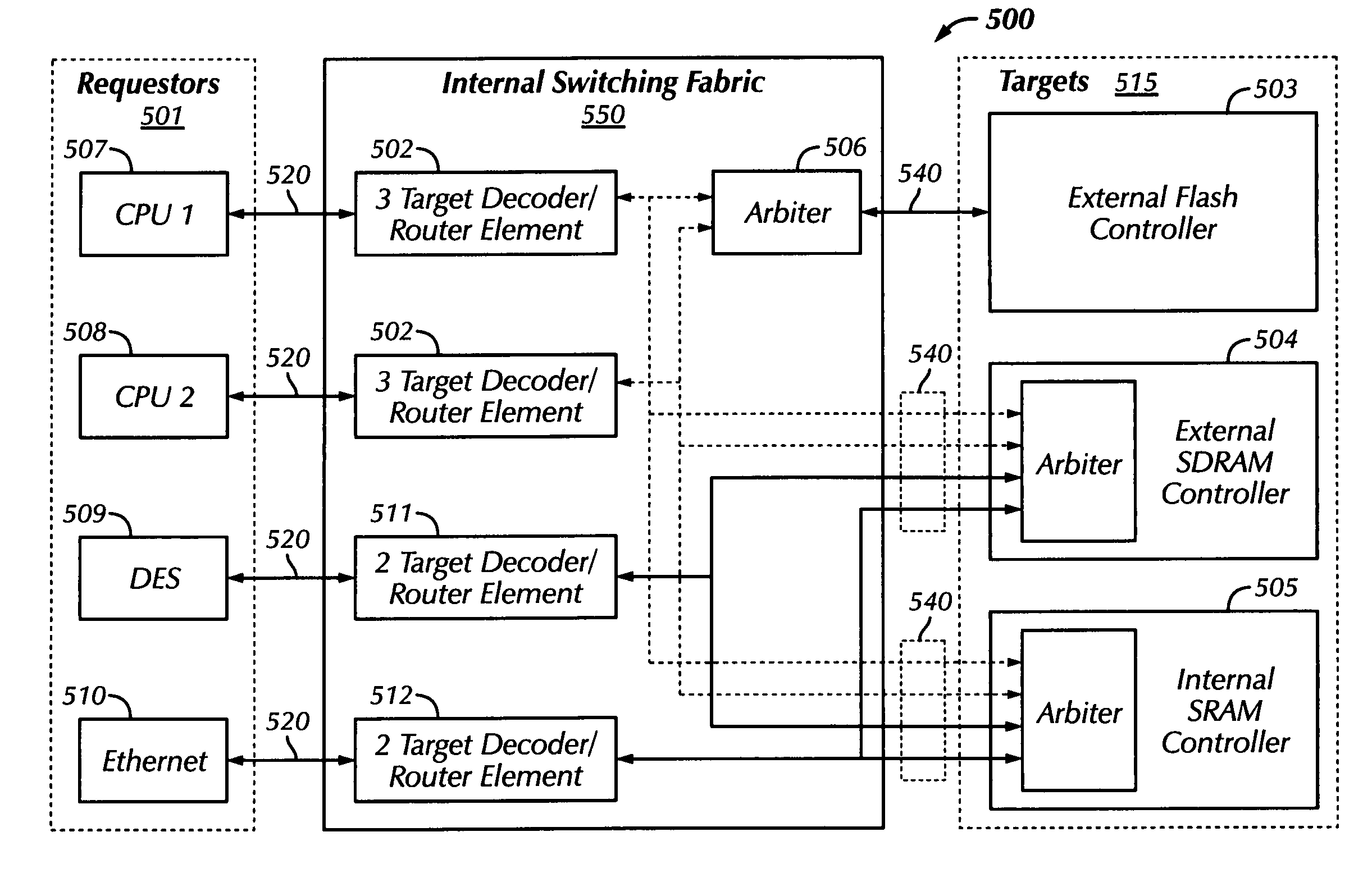

The System-on-Chip (SOC) interconnection apparatus and system discloses an internal switching fabric that interconnects, via standard connection ports, one or more requestors and one or more addressable targets on a single semiconductor integrated circuit. Each target has a unique address space, may or may not have internal arbitration, and may be resident (i.e., on-chip) memory, a memory controller for resident or off-chip memory, an addressable bridge to a device, system, or subsystem, or any combination thereof. Targets and requesters are connected to the internal switching fabric using target and requestor connection ports. The internal switching fabric routes signals between requesters and targets using one or more decoder / router elements that determine which target is the designated target using an internal system memory map. Dedicated arbiters may be included for targets without internal arbitration.

Owner:PALMCHIP CORP

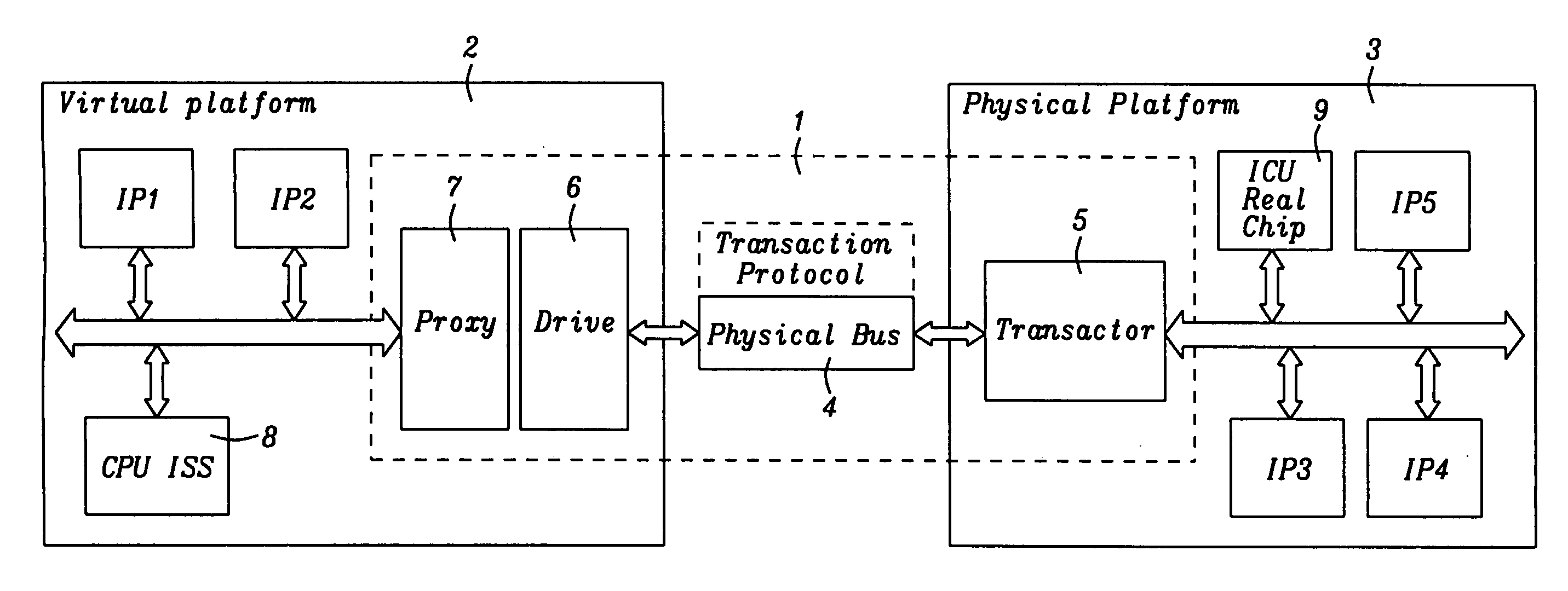

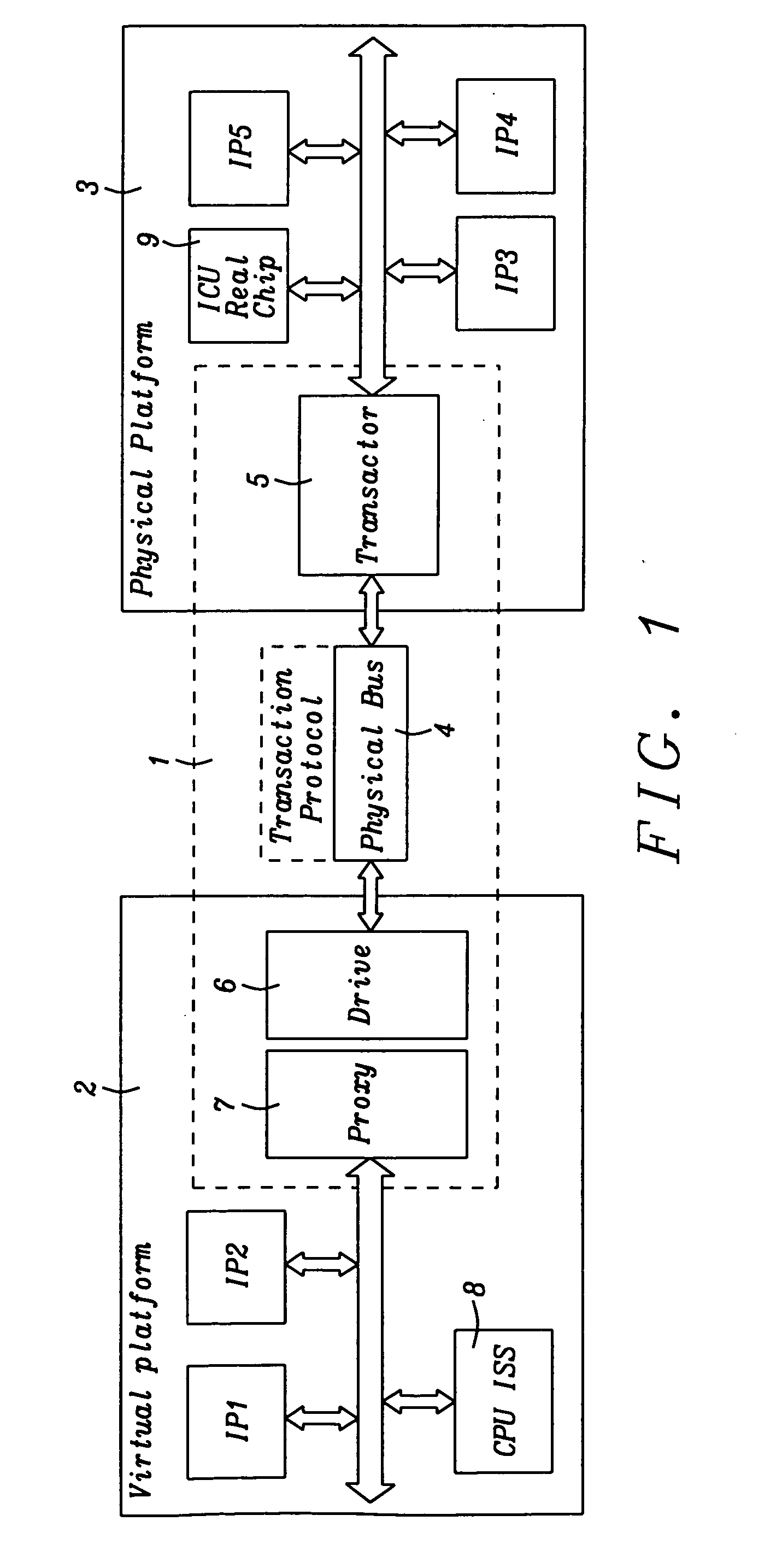

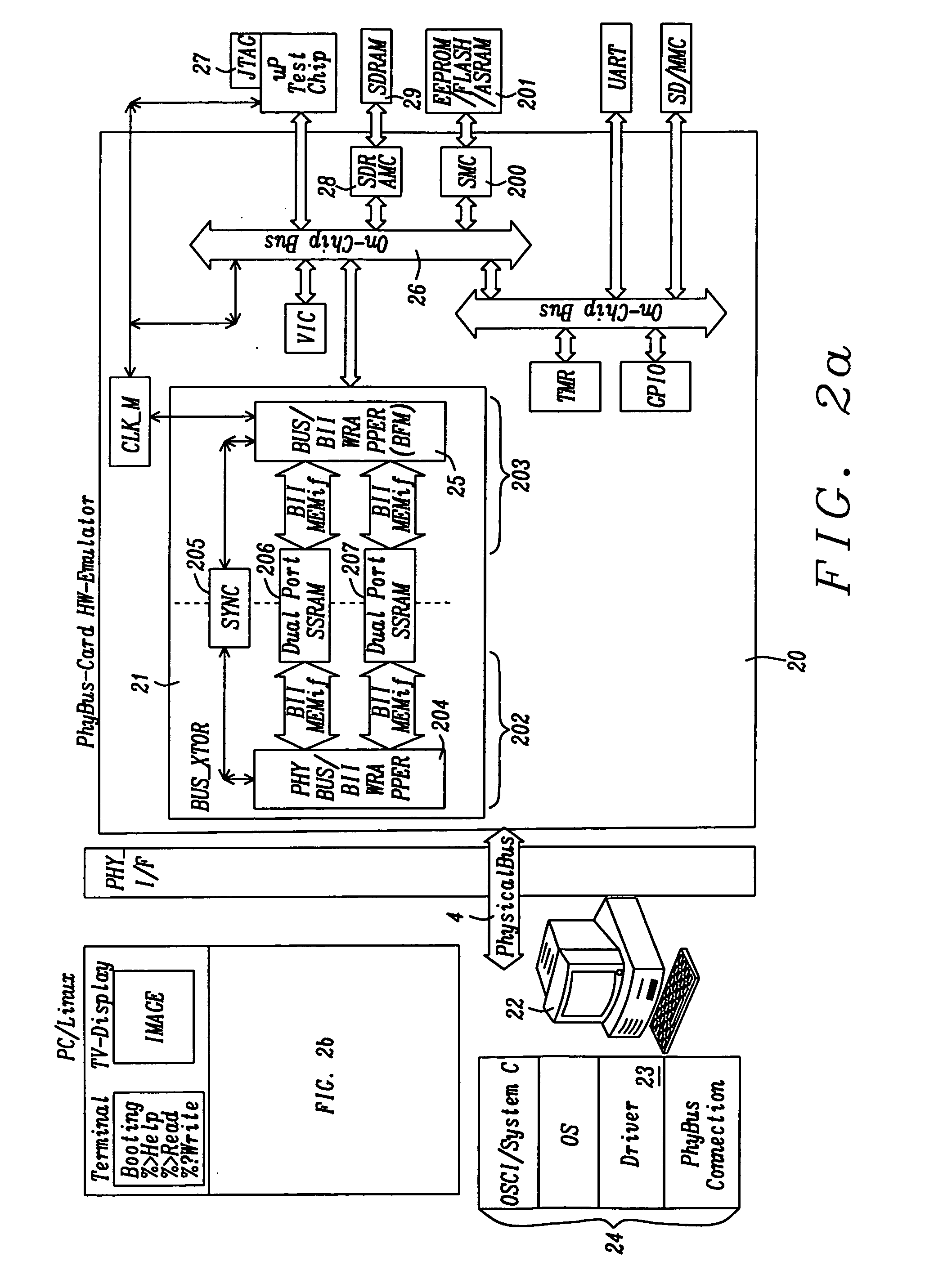

Hybrid system combining TLM simulators and HW accelerators

InactiveUS20110307847A1Simple designLow costCAD circuit designProgram controlHybrid systemComputer architecture

A hybrid system is combining transaction level modeling (TLM) simulators and hardware accelerators so that new system-on chip (SoC) designs are integrated in a virtual platform (VP) to run TLM simulation and existent semiconductor intellectual properties (IP) are added to physical platform (PP) to run hardware accelerator. A new circuit design with TLM is easier to be performed than with register transfer language (RTL) and it is integrated in a virtual platform and existent IP doesn't have to be redesigned to be integrated in a virtual platform.

Owner:GLOBAL UNICHIP CORPORATION

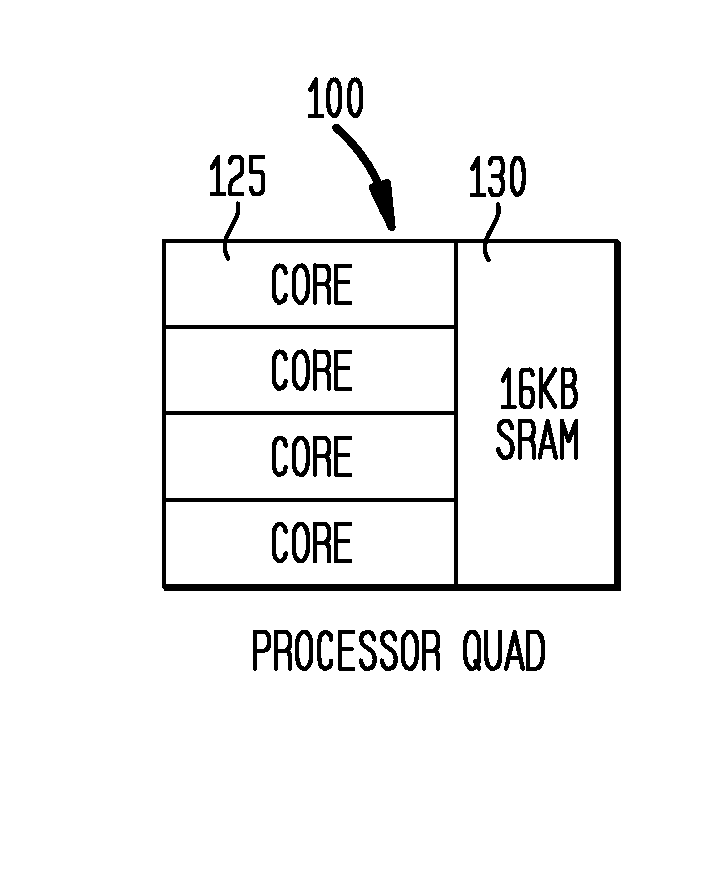

Self-contained processor subsystem as component for system-on-chip design

InactiveUS20070239966A1Increase speedShorten access timeMultiple digital computer combinationsTransmissionComputer architectureCoprocessor

A System-on-Chip (SoC) component comprising a single independent multiprocessor subsystem core including a plurality of multiple processors, each multiple processor having a local memory associated therewith forming a processor cluster; and a switch fabric means connecting each processor cluster within an SoC integrated circuit (IC). The single SoC independent multiprocessor subsystem core is capable of performing multi-threading operation processing for SoC devices when configured as a DSP, coprocessor, Hybrid ASIC, or network processing arrangements. The switch fabric means additionally interconnects a SoC local system bus device with SoC processor components with the independent multiprocessor subsystem core.

Owner:MICROSOFT TECH LICENSING LLC

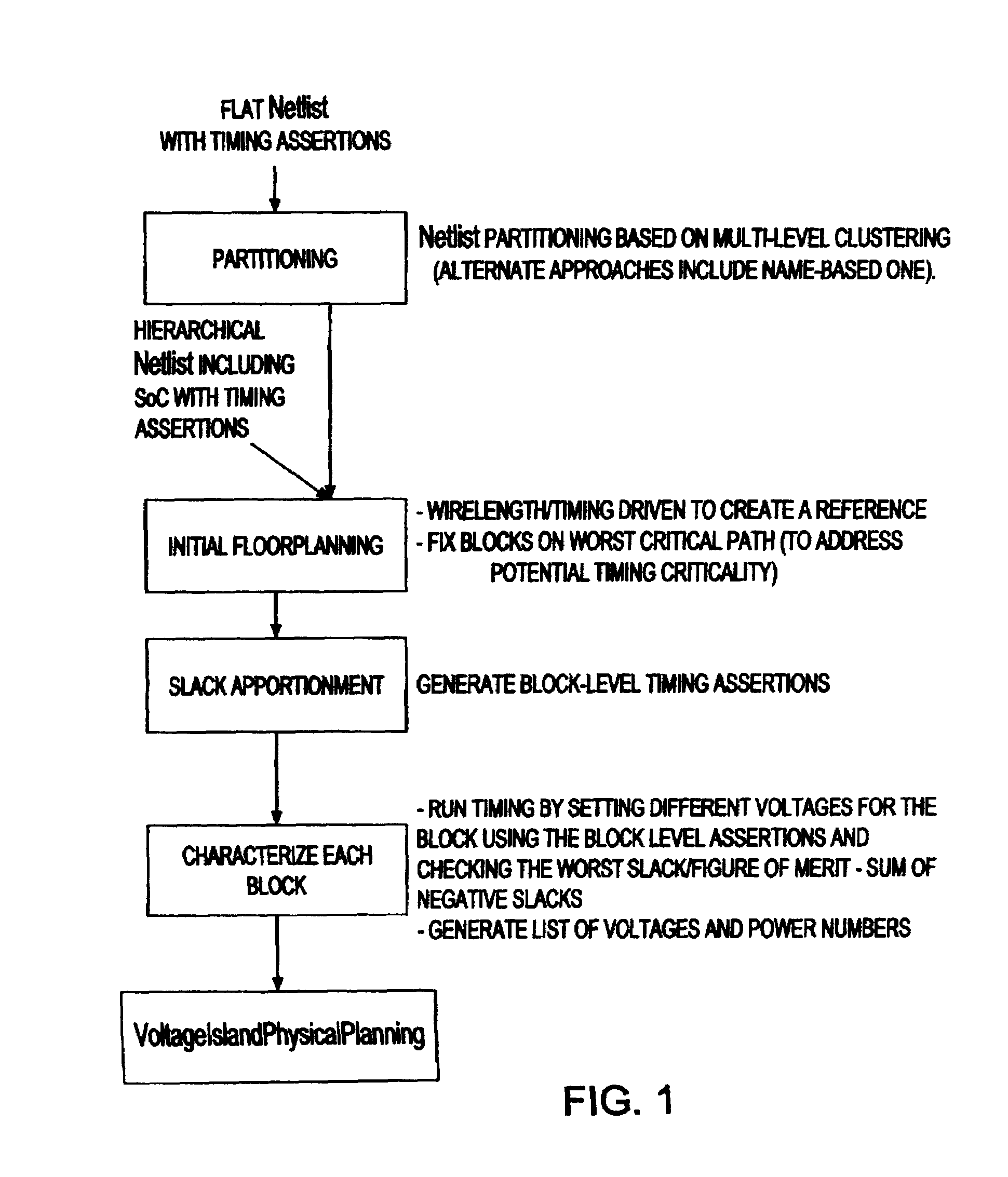

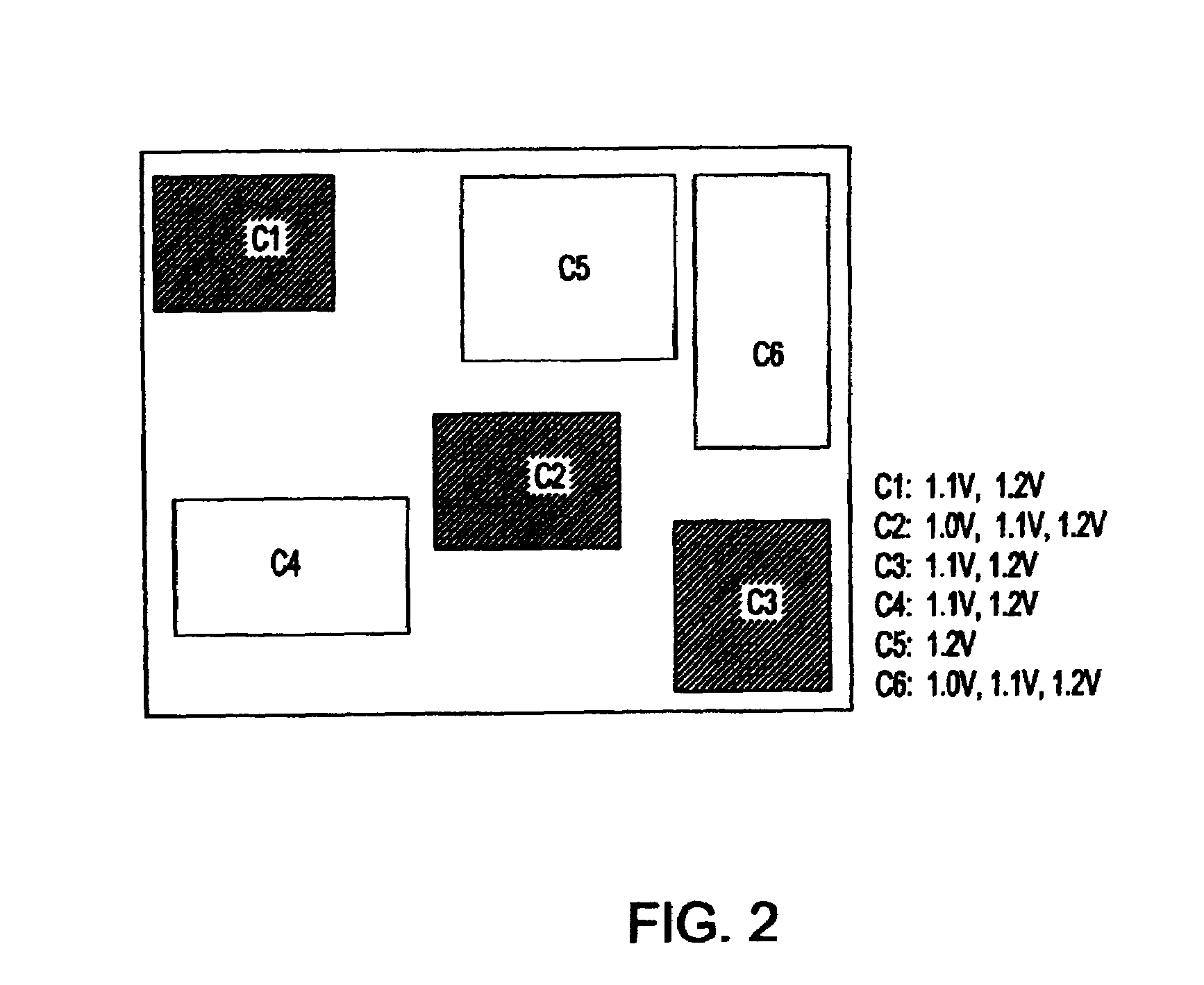

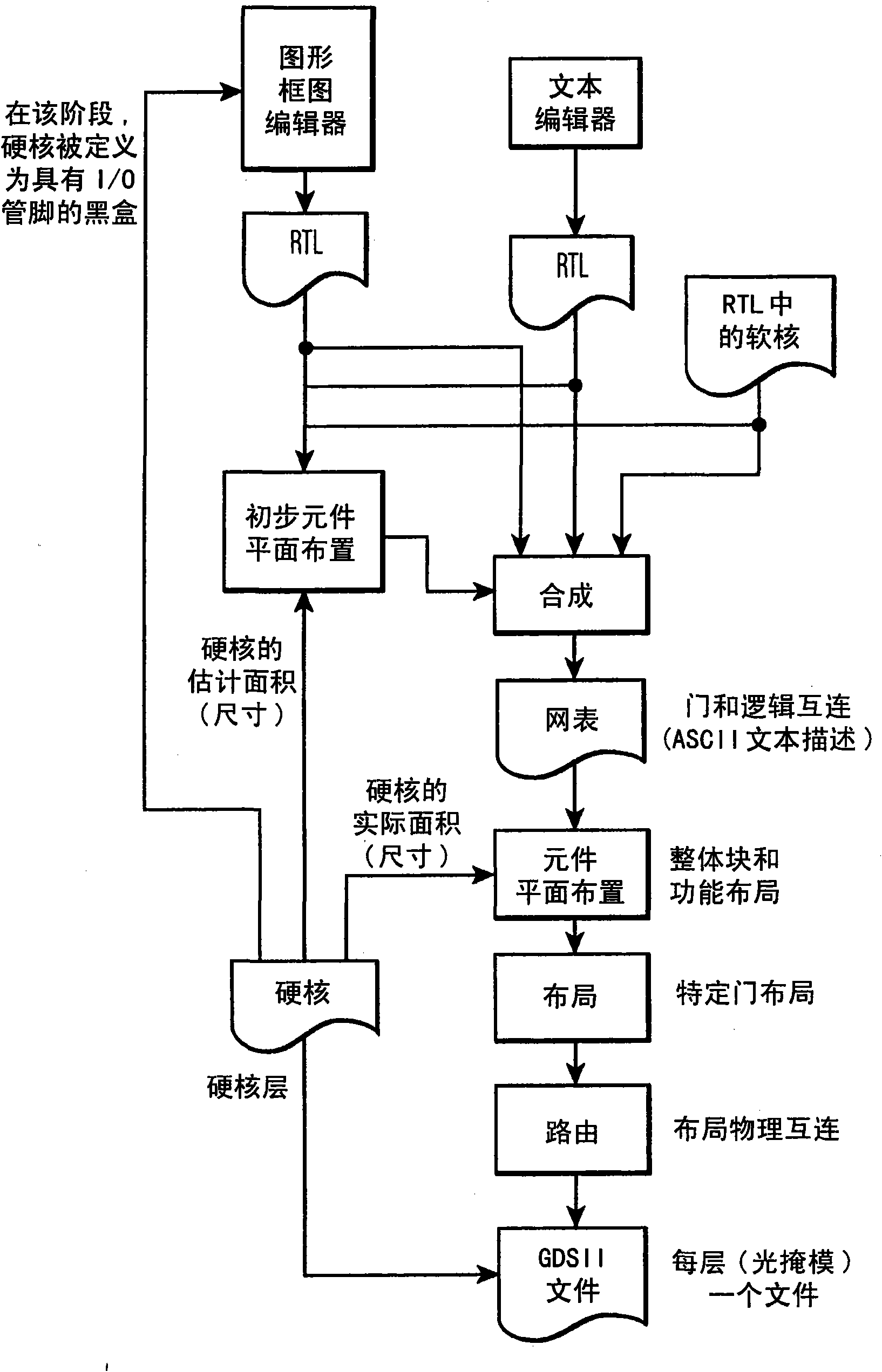

Method of physical planning voltage islands for ASICs and system-on-chip designs

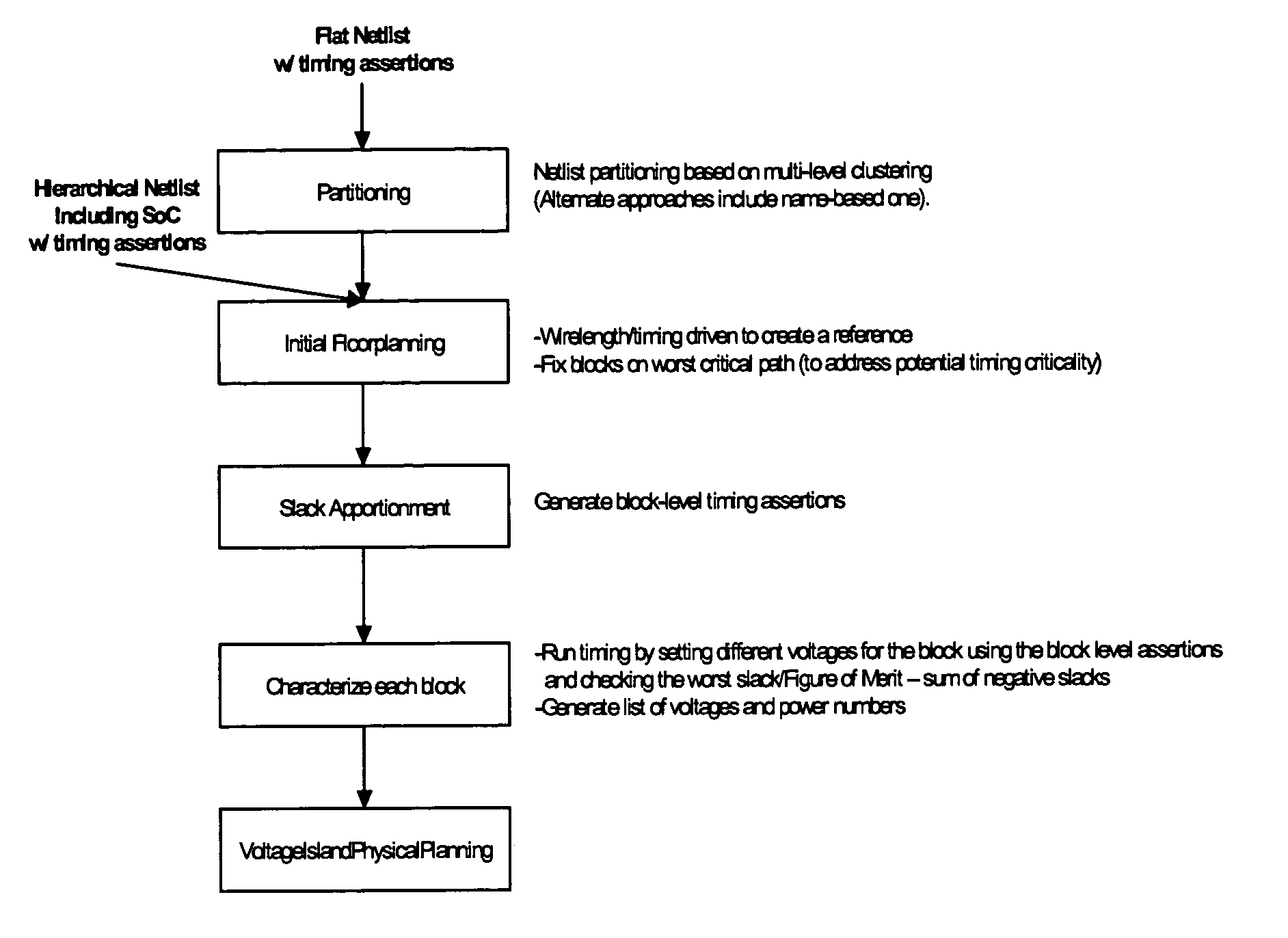

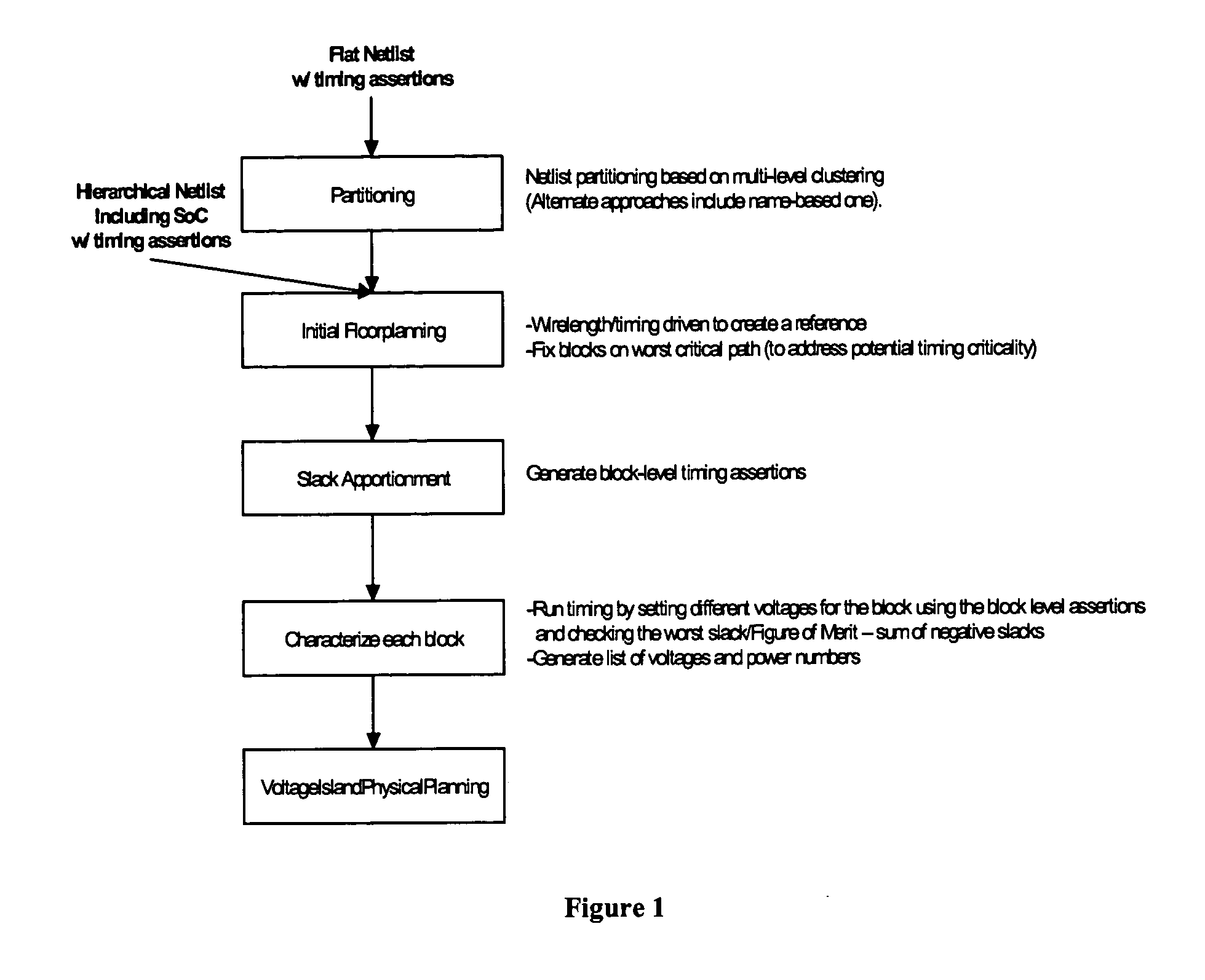

InactiveUS20050278676A1Minimize power consumptionCAD circuit designSoftware simulation/interpretation/emulationPhysical planningIslanding

Voltage islands enable a core-level power optimization of ASIC / SoC designs by utilizing a unique supply voltage for each cluster of the design. Creating voltage islands in a chip design for optimizing the overall power consumption consists of generating voltage island partitions, assigning voltage levels and floorplanning. The generation of voltage island partitions and the voltage level assignment are performed simultaneously in a floorplanning context due to the physical constraints involved. This leads to a floorplanning formulation that differs from the conventional floorplanning for ASIC designs. Such a formulation of a physically aware voltage island partitioning and method for performing simultaneous voltage island partitioning, level assignment and floorplanning are described, as are the definition and the solution of floorplanning for voltage island based designs executed under area, power, timing and physical constraints. The physical planning of voltage islands includes: a) characterizing cell clusters in terms of voltages and power consumption values; b) providing a set of cell clusters that belong to a single voltage island Random Logic Macro (RLM); and c) assigning voltages for the voltage island RLMs, all within the context of generating a physically realizable floorplan for the design.

Owner:GOOGLE LLC

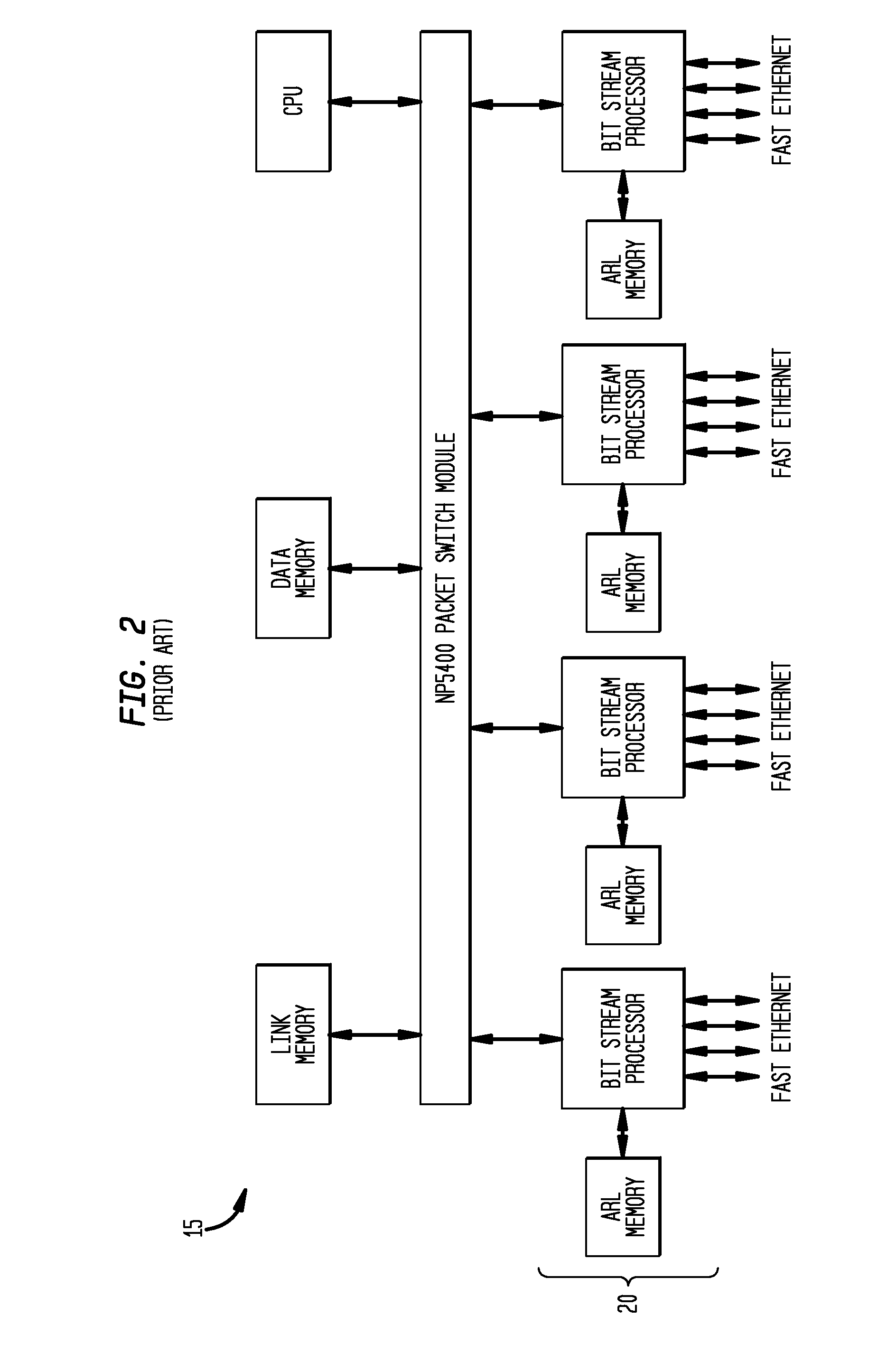

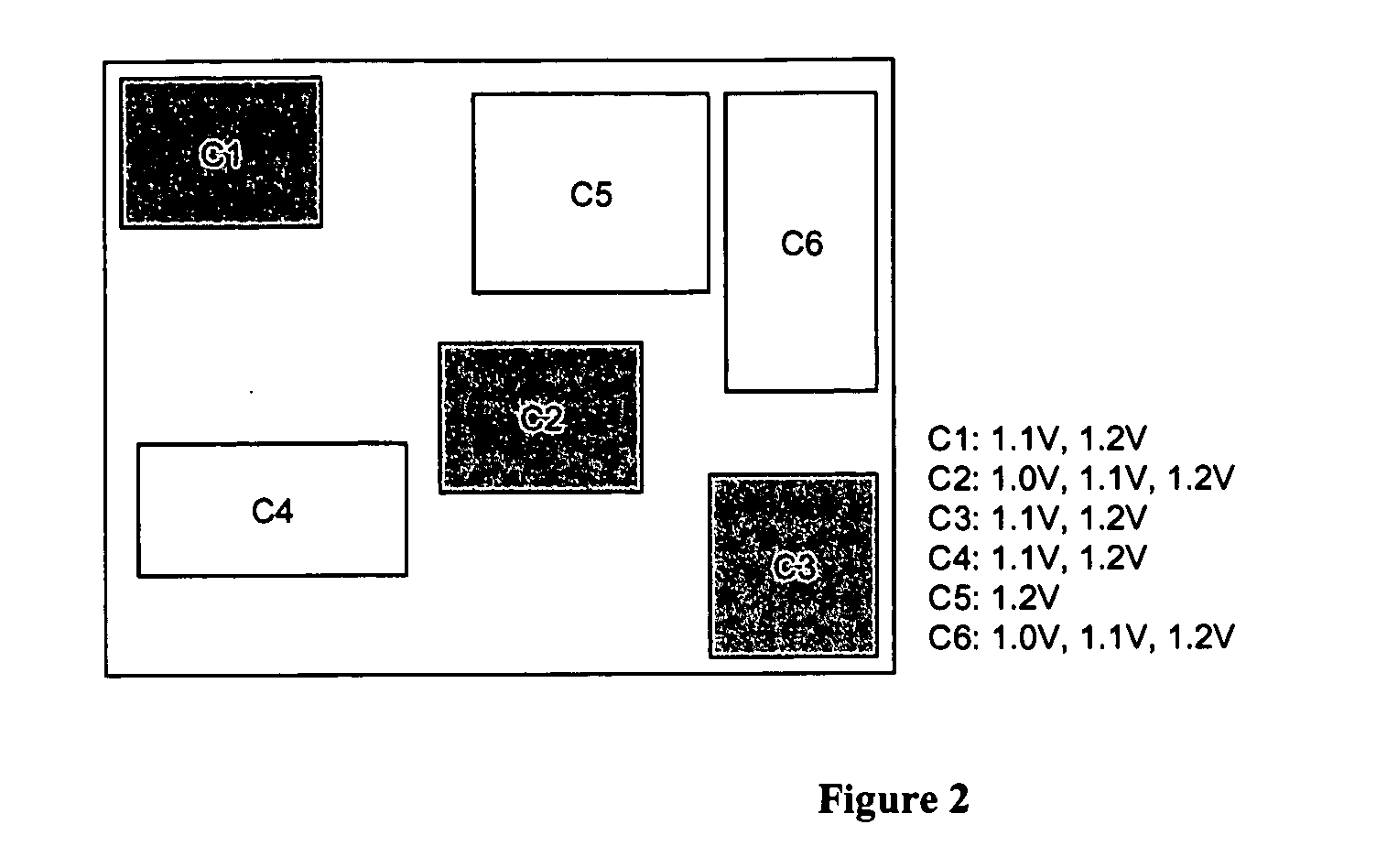

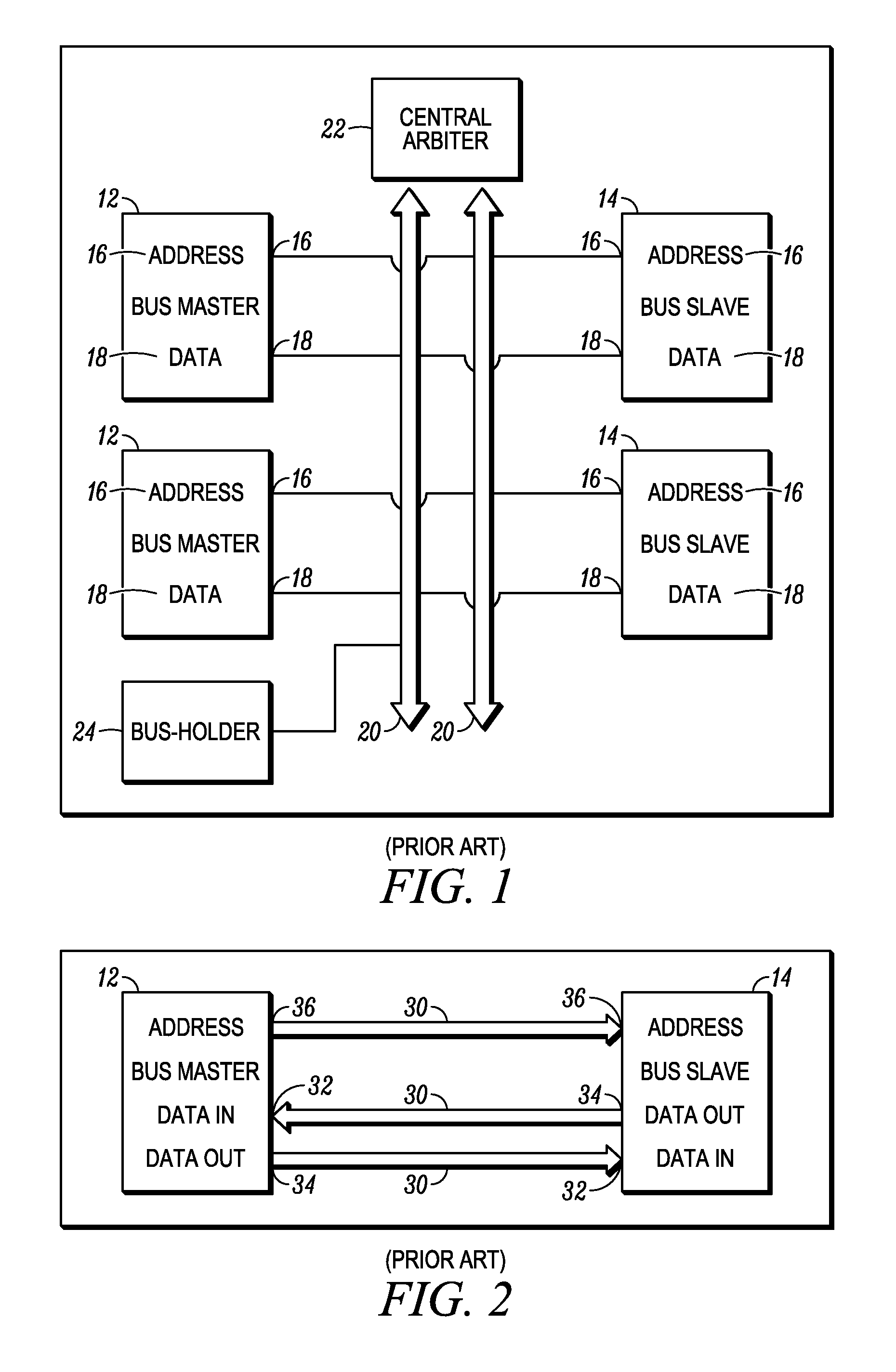

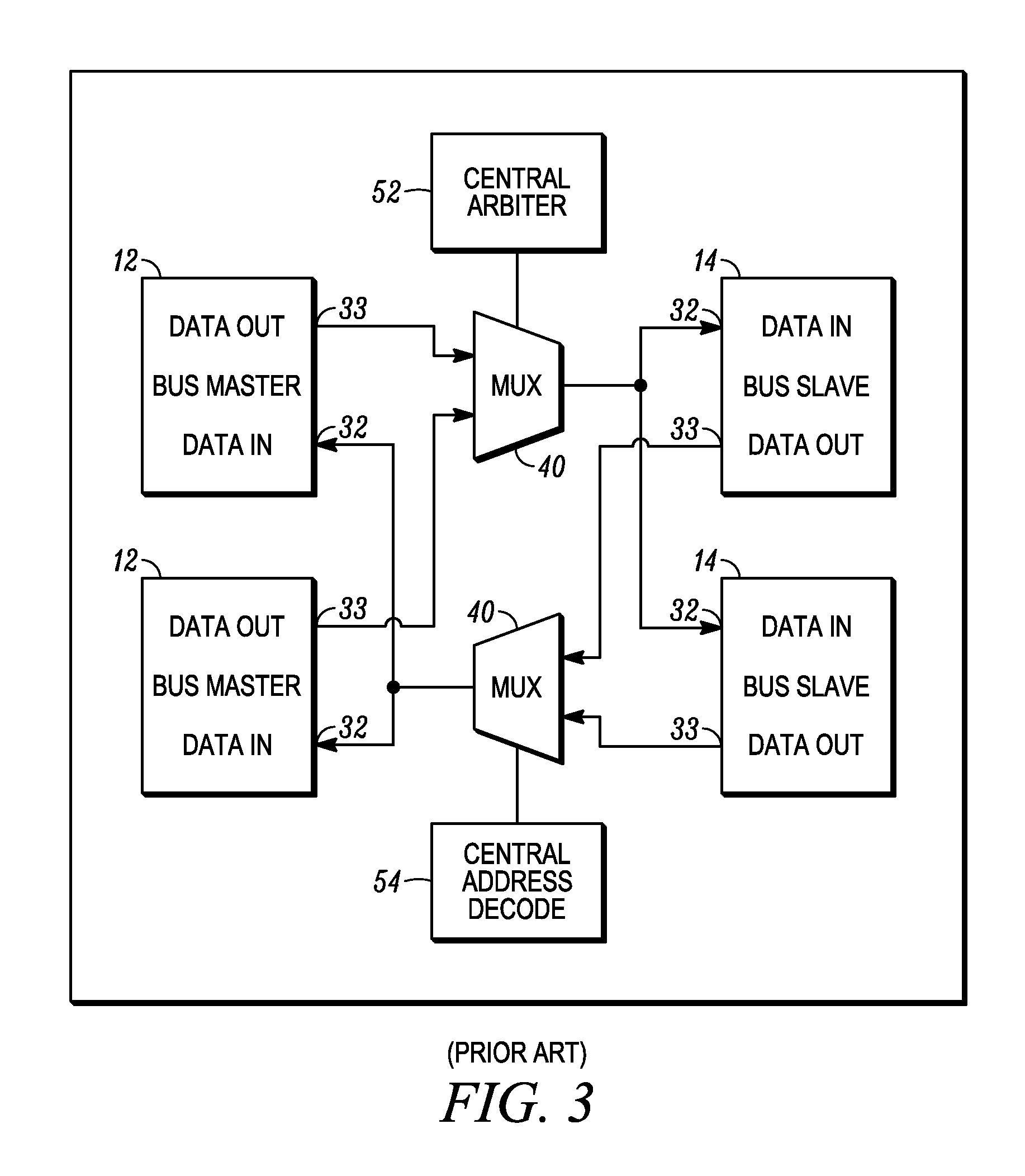

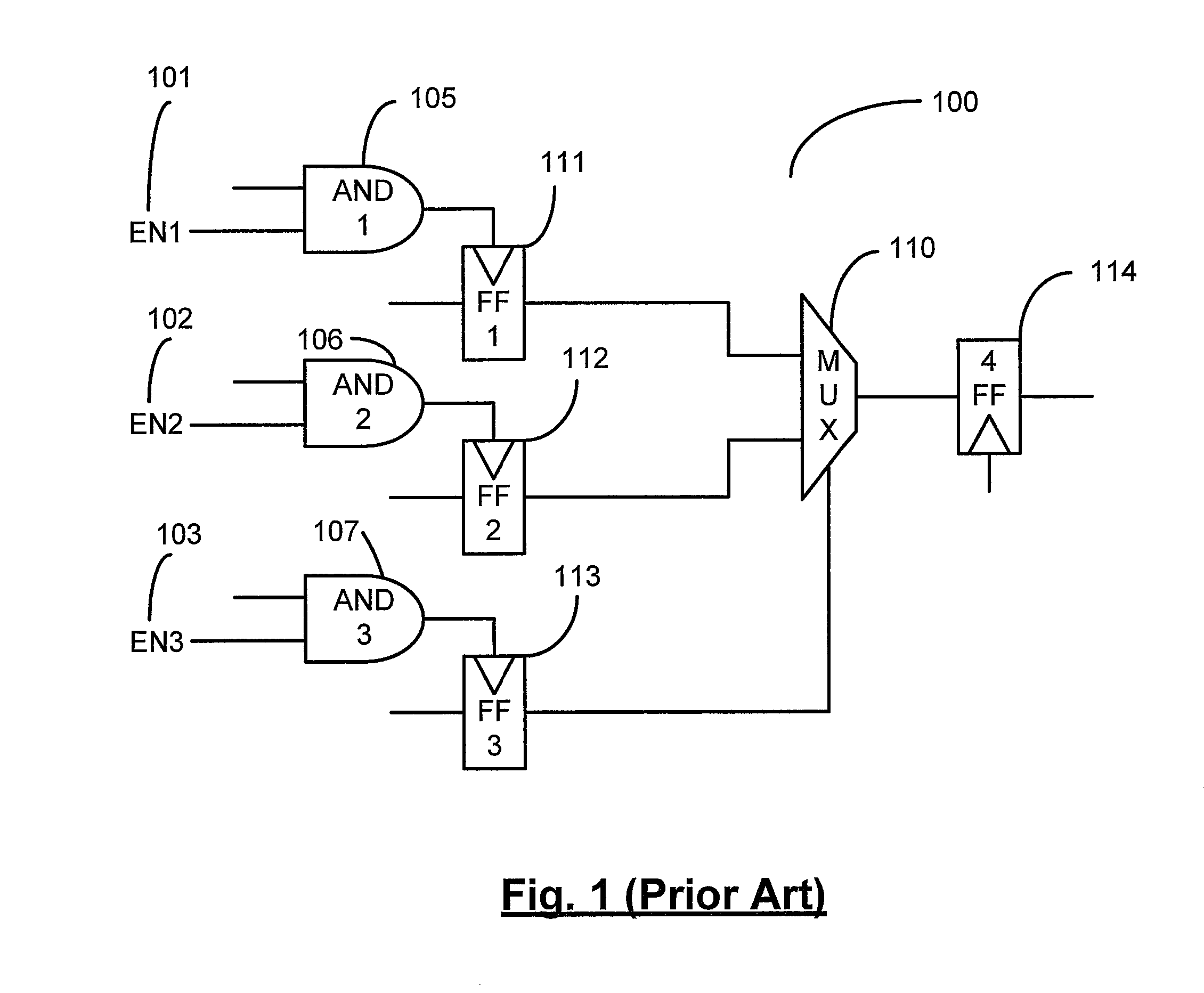

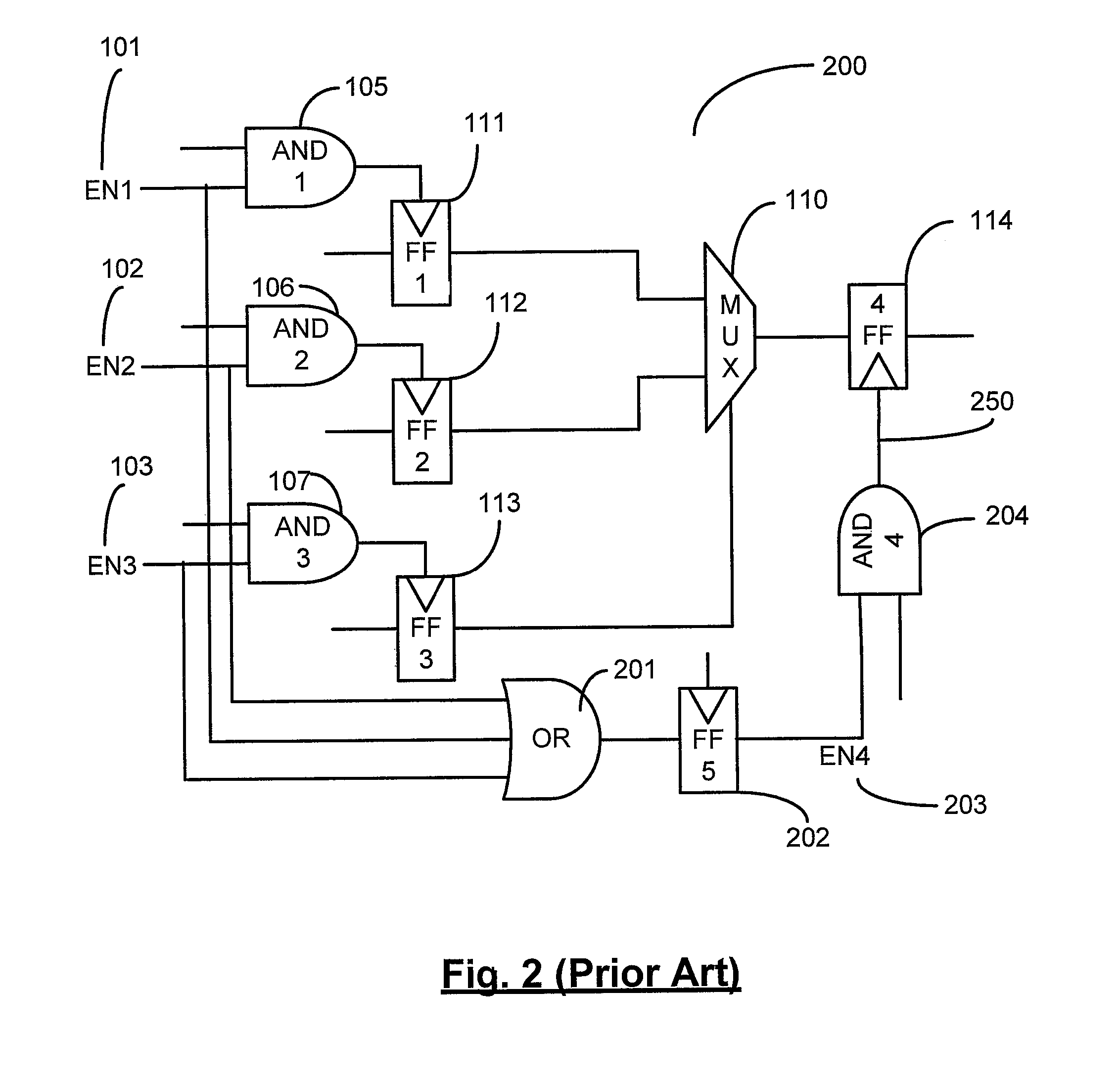

Multi-master bus architecture for system-on-chip designs

ActiveUS7145903B2Facilitate right-first-time developmentImprove reusabilityMultiplex system selection arrangementsTime-division multiplexMultiplexerEmbedded system

A bus architecture system to provide concurrency, fabricated on an integrated circuit for a system on chip design, for connecting a plurality of bus masters to a plurality of bus slaves. The system includes a plurality of multiplexers in communication with each data in port of each bus master and each bus slave. The system also includes a plurality of isolated data paths connecting the port out of each bus master to each multiplexer in communication with each data in port of each bus slave, and a plurality of isolated data paths connecting the port out of each bus slave to each multiplexer in communication with each data in port of each bus master, thereby providing concurrency on the system on chip design. In addition a distributed arbitration is included to allow each bus slave to be selected independently of the other bus slaves.

Owner:STRONG FORCE IOT

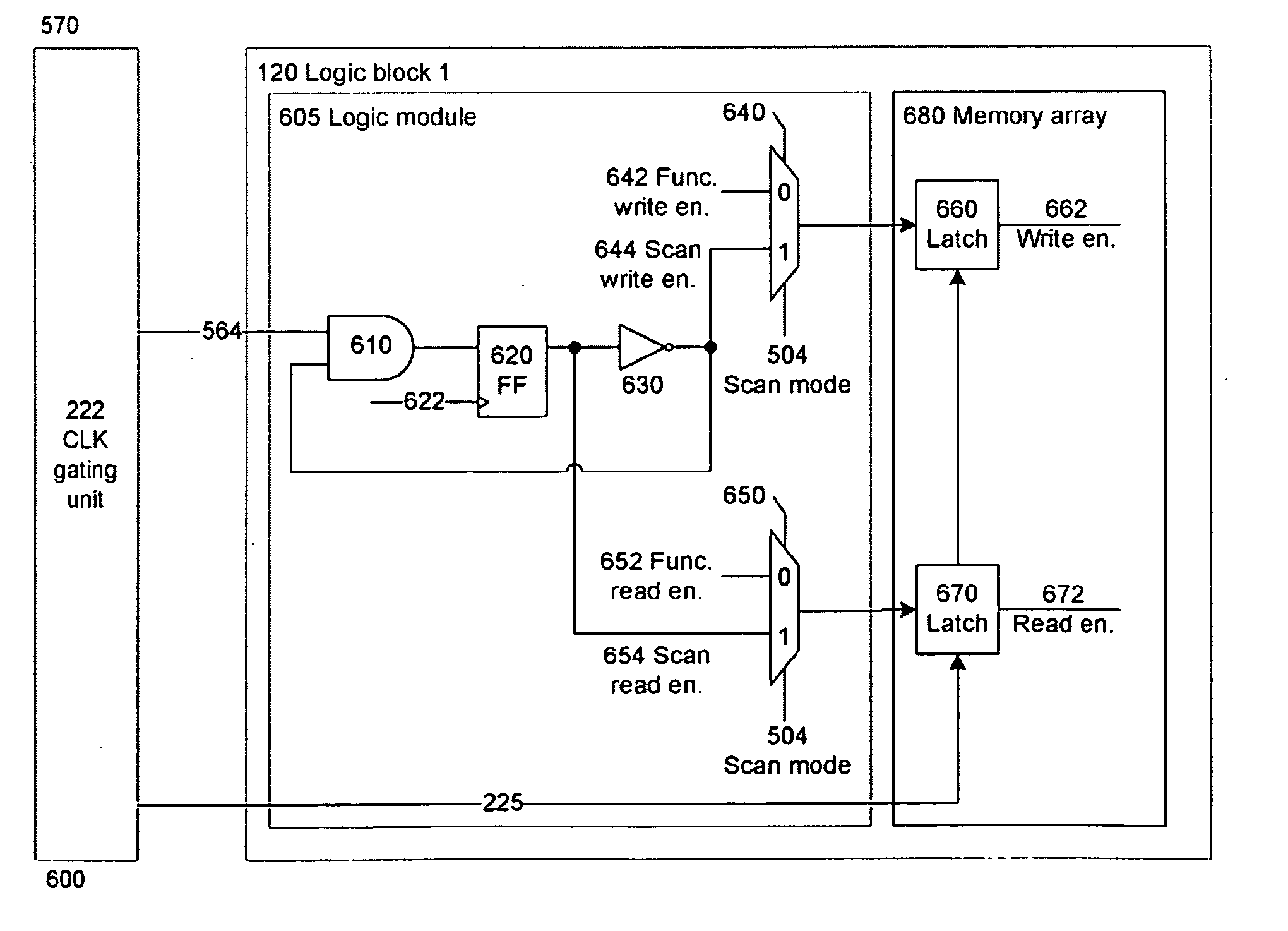

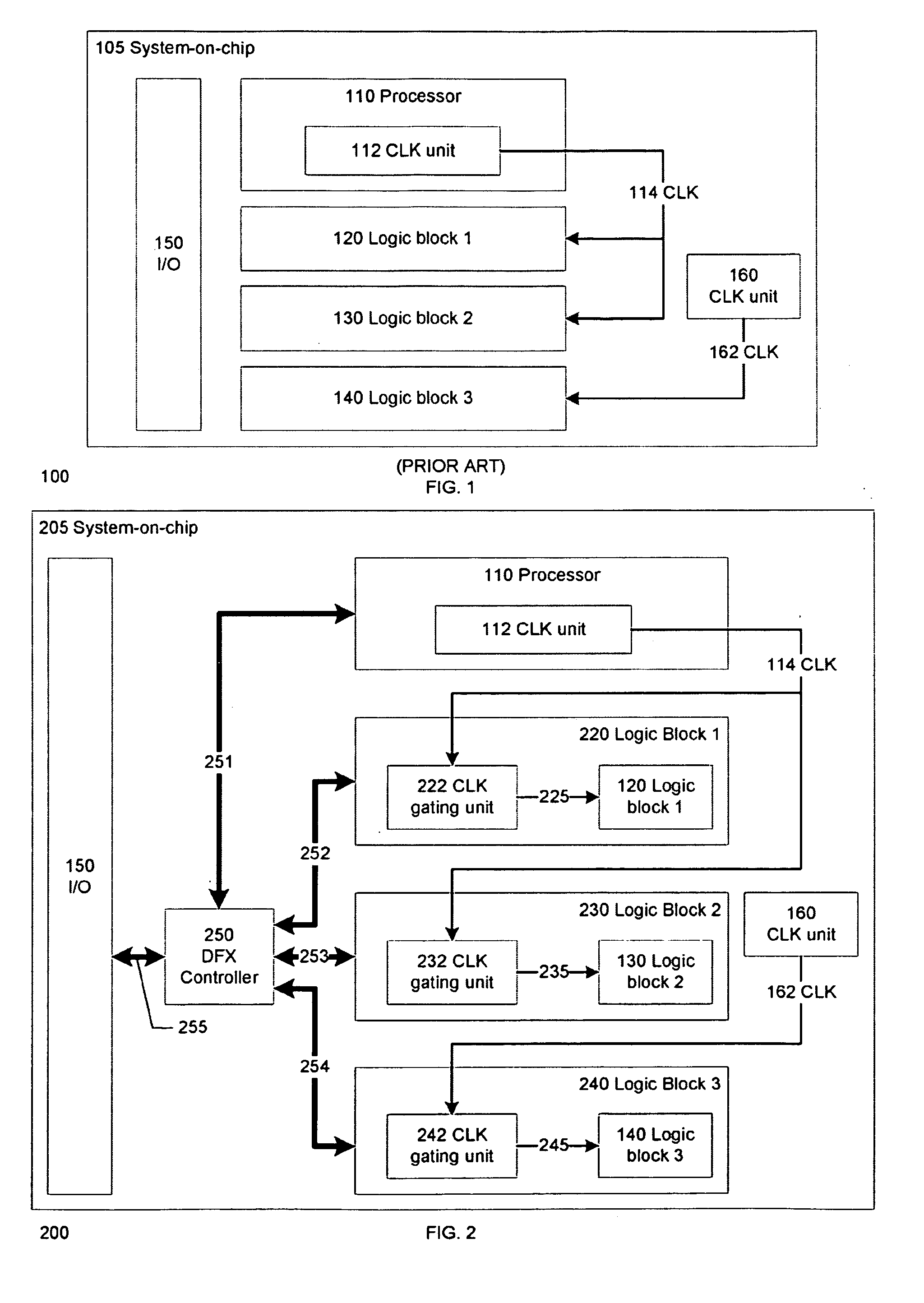

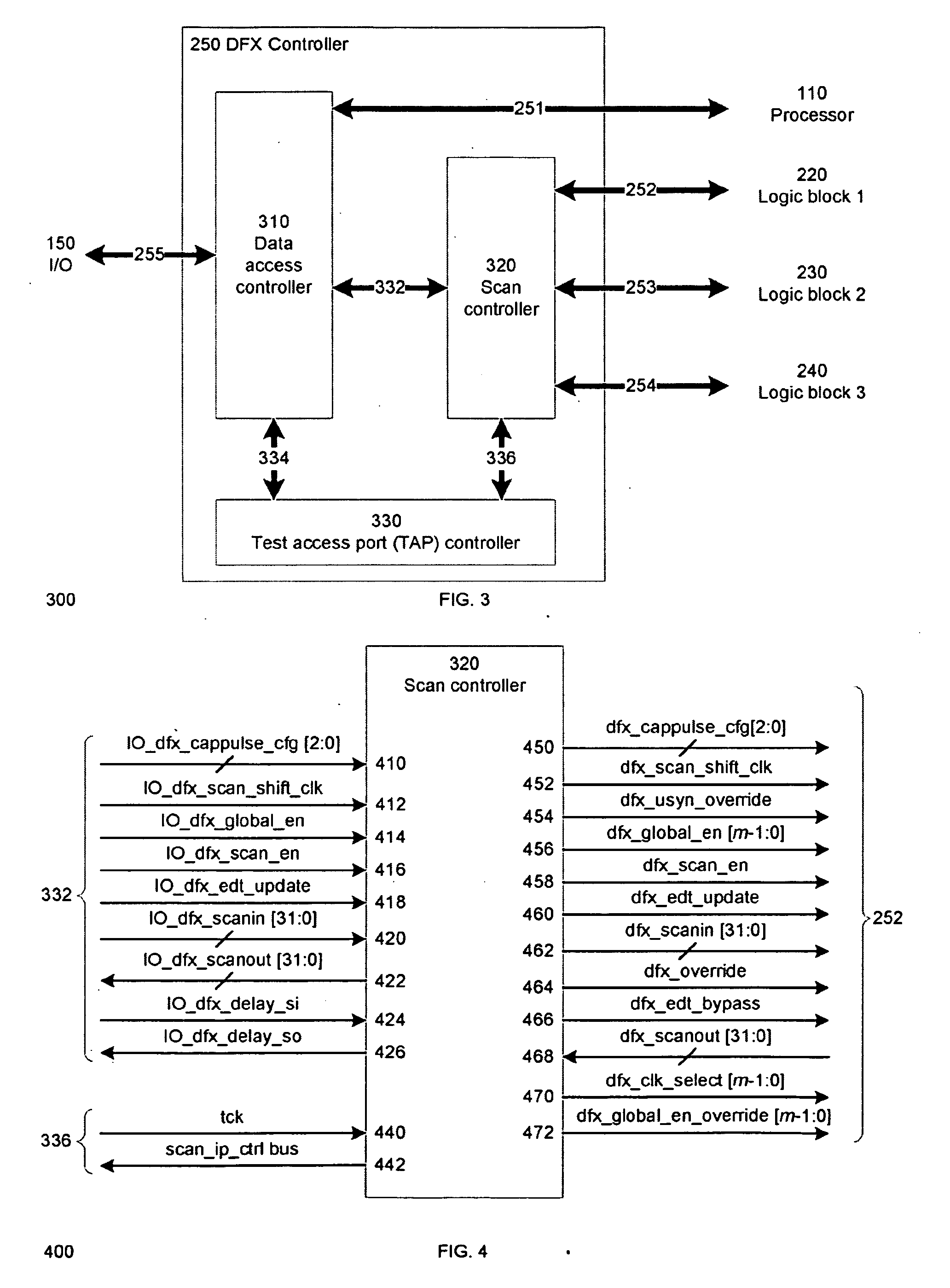

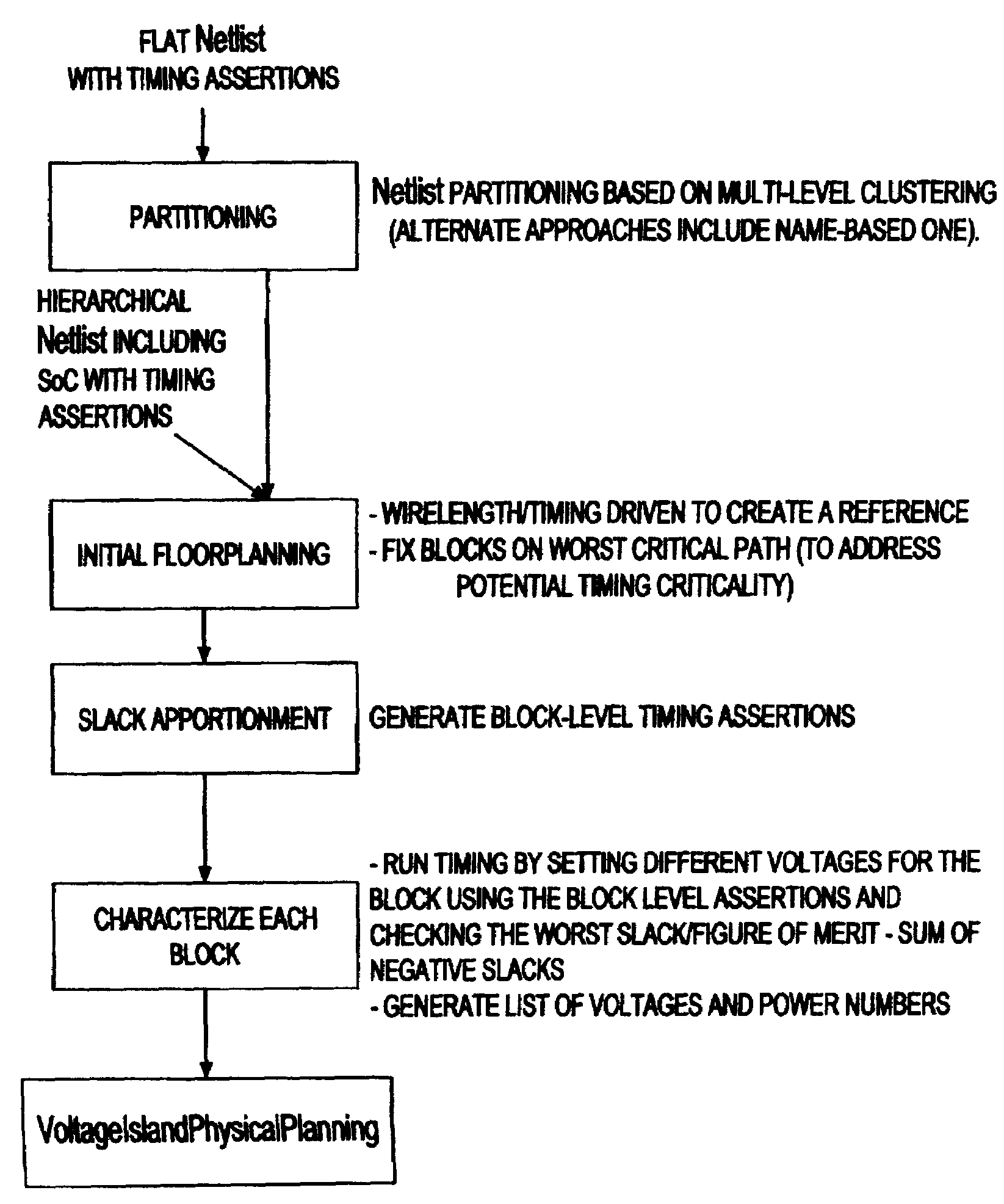

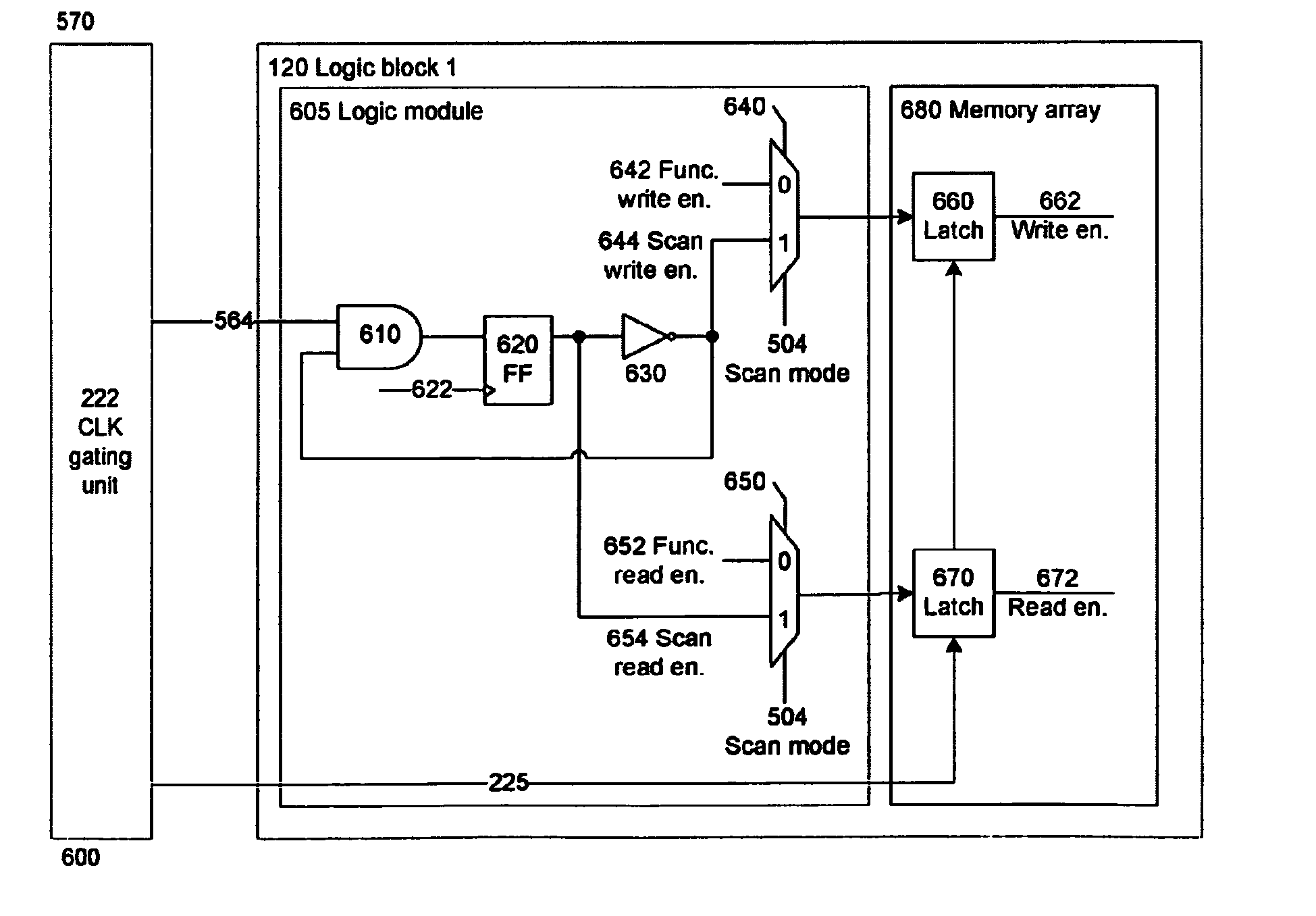

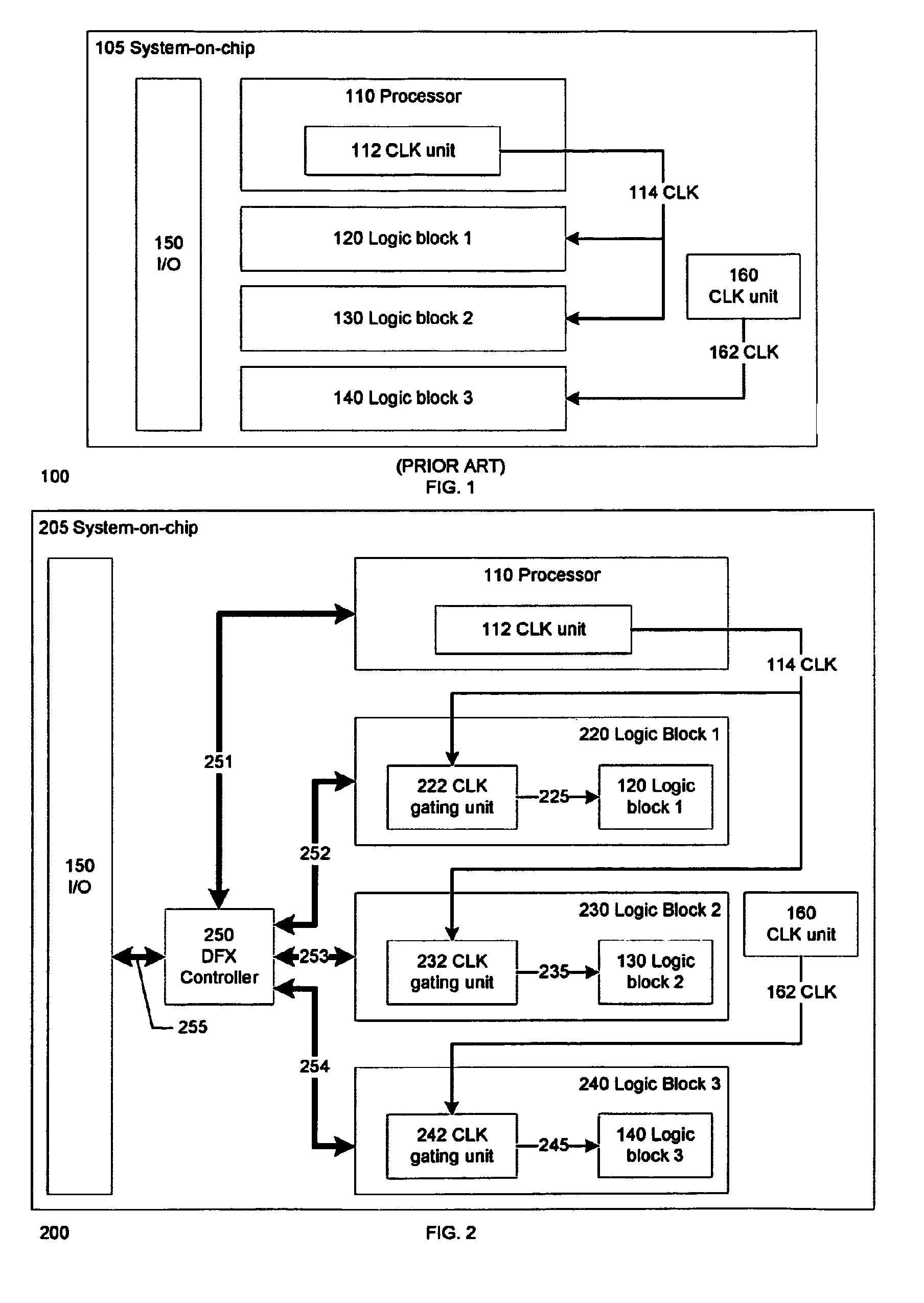

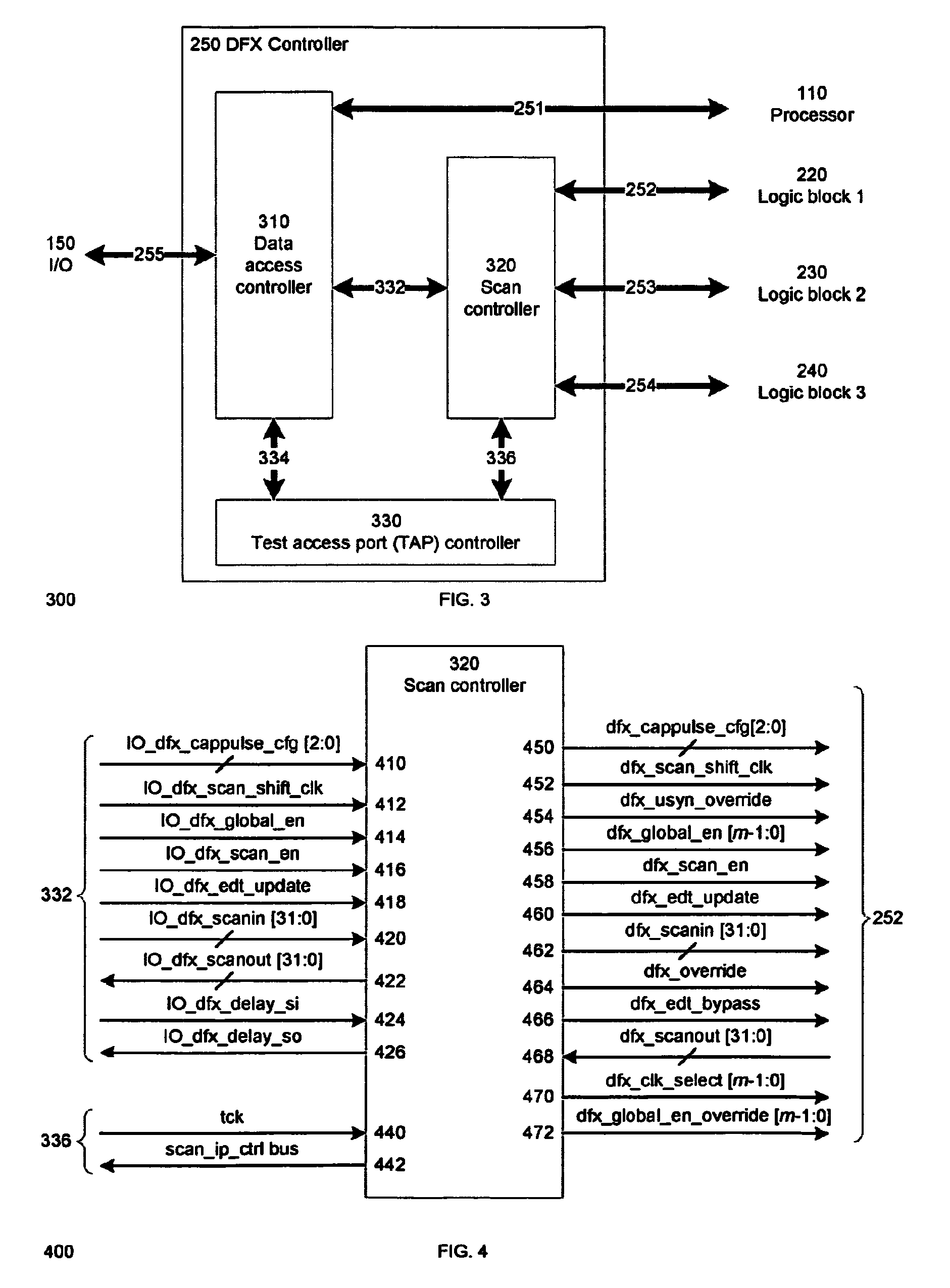

Scalable scan system for system-on-chip design

InactiveUS20100332928A1Electronic circuit testingMemory adressing/allocation/relocationEngineeringBlock level

A method and system to facilitate a scalable scan system in the design of a system-on-chip. In one embodiment of the invention, the system-on-chip includes a controller and one or more clock gating units. The clock gating unit is added to each unique clock domain of each function or logic block in the system-on-chip. By having a controller that connects to each clock gating unit and the scan input and output signals in each logic block of the SOC, this allows a scalable scan system in the design of the SOC and allows frequent block level design changes in the SOC without extensive changes to the scan logic in one embodiment of the invention. In addition, the scalable scan system also allows at-speed scan write-through testing of a memory array that can improves the scan test coverage of the system-on-chip.

Owner:INTEL CORP

Method of physical planning voltage islands for ASICs and system-on-chip designs

InactiveUS7296251B2Minimize power consumptionCAD circuit designSoftware simulation/interpretation/emulationPhysical planningCore level

Owner:GOOGLE LLC

Directional two-dimensional router and interconnection network for field programmable gate arrays, and other circuits and applications of the router and network

ActiveUS10116557B2Reduce switching delayLower latencyData switching networksNetwork sizeFpga implementations

Owner:GRAY RES LLC

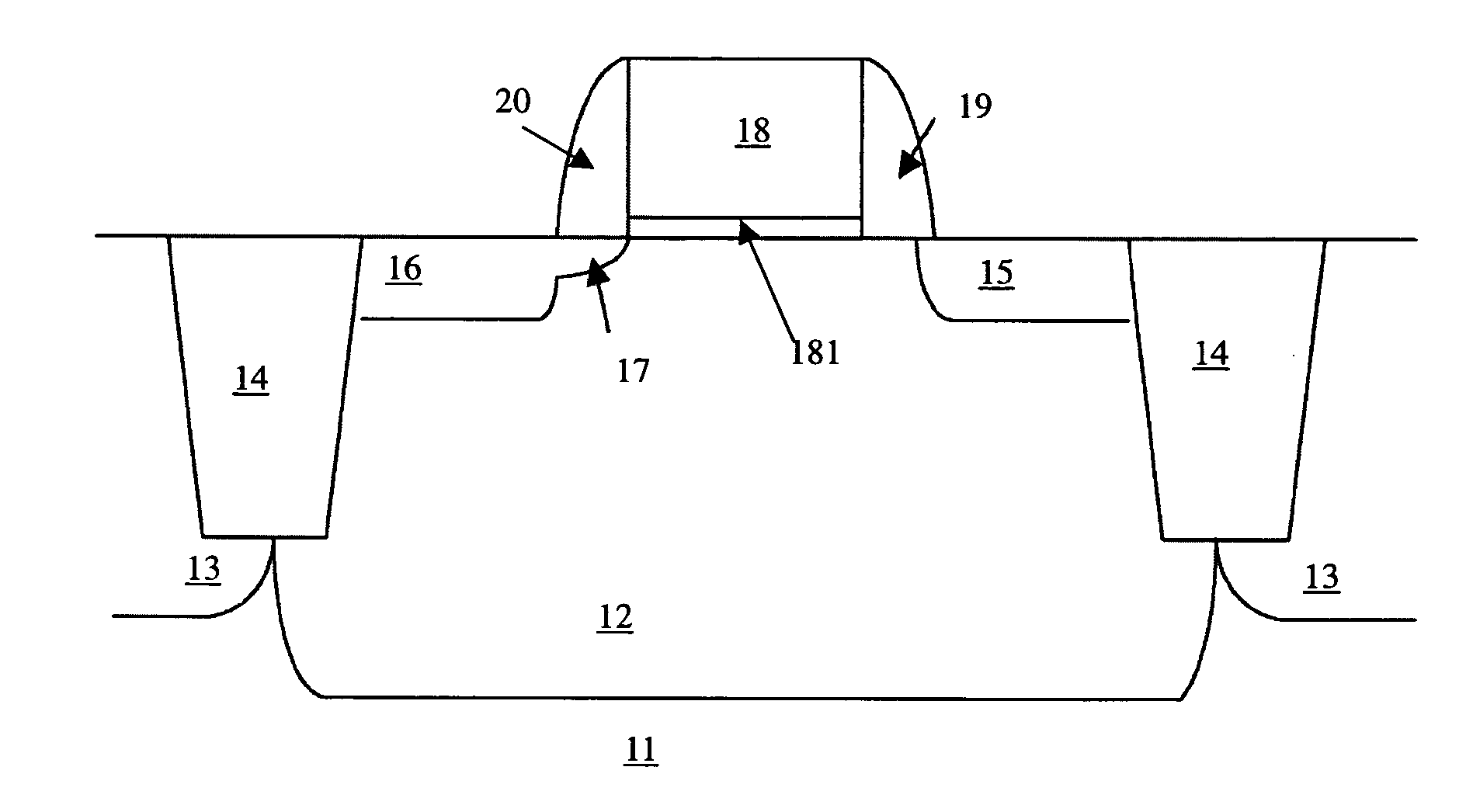

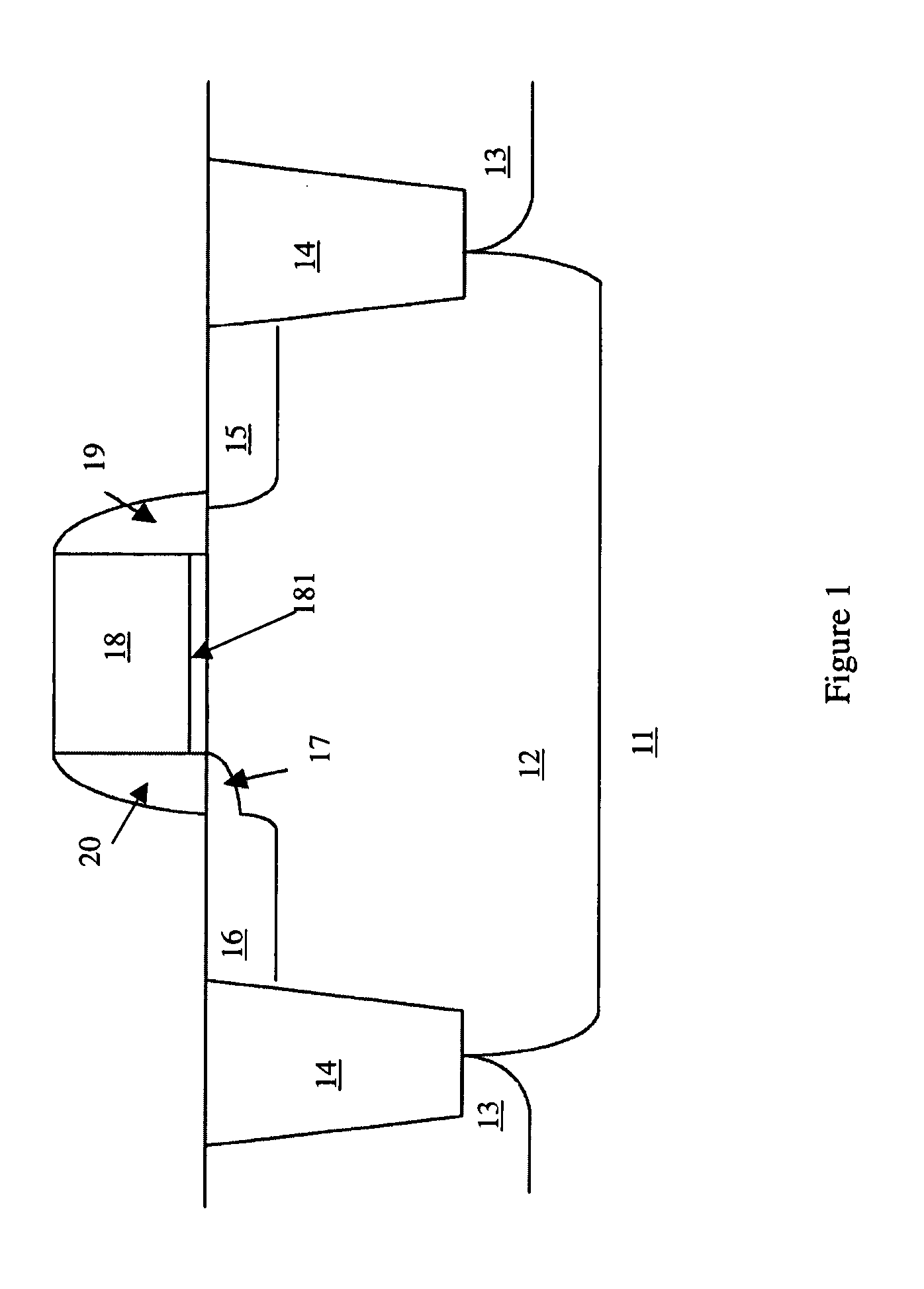

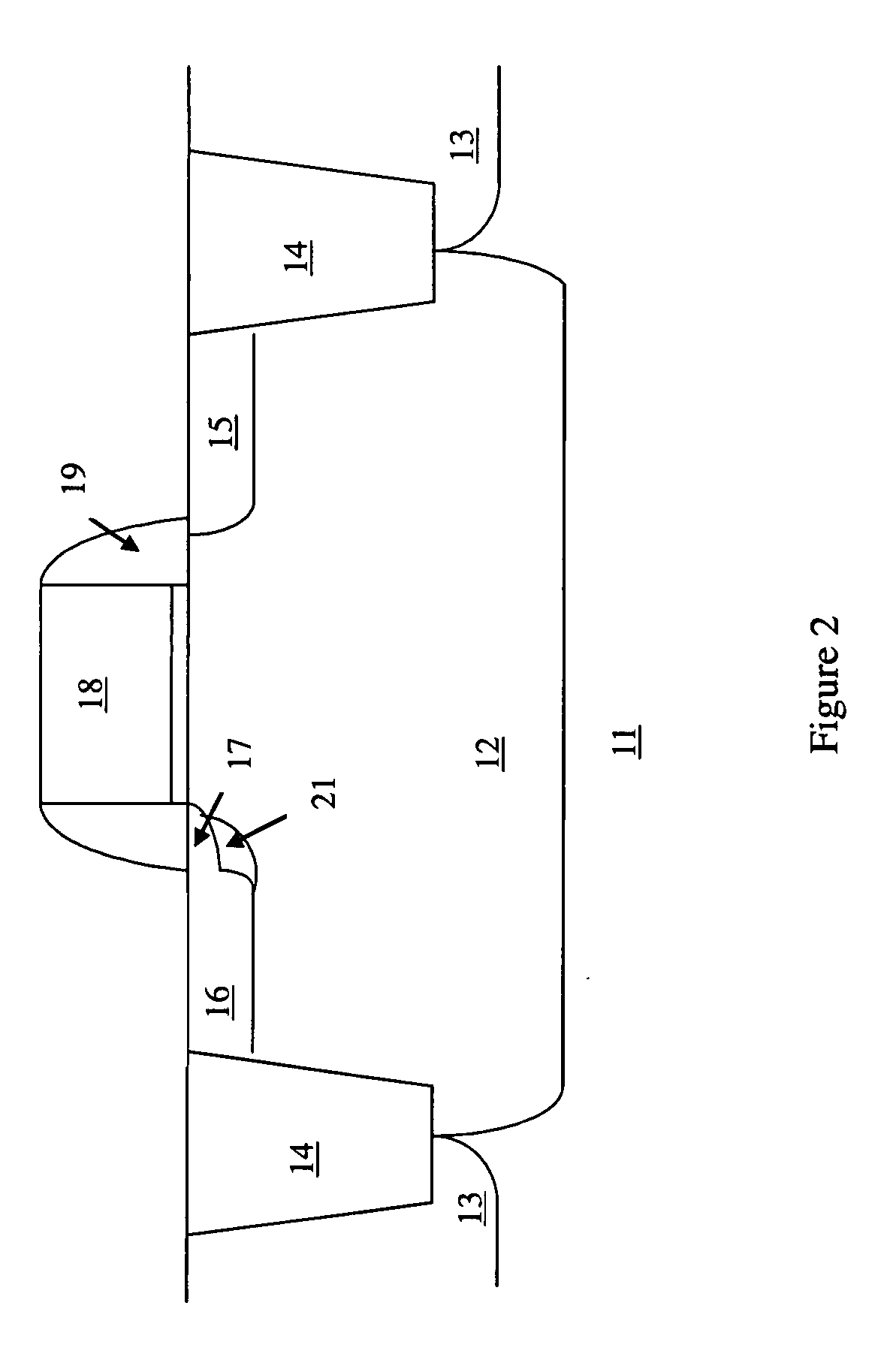

Asymmetric-ldd mos device

InactiveUS20090090980A1Improve RF power performanceLower breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPower-added efficiency

The present invention proposes a new asymmetric-lightly-doped drain (LDD) metal oxide semiconductor (MOS) transistor that is fully embedded in a CMOS logic. The radio frequency (RF) power performance of both conventional and asymmetric MOS transistor is measured and compared. The output power can be improved by 38% at peak power-added efficiency (PAE). The PAE is also improved by 16% at 10-dBm output power and 2.4 GHz. These significant improvements of RF power performance by this new MOS transistor make the RF-CMOS system-on-chip design a step further. Index Terms—Lightly-doped-drain (LDD), metal oxide semiconductor field effect transistor (MOSFET), metal oxide semiconductor (MOS) transistor, radio frequency (RF) power transistor.

Owner:KING MINGCHU +1

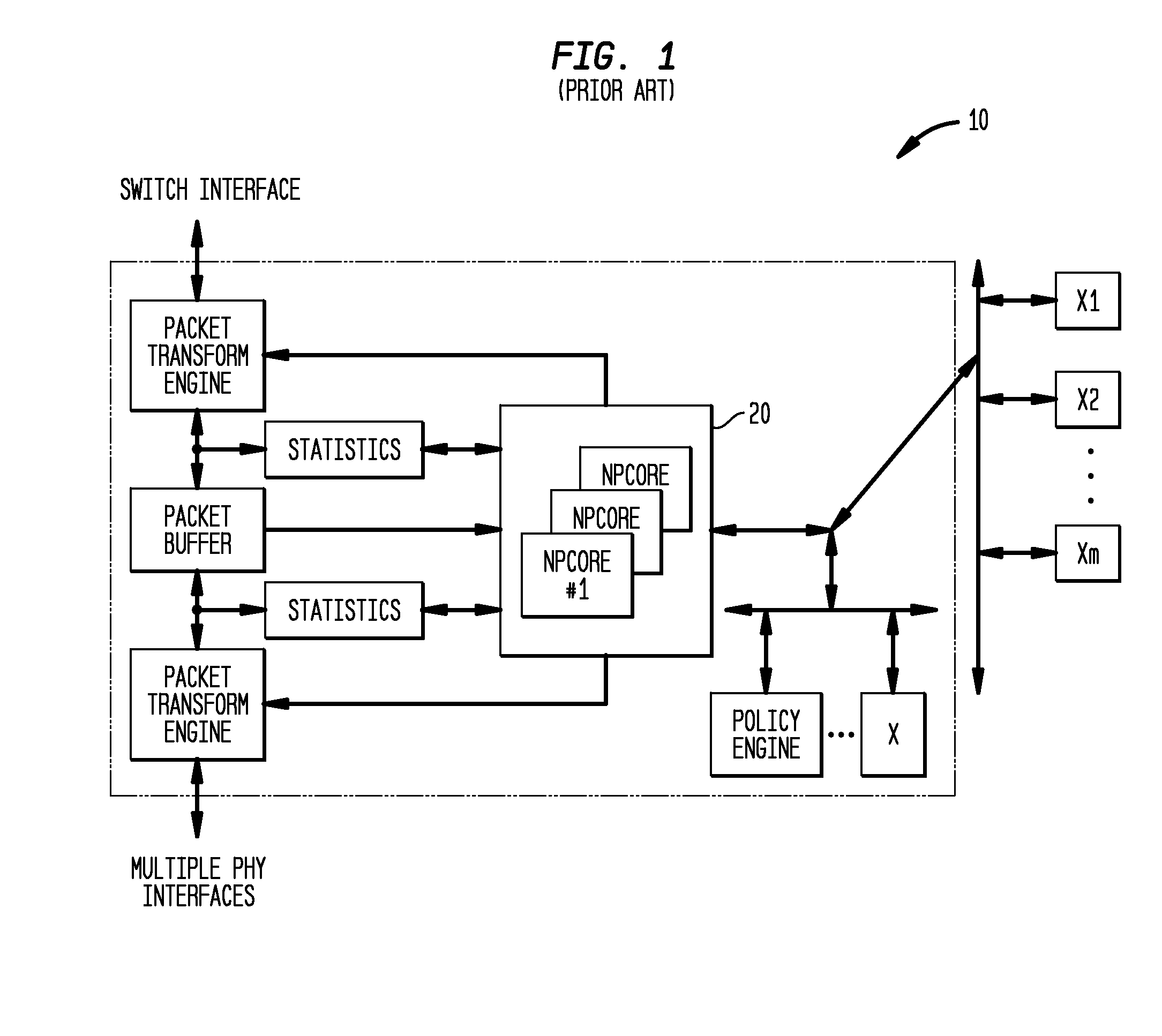

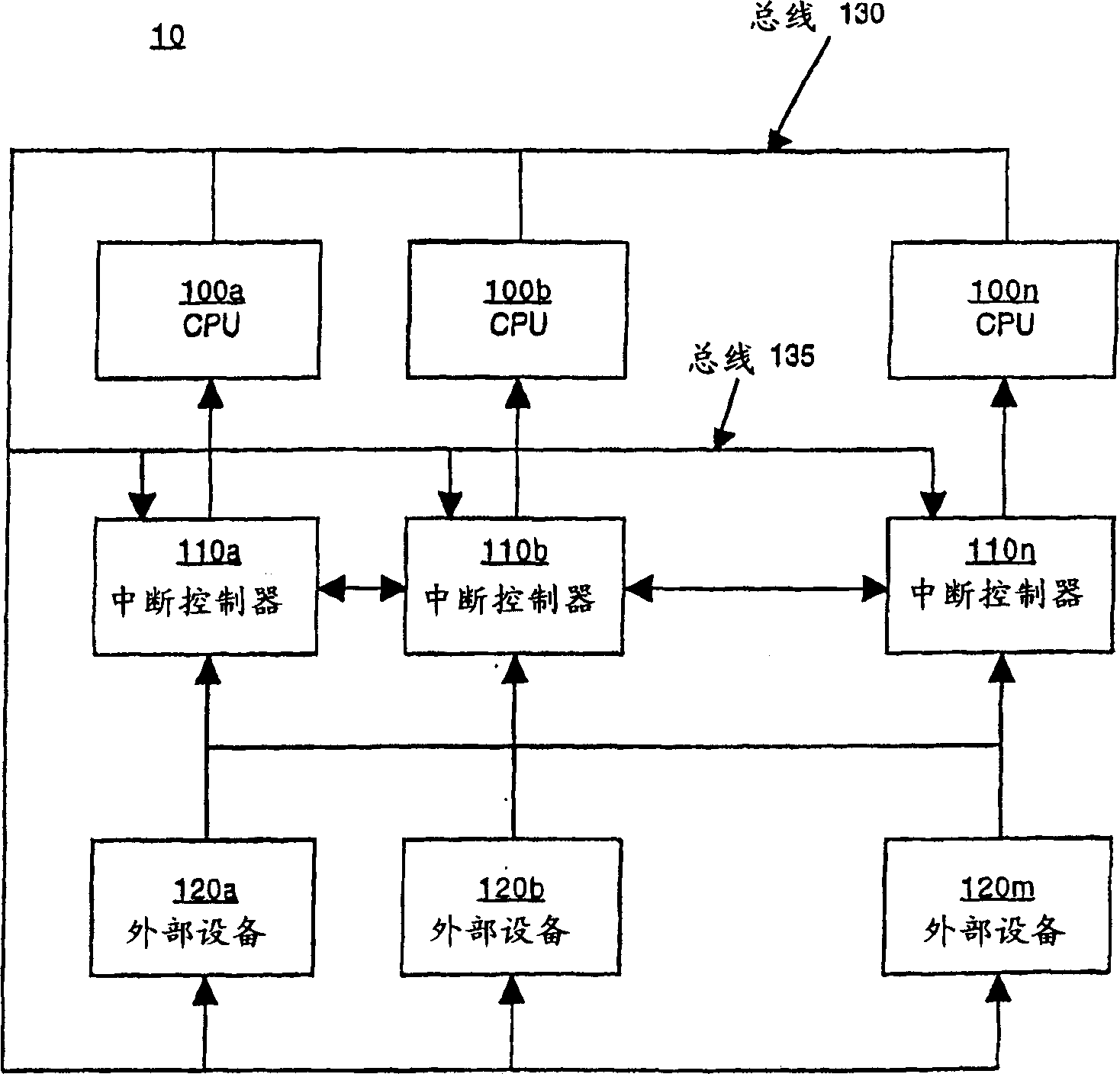

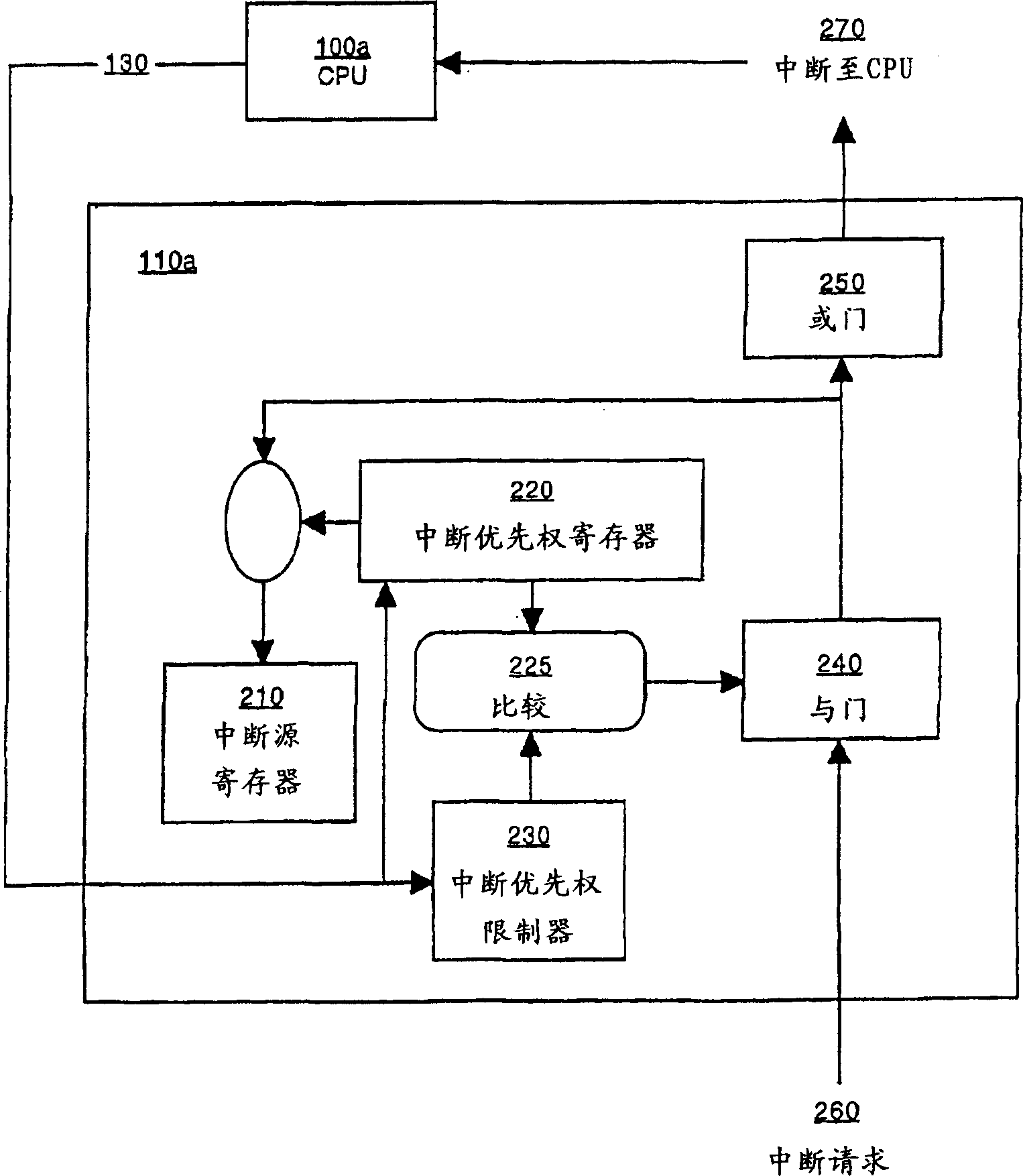

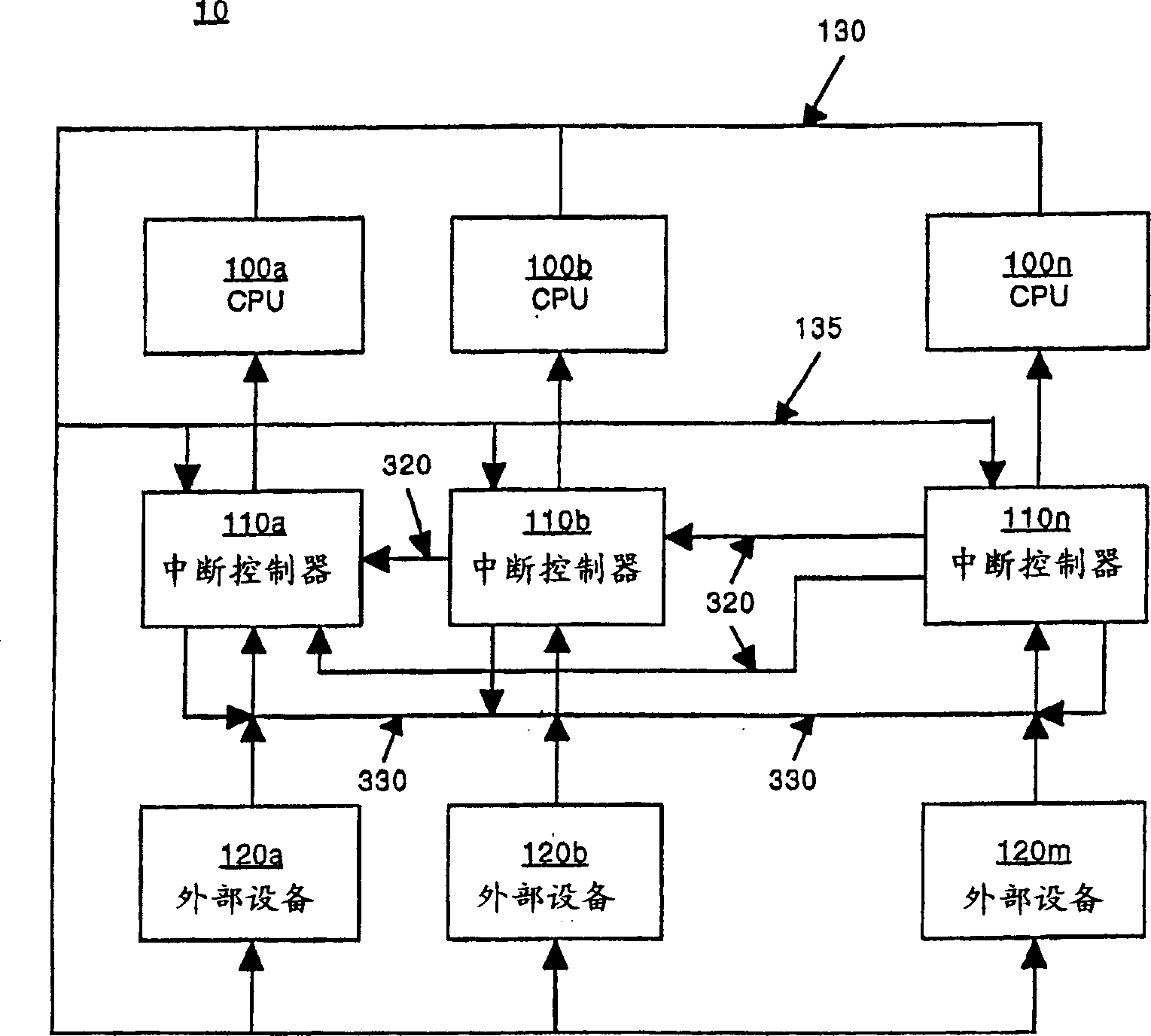

Efficient interrupt system for system on chip design

InactiveCN1535427AInterrupt easilyImproved efficiency of interrupt handlingMultiprogramming arrangementsMultiple digital computer combinationsSystems designEmbedded system

A method (400) and system (10) for managing interrupts in a system on a chip design that includes multiple processors (100a, 100b, ..., 100n) coupled to multiple peripheral devices (120a, 120b, ..., 120m). A plurality of interconnected interrupt controllers (110a, 110b, ..., 110n) are coupled between the processors and the peripheral devices. Interrupts generated by the peripheral devices are received by all of the interrupt controllers. In one embodiment, an interrupt controller is paired with a processor. Each interrupt controller can identify which interrupts will be passed to its respective processor. The interrupt controllers work in concert to pass each interrupt to a particular processor.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Scalable scan system for system-on-chip design

A method and system to facilitate a scalable scan system in the design of a system-on-chip. In one embodiment of the invention, the system-on-chip includes a controller and one or more clock gating units. The clock gating unit is added to each unique clock domain of each function or logic block in the system-on-chip. By having a controller that connects to each clock gating unit and the scan input and output signals in each logic block of the SOC, this allows a scalable scan system in the design of the SOC and allows frequent block level design changes in the SOC without extensive changes to the scan logic in one embodiment of the invention. In addition, the scalable scan system also allows at-speed scan write-through testing of a memory array that can improve the scan test coverage of the system-on-chip.

Owner:INTEL CORP

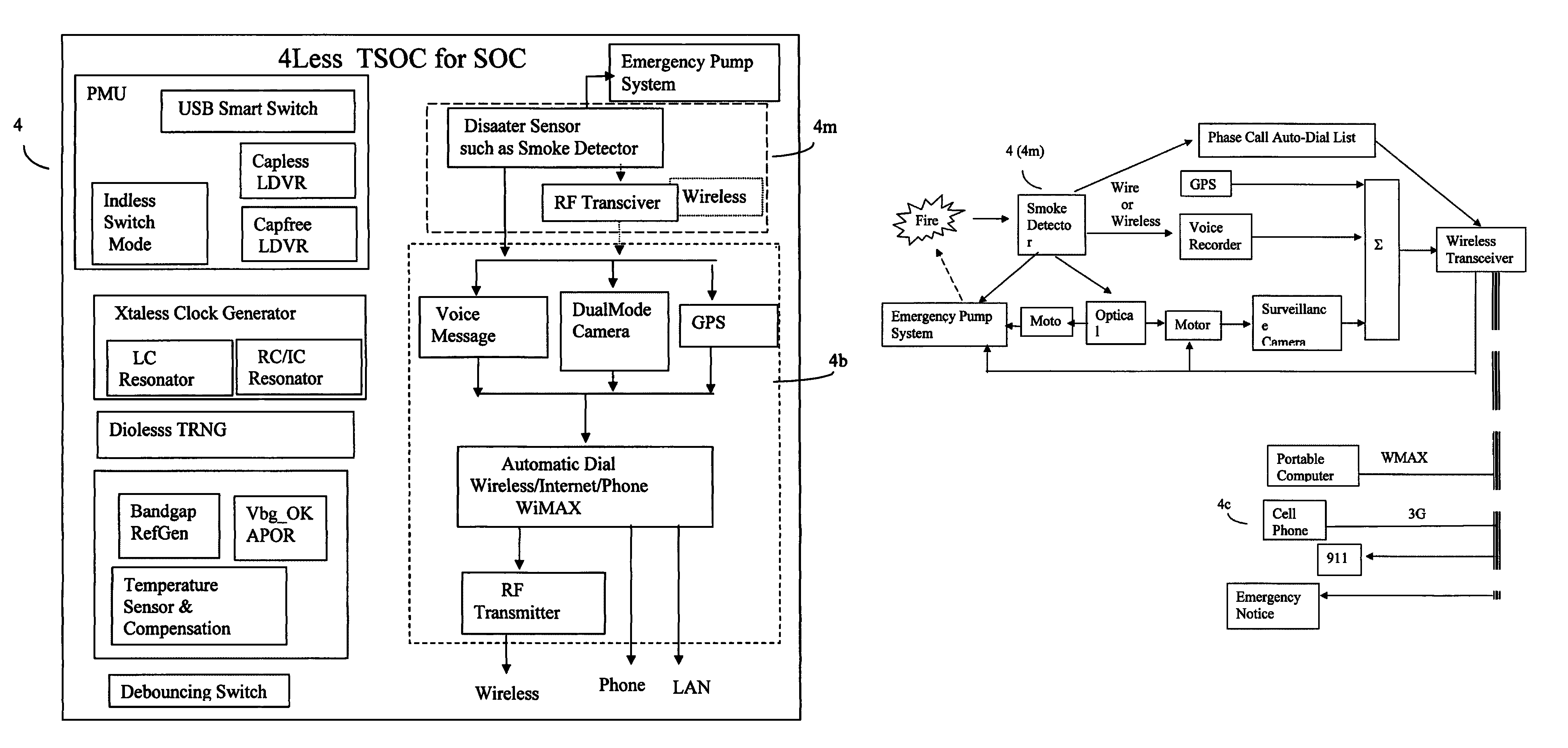

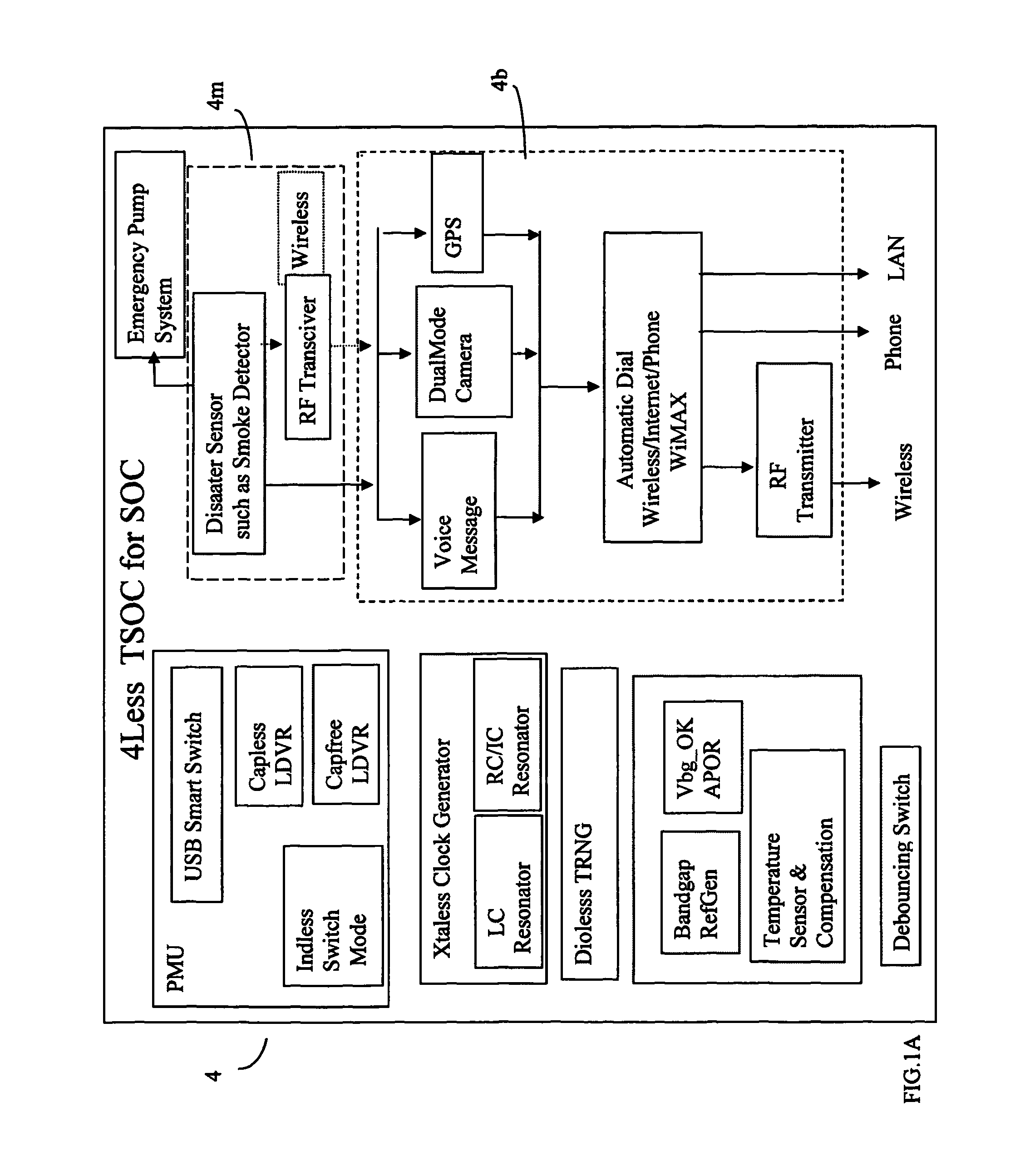

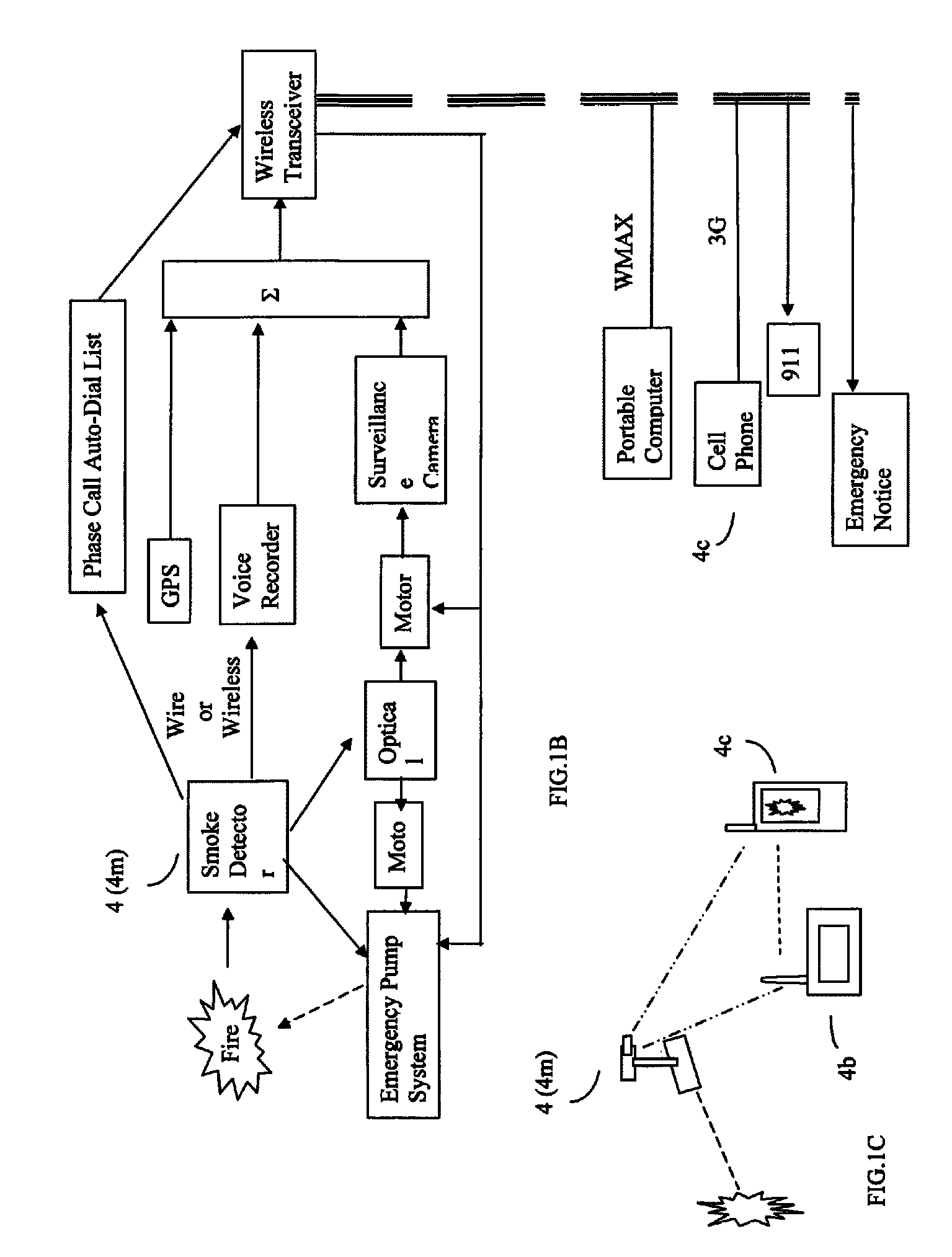

4Less—Xtaless, capless, indless, dioless TSOC design of SOC or 4Free—Xtalfree, capfree, indfree, diofree TSOC design of SOC

InactiveUS8089353B2Reduce system costPulse automatic controlFrequency-division multiplex detailsLc resonatorCapacitance

4Less-Xtaless, Capless, Indless, Dioless TSOC Design of SOC or 4Free-Xtafree, Capfree, Indfree, Diofree TSOC Design of SOC is the True System On Chip Design of Smart Mobile Sensort(SMS) for Sevice Of Community(SOC). Xtaless is Xtaless Clock Generator. Capless has the Capless Toggle and Capless LDVR. Capless Toggle is the de-bouncing circuit. Capless LDVR is the Low Drop Voltage Regulator. The Indless SM adopts the PHM of Pulse Hybrid Modulation of the PWM and PFM. The LDVR and SM can share the same driver. Dioless is the Dioless TRNG which the True Random Number Generator. The Xtaless Clock Generator adopt the PVTNAH design which is Process. Voltage, Temperature, Noise. Aging and Humidity compensation design. The Xtaless Clock using LC resonator of which LC resonator is self-compensation LC resonator over the temperature and humidity. The smart USB switch for SOC design can save the portable battery power. The Triple-Mode Camera for SOC design has the ultra-wide dynamic range for the still camera mode, video camera mode and surveillance camera mode.

Owner:TARNG MIN MING +7

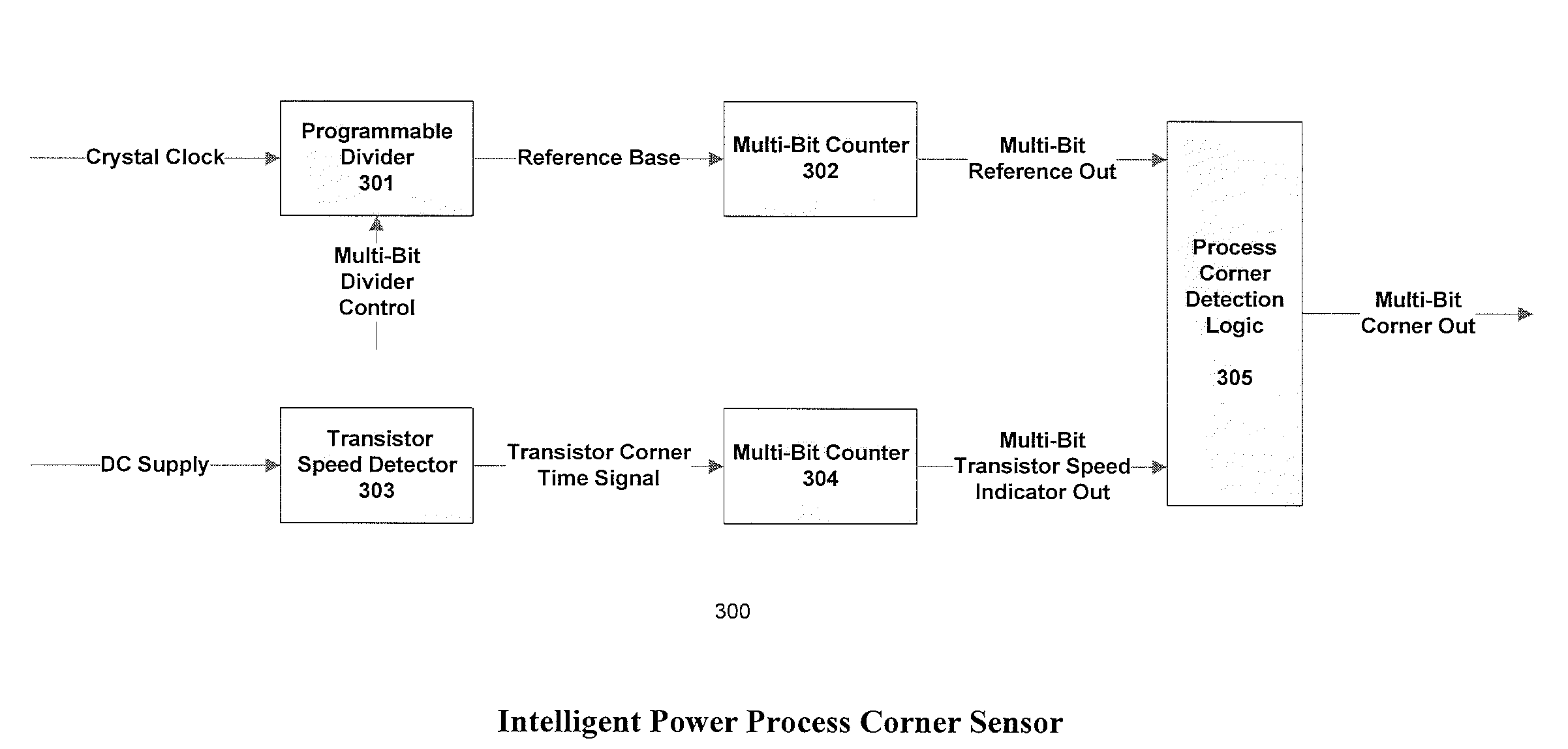

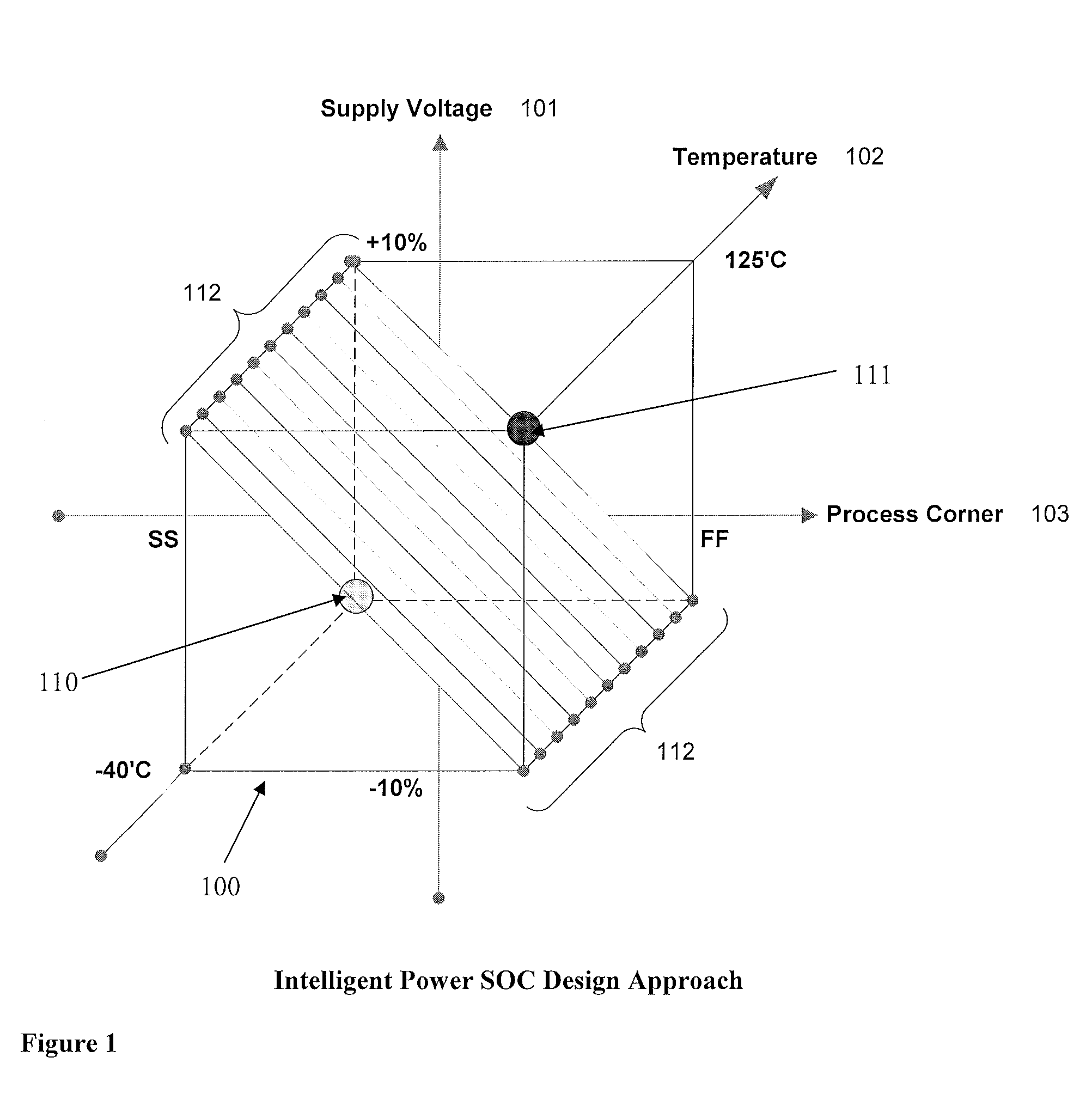

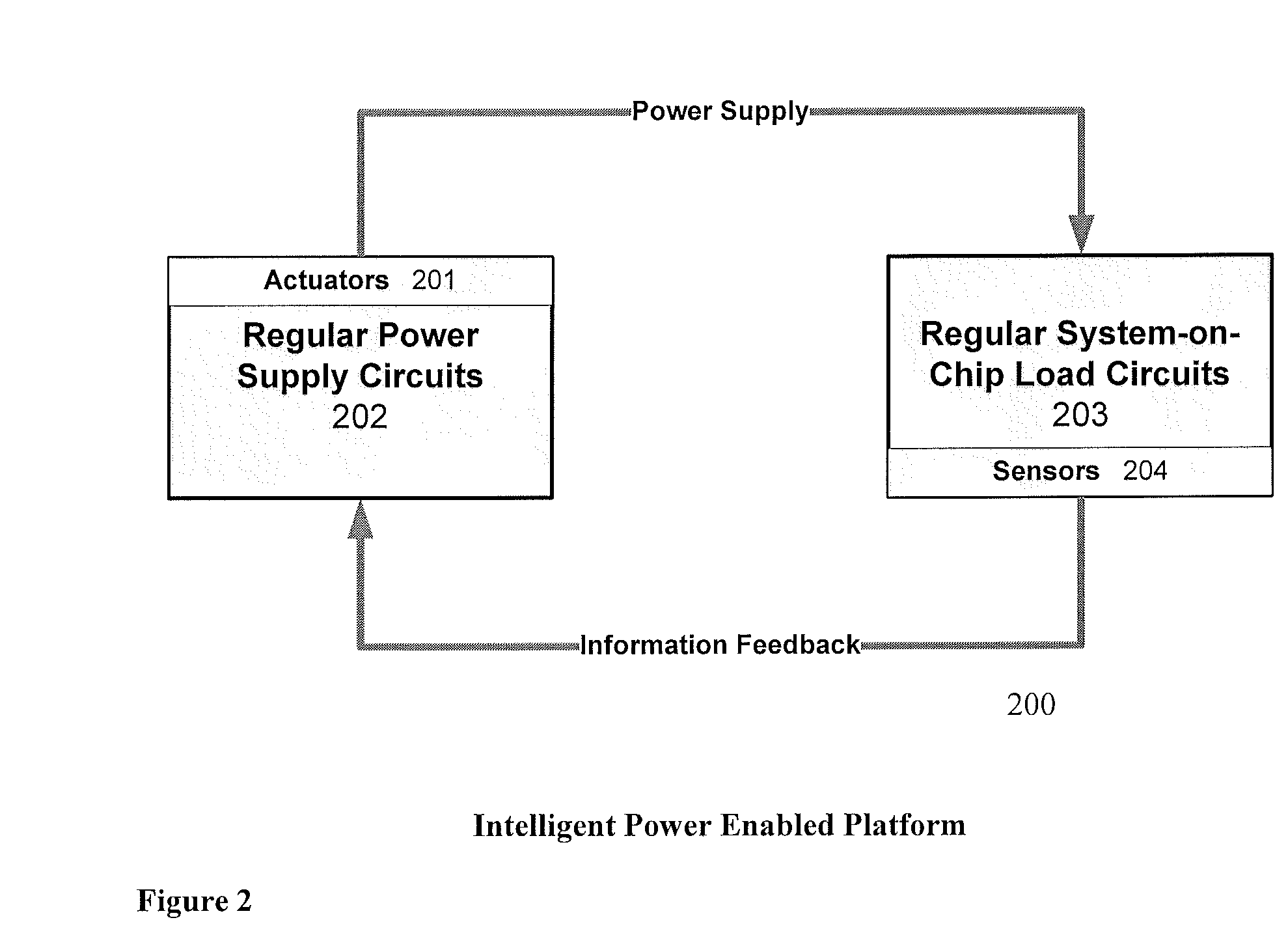

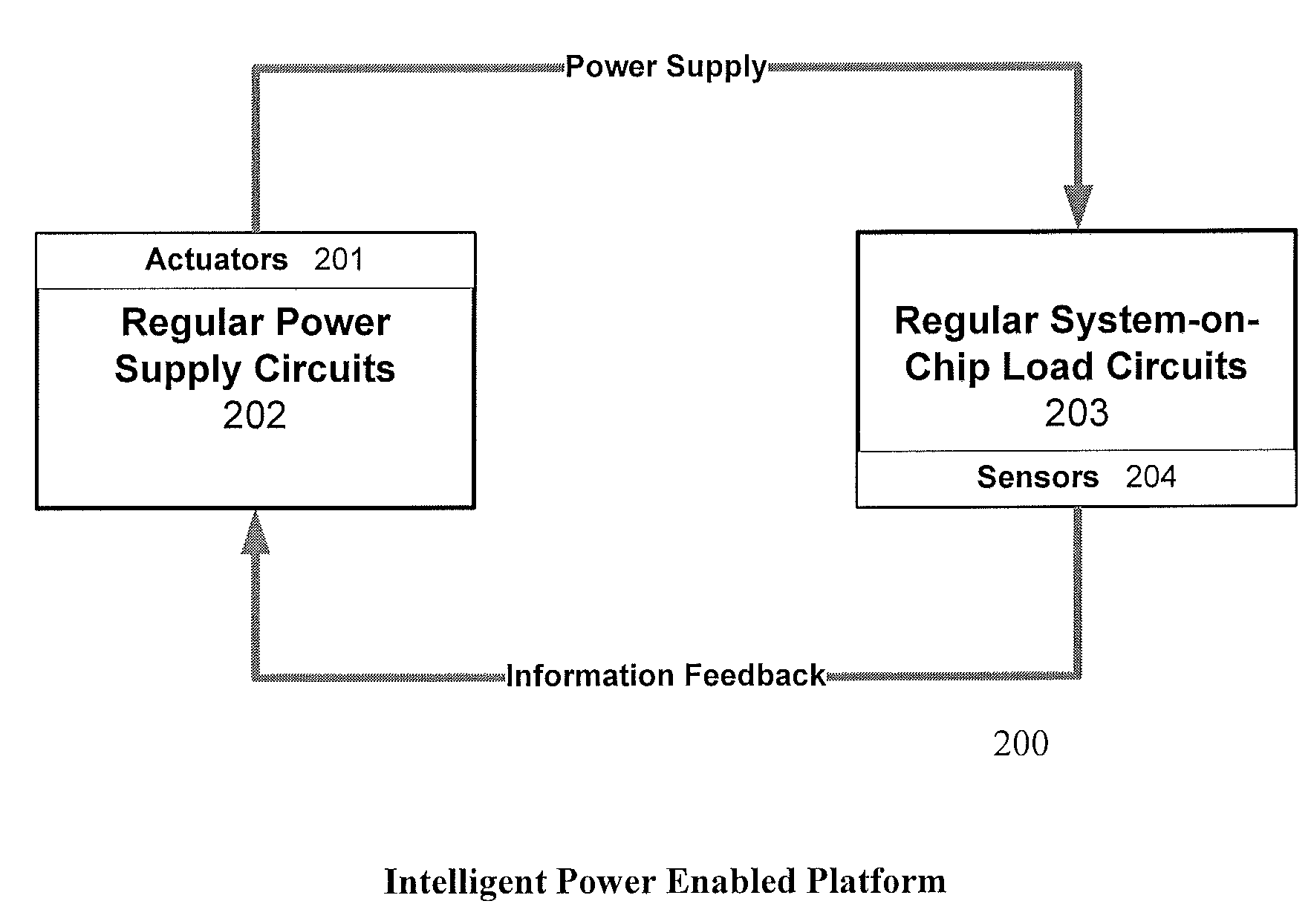

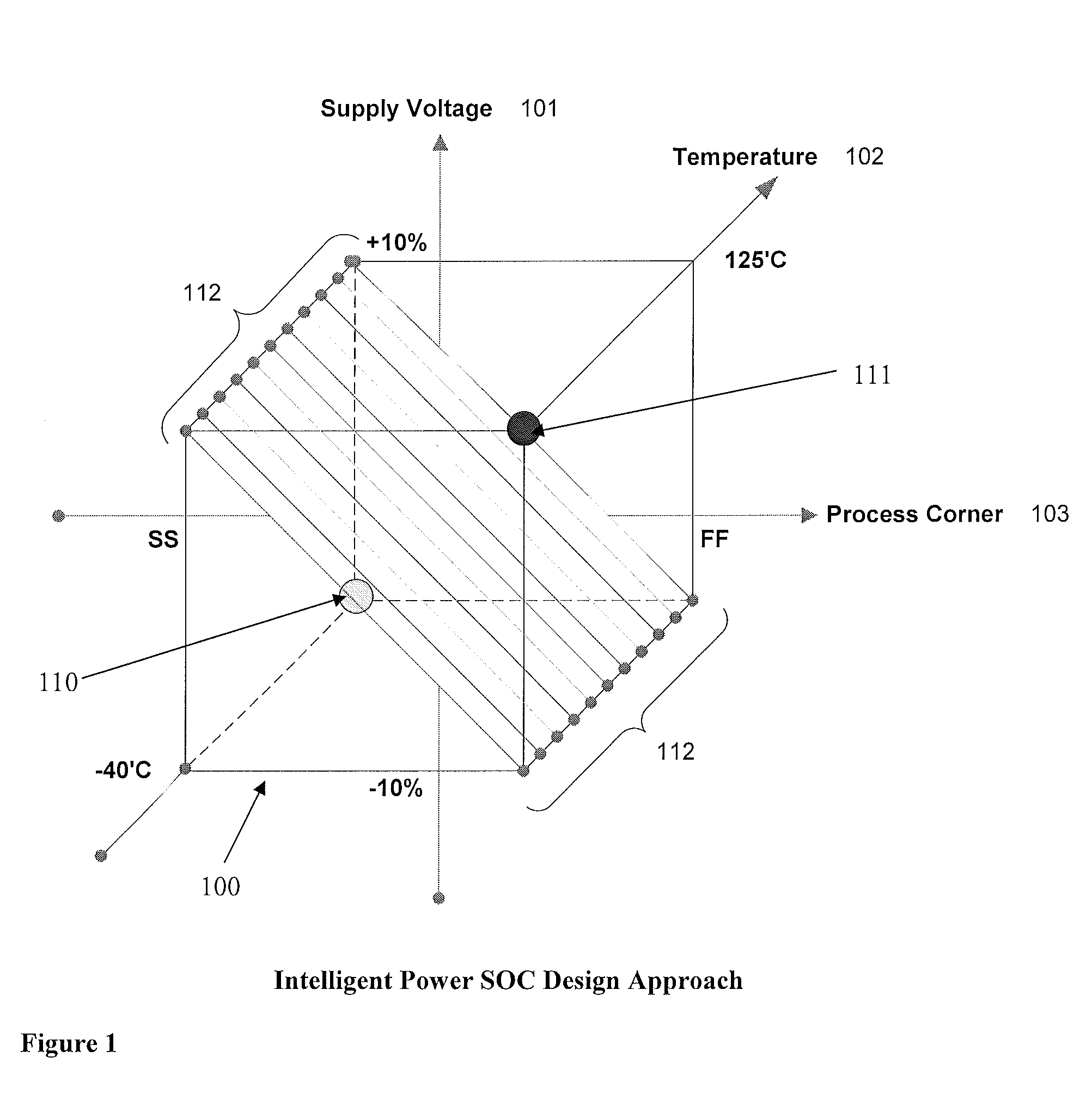

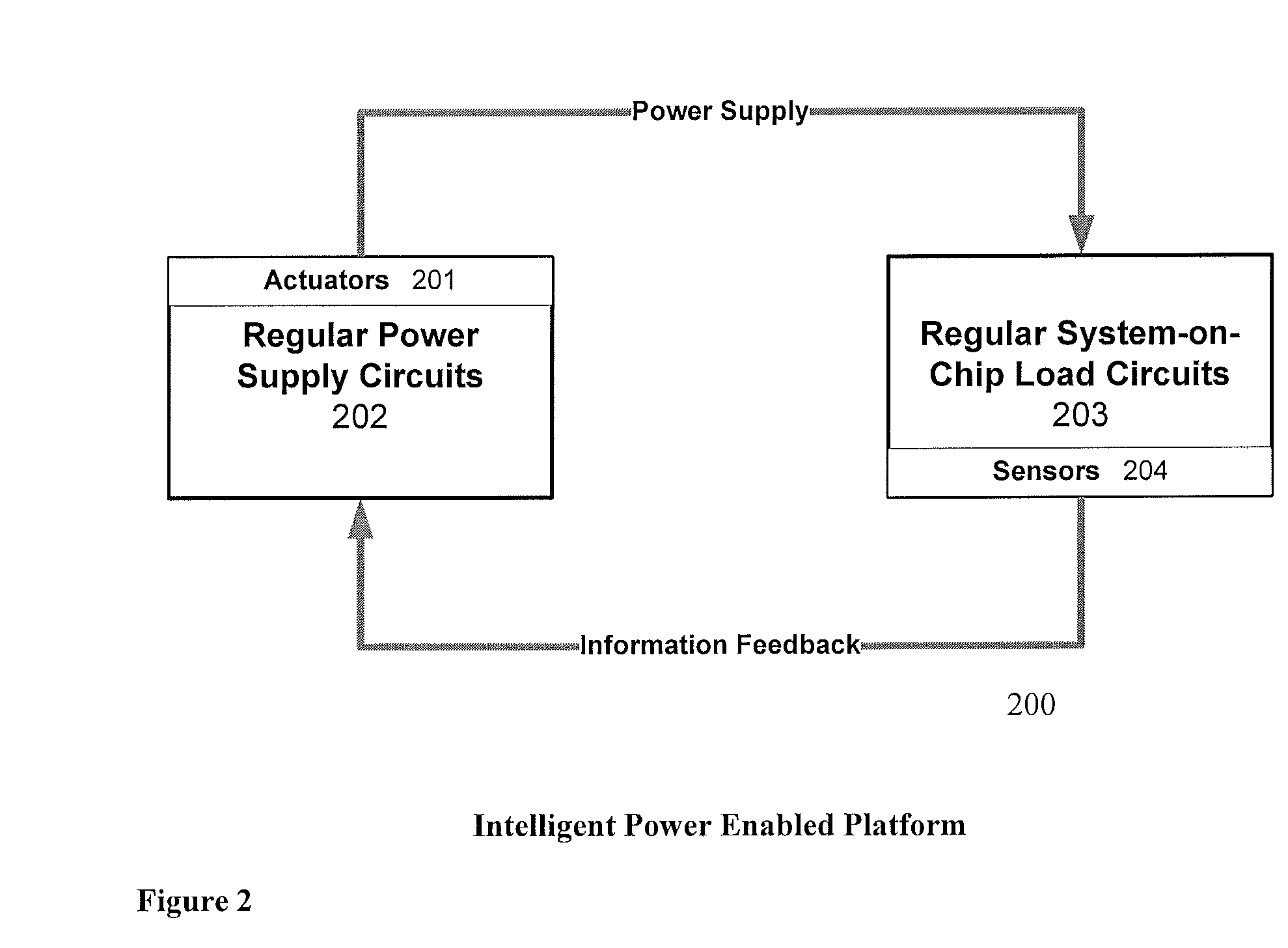

Method and Apparatus for Small Die Low Power System-on-Chip Design with Intelligent Power Supply Chip

ActiveUS20080263482A1Speed up design timeSmall circuit footprintCAD circuit designSoftware simulation/interpretation/emulationDesign phaseSystem of systems

A method and system of system-on-chip design that provides the benefits of reduced design time, a smaller die size, lower power consumption, and reduced costs in chip design and production. The process seeks to remove the worst performance and worst power case scenarios from the design and application phases. This is accomplished by planning the power supply voltage in the design phase along with its tolerance with process corner and temperature combinations. The established plan is then applied with communications between power supply integrated circuits and load system-on-chip.

Owner:DIALOG SEMICONDUCTOR INC

Method and apparatus for small die low power system-on-chip design with intelligent power supply chip

ActiveUS7739626B2Speed up design timeSmall circuit footprintElectrical testingCAD circuit designDesign phaseEngineering

A method and system of system-on-chip design that provides the benefits of reduced design time, a smaller die size, lower power consumption, and reduced costs in chip design and production. The process seeks to remove the worst performance and worst power case scenarios from the design and application phases. This is accomplished by planning the power supply voltage in the design phase along with its tolerance with process corner and temperature combinations. The established plan is then applied with communications between power supply integrated circuits and load system-on-chip.

Owner:DIALOG SEMICONDUCTOR INC

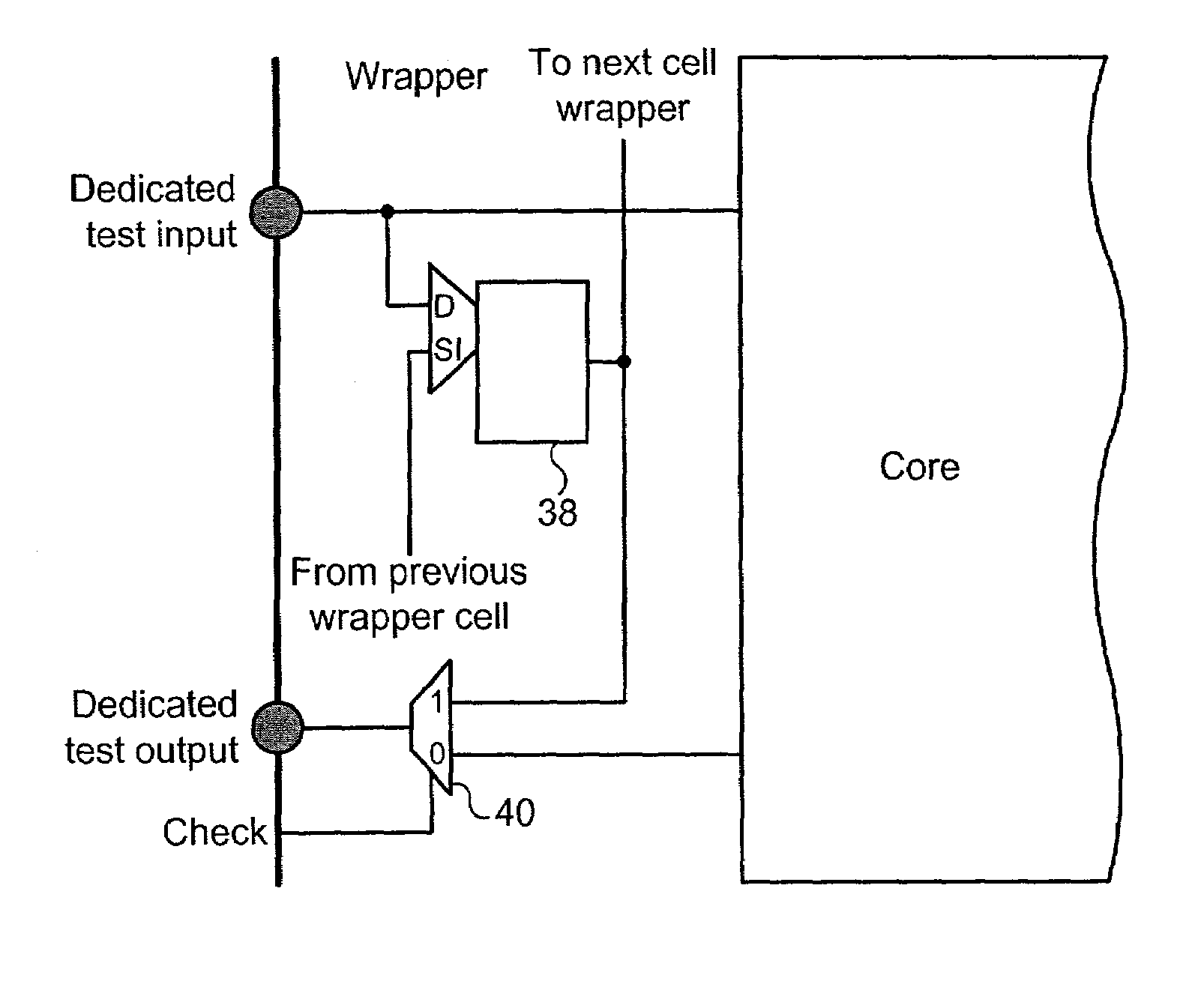

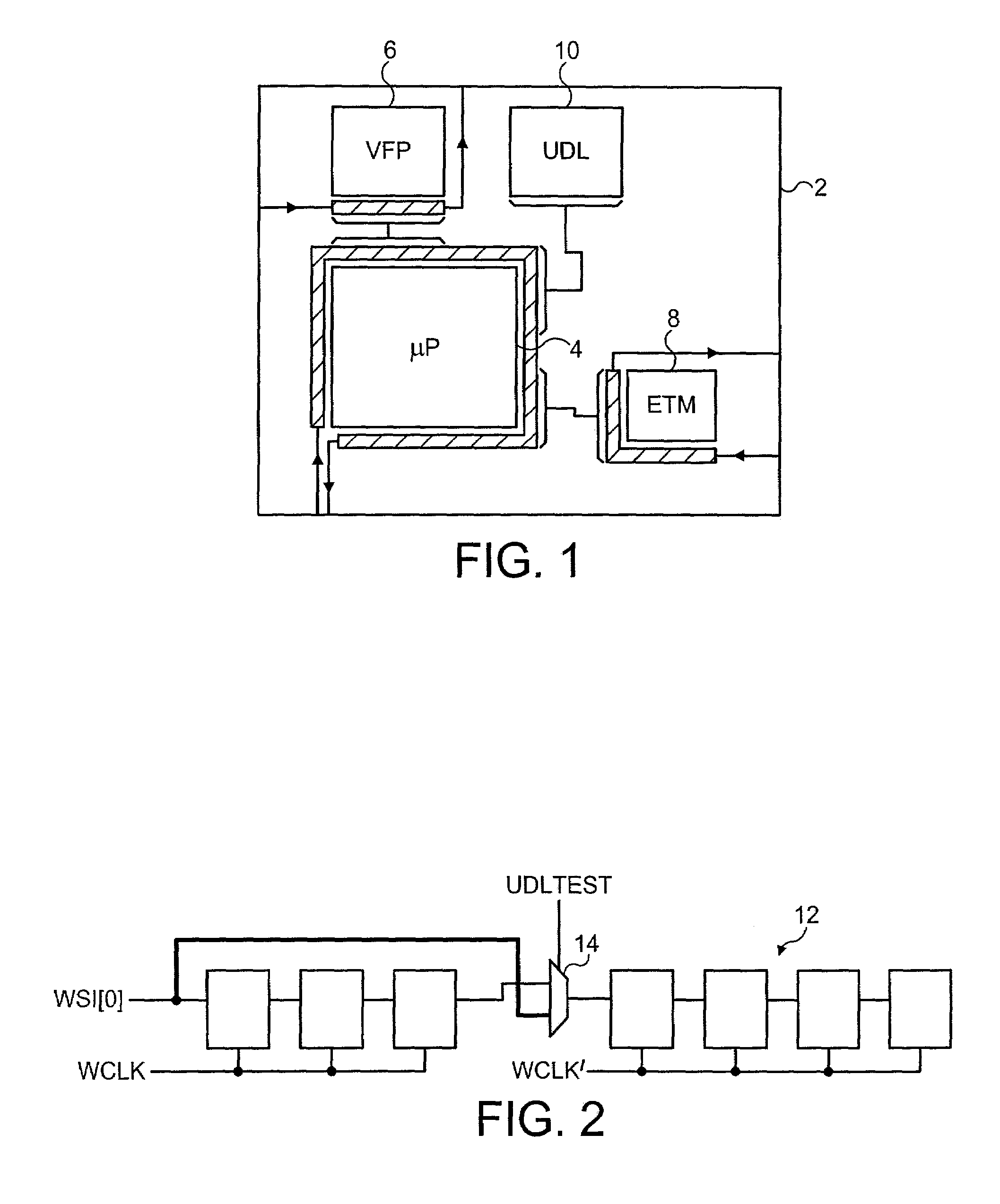

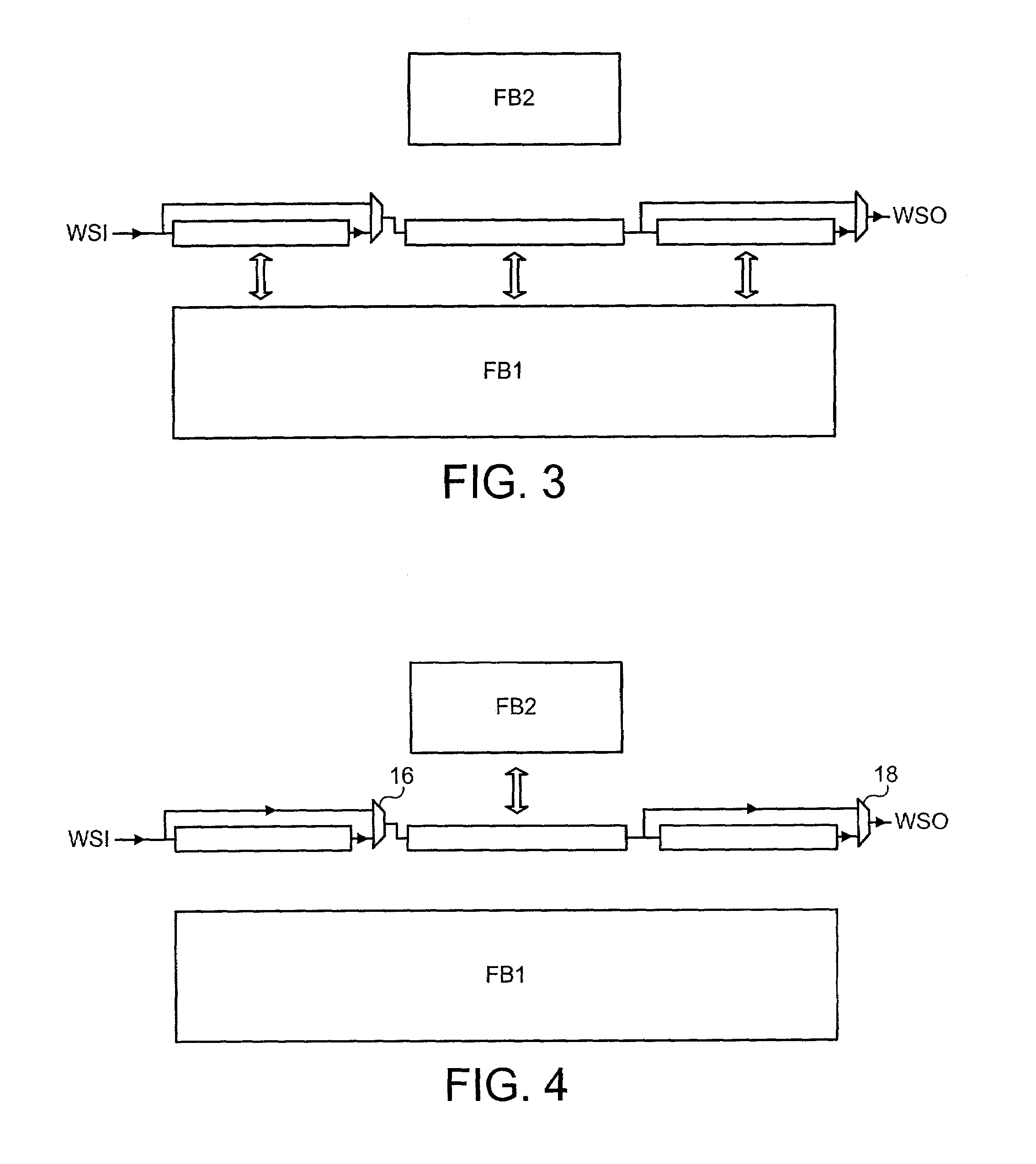

Validating test signal connections within an integrated circuit

InactiveUS7085978B2Increase overheadReduce in quantityElectronic circuit testingElectric connection testingScan chainSystem on chip design

Testing of the test signal connections to a functional block of circuitry within an integrated circuit is made using wrapper serial scan chain cells of a wrapper serial scan chain. These wrapper cells can then be used to validate that the correct signals are reaching test signal inputs and the correct signals are reaching their destination from test signal outputs when that functional block of circuitry is incorporated within a larger design, e.g., a system-on-chip design.

Owner:ARM LTD

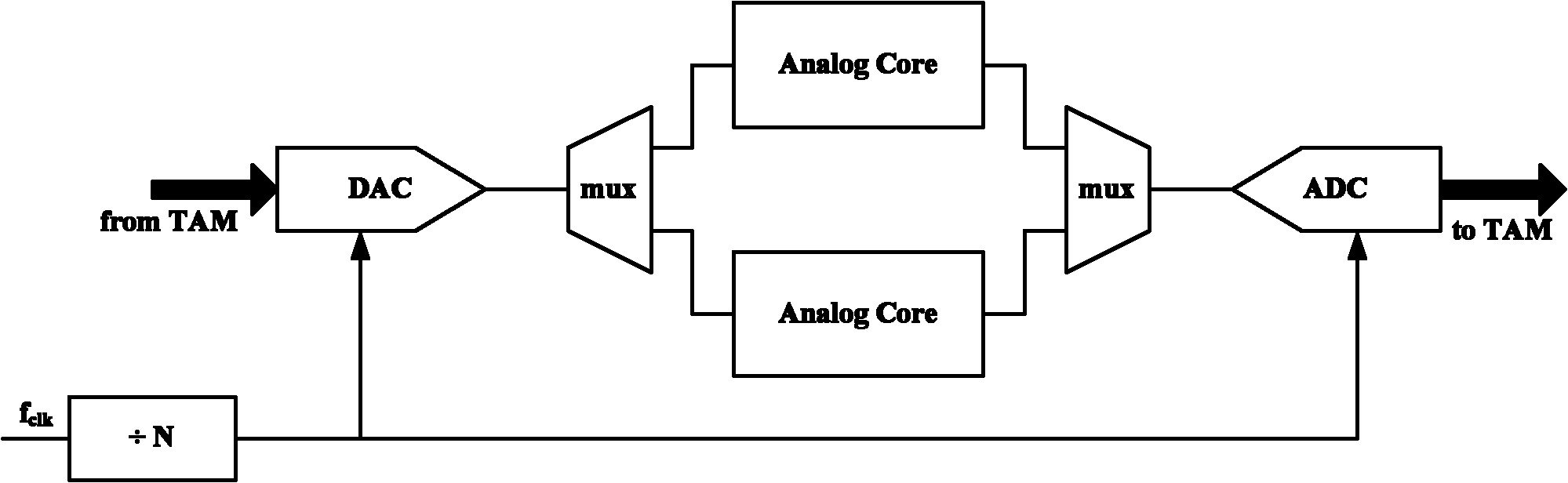

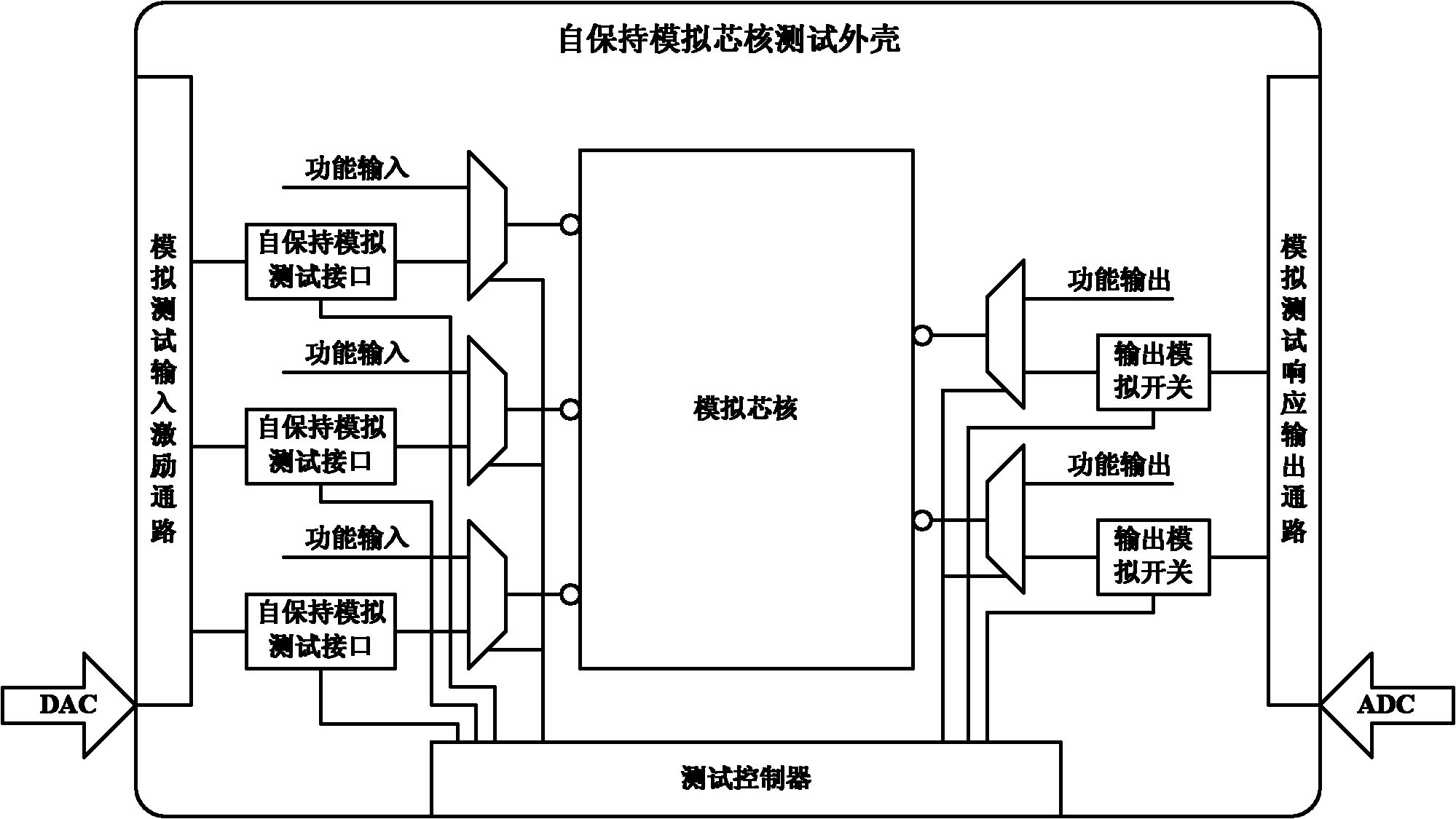

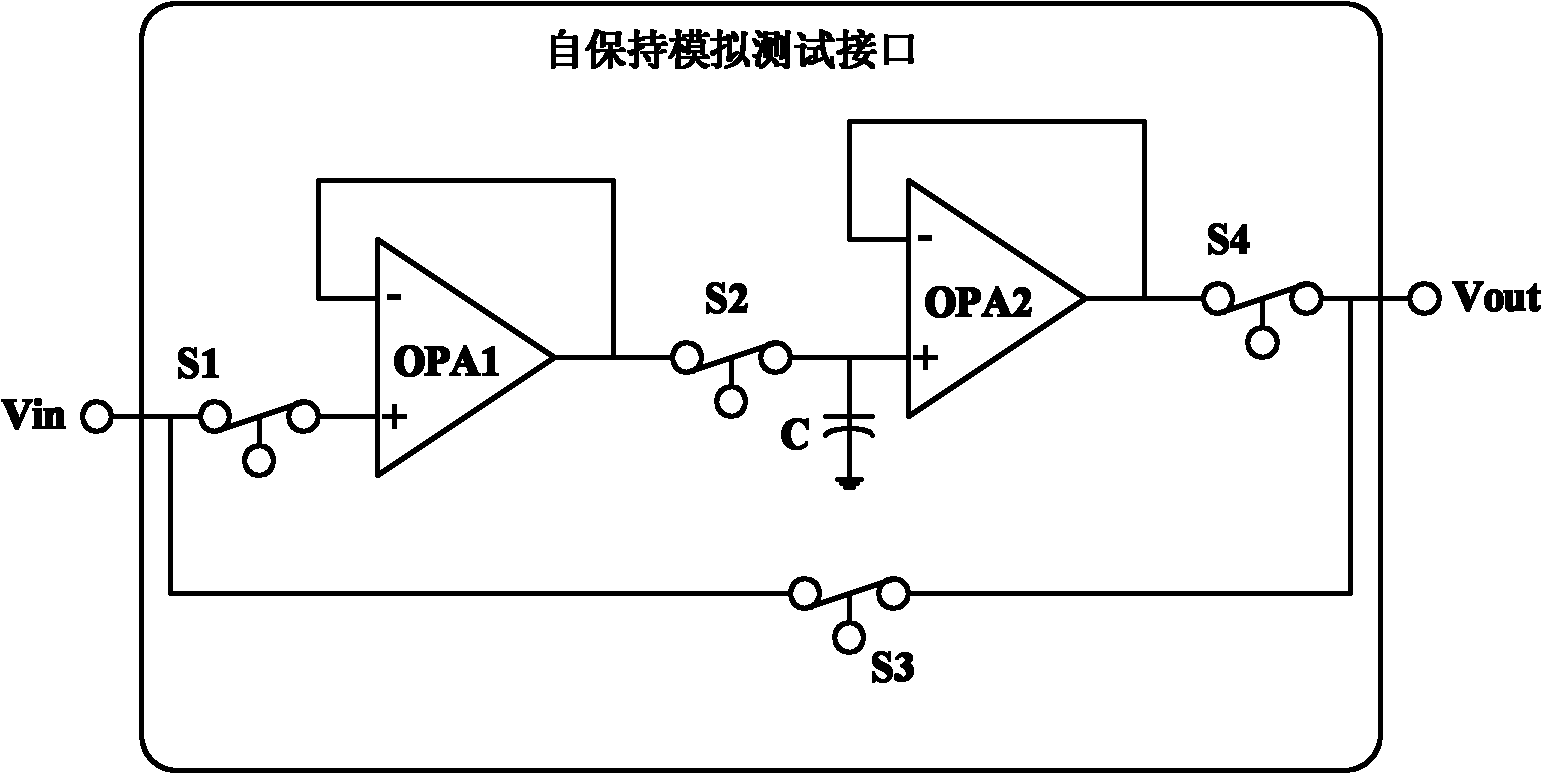

Self-holding analog core testing shell

InactiveCN102156257ASmall area overheadLow costAnalog circuit testingMultiplexingDigital analog converter

The invention discloses a self-holding analog core testing shell in the technical field of system on chip designs of electronic information technology, comprising an analog test input motivating pathway, a self-holding analog testing interface, a test controller, an output analog switch and an analog test response outputting pathway, wherein the analog test input motivating pathway is connected with the self-holding analog testing interface; the self-holding analog testing interface is connected with the test controller; the test controller is connected with the output analog switch; the output analog switch is connected with the analog test response outputting pathway; and the self-holding analog testing interface and the output analog switch are respectively connected with an analog core. By means of the self-holding analog core testing shell provided by the invention, the motivation applying and the response analyzing of the analog test of multiplexing of multiple ports of single DAC (Digital-Analog Converter) and ADC (Analog-Digital Converter) are realized.

Owner:TSINGHUA UNIV

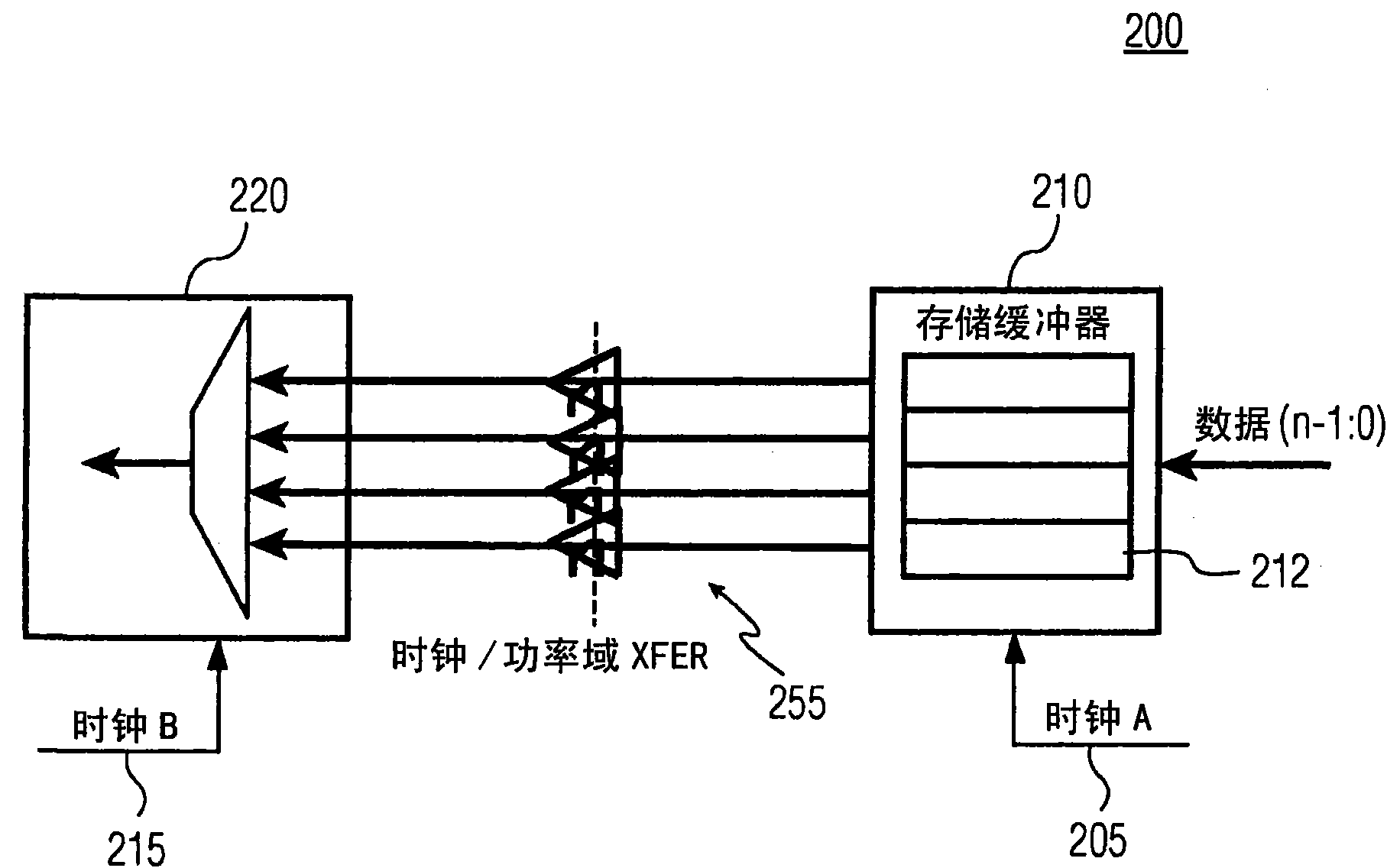

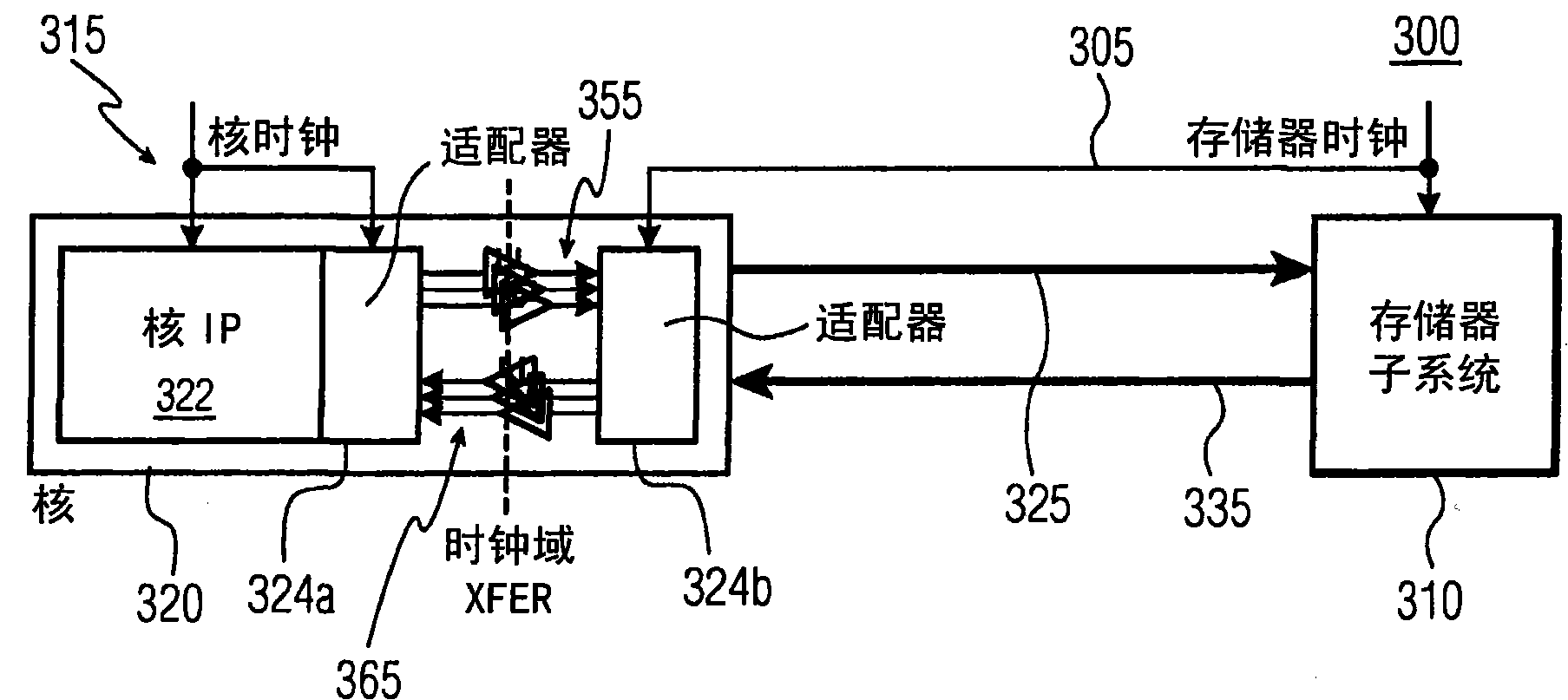

Source-synchronous data link for system-on-chip design

A method of producing an integrated circuit (700) using a system-on-chip (SoC) architecture includes providing a first circuit (710) in a first island of synchronicity (IoS); and providing a source-synchronous data link (755 / 757, 765 / 767) between the first circuit (710) in the first IoS and a hard core (720) in a second IoS for communicating n-bit data elements between the first circuit (710) and the hard core (720). The source-synchronous data link (755 / 757, 765 / 767) includes a set of n data lines (755, 765) for transporting the n-bit data elements between the first circuit (710) and the hard core (720), and a source- synchronous clock line (757, 767) for transporting a source clock between the first circuit (710) and the hard core (720) for clocking the n-bit data elements. The hard core (720) does not include a bus interface adaptor for interfacing with the source-synchronous data link (755 / 757, 765 / 767).

Owner:NXP BV

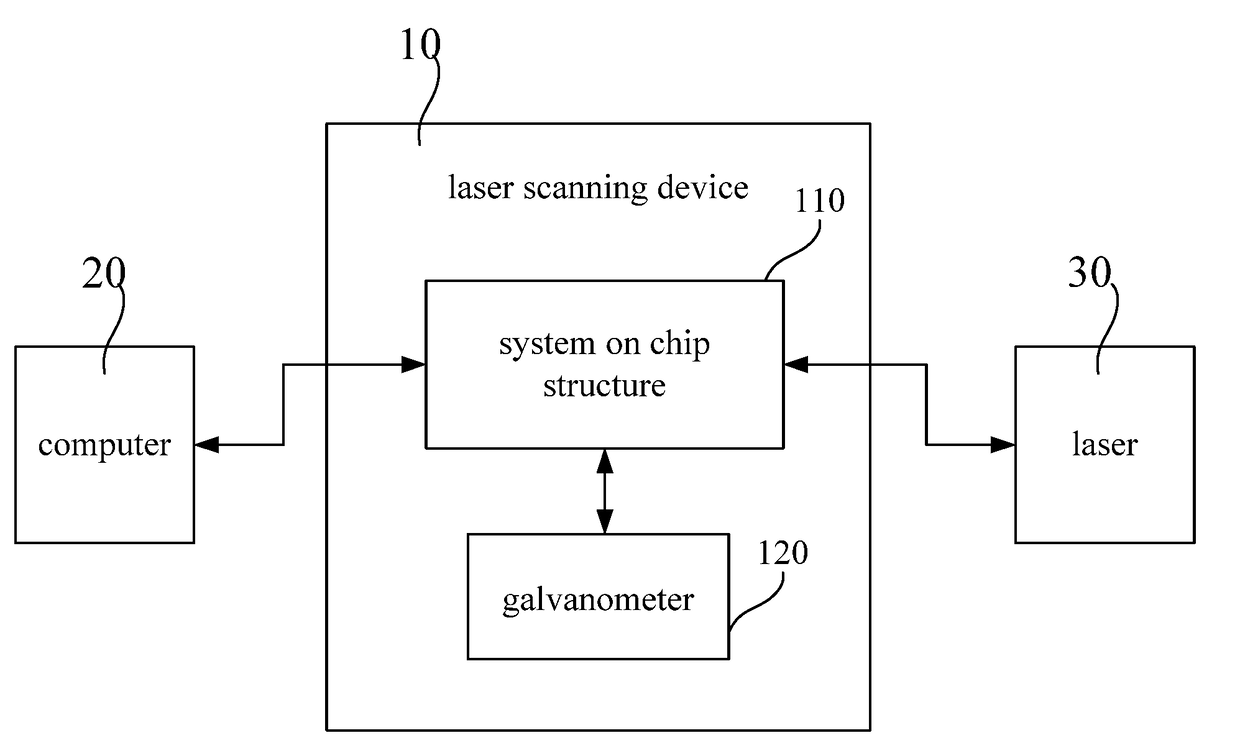

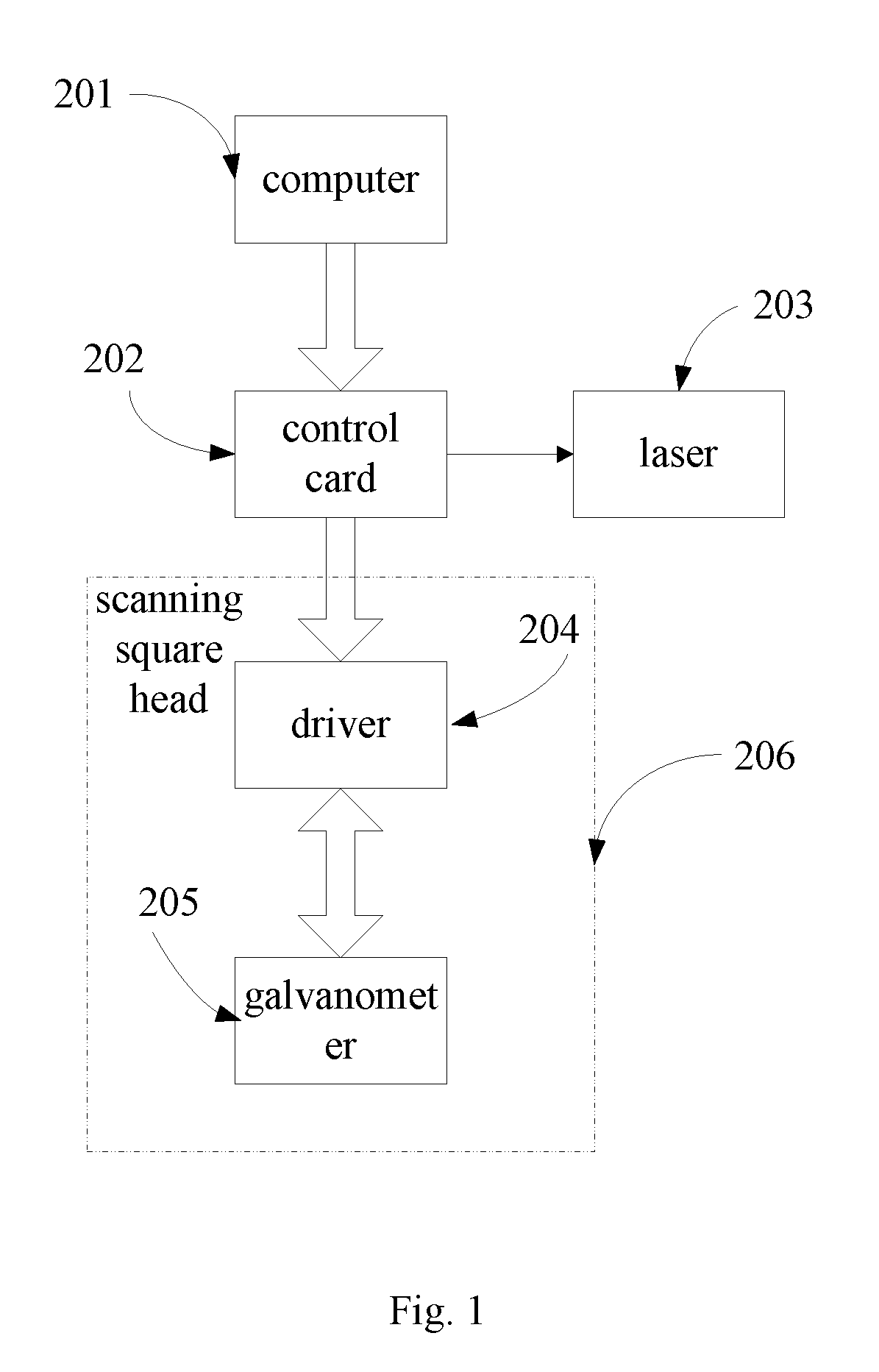

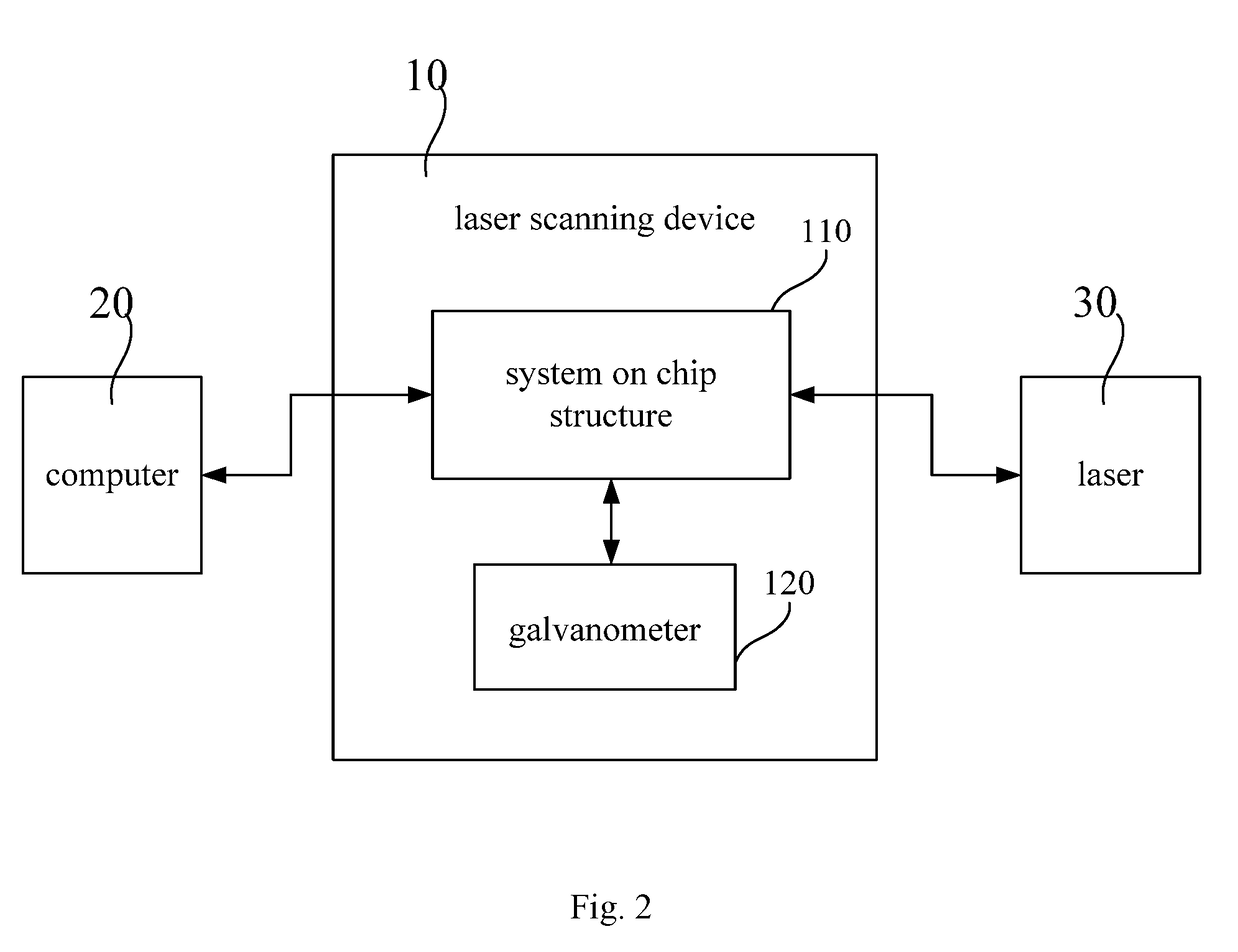

Laser scanning device and laser scanning system

ActiveUS20180031824A1Reduce crosstalkReduce system costPicture reproducers using projection devicesLaser beam welding apparatusGraphicsGalvanometer

A laser scanning device (10), comprising: a system on chip structure (110) configured to receive and process a graphic data transmitted by an external computer (20) to generate a galvanometer movement instruction and a laser control instruction; and galvanometer (120) configured to receive the galvanometer movement instruction and move according to the galvanometer movement instruction; wherein the laser control instruction is transmitted to an external laser (30), so that the laser (30) and the galvanometer (120) move synchronously. The above laser scanning device (10) and scanning system can integrate a laser control function and a galvanometer control function into the same chip by a system on chip design, which does not only reduce cost of the system, but also improve reliability of the system. Because all information are transmitted in the same one chip, there is no signal transmission cable employed between a conventional movement control card and a galvanometer driver, which results in a better real time, and avoids various problems due to transmission from the conventional control card to the galvanometer.

Owner:HANS LASER TECH IND GRP CO LTD +1

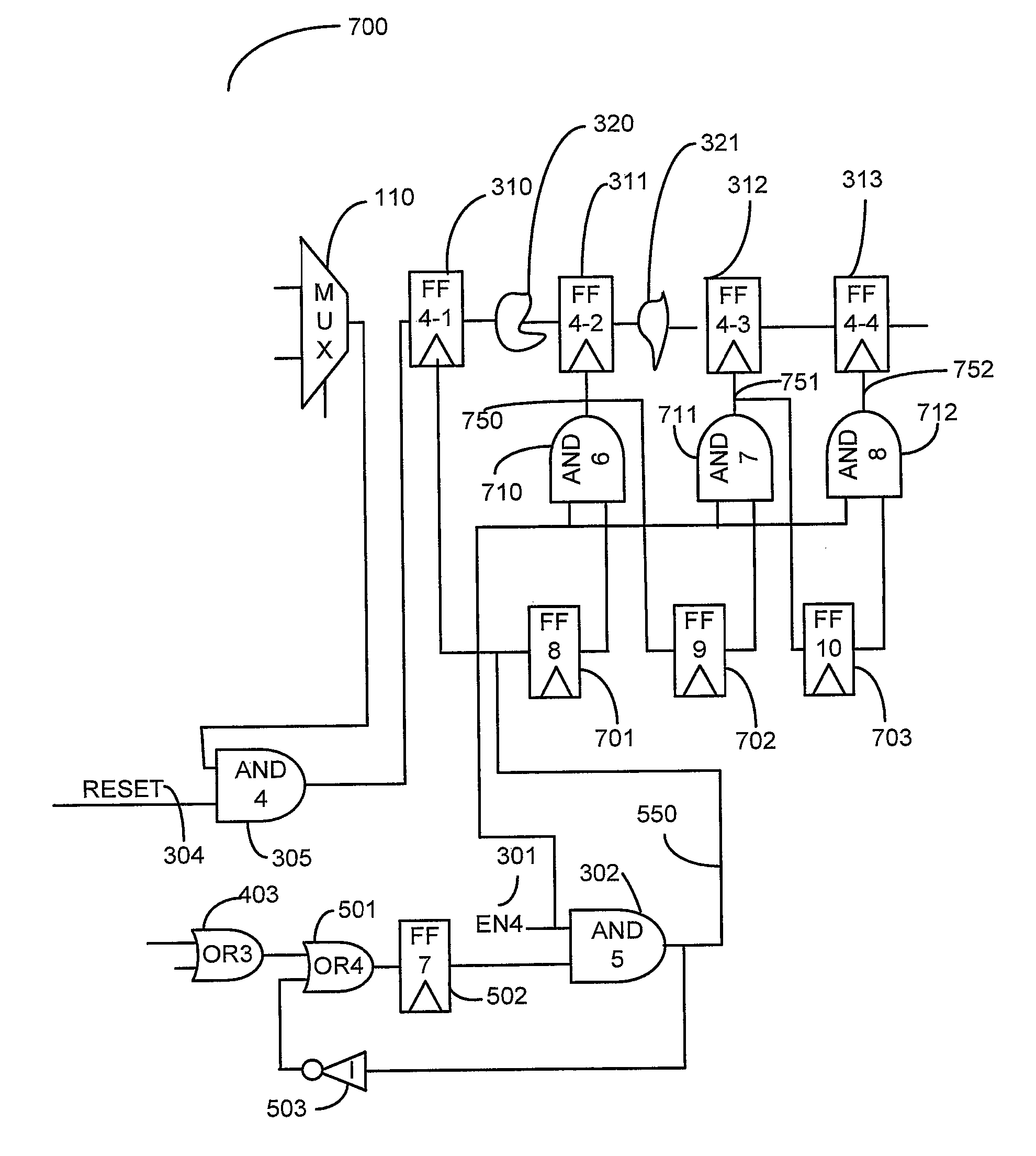

Sequential clock gating using net activity and xor technique on semiconductor designs including already gated pipeline design

ActiveUS8677295B1CAD circuit designSoftware simulation/interpretation/emulationSynthesis methodsExclusive or

The circuit design process requires ways to reduce the power consumption of large integrated circuits and system-on-chip designs. This is typically done by introducing a process of clock gating thereby enabling or disabling flip-flops associated with specific functional blocks within the circuit. However, such changes in the circuit require synthesis and verification to ensure correctness of design and operation as sequential clock gating changes the state function dynamically. It is therefore necessary to define synthesis methods adapted to such dynamic changes in the design. According to an embodiment a sequential clock gating method uses an exclusive-OR technique to overcome the deficiencies of the prior art methods.

Owner:SYNOPSYS INC

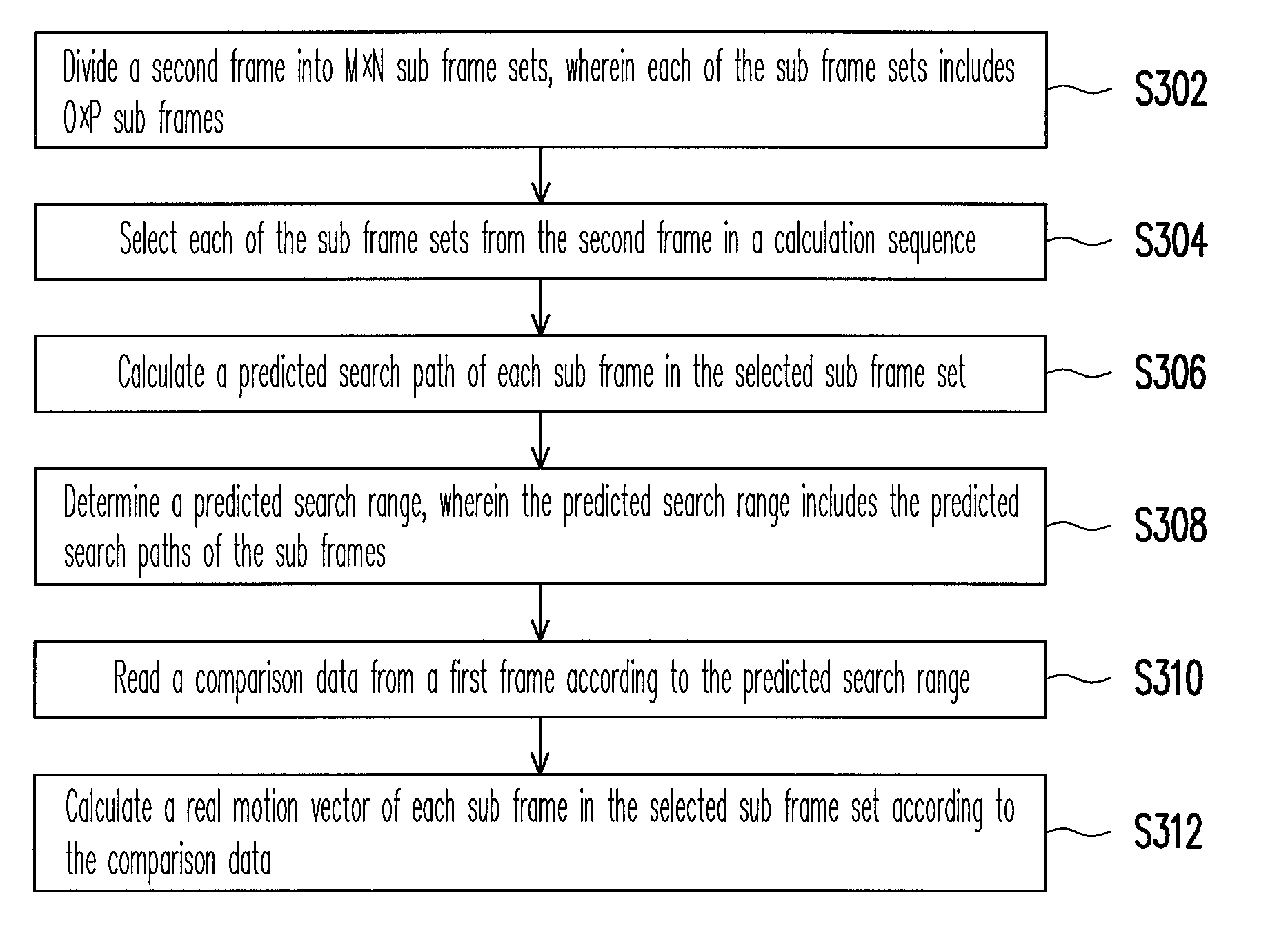

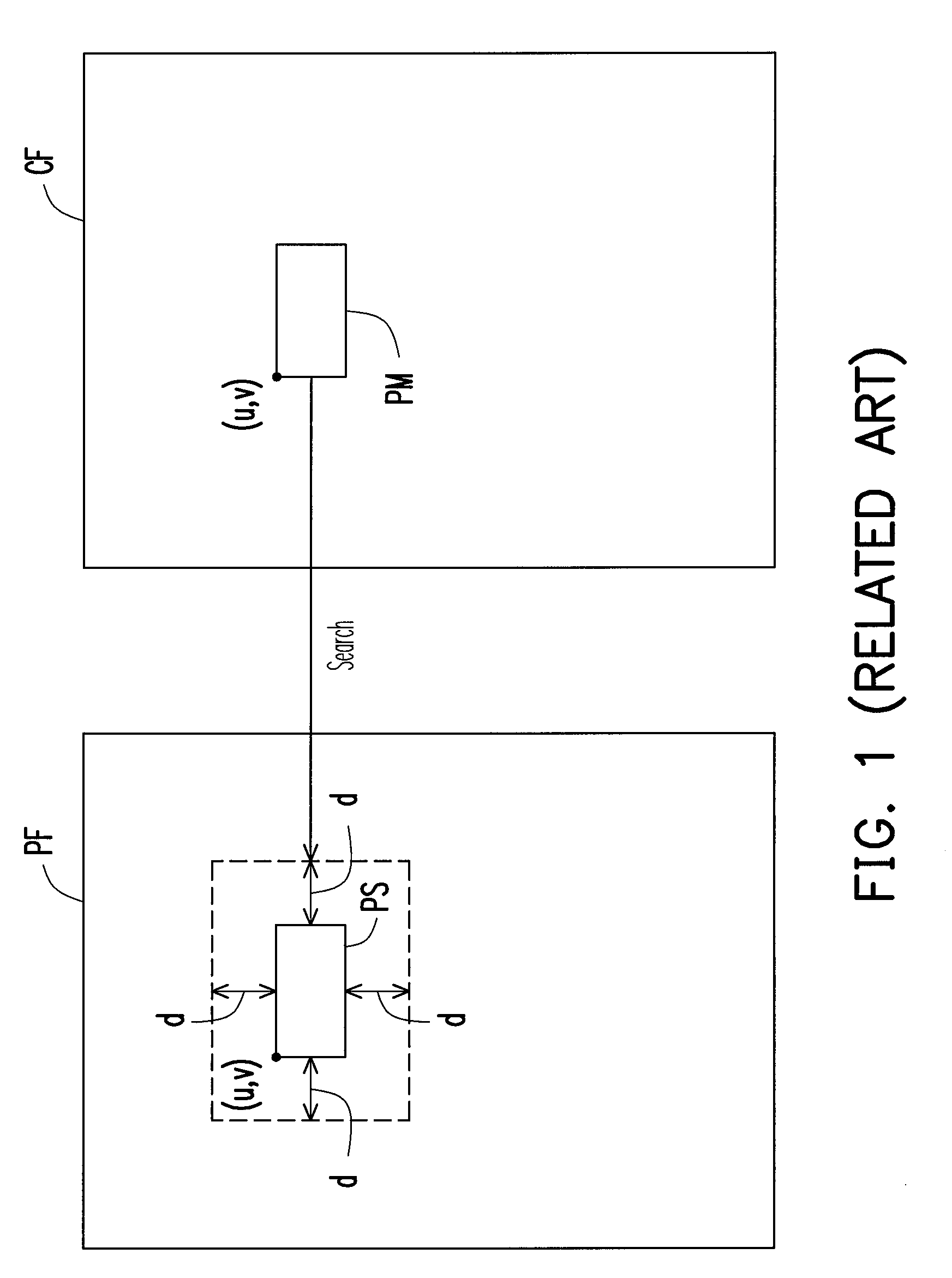

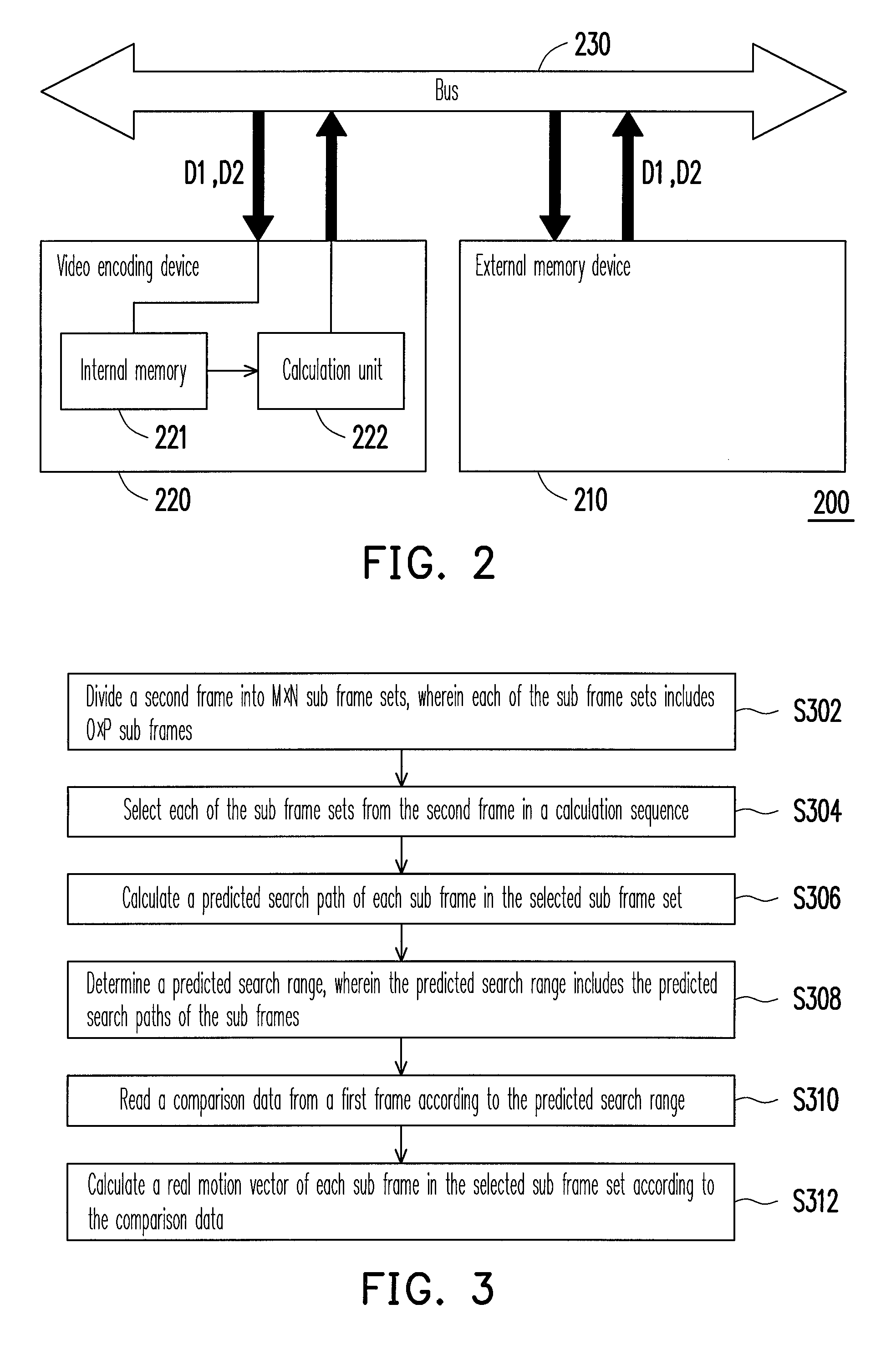

Efficient data prediction and data reuse motion estimation engine for system-on-chip design

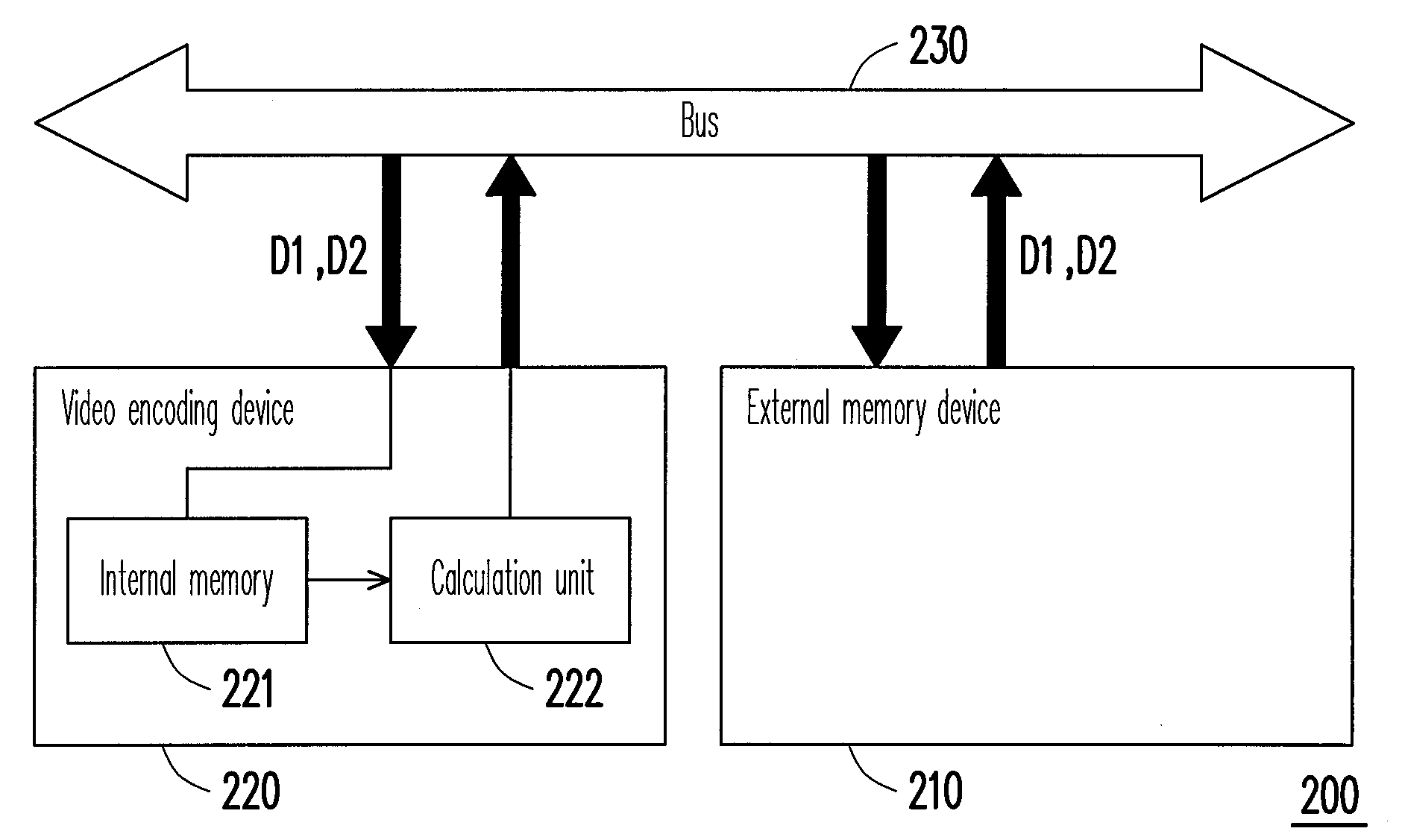

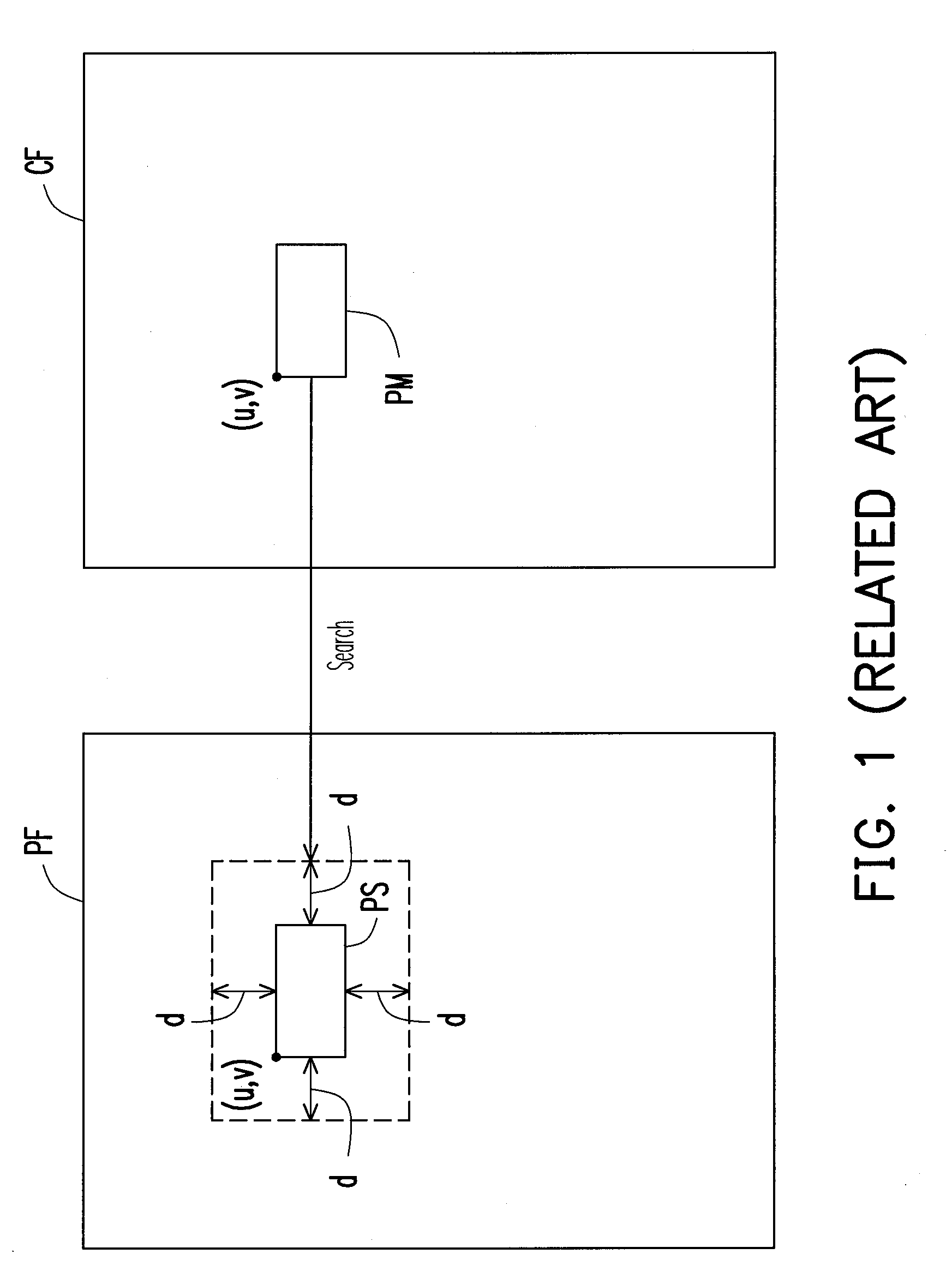

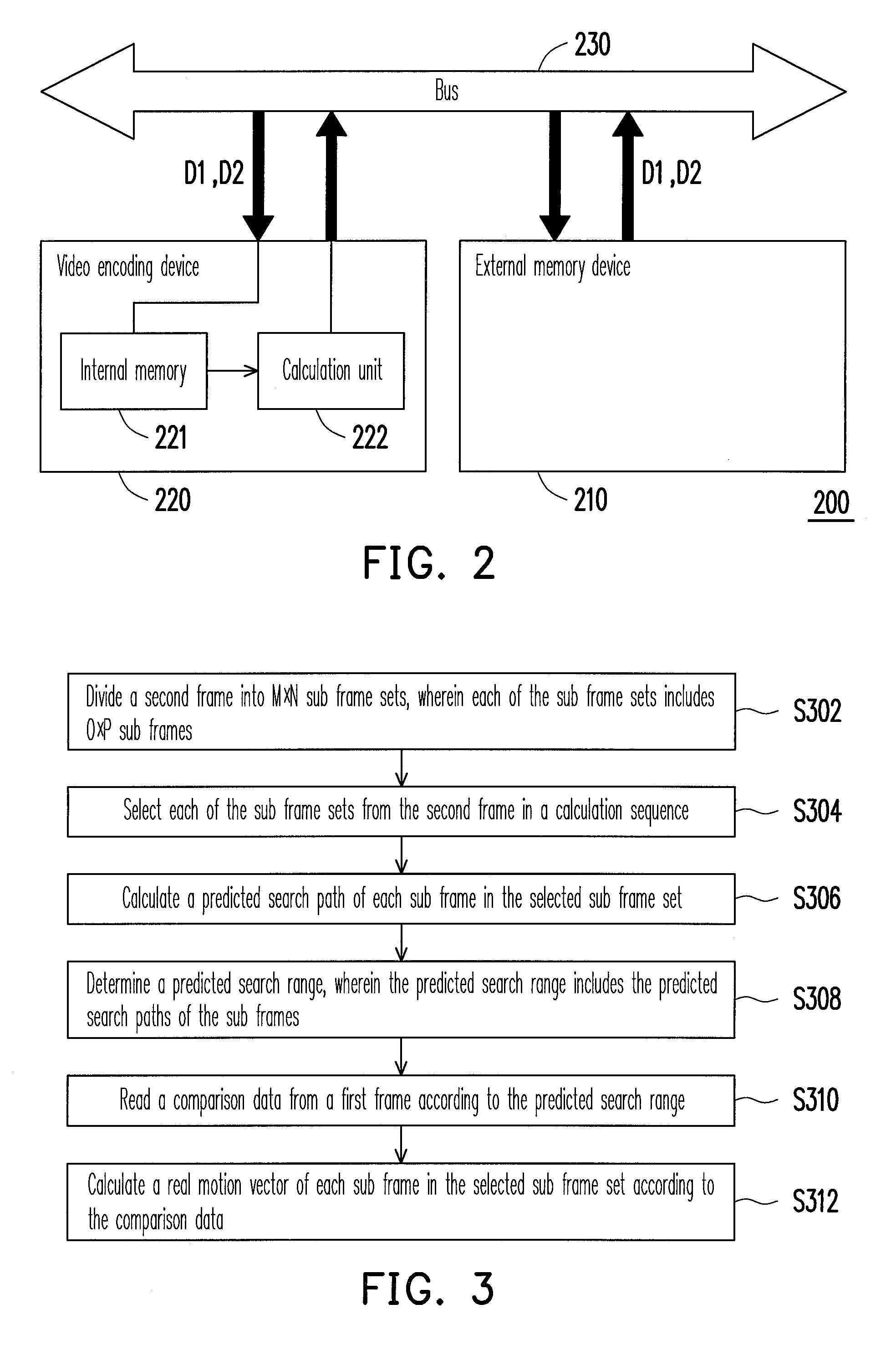

InactiveUS20100266044A1Data quantityReduce memory usageTelevision system detailsPicture reproducers using cathode ray tubesInternal memoryExternal storage

A data reading method for motion estimation in an embedded system is provided. The embedded system includes an external memory device and a video encoding device, wherein the external memory device stores a first frame, and the video encoding device has an internal memory. First, a second frame is divided into M×N sub frame sets, wherein each of the sub frame sets has O×P sub frames. Then, each of the sub frame sets is selected in a calculation sequence, and the selected sub frame set is stored into the internal memory. Next, a predicted search path of each sub frame in the selected sub frame set is calculated. Thereafter; a predicted reading range is determined, wherein the predicted reading range includes the predicted search paths of the sub frames. Finally, a comparison data is read from the first frame according to the predicted reading range.

Owner:NAT TAIWAN UNIV

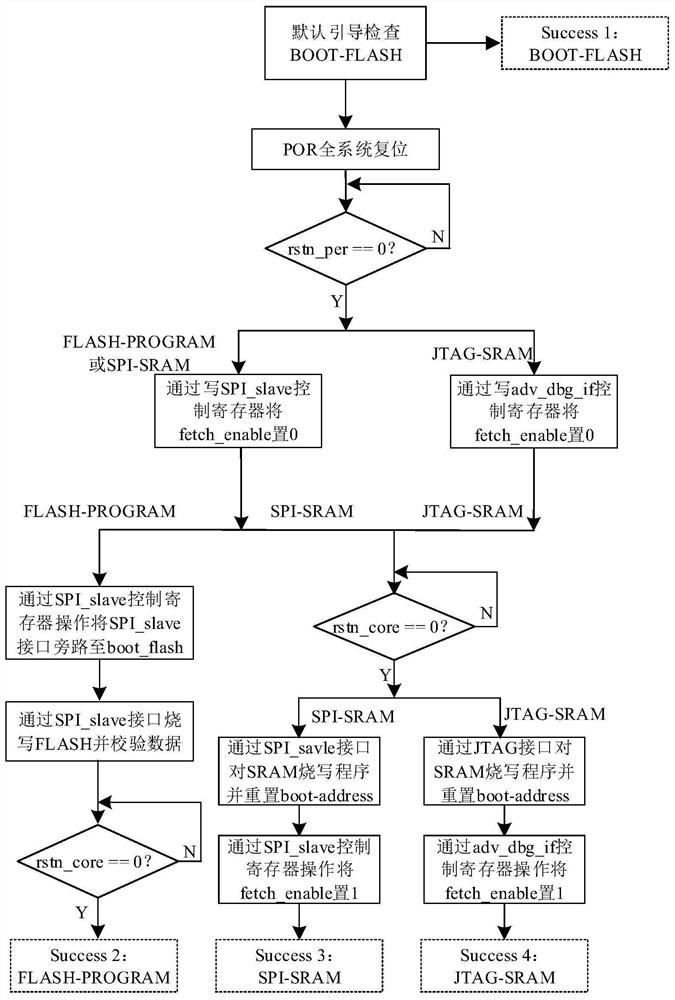

Debugging test-oriented operating system kernel guiding and loading hardware architecture and debugging test-oriented operating system kernel guiding and loading hardware method

ActiveCN112306782AReduce overheadTolerate System State AbnormalitiesDetecting faulty computer hardwareComputer hardwareHardware architecture

The invention discloses a debugging test-oriented operating system kernel guiding and loading hardware architecture and a debugging test-oriented operating system kernel guiding and loading hardware method.The method uses a set storage unit, a peripheral auxiliary interface and a special register to achieve and set four kinds of priority-adjustable kernel guiding and loading modes for a real-timeoperation system. The modes can be mutually backed up. One or more than one of the four real-time operating system kernel guiding and loading modes is or are executed according to a set priority sequence until the operating system kernel guiding and loading are completed. According to the debugging test-oriented operating system kernel guiding and loading hardware architecture and the debugging test-oriented operating system kernel guiding and loading hardware method, auxiliary debugging test and verification can be carried out on a system starting process before system-on-chip design shaping,and system state exception caused by failure of starting the operating system kernel in a single way can be tolerated; The existing peripheral interfaces of a system-on-chip can be reused, so that the additional hardware overhead is low.

Owner:NAT INNOVATION INST OF DEFENSE TECH PLA ACAD OF MILITARY SCI

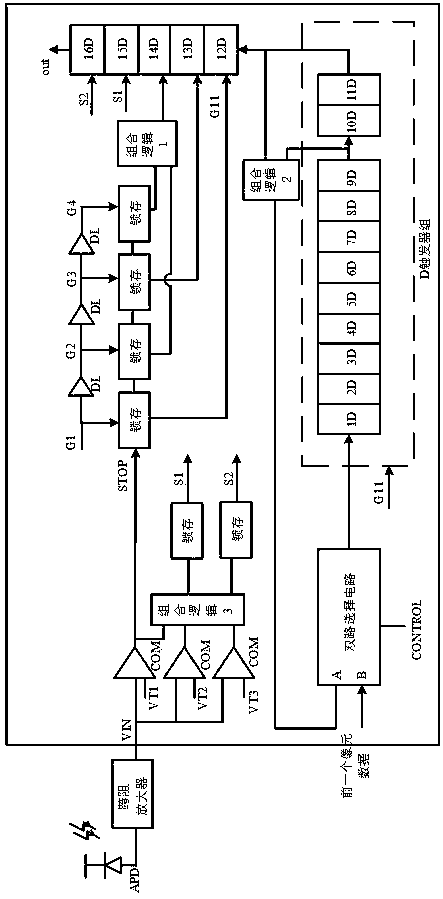

Pixel-level time and intensity digital conversion circuit

PendingCN110308435AIncrease working frequencyReduce difficultyWave based measurement systemsTime informationControl circuit

The invention discloses a pixel-level time and intensity digital conversion circuit. The invention achieves a pixel-level time and intensity digital conversion circuit, for one-time laser pulse, all pixel units can give time information and intensity information of echo signals, in the data reading stage, a row and column selection control circuit is not needed, and all pixel information of each row is read sequentially, thereby greatly improving the working frequency of an area array reading circuit; the information representing the time and intensity of the echo signals is directly output ina digital format, and an on-chip ADC is not required to be quantified twice, thereby reducing the difficulty of design of the on-chip system.

Owner:SUZHOU R&D CENT OF NO 214 RES INST OF CHINA NORTH IND GRP

Efficient data prediction and data reuse motion estimation engine for system-on-chip design

InactiveUS8213513B2Reduce loadEasy to calculateTelevision system detailsPicture reproducers using cathode ray tubesInternal memoryExternal storage

A data reading method for motion estimation in an embedded system is provided. The embedded system includes an external memory device and a video encoding device, wherein the external memory device stores a first frame, and the video encoding device has an internal memory. First, a second frame is divided into M×N sub frame sets, wherein each of the sub frame sets has O×P sub frames. Then, each of the sub frame sets is selected in a calculation sequence, and the selected sub frame set is stored into the internal memory. Next, a predicted search path of each sub frame in the selected sub frame set is calculated. Thereafter; a predicted reading range is determined, wherein the predicted reading range includes the predicted search paths of the sub frames. Finally, a comparison data is read from the first frame according to the predicted reading range.

Owner:NAT TAIWAN UNIV

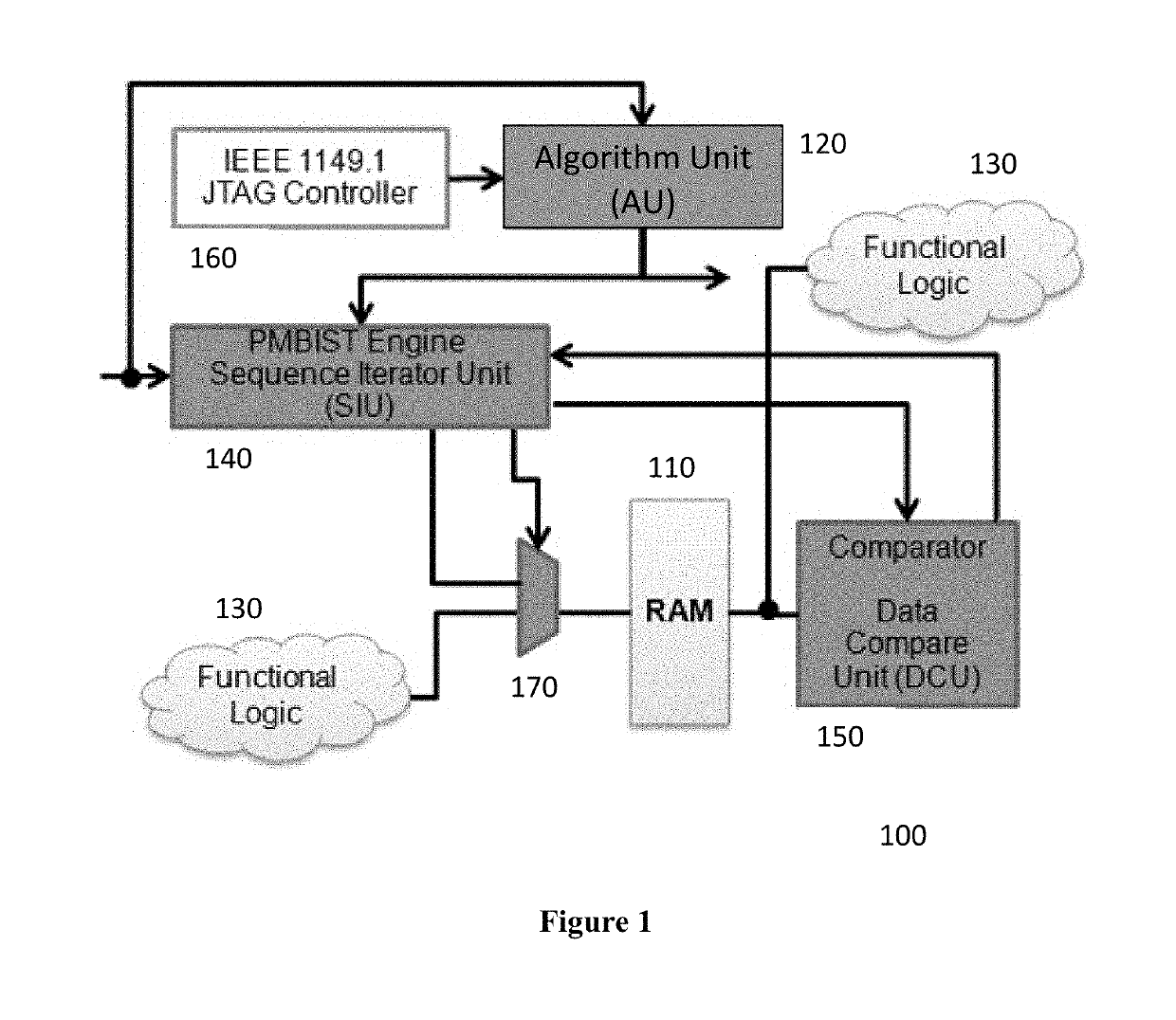

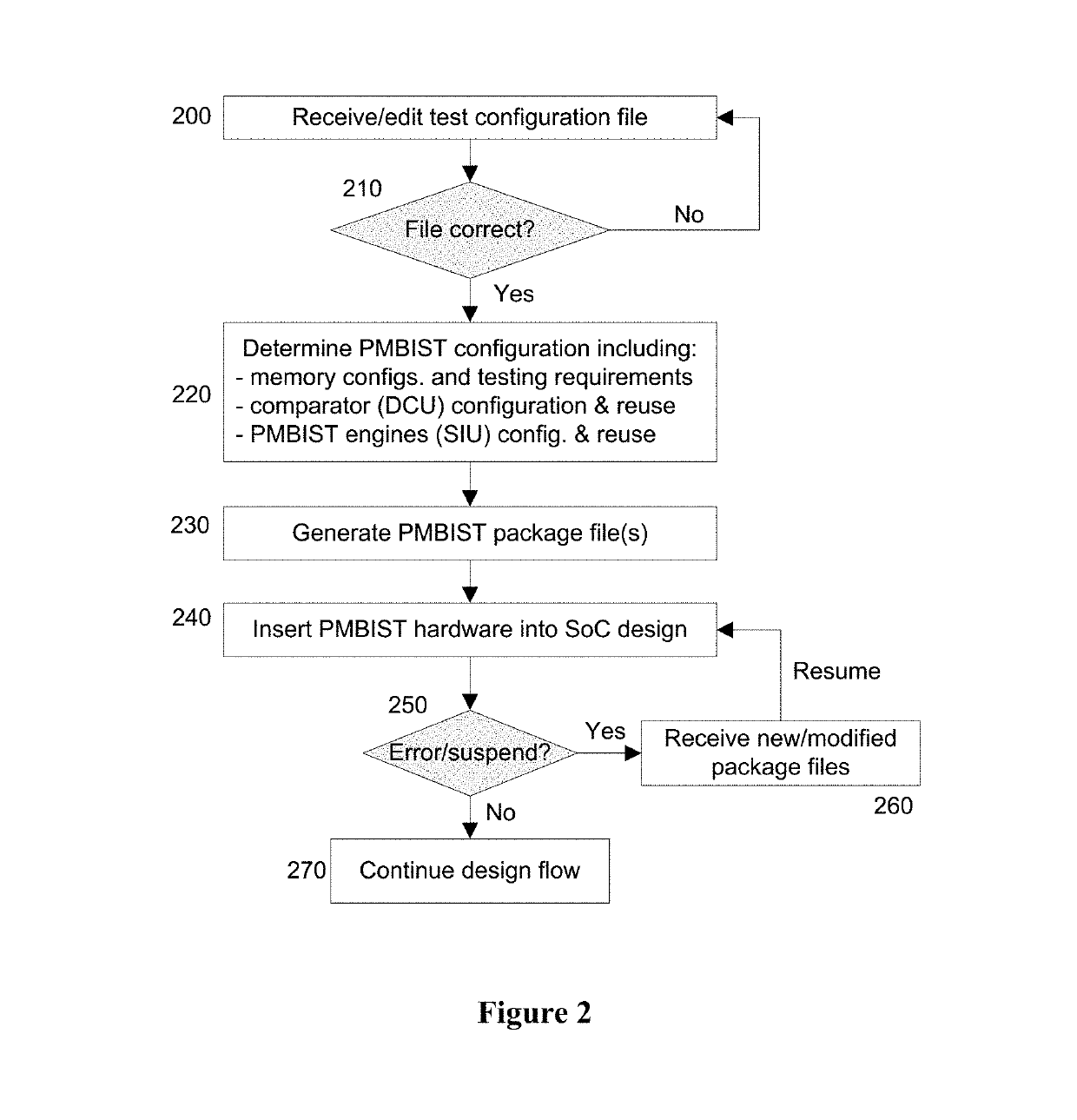

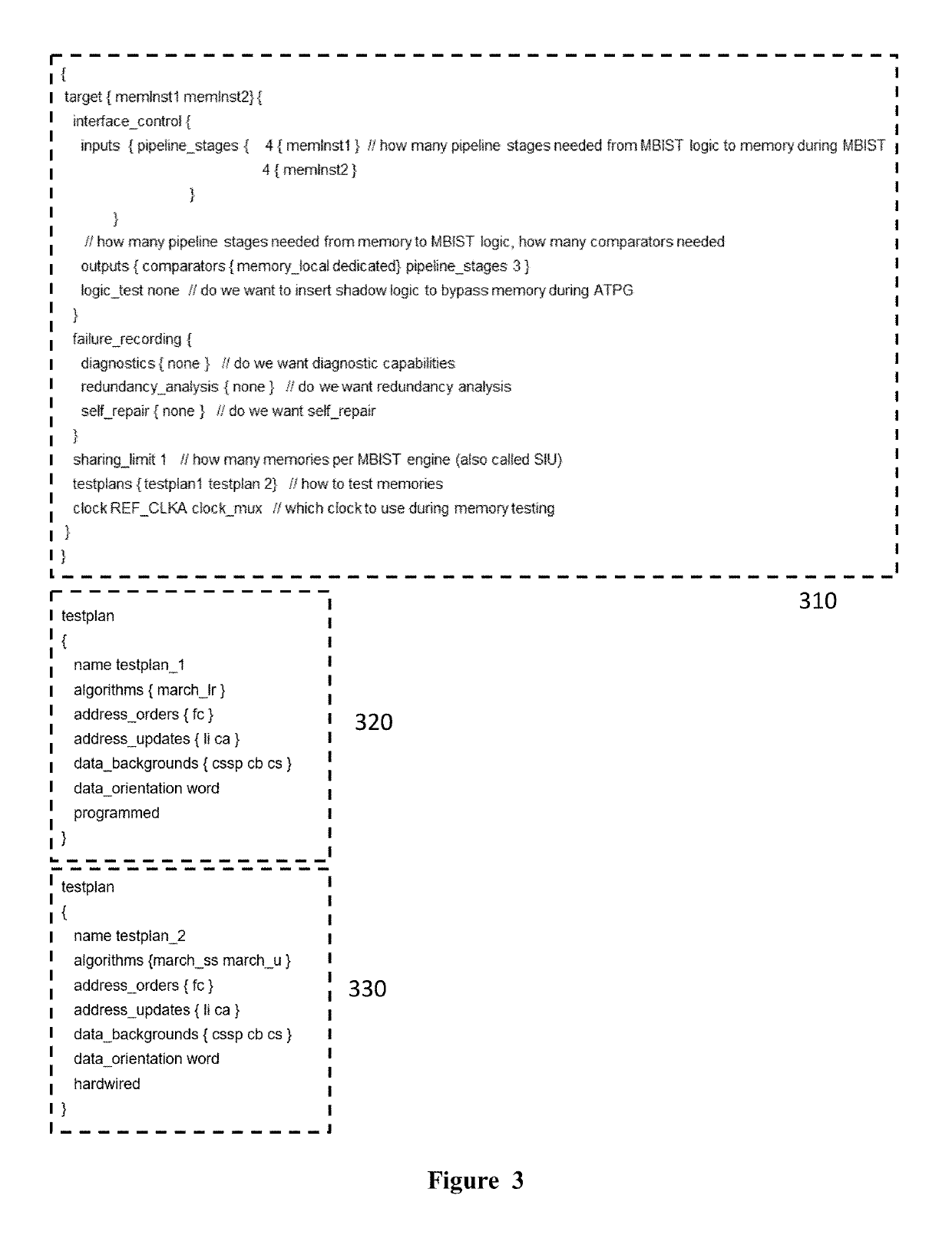

Systems, methods, and computer-readable media utilizing improved data structures and design flow for programmable memory built-in self-test (PMBIST)

ActiveUS10387599B1Robust analysis of requirementElectrical testingFunctional testingArray data structureSystems design

Computer system for programmable built-in self-test (PMBIST) insertion into system-on-chip designs comprising one or more memories, including at least one processor and computer-executable instructions that cause the system to determine a PMBIST configuration based on one or more test configuration files; generate one or more package files based on the PMBIST configuration; insert PMBIST hardware into the SoC design based on the package files and characteristics of the memories; suspend PMBIST hardware insertion after an event related to the package files; and resume PMBIST hardware insertion after receiving one or more updated package files. In some embodiments, the package files are independent of vendor-specific memory models. In some embodiments, the package files comprise a plurality of data structures. Exemplary methods and computer-readable media can also be provided embodying one or more procedures the system is configured to perform.

Owner:CADENCE DESIGN SYST INC

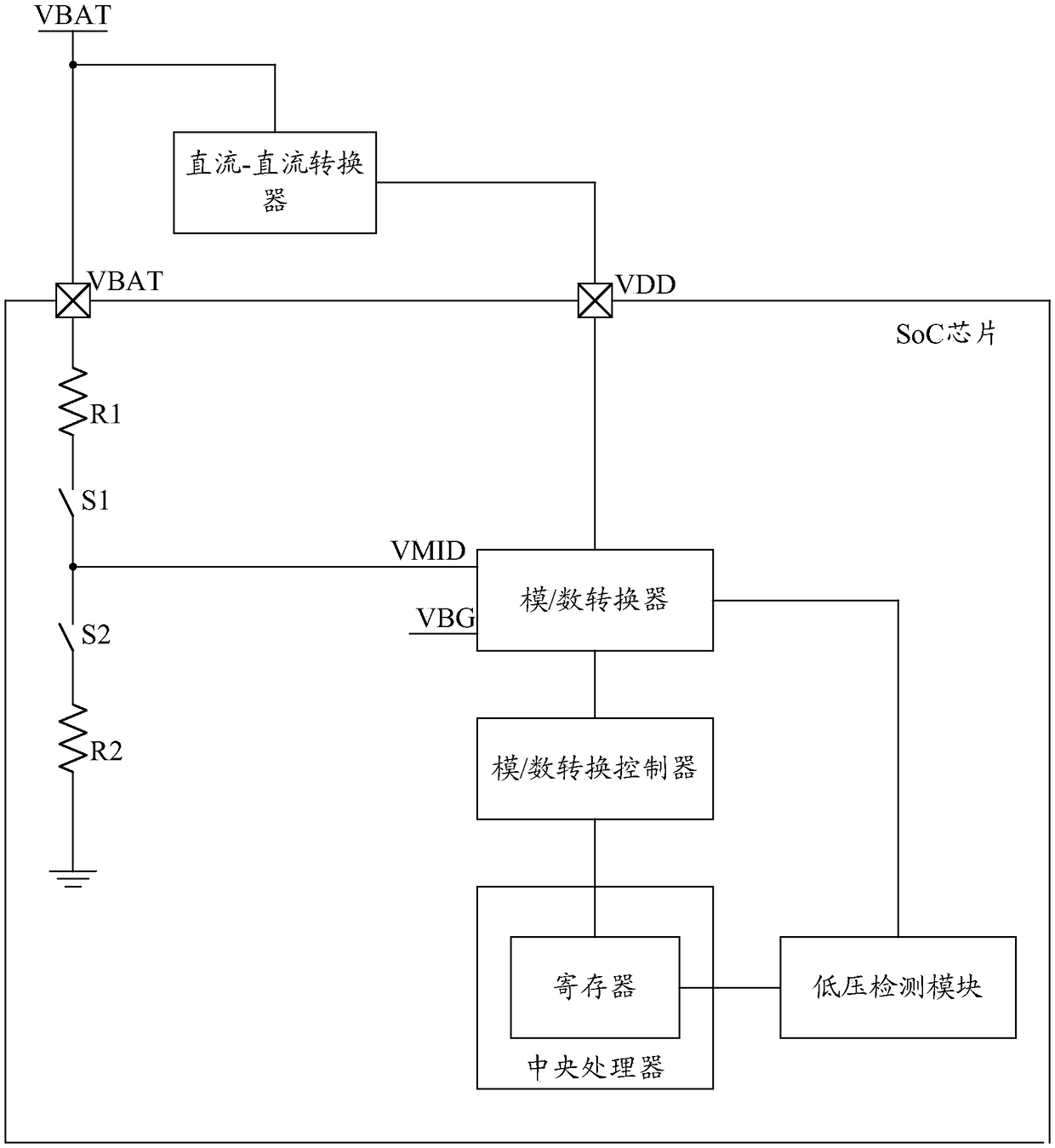

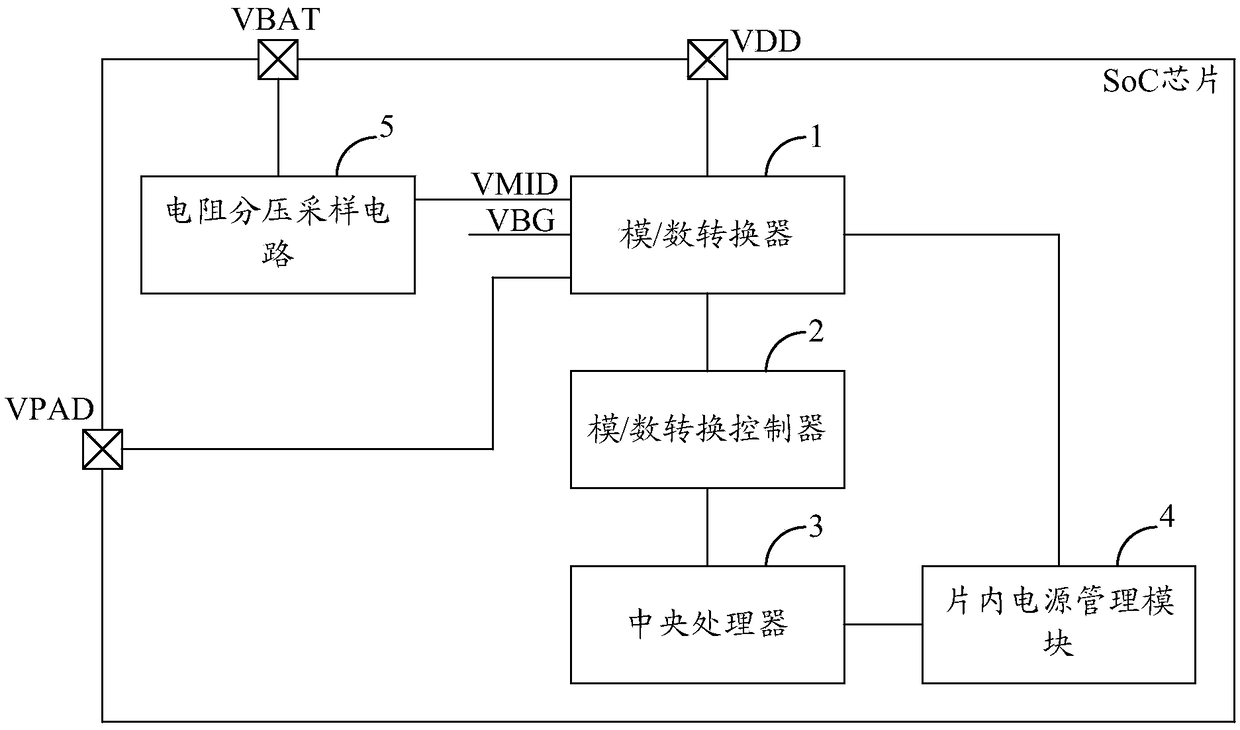

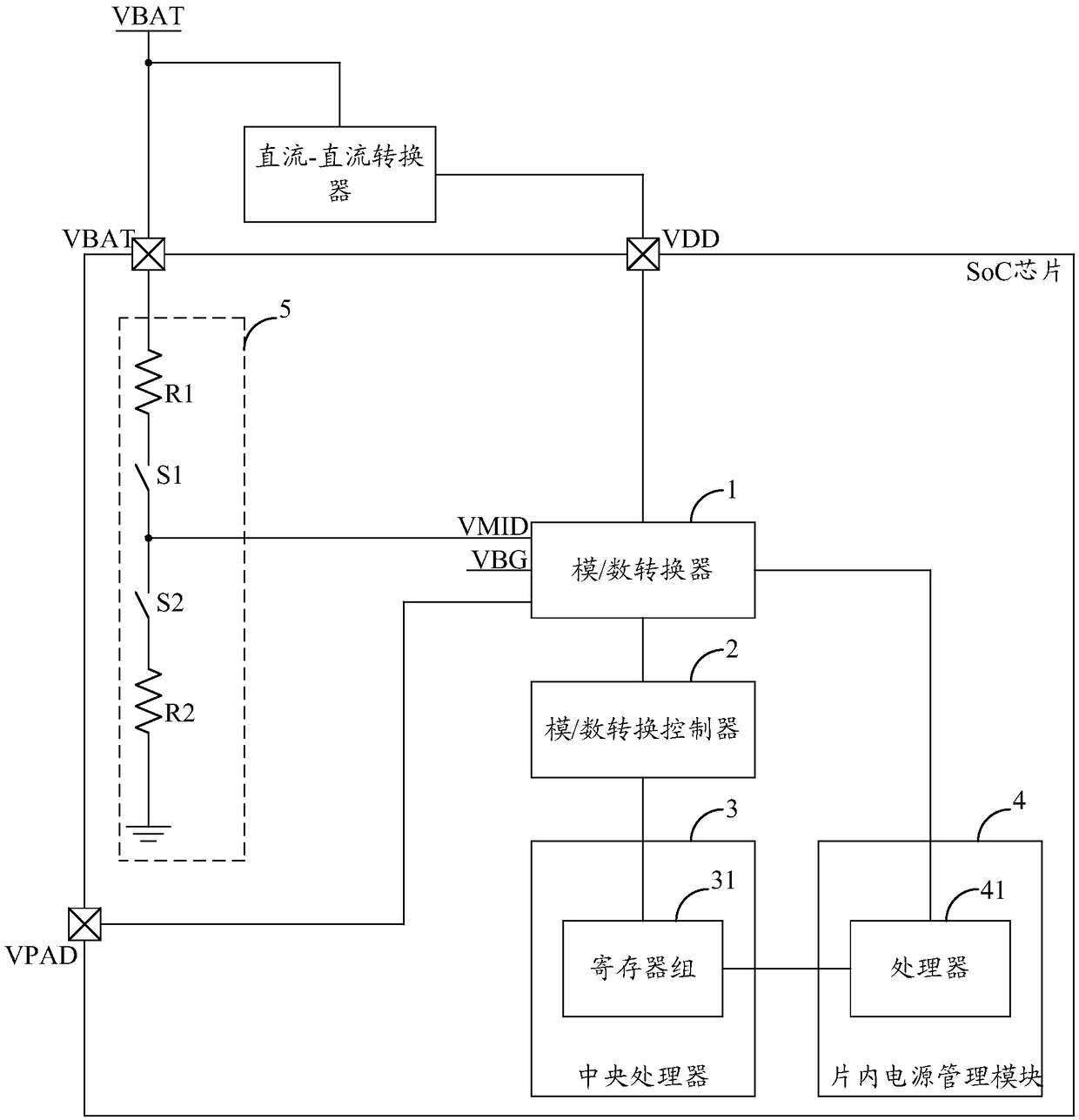

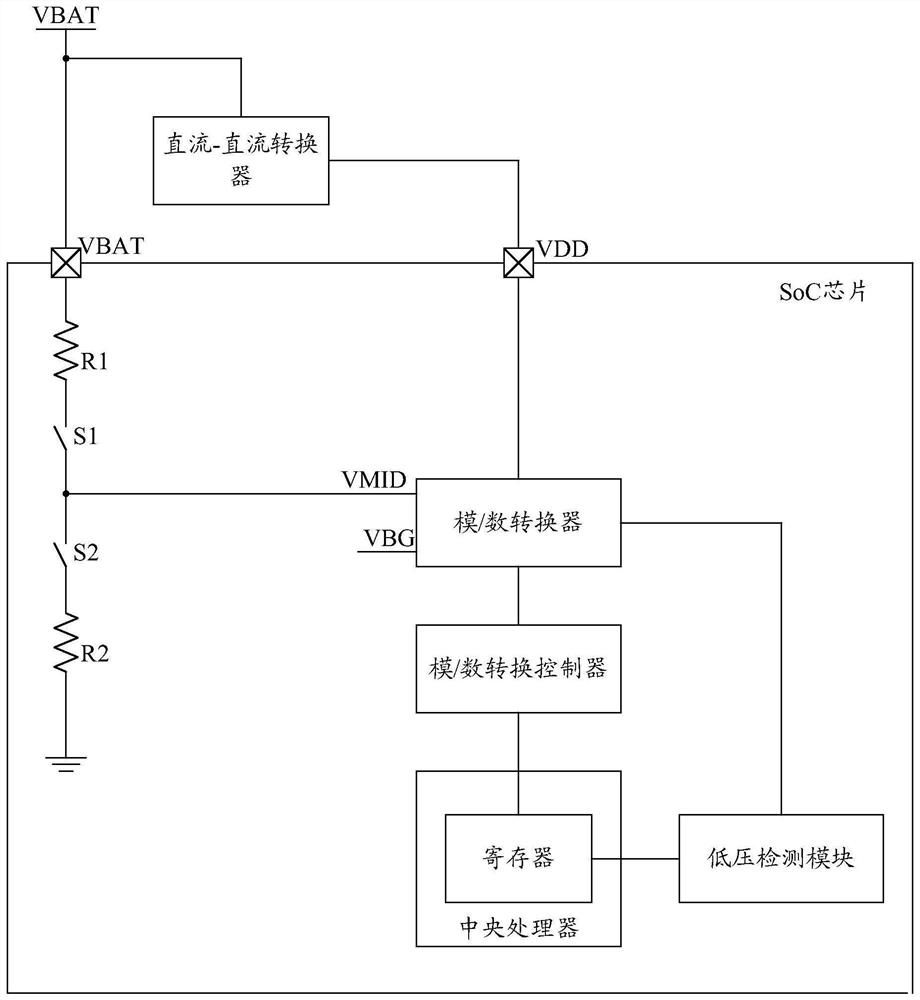

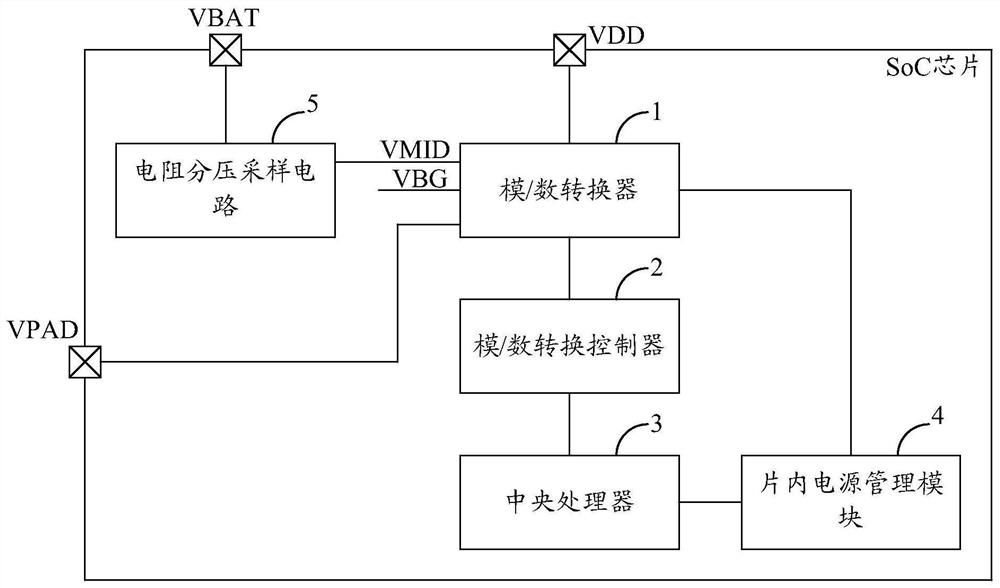

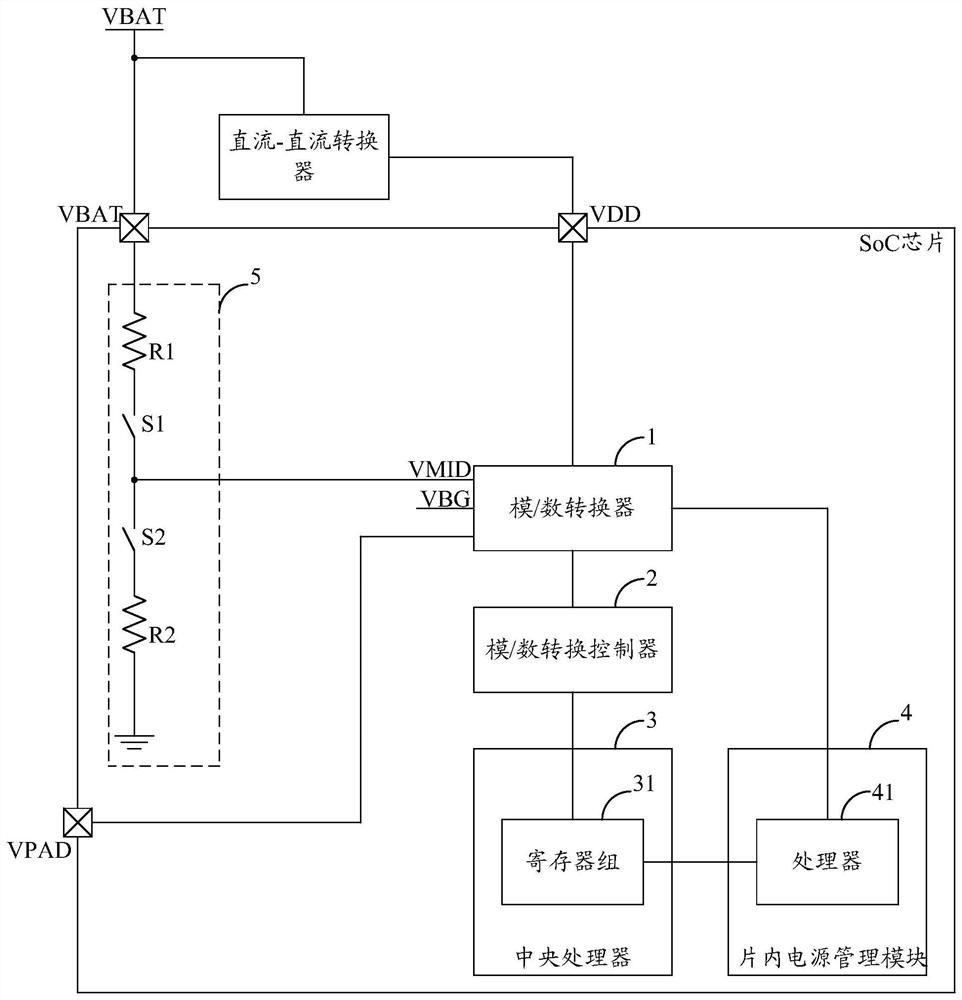

System and detection method for realizing low-voltage real-time detection of an SoC chip

ActiveCN109062743ARich low-voltage detection functionsDetecting faulty hardware by power-on testVolume/mass flow measurementProcessor registerLow voltage

The invention belongs to the field of system-on-chip design, and provides a system for realizing low-voltage real-time detection of an SoC chip and a detection method thereof. Wherein the register bank within the CPU comprises a plurality of registers corresponding to different voltage levels of the VBAT voltage respectively, The processor of the on-chip power management module performs step-by-step monitoring of the VBAT voltage according to the value of each register to generate the corresponding interrupt, and the CPU performs a low-power process according to the fast response of the interrupt type. Through the setting of multiple VBAT voltage grades, multiple VBAT voltage grades can be monitored at the same time, early warning, enriching the low-voltage detection function, and expanding the application range.

Owner:APPOTECH

A system and method for realizing low-voltage real-time detection of SOC chips

ActiveCN109062743BRich low-voltage detection functionsDetecting faulty hardware by power-on testVolume/mass flow measurementLow-voltage detectEmbedded system

The invention belongs to the field of on-chip system design and provides a system and a detection method for realizing low-voltage real-time detection of SoC chips. Among them, the register set inside the central processing unit includes a plurality of registers corresponding to different voltage levels of the VBAT voltage, and the processor of the on-chip power management module monitors the VBAT voltage stepwise according to the value of each register, and generates corresponding interrupt, the CPU will quickly respond to the low-power process according to the interrupt type. Through the setting of multiple VBAT voltage gears, multiple VBAT voltage gears can be monitored and warned at the same time, which enriches the low-voltage detection function and expands the application range.

Owner:APPOTECH

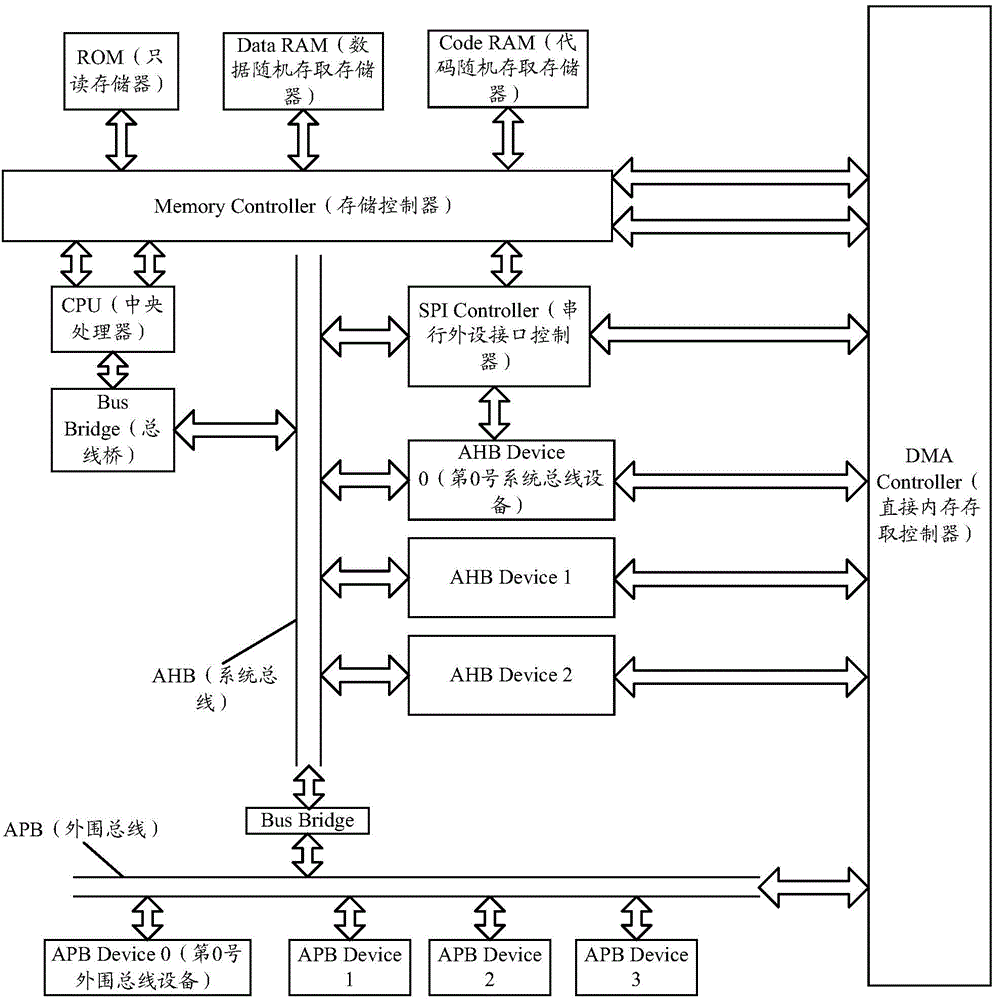

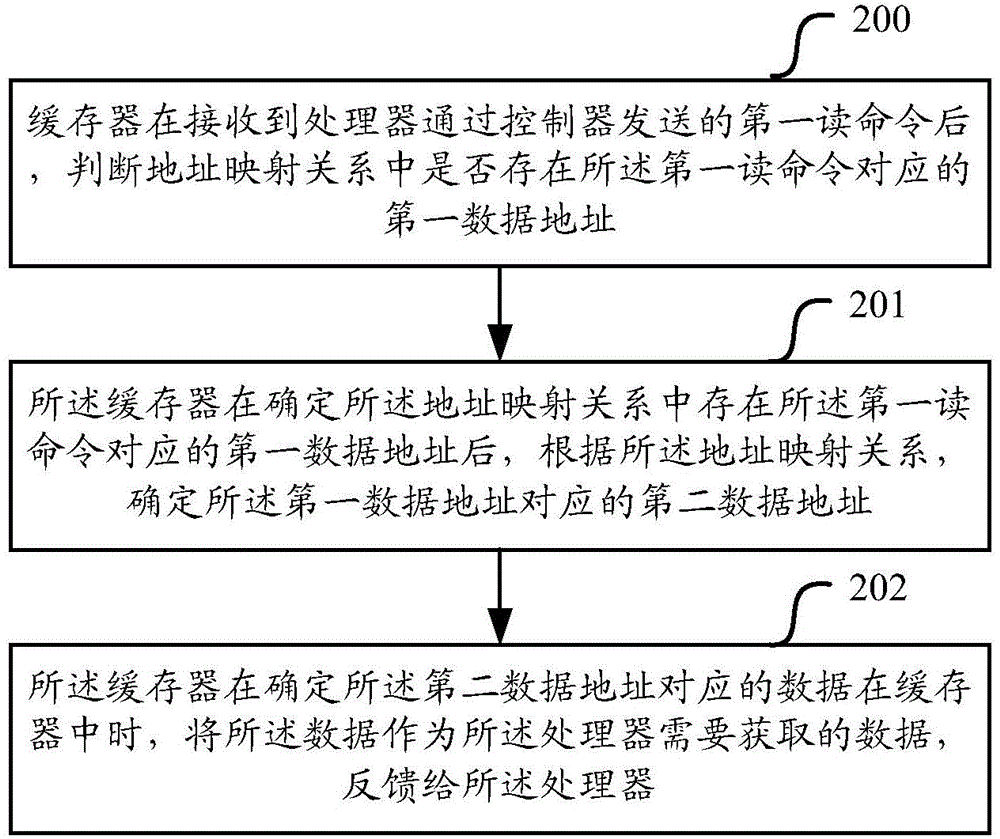

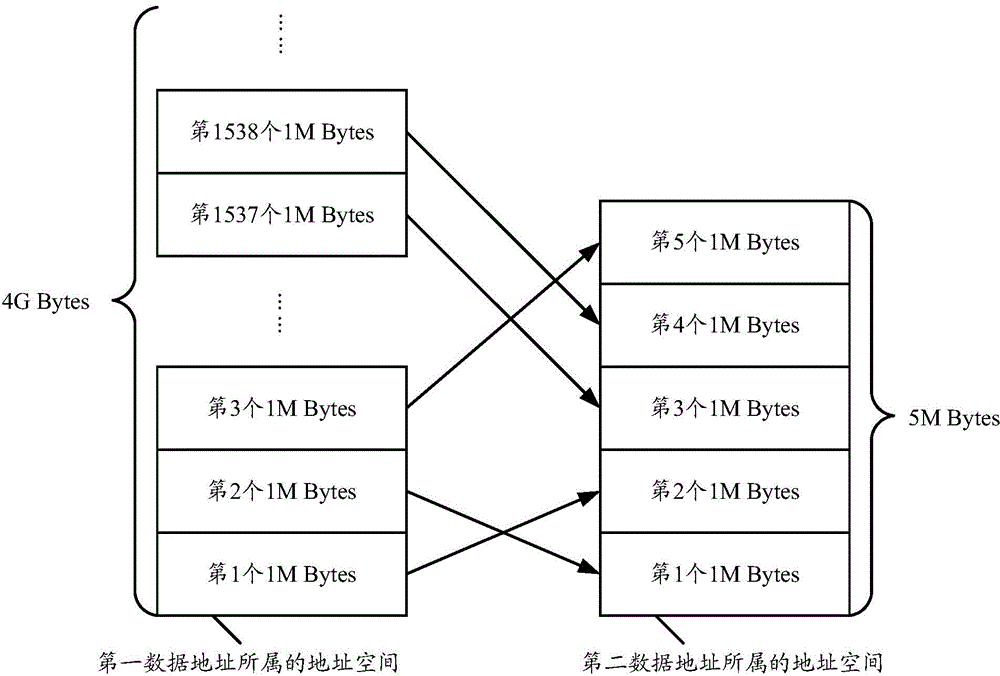

Data feedback method, buffer, controller and system

ActiveCN106294207AEasy to debug and locateMemory adressing/allocation/relocationOperating systemAddress mapping

Embodiments of the invention disclose a data feedback method, a buffer, a controller and a system, and aim to solve the problems that the whole chip area of a system on chip is enlarged and the integration level of the system on chip is reduced because a large amount of Code RAMs need to be designed for storing codes, resident in a memory, of different running scenes in system-on-chip design in the prior art. The method comprises the steps that the buffer judges whether a first data address corresponding to a first read command exists in an address mapping relationship or not after the first read command sent by a processor through the controller is received; the buffer determines a second data address corresponding to the first data address according to the address mapping relationship after determining that the first data address corresponding to the first read command exists in the address mapping relationship; and the buffer feeds back data as data required to be acquired by the processor to the processor when determining that the data corresponding to the second data address is in the buffer. By adopting the method provided by the invention, the integration level of the system on chip can be improved.

Owner:ACTIONS ZHUHAI TECH CO

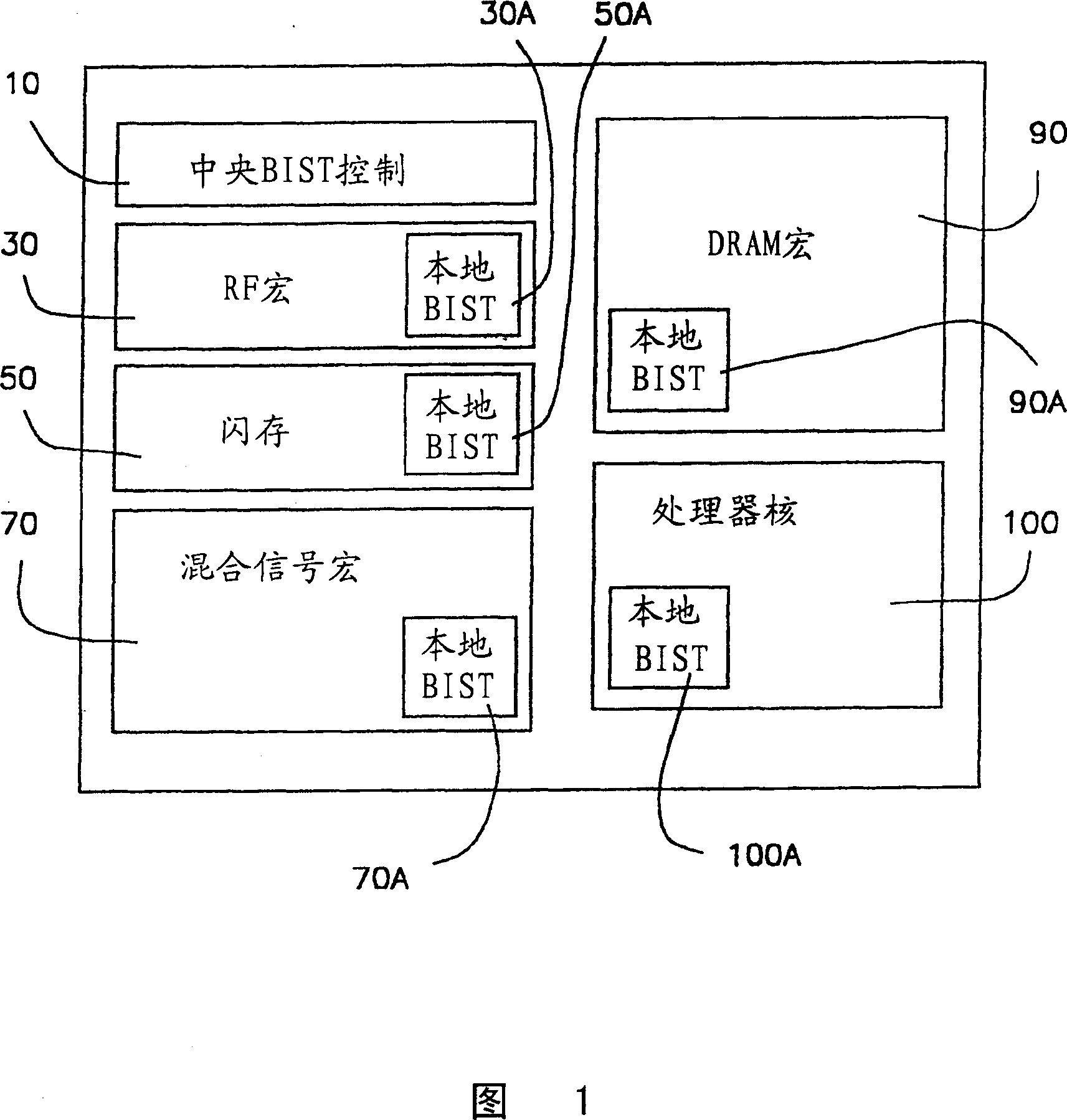

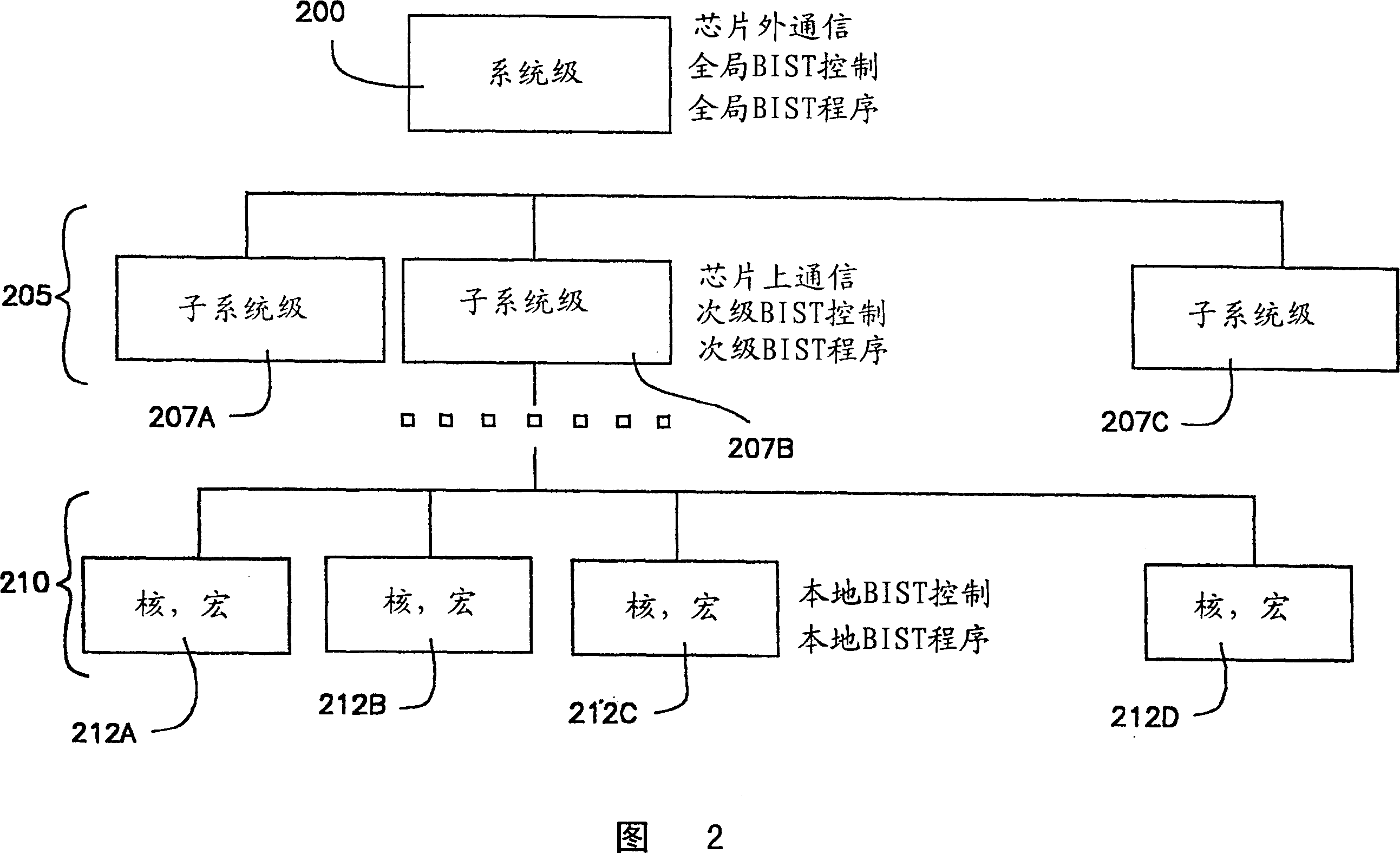

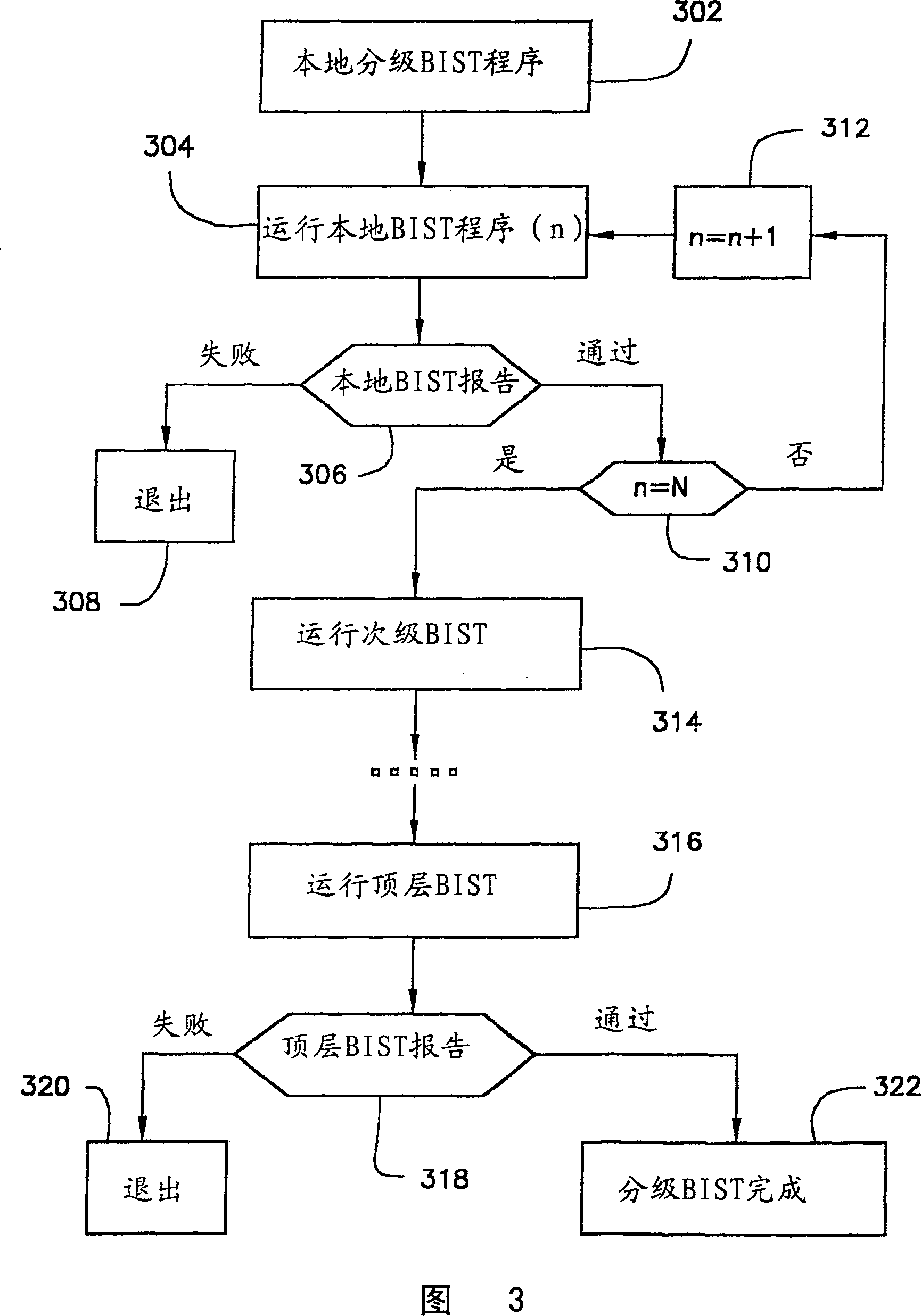

Hierarchical built-in self-test for system-on-chip design

Hierarchical built-in self-test methods and arrangement for verifying system functionality. As a result, an effective built-in self-test methodology is provided for conducting complete system-on-chip testing, to ensure both the circuit reliability and performance of system-on-chip design. As an added advantage, development costs are reduced for system-on-chip applications.

Owner:GLOBALFOUNDRIES INC

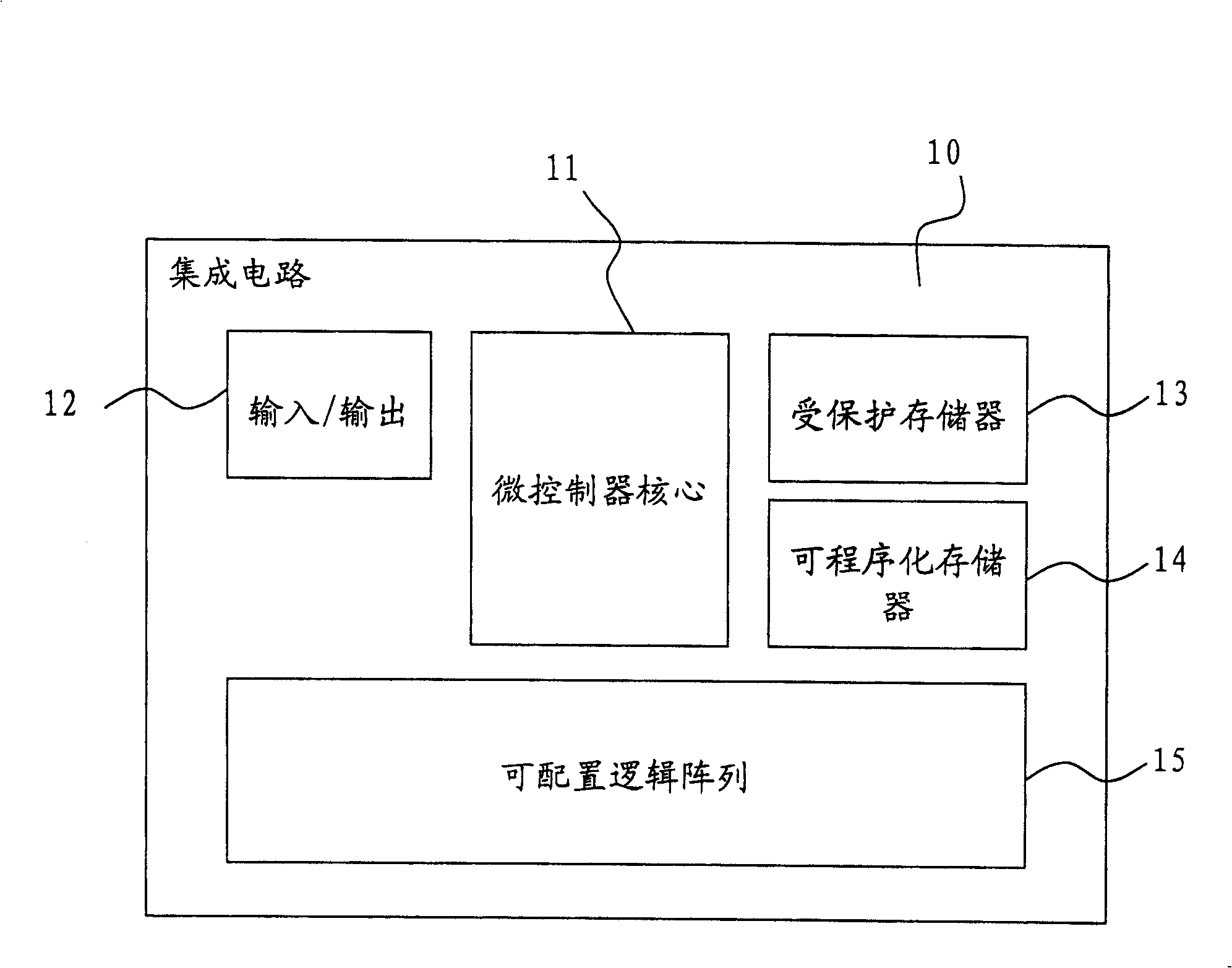

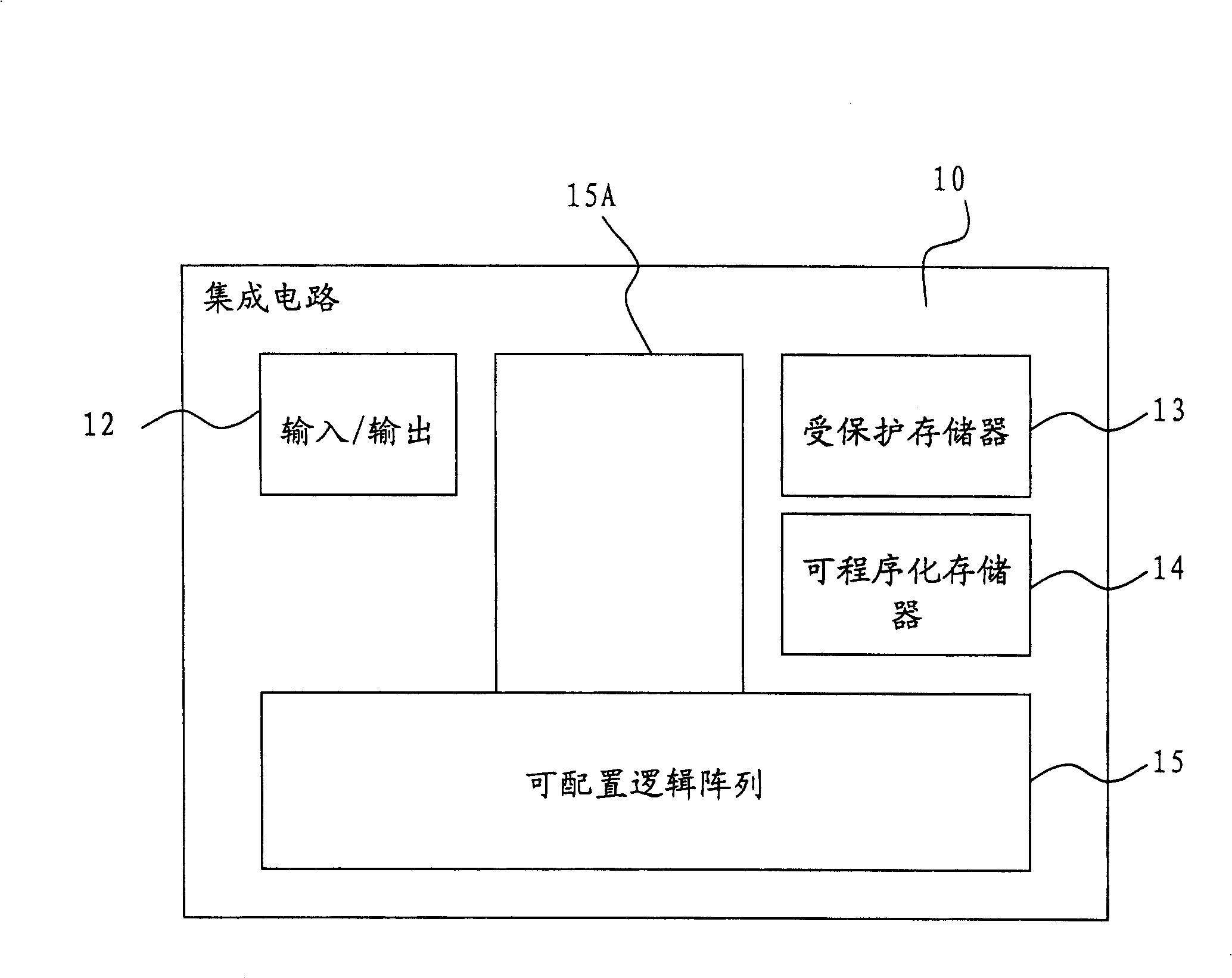

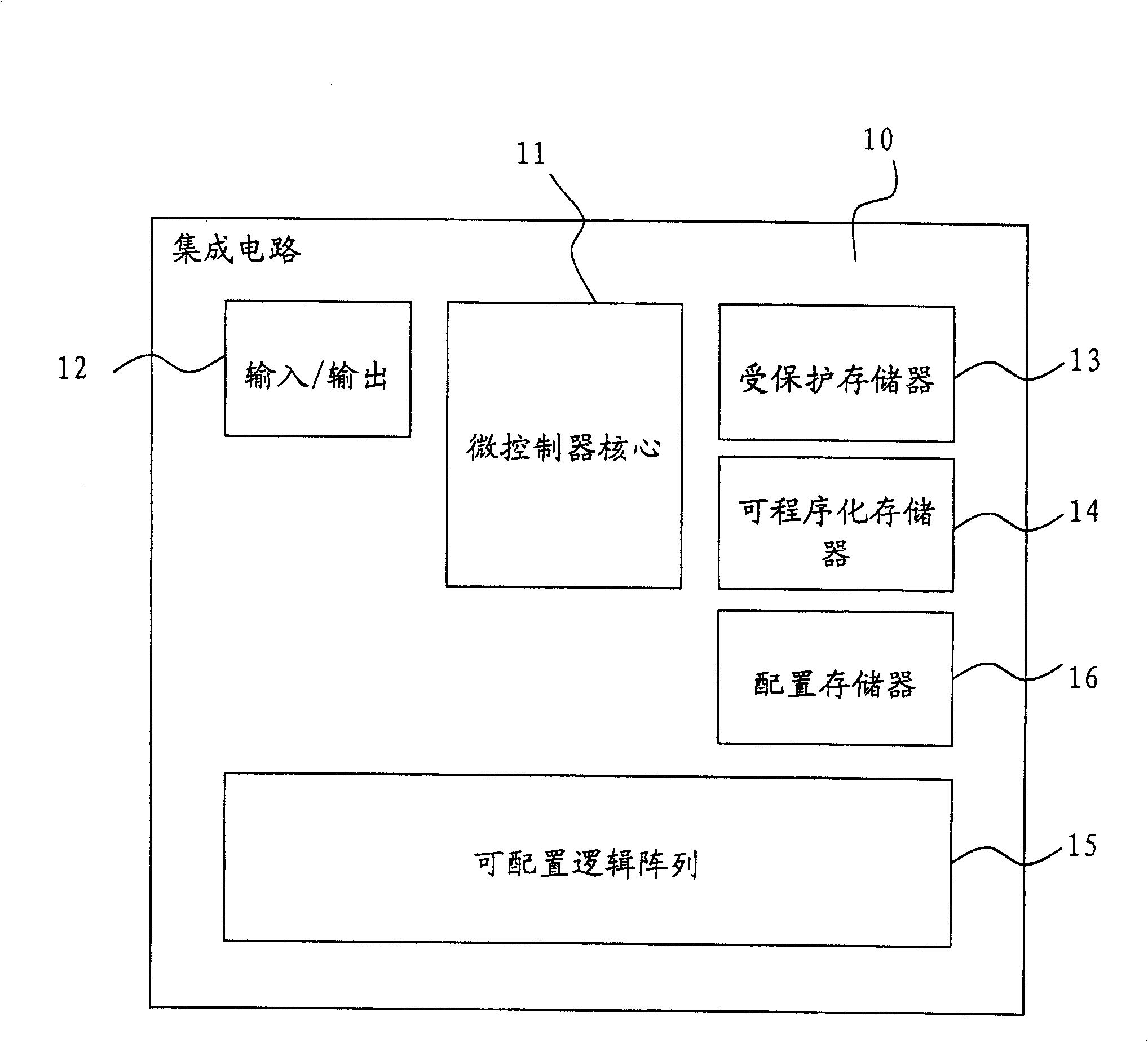

In-circuit configuration architecture for embedded configurable logic array

InactiveCN100421099CError detection/correctionArchitecture with single central processing unitIntegrated circuitExternal source

A system-on-a-chip integrated circuit that includes a configurable logic array, a processor core, and a memory adapted to store instructions for a mission function, and instructions for a configuration load function used to load configuration data on to the integrated circuit via an input port on the integrated circuit from an external source. The processor fetches and executes the instructions from the memory. Configuration data received using the configuration load function is used to configure the configurable logic array. The present invention provided a higher degree of freedom for system-on-chip design using a built-in logic array that can be set, and to provide a setting load of a logic that can be set.

Owner:MACRONIX INT CO LTD