Patents

Literature

462 results about "Register bank" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Register Banks. A register bank is used for the programmable registers used by assembly language programmers. It can be viewed as the hardware equivalent of a software array. It has ports for reading and writing data given an index.

Vector register addressing

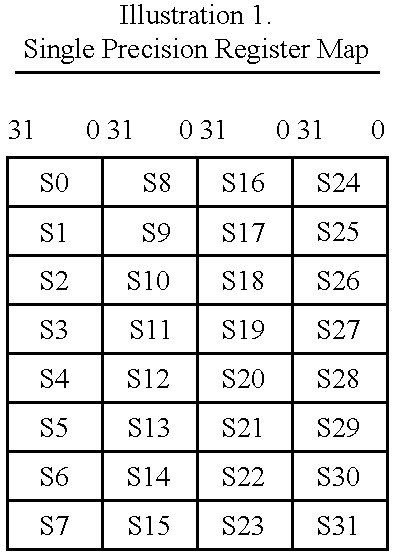

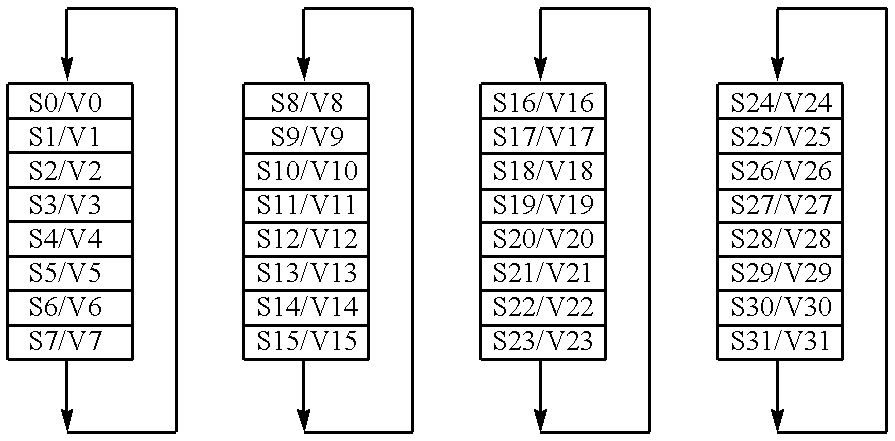

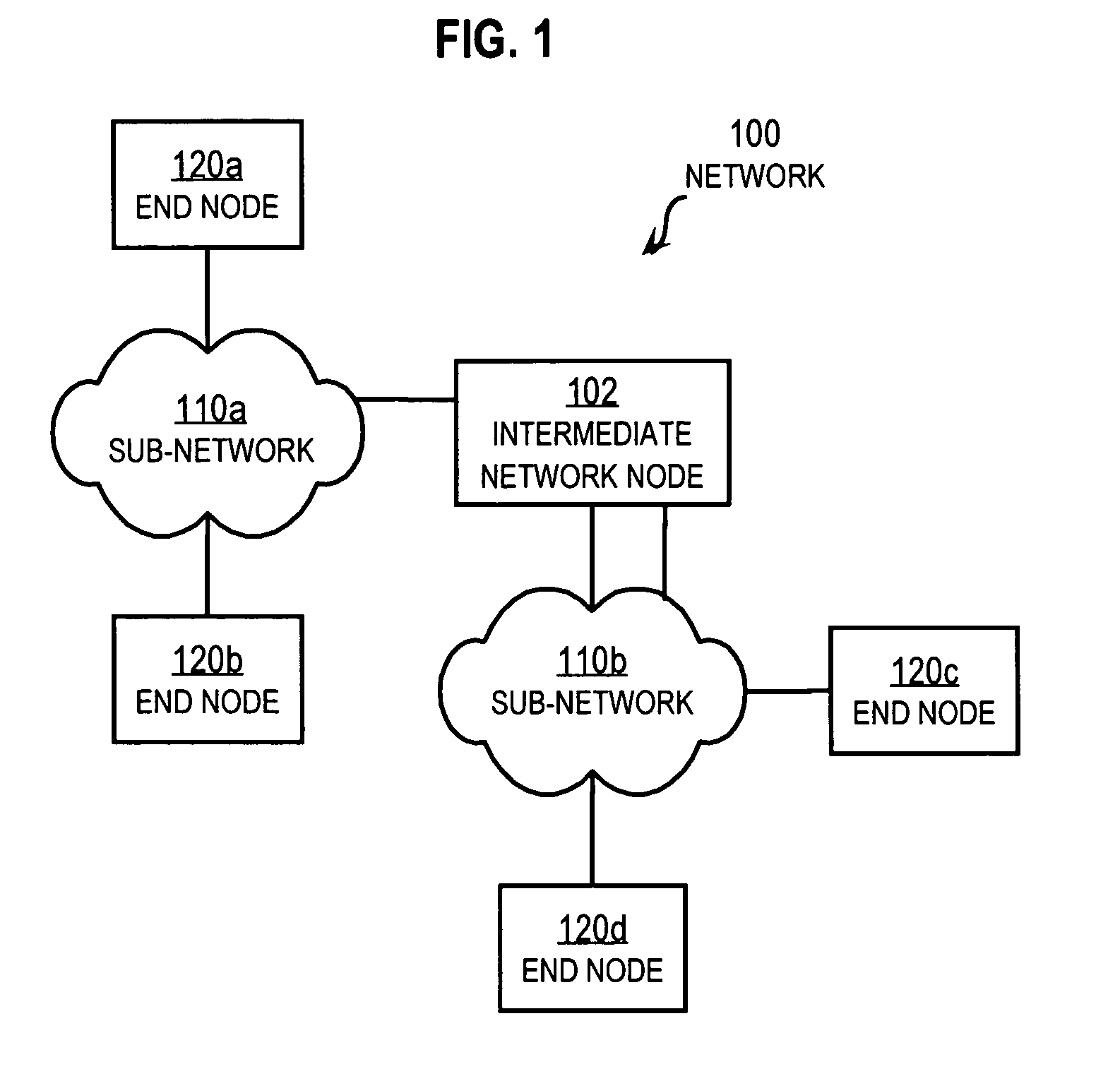

InactiveUS6332186B1Without complexityWithout costRegister arrangementsInstruction analysisMemory addressProcessing Instruction

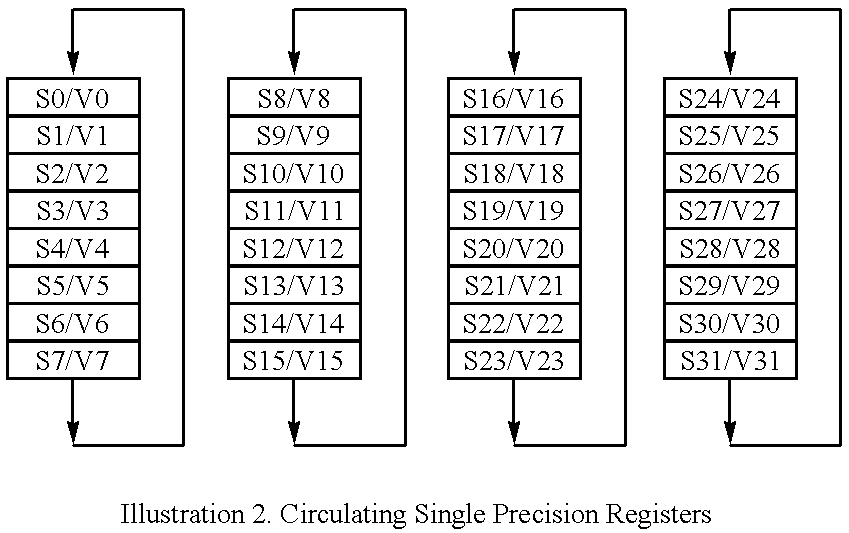

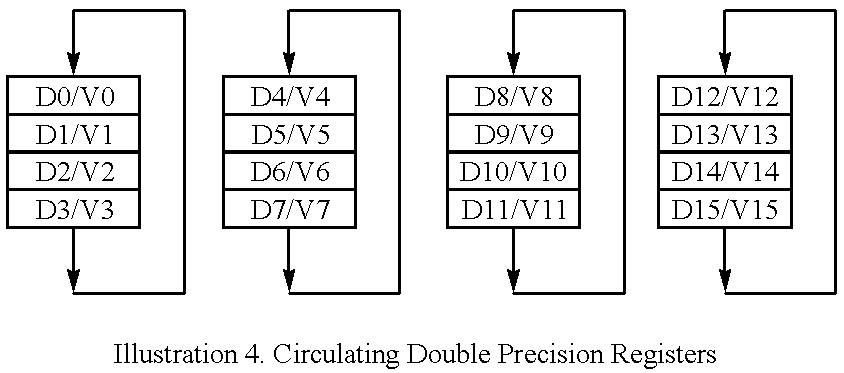

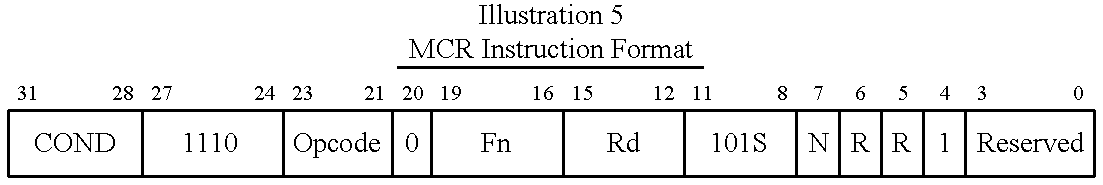

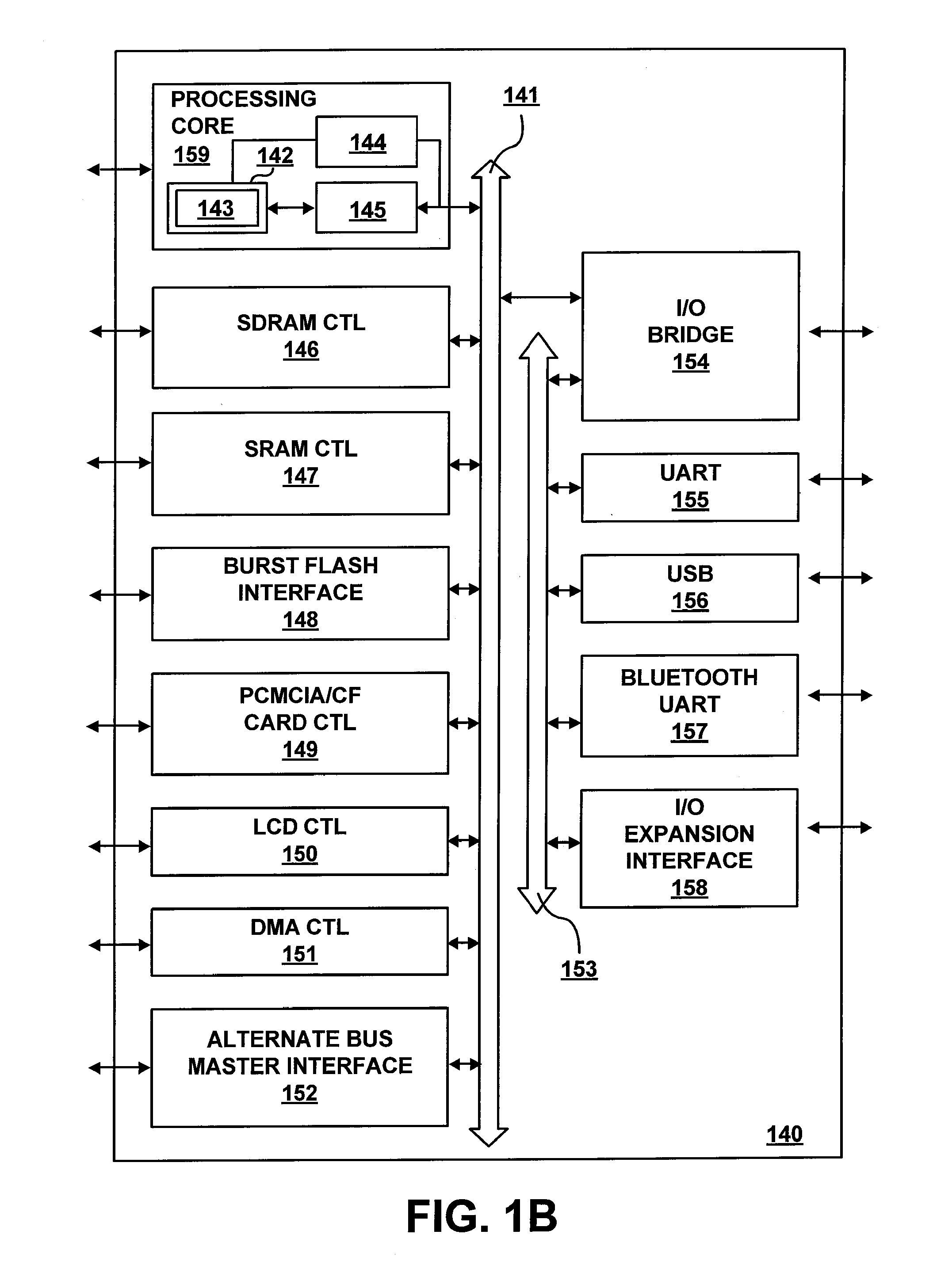

A floating point unit 26 is provided with a register bank 38 comprising 32 registers that may be used as either vector registers V or scalar registers S. Data values are transferred between memory 30 and the registers within the register bank 38 using contiguous block memory access instructions. Vector processing instructions specify a sequence of processing operations to be performed upon data values within a sequence of registers. The register address is incremented between each operation by an amount controlled by a stride value. Accordingly, the register address can be incremented by values such as 0, 1, 2 or 4 between each iteration. This provides a mechanism for retaining block memory access instructions to contiguous memory addresses whilst supporting vector matrix and / or complex operations in which the data values needed for each iteration are not adjacent to one another in the memory 30.

Owner:ARM LTD

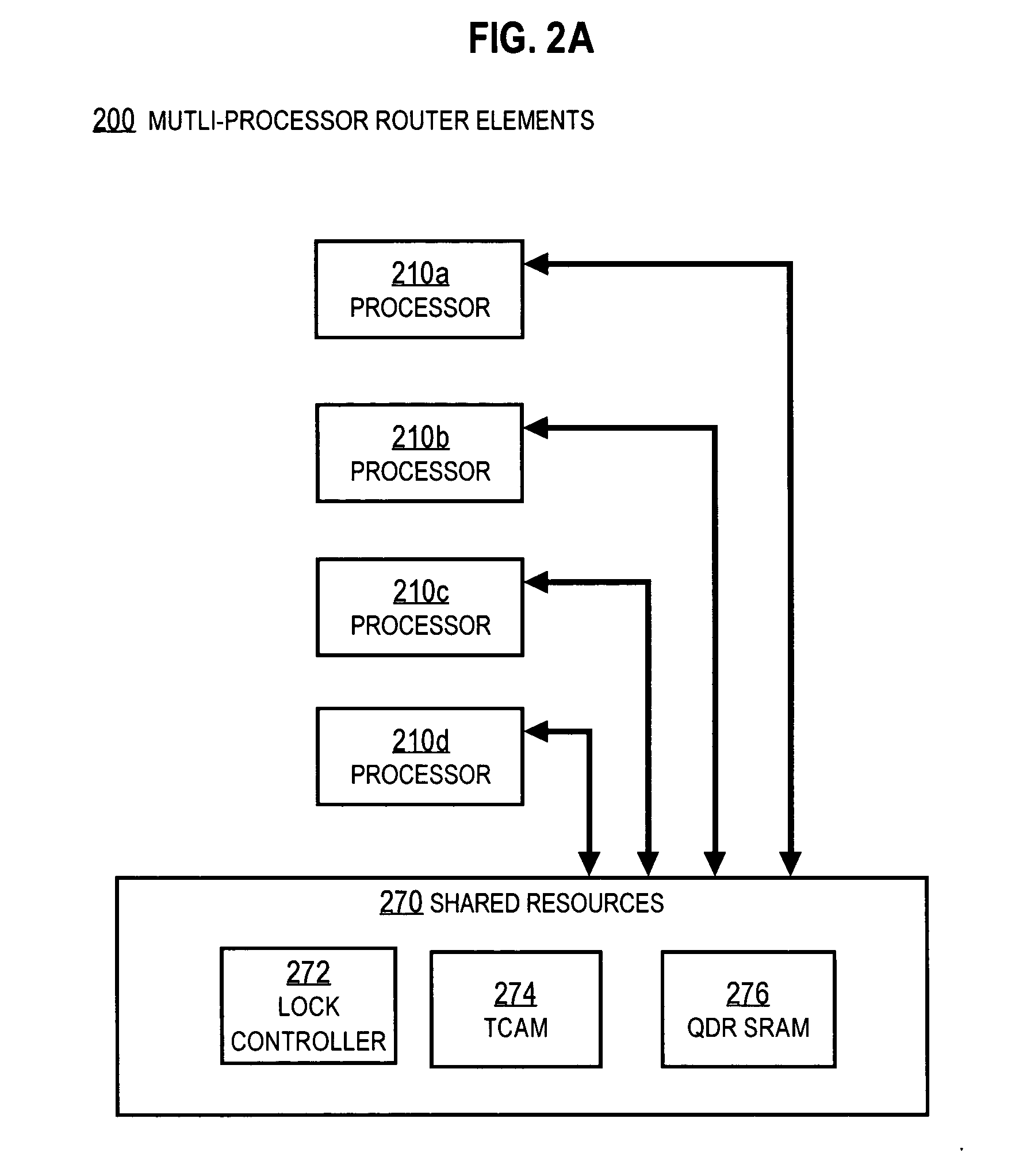

Indirect Register Access Method and System

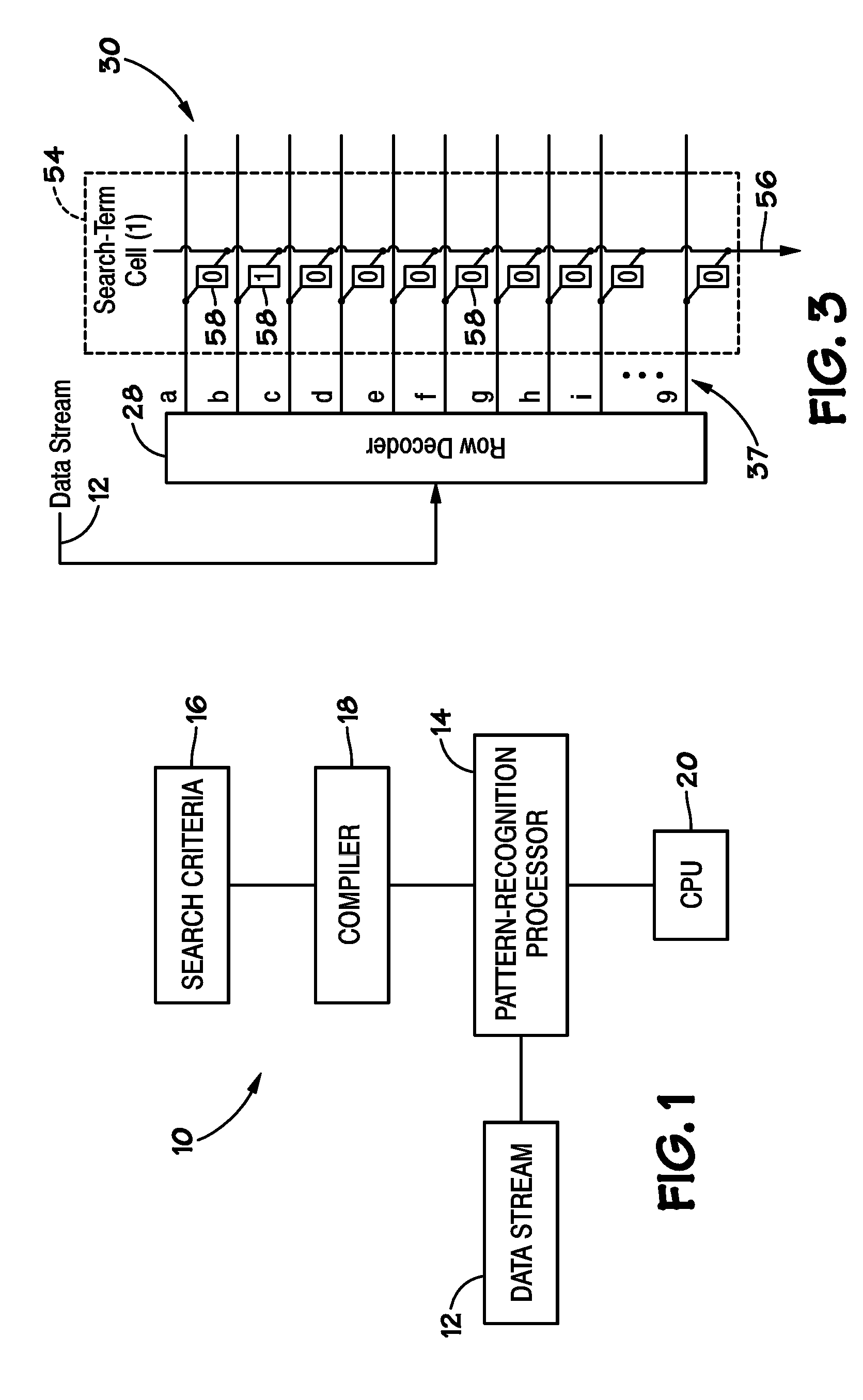

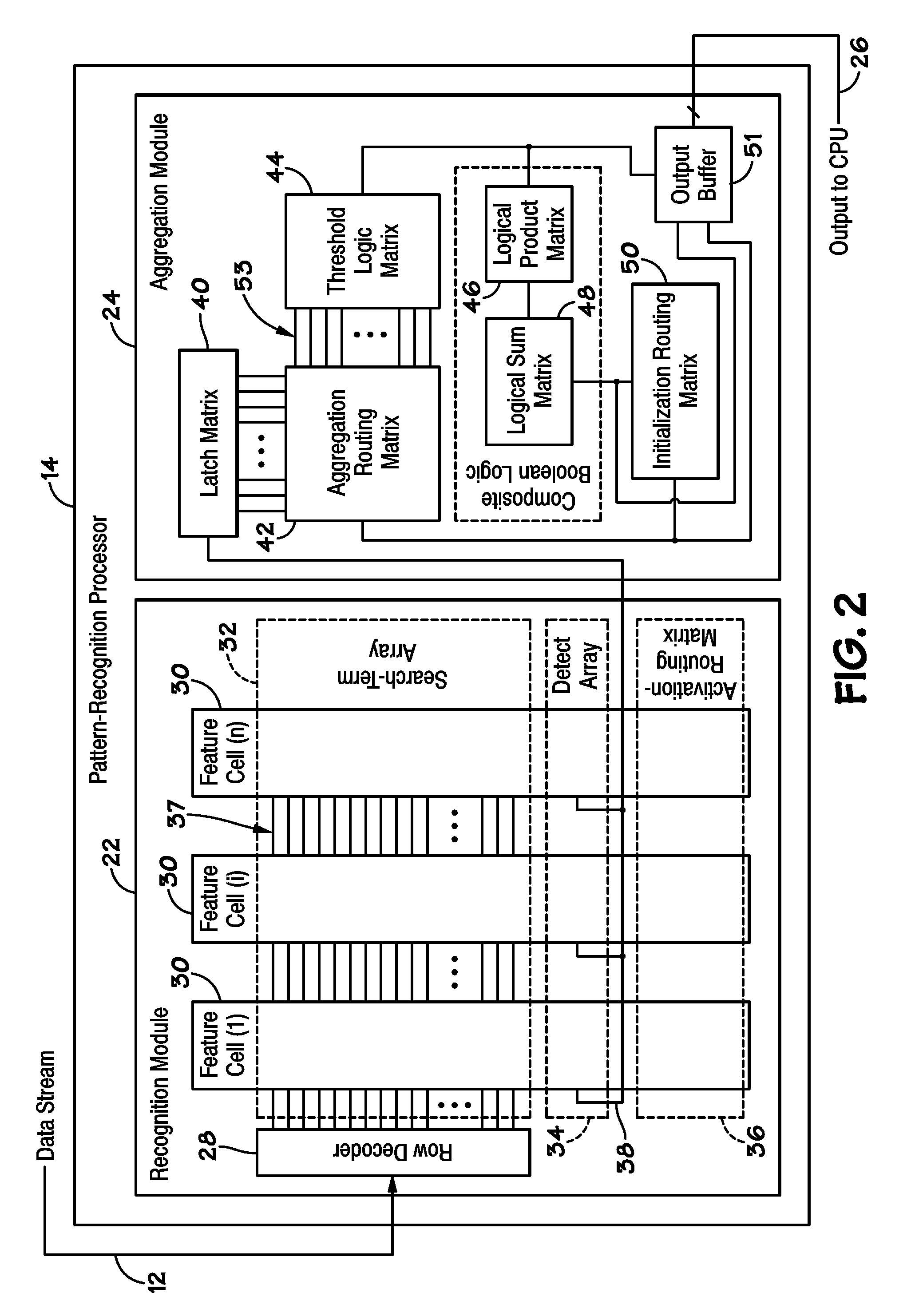

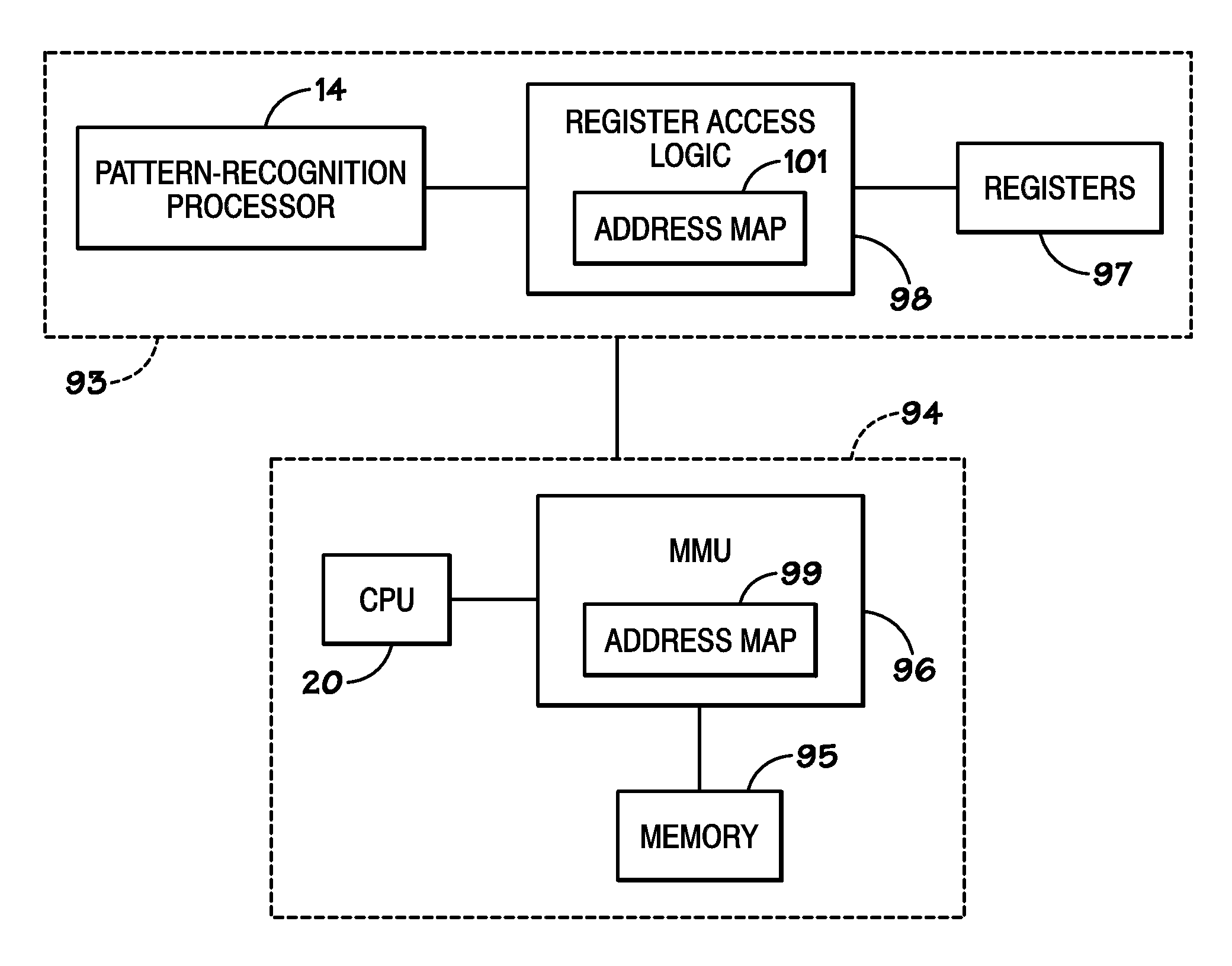

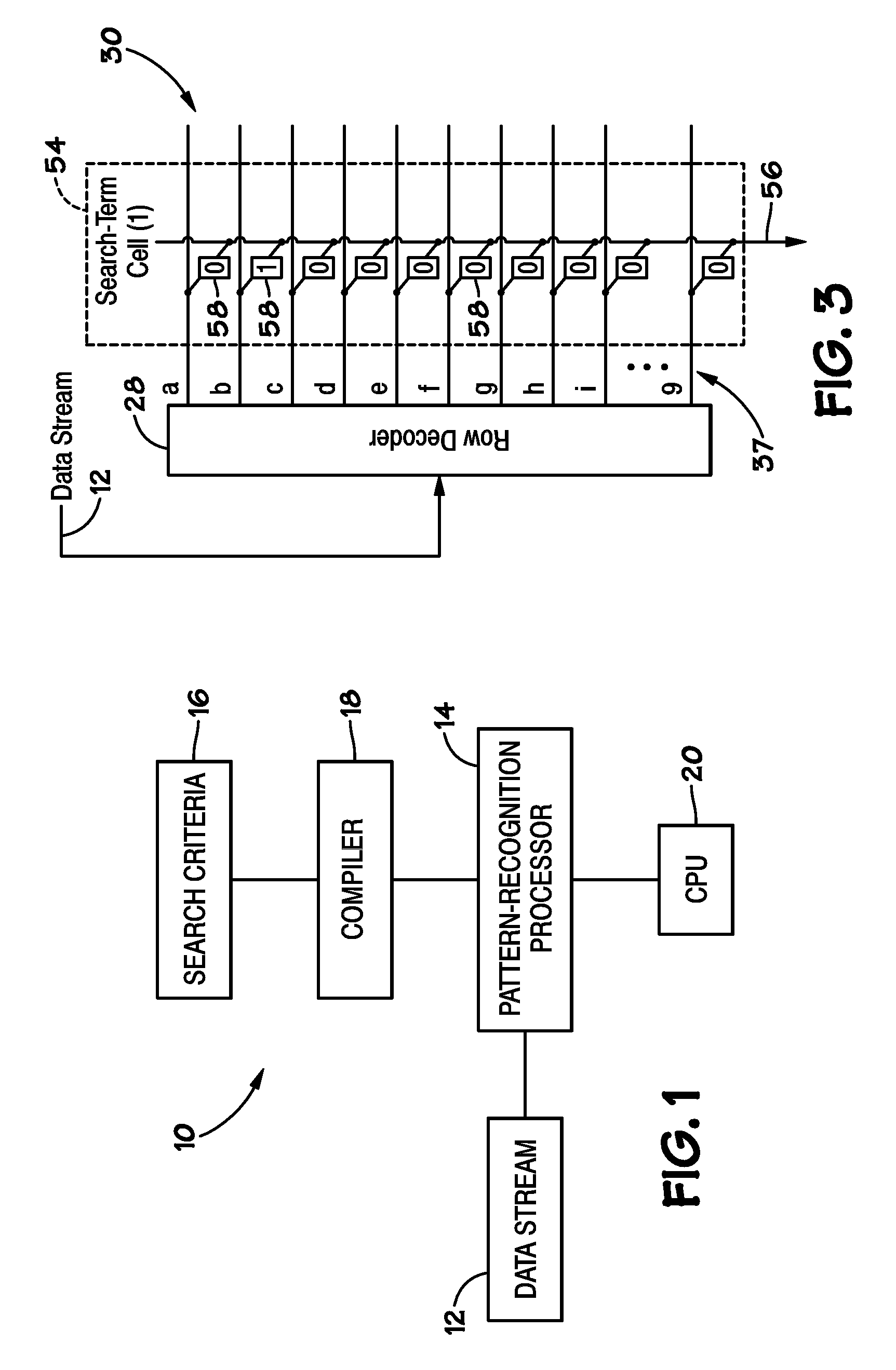

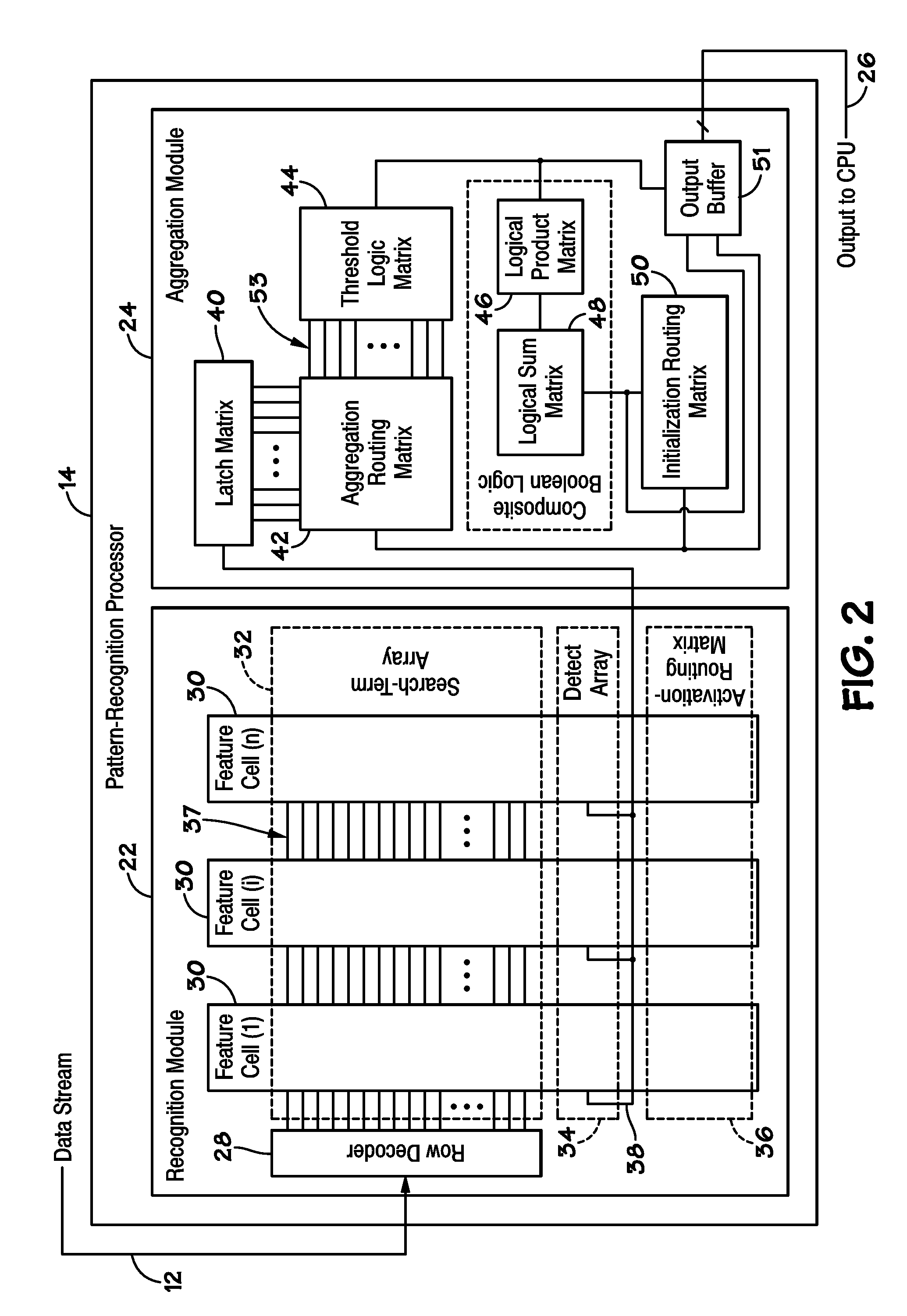

ActiveUS20100100691A1Memory architecture accessing/allocationRegister arrangementsAccess methodProcessor register

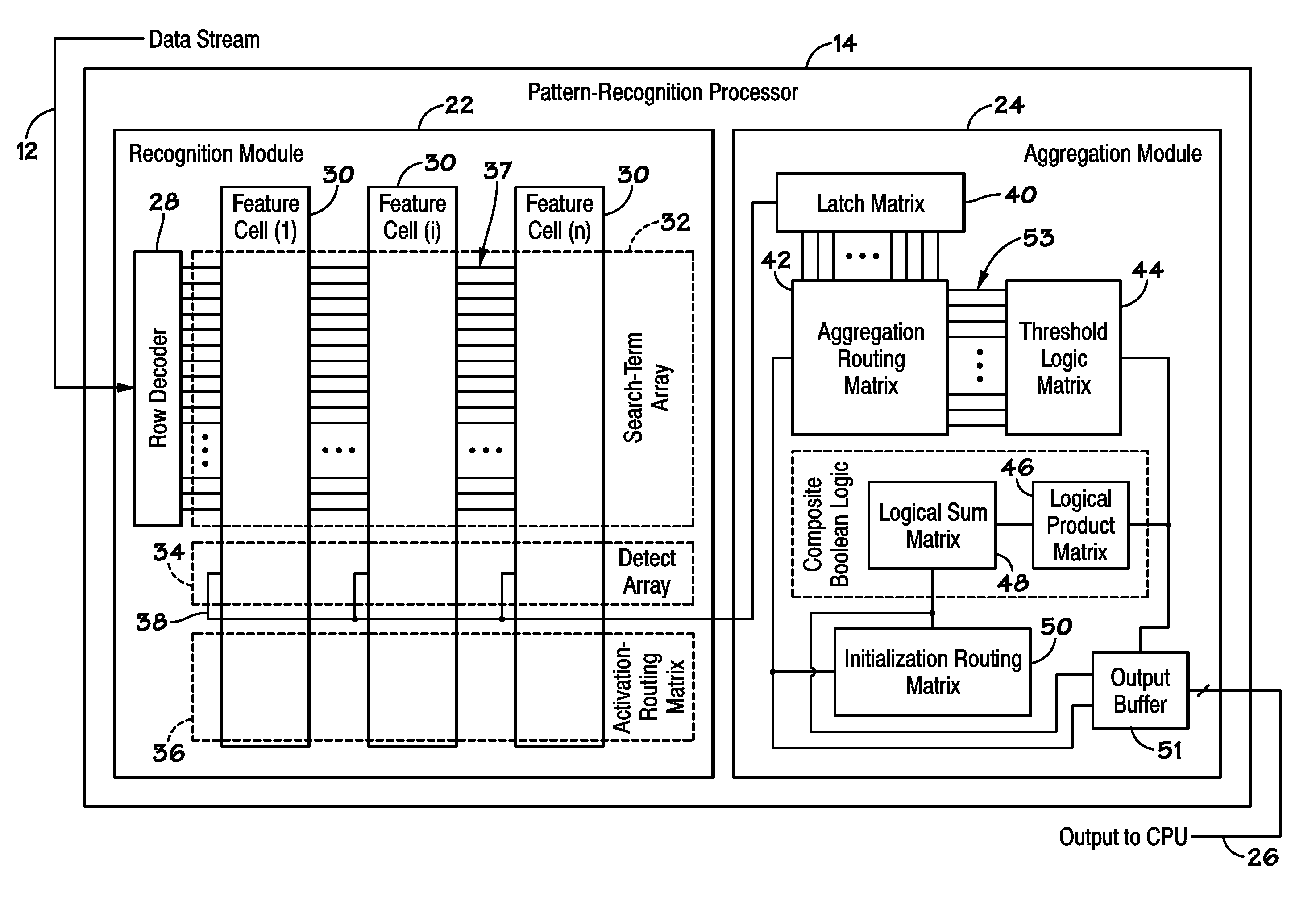

Systems and methods are provided for managing access to registers. In one embodiment, a system may include a processor and a plurality of registers. The processor and the plurality of registers may be integrated into a single device, or may be in separate devices. The plurality of registers may include a first set of registers that are directly accessible by the processor, and a second set of registers that are not directly accessible by the processor. The second set of registers may, however, be accessed indirectly by the processor via the first set of registers. In one embodiment, the first set of registers may include a register for selecting a register bank from the second set of registers, and a register for selecting a particular address within the register bank, to allow indirect access by the processor to the registers of the second set.

Owner:MICRON TECH INC

Digital data processing apparatus having multi-level register file

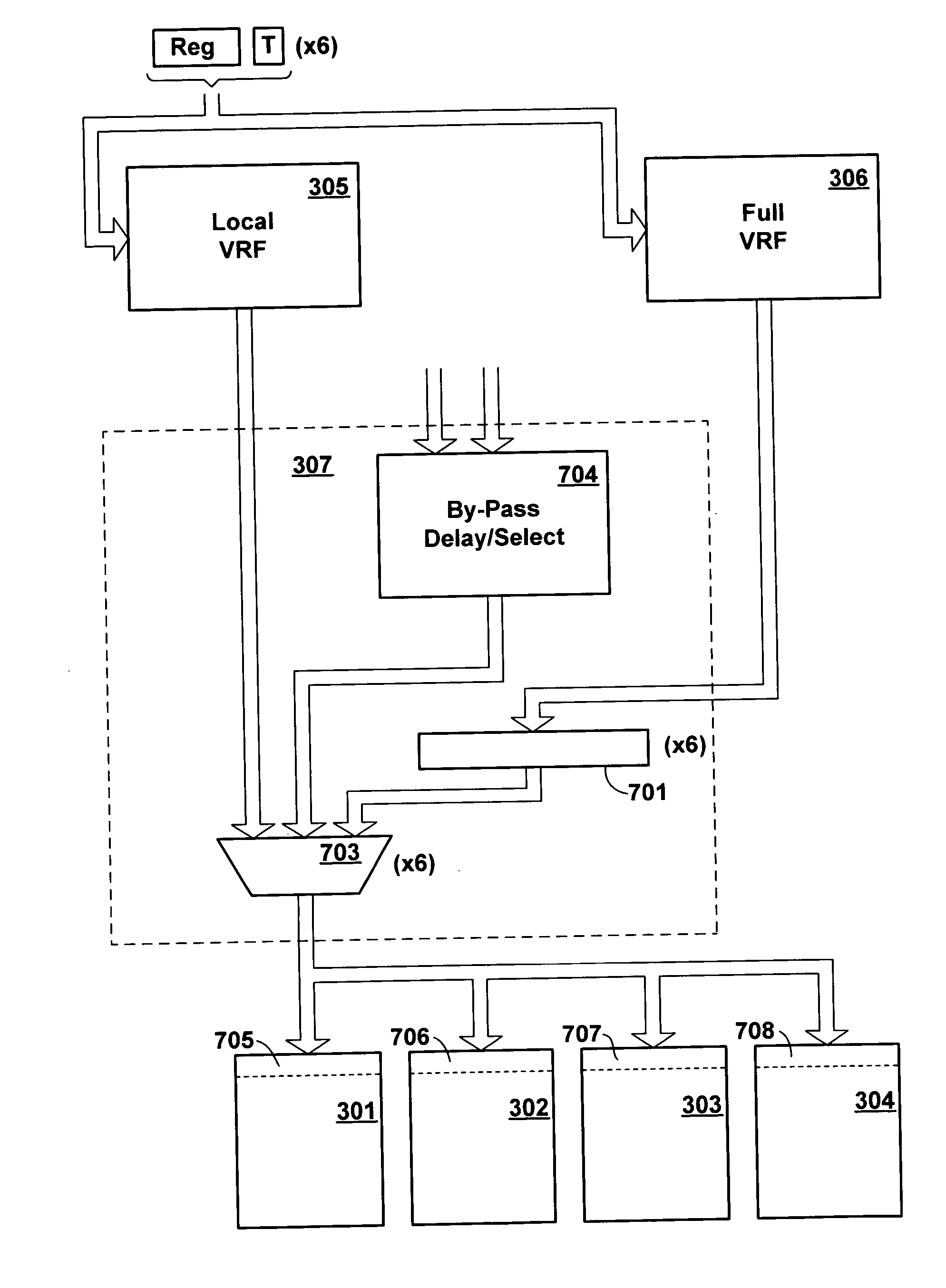

InactiveUS20050289299A1Faster access latency timeSlow access latency timeRegister arrangementsMemory adressing/allocation/relocationDigital dataMemory bank

A processor contains multiple levels of registers having different access latency. A relatively smaller set of registers is contained in a relatively faster higher level register bank, and a larger, more complete set of the registers is contained in a relatively slower lower level register bank. Physically, the higher level register bank is placed closer to functional logic which receives inputs from the registers. Preferably, the lower level bank includes a complete set of all processor registers, and the higher level bank includes a smaller subset of the registers, duplicating information in the lower level bank. The higher level bank is preferably accessible in a single clock cycle.

Owner:IBM CORP

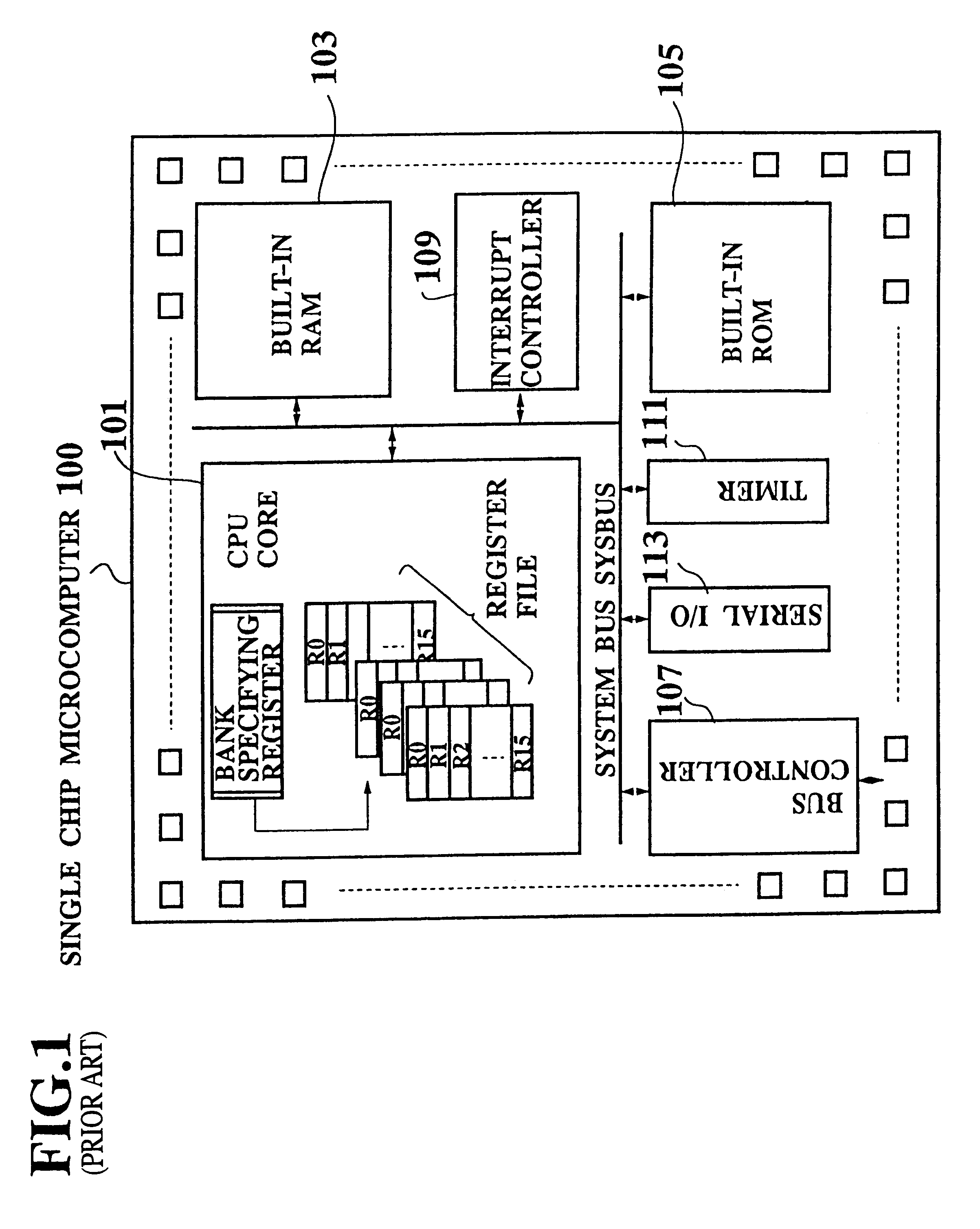

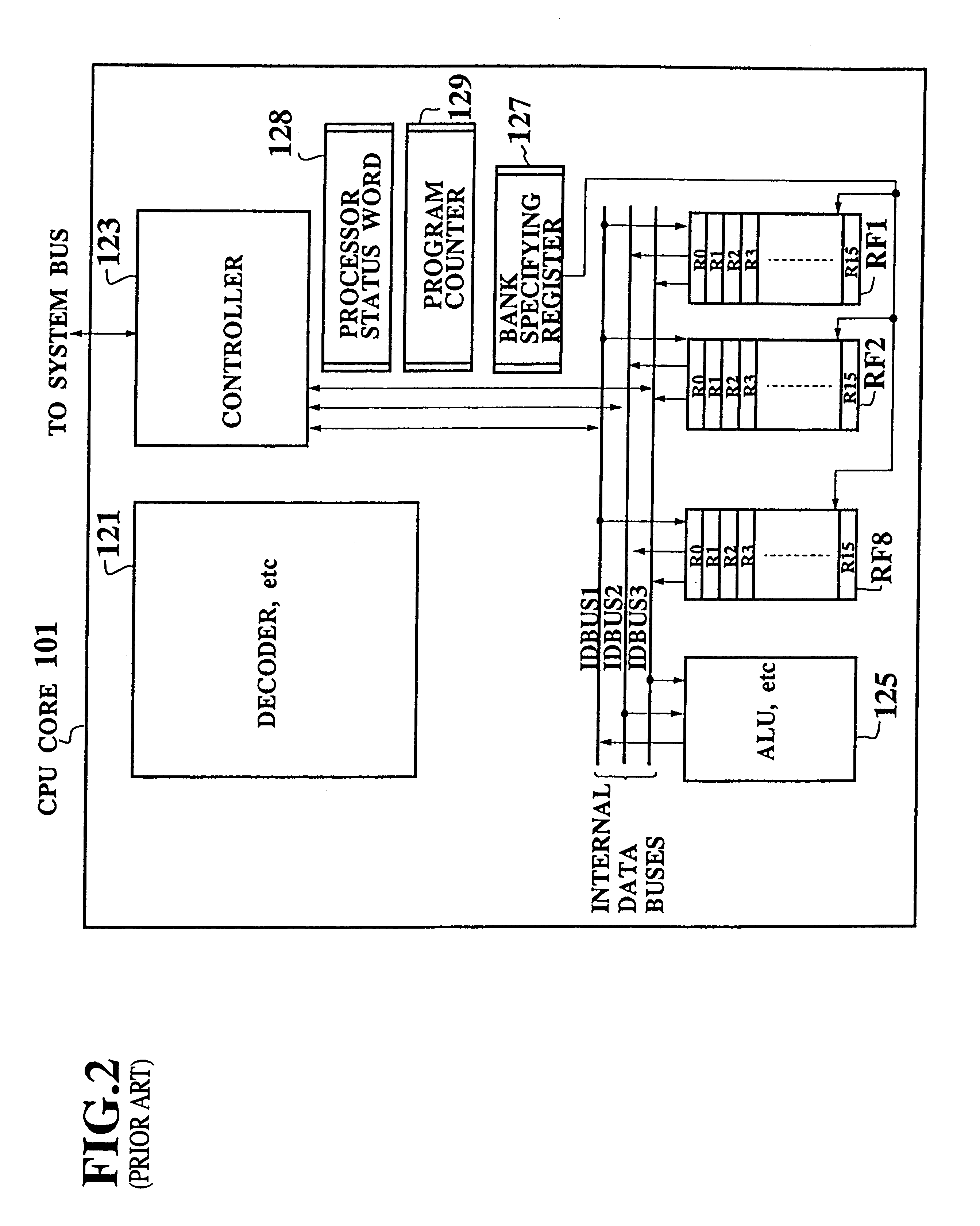

Single chip microcomputer having a dedicated address bus and dedicated data bus for transferring register bank data to and from an on-line RAM

InactiveUS6223279B1Efficiently chip spaceData transferArchitecture with single central processing unitSpecial data processing applicationsGeneral purposeProcessor register

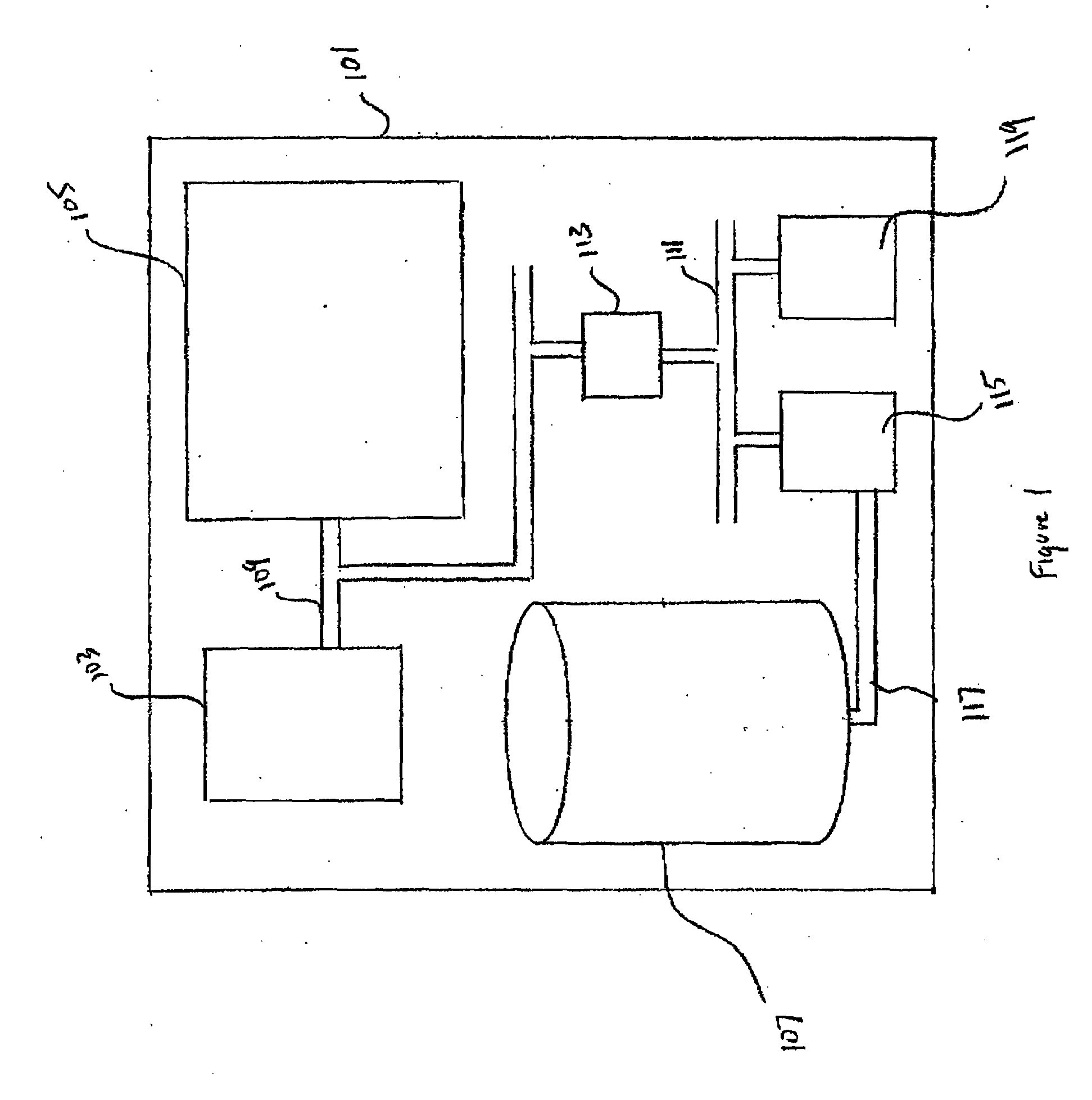

A single chip microcomputer comprises a central processing unit (CPU) 2, a on-chip RAM 3, a on-chip ROM 5, a first bus DBUS for connecting the CPU, RAM, and ROM with one another and transferring data between them, a second bus ABUS for passing address data corresponding to the data passed through the first bus, a third bus SDBUS for connecting the CPU 2 with the RAM 3 and transferring data between them, the number of bits of the third bus SDBUS being larger than that of the first bus DBUS, and a fourth bus BABUS for connecting the CPU 2 with the RAM 3 and passing address data corresponding to the data passed through the third bus SDBUS. The CPU 2 has a data memory RF serving as general purpose registers for providing internal data to the third bus SDBUS, and a bank specifying register BP for holding positional data of a mapping region in the RAM 3 where the contents of the data memory RF are mapped and providing the positional data to the fourth bus BABUS. The RAM 3 has a memory cell array 31, a bank address control circuit 35 connected to the fourth bus BABUS, for generating a real address according to the contents of the bank specifying register BP (BP0, BP1), and a selection circuit 37 for selecting the real address generated by the bank address control circuit 35, or the address provided through the second bus ABUS.

Owner:KK TOSHIBA

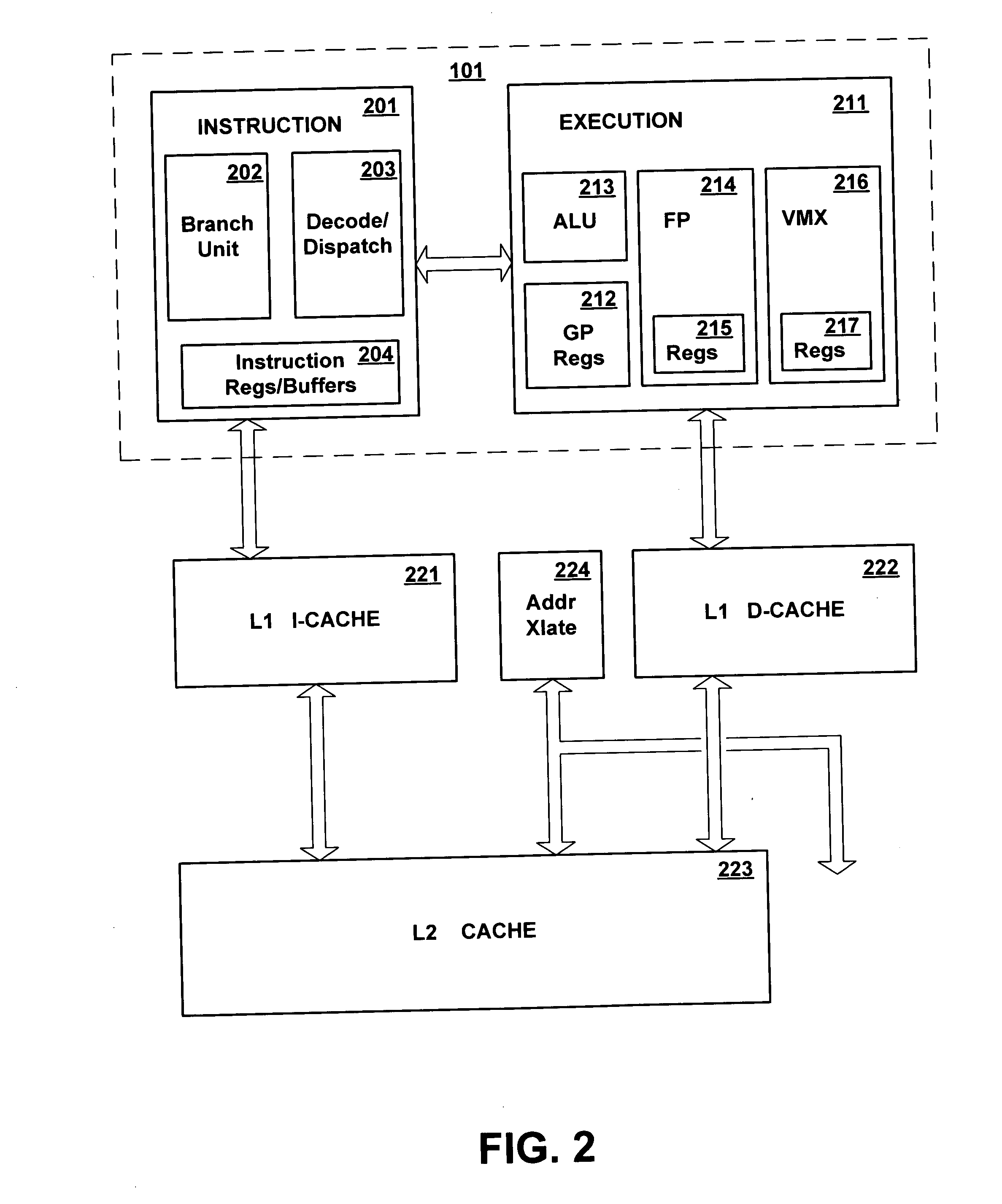

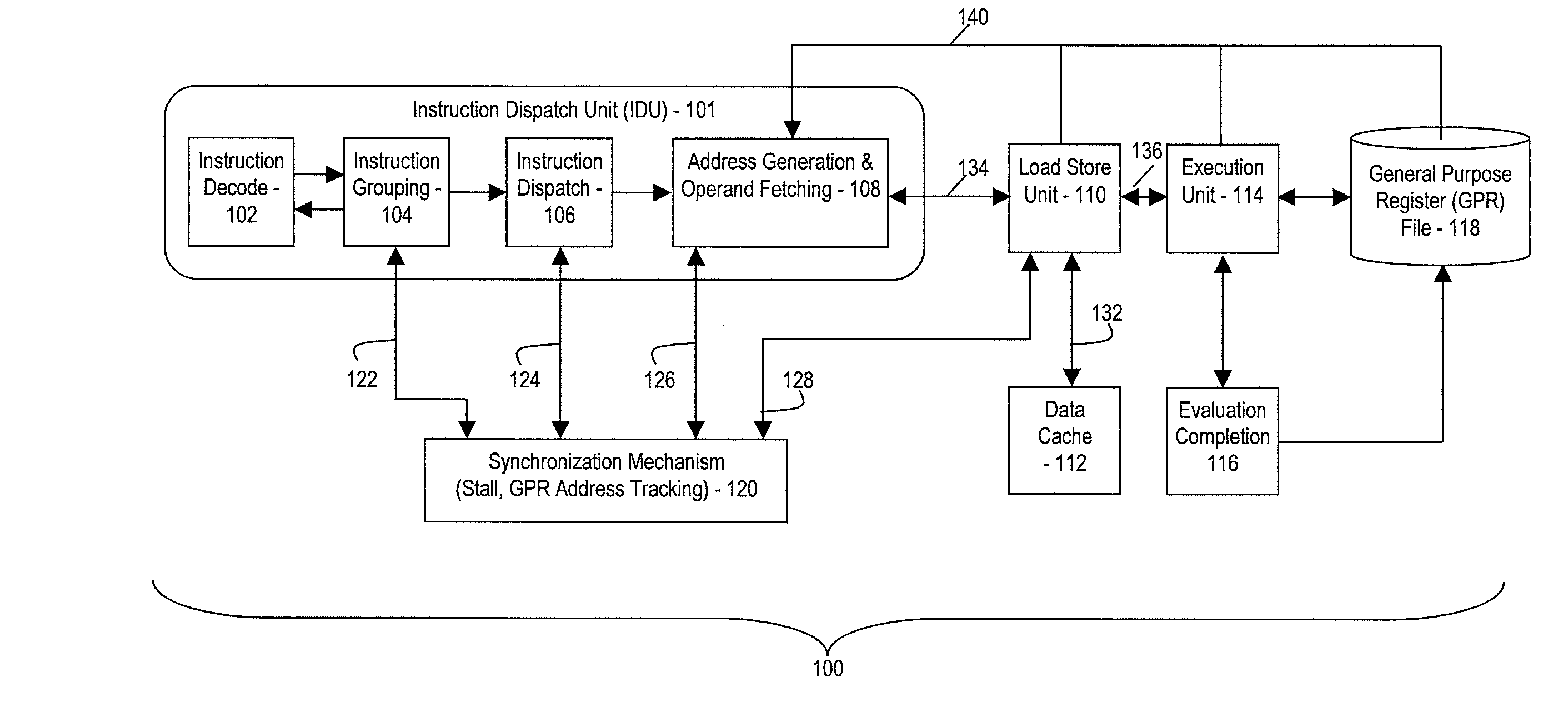

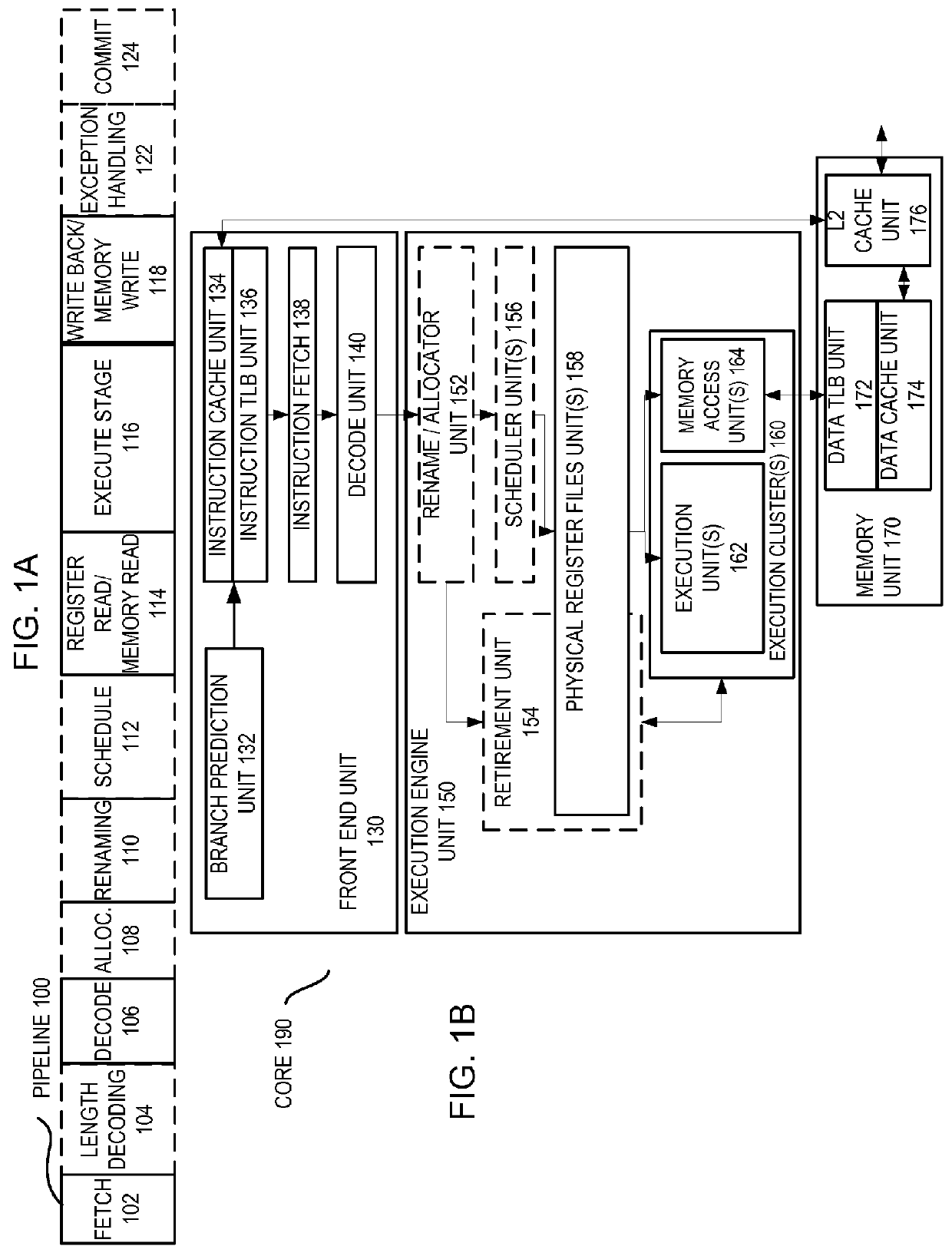

Processor and method for synchronous load multiple fetching sequence and pipeline stage result tracking to facilitate early address generation interlock bypass

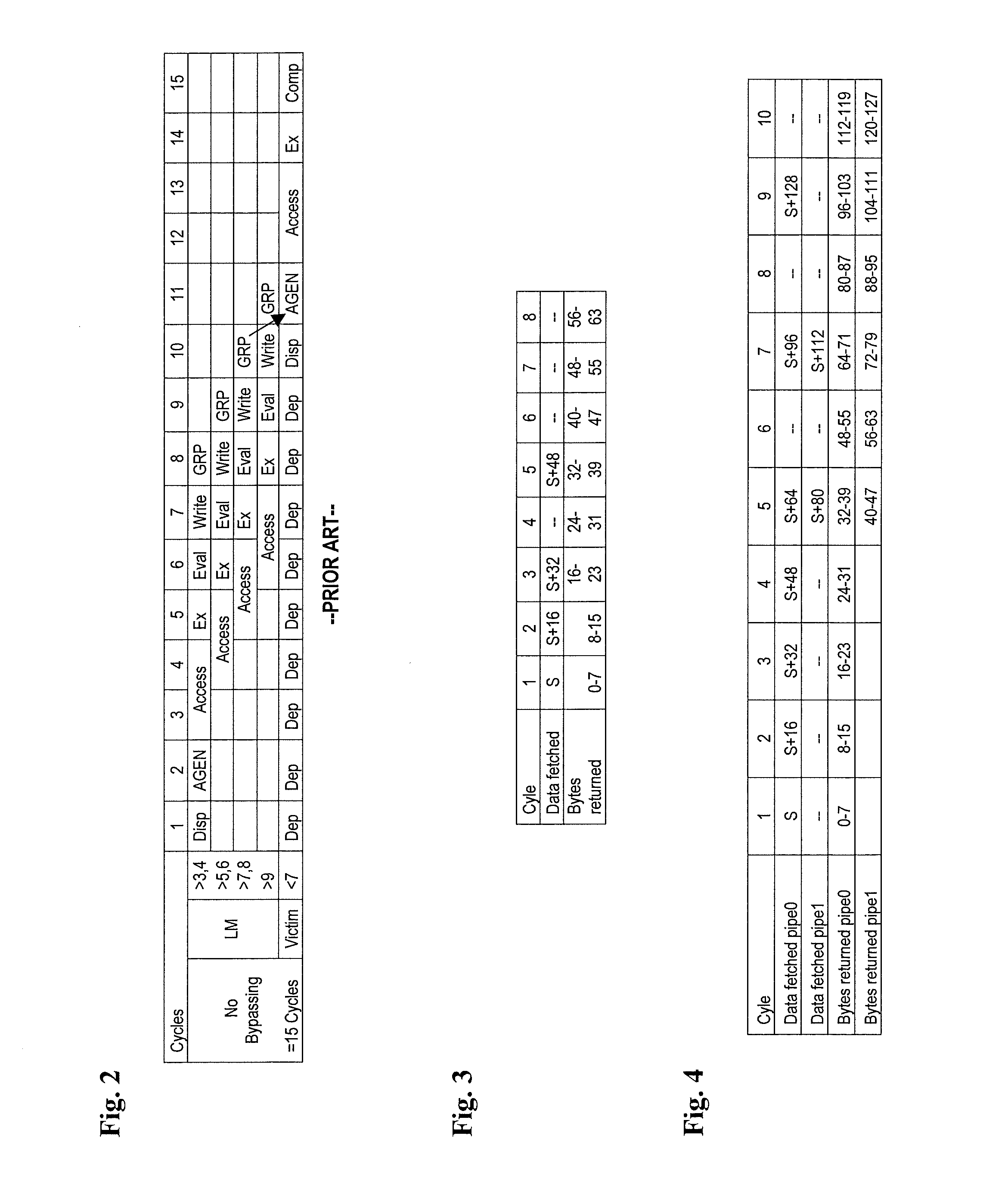

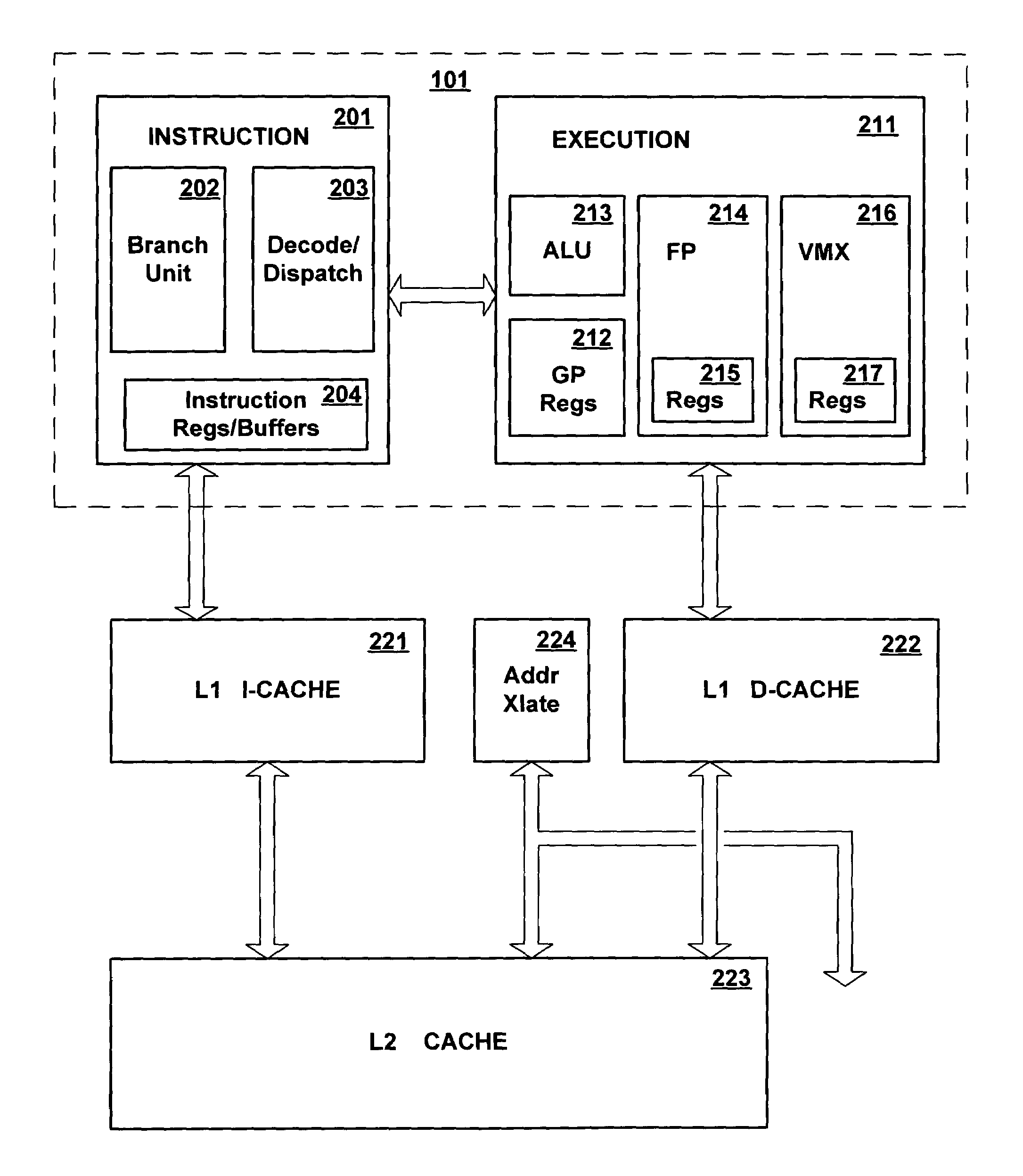

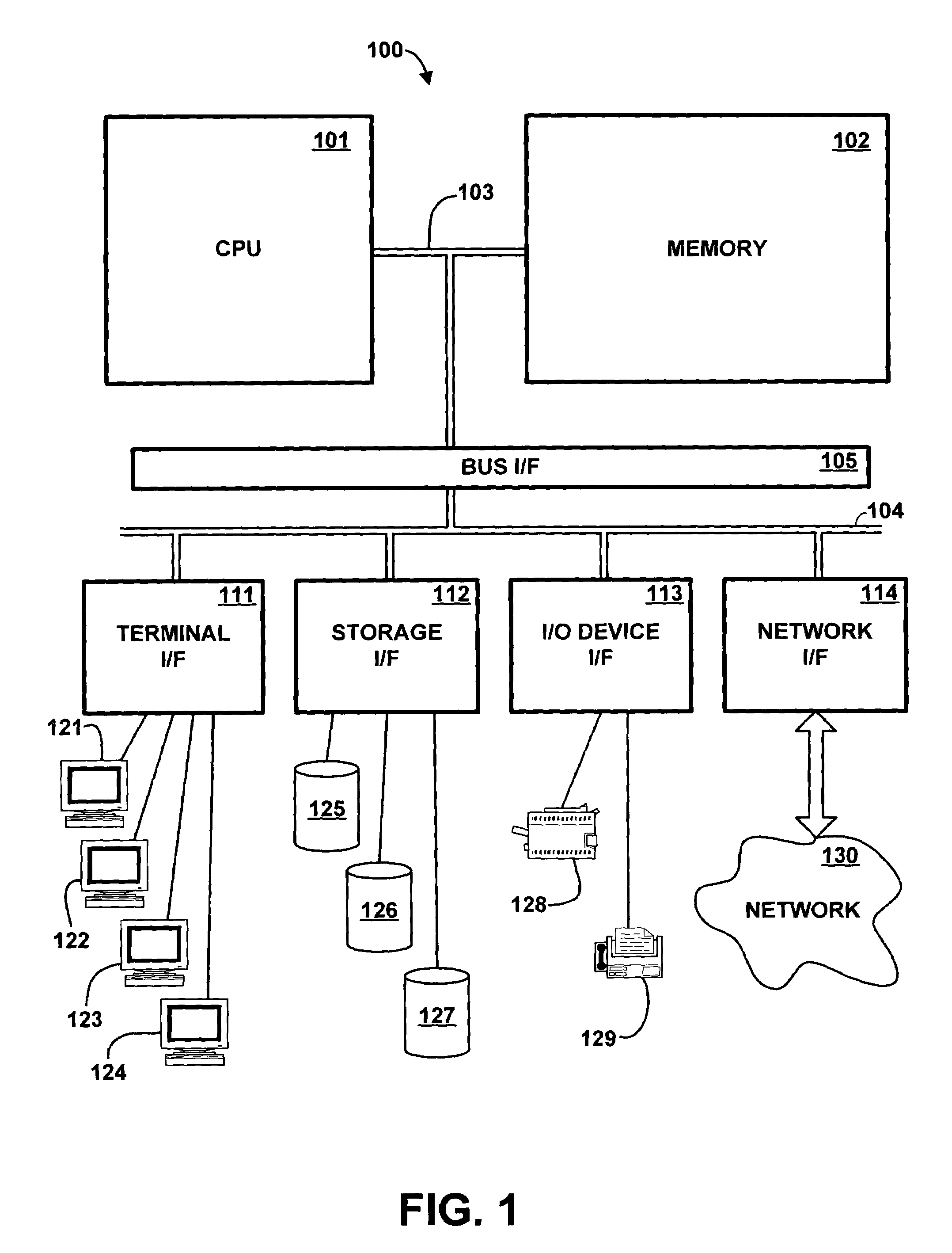

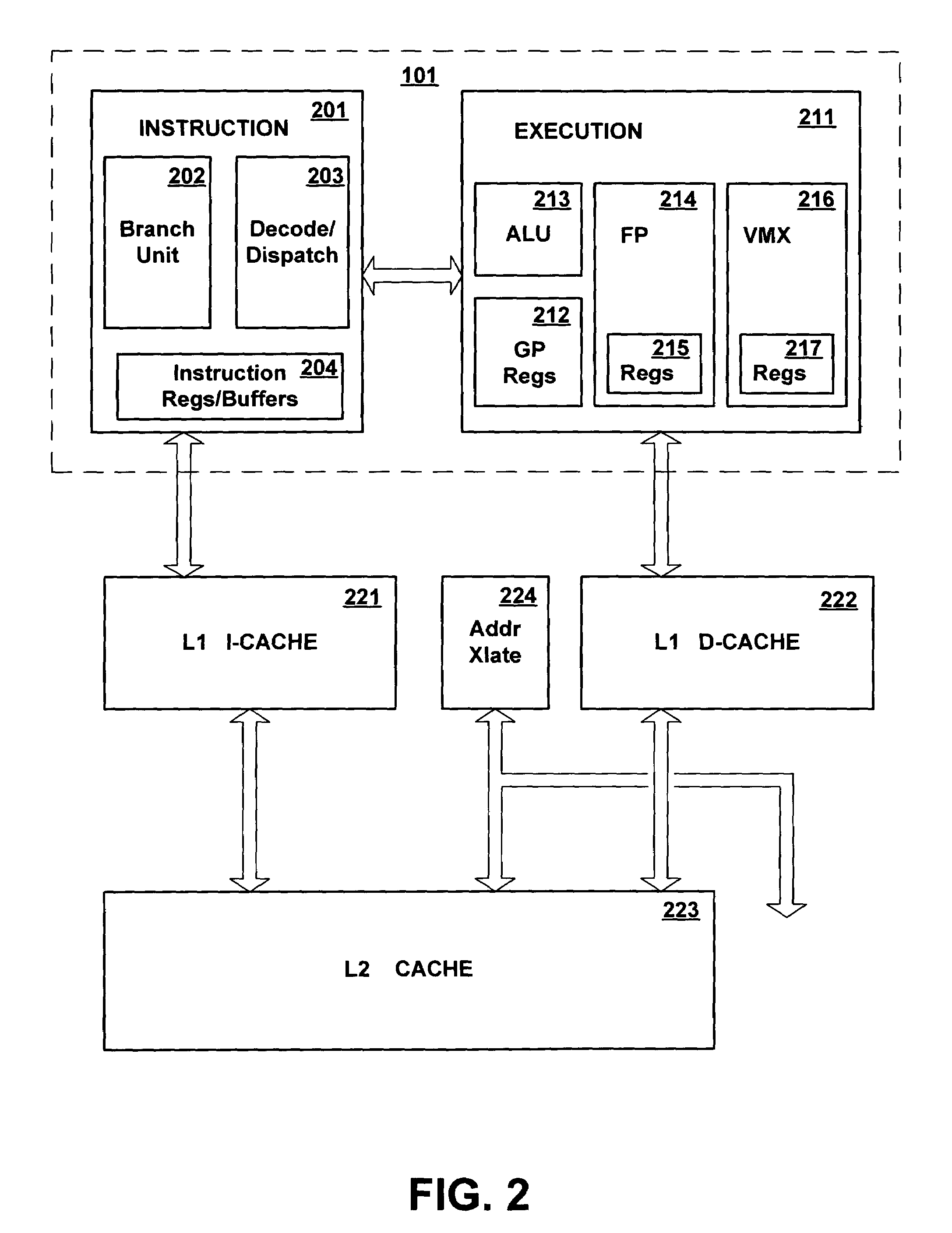

A pipelined processor including an architecture for address generation interlocking, the processor including: an instruction grouping unit to detect a read-after-write dependency and to resolve instruction interdependency; an instruction dispatch unit (IDU) including address generation interlock (AGI) and operand fetching logic for dispatching an instruction to at least one of a load store unit and an execution unit; wherein the load store unit is configured with access to a data cache and to return fetched data to the execution unit; wherein the execution unit is configured to write data into a general purpose register bank; and wherein the architecture provides support for bypassing of results of a load multiple instruction for address generation while such instruction is executing in the execution unit before the general purpose register bank is written. A method and a computer system are also provided.

Owner:IBM CORP

Digital data processing apparatus having multi-level register file

InactiveUS7284092B2Faster access latency timeShorten the timeRegister arrangementsMemory adressing/allocation/relocationProcessor registerElectronic data processing

A processor contains multiple levels of registers having different access latency. A relatively smaller set of registers is contained in a relatively faster higher level register bank, and a larger, more complete set of the registers is contained in a relatively slower lower level register bank. Physically, the higher level register bank is placed closer to functional logic which receives inputs from the registers. Preferably, the lower level bank includes a complete set of all processor registers, and the higher level bank includes a smaller subset of the registers, duplicating information in the lower level bank. The higher level bank is preferably accessible in a single clock cycle.

Owner:IBM CORP

Direct mapped repair cache systems and methods

The present invention facilitates memory devices and operation thereof by employing a repair cache system 600 to correct or repair identified faulty memory locations. The repair cache system 600 includes a repair verification router that compares a memory address 604 for a read / write request to a list or series of repair locations 608. On identifying a matching repair location, a repair register 616 located within a repair register bank 615 is coupled to a data bus 626. Otherwise, a memory location within the main memory 630 and addressed by the memory address 604 is coupled to the data bus 626.

Owner:TEXAS INSTR INC

Techniques for hardware-assisted multi-threaded processing

ActiveUS20070294694A1Digital computer detailsSpecific program execution arrangementsThread schedulingProcessor register

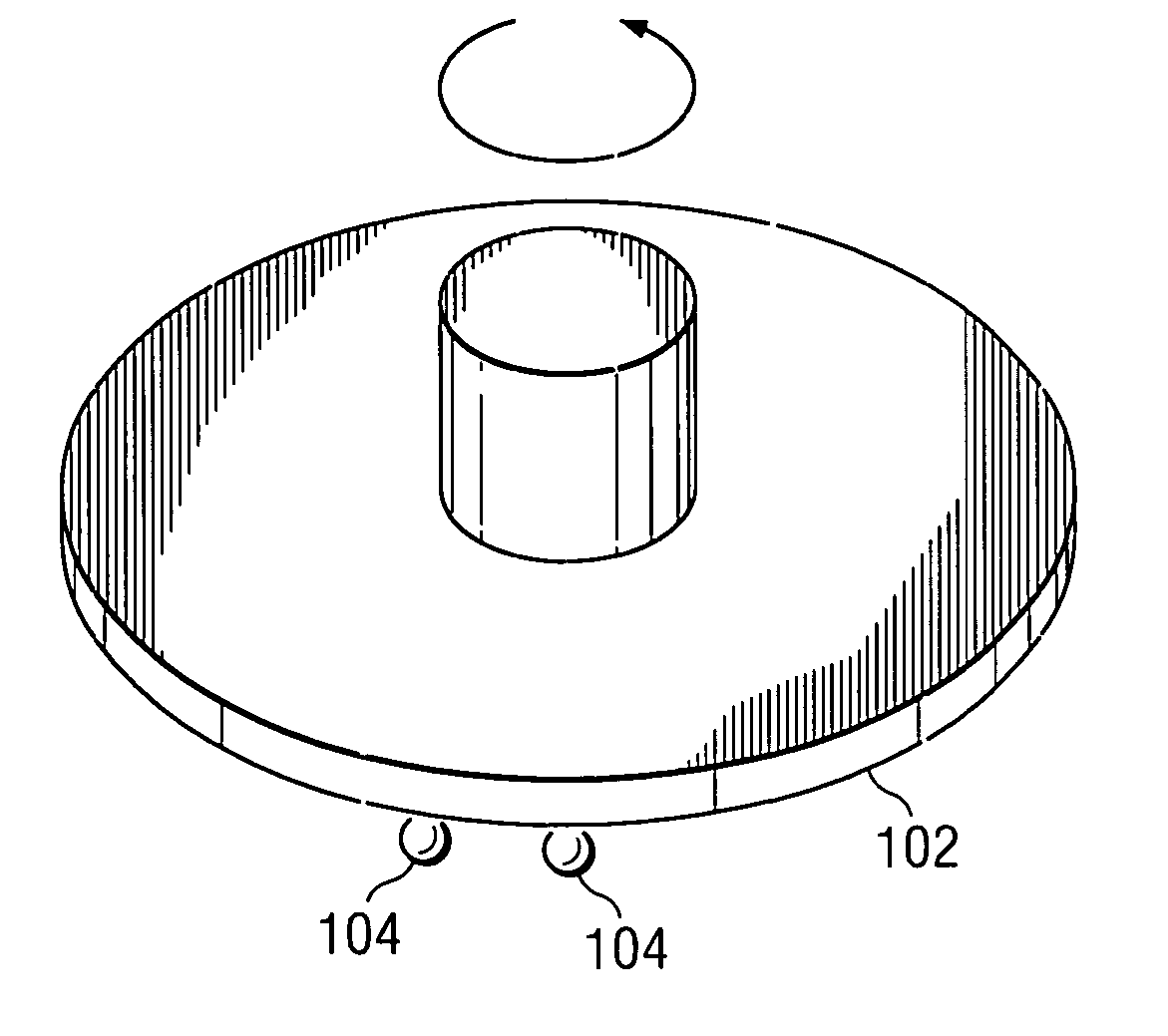

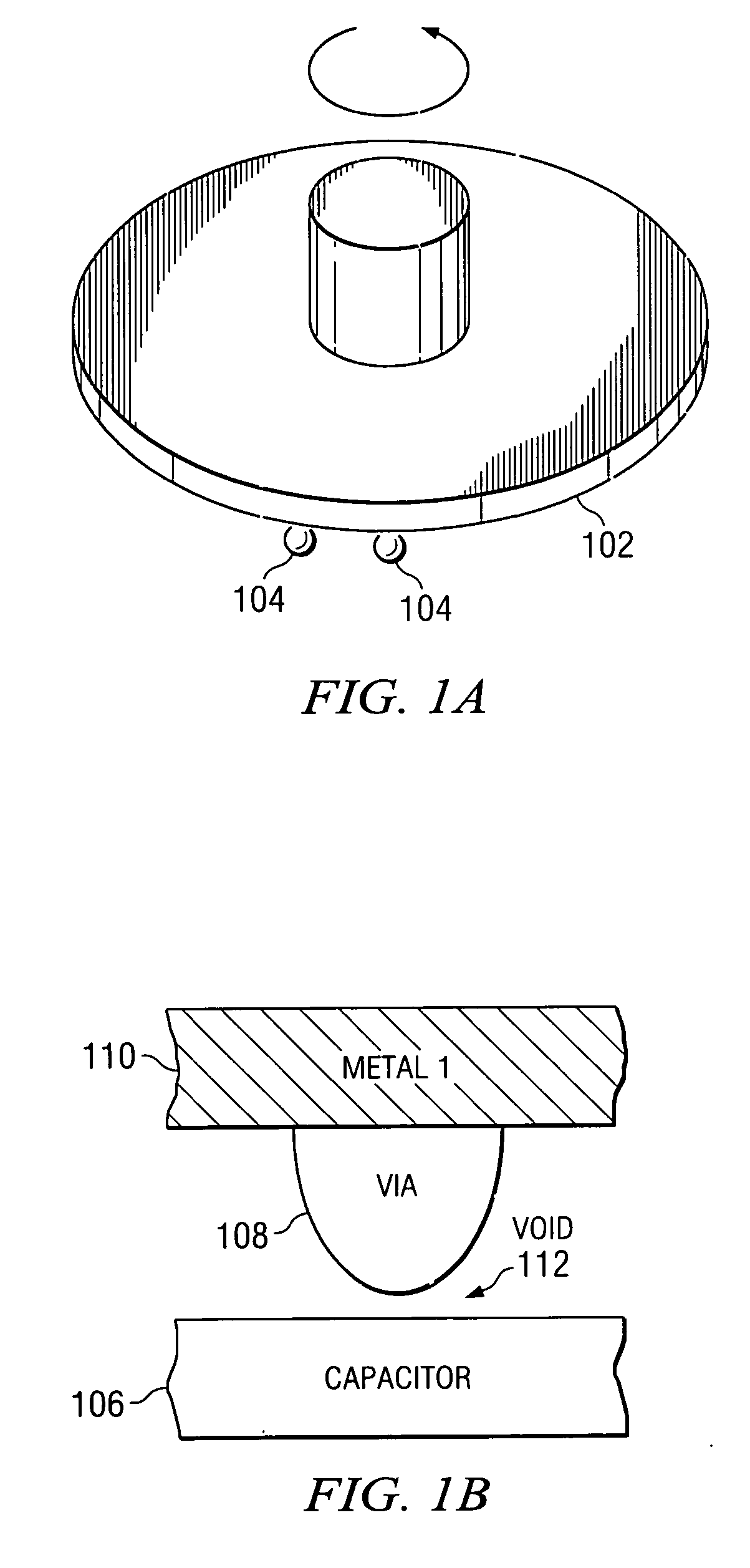

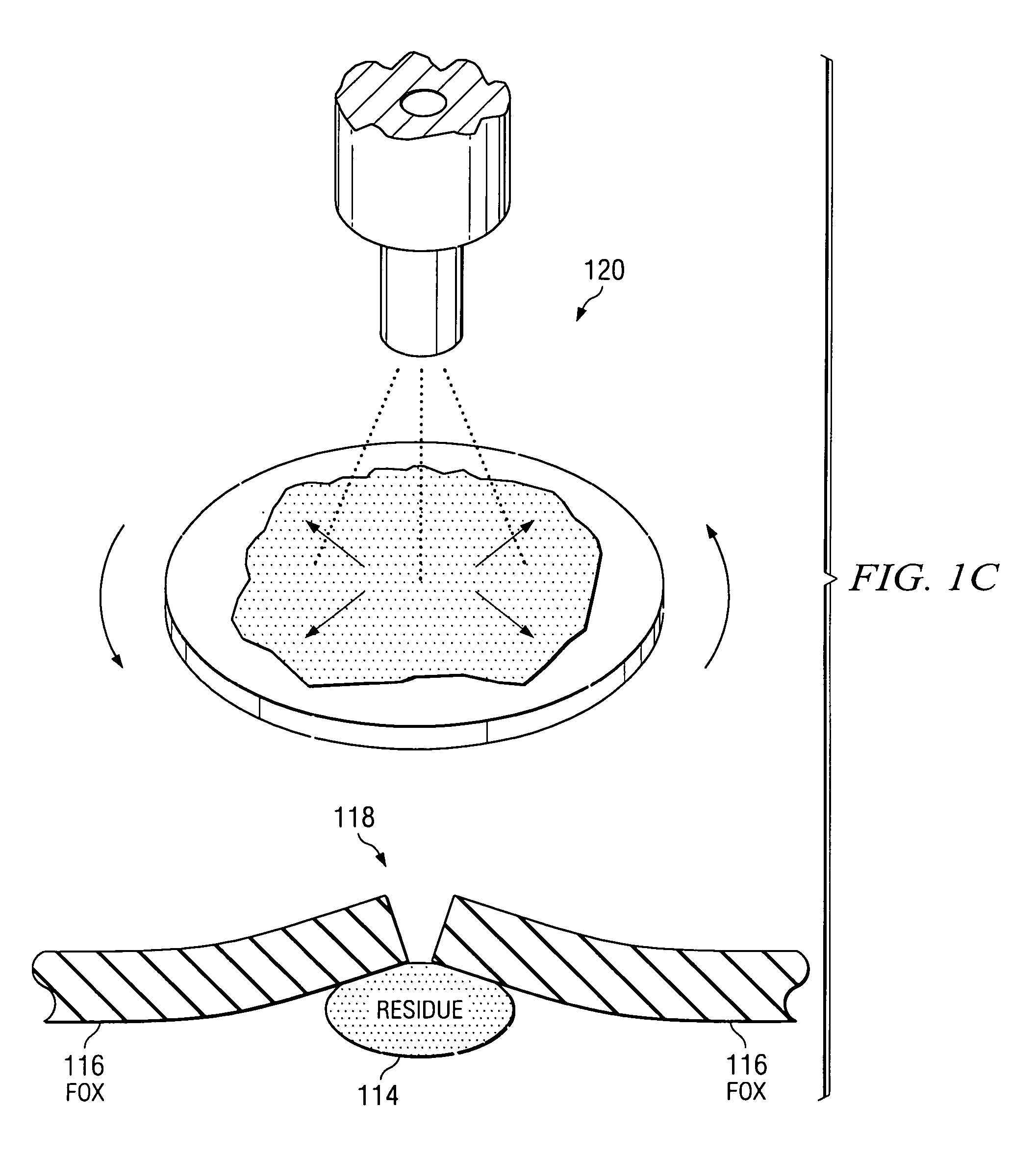

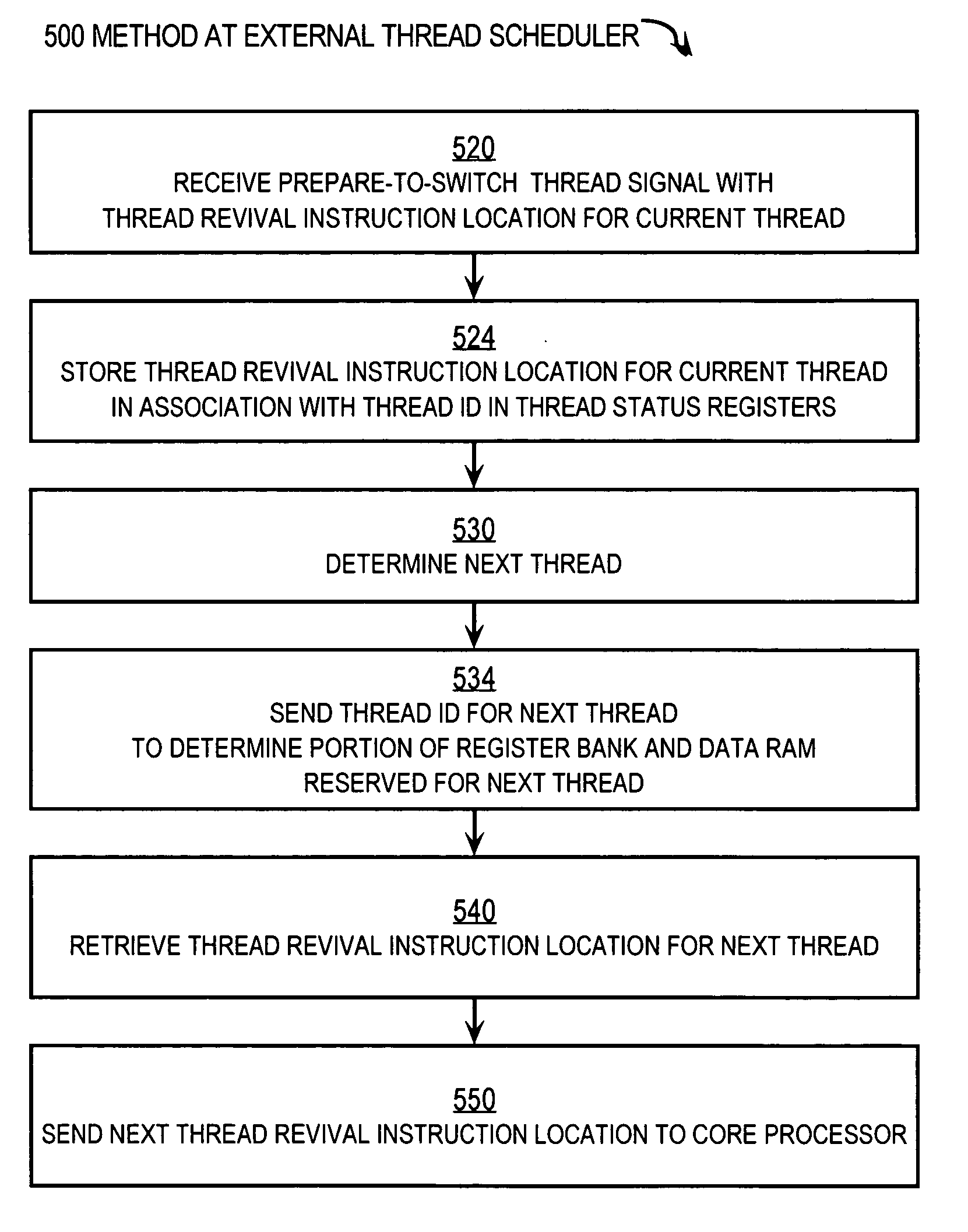

Techniques for processing each of multiple threads that share a core processor include receiving an intra-thread register address from the core processor. This address contains C bits for accessing each of 2c registers for each thread. A thread ID is received from a thread scheduler external to the core processor. The Thread ID contains T bits for indicating a particular thread for up to 2T threads. A particular register is accessed in a register bank that has 2(C+T) registers using an inter-thread address that includes both the intra-thread register address and the thread ID. The particular register holds contents for the intra-thread register address for a thread having the thread ID. Consequently, register contents of all registers of all threads reside in the register bank. Thread switching is accomplished rapidly by simply accessing different slices in the register bank, without swapping contents between a set of registers and memory.

Owner:CISCO TECH INC

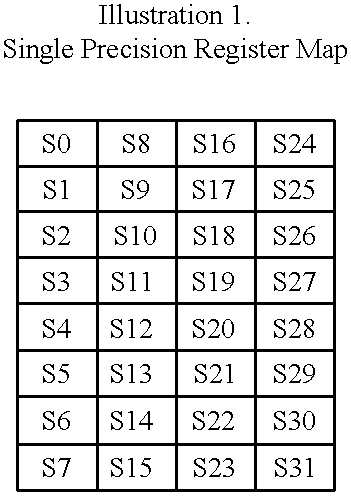

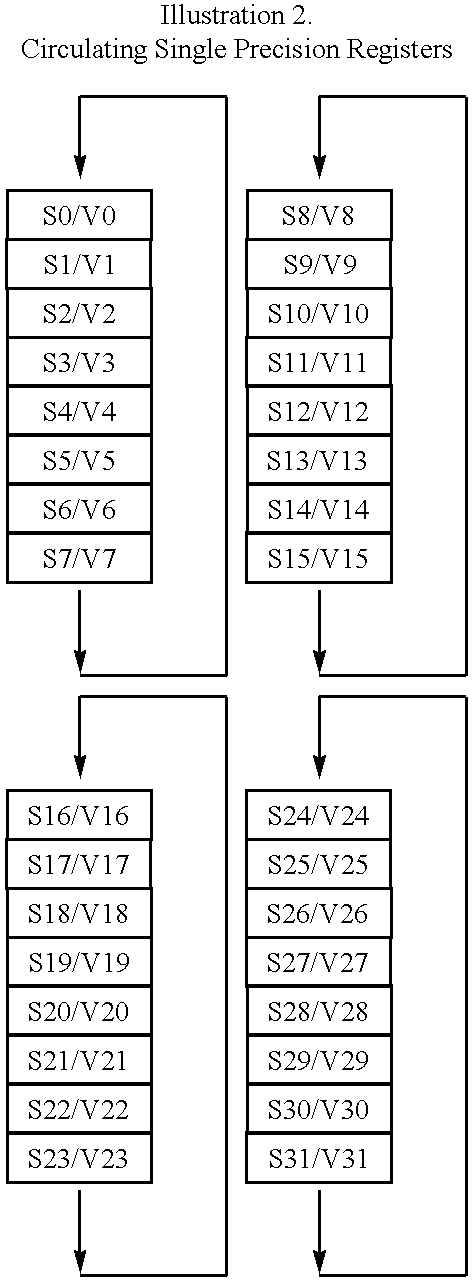

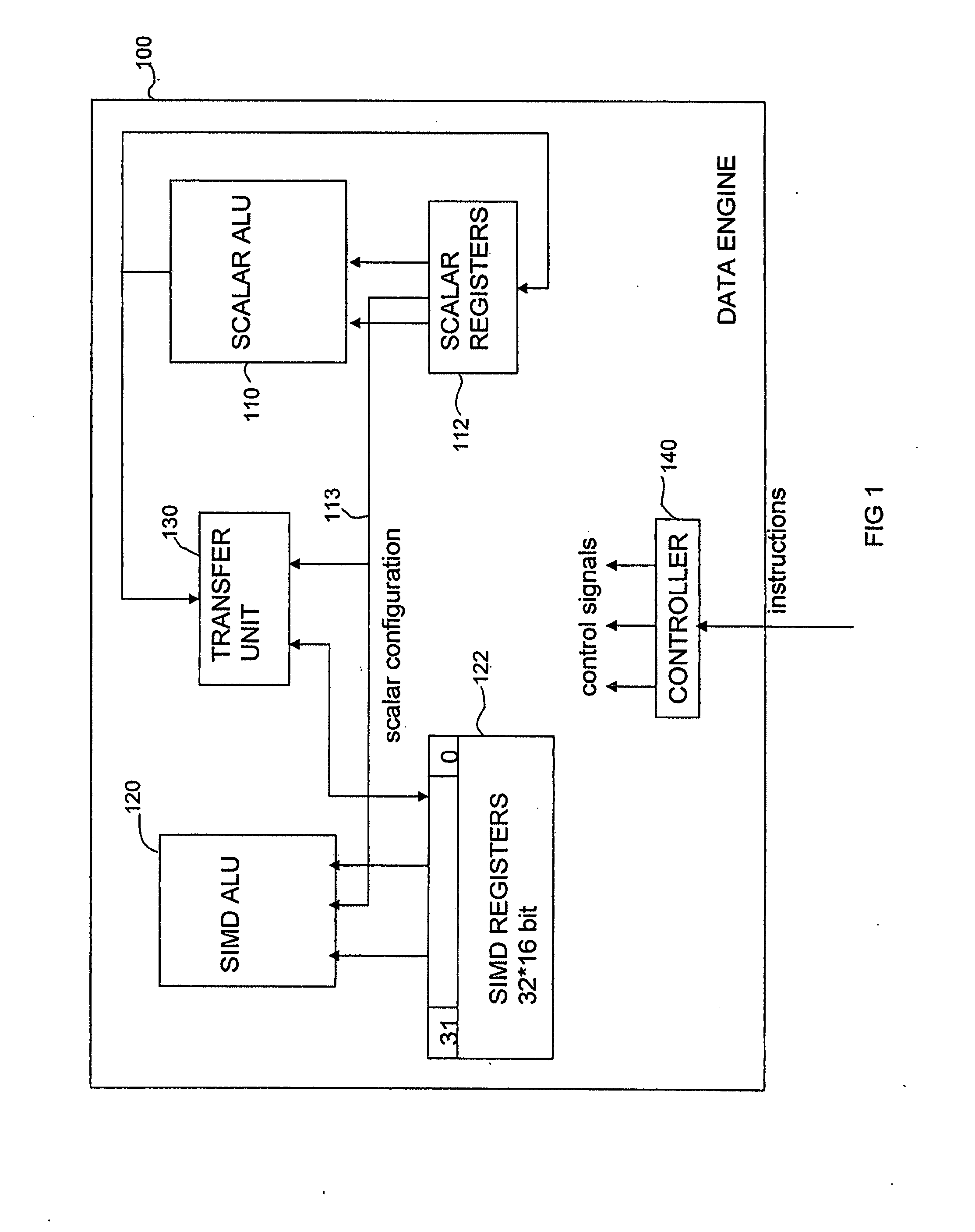

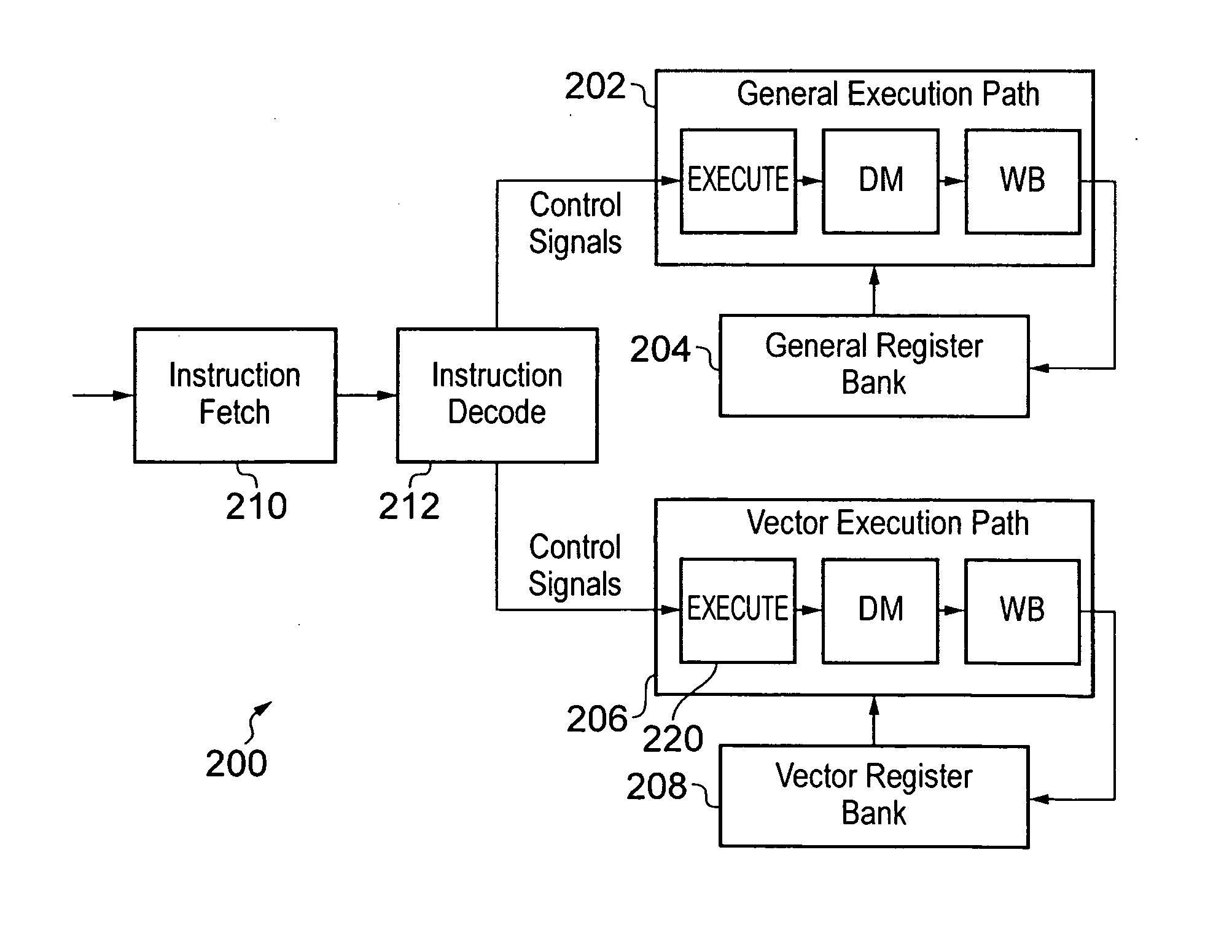

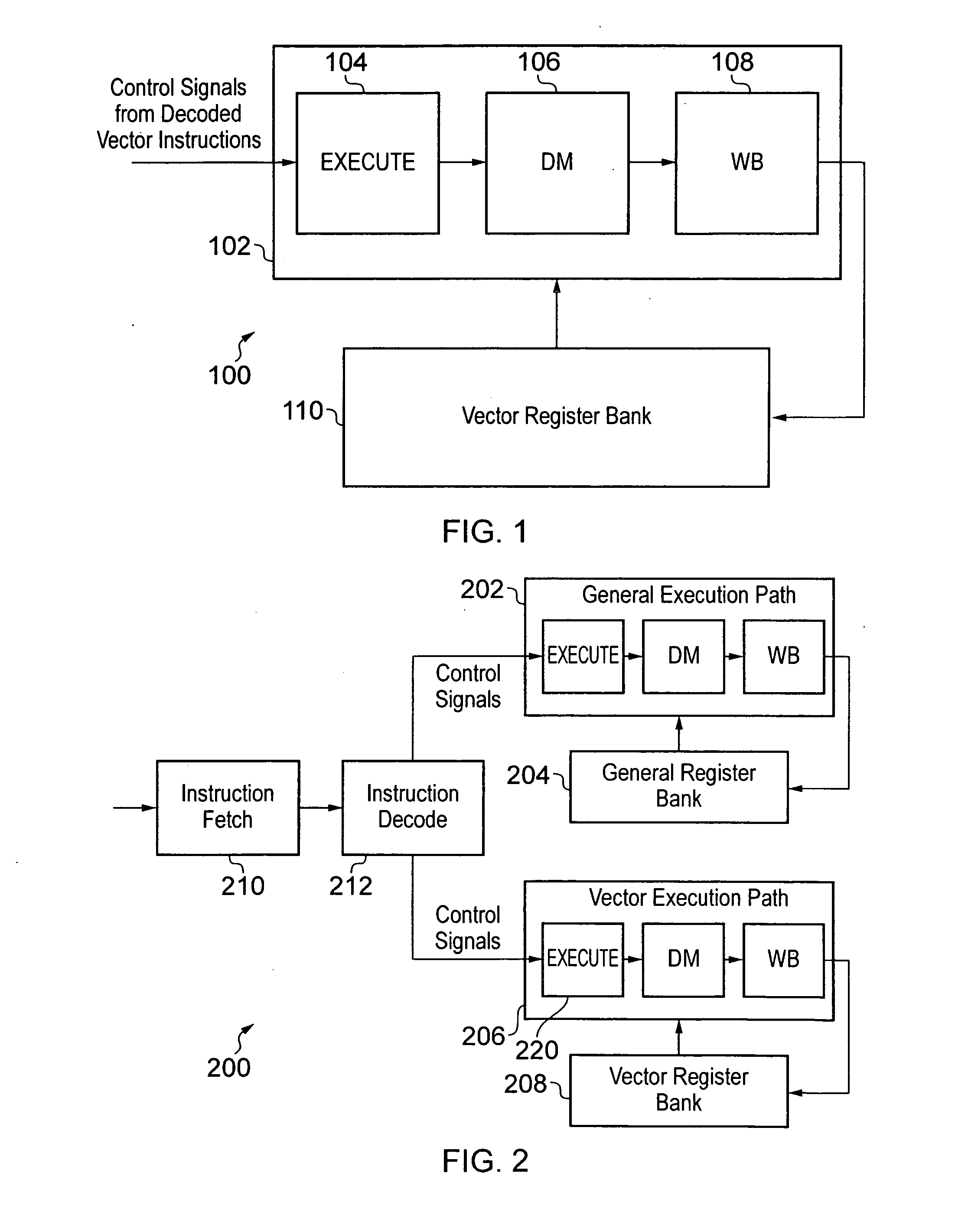

Apparatus and method for processing data having a mixed vector/scalar register file

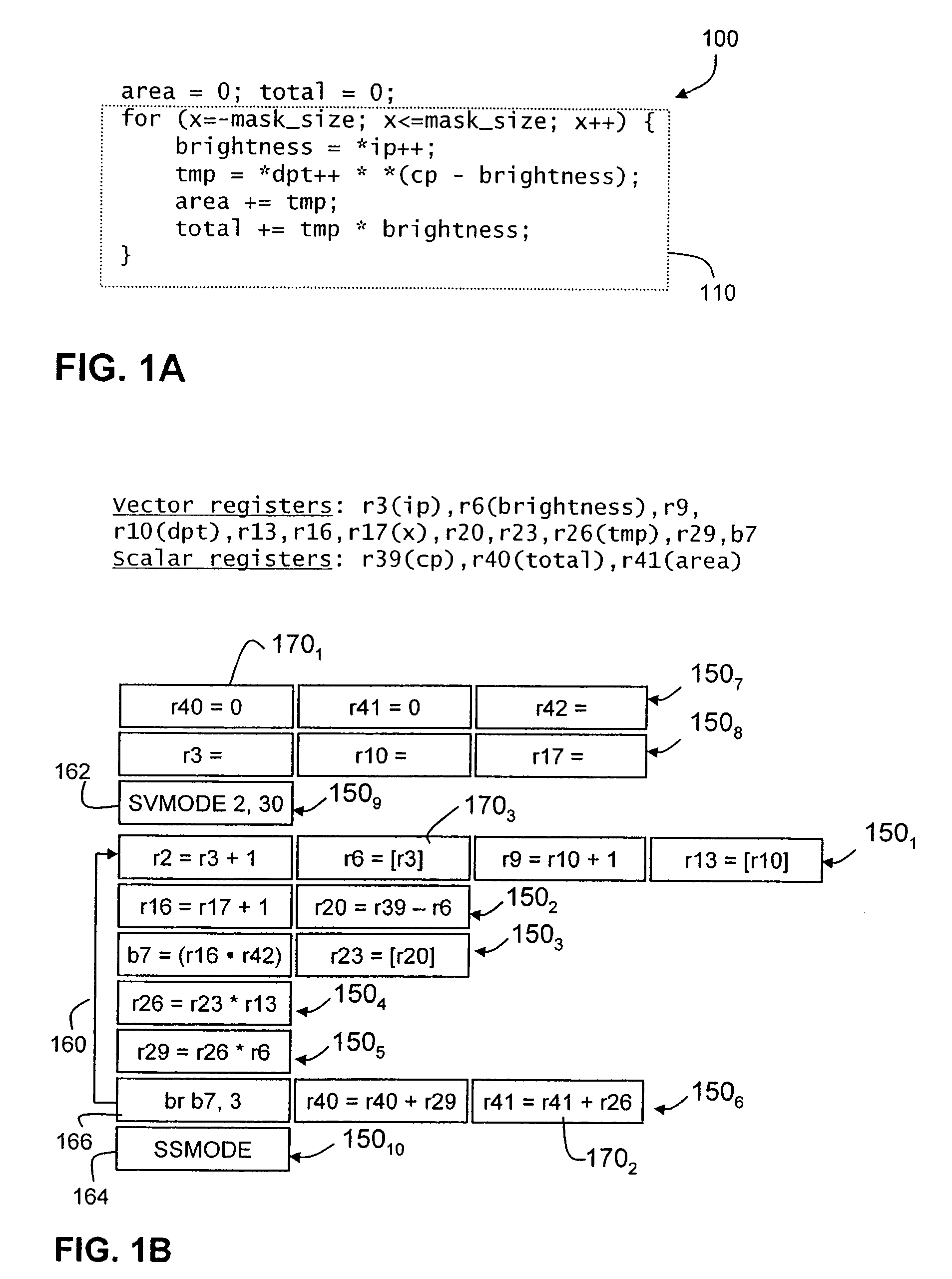

InactiveUS6282634B1Easy to useLarger register bankRegister arrangementsInstruction analysisProcessor registerFloating-point unit

A floating point unit is provided with a register bank comprising 32 registers that may be used as either vector registers of scalar registers. A data processing instruction includes at least one register specifying field pointing to a register containing a data value to be used in that operation. An increase in the instruction bit space available to encode more opcodes or to allow for more registers is provided by encoding whether a register is to be treated as a vector or a scalar within the register field itself. Further, the register field for one register of the instruction may encode whether another register is a vector or a scalar. The registers can be initially accessed using the values within the register fields of the instruction independently of the opcode allowing for easier decode.

Owner:ARM LTD

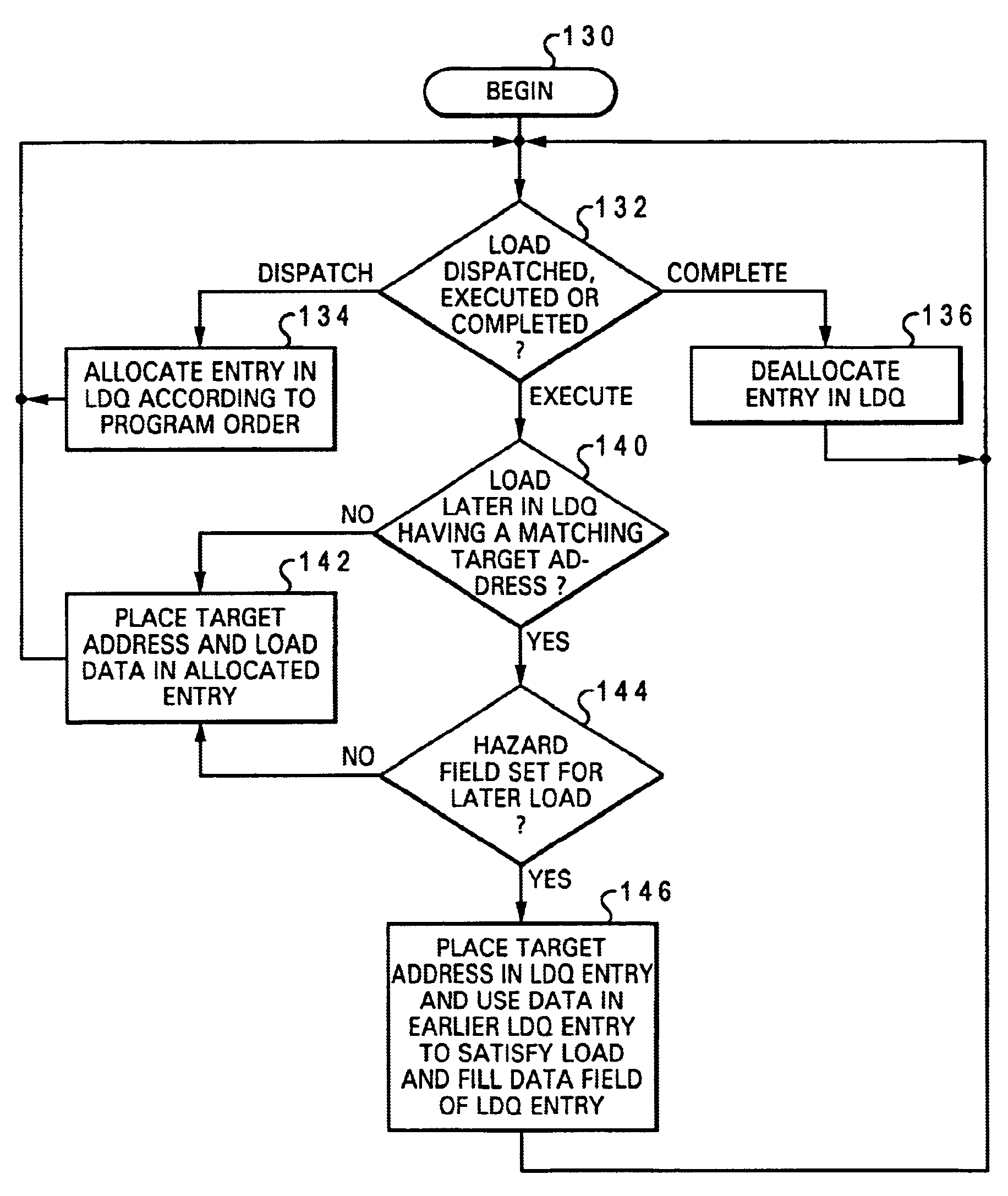

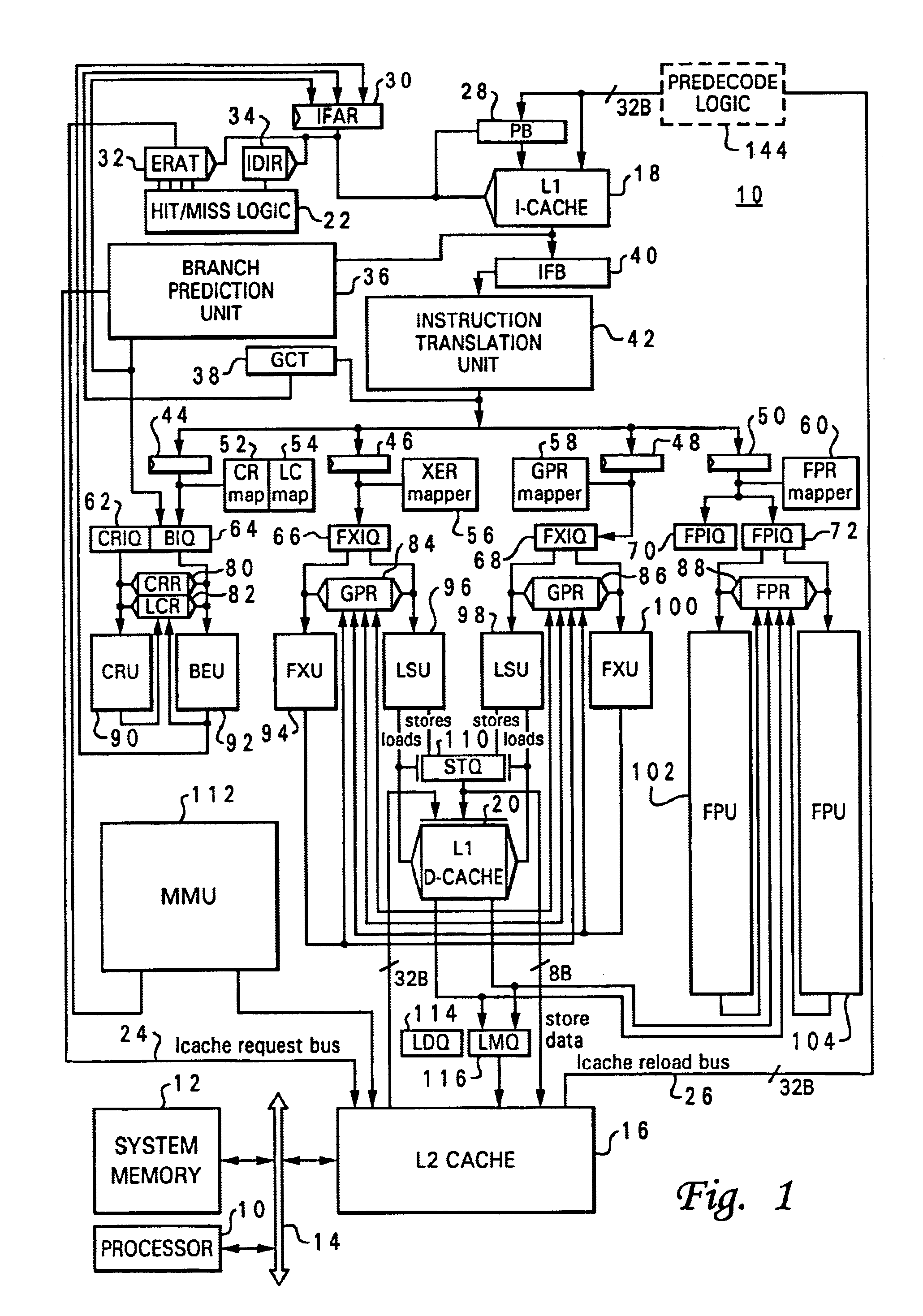

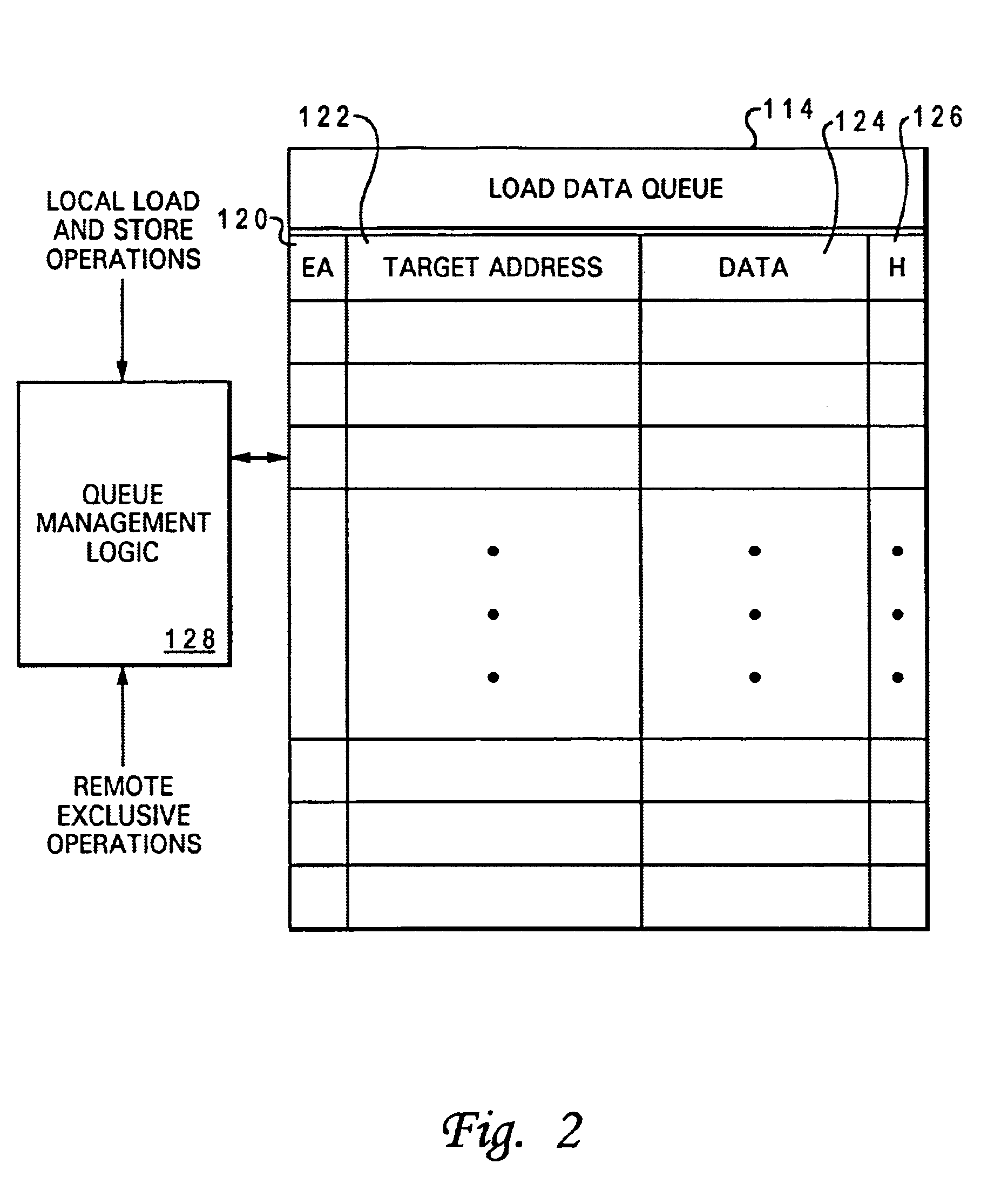

Processor and method of executing load instructions out-of-order having reduced hazard penalty

InactiveUS6868491B1Reduce performance lossLower performance requirementsRuntime instruction translationDigital computer detailsLoad instructionProcessor register

A processor having a reduced data hazard penalty includes a register set, at least one execution unit that executes load instructions to transfer data into the register set, and a load queue. The load queue contains at least one entry, and each occupied entry in the load queue stores load data retrieved by an executed load instruction in association with a target address of the executed load instruction. The load queue has associated queue management logic that, in response to execution by the execution unit of a load instruction, determines by reference to the load queue whether a data hazard exists for the load instruction. If so, the queue management logic outputs load data from the load queue to the register set in accordance with the load instruction, thus eliminating the need to flush and re-execute the load instruction.

Owner:INTEL CORP

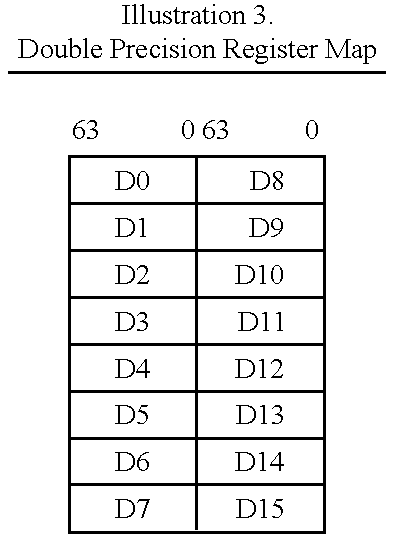

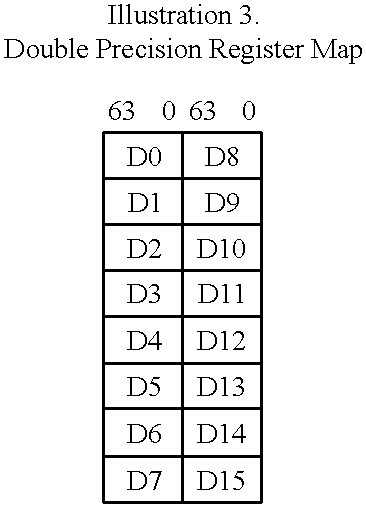

System for transfering format data from format register to memory wherein format data indicating the distribution of single or double precision data type in the register bank

InactiveUS6170001B1Adversely affecting processing speedData processing applicationsRegister arrangementsProcessor registerParallel computing

A data processing apparatus and method is provided, wherein in a first mode of operation, data of a first data type is processed, and in a second mode of operation, data of a second data type consisting of an even multiple of data words is processed. The data processing apparatus comprises a register bank having a plurality of data slots for storing data words of data of said first type data and data words of data of said second type data, and transfer logic, responsive to a store instruction, to control the storing of the data words in the register bank to a memory. Further, a format register is provided for storing format data indicating the distribution in the register bank of data words of data of said first data type and data words of data of said second data type. In said second mode, the transfer logic is responsive to said store instruction specifying an even number of data words to cause those data words to be stored from said register bank to said memory, and is responsive to said store instruction specifying an odd number of data words, to cause the format data from the format register to be stored to said memory along with an even number of data words from the register bank.Hence, in situations where the data in the register bank needs to be temporarily stored to memory for subsequent retrieval into the register bank, all that is required is for the store instruction to be issued in said second mode specifying an odd number of data words, and this will automatically cause the contents of the format register to be stored to memory in addition to the required even number of data words from the register bank.

Owner:ARM LTD

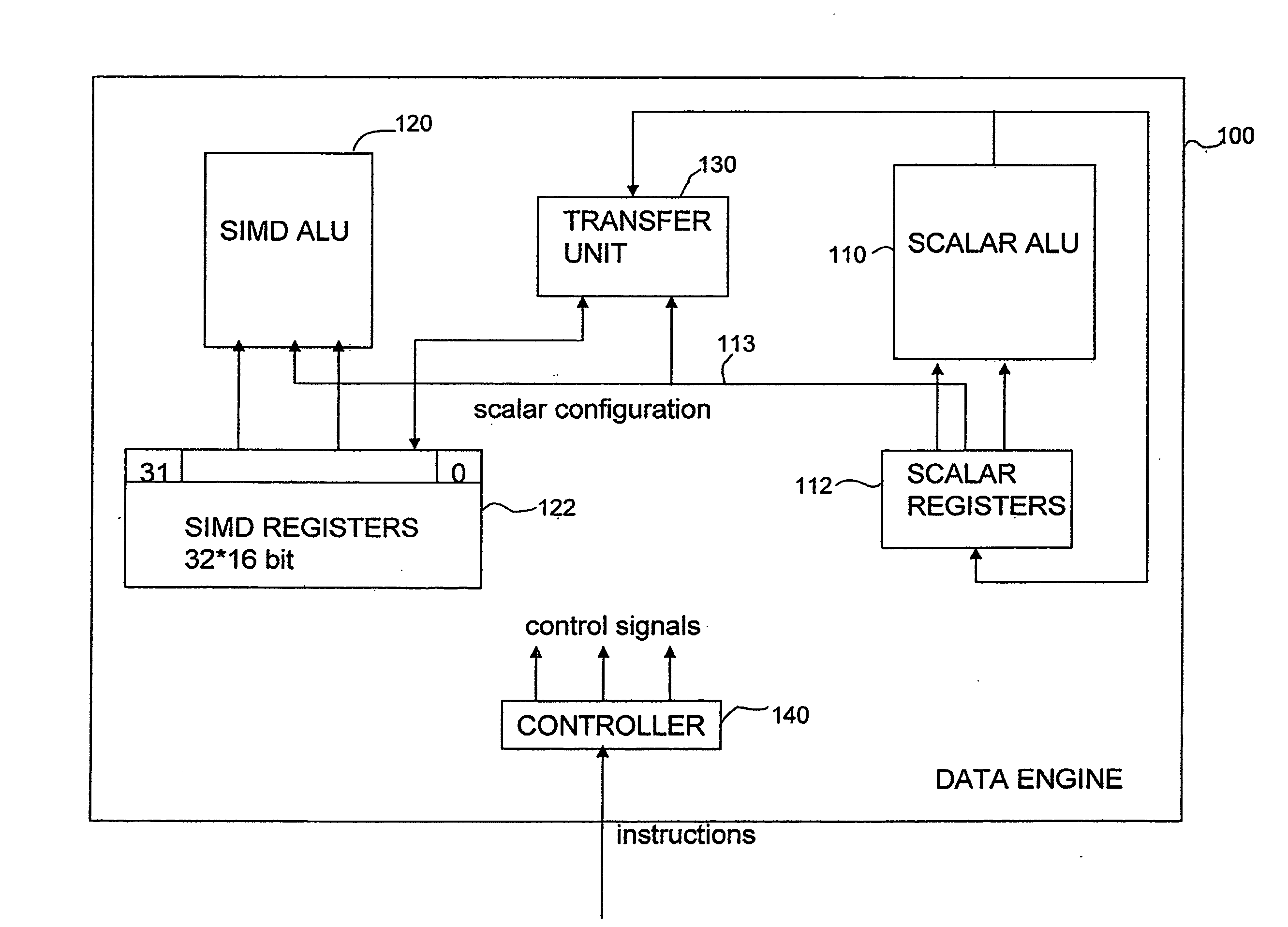

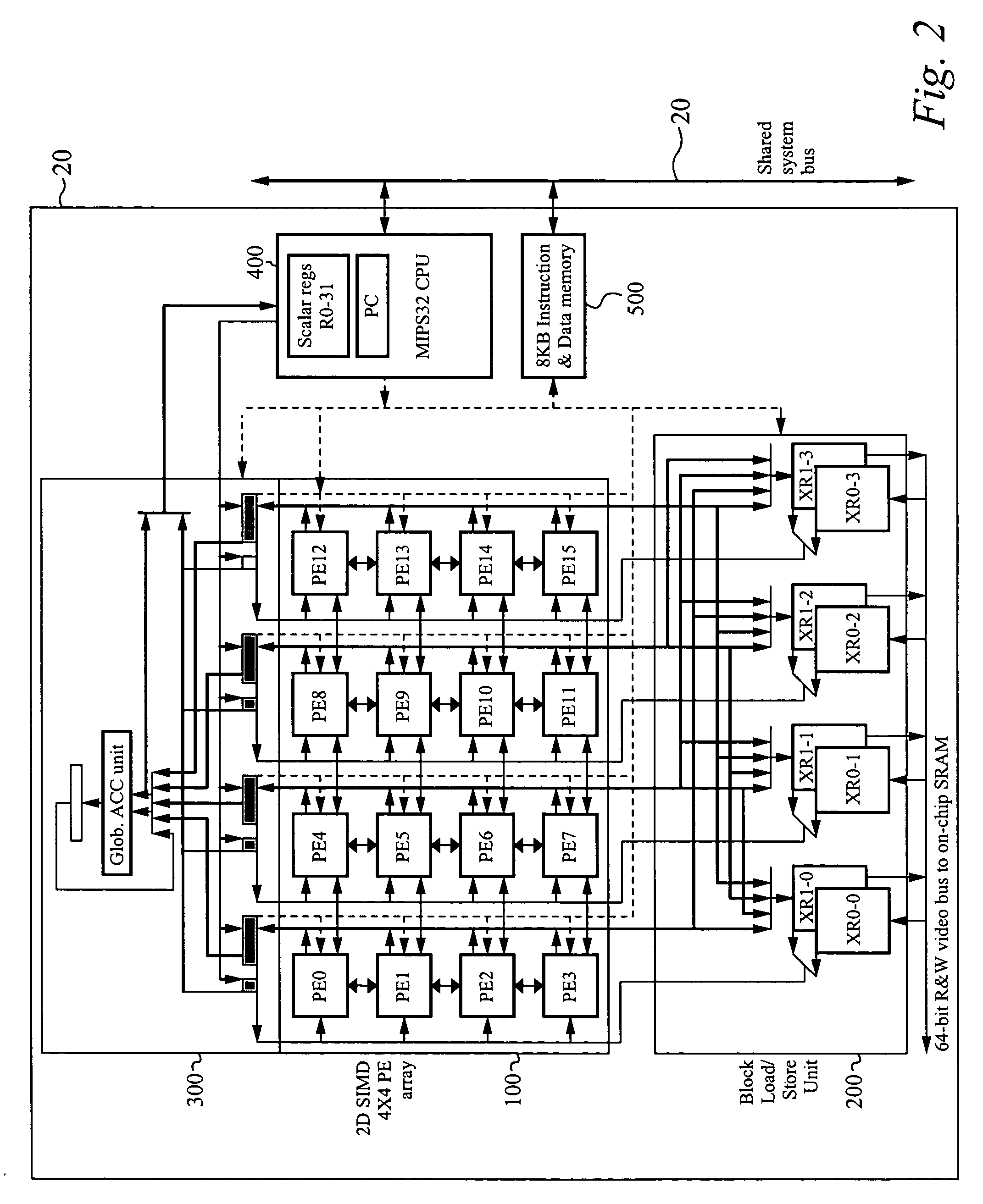

Parallel vector processing

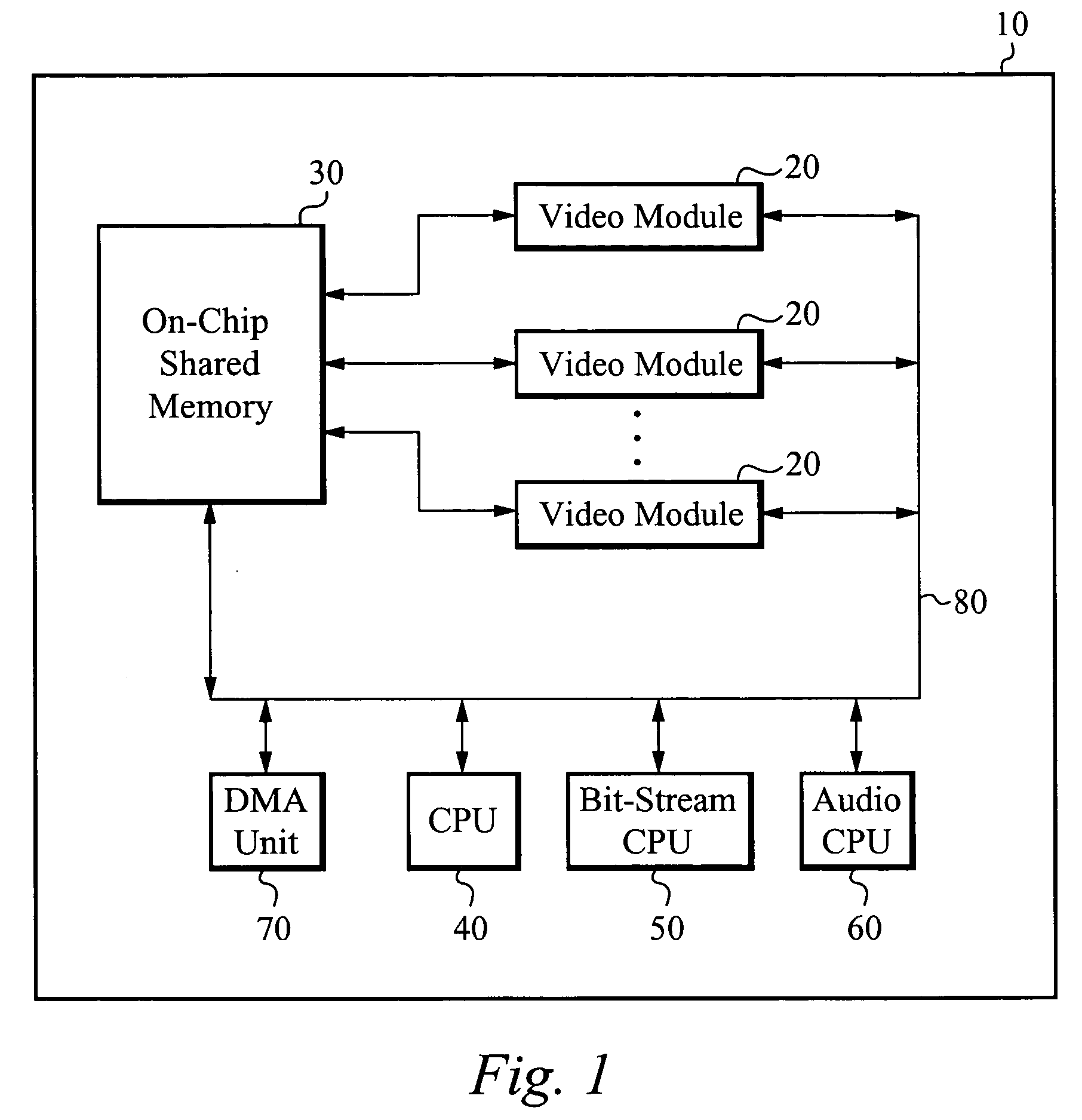

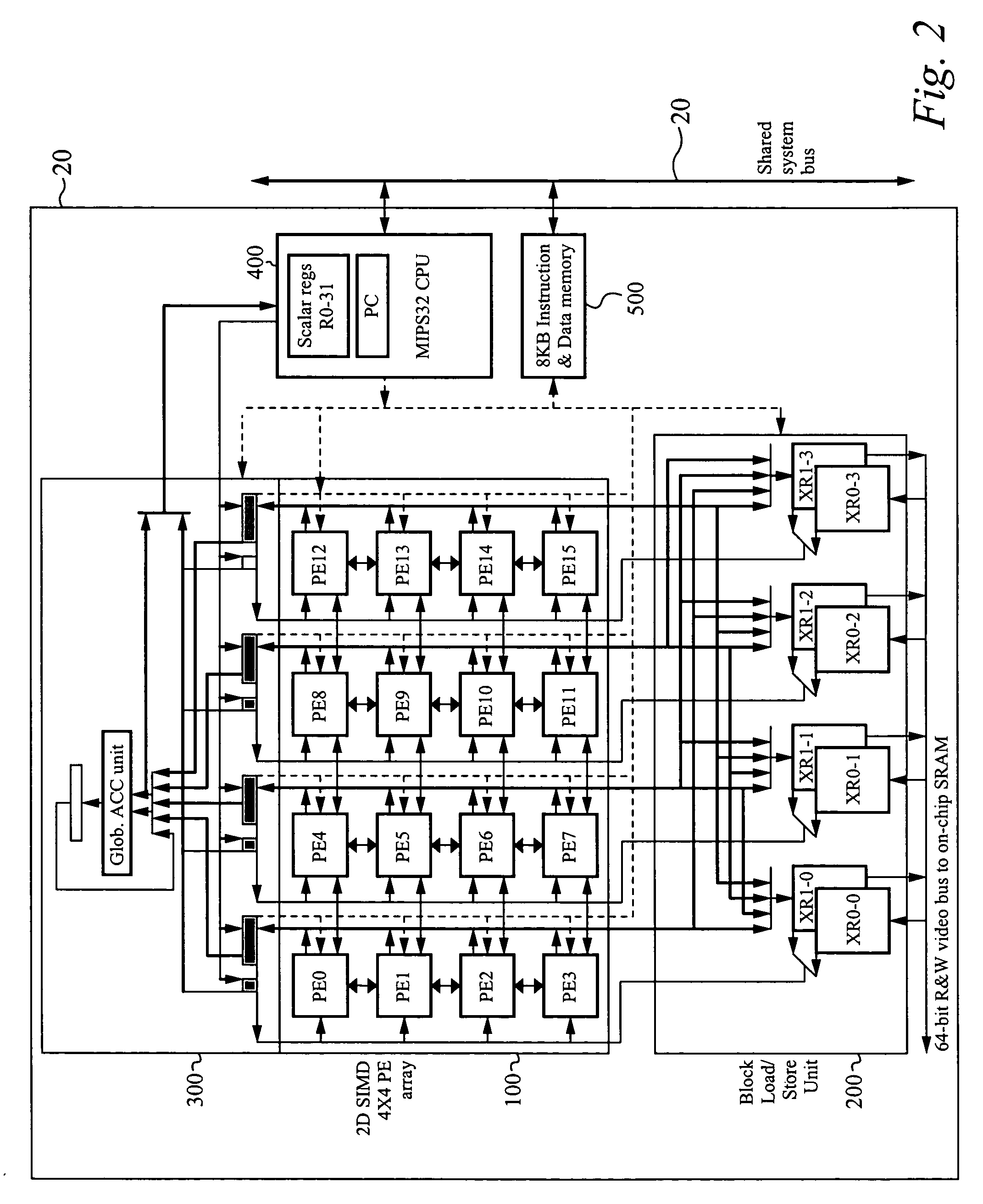

InactiveUS7196708B2Color signal processing circuitsRegister arrangementsArithmetic logic unitProcessor register

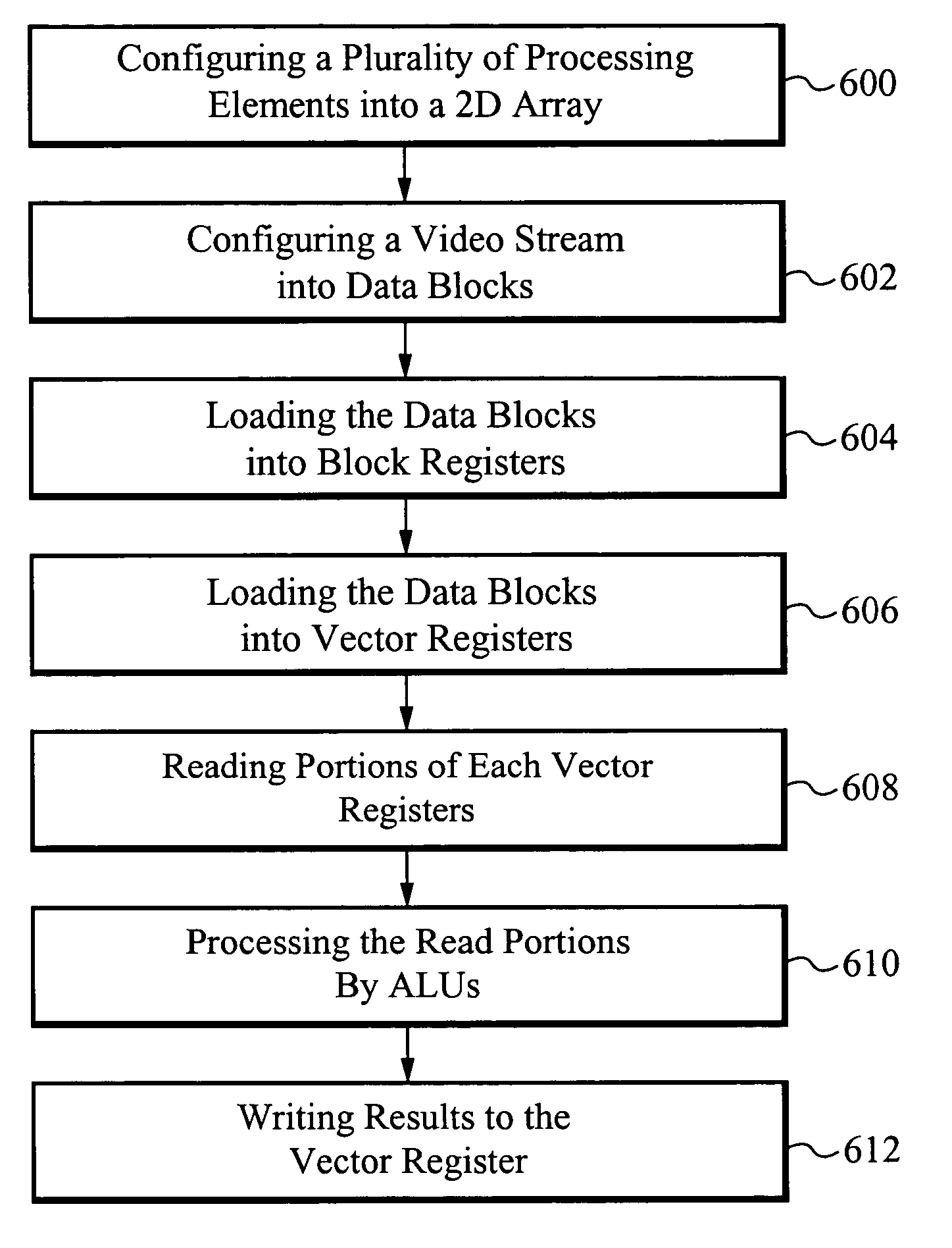

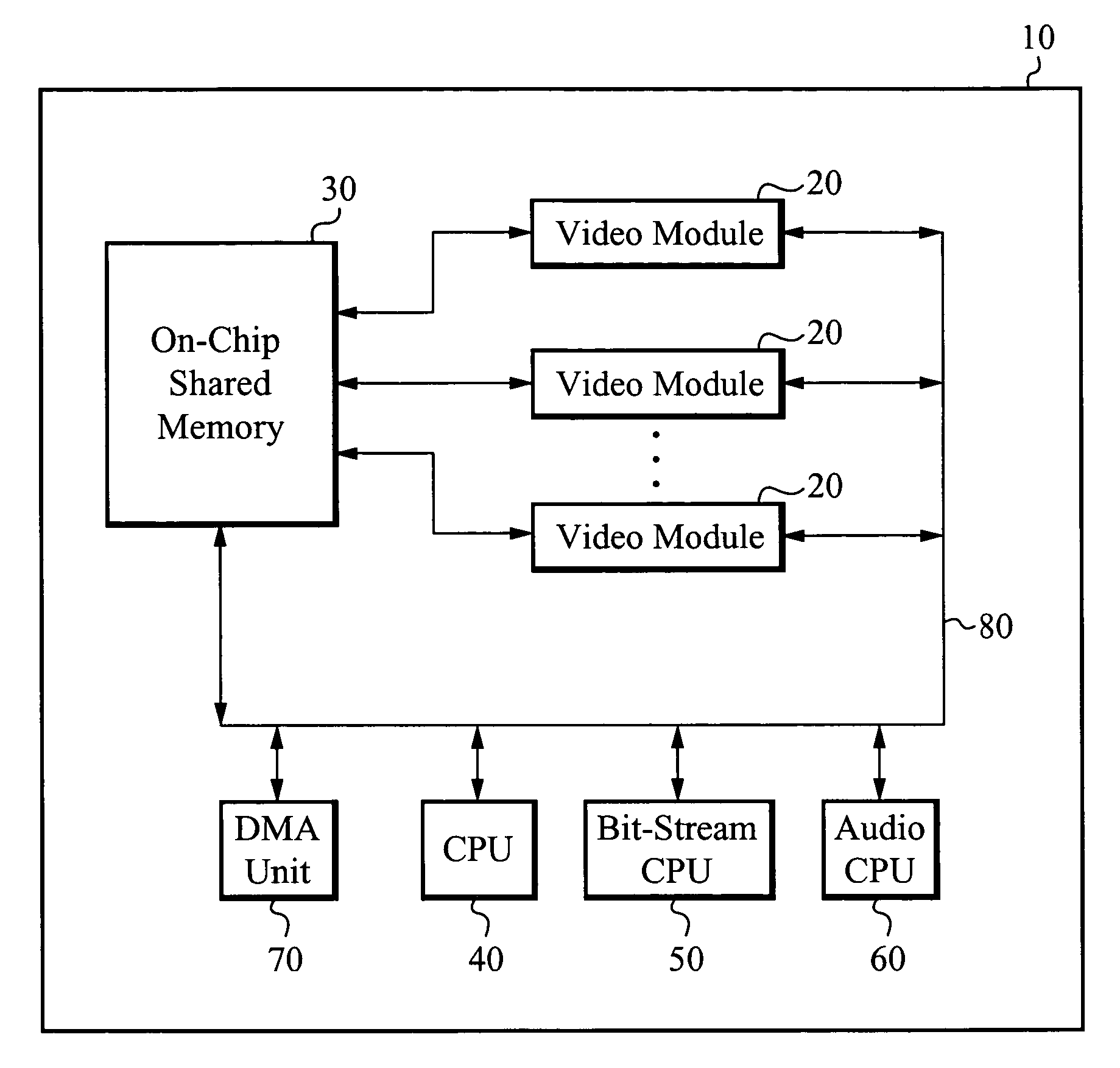

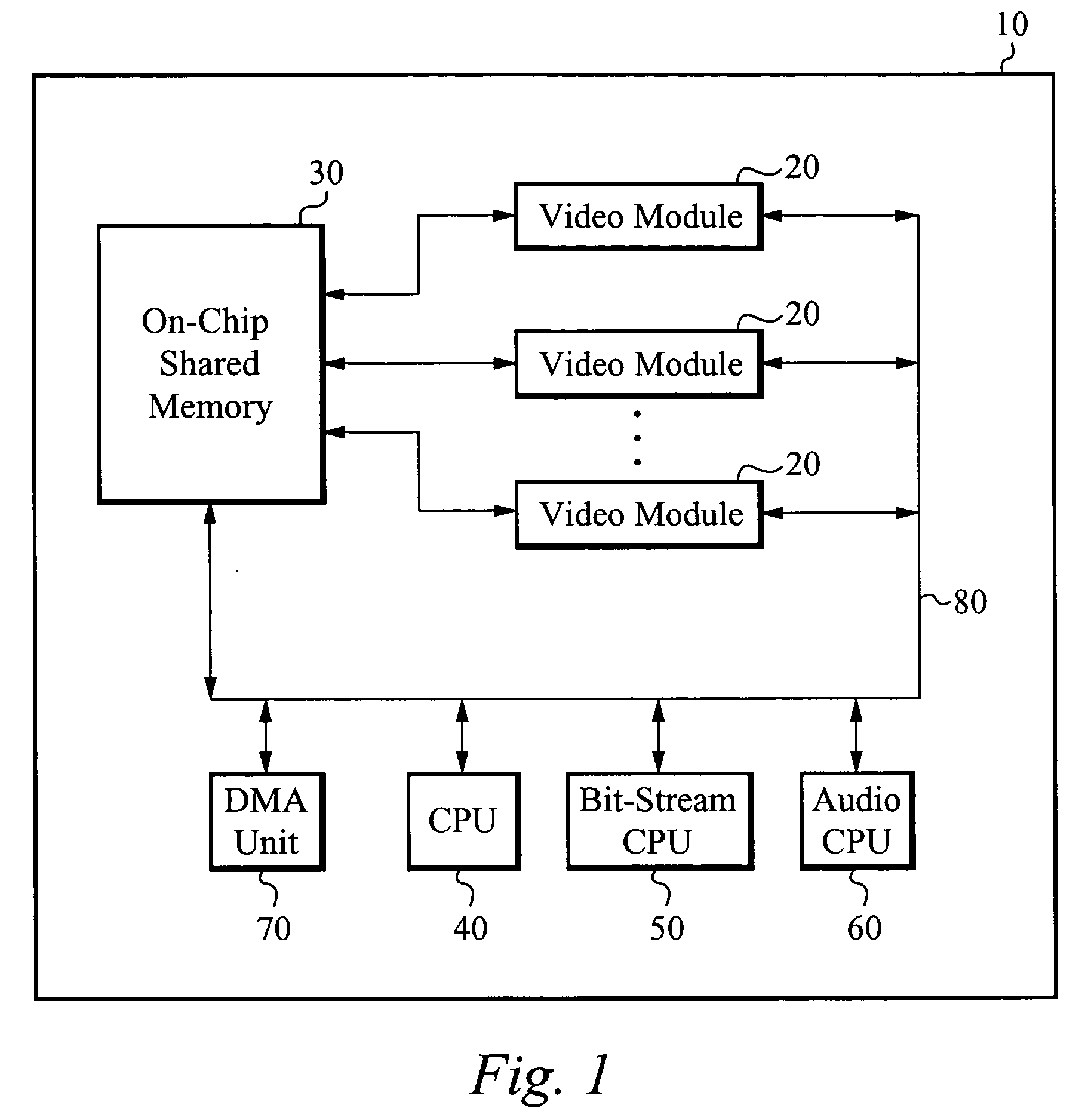

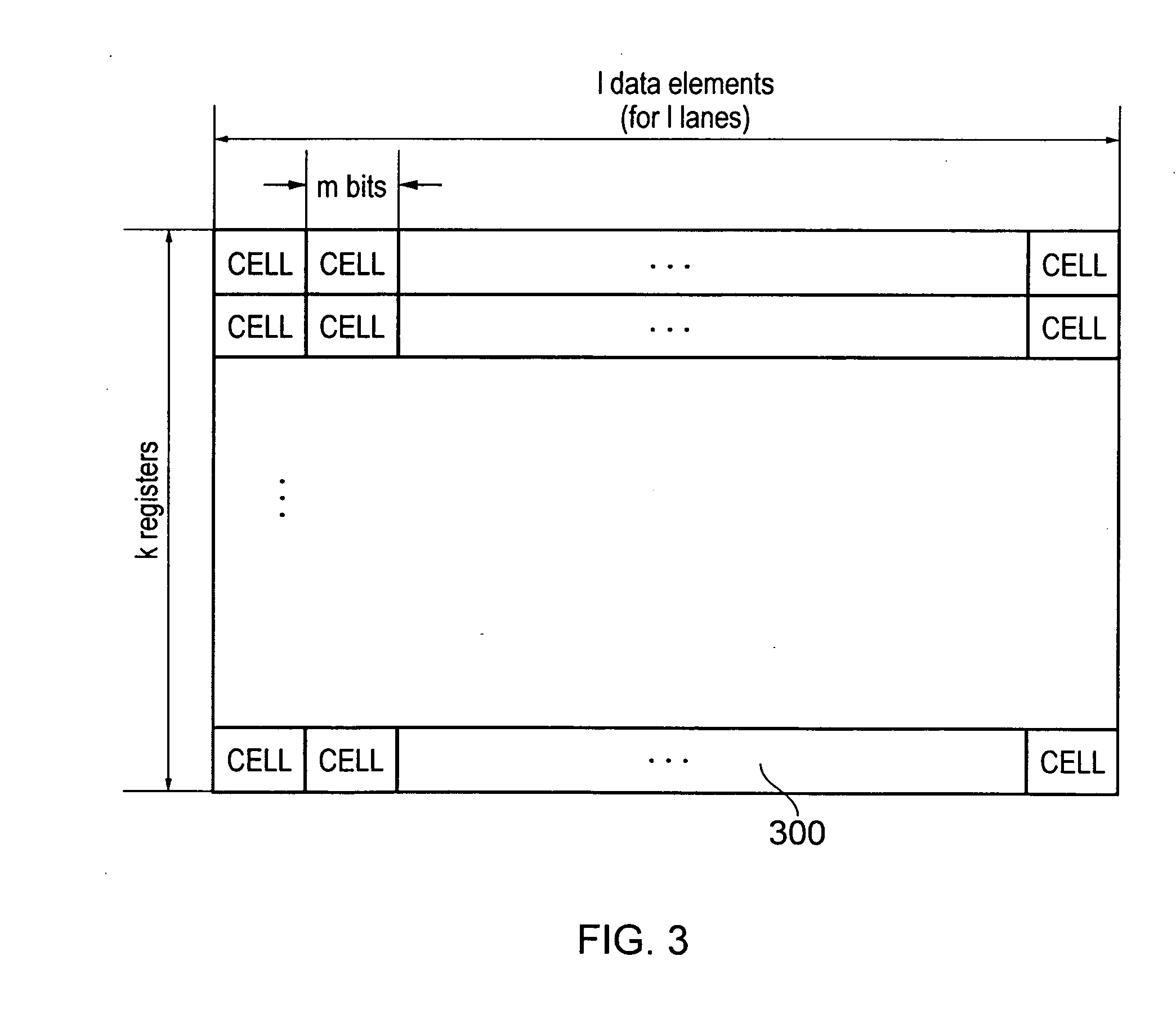

A video platform architecture provides video processing using parallel vector processing. The video platform architecture includes a plurality of video processing modules, each module including a plurality of processing elements (PEs). Each PE provides parallel vector processing. Specifically, means are provided to read all elements of one or two source vector registers in each PE simultaneously, process the read elements by a set of arithmetic-logical units (ALUs), and write back all results to one of the vector registers, all of which occurs in one PE cycle. To provide such parallel vector processing capabilities, the datapath of each PE is built as a set of identical PE processing slices, each of which includes an integer arithmetic-logical unit (ALU), a vector register bank, and a block register bank. A block / vector register bank holds all I elements of row J in a two-dimensional I×J data blocks for all block / vector registers provided by the architecture.

Owner:SONY CORP +1

Single instruction multiple data (SIMD) reconfigurable vector register file and permutation unit

InactiveUS20130339649A1Register arrangementsCathode-ray tube indicatorsProcessor registerData element

An apparatus may comprise a register file and a permutation unit coupled to the register file. The register file may have a plurality of register banks and an input to receive a selection signal. The selection signal may select one or more unit widths of a register bank as a data element boundary for read or write operations.

Owner:INTEL CORP

Instruction vector-mode processing in multi-lane processor by multiplex switch replicating instruction in one lane to select others along with updated operand address

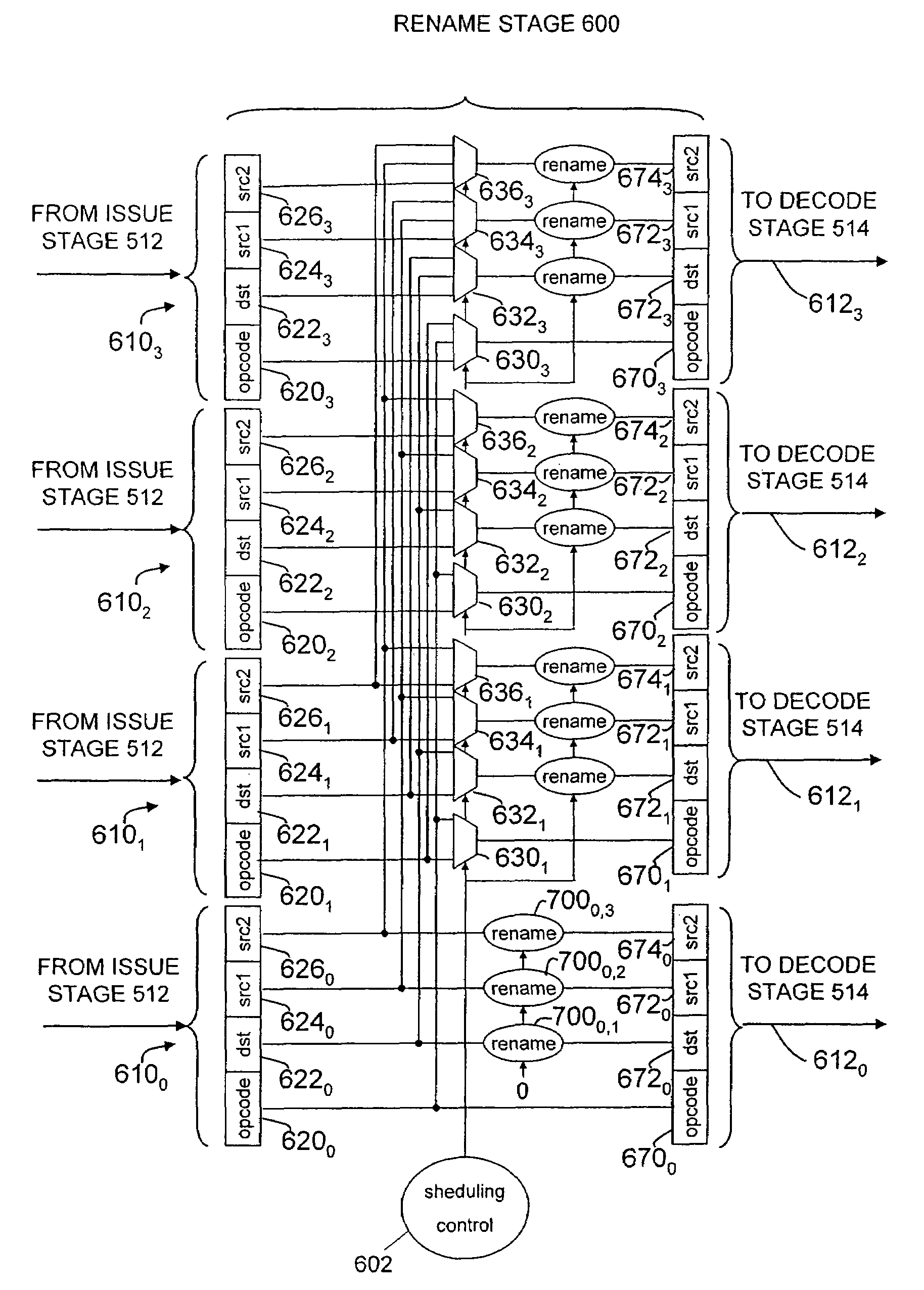

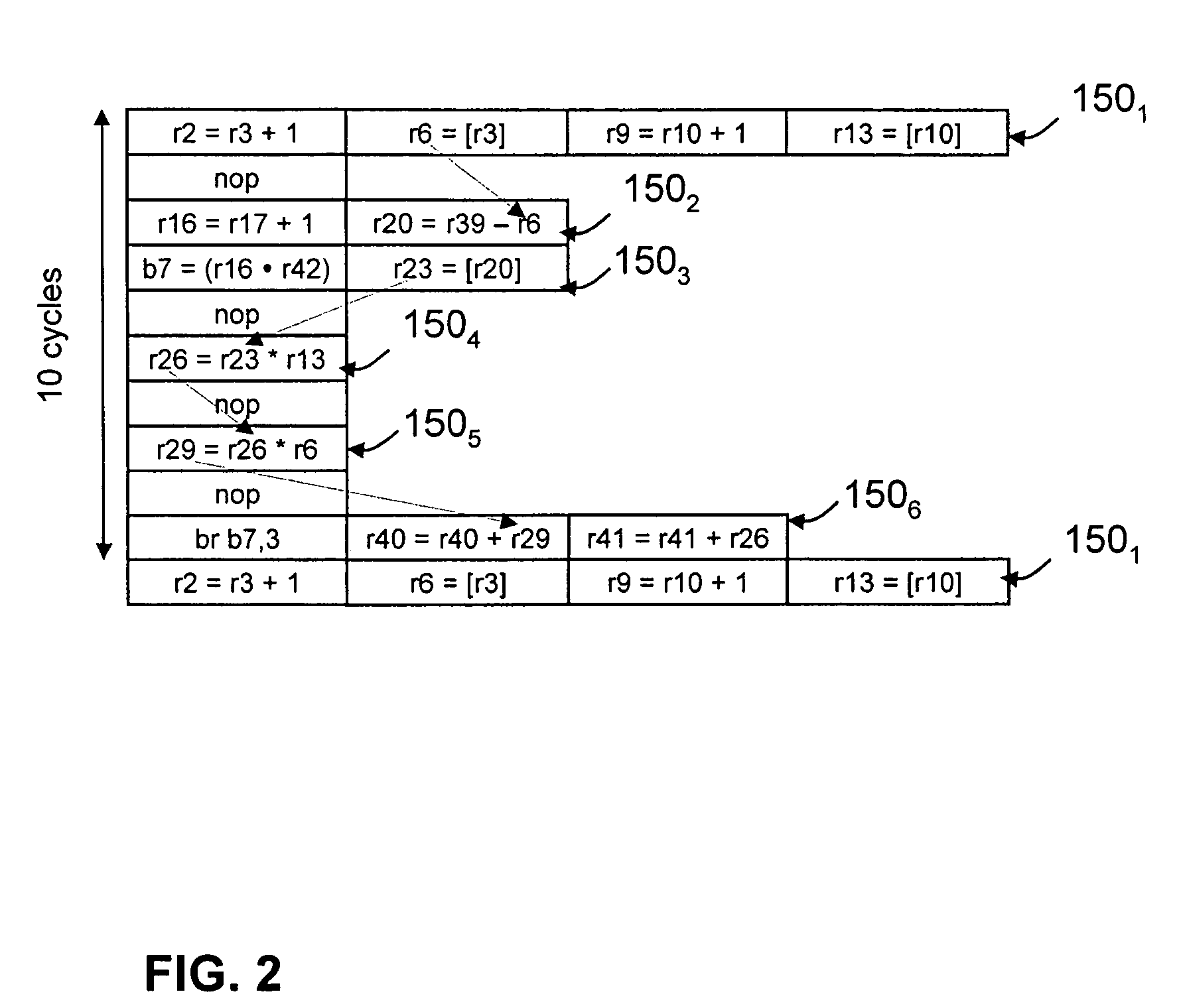

ActiveUS7493475B2Register arrangementsGeneral purpose stored program computerMultiplexingScalar processor

An improved superscalar processor. The processor includes multiple lanes, allowing multiple instructions in a bundle to be executed in parallel. In vector mode, the parallel lanes may be used to execute multiple instances of a bundle, representing multiple iterations of the bundle in a vector run. Scheduling logic determines whether, for each bundle, multiple instances can be executed in parallel. If multiple instances can be executed in parallel, coupling circuitry couples an instance of the bundle from one lane into one or more other lanes. In each lane, register addresses are renamed to ensure proper execution of the bundles in the vector run. Additionally, the processor may include a register bank separate from the architectural register file. Renaming logic can generate addresses to this separate register bank that are longer than used to address architectural registers, allowing longer vectors and more efficient processor operation.

Owner:STMICROELECTRONICS SRL

Indirect register access method and system

ActiveUS8938590B2Memory architecture accessing/allocationRegister arrangementsAccess methodParallel computing

Owner:MICRON TECH INC

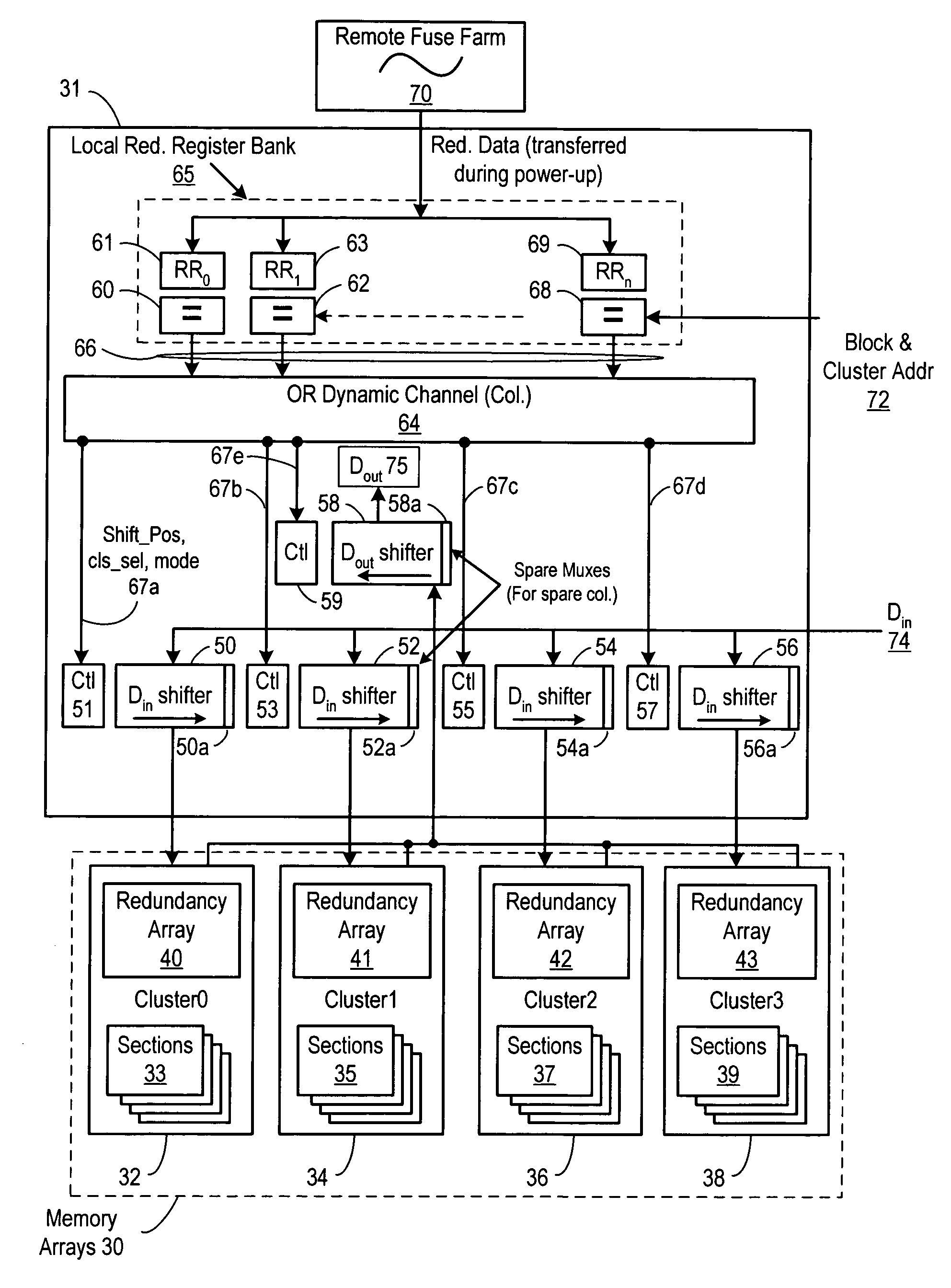

Off-pitch column redundancy using dynamic shifters

ActiveUS7134057B1Improvement in memory redundancy designImproved and efficient column redundancy schemeStatic storageOn boardPitch shift

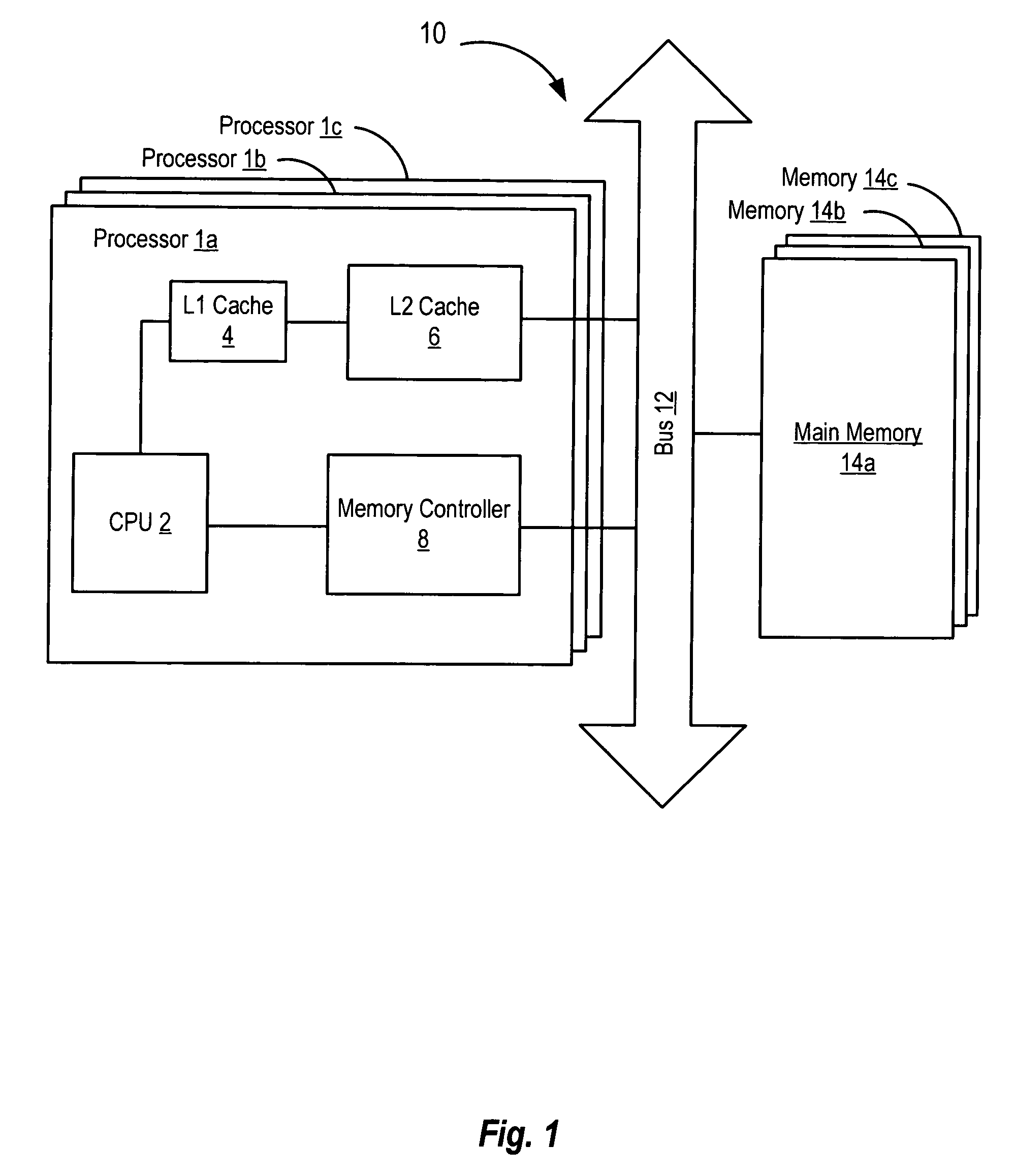

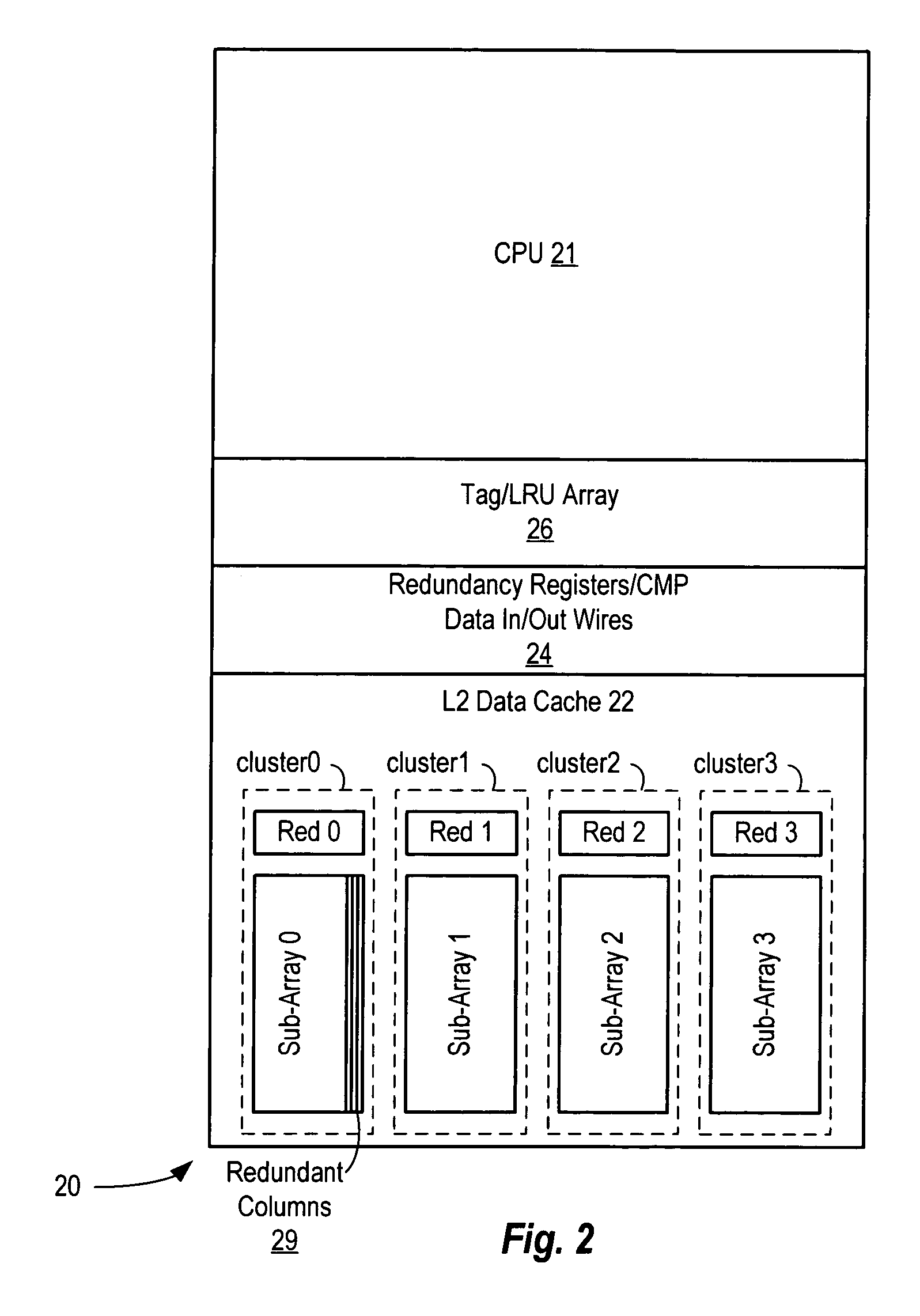

An apparatus and method for controlling and providing off-pitch shifting circuitry for implementing column redundancy in a multiple-array memory is described in connection with an on-board cache memory integrated with a microprocessor. Depending upon the particular sub-array being accessed, shift position data is provided to a shared, off-pitch shift circuit to control the read and / or write operations for the memory. A register bank stores data identifying the defective columns which is compared to the incoming address information to detect any matches. In response to a match, control information is provided to the off-pitch shift circuit for shifting or re-routing the incoming data to a non-defective address in the memory. In this way, defective columns located in different positions in each sub-array can be replaced by redundant paths, thereby repairing the cache and increasing the manufacturing yield of microprocessors with an on-board cache memory.

Owner:ORACLE INT CORP

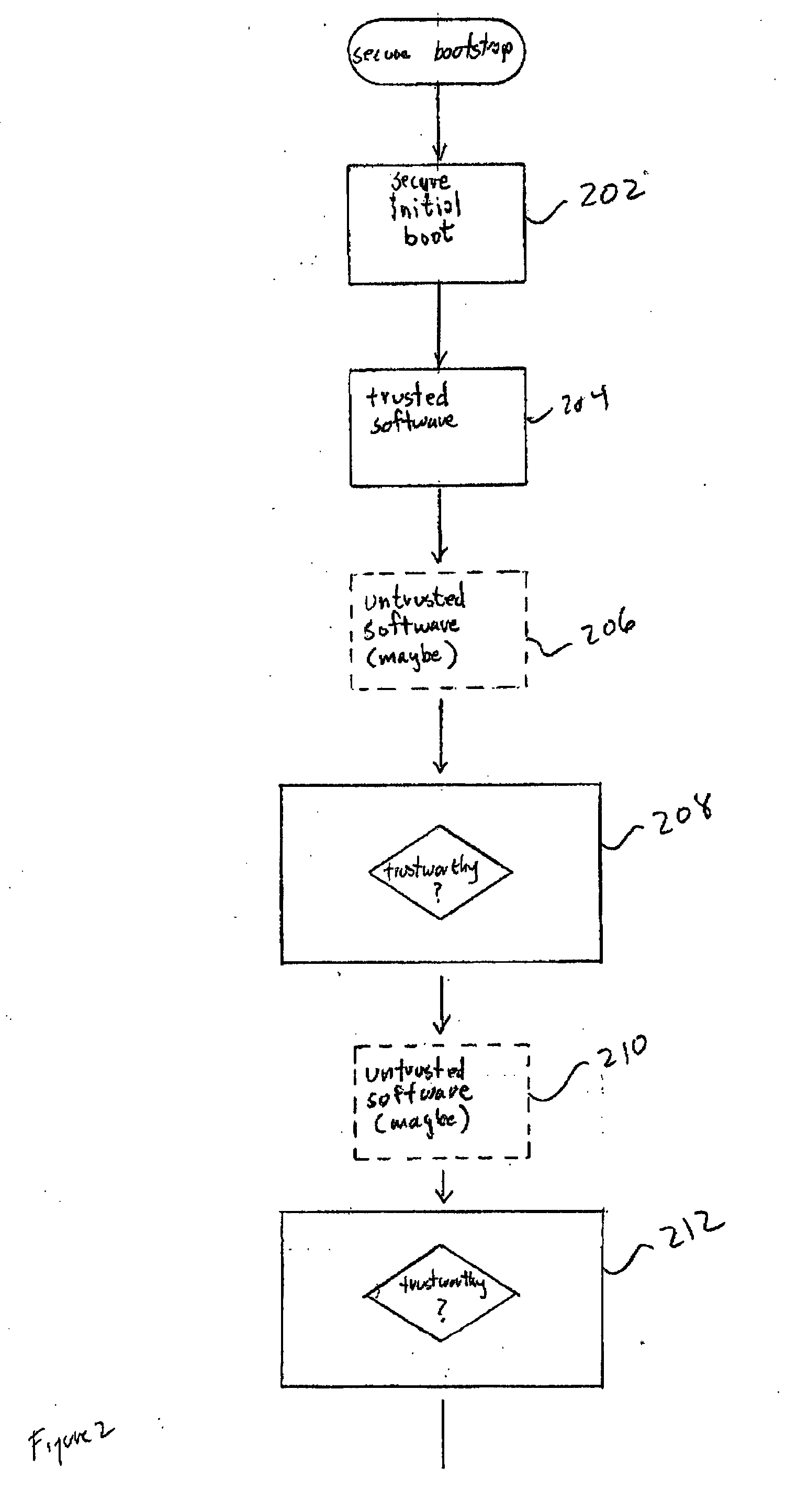

Method and system for securing a computer system

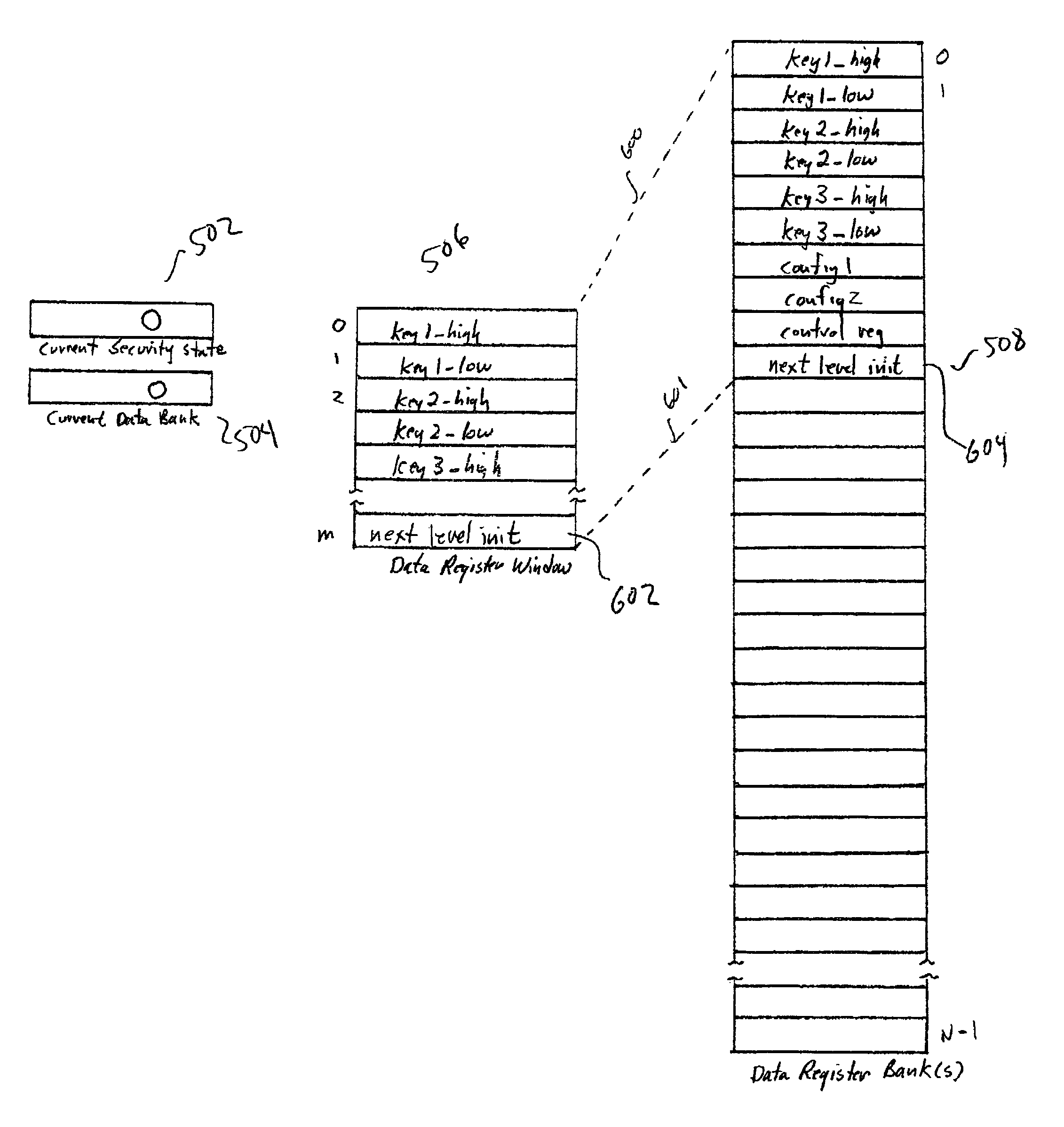

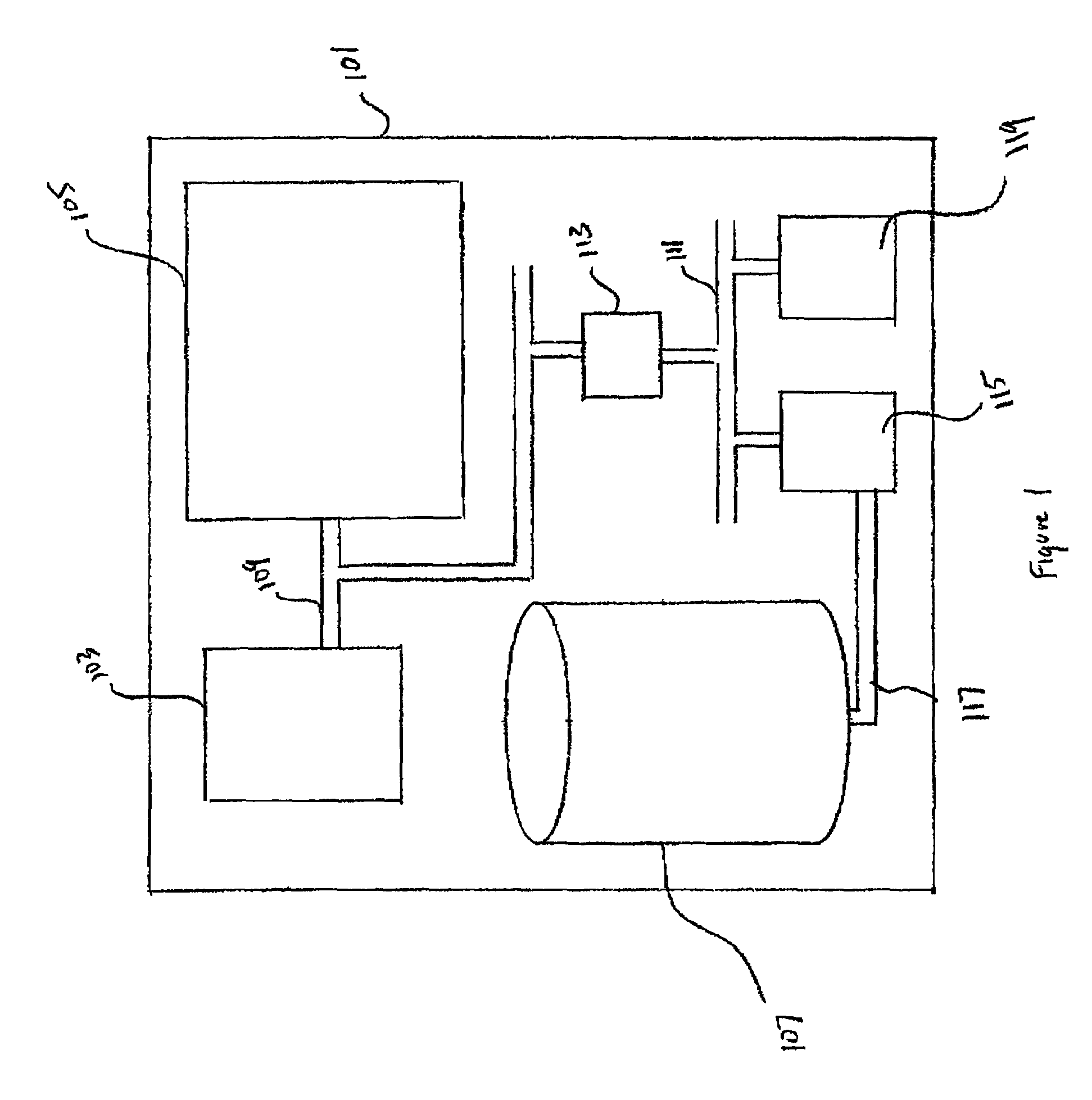

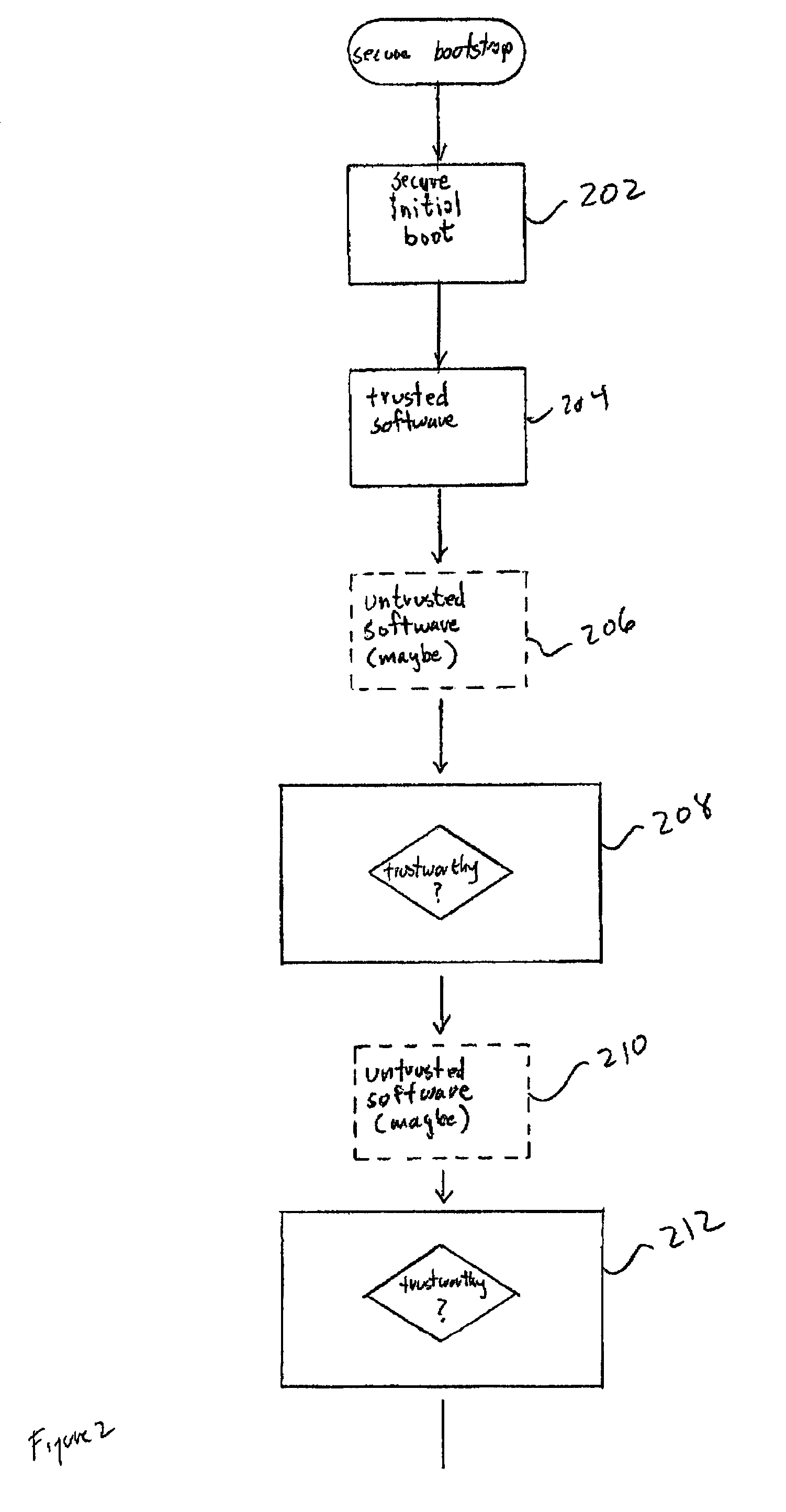

InactiveUS20050033978A1Digital data processing detailsAnalogue secracy/subscription systemsRegister windowControl register

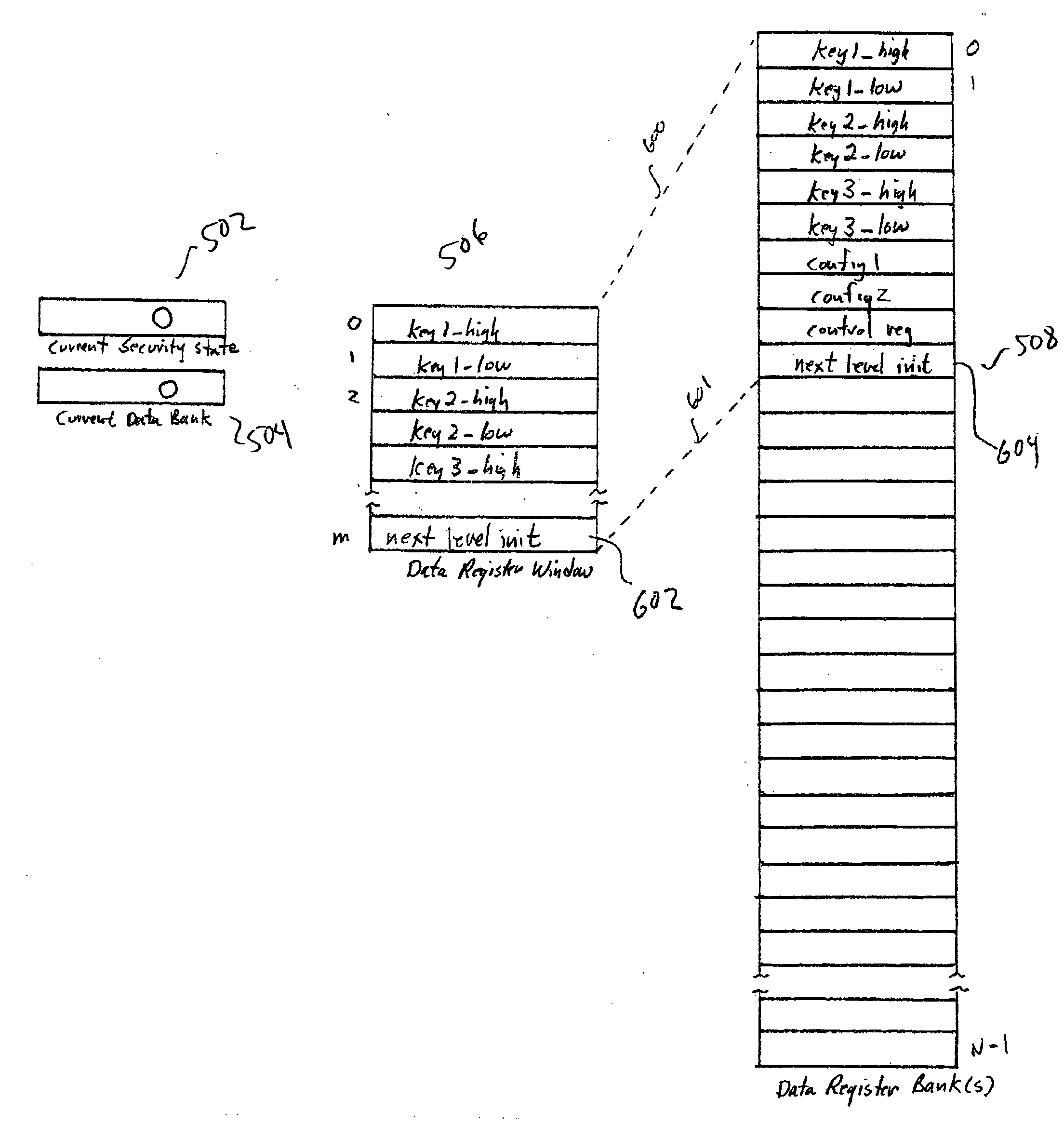

Security-state-reporting and data-control functionality introduced into a computer system to monitor and report the security state of the computer system and to store and make selectively available, for processes executing within a computer system, security-state-associated data. The hardware element includes two control registers, a current-security-state control register (“CSS”) and a current-data-bank control register (“CDB”). When the CSS is read, the CSS reports the current security state of the computer system, with security states represented as unsigned integers starting from a highest security level of 0 and decreasing with unsigned integers of increasing magnitudes. The CDB controls access to one or more data-register banks, positioning a data-register window to allow access only to those data-register-bank registers associated with the currently reported security state.

Owner:GOOGLE LLC

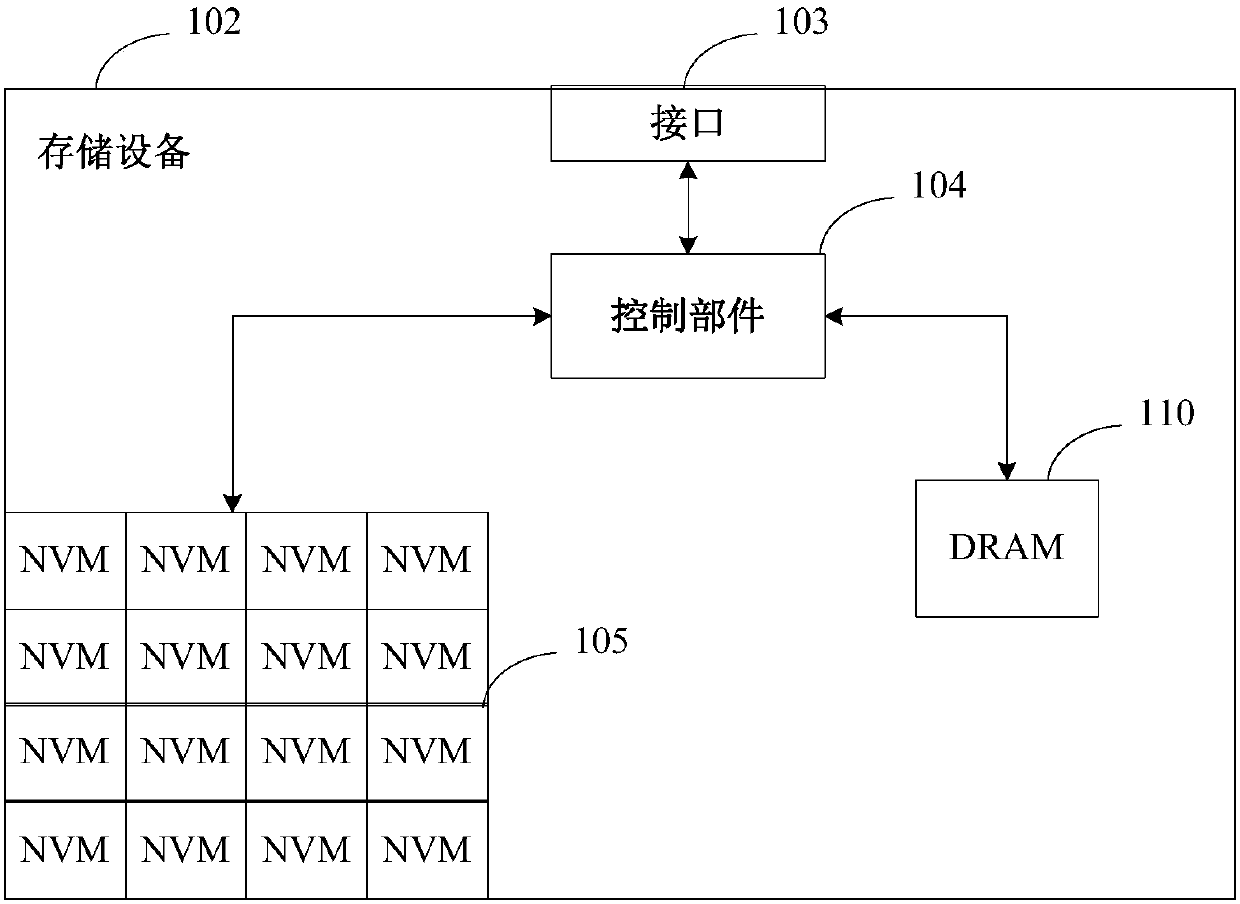

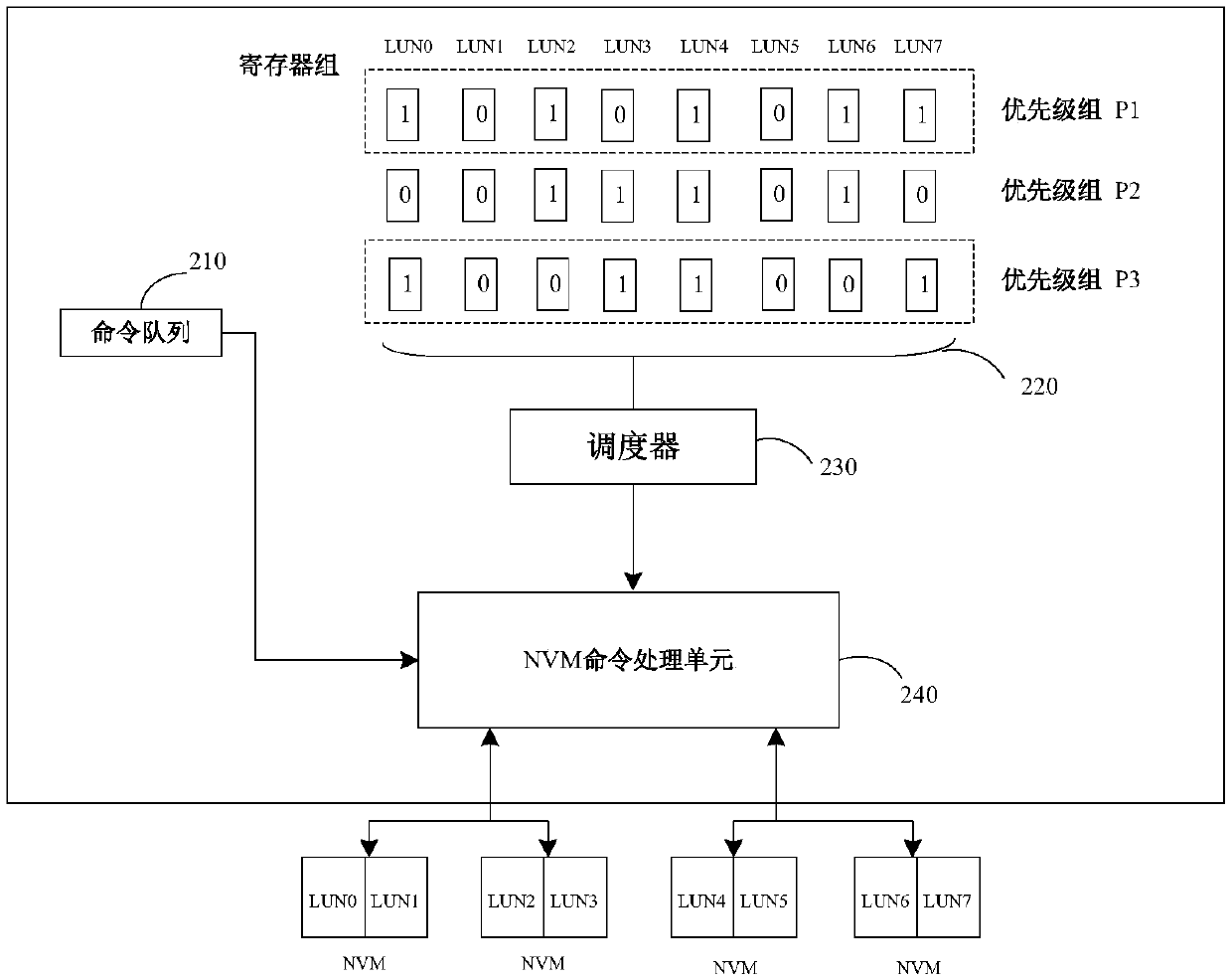

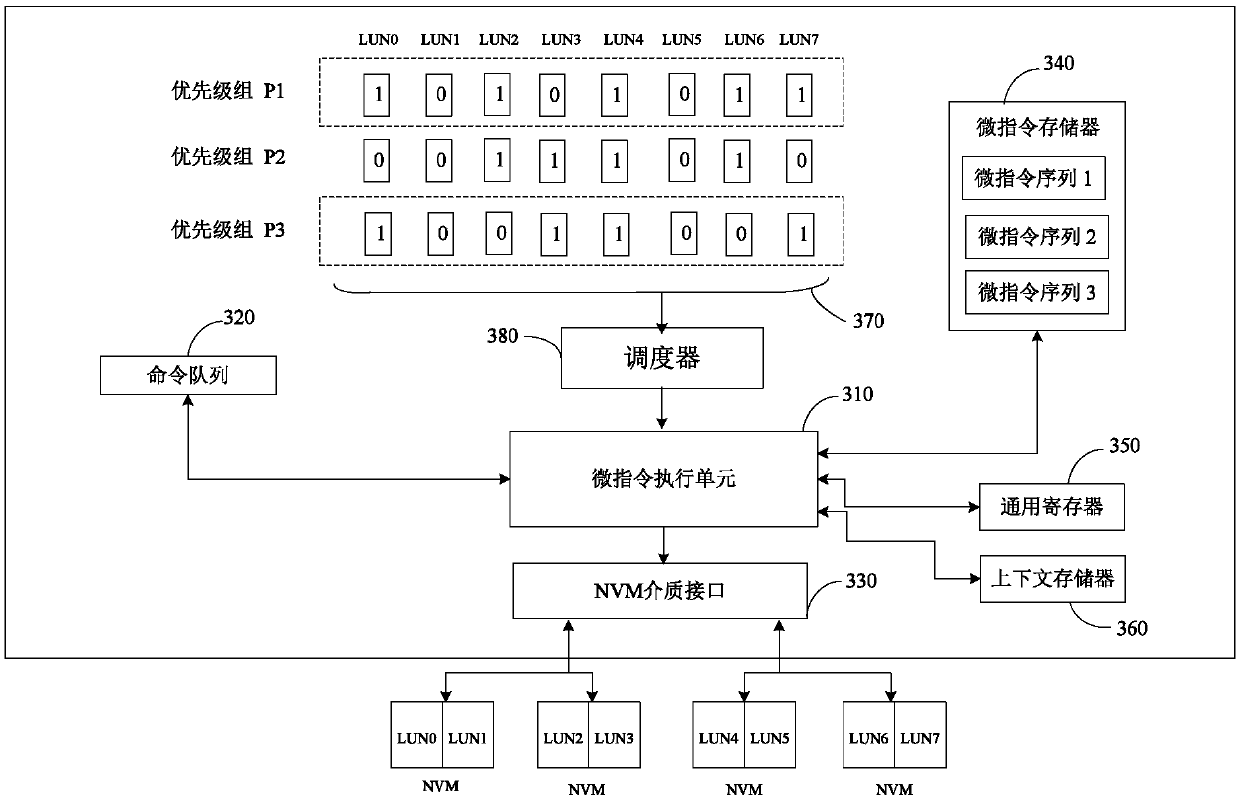

Scheduling method and device

PendingCN107870779AImprove scheduling efficiencyIncrease configuration flexibilityRegister arrangementsInstruction memoryComputer architecture

The invention discloses a scheduling method and device. The scheduling method comprises the following steps of: selecting a first register with a first value from a high-priority group of a register group, wherein the first register corresponds to a first to-be-processed event; and scheduling a first thread corresponding to the first register to process the first to-be-processed event. The scheduling device comprises a command queue, a micro instruction memory, a micro instruction execution unit, the register group, a scheduler and an NVM medium interface, wherein the register group is used for indicating to-be-processed events and priorities of the to-be-processed events; the scheduler is used for scheduling threads according to registers in the register group; and the micro instruction execution unit is used for receiving the indication of the scheduler and executing the scheduled threads.

Owner:BEIJING STARBLAZE TECH CO LTD

Method and system for securing a computer system

InactiveUS7398390B2Digital data processing detailsAnalogue secracy/subscription systemsRegister windowControl register

Security-state-reporting and data-control functionality introduced into a computer system to monitor and report the security state of the computer system and to store and make selectively available, for processes executing within a computer system, security-state-associated data. The hardware element includes two control registers, a current-security-state control register (“CSS”) and a current-data-bank control register (“CDB”). When the CSS is read, the CSS reports the current security state of the computer system, with security states represented as unsigned integers starting from a highest security level of 0 and decreasing with unsigned integers of increasing magnitudes. The CDB controls access to one or more data-register banks, positioning a data-register window to allow access only to those data-register-bank registers associated with the currently reported security state.

Owner:GOOGLE LLC

Method and apparatus for non-speculative fetch and execution of control-dependent blocks

InactiveUS20160055004A1Conditional code generationRuntime instruction translationSpeculative executionRegister bank

An apparatus and method are described for non-speculative execution of conditional instructions. For example, one embodiment of a processor comprises: a register set including a first register to store a set of one or more condition bits; non-speculative execution logic to execute a first instruction to identify a first target instruction strand in response to a first conditional value read from the set of condition bits, the first instruction to wait until the first conditional value becomes known before causing the first target instruction strand to be fetched and executed, the non-speculative execution logic to execute a second instruction to identify an end of the first target instruction strand and responsively identify a new current instruction pointer for instructions which follow the second instruction; and out-of-order execution logic to fetch and execute the instructions which follow the second instruction prior to the execution of the second instruction.

Owner:INTEL CORP

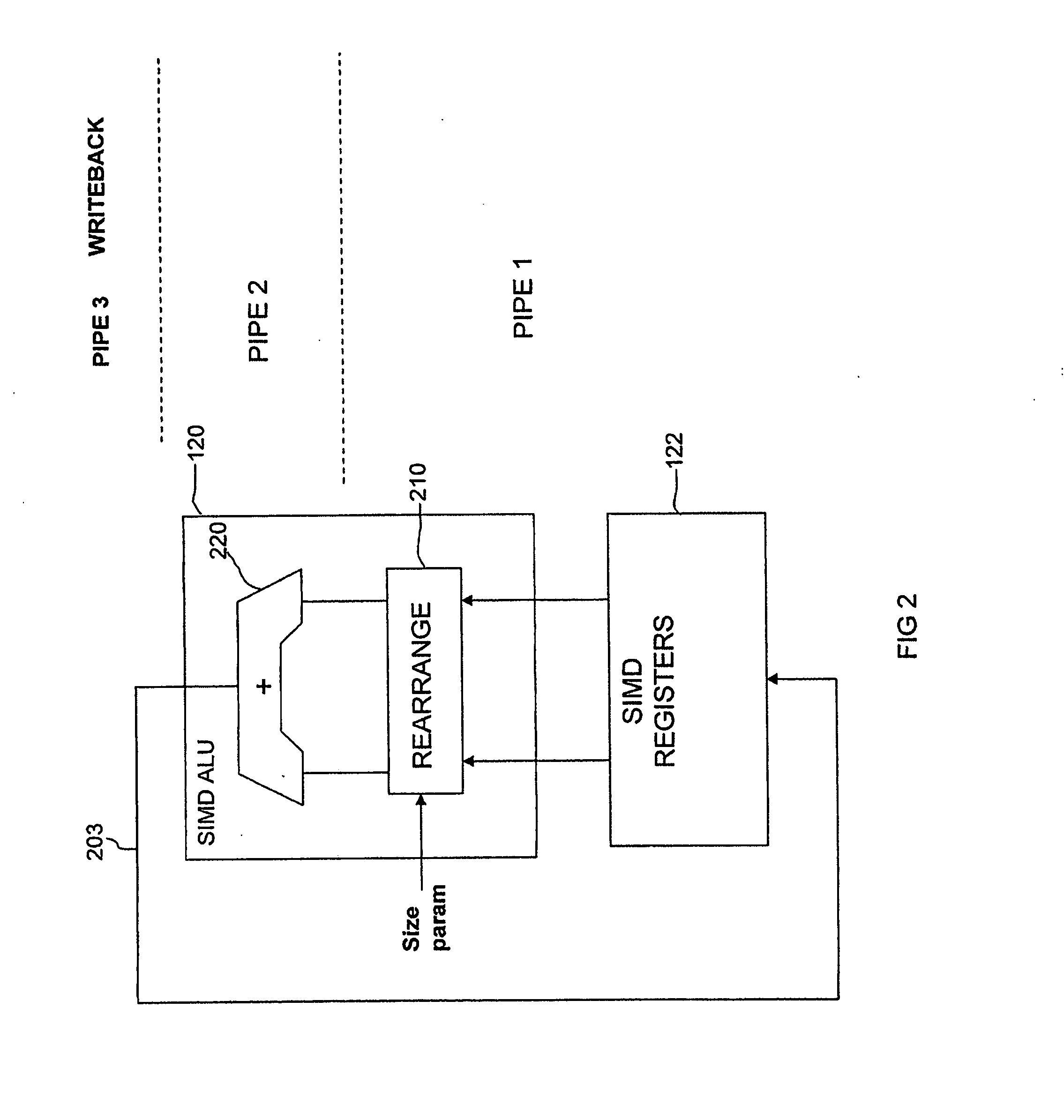

Apparatus and method for performing rearrangement and arithmetic operations on data

ActiveUS20080140750A1Flexible configurationFacilitates rearrangement operationRegister arrangementsComputation using non-contact making devicesProgram instructionData element

An apparatus and method are provided for performing rearrangement operations and arithmetic operations on data. The data processing apparatus has processing circuitry for performing SIMD processing operations and scalar processing operations, a register bank for storing data and control circuitry responsive to program instructions to control the processing circuitry to perform data processing operations. The control circuitry is arranged to responsive to a combined rearrangement arithmetic instruction to control the processing circuitry to perform a rearrangement operation and at least one SIMD arithmetic operation on a plurality of data elements stored in the register bank. The rearrangement operation is configurable by a size parameter derived at least in part from the register bank. The size parameter provides an indication of a number of data elements forming a rearrangement element for the purposes of the rearrangement operation. The associated method involves controlling processing circuitry to perform a rearrangement operation and at least one SIMD arithmetic operation in response to a combined rearrangement arithmetic instruction and providing the scalar logic size parameter to configure the rearrangement operation. Computer program product is also provided comprising at least one combined rearrangement arithmetic instruction.

Owner:ARM LTD

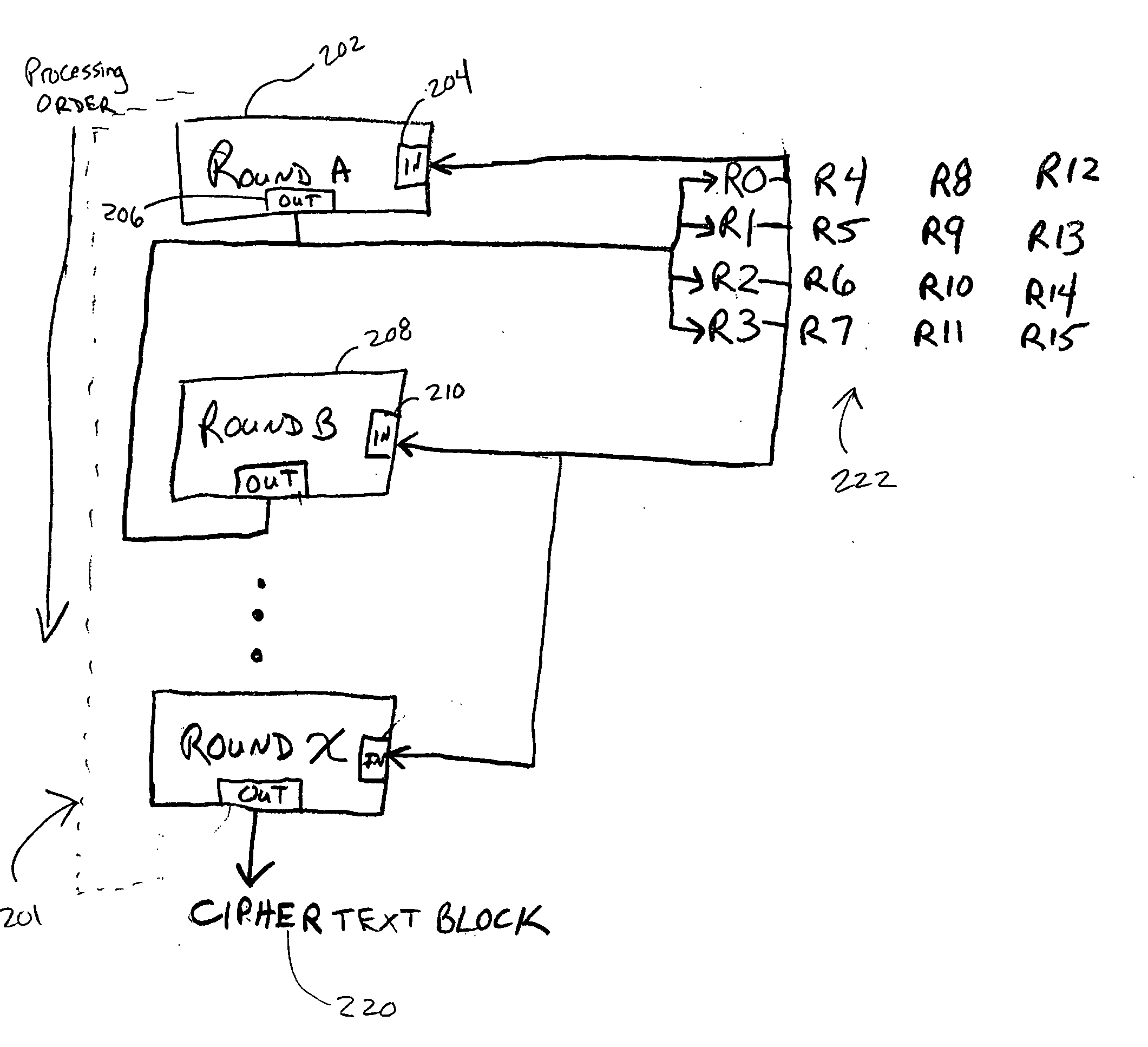

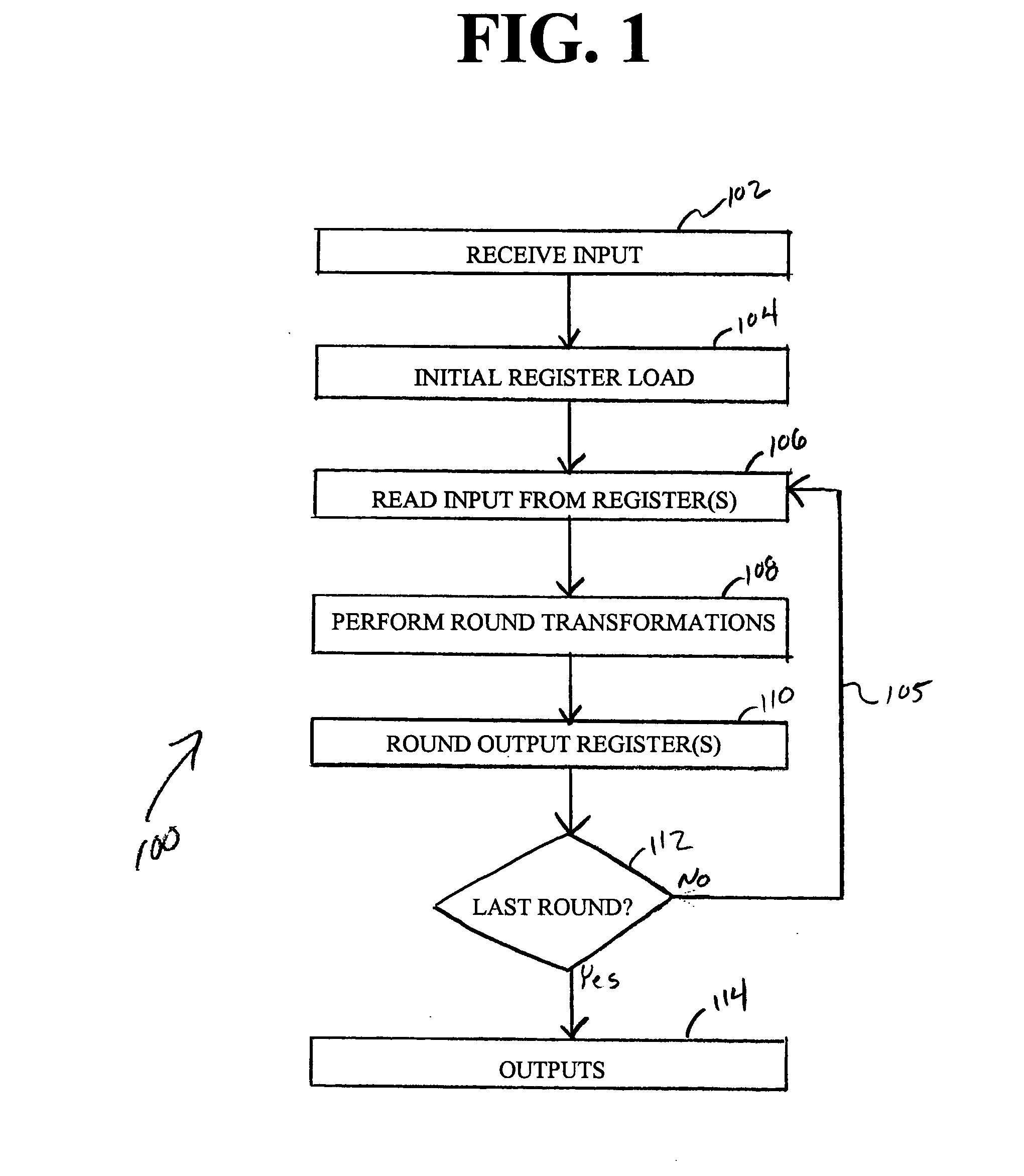

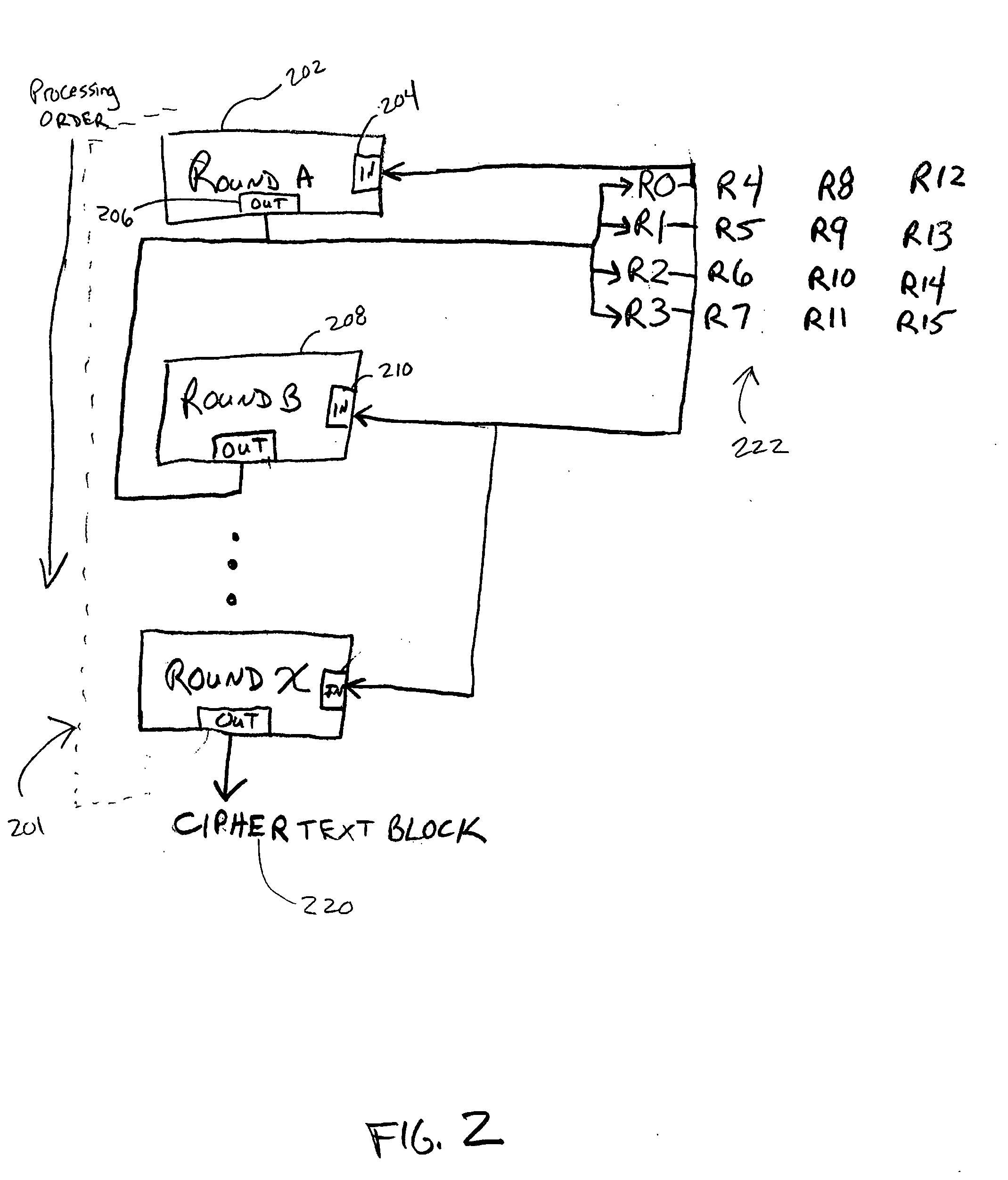

Register scheduling in iterative block encryption to reduce memory operations

InactiveUS20060072746A1Secret communicationSecuring communicationAdvanced encryption standard algorithmProcessor register

Systems and methods encrypt data according to a multi-round, block encryption algorithm, In some embodiments, each round includes transforming data held in a group of registers of a processor register set and maintaining round output in the group of registers to use as input in a subsequent round. In some embodiments, the multi-round, block encryption algorithm is the Advanced Encryption Standard algorithm.

Owner:INTEL CORP

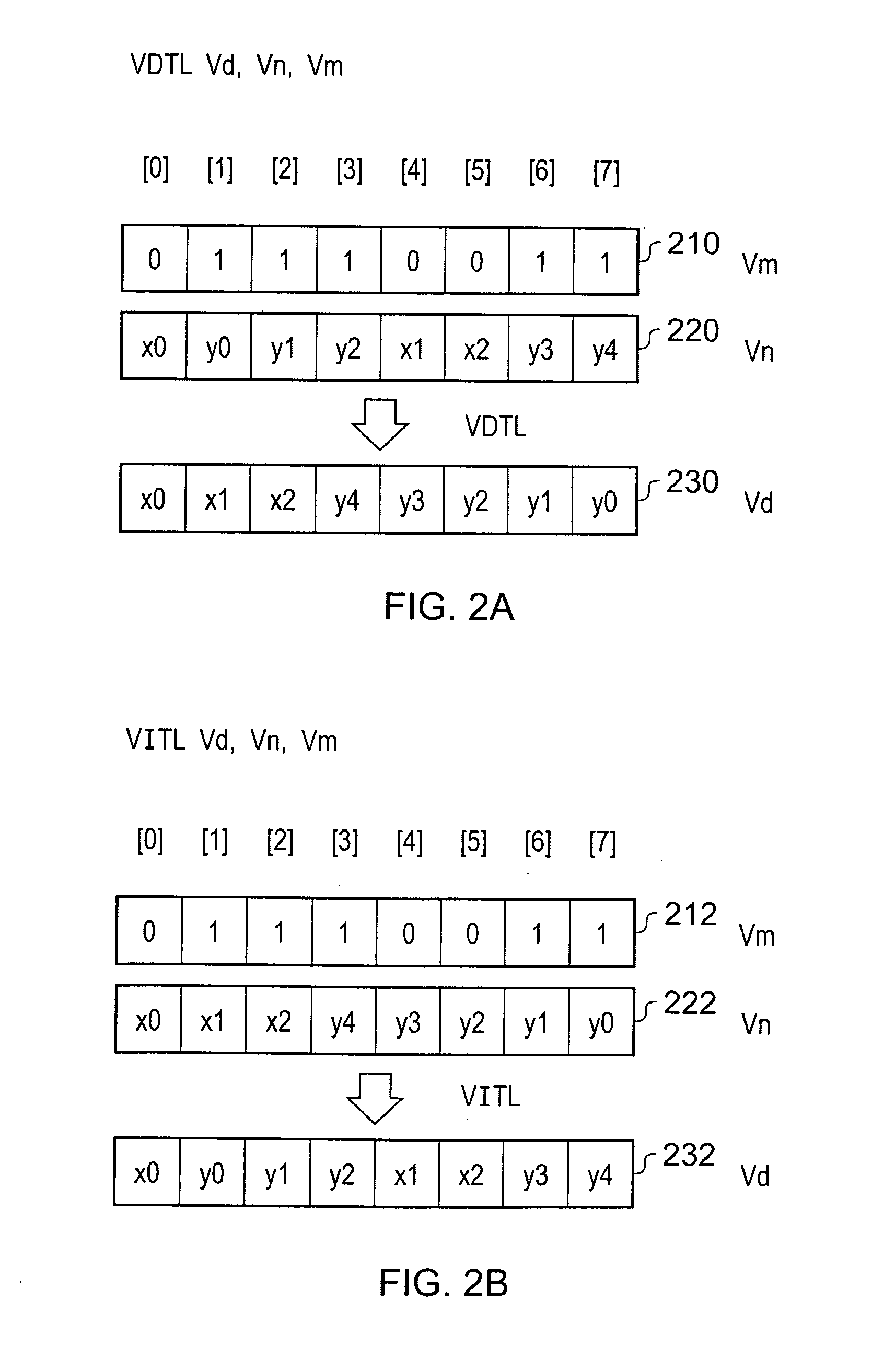

Apparatus and method for performing permutation operations on data

ActiveUS20090187746A1Flexible configurationIncrease data rateData representation error detection/correctionDigital computer detailsProgram instructionControl signal

An apparatus for processing data is provided comprising processing circuitry having permutation circuitry for performing permutation operations, a register bank having a plurality of registers for storing data and control circuitry responsive to program instructions to control the processing circuitry to perform data processing operations. The control circuitry is arranged to be responsive to a control-generating instruction to generate in dependence upon a bit-mask control signals to configure permutation circuitry for performing permutation operation on an input operand. The bit-mask identifies within the input operand the first group of data elements having a first ordering and a second group of data elements having a second ordering and the permutation operation is such that it preserves one of the first ordering and the second ordering but changes the other of the first ordering and the second ordering.

Owner:U-BLOX

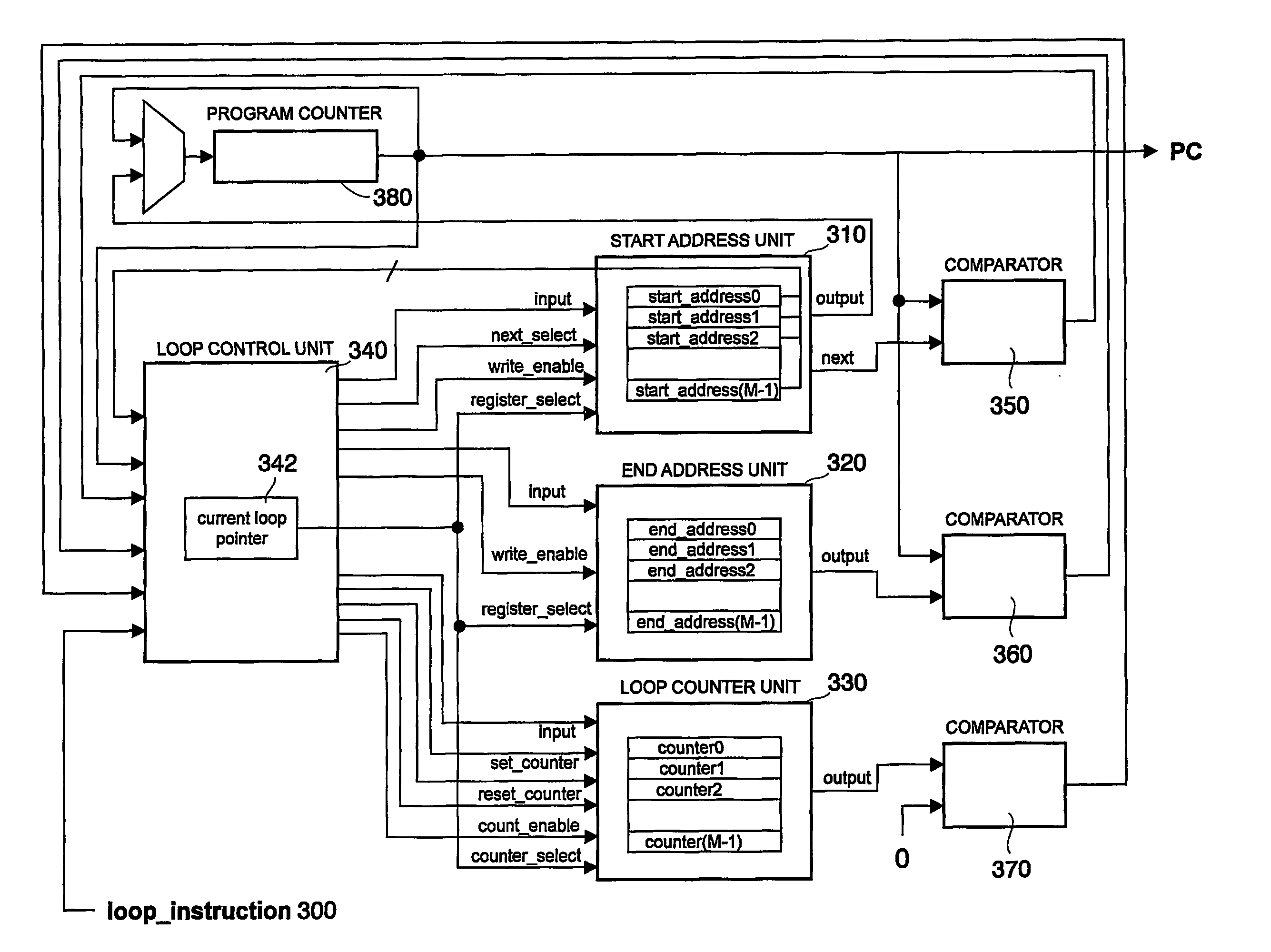

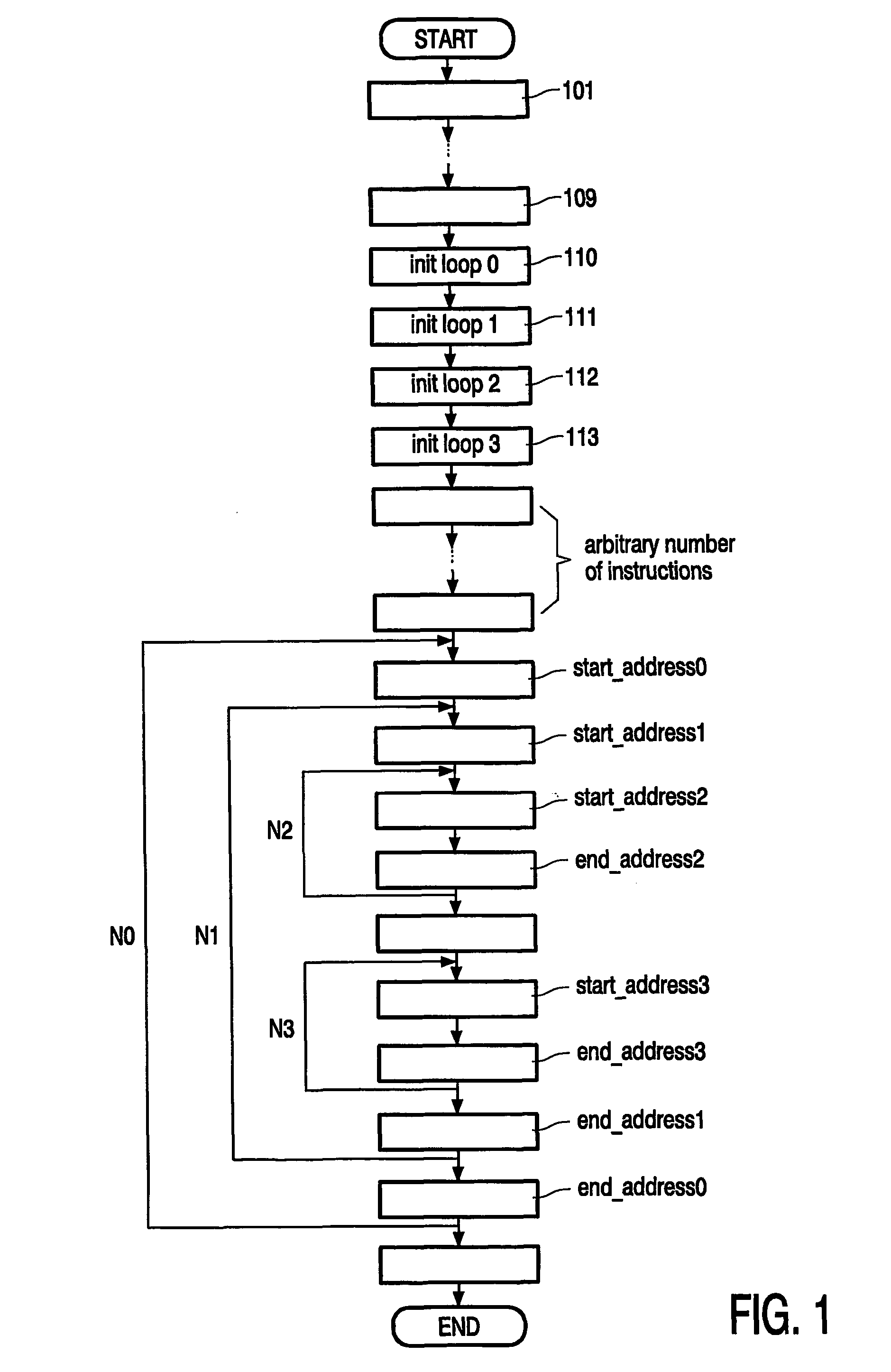

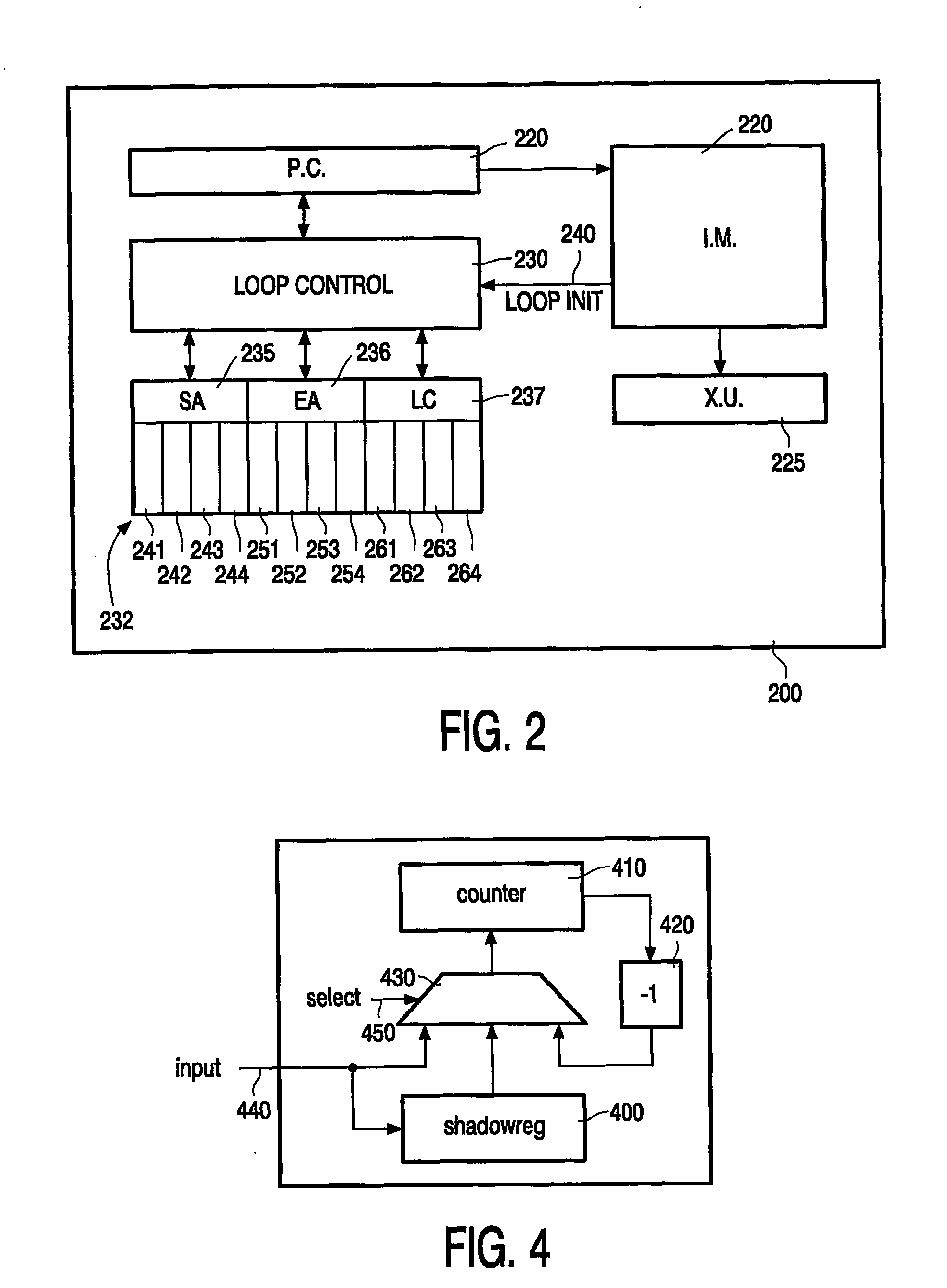

Loop control circuit for a data processor

InactiveUS20060107028A1Good support high-performance processingBetter supports high-performance processingDigital computer detailsNext instruction address formationInstruction memoryLoop control

A data processor (200) includes an operation execution unit (225) for executing instructions from an instruction memory (210) indicated by a program counter (220). A loop control circuit (230) stores respective associated loop information for a plurality of instruction loops in a register bank (232). The loop information includes at least an indication of an end of the loop and a loop count for indicating a number of times the loop should be executed. The loop control circuit (230) detects that one of the loops needs to be executed and in response to said detection, loads the loop information for the corresponding loop, and controls the program counter to execute the corresponding loop according to the loaded loop information. The loop information is initialized in response to a loop initialization instruction (240), where the initialization instruction is issued prior to and independent of a start of the loop initialized by the loop information.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

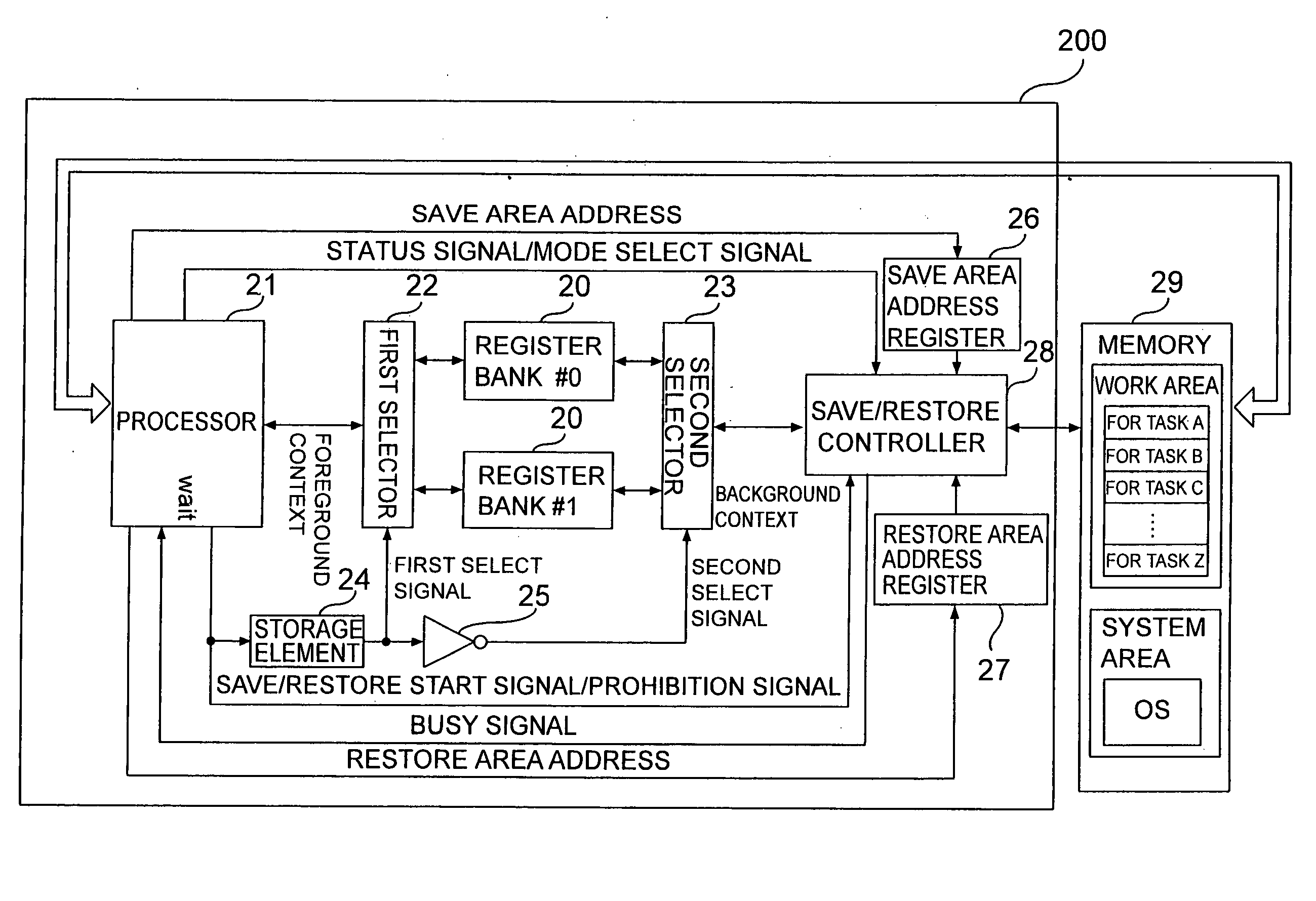

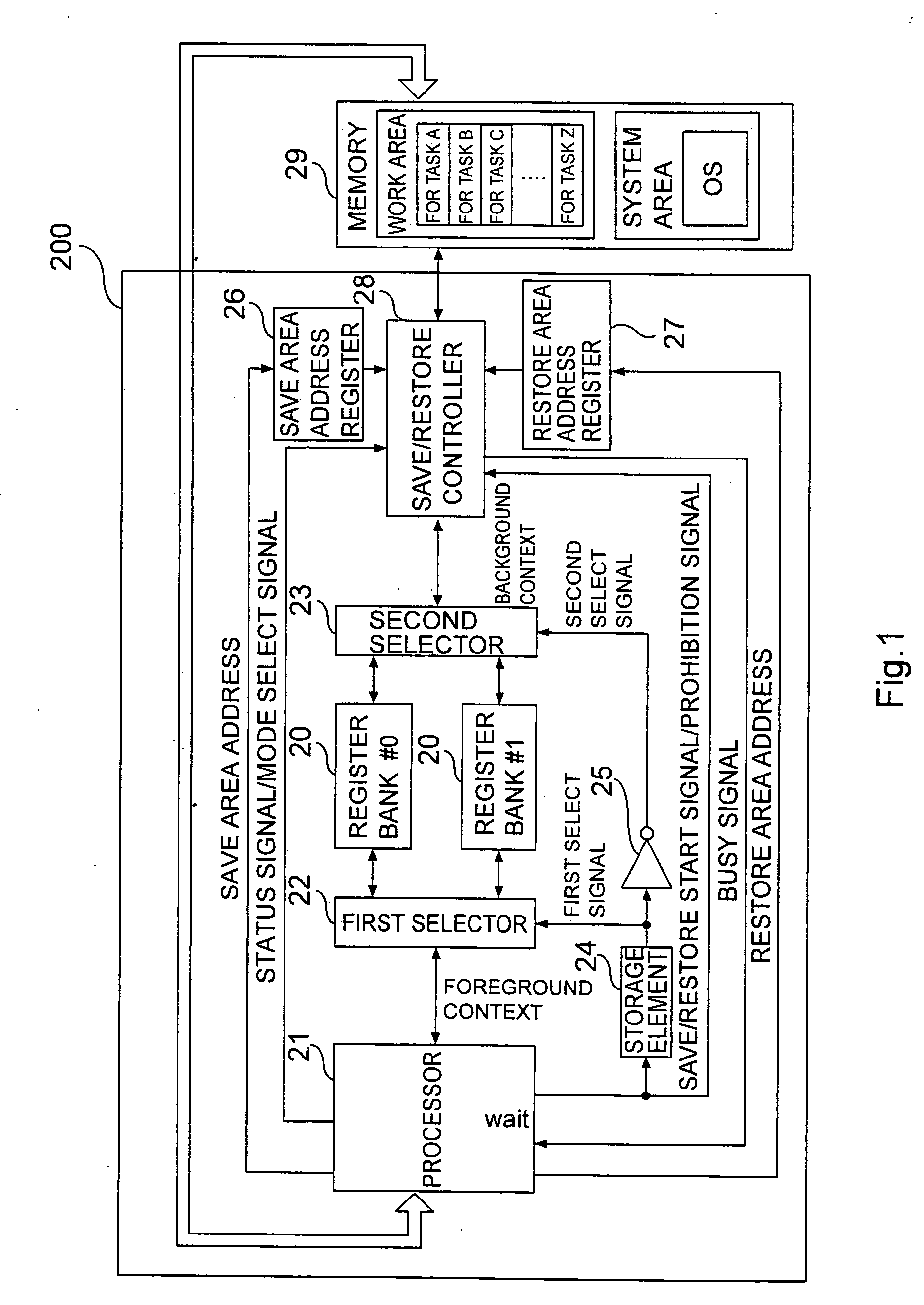

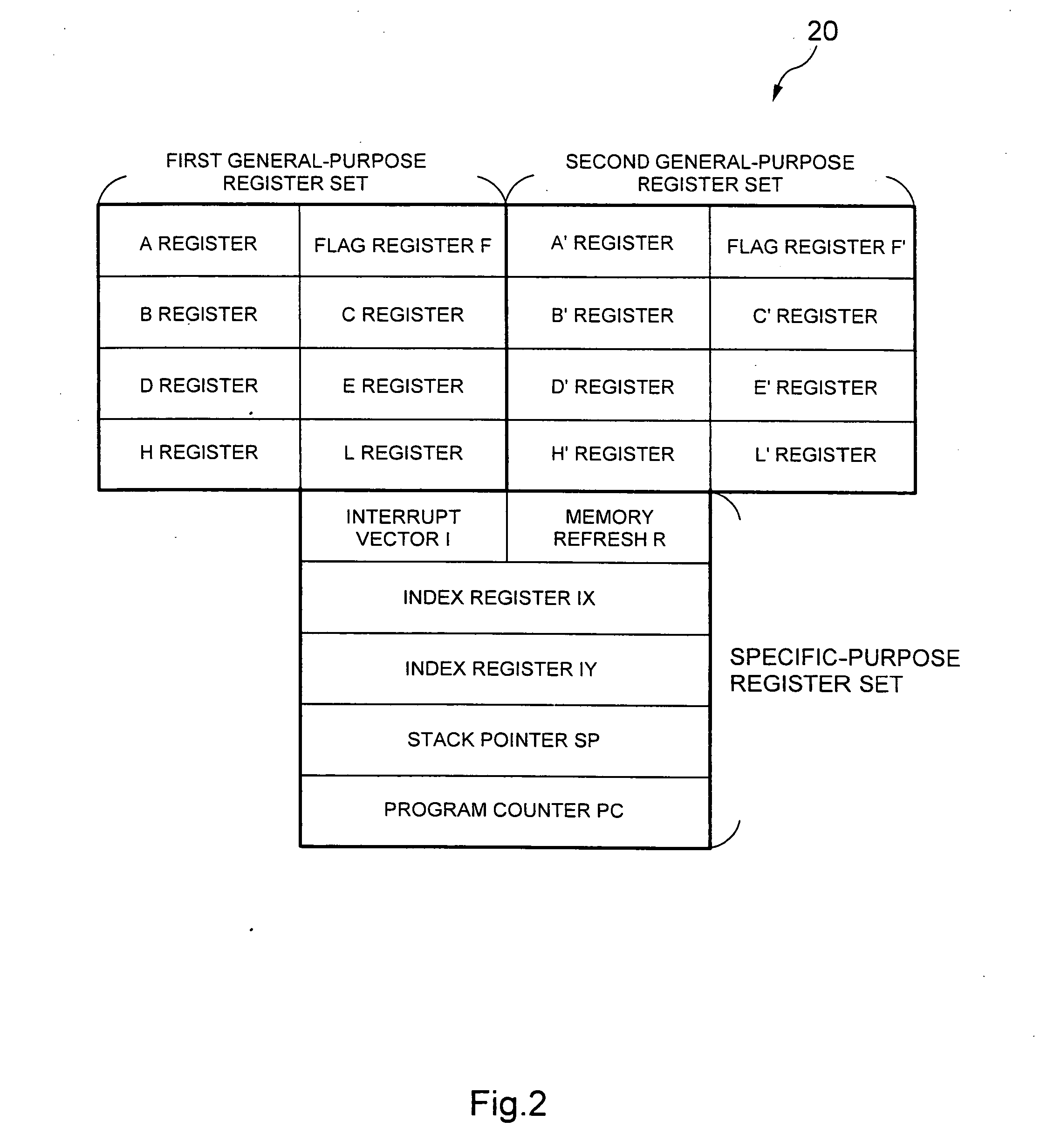

Information processing apparatus and context switching method

InactiveUS20060101252A1Digital computer detailsSpecific program execution arrangementsInformation processingParallel computing

An information processing apparatus which, when executing a plurality of predetermined units of processing, executes the predetermined units of processing in parallel by a processor by switching between contexts associated with the respective predetermined units. The processing apparatus comprises a plurality of register banks that respectively store the contexts associated with the respective predetermined units of processing, the processor that, after the context switching, executes processing associated with a foreground context, and a save / restore controller that, in parallel with the processor executing the processing associated with the foreground context, saves a background context to memory and restores the context of a unit of processing to be executed the next time from the memory to a background register bank.

Owner:SEMICON COMPONENTS IND LLC

Parallel vector processing

InactiveUS20050219422A1Color signal processing circuitsRegister arrangementsArithmetic logic unitVideo processing

A video platform architecture provides video processing using parallel vector processing. The video platform architecture includes a plurality of video processing modules, each module including a plurality of processing elements (PEs). Each PE provides parallel vector processing. Specifically, means are provided to read all elements of one or two source vector registers in each PE simultaneously, process the read elements by a set of arithmetic-logical units (ALUs), and write back all results to one of the vector registers, all of which occurs in one PE cycle. To provide such parallel vector processing capabilities, the datapath of each PE is built as a set of identical PE processing slices, each of which includes an integer arithmetic-logical unit (ALU), a vector register bank, and a block register bank. A block / vector register bank holds all I elements of row J in a two-dimensional I×J data blocks for all block / vector registers provided by the architecture.

Owner:SONY CORP +1

Data processing apparatus and method for performing a predetermined rearrangement operation

ActiveUS20100313060A1Improve performanceReduce complexityProgram control using stored programsRegister arrangementsProcessor registerParallel computing

A data processing apparatus and method are provided for performing a predetermined rearrangement operation. The data processing apparatus comprises a vector register bank having a plurality of vector registers, with each vector register comprising a plurality of storage cells such that the plurality of vector registers provide a matrix of storage cells. Each storage cell is arranged to store a data element. A vector processing unit is provided for executing a sequence of vector instructions in order to apply operations to the data elements held in the vector register bank. Responsive to a vector matrix rearrangement instruction specifying a predetermined rearrangement operation to be performed on the data elements in the matrix of storage cells, the vector processing unit is arranged to issue a set rearrangement enable signal to the vector register bank. The write interface of the vector register bank is modified to provide not only a first input for receiving the data elements generated by the vector processing unit during normal execution, but also has a second input coupled via a data rearrangement path to the matrix of storage cells via which the data elements currently stored in the matrix of storage cells are provided to the write interface in a rearranged form representing the arrangement of data elements that would be obtained by performance of the predetermined rearrangement operation. When the rearrangement enable signal is set, the write interface then performs a write operation to the storage cells of the matrix using the data elements received at the second input. This enables the predetermined rearrangement operation to be performed at high speed and with significantly less complexity than in prior art systems.

Owner:ARM LTD

Method and apparatus for generating a variation-tolerant clock-tree for an integrated circuit chip

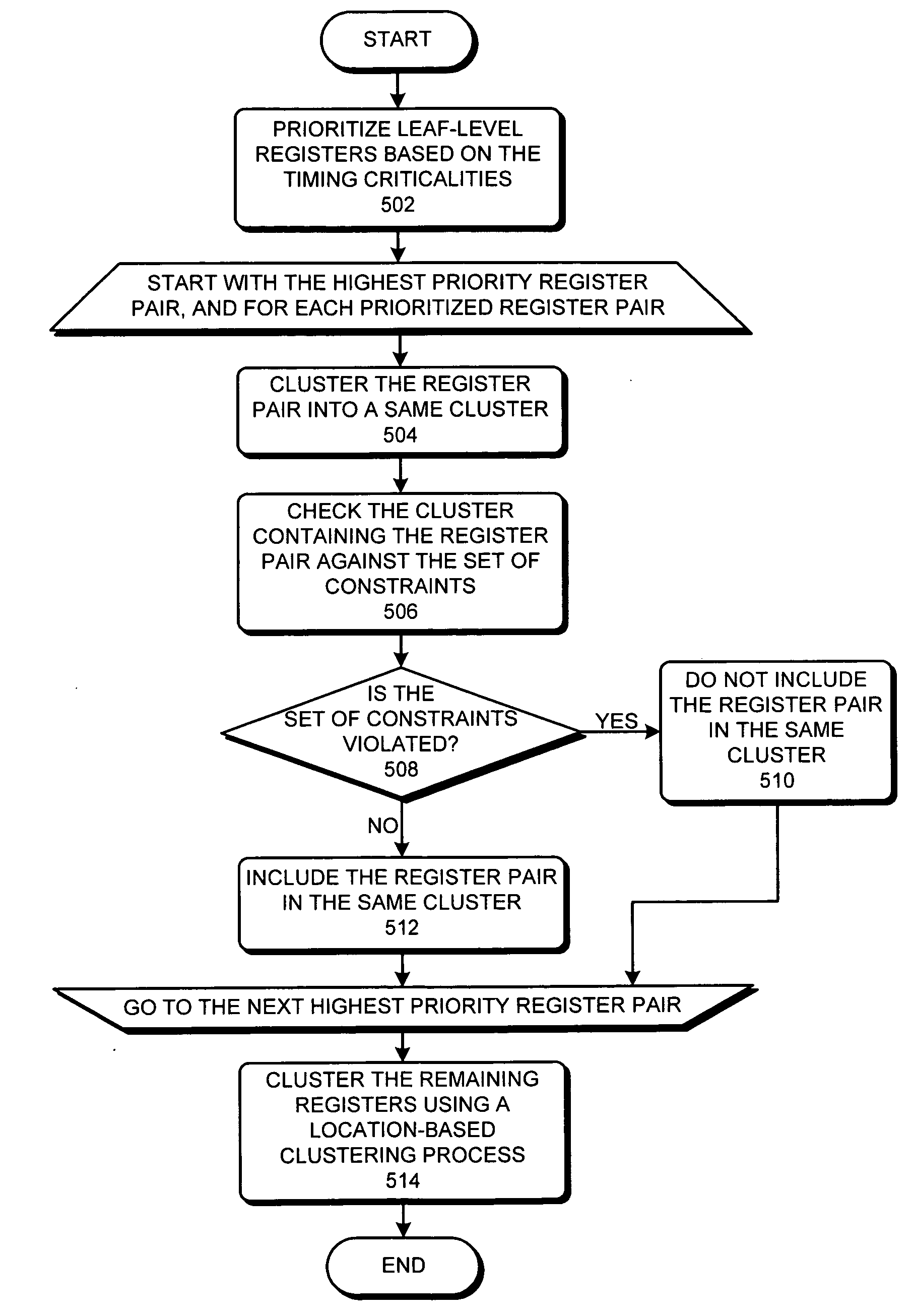

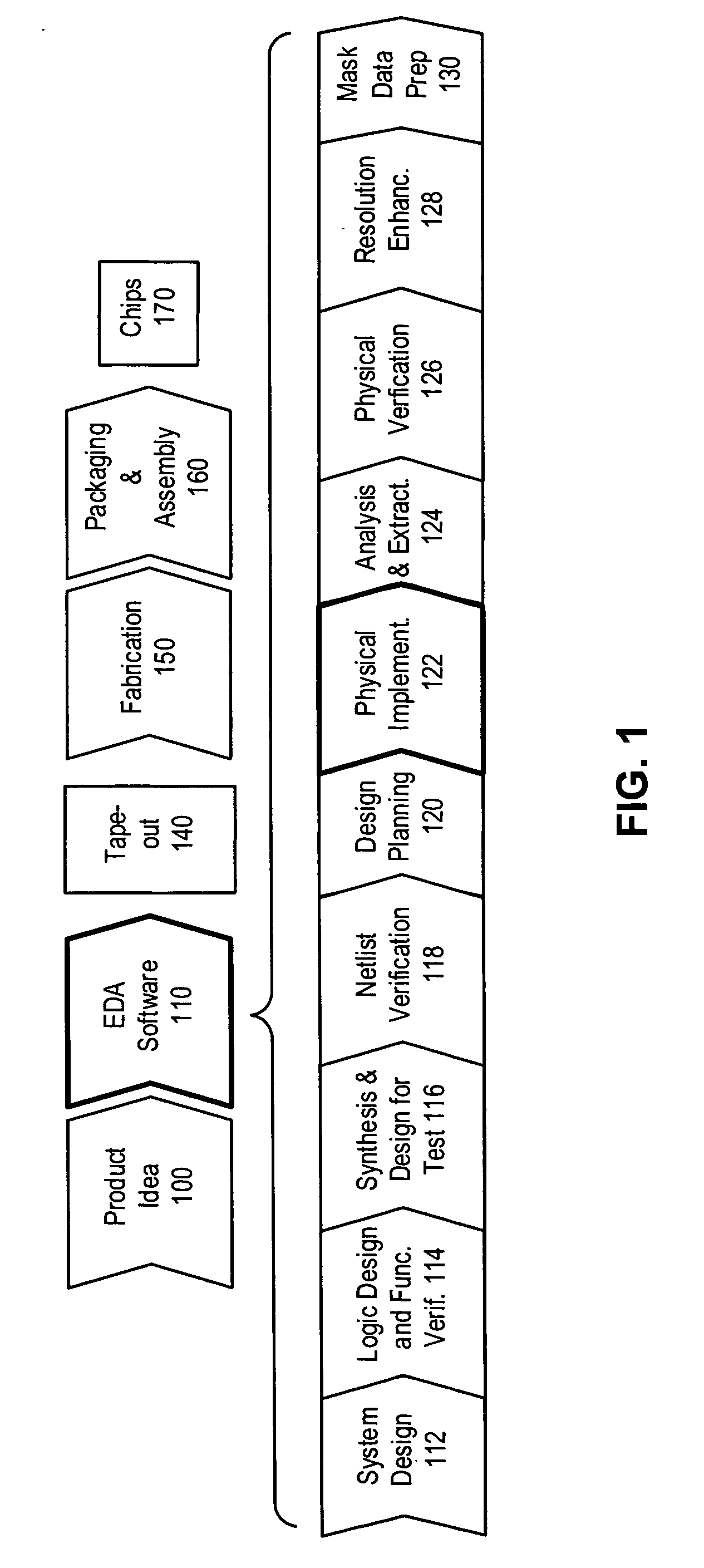

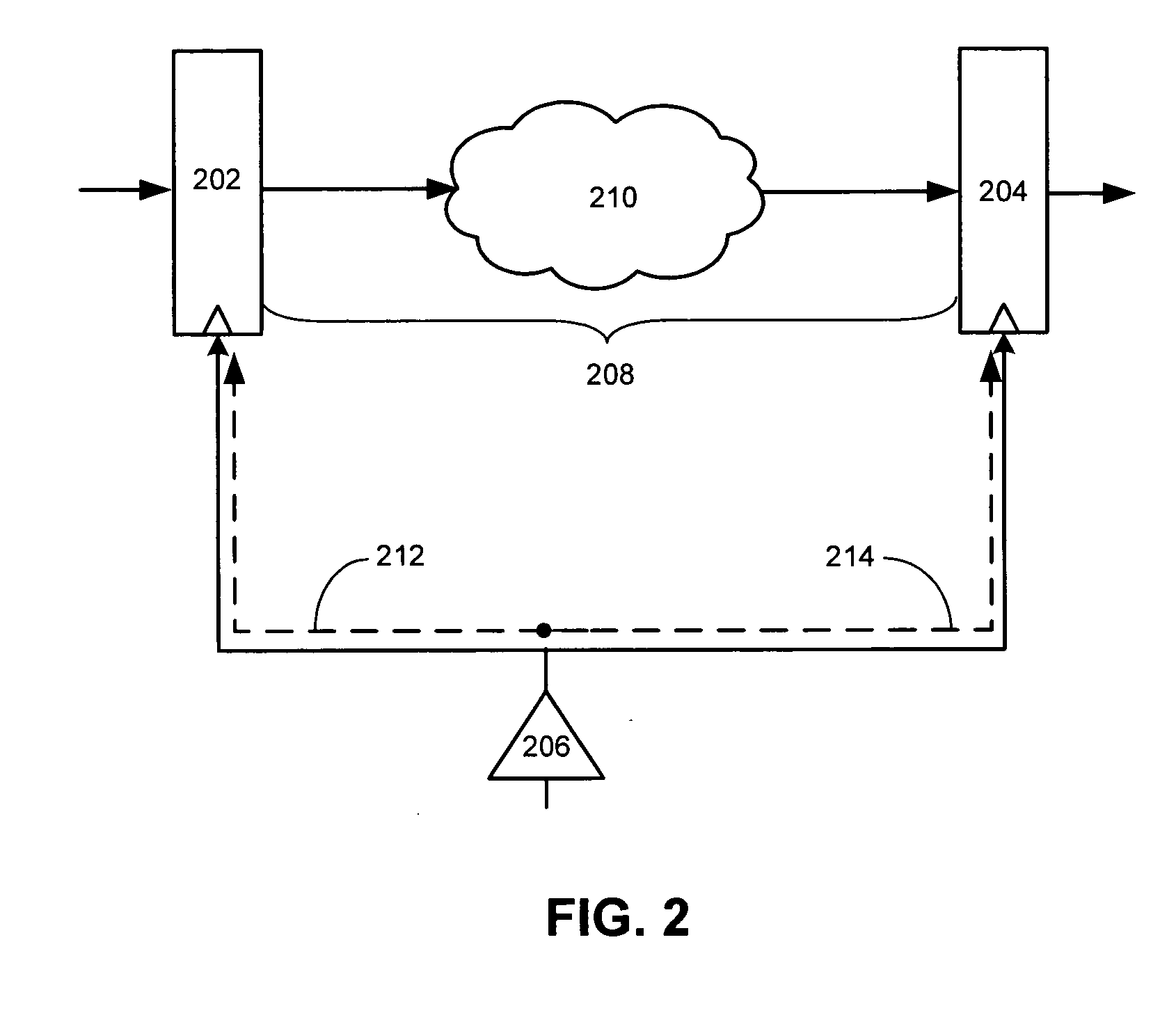

ActiveUS20080168412A1Raise priorityMaximizes inclusionProbabilistic CADSoftware simulation/interpretation/emulationProcessor registerTime critical

One embodiment of the present invention relates to a process that generates a clock-tree on an integrated circuit (IC) chip. During operation, the process starts by receiving a placement for a chip layout, where the placement includes a set of registers at fixed locations in the chip layout. The process then generates a timing criticality profile for the set of registers, wherein the timing criticality profile specifies timing criticalities between pairs of registers in the set of registers. Next, the process clusters the set of registers based on the timing criticality profile to create a clock-tree for the set of registers. By clustering the registers based on the timing criticality profile, the process facilitates using commonly-shared clock paths in the clock-tree to provide clock signals to timing critical register pairs.

Owner:SYNOPSYS INC

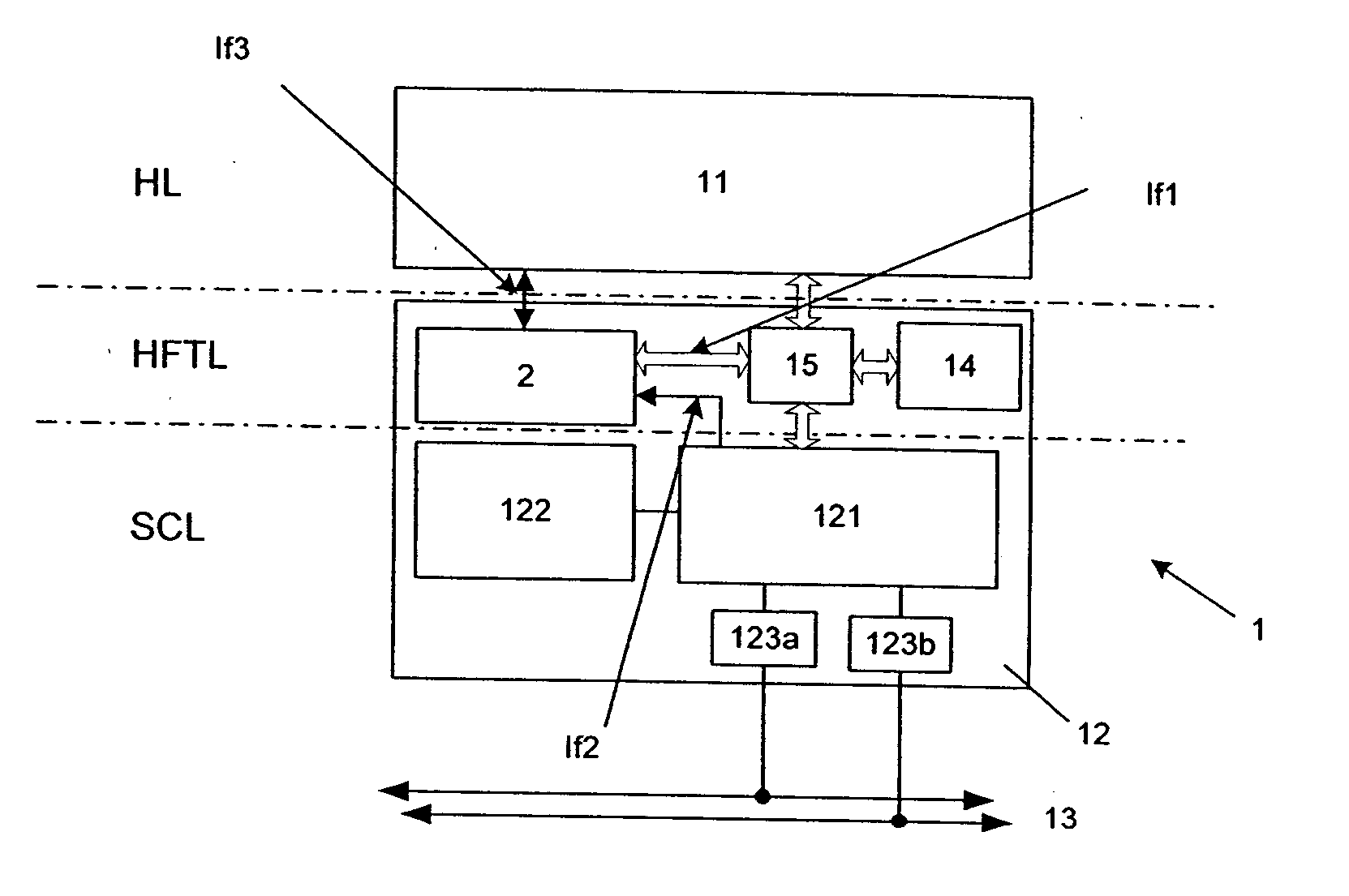

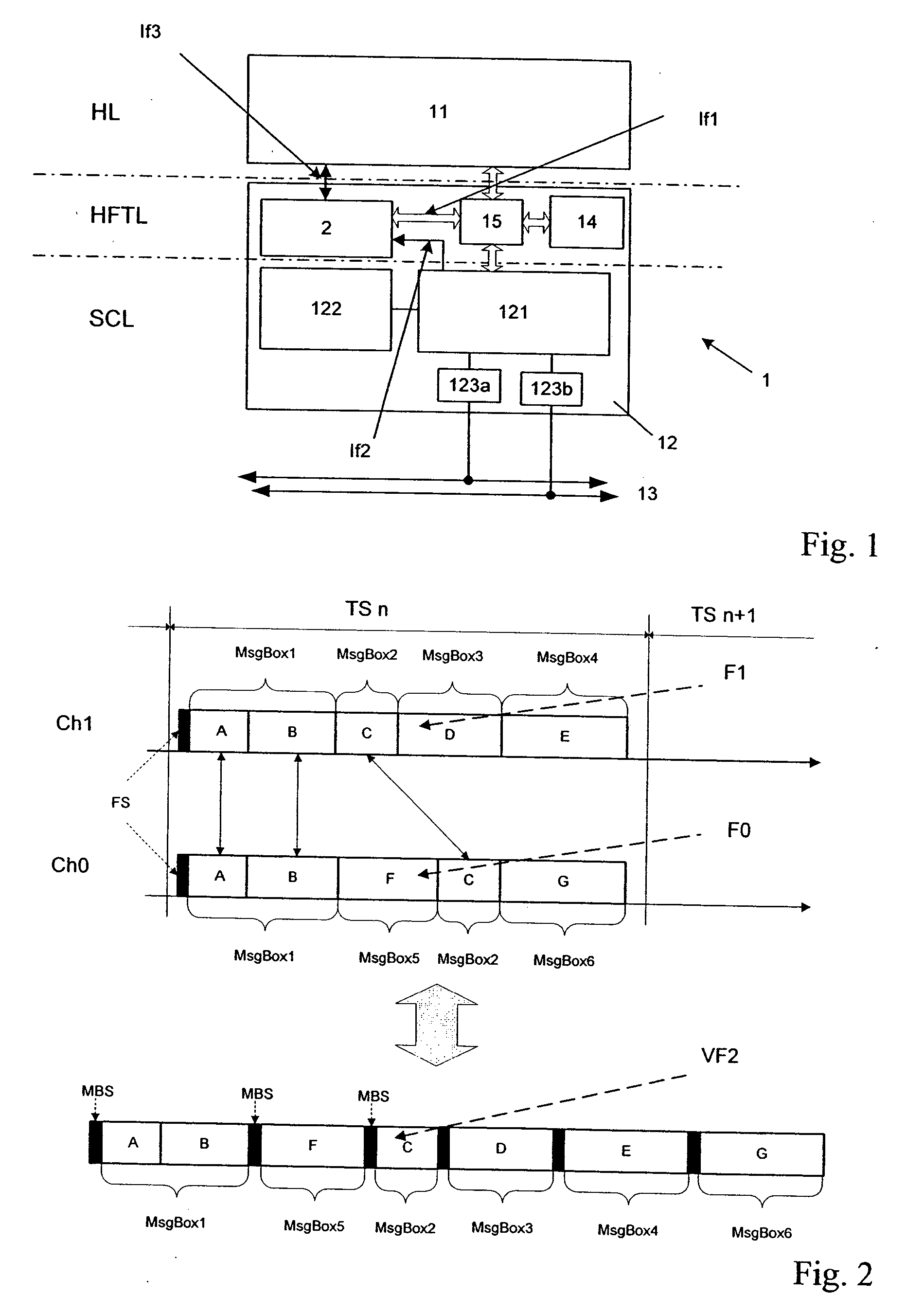

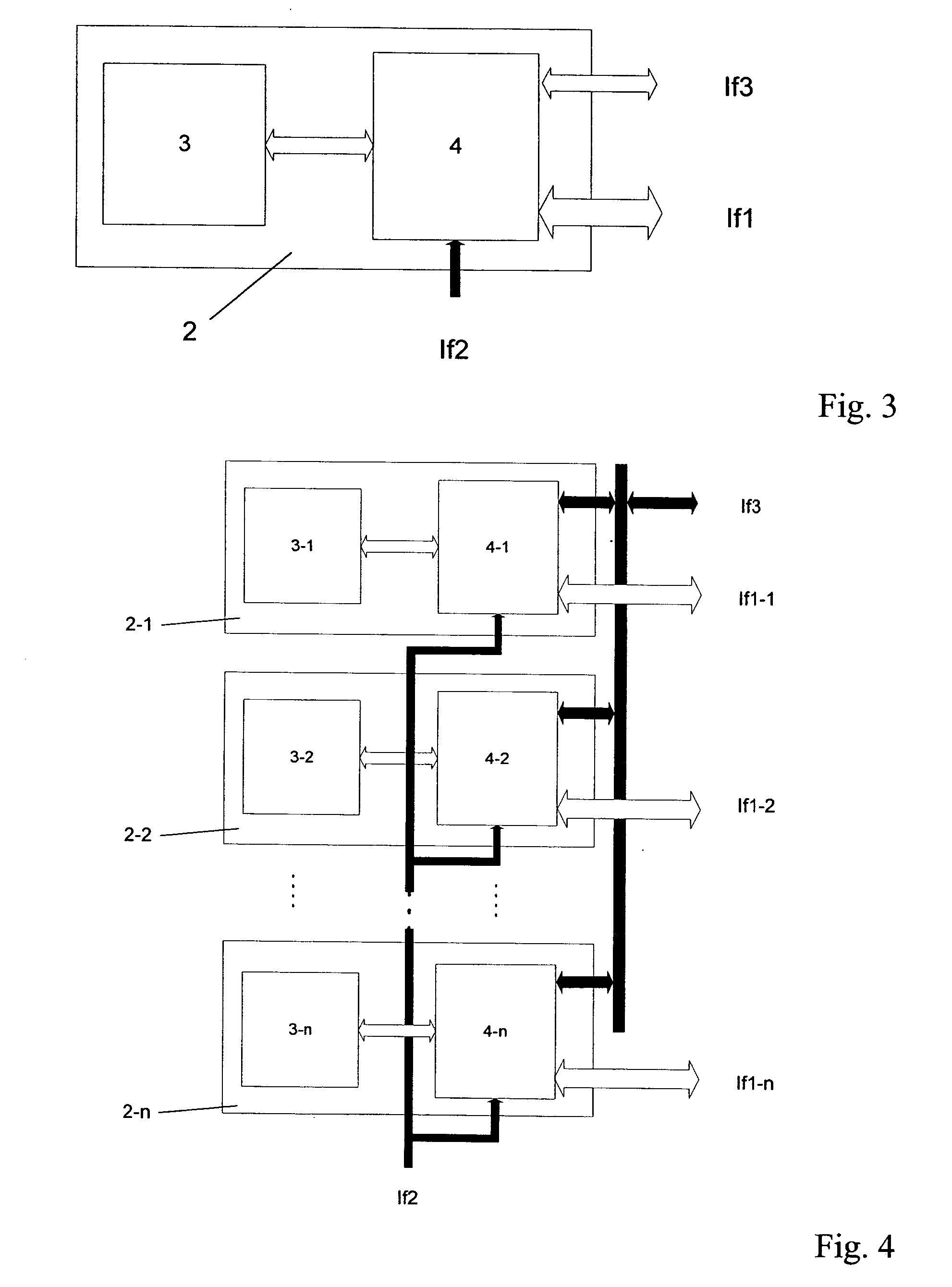

Processing of data frames exchanged over a communication controller in a time-triggered system

InactiveUS20070022209A1Reduce processing requirementsAvoid overheadMultiple digital computer combinationsData switching networksProcessor registerCommunication control

Owner:TTTECH COMPTECHN

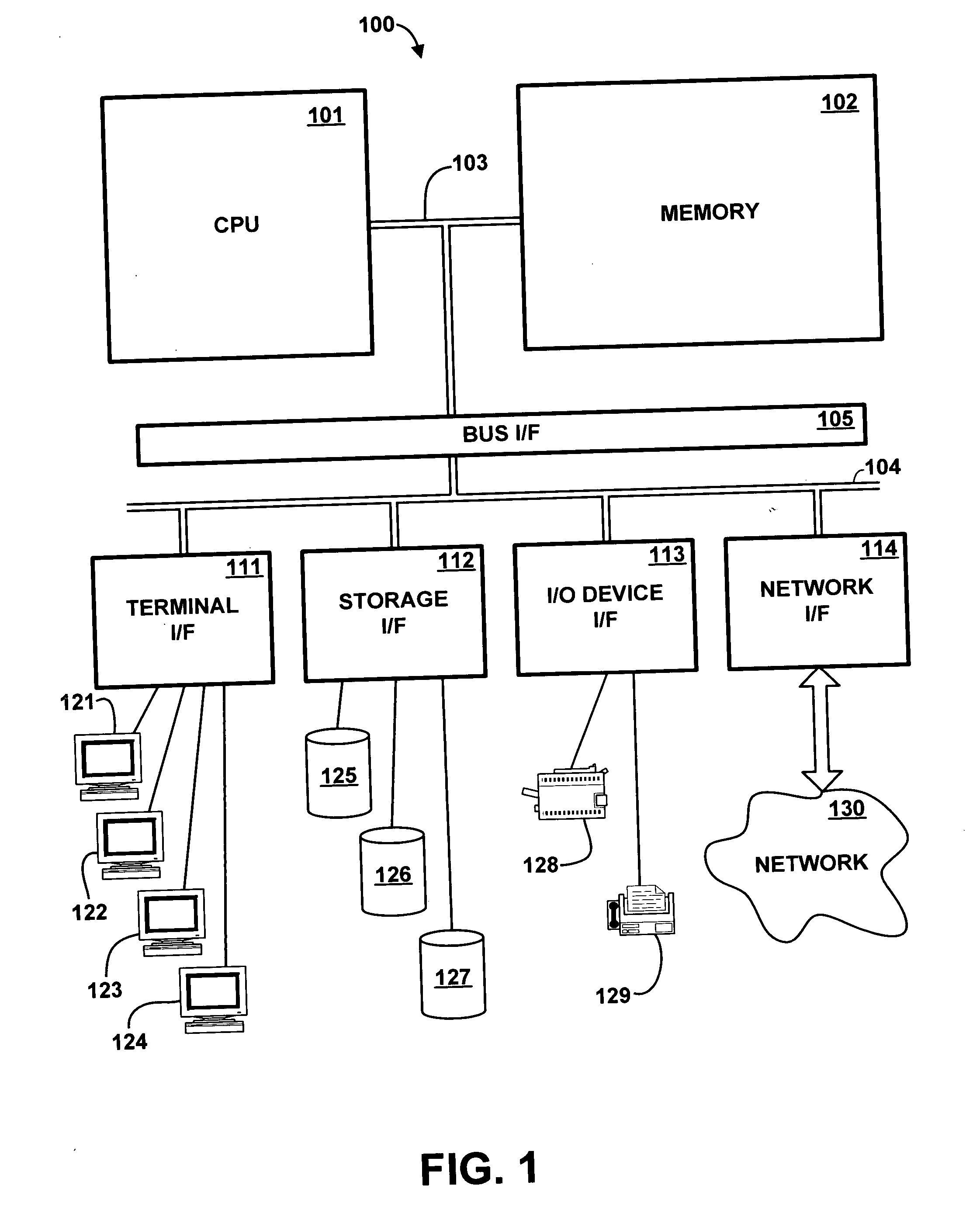

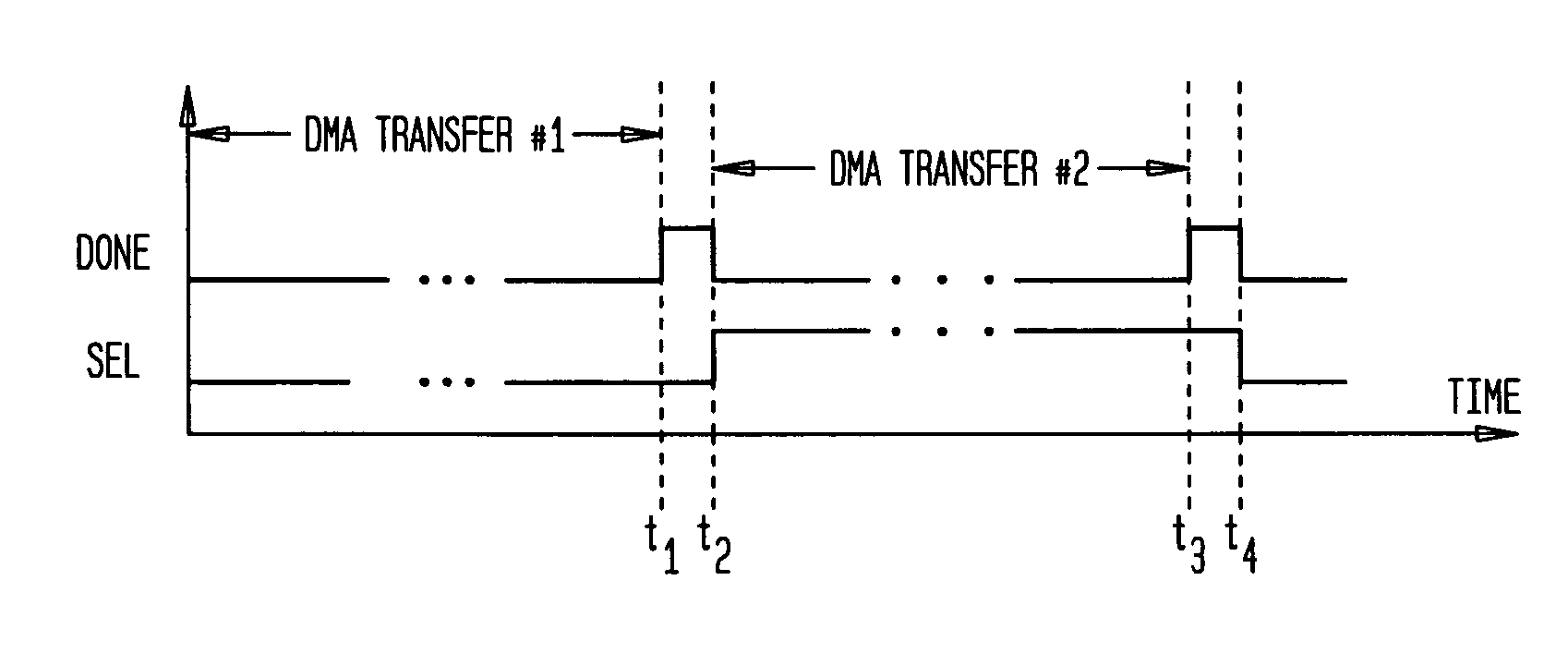

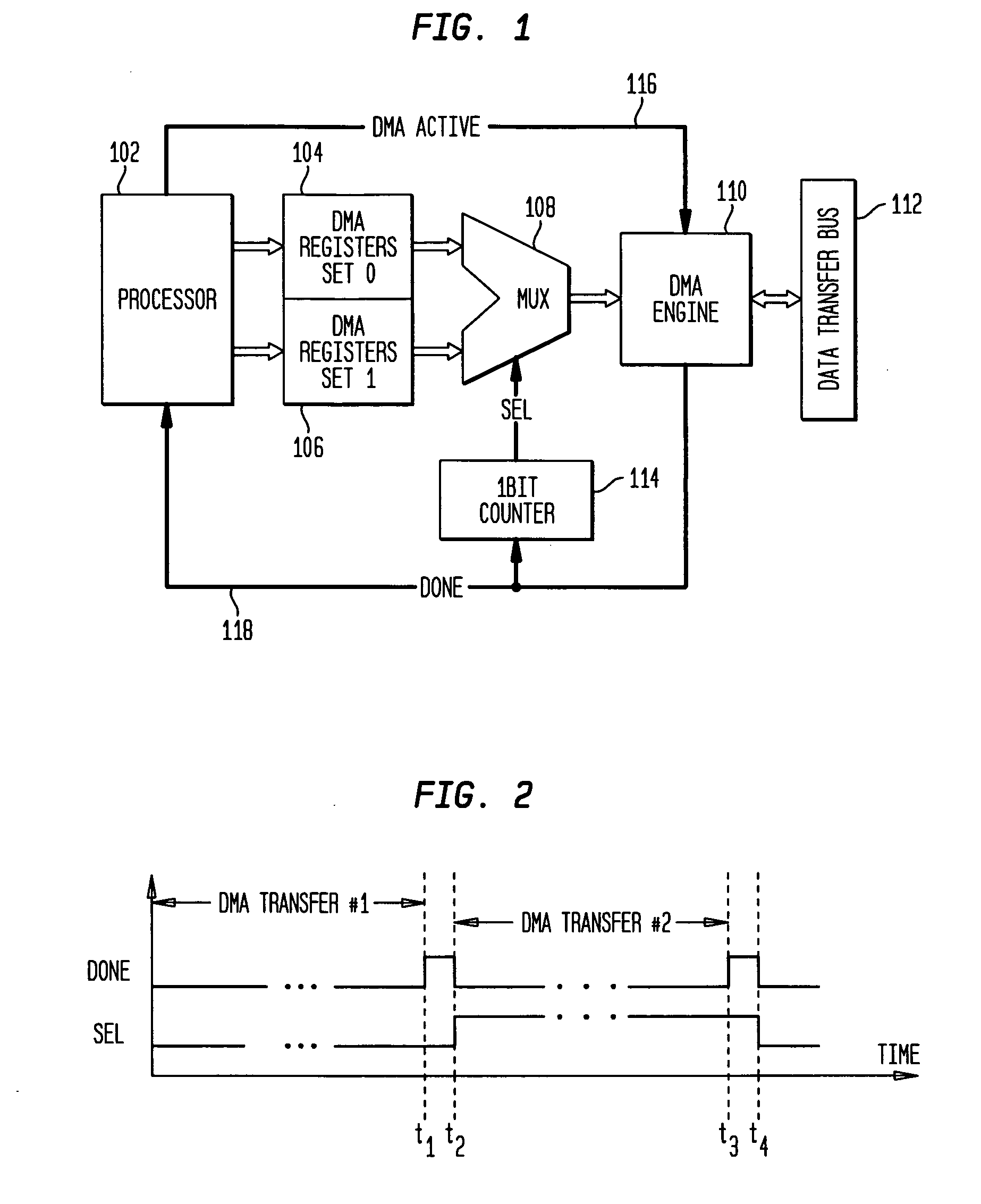

Emulation of independent active DMA channels with a single DMA capable bus master hardware and firmware

InactiveUS20060288128A1Input/output processes for data processingData conversionComputer scienceRegister bank

The present invention utilizes a single DMA engine to process the requests of active DMA channels competing for transfer of data over a single bus. The invention employs two identical sets of DMA request registers which are connected to a processor. These register sets are connected through a switching means to the DMA engine. While a first DMA transfer represented by a first set of registers is active, the process enables preparation of the next request in a second set of registers. Upon completion of the first DMA transfer, the DMA engine is switched to commence processing of the DMA request represented by the second set of registers.

Owner:AVAGO TECH INT SALES PTE LTD