Patents

Literature

420 results about "Instruction memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory reference instruction An instruction that has one or more of its operand addresses referring to a location in memory, as opposed to one of the CPU registers or some other way of specifying an operand. Pick a style below, and copy the text for your bibliography.

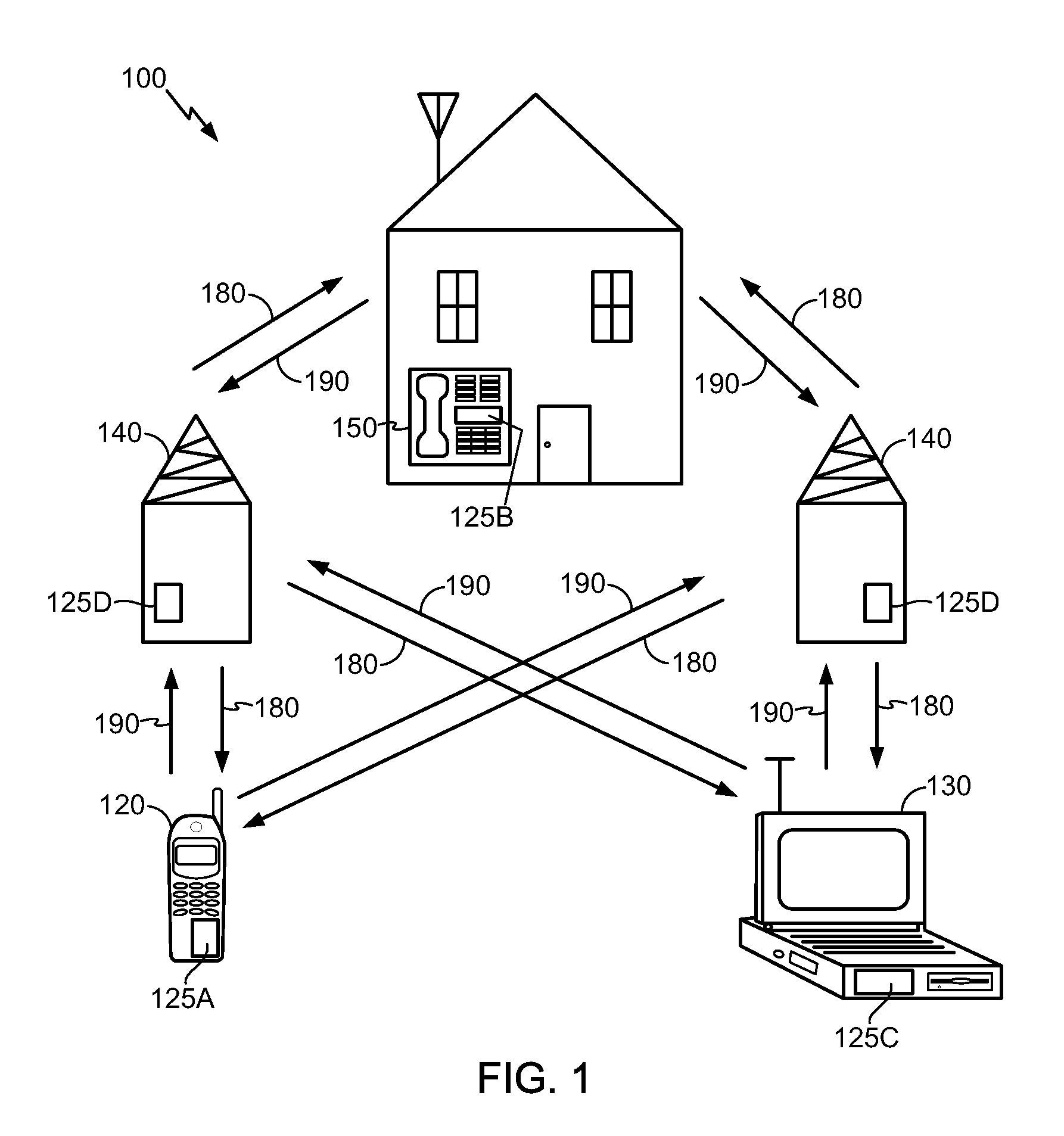

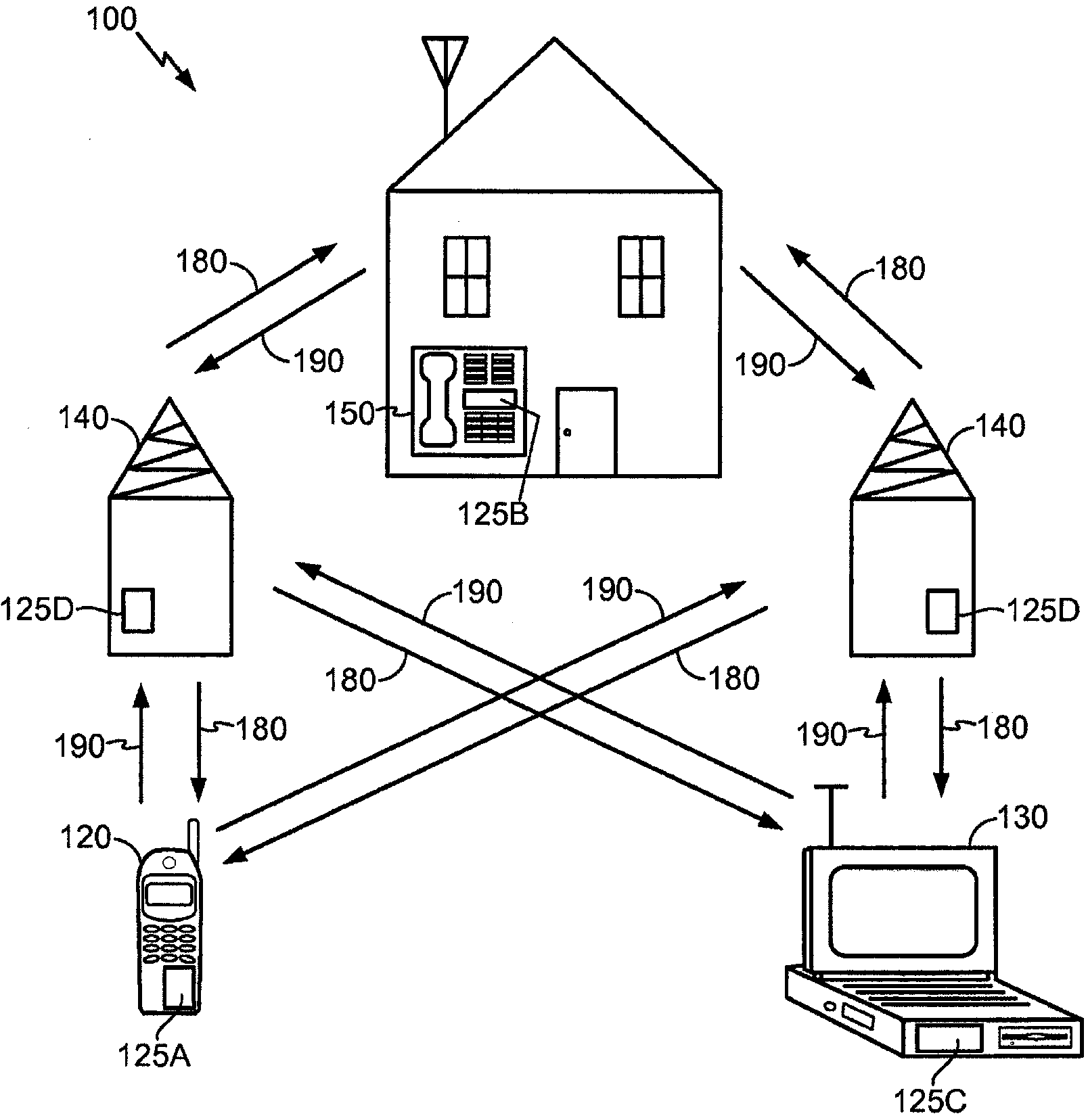

Network manager for cable television system headends

InactiveUS6201536B1Increase flexibilityImprove rendering capabilitiesTelevision system detailsPulse modulation television signal transmissionInformation processingInstruction memory

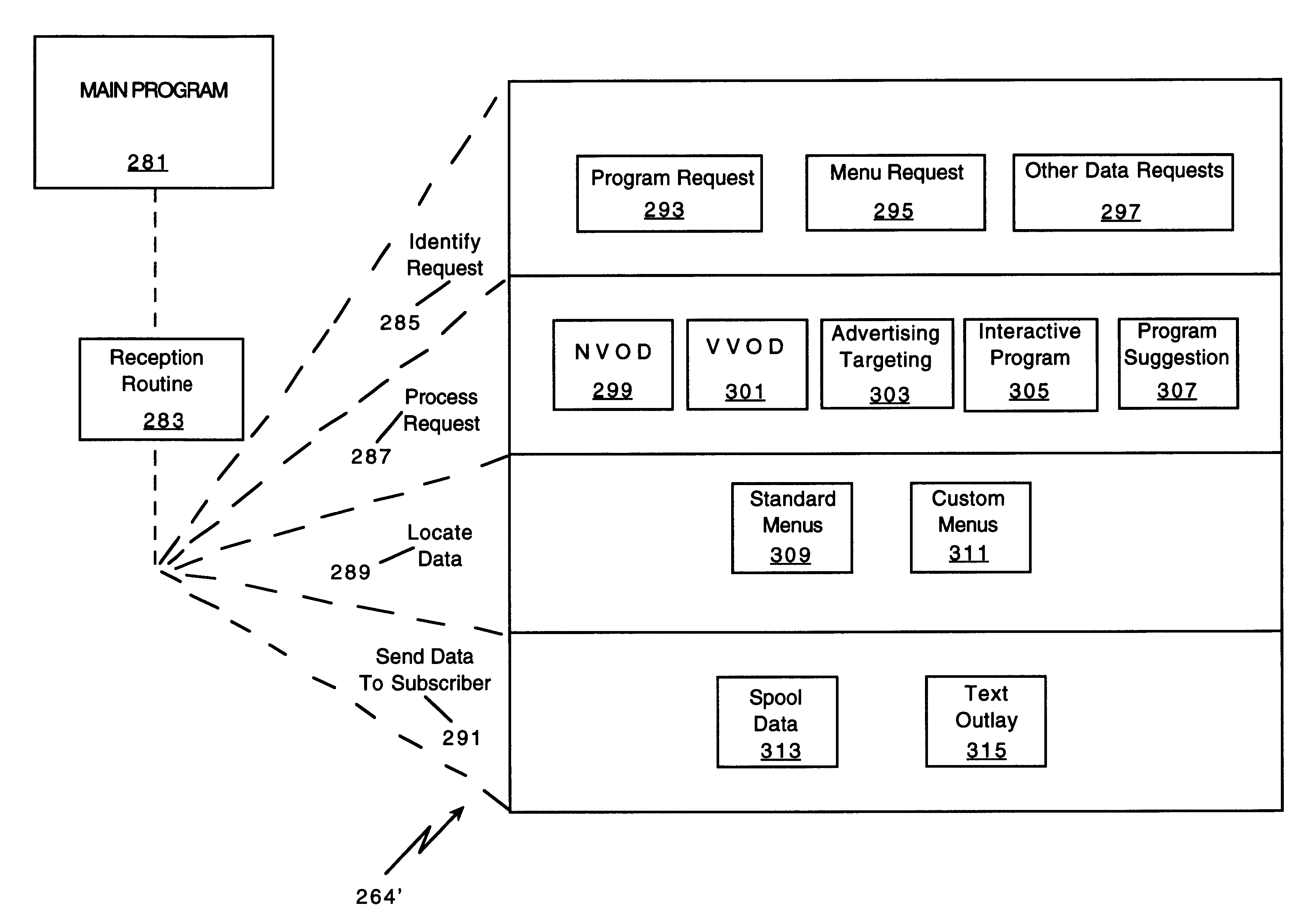

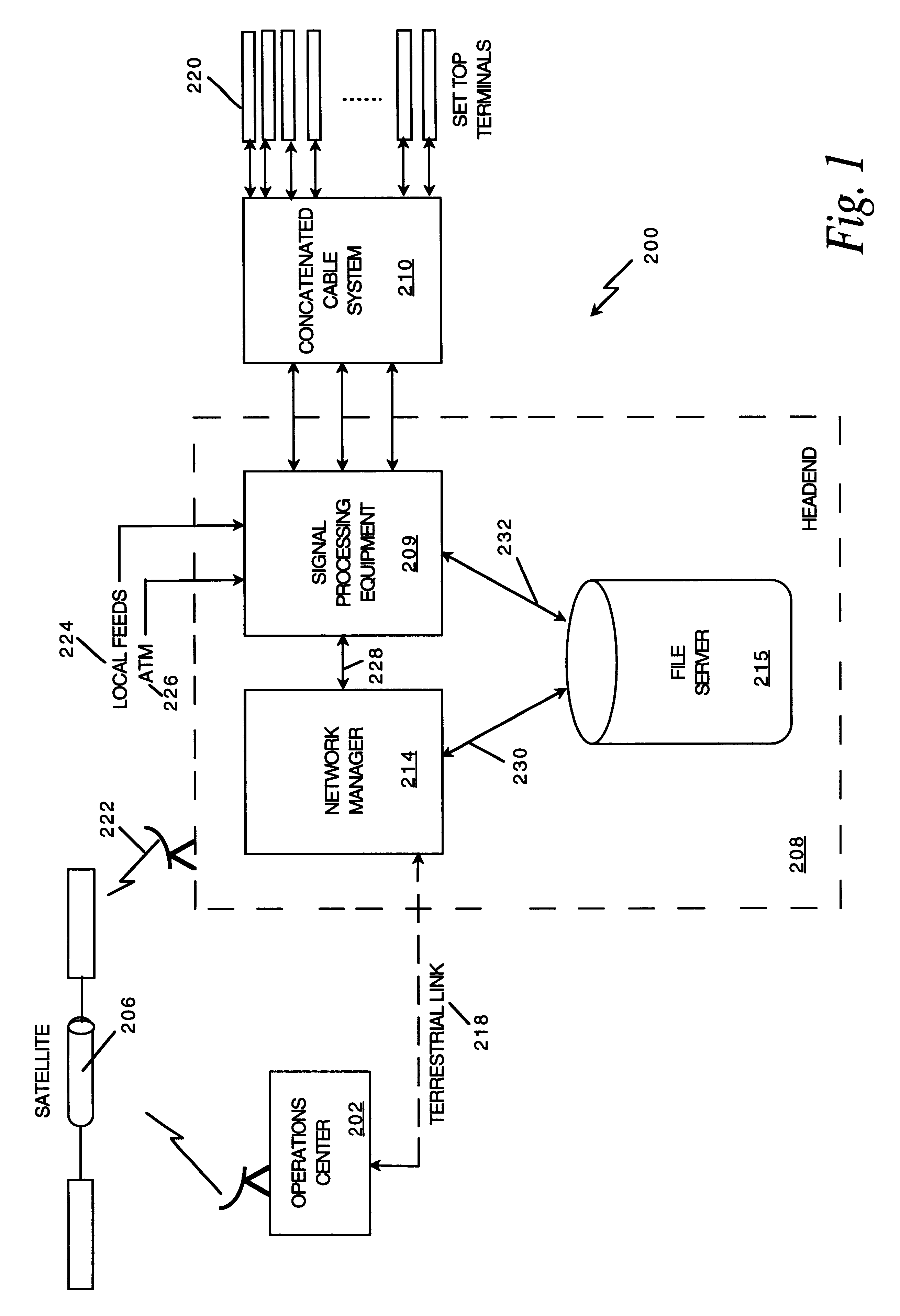

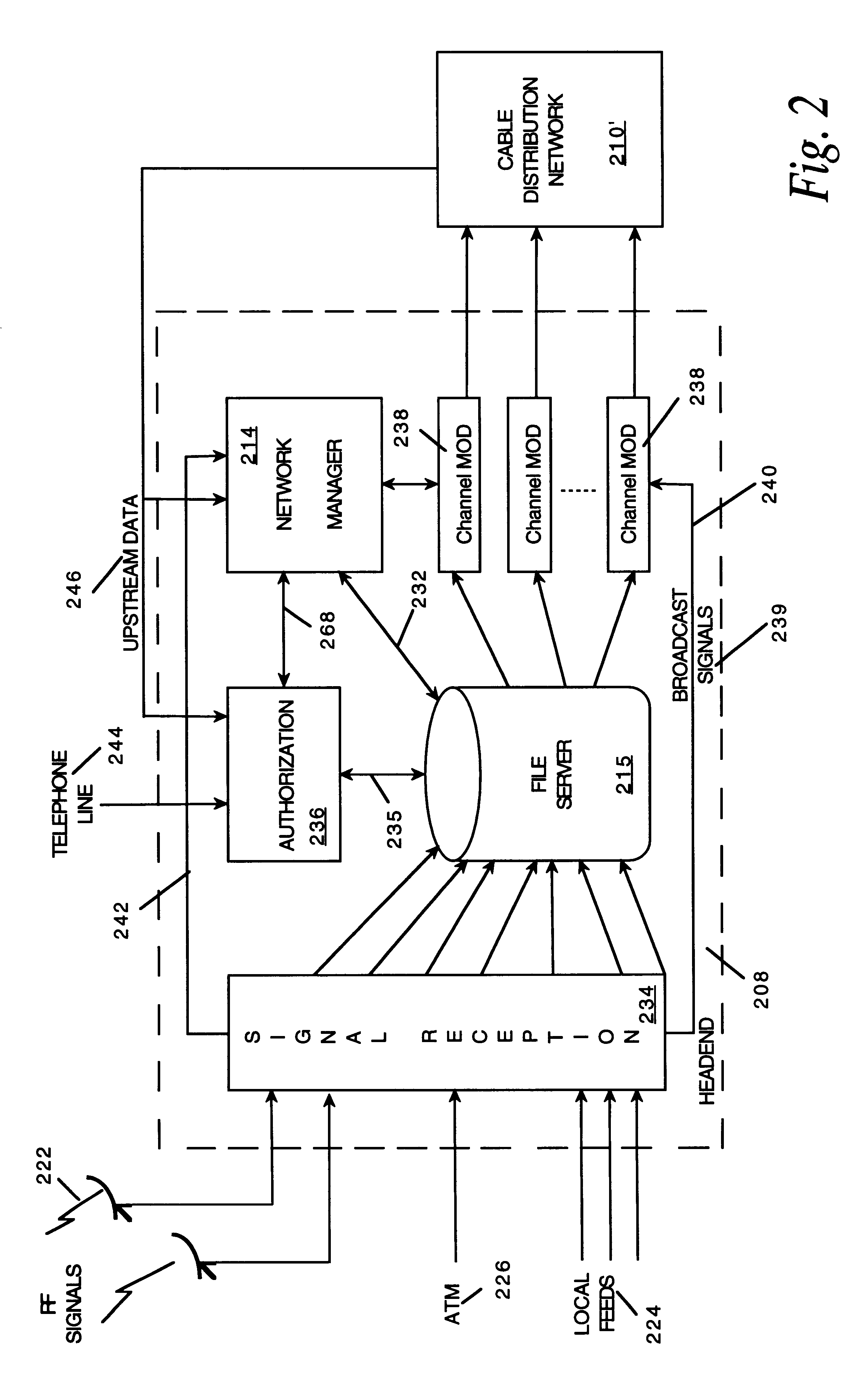

A novel network manager for use with a cable television system headend capable of monitoring and managing headend components and set top terminals in a television delivery system is described. The invention relates to methods and apparatus that manage and coordinate the reception of various programming and control signals at a headend. The invention manages and coordinates the storage of such signals for intelligent selection and distribution to set top terminals. The invention makes use of a receiver or set of receivers, a work station, a program control information processing component, a network management CPU, databases, control software and an instruction memory. The invention uses these components to manage and monitor certain headend components, such as signal reception equipment, an authorization component, a file server, MPEG decoders, a digital buffer with frame repeat and channel modulators. The invention is particularly useful in processing and responding to upstream information and subscriber communications received from set top terminals. In so doing, the invention accommodates various system services, including (1) near video on demand (NVOD), (2) virtual video on demand (VVOD), (3) video on demand (VOD), (4) interactive program services, (5) program suggestion features, (6) advertisement targeting, (7) generation of standard and custom menus, and (8) data spooling and text overlaying.

Owner:COMCAST IP HLDG I

Microprocessors

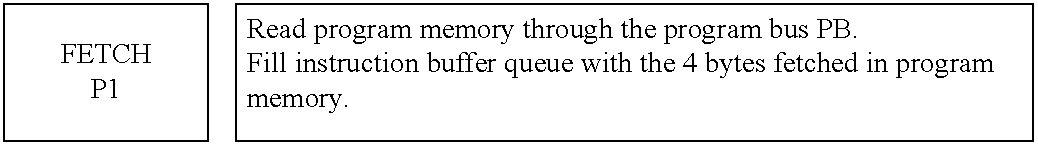

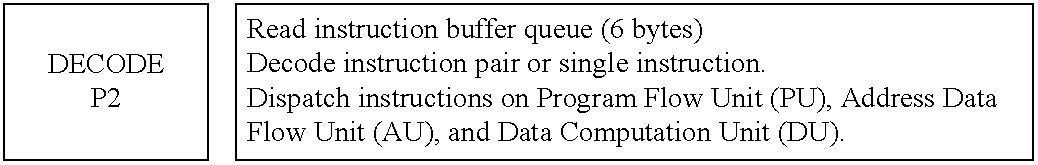

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

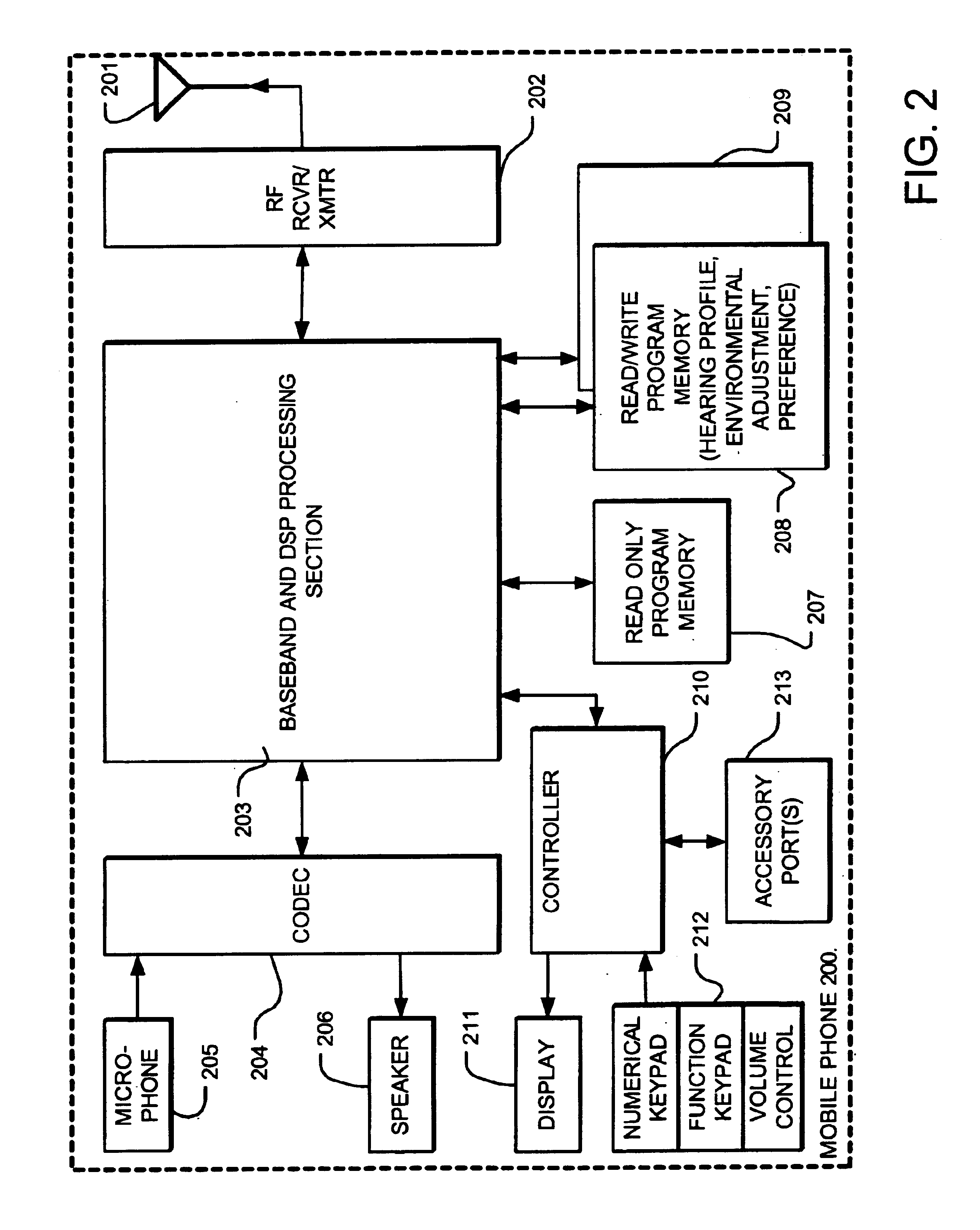

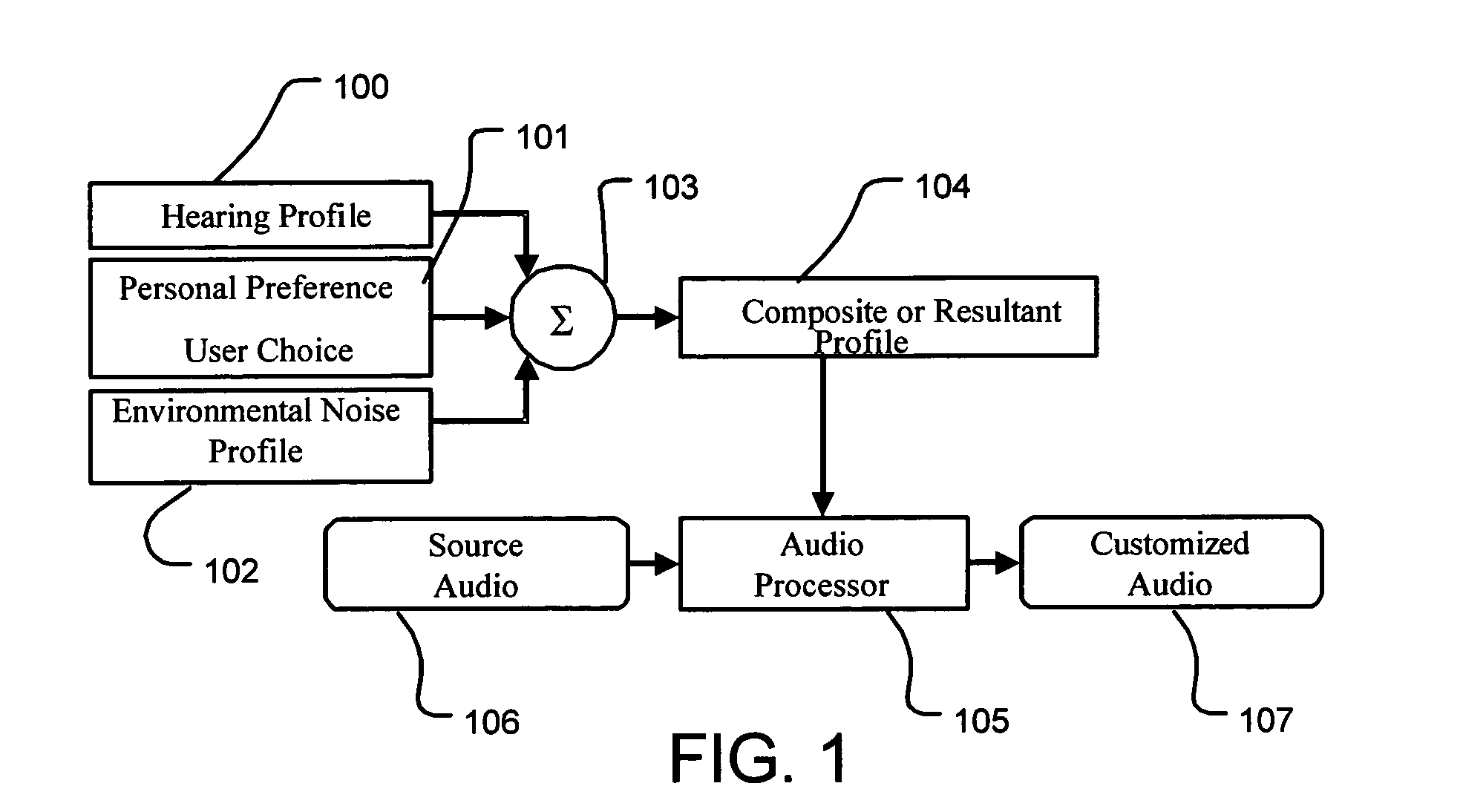

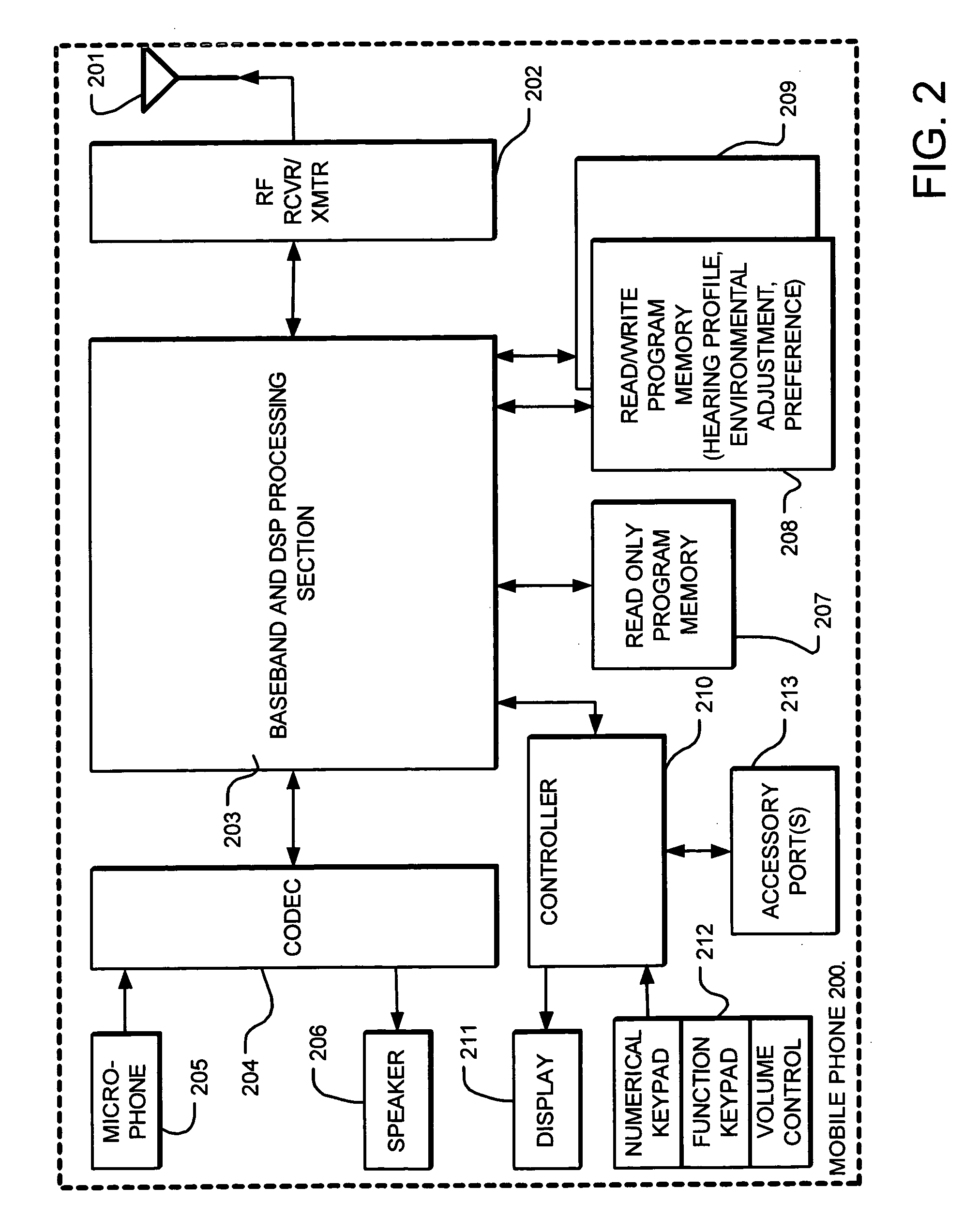

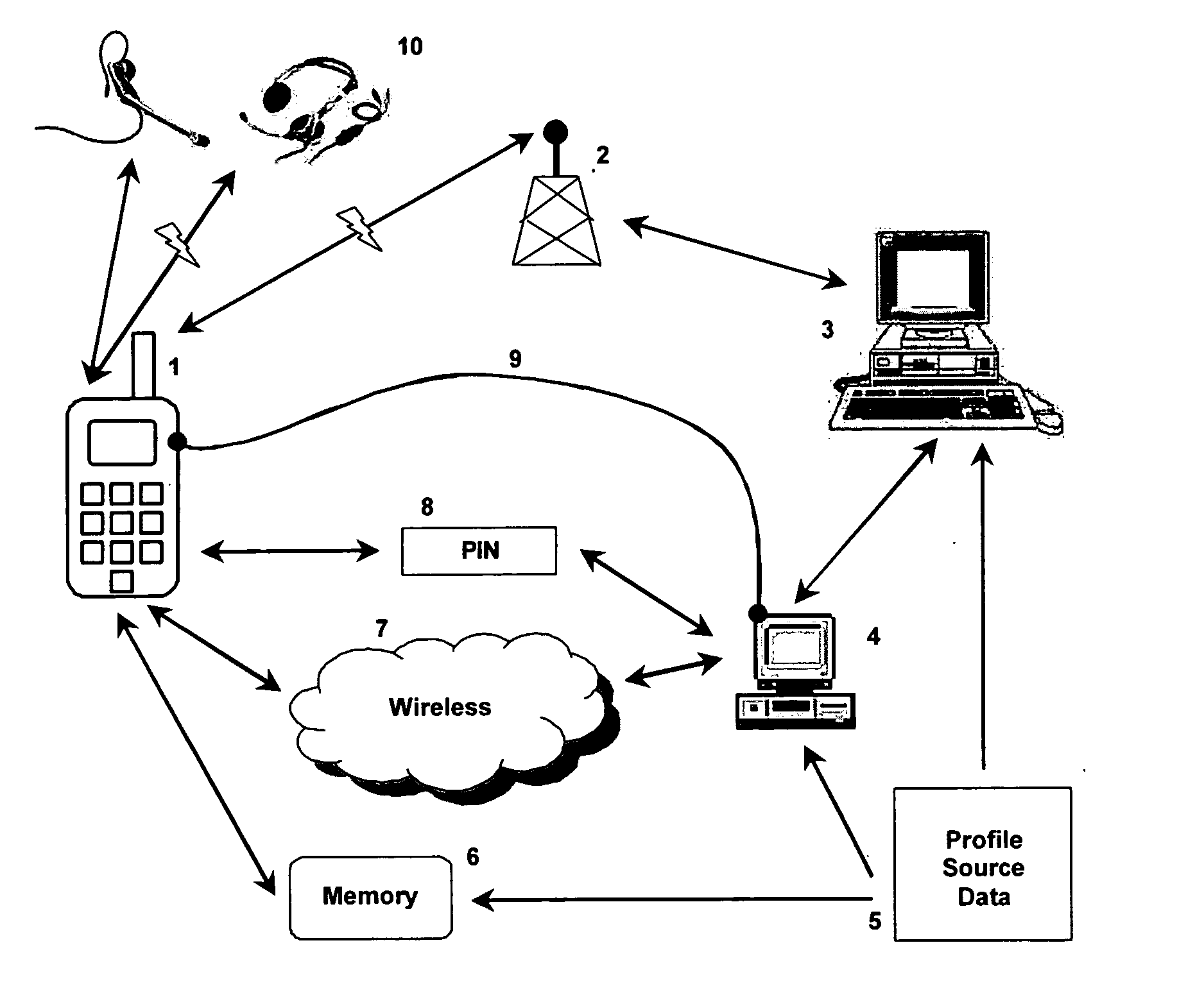

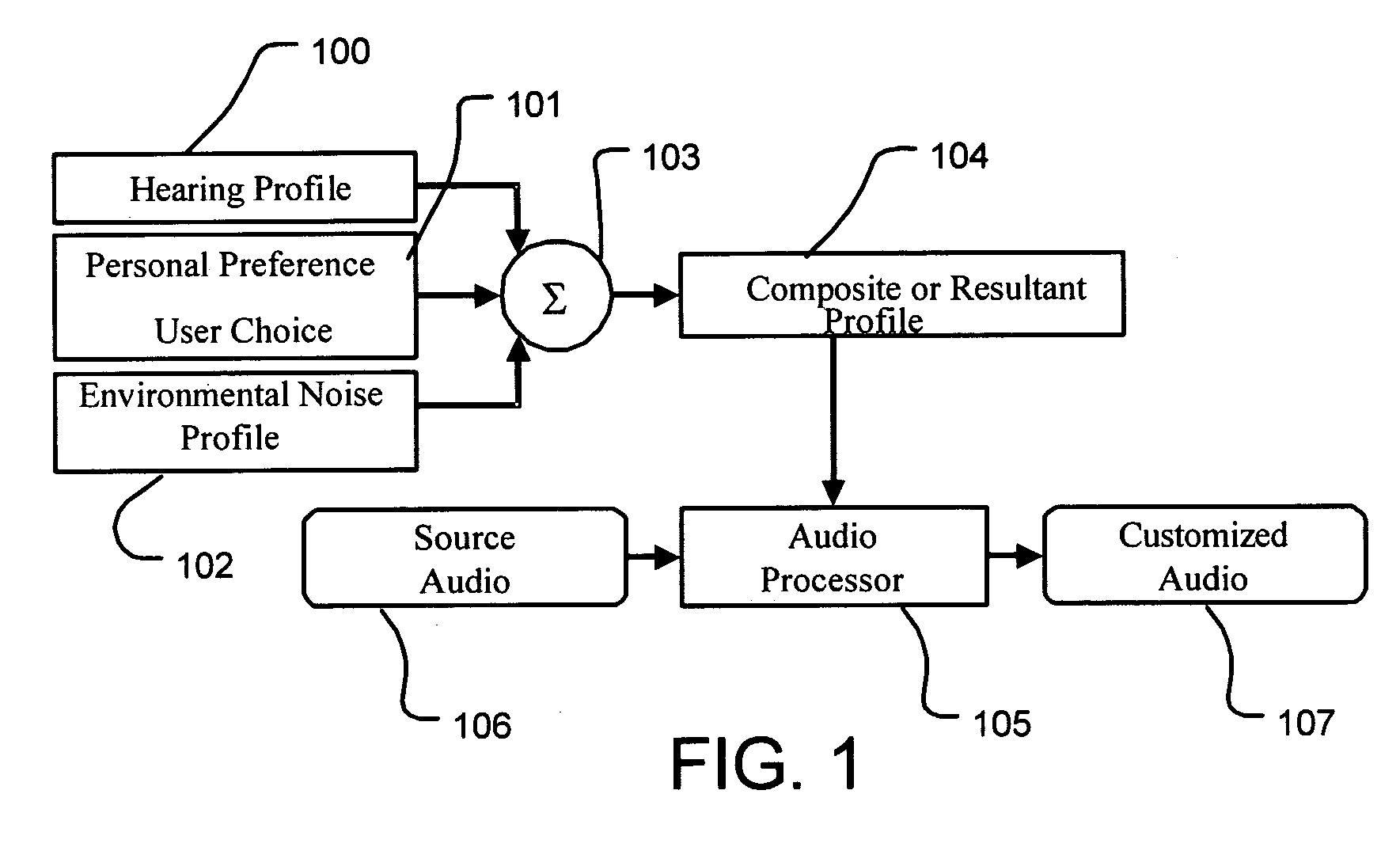

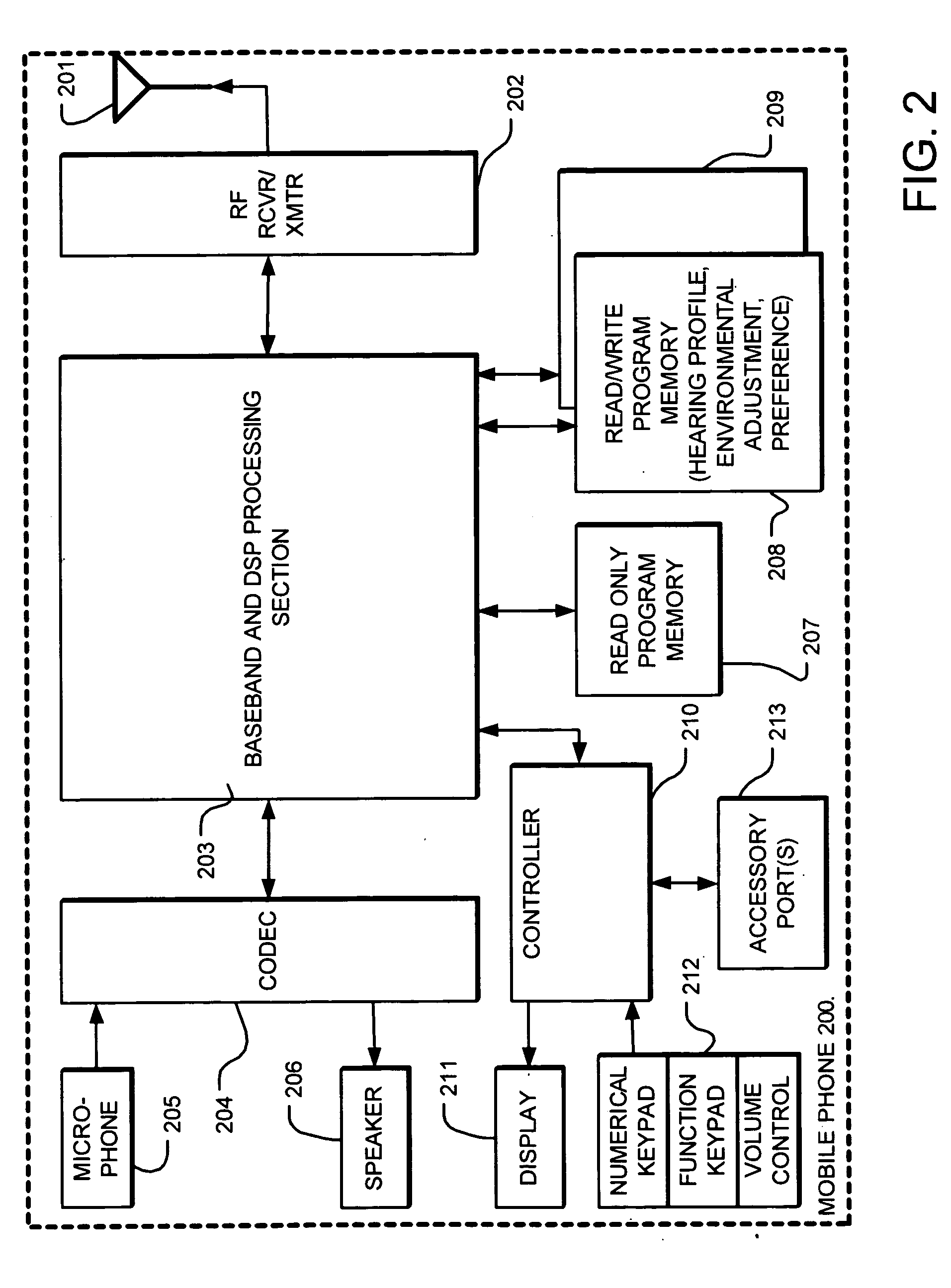

Sound enhancement for mobile phones and other products producing personalized audio for users

InactiveUS6944474B2Easy to receiveImprove soundStereophonic circuit arrangementsHearing impaired stereophonic signal reproductionInstruction memoryEnvironmental noise

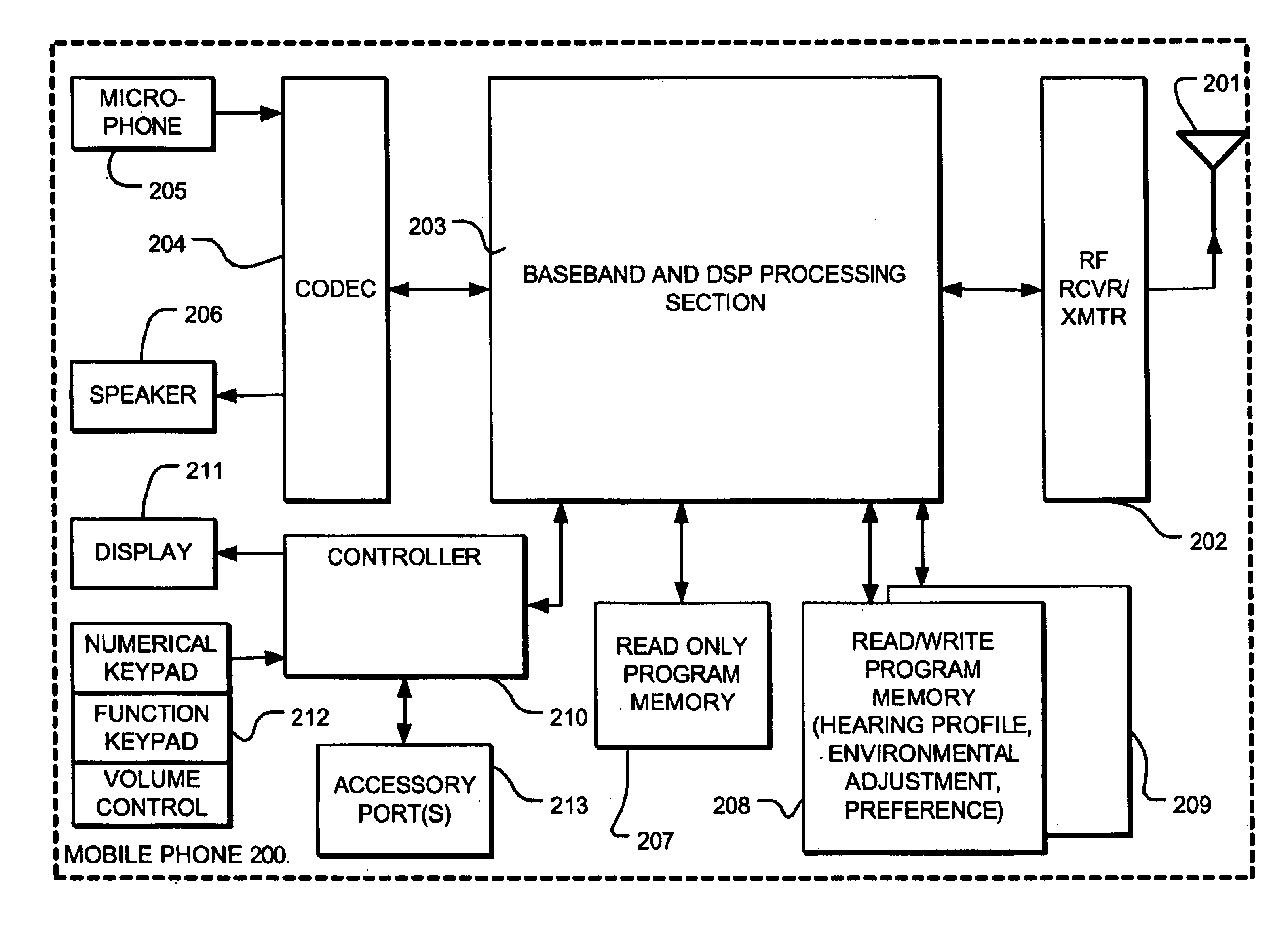

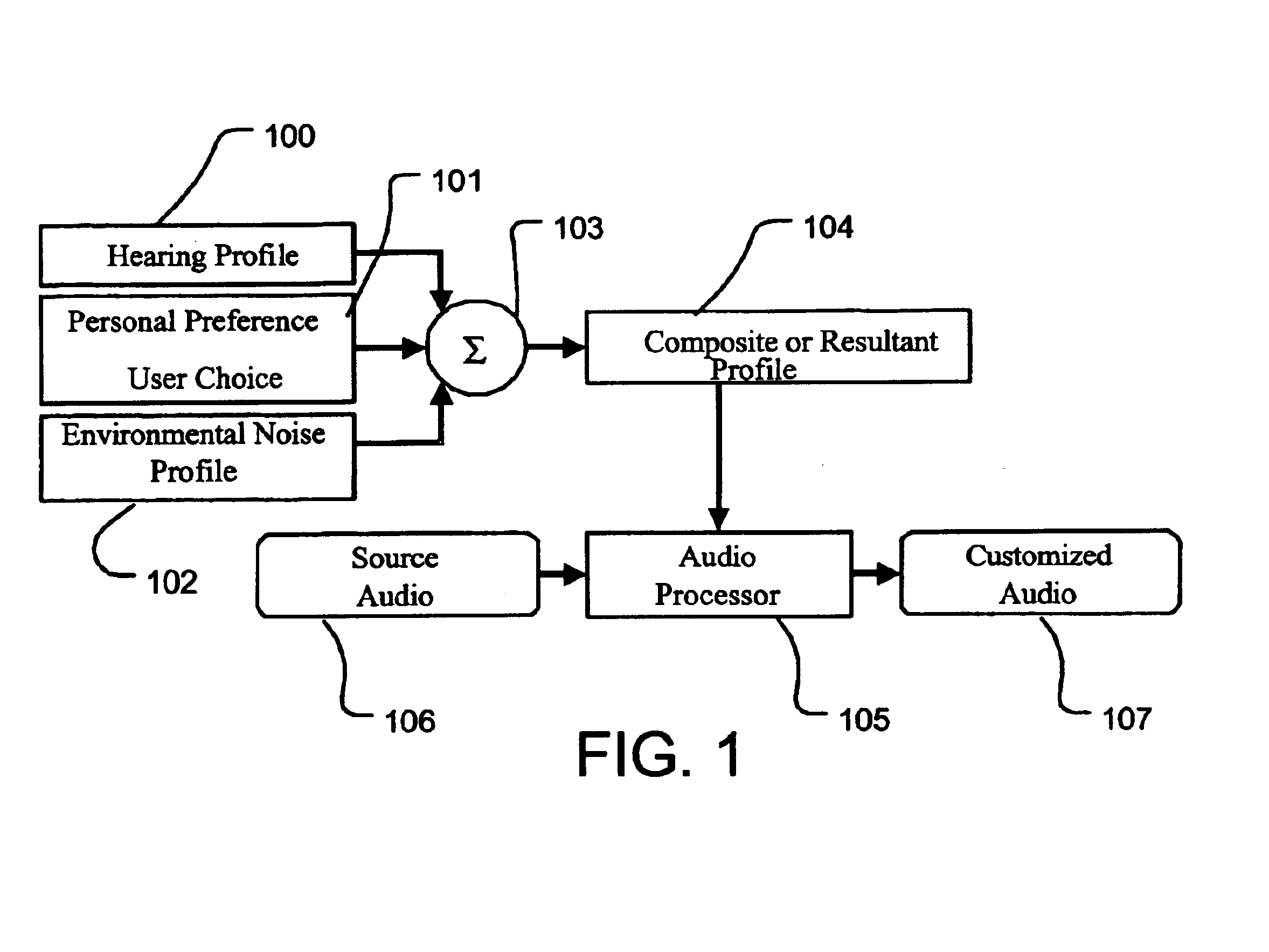

A mobile phone or other personal communication device includes resources applying measures of an individual's hearing profile, personal choice profile, and induced hearing loss profile, separately or in combination, to build the basis of sound enhancement. A personal communication device thus comprises a transmitter / receiver coupled to a communication medium for transmitted receiving audio signals, control circuitry that controls transmission, reception and processing of call and audio signals, a speaker, and a microphone. The control circuitry includes logic applying one or more of a hearing profile of the user, a user preference related hearing, and environmental noise factors in processing the audio signals. The control circuitry may includes instruction memory and an instruction execution processor such as a digital signal processor.

Owner:HIMPP

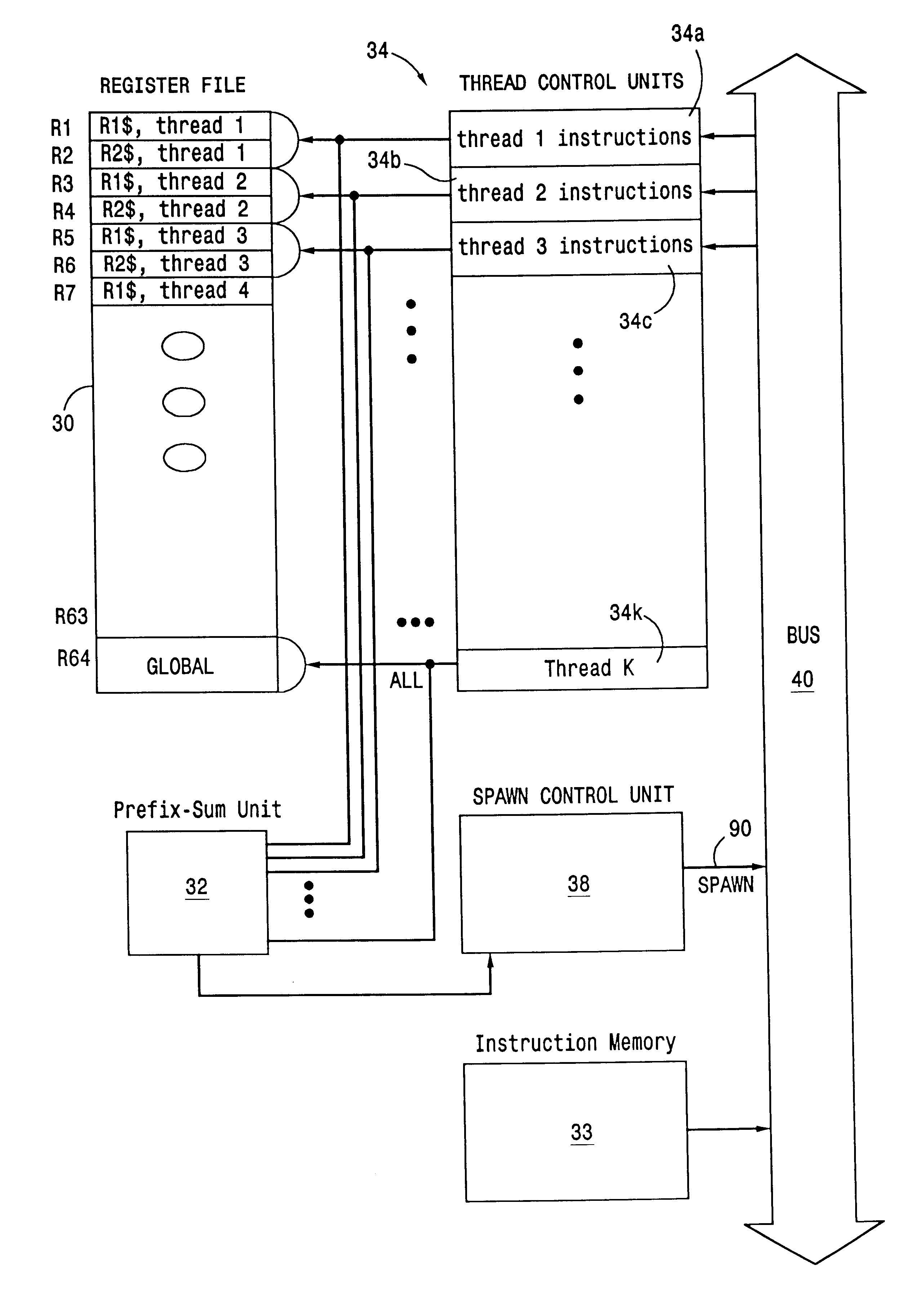

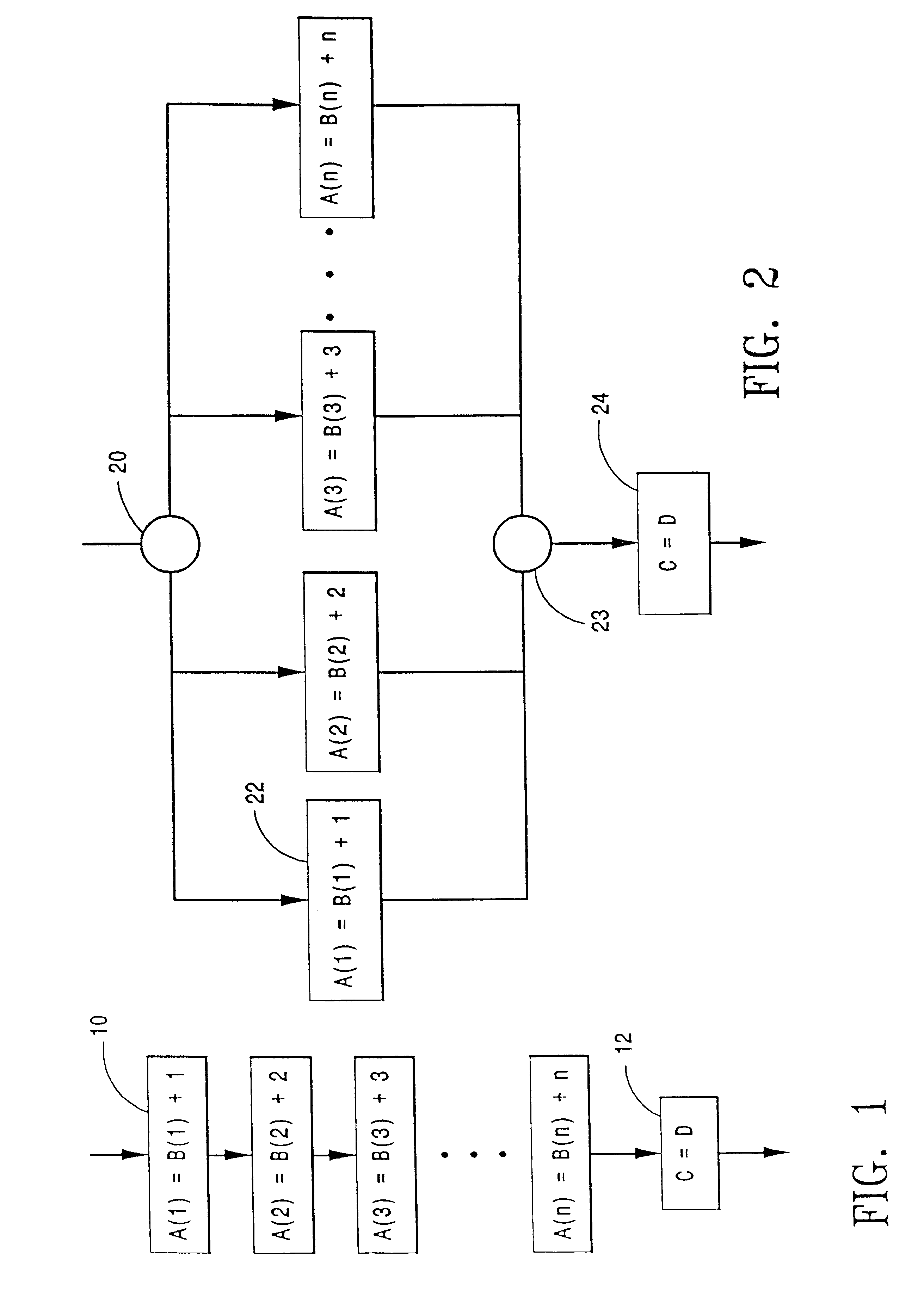

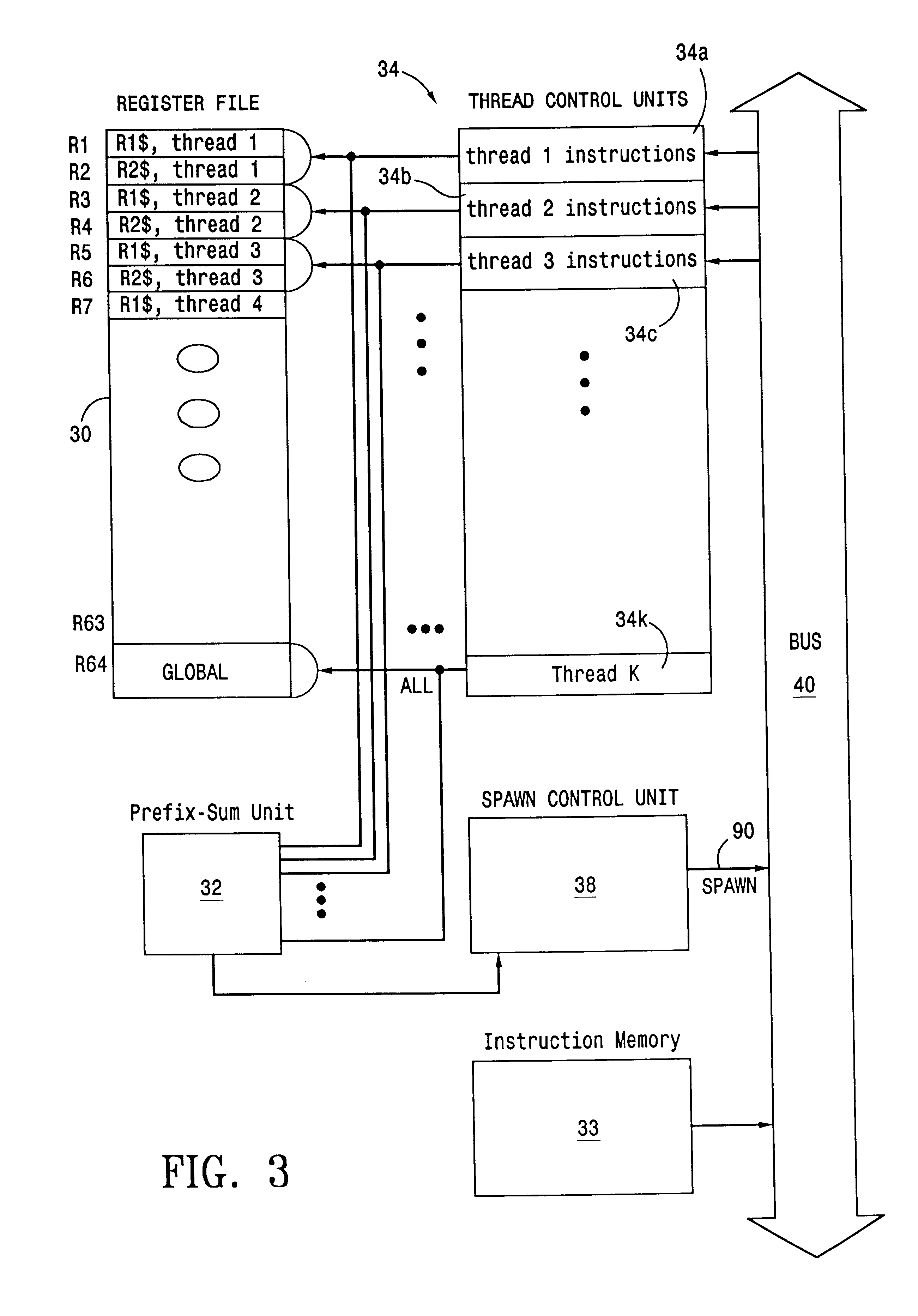

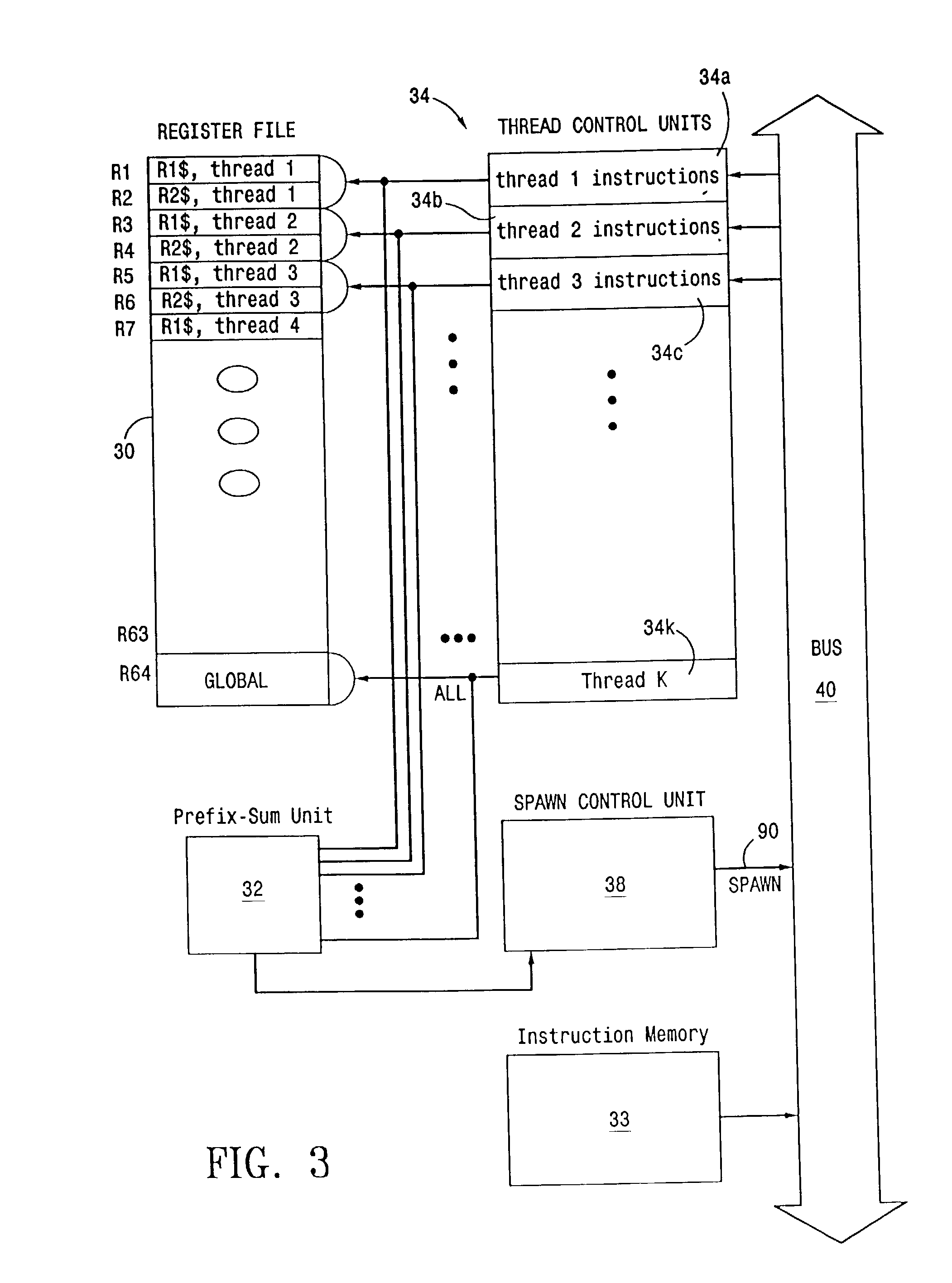

Spawn-join instruction set architecture for providing explicit multithreading

InactiveUS6463527B1Apparent advantageProgram initiation/switchingProgram synchronisationInstruction memoryFrequency spectrum

The invention presents a unique computational paradigm that provides the tools to take advantage of the parallelism inherent in parallel algorithms to the full spectrum from algorithms through architecture to implementation. The invention provides a new processing architecture that extends the standard instruction set of the conventional uniprocessor architecture. The architecture used to implement this new computational paradigm includes a thread control unit (34), a spawn control unit (30), and an enabled instruction memory (50). The architecture initiates multiple threads and executes them in parallel. Control of the threads is provided such that the threads may be suspended or allowed to execute each at its own pace.

Owner:VISHKIN UZI Y

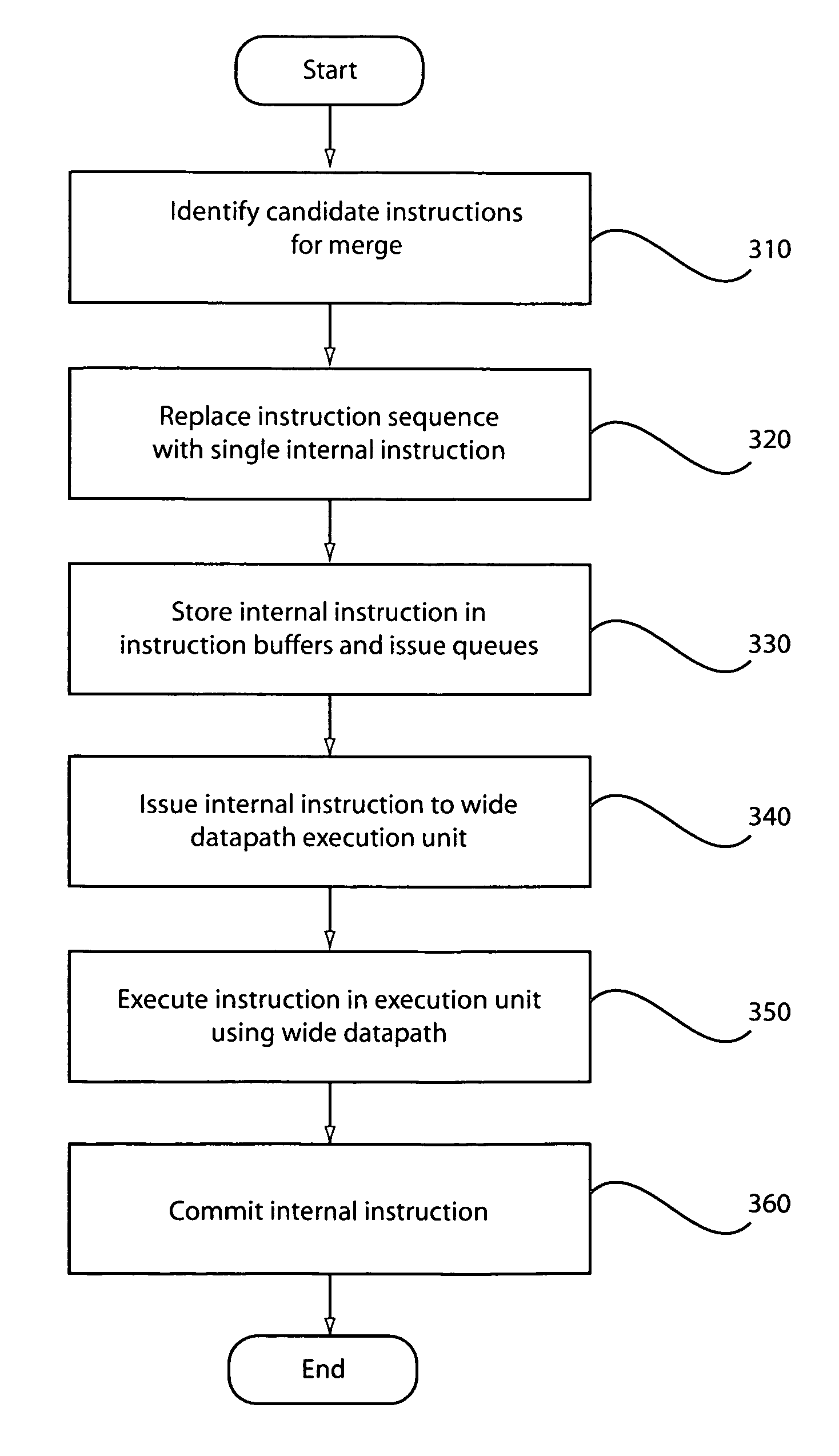

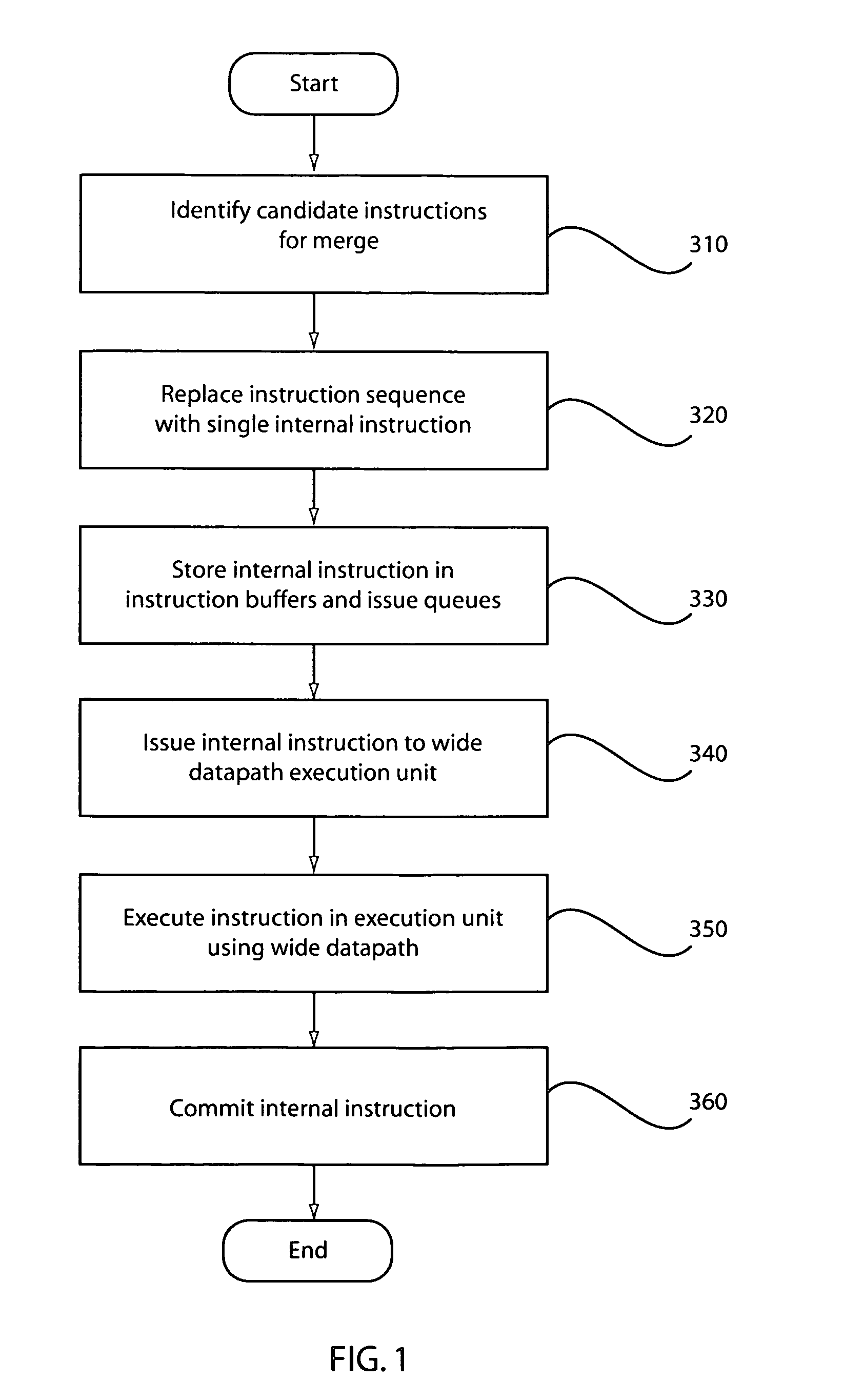

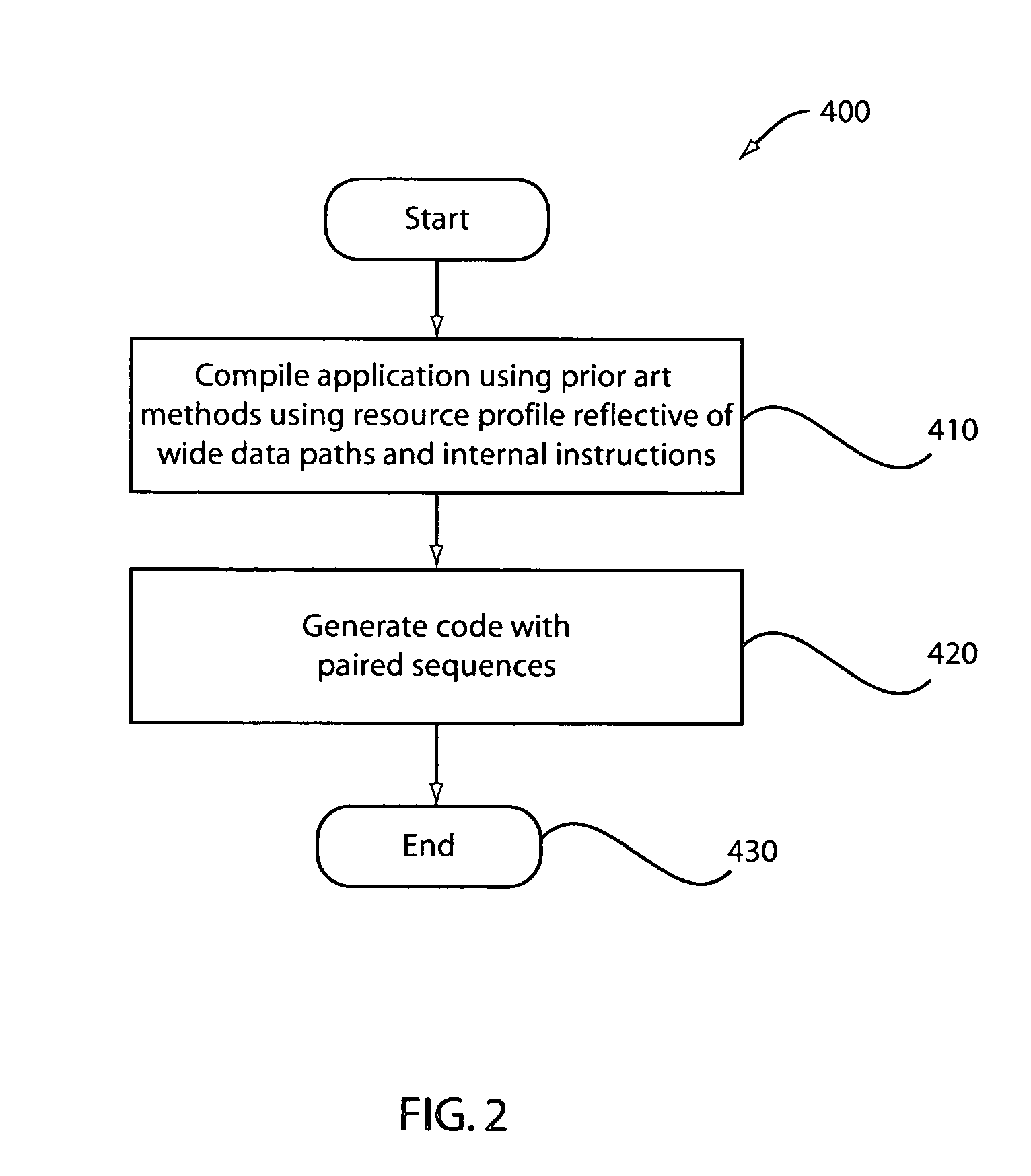

Method and apparatus for the dynamic creation of instructions utilizing a wide datapath

ActiveUS20070260855A1Maintain compatibilityImprove performanceRegister arrangementsInstruction analysisInstruction memoryExecution unit

A processing system and method includes a predecoder configured to identify instructions that are combinable. Instruction storage is configured to merge instructions that are combinable by replacing the combinable instructions with a wide data internal instruction for execution. An instruction execution unit is configured to execute the internal instruction on a wide datapath.

Owner:IBM CORP

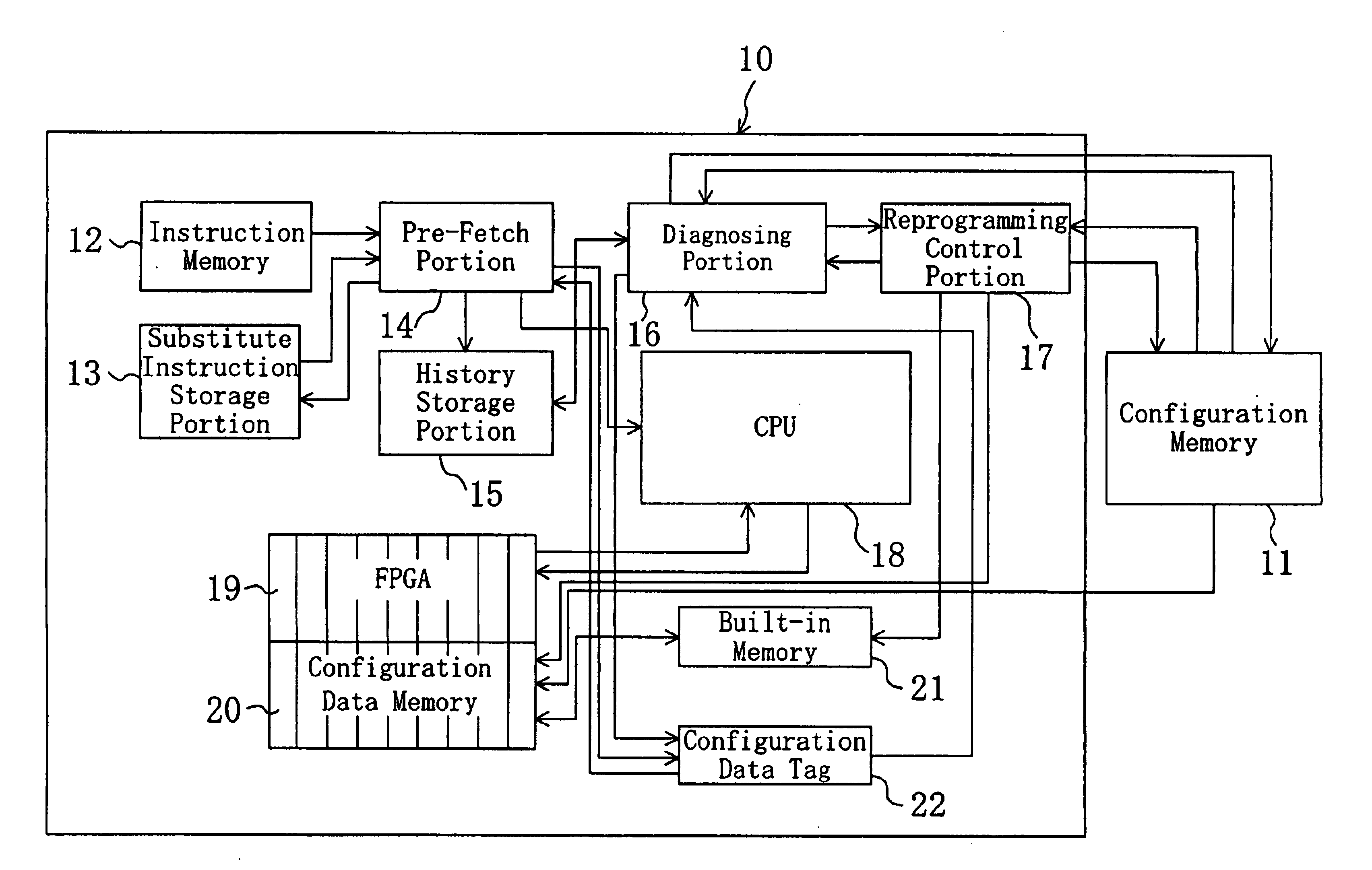

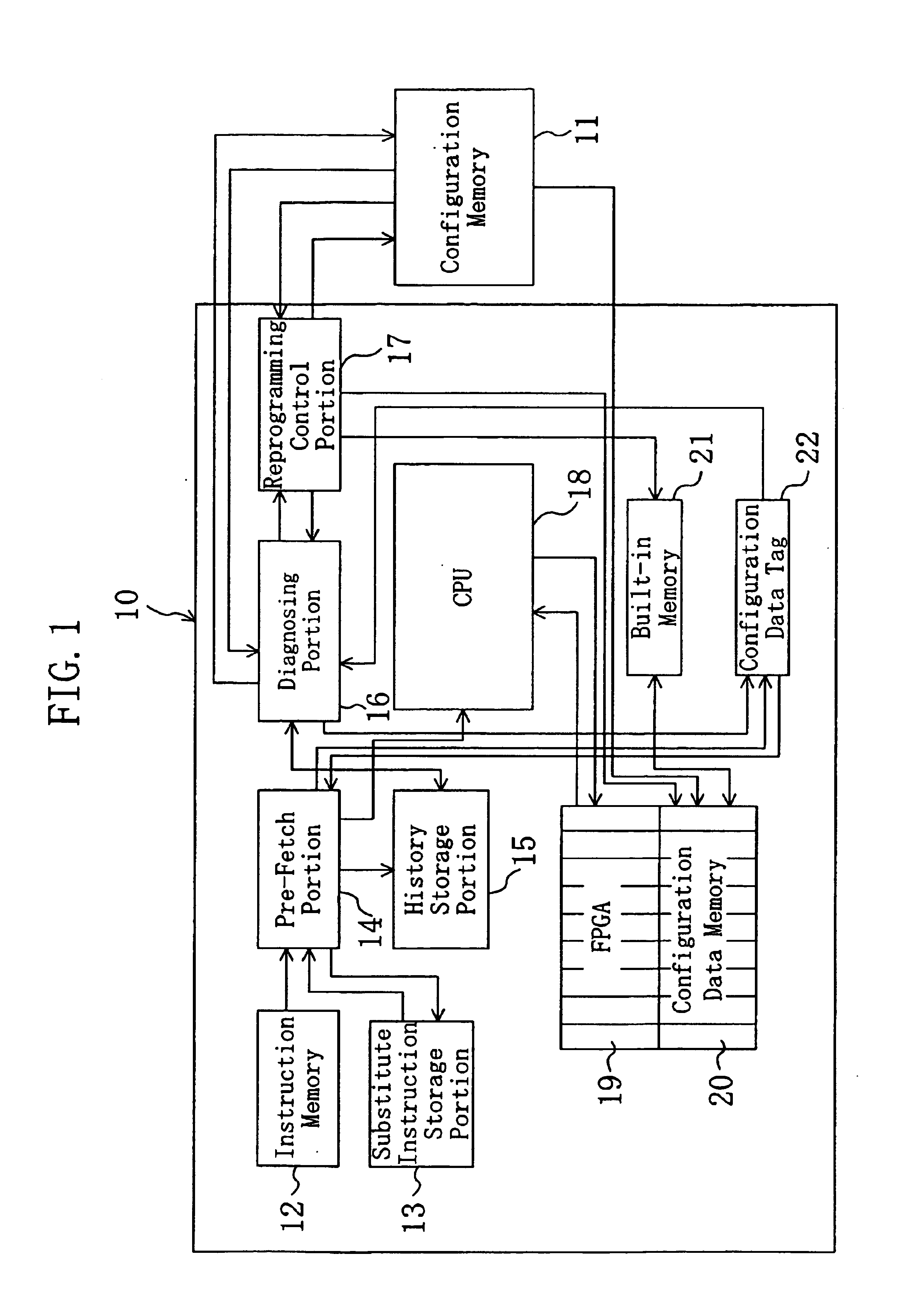

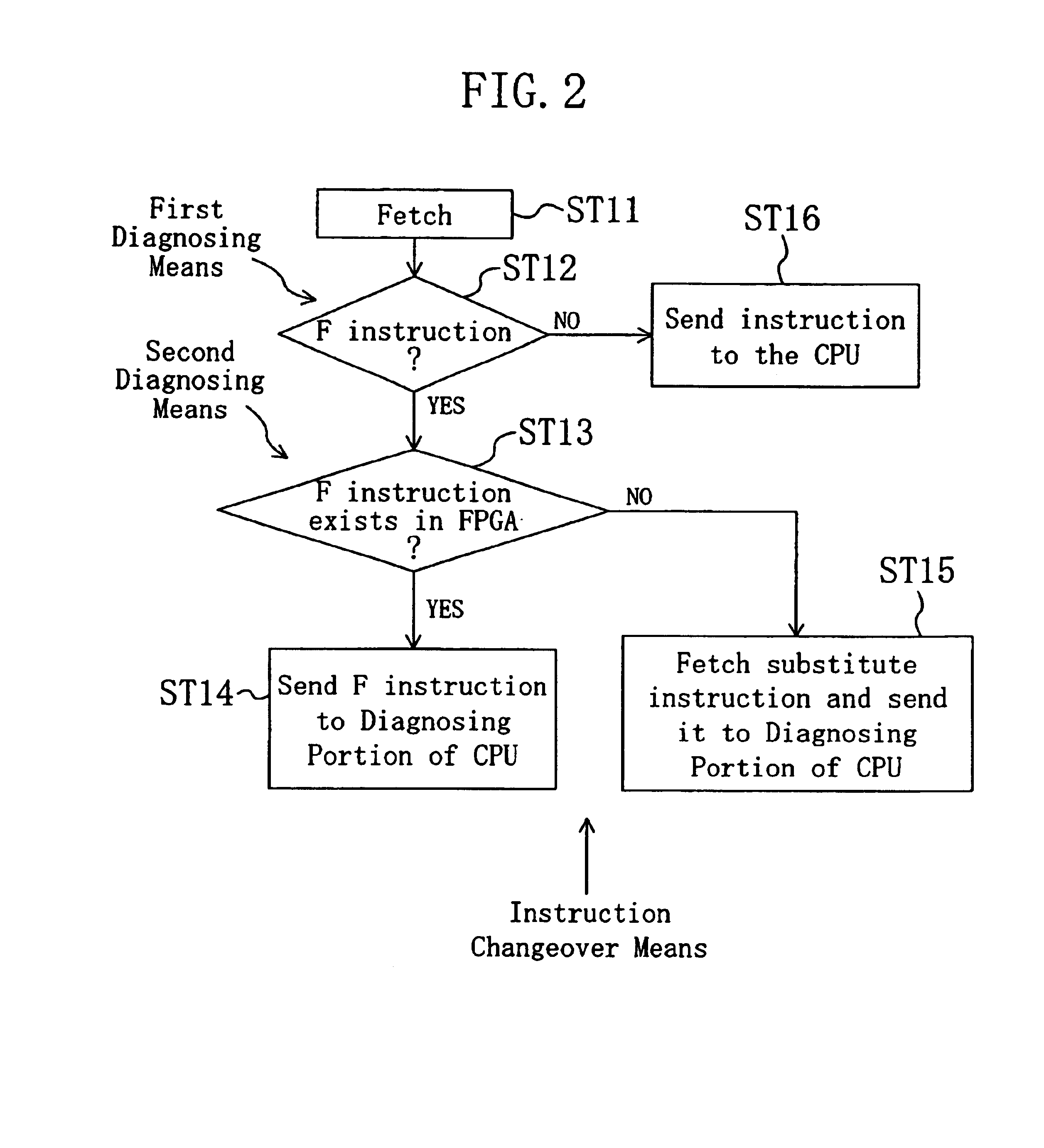

Integrated circuit with CPU and FPGA for reserved instructions execution with configuration diagnosis

InactiveUS6901502B2Easy to processReduce frequency of useError detection/correctionRuntime instruction translationInstruction memoryComputer architecture

A semiconductor integrated circuits can send and receive signals to and form a configuration memory. The semiconductor integrated circuits is provided therein wiht an instruction memory, an instruction storage portion that stores reserved instructions as F instructions, and stores the substantially equivalent processing contents to the F instructions as substitute instructions for processing by the CPU, a pre-fetch portion, a history storage portion, a diagnosing portion for diagnosing the types of instructions, a reprogramming control portion for reprogramming the instructions, a CPU, an FPGA, a configuration data memory, a built-in memory, and a configuration data tag. When the configuration data of the F instruction does not exist in the FPGA, the substantially equivalent processing by FPGA is executed by the CPU by making use of the substitute instructions.

Owner:PANASONIC CORP

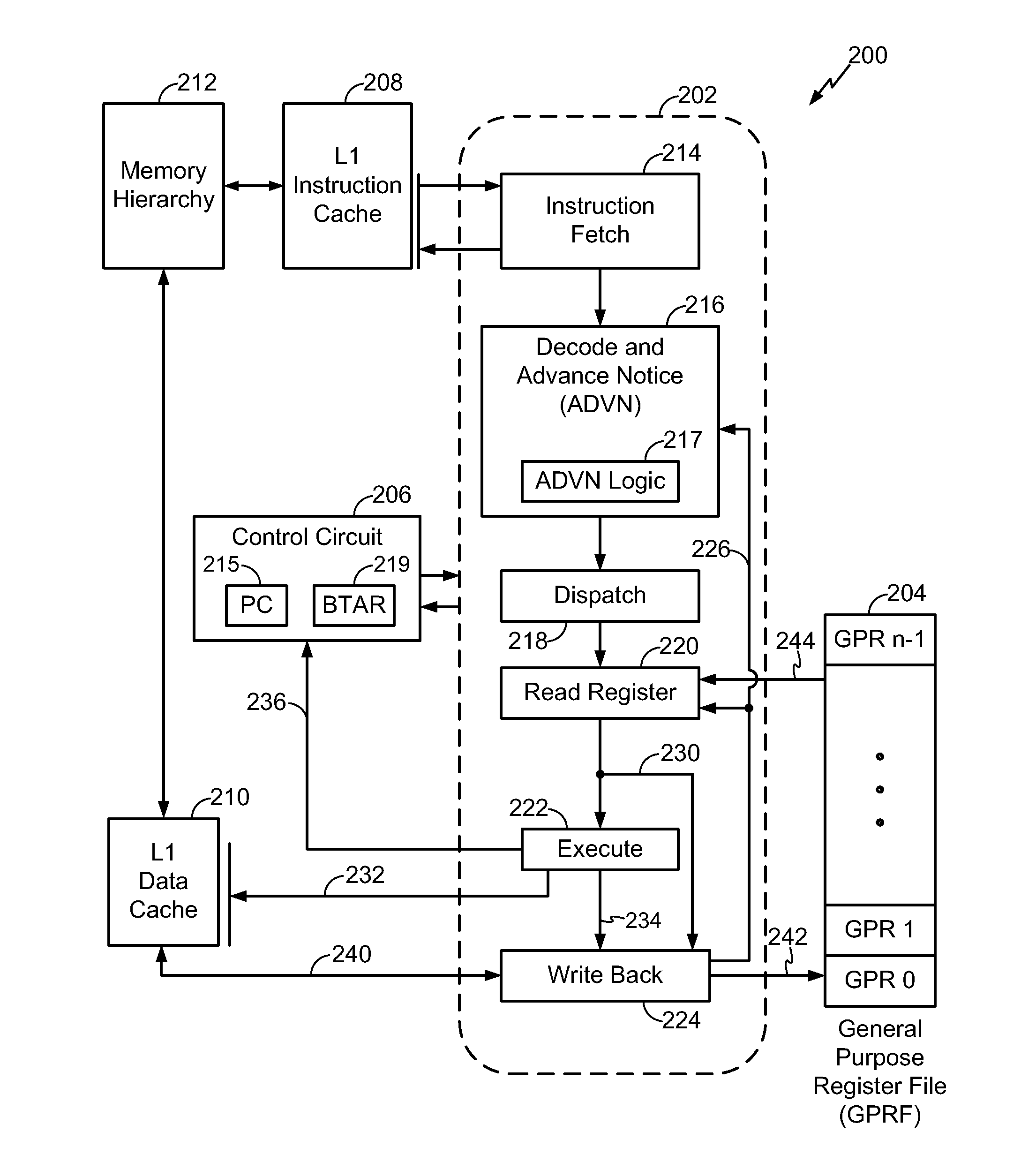

Indirect Branch Hint

InactiveUS20110320787A1Minimize the numberImprove performanceDigital computer detailsNext instruction address formationInstruction memoryProcessor register

A processor implements an apparatus and a method for predicting an indirect branch address. A target address generated by an instruction is automatically identified. A predicted next program address is prepared based on the target address before an indirect branch instruction utilizing the target address is speculatively executed. The apparatus suitably employs a register for holding an instruction memory address that is specified by a program as a predicted indirect address of an indirect branch instruction. The apparatus also employs a next program address selector that selects the predicted indirect address from the register as the next program address for use in speculatively executing the indirect branch instruction.

Owner:QUALCOMM INC

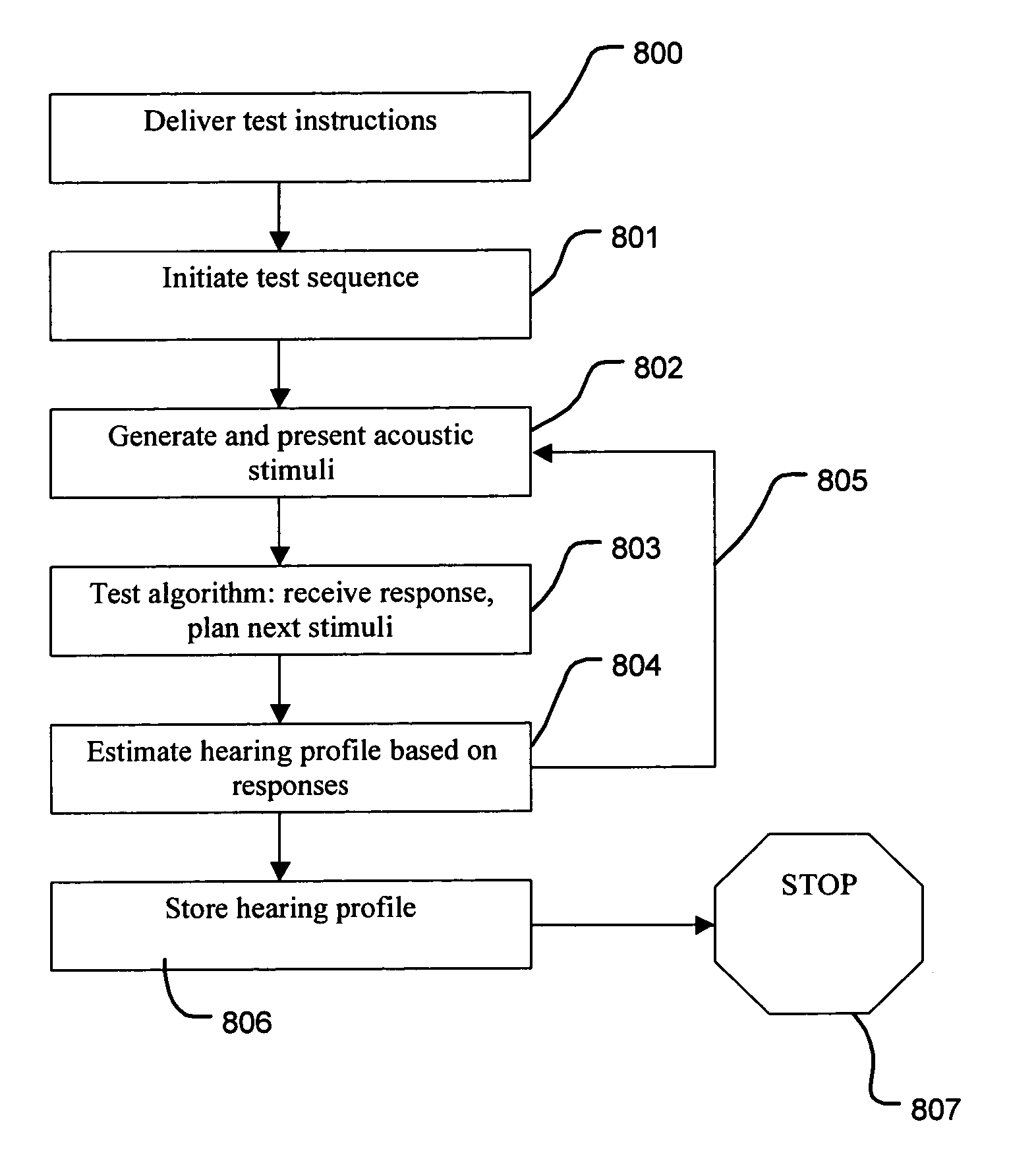

Mobile phones and other products producing personalized hearing profiles for users

InactiveUS20050260985A1Easy to receiveImprove soundStereophonic circuit arrangementsHearing impaired stereophonic signal reproductionEnvironmental noiseInstruction memory

A mobile phone or other personal communication device includes resources applying measures of an individual's hearing profile, personal choice profile, and induced hearing loss profile, separately or in combination, to build the basis of sound enhancement. A personal communication device thus comprises a transmitter / receiver coupled to a communication medium for transmitted receiving audio signals, control circuitry that controls transmission, reception and processing of call and audio signals, a speaker, and a microphone. The control circuitry includes logic applying one or more of a hearing profile of the user, a user preference related hearing, and environmental noise factors in processing the audio signals. The control circuitry may includes instruction memory and an instruction execution processor such as a digital signal processor.

Owner:SOUND ID INC

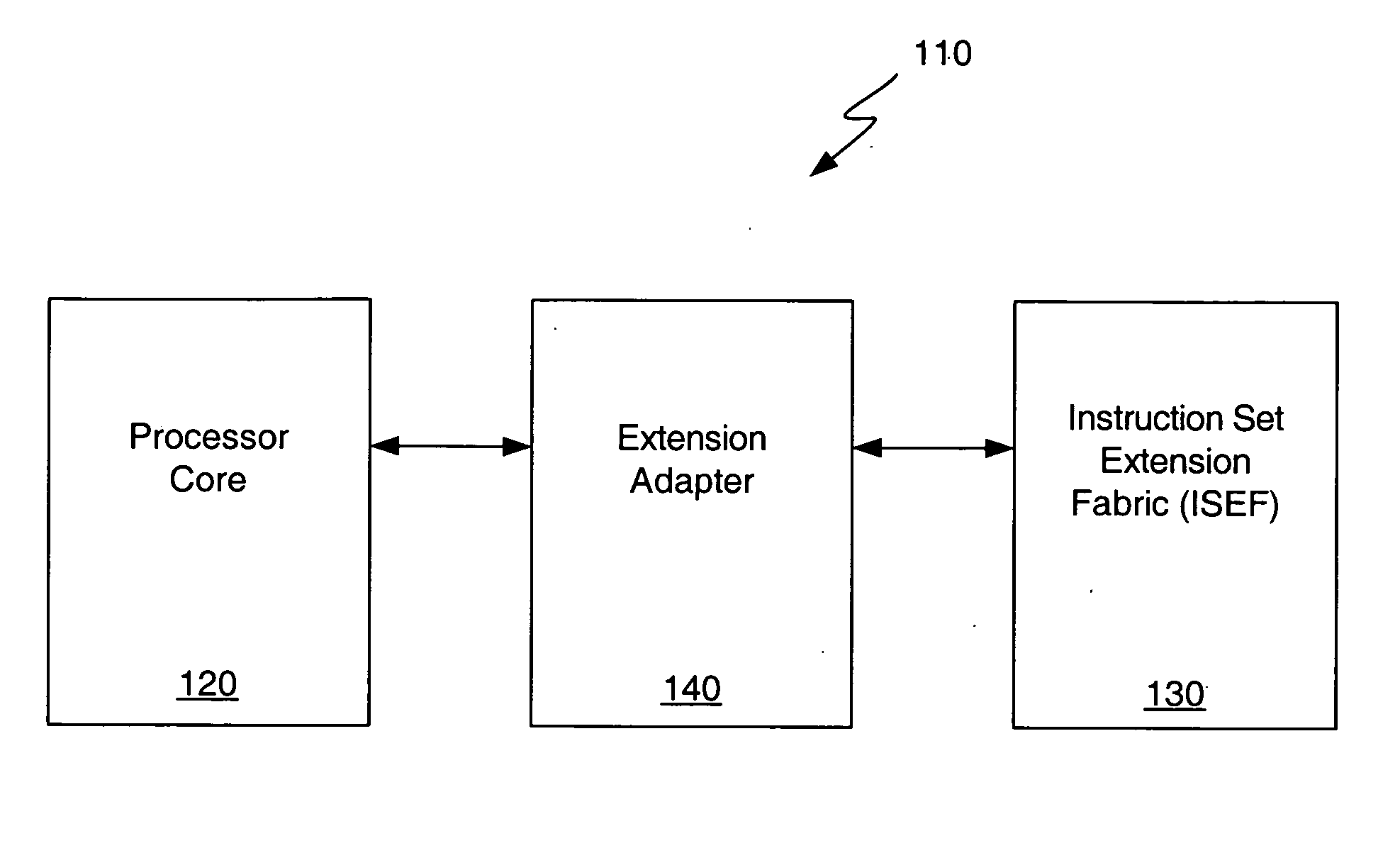

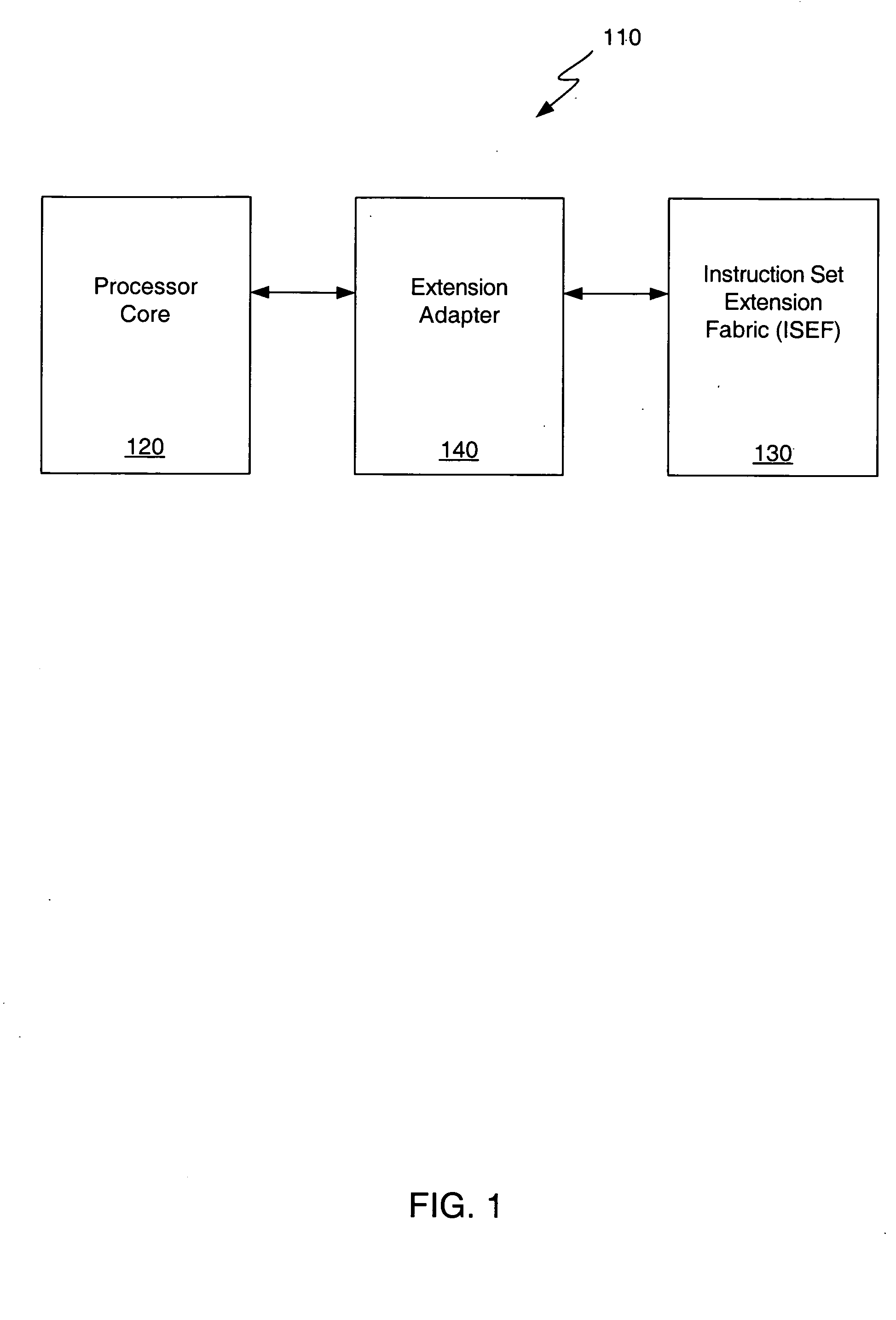

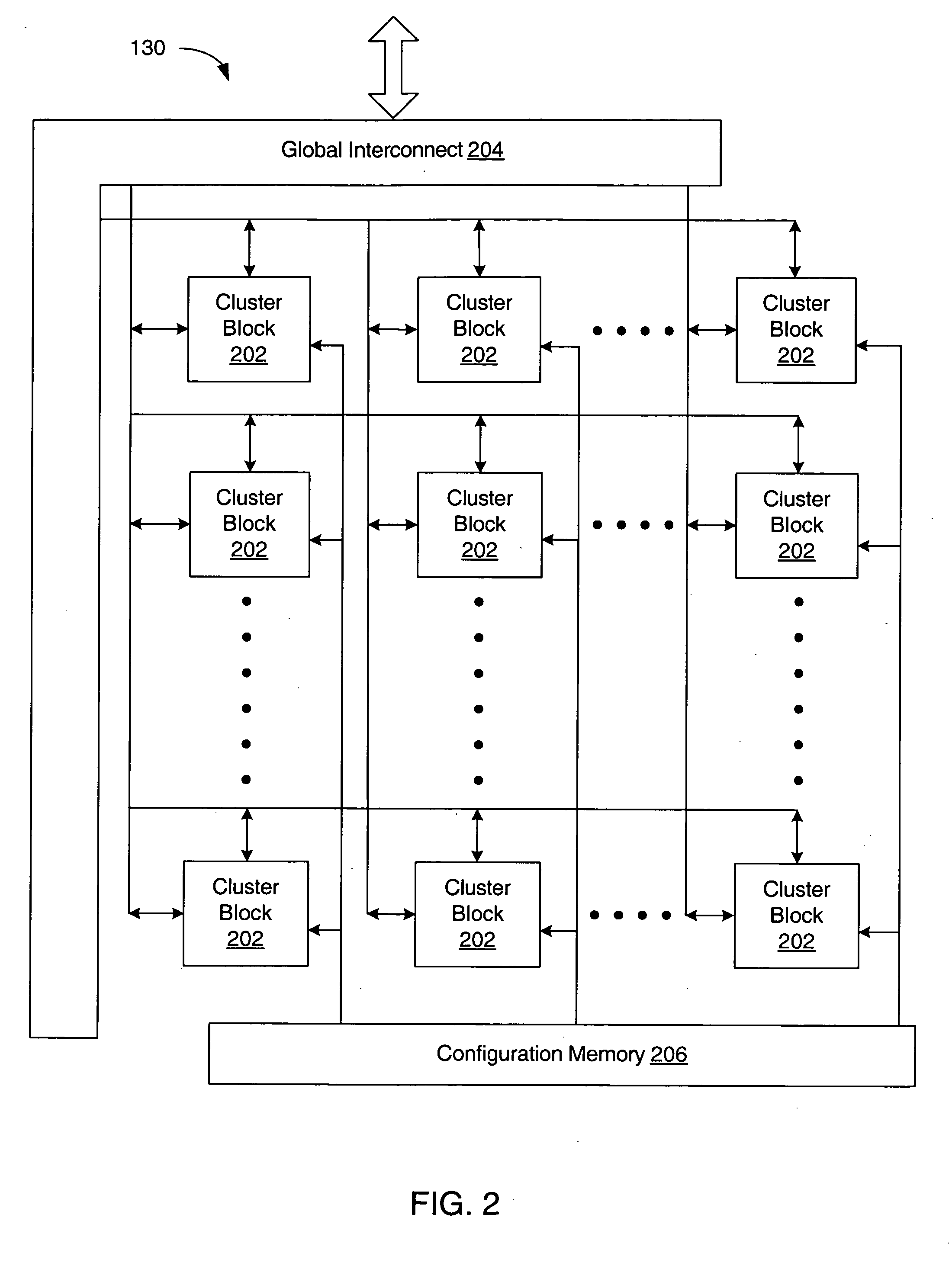

Reconfigurable instruction set computing

InactiveUS20050027970A1General purpose stored program computerConcurrent instruction executionInstruction memoryProgrammable logic device

A system and method for adding reconfigurable computational instructions to a reduced instruction set computer. A computer program contains instruction extensions not native to the instruction set of the processor core and is loaded into an instruction memory accessible by the processor core of the computer. The computer program is then detected for containing the instruction extension. The programmable logic device is then configured to execute the instruction extension. The programmable logic device then executes the instruction extension for use by the processor core in processing the computer program.

Owner:XILINX INC

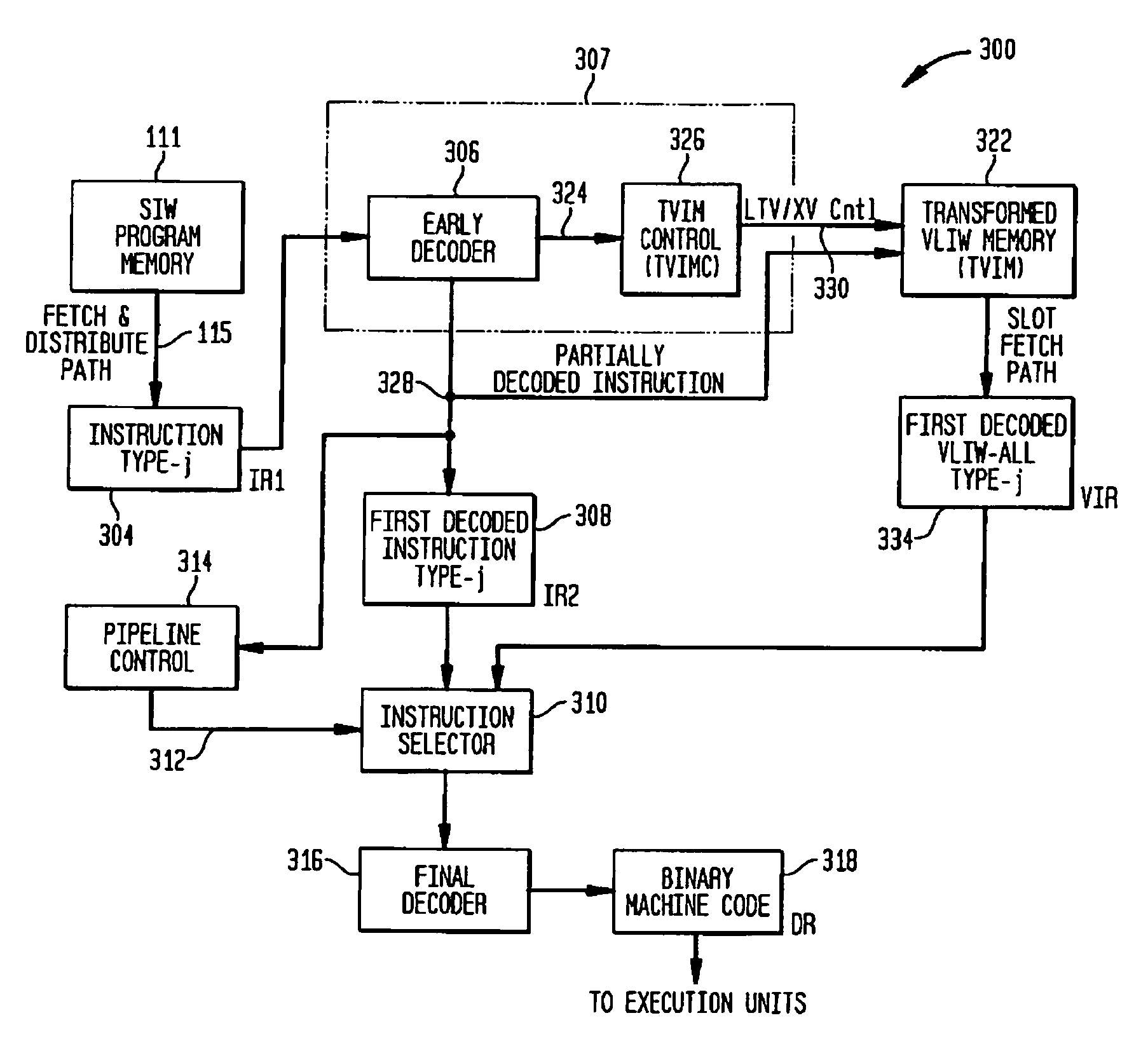

Methods and apparatus for transforming, loading, and executing super-set instructions

InactiveUS7493474B1Eliminate decode stageMinimization of actionRegister arrangementsInstruction analysisInstruction memoryLoad instruction

Techniques are described for loading decoded instructions and super-set instructions in a memory for later access. For loading a decoded instruction, the decoded instruction is a transformed form of an original instruction that was stored in the program memory. The transformation is from an encoded assembly level format to a binary machine level format. In one technique, the transformation mechanism is invoked by a transform and load instruction that causes an instruction retrieved from program memory to be transformed into a new language format and then loaded into a transformed instruction memory. The format of the transformed instruction may be optimized to the implementation requirements, such as improving critical path timing. The transformation of instructions may extend to other needs beyond timing path improvement, for example, requiring super-set instructions for increased functionality and improvements to instruction level parallelism. Techniques for transforming, loading, and executing super-set instructions are described.

Owner:ALTERA CORP

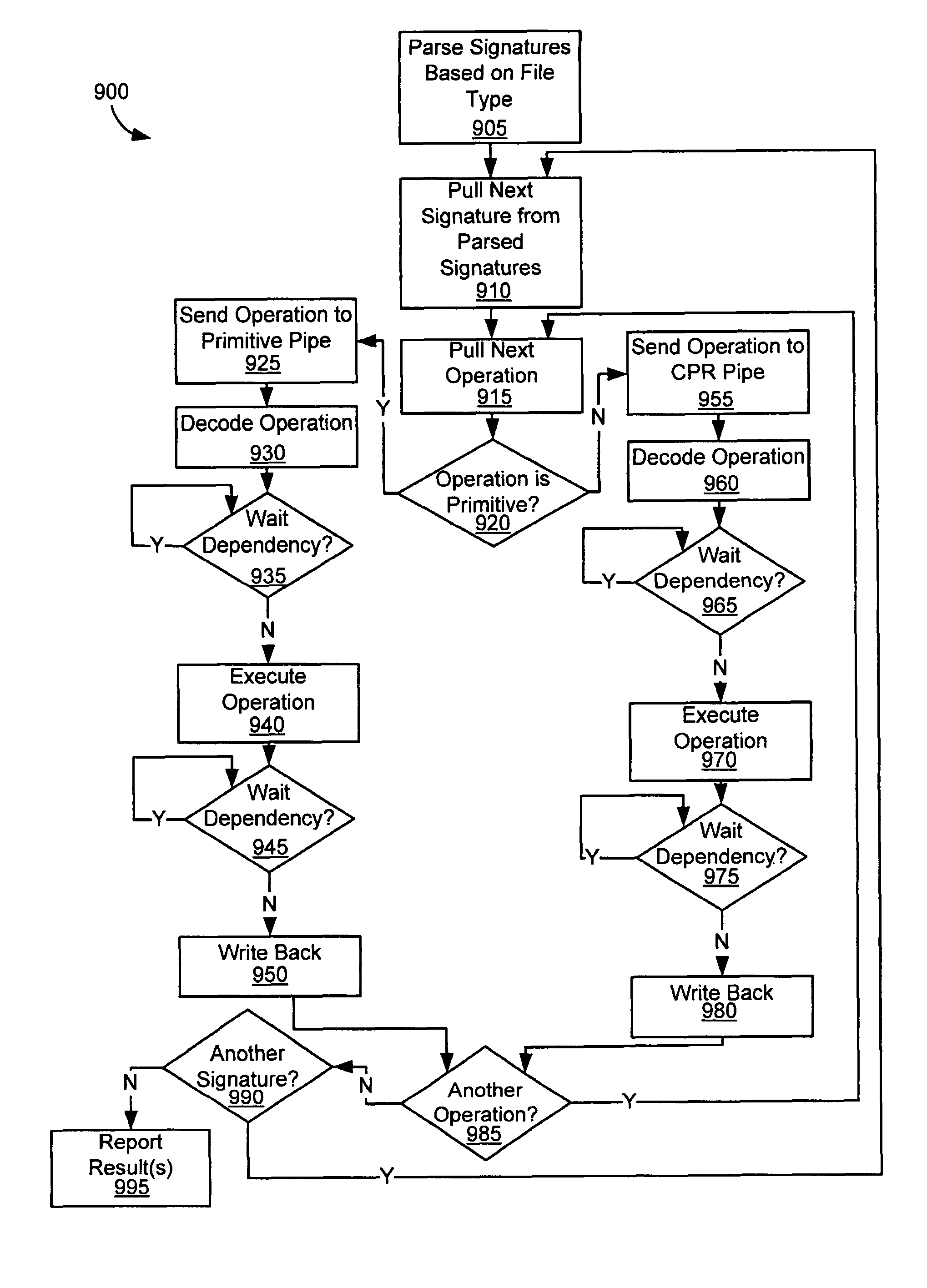

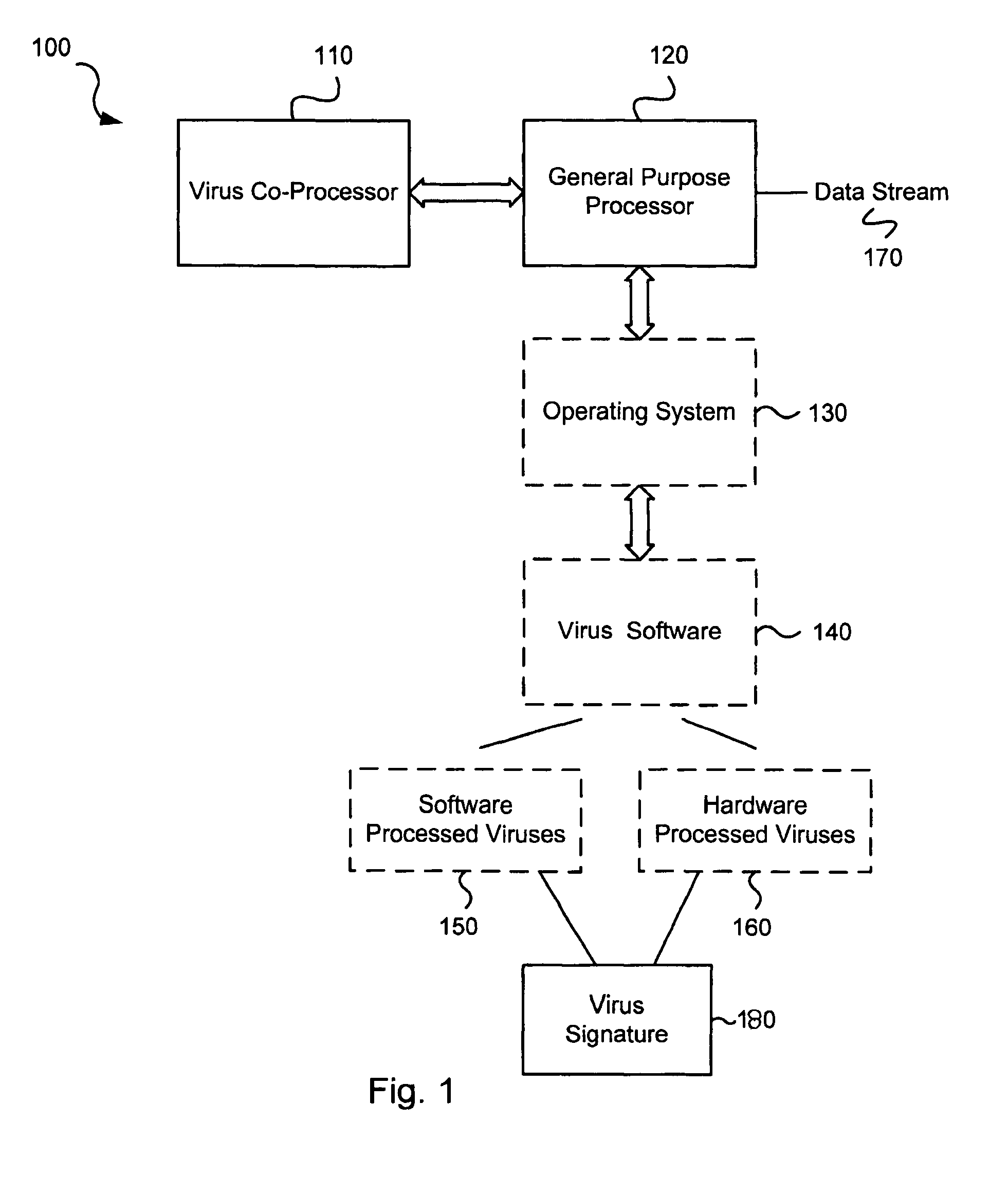

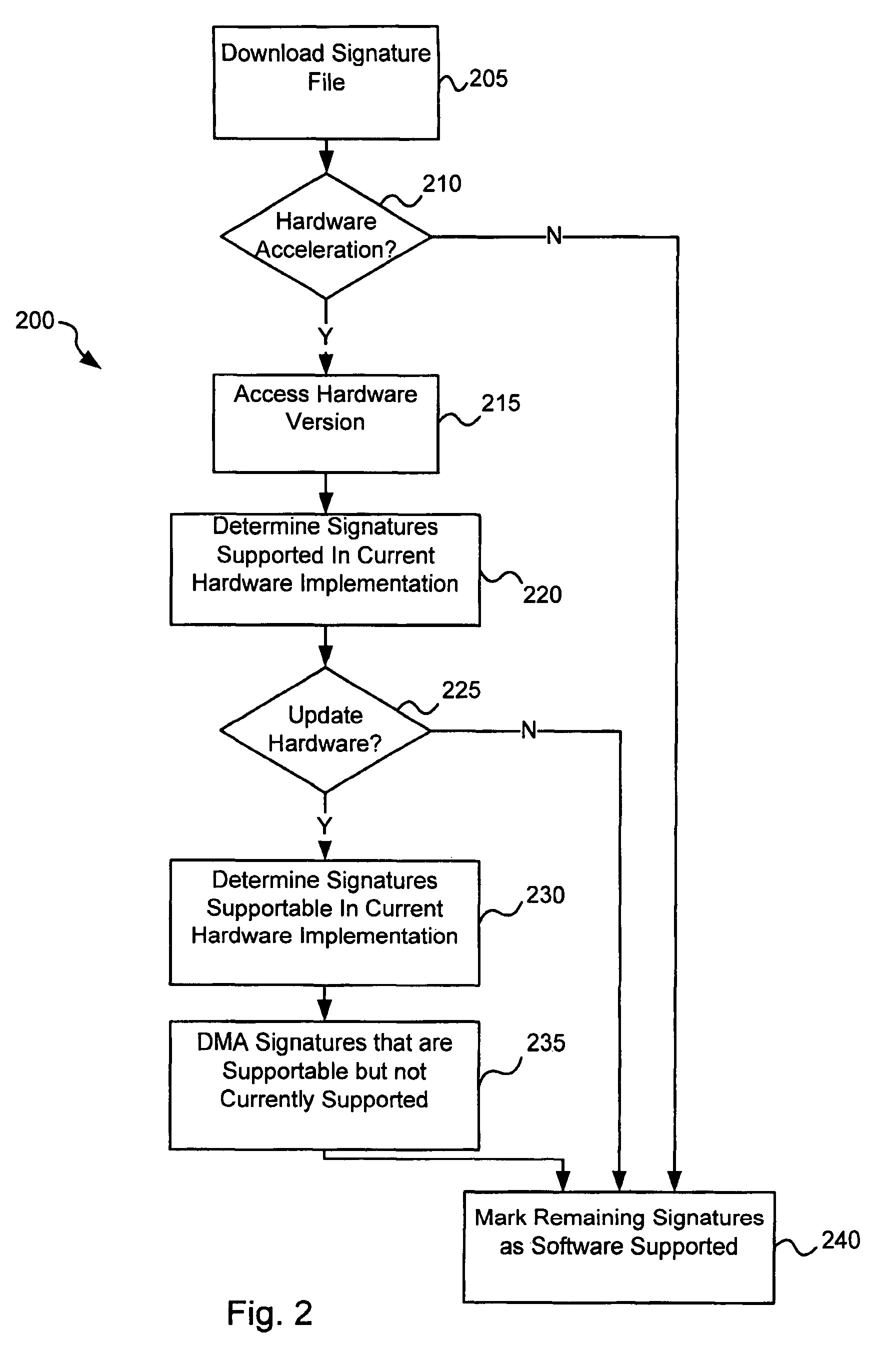

Circuits and methods for operating a virus co-processor

ActiveUS8375449B1Memory loss protectionError detection/correctionInstruction memoryParallel computing

Various embodiments of the present invention provide circuits and methods for improved virus processing. As one example, a virus processing system is disclosed that includes an instruction memory and a virus co-processor. The instruction memory includes a first instruction type and a second instruction type intermixed. The virus co-processor is communicably coupled to the instruction memory, and includes at least a first instruction pipe and a second instruction pipe. The first instruction pipe is operable to execute the first instruction type, and the second instruction pipe is operable to execute the second instruction type.

Owner:FORTINET

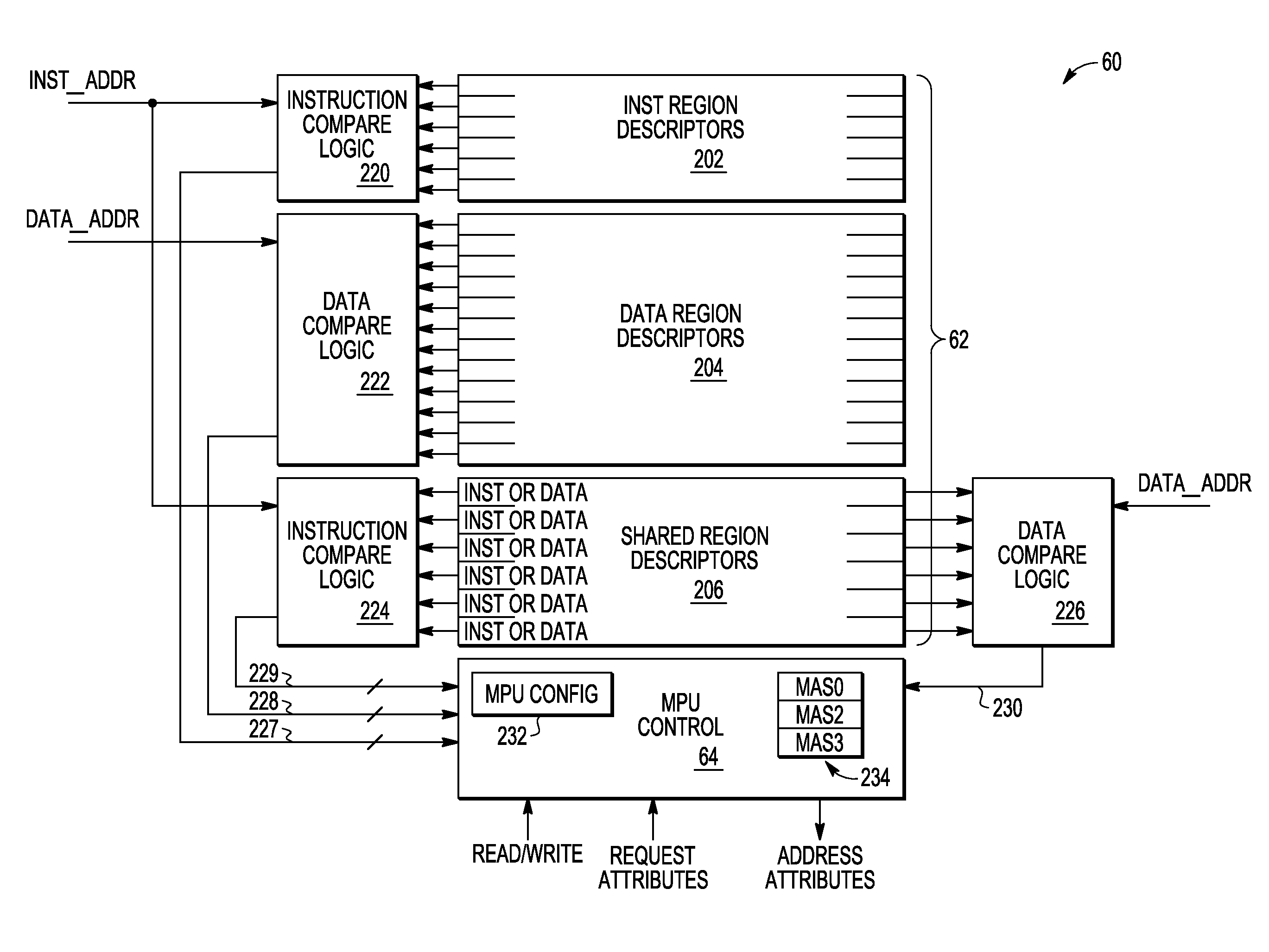

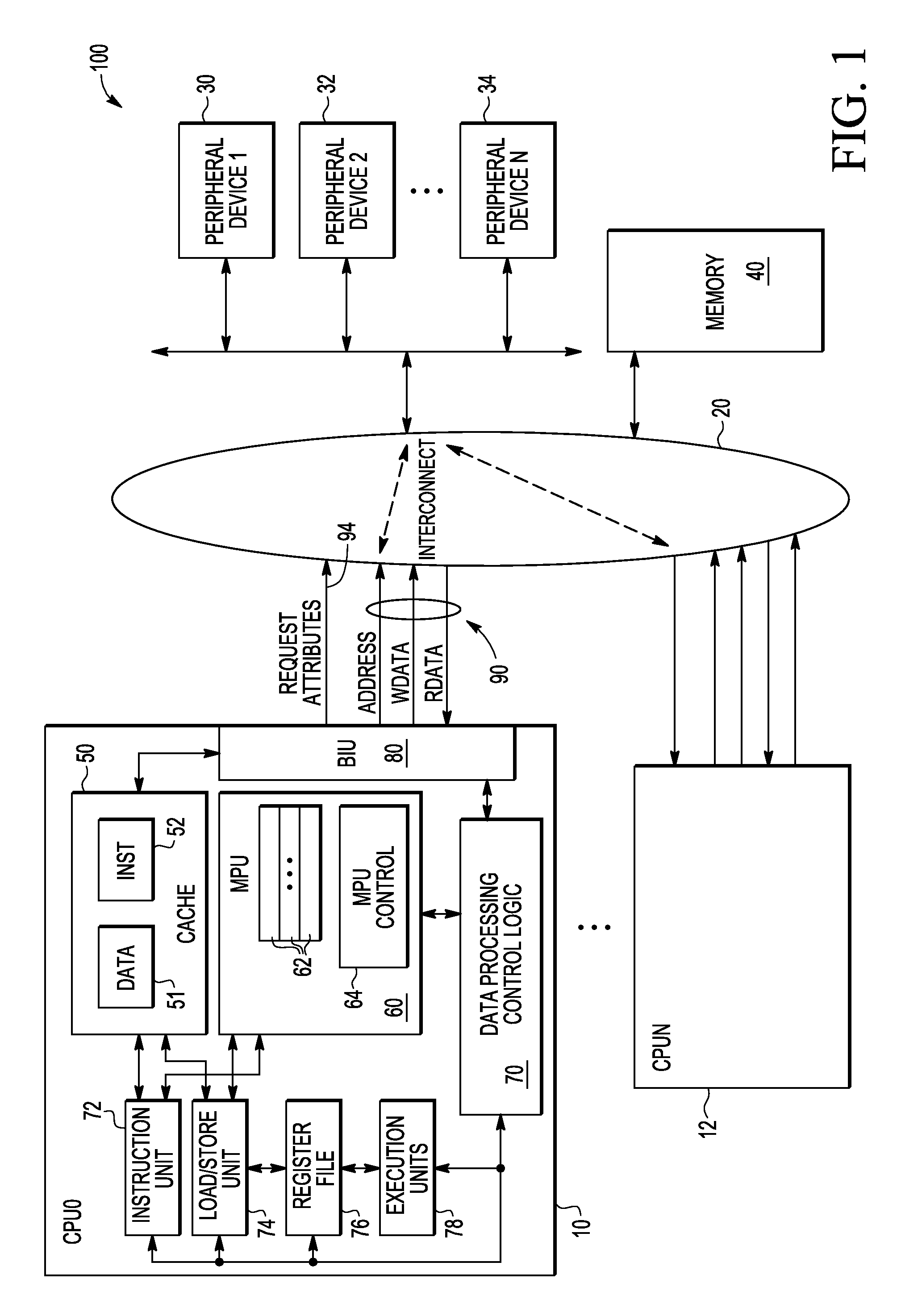

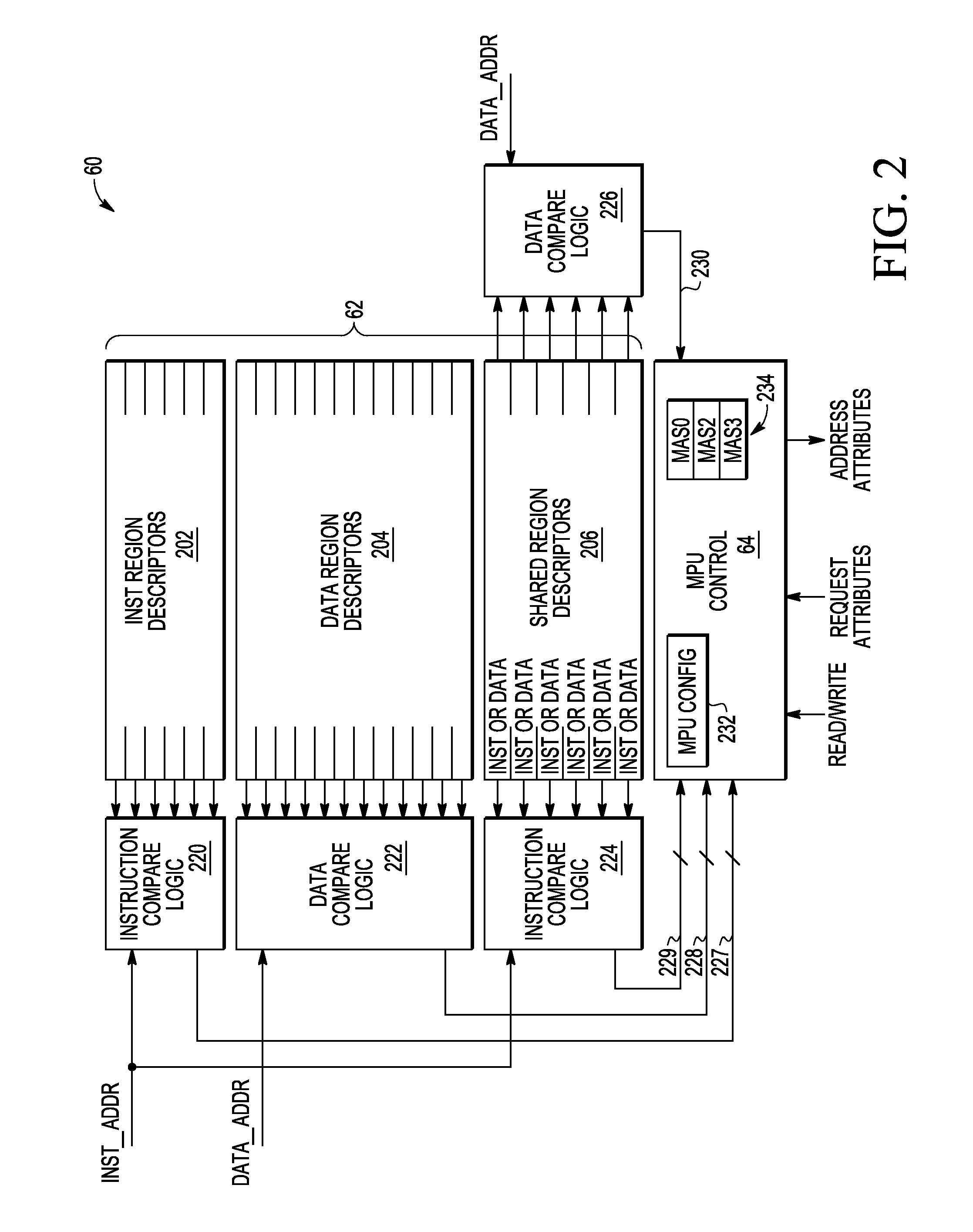

Memory protection unit (MPU) having a shared portion and method of operation

In a disclosed embodiment, a data processing system comprises a memory protection unit (MPU); and a plurality of region descriptors associated with the MPU. Each region descriptor is associated with one of multiple subsets of the region descriptors and includes an address range, protection settings, and attributes for a respective region of memory. The subsets include data-only region descriptors, instruction-only region descriptors, and shared region descriptors. The shared region descriptors are used to access memory regions for data and instruction memory requests.

Owner:NXP USA INC

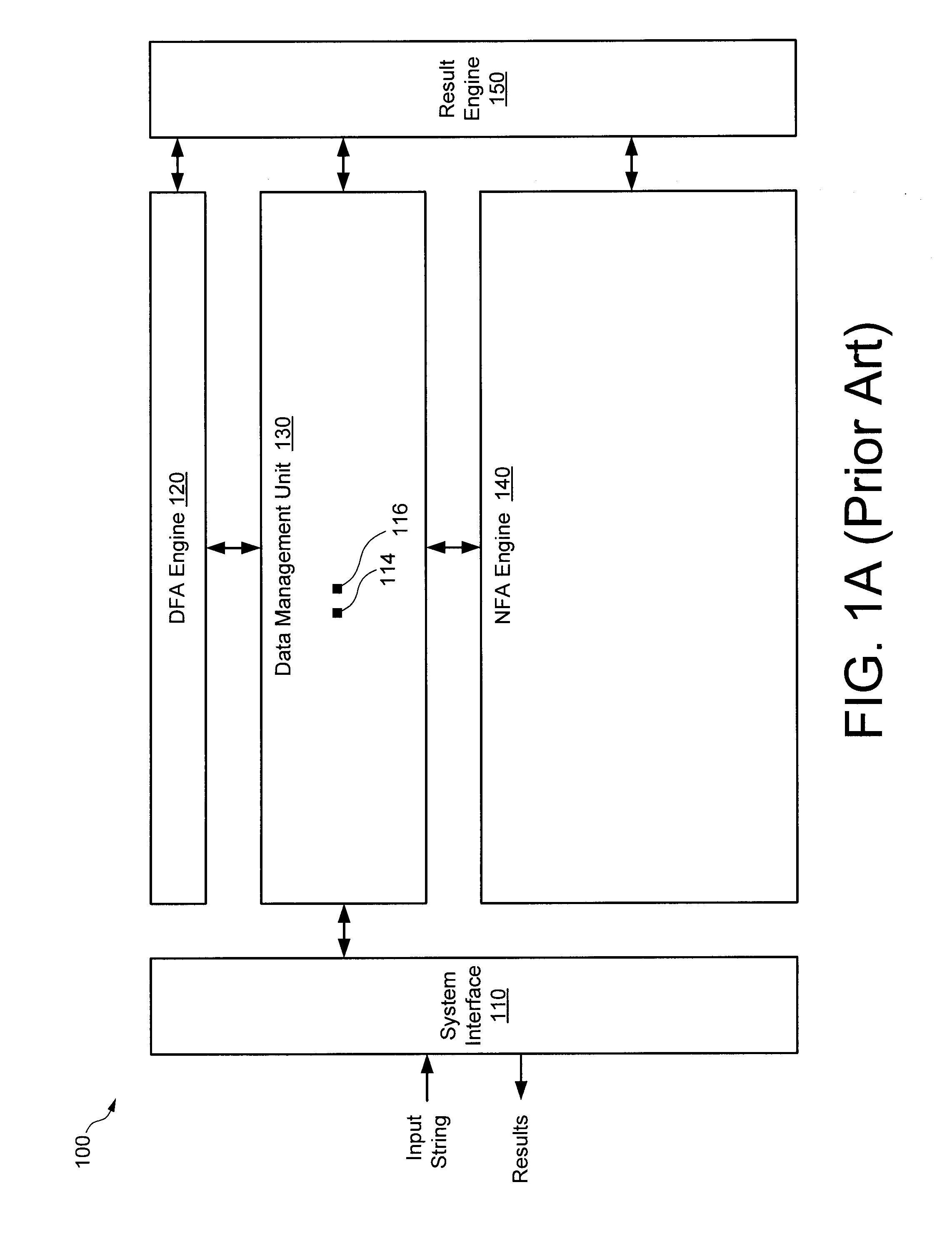

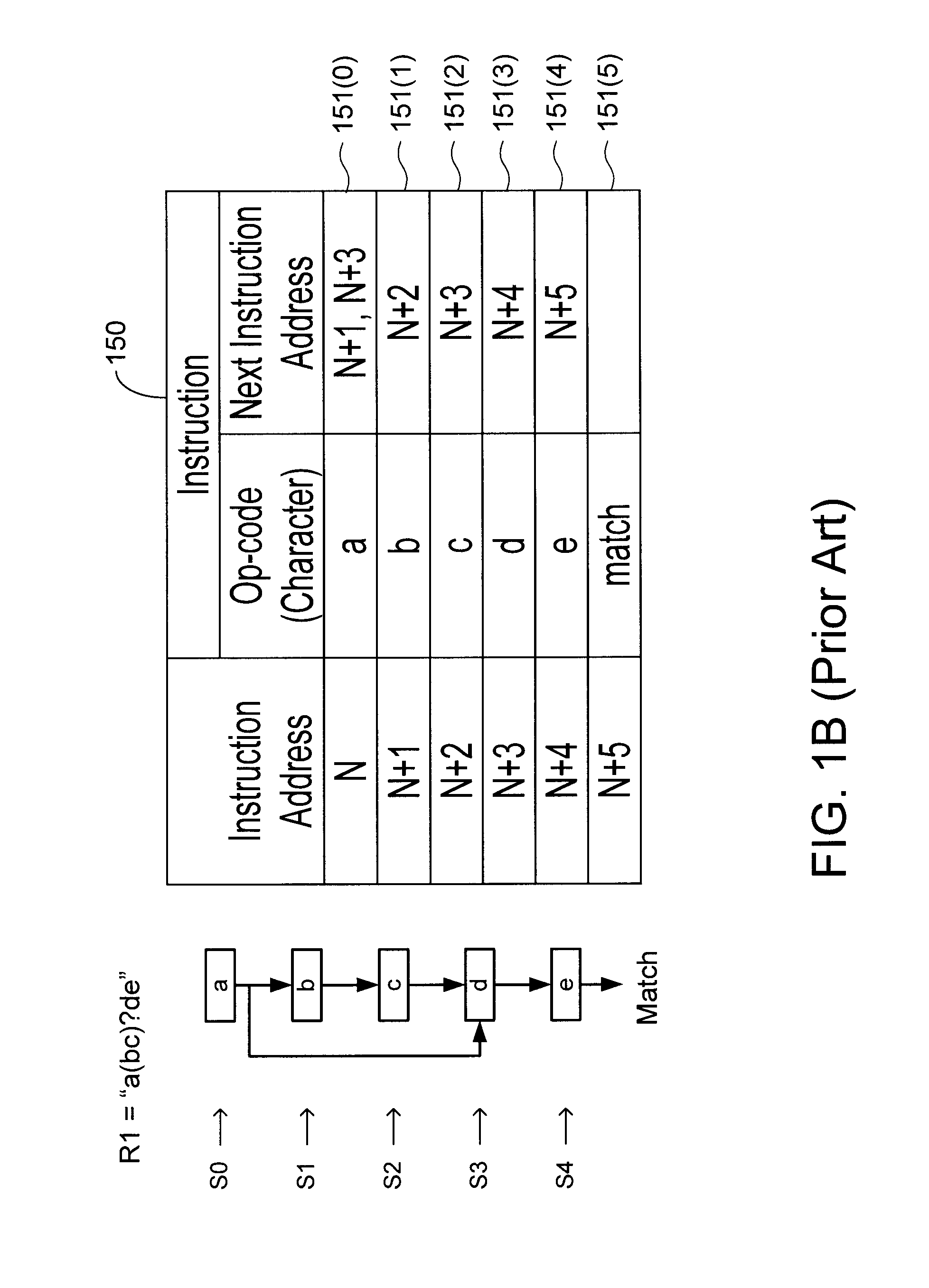

Search circuit having individually selectable search engines

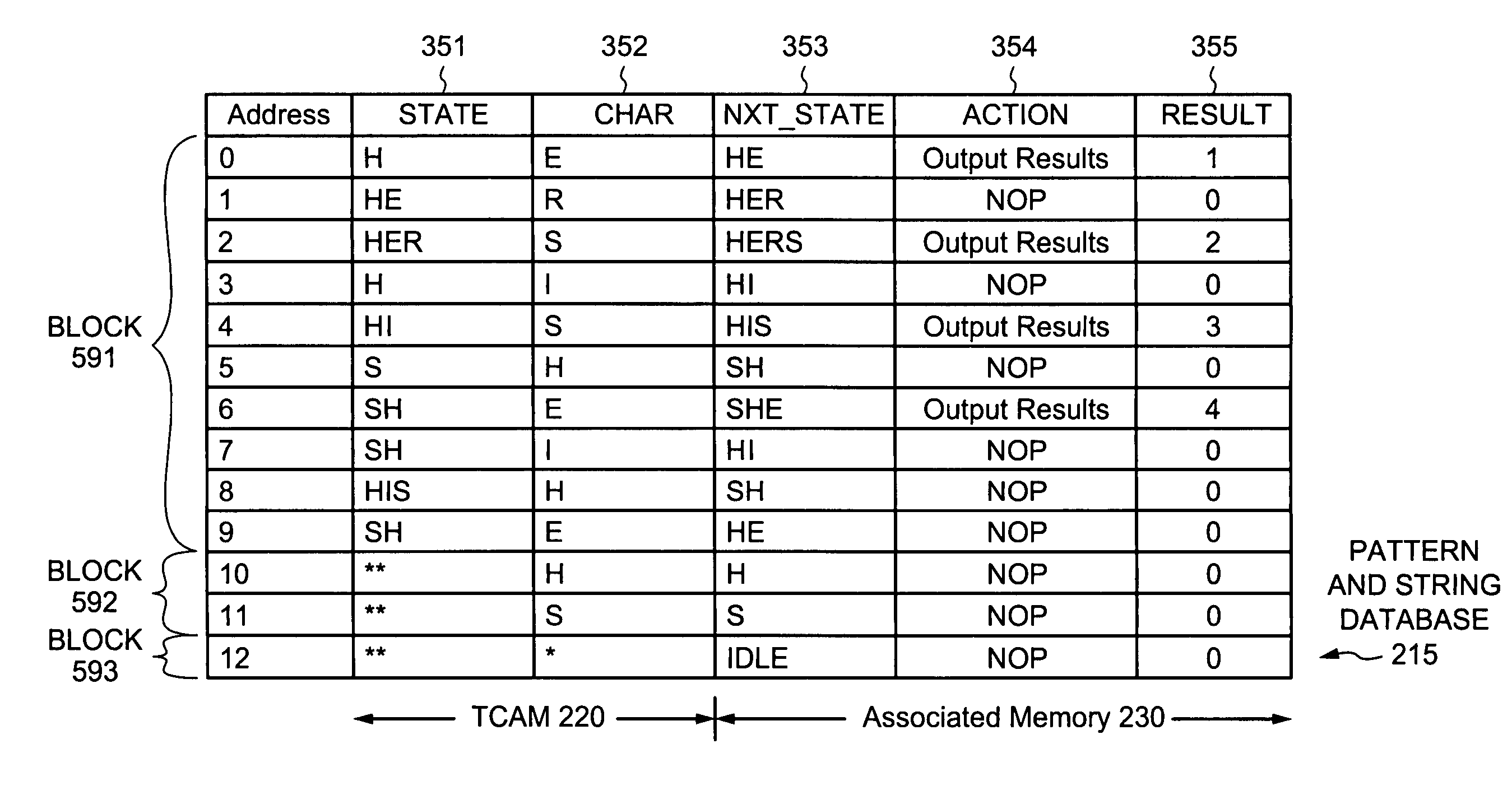

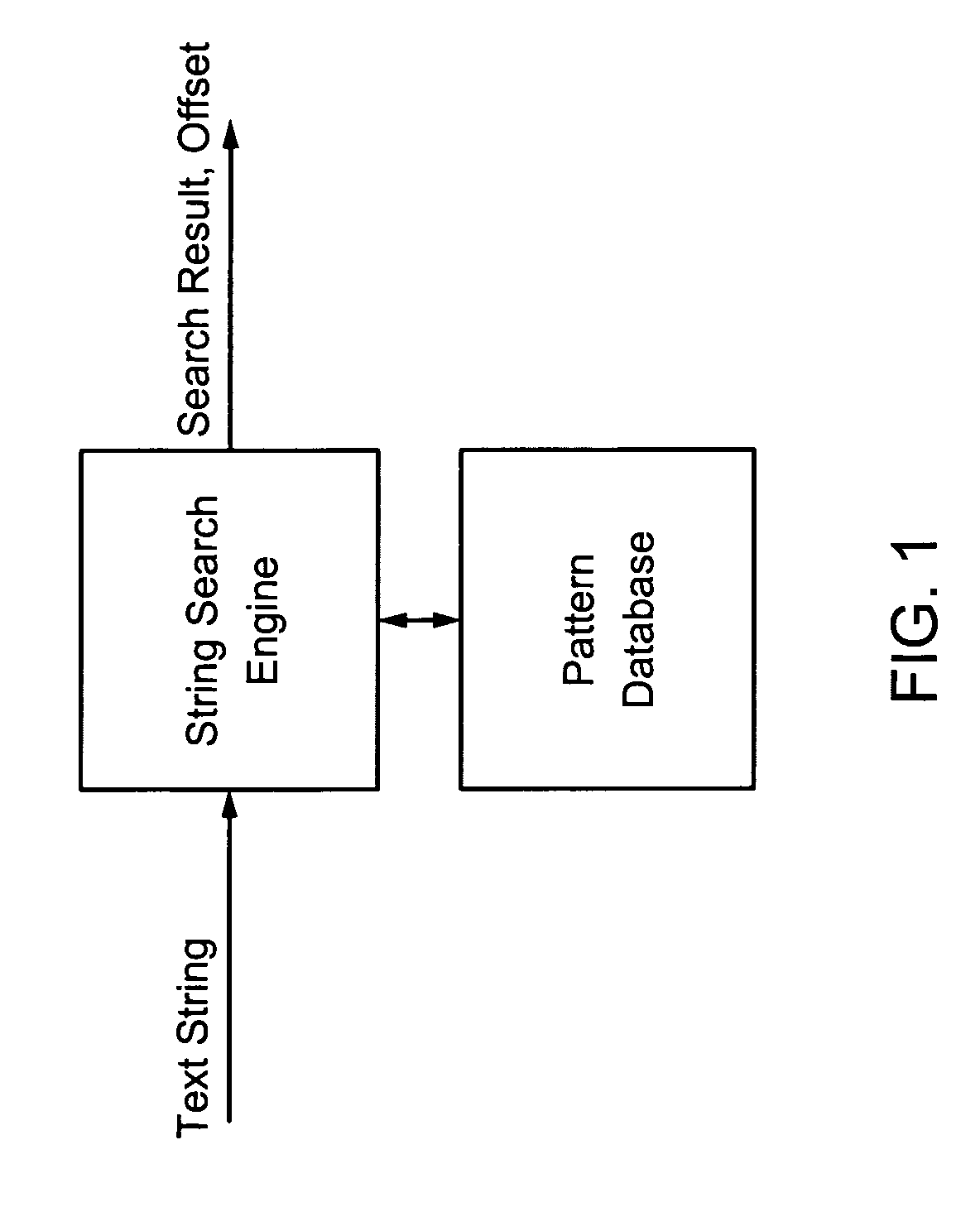

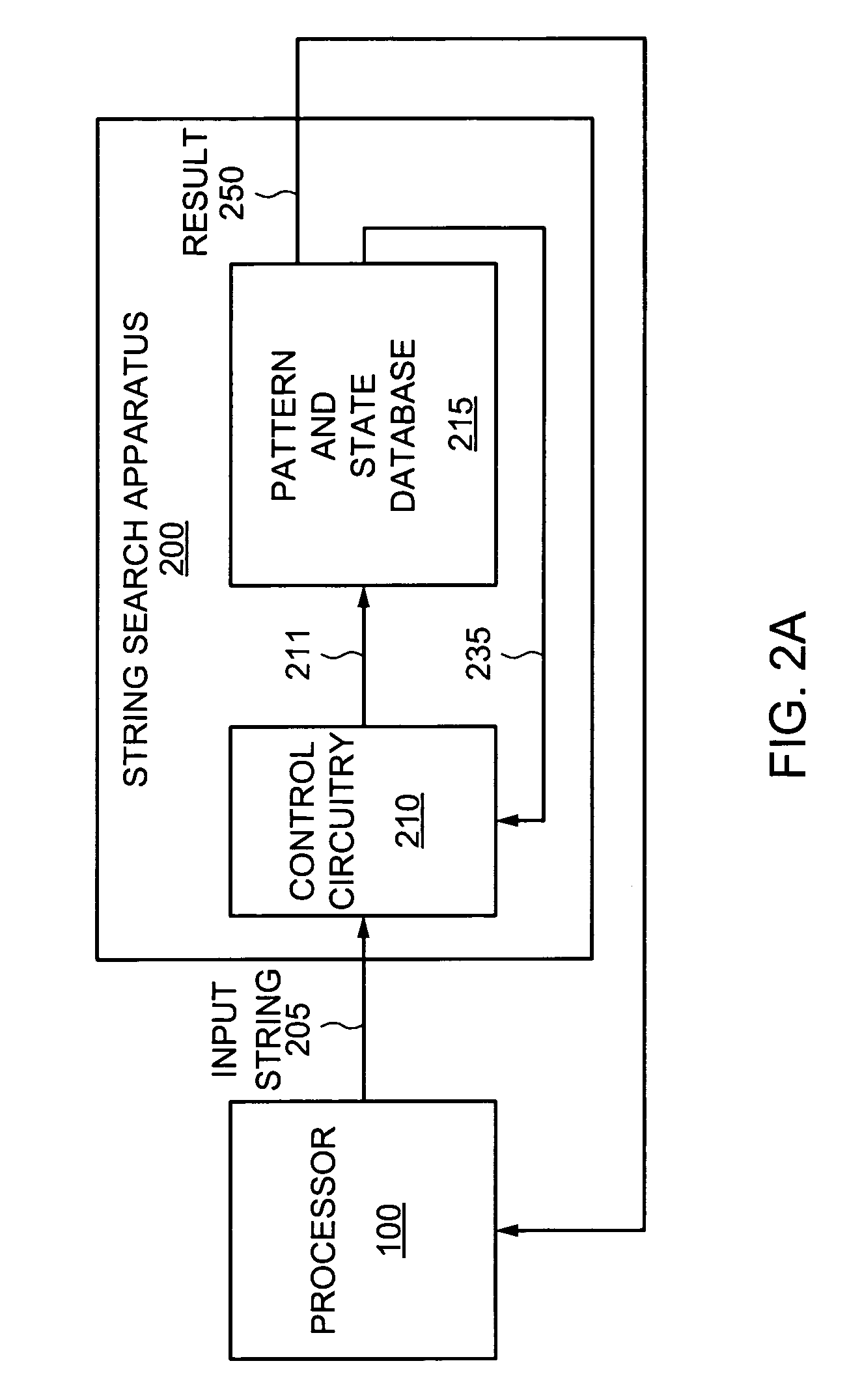

InactiveUS7529746B2Data processing applicationsDigital data information retrievalInstruction memoryTheoretical computer science

A content search circuit for determining whether an input string matches one or more of a plurality of regular expressions, the content search circuit including an instruction memory for storing a plurality of microprograms, each microprogram embodying a corresponding one of the regular expressions, a control circuit having an input to receive the input string, and having a number of outputs, and a plurality of search engines, each having a first input coupled to a corresponding output of the control circuit and having a second input coupled to the instruction memory, wherein each search engine is selectable to execute any of the microprograms stored in the instruction memory to search the input string for any of the regular expressions embodied in the microprograms.

Owner:AVAGO TECH INT SALES PTE LTD

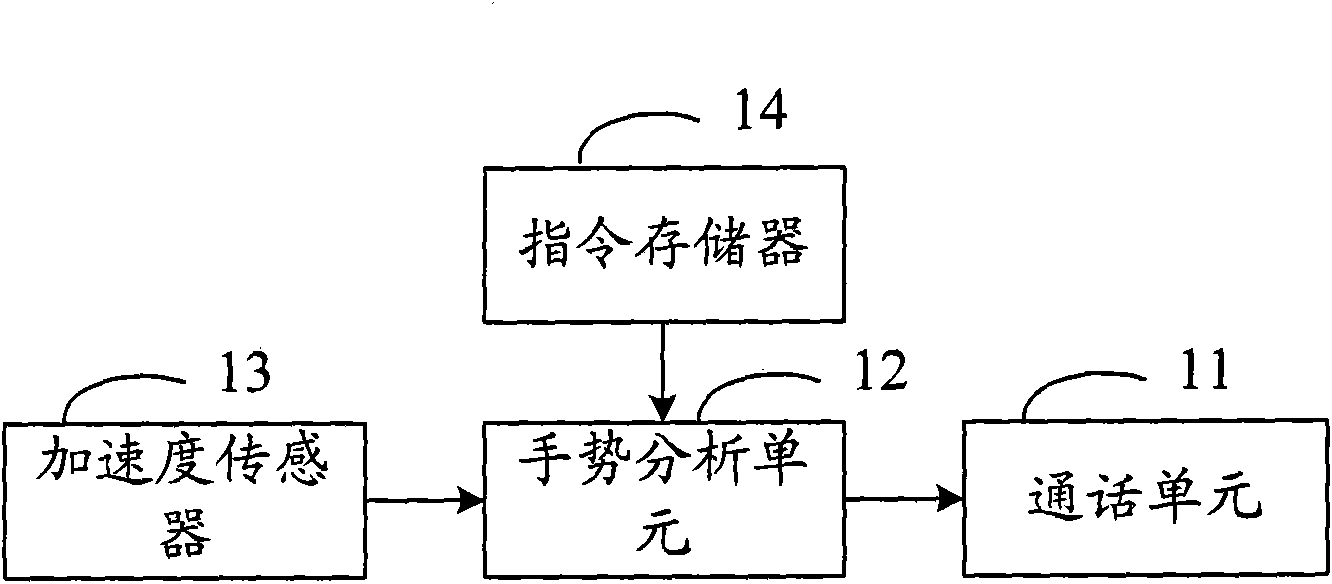

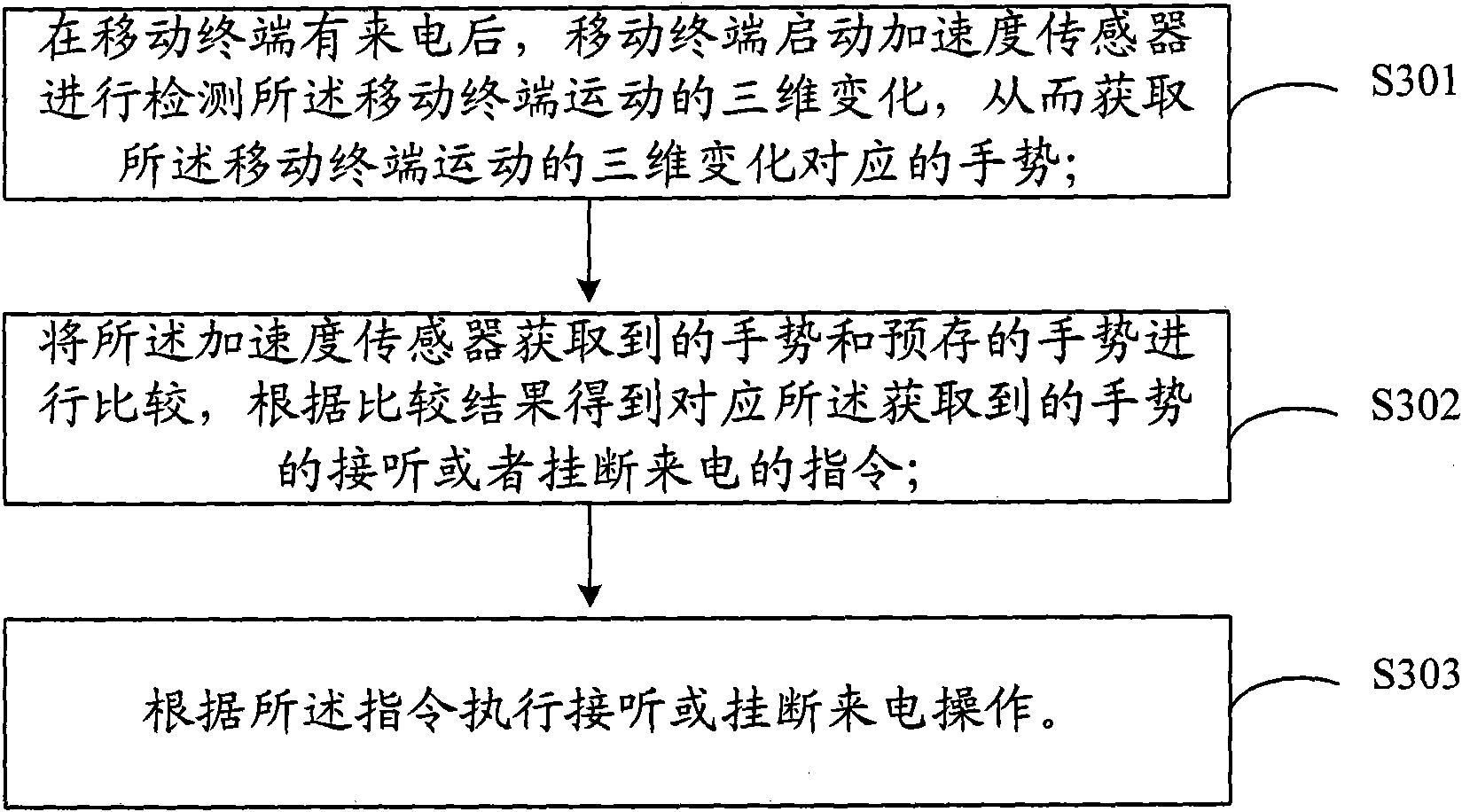

Incoming call processing method, system and mobile terminal

InactiveCN101674368AEasy to answerEasy to hang upAcceleration measurement using interia forcesSubscriber signalling identity devicesInstruction memoryComputer terminal

The invention is applicable to the field of mobile terminals and provides an incoming call processing method, a system and a mobile terminal. The system comprises an instruction memory, an acceleration sensor, a hand signal analysis unit and a conversation unit, wherein, the instruction memory is used for pre-storing a group of hand signals and instructions which correspond to the group of the hand signals and are used for hanging up or receiving incoming calls; the acceleration sensor is used for detecting the three-dimensional change of the motion of the mobile terminal after that the mobileterminal has the incoming call and further obtaining the hand signal which corresponds to the three-dimensional change of the motion of the mobile terminal, the hand signal analysis unit is used forcomparing the hand signal obtained by the acceleration sensor with the hand signals pre-stored in the instruction memory, obtaining the instruction for receiving or hanging up the incoming call whichcorresponds to the obtained hand signal according to the comparison result and then sending to the conversation unit, and the conversation unit is used for receiving or hanging up the incoming call according to the instruction sent form the hand signal analysis unit. The invention realizes the automatic receiving or hanging up of the incoming call according to that a user holds the mobile terminaland carries out the hand signal, thereby facilitating the receiving or hanging up of the incoming call of the user.

Owner:YULONG COMPUTER TELECOMM SCI (SHENZHEN) CO LTD

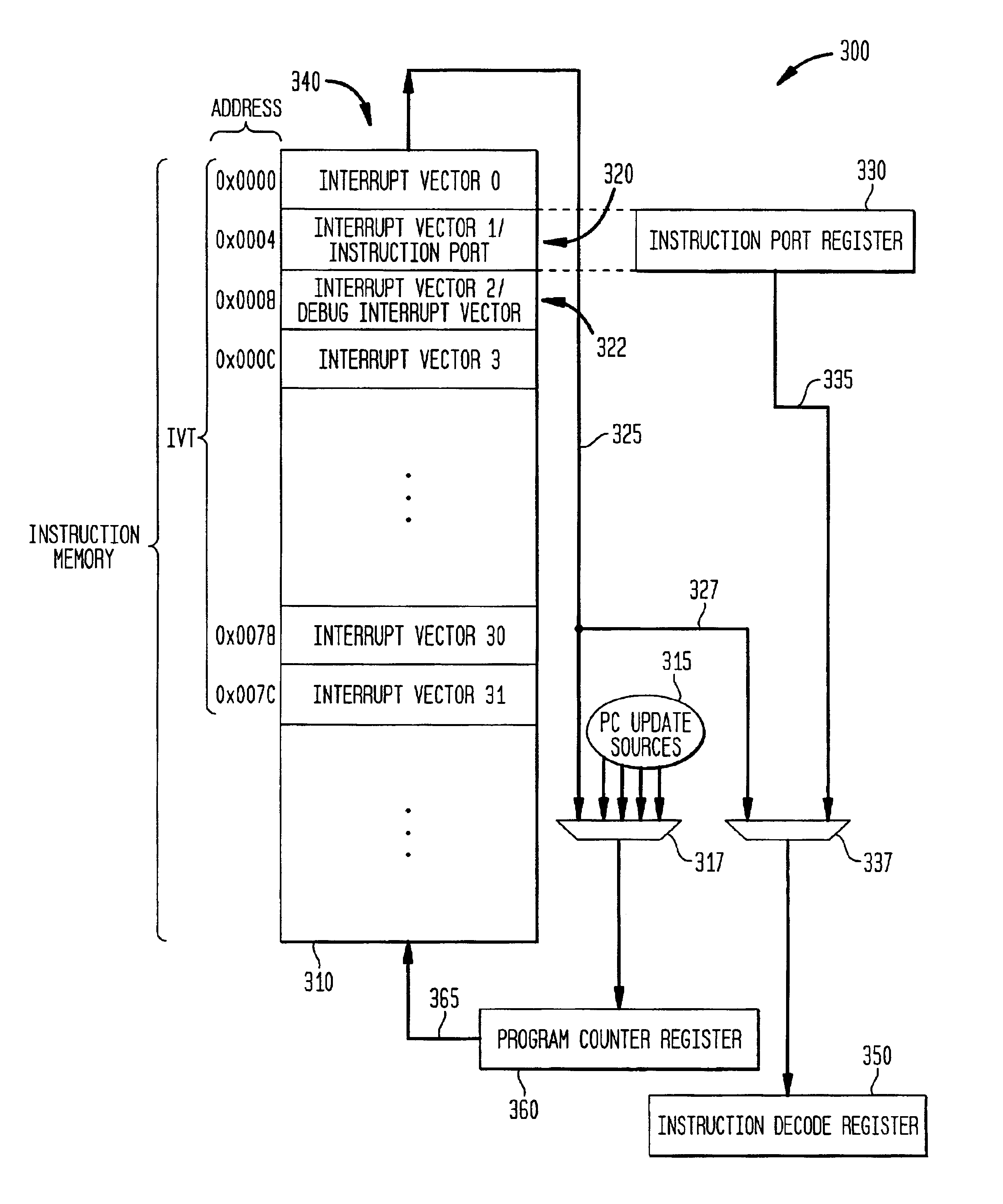

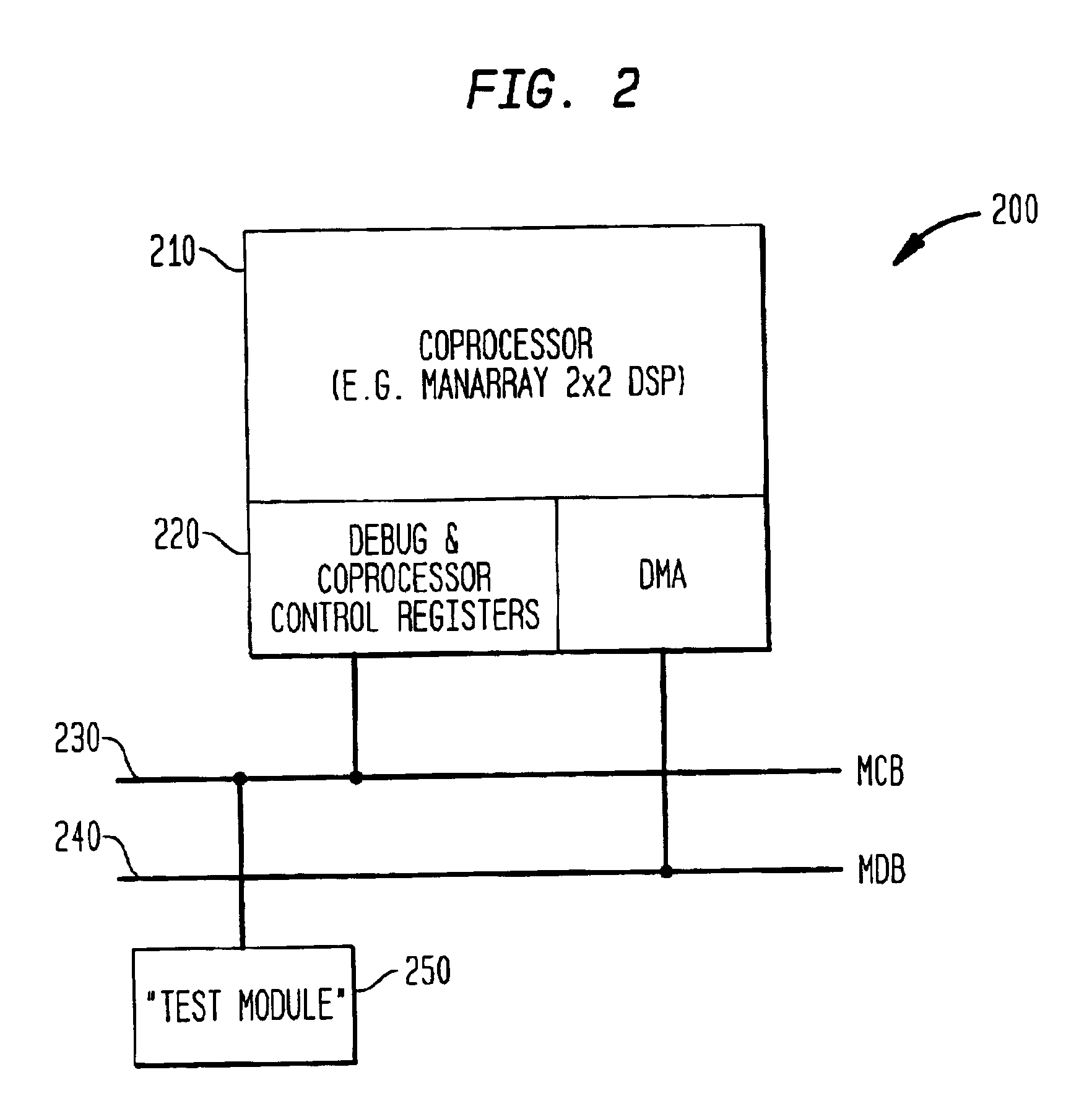

Control processor dynamically loading shadow instruction register associated with memory entry of coprocessor in flexible coupling mode

A method and system are described which provide flexible coupling between a coprocessor and a control processor. The system includes a coprocessor and a system control bus connecting the coprocessor with the control processor. The coprocessor has two modes of access. In the first mode of access, the coprocessor retrieves an instruction stored in instruction memory and, in the second mode of access, the coprocessor retrieves an instruction from the control processor. The system control bus provides a path for loading an instruction to the coprocessor's shadow instruction register. The coprocessor, upon retrieving an entry in its instruction memory associated with the shadow instruction resigter, determines whether to load the instruction as an address in its program counter or to load the contents of the shadow instruction register into the instruction decode register.

Owner:ALTERA CORP

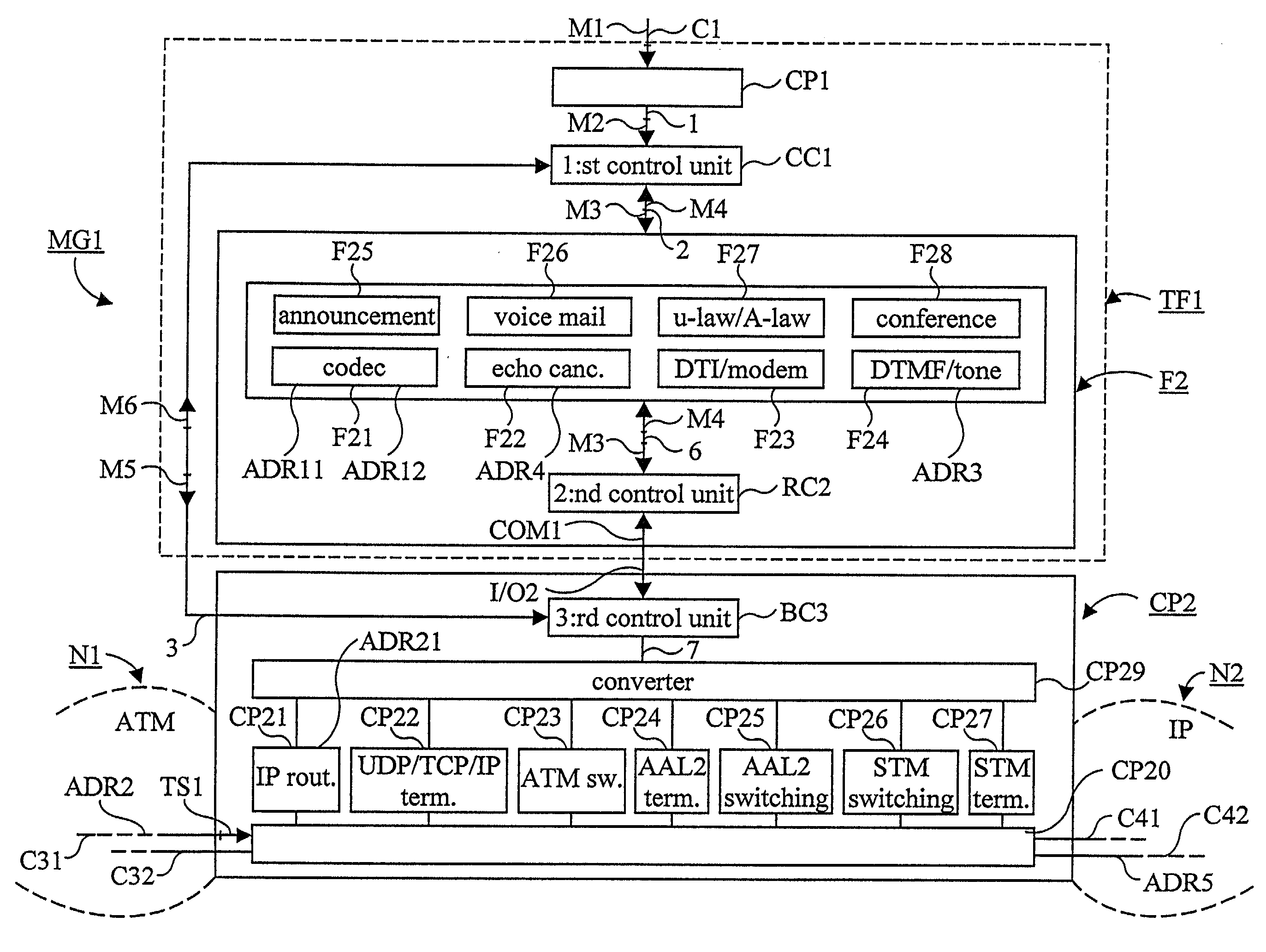

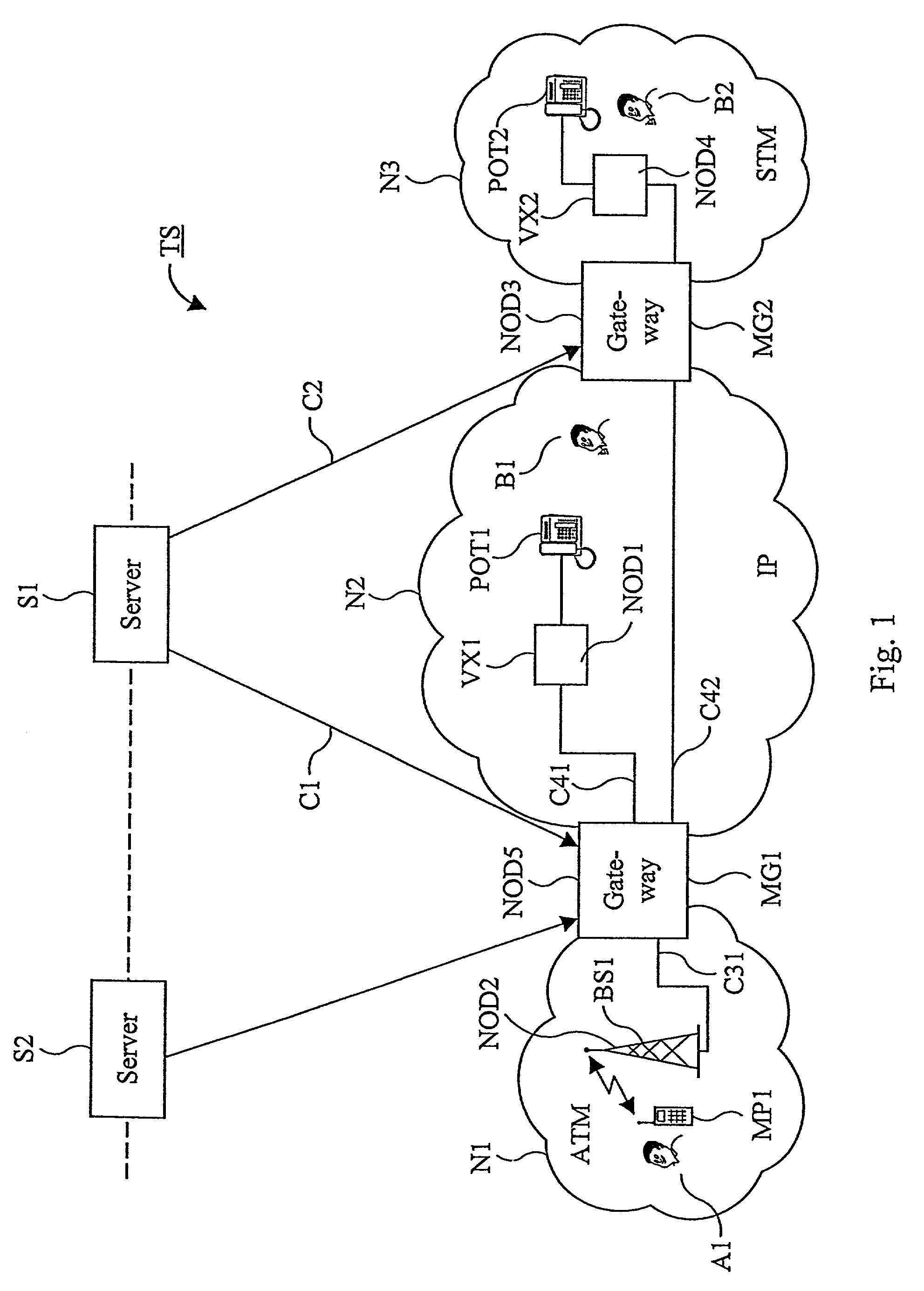

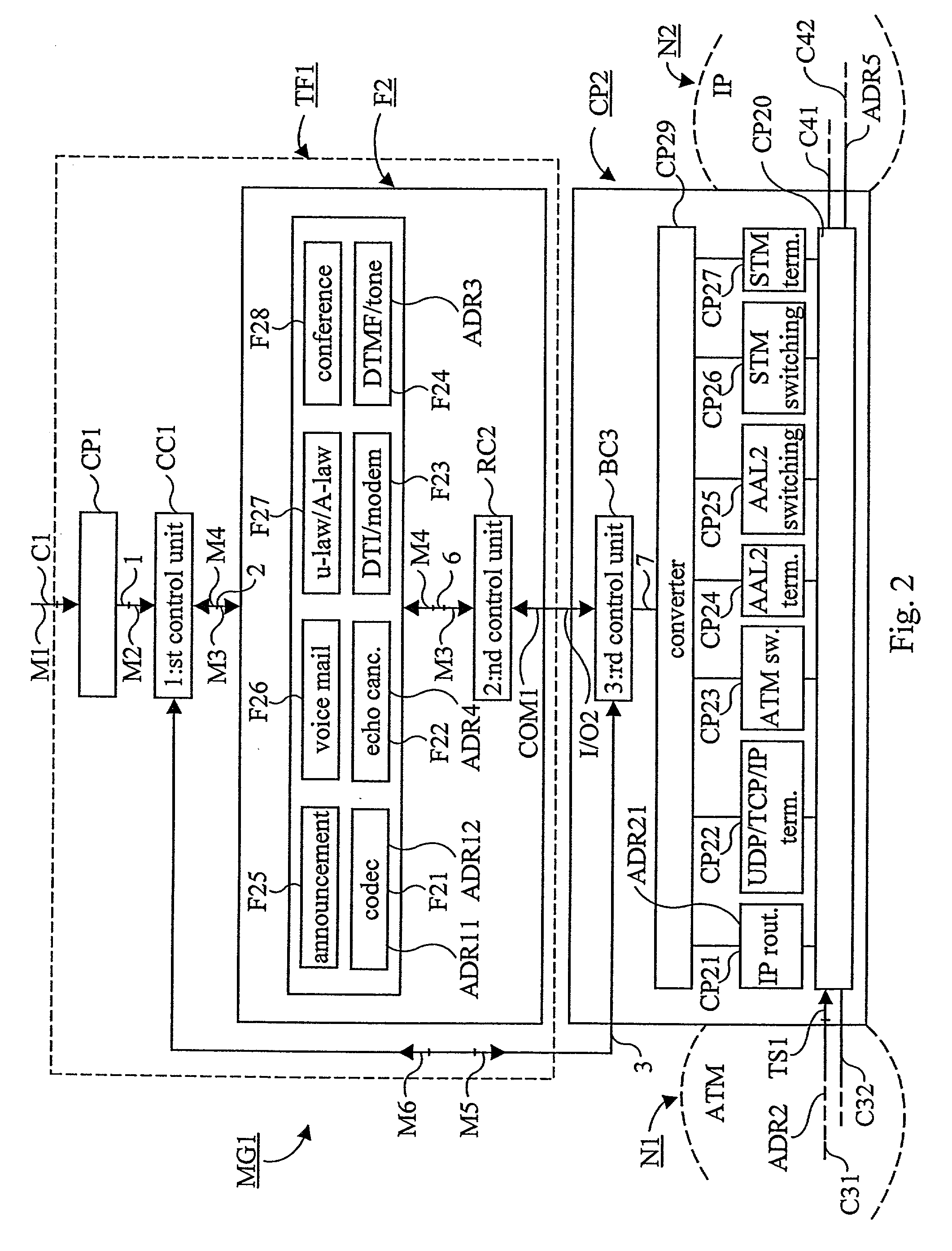

Method and device in a coupling node for a telecommunication system

InactiveUS7065094B2Utilize resourceEfficient use ofMultiplex system selection arrangementsResource allocationInstruction memoryCoupling

Owner:TELEFON AB LM ERICSSON (PUBL)

Sound enhancement for mobile phones and other products producing personalized audio for users

InactiveUS20050260978A1Easy to receiveImprove soundStereophonic circuit arrangementsHearing impaired stereophonic signal reproductionEnvironmental noiseInstruction memory

A mobile phone or other personal communication device includes resources applying measures of an individual's hearing profile, personal choice profile, and induced hearing loss profile, separately or in combination, to build the basis of sound enhancement. A personal communication device thus comprises a transmitter / receiver coupled to a communication medium for transmitted receiving audio signals, control circuitry that controls transmission, reception and processing of call and audio signals, a speaker, and a microphone. The control circuitry includes logic applying one or more of a hearing profile of the user, a user preference related hearing, and environmental noise factors in processing the audio signals. The control circuitry may includes instruction memory and an instruction execution processor such as a digital signal processor.

Owner:HIMPP

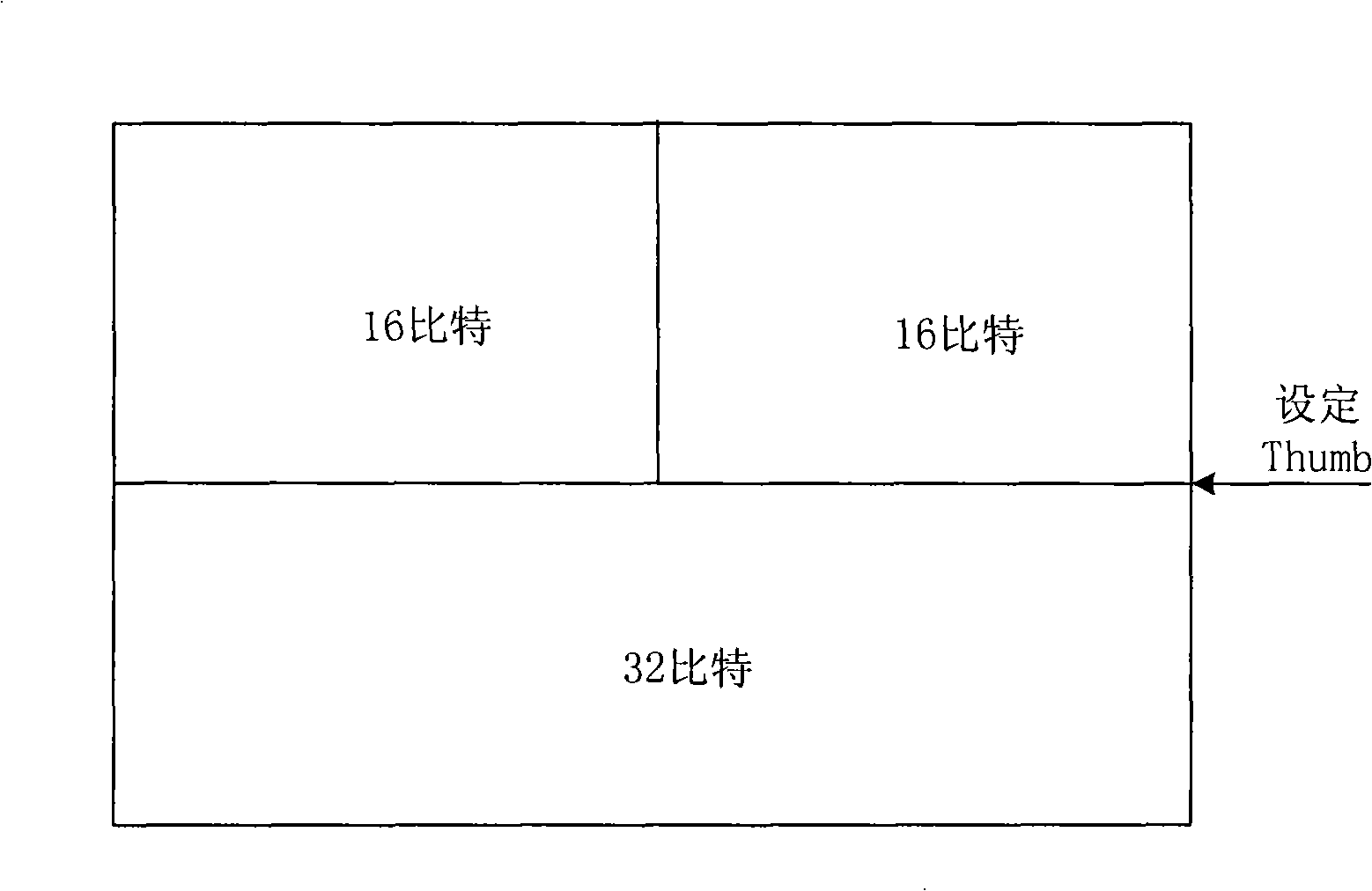

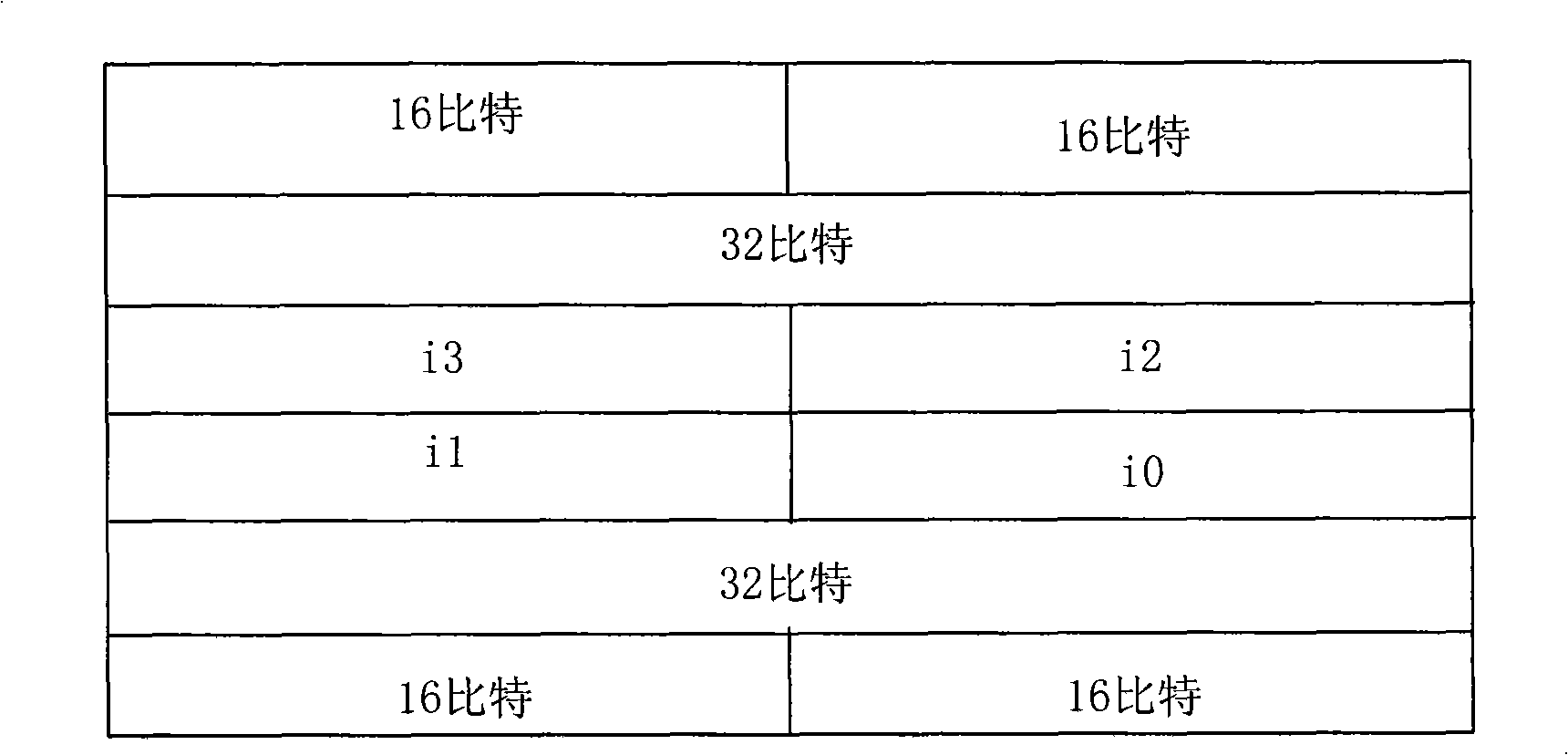

Instruction set optimization

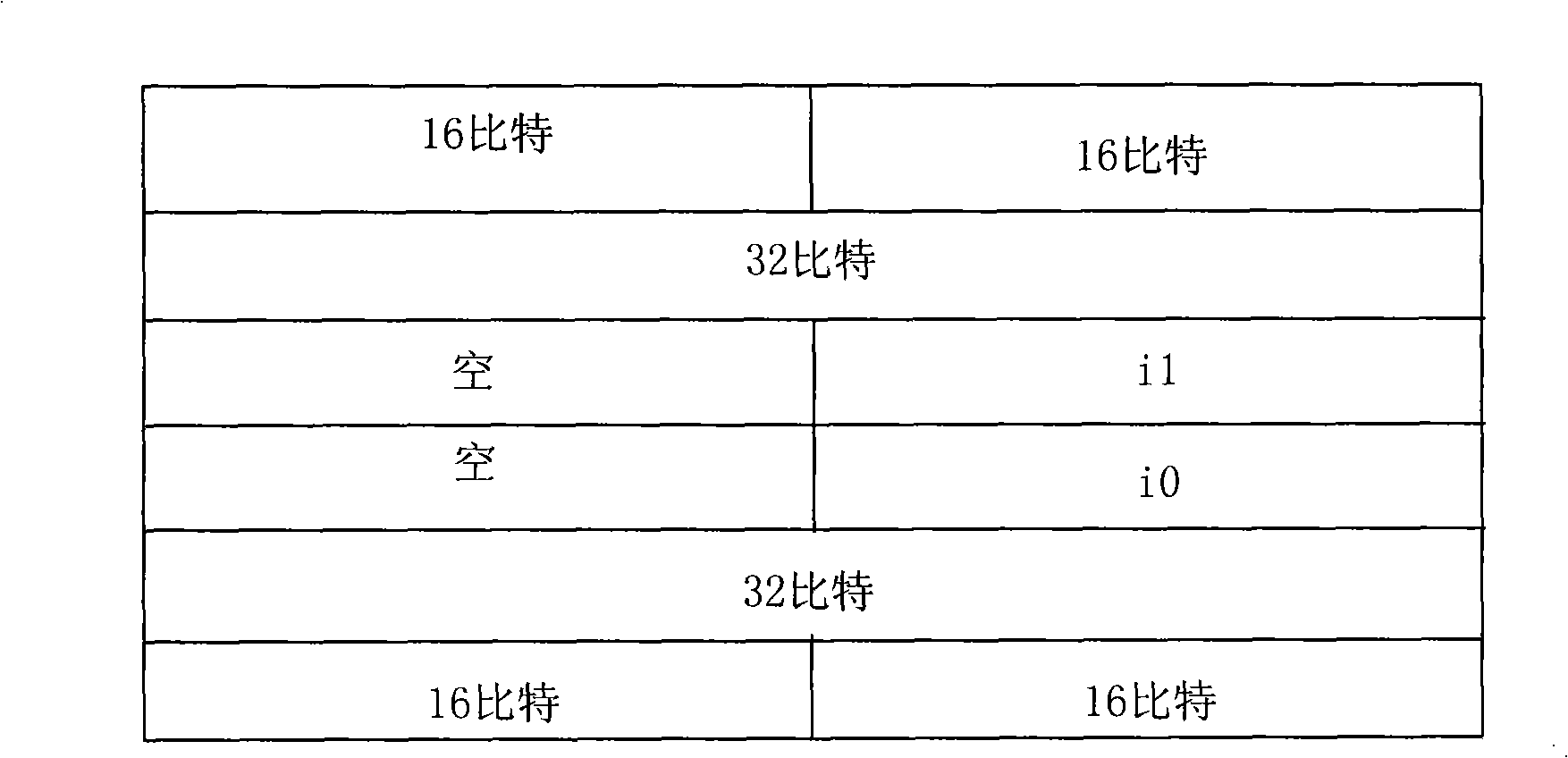

InactiveCN101344840ASolving Hybrid Storage ProblemsSmall sizeMachine execution arrangementsInstruction memoryInstruction set

The invention provides an instruction set optimization method. In one aspect, the invention provides a microprocessor, which comprises: an instruction memory for mixed storage of first-length instructions and second-length instructions with different lengths, the first-length instructions are shorter than the second-length instructions and the two are distinguished by adopting operational codes; an instruction extraction unit, which extracts the instructions in mixed storage from the instruction memory and separates the first-length instructions from the second-length instructions according to the operational codes; an instruction decoding unit, which decodes the first-length instructions and the second-length instructions respectively; and a jump operation unit, which, in jump operation, transfers instructions to the boundary of either the first-length or the second-length instructions. By adopting the optimized instruction set, the program code size can be significantly reduced.

Owner:苏州简约纳电子有限公司

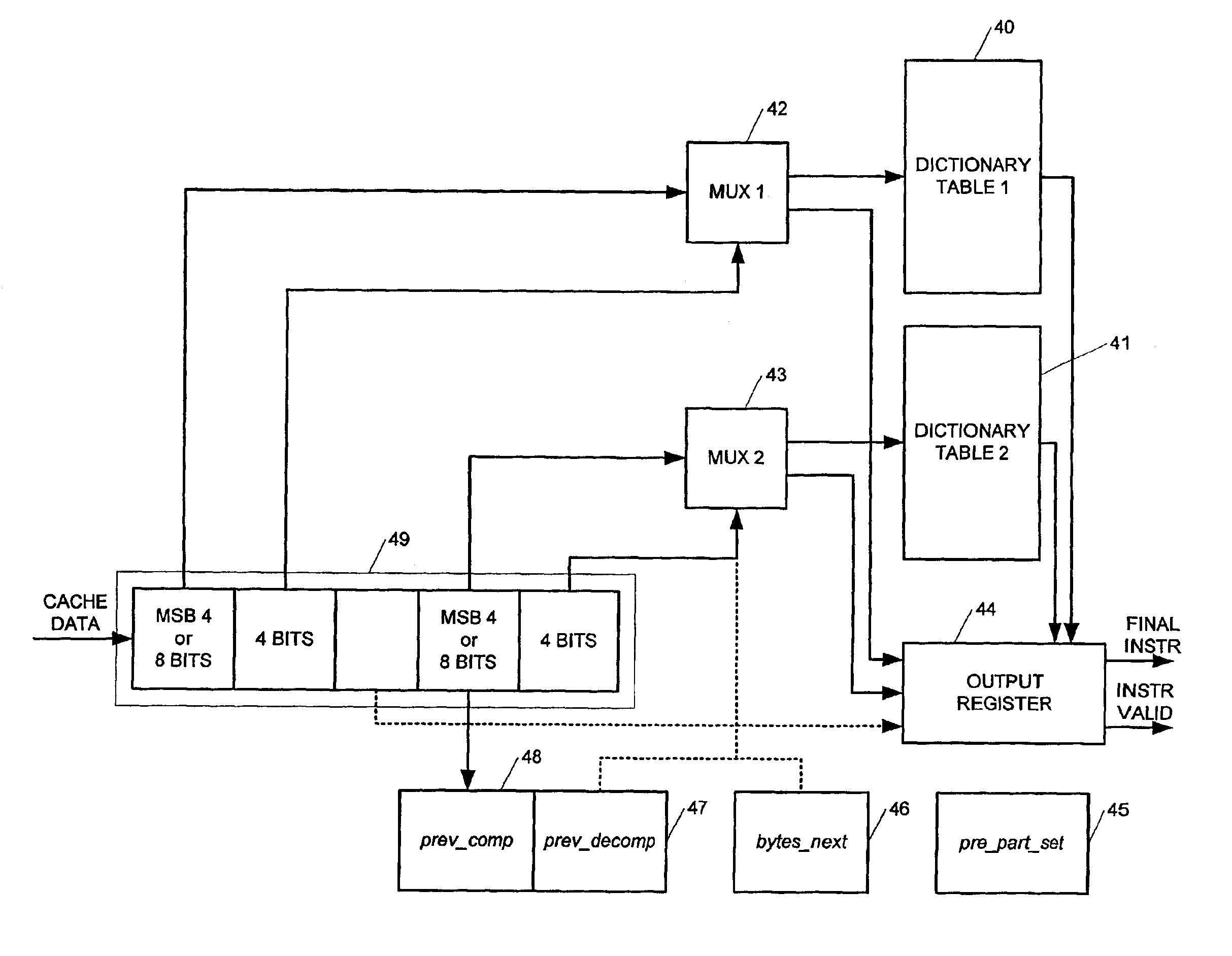

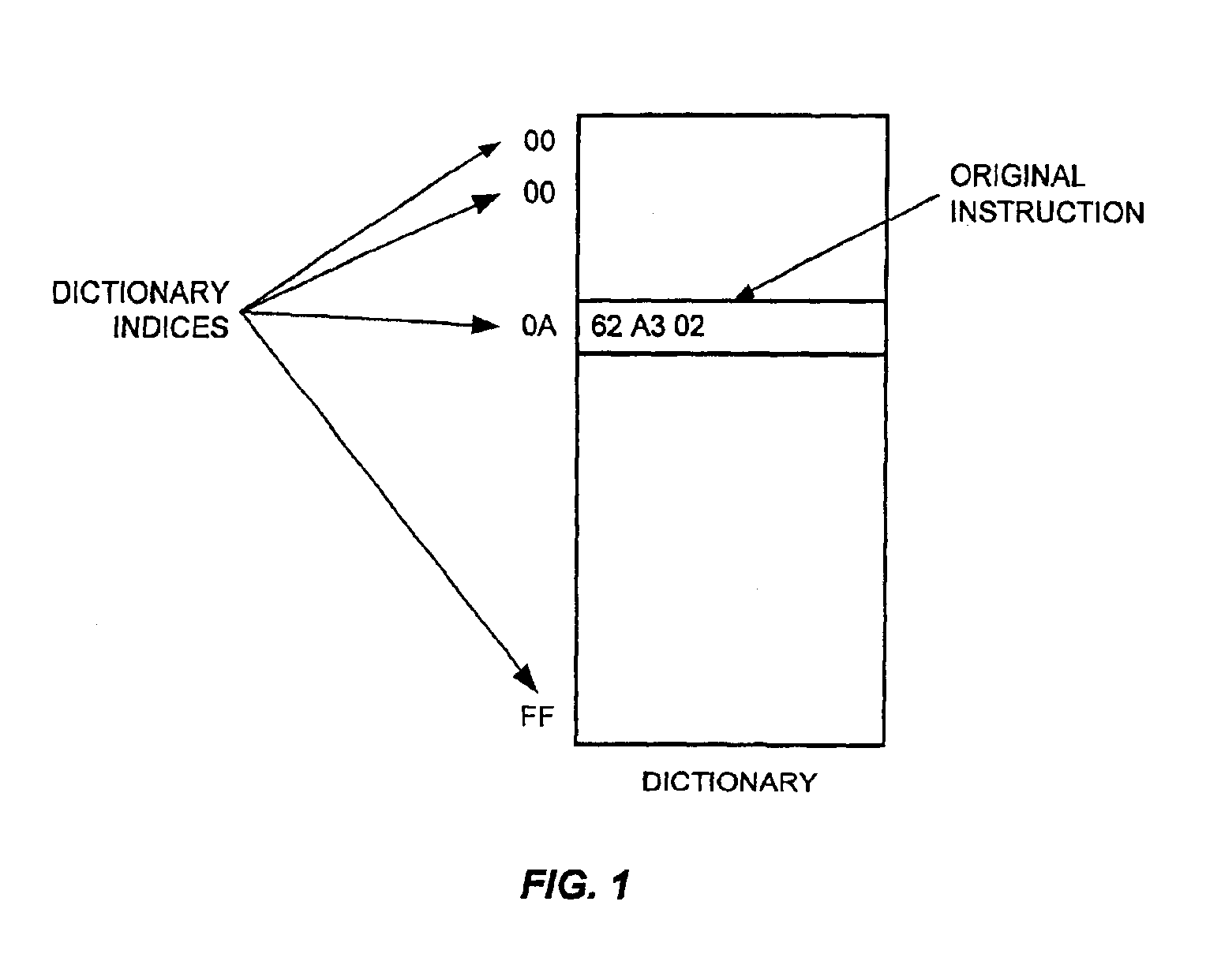

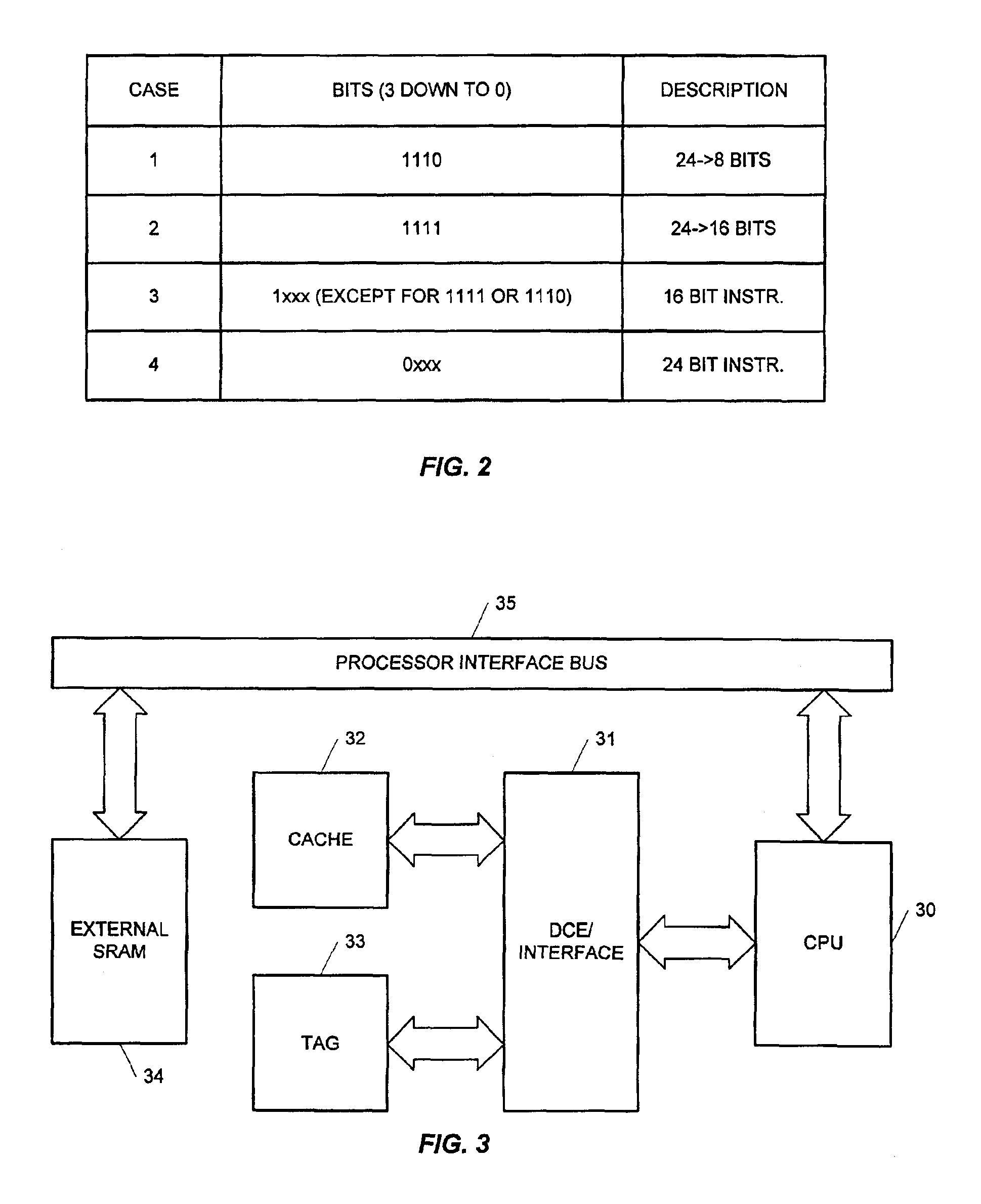

Apparatus for one-cycle decompression of compressed data and methods of operation thereof

Code compression is known as an effective technique to reduce instruction memory size on an embedded system. However, code compression can also be very effective in increasing the processor-to-memory bandwidth and hence provide increased system performance. A code decompression engine having plurality of dictionary tables, coupled with decoding circuitry and appropriate control circuitry, is coupled between the processor core and the instruction cache. The code decompression engine provides one-cycle decompression of compressed instructions that are intermixed with uncompressed instructions, thereby increasing processor-to-memory bandwidth and avoiding processor stalls.

Owner:NEC CORP

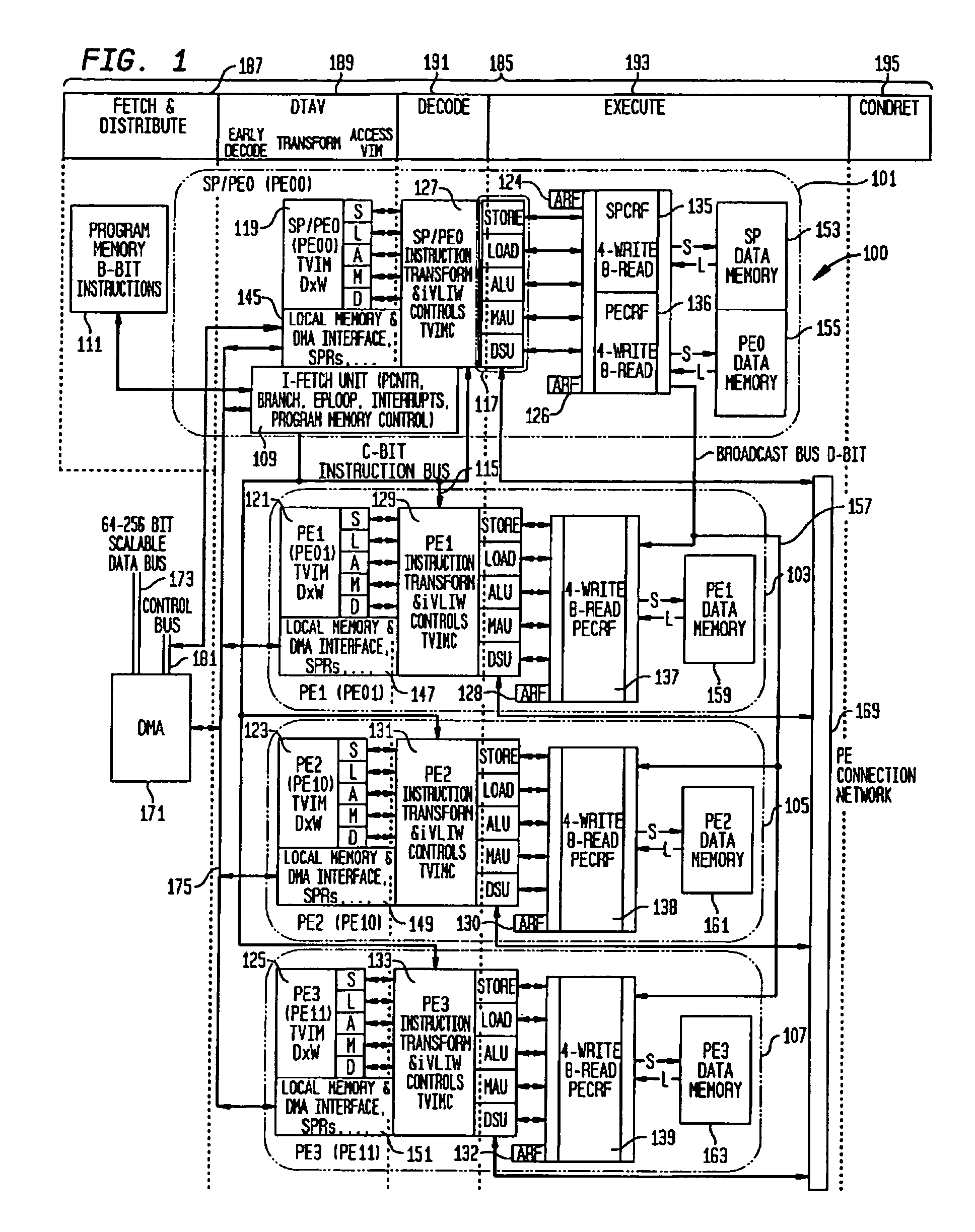

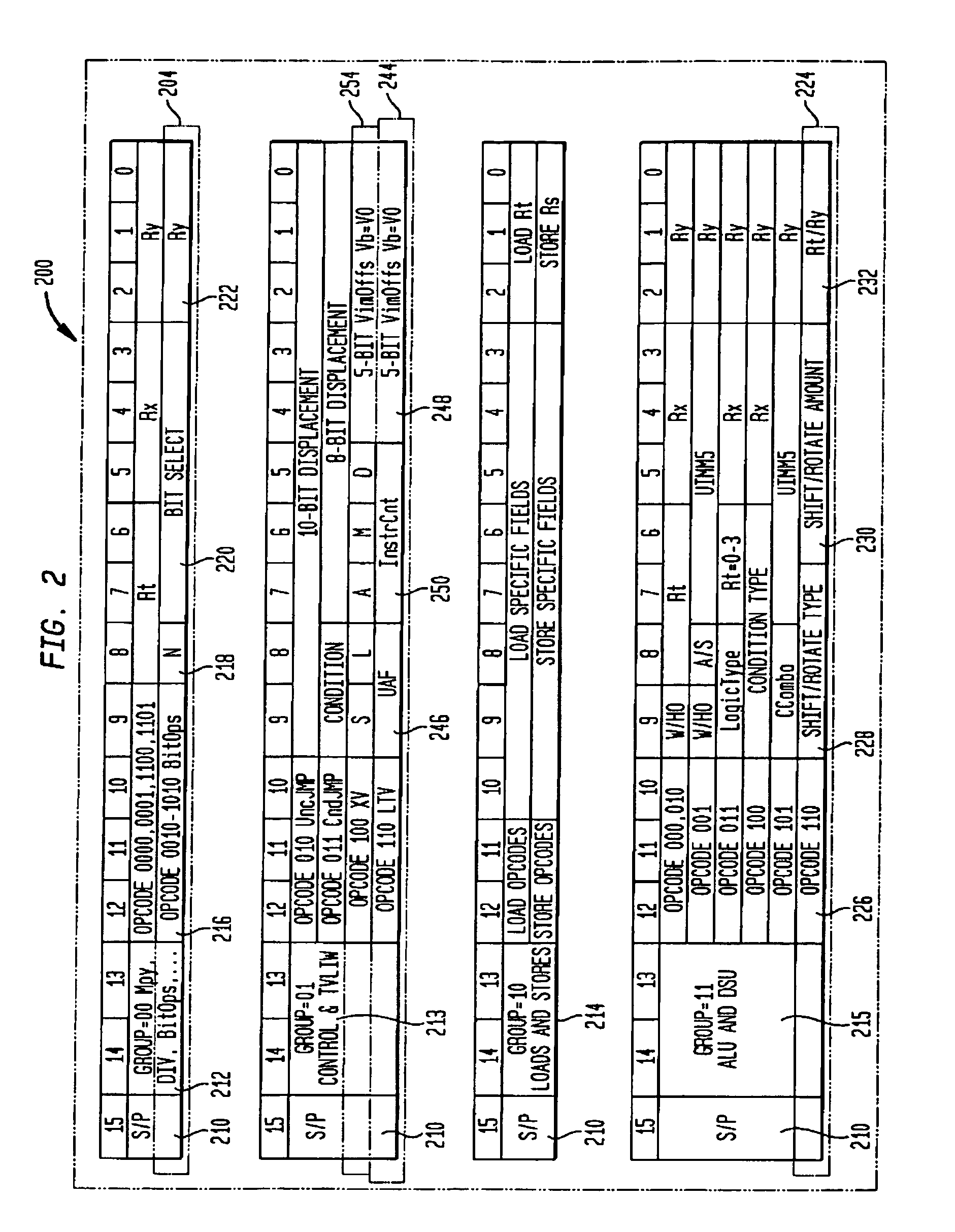

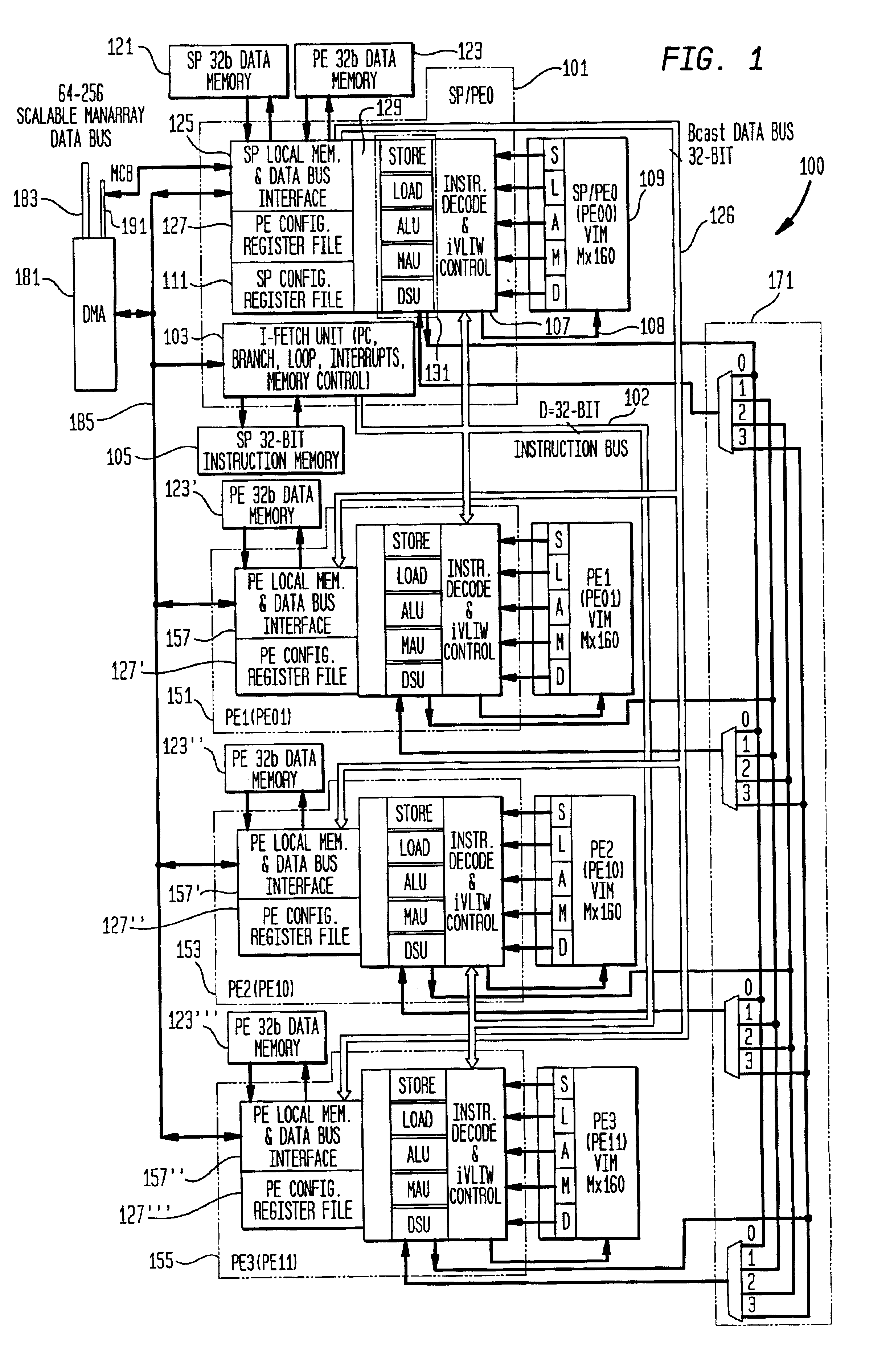

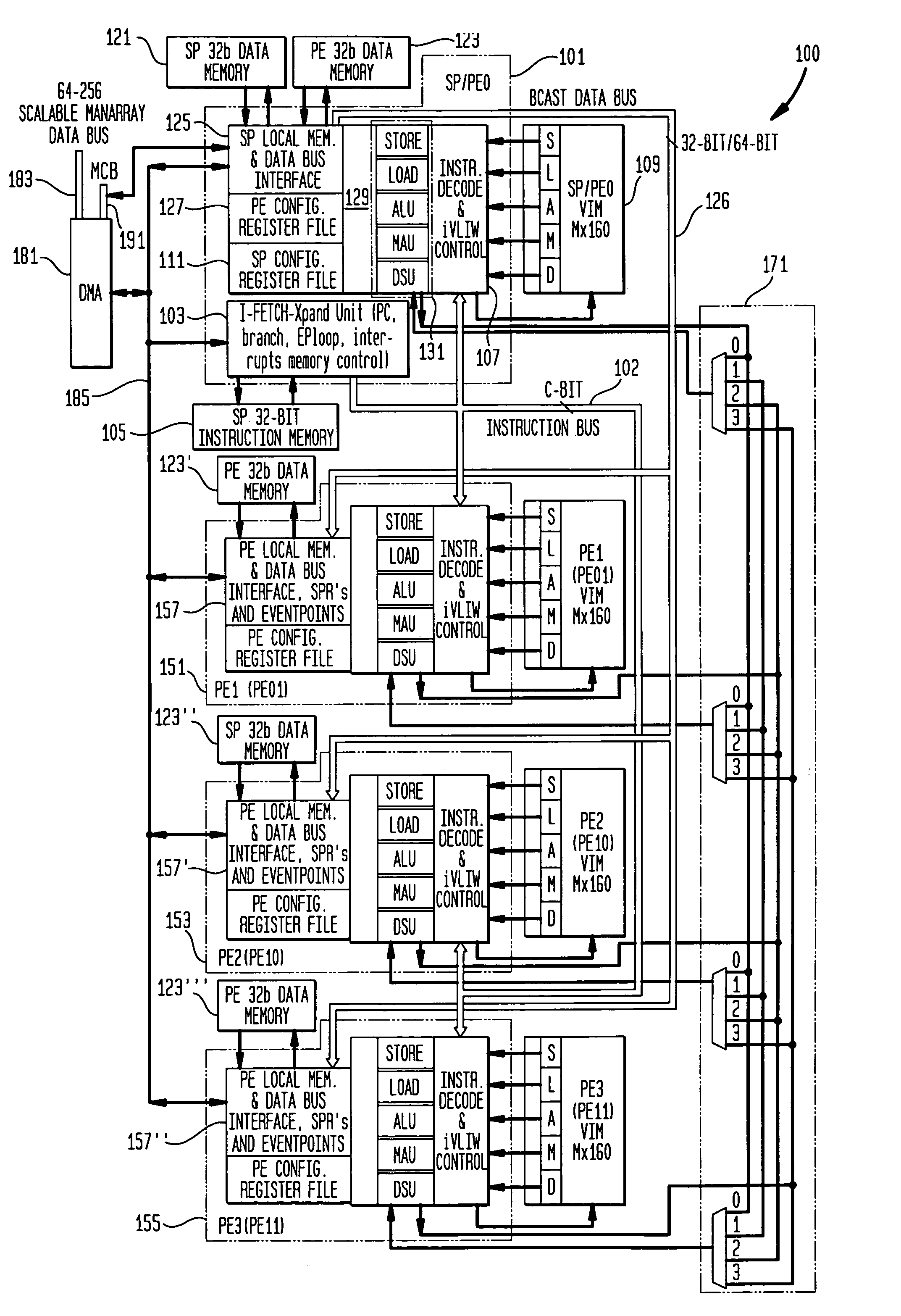

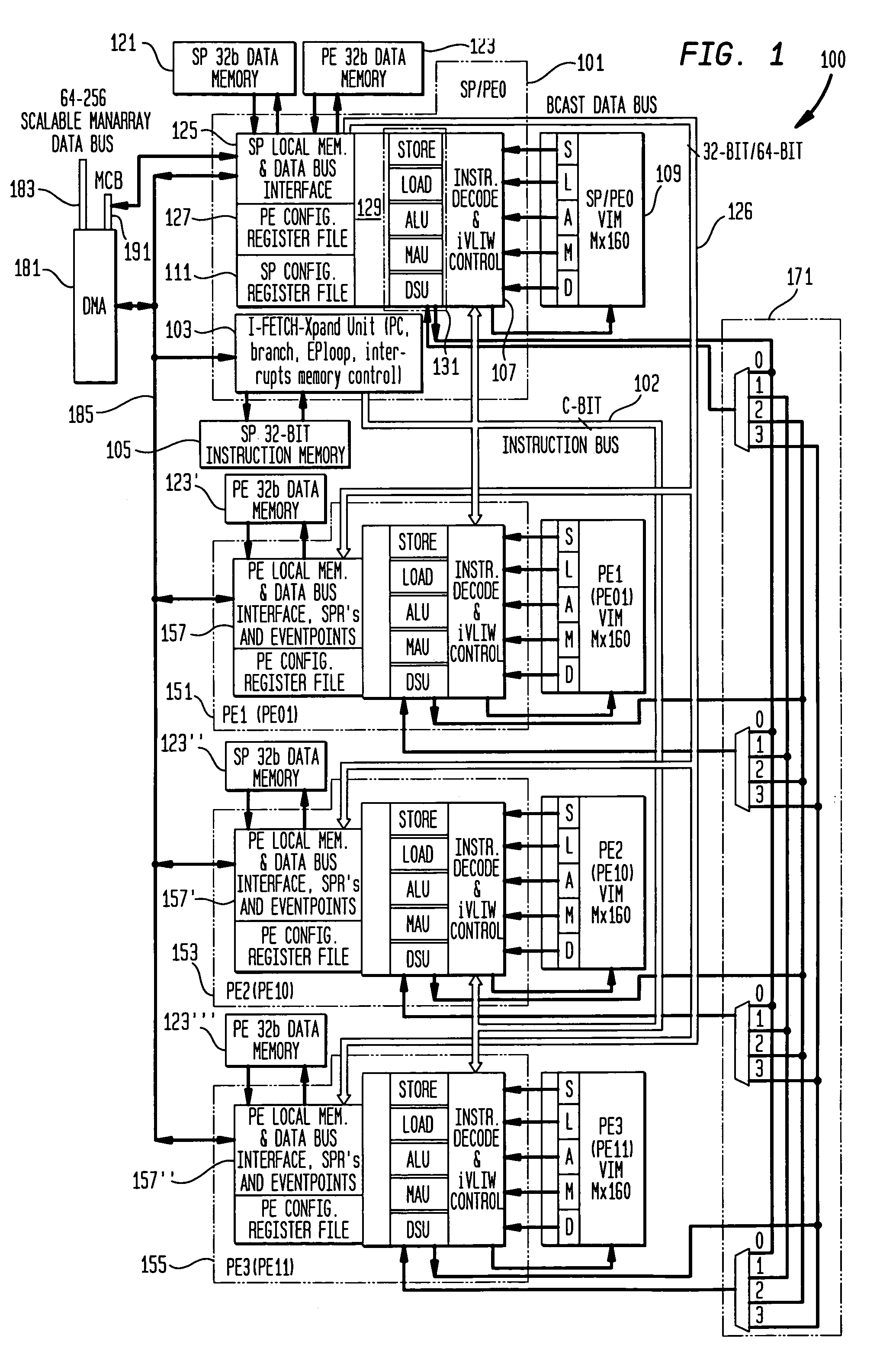

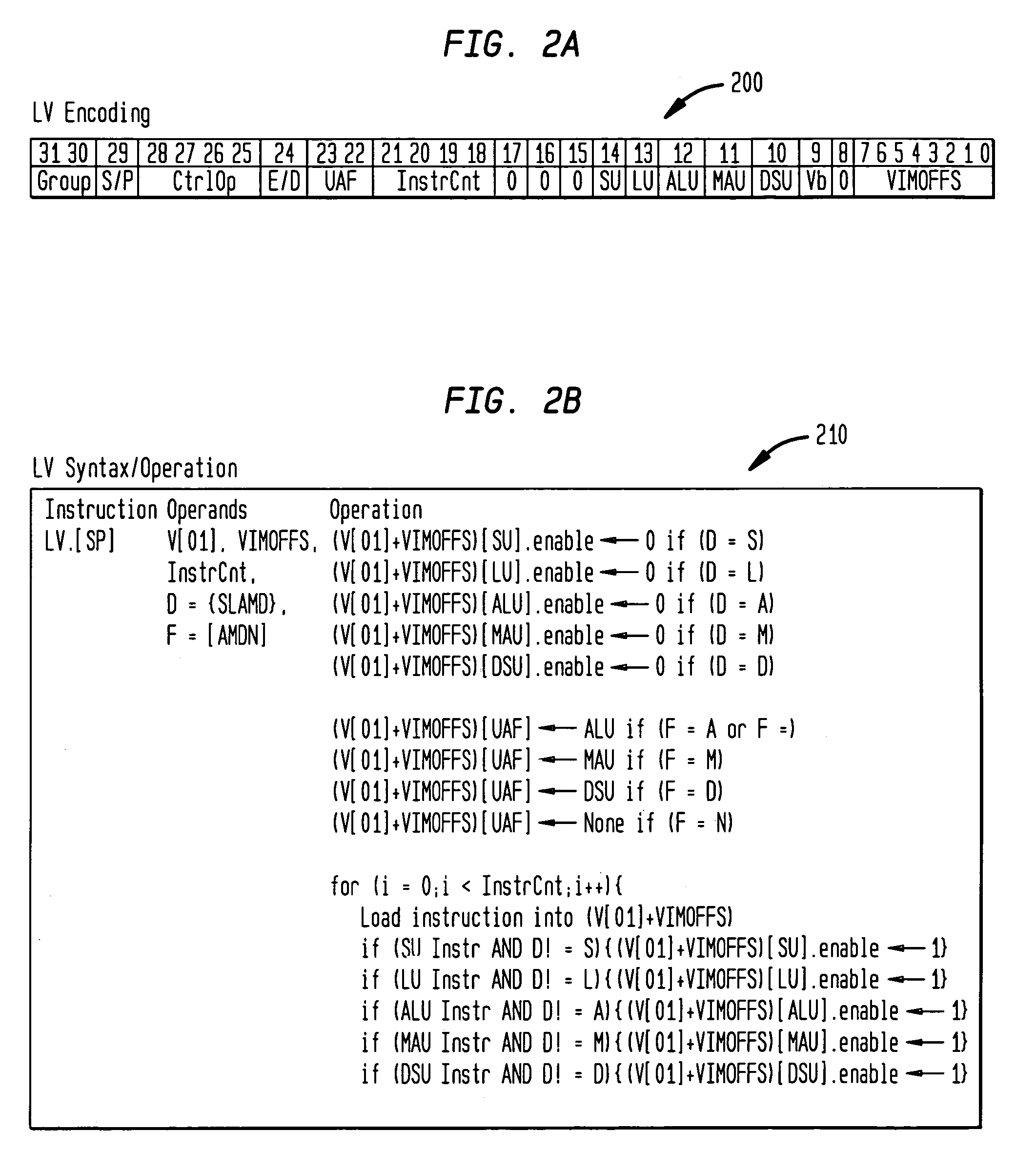

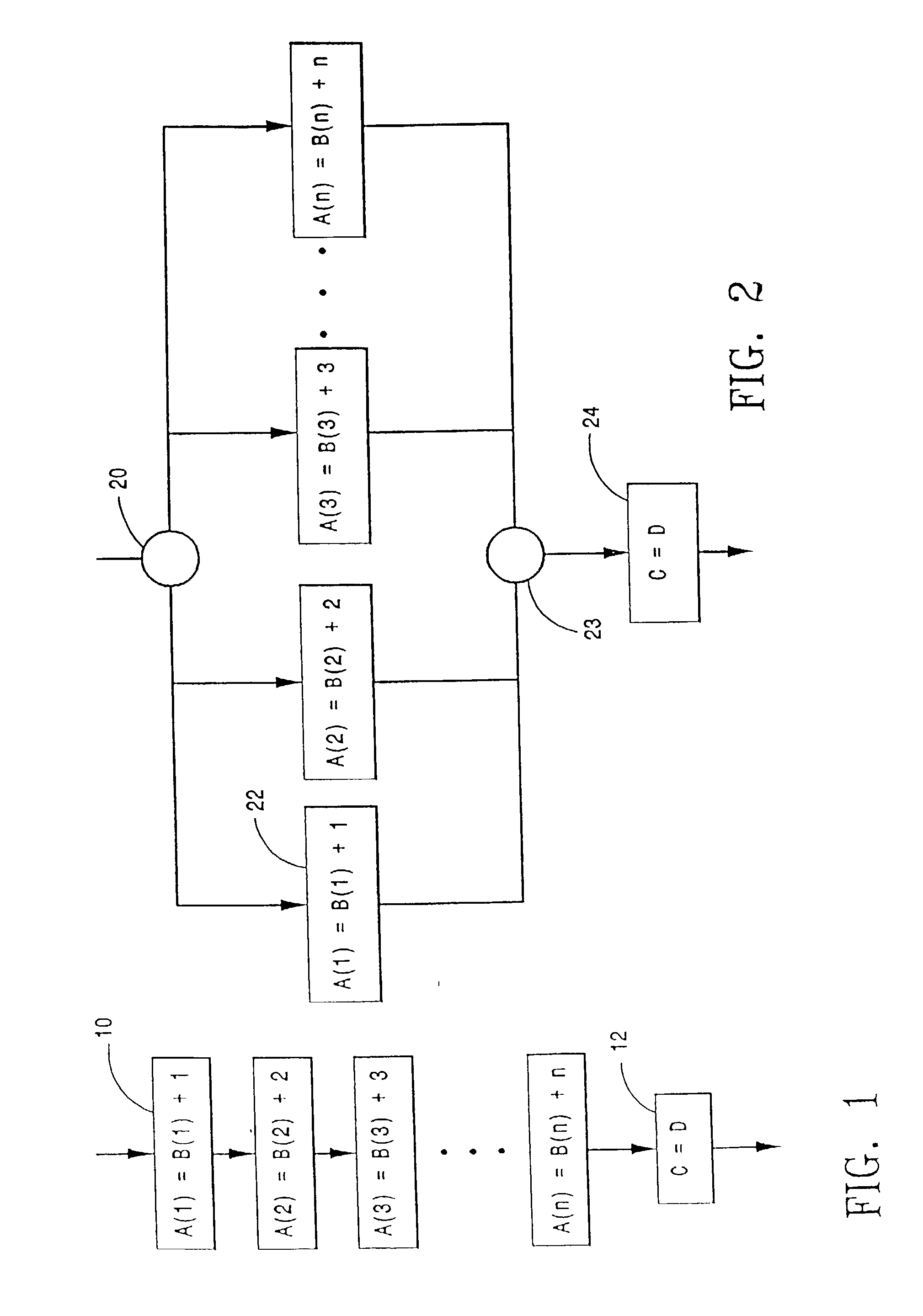

Methods and apparatus for indirect VLIW memory allocation

InactiveUS7181730B2Small sizeAppropriate distributionSoftware engineeringDigital computer detailsInstruction memoryMulti processor

Techniques and a set of heuristics are described to perform allocation of the special instruction memory where indirect very long instruction words (VLIW's) are stored for the ManArray family of multiprocessor digital signal processors (DSP). This approach substantially reduces the cost of pre-initializing the contents of VLIWs.

Owner:ALTERA CORP

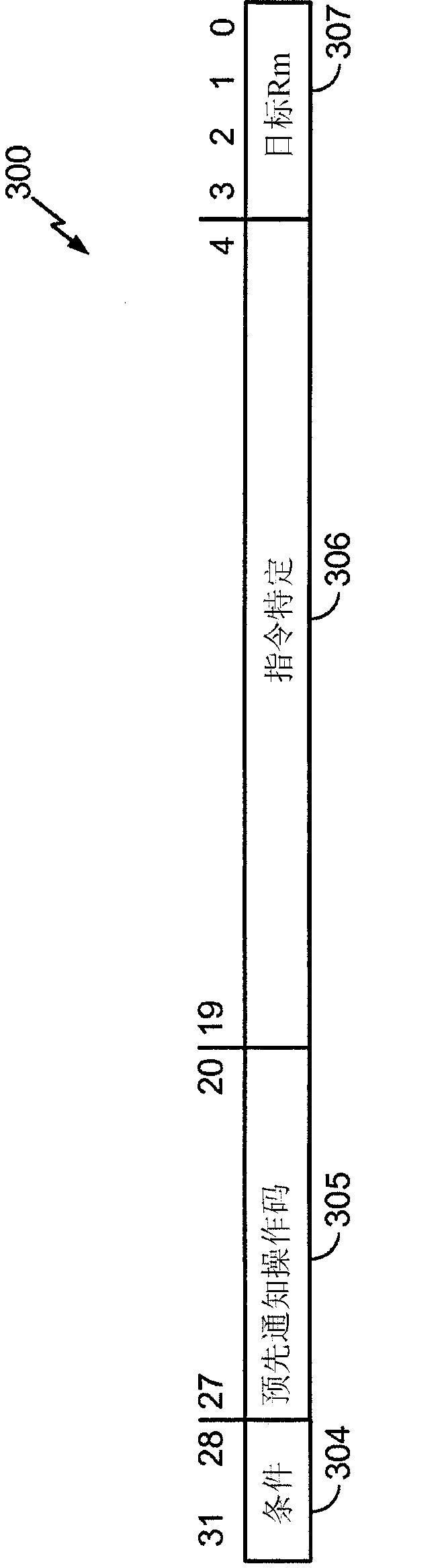

Methods and apparatus for changing a sequential flow of a program using advance notice techniques

InactiveCN102934075ANext instruction address formationConcurrent instruction executionInstruction memoryProcessor register

A processor implements an apparatus and a method for providing advance notice of an indirect branch address. A target address generated by an instruction is automatically identified. A next program address is prepared based on a most current target address before an indirect branch instruction utilizing the most current target address is speculatively executed. The apparatus suitably employs a register for holding an instruction memory address that is specified by a program as a most current indirect address of an indirect branch instruction. The apparatus also employs a next program address selector that selects the most current indirect address from the register as the next program address for use in speculatively executing the indirect branch instruction.

Owner:QUALCOMM INC

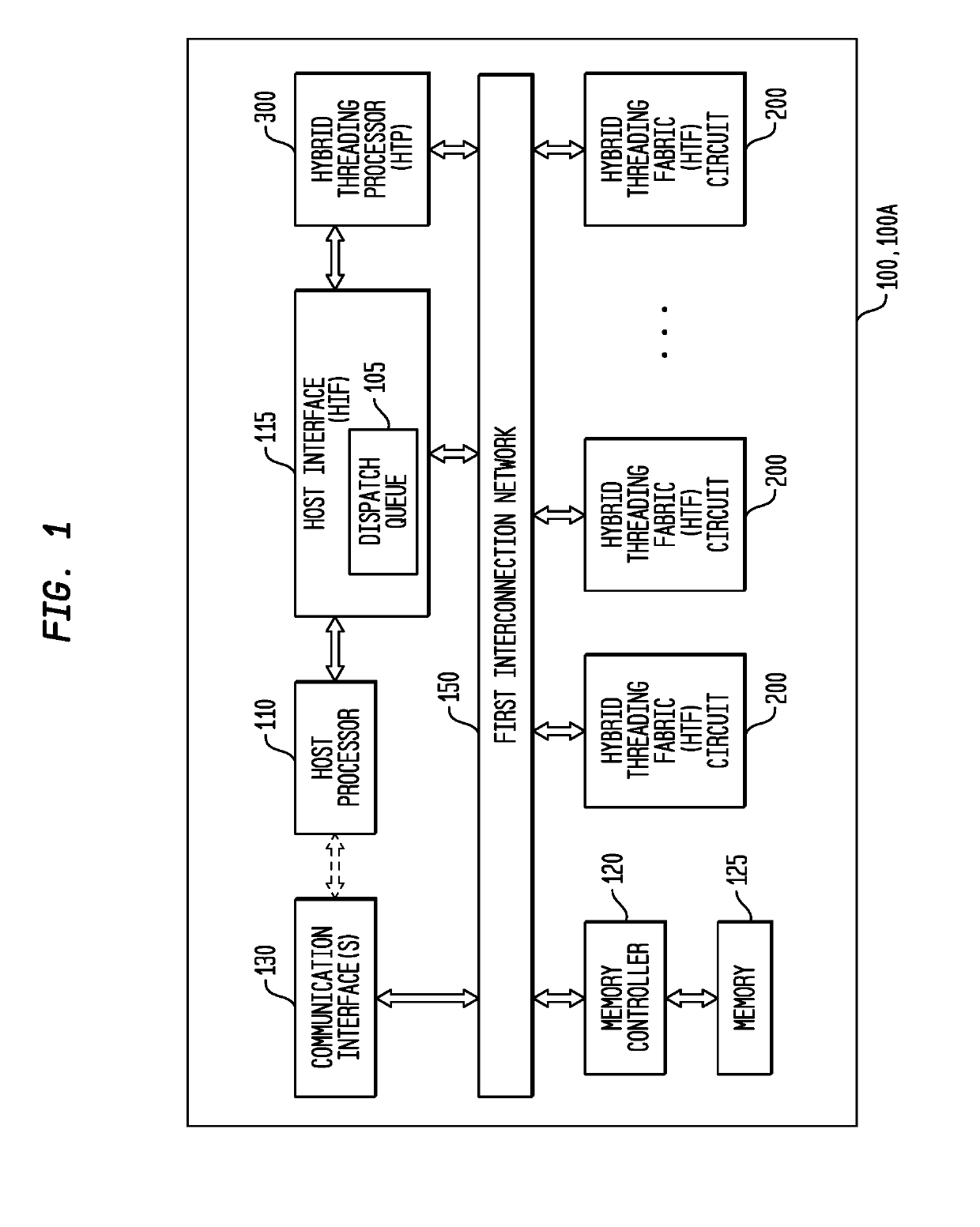

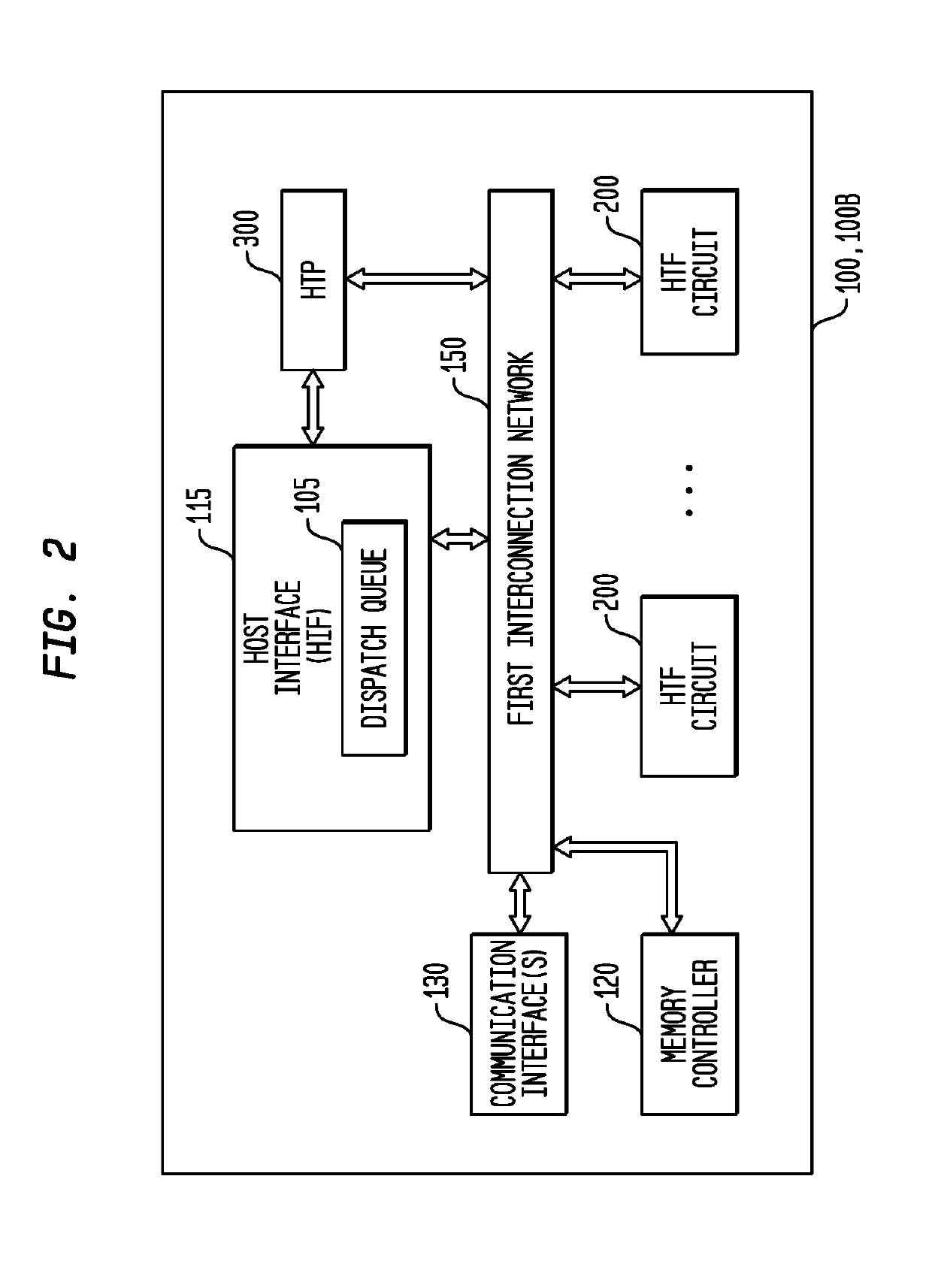

Conditional Branching Control for a Multi-Threaded, Self-Scheduling Reconfigurable Computing Fabric

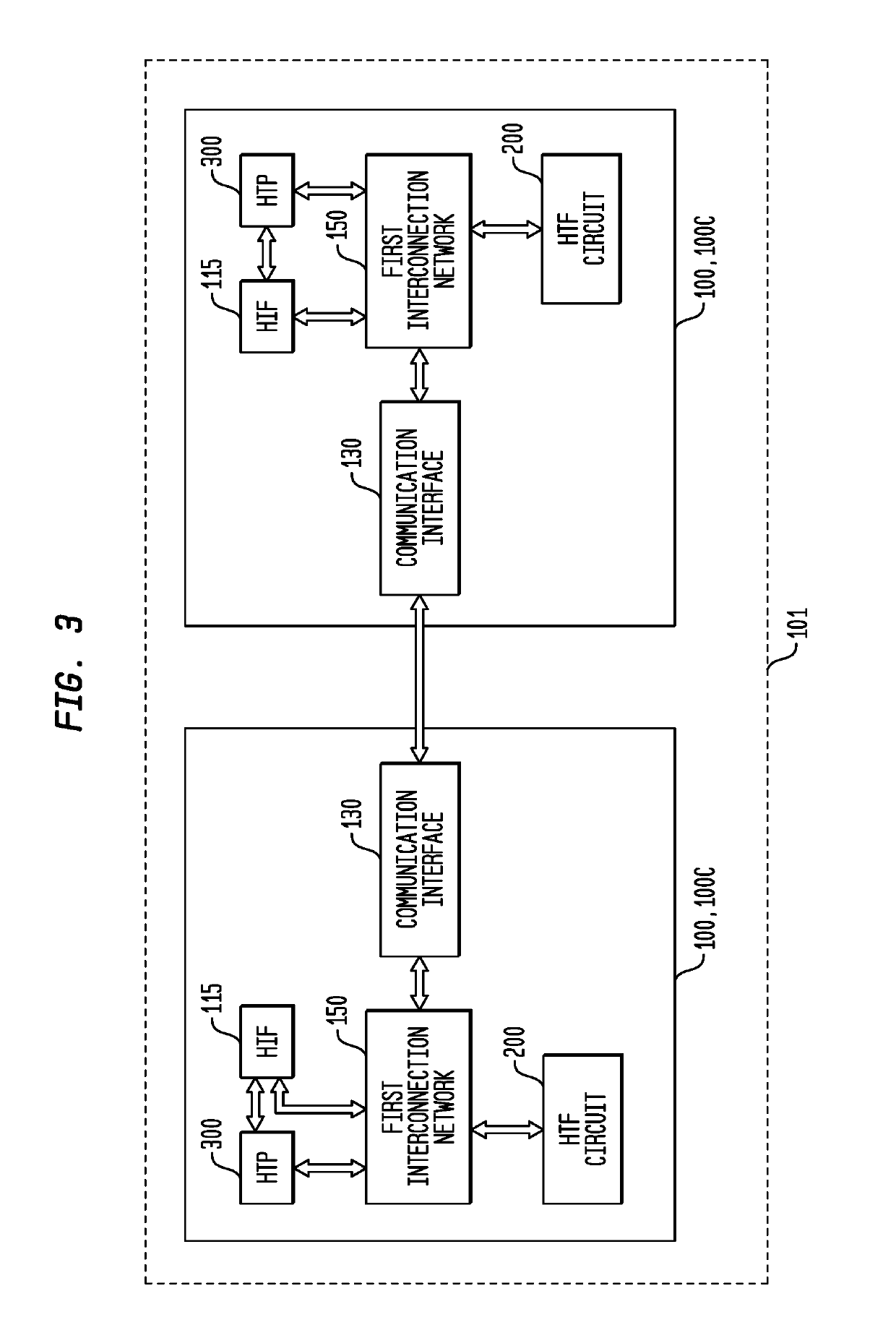

ActiveUS20190303154A1Fast executionRegister arrangementsInterprogram communicationInstruction memoryInterconnection

Representative apparatus, method, and system embodiments are disclosed for configurable computing. A representative system includes an interconnection network; a processor; and a plurality of configurable circuit clusters. Each configurable circuit cluster includes a plurality of configurable circuits arranged in an array; a synchronous network coupled to each configurable circuit of the array; and an asynchronous packet network coupled to each configurable circuit of the array. A representative configurable circuit includes a configurable computation circuit and a configuration memory having a first, instruction memory storing a plurality of data path configuration instructions to configure a data path of the configurable computation circuit; and a second, instruction and instruction index memory storing a plurality of spoke instructions and data path configuration instruction indices for selection of a master synchronous input, a current data path configuration instruction, and a next data path configuration instruction for a next configurable computation circuit.

Owner:MICRON TECH INC

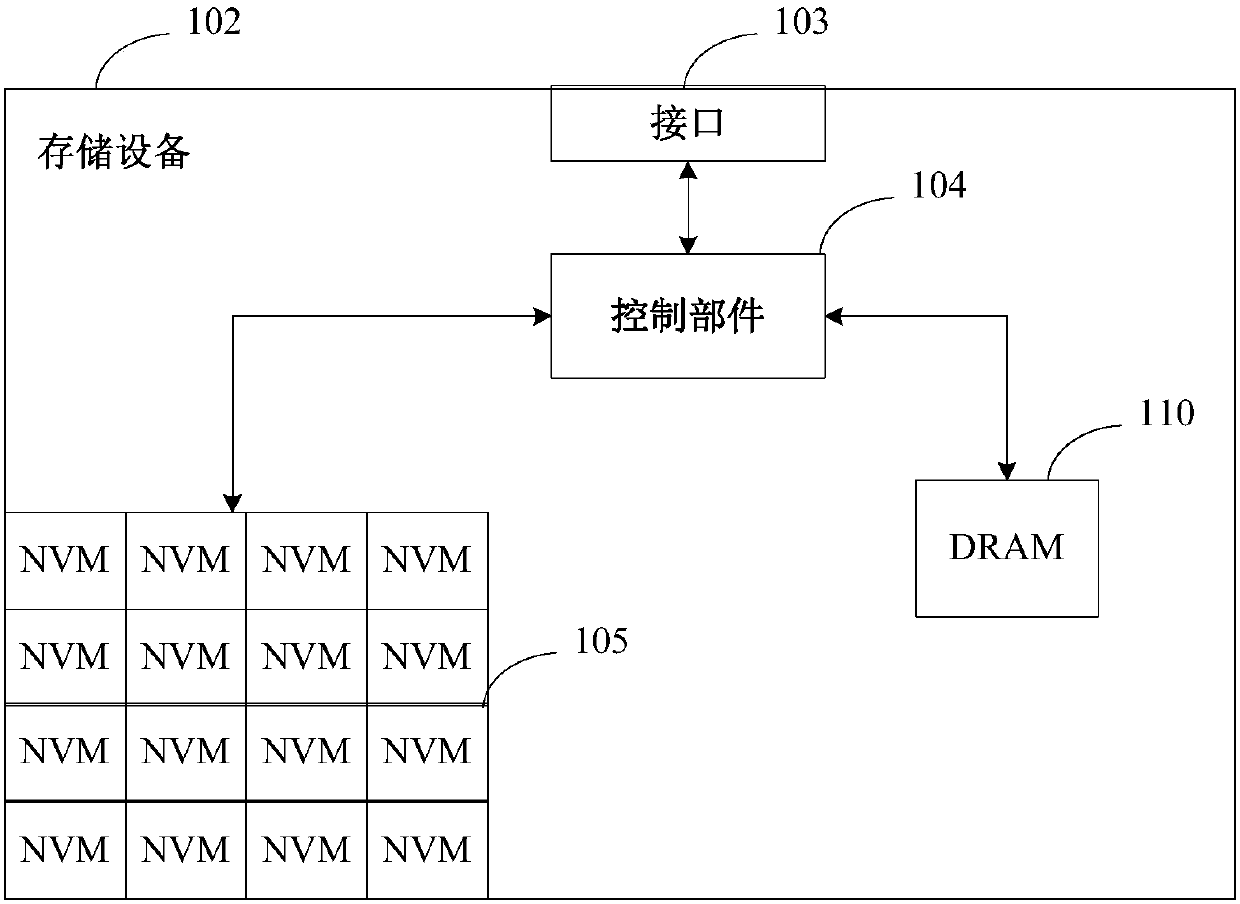

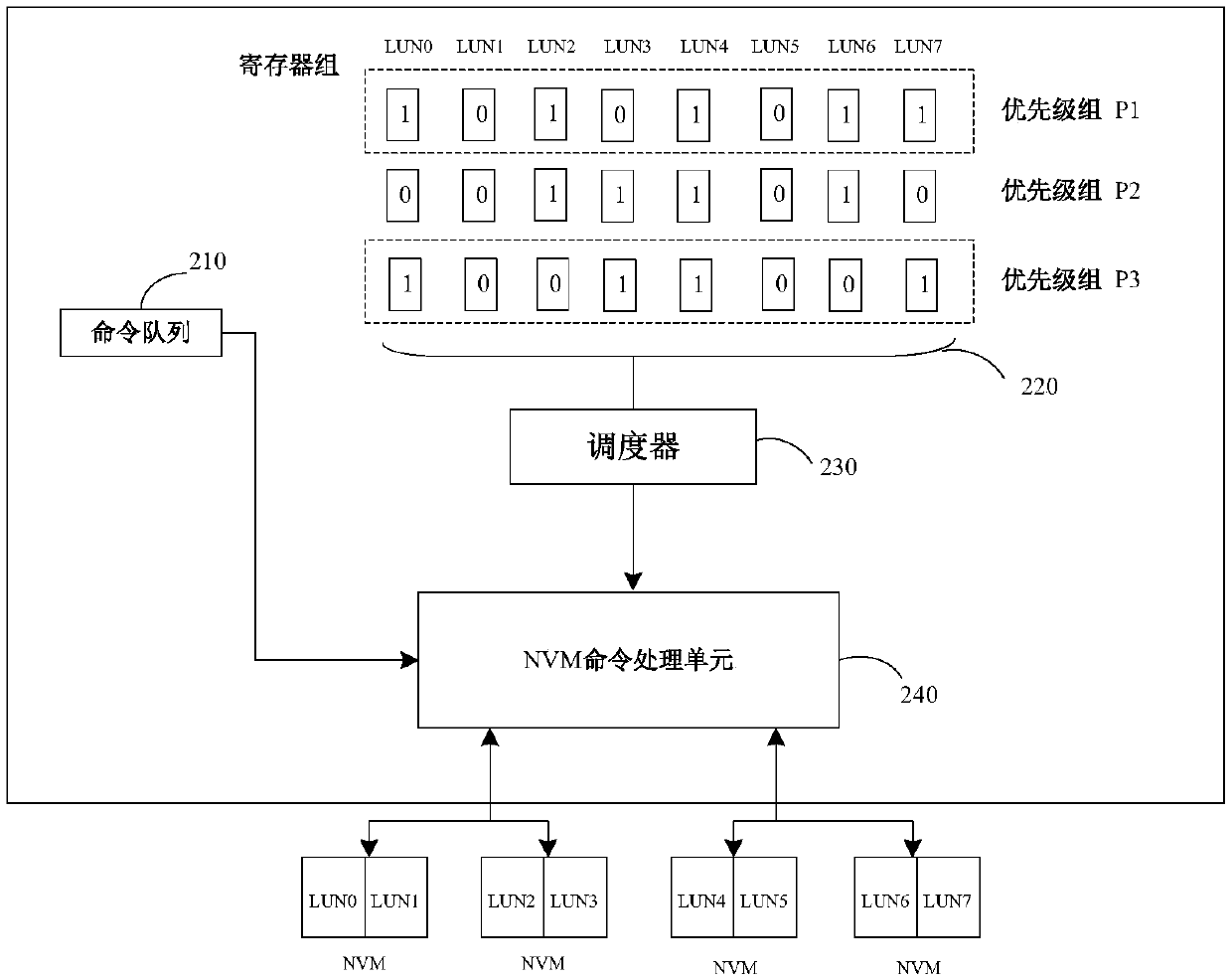

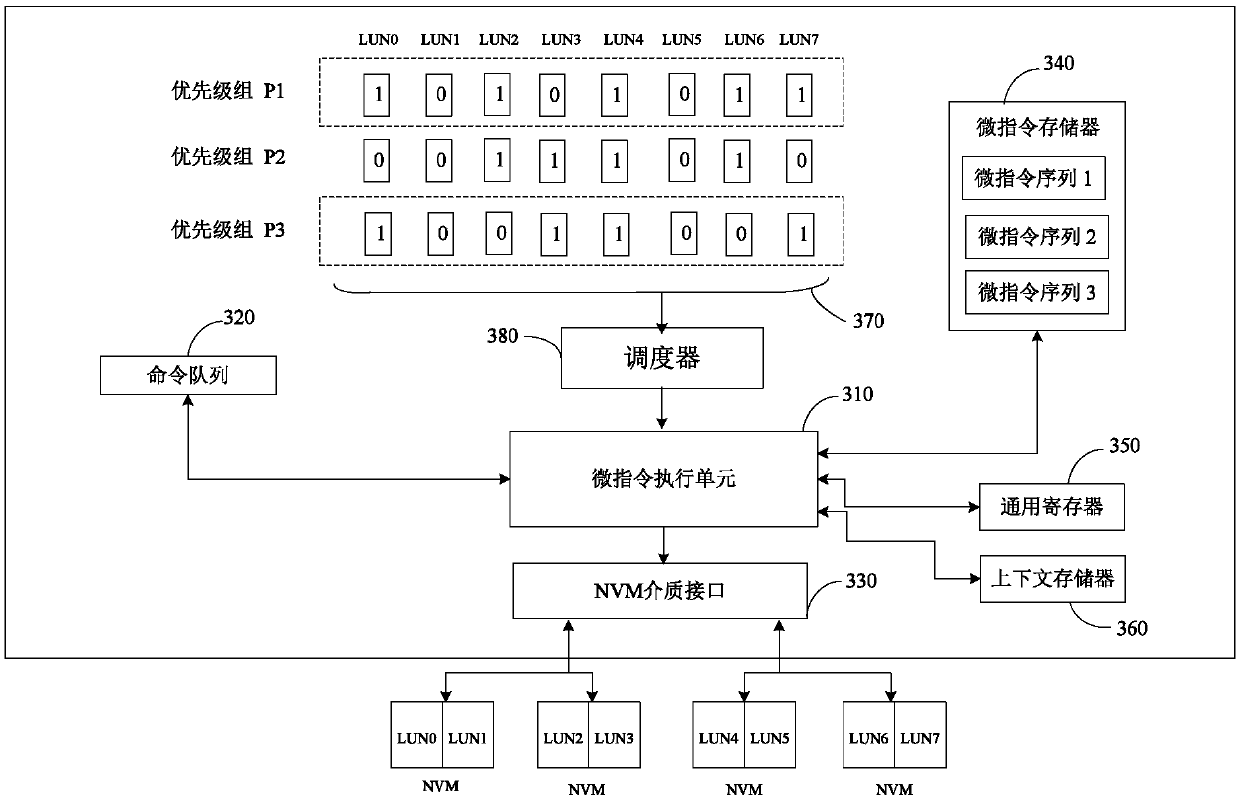

Scheduling method and device

PendingCN107870779AImprove scheduling efficiencyIncrease configuration flexibilityRegister arrangementsInstruction memoryComputer architecture

The invention discloses a scheduling method and device. The scheduling method comprises the following steps of: selecting a first register with a first value from a high-priority group of a register group, wherein the first register corresponds to a first to-be-processed event; and scheduling a first thread corresponding to the first register to process the first to-be-processed event. The scheduling device comprises a command queue, a micro instruction memory, a micro instruction execution unit, the register group, a scheduler and an NVM medium interface, wherein the register group is used for indicating to-be-processed events and priorities of the to-be-processed events; the scheduler is used for scheduling threads according to registers in the register group; and the micro instruction execution unit is used for receiving the indication of the scheduler and executing the scheduled threads.

Owner:BEIJING STARBLAZE TECH CO LTD

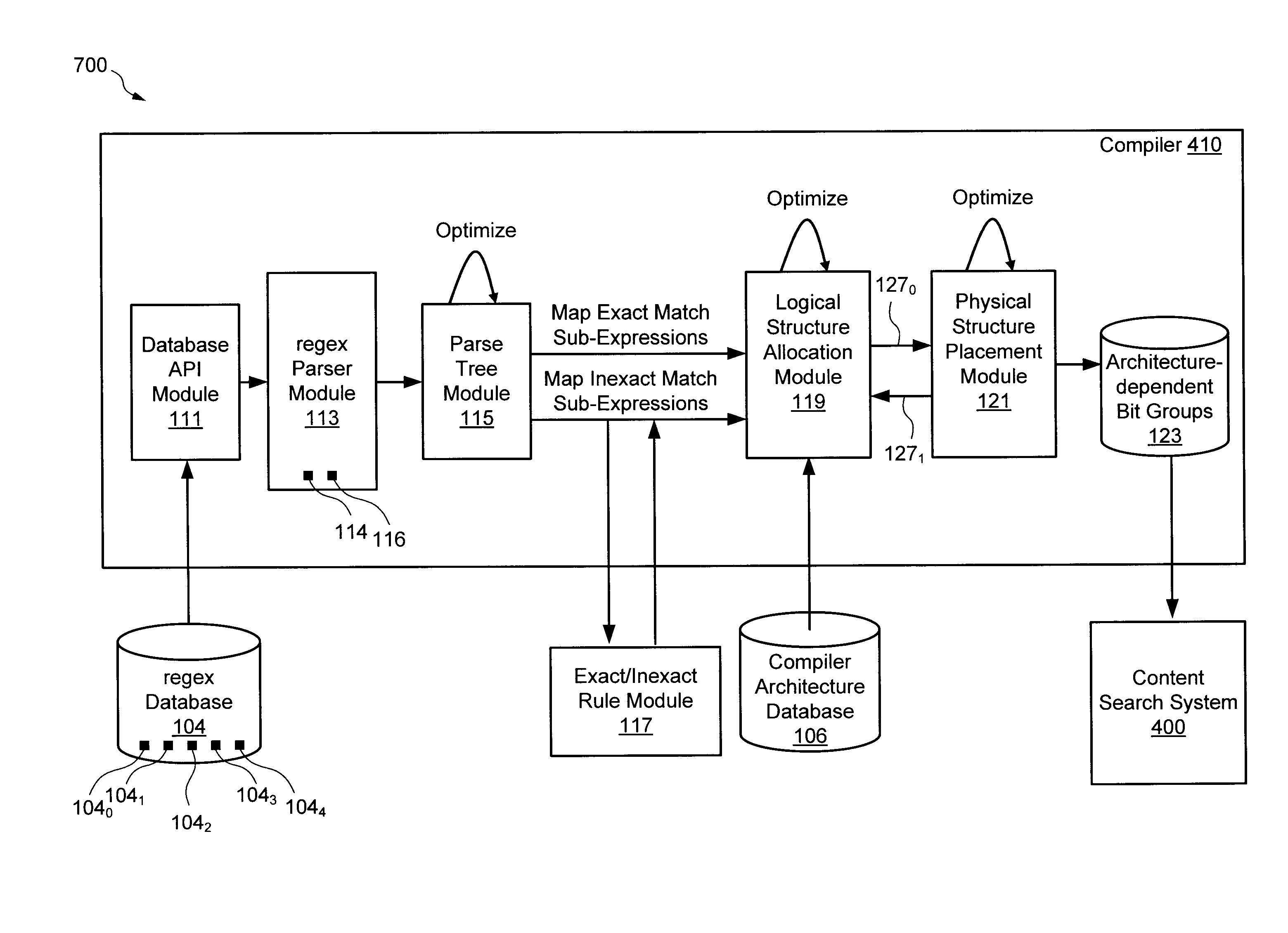

Compact instruction format for content search systems

A system and method are disclosed that compiles a sub-expression associated with an inexact pattern contained in a regular expression into a plurality of microprogram instructions that can be stored in contiguous locations of an instruction memory. At least one of the microprogram instructions includes a next instruction address and a fetch length value, where the next instruction address indicates the instruction memory address of the next instruction to be executed and the fetch length value indicates the number of sequentially-executed instructions that are to be fetched from contiguous locations of the instruction memory.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

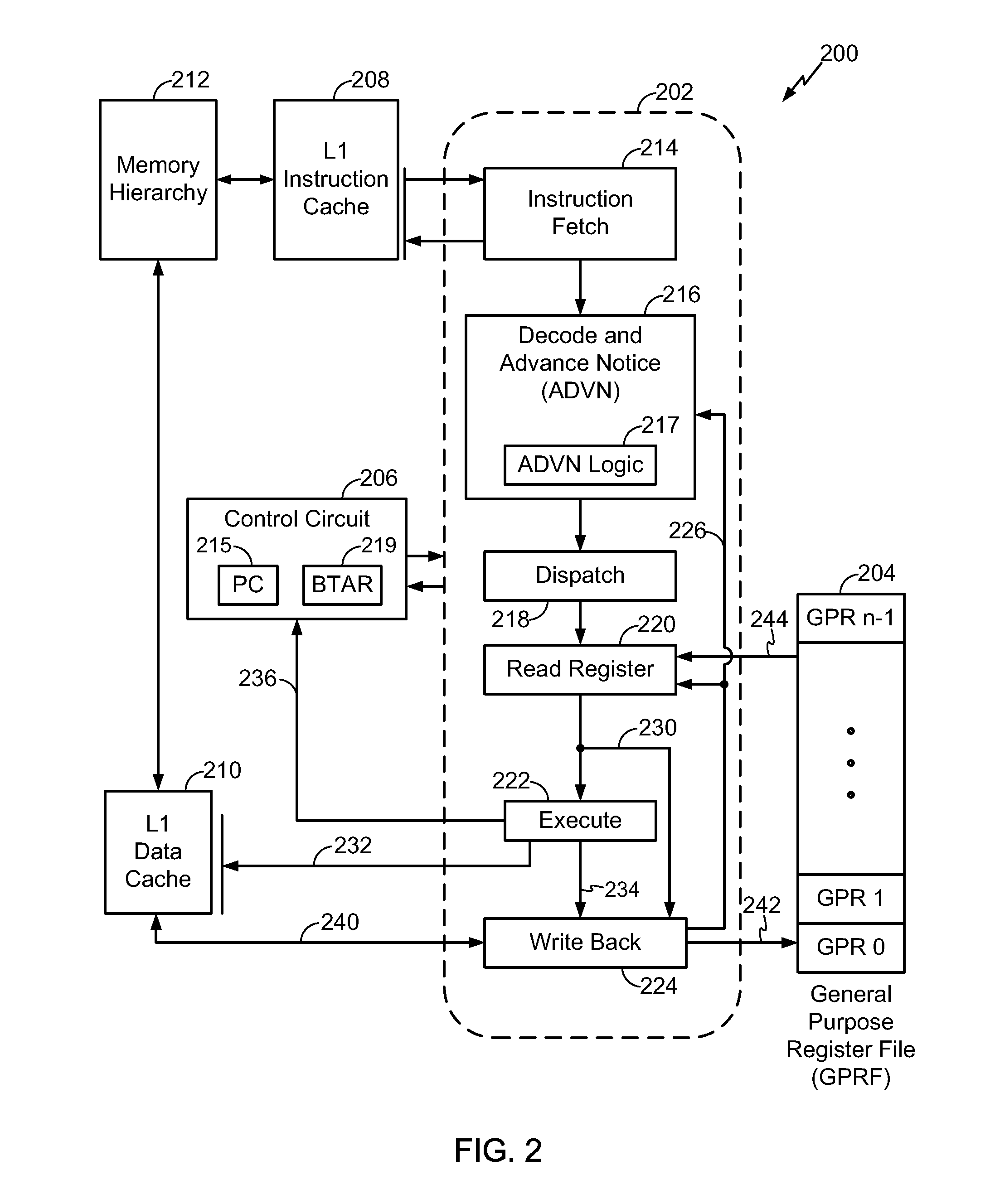

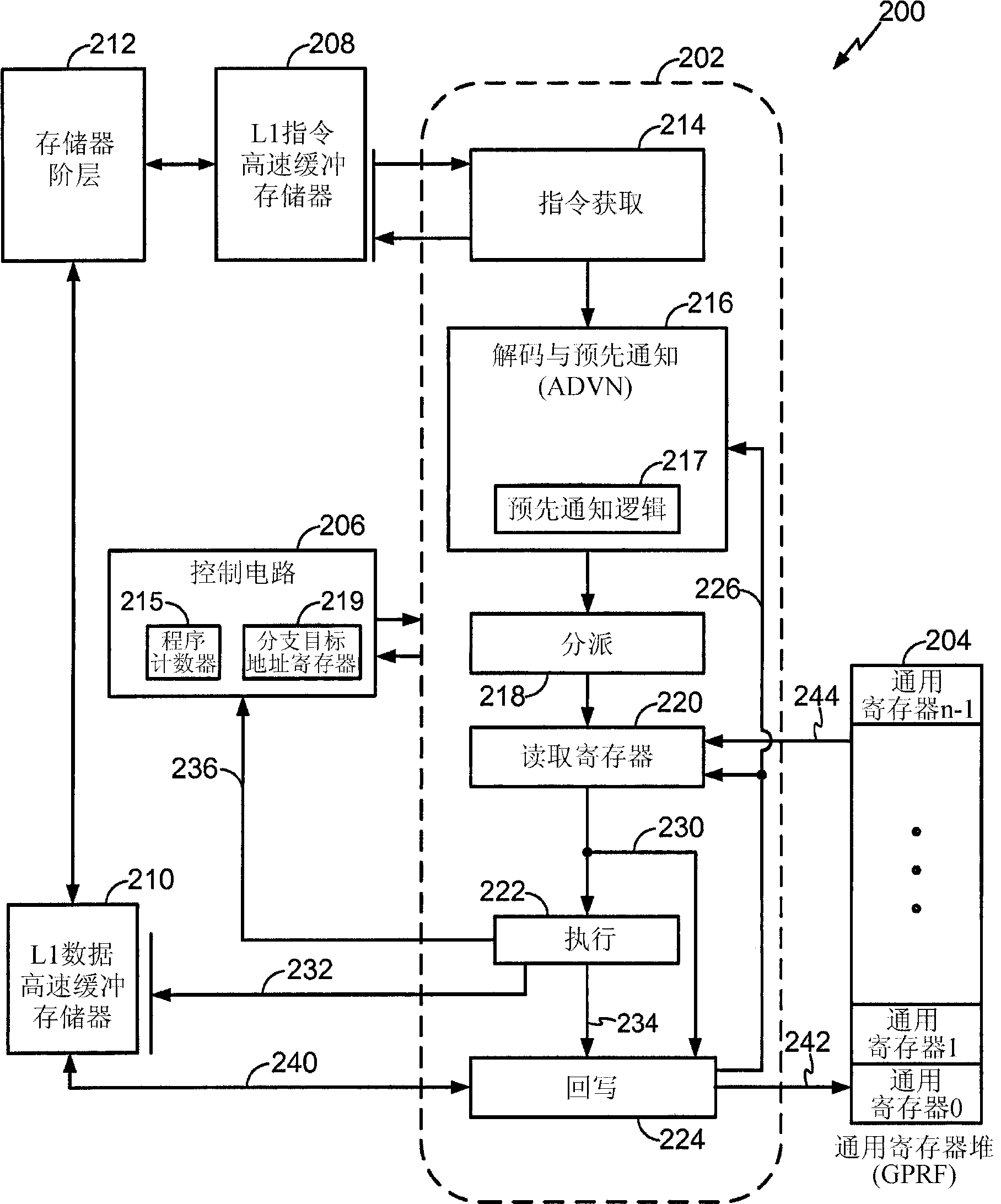

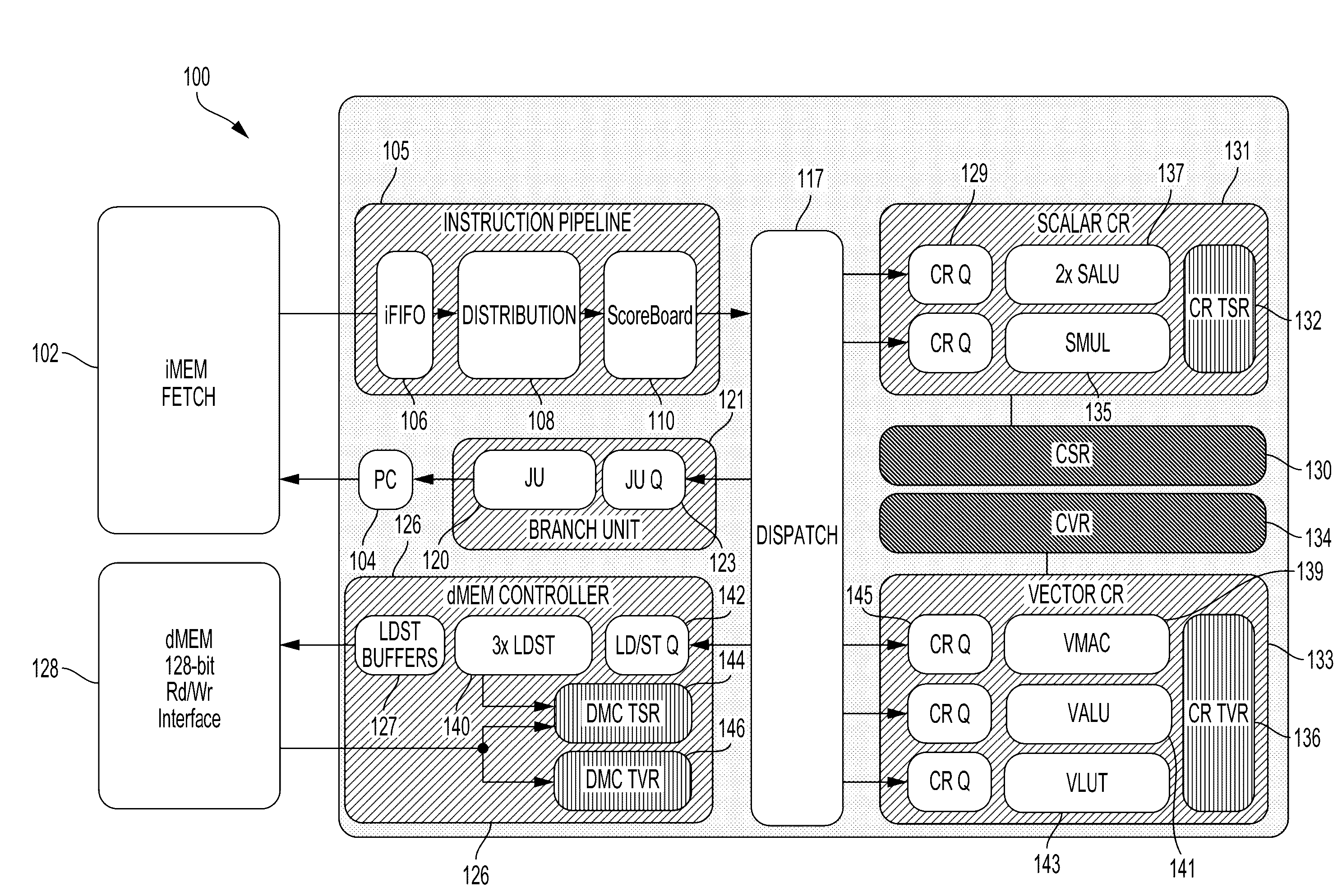

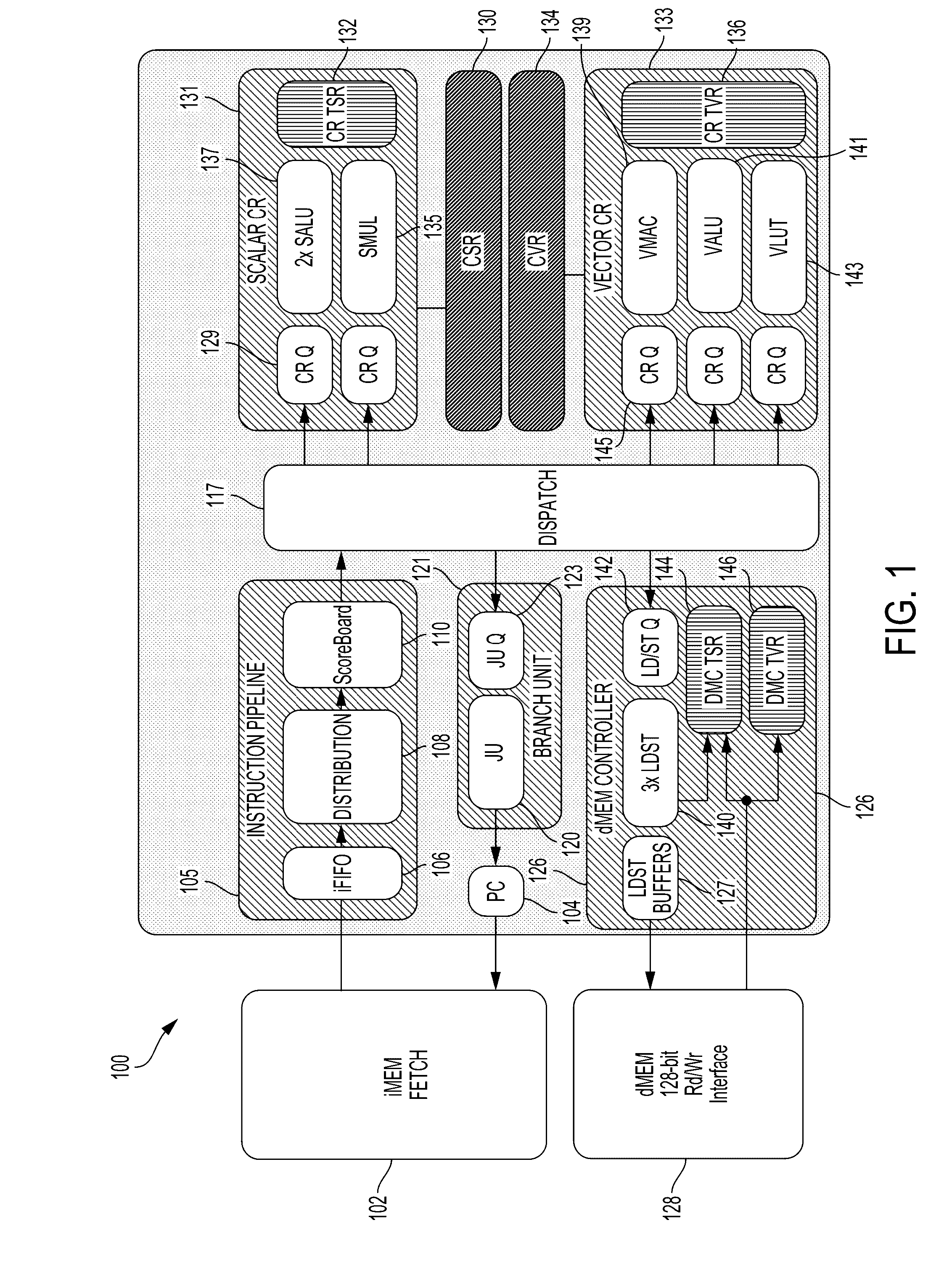

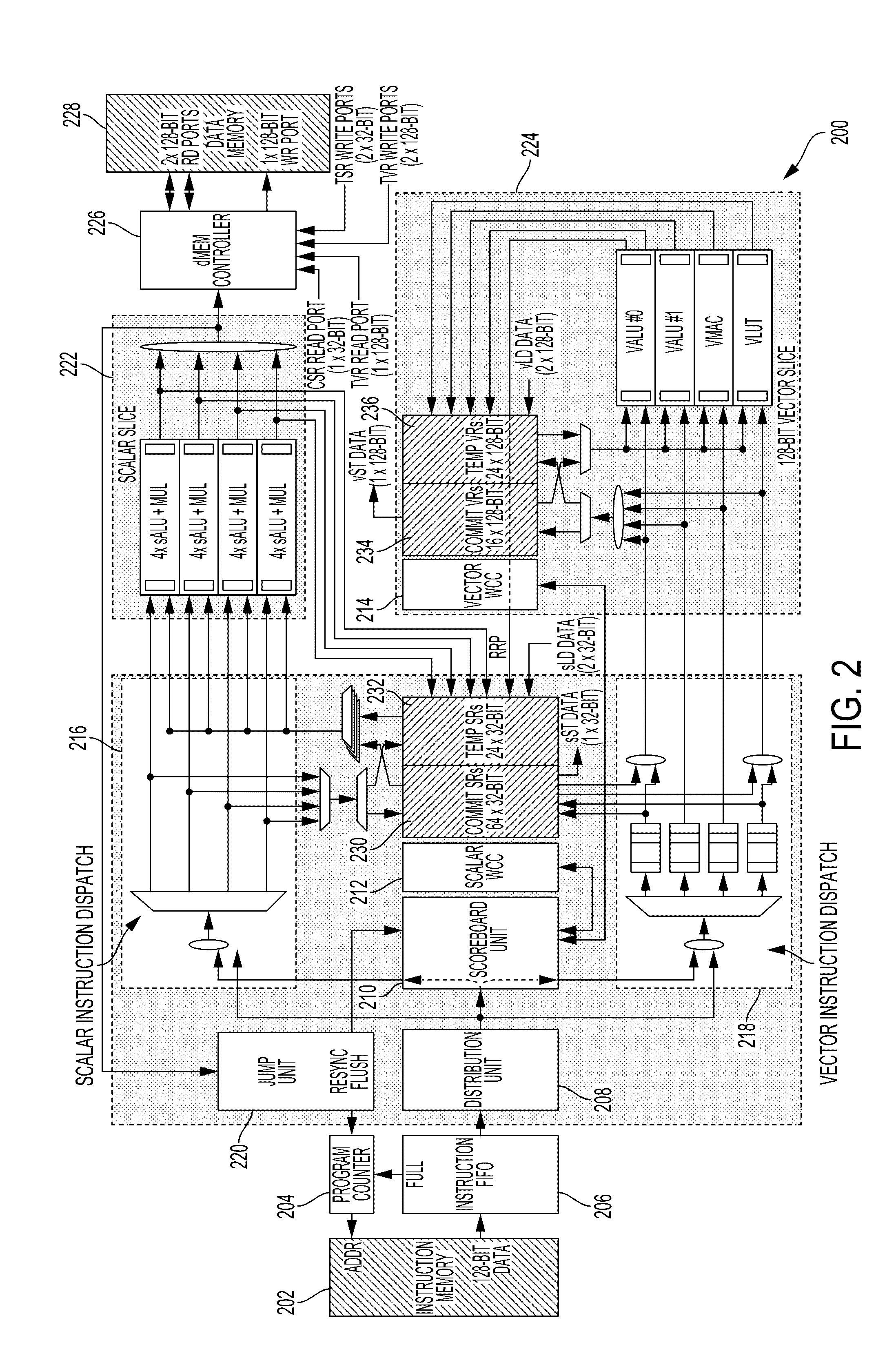

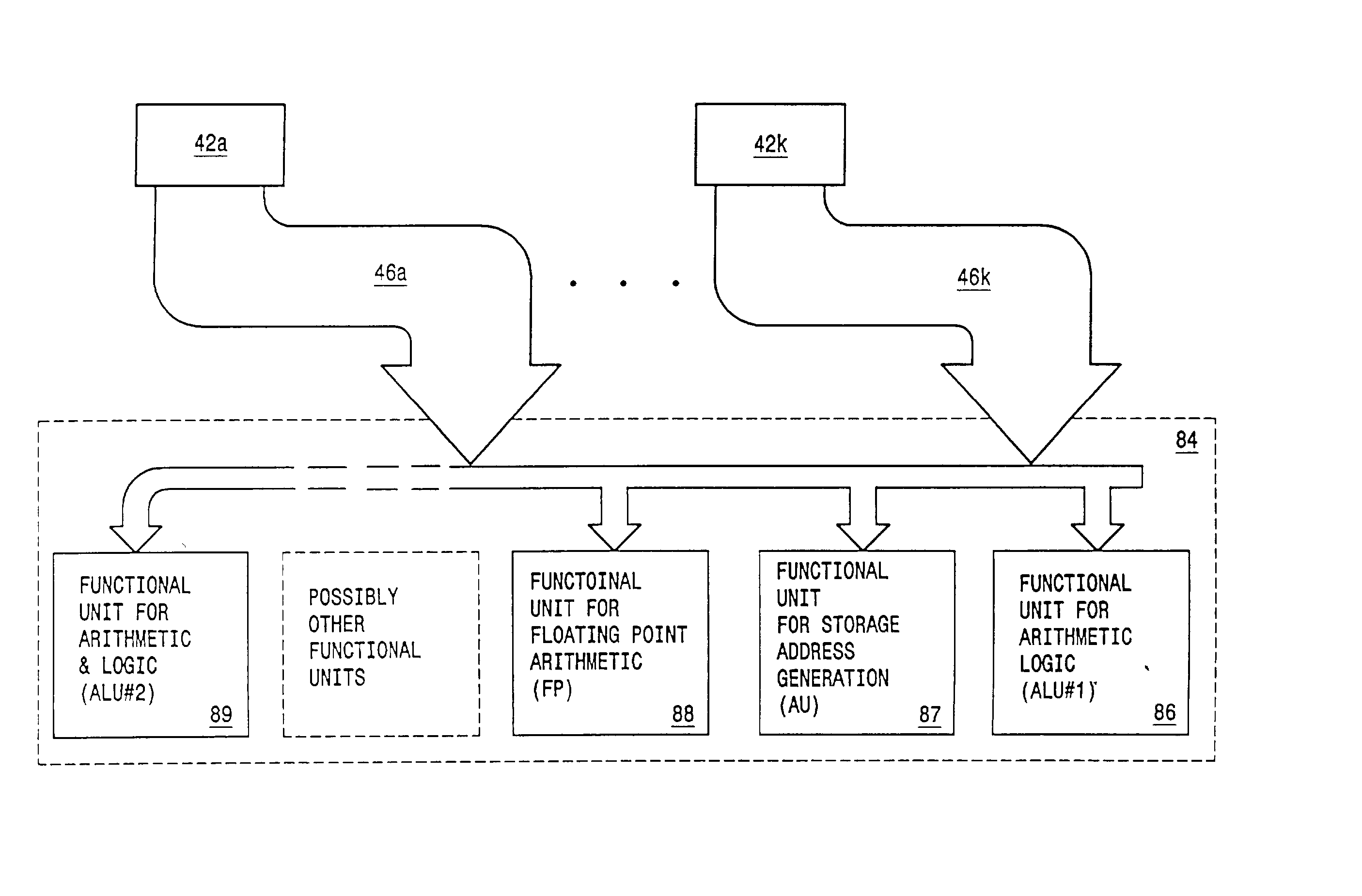

Device and processing architecture for instruction memory efficiency

Different processor architectures are described to evaluate and track dependencies required by instructions. The processors may hold or queue instructions that require output of other instructions until required data and resources are available which may remove the requirement of NOPs in the instruction memory to resolve dependencies and pipeline hazards. The processor may divide instruction data into bundles for parallel execution and provide speculative execution. The processor may include various components to implement an evaluation unit, execution unit and termination unit.

Owner:HUAWEI TECH CO LTD

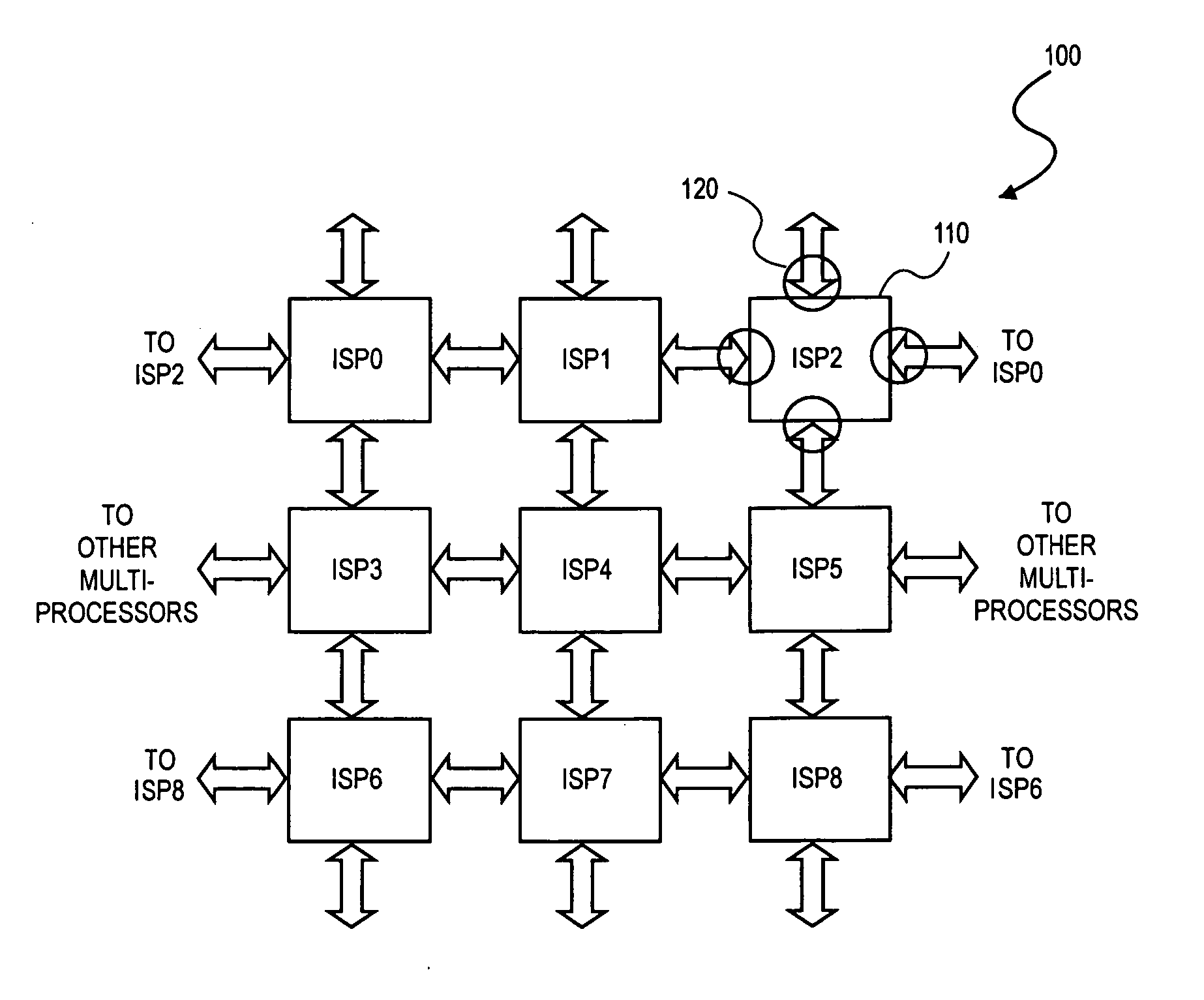

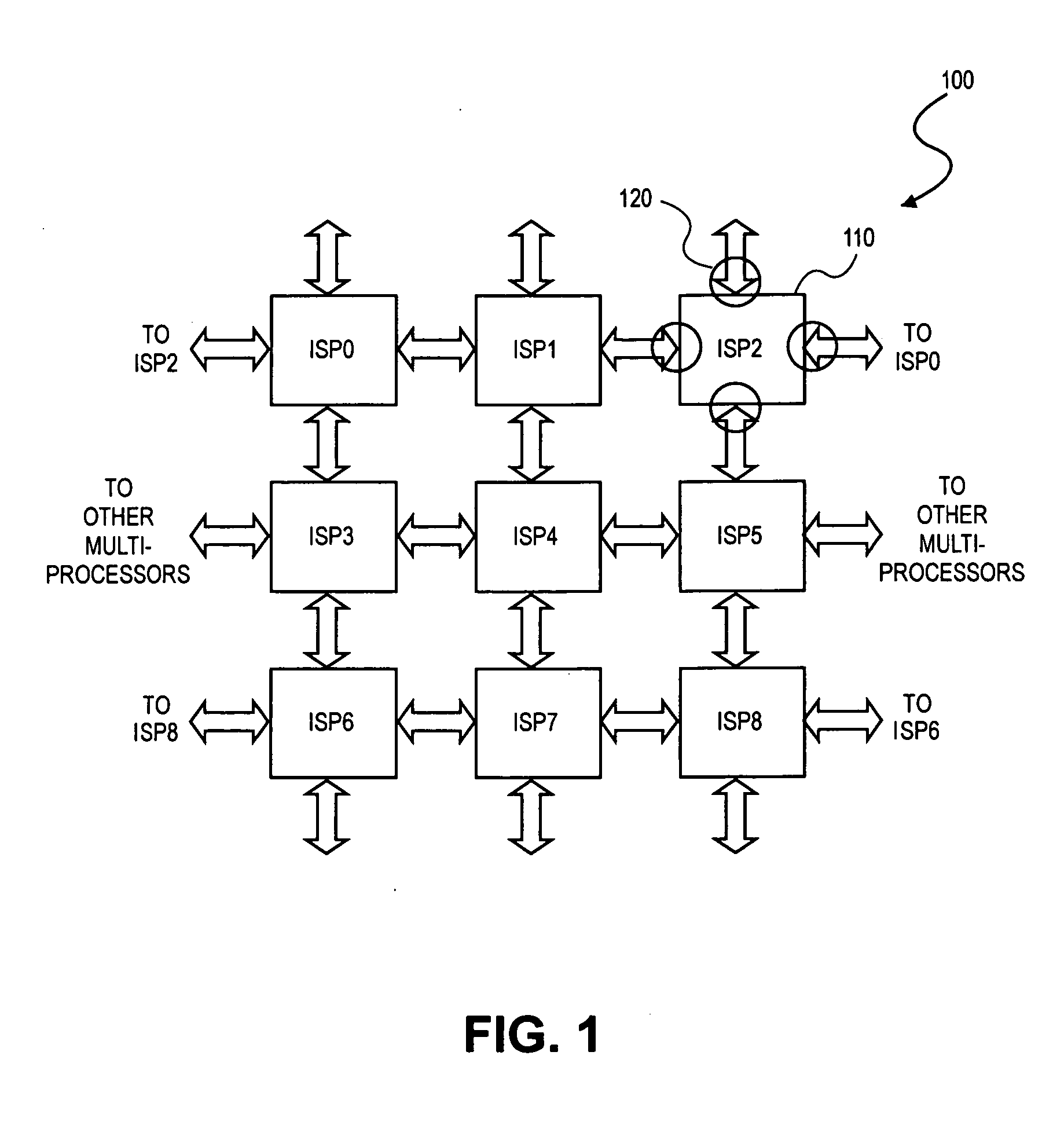

Method and apparatus for multiprocessor debug support

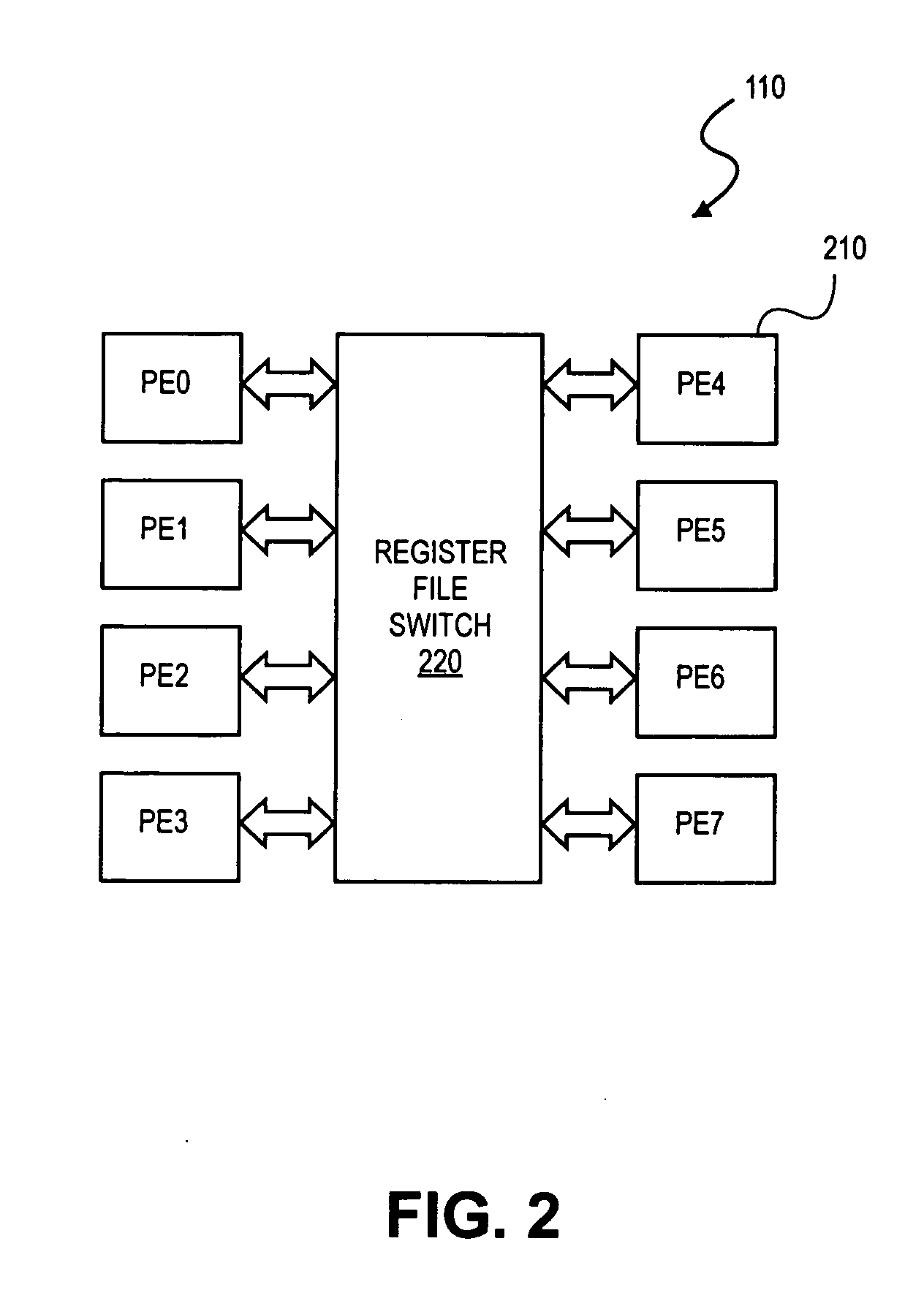

A device having at least one processor connected a controller and a memory; where the controller to execute a debug process. The debug process attaches a breakpoint bit field to each instruction. A system having image signal processors (ISPs), each ISP including processor elements (PEs). The ISPs include a debug instruction register connected to a first mux element. An instruction memory is connected to an instruction register. A decoder is connected to the instruction register. An execution unit is connected to the decoder. A debug executive unit is connected to the instruction memory, and a second mux element is connected to the execution unit and local registers. The decoder decodes a breakpoint bit field of each instruction.

Owner:INTEL CORP

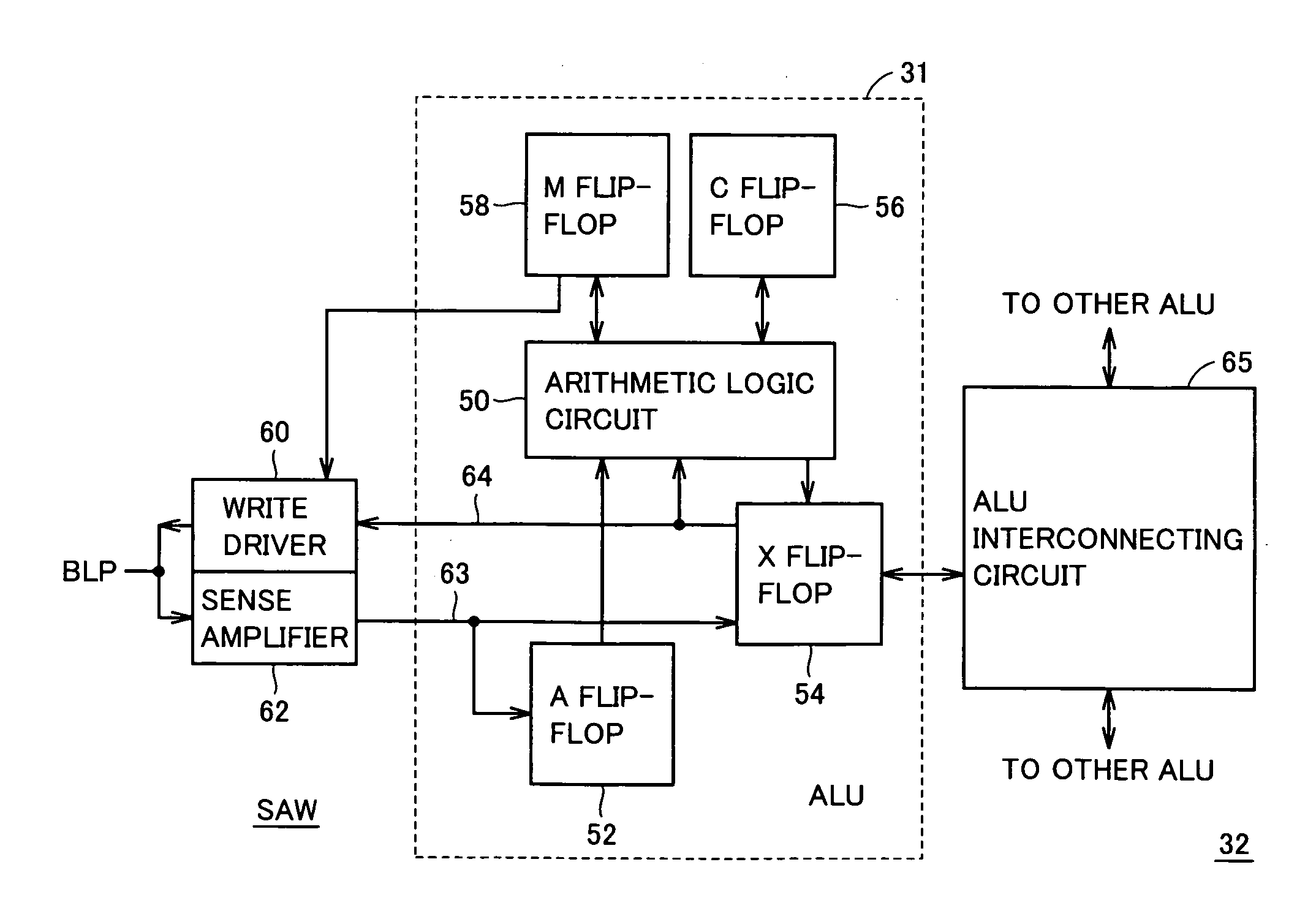

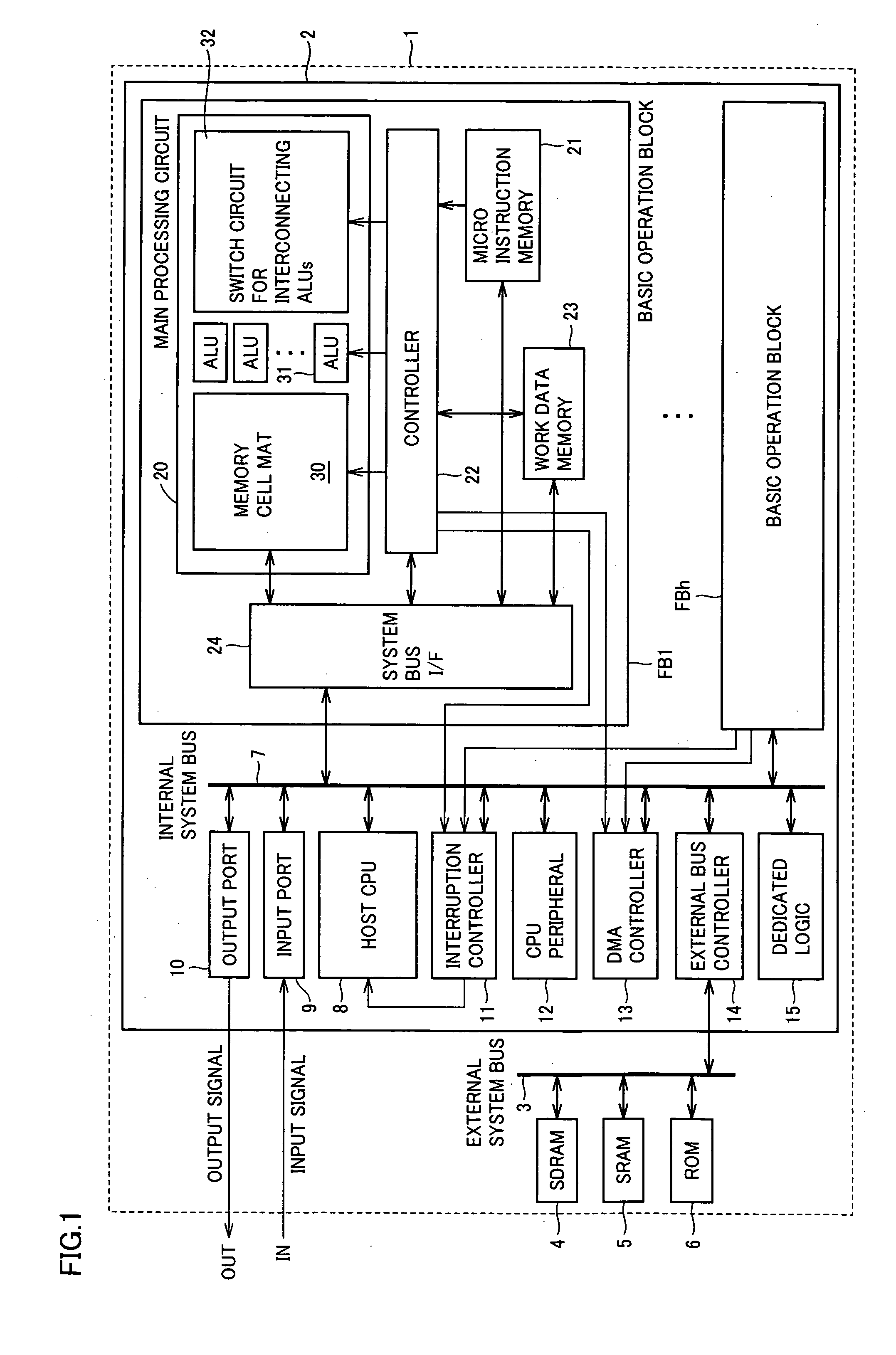

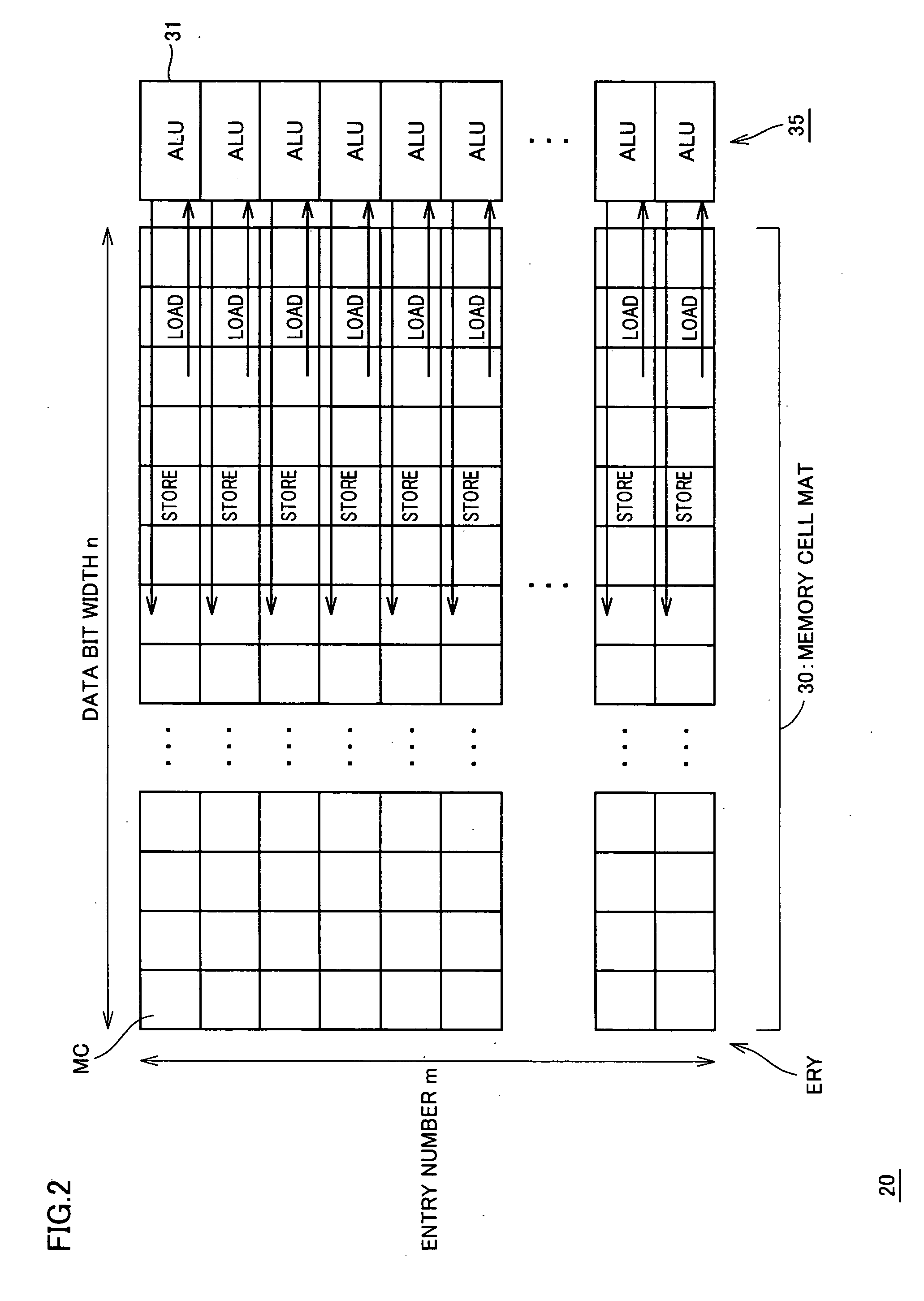

Semiconductor signal processing device

InactiveUS20060101231A1Increase speedBig amount of dataSingle instruction multiple data multiprocessorsSpecific program execution arrangementsInstruction memoryParallel computing

An instruction for an arithmetic / logic operation to a main processing circuit is stored in the form of a micro program in a micro instruction memory, and the operation of the main processing circuit is controlled in accordance with the micro program, under the control of a controller. In the main processing circuit, a memory mat is divided into entries each storing data of a plurality of bits, and for each entry, a processor (ALU) is arranged. Arithmetic / logic operations are performed entry-parallel and in bit-serial manner between each entry and the associated ALU. In accordance with the micro program control method, a large amount of data can be processed efficiently. Thus, a processing device that efficiently performs an arithmetic / logic operation on a large amount of data at high speed is provided.

Owner:RENESAS TECH CORP

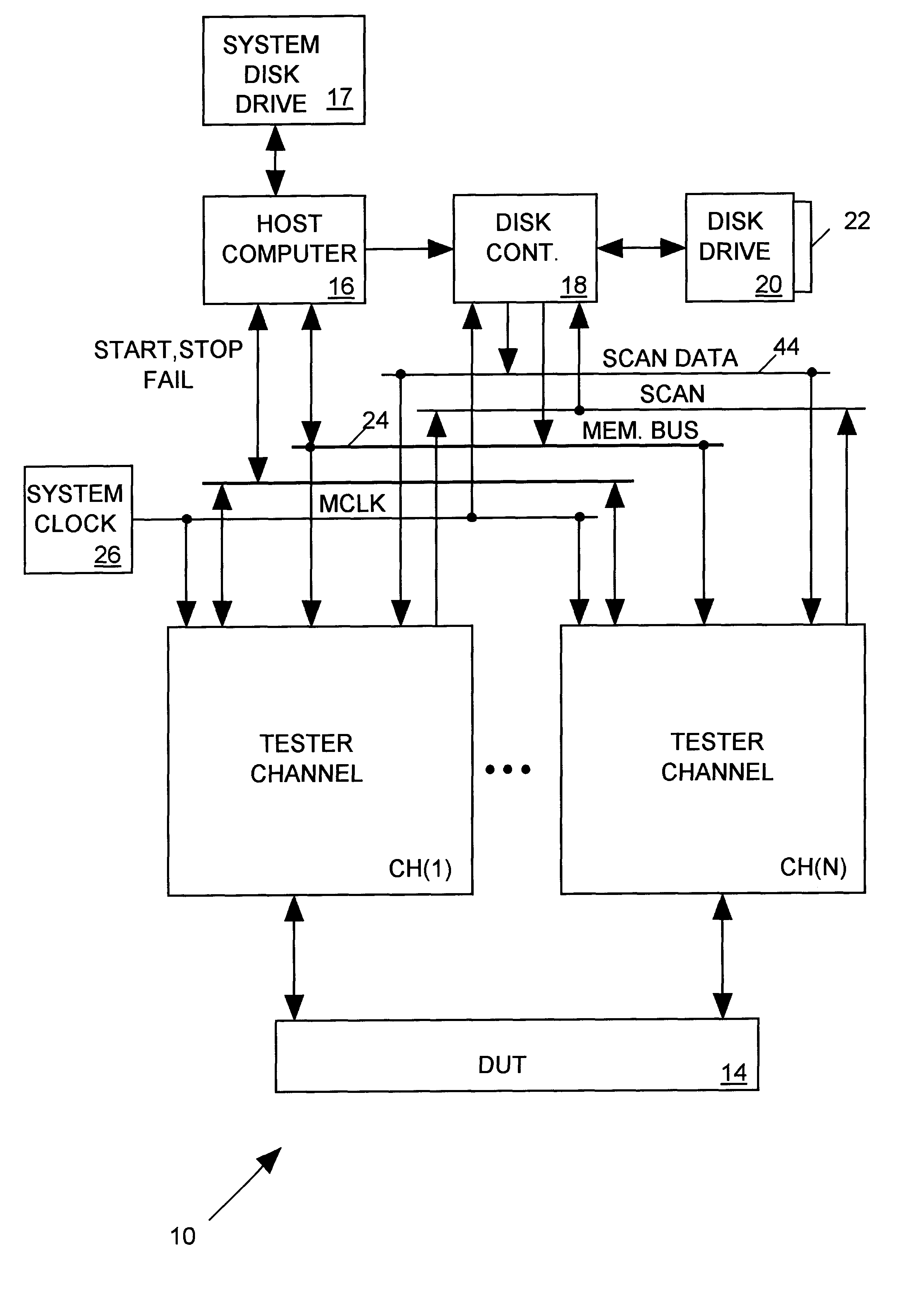

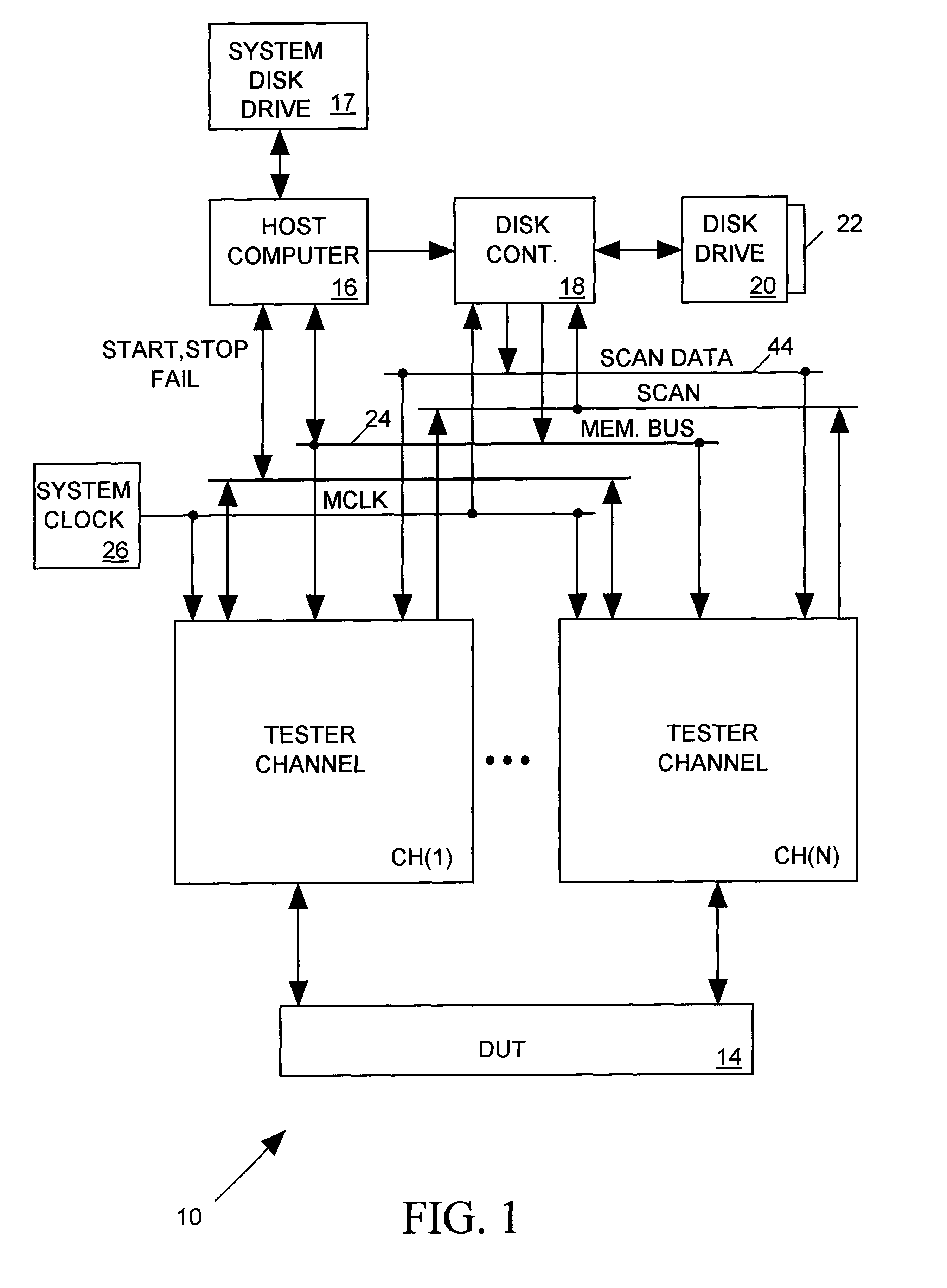

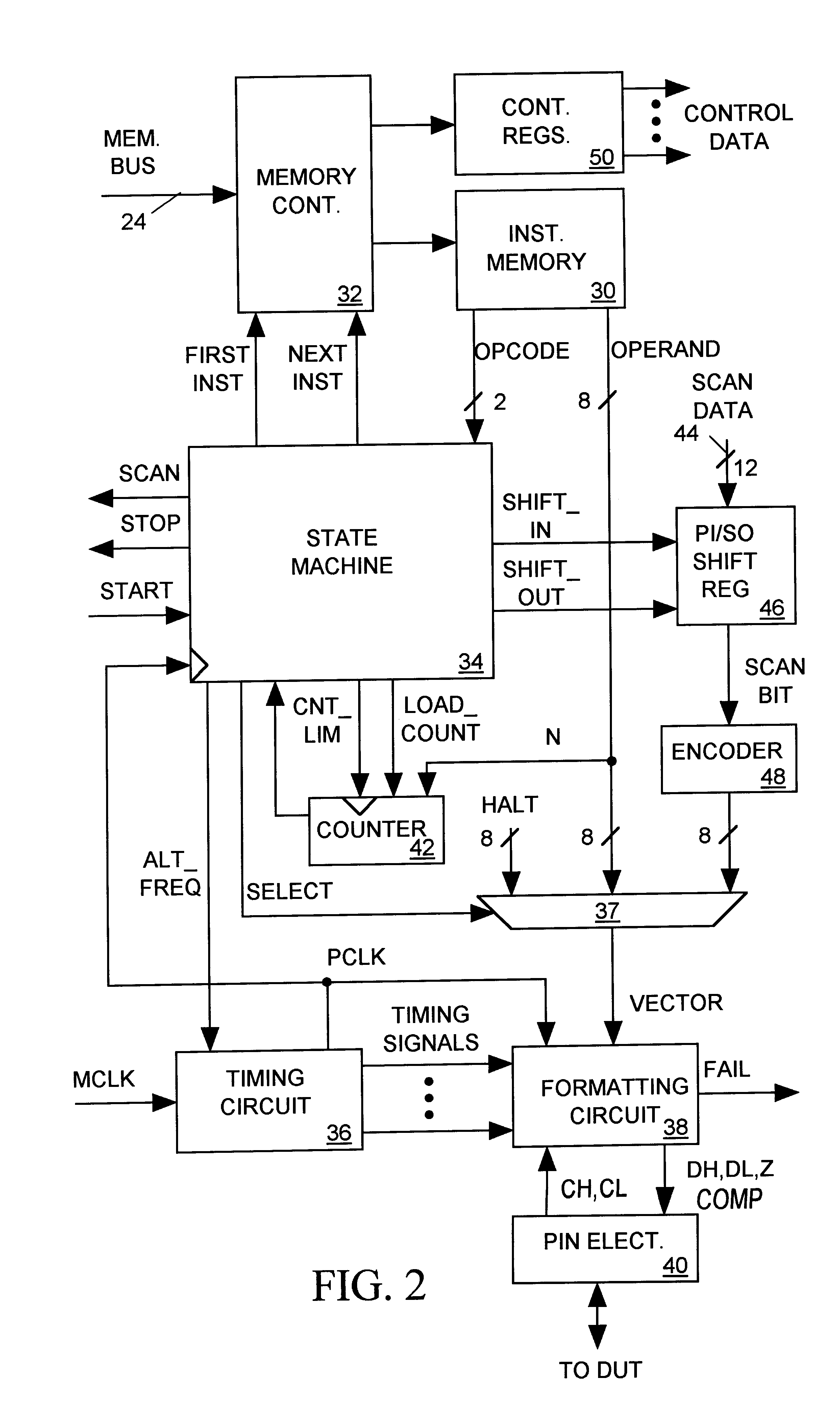

Integrated circuit tester with disk-based data streaming

InactiveUS6181151B1Digital circuit testingDetecting faulty computer hardwareInstruction memoryData stream

An integrated circuit (IC) tester includes set of tester channels, each for carrying out a test activity at a separate terminal of an IC device under test (DUT) during each cycle of a test. The tester also includes a disk drive having a removable disk for reading out scan or programming data to the tester channels during a test. Each tester channel includes an instruction memory for storing a set of instructions, and each tester channel executes its stored instructions during the test. Some of the instructions include VECTOR data directly indicating a particular test activity the tester channel is to carry out at a DUT terminal during a next test cycle. Others of the instructions tell the tester channel to acquire a particular number (N) of serial data bits as they are read out of the disk drive and to carry out an activity during each of the next N test cycles indicated by a state of a corresponding one of the N serial data bits.

Owner:CREDENCE SYSTEMS

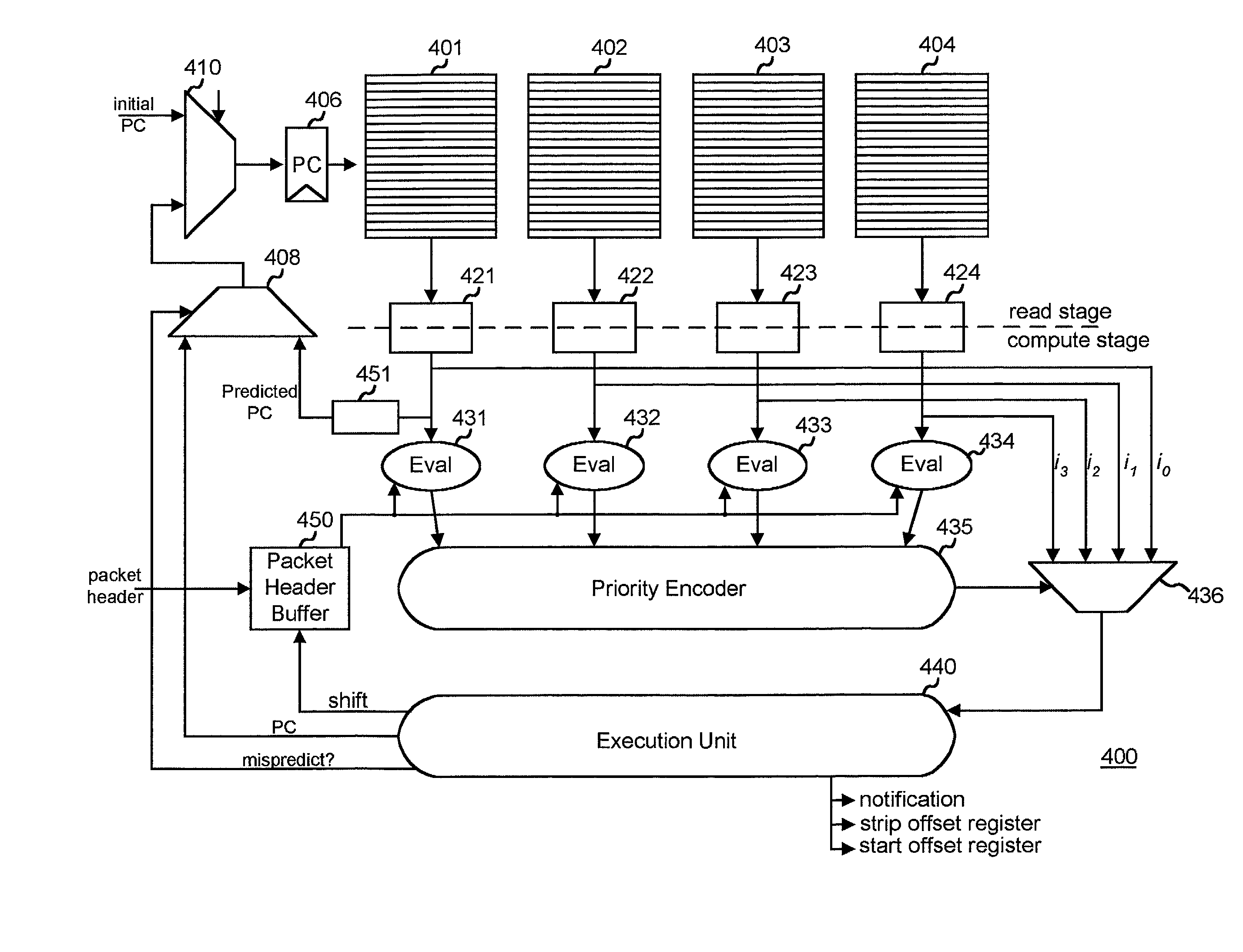

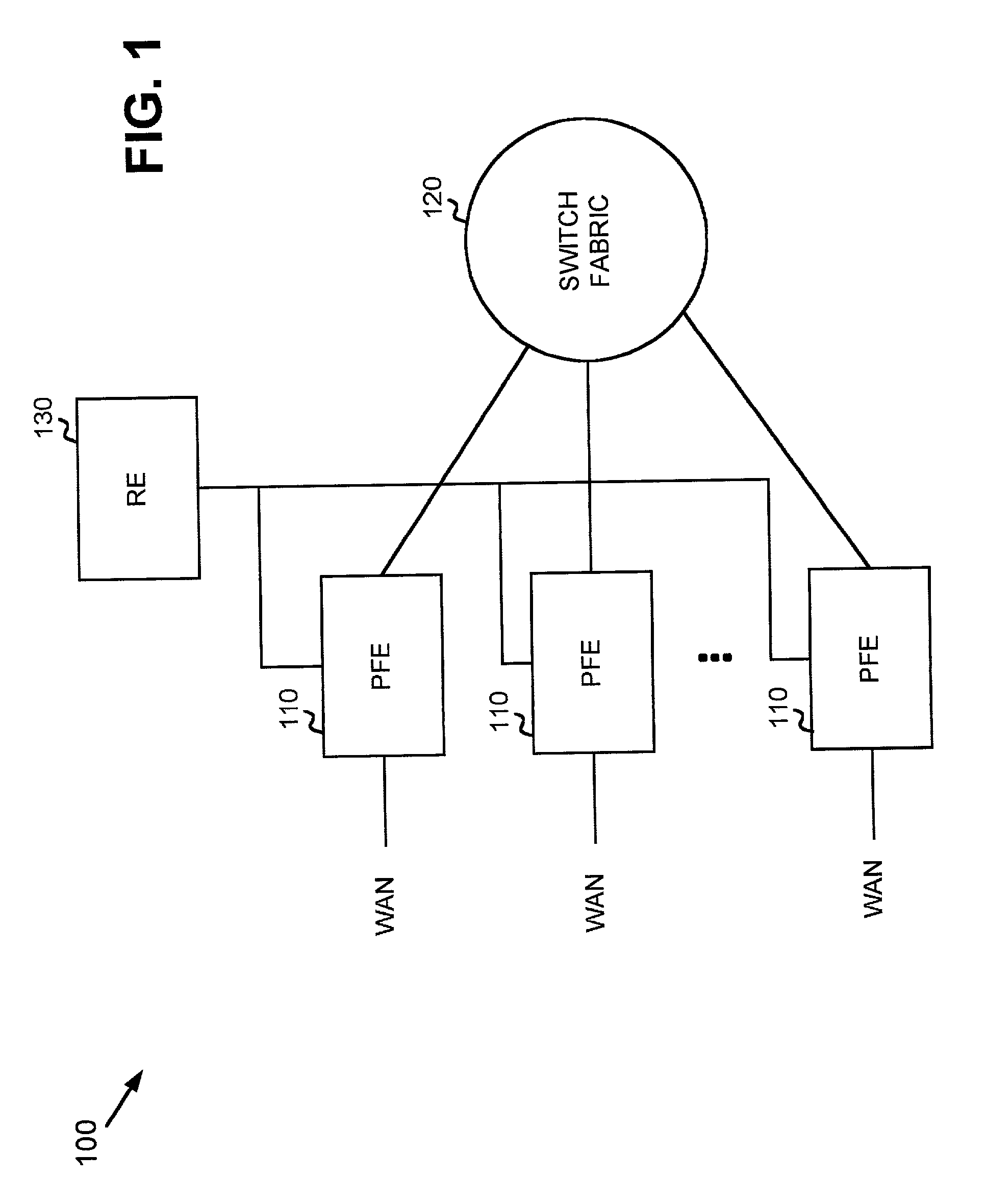

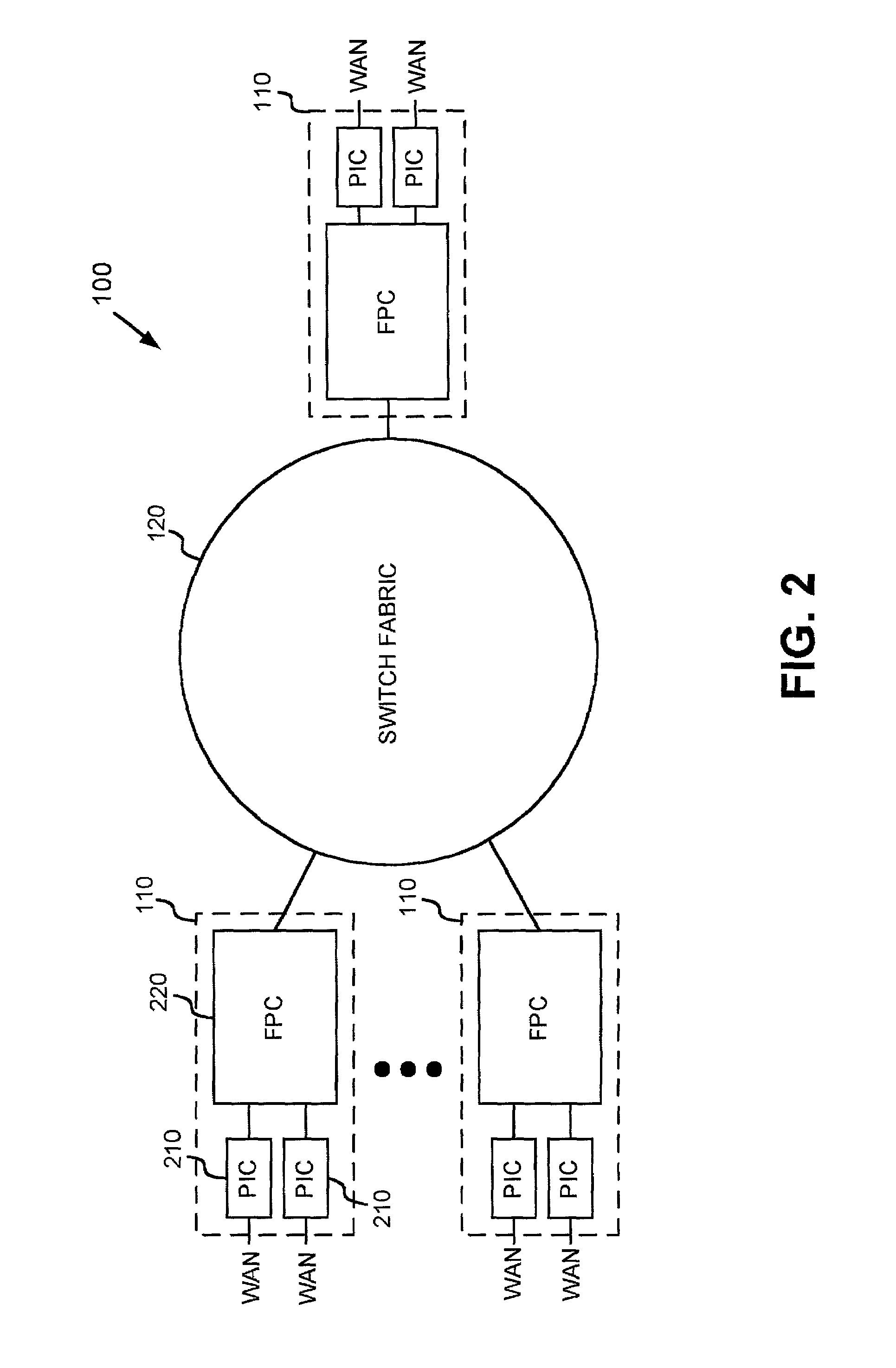

Pipelined processor for examining packet header information

A packet processing engine includes multiple microcode instruction memories implemented in parallel. For each cycle of the pipeline, an instruction from each of the memories is retrieved based on a program counter. One of the instructions is selected by a priority encoder that operates on true / false signals generated based on the instructions. The selected instruction is executed to thereby perform the packet processing operations specified by the instruction.

Owner:JUMIPER NETWORKS INC

Spawn-join instruction set architecture for providing explicit multithreading

InactiveUS20030088756A1Program initiation/switchingGeneral purpose stored program computerInstruction memoryFrequency spectrum

The invention presents a unique computational paradigm that provides the tools to take advantage of the parallelism inherent in parallel algorithms to the full spectrum from algorithms through architecture to implementation. The invention provides a new processing architecture that extends the standard instruction set of the conventional uniprocessor architecture. The architecture used to implement this new computational paradigm includes a thread control unit (34), a spawn control unit (38), and an enabled instruction memory (50). The architecture initiates multiple threads and executes them in parallel. Control of the threads is provided such that the threads may be suspended or allowed to execute each at its own pace.

Owner:VISHKIN UZI Y