Patents

Literature

524 results about "Circular buffer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A circular buffer, circular queue, cyclic buffer or ring buffer is a data structure that uses a single, fixed-size buffer as if it were connected end-to-end. This structure lends itself easily to buffering data streams.

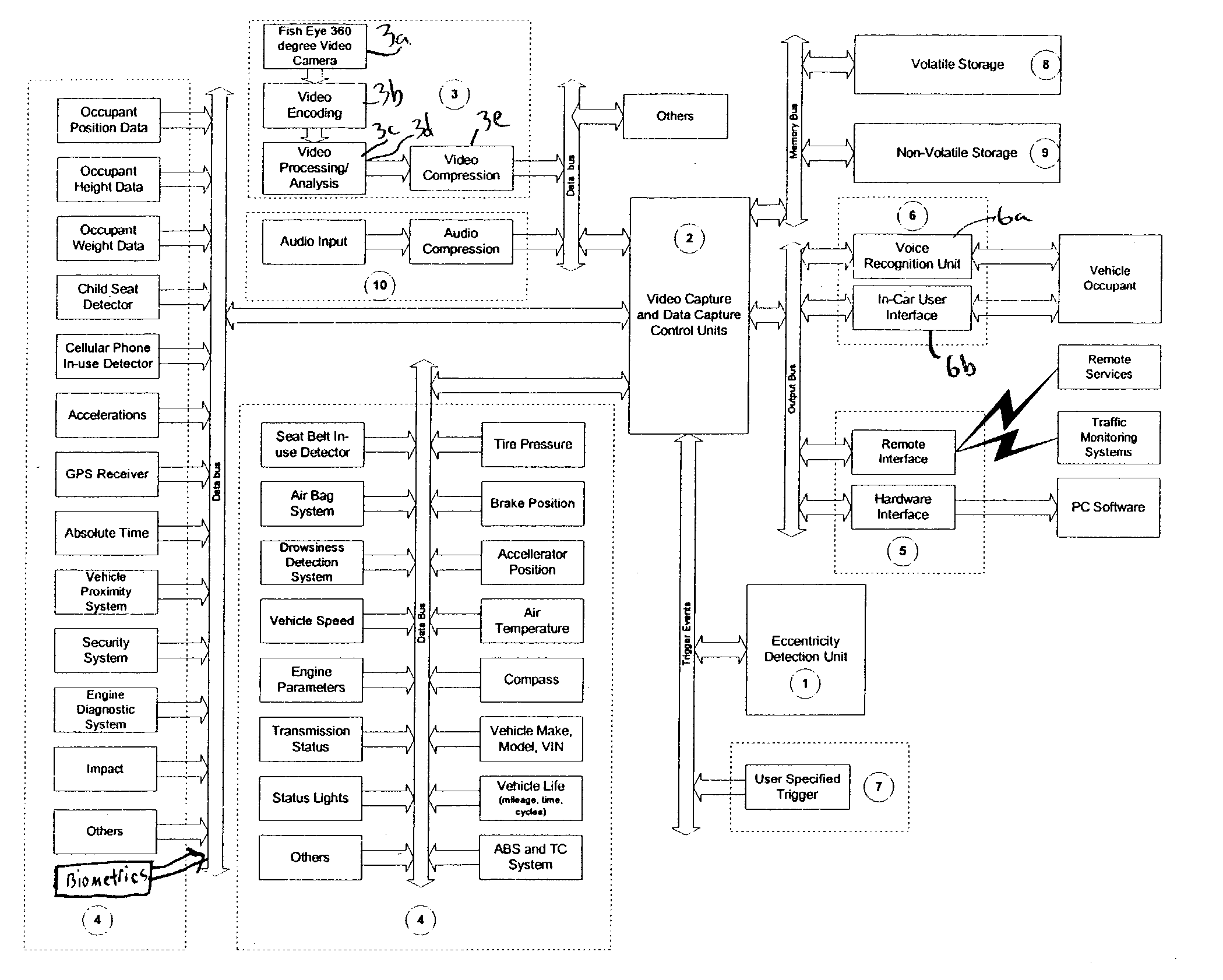

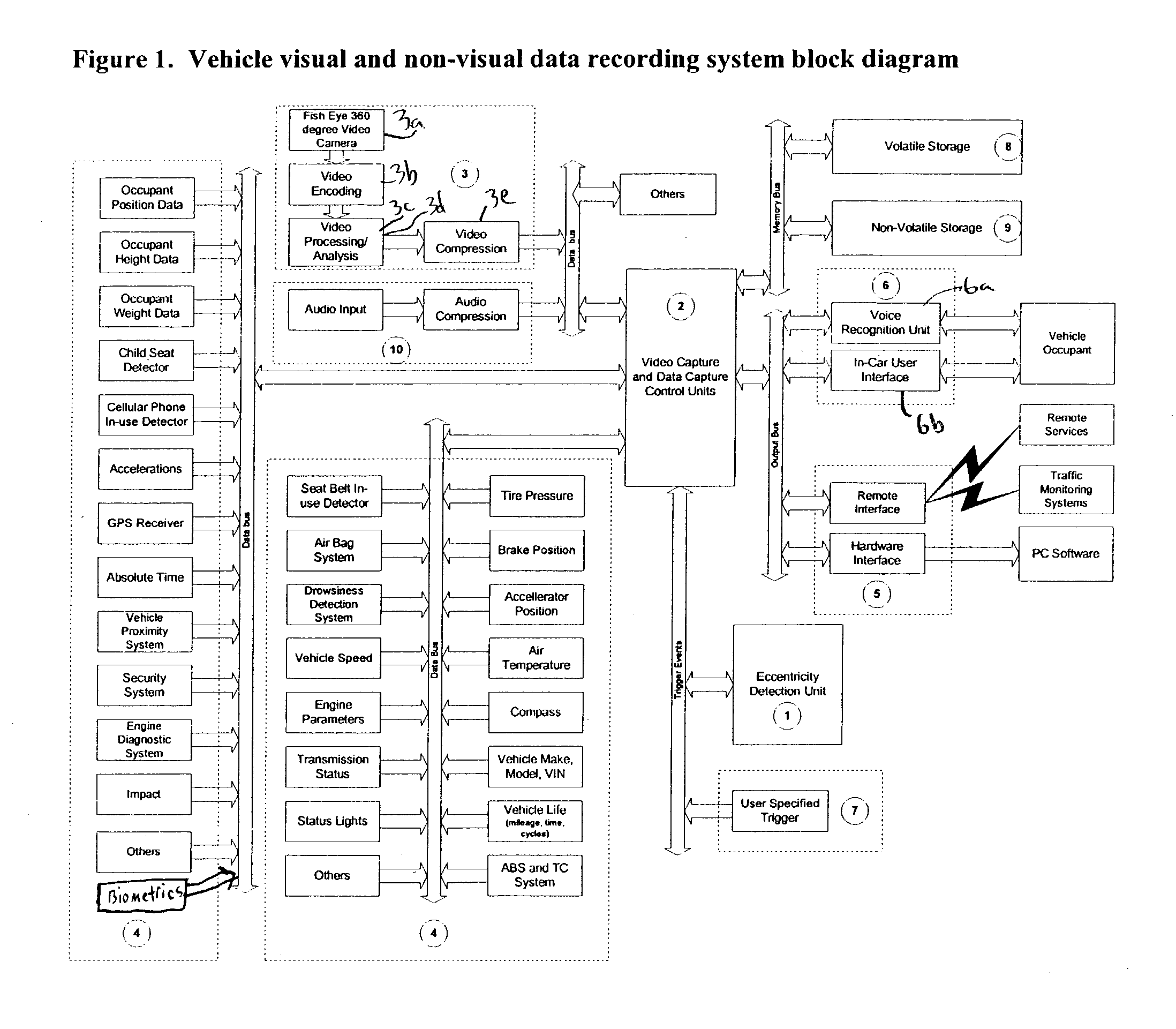

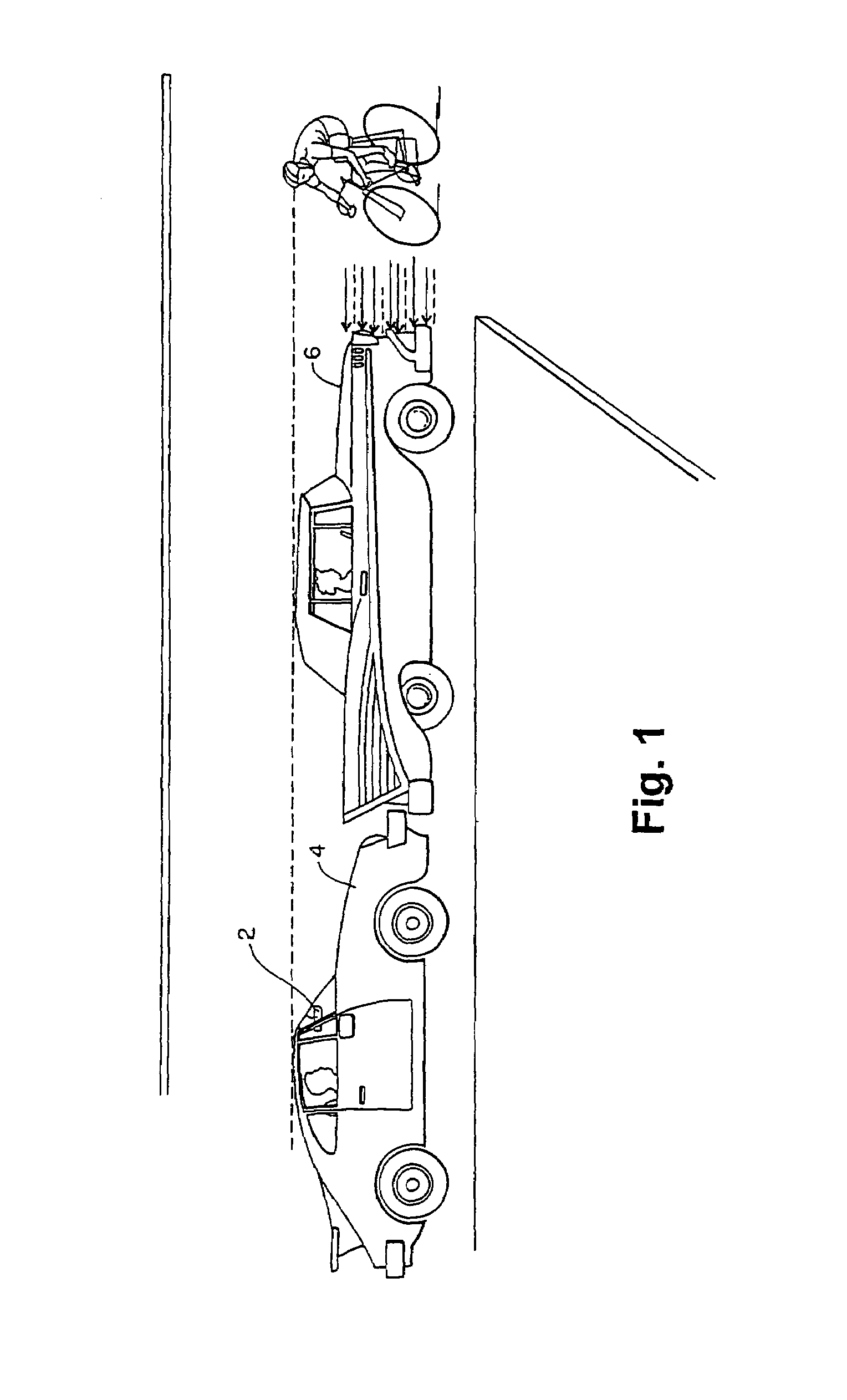

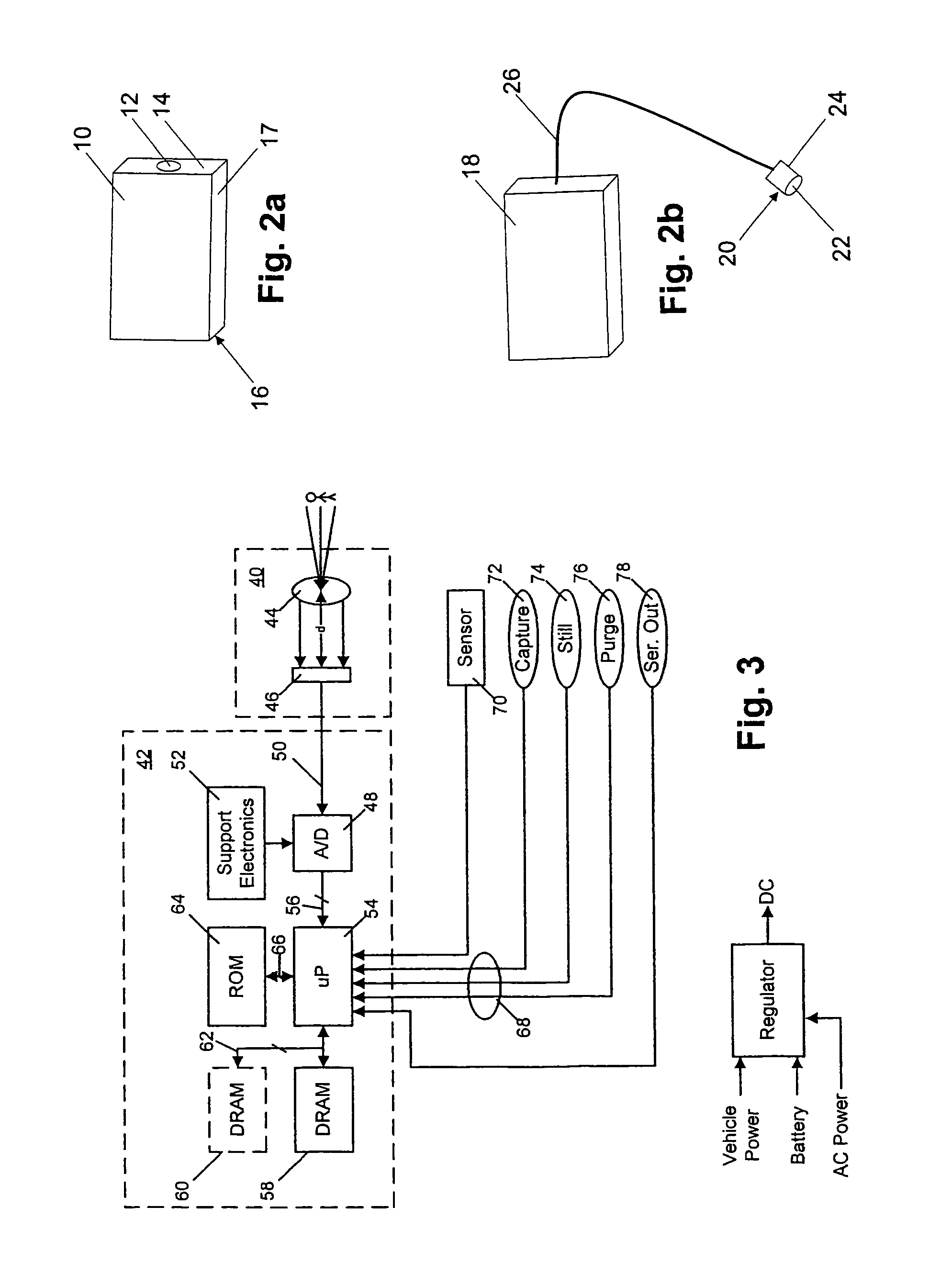

Vehicle visual and non-visual data recording system

ActiveUS7386376B2Vehicle testingRegistering/indicating working of vehiclesData synchronizationDriver/operator

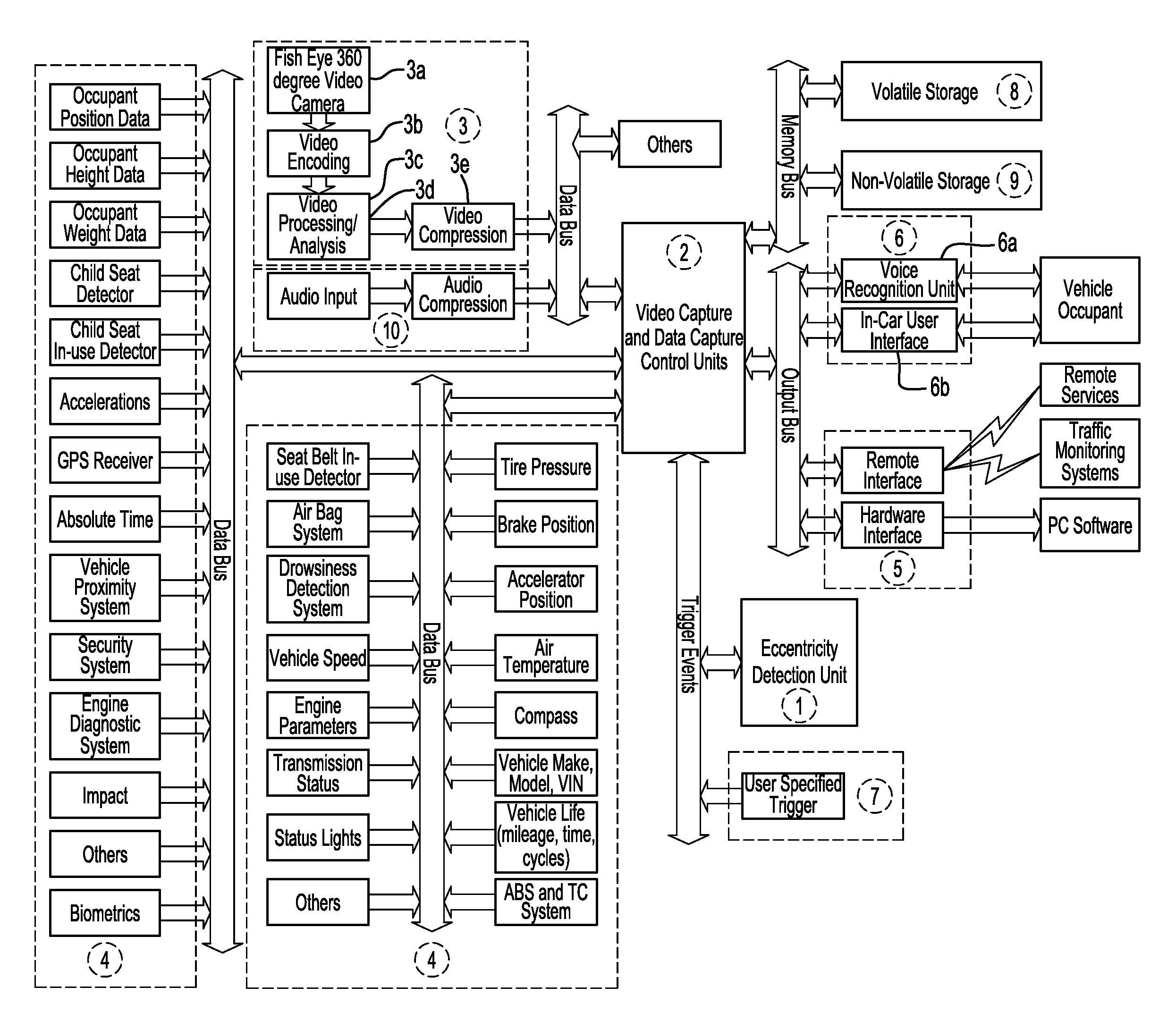

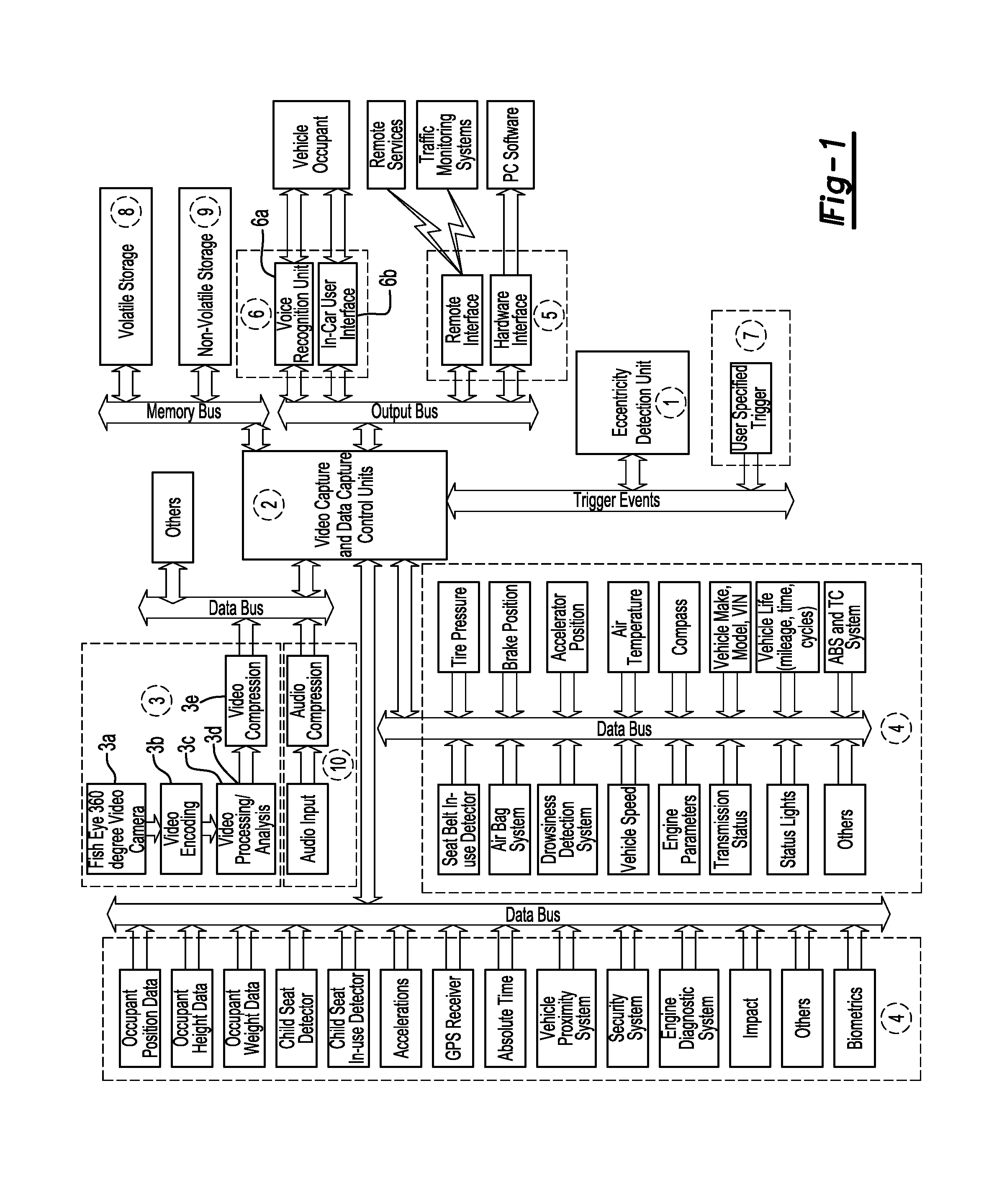

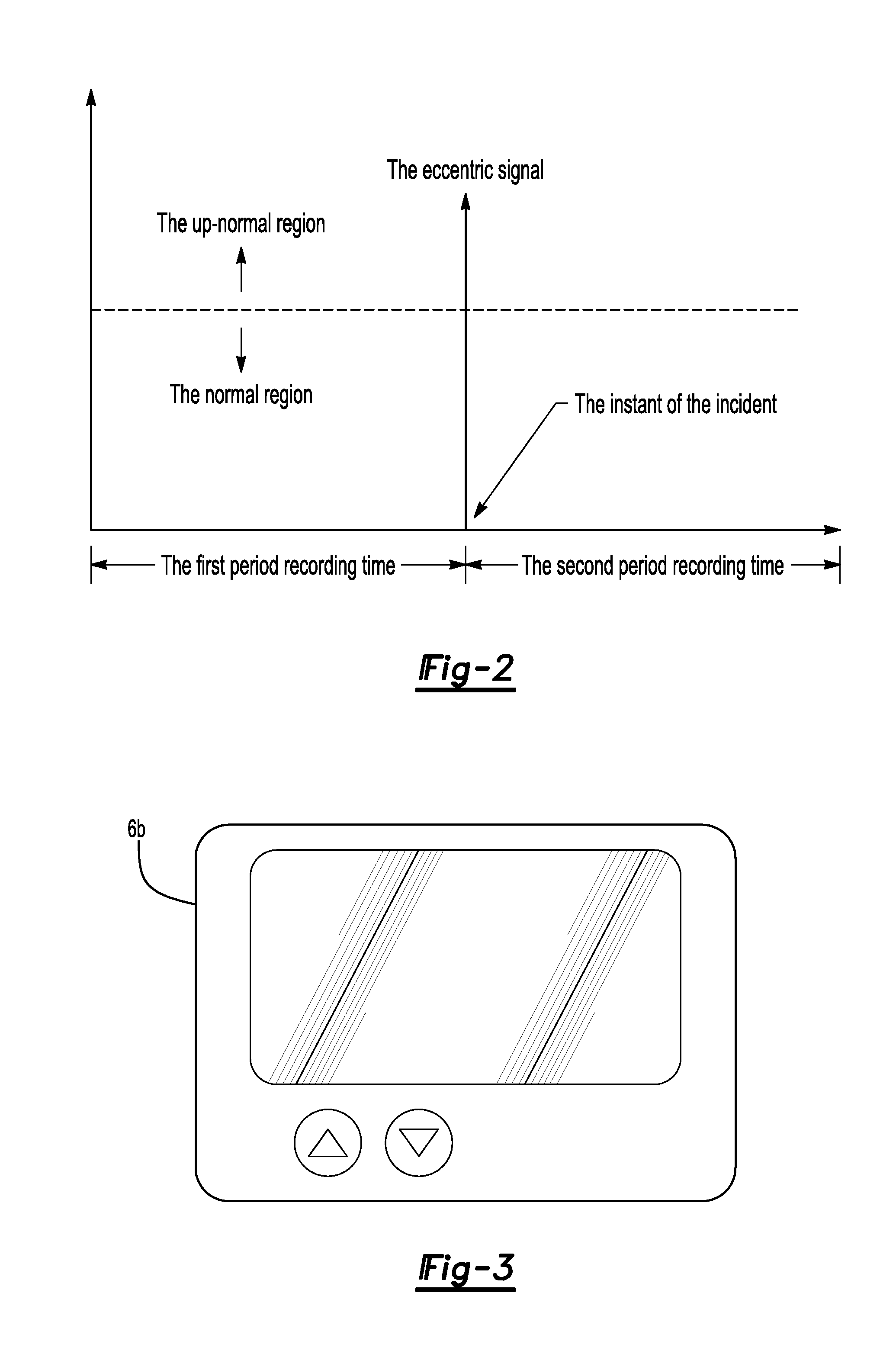

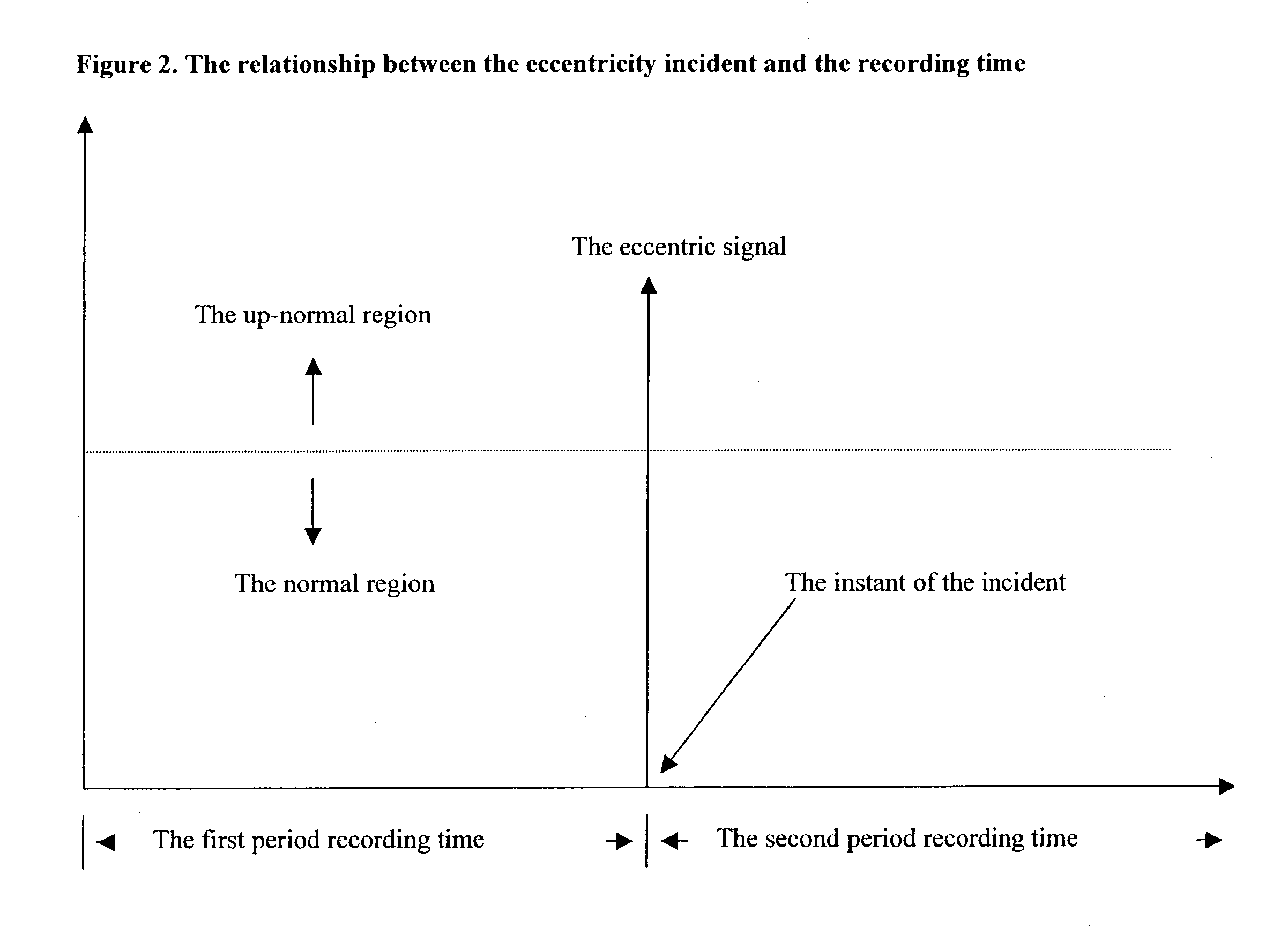

The system described in this invention can be used for monitoring and analyzing real time visual and non-visual information pertaining to the occupant, vehicle, and surroundings prior to, during and post eccentric operating conditions for a given period of time. The system stores vehicle and occupant data from sensors throughout the vehicle and also makes use of existing vehicle sensors that may already be present in the vehicle. The invention also includes a video recording module that makes use of a fish-eye camera to capture video from the inside and the outside of the vehicle. Real-time data analysis is performed to detect and to recognize vehicle occupants, and recognize impending eccentric events. Vehicle, occupant, and video data are stored in circular buffers. When an eccentric event, a collision for example, has been detected, the device continues to record data and video for a fixed period of time. Once this time has elapsed, the data is transferred from volatile to non-volatile memory for later retrieval. A computer may be used to retrieve and display the vehicle and occupant data in a synchronization with the video data for the purposes of accident recreation, driver or vehicle monitoring.

Owner:MINOTAUR SYST LLC

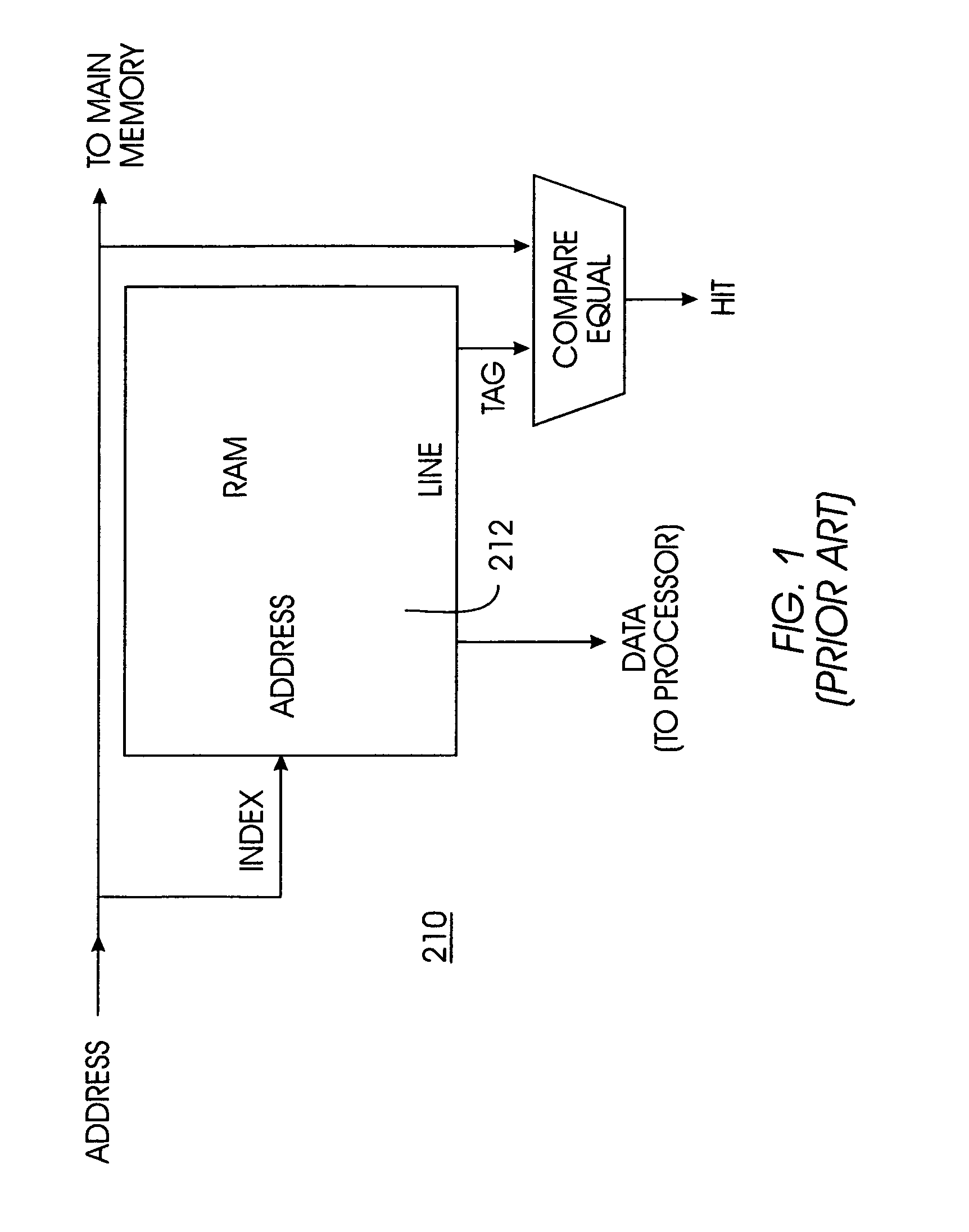

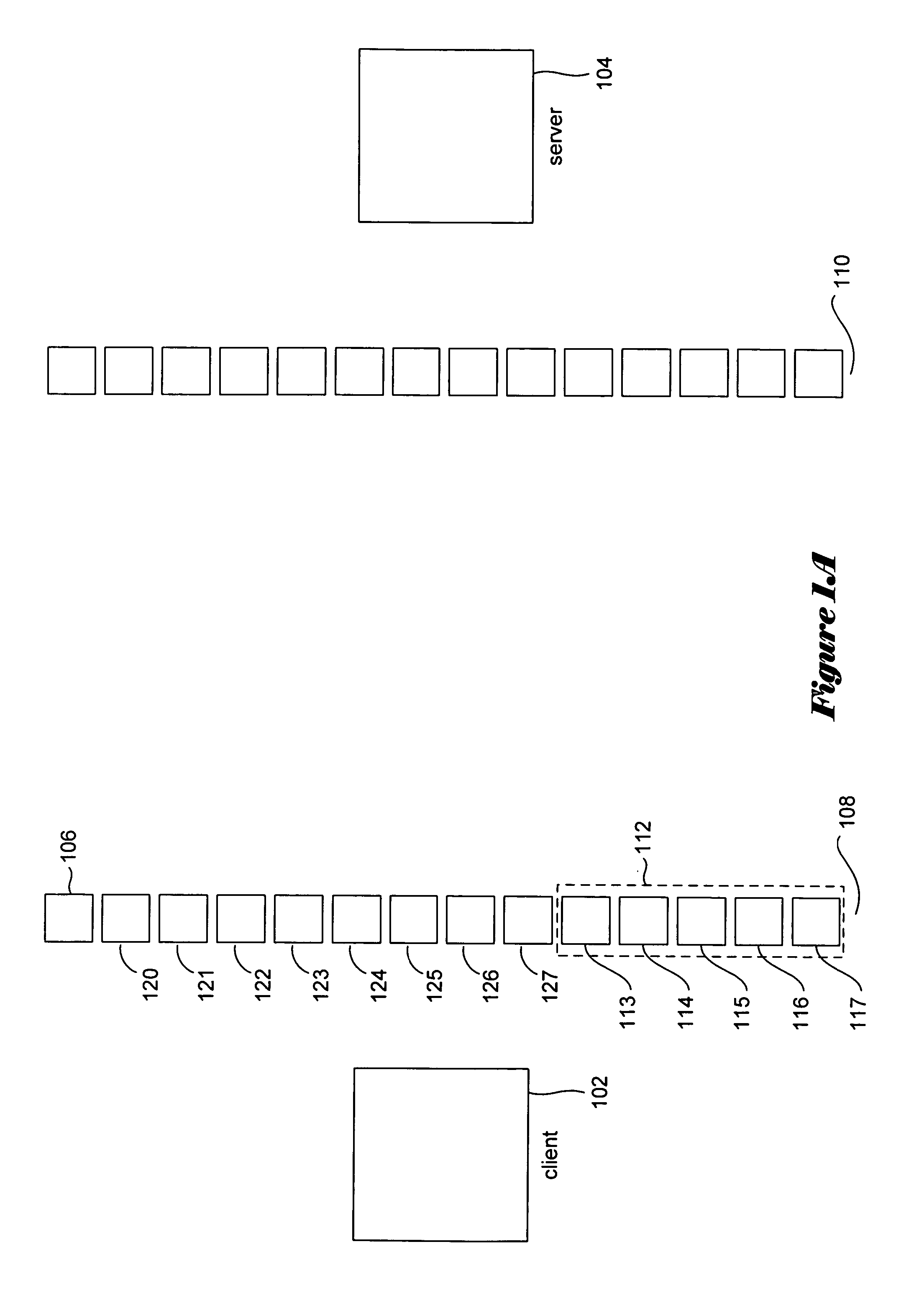

Microprocessors

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

Vehicle visual and non-visual data recording system

ActiveUS20030154009A1Vehicle testingRegistering/indicating working of vehiclesData synchronizationDriver/operator

The system described in this invention can be used for monitoring and analyzing real time visual and non-visual information pertaining to the occupant, vehicle, and surroundings prior to, during and post eccentric operating conditions for a given period of time. The system stores vehicle and occupant data from sensors throughout the vehicle and also makes use of existing vehicle sensors that may already be present in the vehicle. The invention also includes a video recording module that makes use of a fish-eye camera to capture video from the inside and the outside of the vehicle. Real-time data analysis is performed to detect and to recognize vehicle occupants, and recognize impending eccentric events. Vehicle, occupant, and video data are stored in circular buffers. When an eccentric event, a collision for example, has been detected, the device continues to record data and video for a fixed period of time. Once this time has elapsed, the data is transferred from volatile to non-volatile memory for later retrieval. A computer may be used to retrieve and display the vehicle and occupant data in a synchronization with the video data for the purposes of accident recreation, driver or vehicle monitoring.

Owner:MINOTAUR SYST LLC

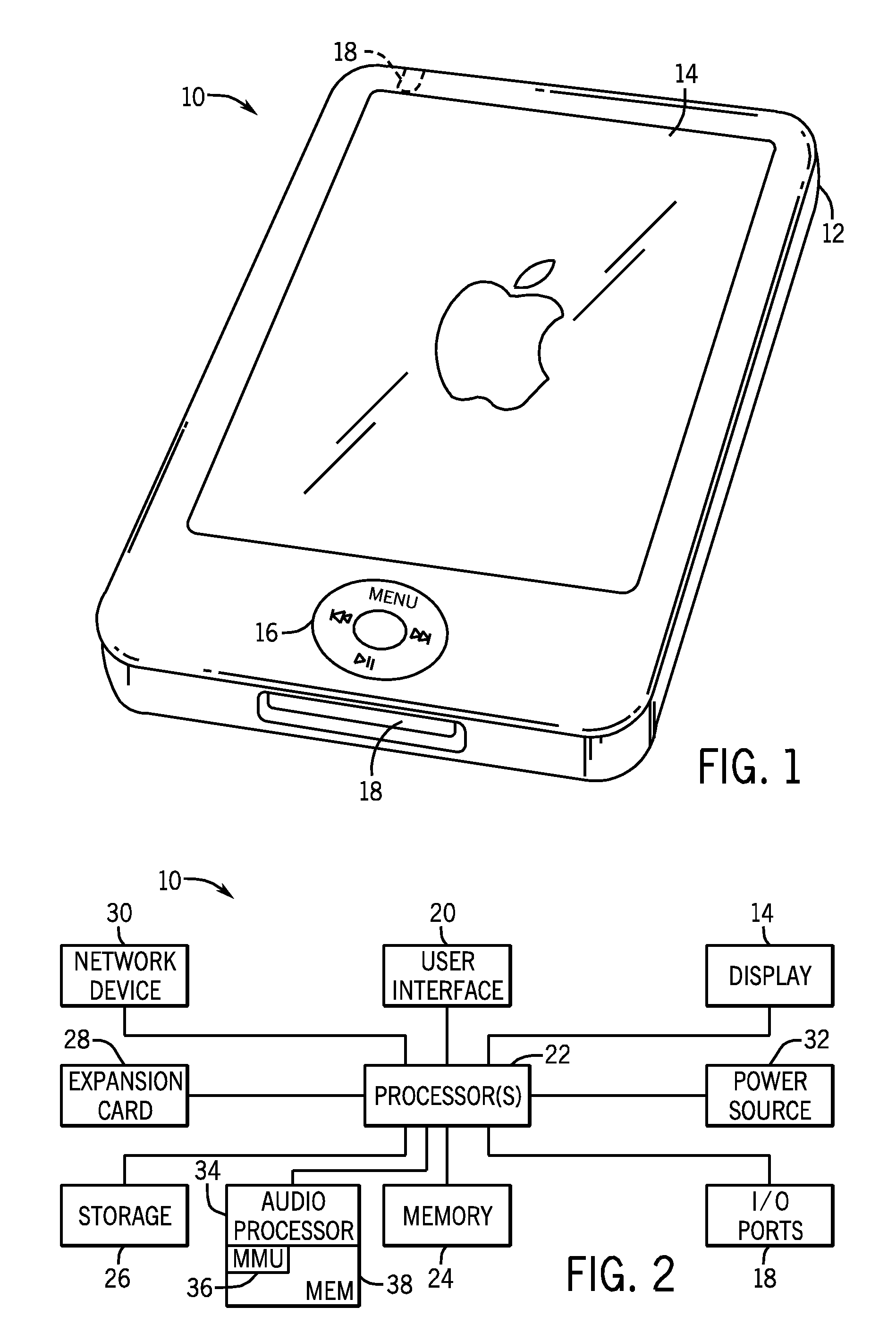

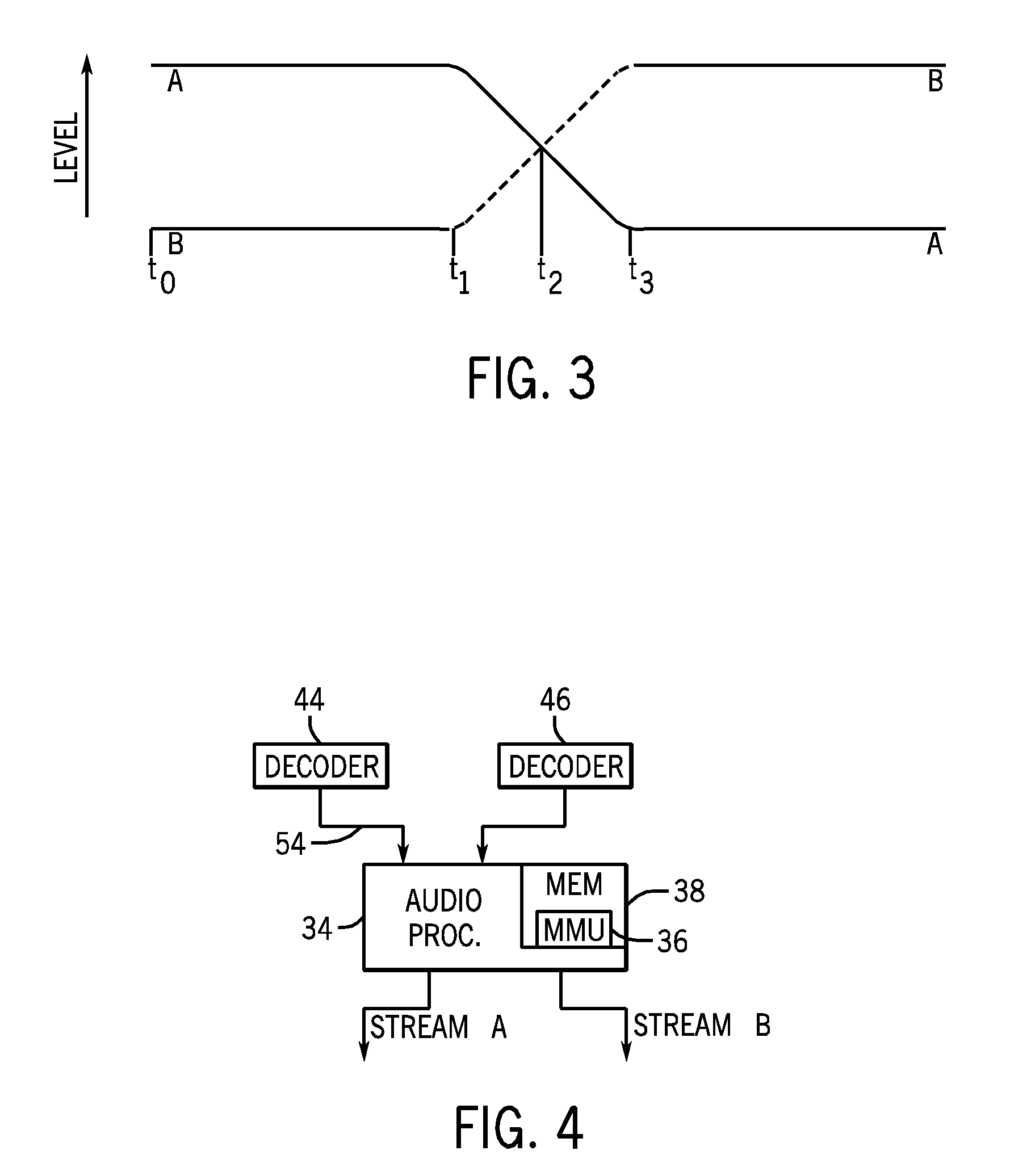

Systems and Methods for Memory Management and Crossfading in an Electronic Device

InactiveUS20100063825A1Sufficient dataLow costElectronic editing digitised analogue information signalsSpeech analysisCircular bufferAudio frequency

Systems and methods are disclosed for the management of memory used in a crossfading operation in an electronic device. In one embodiment, a processor is used to alternately decode two audio streams, one which is being faded out and one which is being faded in to implement a crossfade. The two audio streams may be encoded in the same or different formats and may be alternately decoded such that resource usage is reduced. The amount of decoded data of both audio streams and other parameters may determine which audio stream is to be actively decoded. In certain embodiments, the decoded data may be stored in a circular buffer, and a delta is determined between the decoded data and the empty space of the buffer.

Owner:APPLE INC

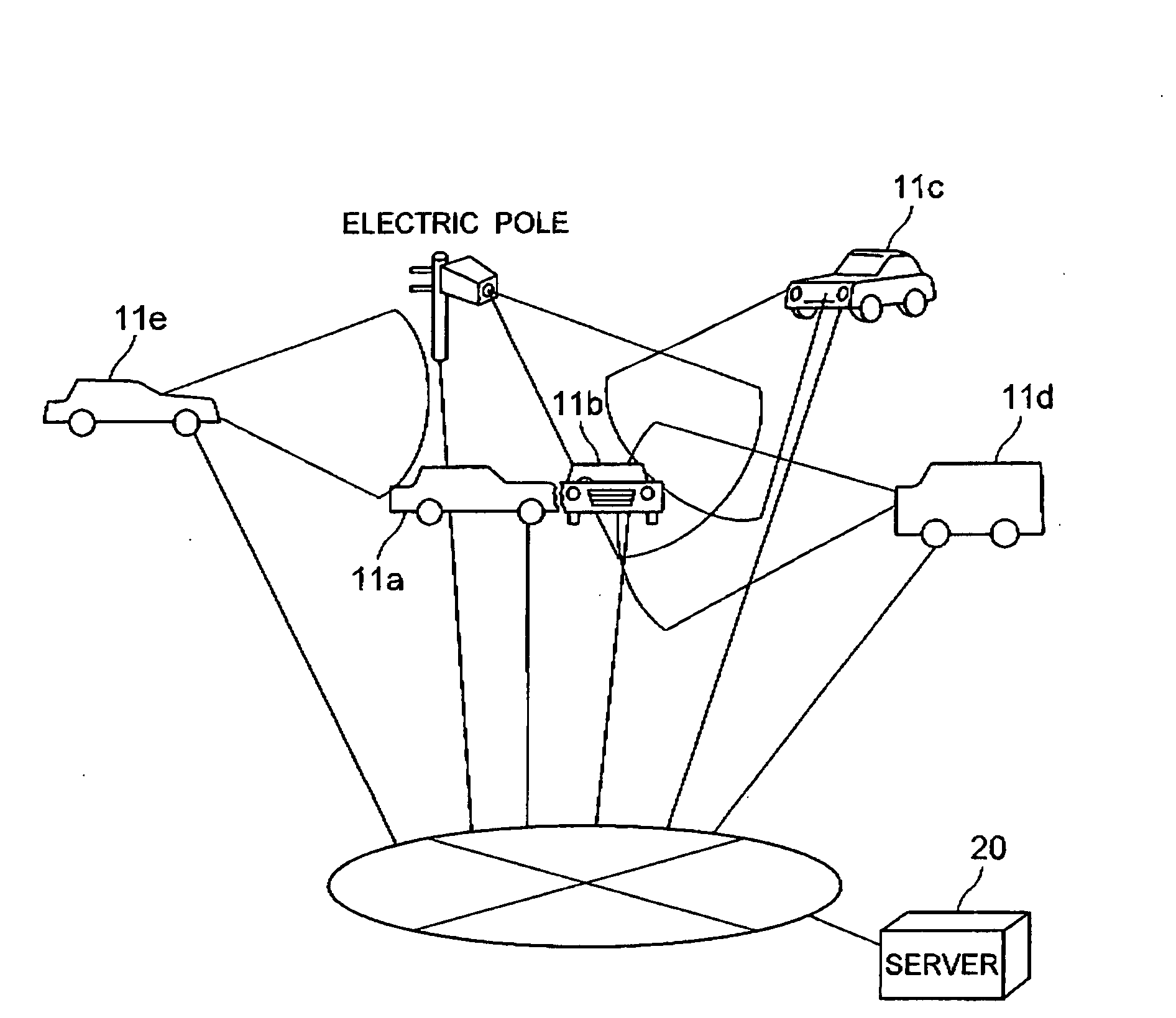

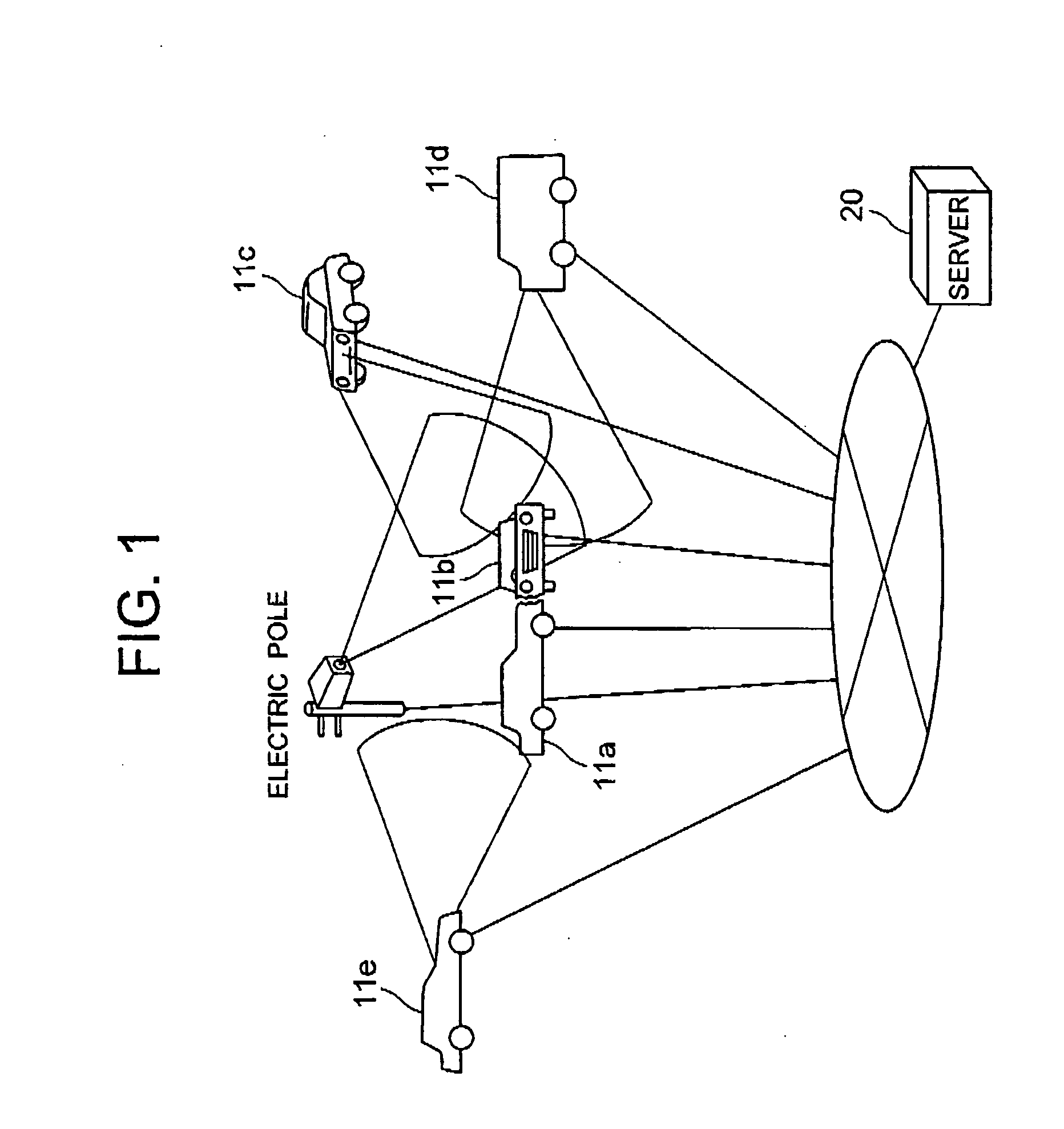

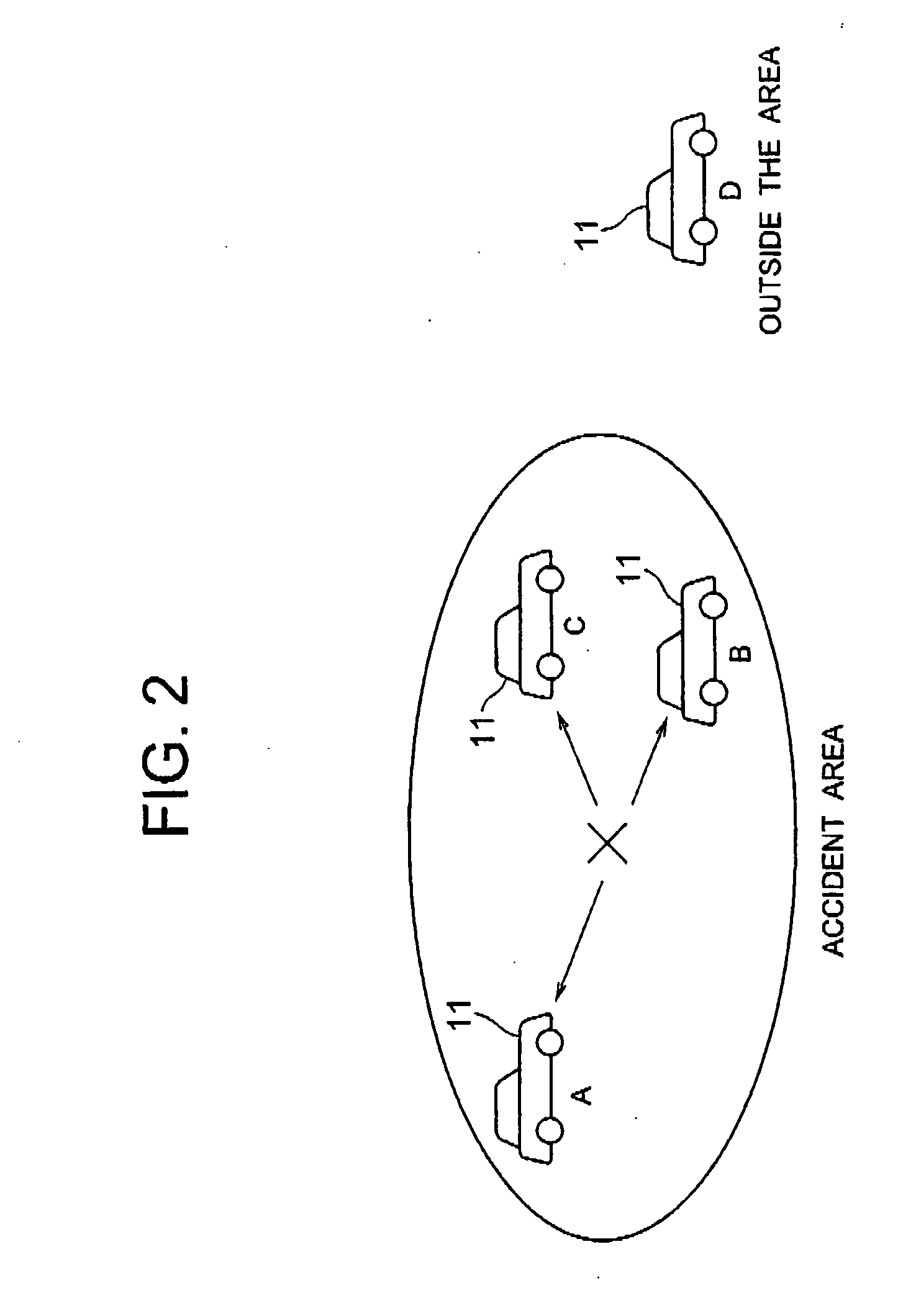

Information Recording System, Information Recording Device, Information Recording Method, and Information Collecting Program

ActiveUS20090015684A1Low costTelevision system detailsRegistering/indicating working of vehiclesImage recordingCircular buffer

An accident judgment device (105) judges whether or not an accident has occurred based on a detection signal of an impact sensor (104). Upon judging that an accident has occurred, an image saving device (106) extracts an image within several seconds before and after occurrence of the accident from a ring buffer (103) to save the same in a save memory (107). Upon judging that the accident has occurred, an image-record requesting device (108) transmits an image-recording request to a drive recorder (10) of target vehicles existing in the vicinity of the accident spot. Upon receiving the image-recording request, an image saving device (106) of the drive recorder (10) on the target vehicle extracts the image within several seconds before and after occurrence of the accident from the ring buffer (103) to save the same into the save memory (107).

Owner:NEC CORP

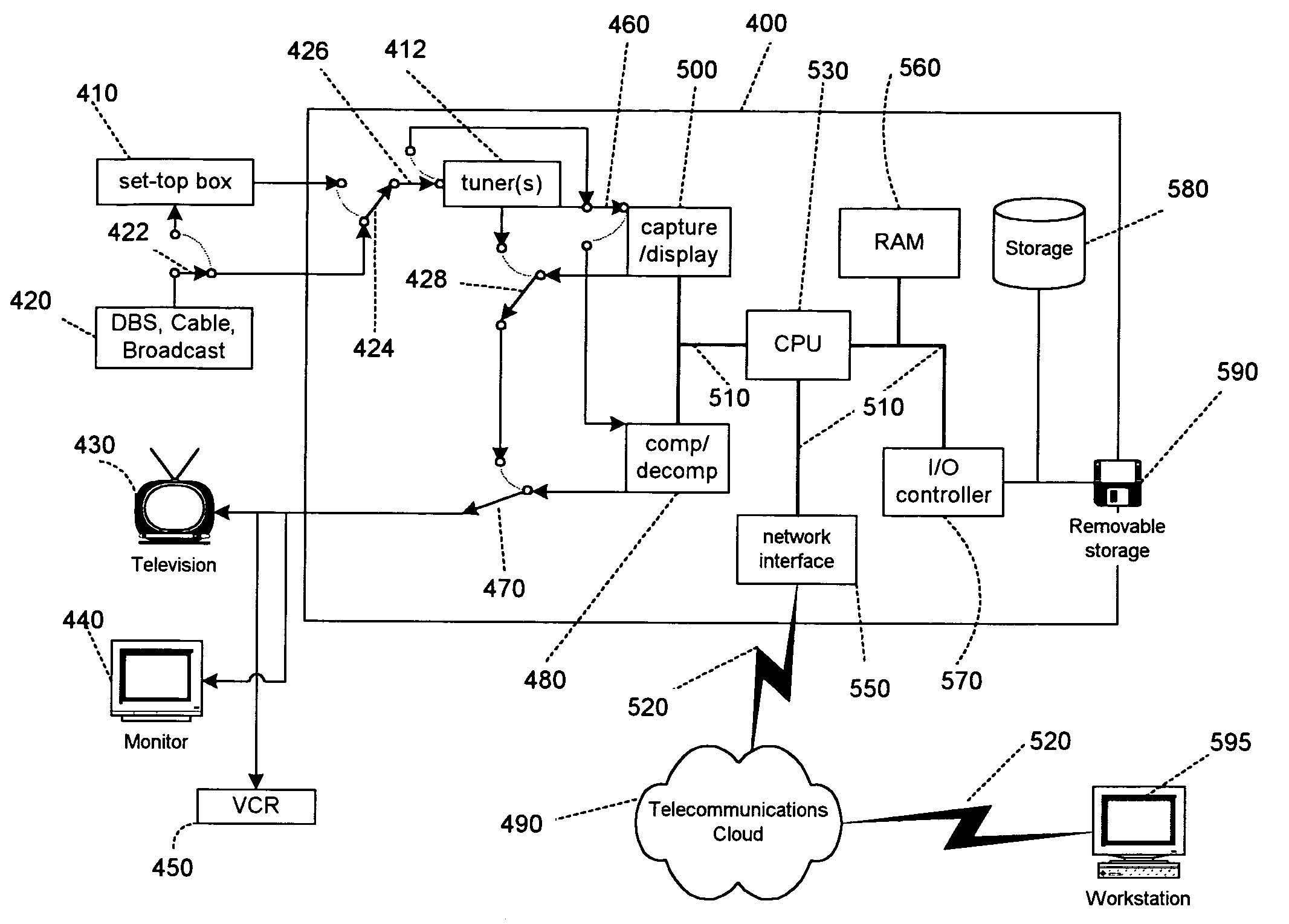

System and method for time-shifted program viewing

InactiveUS7272298B1Television system detailsElectronic editing digitised analogue information signalsDigital videoThe Internet

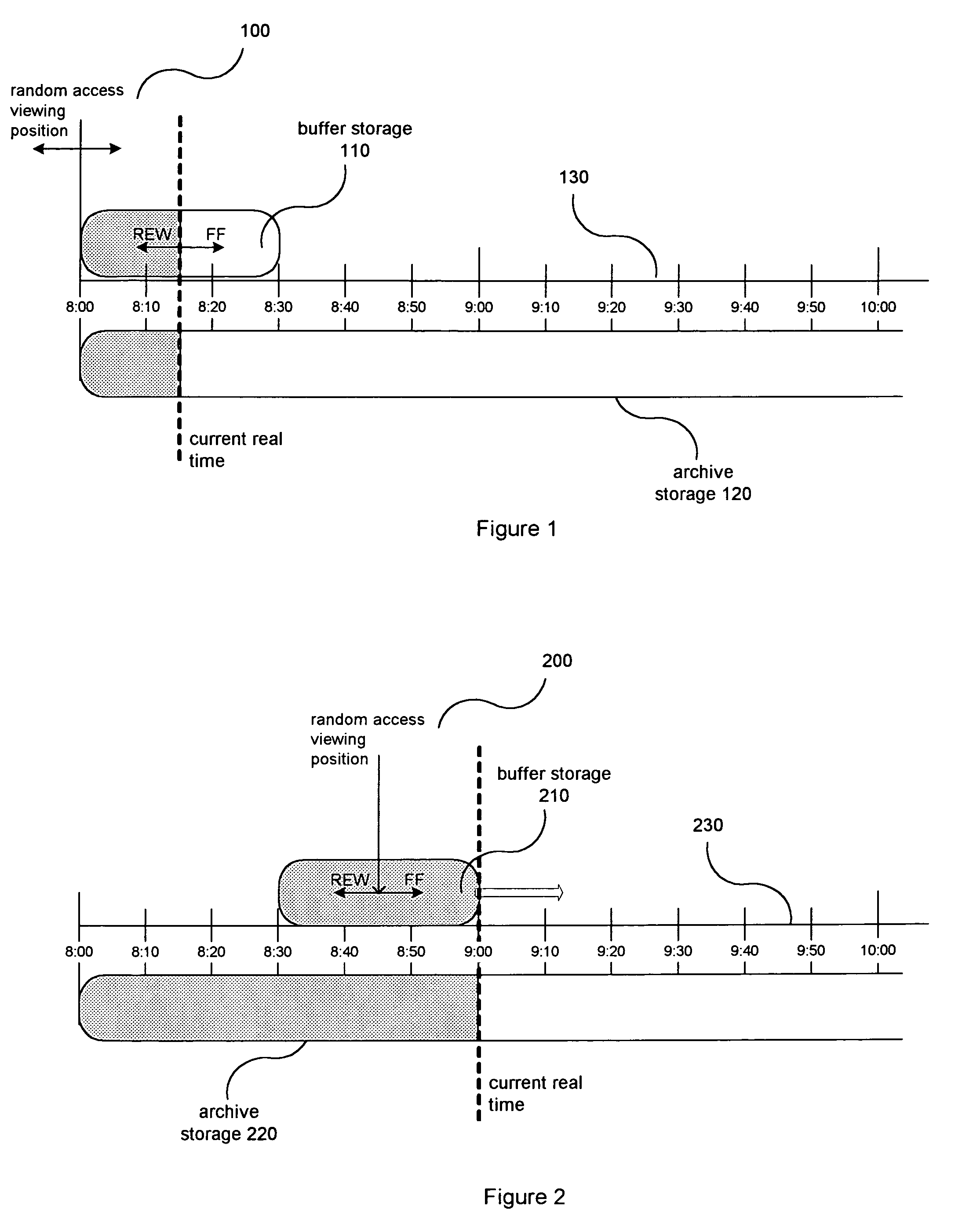

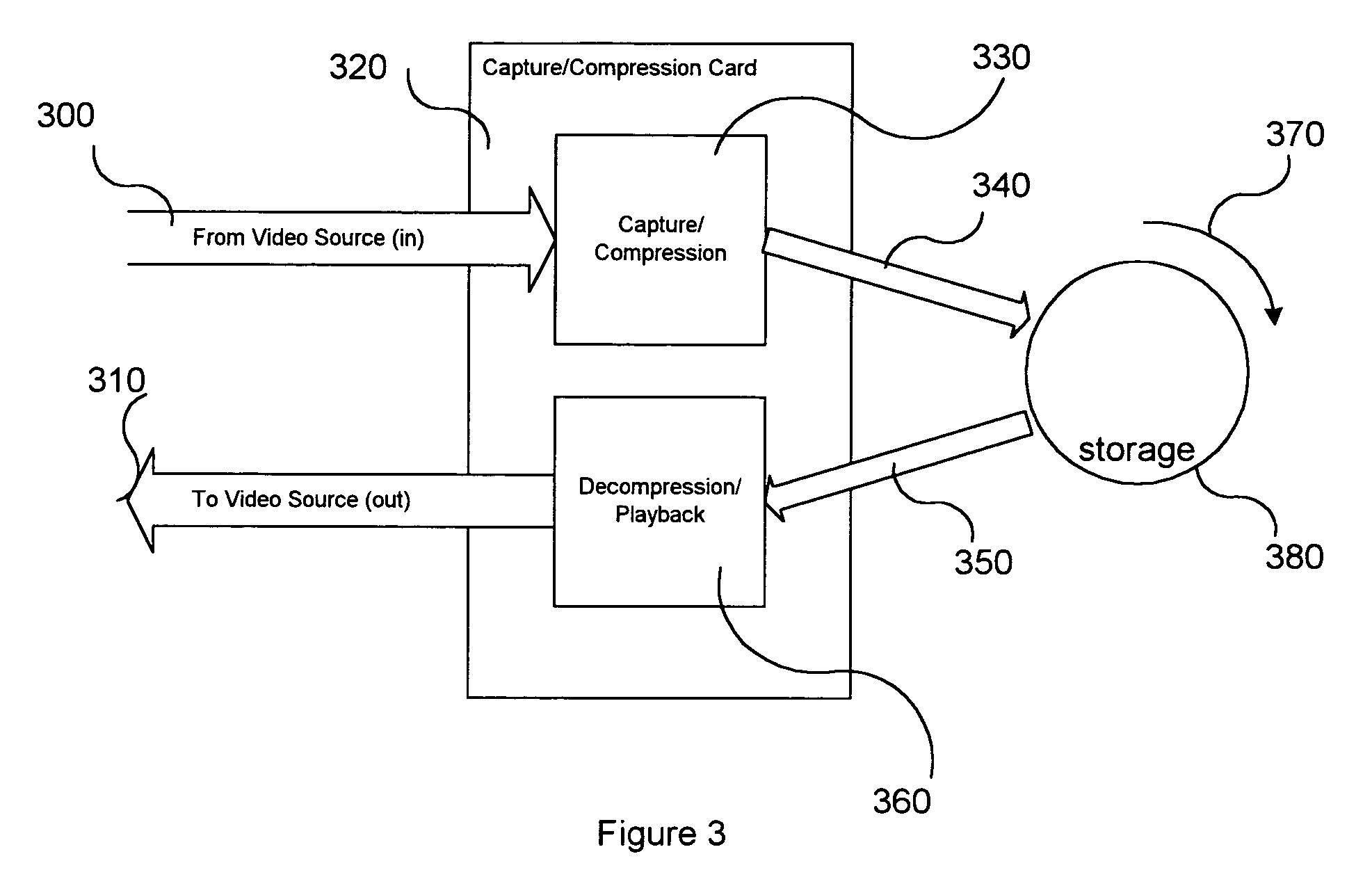

A system and method for time-shifted viewing of broadcast television programs is disclosed. Simultaneous recording and playback are provided by using buffer storage as the source and destination of compressed or uncompressed digital video / audio programs. Full VCR-like control is provided for all playback within the buffer storage. Playback and control of recorded programs may be initiated by the user at any time after initiation of the broadcast program with simultaneous continuous recording of the ongoing live broadcast. Larger archival storage and removable is also provided for storing and building a library of programs. Viewer playback control data may be stored as part of the program or used as edit points prior to archival. Numerous options are provided for features such as continuous automatic recording in a circular buffer fashion, program archival, editing, Internet interfaces, multiple-channel recording and more.

Owner:TIVO INC

Temporal-context-based video browsing interface for PVR-enabled television systems

InactiveUS20060109283A1Improve presentationImprove browsingTelevision system detailsDigital data information retrievalTelevision systemGraphics

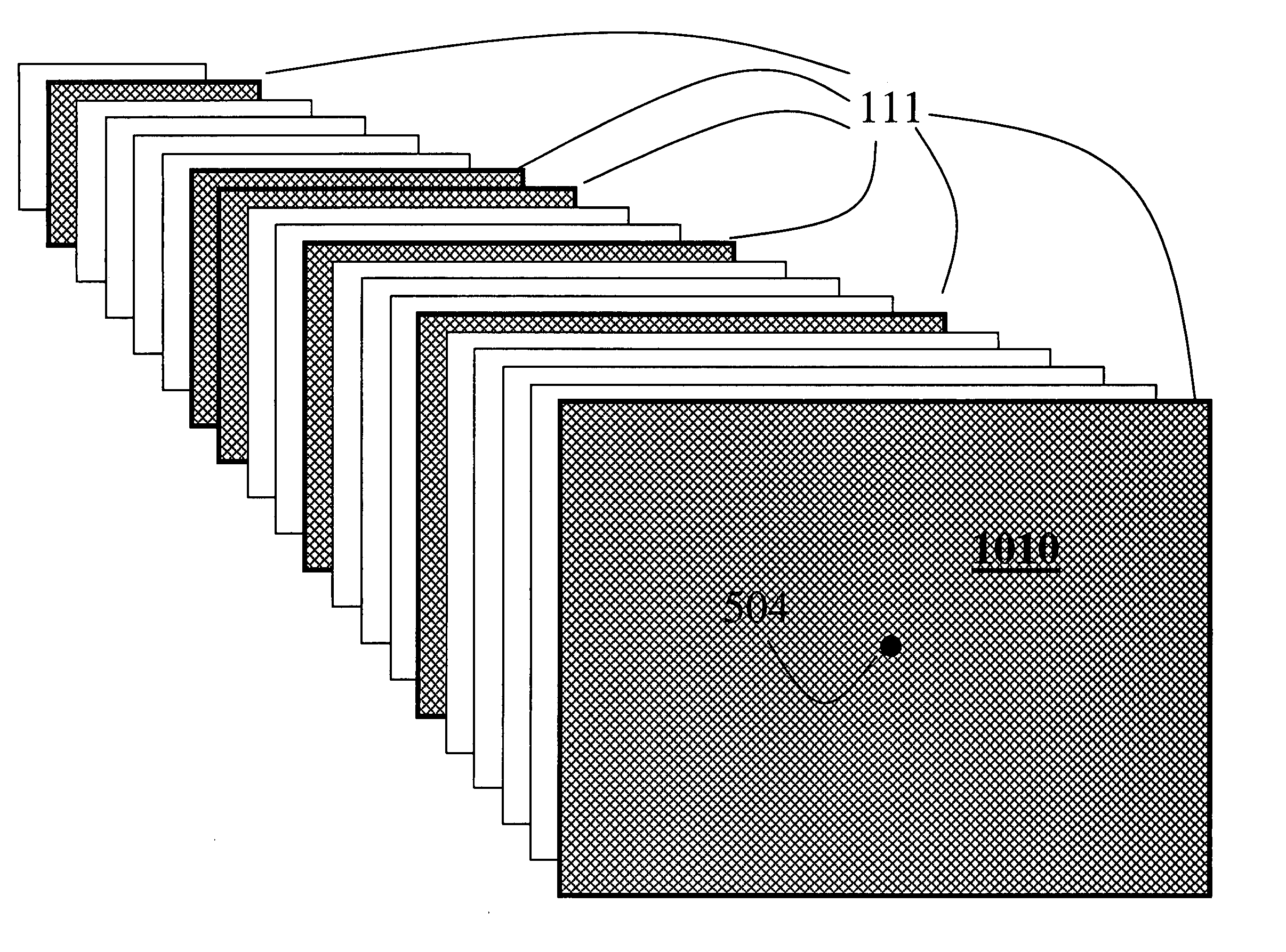

A method and system for presenting a set of graphic images on a television system is presented. A sequence of frames of a video is received. The frames are decoded and scaled to reduced size frames, which are sampled temporally and periodically to provide selected frames. The selected frames are stored in a circular buffer and converted to graphic images. The graphic images are periodically composited and rendered as an output graphic image using a graphic interface.

Owner:MITSUBISHI ELECTRIC RES LAB INC

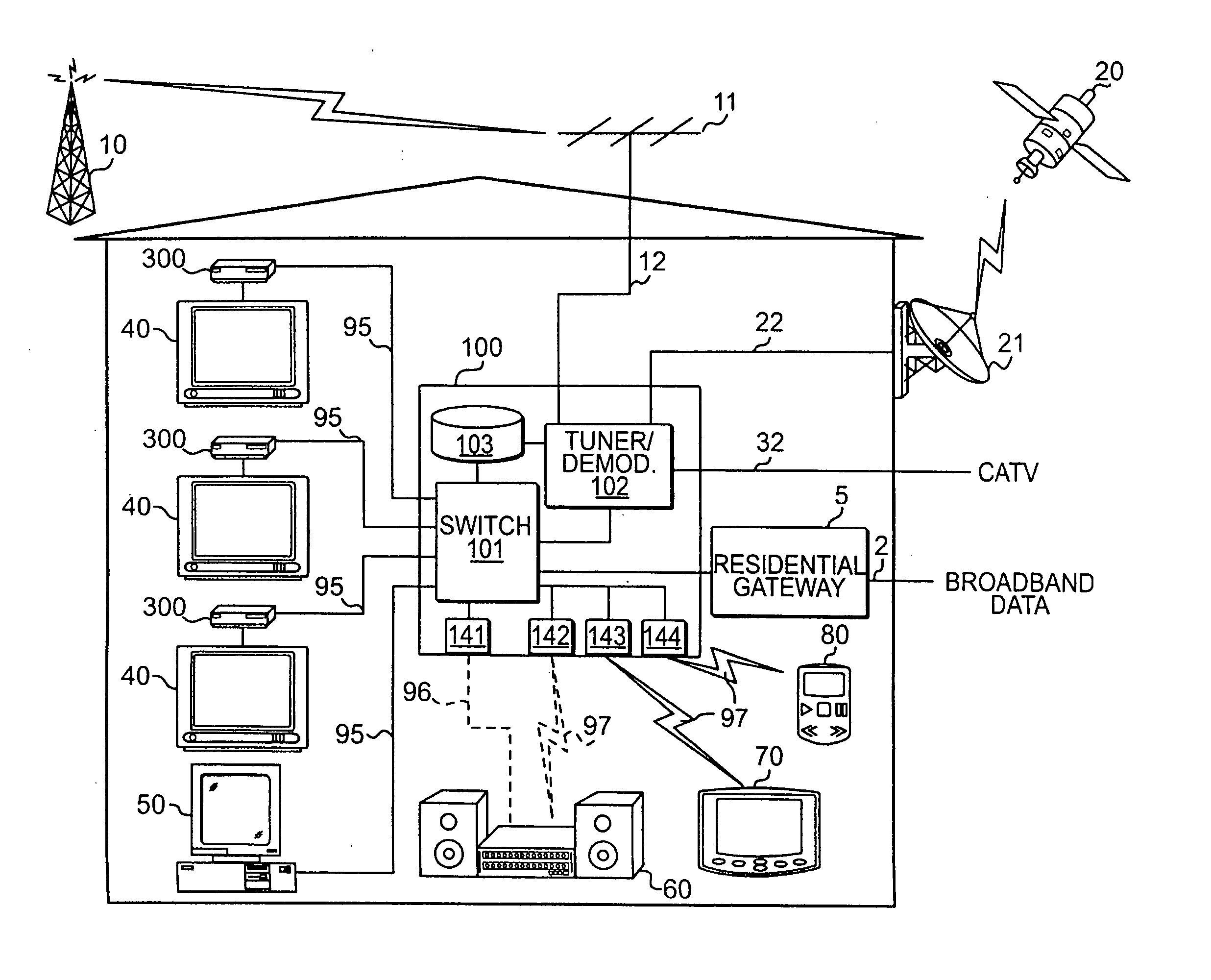

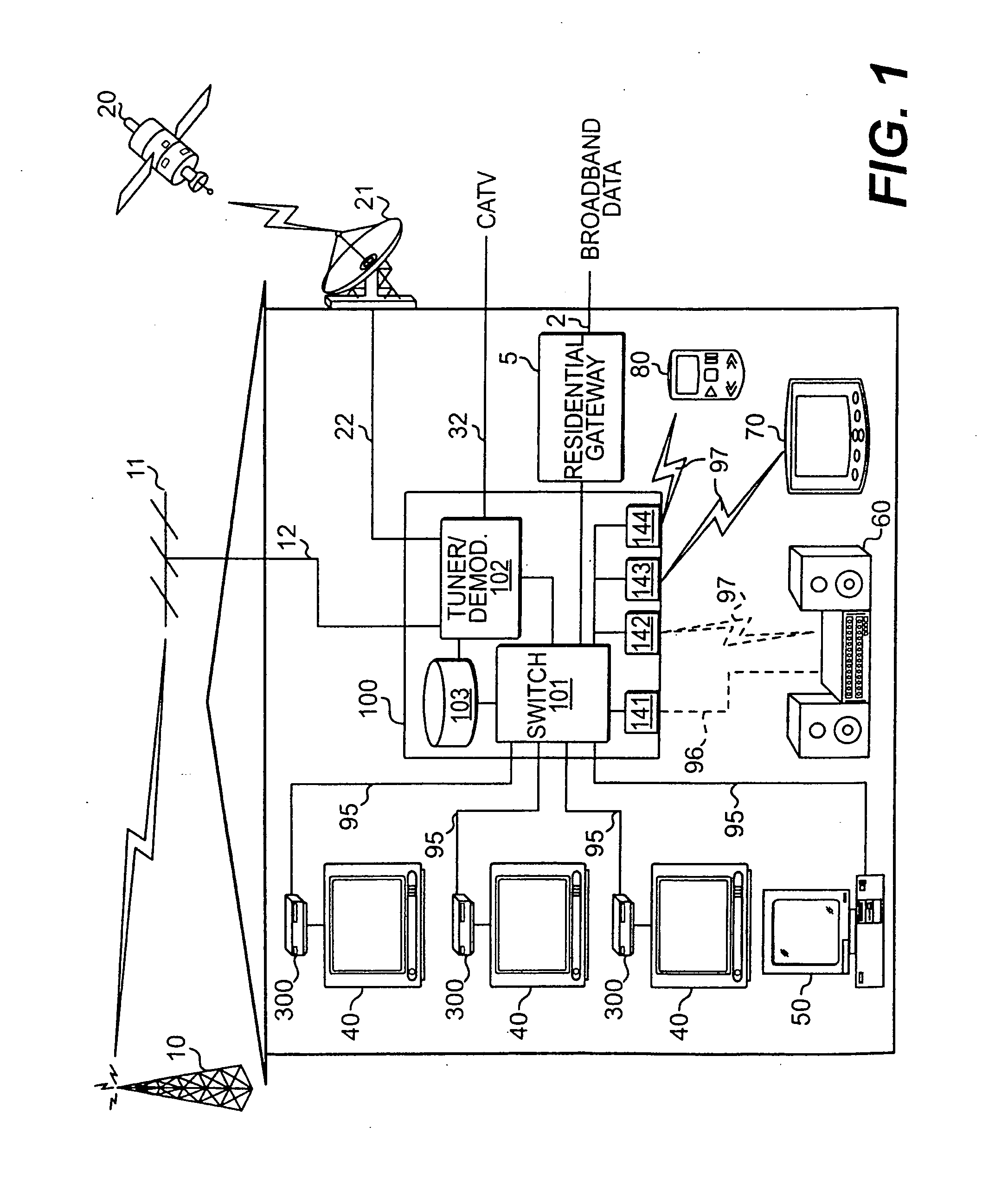

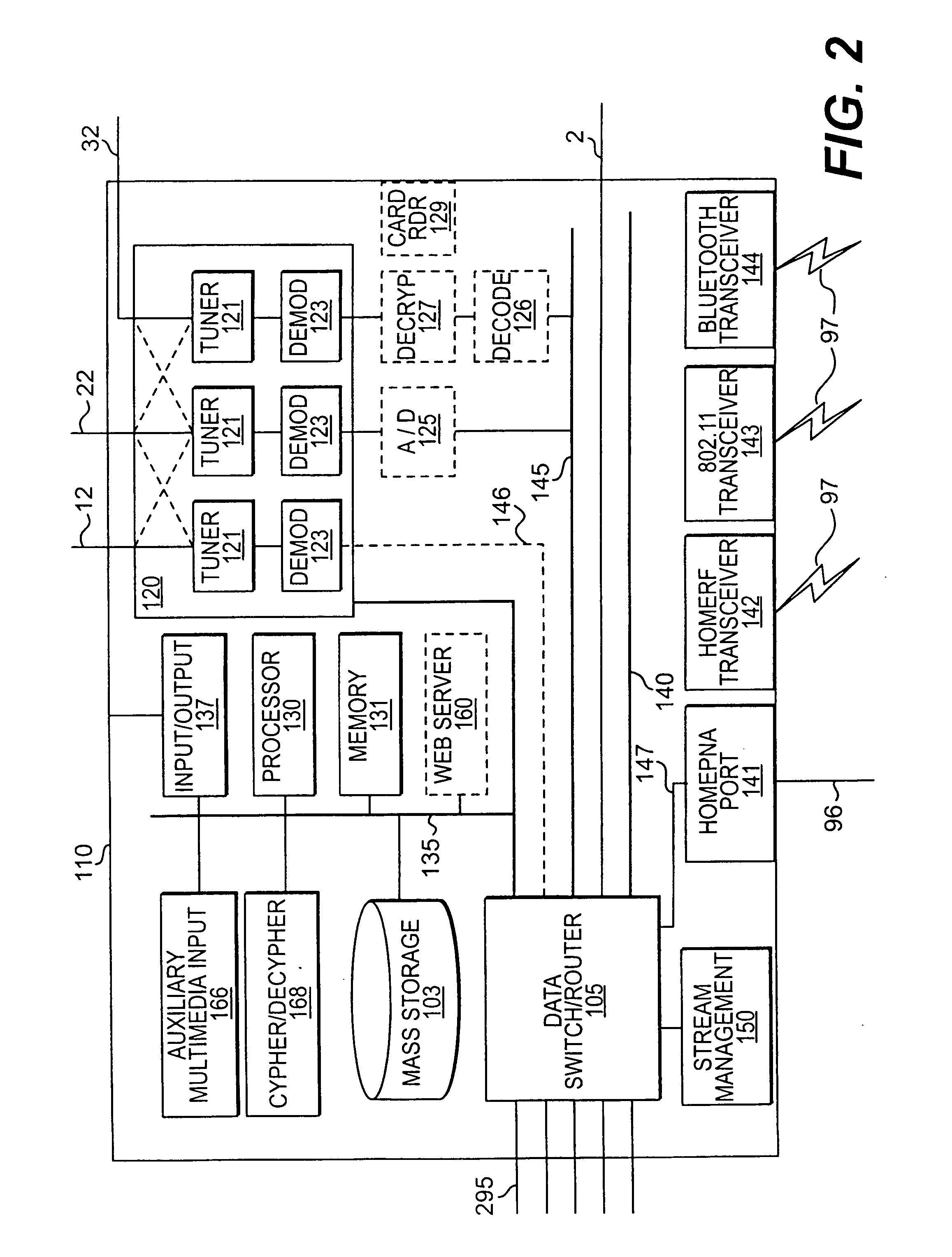

Digital residential entertainment system

InactiveUS20050086694A1Satellite broadcast receivingBroadcast specific applicationsCircular bufferReal-time computing

A digital residential entertainment system is disclosed recording video data of an event. The apparatuses include a processor communicating with memory. The memory stores video data of the event captured by a camera, and the video data includes a series of picture frames of the event. A loop buffer also stores video data of the event captured by the camera. A rule-based engine stored in the memory uses a set of rules to store the contents of the loop buffer in the memory. The apparatus utilizes the loop buffer to provide video data prior to occurrence of the event.

Owner:BELLSOUTH INTPROP COR

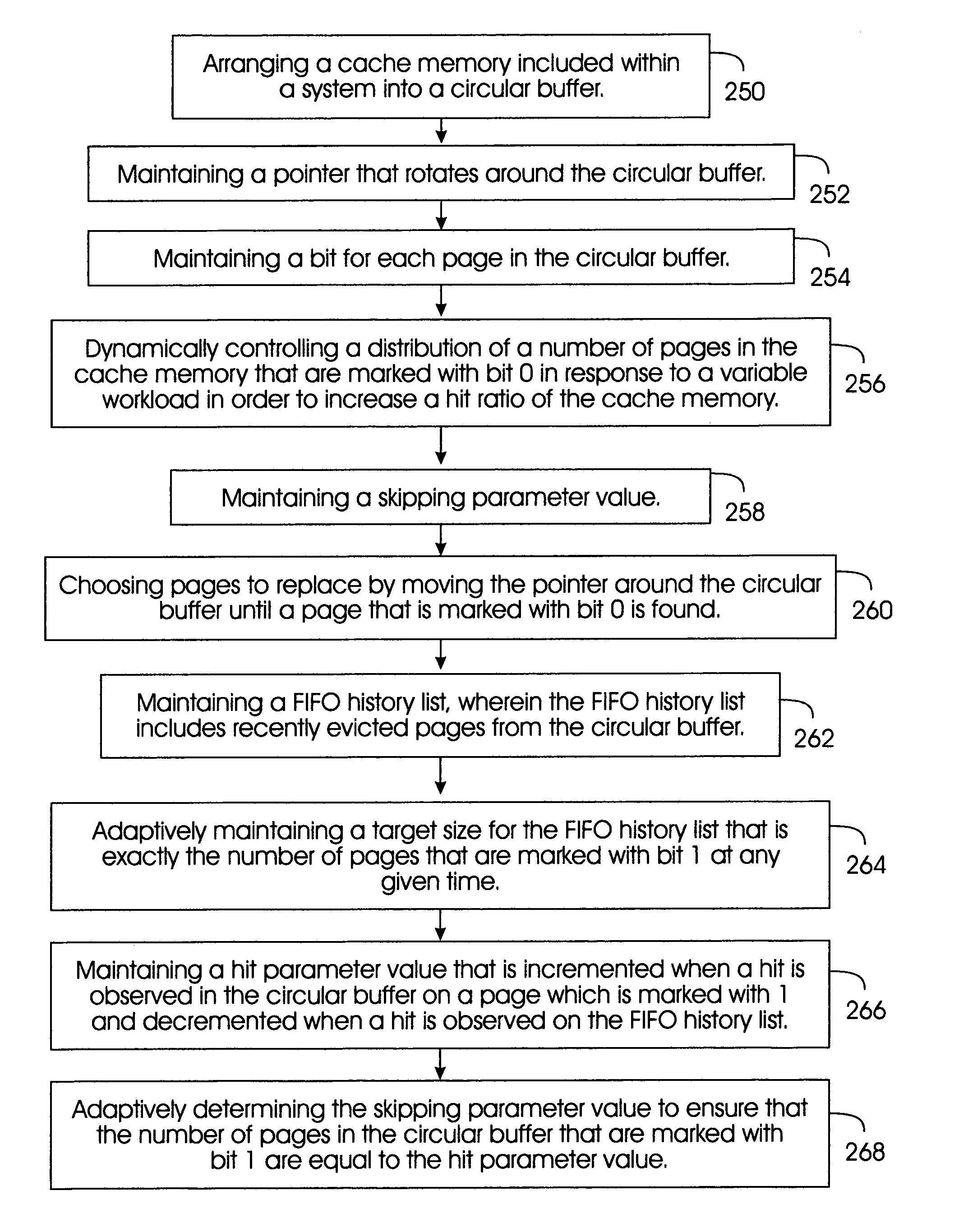

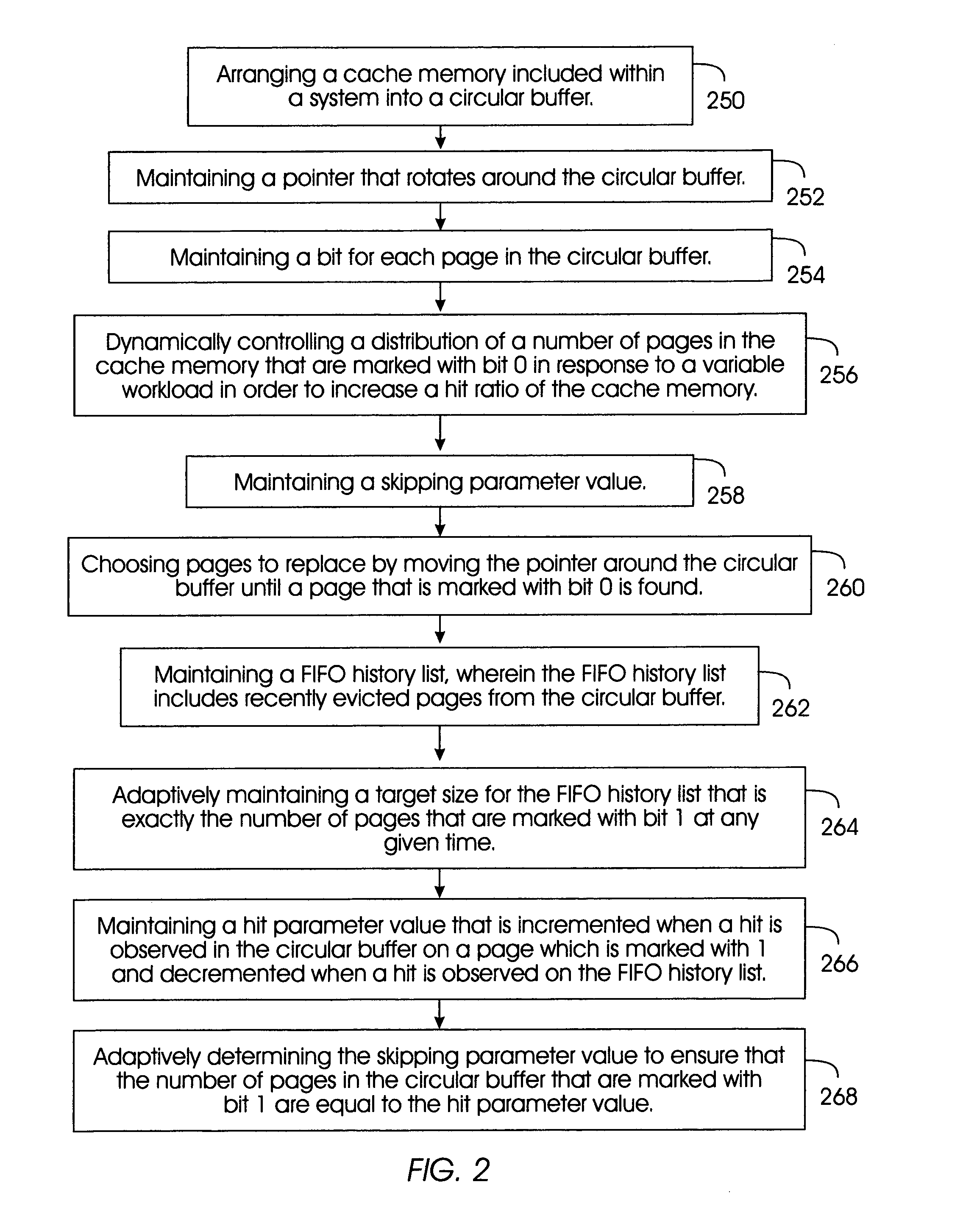

Method and system for a cache replacement technique with adaptive skipping

InactiveUS7096321B2Improve hit rateMemory architecture accessing/allocationMemory adressing/allocation/relocationCircular bufferWorkload

A method, system, and program storage medium for adaptively managing pages in a cache memory included within a system having a variable workload, comprising arranging a cache memory included within a system into a circular buffer; maintaining a pointer that rotates around the circular buffer; maintaining a bit for each page in the circular buffer, wherein a bit value 0 indicates that the page was not accessed by the system since a last time that the pointer traversed over the page, and a hit value 1 indicates that the page has been accessed since the last time the pointer traversed over the page; and dynamically controlling a distribution of a number of pages in the cache memory that are marked with bit 0 in response to a variable workload in order to increase a hit ratio of the cache memory.

Owner:INT BUSINESS MASCH CORP

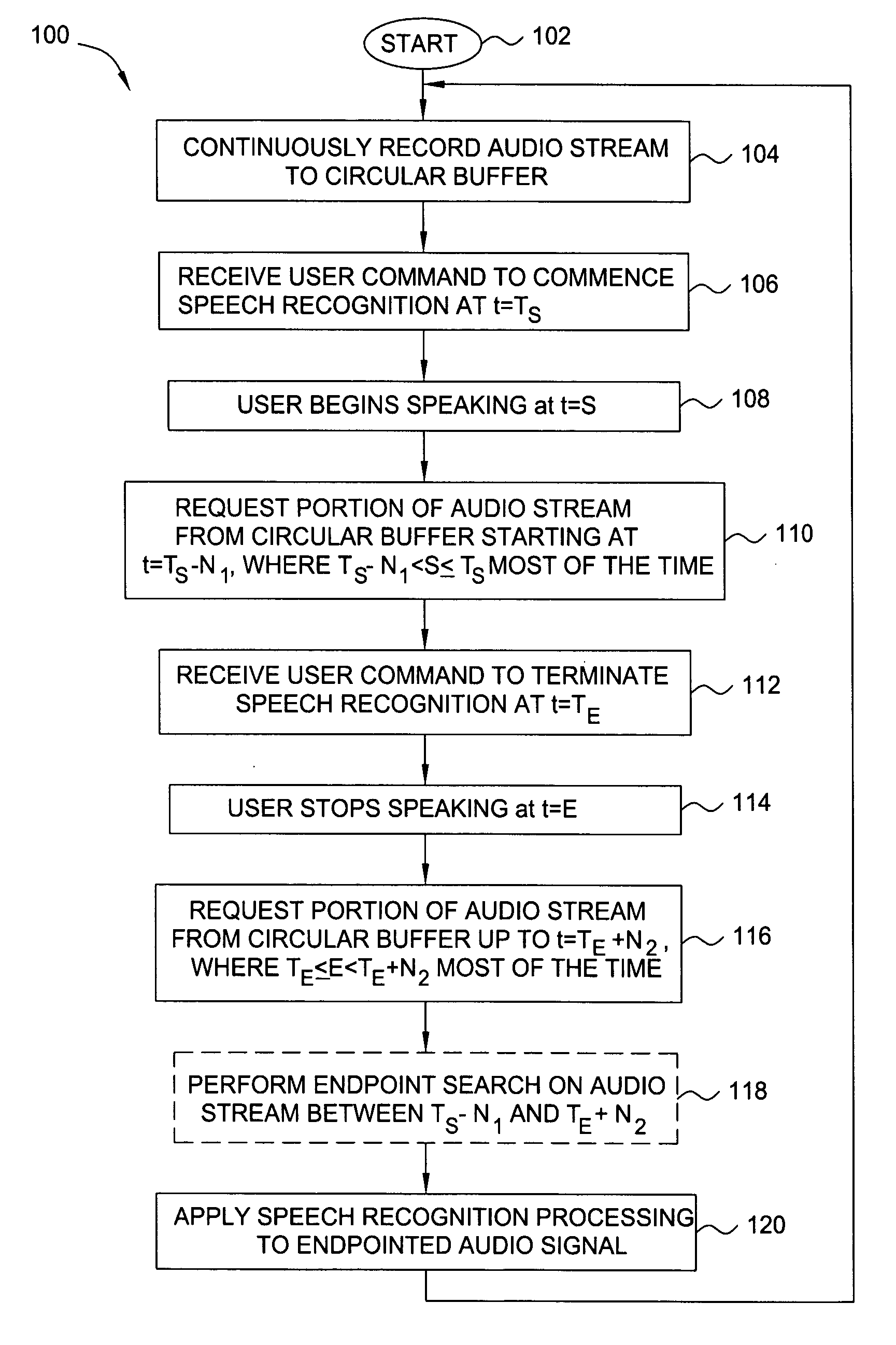

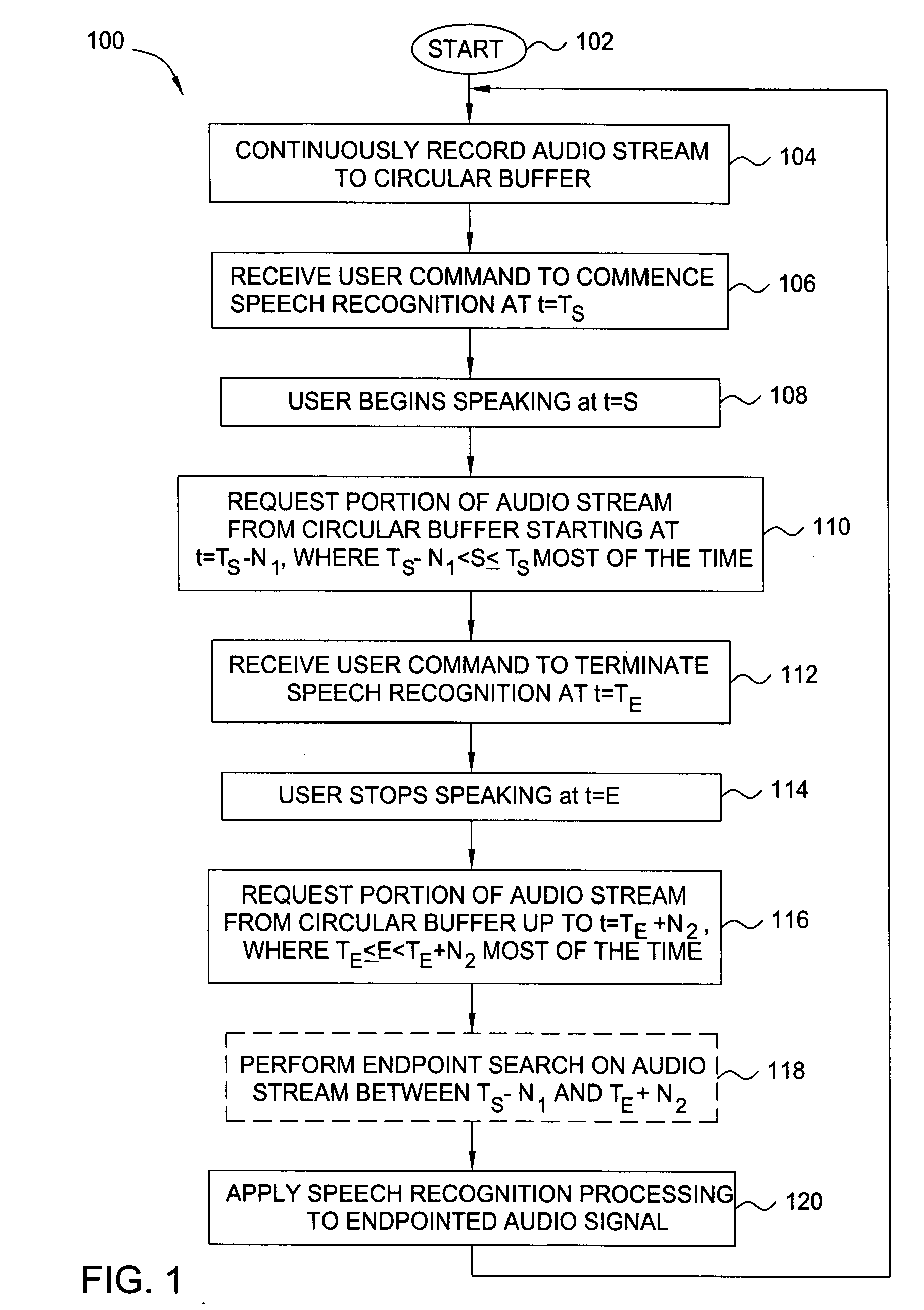

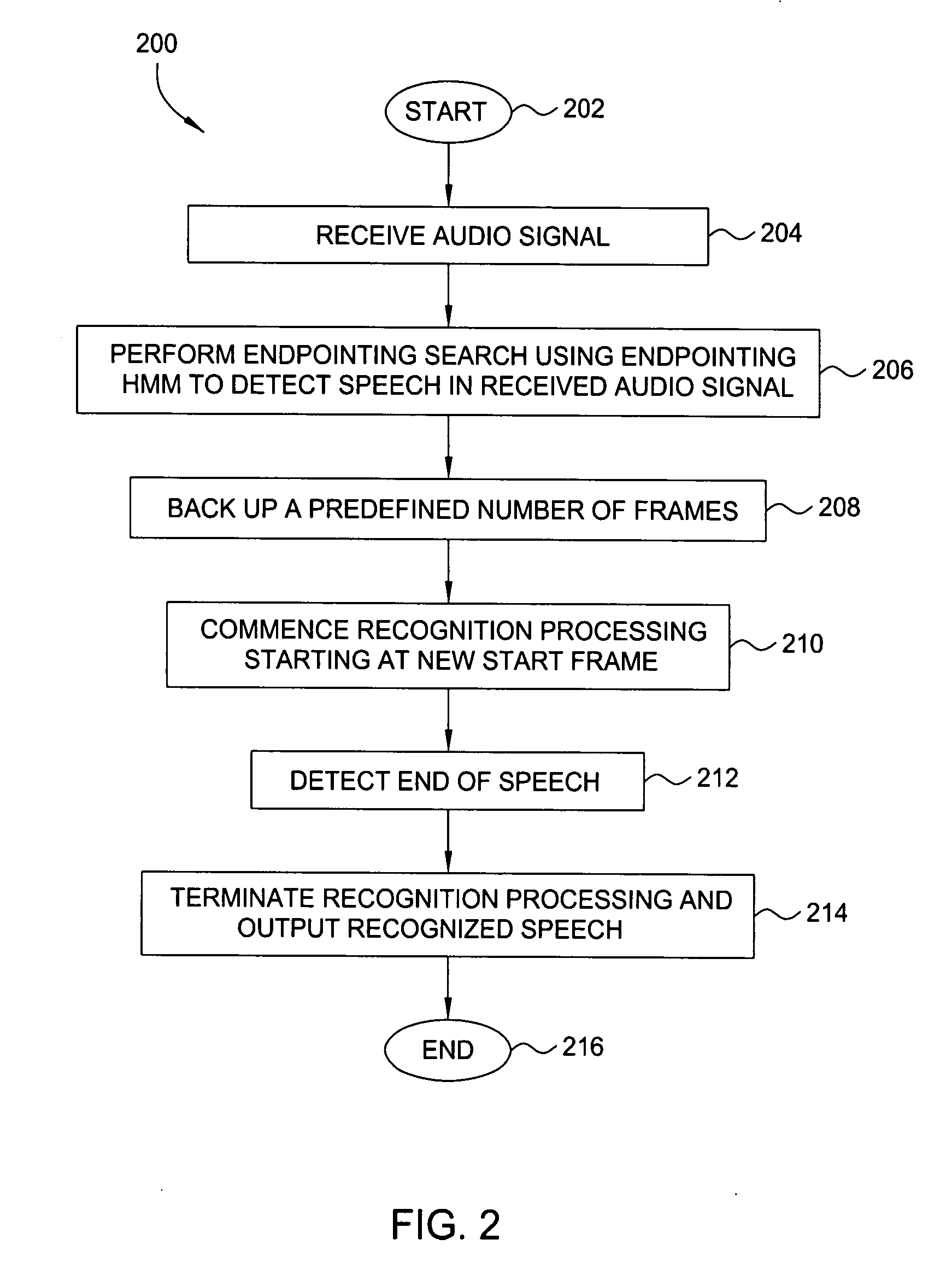

Method and apparatus for obtaining complete speech signals for speech recognition applications

The present invention relates to a method and apparatus for obtaining complete speech signals for speech recognition applications. In one embodiment, the method continuously records an audio stream comprising a sequence of frames to a circular buffer. When a user command to commence or terminate speech recognition is received, the method obtains a number of frames of the audio stream occurring before or after the user command in order to identify an augmented audio signal for speech recognition processing. In further embodiments, the method analyzes the augmented audio signal in order to locate starting and ending speech endpoints that bound at least a portion of speech to be processed for recognition. At least one of the speech endpoints is located using a Hidden Markov Model.

Owner:SRI INTERNATIONAL

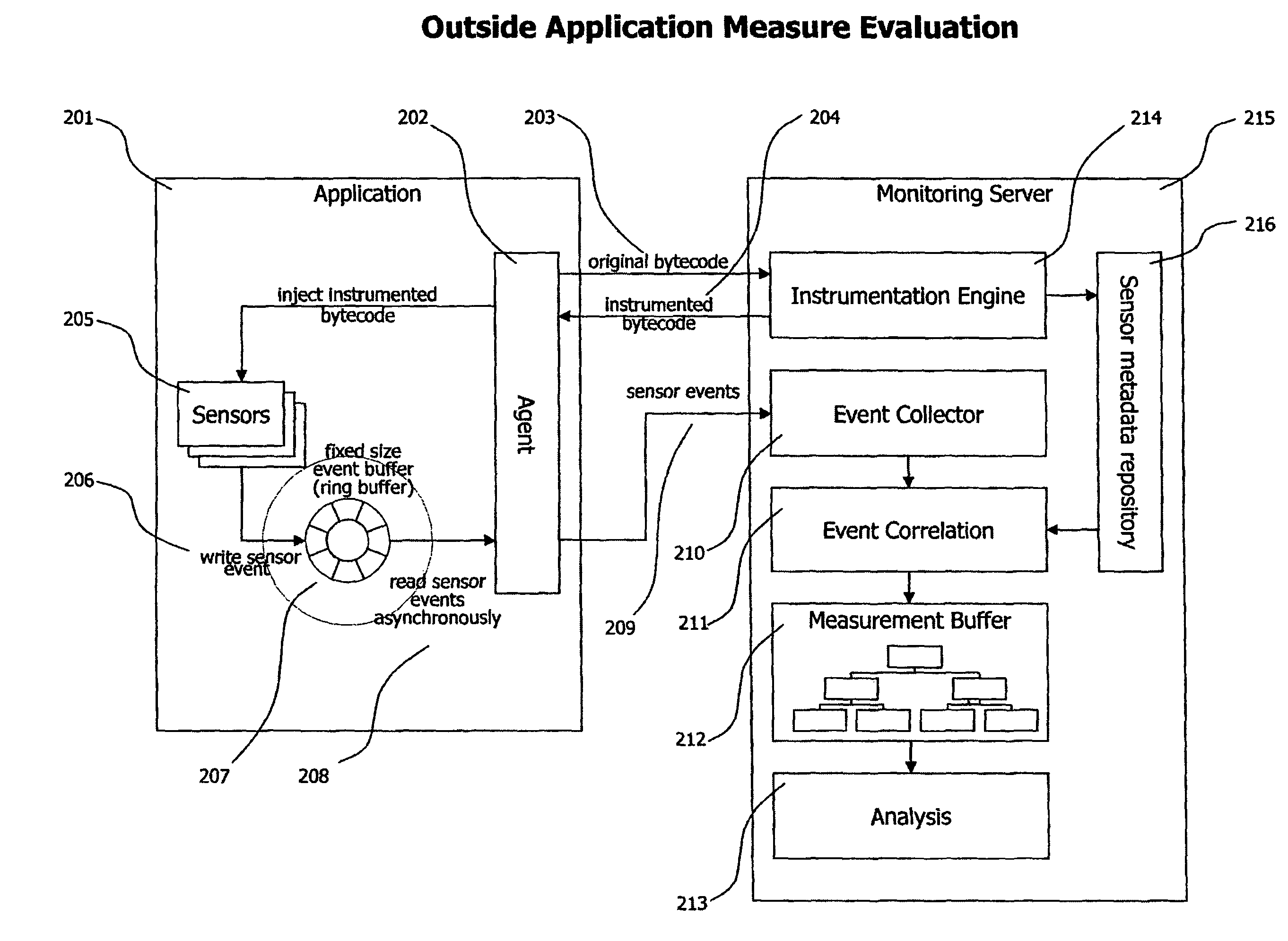

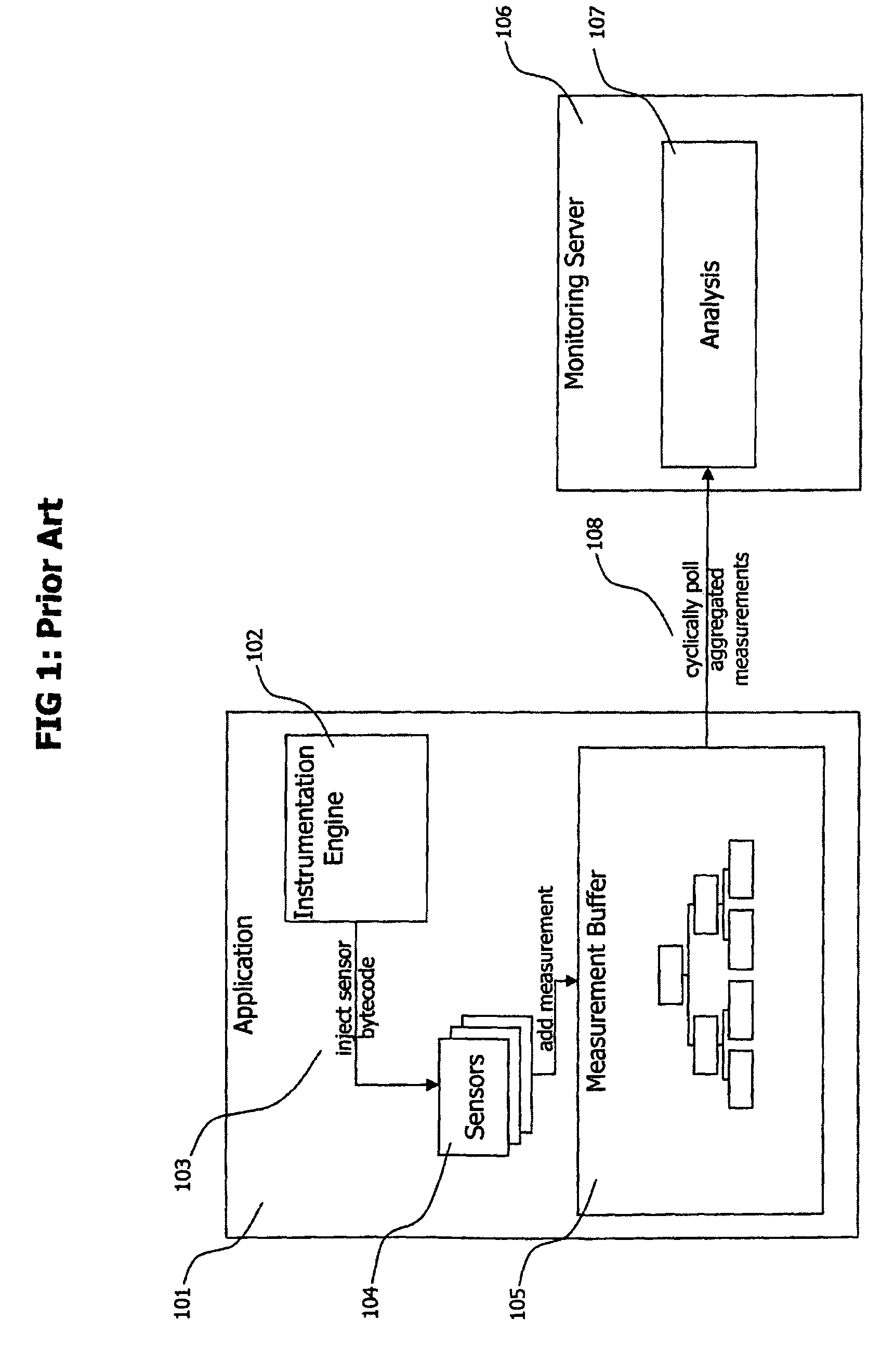

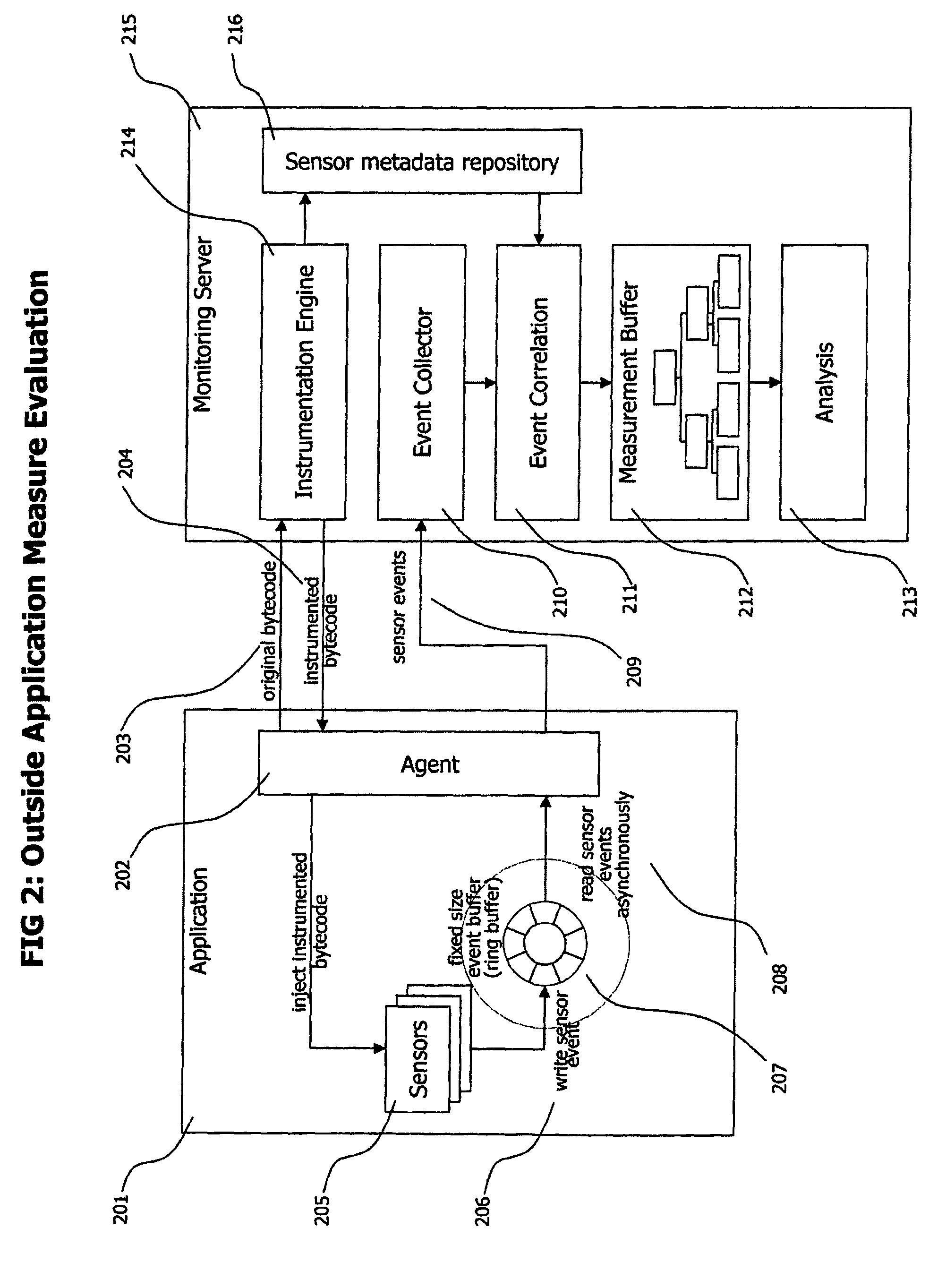

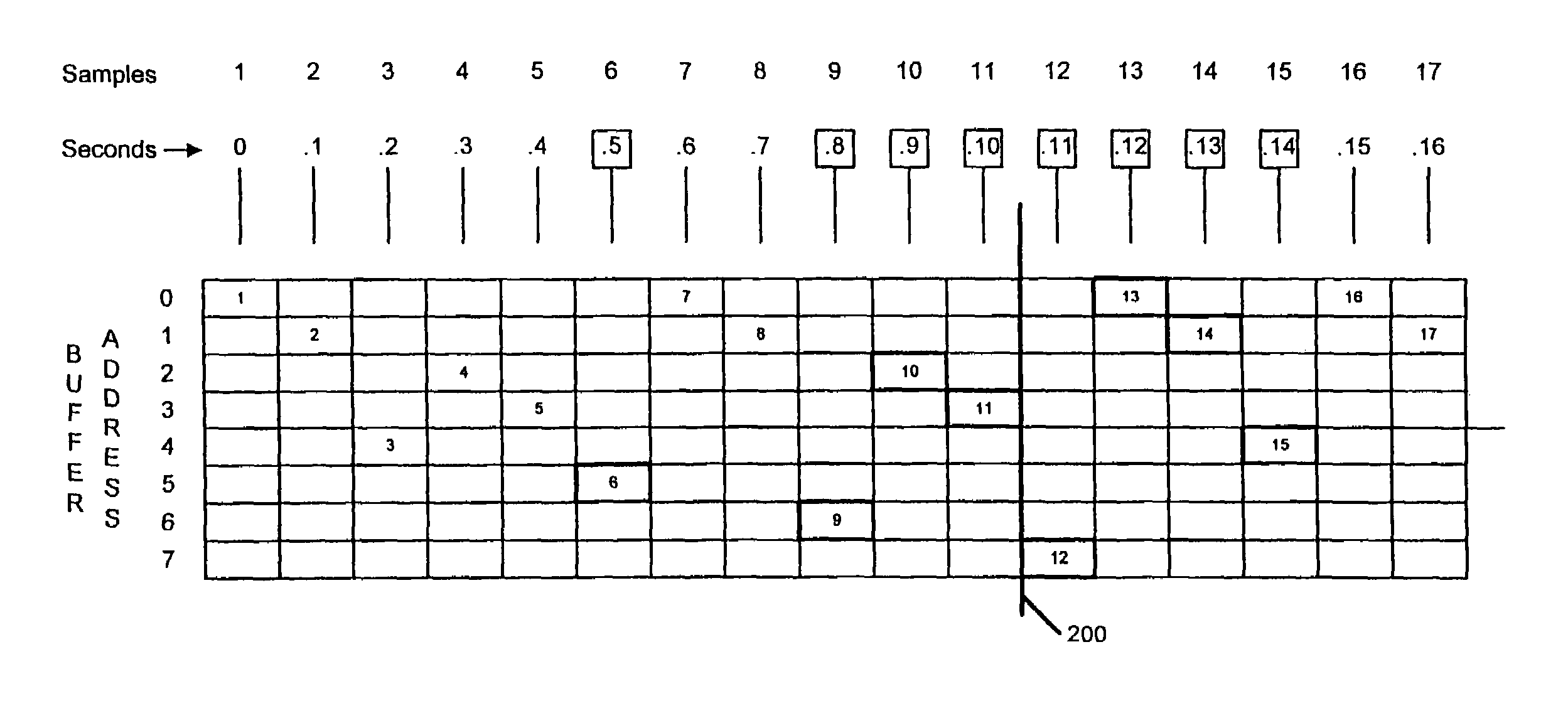

Method and system for processing application performance data outside of monitored applications to limit overhead caused by monitoring

The present invention provides a system and method that aggregates and processes monitoring data acquired inside a monitored application outside of the said application to reduce overhead caused by monitoring tasks in the monitored application. Monitoring data acquired by monitoring sensors is stored in a ring buffer after acquisition, which decouples acquisition of data and its transfer, enabling asynchronous sending of performance data to a monitoring server for analysis. Memory consumption of said ring buffer is limited to a fixed size which keeps memory consumption caused by monitoring processes low and predictable. Correlation, analysis, all computation of monitoring data, and bytecode manipulation to place sensors is performed outside of the monitored application, by a monitoring server.

Owner:DYNATRACE

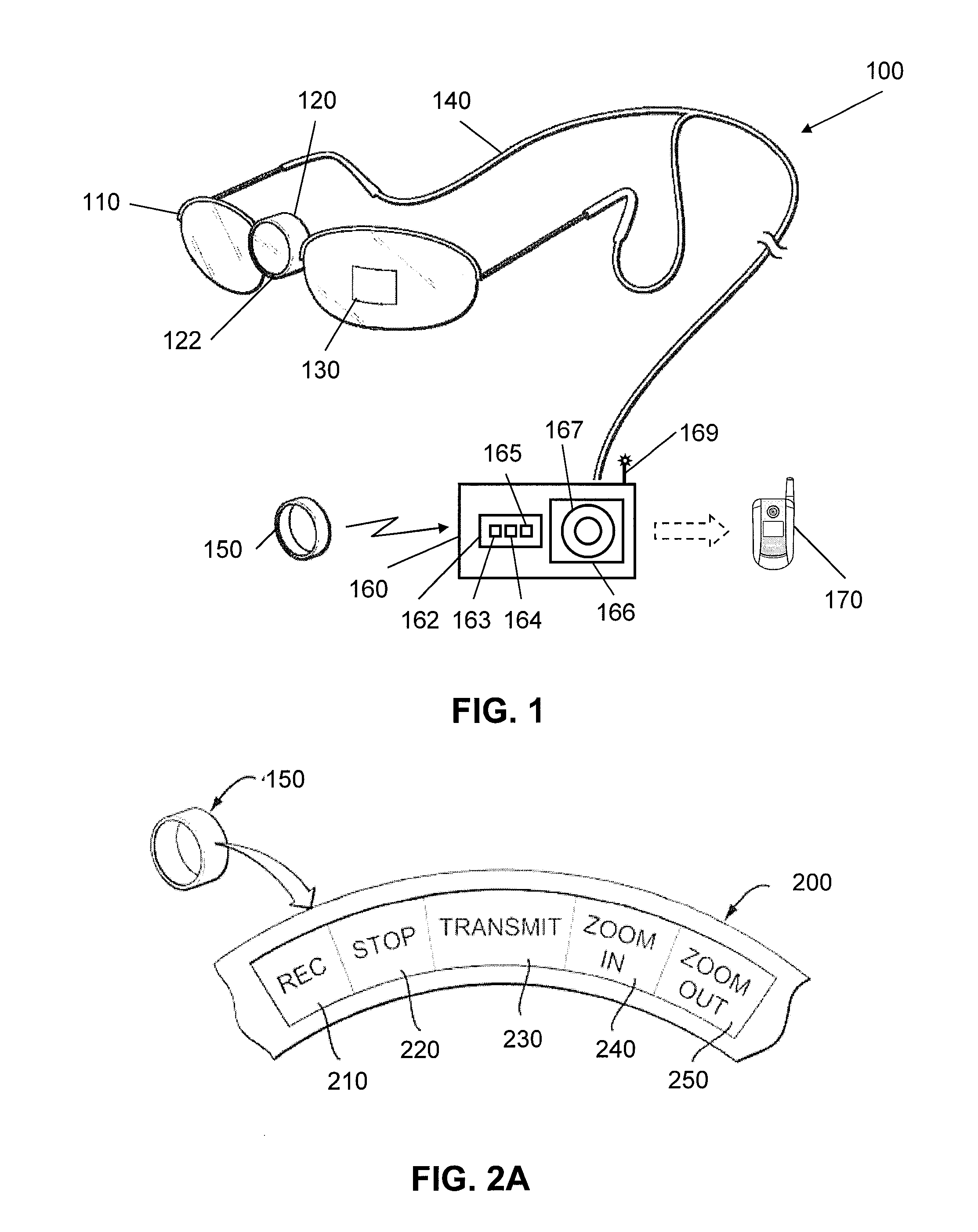

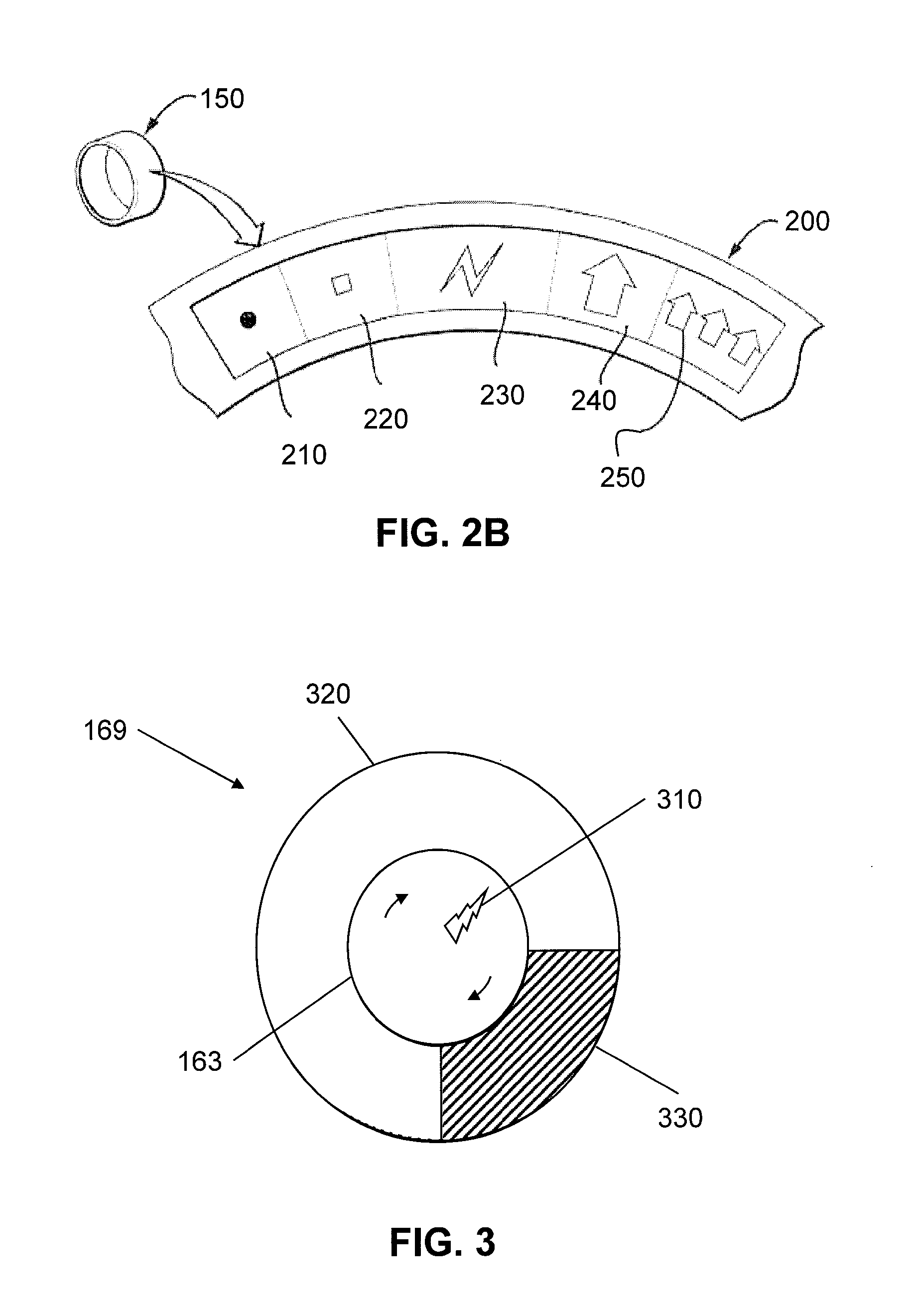

Video recording device for a targetable weapon

InactiveUS7158167B1Improve reliabilitySuitable for commercial applicationTelevision system detailsRecord information storageVideo recordCircular buffer

A compact video image recording device which is mountable to a gun and useful for recording video images before and after the firing of the gun. The recording device includes a camera comprising a lens and a video image sensor. The video recording device is mounted on the gun such that the viewing area of the camera includes the target area of the gun. The video image sensor generates an electronic signal representative of a video image impinging the respective sensor. The output of the image sensor is processed and generally employed to produce frame data which are successively stored in successive frame locations of a semiconductor memory organized as a circular buffer memory while the video recording device is in an active state. Upon the firing of the gun, additional frames are stored in the buffer memory for a short period of time and a portion of the buffer memory is employed to preserve a video record of the shooting both before and after the event. Additional frames are successively stored in the unused portion of the buffer memory. In the event of a further firing of the gun, an additional portion of the buffer memory is dedicated to preserving the image data associated with subsequent firing incident. This process may be repeated until the buffer memory is full in the event the gun is repeatedly fired. A video record is thus generated which documents the circumstances preceding and following the firing of the gun.

Owner:MITSUBISHI ELECTRIC RES LAB INC

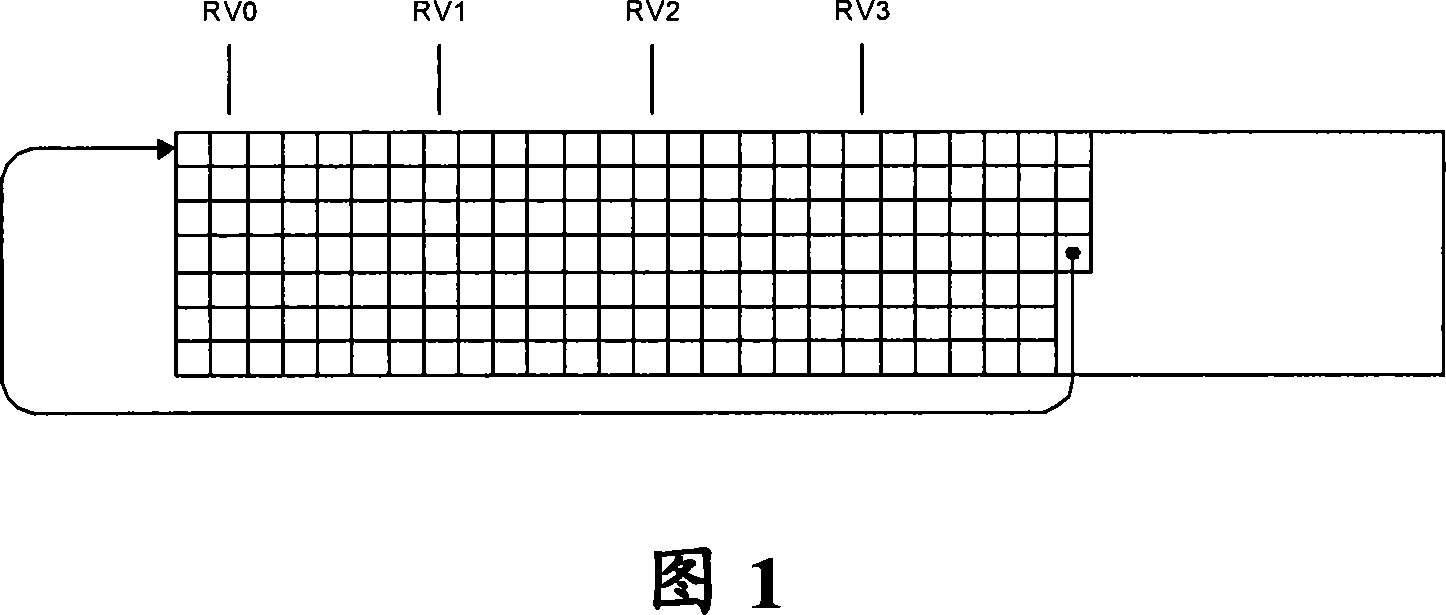

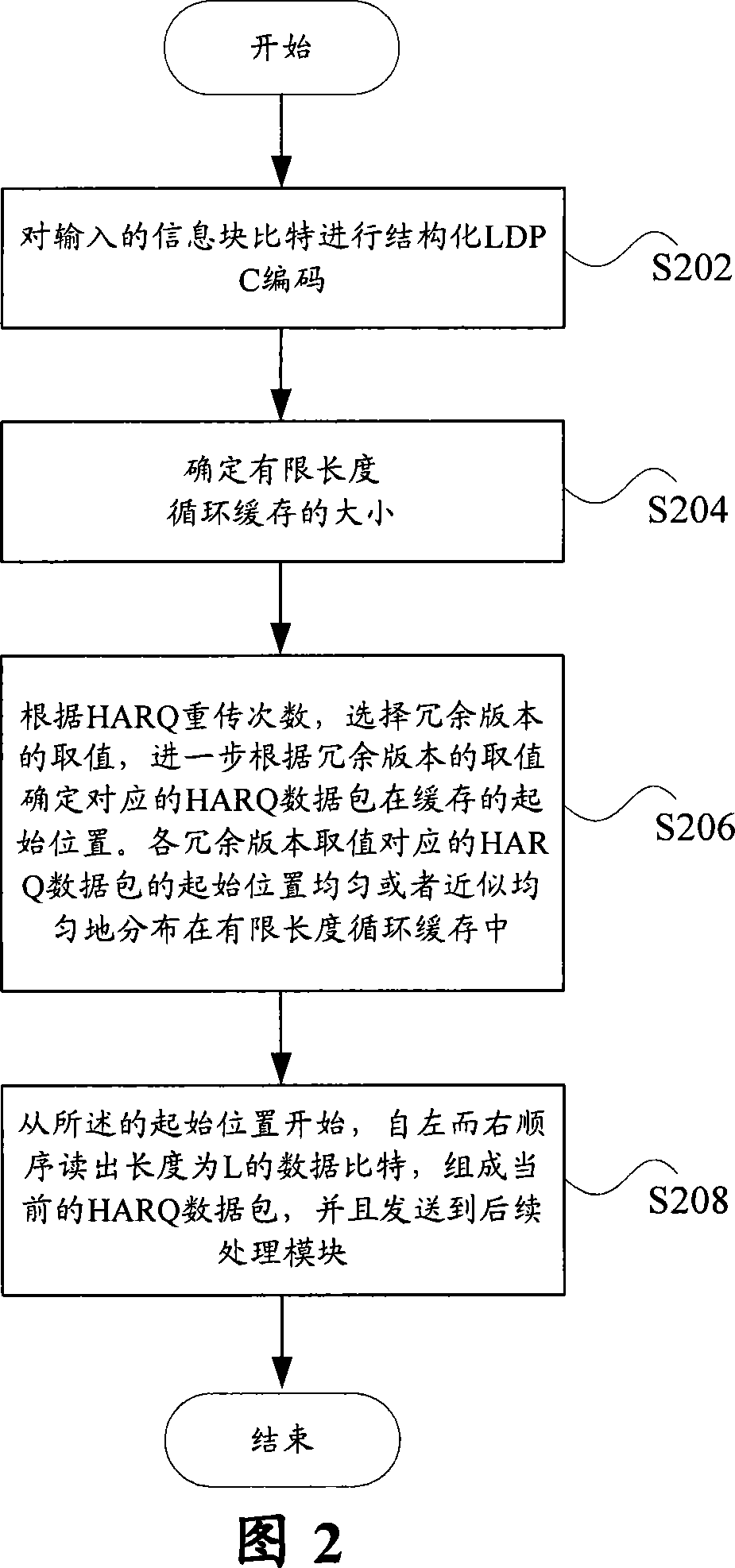

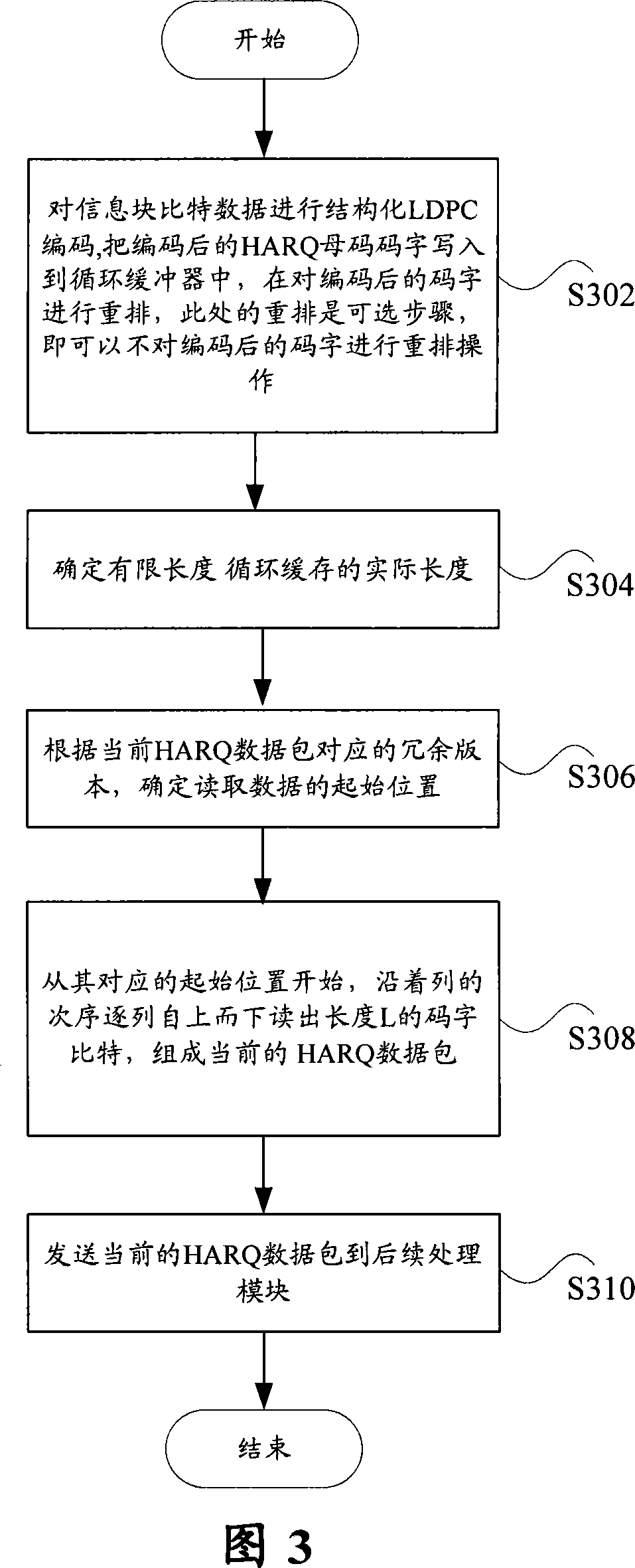

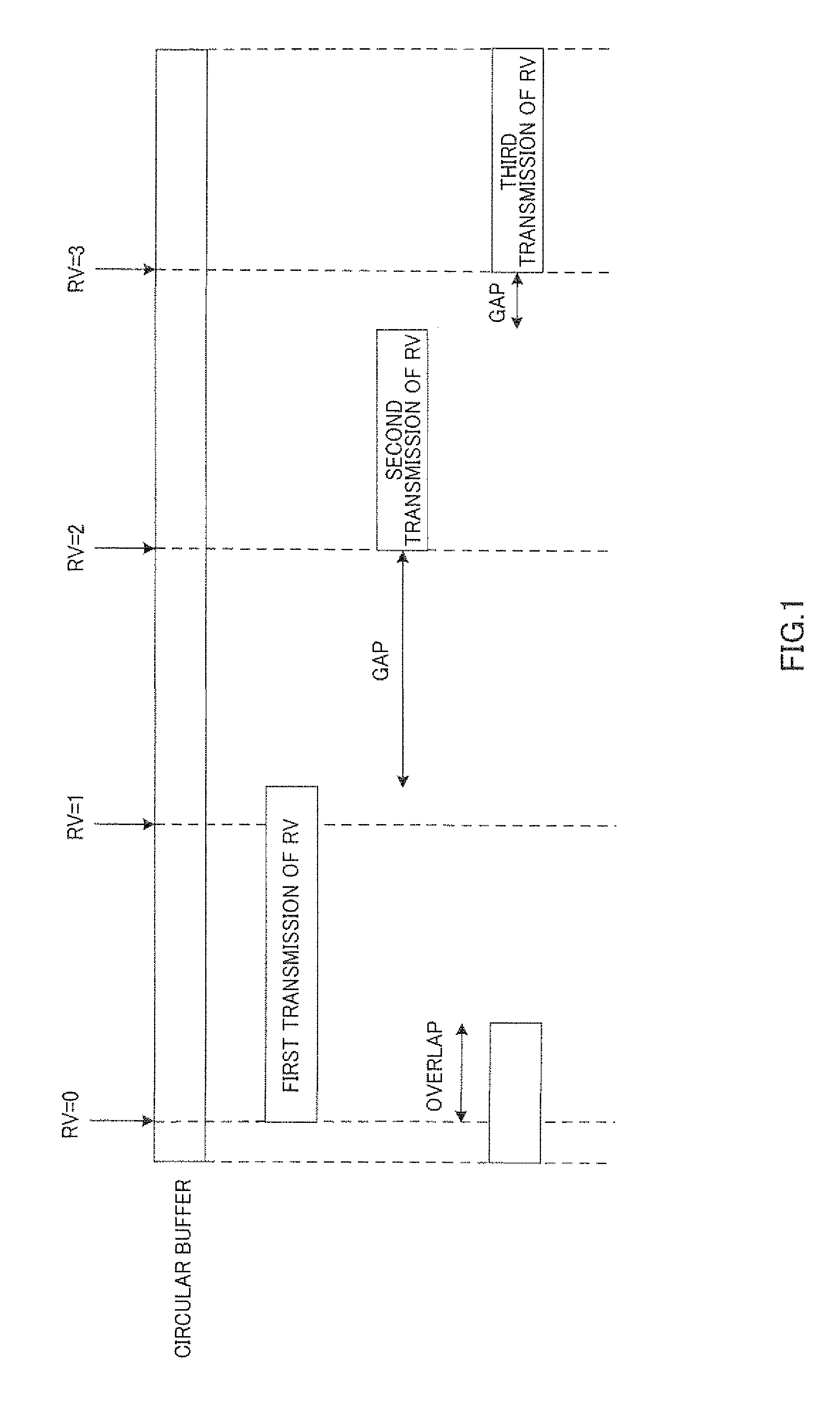

Speed matching method of limited length circular buffer of LDPC code

ActiveCN101188428AImprove retransmission performanceSave cache spaceError correction/detection using multiple parity bitsNetwork packetLow-density parity-check code

The invention discloses a speed matching method of the limited-length circular cache of a low-density parity-check code. The method includes the following steps of conducting a structured low-density parity-check code encoding on the data bit of an inputted information block, and determining the size of the one-dimensional limited-length circular cache according to the encoding result; selecting a redundant version value from a plurality of preset redundant version values according to the retransmission times of the mixed retransmission request, and determining the initial position of the data bit of the formed mixed retransmission request data packet read from the one-dimensional limited-length circular cache according to the selected redundant version value; and reading the mixed automatic retransmission request data packet composed of specific-length data from the initial position in order, and sending the mixed automatic retransmission request data packet out. The respective corresponding initial positions of the multiple preset redundant version values are evenly or almost evenly distributed on the one-dimensional limited-length circular cache.

Owner:ZTE CORP

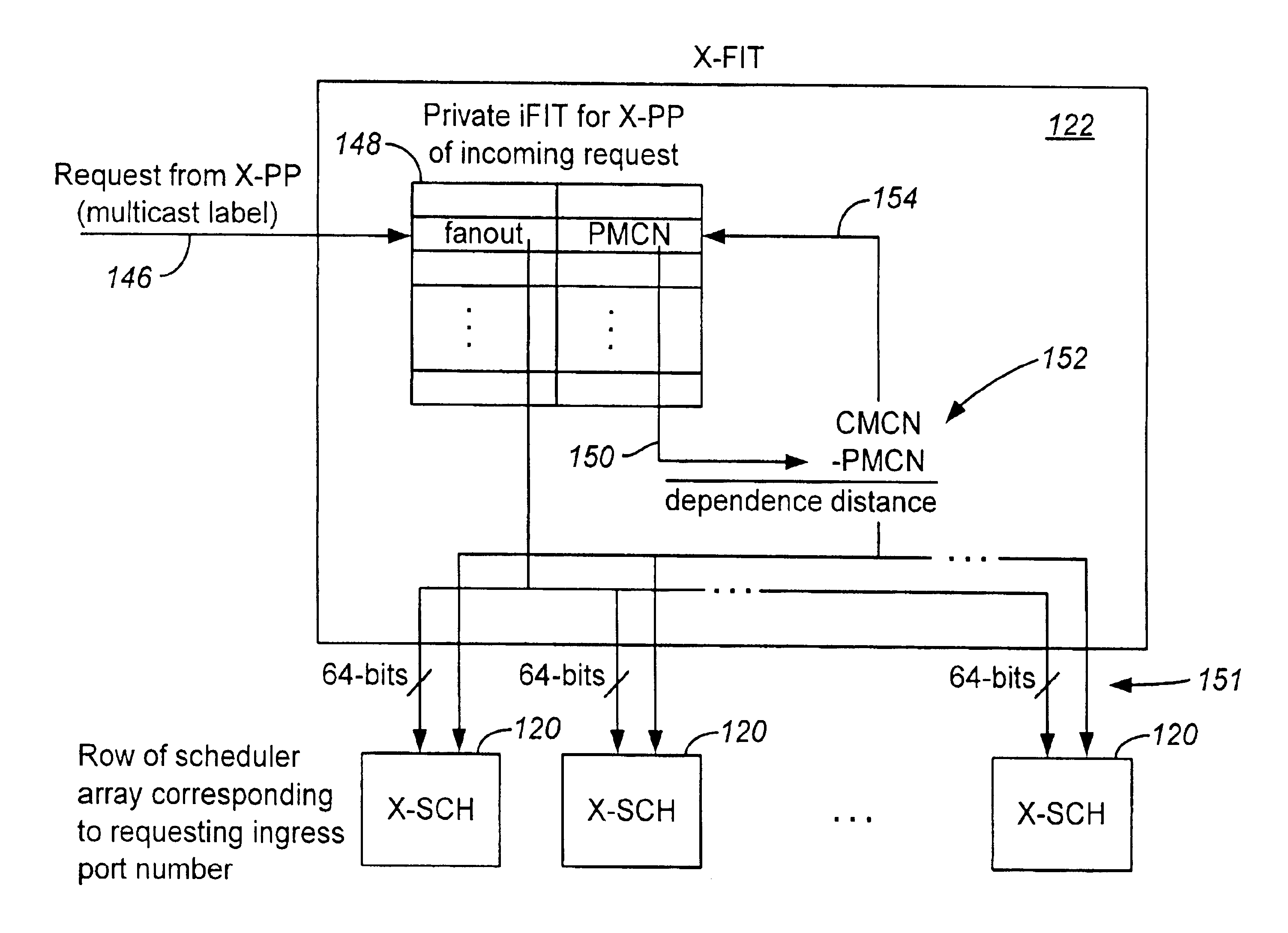

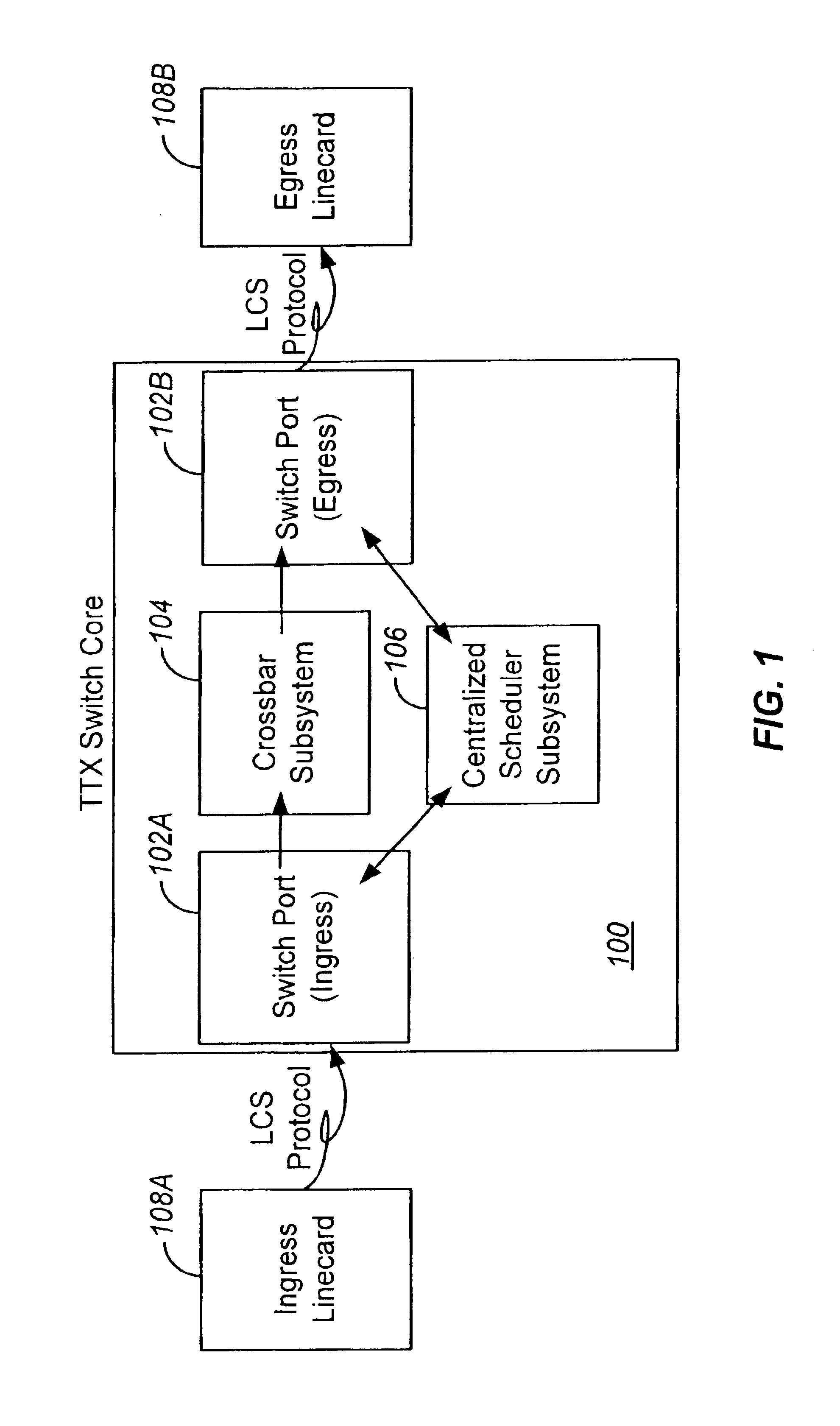

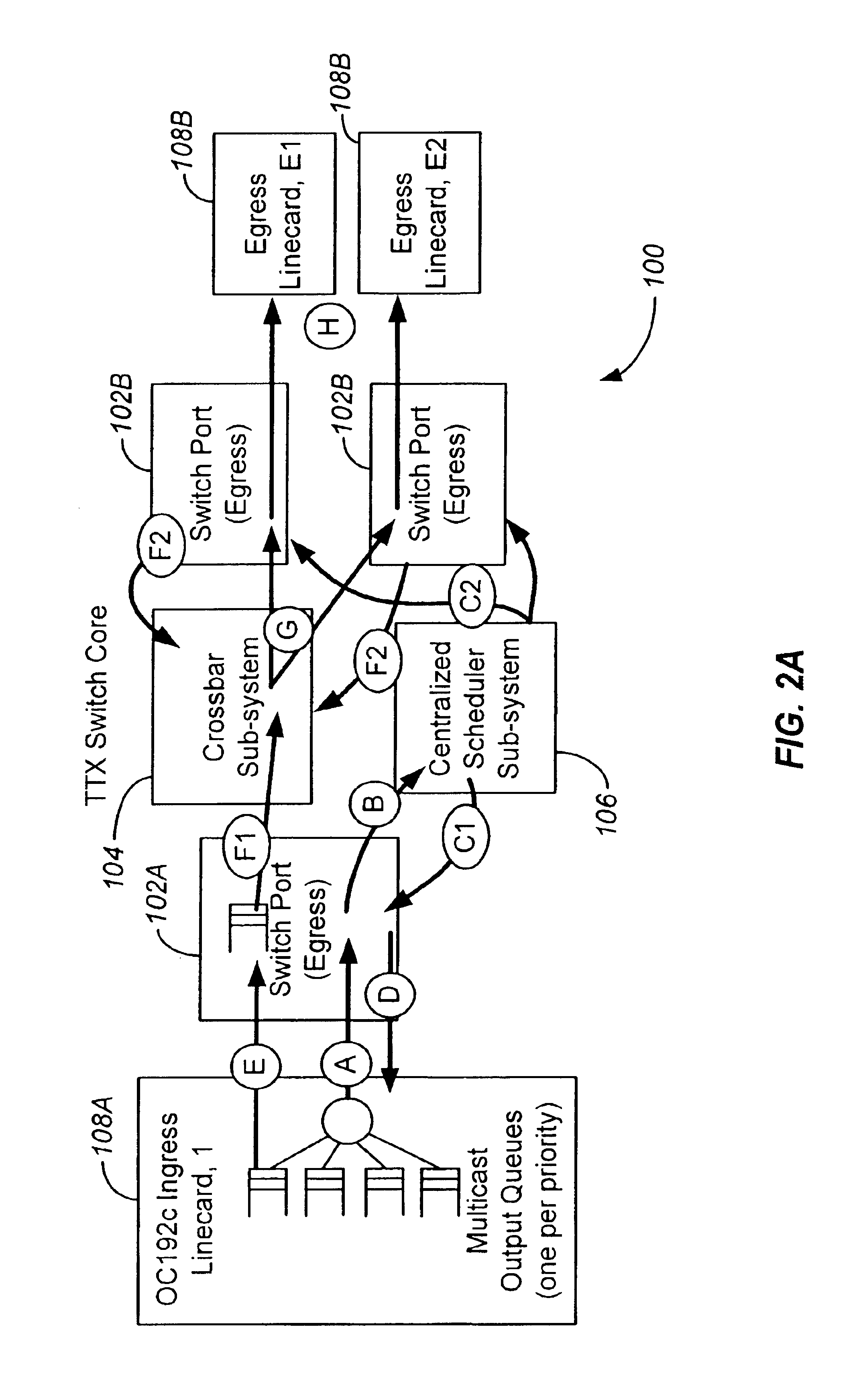

Multicast cell scheduling protocol

InactiveUS6856622B1Convenient ArrangementSpecial service provision for substationData switching by path configurationCell schedulingCircular buffer

A method of facilitating the scheduling of a first multicast request signal of a series of multicast request signals is disclosed, wherein the first request signal is generated to enable the transmission of a multicast data cell by a source port processor to at least one destination port processor. In a preferred embodiment of the invention, the first request signal is received by a roster storage chip associated with a scheduler subsystem. The first request signal has associated therewith a multicast label of a first value and is adapted to schedule transmission of the first multicast cell to the at least one destination port processor at a first time. A roster of the at least one destination port processor to which the first multicast cell is destined is then generated. A dependence distance associated with the first request signal is determined. The dependence distance comprises the numerical value of the difference between a current multicast cell number (CMCN) and a previous multicast cell number (PMCN). The roster and the dependence distance are transmitted to one of the at least one scheduler chips, such transmission causing the roster and the dependence distance to occupy a second tail entry slot of a second circular buffer associated with the one of the at least one scheduler chips. The second tail entry slot has associated therewith a first multicast table index (MTI) comprising a numerical value. The scheduler chip further has associated therewith a head entry slot having associated therewith a second MTI comprising a numerical value. A first numerical parameter comprising the numerical sum of the dependence distance and the first MTI is determined. If the first numerical parameter is higher in value than the second MTI, the first request signal is arbitrated.

Owner:PMC-SIERRA

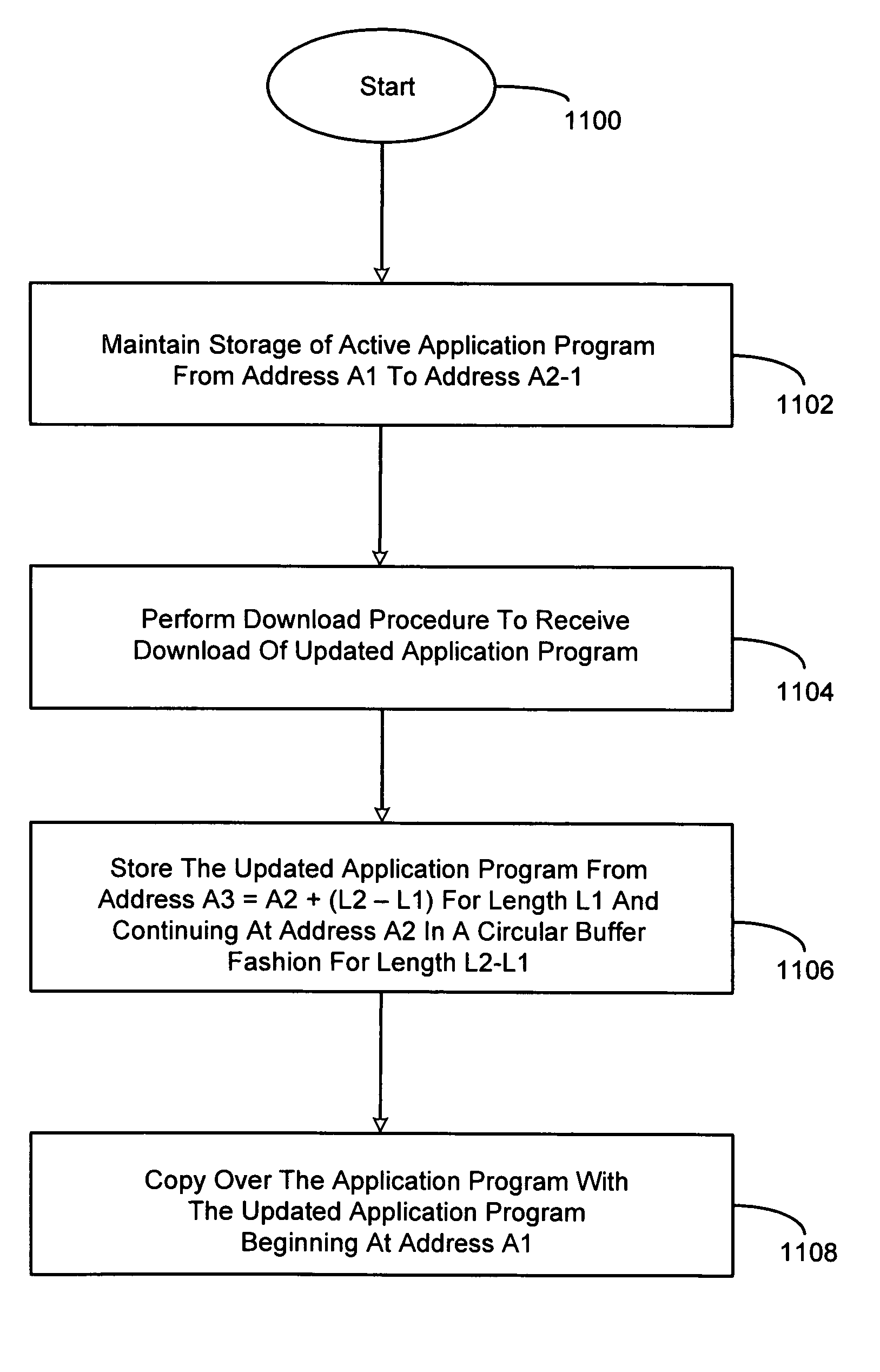

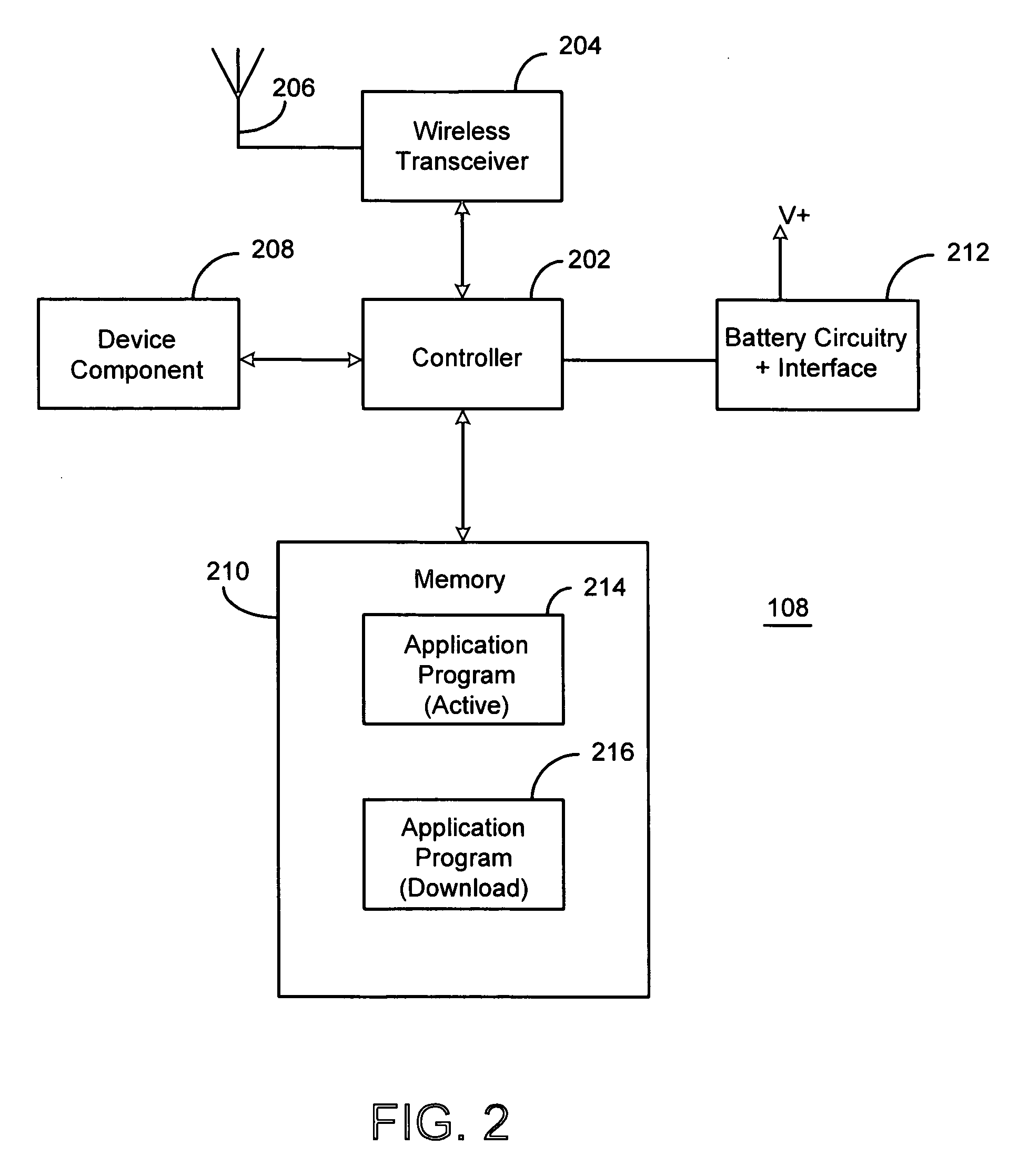

Methods and apparatus for use in updating application programs in memory of a network device

ActiveUS20070169080A1Multiple digital computer combinationsStatic storageMemory addressCircular buffer

An illustrative method of the present application is for use in updating an application program in memory of a network device. An application program having a length L1 is initially stored in memory of the network device from a memory address A1 to a memory address A2−1. A download procedure is performed by the network device to receive an updated application program having a length L2>L1. This updated application program is stored in the memory from a memory address A3=A2+(L2−L1) for the length L1, and continuing in a circular buffer fashion from the memory address A2 for the length L2−L1. The application program is then copied over with the updated application program beginning at the memory address A1. With this technique, if a failure occurs while copying over the application program, no portion of the original updated application program will be written over.

Owner:OSKOREP JOHN J ESQ +1

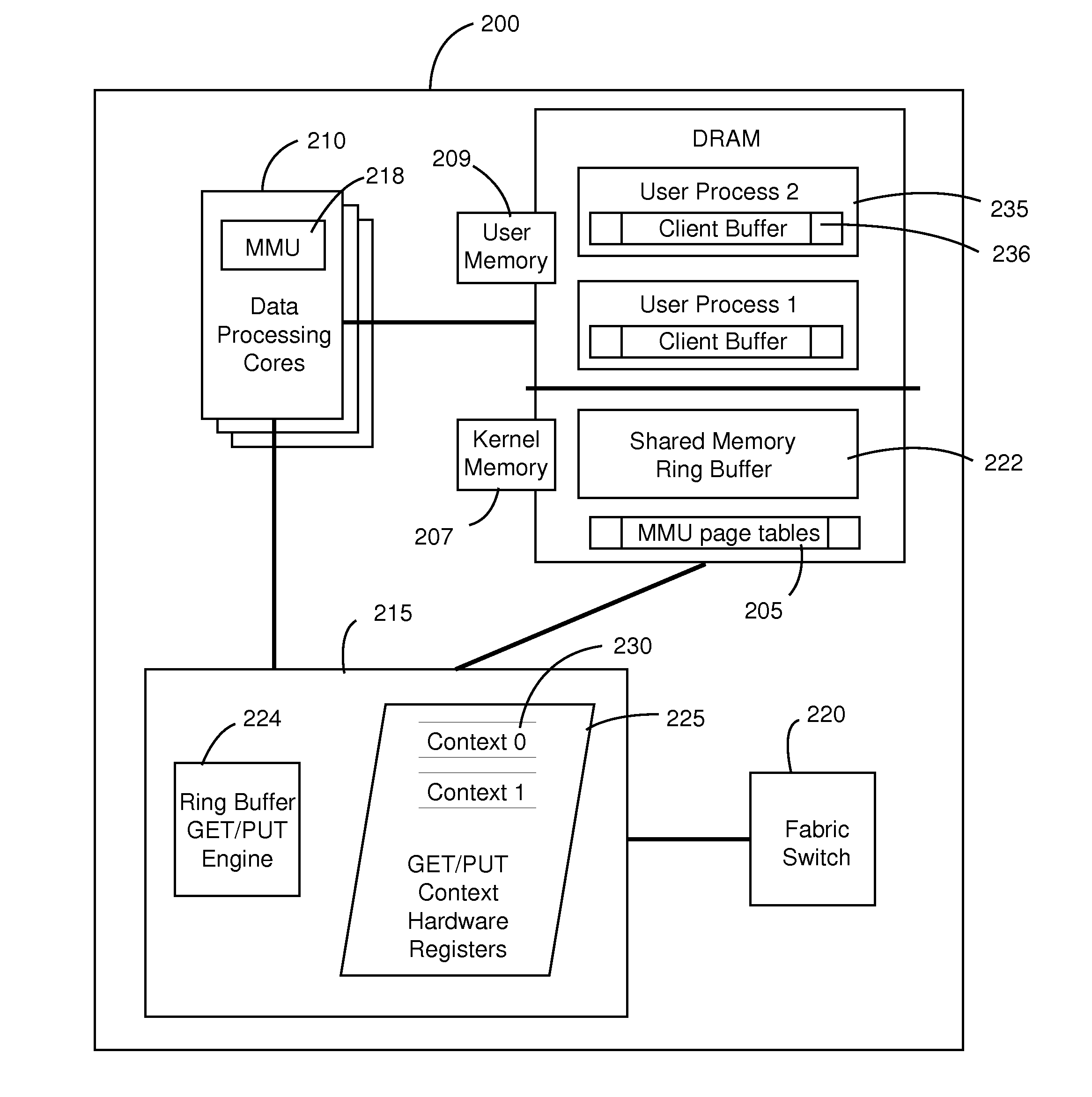

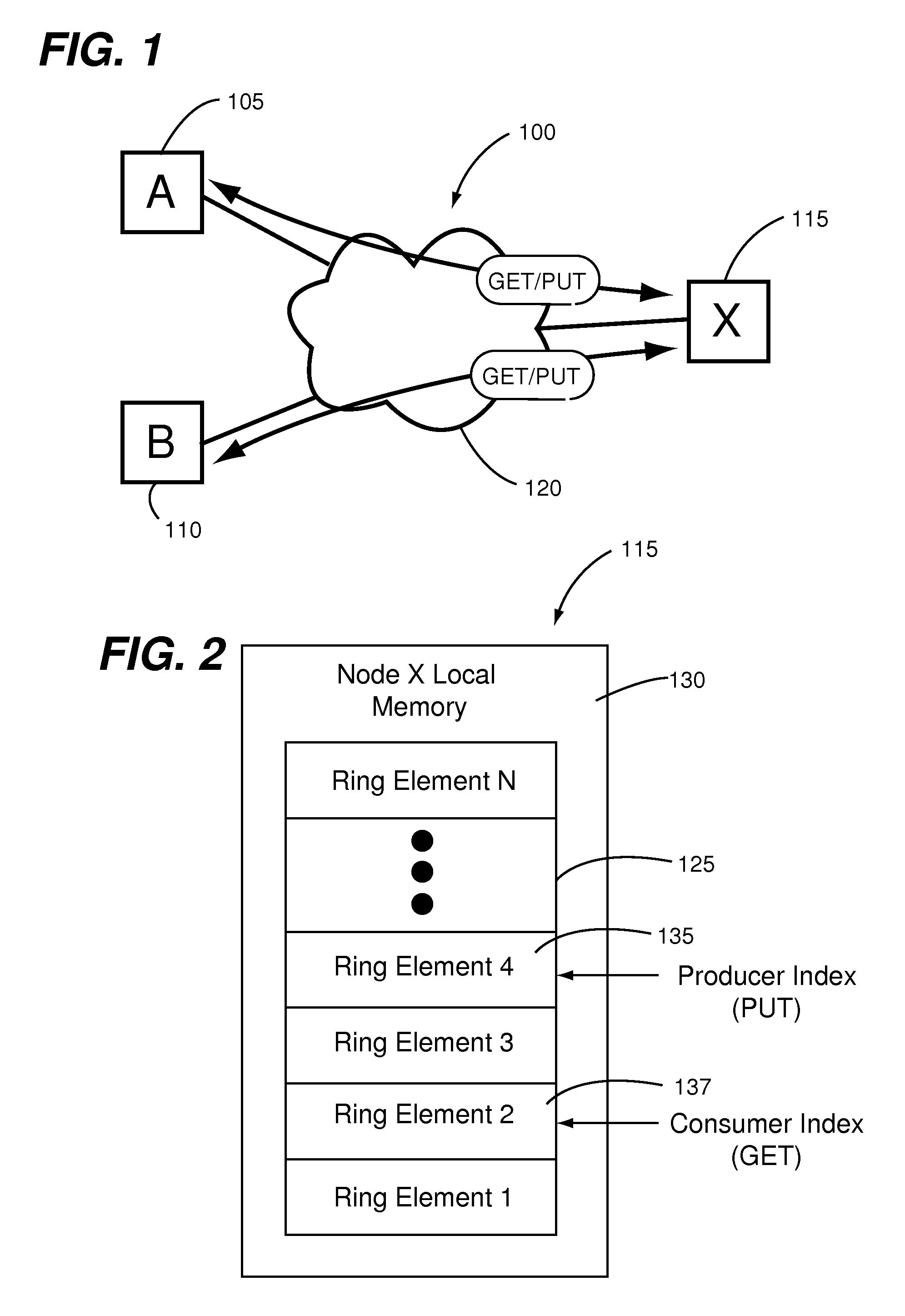

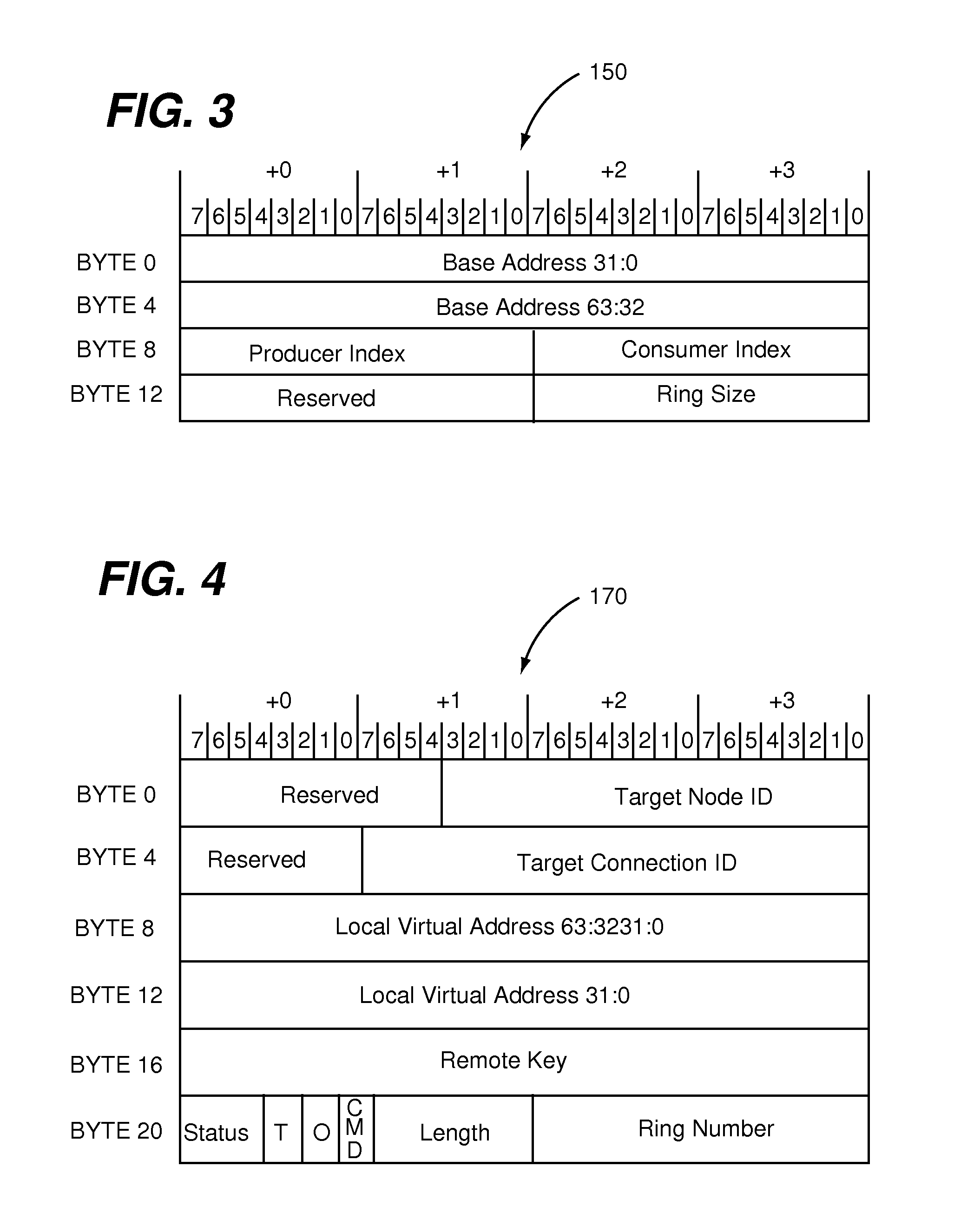

Remote memory ring buffers in a cluster of data processing nodes

ActiveUS20150039840A1Interprogram communicationDigital computer detailsProcessor registerStructure of Management Information

A data processing node has an inter-node messaging module including a plurality of sets of registers each defining an instance of a GET / PUT context and a plurality of data processing cores each coupled to the inter-node messaging module. Each one of the data processing cores includes a mapping function for mapping each one of a plurality of user level processes to a different one of the sets of registers and thereby to a respective GET / PUT context instance. Mapping each one of the user level processes to the different one of the sets of registers enables a particular one of the user level processes to utilize the respective GET / PUT context instance thereof for performing a GET / PUT action to a ring buffer of a different data processing node coupled to the data processing node through a fabric without involvement of an operating system of any one of the data processing cores.

Owner:III HLDG 2

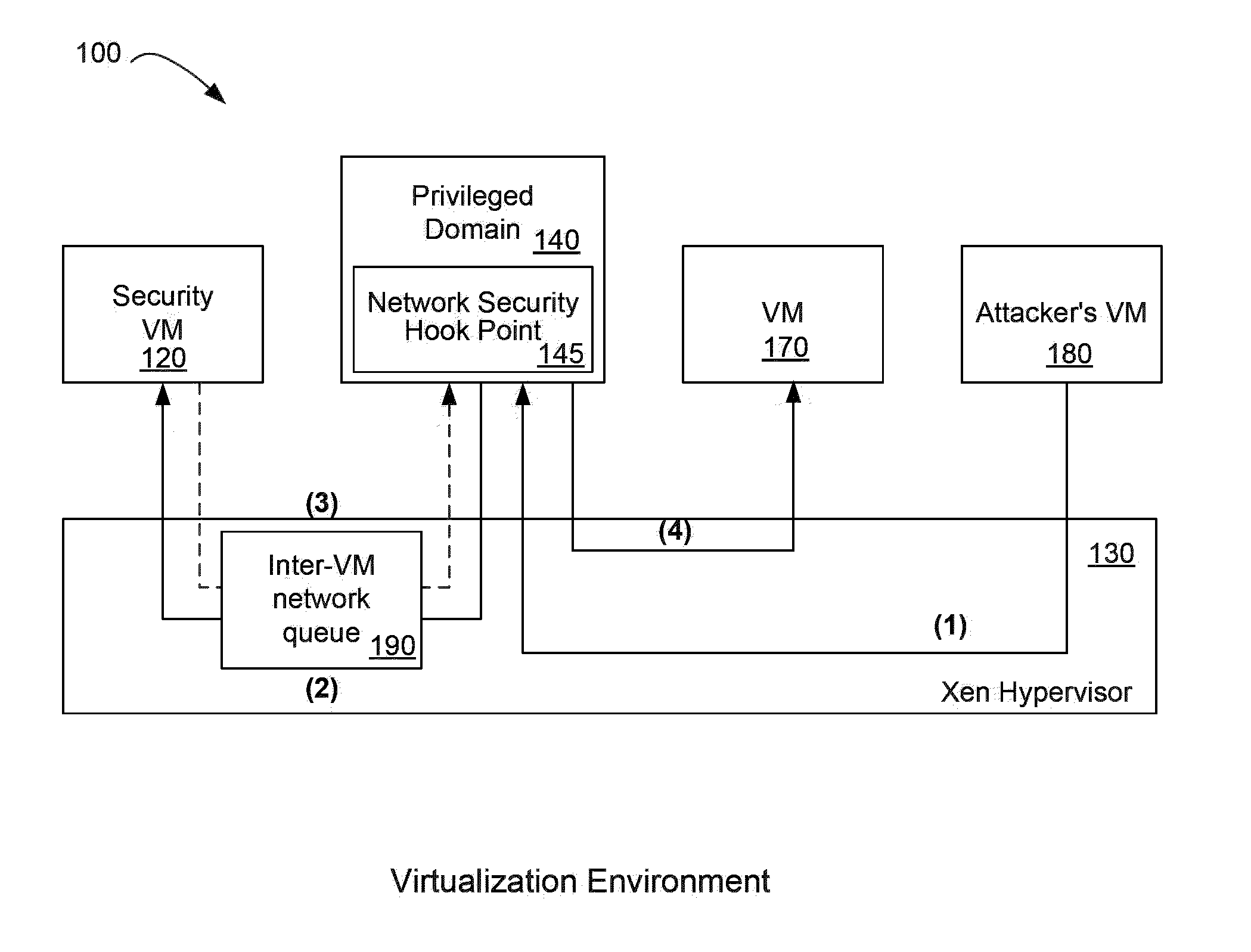

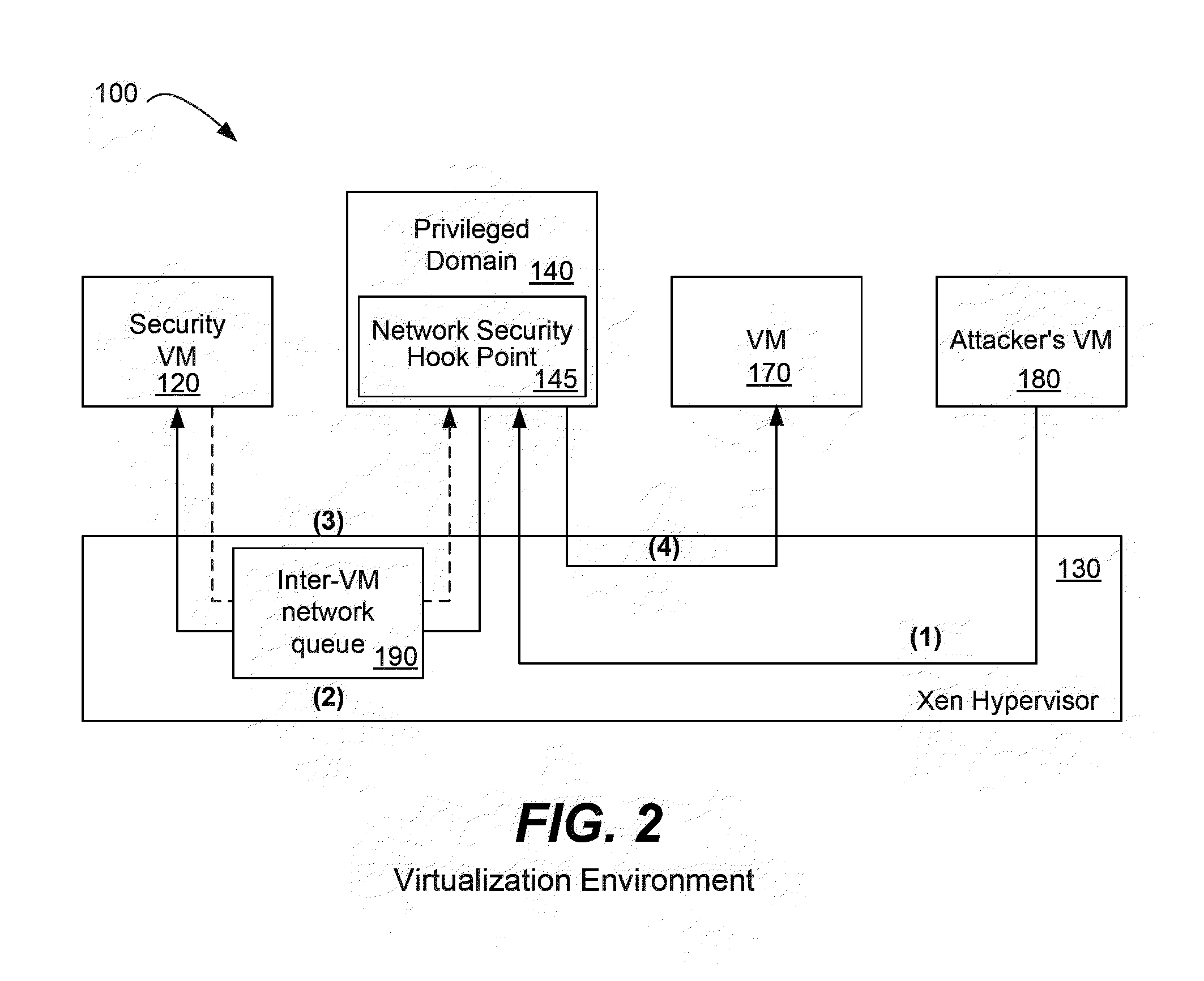

Cross-VM network filtering

ActiveUS20130036470A1Improve performanceMemory loss protectionError detection/correctionVirtualizationNetwork packet

A security virtual machine inspects all data traffic between other virtual machines on a virtualization platform in order to prevent an inter-VM attack. Data traffic between the machines is intercepted at the privileged domain and directed to the security virtual machine via a hook mechanism and a shared memory location. The traffic is read by the security machine and analyzed for malicious software. After analysis, the security machine sends back a verdict for each data packet to the privileged machine which then drops each data packet or passes each data packet on to its intended destination. The privileged domain keeps a copy of each packet or relies upon the security machine to send back each packet. The security machine also substitutes legitimate or warning data packets into a malicious data package instead of blocking data packets. The shared memory location is a circular buffer for greater performance. Traffic is intercepted on a single host computer or between host computers.

Owner:TREND MICRO INC

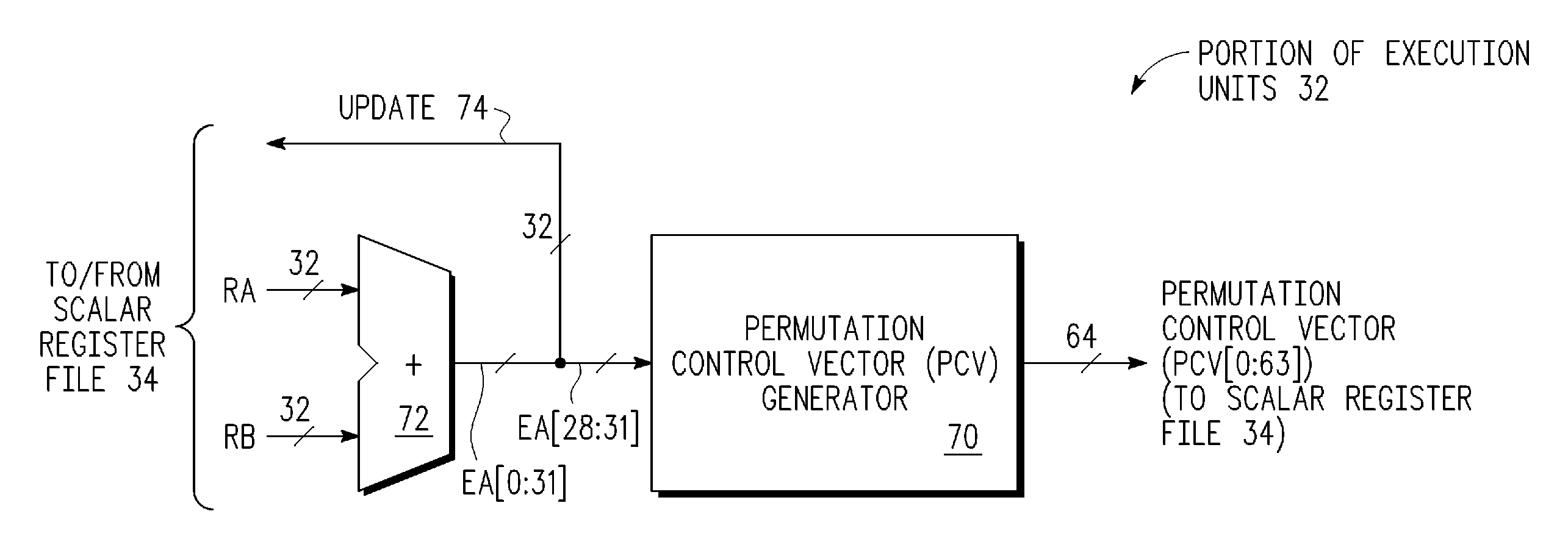

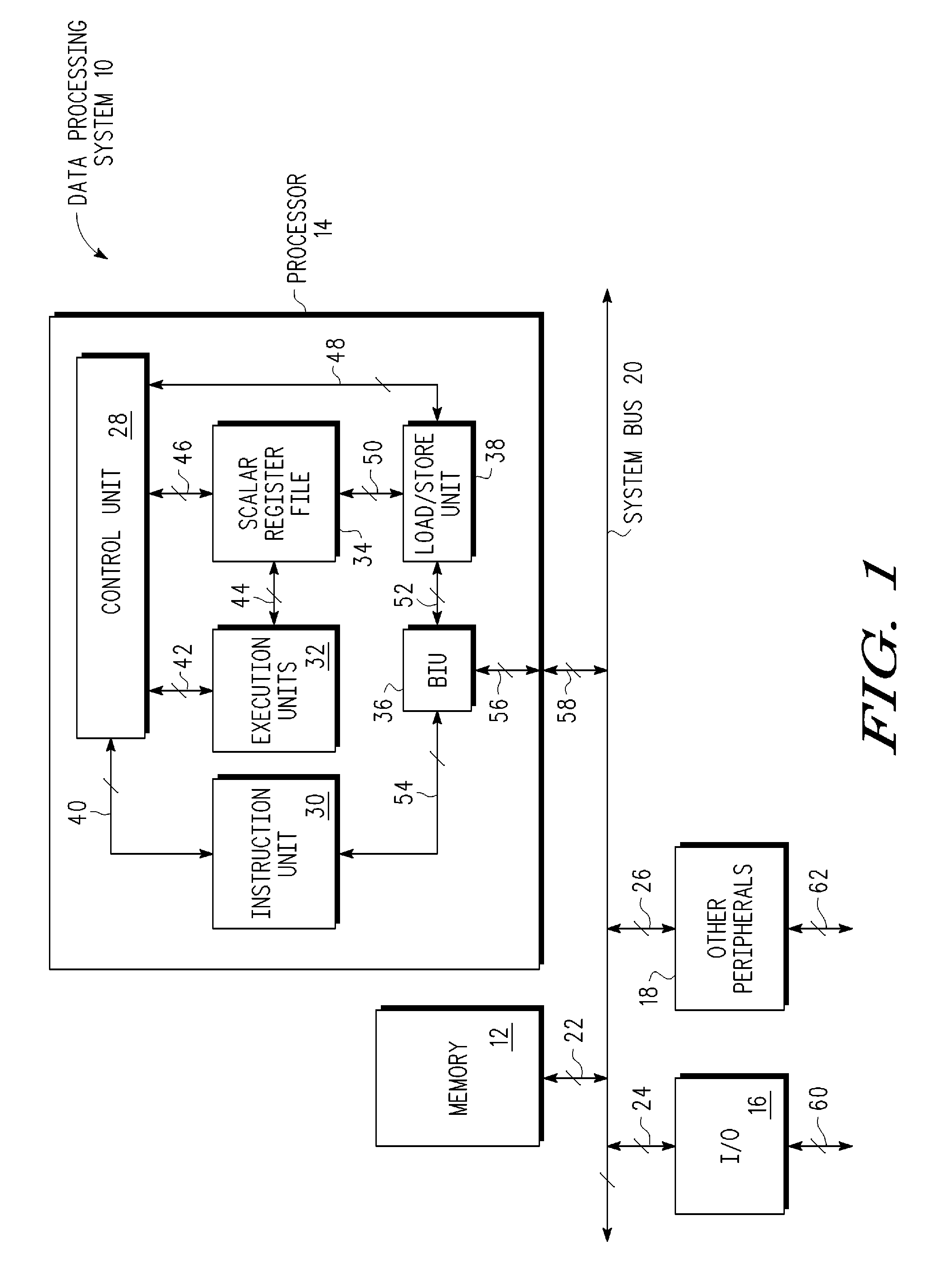

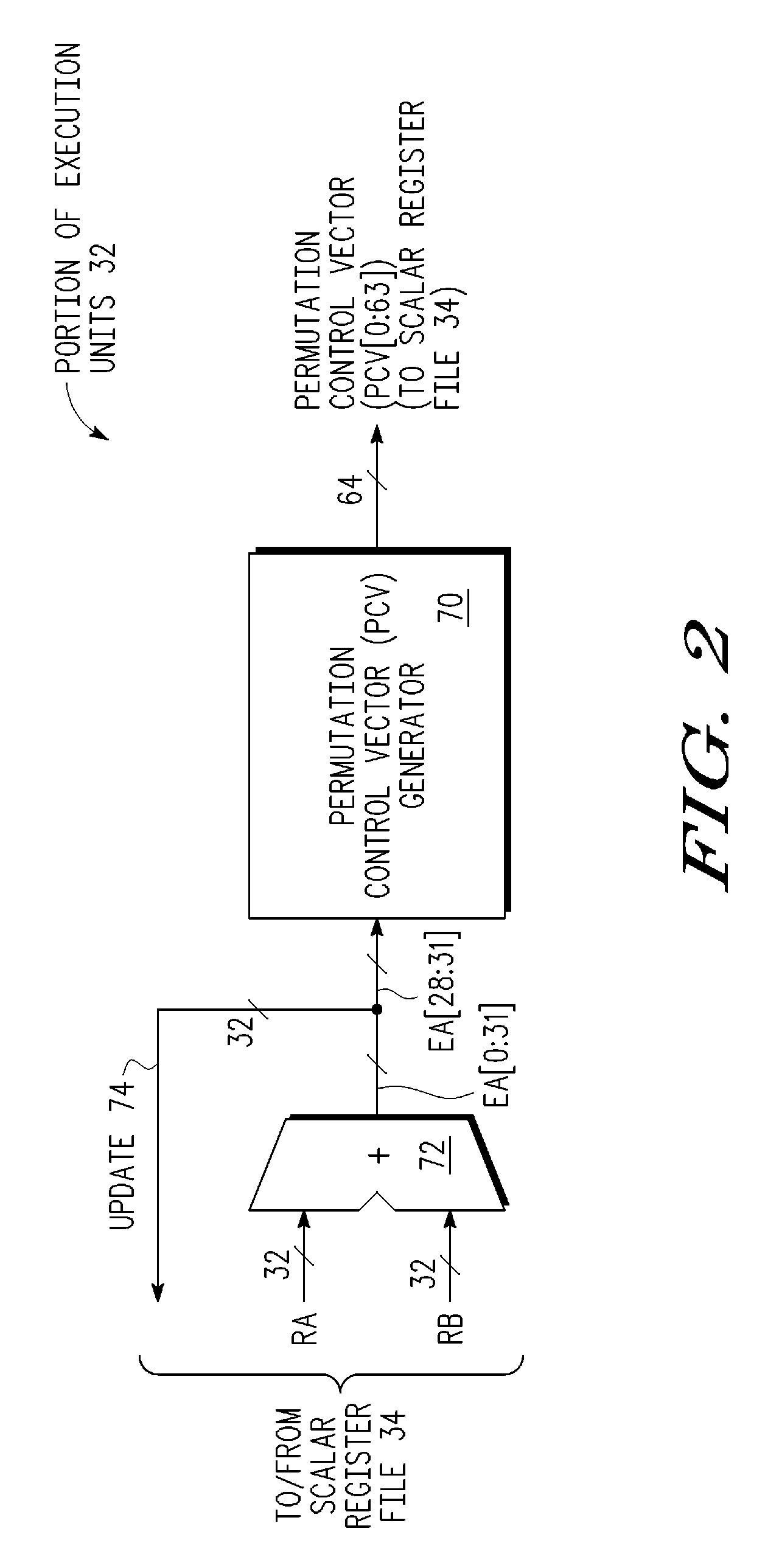

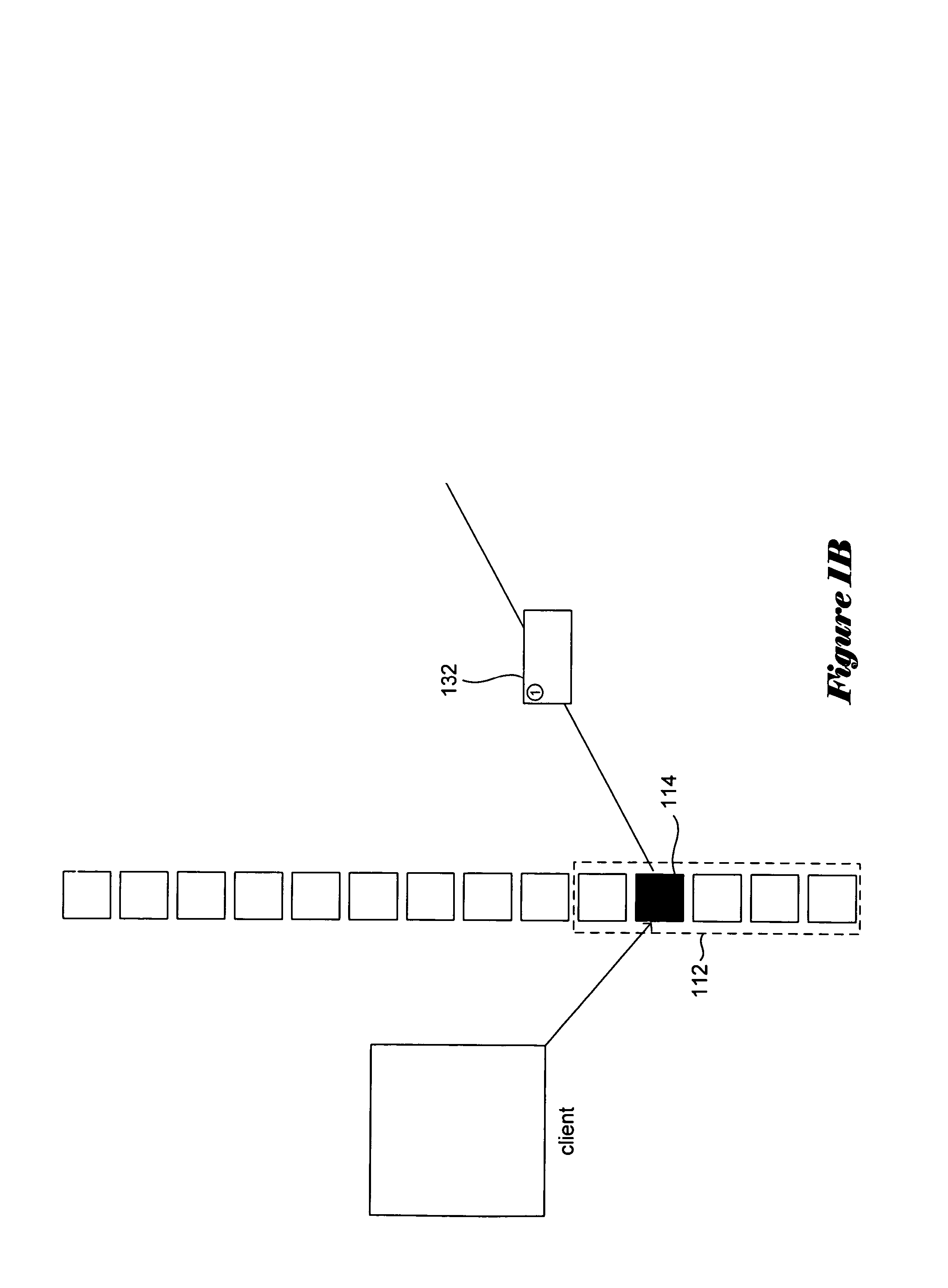

Circular buffer support in a single instruction multiple data (SIMD) data processsor

A method is provided for generating a control vector. The method comprising: providing a circular buffer having a plurality of storage elements that are arranged sequentially from a designated first storage element to a designated last storage element, and when the designated last storage element of the plurality of storage elements is accessed, the access continuing in a sequential order continuing with the designated first storage element; determining a beginning storage element of the plurality of storage elements to be accessed; and generating a control vector, the control vector comprising a plurality of index values, each of the plurality of index values corresponding to one of the plurality of storage elements of the circular buffer to be accessed in the sequential order from the beginning storage element to an ending storage element.

Owner:NORTH STAR INNOVATIONS

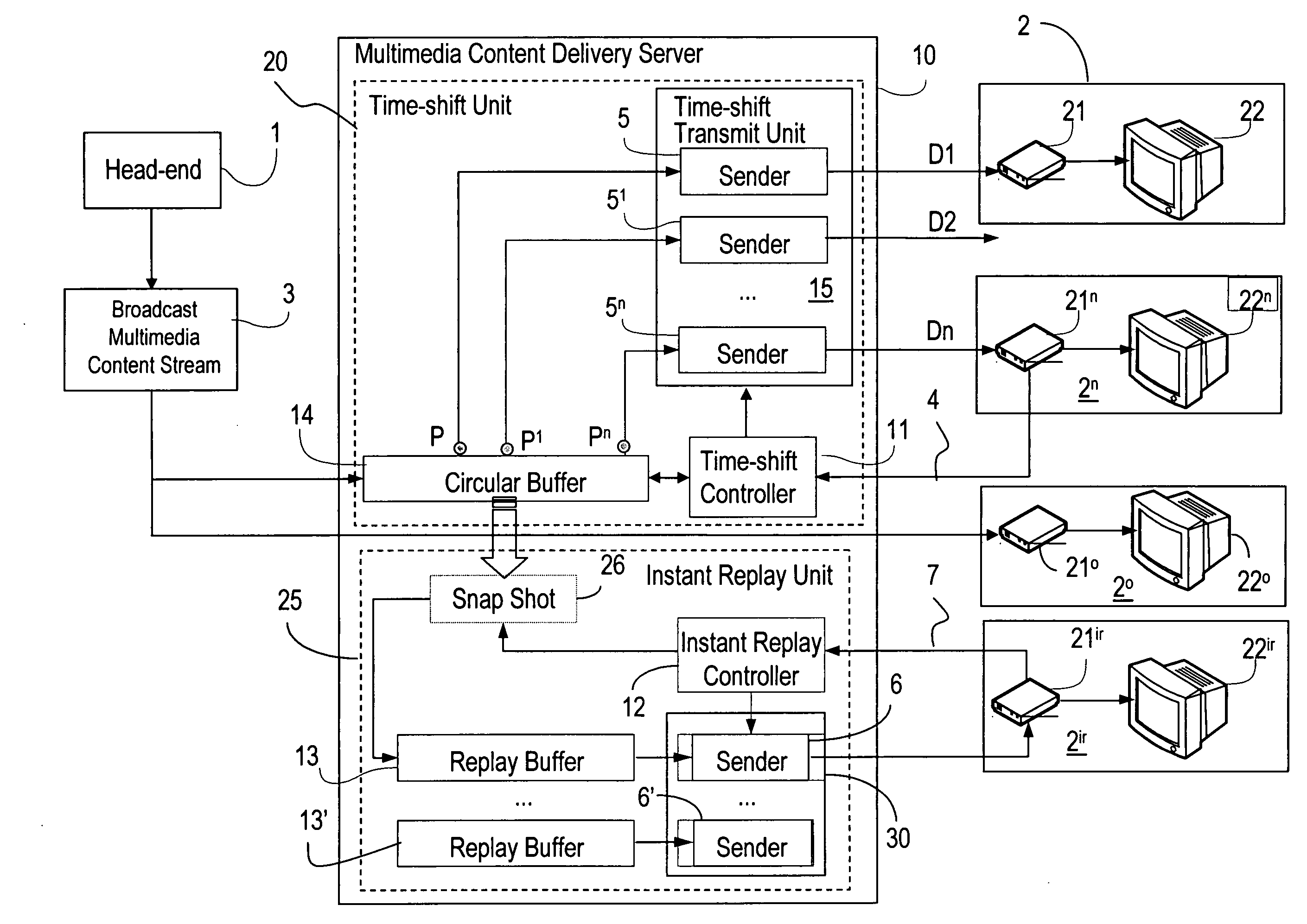

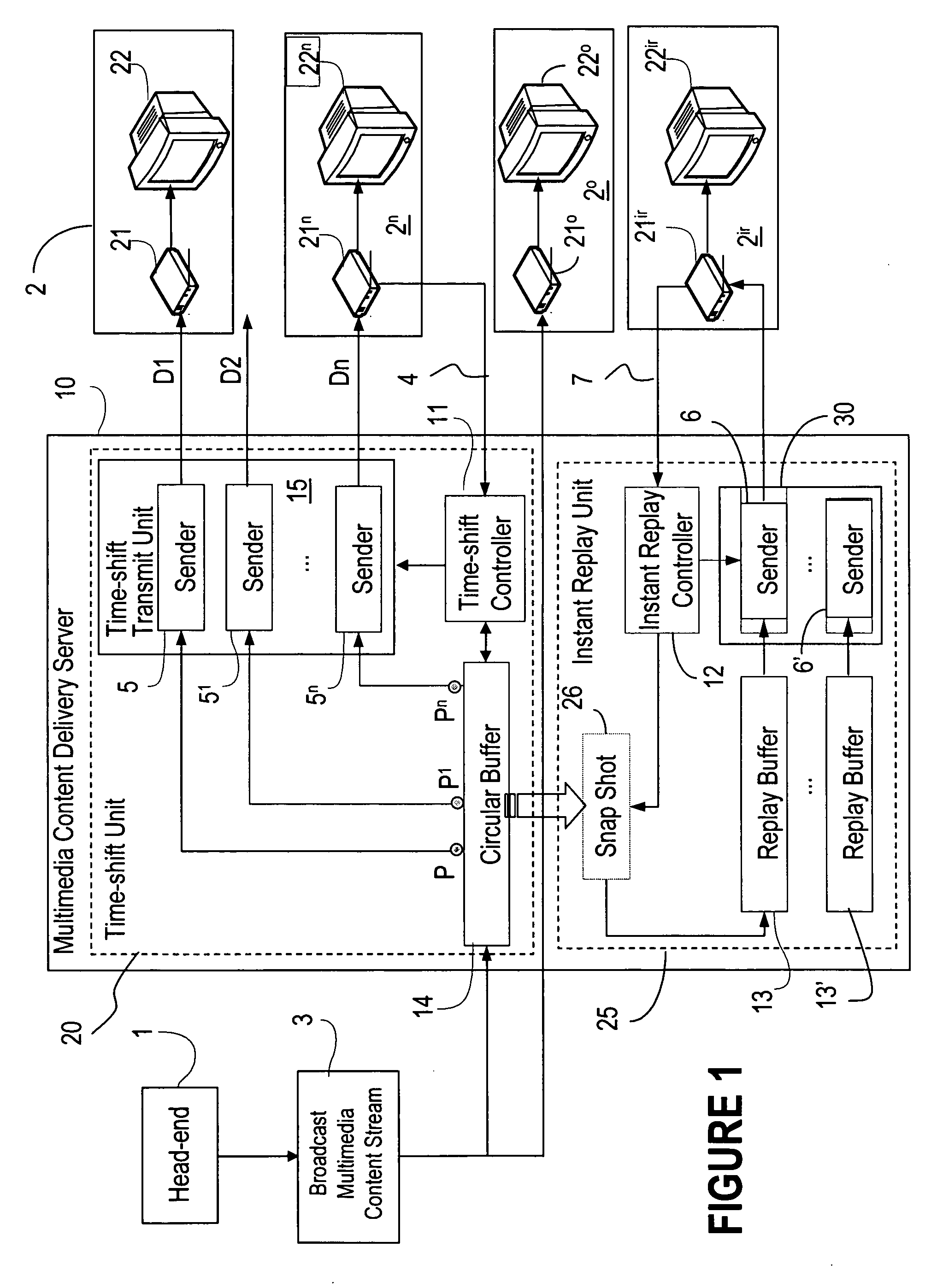

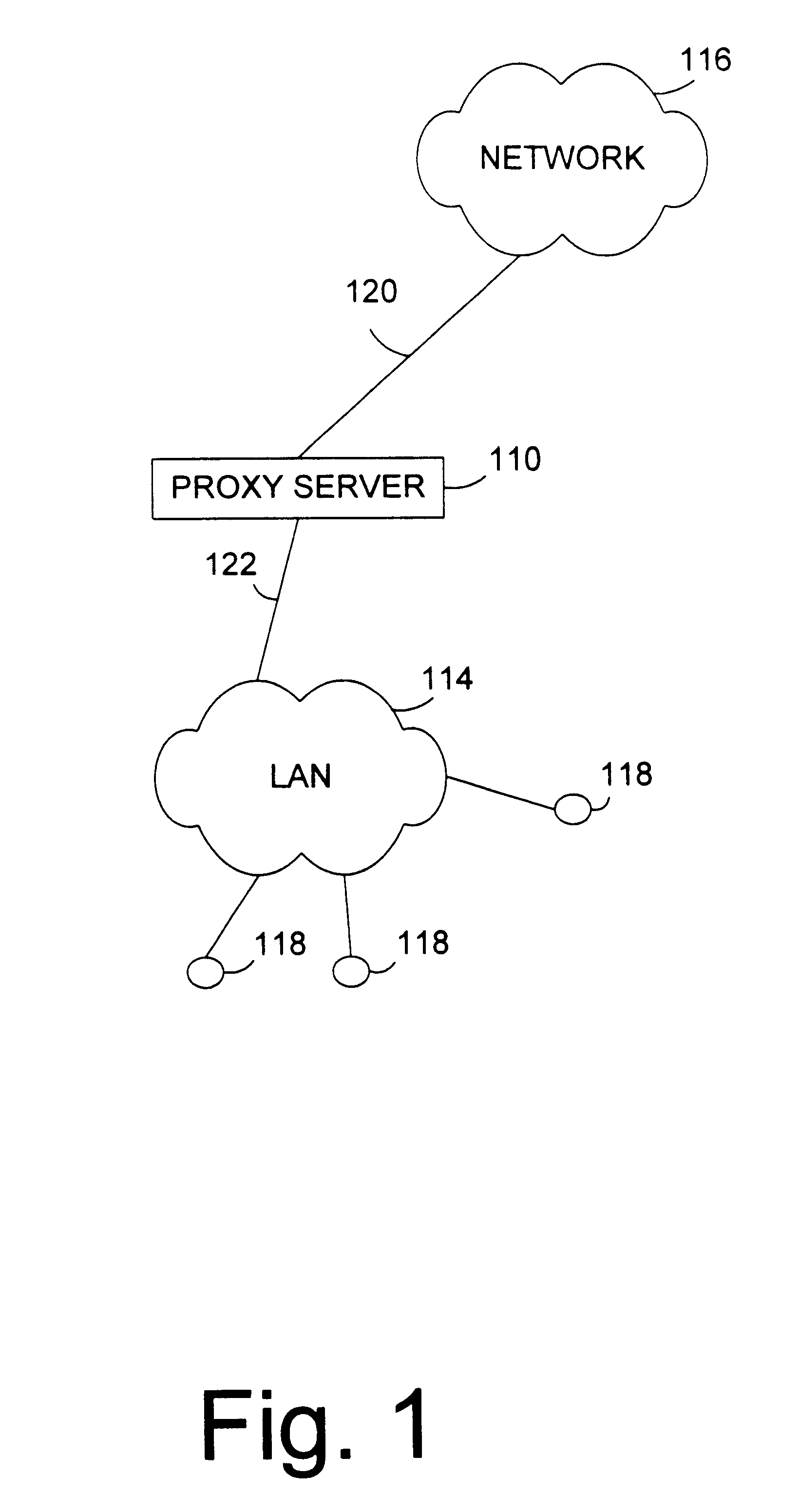

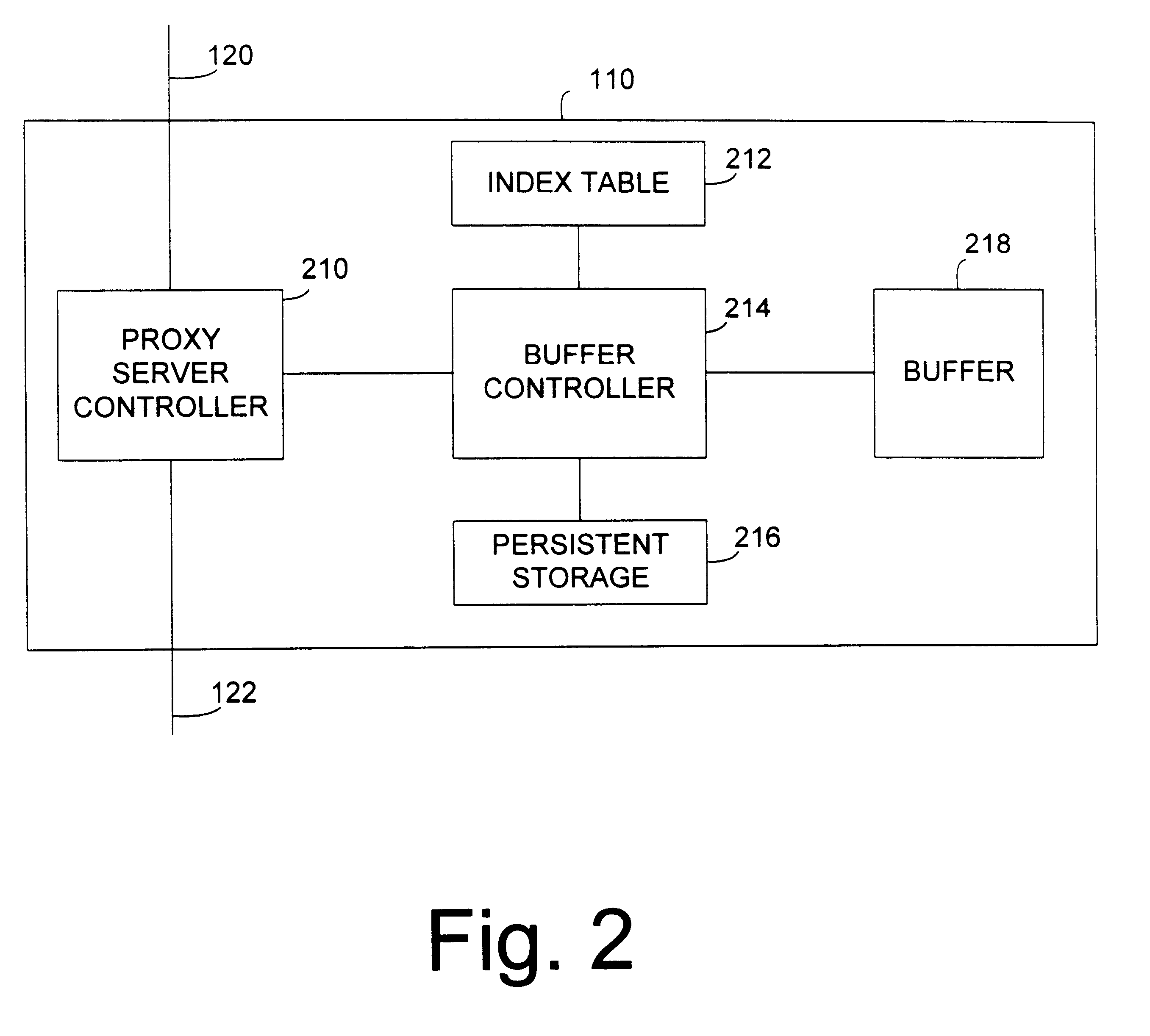

Network based instant replay and time shifted playback

InactiveUS20070130597A1Reduce complexityLess memoryTelevision system detailsBroadcast system return channelsVideo deliveryCircular buffer

A circular buffer in a video delivery server tracks a second copy of a live video stream to provide instant replay capability. When an end-user initiates the instant replay function, the circular buffer is copied to an instant-replay buffer, from which a replay of the video is sent to the end-user. During replay the end-user can use playback functions such as pause, slow-play, freeze frame, etc. Upon leaving the replay function the end user rejoins the live stream. The circular buffer also enables transmission of delayed copies of the live stream, time-shifted by predetermined intervals, which copies are multicasted to end-users. Upon request, an end-user may join a delayed version of interest. This allows the user to replay interesting content by jumping to a time-delayed version without missing the show and to catch up with real-time during e.g. commercial breaks.

Owner:ALCATEL LUCENT SAS

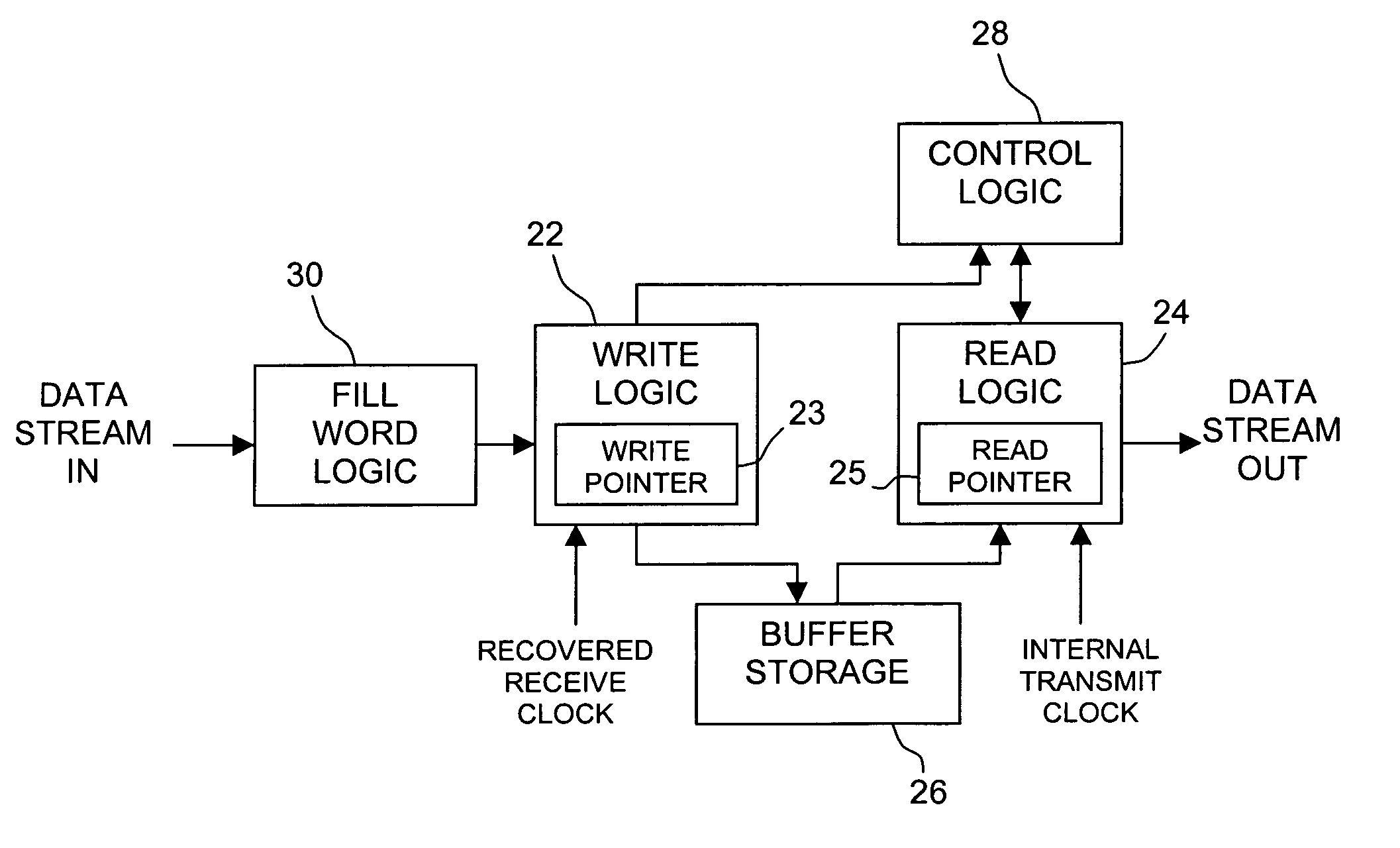

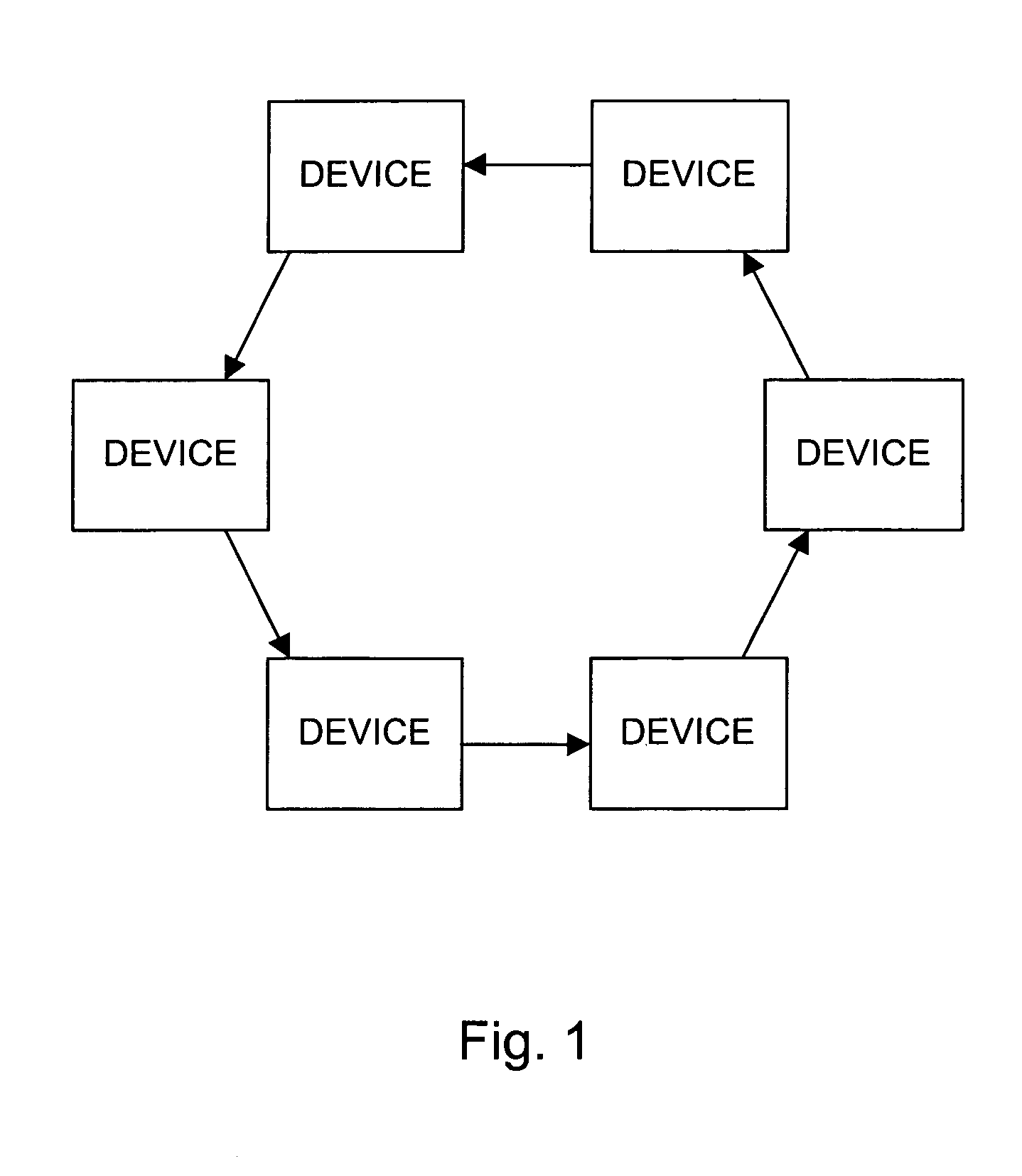

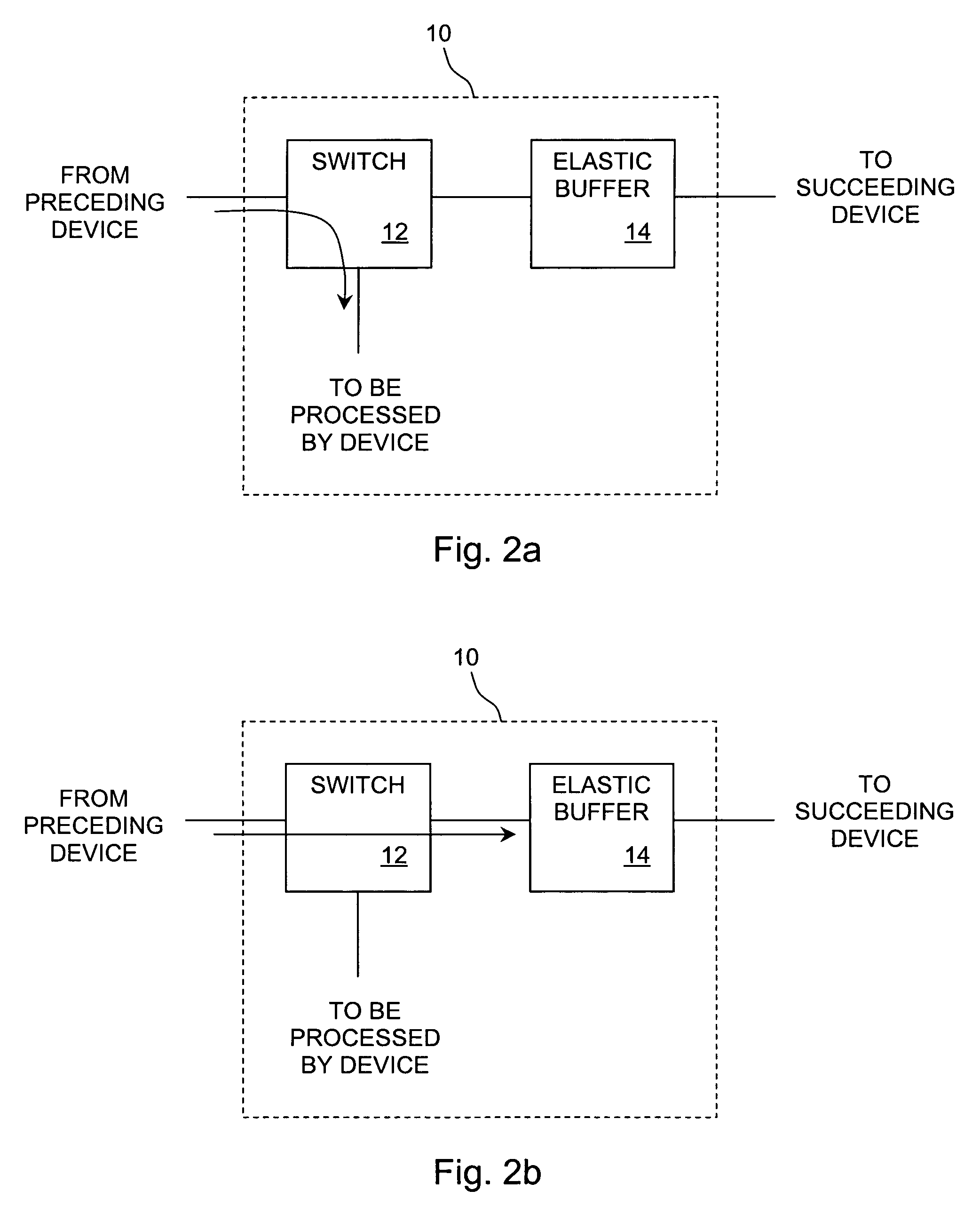

System and method for jitter compensation in data transfers

InactiveUS6977897B1Reduce in quantitySimplify comparison logicError preventionFrequency-division multiplex detailsCircular bufferData Corruption

A system and method for compensating for differences between a recovered receive clock and an internal transmit clock in an elastic buffer and thereby preventing corruption of data. In one embodiment, the system comprises a circularly accessed buffer coupled to read and write logic. The read and write logic read and write to locations within the circular buffer as indicated by respective read and write pointers. The system further comprises control logic which compares the pointers to determine whether the buffer is approaching an underflow or overflow condition and adds or deletes fill words between frames of data to compensate for the underflow or overflow condition. In one embodiment, the system includes fill word logic which is configured to add a fill word bit to each received word and to set or clear the fill word bit to indicate whether or not the corresponding word is a fill word.

Owner:CF DB EZ +1

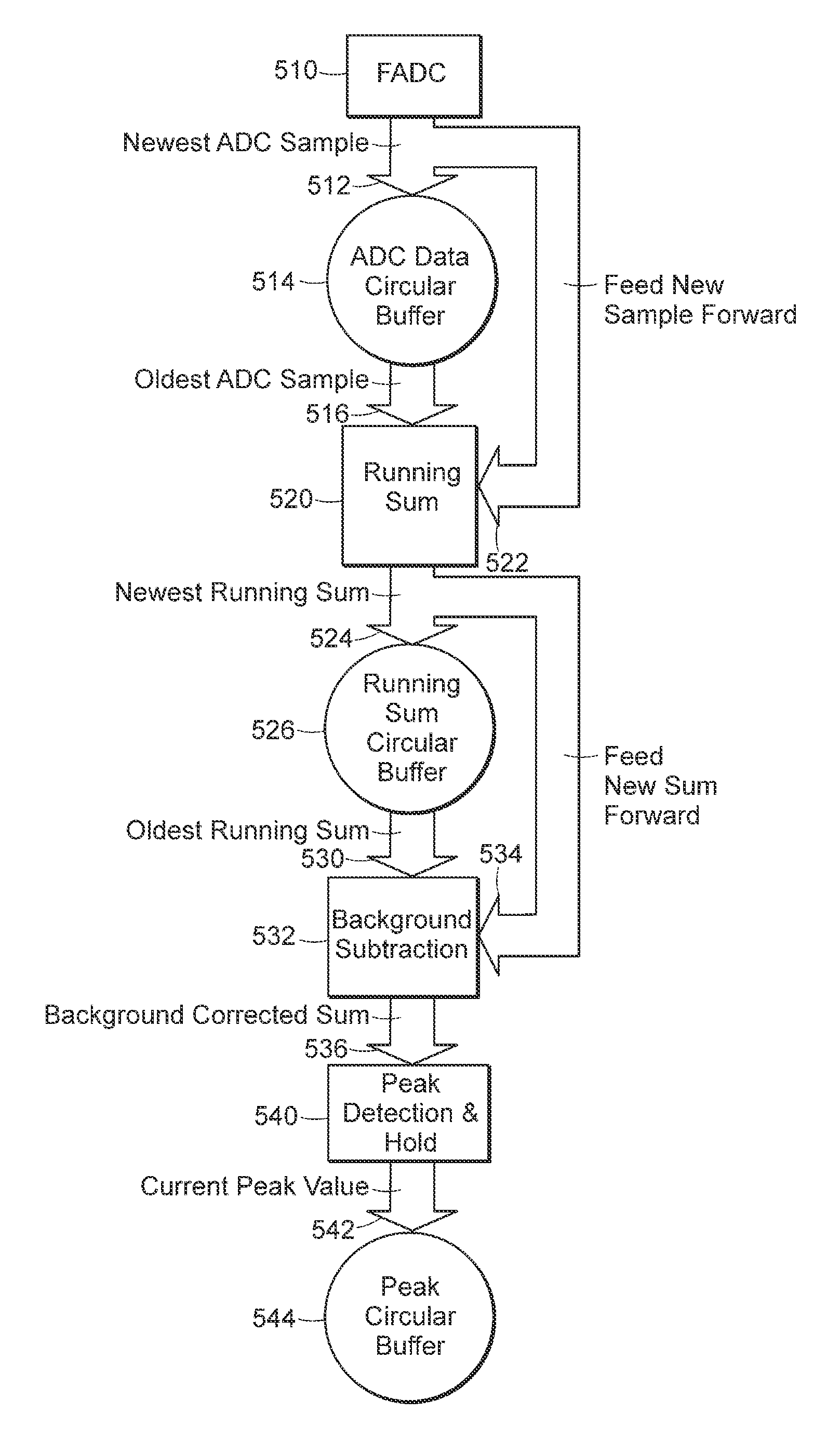

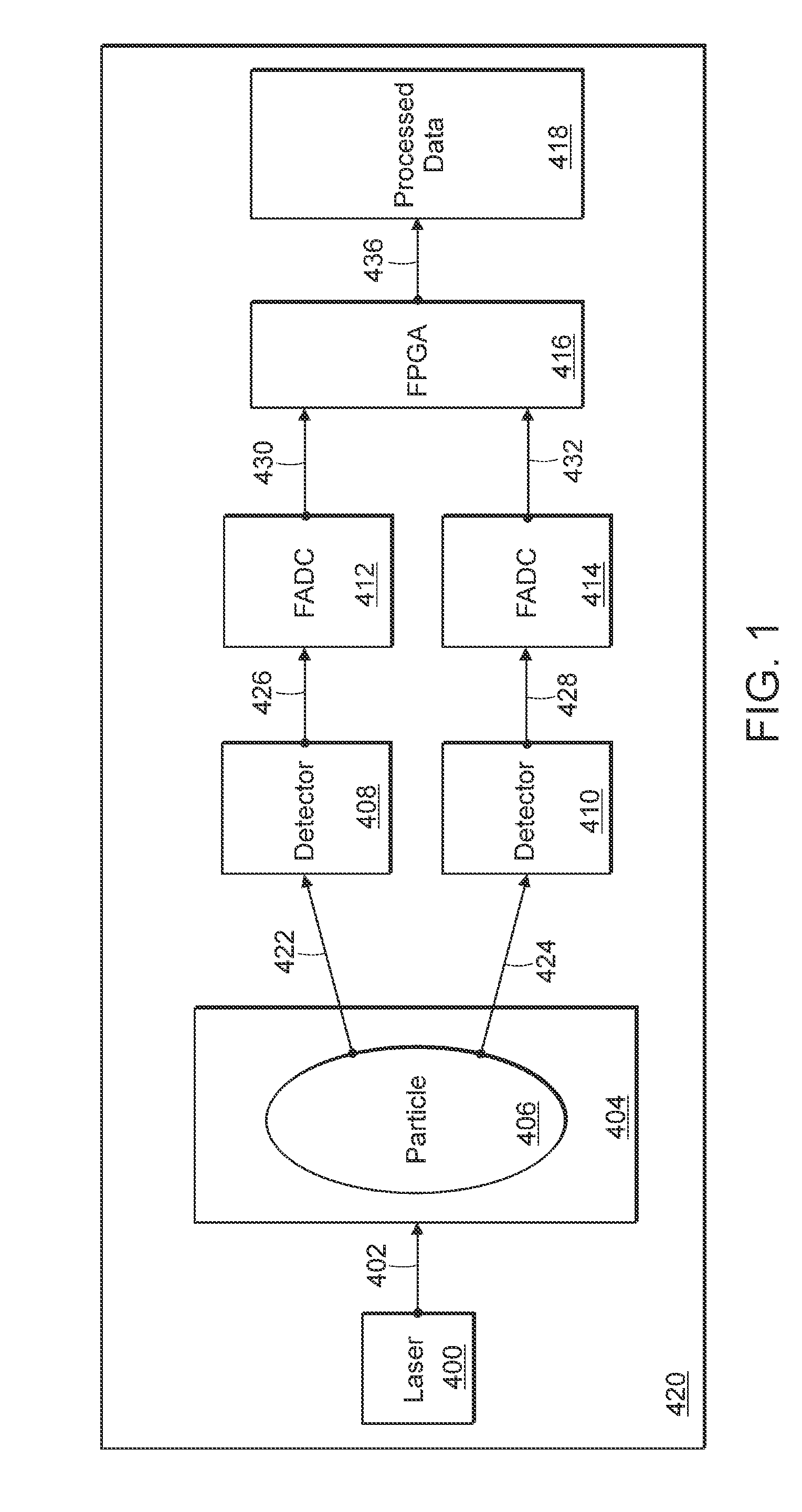

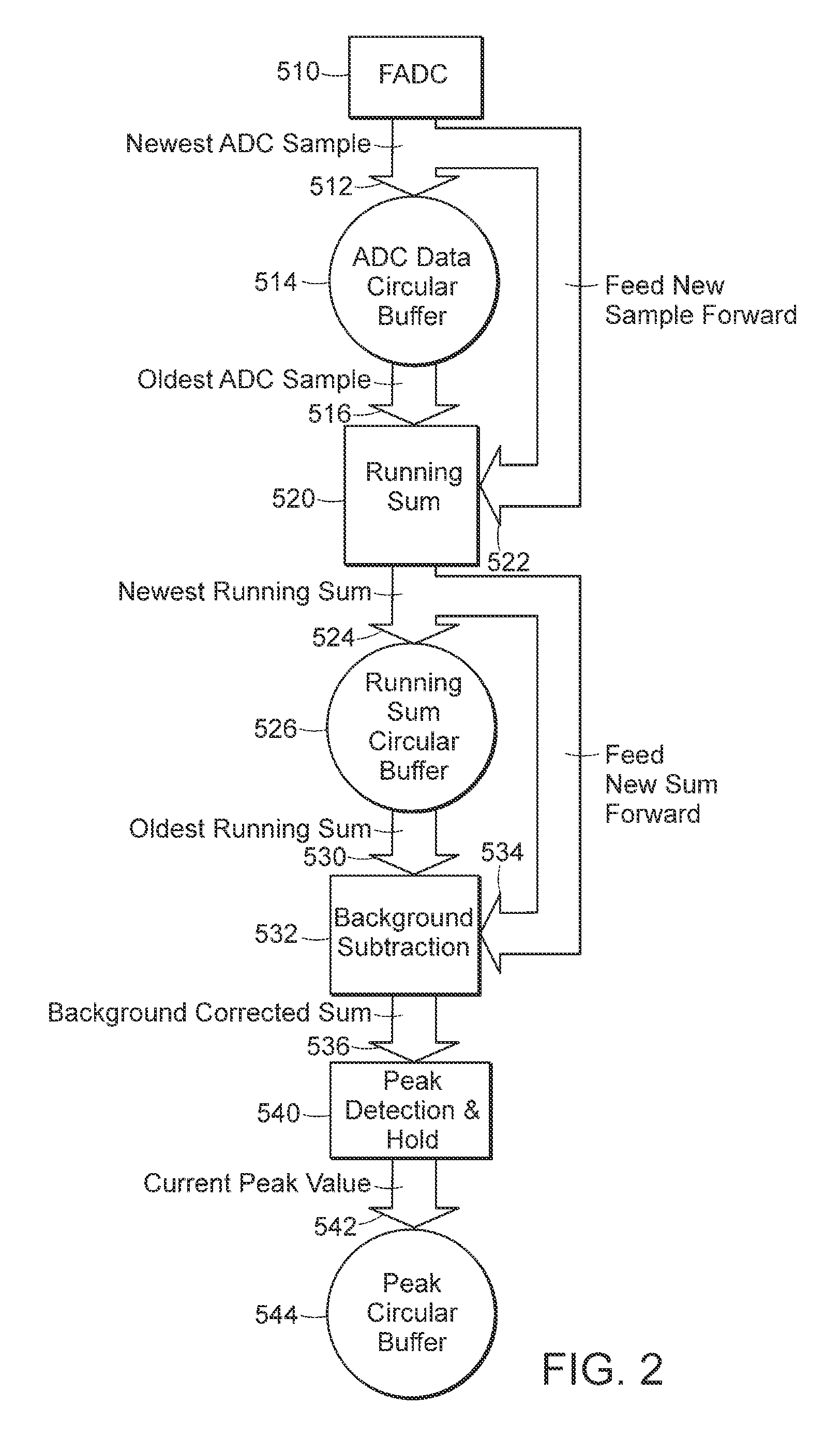

System and method for managing data from a flow analyzer

InactiveUS7274316B2Increase the number ofIncrease the amount of dataAnalogue/digital conversionElectric signal transmission systemsParallel computingData acquisition

Owner:LUMINEX

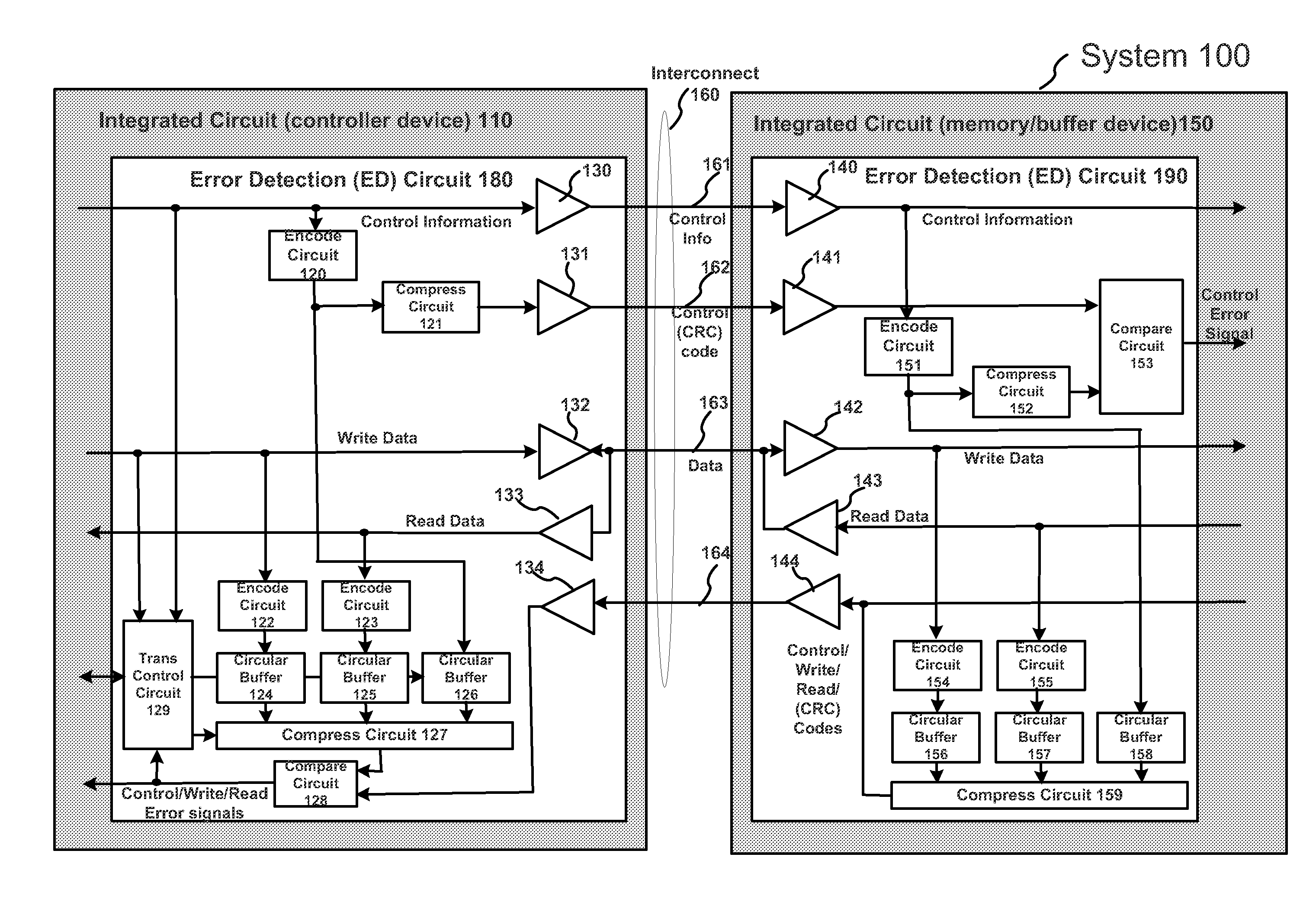

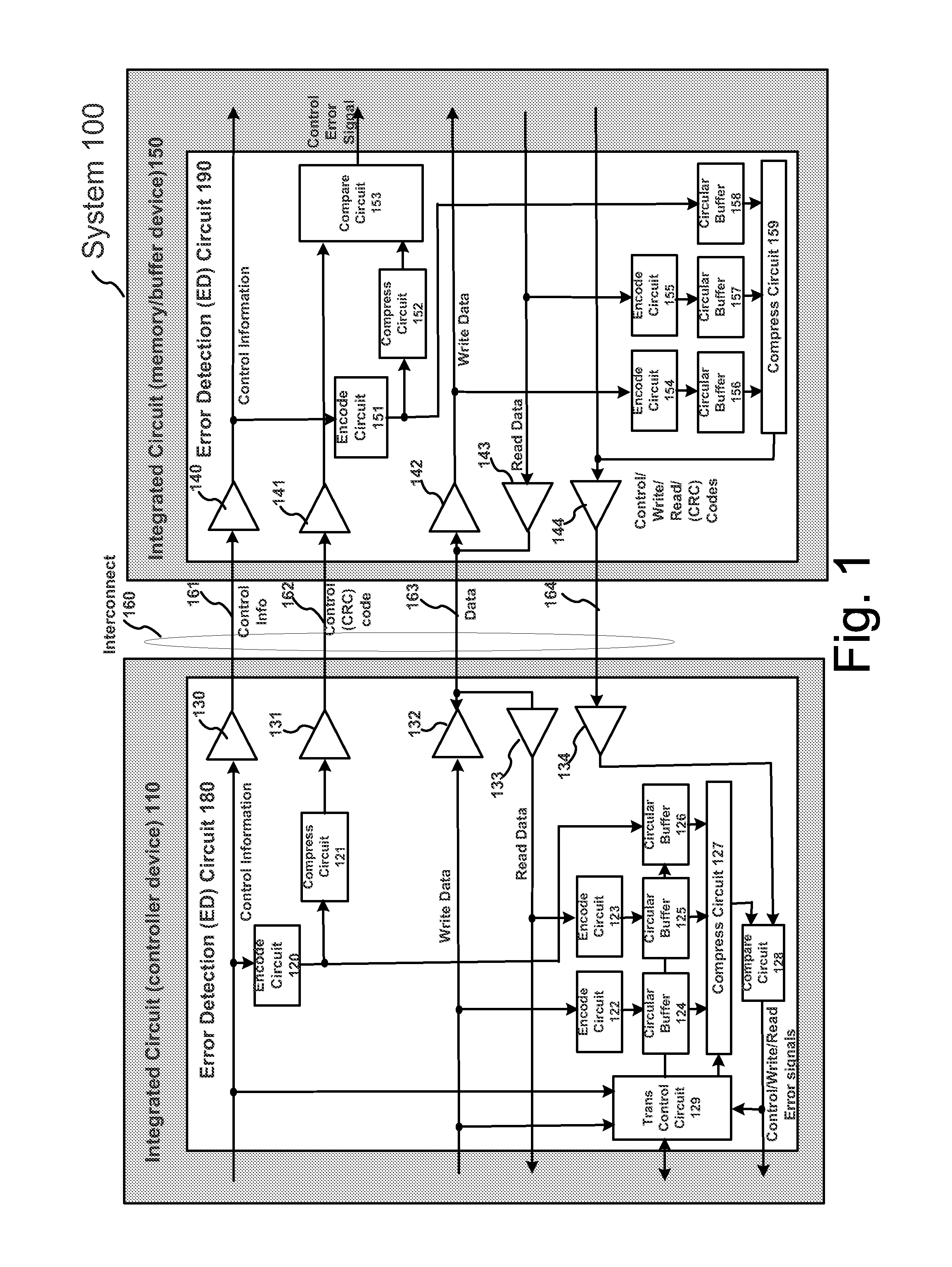

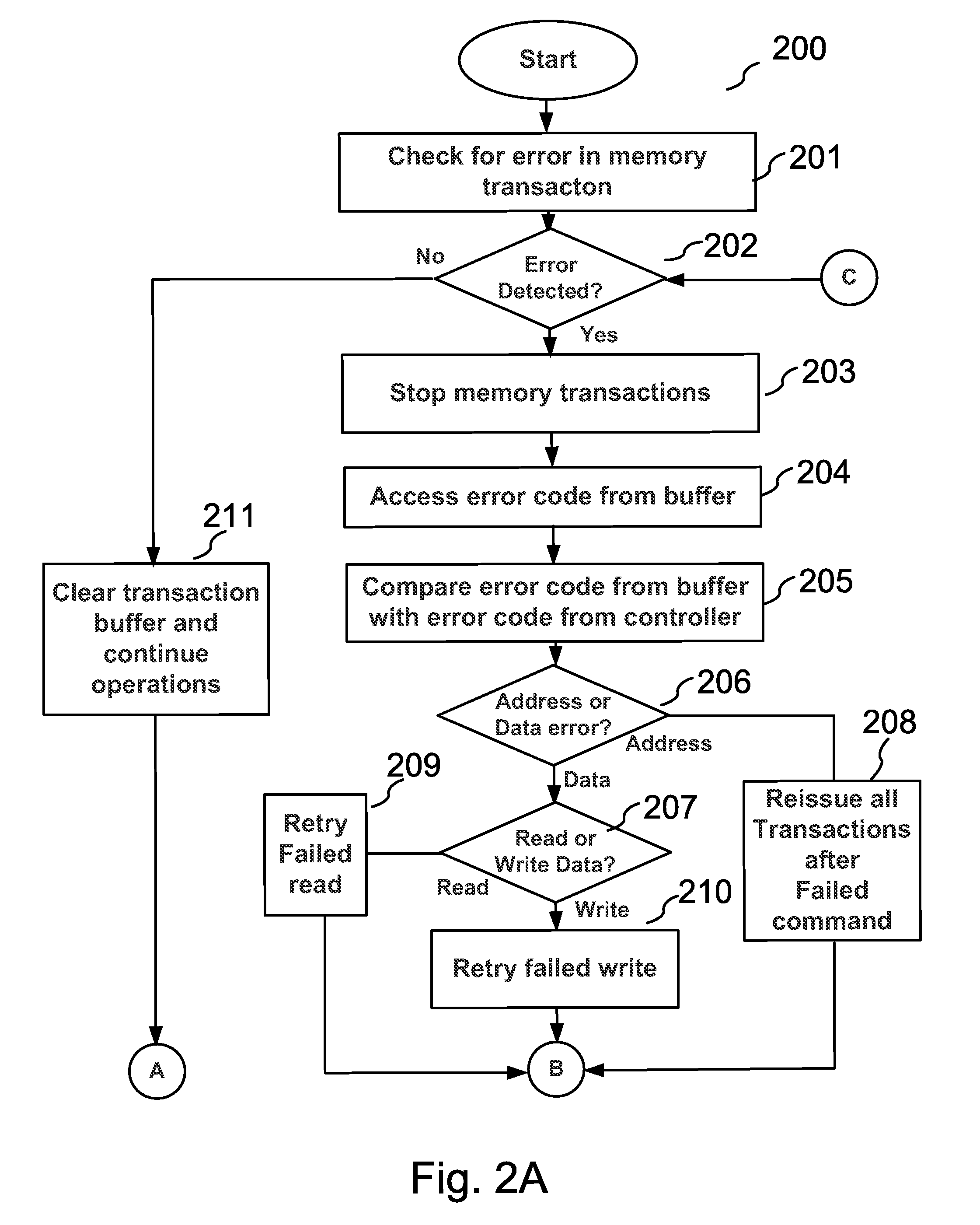

System To Detect And Identify Errors In Control Information, Read Data And/Or Write Data

An integrated circuit, such as an integrated circuit memory or buffer device, method and system, among other embodiments, generate a plurality of error codes, such as CRC codes, corresponding to control information, write data and read data transactions, respectively. The plurality of separately generated CRC codes is logged or stored in respective storage circuits, such as circular buffers. The stored plurality of CRC codes corresponding to each transaction then may be used to determine whether an error occurred during a particular transaction and thus whether a retry of the particular transaction is issued. The integrated circuit includes a compare circuit to compare a CRC code generated by the integrated circuit with a CRC code provided by a controller device. A CRC code corresponding to read data is transferred to a controller device using a data mask signal line that is not being used during a read transaction. The CRC code generated by the integrated circuit then may be compared to a CRC code generated by the controller device to determine whether an error occurred. The controller device generates and stores a plurality of CRC codes, corresponding to control information, write data and read data. The controller device then compares the CRC codes generated by the controller device with CRC codes generated and stored in the integrated circuit to determine whether an error has occurred during a particular transaction.

Owner:RAMBUS INC

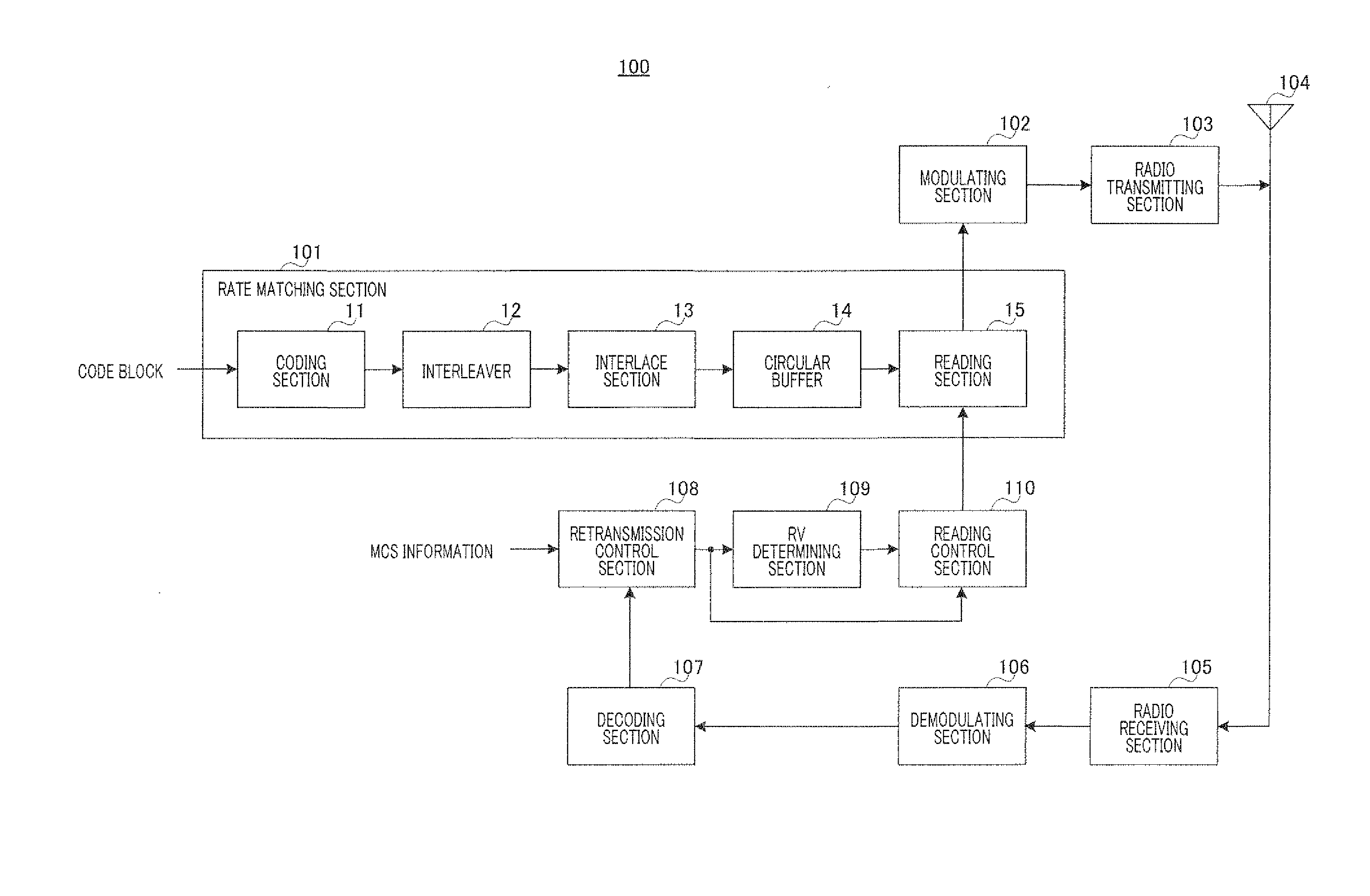

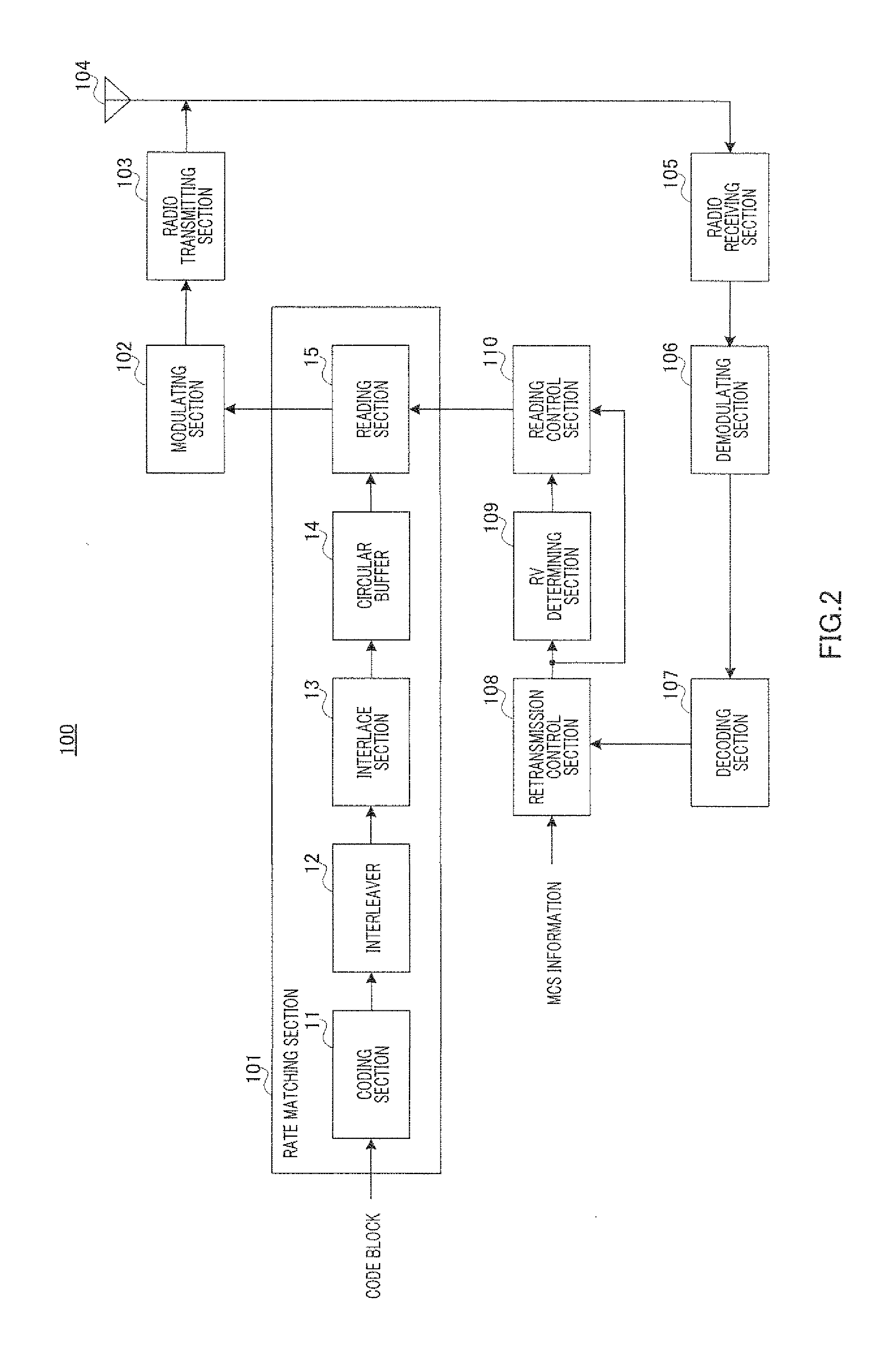

Wireless communication device and circular buffer control method

ActiveUS20100199157A1Improve decoding performanceError preventionError detection/correctionCircular bufferSelection criterion

There is provided a wireless communication device capable of improving a decoding performance by using an optimal selection criterion for a start address and a read direction in a circular buffer. An interlacer (13) writes an interleaved and interlaced bit sequence into a circular buffer (14). An RV decision unit (109) decides the read start address and read direction of the circular buffer (14) based on the number of non-transmitted systematic bits, the number of non-transmitted important parity bits, and / or the number of non-transmitted unimportant parity bits. A read control unit (110) controls the read start address and read end address of the circular buffer (14). A read unit (15) is controlled by the read control unit (110) to continuously read encoded bits from the circular buffer (14).

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

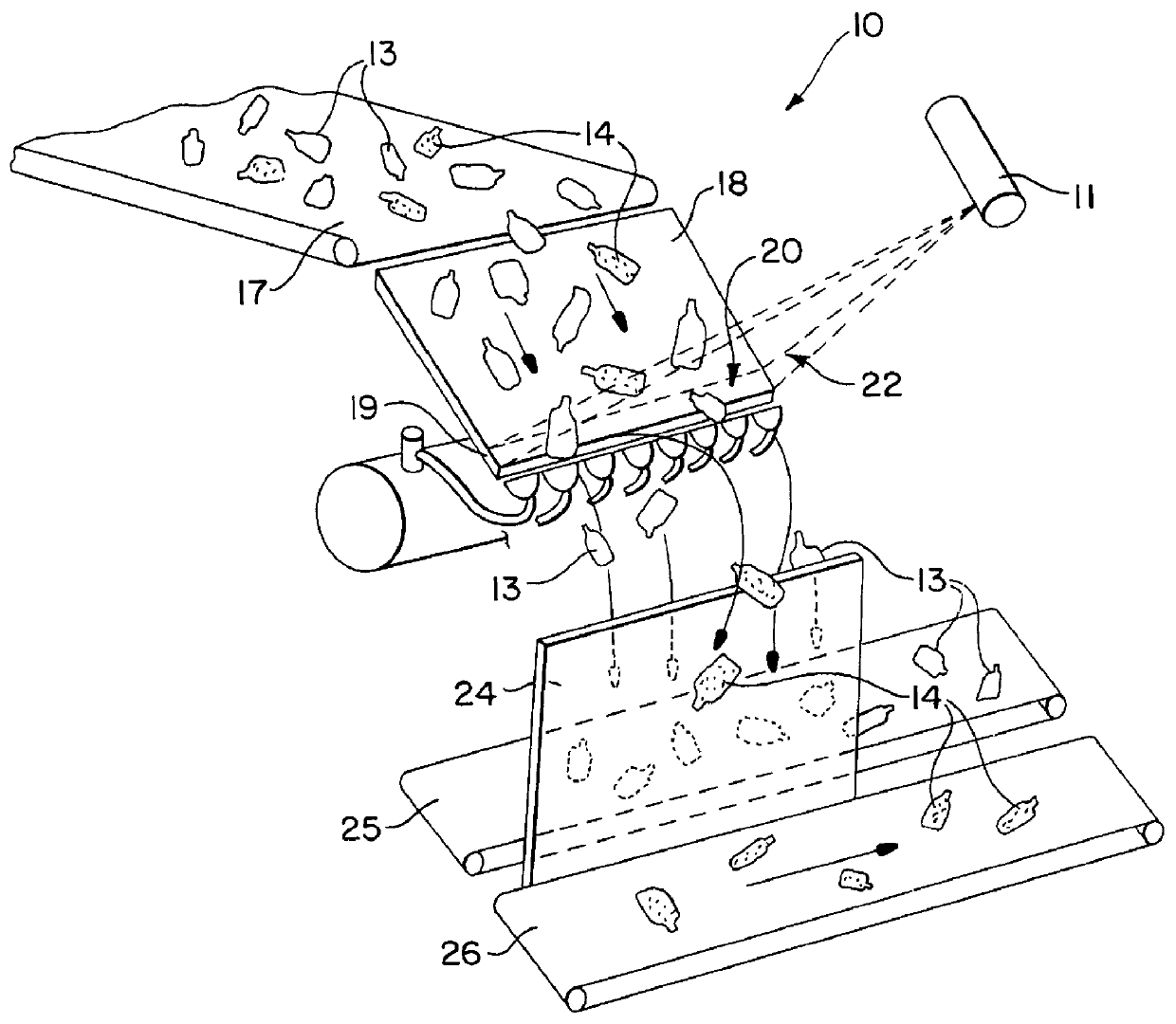

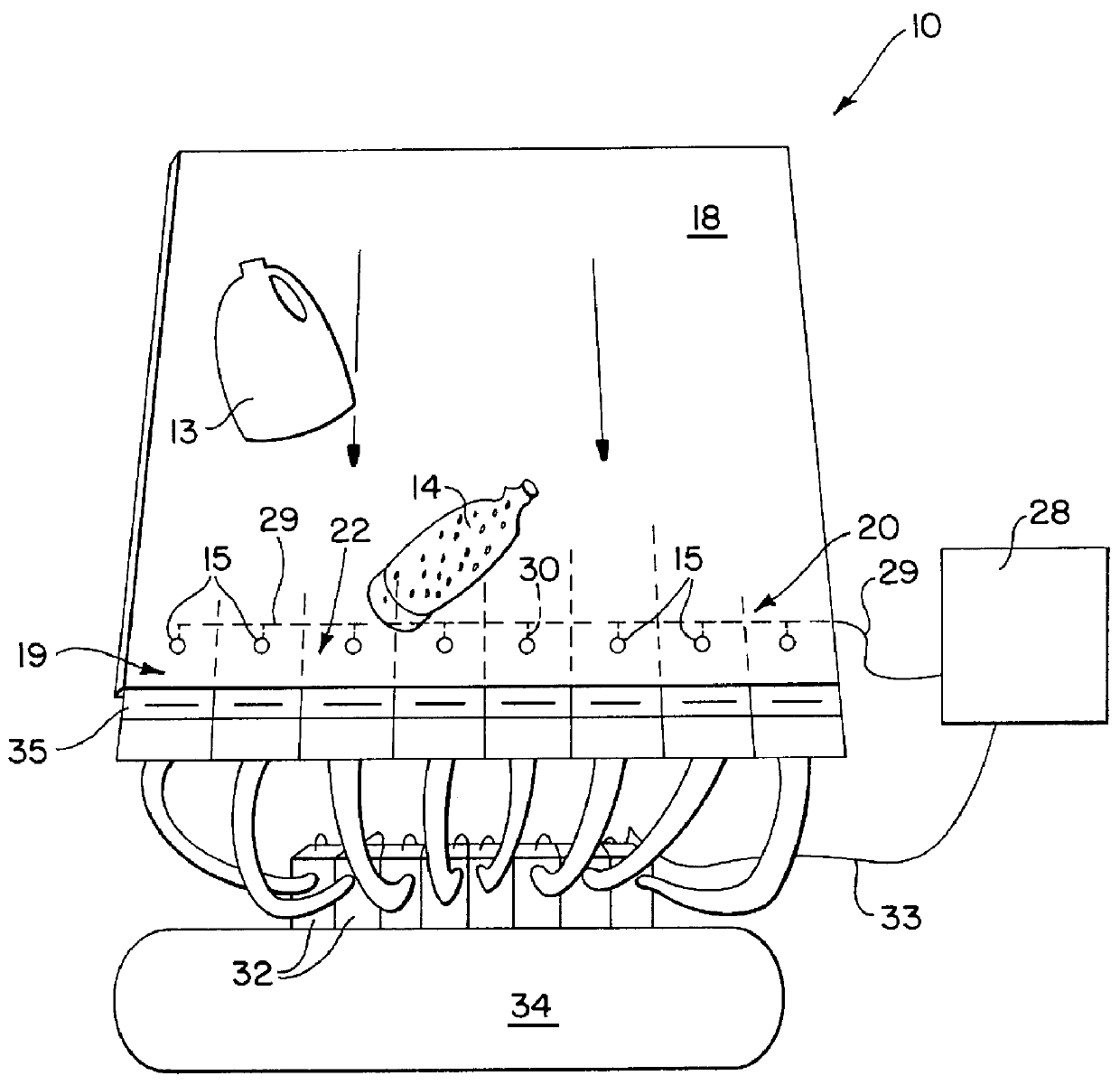

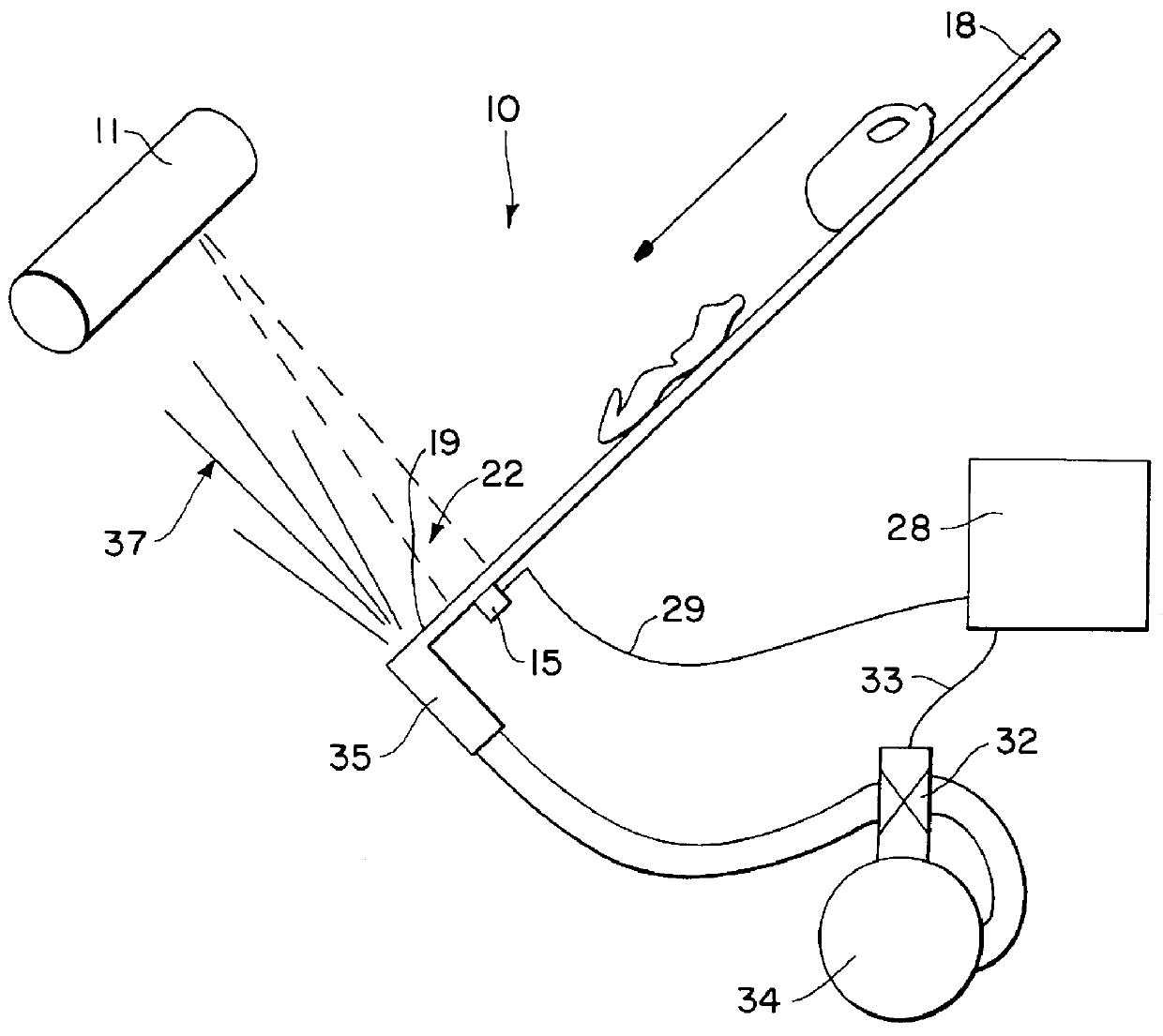

Method and apparatus for sorting materials using electromagnetic sensing

InactiveUSRE36537E1Efficient high volume separationImprove throughputRadiation pyrometryVolume/mass flow measurementEngineeringCircular buffer

An automated interrupt driven system which employs a circular buffer is used to sort materials based on differing electromagnetic radiation absorption and penetration characteristics. The system has a conveyor and a source of electromagnetic radiation which radiates materials travelling along the conveyor. A controller samples detector outputs at various times to evaluate the absorption and penetration characteristics of the materials to be sorted, based on a plurality of samples. Portions of the materials are ignored to obtain accurate readings from the detectors. Based on the detected penetration and absorption characteristics, the controller activates ejection mechanisms causing materials of different compositions to be deposited into different bins. The controller executes interrupts to cause detection, ejection, testing, and system history maintenance at required times. The circular buffer contains indices which point to various locations which are programmed in memory to trigger and perform specific events. The location of the indices in the circular buffer is used to control event timing, such as activating and deactivating the ejection mechanisms. This configuration, allows several events to be executed simultaneously by moving to the next location in the circular buffer while the event indicated by the index in the previous location continues in progress.

Owner:NAT RECOVERY TECH

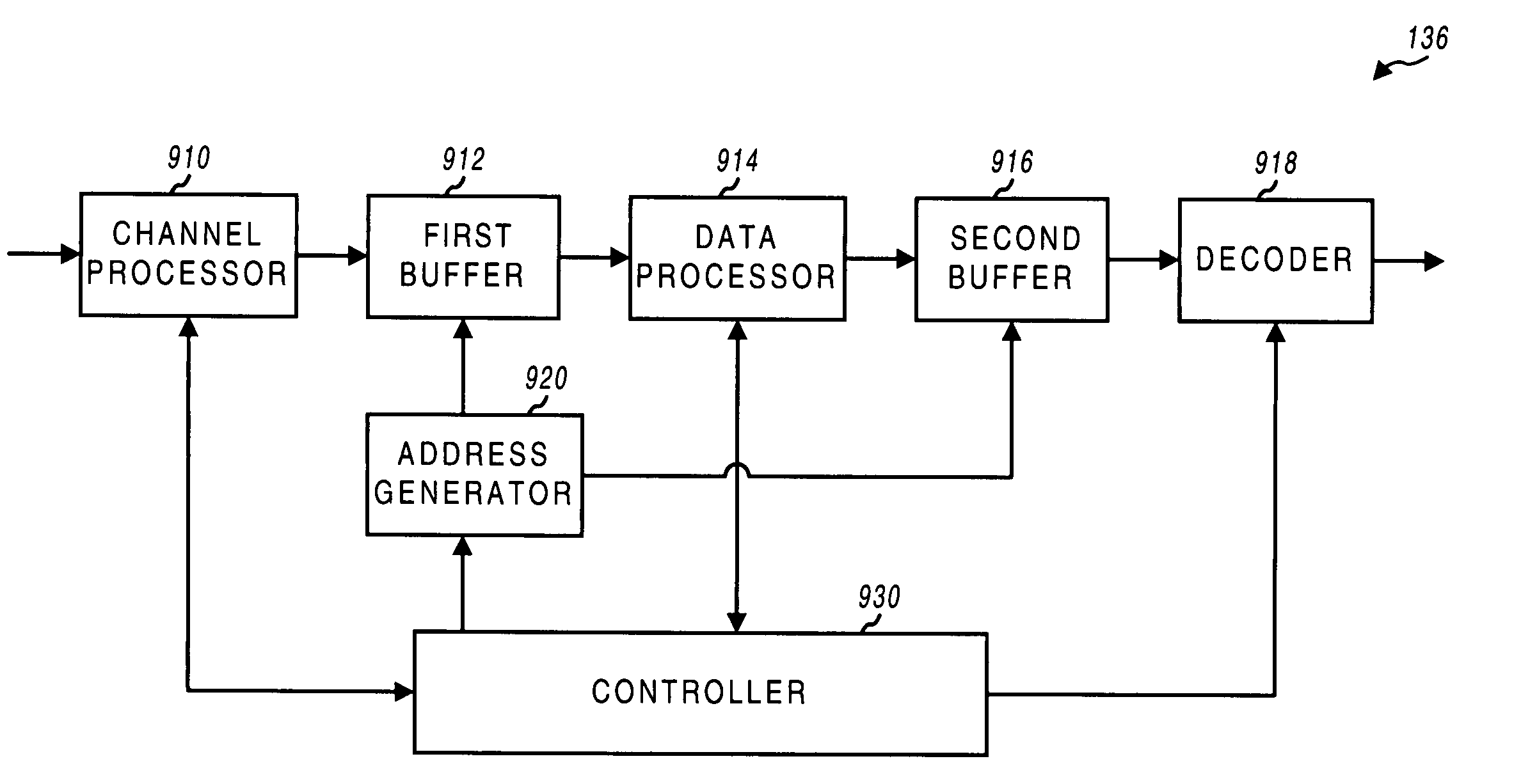

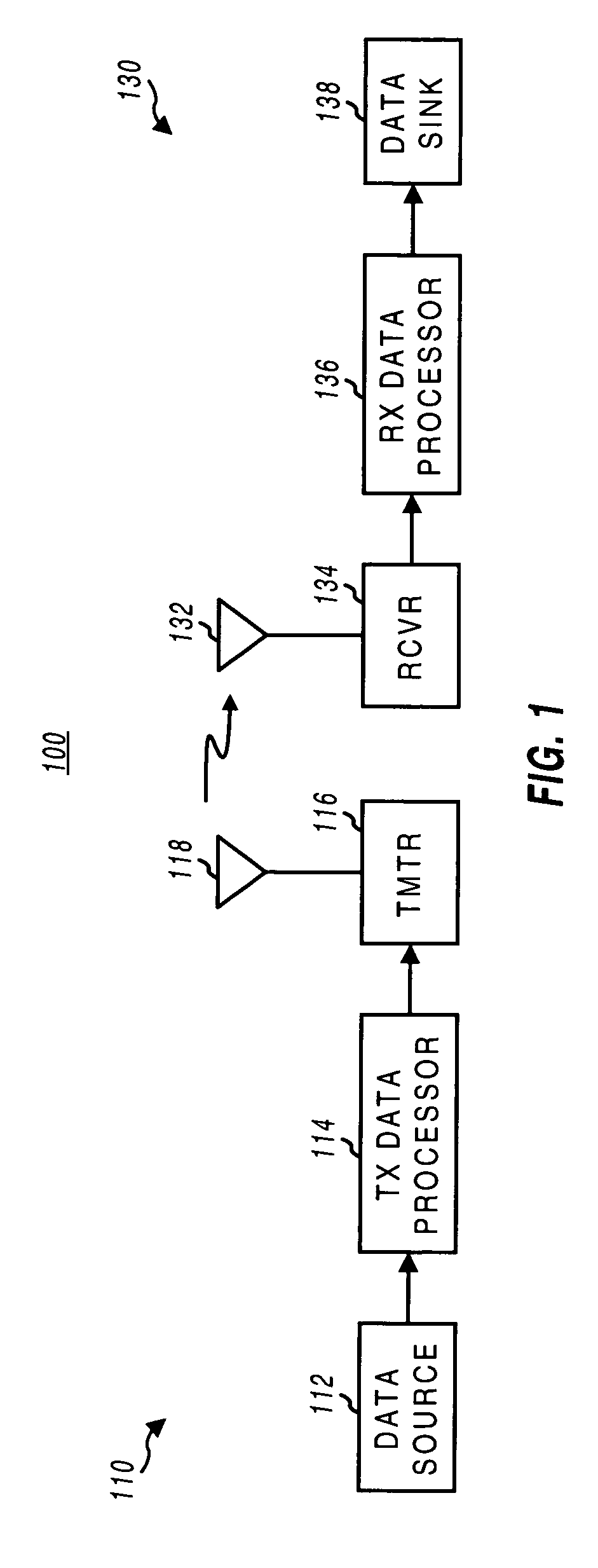

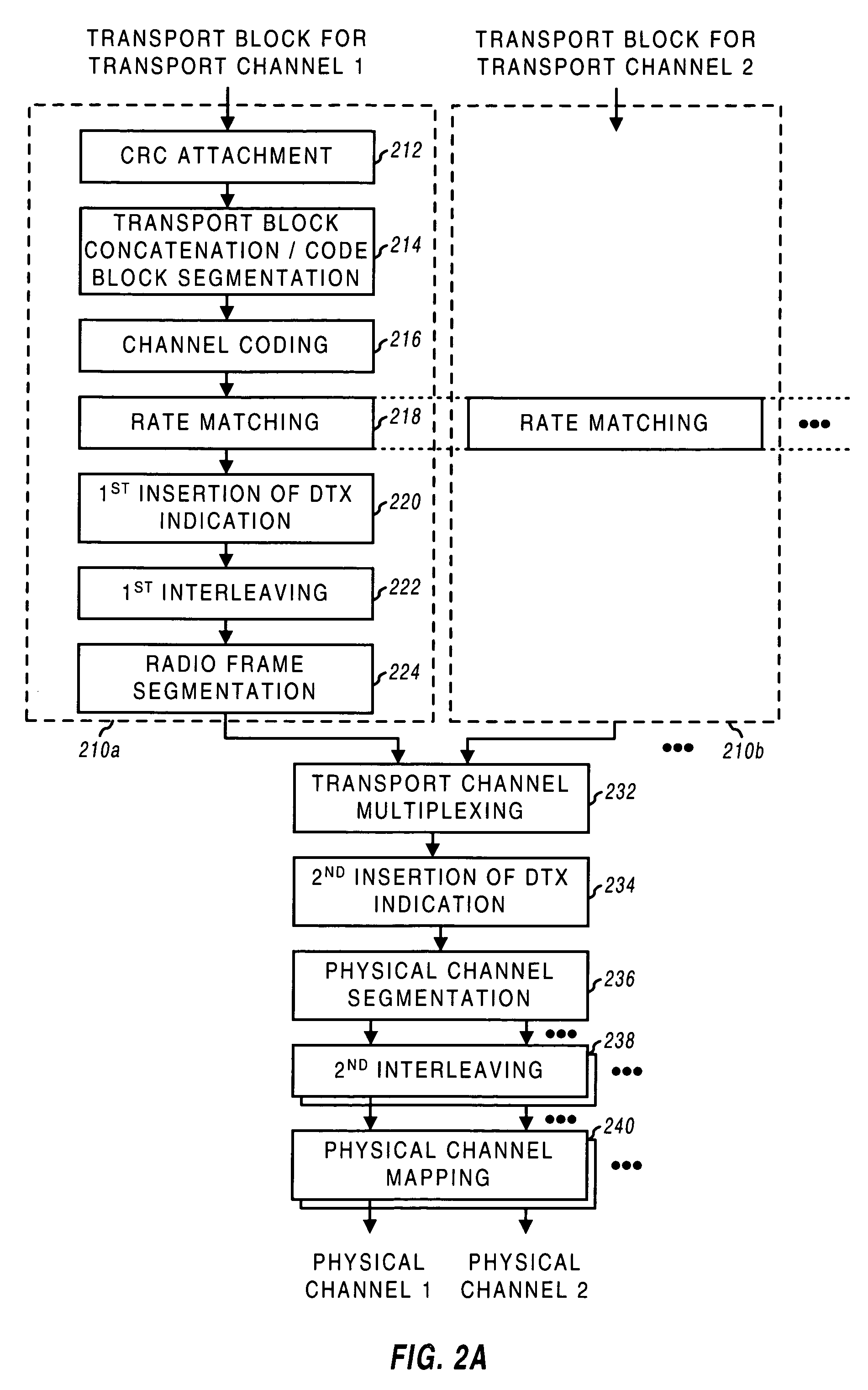

Data buffer structure for physical and transport channels in a CDMA system

InactiveUS7187708B1Efficient storageEasy maintenanceError preventionTransmission systemsAddress generatorCircular buffer

A buffer structure for storing symbols received via a number of (e.g., physical or transport) channels. Each channel is associated with a particular time interval (e.g., a radio frame period or a transmission time interval (TTI)) over which the received symbols are processed (e.g., interleaved). The buffer structure includes a buffer and an address generator. The buffer is partitioned into a number of sections. One section is assigned to each channel being processed. Each section can be operated as a circular buffer. The address generator provides addresses for writing symbols to the assigned sections. If the buffer structure is used for the transport channels, the sections can be assigned to the transport channels based on the associated TTIs (e.g., in descending order of TTIs). For each coded composite transport channel (CCTrCH), the transport channels in the CCTrCH can be assigned to sections defined starting from a respective initial location (e.g., the top or bottom of the buffer) and continuing along a respective direction of the buffer (e.g., downward or upward).

Owner:QUALCOMM INC

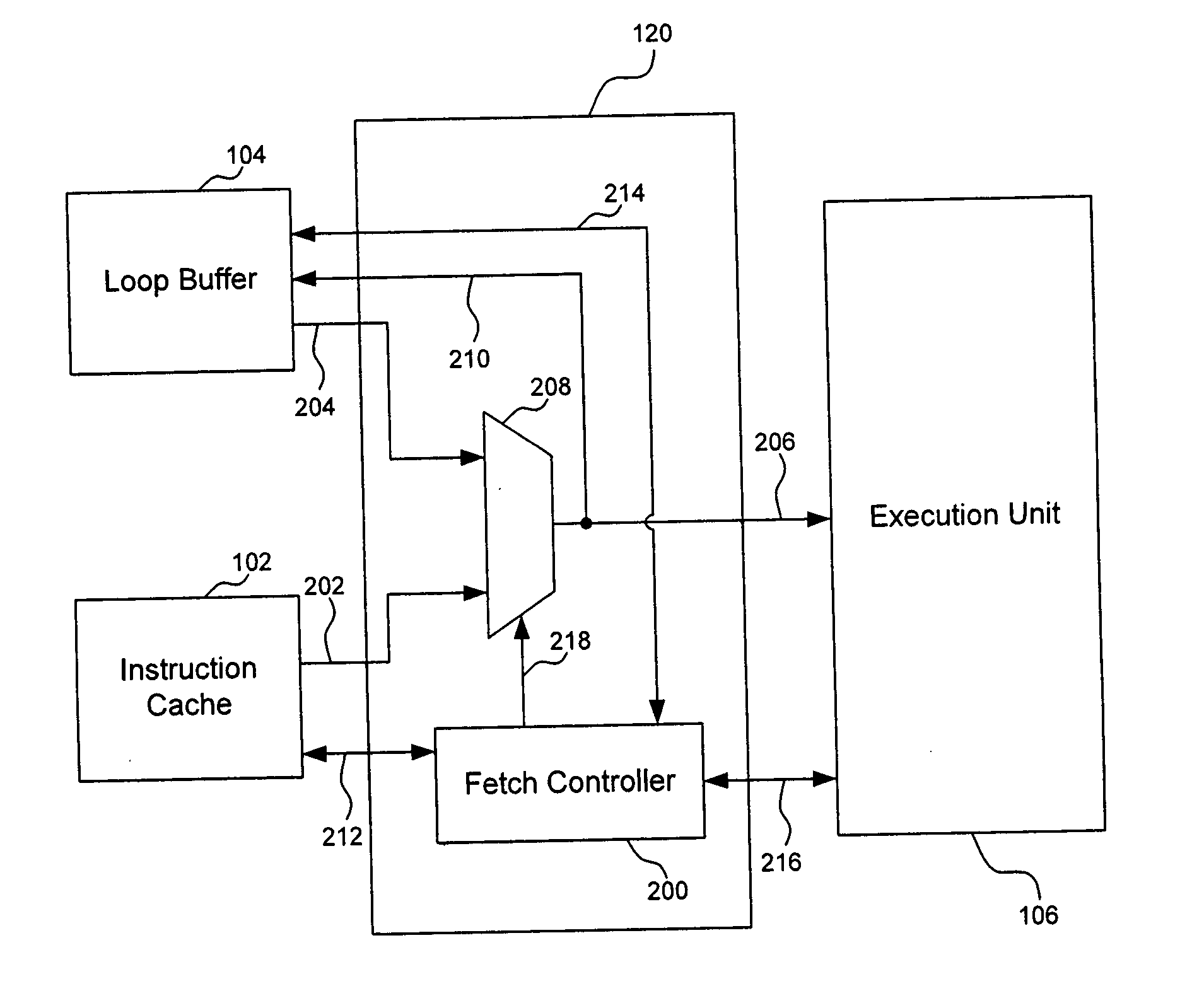

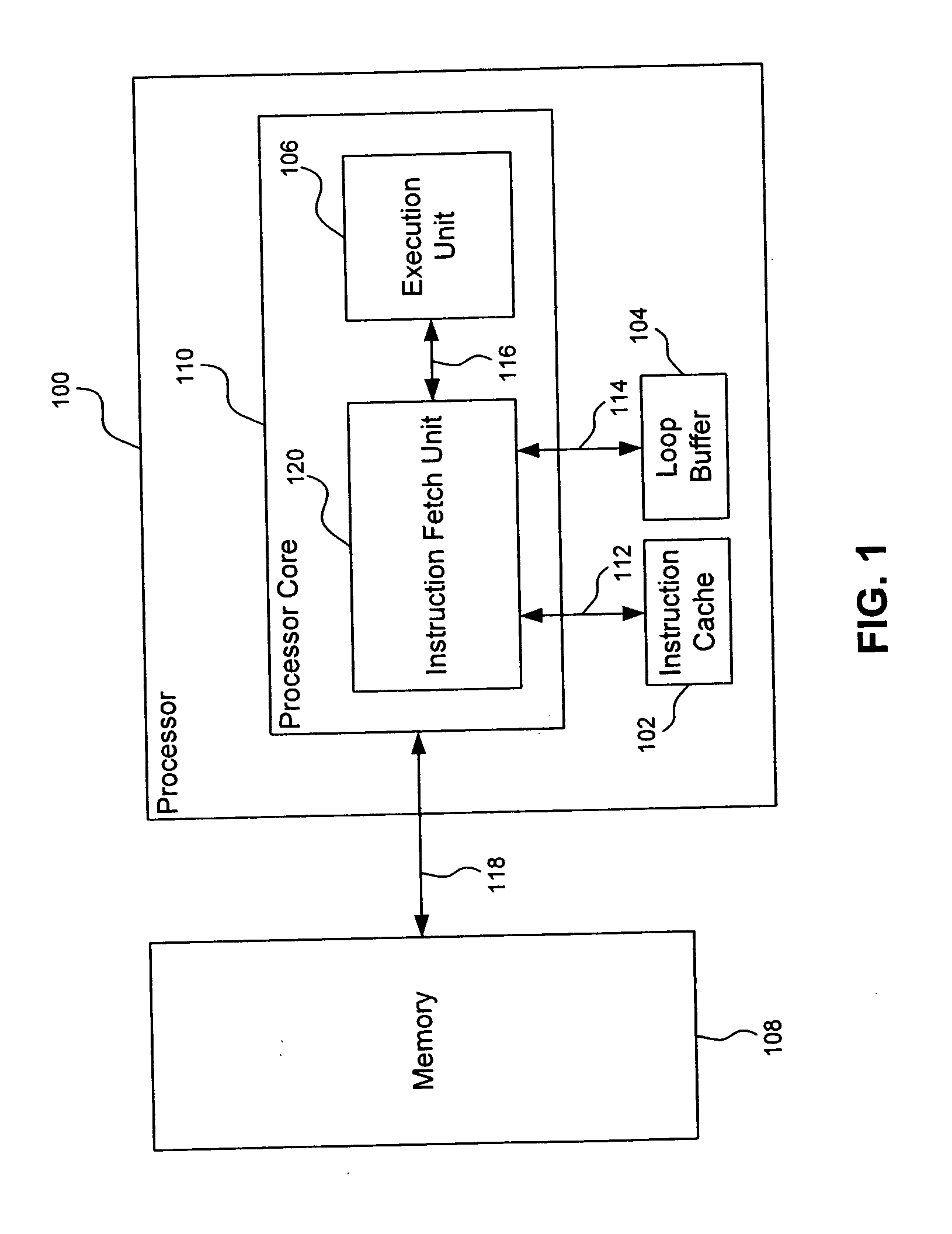

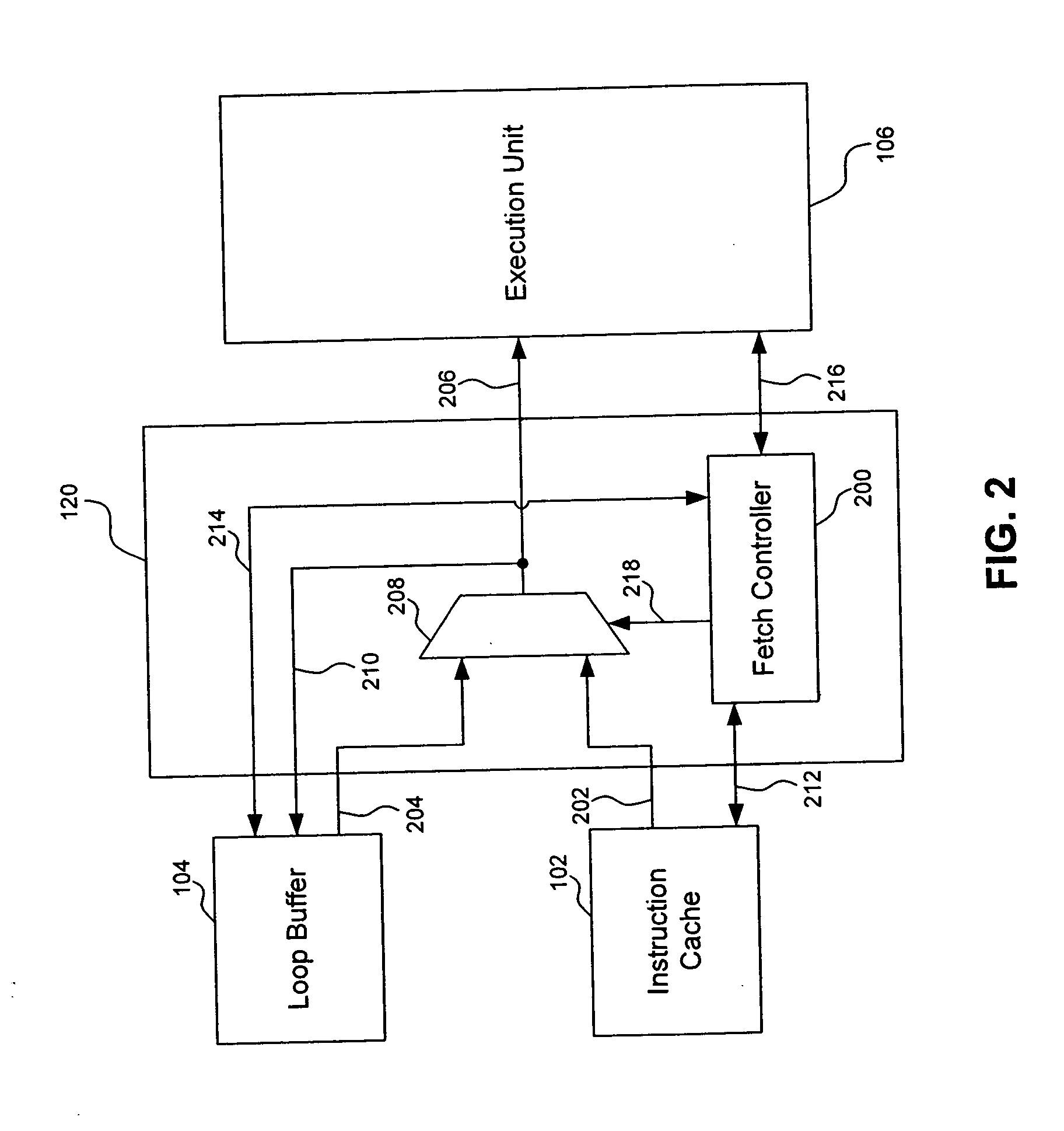

Processor utilizing a loop buffer to reduce power consumption

InactiveUS20070113057A1Reduce power consumptionEnergy efficient ICTDigital computer detailsParallel computingExecution unit

The present invention provides processing systems, apparatuses, and methods that reduce power consumption with the use of a loop buffer. In an embodiment, an instruction fetch unit of a processor initially provides instructions from an instruction cache to an execution unit of the processor. While instructions are provided from the instruction cache to the execution unit, instructions forming a loop are stored in a loop buffer. When a loop stored in the loop buffer is being iterated, the instruction cache is disabled to reduce power consumption and instructions are provided to the execution unit from the loop buffer. When the loop is exited, the instruction cache is re-enabled and instructions are provided to the execution unit from the instruction cache.

Owner:ARM FINANCE OVERSEAS LTD

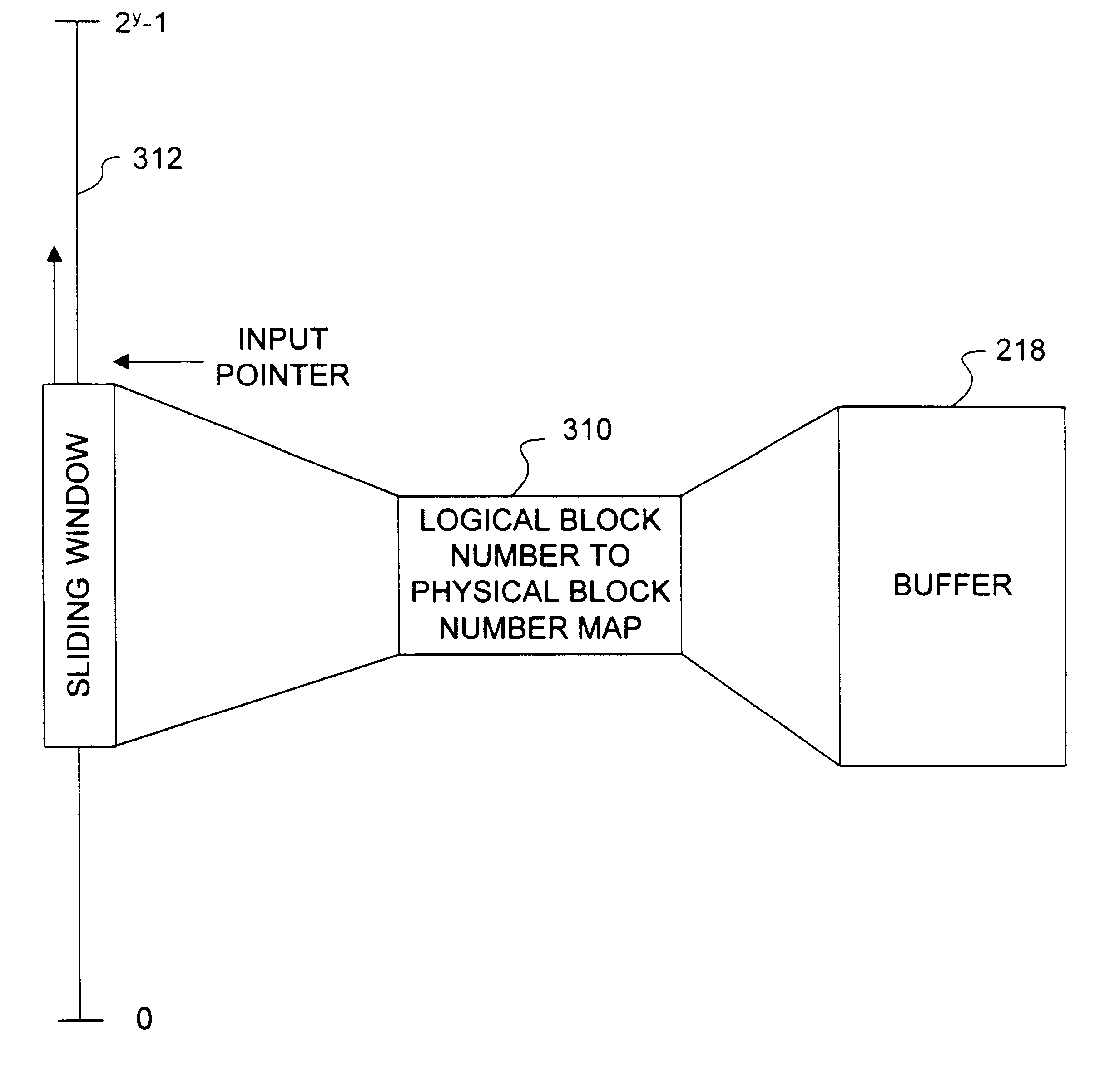

Apparatus and method for providing a cyclic buffer using logical blocks

InactiveUS6807615B1Overcome problemsMemory adressing/allocation/relocationInput/output processes for data processingCircular bufferData buffer

An apparatus and method for creating and maintaining a cyclic or circular buffer are implemented using logical blocks corresponding to the physical blocks of the buffer. The logical blocks are mapped to the physical blocks of the cyclic buffer, and are used to create an index table for the buffer. Each entry in the index table corresponds to one or more blocks in the buffer, and has a logical block number respectively associated with a buffer block. When information from the buffer is accessed, the index table is consulted to determine if the requested information is stored in the buffer. If the information is stored in the buffer, the logical block number corresponding to the information is retrieved from the entry and translated into a corresponding physical block number. Using logical block numbers allows simple determination of whether the buffer block is valid, and how new or fresh the buffer block is without requiring a generation or cycle number.

Owner:ORACLE INT CORP

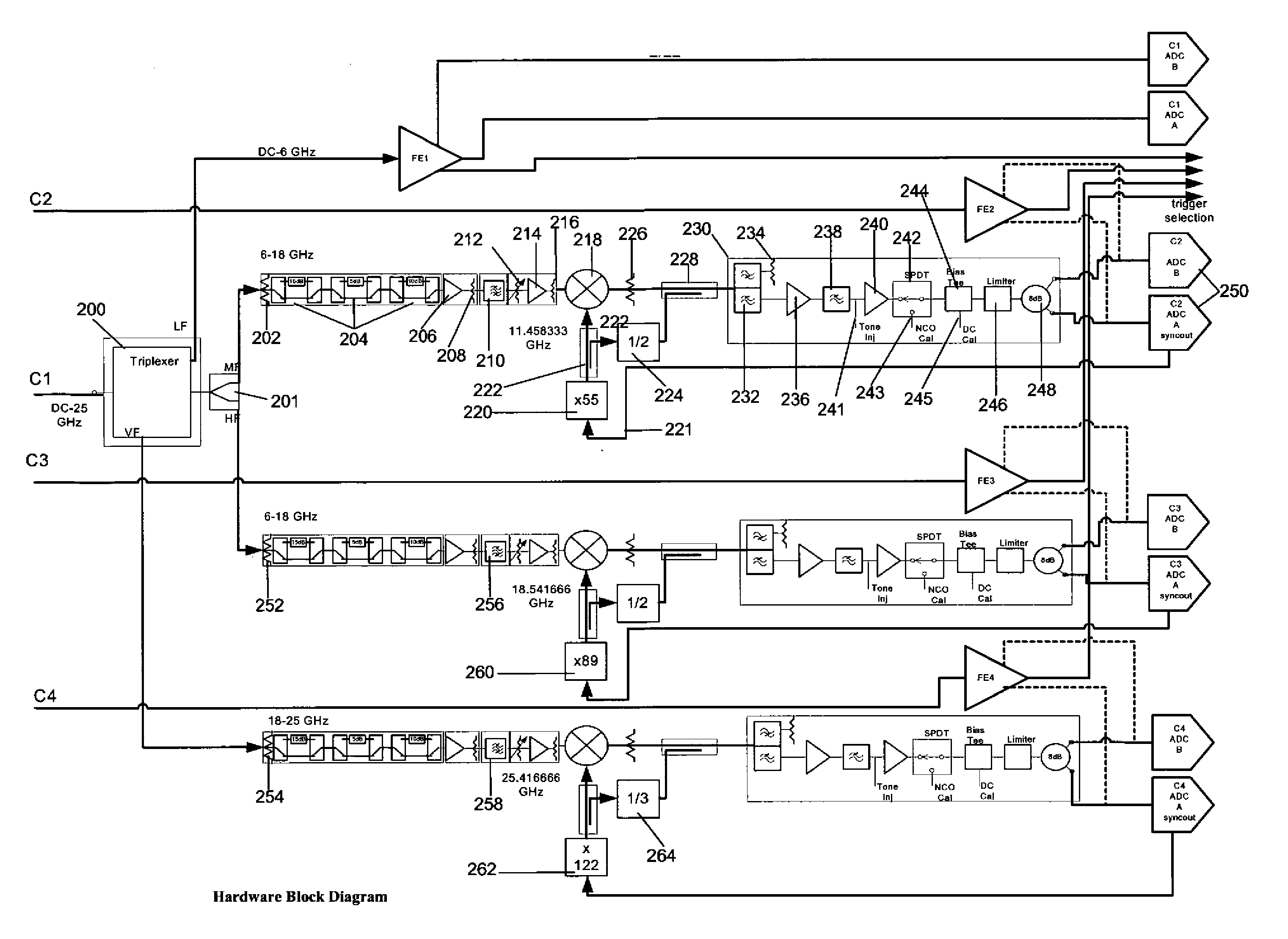

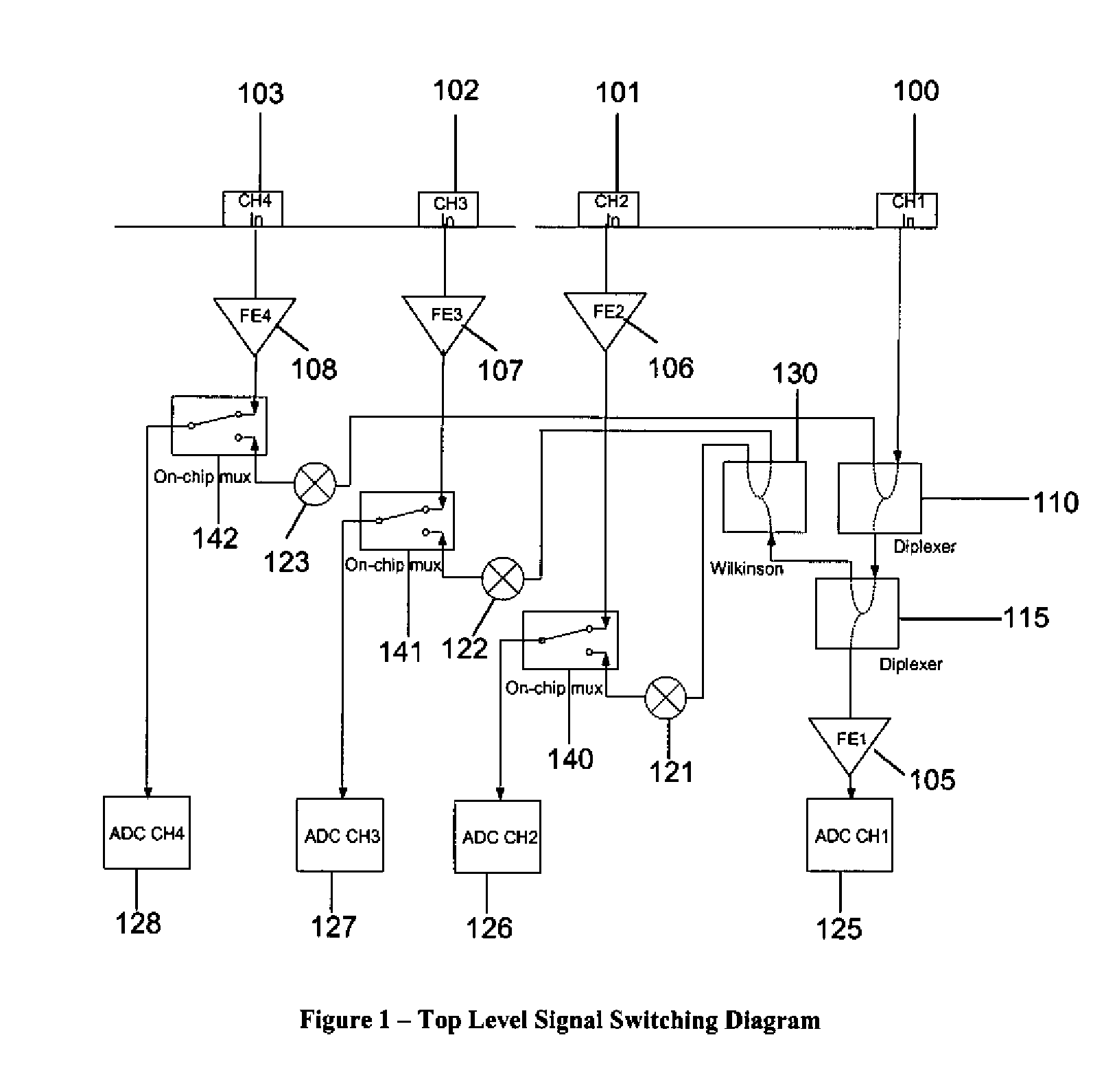

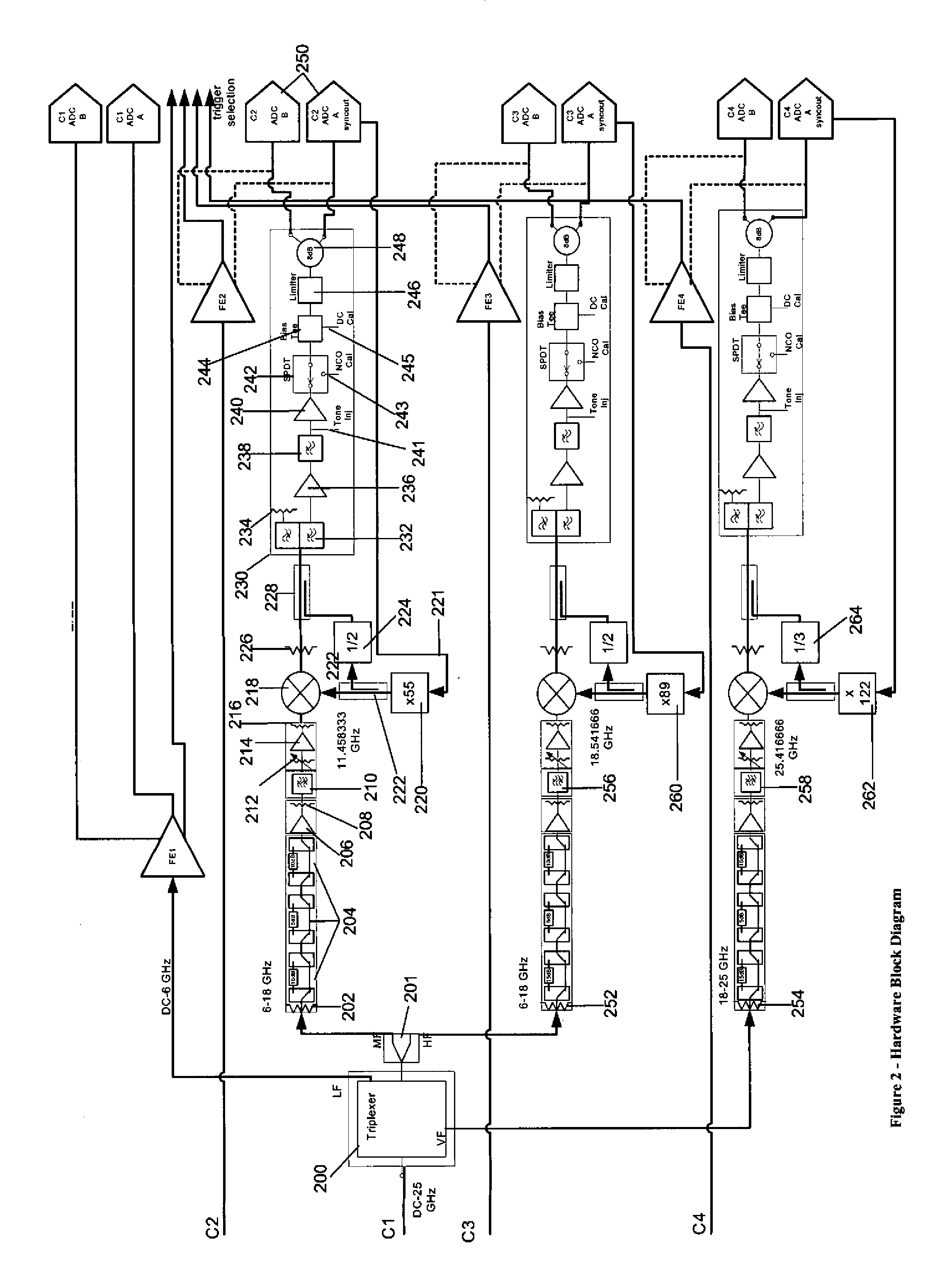

Method and Apparatus for a High Bandwidth Oscilloscope Utilizing Multiple Channel Digital Bandwidth Interleaving

ActiveUS20090002213A1Spectral/fourier analysisElectric signal transmission systemsHigh bandwidthLocal oscillator

A method of digitizing an analog signal is provided, comprising the steps of separating the analog signal spanning a frequency range into a plurality of frequency bands, each frequency band spanning a corresponding predefined frequency range, at least a portion of each of the plurality of corresponding frequency ranges not overlapping any other of the plurality of corresponding predefined frequency ranges and then translating at least one of the signals in the plurality of frequency bands to a lower frequency band in accordance with a local oscillator and digitizing the at least one translated signal with digitizing elements having a frequency range less than the analog signal frequency range. A fixed relationship of the phase of the local oscillator and a repetitive signal generated in accordance with a writing to a circular buffer of the digitized representation of the at least one of the plurality of frequency bands is then defined. Signals corresponding to the other of the plurality of frequency bands are digitized and written to corresponding circular buffers in accordance with one or more corresponding local oscillators. Finally, a digital representation of the analog signal is formed from the digitized signals, the digital representation substantially spanning the frequency range of the analog signal, and the digital representation is stored in a computer readable medium.

Owner:TELEDYNE LECROY

Loop Recording With Book Marking

A surveillance apparatus continuously records imaged data from a camera into a circular buffer in a local memory. When a record signal is received, the system records the video stream that was recorded before the record signal was received, and the video stream that is recorded after the record signal was received. The recorded segment is then write-protected, so that the surveillance apparatus does not overwrite the recorded segment. The recorded segment could then be sent to a remote memory via a wireless connection to free up local memory for future recording sessions.

Owner:STELLAR

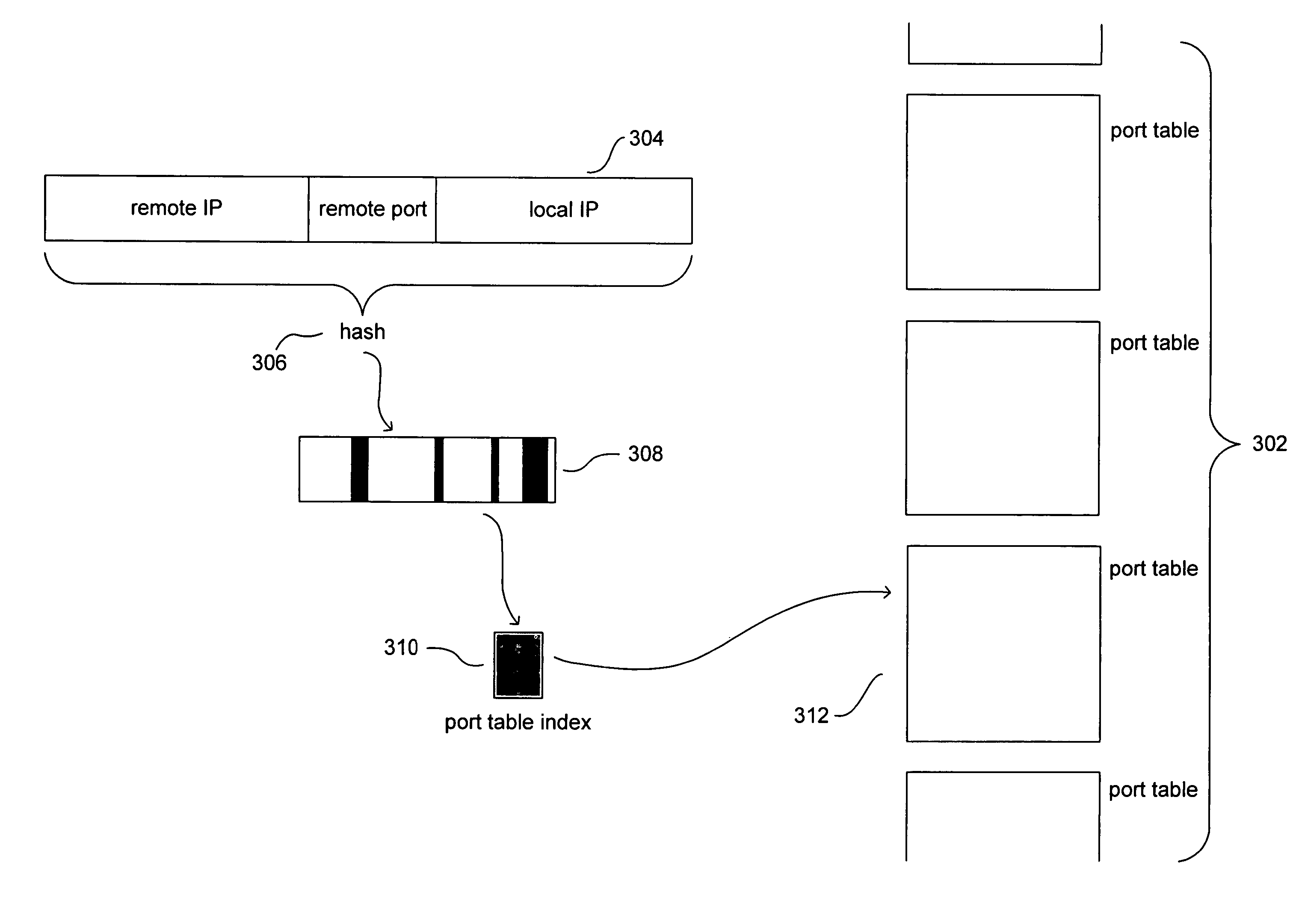

Method and system for reallocating computational resources using resource reallocation enabling information

InactiveUS8464265B2Facilitates immediate reallocation and useEfficient managementMultiprogramming arrangementsData switching by path configurationResource poolIp address

Various embodiments of the present invention are directed to an efficient and flexible method and system for managing a pool of computational resources that can be allocated from a resource pool, used for varying periods of time, and eventually returned to the resource pool. Certain embodiments of the present invention are directed to a method and system for efficiently managing ephemeral ports used for short-duration communications connections. In one embodiment of the present invention, an array of port tables is employed to store and manage a large space of ephemeral protocol ports. Each port table is a circular buffer, each entry of which includes a port number that uniquely identifies a communications port, a sequence number that allows the port to be immediately reallocated, and any other additional protocol-specific information that may be associated with the port. A non-local-port-number portion of a connection address, comprising a remote IP address, a remote port number, and a local IP address, may be hashed to generate a numerical reference to a particular port table within the array, or list, of port tables, and ephemeral ports for the non-local-port-number portion of a connection address are allocated from, and deallocated and returned to, the numerically identified port table.

Owner:SECURE64 SOFTWARE