Patents

Literature

1503 results about "Memory interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

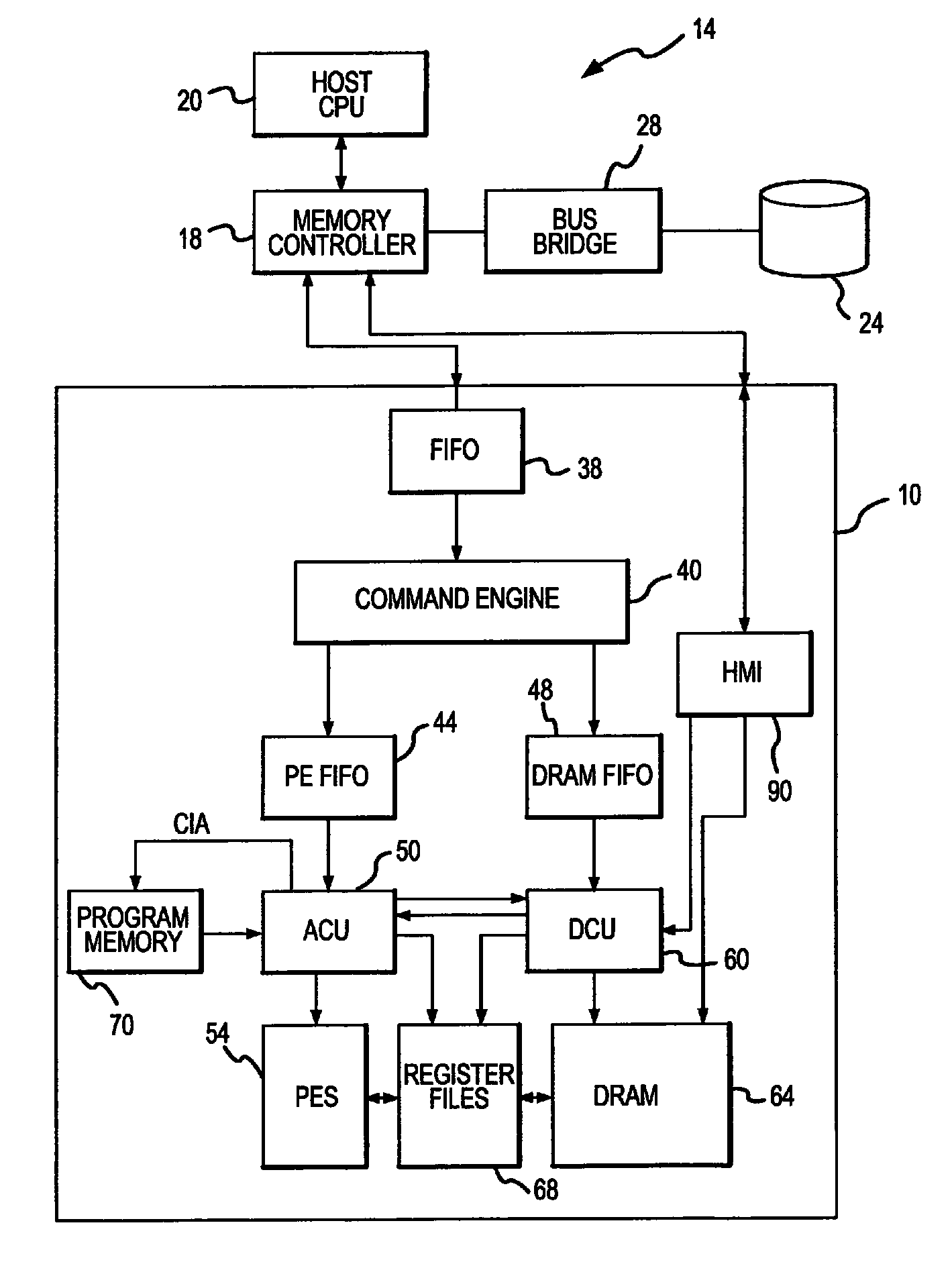

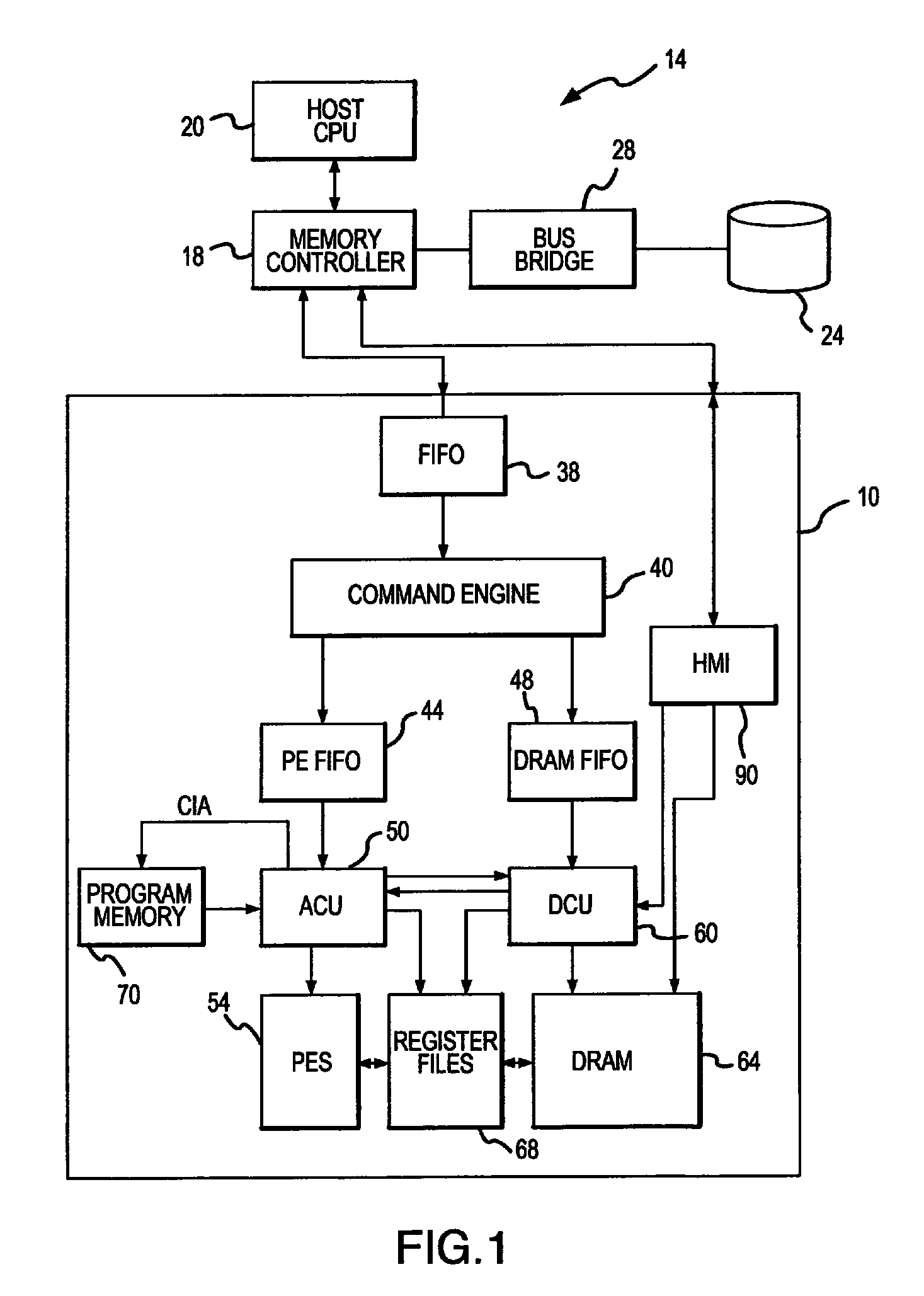

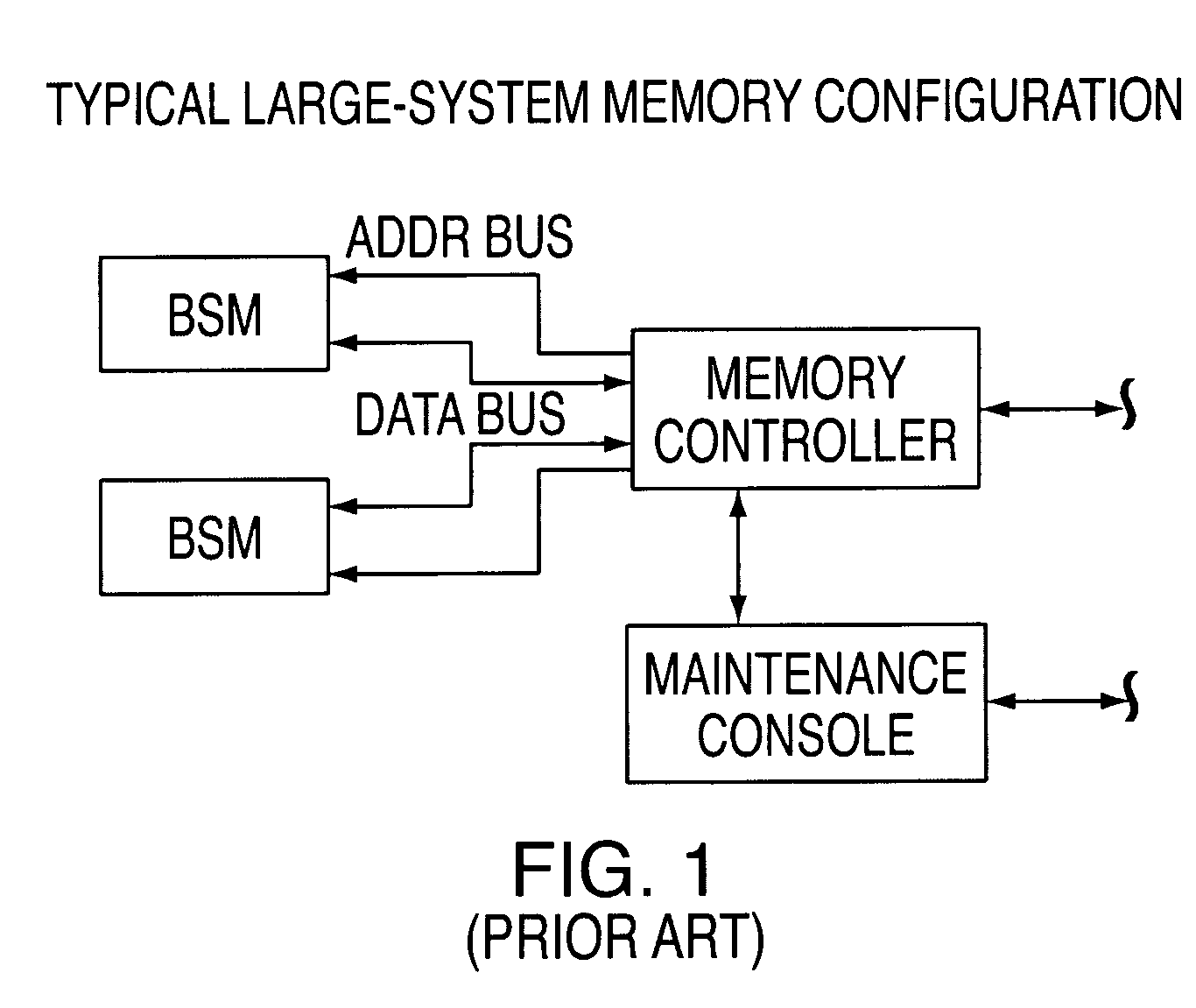

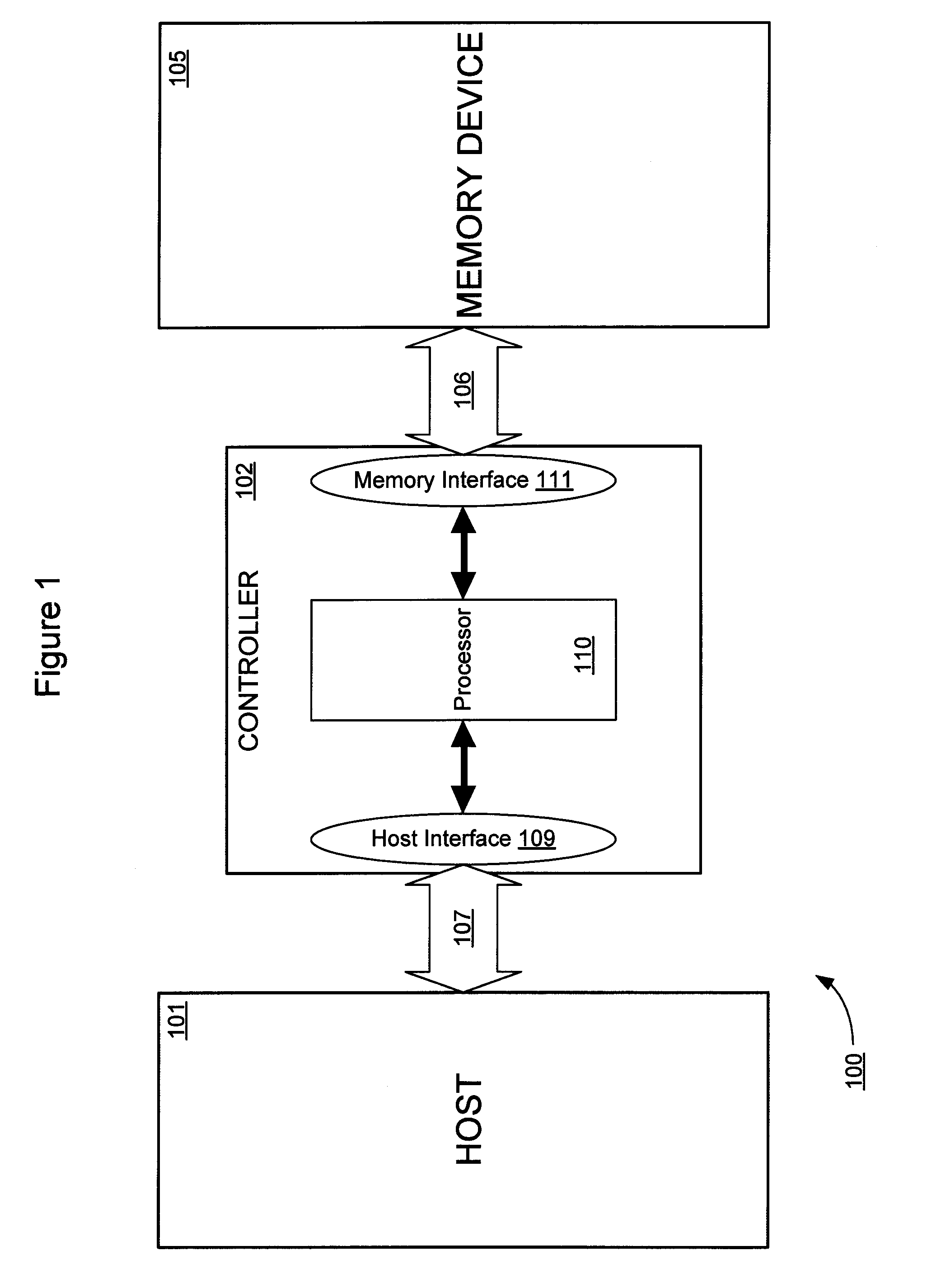

Active memory data compression system and method

ActiveUS9015390B2Concurrent instruction executionArchitecture with single central processing unitMass storageData compression

An integrated circuit active memory device receives task commands from a component in a host computer system that may include the active memory device. The host system includes a memory controller coupling the active memory device to a host CPU and a mass storage device. The active memory device includes a command engine issuing instructions responsive to the task commands to either an array control unit or a DRAM control unit. The instructions provided to the DRAM control unit cause data to be written to or read from a DRAM and coupled to or from either the processing elements or a host / memory interface. The processing elements execute instructions provided by the array control unit to decompress data written to the DRAM through the host / memory interface and compress data read from the DRAM through the host / memory interface.

Owner:MICRON TECH INC

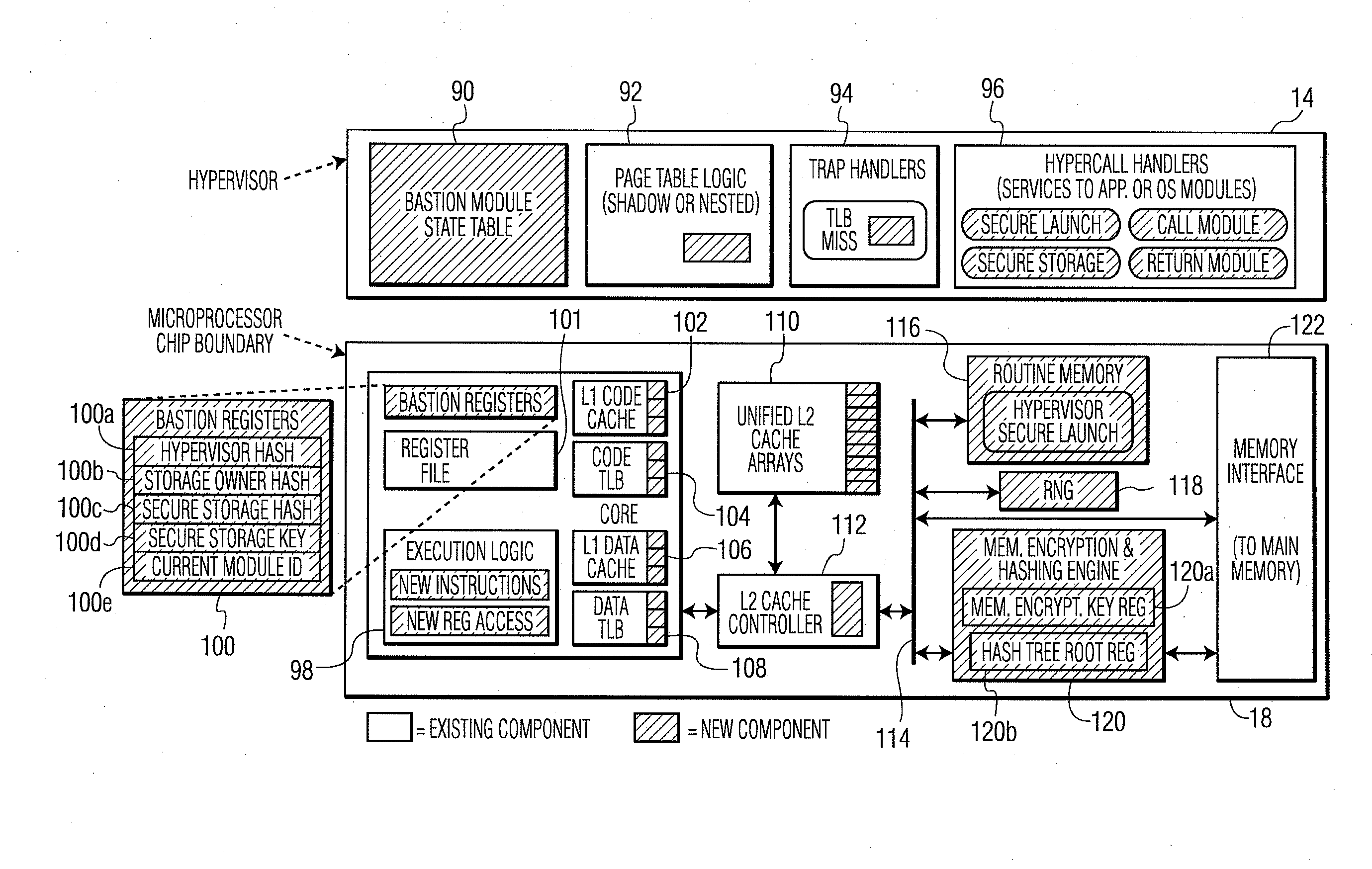

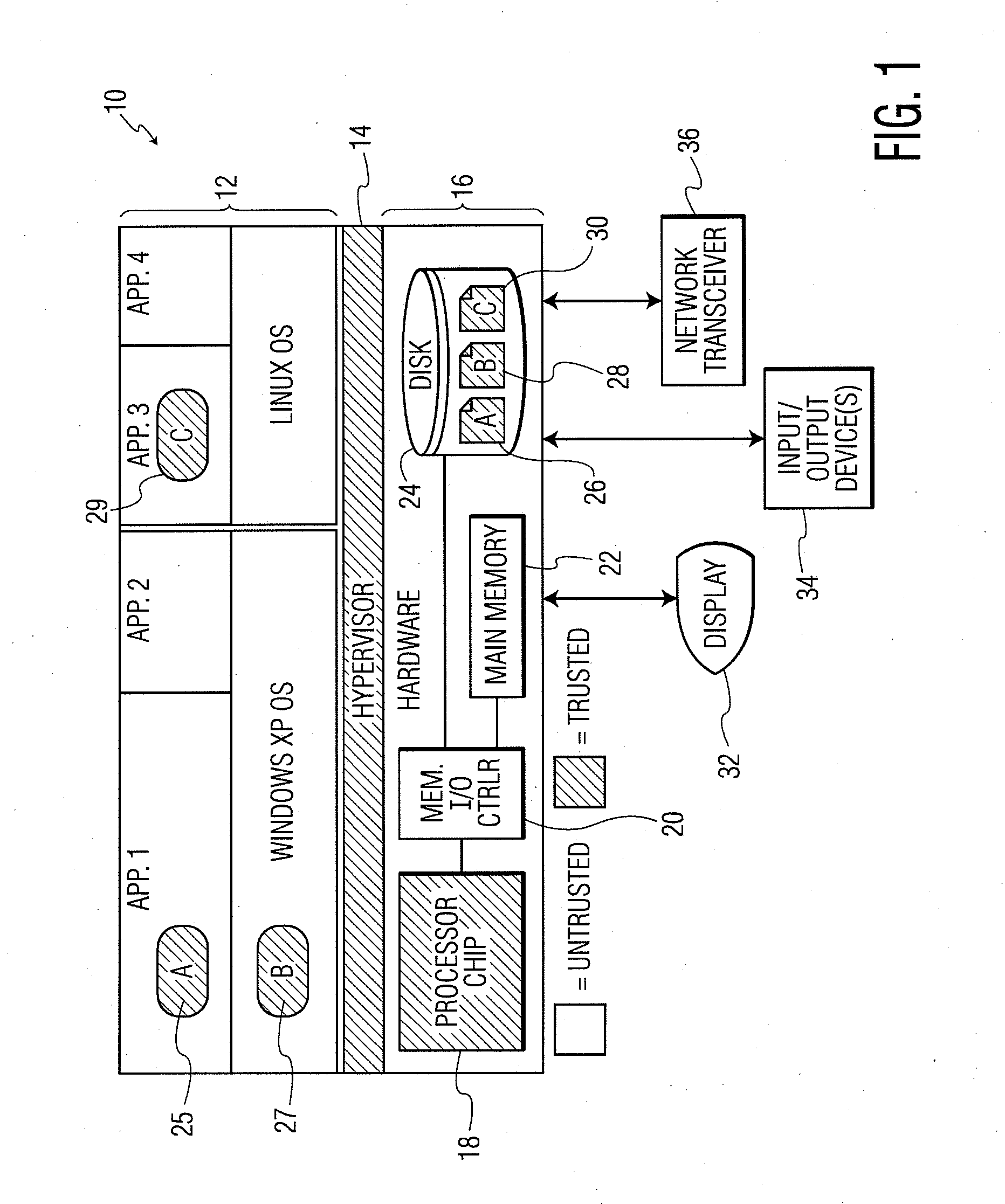

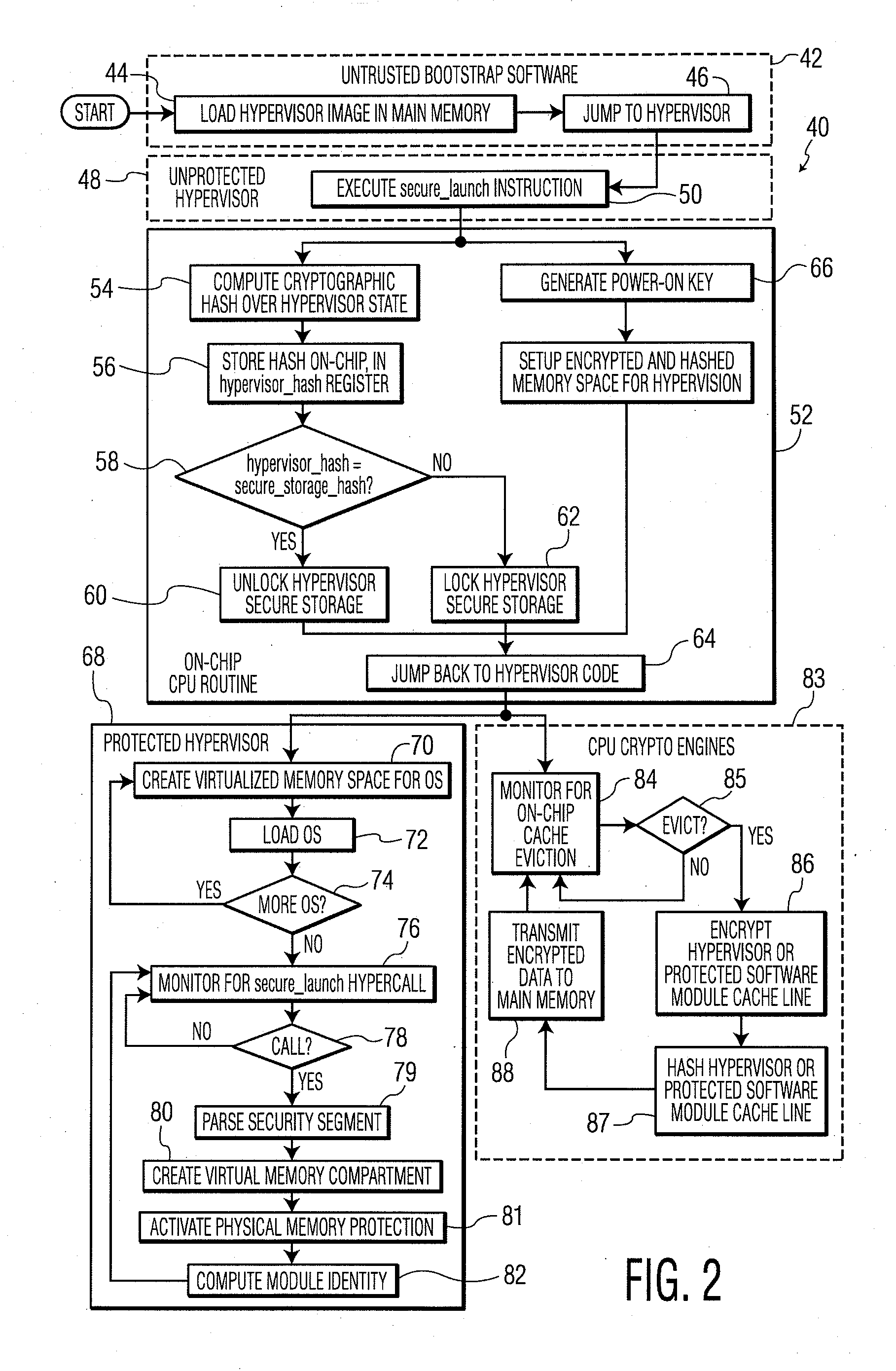

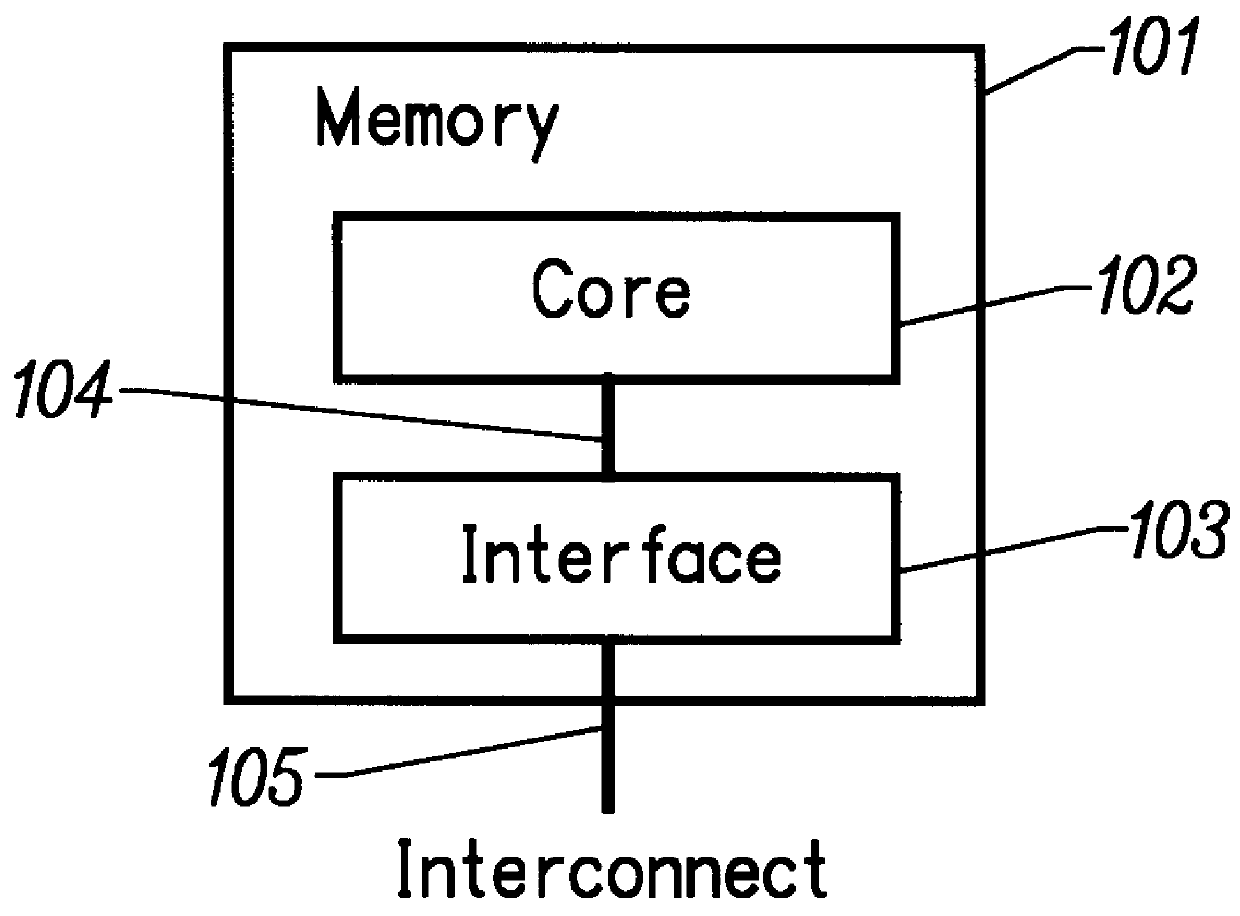

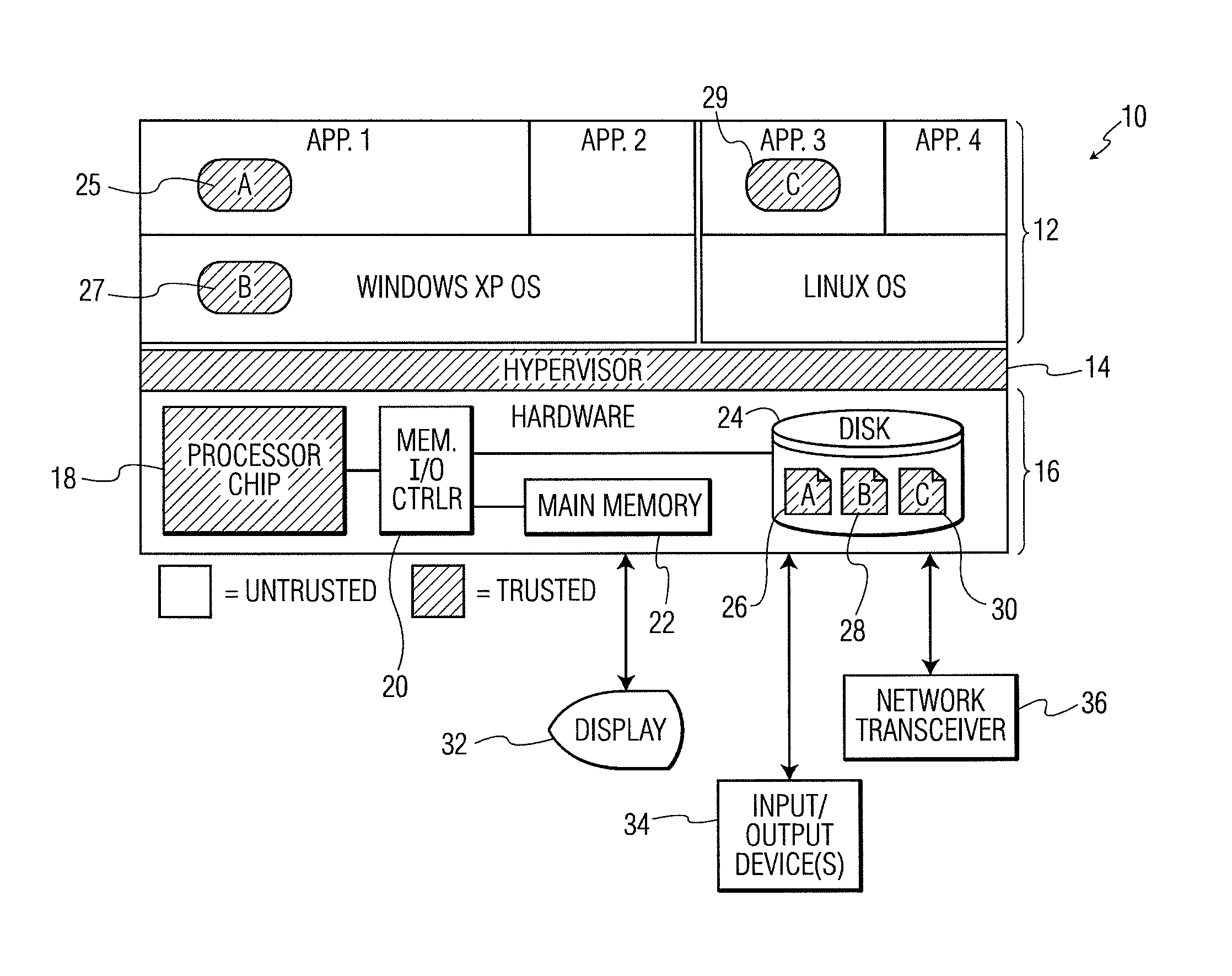

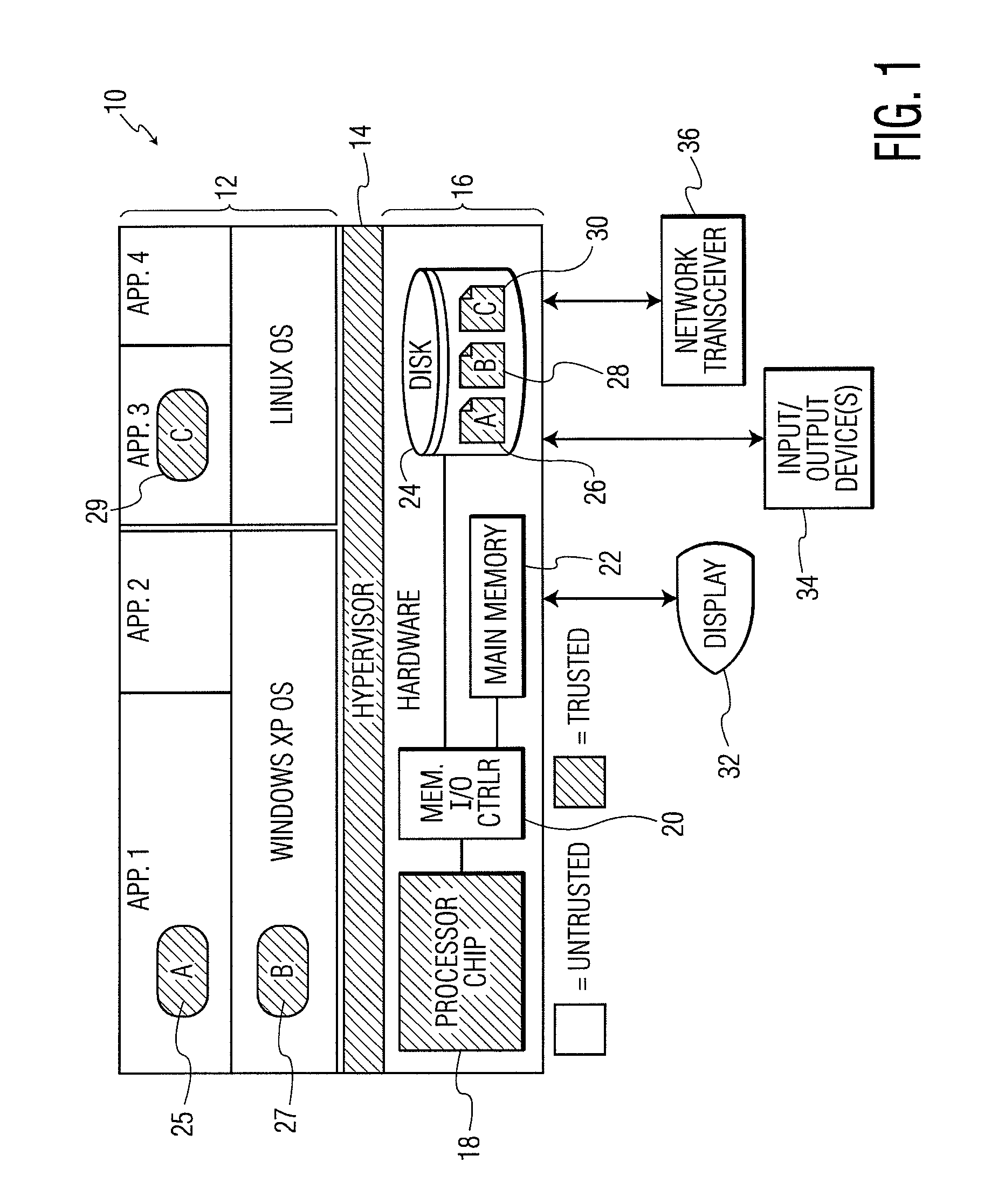

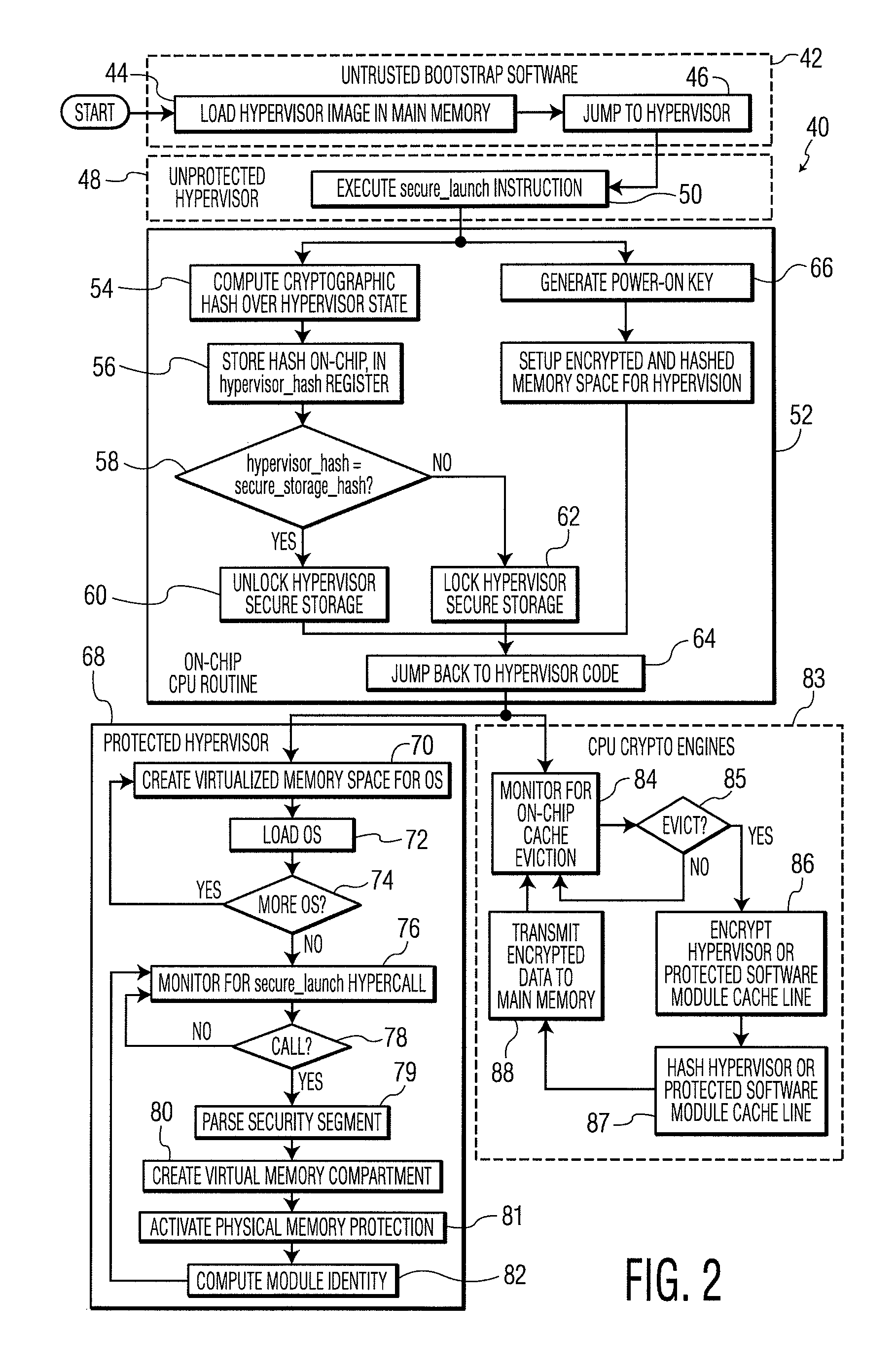

System and Method for Processor-Based Security

ActiveUS20100281273A1Avoid accessUnauthorized memory use protectionHardware monitoringExternal storageMemory interface

A system and method for processor-based security is provided, for on-chip security and trusted computing services for software applications. A processor is provided having a processor core, a cache memory, a plurality of registers for storing at least one hash value and at least one encryption key, a memory interface, and at least one on-chip instruction for creating a secure memory area in a memory external to the processor, and a hypervisor program executed by the processor. The hypervisor program instructs the processor to execute the at least one on-chip instruction to create a secure memory area for a software area for a software module, and the processor encrypts data written to, and decrypts data read from, the external memory using the at least one encryption key and the verifying data read from the external memory using the at least one hash value. Secure module interactions are provided, as well as the generation of a power-on key which can be used to protect memory in the event of a re-boot event. Lightweight, run-time attestation reports are generated which include selected information about software modules executed by the processors, for use in determining whether the processor is trusted to provide secure services.

Owner:CORESECURE TECH LLC

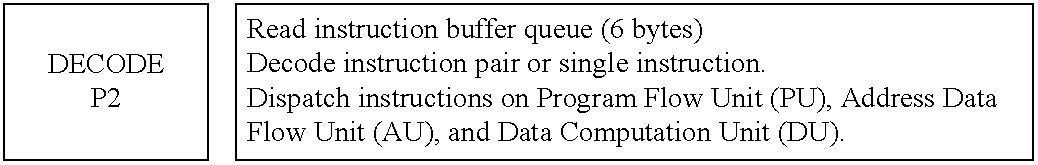

Microprocessors

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

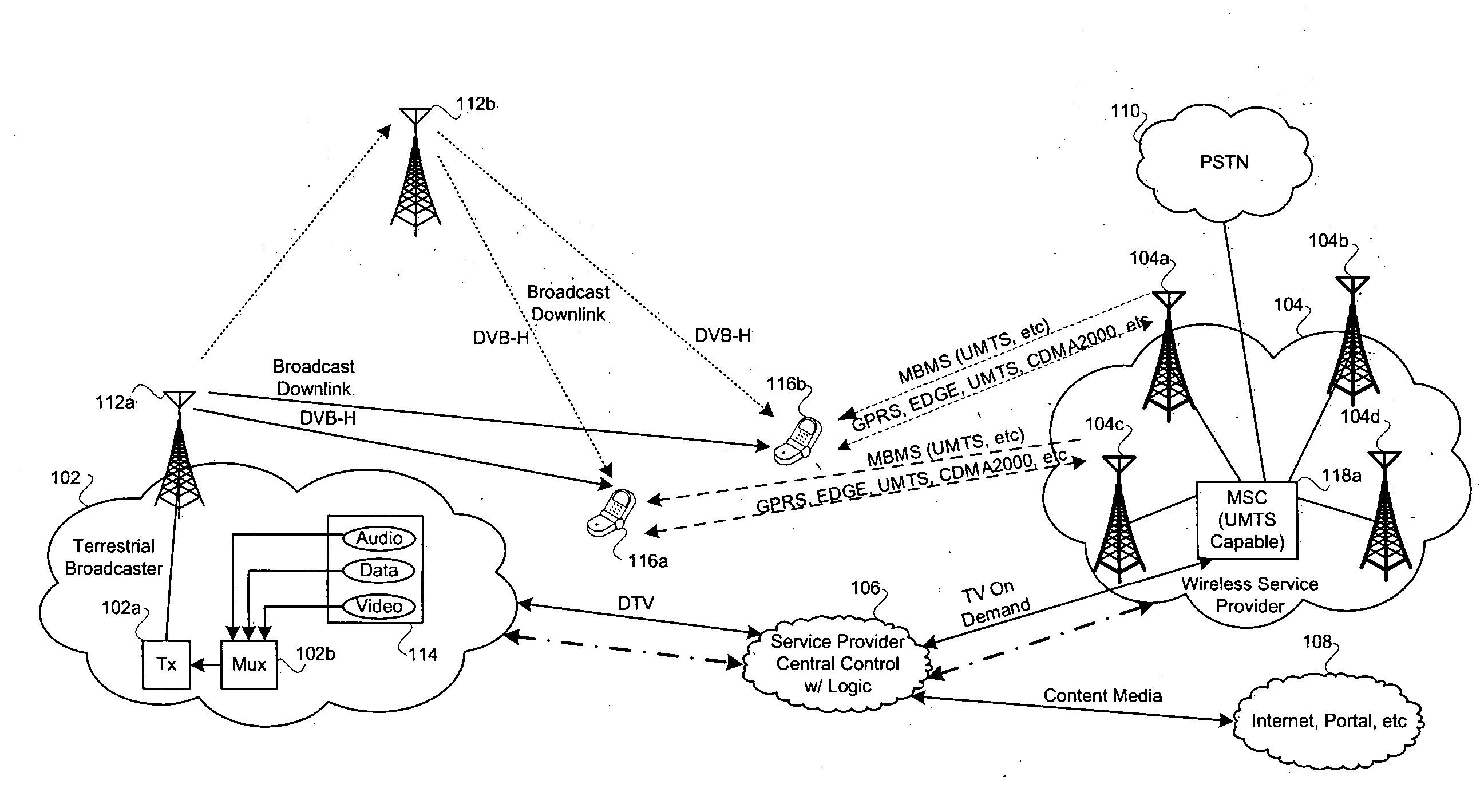

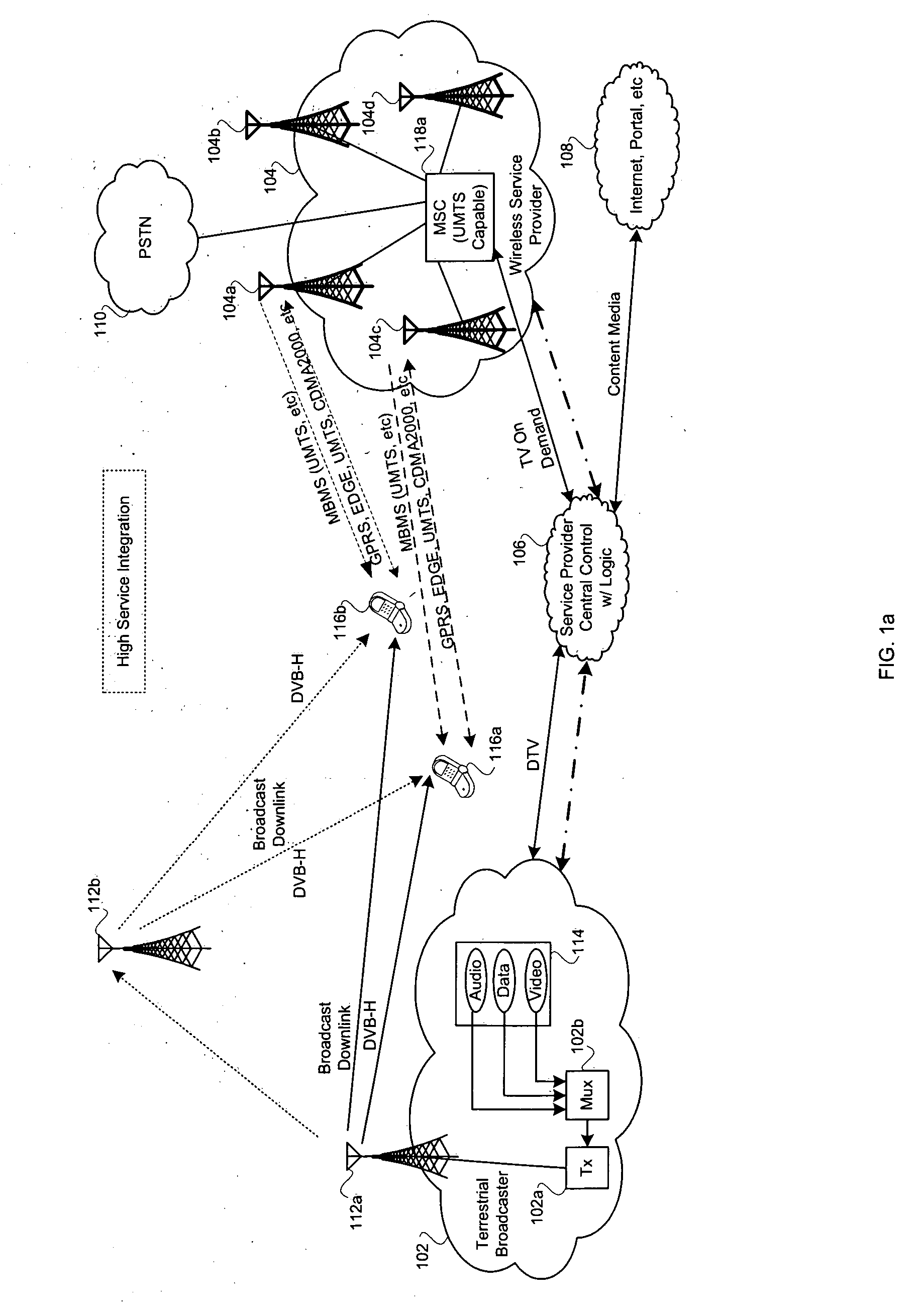

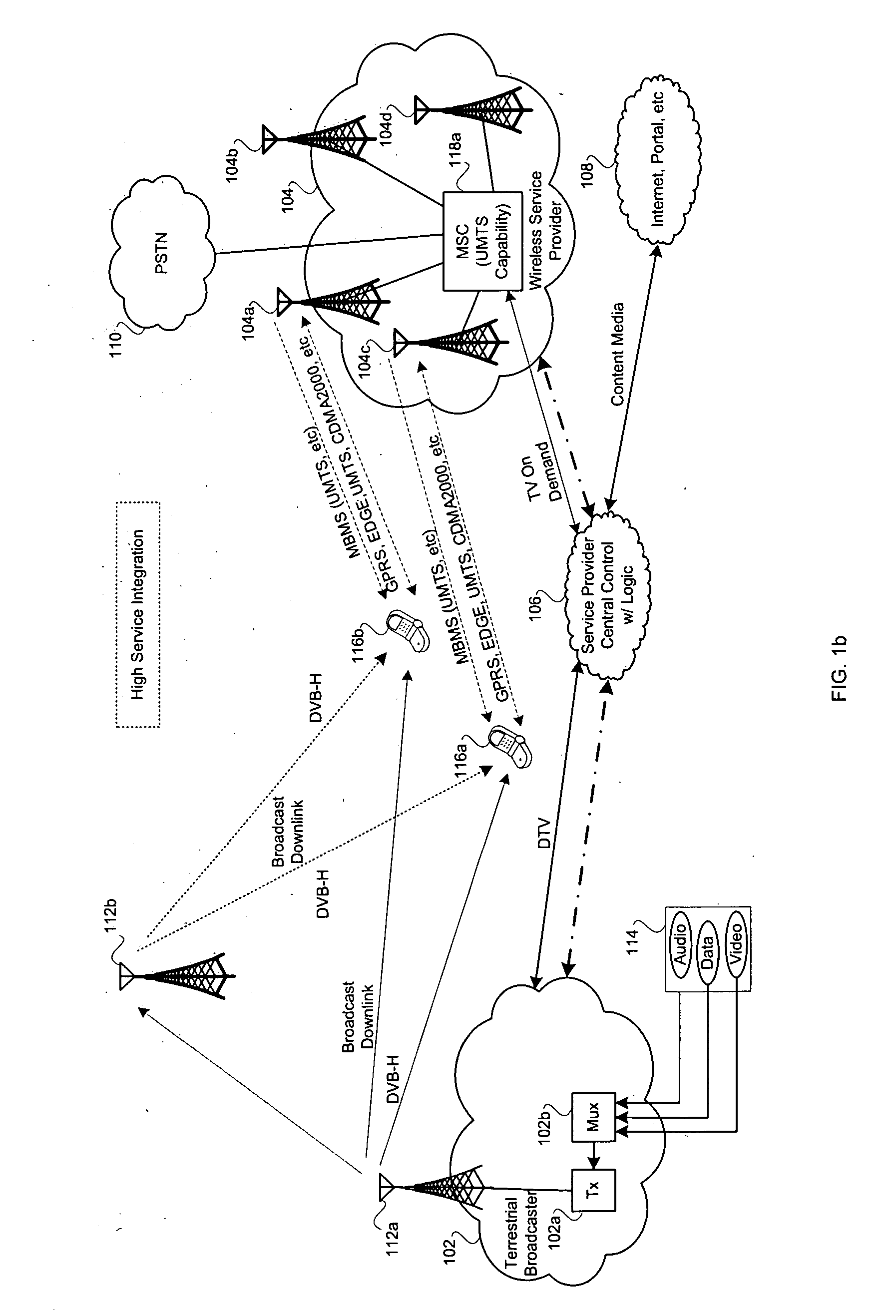

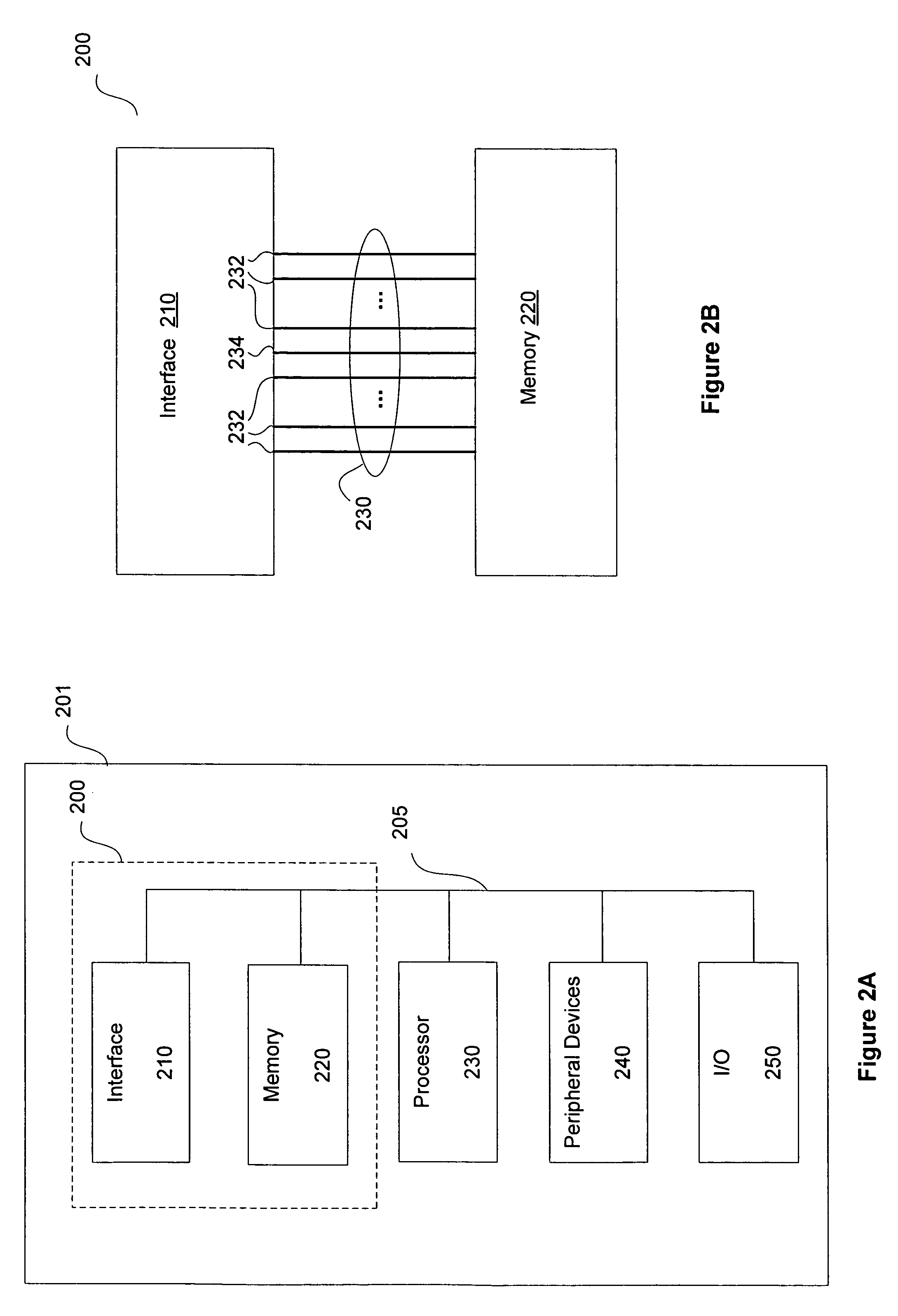

Method and system for cellular network and integrated broadcast television (TV) downlink with intelligent service control without feedback

InactiveUS20060130099A1Broadcast specific applicationsBroadcast-related systemsMemory interfaceService control

Methods and systems for communicating with a plurality of communications networks are provided herein. Aspects of the system may comprise cellular processing circuitry that processes a plurality of cellular frequency band communications services, comprising at least one cellular voice service and at least one cellular data service. The cellular processing circuitry may comprise a plurality of cellular processing integrated circuits within a mobile terminal. Broadcast processing circuitry may processes VHF / UHF frequency band broadcast services in at least one single broadcast processing integrated circuit within the mobile terminal. One or more of the cellular processing integrated circuits may communicate with, and shares at least a single memory with, the single broadcast processing integrated circuit. The single memory may be coupled to one or more of the cellular processing integrated circuits and the single broadcast processing integrated circuit via a memory interface.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

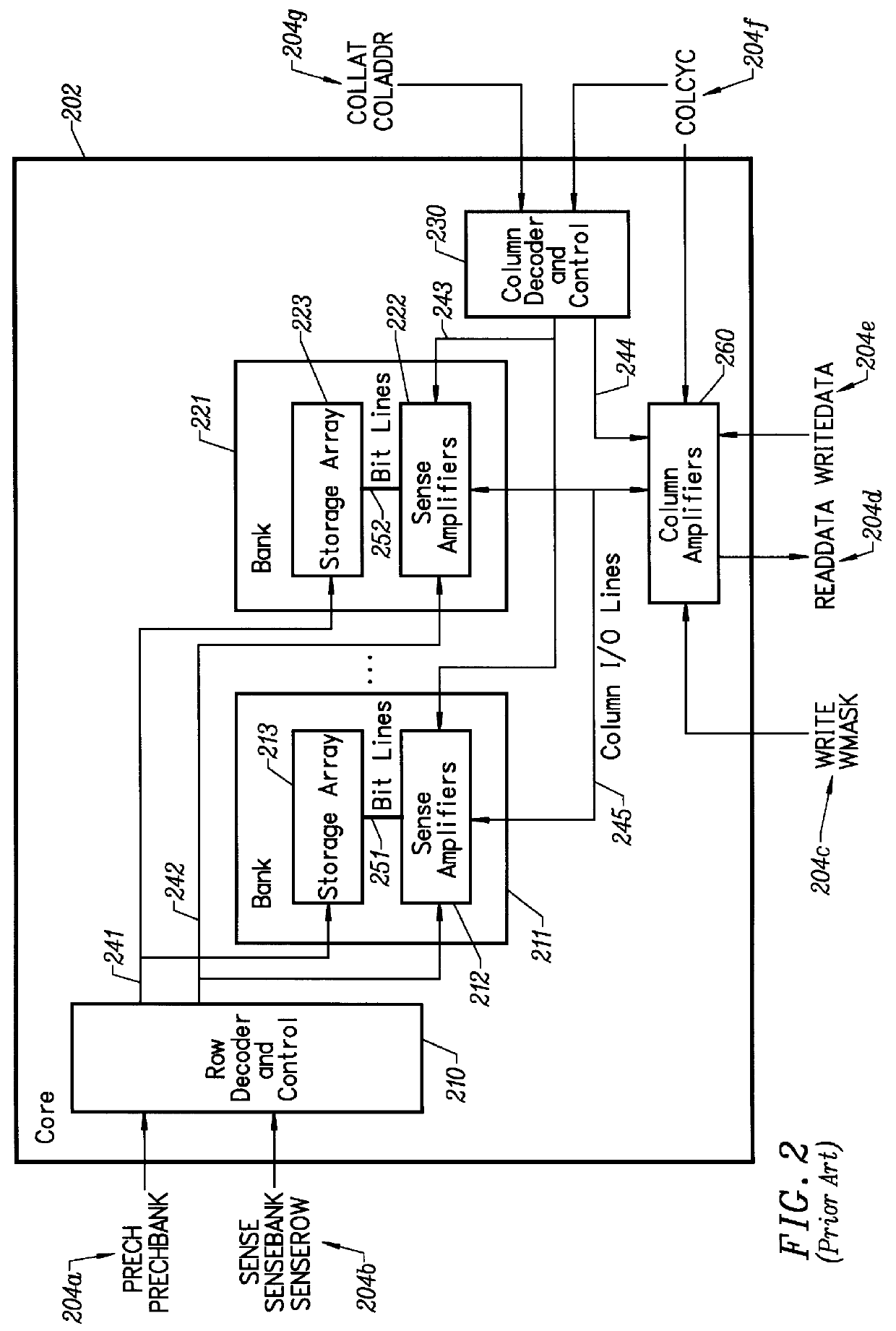

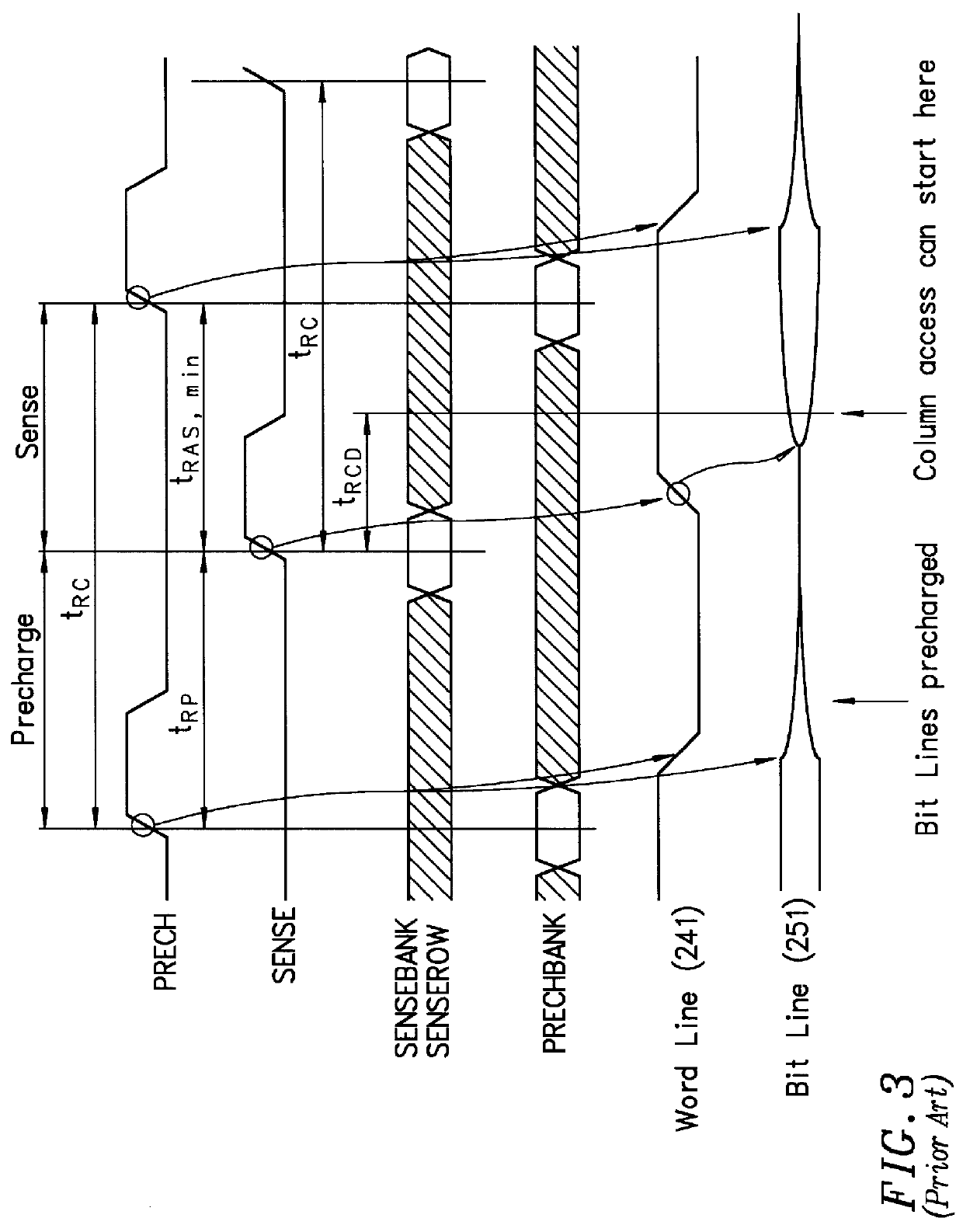

High performance cost optimized memory with delayed memory writes

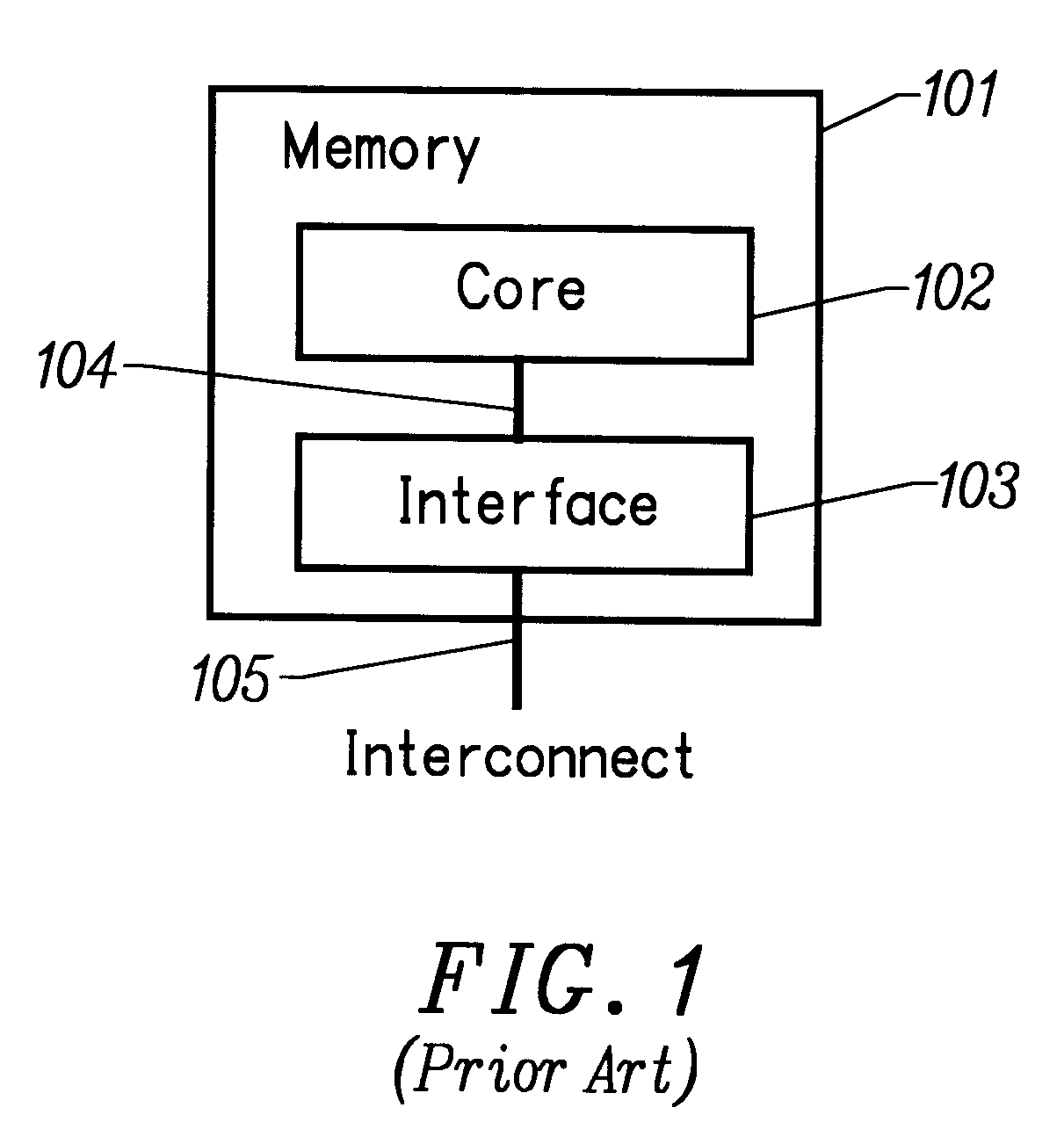

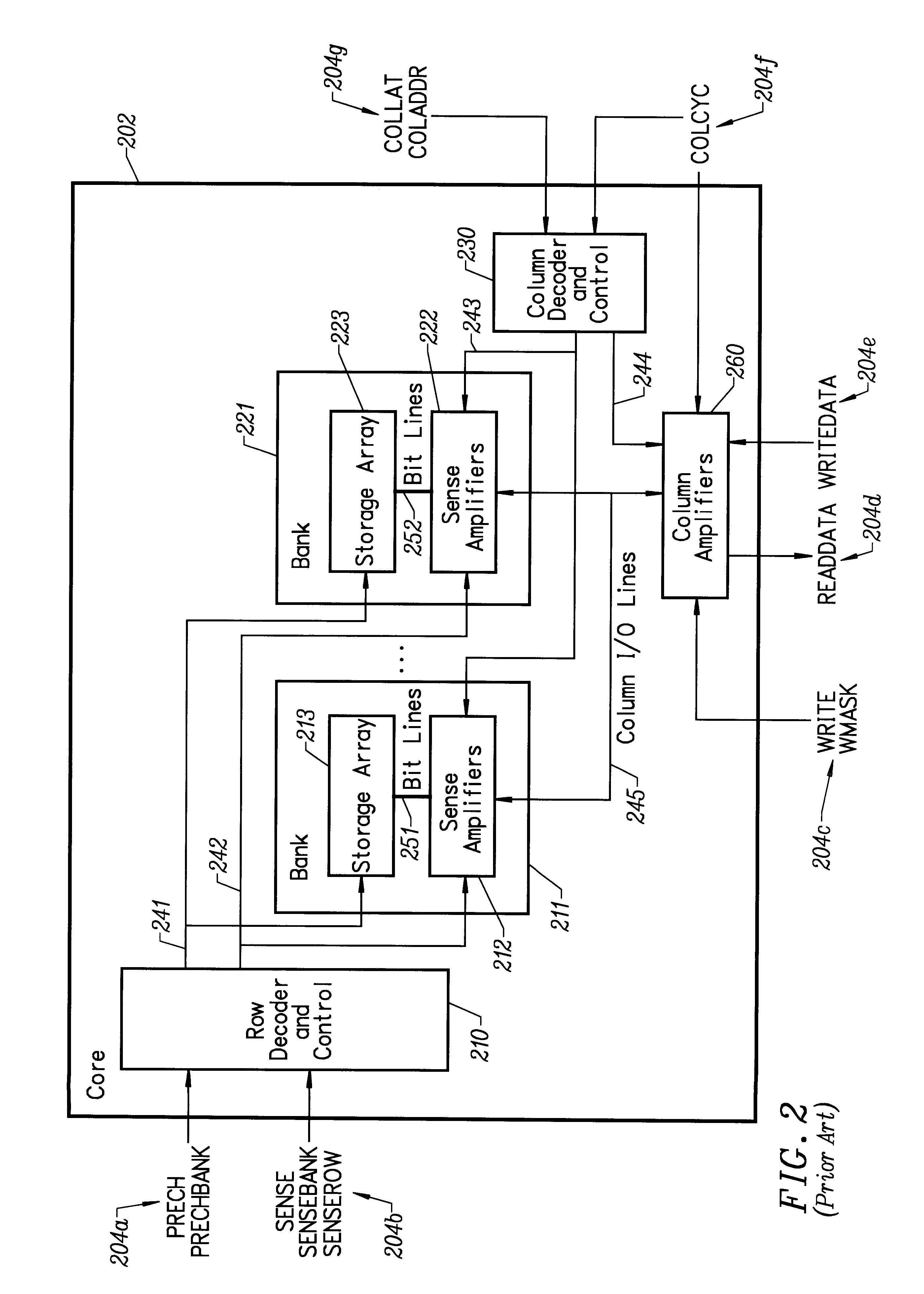

A memory device includes an interconnect with control pins and bidirectional data pins. A memory core stores data. A memory interface circuit is connected to the interconnect and the memory core. The memory interface circuit includes a delay circuit to establish a write delay during a memory core write transaction such that the memory core write transaction has a processing time that is substantially equivalent to a memory core read transaction. The delay circuit delays the memory core write transaction for a time corresponding to the time required for signals to travel on the interconnect.

Owner:RAMBUS INC +1

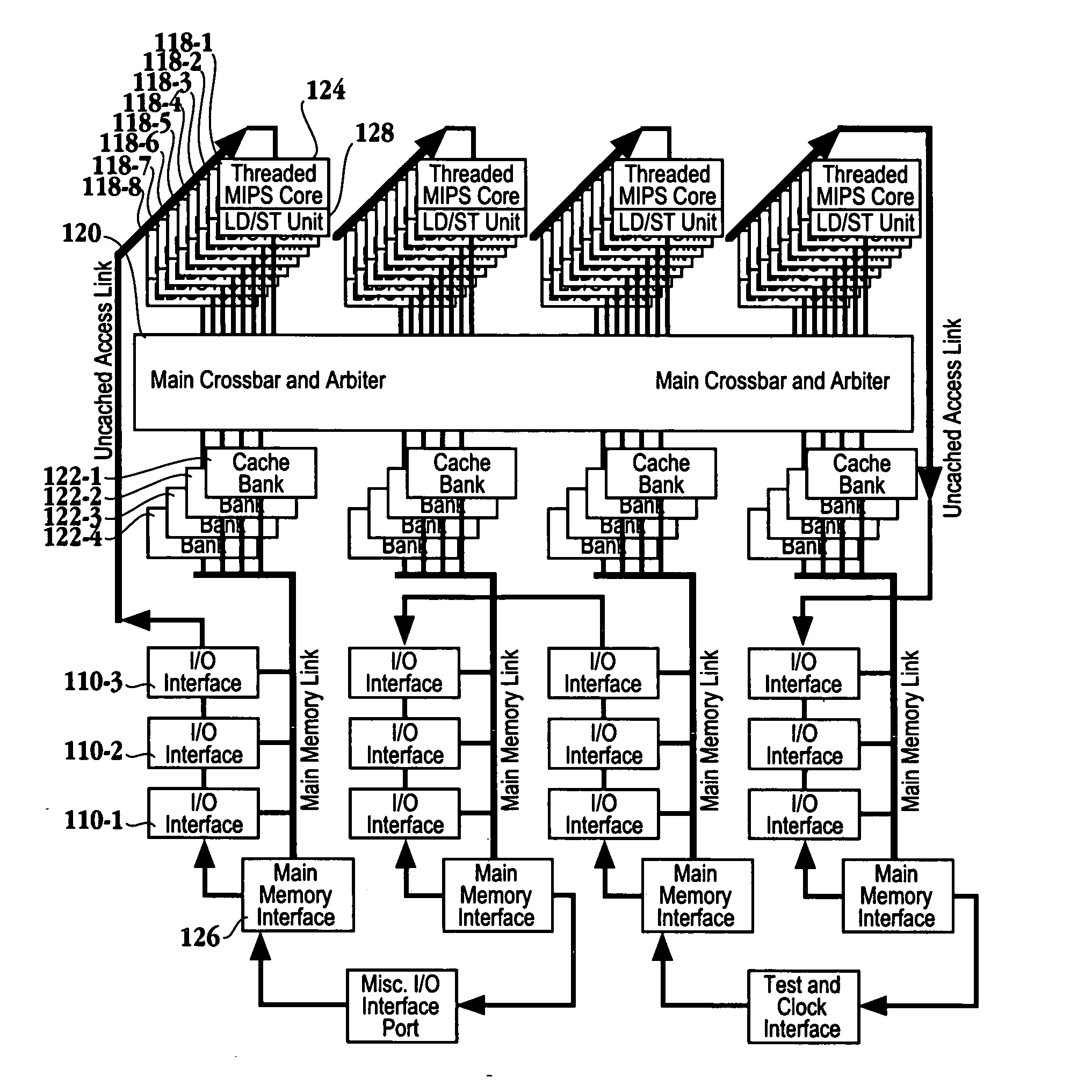

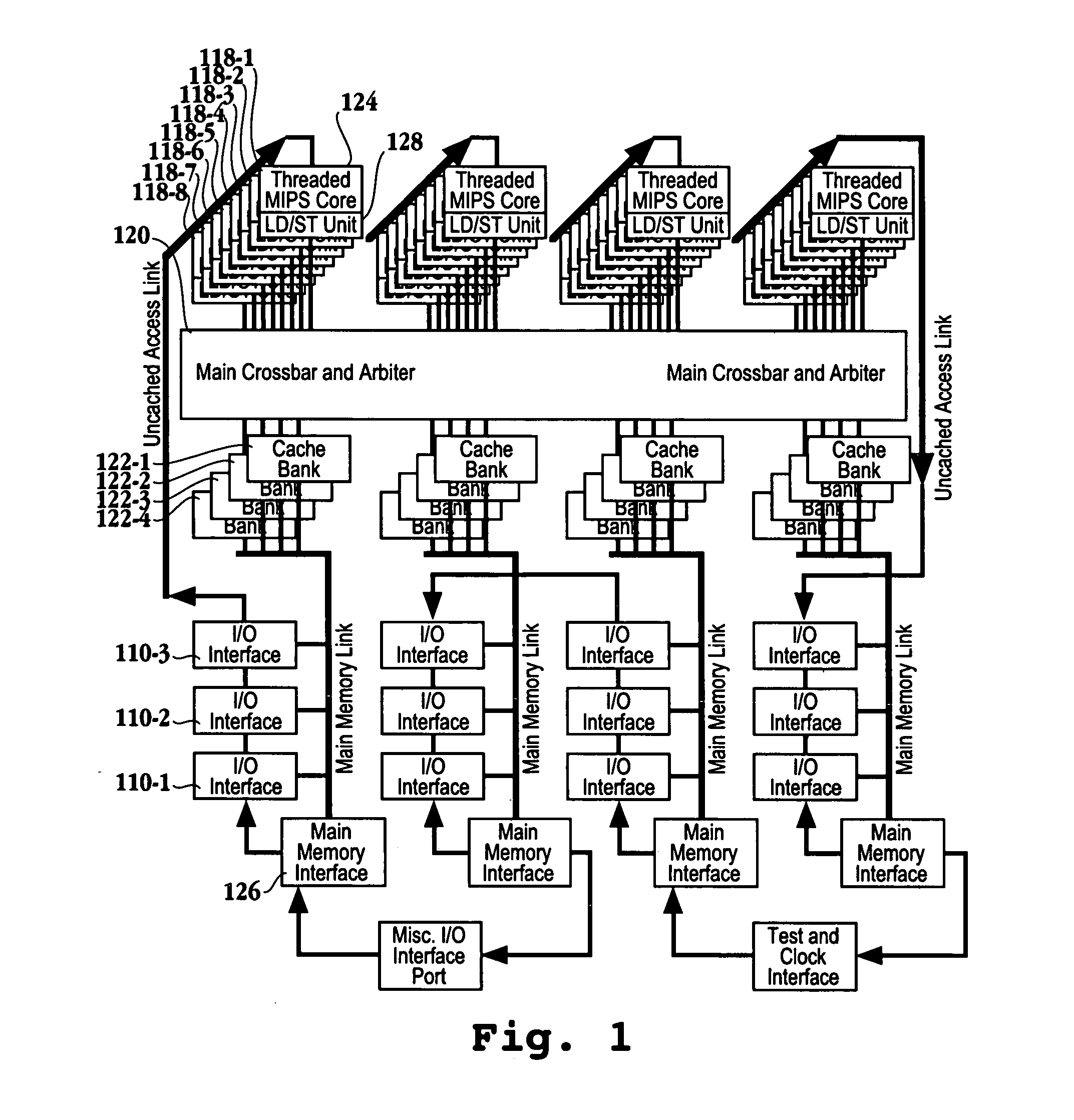

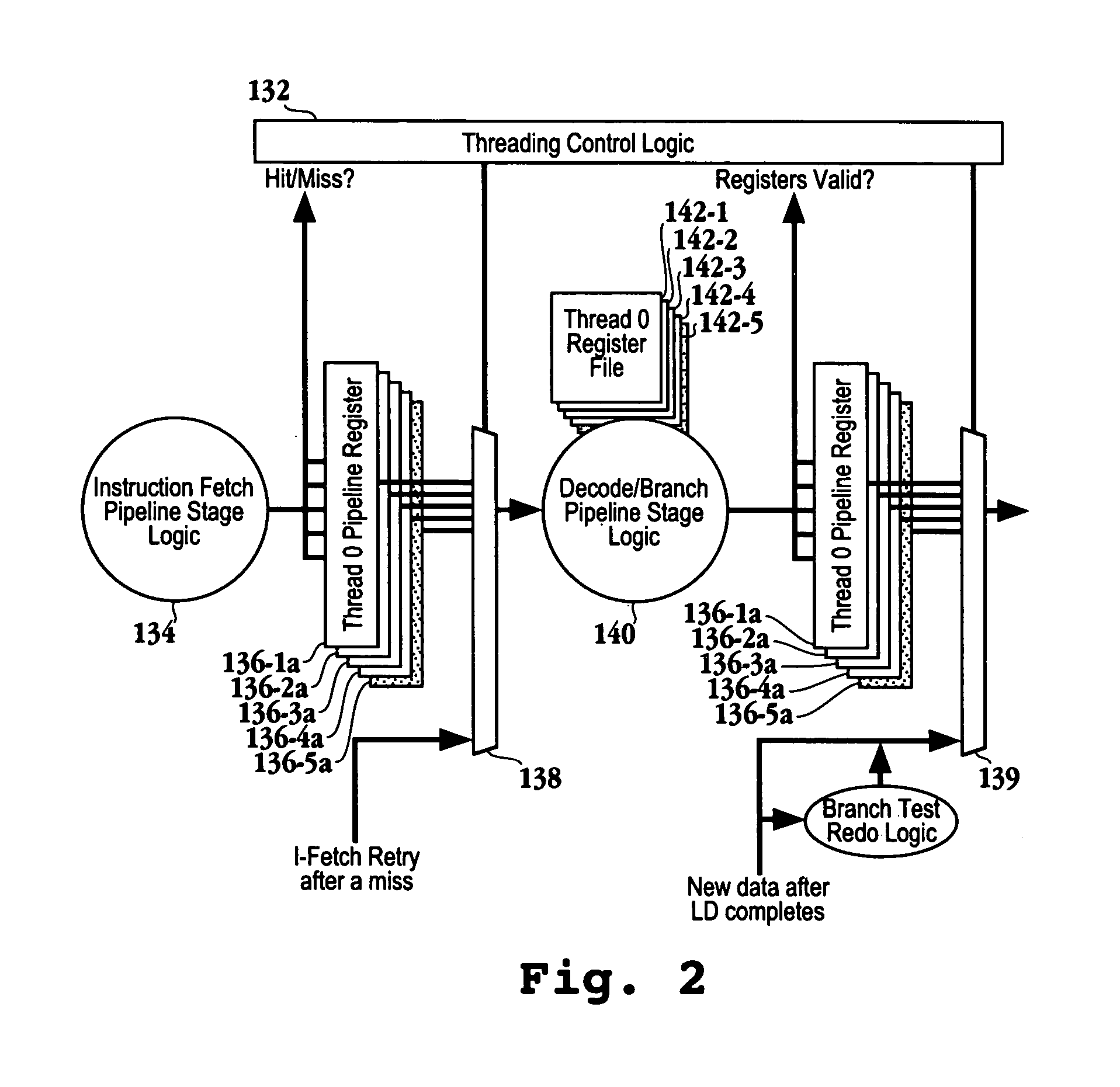

Multi-core multi-thread processor

ActiveUS20050044319A1Easy accessRegister arrangementsMemory adressing/allocation/relocationMemory interfaceParallel computing

A processor is provided. The processor includes at least two cores. The at least two cores have a first level cache memory and are multi-threaded. A crossbar is included. A plurality of cache bank memories in communication with the at least two cores through the crossbar is provided. Each of the plurality of cache bank memories communicates with a main memory interface. A plurality of input / output interface modules in communication with the main memory interface and providing a link to the at least two cores are included. The link bypasses the plurality of cache bank memories and the crossbar. Threading hardware configured to enable the at least two cores to switch from a first thread to a second thread in a manner hiding delays caused by cache accesses is included. A server and a method for determining when to switch threads in a multi-core multi-thread environment are included.

Owner:ORACLE INT CORP

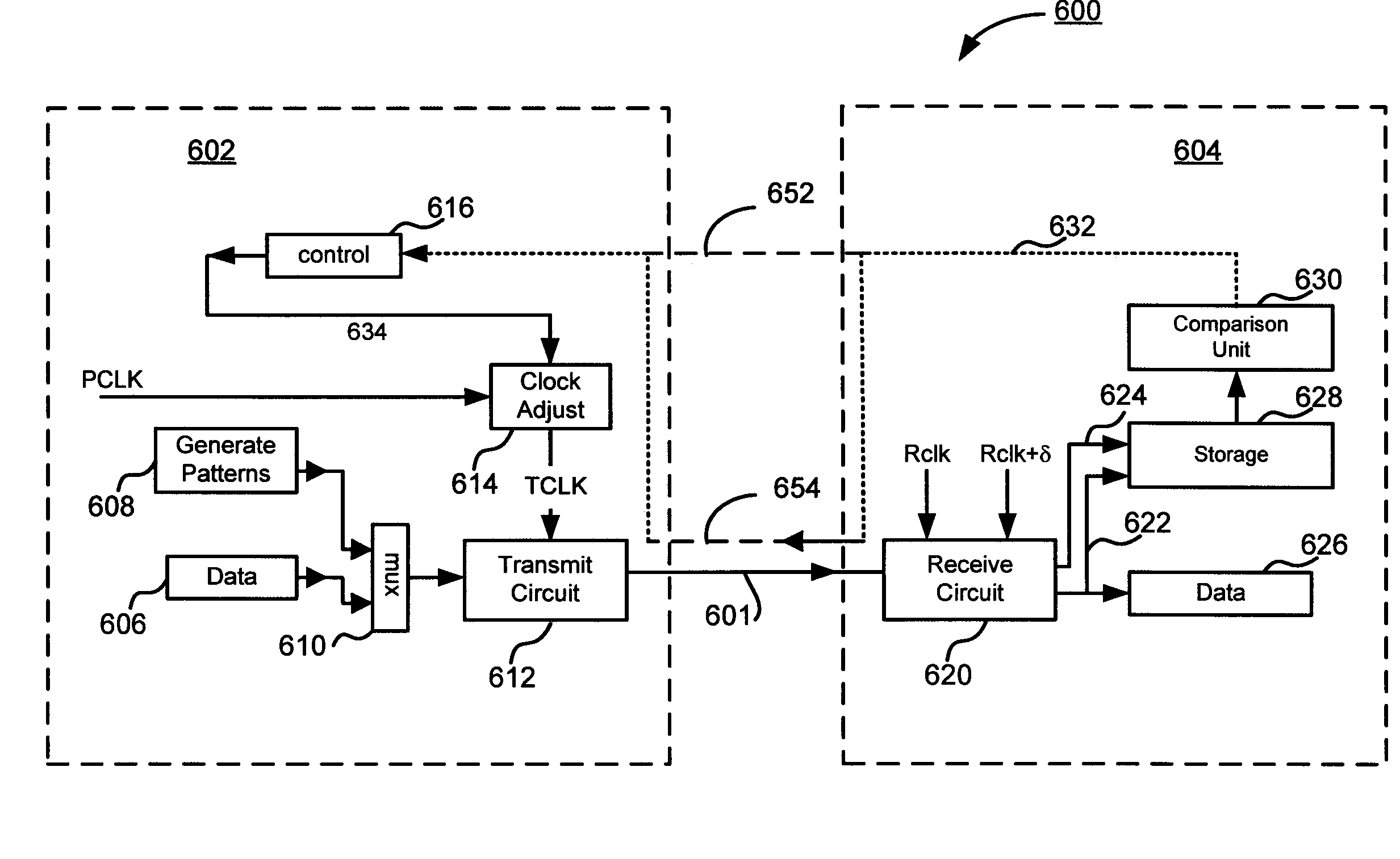

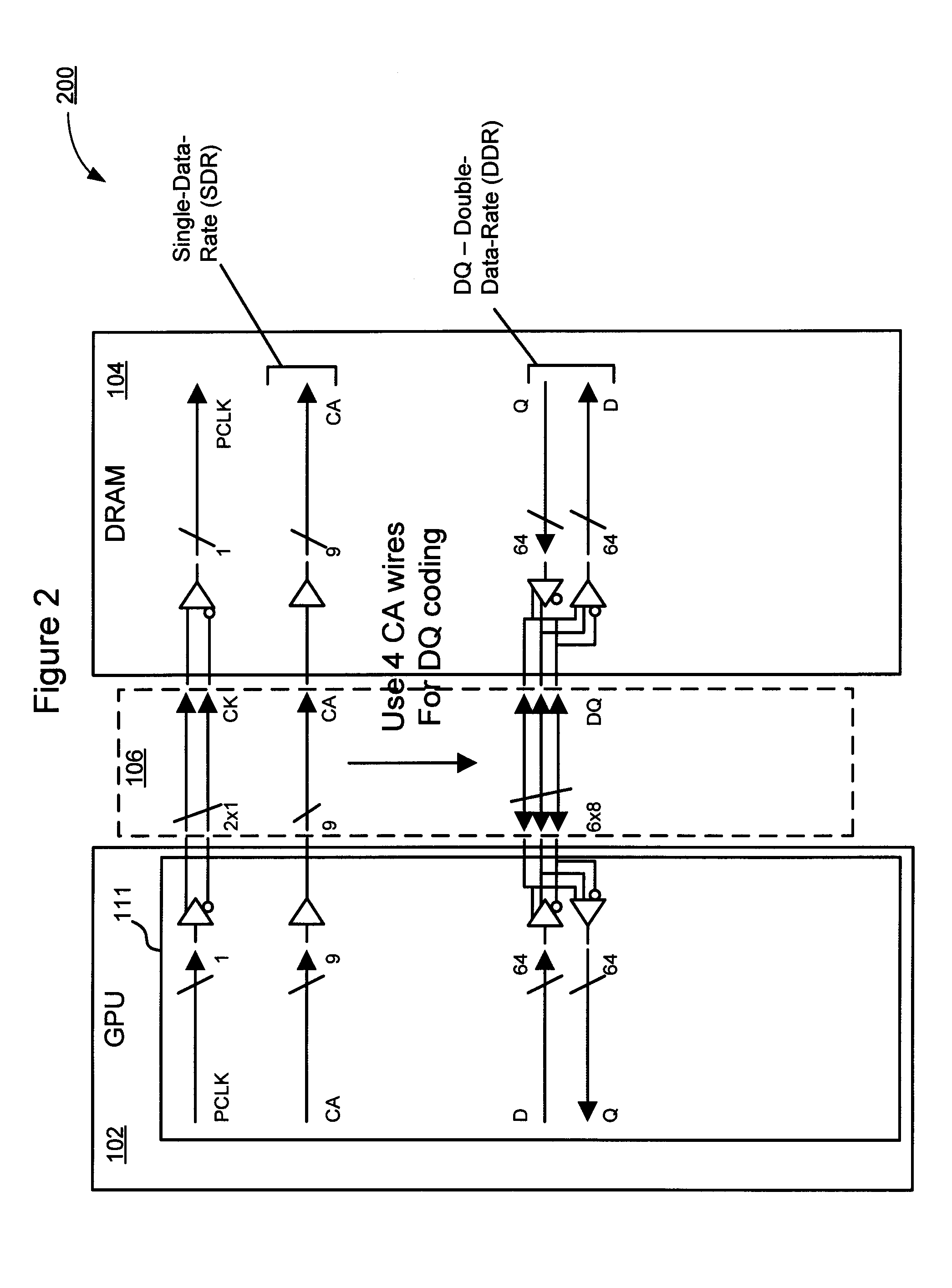

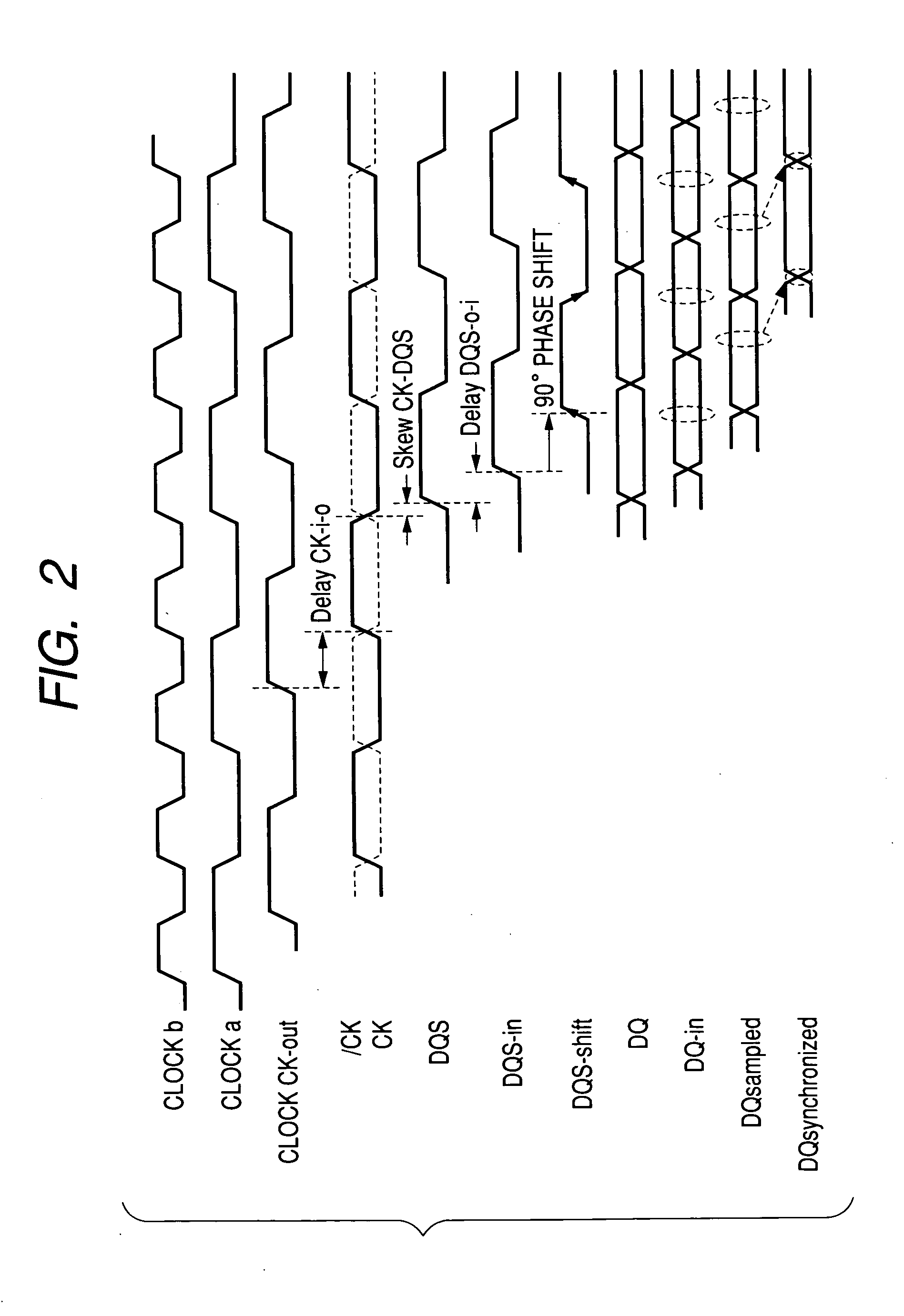

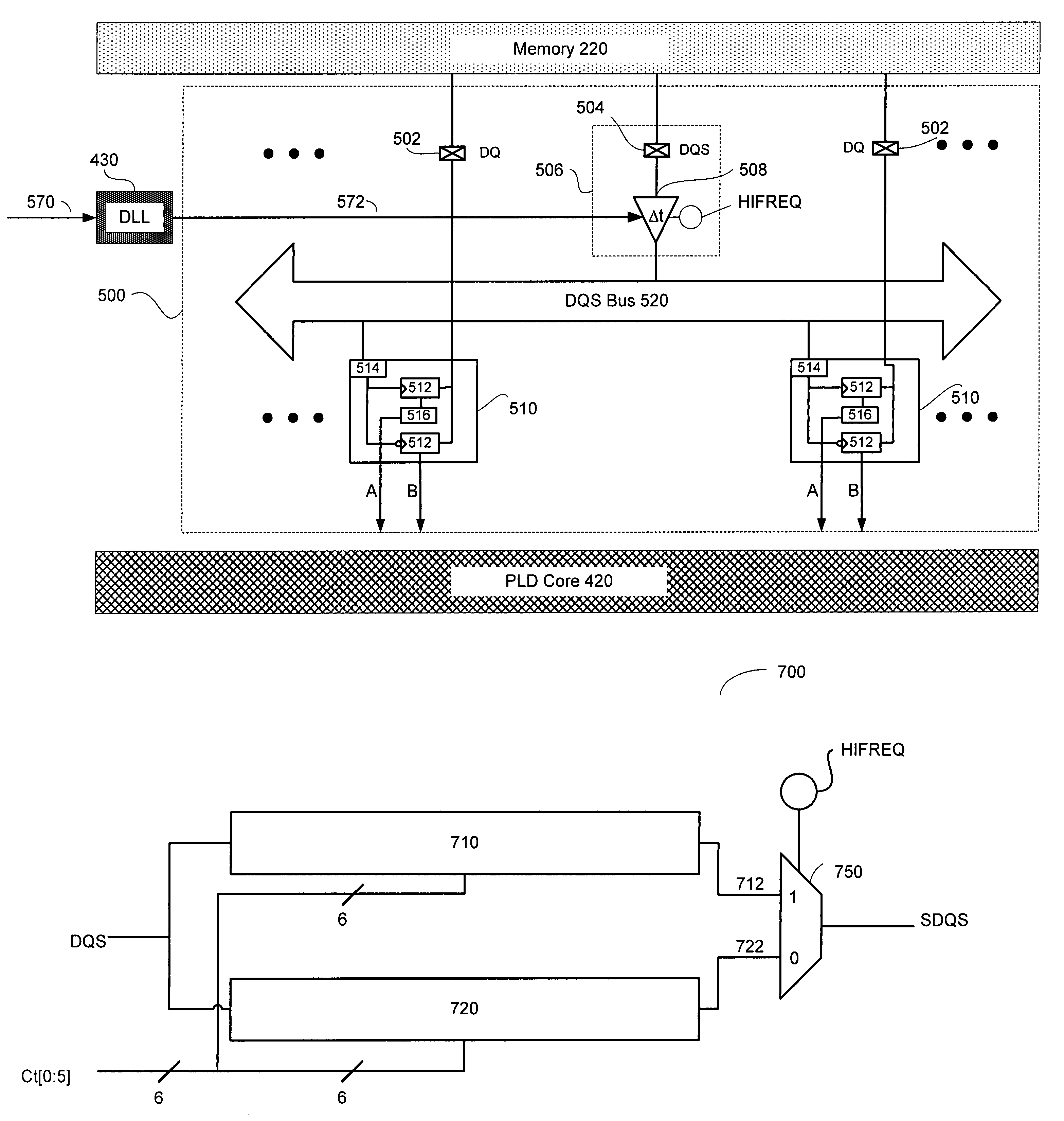

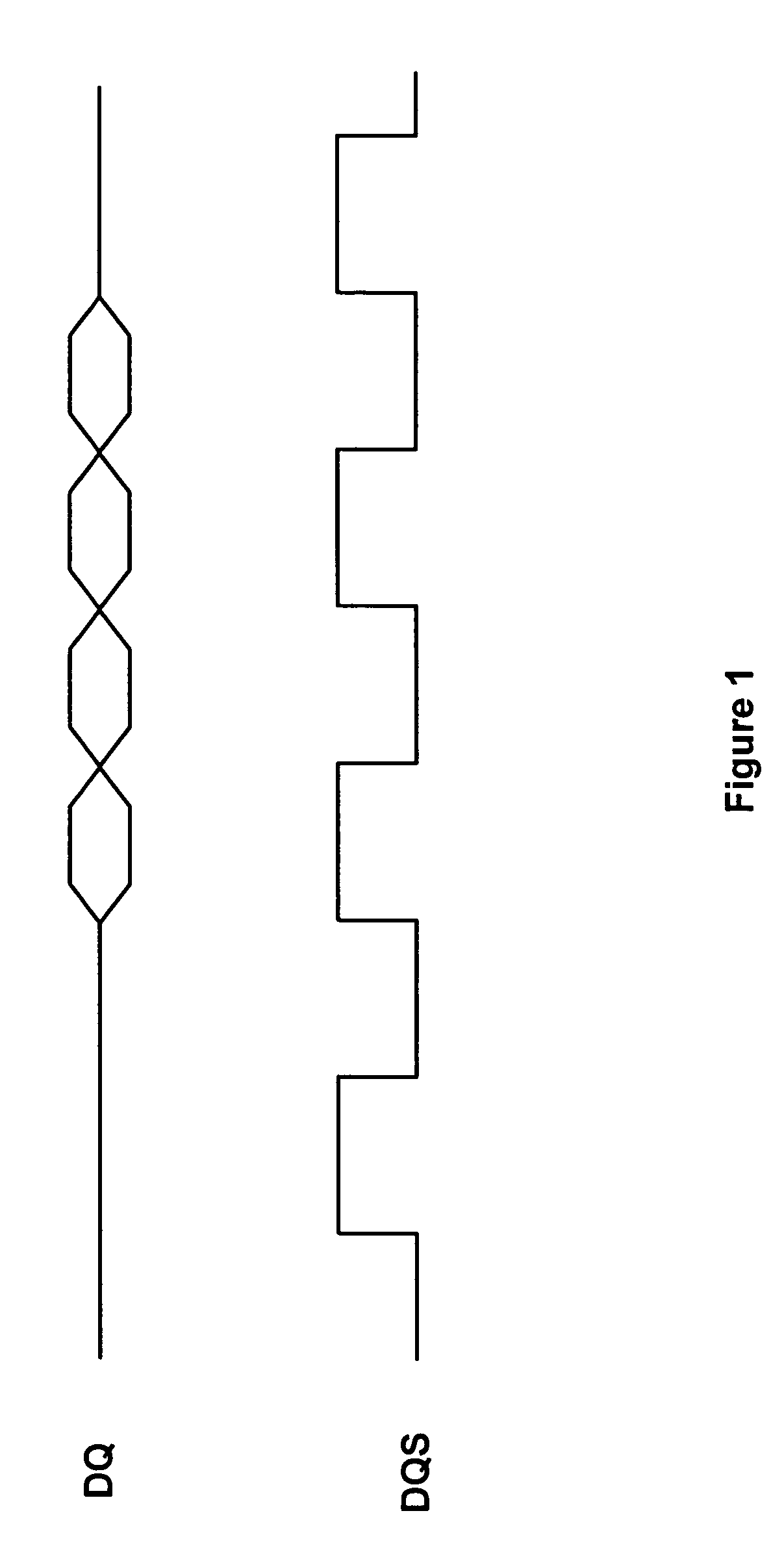

Techniques for improved timing control of memory devices

InactiveUS20100180143A1Digital storageGenerating/distributing signalsElectrical conductorTelecommunications link

Techniques for improved timing control of memory devices are disclosed. In one embodiment, the techniques may be realized as a memory controller to communicate with a memory device via a communications link. The memory controller may comprise a memory interface to exchange data with the memory device via a set of N conductors according to at least one clock, the data being encoded such that each M bits of data are represented by at least one symbol and each symbol is associated with a combination of signal levels on a group of n conductors, wherein M<N and n is equal to at least one and at most N. The memory may also comprise clock control logic to receive timing calibration information from the memory device and to output a signal to adjust a phase of the at least one clock based on the timing calibration information.

Owner:RAMBUS INC

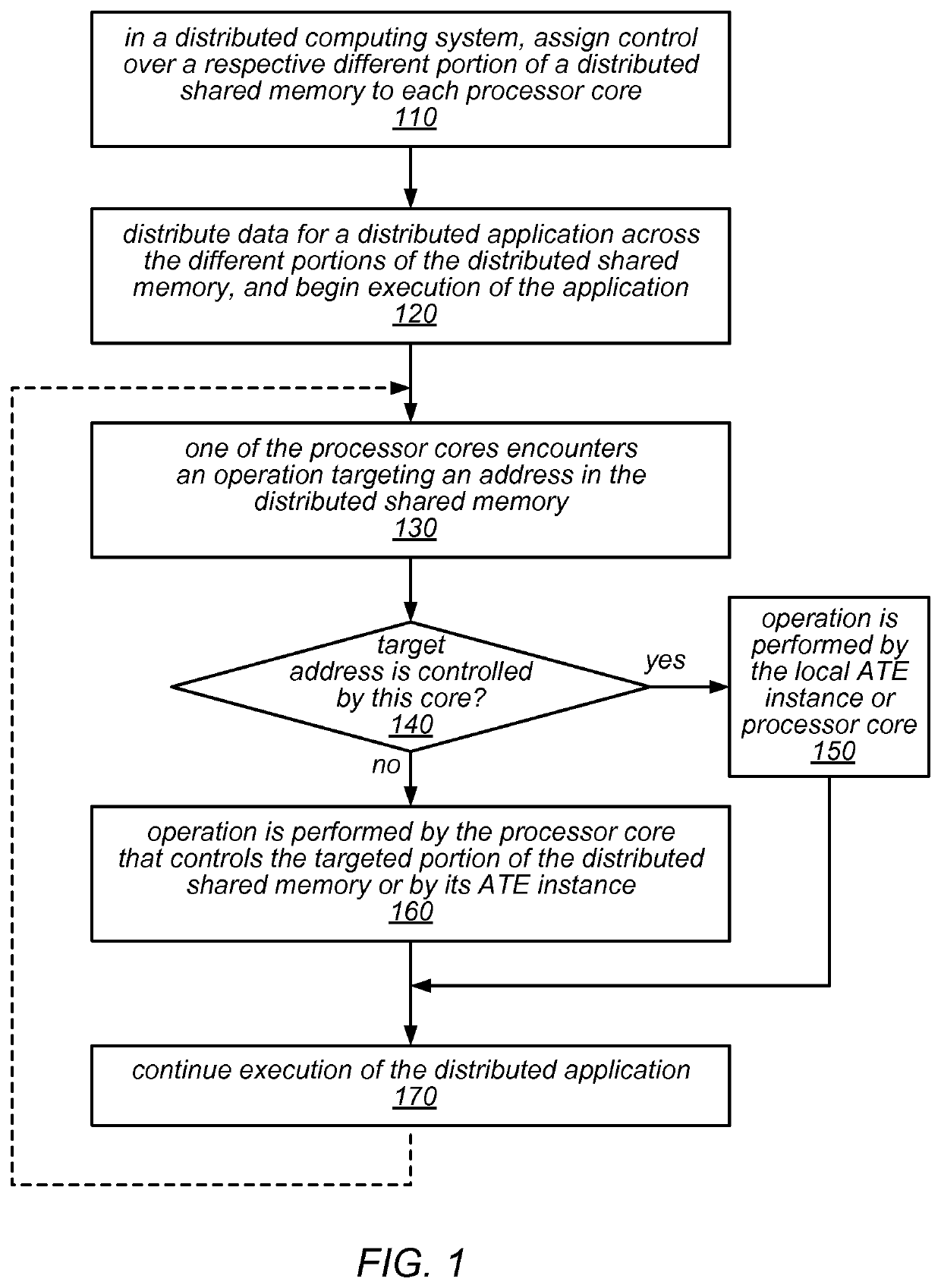

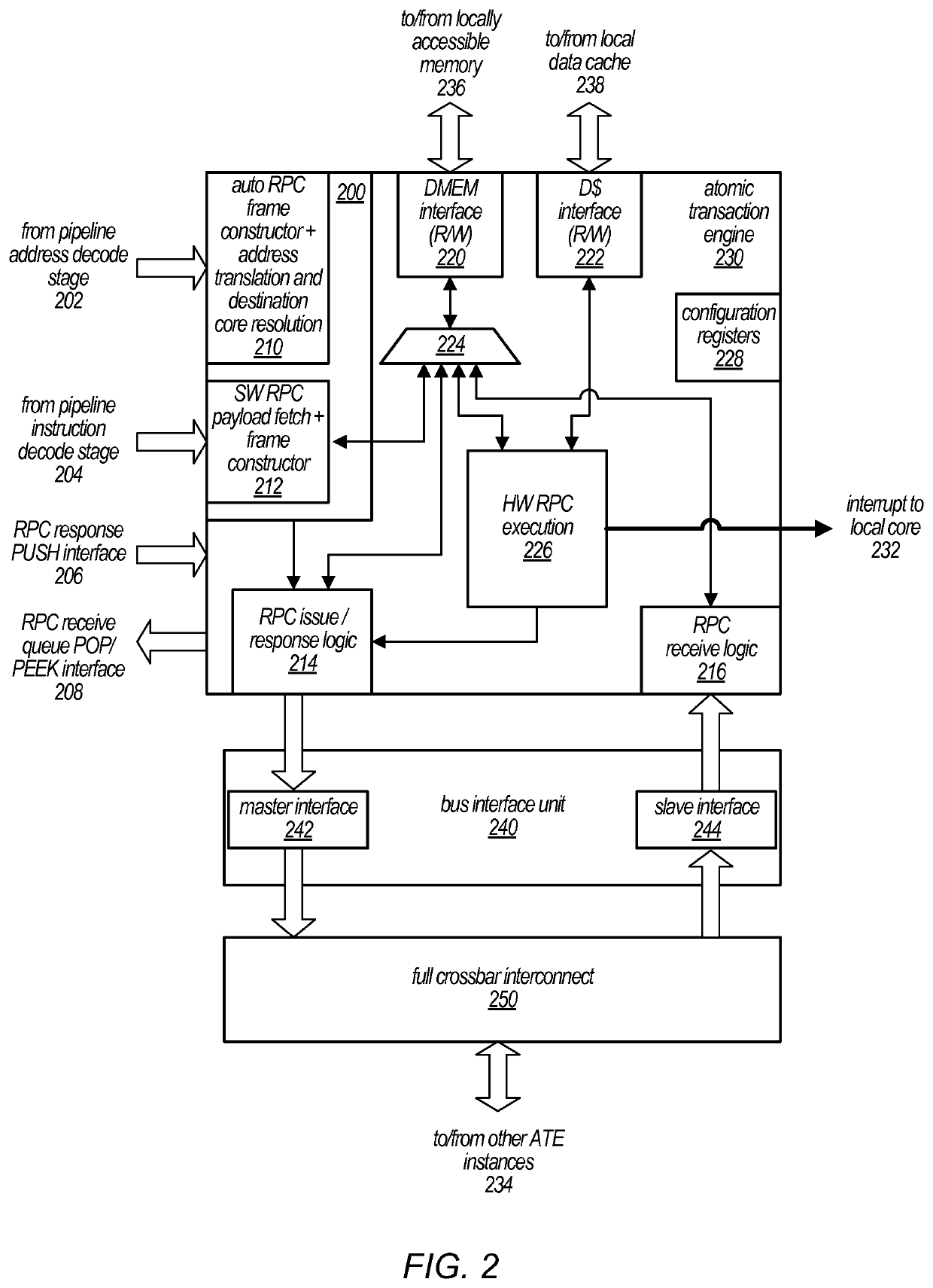

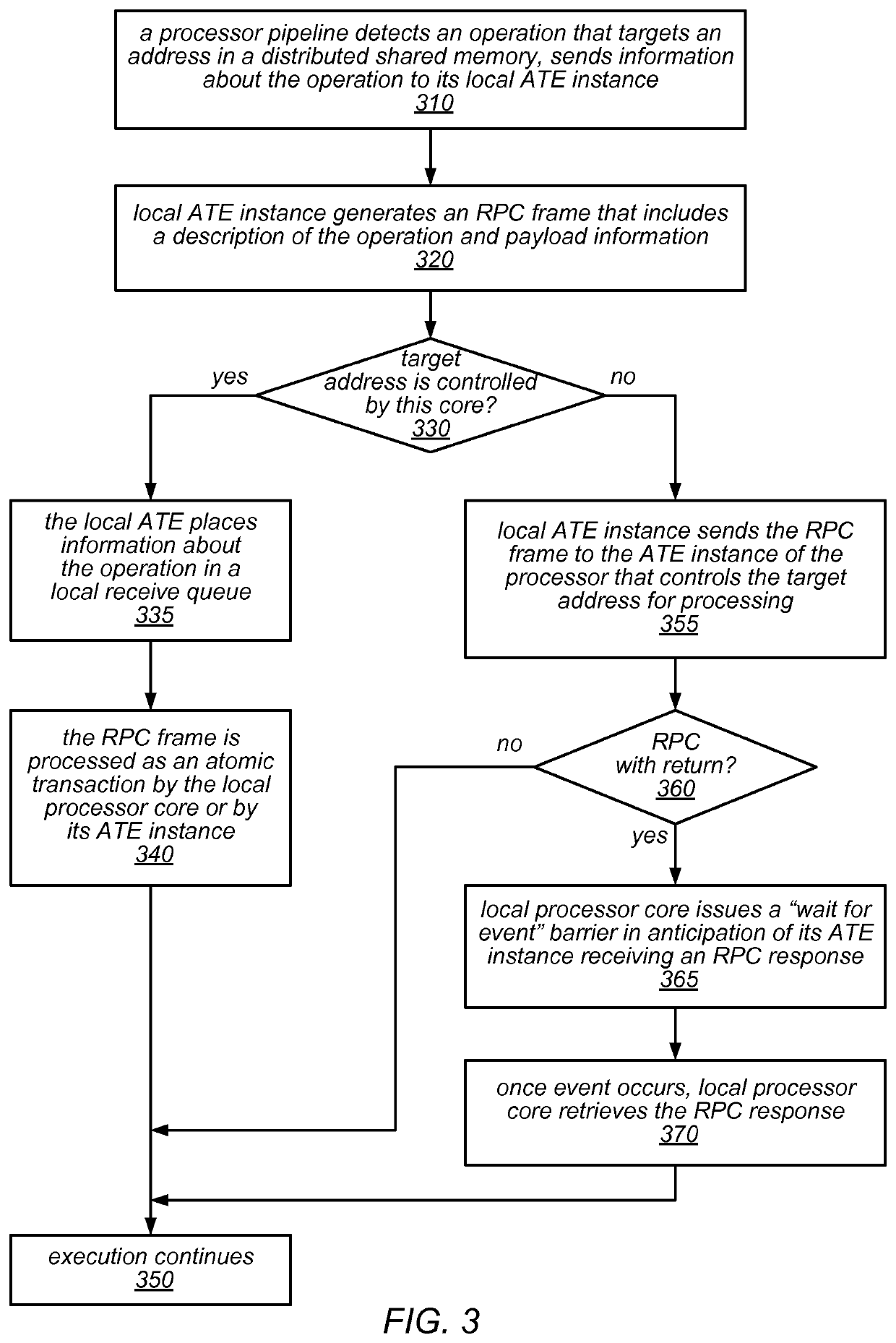

Distributed shared memory using interconnected atomic transaction engines at respective memory interfaces

ActiveUS10732865B2Light weightLess complexInput/output to record carriersProgram synchronisationComputer architectureMemory interface

A hardware-assisted Distributed Memory System may include software configurable shared memory regions in the local memory of each of multiple processor cores. Accesses to these shared memory regions may be made through a network of on-chip atomic transaction engine (ATE) instances, one per core, over a private interconnect matrix that connects them together. For example, each ATE instance may issue Remote Procedure Calls (RPCs), with or without responses, to an ATE instance associated with a remote processor core in order to perform operations that target memory locations controlled by the remote processor core. Each ATE instance may process RPCs (atomically) that are received from other ATE instances or that are generated locally. For some operation types, an ATE instance may execute the operations identified in the RPCs itself using dedicated hardware. For other operation types, the ATE instance may interrupt its local processor core to perform the operations.

Owner:ORACLE INT CORP

High performance cost optimized memory

A memory device includes an interconnect with mask pins and a memory core for storing data. A memory interface circuit is connected between the interconnect and the memory core. The memory interface circuit selectively processes write mask data from the mask pins or precharge instruction signals from the mask pins.

Owner:RAMBUS INC

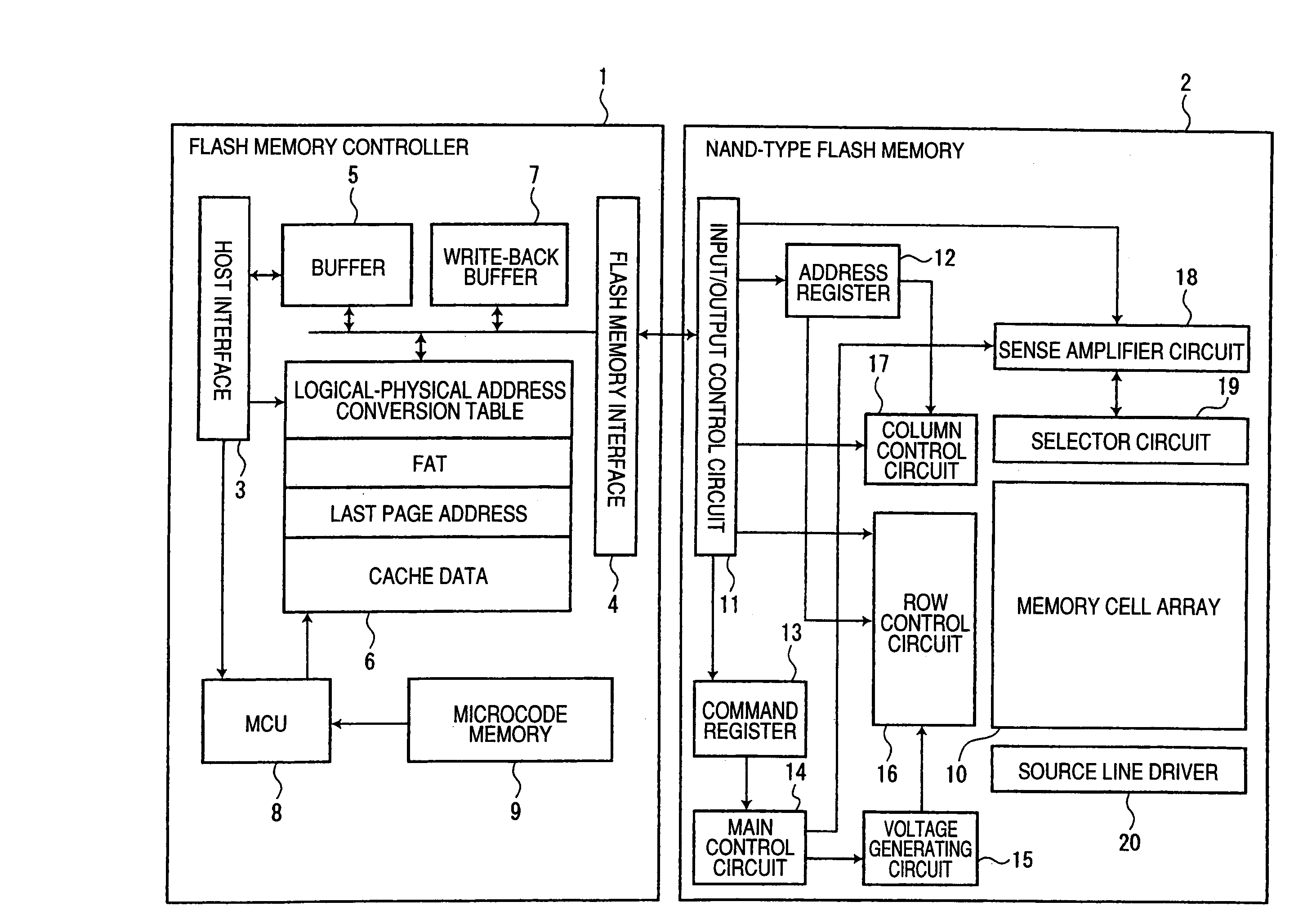

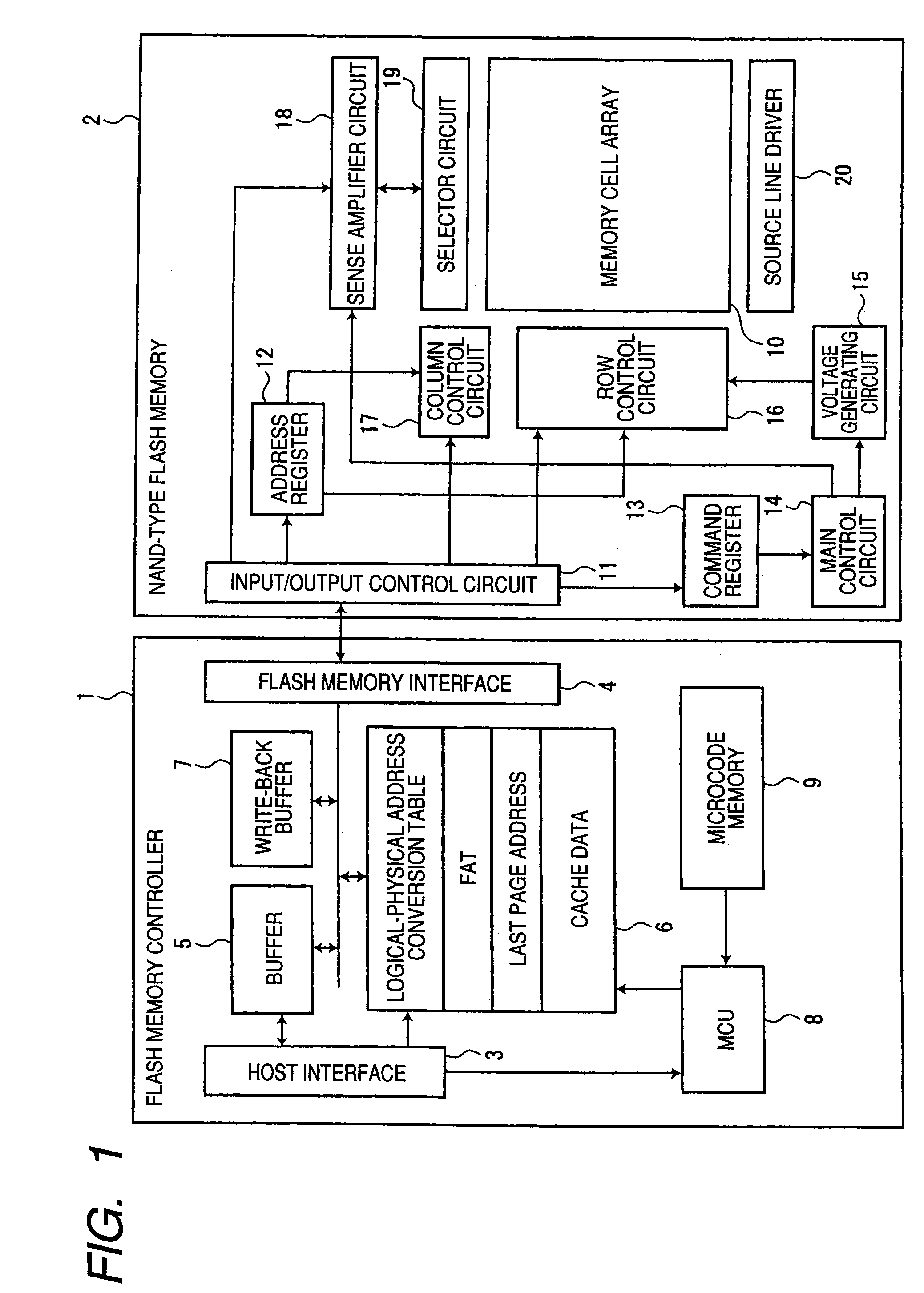

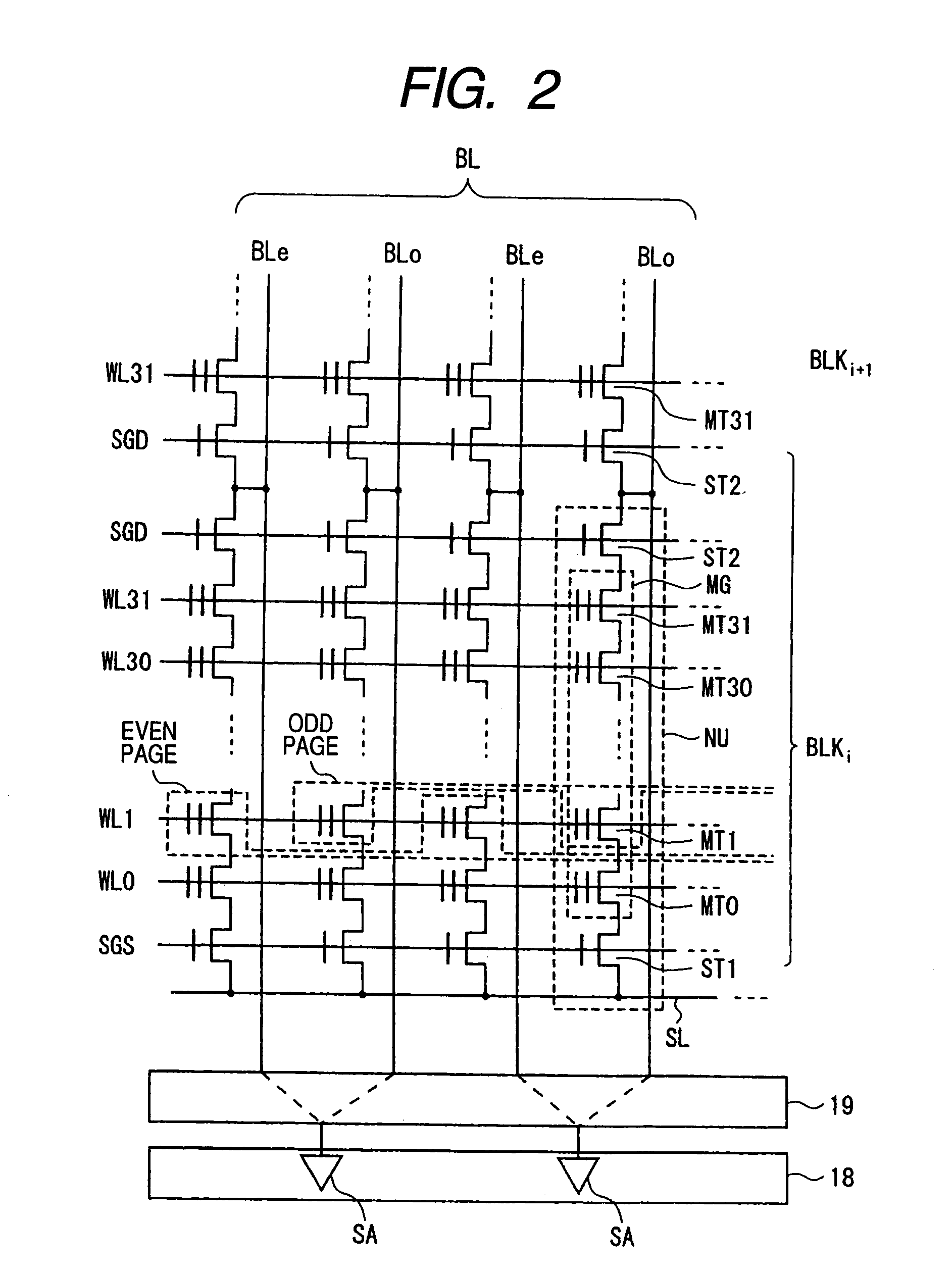

Nonvolatile semiconductor memory system

According to an embodiment, a nonvolatile semiconductor memory system includes: a nonvolatile semiconductor memory; and a memory controller having: a memory interface unit that inputs commands to the nonvolatile semiconductor memory and inputs or outputs data between the nonvolatile semiconductor memory; a memory that stores writing information indicating a memory cell transistor that is written the latest in each of the NAND cell units; and a processor that sets a read voltage based on the writing information to readout data from the memory cell transistors connected to a first word line; wherein a row controller is configured to set a plurality of levels of the read voltage to be applied to the first word line, with respect to one threshold for discriminating data stored in a memory cell transistors.

Owner:KK TOSHIBA

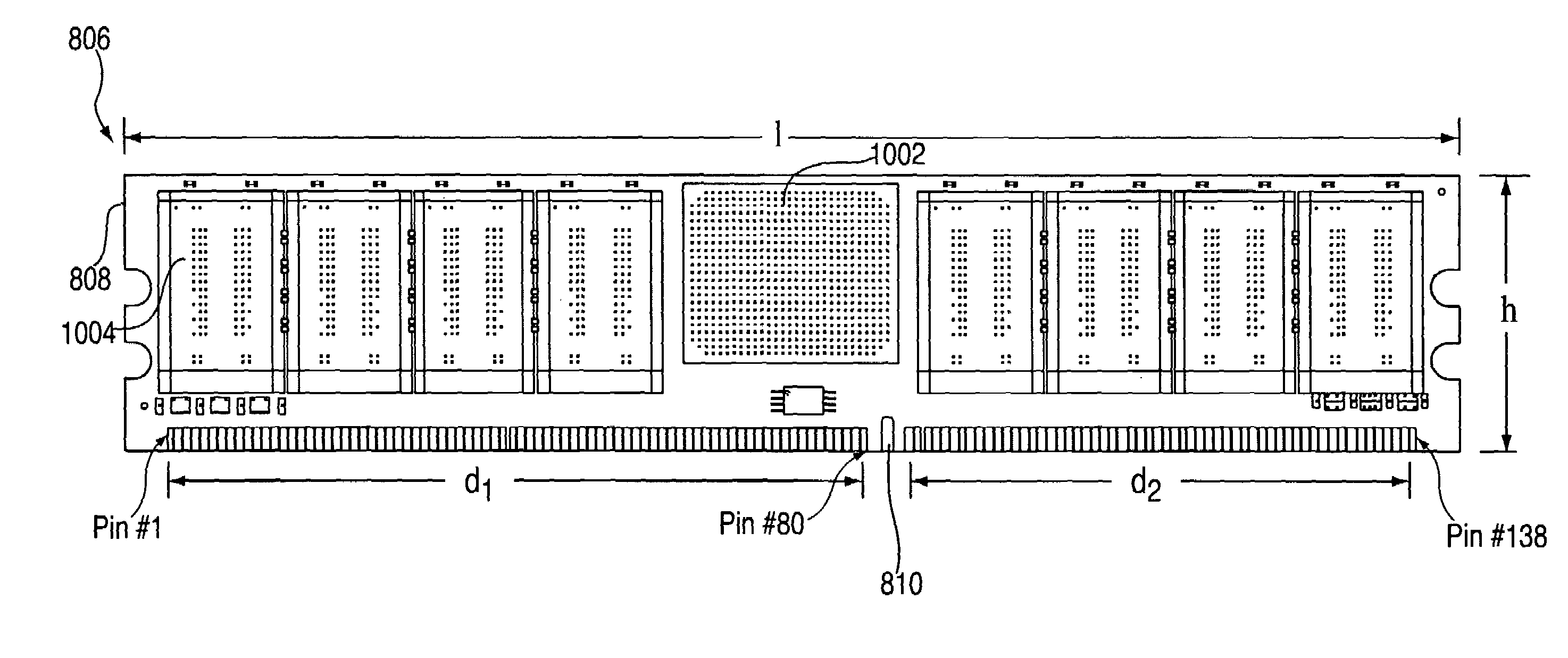

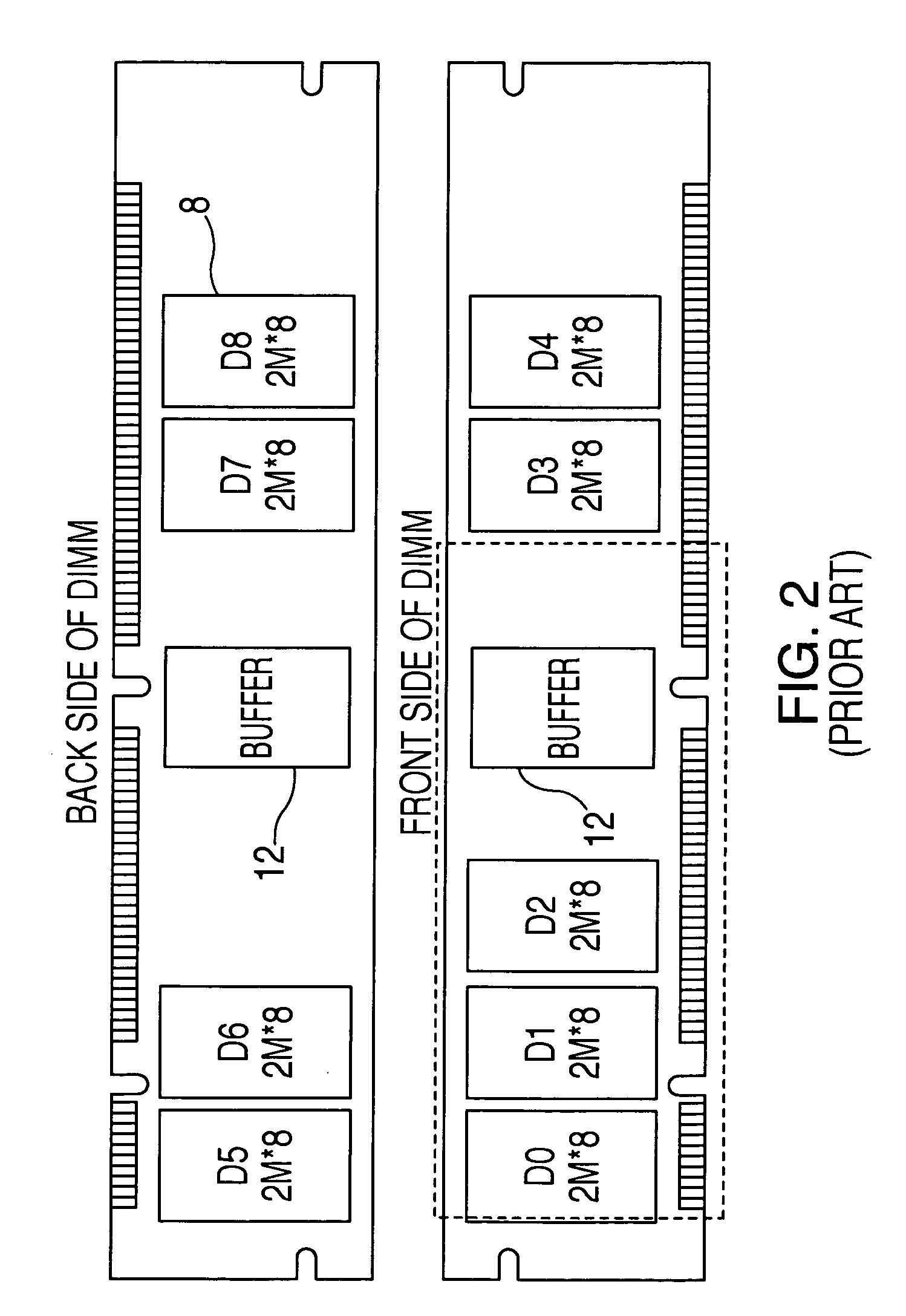

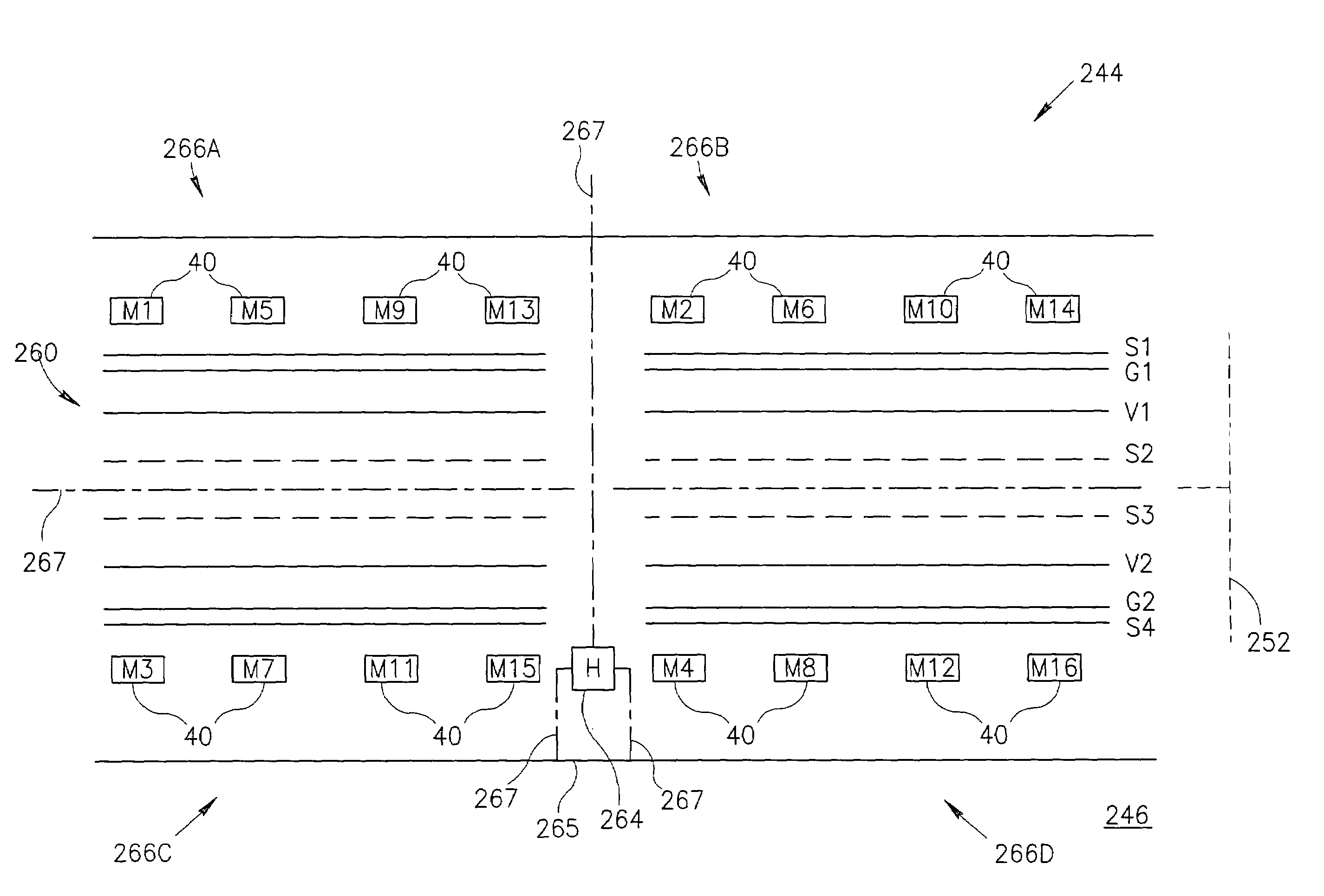

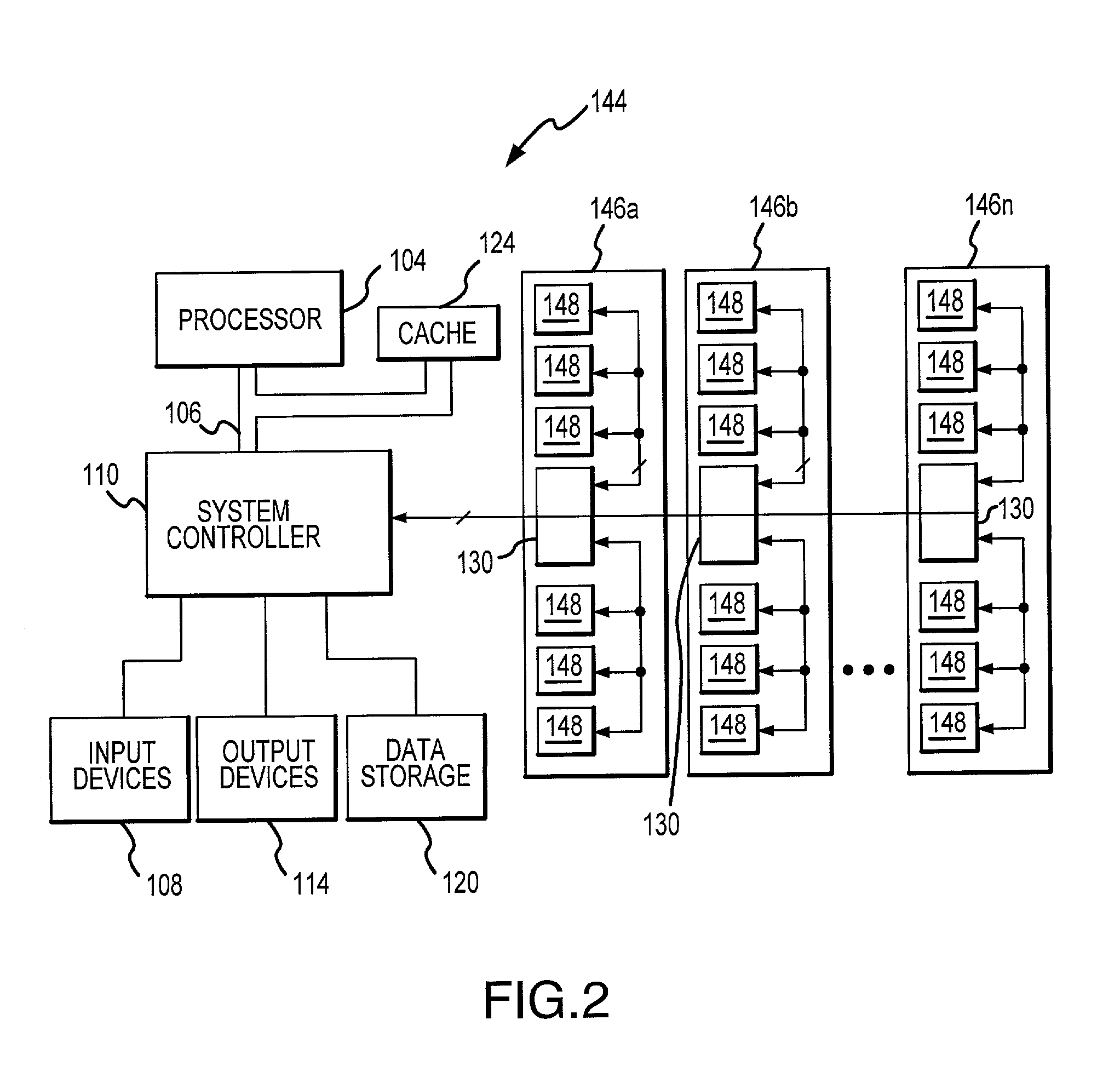

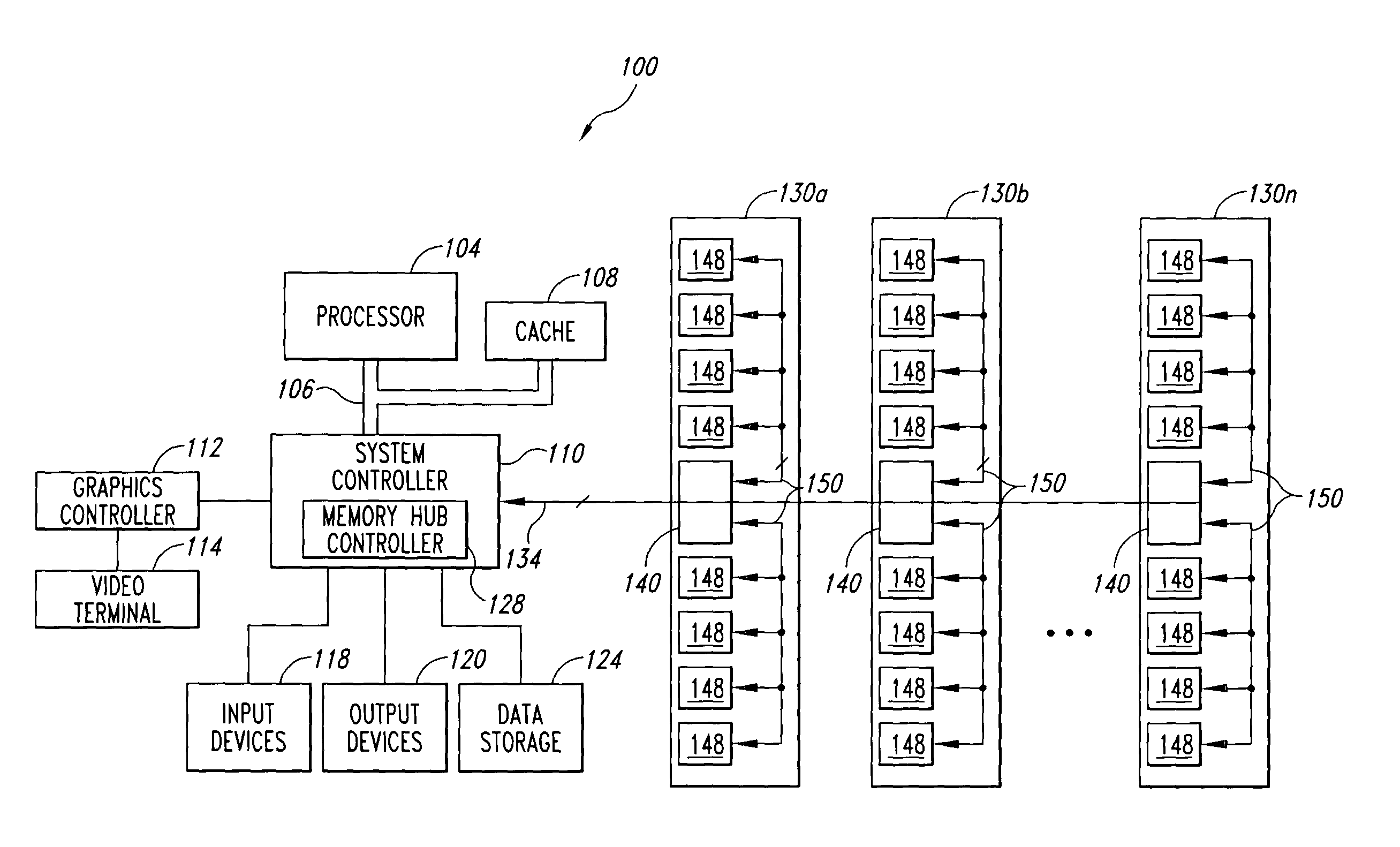

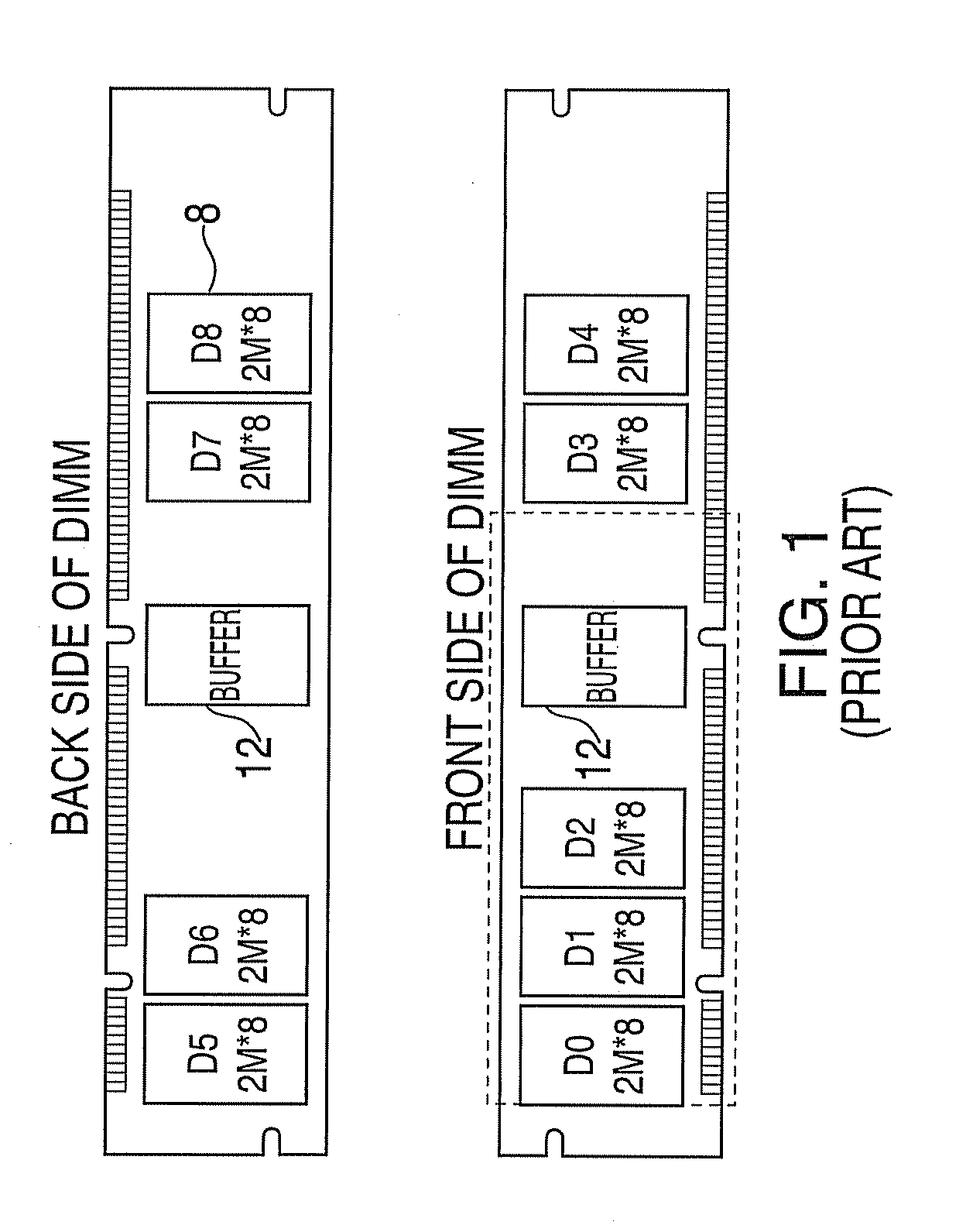

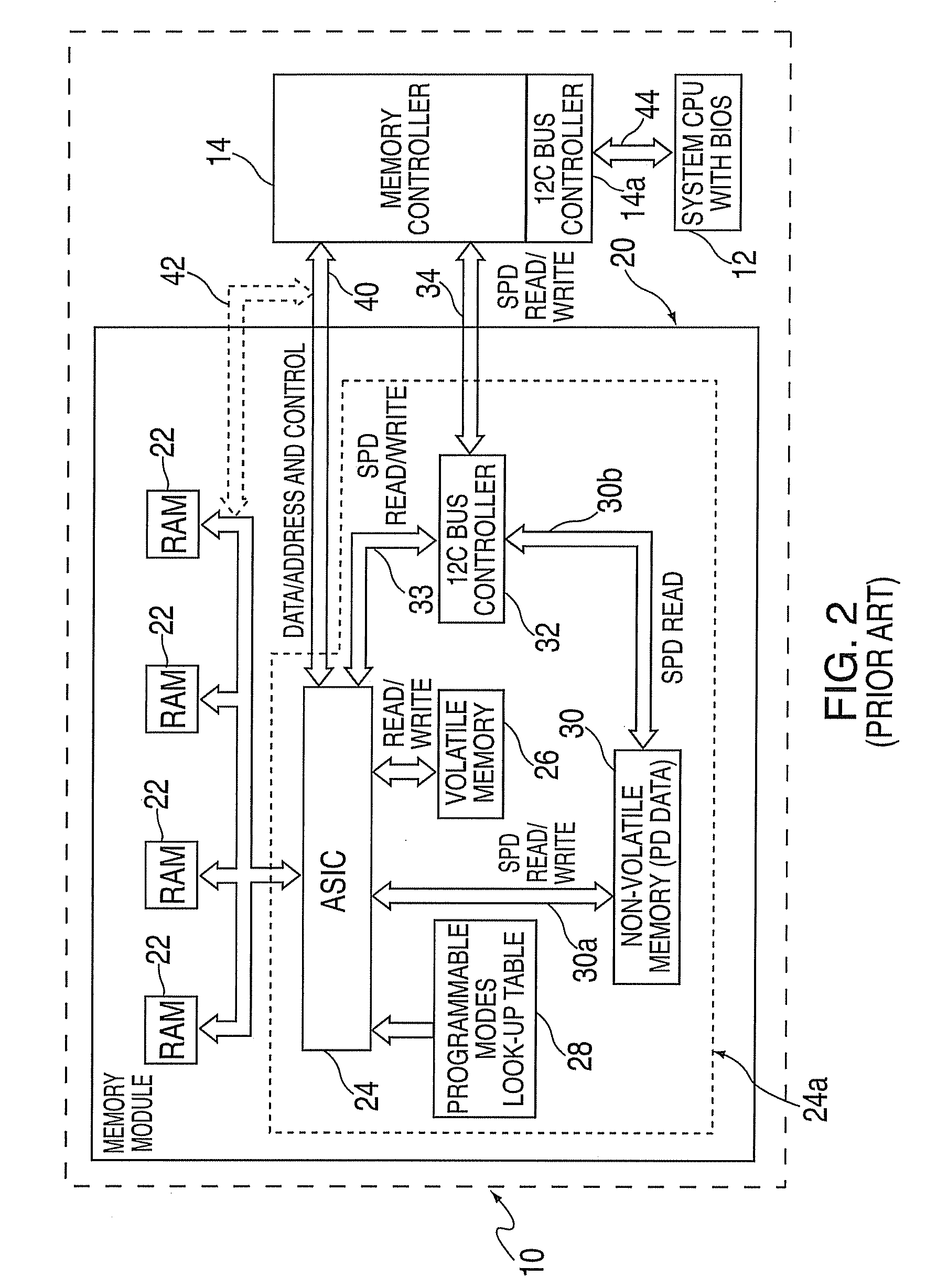

Apparatus and methods for a physical layout of simultaneously sub-accessible memory modules

ActiveUS6982892B2Improve performanceFinal product manufacturePrinted circuit aspectsMemory interfaceComputer module

A layout for simultaneously sub-accessible memory modules is disclosed. In one embodiment, a memory module includes a printed circuit board having a plurality of sectors, each sector being electrically isolated from the other sectors and having a multi-layer structure. At least one memory device is attached to each sector, the memory devices being organized into a plurality of memory ranks. A driver is attached to the printed circuit board and is operatively coupled to the memory ranks. The driver is adapted to be coupled to a memory interface of the computer system. Because the sectors are electrically-isolated from adjacent sectors, the memory ranks are either individually or simultaneously, or both individually and simultaneously accessible by the driver so that one or more memory devices on a particular sector may be accessed at one time. In an alternate embodiment, the printed circuit board includes a driver sector electrically isolated from the other sectors and having a multi-layer structure, the driver being attached to the driver sector.

Owner:MICRON TECH INC

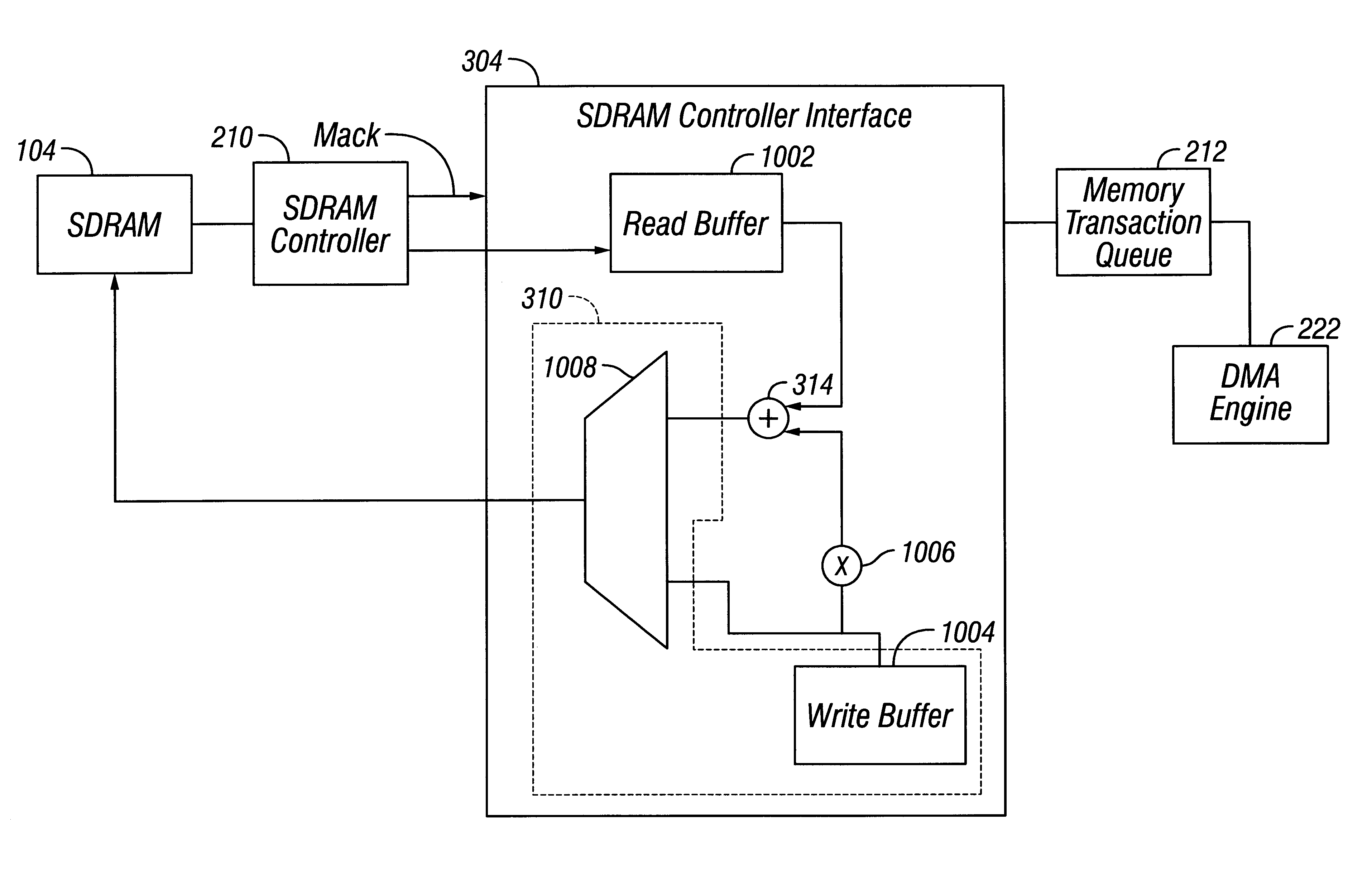

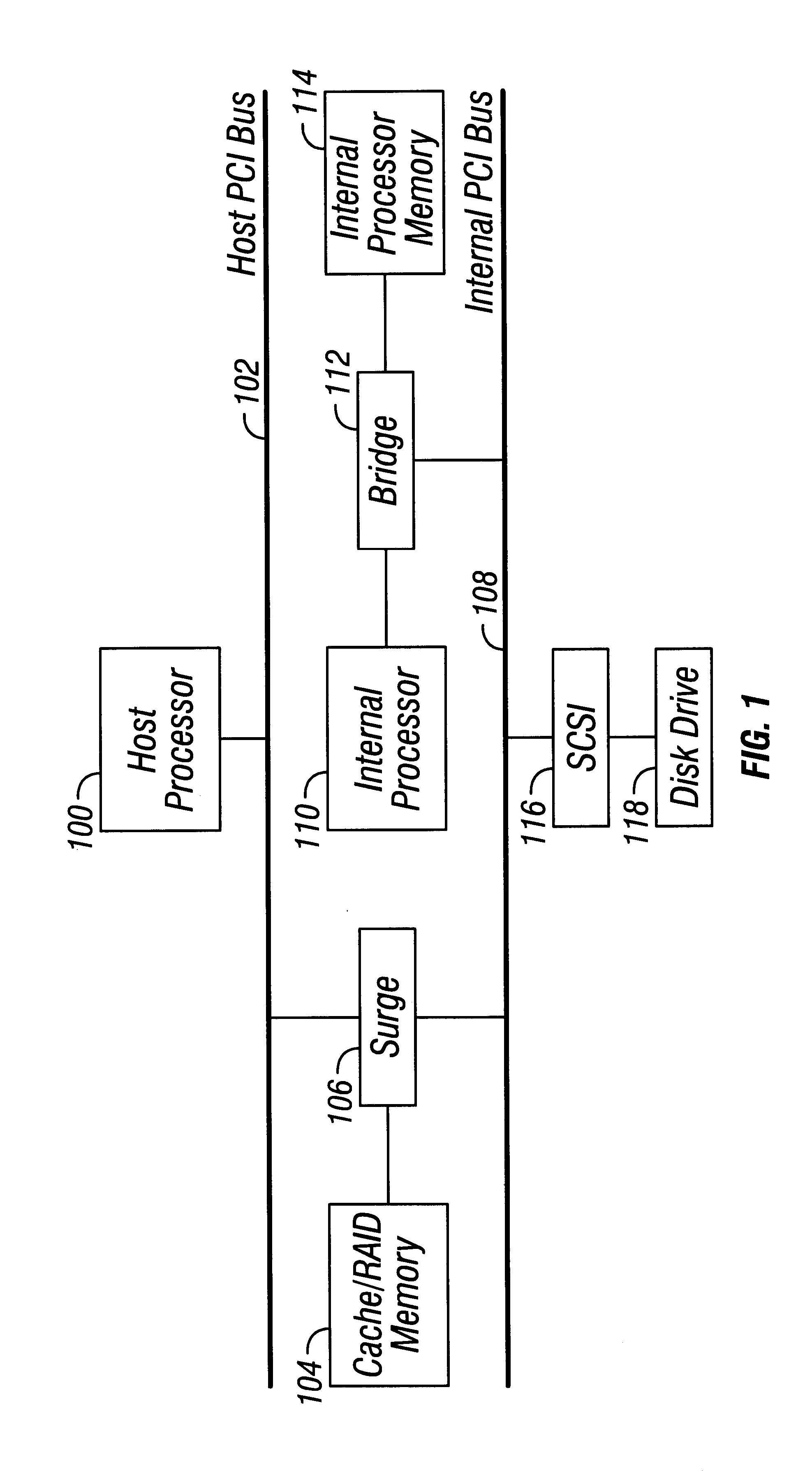

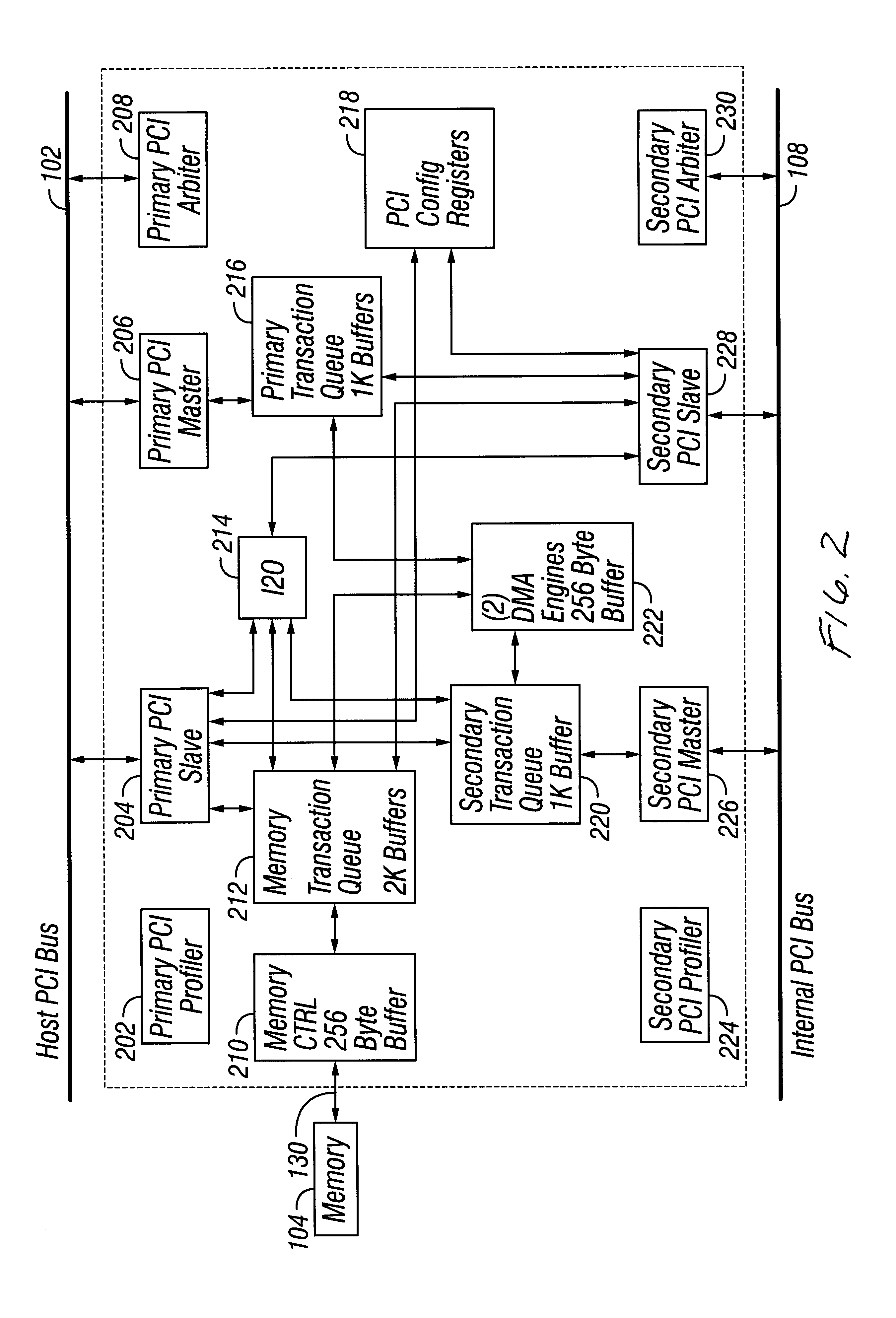

Raid XOR operations to synchronous DRAM using a read buffer and pipelining of synchronous DRAM burst read data

A memory interface controller includes a read buffer to pipeline data from a synchronous dynamic random access memory (DRAM) in response to a plurality of consecutive SDRAM burst read requests, a write buffer to store write data, an exclusive or (XOR) engine to XOR the write data with the data from the read buffer, and a write interface to write resulting data from XORing the write data and the data from the read buffer to the synchronous DRAM. Data is pipelined in the read buffer by repeatedly issuing an SDRAM burst read request before data is transferred out of the synchronous DRAM in response to a previous SDRAM burst read request until a desired amount of data is stored in the read buffer. The memory interface controller thus can perform an external read-modify-write cycle for the synchronous DRAM. The synchronous DRAM can serve as a RAID (Redundant Array s of Inexpensive Disks) memory.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

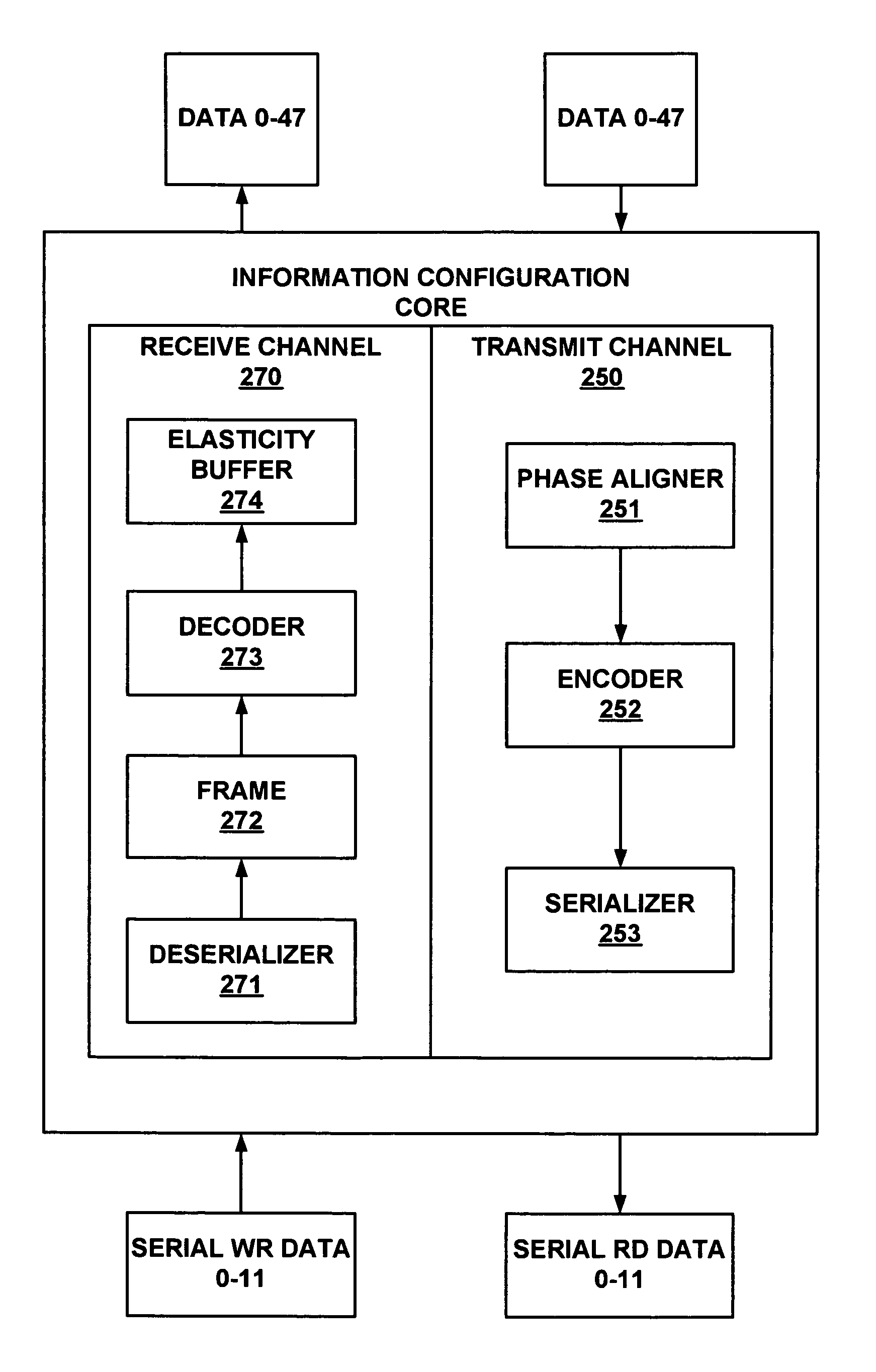

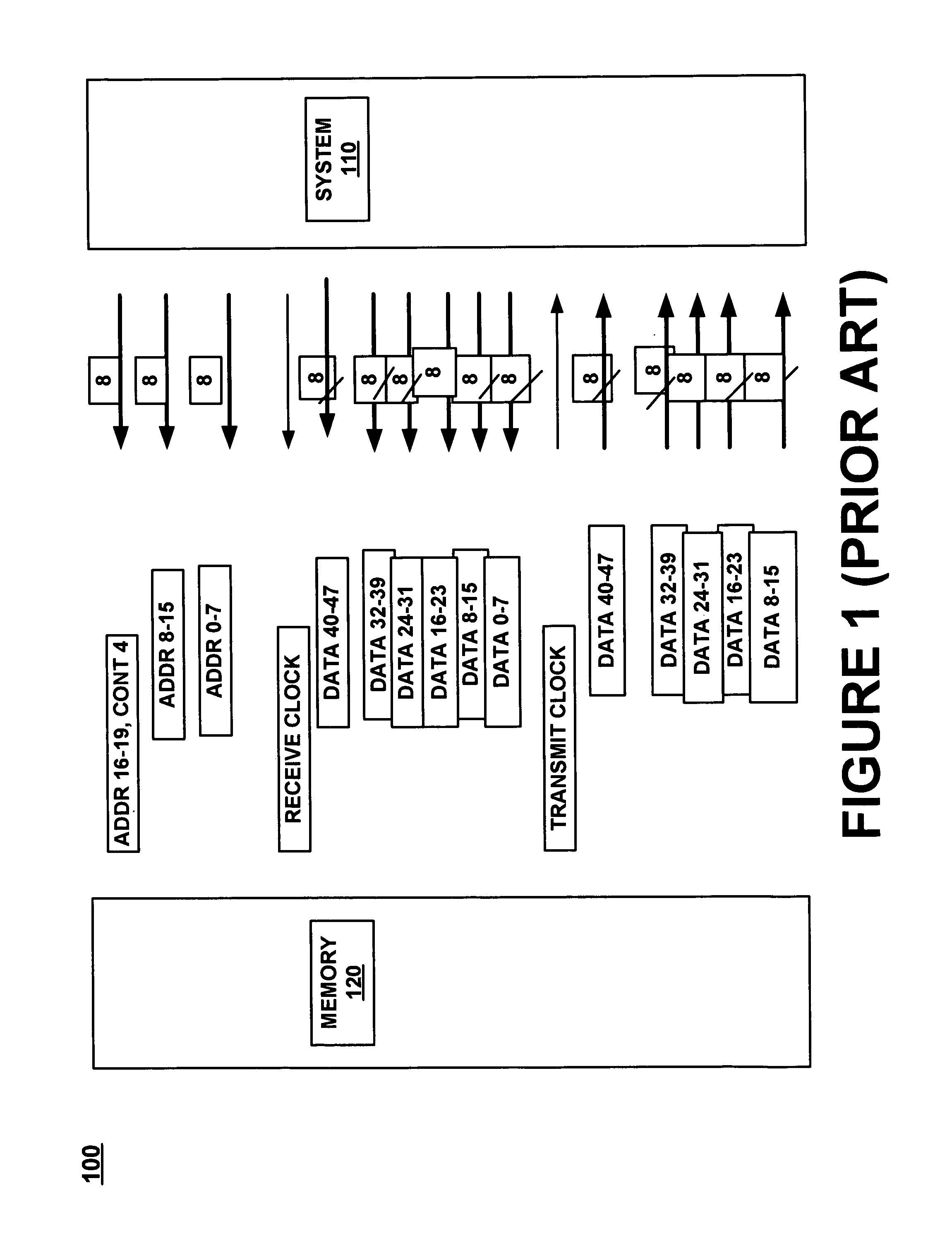

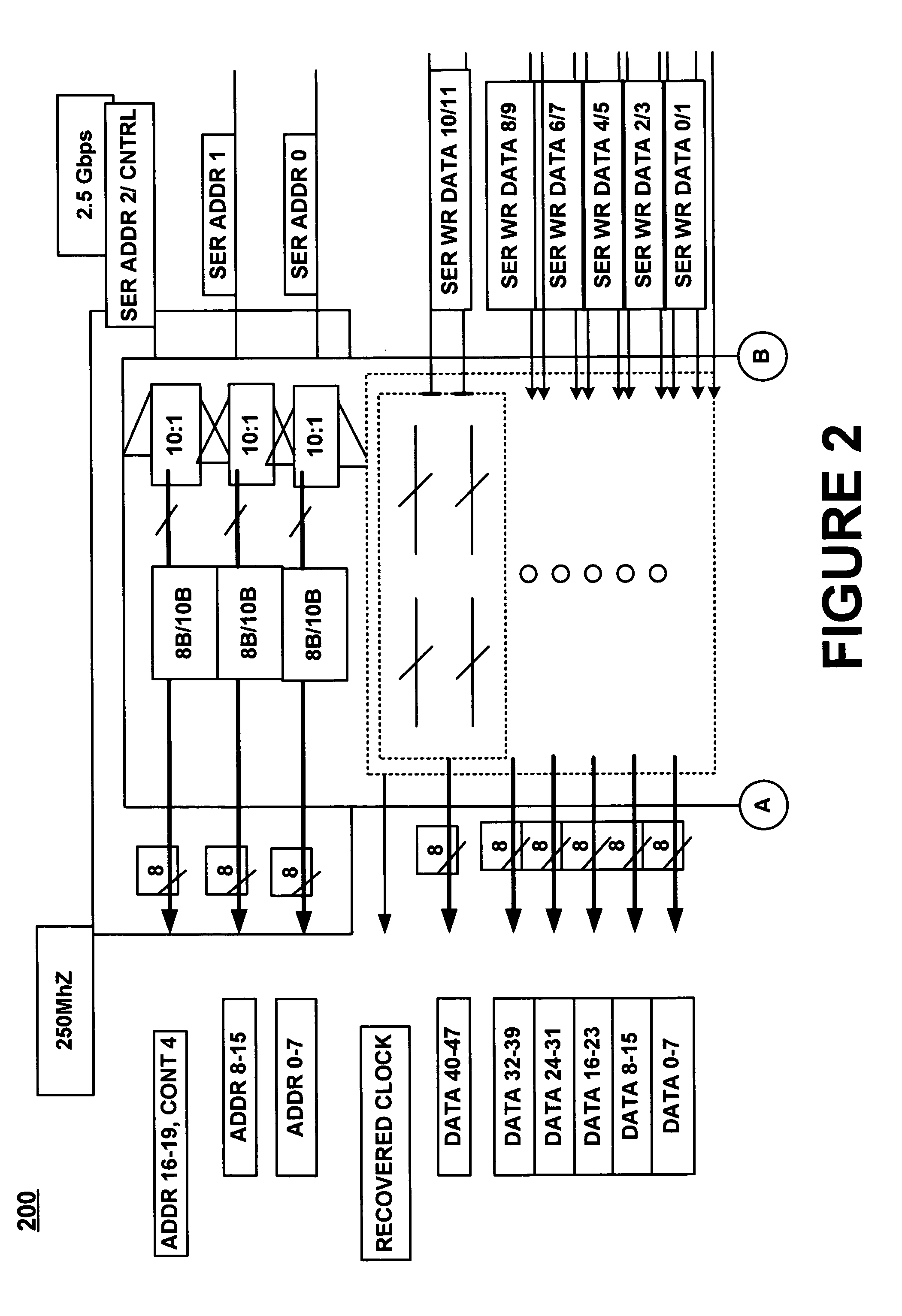

High speed memory interface system and method

InactiveUS7013359B1Facilitate efficient communicationIncrease speedElectric digital data processingHigh speed memoryMemory interface

The present invention is a high speed serial memory interface system and method that facilitates efficient communication of information between a system controller operating at a relatively high speed serial communication rate and a memory array operating at a relatively slow speed serial communication rate. In one embodiment the present invention is a high speed serial memory interface system with an information configuration core for coordinating proper alignment of information communication signals, a system interface for communicating with a system controller, and a memory array interface for communicating with a memory array. A memory module array for storing information and a high speed serial memory interface system for providing interface configuration management are integrated on a single substrate.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

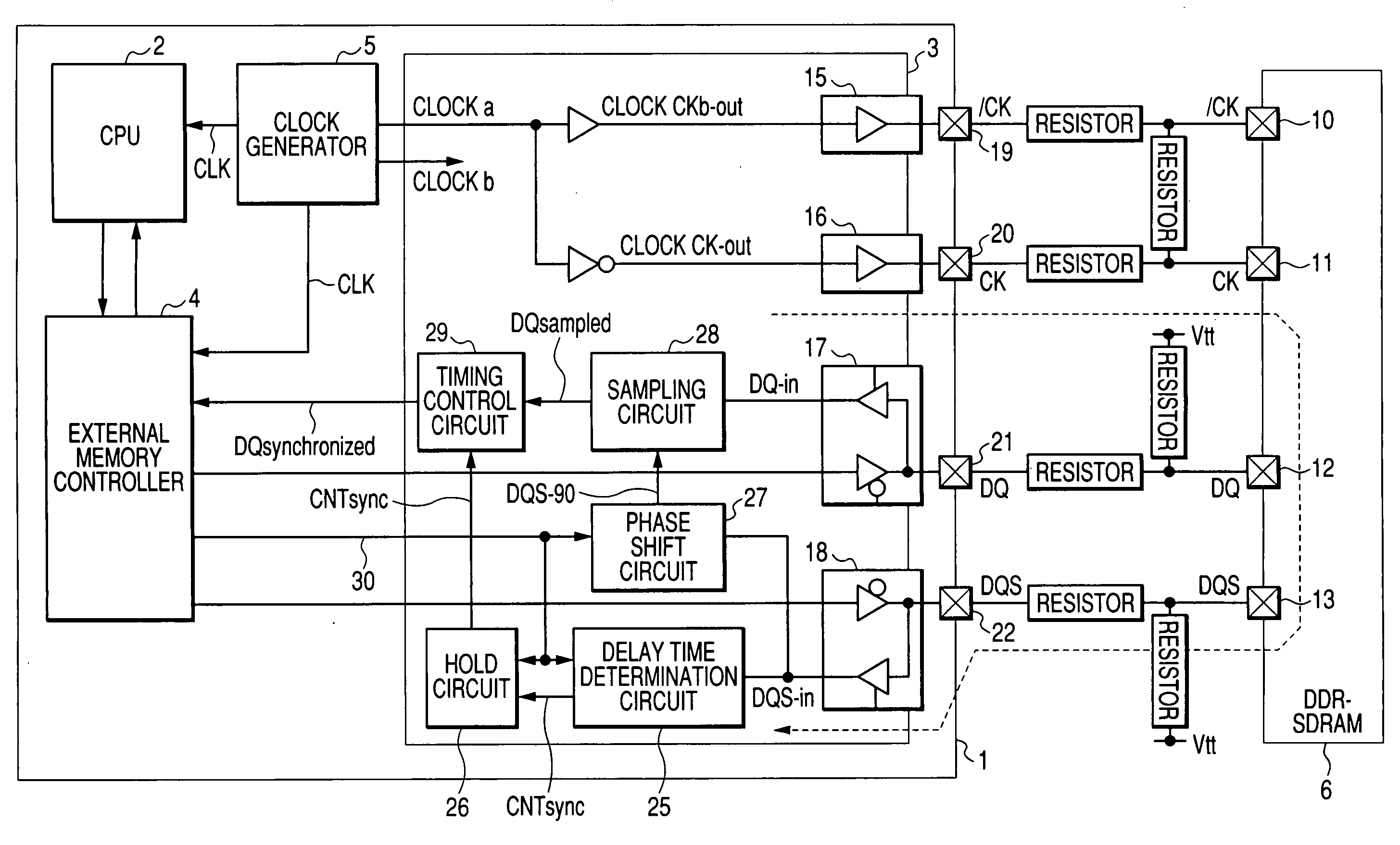

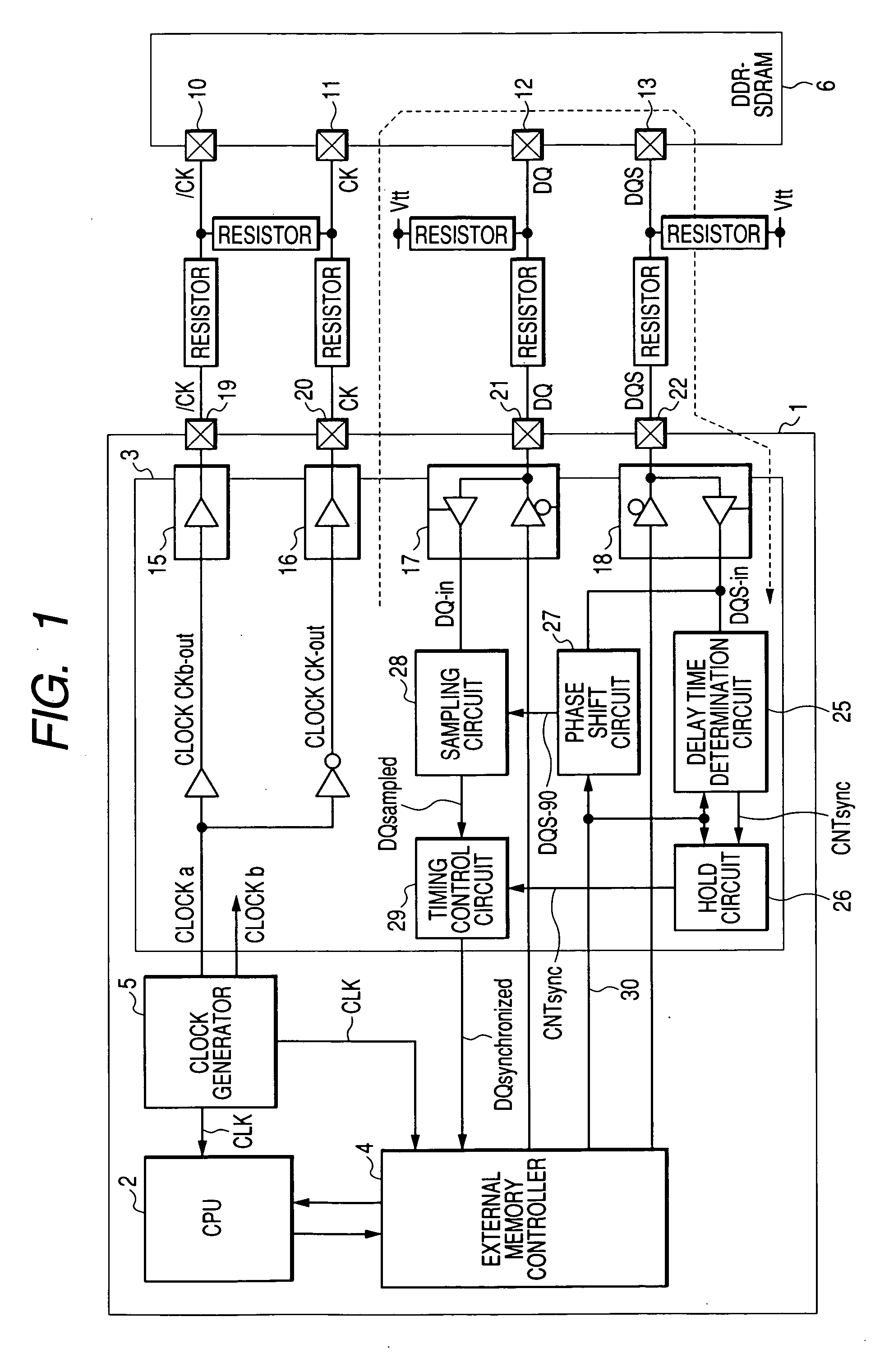

Semiconductor integrated circuit

ActiveUS20050047192A1Improve accuracyGuaranteed uptimeDigital storageGenerating/distributing signalsMemory interfaceComputer science

Owner:RENESAS ELECTRONICS CORP

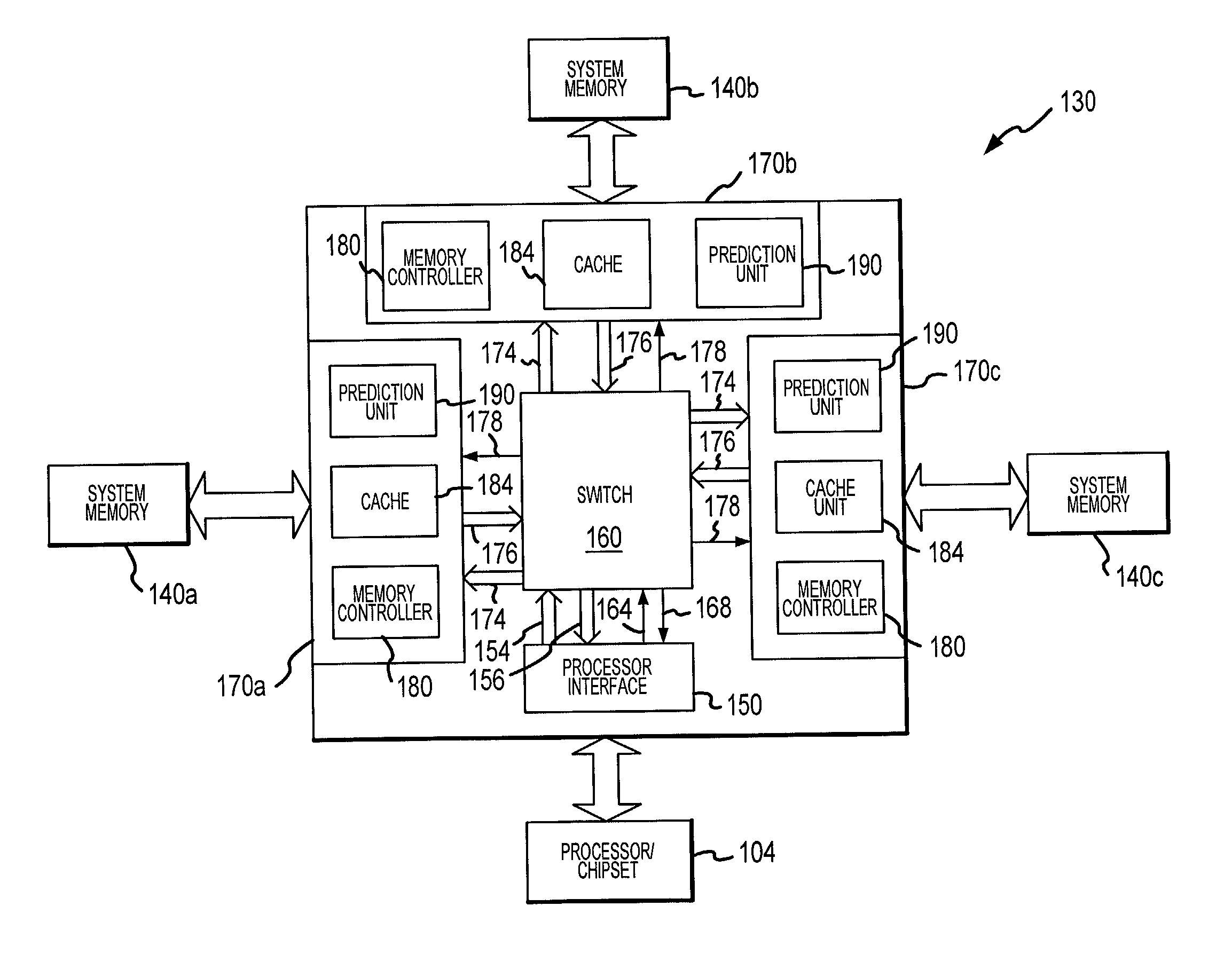

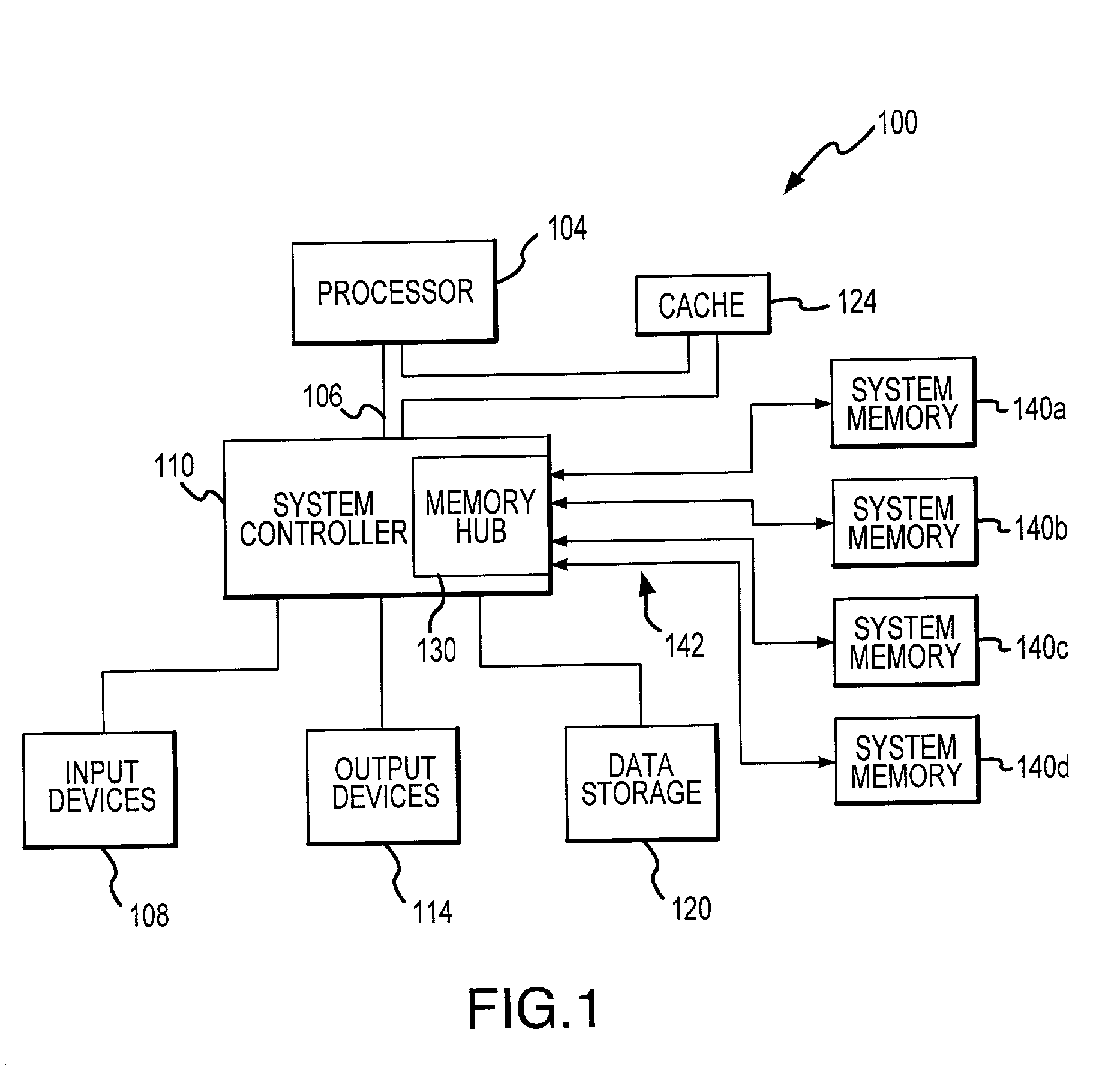

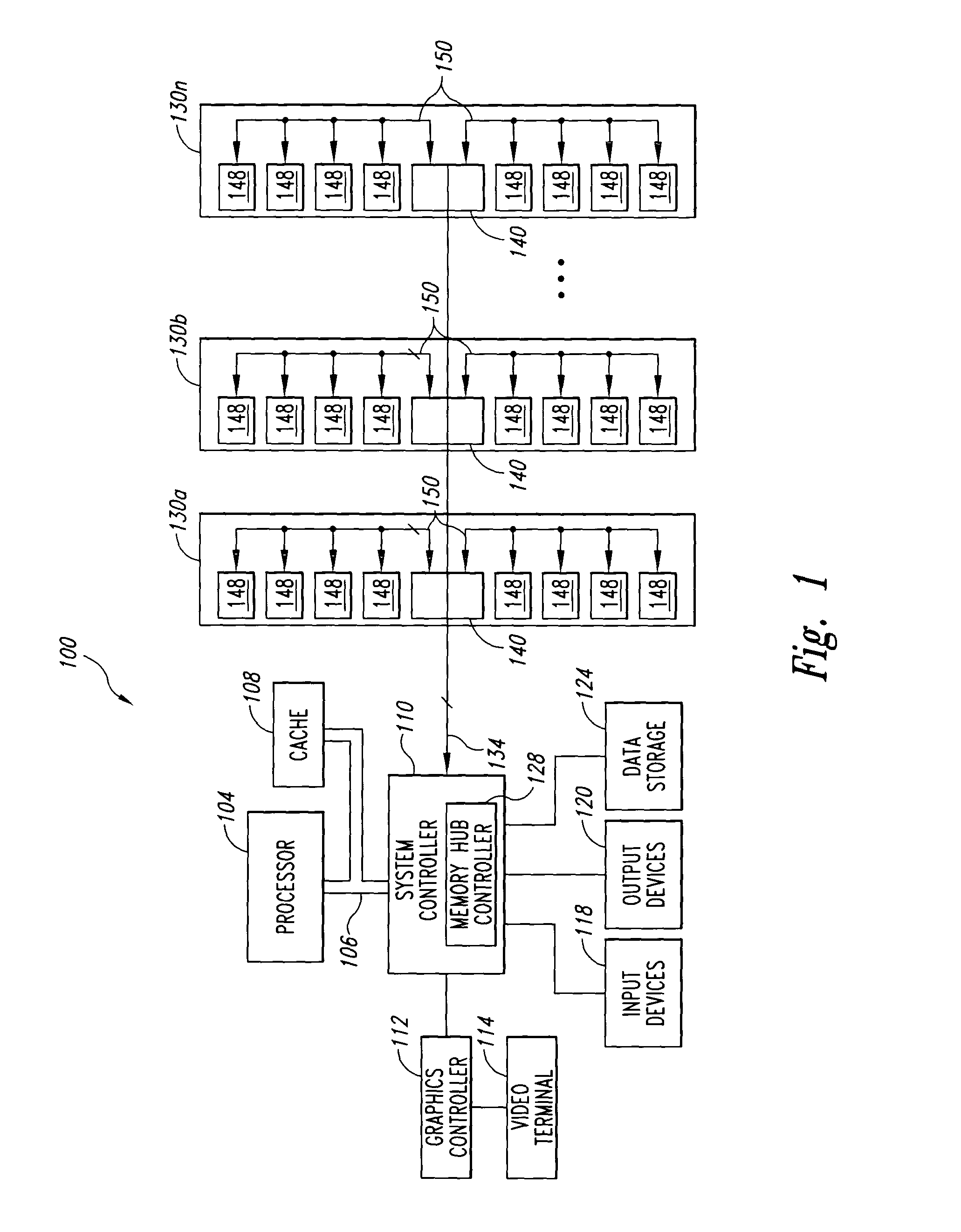

Memory hub with internal cache and/or memory access prediction

InactiveUS7133972B2Memory adressing/allocation/relocationMultiple digital computer combinationsRandom access memoryMemory interface

A computer system includes a memory hub for coupling a processor to a plurality of synchronous dynamic random access memory (“SDRAM”) devices. The memory hub includes a processor interface coupled to the processor and a plurality of memory interfaces coupled to respective SDRAM devices. The processor interface is coupled to the memory interfaces by a switch. Each of the memory interfaces includes a memory controller, a cache memory, and a prediction unit. The cache memory stores data recently read from or written to the respective SDRAM device so that it can be subsequently read by processor with relatively little latency. The prediction unit prefetches data from an address from which a read access is likely based on a previously accessed address.

Owner:ROUND ROCK RES LLC

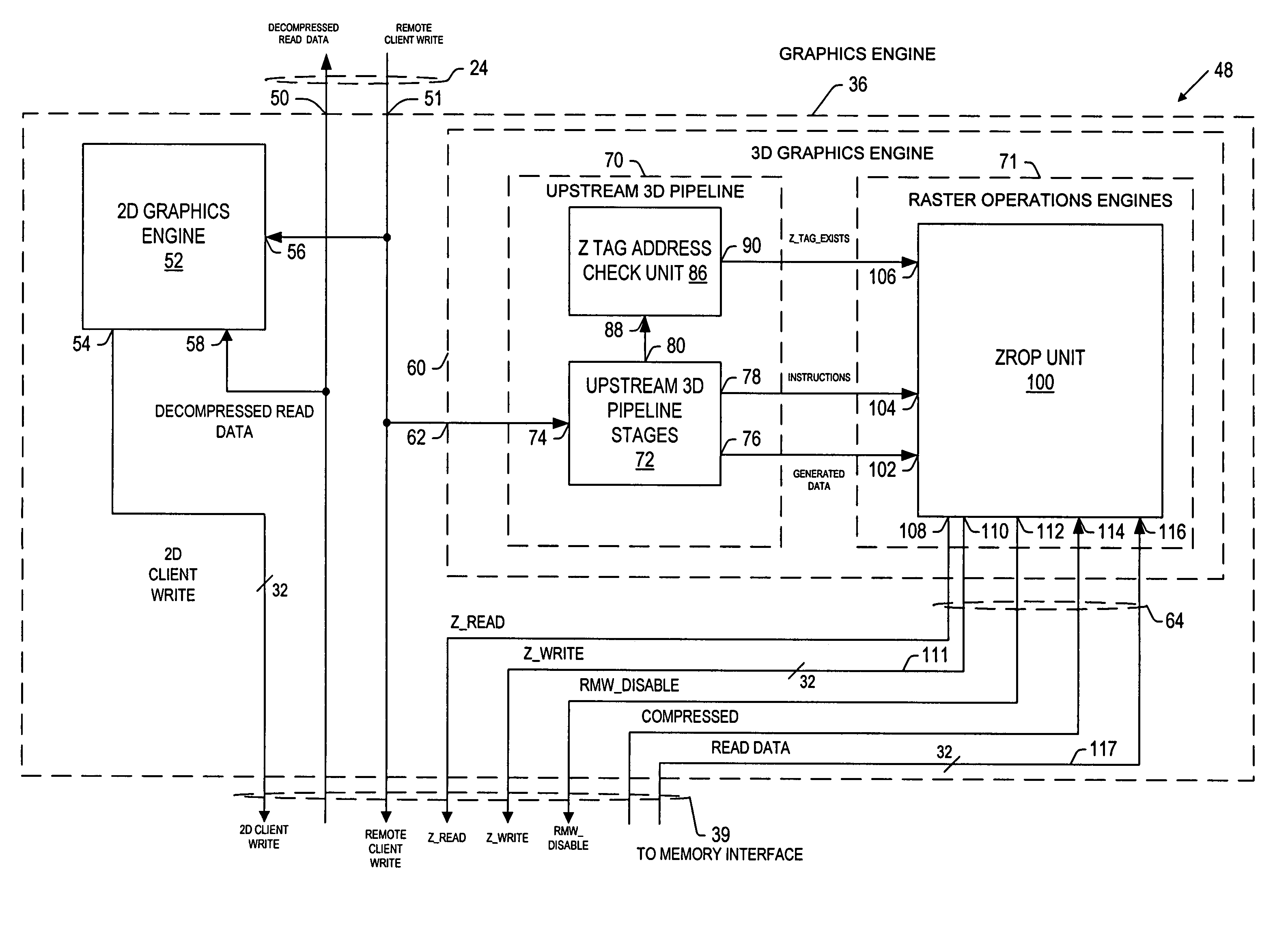

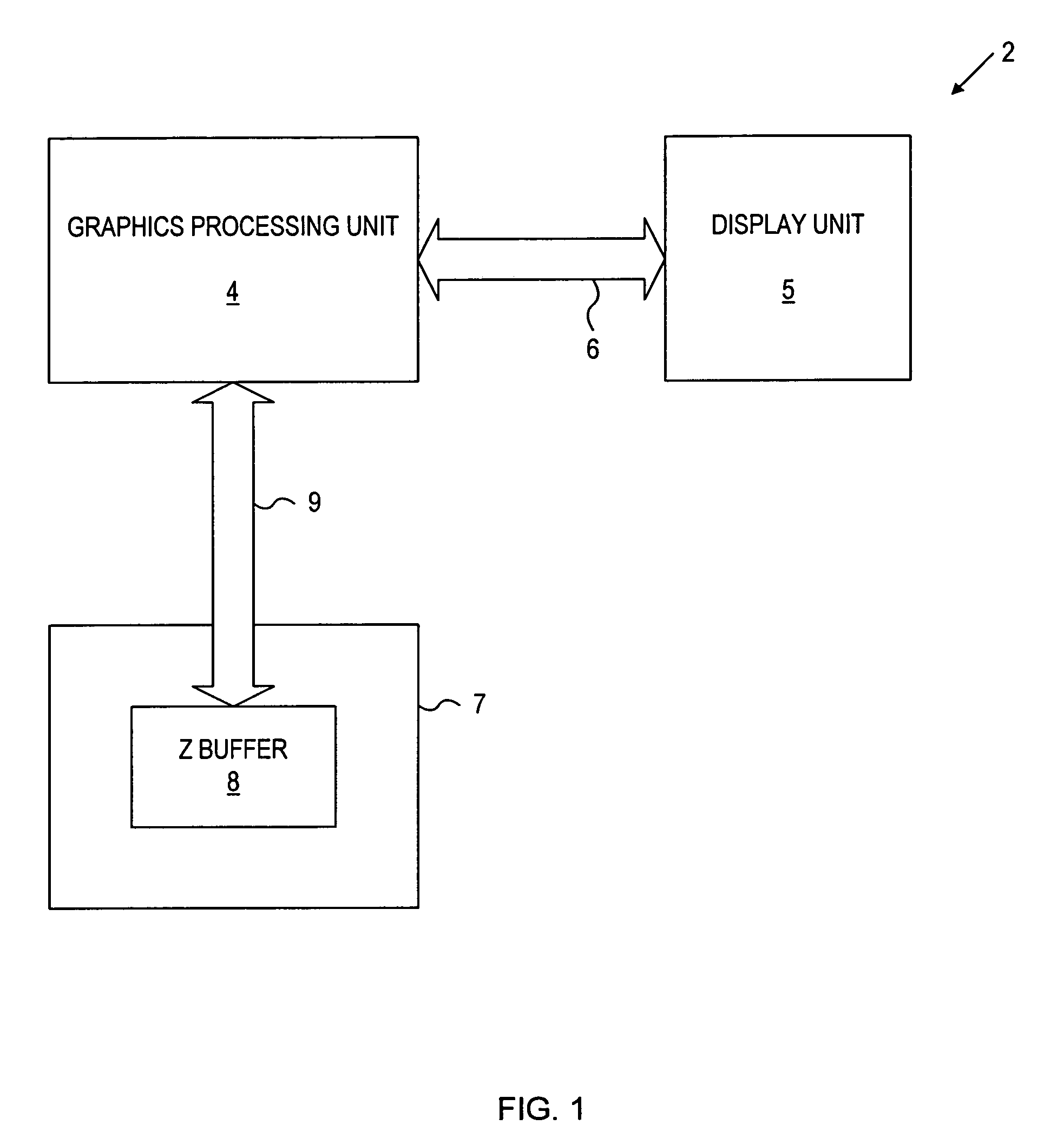

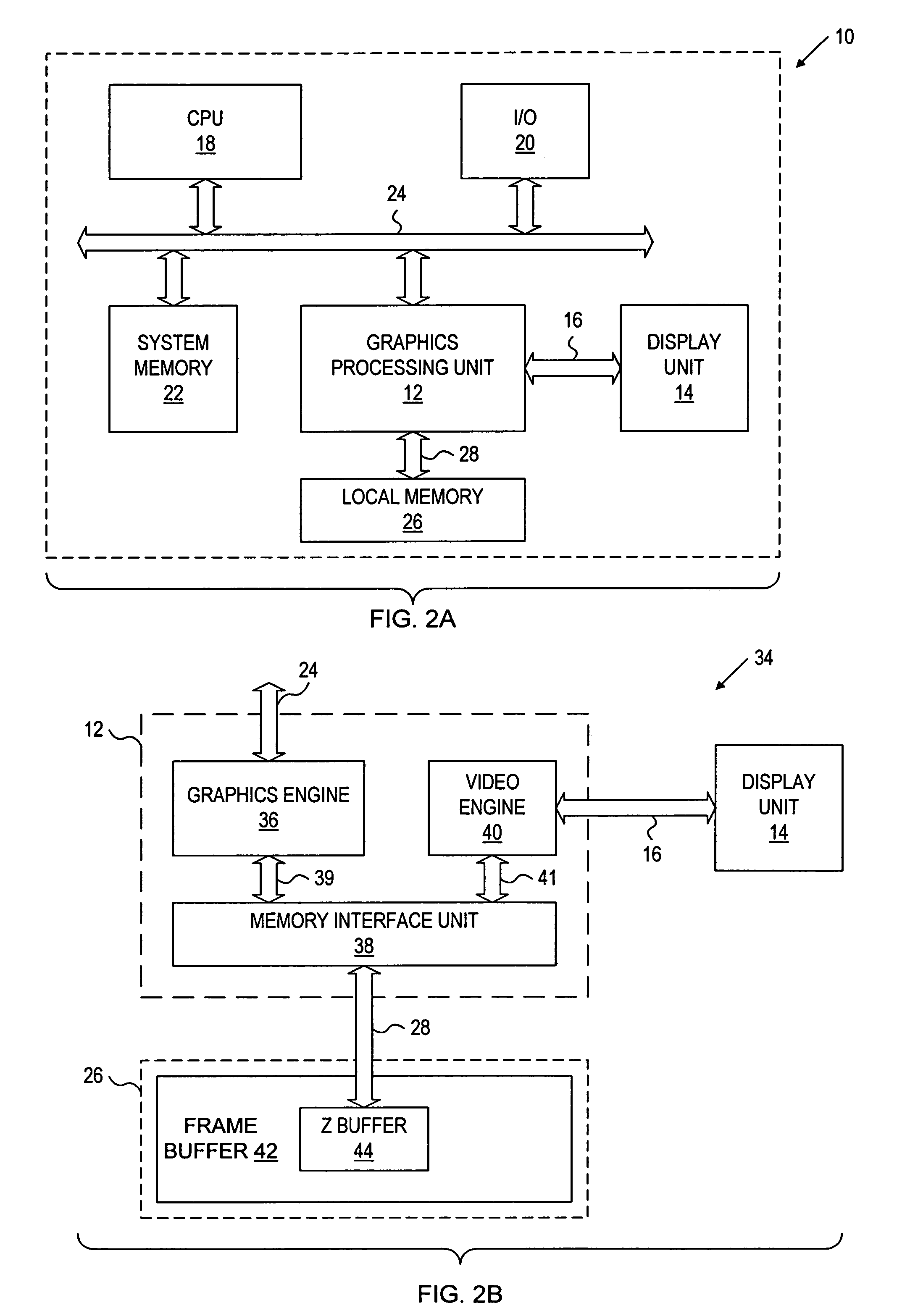

Method and apparatus for managing and accessing depth data in a computer graphics system

A computer graphics system provides for processing image data including Z data for use in displaying three-dimensional images on a display unit. The system includes: a depth buffer providing for temporary storage of Z data; and a graphics processing unit having a graphics engine for generating image data including Z data, and a memory interface unit communicatively coupled to the graphics engine and communicatively coupled to the depth buffer via a depth buffer interface. The graphics processing unit is operative to compress at least a portion of the generated Z data, to write the compressed portion of Z data to the depth buffer via the depth buffer interface in a compressed format, to read portions of compressed Z data from the depth buffer via the depth buffer interface, and to decompress the compressed Z data read from the buffer. An advantage of the present invention is that effective Z data bandwidth through the depth buffer interface is maximized in order to facilitate fast depth buffer access operations.

Owner:NVIDIA CORP

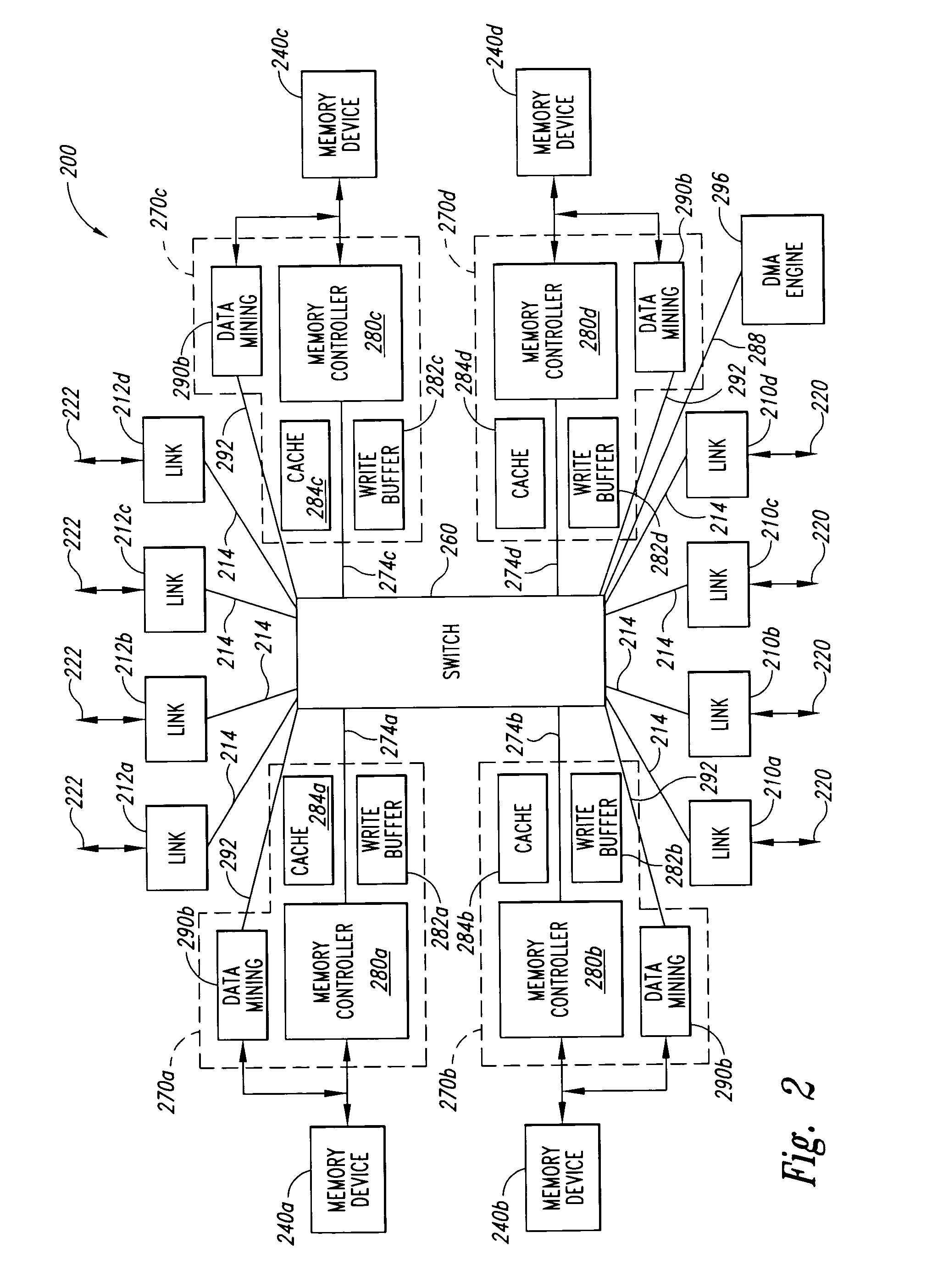

Memory module and method having on-board data search capabilities and processor-based system using such memory modules

InactiveUS20050050237A1Faster rateDigital data information retrievalStatic storageCrossbar switchWrite buffer

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory interfaces coupled to respective memory devices, and a cross-bar switch coupling any of the link interfaces to any of the memory interfaces. Each memory interface includes a memory controller, a write buffer, a read cache, and a data mining module. The data mining module includes a search data memory that is coupled to the link interface to receive and store at least one item of search data. A comparator receives both the read data from the memory device and the search data. The comparator then compares the read data to the respective item of search data and provides a hit indication in the event of a match.

Owner:MICRON TECH INC

Smart memory based synchronization controller for a multi-threaded multiprocessor SoC

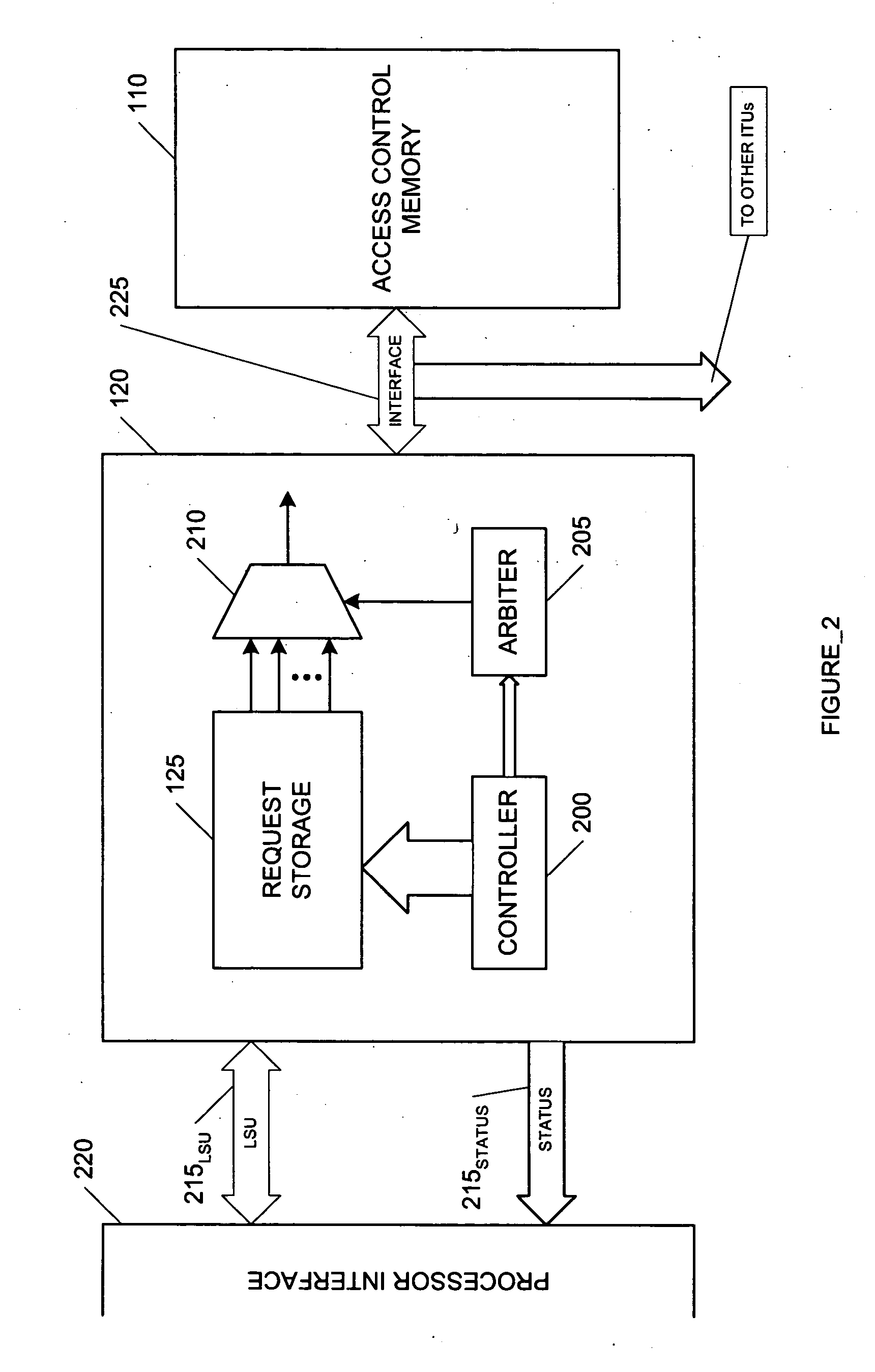

A memory interface for use with a multiprocess memory system having a gating memory, the gating memory associating one or more memory access methods with each of a plurality of memory locations of the memory system wherein the gating memory returns a particular one access method for a particular one memory location responsive to a memory access instruction relating to the particular one memory location, the interface including: a request storage for storing a plurality of concurrent memory access instructions for one or more of the particular memory locations, each the memory access instruction issued from an associated independent thread context; an arbiter, coupled to the request storage, for selecting a particular one of the memory access instructions to apply to the gating memory; and a controller, coupled to the request storage and to the arbiter, for: storing the plurality of memory access instructions in the request storage; initiating application of the particular one memory access instruction selected by the arbiter to the gating memory; receiving the particular one access method associated with the particular one memory access method from the gating memory; and initiating a communication of the particular access method to the thread context associated with the particular one access instruction.

Owner:MIPS TECH INC

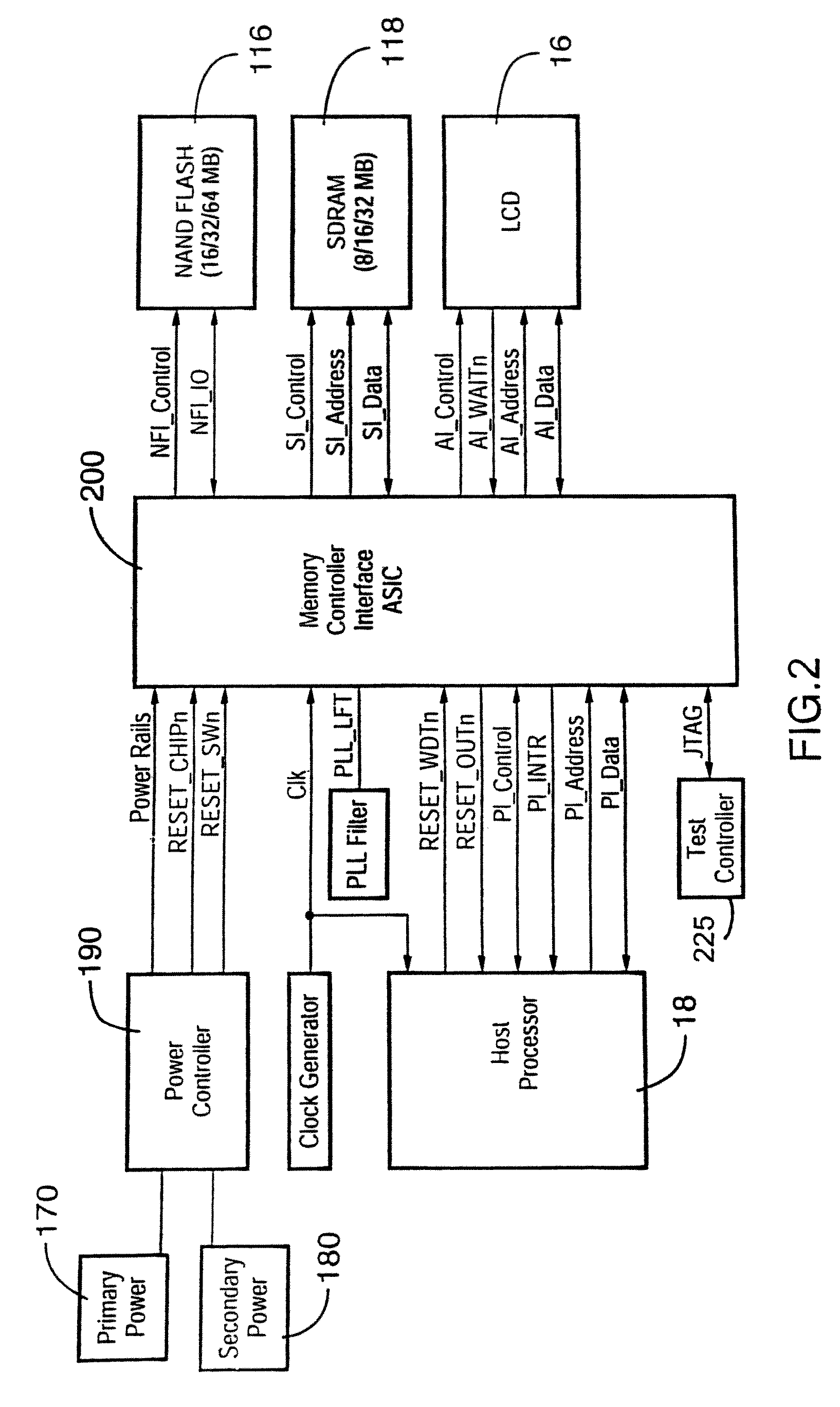

Memory controller interface

ActiveUS7610433B2Memory architecture accessing/allocationMemory loss protectionStatic random-access memoryMemory interface

A memory interface controller and method to allow a processor designed and configured to operate with NOR flash and static random access memory (SRAM) memory devices to instead operate using NAND flash and synchronous dynamic random access memory (SDRAM). The system accomplishes this by caching sectors out of NAND flash into SDRAM, where the data can be randomly accessed by the processor as though it were accessing data from NOR flash / SRAM. Sectors containing data required by the processor are read out of NAND flash and written into SDRAM, where the data can be randomly accessed by the processor.

Owner:MALIKIE INNOVATIONS LTD

Memory interface phase-shift circuitry to support multiple frequency ranges

The present invention provides a phase shift circuit that supports multiple frequency ranges. The phase shift circuit receives a plurality of control bits and causes a phase shift in a received signal, the phase shift corresponding to a number of time steps, the number depending on the control bits, and the time step is selected from a plurality of different time steps based on a frequency range associated with the received signal.

Owner:BROOKE LAWRENCE L +1

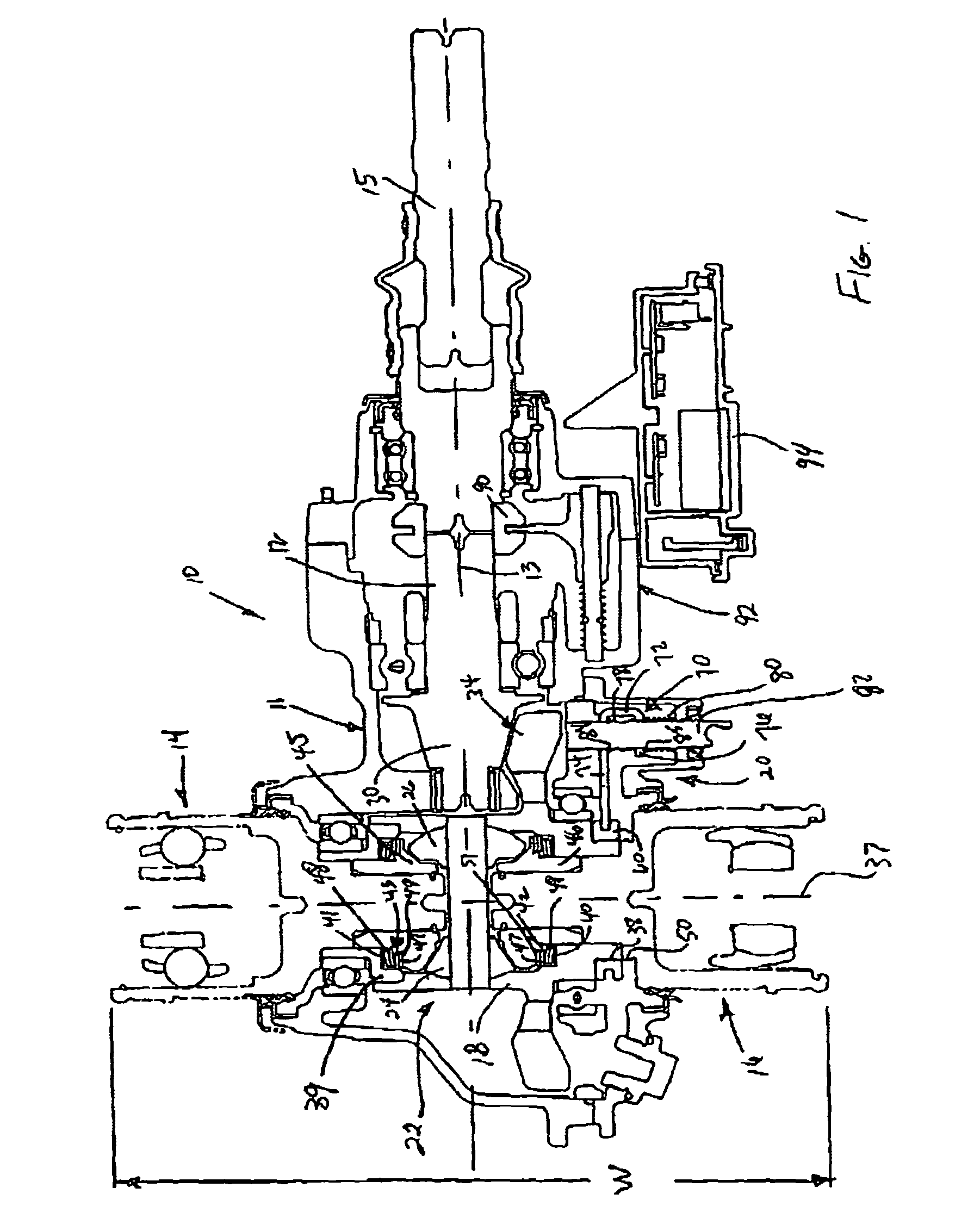

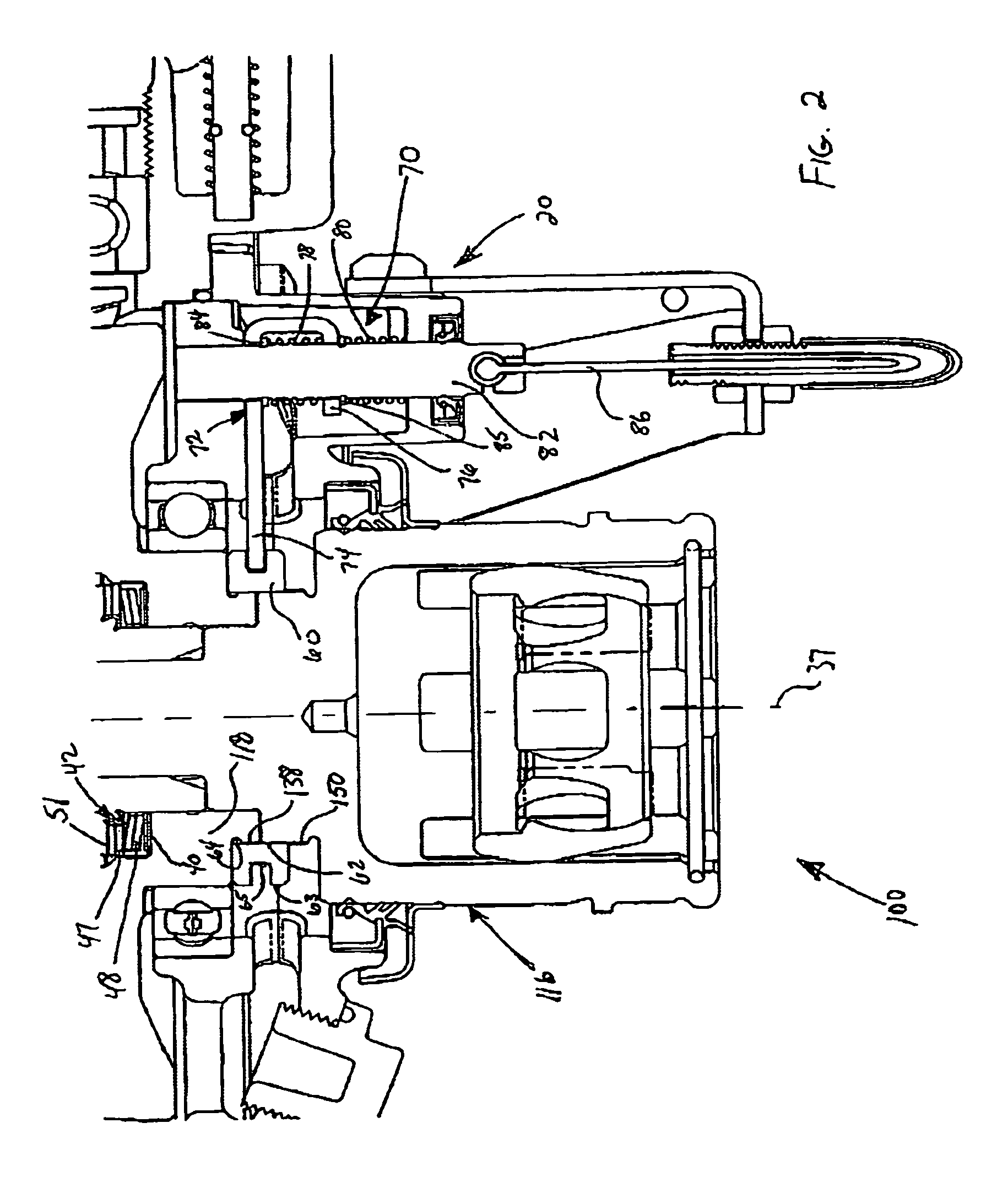

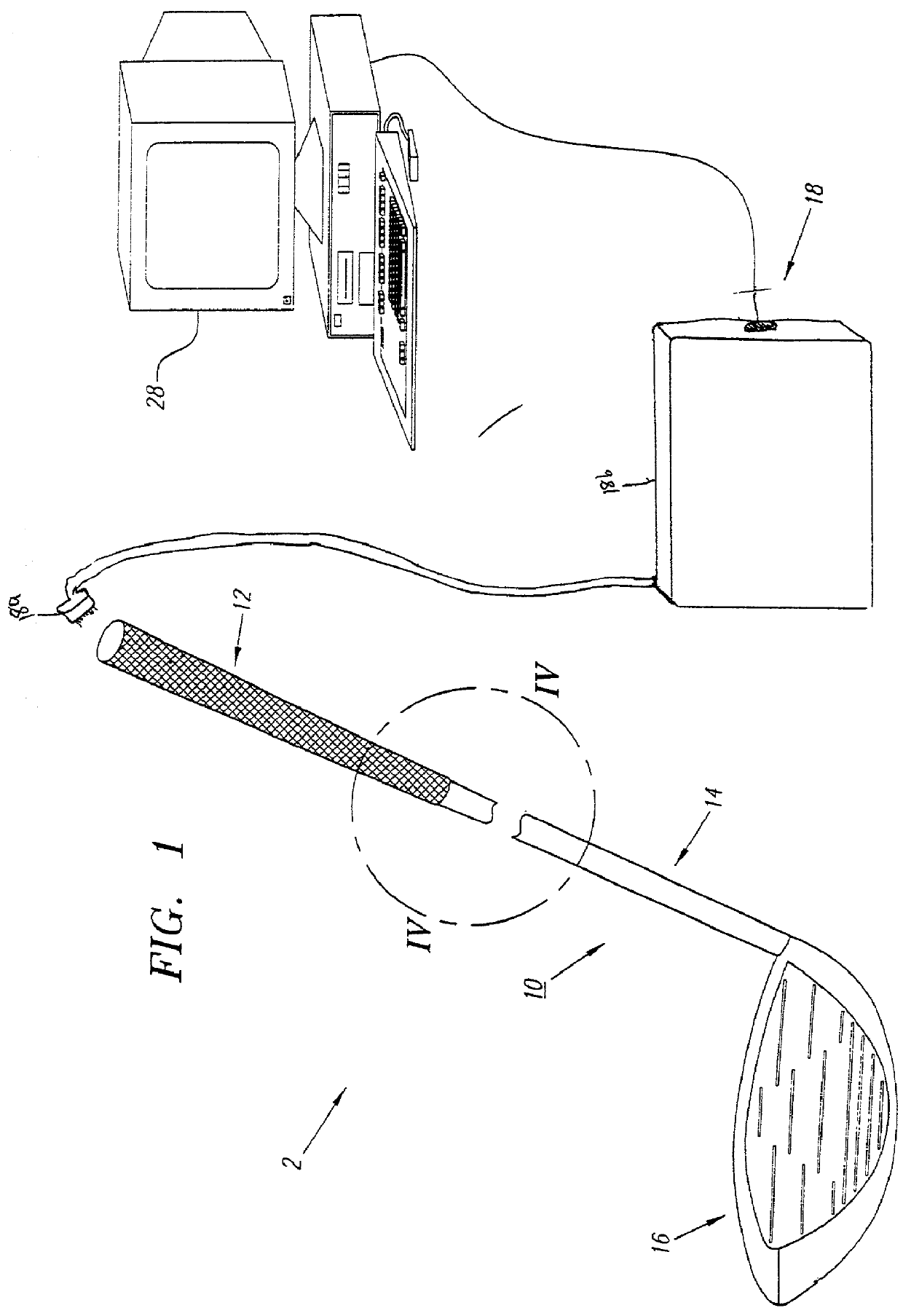

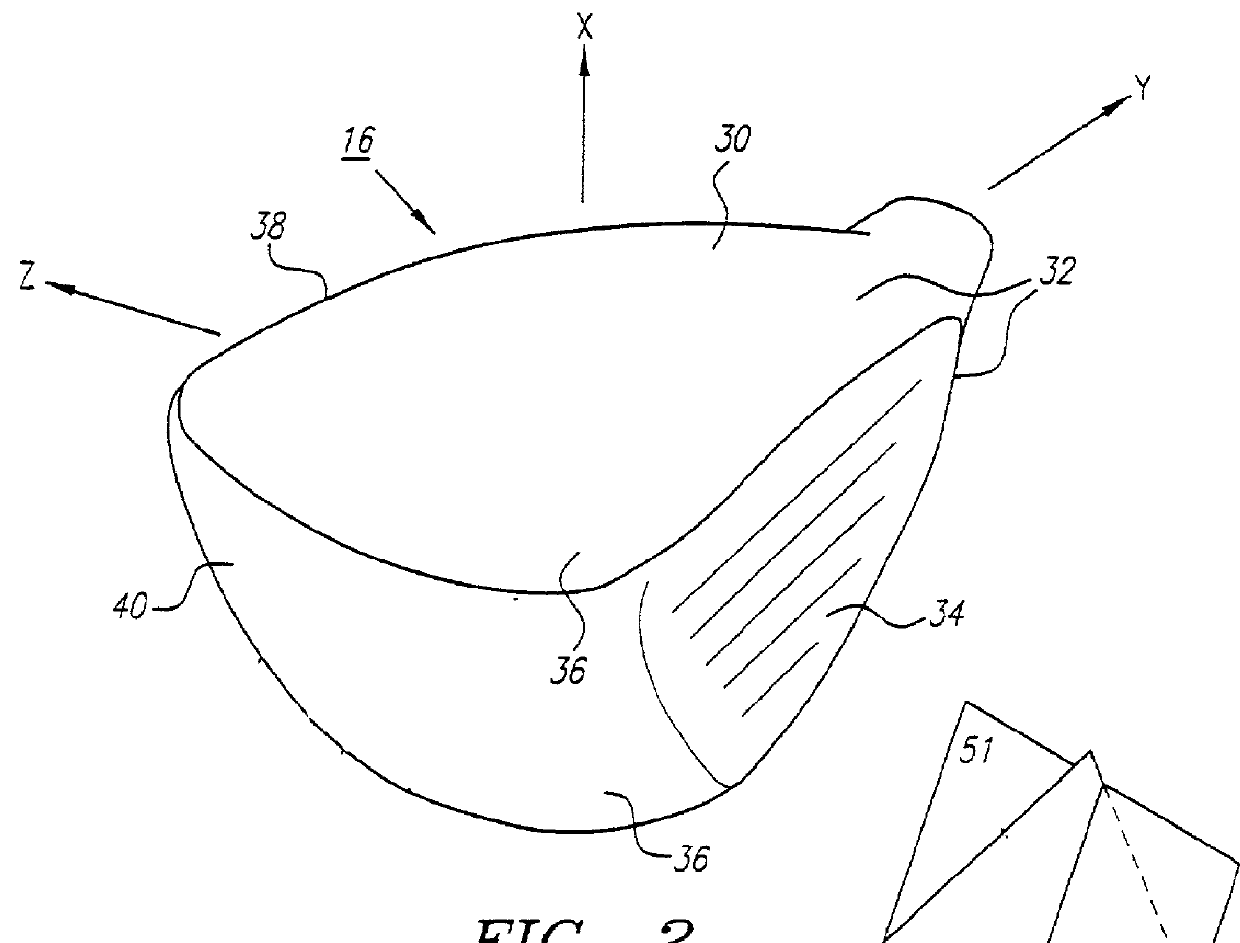

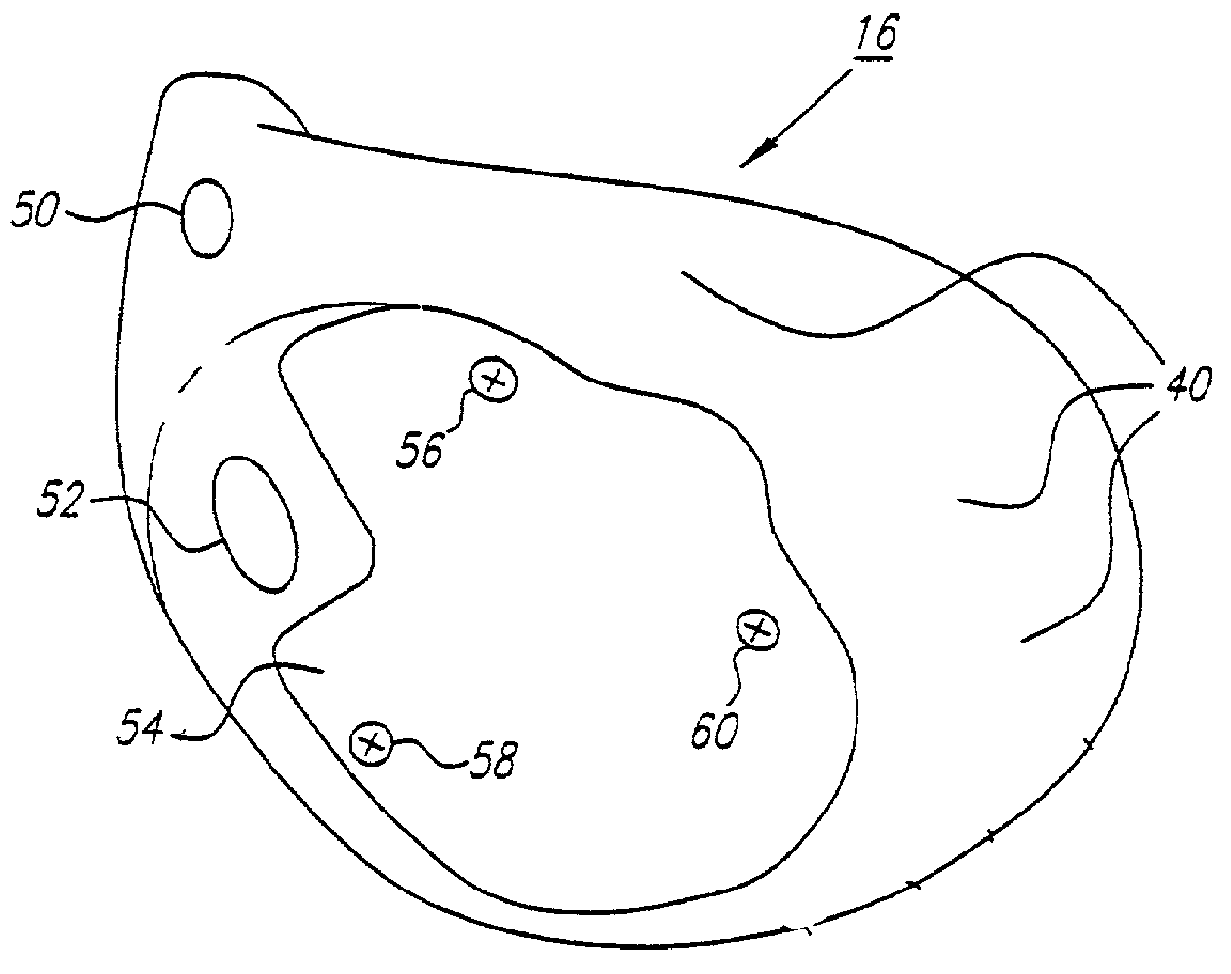

Instrumented golf club system & method of use

An instrumented golf club system having an instrumented golf club, an interface means and a computing means is disclosed herein. The instrumented golf club includes a plurality of sensors, an internal power supply, an angular rate sensor and an internal ring buffer memory for capturing data relating to a golf swing. The interface means is capable of transferring data from the instrumented golf club to the computing means for processing the data and presenting the data in a useful and informative format. The data may be used to assist a golfer's swing, or to design an appropriate golf club for a specific type of golfer.

Owner:CALLAWAY GOLF CO

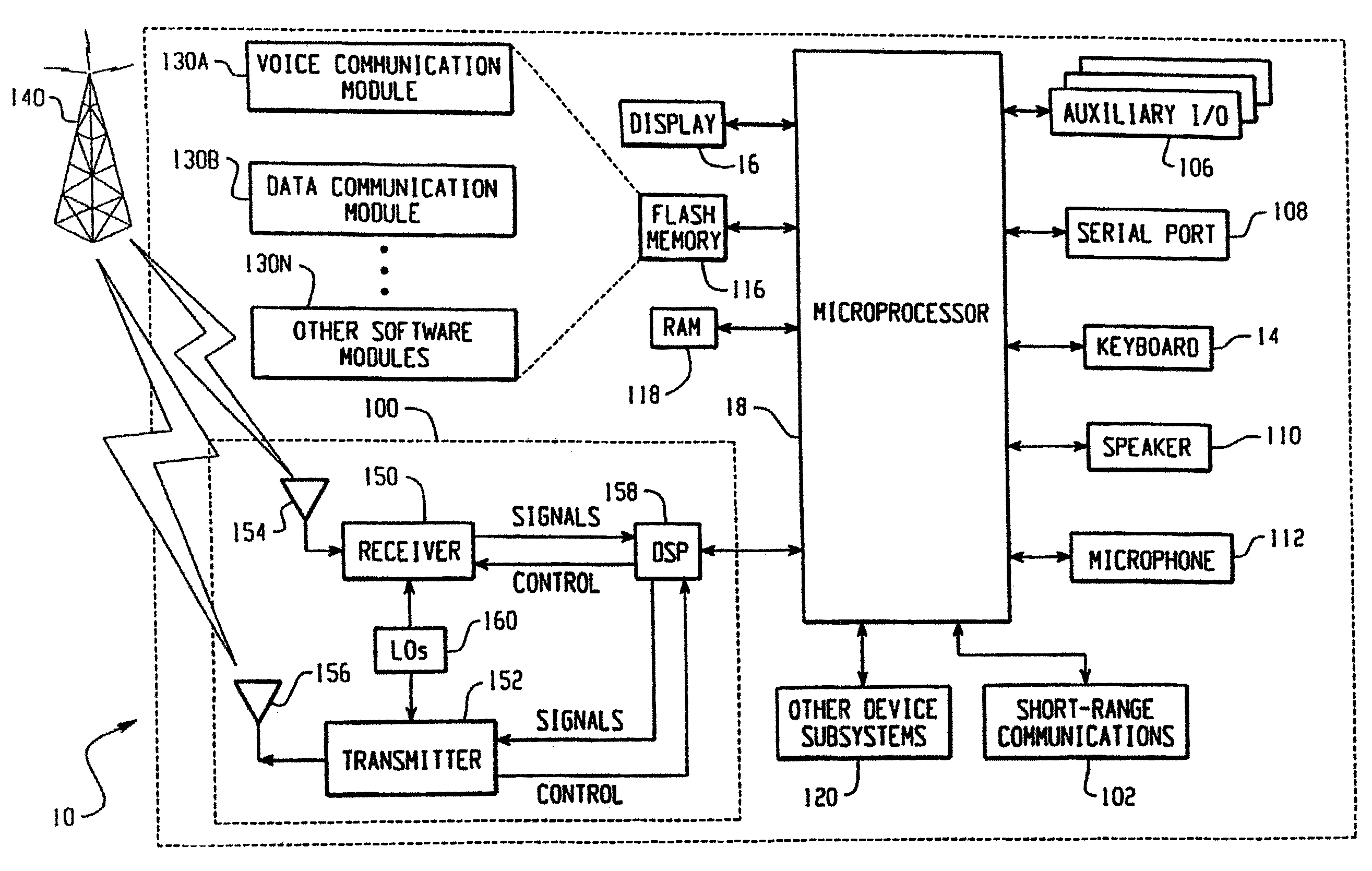

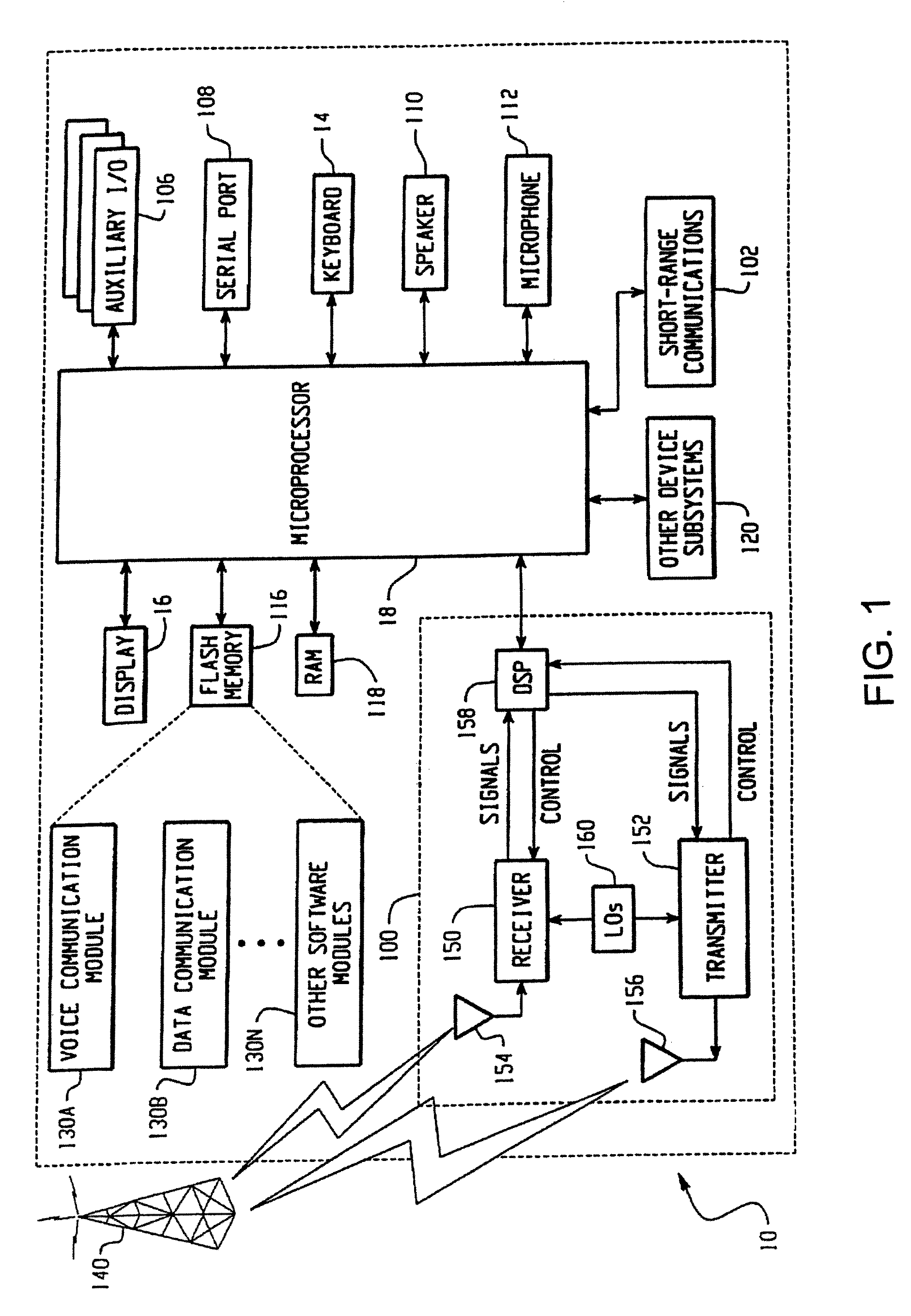

System and method for processor-based security

ActiveUS8738932B2Avoid accessDigital data processing detailsUser identity/authority verificationExternal storageProcessor register

A system and method for processor-based security is provided, for on-chip security and trusted computing services for software applications. A processor is provided having a processor core, a cache memory, a plurality of registers for storing at least one hash value and at least one encryption key, a memory interface, and at least one on-chip instruction for creating a secure memory area in a memory external to the processor, and a hypervisor program executed by the processor. The hypervisor program instructs the processor to execute the at least one on-chip instruction to create a secure memory area for a software area for a software module, and the processor encrypts data written to, and decrypts data read from, the external memory using the at least one encryption key and the verifying data read from the external memory using the at least one hash value. Secure module interactions are provided, as well as the generation of a power-on key which can be used to protect memory in the event of a re-boot event. Lightweight, run-time attestation reports are generated which include selected information about software modules executed by the processors, for use in determining whether the processor is trusted to provide secure services.

Owner:CORESECURE TECH LLC

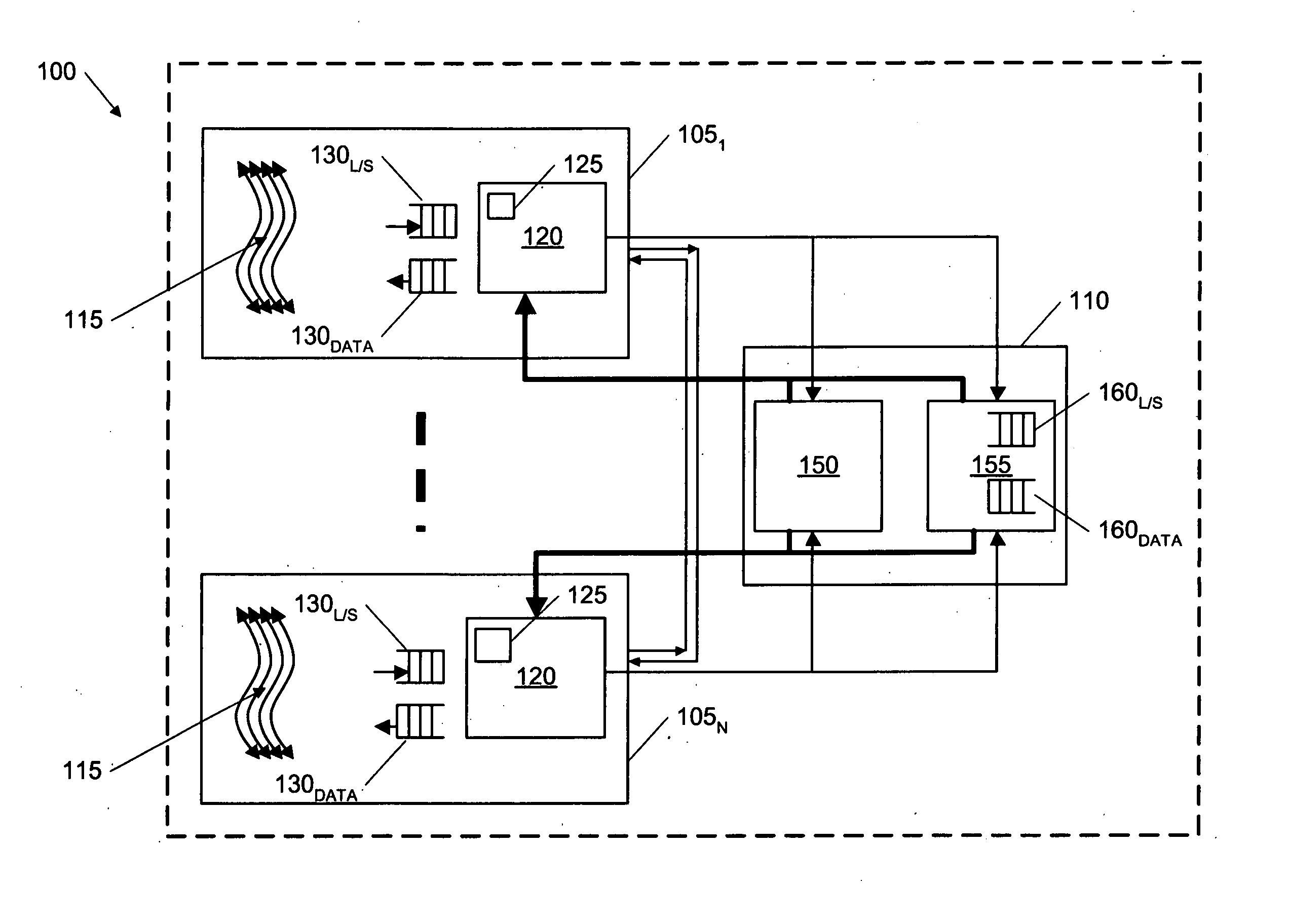

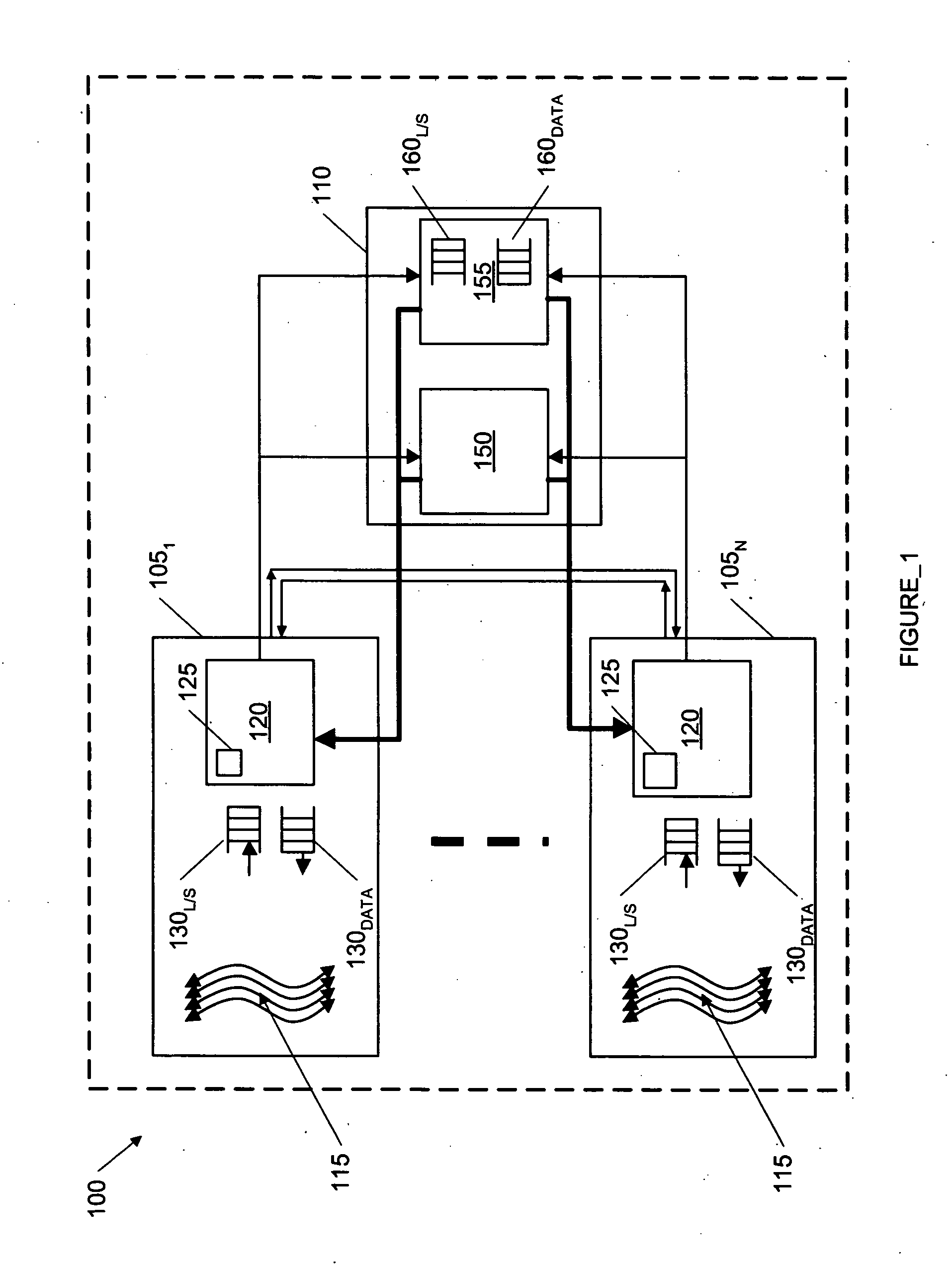

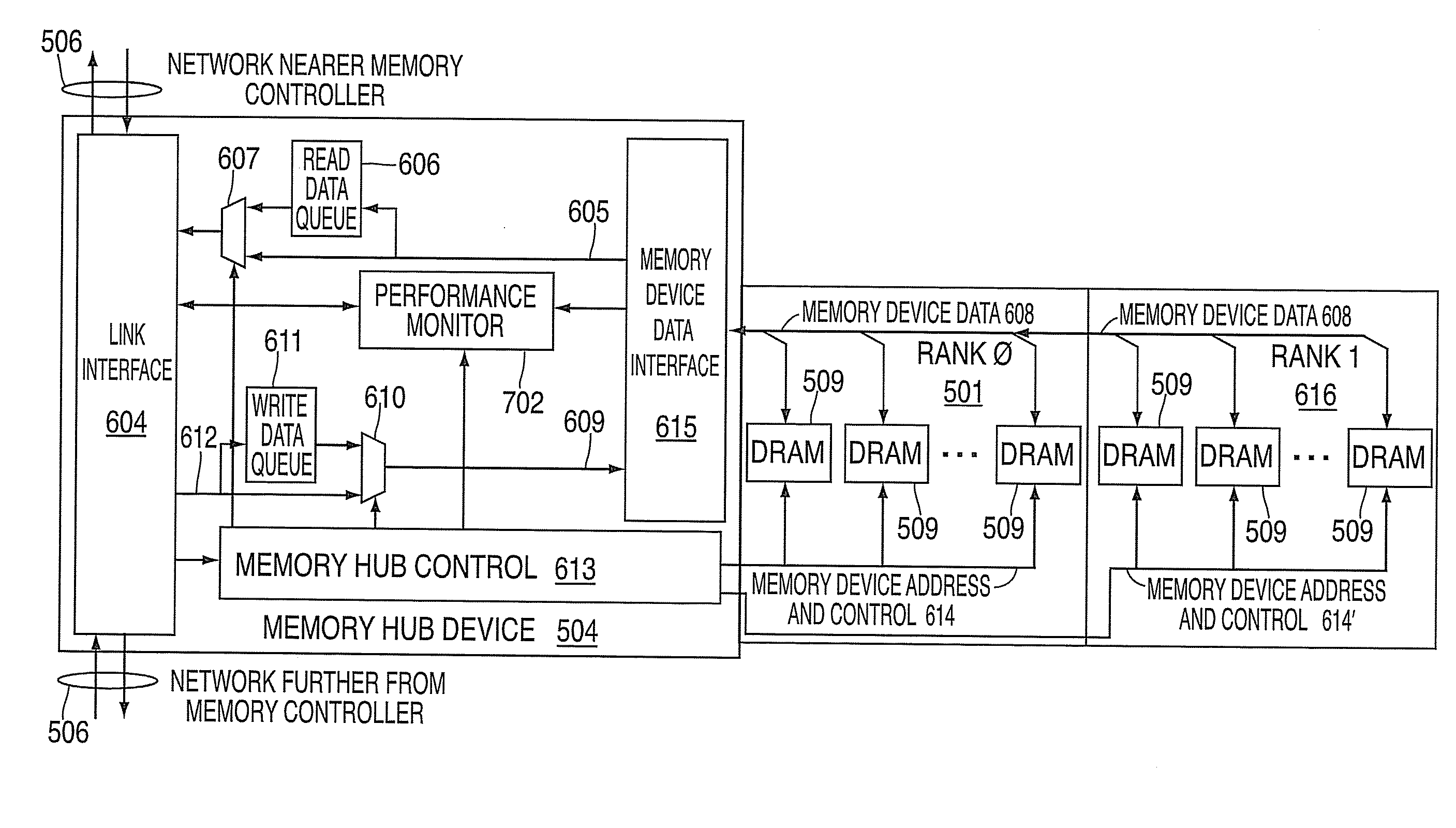

Systems and methods for providing performance monitoring in a memory system

Systems and methods for providing performance monitoring in a memory system. Embodiments include a memory system for storing and retrieving data for a processing system. The memory system includes a memory controller, a plurality of memory devices, a memory bus and a memory hub device. The memory controller receives and responds to memory access requests. The memory bus is in communication with the memory controller. The memory hub device is in communication with the memory bus. The memory hub device includes a memory interface for transferring one or more of address, control and data information between the memory hub device and the memory controller via the memory bus. The memory hub device also includes a memory device interface for communicating with the memory devices. The memory hub device further includes a performance monitor for monitoring and reporting one or more of memory bus utilization, memory device utilization, and performance characteristics over defined intervals during system operation.

Owner:IBM CORP

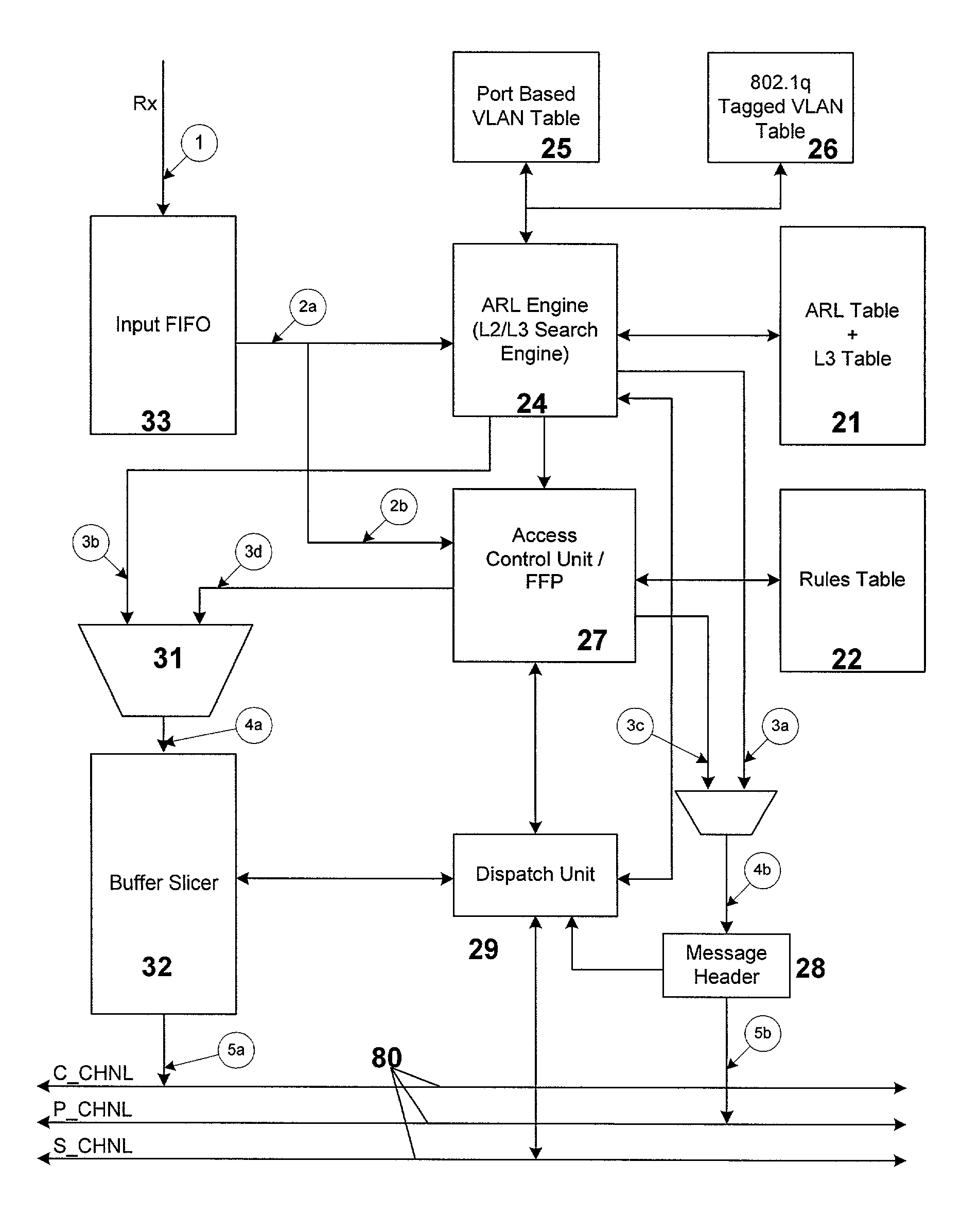

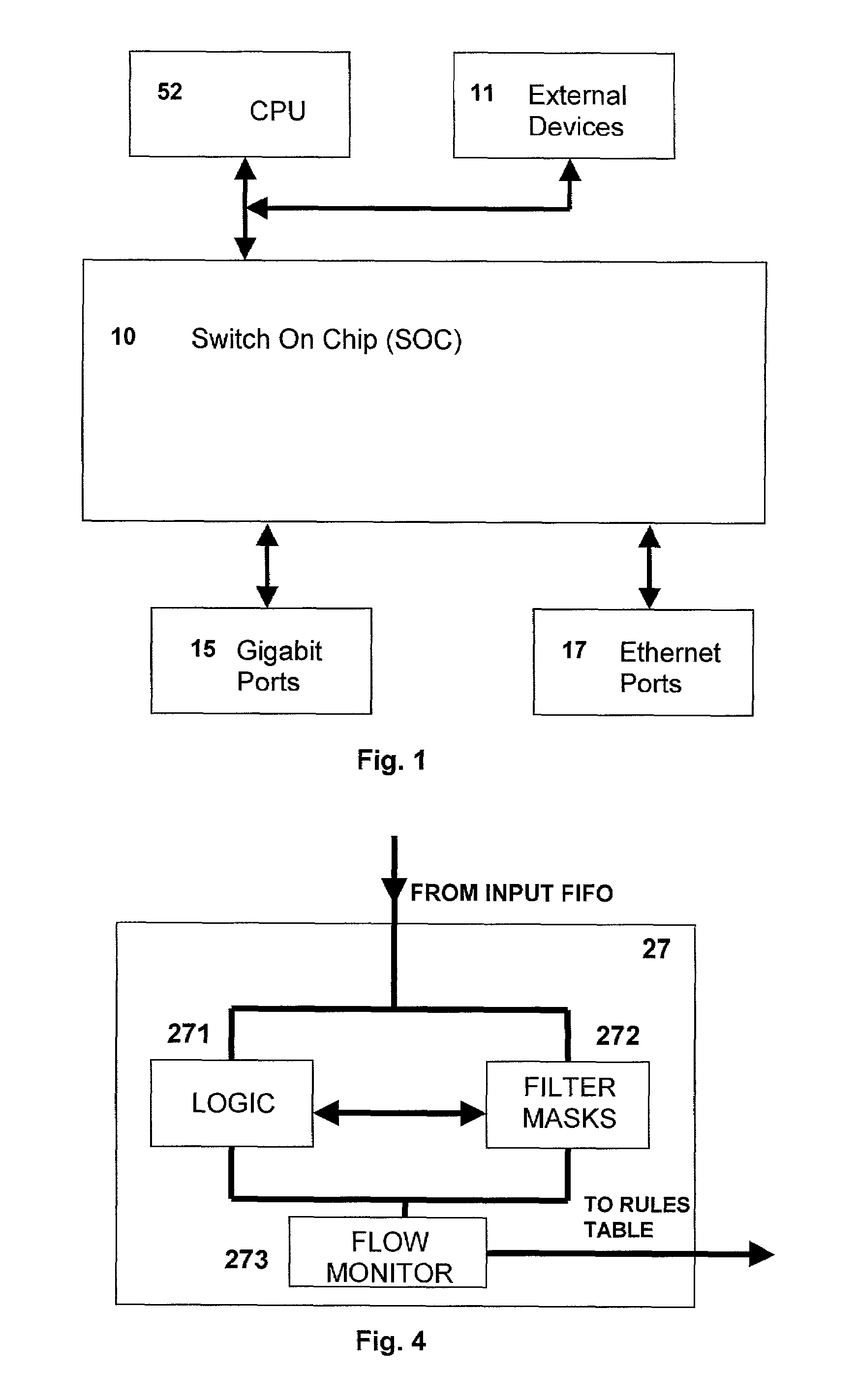

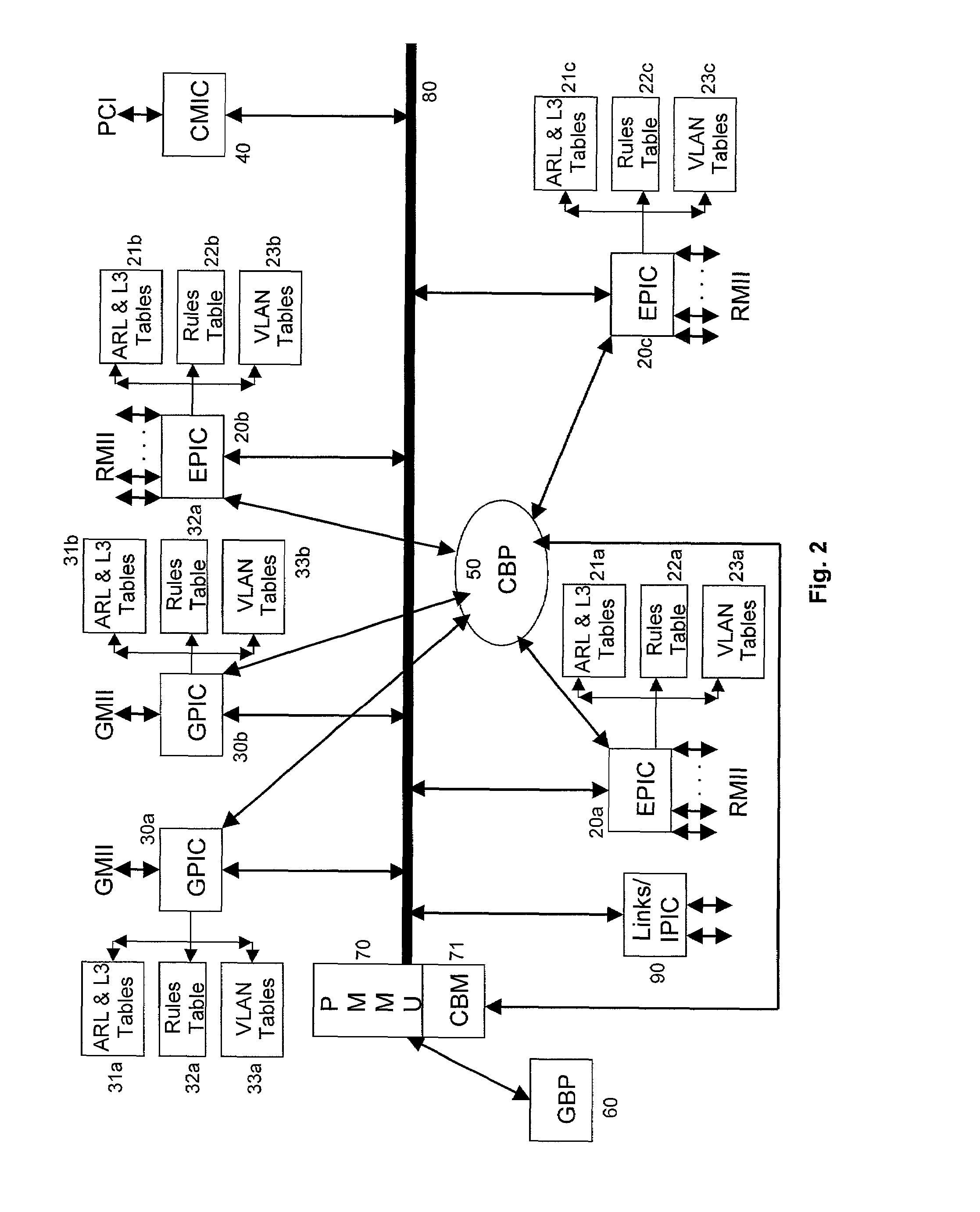

Method and apparatus for enabling access on a network switch

A data switch for network communications includes a data port interface which supports at least one data port which transmits and receives data. The switch also includes a CPU interface, where the CPU interface is configured to communicate with a CPU, and a memory management unit, including a memory interface for communicating data from the data port interface to the switch memory. A communication channel is also provided, communicating data and messaging information between the data port interface, the CPU interface, the switch memory, and the memory management unit. The data port interface also includes an access control unit that filters the data coming into the data port interface and takes selective action on the data by applying a set of filter rules such that access to the switch is controlled by the set of filter rules.

Owner:AVAGO TECH INT SALES PTE LTD

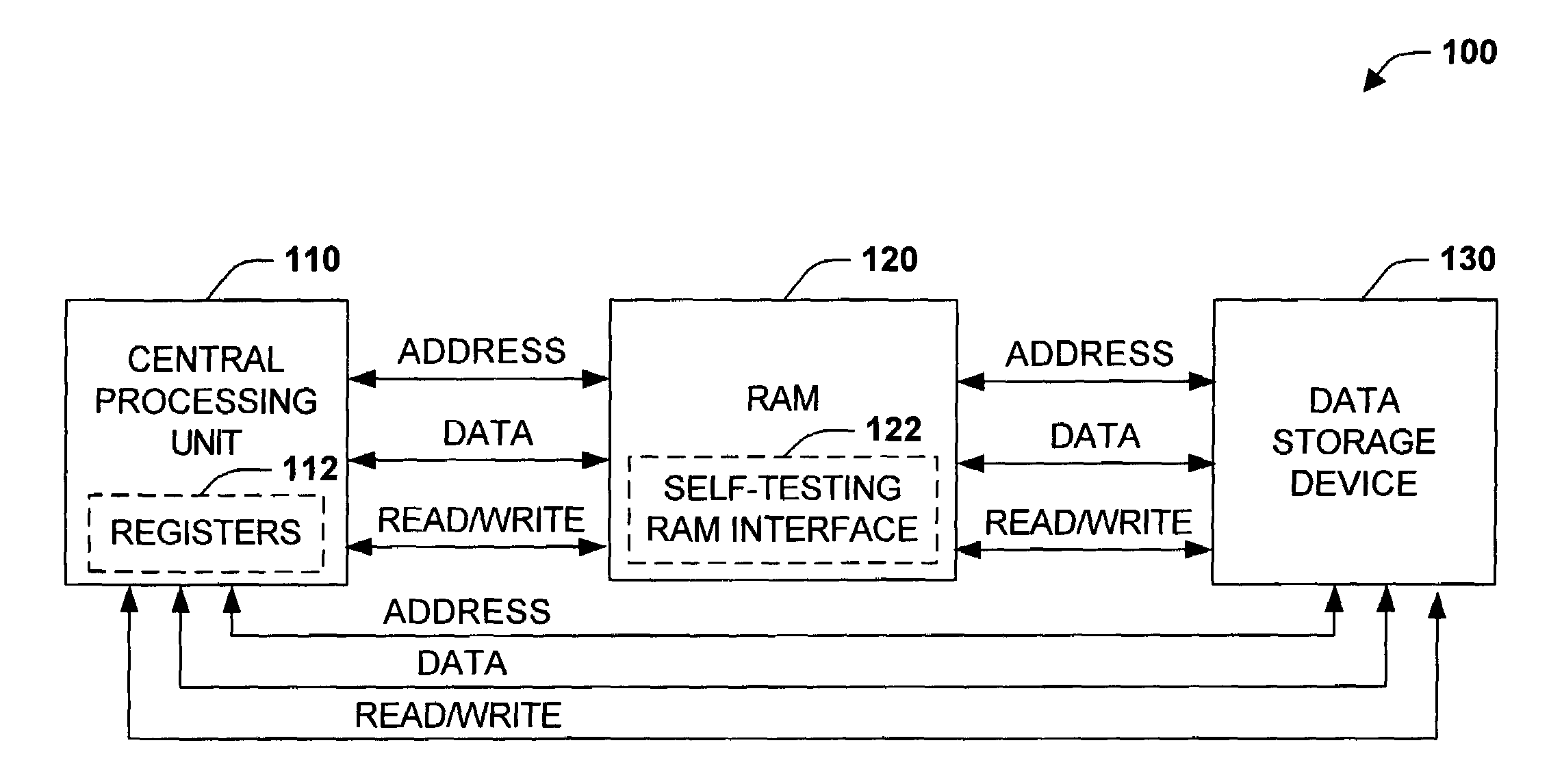

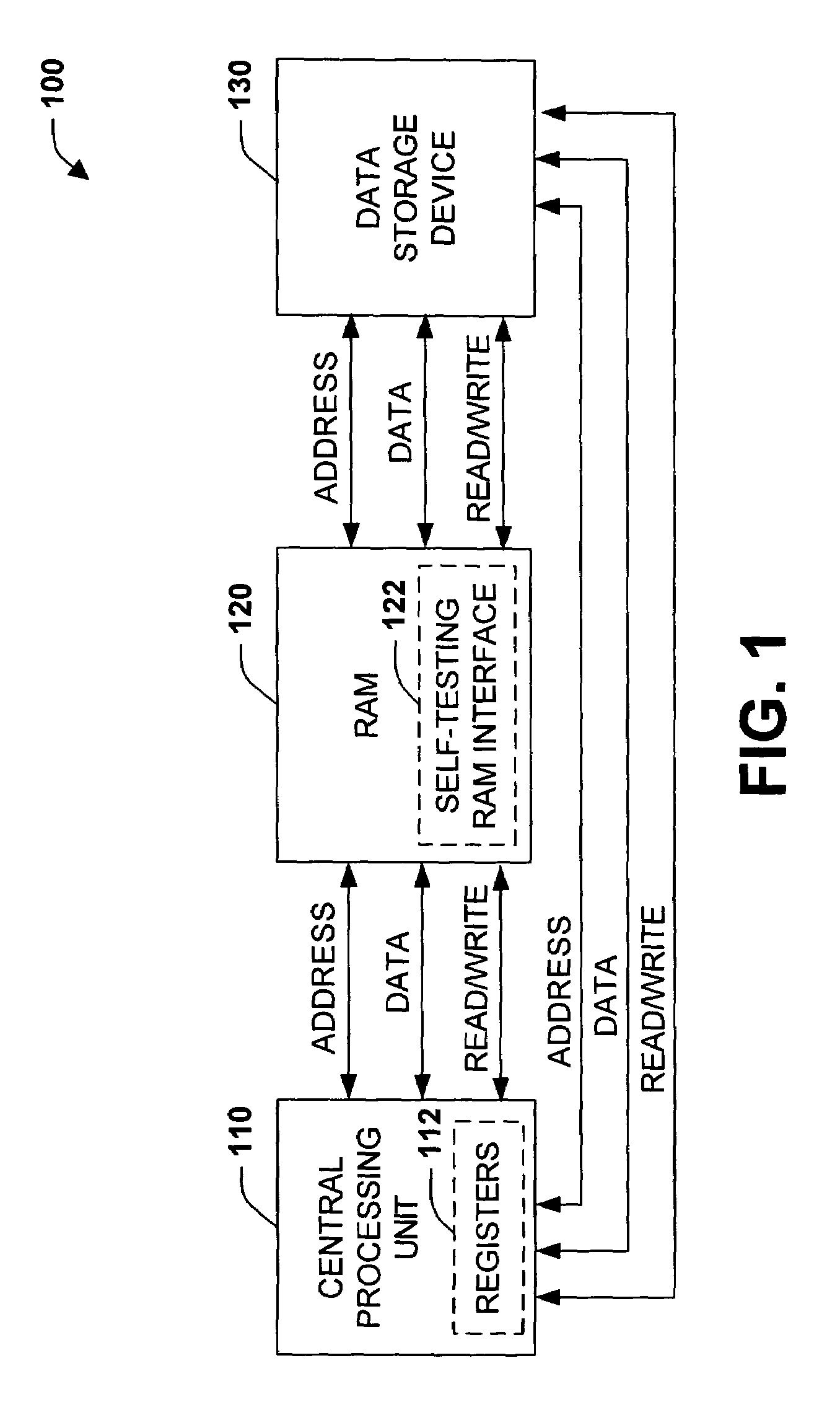

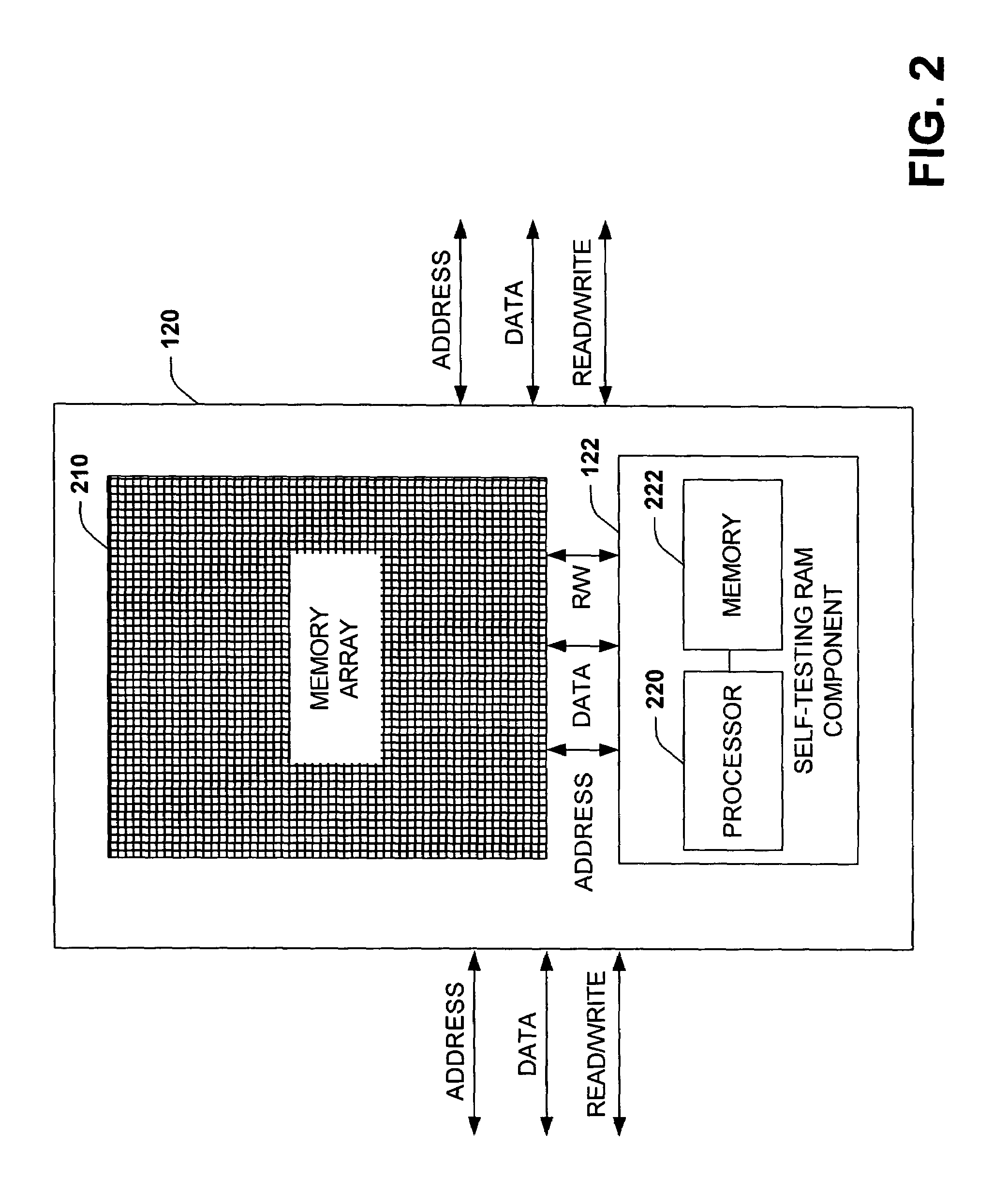

Self-testing RAM system and method

ActiveUS7334159B1Easy to testTedious to testUnauthorized memory use protectionDigital storageData integrityMemory interface

A self-testing and correcting random access memory (RAM) device and methodology is disclosed herein. The device includes at least one array of memory to enable data storage and self-testing RAM interface for evaluating, correcting, and / or compensating for memory cell errors. The RAM device, via the self-testing RAM interface, supports interaction with a central processing unit (CPU) to facilitate testing of the CPU to memory interface as well as the device memory array. Upon detection of memory errors, the self-testing RAM interface can notify the CPU, notify an exception handler, correct, and / or compensate for the errors. Error correction can be accomplished using error correction codes (ECCs) alone or in combination with retrieval and replacement of erroneous data with correct data stored in different locations. Memory cells that are physically defective and incapable of maintaining data integrity can be compensated for by mapping defective cells to a plurality of reserved replacement cells.

Owner:XENOGENIC DEV LLC

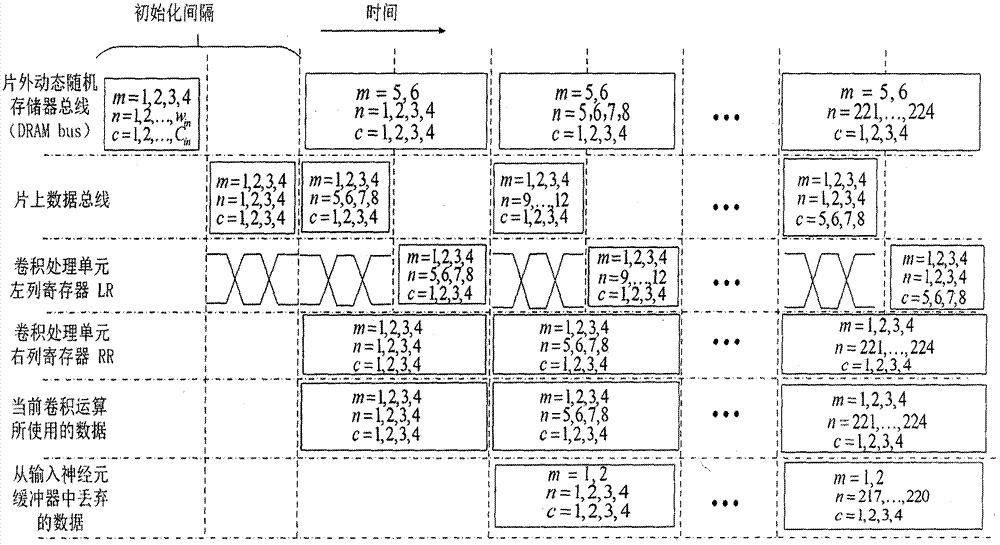

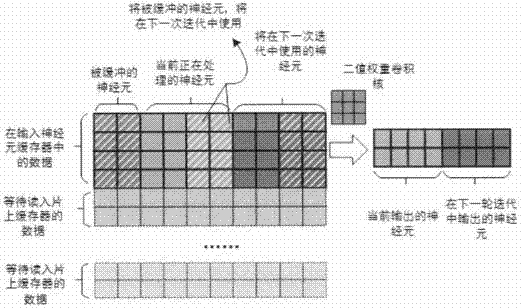

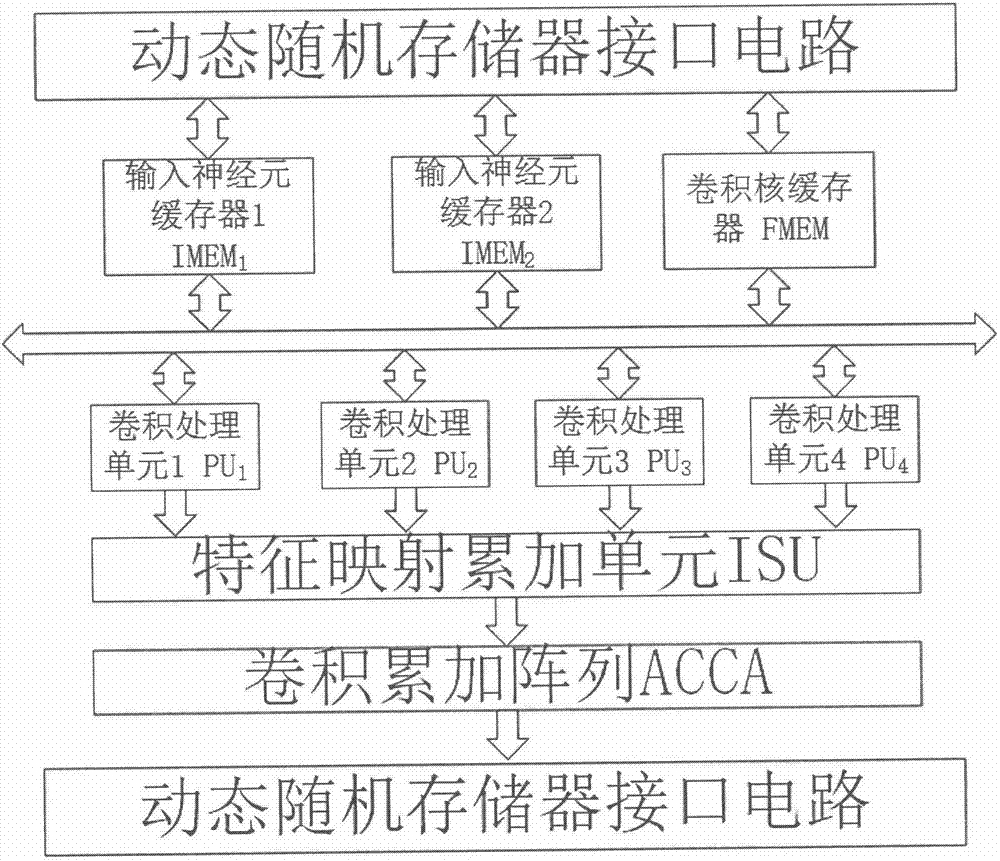

Hardware architecture of binary weight convolution neural network accelerator and calculation process thereof

ActiveCN106875011AReduce accessReduce power consumptionPhysical realisationStatic random-access memoryMemory interface

The invention discloses the hardware architecture of a binary weight convolution neural network accelerator and a calculation process thereof. The hardware architecture comprises three double-ended on-chip static random access memories which are used for buffering the binary weight of input neurons and a convolution layer, four convolution processing units capable of controlling calculation parts to complete major convolution calculation operation according to the calculation process, a feature map accumulation unit and a convolutional accumulation array. The feature map accumulation unit and the convolutional accumulation array are used for further processing the operation result of the convolution processing units to acquire a final correct output neuron value. The entire design exchanges data with an off-chip memory via a dynamic random access memory interface. In addition to the hardware architecture, the invention further provides the detailed calculation process which optimizes the hardware architecture and uses four lines of input feature map as a complete calculation unit. According to the invention, input data are reused to the greatest extent; the access of the off-chip memory is eliminated as much as possible; the power consumption of the deep binary convolution neural network calculation can be effectively reduced; a deep network is supported; and the scheme provided by the invention is a reasonable scheme which can be applied to an embedded system of visual application.

Owner:南京风兴科技有限公司

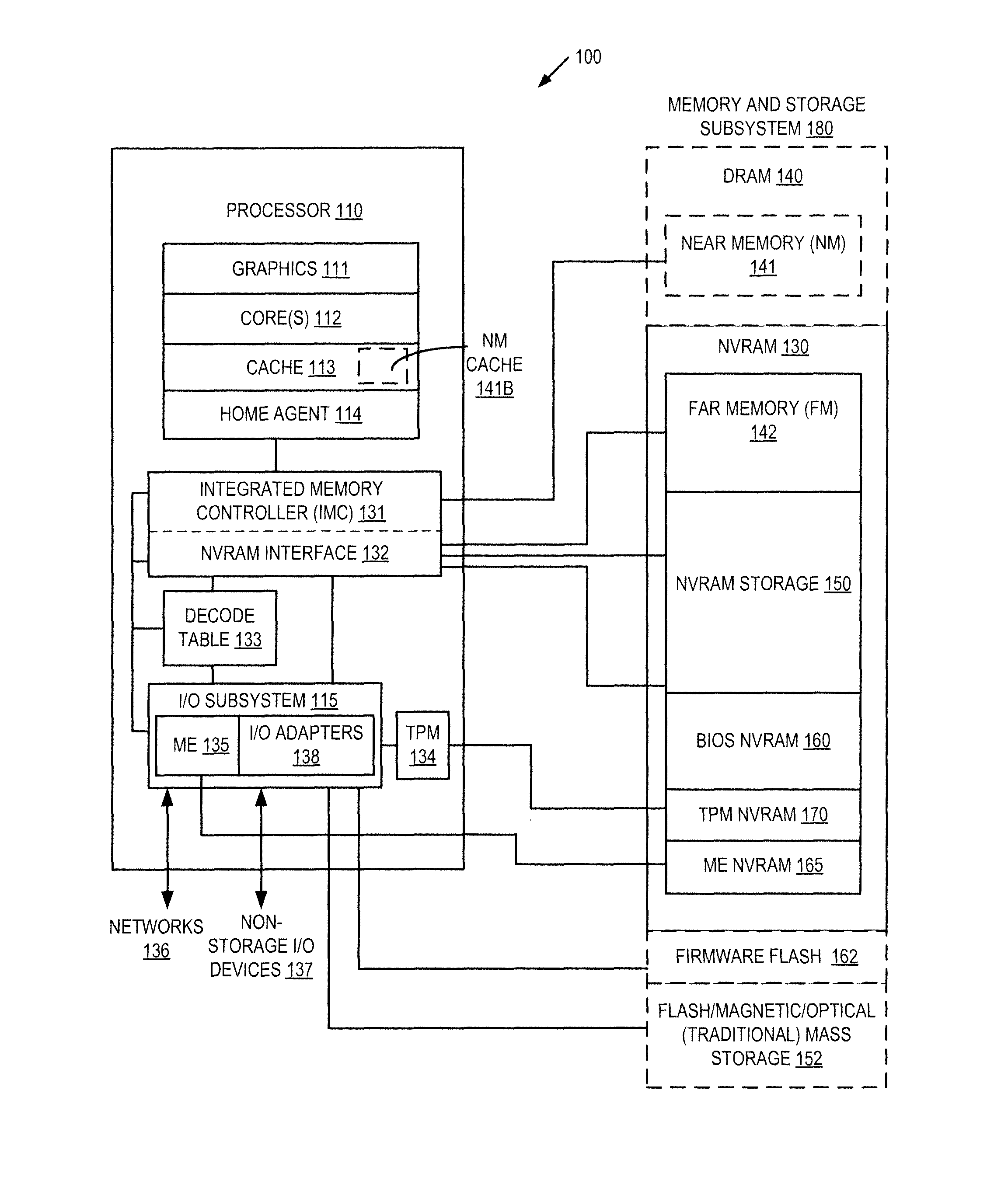

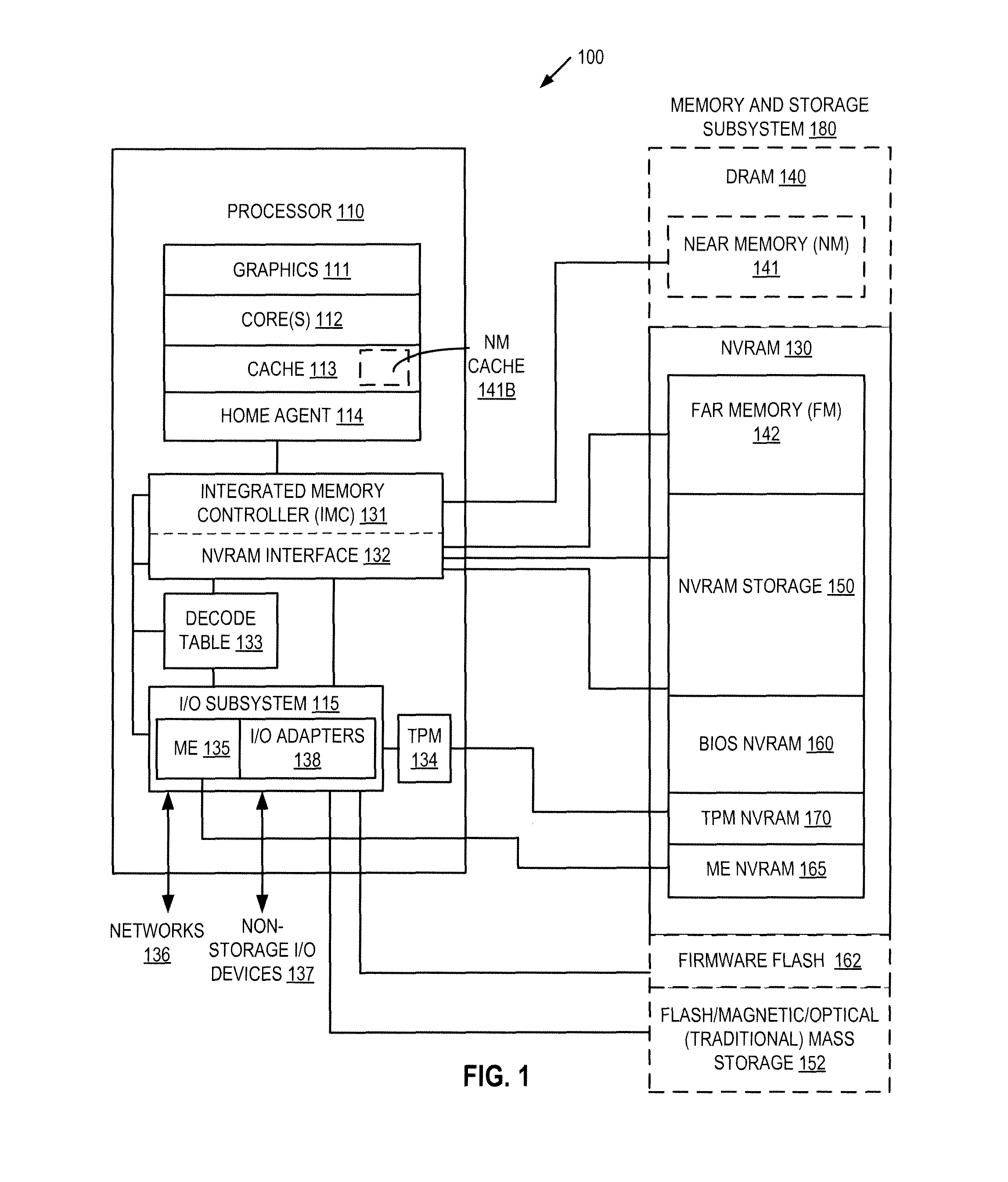

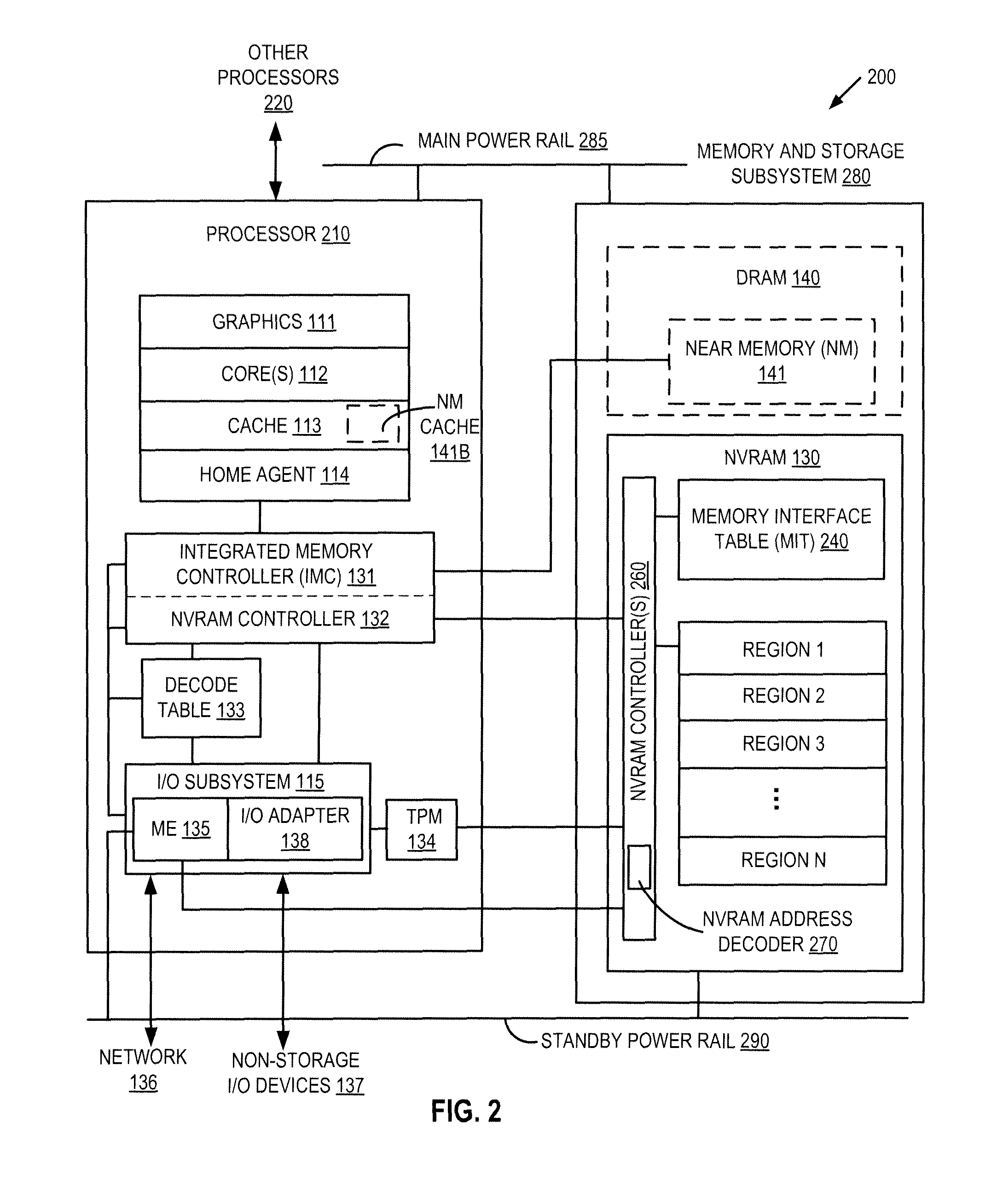

Autonomous initialization of non-volatile random access memory in a computer system

A non-volatile random access memory (NVRAM) is used in a computer system to store information that allows the NVRAM to autonomously initialize itself at power-on. The computer system includes a processor, an NVRAM controller coupled to the processor, and an NVRAM that comprises the NVRAM controller. The NVRAM is byte-rewritable and byte-erasable by the processor. The NVRAM stores a memory interface table containing information for the NVRAM controller to autonomously initialize the NVRAM upon power-on of the computer system without interacting with the processor and firmware outside of the NVRAM. The information is provided by the NVRAM controller to the processor to allow the processor to access the NVRAM.

Owner:INTEL CORP

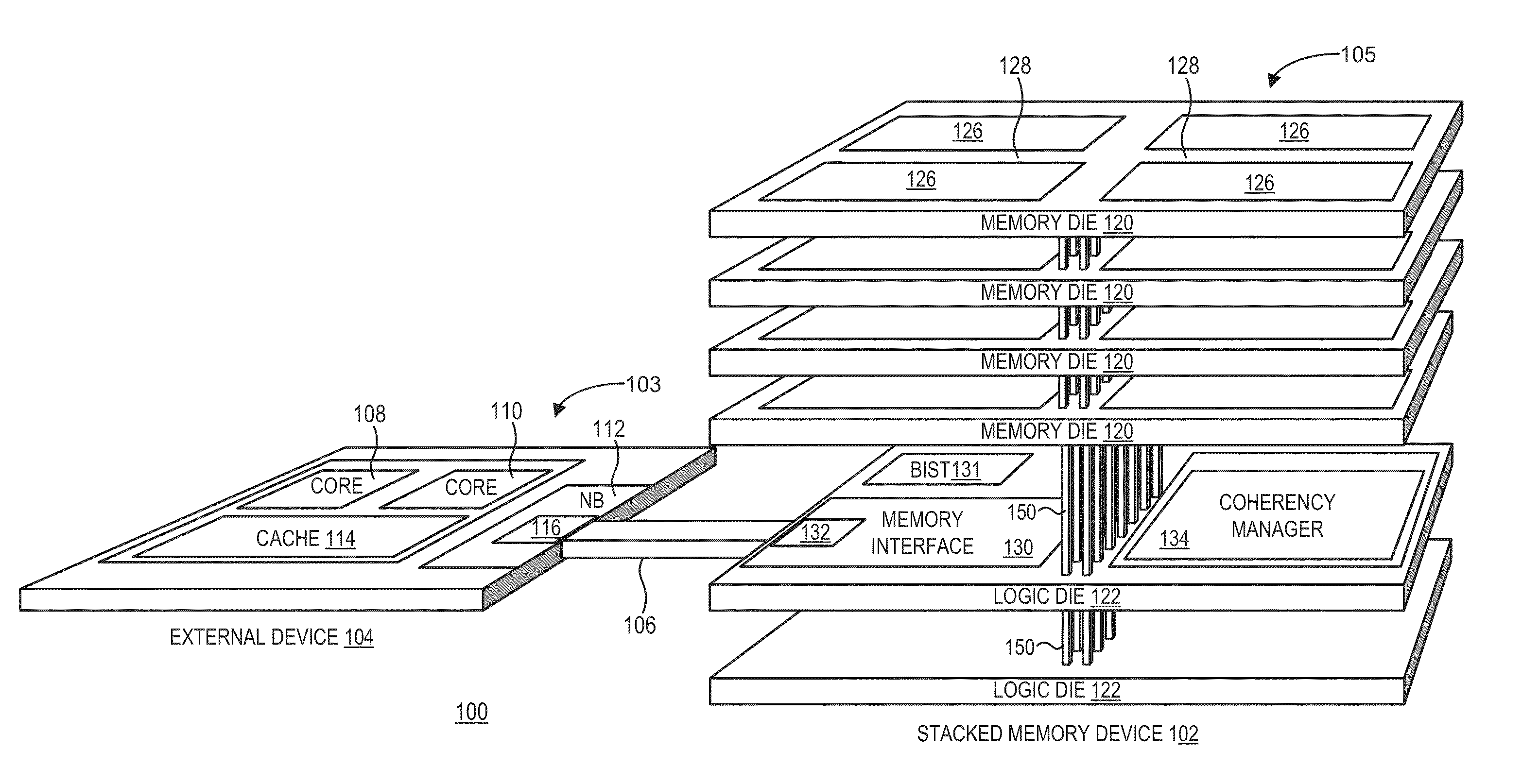

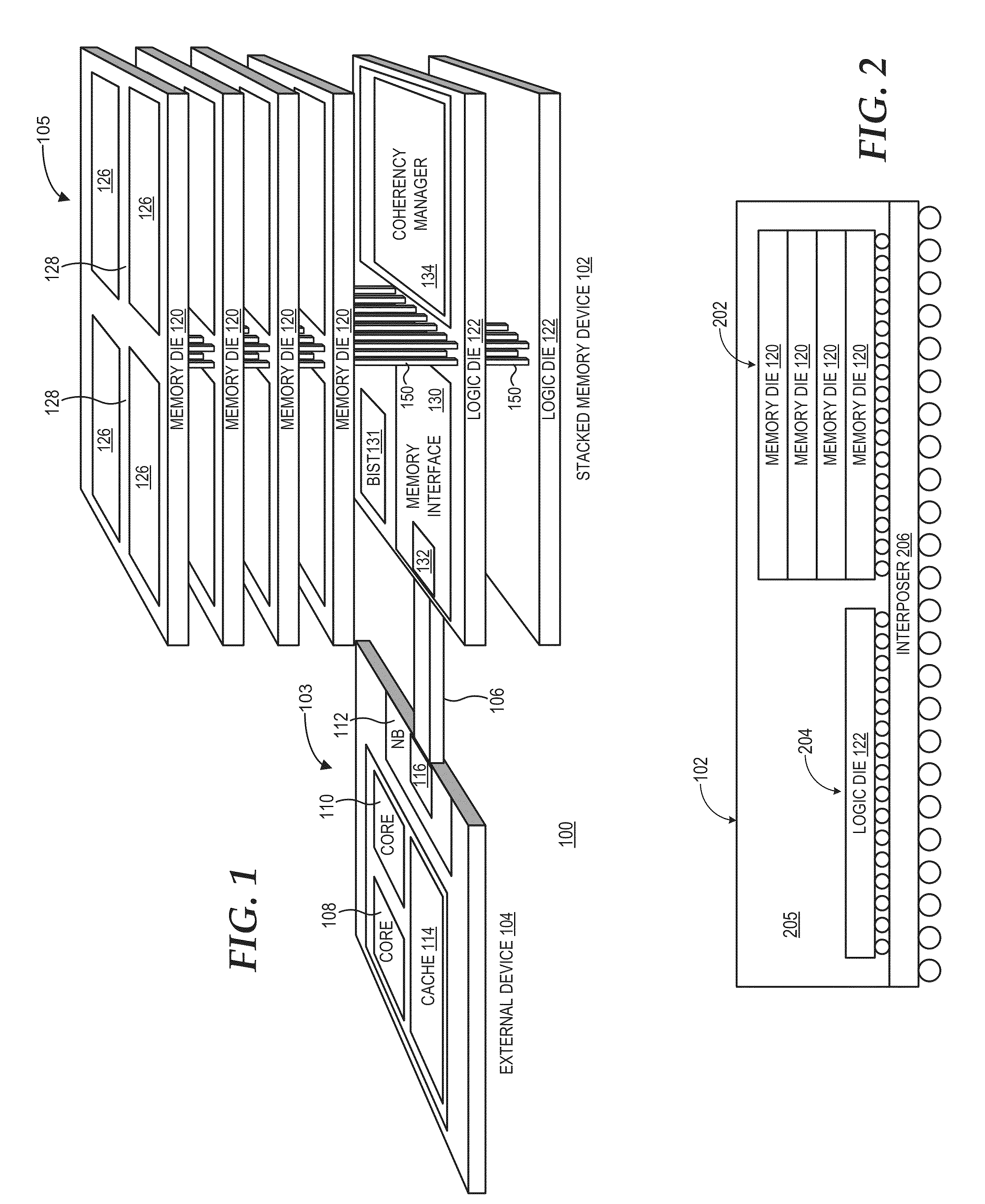

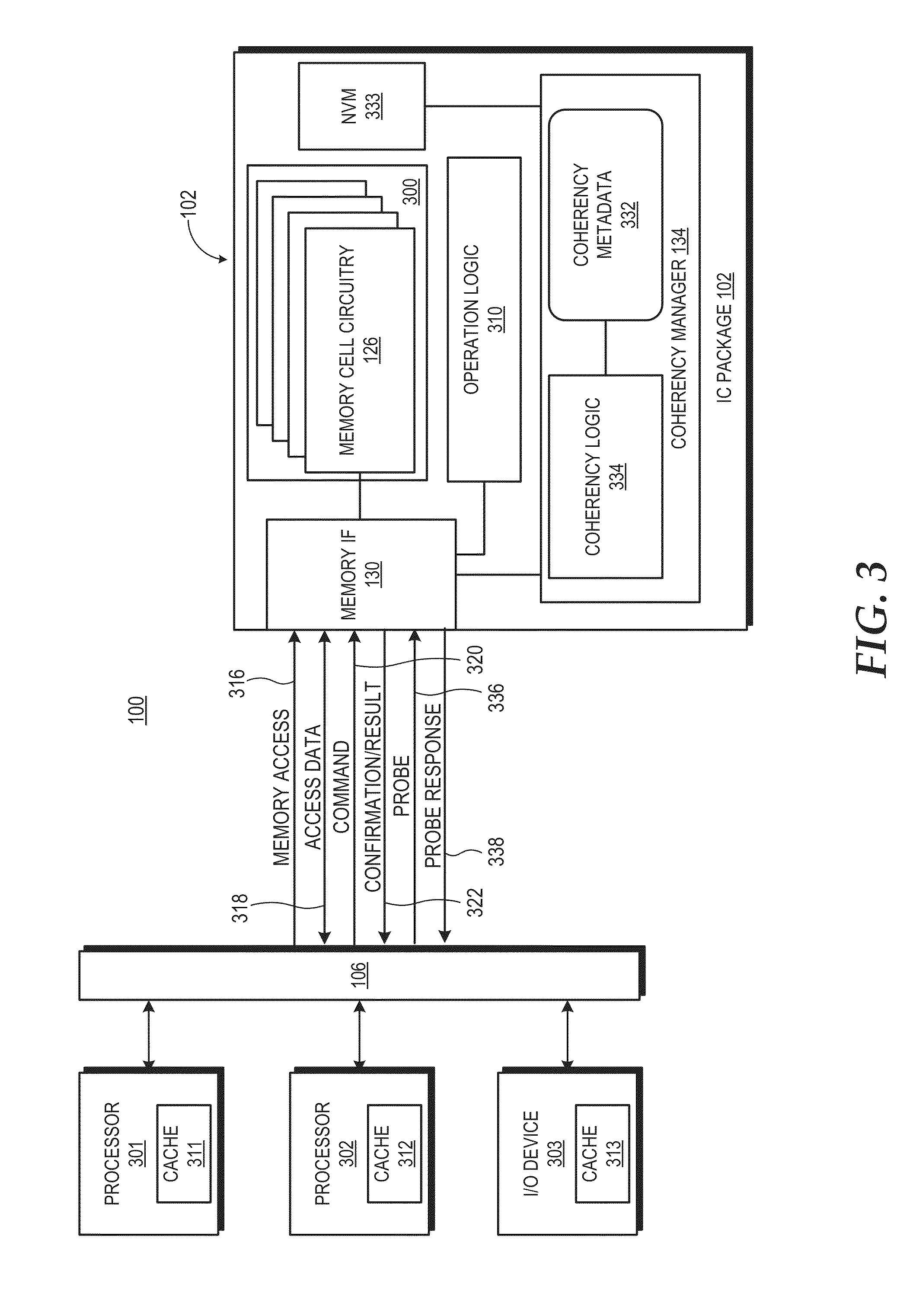

Cache coherency using die-stacked memory device with logic die

ActiveUS20140181417A1Solid-state devicesMemory adressing/allocation/relocationHigh bandwidthMemory interface

A die-stacked memory device implements an integrated coherency manager to offload cache coherency protocol operations for the devices of a processing system. The die-stacked memory device includes a set of one or more stacked memory dies and a set of one or more logic dies. The one or more logic dies implement hardware logic providing a memory interface and the coherency manager. The memory interface operates to perform memory accesses in response to memory access requests from the coherency manager and the one or more external devices. The coherency manager comprises logic to perform coherency operations for shared data stored at the stacked memory dies. Due to the integration of the logic dies and the memory dies, the coherency manager can access shared data stored in the memory dies and perform related coherency operations with higher bandwidth and lower latency and power consumption compared to the external devices.

Owner:ADVANCED MICRO DEVICES INC

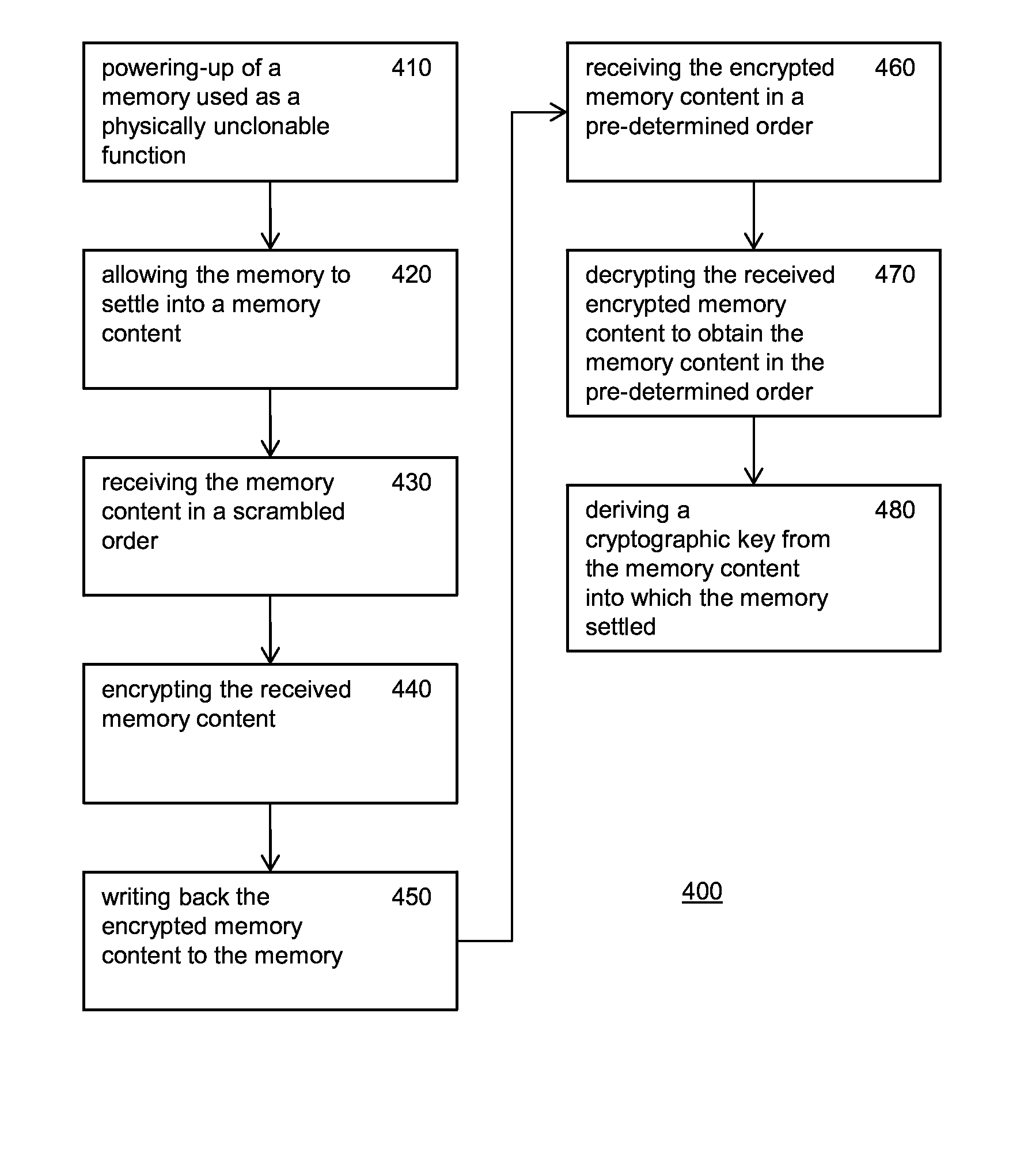

System for generating a cryptographic key from a memory used as a physically unclonable function

ActiveUS20150234751A1Reduce side channel leakageMore informationMemory architecture accessing/allocationDigital data processing detailsElectricityElectronic systems

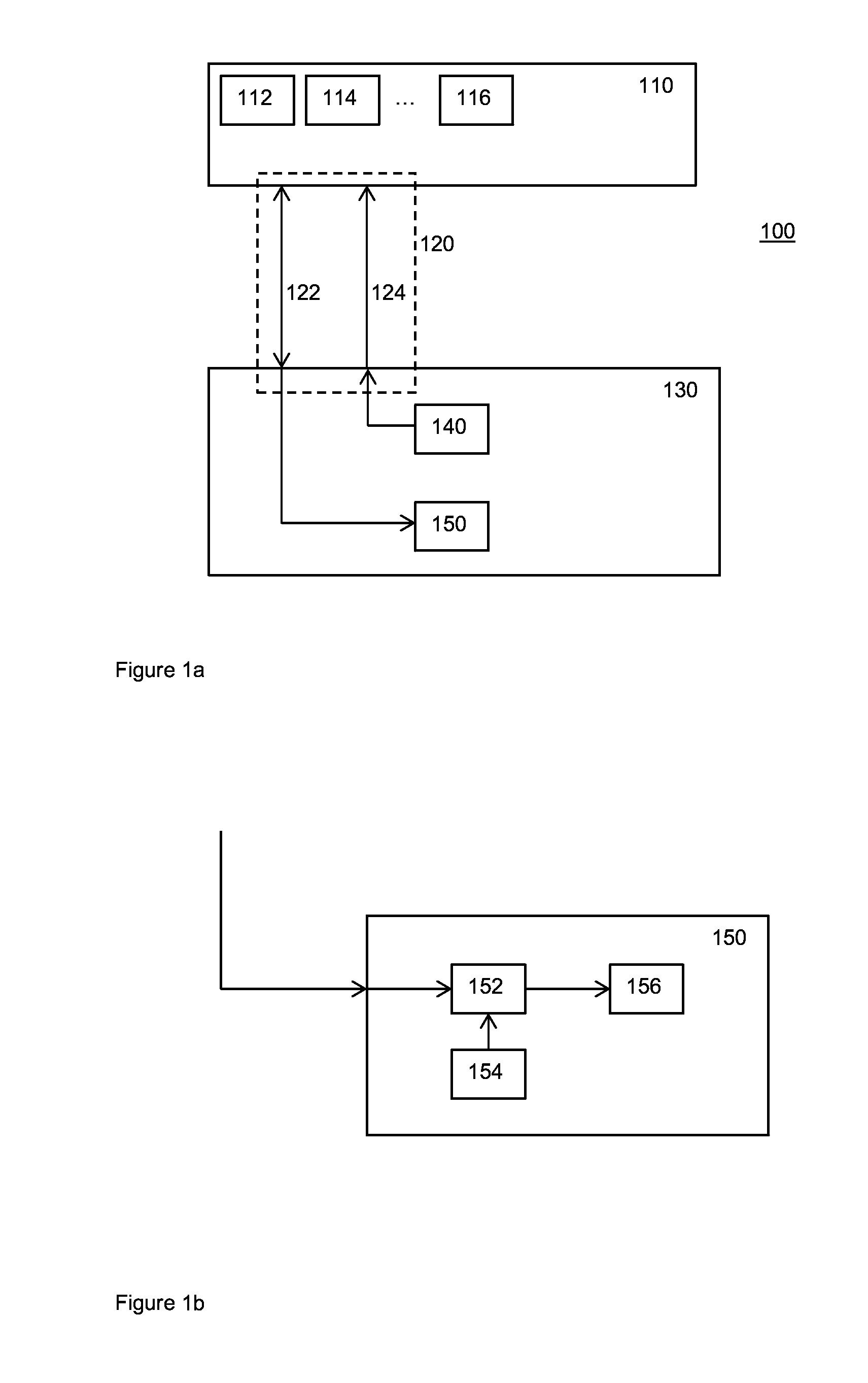

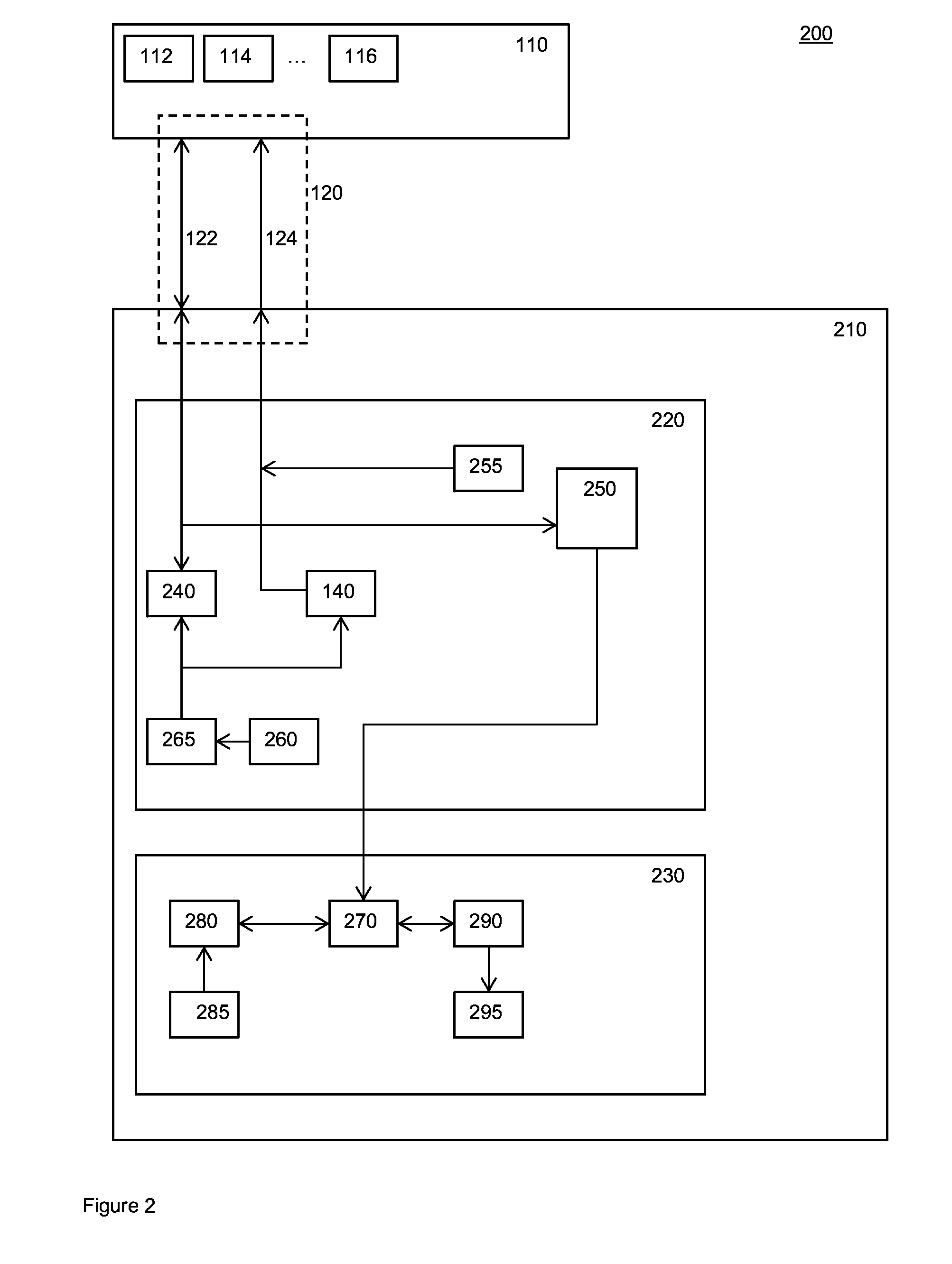

An electronic system 100 for generating a cryptographic key, the system comprisinga memory 110 used as a physically unclonable function, the memory being writable, volatile and configured such that upon each powering-up of the memory the memory settles into a memory content which depends upon at least partially random physical characteristics of the memory, the memory being accessible through a memory interface, anda key derivation unit 150 configured to derive the cryptographic key from the memory content into which the memory settled,wherein the electronic system for generating a cryptographic key further comprises,a memory read-out unit connected to the memory through the memory interface and to the key derivation unit, the memory read-out unit comprising an address scrambler 140 for retrieving the memory content over the memory interface in a scrambled order.

Owner:INTRINSIC ID