Patents

Literature

12283results about "Generating/distributing signals" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reference time distribution over a network

InactiveUS8014423B2Time-division multiplexGenerating/distributing signalsTime informationData stream

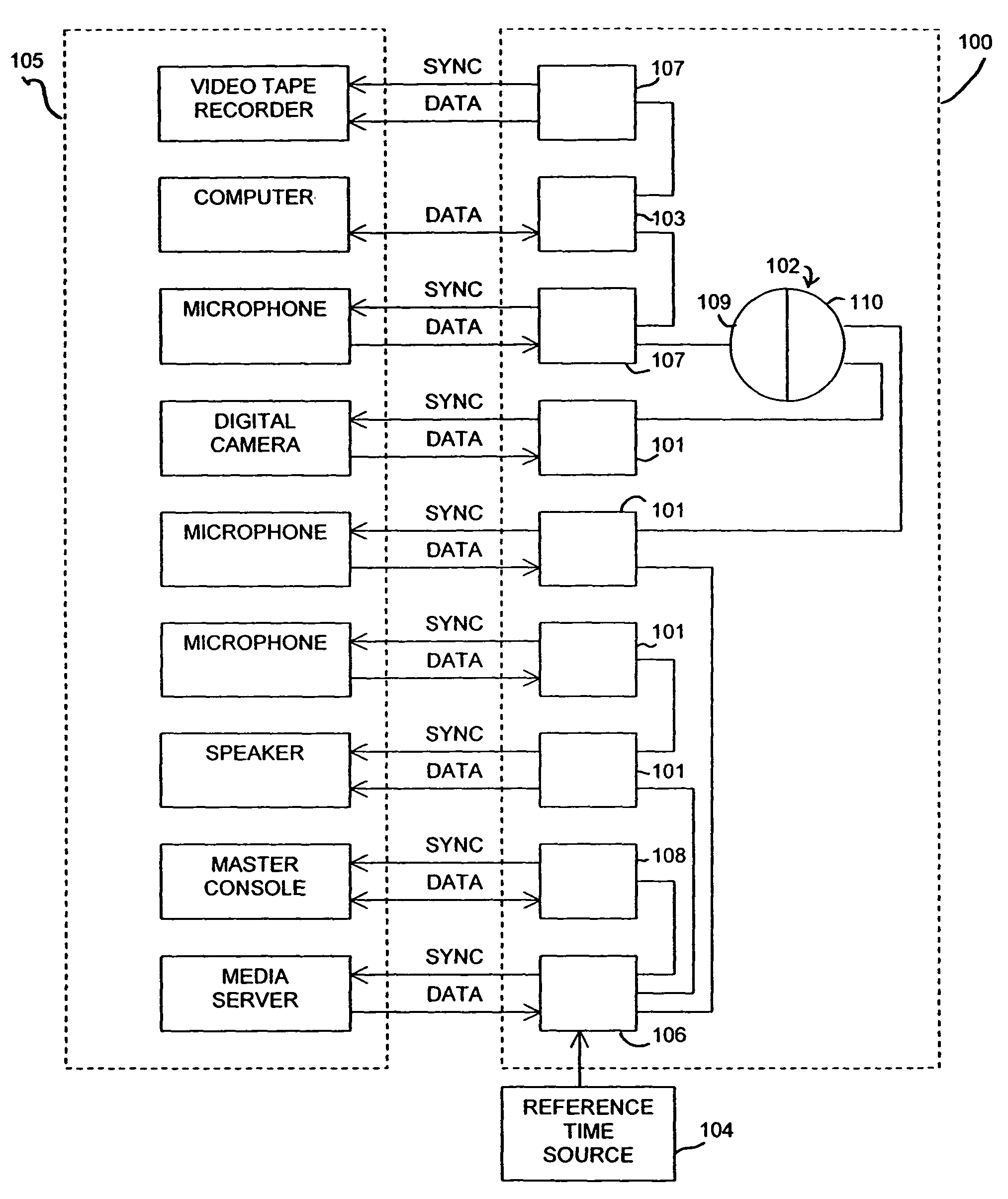

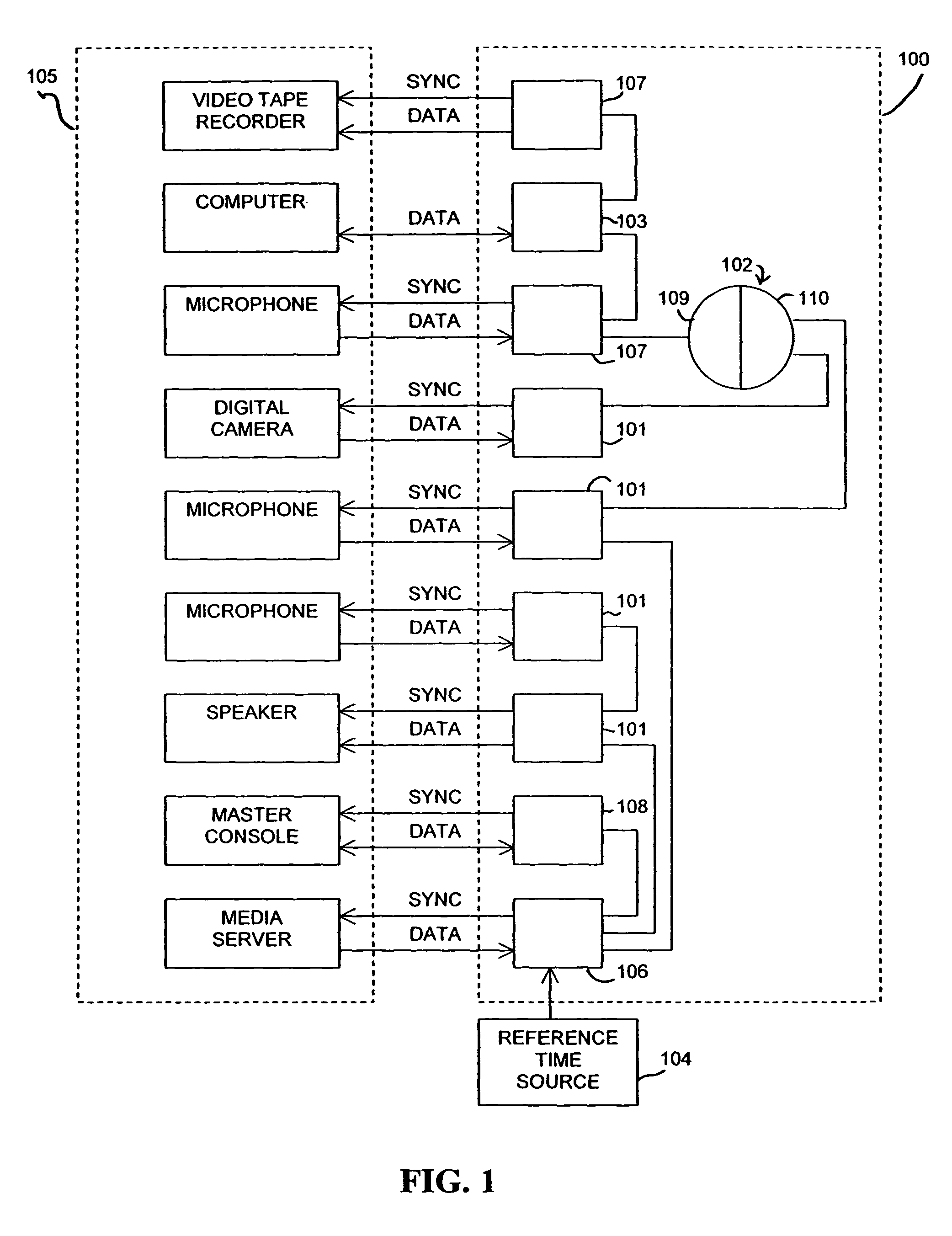

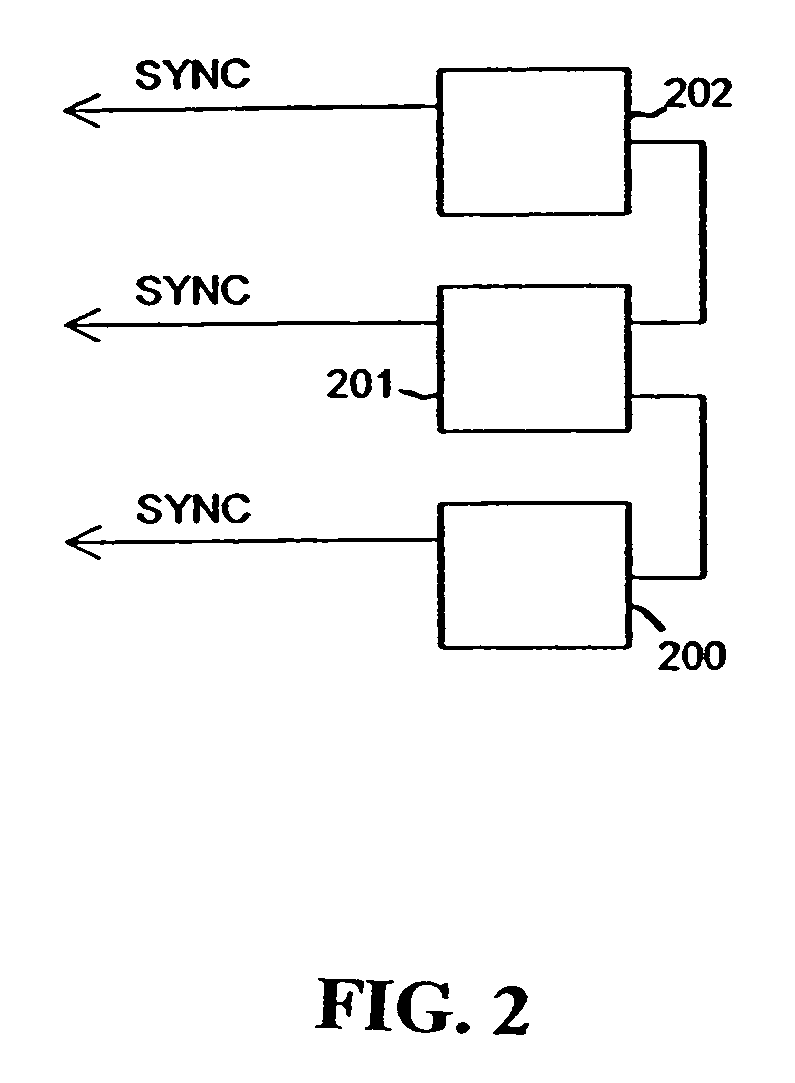

A reference time distribution system and method use a data transmission network having a plurality of nodes to distribute the House Sync signal. A network-wide time signal is generated using a reference time generator, and the network-wide time signal is then distributed over the network to the plurality of nodes. At each node, the network-wide time signal is converted to a local synchronization signal for use in performing synchronization of the timing of each node. Either network-inherent timing and / or additional time signaling is used to provide the nodes attached to this network with a network-wide notion of time. The time information is converted locally into synchronization signals or time information as required by a respective application. When data is transported over the network, delay compensation is performed to simultaneously output different data streams that have been synchronously input into the network, regardless of the data path.

Owner:POLARIS POWERLED TECH LLC

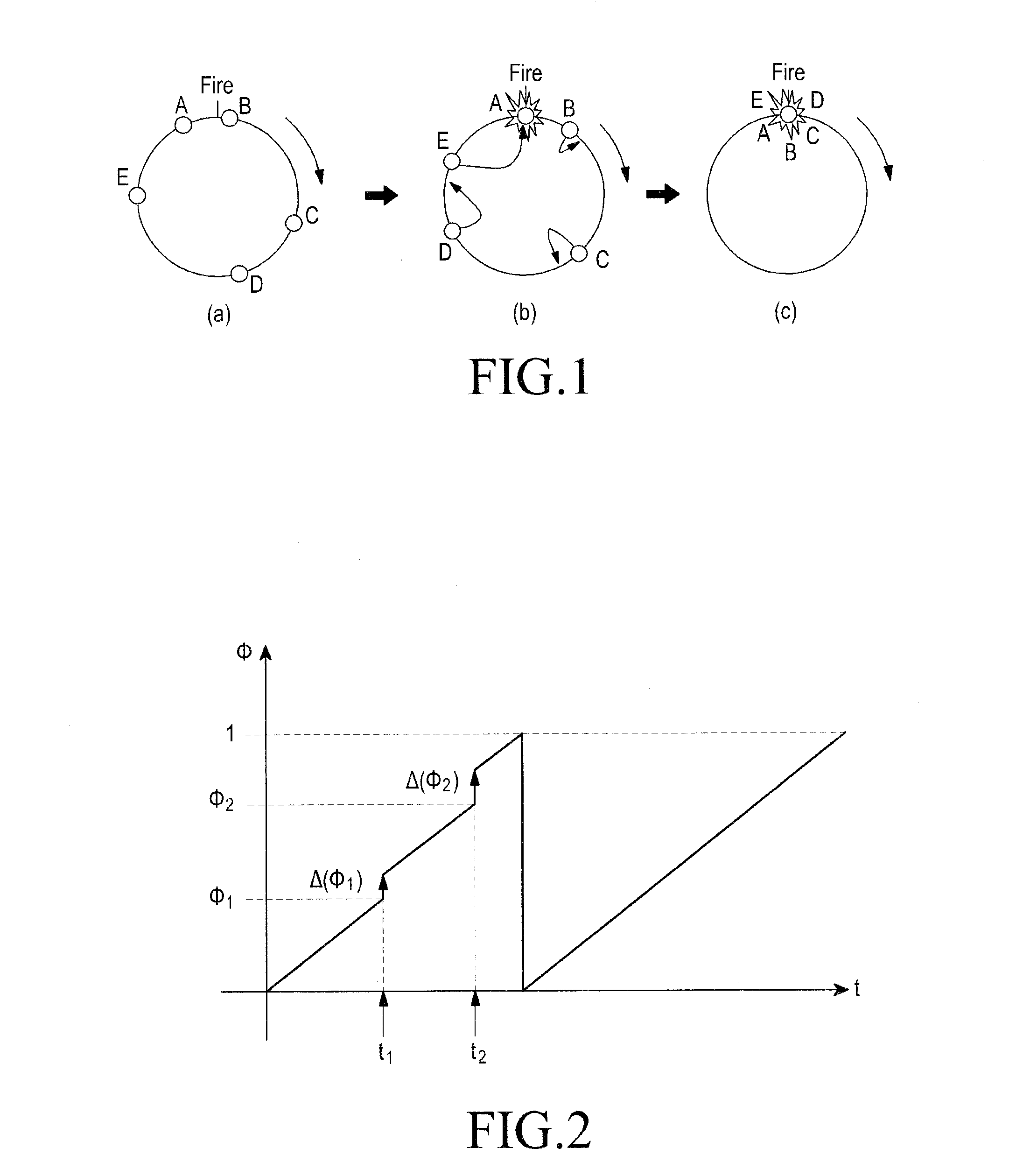

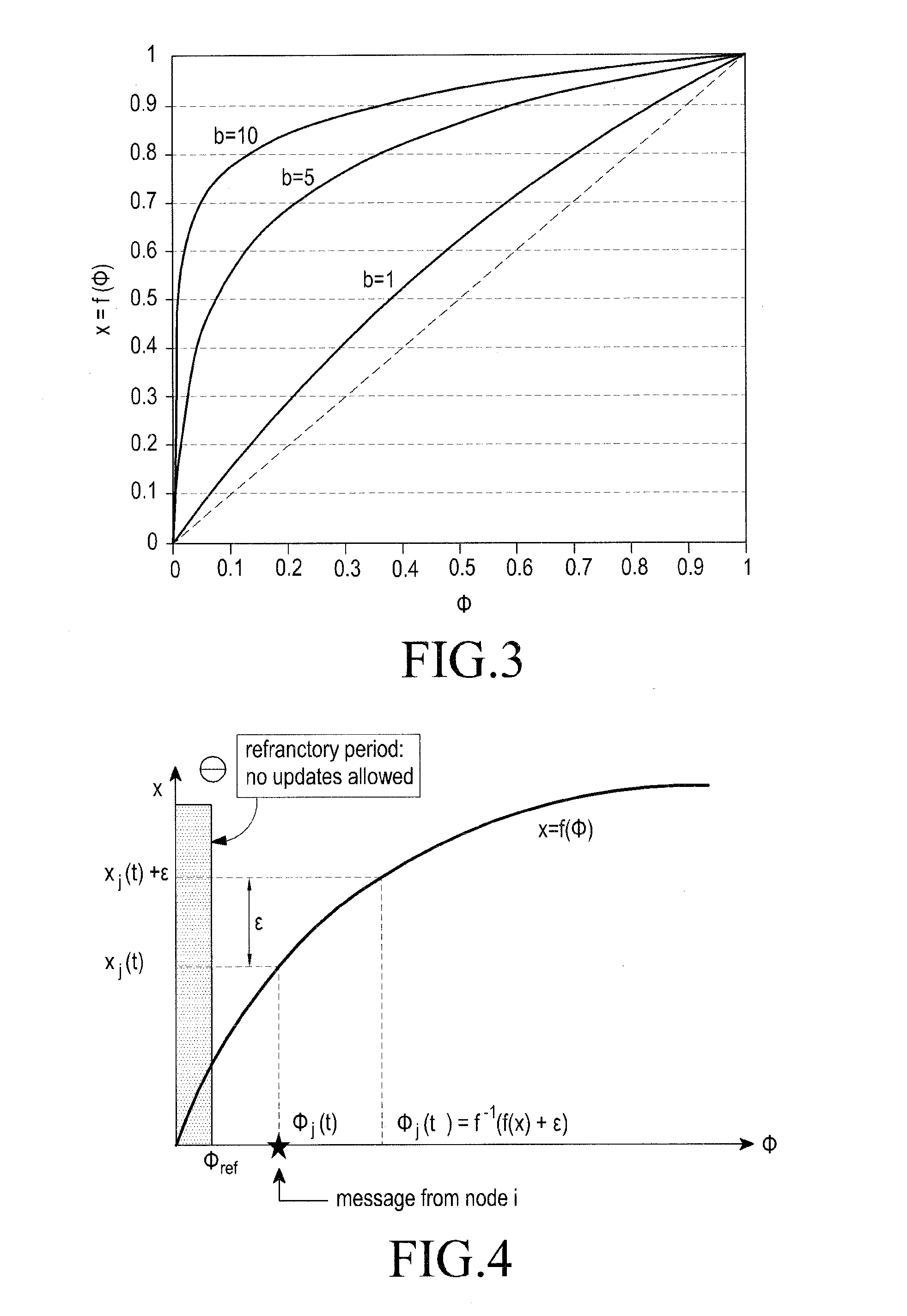

Method and apparatus for performing synchronization in device-to-device network

ActiveUS20130308625A1Perform synchronizationSynchronisation arrangementTime-division multiplexComputer sciencePhase adjustment

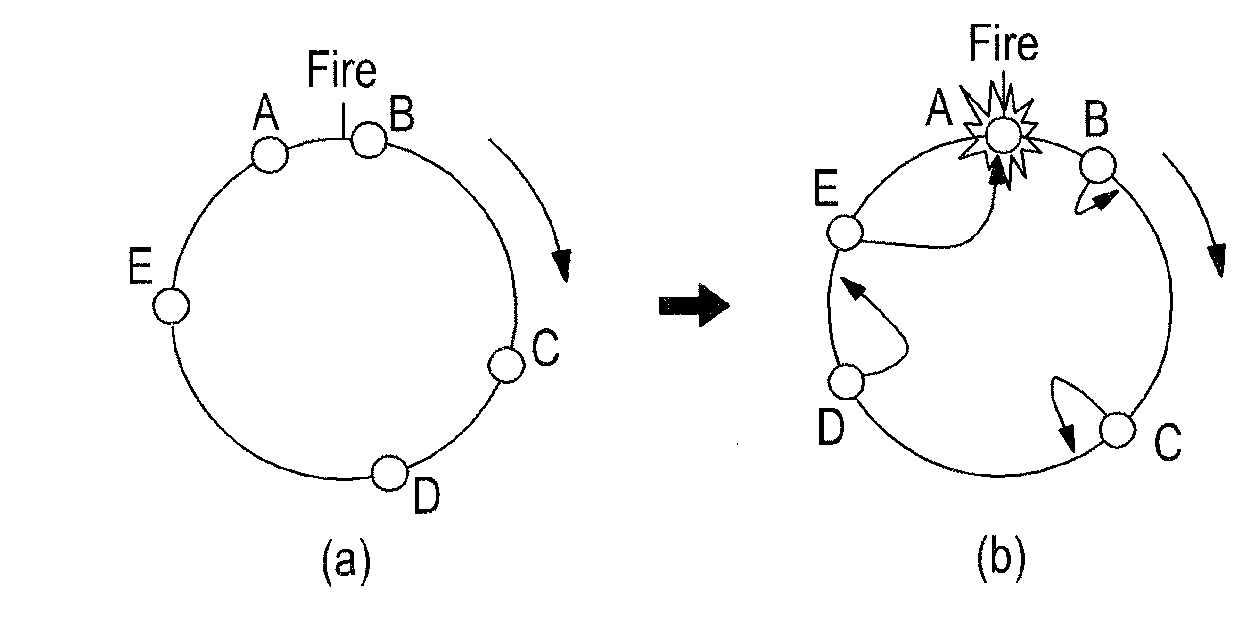

A method and an apparatus for performing synchronization by a first device in a Device-to-Device (D2D) network are provided. The method includes detecting a synchronization signal from at least one second device during one period, determining a phase adjustment value depending on a number of synchronization signals, which have been detected from the at least one second device during the one period, adjusting a phase value of a first device using the phase adjustment value, and transmitting a synchronization signal if the phase value of the first device reaches a predetermined specific value.

Owner:SAMSUNG ELECTRONICS CO LTD

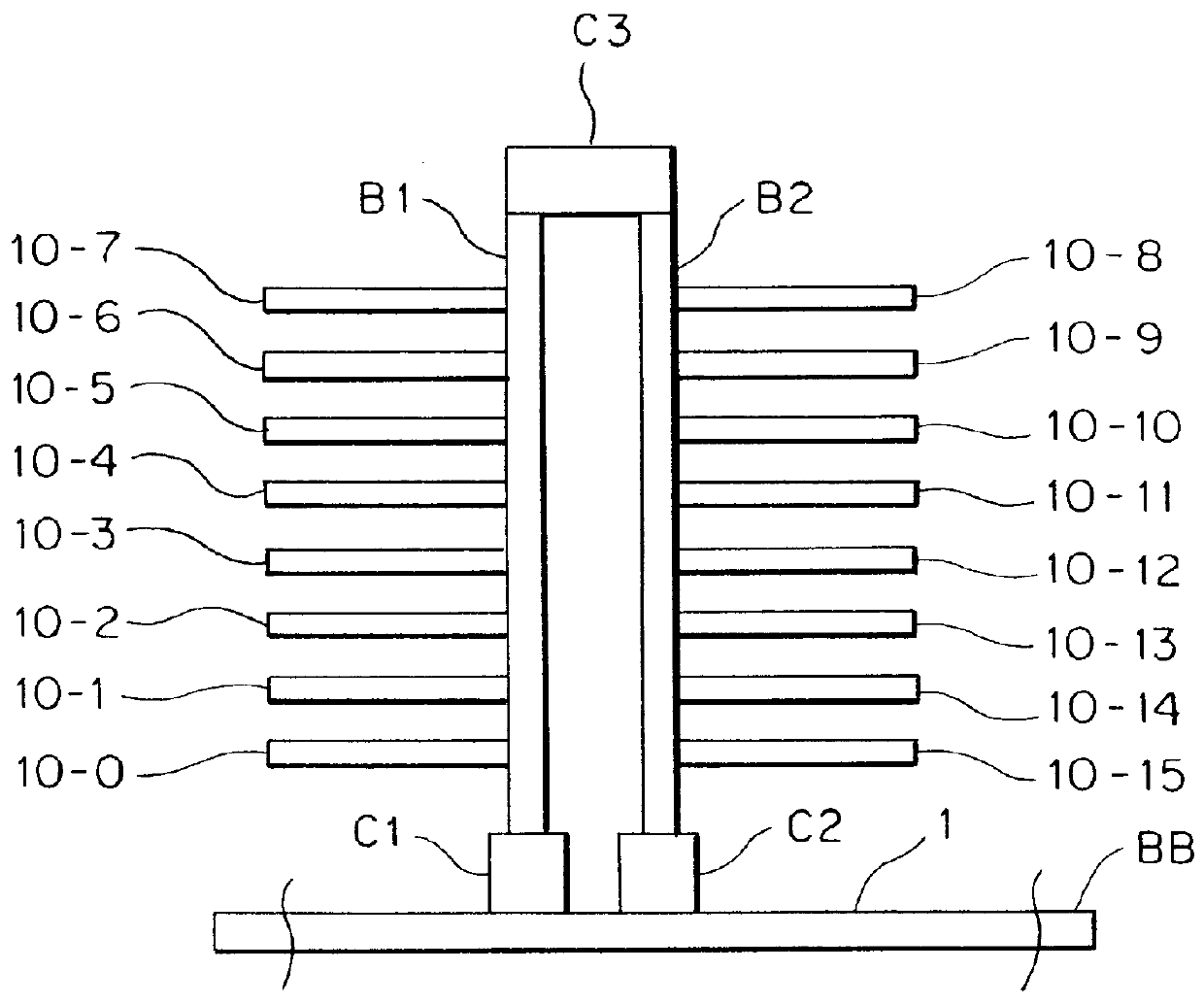

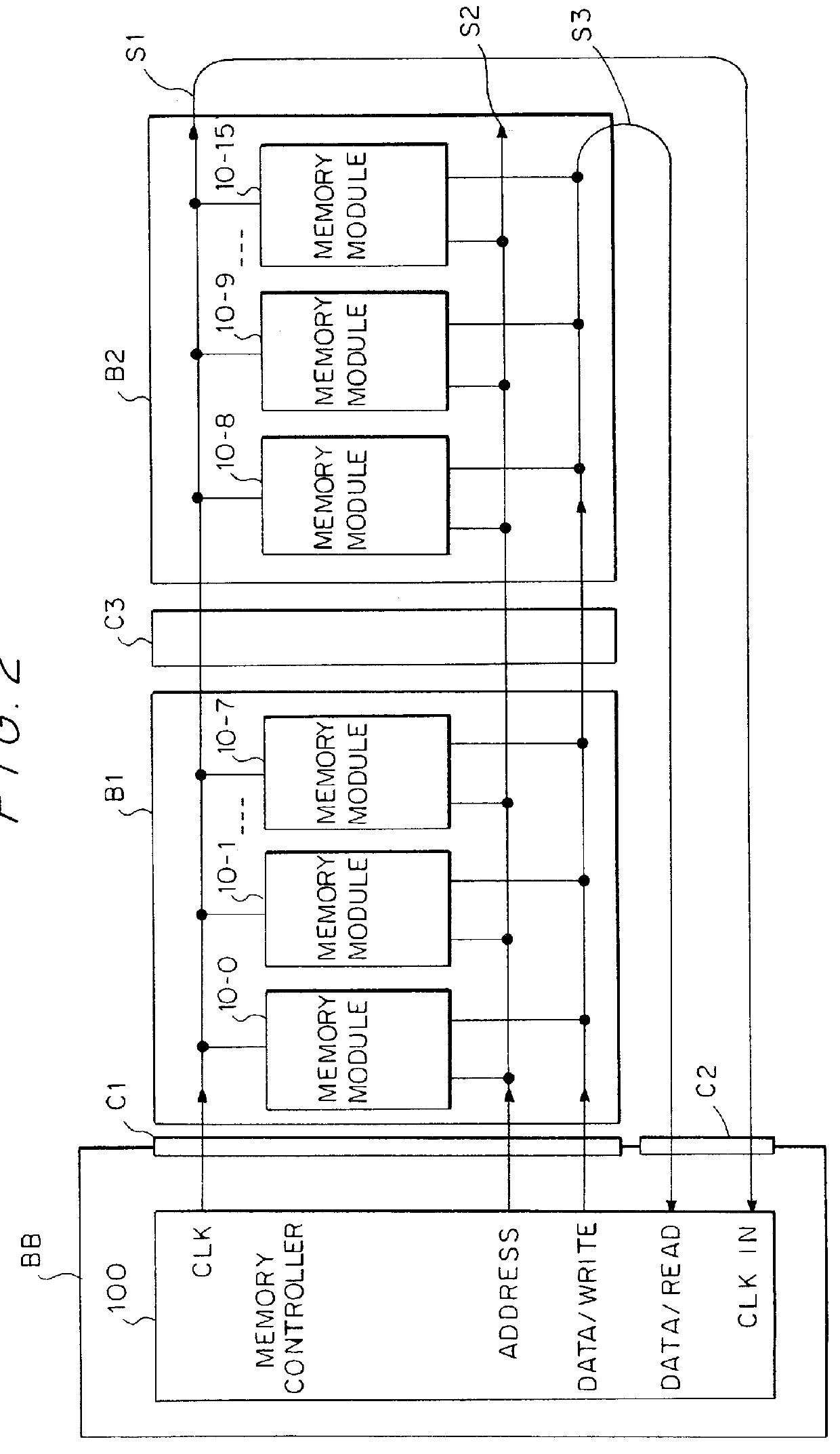

Source-clock-synchronized memory system and memory unit

InactiveUS6034878ALarge data storage capacity per memoryImprove installation densityMemory adressing/allocation/relocationDigital storageMemory bankComputer module

A source-clock-synchronized memory system having a large data storage capacity per memory bank and a high mounting density. The invention includes a memory unit having a first memory riser board B1 mounted on a base board through a first connector C1 and a second memory riser board B2 mounted on the base board BB through a second connector C2. The first memory riser board has a plurality of first memory modules mounted on the front surface thereof and the second memory riser board has a plurality of second memory modules mounted on the front surface thereof. The first and second memory riser boards are arranged in such a way that the back surface of the first memory riser board faces the back surface of the second memory riser board. The invention further includes a board linking connector for connecting signal lines on the first memory riser board to corresponding signal lines on the second memory riser board.

Owner:DELTA KOGYO CO LTD +1

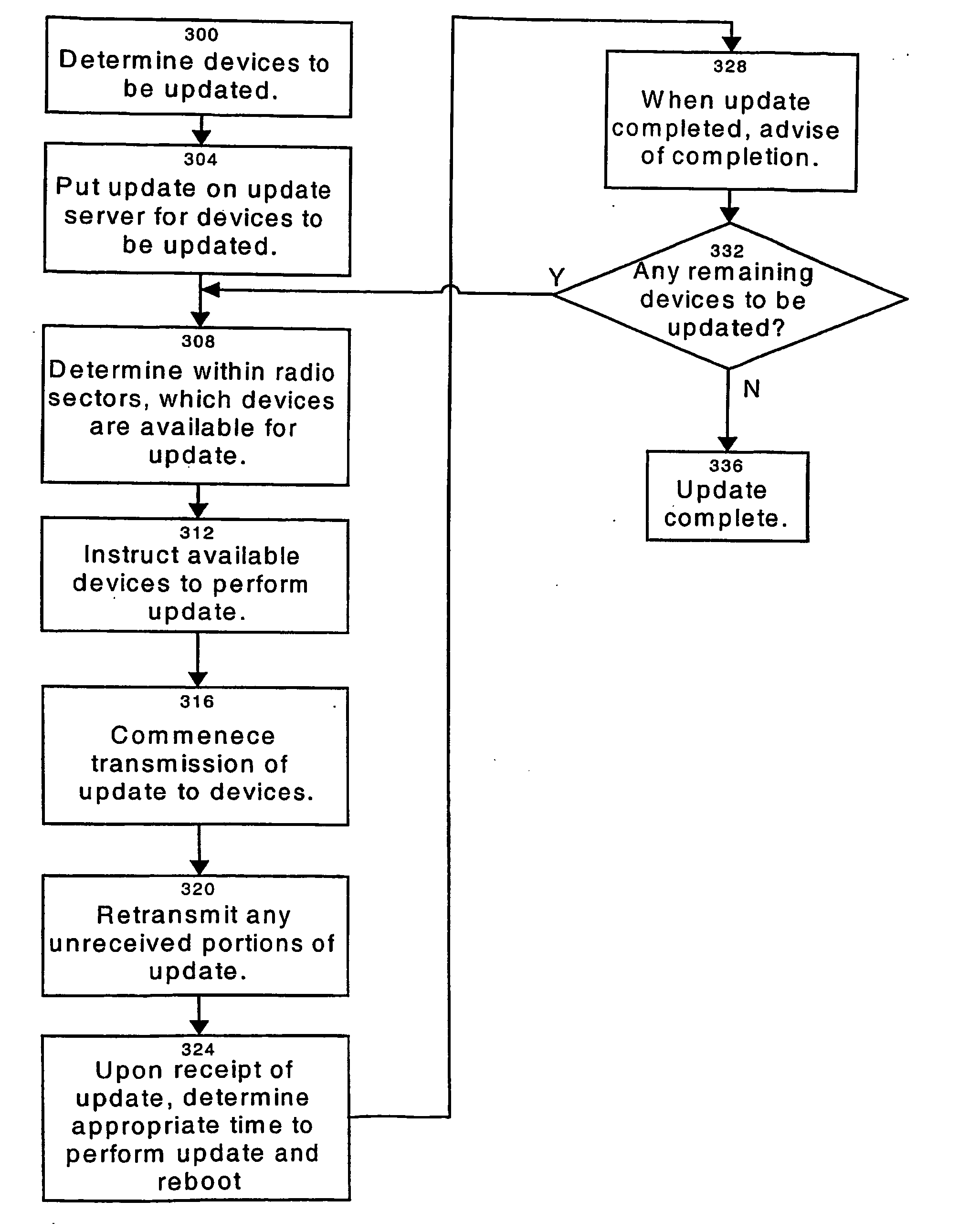

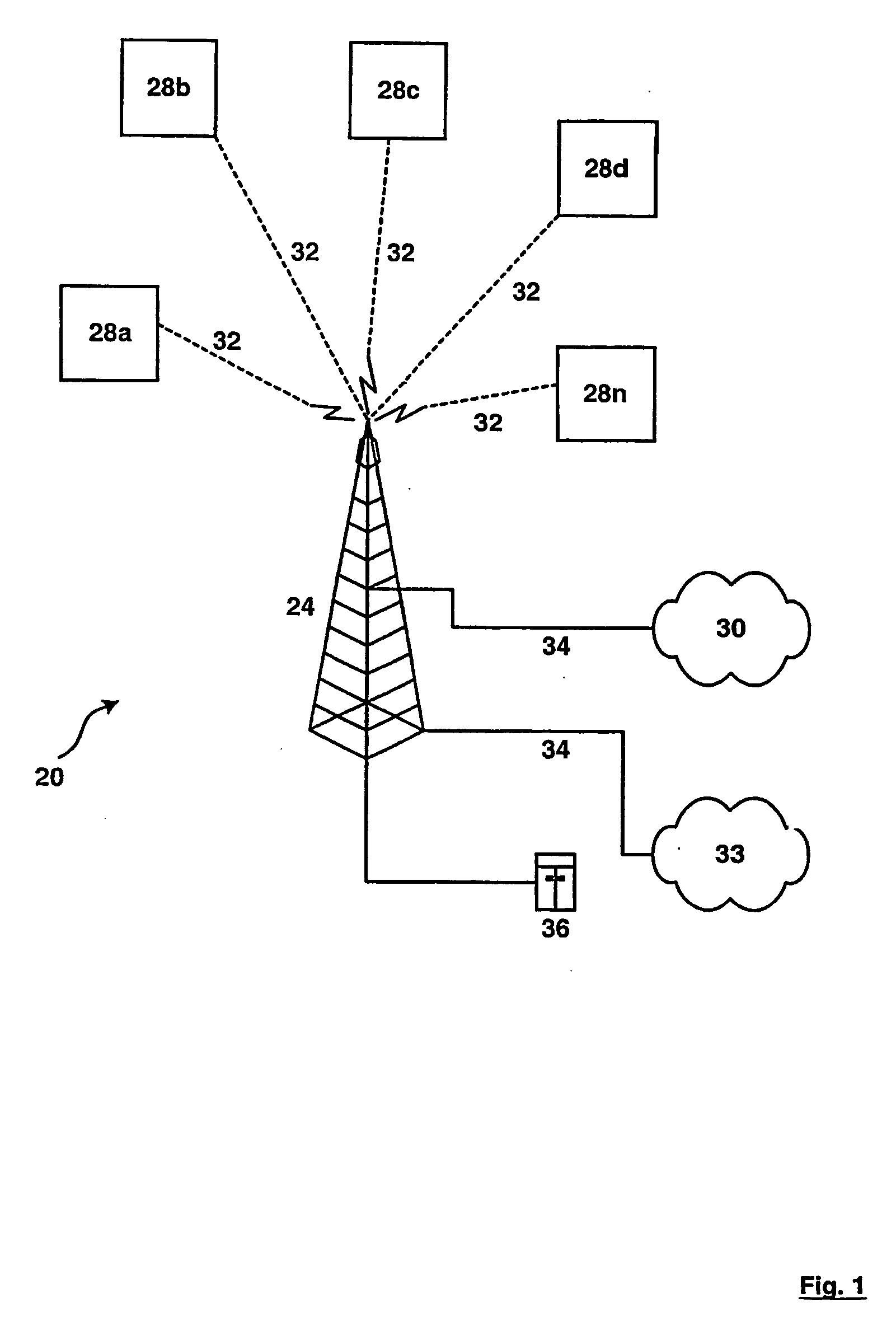

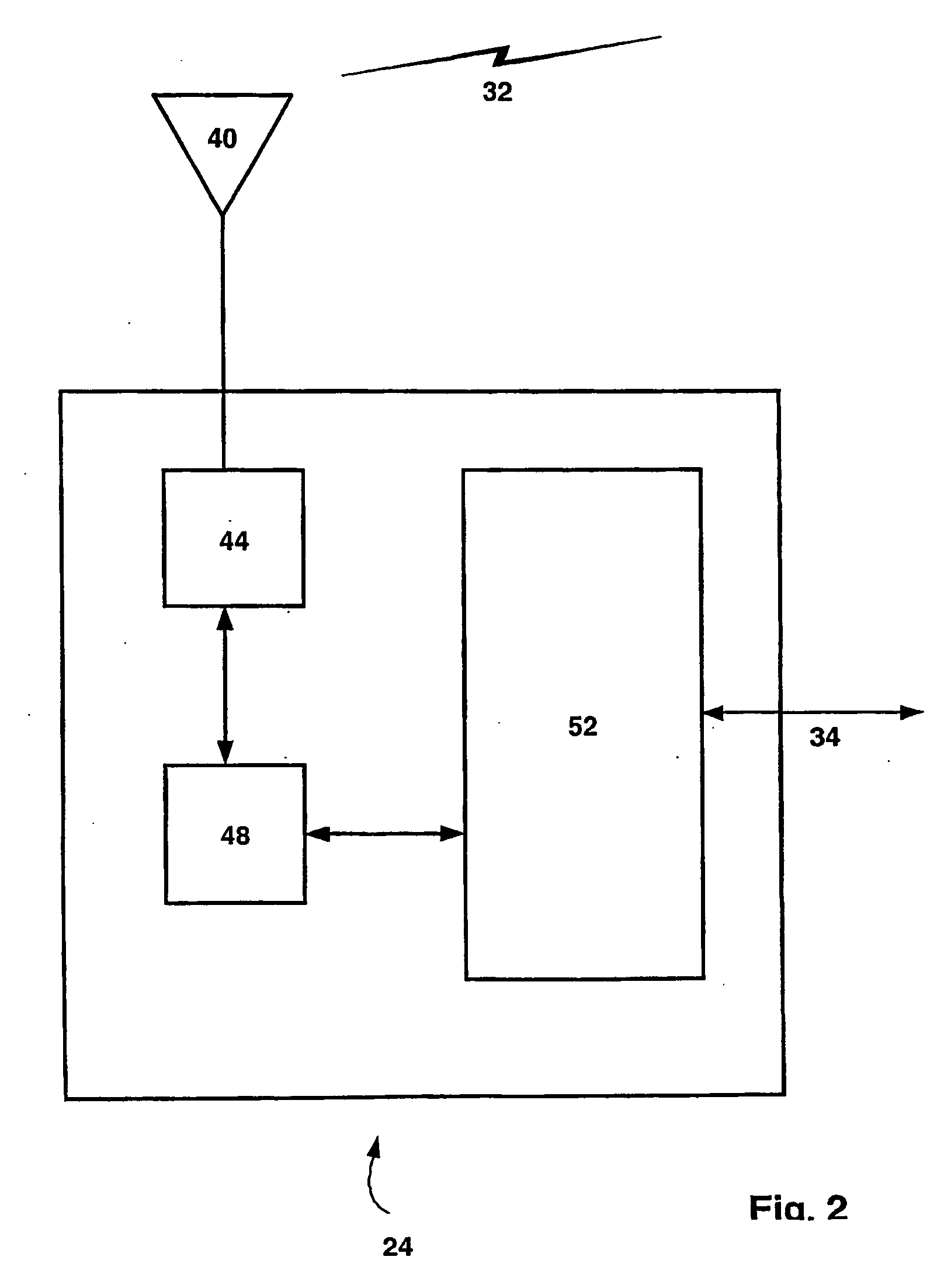

Software update method, apparatus and system

A system for remotely updating software on at least one electronic device connected to a network. The electronic devices have a non-volatile rewritable storage unit divided into at least two partitions, one of which will contain core firmware and the other of which will contain auxiliary software. When an update is received at the device, the updated core firmware is written to overwrite the partition in the rewritable storage unit that contained the auxiliary software. When this is completed and verified, the previous version of the core firmware stored in the storage unit is disabled from execution by the device. Next, the updated auxiliary software is written to overwrite the old version of the core firmware. When this write is complete, the device determines a suitable time for it to be rebooted to execute the updated software. In another embodiment, the present core firmware in the device is copied from the partition it is in to the other partition, overwriting the auxiliary software stored there. The new core firmware received to update the device is overwritten into the first partition, the old copied core firmware being present in case of an upgrade failure, and upon a successful update of the first partition, the auxiliary software is written to the second partition, overwriting the copied old core firmware. In this manner, the position of the core firmware and auxiliary software within the partitions is preserved during normal operation of the device.

Owner:WI LAN INC

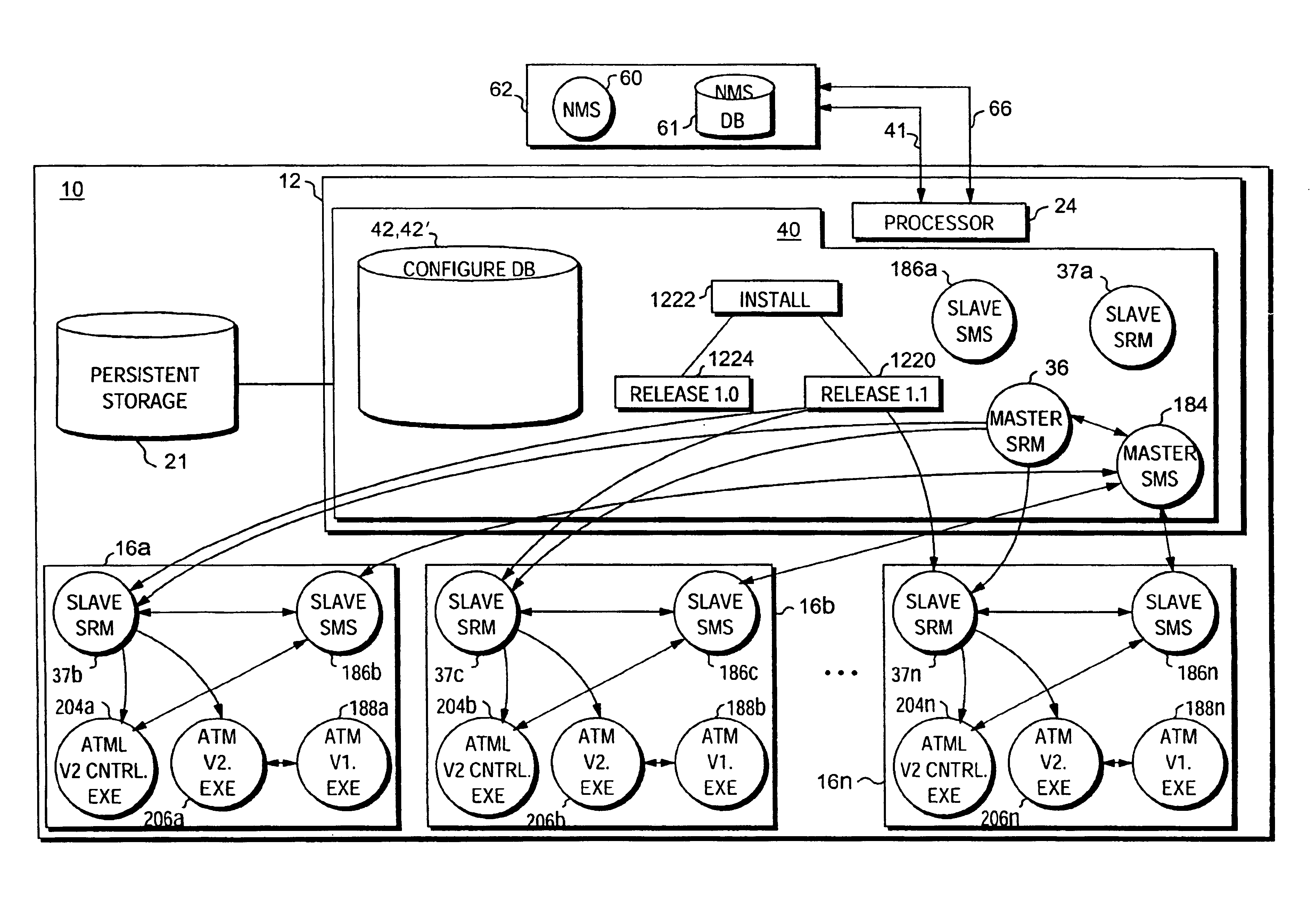

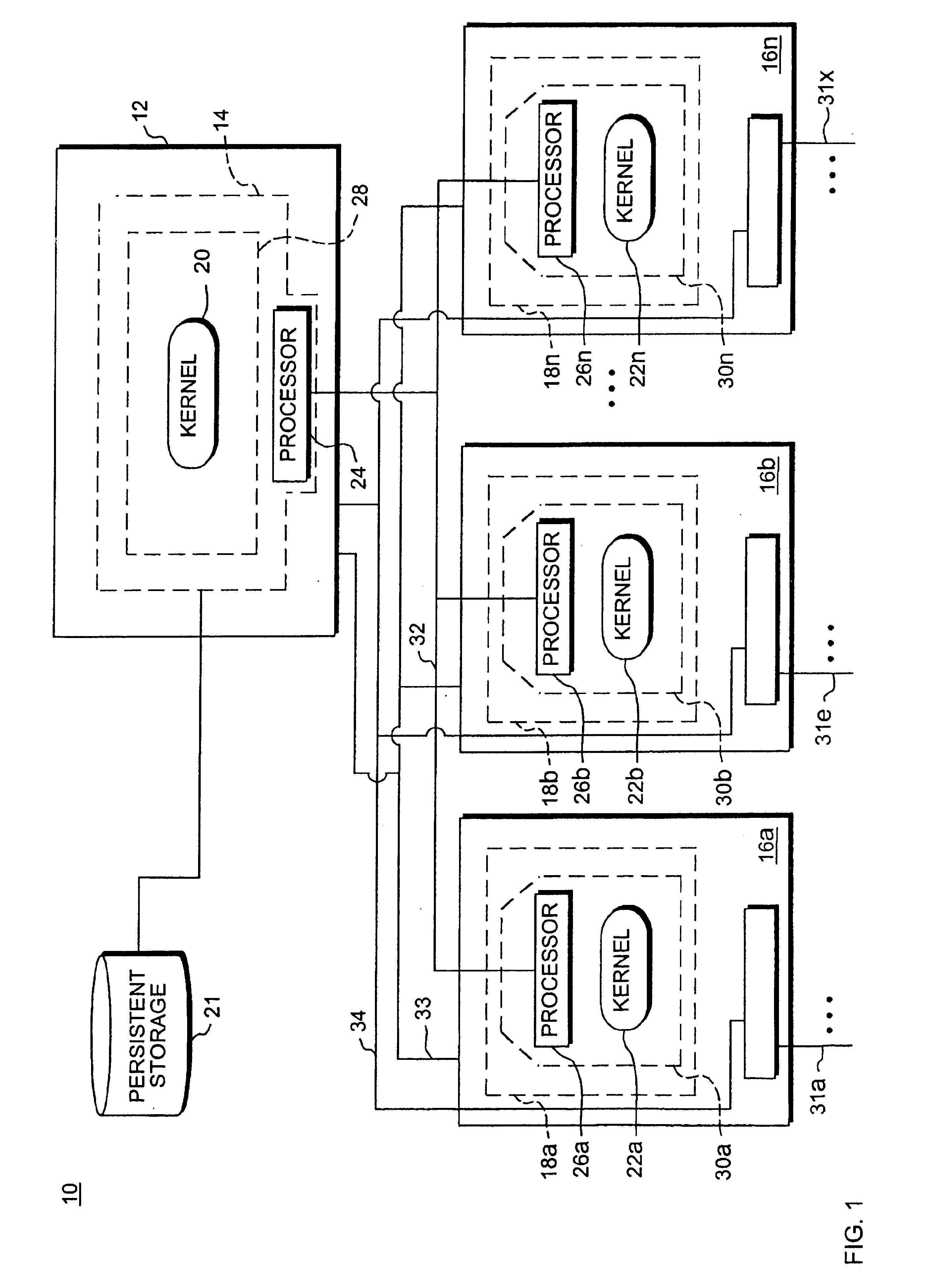

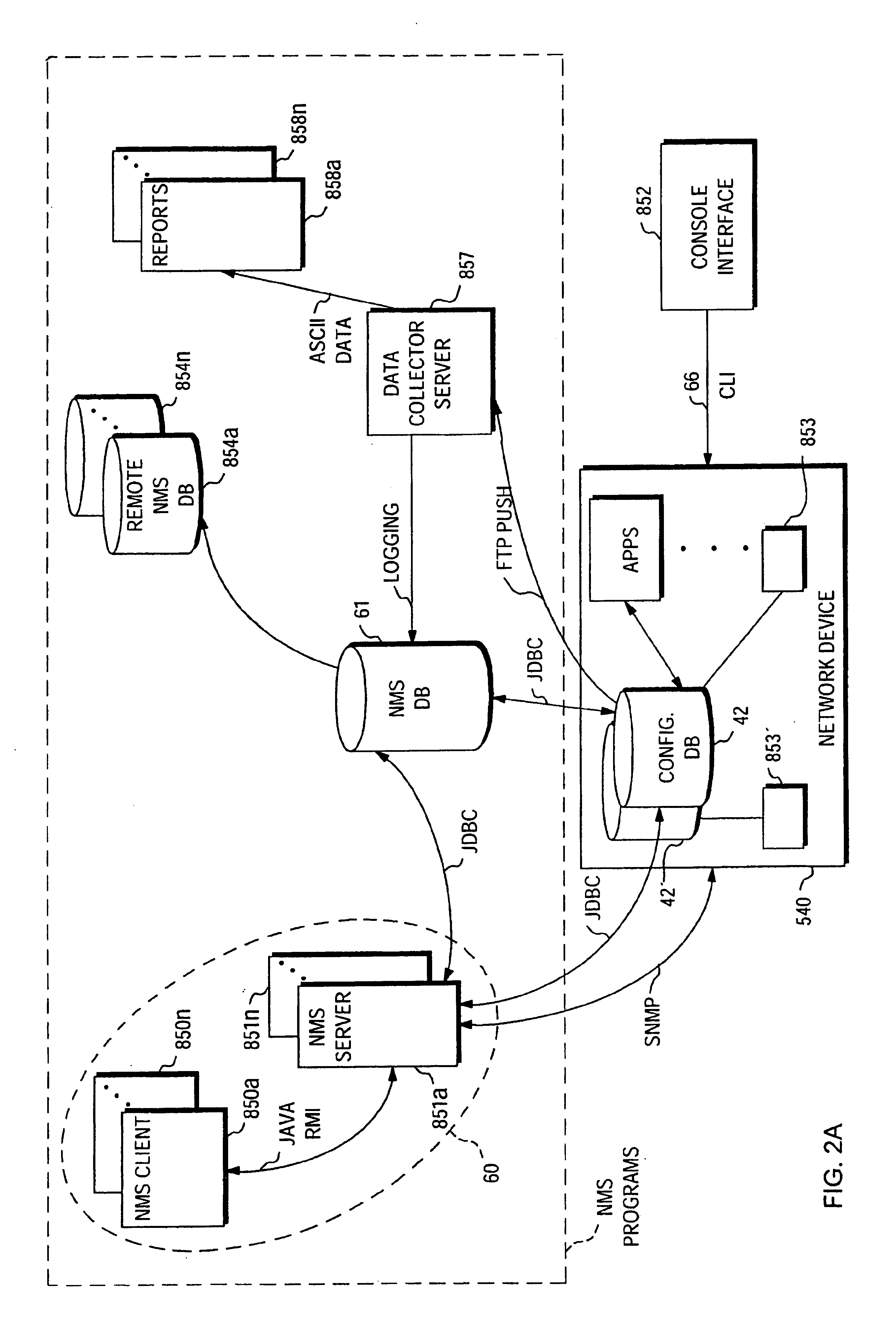

Signatures for facilitating hot upgrades of modular software components

InactiveUS6880086B2Facilitating hot upgradeAccurately determineSynchronisation information channelsMemory loss protectionComputer hardwareTelecommunications network

The present invention provides a method and apparatus for facilitating hot upgrades of software components within a telecommunications network device through the use of “signatures” generated by a signature generating program. After installation of a new software release within the network device, only those software components whose signatures do not match the signatures of corresponding and currently executing software components are upgraded. Signatures promote hot upgrades by identifying only those software components that need to be upgraded. Since signatures are automatically generated for each software component as part of putting together a new release a quick comparison of two signatures provides an accurate assurance that either the software component has changed or has not. Thus, signatures provide a quick, easy way to accurately determine the upgrade status of each software component.

Owner:CIENA

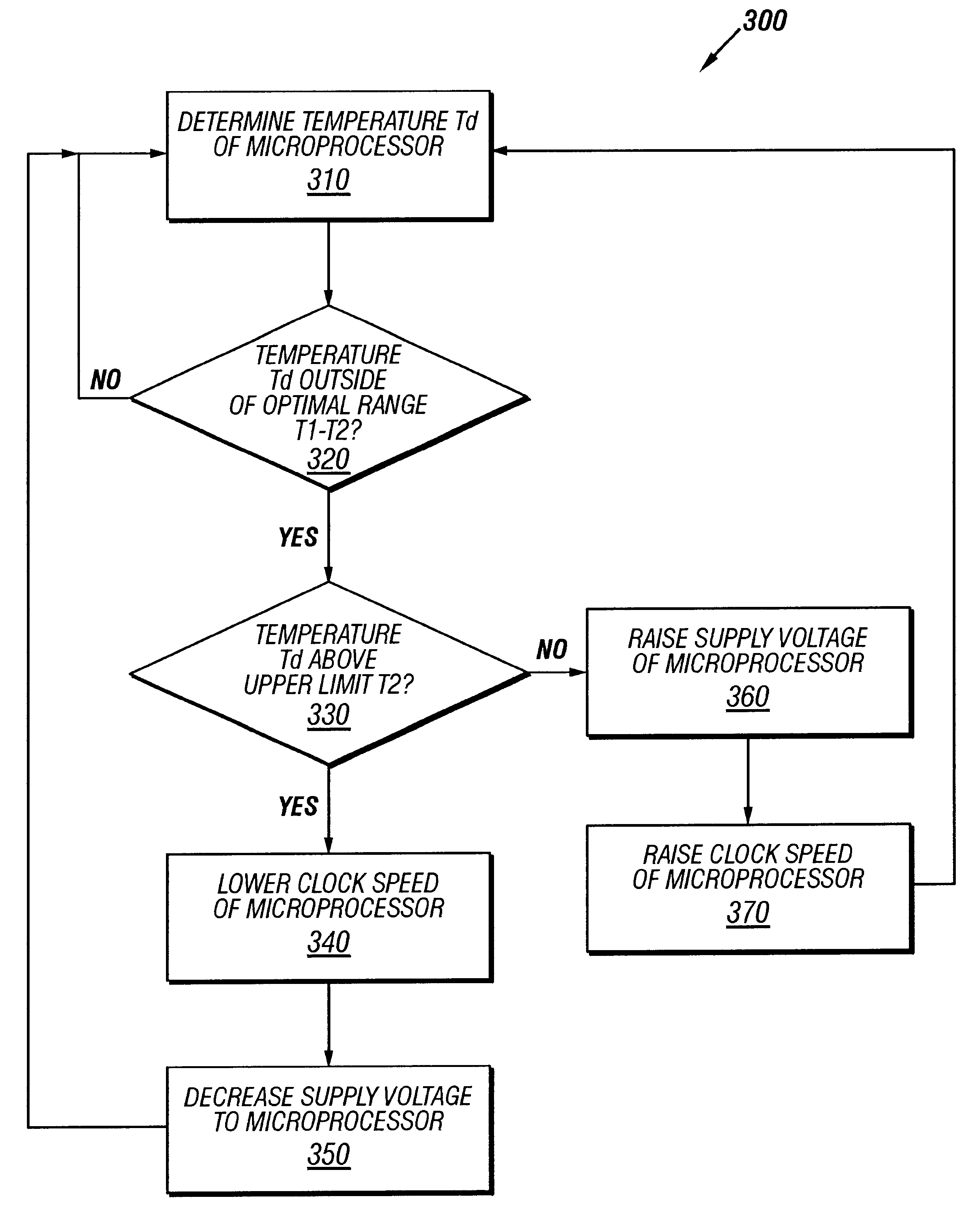

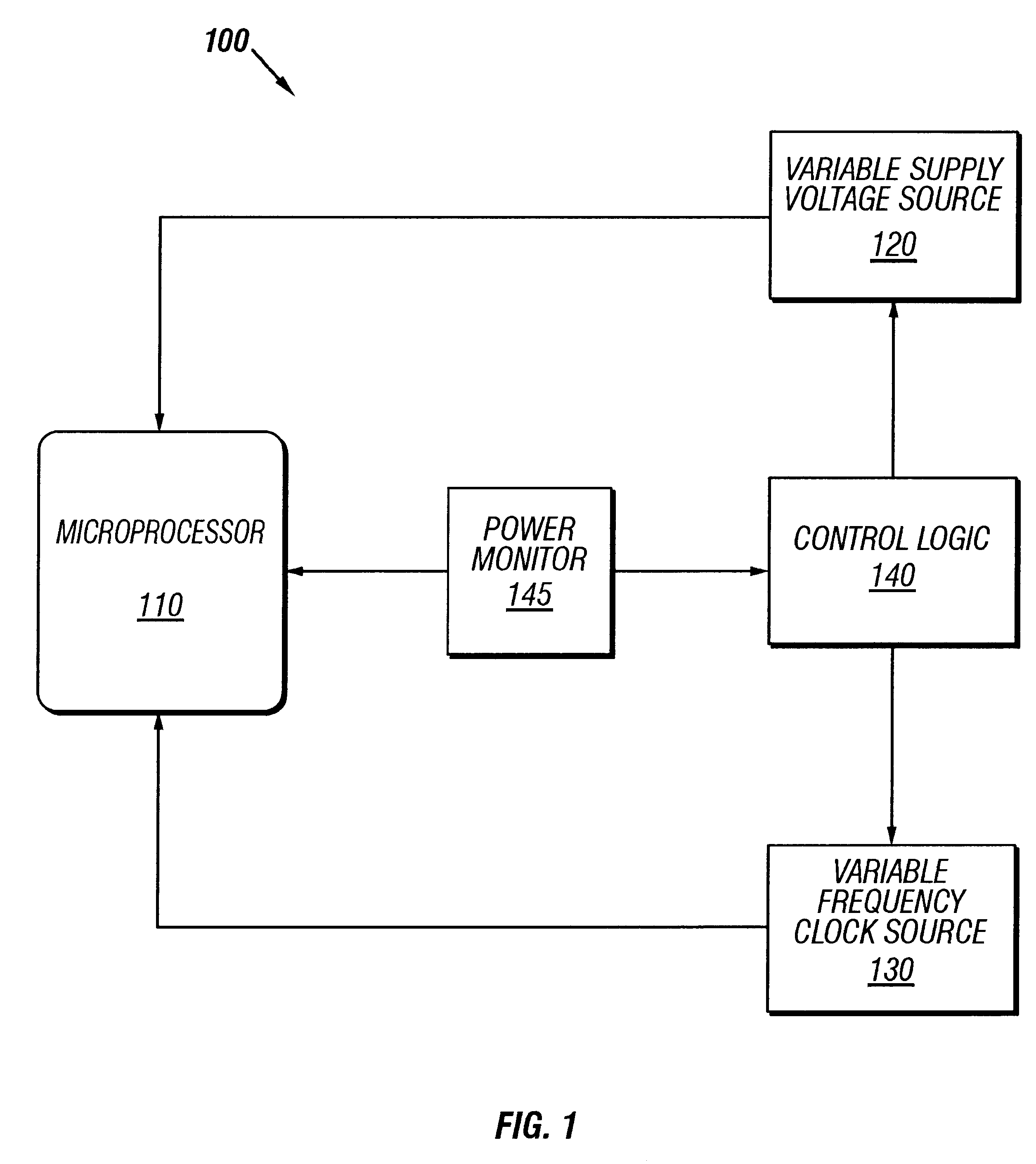

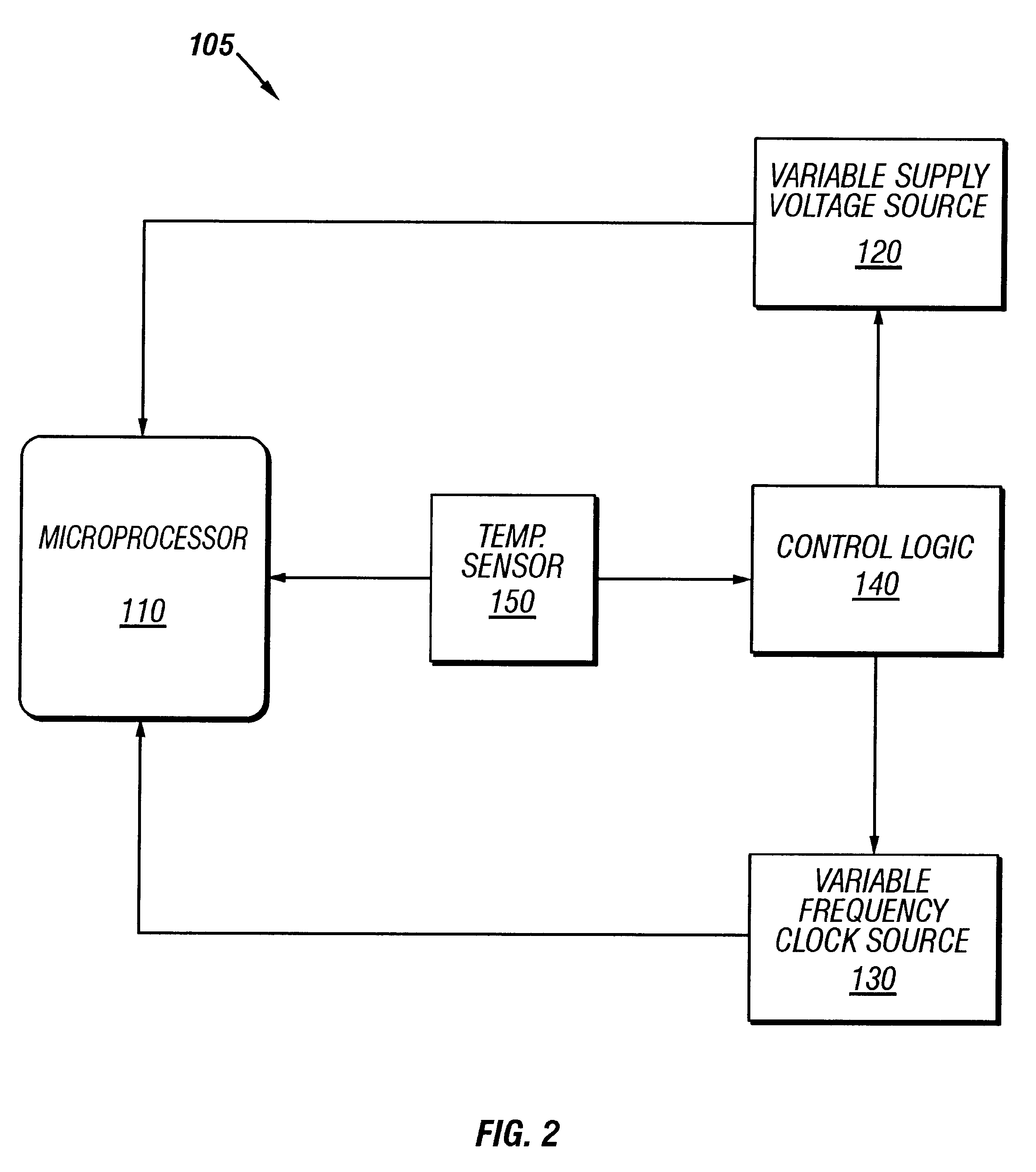

Method and apparatus for power throttling in a microprocessor using a closed loop feedback system

A method and apparatus for power throttling in a microprocessor. A voltage source supplies voltage to the microprocessor, and a clock source operates the microprocessor at a desired frequency. In one embodiment, a power monitor is configured to measure the short term power consumption of the microprocessor. In another embodiment, a temperature sensor measures the temperature of the microprocessor. Control logic is coupled to the voltage source and the clock source. The control logic receives an indication of the power consumption or temperature, as applicable, and compares it to a predetermined value. In response to the comparison, the control logic varies the supply voltage and the frequency.

Owner:INTEL CORP

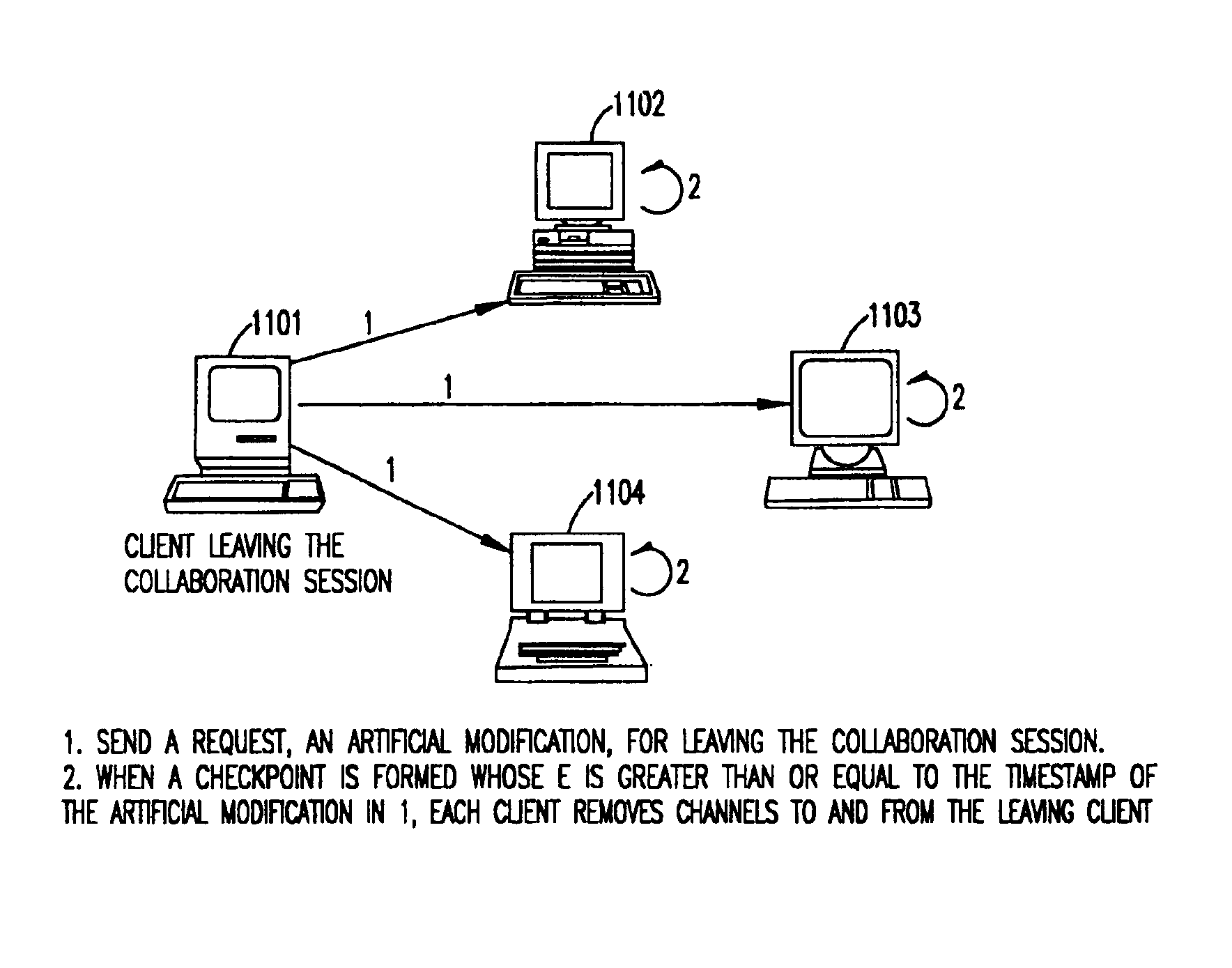

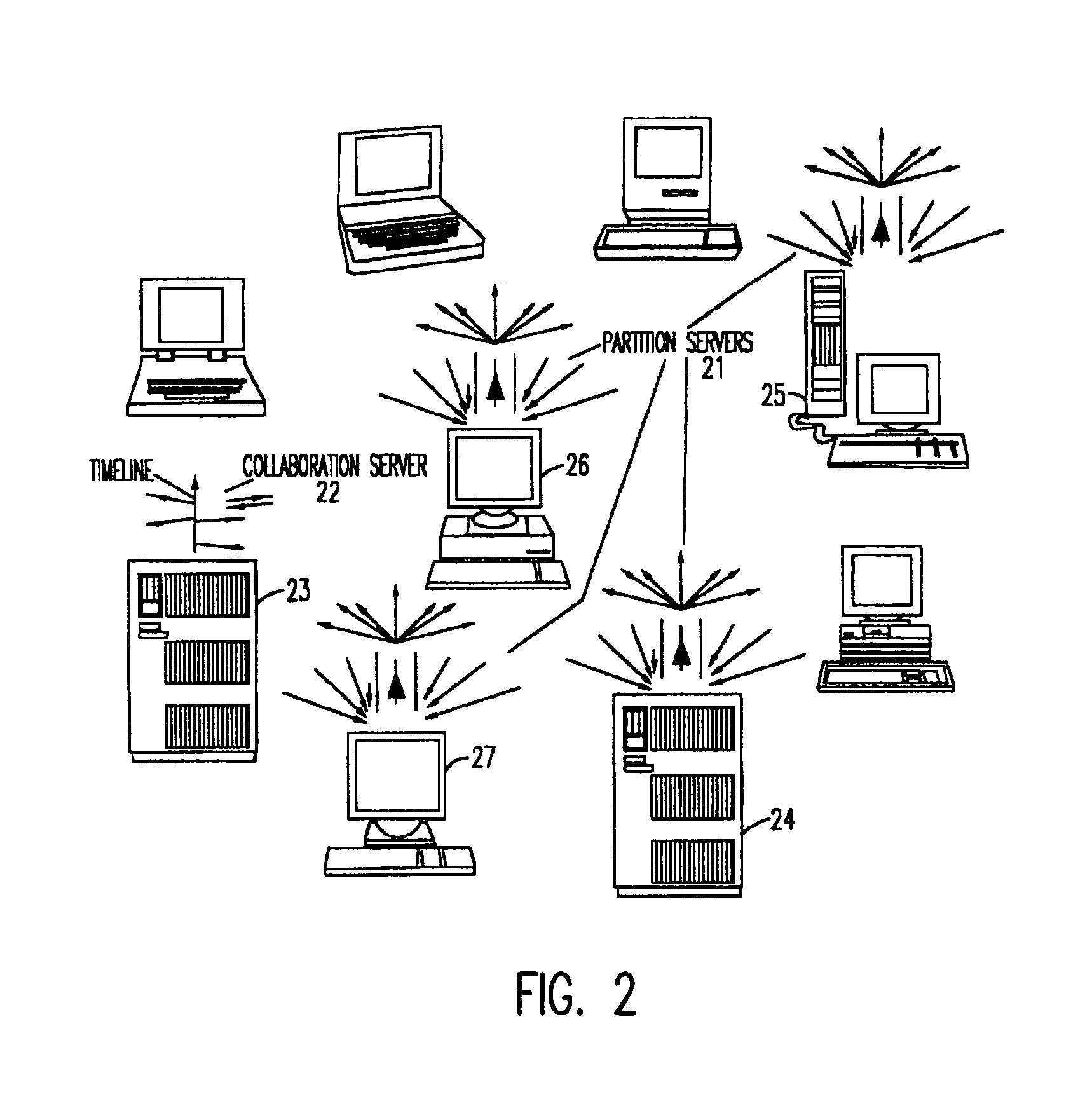

Synchronous collaboration based on peer-to-peer communication

InactiveUS6898642B2Eliminate useFully treatDigital data information retrievalMultiple digital computer combinationsTimestampWorkspace

A peer-to-peer protocol is based on the use of global timestamps and client priorities in serializing modifications to a shared workspace of real-time collaboration. The method caters to dynamic clients wherein a client can leave or join an ongoing collaboration session as long as there is always at least one client present / remaining in the collaboration session. The method can support multiple definitions of a modification, including partitioning-based definitions, wherein the method provides full support for locking of partitions, and a full treatment of inter-partition synchronization via a modification definition over multiple partitions. The method is capable of utilizing the many standard methods of creating a global, distributed, synchronized clock for the global timestamps utilized by it. The method is rollback-based for correcting tentative but incorrect serializations, and provides additional backup in terms of checkpoints for additional safety and for the support of lightweight, pervasive clients. The method includes many optimizations for efficiency, and includes a method of switching to and back from distributed server-based serialization for the periods when the network response is better suited to a distributed server than the peer-to-peer protocol.

Owner:INT BUSINESS MASCH CORP

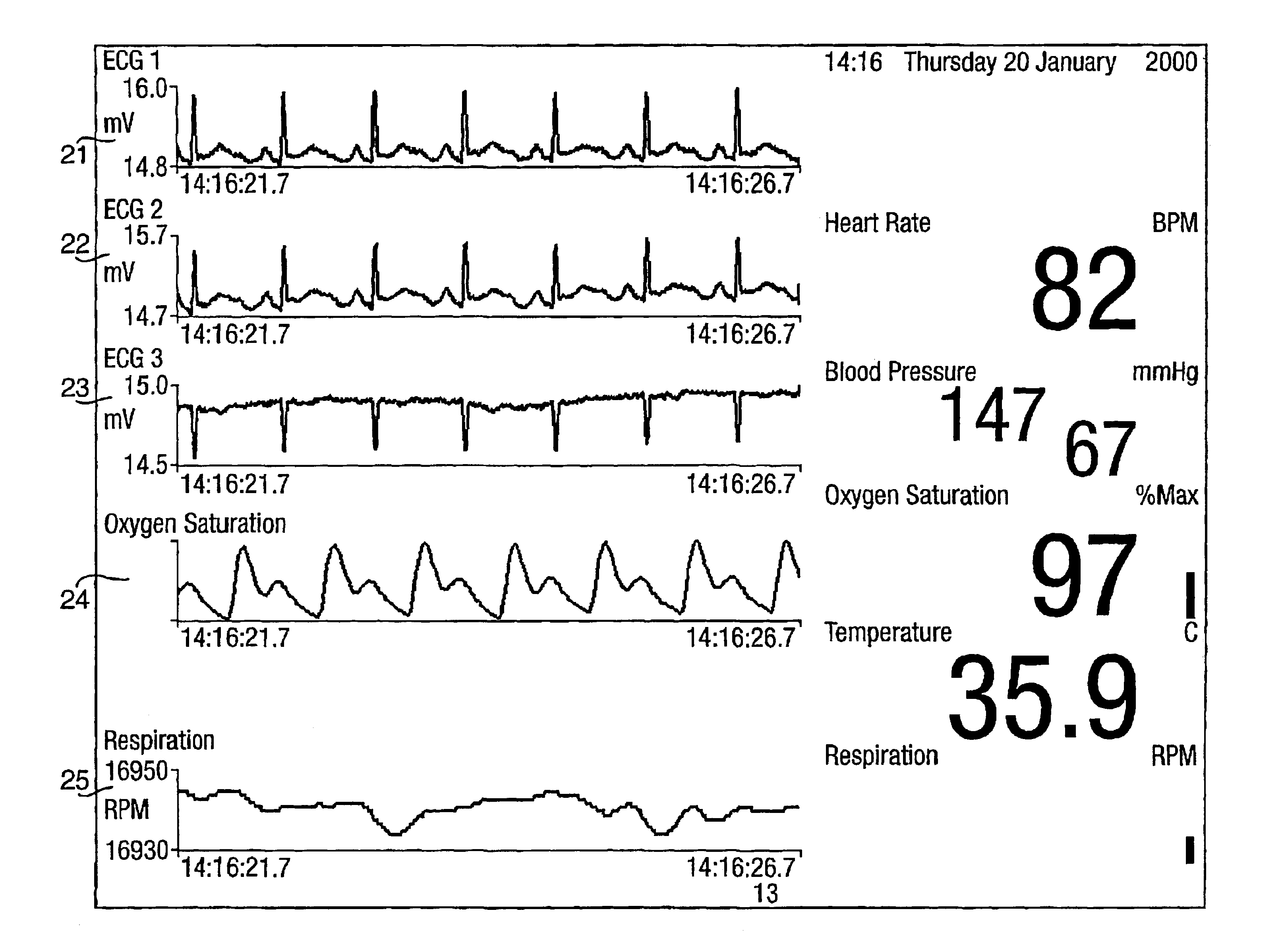

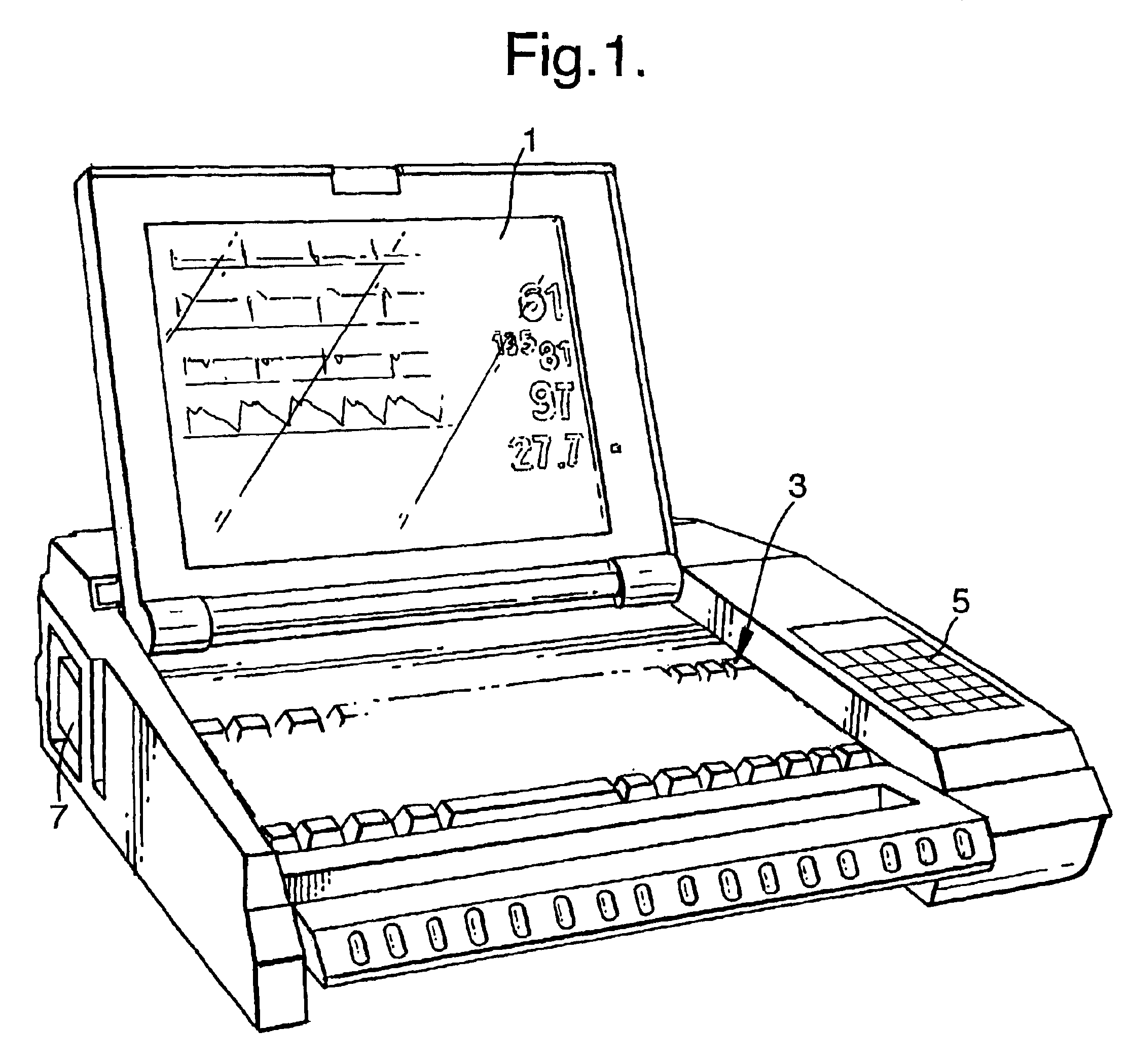

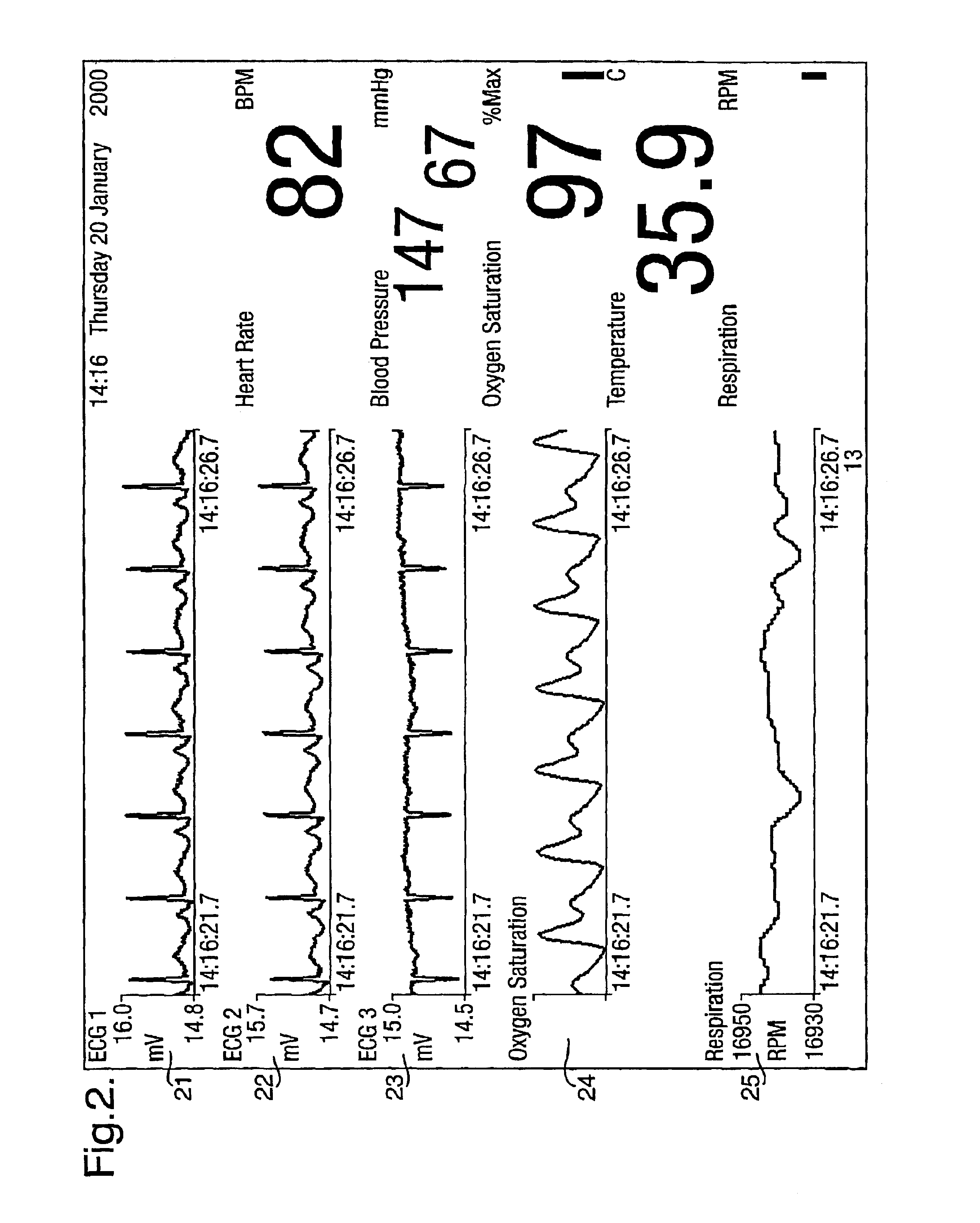

System and method for acquiring data

InactiveUS6839659B2Easy to carryImprove clarityAngiographyData acquisition and loggingData connectionHigh rate

A system for acquiring, and displaying, data such as physiological data, from a plurality of data connection devices, each of which monitor one or more different parameters and output data at different sampling frequencies based on their own system clocks. The system receives the data signals at different sampling frequencies and associates each sample of each signal with a time stamp derived from a single master clock. Low rate and high rate data are treated differently. Low rate data is associated with the current value of the master clock, where as high rate data is time stamped by giving the first sample a time stamp equal to the current value of the current master clock, subsequent samples being given an estimated time stamp based on the expected interval between samples derived from the sampling frequency of the data collection device, and the timescale given to the first example. The estimated time stamp may be periodically corrected, and the estimation calculation can be improved by correcting the value used for the interval between samples. The different signals can be displayed together on a display aligned with respect to a time axis. The system can display, the data in two different timescales, one showing a few seconds of data and one showing a few hours of data. The data traces are scrolled across the time axis, new data being added to one end of the trace.

Owner:ISIS INNOVATION LTD

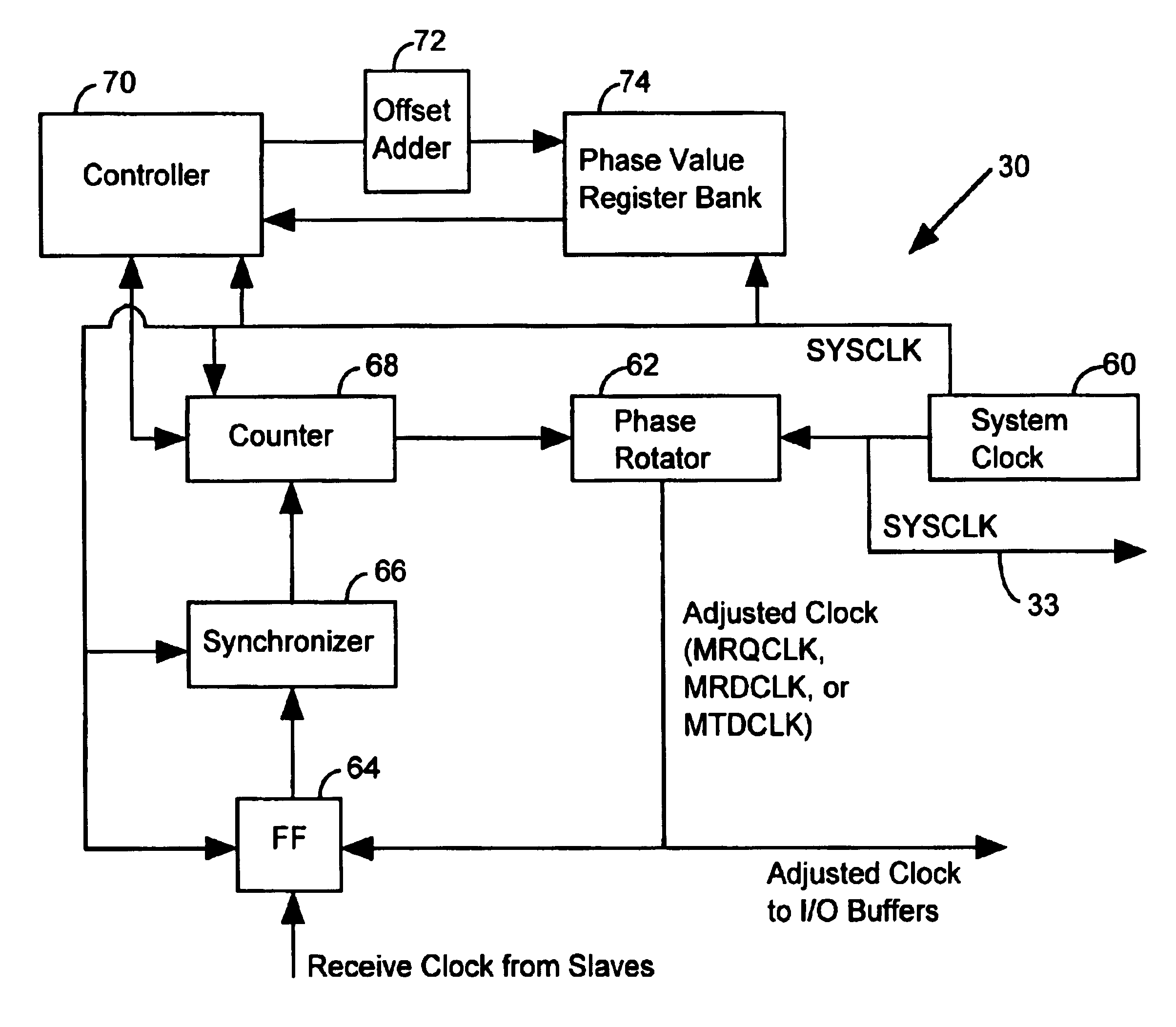

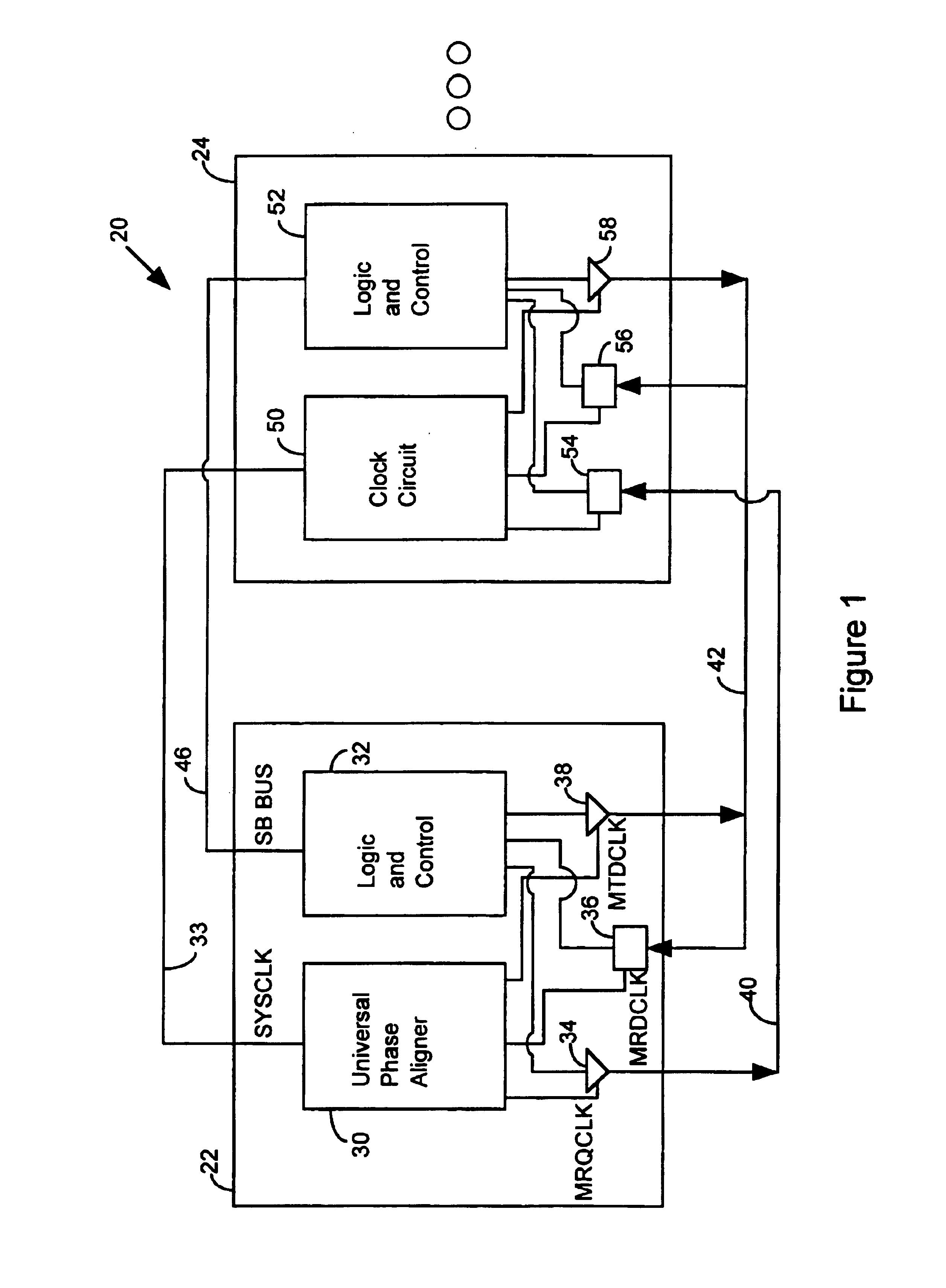

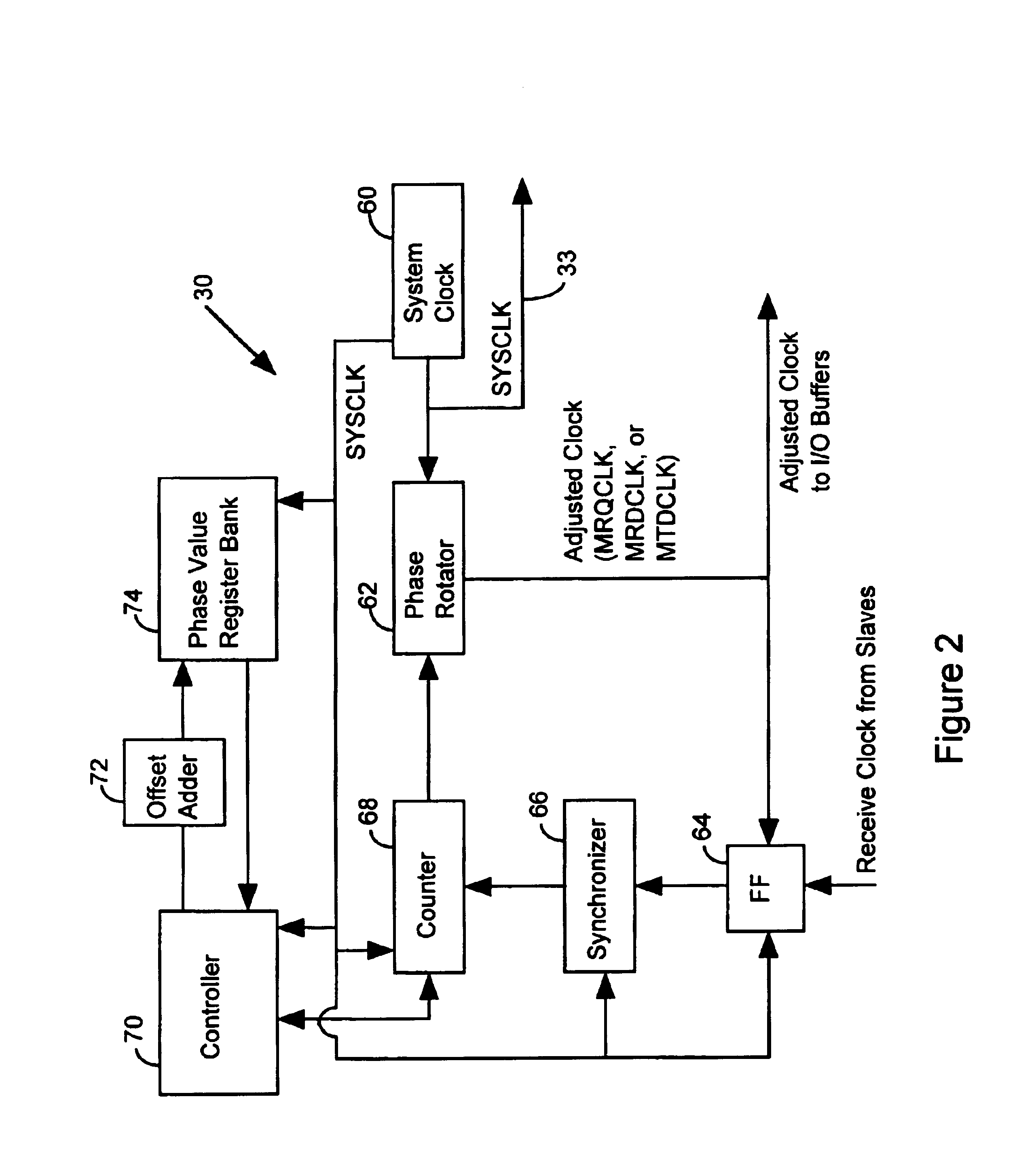

Apparatus and method for controlling a master/slave system via master device synchronization

InactiveUS6839393B1Reduce power consumptionImprove throughputEnergy efficient ICTPulse automatic controlComputer hardwareData shipping

A method of operating a master / slave system includes the step of identifying a master receive data phase value to coordinate the transfer of data from a slave device without phase alignment circuitry to a master device with a universal phase aligner. Data is transferred from the slave device to the master device in accordance with the master receive data phase value. The master device characterizes a master transmit data phase value to coordinate the transfer of data from the master device to the slave device. Subsequently, the master device routes data to the slave device in accordance with the master transmit data phase value.

Owner:RAMBUS INC

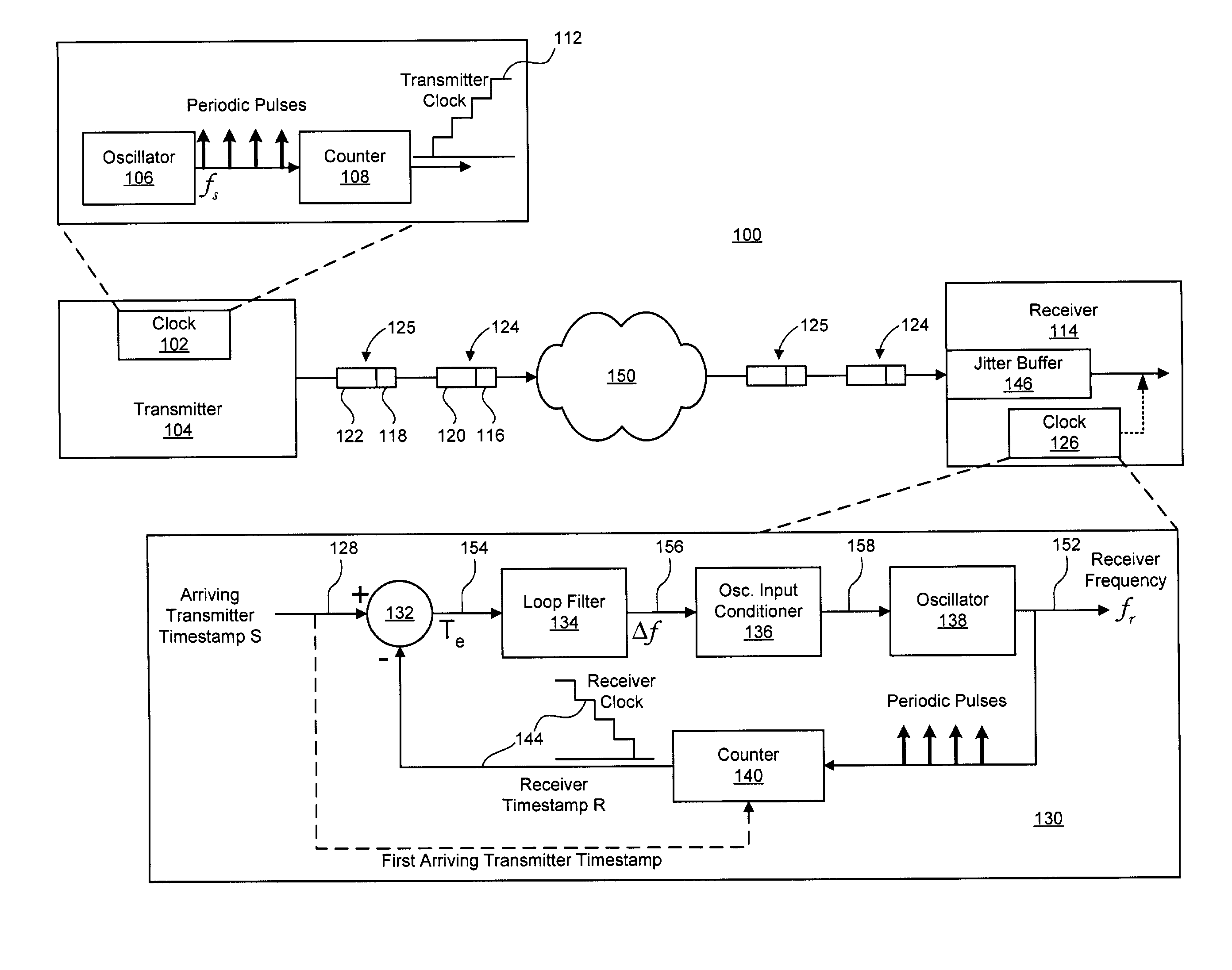

Clock recovery using a double-exponential smoothing process

A system and method for synchronizing a local clock to a reference clock using a linear model of the clock error between the local clock and the reference clock is disclosed. In one embodiment, a double-exponential smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the double-exponential smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:RPX CLEARINGHOUSE

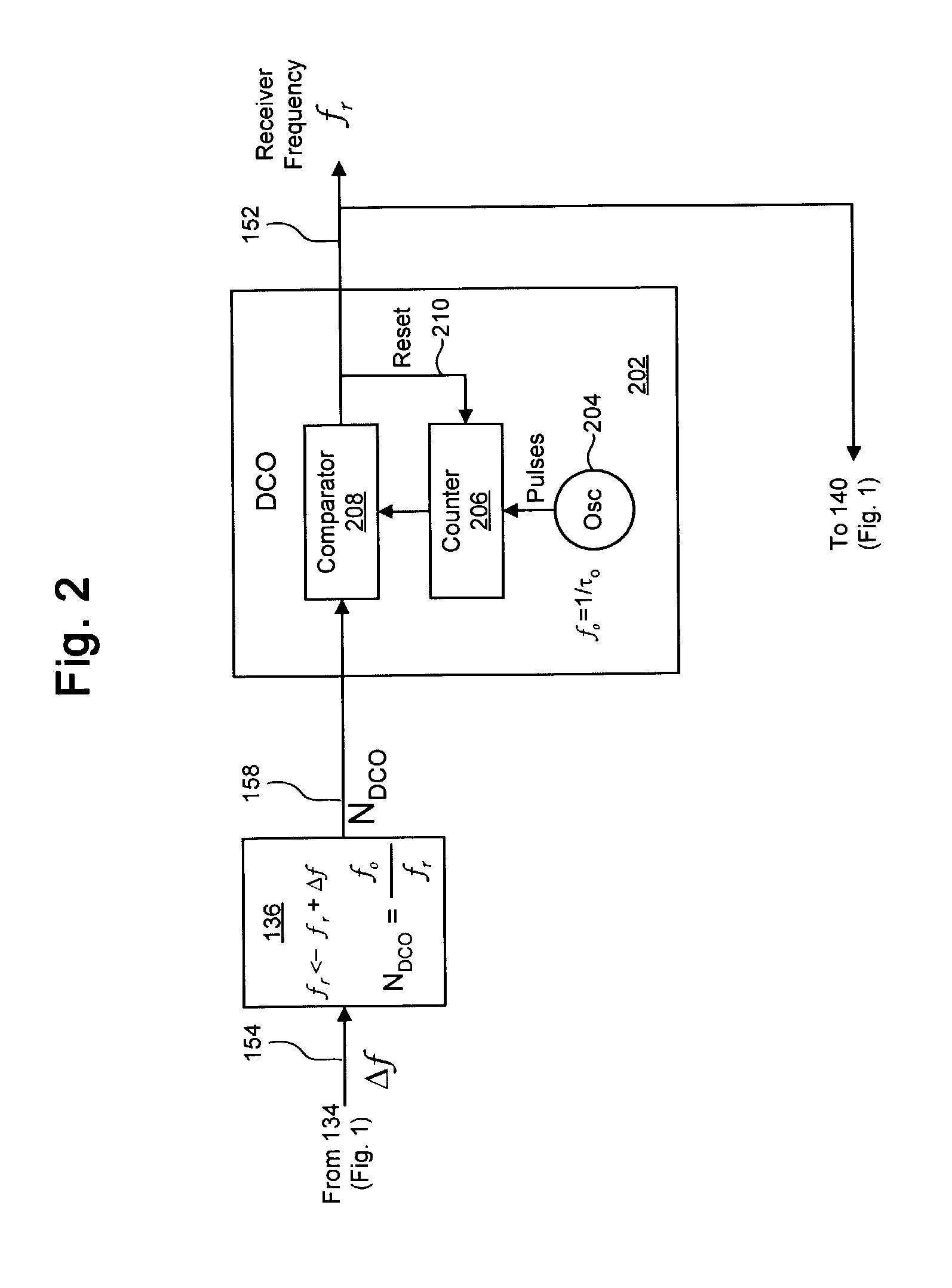

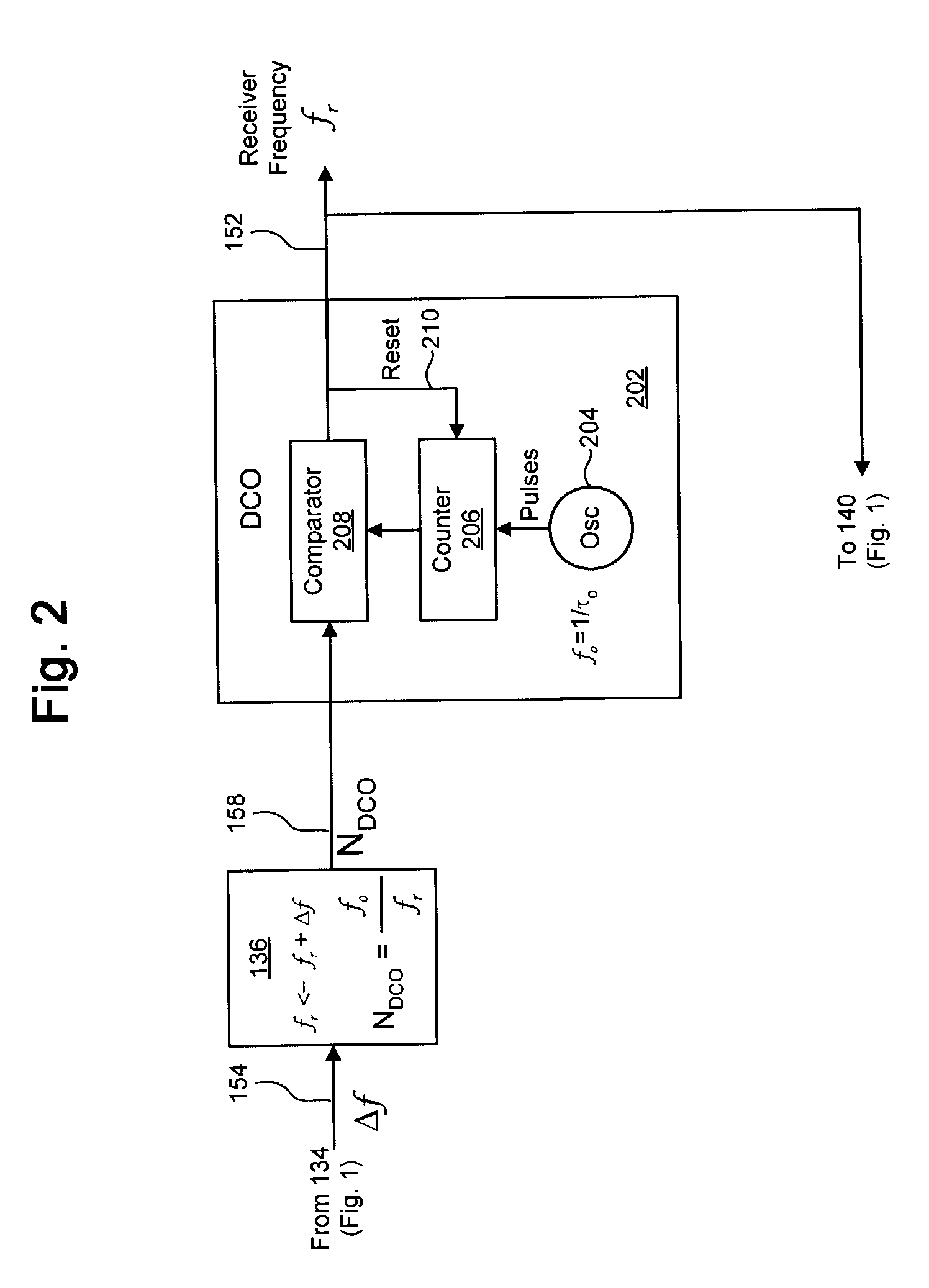

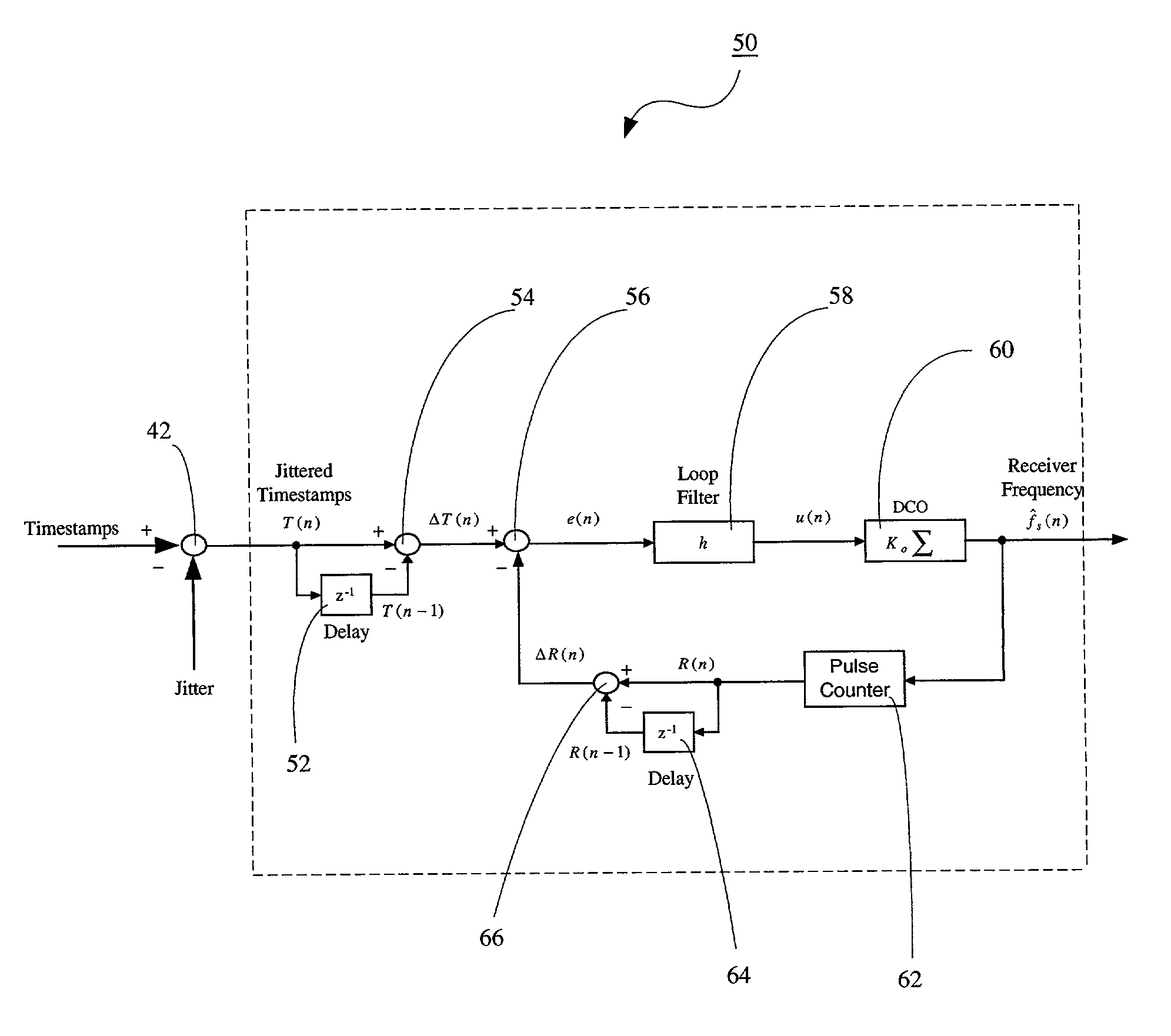

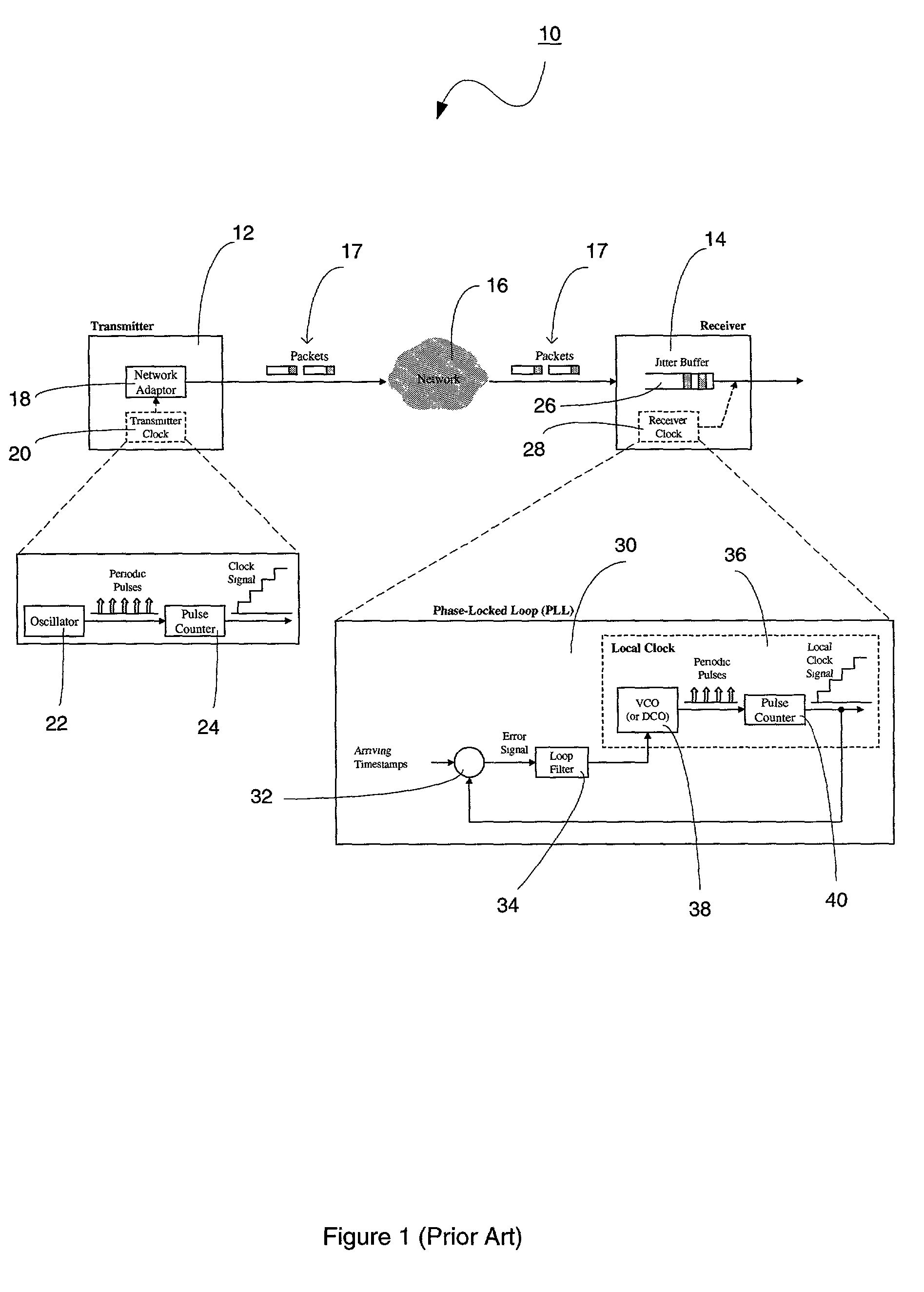

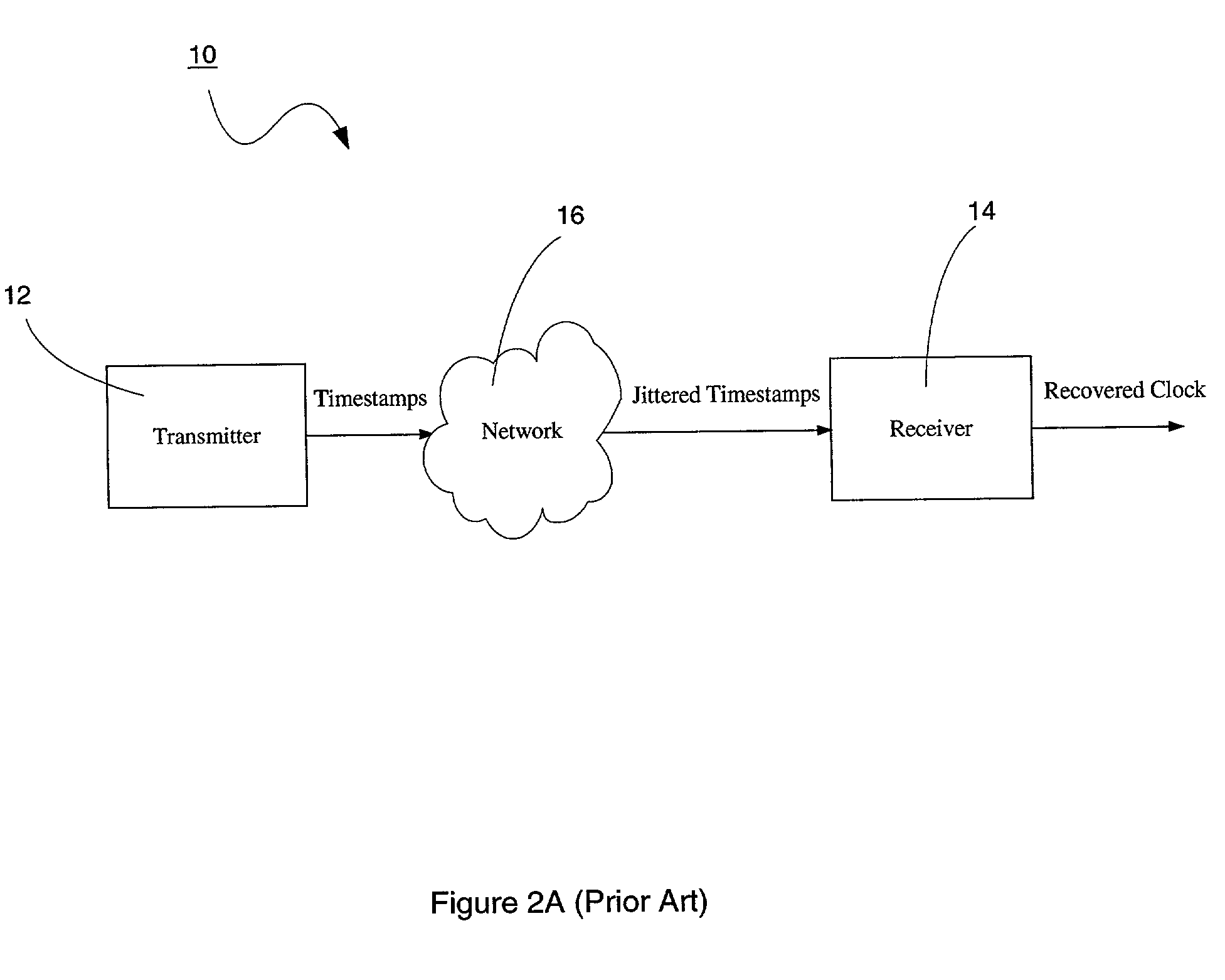

Clock recovery using a direct smoothing process

ActiveUS7130368B1Guaranteed maximum utilizationPulse automatic controlModulated-carrier systemsClock recoveryLinear model

A system and method for synchronizing a local clock to a reference clock using a linear model of the error between the local clock and the reference clock is disclosed. In one embodiment, a direct smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the direct smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:CIENA

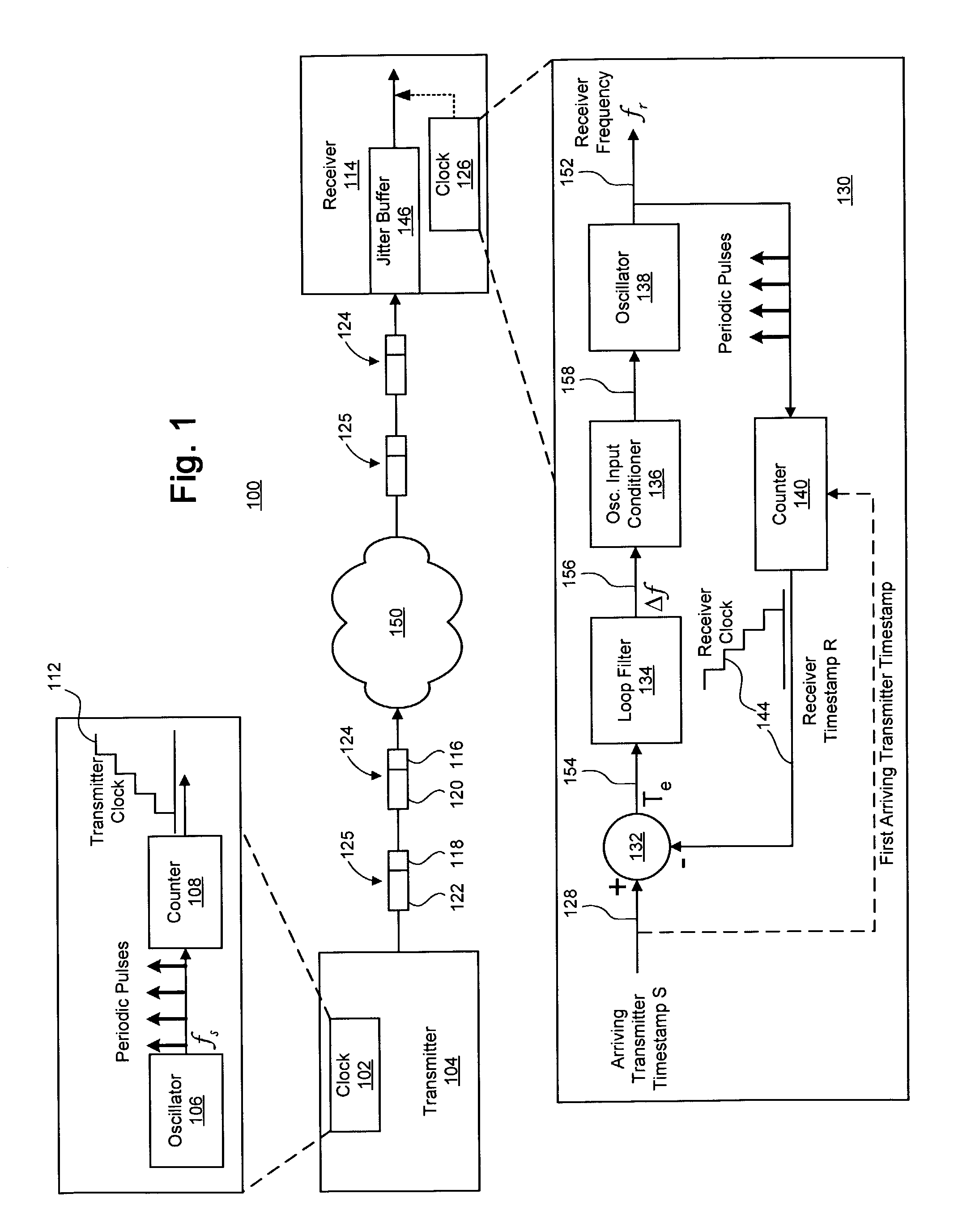

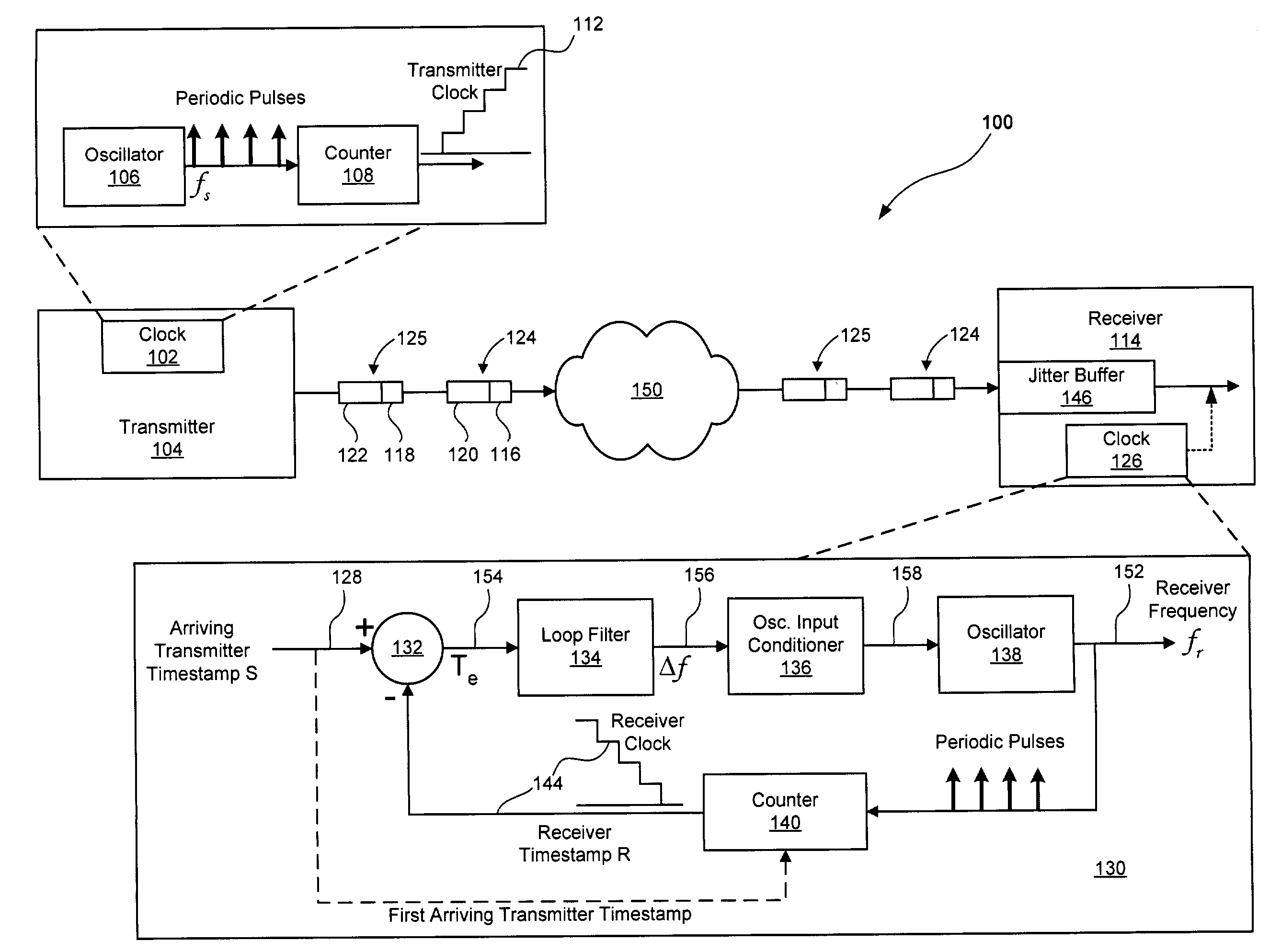

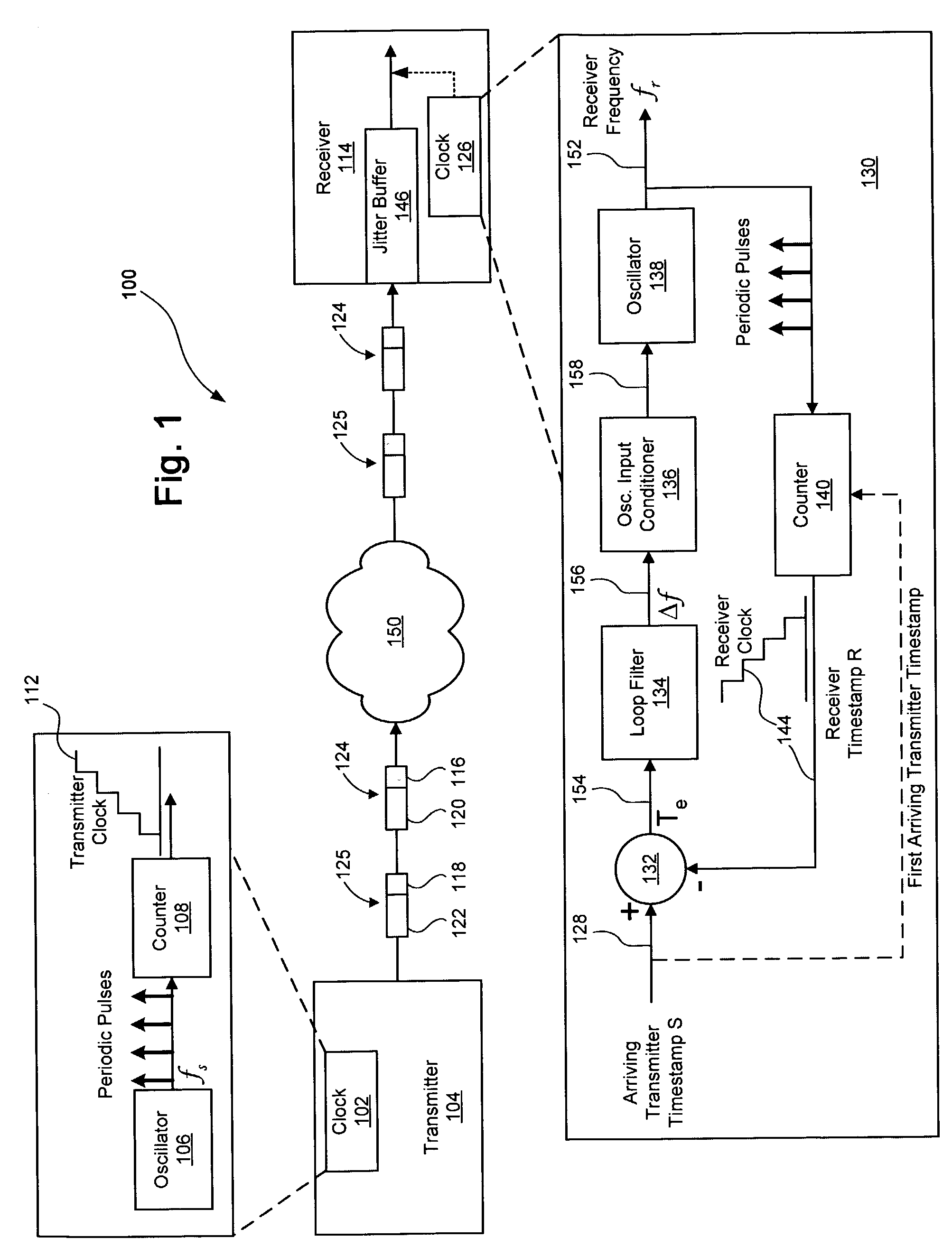

Technique for synchronizing clocks in a network

A technique for synchronizing clocks in a network is disclosed. In one exemplary embodiment, the technique may be realized as a method for synchronizing clocks in a network. The method comprises receiving a first timestamp and a second timestamp, each indicating a respective time instance as determined by a first clock signal within the network. The method also comprises measuring a first time interval between the first timestamp and the second timestamp. The method further comprises generating a difference signal representing a difference between the first time interval and a second time interval, and generating a second clock signal based upon the difference signal such that the second clock signal is synchronized with the first clock signal.

Owner:RPX CLEARINGHOUSE

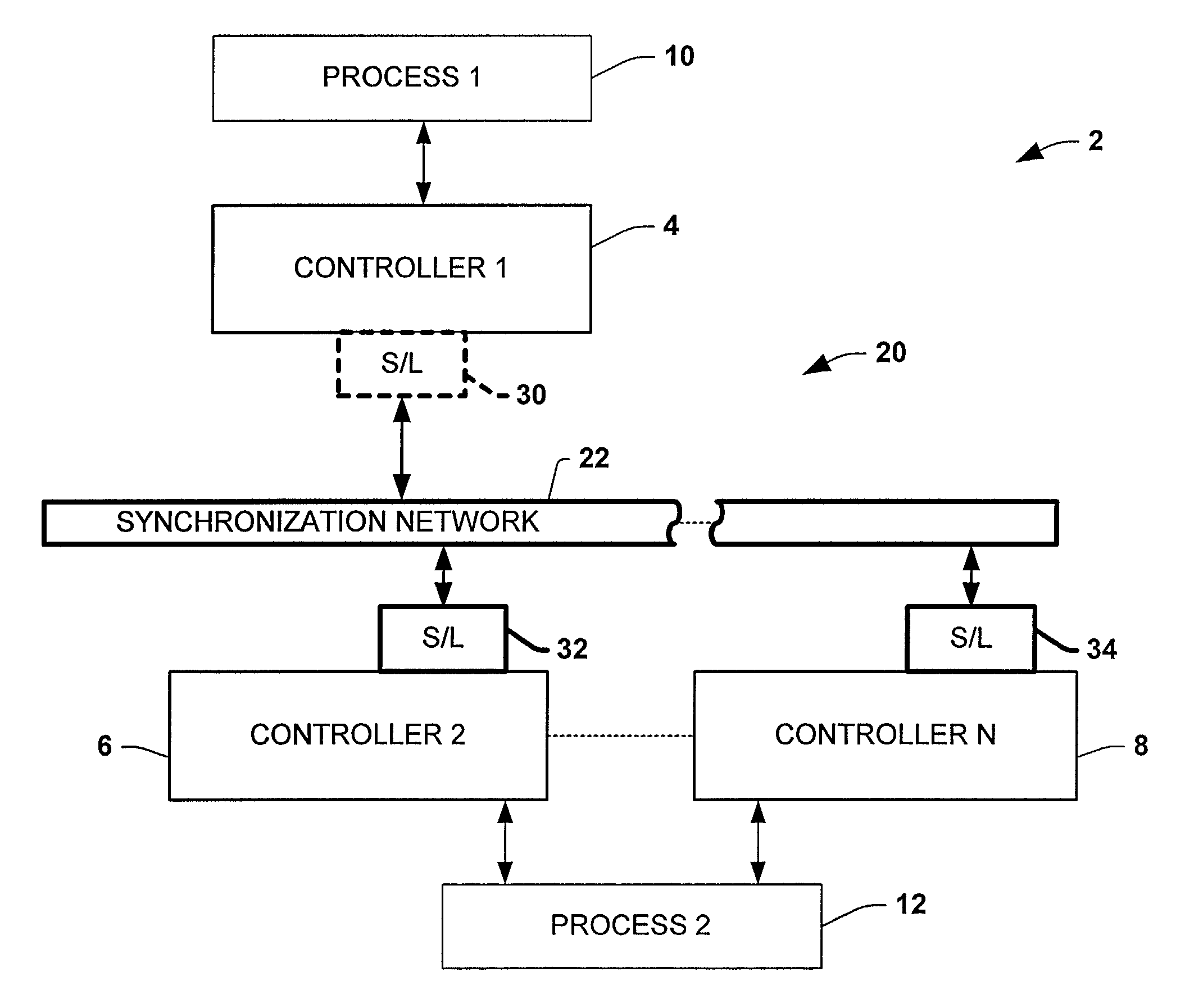

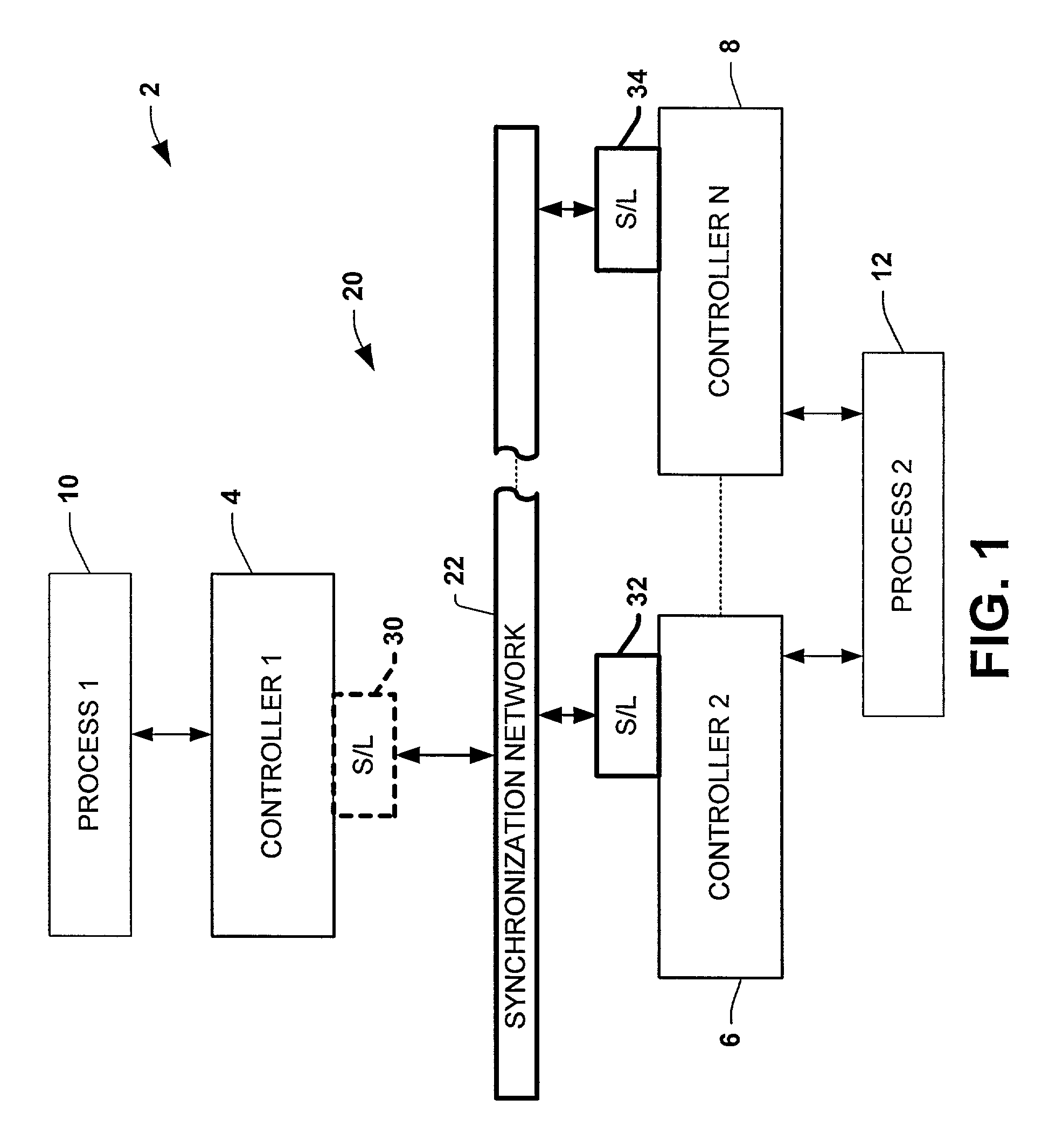

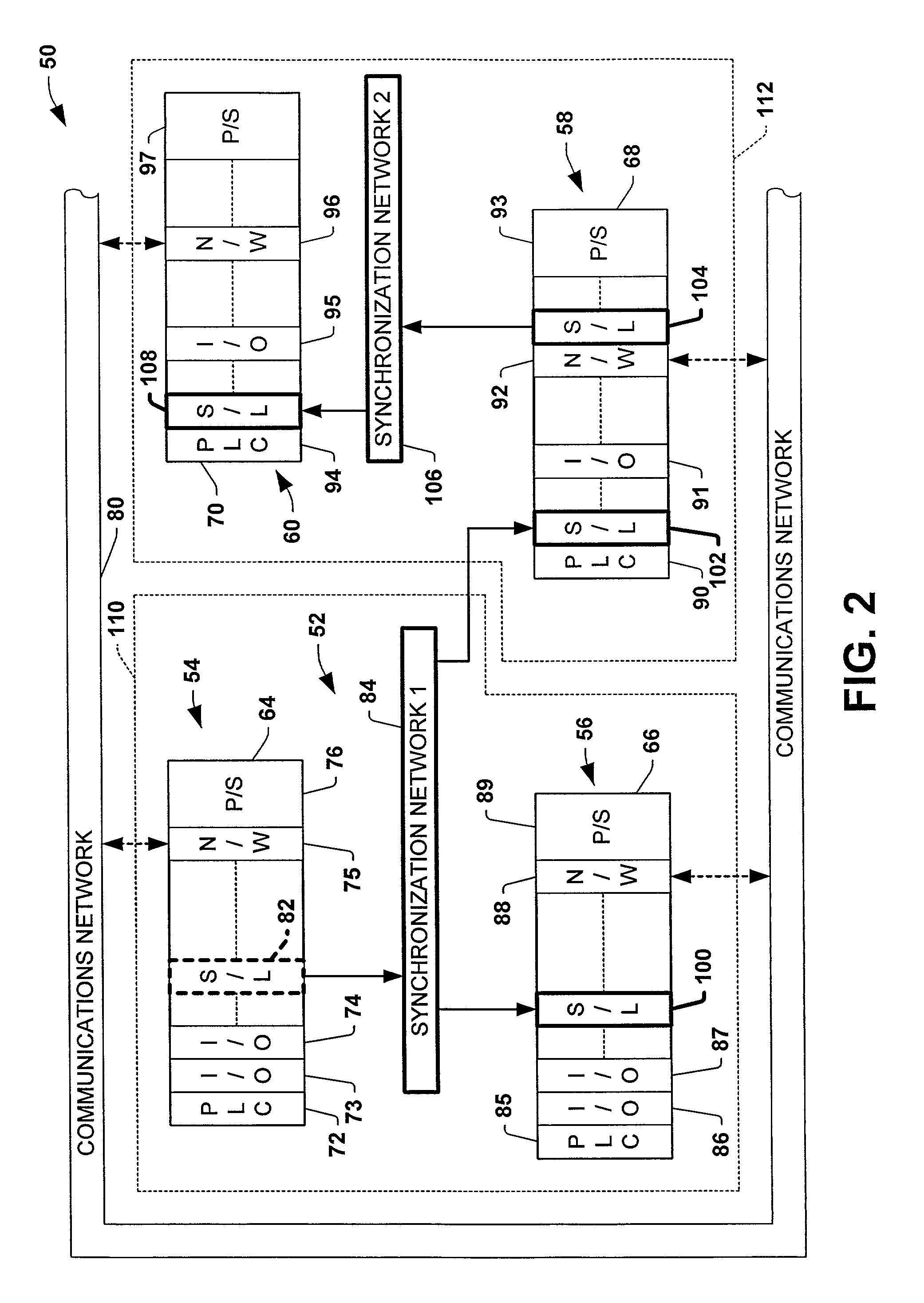

Protocol and method for multi-chassis configurable time synchronization

ActiveUS7007106B1Data representation error detection/correctionCode conversionSynchronous controlControl system

Systems and methods are disclosed for time synchronization of operations in a control system. Synchronization networks and devices are provided for transferring synchronization information between controllers in a distributed or localized control system, which is employed in order to allow operation of such controllers to be synchronized with respect to time. Also disclosed are synchronization protocols and hardware apparatus employed in synchronizing control operations in a control system.

Owner:ROCKWELL TECH

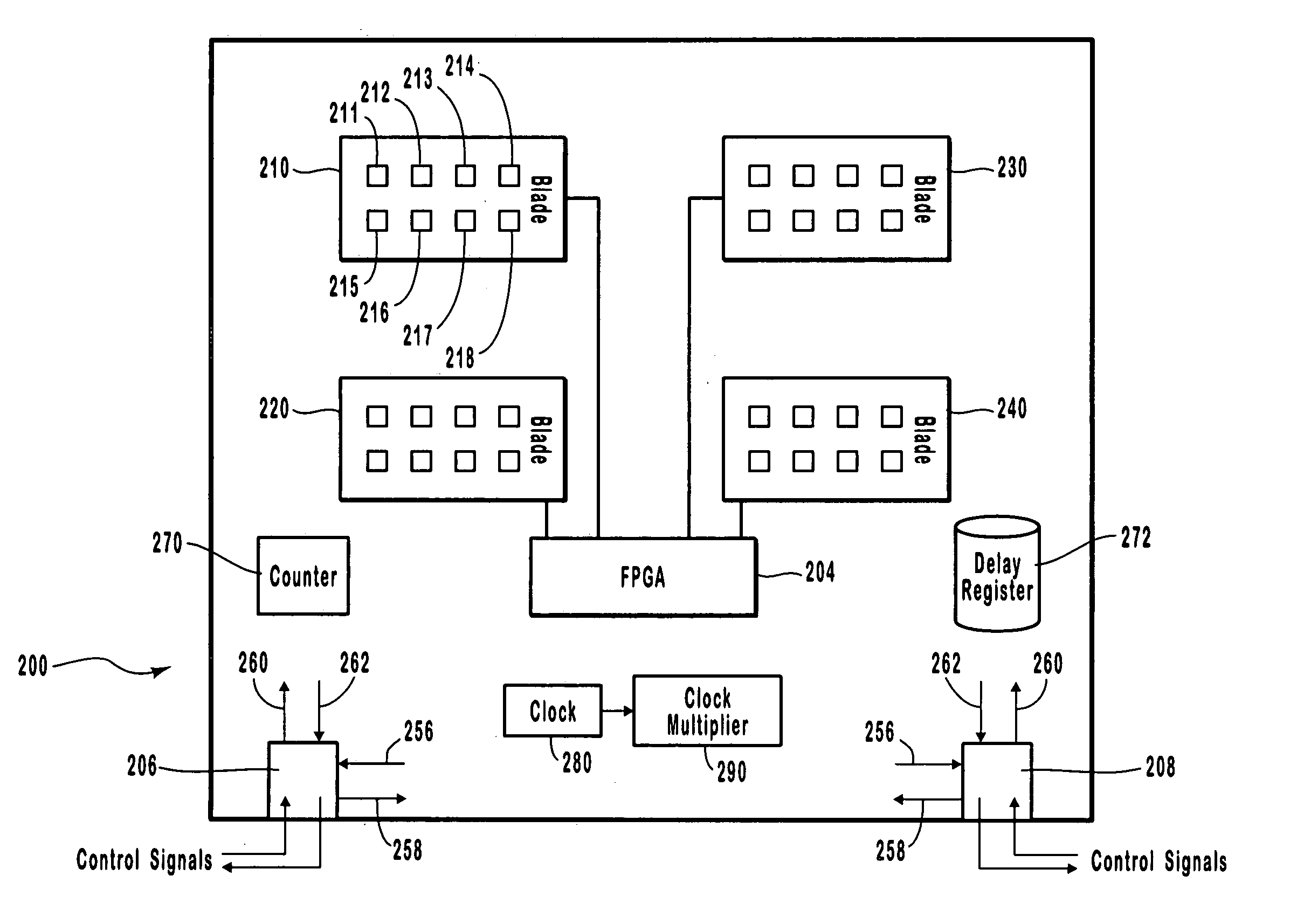

Synchronization of timestamps to compensate for communication latency between devices

InactiveUS20050010691A1To overcome the large delayTime-division multiplexMultiple digital computer combinationsTimestampControl signal

Protocol analyzer systems enable synchronization of timestamps and the capture of data across serially chained boxes that are used together to monitor and capture network data. Through experiment, it can be determined how long it takes to propagate a signal to each box in the chain. These values are then recorded in each box in a delay register so that each box has a recorded delay value corresponding to the time required to propagate a signal to or receive a signal from every other box. Each box applies a control signal, such as a run signal or a trigger signal, to the ports in the box only after the expiration of the delay value indicated in the delay register. The box initiating the signal has the largest delay since the other boxes need to get the signal before the boxes can begin to operate with a common counter, with successive boxes having smaller delays.

Owner:VIAVI SOLUTIONS INC

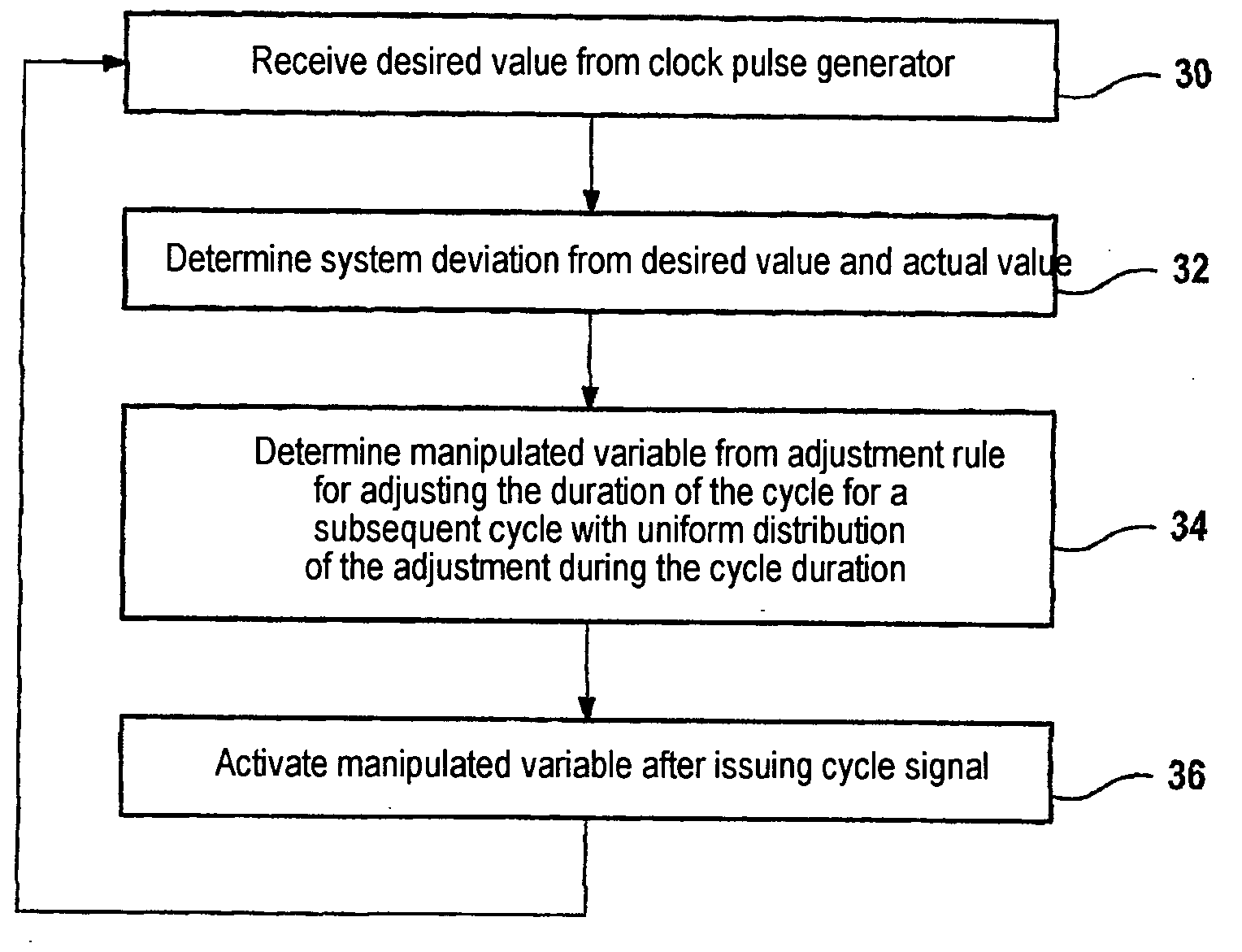

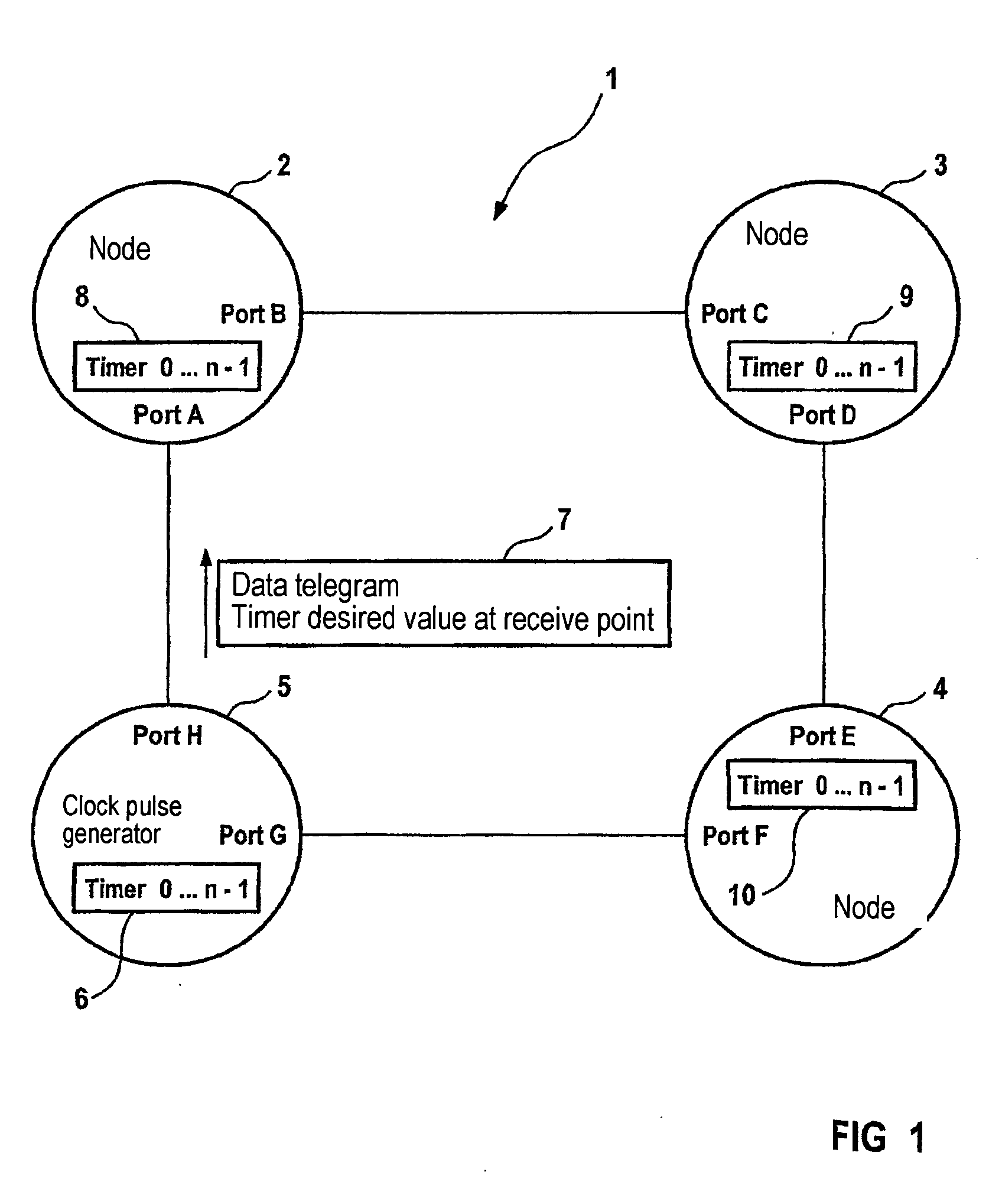

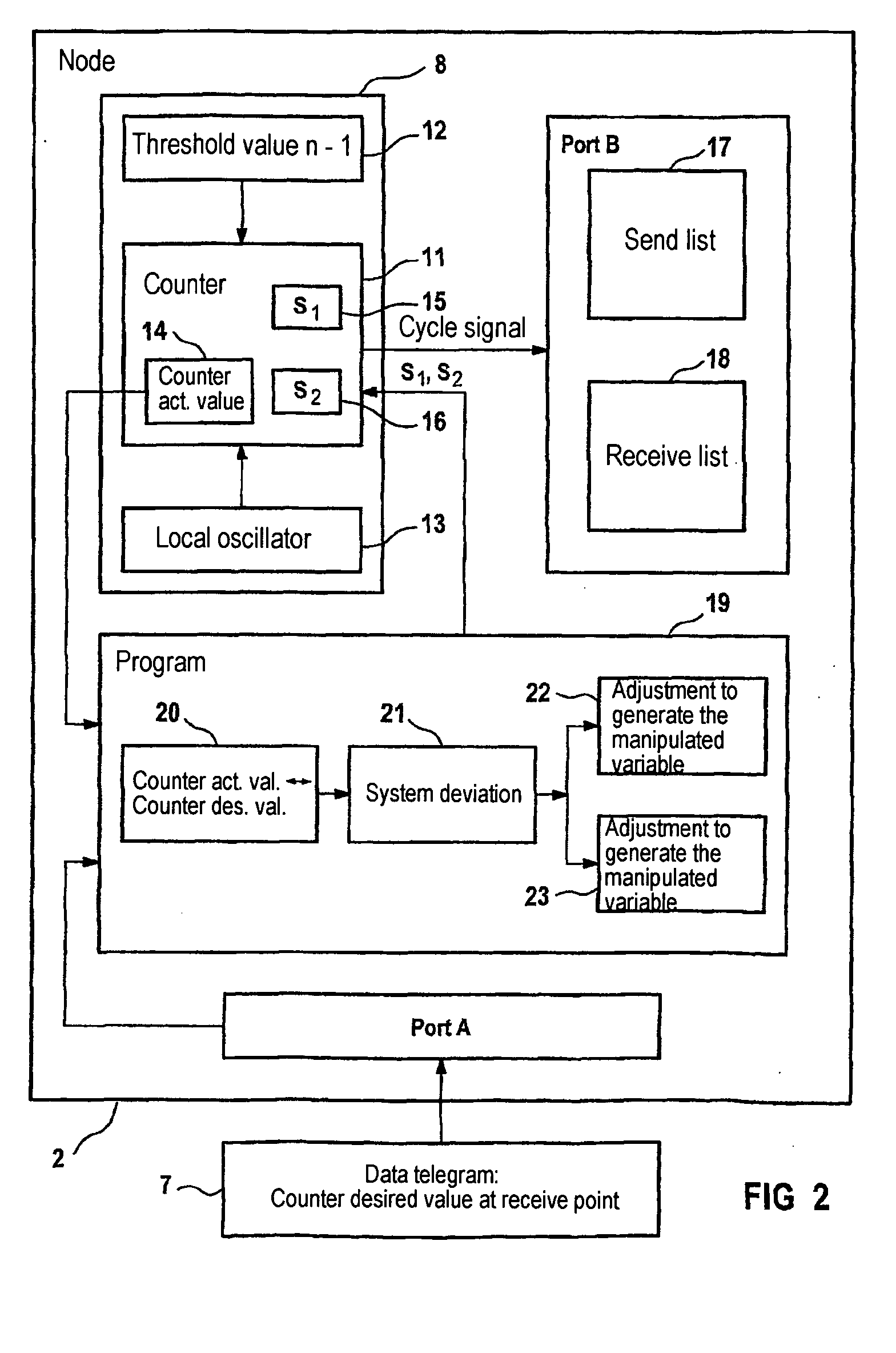

Communications system and method for synchronizing a communications cycle

ActiveUS20040249982A1Programme controlTime-division multiplexTelecommunications linkCommunications system

The invention relates to a method for synchronizing a communications cycle and a communications node in a network. Said node comprises: devices for receiving a desired value for a time base of a communications cycle of the communications node in a communications link to an additional communications node of the network; devices for determining a system deviation between the desired value and an actual value of the time base; and a device for generating a manipulated variable for correcting the time base in accordance with the system deviation.

Owner:SIEMENS AG

Method and apparatus for reducing power consumption

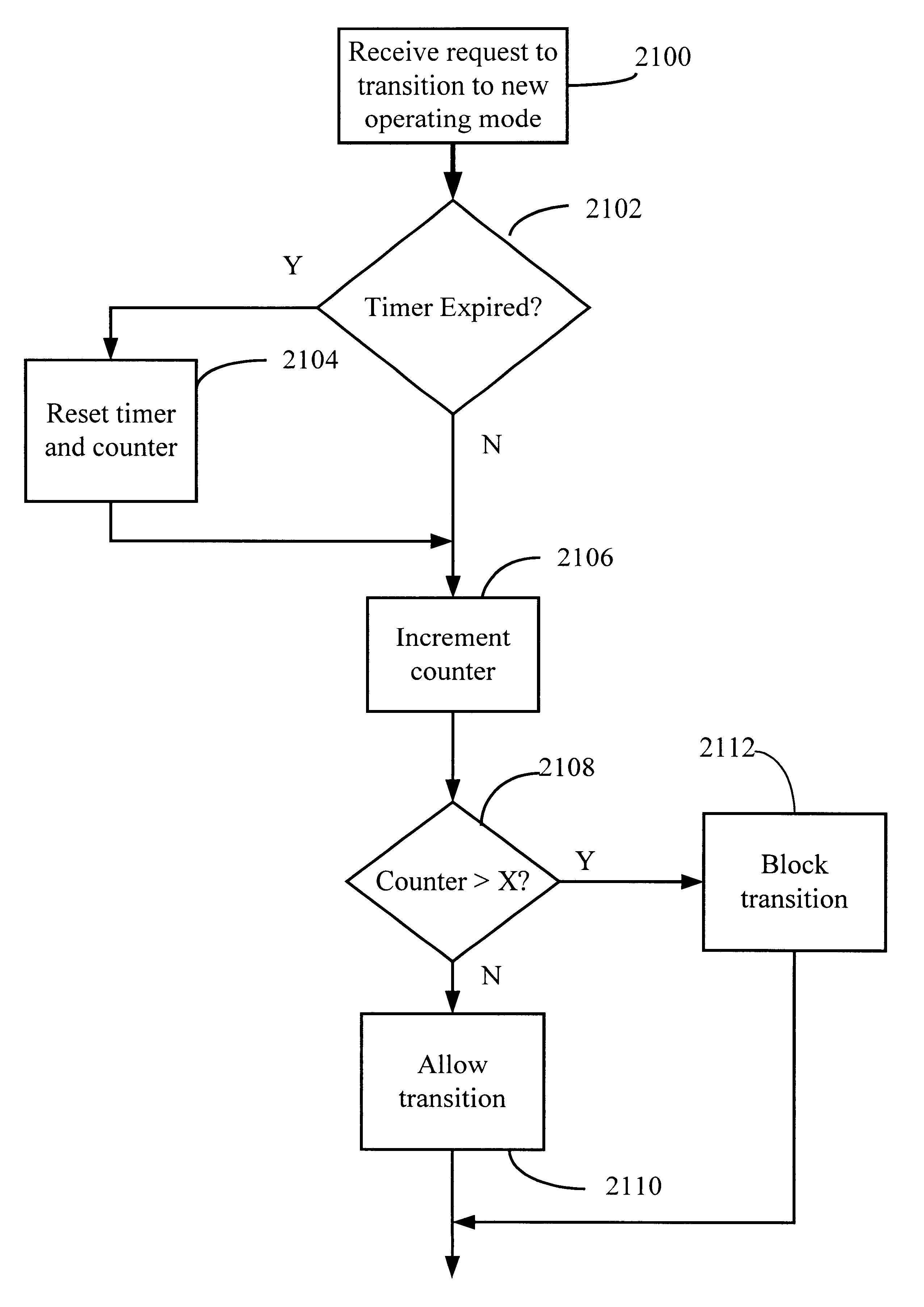

A method for controlling thermal cycles in a computer system is provided. The method is comprised of receiving a request to transition the computer system from a first operating mode to a second operating mode, where less power is consumed in the second operating mode. A historical rate at which the computer system has transitioned between the first and second operating modes is determined, and the requested transition is permitted in response to the historical rate being less than a first preselected setpoint, but denied in response to the historical rate being greater than the first preselected setpoint.

Owner:ORACLE INT CORP

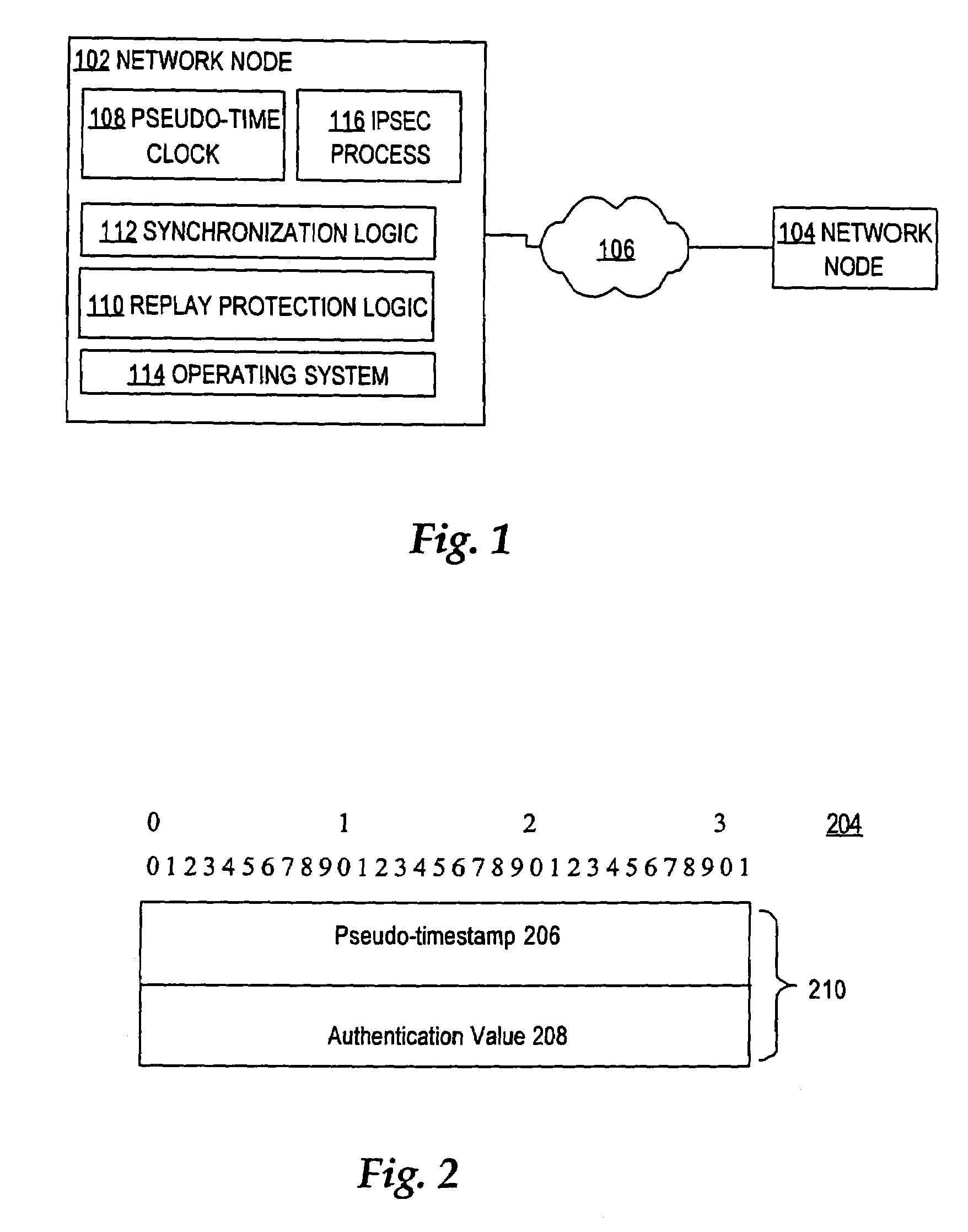

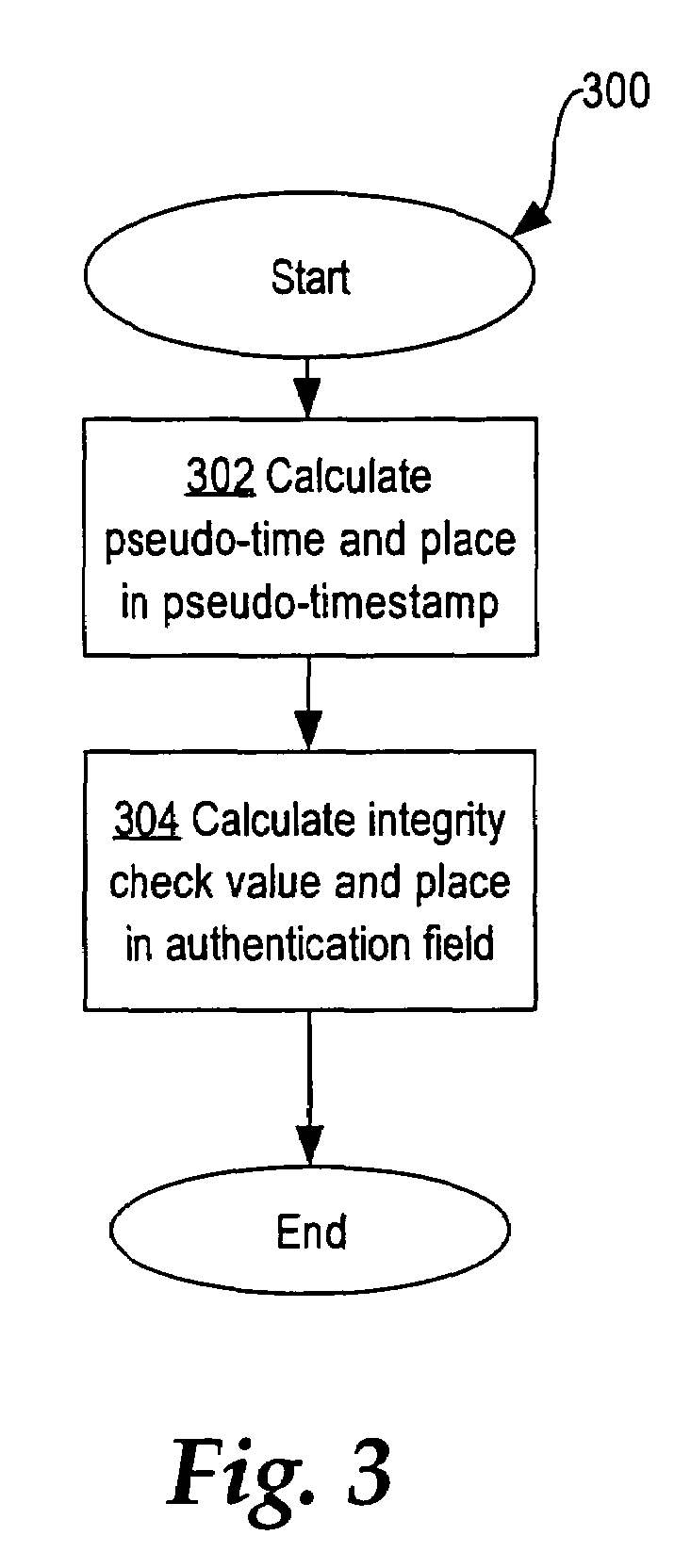

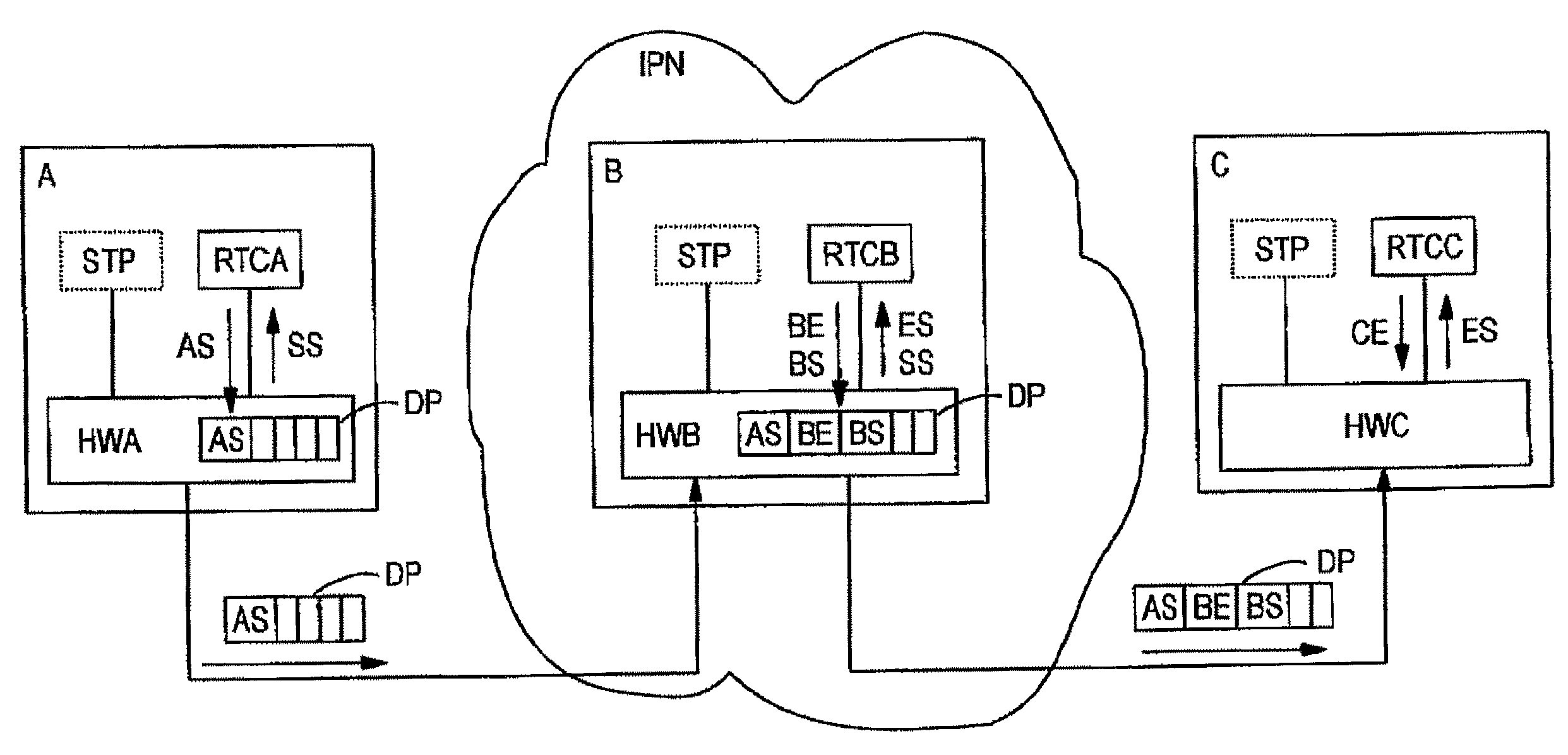

Method for self-synchronizing time between communicating networked systems using timestamps

ActiveUS7676679B2Synchronising transmission/receiving encryption devicesError detection/correctionTimestampNetworked system

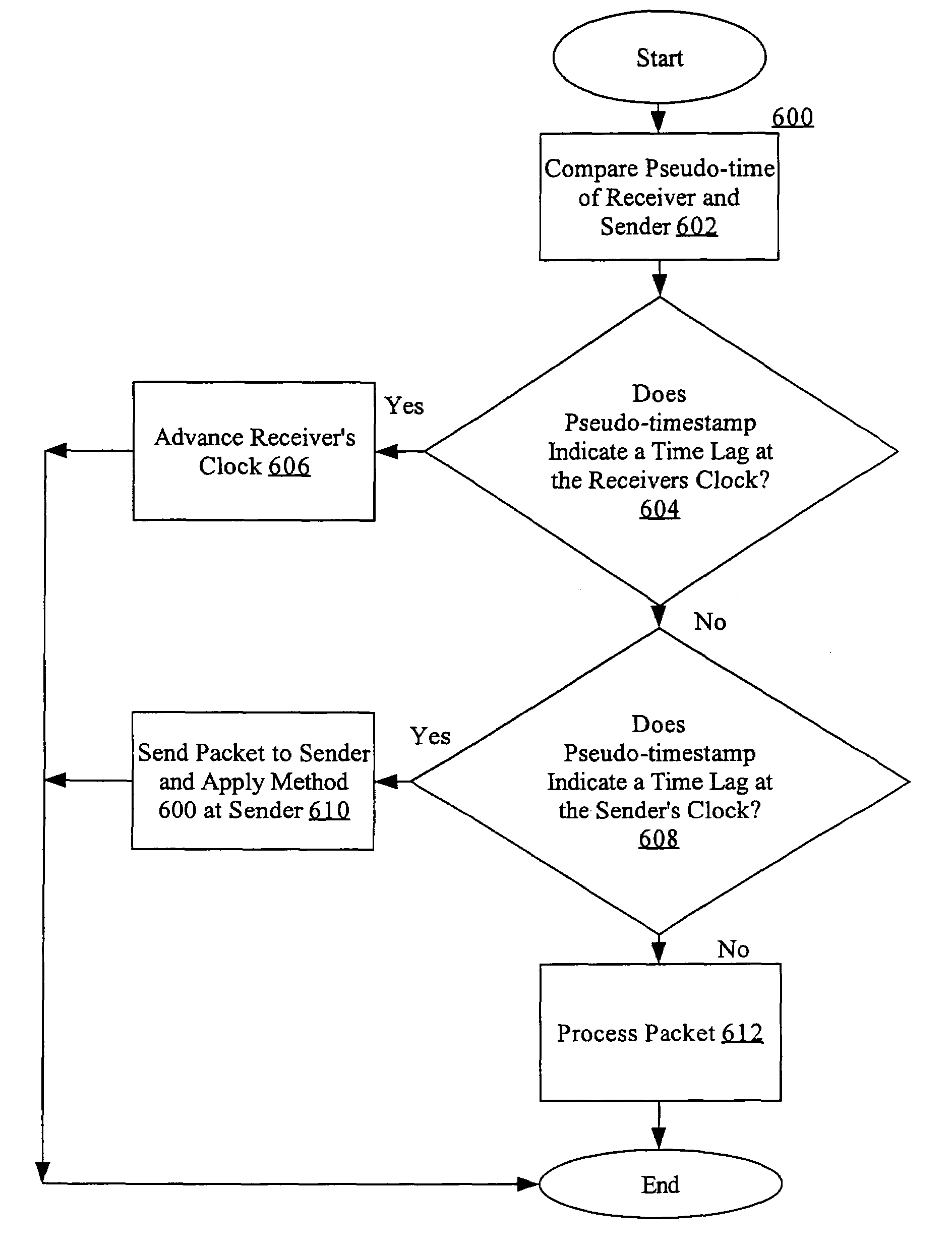

Nodes in a network include a pseudo-timestamp in messages or packets, derived from local pseudo-time clocks. When a packet is received, a first time is determined representing when the packet was sent and a second time is determined representing when the packet was received. If the difference between the second time and the first time is greater than a predetermined amount, the packet is considered to be stale and is rejected, thereby deterring replay. Because each node maintains its own clock and time, to keep the clocks relatively synchronized, if a time associated with a timestamp of a received packet is later than a certain amount with respect to the time at the receiver, the receiver's clock is set ahead by an amount that expected to synchronize the receiver's and the sender's clocks. However, a receiver never sets its clock back, to deter attacks.

Owner:CISCO TECH INC

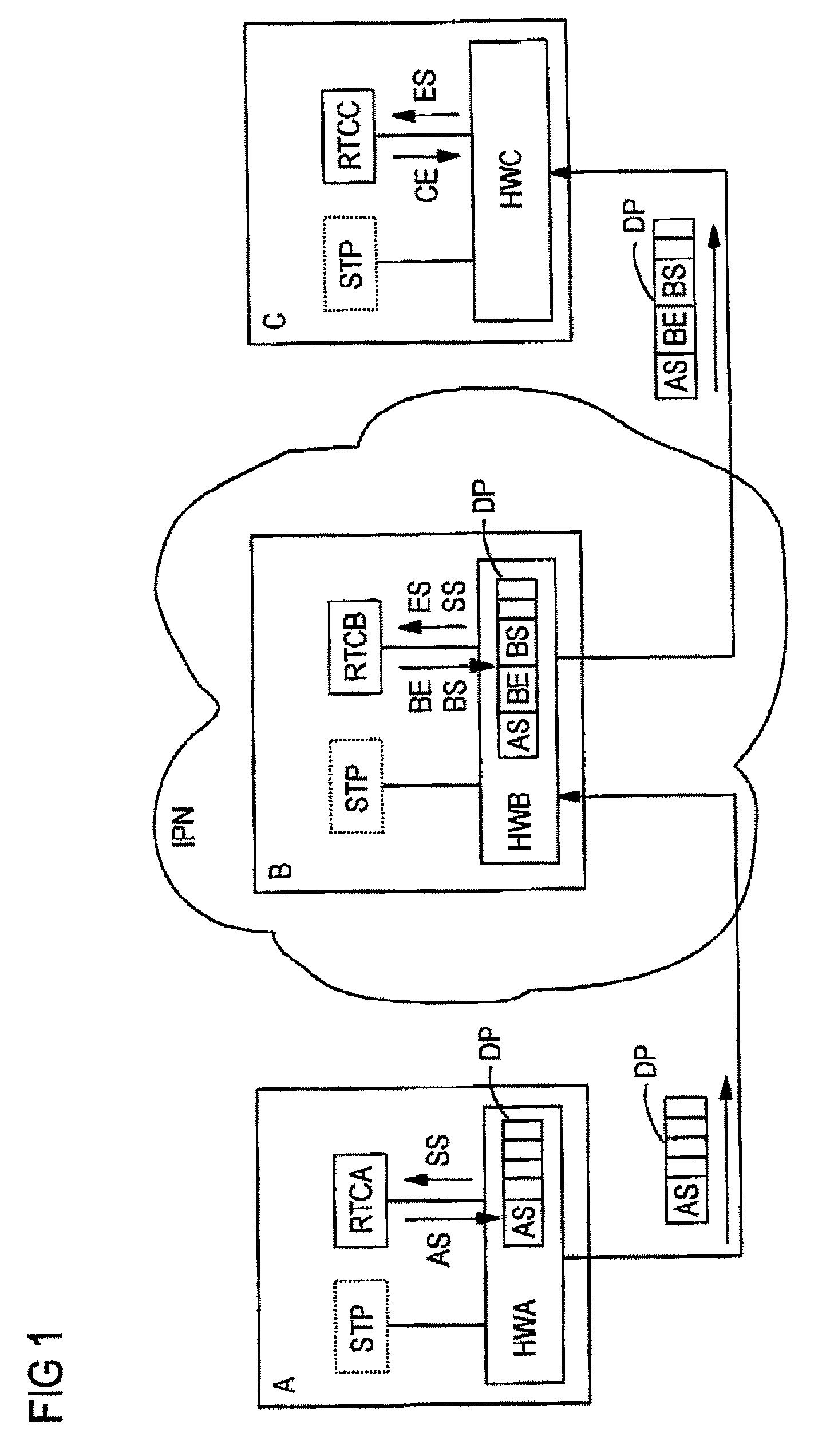

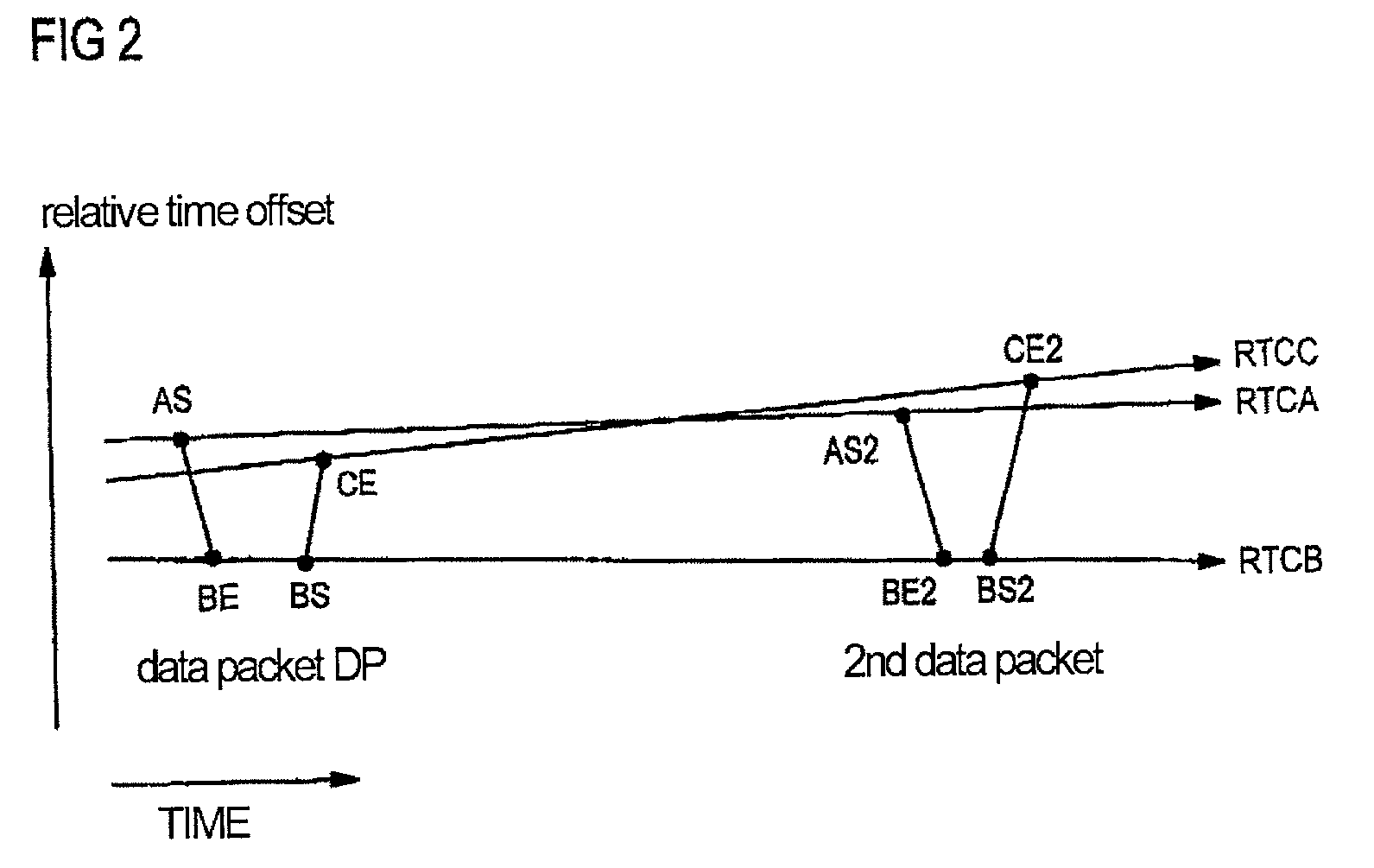

Method for transmitting time information via a data packet network

InactiveUS7372846B2Accurate timingHigh synchronization accuracyTime-division multiplexData switching by path configurationTemporal informationNetworked Transport of RTCM via Internet Protocol

Time information which is to be transmitted via a data packet network is called up from a time information source and is transmitted to a data packet transmission module. The data packet transmission module controls the transmission time of a data packet in which the time information is transmitted via the data packet network. The transmission time and the calling of the time information are aligned with respect to one another in time by a transmission signal which is generated by the time information source or by the data packet transmission module and indicates the transmission time.

Owner:RINGCENTRAL INC

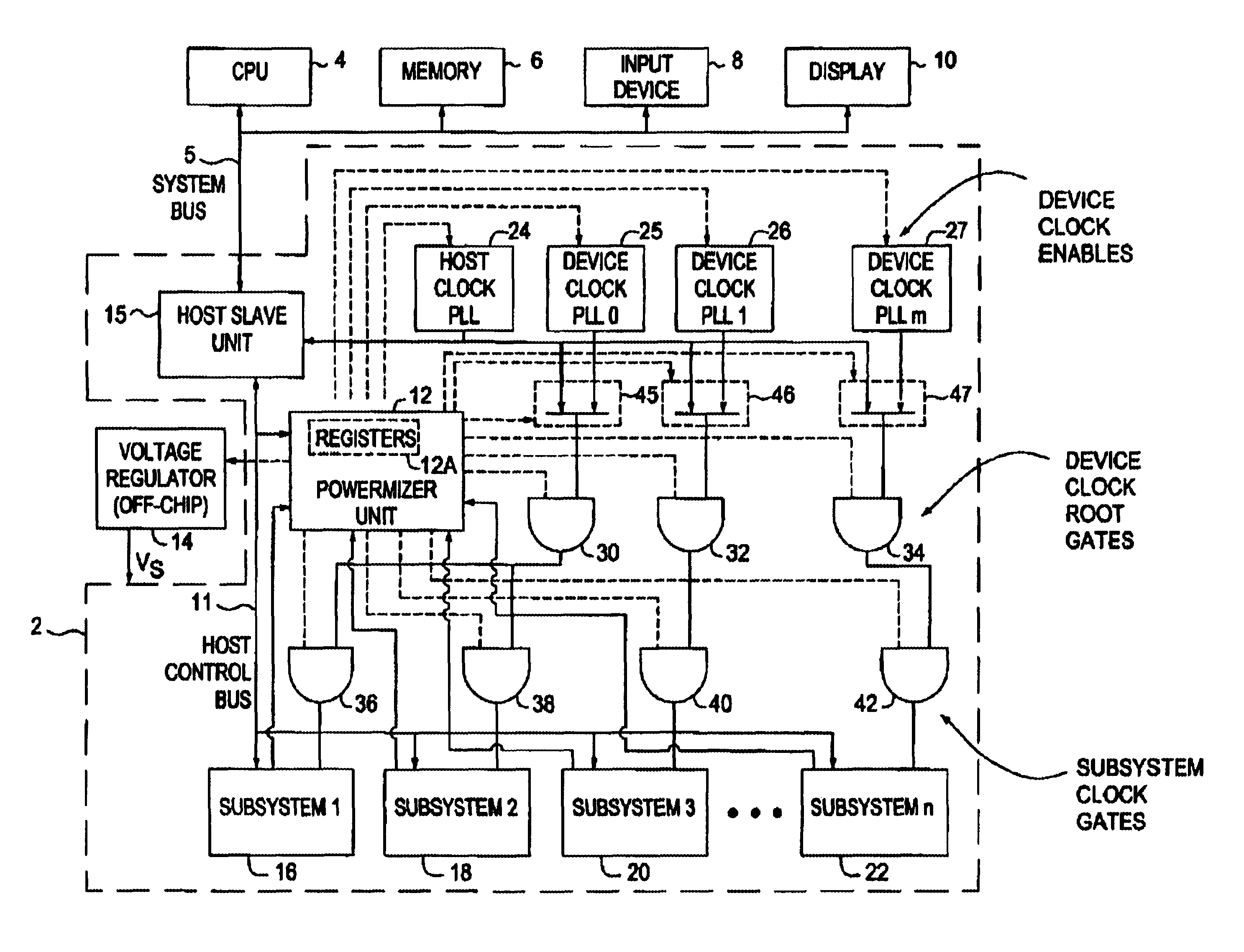

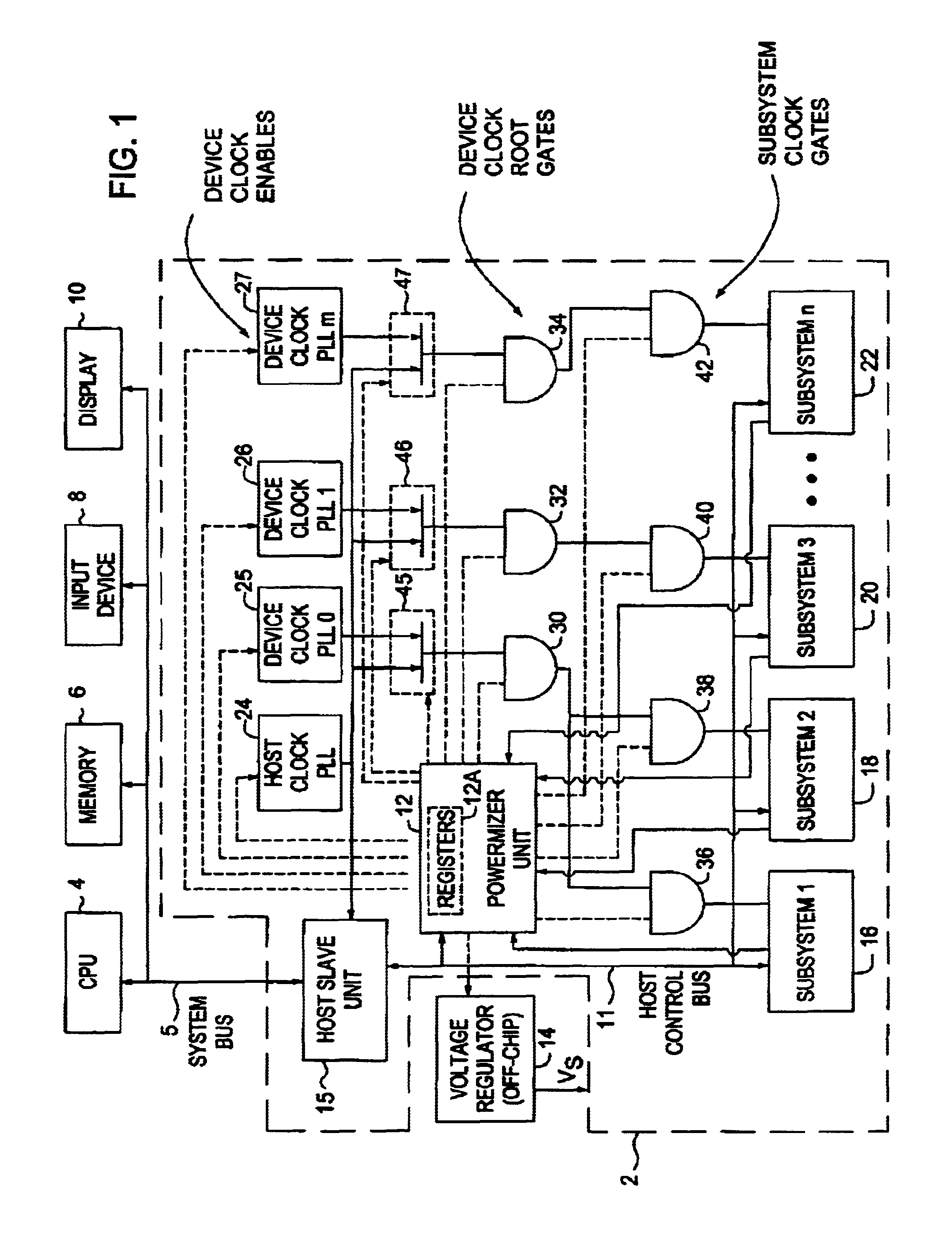

Method and apparatus for power management of graphics processors and subsystems that allow the subsystems to respond to accesses when subsystems are idle

InactiveUS6938176B1Reduce power consumptionEnergy efficient ICTStatic indicating devicesGraphicsComputer science

A graphics processing device implementing a set of techniques for power management, preferably at both a subsystem level and a device level, and preferably including peak power management, a system including a graphics processing device that implements such a set of techniques for power management, and the power management methods performed by such a device or system. In preferred embodiments, the device includes at least two subsystems and hardware mechanisms that automatically seek the lowest power state for the device that does not impact performance of the device or of a system that includes the device. Preferably, the device includes a control unit operable in any selected one of multiple power management modes, and system software can intervene to cause the control unit to operate in any of these modes.

Owner:NVIDIA CORP

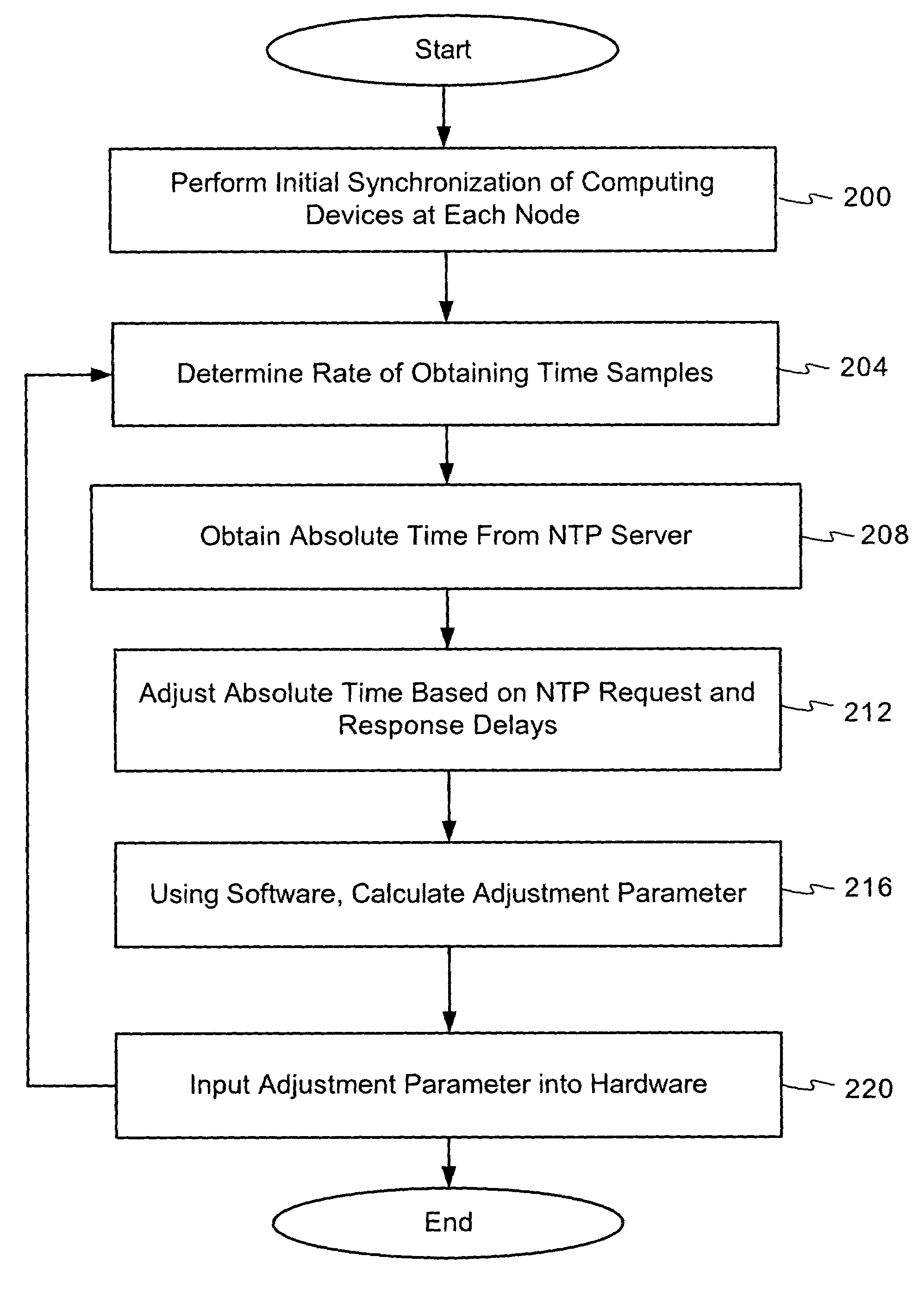

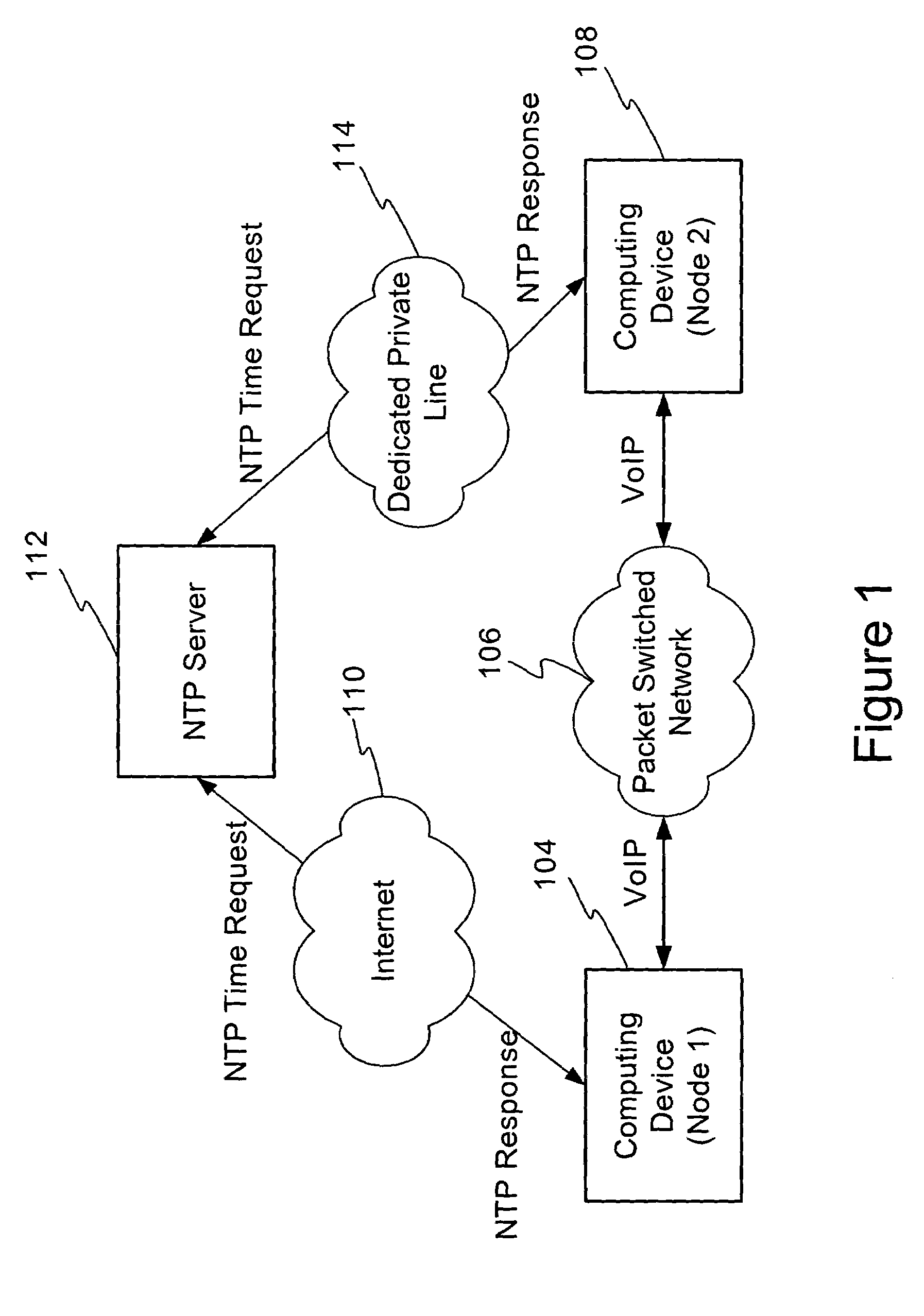

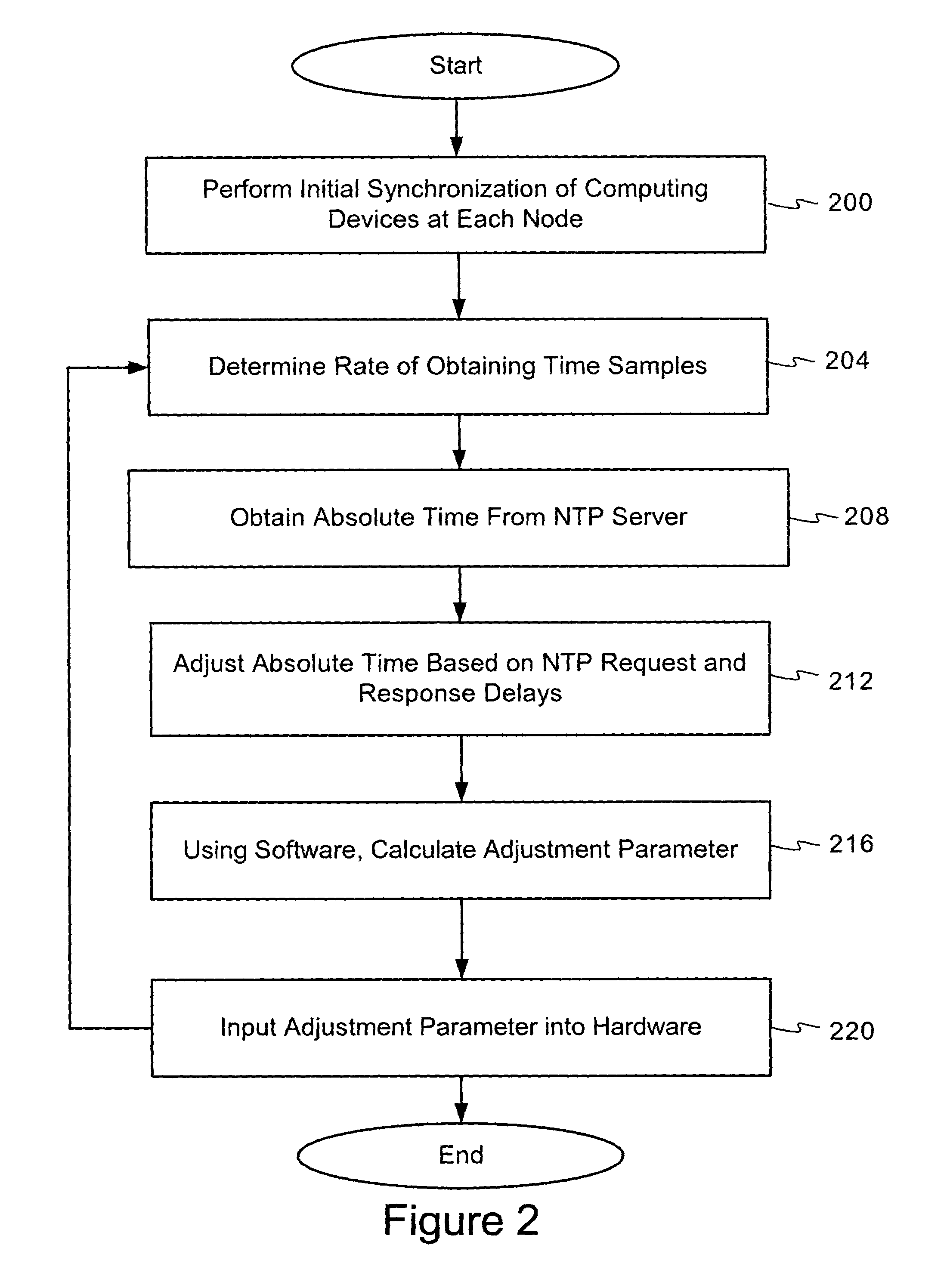

Using network time protocol in voice over packet transmission

ActiveUS7602815B2Guaranteed normal transmissionEffective maintenanceTime-division multiplexData switching by path configurationTTEthernetVoice over packet

One or more methods and systems of effectively transmitting voice and voice band data from one node to another are presented. In one embodiment, the system comprises an NTP time server generating absolute times to computing devices such as residential voice over internet protocol (VoIP) gateways. The NTP time server generates absolute times in response to NTP time requests made by one or more computing devices such as residential VoIP gateways. In one embodiment, the method comprises determining an adequate rate for requesting absolute times from an NTP server, making periodic requests to the NTP server, obtaining the absolute times from the NTP server, and generating an adjustment parameter for use by a computing device such as a residential VoIP gateway.

Owner:AVAGO TECH INT SALES PTE LTD

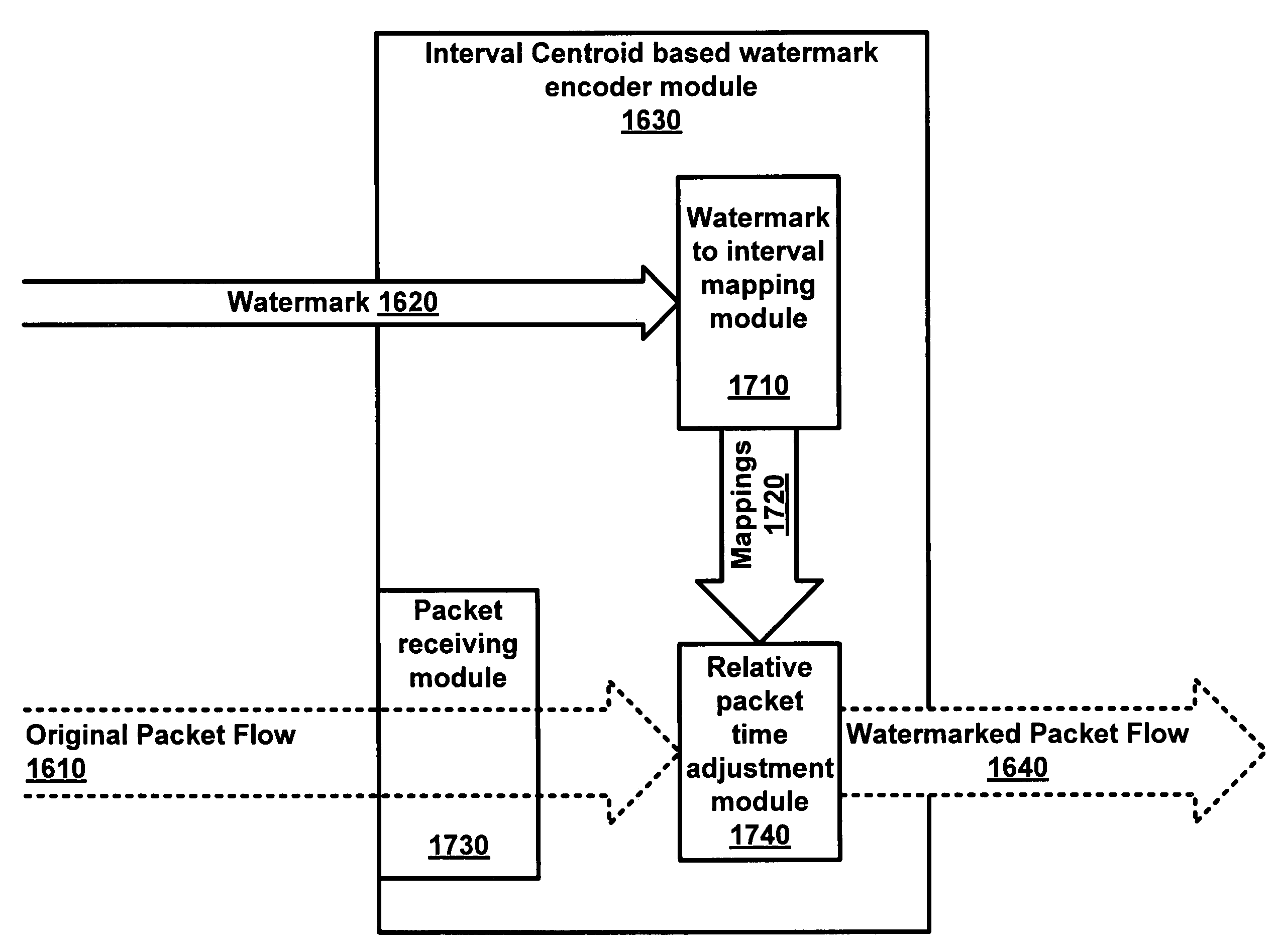

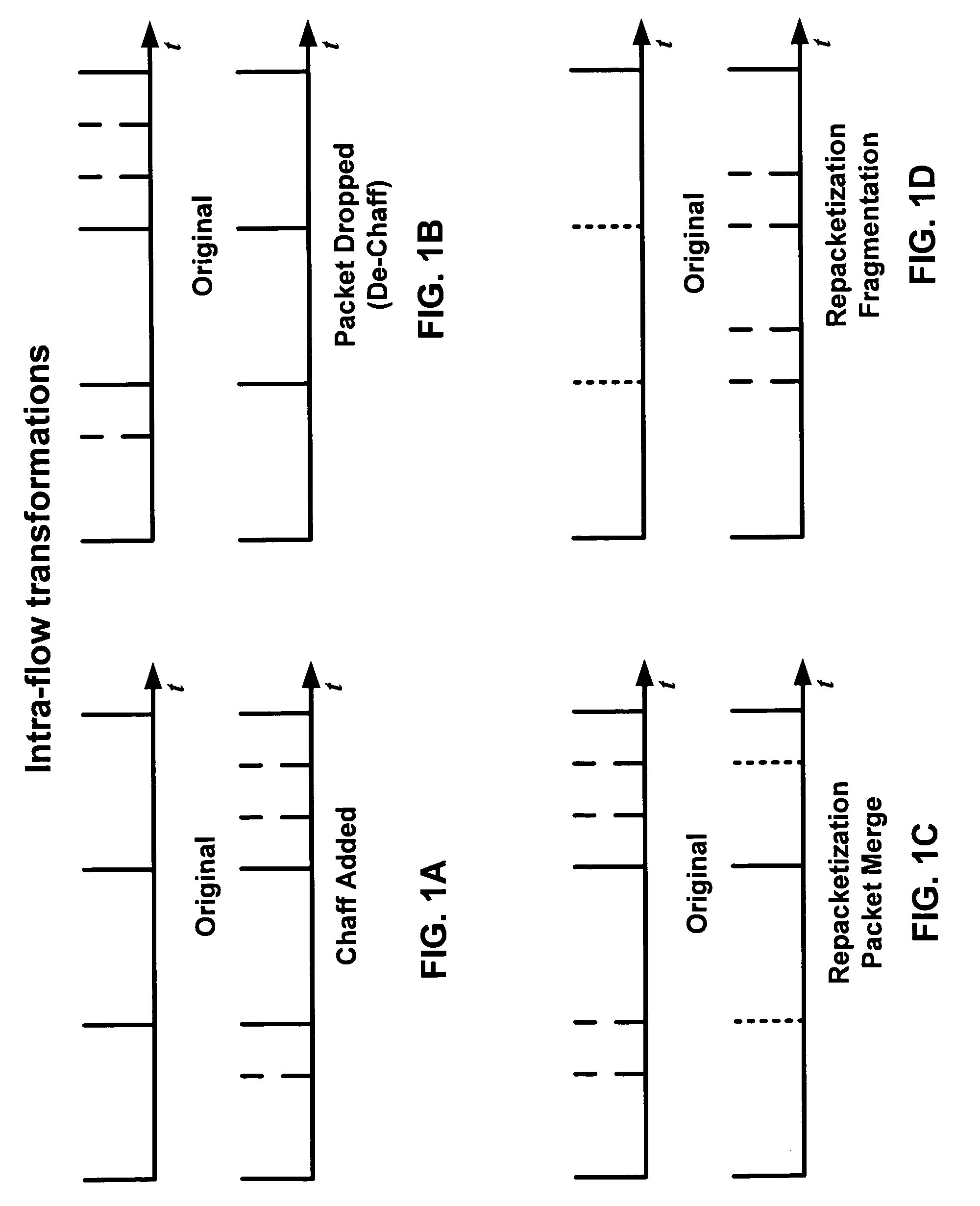

Interval centroid based watermark

An interval centroid-based watermark encoder encodes a watermark into a packet flow. Intervals are defined for the packet flow. Some of the intervals are selected as group A intervals while other intervals are selected as group B intervals. Group A and group B intervals are paired and assigned to watermark bits. A first or second value may be encoded by increasing the relative packet time between packets in either the group A (for the first bit value) or group B (for the second bit value) interval(s) of the interval pair(s) assigned to the watermark bits that are to represent the first or second bit value and the beginning of the same group interval(s). The relative packet times may be measured by a decoder and used to calculate a centroid difference for each interval pair. The centroid differences may be used to reconstruct the watermark.

Owner:GEORGE MASON INTPROP INC

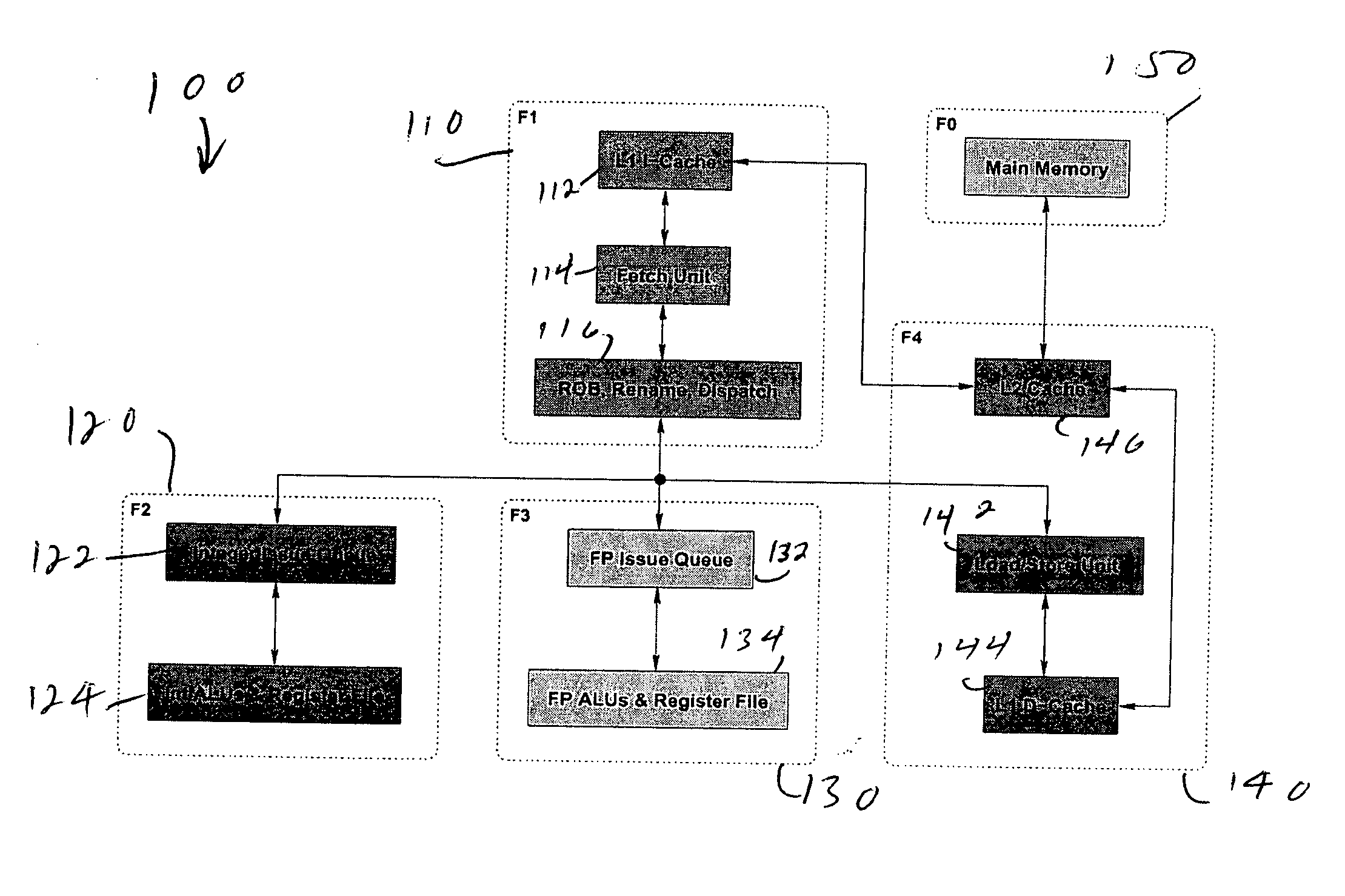

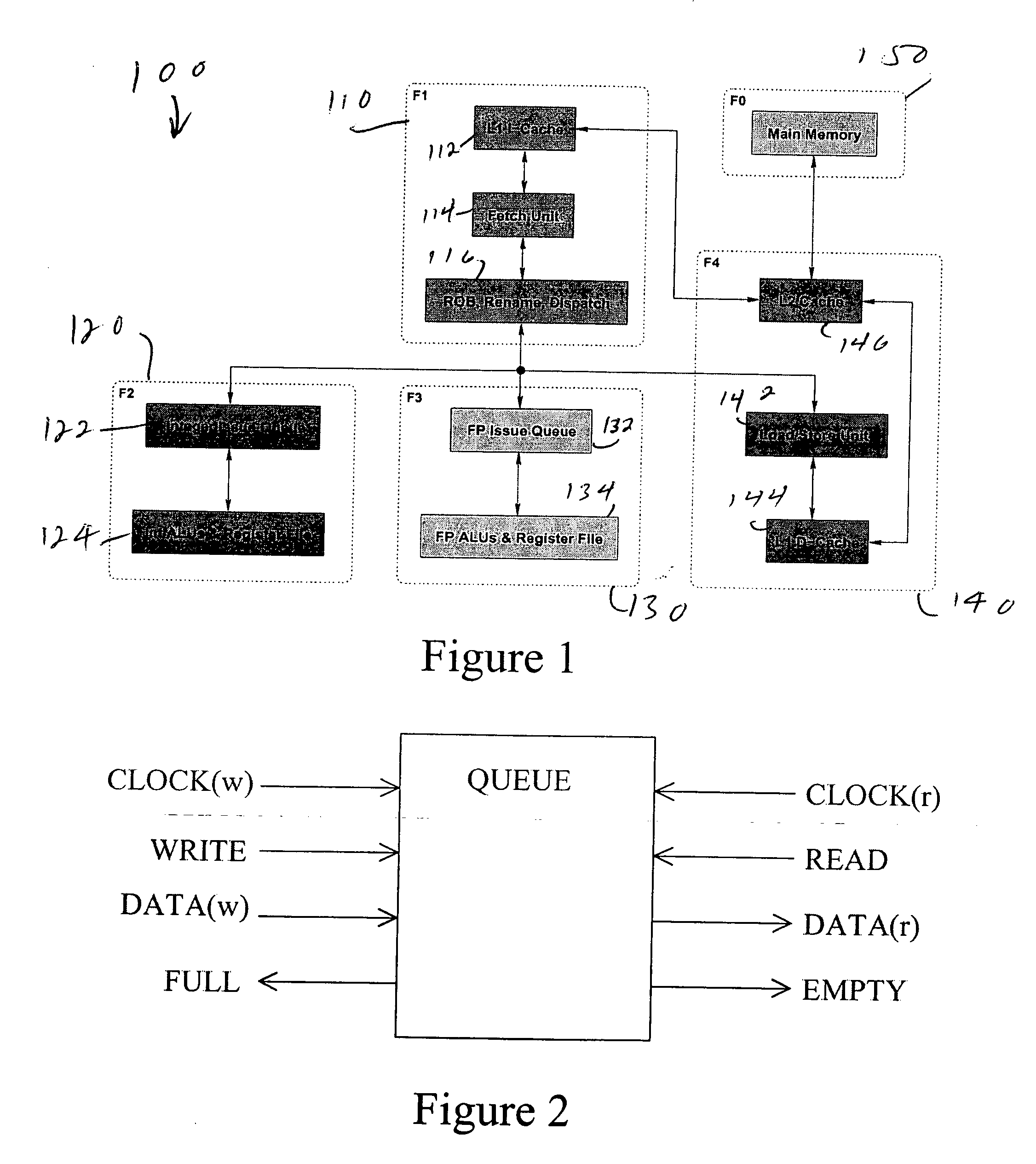

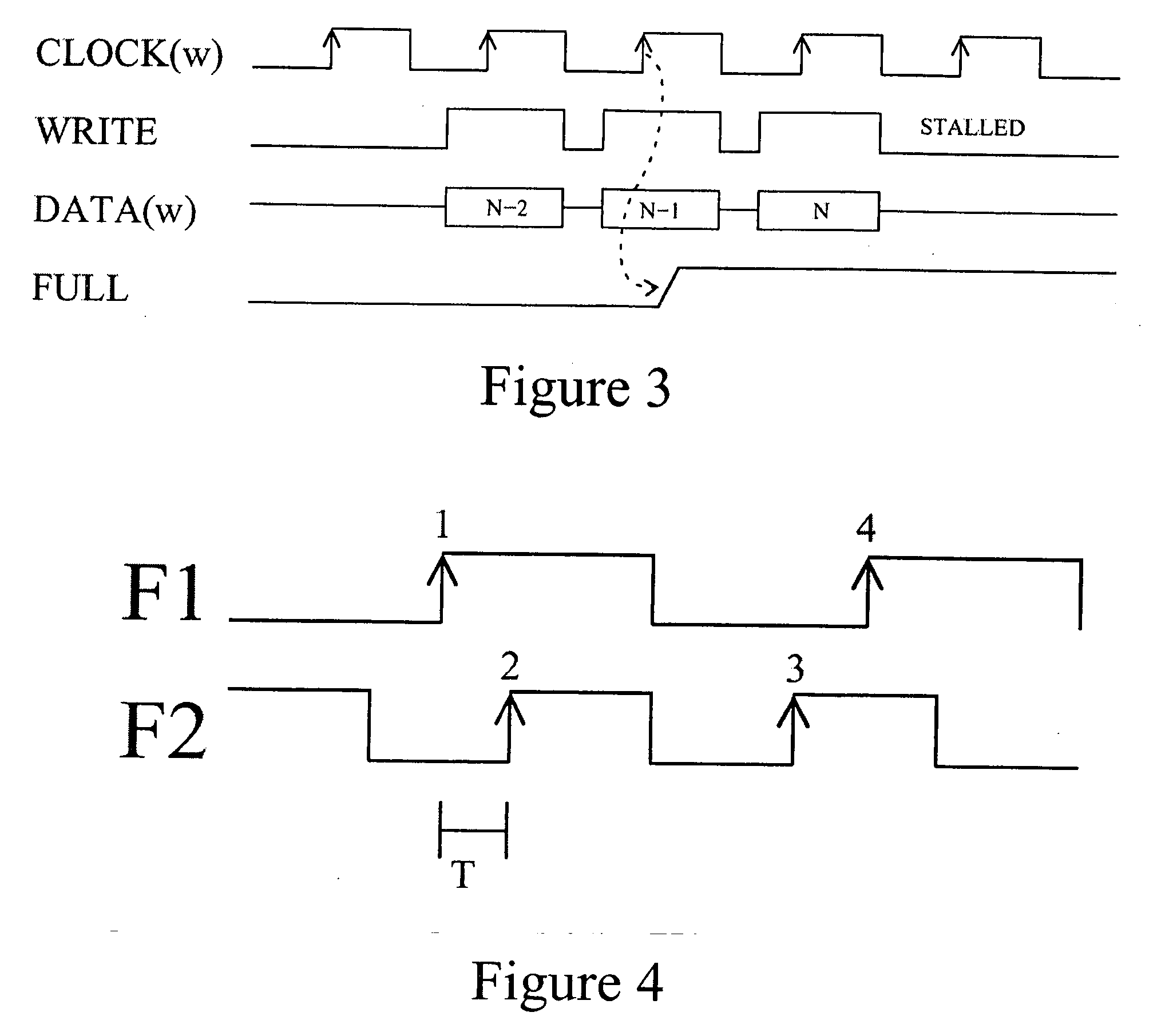

Multiple clock domain microprocessor

ActiveUS20070016817A1High frequencyImprove good performanceEnergy efficient ICTPower supply for data processingComputer scienceInter-domain

A multiple clock domain (MCD) microarchitecture uses a globally-asynchronous, locally-synchronous (GALS) clocking style. In an MCD microprocessor each functional block operates with a separately generated clock, and synchronizing circuits ensure reliable inter-domain communication. Thus, fully synchronous design practices are used in the design of each domain.

Owner:ALBONESI DAVID +5

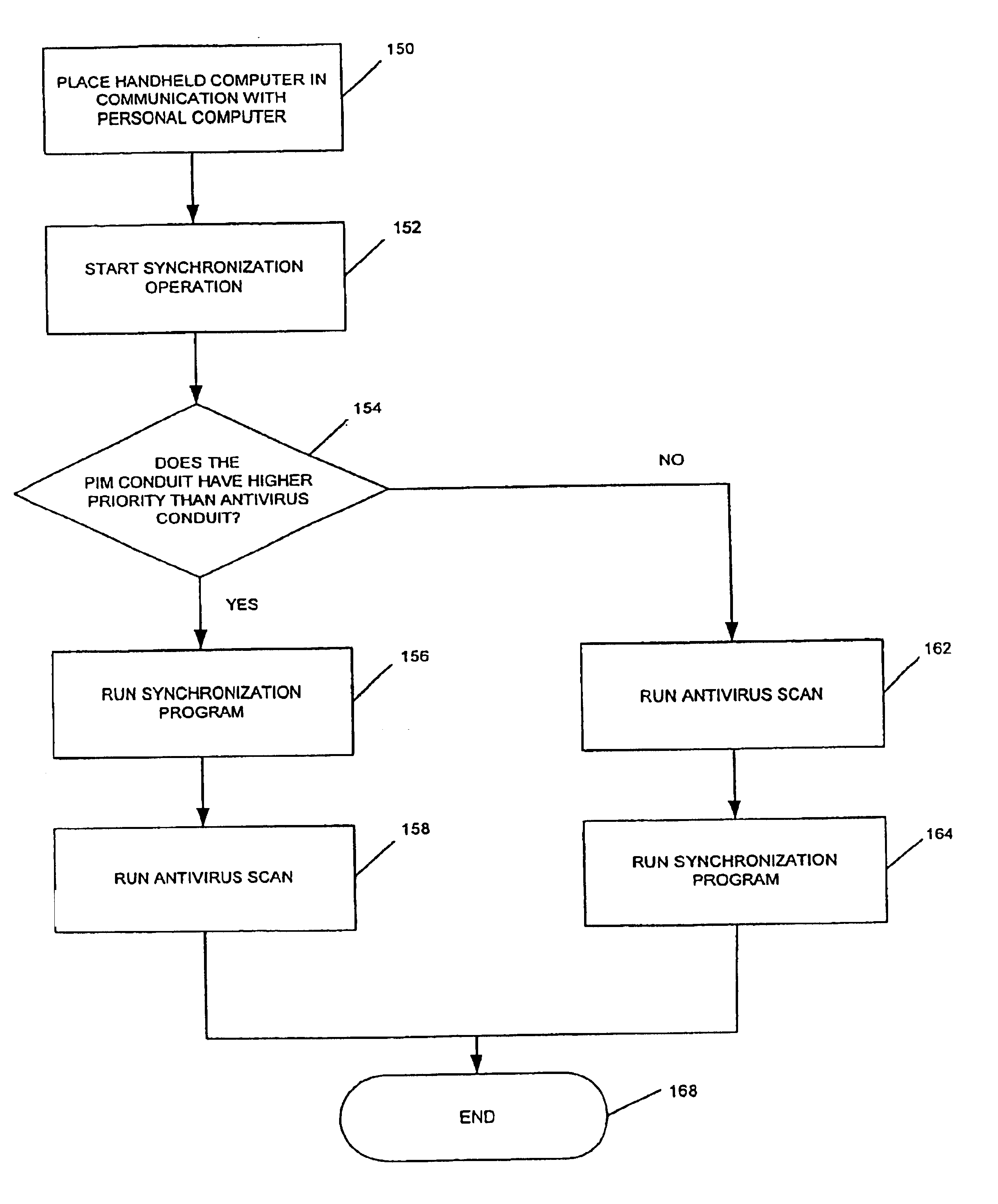

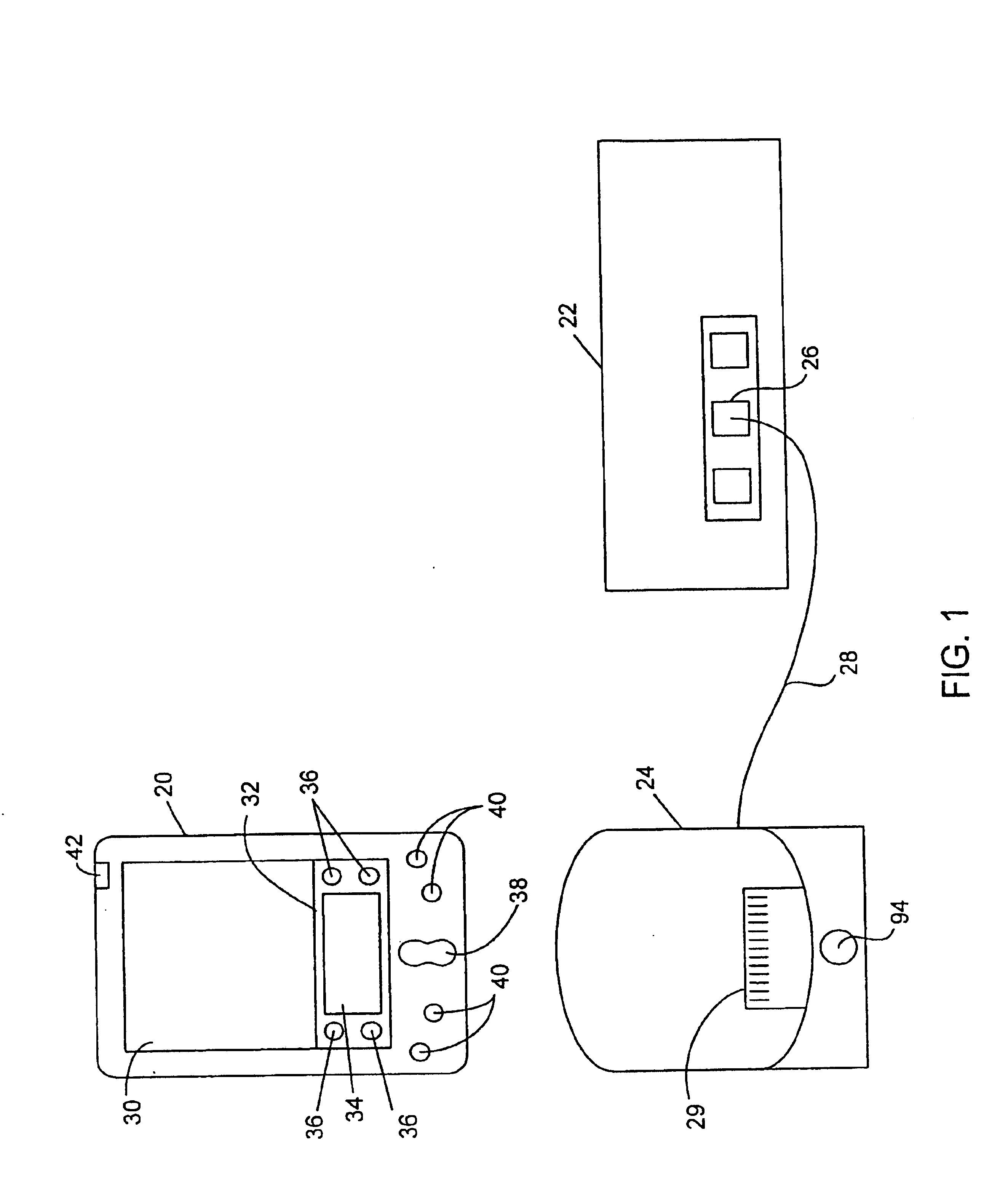

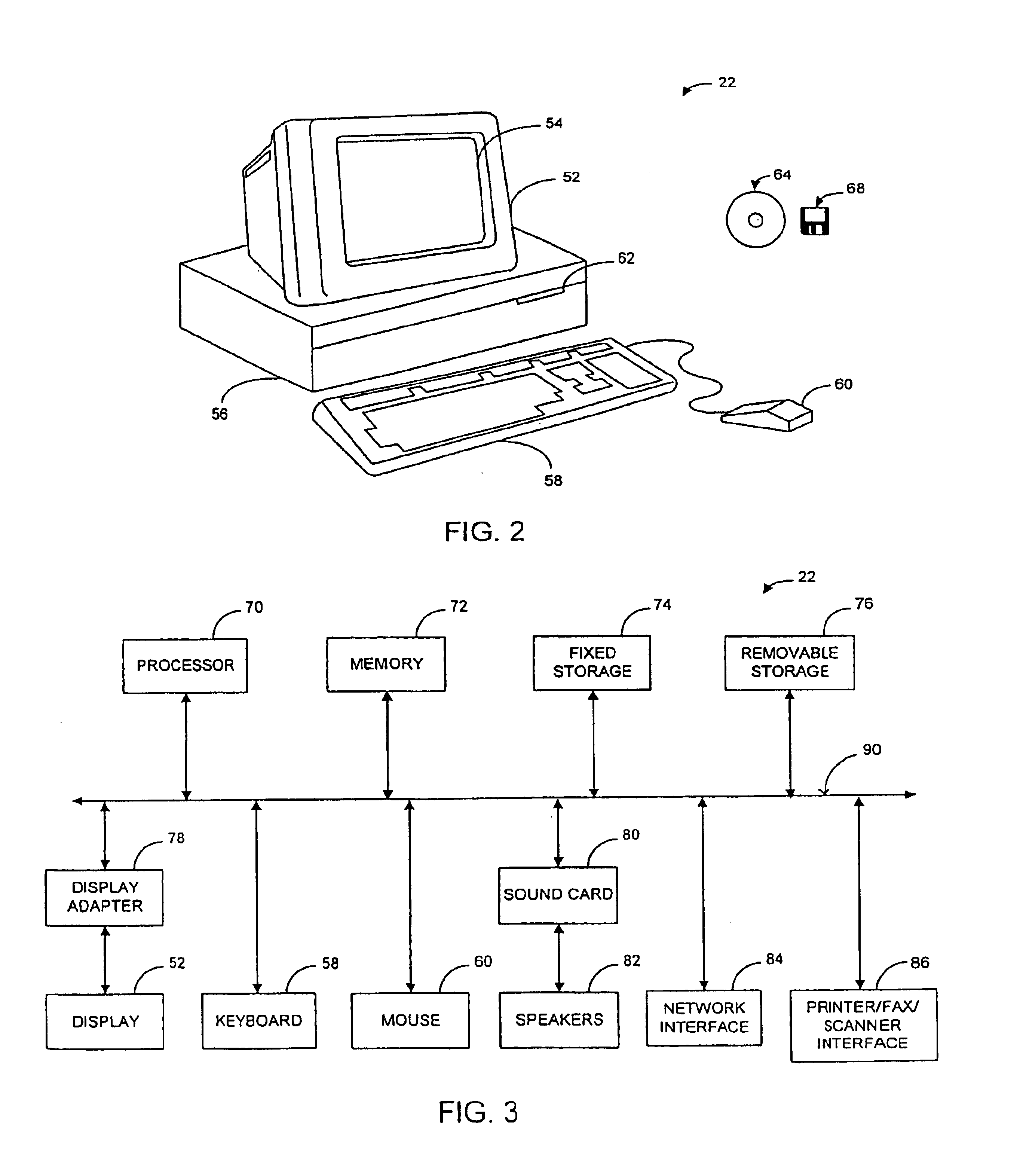

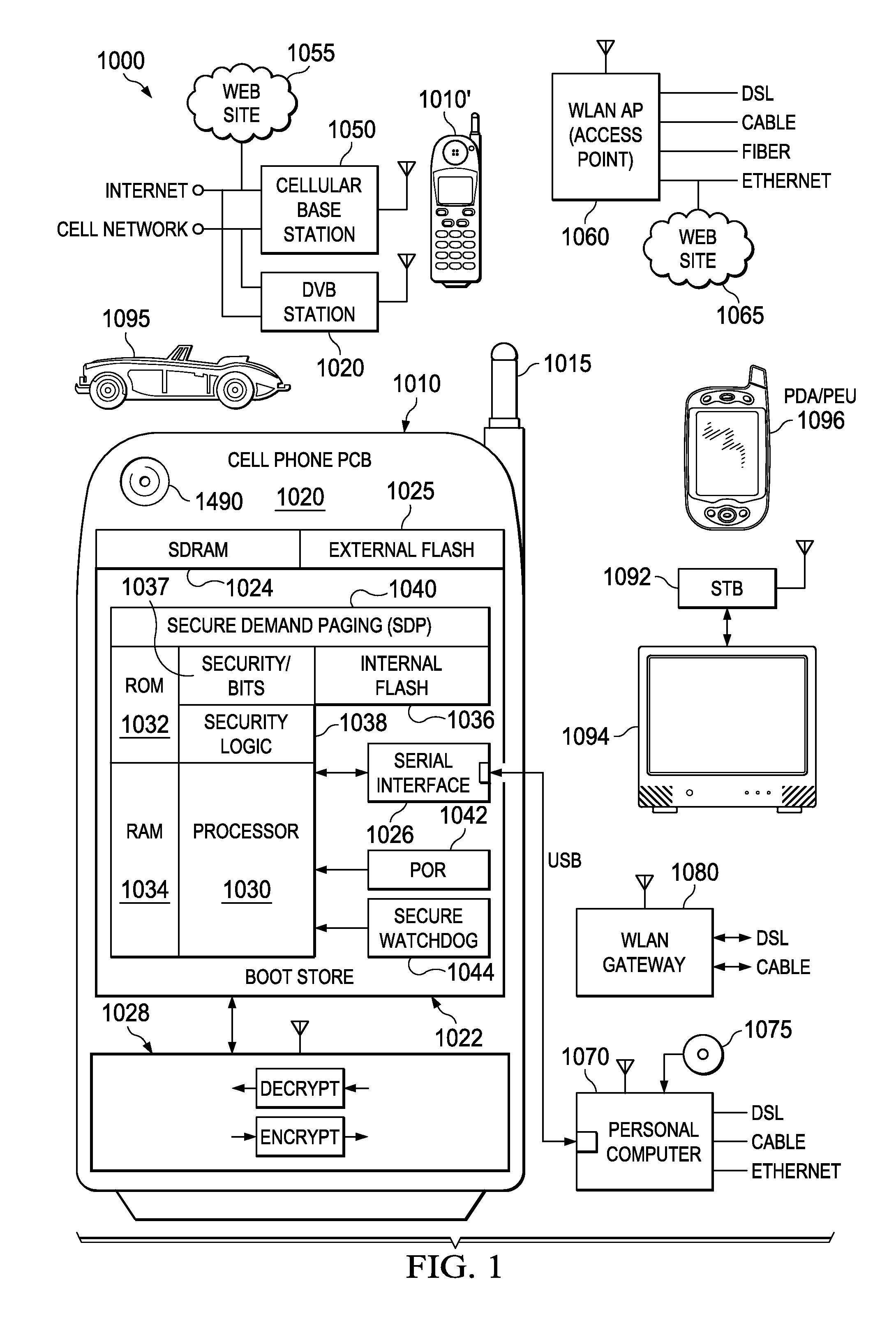

Method and system for detecting viruses on handheld computers

InactiveUS6842861B1Memory loss protectionUnauthorized memory use protectionComputerized systemHand Held Computer

A method and system for detecting viruses on handheld computers. The handheld computer is in communication with a computer system having a virus detection program. The method includes reading data from the handheld computer and writing the data at least temporarily to a database on the computer system. The data is scanned for viruses with the virus detection program. The method further includes updating data on the handheld computer based on results of the scanning.

Owner:MCAFEE INC

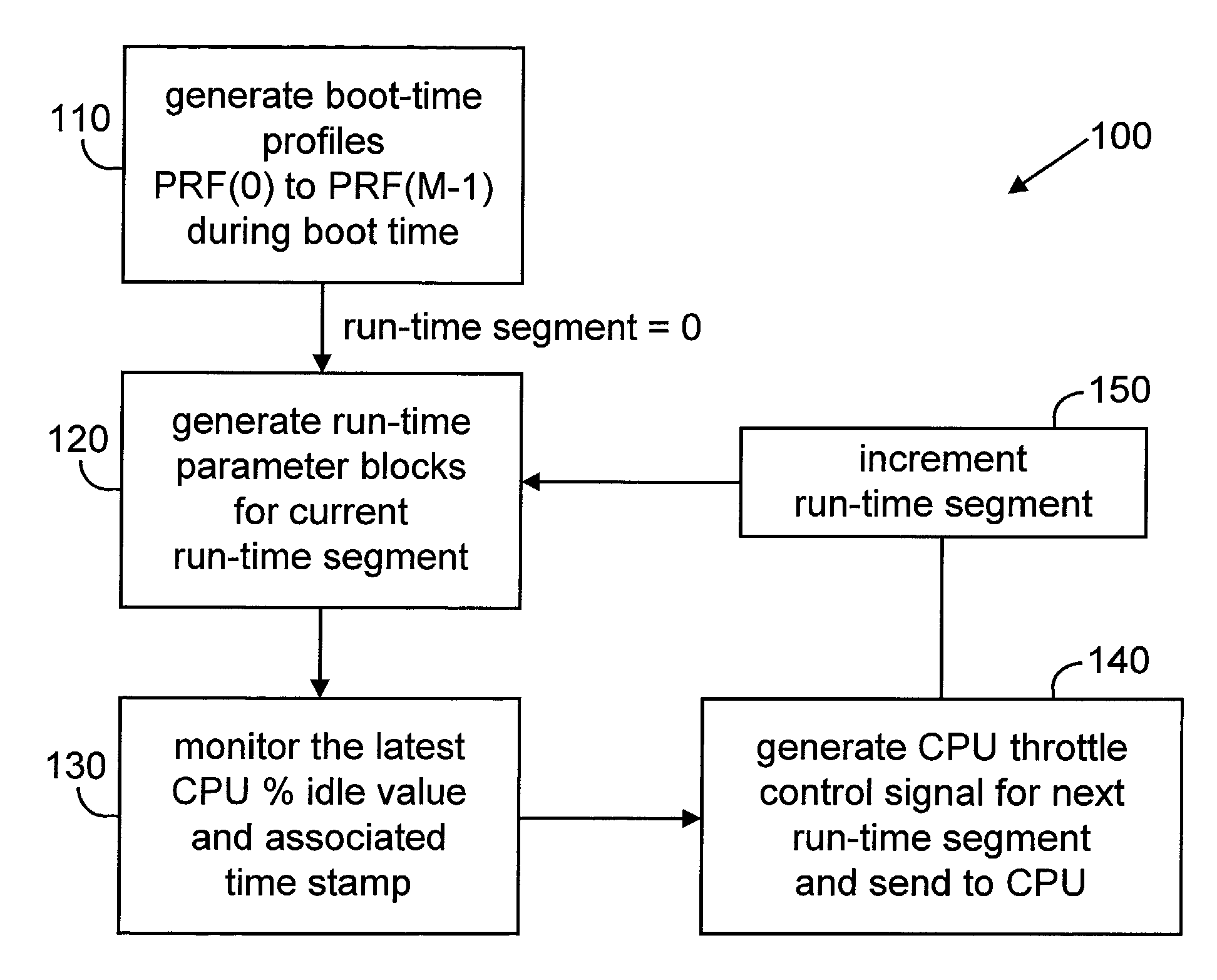

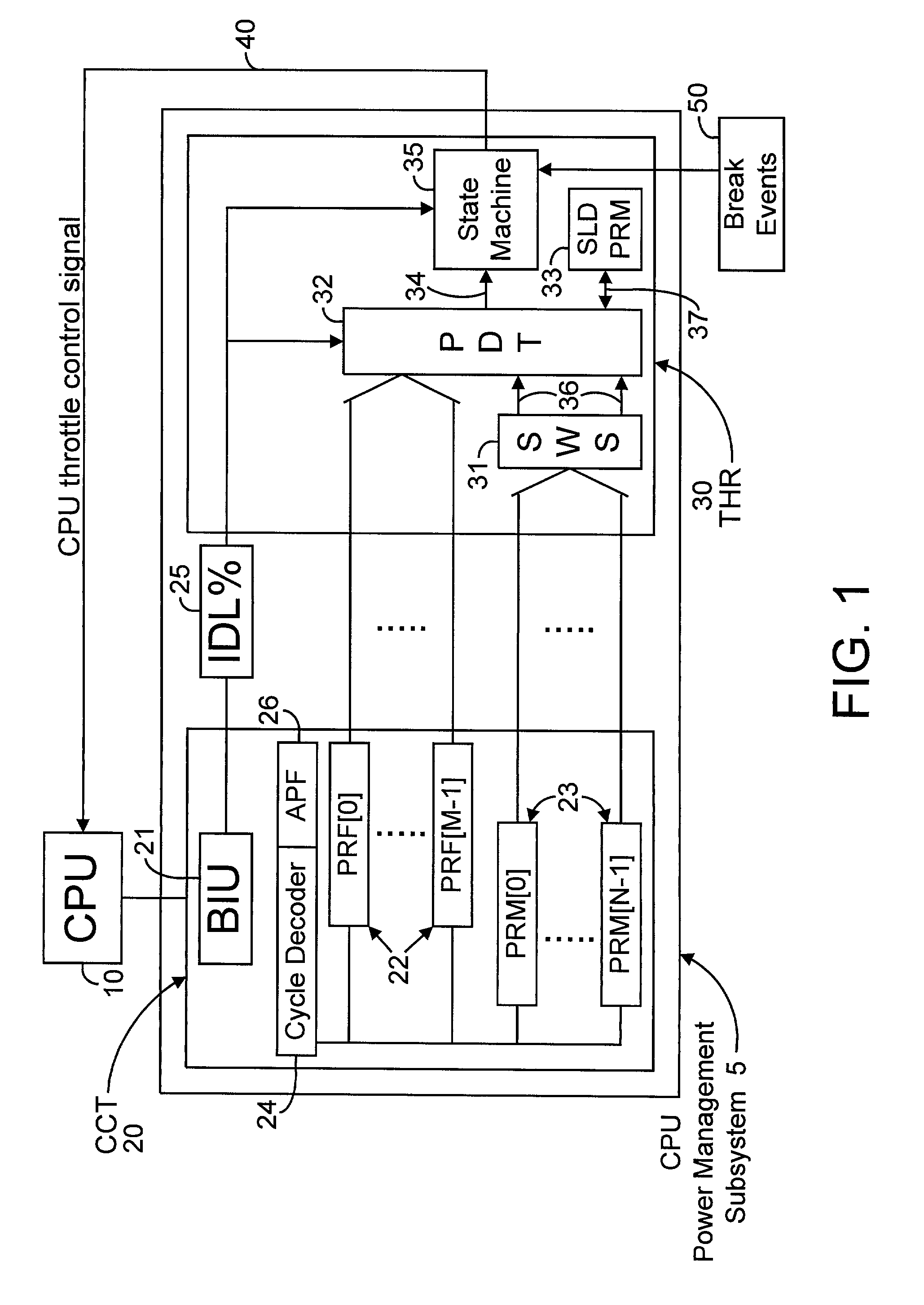

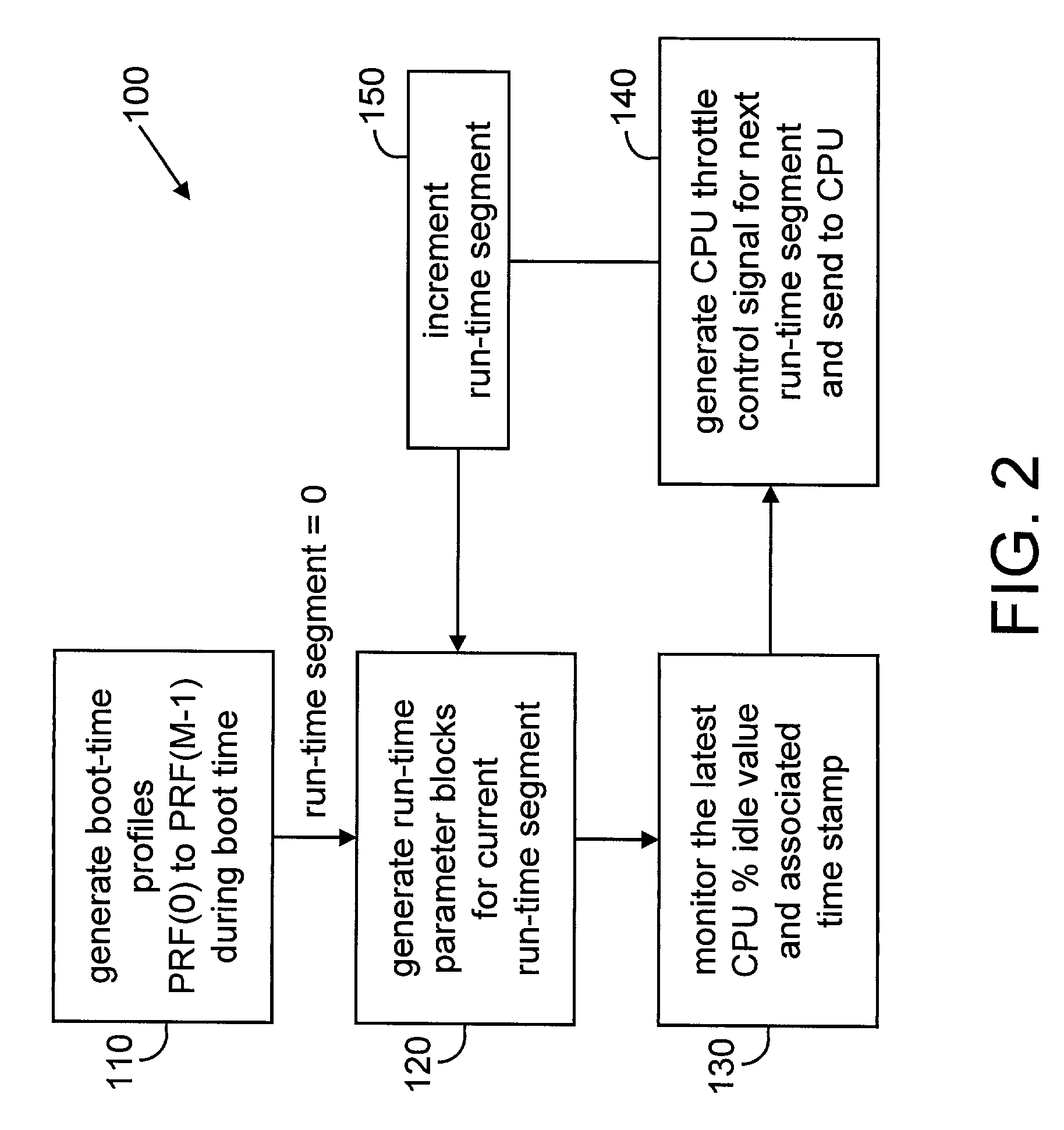

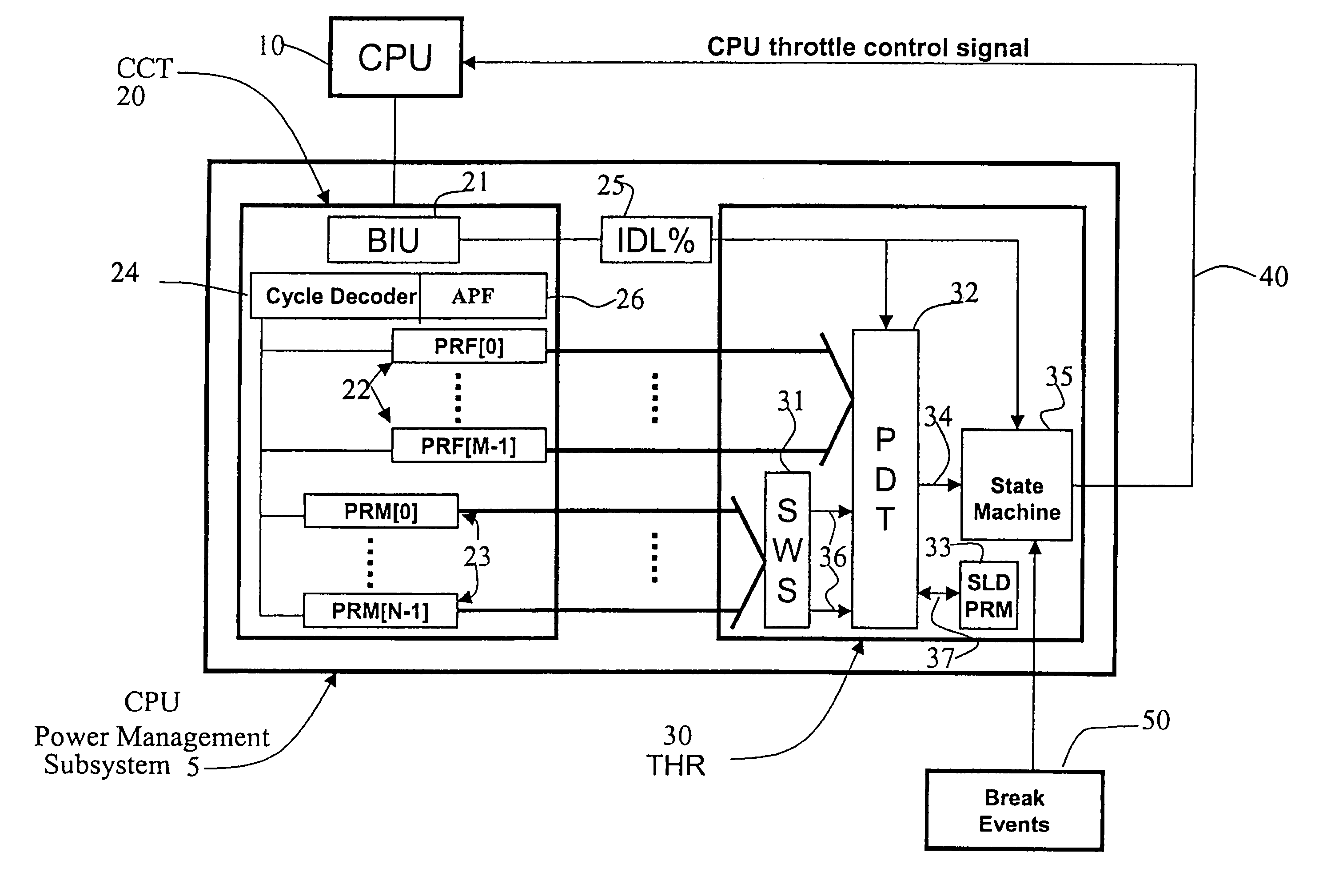

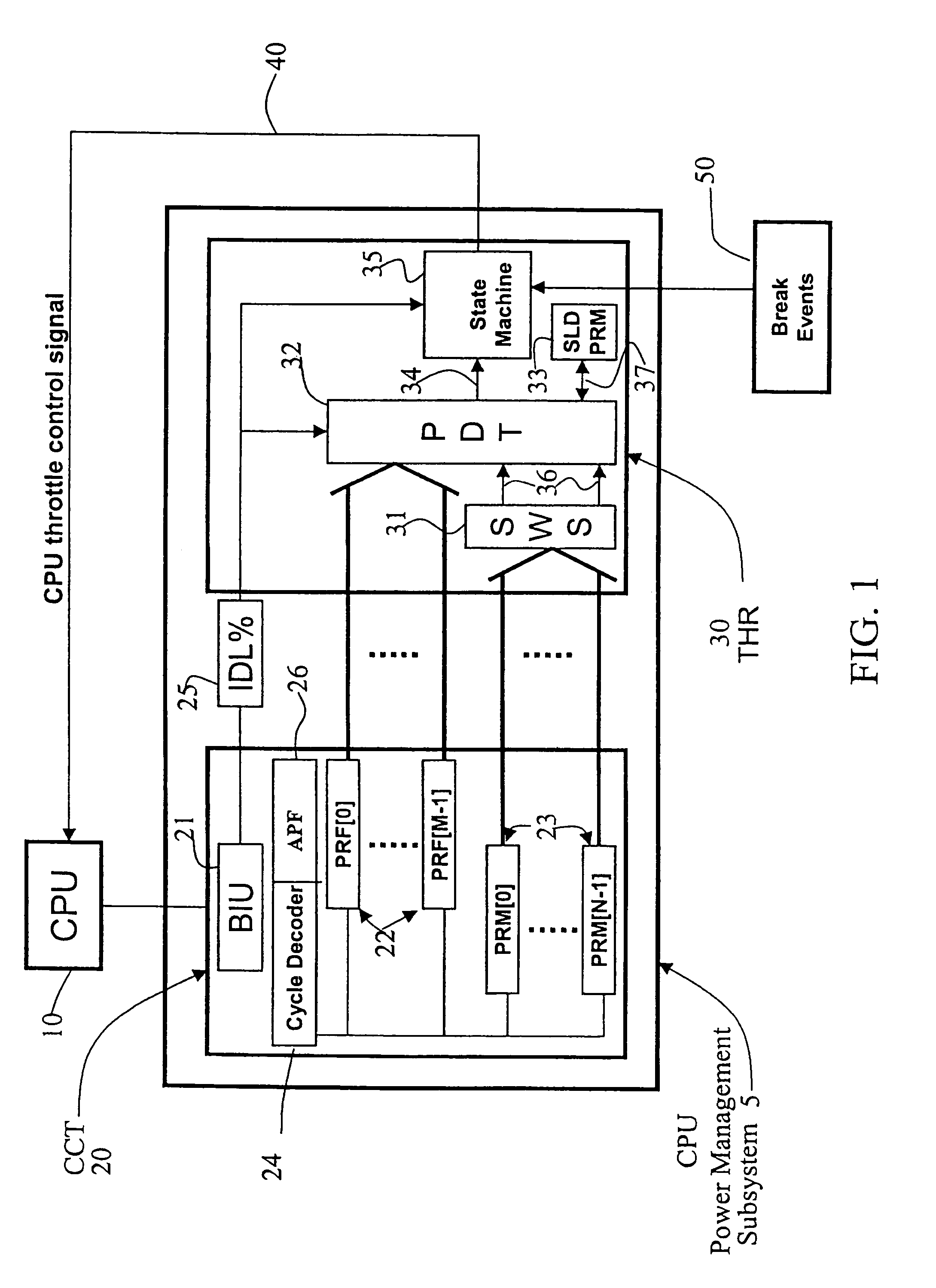

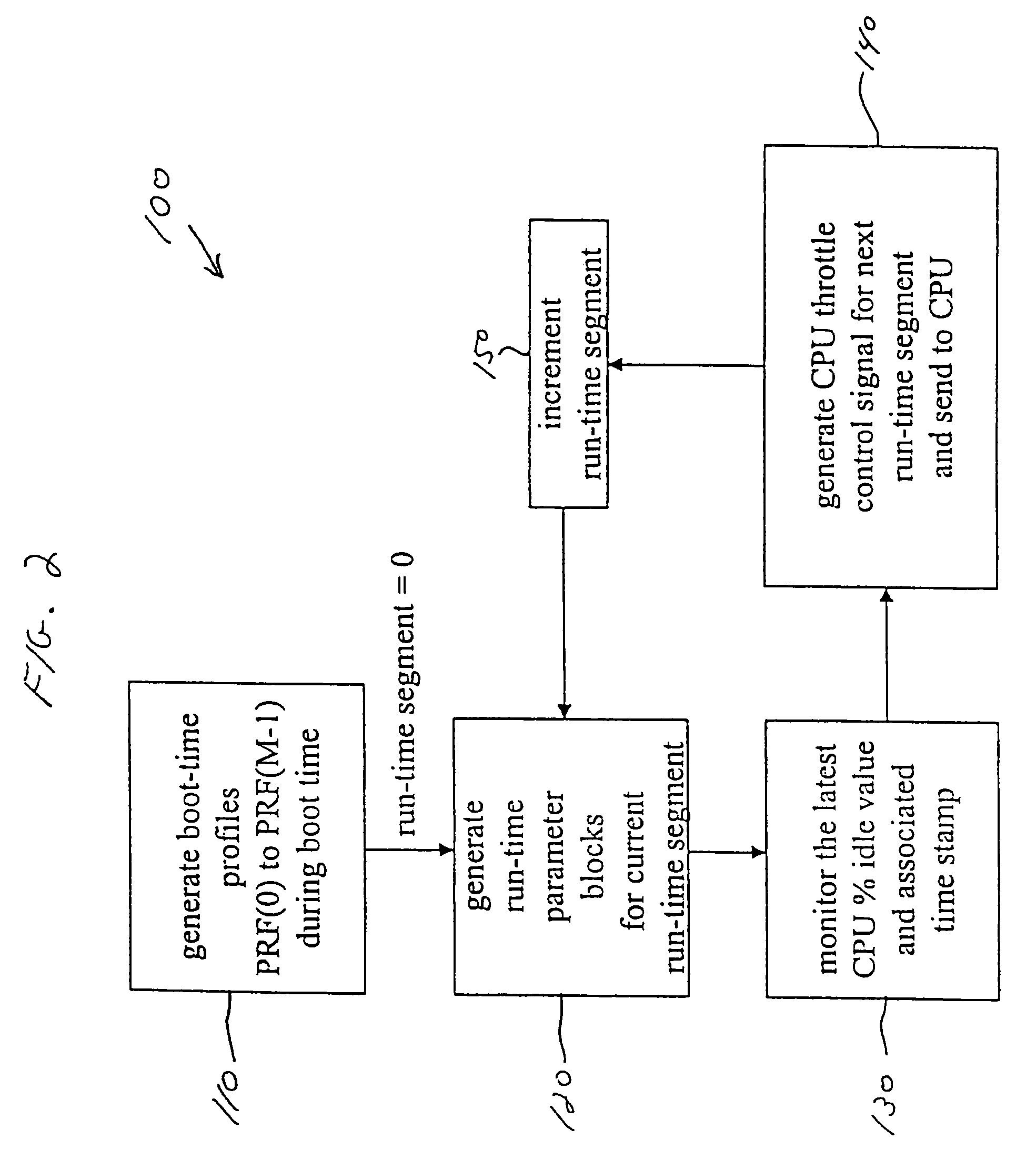

Method and apparatus for adaptive CPU power management

A method and apparatus are disclosed for performing adaptive run-time power management in a system employing a CPU and an operating system. A CPU cycle tracker (CCT) module monitors critical CPU signals and generates CPU performance data based on the critical CPU signals. An adaptive CPU throttler (THR) module uses the CPU performance data, along with a CPU percent idle value fed back from the operating system, to generate a CPU throttle control signal during predefined run-time segments of the CPU run time. The CPU throttle control signal links back to the CPU and adaptively adjusts CPU throttling and, therefore, power usage of the CPU during each of the run-time segments.

Owner:AVAGO TECH INT SALES PTE LTD

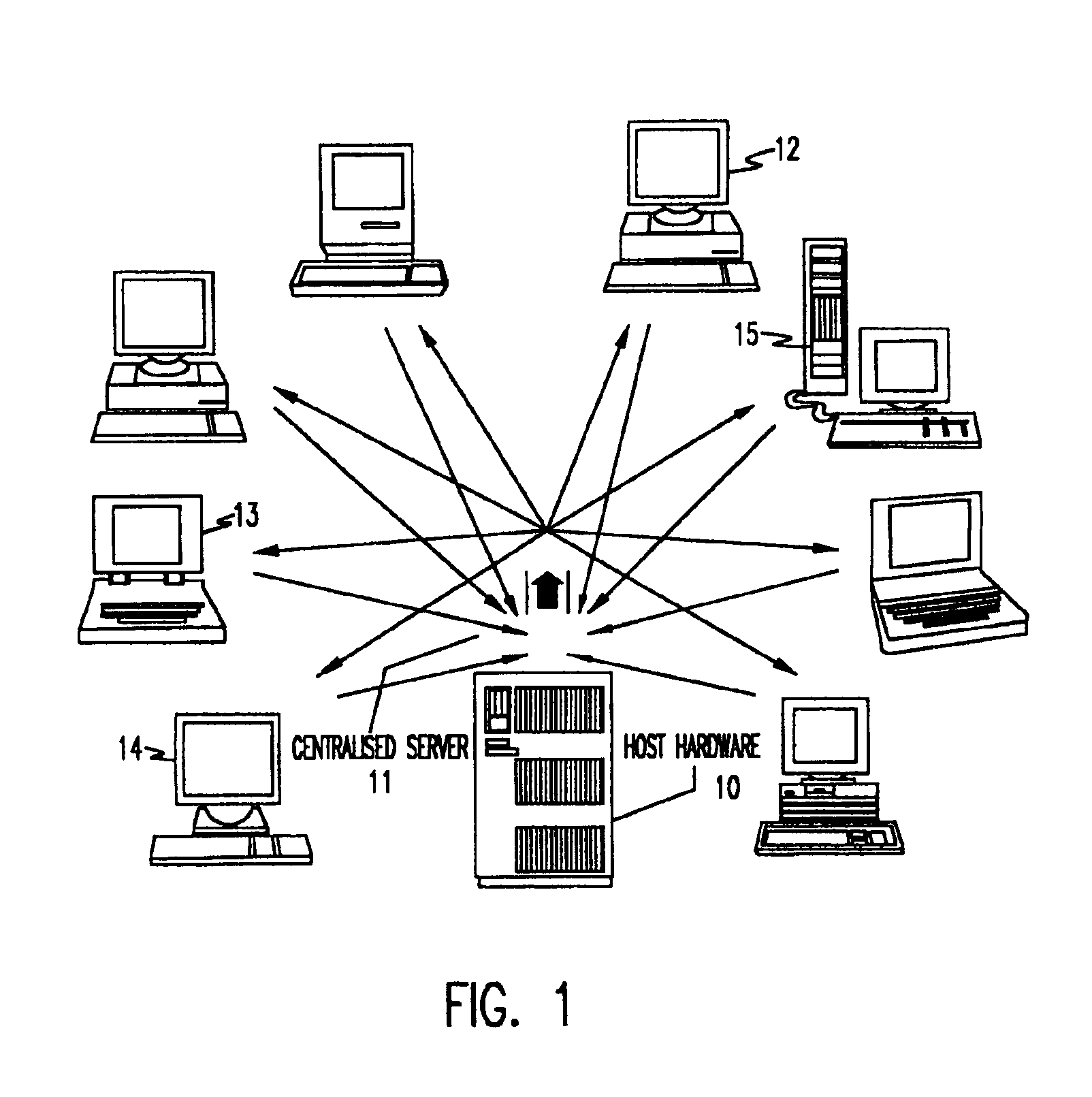

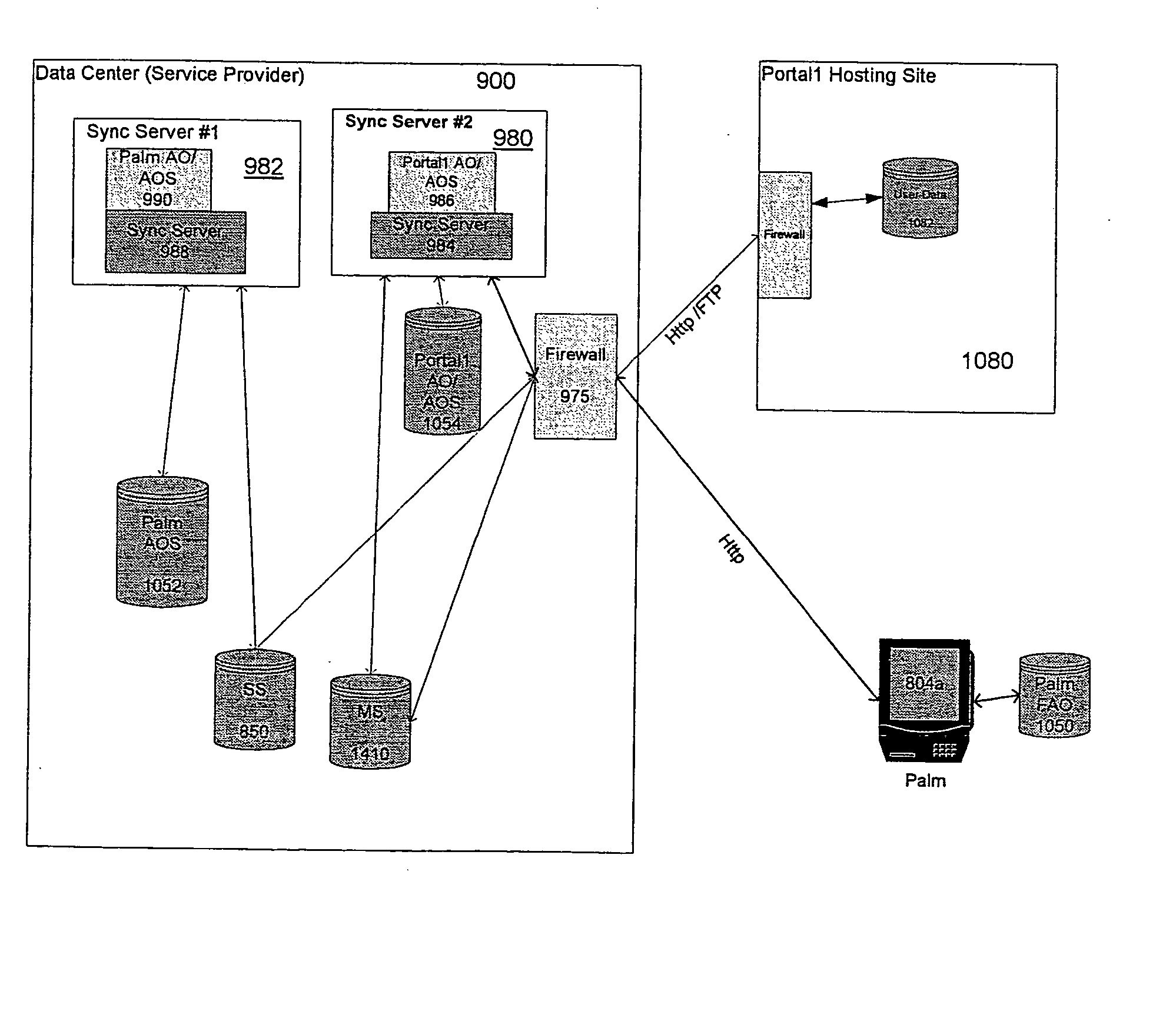

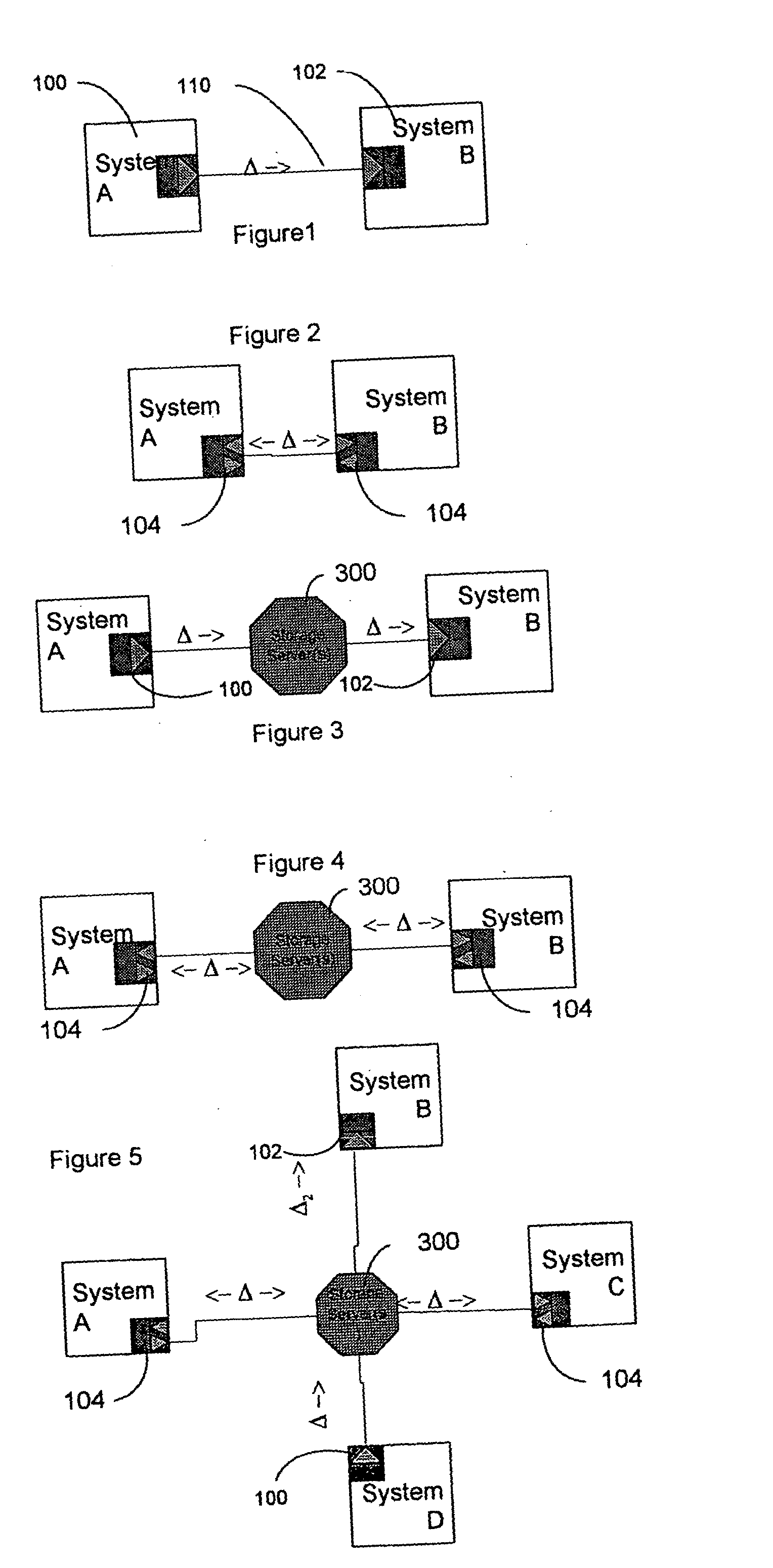

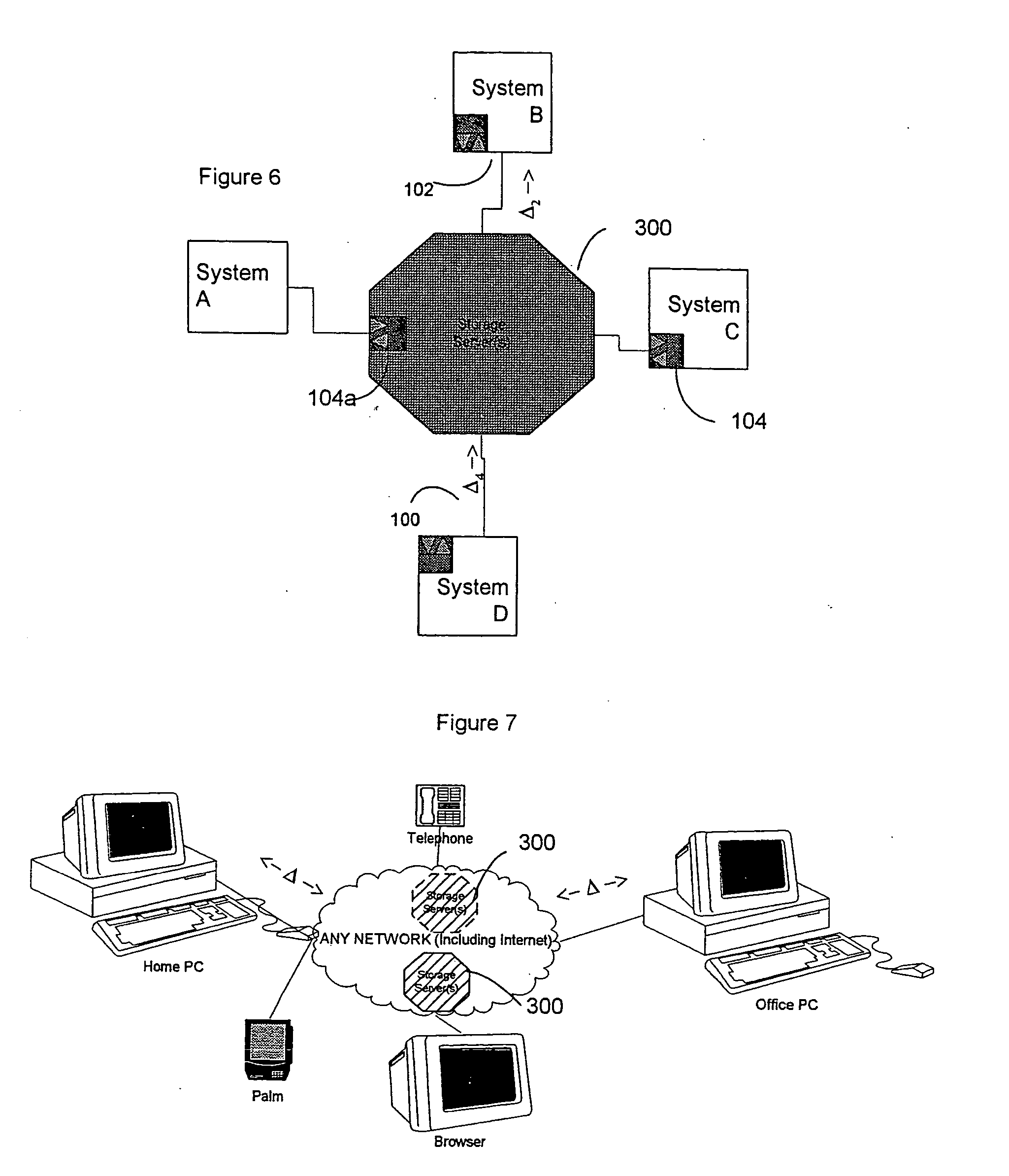

Data transfer and synchronization system

InactiveUS20040054711A1Data processing applicationsMultiple digital computer combinationsFile synchronizationData information

A system and method for synchronizing devices which can couple to the Internet, or any network. In one aspect a system for synchronizing data between a first system and a second system is provided. The system includes a first sync engine on the first system interfacing with data on the first system to provide difference information. A data store is coupled to network and in communication with the first and second systems. A second sync engine is provided on the second system coupled to receive the difference information from the data store via the network, and interfacing with data on the second system to update said data on the second system with said difference information. Difference information is transmitted to the data store by the first sync engine and received from the data store from the second sync engine. The system may include a management server coupled to the network and in communication with the first sync engine, the second sync engine and the data store. The system may include a plurality of sync engines on a respective plurality of systems, each of said plurality of engines being coupled to receive difference information from each of said first, second and plurality of sync engines from the data store via the network. Each said engine interfaces with data on the system on which it resides to update said data on said system on which it resides with said difference information, and interfaces with data on said system on which it resides to provide difference data information from the system on which it resides to the data store. In a further embodiment, the invention comprises a method for synchronizing at least a first file and a second file resident on a first and a second systems, respectively, coupled to the Internet, respectively. The method includes the steps of: determining difference data resulting from changes to the first file on the first system; transmitting the difference data to a server via the Internet; querying the server from a second system to determine whether difference data exists for files on the second system; retrieving the difference data to the second system; and updating the second file on the second system with the difference data.

Owner:SYNCHRONOSS TECH

Method and apparatus for adaptive CPU power management

A method and apparatus are disclosed for performing adaptive run-time power management in a system employing a CPU and an operating system. A CPU cycle tracker (CCT) module monitors critical CPU signals and generates CPU performance data based on the critical CPU signals. An adaptive CPU throttler (THR) module uses the CPU performance data, along with a CPU percent idle value fed back from the operating system, to generate a CPU throttle control signal during predefined run-time segments of the CPU run time. The CPU throttle control signal links back to the CPU and adaptively adjusts CPU throttling and, therefore, power usage of the CPU during each of the run-time segments.

Owner:AVAGO TECH INT SALES PTE LTD

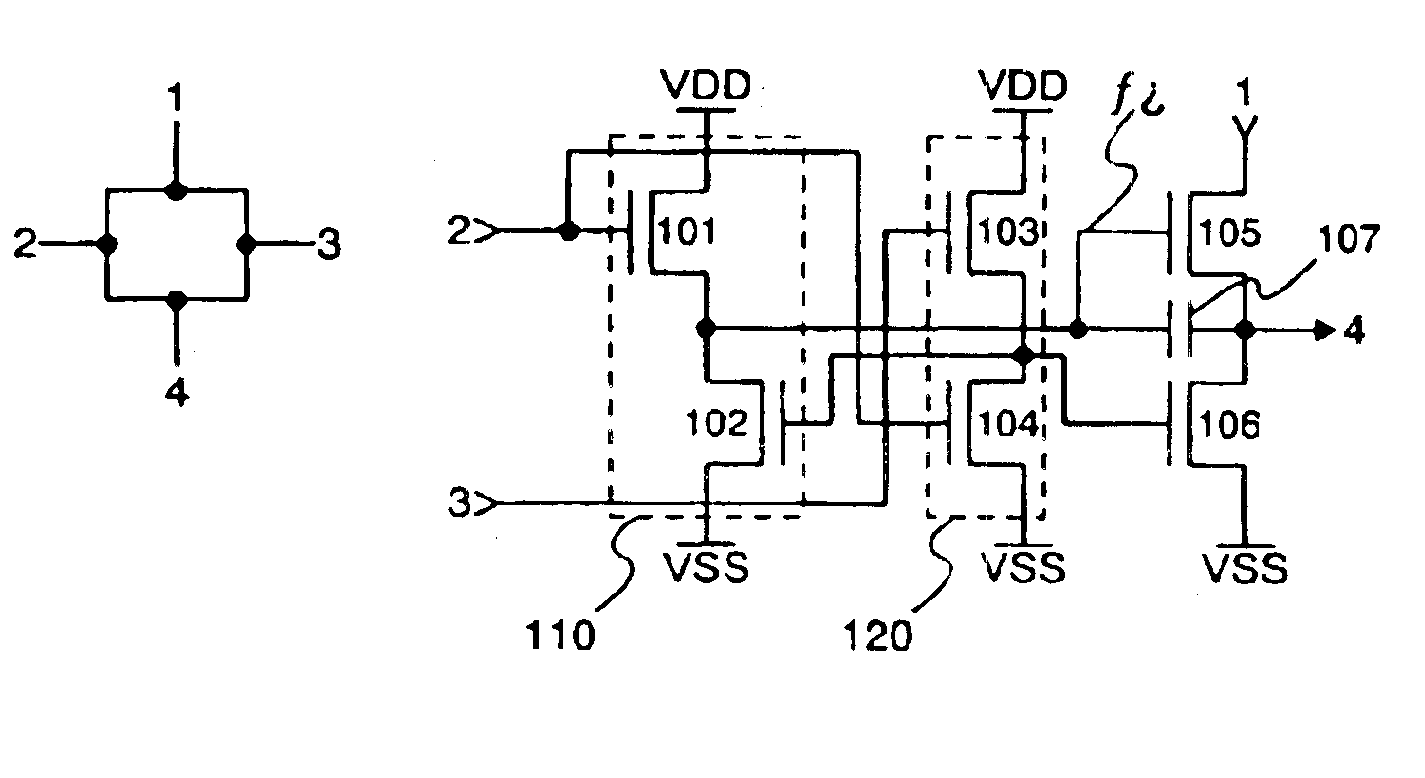

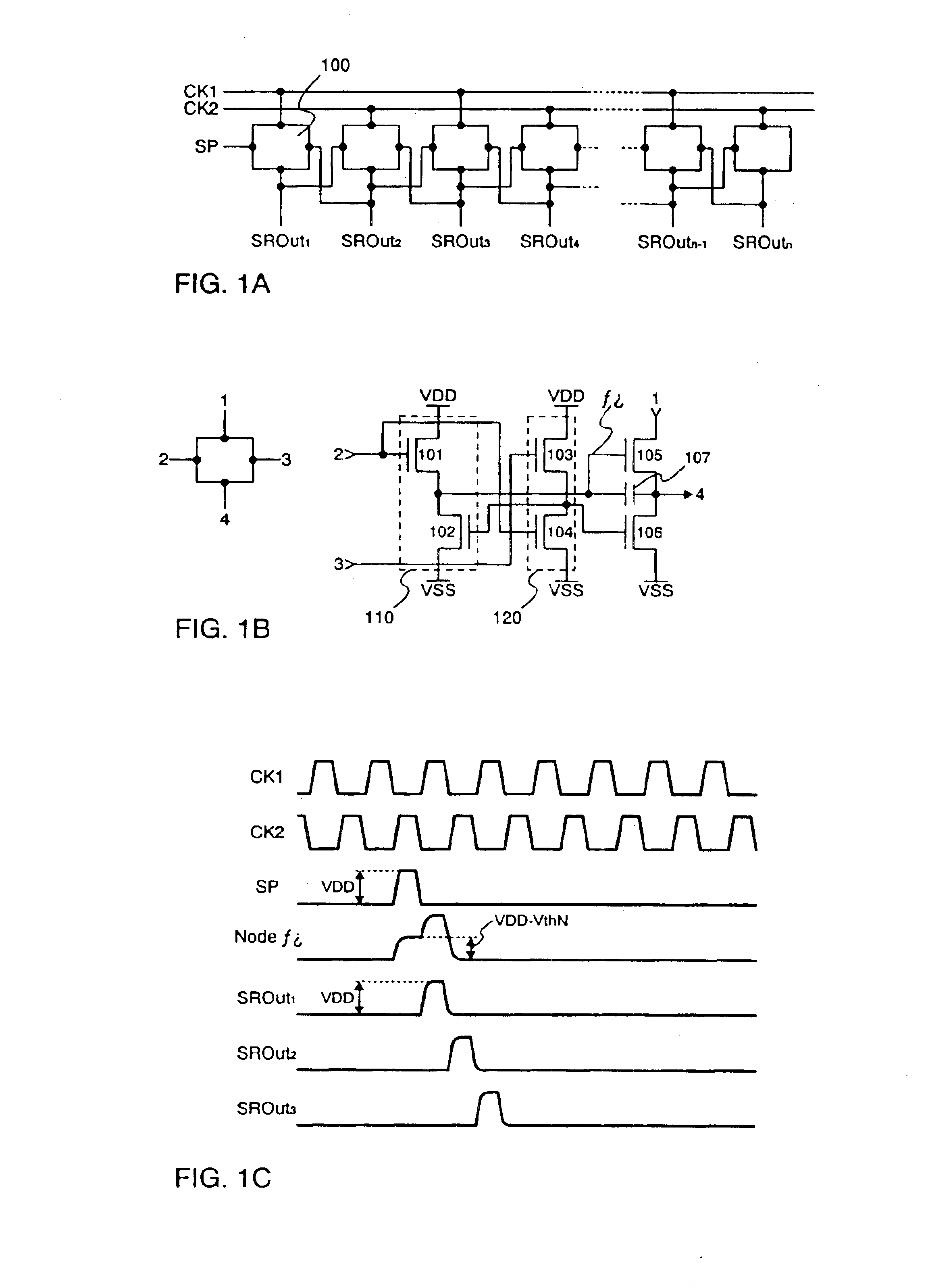

Pulse output circuit, shift register and electronic equipment

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 On, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

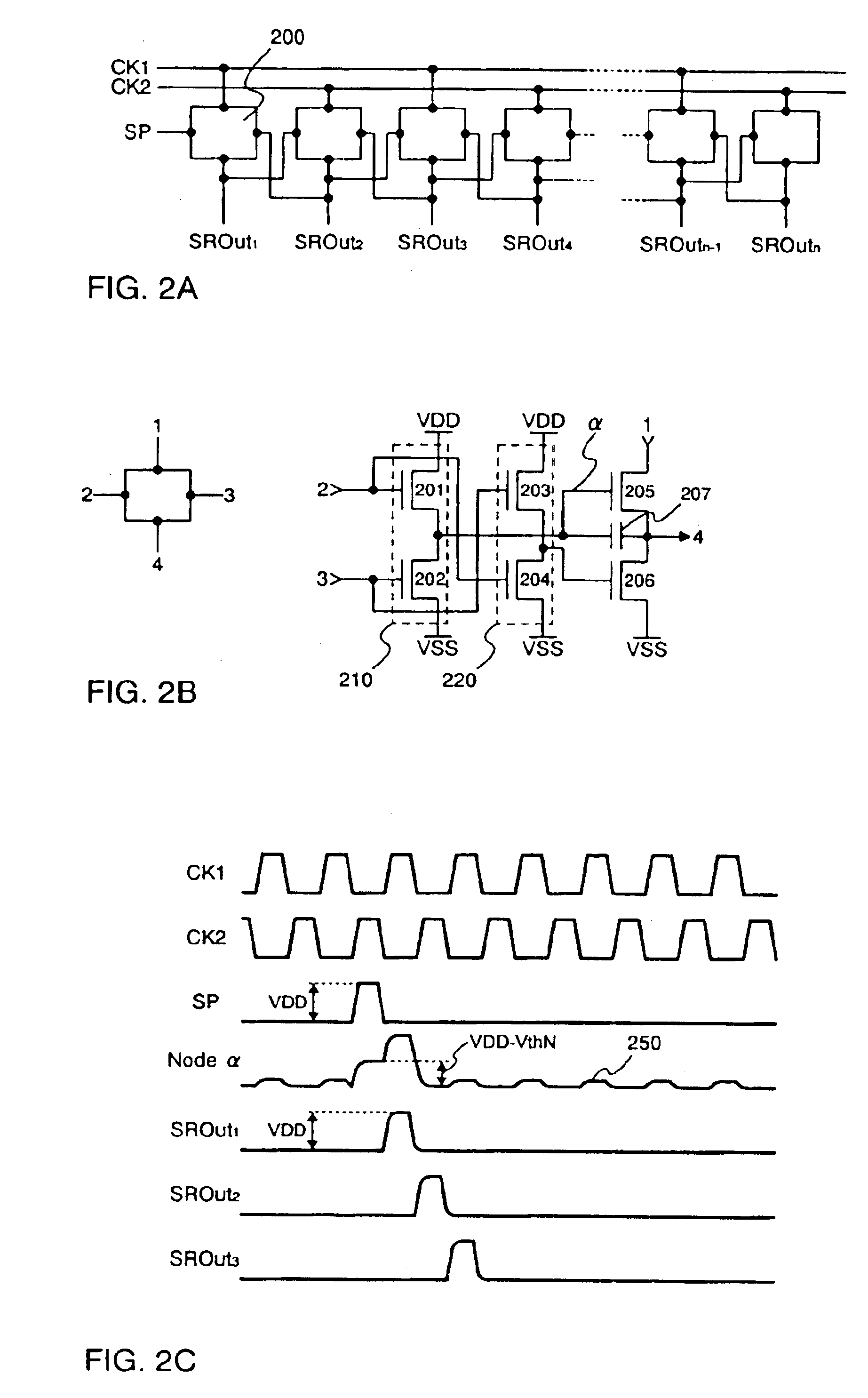

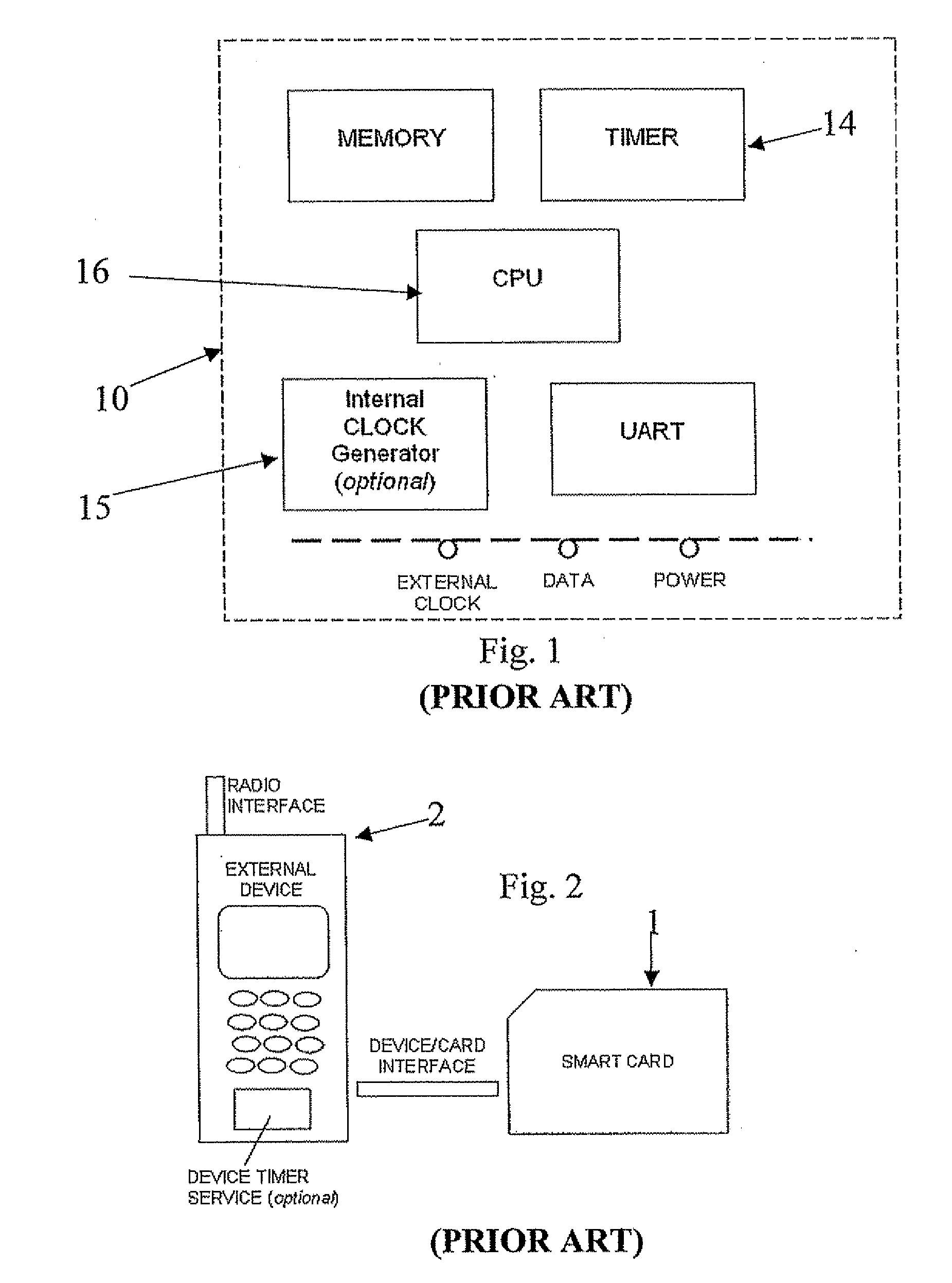

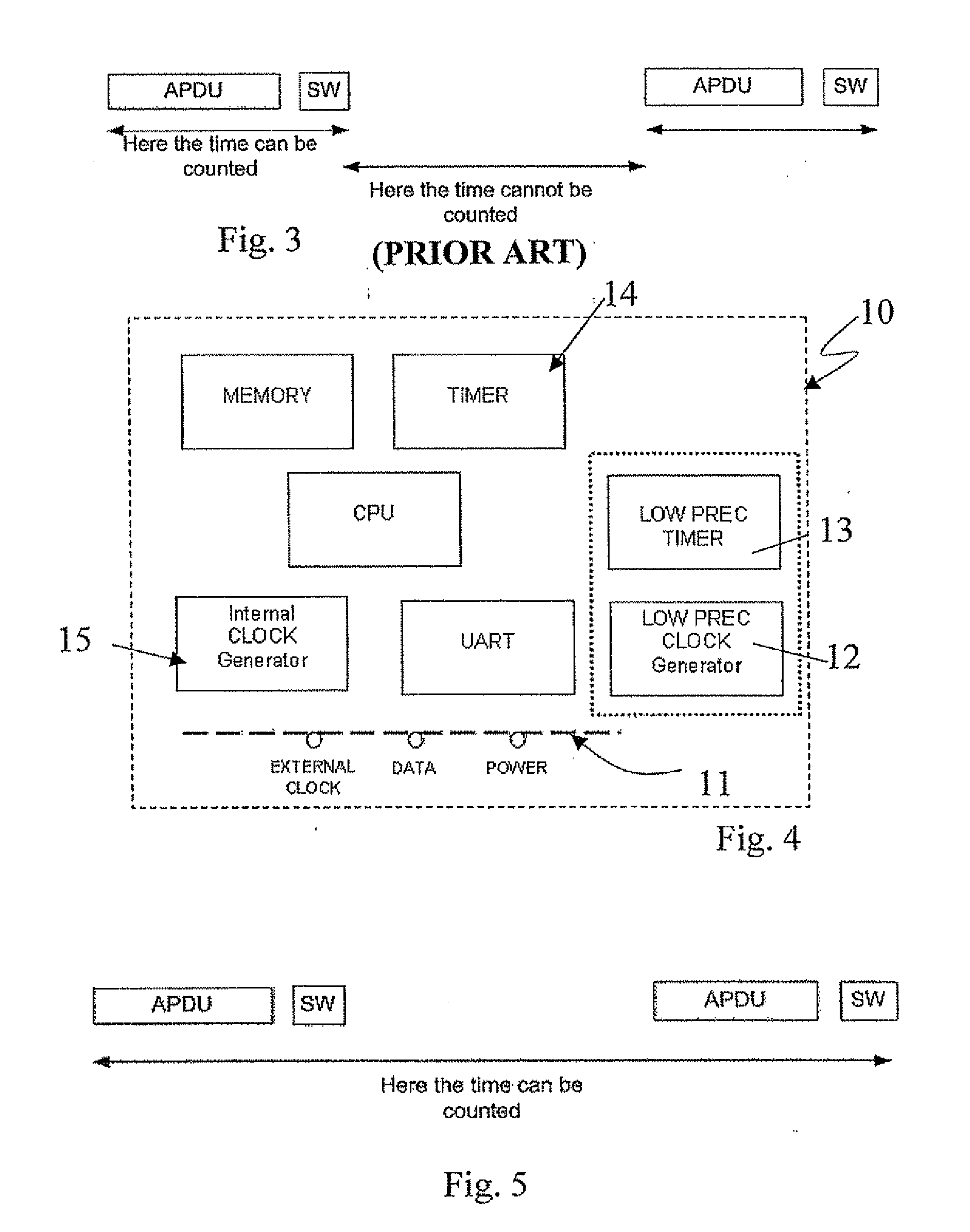

IC card with low precision clock

ActiveUS20080294930A1Avoid power consumptionHigh power consumptionGenerating/distributing signalsData conversionElectronic componentPower consumption

An IC Card may include electronic components to receive a power supply and a main clock signal by a reader device. The power supply may be provided to a subset of the electronic components during a main clock stop status wherein the main clock signal is suspended for avoiding a maximum power consumption threshold. The IC Card may also include a low precision clock included in the subset of electronic components for measuring time in the main clock stop status.

Owner:STMICROELECTRONICS INT NV

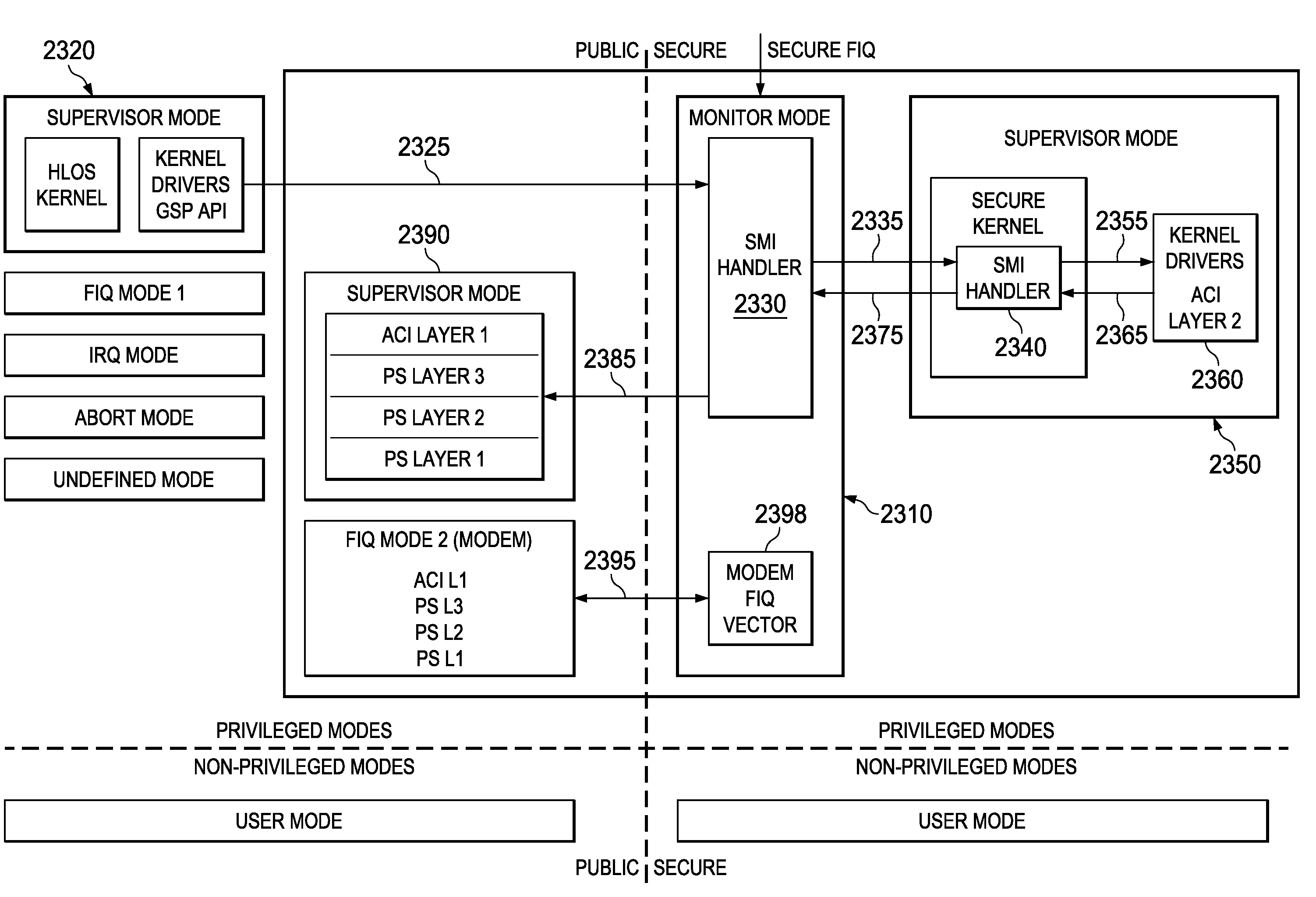

Interrupt morphing and configuration, circuits, systems, and processes

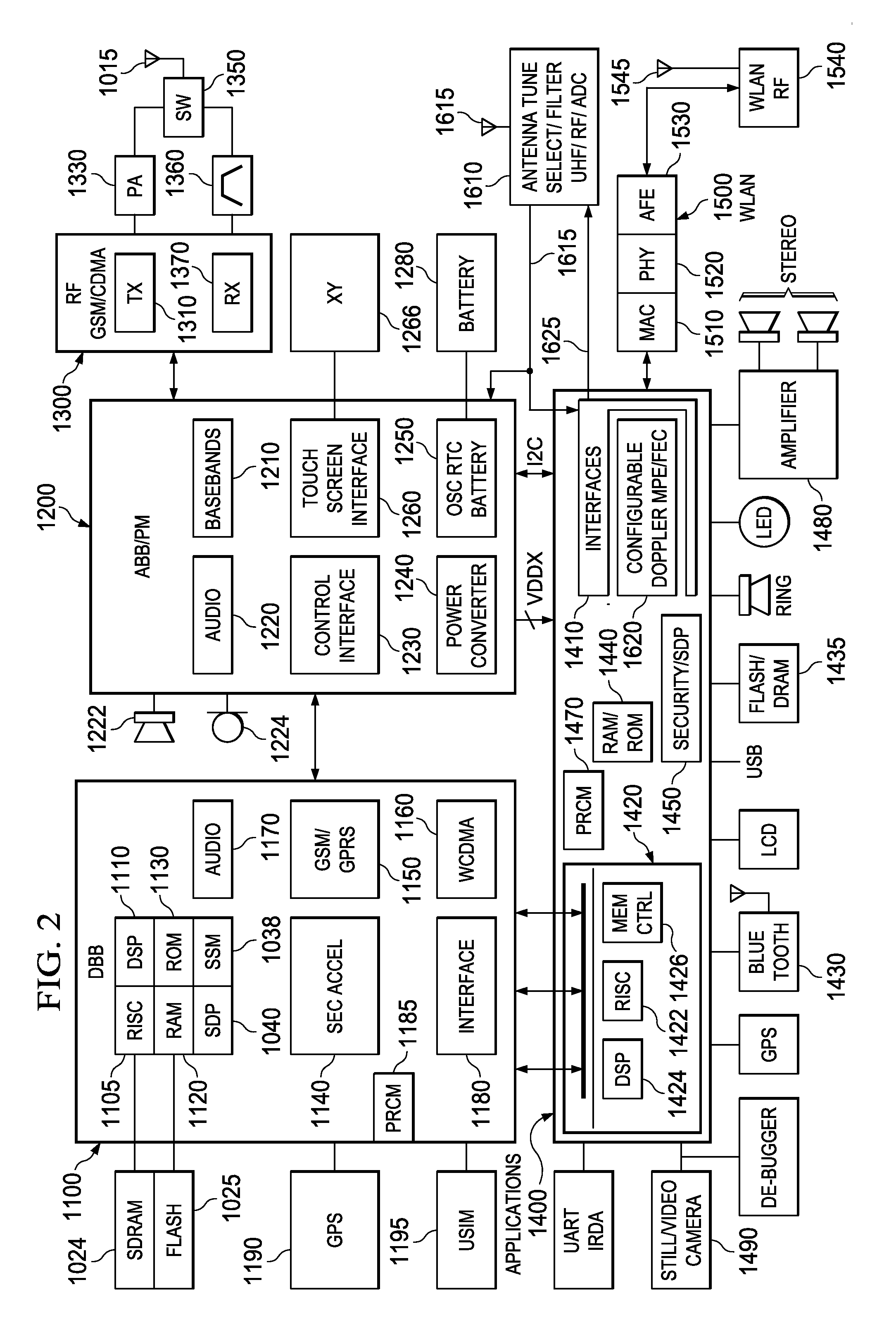

ActiveUS20090157936A1Energy efficient ICTInternal/peripheral component protectionMorphingProcessor register

An electronic configuration circuit includes a processing circuit (2610) operable for executing instructions and responsive to interrupt requests and operable in a plurality of execution environments (EE) selectively wherein a said execution environment (EE) is activated or suspended, a first configuration register (SCR) coupled to the processing circuit (2610) for identifying the interrupt request as an ordinary interrupt request IRQ when the execution environment (EE) is activated (EE_Active); and a second configuration register (SSM_FIQ_EE_y) for associating an identification of that execution environment (EE) with the same interrupt request, the processing circuit (2610) coupled (5910) to the second configuration register (SSM_FIQ_EE_y) to respond to the same interrupt request as a more urgent type of interrupt request when that execution environment (EE) is suspended (5920).

Owner:TEXAS INSTR INC

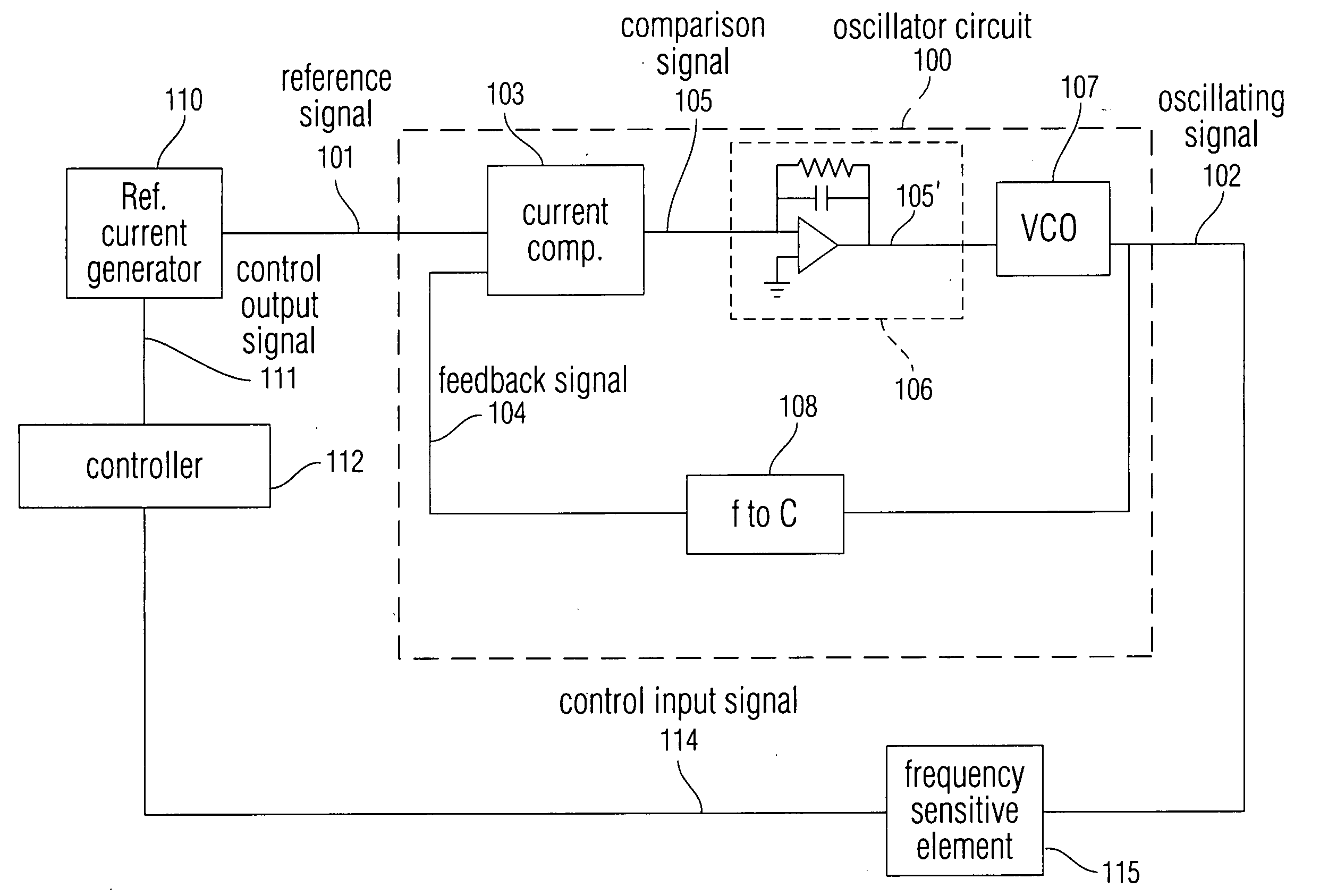

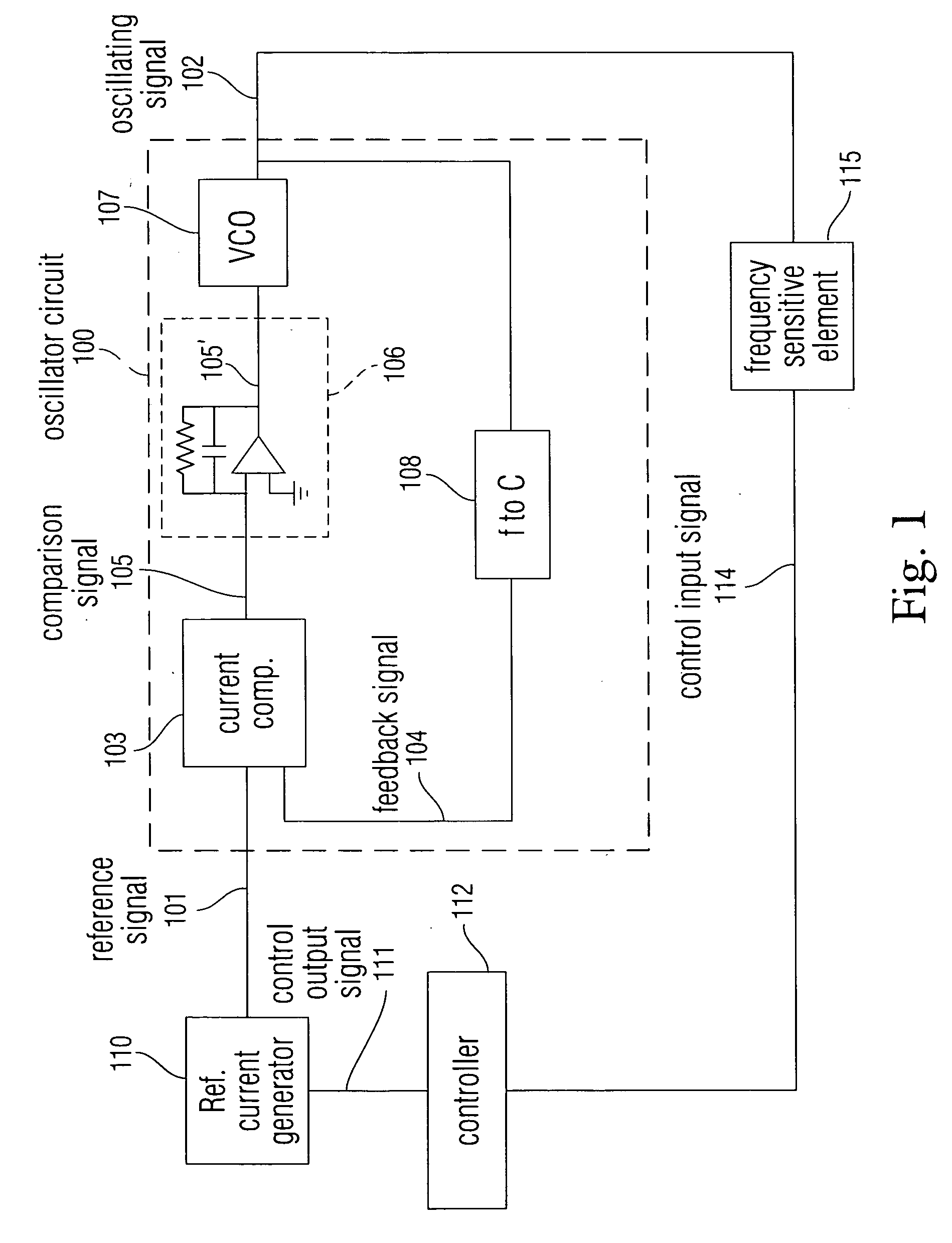

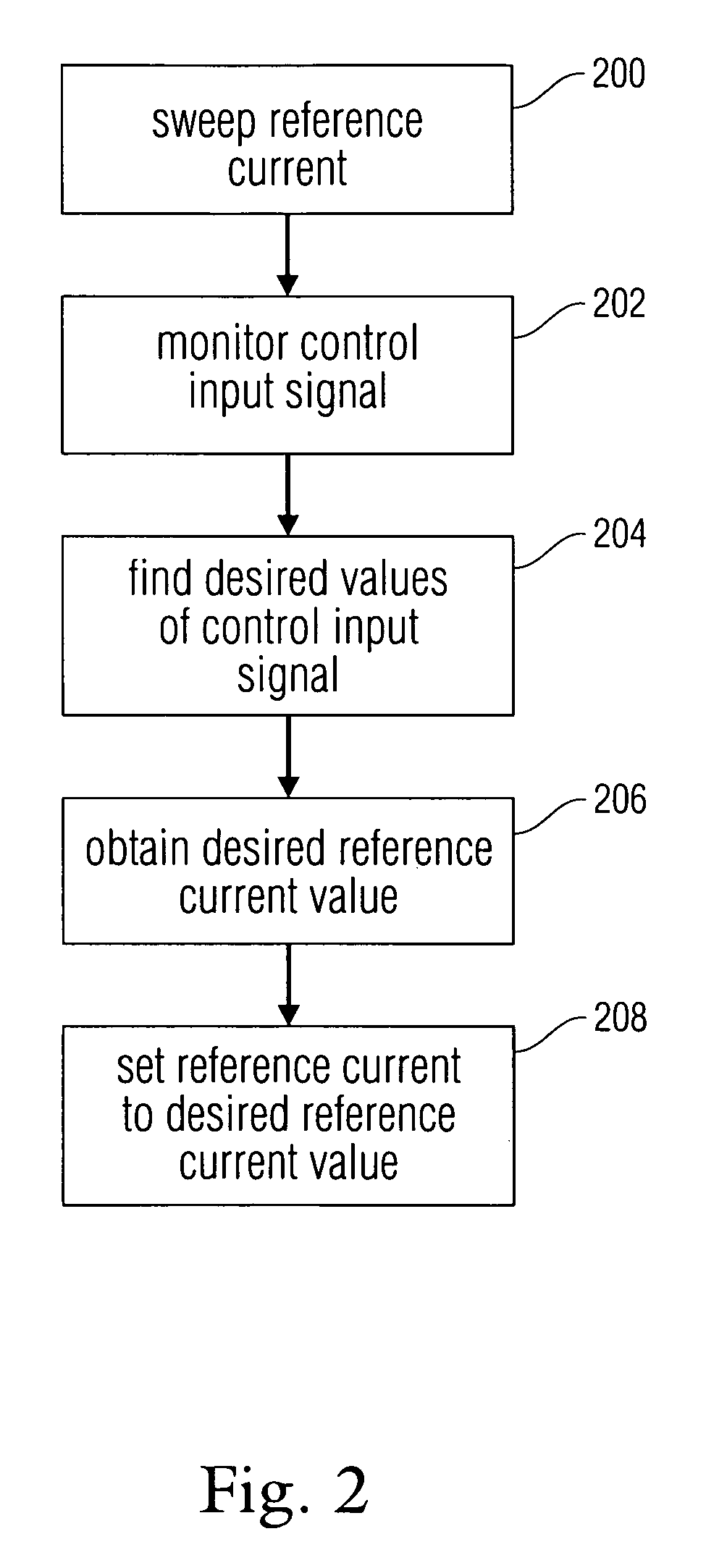

Noise reduction within an electronic device using automatic frequency modulation

ActiveUS20080157893A1High frequencyLimitation to input signalPulse automatic controlFrequency analysisEngineeringNoise reduction

Disclosed is a system and method for providing an oscillating signal of relatively precise frequency without using a signal provided by a crystal as a reference. Disclosed is a feedback oscillator circuit configured to output an oscillating signal having a frequency defined by a reference signal. The oscillating signal can be sent to one or more circuits including at least one frequency sensitive element. The frequency sensitive element produces an output signal which depends on the frequency of the oscillating signal. A controller controls the reference signal in order to cause an attribute of the output signal to have a value within a desired range.

Owner:APPLE INC