Patents

Literature

26785 results about "Clock signal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics and especially synchronous digital circuits, a clock signal is a particular type of signal that oscillates between a high and a low state and is used like a metronome to coordinate actions of digital circuits.

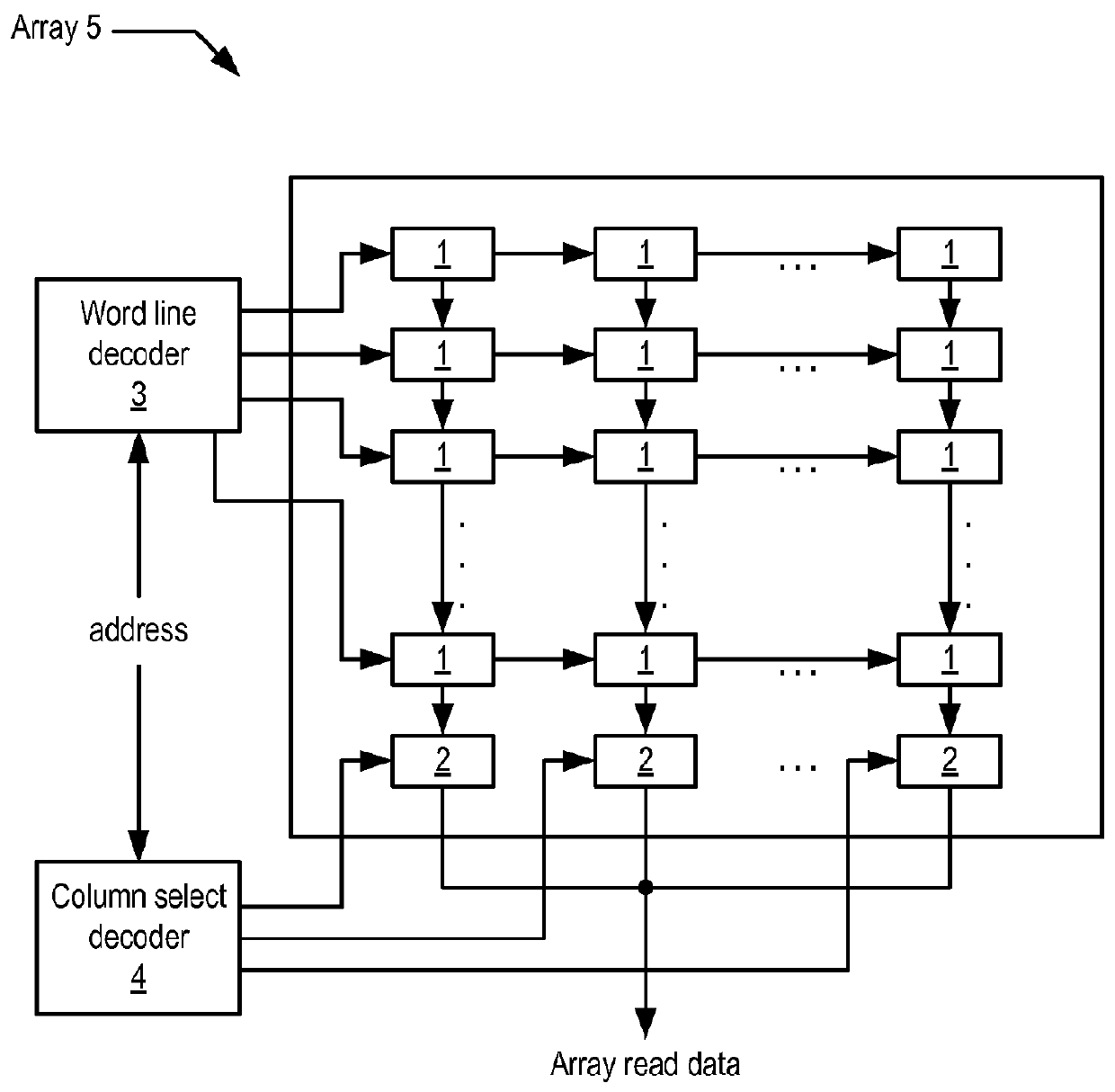

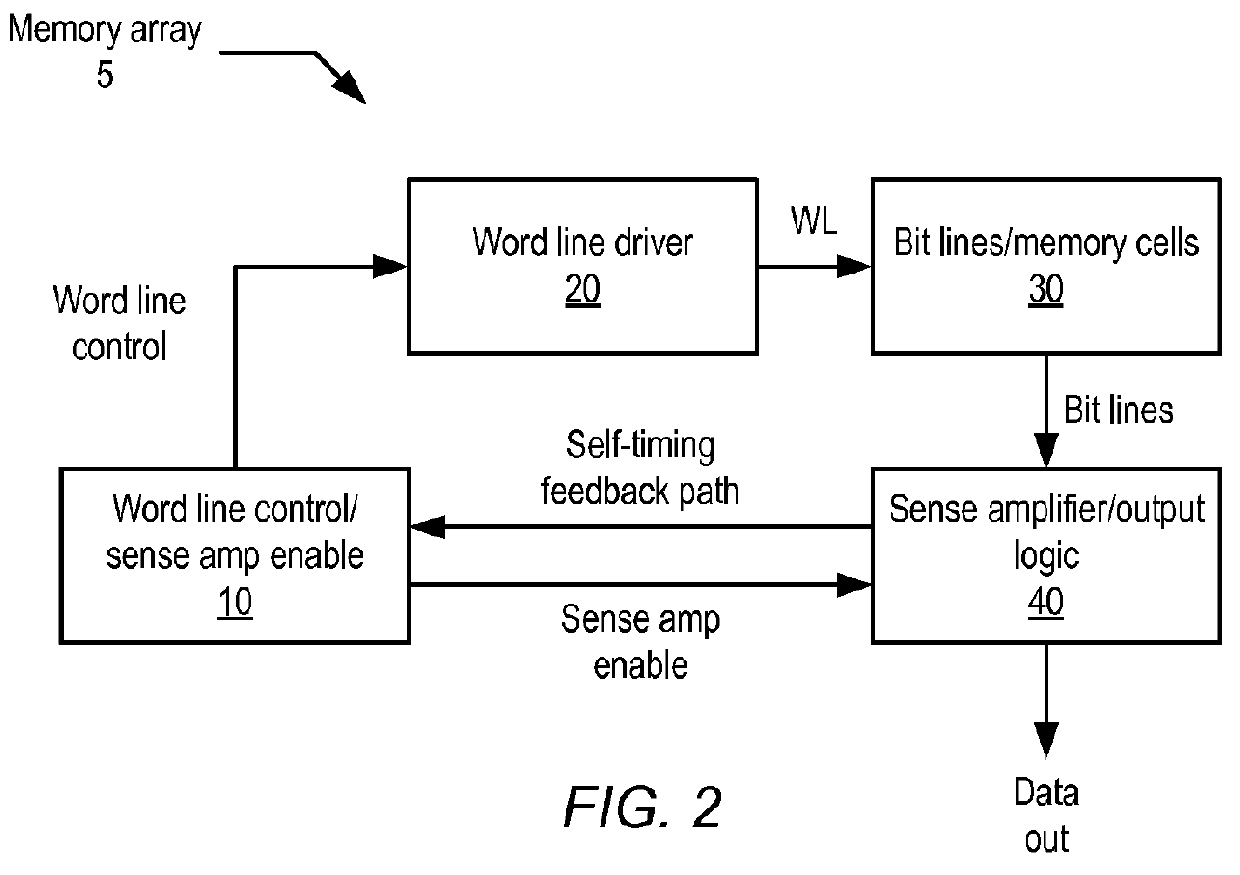

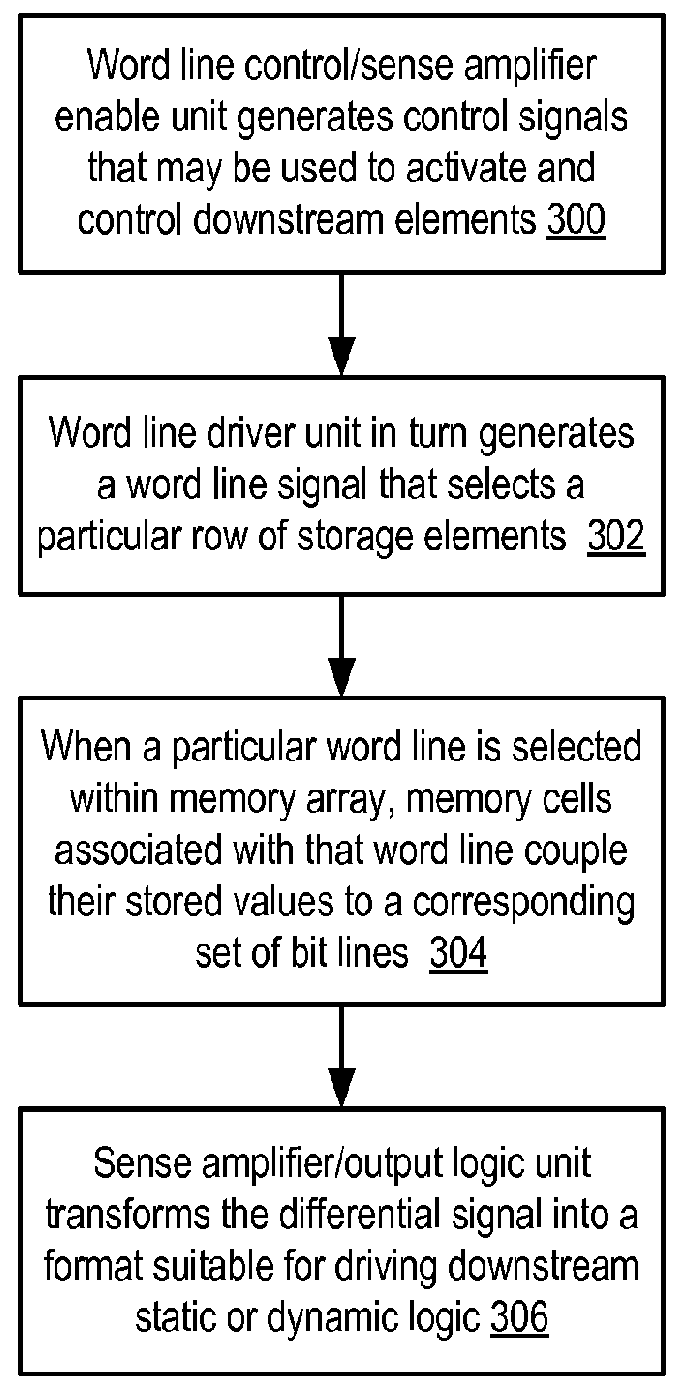

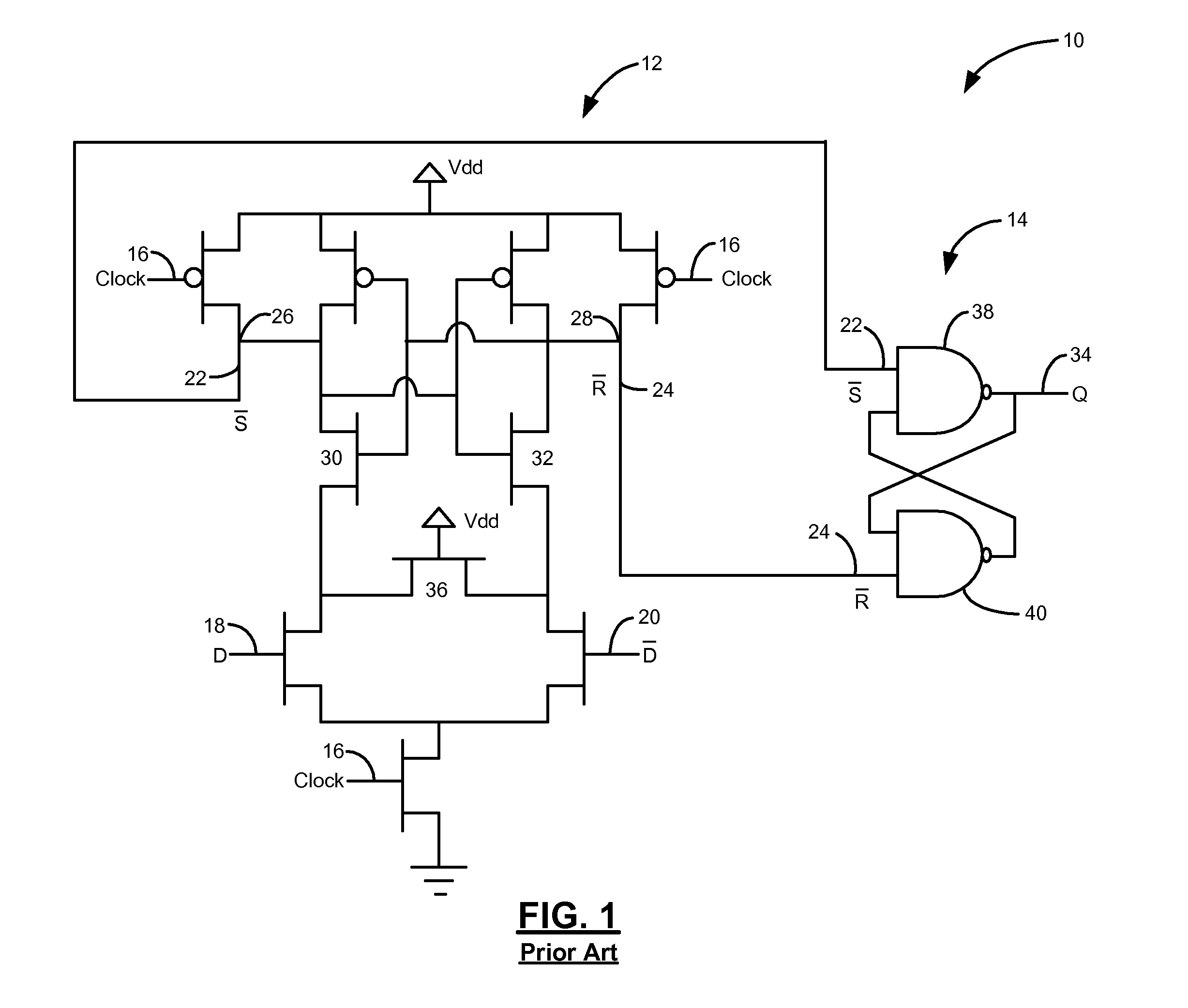

Sense amplifier and sense amplifier latch having common control

A sense amplifier of a memory array may be provided to amplify data presented from storage cells of the memory array. Additionally, a sense amplifier latch may be provided to store data received from the sense amplifier. The sense amplifier may be enabled for operation by a sense amplifier enable signal that is distinct from a clock signal. Moreover, the latch enable signal of the sense amplifier latch may be controlled by the sense amplifier enable signal, such that the sense amplifier latch opens in response to activation of the sense amplifier and closes in response to deactivation of the sense amplifier.

Owner:APPLE INC

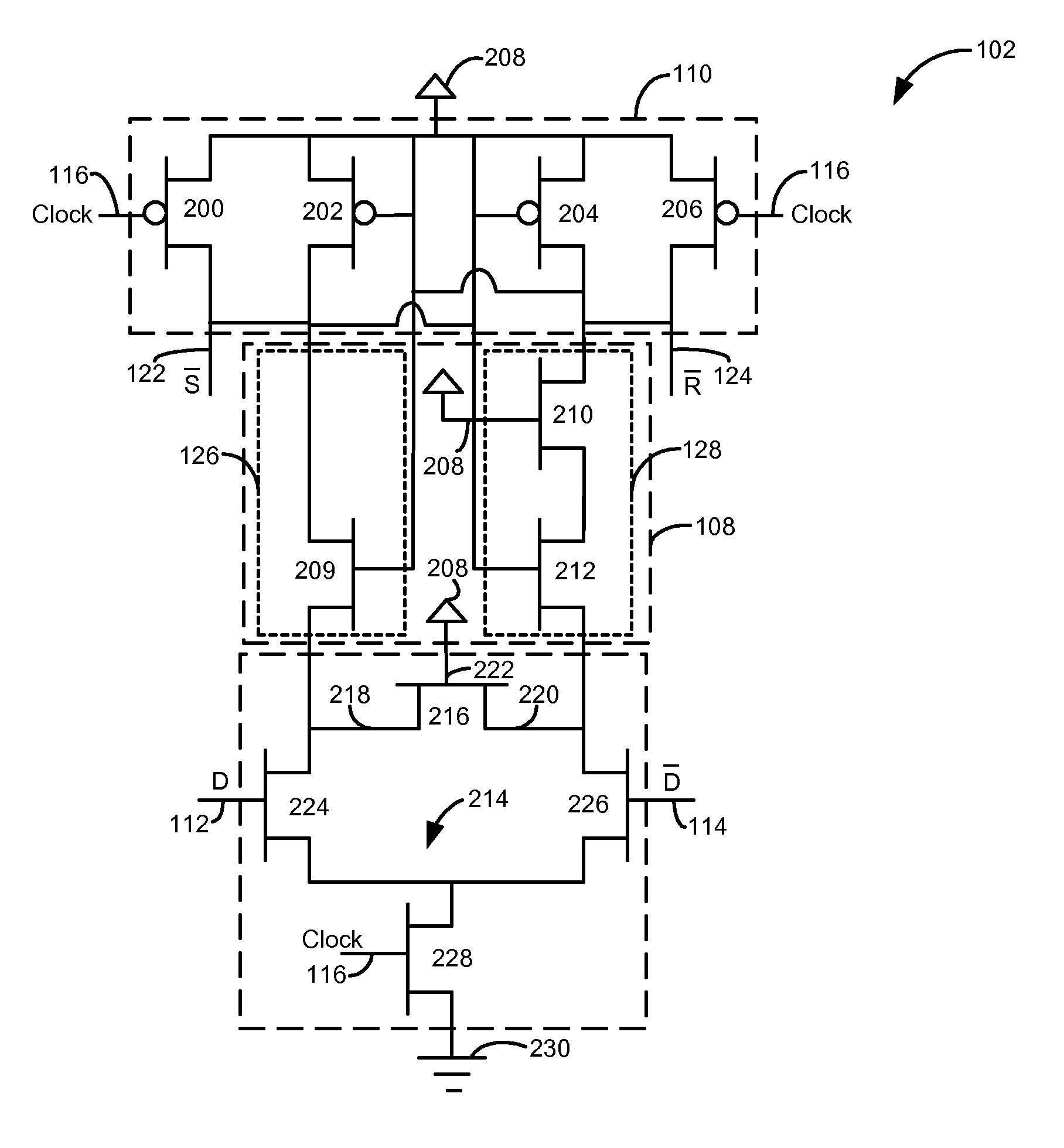

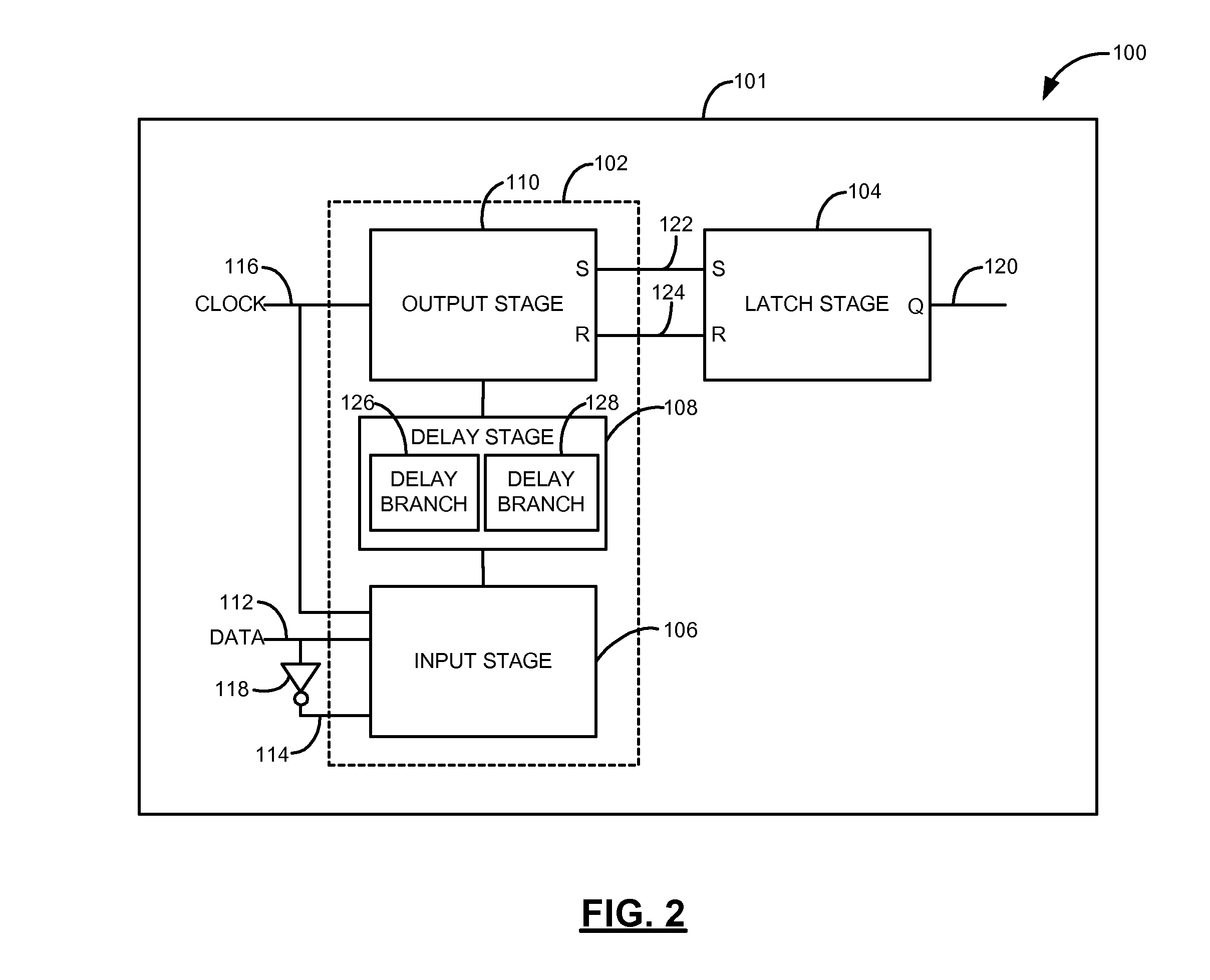

Sense amplifier based flip-flop

A circuit includes an input stage, an output stage, and a delay stage. The input stage is operative to receive a clock signal and a first and second input signal. The output stage is operative to receive the clock signal. The output stage is also operative to generate a first and second output signal based on the clock signal and the first and second input signals. The delay stage is operatively coupled to the input and output stages. The delay stage includes a first and second branch. The second branch includes at least one more delay element than the first branch.

Owner:ATI TECH INC

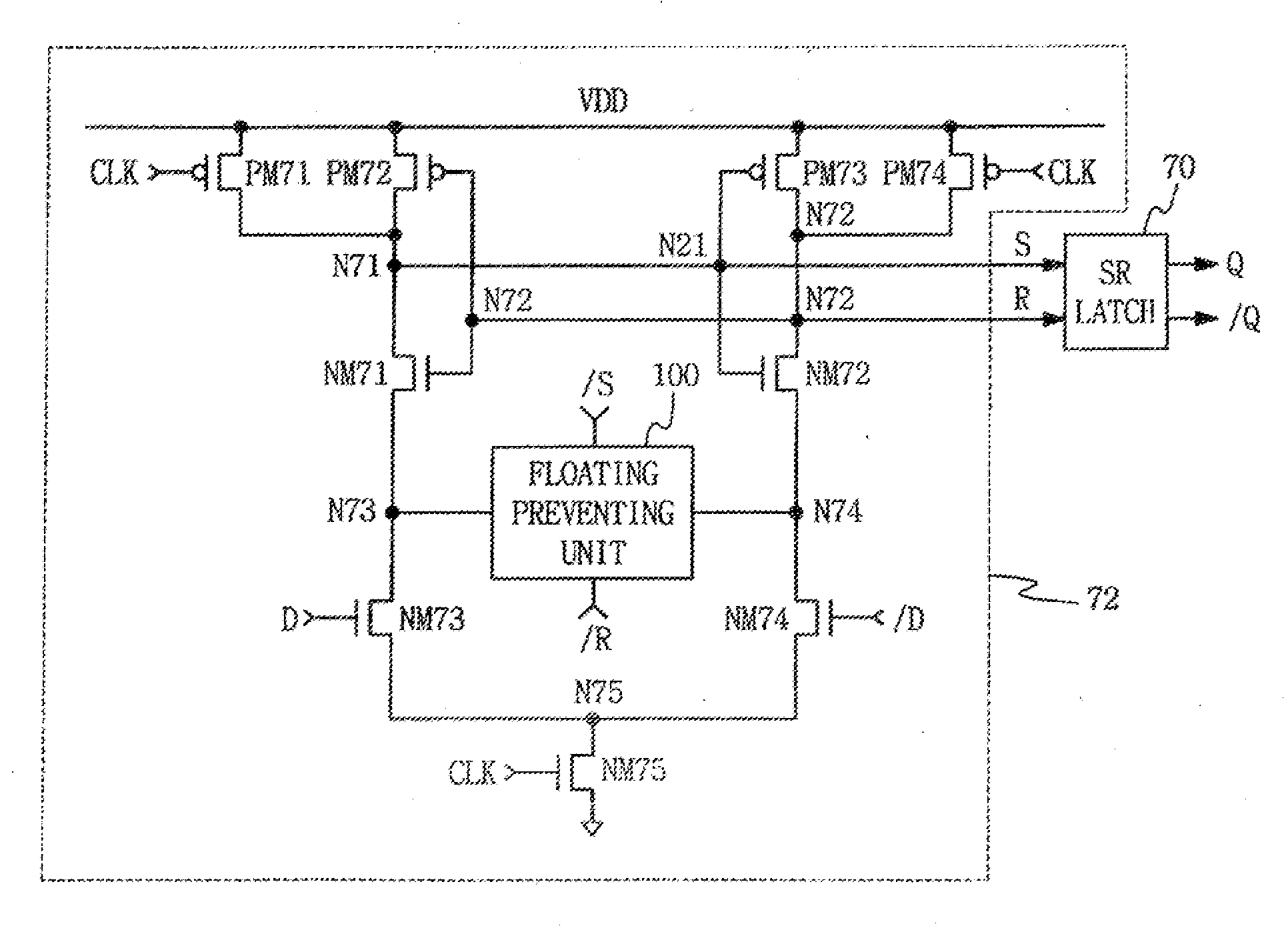

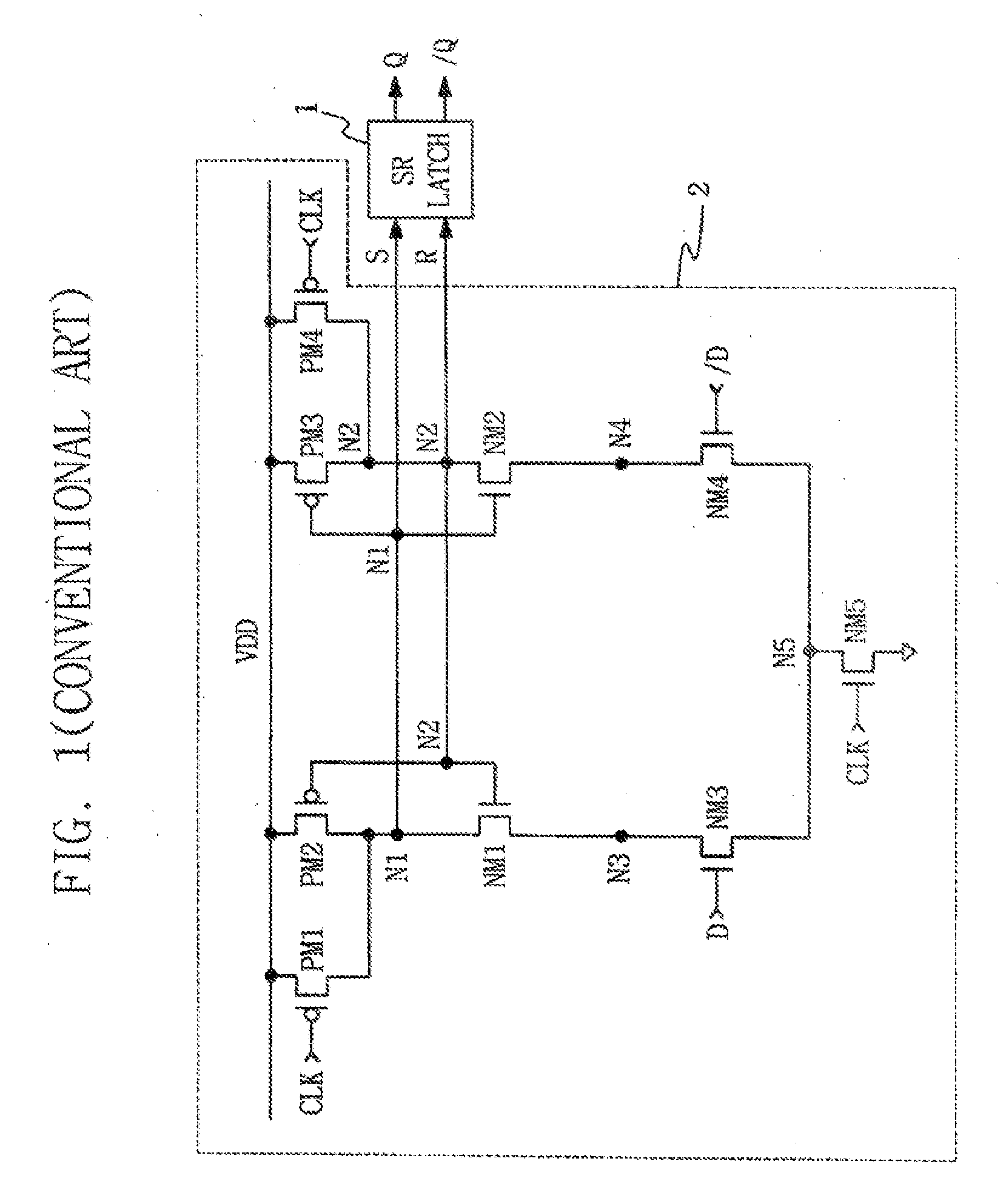

Sense amplifier circuit and sense amplifier-based flip-flop having the same

ActiveUS20070285131A1Reducing signal delay timePrevent degradation of outputCurrent/voltage measurementDigital storageAudio power amplifierControl delay

A sense amplifier-based flip-flop includes a first latch, a second latch, a floating reduction unit, an input signal applying unit, a ground switch and a delay reduction unit. The first latch outputs a signal to a first output terminal pair, and outputs an evaluation signal pair corresponding to an input single pair to the first output terminal pair. The second latch latches the evaluation signal pair and outputs the evaluation signal pair to a second output terminal pair. The floating reduction unit is controlled by signals of the first output terminal pair and is operationally connected between current passing nodes of the first latch to prevent the first output terminal pair from floating. The input signal applying unit is disposed between the current passing nodes and a ground terminal, and receives the input signal pair. The ground switch is disposed between the input signal applying unit and the ground terminal, and is controlled by the clock signal. The delay reduction unit is disposed between the input signal applying unit and the ground switch, and reduces a signal delay from when the clock signal to when the evaluation signal pair is output from the second output terminal pair.

Owner:SAMSUNG ELECTRONICS CO LTD

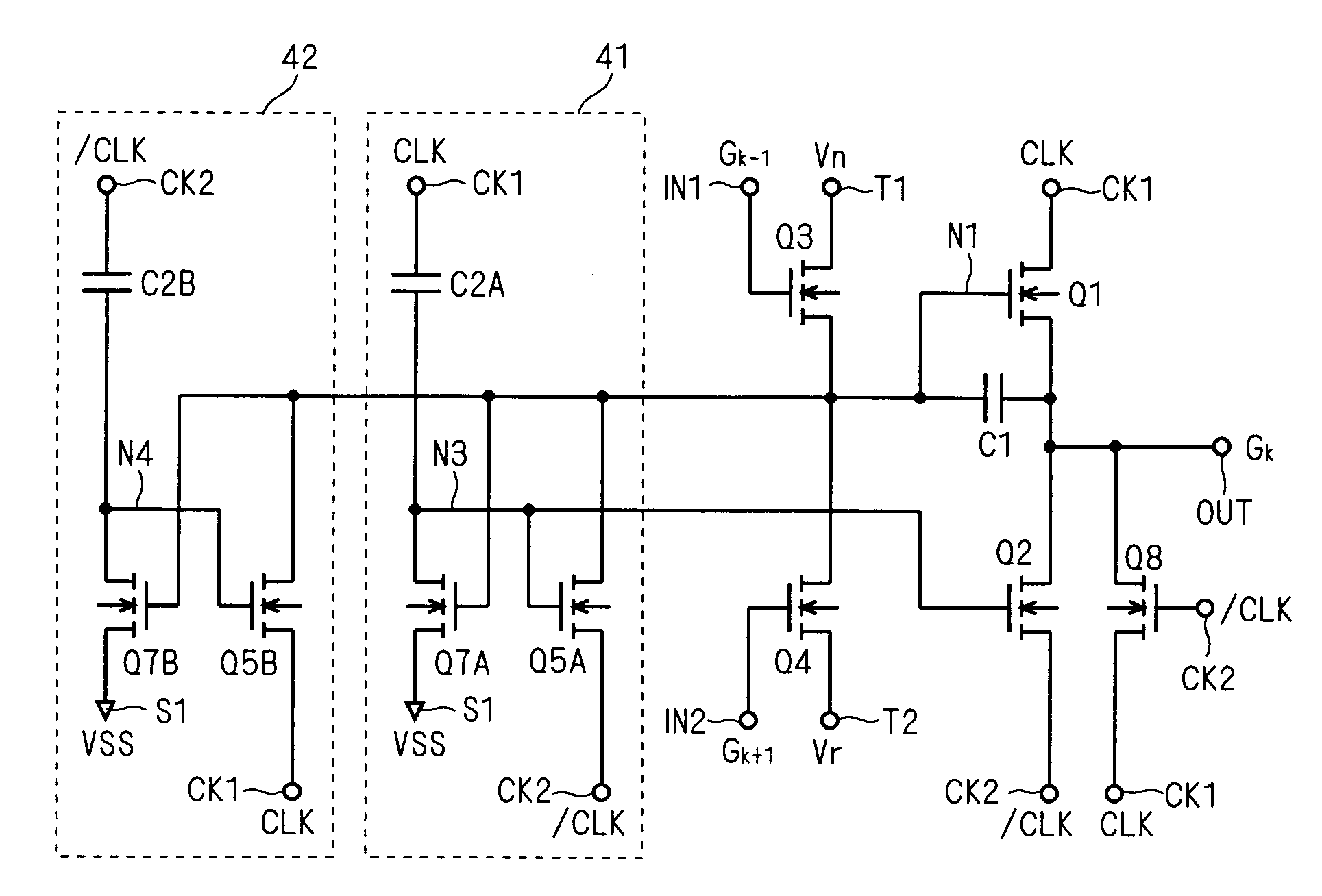

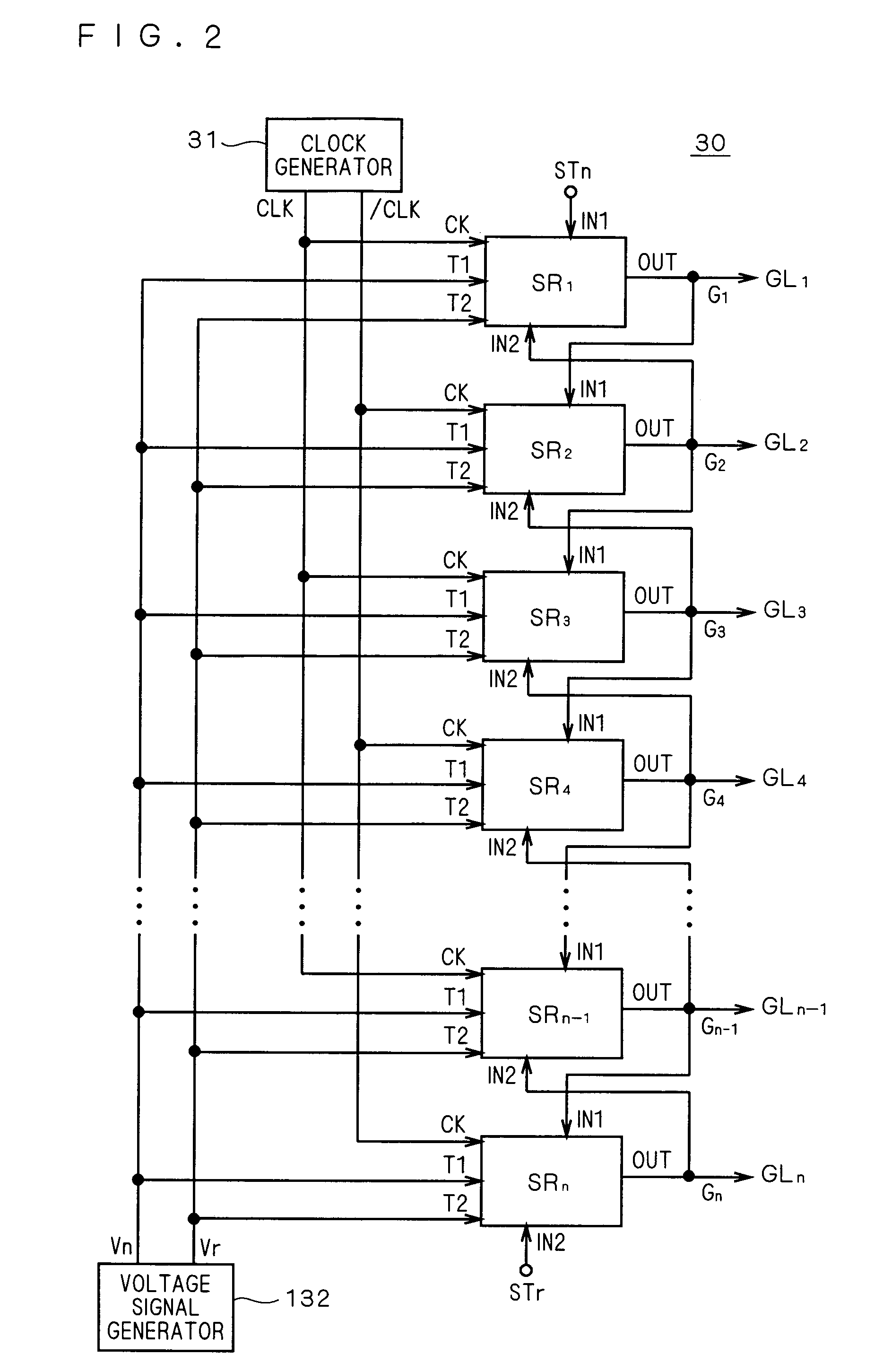

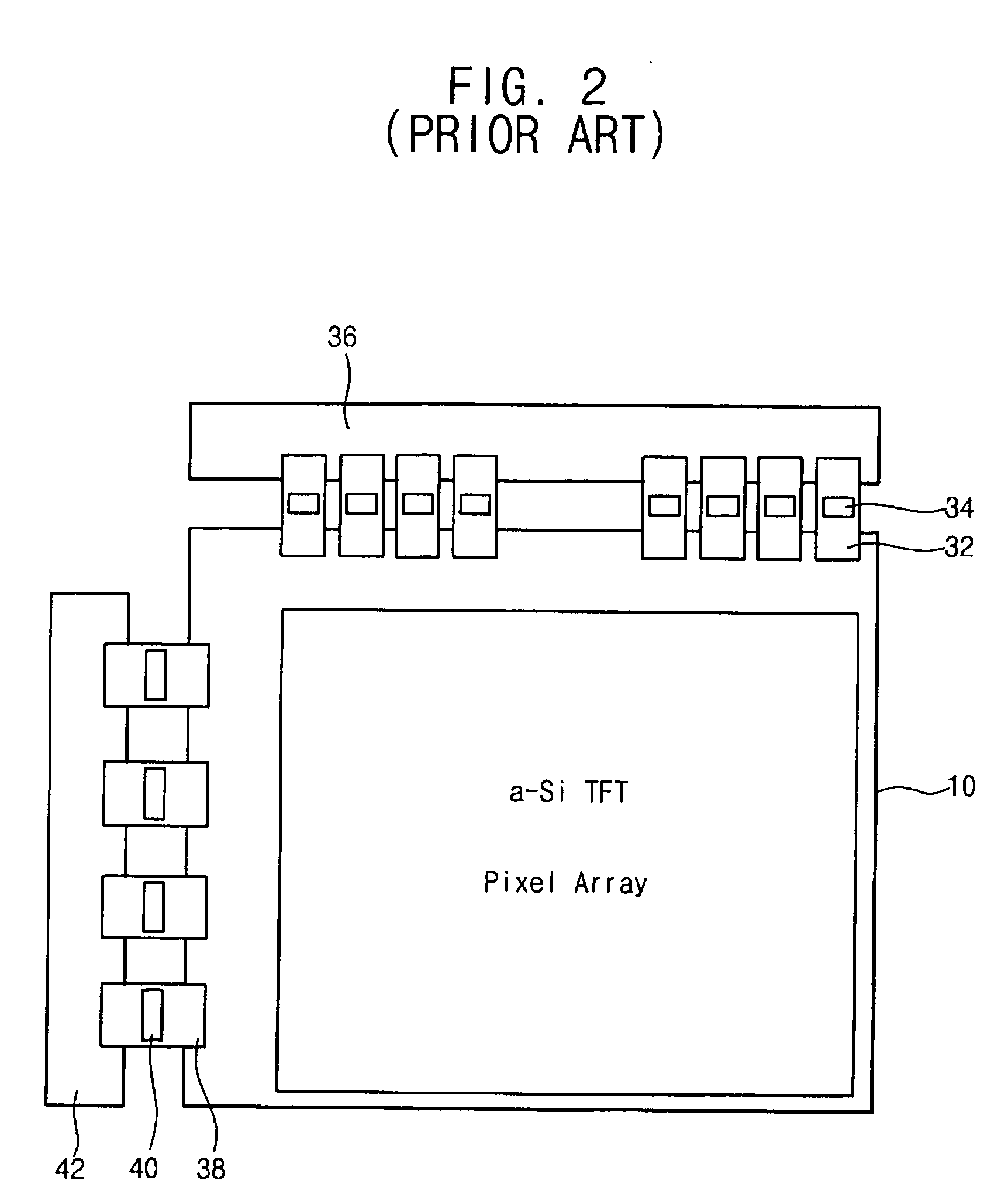

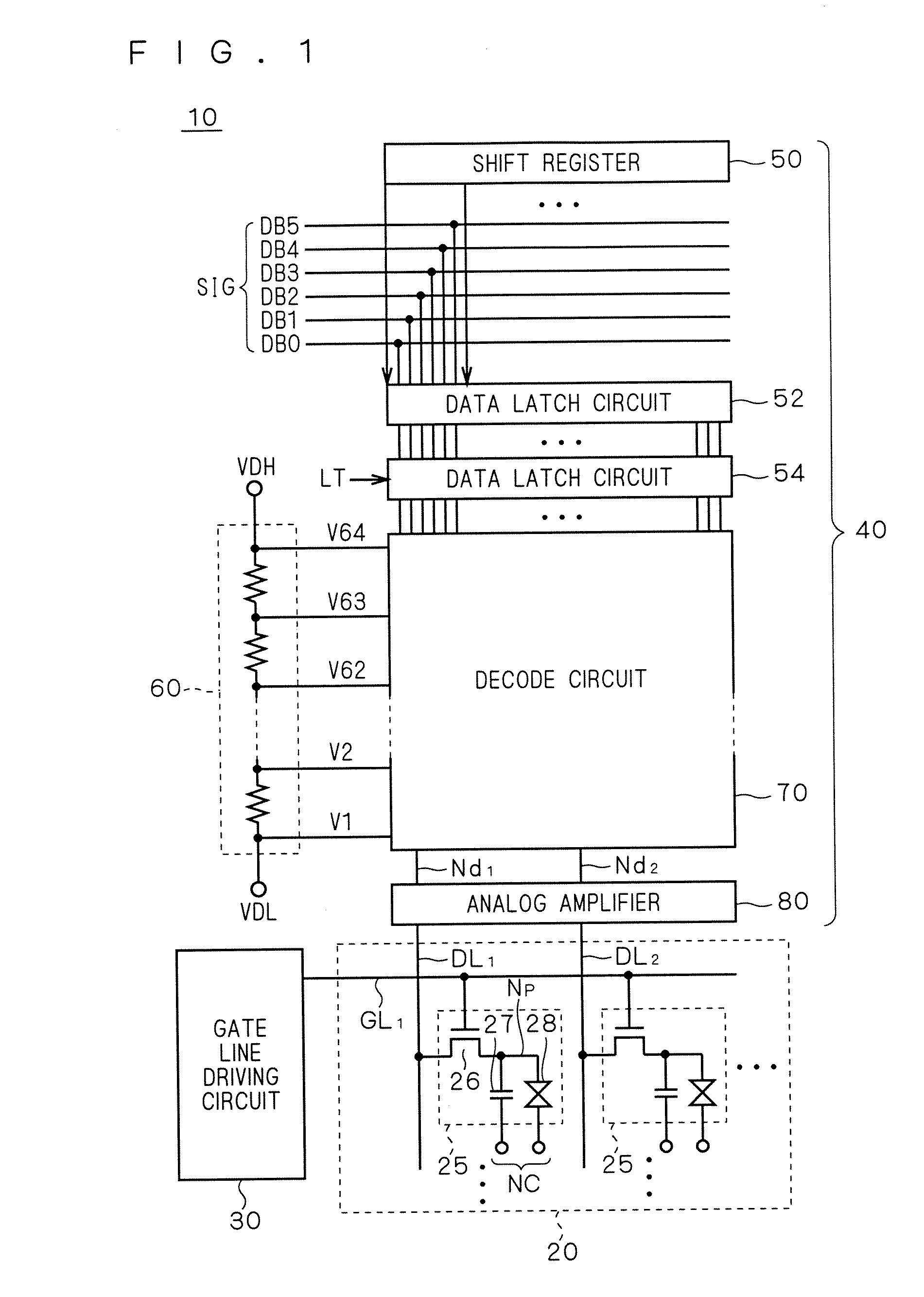

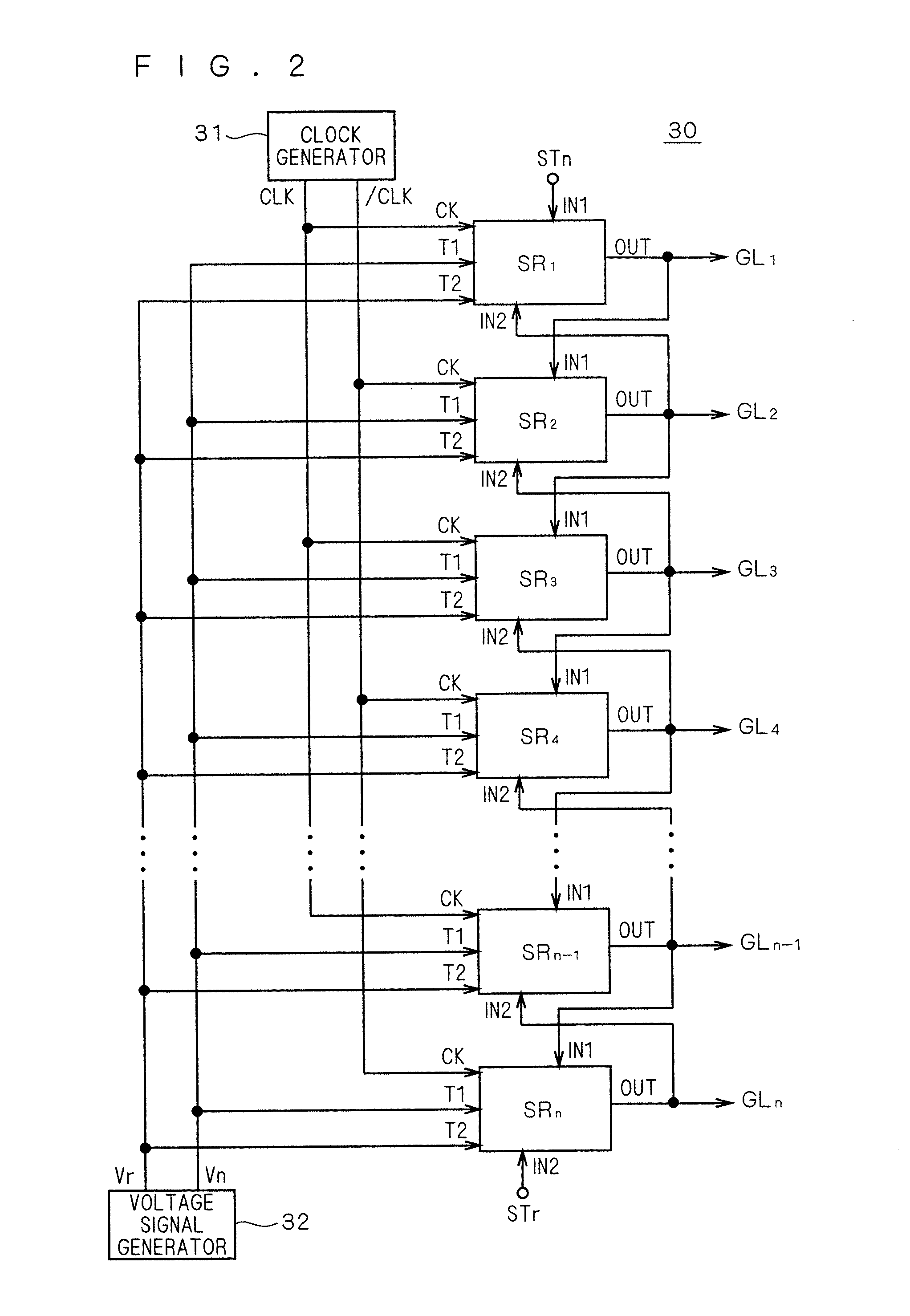

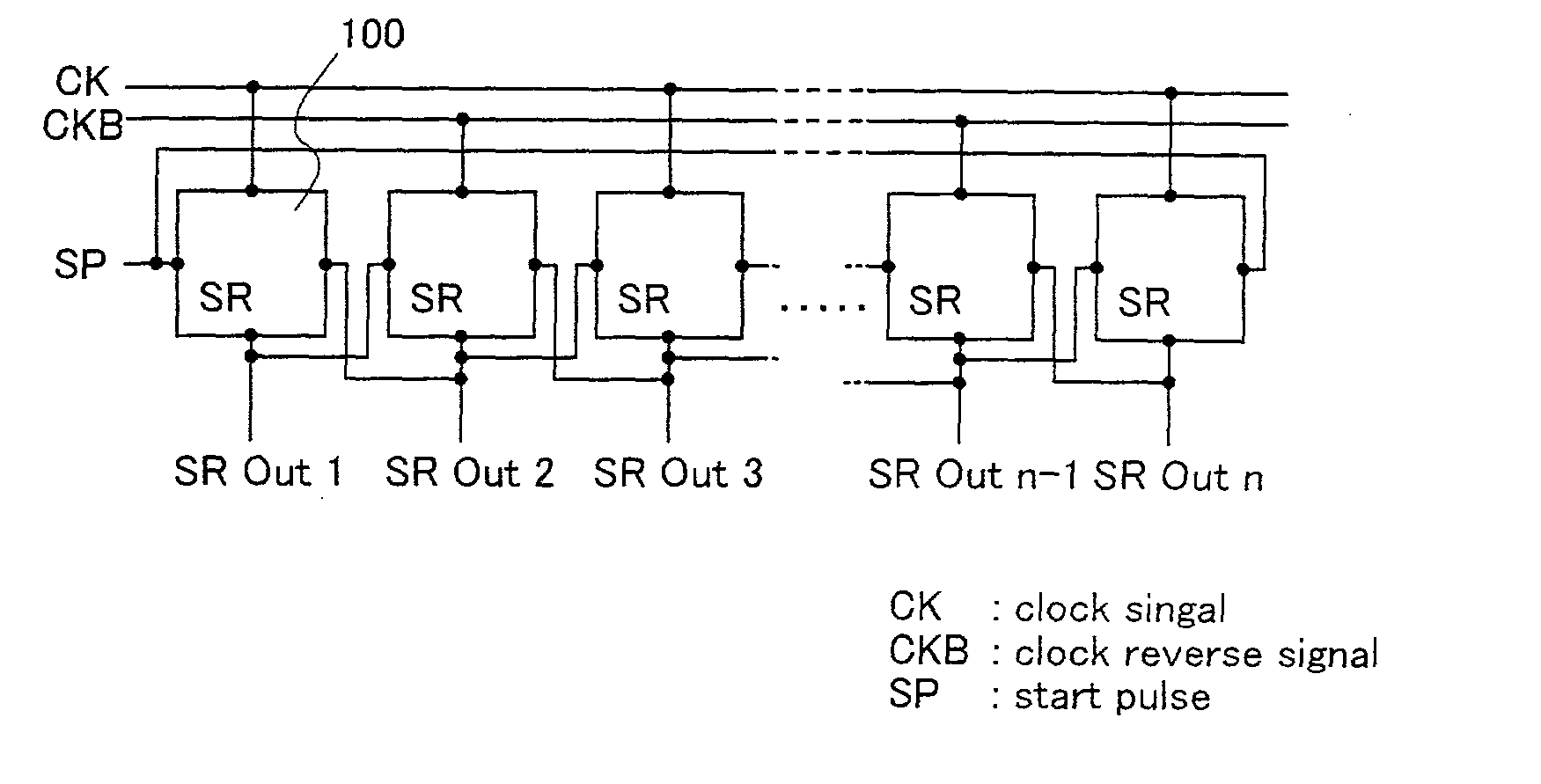

Shift register circuit and image display apparatus containing the same

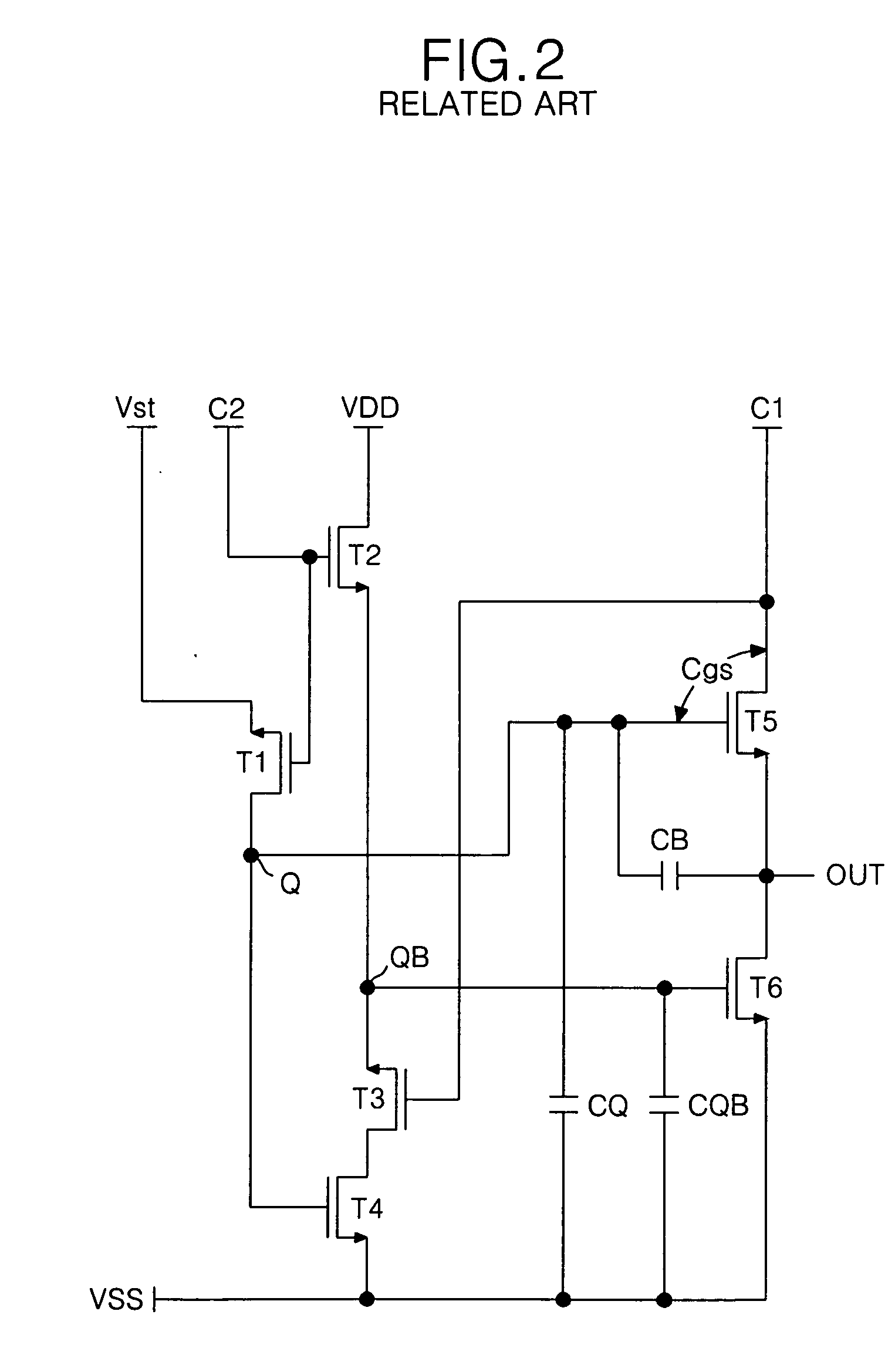

InactiveUS20080219401A1Avoid failureReduced driving abilityStatic indicating devicesDigital storageShift registerProcessor register

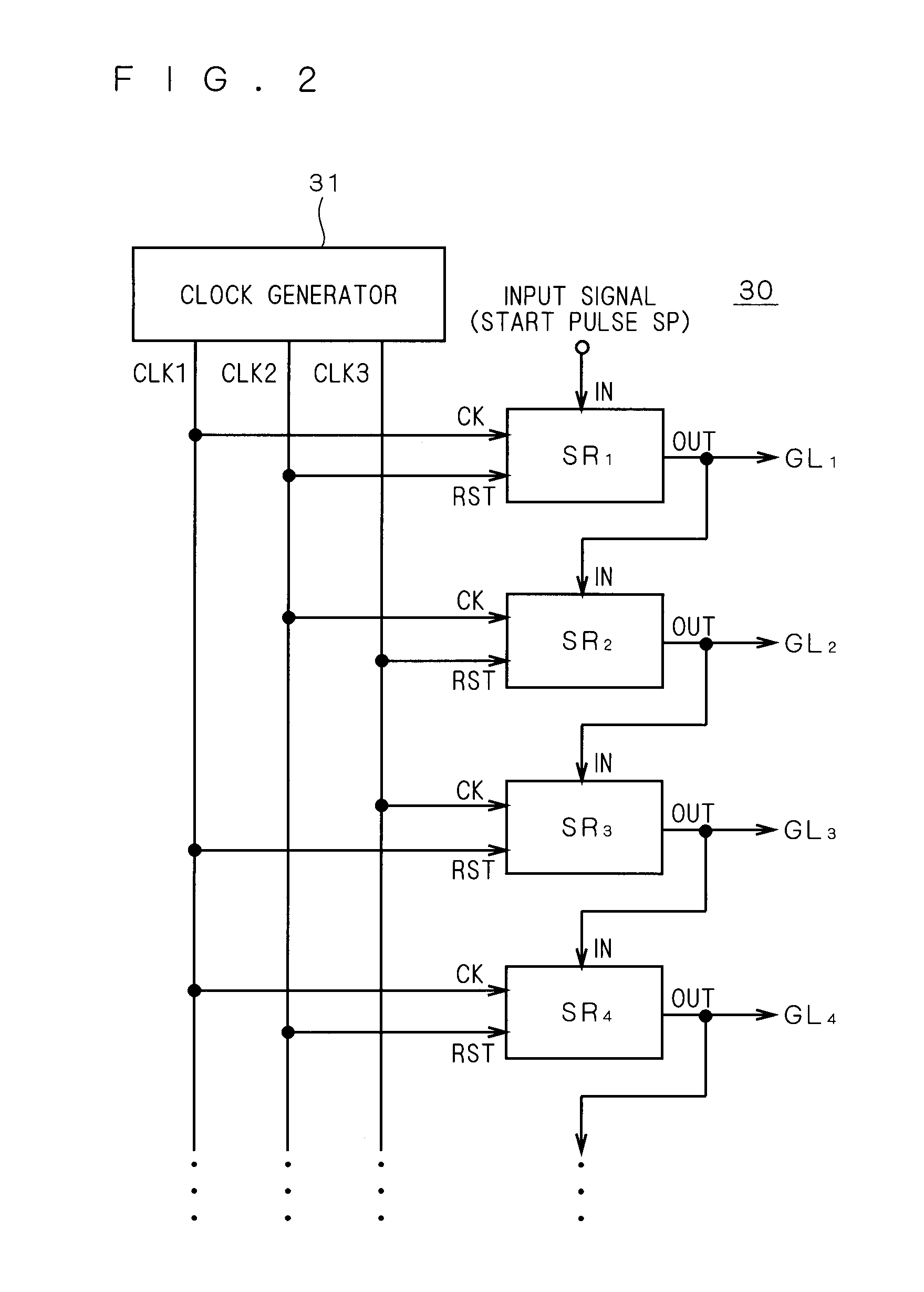

Threshold voltage shifts of transistors which are constituents of a bidirectional shift register are reduced to prevent a malfunction in the shift register. A bidirectional unit shift register includes first and second pull-down circuits (41, 42) connected to the gate of a first transistor (Q1) that supplies a first clock signal (CLK) to an output terminal (OUT). The first pull-down circuit (41) includes a first inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by the first clock signal (CLK), and a second transistor (Q5A) that discharges the gate of the first transistor (Q1) according to the output of the first inverter. The second pull-down circuit (42) includes a second inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by a second clock signal ( / CLK) having a different phase from the first clock signal (CLK), and a third transistor (Q5A) that discharges the gate of the first transistor according to the output of the second inverter.

Owner:TRIVALE TECH LLC

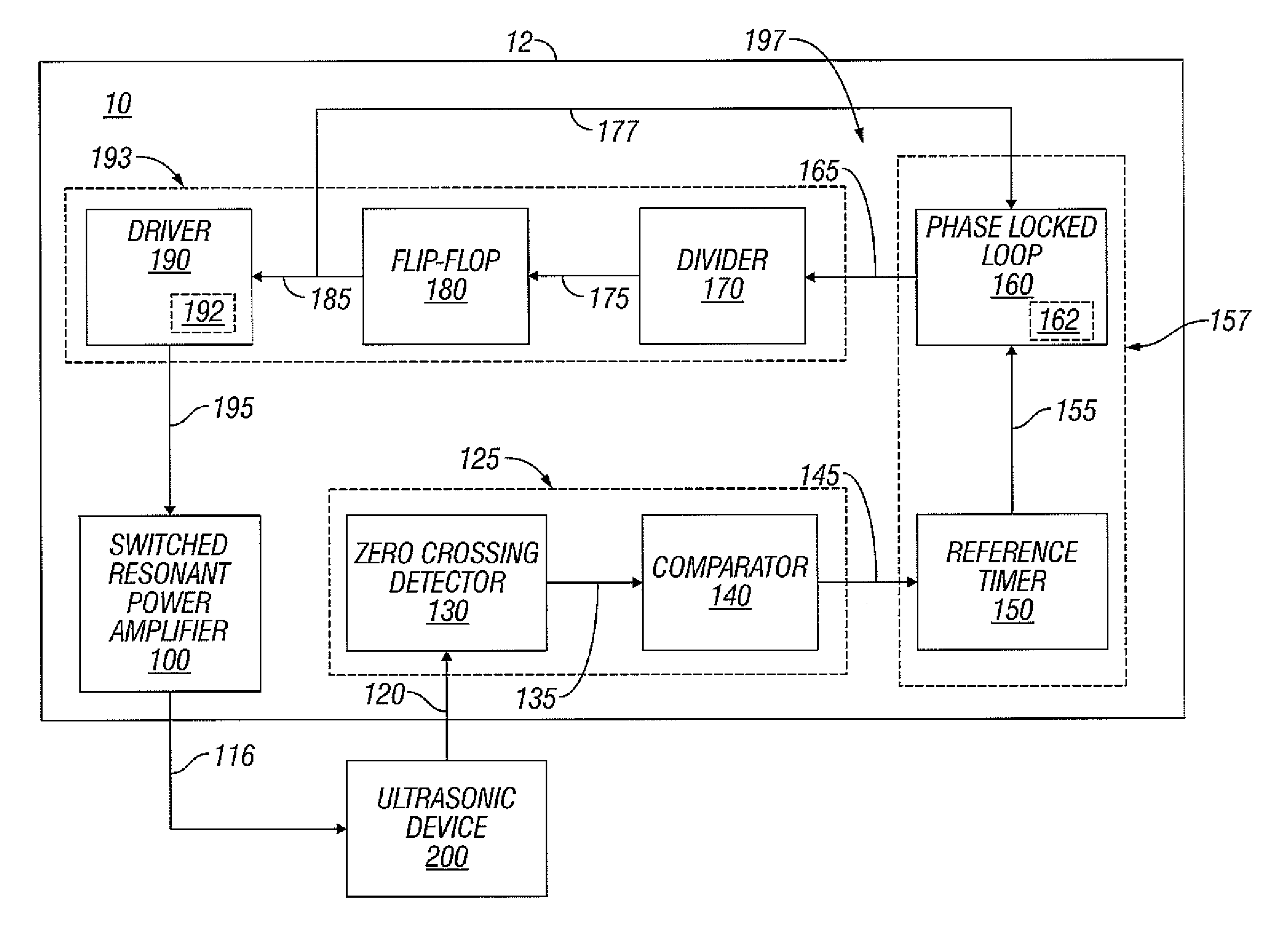

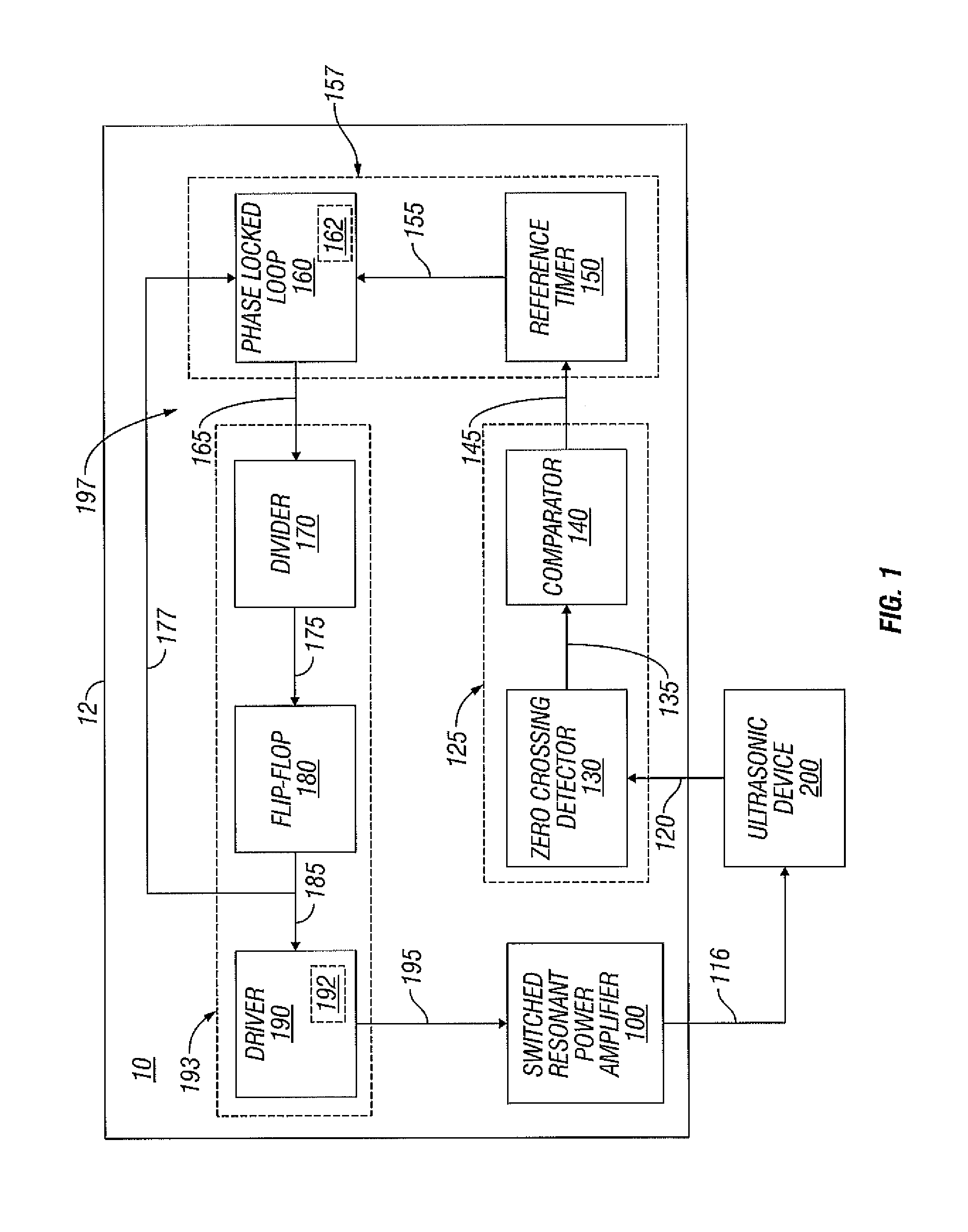

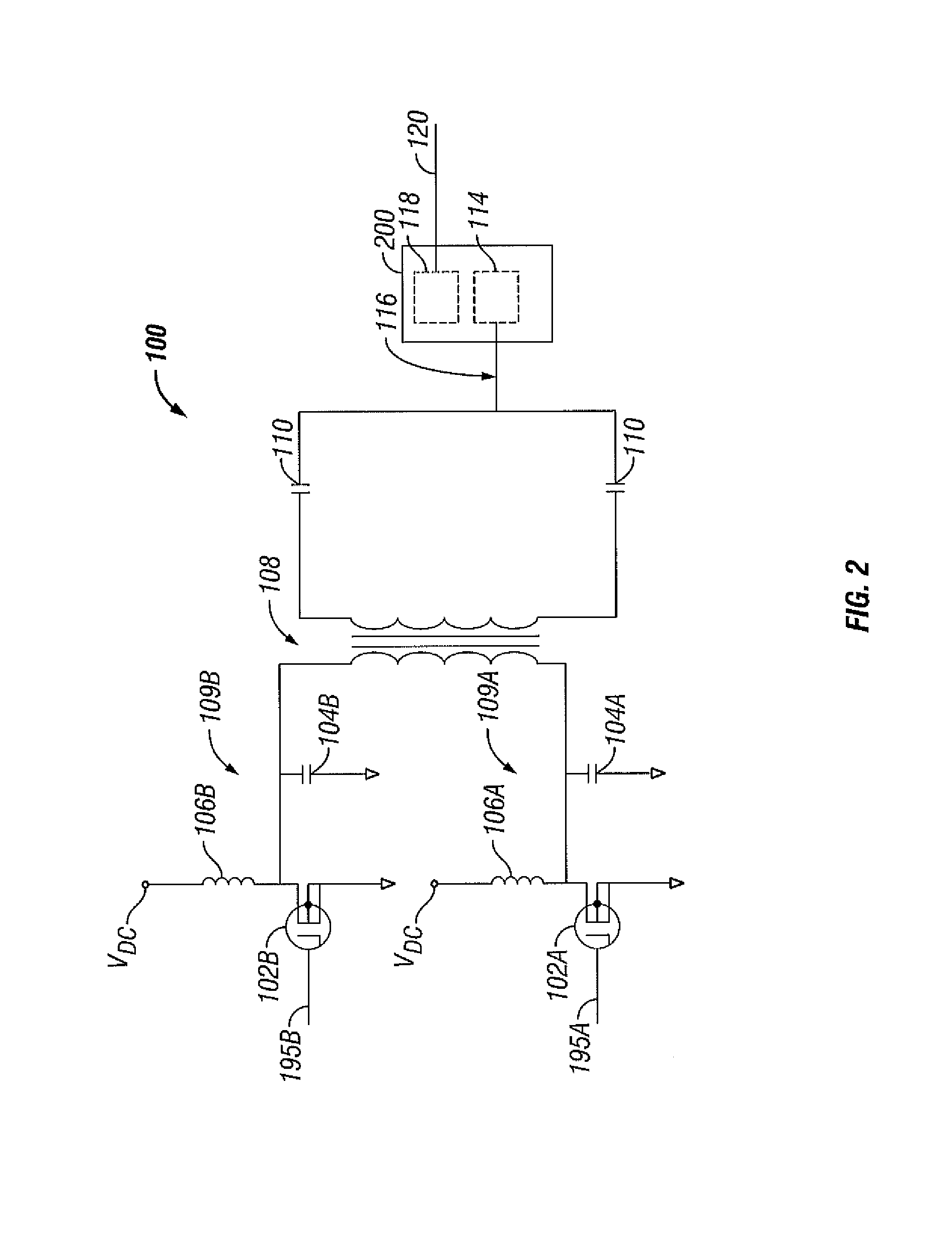

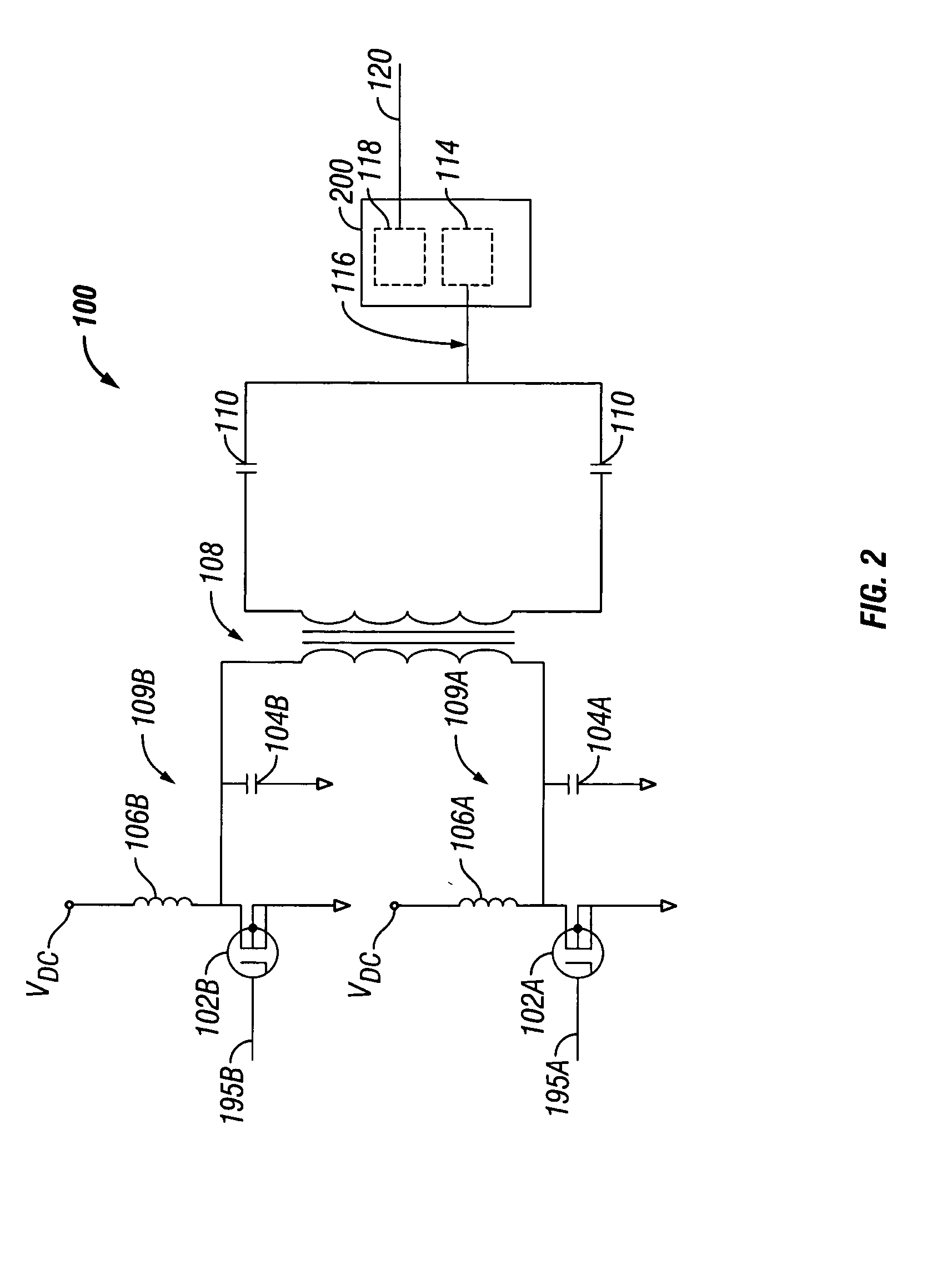

Switched resonant ultrasonic power amplifier system

ActiveUS7396336B2Operation efficiency can be improvedSmall footprintUltrasound therapyAmplifier modifications to raise efficiencyHemt circuitsControl ultrasound

Owner:COVIDIEN AG

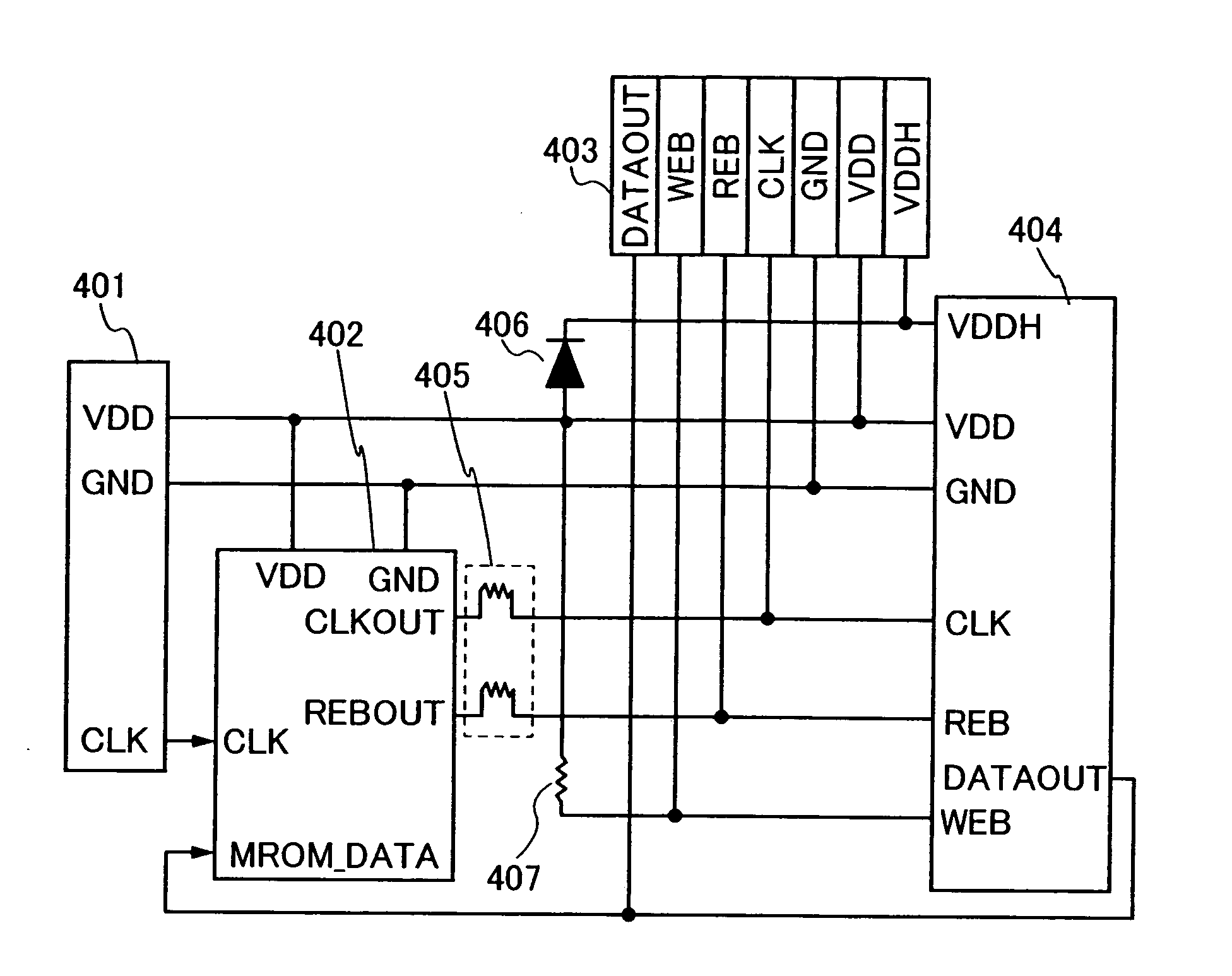

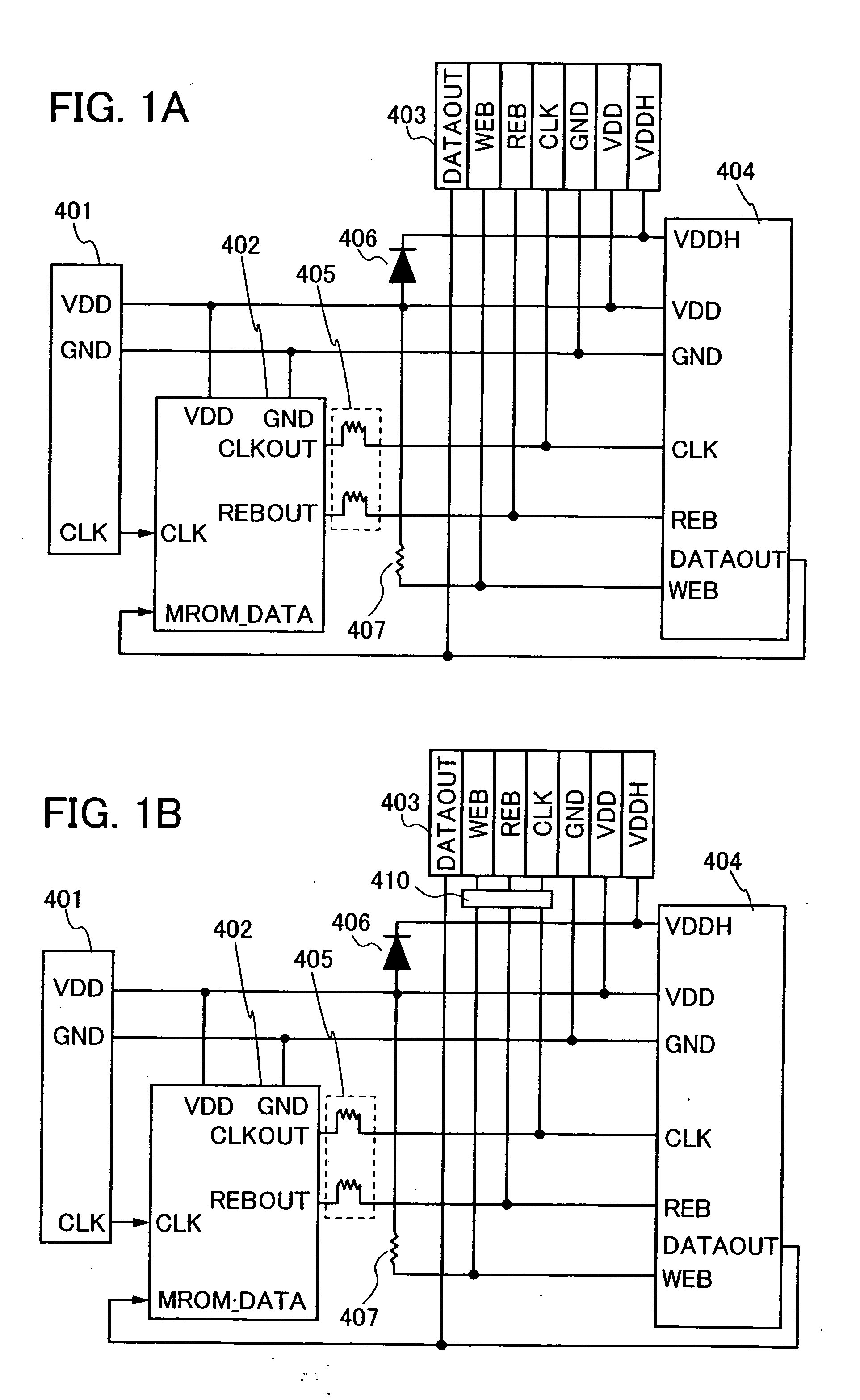

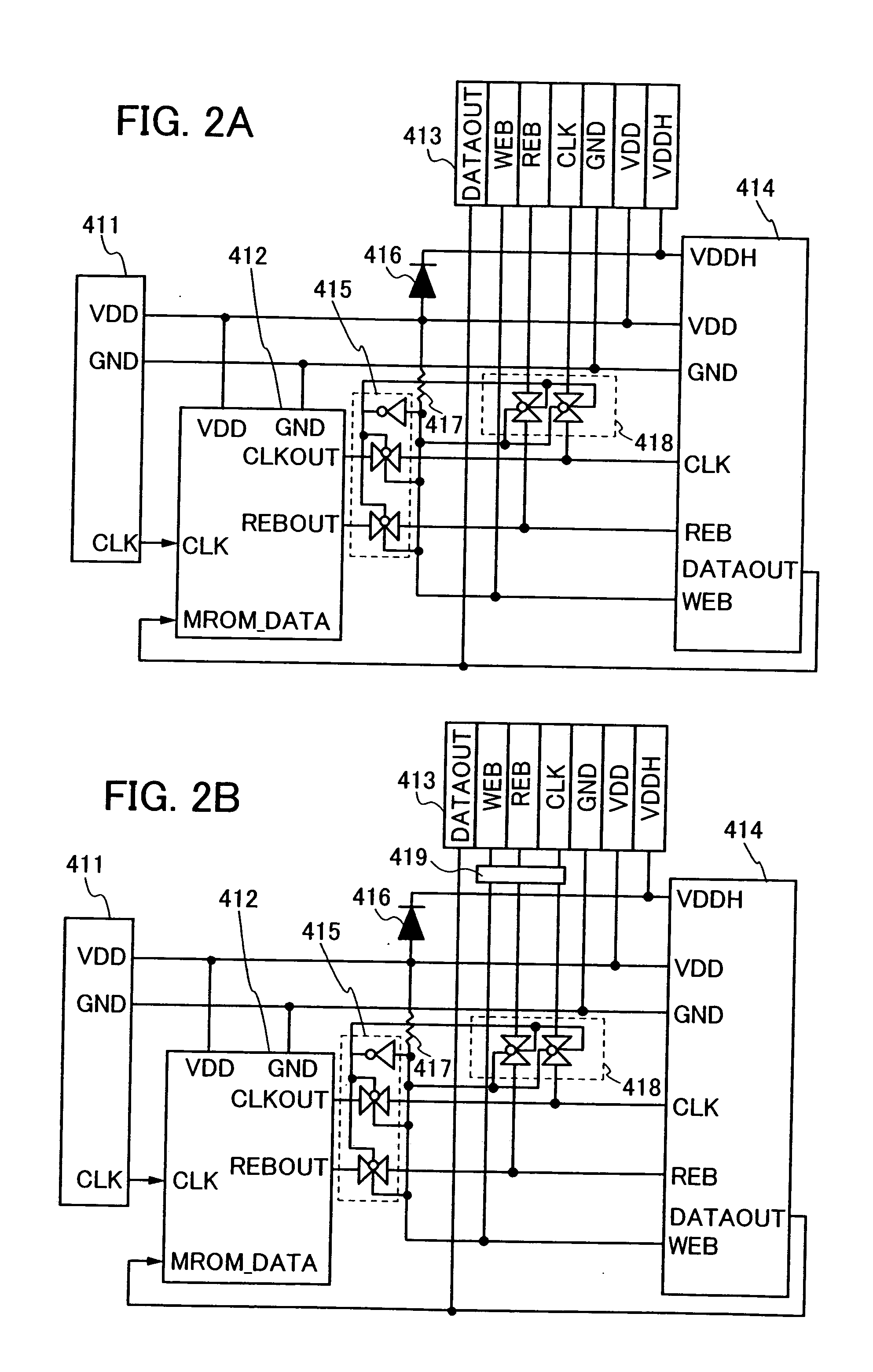

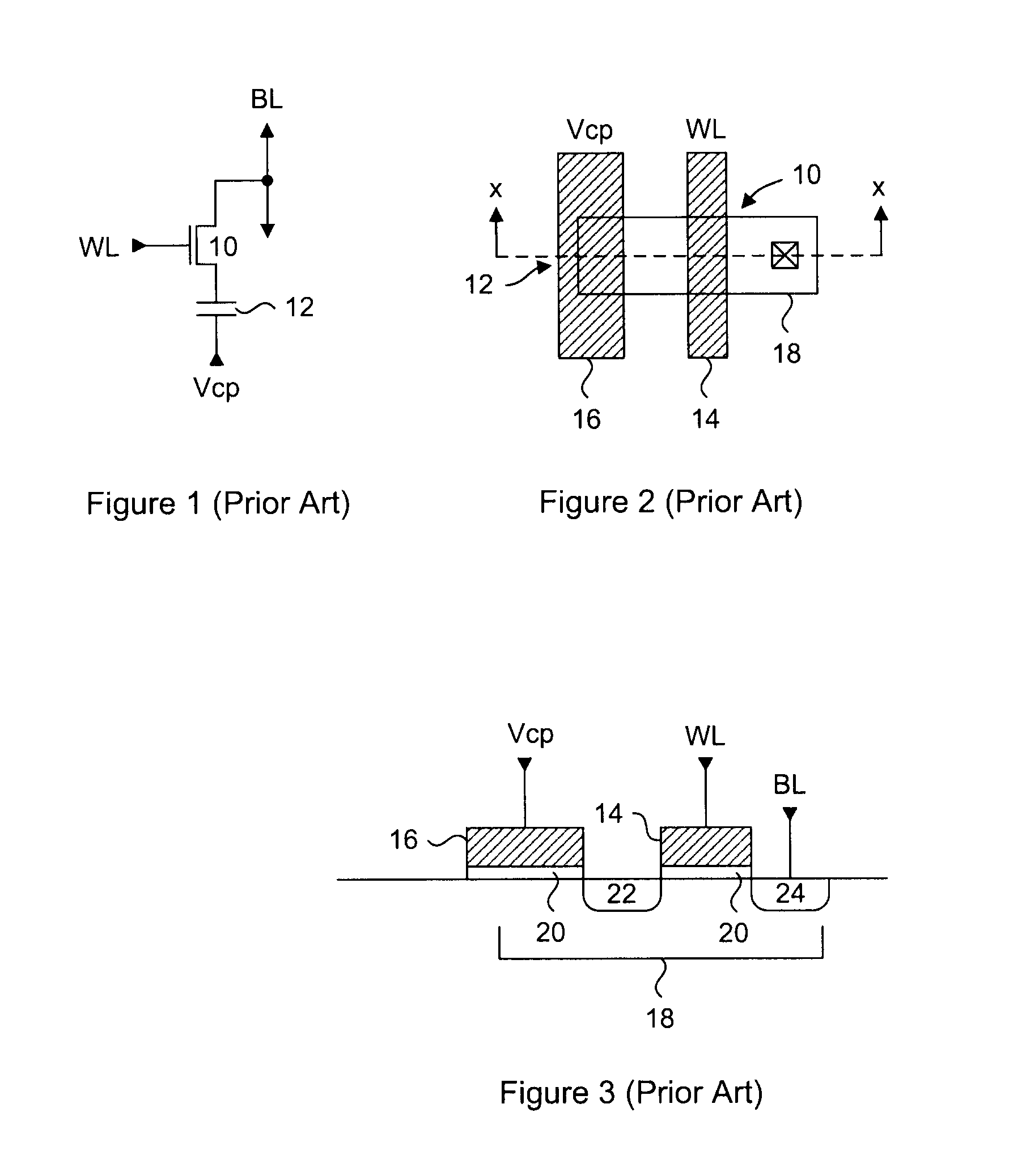

Semiconductor device and operating method thereof

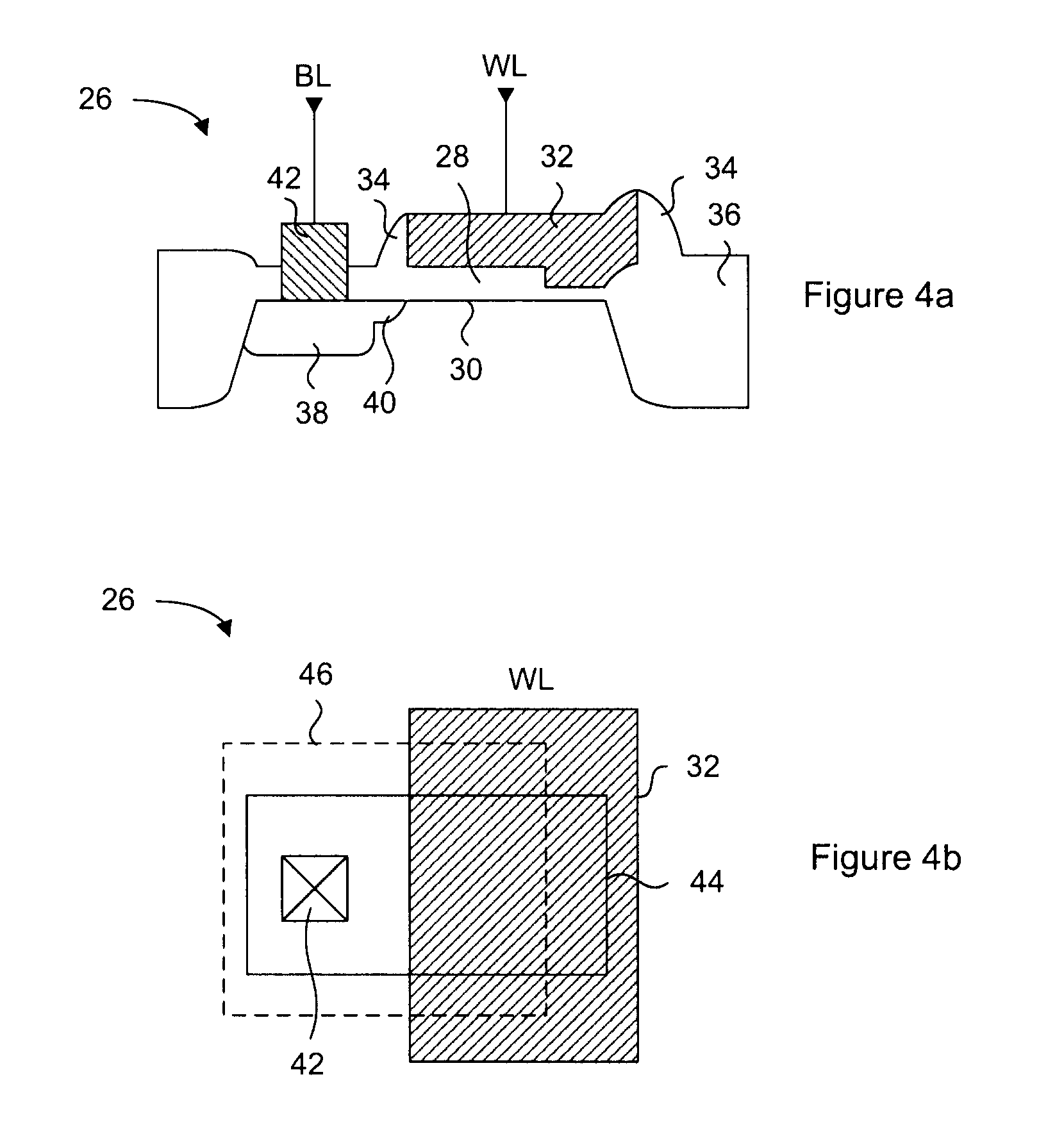

InactiveUS20070123189A1Lower unit costReduce memory areaNanoinformaticsSolid-state devicesOrganic memoryBit line

In an organic memory which is included in a radio chip formed from a thin film, data are written to the organic memory by a signal inputted with a wired connection, and the data is read with a signal by radio transmission. A bit line and a word line which form the organic memory are each selected by a signal which specifies an address generated based on the signal inputted with a wired connection. A voltage is applied to a selected memory element. Thus writing is performed. Reading is performed by a clock signal or the like which are generated from a radio signal.

Owner:SEMICON ENERGY LAB CO LTD

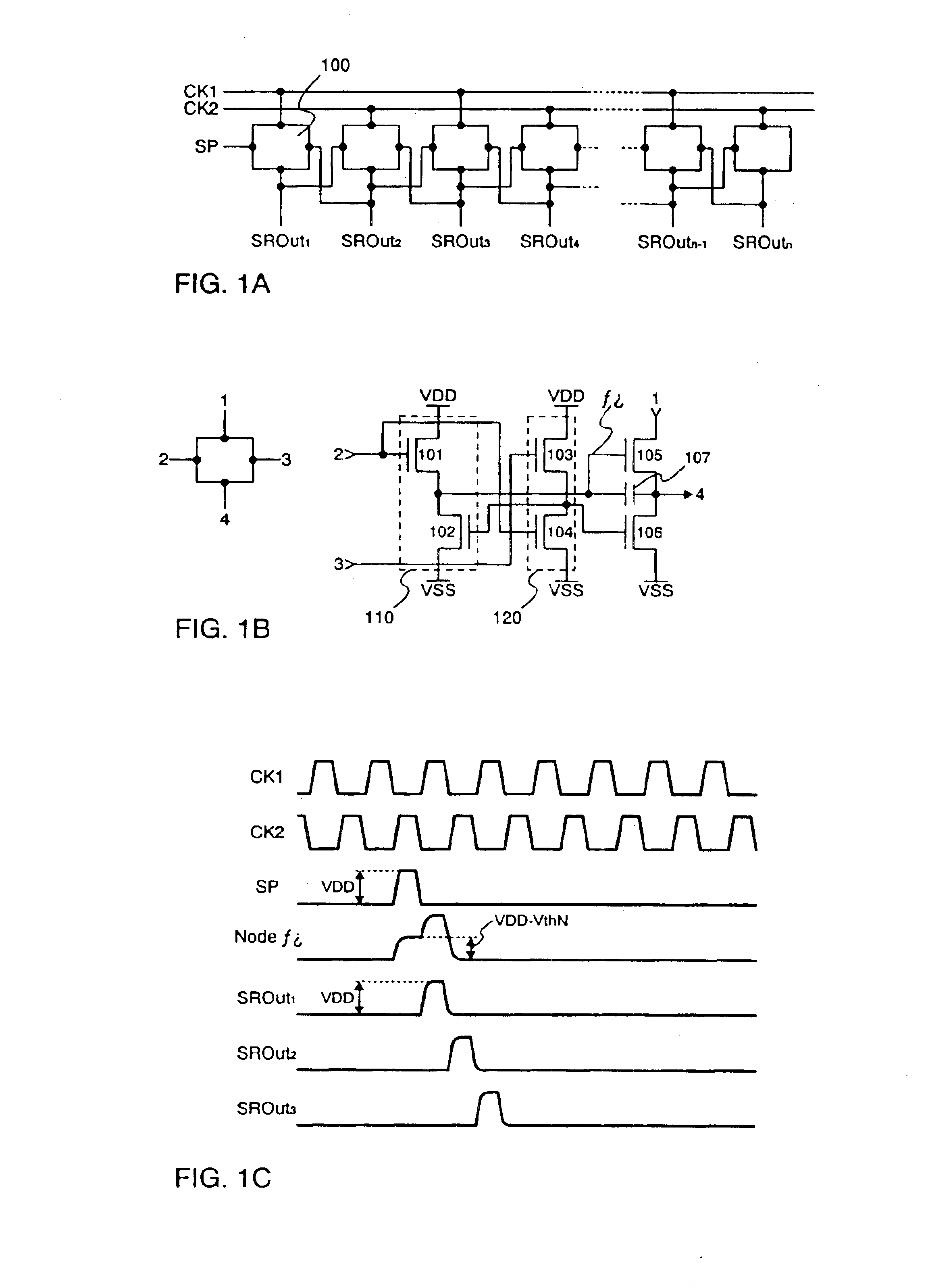

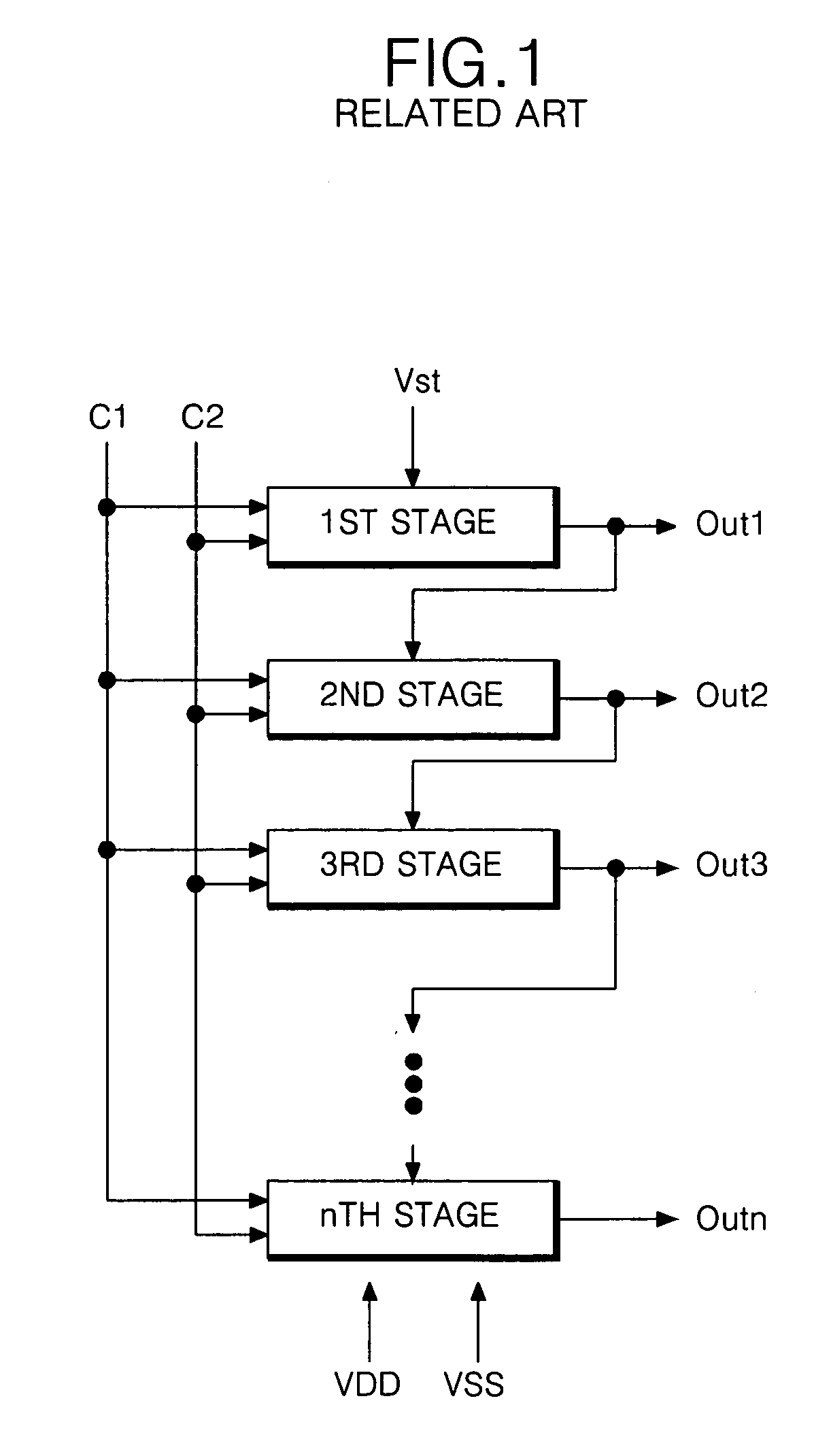

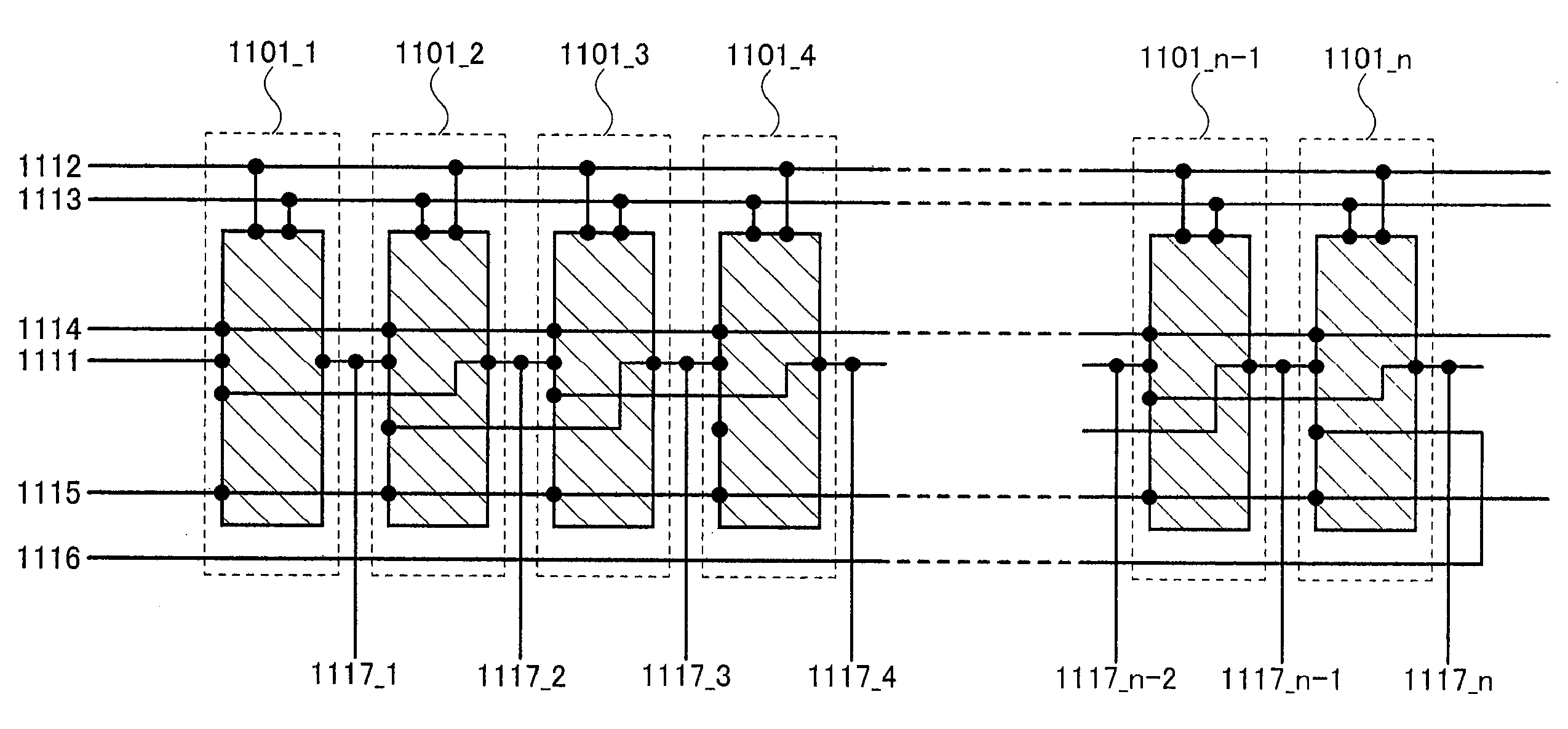

Shift register, display device having the same and method of driving the same

ActiveUS20060001637A1Improve reliabilitySize of display is limitedStatic indicating devicesDigital storageShift registerControl signal

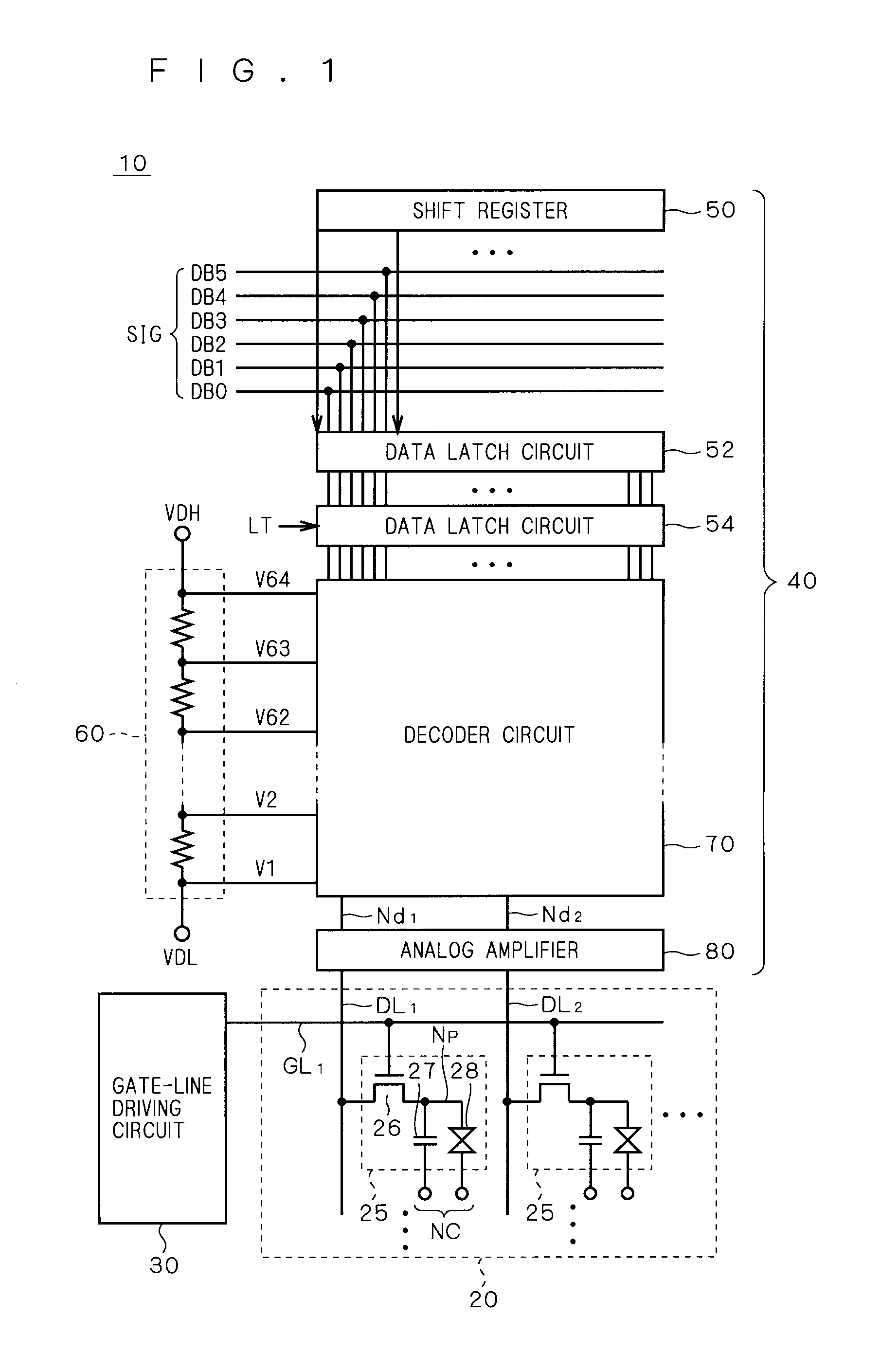

A shift register includes stages to generate gate signals in sequence. Each of the stages includes a first pull up drive control section, a pull up drive section and a pull down drive section. The first pull up drive control section outputs a control signal based on the gate signal of an adjacent stage. The pull up drive section receives a first clock signal and outputs the first clock signal as the gate signal to a corresponding gate line in response to the control signal. The pull down drive section inactivates the corresponding gate line in response to a second clock signal.

Owner:SAMSUNG DISPLAY CO LTD

Clock reproduction circuit that can reproduce internal clock signal correctly in synchronization with external clock signal

InactiveUS6166990ASolid-state devicesSemiconductor/solid-state device manufacturingFrequency determinationPhase synchronization

A frequency determination circuit generating a clock signal phase-locking with an external clock signal at a coarse precision and a fine adjust circuit generating an internal synchronizing signal phase-locking with the external clock signal at a fine precision are provided. The fine adjust circuit has a function of adjusting the phase of the frequency determination circuit when phase synchronization is to be carried out exceeding the adjust range thereof. The frequency determination circuit and the fine adjust circuit receive a clock power supply voltage. A clock reproduction circuit is provided which generates an internal clock signal phase-locking with an external clock signal or a reference clock signal stably even when the operating environment changes.

Owner:HITACHI LTD +2

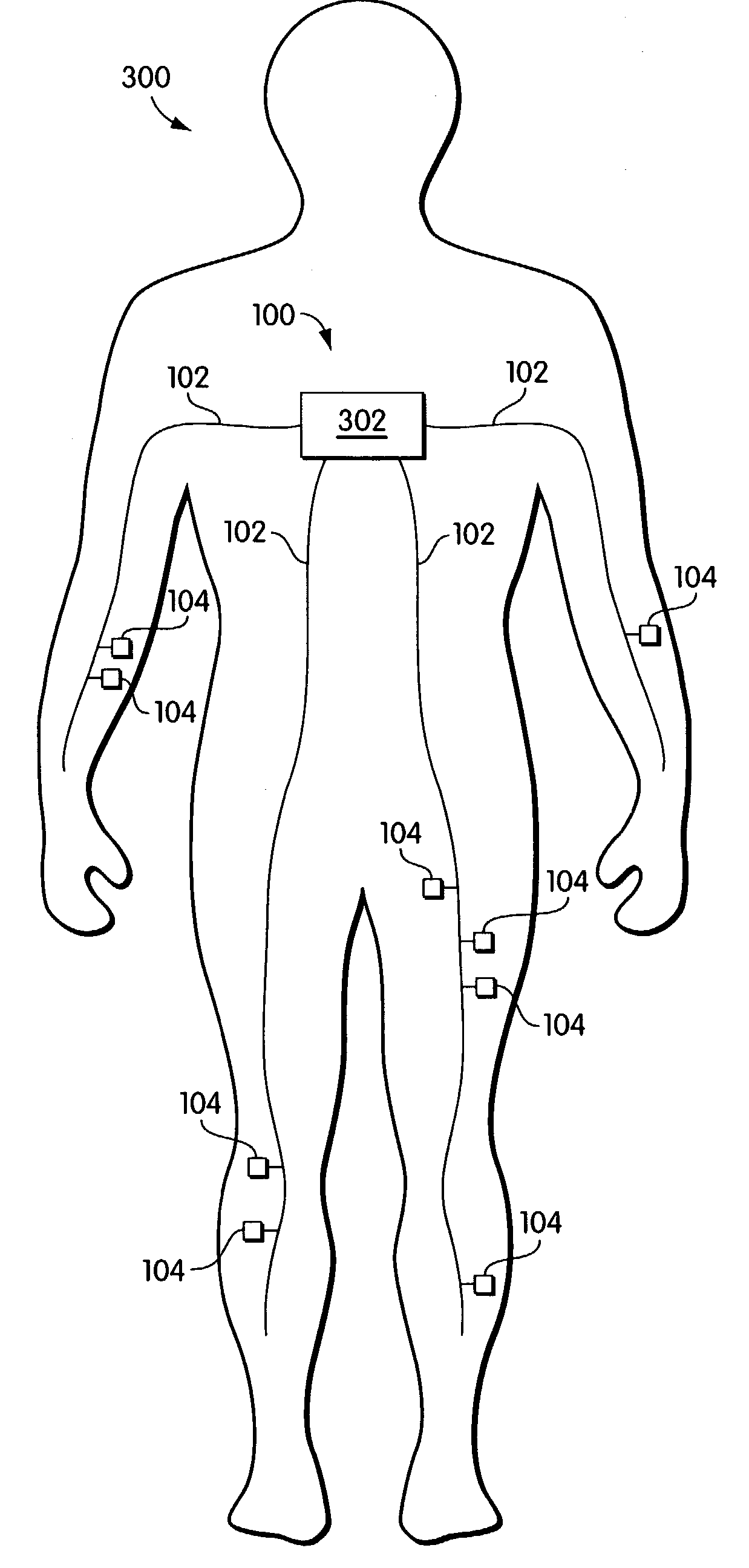

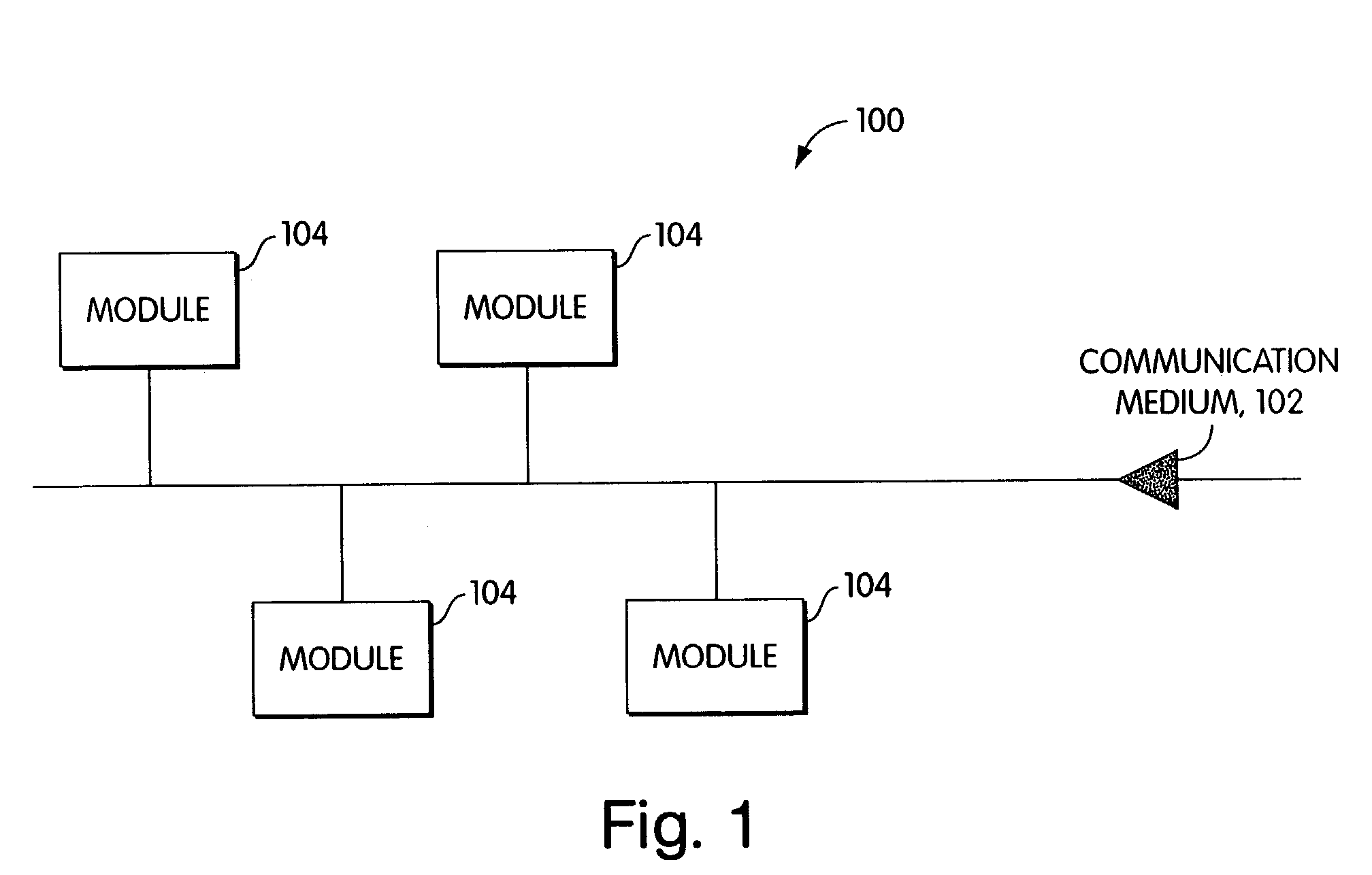

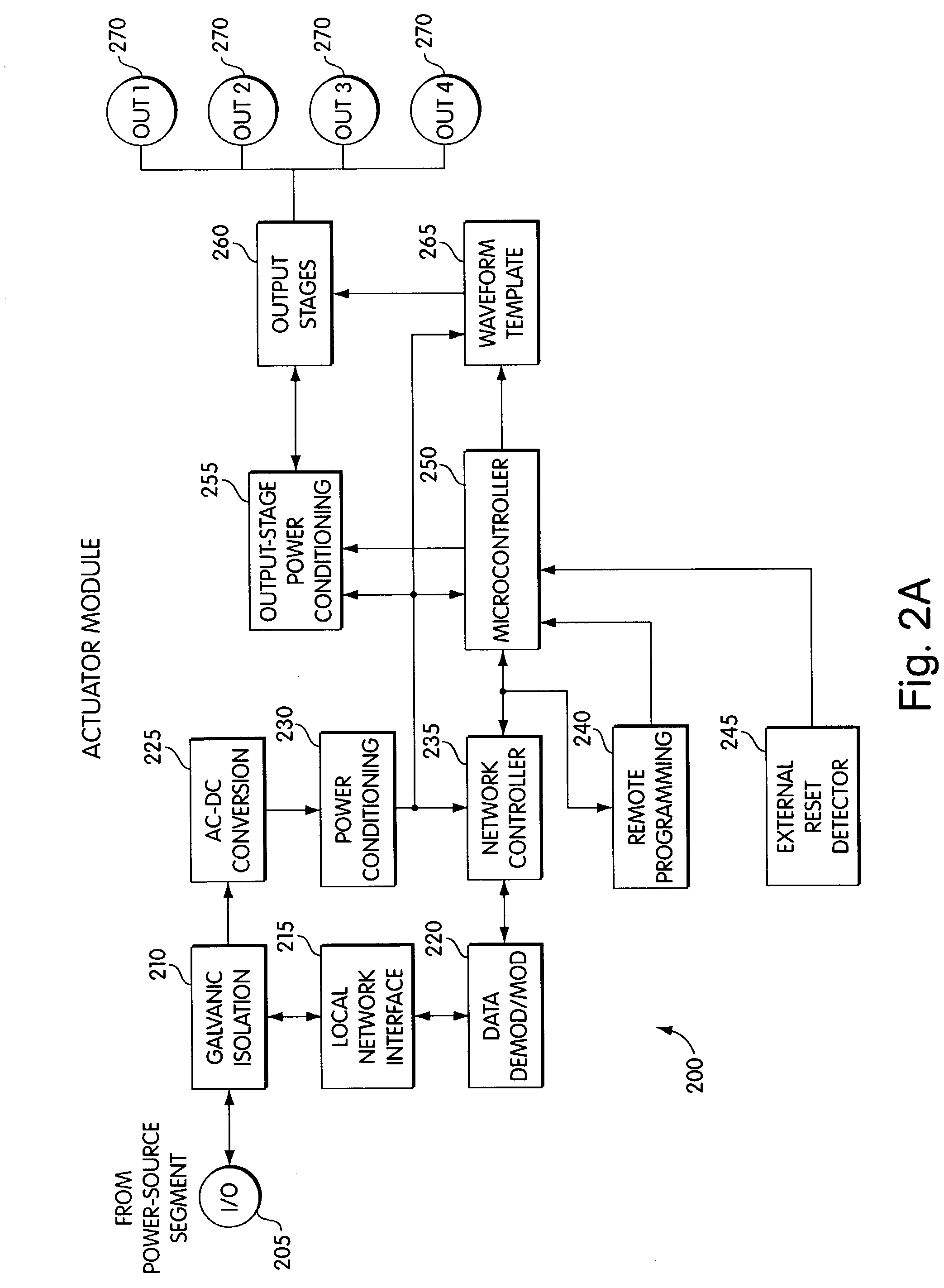

Implantable networked neural system

A neural prosthesis includes a centralized device that can provide power, data, and clock signals to one or more individual neural prosthesis subsystems. Each subsystem may include a number of individually addressable, programmable modules that can be dynamically allocated or shared among neural prosthetic networks to achieve complex, coordinated functions or to operate in autonomous groups.

Owner:CASE WESTERN RESERVE UNIV

Shift register and image display apparatus containing the same

ActiveUS20080101529A1Increased circuit areaImprove driving reliabilityStatic indicating devicesDigital storagePower inverterShift register

A shift register includes a first transistor supplying an output terminal with a clock signal input to a first clock terminal and a second transistor discharging the output terminal. Defining the gate node of the first transistor as a first node, and the gate node of the second transistor as a second node, the shift register includes an inverter circuit in which the first node serves as its input node and a capacitive element serves as a load, and a buffer circuit receiving the output from the inverter circuit and outputting a signal to the second node.

Owner:TRIVALE TECH

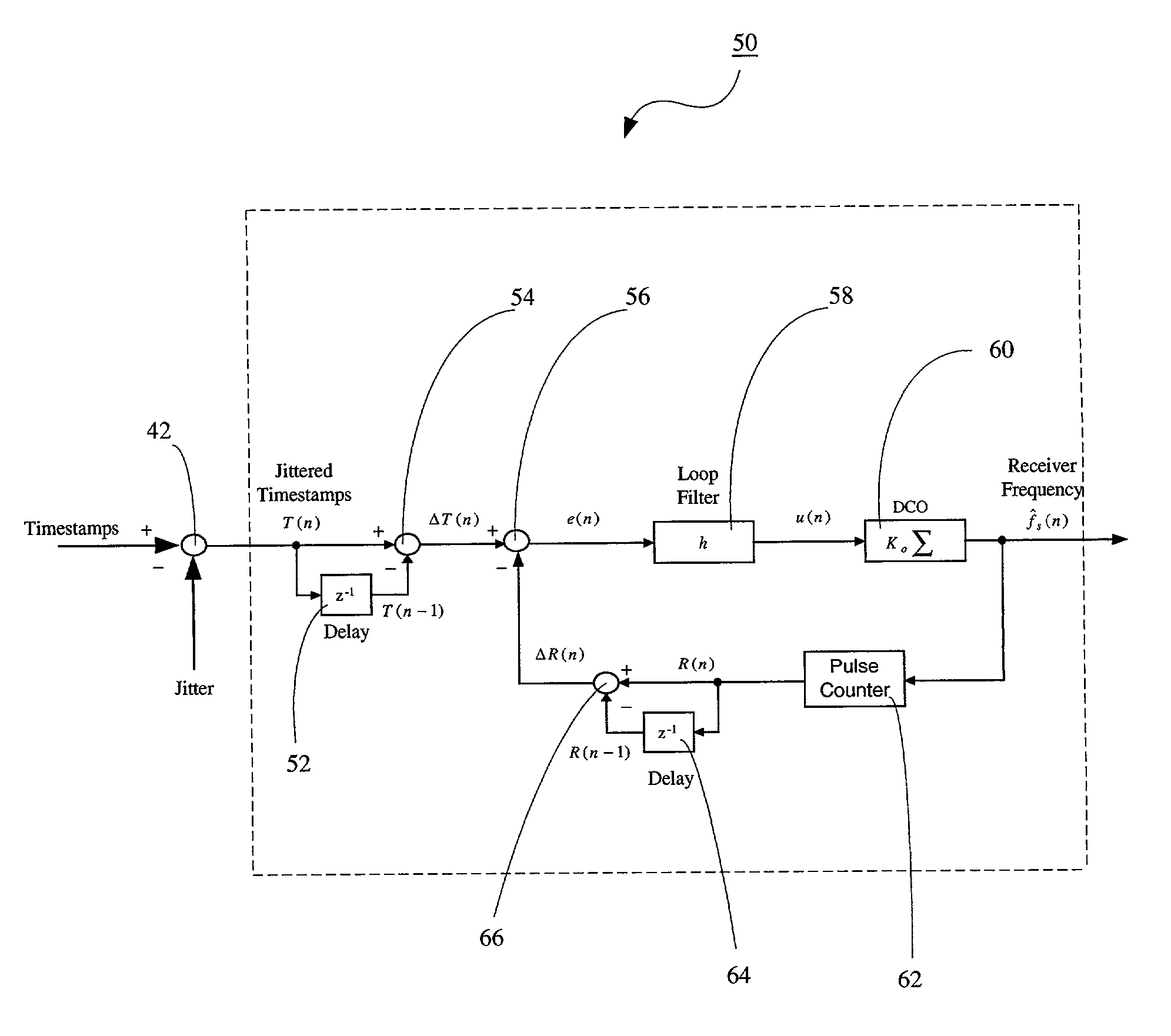

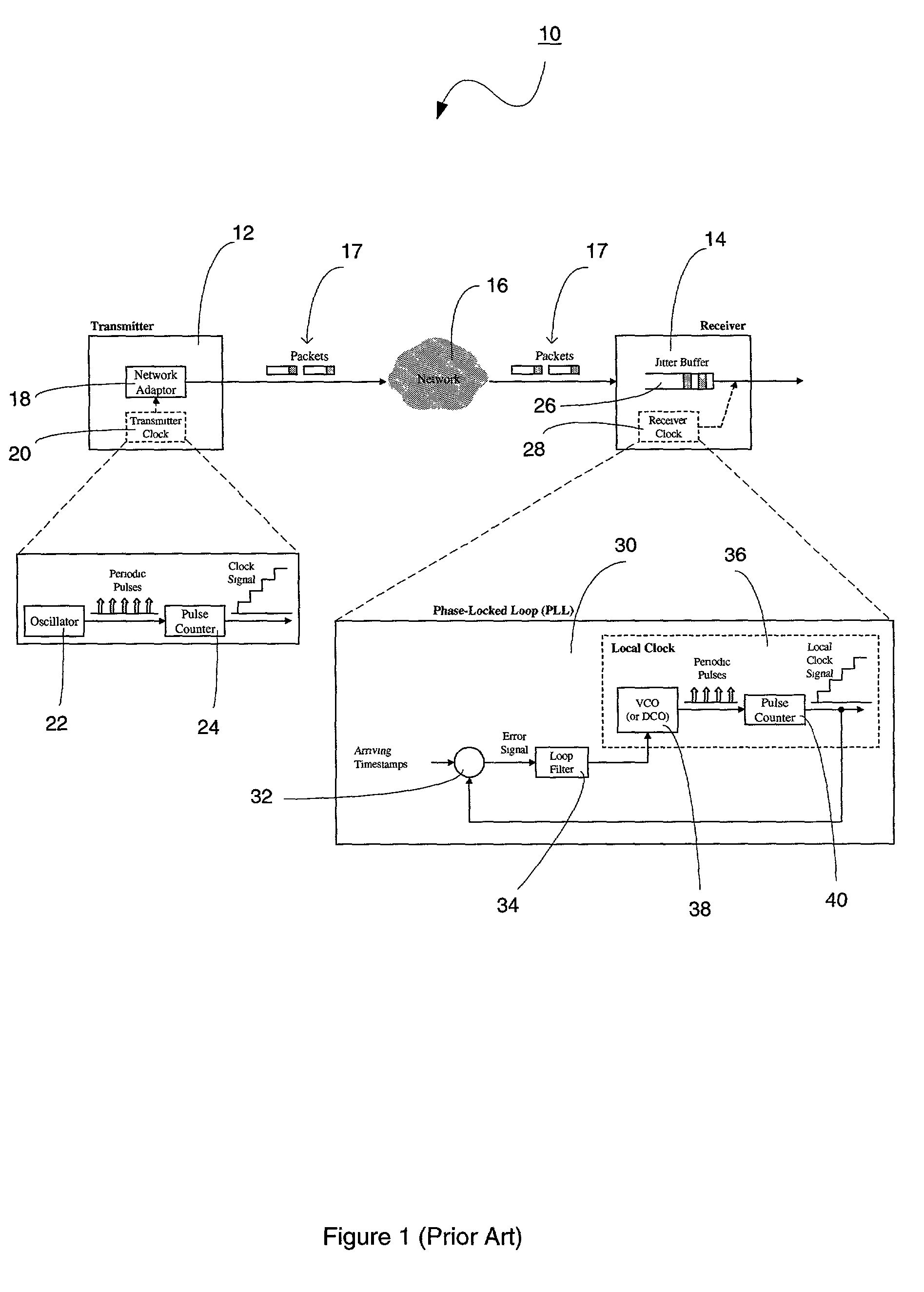

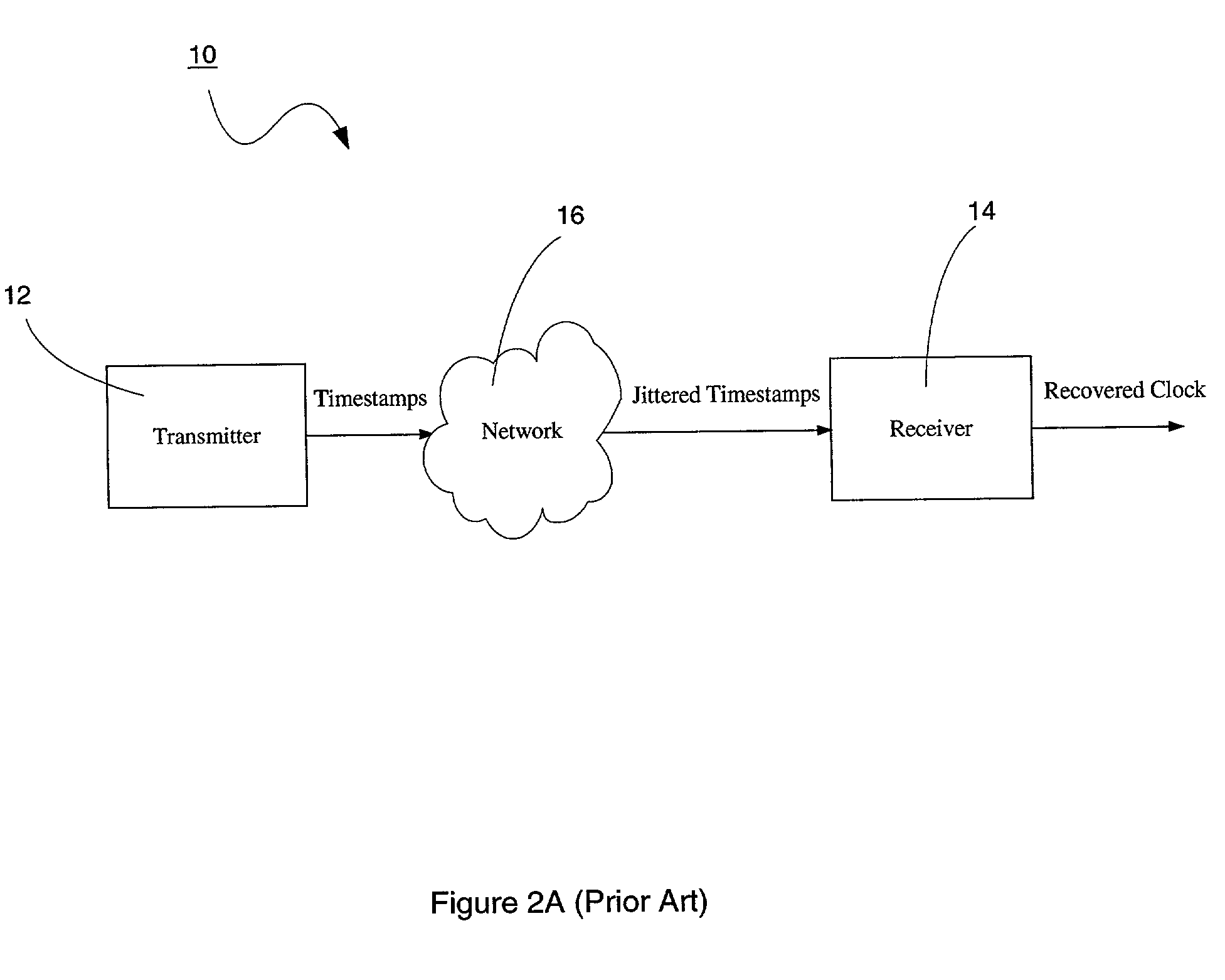

Technique for synchronizing clocks in a network

A technique for synchronizing clocks in a network is disclosed. In one exemplary embodiment, the technique may be realized as a method for synchronizing clocks in a network. The method comprises receiving a first timestamp and a second timestamp, each indicating a respective time instance as determined by a first clock signal within the network. The method also comprises measuring a first time interval between the first timestamp and the second timestamp. The method further comprises generating a difference signal representing a difference between the first time interval and a second time interval, and generating a second clock signal based upon the difference signal such that the second clock signal is synchronized with the first clock signal.

Owner:RPX CLEARINGHOUSE

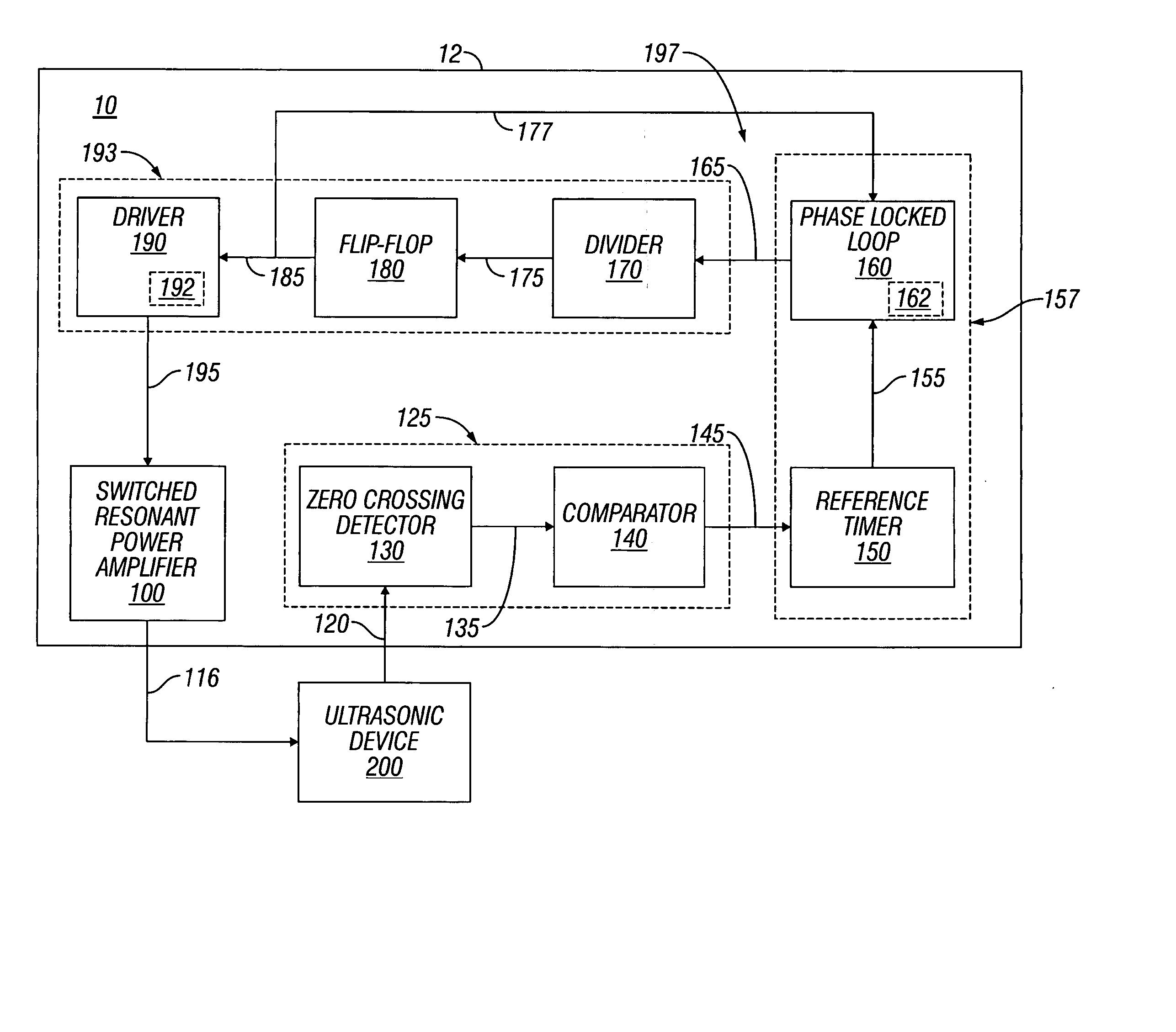

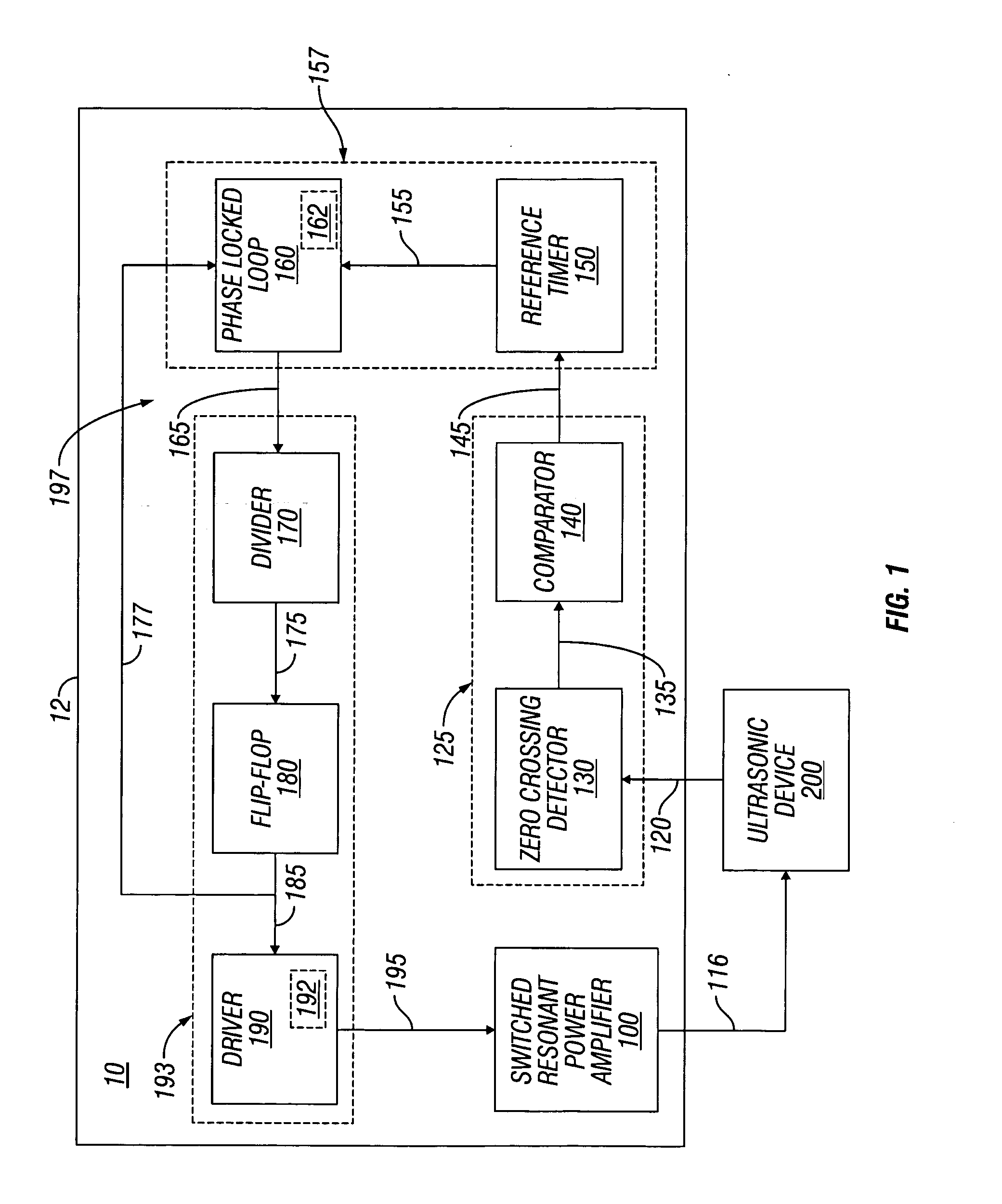

Switched resonant ultrasonic power amplifier system

ActiveUS20050149151A1Reduce frequencyControl outputUltrasound therapyAmplifier modifications to raise efficiencySonificationAudio power amplifier

A switched resonant power amplifier system for ultrasonic transducers is disclosed. The system includes an amplifier that receives and processes a driver output signal for generating a drive signal that is provided to an ultrasonic device for controlling output of the ultrasonic device. An output control circuit receives and processes a signal related to a feedback signal generated by the ultrasonic device and a divider reference signal, and generates a compensated clock signal that is adjusted for at least one of phase and frequency differences between the received feedback signal and the divider reference signal. A compensated drive circuit receives and processes the compensated clock signal for generating the divider reference signal, and for generating the driver output signal.

Owner:COVIDIEN AG

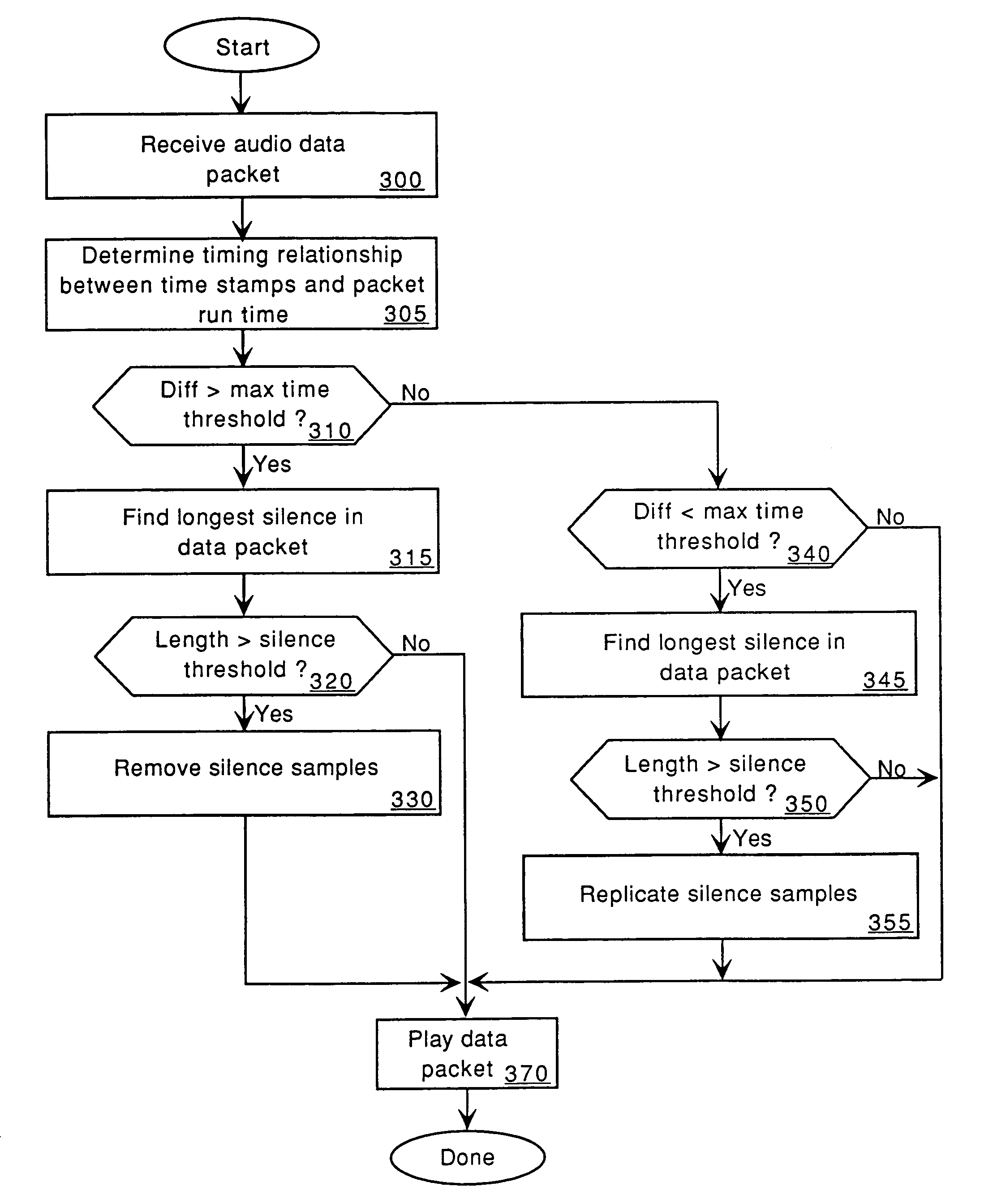

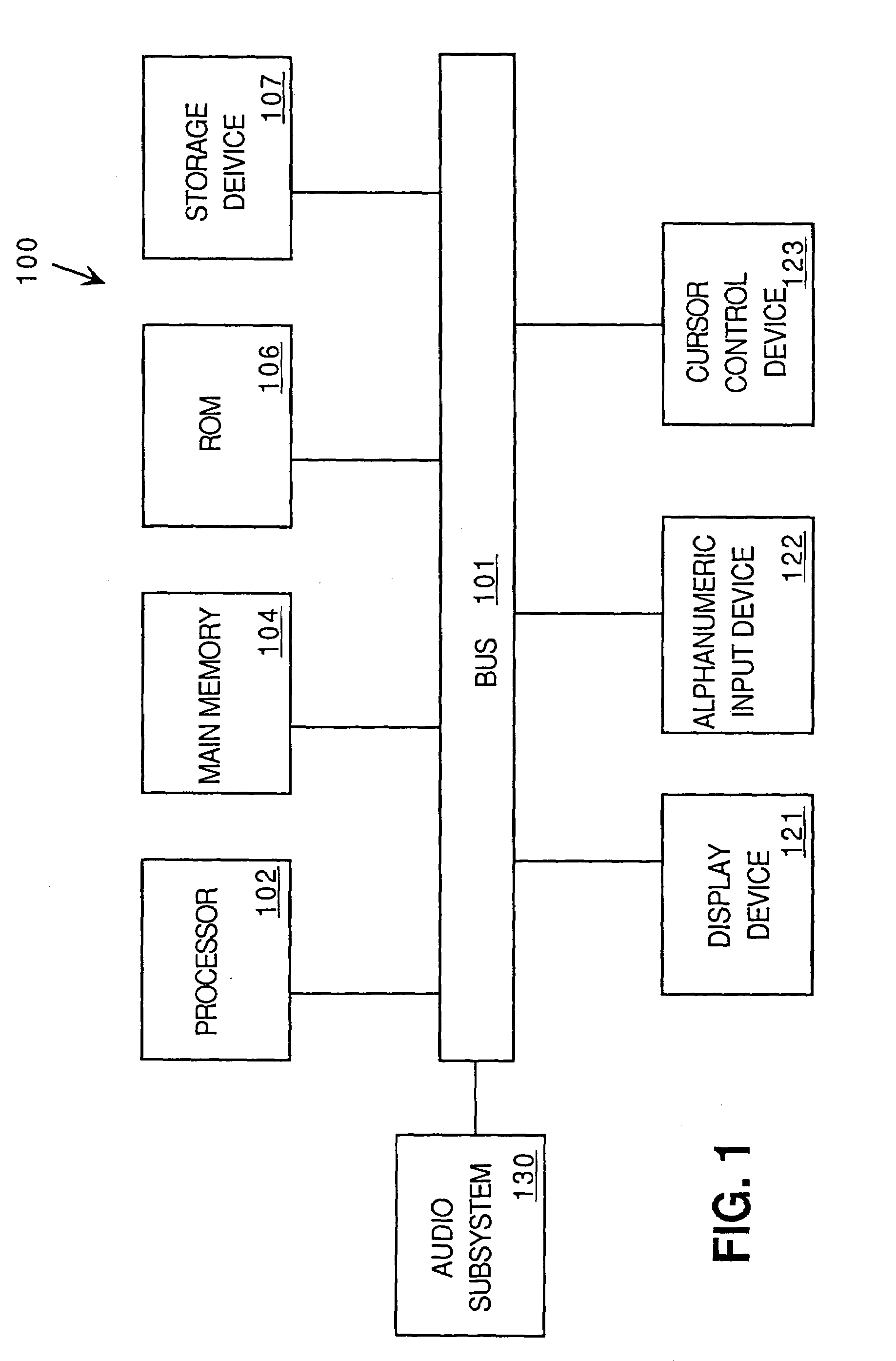

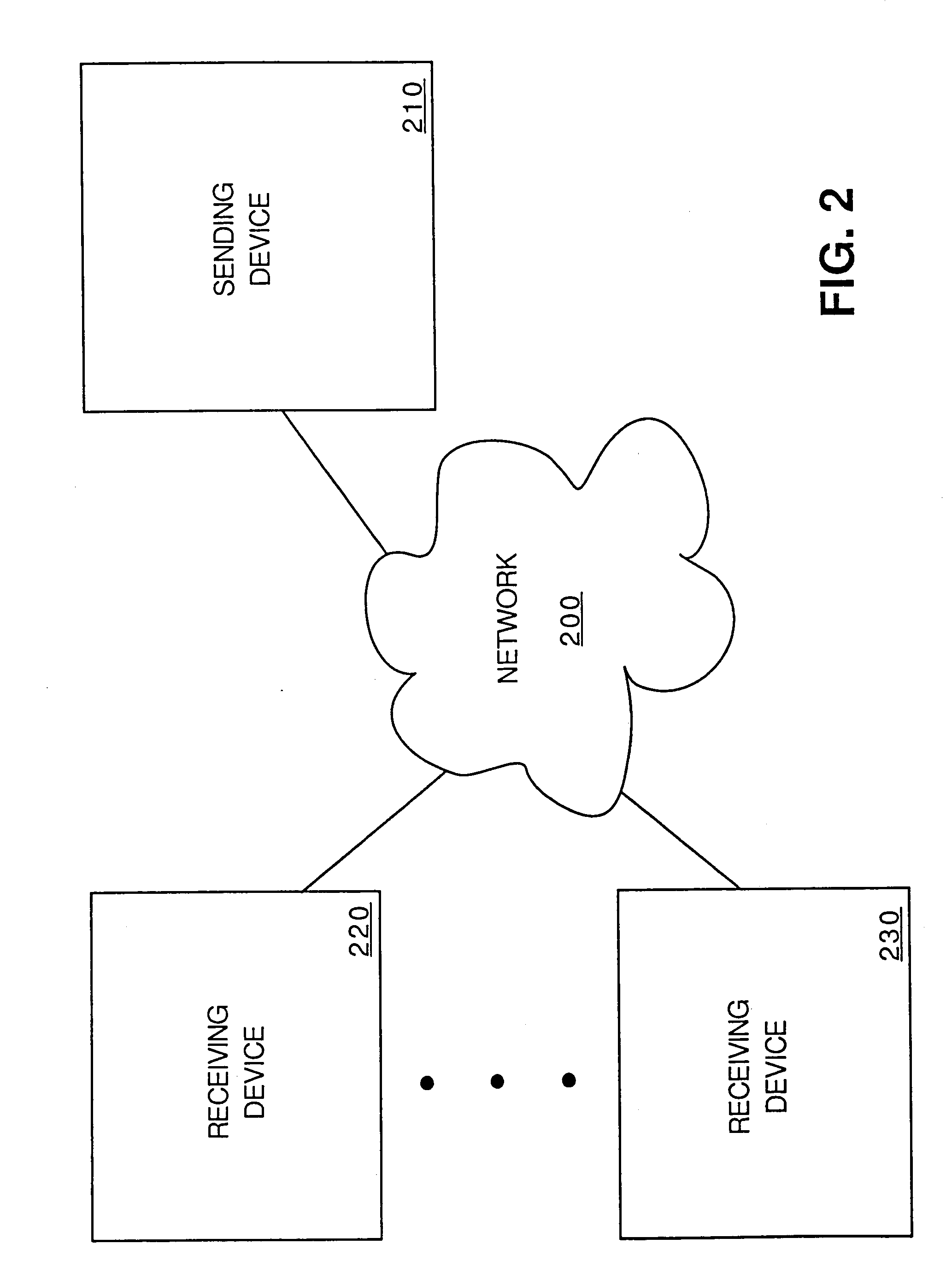

Digital audio compensation

A method and apparatus for audio compensation is disclosed. If audio input components and audio output components are not driven by a common clock (e.g., input and output systems are separated by a network, different clock signals in a single computer system), input and output sampling rates may differ. Also, network routing of the digital audio data may not be consistent. Both clock synchronization and routing considerations can affect the digital audio output. To compensate for the timing irregularities caused by clock synchronization differences and / or routing changes, the present invention adjusts periods of silence in the digital audio data being output. The present invention thereby provides an improved digital audio output.

Owner:MICROSOFT TECH LICENSING LLC

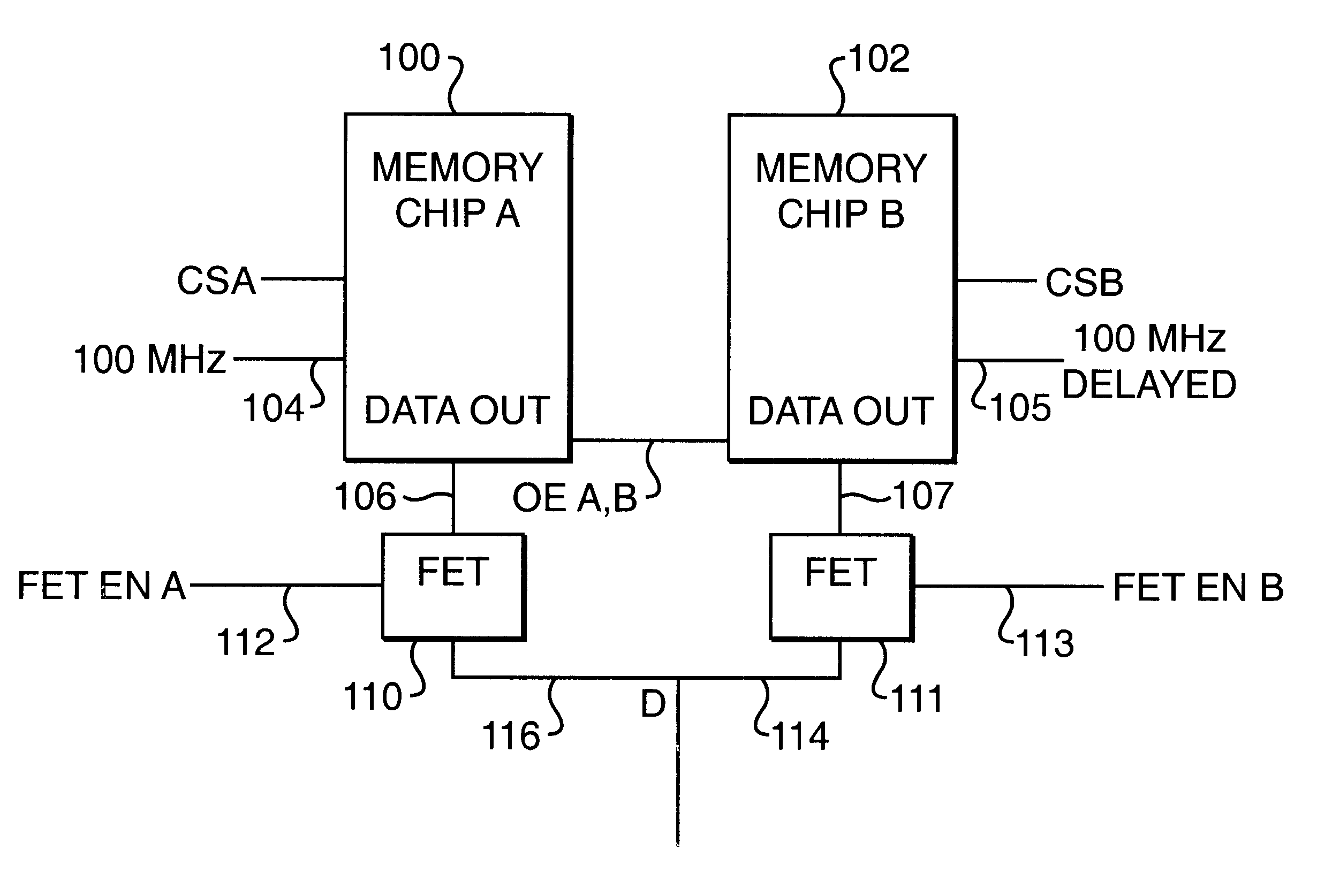

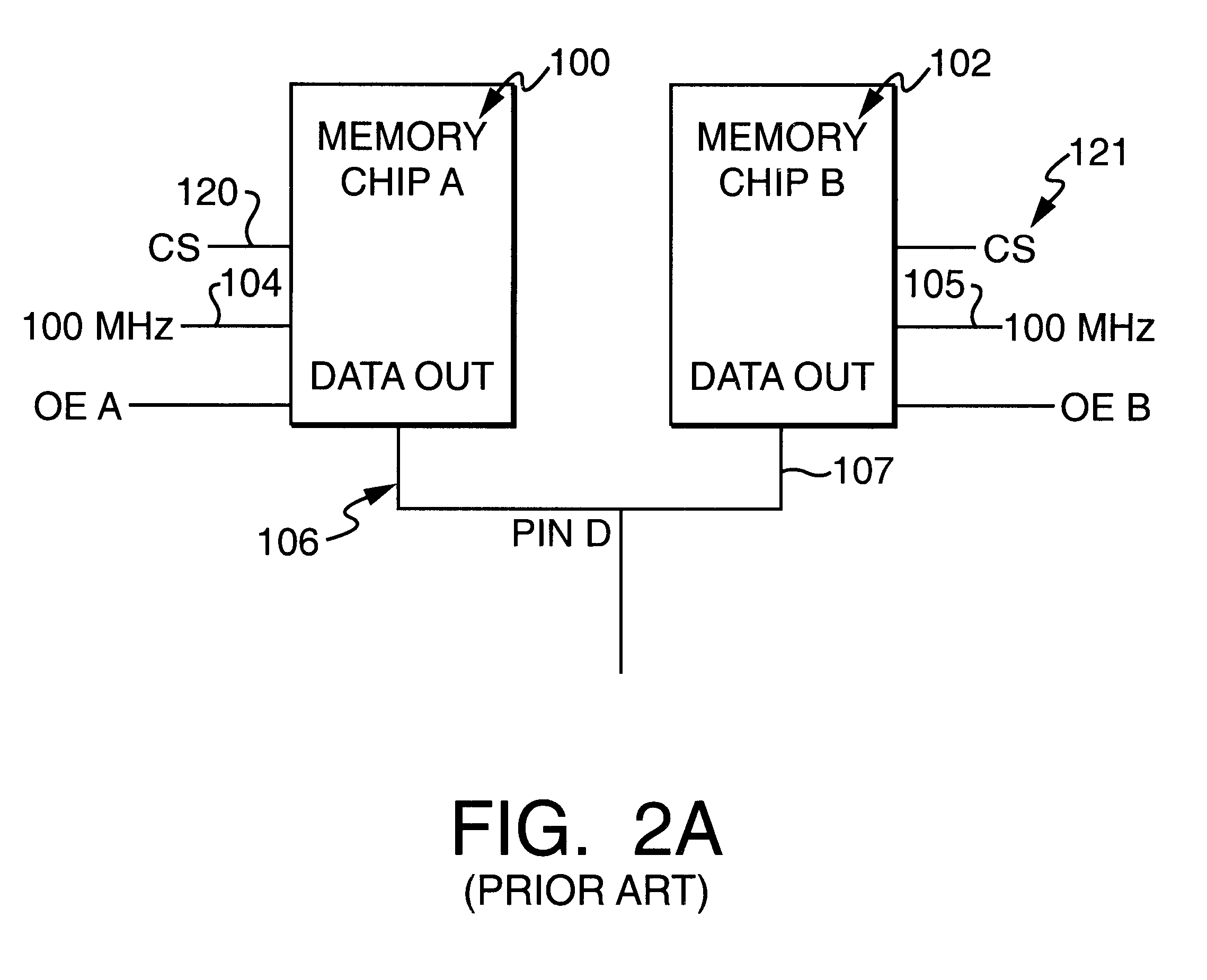

Memory system using FET switches to select memory banks

A computer memory system provides a double data rate (DDR) memory output while requiring memory chips with only half the frequency limit of the prior art DDR memory chips. The system contains a first memory bank having data lines and a second memory bank having data lines. The first and second memory banks are associated with first and second clock signals, respectively, where the second clock signal is delayed from the first clock signal such that the data lines of the first memory bank are connected to a data bus in synchronism with the first clock signal while the data lines of the second memory bank are connected with the data bus in synchronism with the second clock signal. In one embodiment, a first FET switch connects the data lines of the first memory bank with the data bus and a second FET switch connects the data lines of the second memory bank with the data bus. The second FET switch is connected to the data bus at a time delayed from the beginning after the start of each clock cycle of the second clock signal. As a result, the data bus is never connected to the data lines of both memory banks at the same time, but rather, the data bus is alternately connected with the first memory bank and then the second memory bank.

Owner:FOOTHILLS IP LLC

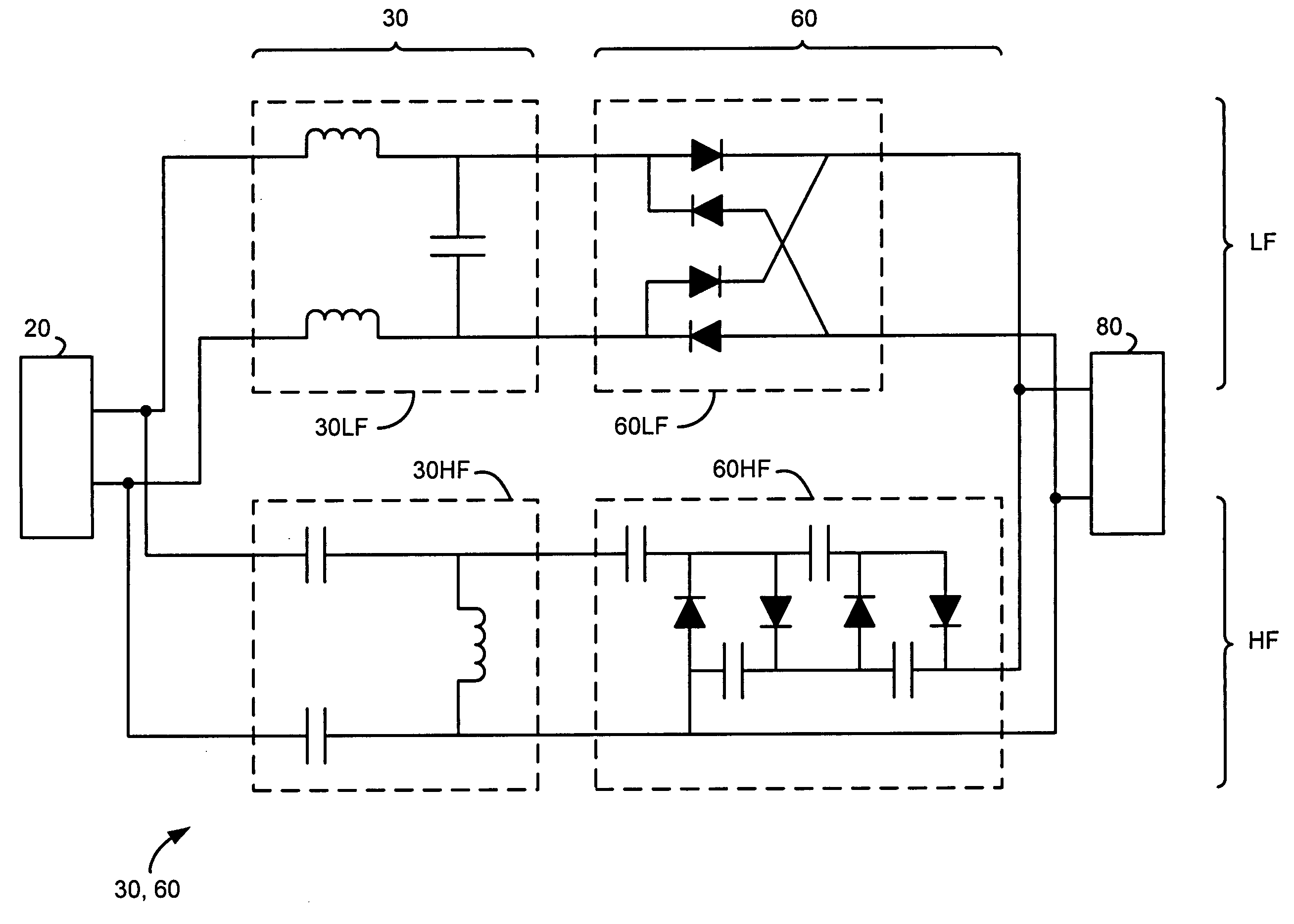

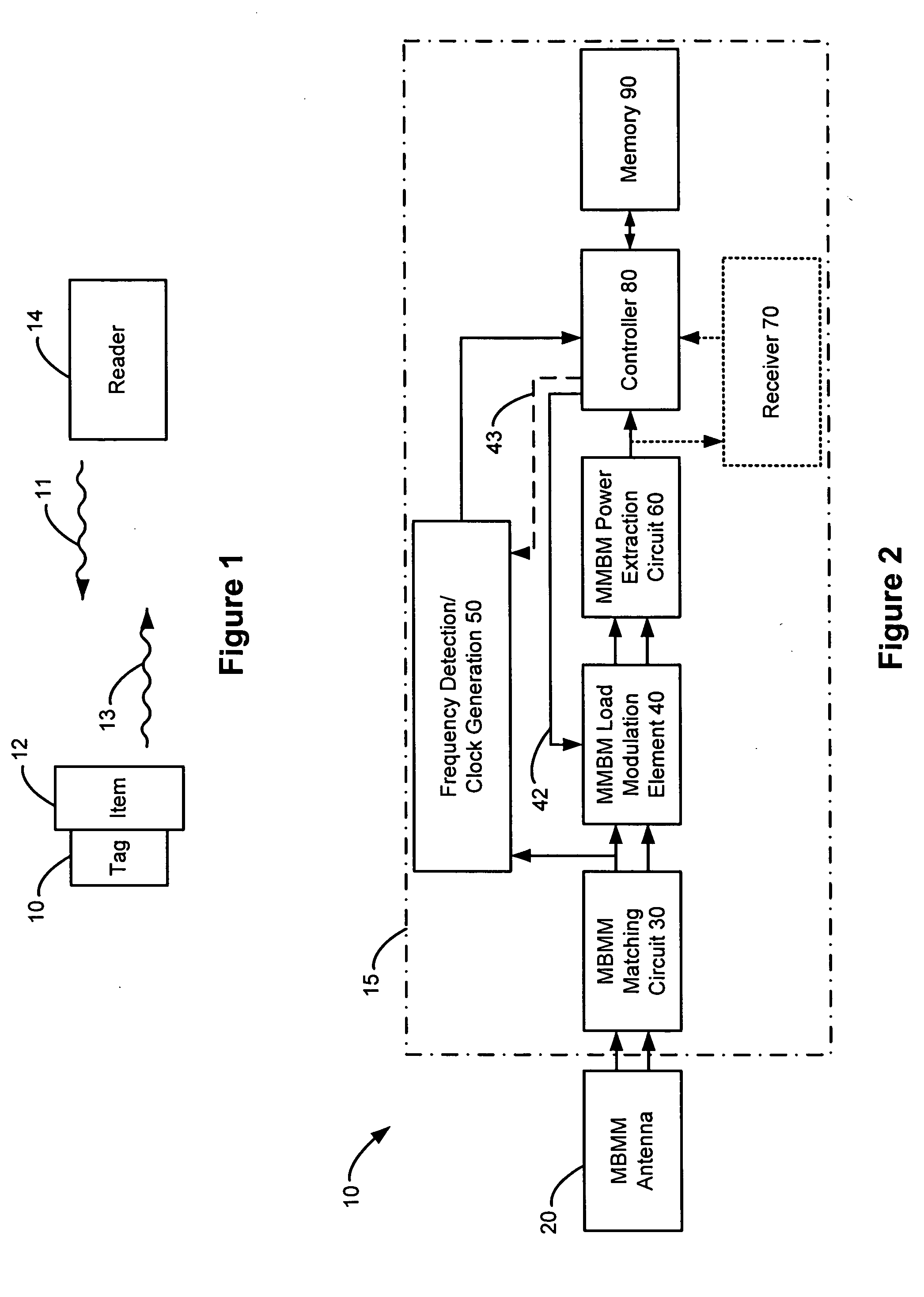

Method and apparatus for multiple frequency RFID tag architecture

ActiveUS20050052283A1Reduce conductivityAntenna arraysSubscribers indirect connectionMulti bandTagged architecture

The present invention provides a multi-band, multi-mode RFID tag that uses a single antenna structure and integrated circuit to provide asset location information at any stage of a supply chain. The unified tag design operates at multiple frequencies (or bands) using the antenna structure, for example, 125 kHz, 13.56 MHz, 915 MHz, and 2.45 GHz, and preferably operates electrostatically (at lower frequencies) and electromagnetically (ay higher frequencies). An on-chip frequency monitor in the integrated circuit automatically determines which frequency is present and derives a local clock for the tag's integrated circuit, which can vary in accordance with the frequency or which can be constant. Alternatively, a phase locked loop circuit can be used to derive a local clock signal modulated into the interrogation signal. On-chip matching and power extraction circuits derive power for the tag from the interrogation signal, which is preferably passive. Additionally, a receiver can receive data from the interrogation signal.

Owner:MOTOROLA SOLUTIONS INC

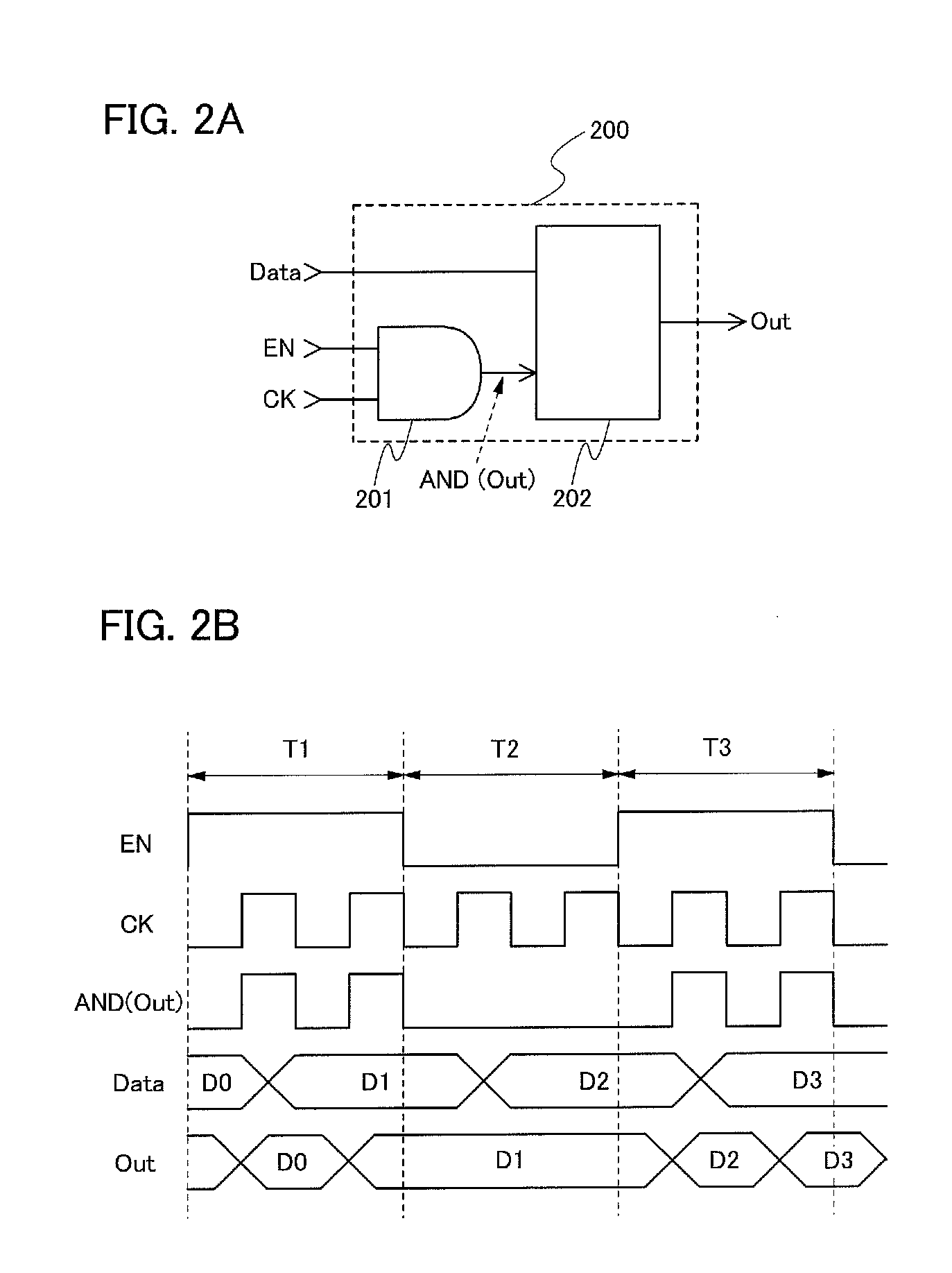

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

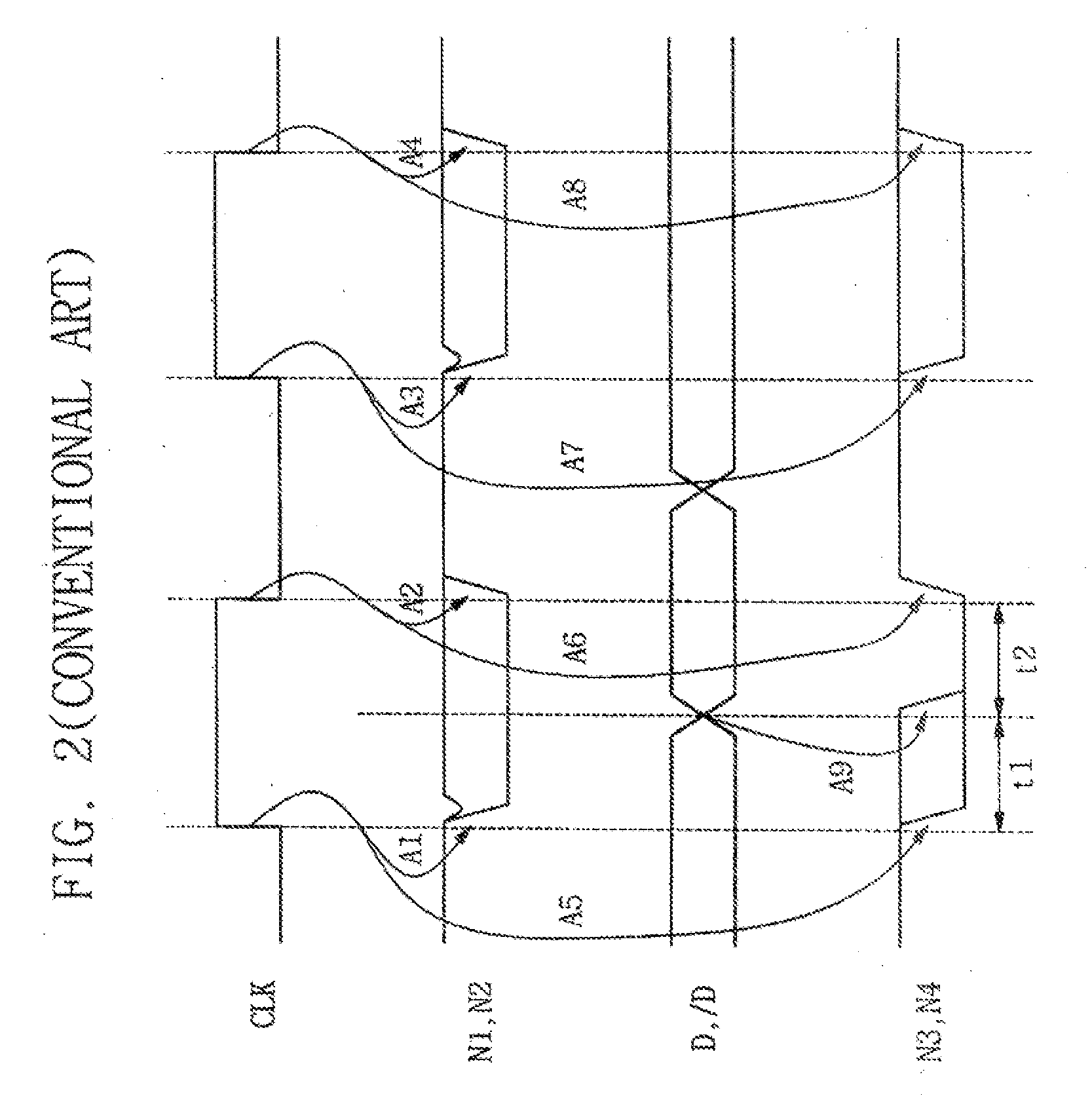

Shift register circuit and image display apparatus equipped with the same

InactiveUS20070274433A1Suppress failureIncrease computing speedStatic indicating devicesDigital storageShift registerElectricity

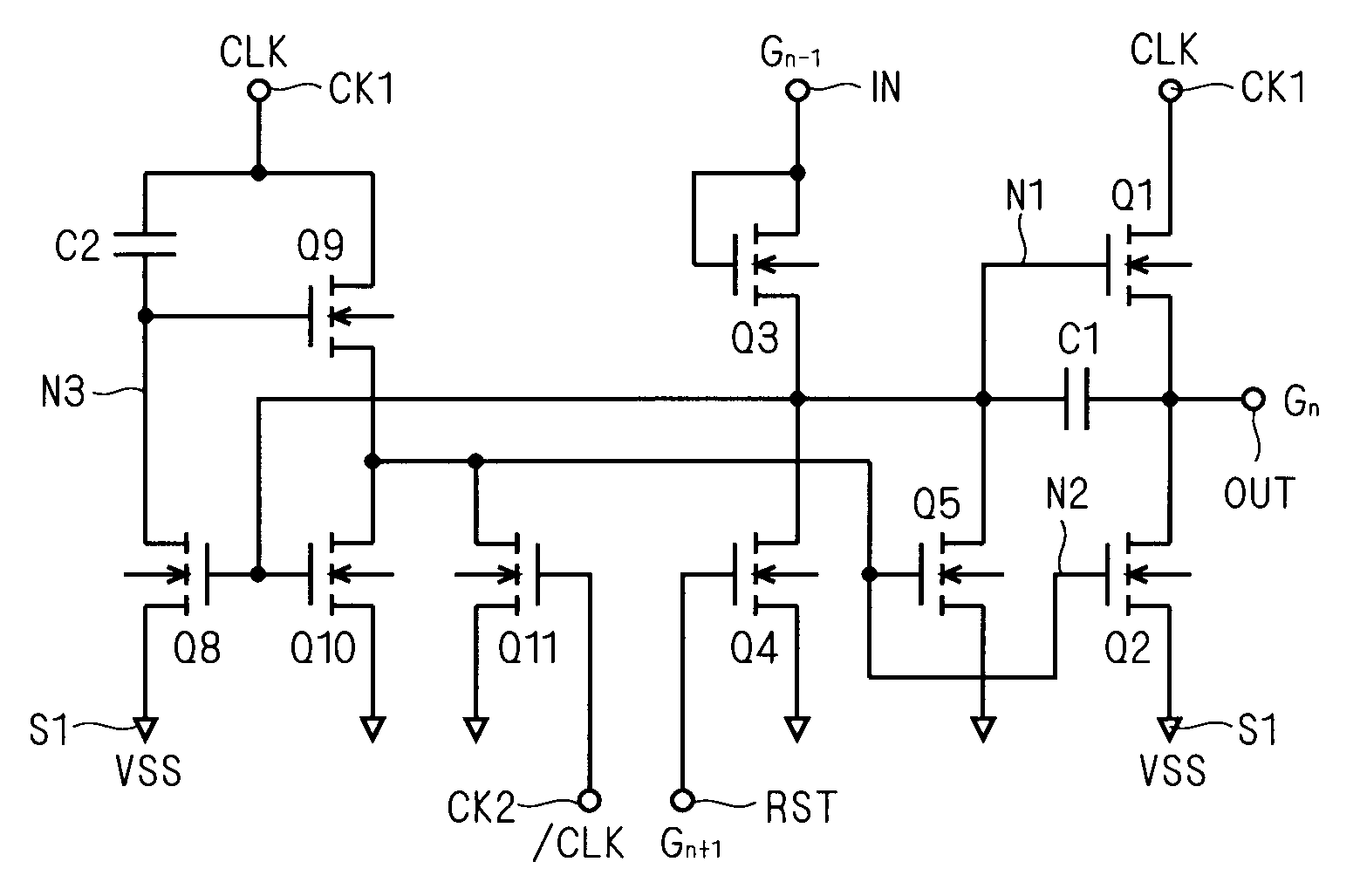

Malfunction caused by leakage current of the transistor and shift in threshold voltage is prevented in the shift register in which the signal can be shifted bi-directionally. The bi-directional unit shift register includes a first transistor Q1 for providing a first clock signal CLK to an output terminal OUT, a second transistor Q2 for discharging the output terminal OUT based on a second clock signal, third and fourth transistors Q3, Q4 for providing first and second voltage signals Vn, Vr complementary to each other to a first node, which is a gate node of the first transistor Q1, and a fifth transistor Q5 connected between the first node and the output terminal OUT. The fifth transistor Q5 is in an electrically conducted state based on the first clock signal CLK when the gate of the transistor Q1 is at L (Low) level.

Owner:MITSUBISHI ELECTRIC CORP

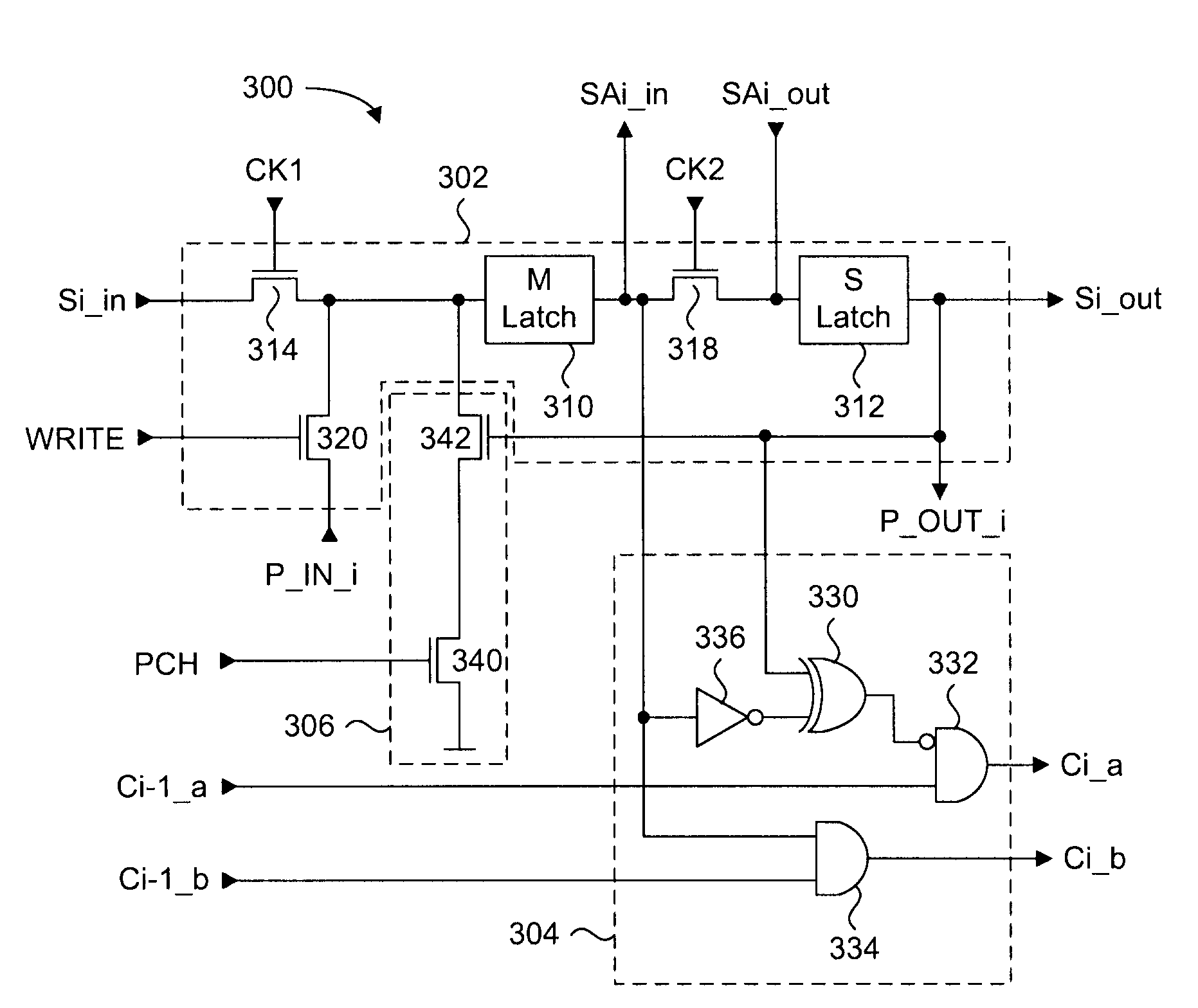

Dual function data register

ActiveUS20090290434A1Reduce disadvantagesRead-only memoriesDigital storageProcessor registerTheoretical computer science

A dual function serial and parallel data register with integrated program verify functionality. The master and slave latching circuits of the dual function data register can concurrently store two different words of data. In a program verify operation, the master latch stores program data and the slave latch will receive and store read data. Comparison logic in each register stage will compare the data of both latches, and integrate the comparison result to that of the previous register stage. The final single bit result will indicate the presence of at least one bit that has not been programmed. Automatic program inhibit logic in each stage will prevent successfully programmed bits from being re-programmed in each subsequent reprogram cycle. Either data word can be serially clocked out by selectively starting the shift operations on either the low or high active logic level of a clock signal.

Owner:SYNOPSYS INC

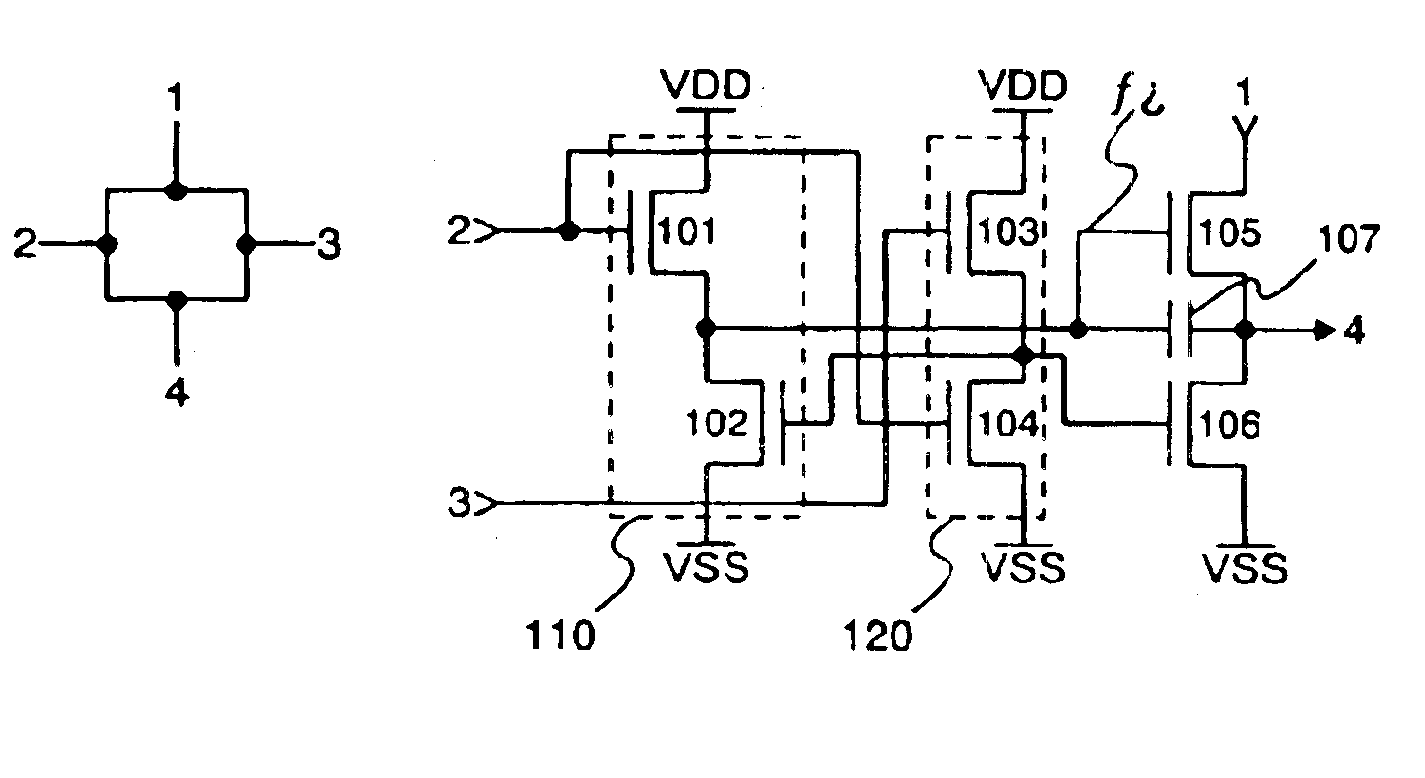

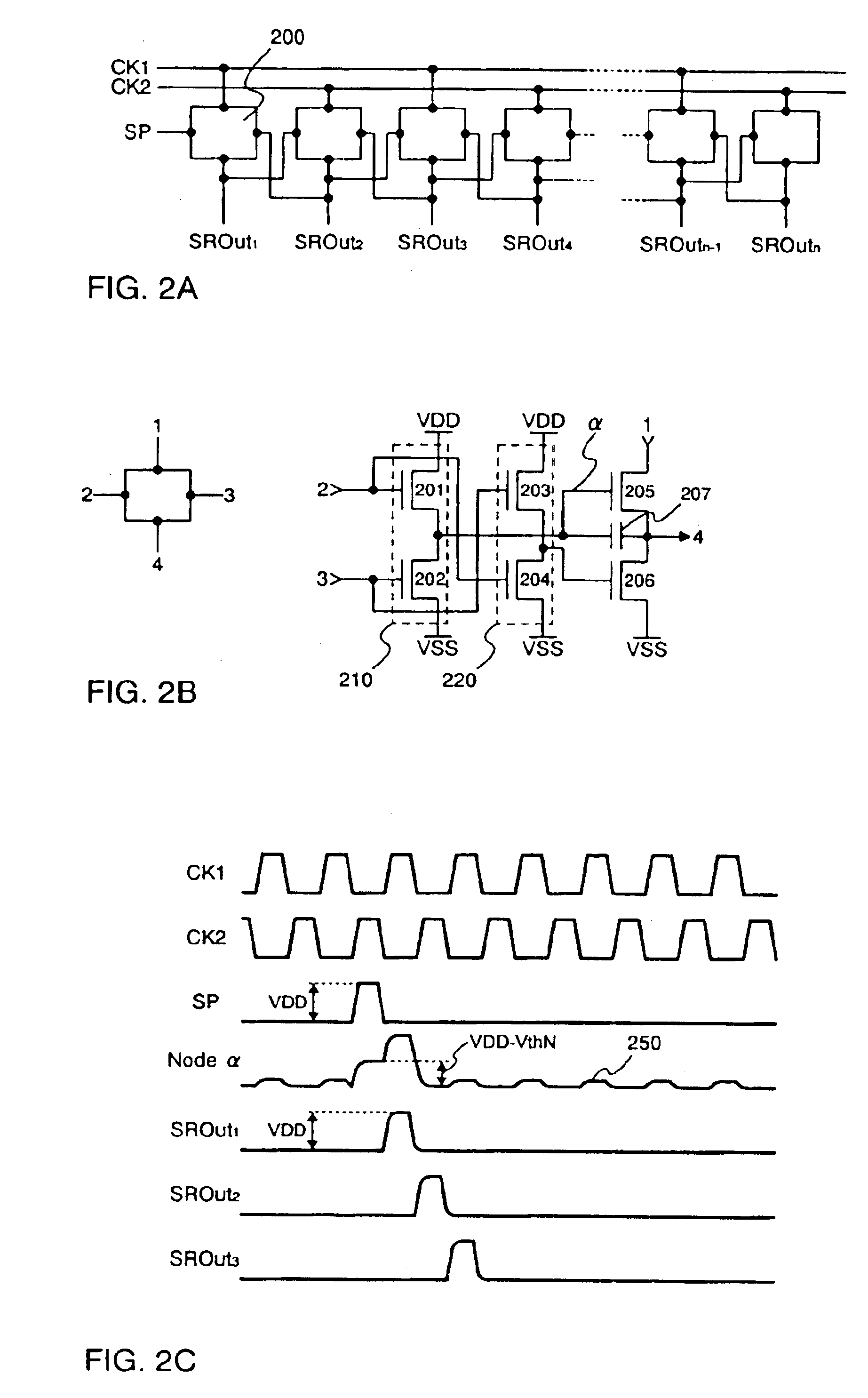

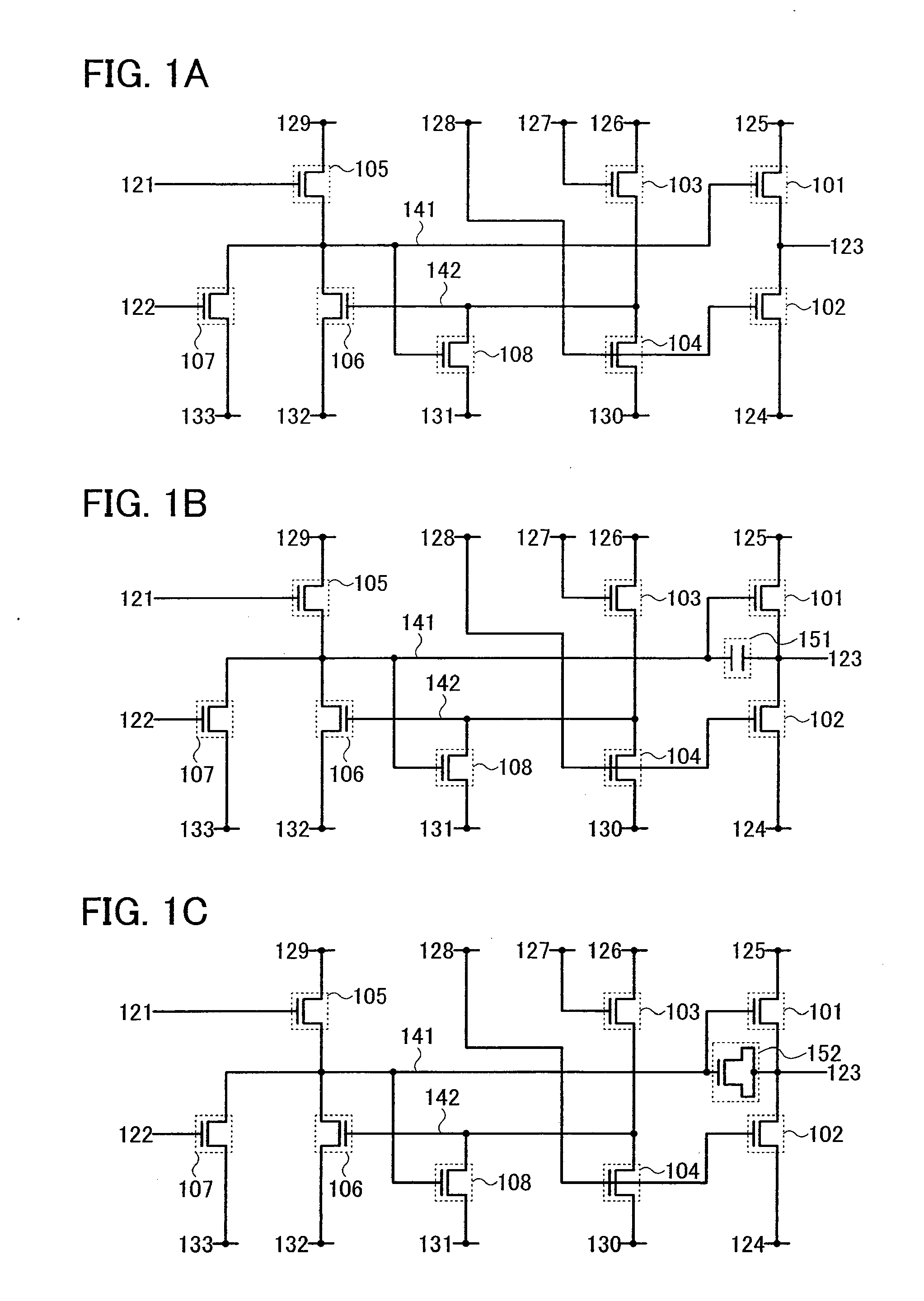

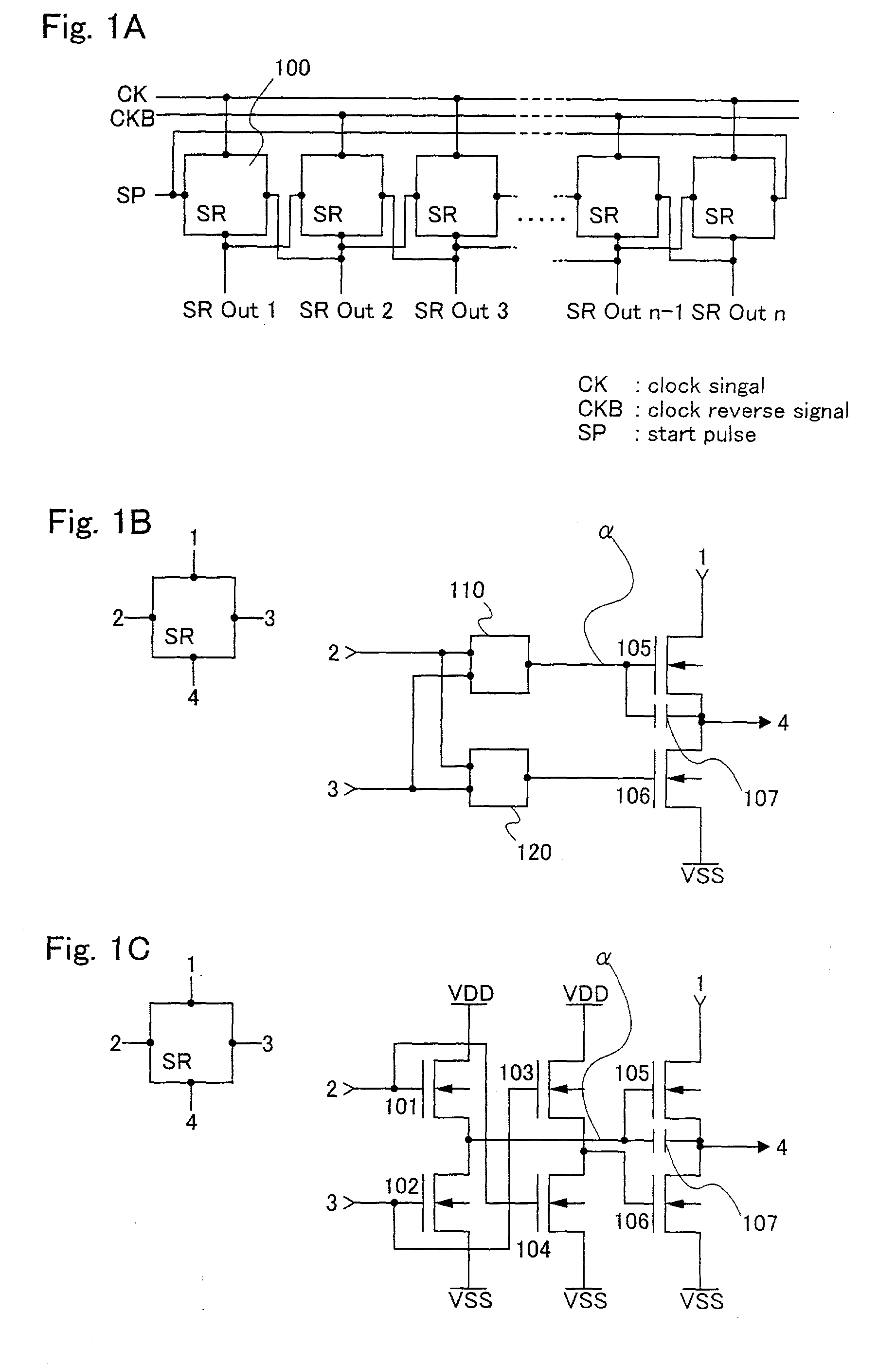

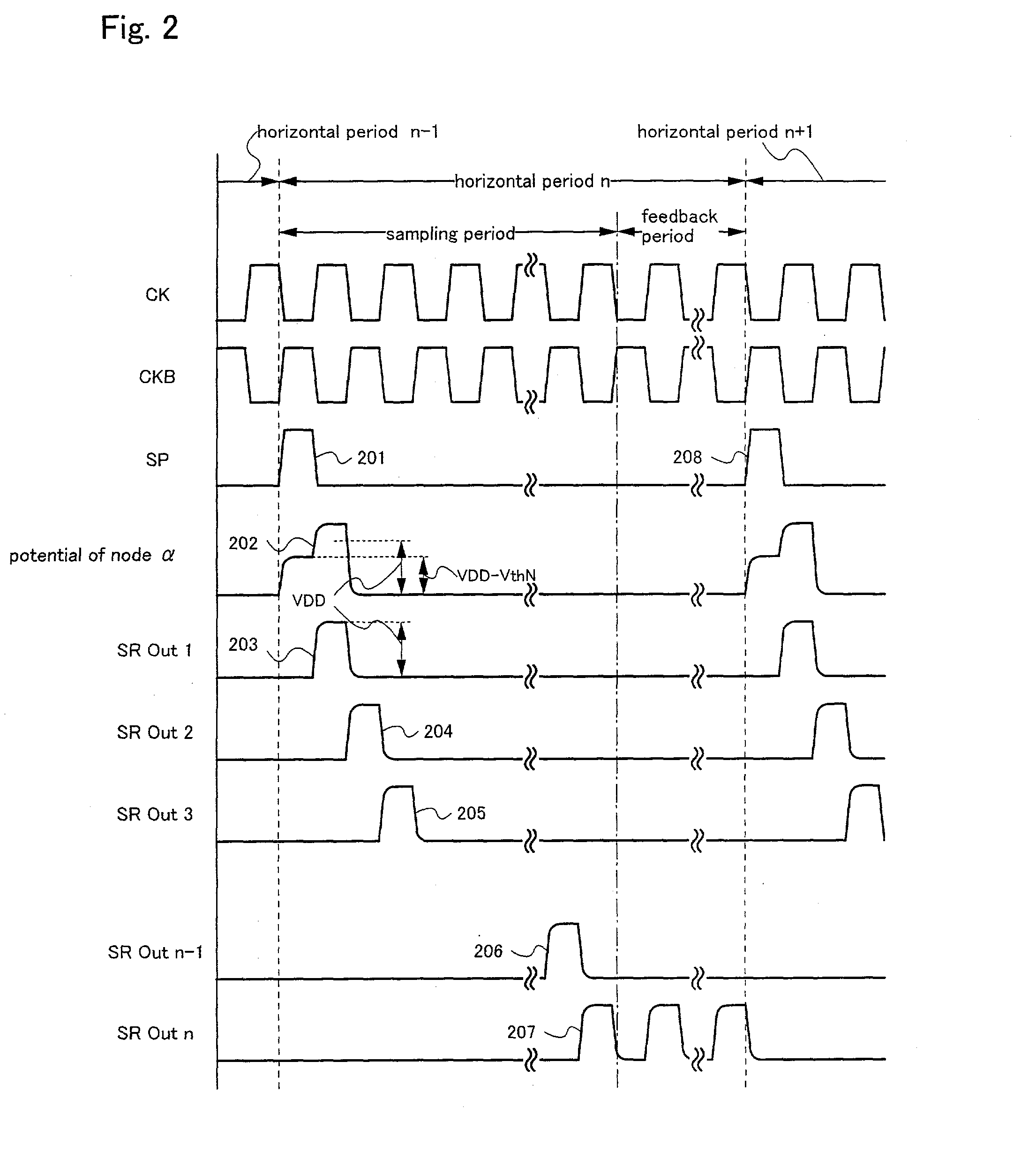

Pulse output circuit, shift register and electronic equipment

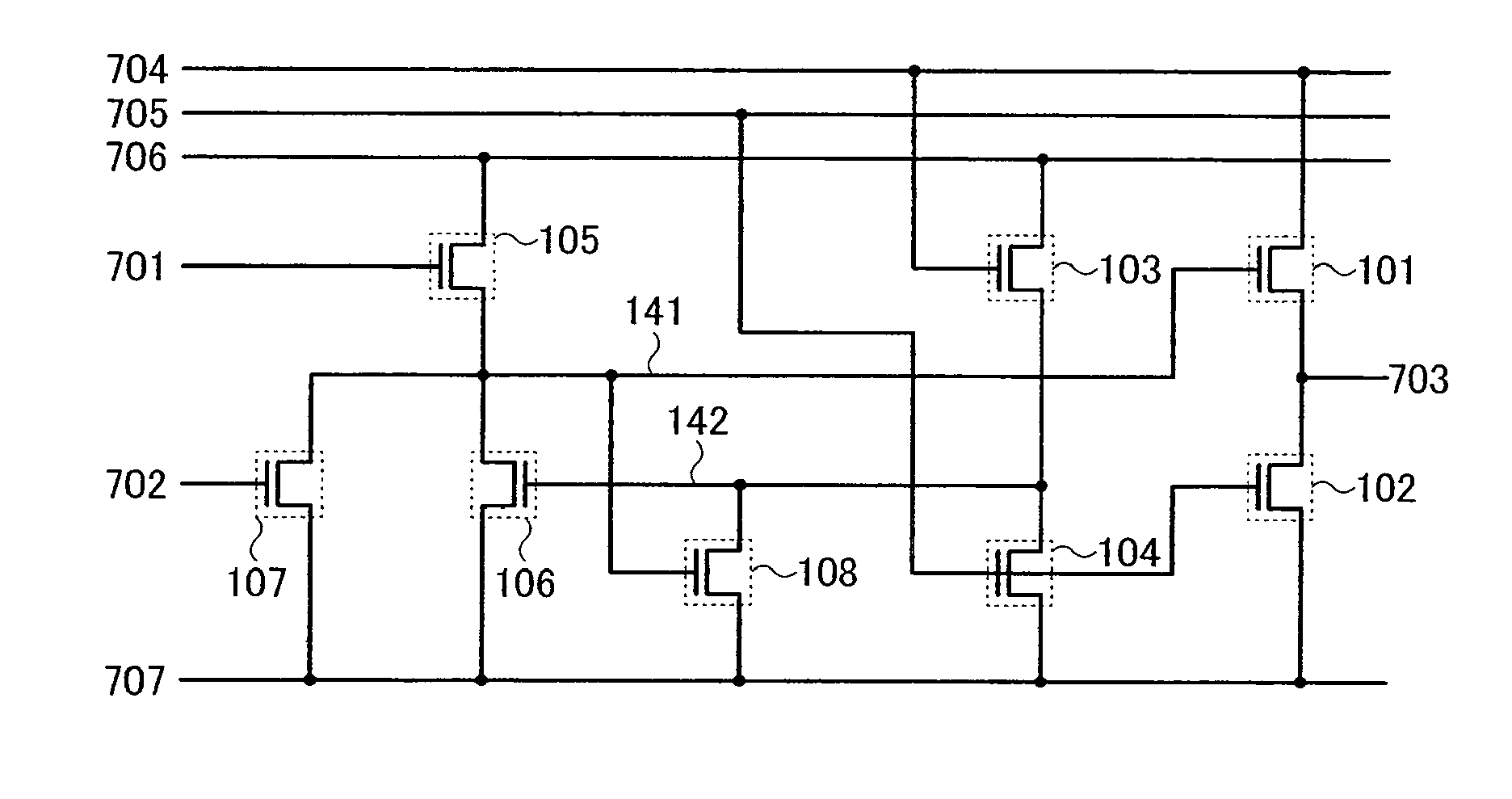

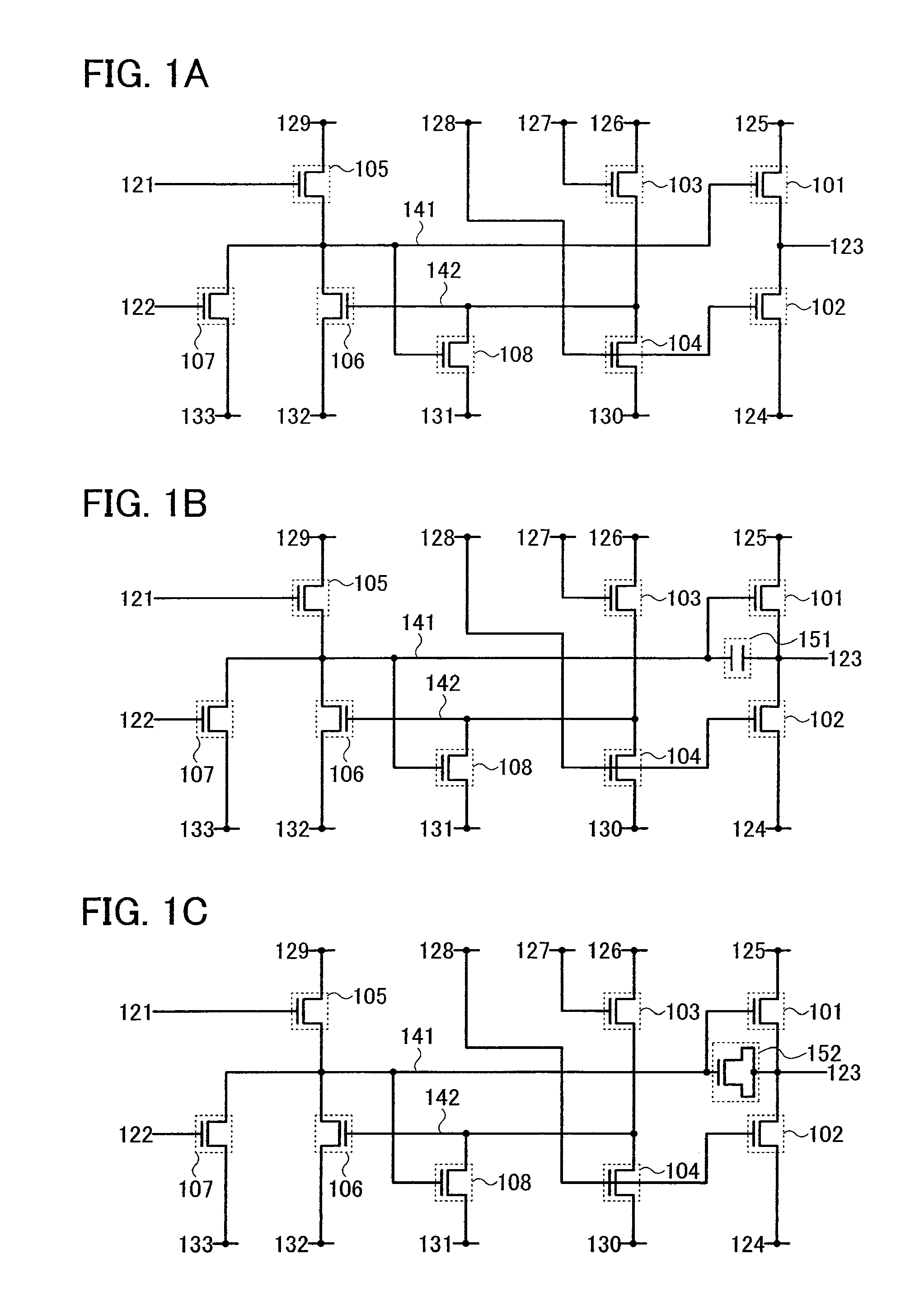

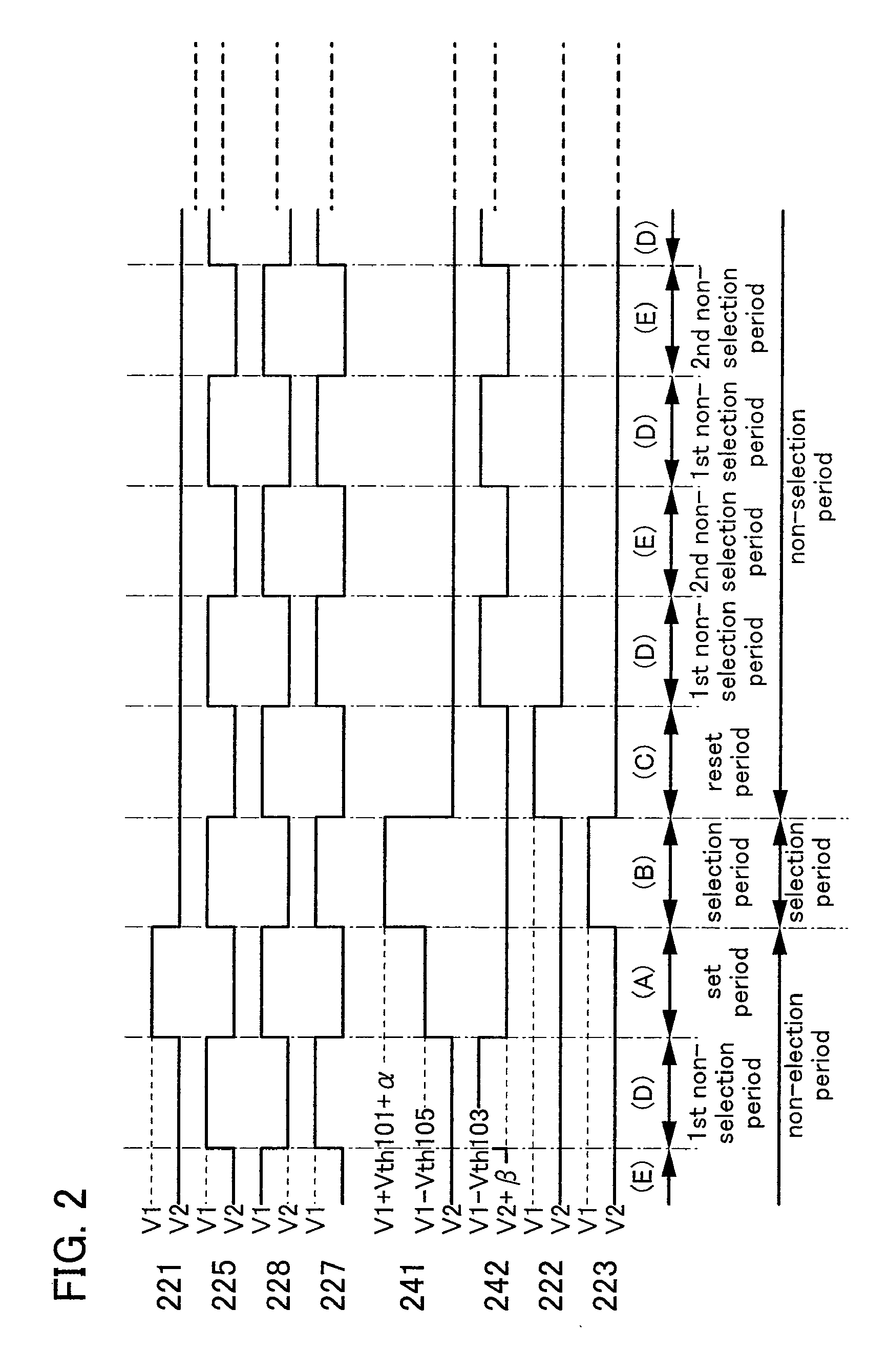

A driver circuit of a display device, which includes TFTs of a single conductivity type and outputs an output signal with normal amplitude. A pulse is inputted to TFTs 101 and 104 to turn ON the TFTs and a potential of a node alpha is raised. When the potential of the node alpha reaches (VDD-VthN), the node alpha becomes in a floating state. Accordingly, a TFT 105 is turned ON and a potential of an output node is raised as a clock signal becomes High level. On the other hand, a potential of a gate electrode of the TFT 105 is further raised due to an operation of a capacitance means 107 as the potential of the output node is raised, so that the potential of the gate electrode of the TFT 105 becomes higher than (VDD+VthN). Thus, the potential of the output node is raised to VDD without causing a voltage drop due to a threshold voltage of the TFT 105. An output at the subsequent stage is then inputted to a TFT 103 to turn the TFT 103 On, while the potential of the node alpha of TFTs 102 and 106 is dropped to turn the TFT 105 OFF. As a result, the potential of the output node becomes Low level.

Owner:SEMICON ENERGY LAB CO LTD

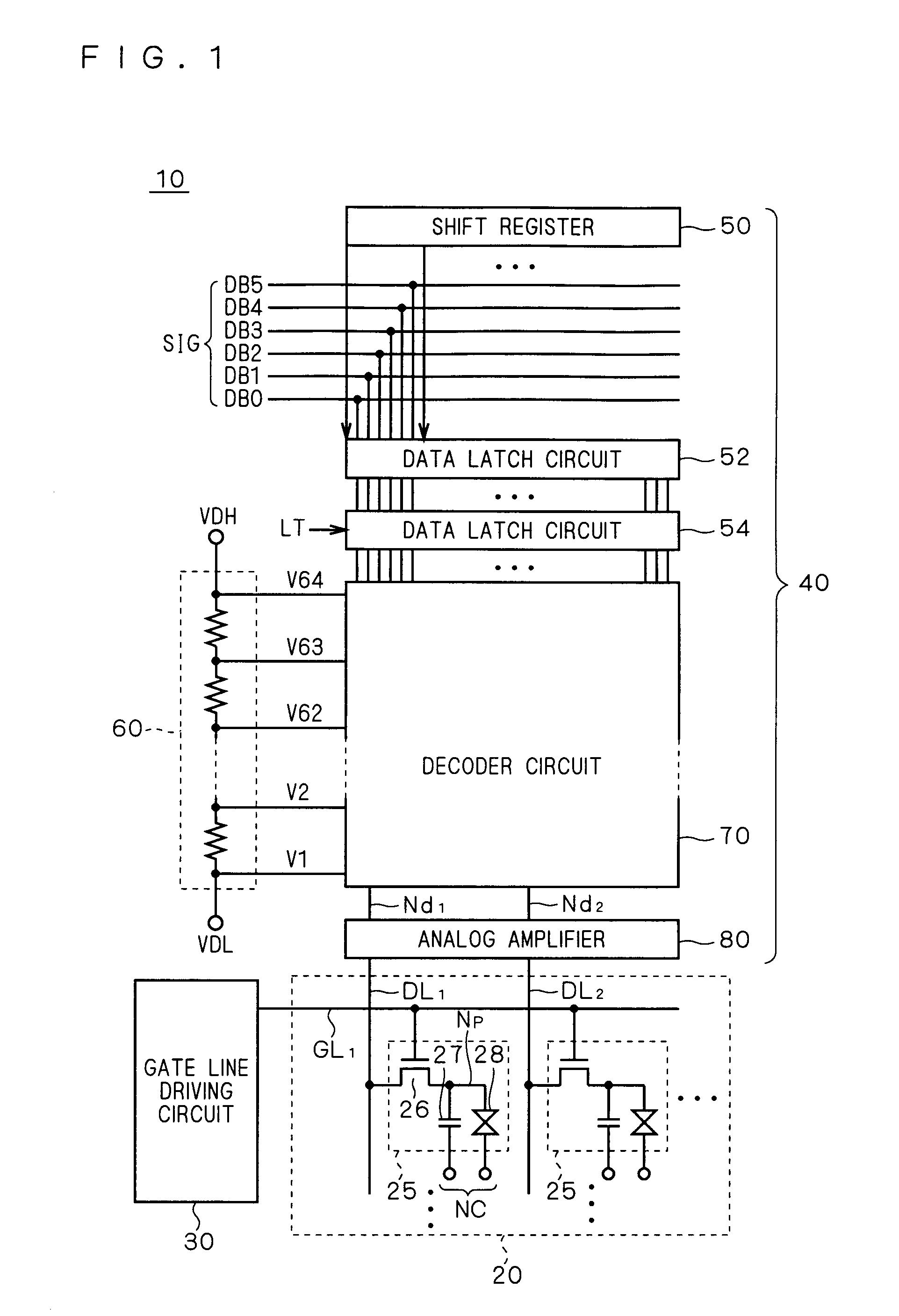

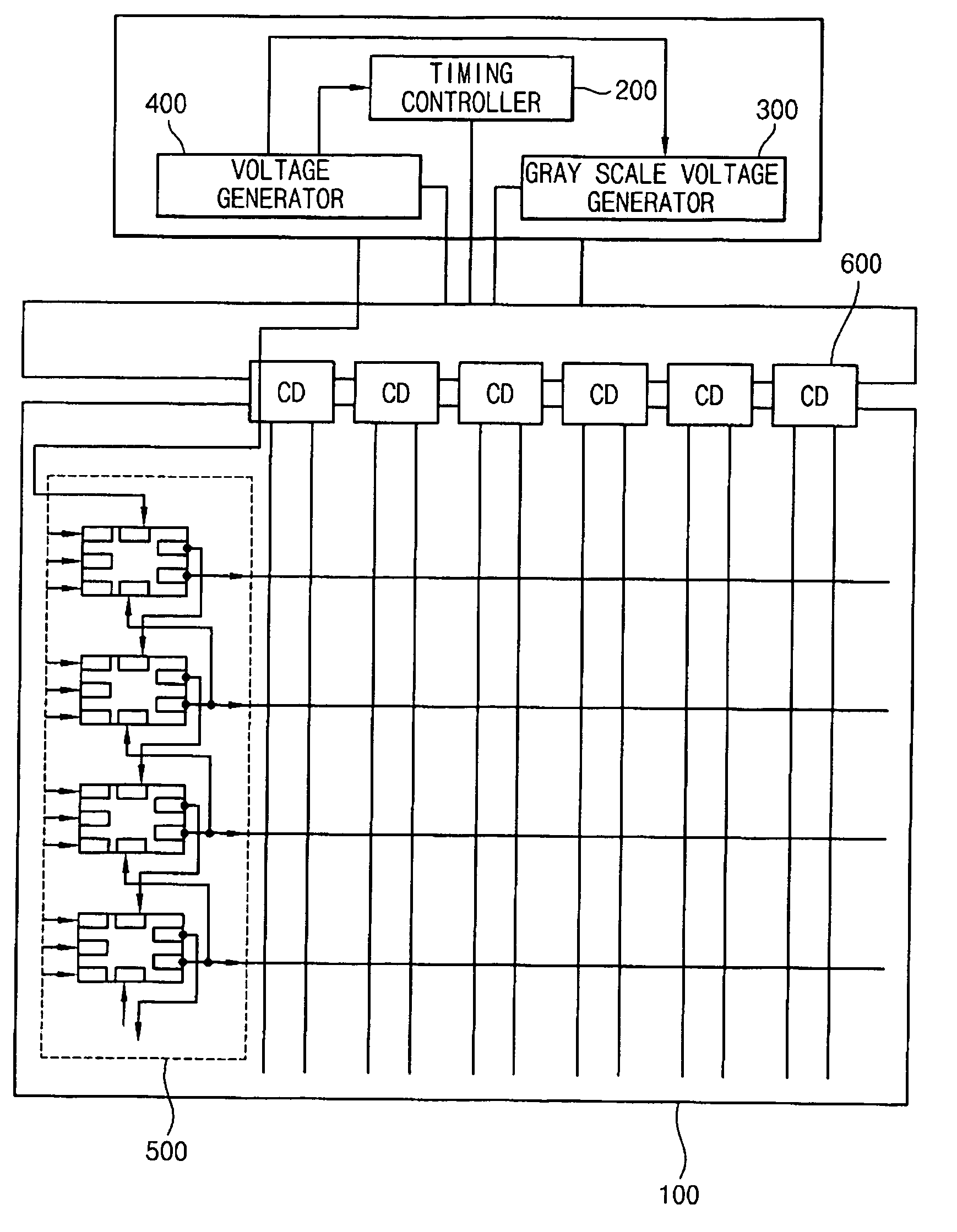

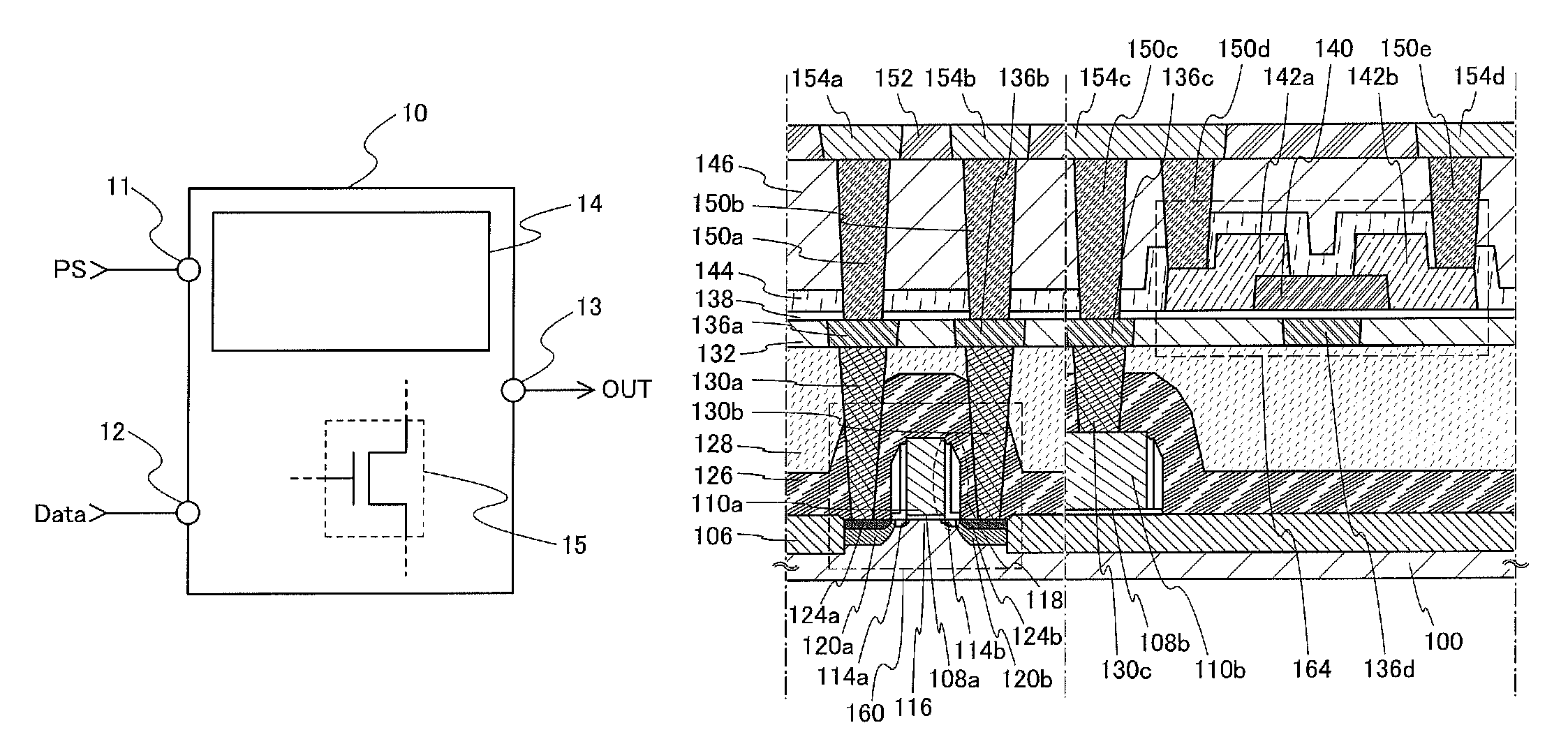

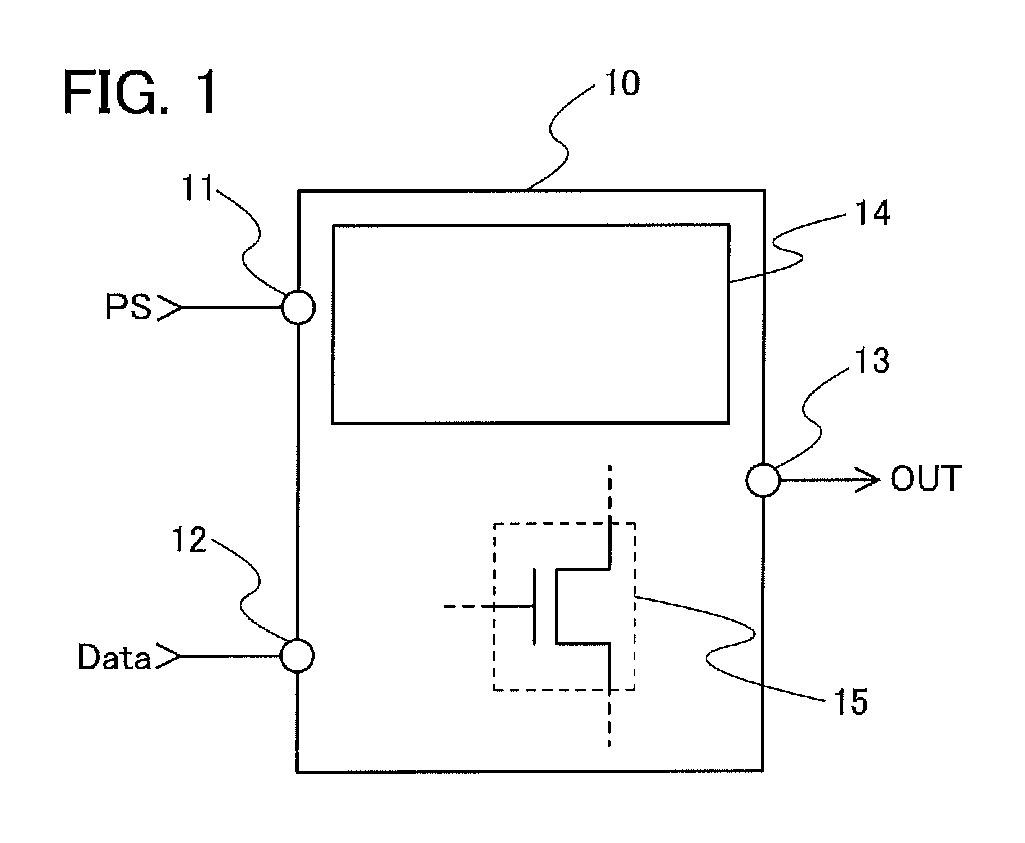

Display device

ActiveUS8054279B2Suppression voltageEasily deterioratedStatic indicating devicesSolid-state devicesDisplay deviceHigh definition

To suppress fluctuation in the threshold voltage of a transistor, to reduce the number of connections of a display panel and a driver IC, to achieve reduction in power consumption of a display device, and to achieve increase in size and high definition of the display device. A gate electrode of a transistor which easily deteriorates is connected to a wiring to which a high potential is supplied through a first switching transistor and a wiring to which a low potential is supplied through a second switching transistor; a clock signal is input to a gate electrode of the first switching transistor; and an inverted clock signal is input to a gate electrode of the second switching transistor. Thus, the high potential and the low potential are alternately applied to the gate electrode of the transistor which easily deteriorates.

Owner:SEMICON ENERGY LAB CO LTD

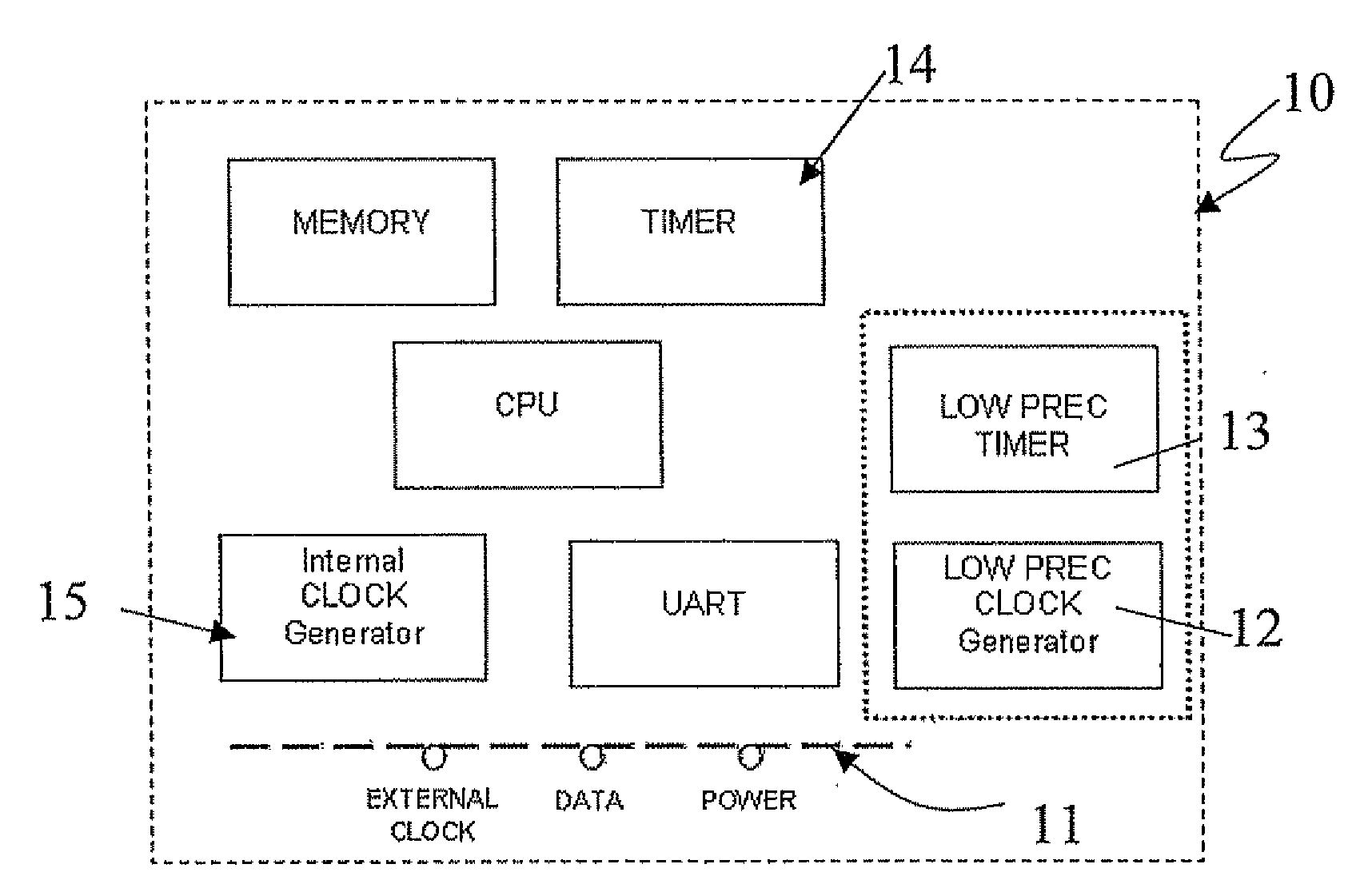

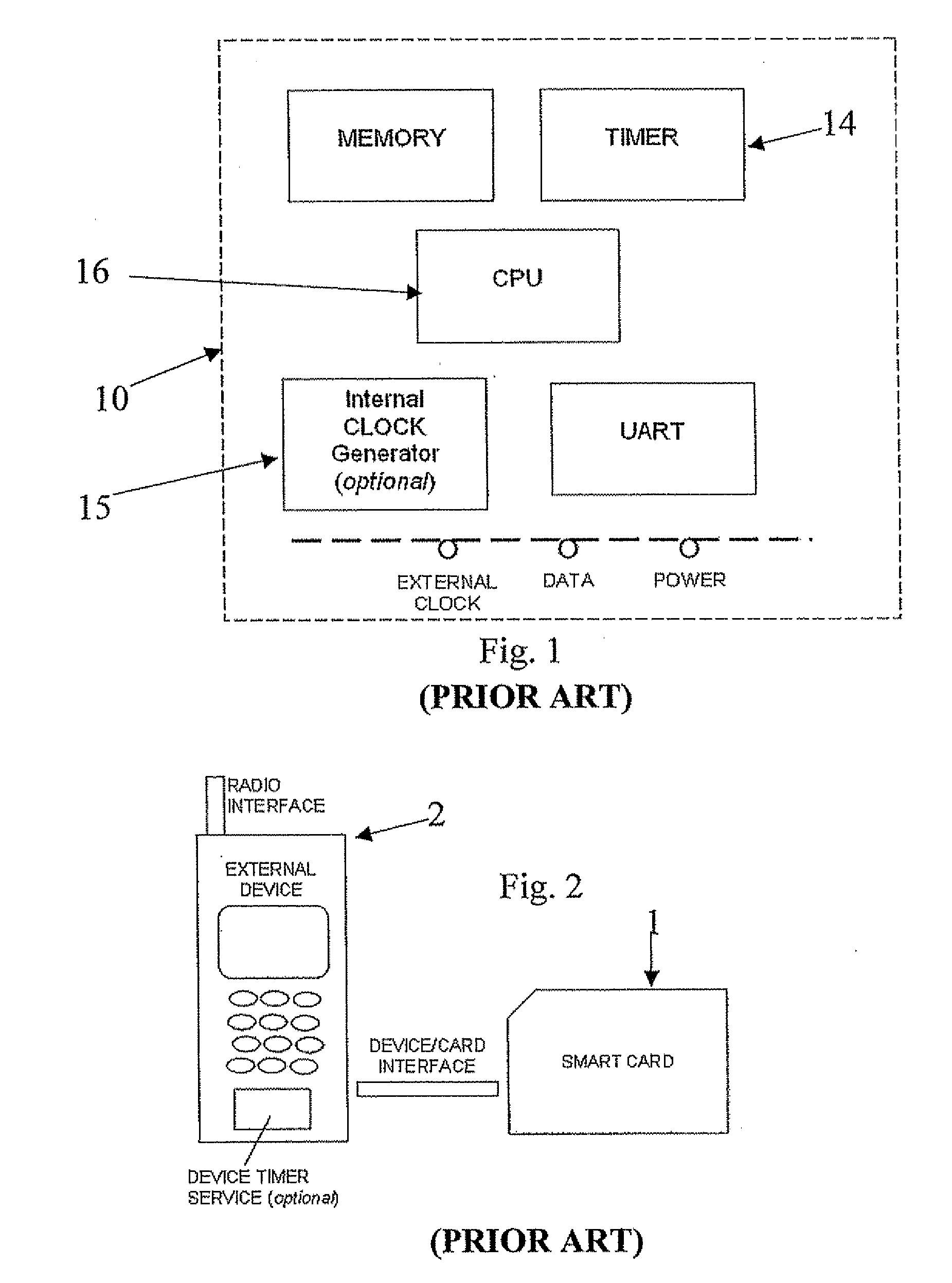

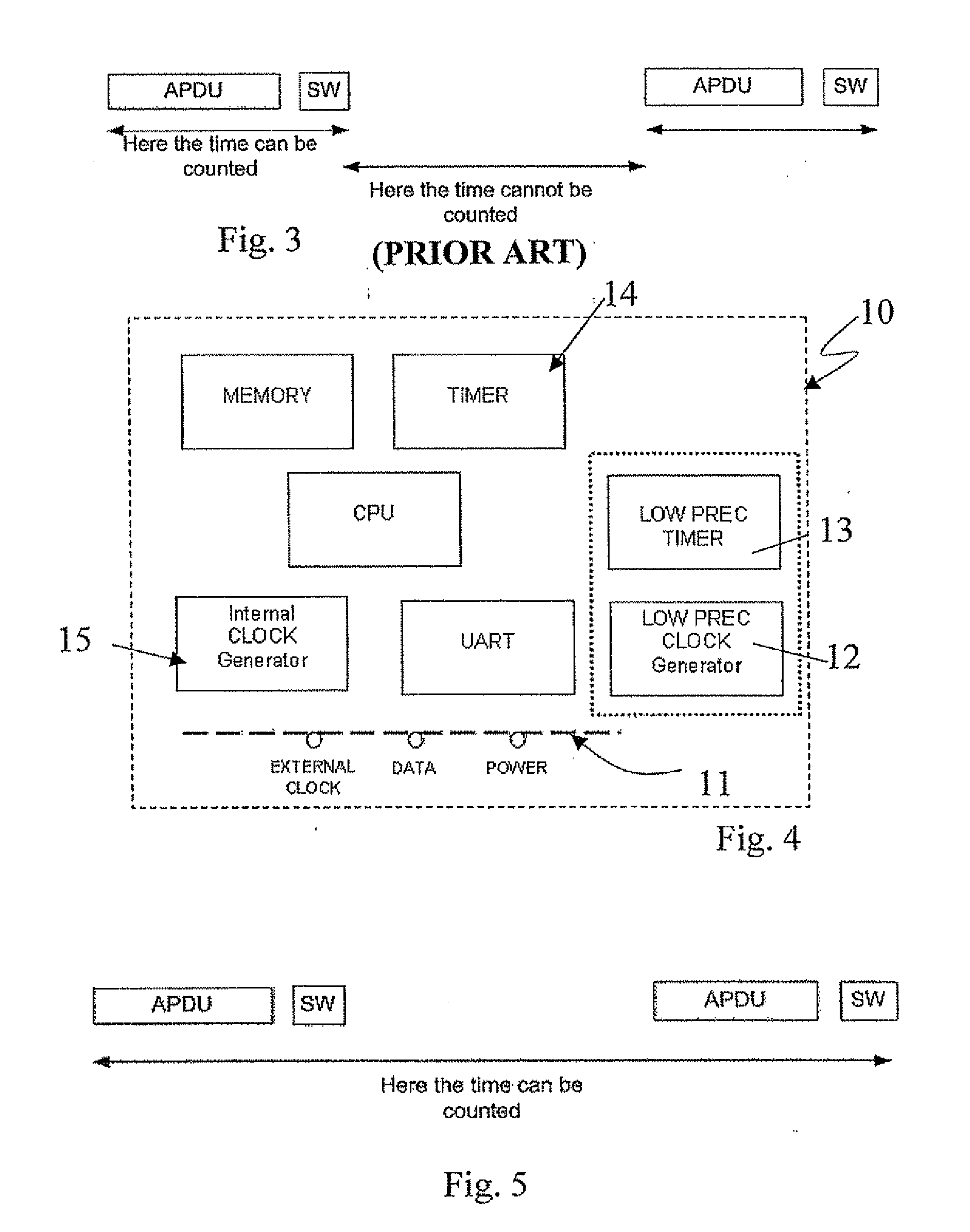

IC card with low precision clock

ActiveUS20080294930A1Avoid power consumptionHigh power consumptionGenerating/distributing signalsData conversionElectronic componentPower consumption

An IC Card may include electronic components to receive a power supply and a main clock signal by a reader device. The power supply may be provided to a subset of the electronic components during a main clock stop status wherein the main clock signal is suspended for avoiding a maximum power consumption threshold. The IC Card may also include a low precision clock included in the subset of electronic components for measuring time in the main clock stop status.

Owner:STMICROELECTRONICS INT NV

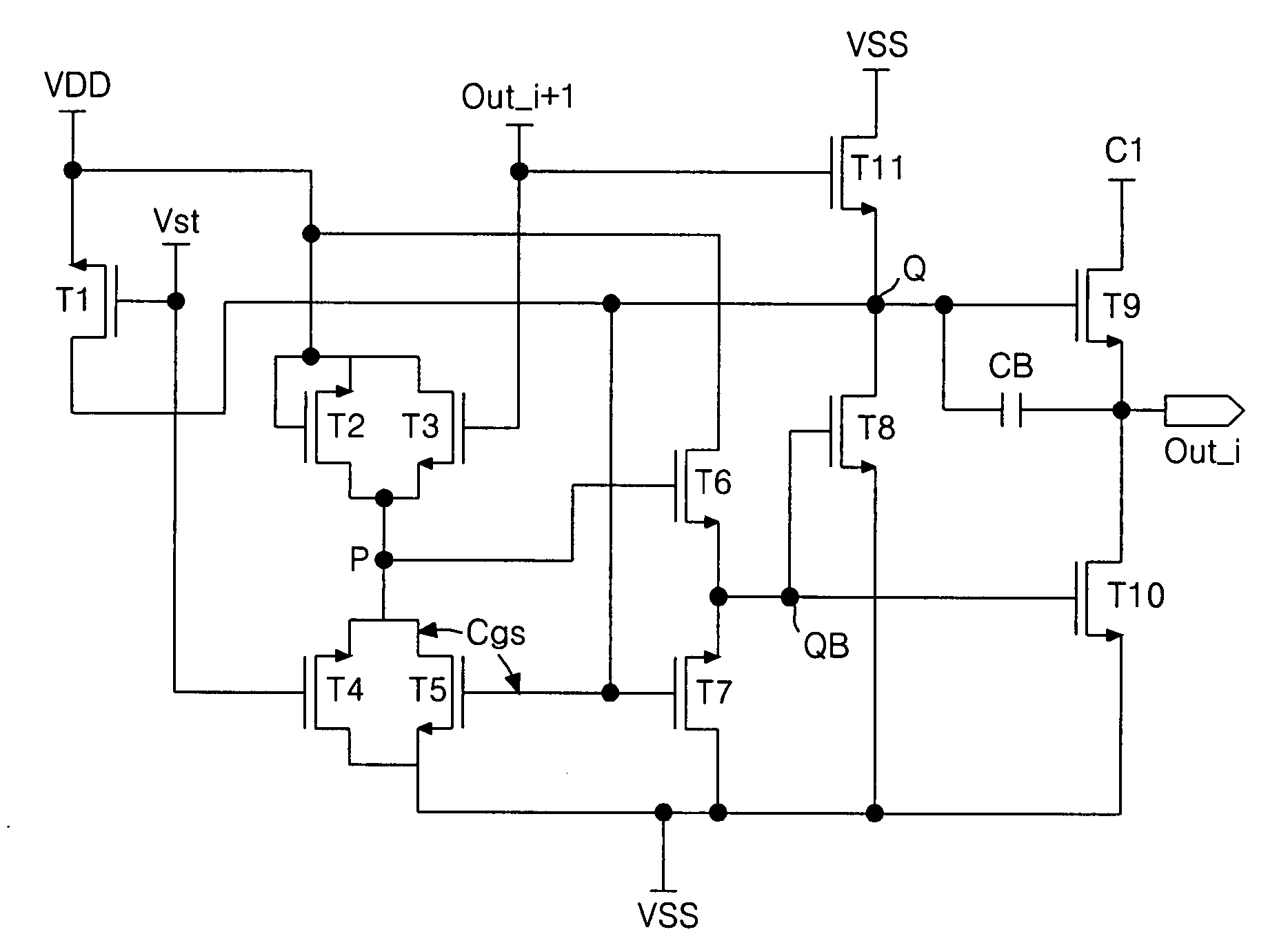

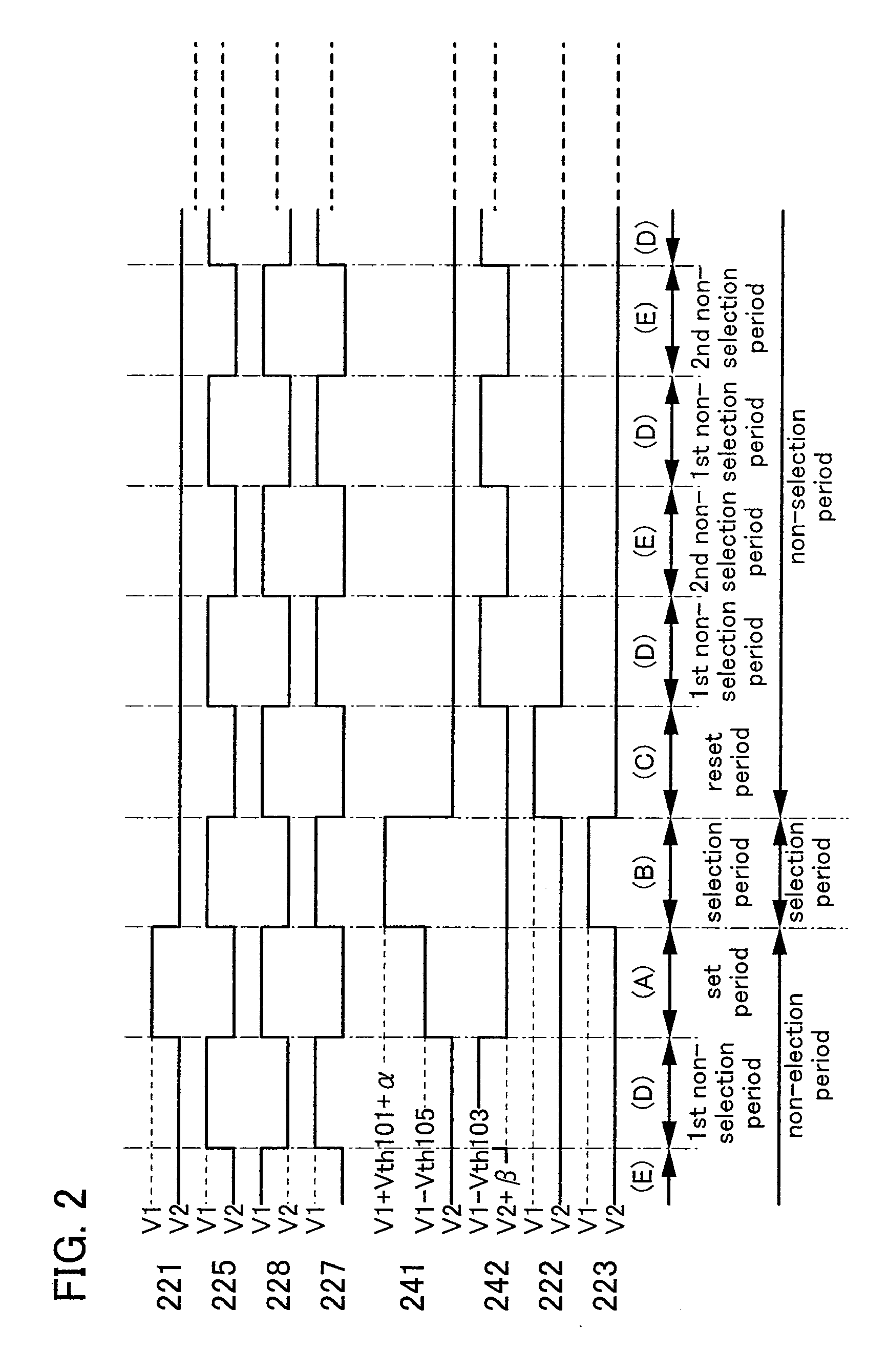

Shift register

An output buffer in each stage of a shift register applies a first clock signal to an output line under control of a first node and a second driving voltage to the output line under control of second and third nodes. A first node controller controls the first node using a start pulse and an output signal of the next stage. A second node controller selectively applies a voltage at a fourth node and the second driving voltage to the second node under control of the first and second clock signals. A third node controller applies the voltage at the fourth node and the second driving voltage to the third node opposite to the second node. A fourth node controller controls the fourth node such that the fourth node has a voltage opposite to the first node using a voltage at the first node and the first driving voltage.

Owner:LG DISPLAY CO LTD

Display device

ActiveUS20080079685A1Suppression voltageEasily deterioratedStatic indicating devicesSolid-state devicesDisplay deviceEngineering

To suppress fluctuation in the threshold voltage of a transistor, to reduce the number of connections of a display panel and a driver IC, to achieve reduction in power consumption of a display device, and to achieve increase in size and high definition of the display device. A gate electrode of a transistor which easily deteriorates is connected to a wiring to which a high potential is supplied through a first switching transistor and a wiring to which a low potential is supplied through a second switching transistor; a clock signal is input to a gate electrode of the first switching transistor; and an inverted clock signal is input to a gate electrode of the second switching transistor. Thus, the high potential and the low potential are alternately applied to the gate electrode of the transistor which easily deteriorates.

Owner:SEMICON ENERGY LAB CO LTD

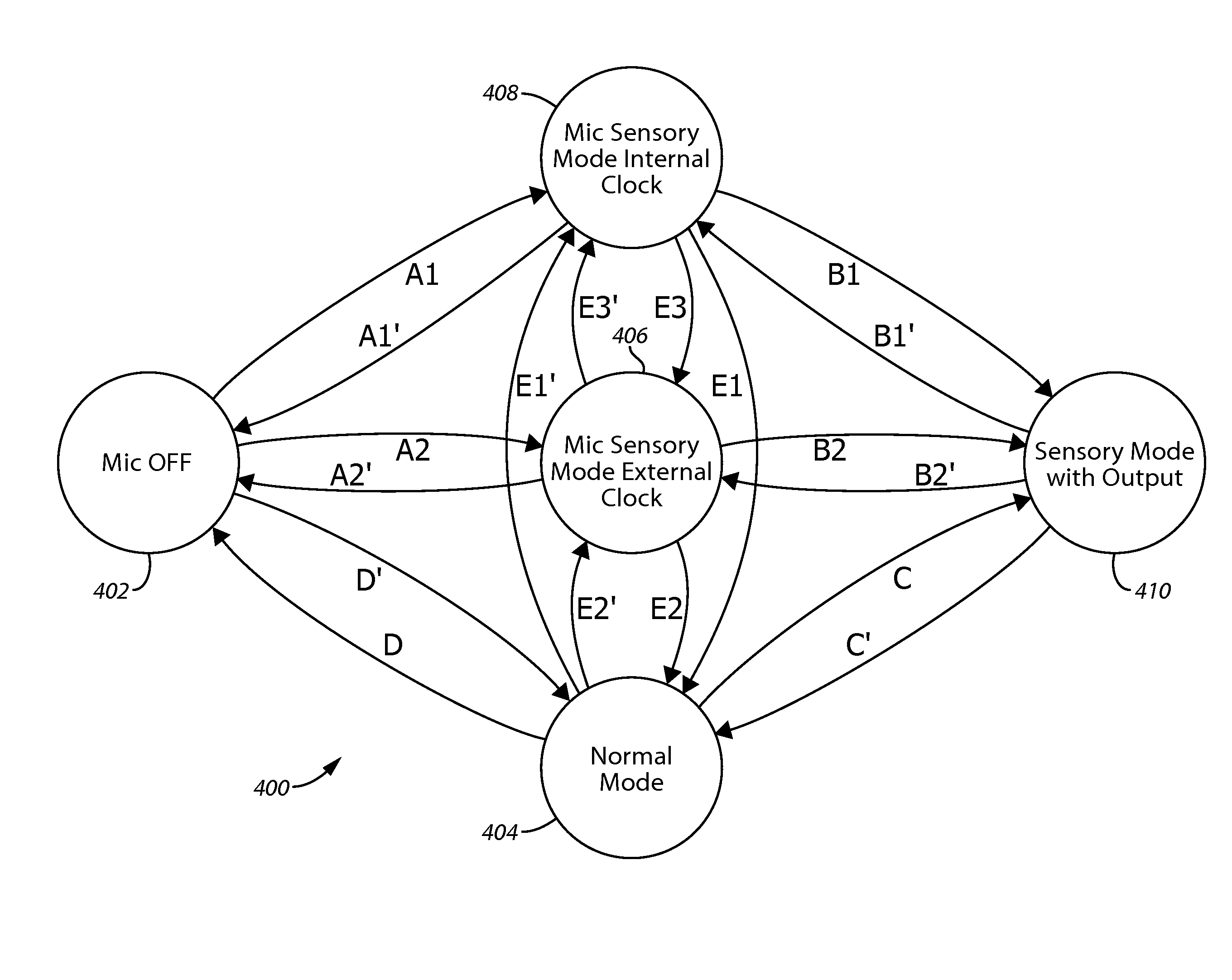

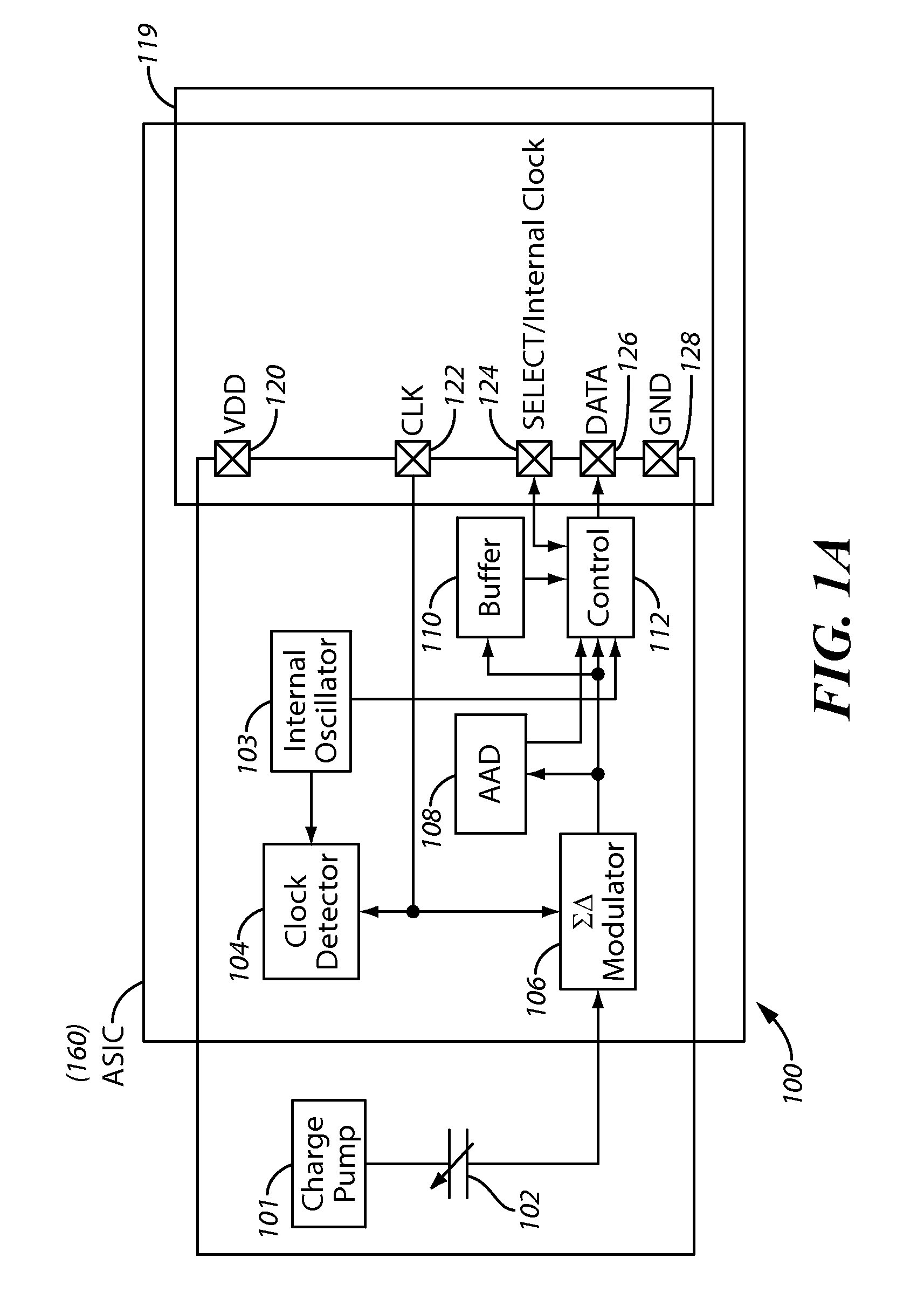

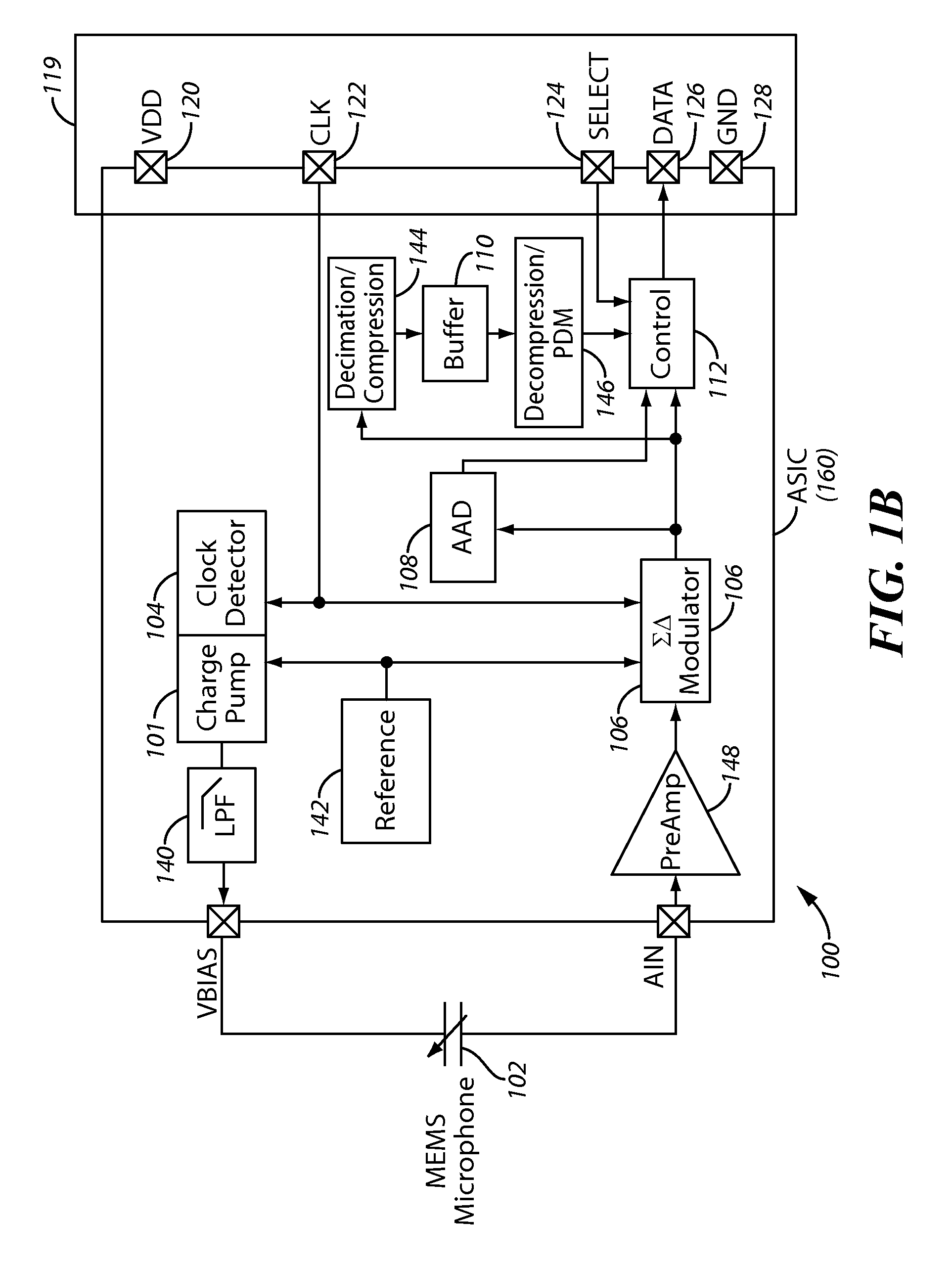

Synchronization of buffered data in multiple microphones

InactiveUS9111548B2Semiconductor electrostatic transducersElectrostatic transducer microphonesDigital dataAnalog signal

Owner:KNOWLES ELECTRONICS INC

Pulse output circuit, shift register and display device

A drive circuit of a display device, which comprise only single conductive TFTs and in which amplitude of an output signal is normal, is provided. A pulse is inputted to TFTs 101 and 104 so that the TFTs would turn ON and then potential of a node á rises. When the potential of the node á reaches (VDD-VthN), the node á became in a floating state. Accordingly, a TFT 105 then turns ON, and potential of an output node rises as a clock signal reaches the level H. On the other hand, potential of a gate electrode of the TFT 105 further rises due to an operation of capacitance 107 as the potential of the output node rises, so that the potential of the output node would be higher than (VDD+VthN). Thus, the potential of the output node rises to VDD without voltage drop caused by a threshold of the TFT 105. An output at the subsequent stage is then inputted to TFTs 102 and 103 to turn the TFTs 102 and 103 ON, while the potential of the node á drops down to turn the TFT 105 OFF. A TFT 106 turns ON at the same time so that the potential of the output node would reach the level L.

Owner:SEMICON ENERGY LAB CO LTD

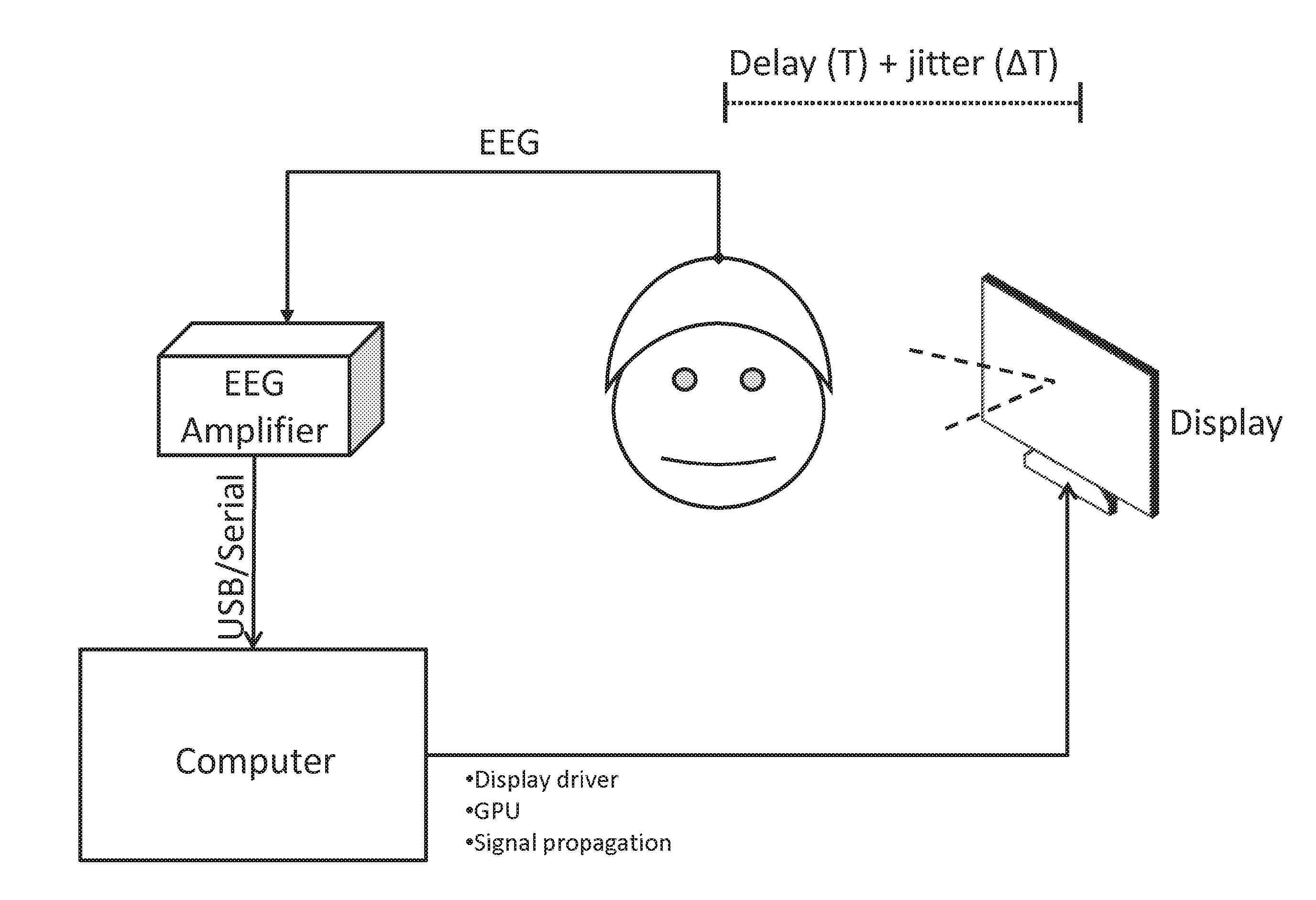

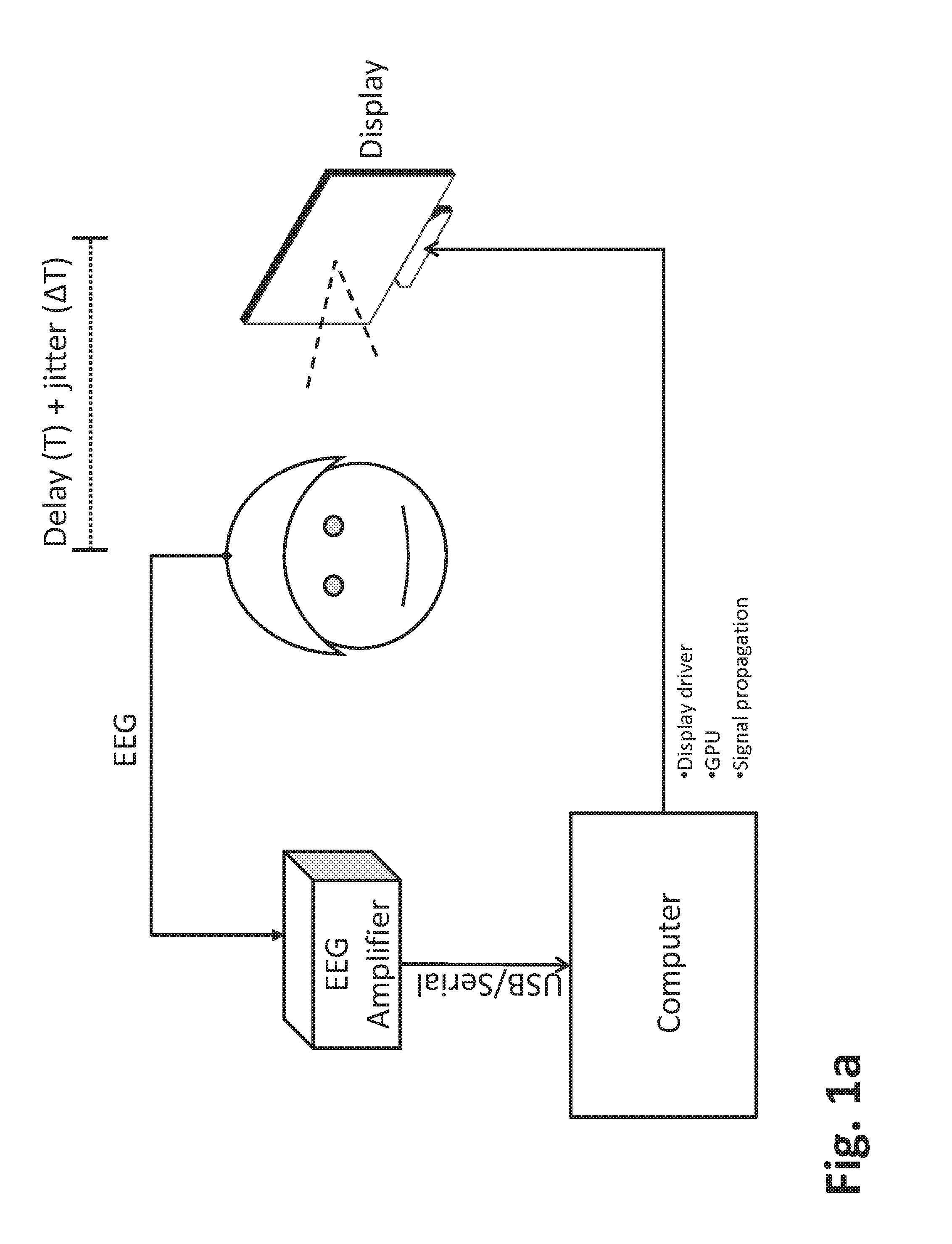

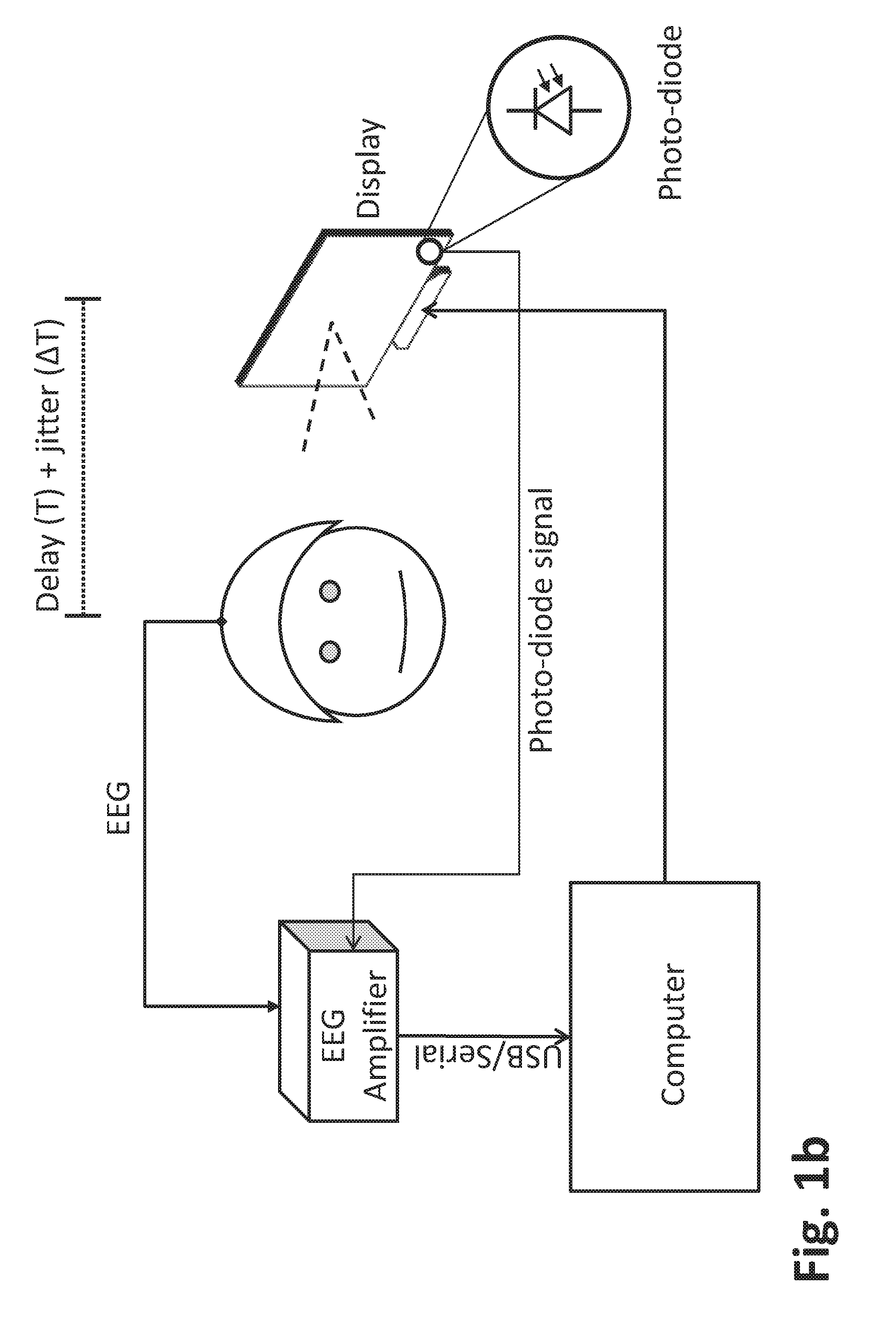

Physiological parameter measurement and feedback system

InactiveUS20160235323A1Improve responseAccurate timingPhysical therapies and activitiesRespiratory organ evaluationControl systemEngineering

A physiological parameter measurement and motion tracking system including a control system, a sensing system, and a stimulation system is disclosed. The sensing system includes one or more physiological sensors including at least brain electrical activity sensors. The stimulation system includes one or more stimulation devices including at least a visual stimulation system. The control system includes an acquisition module configured to receive sensor signals from the sensing system, and a control module configured to process the signals from the acquisition module and control the generation of stimulation signals to one or more devices of the stimulation system. The control system further includes a clock module and the control system is configured to receive content code signals from the stimulation system and to time stamp the content code signals and the sensor signals with a clock signal from the clock module.

Owner:MINDMAZE HLDG SA

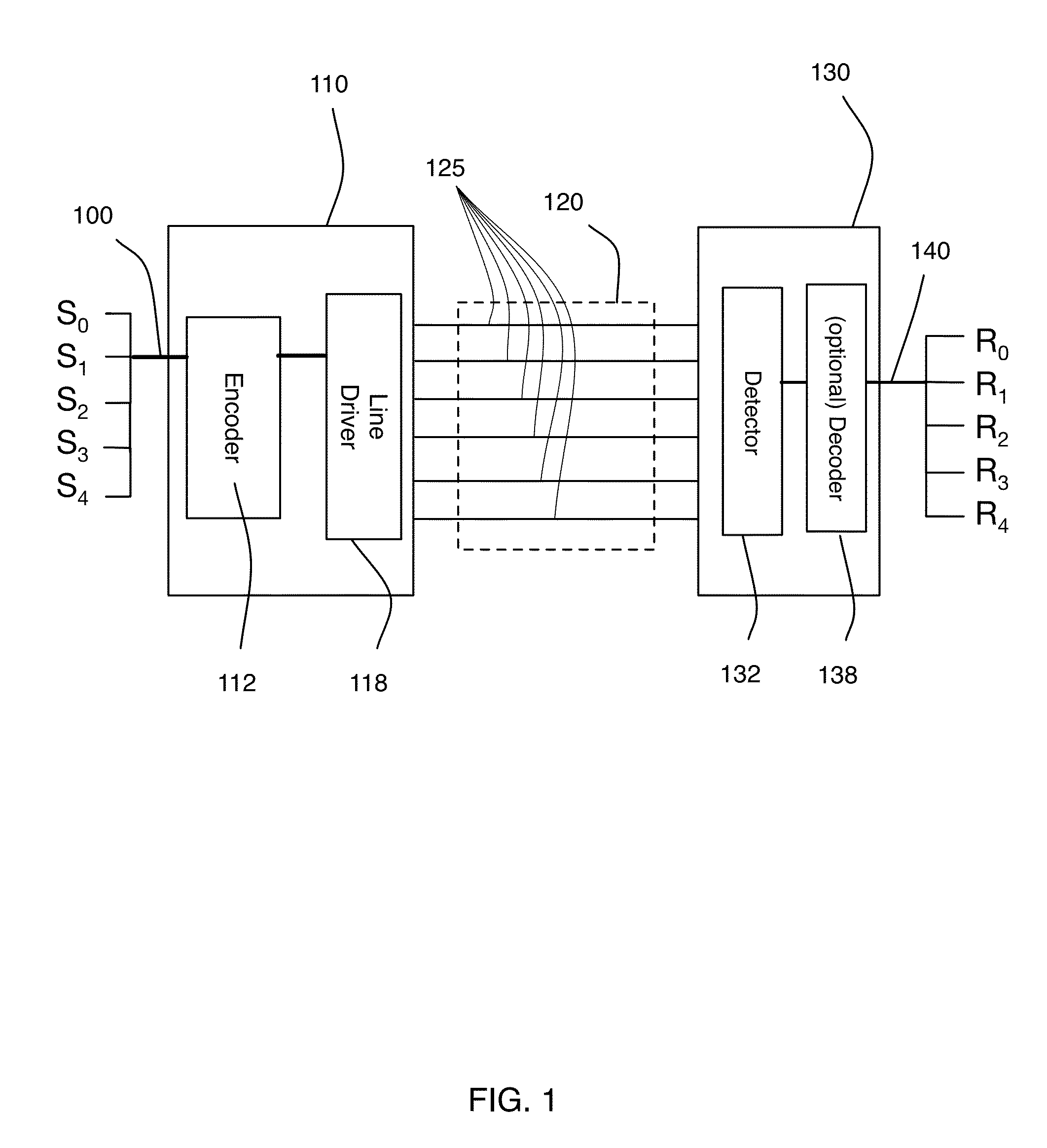

Method for code evaluation using ISI ratio

ActiveUS9100232B1Fast communication speedReduce power consumptionChannel dividing arrangementsCode division multiplexComputer architectureCode assessment

An efficient communications apparatus is described for a vector signaling code to transport data and optionally a clocking signal between integrated circuit devices. Methods of designing such apparatus and their associated codes based on a new metric herein called the “ISI Ratio” are described which permit higher communications speed, lower system power consumption, and reduced implementation complexity.

Owner:KANDOU LABS

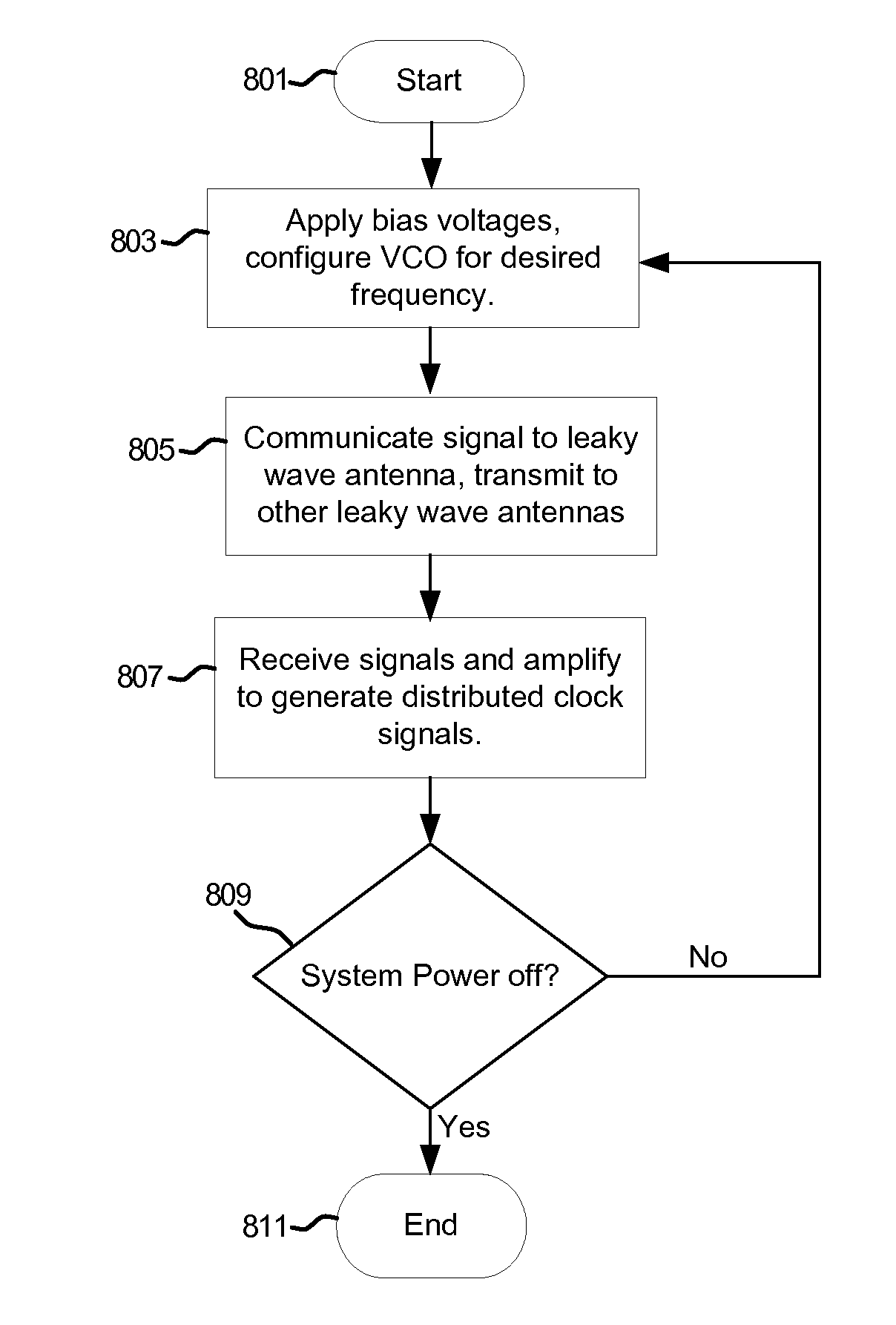

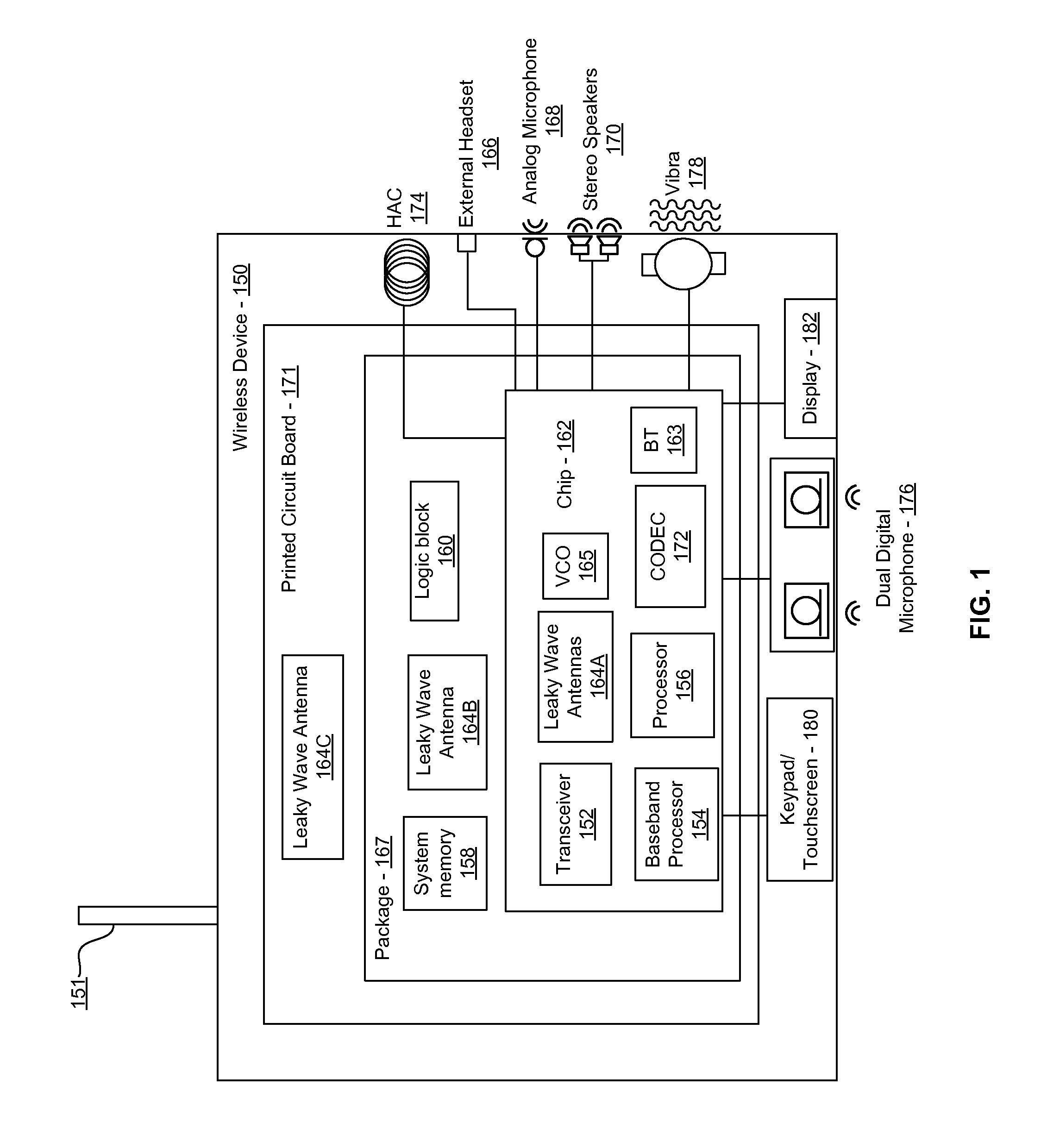

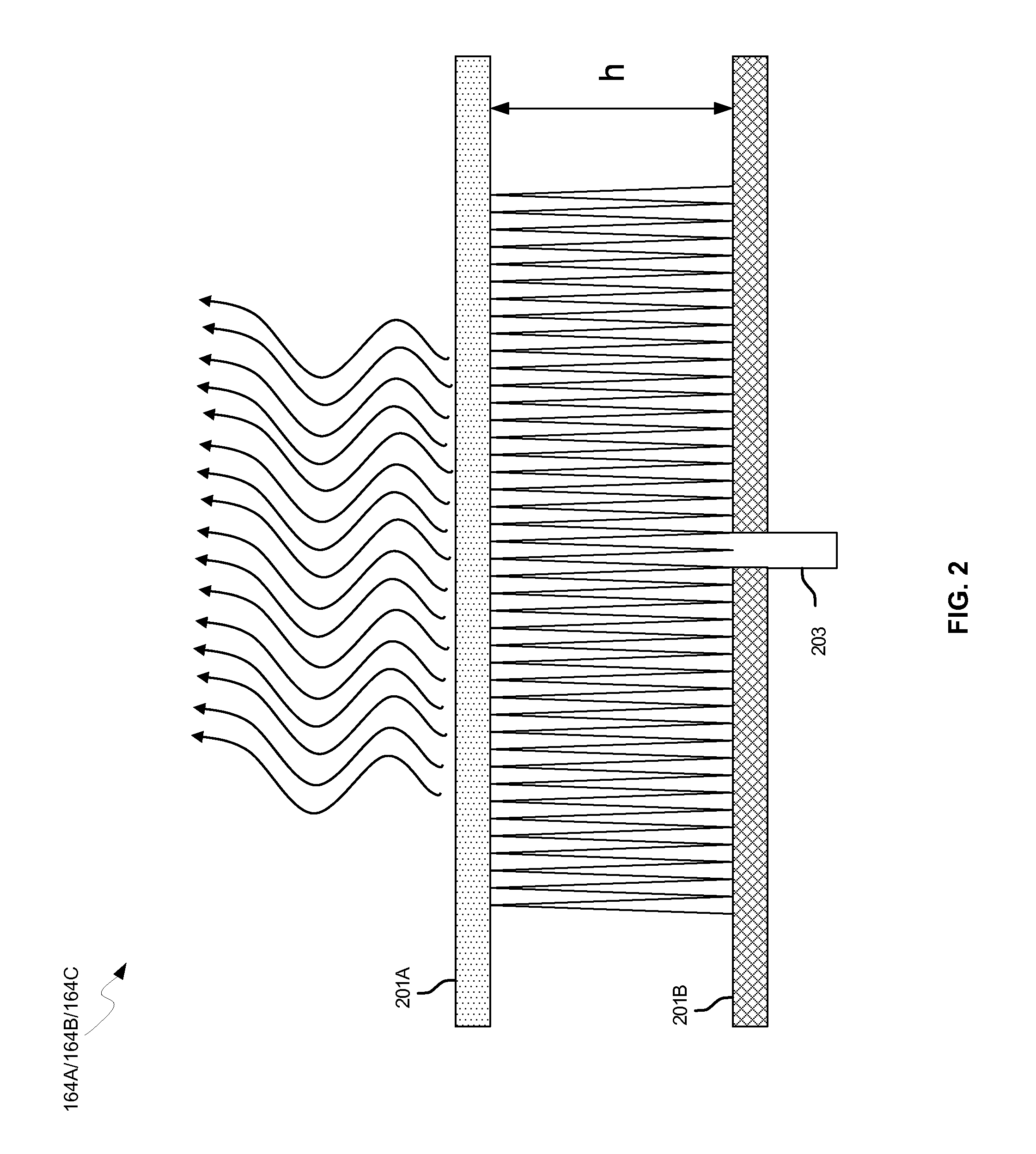

Method and system for an integrated voltage controlled oscillator-based transmitter and on-chip power distribution network

Methods and systems for an integrated voltage controlled oscillator (VCO)-based transmitter and on-chip power distribution network are disclosed and may include supplying bias voltages and / or ground to a chip utilizing conductive lines. One or more VCOs and low-noise amplifiers (LNAs) may each be coupled to a leaky wave antenna (LWA) integrated in the bias voltage and / or ground lines. One or more clock signals may be generated utilizing the VCOs, which may be transmitted from the LWAs coupled to the VCOs, to the LWAs coupled to the LNAs. RF signals may be transmitted via the LWAs, and may include 60 GHz signals. The LWAs may include microstrip and / or coplanar waveguides, where a cavity length of the LWAs may be dependent on a spacing between conductive lines in the waveguides. The LWAs may be dynamically configured to transmit the clock signals at a desired angle from a surface of the chip.

Owner:AVAGO TECH INT SALES PTE LTD

Logic circuit and semiconductor device

ActiveUS8207756B2Reduce dynamic power consumptionLeakage of highTransistorPower reduction by control/clock signalHydrogen concentrationPower semiconductor device

In a logic circuit where clock gating is performed, the standby power is reduced or malfunction is suppressed. The logic circuit includes a transistor which is in an off state where a potential difference exists between a source terminal and a drain terminal over a period during which a clock signal is not supplied. A channel formation region of the transistor is formed using an oxide semiconductor in which the hydrogen concentration is reduced. Specifically, the hydrogen concentration of the oxide semiconductor is 5×1019 (atoms / cm3) or lower. Thus, leakage current of the transistor can be reduced. As a result, in the logic circuit, reduction in standby power and suppression of malfunction can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

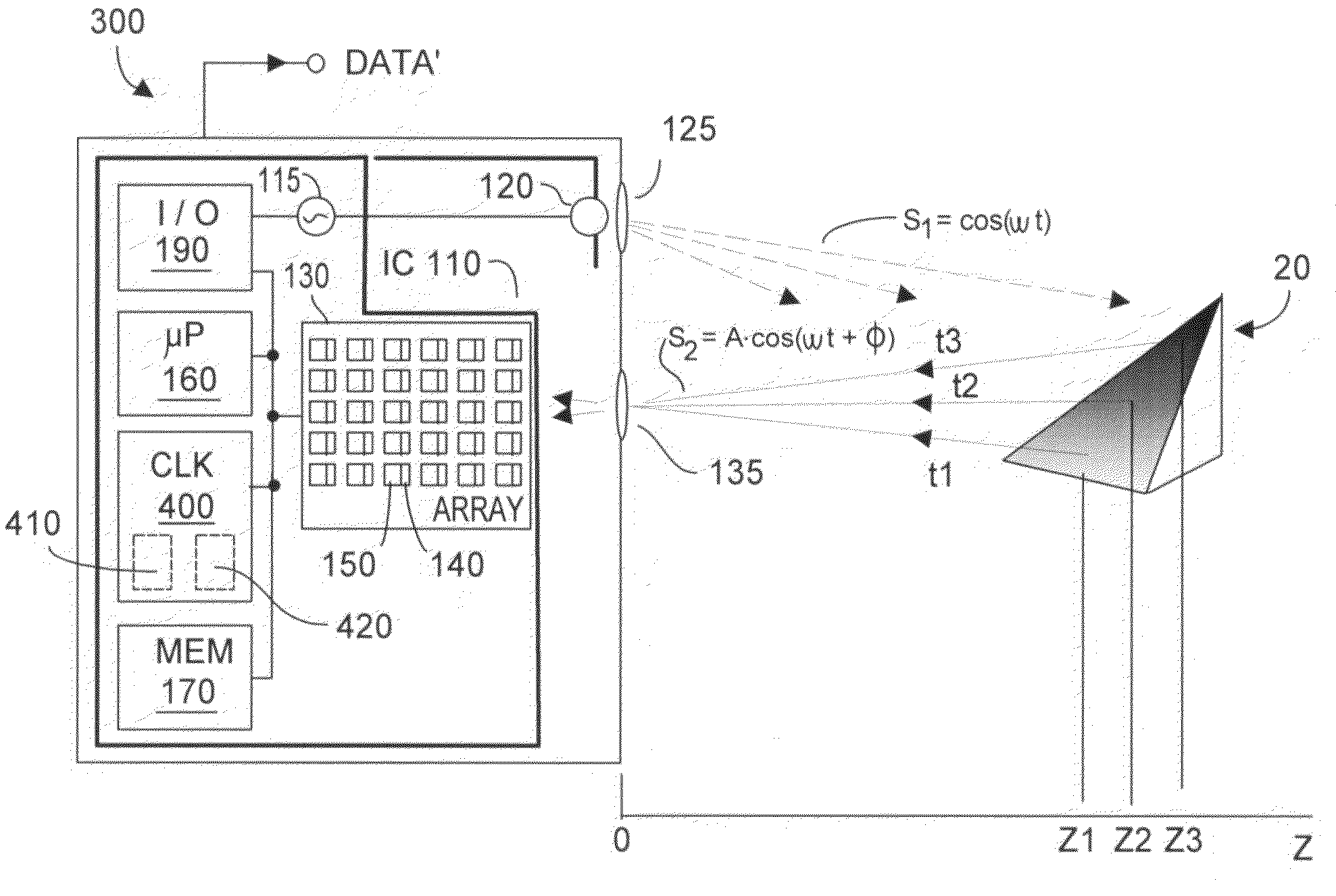

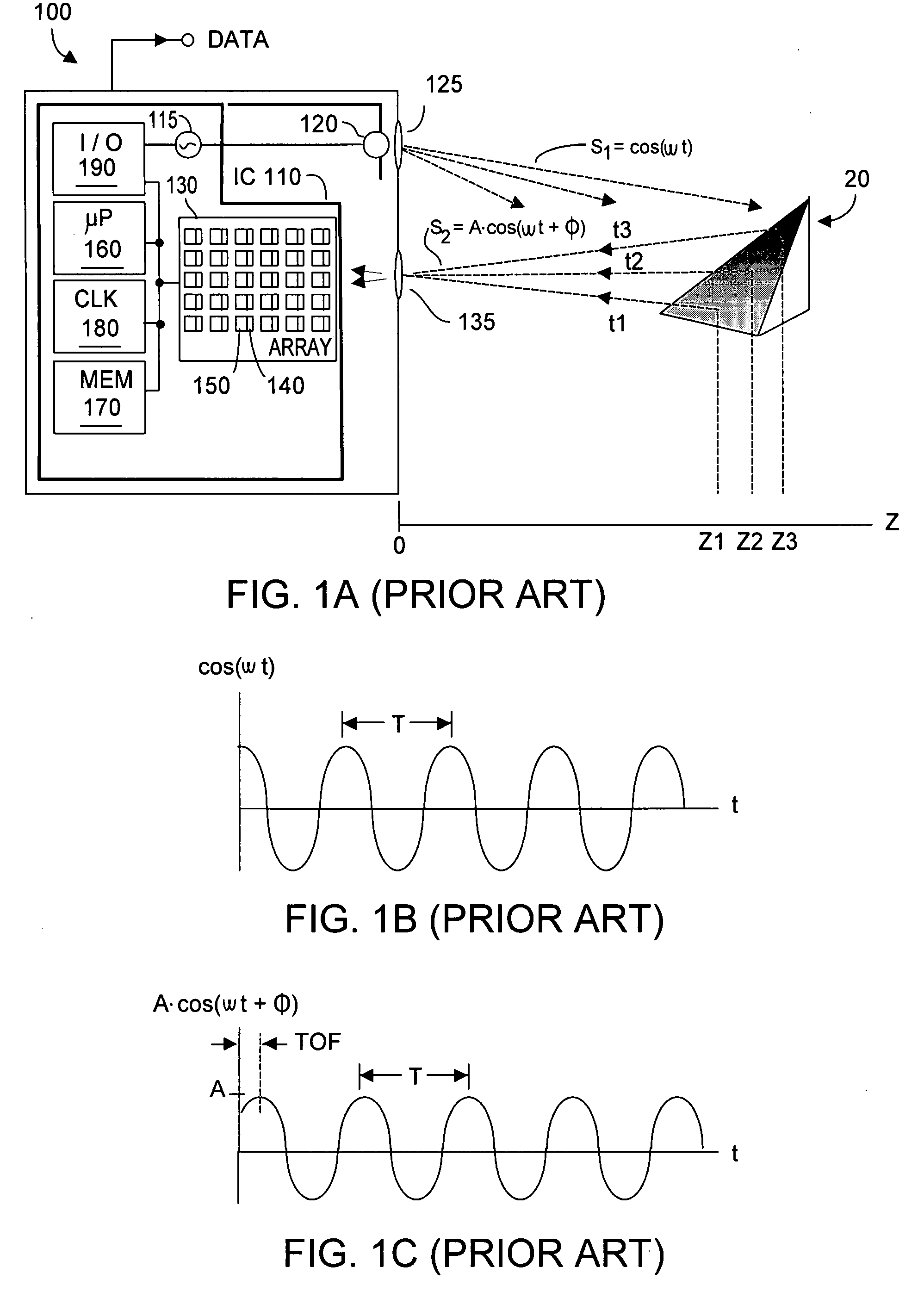

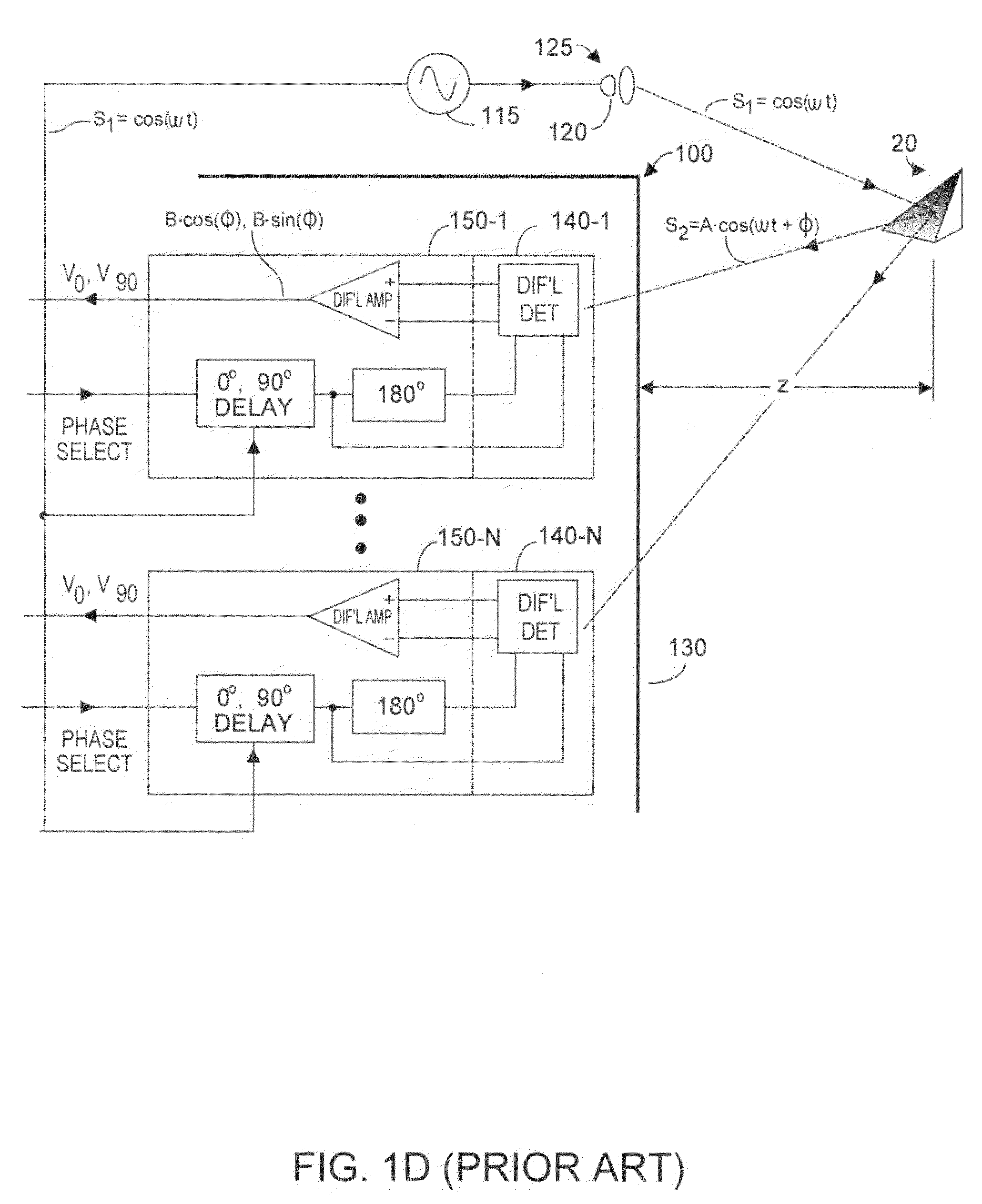

Method and system to avoid inter-system interference for phase-based time-of-flight systems

ActiveUS7405812B1Likelihood of interferenceReduce distractionsOptical rangefindersElectromagnetic wave reradiationClock rateOptical energy

Inter-system interference cross-produce P12 is reduced in a phase-based TOF system by randomizing instantaneous phase and / or frequency within a capture interval (or detection integration period). In one aspect, the TOF clock system frequency preserves long-term clock frequency stability but intentionally includes random or pseudo-random clock noise. The noise ensures the generated clock signals are temporally imperfect and lack substantial perfect periodicity. A second aspect causes the TOF clock system to hop frequency, preferably pseudo-randomly. TOF system homodyning favors detection of optical energy whose frequency correlates to the time-varying frequency of the emitted optical energy. Thus, the varying spectral spacing of the emitted optical energy reduces likelihood that an adjacent TOF system at any given time will emit optical energy of an interfering frequency. At least one aspect is employed, both aspects being mutually complementary to reduce the cross-correlation product P12 without substantially affecting TOF system performance.

Owner:MICROSOFT TECH LICENSING LLC