Patents

Literature

7555 results about "Phase-locked loop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is related to the phase of an input signal. There are several different types; the simplest is an electronic circuit consisting of a variable frequency oscillator and a phase detector in a feedback loop. The oscillator generates a periodic signal, and the phase detector compares the phase of that signal with the phase of the input periodic signal, adjusting the oscillator to keep the phases matched.

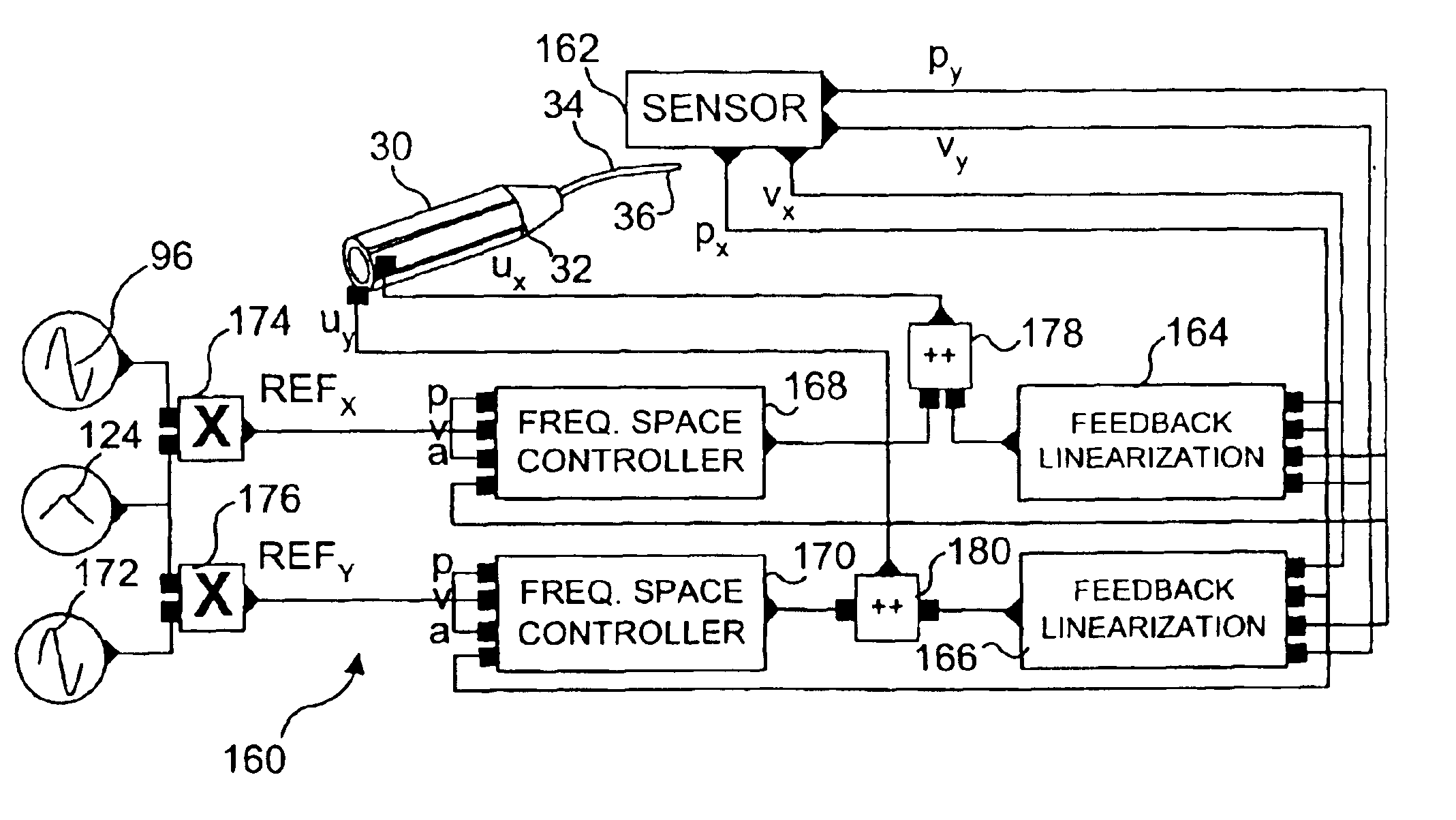

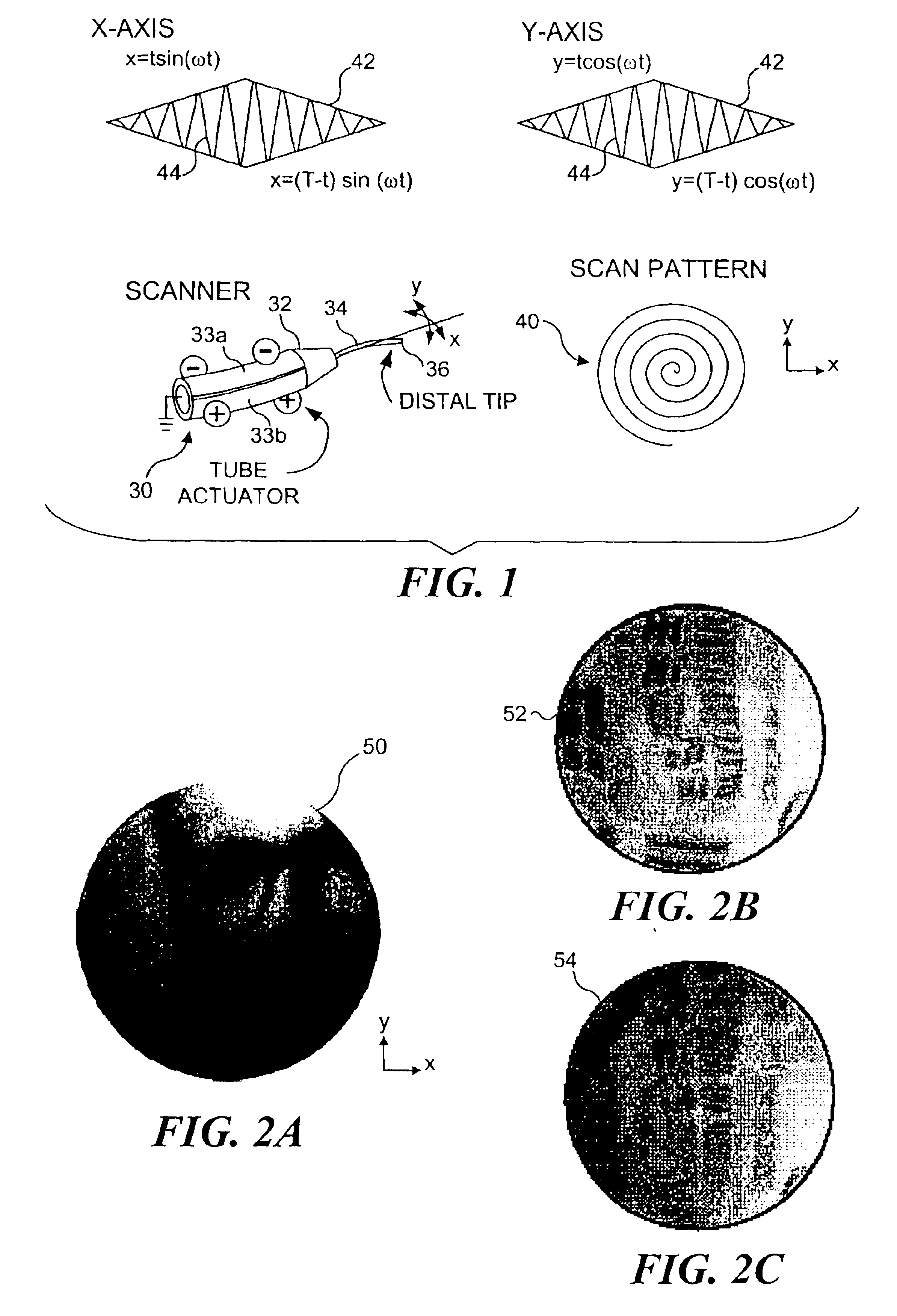

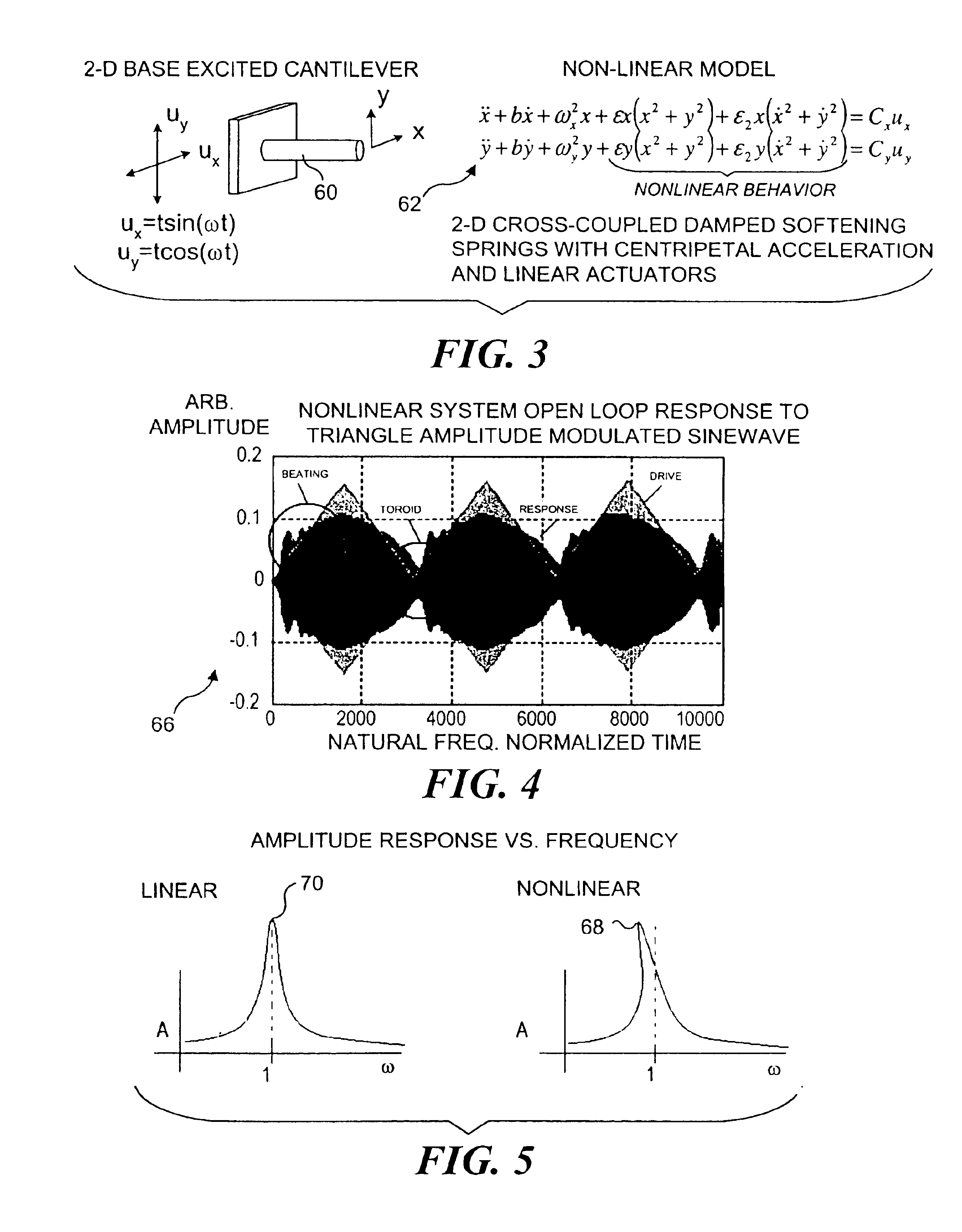

Control of an optical fiber scanner

InactiveUS6845190B1Remove nonlinear behaviorRobust cancellationSurgeryEndoscopesOptical scannersPhotodetector

Controls for an optical scanner, such as a single fiber scanning endoscope (SFSE) that includes a resonating optical fiber and a single photodetector to produce large field of view, high-resolution images. A nonlinear control scheme with feedback linearization is employed in one type of control to accurately produce a desired scan. Open loop and closed loops controllers are applied to the nonlinear optical scanner of the SFSE. A closed loop control (no model) uses either phase locked loop and PID controllers, or a dual-phase lock-in amplifier and two PIDs for each axis controlled. Other forms of the control that employ a model use a frequency space tracking control, an error space tracking control, feedback linearizing controls, an adaptive control, and a sliding mode control.

Owner:UNIV OF WASHINGTON

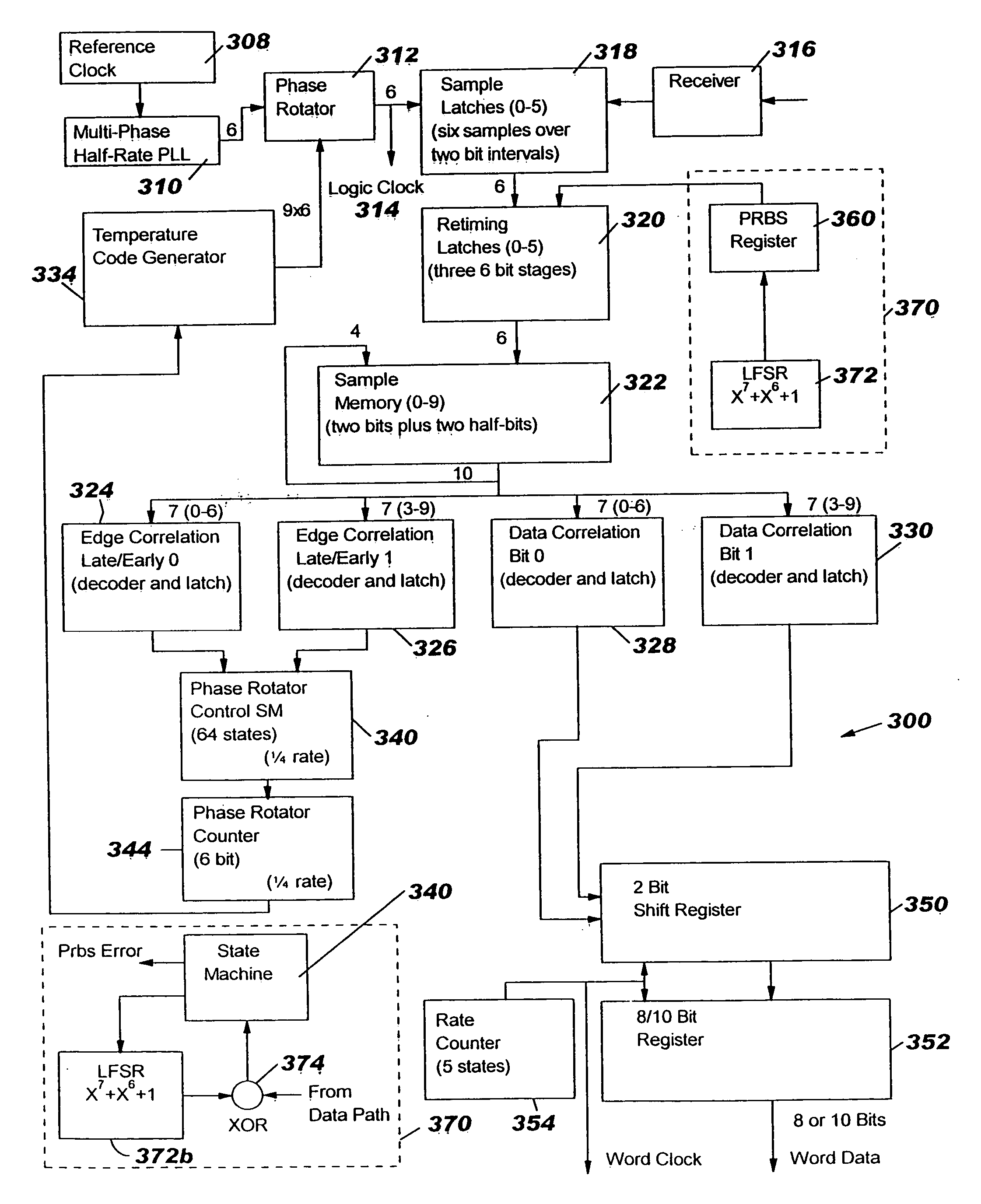

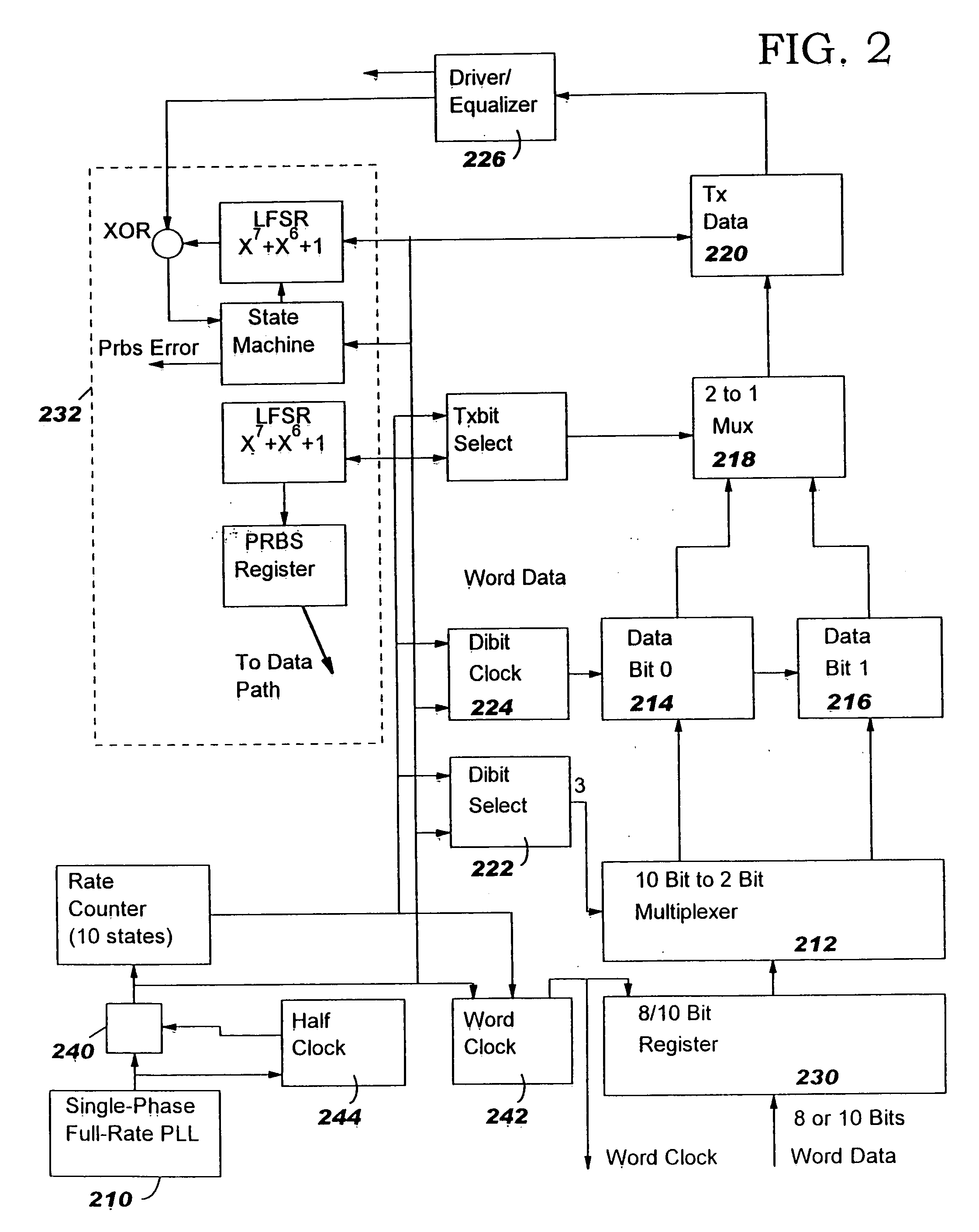

Unified digital architecture

InactiveUS20060029177A1Pulse automatic controlModulated-carrier systemsFinite impulse responseComputer science

A unified, unidirectional serial link is described for providing data across wired media, such as a chip-to chip or a card-to-card interconnect. It consists of a transmit section and a receive section that are operated as pairs to allow the serial data communication. The serial link is implemented as part of a VLSI ASIC module and derives its power, data and clocking requirements from the host modules. The logic transmitter portion contains a phase locked loop (PLL), a dibit data register, a finite impulse response (FIR) filter and a transmit data register. The phase locked loop comprises both a digital coarse loop and an analog fine loop. The digital receiver portion contains a PLL, an FIR phase rotator, a phase rotator control state machine, and a clock buffer. The transmitter and the receiver each preferably utilize a pseudo-random bit stream (PRBS) generator and checker.

Owner:IBM CORP

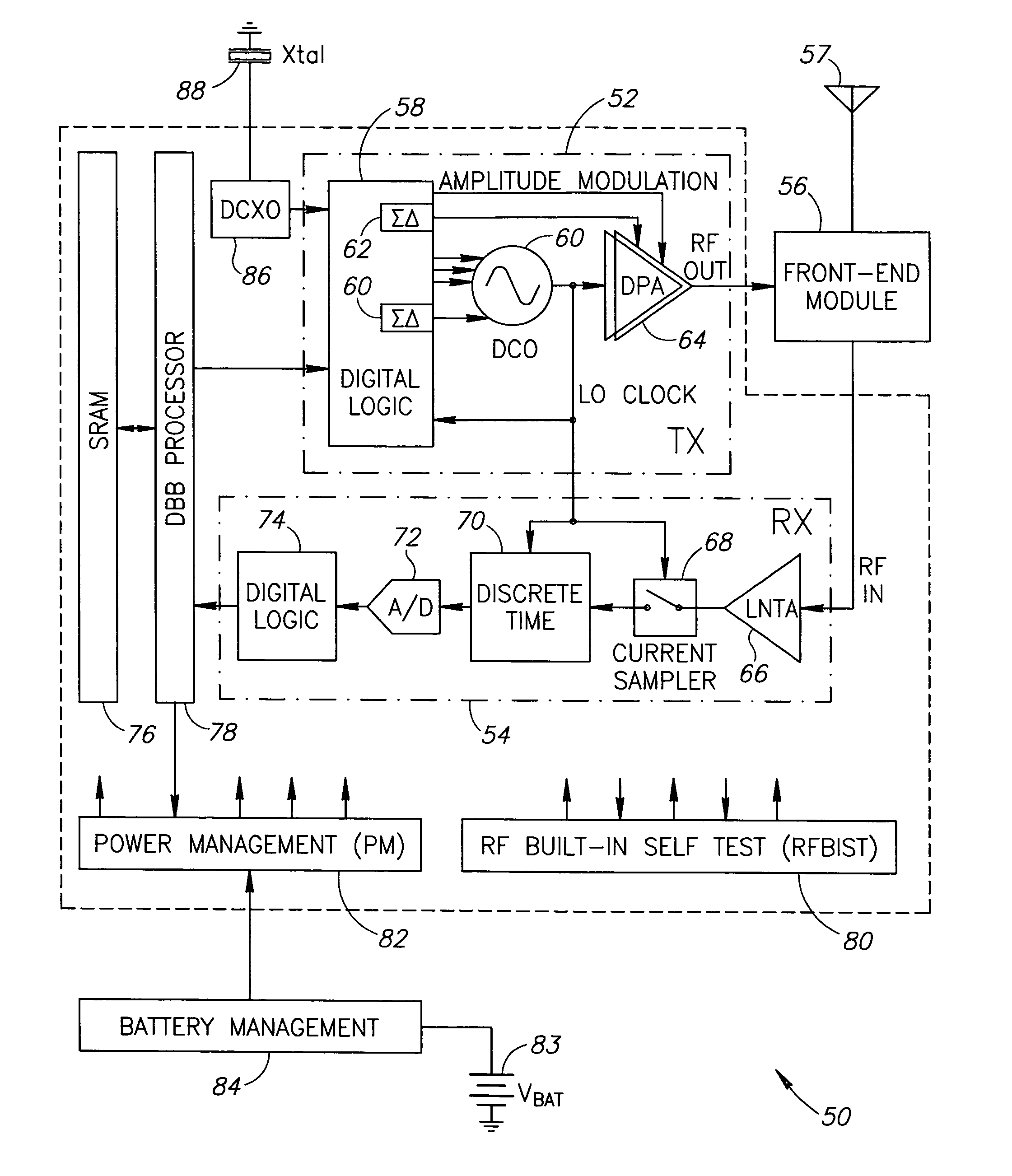

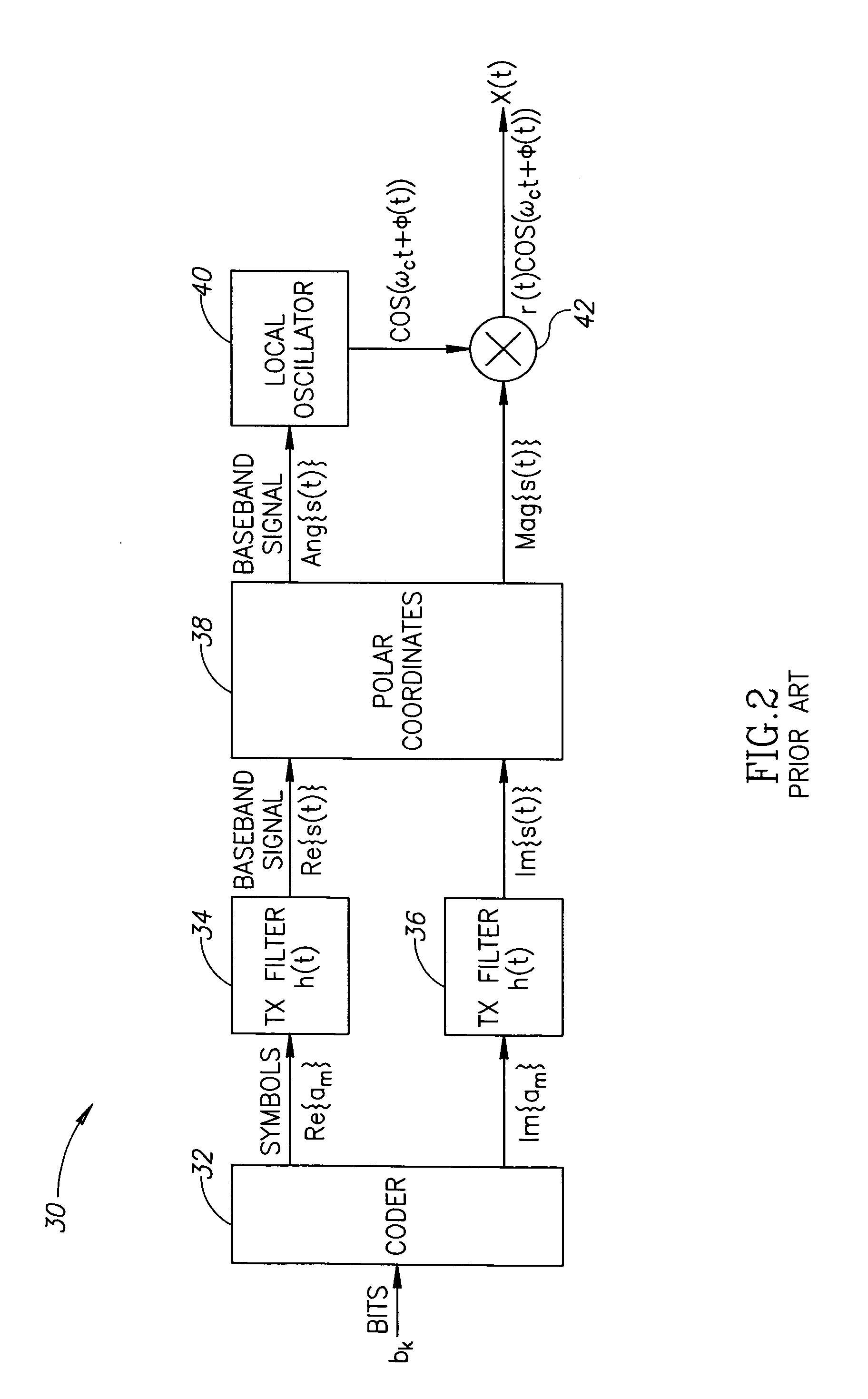

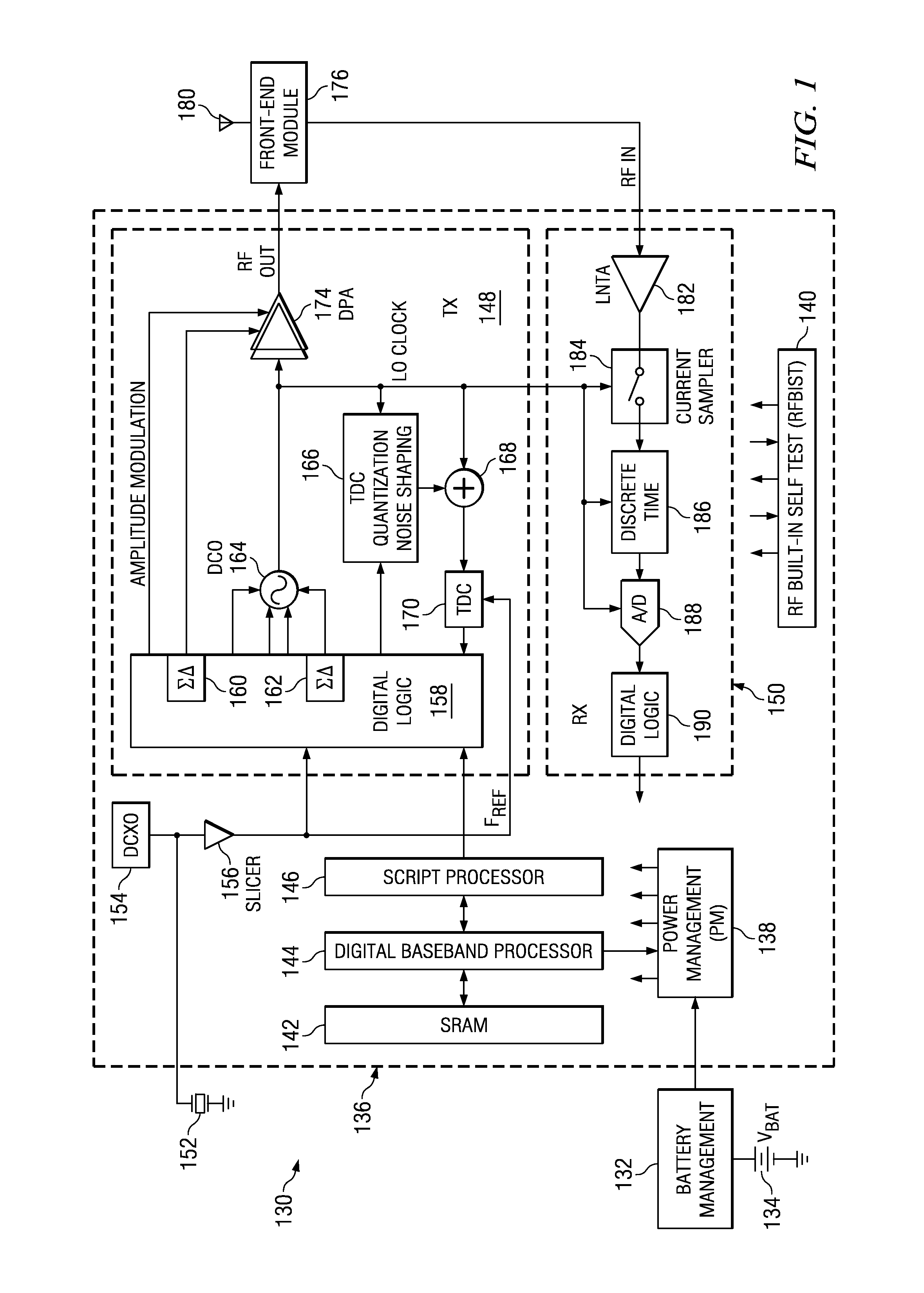

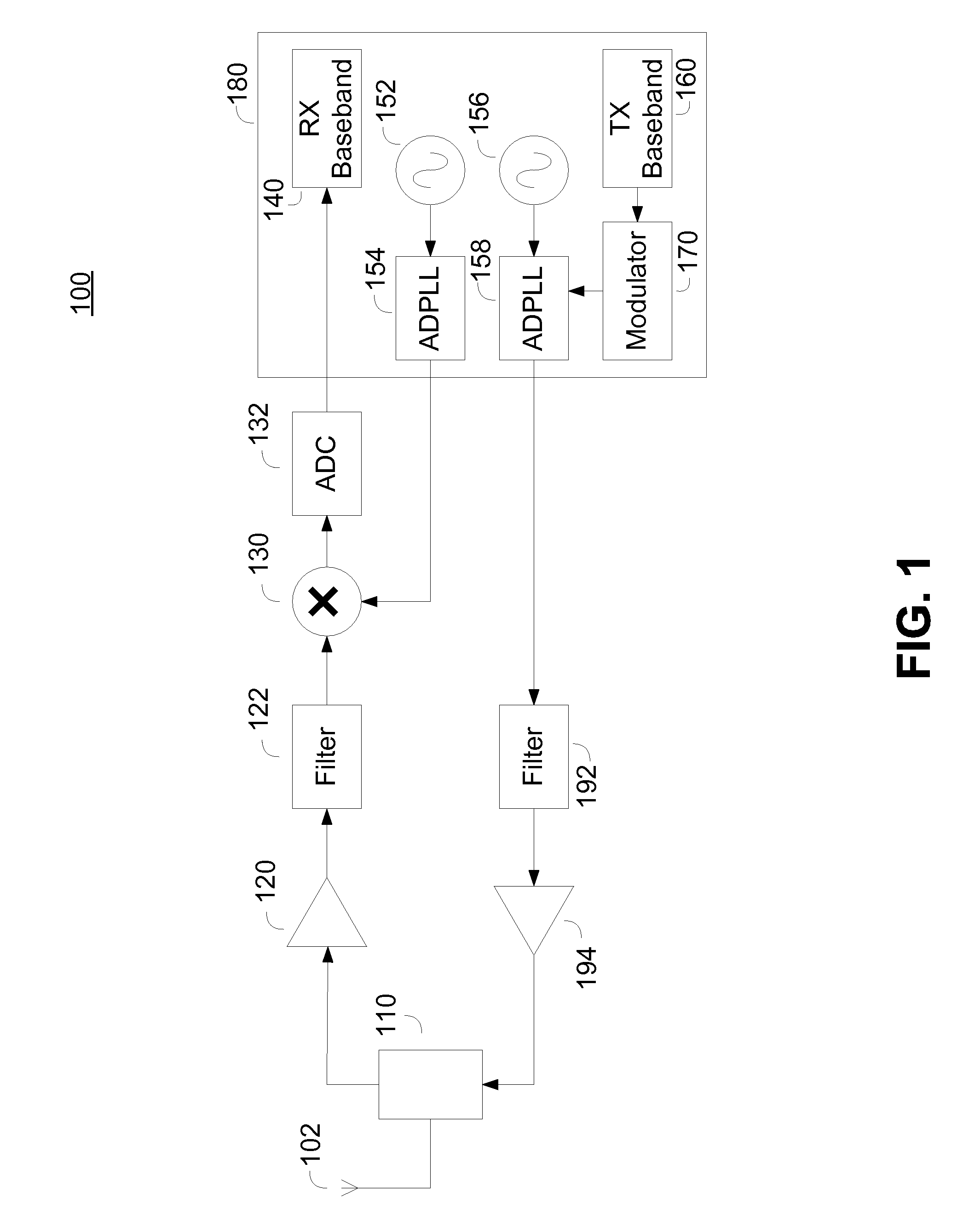

Hybrid polar/cartesian digital modulator

ActiveUS20060038710A1Reconfigurable analogue/digital convertersAnalogue conversionControl powerEngineering

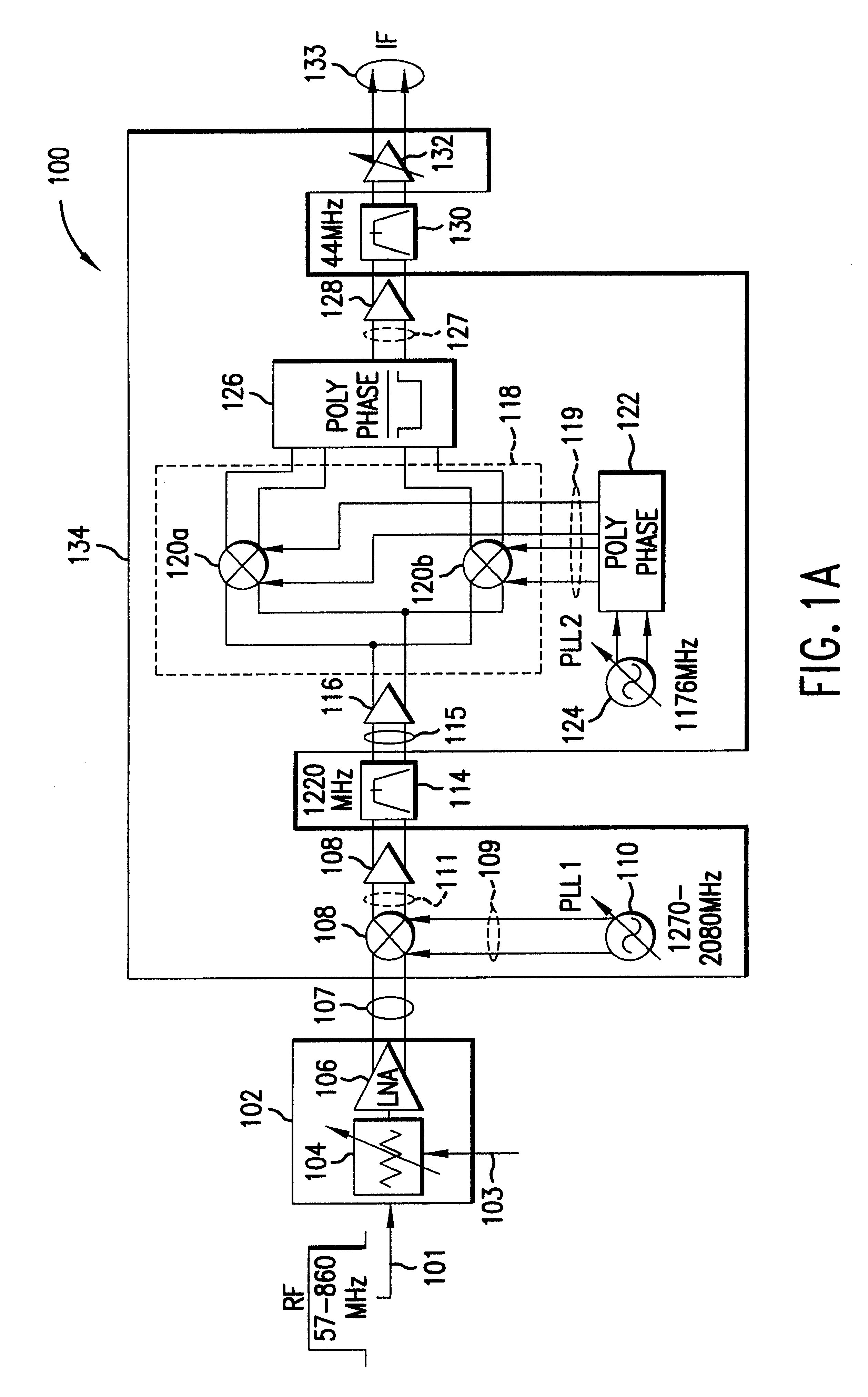

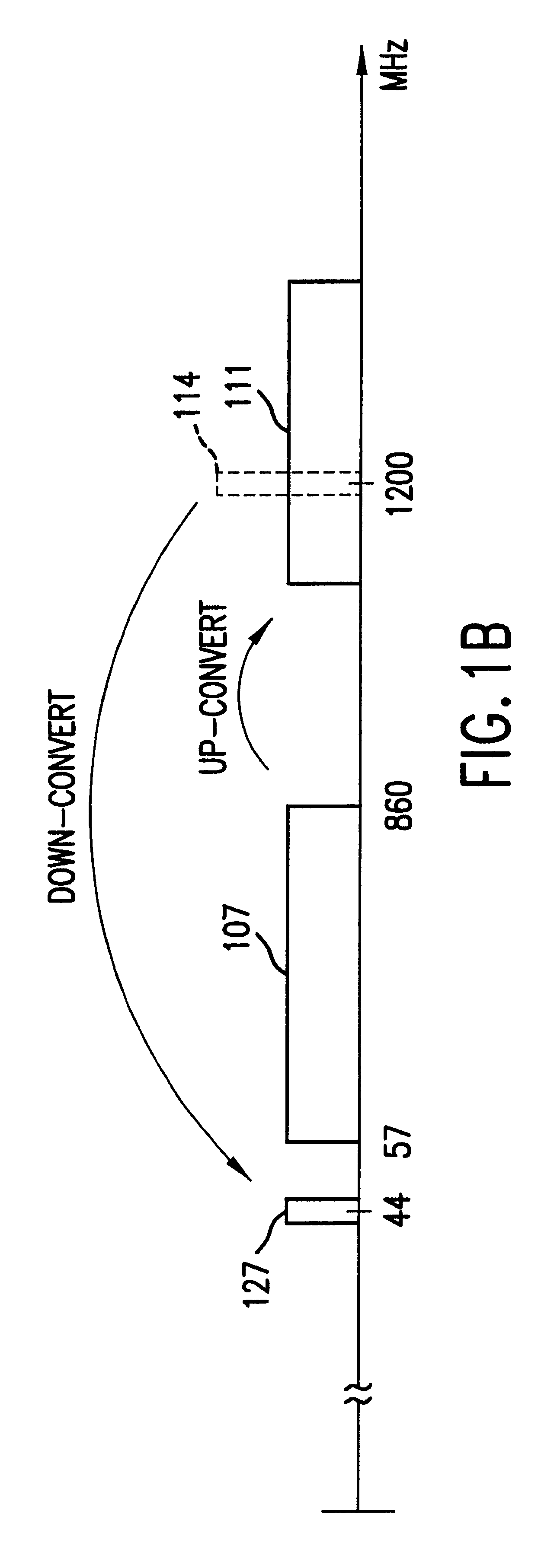

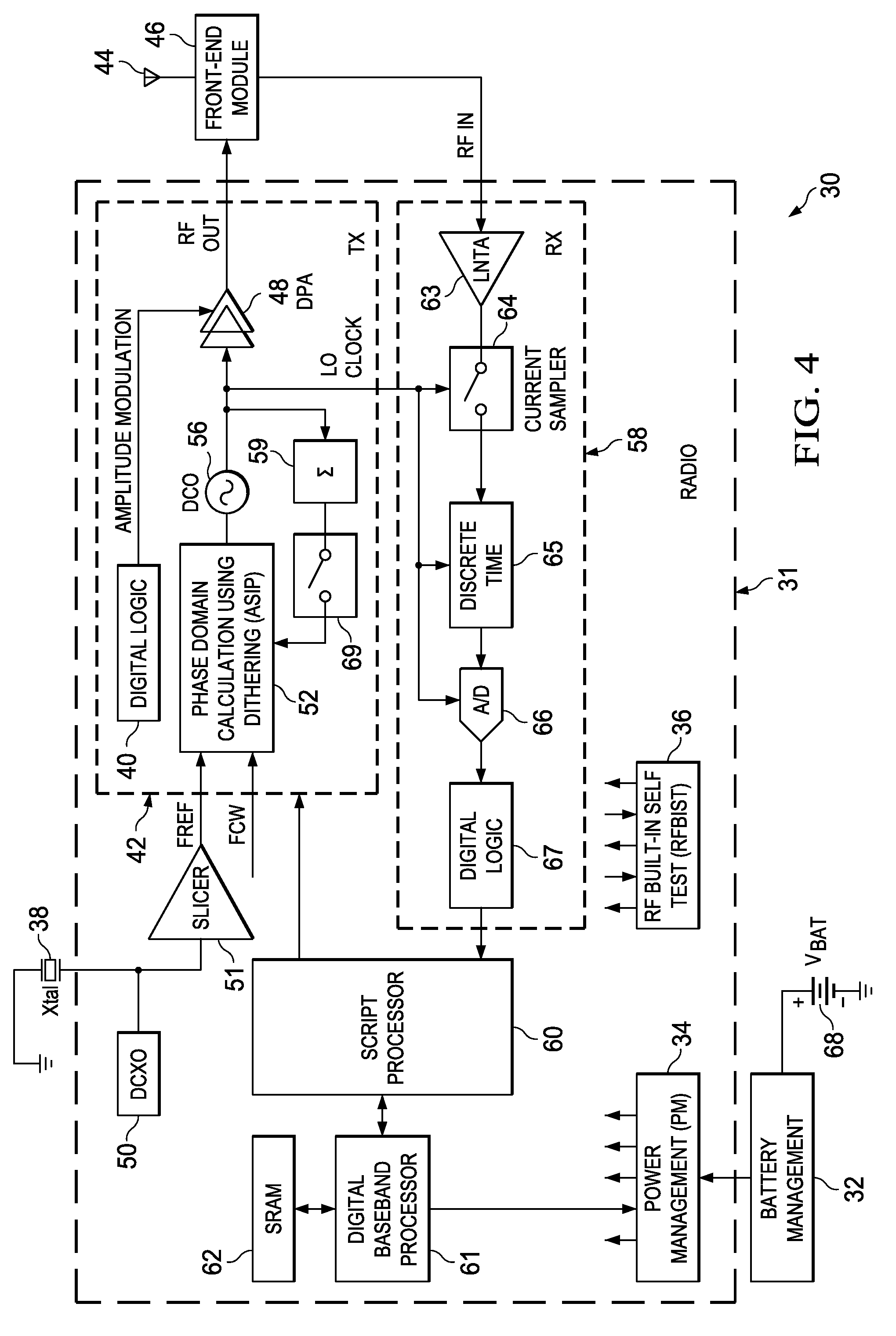

A novel apparatus and method for a hybrid Cartesian / polar digital QAM modulator. The hybrid technique of the present invention utilizes a combination of an all digital phase locked loop (ADPLL) that features a wideband frequency modulation capability and a digitally controlled power amplifier (DPA) that features interpolation between 90 degree spaced quadrature phases. This structure is capable of performing either a polar operation or a Cartesian operation and can dynamically switch between them depending on the instantaneous value of a metric measured by a thresholder / router. In this manner, the disadvantages of each modulation technique are avoided while the benefits of each are exploited.

Owner:TEXAS INSTR INC

Clock recovery using a double-exponential smoothing process

A system and method for synchronizing a local clock to a reference clock using a linear model of the clock error between the local clock and the reference clock is disclosed. In one embodiment, a double-exponential smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the double-exponential smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:RPX CLEARINGHOUSE

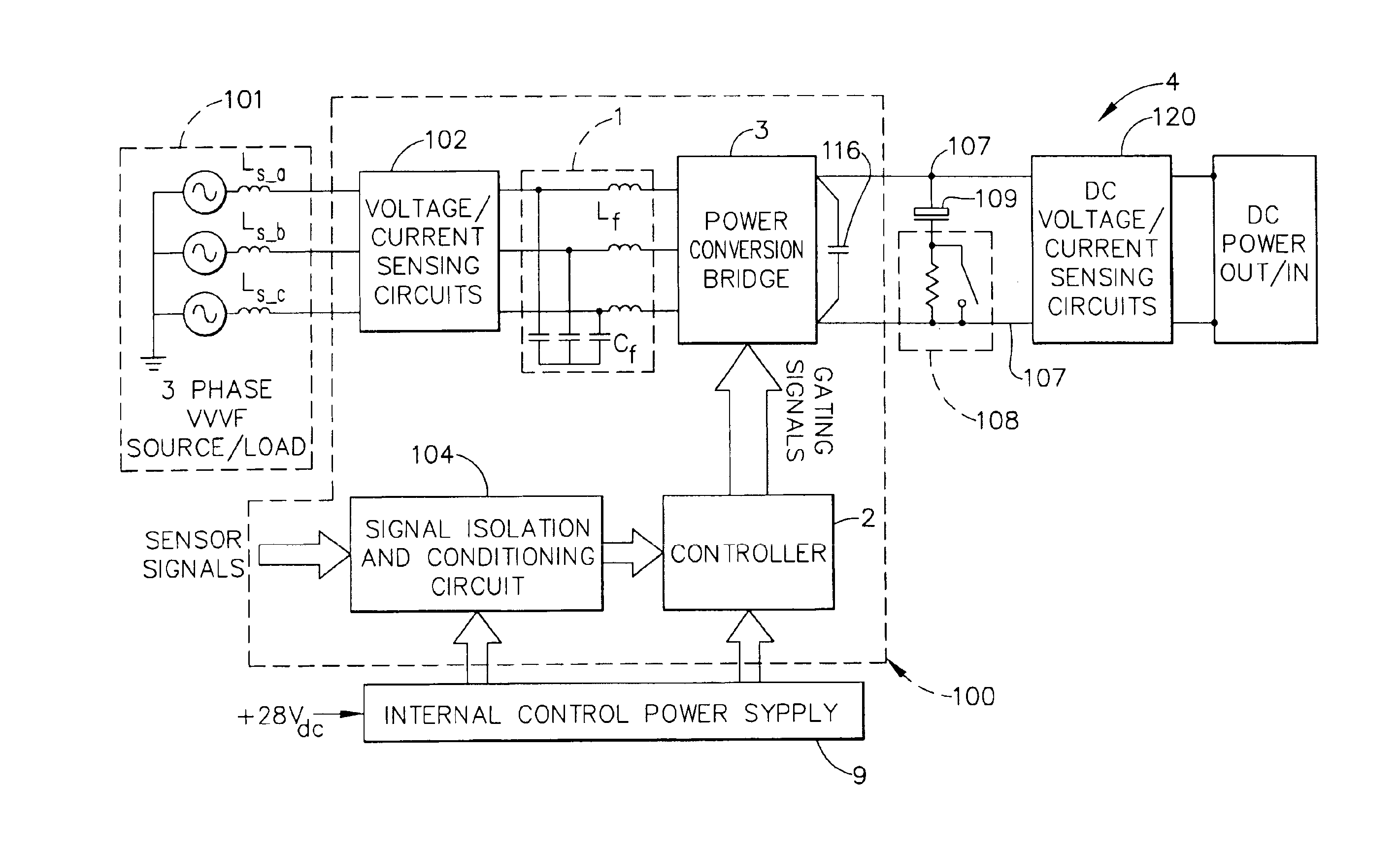

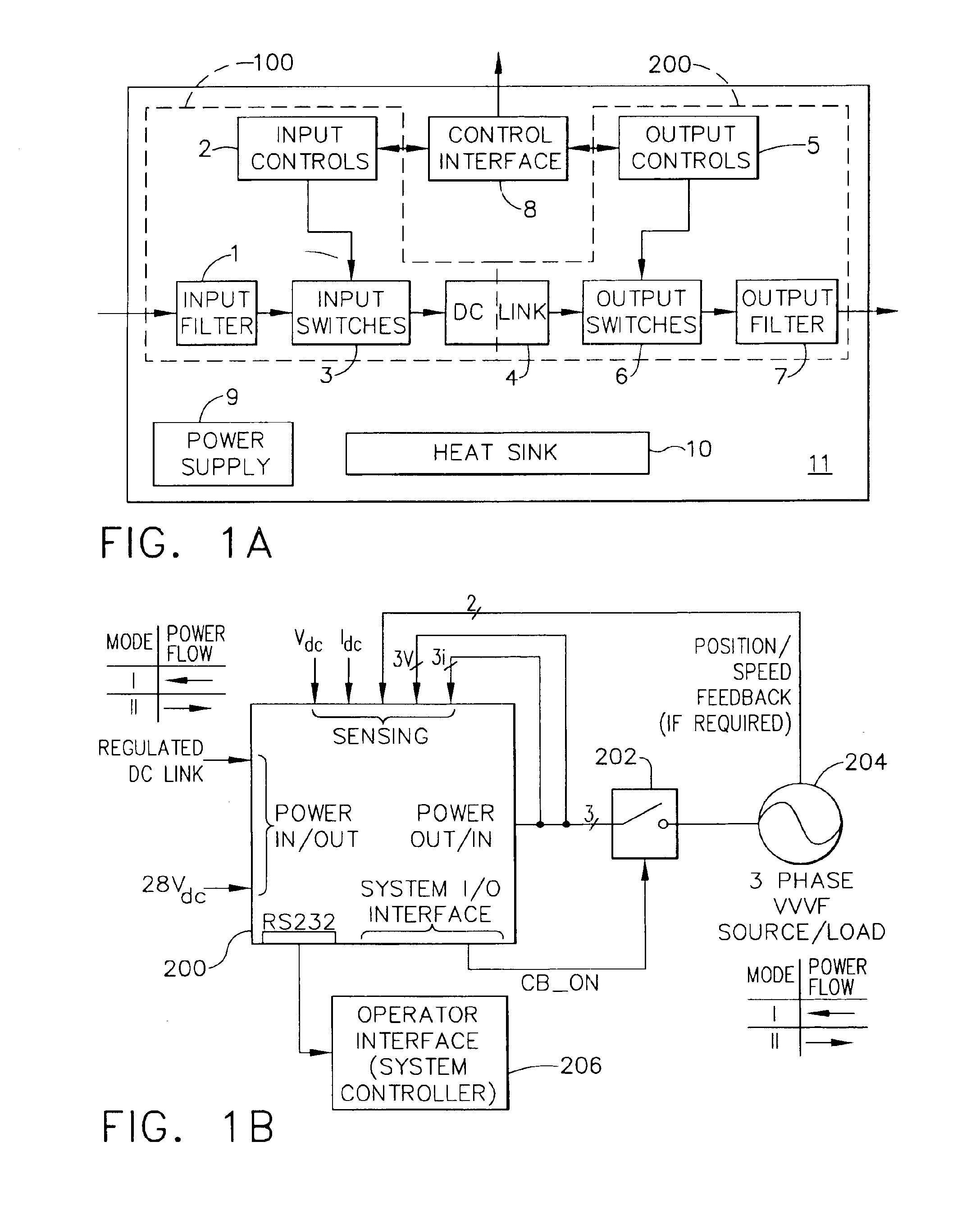

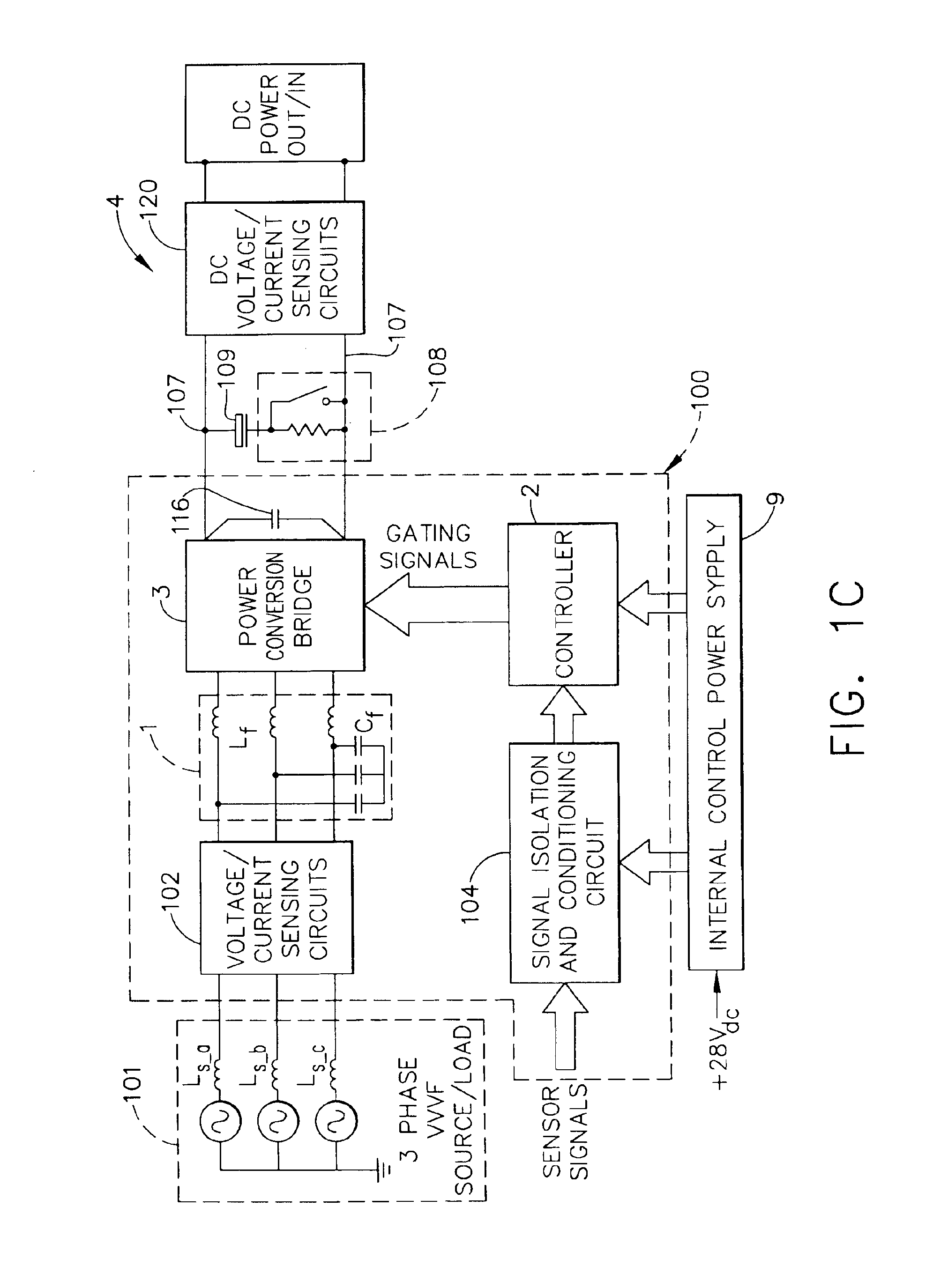

Synchronous and bi-directional variable frequency power conversion systems

InactiveUS6850426B2Facilitate easeLow costAc-dc conversion without reversalDc-dc conversionDigital controlAC power

A synchronous bi-directional active power conditioning system (11) suitable for wide variable frequency systems or active loads such as adjustable speed drives which require variable voltage variable frequency power management systems is disclosed. Common power electronics building blocks (100, 200) (both hardware and software modular blocks) are presented which can be used for AC-DC, DC-AC individually or cascaded together for AC-DC-AC power conversion suitable for variable voltage and / or wide variable frequency power management systems. A common control software building block (2, 5) includes a digital control strategy / algorithm and digital phase lock loop method and apparatus which are developed and implemented in a digital environment to provide gating patterns for the switching elements (3, 6) of the common power-pass modular power electronics building blocks (100, 200).

Owner:HONEYWELL INT INC

Clock recovery using a direct smoothing process

ActiveUS7130368B1Guaranteed maximum utilizationPulse automatic controlModulated-carrier systemsClock recoveryLinear model

A system and method for synchronizing a local clock to a reference clock using a linear model of the error between the local clock and the reference clock is disclosed. In one embodiment, a direct smoothing process is used in conjunction with the linear model to estimate a frequency offset by which the frequency of an oscillator of the local clock is adjusted. Also disclosed herein is a phased-lock loop (PLL) adapted to synchronize a local clock with a reference clock using the direct smoothing process, as well as a system implementing the PLL for timing the playout of data received from a transmitter.

Owner:CIENA

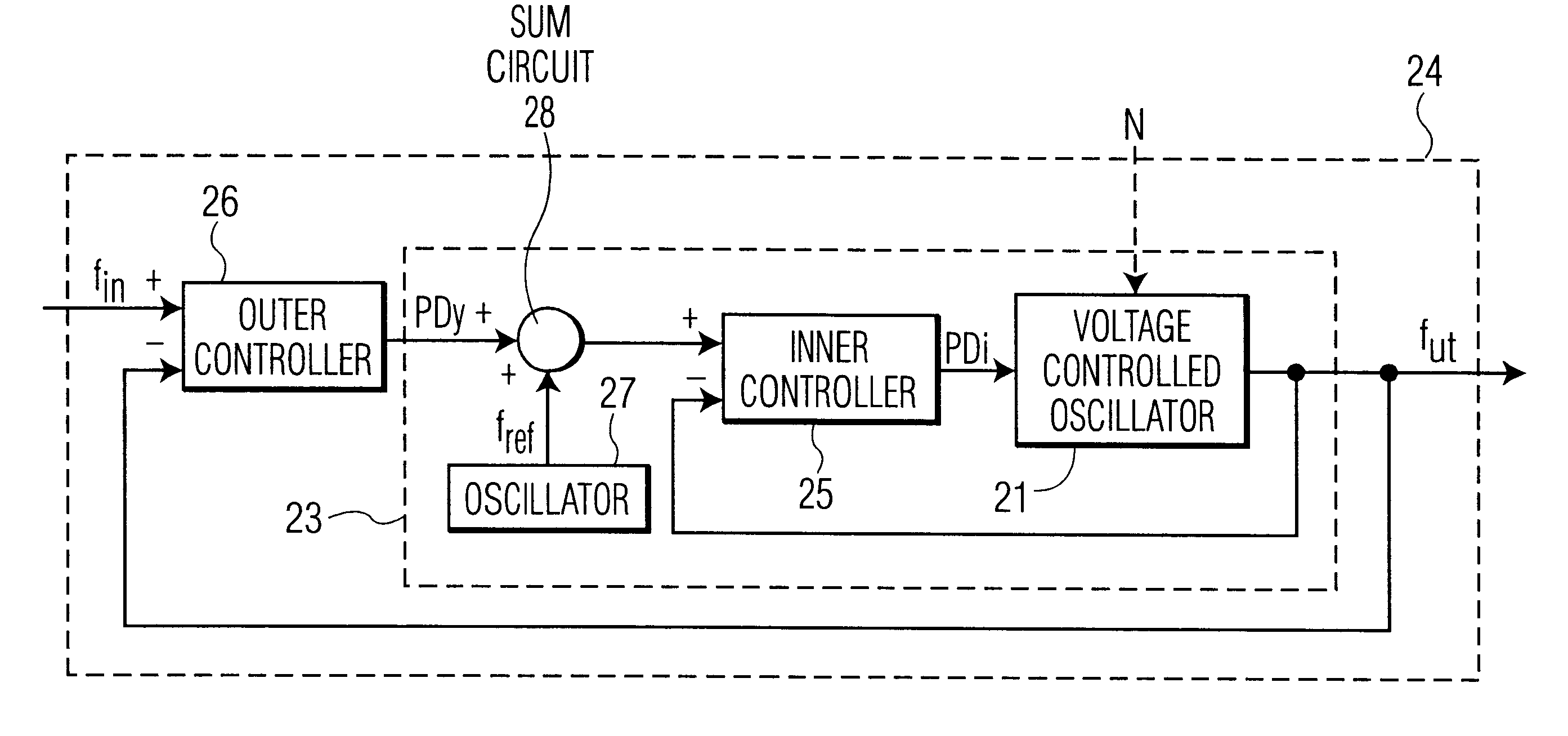

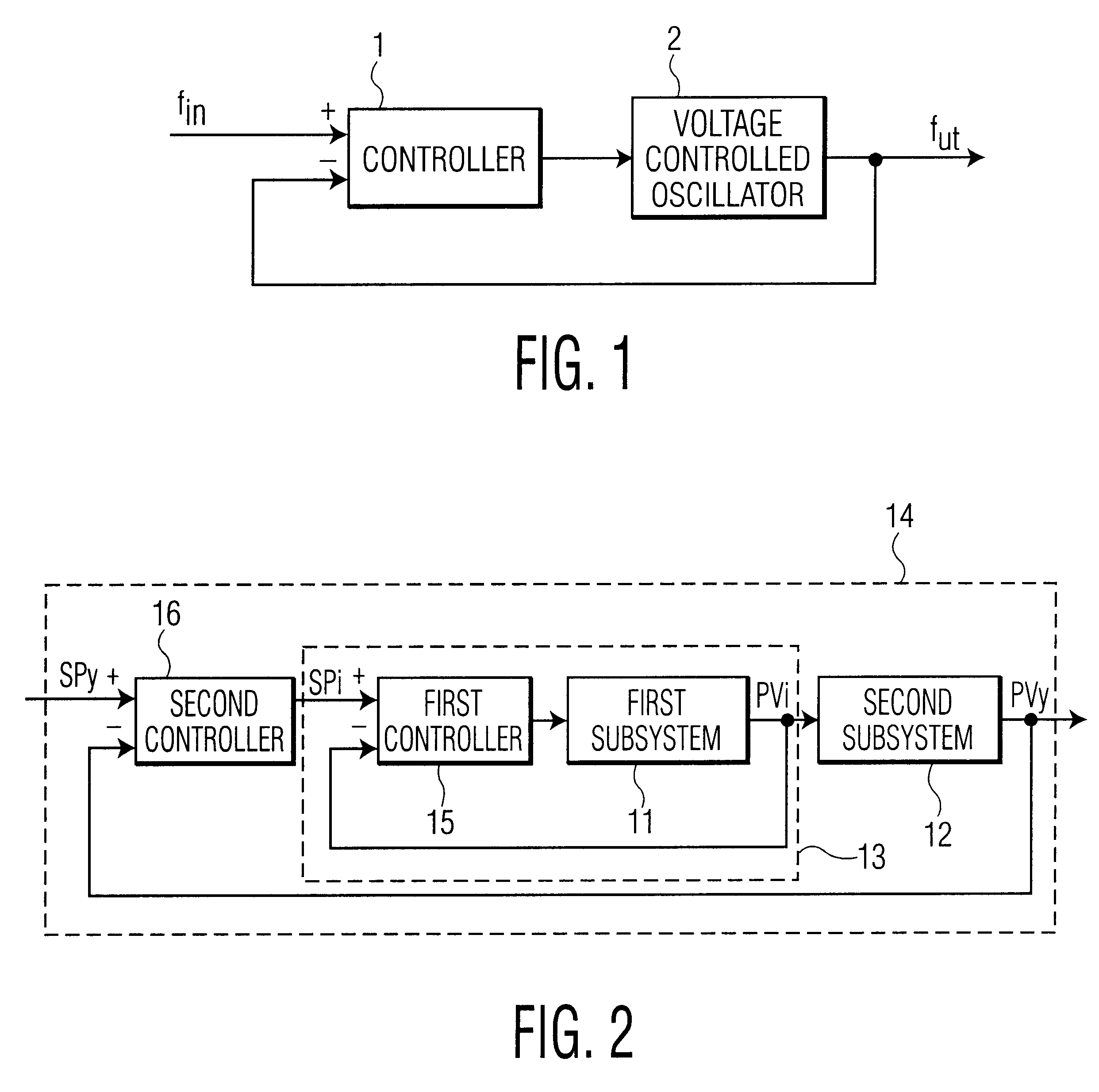

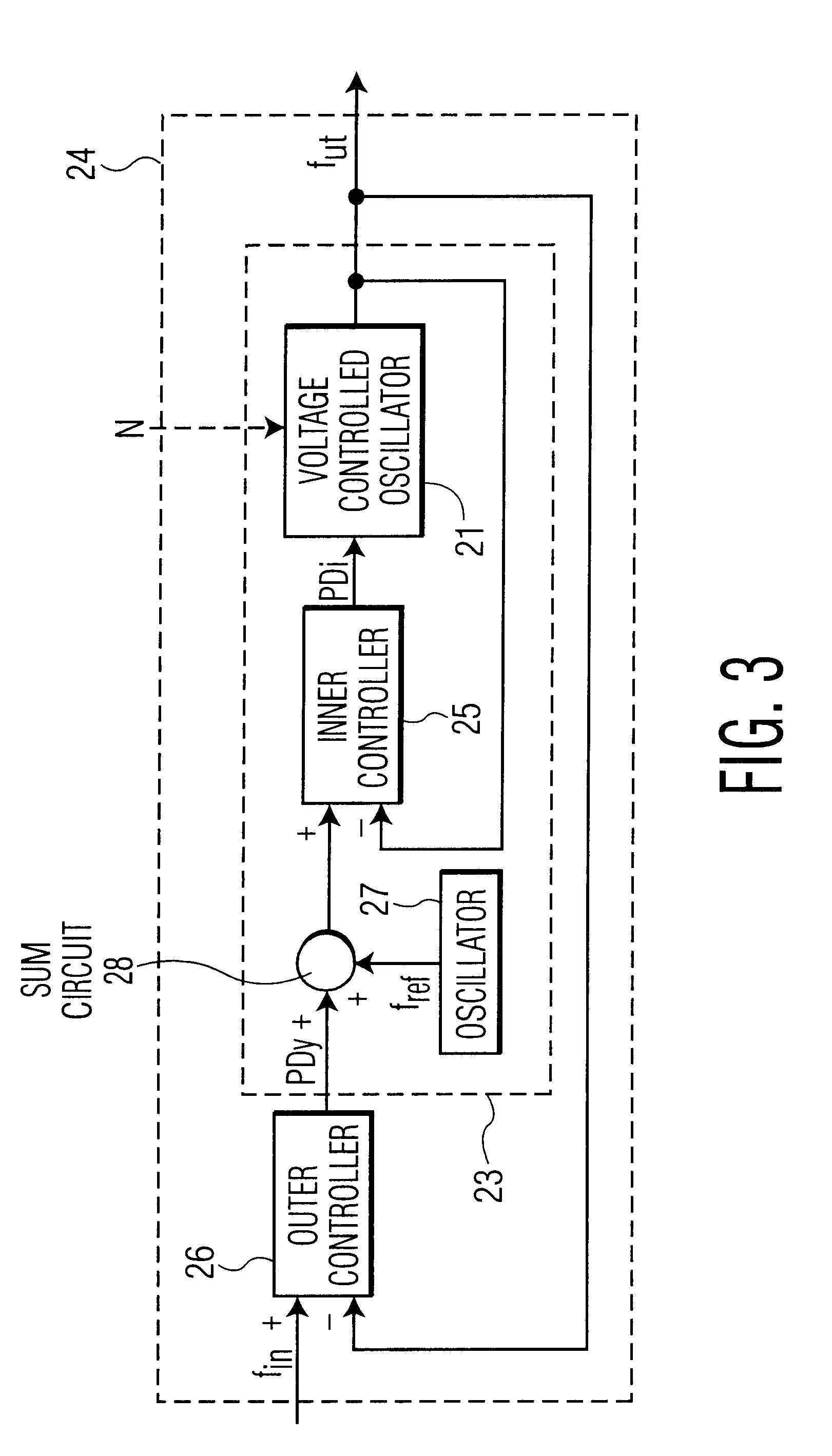

Phase locked loop control via inner and outer feedback control circuits

InactiveUS6384690B1Reduce inputGood frequencyPulse automatic controlNegative feedbackControl circuit

A phase locked loop includes at least one control circuit, where a voltage-controlled oscillator provides an output frequency which is arranged to strive to follow an input frequency. The phase locked loop also includes an outer, slow, negative feedback control circuit, having the input frequency as a setpoint, the output frequency as a process value and an outer output signal. The phase locked loop also includes an inner, fast, negative feedback control circuit, having the sum of a reference frequency from a stable oscillator and the outer output signal as a setpoint, the output frequency as the process value and an inner output signal for controlling the voltage controlled oscillator.

Owner:TELEFON AB LM ERICSSON (PUBL)

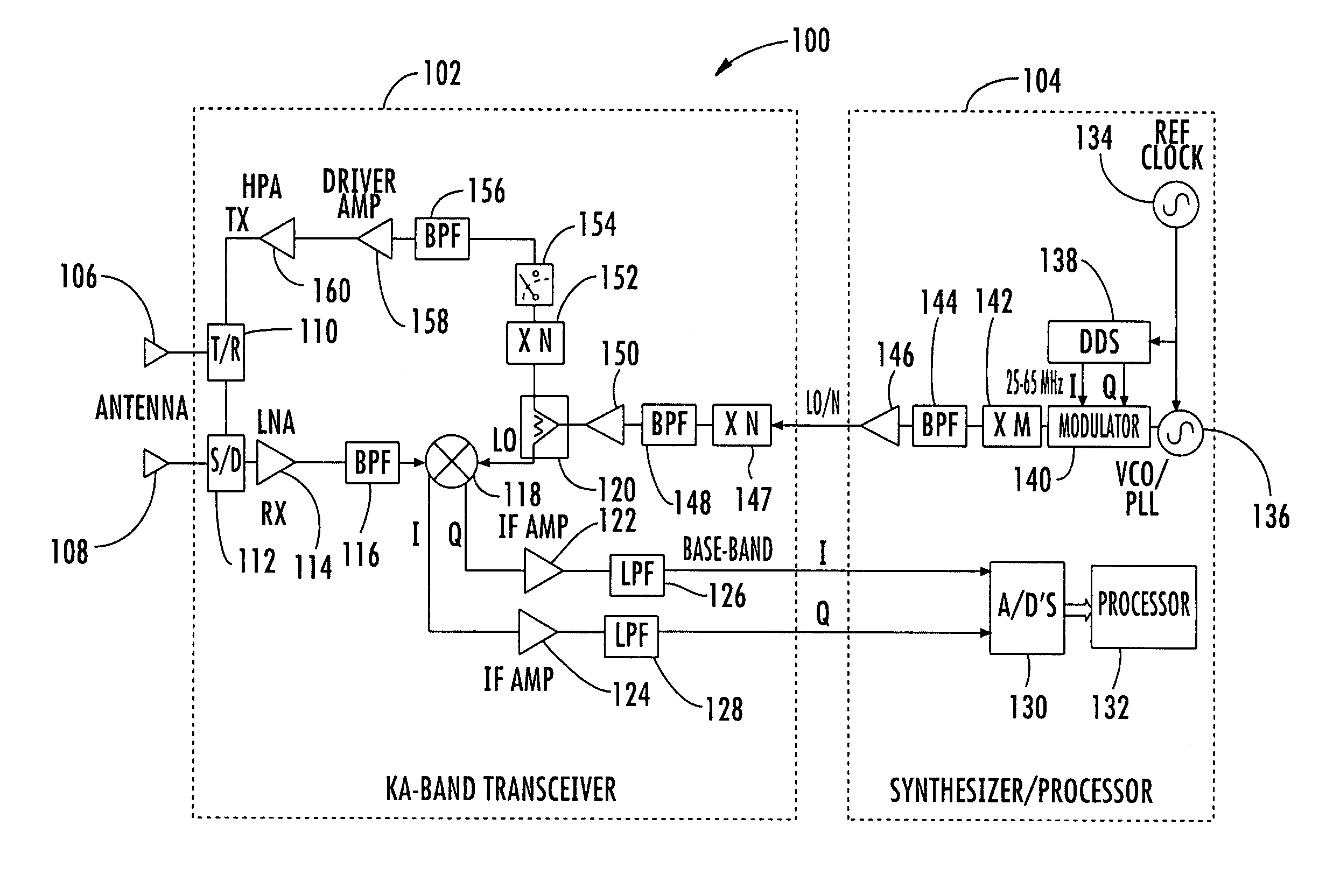

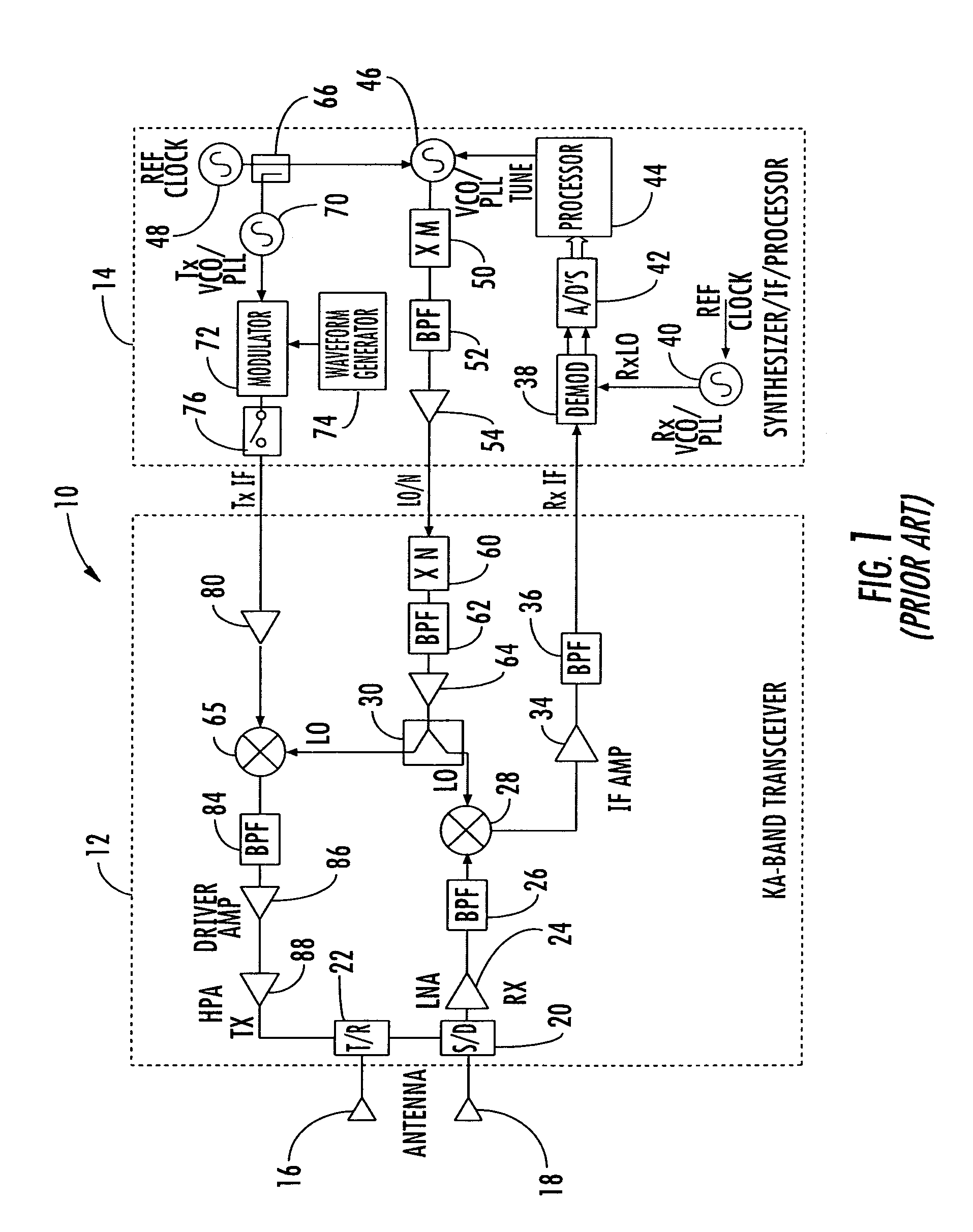

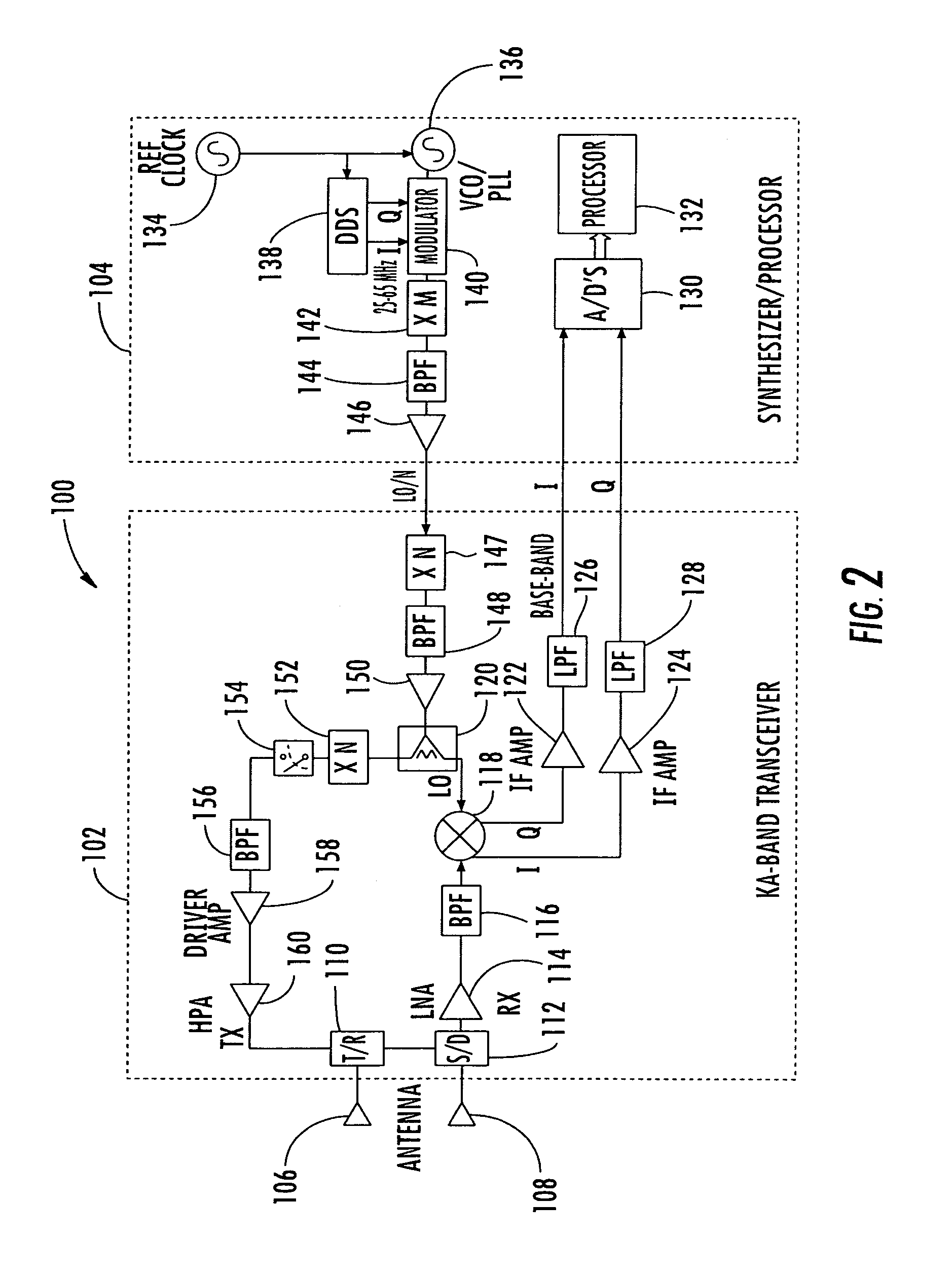

Millimeter wave pulsed radar system

InactiveUS7002511B1Improve efficiencySimplified frequency synthesizer designRadio wave reradiation/reflectionQuadrature modulatorLocal oscillator signal

A millimeter wave pulsed radar system includes a radar synthesizer having a voltage controlled oscillator / phase locked loop (VCO / PLL) circuit, direct digital synthesizer (DDS) circuit and quadrature modulator circuit that are operative to generate an intermediate frequency local oscillator signal (IF / LO signal). A radar transceiver is operative with the radar synthesizer for receiving the IF / LO signal. A transmitter section has a frequency multiplier that multiplies the IF / LO signal up to a millimeter wave (MMW) radar signal and a receiver section and includes a direct conversion mixer that receives a MMW radar signal and the IF / LO signal to produce I / Q baseband signals that are later digitized and processed.

Owner:REVEAL IMAGING

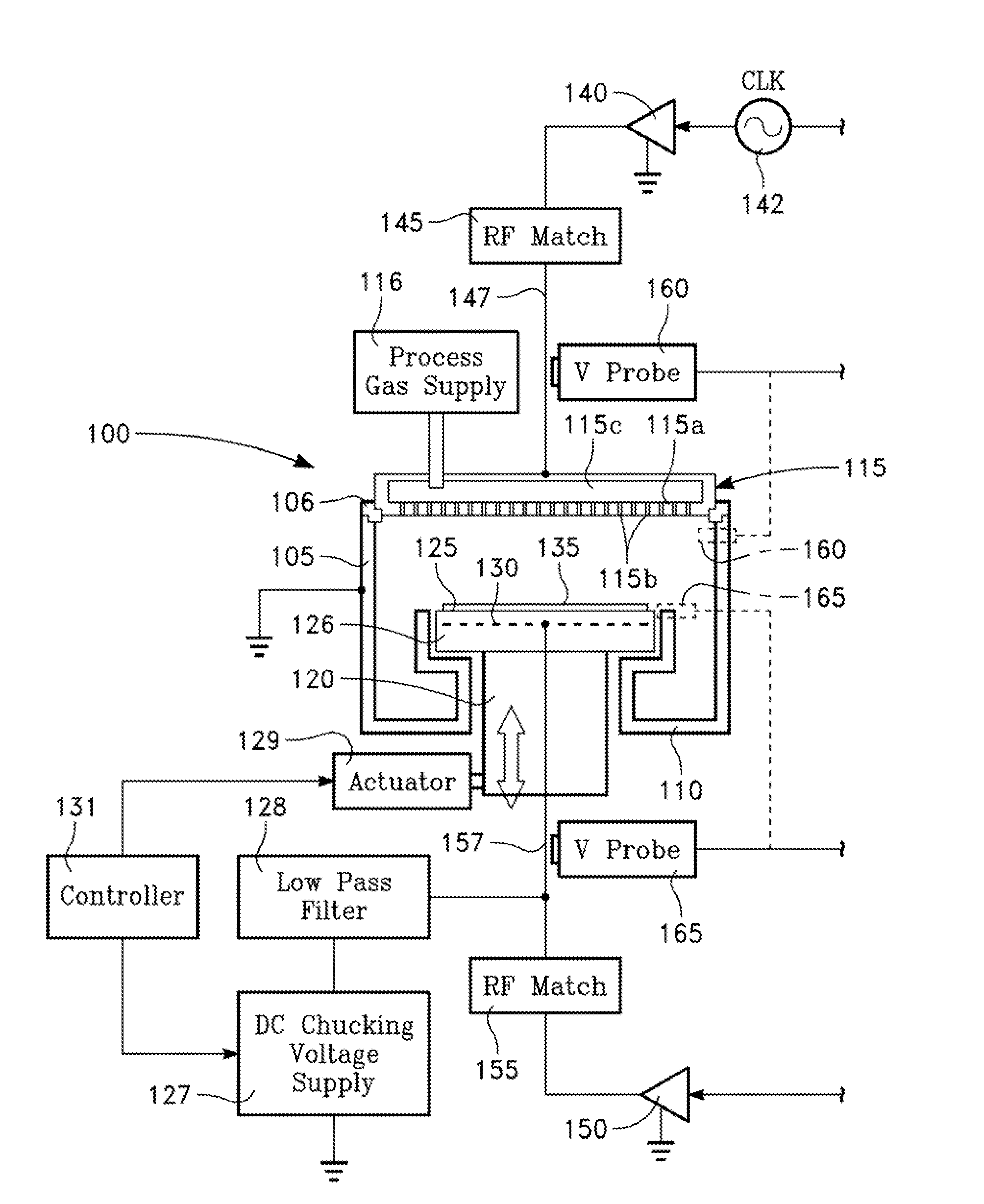

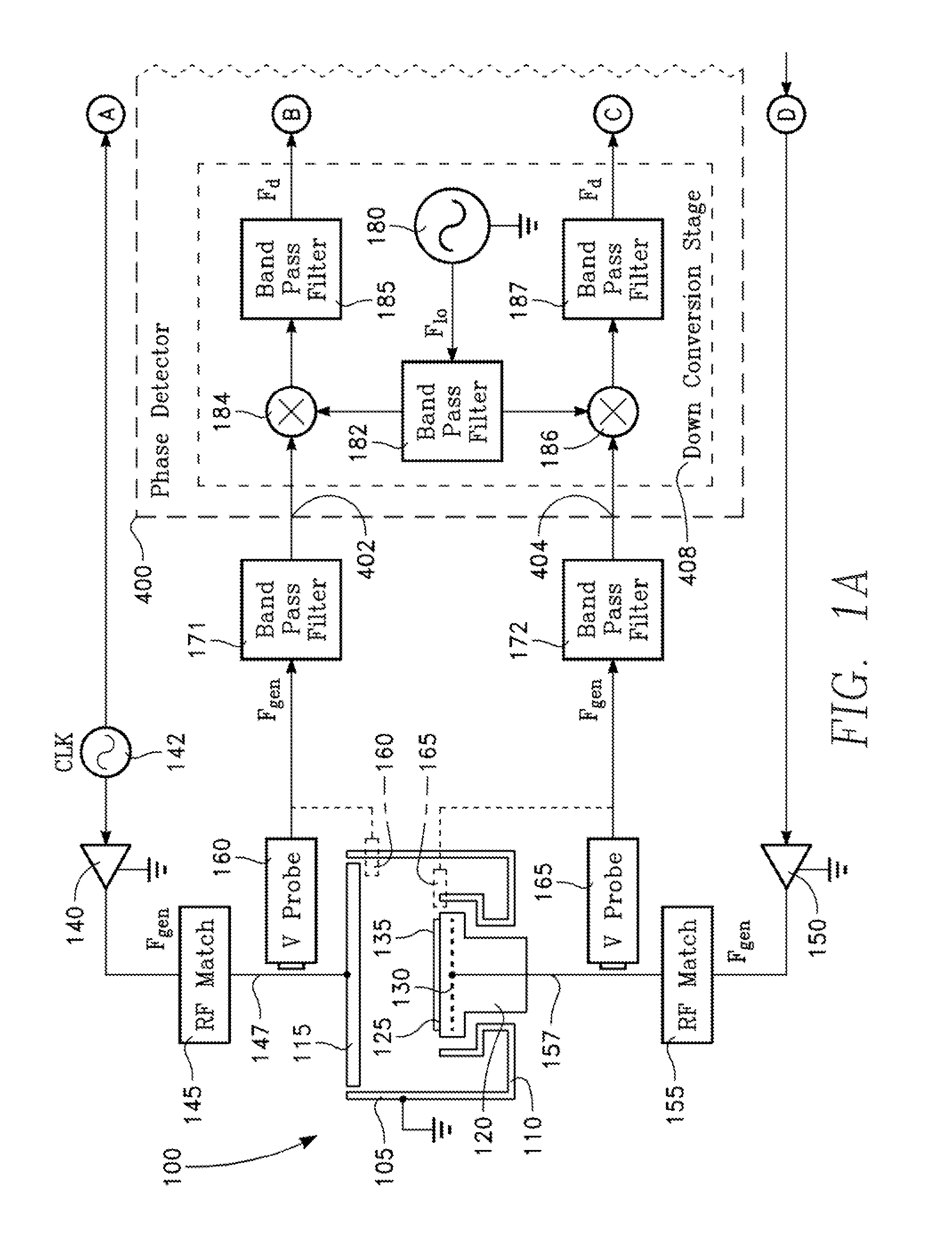

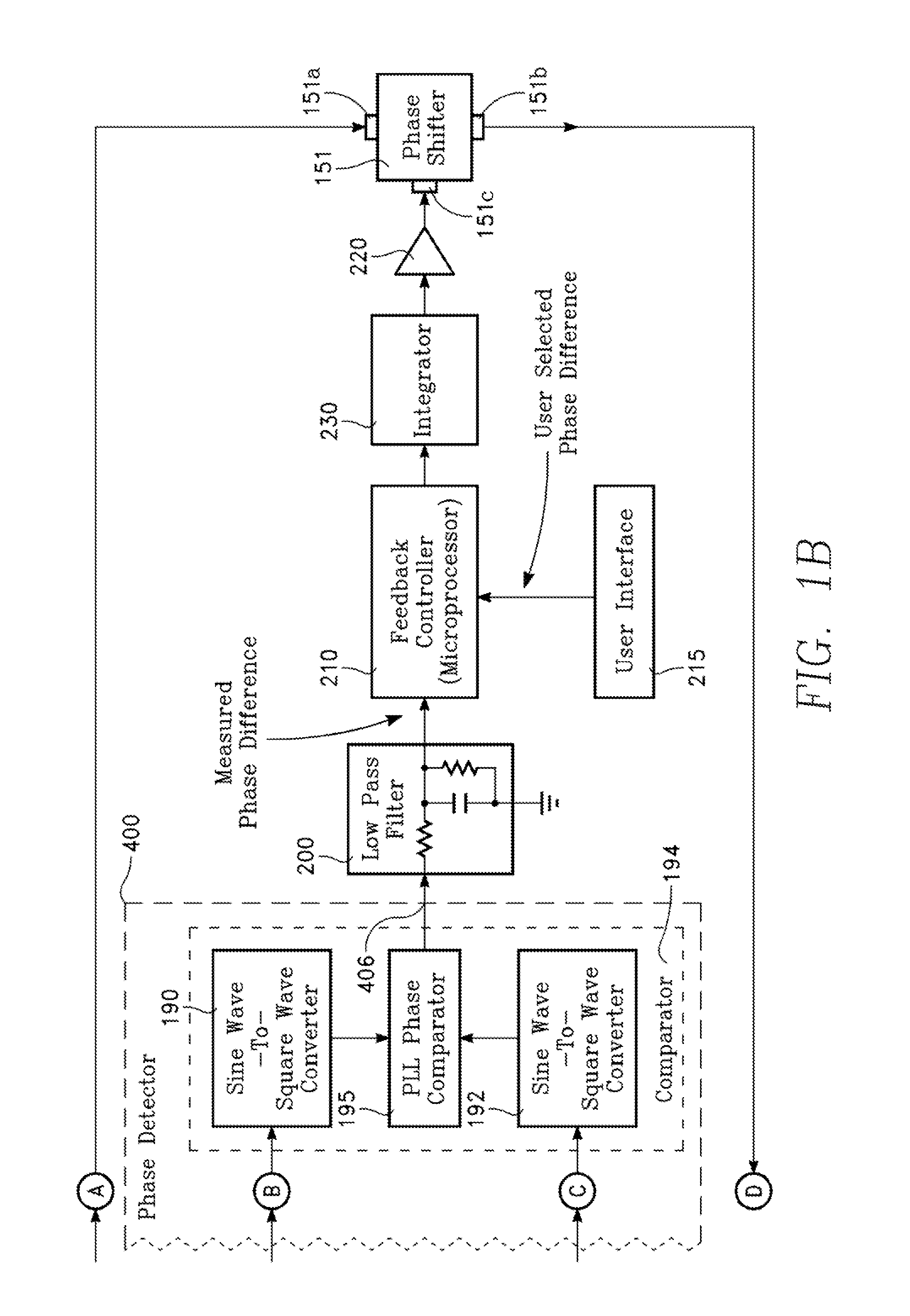

Two-phase operation of plasma chamber by phase locked loop

InactiveUS20130284369A1Liquid surface applicatorsElectric discharge tubesPhase differenceEngineering

Plasma distribution is controlled in a plasma reactor by controlling the phase difference between opposing RF electrodes, in accordance with a desired or user-selected phase difference, by a phase-lock feedback control loop.

Owner:APPLIED MATERIALS INC

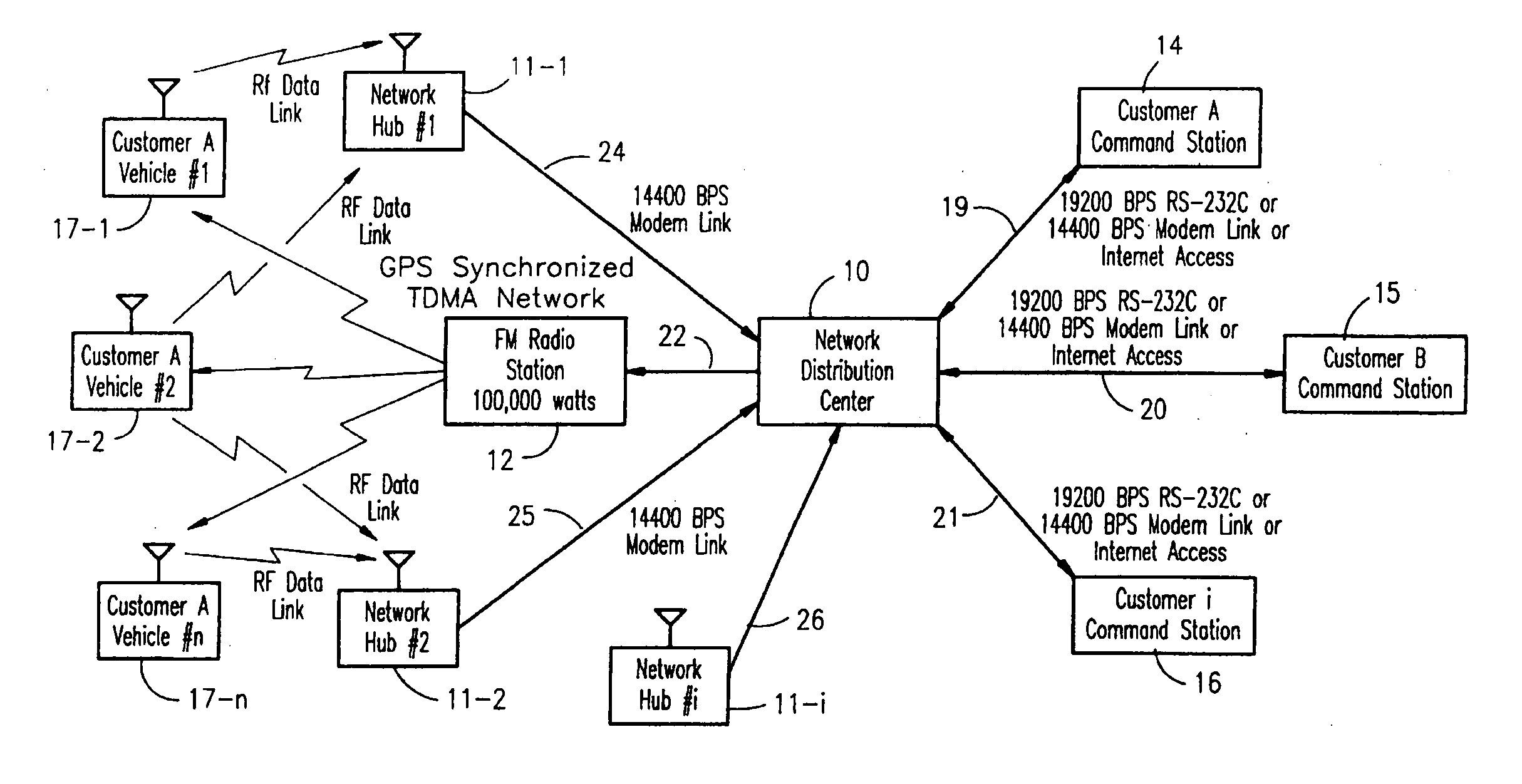

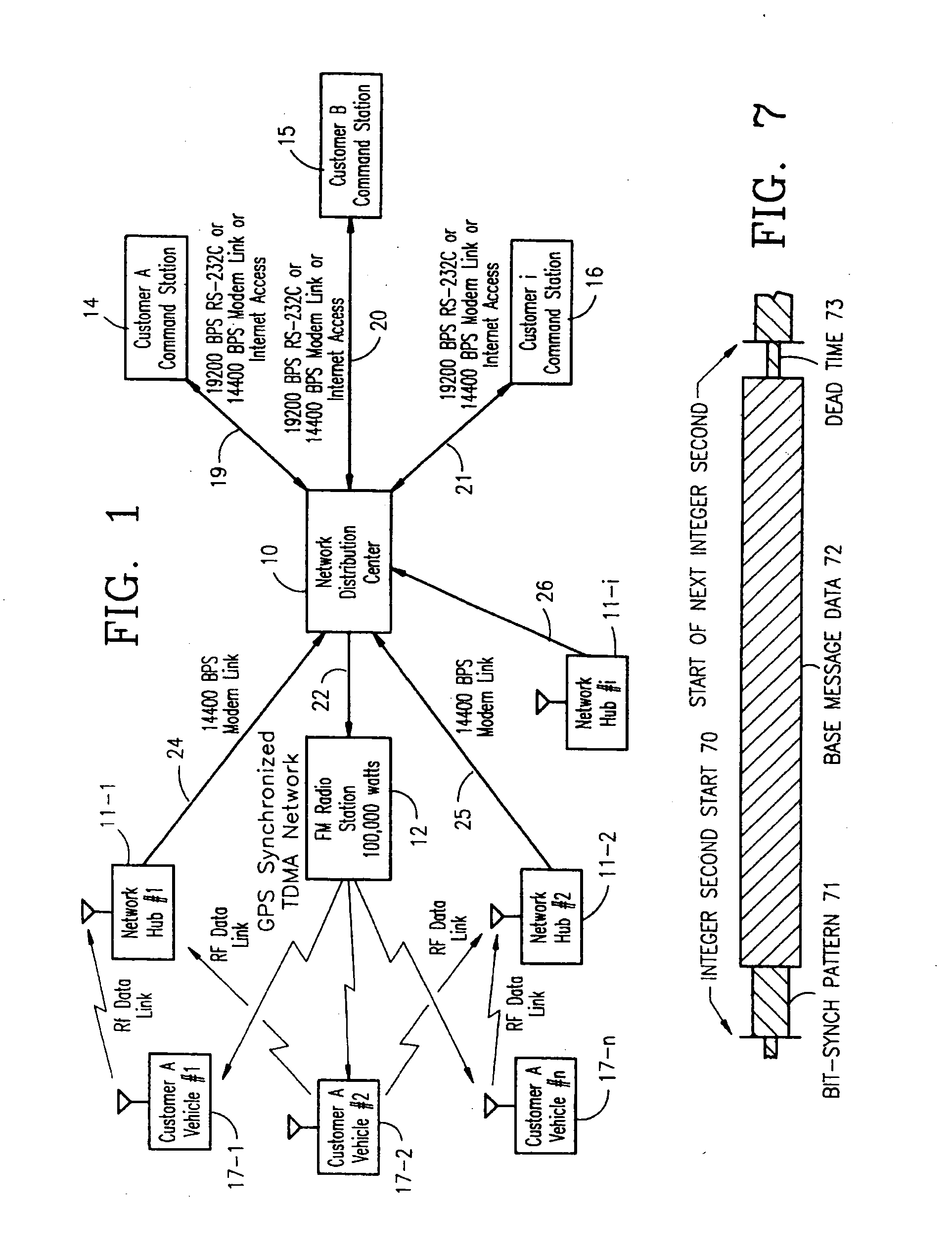

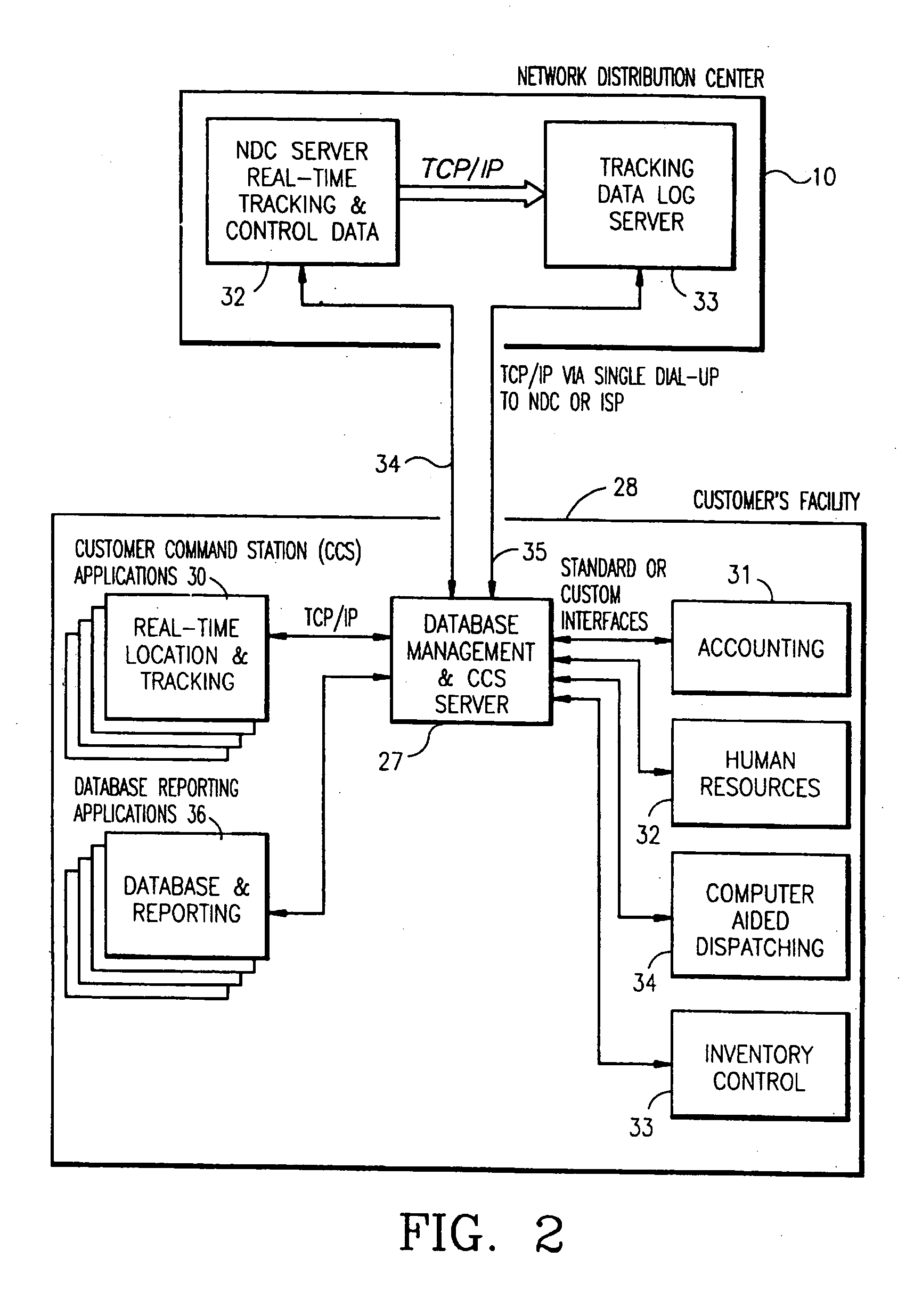

Vehicle tracking, communication and fleet management system

InactiveUS20060142913A1Management moreEfficient and reliableVehicle testingRegistering/indicating working of vehiclesFleet managementEngineering

A vehicle fleet management information system identifies location and direction of movement of each vehicle in a fleet in real-time, and automatically reports such information, as well as status of predetermined events in which the vehicle is engaged, directly to the fleet manager. Each fleet vehicle has an assigned time slot to transmit its reporting information over a communications network without interfering with transmissions from other vehicles in their own respective time slots. A timing control phase lock loop (PLL) provides precise time synchronization for timing corrections from a global positioning system (GPS) based time reference. A dual band full-duplex interface of the network has TDMA on one-half and broadcast on the other half. Microprocessor time processing units in components of the network perform precise clock synchronization. Space diversity performed on received vehicle transmitted messages avoids data corruption. Different vehicles have different periodic transmission intervals, by dynamically allocating the slots for various update rates. Auxiliary reporting slots enable prompt reporting of important data by the respective vehicle transmitters independent of the slower periodic transmission intervals.

Owner:TRIMBLE NAVIGATION LTD

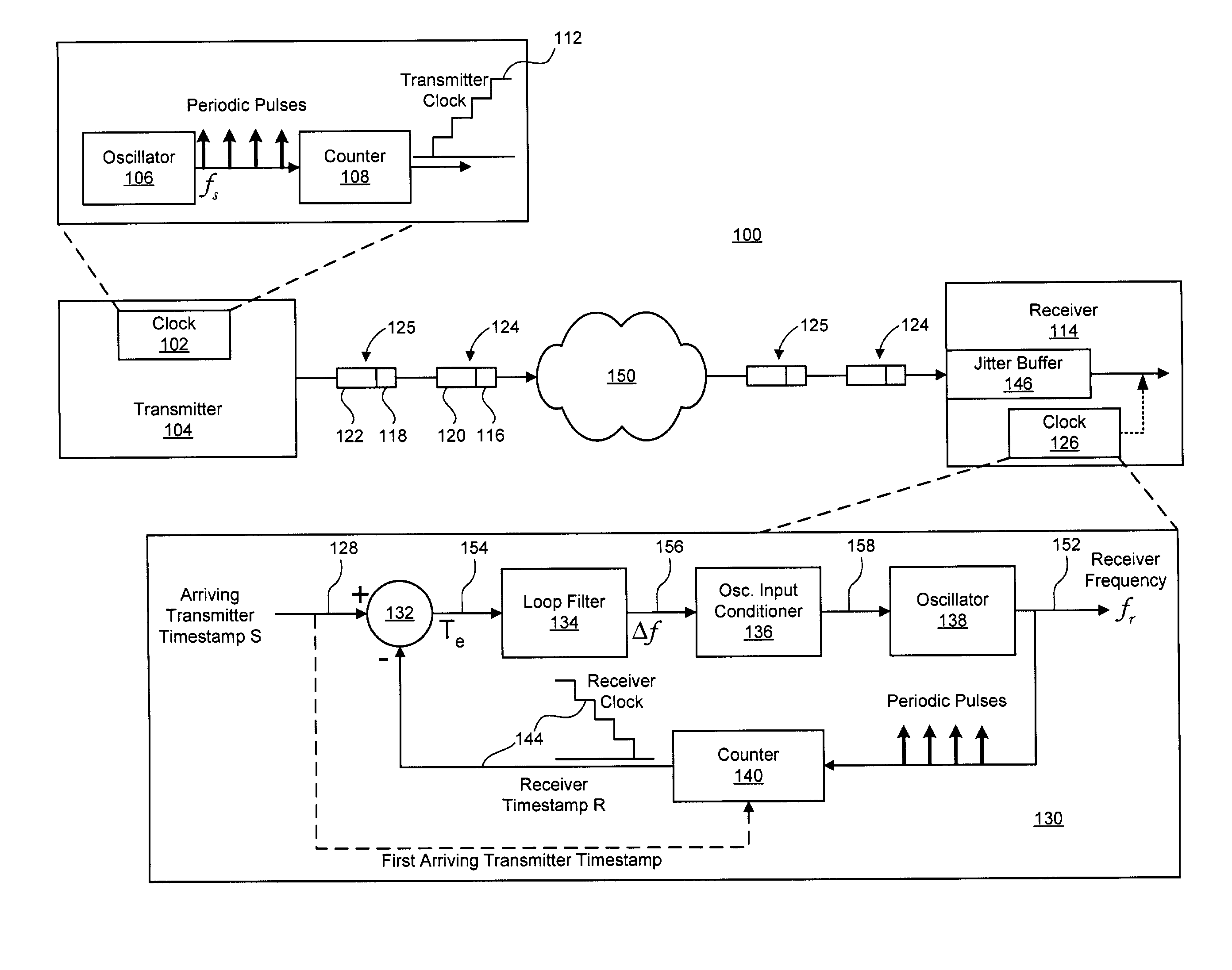

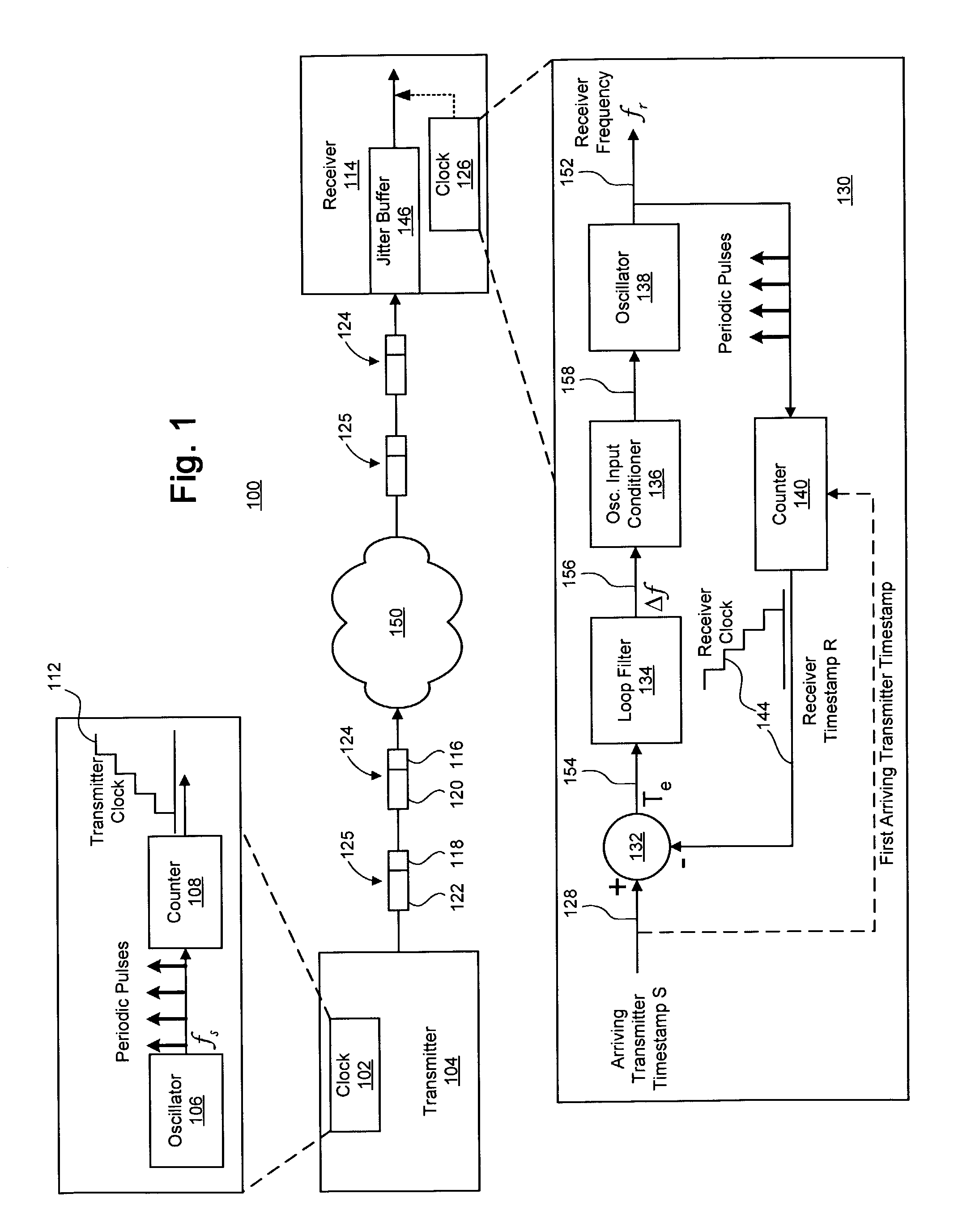

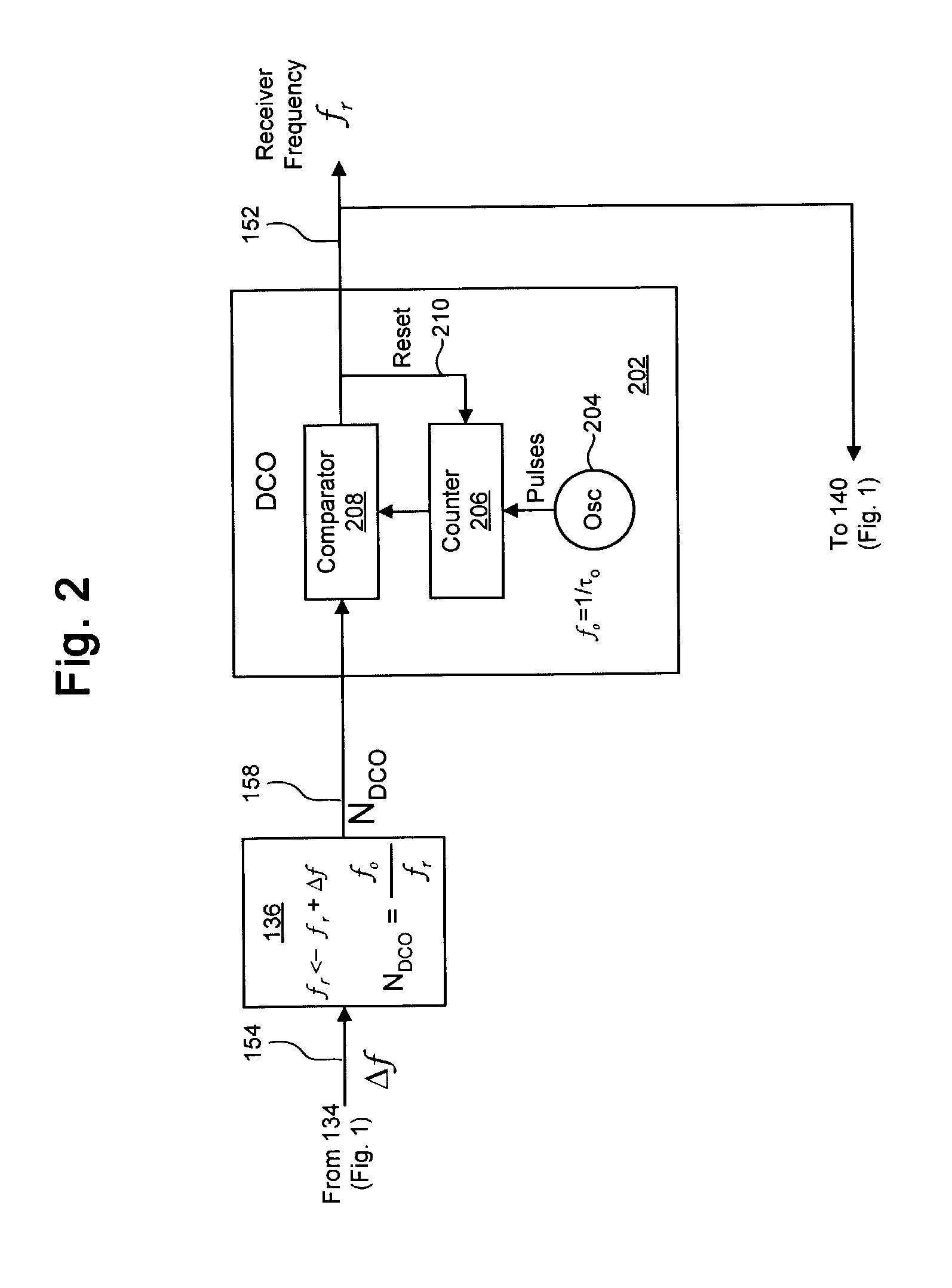

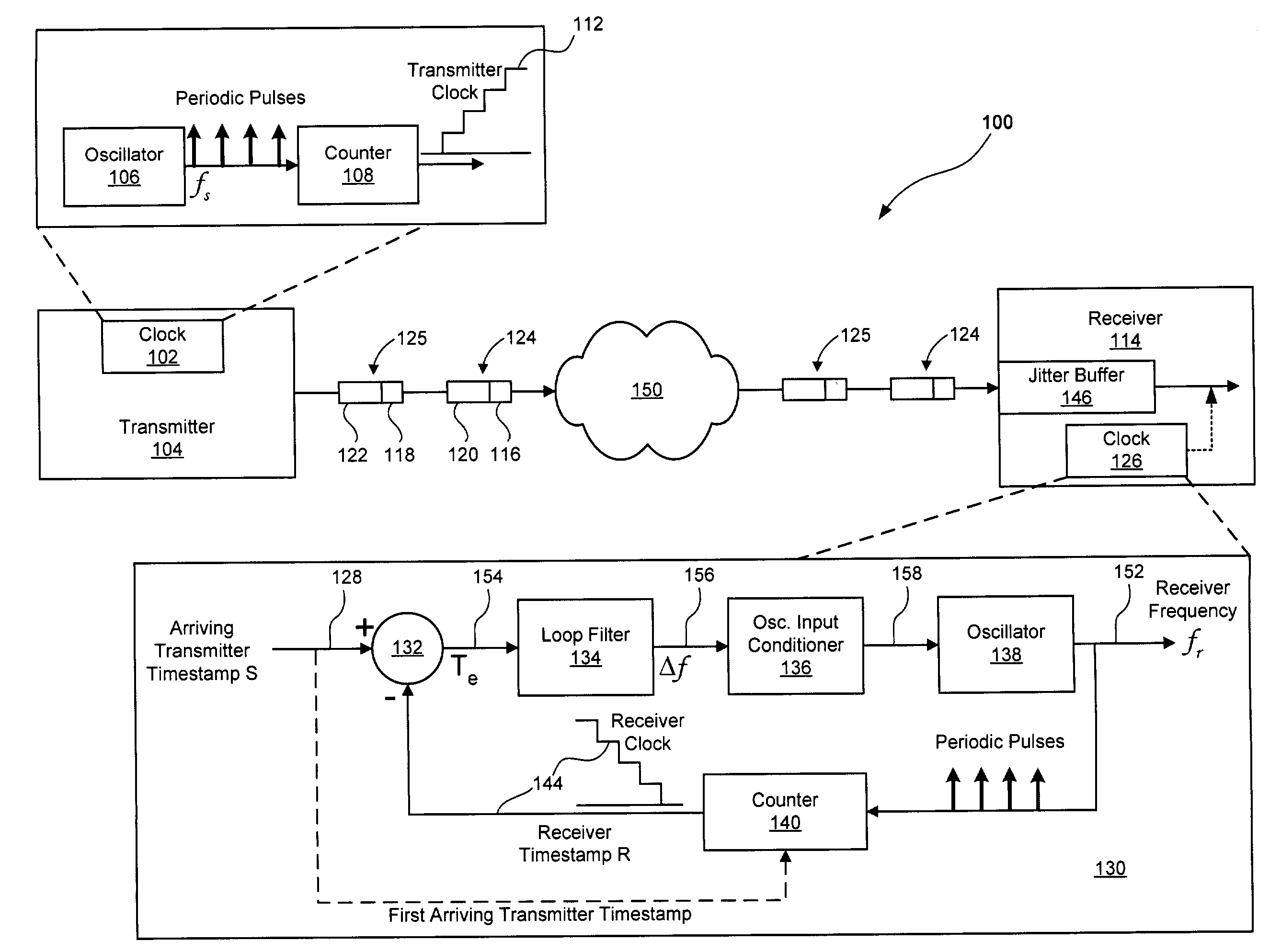

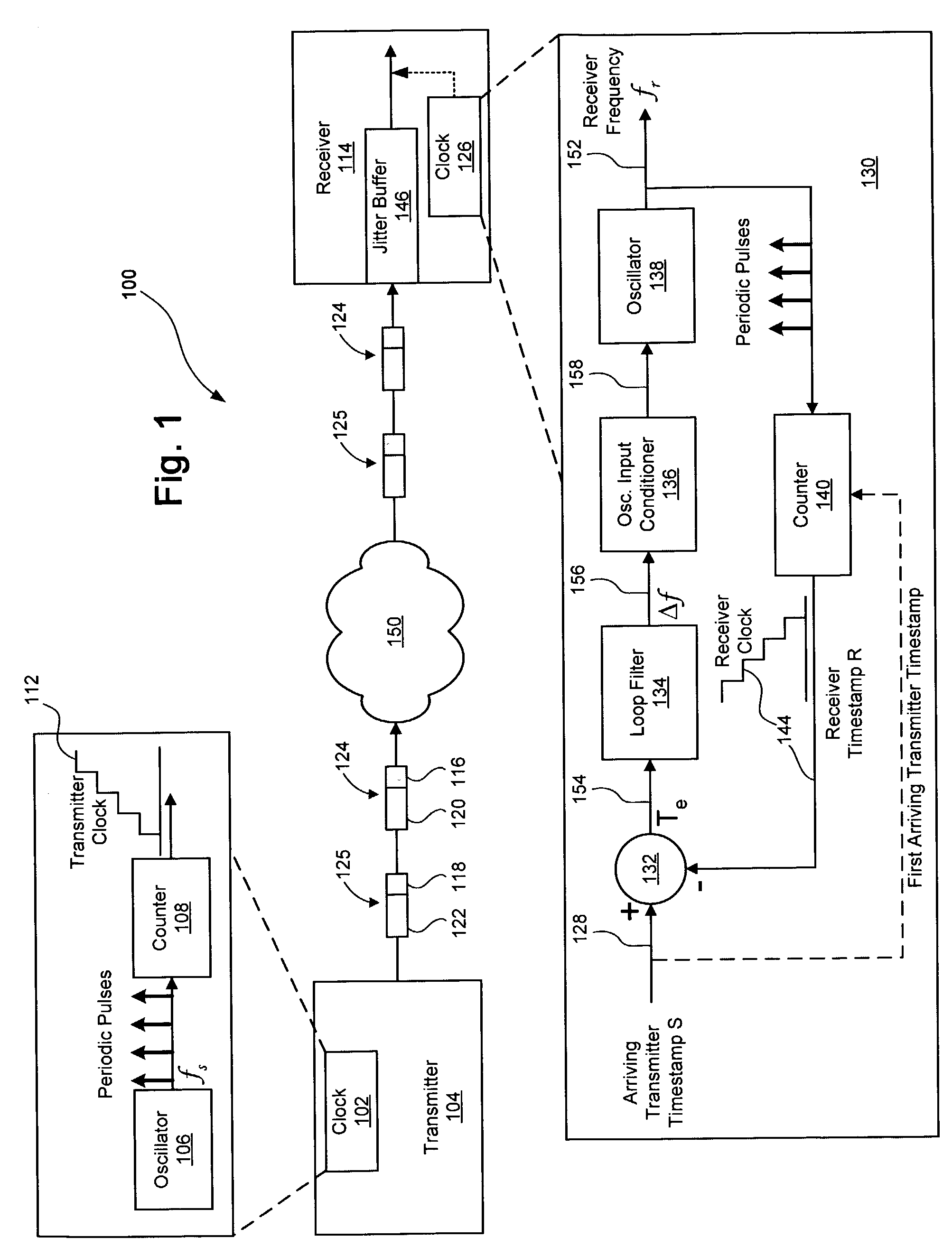

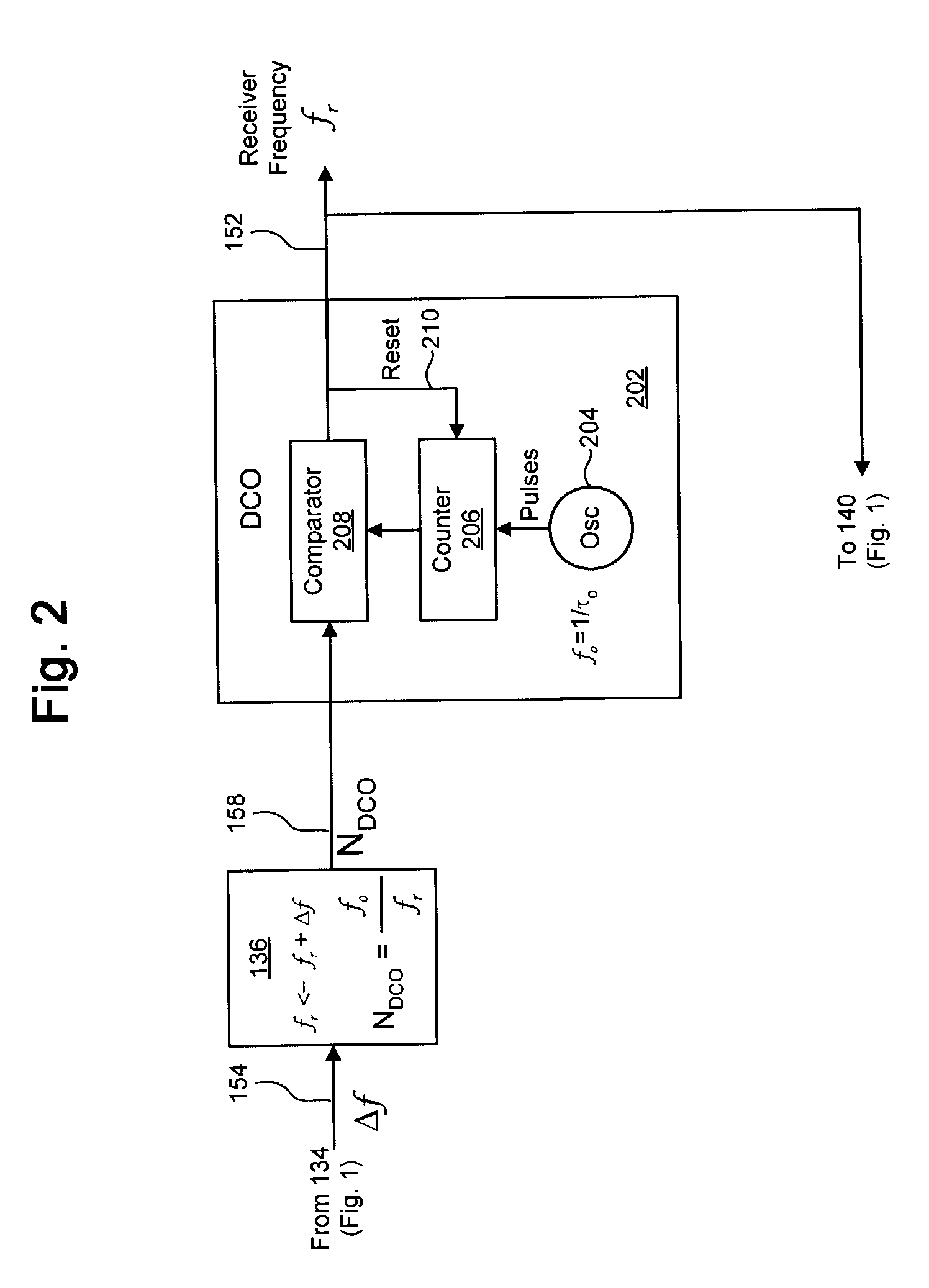

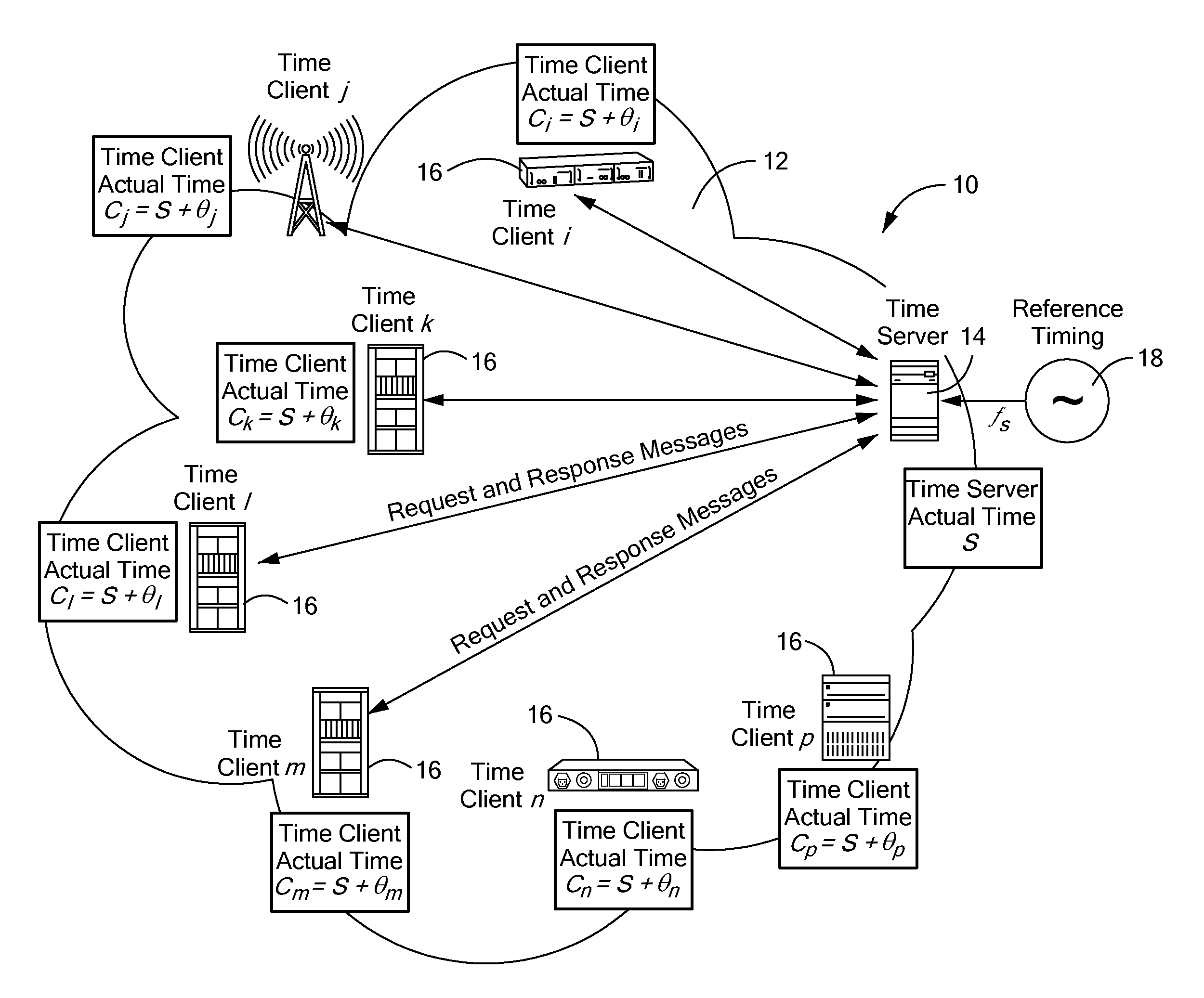

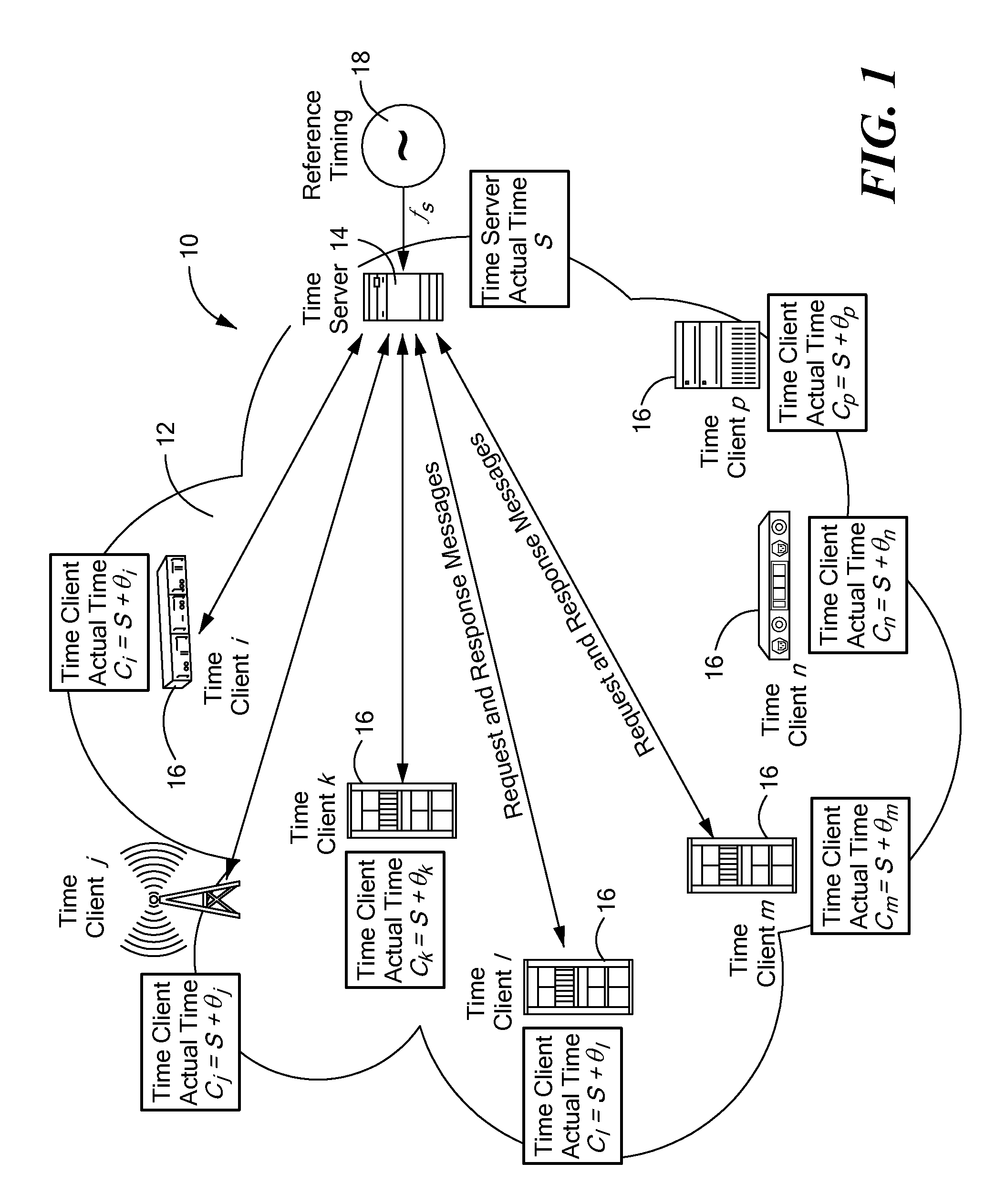

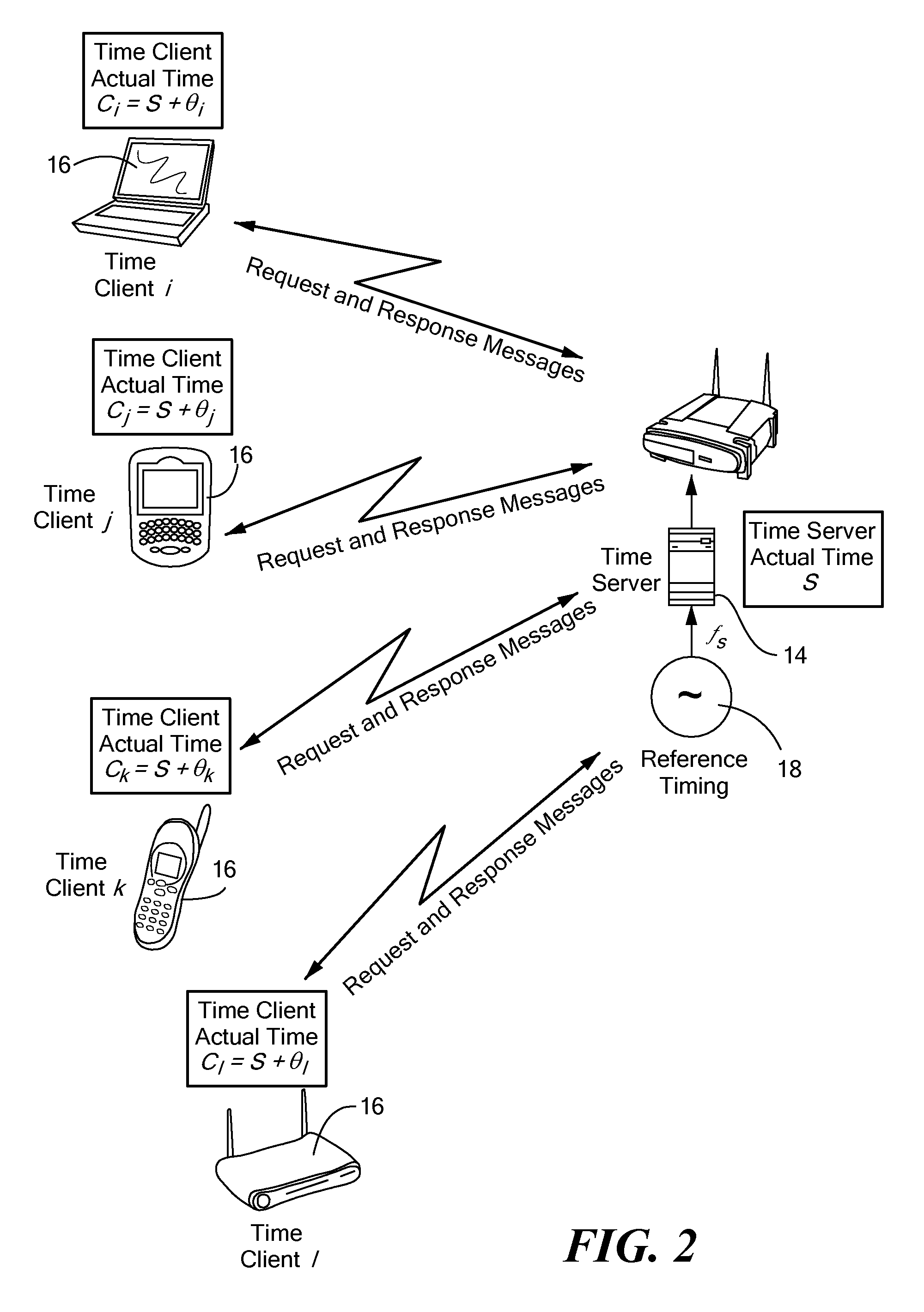

Method and apparatus for time and frequency transfer in communication networks

A timing system for time synchronization between a time server and a time client over a packet network. The timing system includes a time server for generating current timestamp information and a time client having a phase-locked loop driven client clock counter. The time client periodically exchanges time transfer protocol messages with the time server over the packet network, and calculates an estimated client time based on the timestamp information. The phase-locked loop in the time client receives periodic signals representing the estimated server time as its input and calculates a signal which represents the error difference between the estimated server time and the time indicated by the time client clock counter. The error difference eventually converges to zero or a given error range indicating the time presented by the client clock counter, which is driven by the phase-locked loop having locked onto the time of the time server.

Owner:RPX CLEARINGHOUSE +1

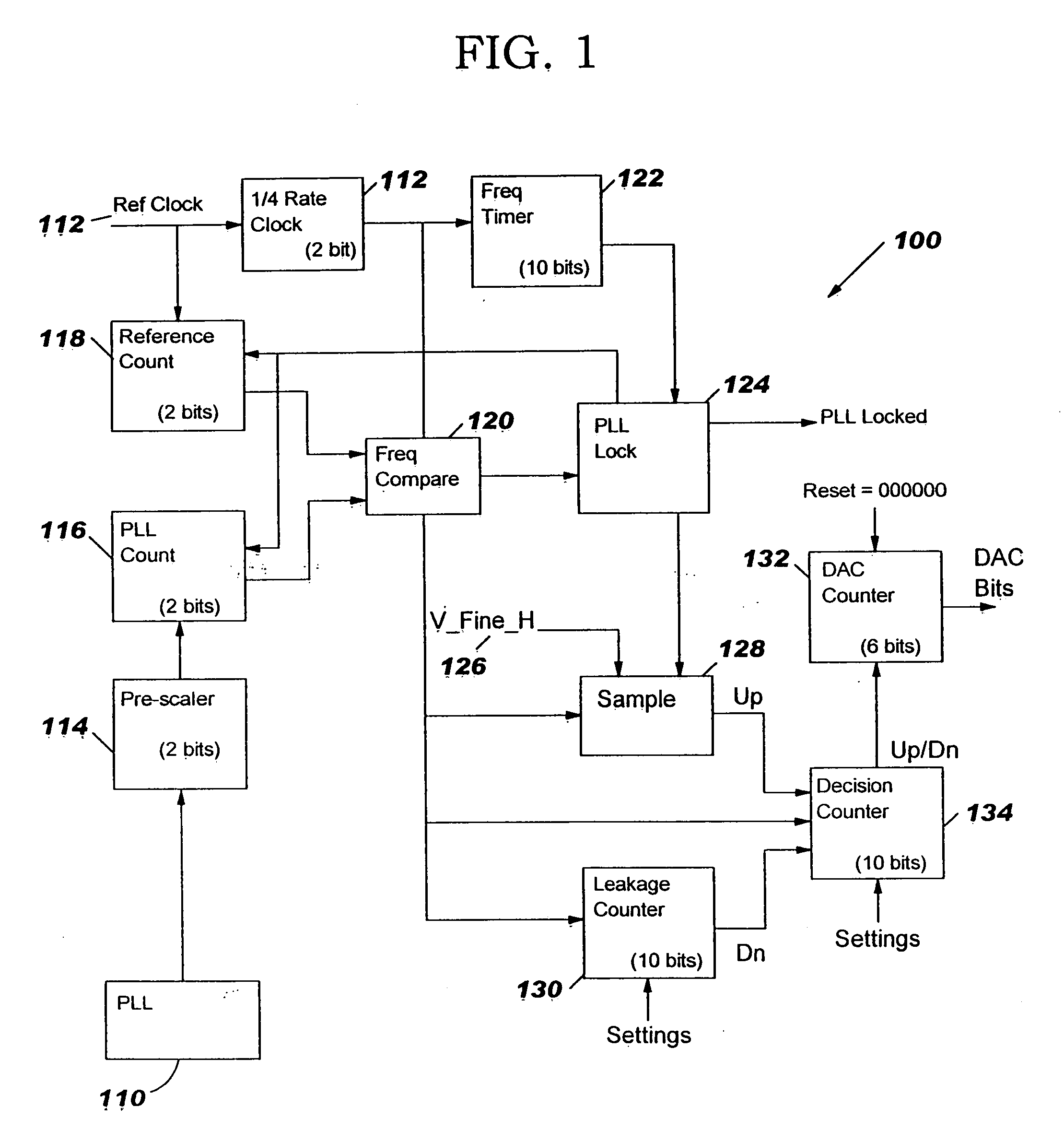

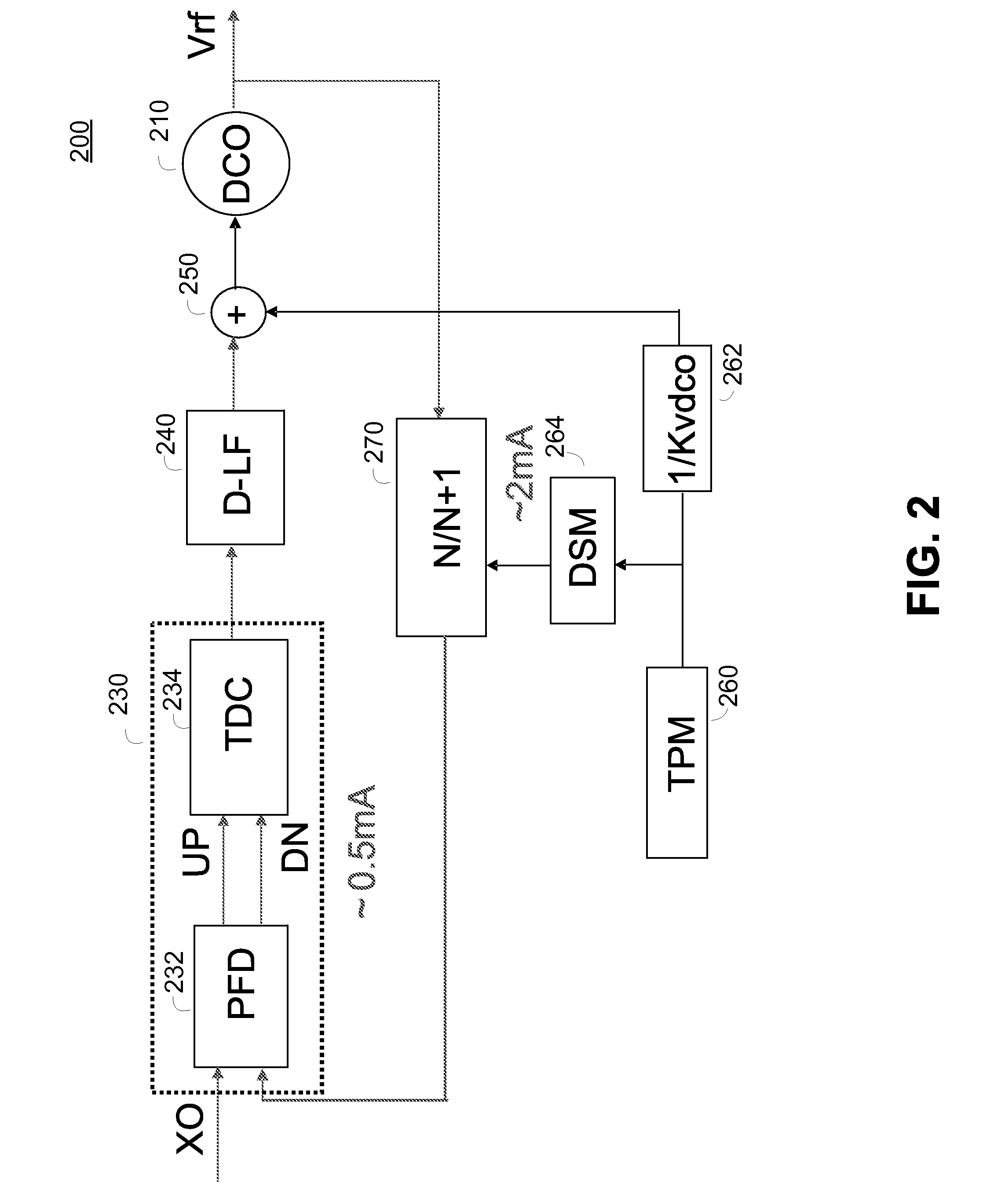

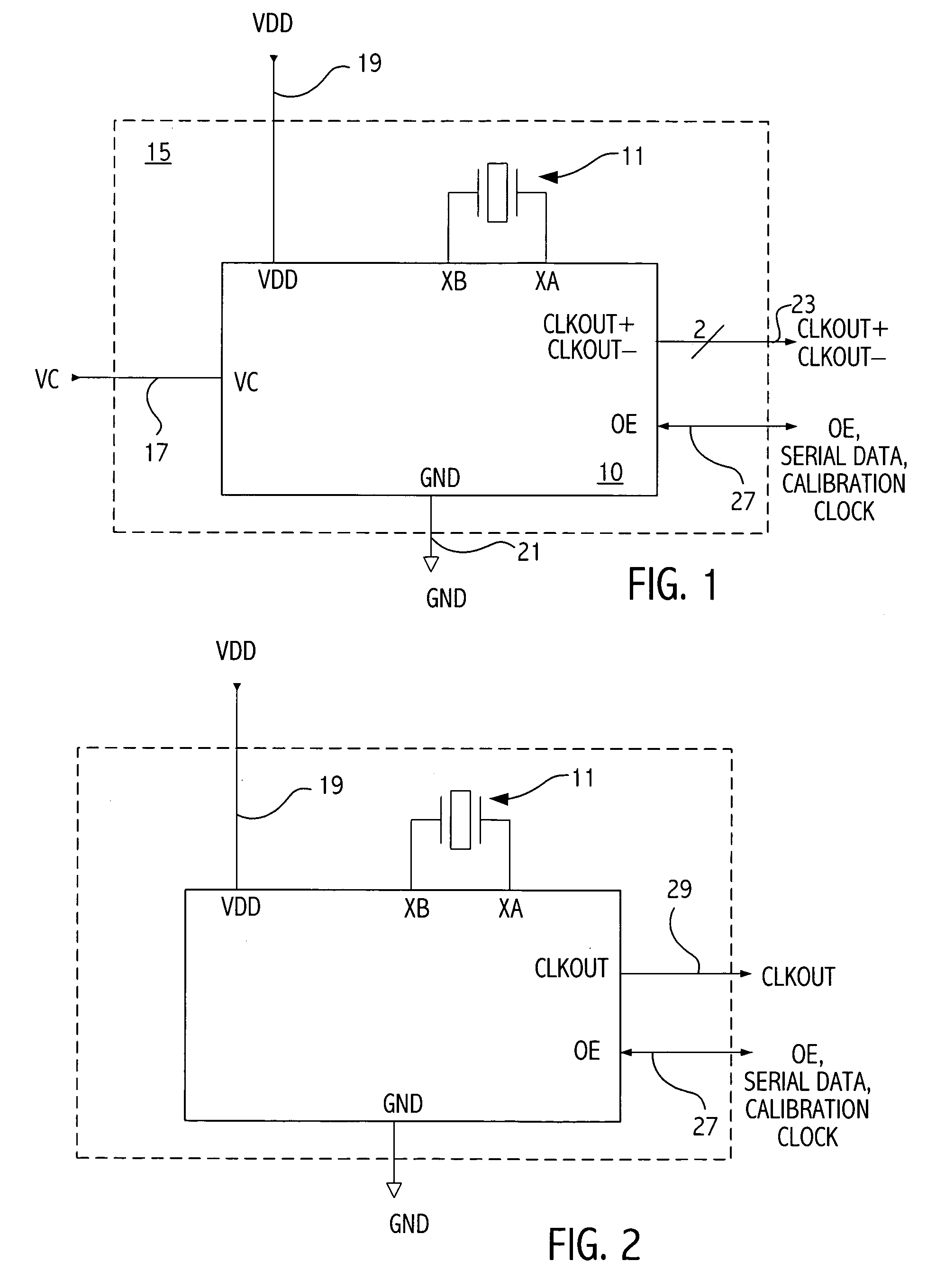

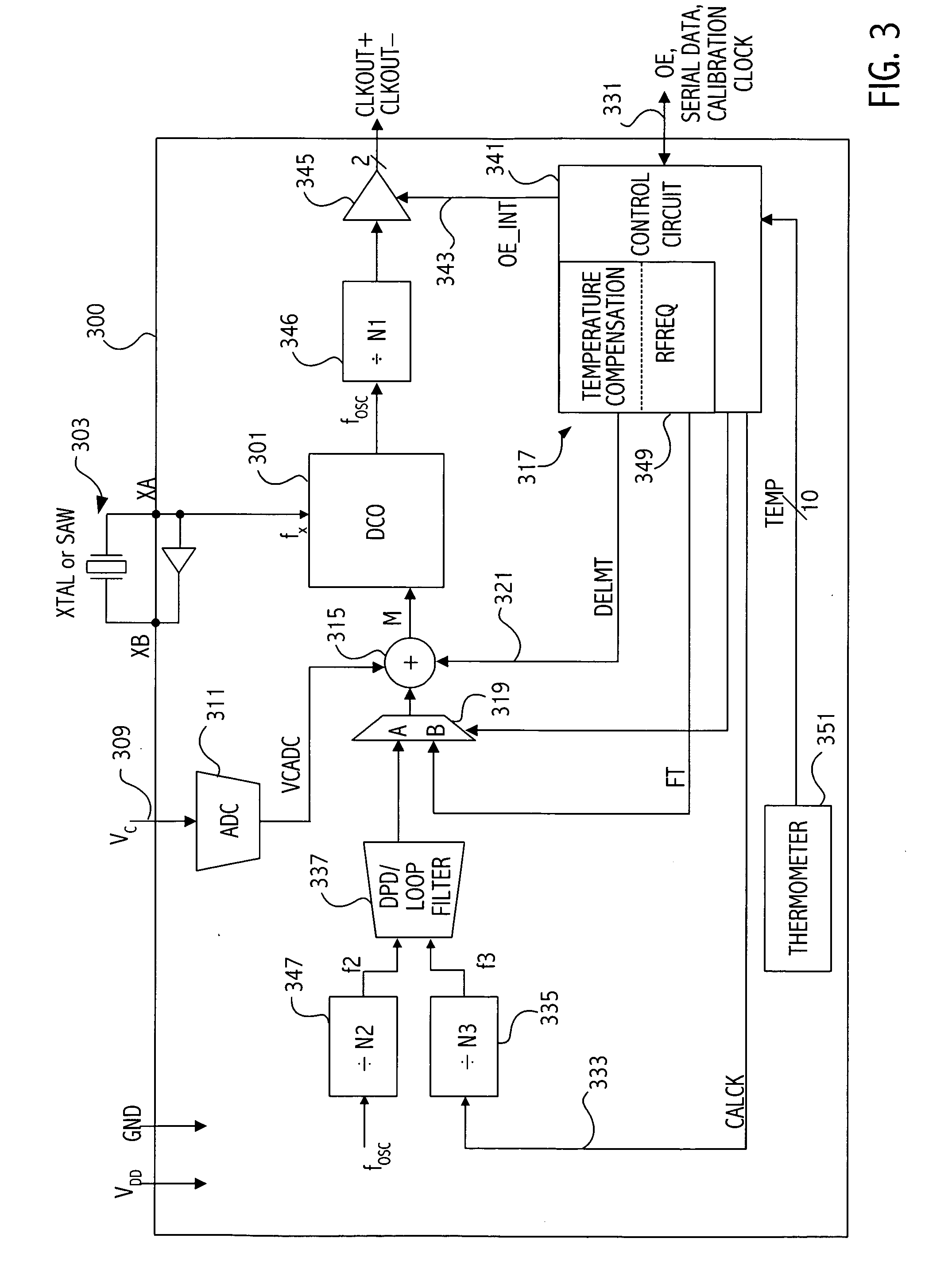

Digital Phase Locked Loop with Integer Channel Mitigation

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal with a plurality of phases. A switch is coupled to receive the RF clock, and is operative to select one of the plurality of phases. A phase detection circuit is coupled to the switch and is operable to receive a selected phase and to provide digital phase error samples indicative of a time difference between the reference clock and the selected phase.

Owner:TEXAS INSTR INC

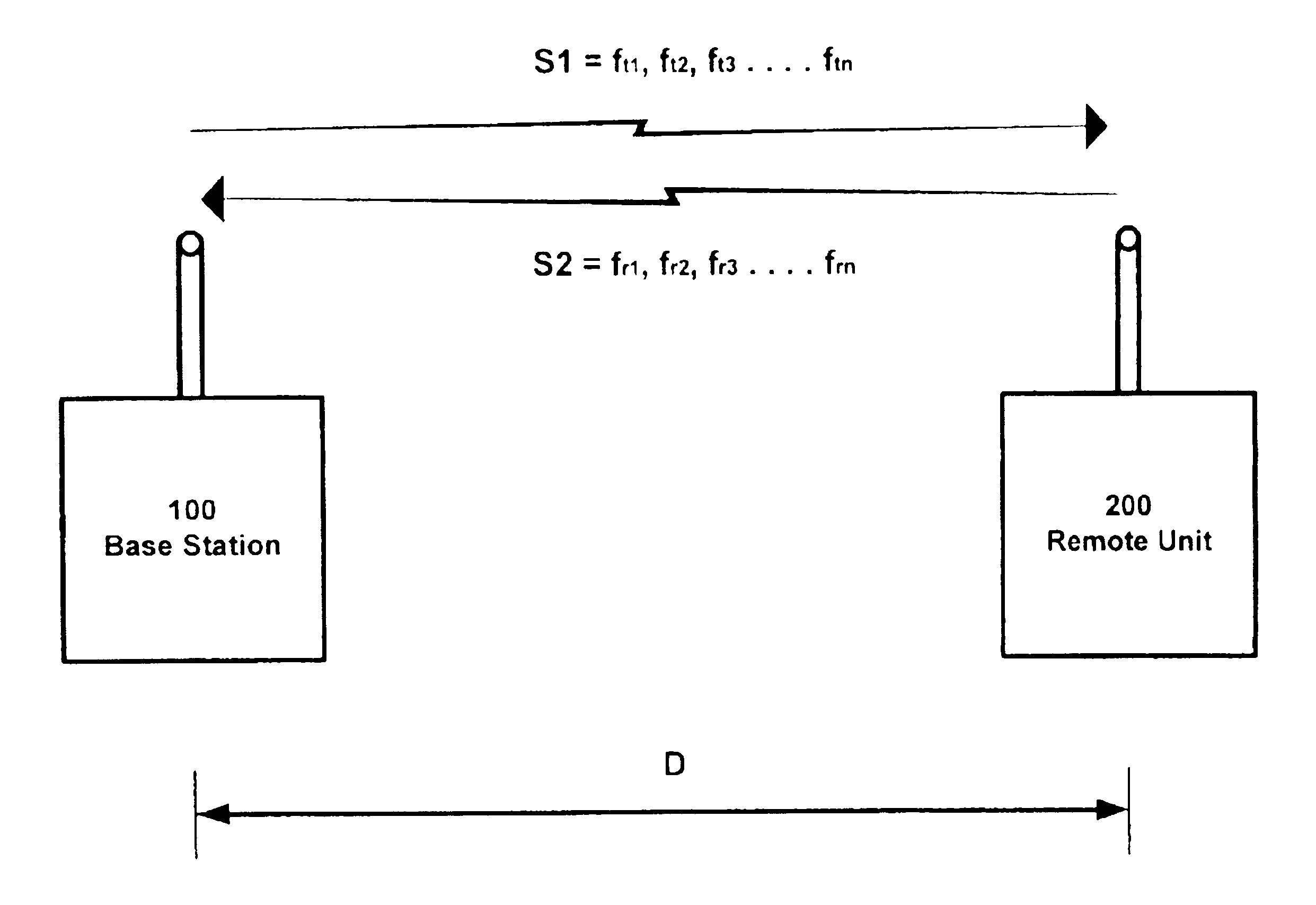

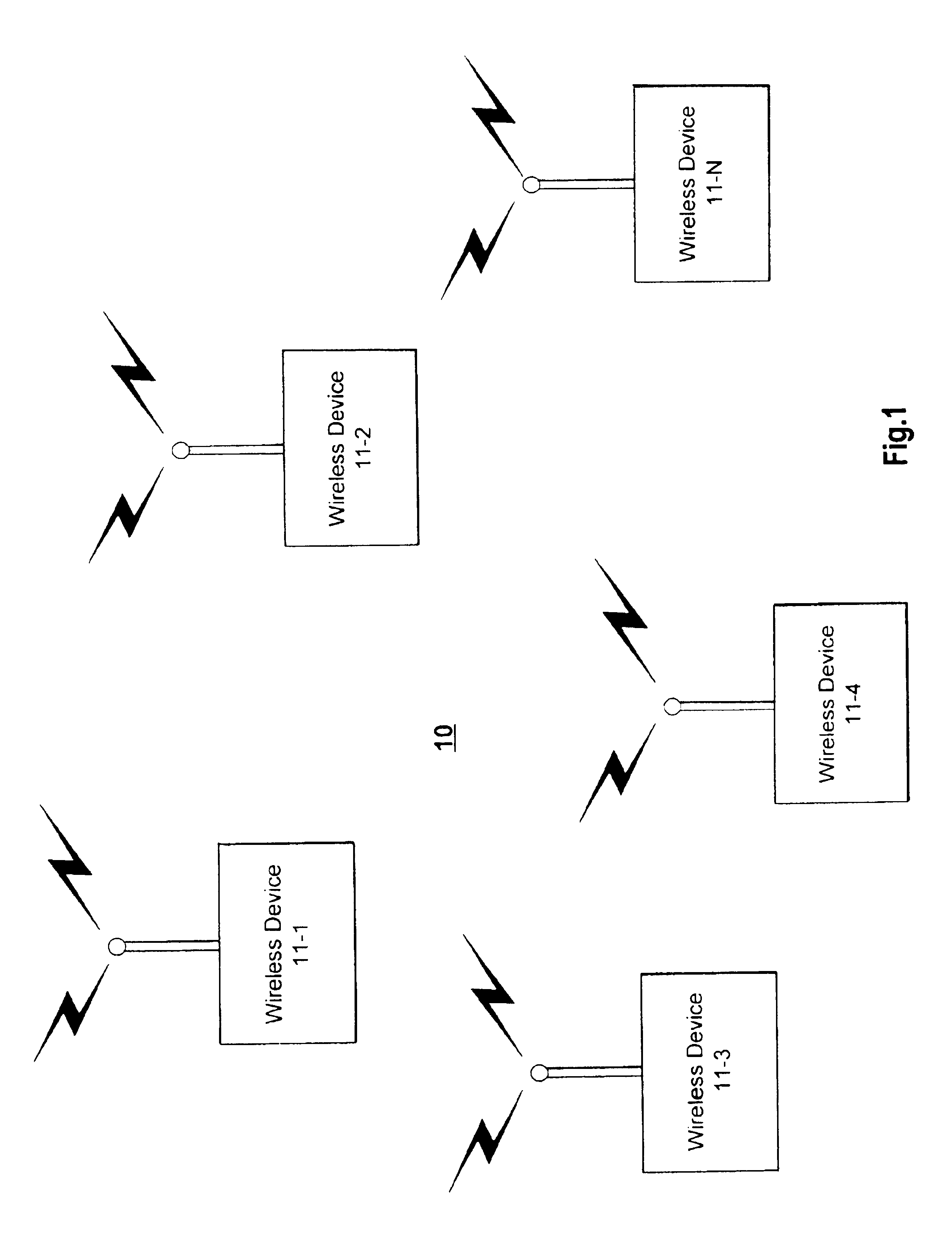

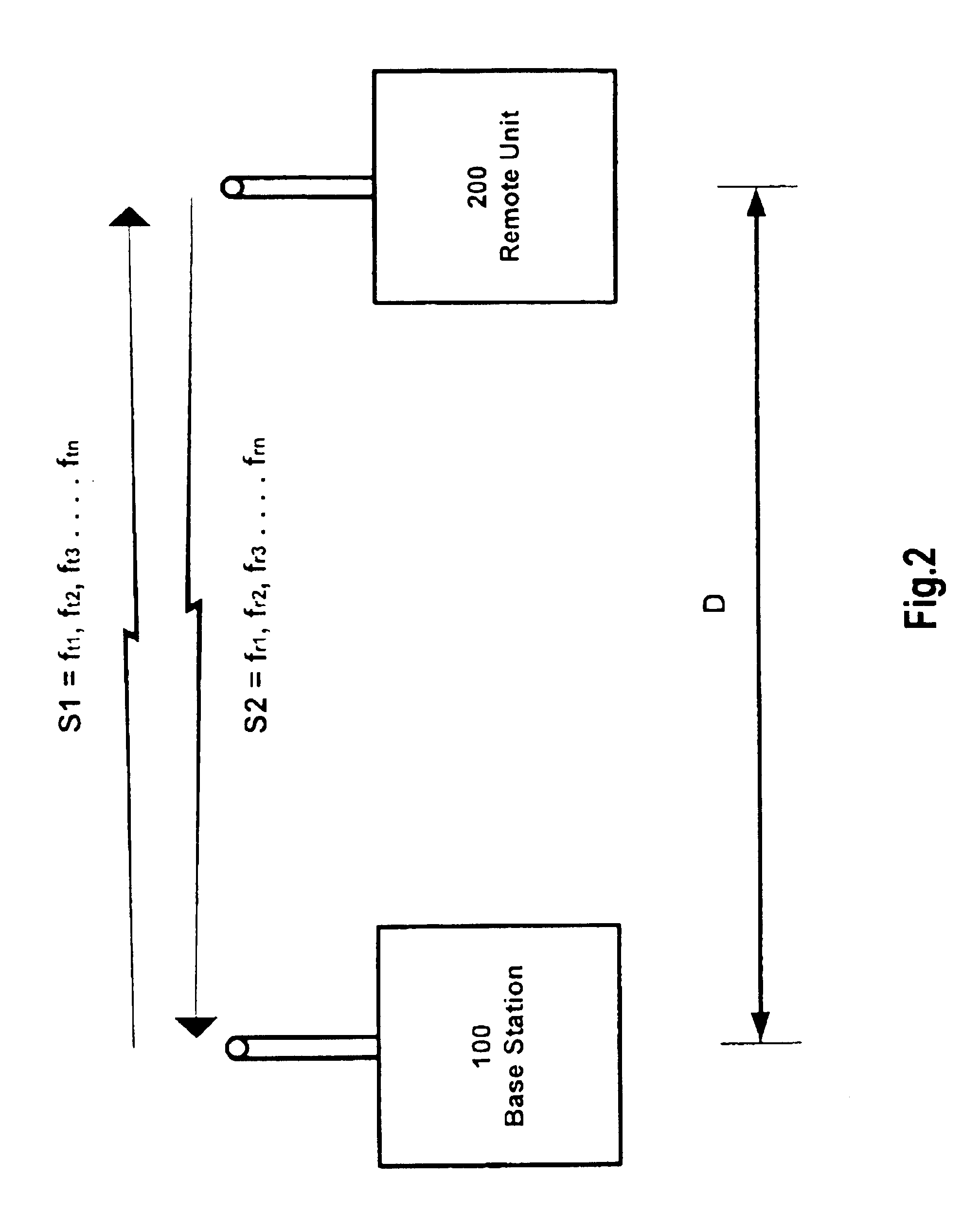

Distance measurement using half-duplex RF techniques

A system, apparatus, and method for determining the distance between two objects using an indirect propagation delay measurement is disclosed. A frequency hopping scheme (such as the Bluetooth.TM. technology) is used to measure the relative phase offset of the received signal between the various frequencies. For a given distance between the objects, the phase offset vs. frequency curve is a straight line with the slope dependent upon the measured distance. After the phase of the received signals is detected, the data is plotted on a curve and the slope is calculated. A wireless slave device remains phase locked with another device in a half-duplex communication mode by employing a low-drift phase locked loop employing a voltage controlled crystal oscillator. The phase locked loop further employs a mechanism that provides immunity from transitory phase slip at a time when the loop is opened.

Owner:AEROSCOUT

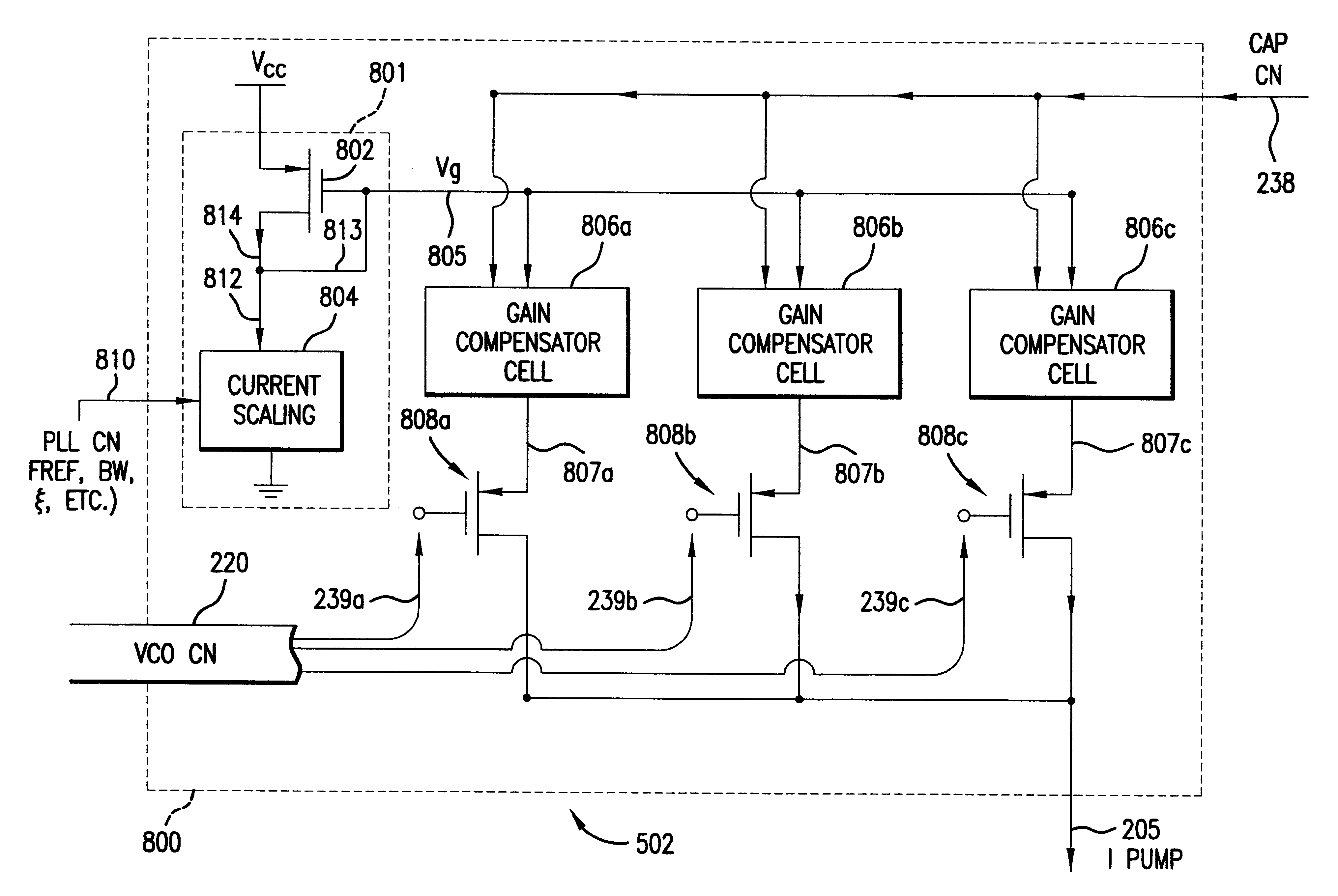

Apparatus and method for phase lock loop gain control using unit current sources

InactiveUS6583675B2Pulse automatic controlDiscontinuous tuning for band selectionFixed capacitorReference current

A gain compensator compensates for the gain variation of a varactor-tuned voltage tuned oscillator (VCO) in a phase lock loop (PLL). The VCO includes a parallel LC circuit having multiple fixed capacitors that can be switched-in or switched-out of the LC circuit according to a capacitor control signal to perform band-select tuning of the VCO. The gain compensator compensates for the variable VCO gain by generating a charge pump reference current that is based on the same capacitor control signal that controls the fixed capacitors in the LC circuit. The gain compensator generates the charge pump reference current by replicating a reference scale current using unit current sources. The number of times the reference scale current is replicated is based on the fixed capacitance that is switched-in to the LC circuit and therefore the frequency band of the PLL. The reference scale current is generated based on a PLL control that specifics certain PLL characteristics such as reference frequency, loop bandwidth, and loop damping. Therefore, the reference pump current can be efficiently optimized for changing PLL operating conditions, in addition to compensating for variable VCO gain.

Owner:AVAGO TECH INT SALES PTE LTD

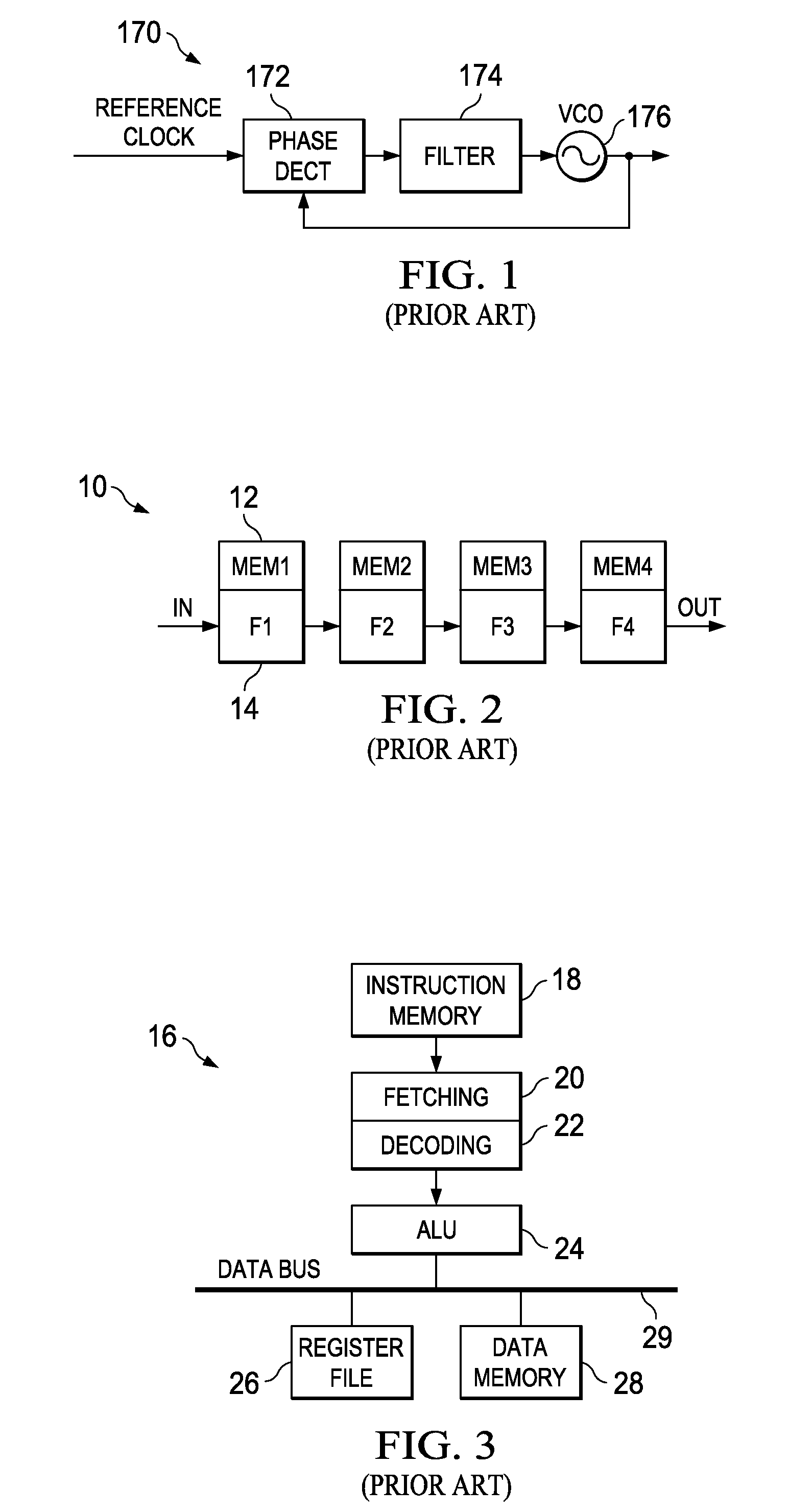

Computation spreading utilizing dithering for spur reduction in a digital phase lock loop

ActiveUS20090262877A1Easy to reconfigureReduce generationPulse automatic controlGenerator stabilizationFrequency spectrumClock rate

A novel and useful apparatus for and method of spur reduction using computation spreading with dithering in a digital phase locked loop (DPLL) architecture. A software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU is adapted to spread the computation of the atomic operations out over a PLL reference clock period wherein each computation is performed at a much higher processor clock frequency than the PLL reference clock rate. This significantly reduces the per cycle current transient generated by the computations. The frequency content of the current transients is at the higher processor clock frequency which results in a significant reduction in spurs within sensitive portions of the output spectrum. Further reduction in spurs is achieved by dithering the duration of the software loop of atomic operations and / or by randomly shuffling one or more non-data dependent instructions within each iteration of the software loop.

Owner:TEXAS INSTR INC

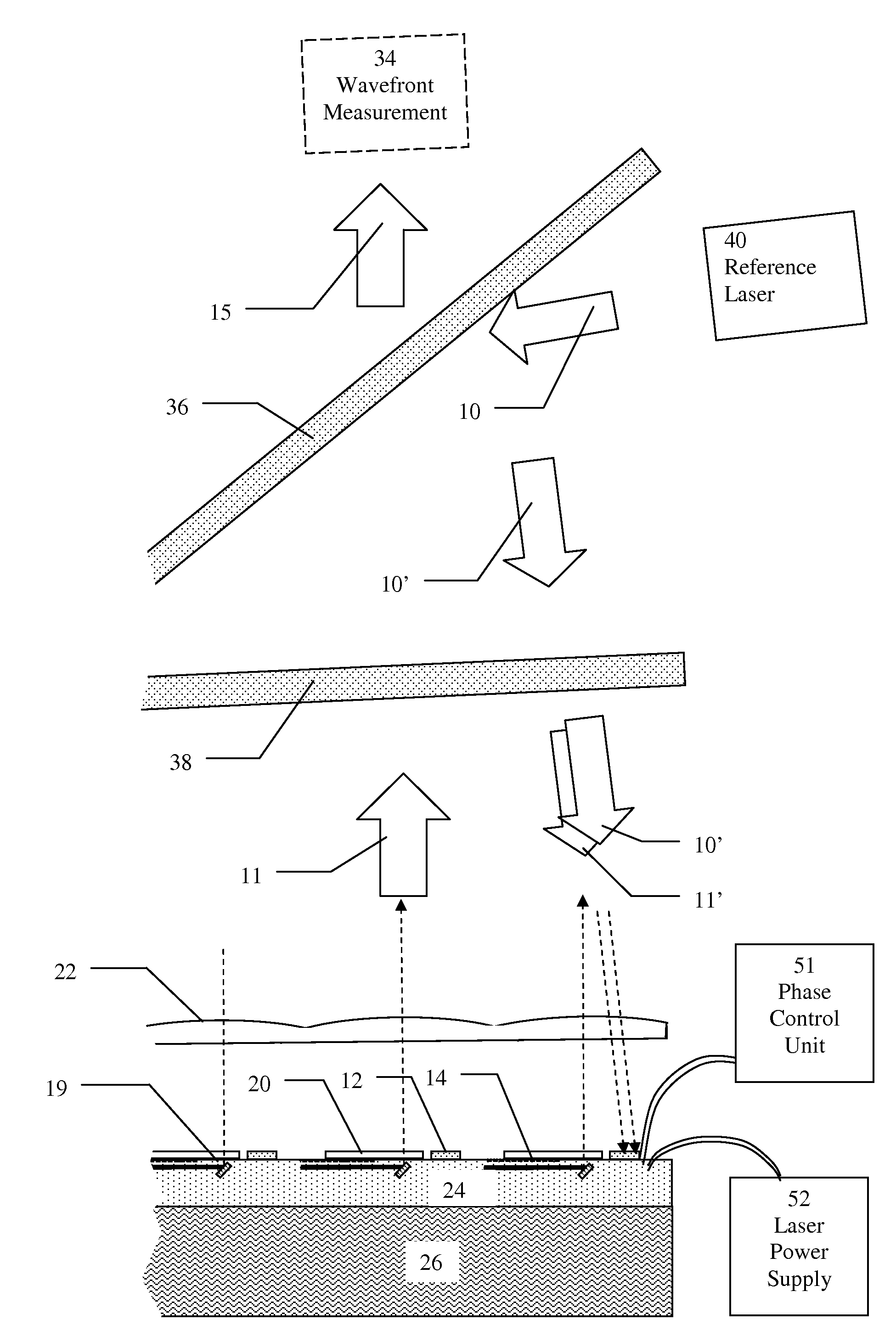

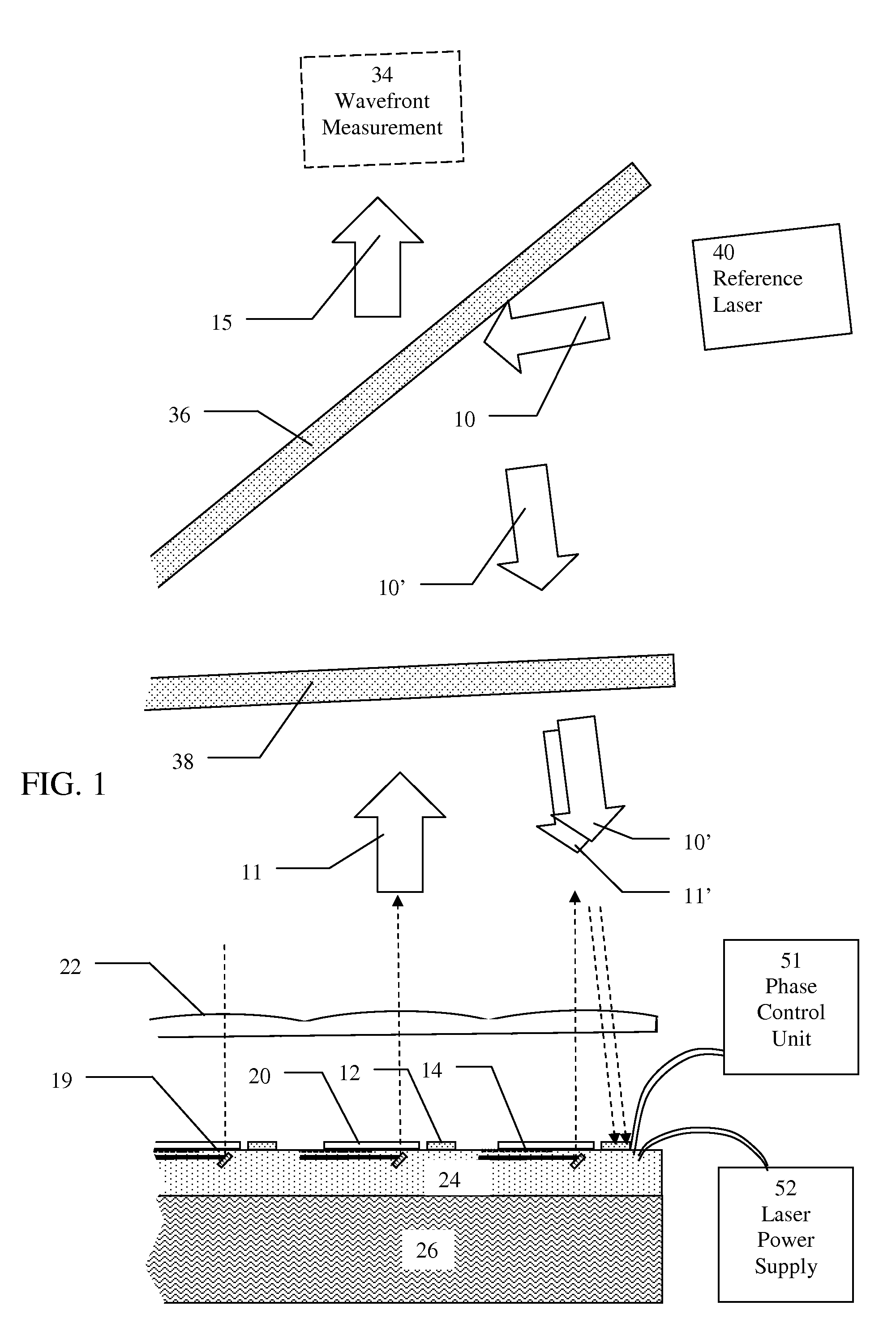

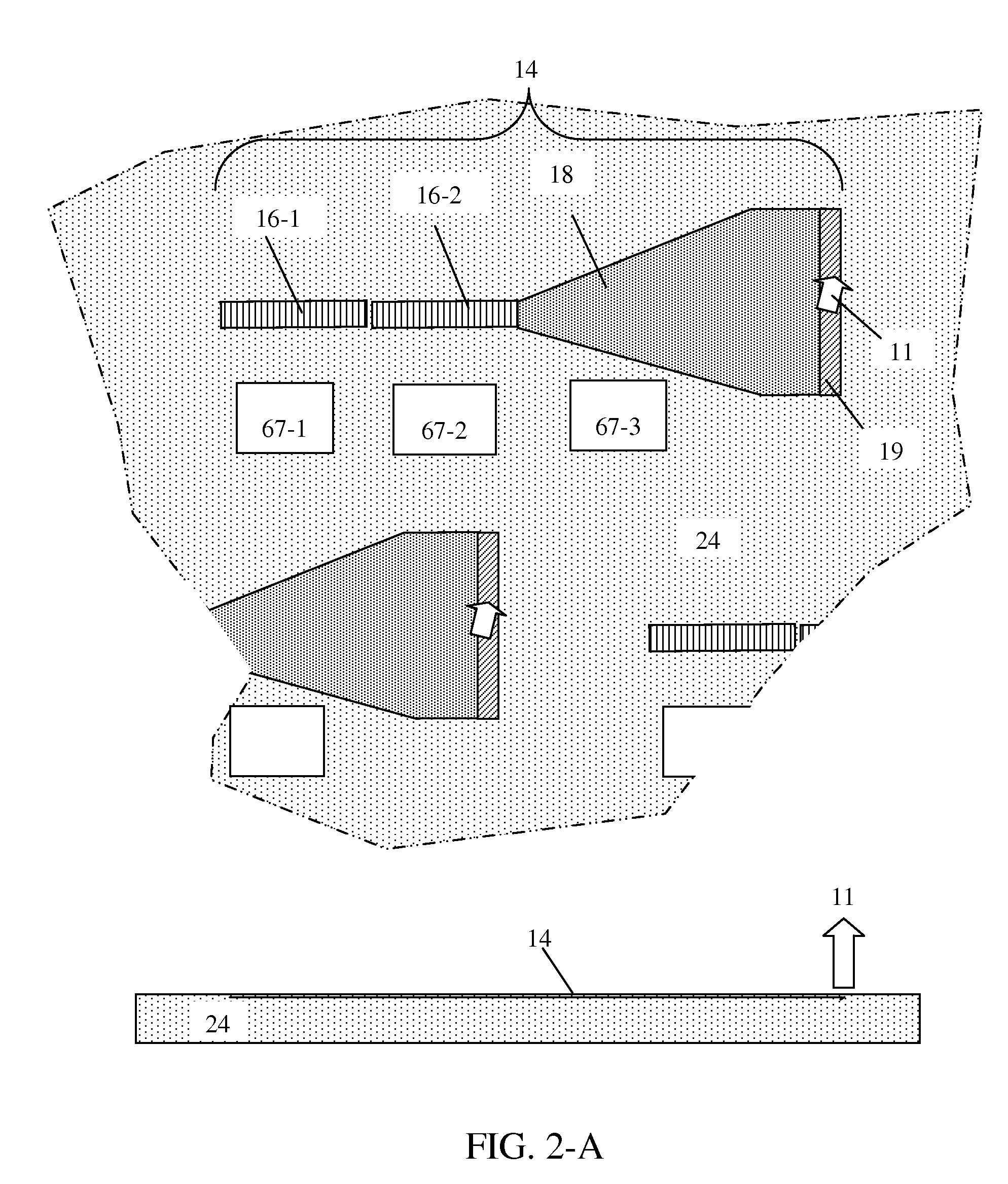

Semiconductor Lasers in Optical Phase-Locked Loops

InactiveUS20060239312A1Increase optical powerHigh beam qualityLaser detailsSemiconductor laser optical devicePhase noiseLaser array

This invention relates to opto-electronic systems using semiconductor lasers driven by feedback control circuits that control the laser's optical phase and frequency. Feedback control provides a means for coherent phased laser array operation and reduced phase noise. Systems and methods to coherently combine a multiplicity of lasers driven to provide high power coherent outputs with tailored spectral and wavefront characteristics are disclosed. Systems of improving the phase noise characteristics of one or more semiconductor lasers are further disclosed.

Owner:TELARIS

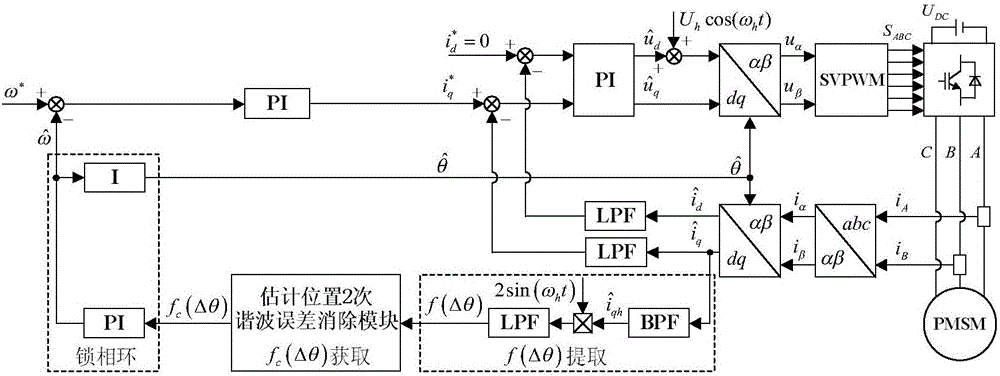

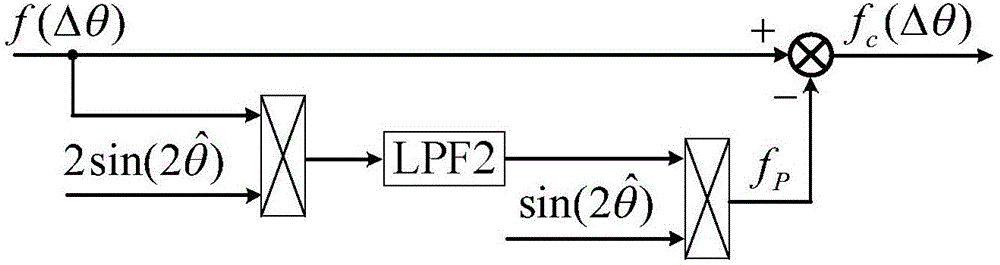

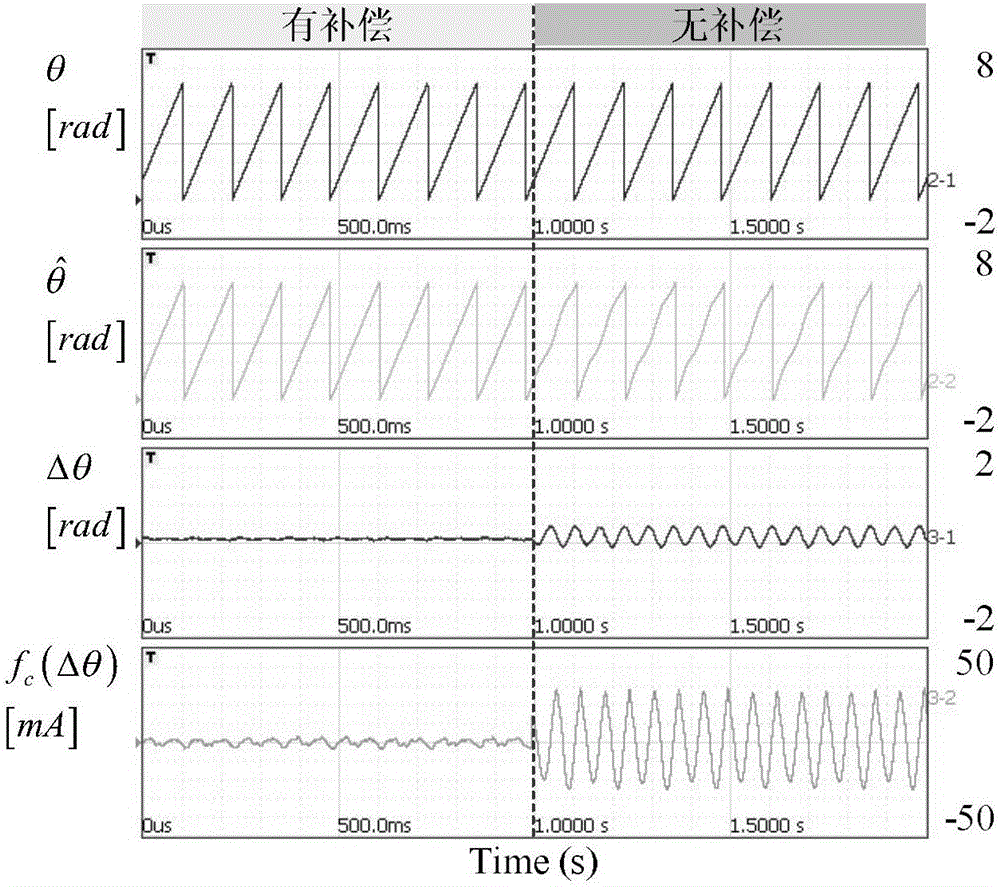

Method for improving estimation accuracy of rotor position of permanent magnet synchronous motor

ActiveCN106788071AEasy to implementReduce computing burdenElectronic commutation motor controlAC motor controlControl systemHarmonic

The invention discloses a method for improving the estimation accuracy of the rotor position of a permanent magnet synchronous motor. The method comprises the following steps: on the basis of realizing estimation of the rotor position of the permanent magnet synchronous motor by utilizing a pulse-shake high frequency voltage injection method, processing the extracted position estimation error function, eliminating a second harmonic component introduced due to asymmetric motor parameters, so as to obtain a processed position estimation error function, then establishing a phase-locked loop, and adjusting the phase-locked loop to be 0, thus obtaining estimated rotor speed and estimated rotor position. The method disclosed by the invention can effectively inhibit position estimation second harmonic error caused by the asymmetric motor parameters, and the performance of a control system without a position sensor can be improved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

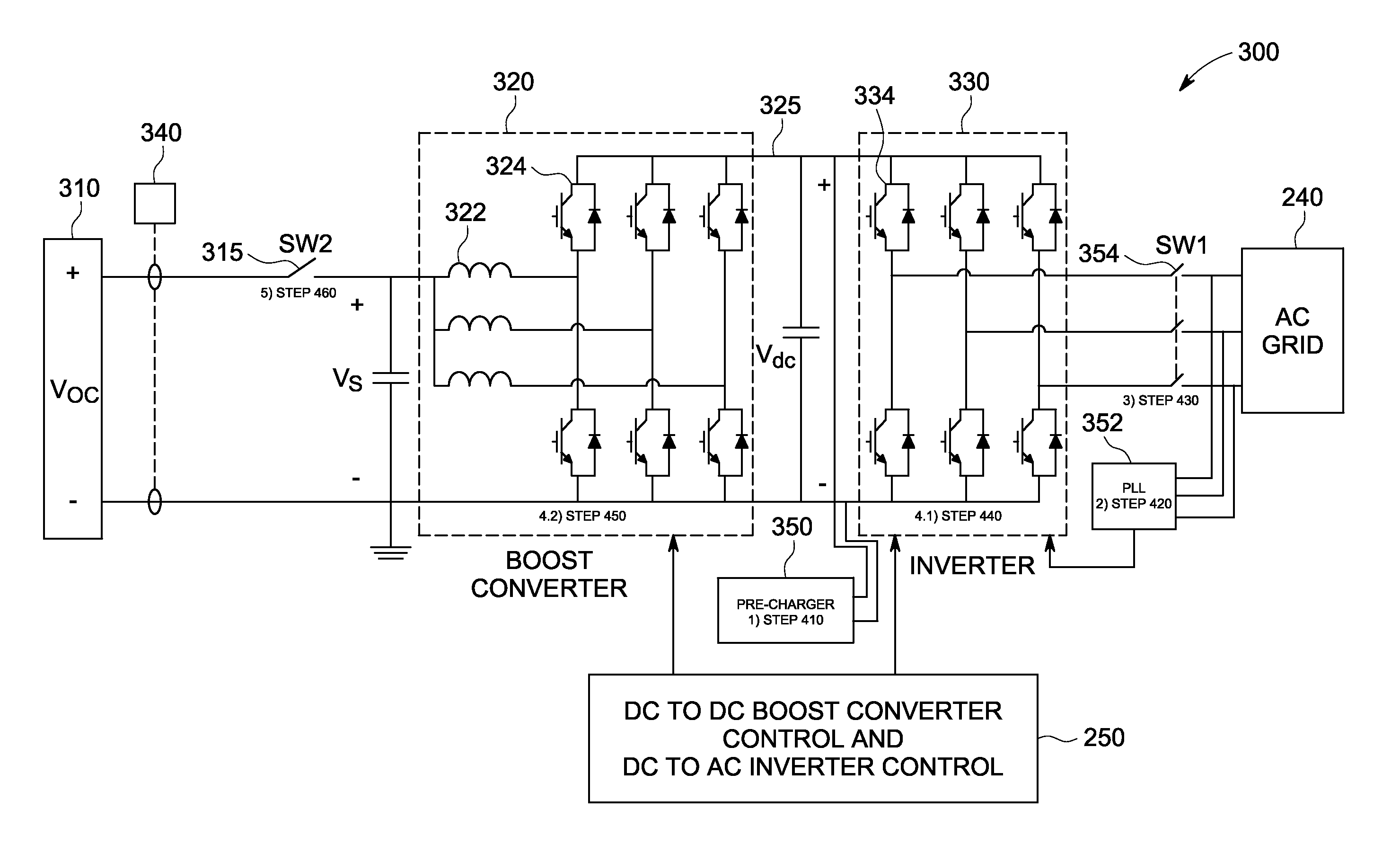

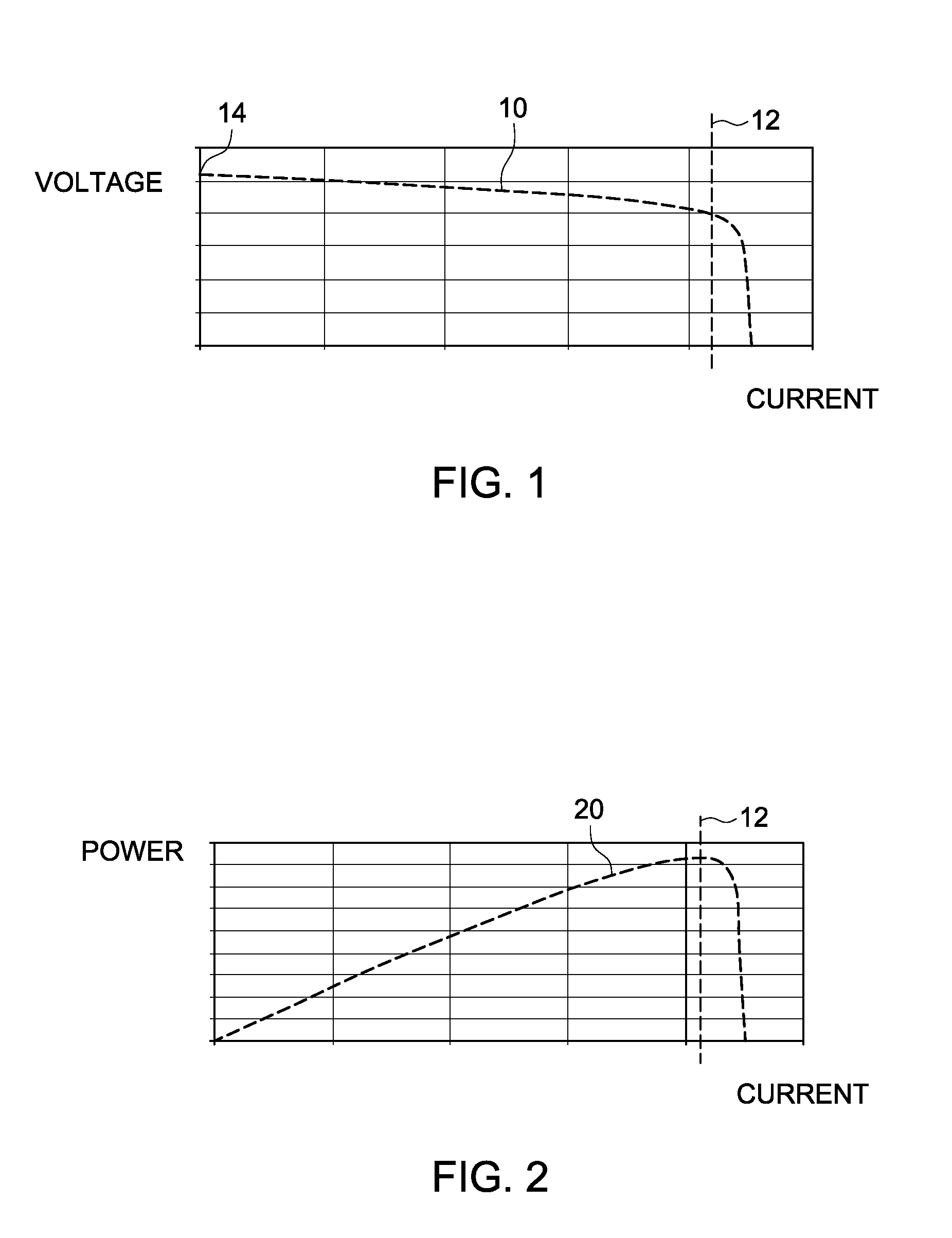

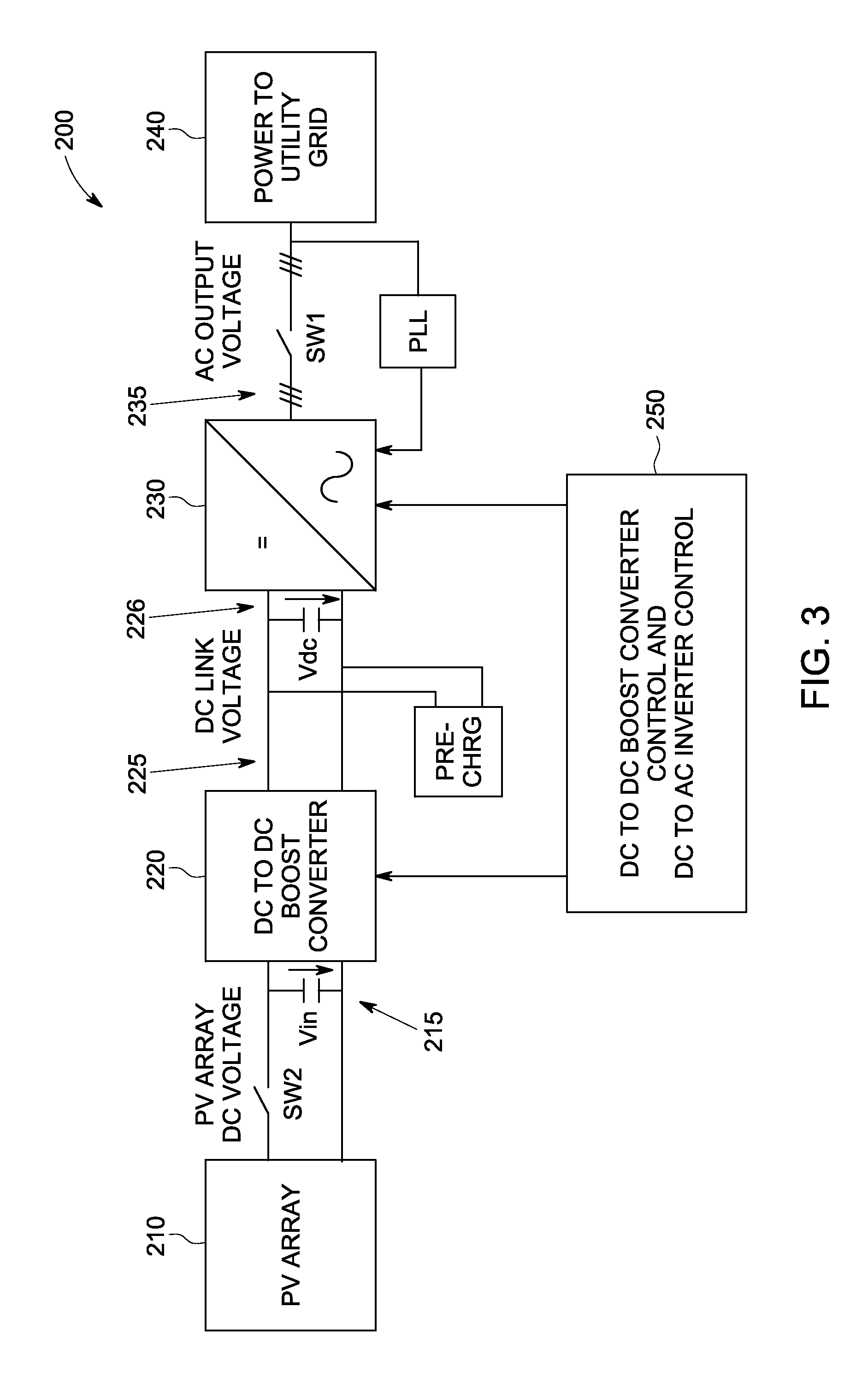

Photovoltaic inverter system and method of starting same at high open-circuit voltage

ActiveUS20120026769A1Dc-dc conversionSingle network parallel feeding arrangementsPre-chargeEngineering

A power inverter system includes a DC to AC inverter configured to convert DC voltage from a DC power source to AC voltage. A DC link couples the DC power source and the inverter. An inverter pre-charger operates to pre-charge the inverter to achieve a desired DC link voltage prior to connecting the power inverter system to an AC power grid. A phased lock loop synchronizes the pre-charged inverter to the AC power grid prior to connecting the power inverter system to the AC power grid. The pre-charged inverter regulates the DC link voltage to about the minimum voltage level that allows control of AC grid currents via the inverter subsequent to connecting the power inverter system to the AC grid. The inverter operates in a maximum power point tracking control mode only subsequent to a first voltage transient caused by connecting the DC power source to energize the power inverter system.

Owner:GENERAL ELECTRIC CO

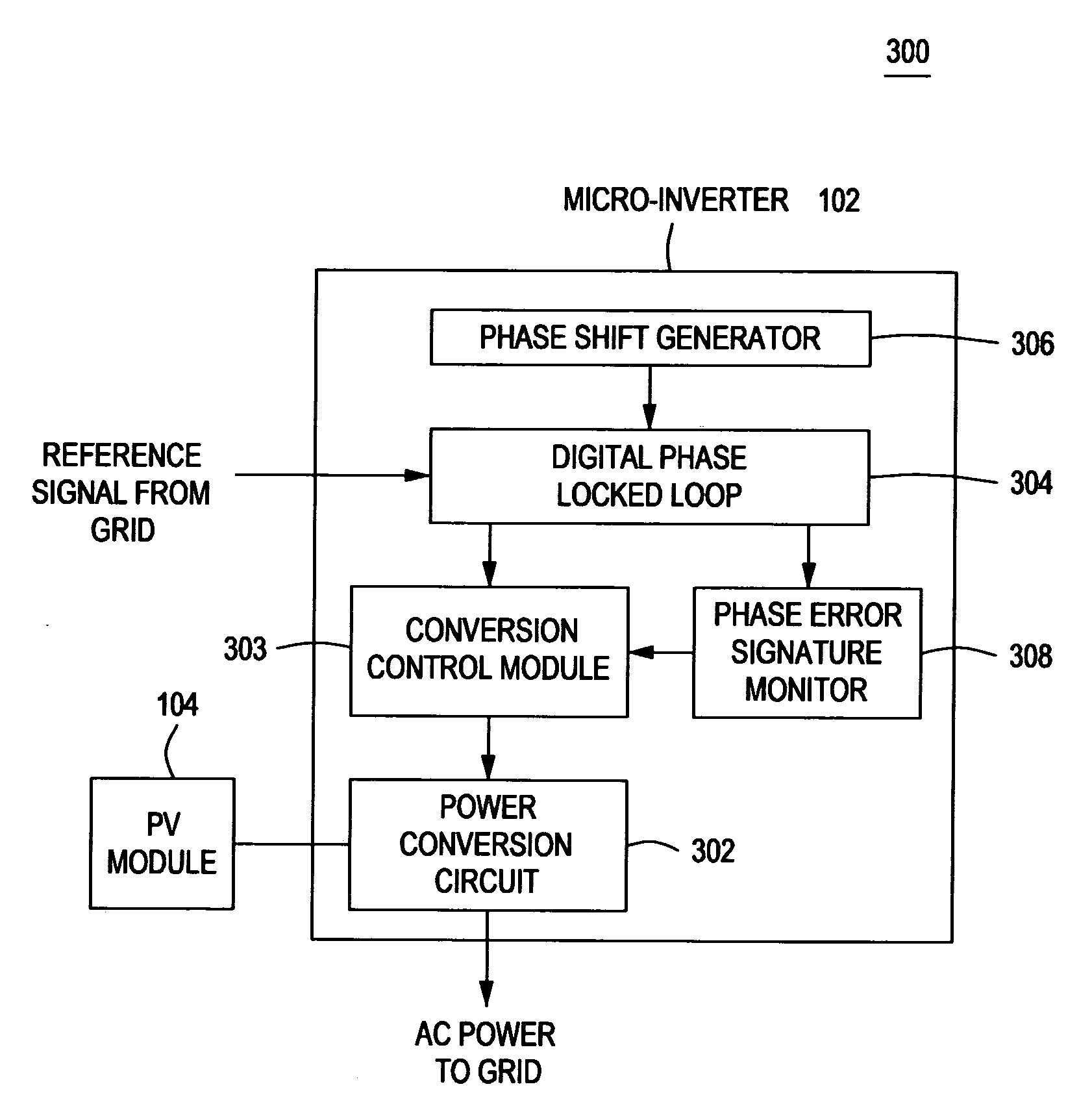

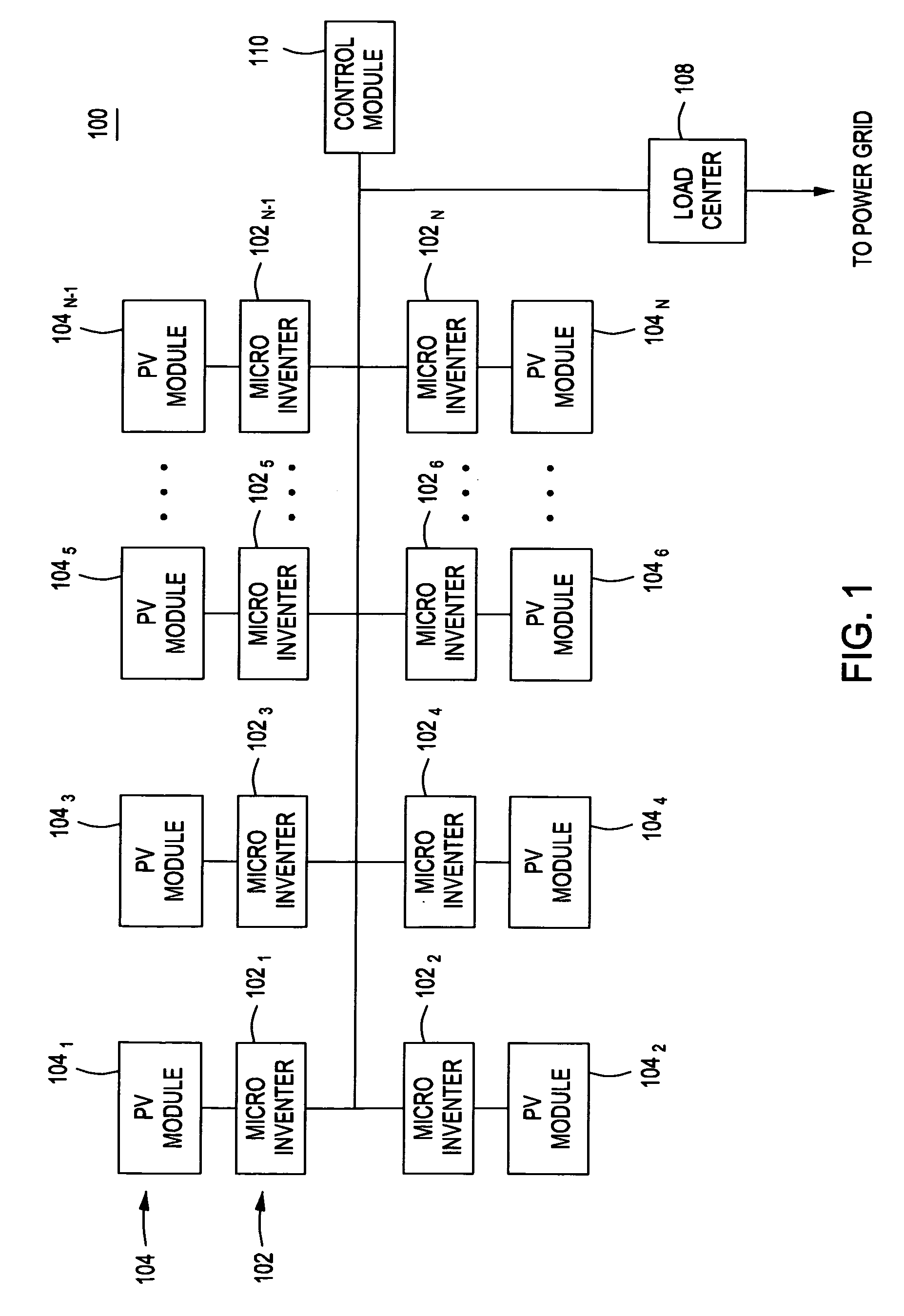

Method and apparatus for anti-islanding of distributed power generation systems

InactiveUS20090021877A1Noise figure or signal-to-noise ratio measurementApparatus with intermediate ac conversionIslandingPhase shifted

A method and apparatus for anti-islanding of distributed power generation systems having an inverter comprising a phase locked loop (PLL), a phase shift generator for injecting a phase shift into the PLL during at least one sample period, and a phase error signature monitor for monitoring at least one phase error response of the PLL during the at least one sample period.

Owner:ENPHASE ENERGY

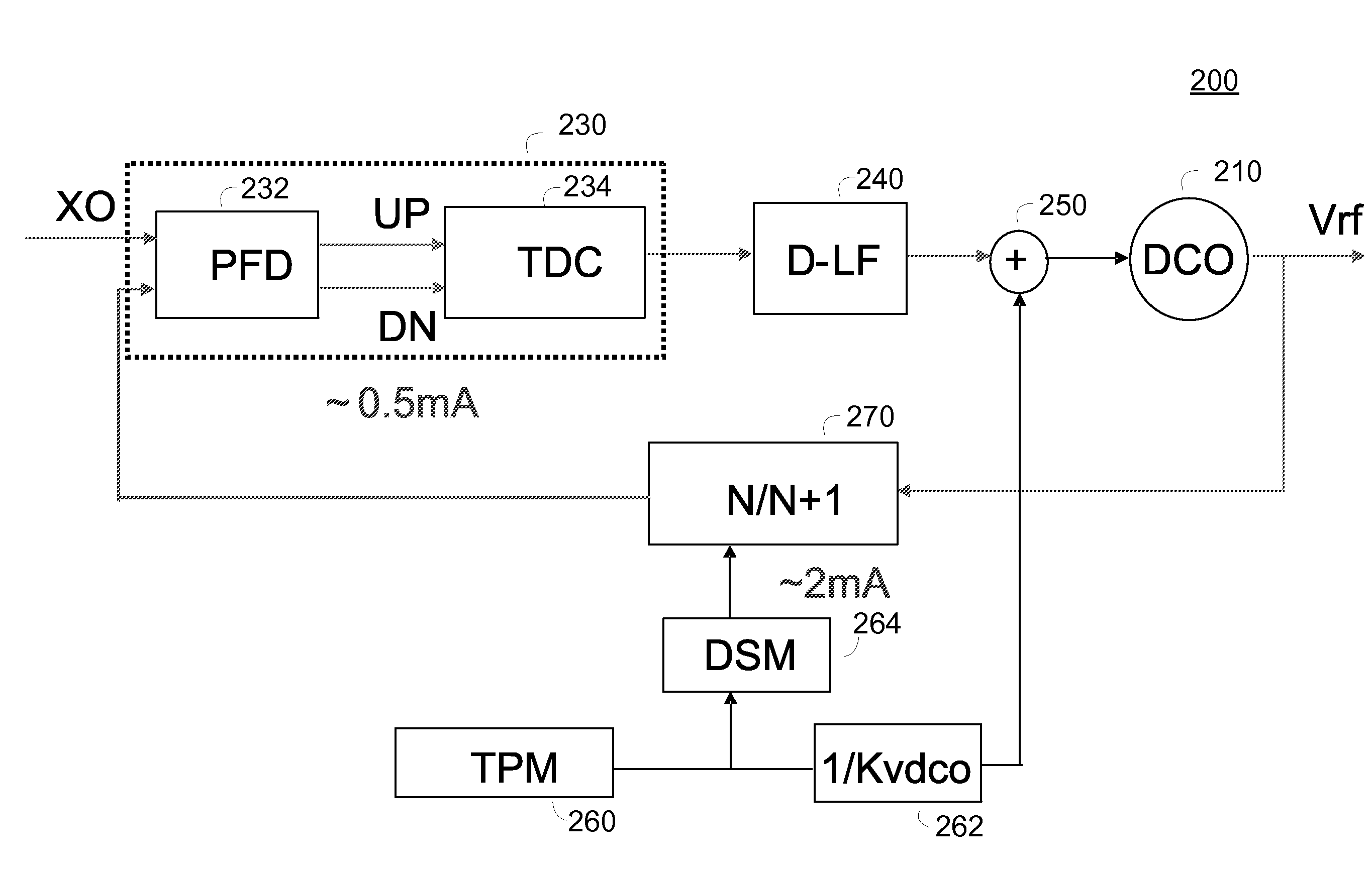

Phase to digital converter in all digital phase locked loop

ActiveUS20090256601A1Low power operationLower requirementElectric signal transmission systemsPulse automatic controlDigital down converterReference Period

A phase to digital converter, all digital phase locked loop, and apparatus having an all digital phase locked loop are described herein. The phase to digital converter includes a phase to frequency converter driving a time to digital converter. The time to digital converter determines a magnitude and sign of the phase differences output by the phase to frequency converter. The time to digital converter utilizes tapped delay lines and looped feedback counters to enable measurement of small timing differences typical of a loop tracking process and large timing differences typical of an loop acquisition process. The tapped delay lines permit the measurement of fractions of a reference period and enable lower power operation of the phase to digital converter by reducing requirements on the speed of the reference clock.

Owner:QUALCOMM INC

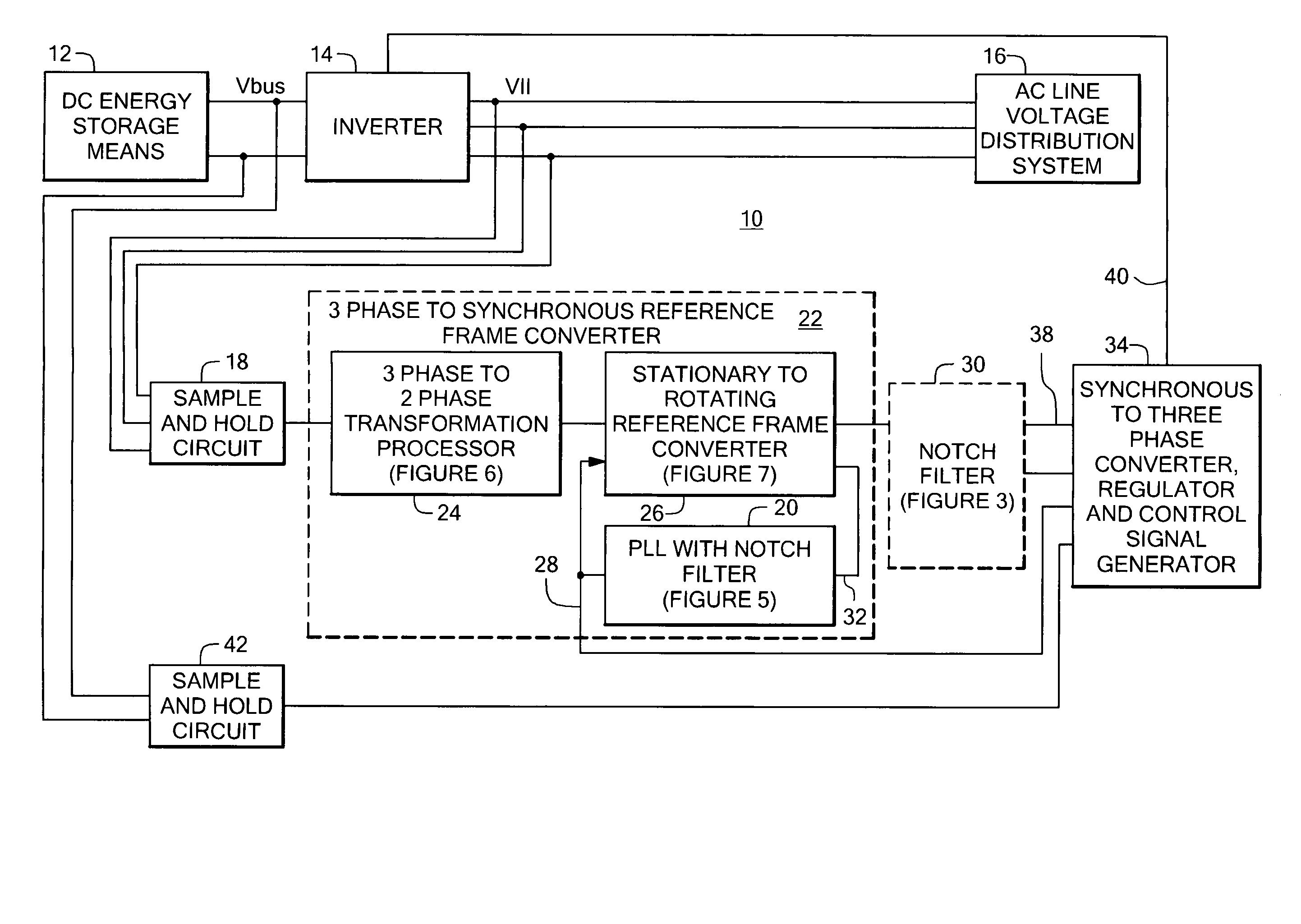

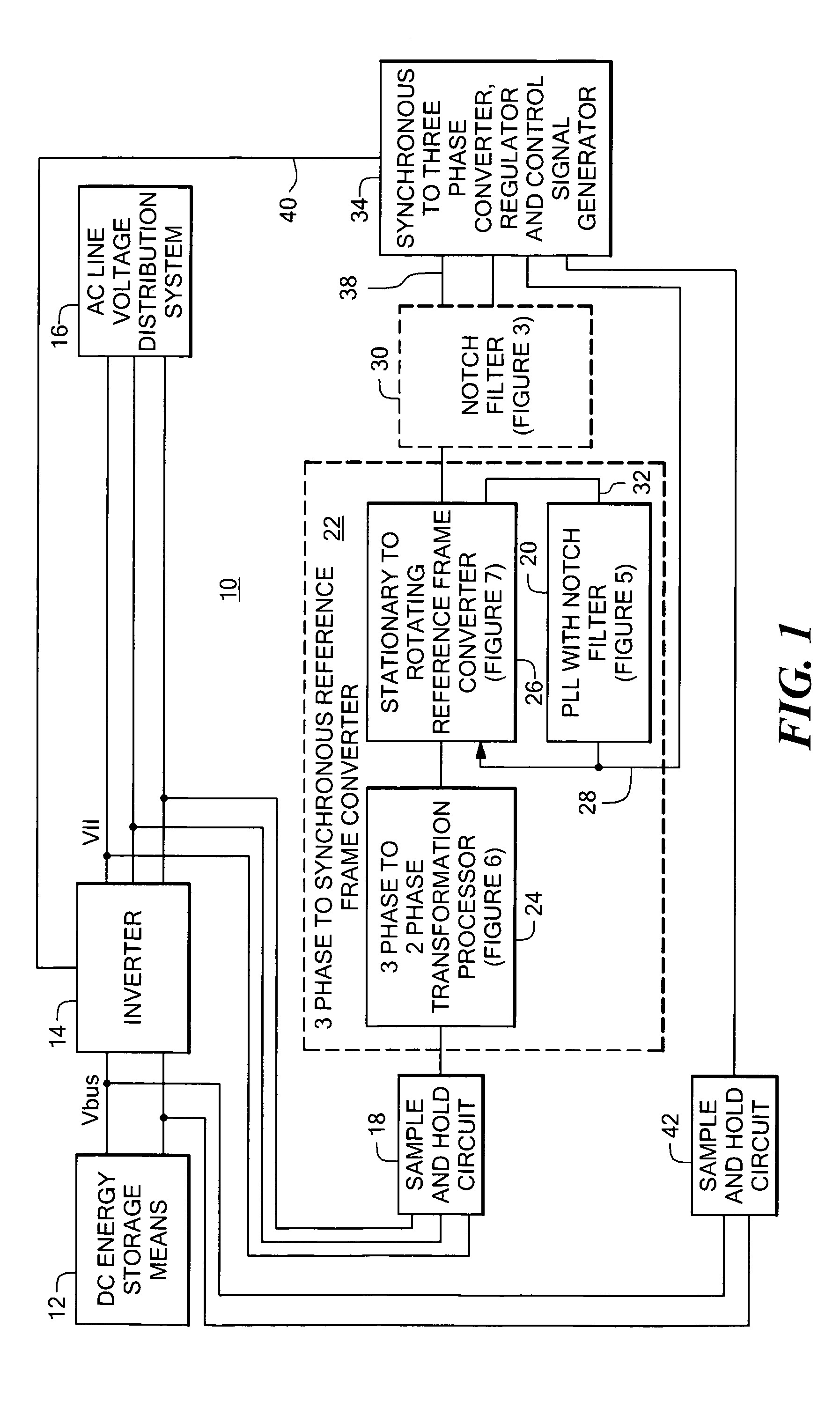

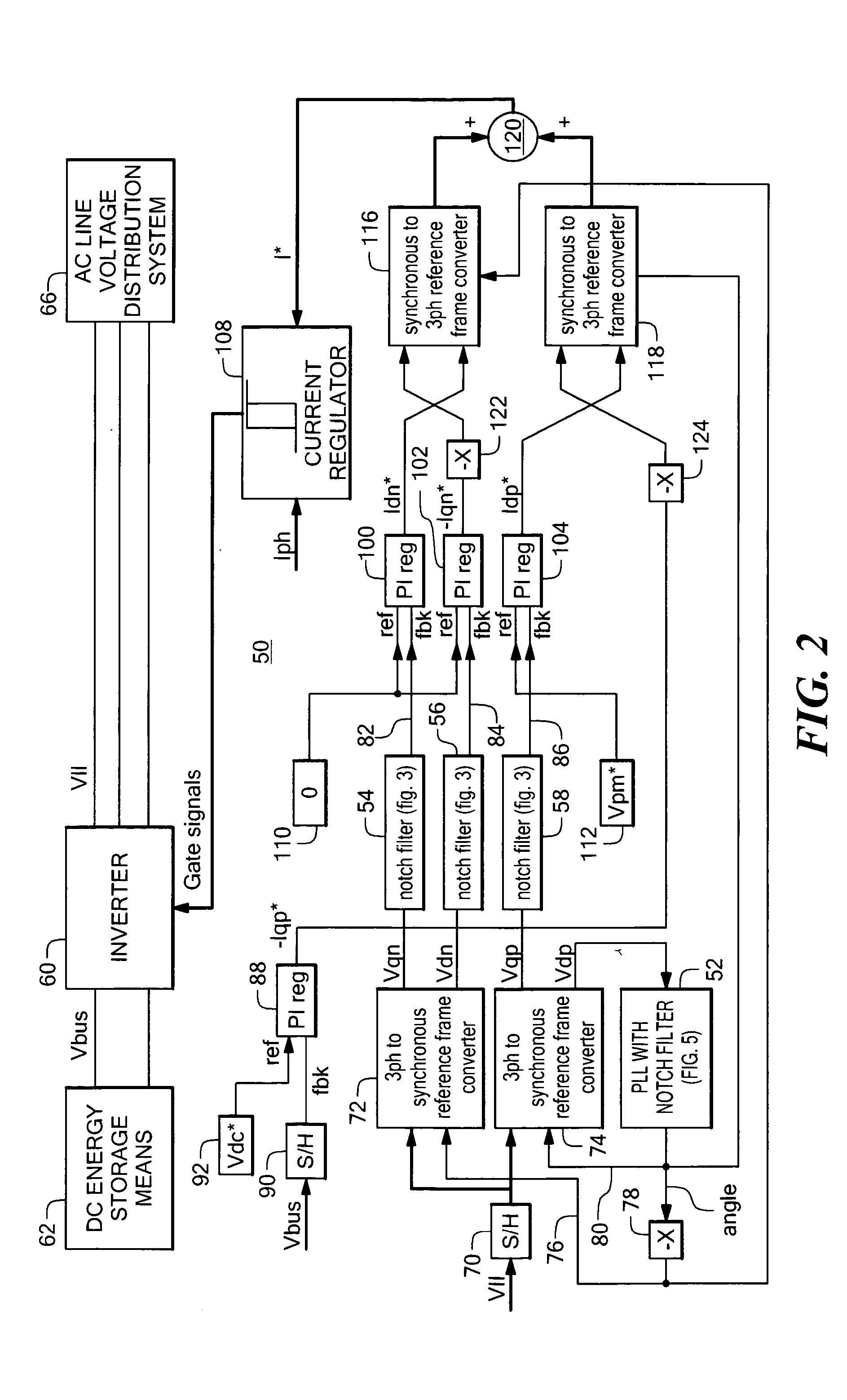

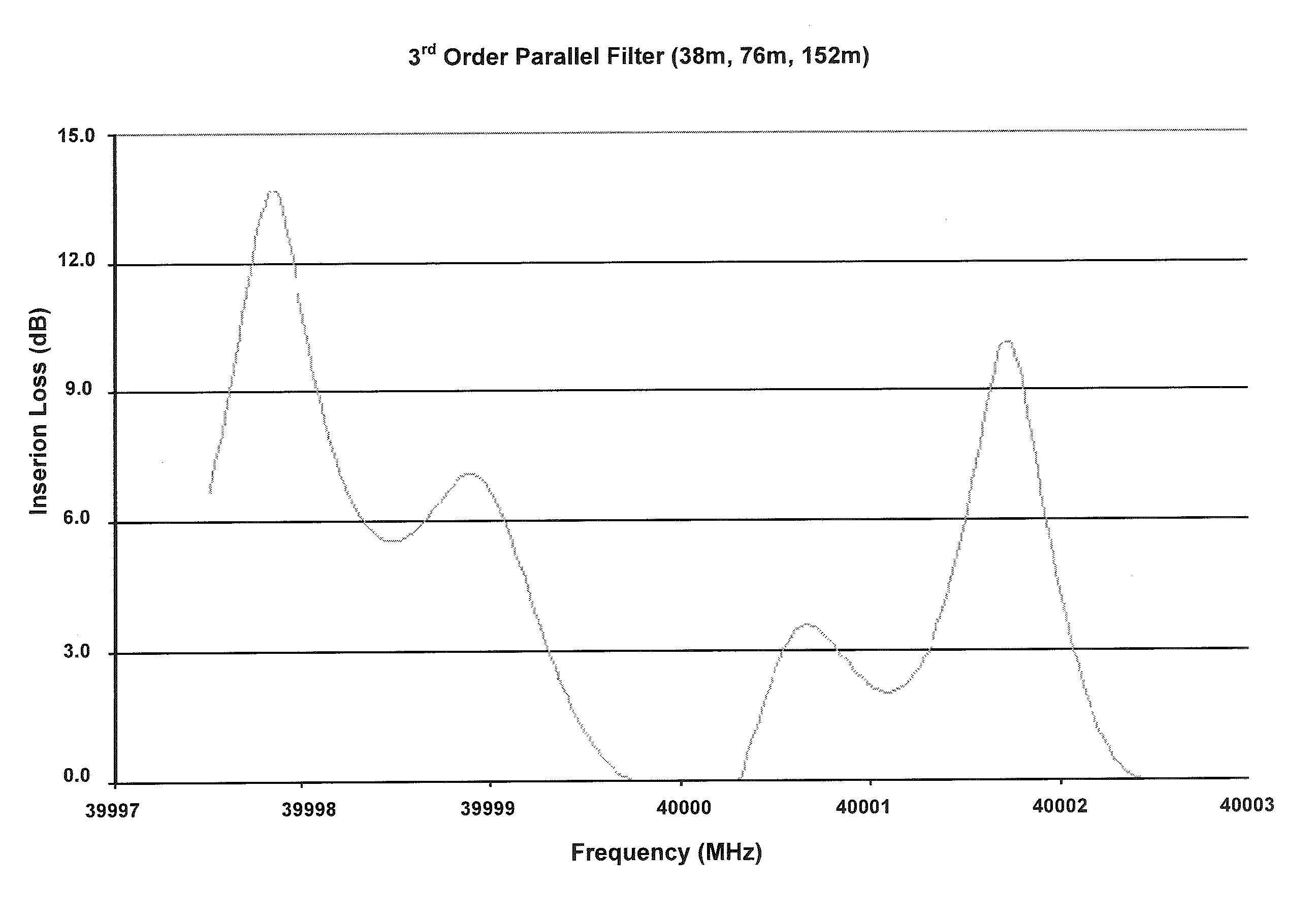

Power system having a phase locked loop with a notch filter

InactiveUS20050207190A1Highly accurate frequencyHighly accurate amplitudeAc-dc conversionElectric variable regulationIntegratorHarmonic

A power system having a phase locked loop (PLL) with a notch filter for synchronous reference frame sequence separation. The notch filter includes a generalized integrator tuned to the notch frequency. The output of the generalized integrator is summed with the filter input signal and the output of the summer is fed back to the integrator input. In one embodiment, the notch filter is programmable by a control signal generated in response to the filter output signal, thereby causing the filter to self-regulate to a frequency related to the PLL input signal. Illustrative power systems include active VAR generators and active rectifiers. One or more additional notch filters may be used to remove harmonic components from derived synchronous reference frame sequence components.

Owner:AMERICAN SUPERCONDUCTOR

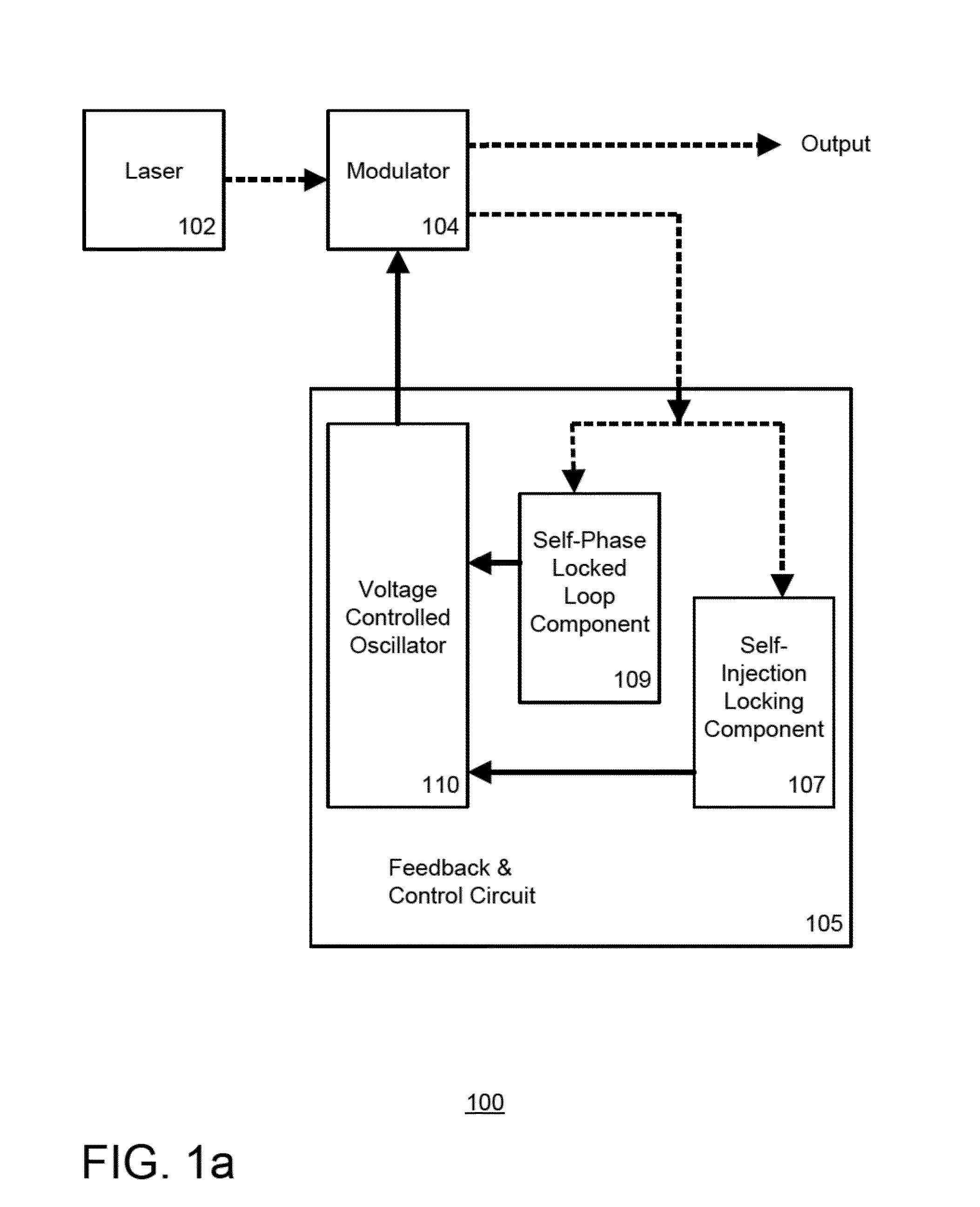

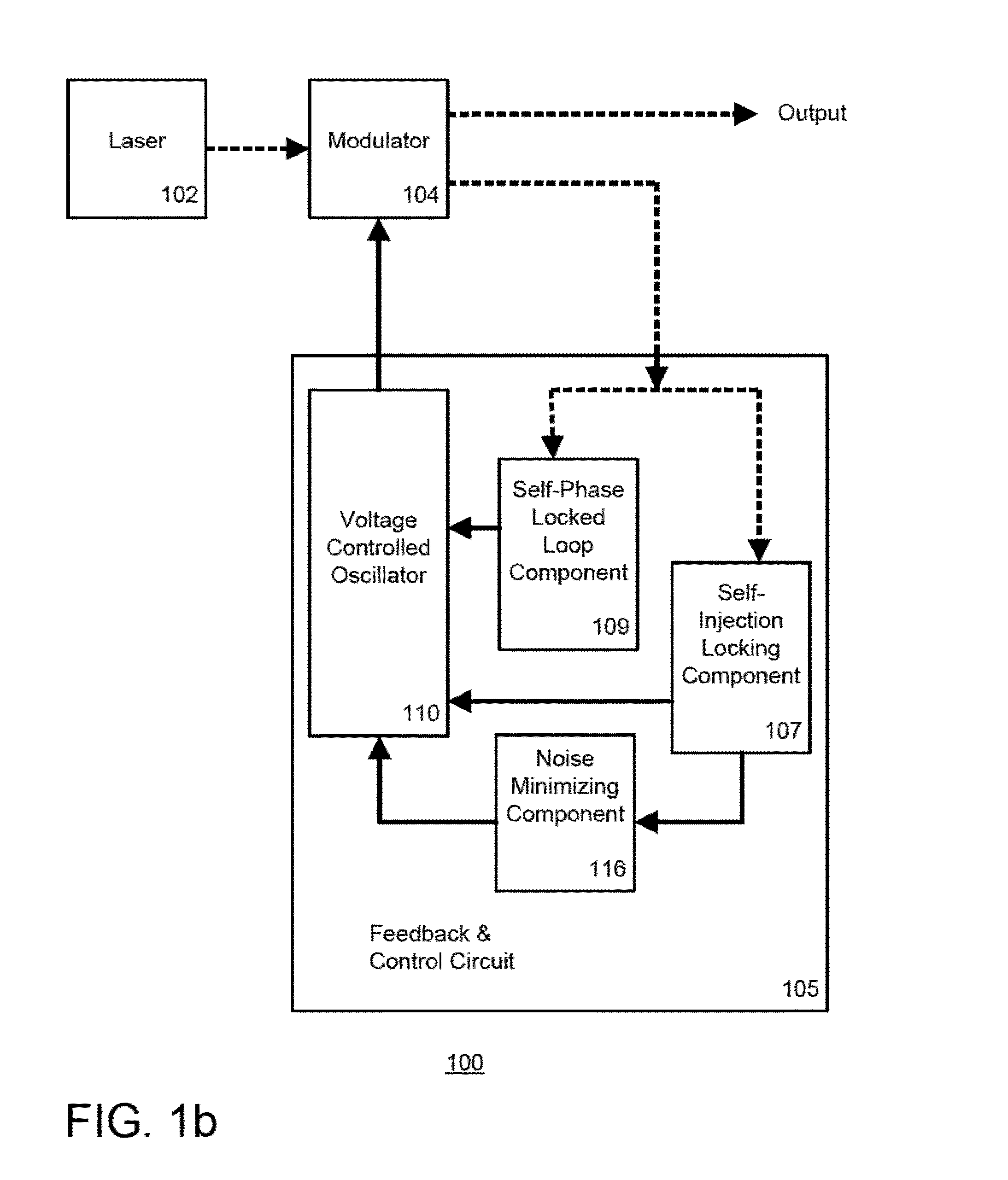

Self injection locked phase locked looped optoelectronic oscillator

Aspects of the disclosure relate generally to a circuit for sustaining an radio frequency (RF) modulated optical signal. The circuit may comprise a self injection locking component having a fiber optic delay line over which a portion of the optical signal propagates. The circuit may also comprise a self phase locked loop component having at least two fiber optic cables having different lengths and over which another portion of the optical signal propagates and a phase detector coupled to the at least two fiber optic cables and configured to determine a phase difference between the signals propagating over one of the respective fiber optic cables. The circuit may further comprise a voltage controlled oscillator configured to generate a stable oscillating signal in response to signals generated by each of the self injection locking and self phase locked loop components, the stable oscillating signal being configured to sustain the optical signal.

Owner:SYNERGY MICROWAVE CORP

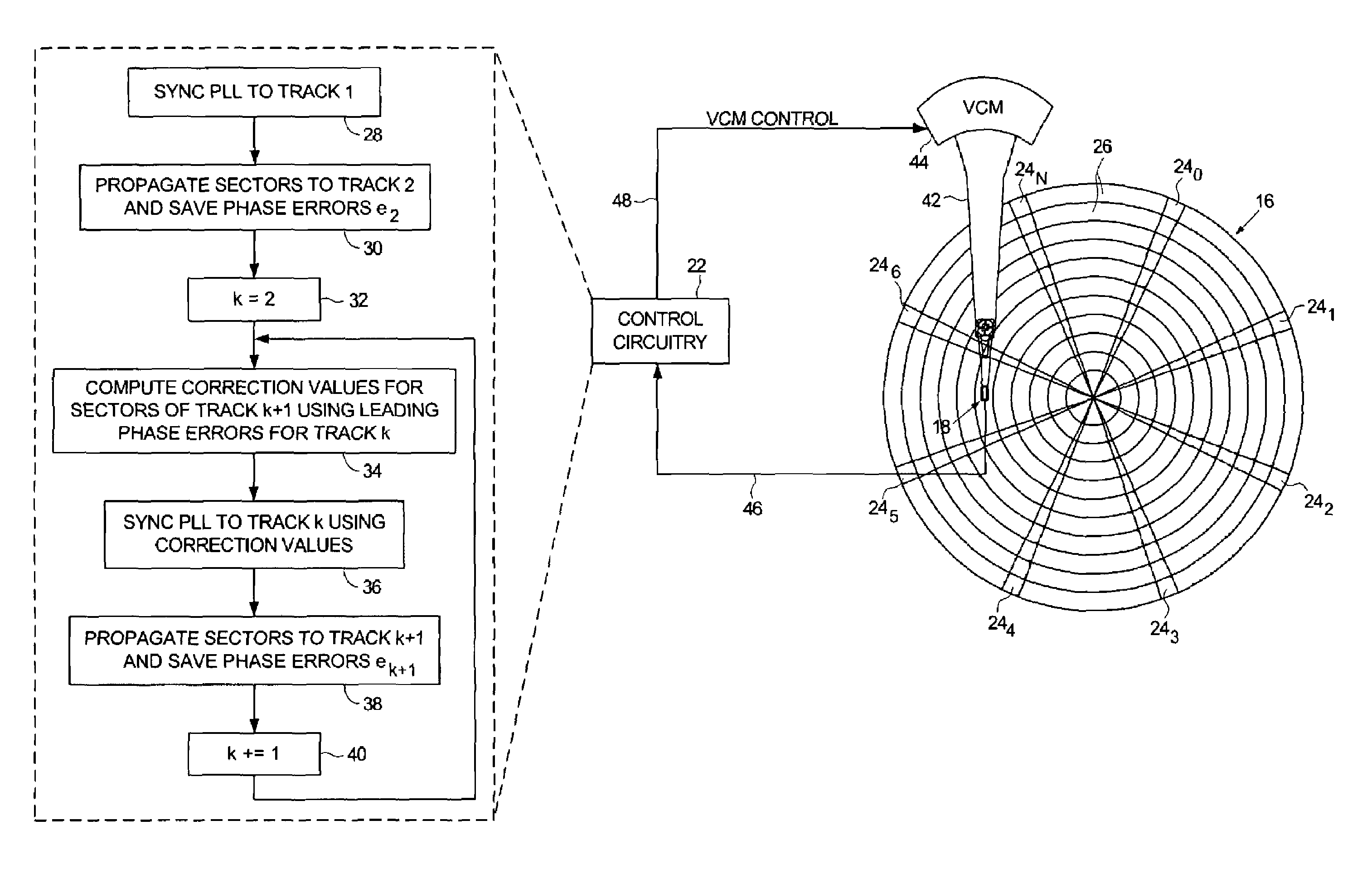

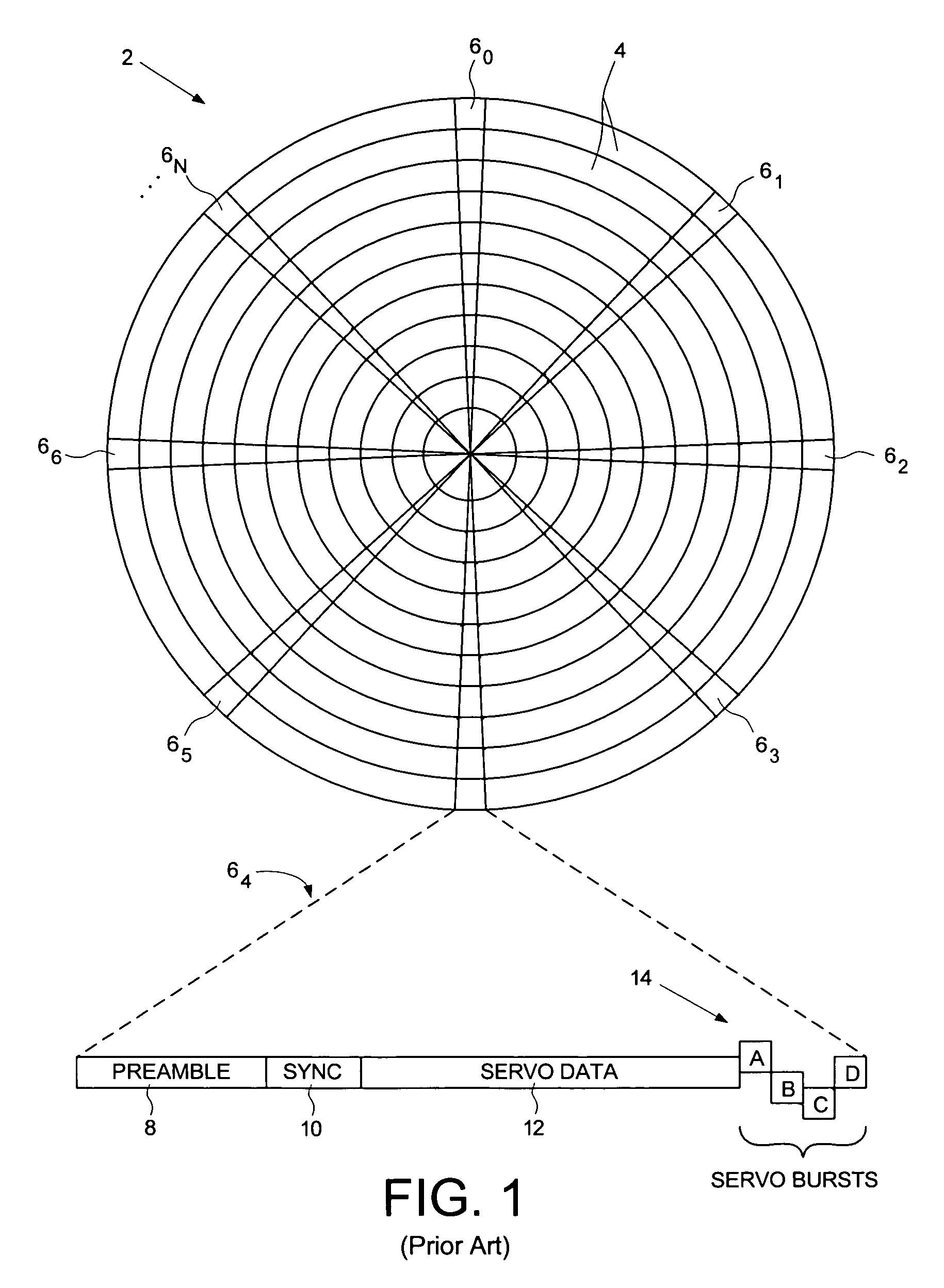

Servo writing a disk drive using correction values that attenuate phase error propagation

InactiveUS7298574B1Filamentary/web carriers operation controlDriving/moving recording headsPhase-locked loopPhase error

Servo writing a disk of a disk drive is disclosed. A phase locked loop (PLL) is synchronized to first sectors previously written on a first track, and second sectors are written to a second track using the PLL, wherein a plurality of phase errors corresponding to the second sectors are saved. A correction value is computed corresponding to a selected one of the second sectors, wherein the correction value is computed in response to a plurality of the phase errors generated for a plurality of the second sectors leading the selected sector. The PLL is synchronized to the second sectors using the correction value, a third sector is written to a third track using the PLL, and a phase error is saved corresponding to the third sector.

Owner:WESTERN DIGITAL TECH INC

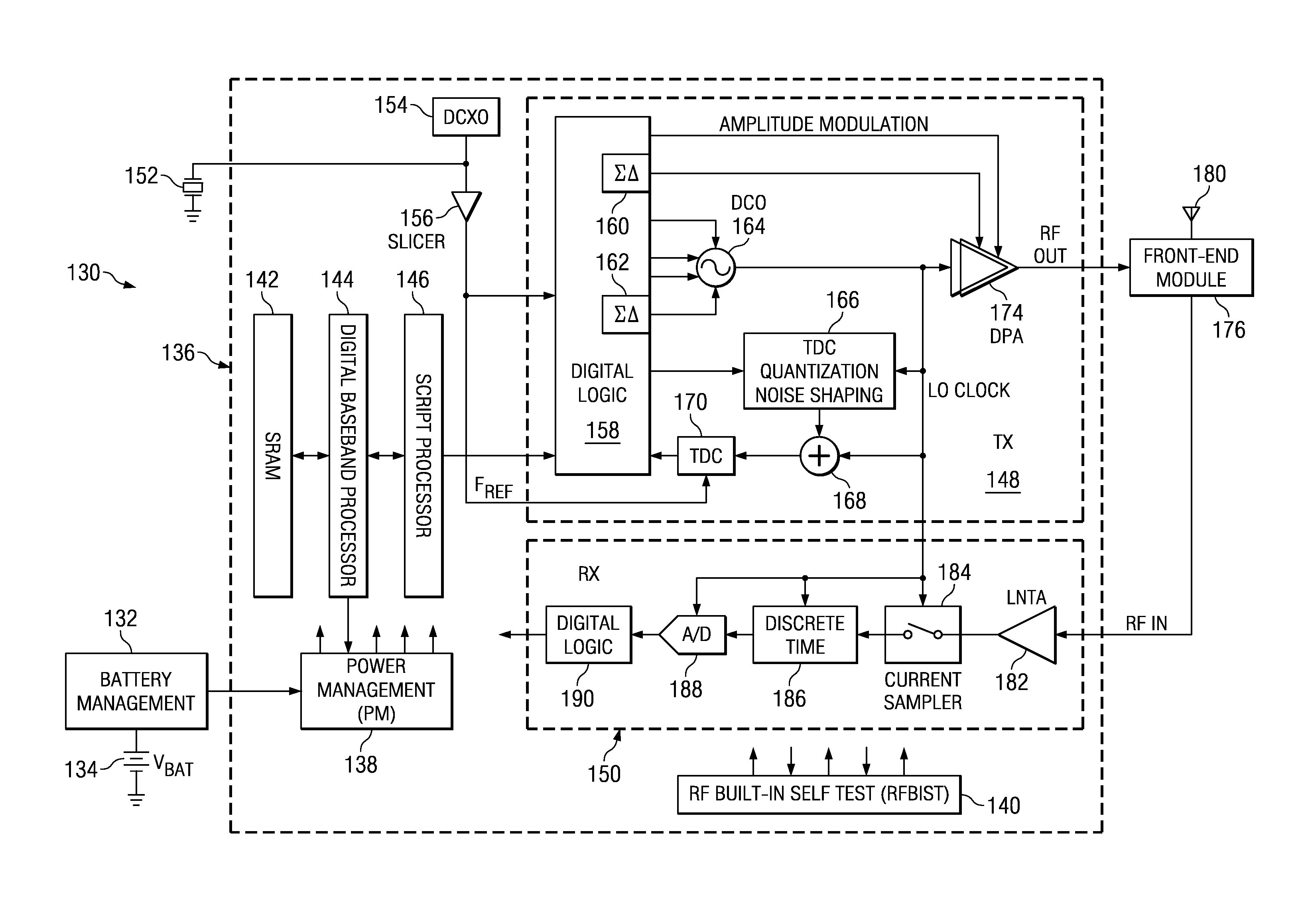

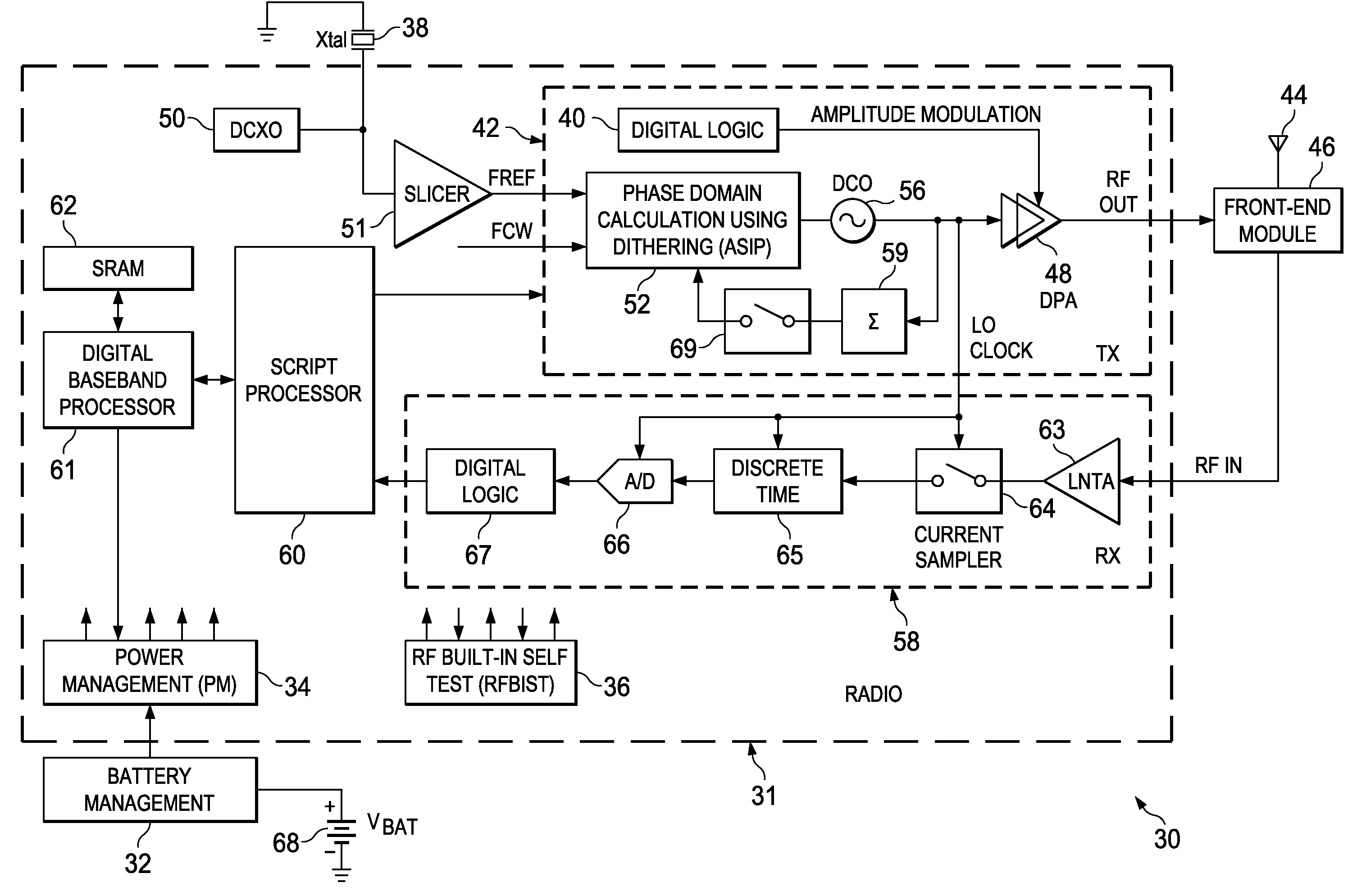

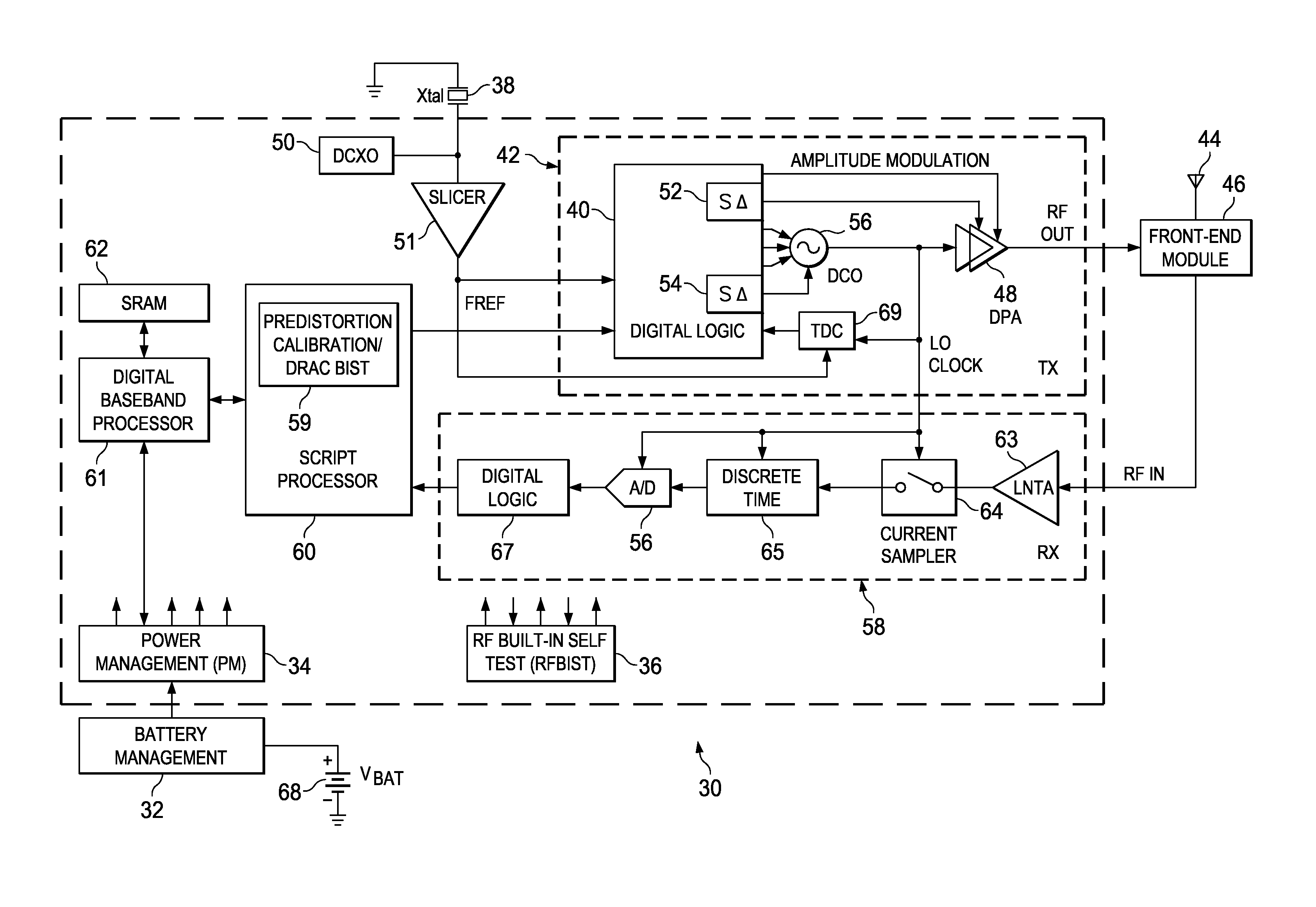

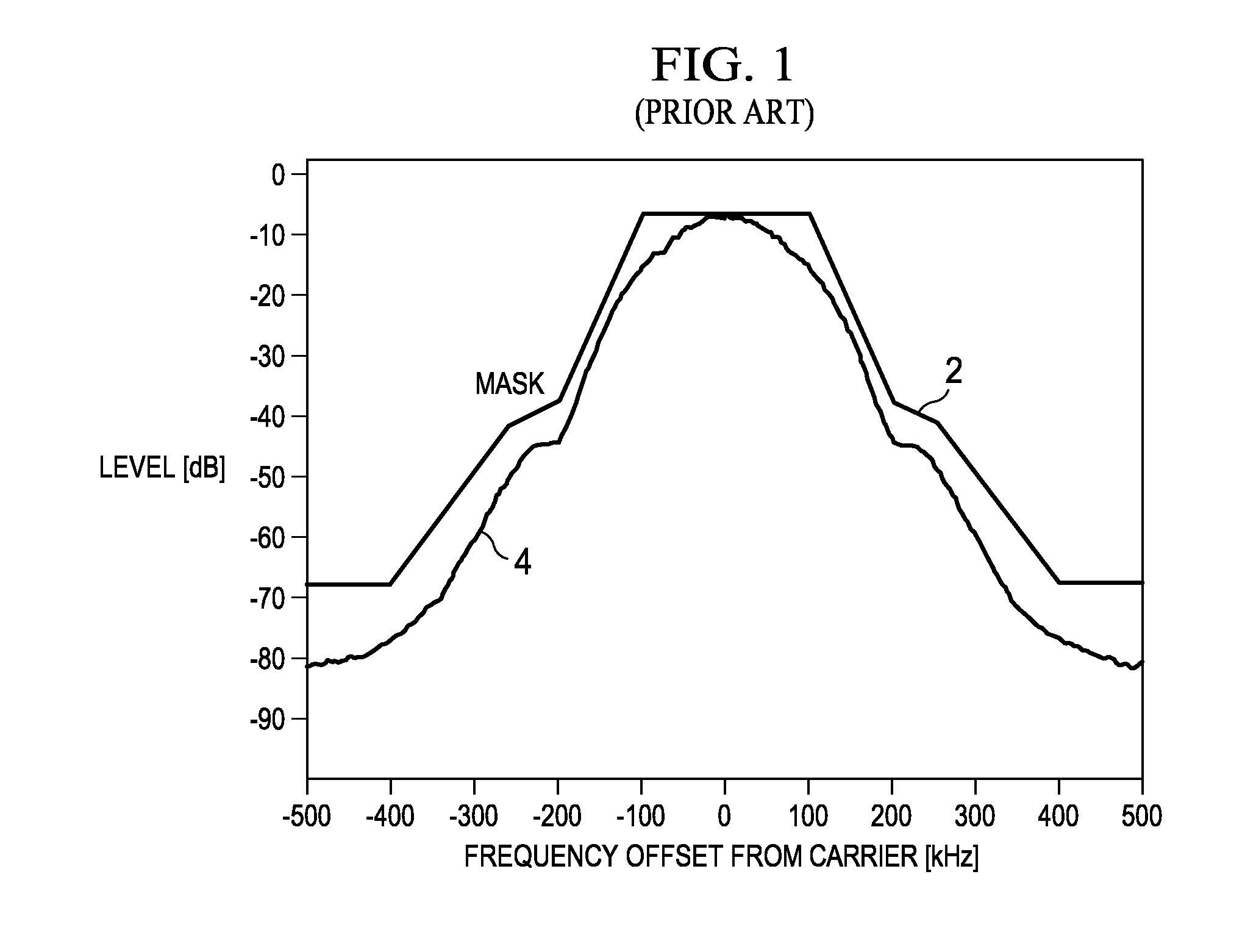

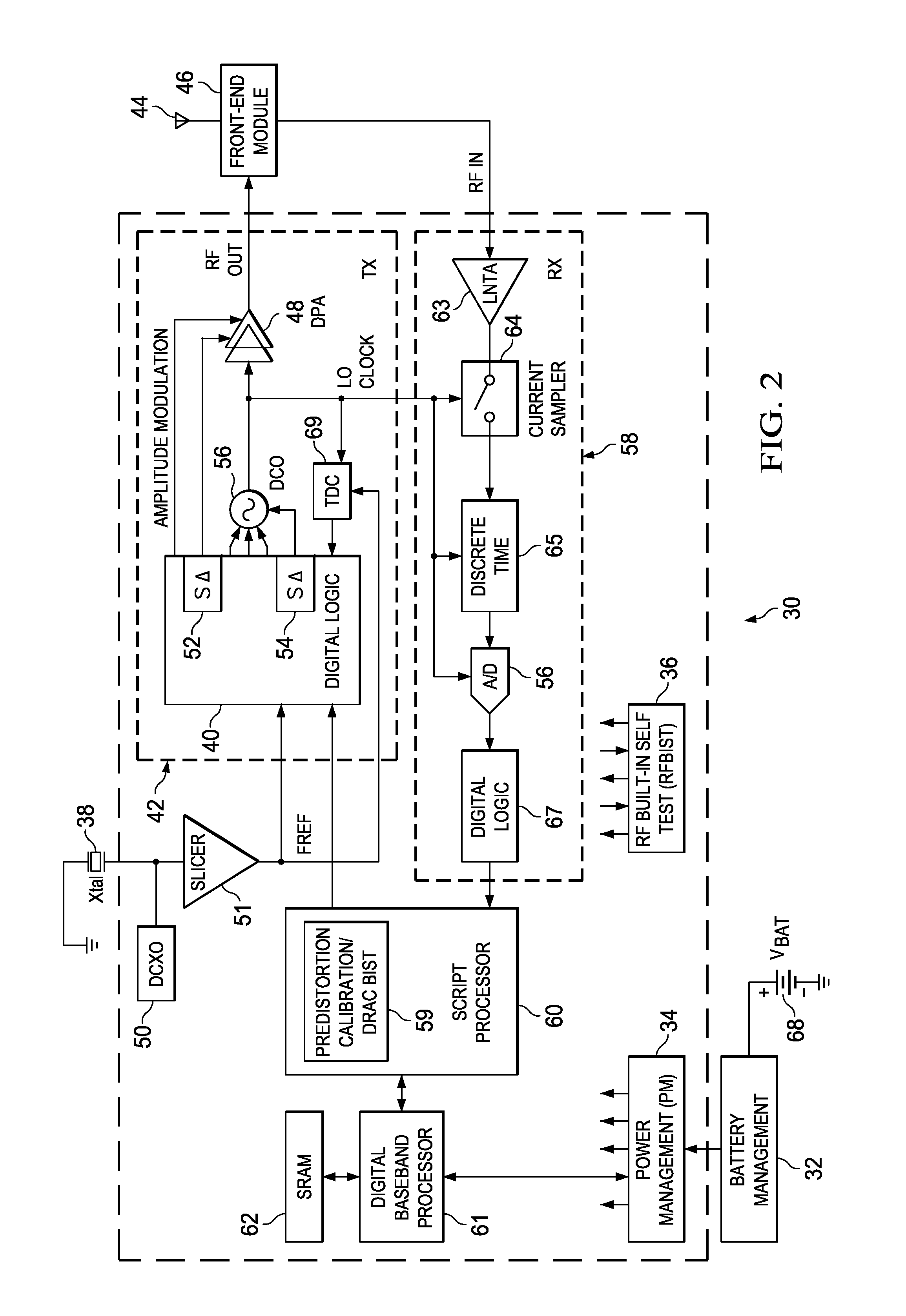

Predistortion calibration and built in self testing of a radio frequency power amplifier using subharmonic mixing

ActiveUS20120252382A1No significant hardware overheadStrain is placedTransmitters monitoringPower amplifiersHarmonicTested time

A novel and useful apparatus for and method of predistortion calibration and built-in self testing (BIST) of a nonlinear digitally-controlled radio frequency (RF) power amplifier (DPA) using subharmonic mixing. The RF power amplifier output is temporarily coupled into the frequency reference (FREF) input and the phase error samples generated in the phase locked loop (PLL) are then observed and analyzed. The digital predistortion and BIST mechanisms process the phase error samples to calibrate and test the DPA in the transmitter of the Digital RF Processor (DRP). The invention enables the characterization of nonlinearities, the configuration of internal predistortion, as well as the testing of the transmitter's analog / RF circuitry, thereby eliminating commonly employed RF performance testing using high-cost test equipment and associated extended test times.

Owner:TEXAS INSTR INC

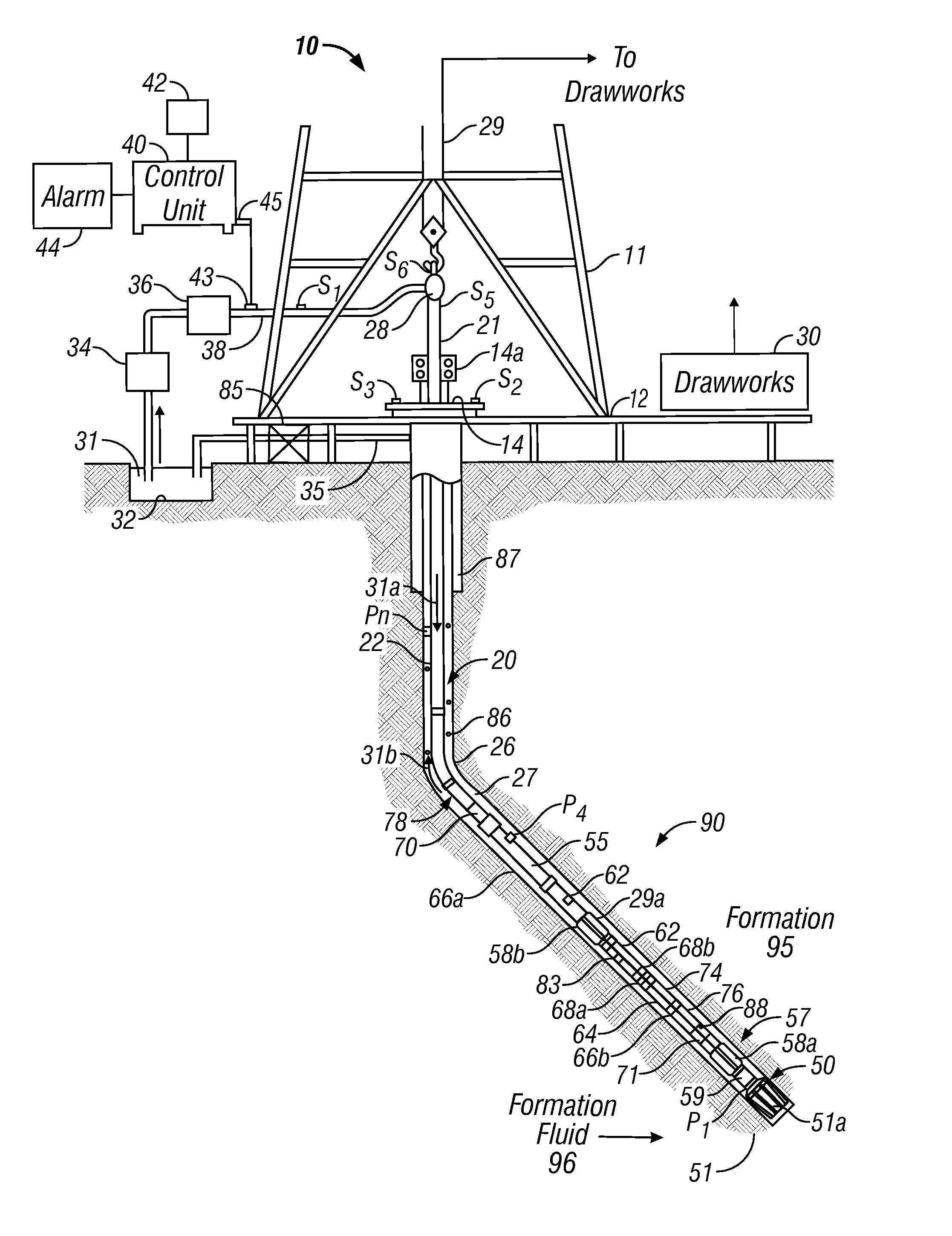

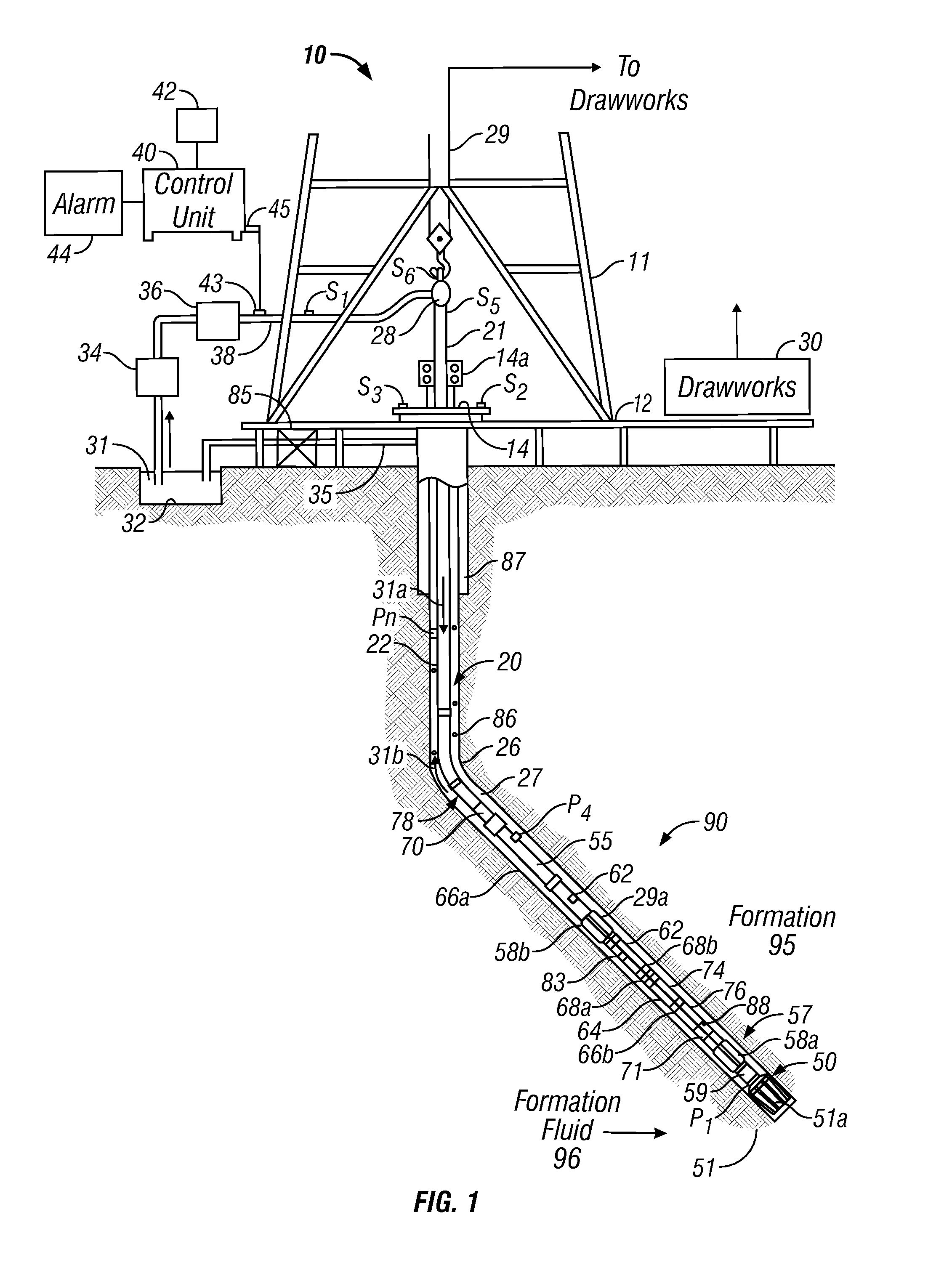

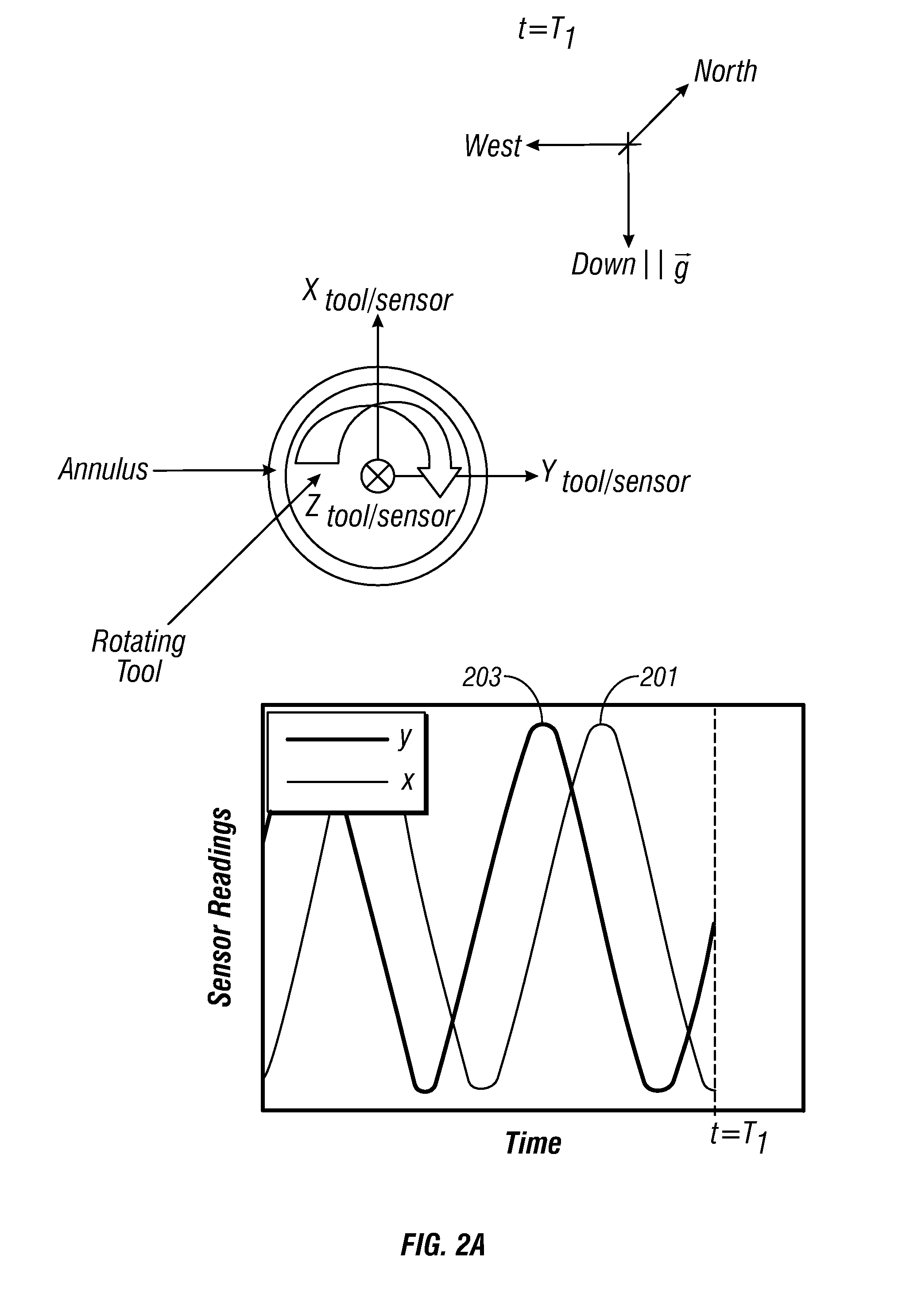

Phase Estimation From Rotating Sensors To Get a Toolface

Measurements made by a rotating sensor on a bottomhole assembly are used to determine the toolface angle of the BHA. The method includes using a phase locked loop (PLL) to determine a phase difference between the sensor output and a reference signal.

Owner:BAKER HUGHES INC

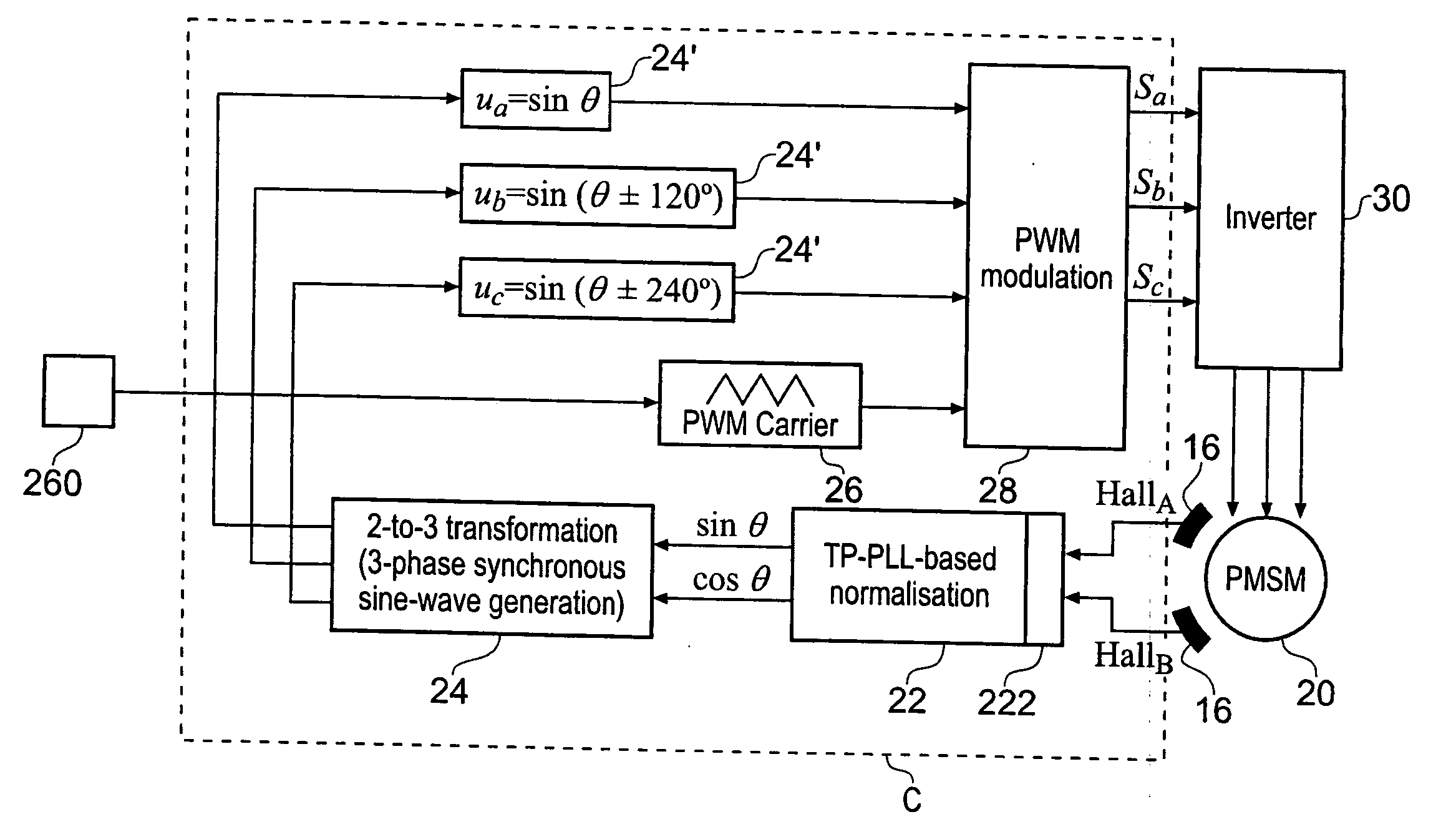

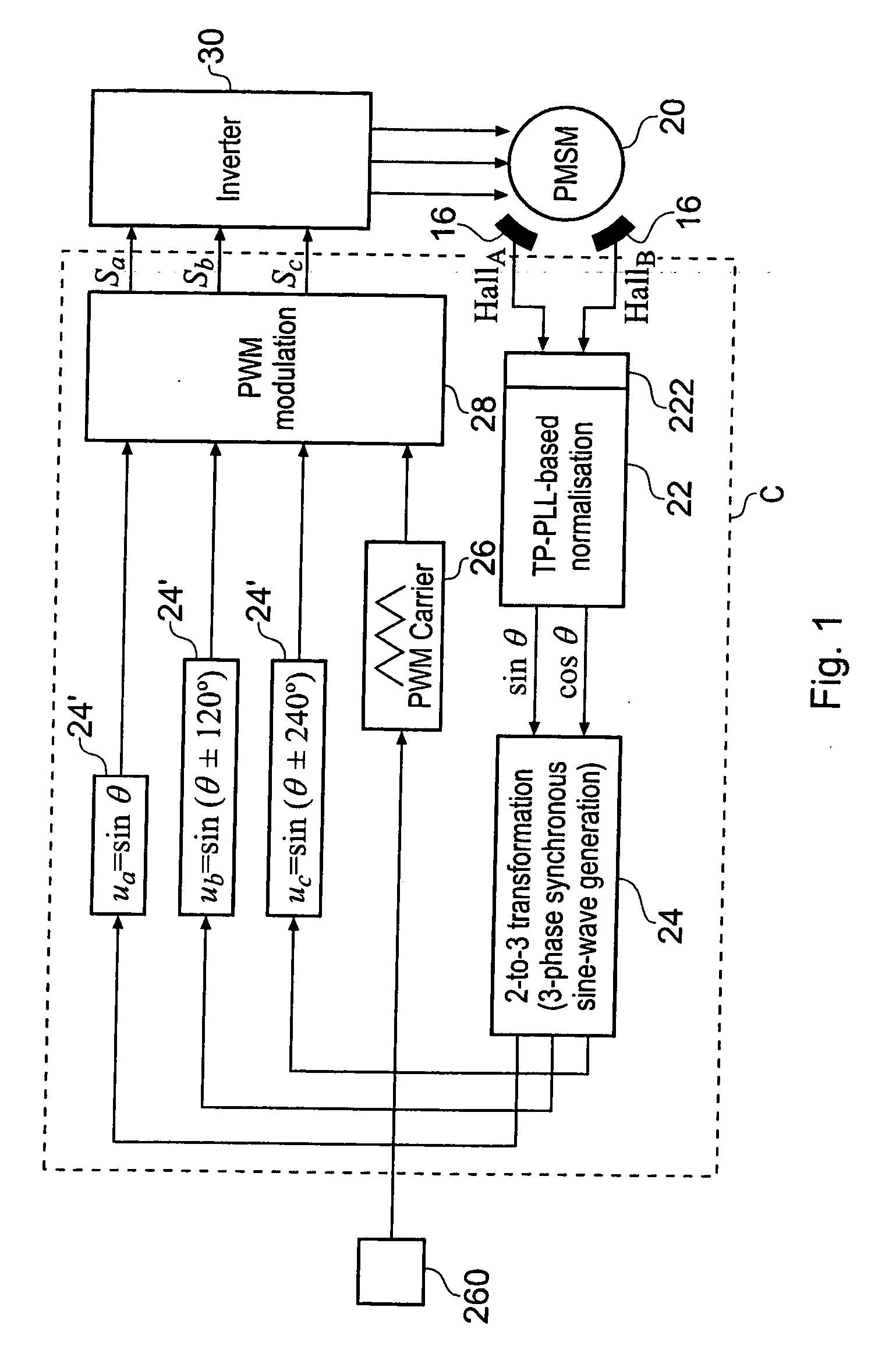

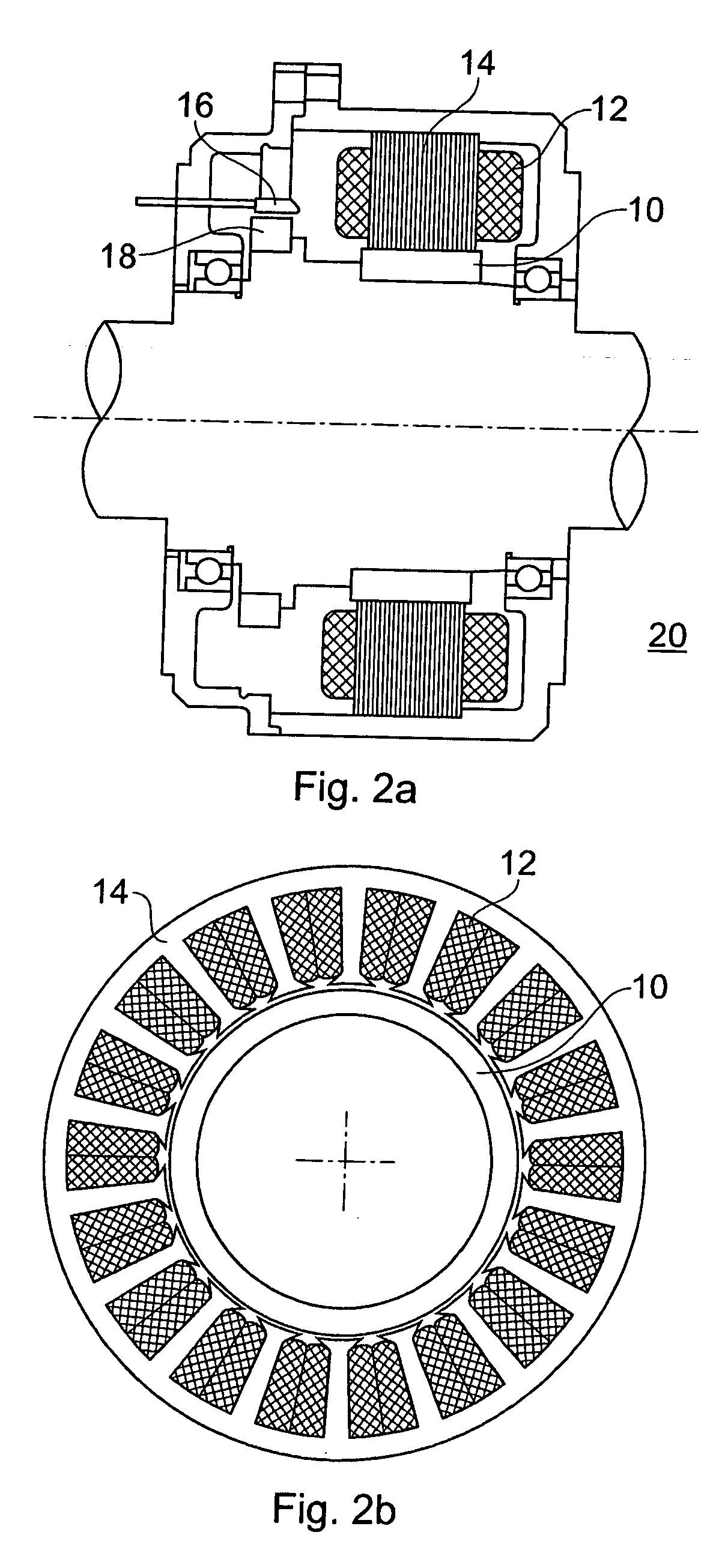

Permanent magnet synchronous motor and controller therefor

InactiveUS20050248306A1Low costReduce impactTorque ripple controlMotor/generator/converter stoppersPhase currentsLoop control

A low-cost sine-wave drive for a 3-phase permanent magnet synchronous AC machines (PMSM) in open-loop control is based on the measurements of two linear Hall sensors. The two Hall sensors are excited by a magnetic ring with the same pole number as the PMSM rotor magnet and sinusoidal flux distributions. The output signals of the Hall sensors are unified through a two-phase-type phase-lock-loop in order to reduce the impact of the sensor mounting non-uniformity during mass production. The peak torque and speed of motor is simply controlled by adjusting the amplitude of pulse-width-modulation carrier. Smooth torque control is achieved due to sinusoidal 3-phase currents. Such a simple sine-wave drive can be achieved with or without the assistance of a micro-controller unit (MCU). No current sensor is required for the motor phase current detection. This motor can be used in industrial applications where there is no strict requirement on torque response and constant speed control of PMSM machines.

Owner:AISIN SEIKI KK

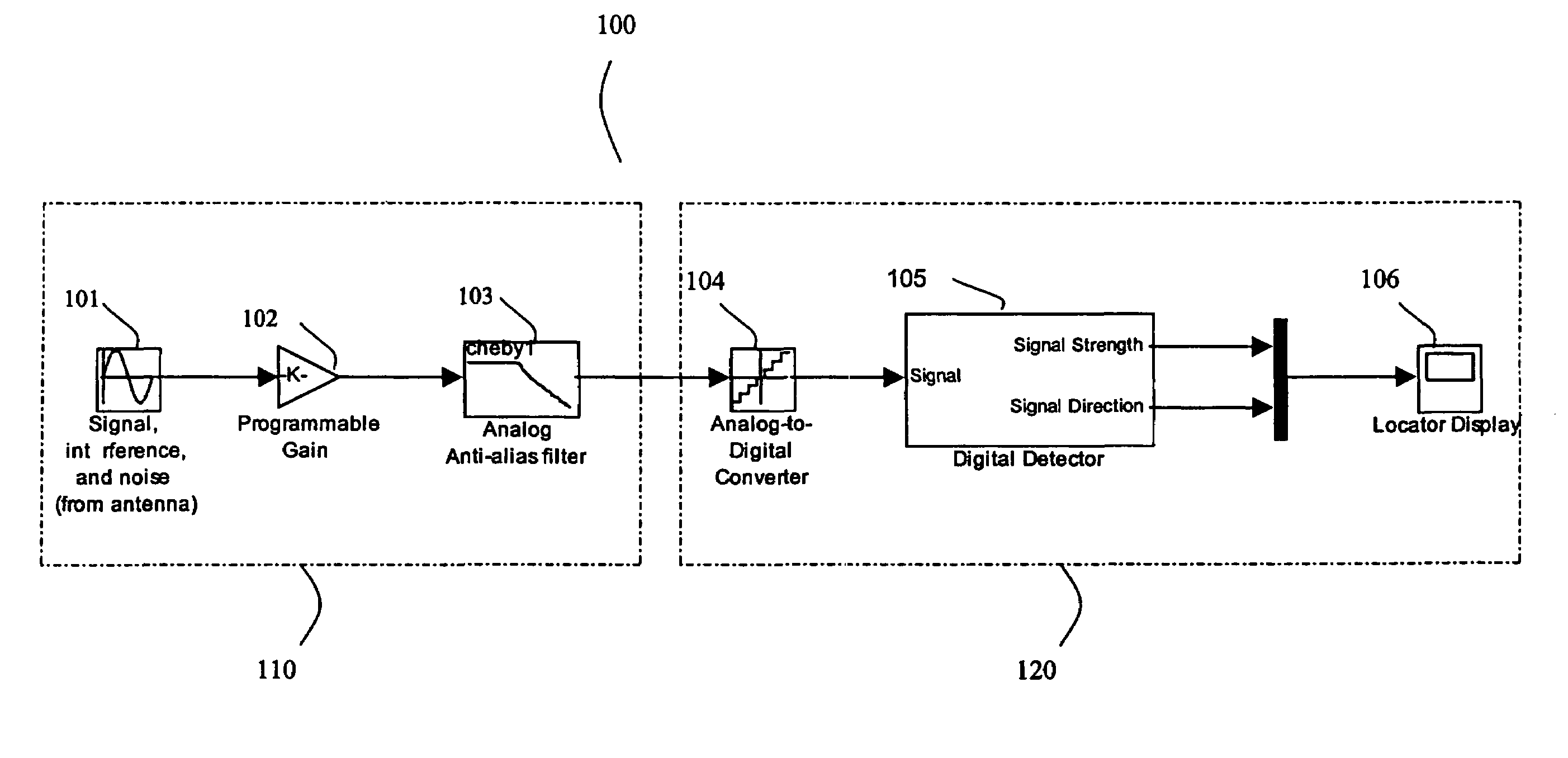

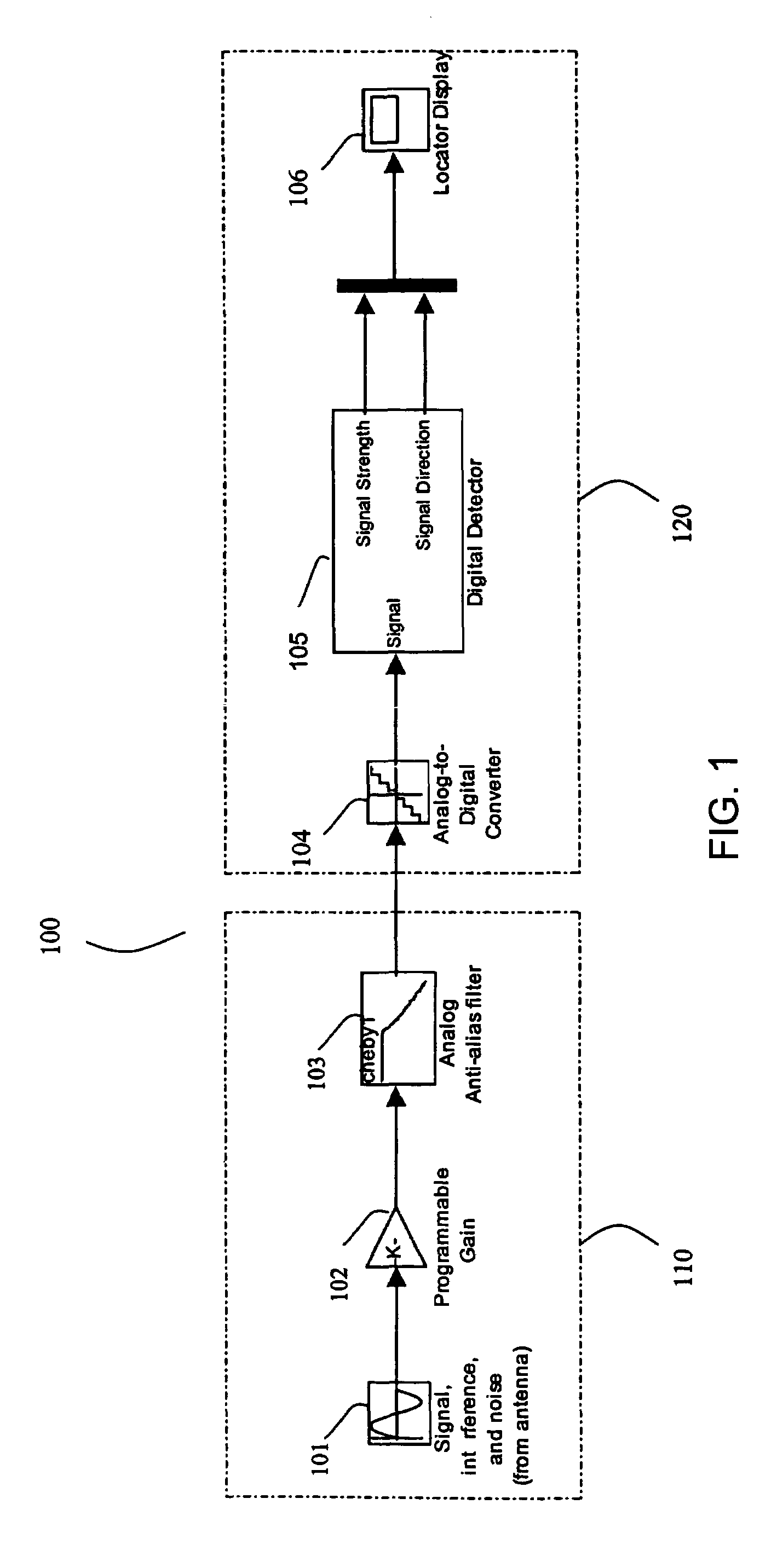

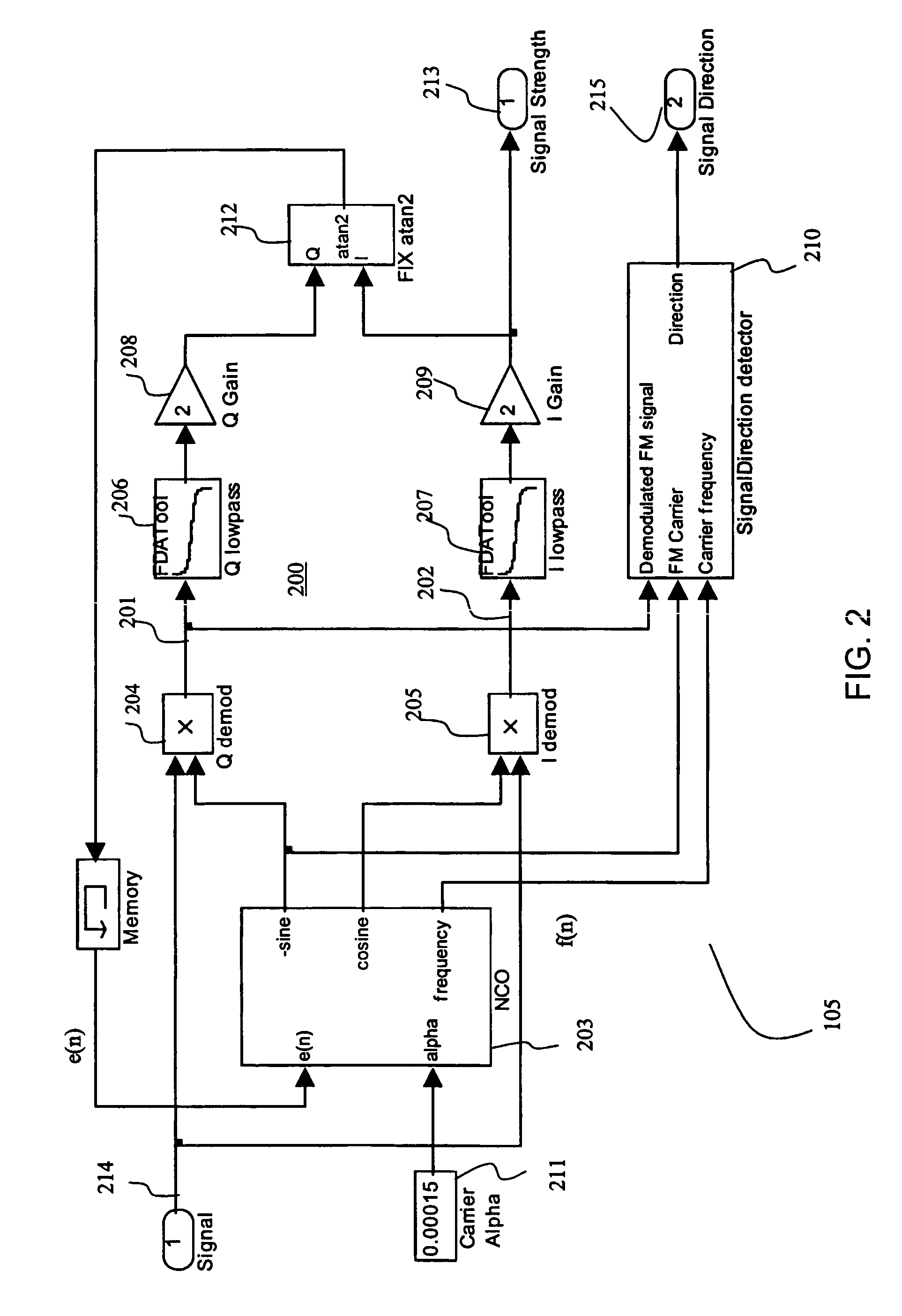

Method and apparatus for digital detection of electromagnetic signal strength and signal direction in metallic pipes and cables

InactiveUS7062414B2Low hardware requirementsWide resistance to component tolerancesAmplifier modifications to reduce noise influenceDigital computer detailsDigital signal processingCarrier signal

A new digital architecture for metallic pipe and cable locators, providing accurate estimation of the fundamental locate parameters, electromagnetic signal strength and signal direction, and utilizing a nested Digital Phase-Locked Loop (DPLL) structure is disclosed. The obstacles to signal direction measurement in low SINR environments using the signal select method are overcome and a more precise phase comparison between the carrier and the FM modulation signals is obtained. The architecture further significantly reduces analog front-end hardware requirements, offers wider resistance to component tolerances, lower calibration and test time, and provides flexible frequency selectivity. Locators according to the present invention provide accurate estimation of the fundamental physical parameters of line location (electromagnetic signal strength and signal direction) in extremely noisy environments, using Digital Signal Processing (DSP) methods.

Owner:BUSAN TRANSPORTATION CORPORATION

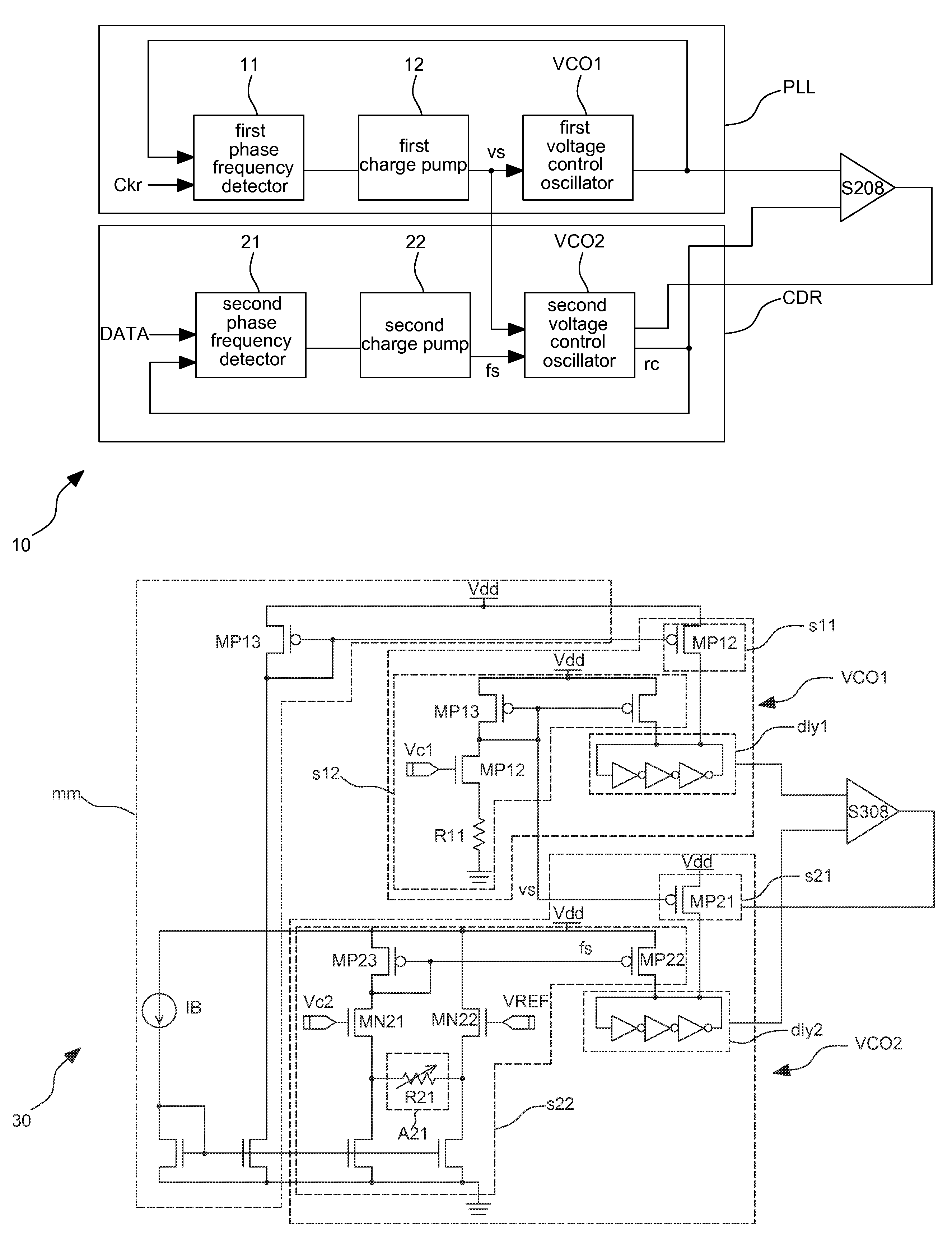

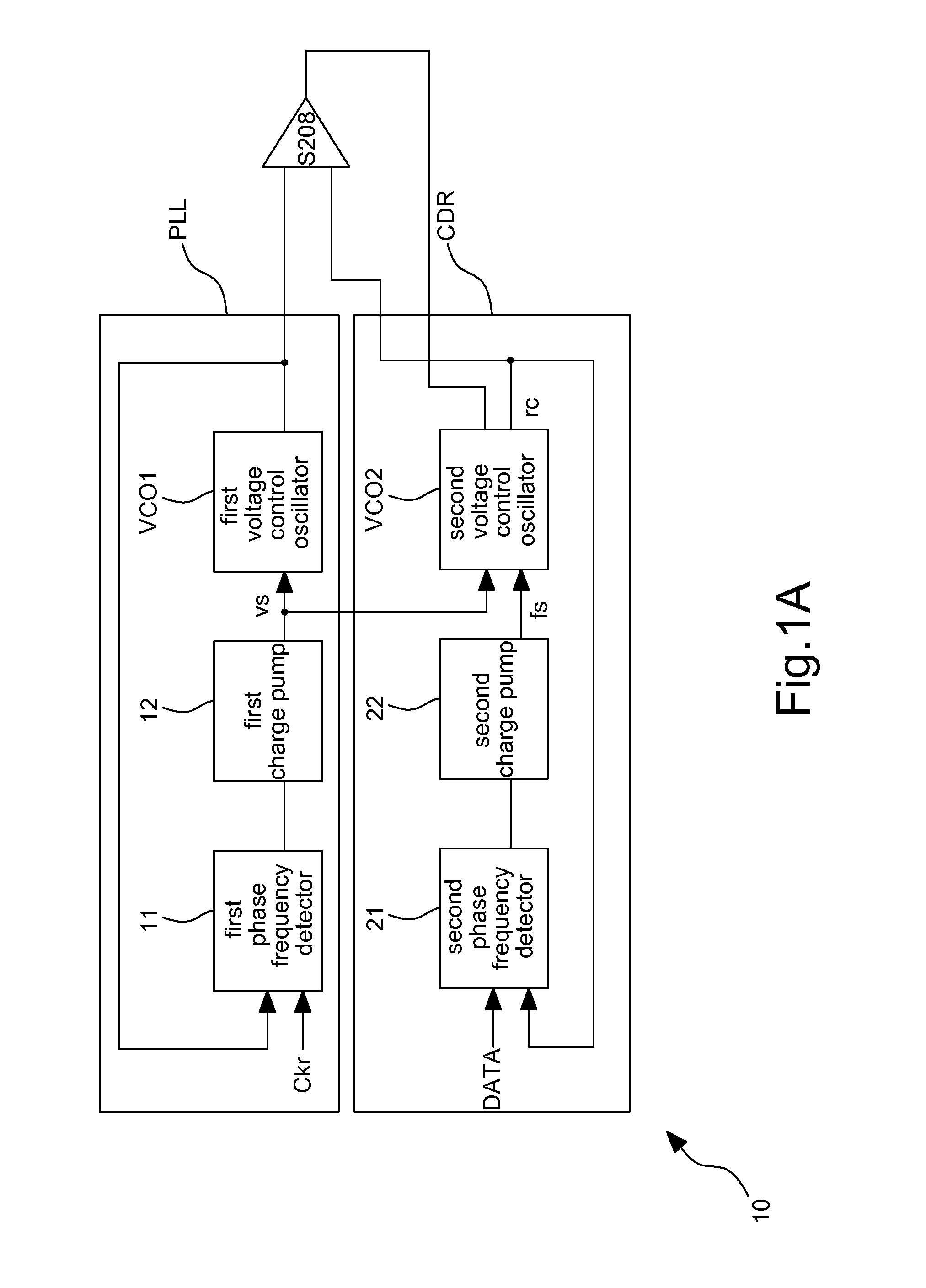

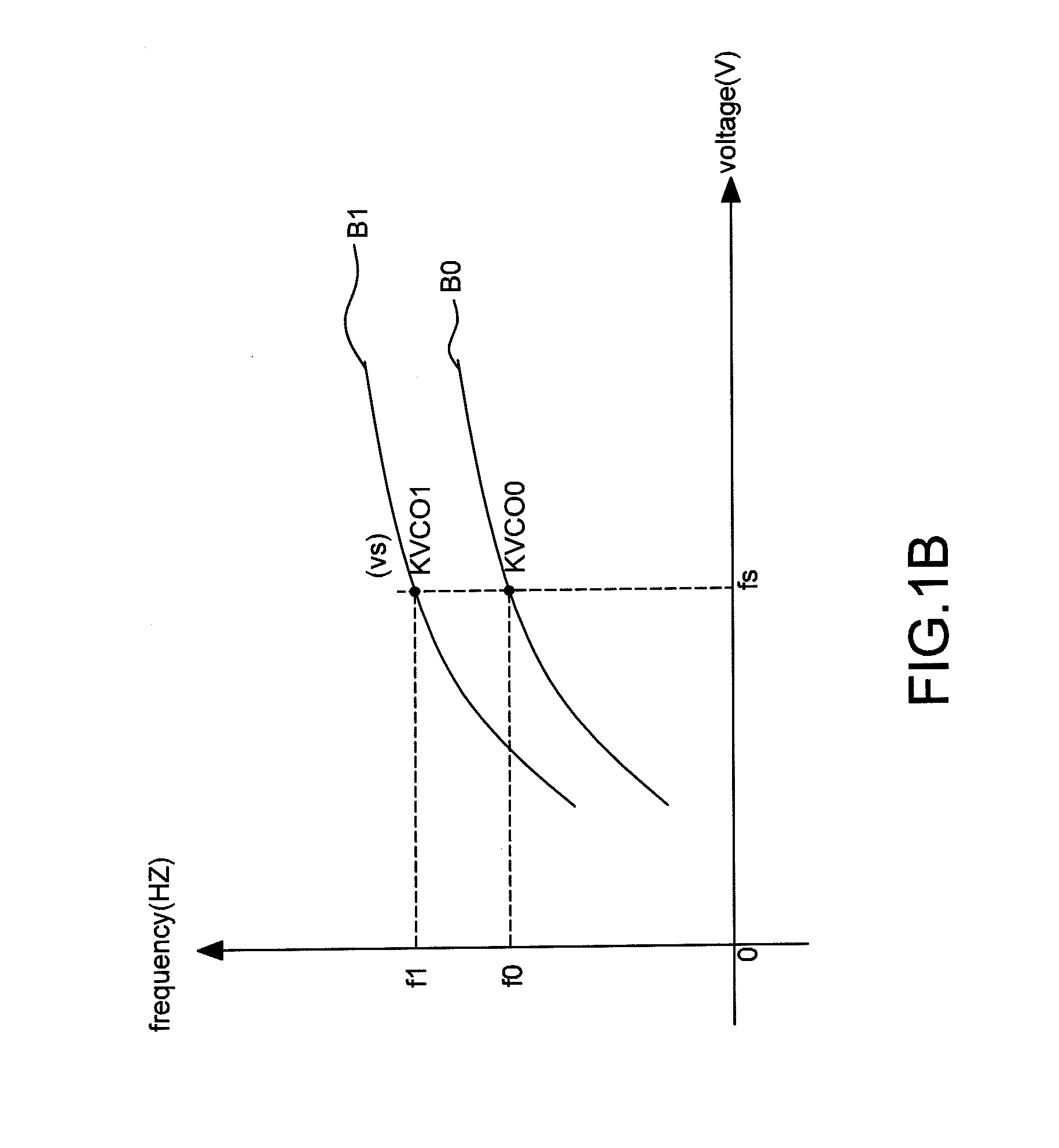

Transceiver, voltage control oscillator thereof and control method thereof

ActiveUS8928416B2Smaller VCO gainLarge rangePulse automatic controlPulse generation by logic circuitsTransceiverControl signal

A transceiver includes a phase lock loop (PLL) and a clock data recovery circuit (CDR). The phase lock loop generates a first level control signal. The clock data recovery circuit, coupled to the phase lock loop, locks an incoming data signal to generate a data recovery clock according to a second level control signal. Wherein the clock data recovery circuit receives the first level control signal to further control a frequency range of the data recovery clock.

Owner:REALTEK SEMICON CORP

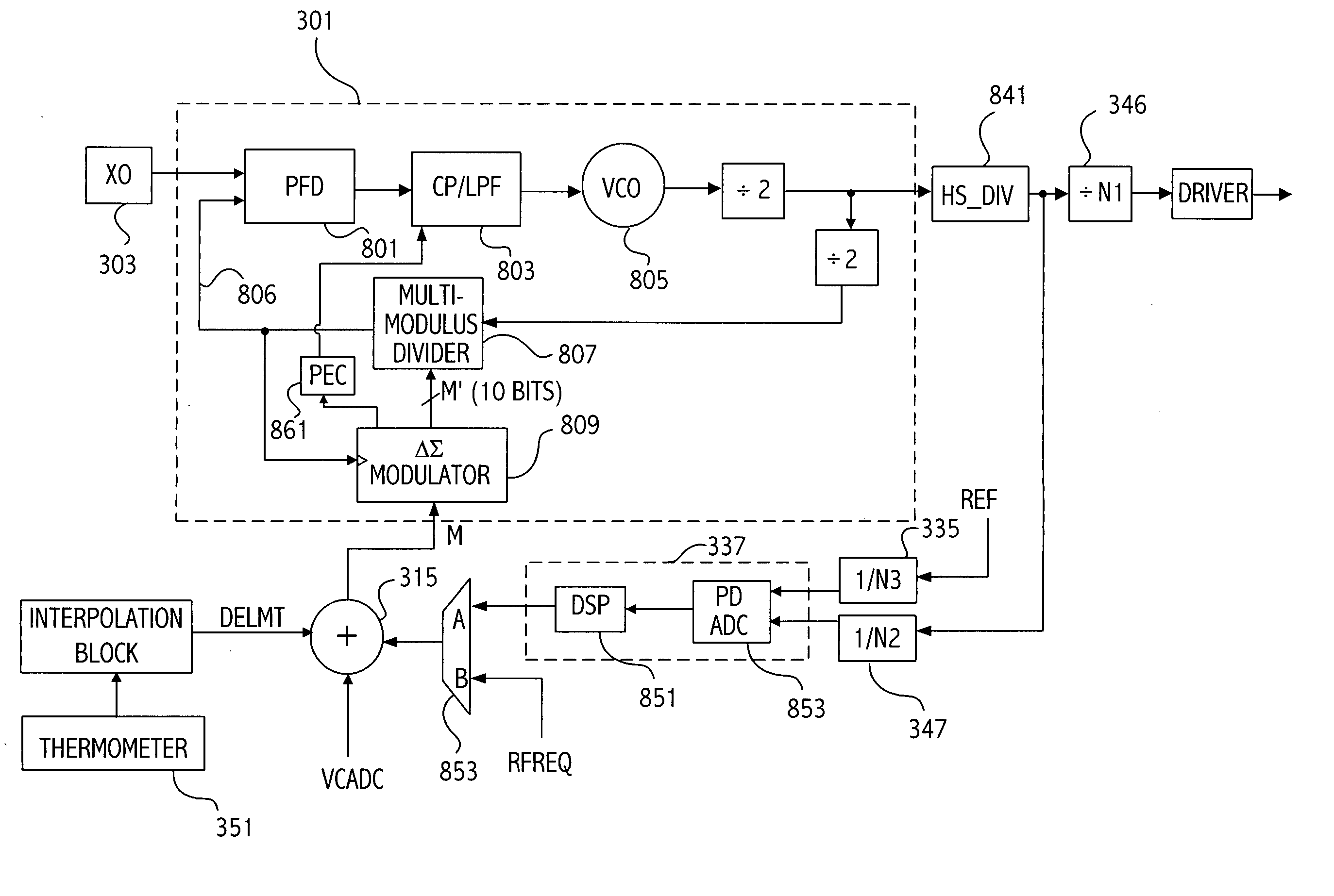

Dual loop architecture useful for a programmable clock source and clock multiplier applications

InactiveUS20040232995A1Pulse automatic controlGenerator stabilizationFrequency multiplierDigital control

A first phase-locked loop (PLL) circuit includes an input for receiving a timing reference signal from an oscillator, a controllable oscillator circuit supplying an oscillator output signal, and a multi-modulus feedback divider circuit. A second control loop circuit is selectably coupled through a select circuit to supply a digital control value (M) to the multi-modulus feedback divider circuit of the first loop circuit to thereby control the oscillator output signal. While the second control loop is coupled to supply the control value to the feedback divider circuit, the control value is determined according to a detected difference between the oscillator output signal and a reference signal coupled to the second control loop circuit at a divider circuit. While the second control loop circuit is not coupled to control the first PLL circuit, the first PLL circuit receives a digital control value to control a divide ratio of the feedback divider, the digital control value is determined at least in part according to a stored control value stored in nonvolatile storage, the stored control value corresponding to a desired frequency of the oscillator output signal.

Owner:SKYWORKS SOLUTIONS INC

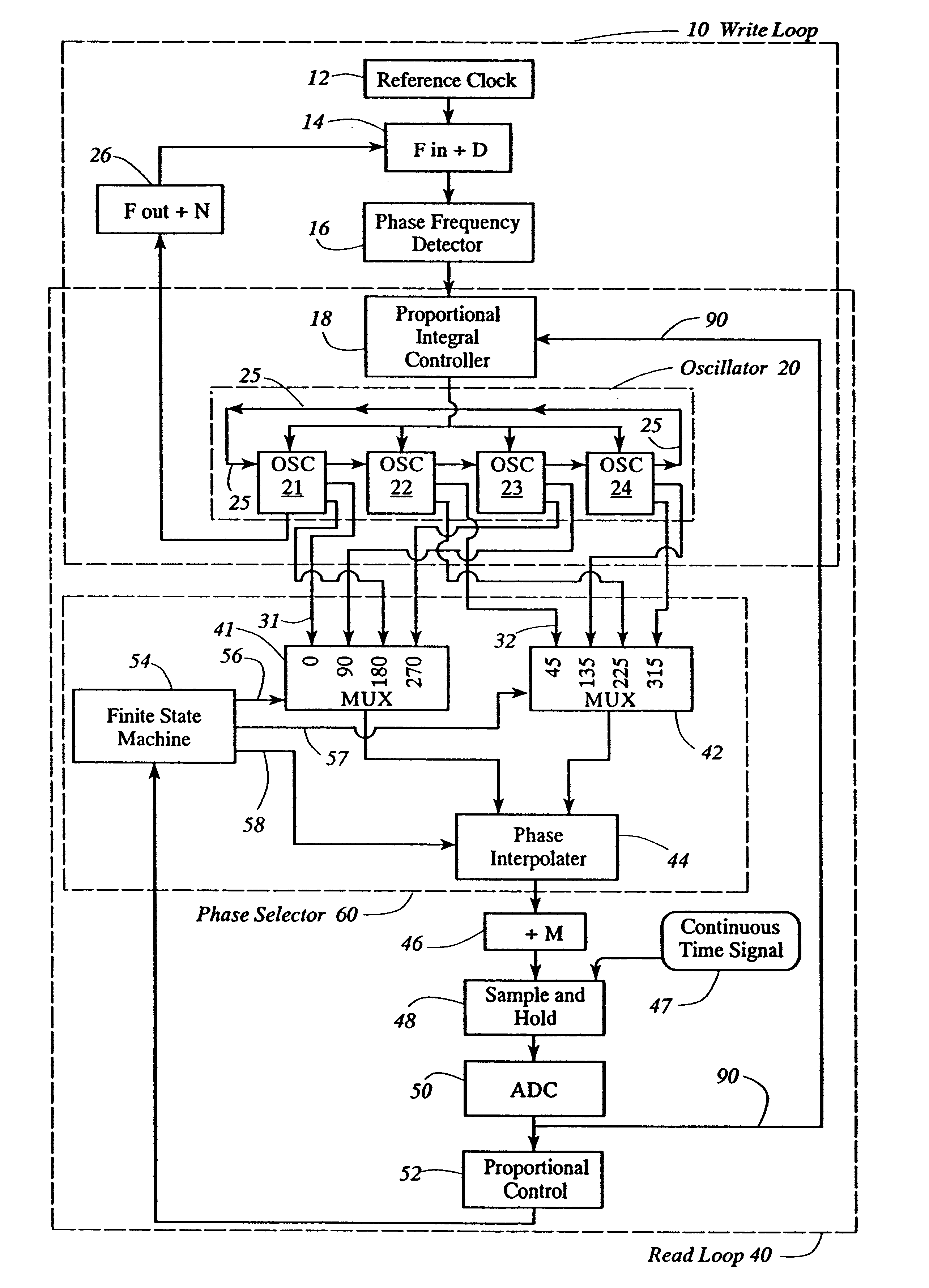

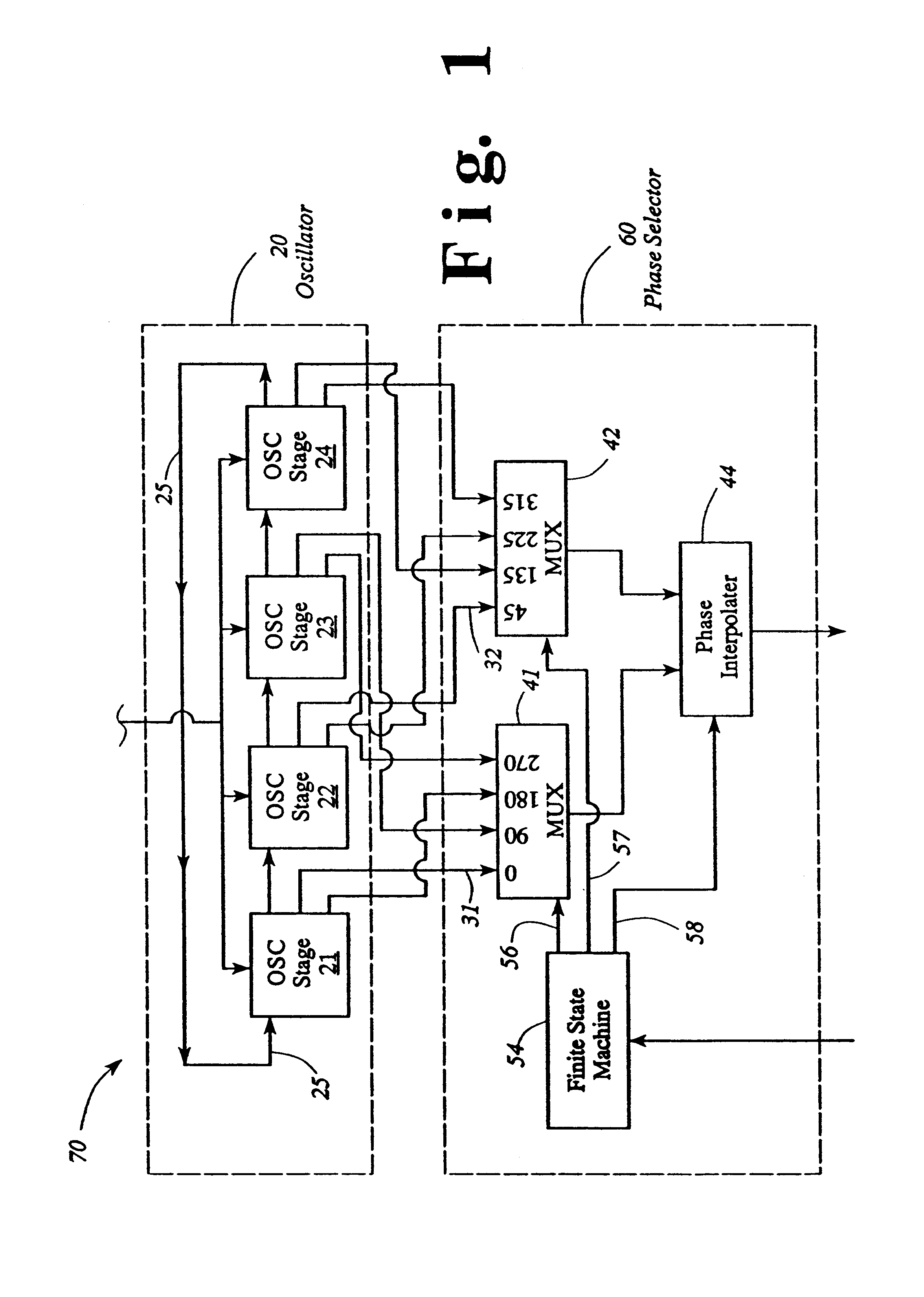

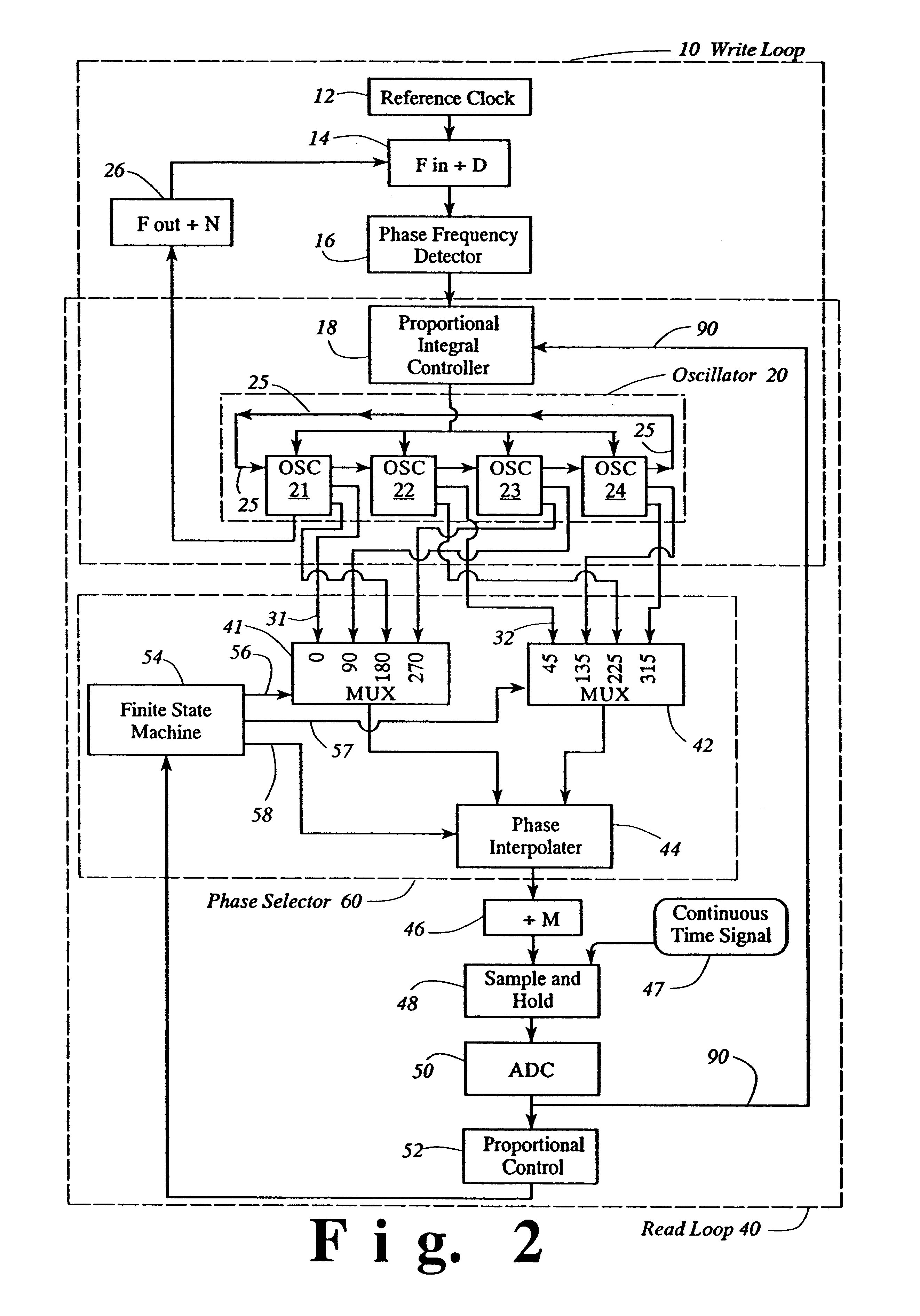

Oscillator with digitally variable phase for a phase-locked loop

InactiveUS6525615B1Disposition/mounting of recording headsPulse automatic controlMultiplexerImproved method

The present invention provides an improved method and apparatus for independently controlling phase and frequency using an oscillator having a plurality of stages in combination with a phase selector within a digitally controlled phase-locked loop, preferably, a read phase locked loop. The present invention provides a digitally controlled variable phase of the read timing loop in read channel integrated circuits associated with data storage devices. The phase selector has a digitally controlled fine interpolator with 12 states for further fine interpolation between at least two multiplexer phase outputs to provide a single phase output selected from a range comprising at least 2pi in selectable variable phase increments of 2pi / 96 radian. The combined oscillator with the phase selector within a phase locked loop controls phase by exact fractional increments of equally space phases of the operating frequency within the phase locked loop, therein controlling phase at all operating frequencies.

Owner:GLOBALFOUNDRIES INC