Patents

Literature

680 results about "Data recovery circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

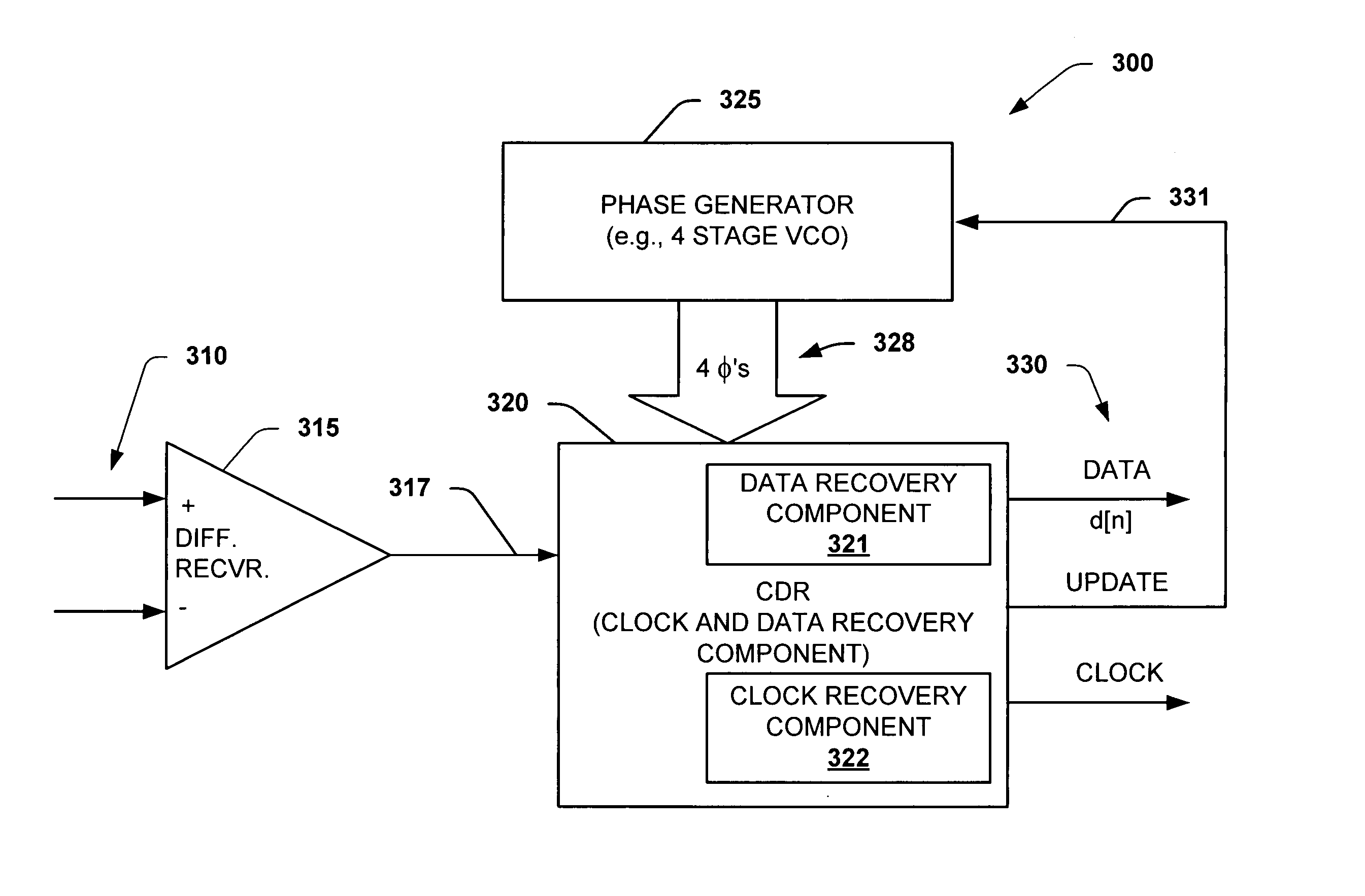

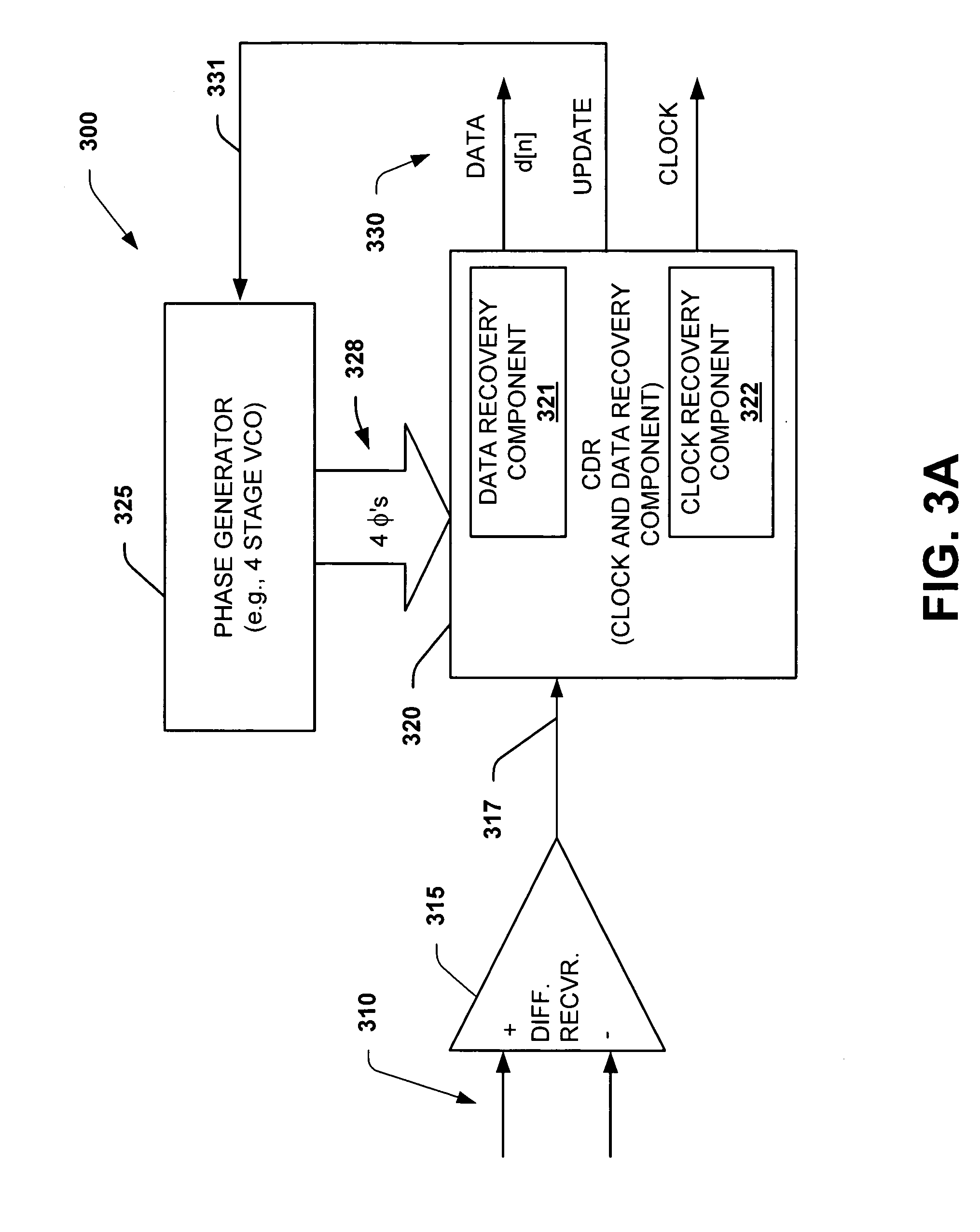

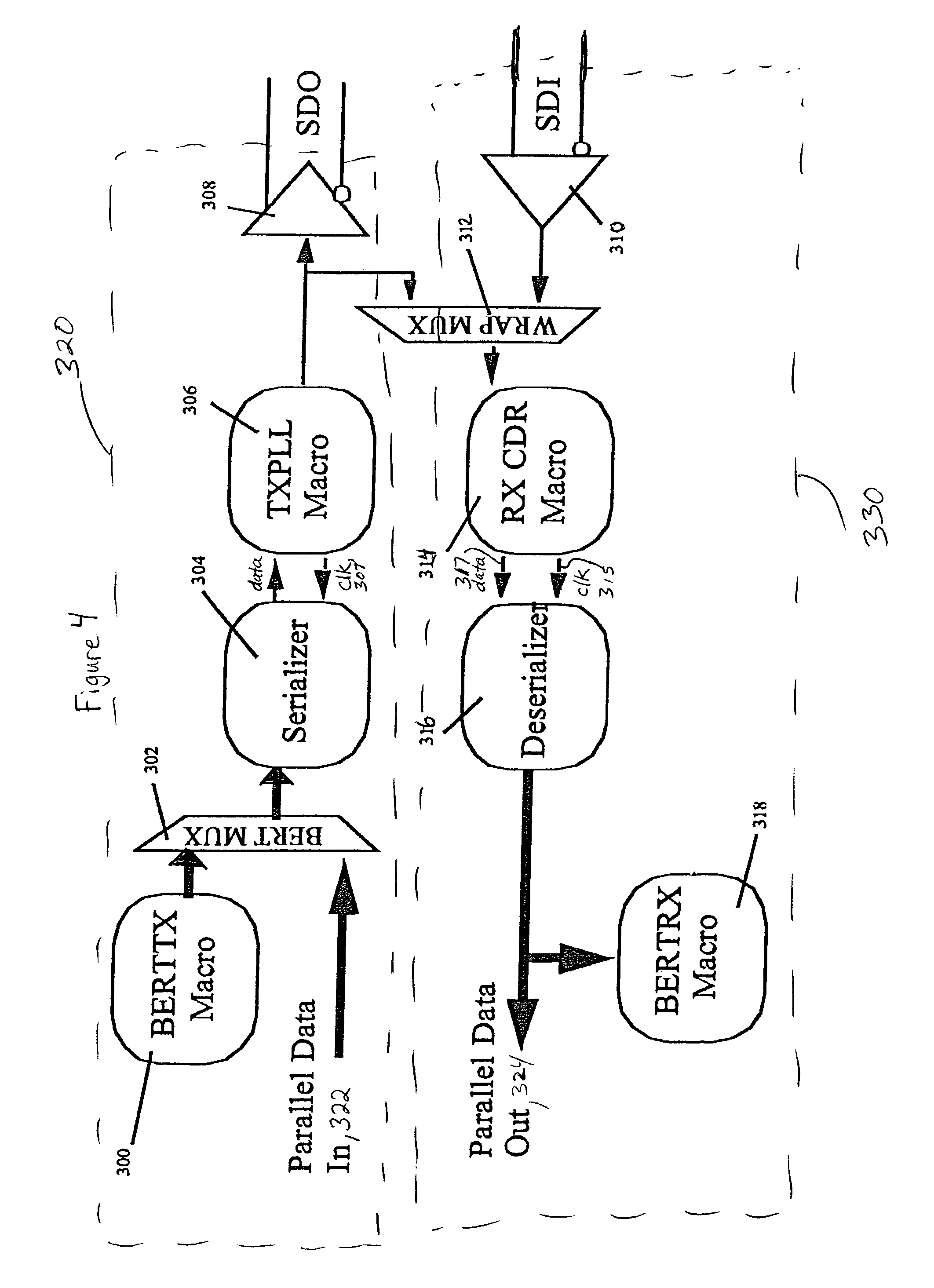

Interpolator based clock and data recovery (CDR) circuit with digitally programmable BW and tracking capability

ActiveUS20050180536A1High bandwidthLower latencyPulse automatic controlSynchronising arrangementPhase correctionData stream

The present invention facilitates clock and data recovery (330,716 / 718) for serial data streams (317,715) by providing a mechanism that can be employed to maintain a fixed tracking capability of an interpolator based CDR circuit (300,700) at multiple data rates (e.g., 800). The present invention further provides a wide data rate range CDR circuit (300,700), yet uses an interpolator design optimized for a fixed frequency. The invention employs a rate programmable divider circuit (606,656,706) that operates over a wide range of clock and data rates (e.g., 800) to provide various phase correction step sizes (e.g., 800) at a fixed VCO clock frequency. The divider (606,656,706) and a finite state machine (FSM) (612,662,712) of the exemplary CDR circuit (600,650,700) are manually programmed based on the data rate (614,667). Alternately, the data rate may be detected from a recovered serial data stream (718) during CDR operations (on-the-fly) utilizing a frequency detection circuit (725) to automatically program the divider (706) and FSM (712) to provide CDR circuit operation at the nearest base clock rate (716).

Owner:TEXAS INSTR INC

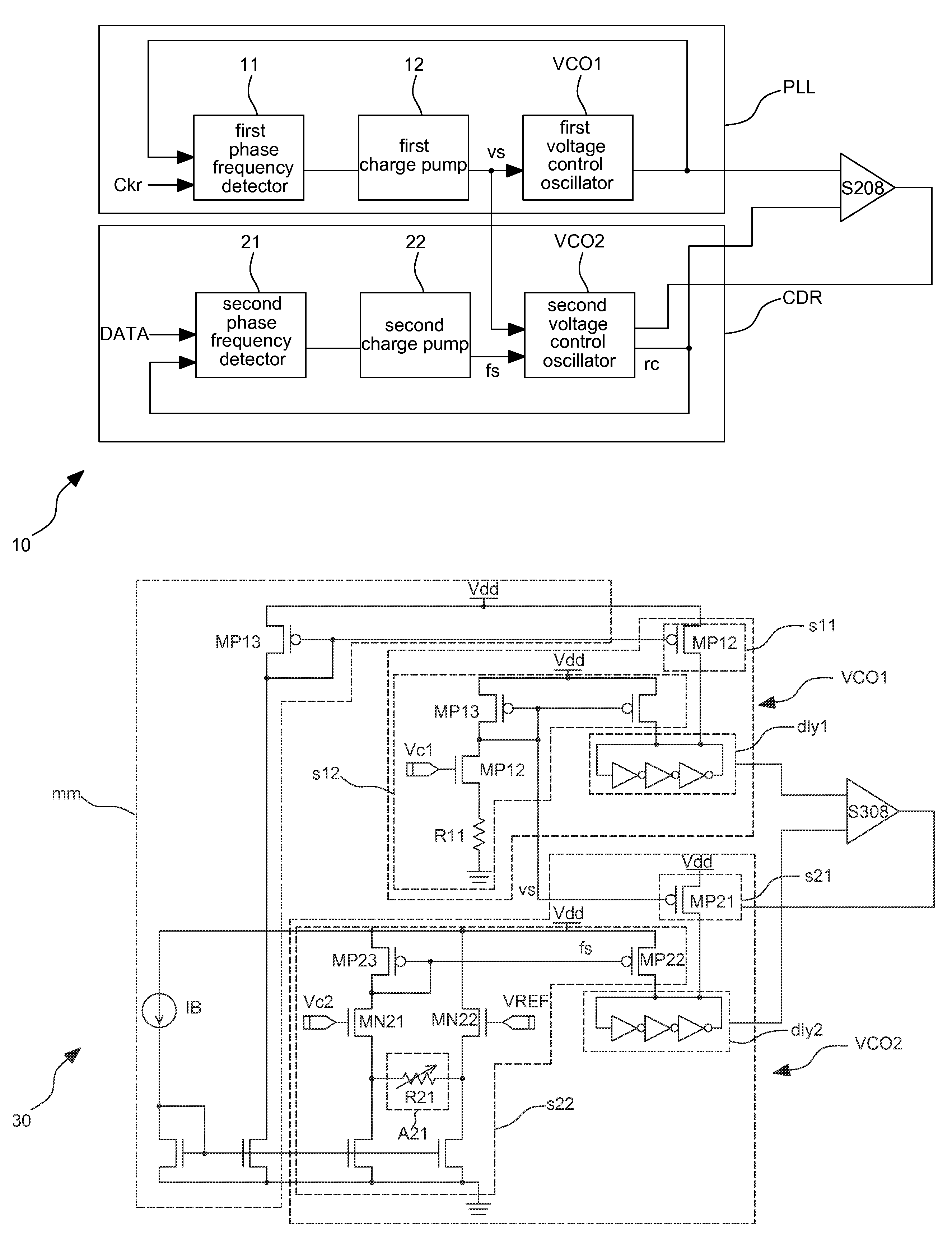

Transceiver, voltage control oscillator thereof and control method thereof

ActiveUS8928416B2Smaller VCO gainLarge rangePulse automatic controlPulse generation by logic circuitsTransceiverControl signal

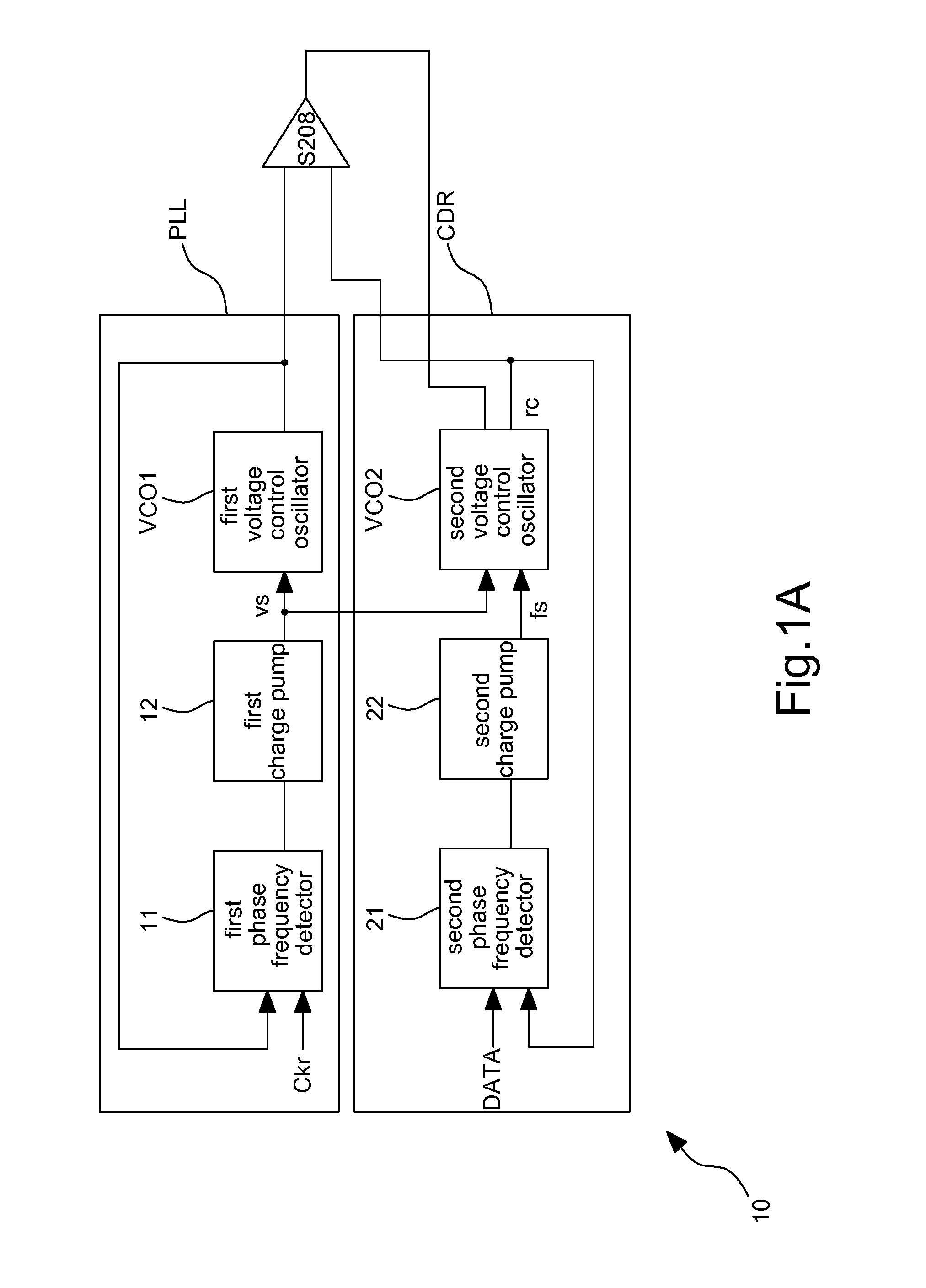

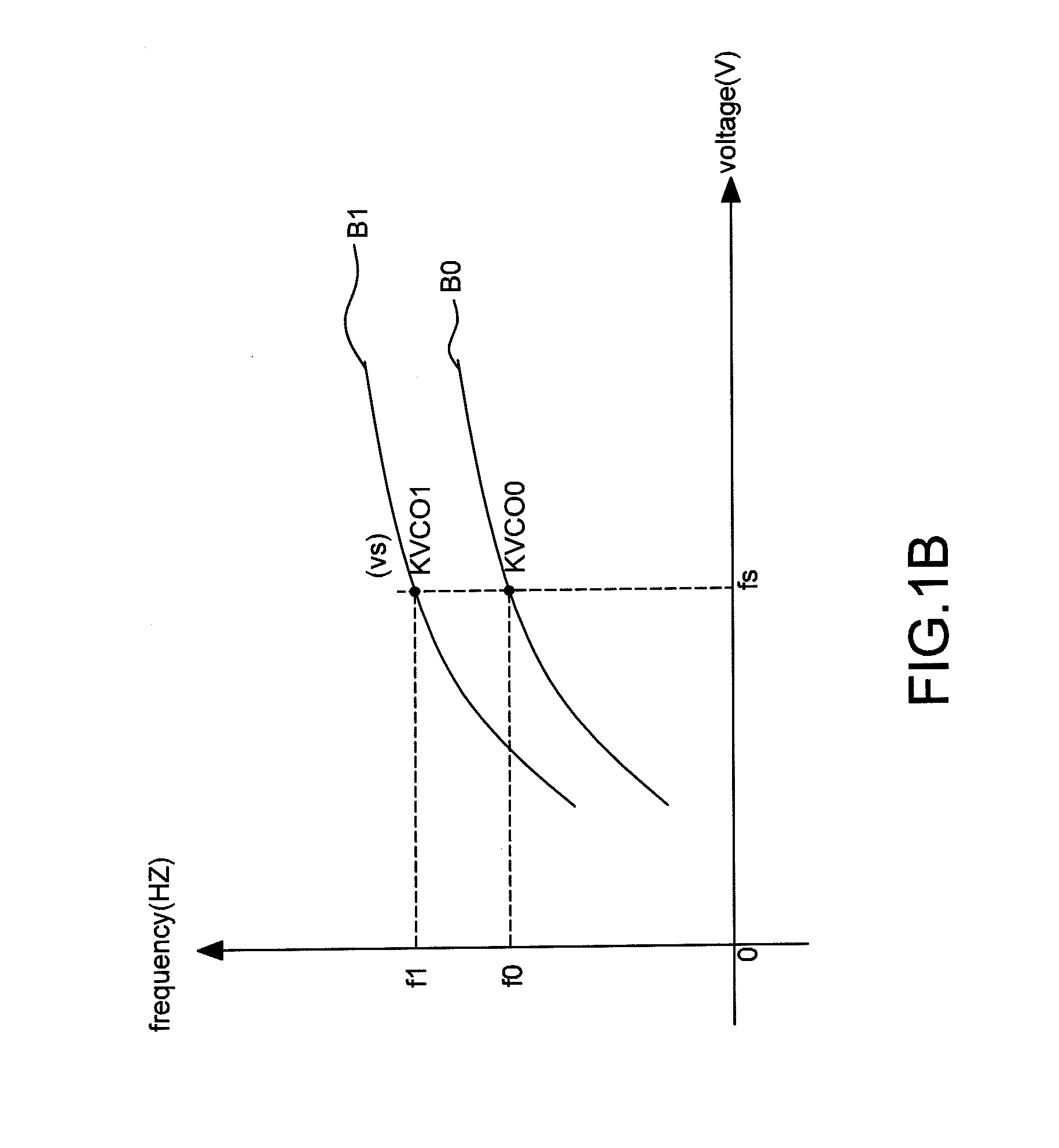

A transceiver includes a phase lock loop (PLL) and a clock data recovery circuit (CDR). The phase lock loop generates a first level control signal. The clock data recovery circuit, coupled to the phase lock loop, locks an incoming data signal to generate a data recovery clock according to a second level control signal. Wherein the clock data recovery circuit receives the first level control signal to further control a frequency range of the data recovery clock.

Owner:REALTEK SEMICON CORP

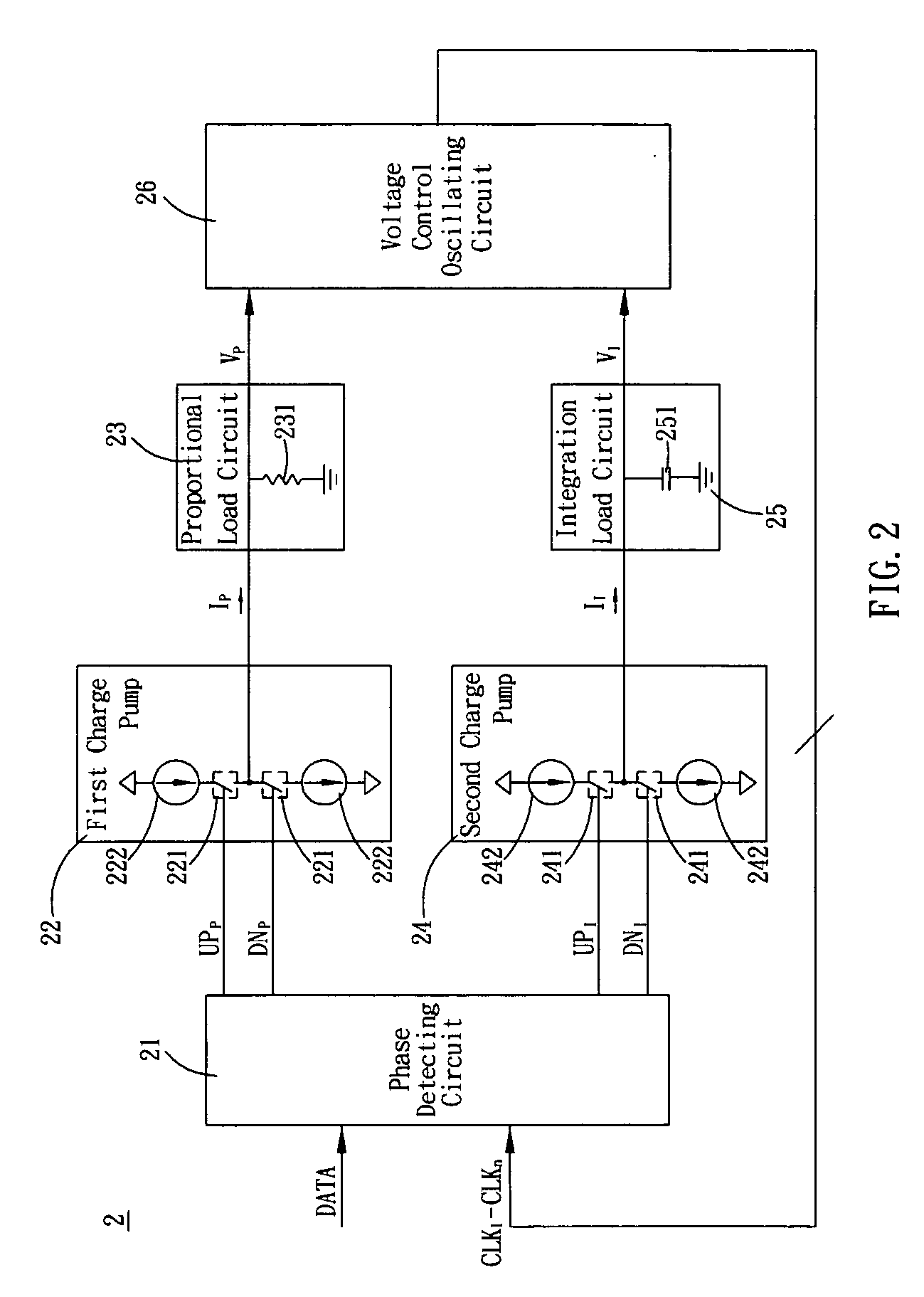

Clock and data recovery circuit and method thereof

ActiveUS20070001723A1Easy to optimizeEasy to regulatePulse automatic controlSynchronising arrangementLoad circuitProportional control

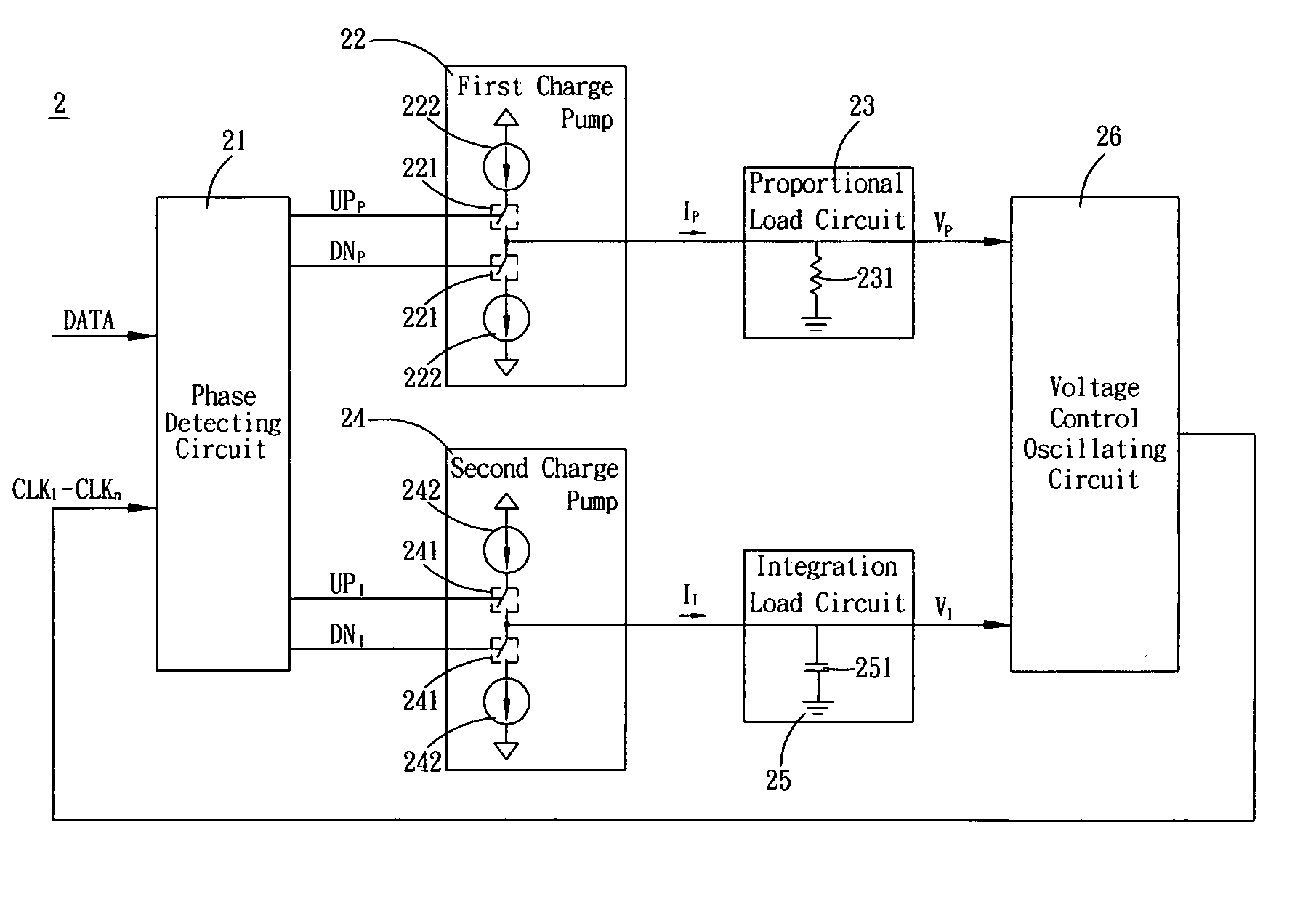

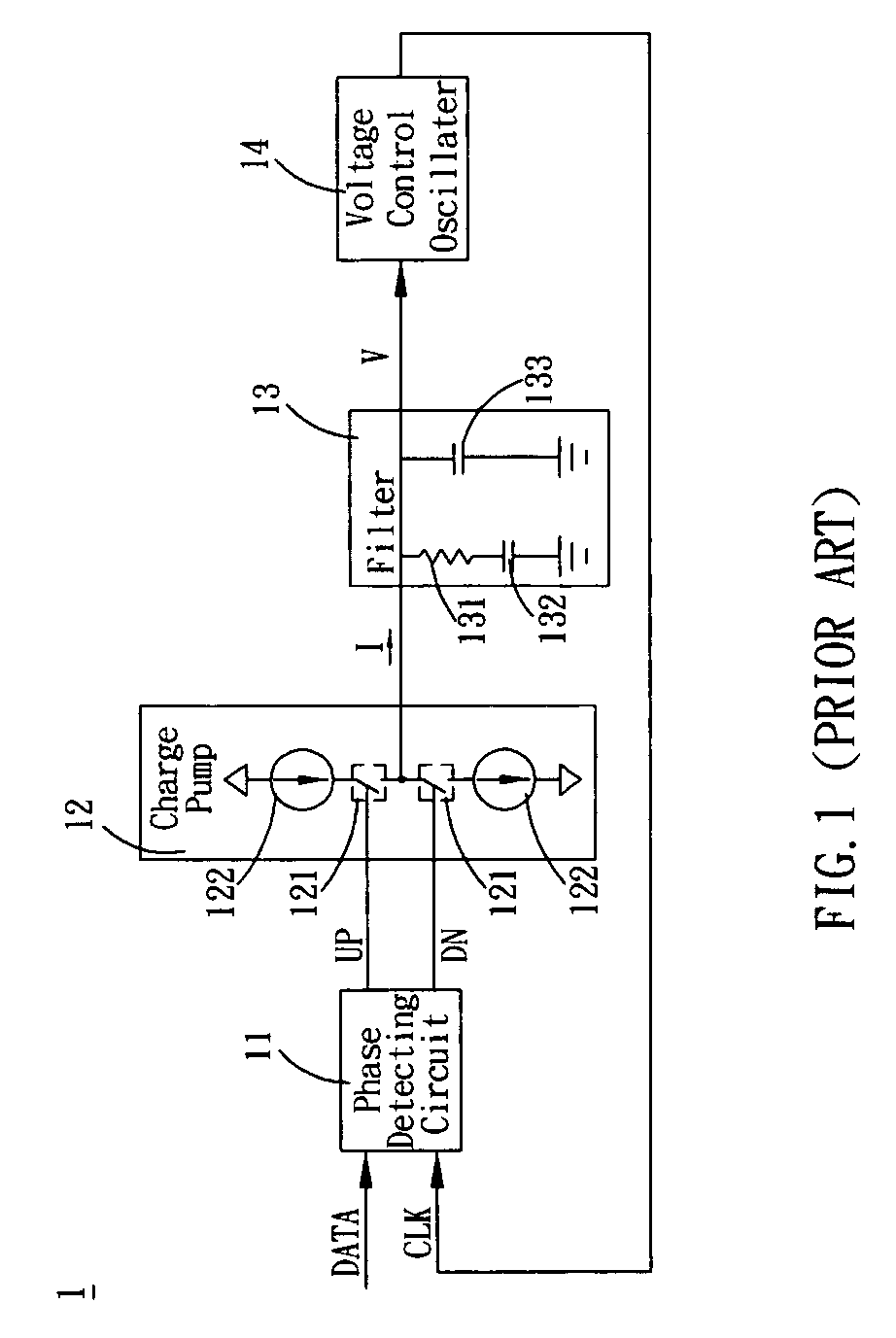

A clock and data recovery circuit having parallel dual path is disclosed, which includes a phase detecting circuit, a first charge pump, a proportional load circuit, a second charge pump, an integration load circuit, and a voltage control oscillating circuit. The phase detecting circuit respectively compares a phase difference between a data signal and a plurality of clock signals to generate two proportional control signal and two integration control signal for respectively controlling the first charge pump and the second charge pump to generate a first current and a second current. The proportional load circuit and the integration load circuit respectively receive the first current and the second current to output a proportional voltage and an integration voltage. The voltage control oscillating circuit adjusts the phase and frequency of the plurality of clock signals in response to the proportional voltage and the integration voltage.

Owner:VIA TECH INC

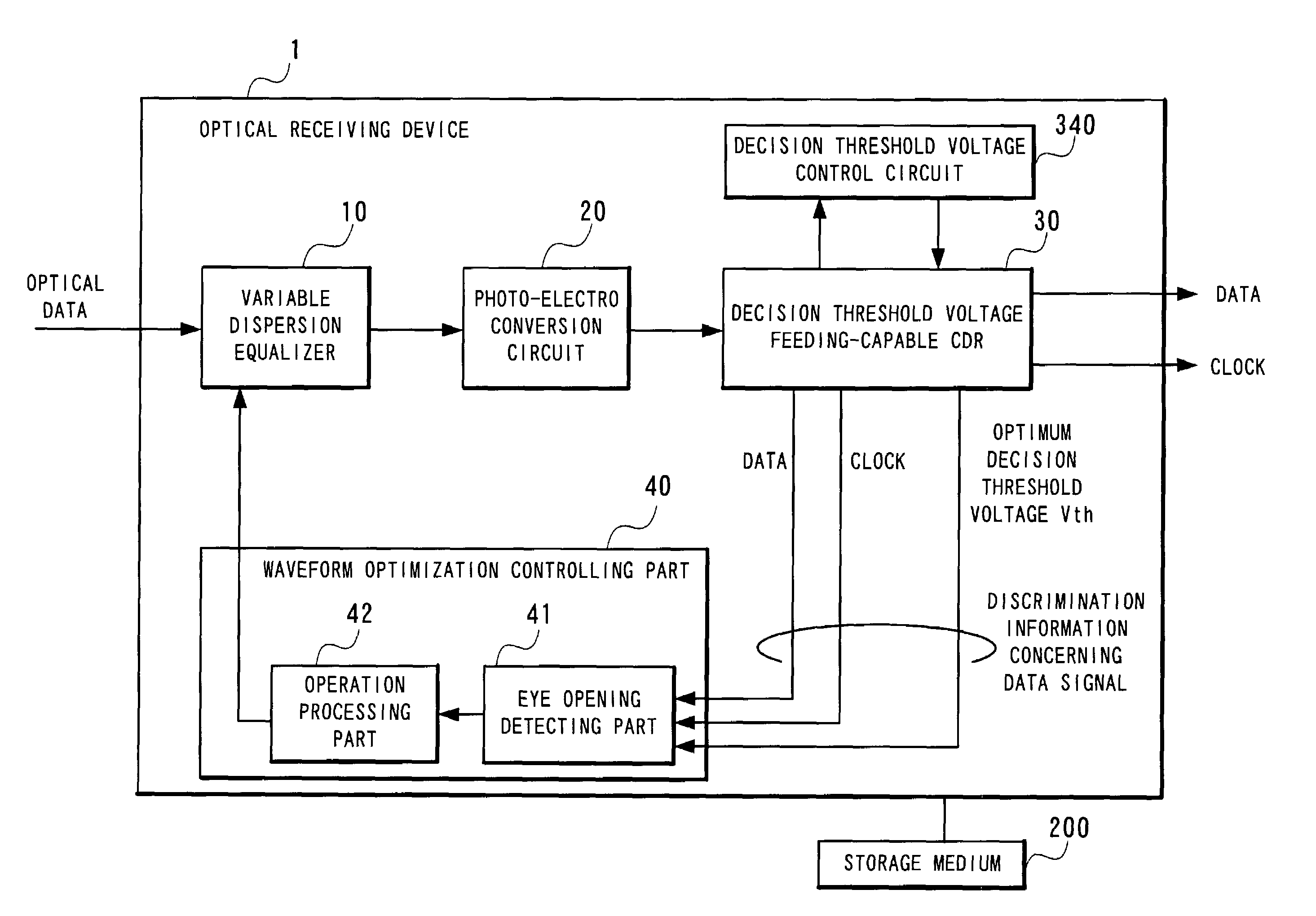

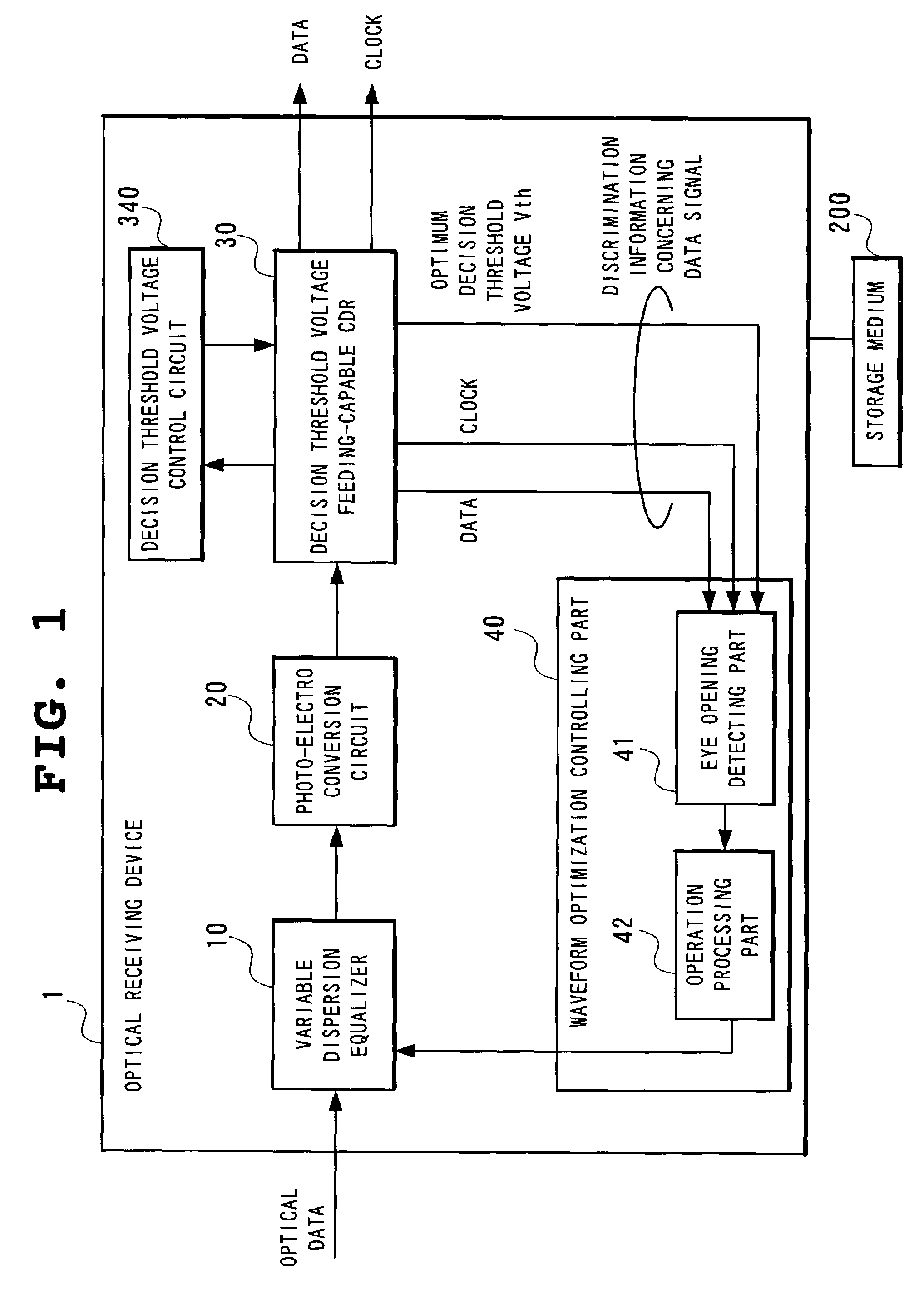

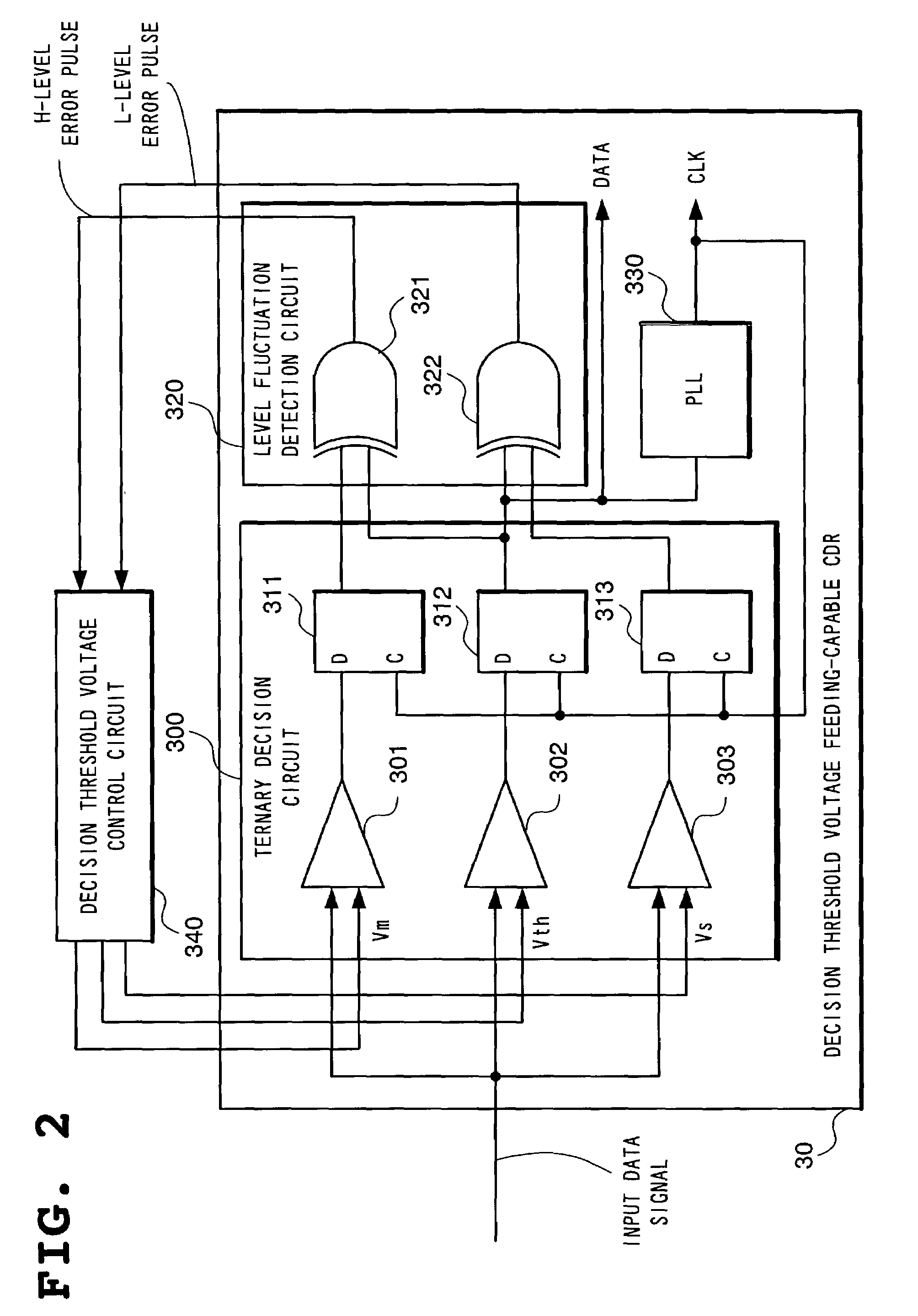

Optical receiving device, waveform optimization method for optical data signals, and waveform optimization program for optical data signals

InactiveUS7123846B2Improve waveformOptimize optical waveformTelevision system detailsFilamentary/web record carriersData signalControl data

This optical receiving device for discriminating and recovering a data signal, which results from converting an optical signal input through a dispersion equalizer into an electrical signal and amplifying it to a pre-determined amplitude, by using a clock and data recovery circuit for discriminating a data signal at the decision point controlled to achieve the optimum position controls the dispersion characteristics of a dispersion equalizer so that the error count in the recovered data signal by using a clock and data recovery circuit will be minimized by controlling the eye pattern of the data signal which has been amplified to a pre-determined amplitude.

Owner:NEC CORP

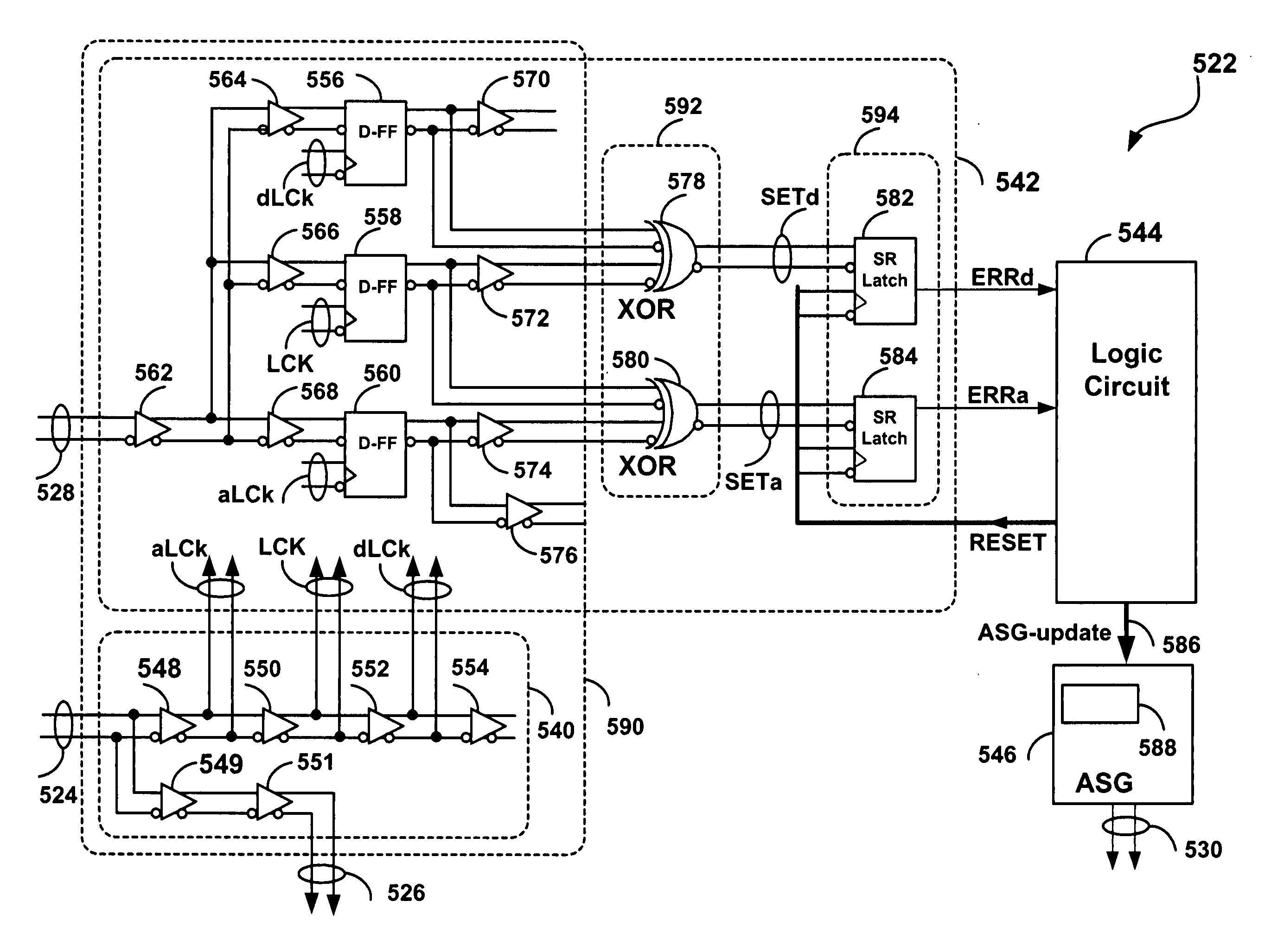

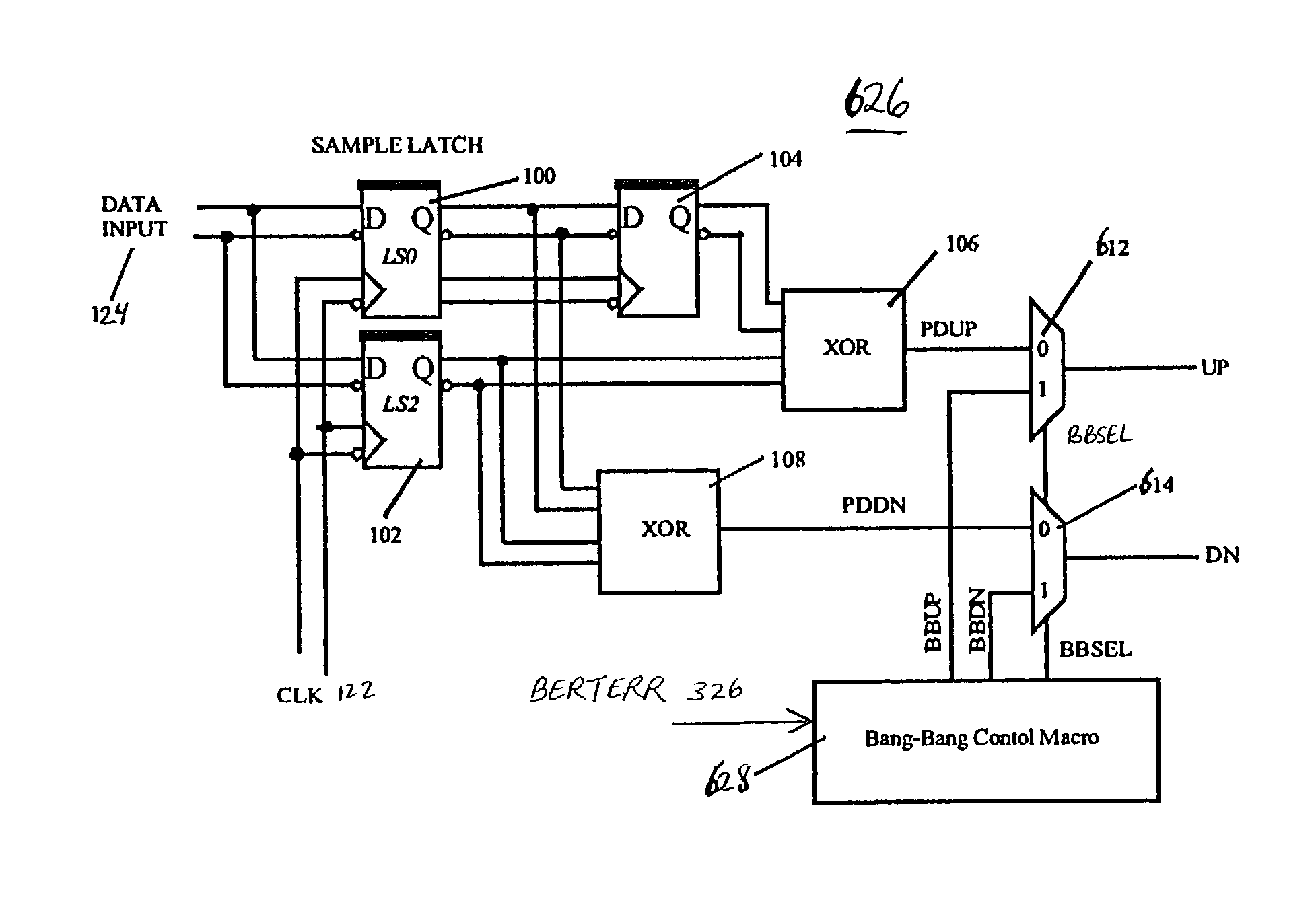

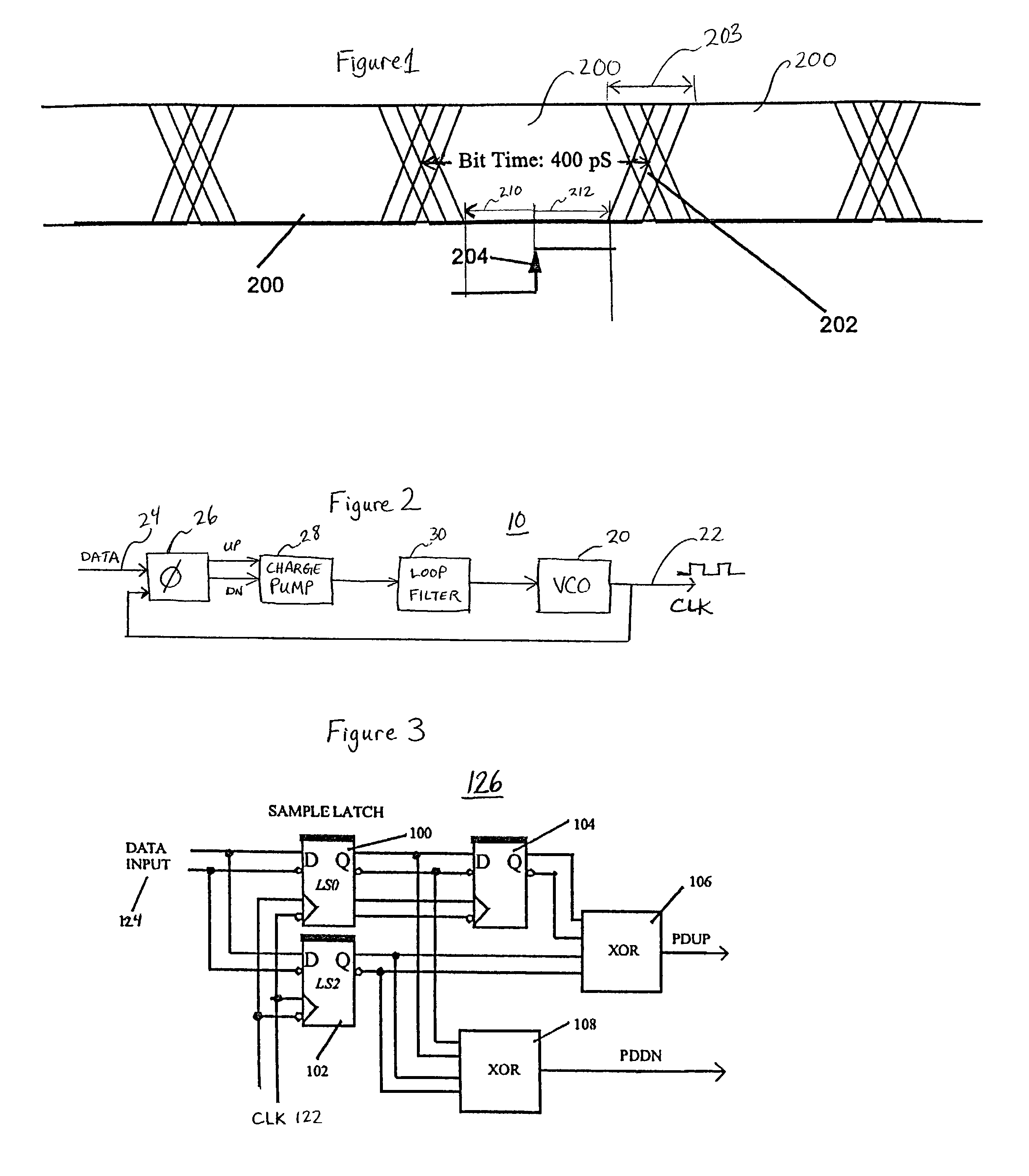

Circuit for adaptive sampling edge position control and a method therefor

ActiveUS20060034394A1Pulse automatic controlPhase-modulated carrier systemsDigital dataPosition control

A clock and data recovery circuit (CDR) for receiving high-speed digital data, and having an analog phase offset control capability, is improved by providing an adaptive sampling edge position control. A differential circuit samples the raw data signal at three closely spaced sampling points of the eye, and compares advanced and delayed sampled data with the nominal sampled data. If either the advanced or delayed sampled data differ from the nominal sampled data, i.e. if advanced or delayed errors are detected, a shift in the sampling edge position may be required. A logic circuit performs a method determining the occurrence of advanced or delayed errors over progressively longer time intervals, and to adjust the sampling edge position of the CDR by controlling the phase offset.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

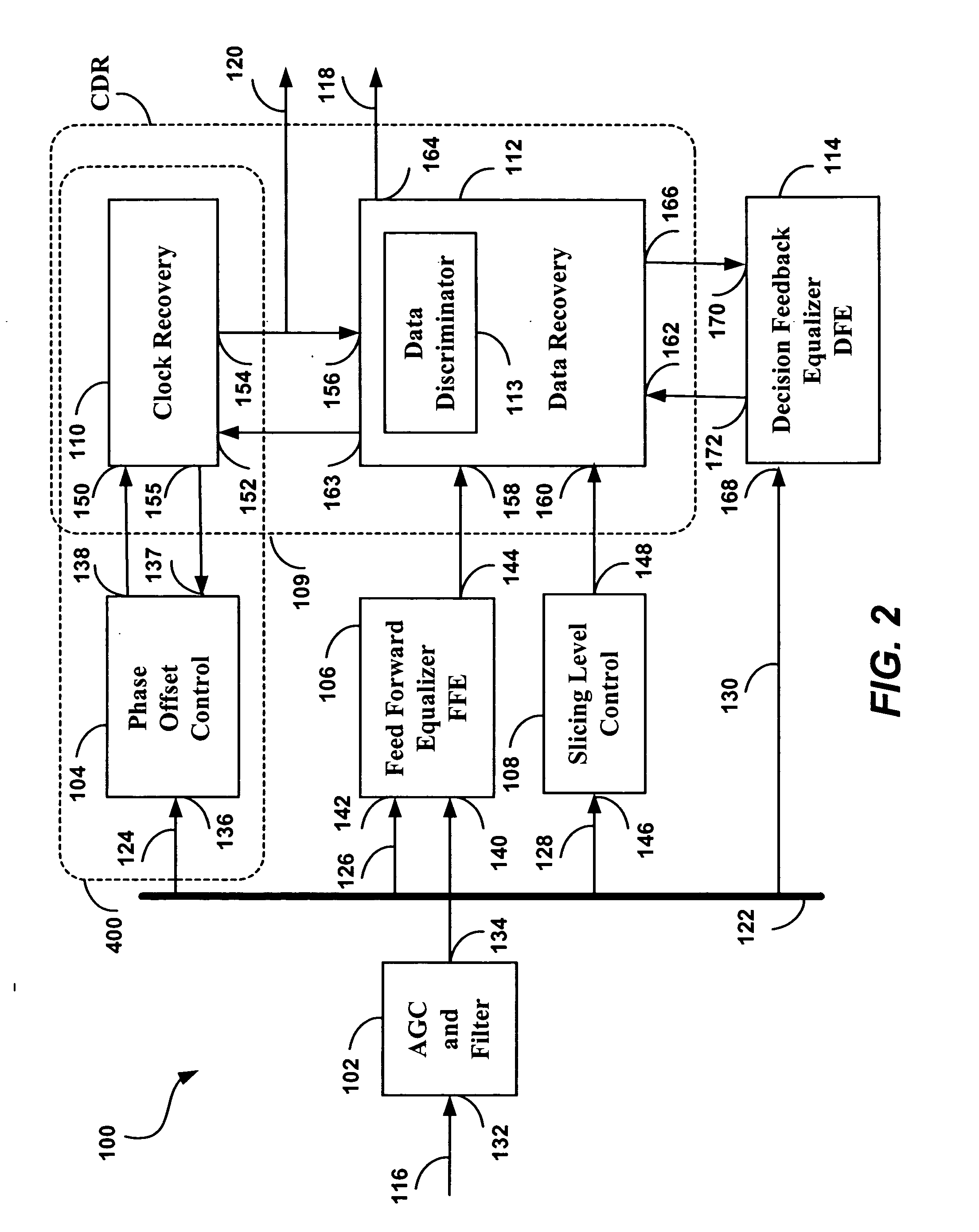

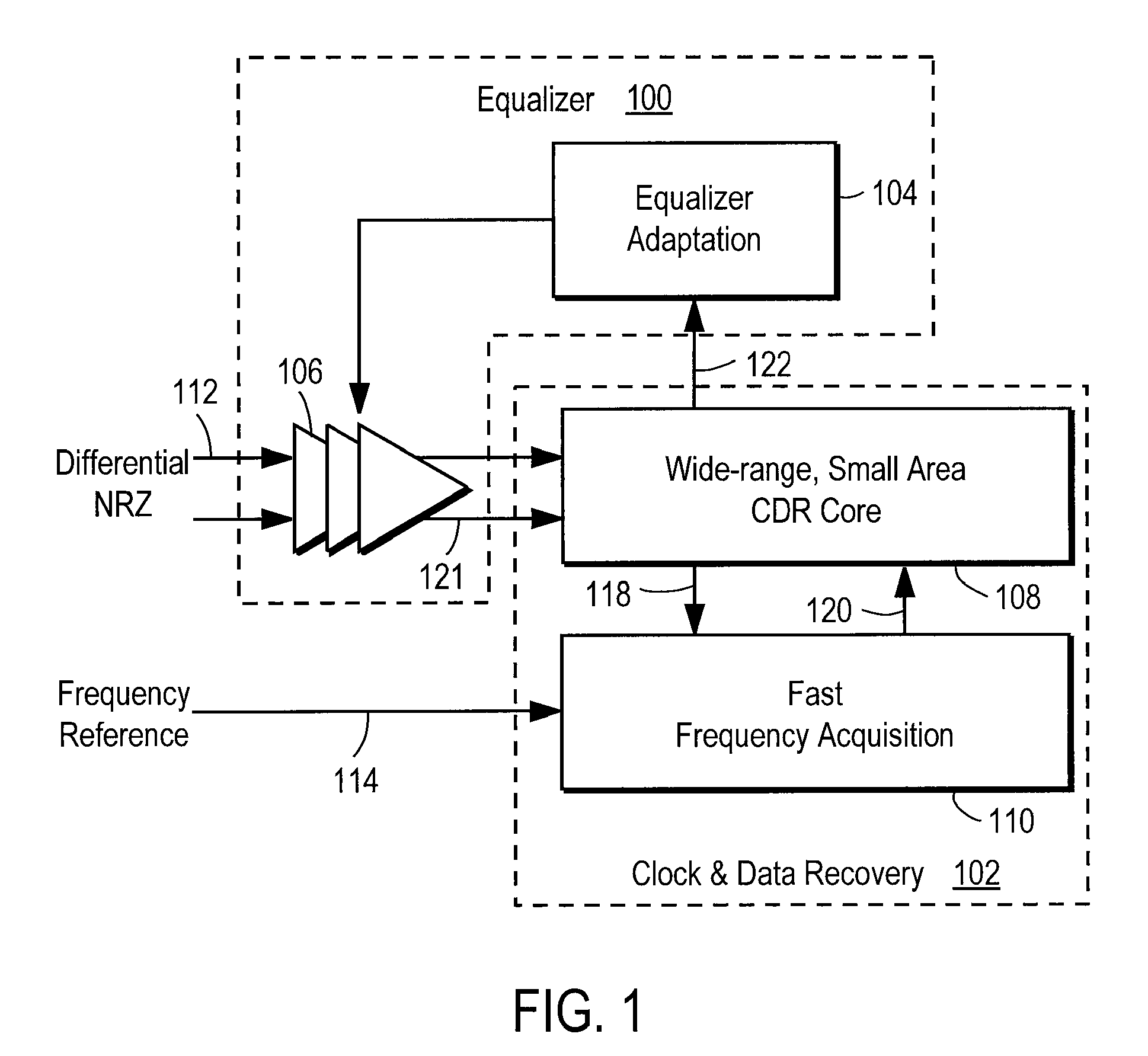

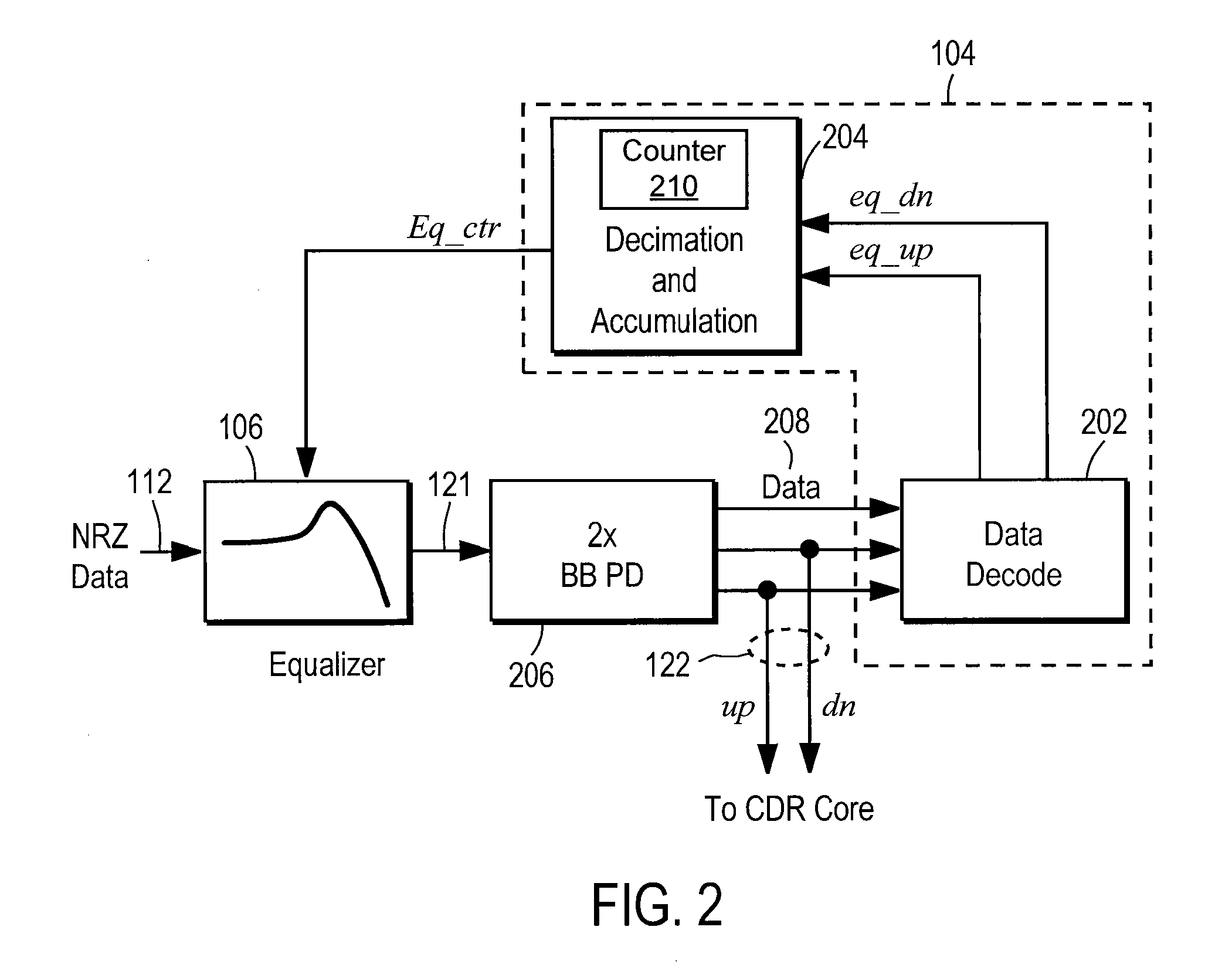

Adaptive equalizer for use with clock and data recovery circuit of serial communication link

ActiveUS20080247452A1Low costEffort-saving designMultiple-port networksReceiver initialisationPhase detectorTime information

An adaptive equalizer system for use in a serial communication link uses timing information generated by a phase detector of a clock and data recovery circuit of the serial communication link and a frequency pattern of the recovered data to determine whether the data received over the serial communication link is over-equalized or under-equalized. The equalizer strength of the adaptive equalizer system is adjusted based on such determination.

Owner:SILICON IMAGE INC

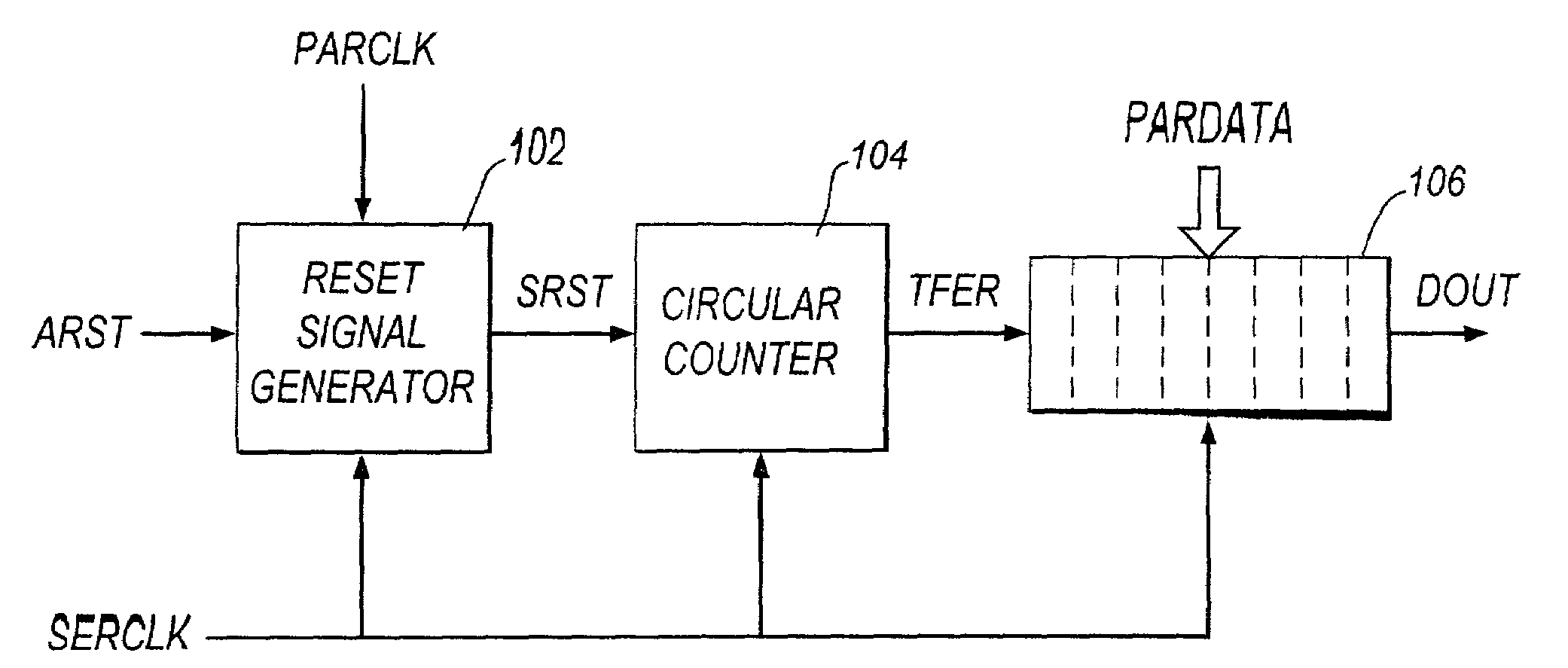

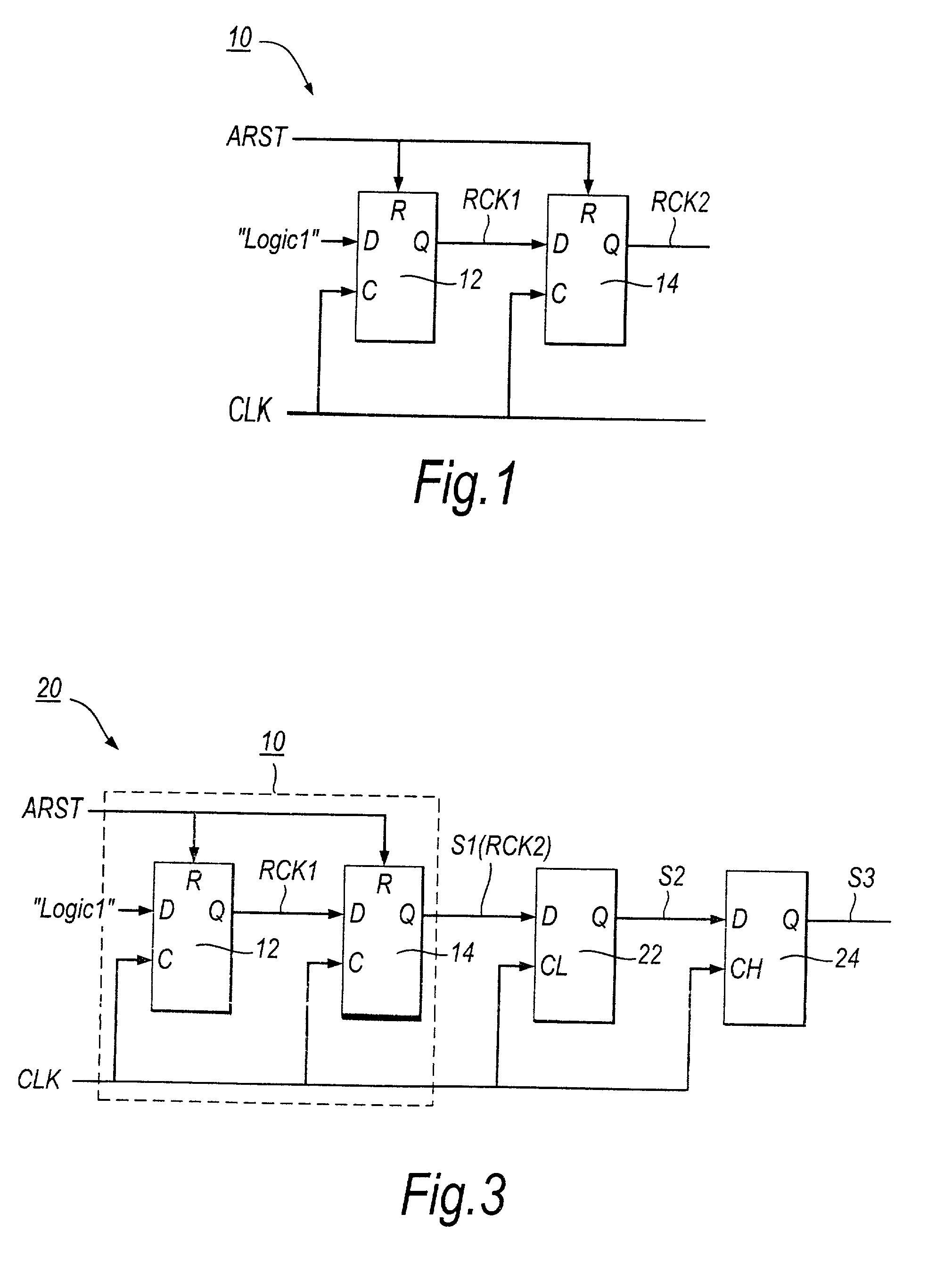

Processing high-speed digital signals

ActiveUS7187738B2Reduce controlMeet high-speed operationChannel dividing arrangementsPulse automatic controlData synchronizationData stream

A first transparent latch receives a first synchronised signal changing its logic state synchronously with respect to a clock signal. A second transparent latch receives a second synchronised signal output by the first latch. When the clock signal has a first logic state the first latch has a non-responsive state and the second latch has a responsive state, and when the clock signal has a second logic state the first latch has the responsive state and the second latch has the non-responsive state. The change in logic state of a third synchronised signal output by the second latch is guaranteed to occur in a particular half-cycle of the clock signal, irrespective of process / voltage / temperature (PVT) variations of the circuitry. Clock recovery circuitry may have rising-edge and falling-edge latches; circulating control pattern verification circuitry; data synchronising circuitry for converting parallel data clocked by a first clock signal into serial data clocked by a second clock signal asynchronous with the first clock signal; and data recovery circuitry for producing an offset clock signal which suits a data eye shape of a received serial data stream.

Owner:SOCIONEXT INC

On-chip system and method for measuring jitter tolerance of a clock and data recovery circuit

An integrated circuit is operable to measure tolerance to jitter in a data stream signal. A Clock And Data Recovery Circuit (“CDR”) thereon recovers a phase of a clock for sampling a data stream signal containing a repeatable known sequence of data values and then samples the data stream signal with the recovered clock phase to obtain data stream sample data. An error rate determination circuit independently generates the repeatable known sequence of data values and compares them with the data stream sample data to determine an associated error rate. A control circuit coupled to the CDR delays the recovered clock phase by a predetermined amount a plurality of times and monitors the error rate after each time it delays the recovered clock phase. In this way, a maximum delayed clock phase is determined, representing a right timing signal margin for which the data stream signal can be sampled.

Owner:IBM CORP

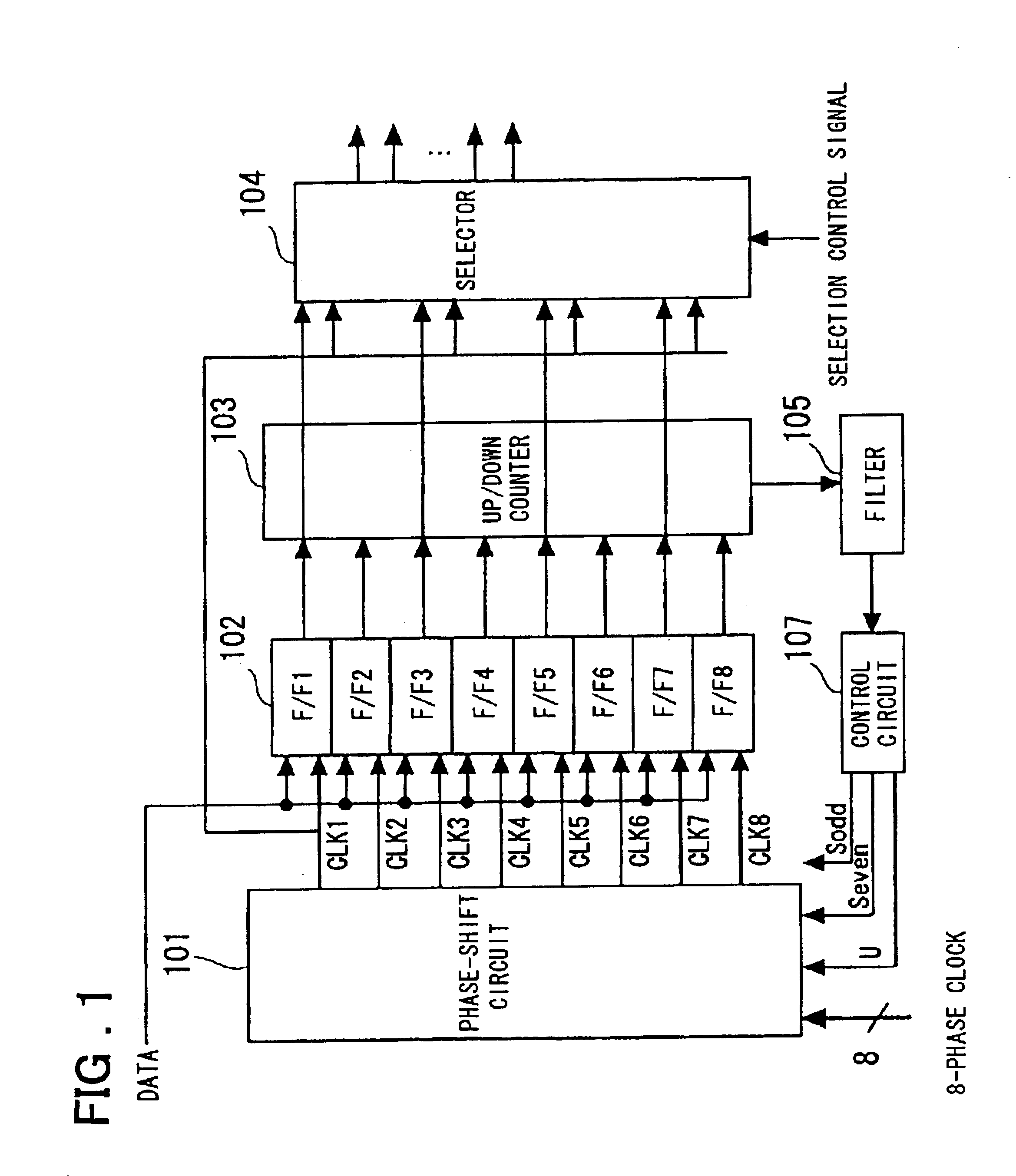

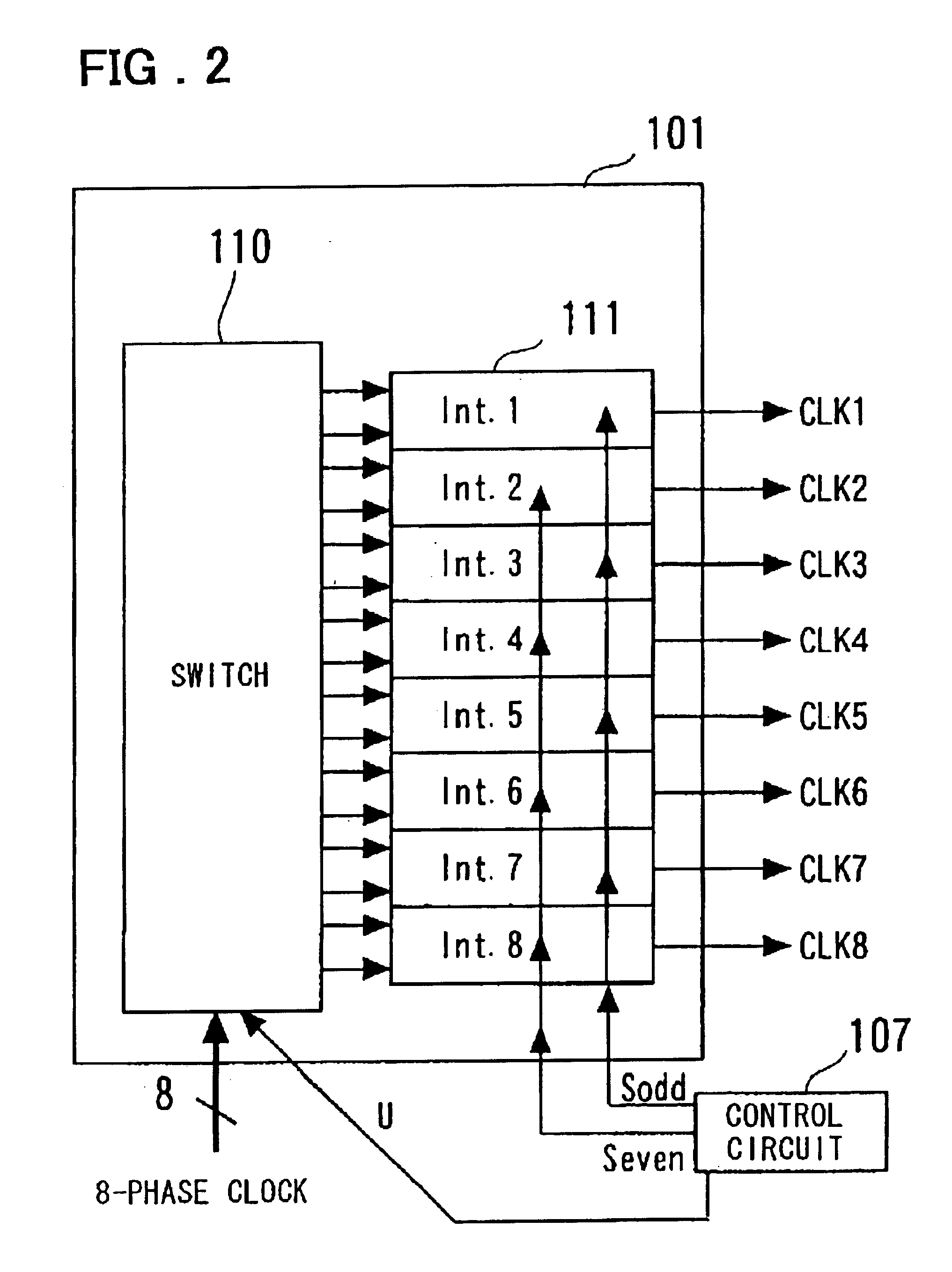

Clock and data recovery circuit and clock control method

InactiveUS20020079938A1Easy to characterizeFacilitate change of frequencyPulse automatic controlSingle output arrangementsPhase shiftedPhase difference

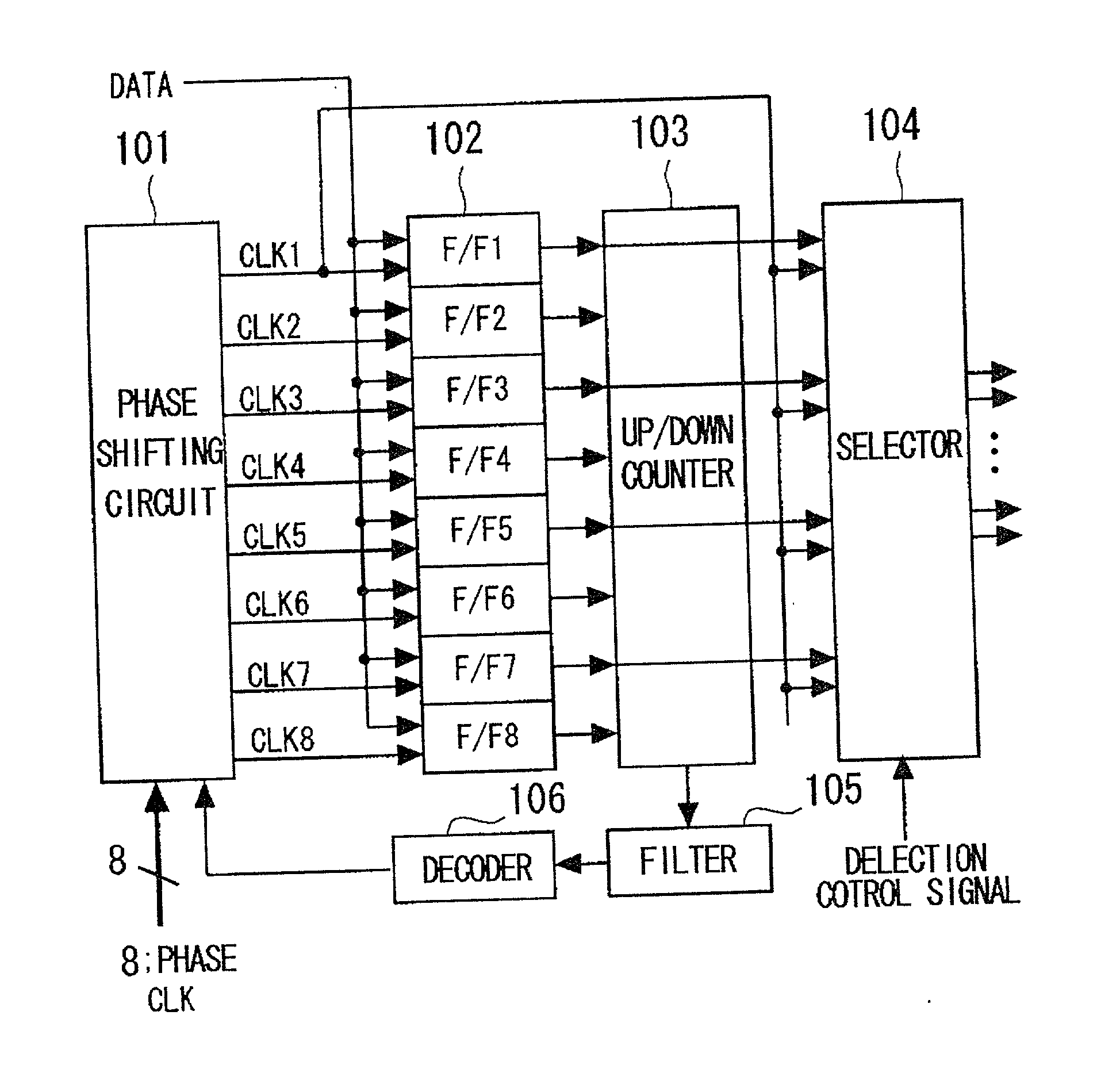

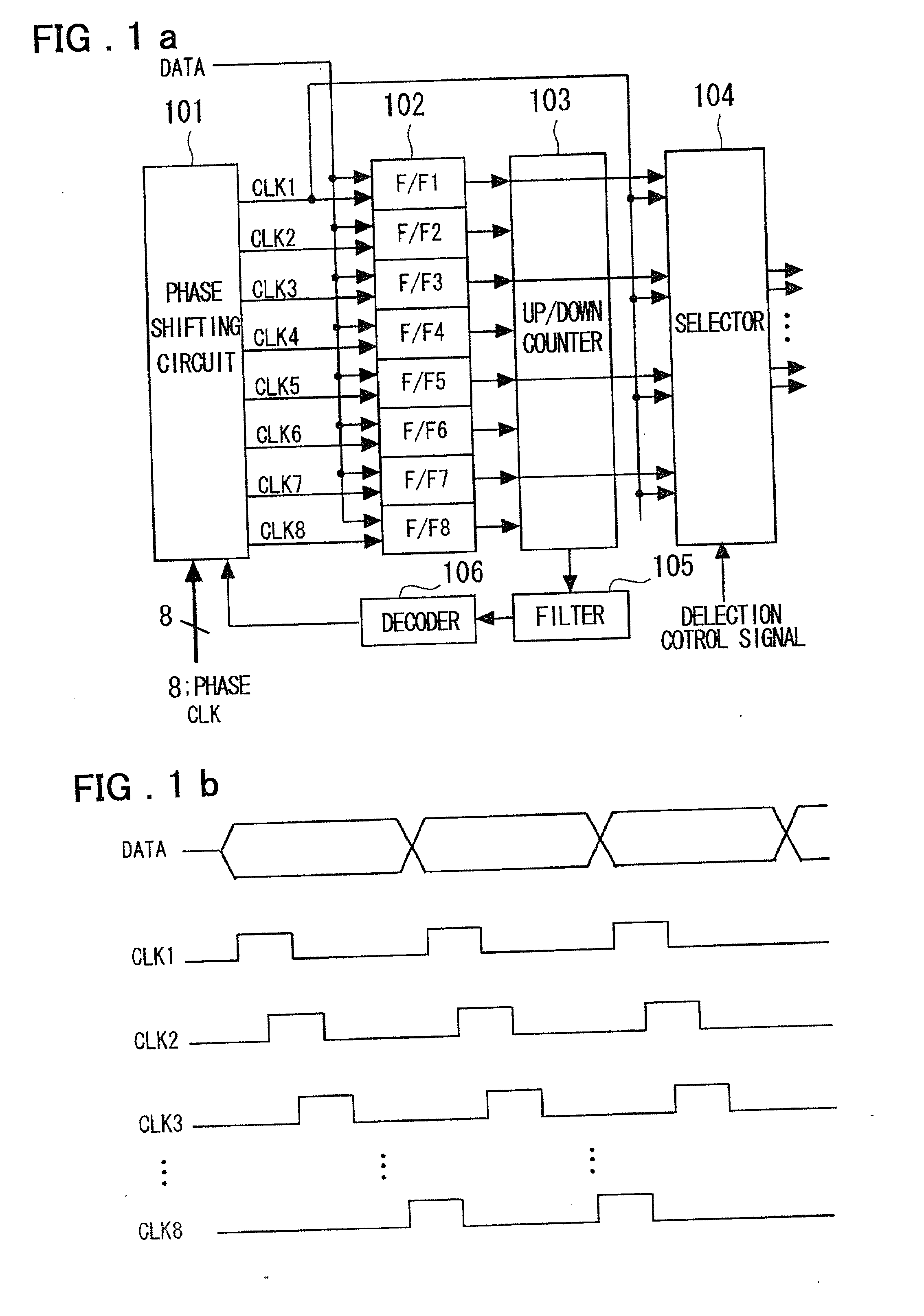

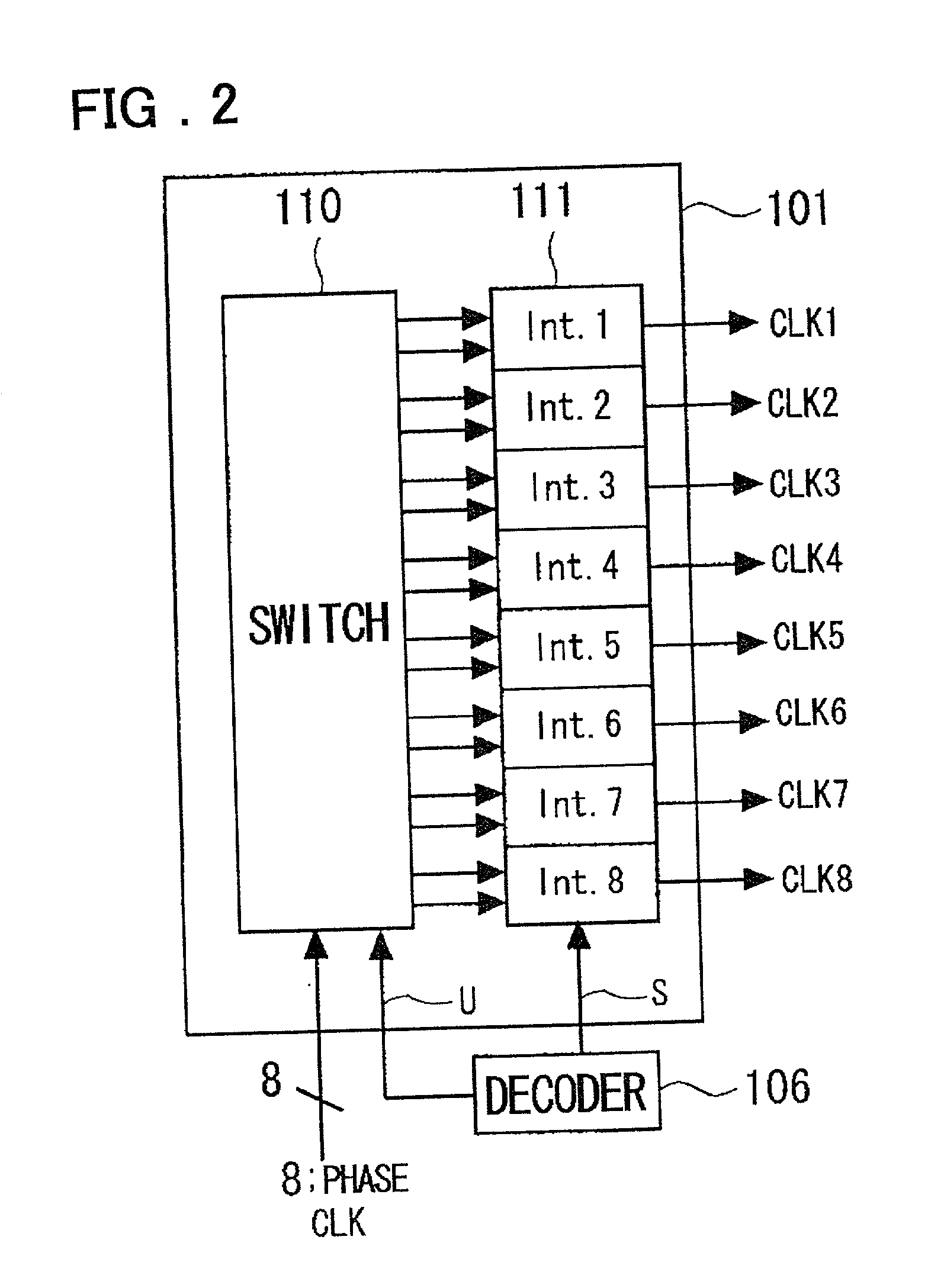

To provide a clock and data recovery circuit which facilitates alteration of the frequency range and adjustment of characteristics. The clock and data recovery circuit includes a phase shift circuit 101 having a switch receiving as inputs multi-phase clocks for selecting and outputting plural sets of the paired clocks from the input multi-phase clocks and a plural number of interpolators receiving the plural number of clock pairs output from the switch to output signals having the delay prescribed by the time corresponding to interior division of the phase difference of the clock pairs, a plural number of latch circuits 102 for latching the input data based on the signals output from the phase shift circuit 101, a counter 103 for counting the outputs of the plural latch circuits, a filter 105 for averaging the counter output over a preset time, a decoder 106 for decoding an output of the filter and a selection circuit 104 fed with a plural number of sets of data output by the plural latch circuits and clocks output from a preset one of the plural interpolators to select pairs of output data and clocks.

Owner:RENESAS ELECTRONICS CORP

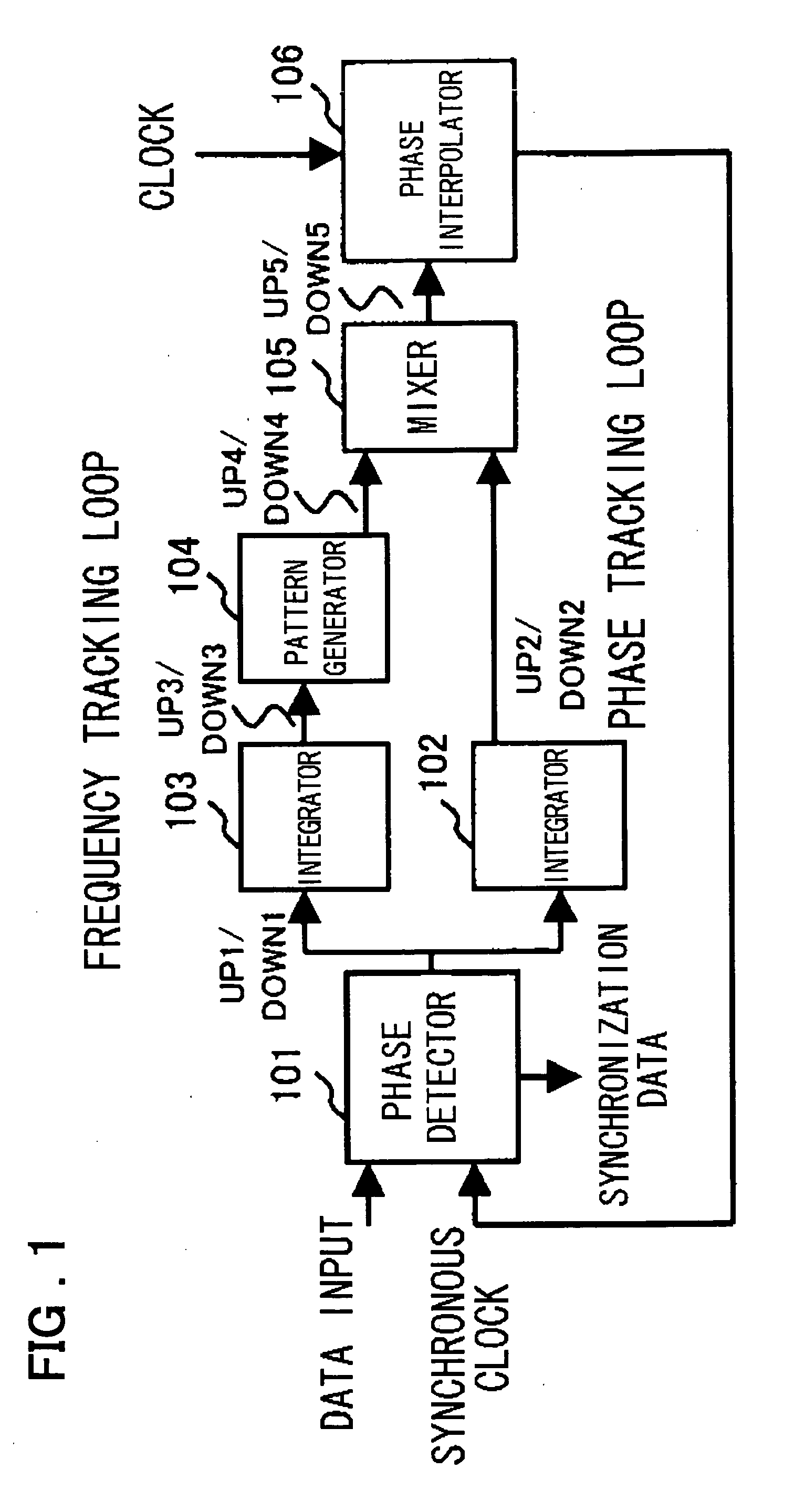

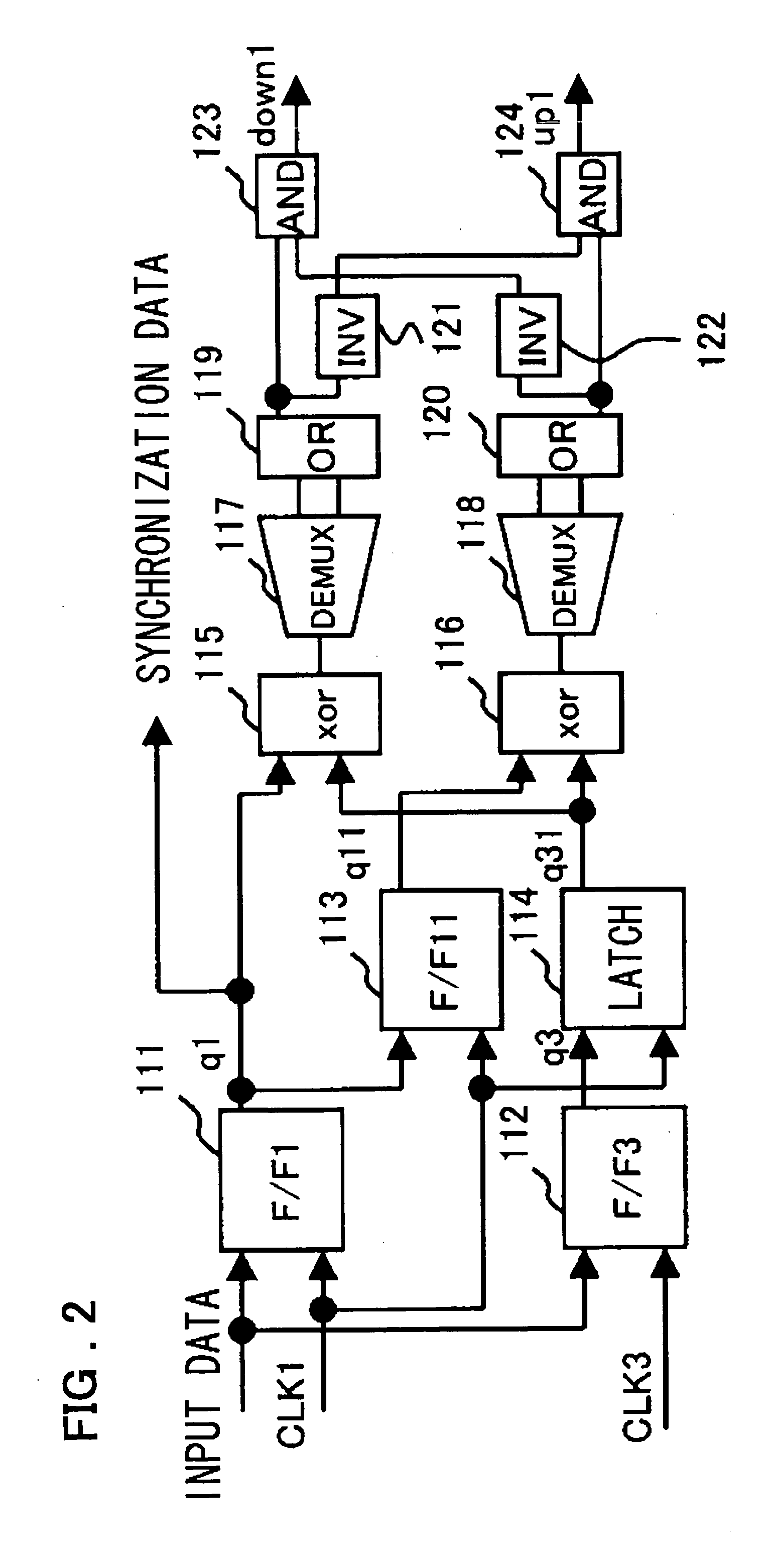

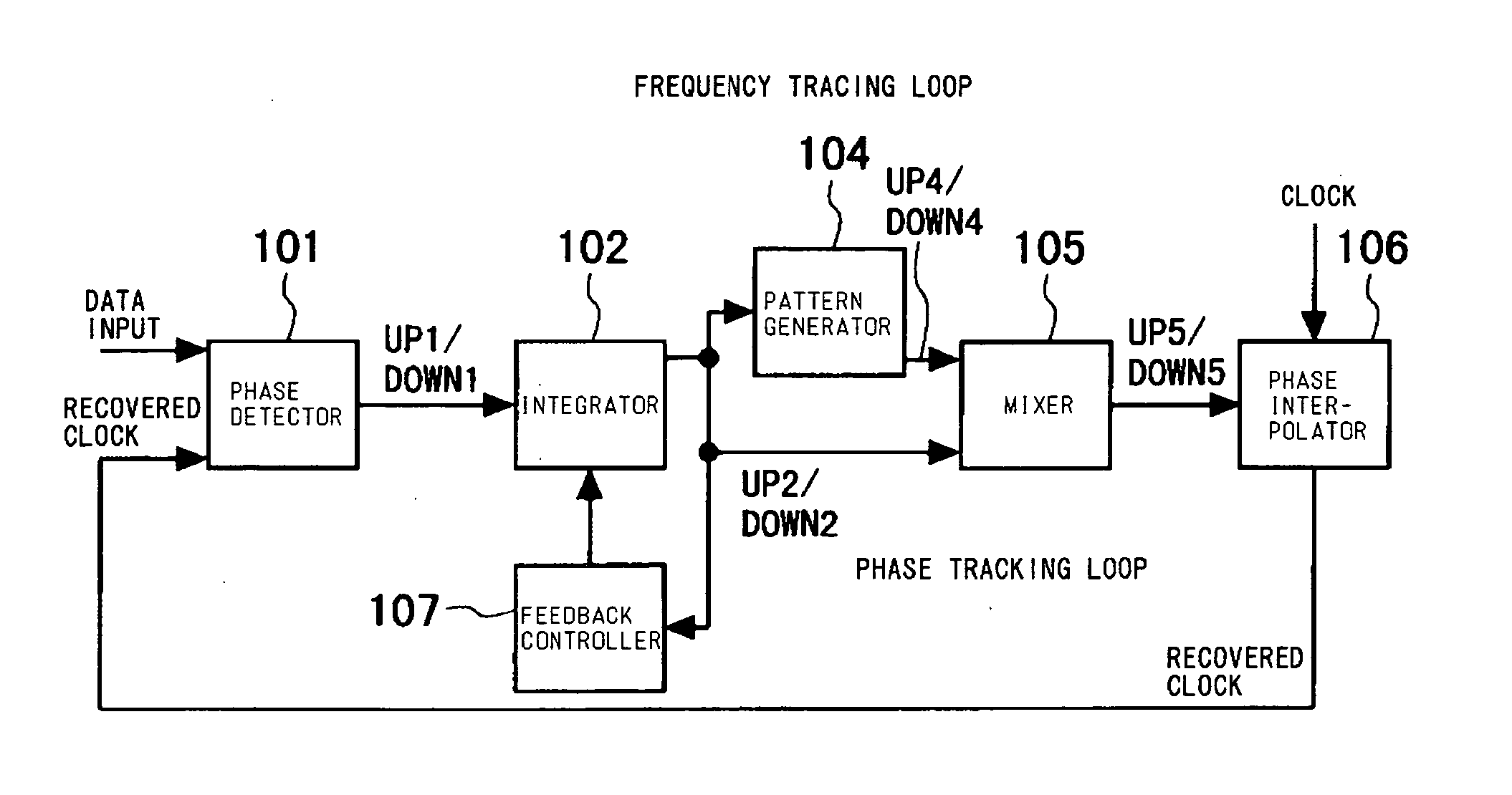

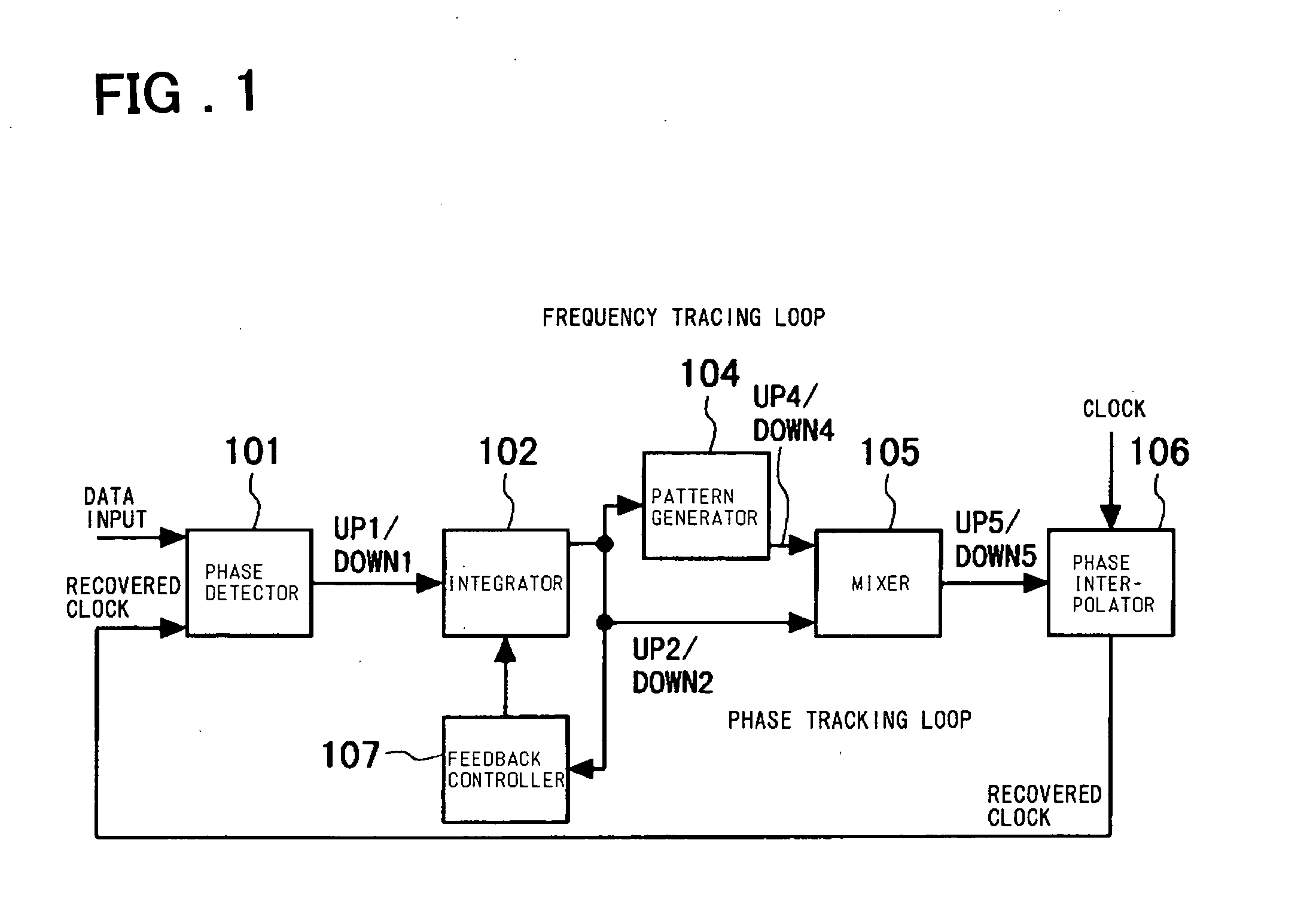

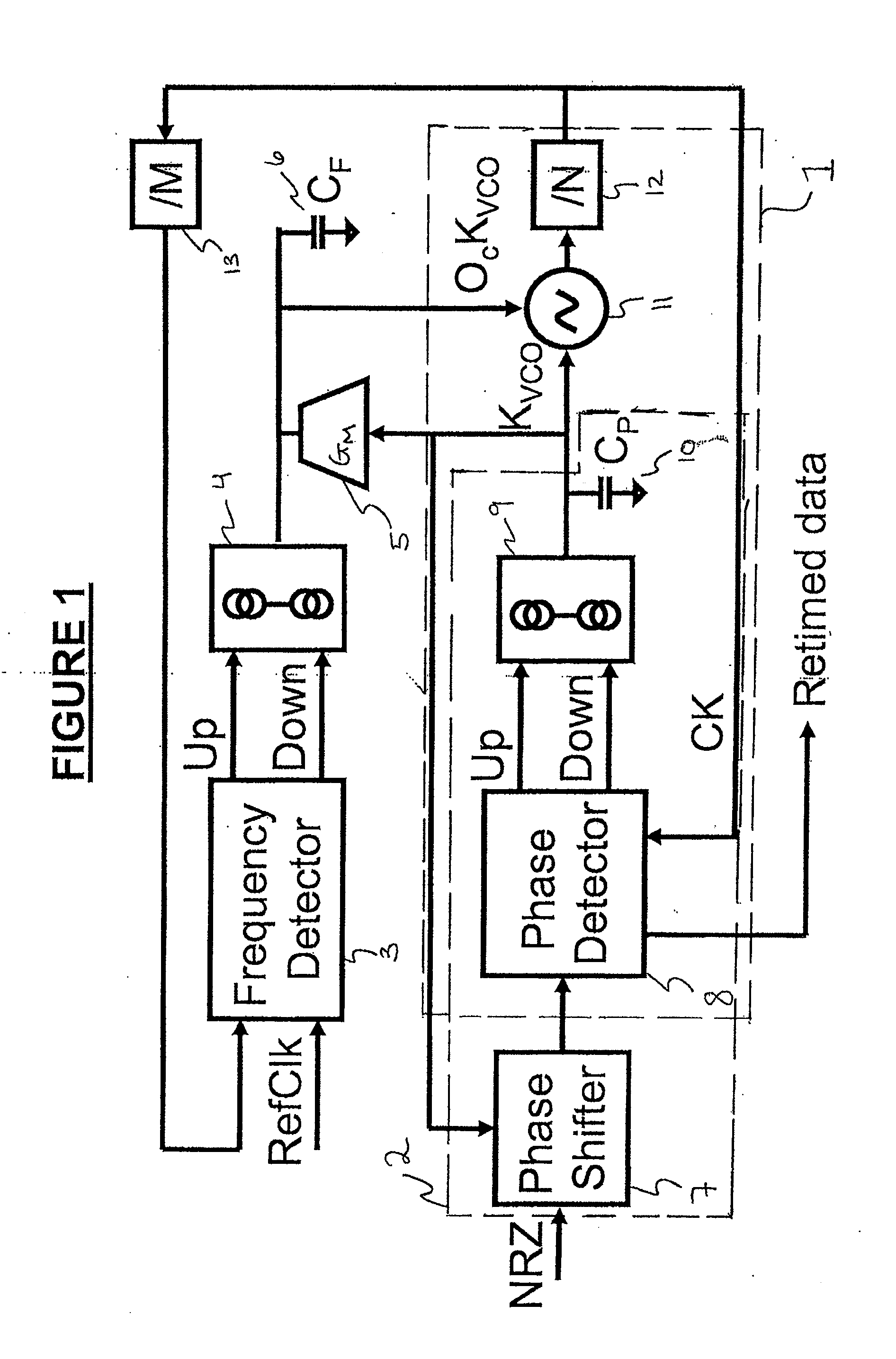

Clock and data recovery circuit

ActiveUS20040252804A1Increase in chip sizeIncreasing chip sizePulse automatic controlOscillations comparator circuitsPhase detectorIntegrator

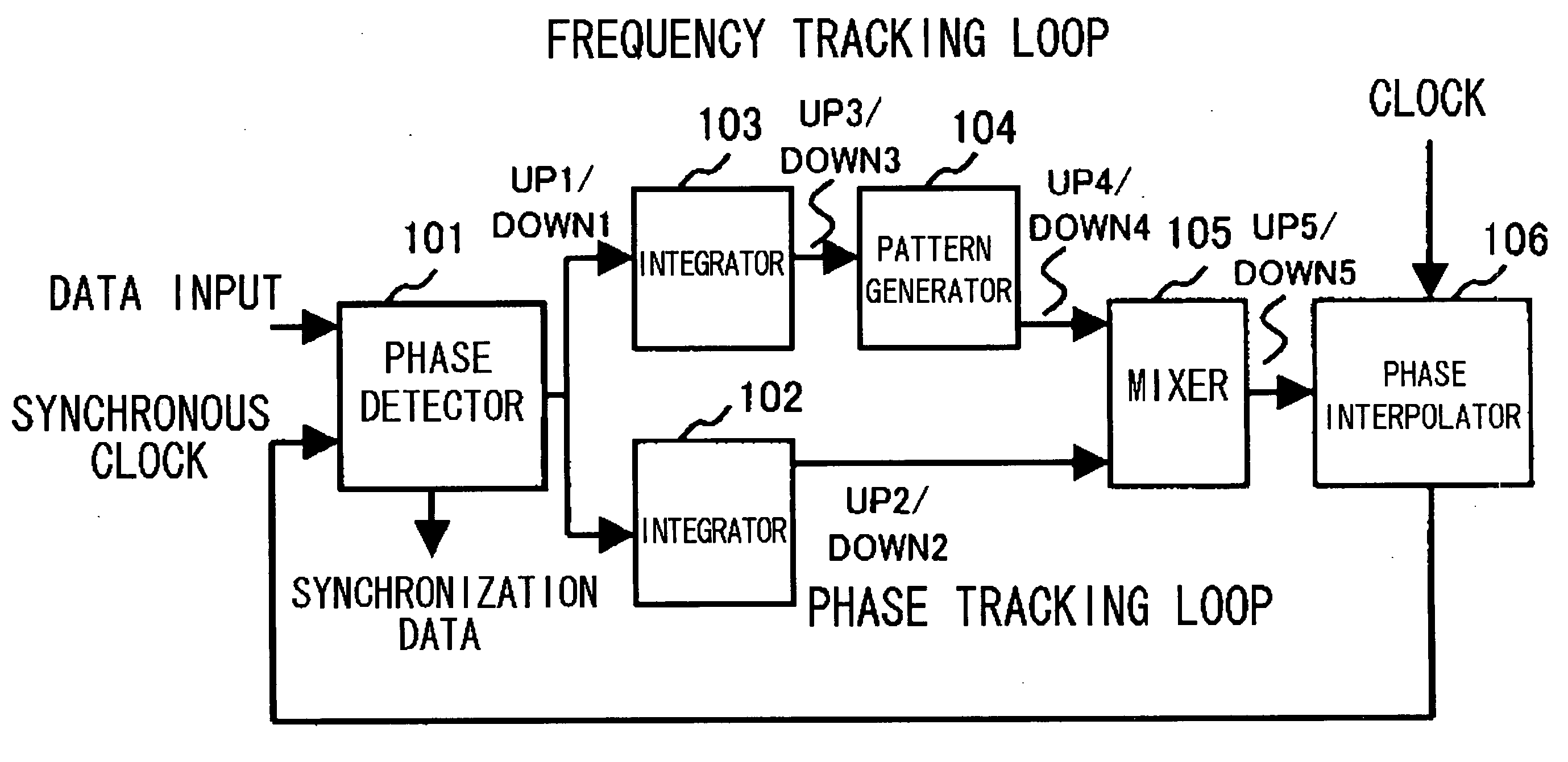

A clock and data recovery circuit, for tracking frequency-modulated input data, comprises a phase detector for receiving a data signal and a synchronous clock signal, detecting a phase delay or a phase advance, and outputting an UP1 / DOWN1 signal, first and second integrators for integrating the UP1 / DOWN1 signal and outputting an UP2 / DOWN2 signal and an UP3 / DOWN3 signal, respectively, a pattern generator for receiving the UP3 / DOWN3 signal from the second integrator to output an UP4 / DOWN4 signal, a mixer for receiving the UP2 / DOWN2 signal from the first integrator and the UP4 / DOWN4 signal from the pattern generator and generating an UP5 / DOWN5 signal for output, and a phase interpolator for interpolating the phase of an input clock signal based on the UP5 / DOWN5 signal from the mixer, for output are provided. A clock signal output from the interpolator is fed back to the phase detector as the clock.

Owner:RENESAS ELECTRONICS CORP

Apparatus and method for calibrating the frequency of a clock and data recovery circuit

Embodiments of the invention include an apparatus and method for continuously calibrating the frequency of a clock and data recovery (CDR) circuit. The apparatus includes a delay arrangement that generates a gating signal, and a gated voltage-controlled oscillator that is enabled by the gating signal. The gated voltage-controlled oscillator generates a recovered clock signal that is based on the data signal input to the CDR circuit. The apparatus also includes a frequency control loop that continuously calibrates the gated voltage-controlled oscillator in such a way that the frequency of the clock signal generated by the gated voltage-controlled oscillator continues to be one half of the period of the data bits in the input data signal and the clock signal remains synchronized to the center of the data state transitions of the input data signal. Alternatively, a secondary frequency control loop adjusts the amount of delay in the frequency control loop.

Owner:AVAGO TECH INT SALES PTE LTD

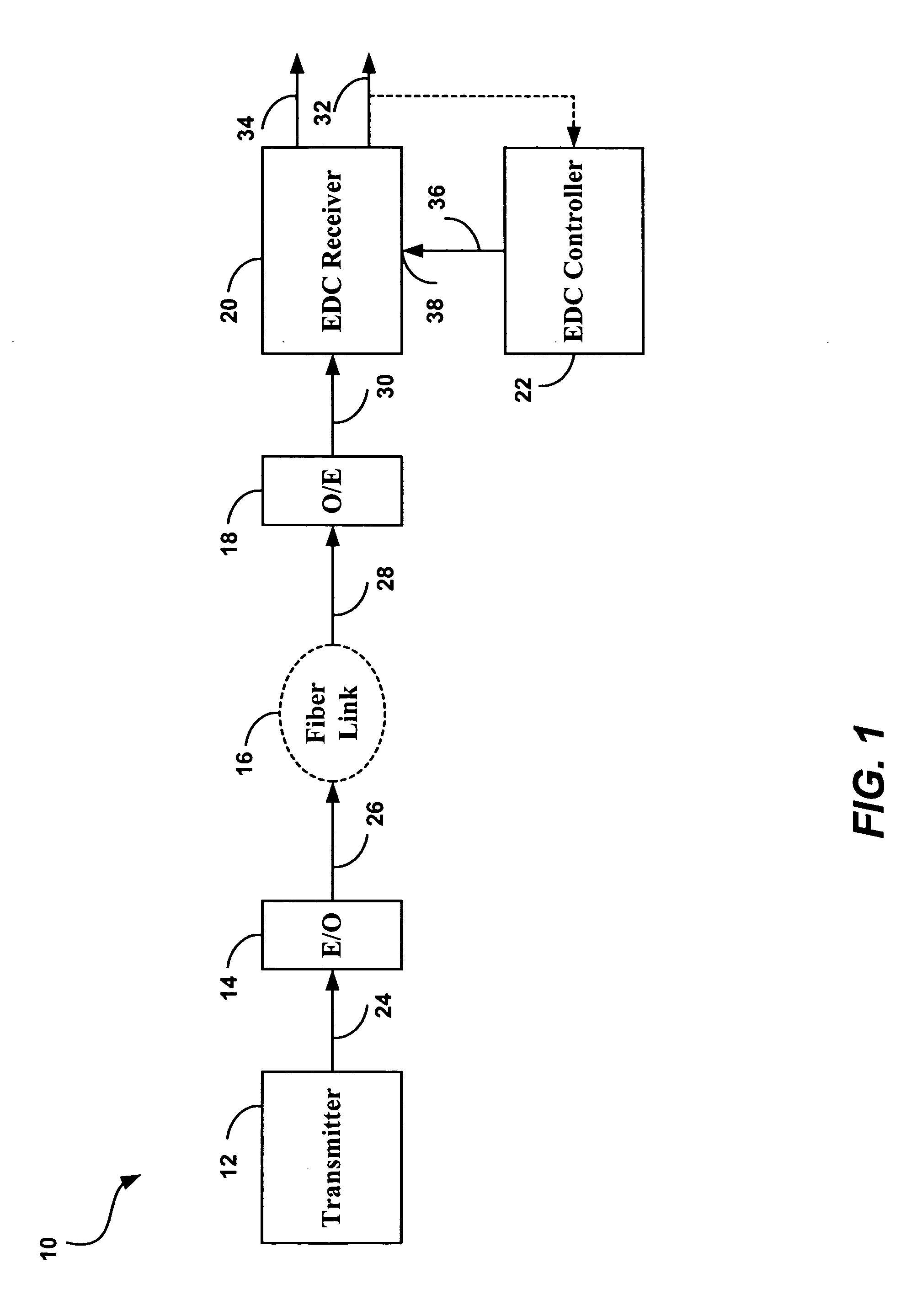

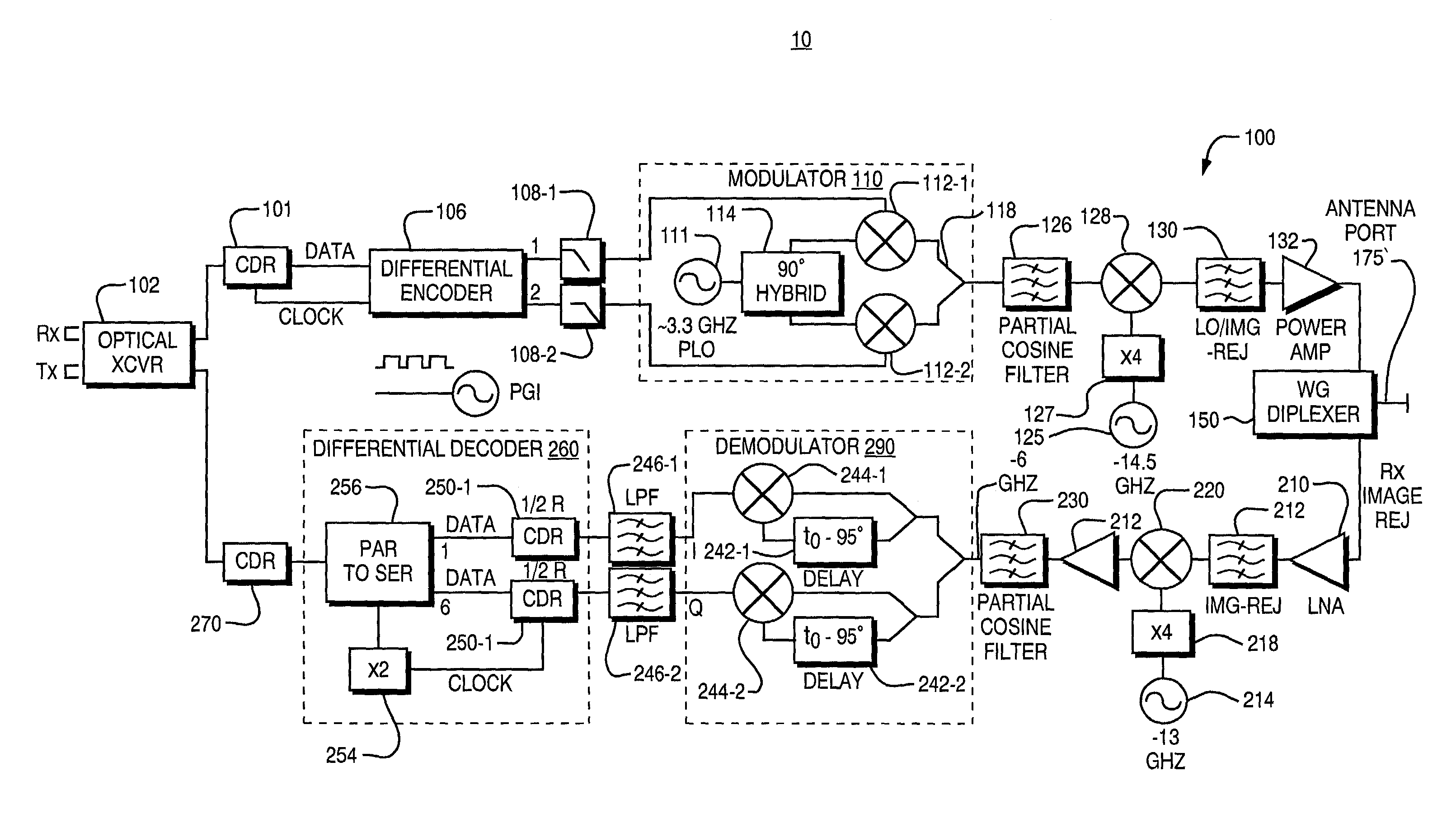

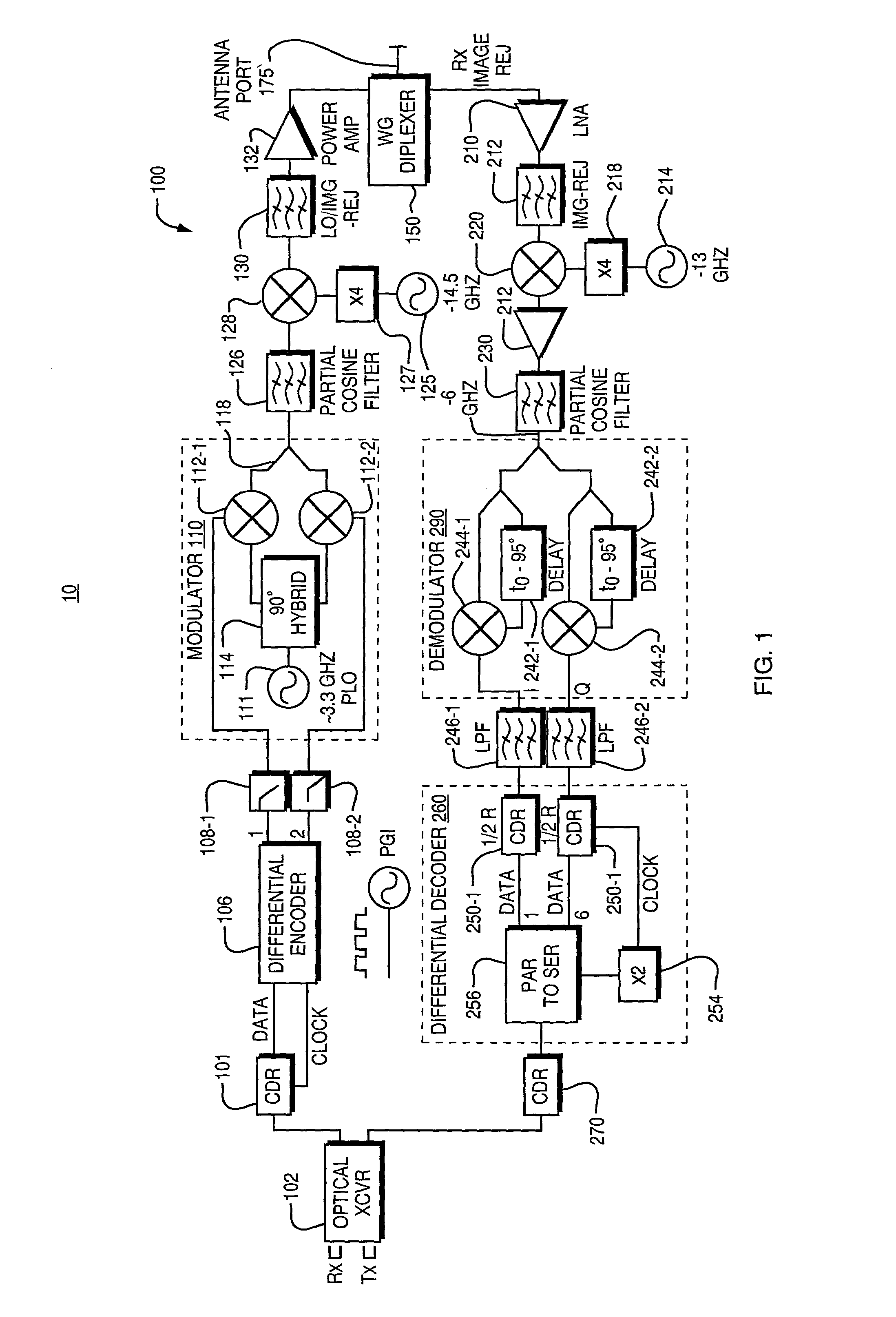

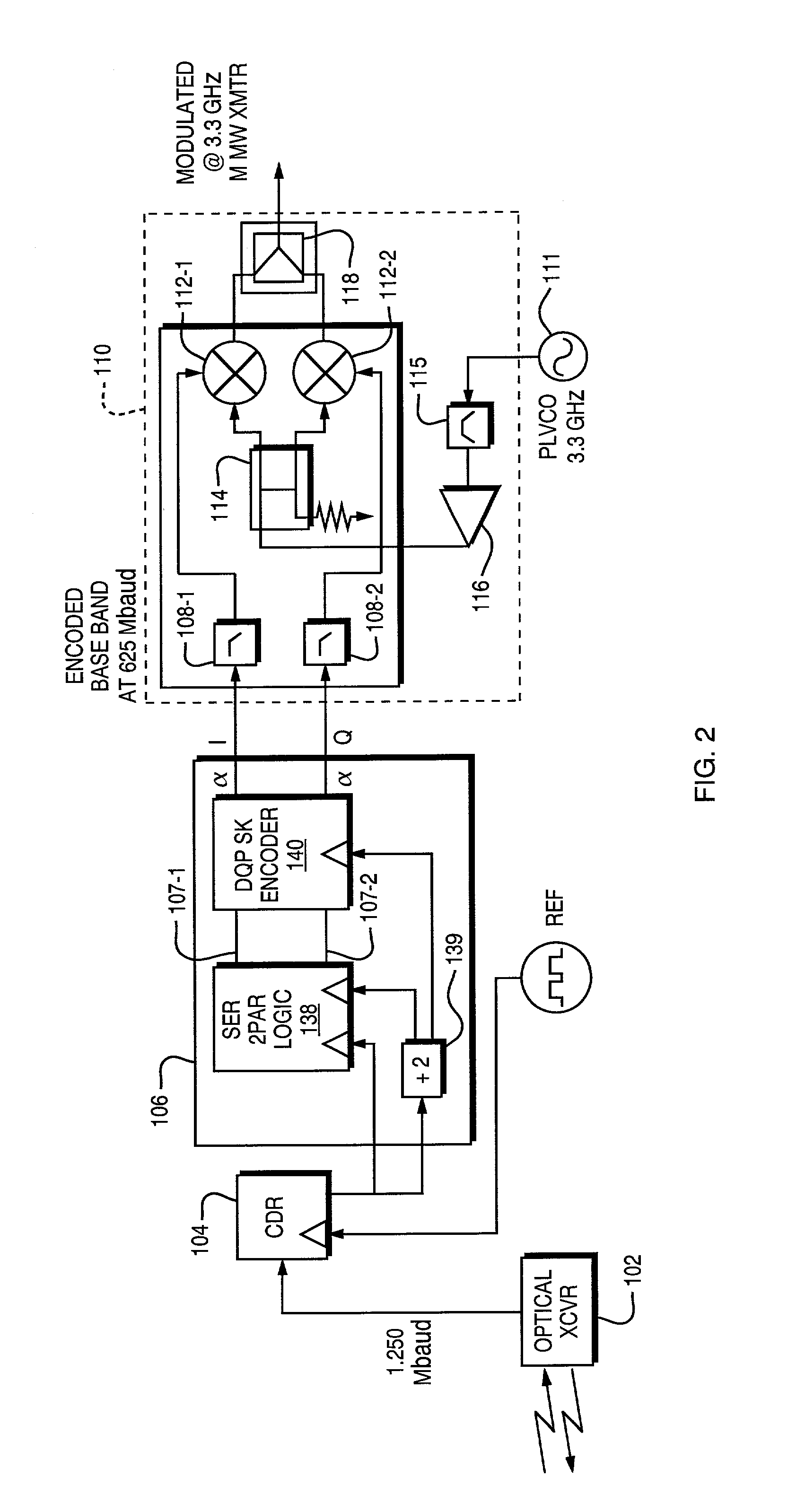

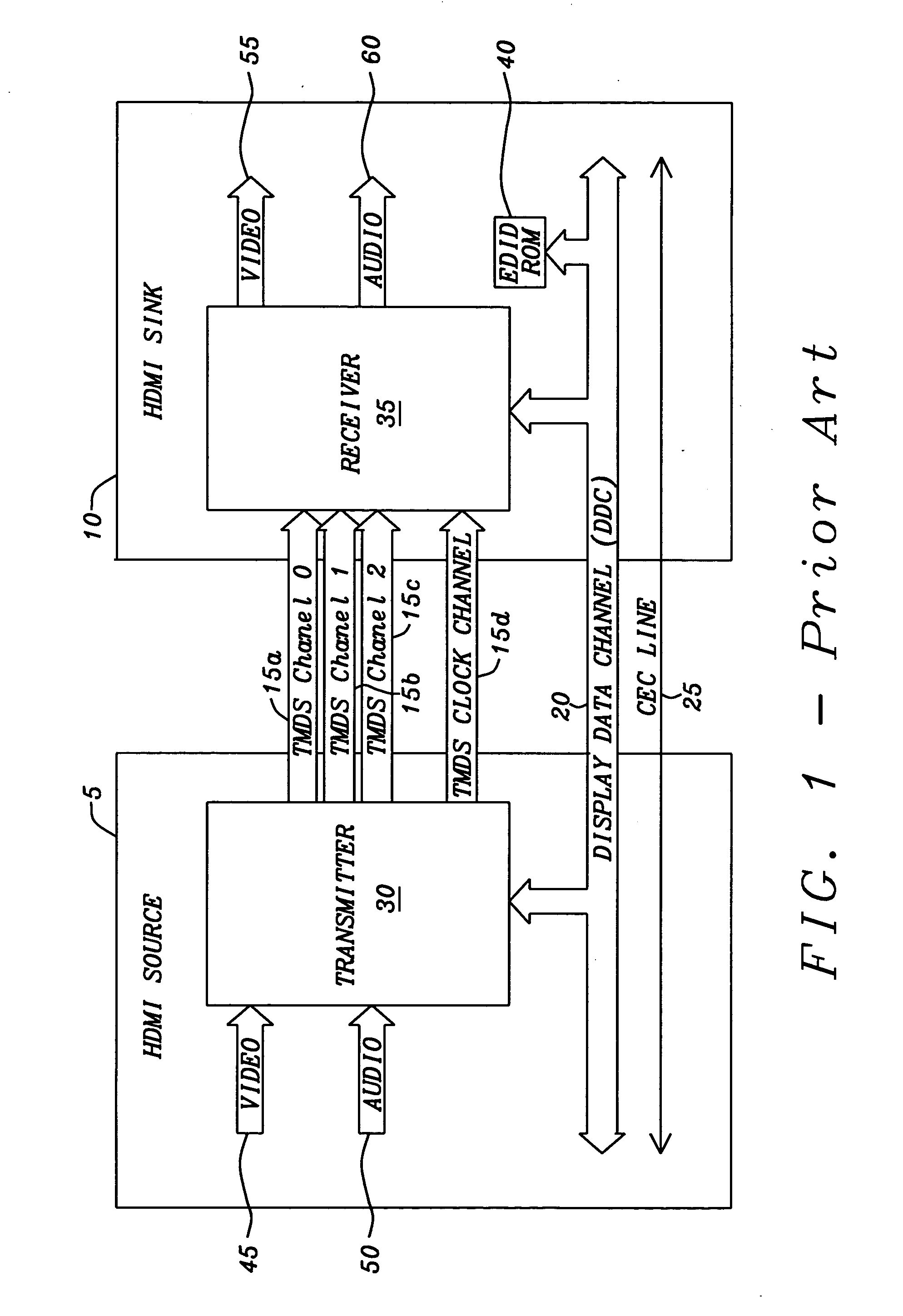

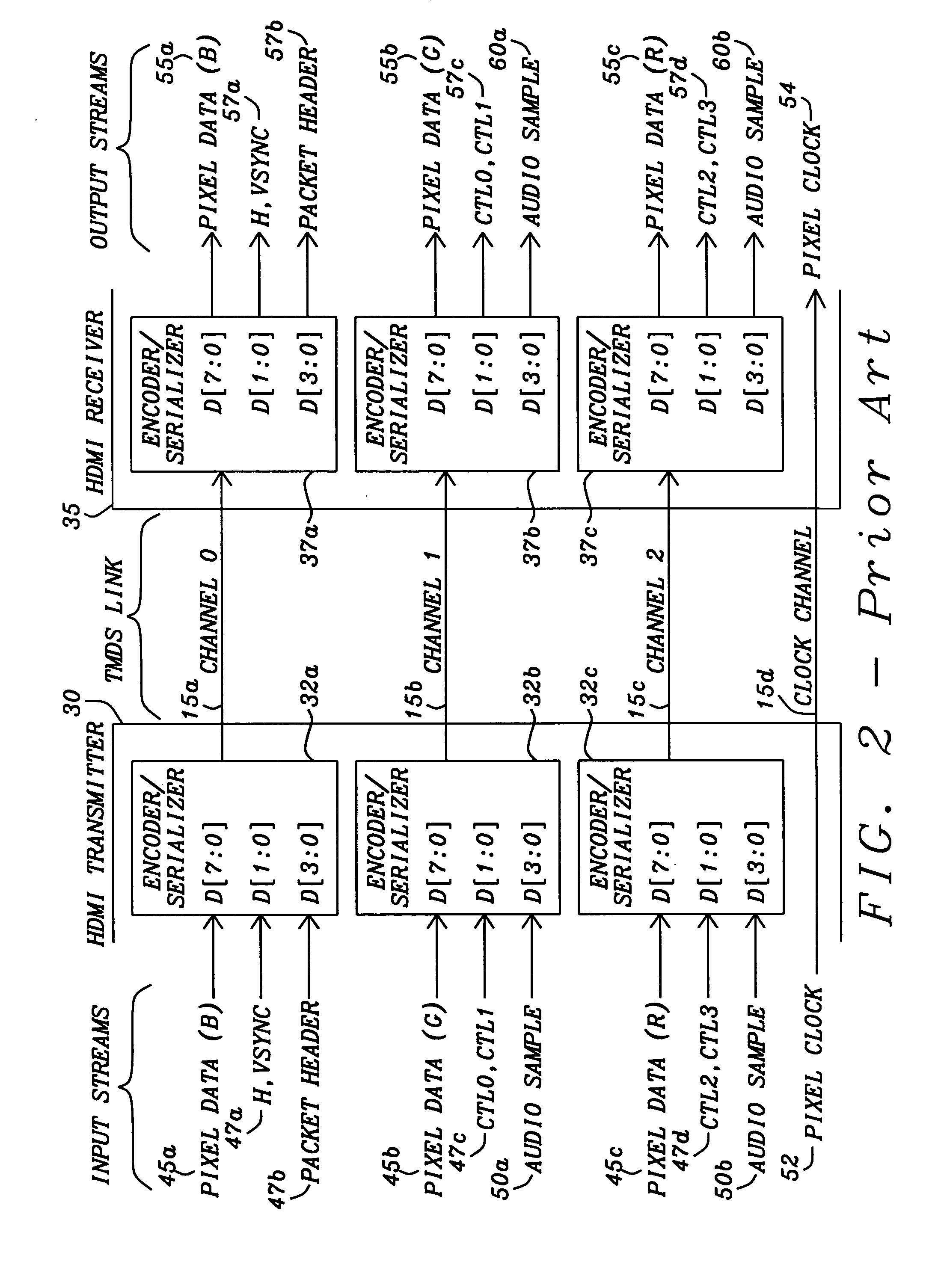

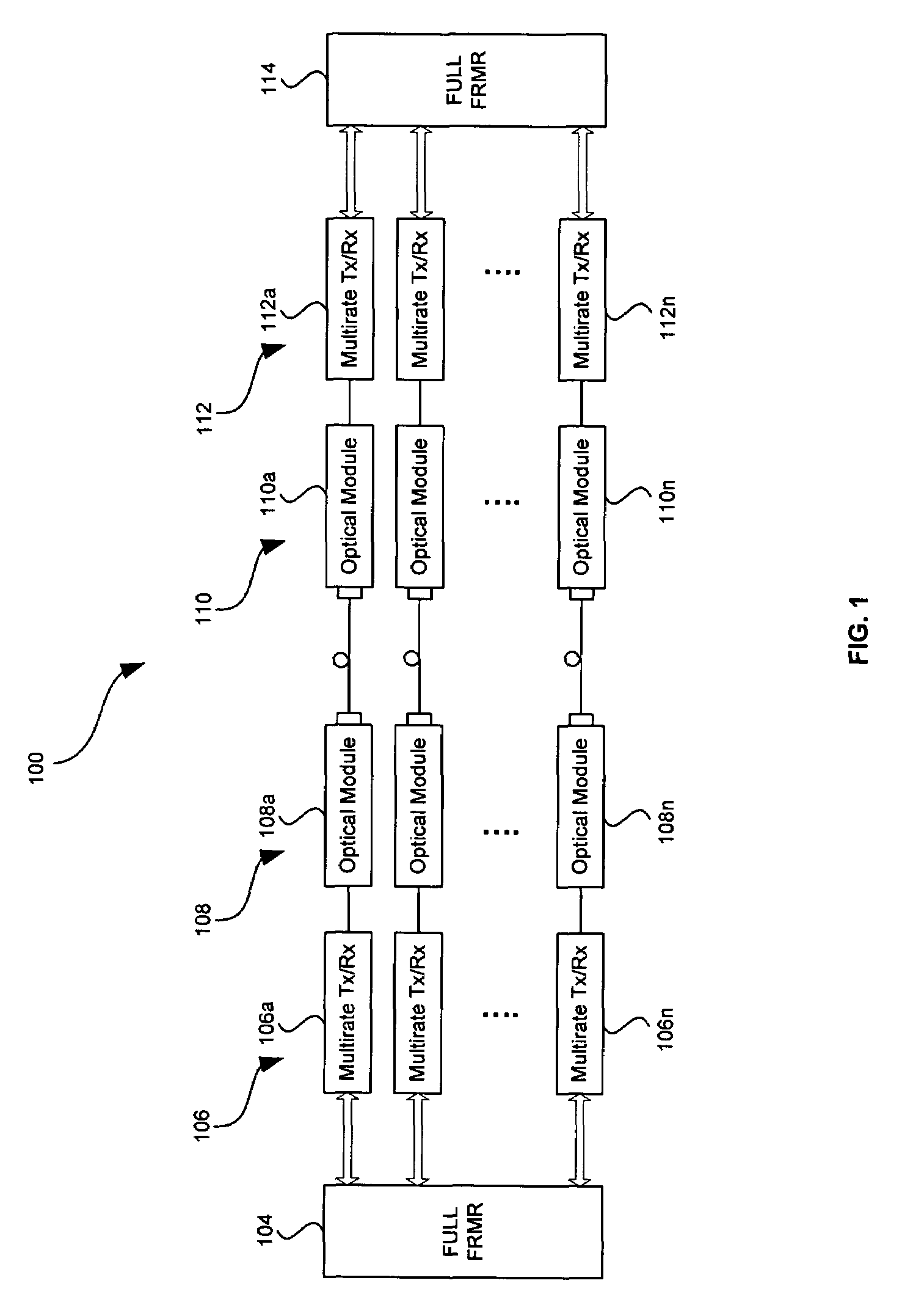

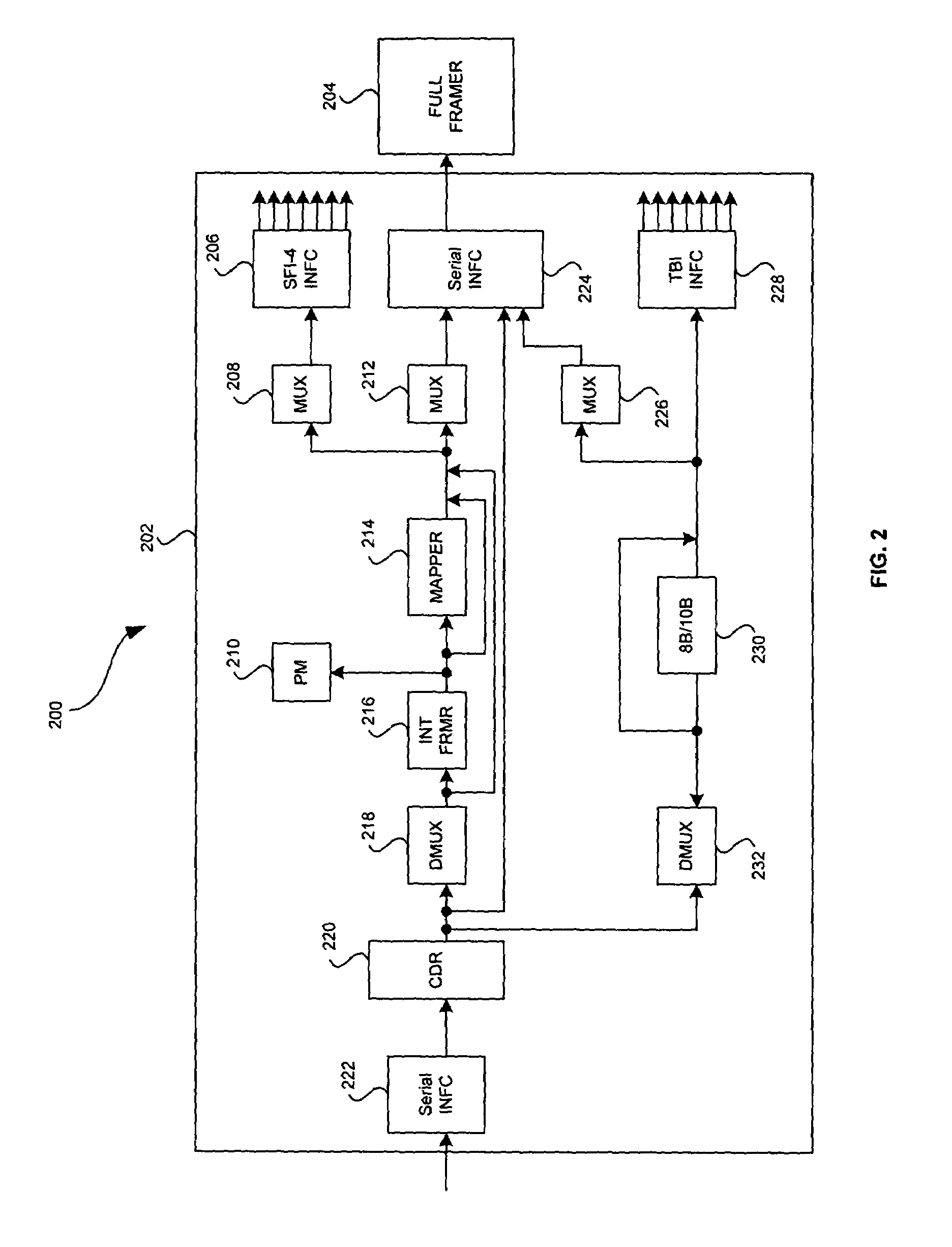

Architecture for wireless transmission of high rate optical signals

InactiveUS7103279B1Minimize intersymbol interferenceReduce noiseLine-of-sight transmissionElectromagnetic transmittersFiberHigh rate

An apparatus for a wireless transmission of high data rate signals such as received from an optical interface including gigabit fiber channel or a sonet. The architecture combines direct detection of the optical signal with clock and data recovery circuit and a differential signal encoder which is preferably a differential quadrature phase shift encoder and modulator pair. A millimeter wave, local oscillator and up conversion chain converts the optical input signal to a microwave carrier. In the opposite direction, the down converted signal is non-coherently phase detected and fed to a pair of synchronized clock and data recovery circuits to recover I and Q channel signals. These recovered signals are then combined prior to re-timing before they are fed back to the optical transceiver.

Owner:OL SECURITY LIABILITY CO

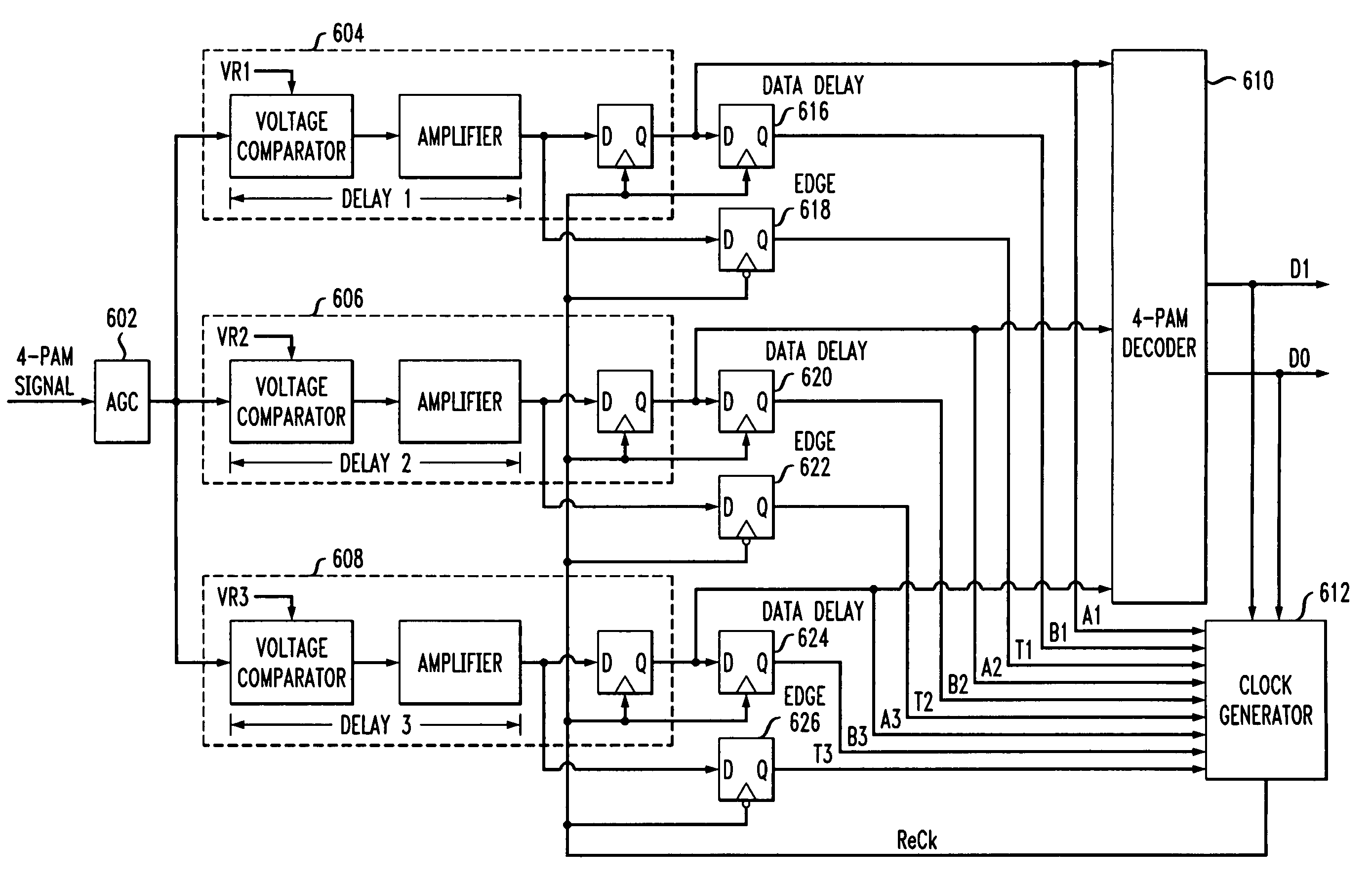

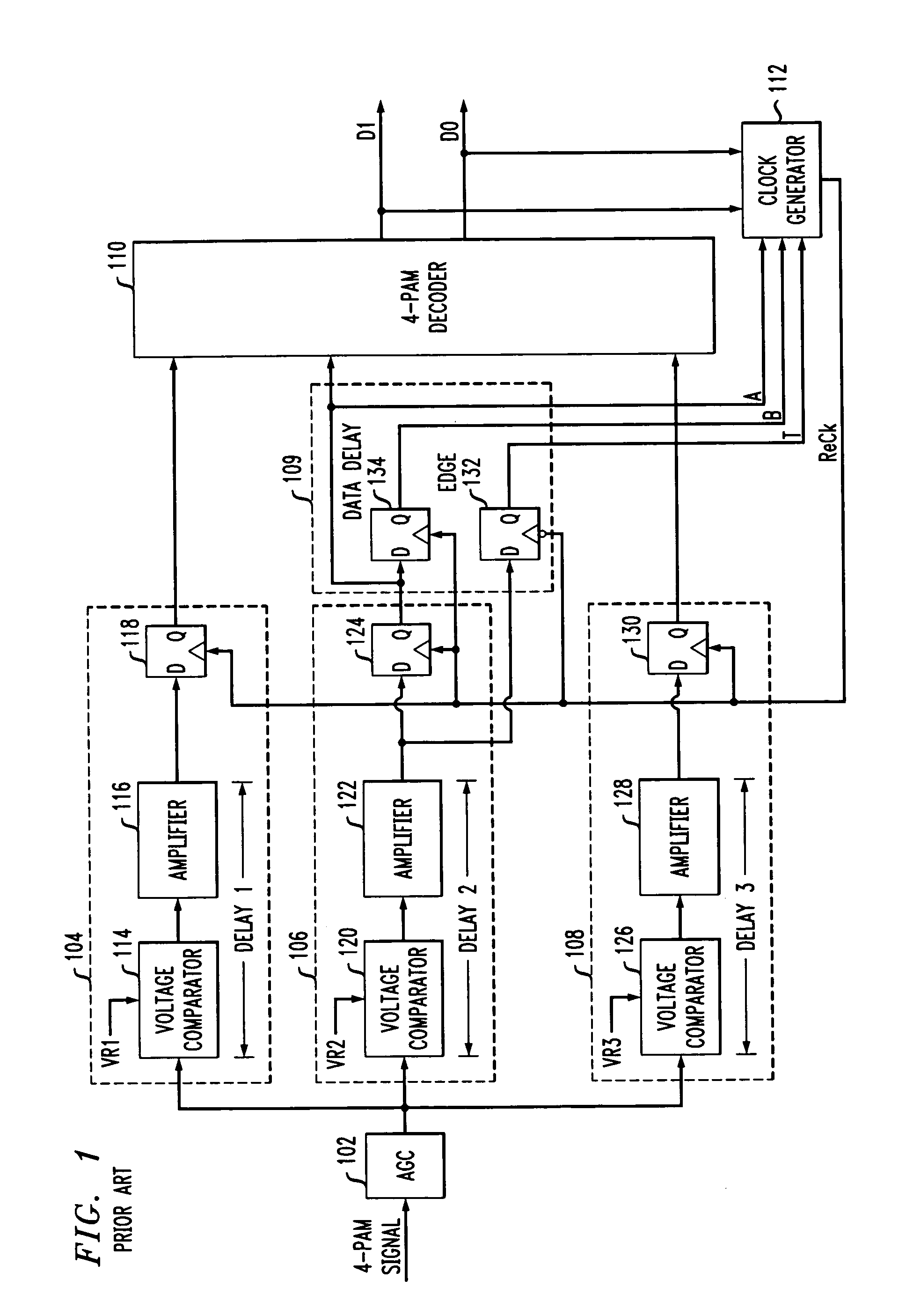

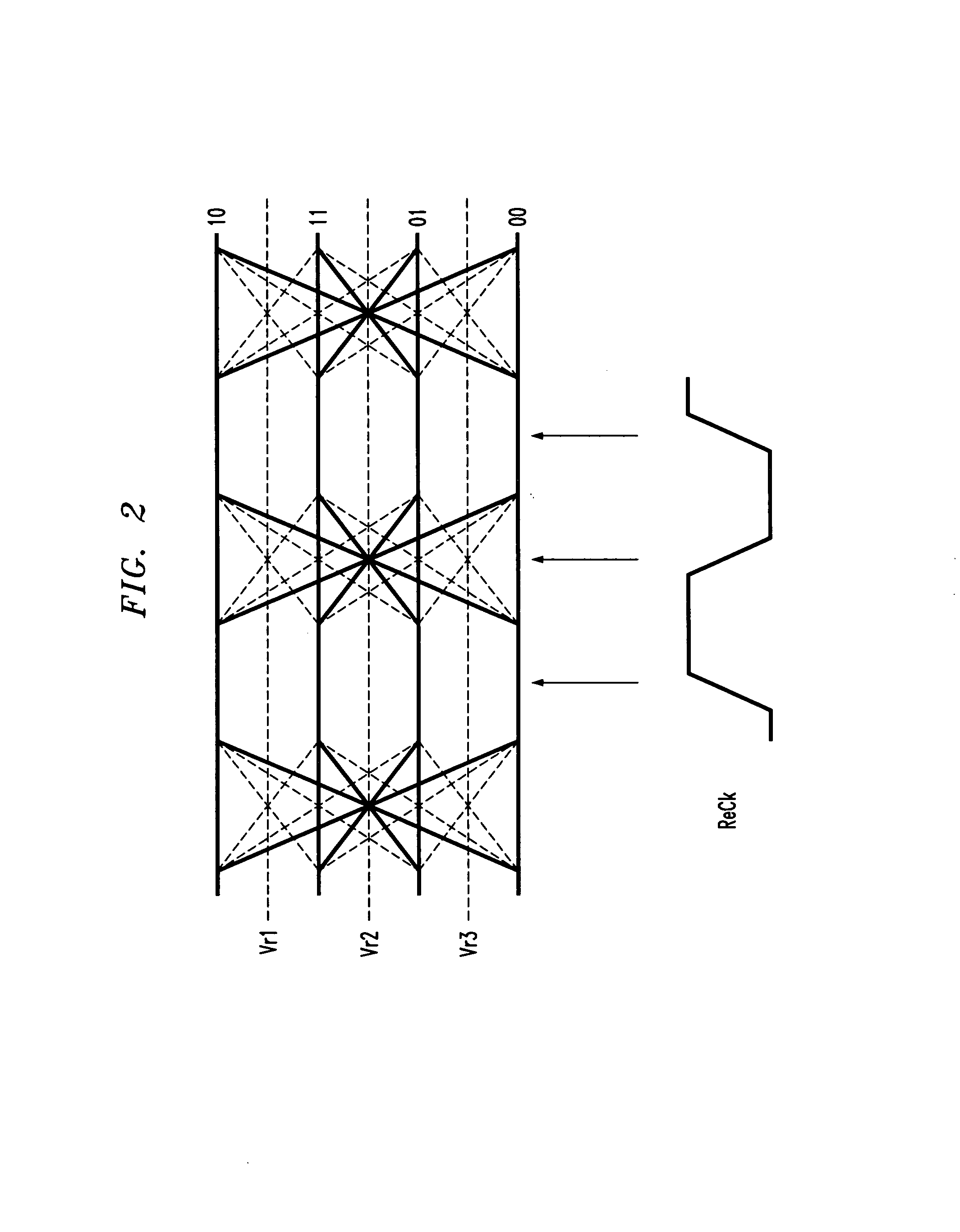

Multi-level pulse amplitude modulation receiver

InactiveUS7099400B2Pulse automatic controlDc level restoring means or bias distort correctionPhase detectorComputer science

Multiple-level phase amplitude (M-PAM) clock and data recovery circuitry uses information from multiple phase detectors to generate one or more data sampling clocks that are optimized for each of the data slicers. One possible 4-PAM implementation includes 3 data slicers, 3 edge slicers, 3 phase detectors, and a single VCO. The phase detector outputs are combined (e.g., via weighted voting, weighted average, minimum error, and / or minimum variance) to determine an optimized phase estimate for the clock used to sample the data at all three data slicers. Another 4-PAM implementation similarly includes 3 data slicers, 3 edge slicers, 3 phase detectors, and a single VCO. The mid-amplitude edge slicer and phase detector are used in combination with the VCO to generate a central phase while a multiple-tap delay line provides N phase variants before and after the central phase. Information from the non-mid-amplitude edge slicers and phase detectors is used to choose a phase from among the phase variants that best suits the other data slicers. In yet another implementation, a single edge slicer, single phase detector, and single VCO is used to generate a key clock which is used by the edge slicer to track the symbol timing. A clock generator provides a single optimized clock (that is offset from the key clock) that is used by the data slicers. Bit error rates from the data slicers are used to adjust the offset until the data slicer clock is optimized with respect to all the slicers. Alternatively, multiple clocks are generated via offsets from the key clock, each being optimized to the data slicer group that it drives.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

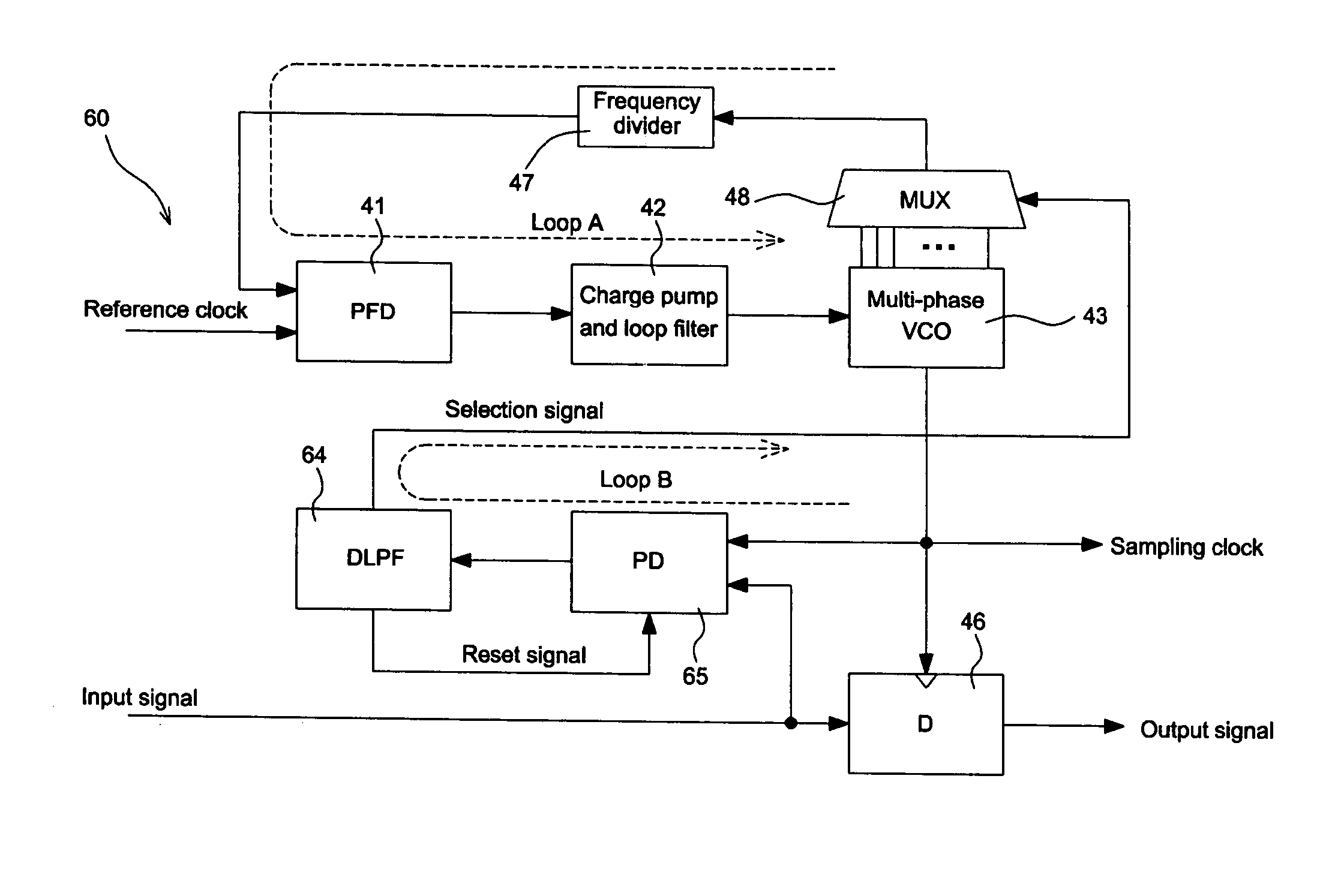

Clock generator and data recovery circuit using the same

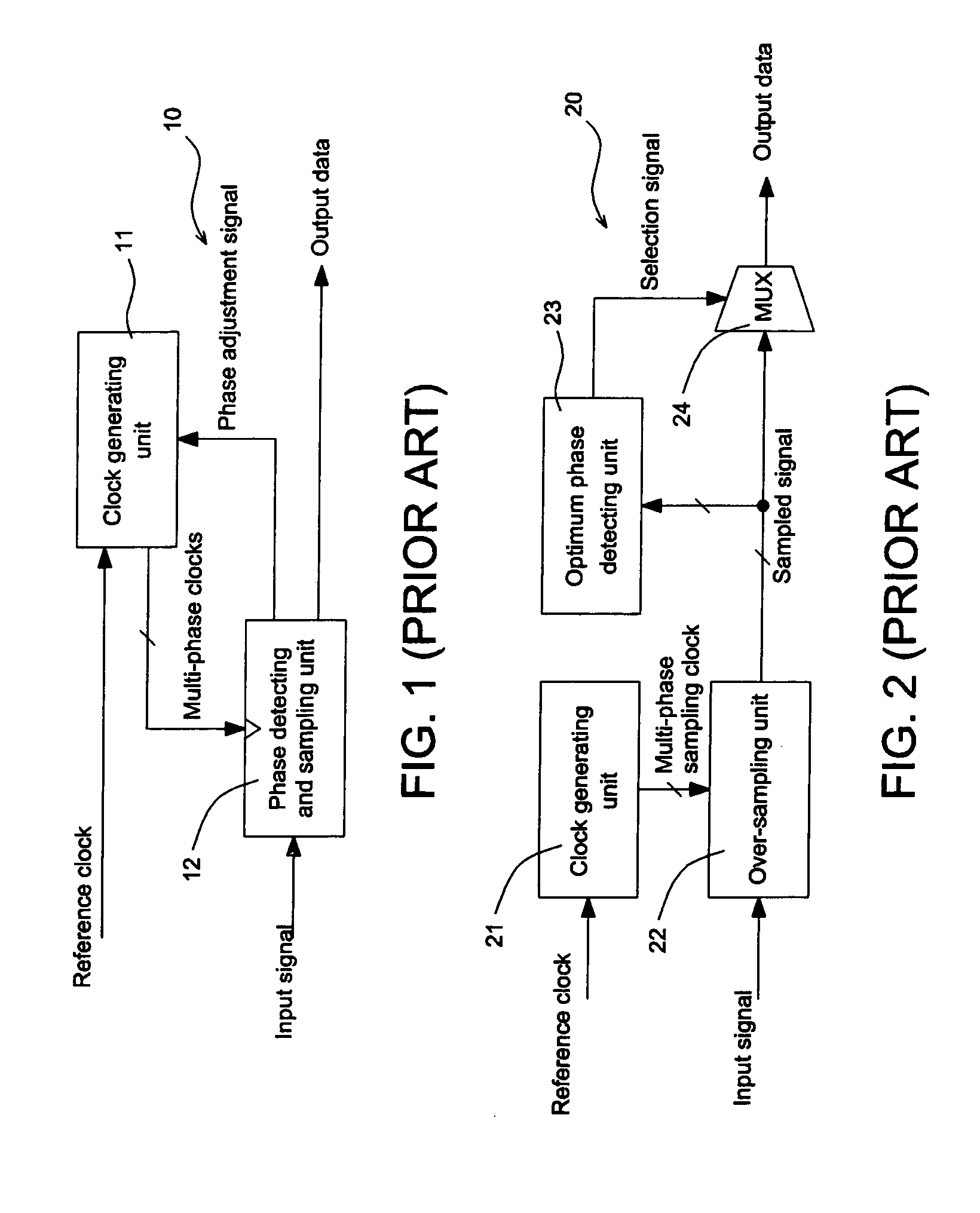

ActiveUS20060078079A1Reduce tracking timePulse automatic controlAngle demodulation by phase difference detectionPhase detectorLoop filter

A clock generator and a data recovery circuit. The clock generator includes a voltage control oscillator (VCO) for generating a sampling clock and multi-phase clocks, a multiplexer for receiving the multi-phase clocks and selecting one of the multi-phase clocks to generate a selected clock according to a selection signal, a phase-frequency detector for receiving the selected clock and a reference clock and generating a phase-frequency error signal, a charge pump and loop filter for receiving the phase-frequency error signal and generating a control voltage, a phase detector for receiving the sampling clock and an input signal and generating a phase error signal, and a digital low-pass filter for receiving the phase error signal and generating the selection signal. The digital low-pass filter clears an accumulated phase error when it generates the selection signal to force the multiplexer to change the phase.

Owner:REALTEK SEMICON CORP

Clock and data recovery circuit having wide phase margin

InactiveUS20070047683A1Wide phase marginIncrease speedPulse automatic controlSynchronisation receiversSerial samplingPhase control

A clock and data recovery (CDR) circuit includes a sampler, a CDR loop and a phase interpolator. The sampler samples serial data in response to a recovery clock signal to generate a serial sampling pulse. The CDR loop transforms the serial sampling pulse into parallel data, generates a plurality of phase signals with a first speed based on the parallel data, and generates a phase control signal with a second speed higher than the first speed based on the plurality of phase signals. The phase interpolator generates the recovery clock signal by controlling a phase of a reference clock signal in response to the phase control signal. Therefore, the CDR circuit may recover data and a clock with a relatively high speed.

Owner:SAMSUNG ELECTRONICS CO LTD

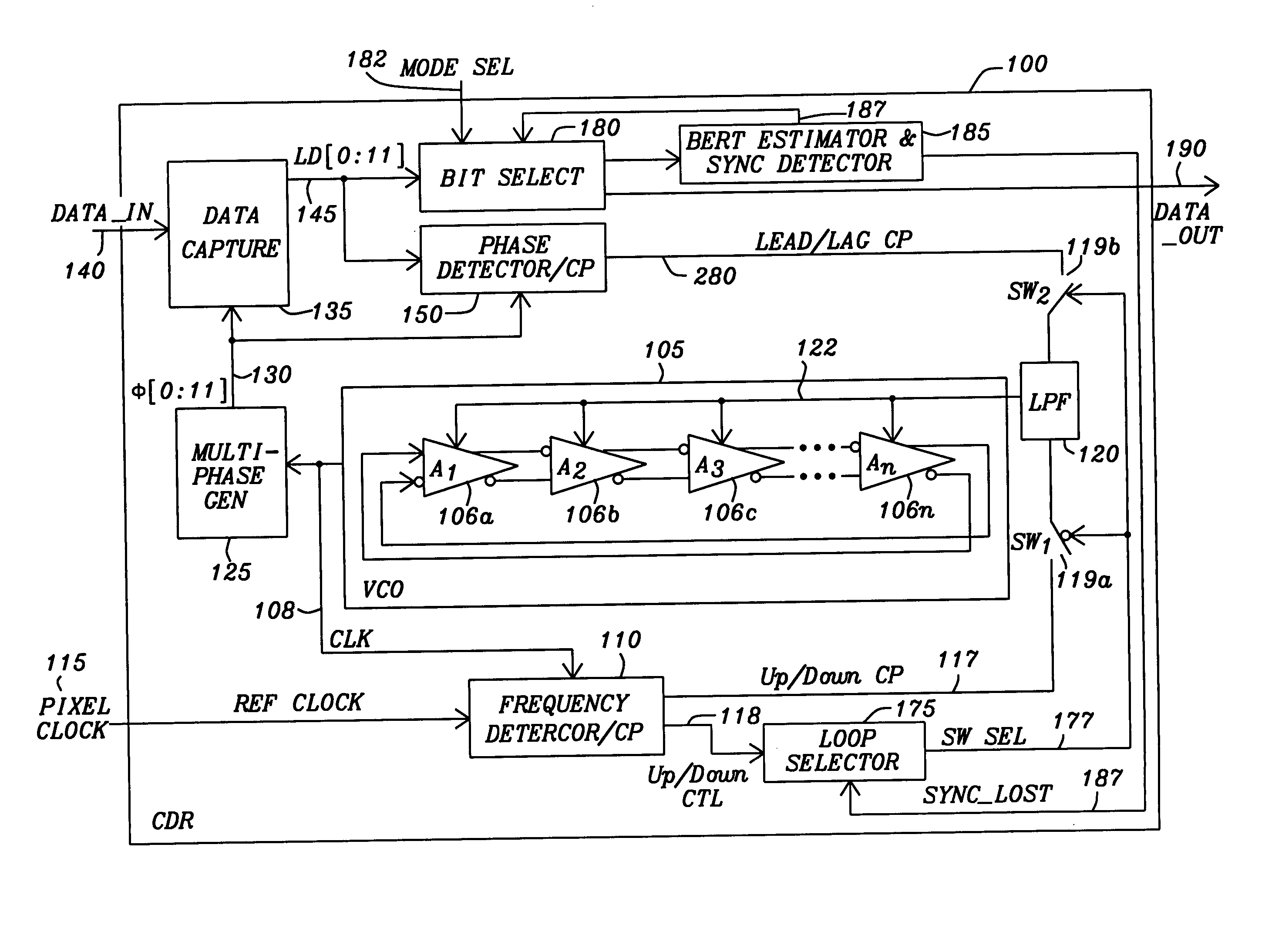

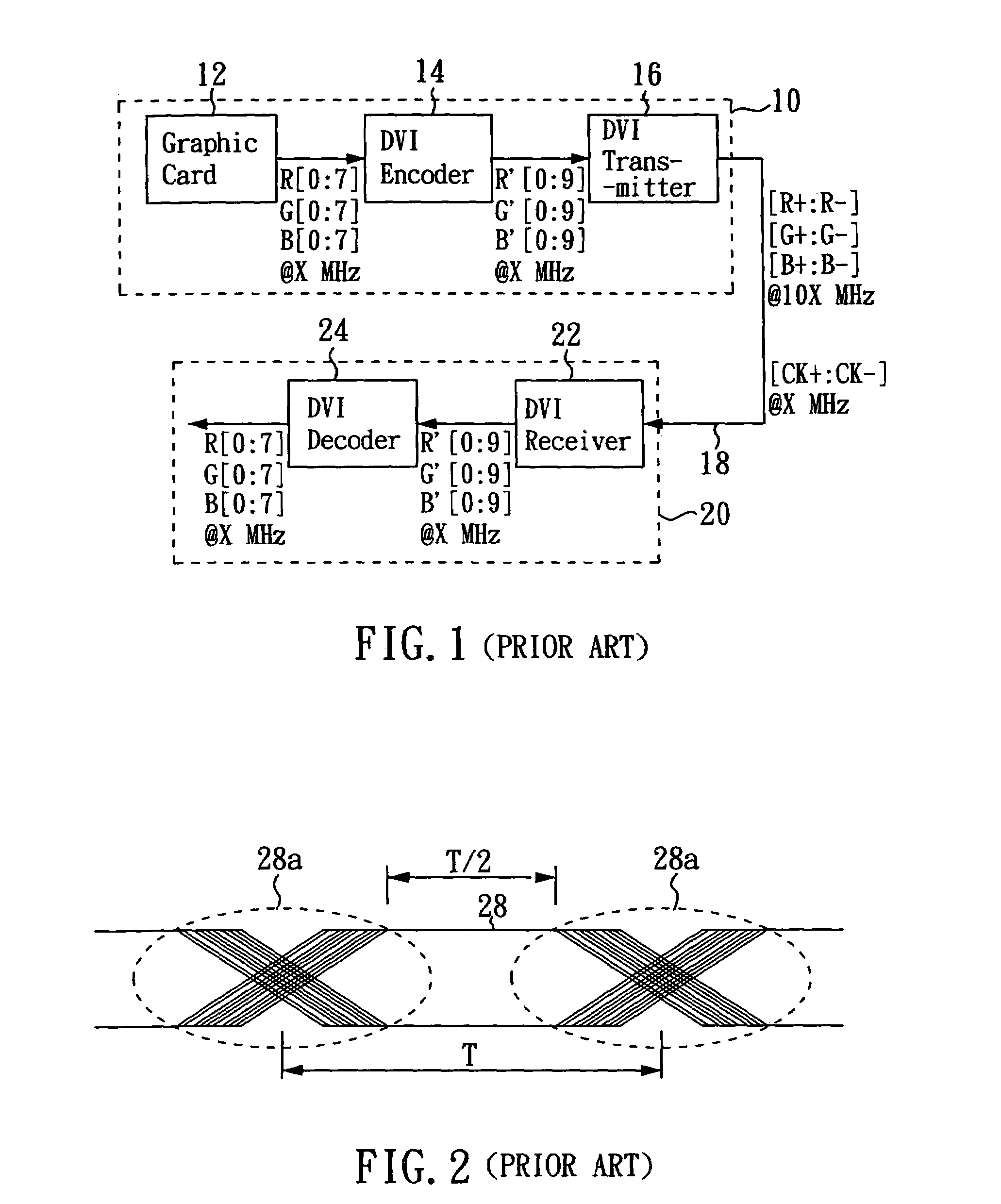

Single-VCO CDR for TMDS data at gigabit rate

InactiveUS20060256909A1Improve toleranceReceiver initialisationSynchronisation information channelsPhase detectorMultiplexer

A clock and data recovery circuit has a voltage controlled oscillator that provides a clocking signal synchronized to a received serialized data. A multiple phase generator converts the clocking signal to a plurality of multiple phased clocking signals. A data capture device acquires the serialized data with each of the plurality of multiple phased clocking signals to create multiple phased data signals. A phase detector determines if the clocking signal is in phase with the recovered serialized data and providing a lead signal and a lag signal indicating whether the clocking signal is in phase with the recovered serialized data. A frequency initializing device assists acquisition of lock of the voltage controlled oscillator to a reference clock signal. A recovered data selector selects which of the multiple phased data signals are to be transferred to external circuitry for further processing.

Owner:KARMIC DESIGN USA

Apparatus for clock data recovery

InactiveUS7295644B1Increase coverageMinimal amountPulse automatic controlAngle demodulation by phase difference detectionData streamClock rate

Circuits, architectures, a system and methods for clock data recovery. The circuit generally includes (a) a clock phase adjustment circuit, receiving clock phase information and providing a clock phase adjustment signal, (b) a clock frequency adjustment circuit, receiving clock frequency information and providing a clock frequency adjustment signal, and (c) an adder circuit, receiving the clock phase adjustment signal and the clock frequency adjustment signal, and providing a clock recovery adjustment signal. The architectures and / or systems generally comprise those that include a clock data recovery circuit embodying one or more of the inventive concepts disclosed herein. The method generally comprises the steps of (1) sampling the data stream at predetermined times, (2) generating clock frequency information and clock phase information from sampled data, and (3) altering a frequency and / or a phase of the clock signal in response to the clock frequency information and the clock phase information. The present invention prevents or reduces the likelihood of the potential nonconvergence / clock runaway problem, advantageously with minimal or no changes to existing designs and logic. The present invention further advantageously improves system stability, reliability and performance with a minimum of additional circuitry.

Owner:MARVELL ASIA PTE LTD

Method and system for pattern-independent phase adjustment in a clock and data recovery (CDR) circuit

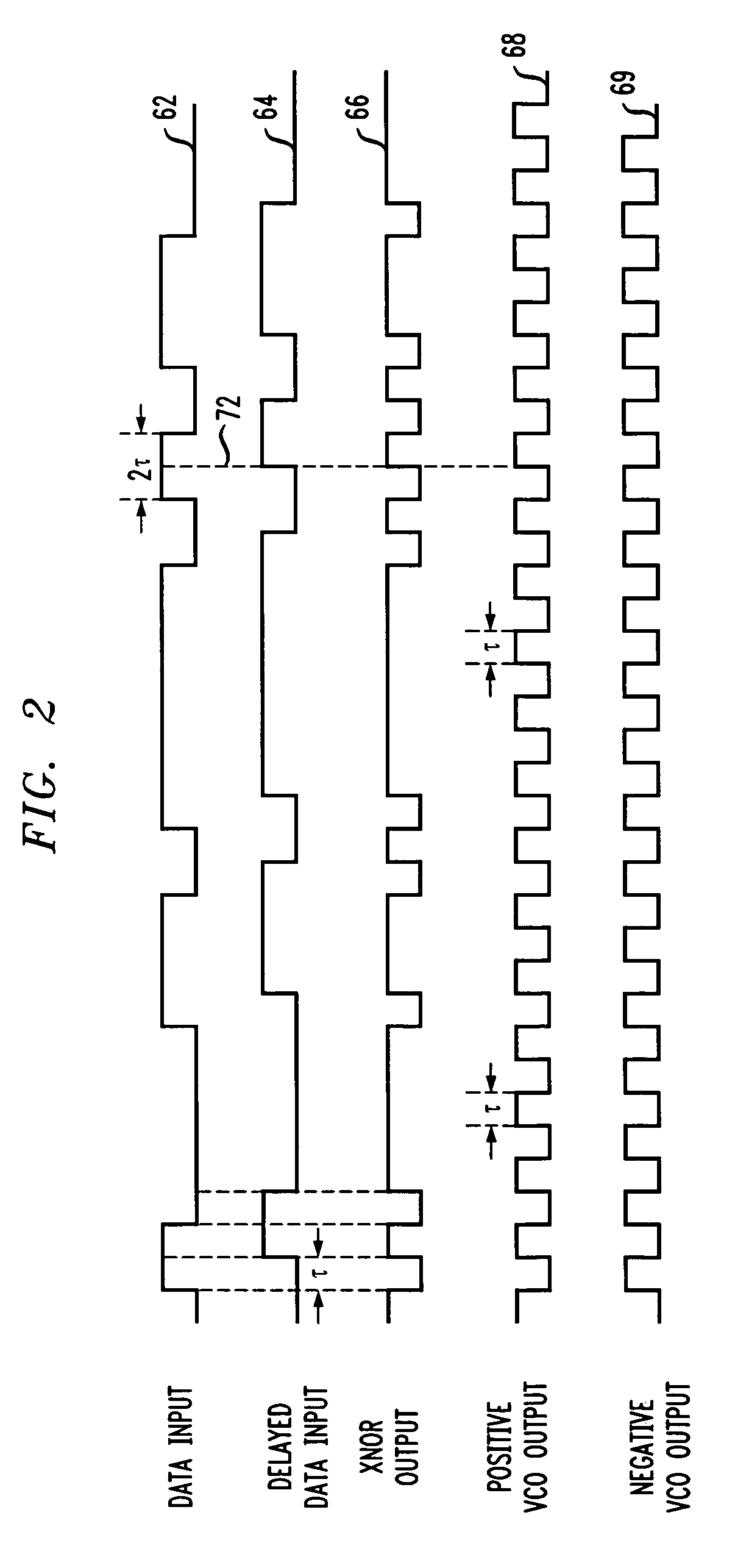

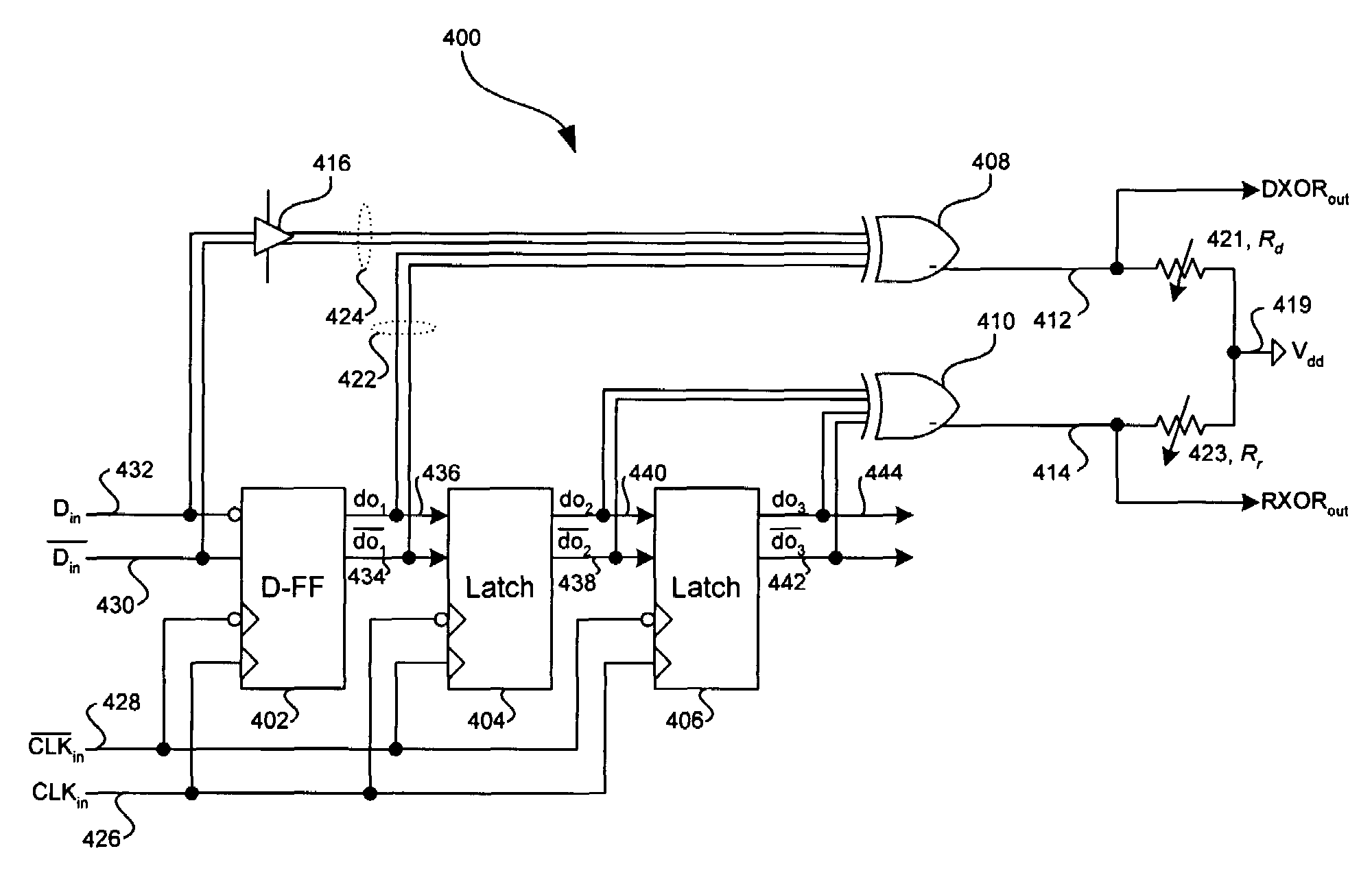

Aspects of the pattern-independent phase adjustment system includes a single output data XOR gate coupled to a differential input data signal and a bias voltage through a first variable resistor. A single output reference XOR gate may be coupled to a latched differential input signal and the bias voltage through a second variable resistor. At least one latch may be coupled to at least one differential input of the data and reference XOR gate. The single output of the data XOR gate may be a data output of a clock and data recovery circuit (CDR) and the single output of the reference XOR gate may be a reference output of the clock and CDR. No current may flow at the data output of the data XOR gate and the reference output of the reference XOR gate when there are no transitions occurring at an input of the phase detector.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

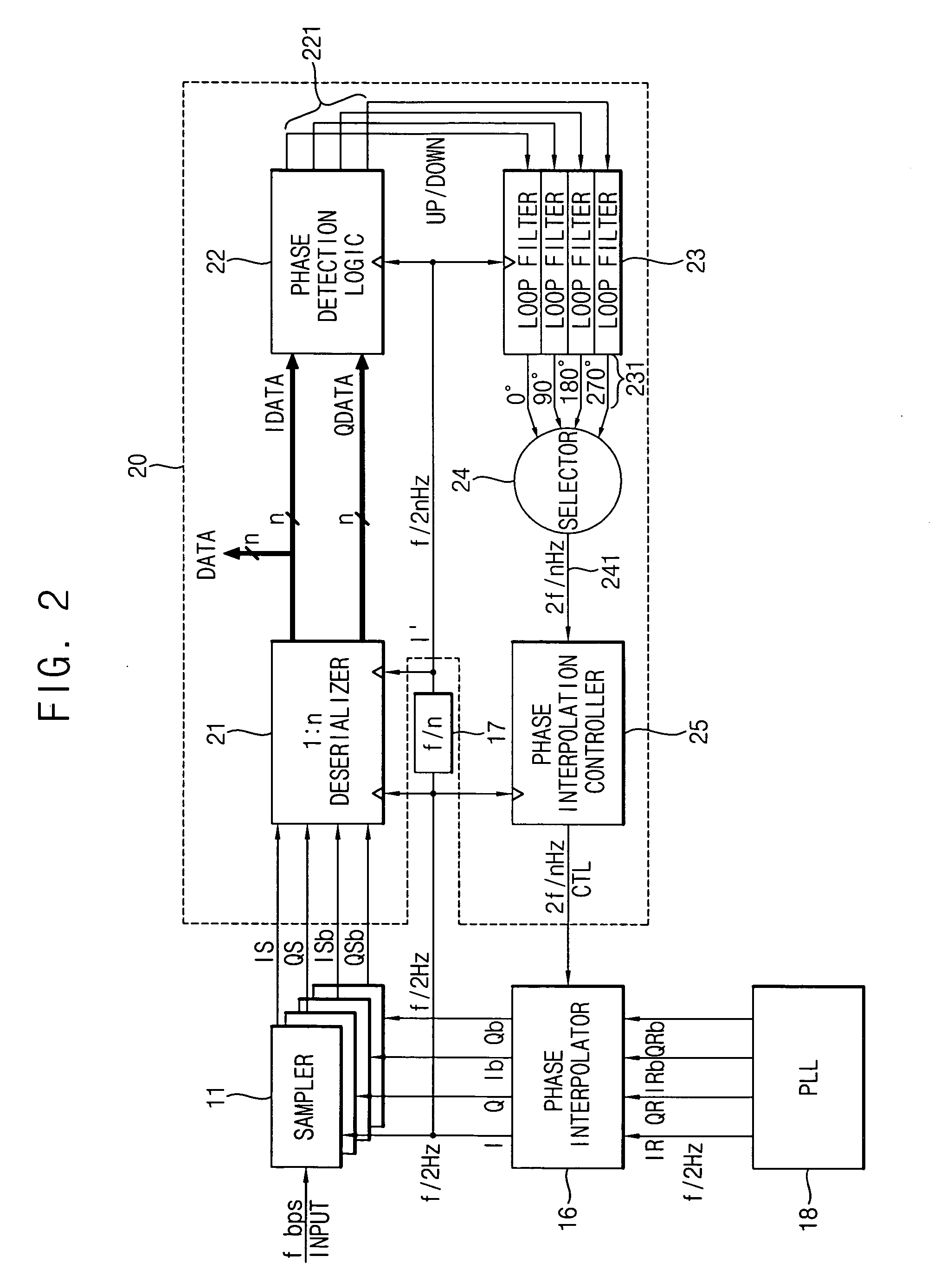

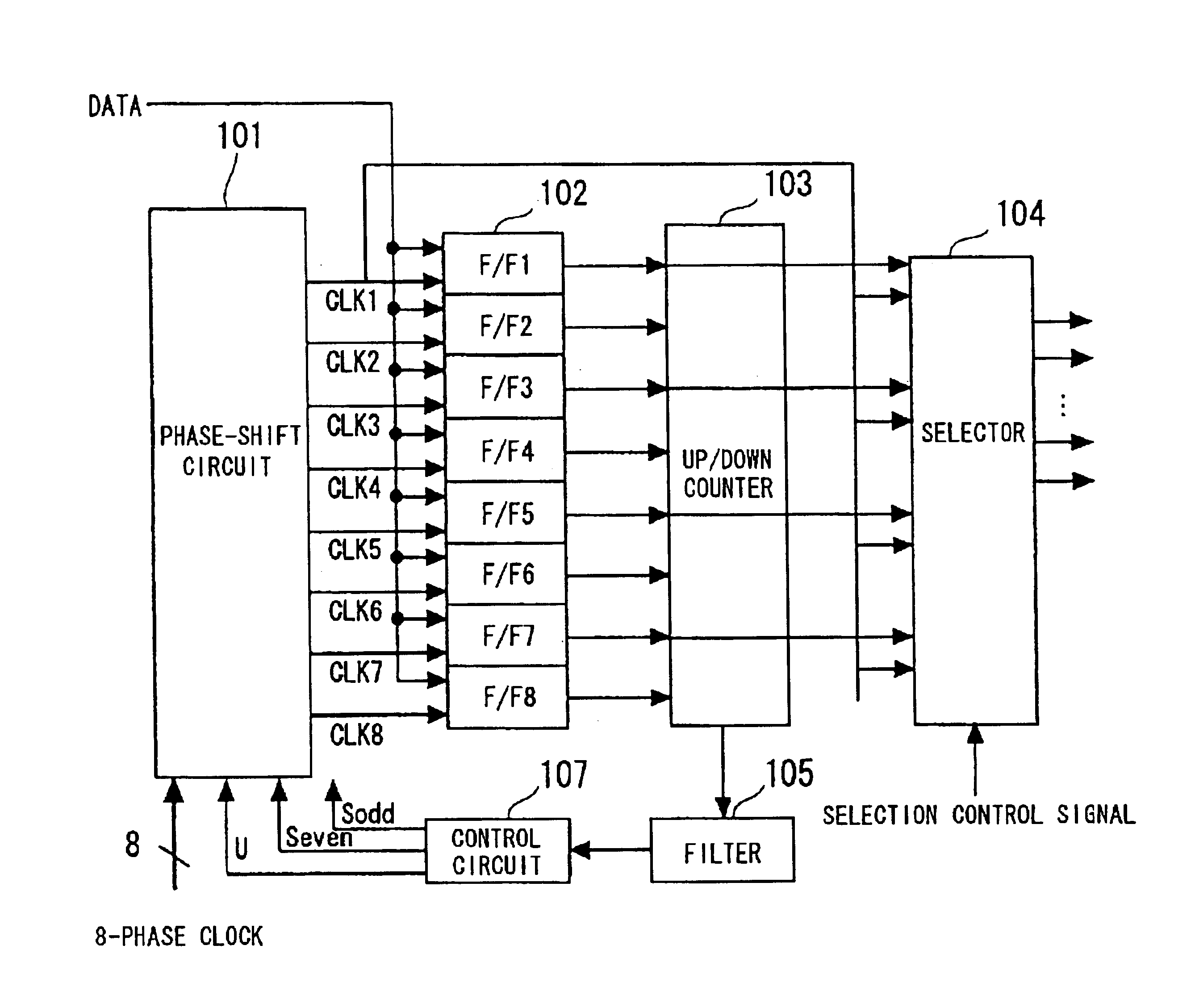

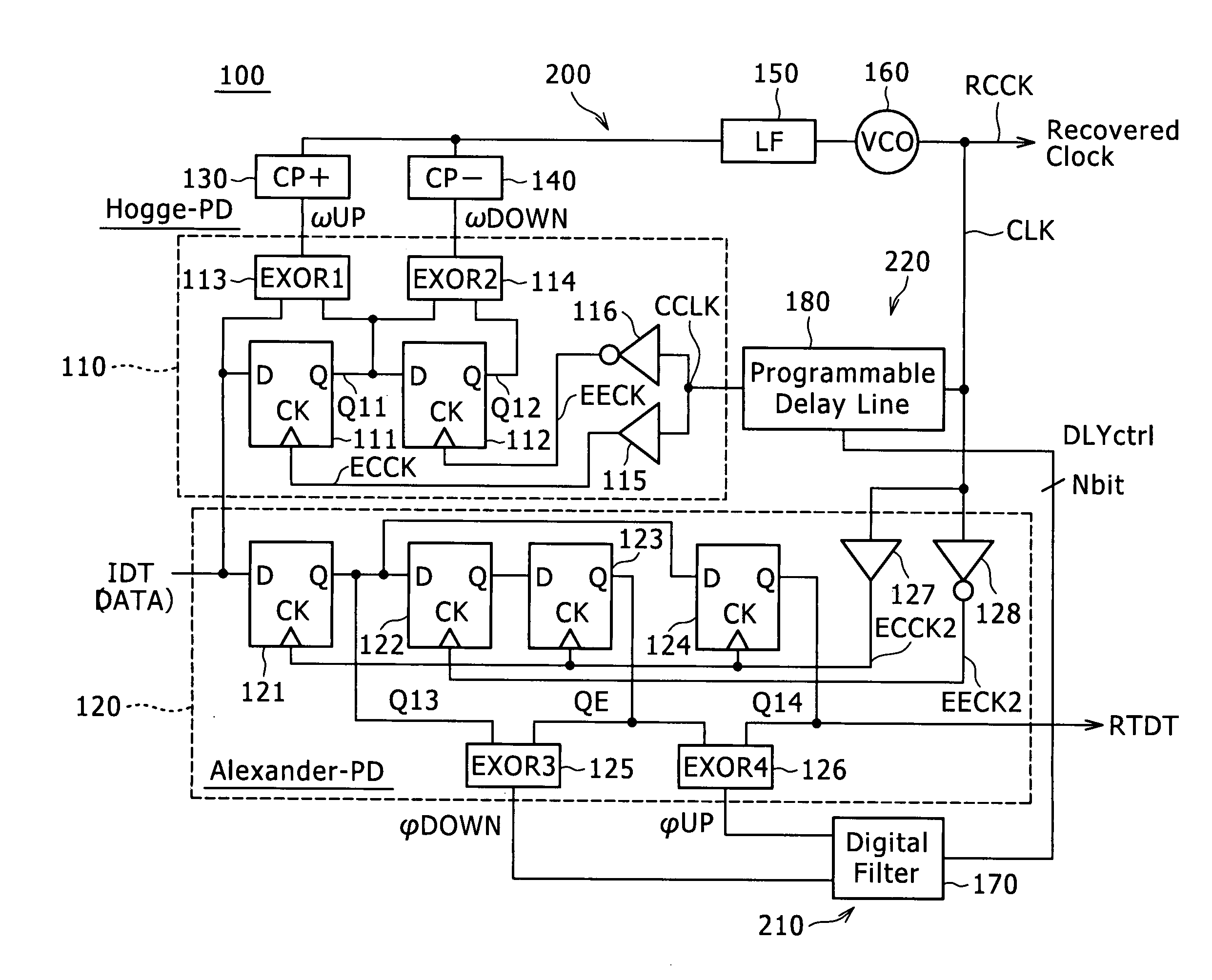

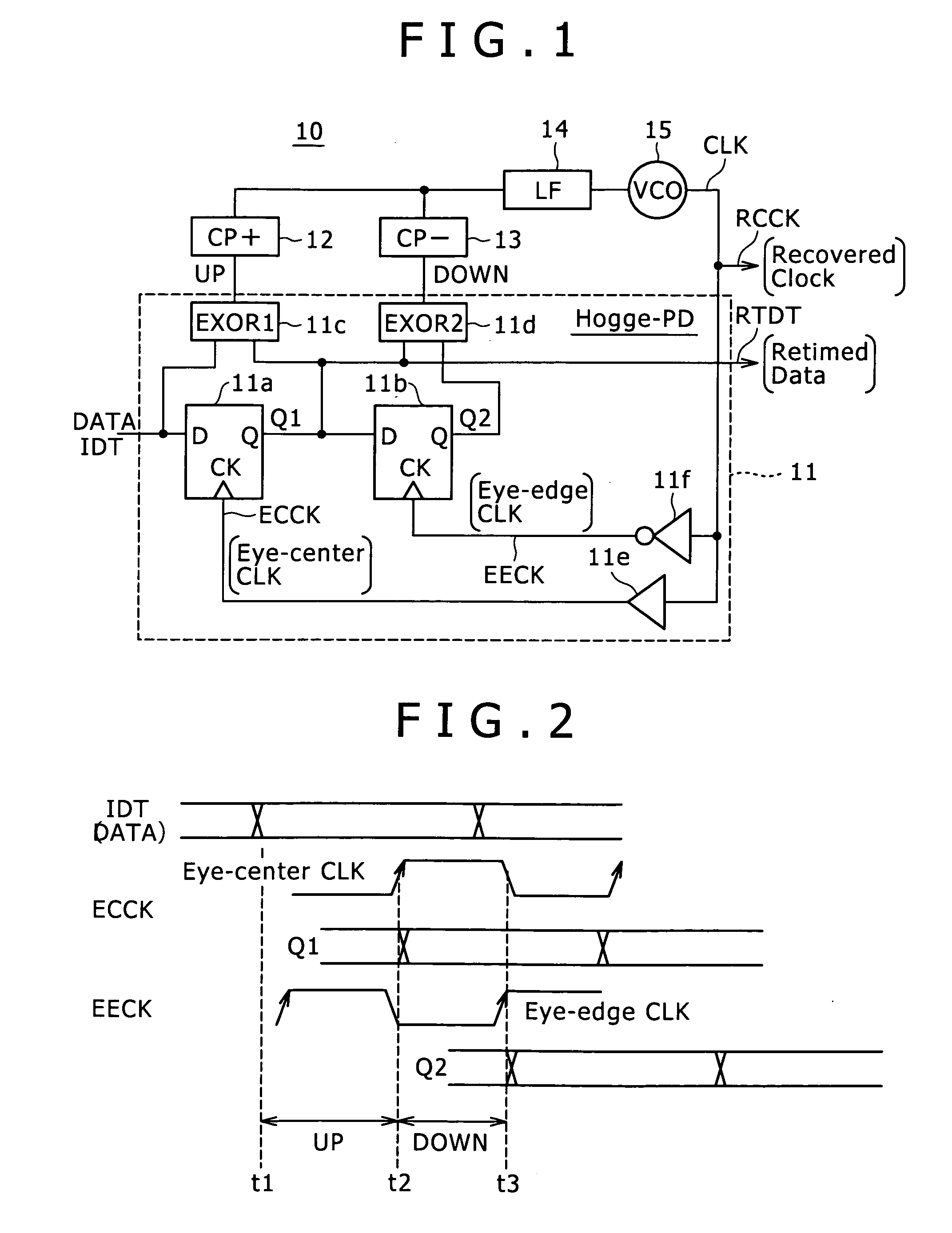

Clock and data recovery circuit and clock control method thereof

InactiveUS6753712B2Eliminate the effects ofAccurate dataPulse automatic controlSingle output arrangementsPhase shiftedControl signal

A clock and data recovery circuit includes a phase-shift circuit having a switch, which receives multiphase clocks, for selecting and outputting a plurality of clock pairs from among the multiphase clocks, and a plurality of interpolators, which receive the plurality of clock pairs output from the switch, for outputting clock signals in which delay time is stipulated by time obtained by performing interior division of the phase difference between the clocks of the pair; a plurality of latch circuits which receive input data in common; a phase detecting circuit for detecting and outputting phase, with respect to the clock, of a transition point of the input data from the outputs of the plurality of latch circuits; a filter for smoothing the output of the phase detecting circuit; and a control circuit for controlling clock phase by outputting control signals for controlling the interpolators and / or switch of the phase-shift circuit based upon the filter output.

Owner:RENESAS ELECTRONICS CORP

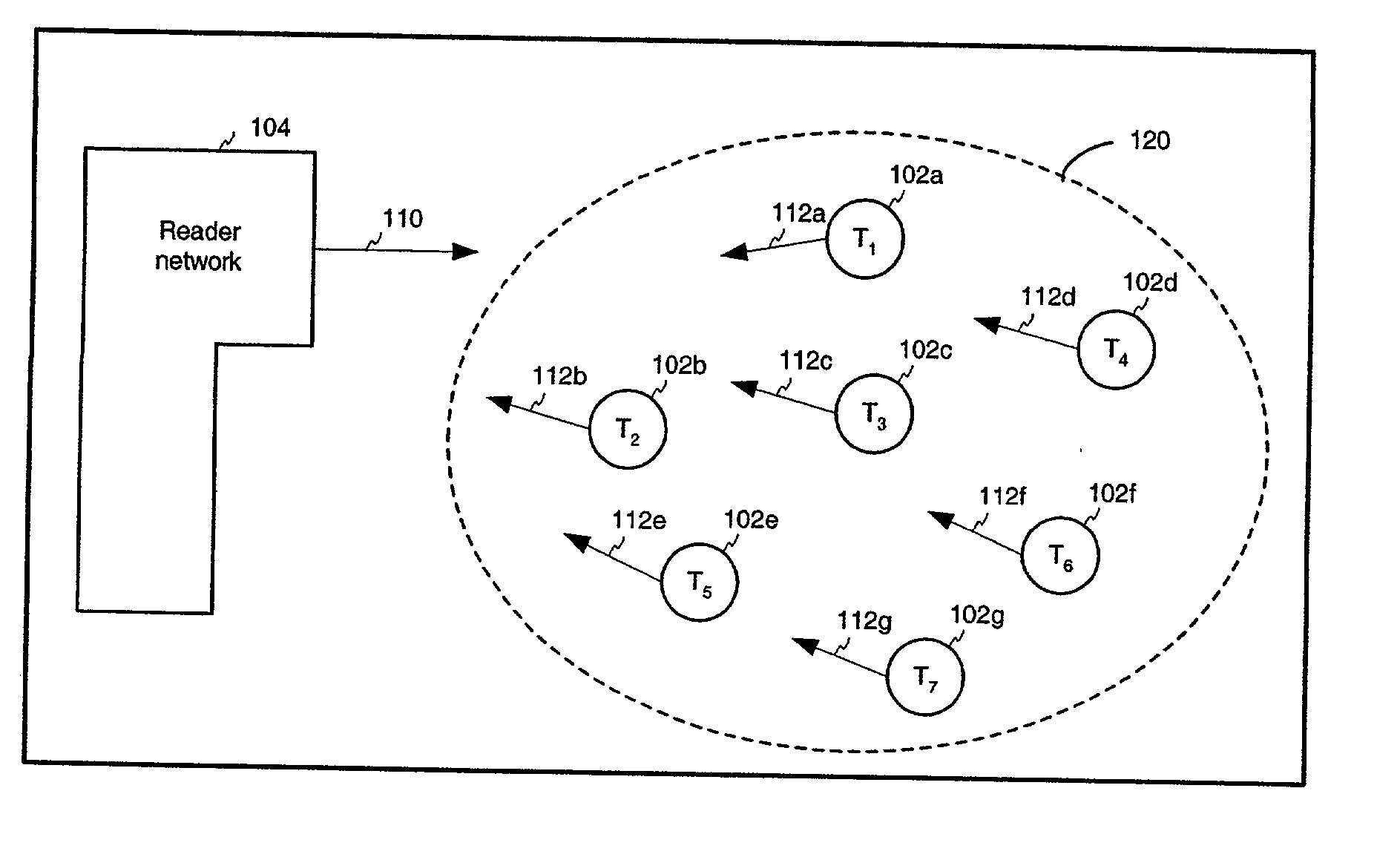

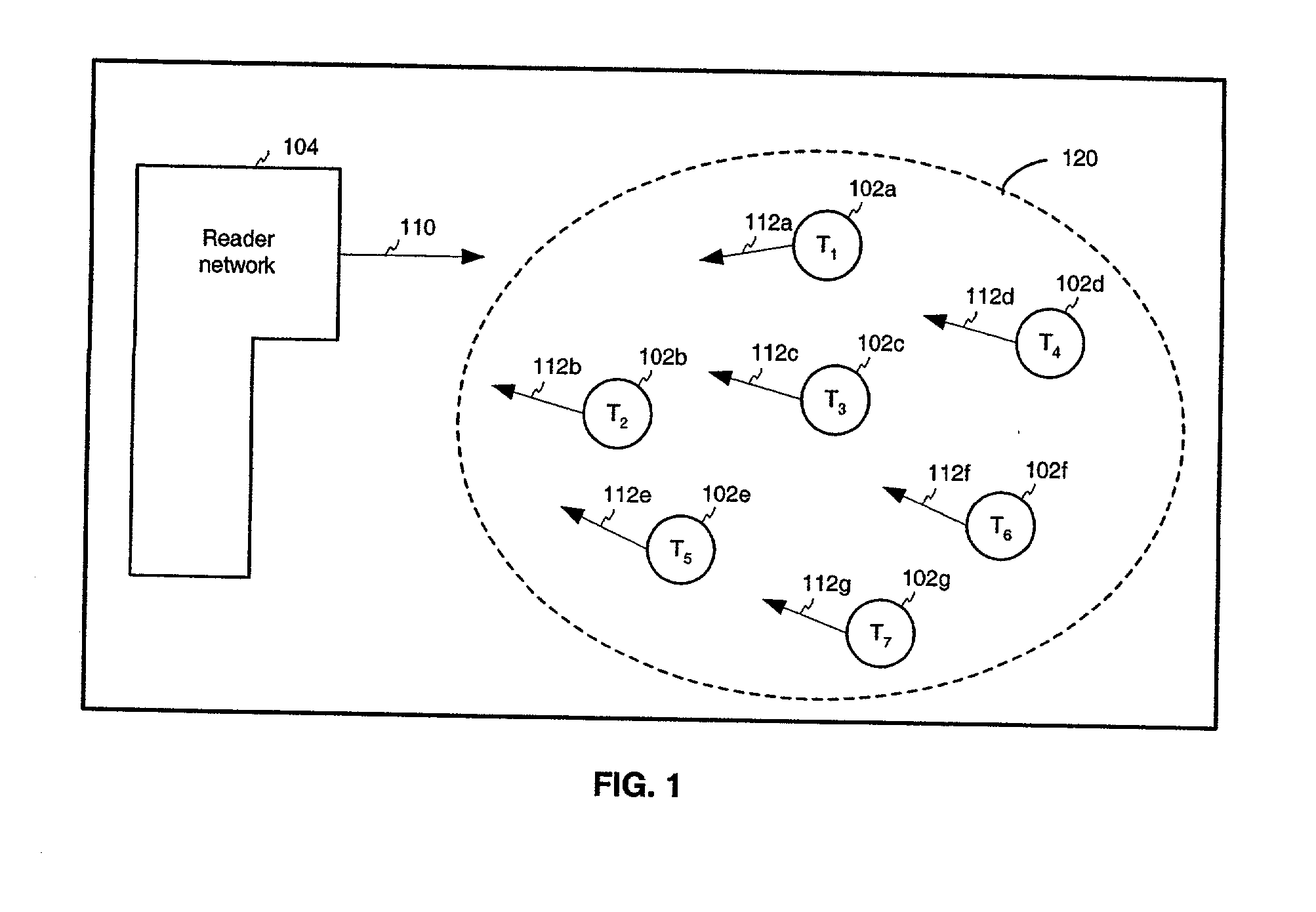

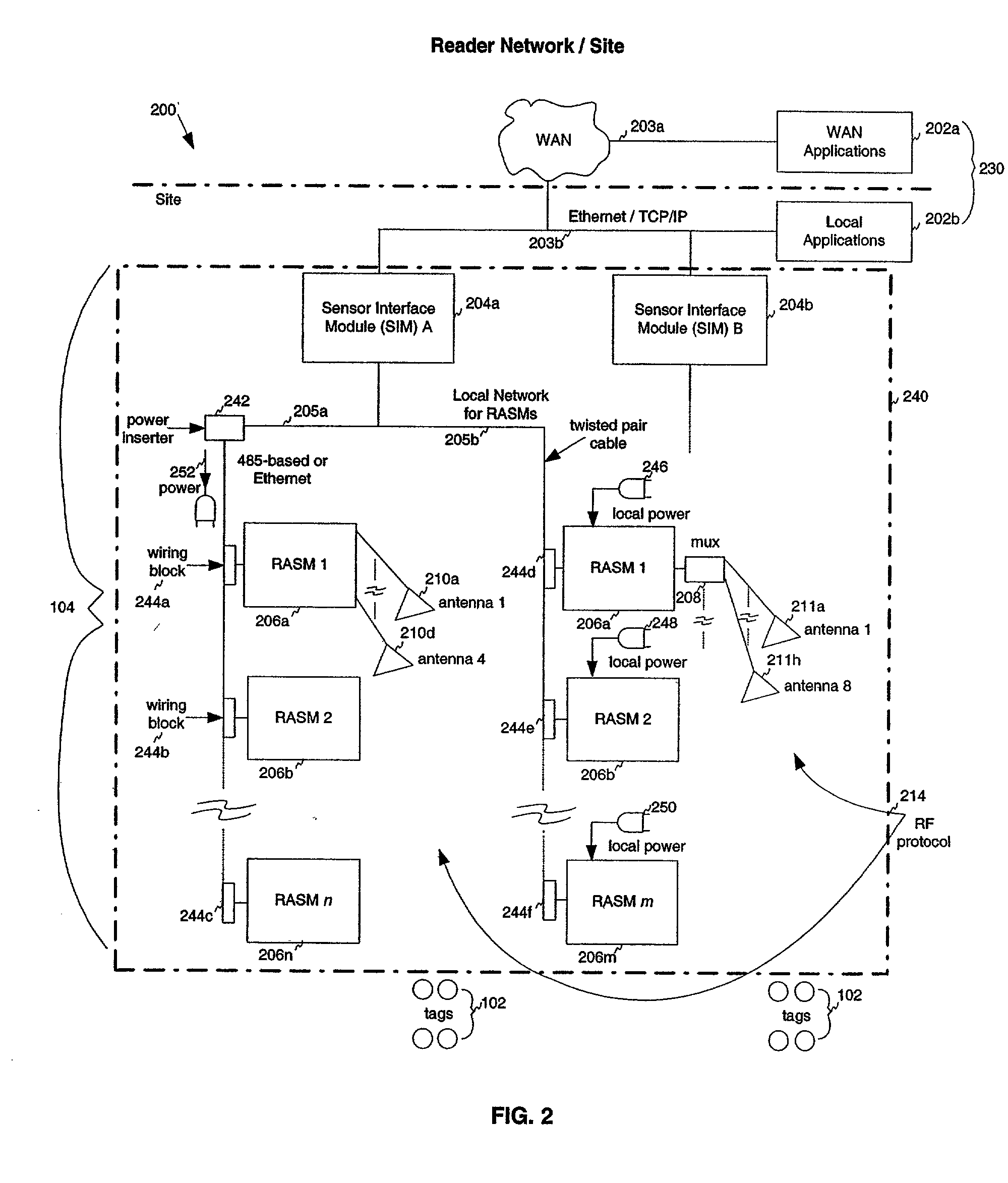

Identification tag utilizing charge pumps for voltage supply generation and data recovery

InactiveUS20020149482A1Memory record carrier reading problemsCo-operative working arrangementsControl signalRadio frequency

An identification (ID) tag includes a substrate having an input capable of receiving a high frequency signal. For instance, the high frequency signal can be a radio frequency (RF) signal that is generated as part of a radio frequency (RF) ID system. A first charge pump is coupled to the input and is configured to convert the high frequency signal to a substantially direct current (DC) voltage. A data recovery circuit is coupled to the input and is capable of recovering data from the high frequency signal. A back scatter switch is coupled to the input and is capable of modifying an impedance of the input, responsive to a control signal. A state machine is disposed on the substrate and is responsive to the data recovered by the second charge pump, where the state machine is capable of generating the control signal for the back scatter switch in response to the data. The DC voltage from the first charge pump is capable of providing a voltage supply for at least one of the data recovery circuit, the back scatter switch, and the state machine. The data recovery circuit includes a second charge pump that is capable of operating on the high frequency signal simultaneously with the first charge pump. In other words, the first charge pump can generate the supply voltage for the ID tag from the high frequency signal, while the second charge pump simultaneously retrieves the data from the high frequency signal. The first charge pump also includes a means for limiting the amplitude of the DC voltage by reducing the charge pump efficiency, once a threshold voltage is reached.

Owner:SYMBOL TECH LLC

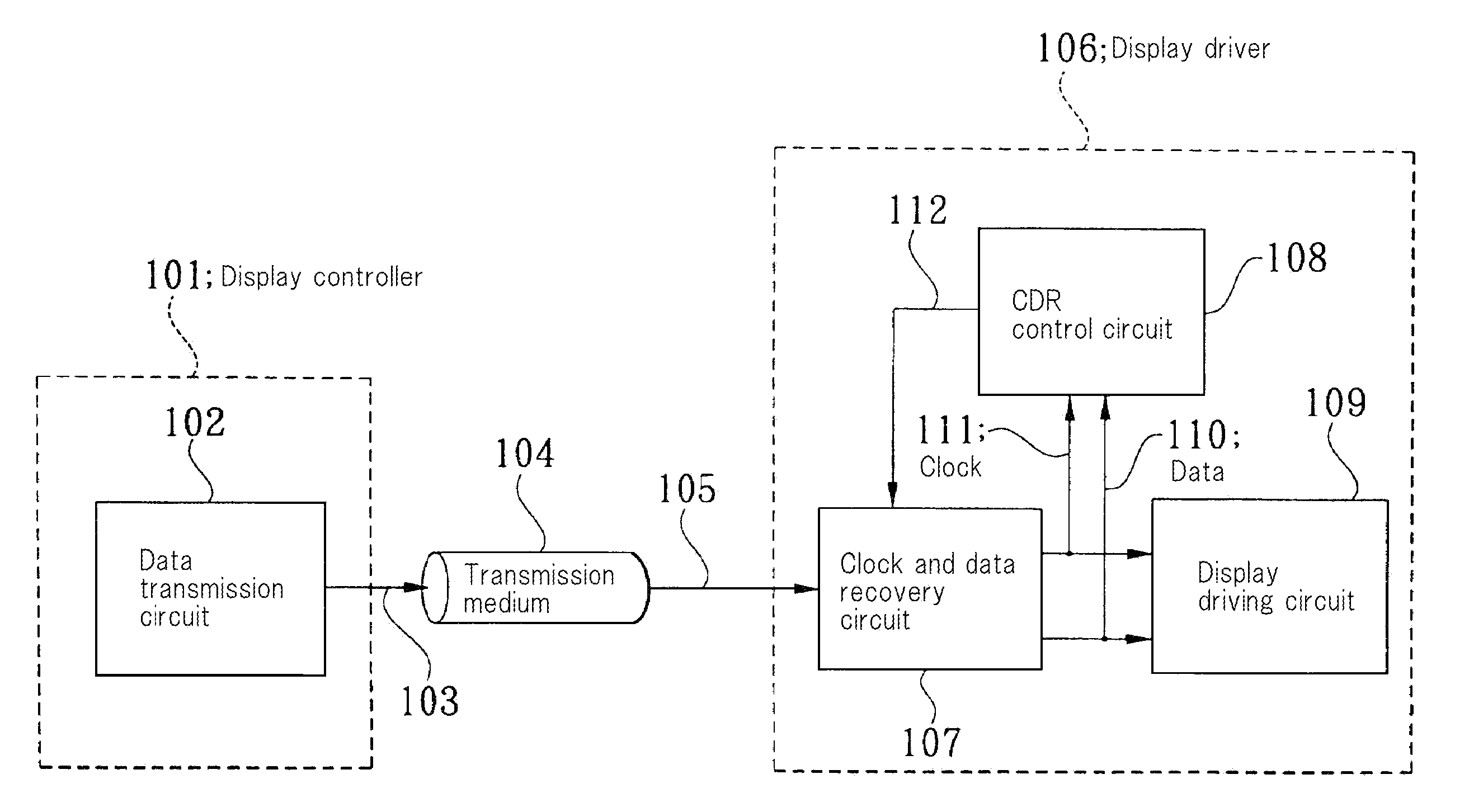

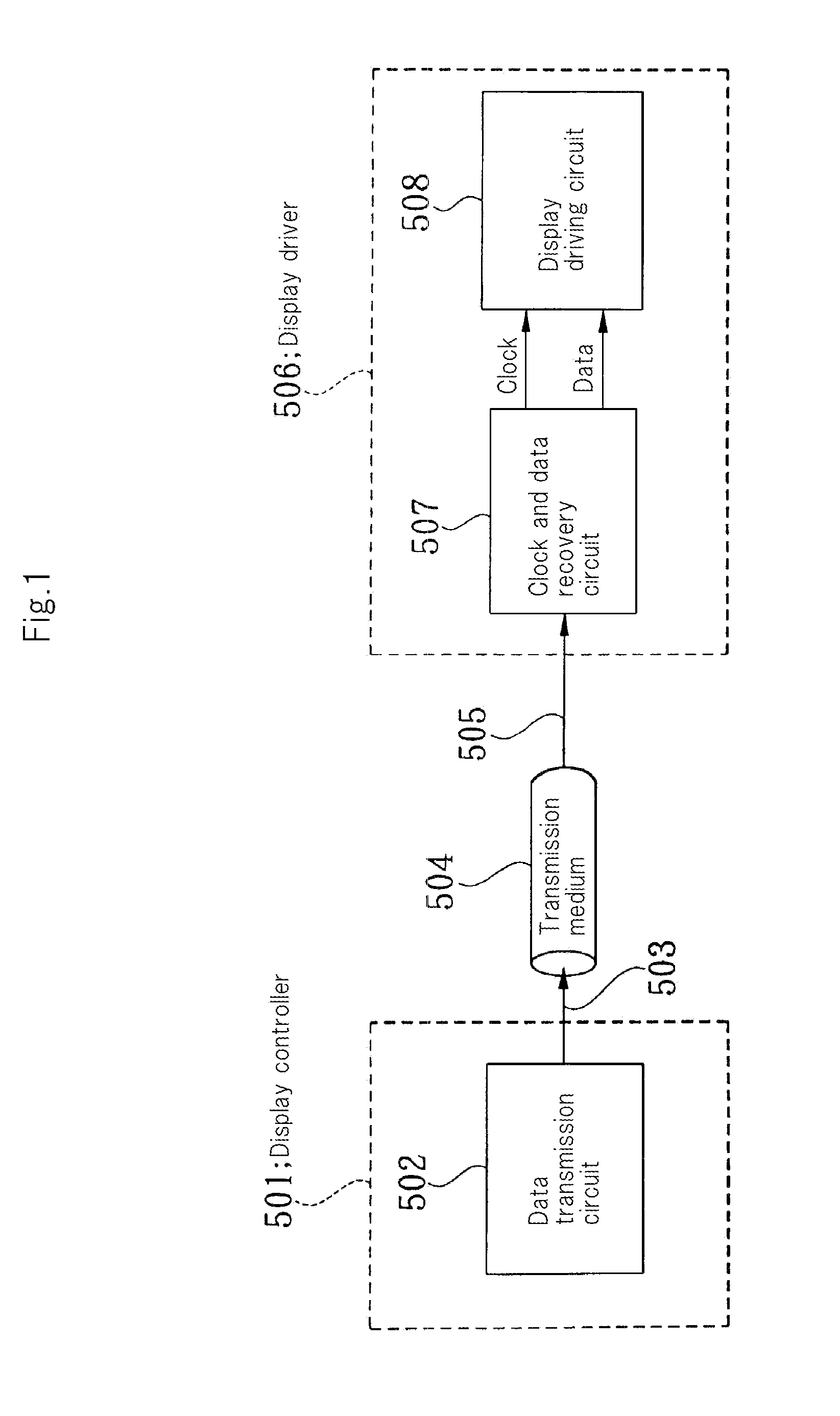

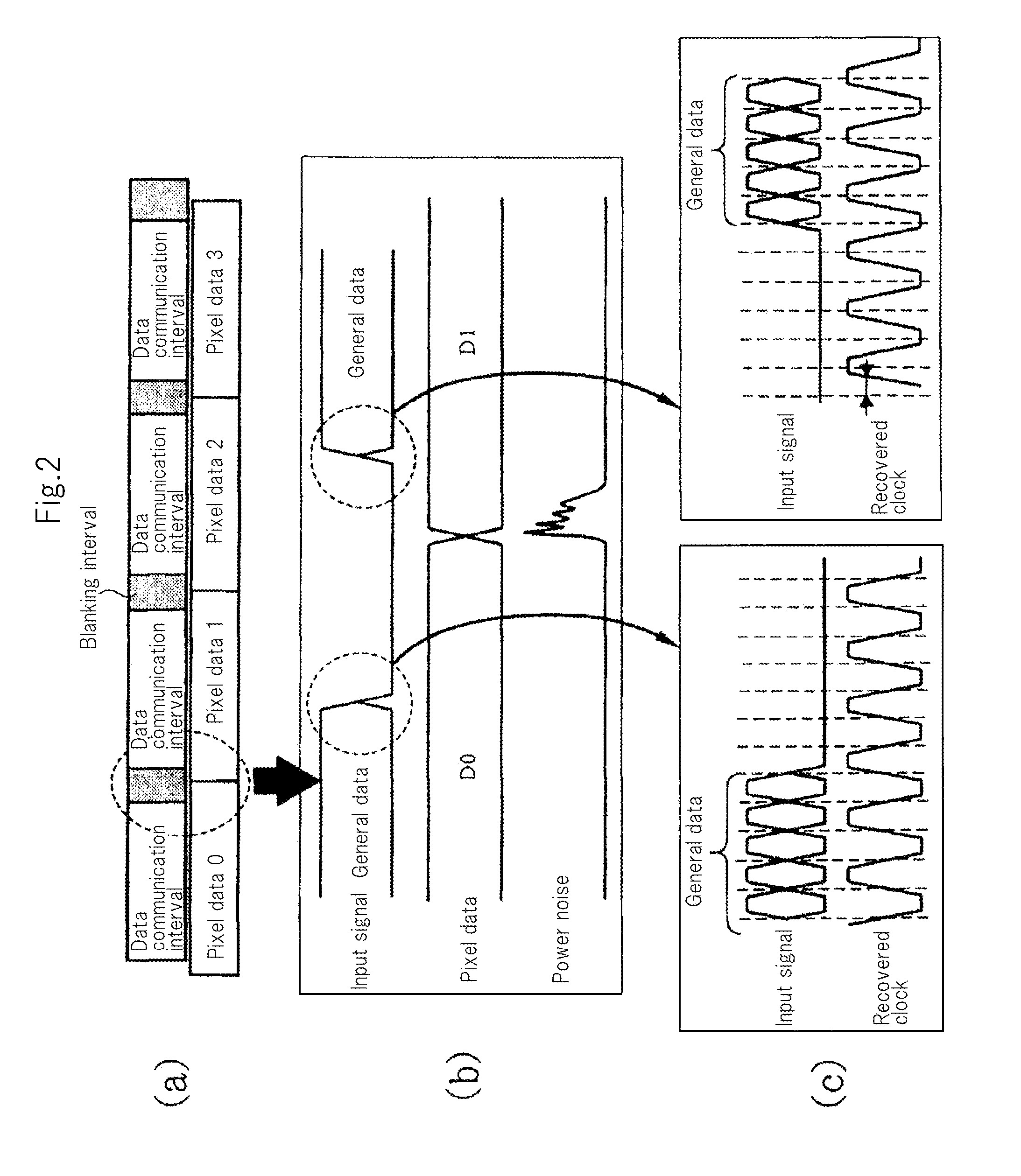

Clockless transmission system and clockless transmission method

ActiveUS20100039156A1Improve noise marginSignal transmission is convenientPulse automatic controlCathode-ray tube indicatorsControl signalControl data

A clockless transmission system includes display controller 101 and display driver 106. Display controller 101 includes data transmission circuit 102 configured to output general data obtained by multiplexing a clock by coding serialized pixel data for each pixel data during a data communication interval and also to output a predetermined control signal during a blanking interval. Display driver 106 includes clock and data recovery circuit 107 configured to output the pixel data from the general data transferred from the display controller and to increase a loop gain of a feedback loop in clock recovery such that the loop gain is larger than that when the general data is received, according to control data of the control signal, to recover and output a clock, and display driving circuit 109 configured to output a signal for driving a display based on the pixel data and the recovered clock.

Owner:NEC CORP

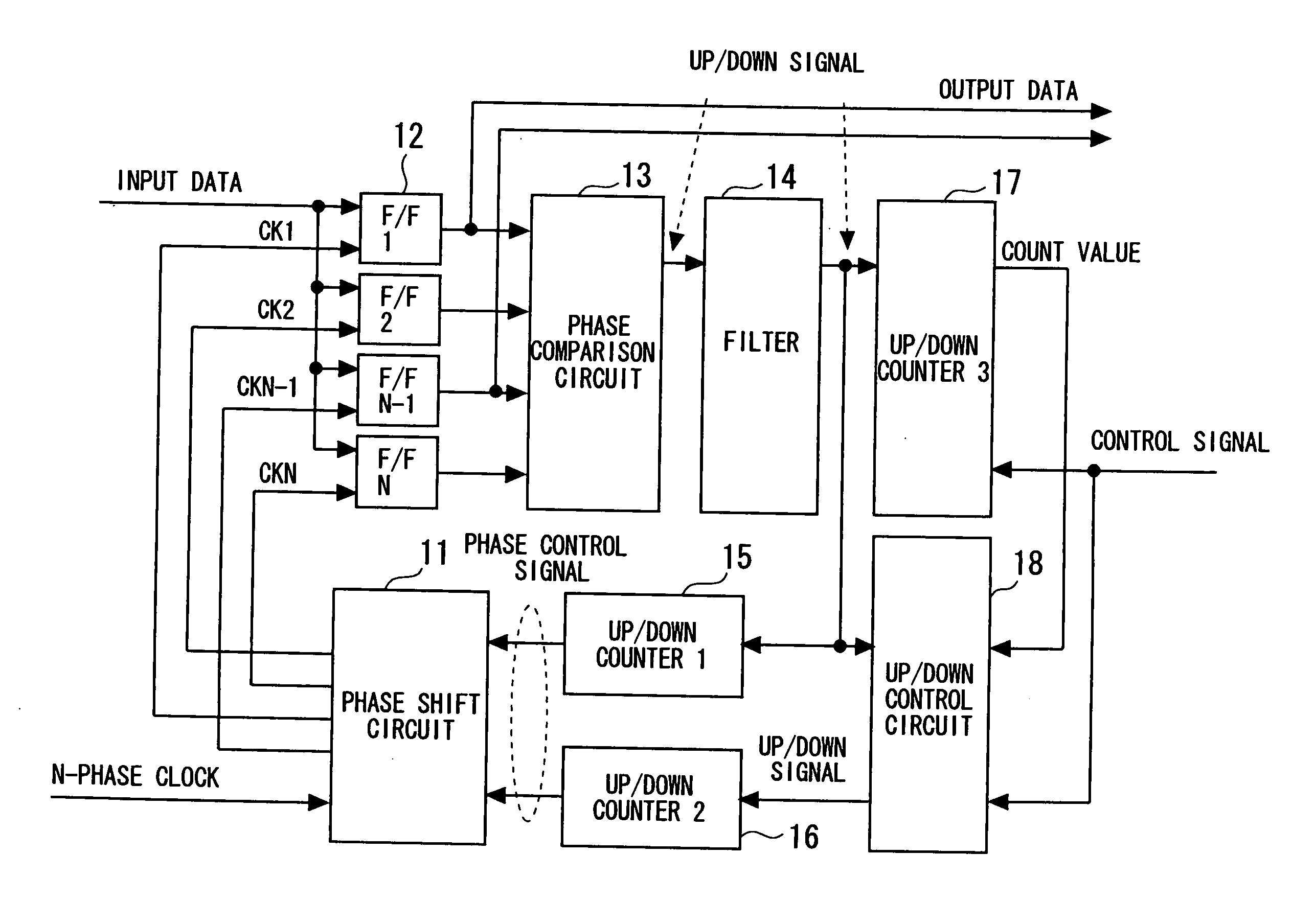

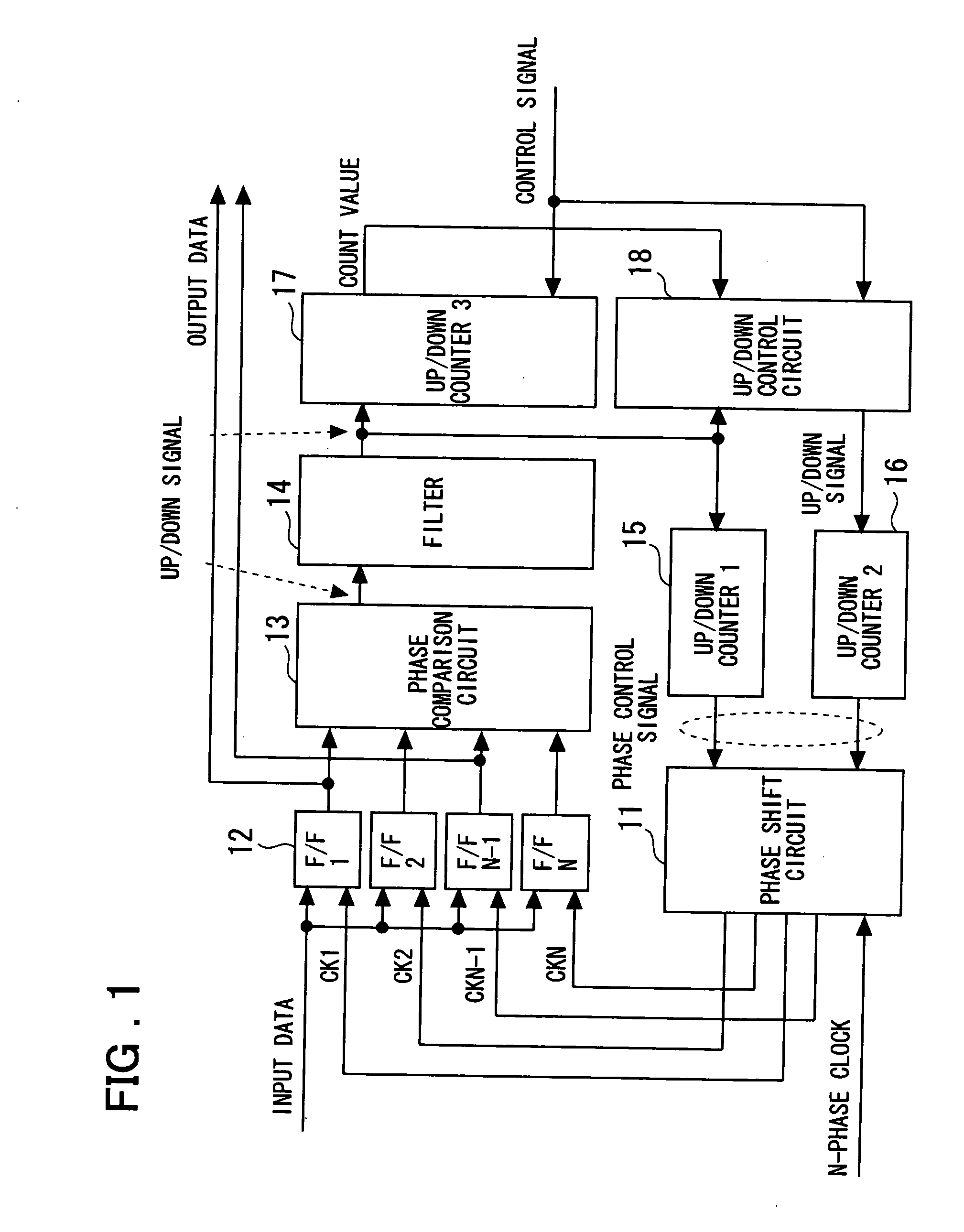

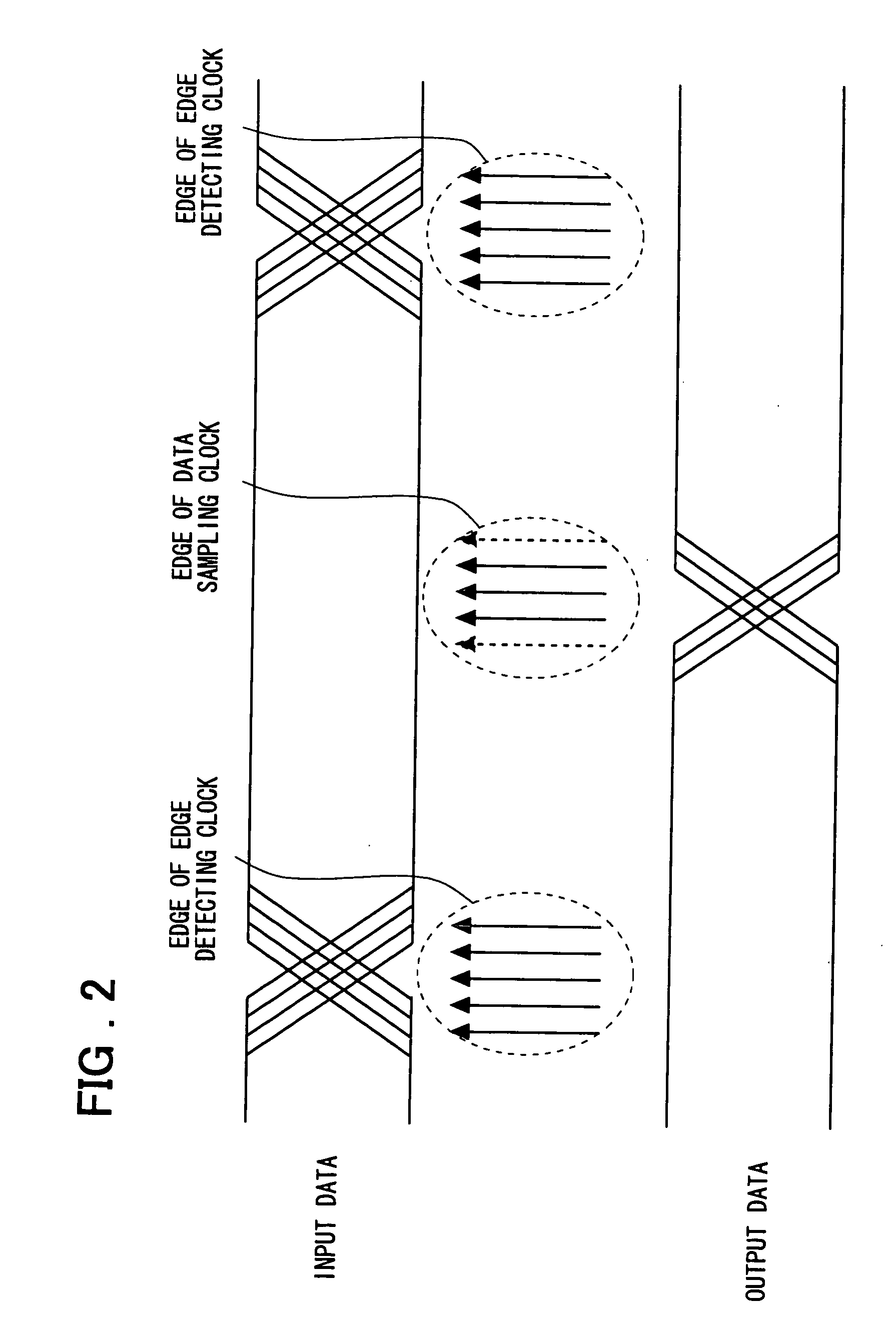

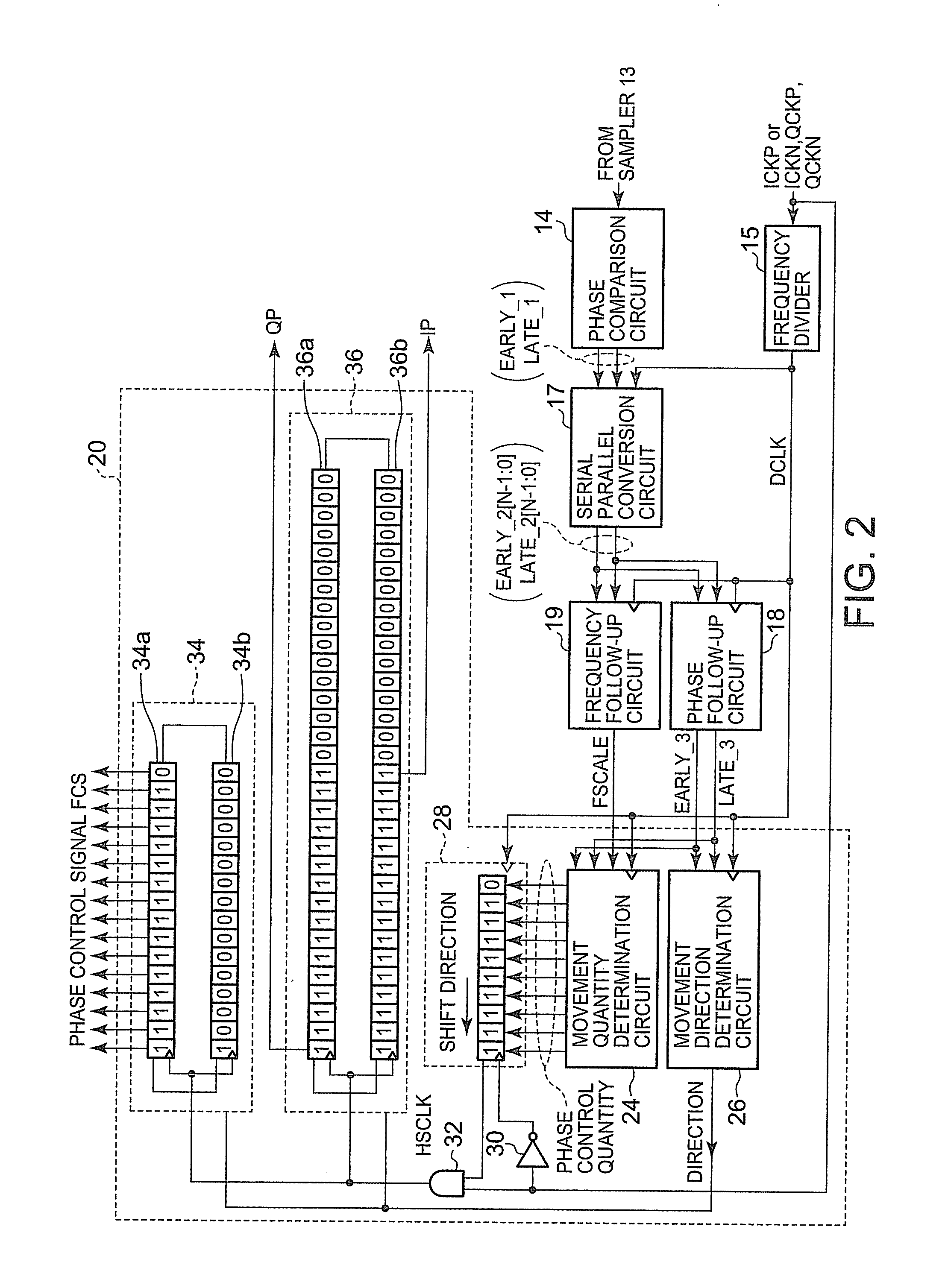

Clock and data recovery circuit

InactiveUS20070047686A1Pulse automatic controlAngle demodulation by phase difference detectionPhase shiftedControl signal

Disclosed is a clock and data recover circuit including N flip-flops (F / Fs) for sampling an input data signal using N-phase clocks, a phase comparison circuit for performing phase comparison based on outputs of the F / Fs, a filter or smoothing a result of the phase comparison and outputting an up / down signal, up / down counters, each for receiving an output of the filter and counting up or down a count value thereof, a phase shift circuit for adjustably controlling phases of the clocks for edge detection and the clocks for data sampling according to phase control signals from an up / down counter and an up / down counter, respectively, and an up / down control circuit for receiving a control signal for controlling maximum and minimum values of count values of the up / down counter, generating a signal for controlling counting up and down of the up / down counter based on the count value of the up / down counter, and supplying the generated signal to the up / down counter.

Owner:RENESAS ELECTRONICS CORP

Clock data recovery circuit and multiplied-frequency clock generation circuit

InactiveUS20100264963A1Avoid receivingIncrease probabilityPulse automatic controlFrequency-modulated carrier systemsPhase correctionPhase detector

Disclosed herein is a clock data recovery circuit including: a first phase detector; a loop filter; a charge pump; a voltage-controlled oscillator; a second phase detector; a phase correction information generation section; and a phase correction information addition section.

Owner:SONY CORP

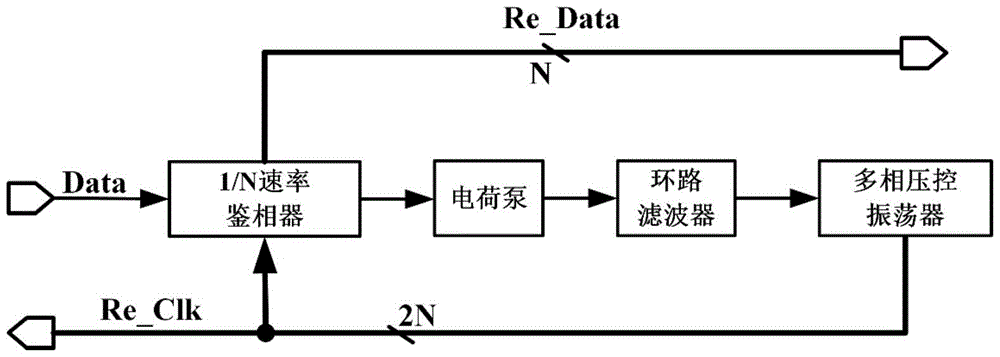

High-energy-efficiency low-jitter single loop clock data recovery circuit

ActiveCN105703767ASimple structureEliminate the effects of jitter performance degradationPulse automatic controlDiscriminatorHigh energy

The invention discloses a high-energy-efficiency low-jitter single loop clock data recovery circuit. The circuit comprises an 1 / N rate Bang-Bang phase discriminator with a 1:N demultiplexer function, a voltage-current converter, a loop filter and a multi-phase clock generator. An orthogonal clock signal generated by an orthogonal voltage control oscillator in the multi-phase clock generator is synthesized into a needed (N+2) phase recovery clock signal through a cascaded digital phase interpolator. And then the 1 / N rate Bang-Bang phase discriminator receives input data and a phase clock signal, detects a phase relationship between the two to generate a lead / lag voltage signal and recovers N paths of parallel 1 / N rate data signals. Then, the lead / lag voltage signal is converted into a current signal through the voltage-current converter. A current passes through loop filter filtering and then controls an output clock frequency and a phase relationship of the multi-phase clock generator so as to reduce a frequency deviation so that phase locking of a clock data recovery loop is reached. Jitter performance of the clock data recovery loop is effectively improved.

Owner:INST OF ADVANCED TECH UNIV OF SCI & TECH OF CHINA

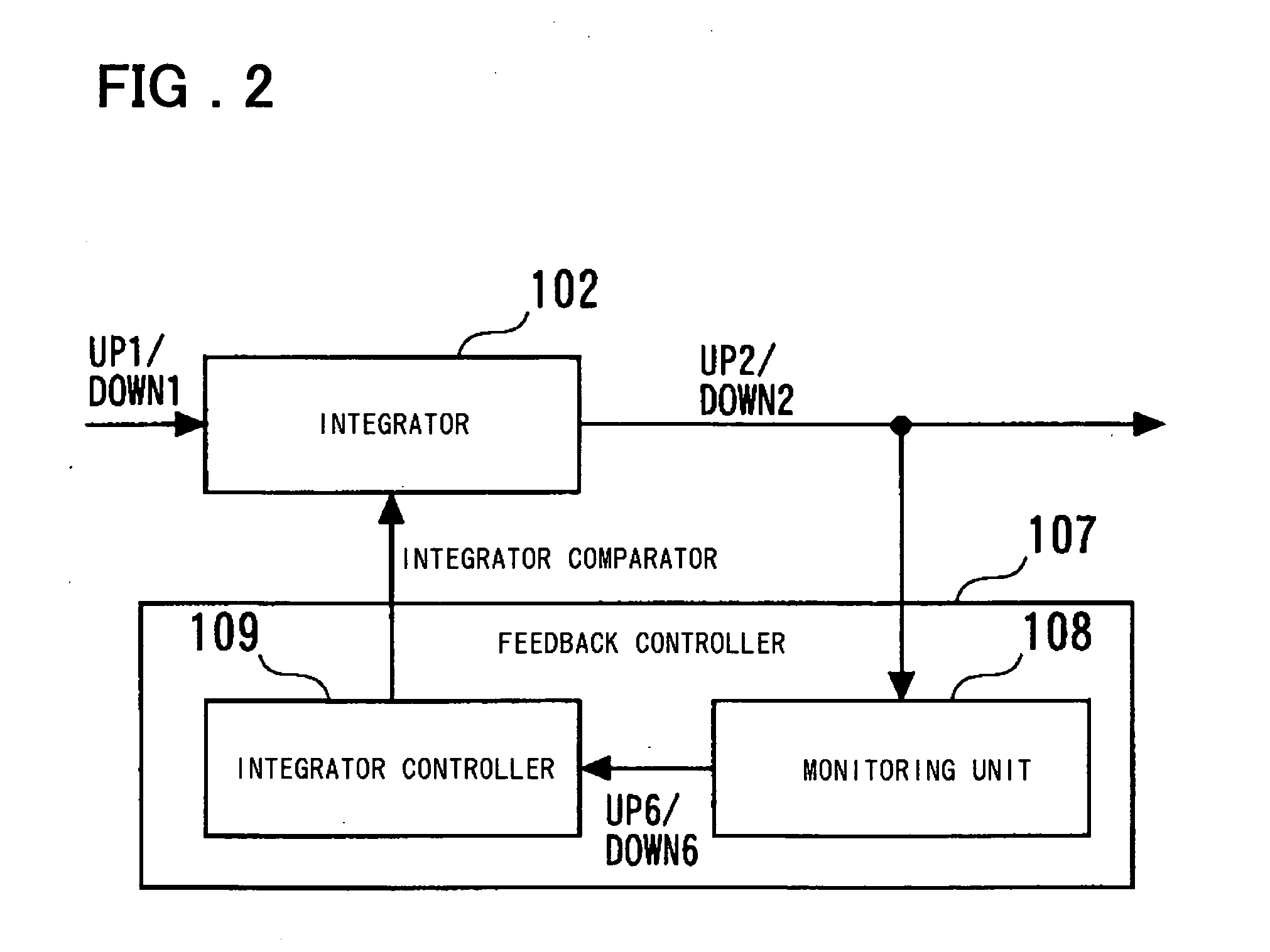

Clock and data recovery circuit

InactiveUS20060056564A1Excellent jitter tolerance characteristicImprove jitter tolerance characteristicReceiver initialisationPulse automatic controlIntegratorFeedback controller

A clock and data recovery circuit that tracks the frequency and phase fluctuation of serial data includes a feedback controller for monitoring tracking speed of an extraction clock with respect to the frequency and phase fluctuation of the serial data and applying feedback control to an integrator adaptively and moment to moment, thereby raising the tracking speed of the recovered clock and improving the jitter tolerance characteristic.

Owner:RENESAS ELECTRONICS CORP

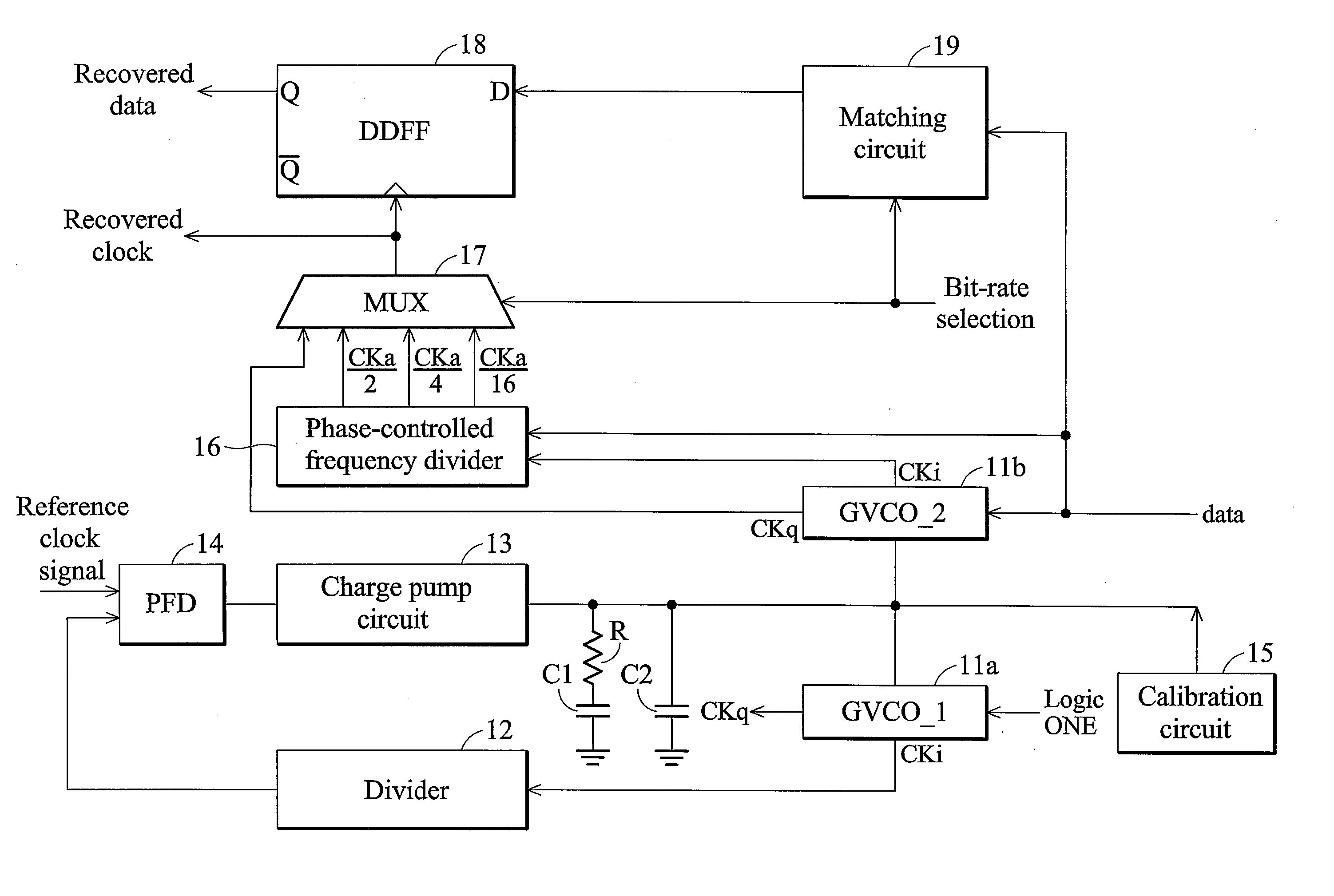

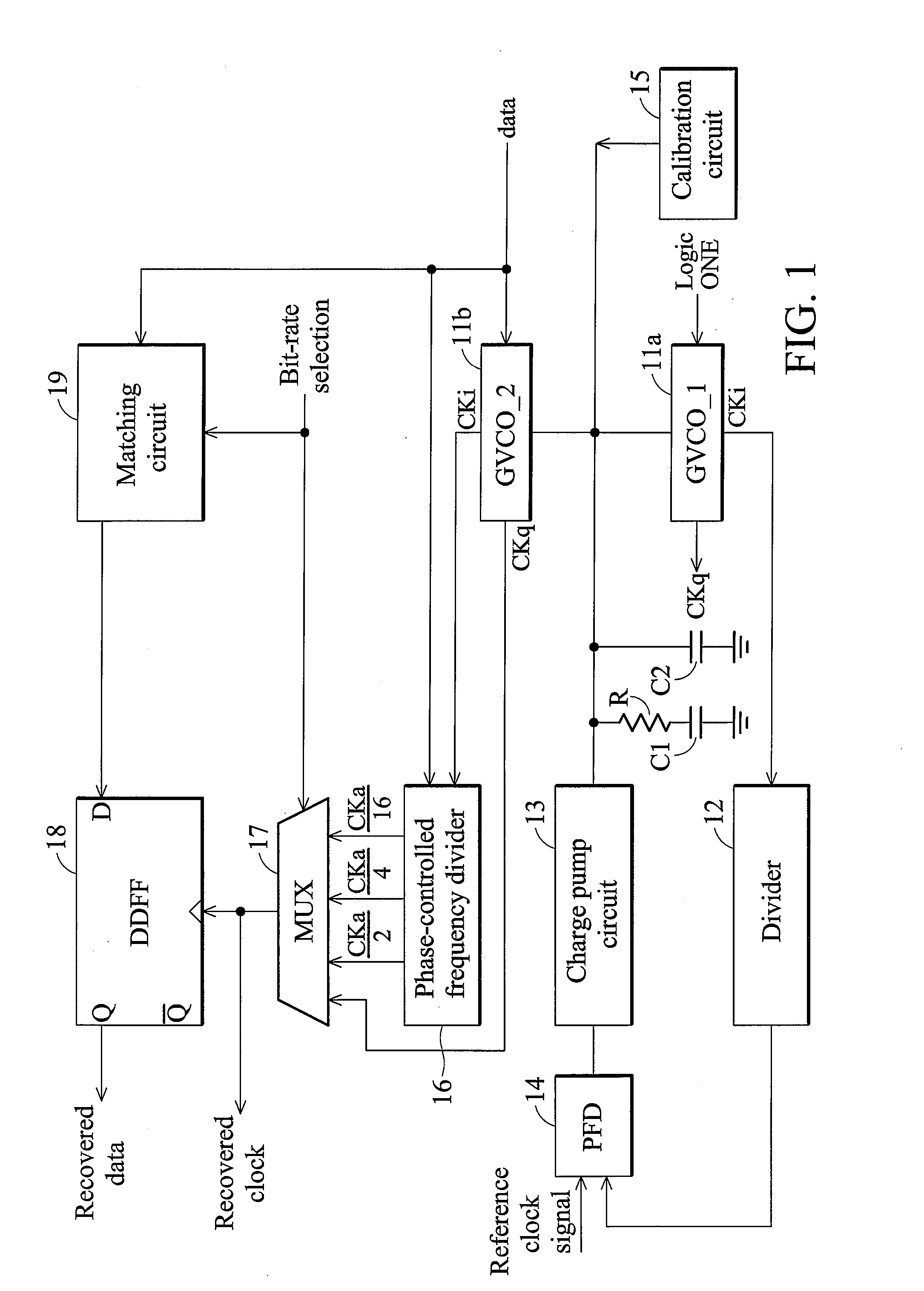

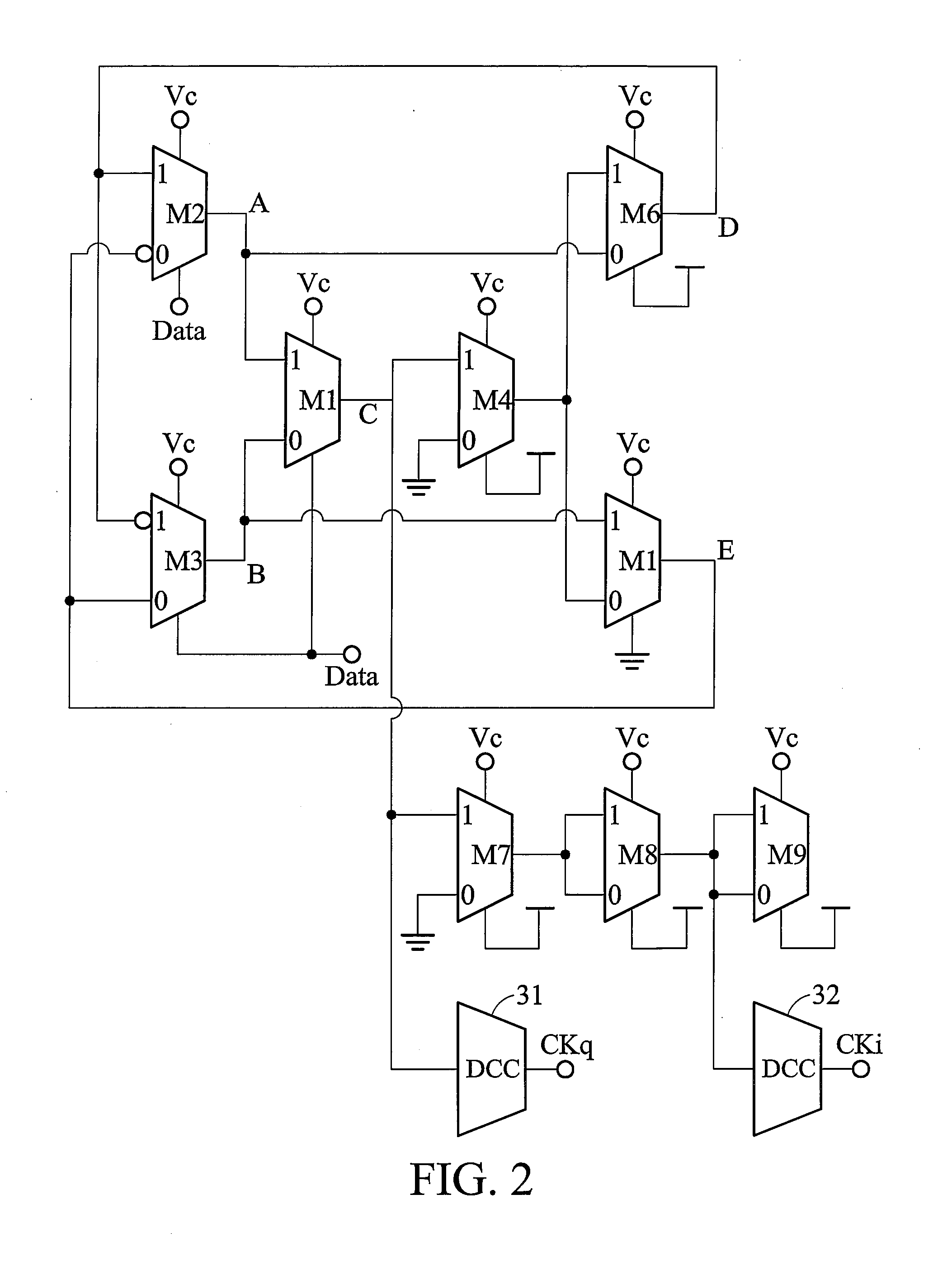

Multi-band burst-mode clock and data recovery circuit

ActiveUS20080260087A1Pulse automatic controlPulse generation by logic circuitsMulti bandVoltage reference

A clock and data recovery circuit is disclosed and comprises a first gated voltage-controlled oscillator, a PLL unit, a phase-controlled frequency divider, a multiplexer, a matching circuit and a double-edge-triggered D flip-flop. The first GVCO receives a data signal and a reference voltage to generate a first clock signal and a second clock signal based on the data signal. The PLL unit receives a reference clock signal and generates the reference voltage to adjust the frequency of the first clock signal and the second clock signal at the vicinity of the predetermined frequency. The phase-controlled frequency divider receives and divides the first clock signal by N to output a third clock signal. The multiplexer controlled by a selection signal receives and outputs the second clock signal or the third clock signal. The matching circuit receives the data signal and the selection signal to match the delays therebetween. The double-edge-triggered D flip-flop comprises a data input terminal receiving the output signal from the matching circuit, a clock input terminal receiving the output signal from the multiplexer, and an output terminal outputting a recovered data signal.

Owner:MEDIATEK INC +1

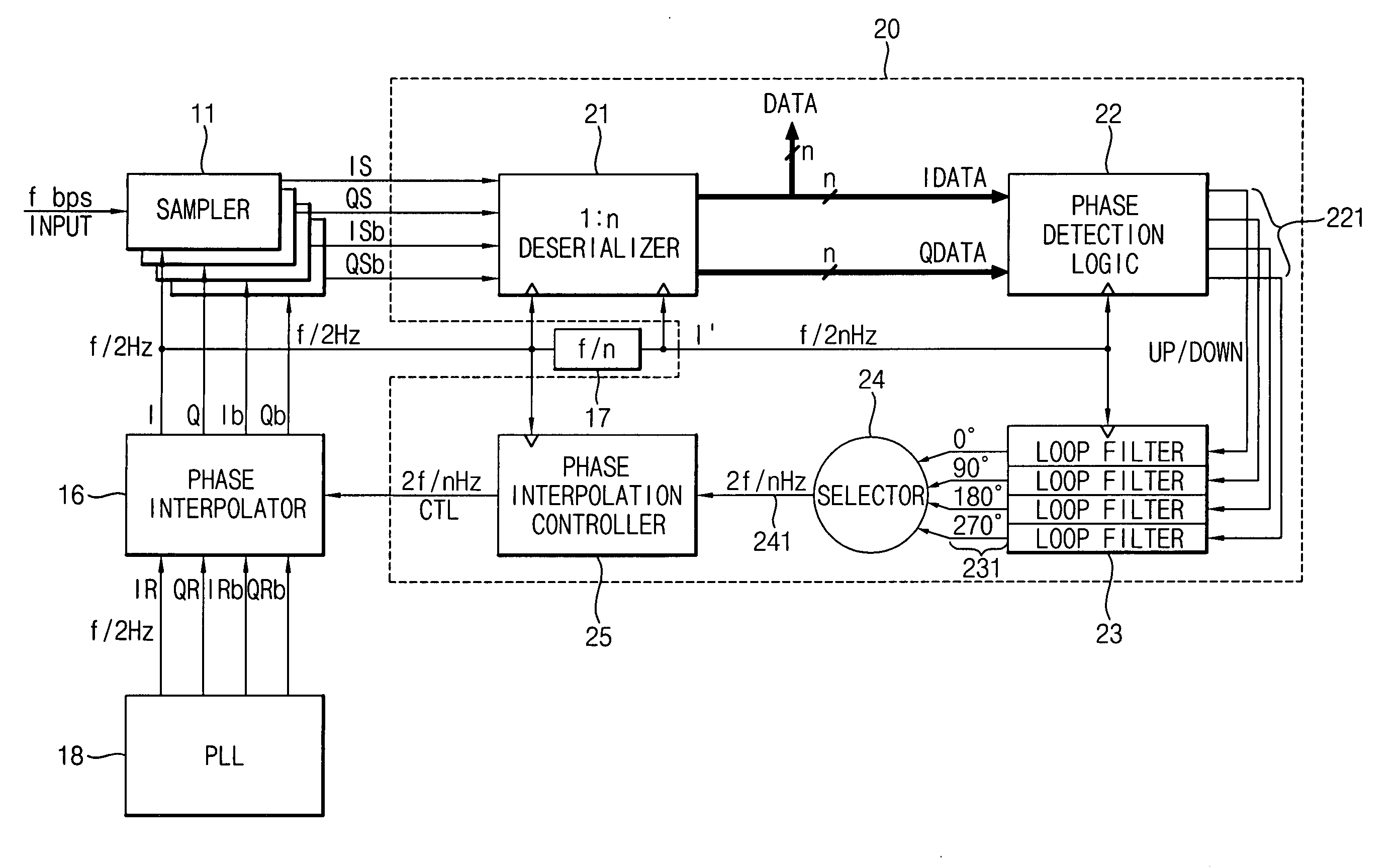

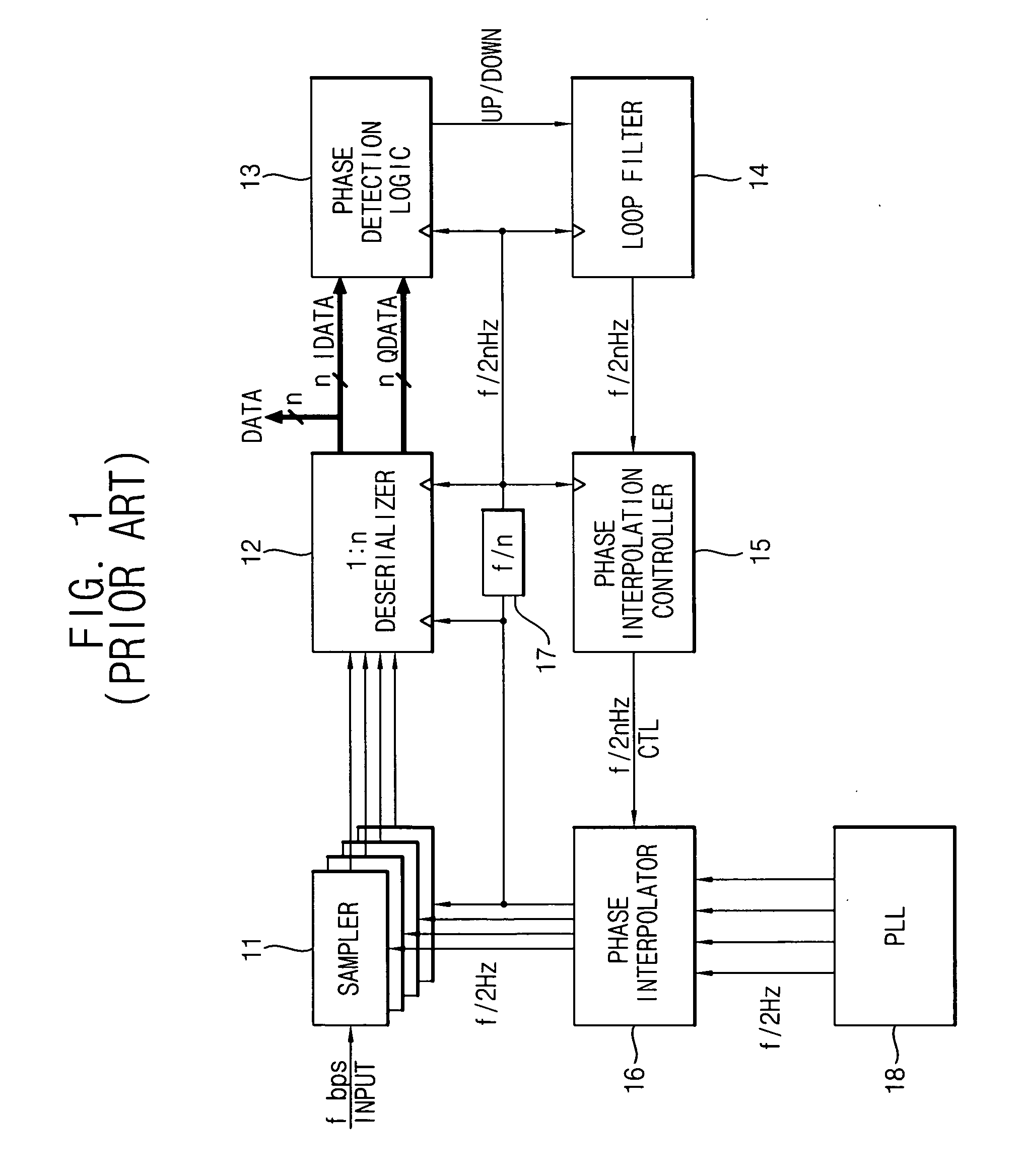

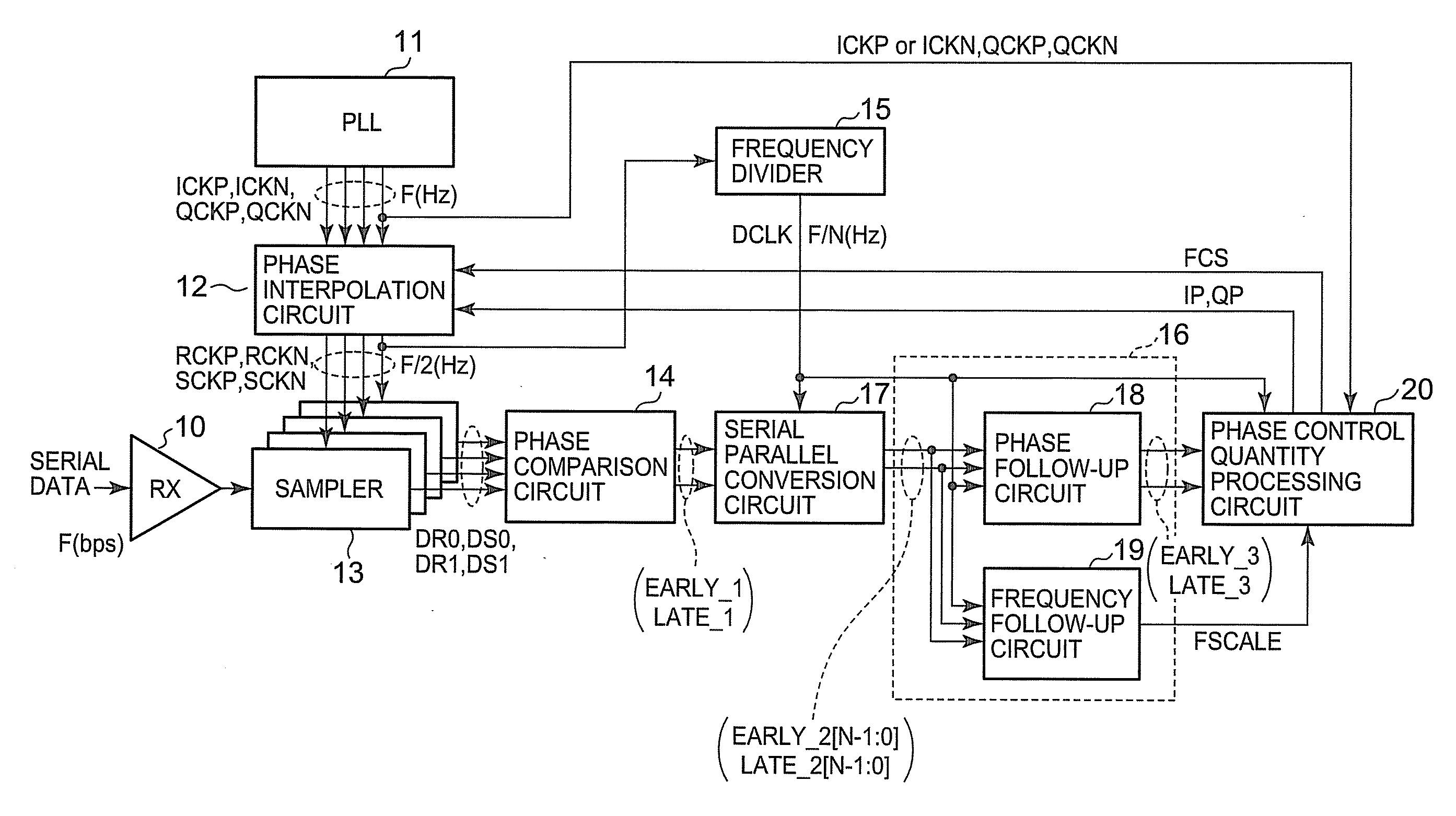

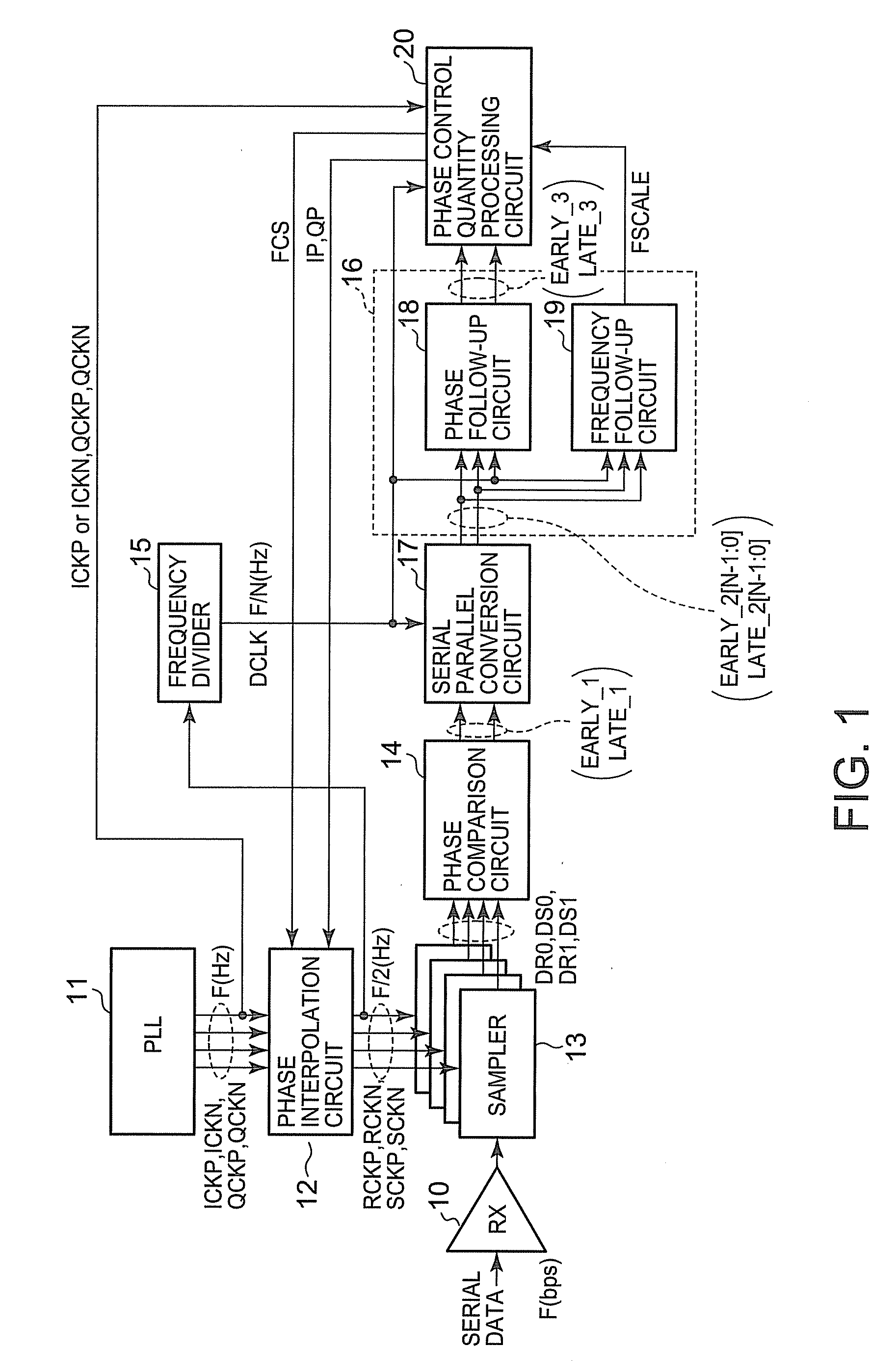

Clock recovery circuit and data recovery circuit

A serial input signal is sampled in synchronization with a plurality of first clock signals to obtain a plurality of sampling data pieces. A phase comparison circuit outputs a serial phase information signal based on the sampling data pieces. A serial-parallel conversion circuit performs a serial-to-parallel conversion on the serial phase information signal in synchronization with a second clock signal having a lower frequency, to output a parallel phase information signal. A digital filtering circuit calculates phase deviation and phase advance-delay signals based on the parallel phase information signal in synchronization with the second clock signal. By these signals, a phase control amount processing circuit generates a phase control signal. The phase control signal is in synchronization with third clock signals having a higher frequency. A phase interpolation circuit adjusts the phases of the third clock signals based on the phase control signal to output the first clock signals.

Owner:KK TOSHIBA

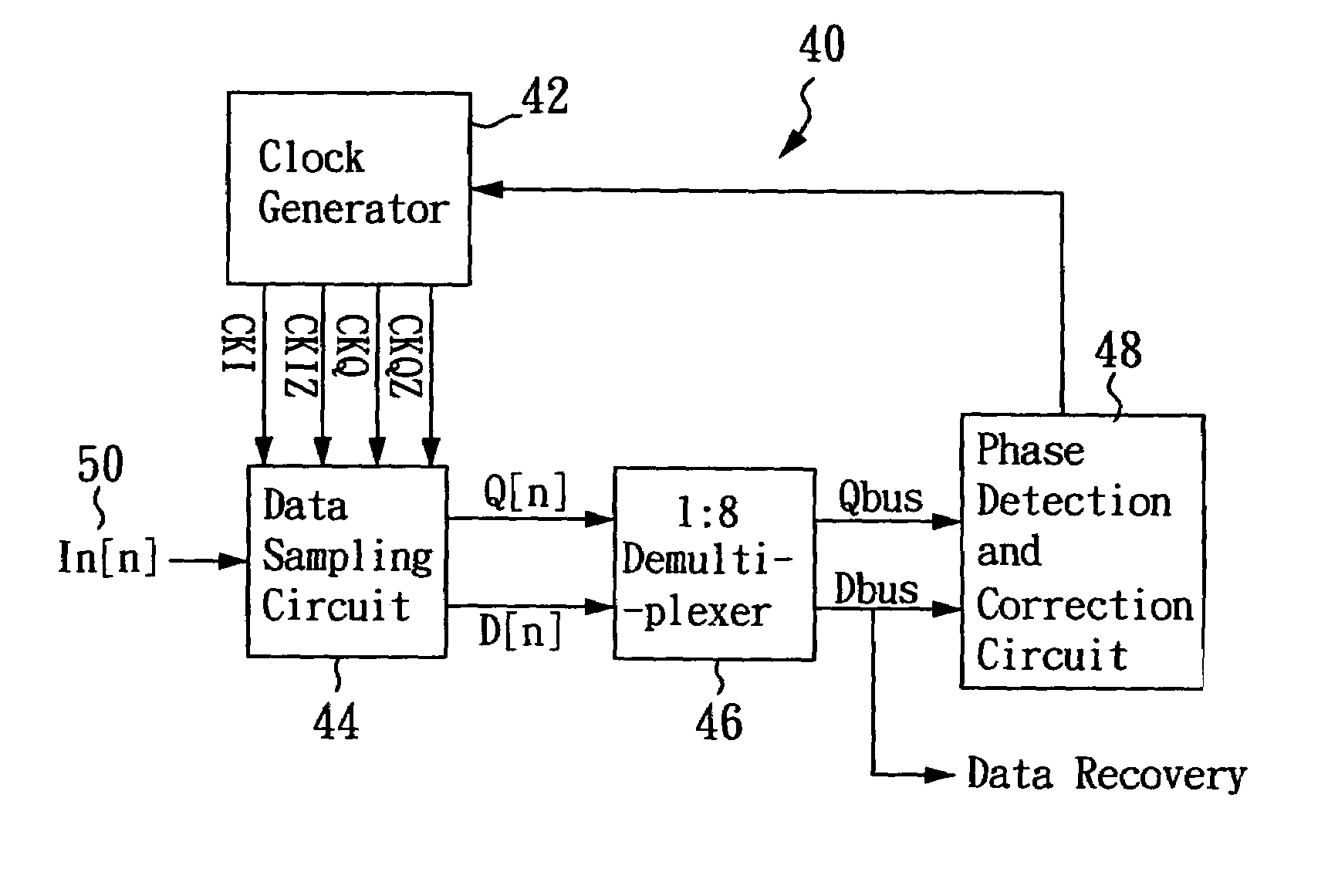

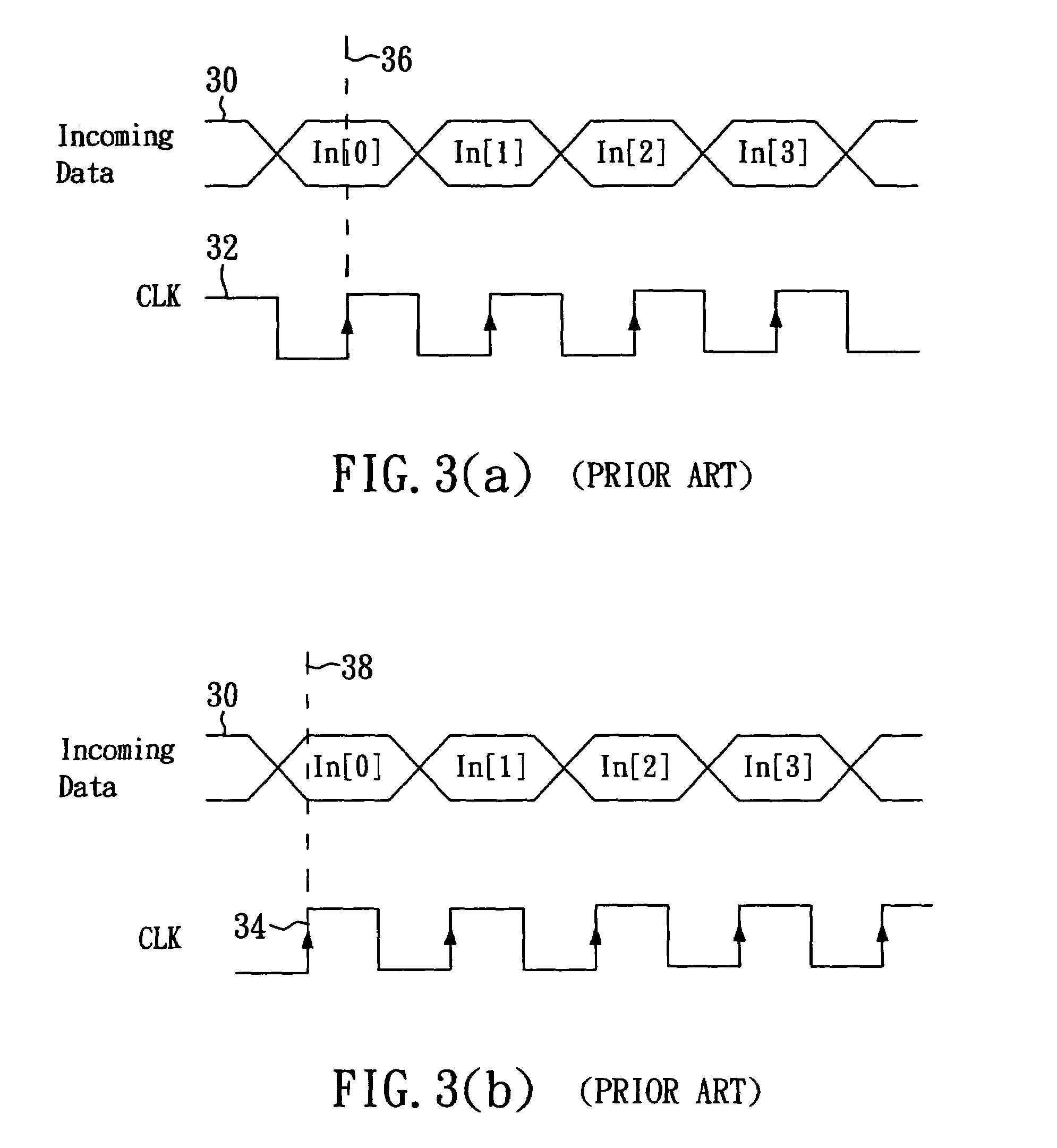

Data recovery circuit, phase detection circuit and method for detecting and correcting phase conditions

ActiveUS7310397B2Reduce frequencyPulse automatic controlVoltage-current phase angleData streamData recovery circuit

In the data recovery circuit of the invention, a first group of sampling clock pulses is used for sampling approximately the central portions of the data bits in an incoming data stream to produce a first sampled data stream, while a second group of sampling clock pulses is used for sampling approximately the transition portions between every two adjacent data bits in the incoming data stream to produce a second sampled data stream. By detecting the resemblance of each bit in the second sampled data stream to the corresponding two adjacent bits in the first sampled data stream, a phase detection and correction circuit determines an early condition or a late condition for the phases of the sampling clocks and produces a signal to correct the phases of the sampling clocks by shifting the phases backwards or forwards. According to the invention, sampling clocks with lower frequencies can be used for sampling, and the phase error can be corrected to obtain the correct data recovery.

Owner:XUESHAN TECH INC

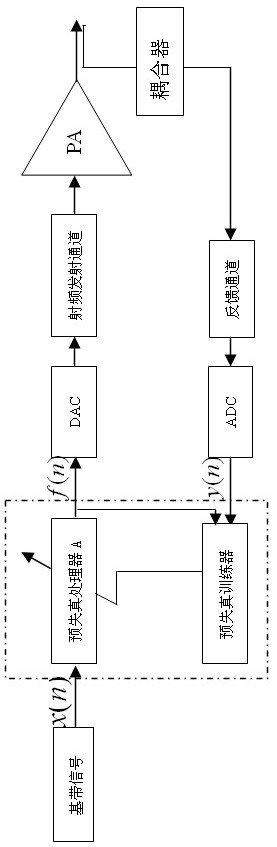

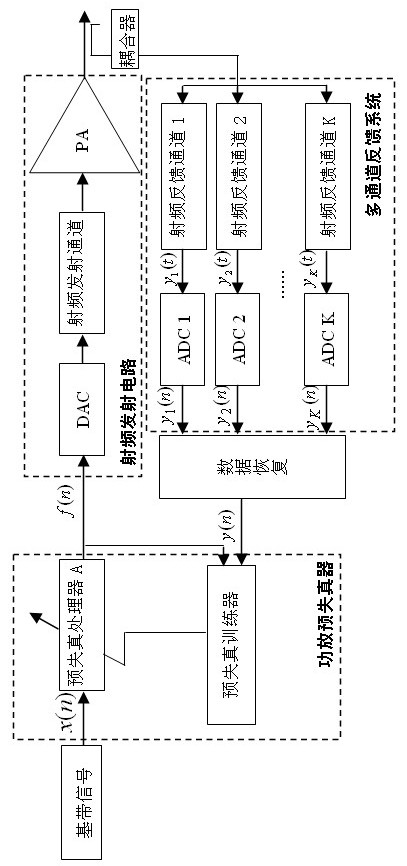

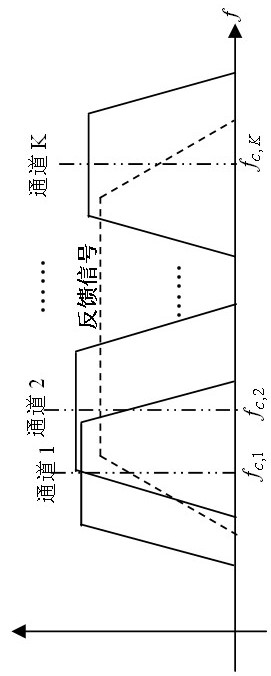

Power amplifier linearization correcting circuit and method based on multi-channel feedback

ActiveCN102055411ASolve problems that are difficult to achieve high linearityAmplifier modifications to reduce non-linear distortionPower amplifiersNonlinear distortionFrequency spectrum

The invention discloses a power amplifier linearization correcting circuit and method based on multi-channel feedback, relates to a linearization technology in the technical field of communication, and aims to provide a power amplifier linearization correcting circuit and method capable of self-adaptively regulating a predistortion parameter of a system by tracking the linearization characteristic of a radio frequency power amplifier. The power amplifier linearization correcting method is technically characterized in that a signal output by a power amplifier is subjected to frequency spectrumdivision and is coupled to a feedback system by utilizing a plurality of paths of channels; a data recovery circuit recovers a plurality of paths of feedback information to form a path of signal; a predistortion trainer calculates the predistortion parameter by utilizing a baseband signal and a recovered feedback signal; a predistortion trainer A adds a predistortion signal complementing a nonlinear distorted signal of the power amplifier according to the predistortion parameter; and the predistortion signal in the baseband signal is counteracted in the power amplifier, thereby realizing the linearization correction of the power amplifier. The invention is mainly used for nonlinear predistortion correction of a radio frequency signal emission system.

Owner:CHENGDU KAITENG SIFANG DIGITAL RADIO & TELEVISION EQUIP CO LTD

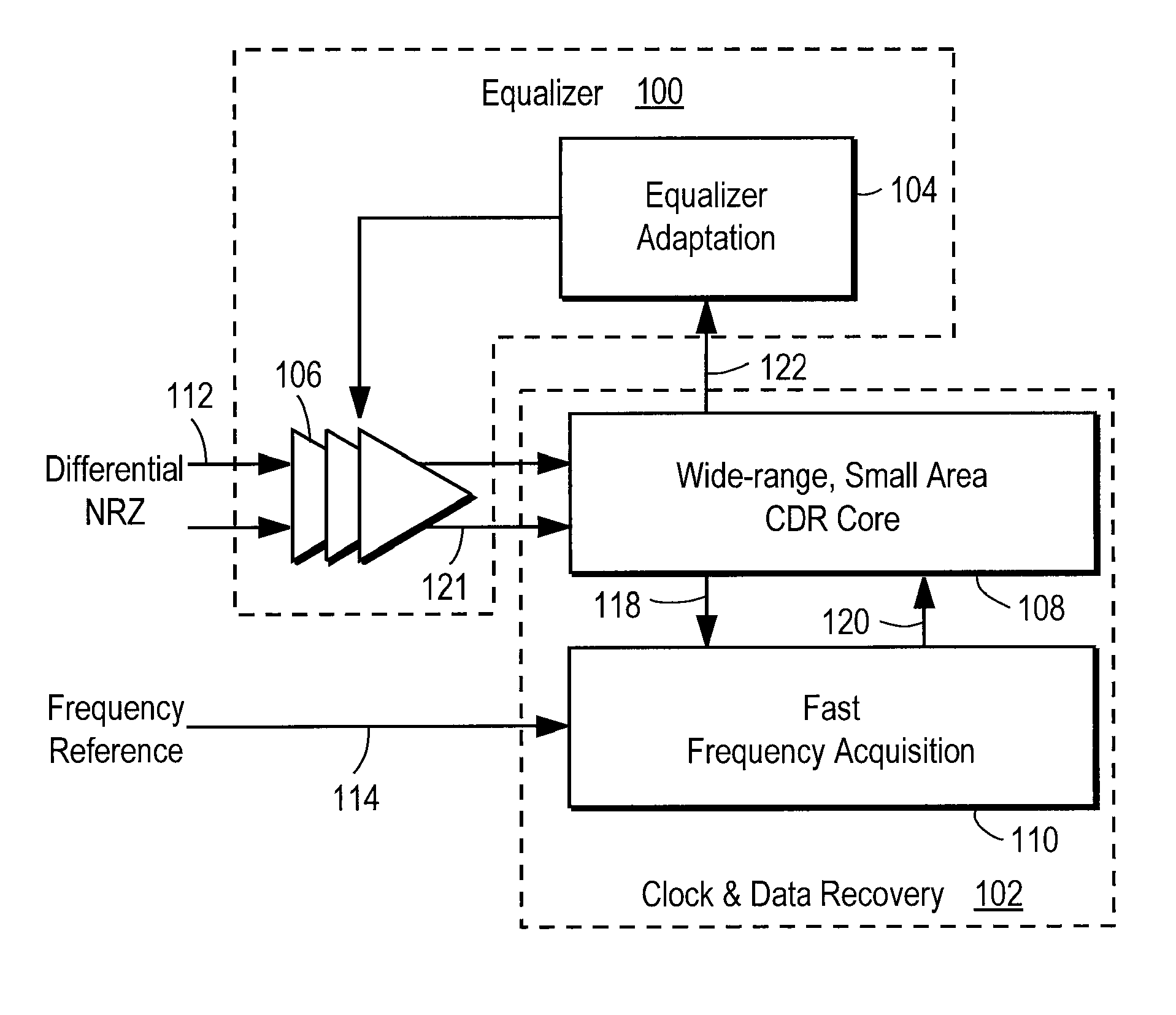

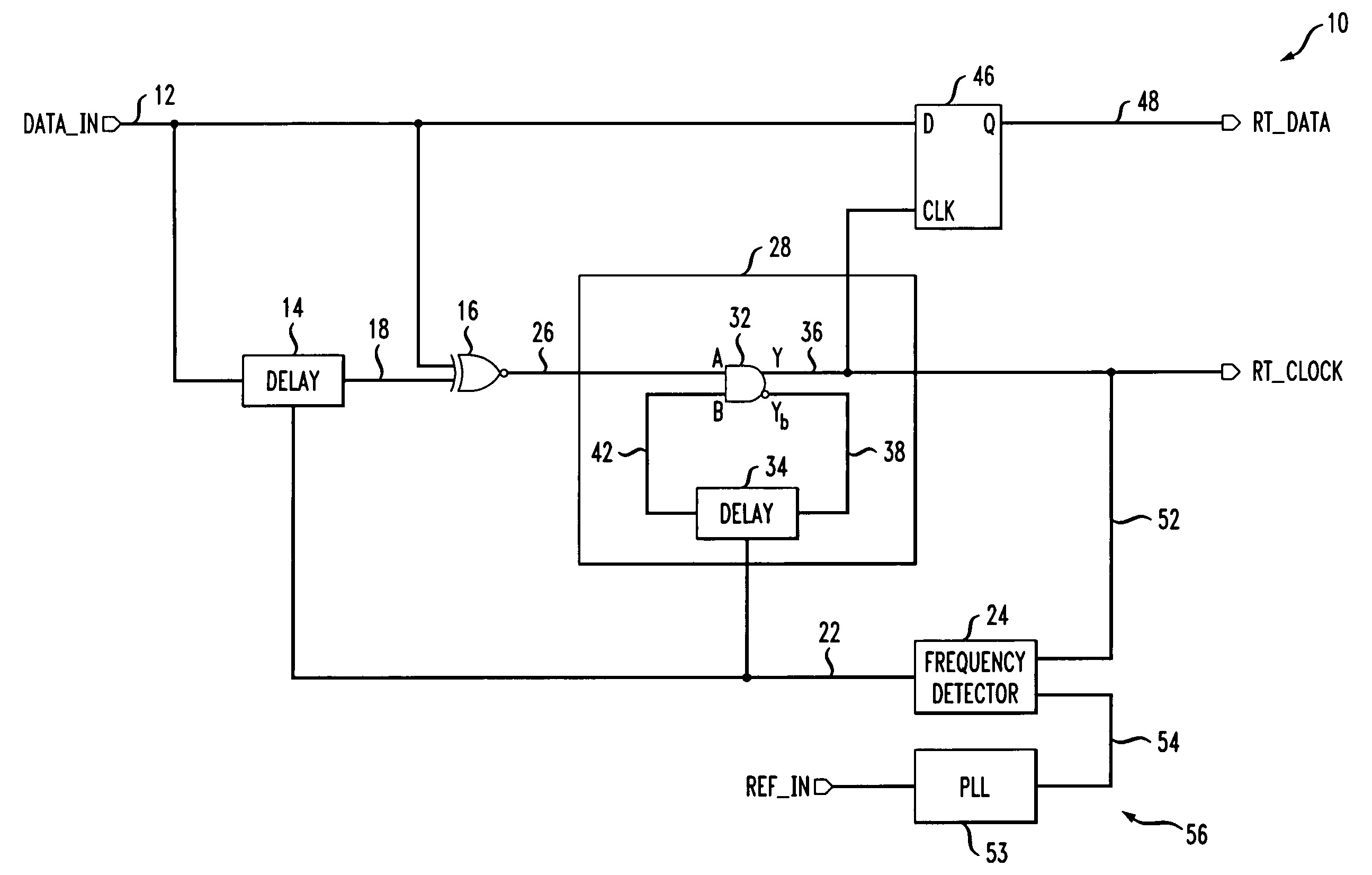

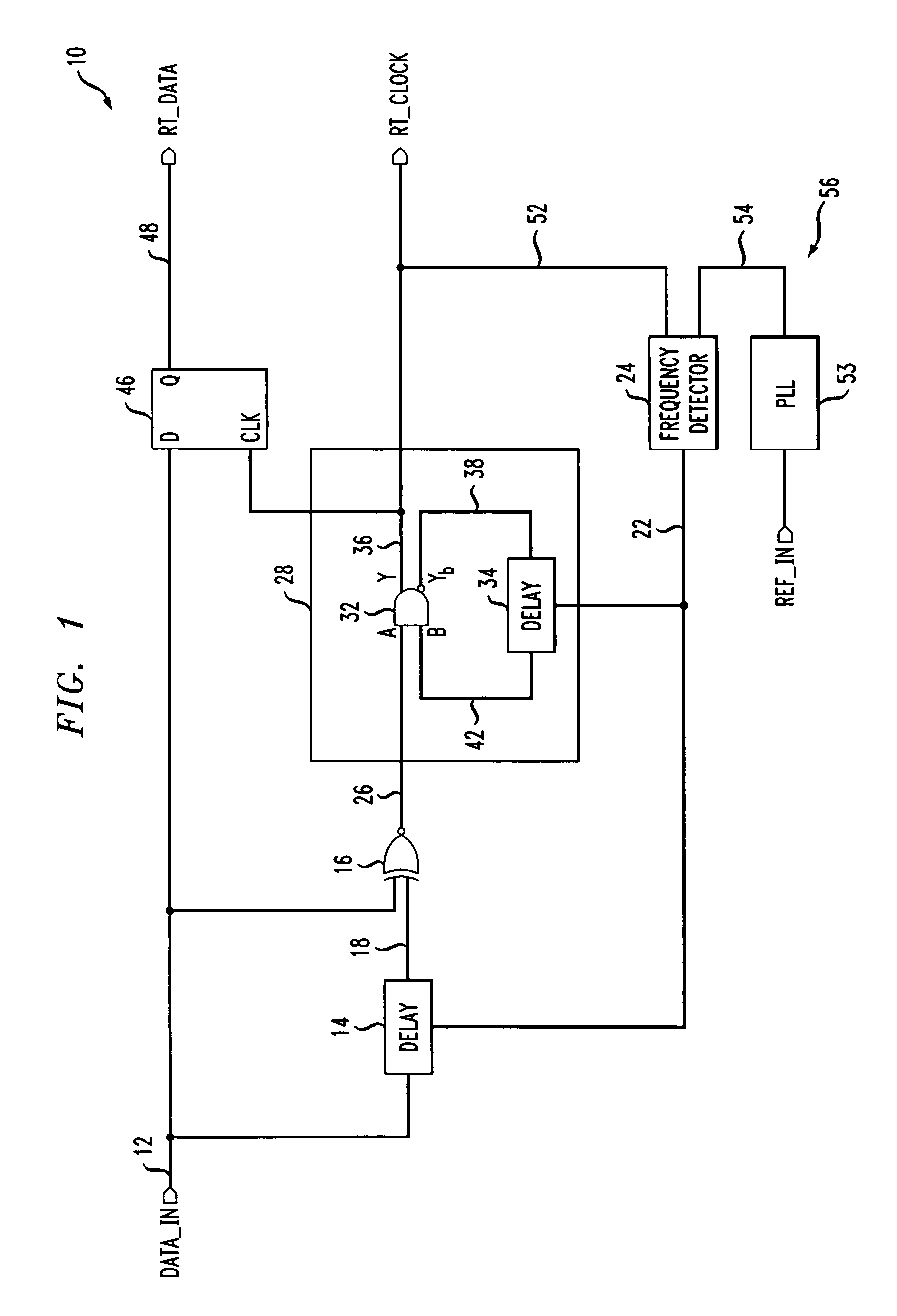

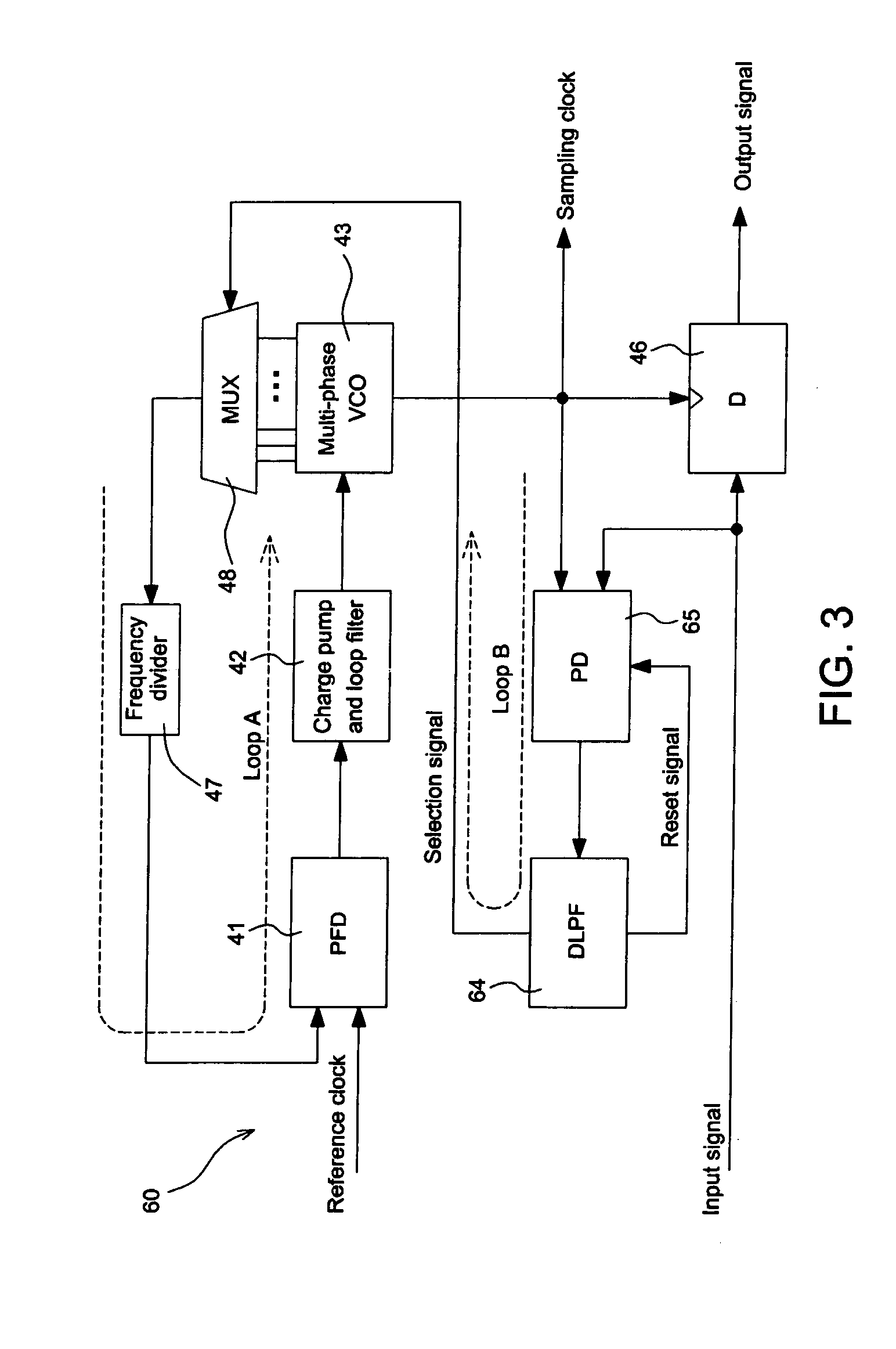

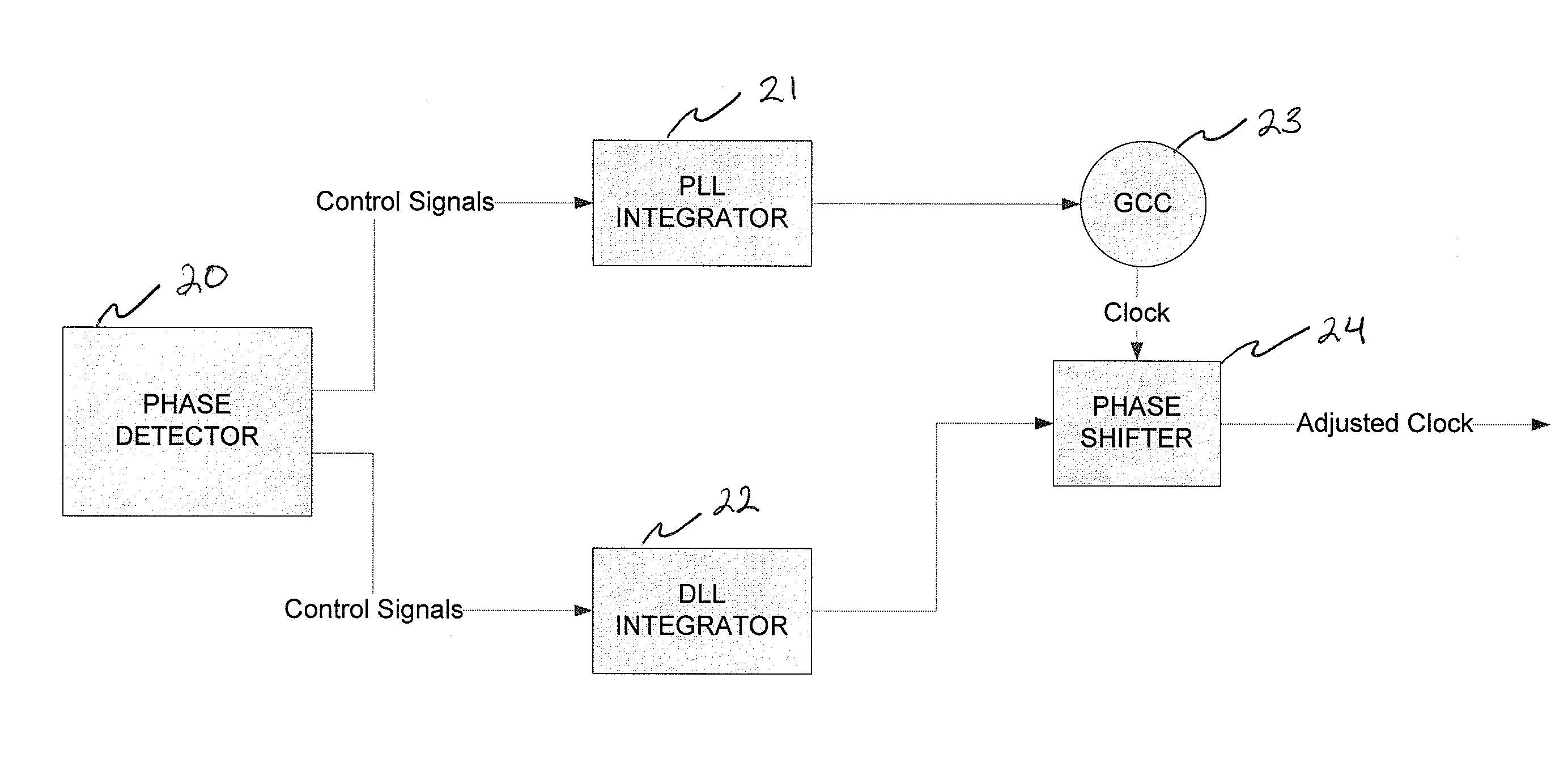

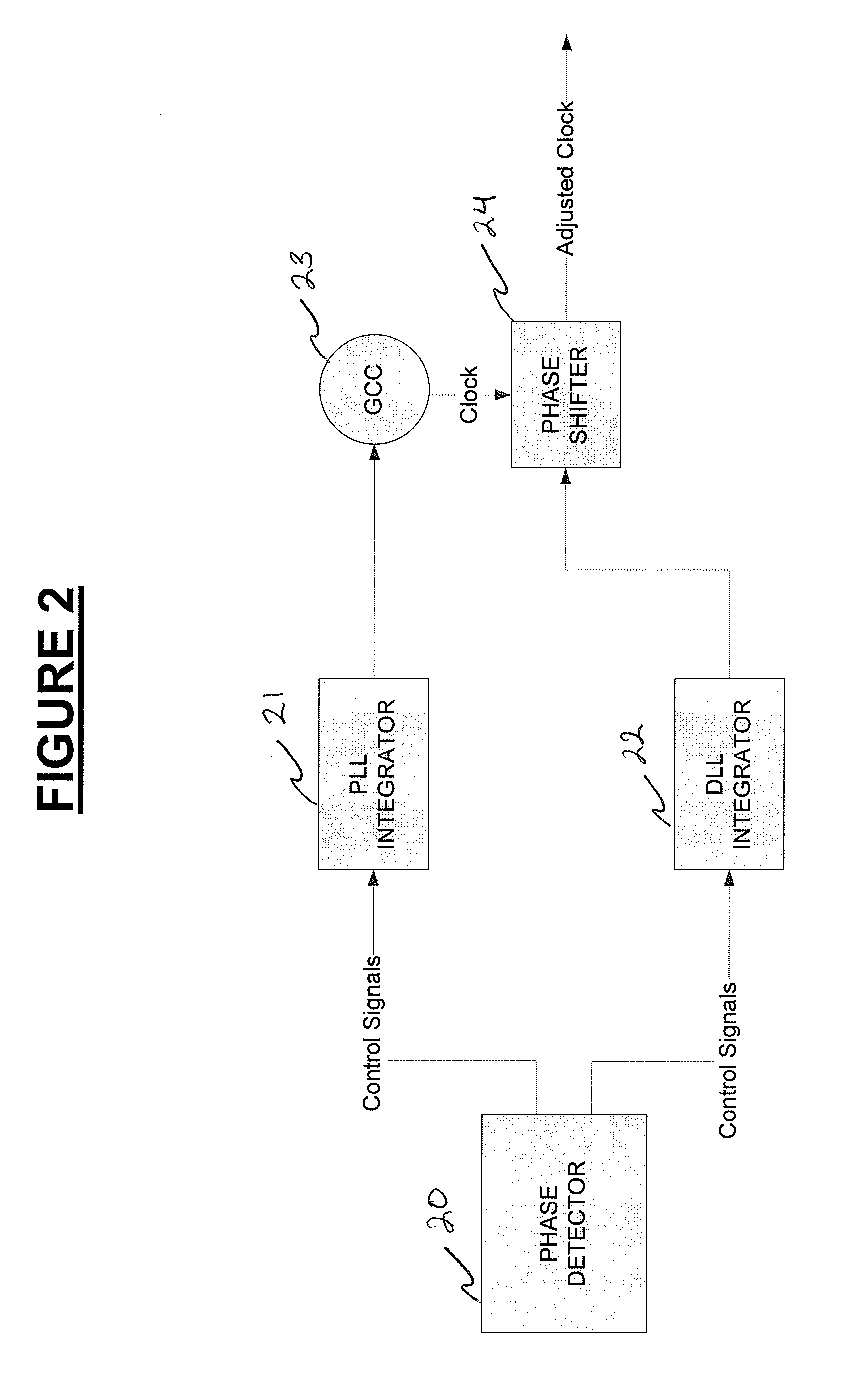

Continuous-rate clock recovery circuit

ActiveUS20110075781A1Circuit stabilityLow jitter transfer bandwidthPulse automatic controlModulated-carrier systemsIntegratorDelay-locked loop

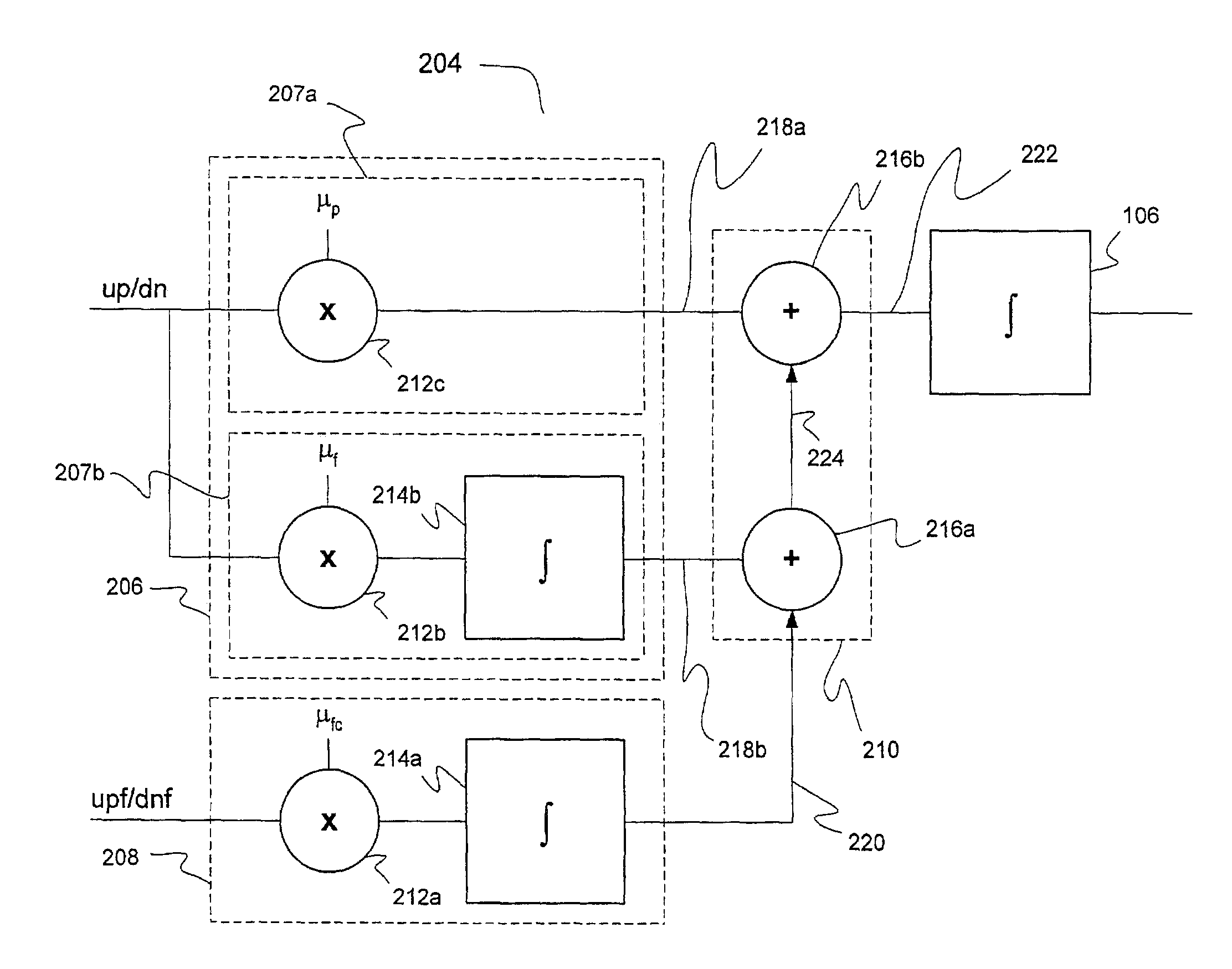

A continuous-rate clock and data recovery circuit includes a delay locked loop with a first integrator and a phase locked loop with a separate integrator. The delay locked loop and the phase locked loop are in a dual loop architecture. The first integrator is a digital accumulator that wraps upon exceeding a maximum or minimum value. The second integrator is a digital accumulator that saturates at its maximum or minimum value.

Owner:ANALOG DEVICES INC