Patents

Literature

196 results about "Phase advance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

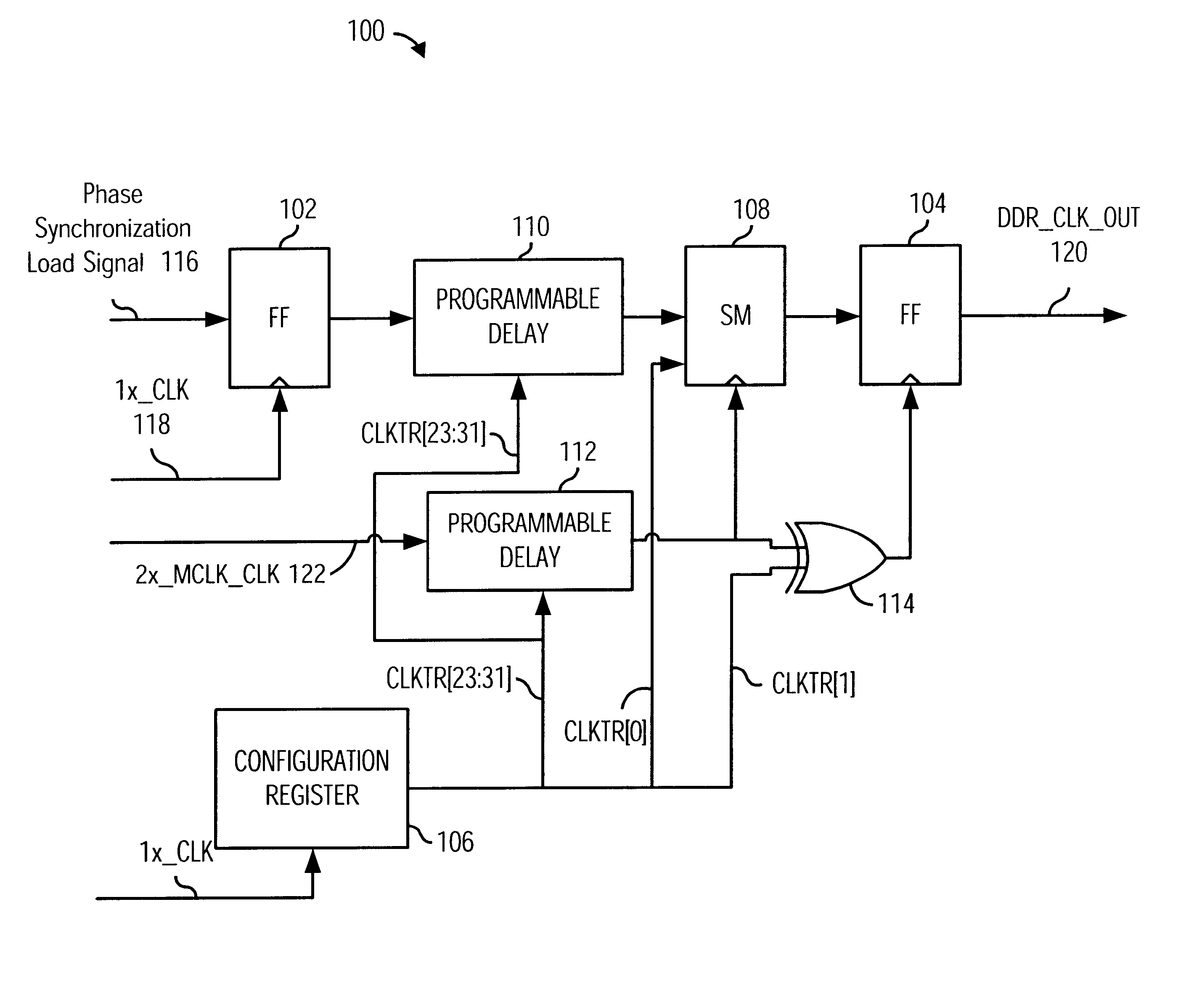

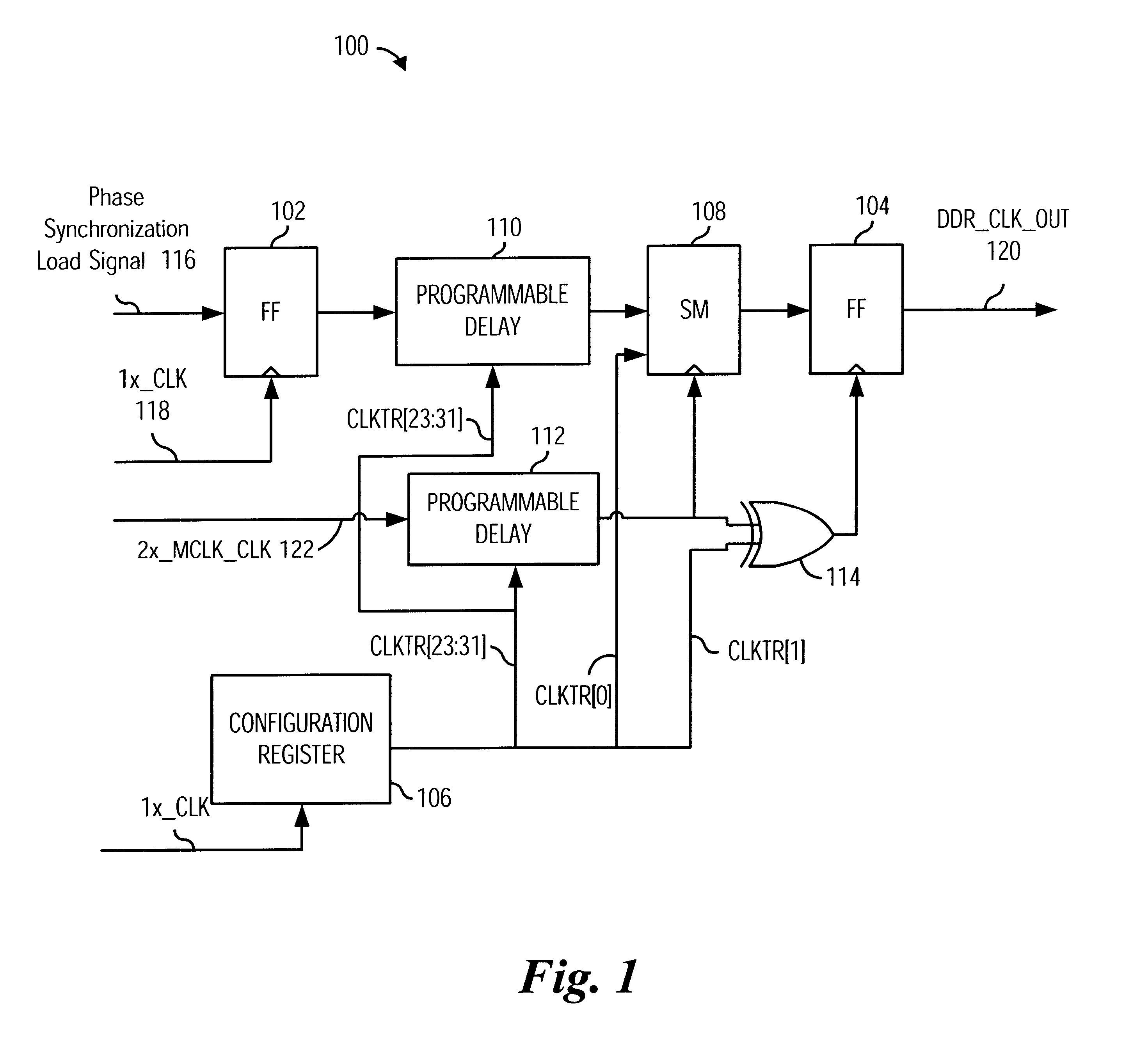

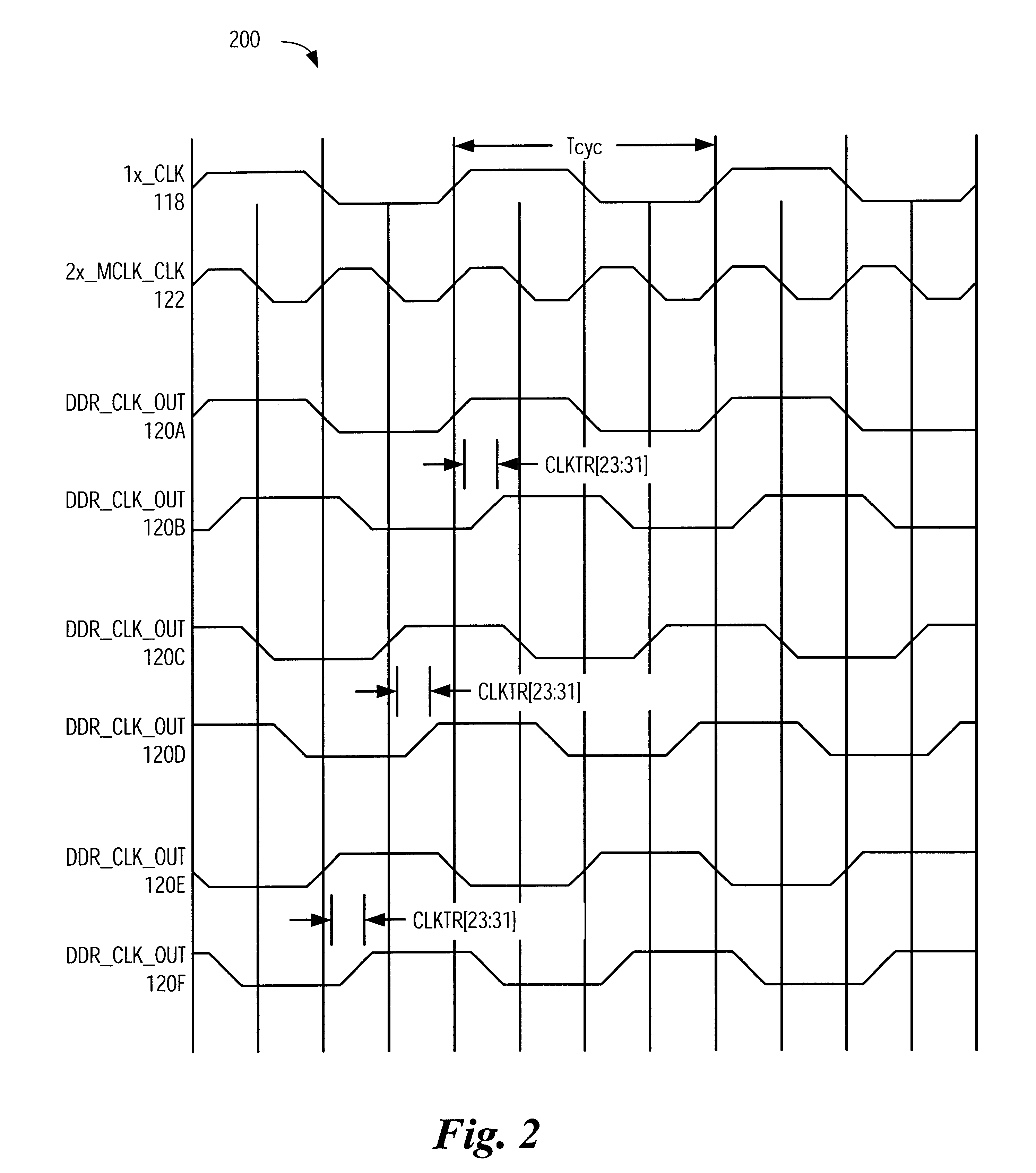

Memory clock generation with configurable phase advance and delay capability

A circuit generating memory clock with phase advance and delay capability is provided. The phase of the memory clock is controlled by adjusting the configuration register bits. The circuit allows for a high degree of control and flexibility in the memory clock generation in that the memory clock relationship with respect to the memory command and data can be adjusted independently, thereby creating the ability to effectively adjust the memory interface timings such as setup time, hold time, and memory read data access time. Specifically, 0, 90, and 180 degree phase advance ability is combined with the ability to add delay in fine increments to achieve a more granular degree of phase adjustment.

Owner:LINKEDIN

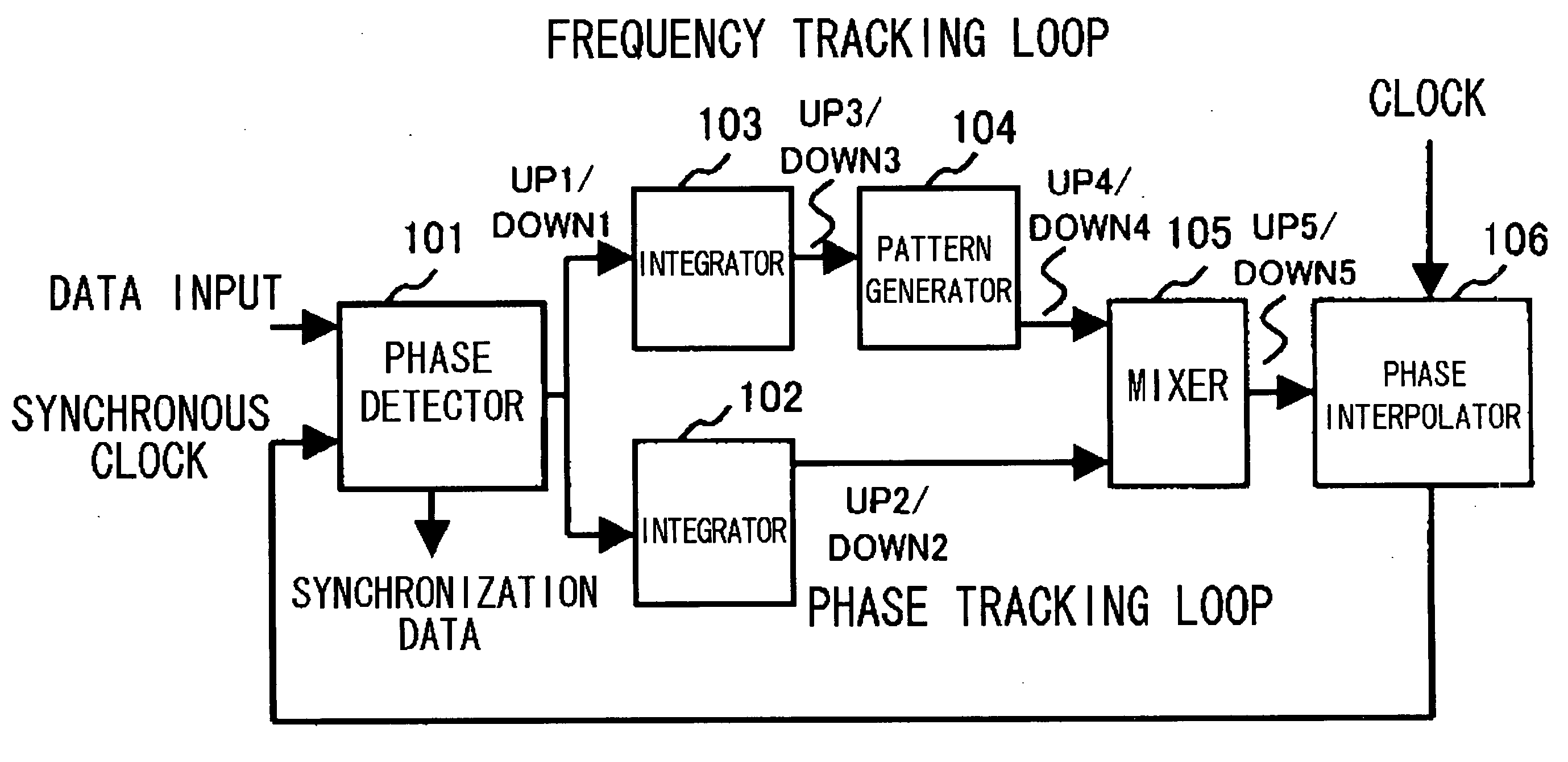

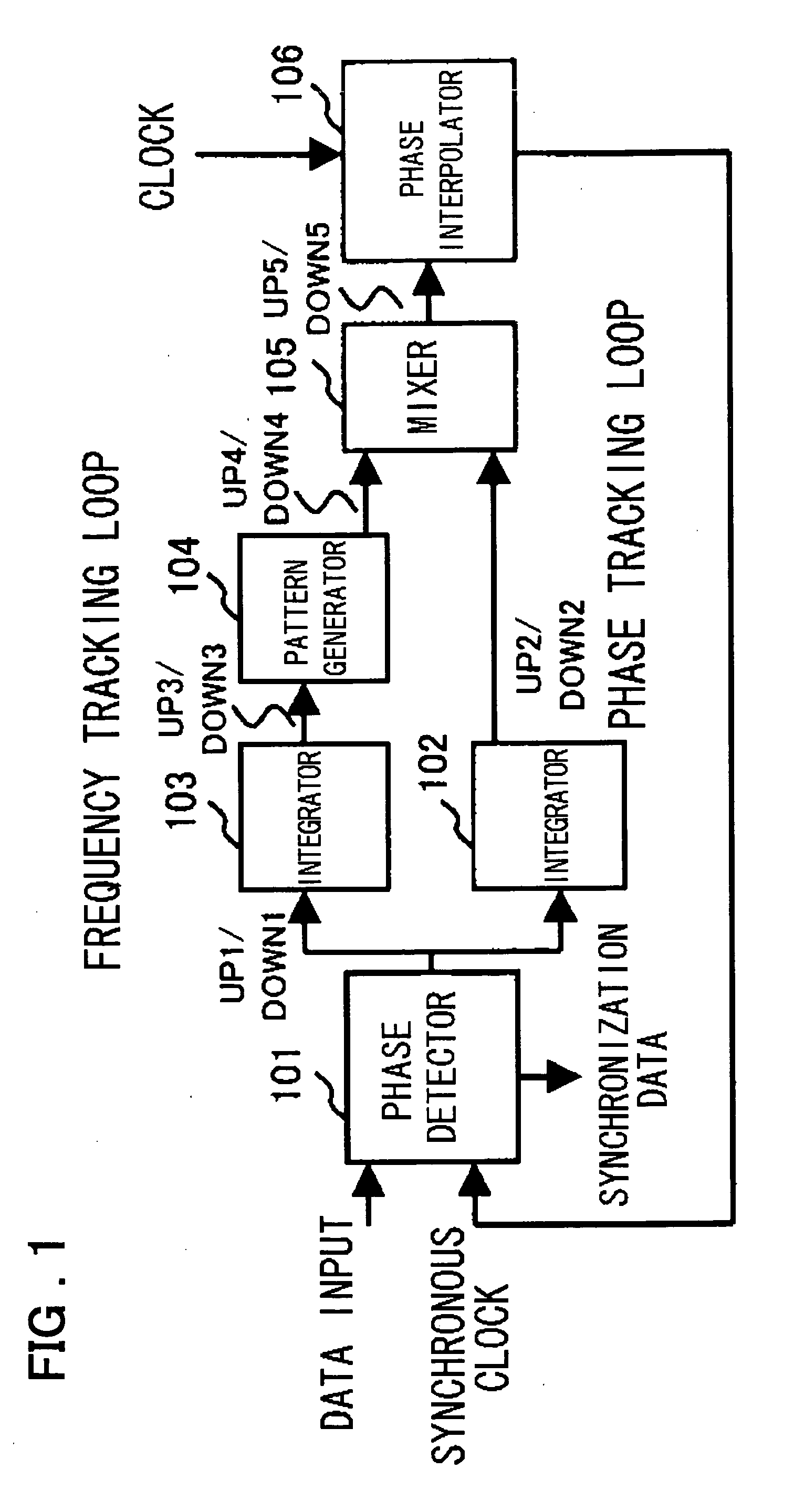

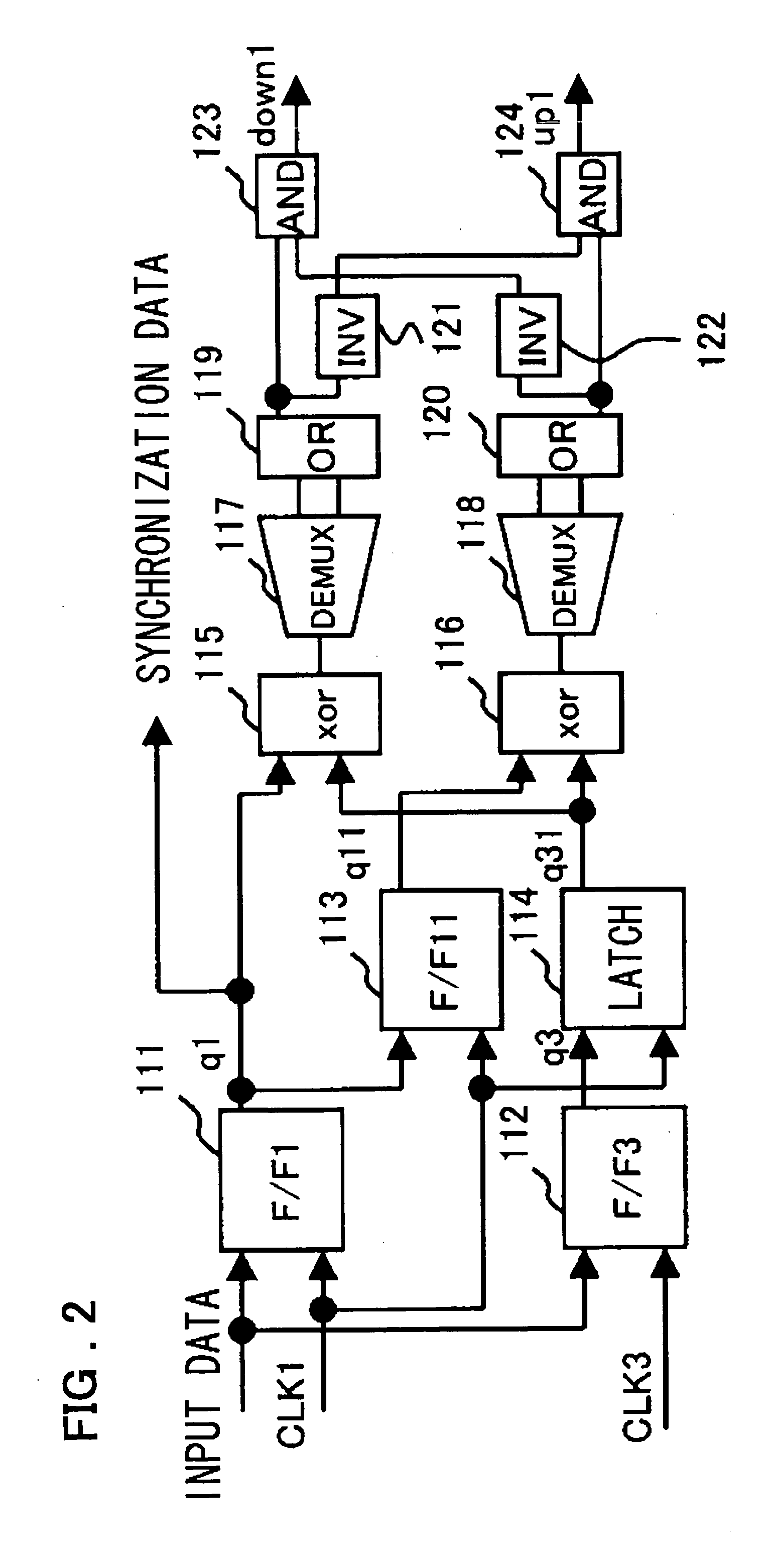

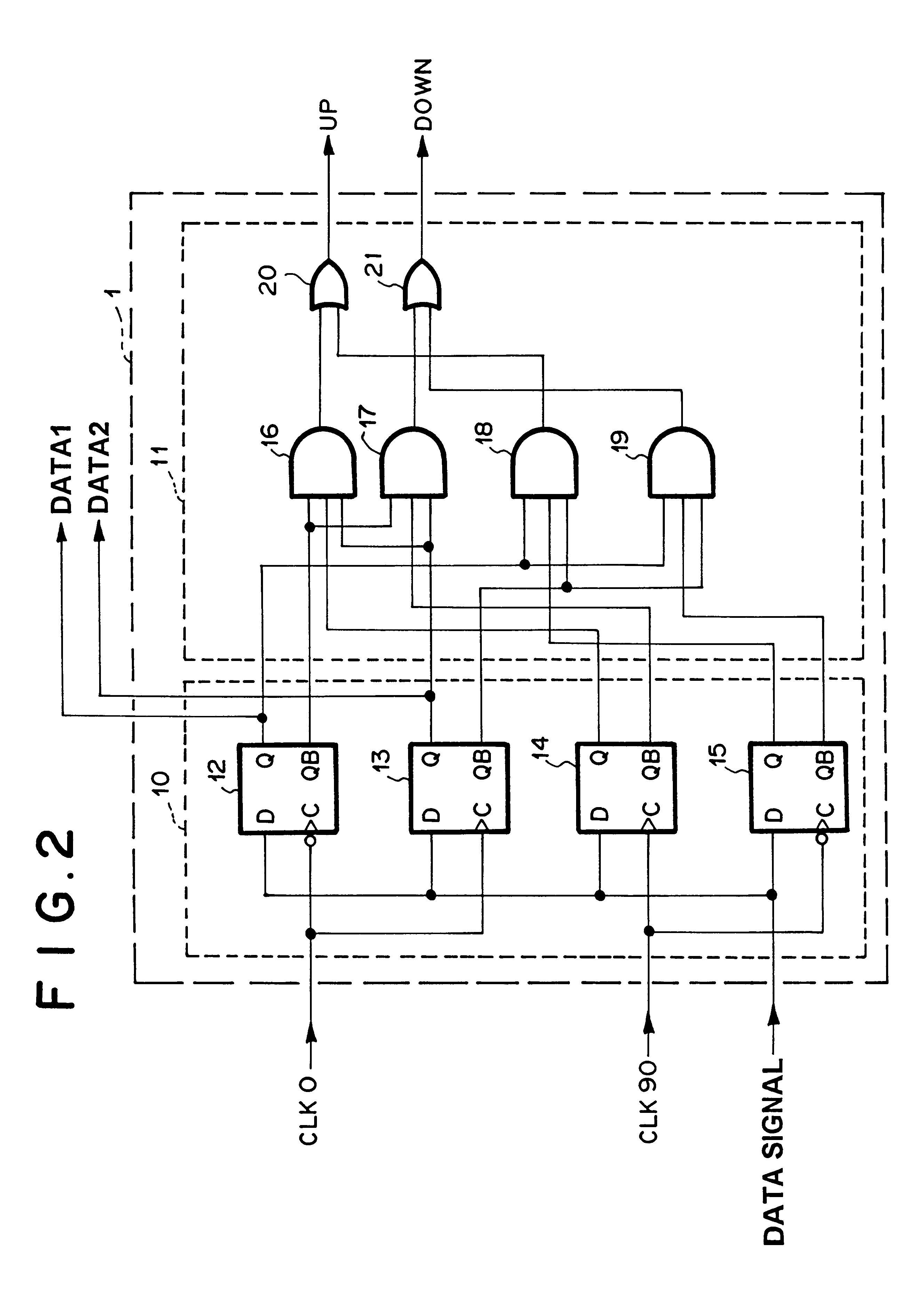

Clock and data recovery circuit

ActiveUS20040252804A1Increase in chip sizeIncreasing chip sizePulse automatic controlOscillations comparator circuitsPhase detectorIntegrator

A clock and data recovery circuit, for tracking frequency-modulated input data, comprises a phase detector for receiving a data signal and a synchronous clock signal, detecting a phase delay or a phase advance, and outputting an UP1 / DOWN1 signal, first and second integrators for integrating the UP1 / DOWN1 signal and outputting an UP2 / DOWN2 signal and an UP3 / DOWN3 signal, respectively, a pattern generator for receiving the UP3 / DOWN3 signal from the second integrator to output an UP4 / DOWN4 signal, a mixer for receiving the UP2 / DOWN2 signal from the first integrator and the UP4 / DOWN4 signal from the pattern generator and generating an UP5 / DOWN5 signal for output, and a phase interpolator for interpolating the phase of an input clock signal based on the UP5 / DOWN5 signal from the mixer, for output are provided. A clock signal output from the interpolator is fed back to the phase detector as the clock.

Owner:RENESAS ELECTRONICS CORP

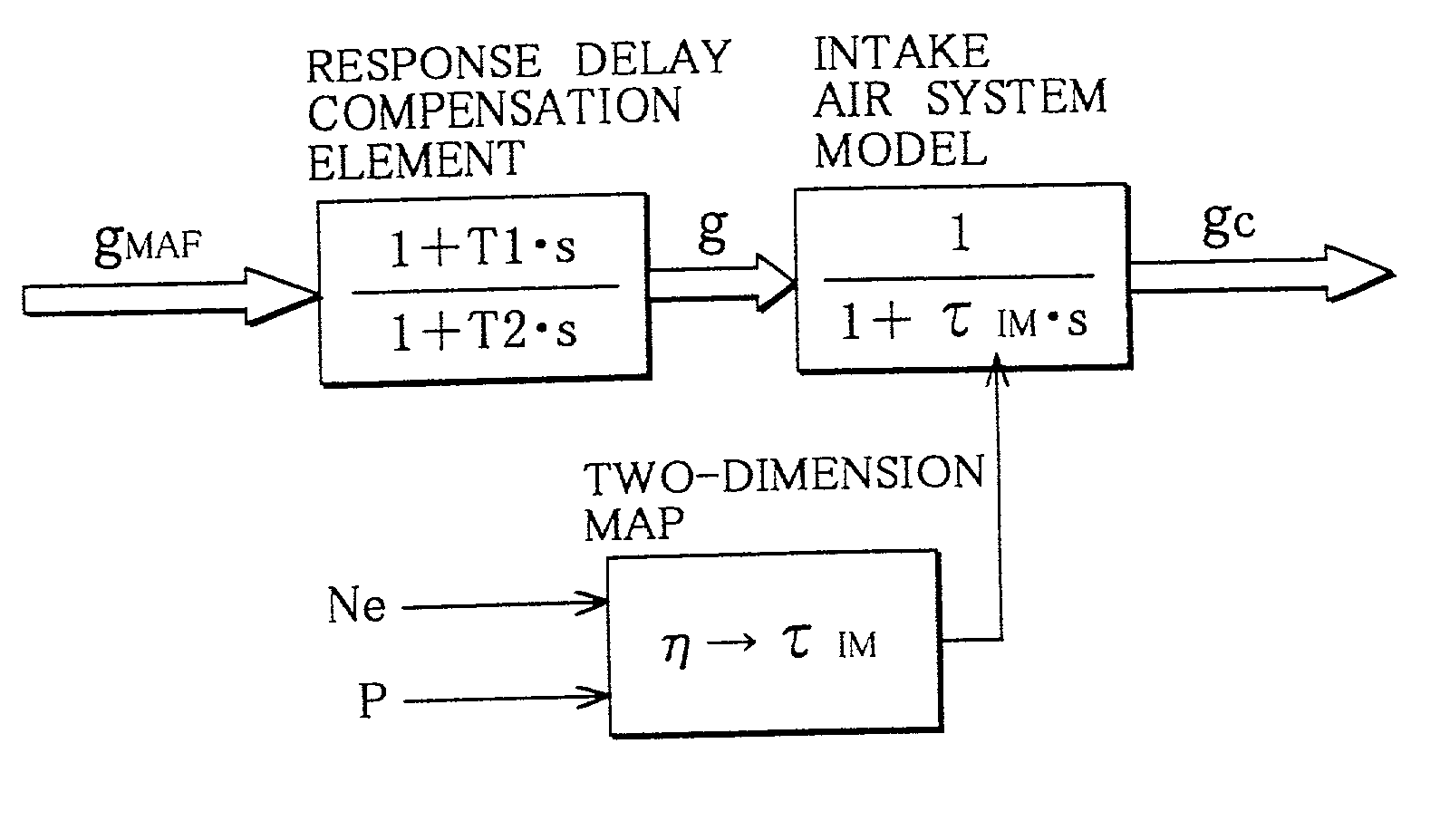

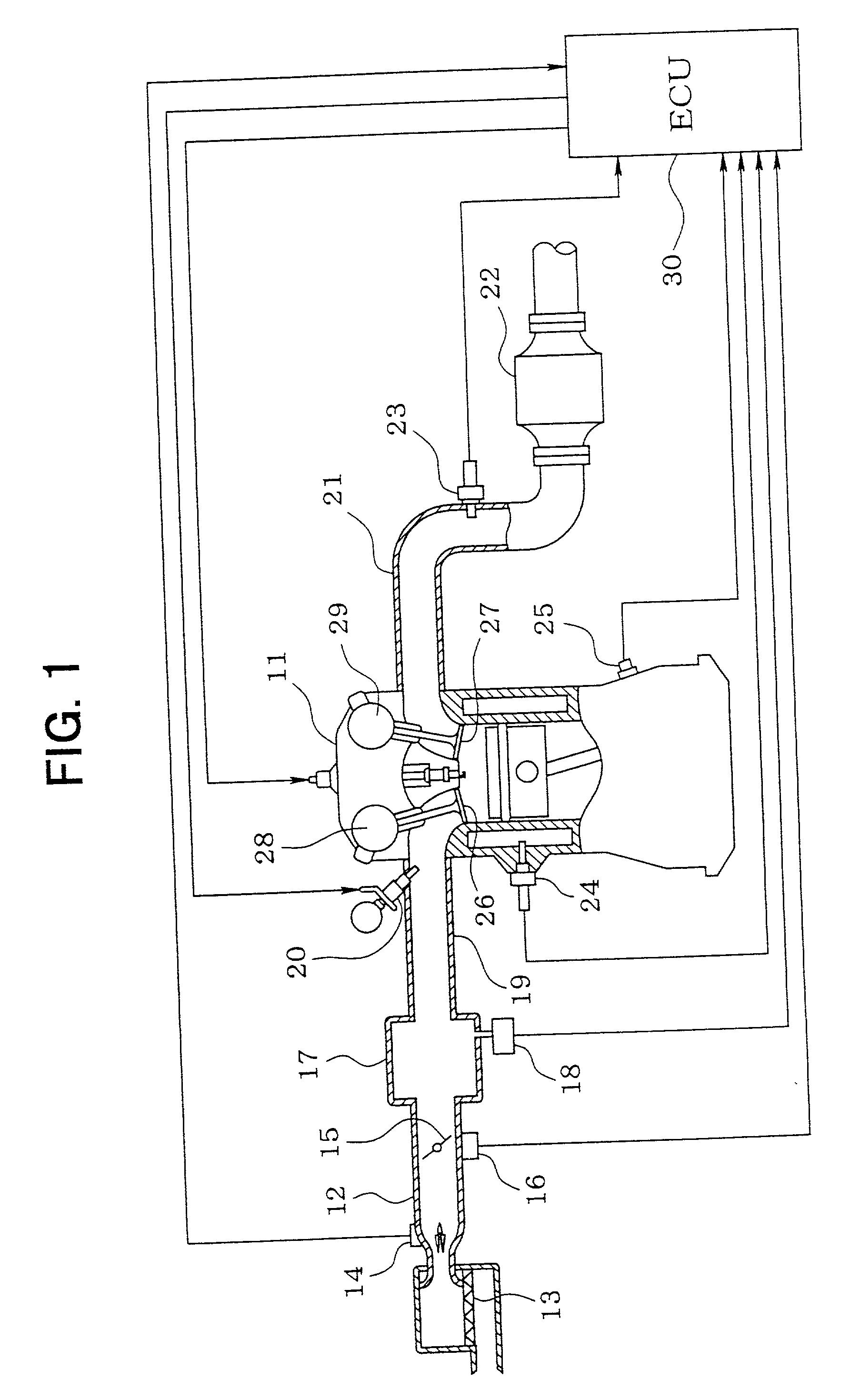

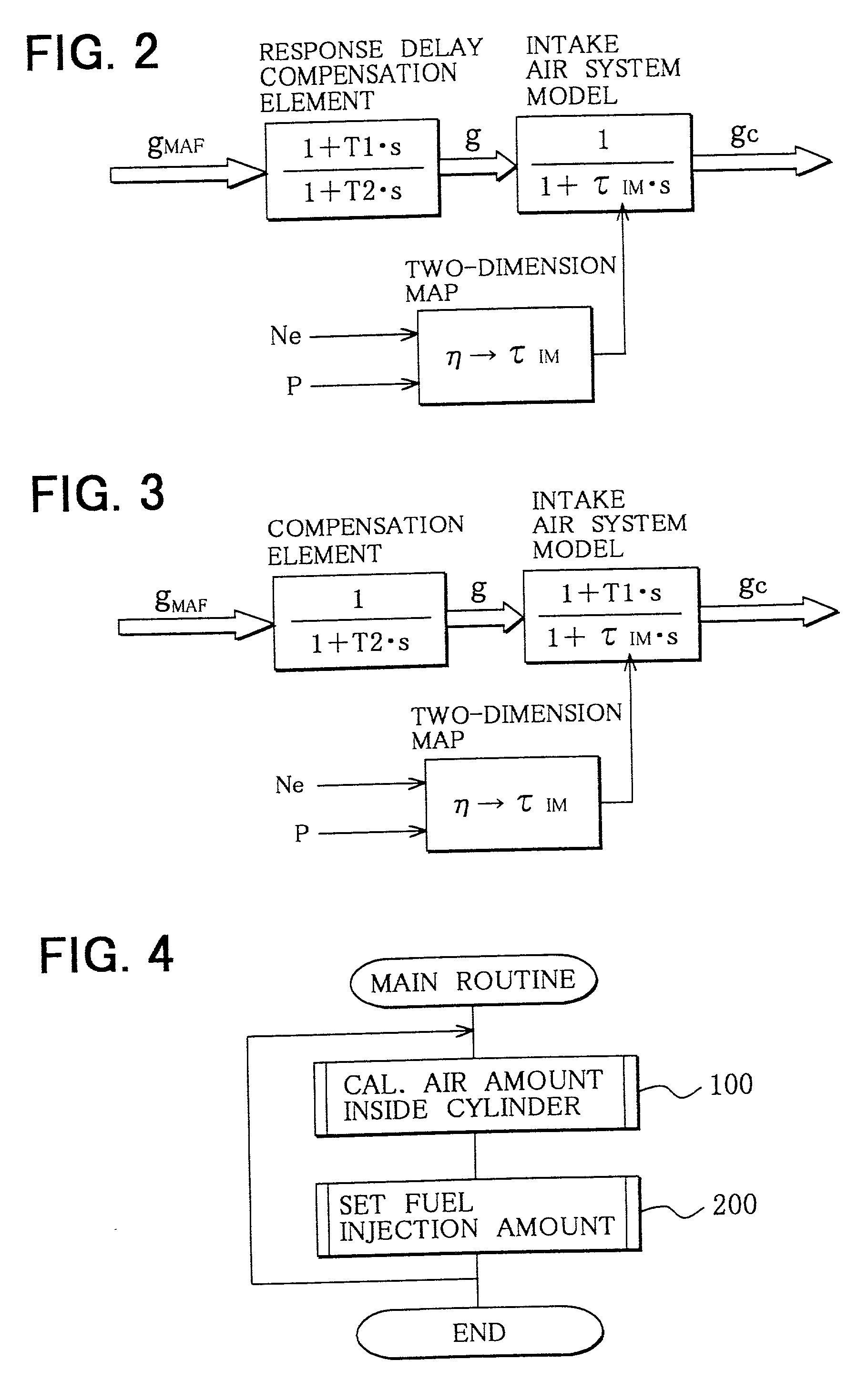

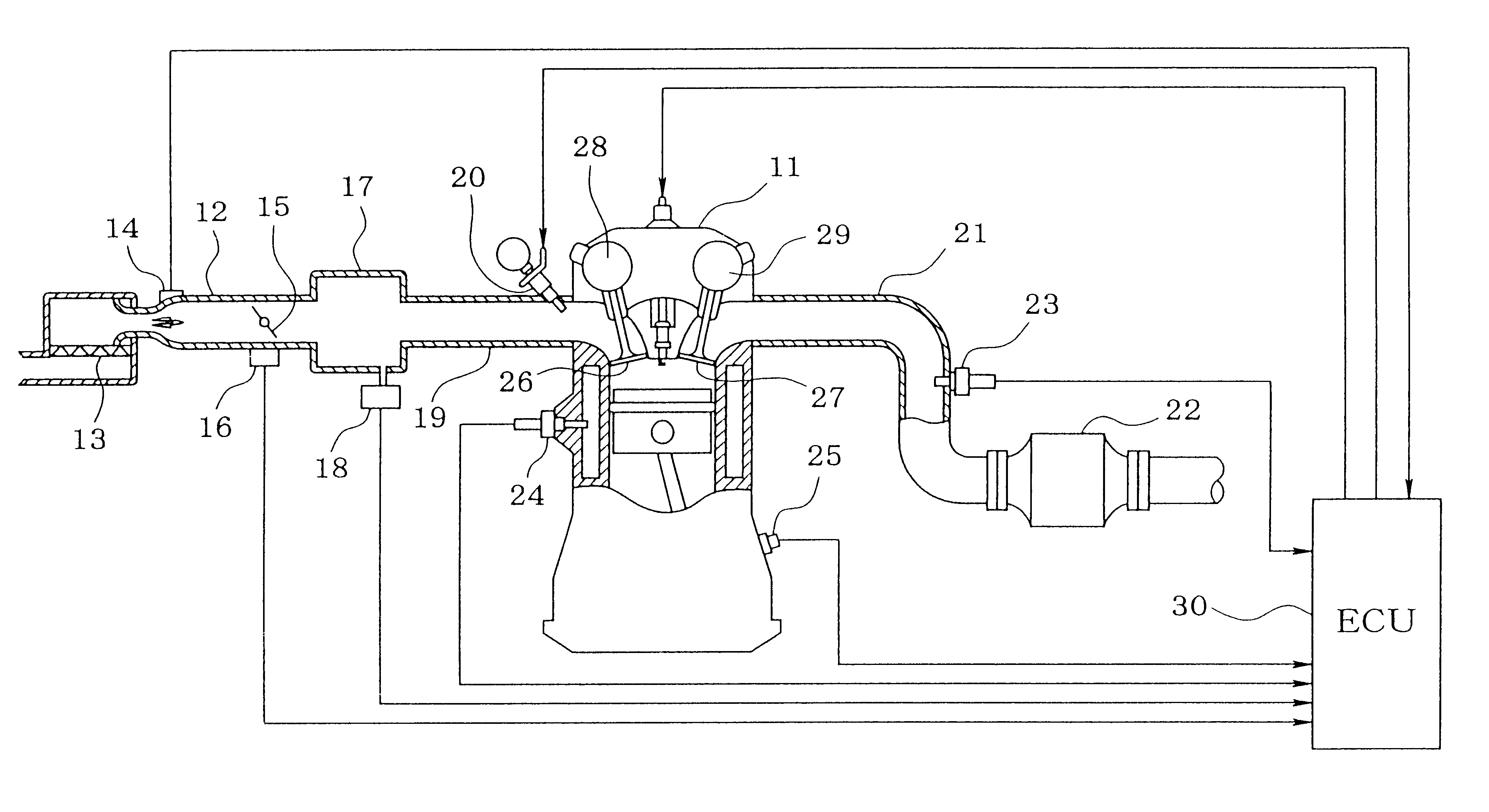

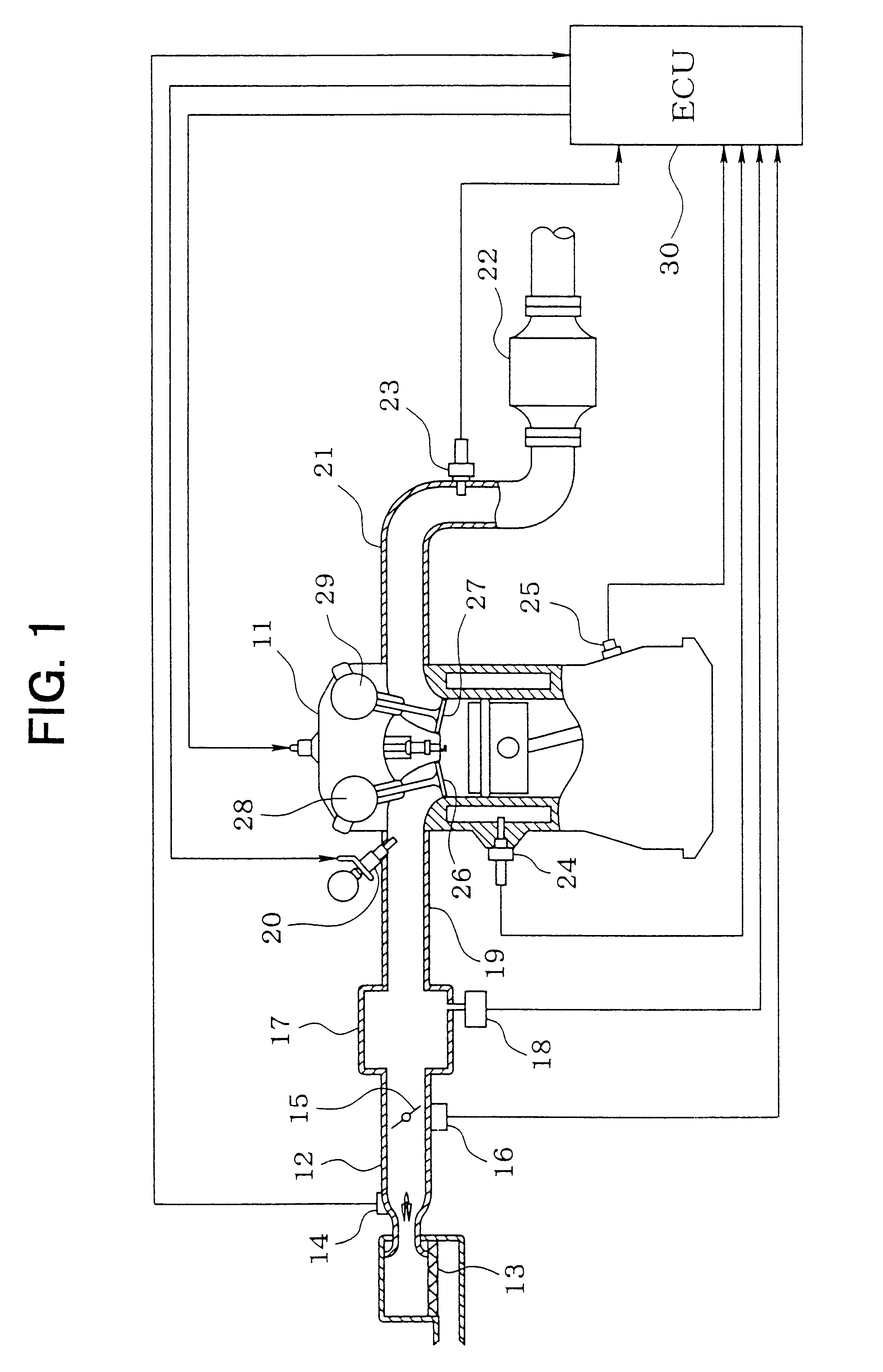

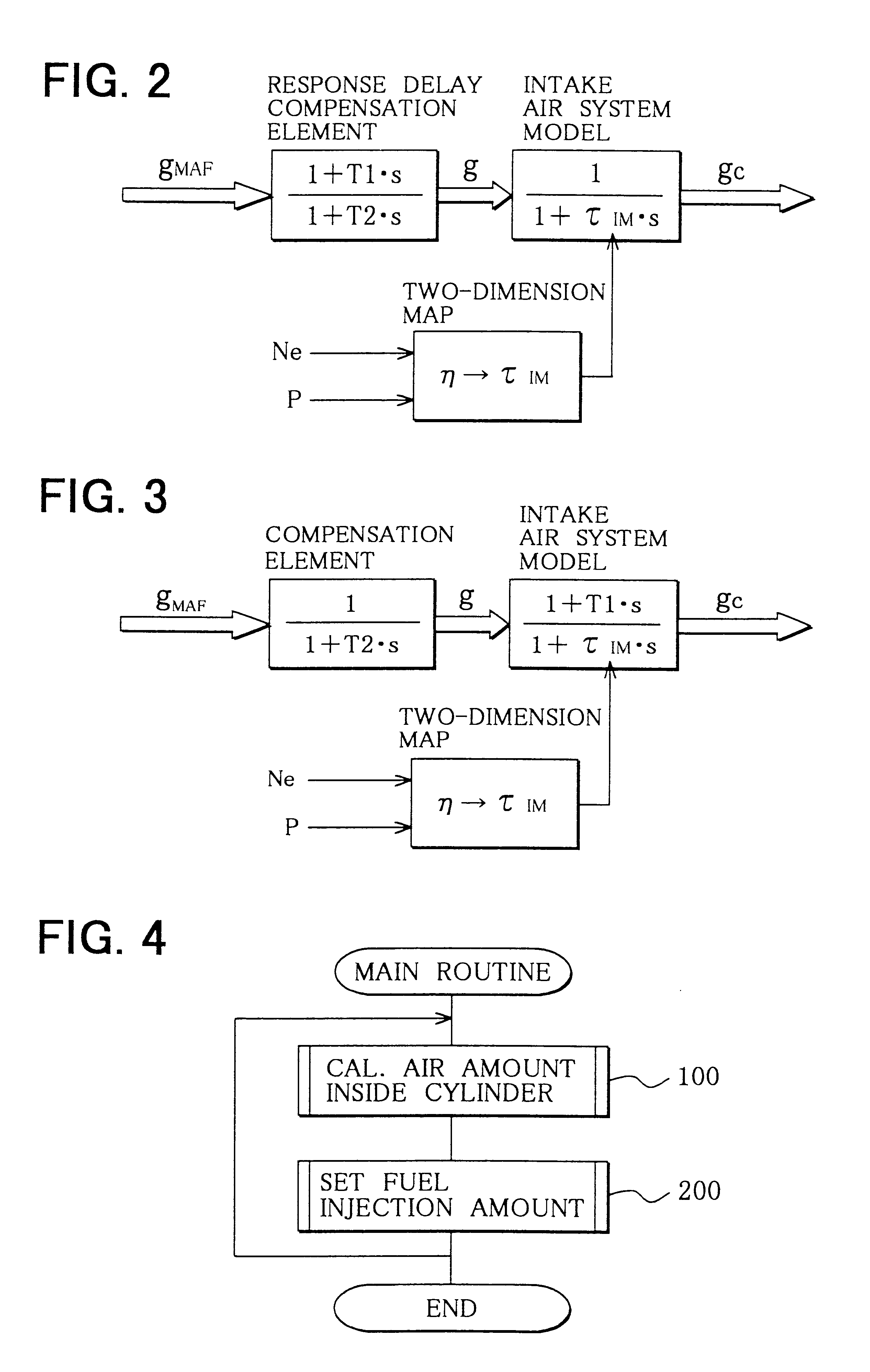

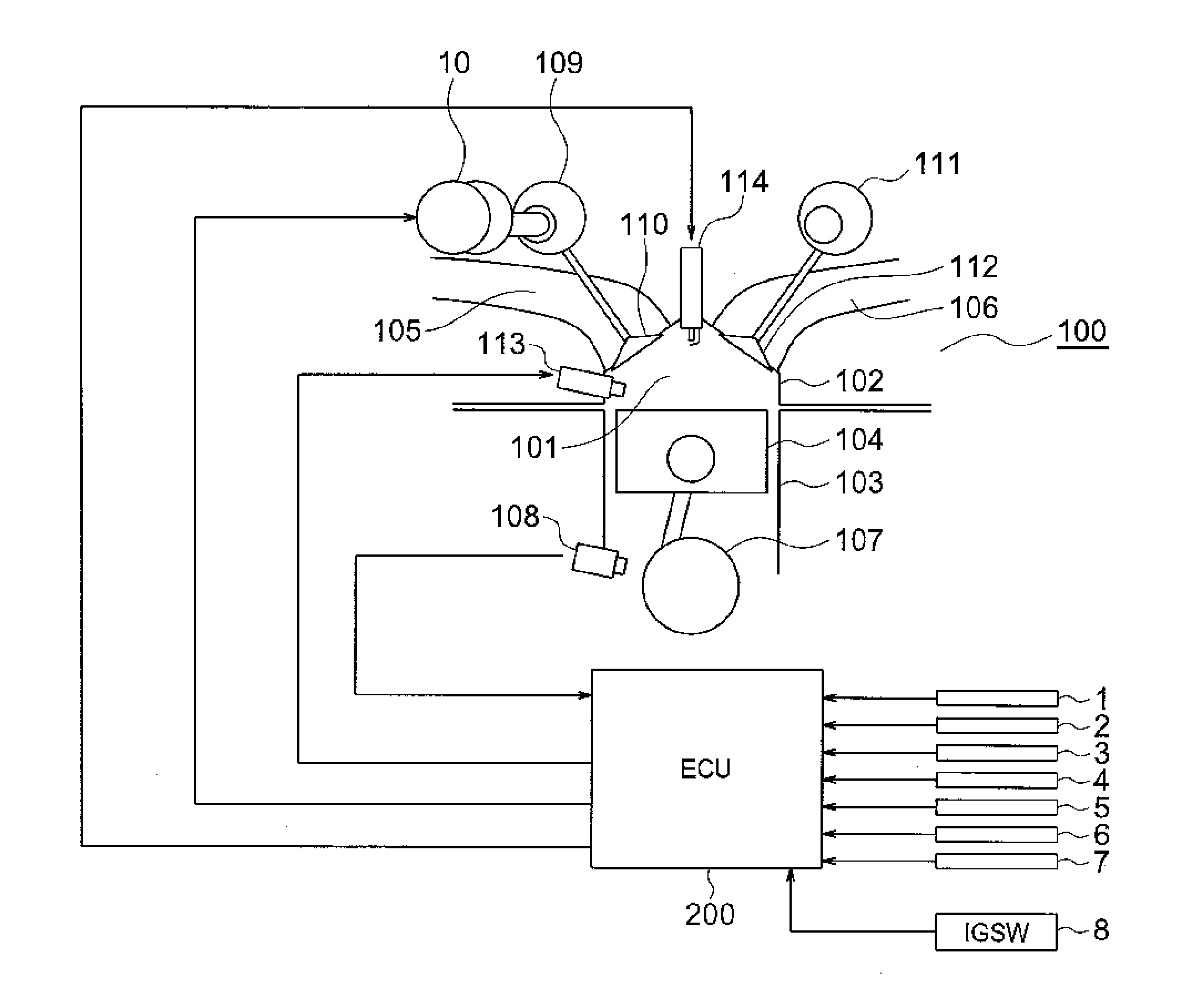

Air amount detector for internal combustion engine

InactiveUS20020107630A1Improve calculation accuracyAnalogue computers for vehiclesElectrical controlResponse delayPhase advance

A response delay compensation element for compensating a response delay of an output gMAF of an airflow meter by a phase advance compensation is provided so that an output g of the response delay compensation element is input to the intake air system model. A transfer function of the phase advance compensation is <paragraph lvl="0"><in-line-formula>g=(1+T1.s) / (1+T2s).gMAF< / in-line-formula>where T1 and T2 are time constant of the phase advance compensation, which is set based on at least one of the output gMAF of the airflow meter, engine speed, an intake air pressure, and a throttle angle. The model time constant τIM of the intake air system model is calculated by variables including volumetric efficiency and the engine speed. The volumetric efficiency is calculated by two-dimensional map having the engine speed and the intake air pressure as parameters thereof.

Owner:DENSO CORP

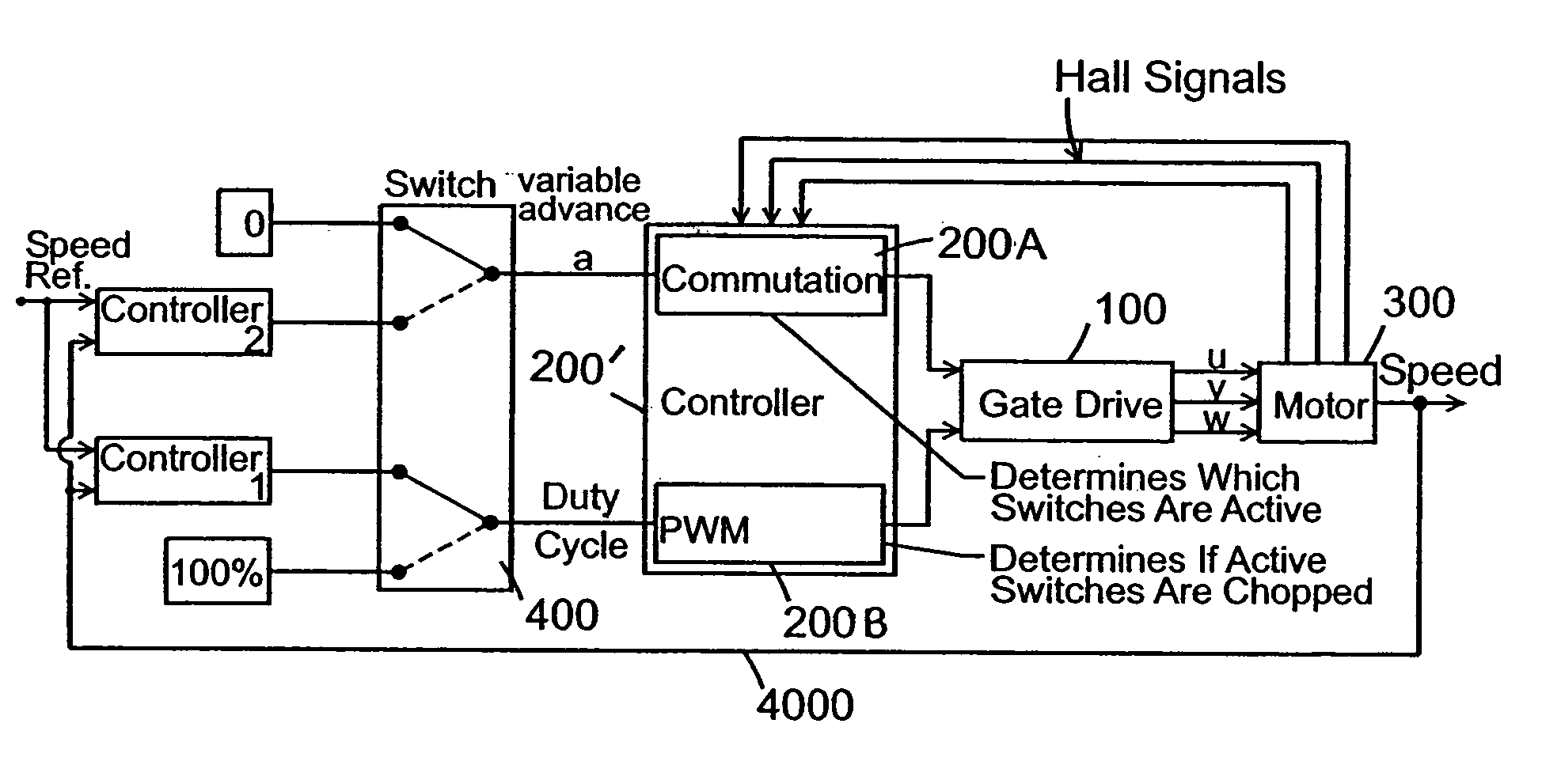

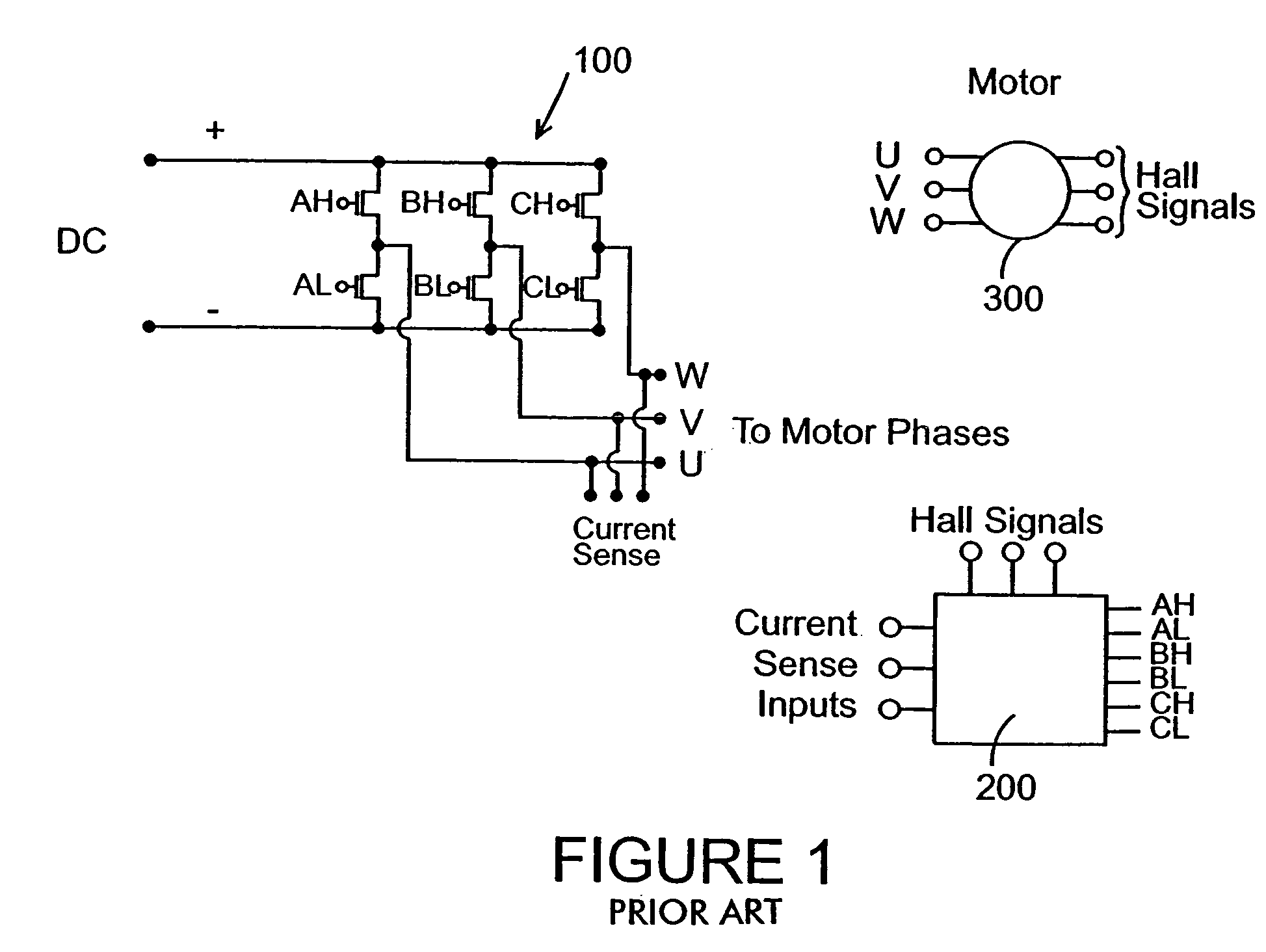

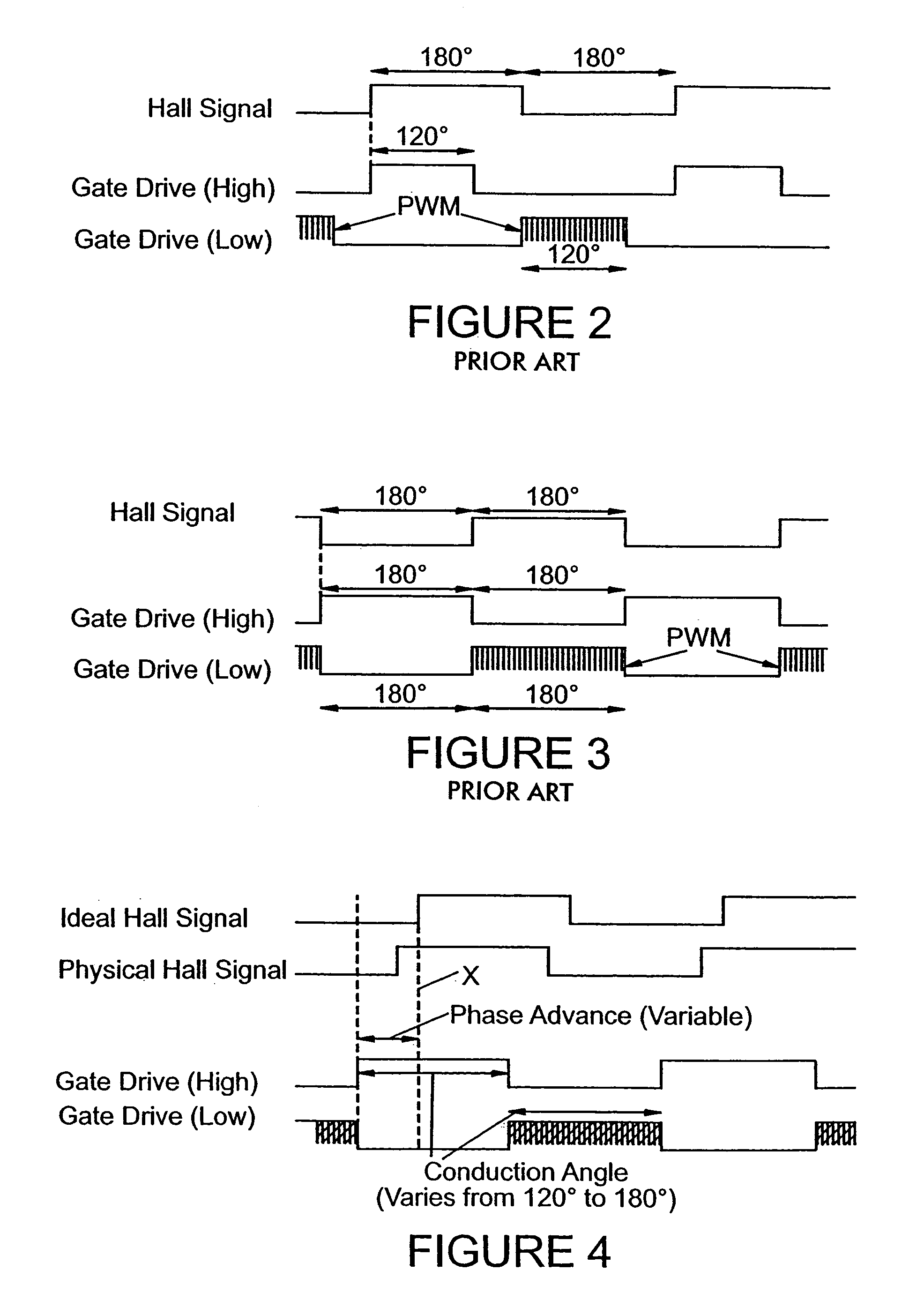

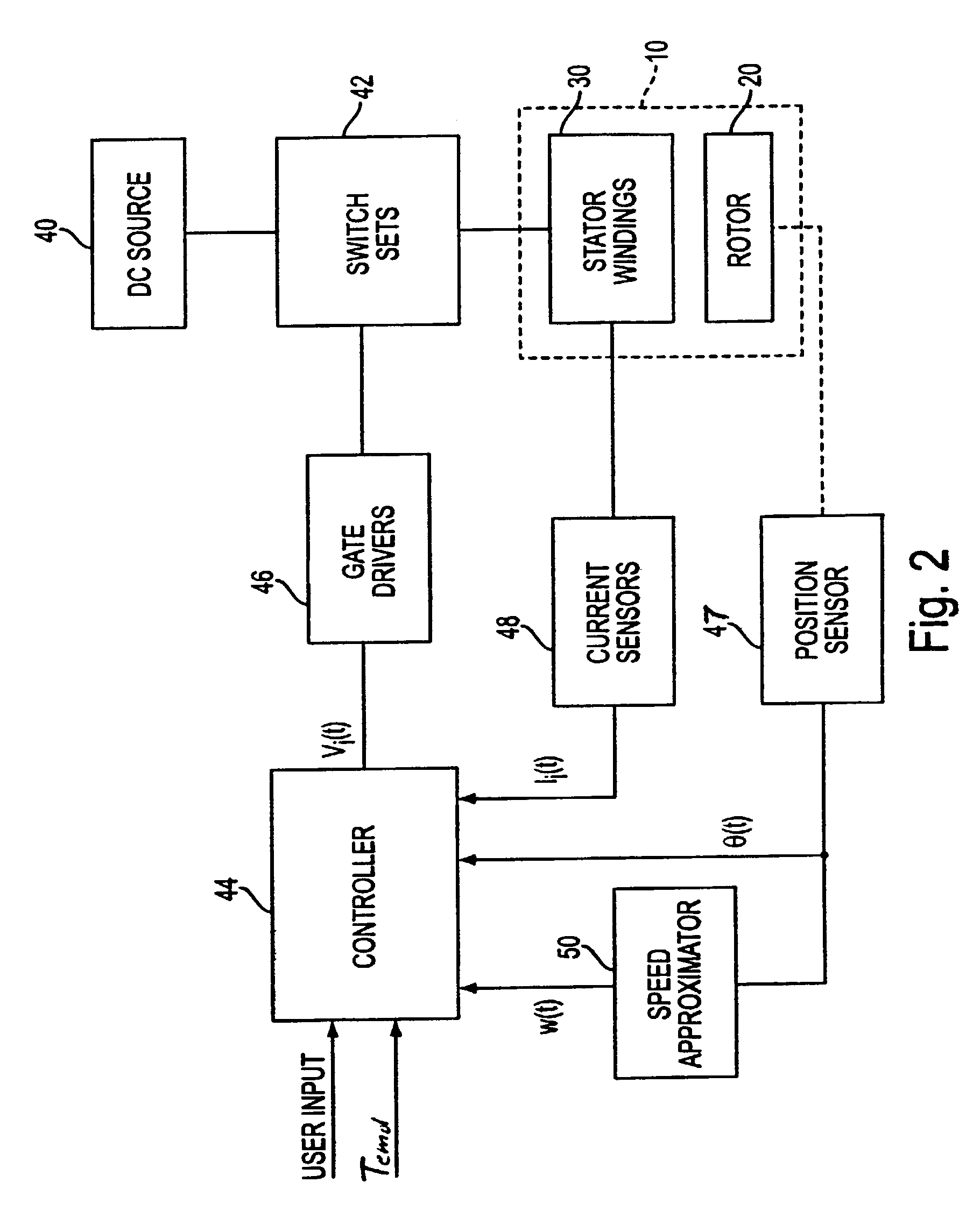

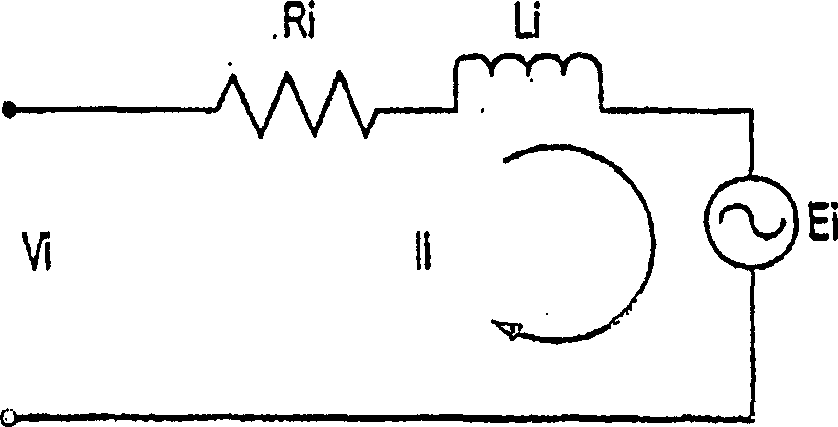

Method for controlling an electric motor to reduce EMI

InactiveUS7202622B2Reduce the amount requiredLow costDC motor speed/torque controlSynchronous motors startersPhase advanceDC-BUS

A method for reducing EMI emissions in the control of an electric motor supplied by a switching inverter fed by a DC bus comprising controlling a phase advance of a conduction angle period during which a phase of the motor is fed power by the inverter to control the conduction angle to control the speed of the motor, thereby to reduce the number of switching operations of the inverter and thereby reduce EMI.

Owner:INFINEON TECH AMERICAS CORP

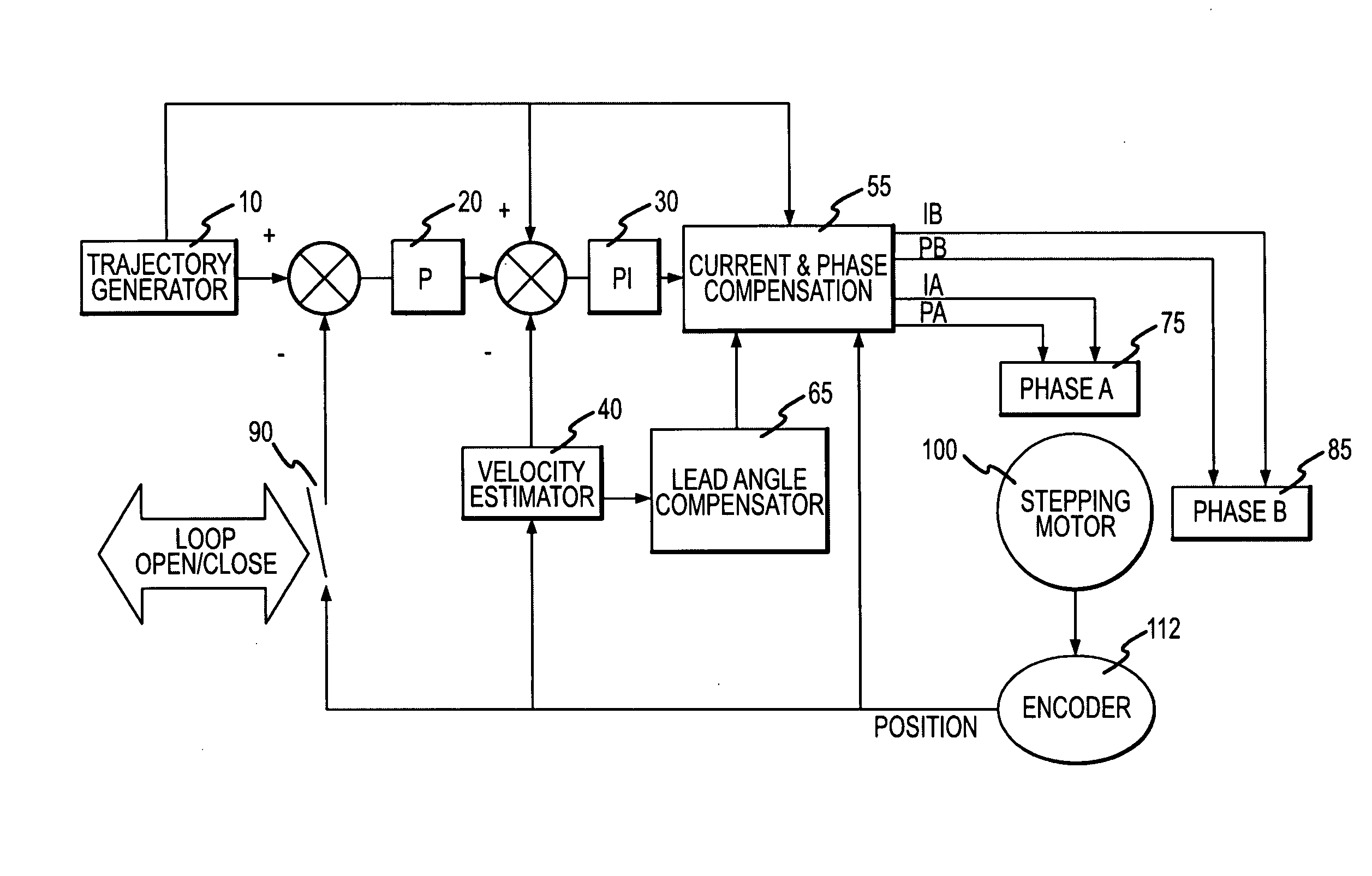

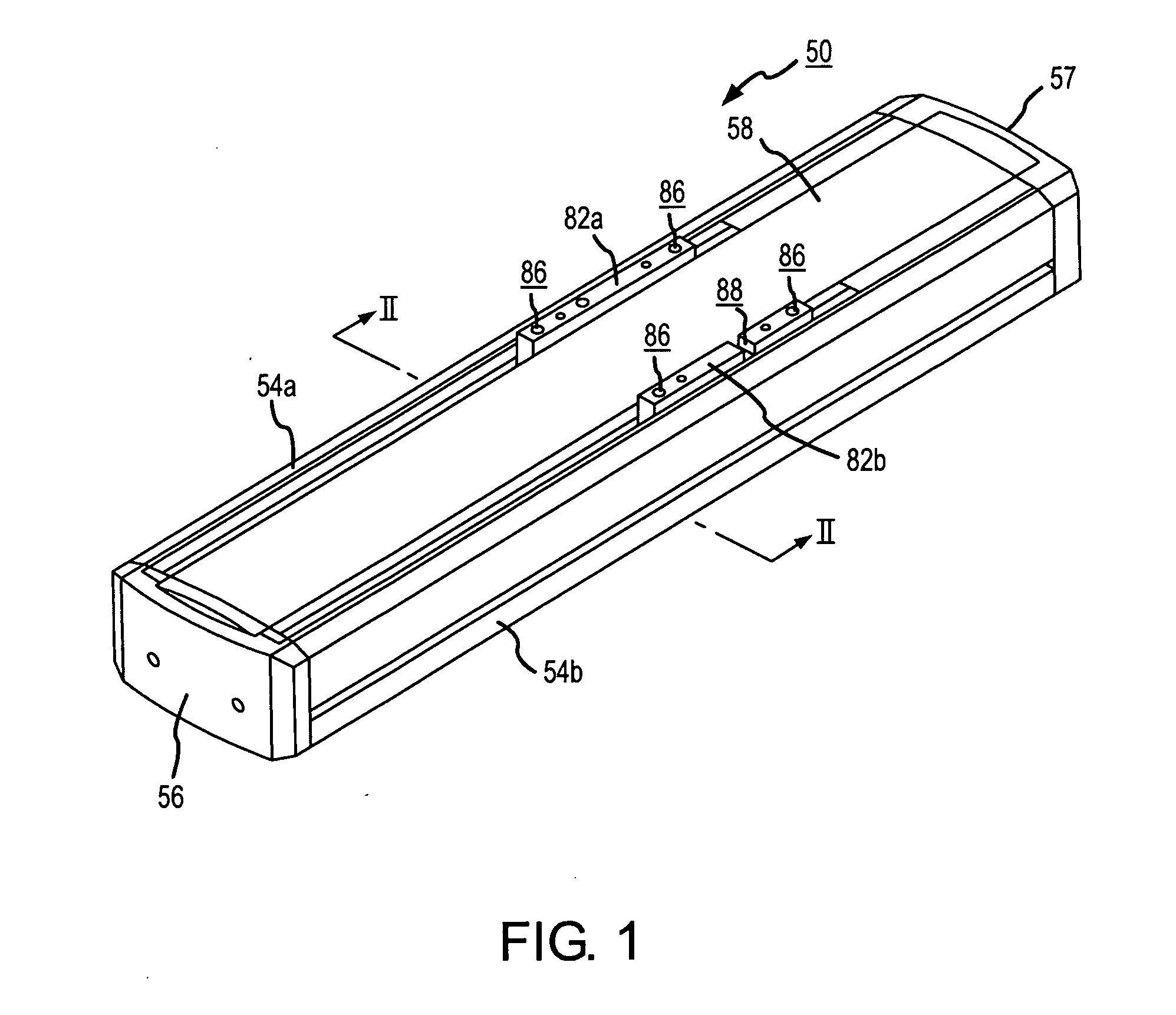

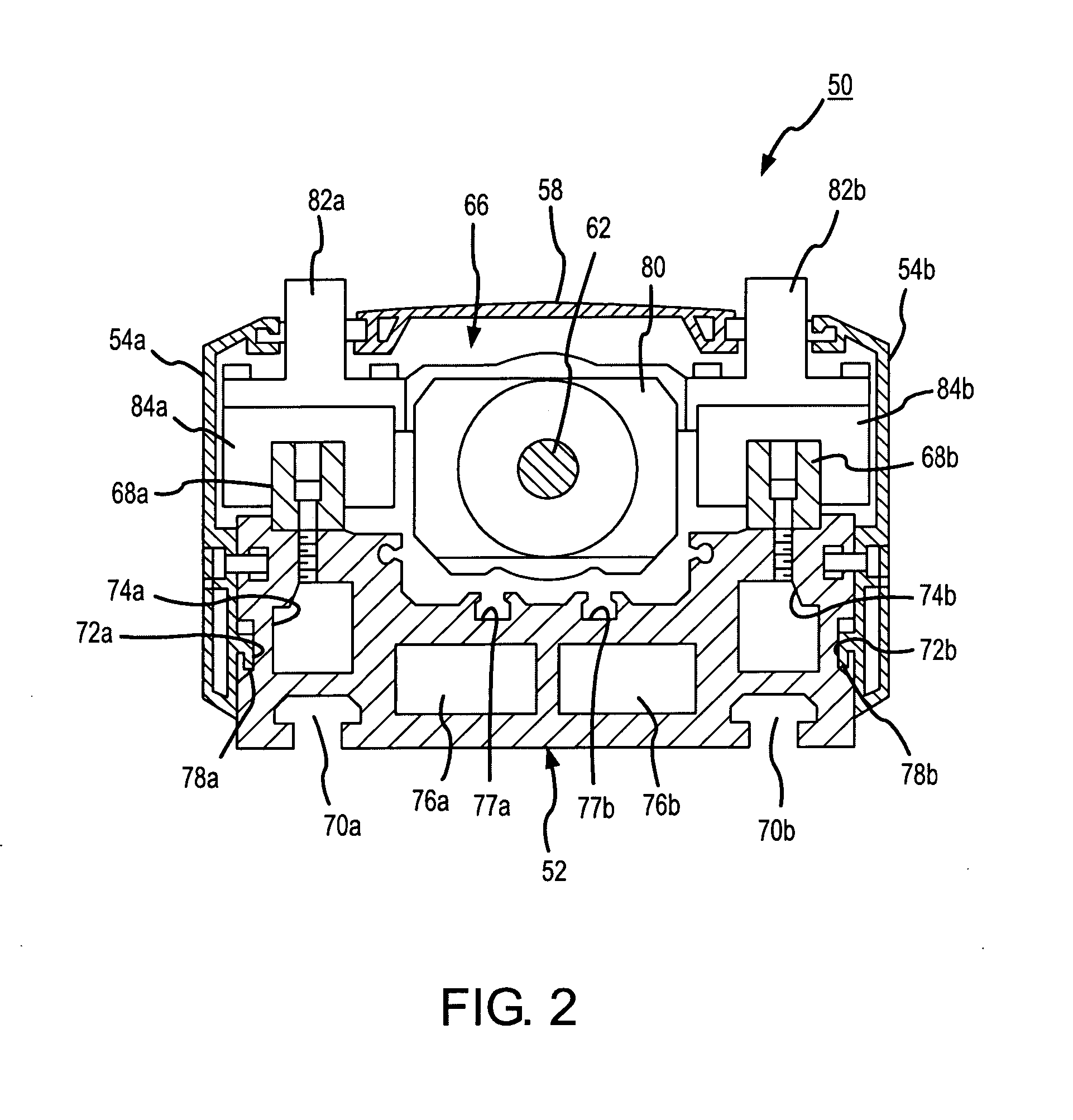

Stepping motor control system and method for controlling a stepping motor using closed and open loop controls

InactiveUS20070040529A1Good for high speedImprove torque performanceComputer controlSimulator controlMotor speedLoop control

A stepping motor is driven in both closed-loop and open-loop modes while initiating microstepping after a predetermined threshold velocity has been reached. A feedback device such as an encoder is mounted on the stepping motor shaft and the encoder keeps track of the mechanical position of the rotor. Based on feedback from the encoder, stator phases are activated to maintain a 90° phase advance and produce maximum torque. A lead angle compensation technique is used to advance the motor lead angle, to allow for the excitation currents to reach maximum even at higher speeds. The stepping motor controller employs this strategy in order to produce maximum torque across a wide range of motor speeds and actuator motions.

Owner:SMC CORP OF AMERICA

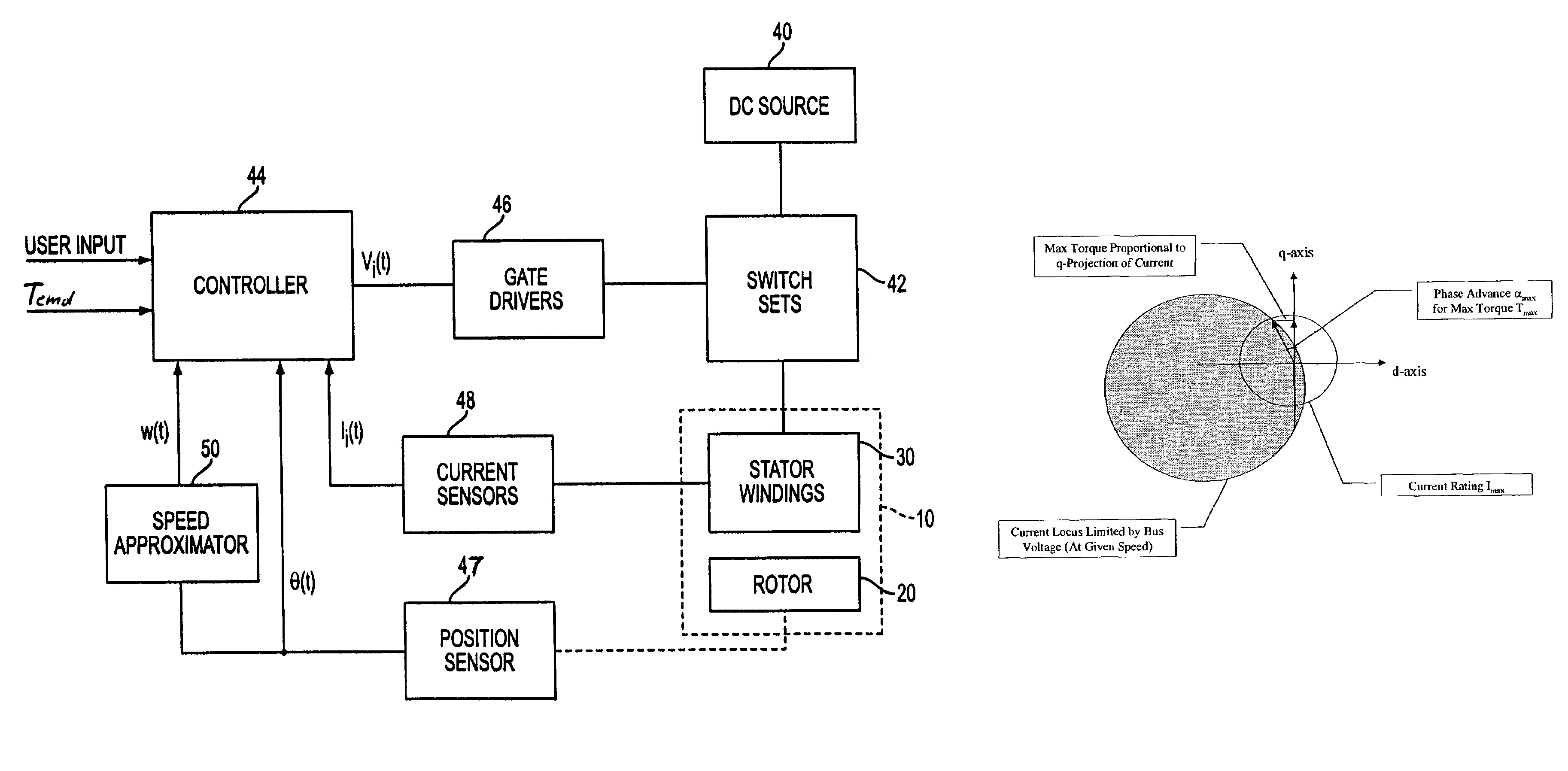

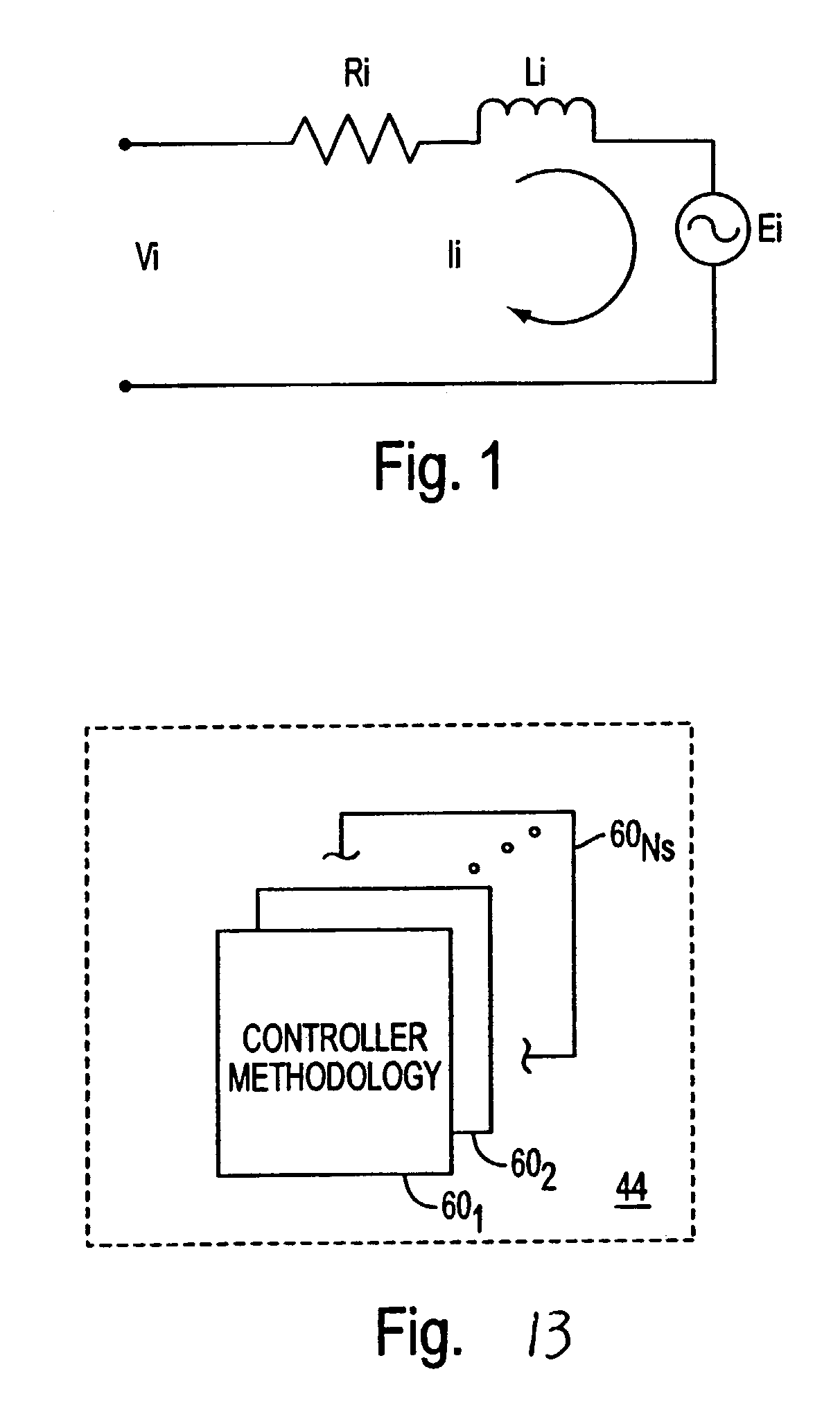

Phase advance angle optimization for brushless motor control

InactiveUS7436139B2High degree of precision controllabilityMaximizes output torqueCommutation monitoringMotor/generator/converter stoppersBrushless motorsPhase currents

A control system for a multiphase permanent magnet motor having a controller for producing a control signal to energize each phase winding. The controller includes a current value calculator for determining a value of phase current advanced in phase with respect to back-EMF by a phase advance angle, and a phase advance optimization circuit for producing a value of the phase advance angle optimized so as to maximize output torque of the motor and mimimize the phase current. The phase advance optimization circuit determines the phase advance angle optimized for each phase of the motor.

Owner:MATRA MFG & SERVICES

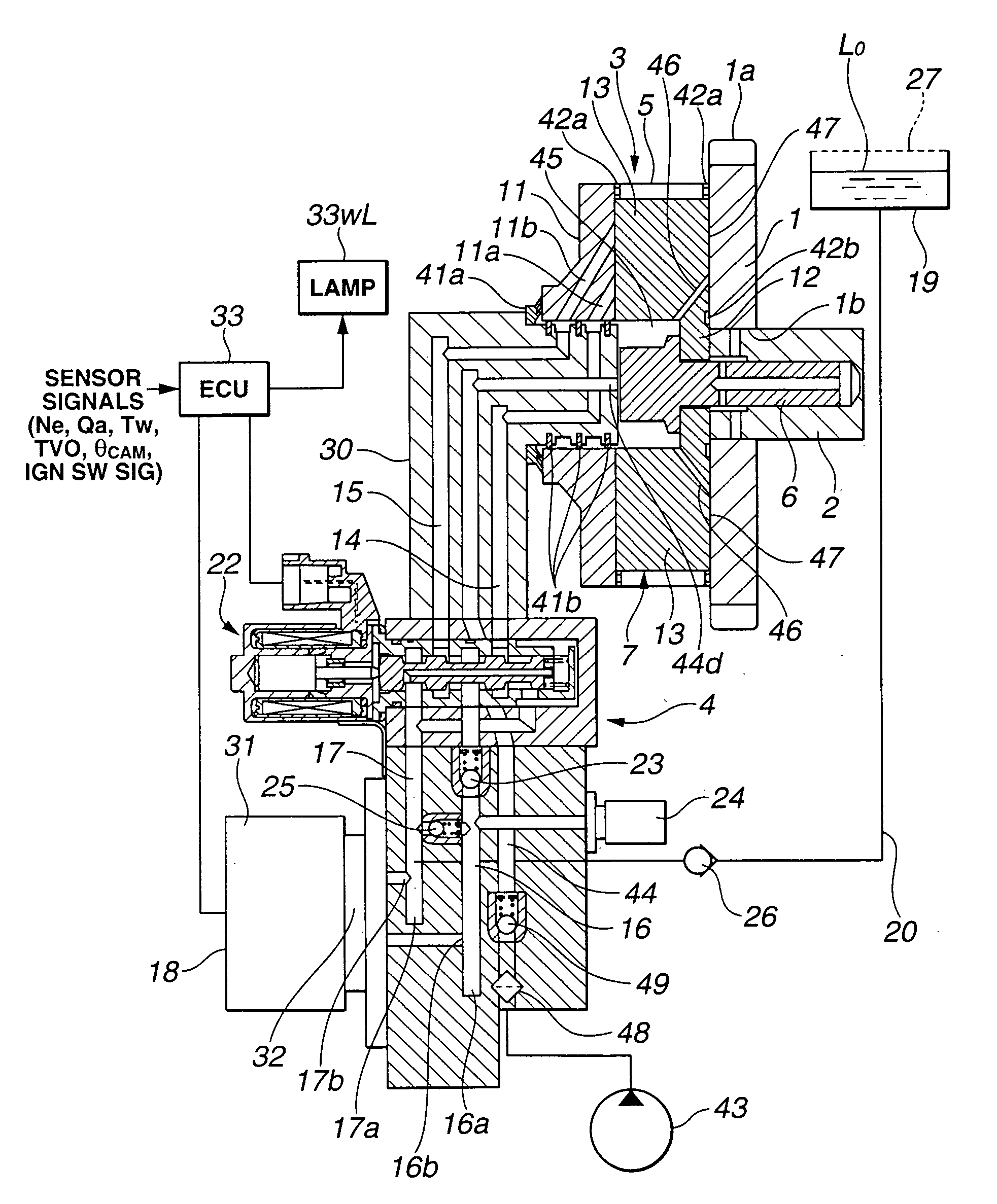

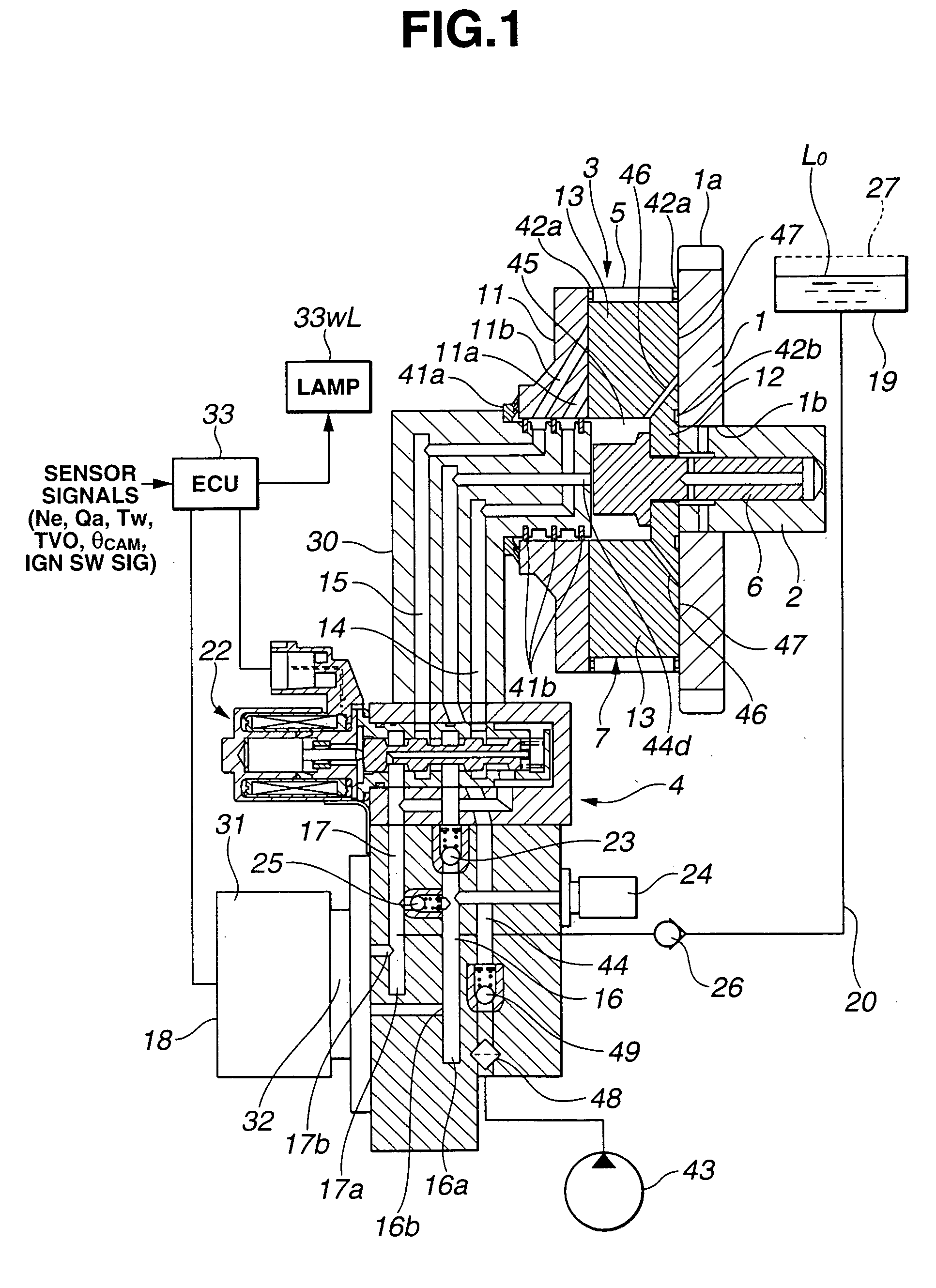

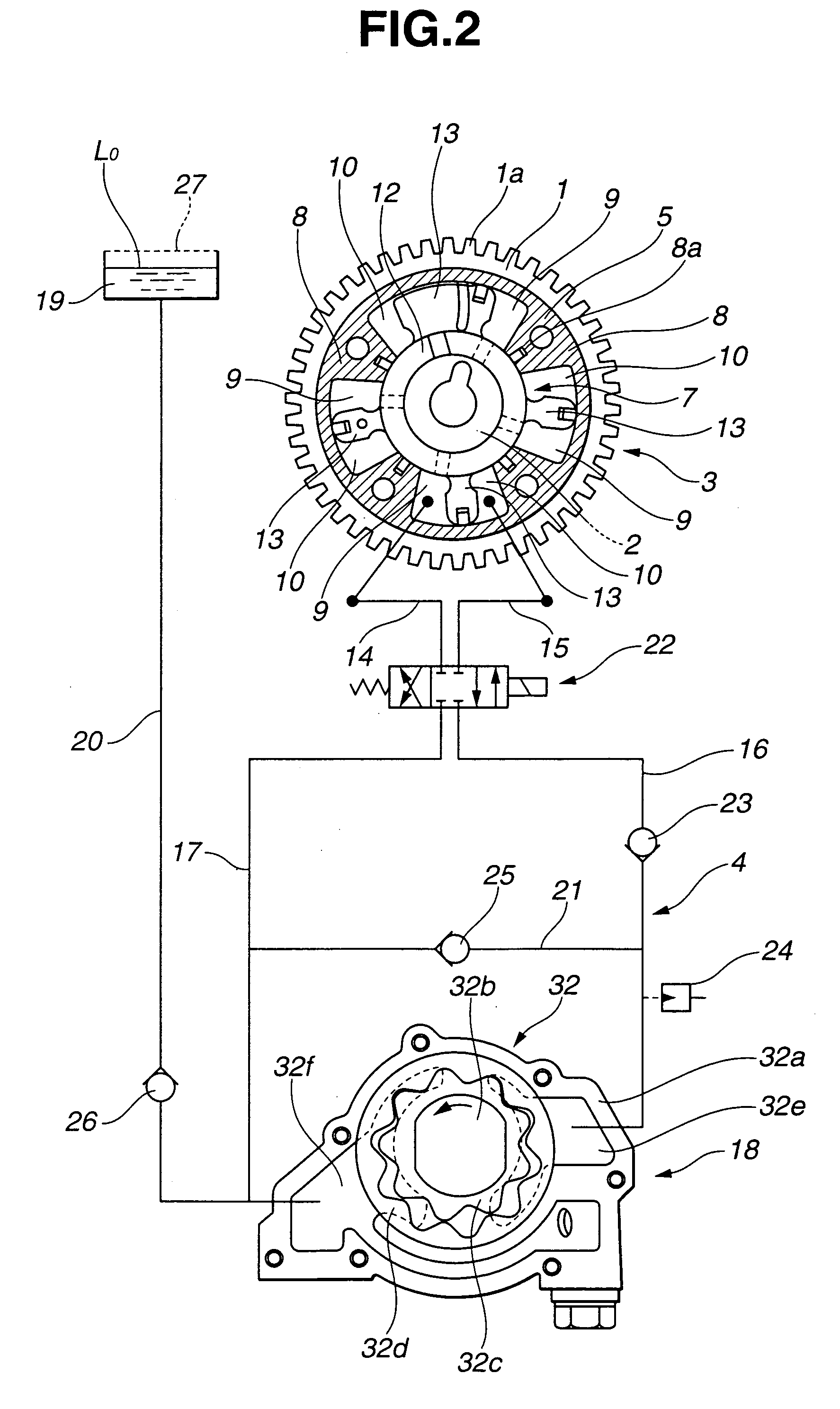

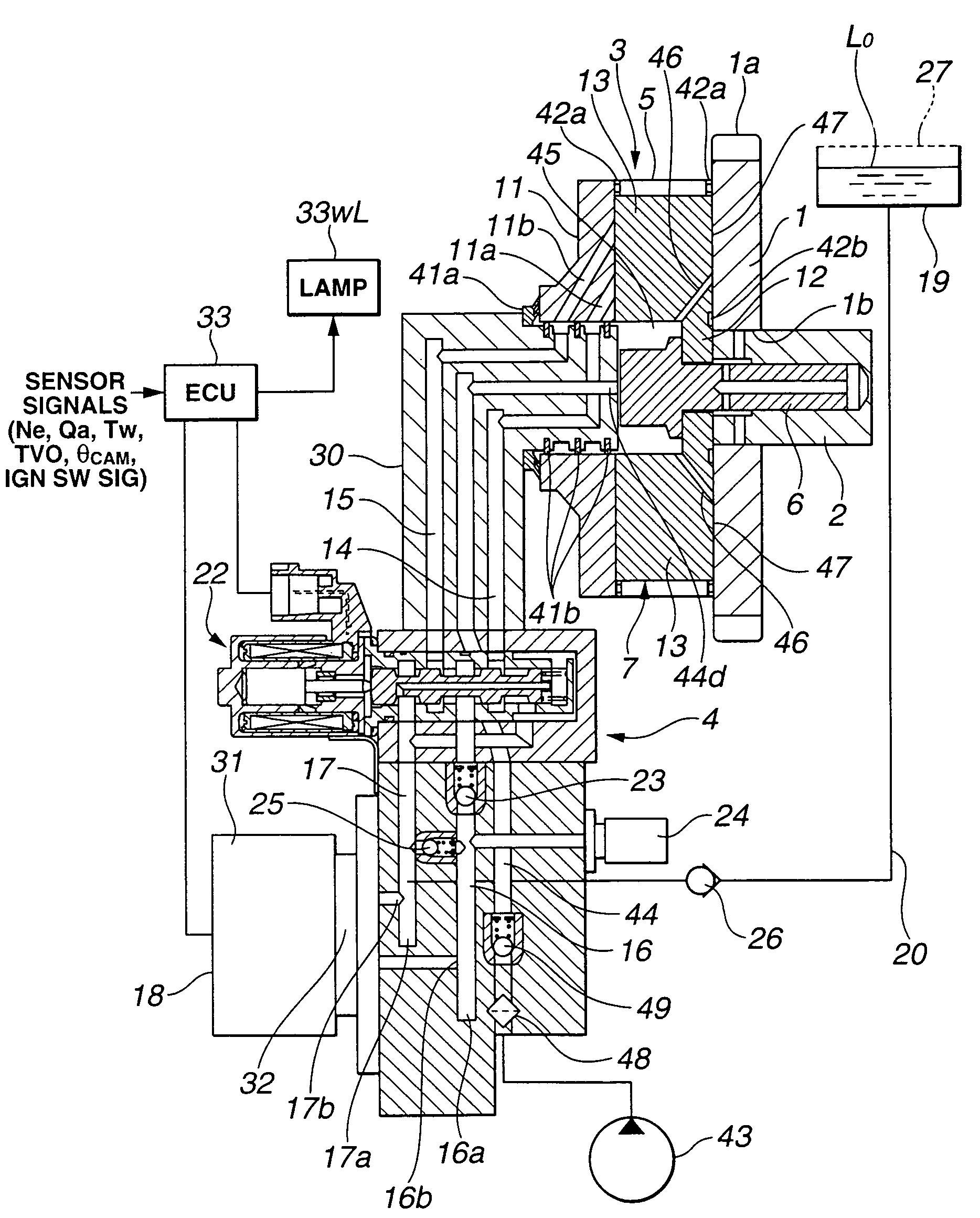

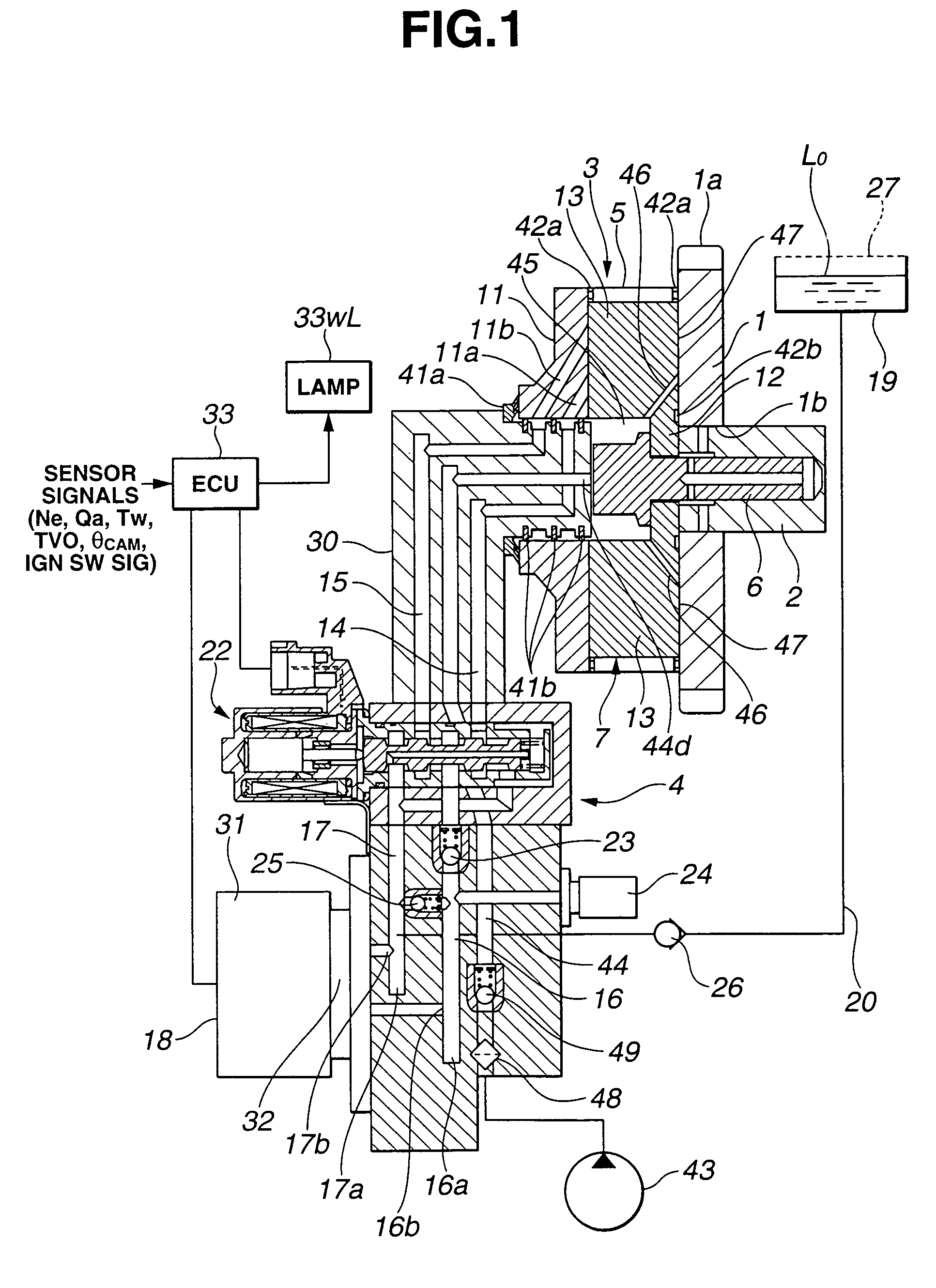

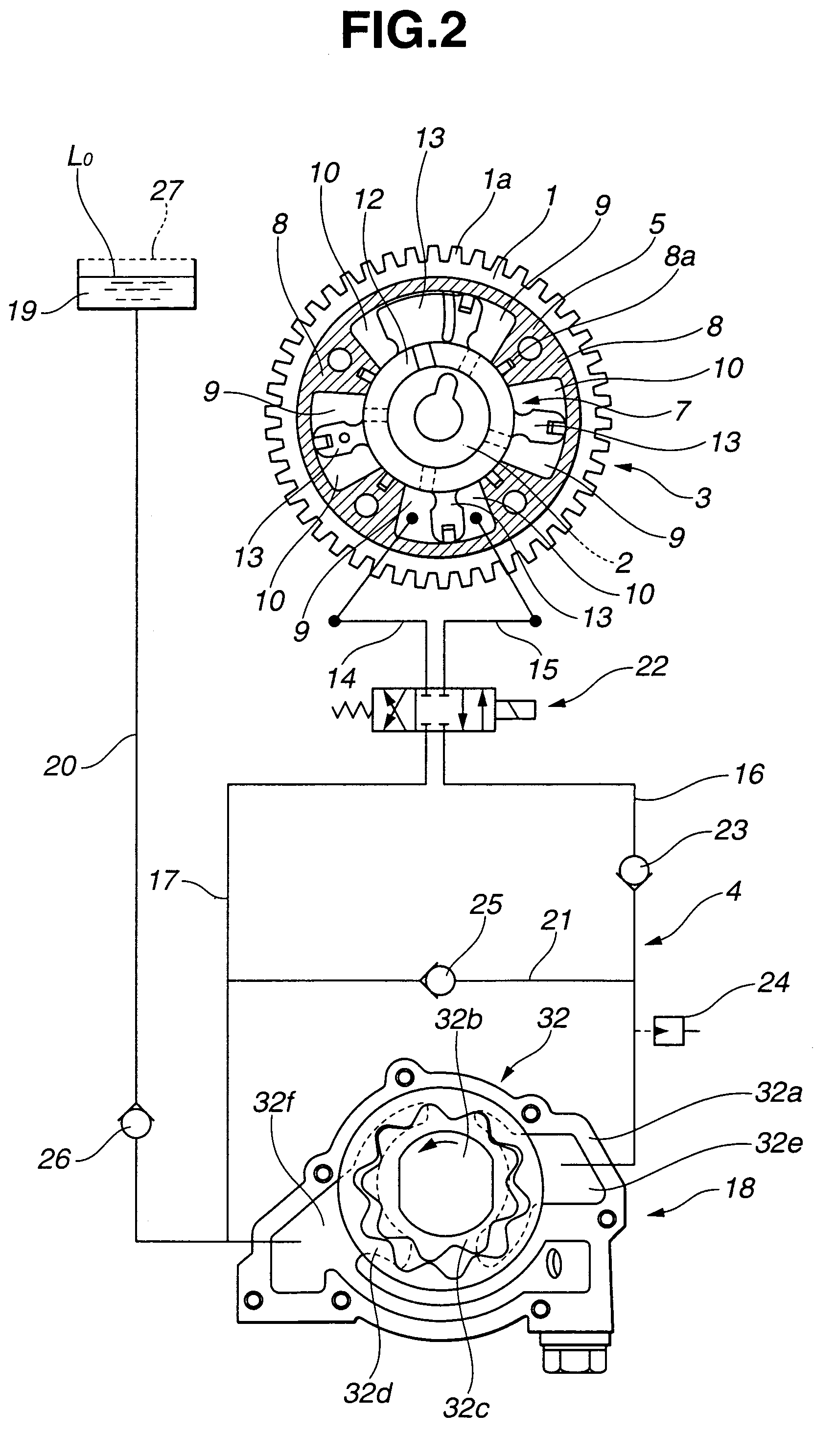

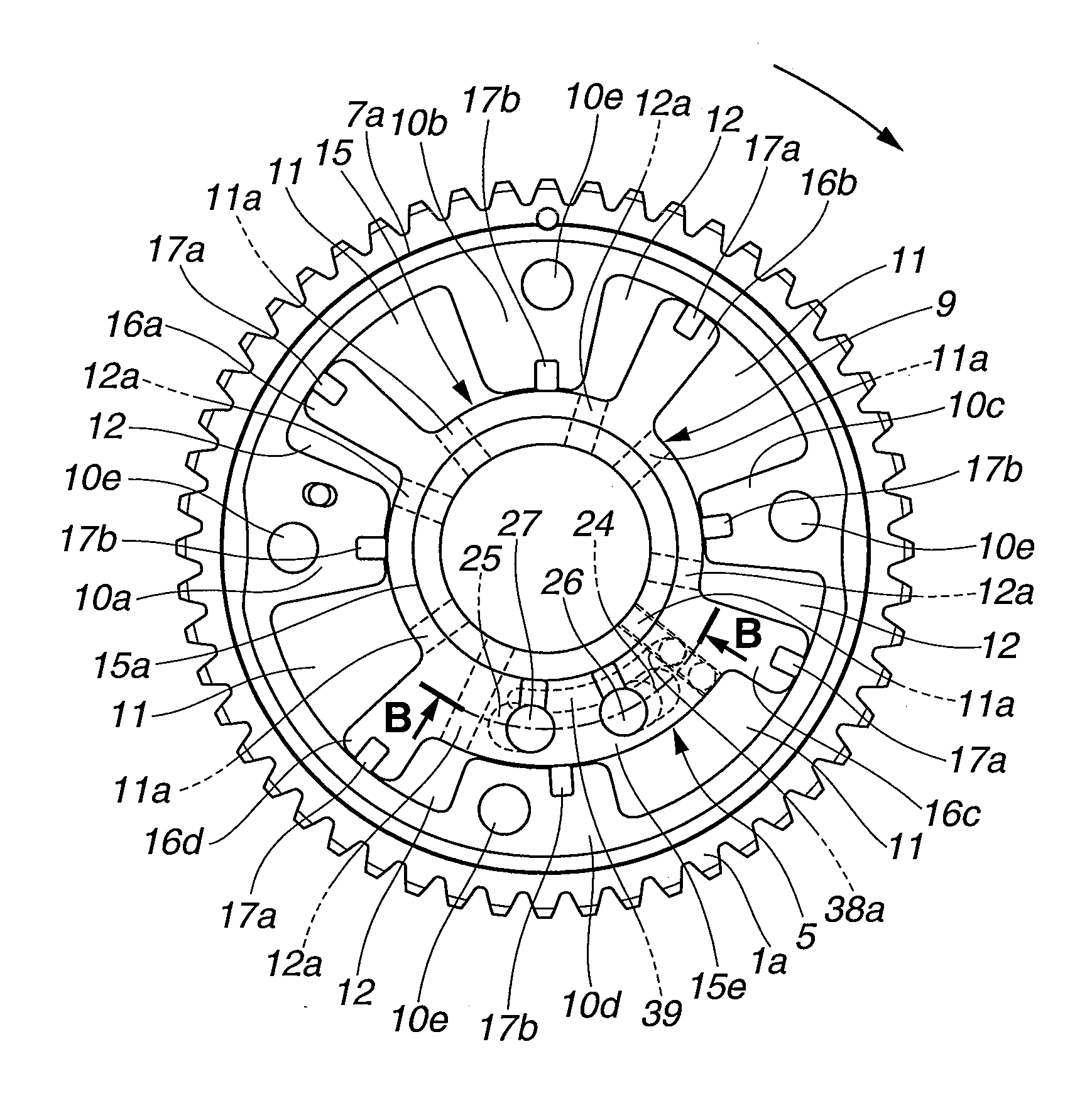

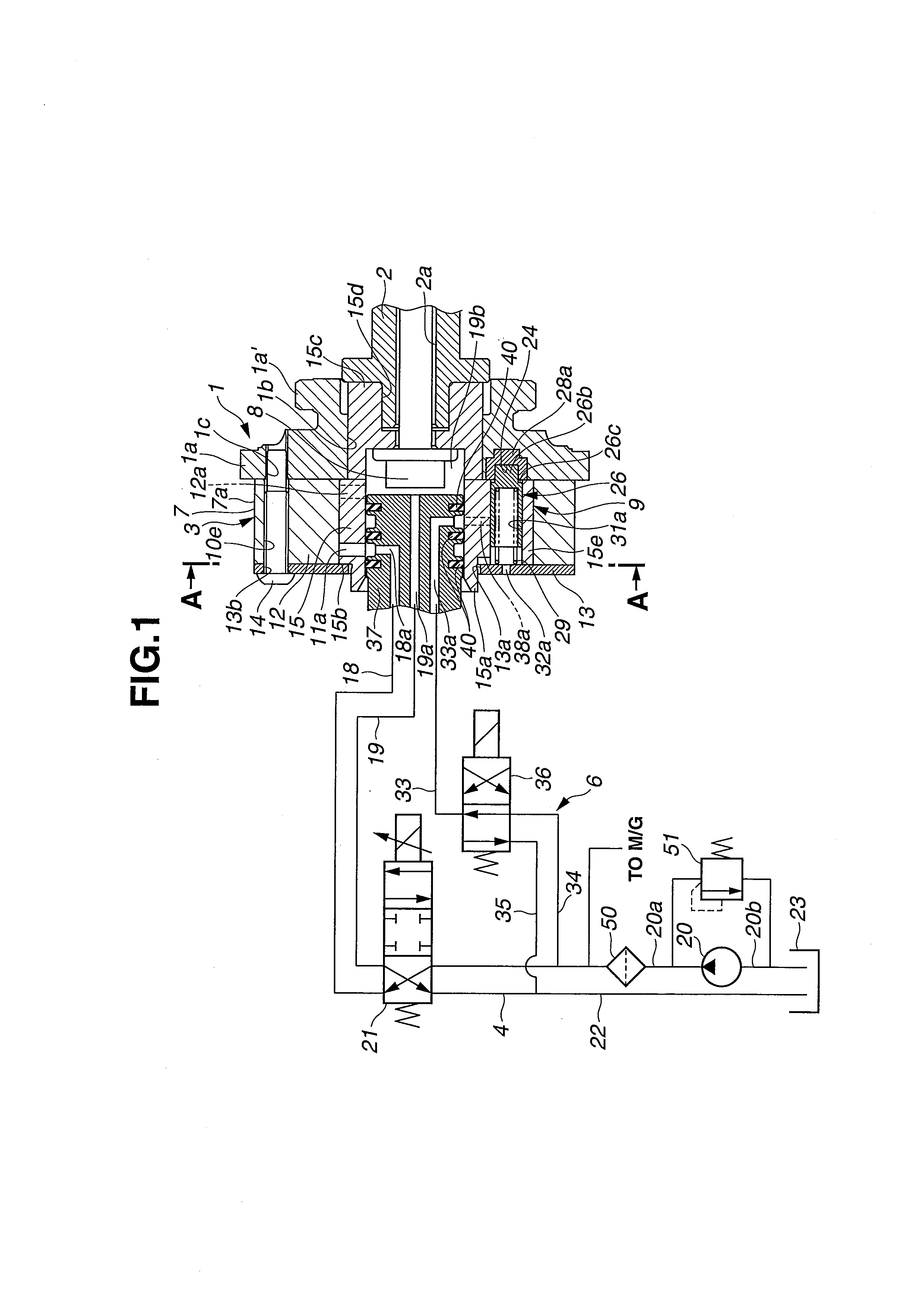

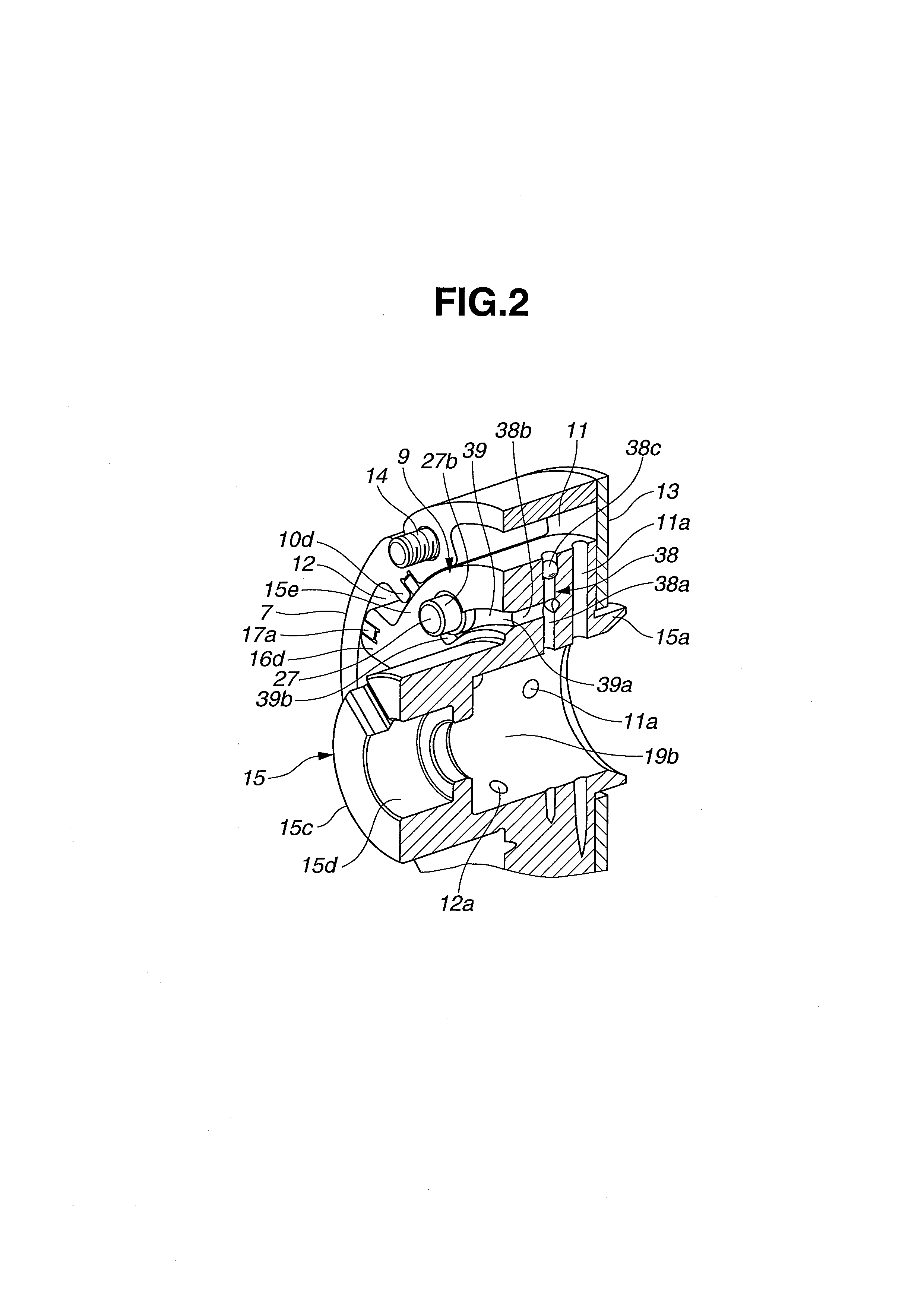

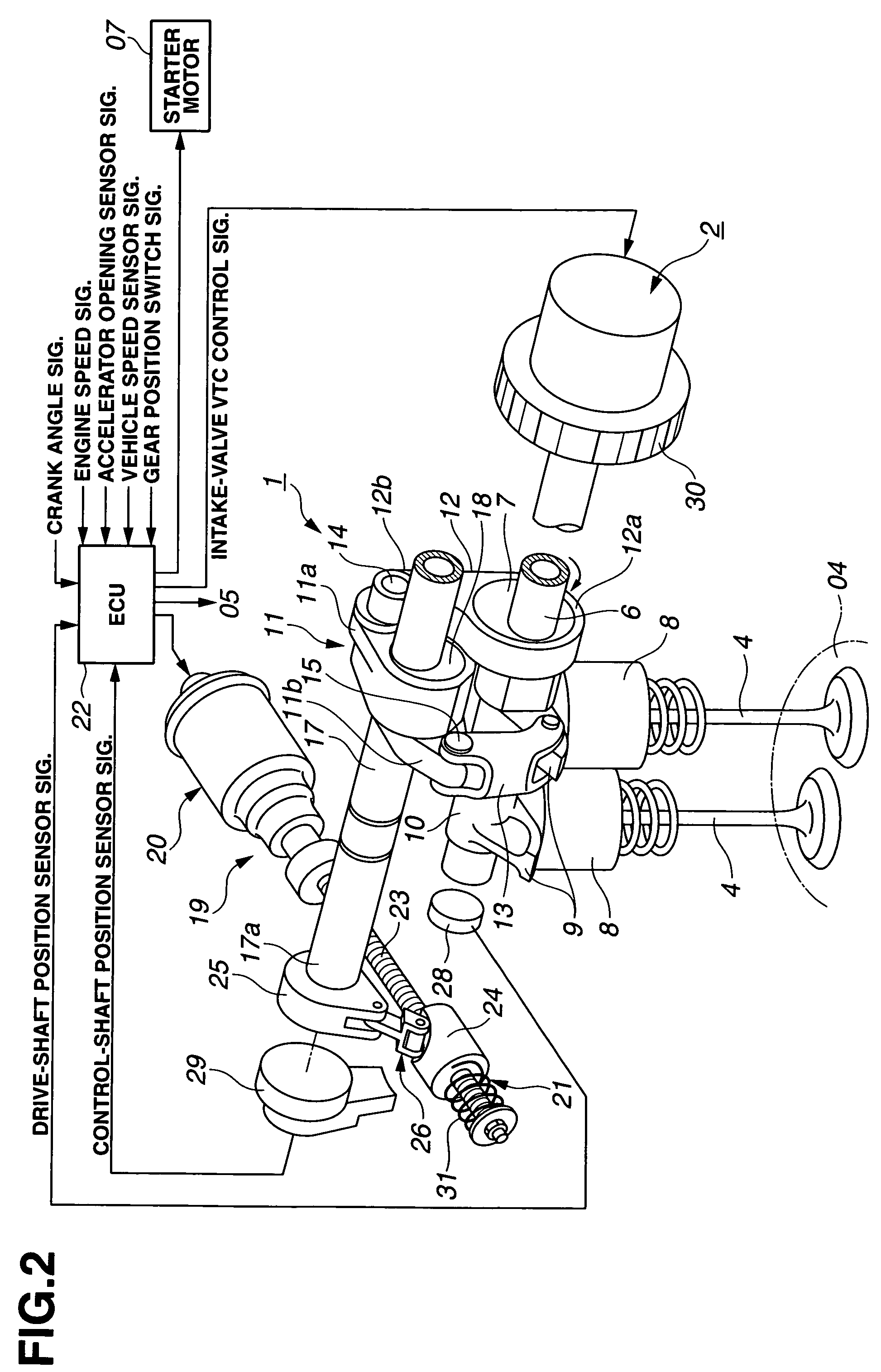

Variable valve timing control system of internal combustion engine

InactiveUS20050257762A1Tendency increaseIncrease system costValve drivesMachines/enginesWorking fluidVariable valve timing

A variable valve timing control system of an internal combustion engine includes a hydraulically-operated phase converter disposed between a sprocket and a camshaft, and having a phase-advance hydraulic chamber and a phase-retard hydraulic chamber for changing an angular phase of the camshaft relative to the sprocket. An electric pump is provided to supply working fluid selectively to one of the hydraulic chambers via a directional control valve. Also provided is a check valve disposed in a discharge line of the pump for permitting flow in a direction that the working fluid flows from the pump to the directional control valve and preventing any flow in the opposite direction, so as to prevent a pulse pressure arising from alternating torque exerted on the camshaft from being transmitted from either one of the hydraulic chambers via the discharge line to a discharge port of the pump.

Owner:HITACHI LTD

Air amount detector for internal combustion engine

InactiveUS6662640B2Improve calculation accuracyAnalogue computers for vehiclesElectrical controlResponse delayPhase advance

A response delay compensation element for compensating a response delay of an output gMAF of an airflow meter by a phase advance compensation is provided so that an output g of the response delay compensation element is input to the intake air system model. A transfer function of the phase advance compensation iswhere T1 and T2 are time constant of the phase advance compensation, which is set based on at least one of the output gMAF of the airflow meter, engine speed, an intake air pressure, and a throttle angle. The model time constant tauIM of the intake air system model is calculated by variables including volumetric efficiency and the engine speed. The volumetric efficiency is calculated by two-dimensional map having the engine speed and the intake air pressure as parameters thereof.

Owner:DENSO CORP

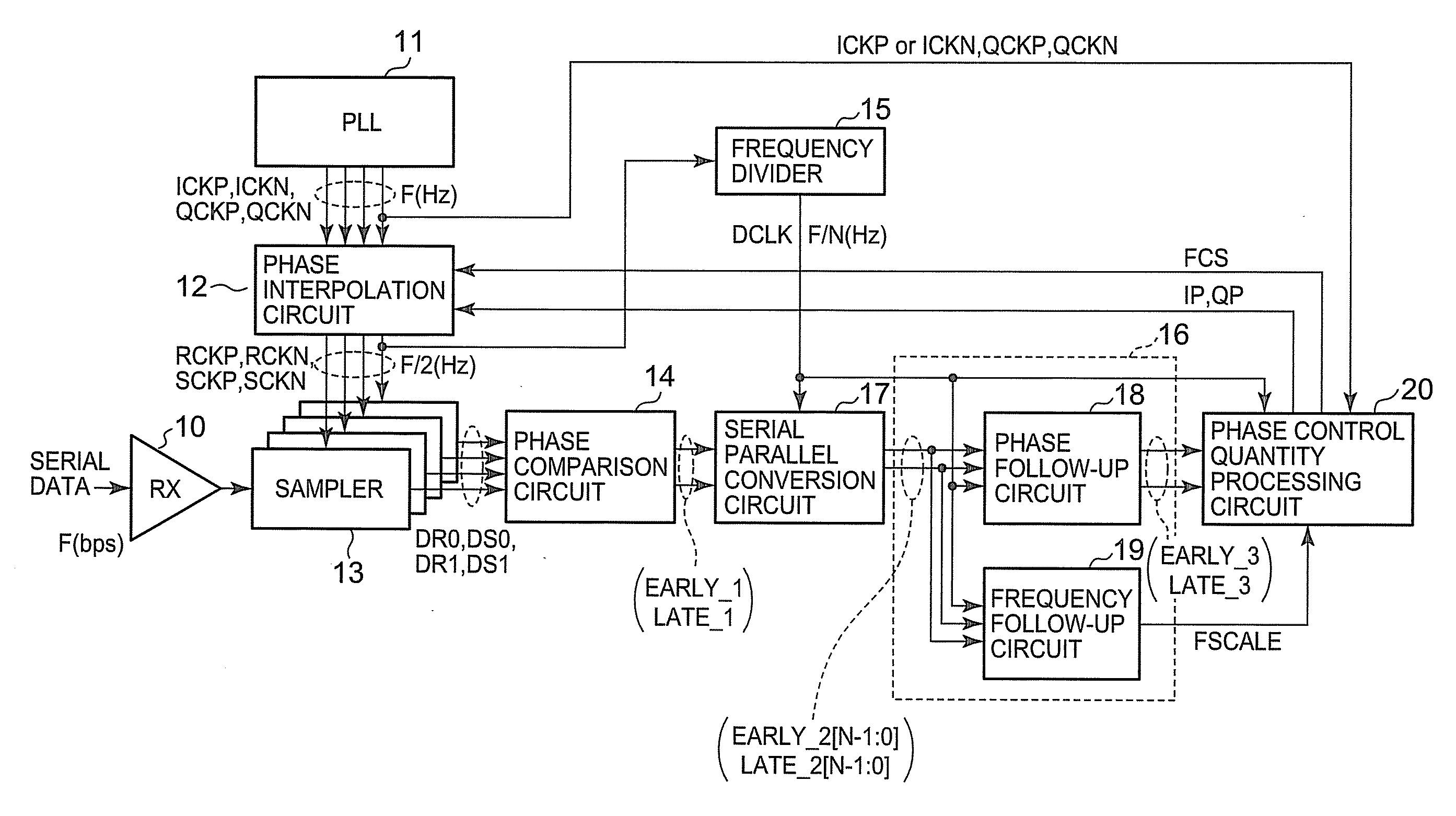

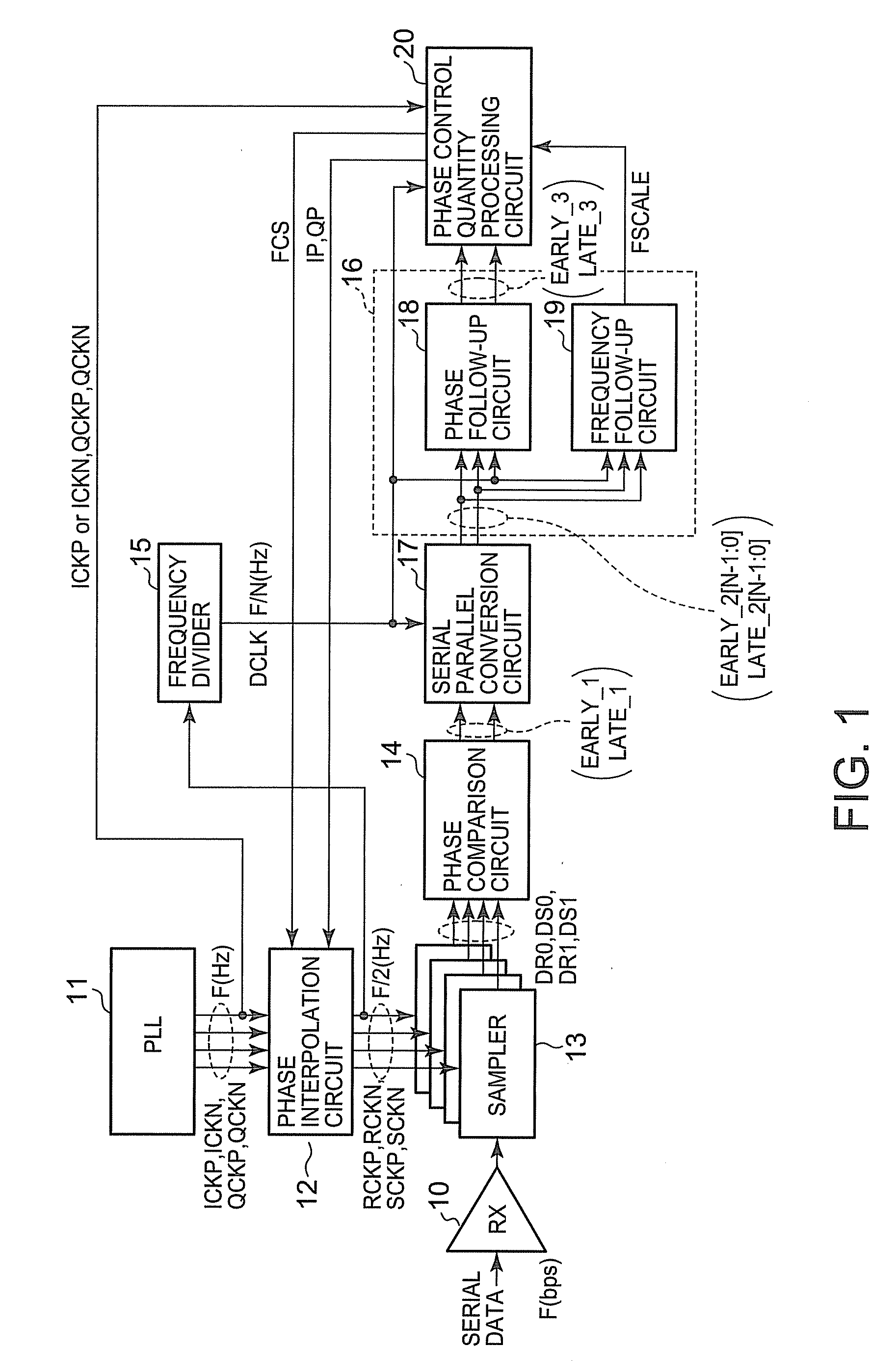

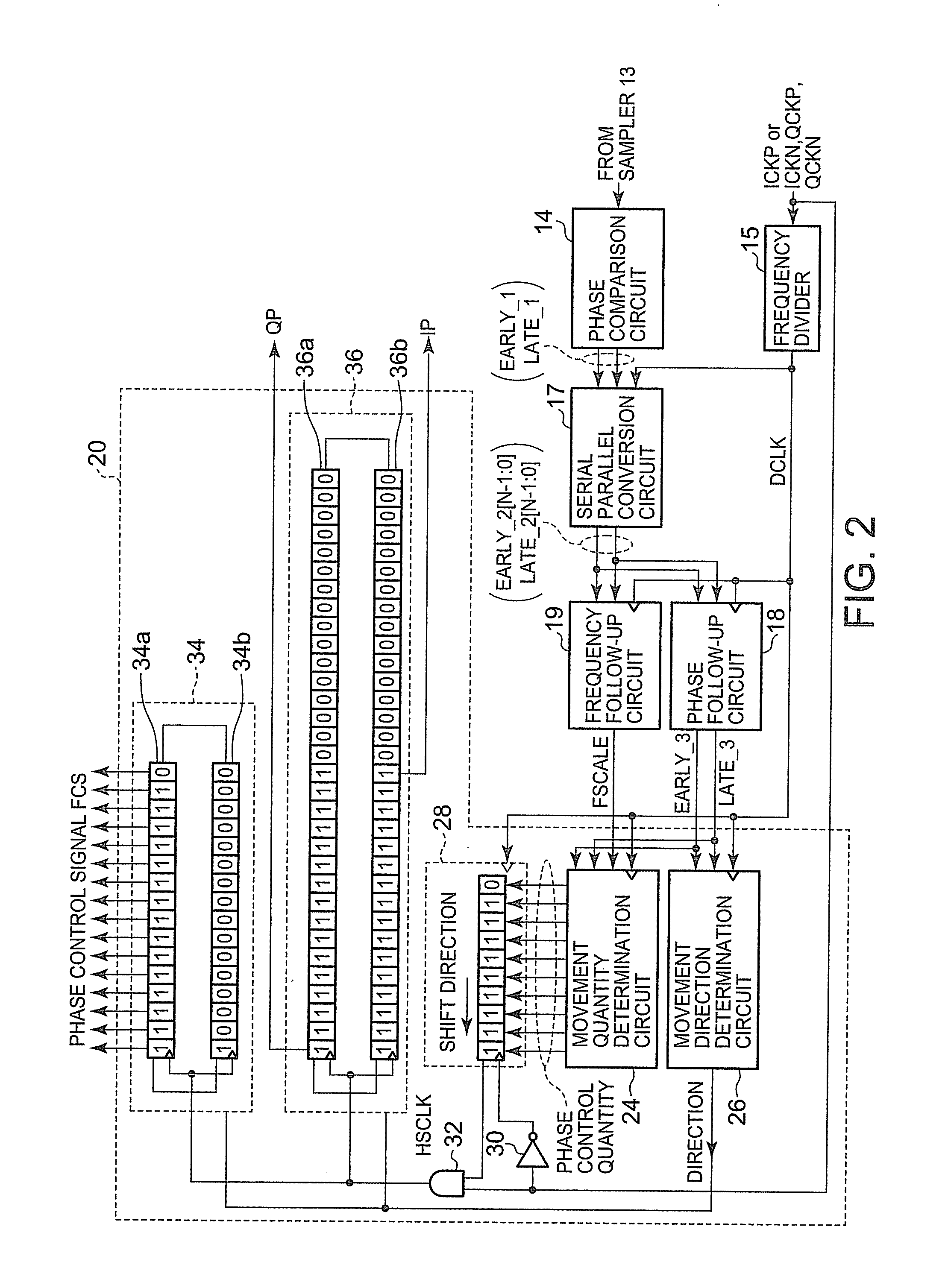

Clock recovery circuit and data recovery circuit

A serial input signal is sampled in synchronization with a plurality of first clock signals to obtain a plurality of sampling data pieces. A phase comparison circuit outputs a serial phase information signal based on the sampling data pieces. A serial-parallel conversion circuit performs a serial-to-parallel conversion on the serial phase information signal in synchronization with a second clock signal having a lower frequency, to output a parallel phase information signal. A digital filtering circuit calculates phase deviation and phase advance-delay signals based on the parallel phase information signal in synchronization with the second clock signal. By these signals, a phase control amount processing circuit generates a phase control signal. The phase control signal is in synchronization with third clock signals having a higher frequency. A phase interpolation circuit adjusts the phases of the third clock signals based on the phase control signal to output the first clock signals.

Owner:KK TOSHIBA

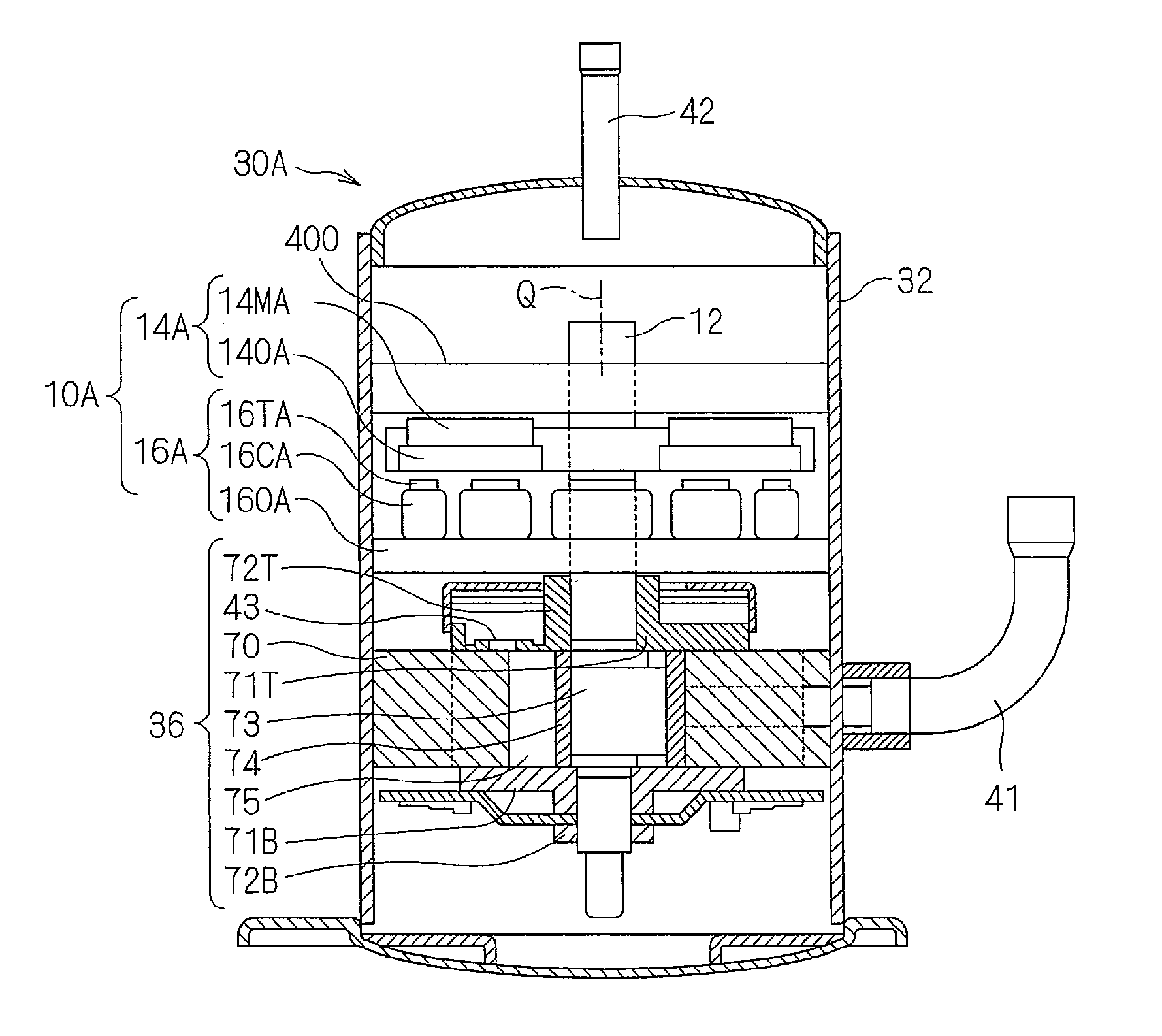

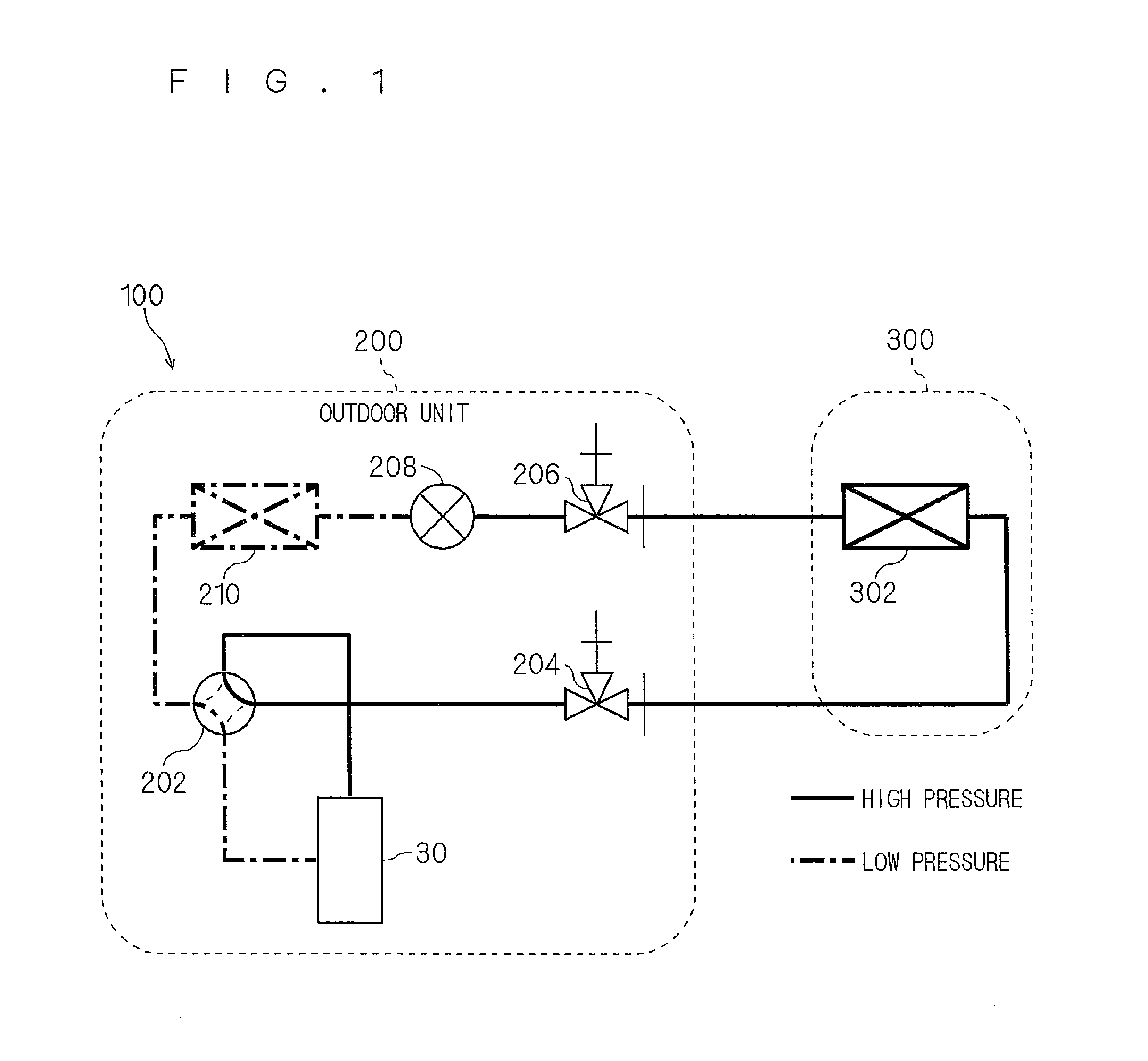

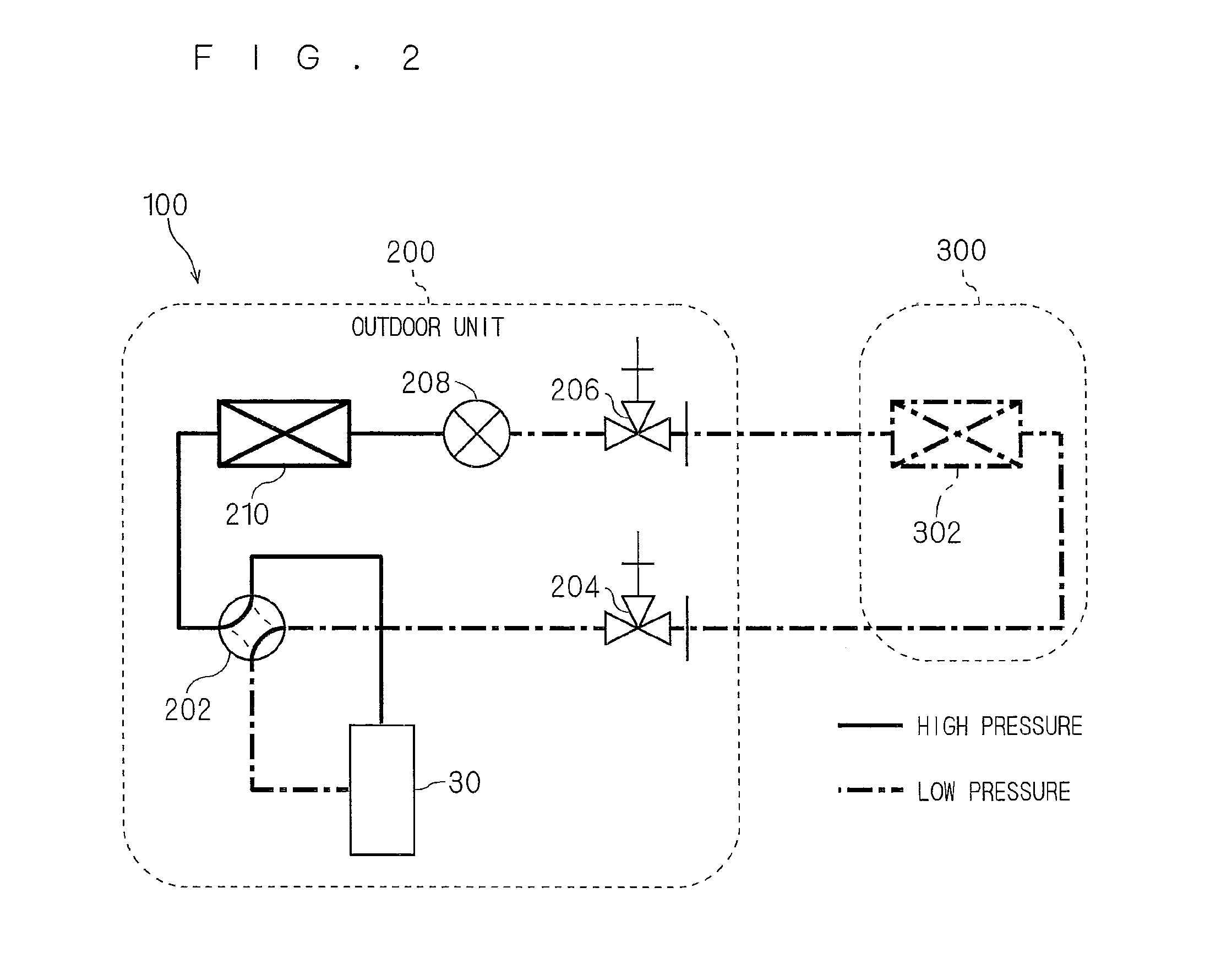

Air conditioner, air conditioner manufacturing method, and compressor

ActiveUS20110083467A1Increased number of spinsHigh voltageWindingsSpace heating and ventilationPower flowPower conditioner

At a time of a heating high-load operation, a harmonic current is flown in an armature winding to induction-heat rare-earth magnets, thus reducing a residual magnetic flux density. Thereby, the number of rotations of a radial gap type motor is improved. The rare-earth magnets are provided near a cooling medium passage extending substantially in parallel with a flow line of a cooling medium, so that the cooling medium recovers heat of the heated rare-earth magnets. At a time of a cooling high-load operation, a greater number of rotations are obtained with respect to the same torque command value, by a field weakening control by means of a current-phase advance.

Owner:DAIKIN IND LTD

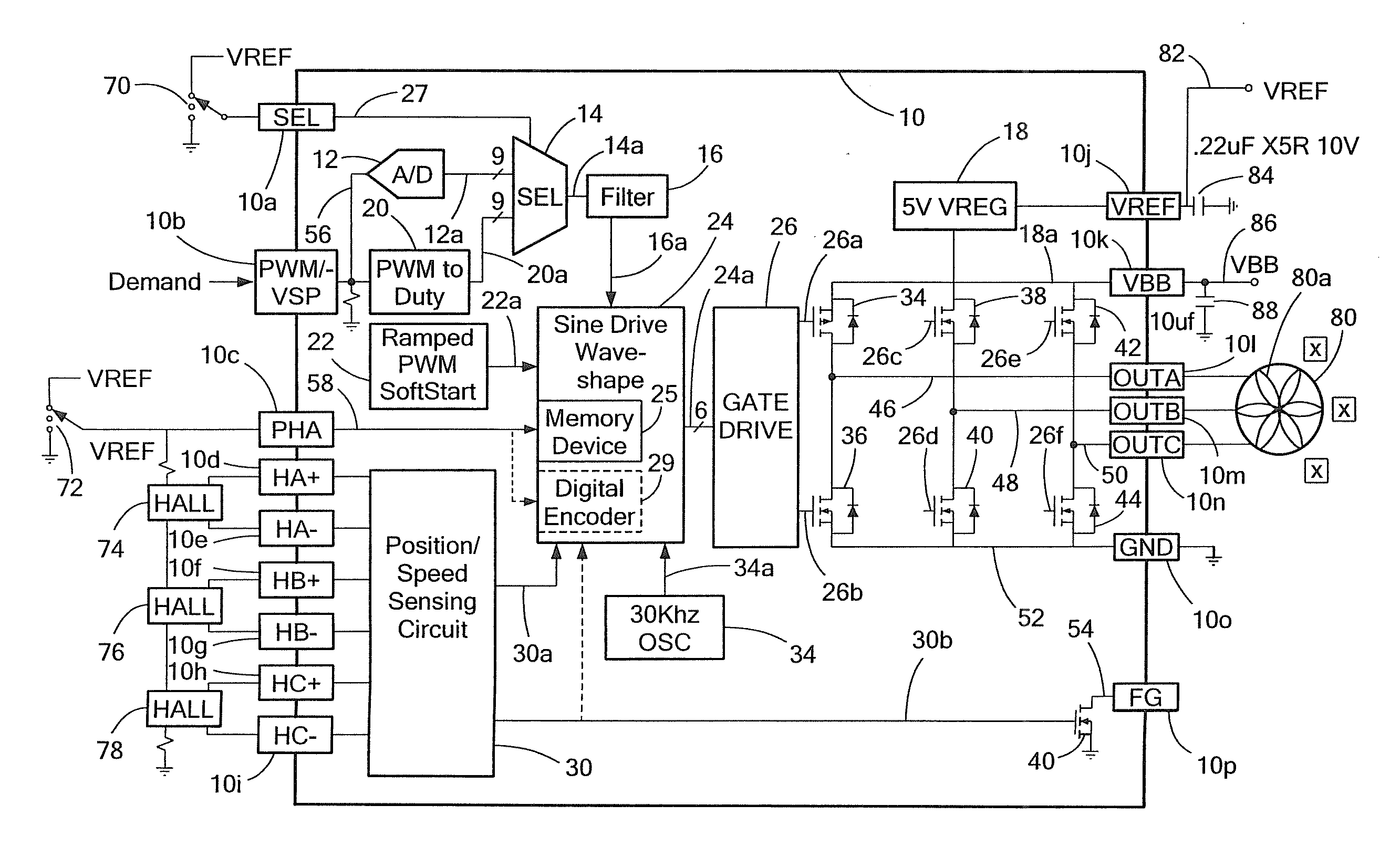

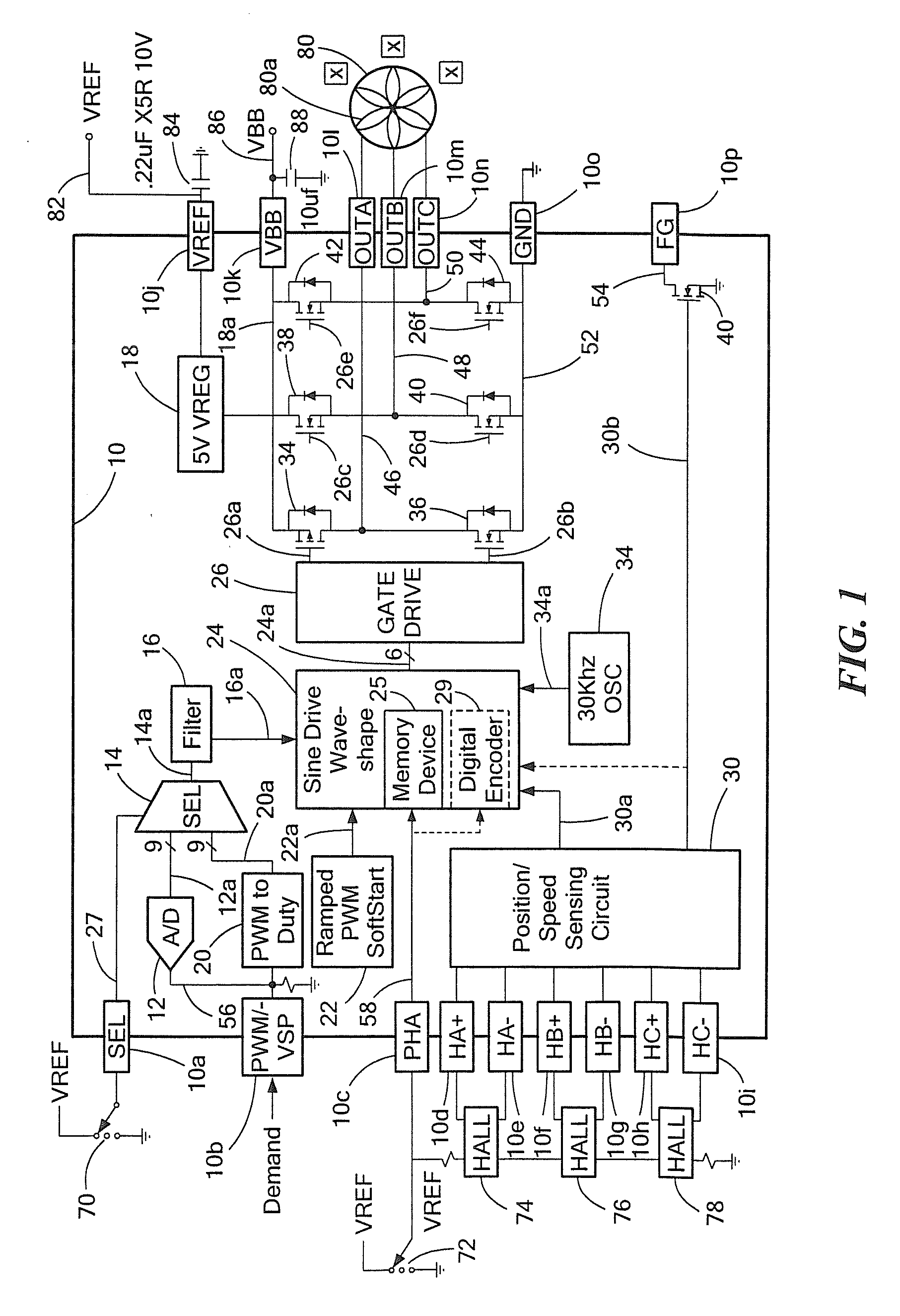

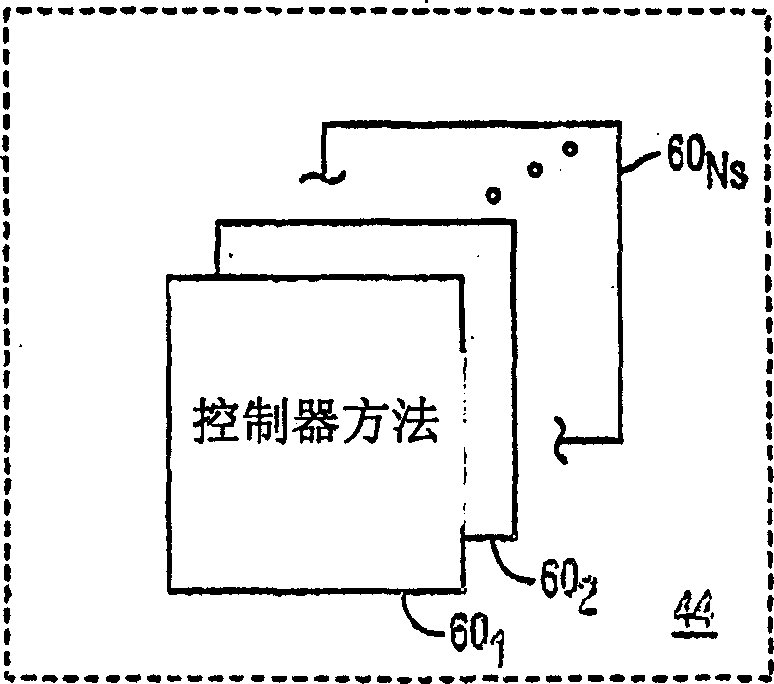

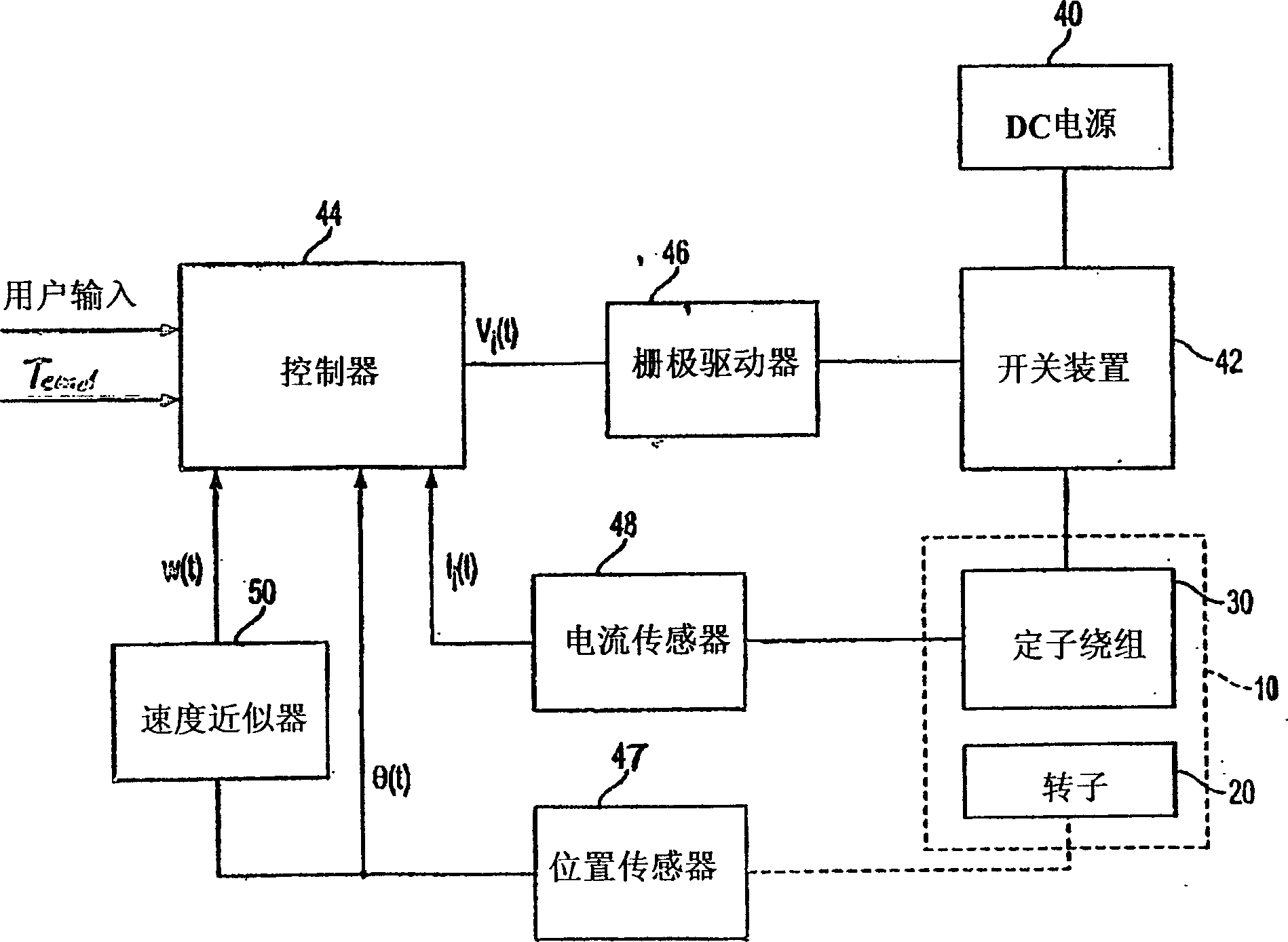

Electronic circuit and method generating electric motor drive signals having phase advances in accordance with a user selected relationship between rotational speed of an electric motor and the phase advances

ActiveUS20130009578A1Improve electricity efficiencyTorque ripple controlMotor/generator/converter stoppersControl theoryPhase advance

An electronic circuit and an associated method used to drive an electric motor provide a user selectable relationship between rotational speed of the electric motor and phase advances of signals used to drive the electric motor. By selecting the relationship, efficiency of the electric motor drive can be improved.

Owner:ALLEGRO MICROSYSTEMS INC

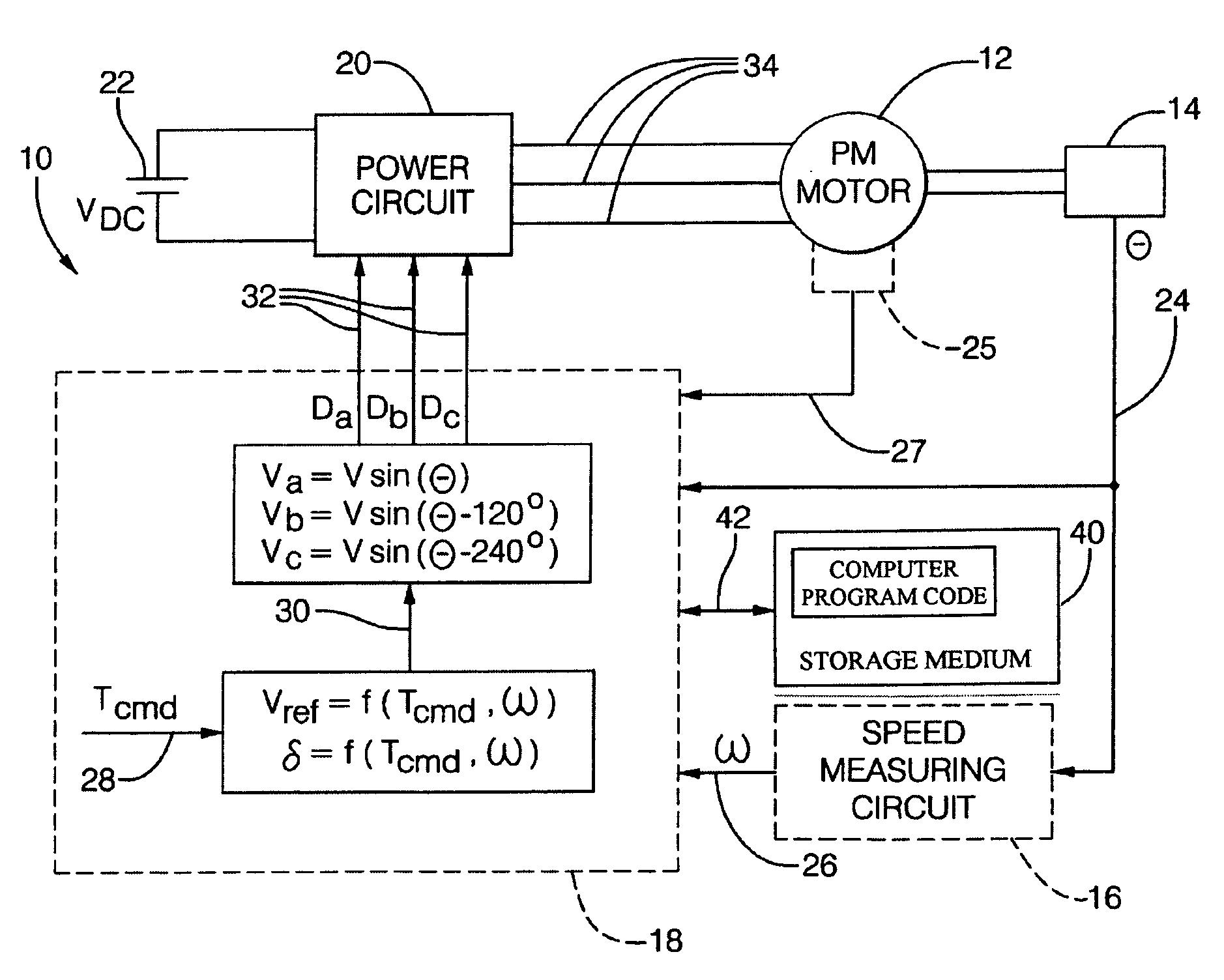

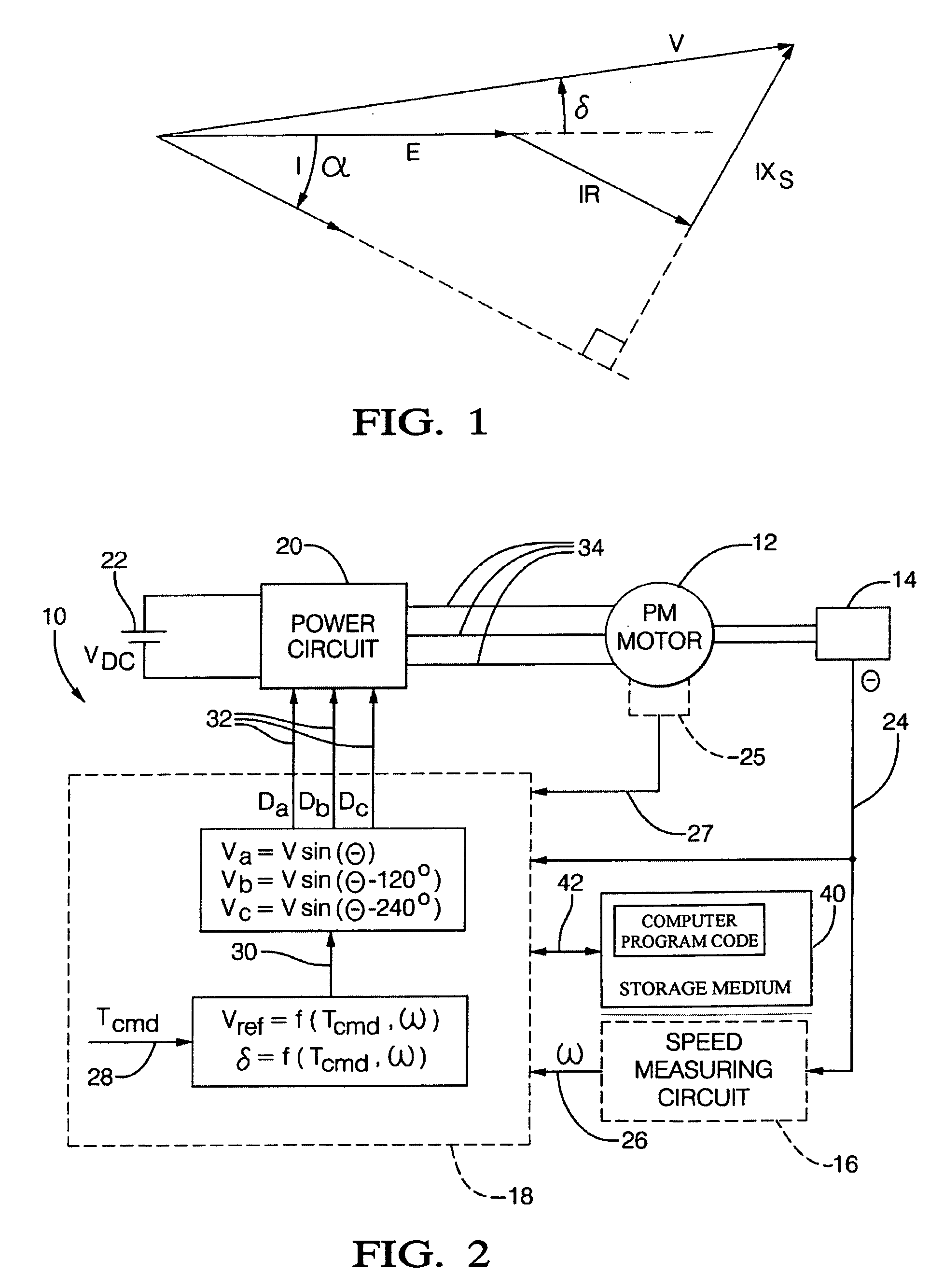

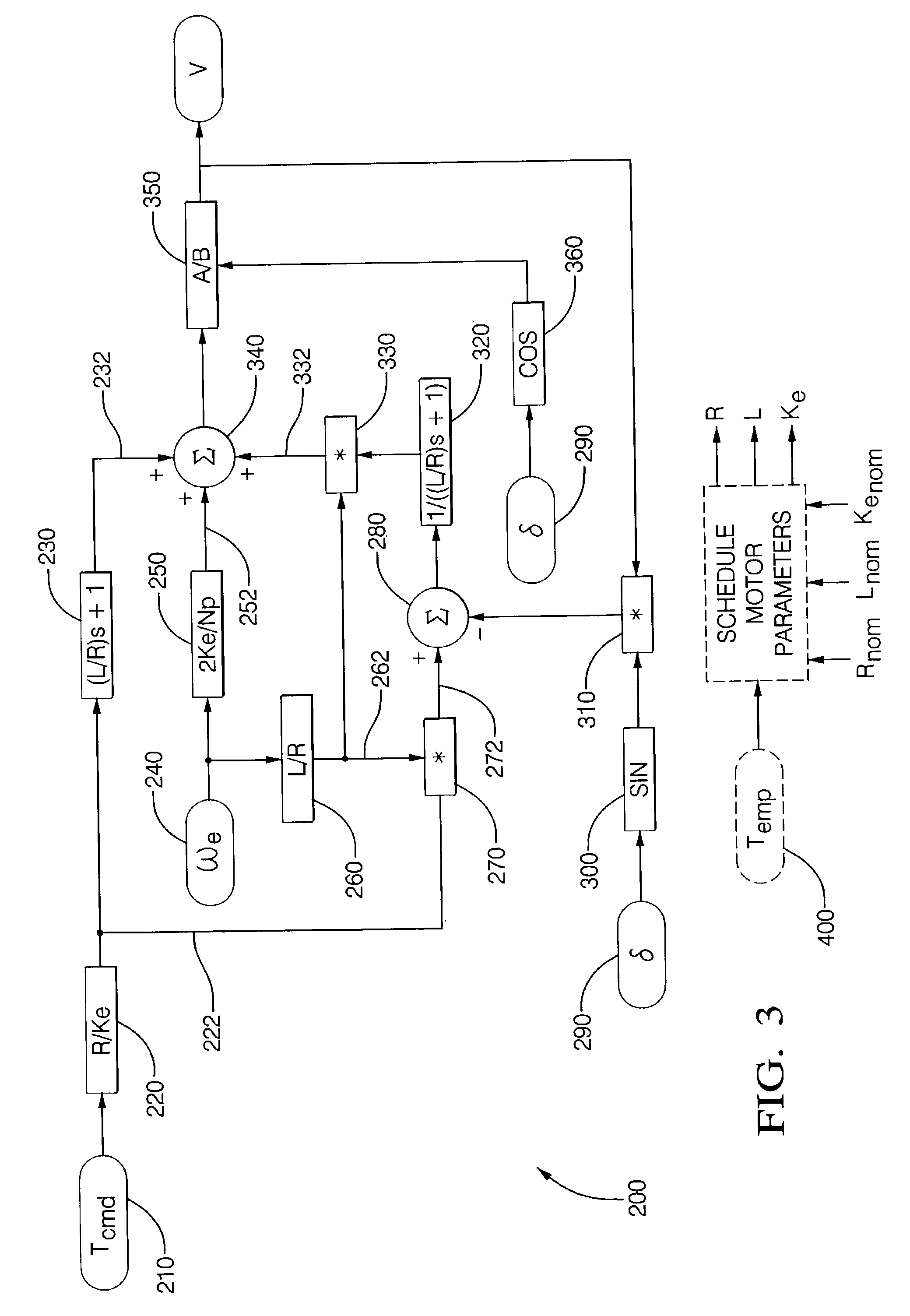

Transient compensation voltage estimation for feedforward sinusoidal brushless motor control

InactiveUS7157878B2Single-phase induction motor startersAC motor controlBrushless motorsTransient state

A method for controlling a voltage mode controlled electric machine comprising: receiving a torque value representative of a desired torque; obtaining a speed value indicative of a rotational velocity of the electric machine; acquiring a phase advance value indicative of a desired phase advance angle; generating a voltage command responsive to the torque value, the position value; the generating is responsive to the torque value, the speed value, and the phase advance value.

Owner:STEERING SOLUTIONS IP HLDG +1

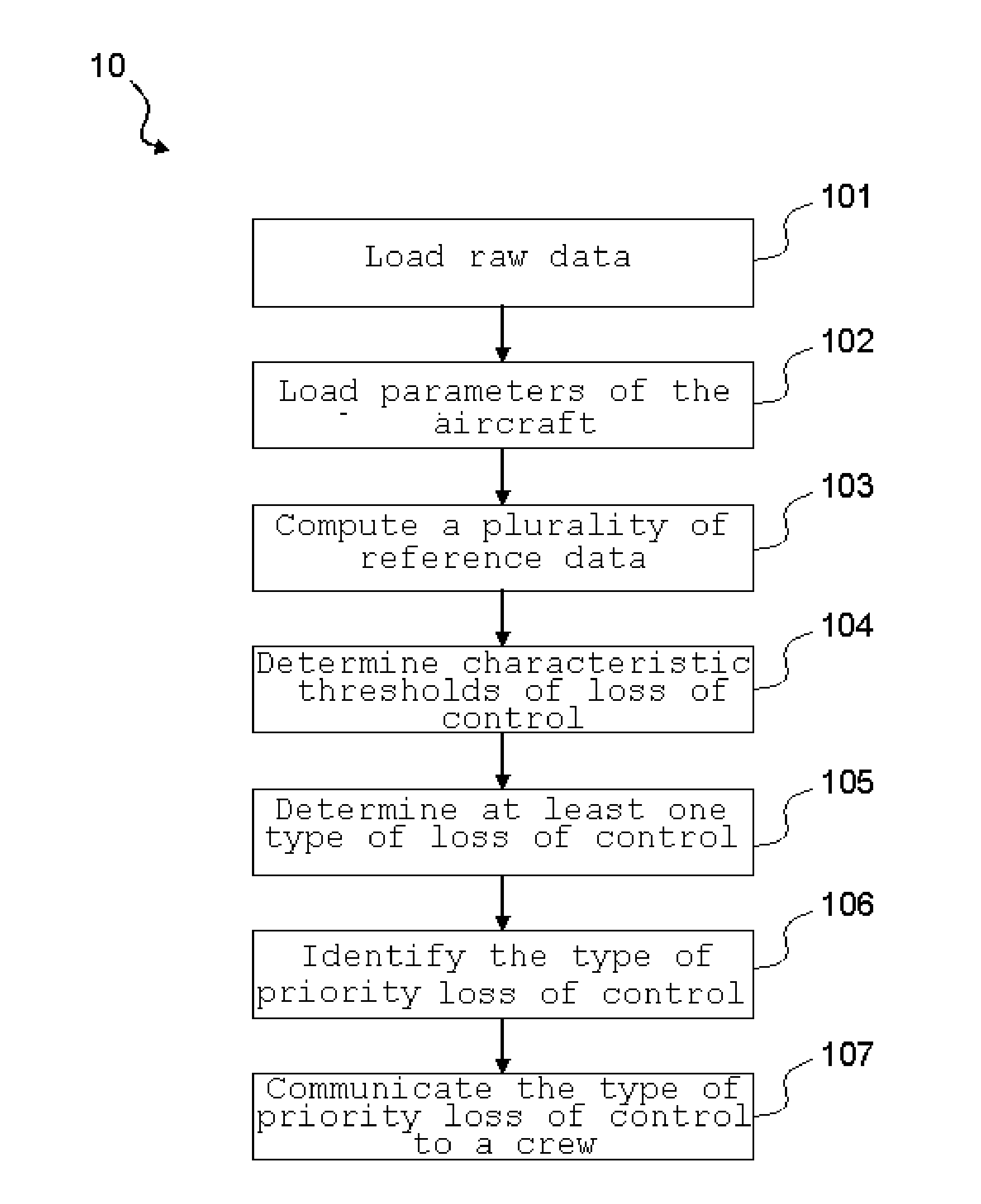

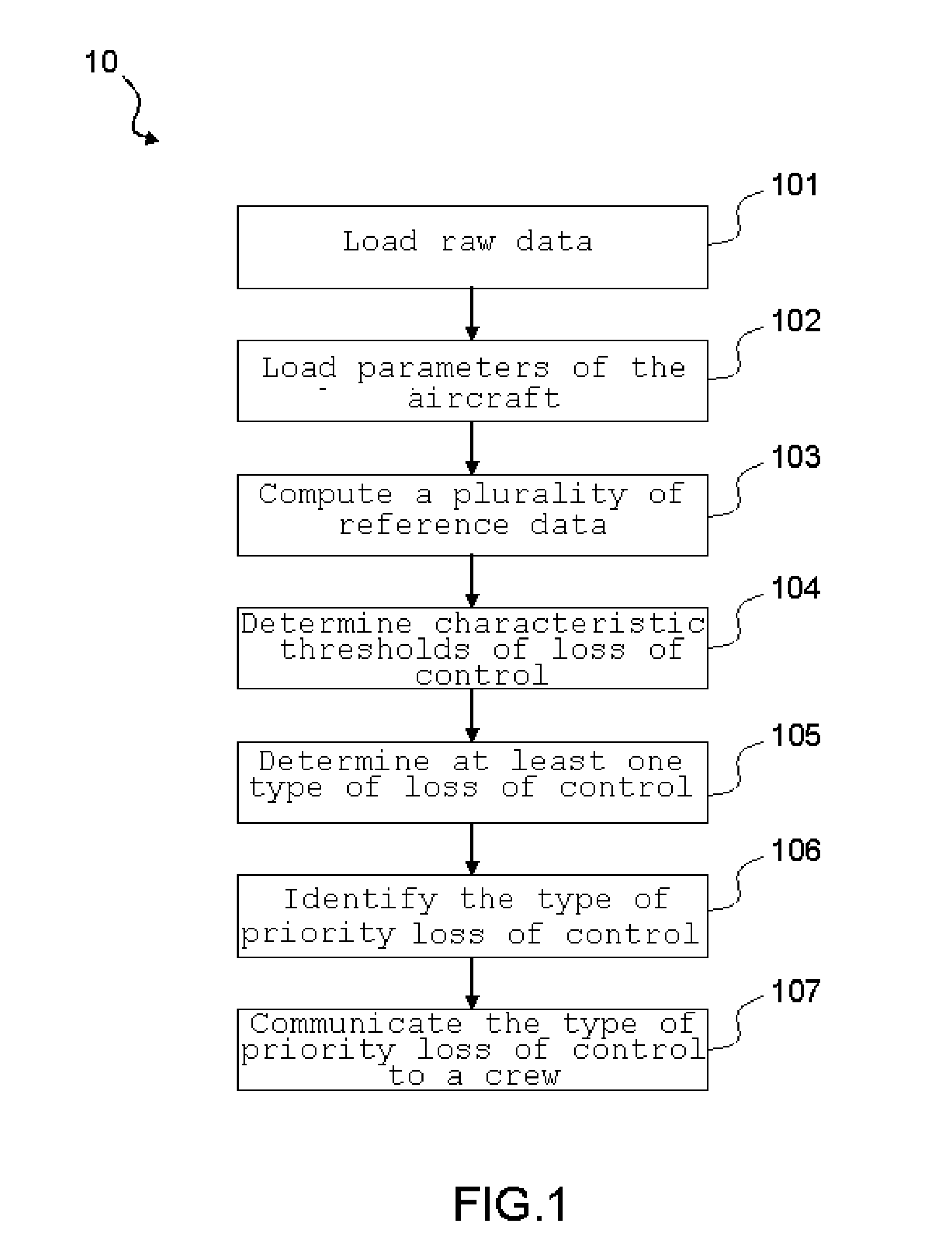

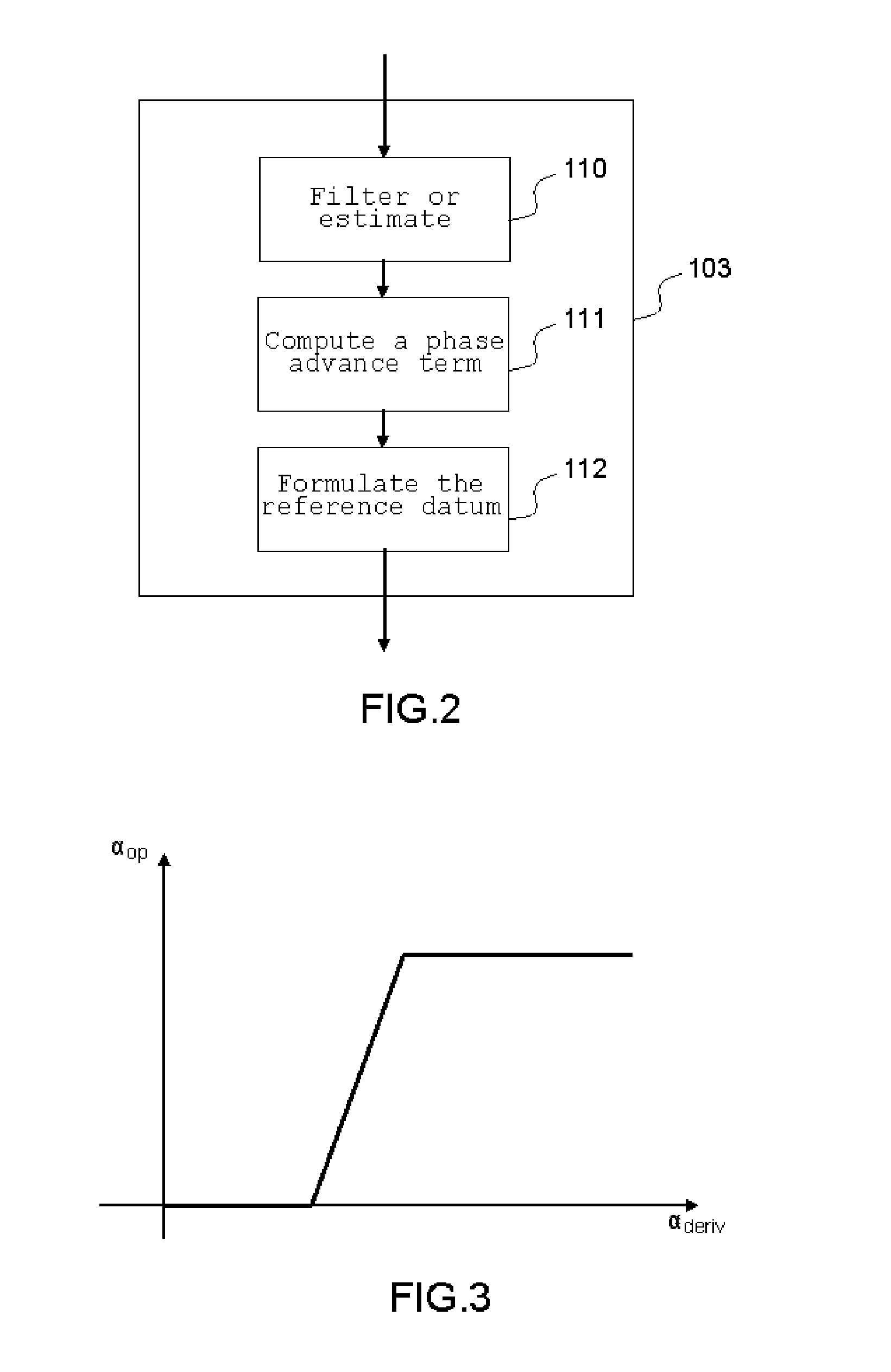

Method and device for diagnosis of a loss of control of an aircraft

InactiveUS20140371957A1Mitigate such drawbackControl safety arrangementsDigital data processing detailsPhase advanceComputer science

A method for diagnosis of a loss of control of an aircraft comprises the steps: loading raw data; loading parameters of the aircraft; computing a plurality of reference data comprising a preprocessing comprising for at least one reference datum a sub-step of computing a phase advance term; determining the characteristic thresholds indicative of loss of control; detecting at least one type of loss of control by comparing the reference data with characteristic thresholds; and, when at least one type of loss of control is detected: identifying the type of priority loss of control corresponding to the type of loss of control exhibiting the highest priority level, and communicating the type of priority loss of control to a crew.

Owner:THALES SA

Air conditioner

InactiveUS20070283707A1Increases starting torqueCheap constructionSingle-phase induction motor startersAC motor controlEngineeringPhase advance

An air conditioner having two compressors enables, when one compressor is started, the phase advance capacitor for the other compressor to be temporarily separated and used in parallel with the phase advance capacitor for the one compressor. These compressors can have an increased starting torque without using a starting capacitor. This structure allows the effective use of expensive capacitors, making the system inexpensive.

Owner:PANASONIC CORP

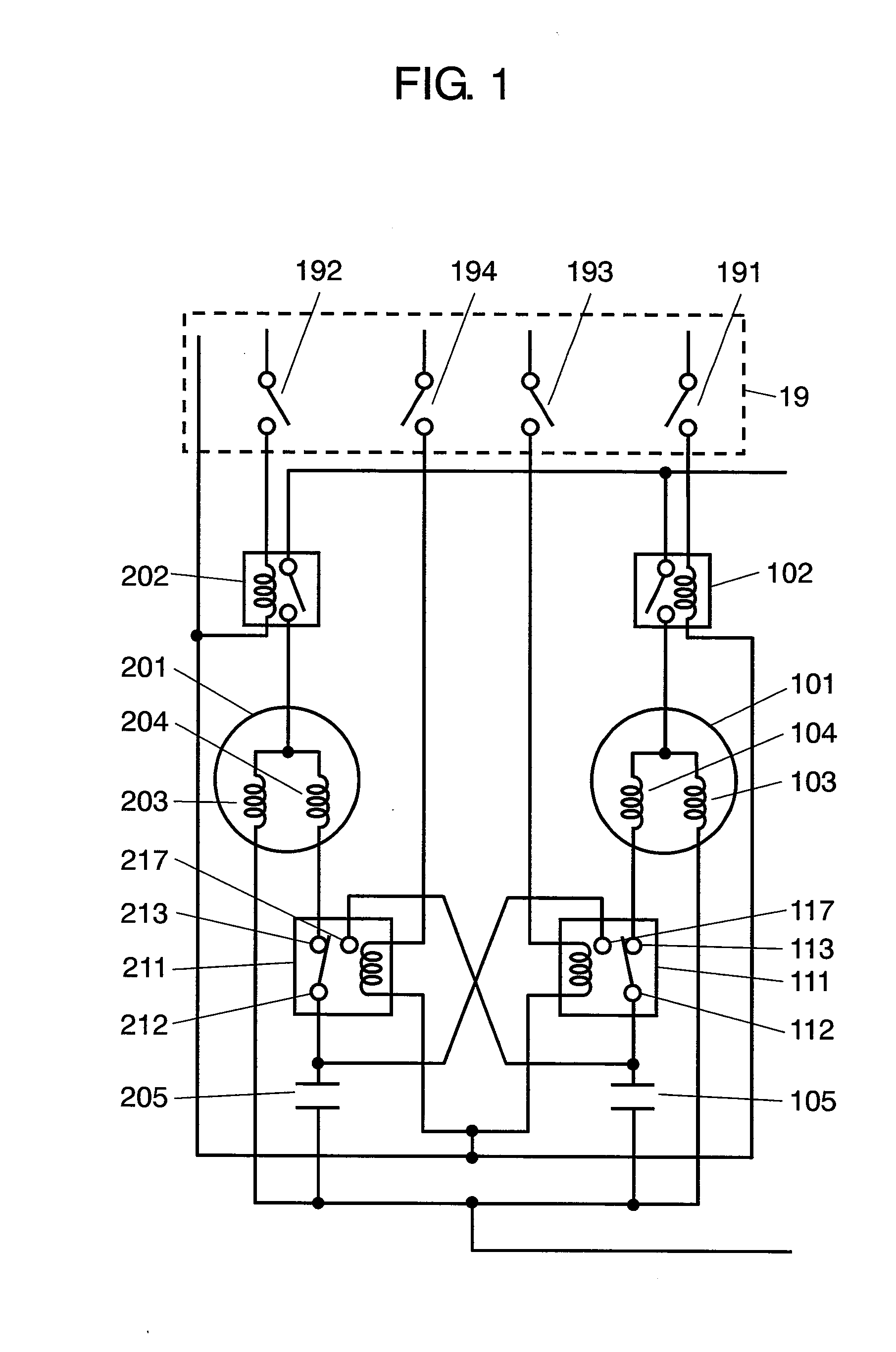

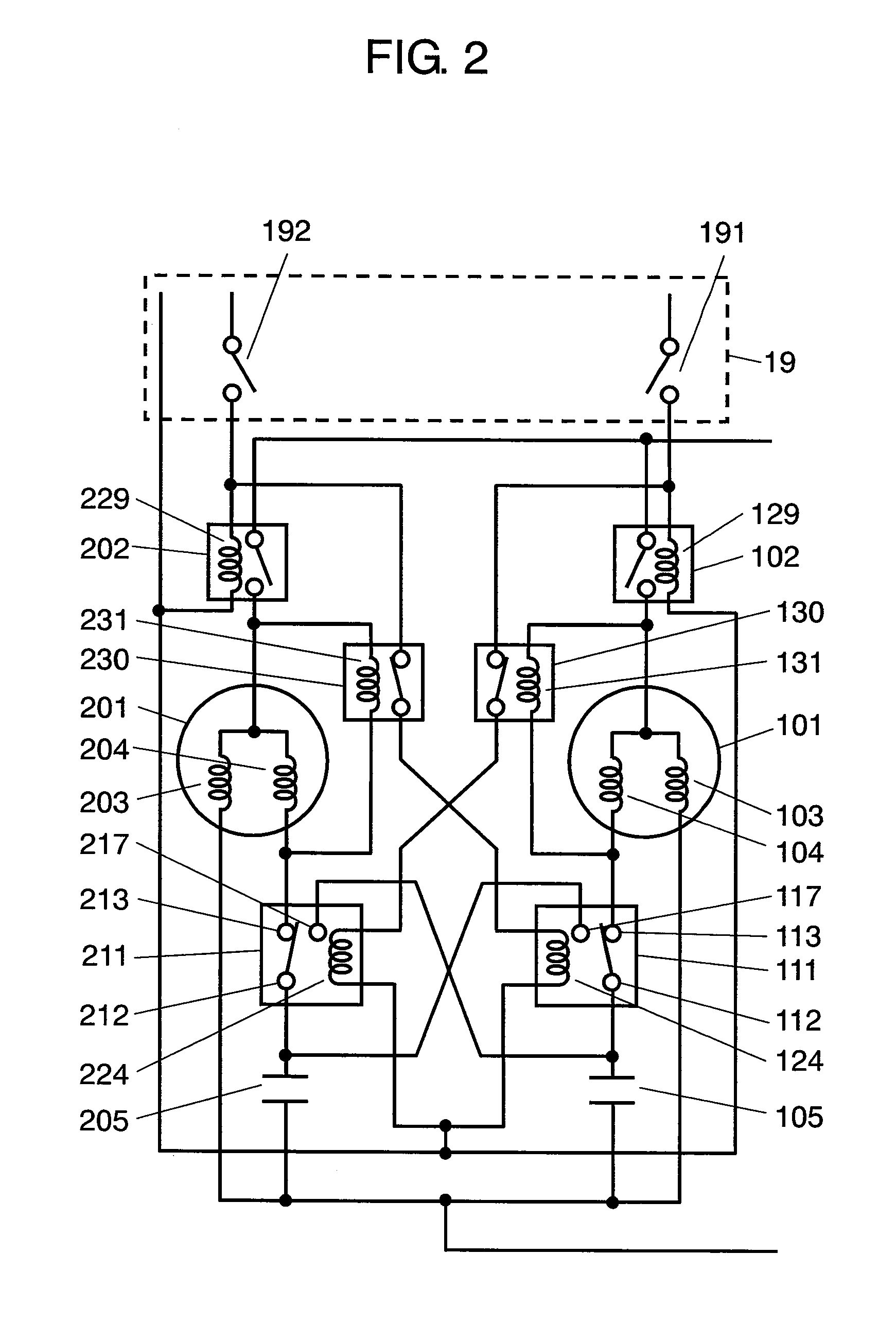

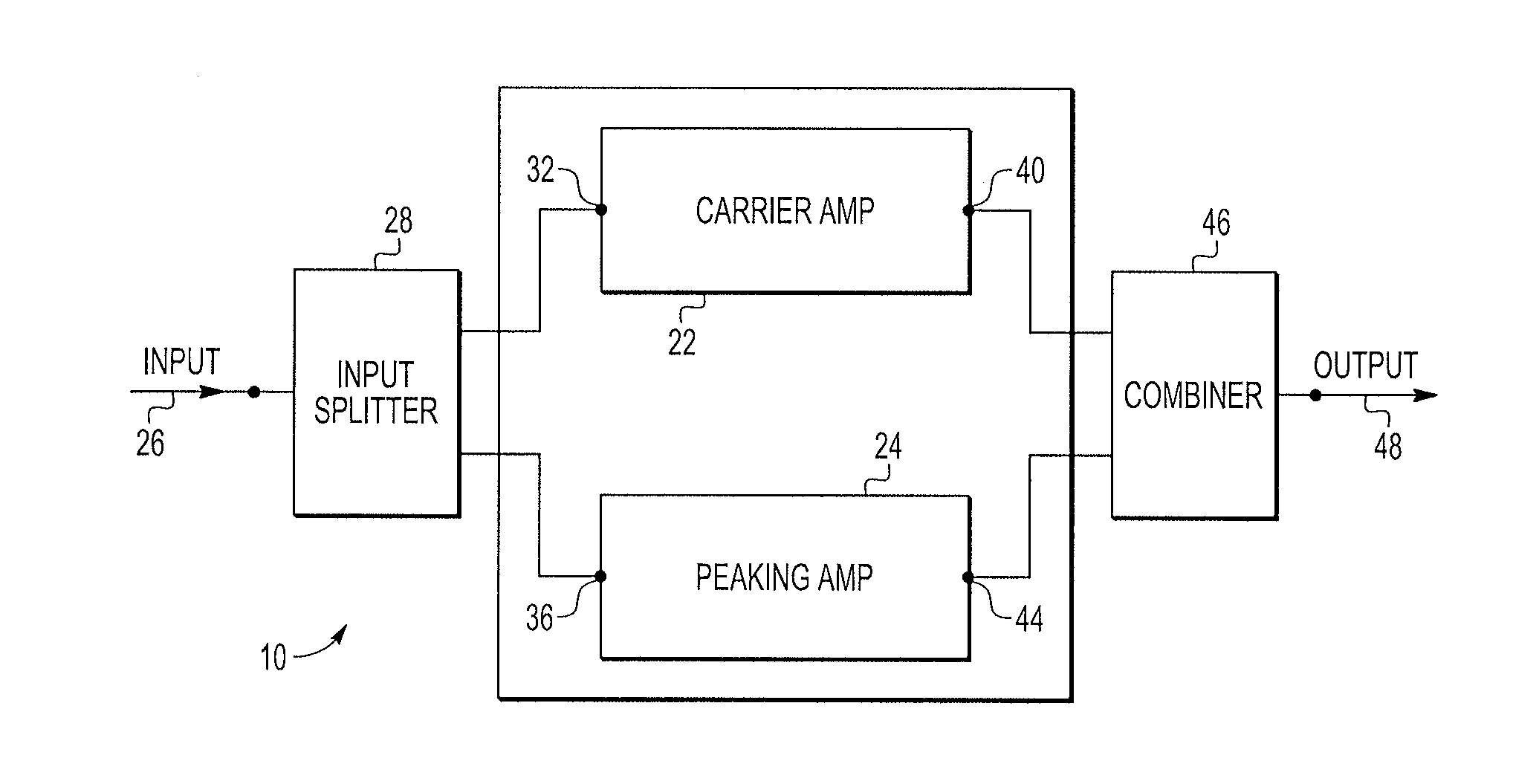

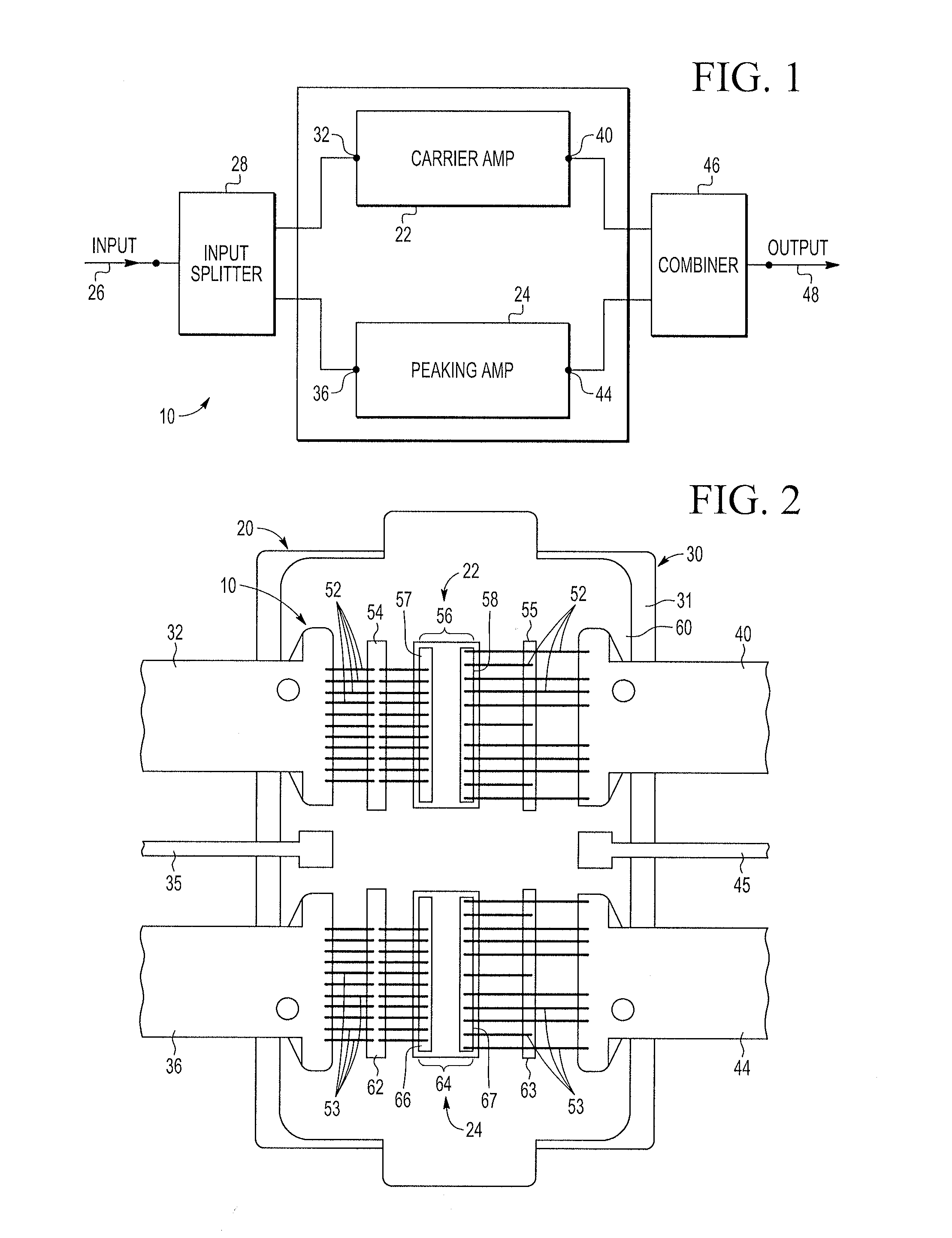

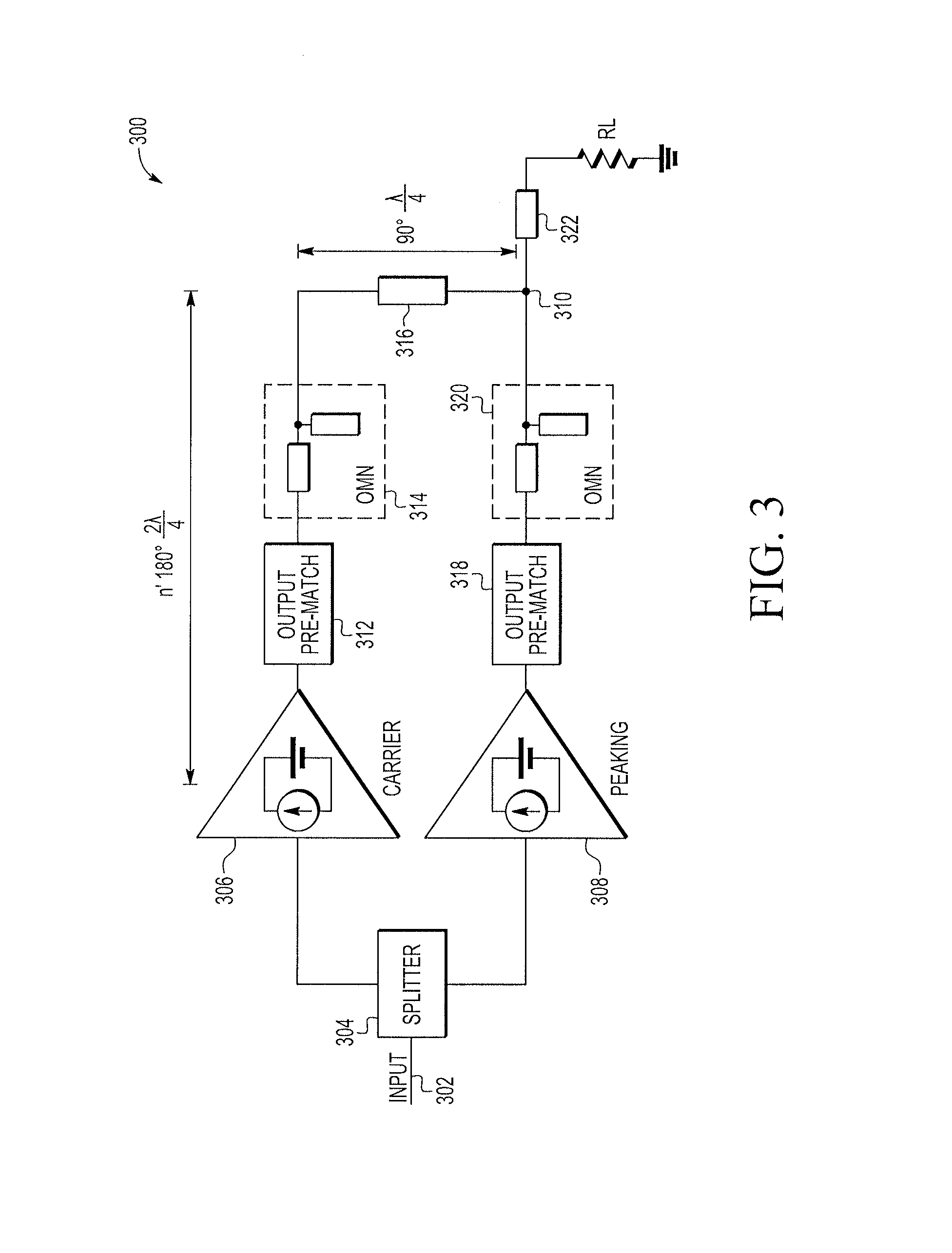

Phase correction in a doherty power amplifier

In various embodiments, a semiconductor package includes a carrier amplifier connected to a first output of a power divider, and a first output matching network connected to the carrier amplifier and an output combining node. The first output matching network exhibits a phase delay during operation of the carrier amplifier. The semiconductor package includes a phase advance network connected to the first output matching network. The phase advance network is configured to offset at least a portion of the phase delay of the first output matching network. The semiconductor package includes a peaking amplifier connected to a second output of the power divider and the output combining node, and a second output matching network connected to the peaking amplifier.

Owner:NXP USA INC

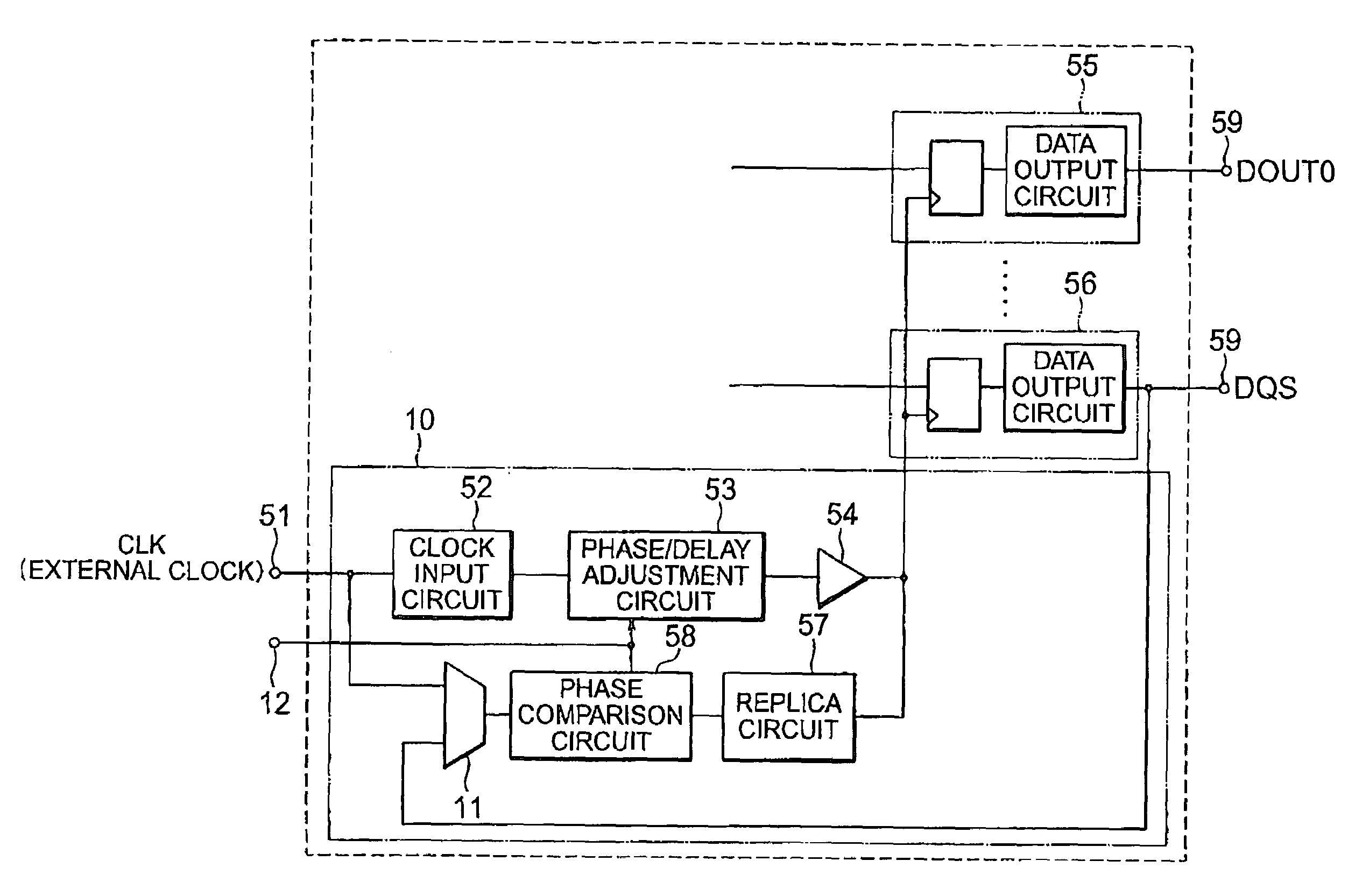

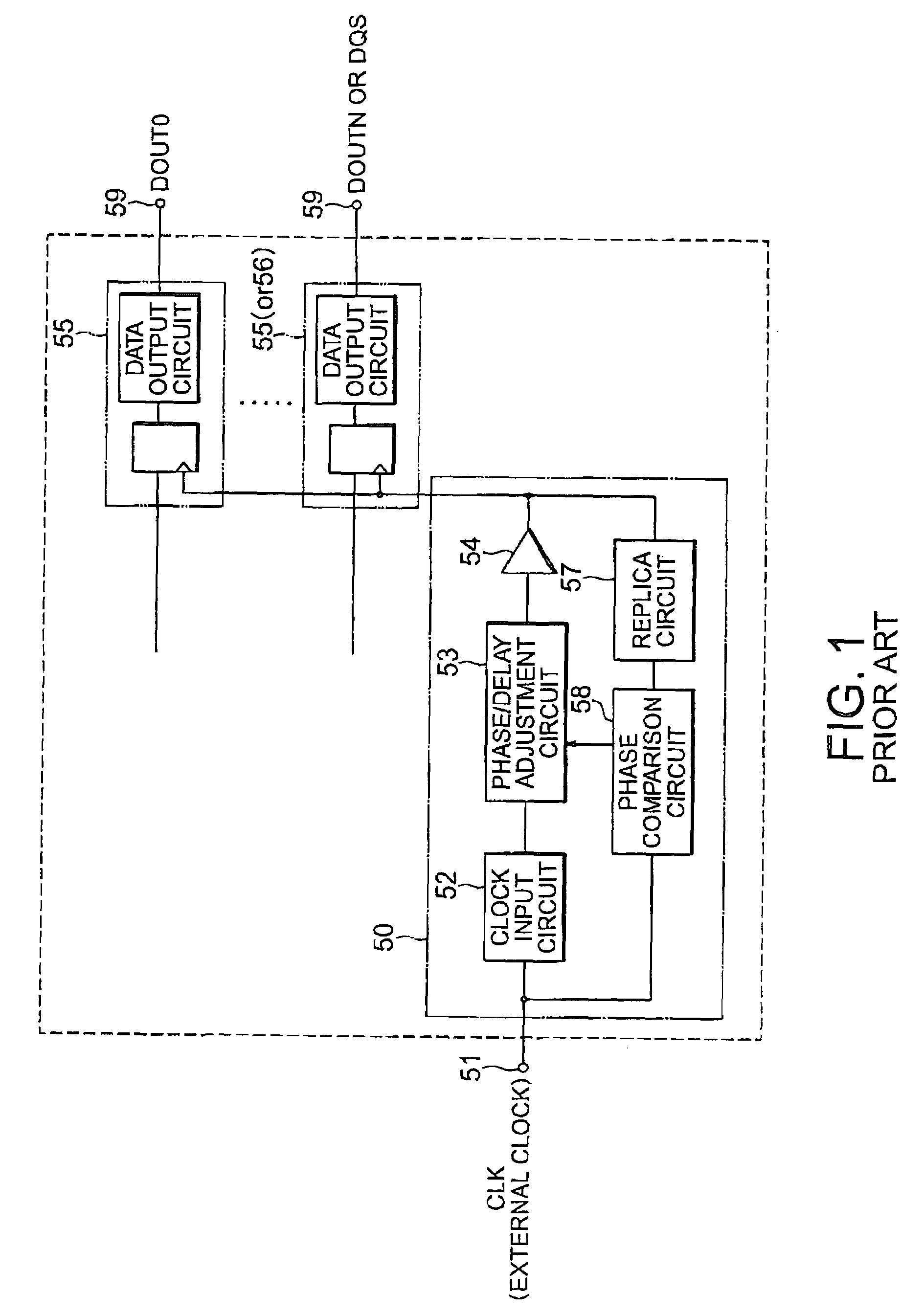

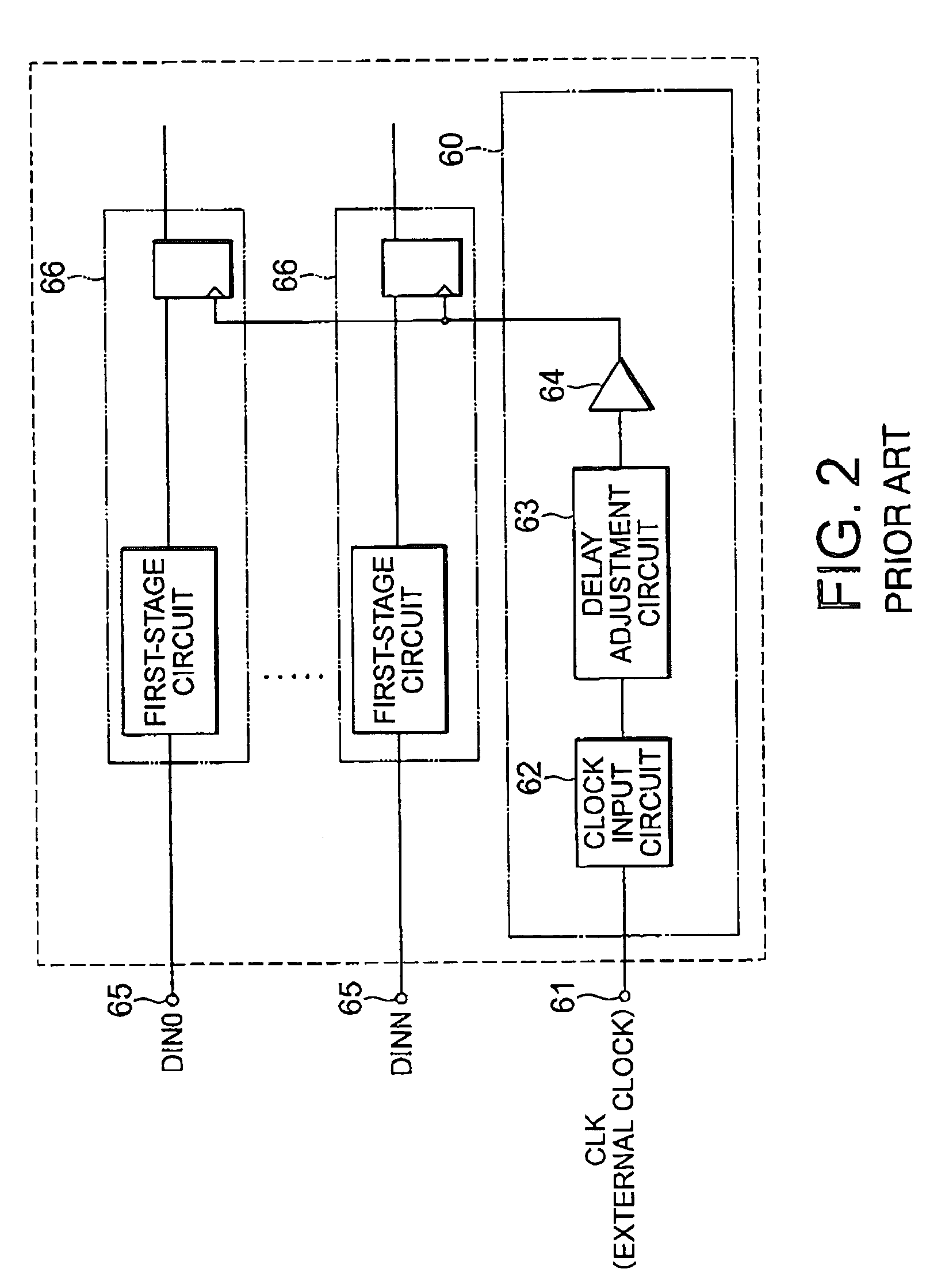

Timing adjustment circuit and semiconductor device including the same

InactiveUS7137022B2Improve accuracyPulse automatic controlElectronic circuit testingEngineeringPhase advance

In order to compare a phase of an internal clock signal outputted from a clock driver with that of a data strobe signal from a data strobe output circuit driven by the internal clock signal, a selector is disposed to supply a data strobe signal instead of an external clock signal inputted into a phase comparison circuit. While the selector selects the data strobe signal, the selector, a replica circuit, and the phase comparison circuit operate as a phase advance / delay signal generation circuit to output a phase advance / delay signal indicating a timing deviation to an external output terminal.

Owner:LONGITUDE SEMICON S A R L

Variable valve timing control system of internal combustion engine

InactiveUS7219636B2Tendency increaseIncreased torque capacityValve drivesMachines/enginesWorking fluidVariable valve timing

A variable valve timing control system of an internal combustion engine includes a hydraulically-operated phase converter disposed between a sprocket and a camshaft, and having a phase-advance hydraulic chamber and a phase-retard hydraulic chamber for changing an angular phase of the camshaft relative to the sprocket. An electric pump is provided to supply working fluid selectively to one of the hydraulic chambers via a directional control valve. Also provided is a check valve disposed in a discharge line of the pump for permitting flow in a direction that the working fluid flows from the pump to the directional control valve and preventing any flow in the opposite direction, so as to prevent a pulse pressure arising from alternating torque exerted on the camshaft from being transmitted from either one of the hydraulic chambers via the discharge line to a discharge port of the pump.

Owner:HITACHI LTD

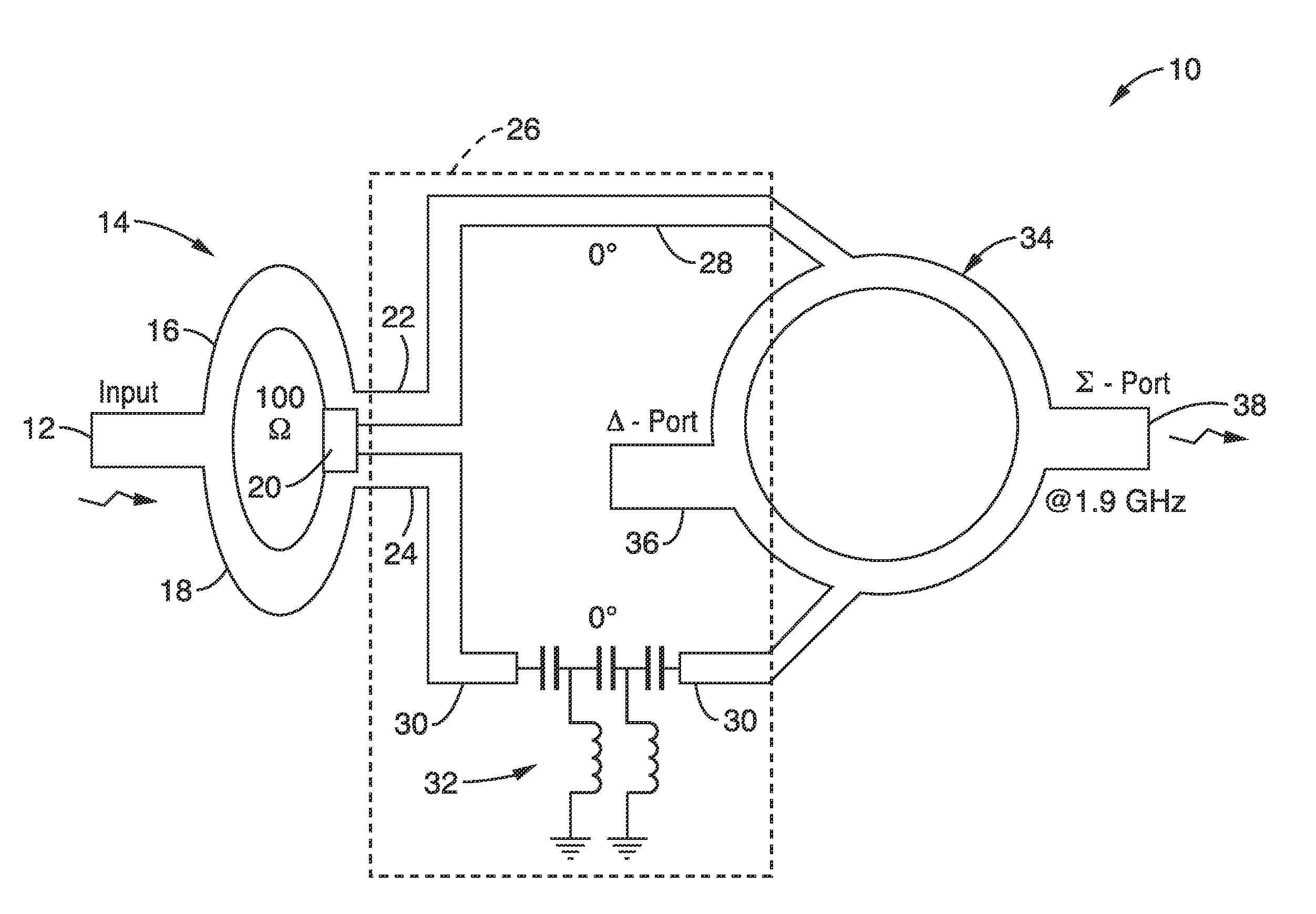

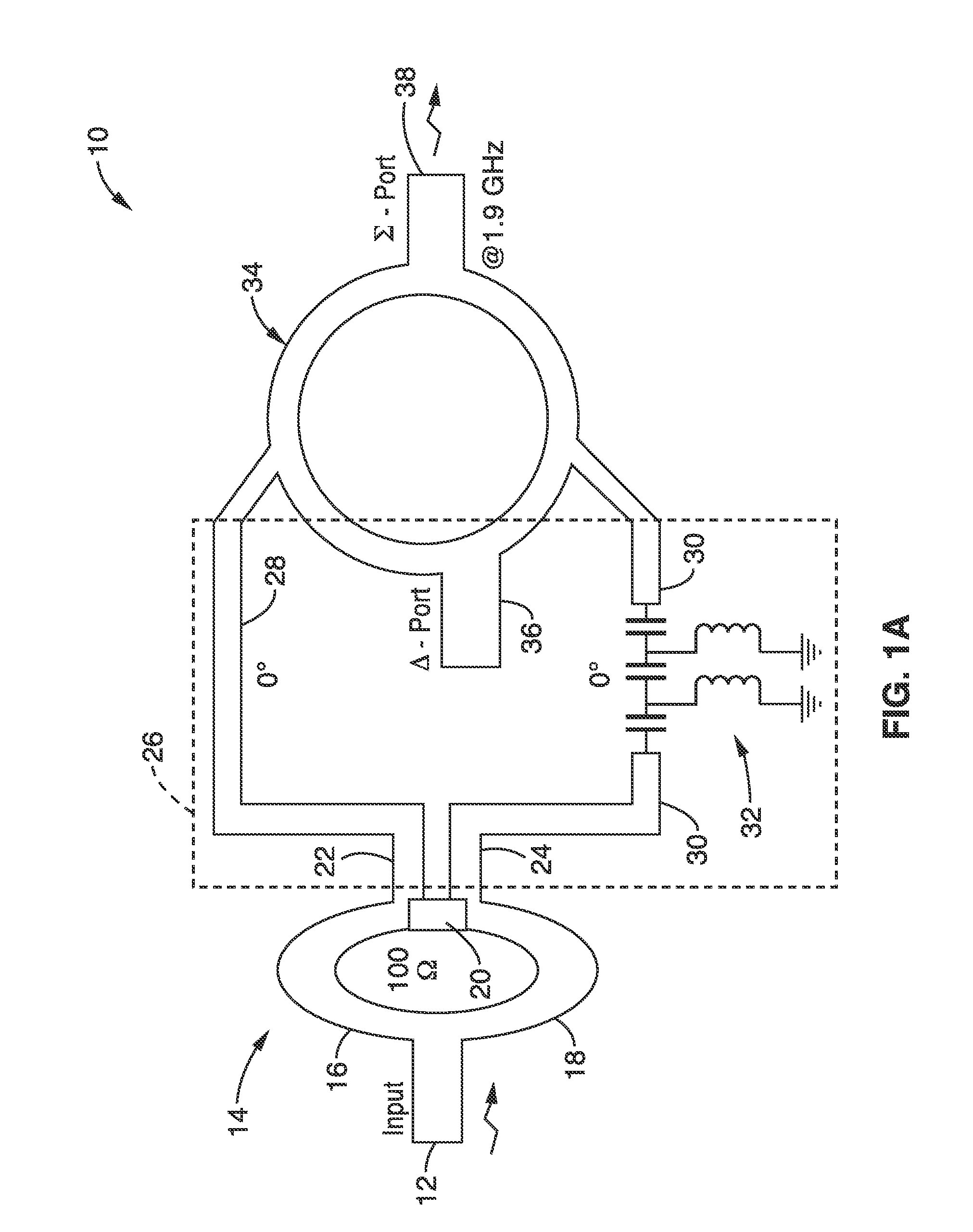

Diplexer synthesis using composite right/left-handed phase-advance/delay lines

ActiveUS20100295630A1Improve the level ofAvoid design complexityCoupling devicesHybrid couplerPhase response

A diplexing apparatus and method which utilizes composite right / left-handed (CRLH) phase-advance / delay lines combined with a coupler. By engineering CRLH-based transmission lines with desired phase responses at two arbitrary frequencies of interest, the connected CRLH delay line and / or CRLH coupler are excited in a manner such that signals at designated frequencies are separated to the corresponding output ports of the hybrid coupler. Benefits of the apparatus include elimination of design complexities such as optimization of the interconnection junctions and the harmonic spurious suppression involved in conventional filter-based diplexers. In addition, channel isolation is beneficially achieved from the isolation property of directional couplers. Measured insertion loss on the implementations was found to be less than 1 dB, with isolation greater than 20 dB in the dual bands. A high level of agreement was observed between simulated and measured results.

Owner:RGT UNIV OF CALIFORNIA

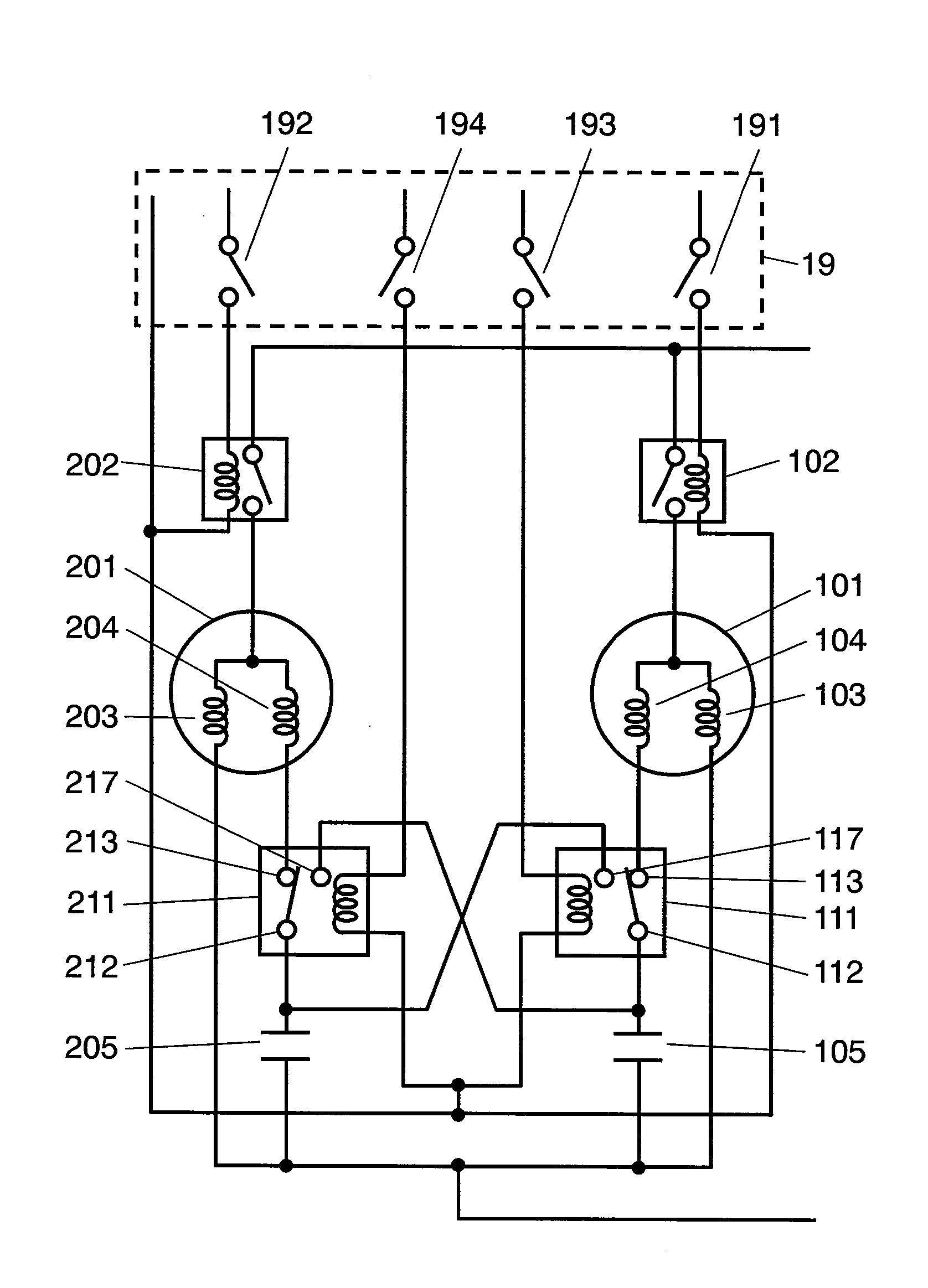

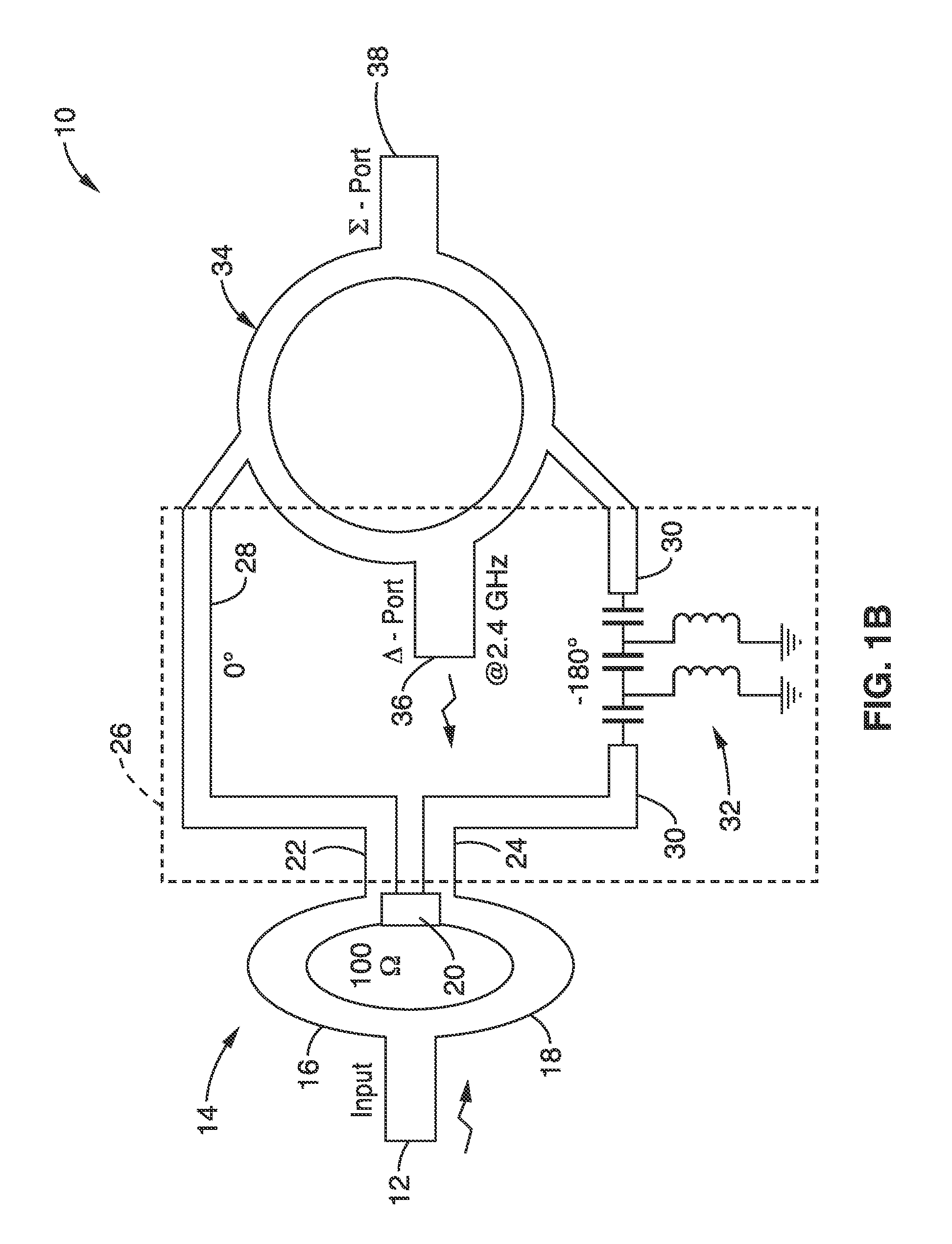

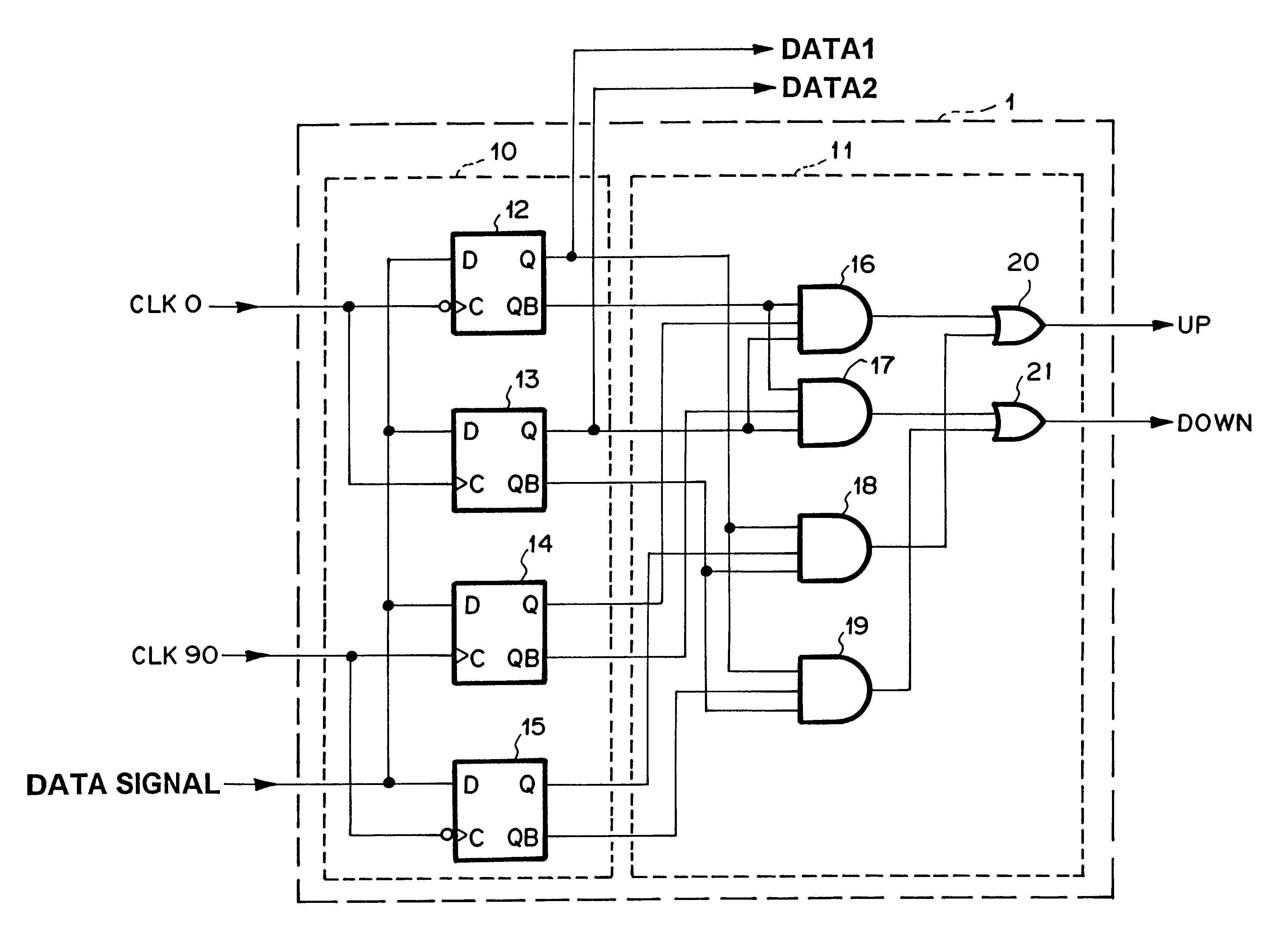

Two phase digital phase locked loop circuit

InactiveUS6594331B1Multiple input and output pulse circuitsPulse automatic controlPhase locked loop circuitData signal

To provide a high speed digital PLL circuit which is easily manufactured by IC process. The phase of data signal is locked with a first clock of which frequency is the half of the data signal. Further, a second clock of which phase is shifted by pi / 2 compared with the first clock is used for determining phase delay or phase advance of the data signal compared with the first clock. VCO outputs the first clock and the second clock. The phase comparator for inputting the data signal, the first and second clock, outputs a first data sampled at rise up of the first clock, a second data sampled at fall down of the first clock, a first indication signal indicating the phase delay, and a second indication signal indicating the phase advance. The filter for inputting the first and second indication signal outputs a control voltage for VCO.

Owner:NEC ELECTRONICS CORP

Phase advance angle optimization for brushless motor control

A control system for a multiphase permanent magnet motor having a controller for producing a control signal to energize each phase winding. The controller includes a current value calculator for determining a value of phase current advanced in phase with respect to back-EMF by a phase advance angle, and a phase advance optimization circuit for producing a value of the phase advance angle optimized so as to maximize output torque of the motor and mimimize the phase current. The phase advance optimization circuit determines the phase advance angle optimized for each phase of the motor.

Owner:WAVECREST LAB LLC

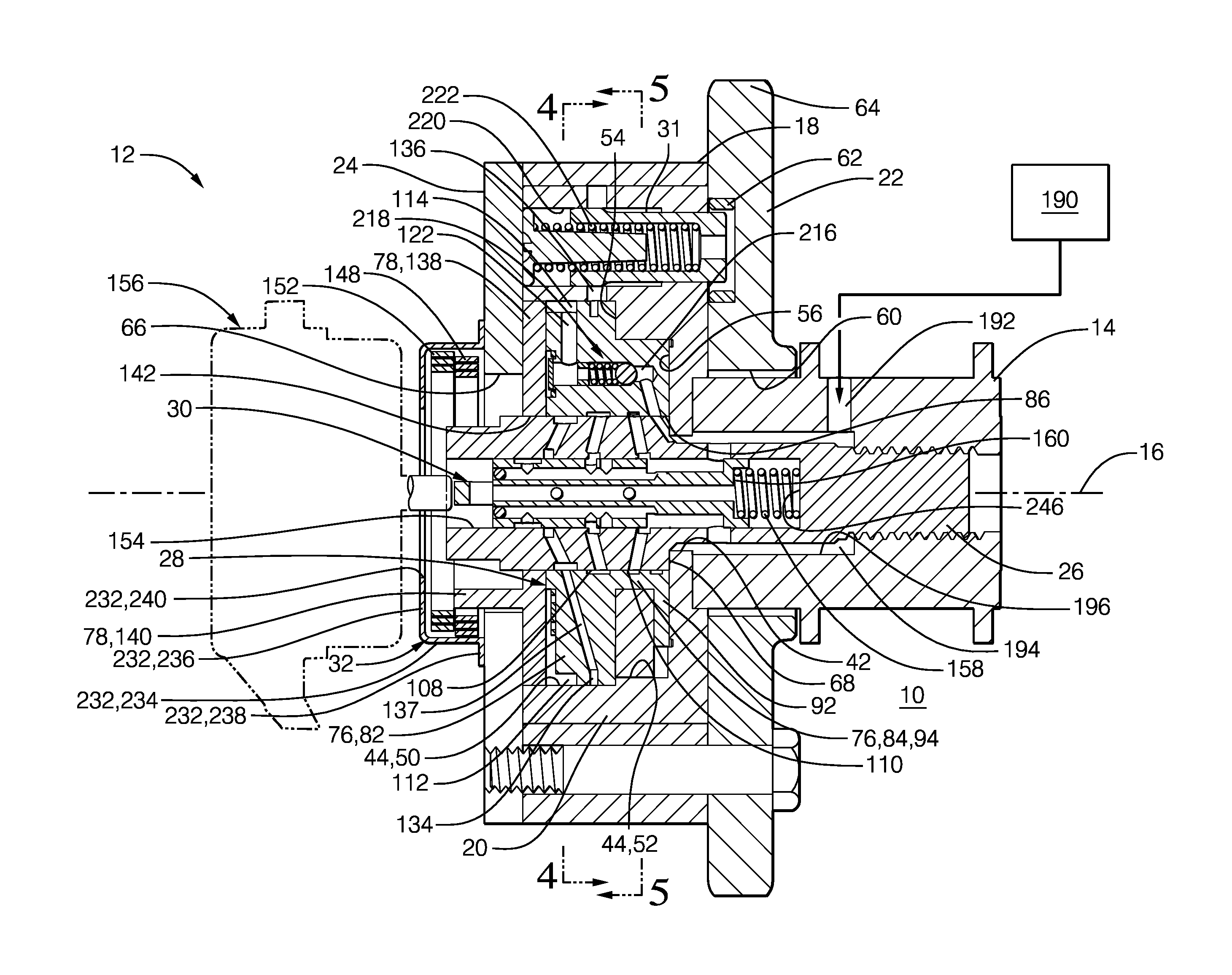

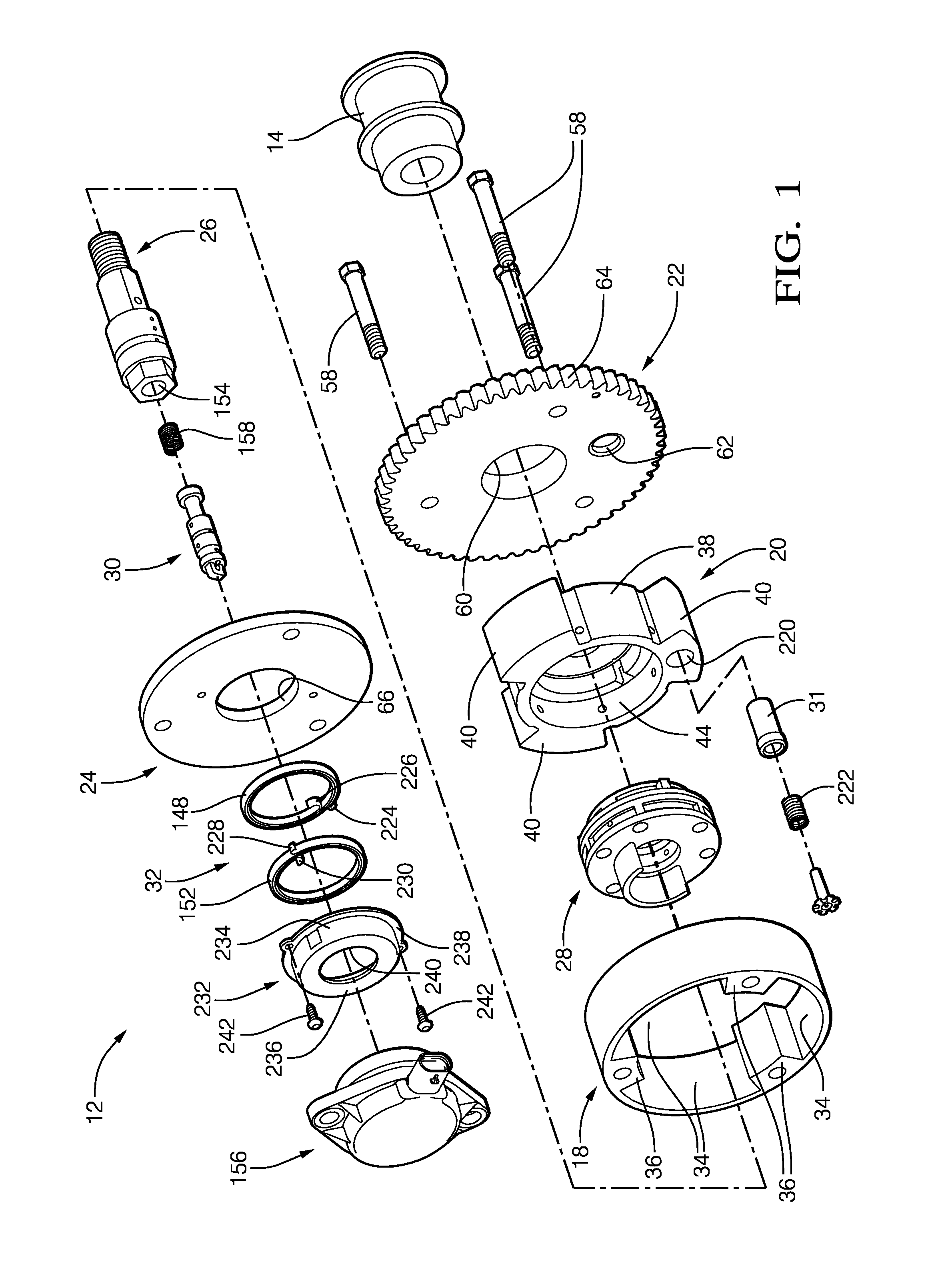

Camshaft phaser with a rotary valve spool positioned hydraulically

A camshaft phaser includes an input member; an output member defining a phasing advance chamber and a phasing retard chamber with the input member; and a rotary valve spool coaxially disposed within the output member such that the rotary valve spool is rotatable relative to the output member and the input member, the valve spool defining a rotary valve spool advance chamber and a rotary valve spool retard chamber. Oil supplied to the rotary valve spool advance chamber causes the rotary valve spool to rotate relative to the output member and relative to the input member in a retard direction and oil supplied to the rotary valve spool retard chamber causes the rotary valve spool to rotate relative to the output member and relative to the input member in an advance direction.

Owner:DELPHI TECH IP LTD

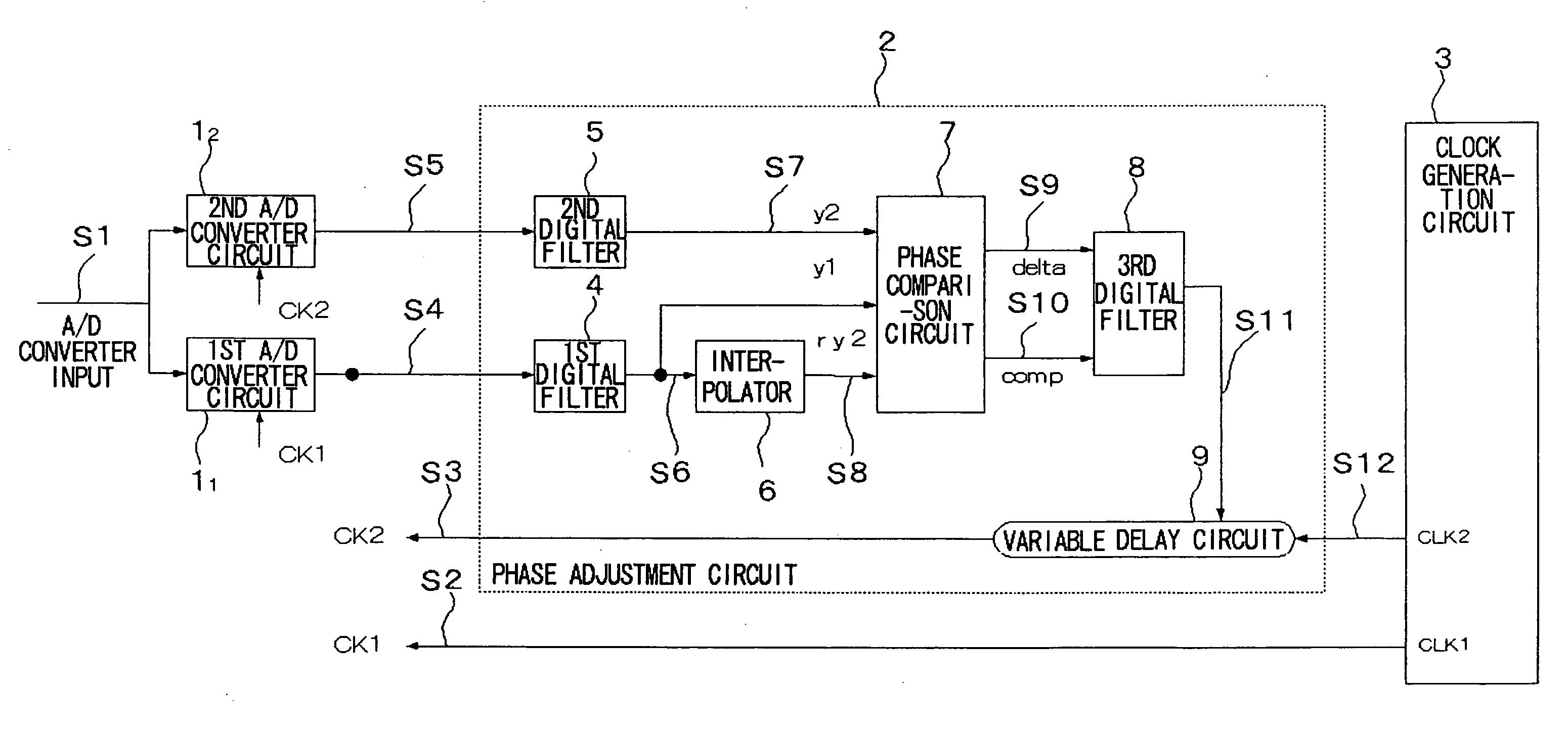

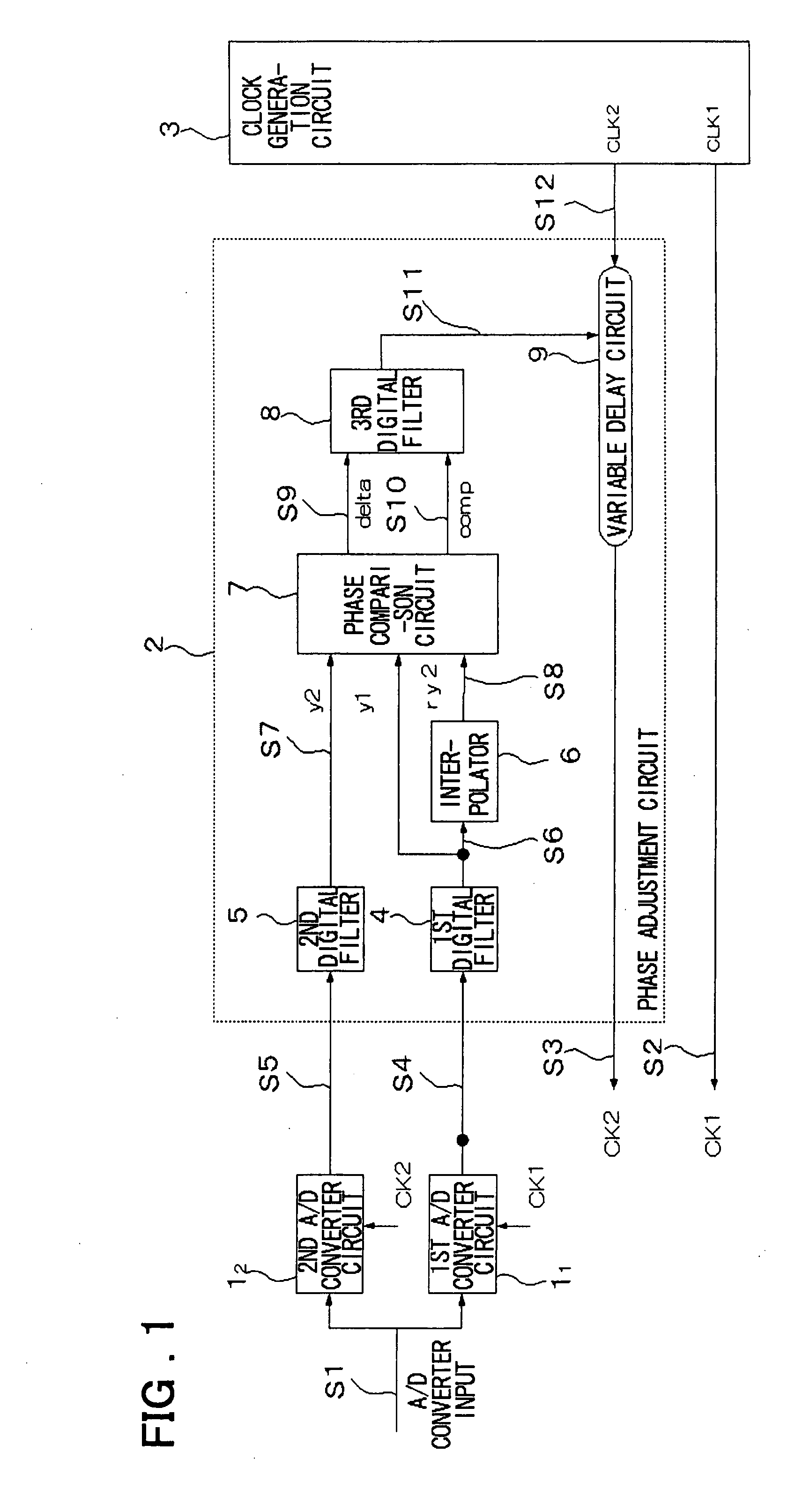

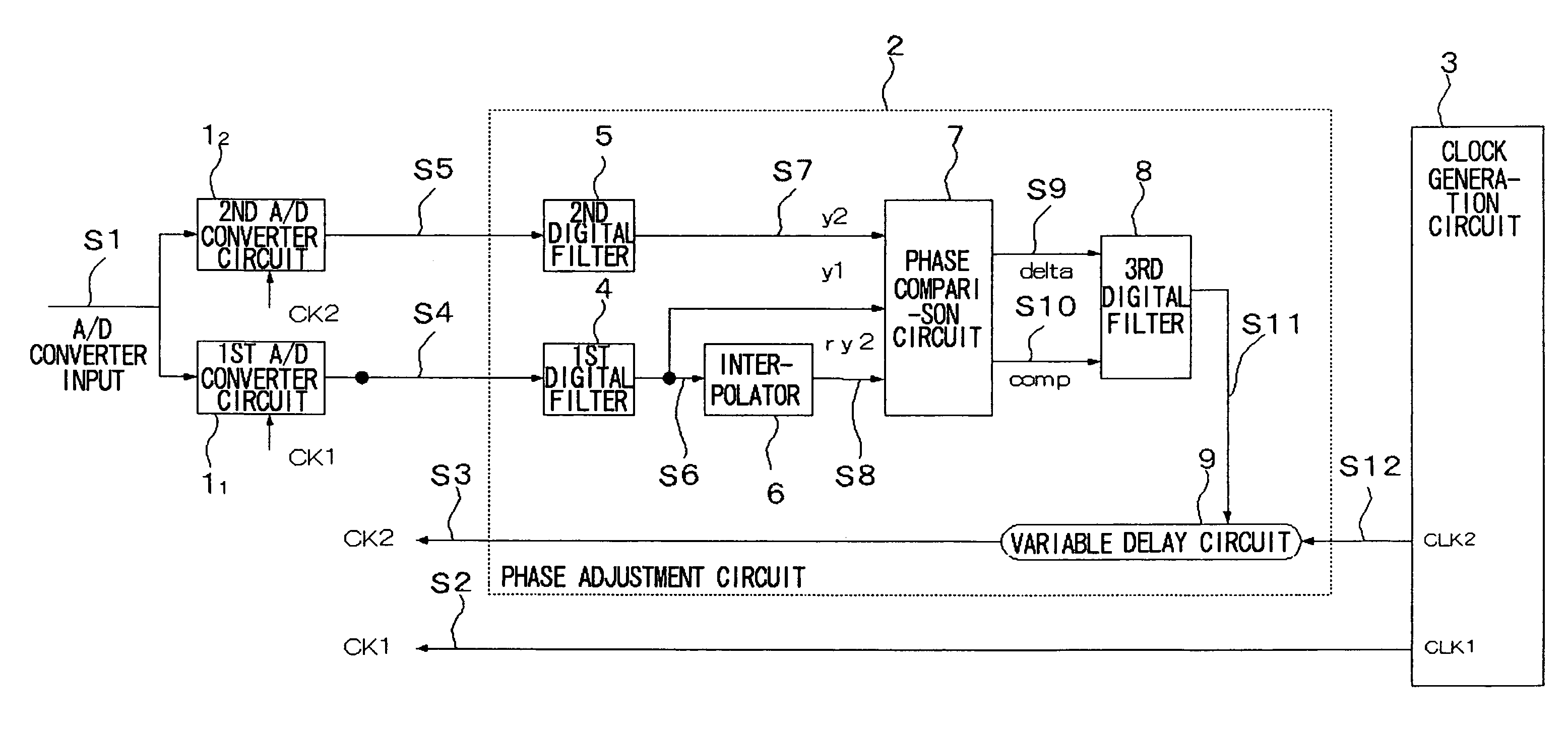

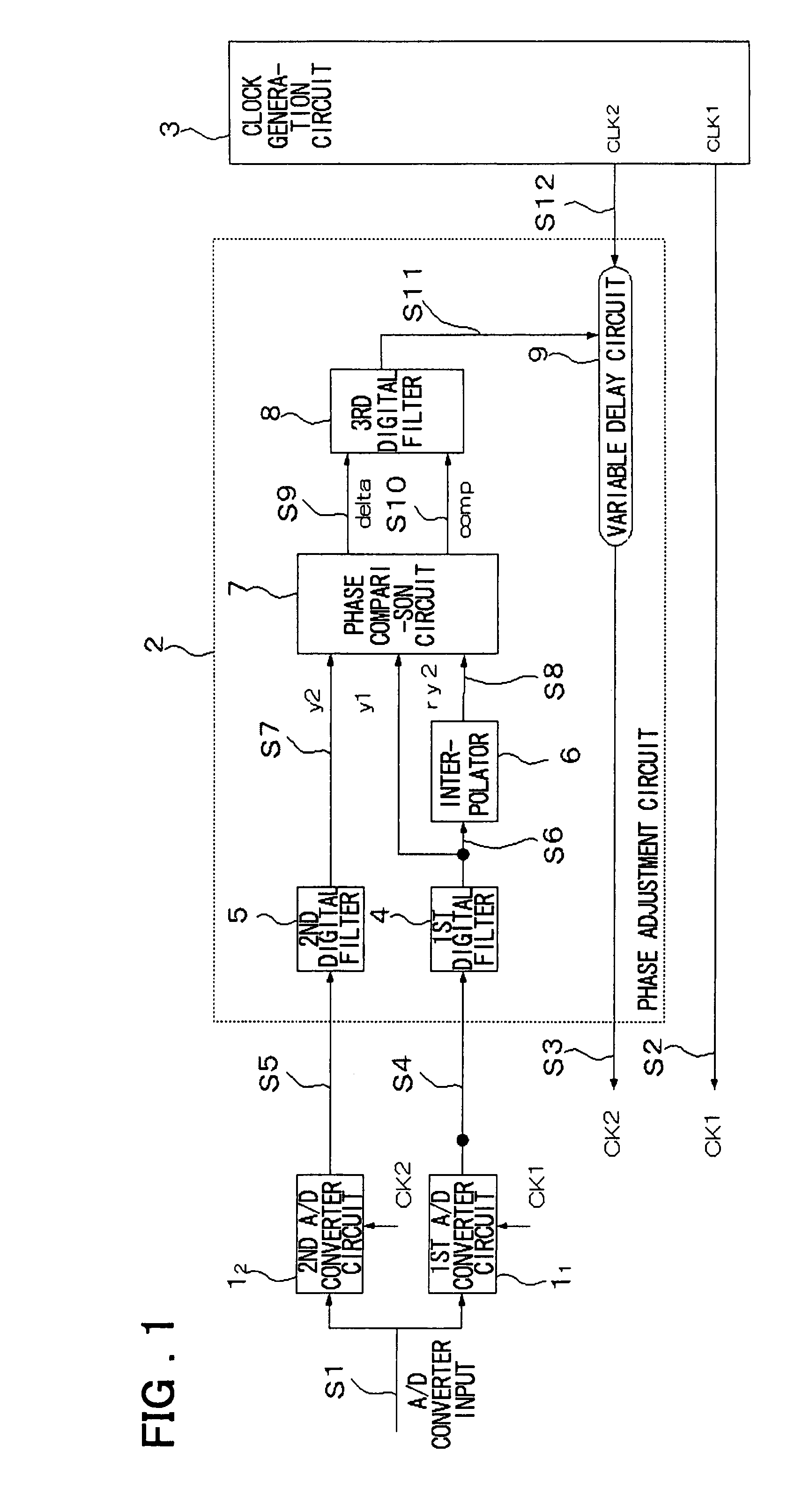

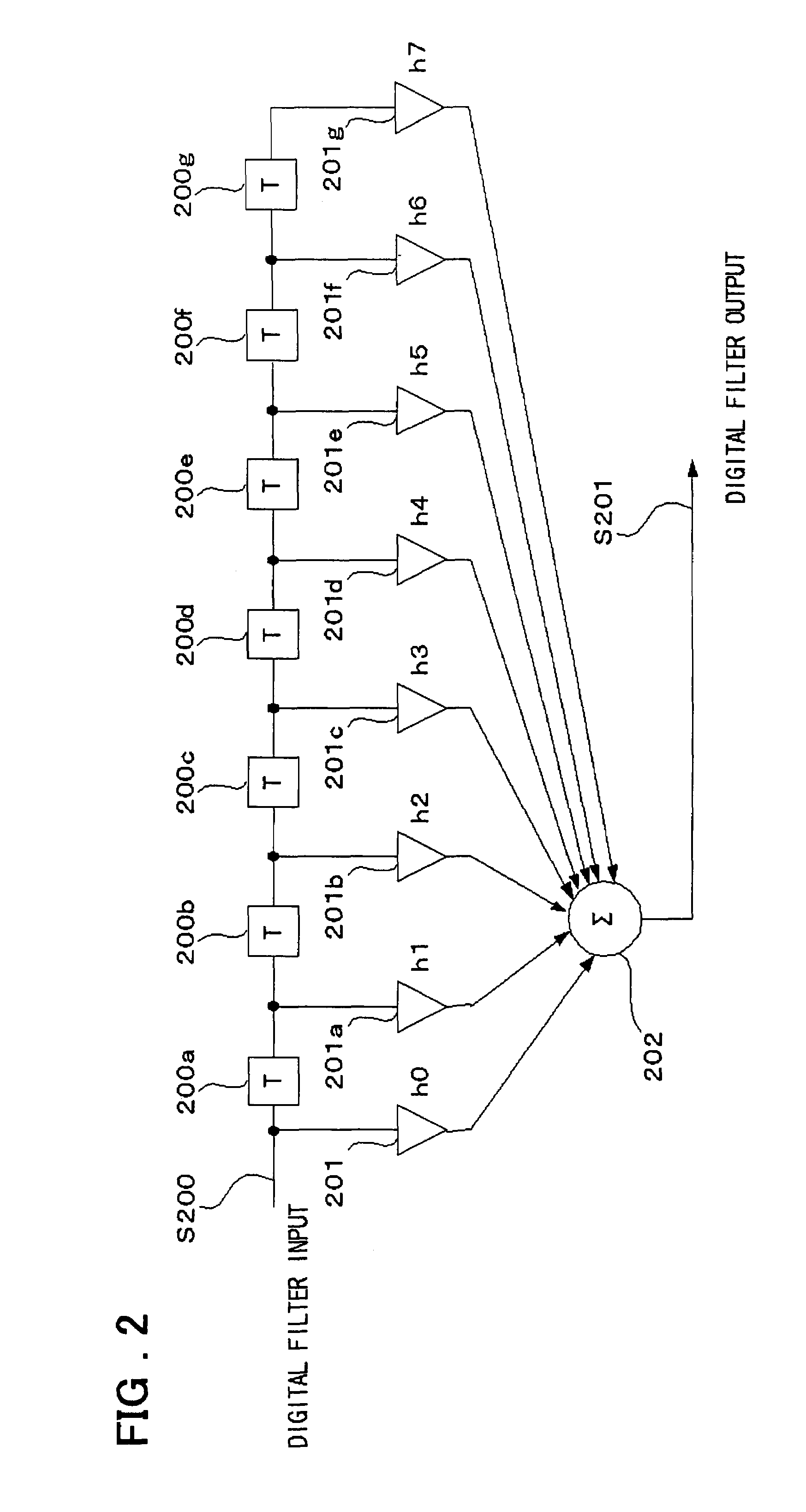

Time-interleaved A/D converter device

InactiveUS20080001806A1Broaden applicationElectric signal transmission systemsAnalogue-digital convertersA d converterDigital filter

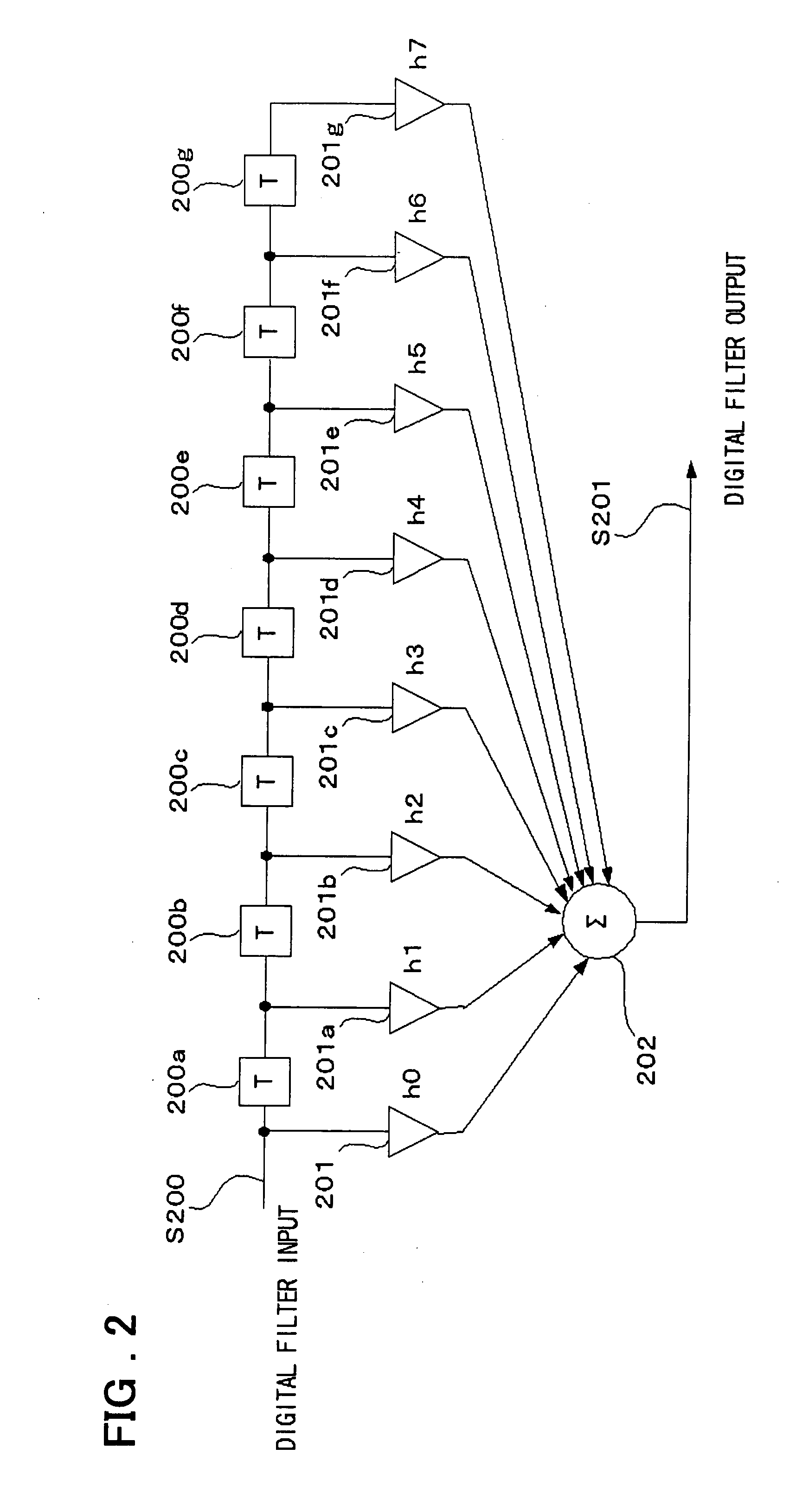

Disclosed is a time-interleaved A / D converter device that including first and second digital filters that respectively perform filter processing on output signals of first and second A / D converter circuits driven by first and second clocks, respectively, an interpolator that receives an output signal of the first digital filter and derives an interpolation value corresponding to a case where an input signal is sampled using the second clock signal free of a clock skew and having a predetermined phase relationship with respect to the first clock signal, a phase comparison circuit that receives the output of the first digital filter, an output of the second digital filter, and an interpolation signal from the interpolator, and outputs a first signal indicating a phase advance or a phase delay of the second signal responsive to a gradient of the input signal and a second signal indicating whether the output signal of the second digital filter matches the interpolation signal or not, a digital filter that receives the first and second signals output from the phase comparison circuit, and outputs zero when the second signal indicates a match and outputs a polarity of a value obtained b by selecting a positive value or a negative value according to the delay or advance indicated by the first signal and averaging selected values when the second signal indicates a mismatch, and a variable delay circuit that receives an output of the digital filter and changes a delay time of the second clock signal.

Owner:NEC ELECTRONICS CORP

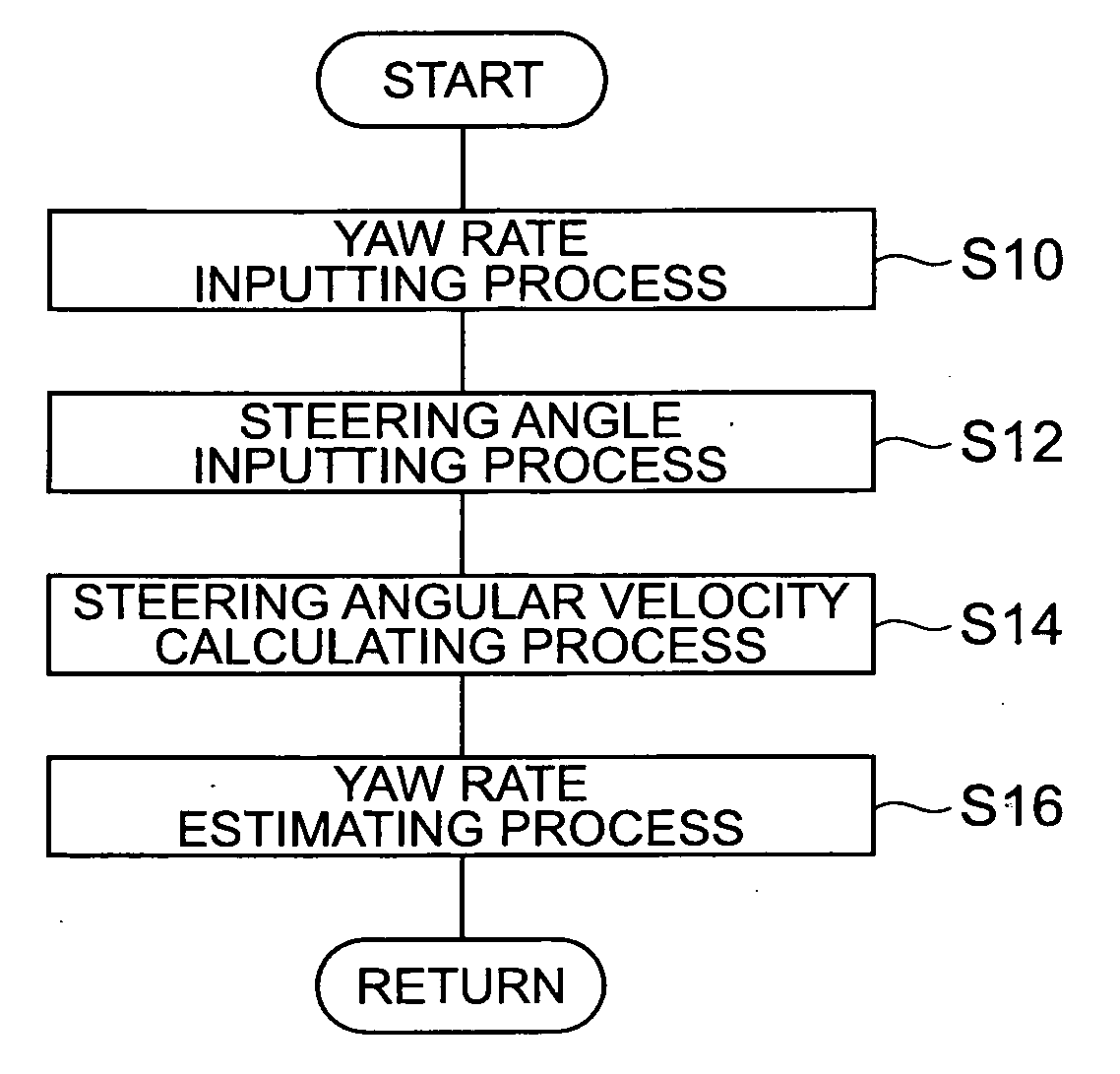

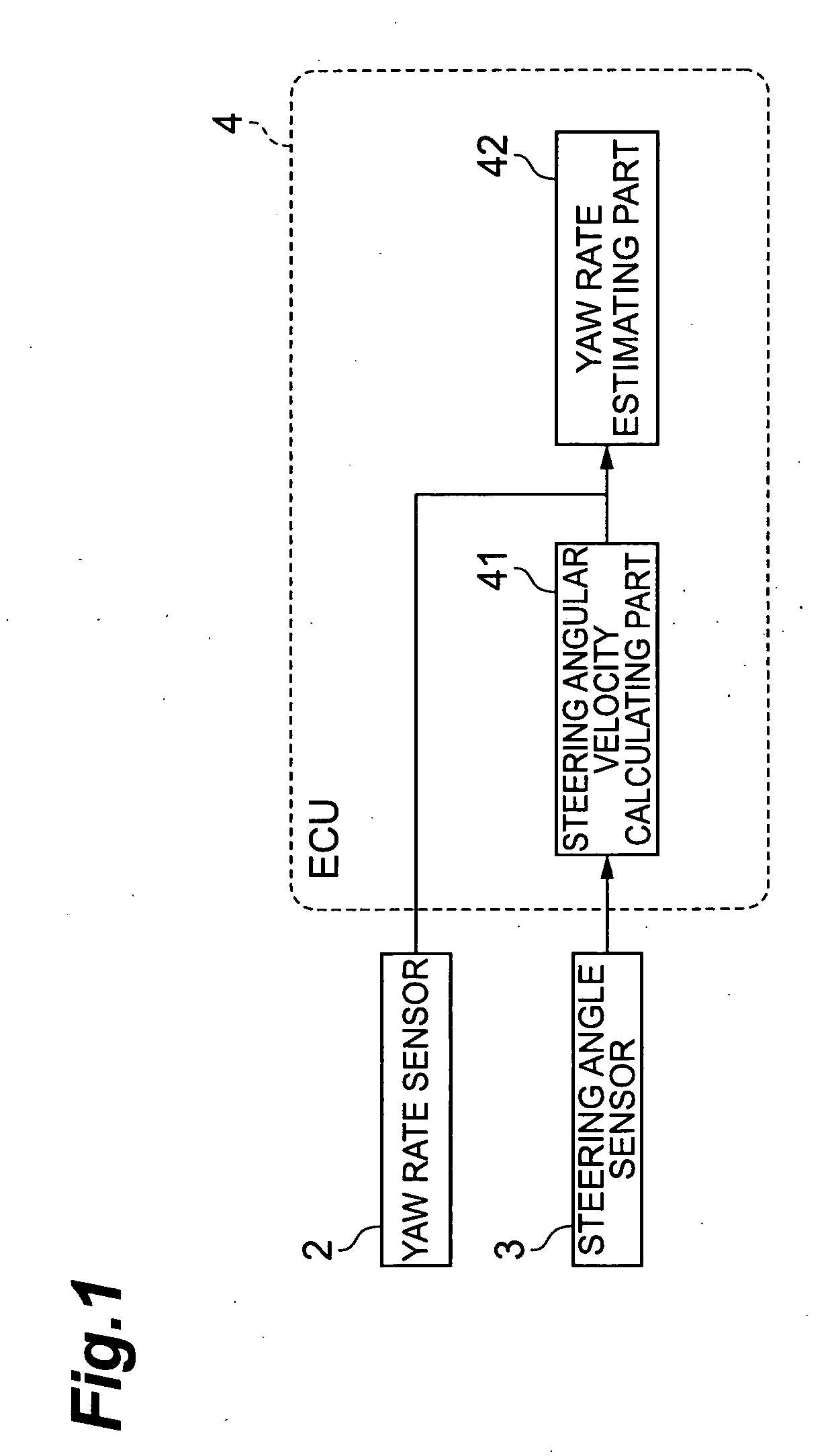

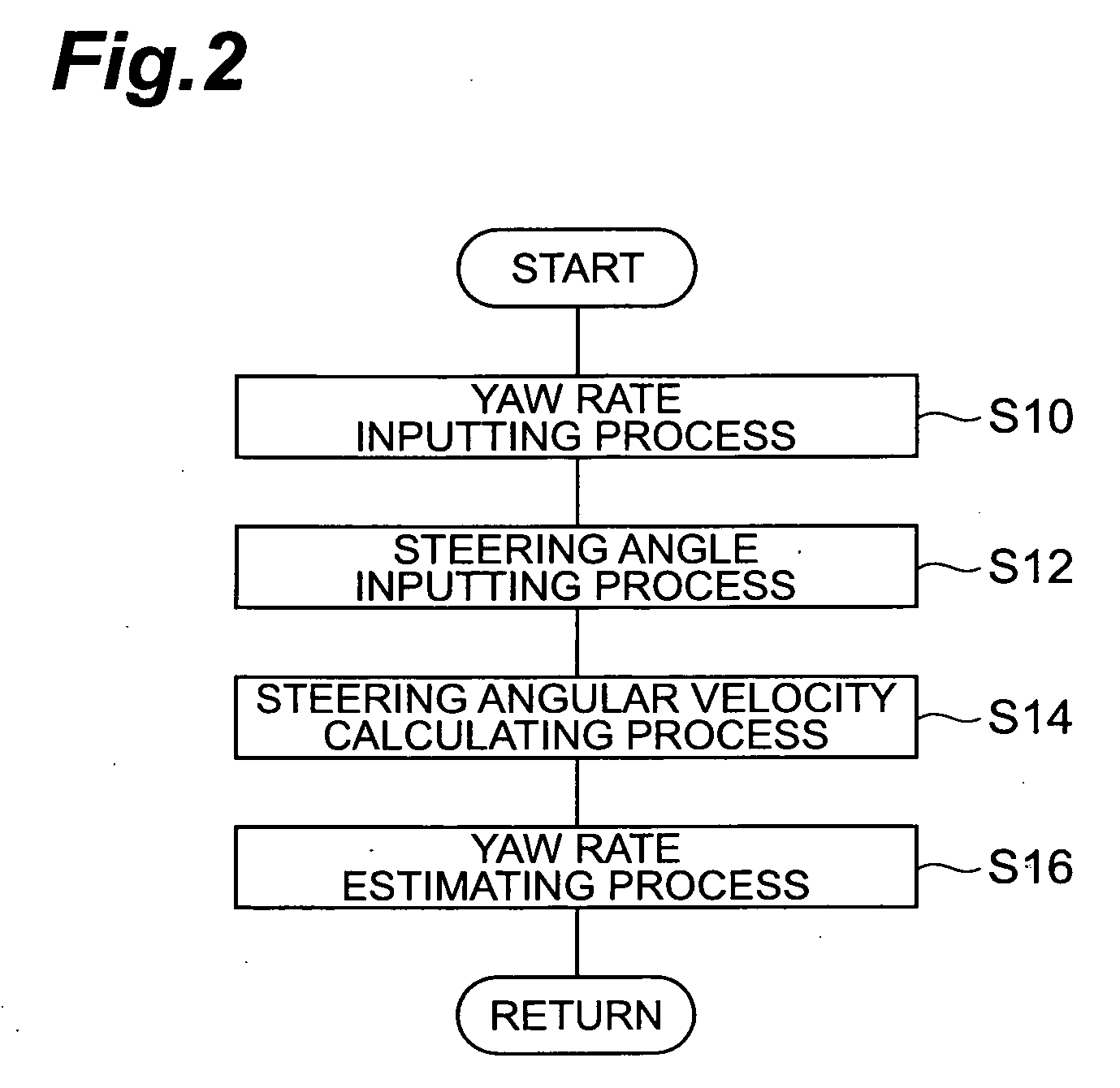

Apparatus for Estimating Yaw Rate

ActiveUS20080189013A1Improve accuracyHigh precision estimationSteering initiationsDigital data processing detailsTime lagAngular velocity

A future yaw rate γ(t) is estimated according to a current yaw rate γ(t) and a steering angular velocity. As compared with directly detecting the yaw rate γ(t) from a vehicle body, calculating the yaw rate γ(t) from a steering operation can attain a yaw rate having a phase advanced by a time lag Δt, whereby the future yaw rate γ(t) can be estimated accurately.

Owner:TOYOTA JIDOSHA KK

Valve timing control apparatus for internal combustion engine

ActiveUS20130180481A1Improve layout freedomControl freedomValve arrangementsMachines/enginesEngineeringInternal combustion engine

A valve timing control apparatus including a housing, a vane rotor rotatable relative to the housing toward a phase-advance side and a phase-retard side, a first lock member and a second lock member disposed on the vane rotor, a first lock concave portion disposed on the housing so as to be engaged with a tip end portion of the first lock member, a second lock concave portion disposed on the housing so as to be engaged with a tip end portion of the second lock member, and a communication passage formed in the vane rotor and serving to always establish fluid communication between the first and second lock concave portions.

Owner:HITACHI ASTEMO LTD

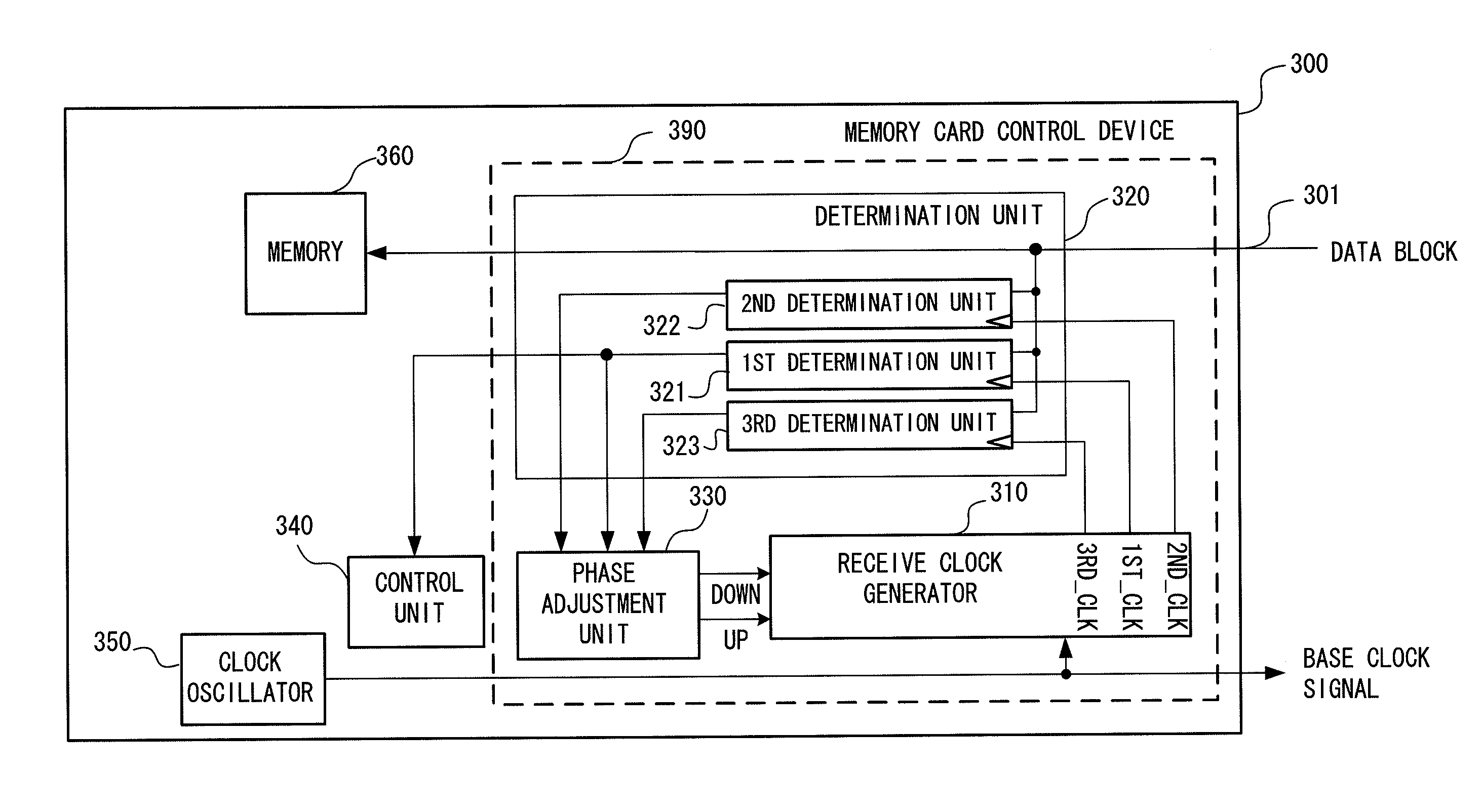

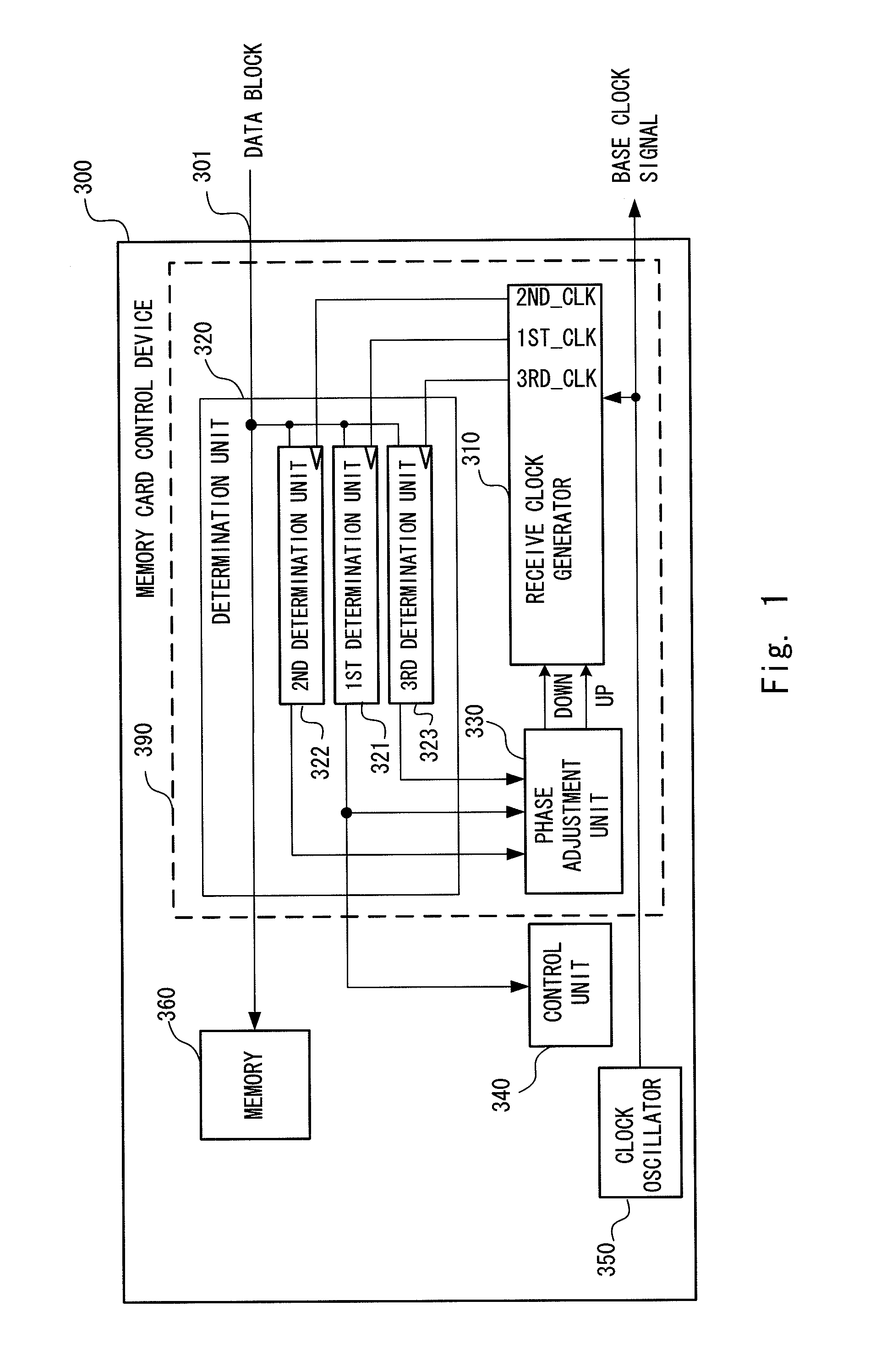

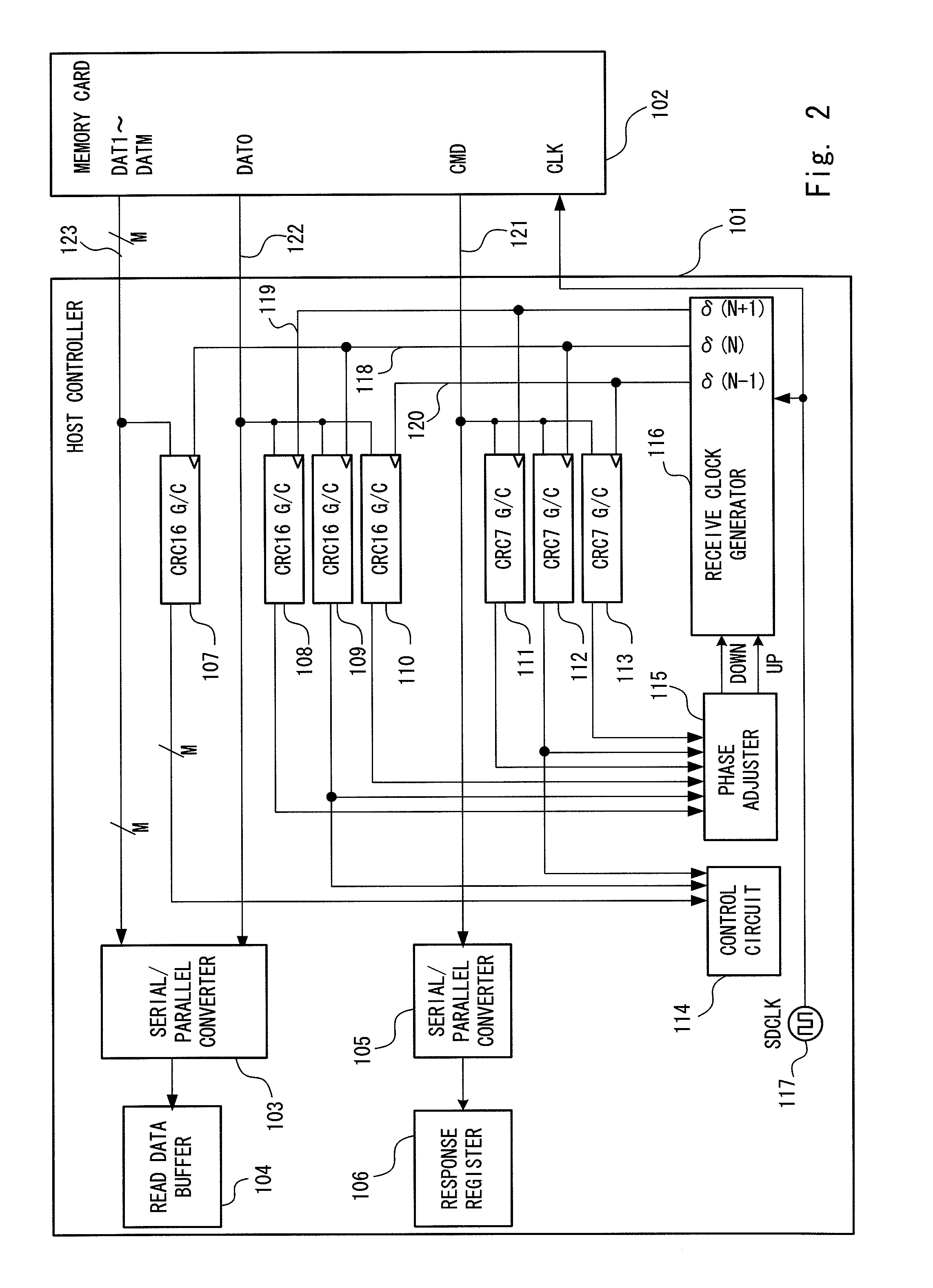

Phase calibration circuit, memory card control device, and phase calibration method

InactiveUS20110093753A1Improve transfer efficiencyPrevent degradationError preventionPulse automatic controlPhase shiftedPhase advance

Provided is a phase calibration circuit to suppress degradation of transfer efficiency when reading data from a memory card. The phase calibration circuit includes a receive clock generator that generates clock signals including a first clock signal (FCS) with a phase shifted with respect to a base clock signal, a second clock signal with a phase advanced with respect to the FCS, and a third clock signal with a phase delayed with respect to the FCS; a determination unit that acquires data blocks, each of which including a data body and detection information for detecting an error, in accordance with the clock signals, determines whether an error occurs by using the detection information of the data blocks, and outputs determination results; and a phase adjustment unit that instructs the receive clock generator to adjust a phase of the FCS depending on the determination results.

Owner:RENESAS ELECTRONICS CORP

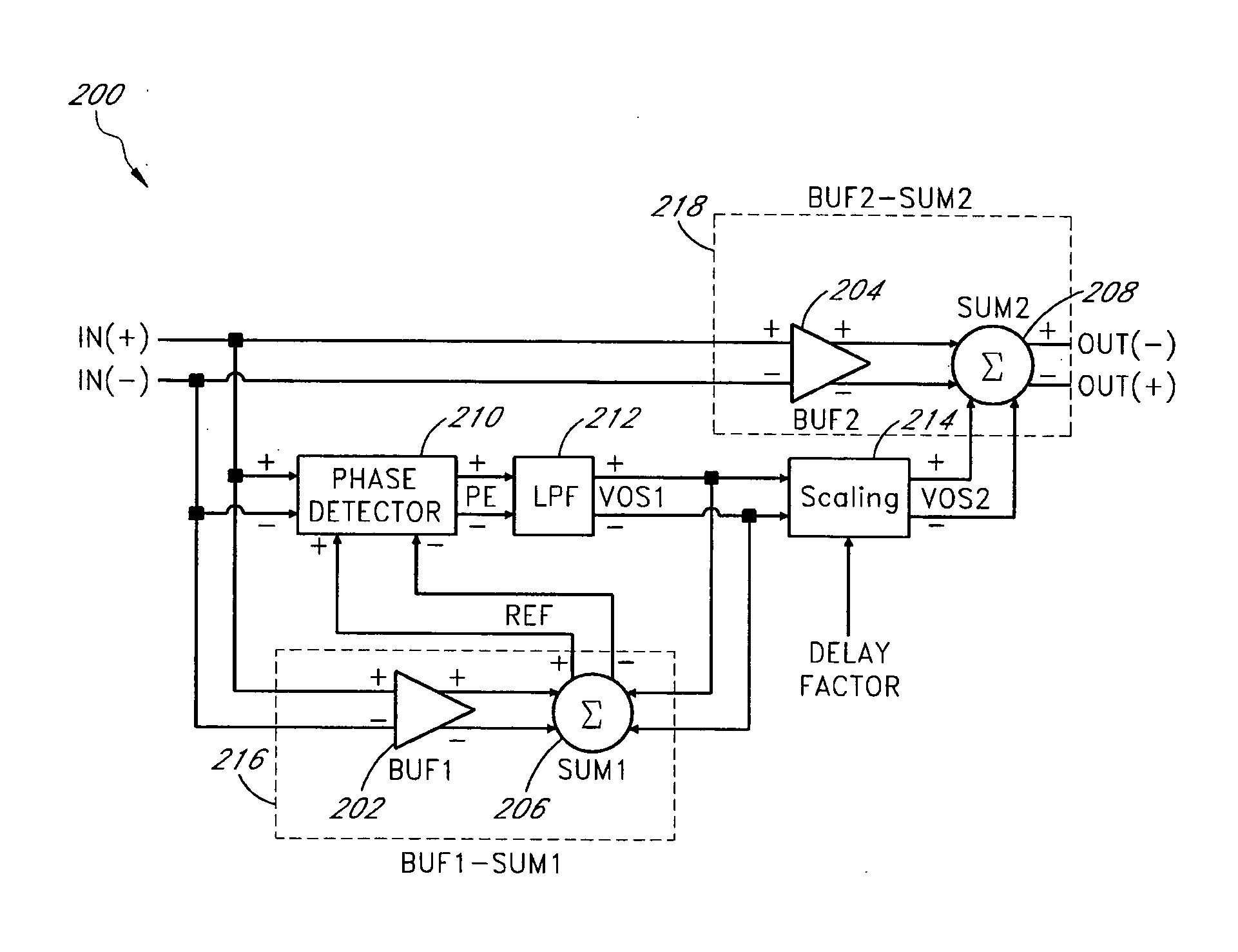

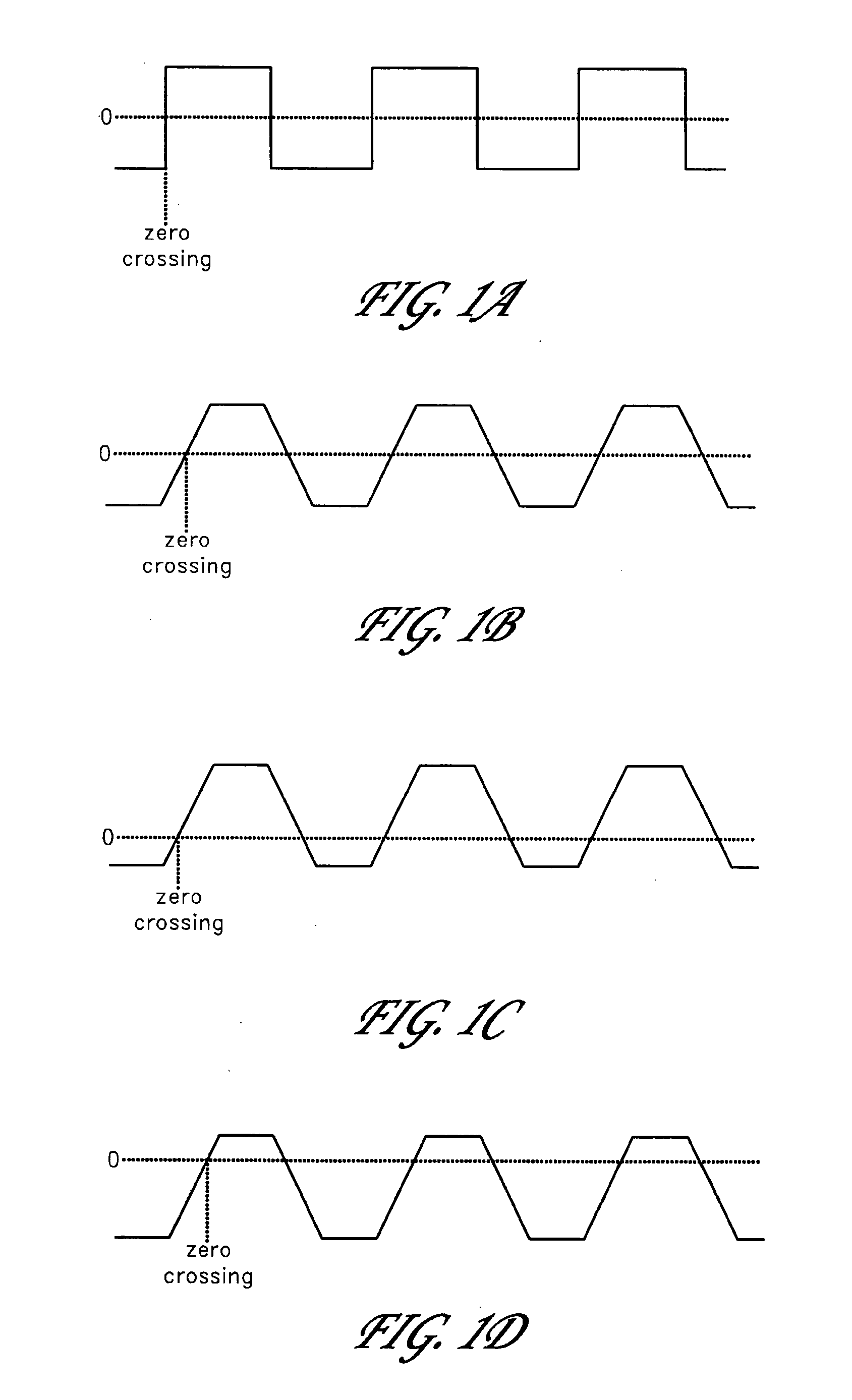

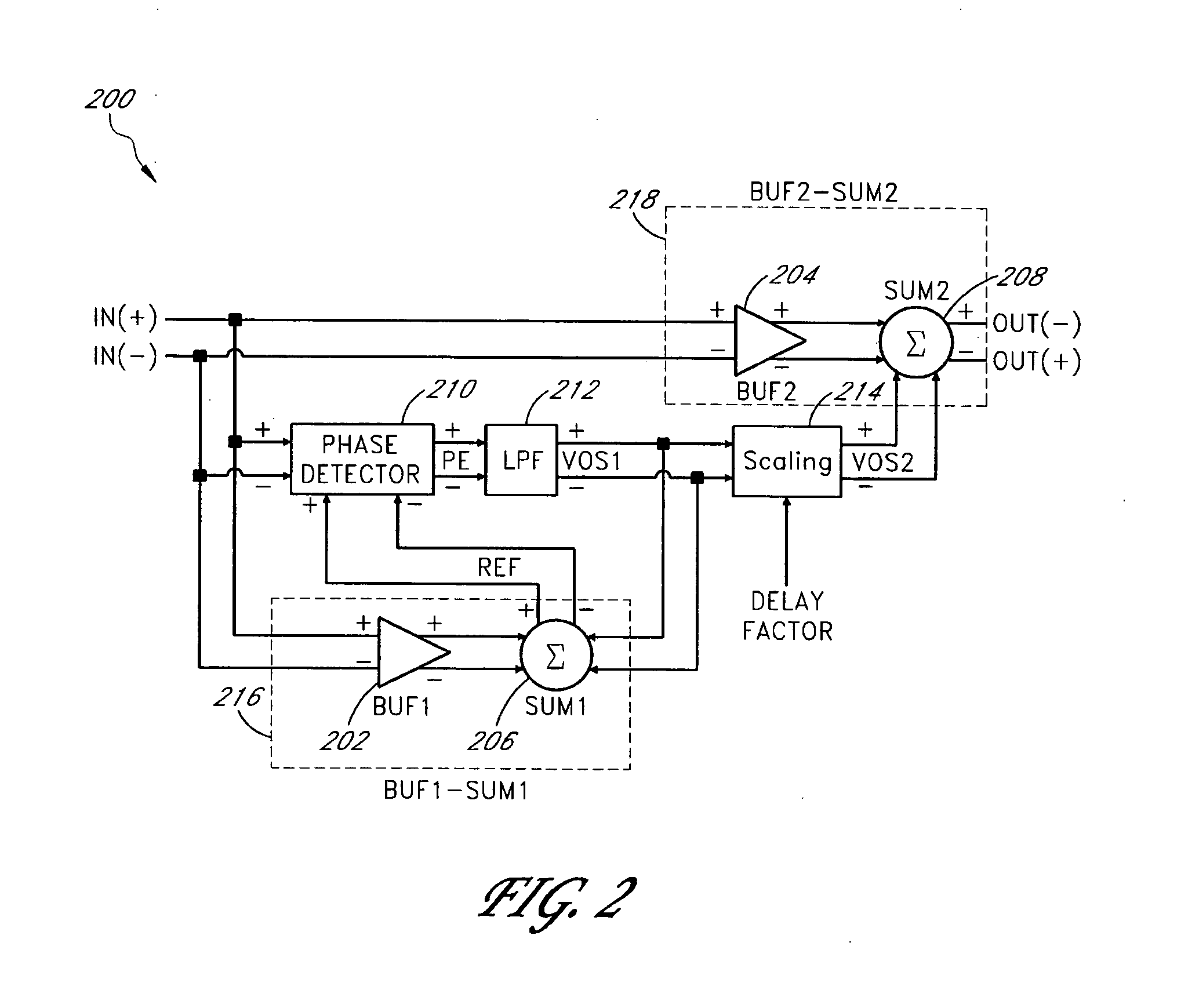

Variable delay clock synthesizer

In an embodiment, a fine resolution of variable clock delay is implemented using a variable DC offset having fine resolution. The proportional ratio between the DC offset and the phase delay / advance of the clock is calibrated in a closed-loop manner. In an embodiment, in a calibration circuit, an adaptive positive DC offset is added to the output of a delay buffer to advance the phase of the clock output, which also has a phase delay from the delay buffer. The DC offset is adjusted in a closed-loop manner to make the phase advance, due to the DC offset, compensate for the phase delay, due to the delay buffer. Once the phase relationship of the DC offset to the clock phase advance is calibrated, the DC offset can be scaled and added to the output of another buffer of the same type to achieve a desired phase delay or advance of the clock signal.

Owner:REALTEK SEMICON CORP

Time-interleaved A/D converter device

InactiveUS7466251B2Electric signal transmission systemsAnalogue-digital convertersA d converterEngineering

Disclosed is a time-interleaved A / D converter device that including first and second digital filters that respectively perform filter processing on output signals of first and second A / D converter circuits driven by first and second clocks, respectively, an interpolator that receives an output signal of the first digital filter and derives an interpolation value corresponding to a case where an input signal is sampled using the second clock signal free of a clock skew and having a predetermined phase relationship with respect to the first clock signal, a phase comparison circuit that receives the output of the first digital filter, an output of the second digital filter, and an interpolation signal from the interpolator, and outputs a first signal indicating a phase advance or a phase delay of the second signal responsive to a gradient of the input signal and a second signal indicating whether the output signal of the second digital filter matches the interpolation signal or not, a digital filter that receives the first and second signals output from the phase comparison circuit, and outputs zero when the second signal indicates a match and outputs a polarity of a value obtained b by selecting a positive value or a negative value according to the delay or advance indicated by the first signal and averaging selected values when the second signal indicates a mismatch, and a variable delay circuit that receives an output of the digital filter and changes a delay time of the second clock signal.

Owner:NEC ELECTRONICS CORP

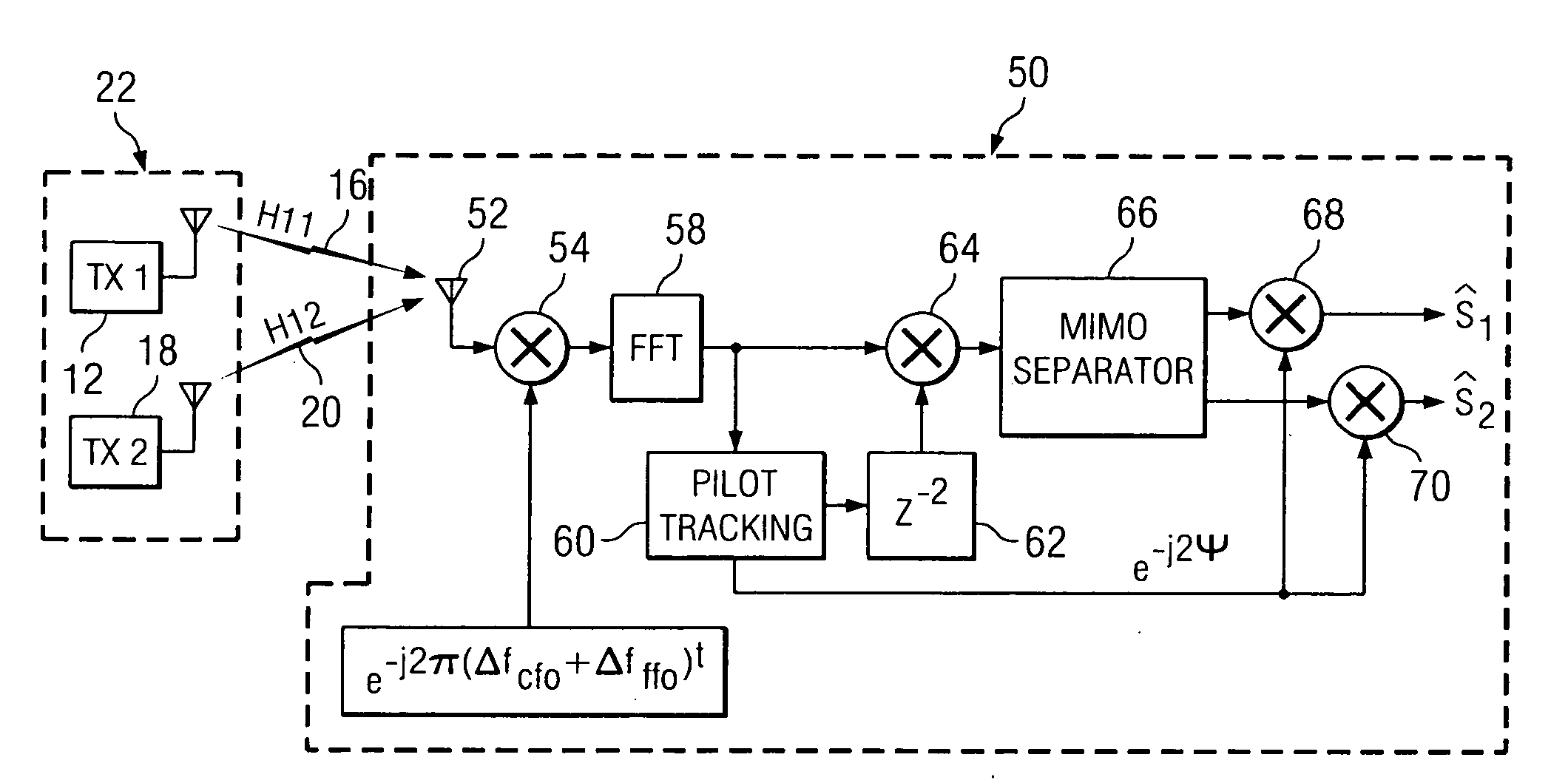

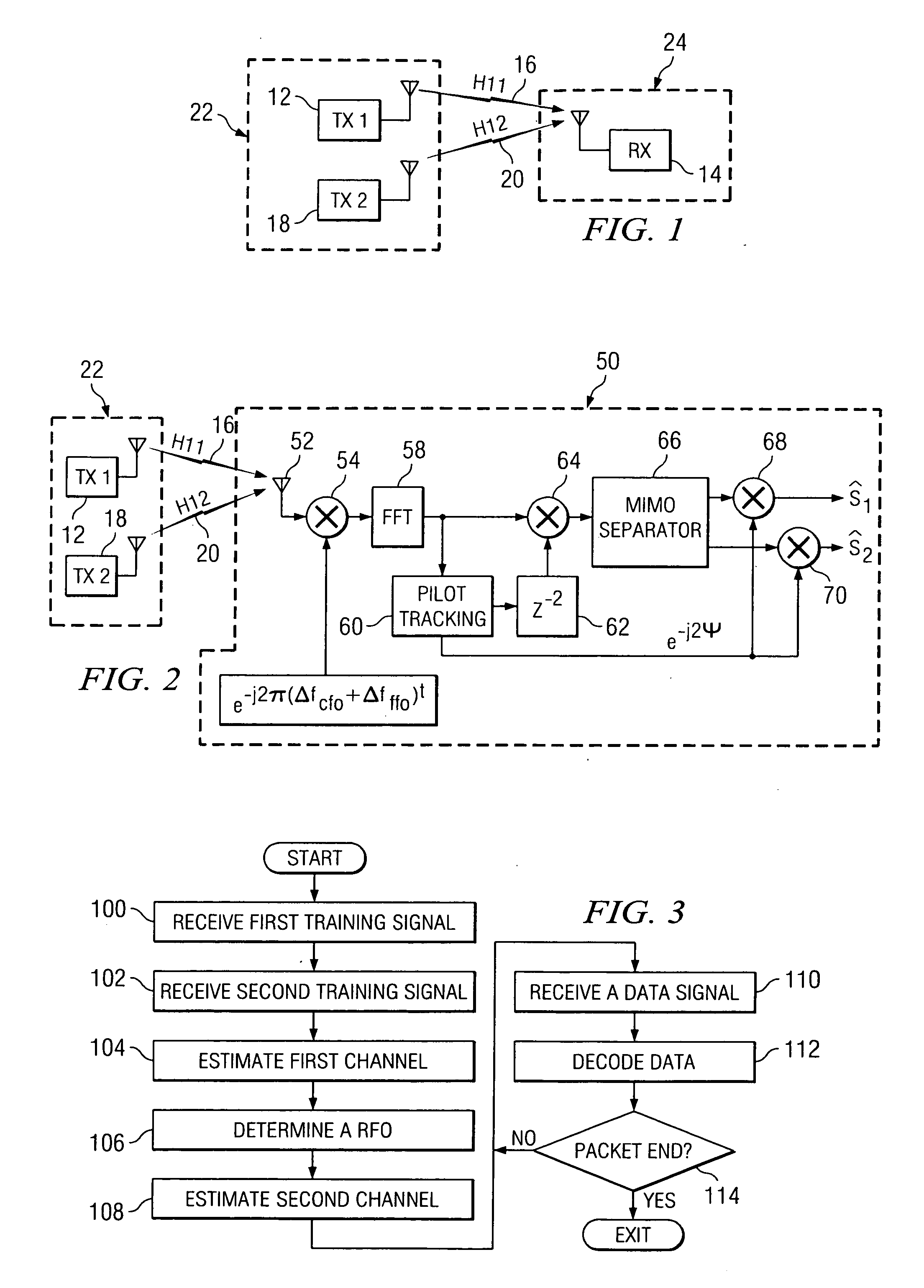

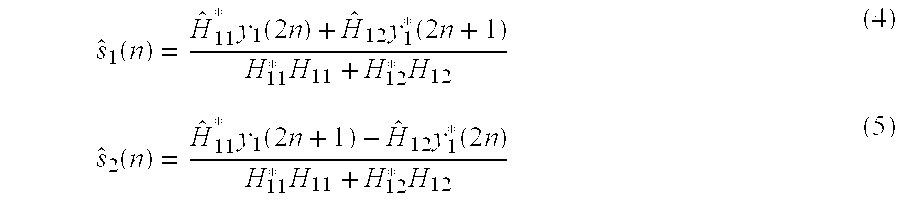

Phase advance compensation for MIMO time-switch preamble modes

A communications receiver is provided that includes a first and second compensators 64 and 68, a pilot tracker 60, and a demodulator 66. The first compensator 64 is operable to adjust an input signal based on both a coarse frequency offset and a fine frequency offset to produce an adjusted input signal. The pilot tracker 60 determines an estimated residual frequency offset based on at least a portion of the adjusted input signal. The demodulator 66 determines at least a first symbol sequence and a second symbol sequence based on the adjusted input signal. The second compensator 68 is operable to adjust the first symbol sequence and the second symbol sequence based on the estimate residual frequency offset.

Owner:TEXAS INSTR INC

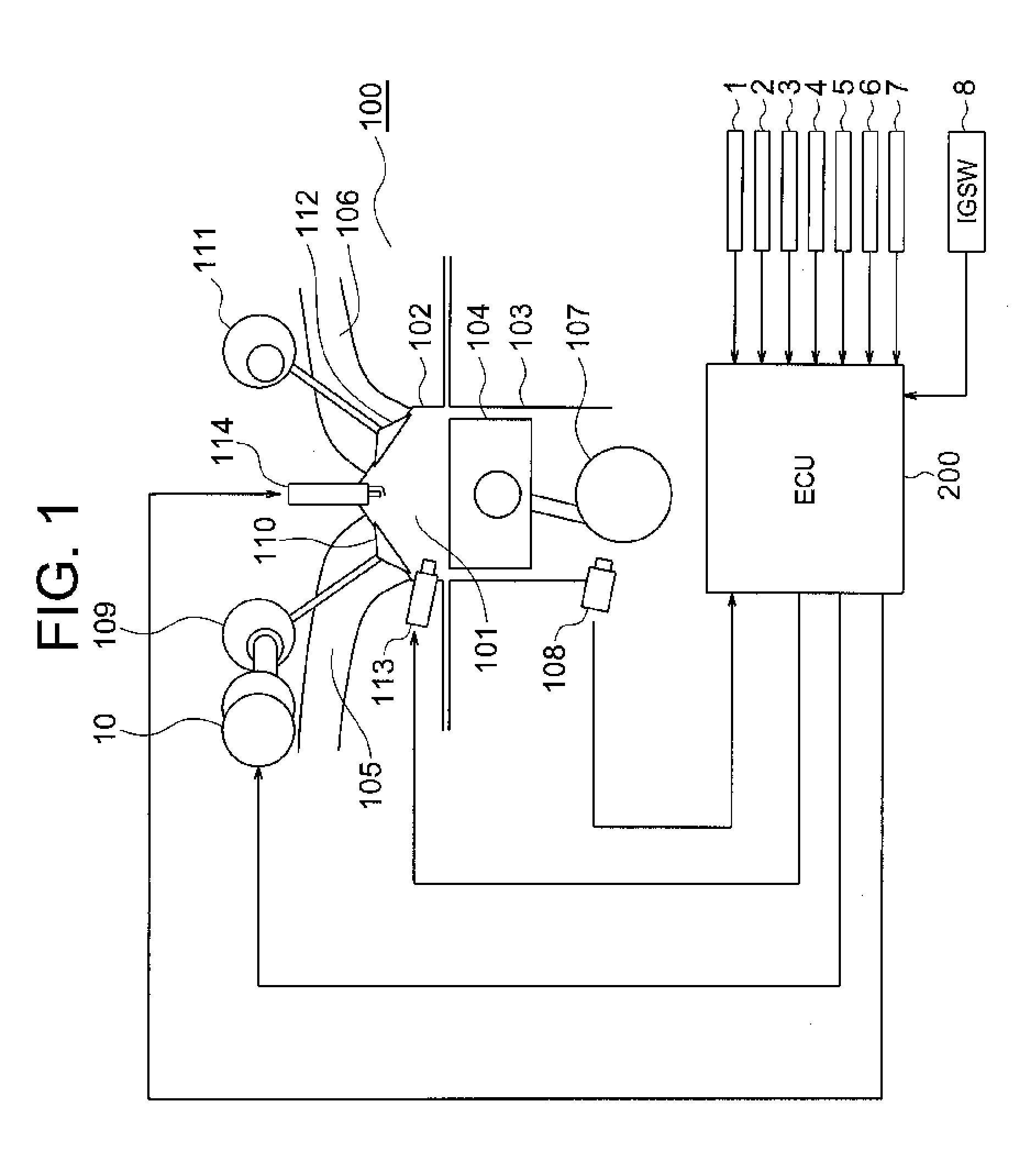

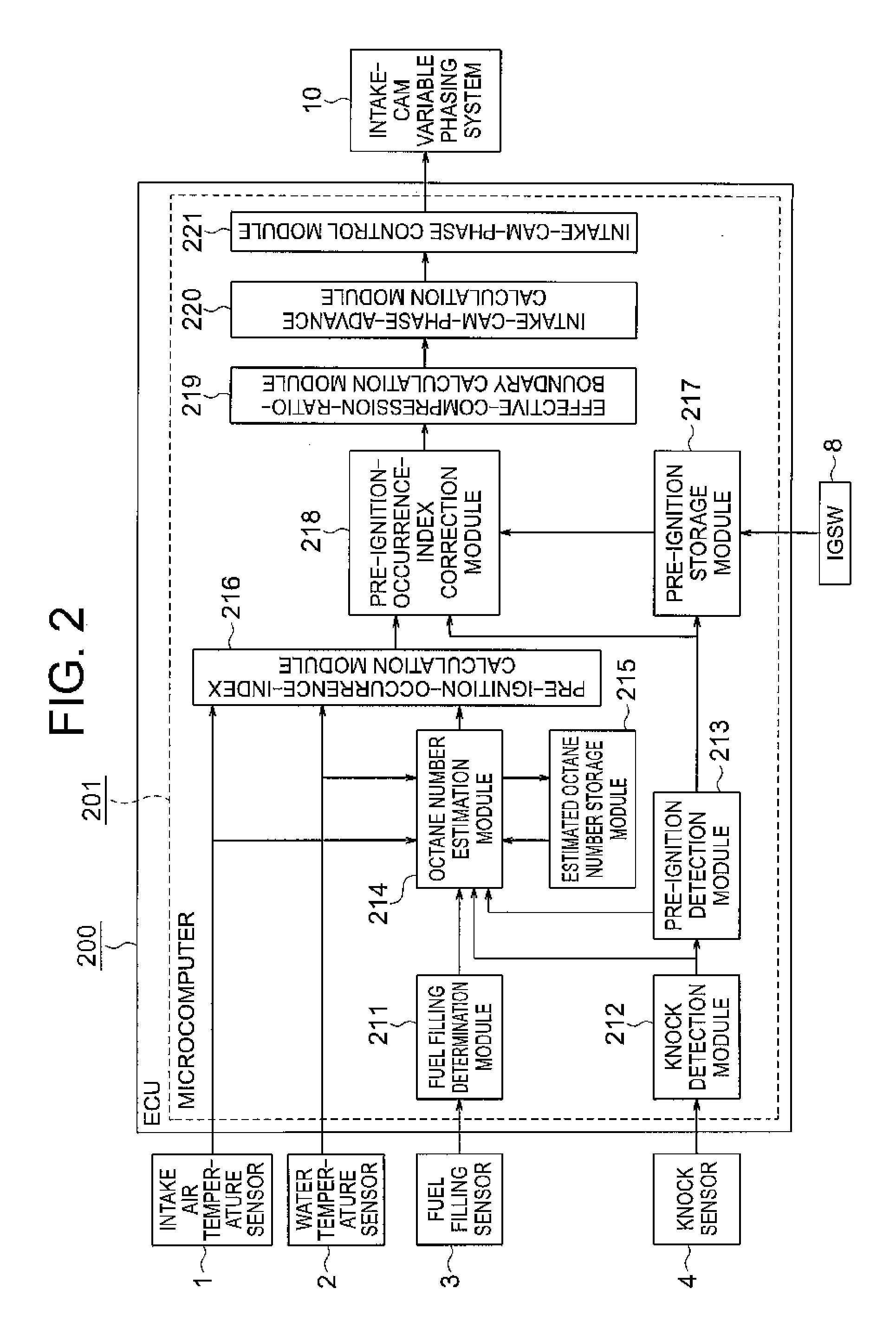

Pre-ignition estimation/control device for an internal combustion engine

ActiveUS20120089315A1Control changesEffective compression ratioAnalogue computers for vehiclesElectrical controlPhase controlEngineering

A pre-ignition estimation / control device includes: an octane number estimation module for estimating an octane number of a fuel based on detection signals received from an intake air temperature sensor, a water temperature sensor, etc; a pre-ignition-occurrence-index calculation module for calculating a pre-ignition occurrence index based on the estimated octane number and the like; a pre-ignition-occurrence-index correction module for correcting the pre-ignition occurrence index so as to cause the pre-ignition more likely to occur; an effective-compression-ratio-boundary calculation module for calculating a boundary of an effective compression ratio based on the pre-ignition occurrence index; an intake-cam-phase-advance calculation module for calculating a phase advance of an intake cam based on the boundary of the effective compression ratio and the like; and an intake-cam-phase control module for controlling an intake-cam variable phasing system based on the phase advance of the intake cam, to thereby restrict a change in phase advance.

Owner:MITSUBISHI ELECTRIC CORP

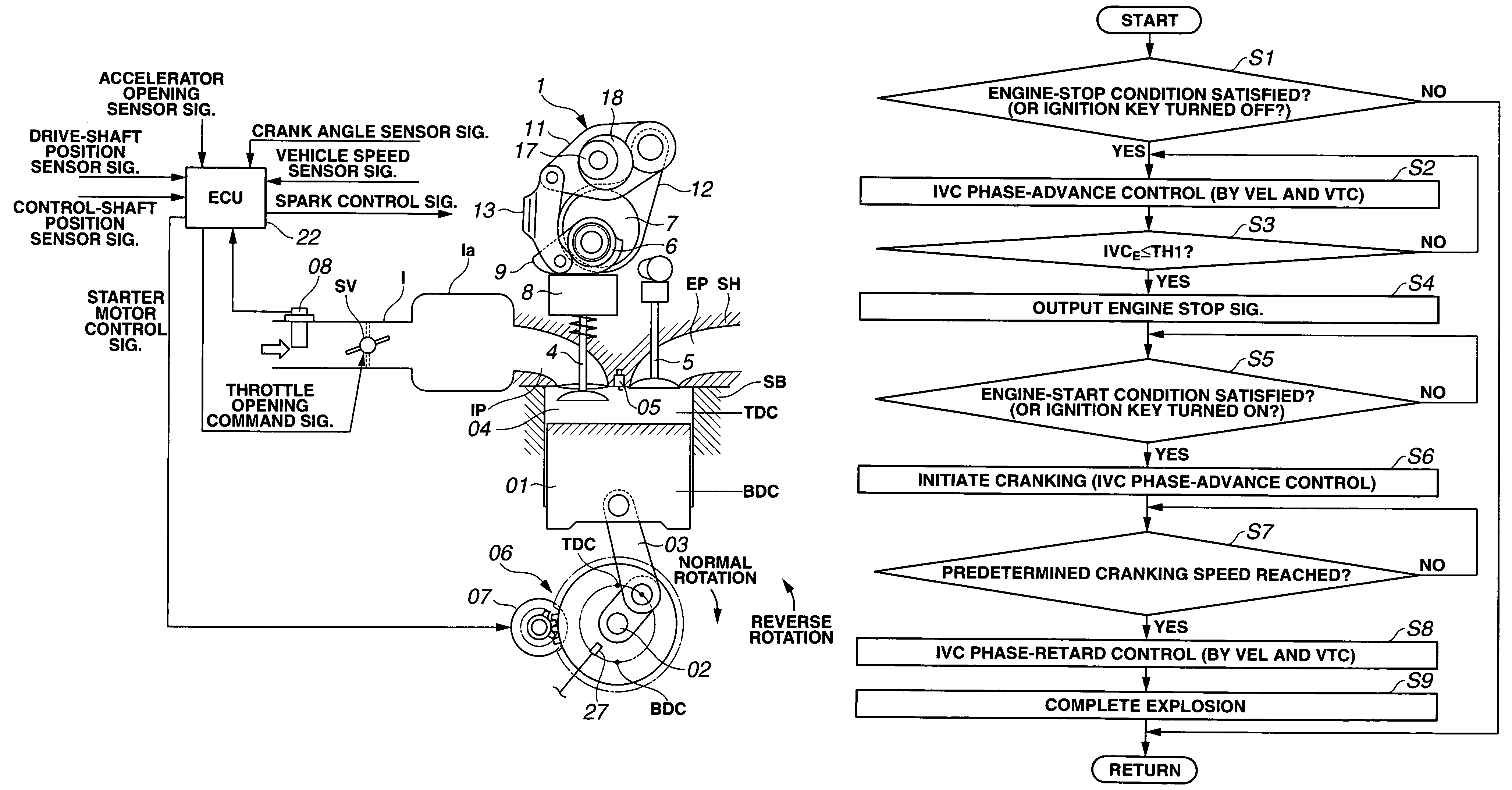

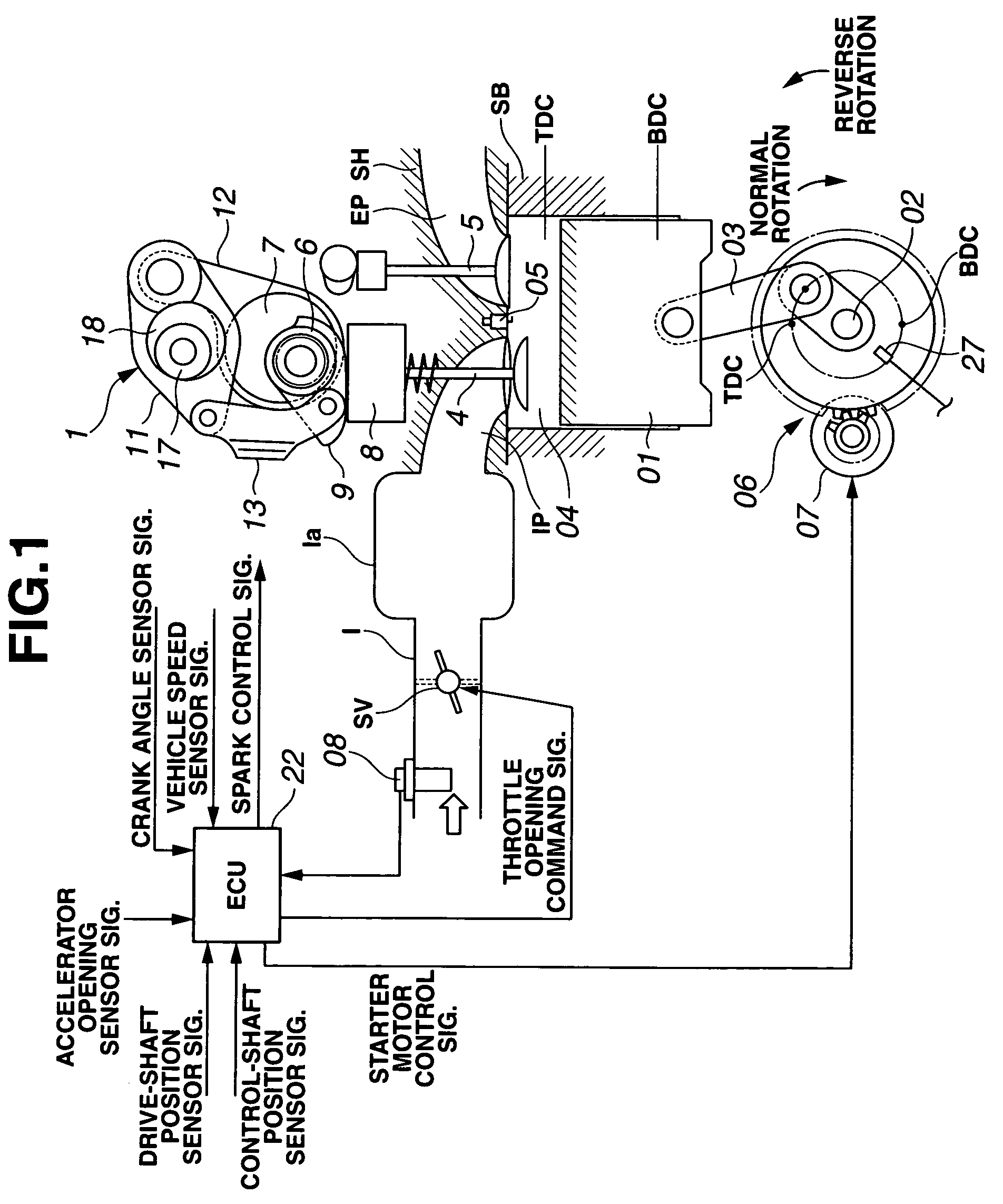

Variable valve actuation system of internal combustion engine

InactiveUS7703424B2Increase friction lossReduce noiseValve arrangementsOutput powerTop dead centerValve actuator

In a variable valve actuation system of an internal combustion engine employing a variable valve actuator capable of variably adjusting at least intake valve closure timing depending on engine operating conditions, a processor of a control unit is programmed to phase-advance the intake valve closure timing to a predetermined timing value after a piston top dead center position and before a piston bottom dead center position on intake stroke during at least one of an engine starting period and an engine stopping period. The variable valve actuator includes a biasing device by which the intake valve closure timing is permanently biased toward the predetermined timing value.

Owner:HITACHI LTD