Patents

Literature

3856results about "Multiple input and output pulse circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

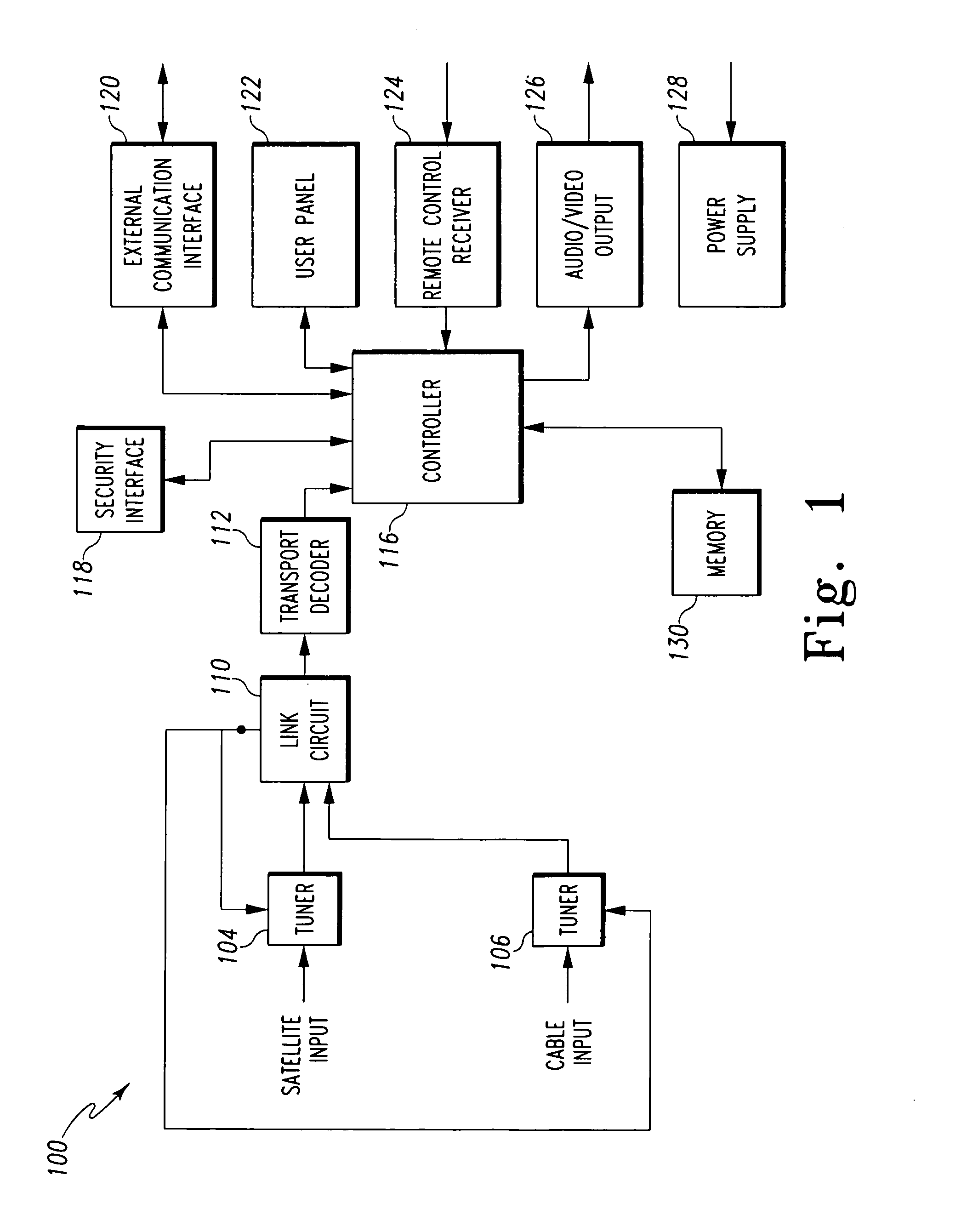

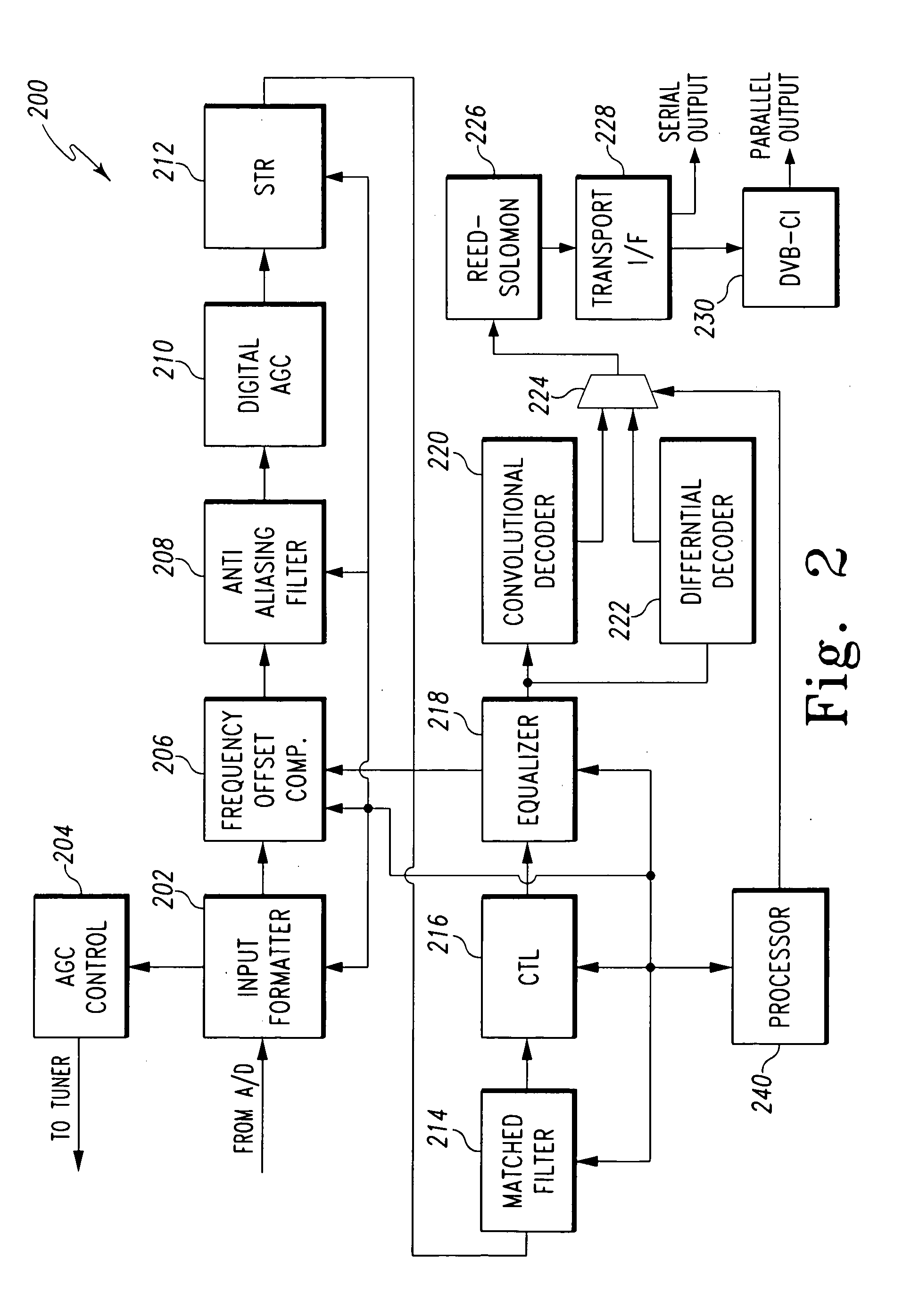

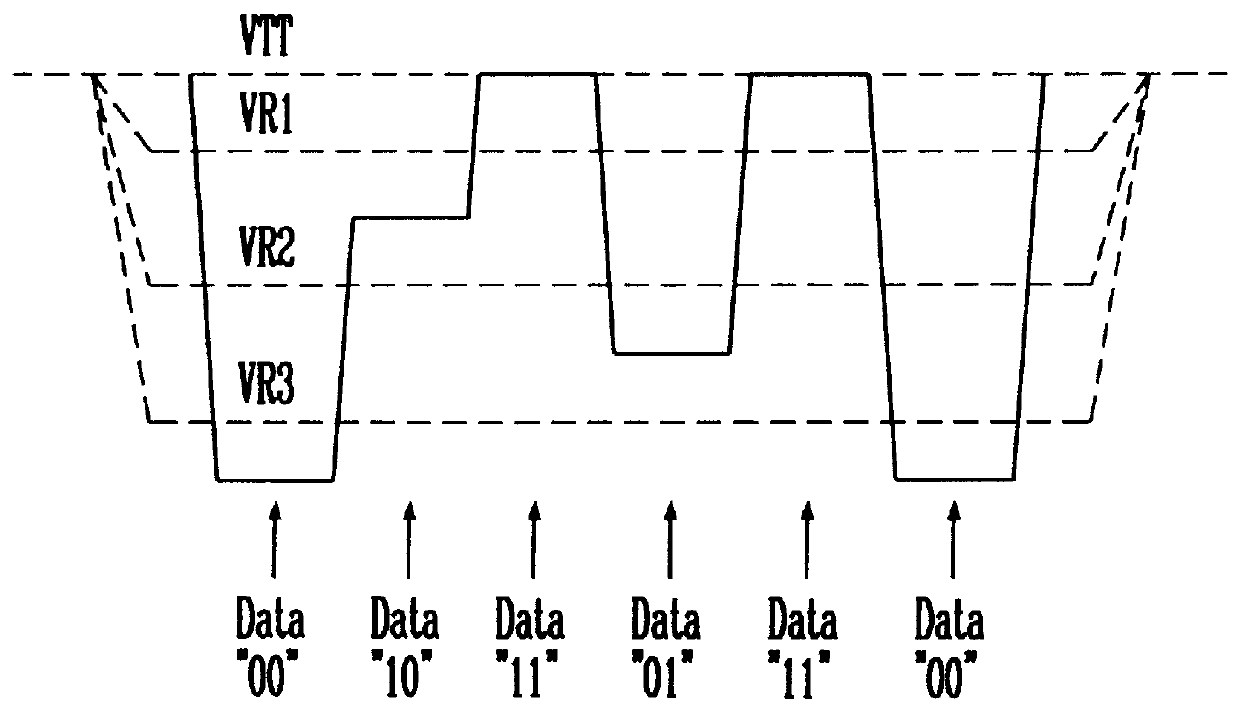

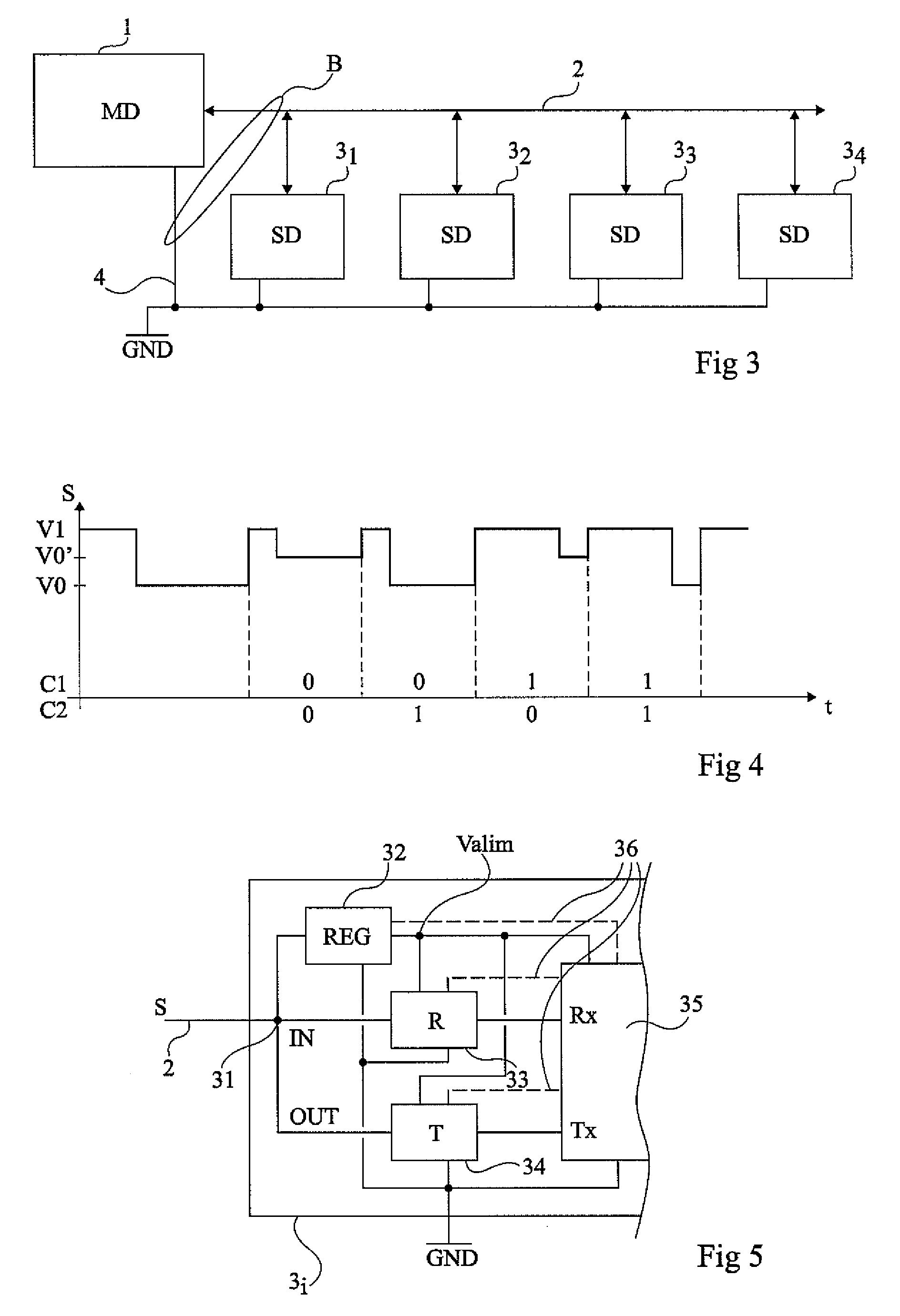

Multiple-channel transmission over a single-wire bus

ActiveUS8509318B2Batteries circuit arrangementsTransmission/receiving by adding signal to waveTransmission channelPower over

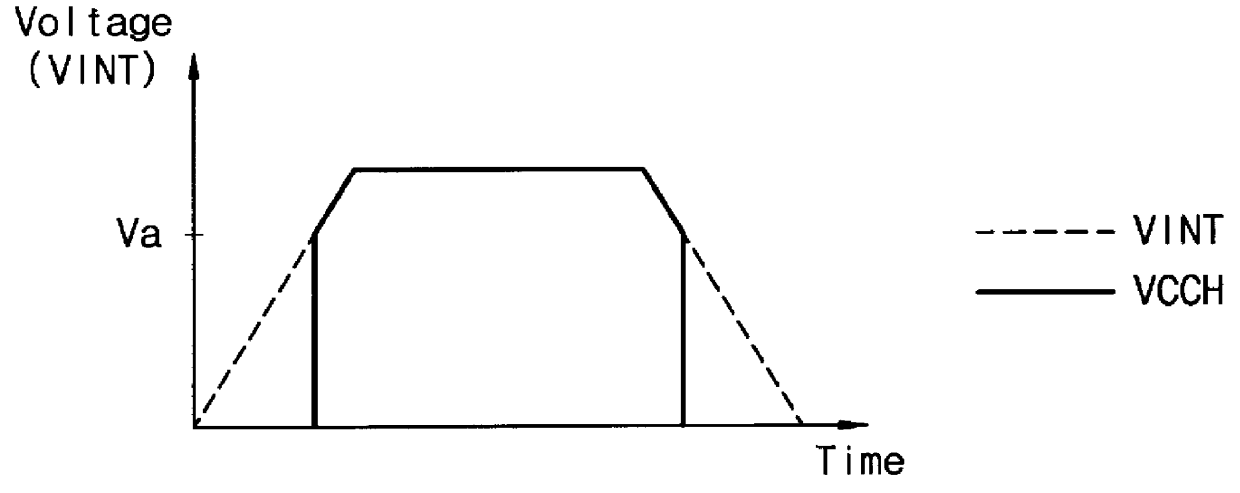

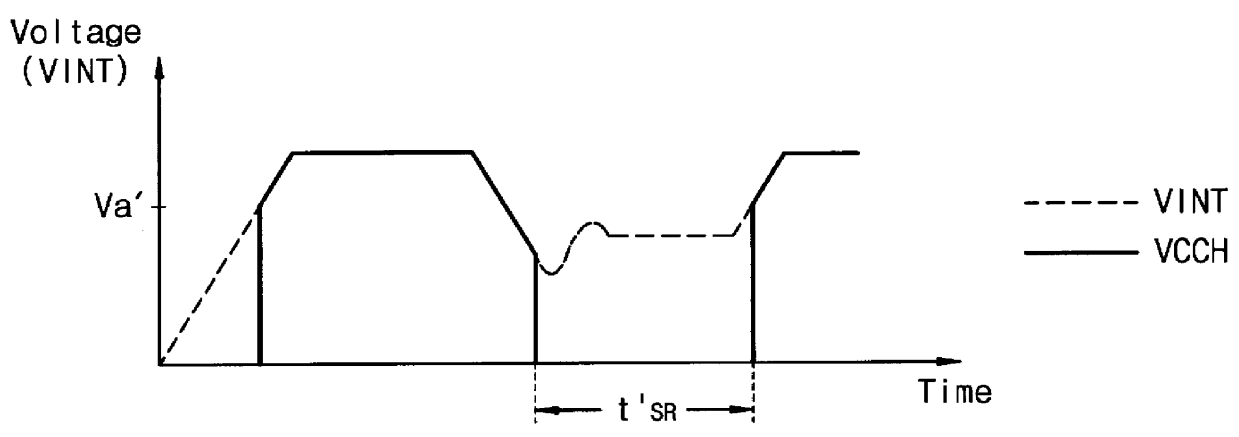

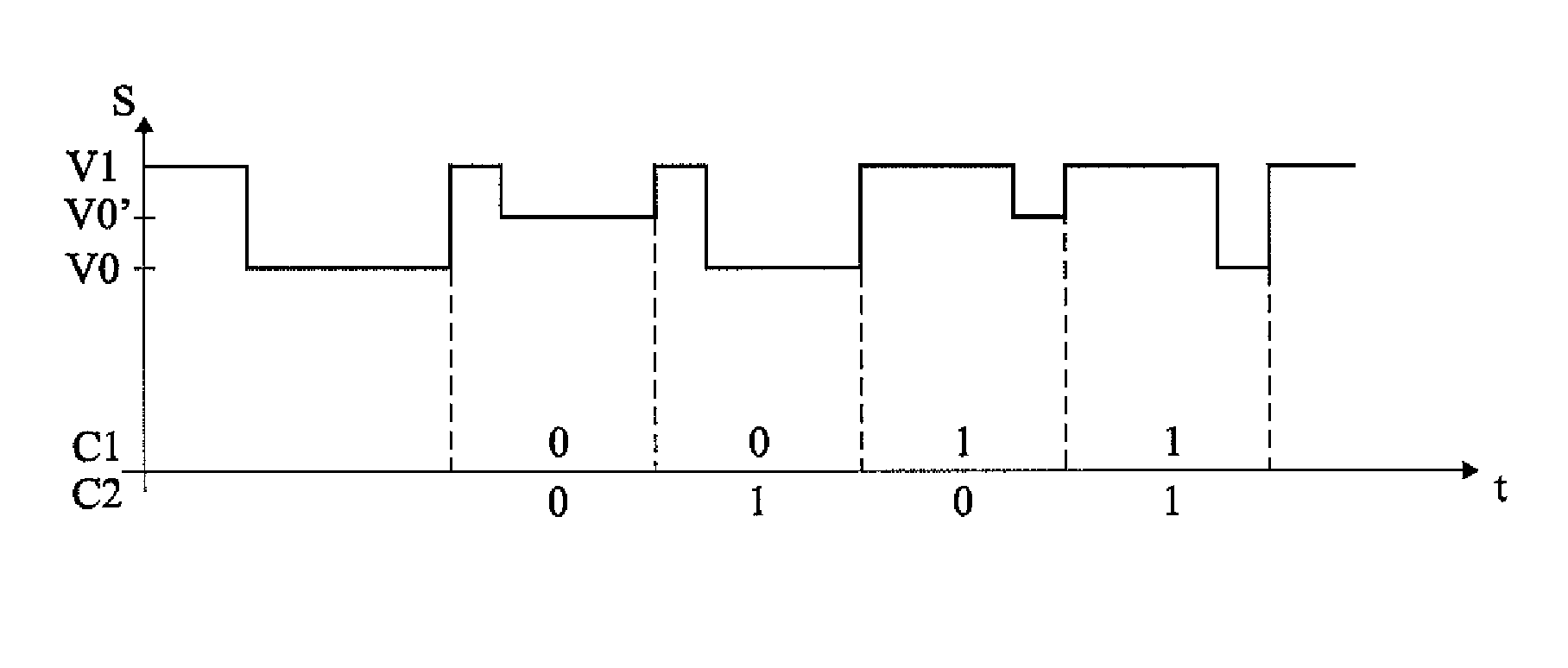

Apparatus and methods are described that enable concurrent transmission of multiple data signals including clock, synchronization, and power over a single-wire bus between a master device and one or more slave devices. A first transmission channel from the master device to the slave device may modulate the width of periodic pulses between a first voltage level and a second voltage level with respect to a reference potential. A second transmission channel may modulate the amplitude of at least one of the first and second voltage levels to at least one third voltage level. Concurrent communications between a master device and one or more slave devices over a single-wire bus can be achieved.

Owner:STMICROELECTRONICS (ROUSSET) SAS

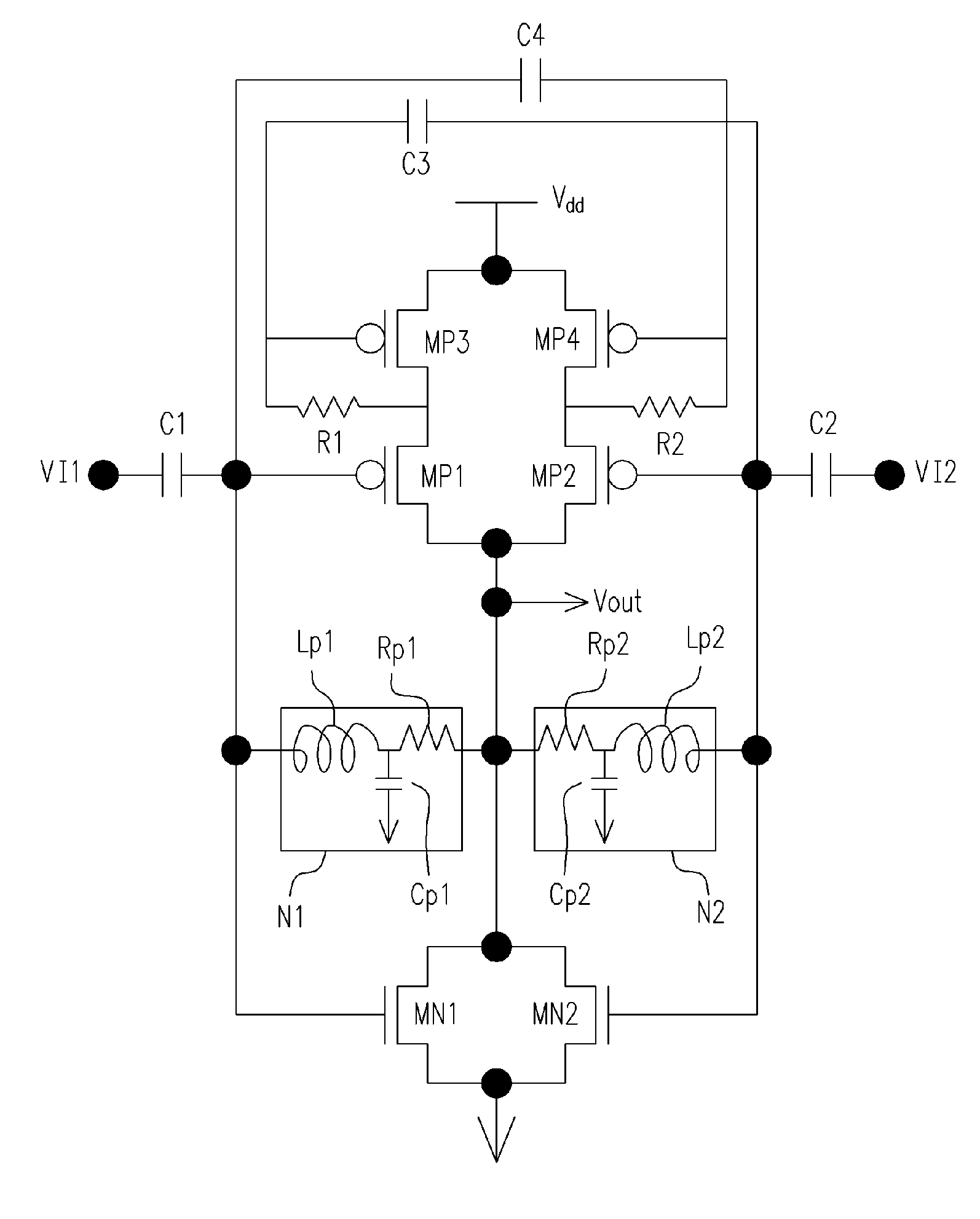

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

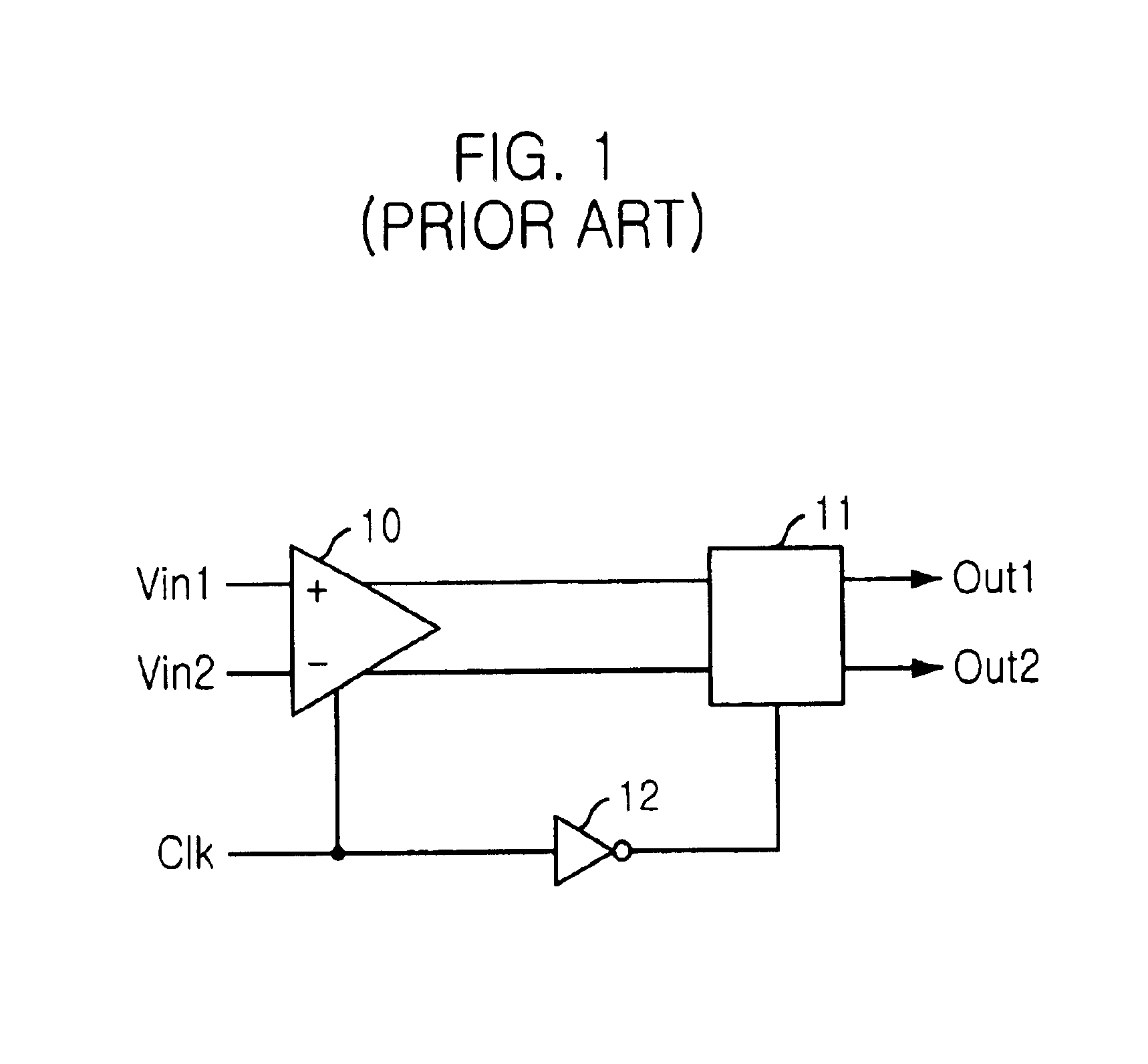

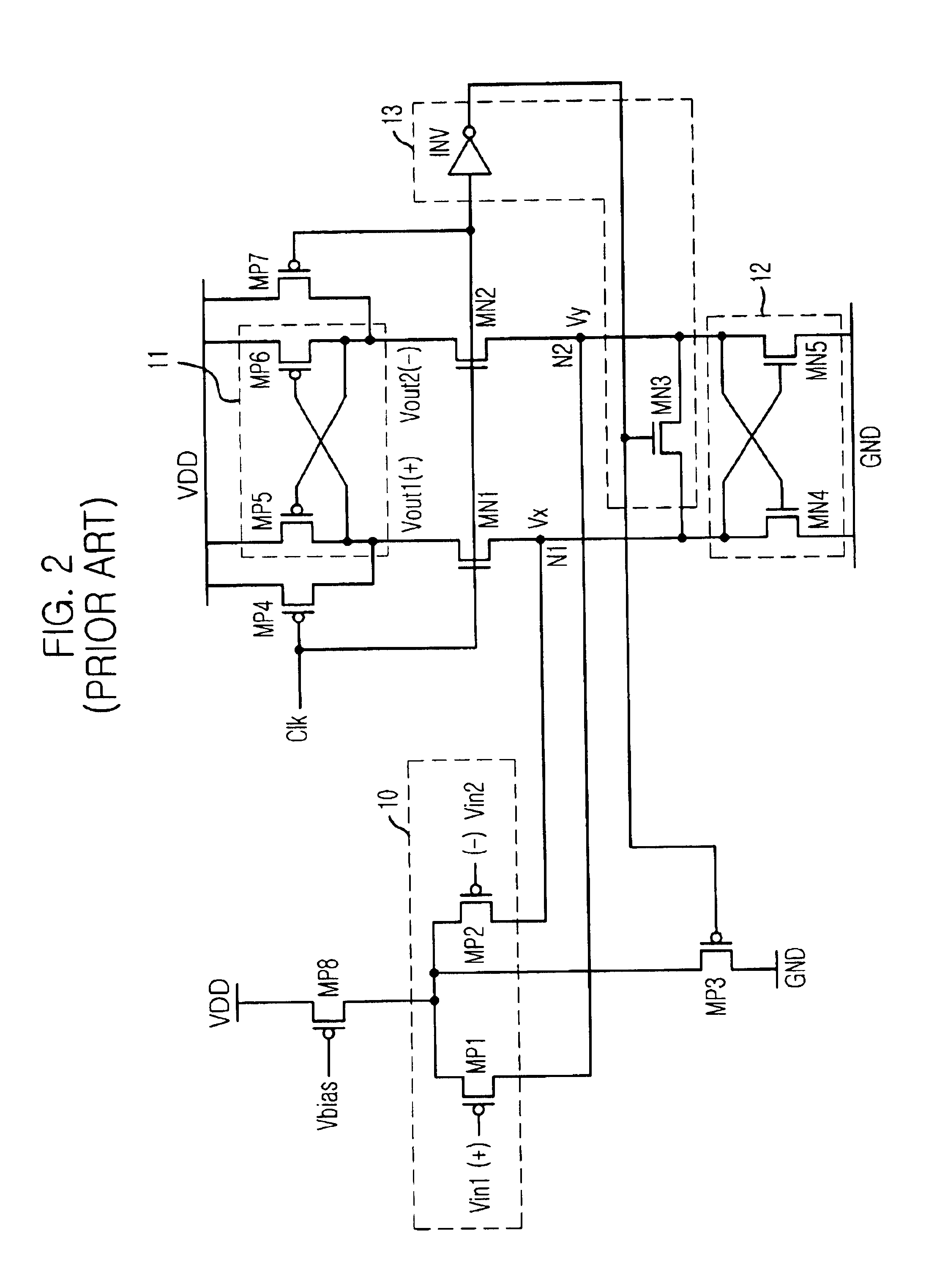

Comparison apparatus operated at a low voltage

InactiveUS6847234B2Inhibition of changes in propertiesGuaranteed uptimeElectric signal transmission systemsMultiple input and output pulse circuitsCmos comparatorLow voltage

The present invention provide an CMOS comparator outputting one bit digital signal after comparing two analog input signals through alternately performing a track mode operation and latch mode operation decided by a clock signal having a constant period, including: a latching unit having the main / sub input terminal; a first switching transistor having the clock signal as a gate input and having one end coupled to main input terminal; a first load transistor diode-connected to the other end of the first switching transistor and a ground end; a second switching transistor having a gate receiving the clock signal as a gate input and one end coupled to the sub input terminal; and a second load transistor diode-connected to the second switching transistor and to the other end of the ground terminal.

Owner:KEY FOUNDRY CO LTD

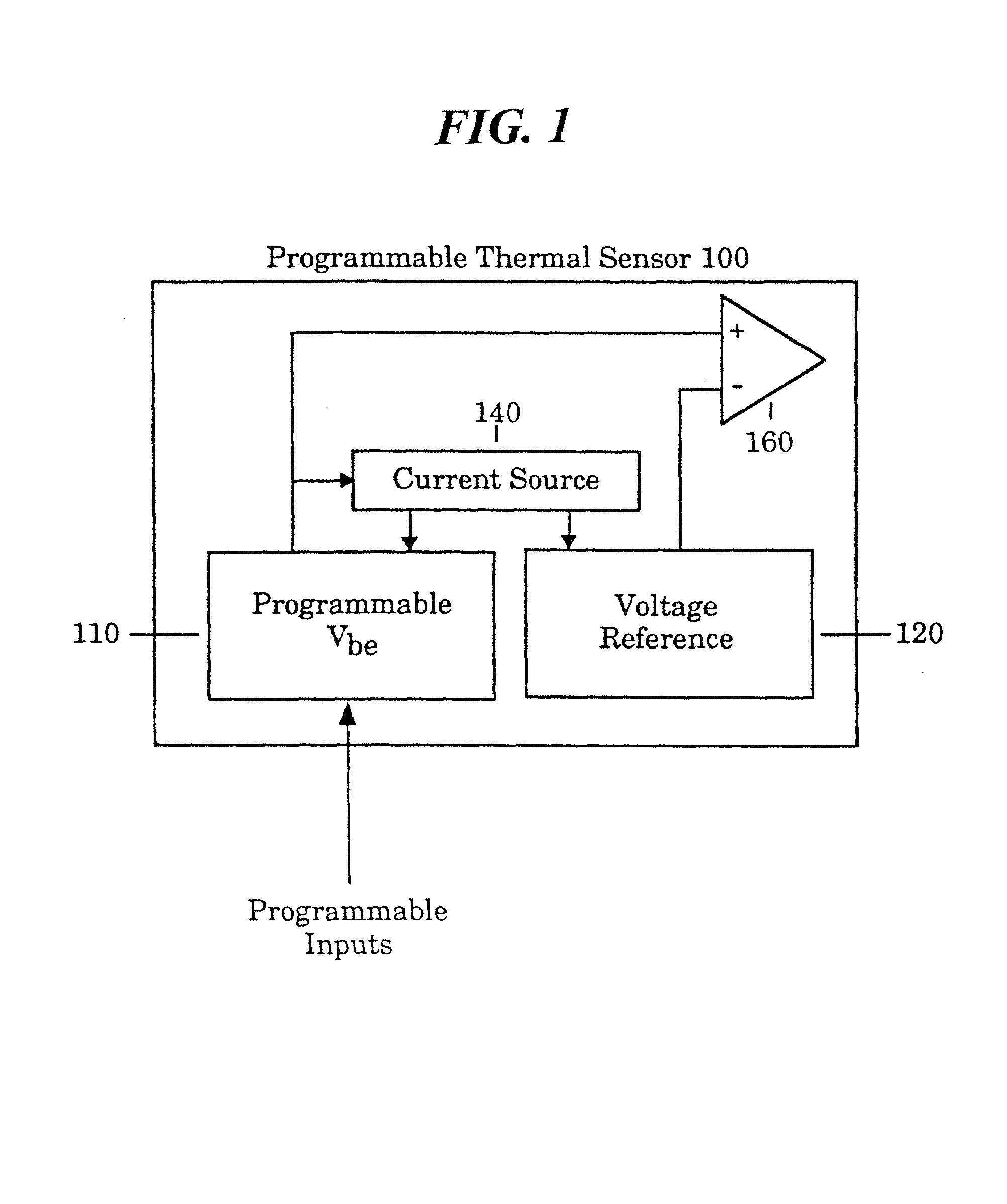

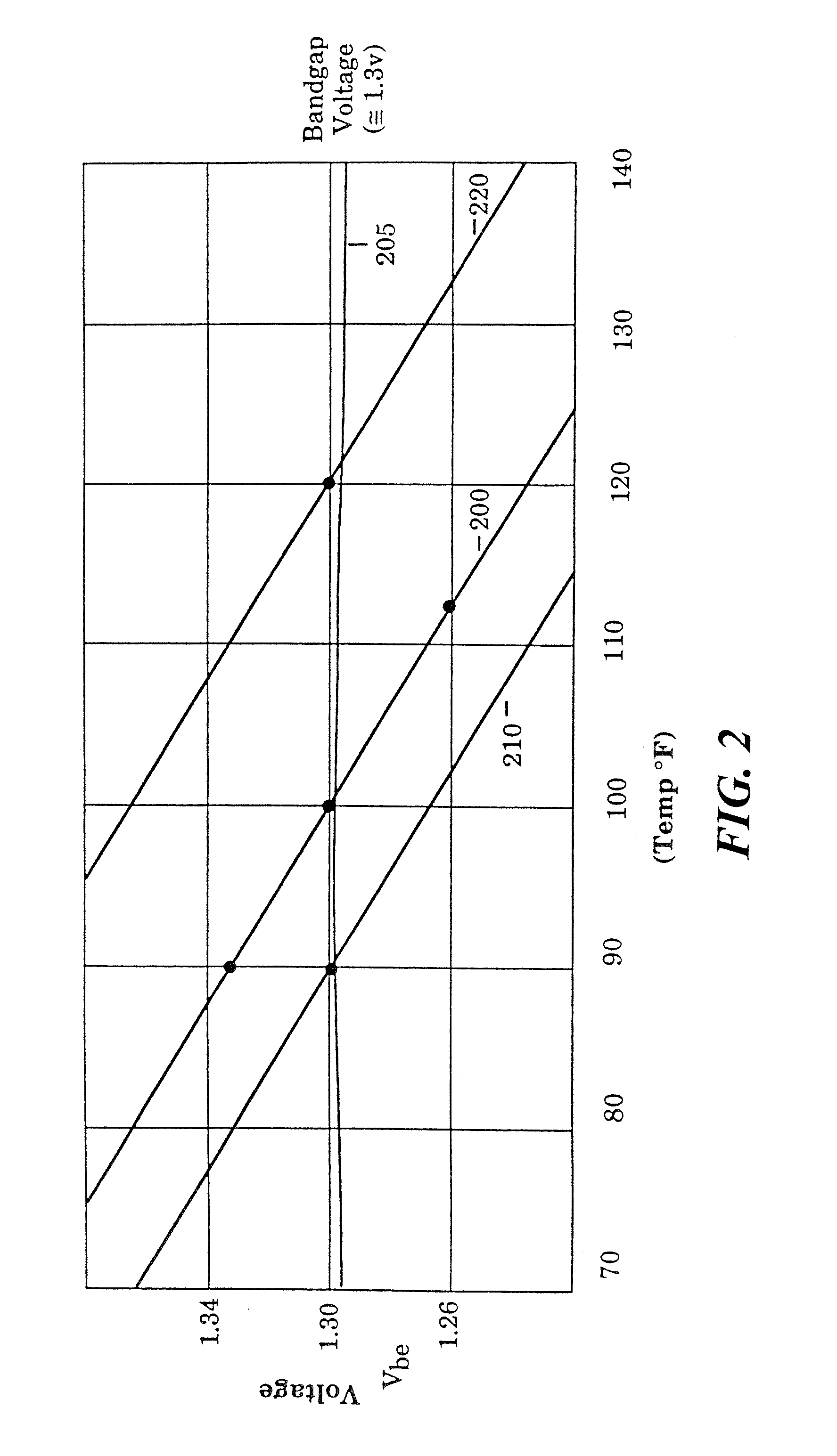

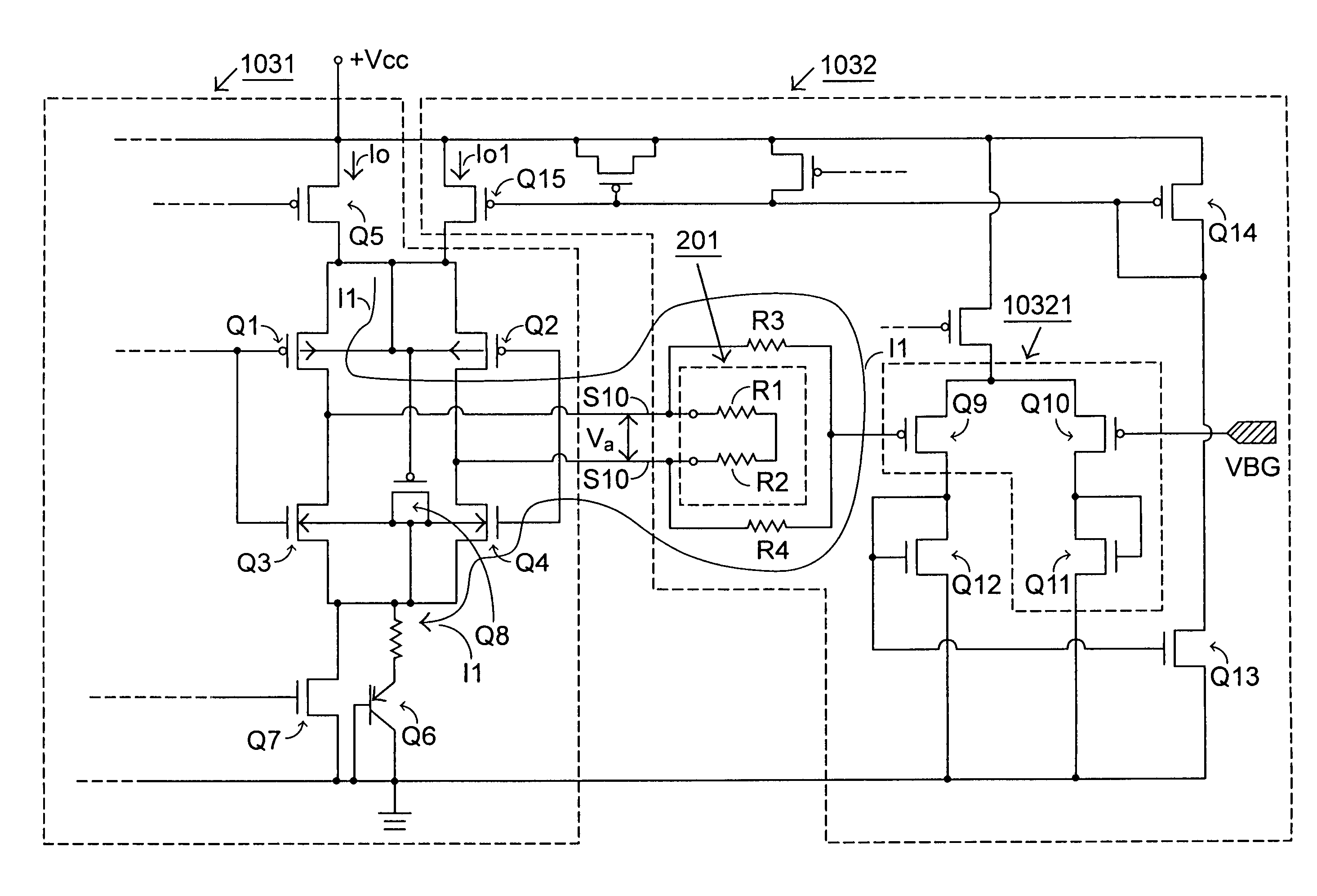

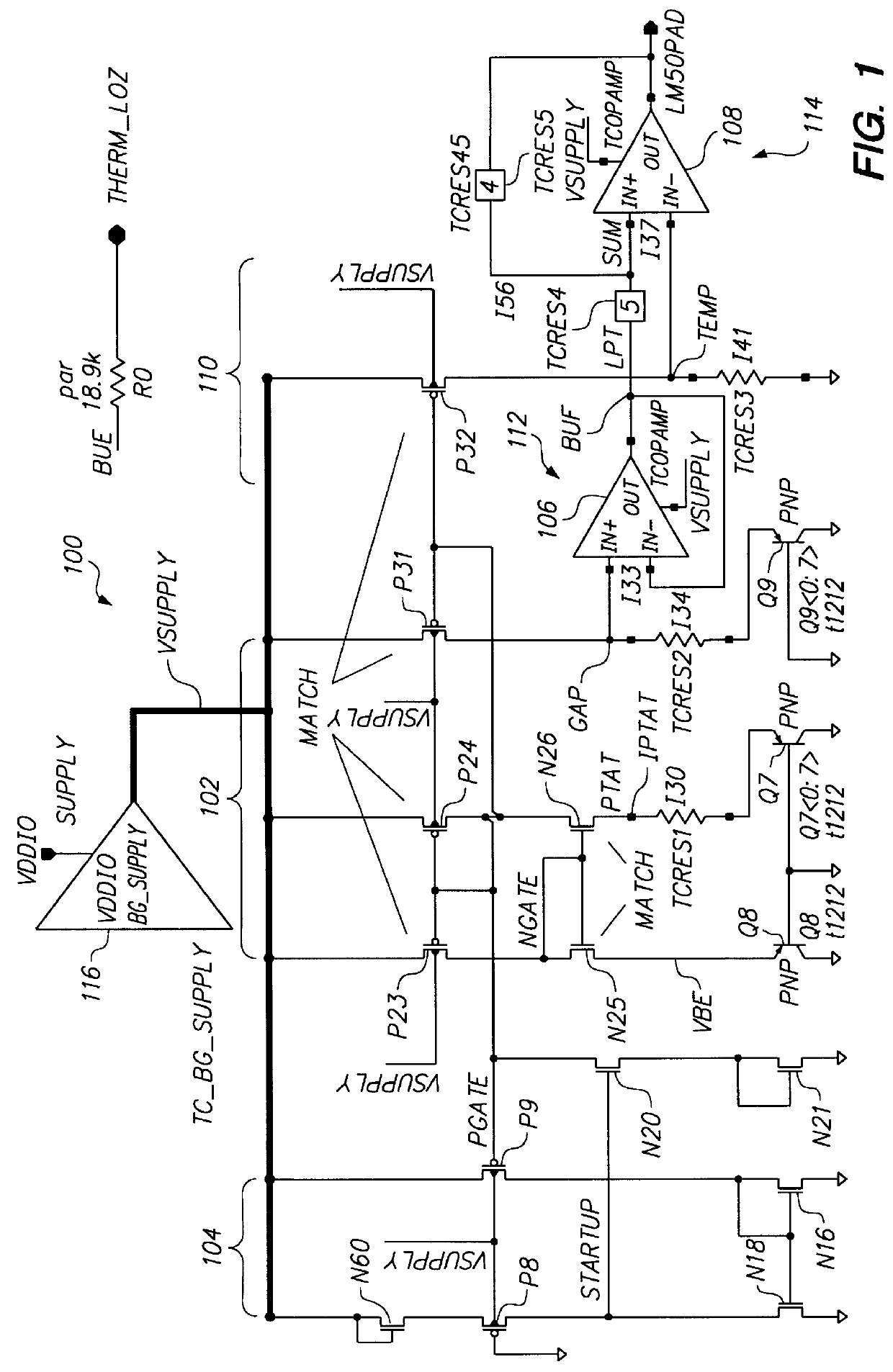

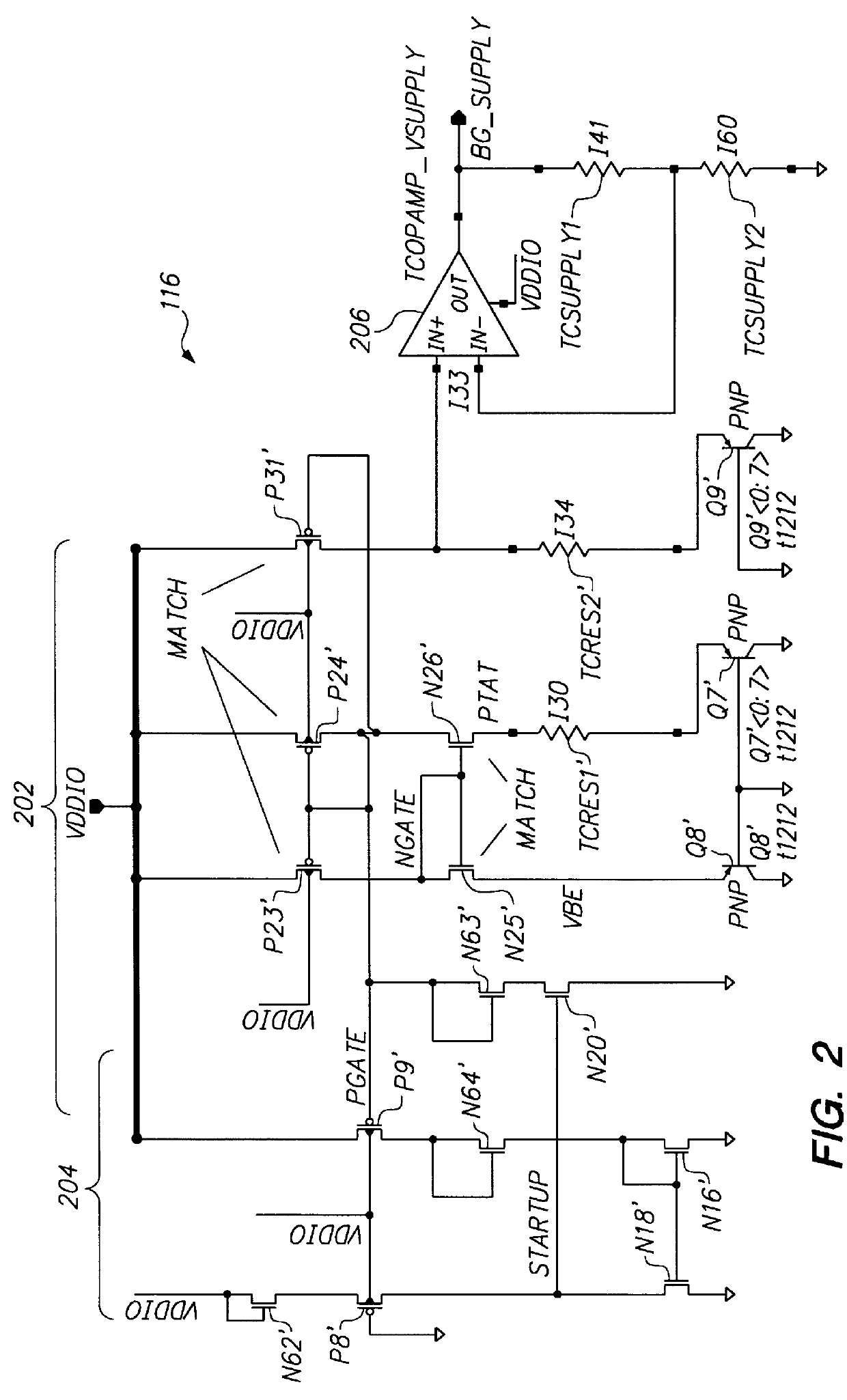

Power supply independent temperature sensor

InactiveUS6157244AMultiple input and output pulse circuitsInstant pulse delivery arrangementsAudio power amplifierEngineering

A temperature sensor is fabricated in an integrated circuit in combination with another device such as a microprocessor using a fabrication technology that is suitable for fabricating the device. Operation of the temperature sensor is based on the bandgap physics of semiconductors using a bandgap reference circuit and an amplifier that generate two measurement voltages, a voltage that is temperature-dependent and a voltage that is temperature-independent. The temperature sensor includes a bandgap power supply circuit that supplies a power supply voltage that is very stable to drive the temperature sensor so that the temperature sensor generates an output signal that is essentially independent of the power supply voltage.

Owner:GLOBALFOUNDRIES INC

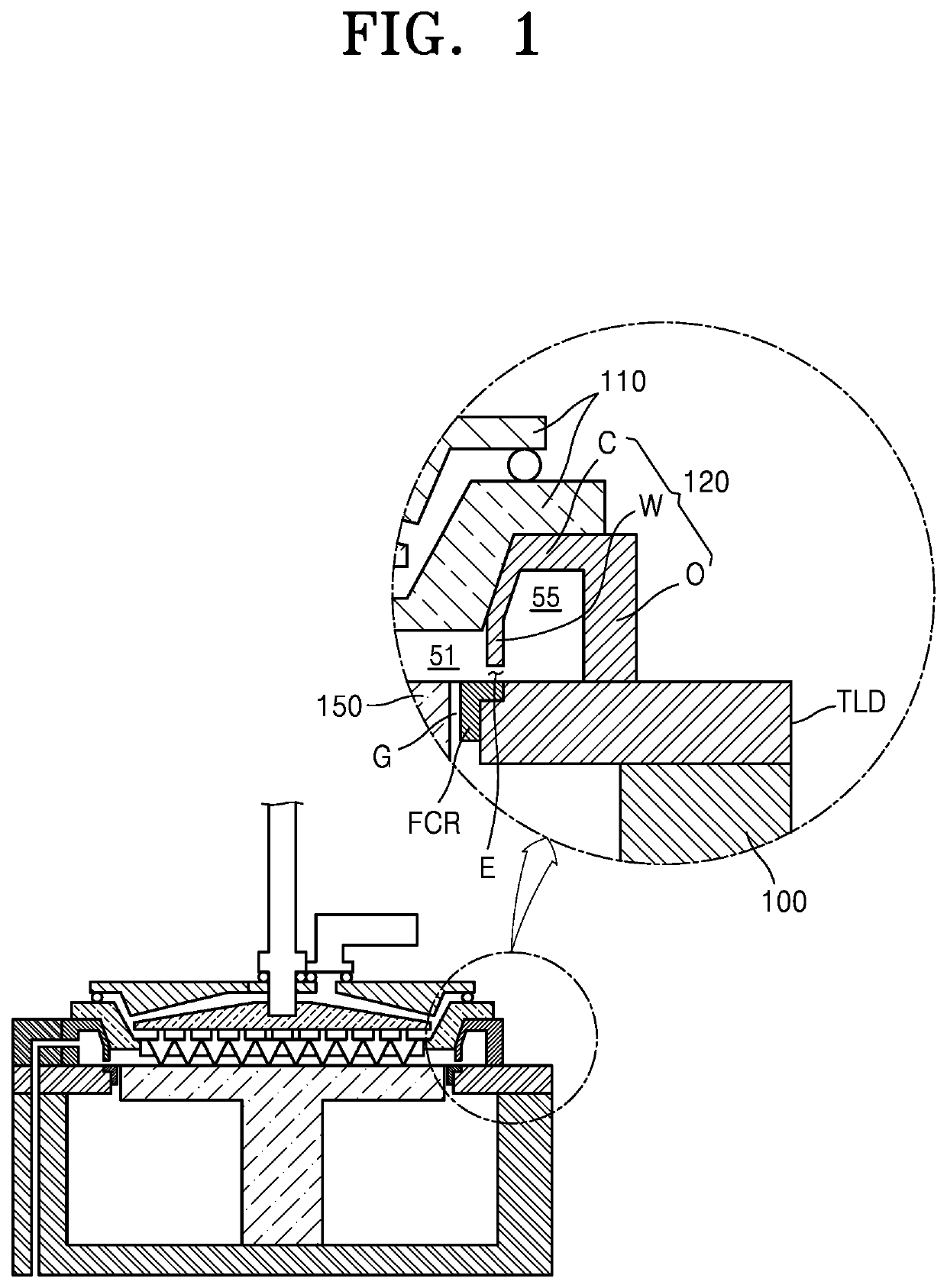

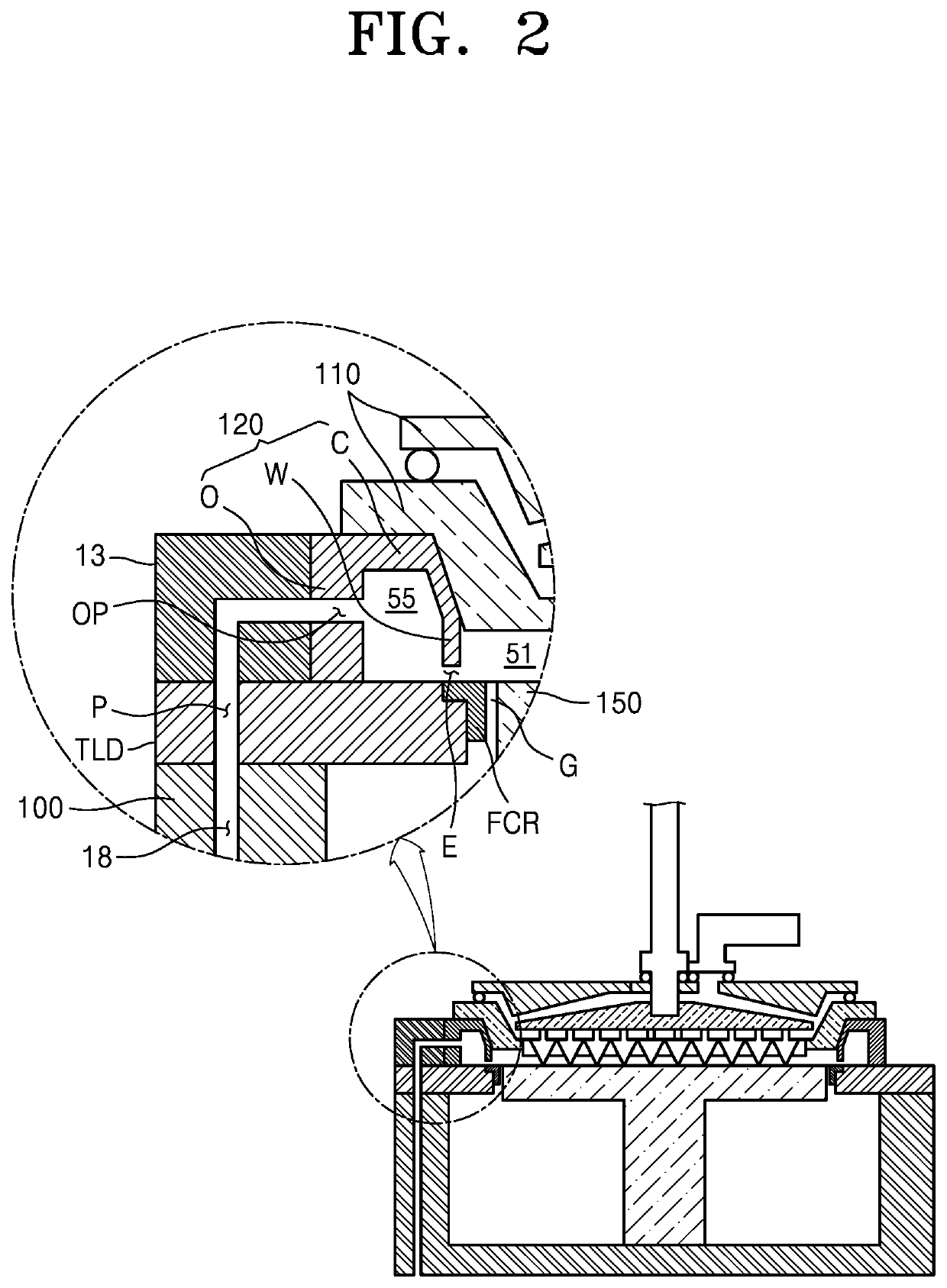

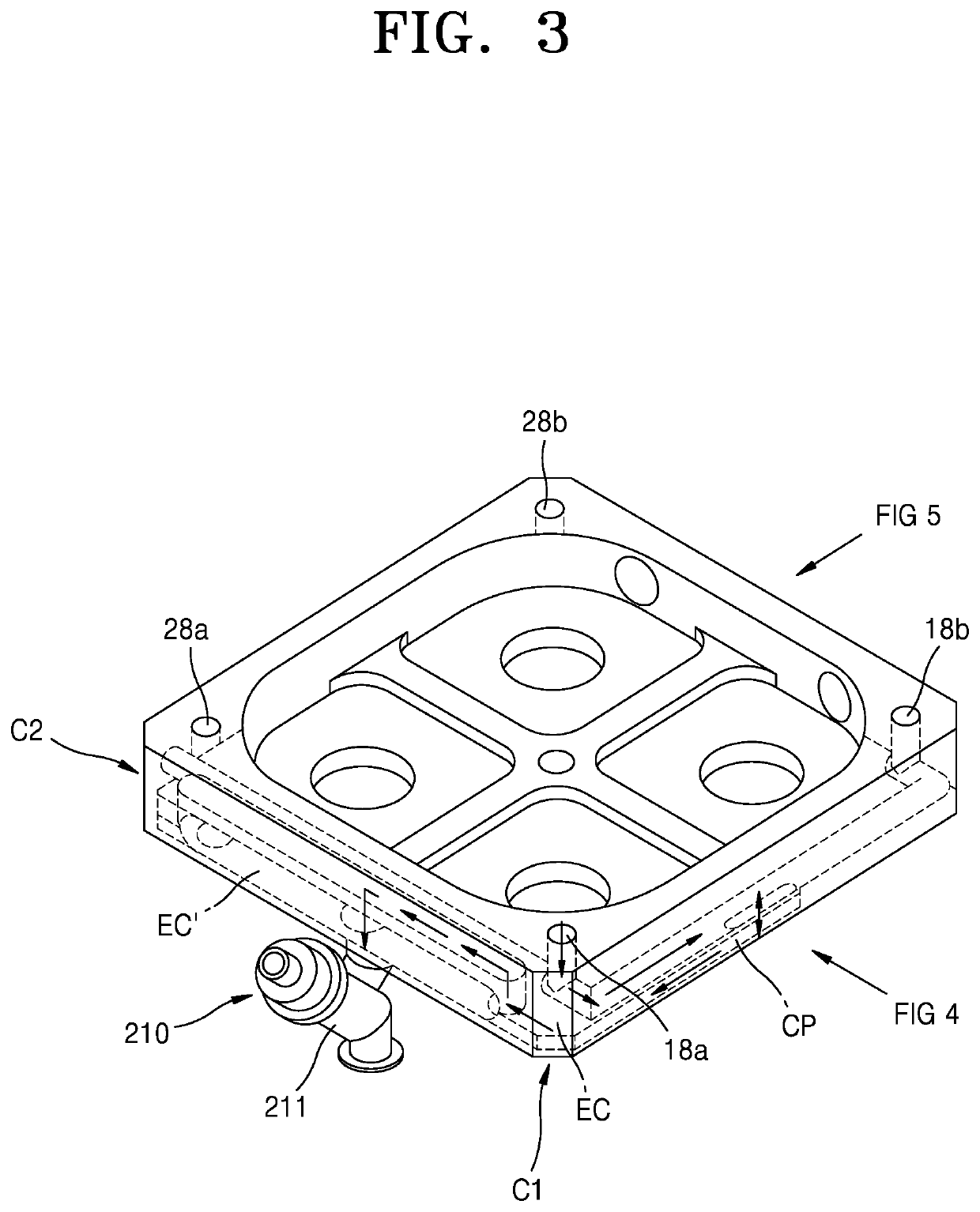

Substrate processing apparatus

PendingUS20210287878A1Preventing unstable mismatchingStable voltageMultiple input and output pulse circuitsElectric discharge tubesProcess engineeringElectric generator

A substrate processing apparatus capable of removing signal interference between reactors includes: a first reactor, a second reactor adjacent to the first reactor, and a power generator configured to supply first power to the first reactor and supply second power to the second reactor, wherein the power generator is further configured to synchronize phases of the first power and the second power.

Owner:ASM IP HLDG BV

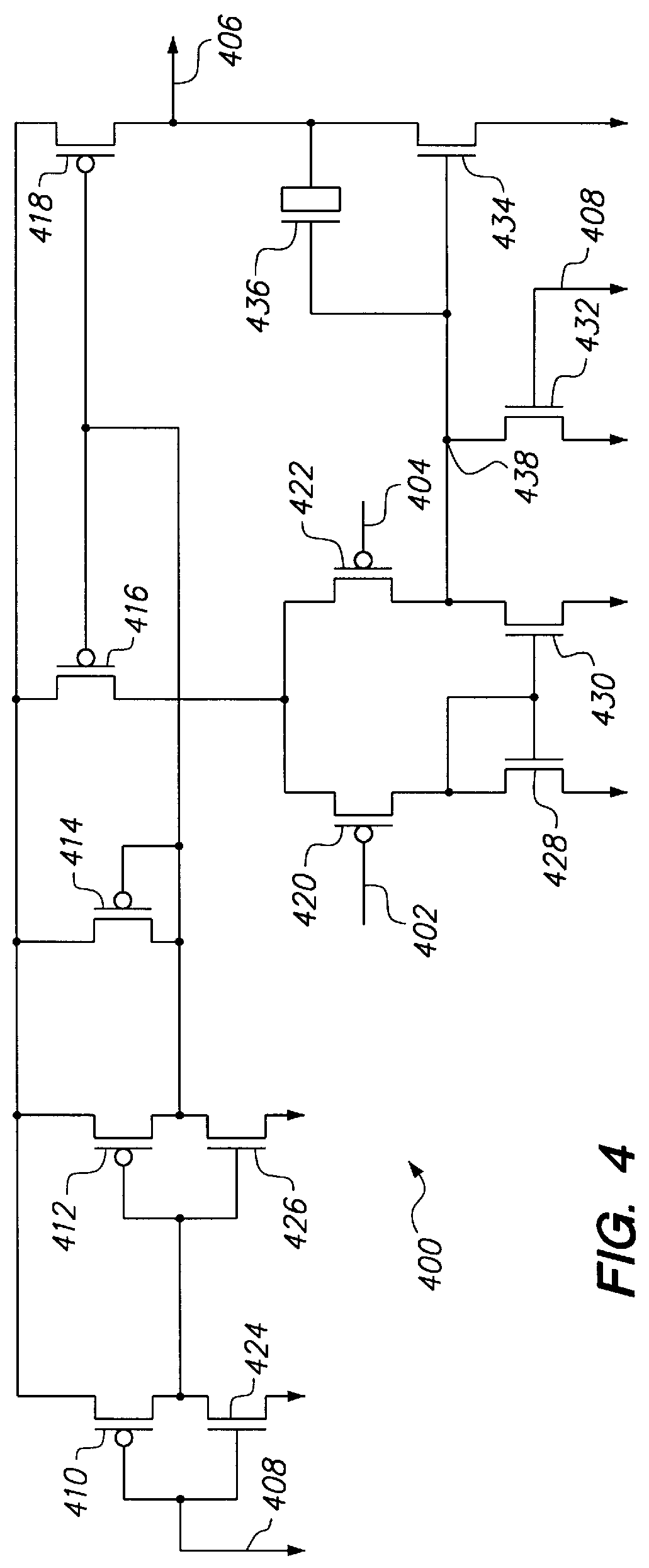

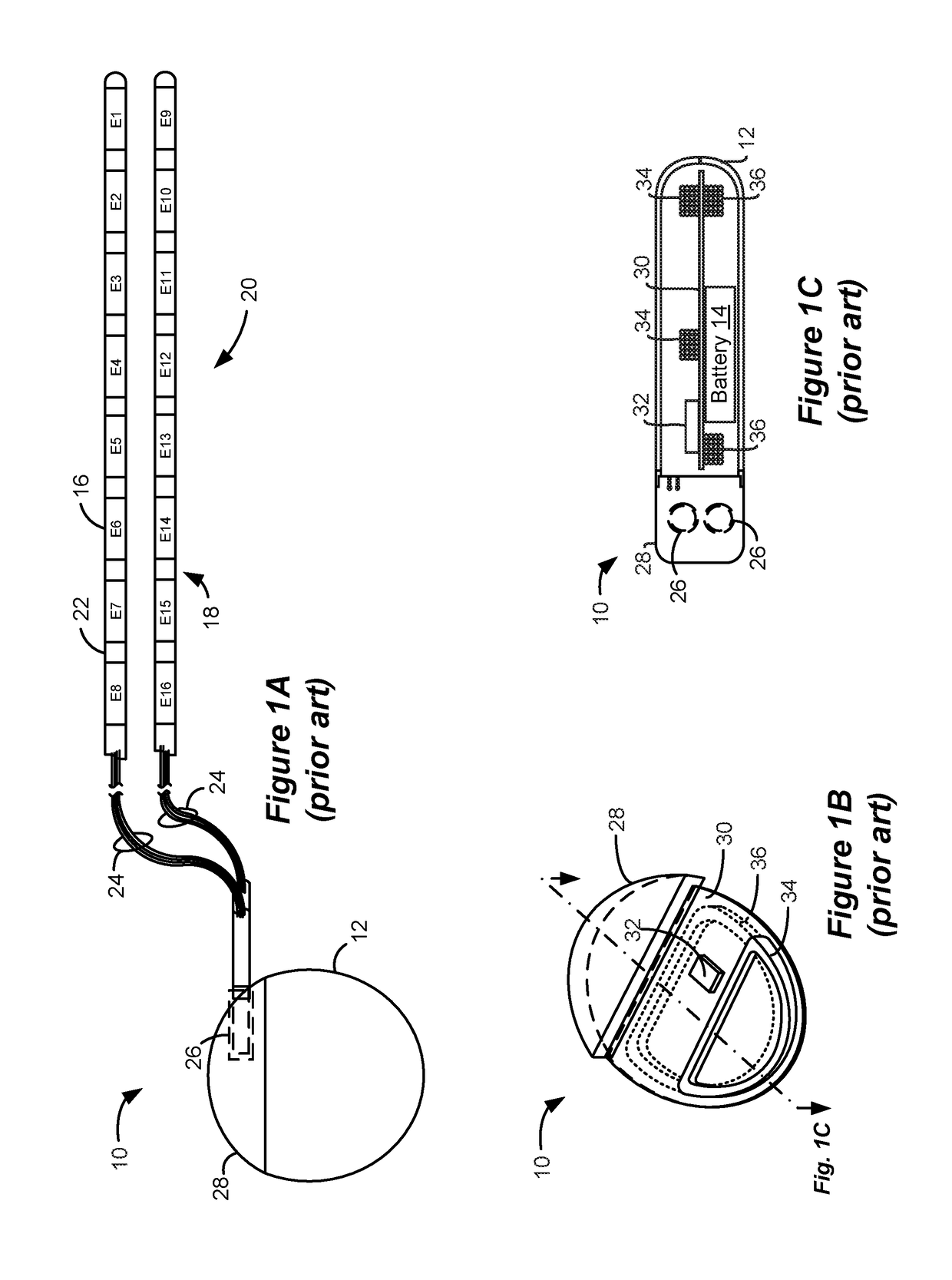

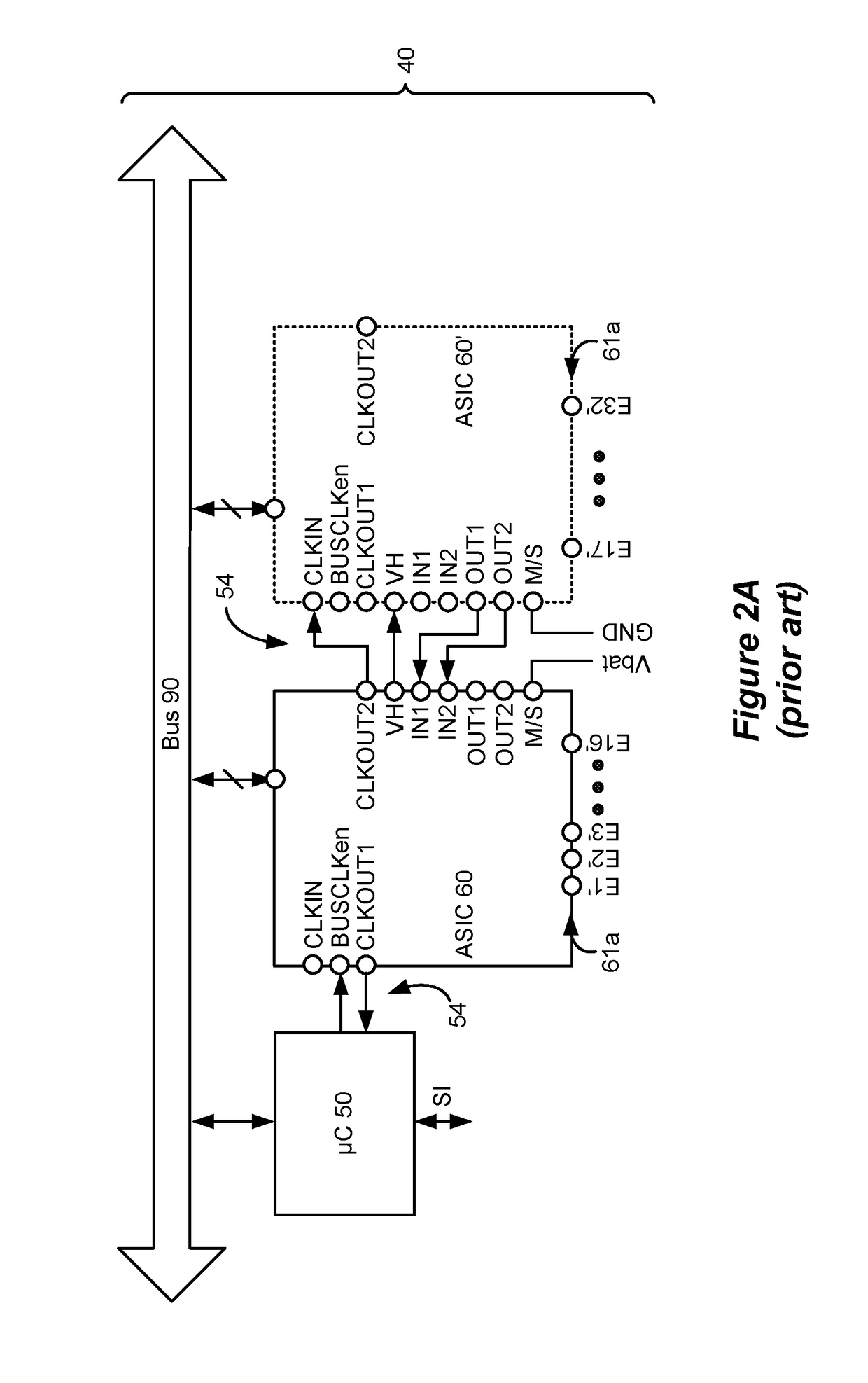

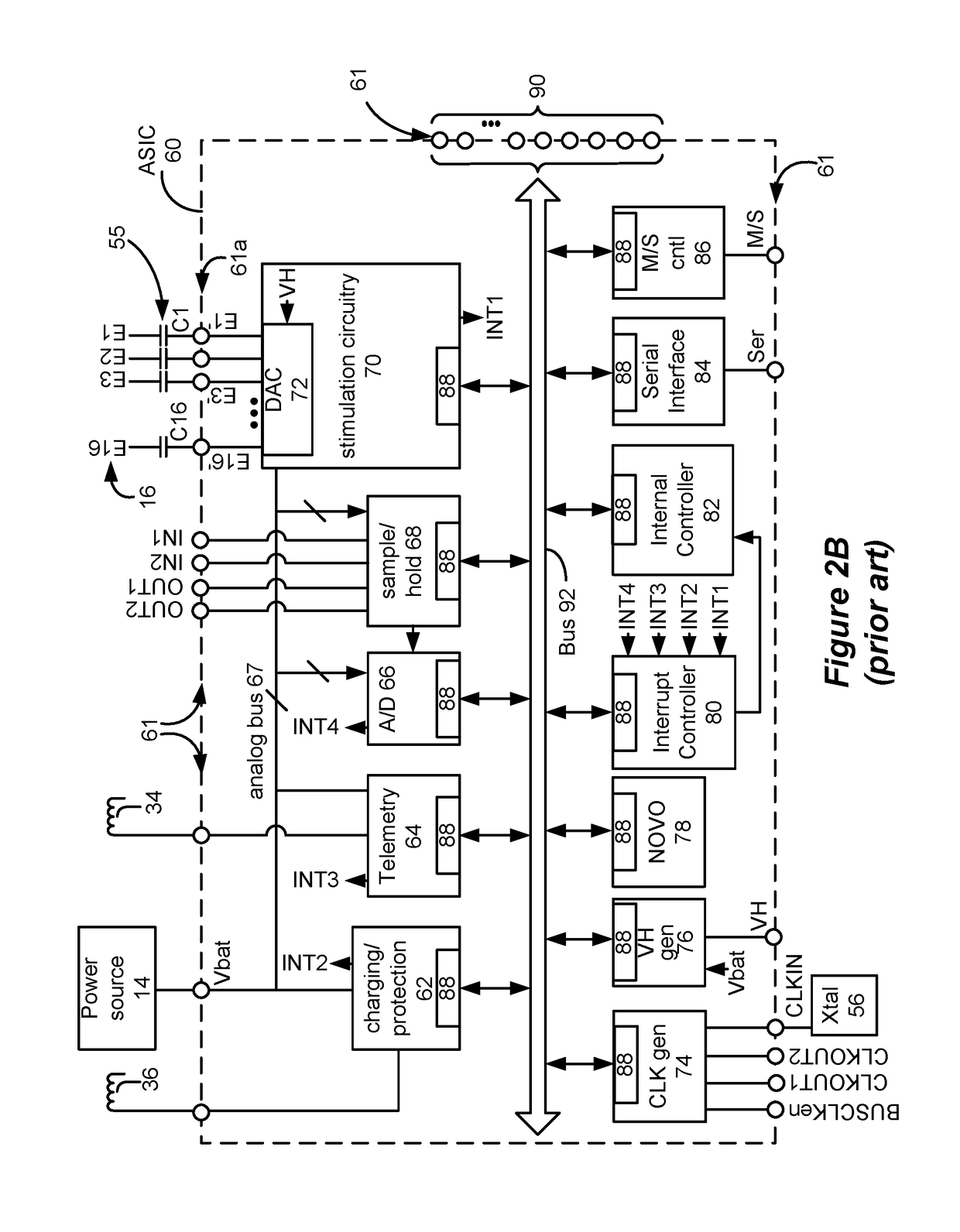

Current Generation Architecture for an Implantable Stimulator Device to Promote Current Steering Between Electrodes

ActiveUS20190083796A1Analogue/digital conversionMultiple input and output pulse circuitsControl signalImage resolution

An implantable pulse generator (IPG) is disclosed having an improved ability to steer anodic and cathodic currents between the IPG's electrodes. Each electrode node has at least one PDAC / NDAC pair to source / sink or sink / source a stimulation current to an associated electrode node. Each PDAC and NDAC receives a current with a magnitude indicative of a total anodic and cathodic current, and data indicative of a percentage of that total that each PDAC and NDAC will produce in the patient's tissue at any given time, which activates a number of branches in each PDAC or NDAC. Each PDAC and NDAC may also receive one or more resolution control signals specifying an increment by which the stimulation current may be adjusted at each electrode. The current received by each PDAC and NDAC is generated by a master DAC, and is preferably distributed to the PDACs and NDACs by distribution circuitry.

Owner:BOSTON SCI NEUROMODULATION CORP

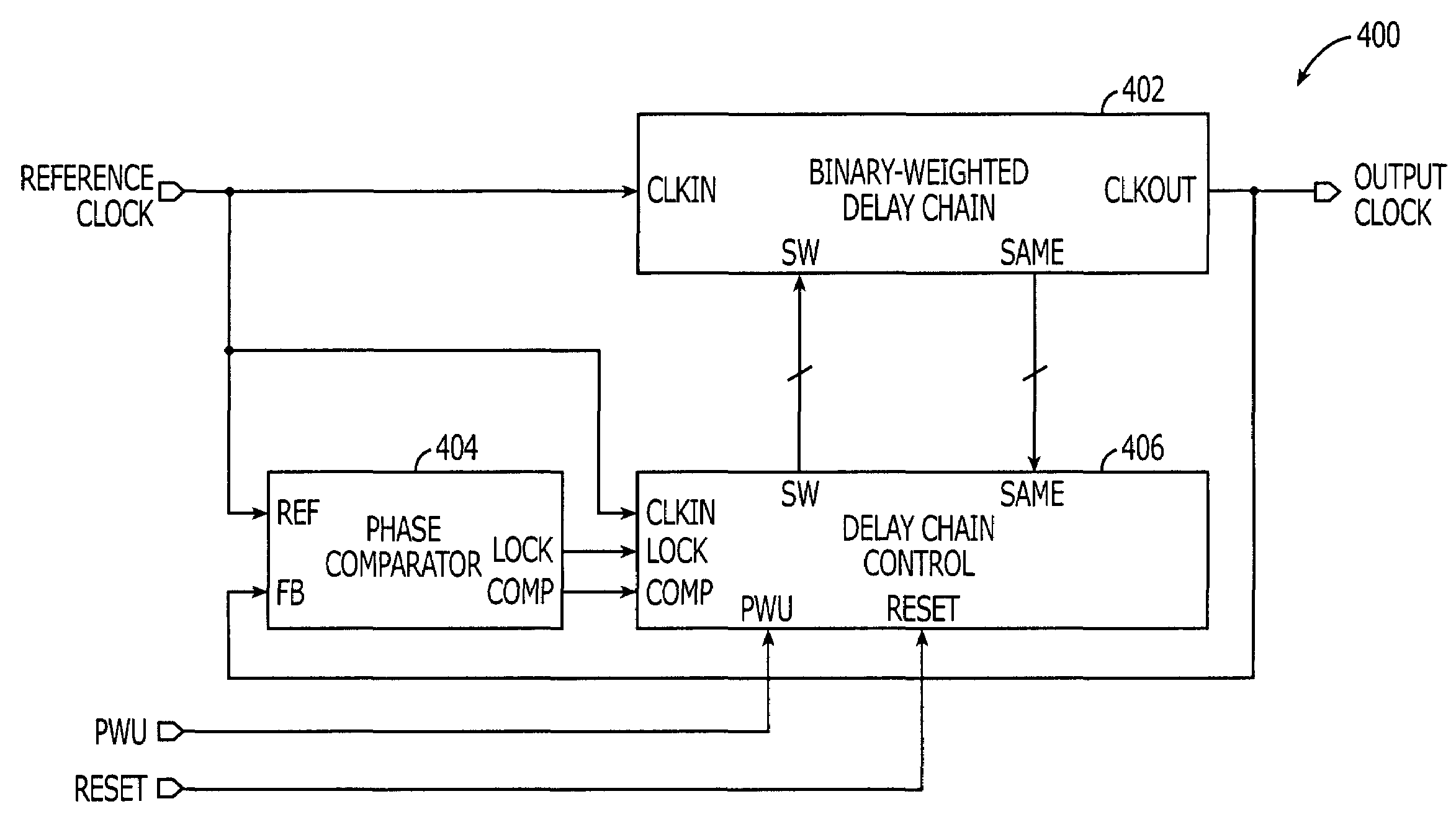

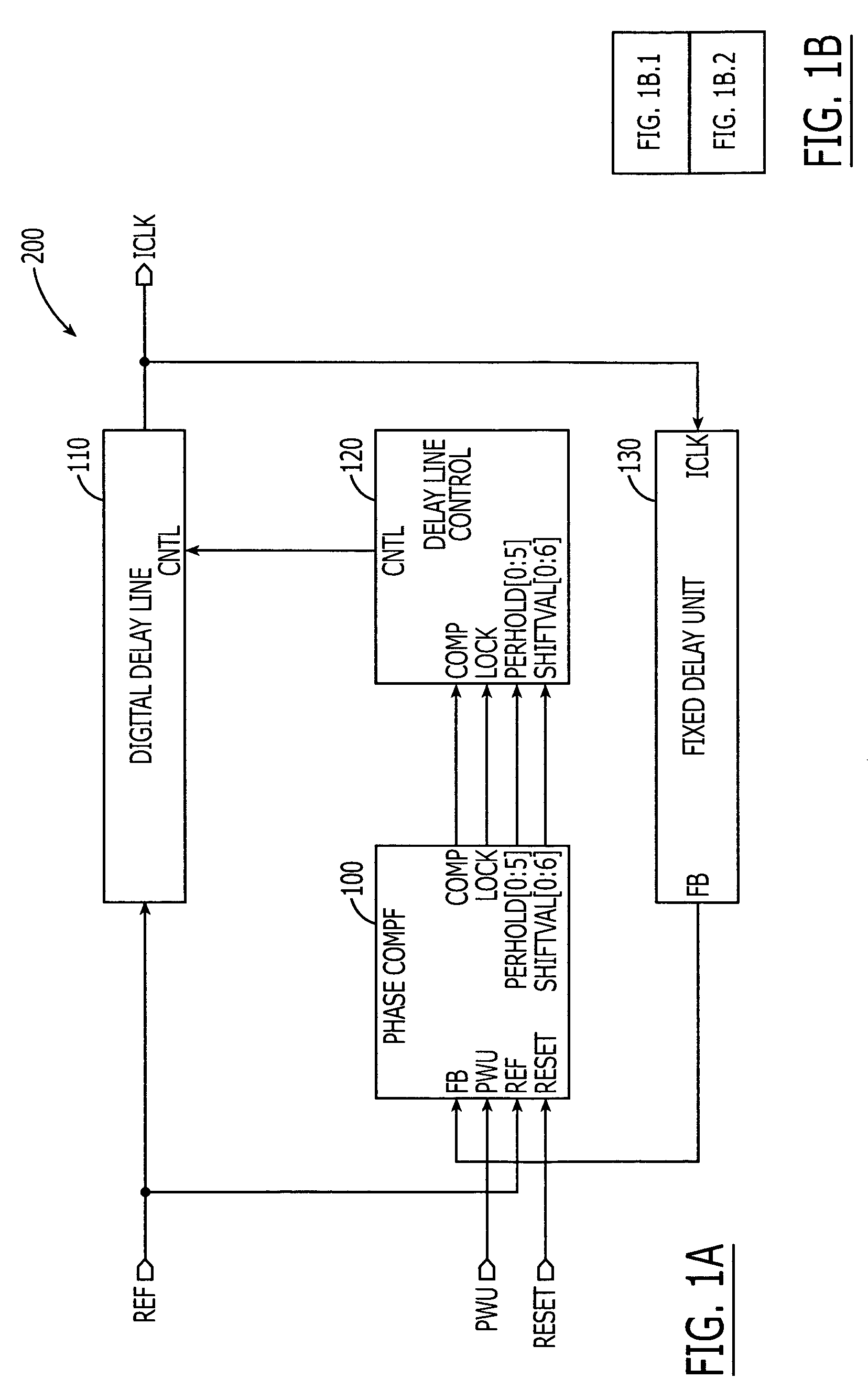

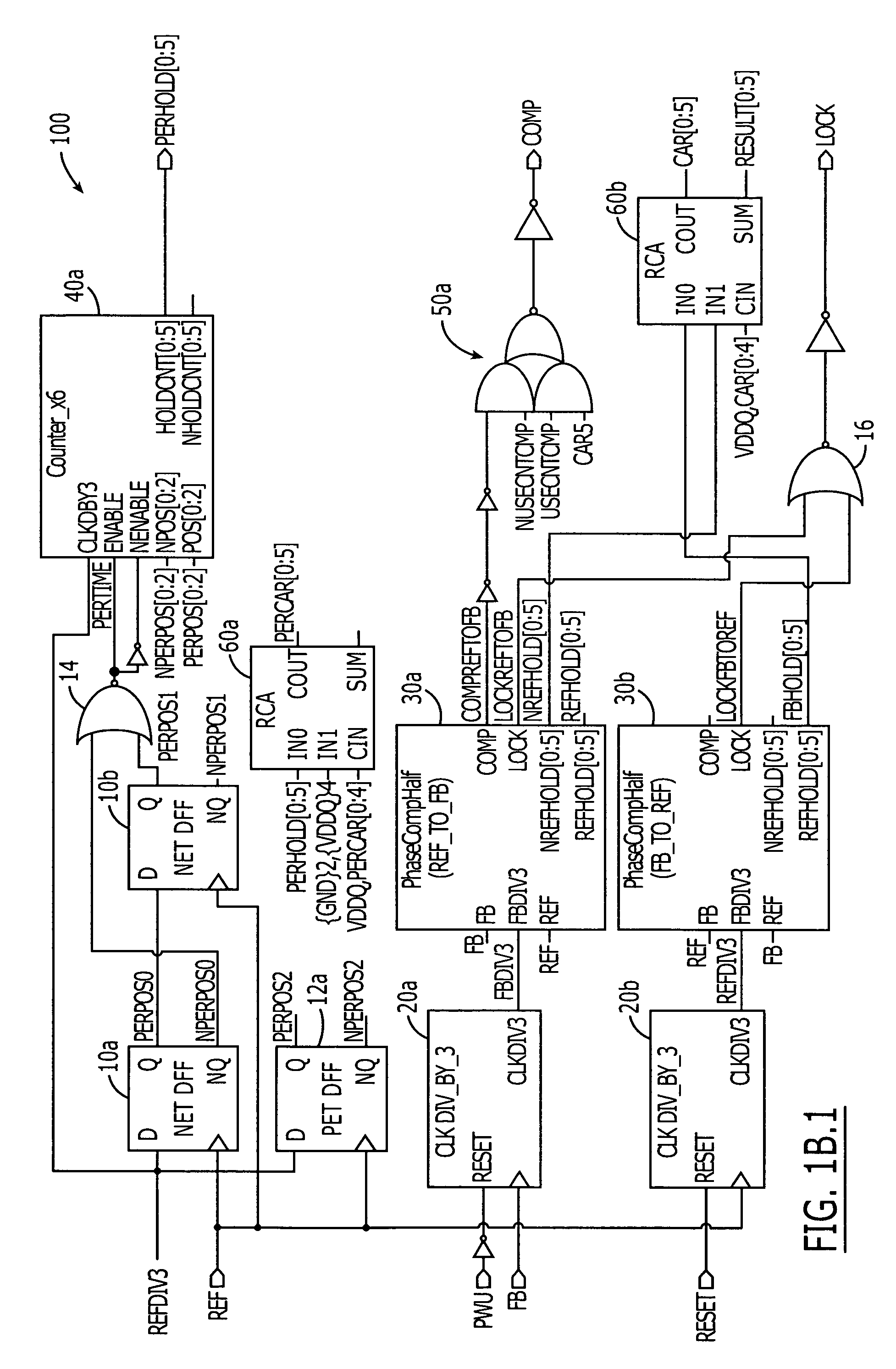

Delay-locked loop (DLL) integrated circuits having binary-weighted delay chain units with built-in phase comparators that support efficient phase locking

ActiveUS7119591B1Facilitates efficient locking of lockedMultiple input and output pulse circuitsPulse automatic controlDelay-locked loopEngineering

Owner:INTEGRATED DEVICE TECH INC

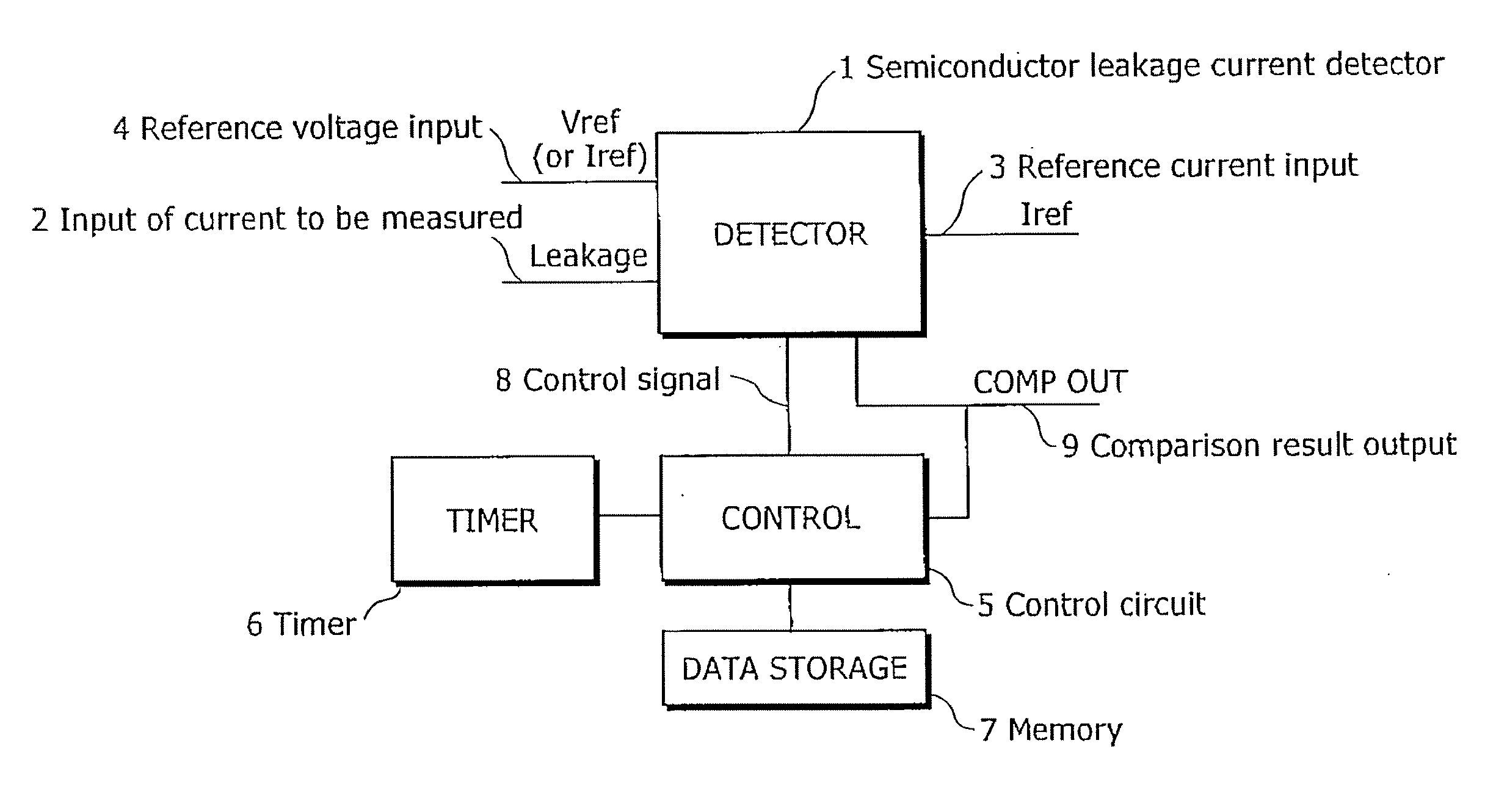

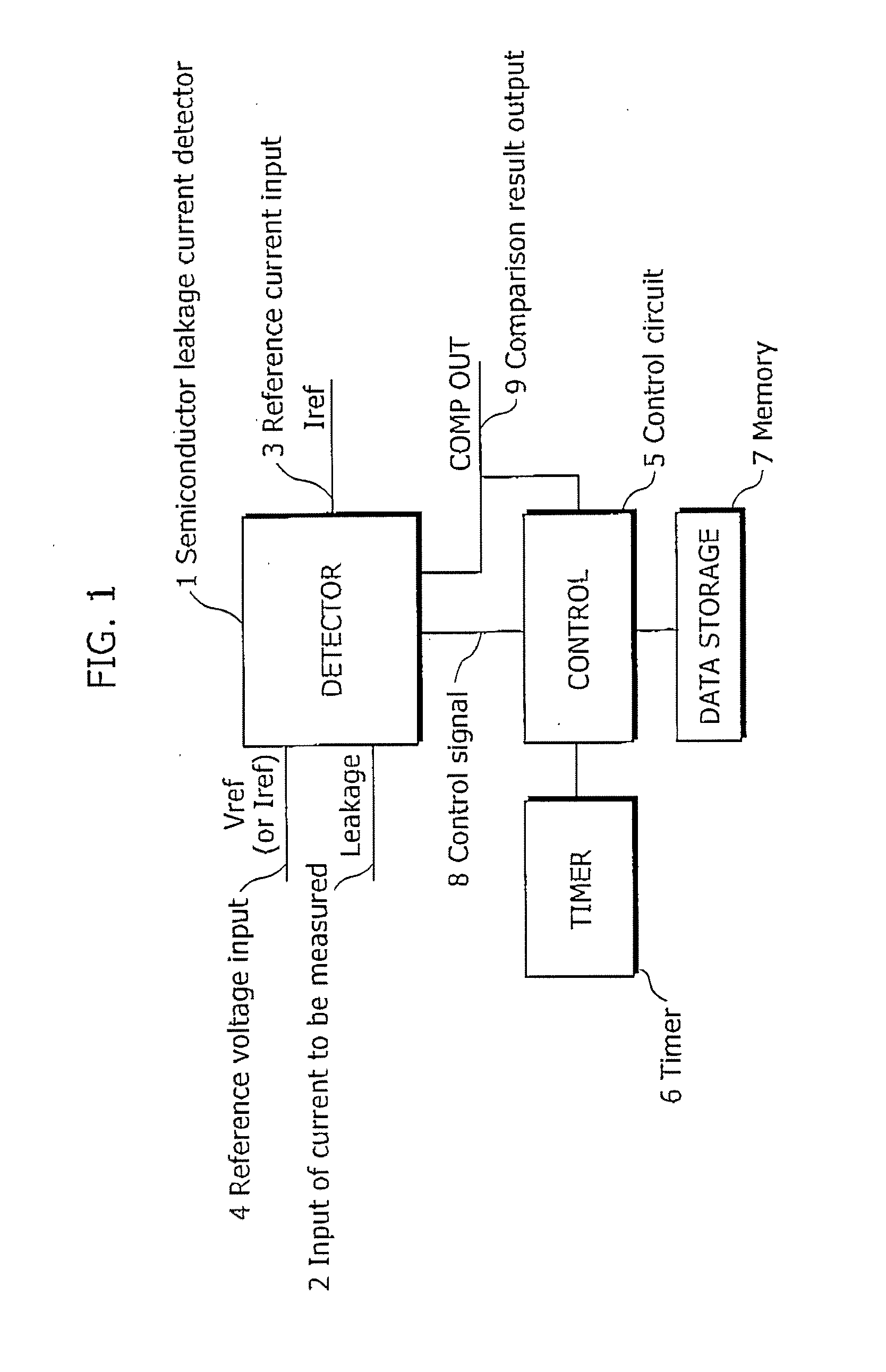

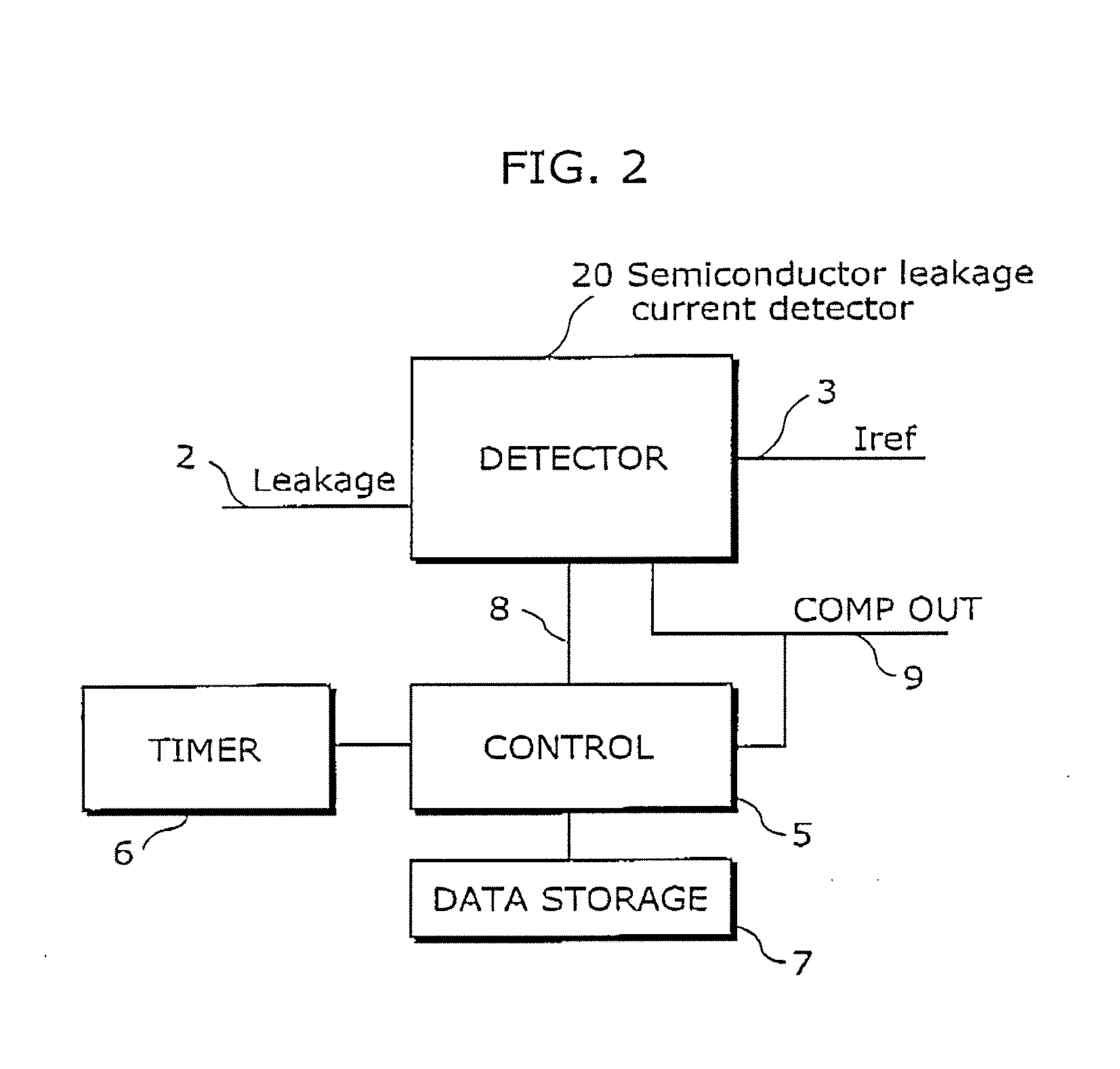

Semiconductor leakage current detector and leakage current measurement method, semiconductor leakage current detector with voltage trimming function and reference voltage trimming method, and semiconductor intergrated circuit thereof

ActiveUS20070145981A1Improve search speedReduce trimming timeMultiple input and output pulse circuitsDirection of current indicationCapacitanceReference current

A semiconductor leakage current detector of the present invention includes a first analog switch which causes a current to be measured to flow or to be cut off, a second analog switch which causes a reference current to flow or to be cut off, an integral capacitance element which is connected by the first analog switch and the second analog switch and is charged with the current to be measured or the reference current, a discharge unit which discharges the integral capacitor, and a comparison unit which compares the reference voltage with each of an integral voltage generated in the integral capacitor by a reference current after the discharge of the integral capacitor and an integral voltage generated in the integral capacitance element by the current to be measured after the discharge of the integral capacitor

Owner:III HLDG 12 LLC

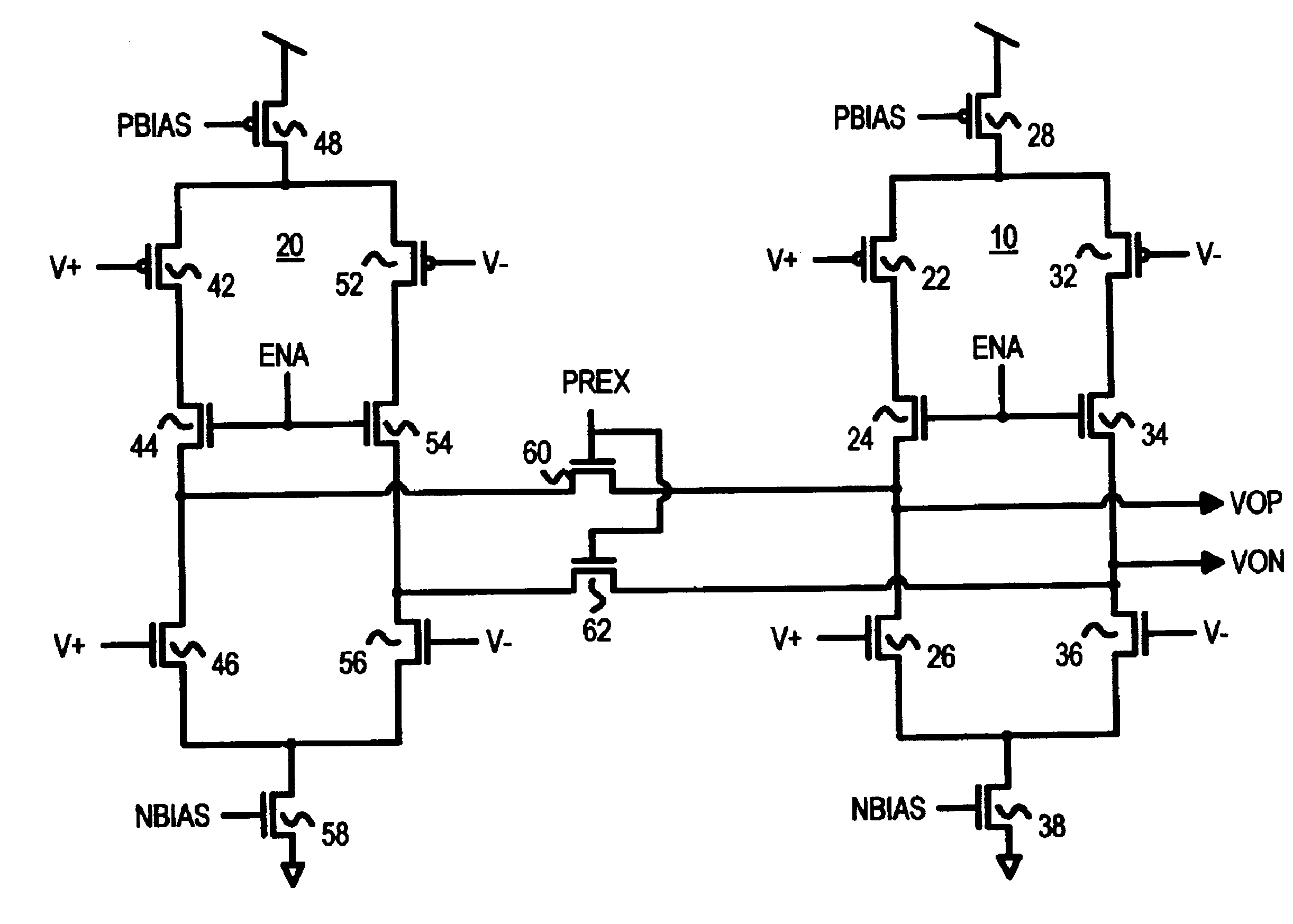

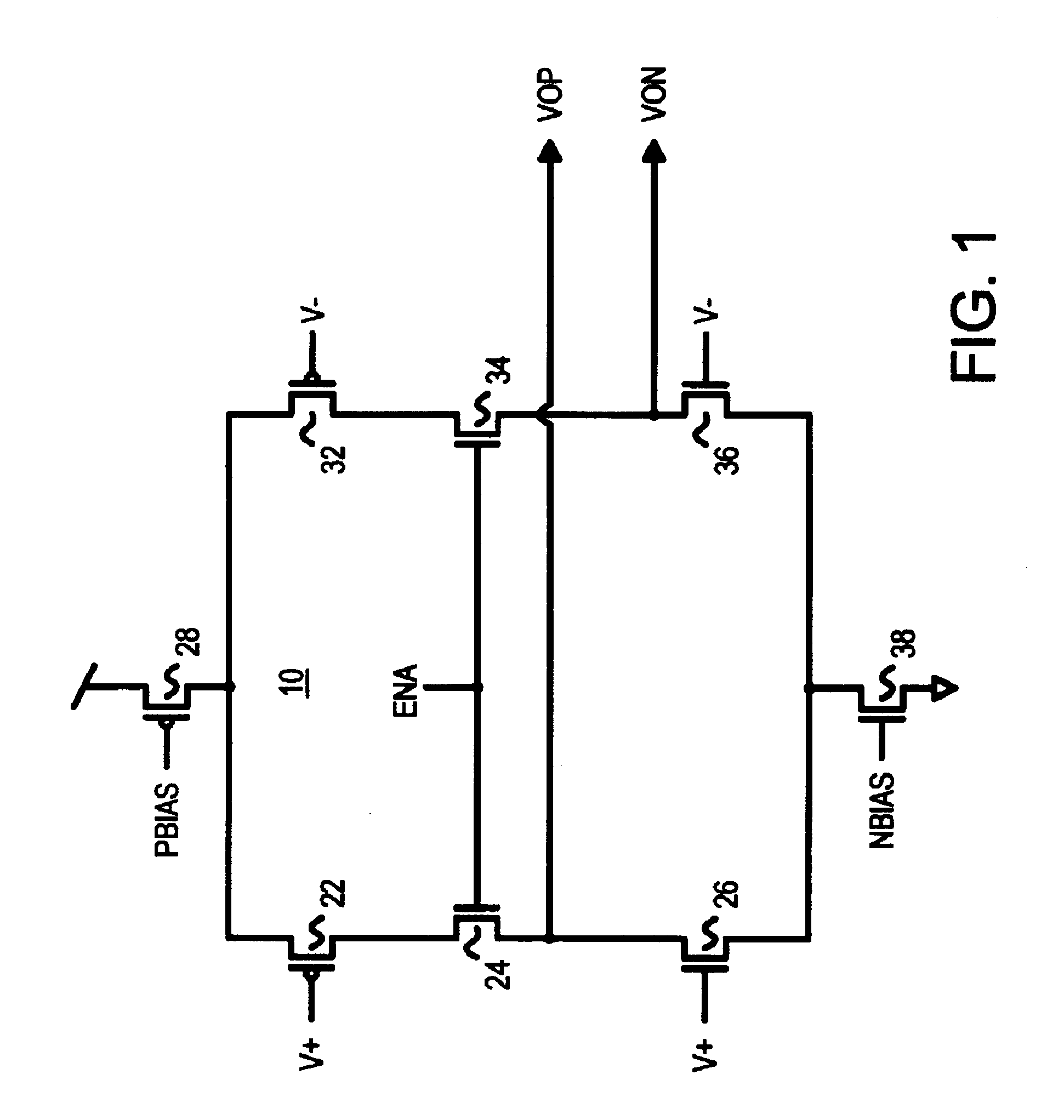

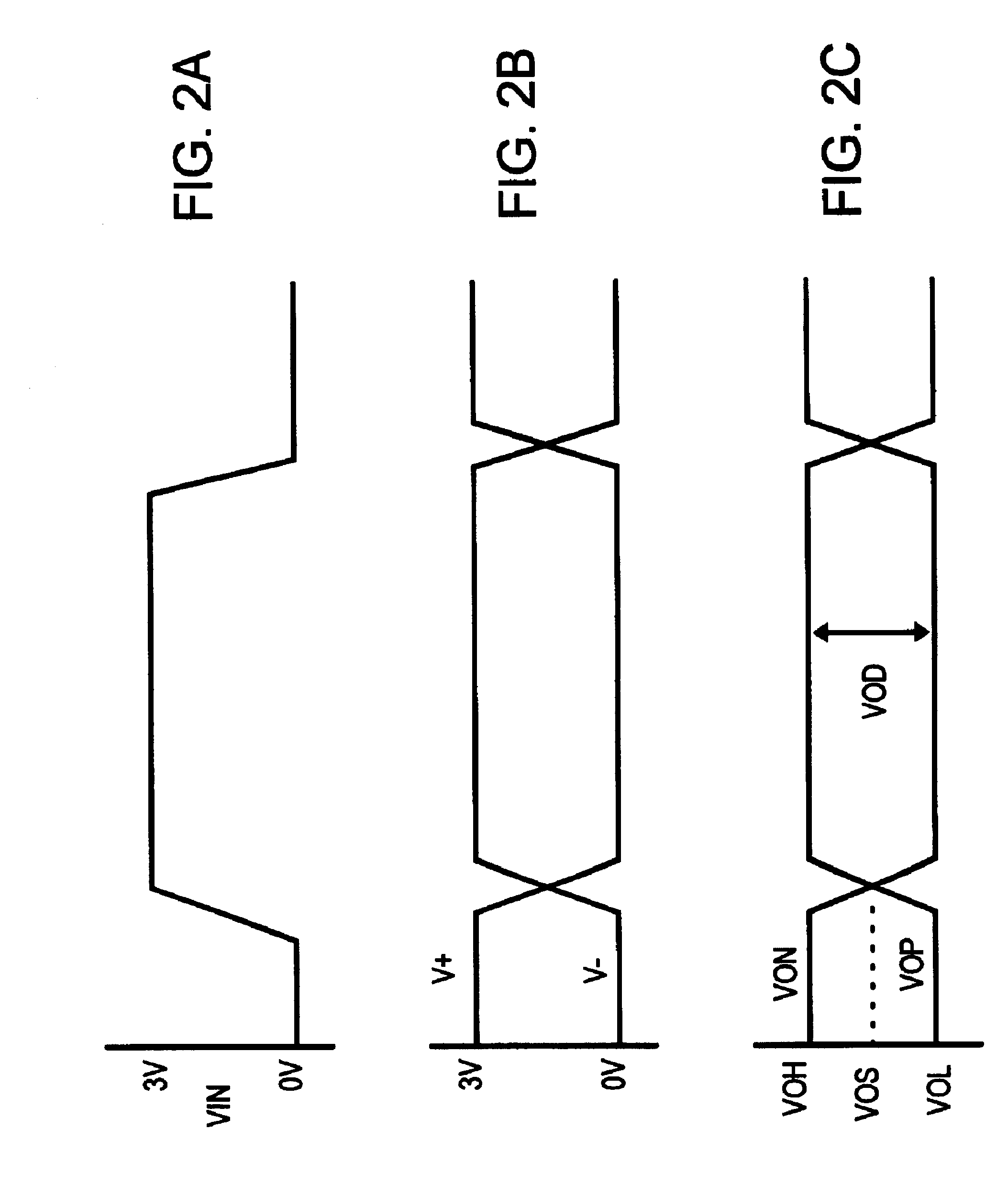

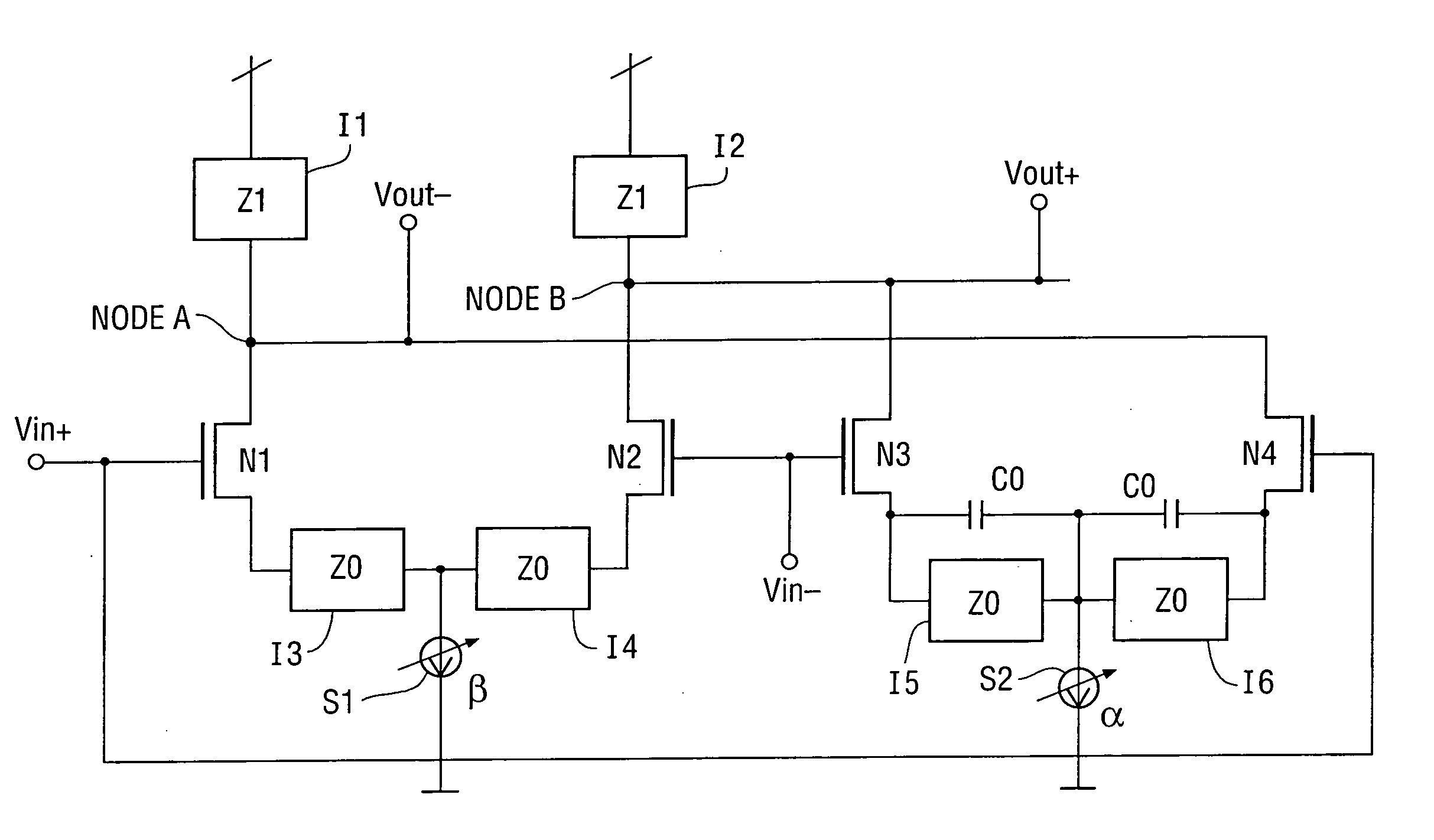

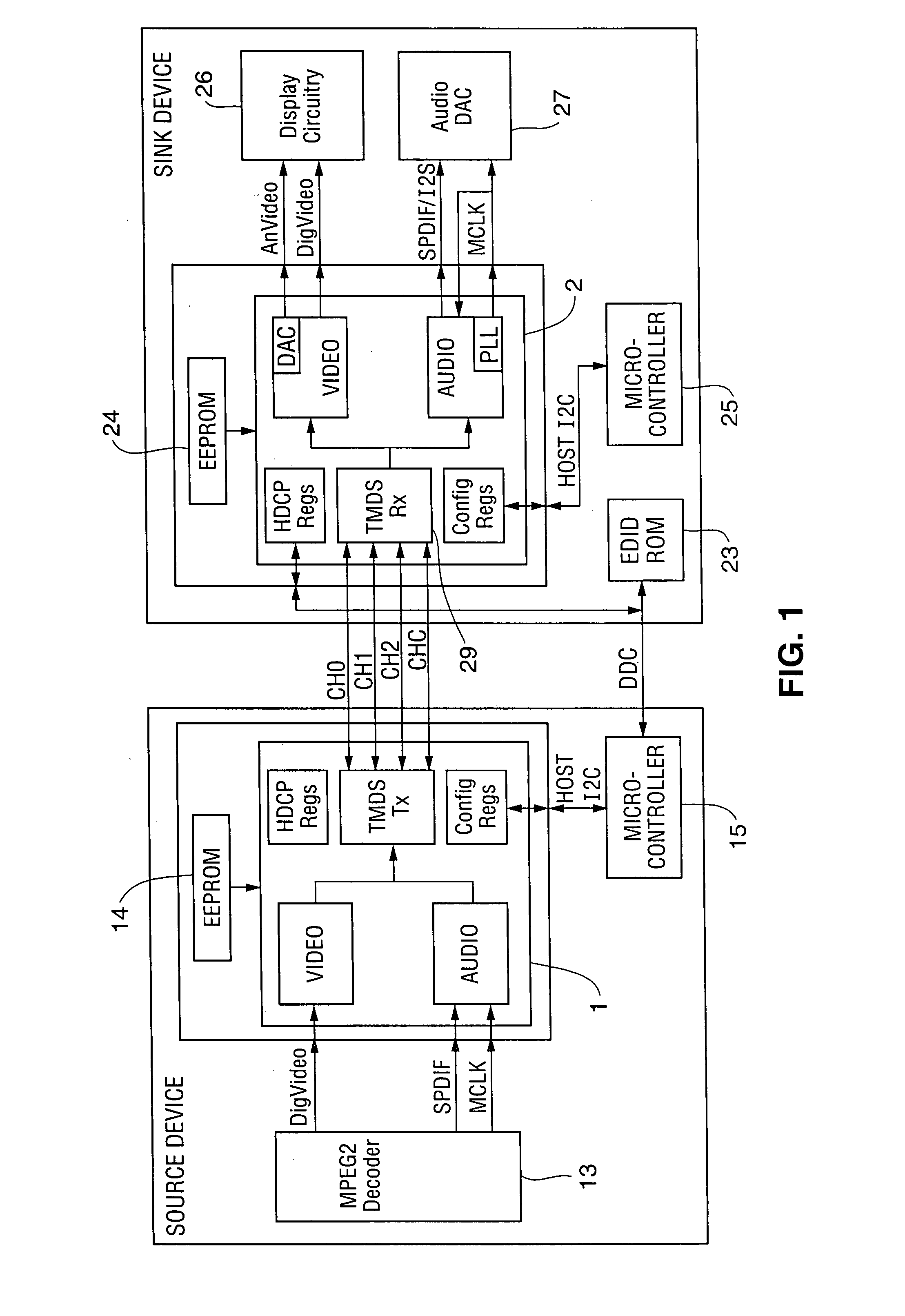

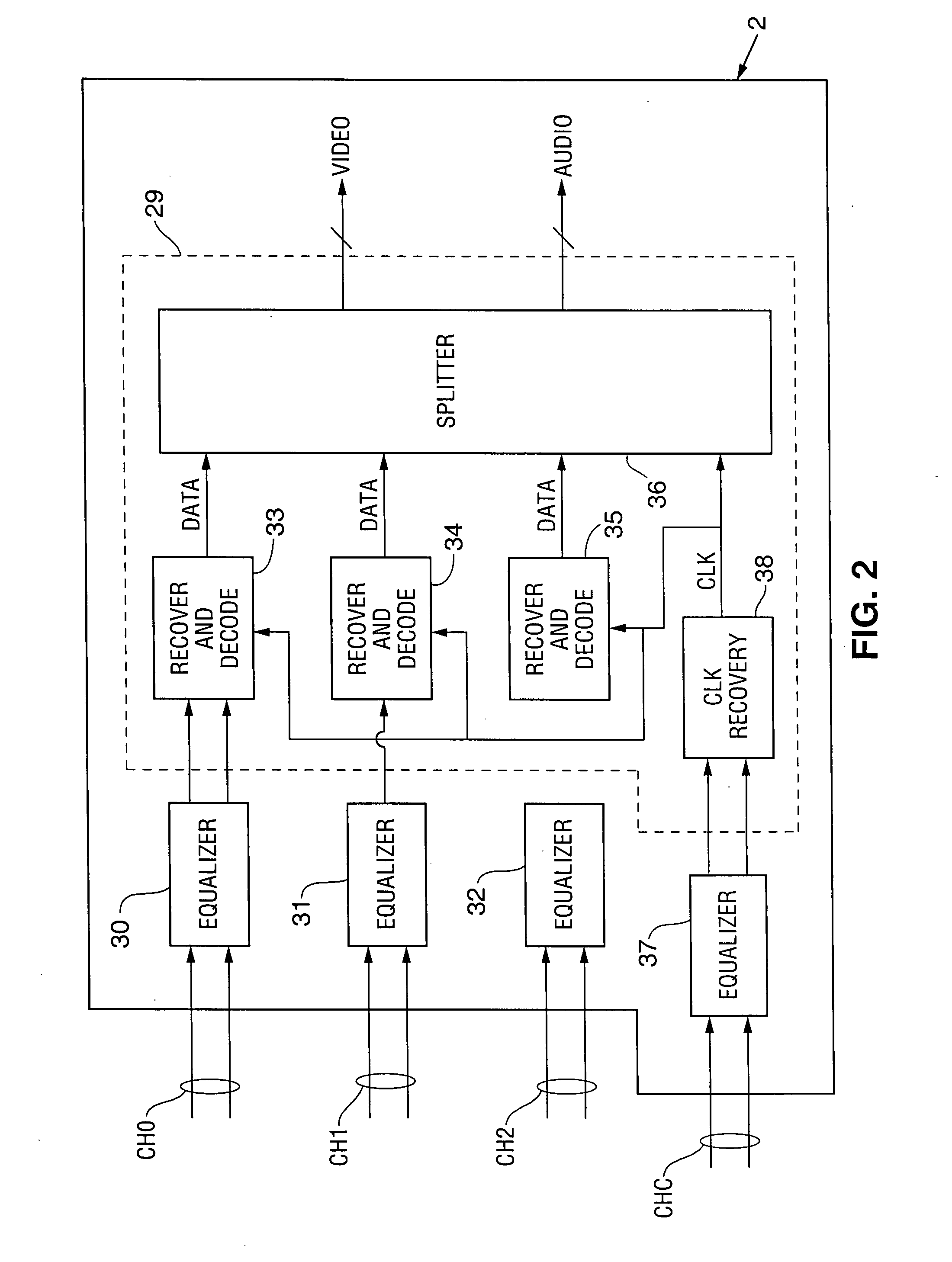

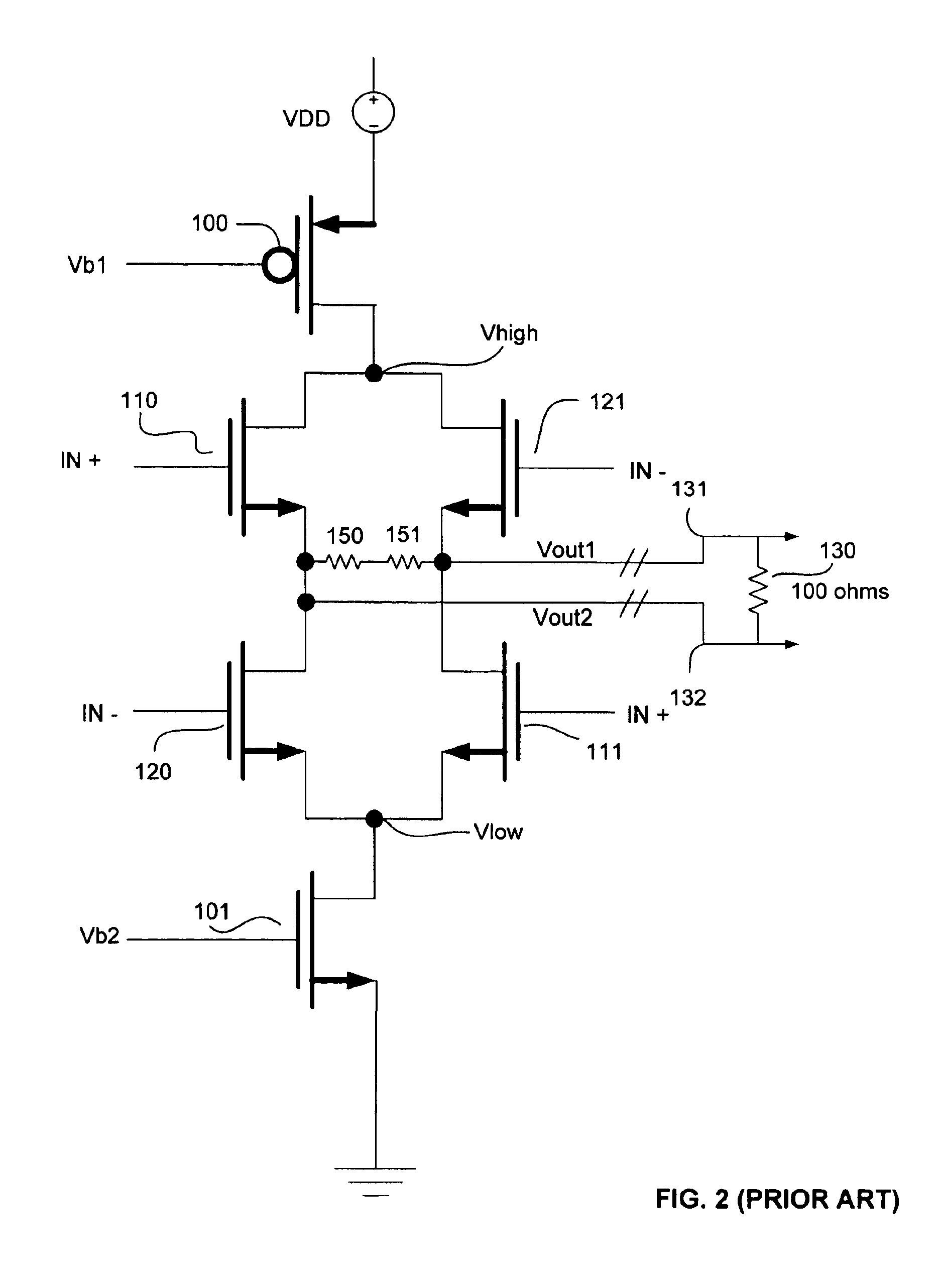

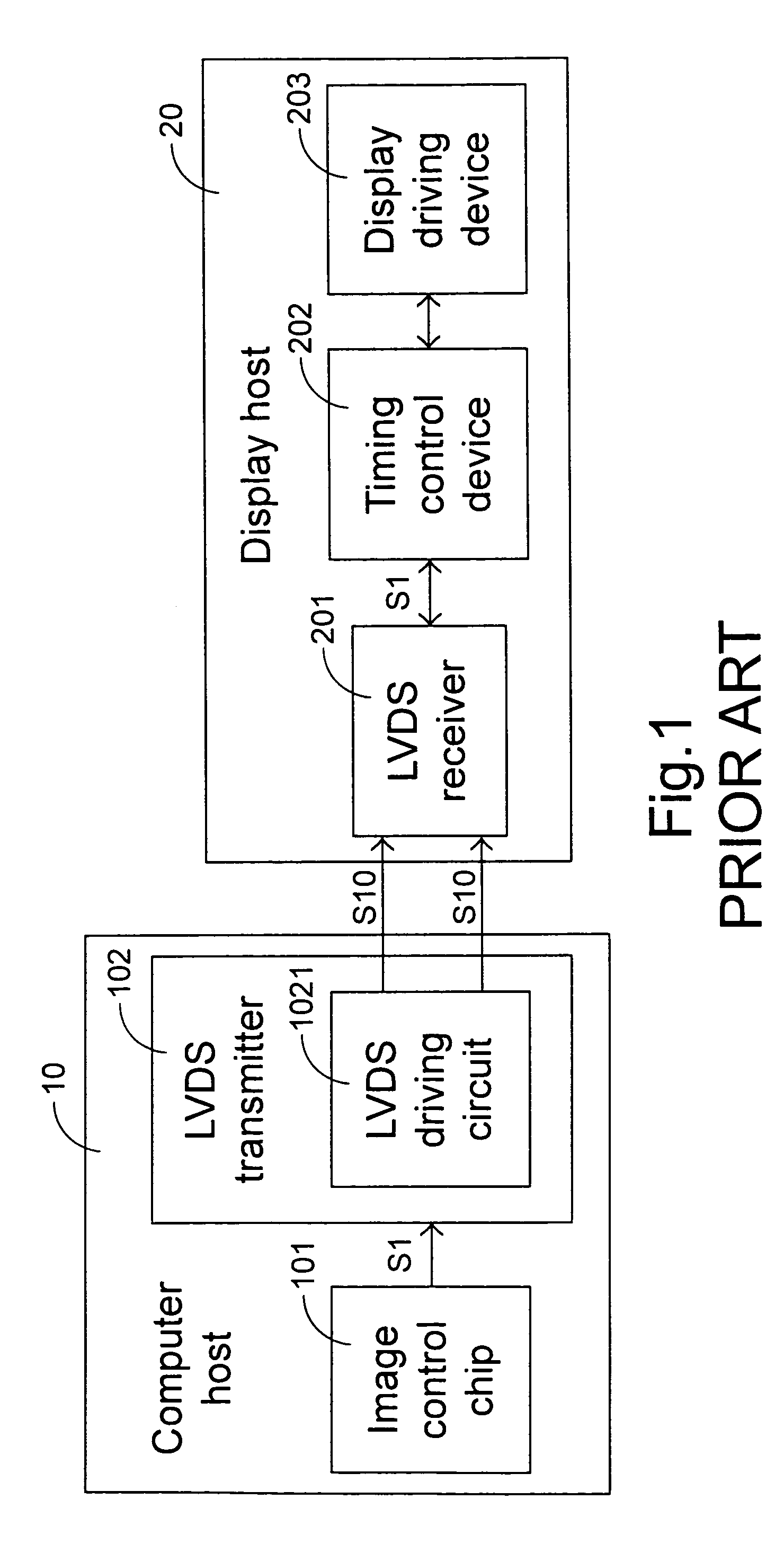

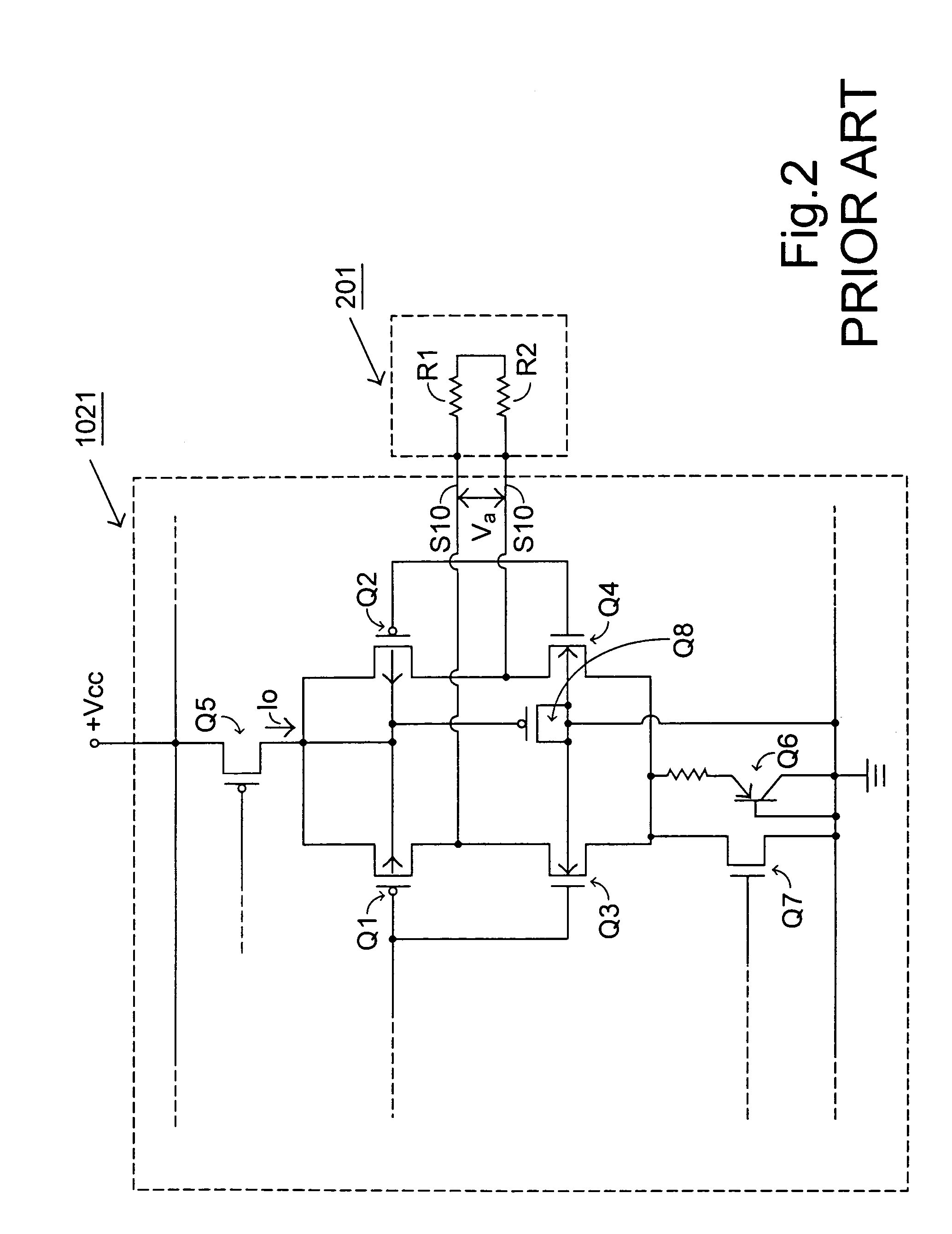

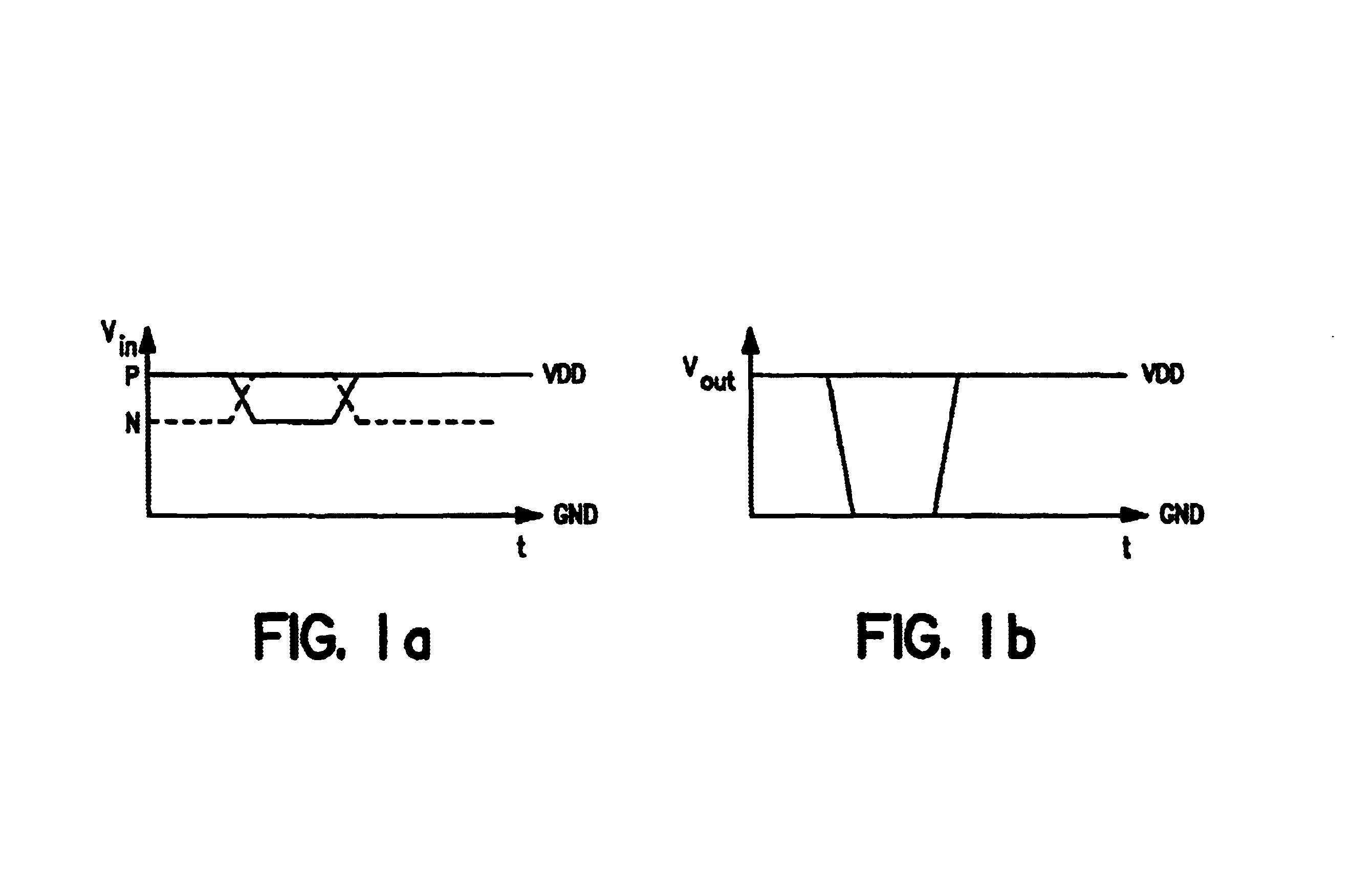

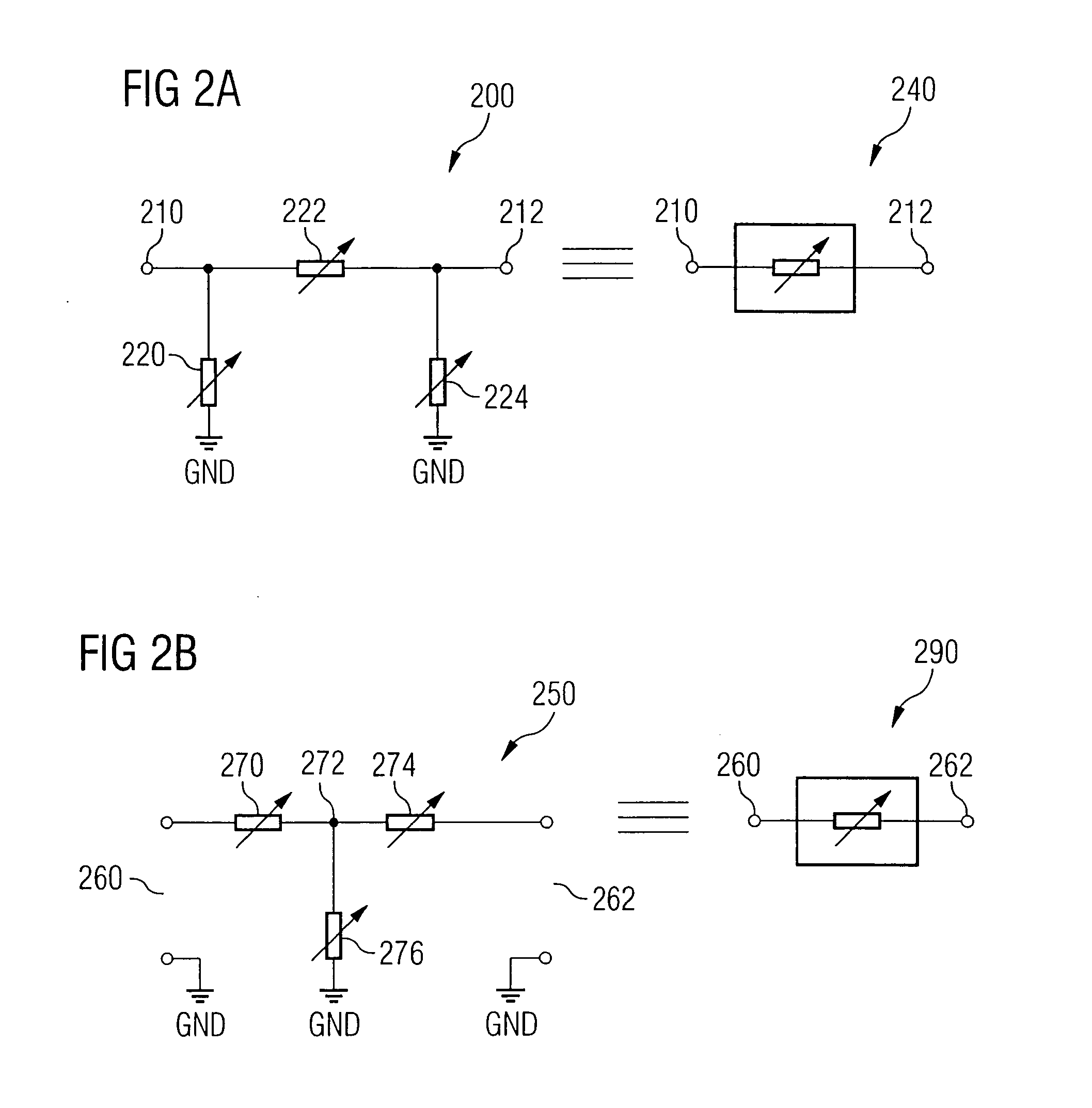

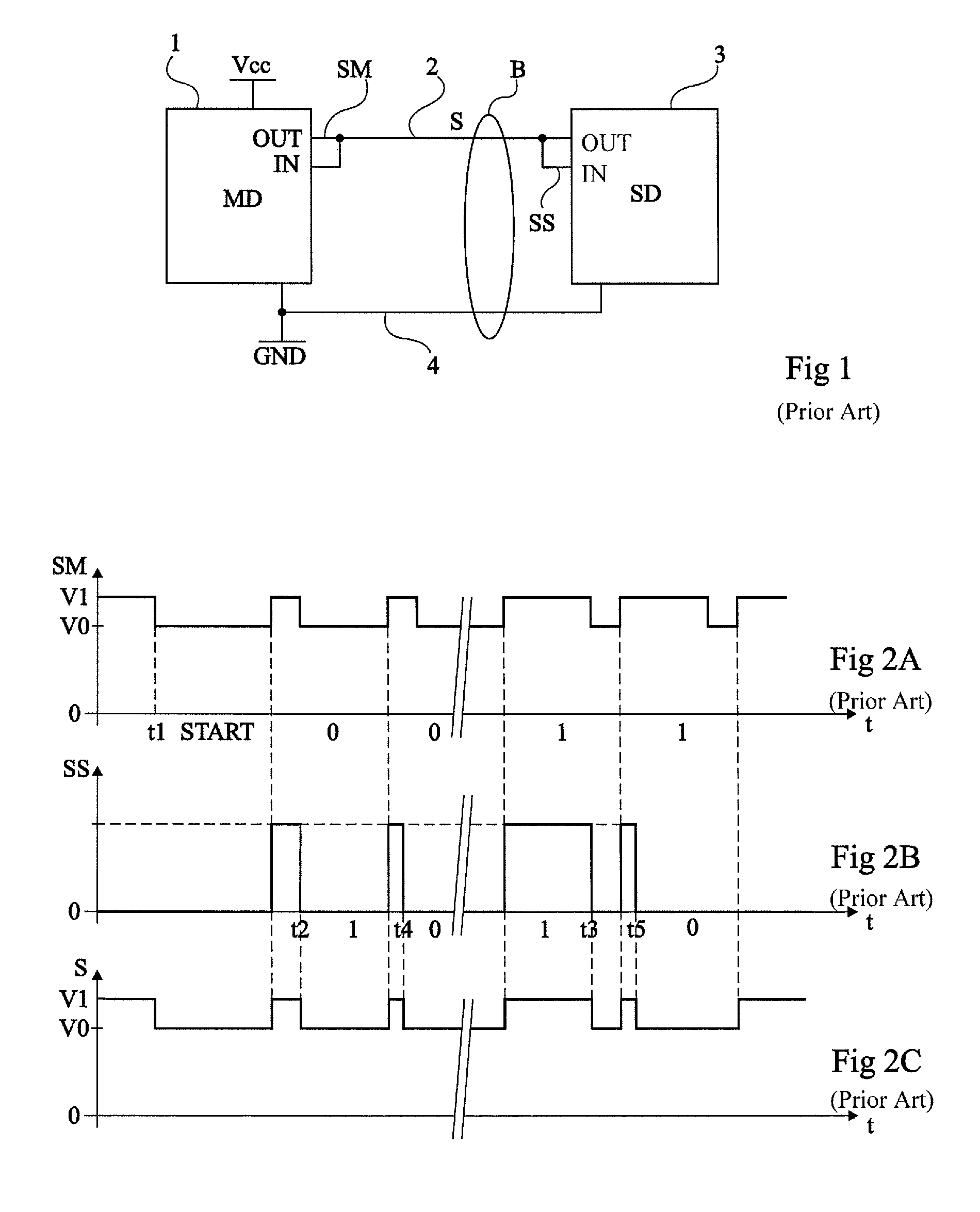

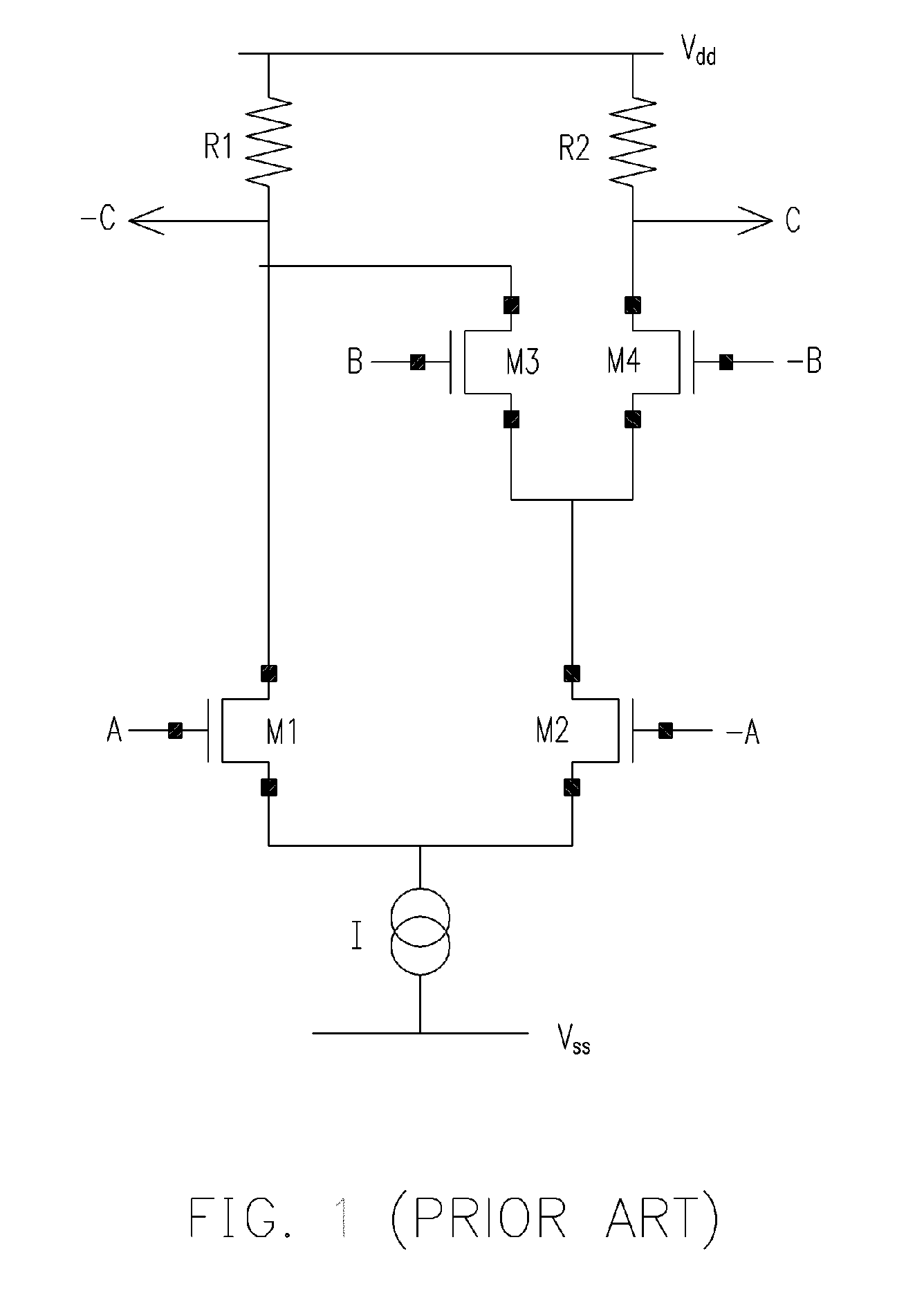

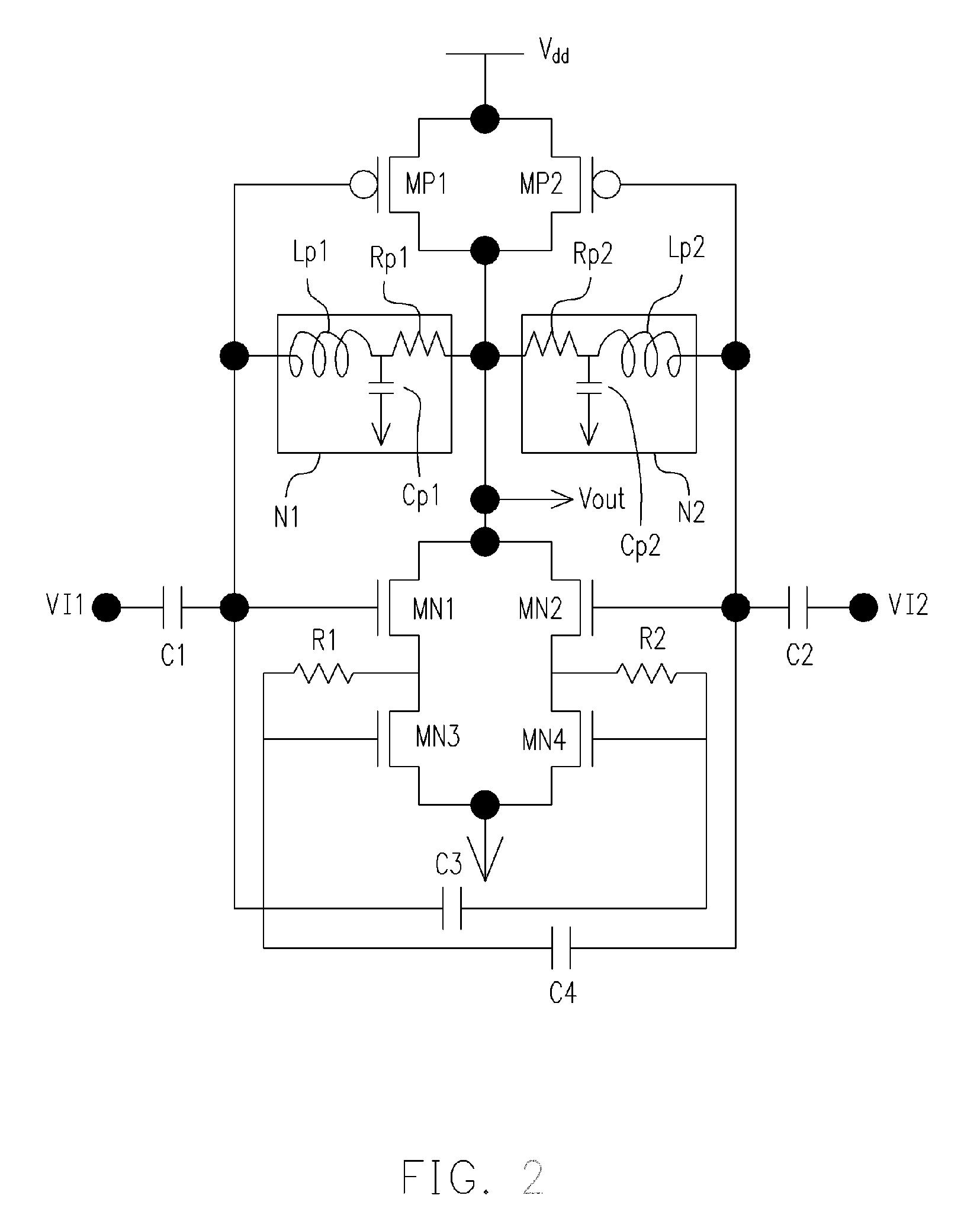

Low voltage differential signaling [LVDS] driver with pre-emphasis

ActiveUS6977534B2Reduce data jitterMultiple input and output pulse circuitsBaseband system detailsControl signalSecondary stage

A Low Voltage Differential Signaling Driver with Pre-emphasis and including a primary stage having a first switching circuit providing an output representing a sequence of pulses at a predetermined current level, a secondary stage having a second switching circuit arranged to provide an additional current level for the pulses, and a control circuit arranged to provide control signals for controlling the first and second switching circuits. The control circuit detects a difference in level between two consecutive pulses of the sequence and provides accordingly control signals to the first and second switching circuits. The control signals are such that when two consecutive pulses of the sequence are different, the additional current level is added to the predetermined current level, whilst when two consecutive pulses of the sequence are identical, the additional current level is subtracted from the predetermined current level.

Owner:RPX CORP

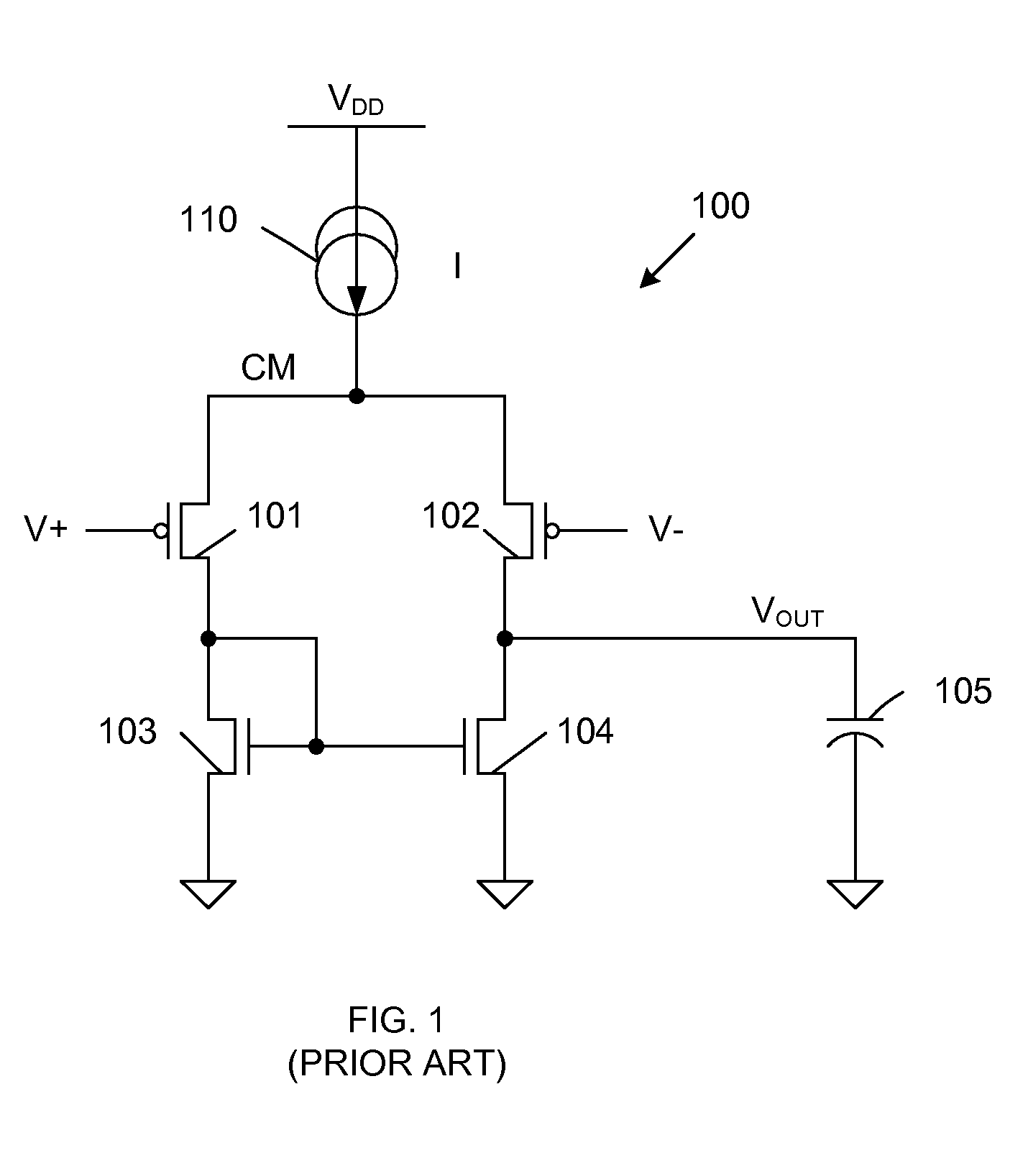

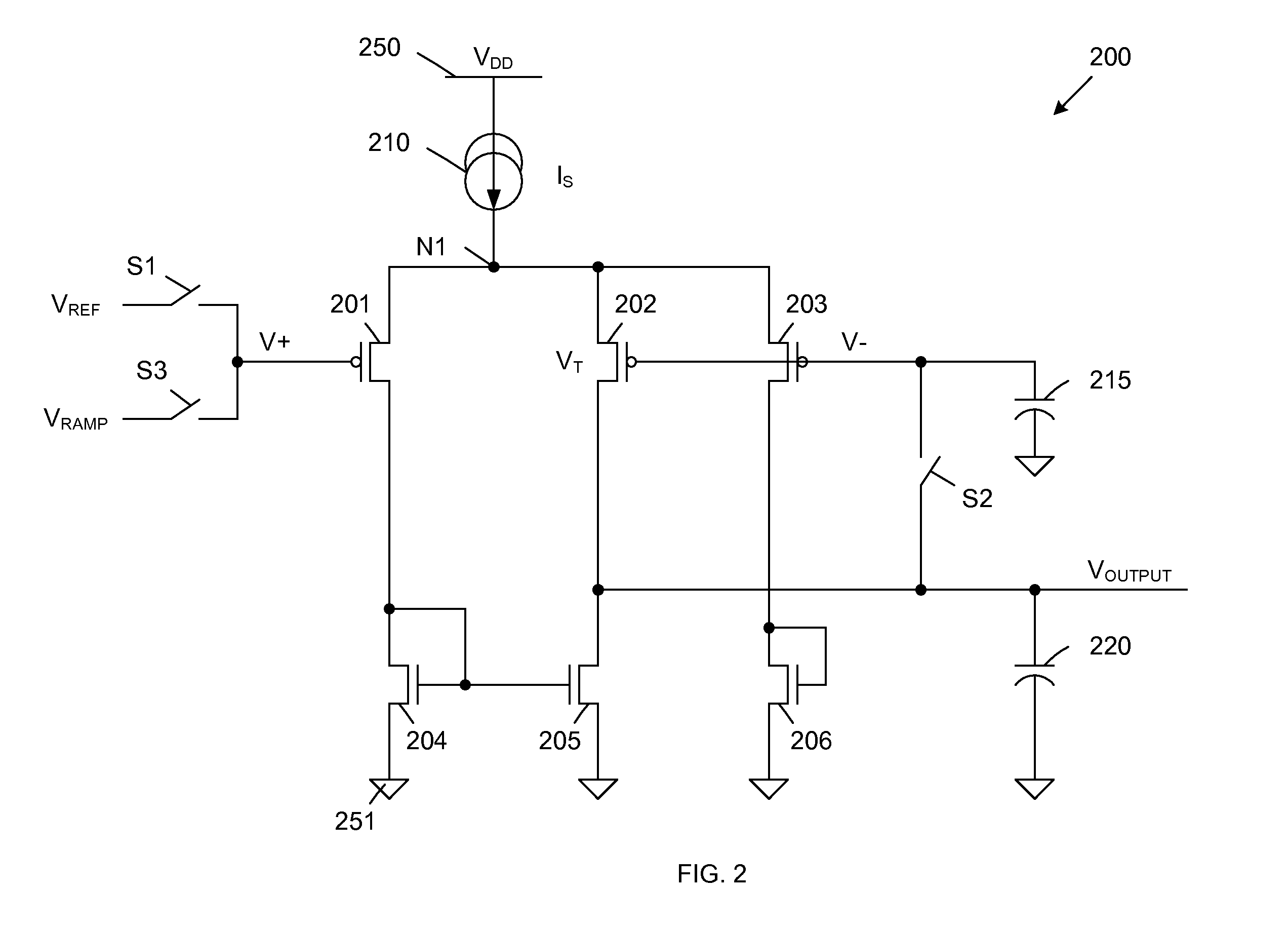

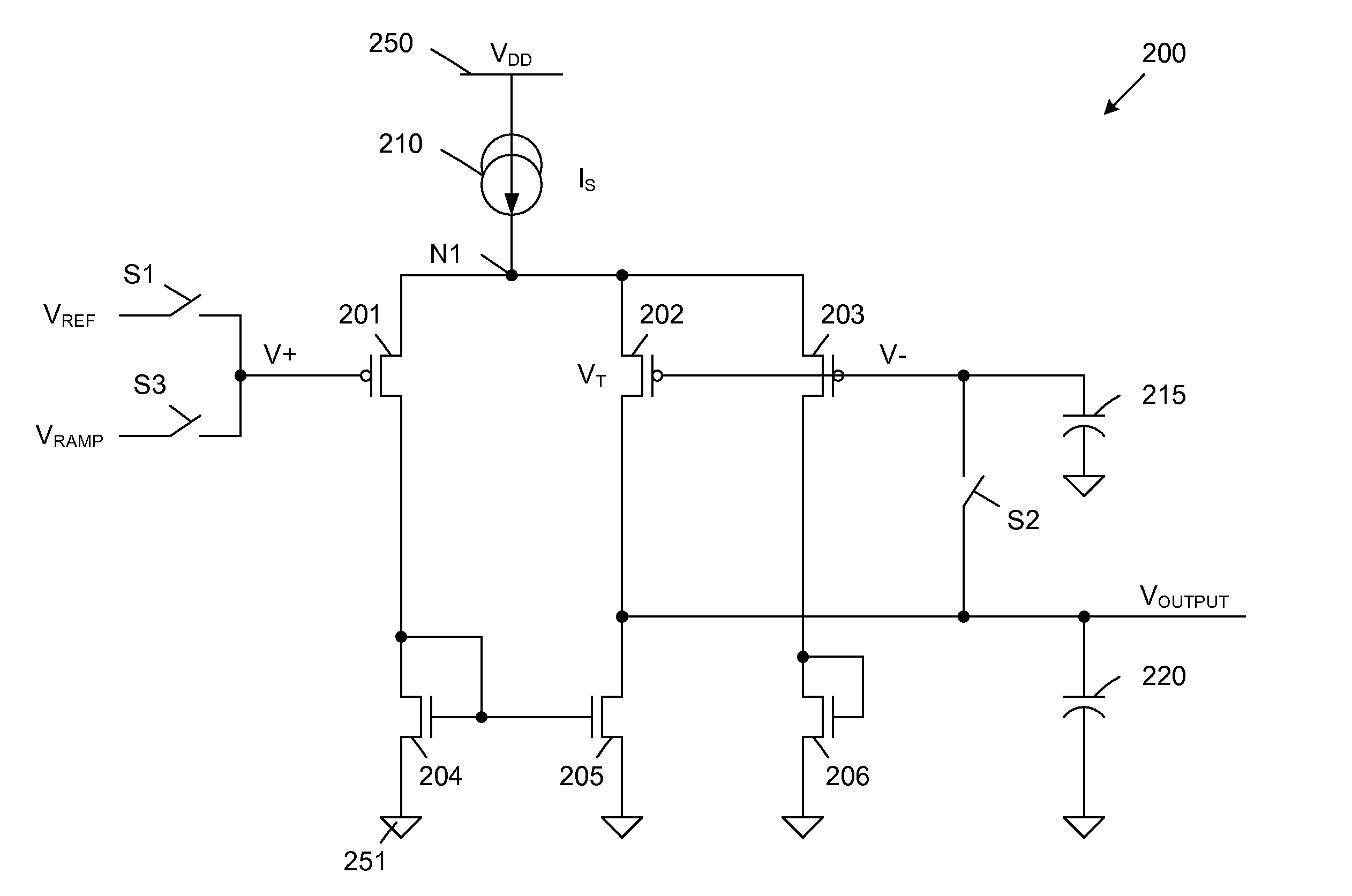

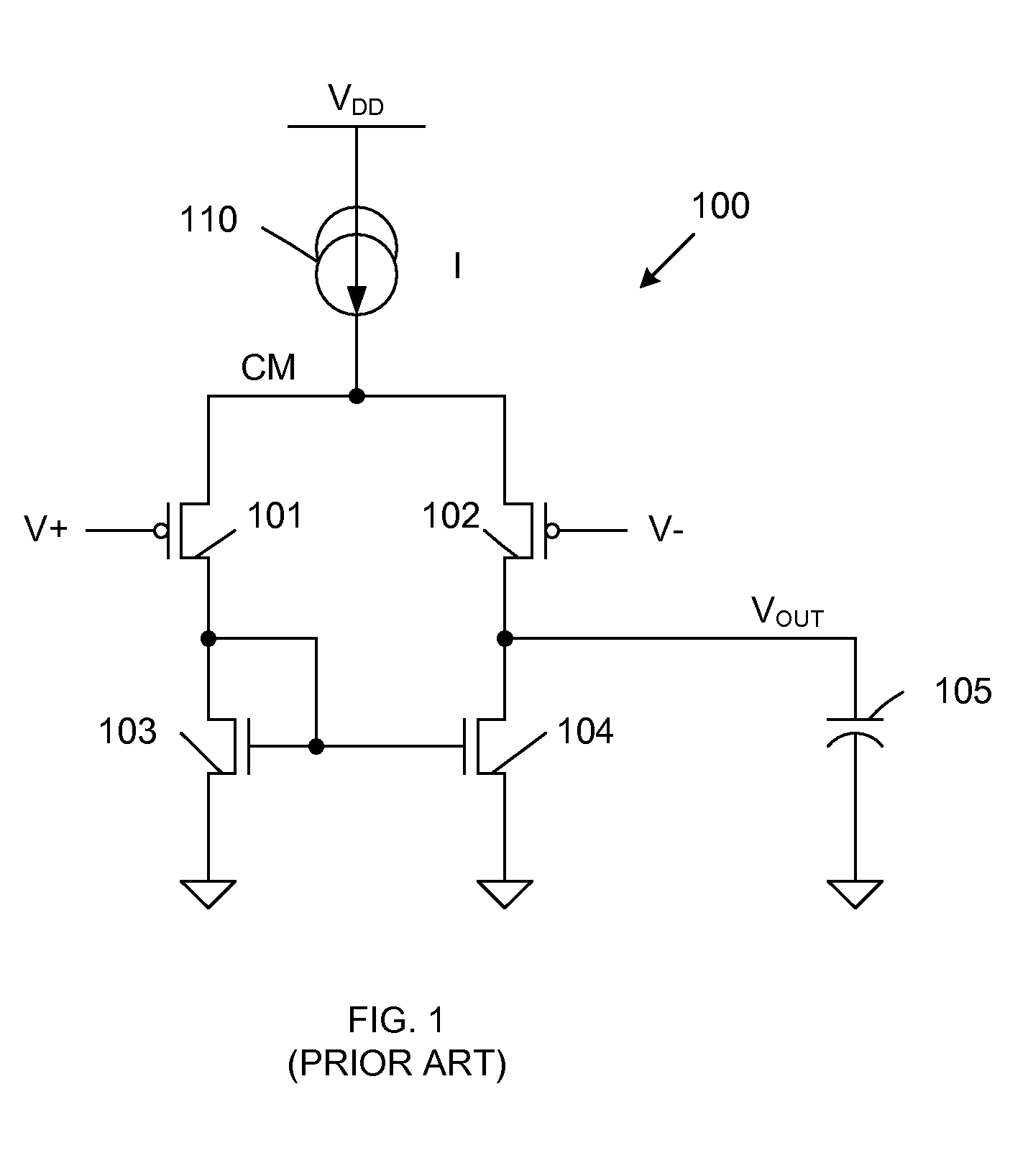

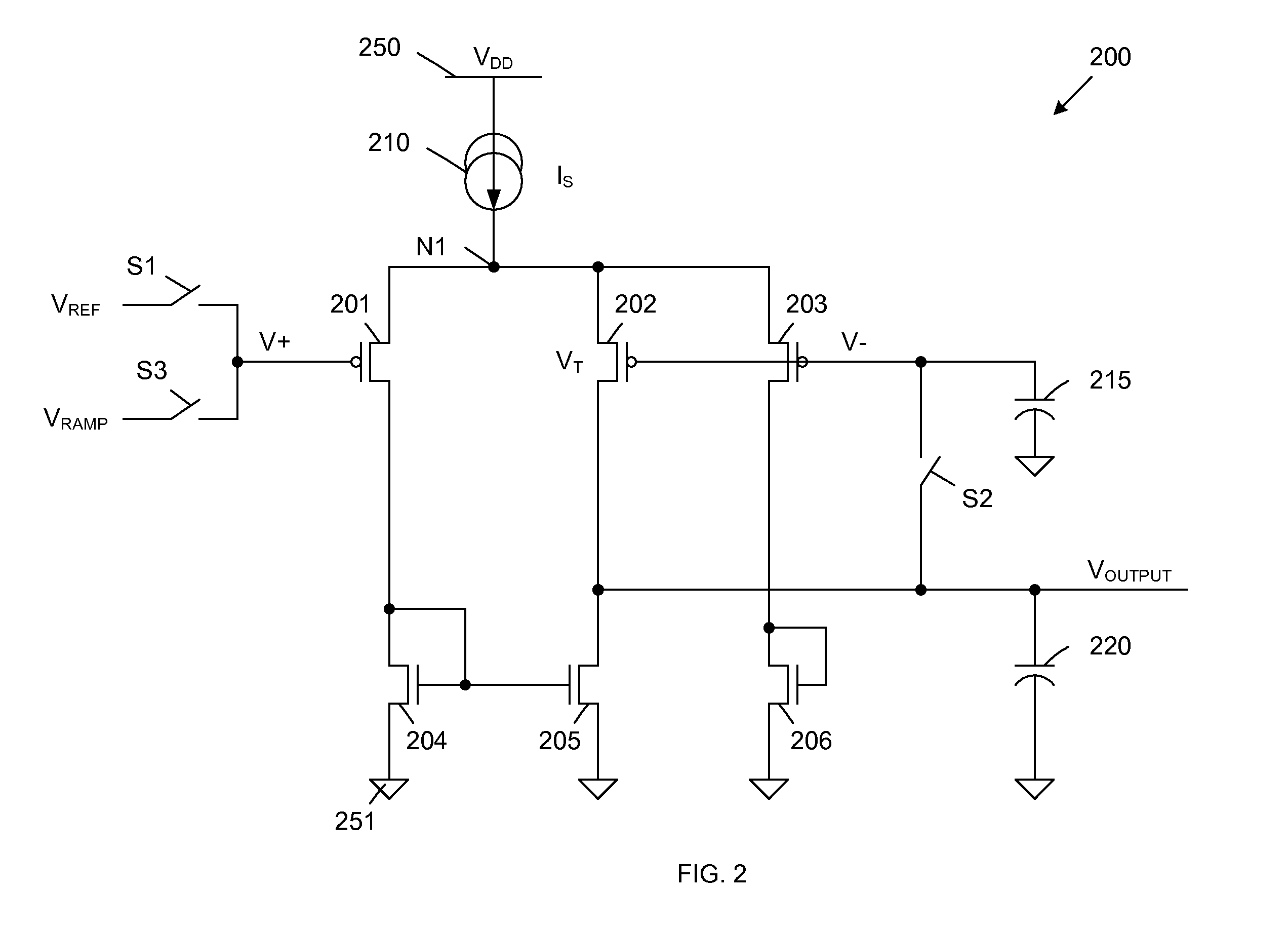

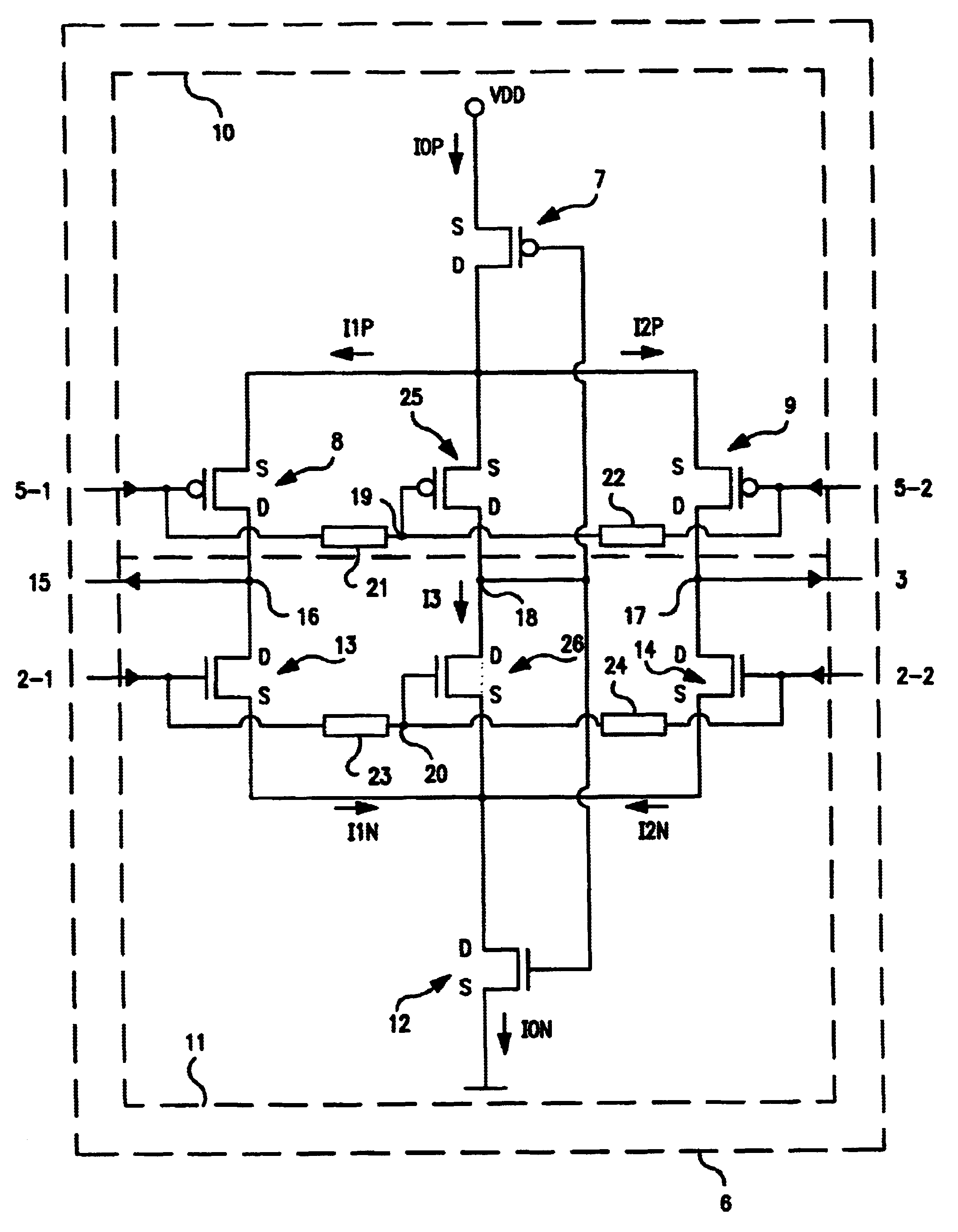

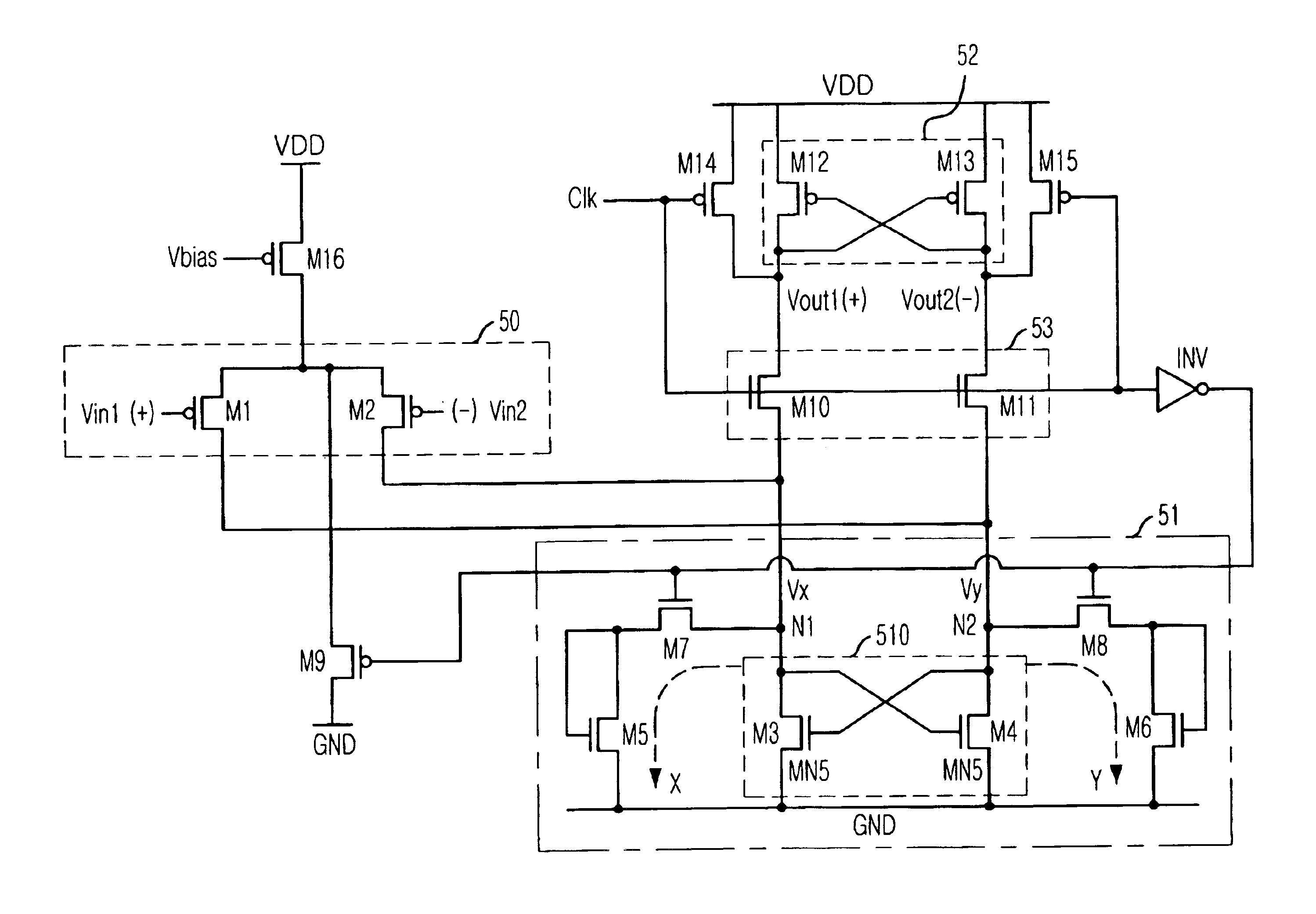

Comparator with low supply current spike and input offset cancellation

ActiveUS7609093B2Multiple input and output pulse circuitsInstant pulse delivery arrangementsOffset cancellationComparators circuits

A current control circuit is coupled in parallel with the current paths of a differential comparator circuit to ensure that a substantially constant current is drawn from a current source during all operating phases of a comparator. The current control circuit is biased by a reference voltage, which is also used to bias a V− input terminal of the differential comparator circuit. The reference voltage is stored by a sample capacitor, which is charged by applying the reference voltage to a V+ input terminal of the differential comparator circuit while coupling an output terminal of the differential comparator circuit to the sample capacitor in a unity feedback configuration.

Owner:TOWER SEMICONDUCTOR

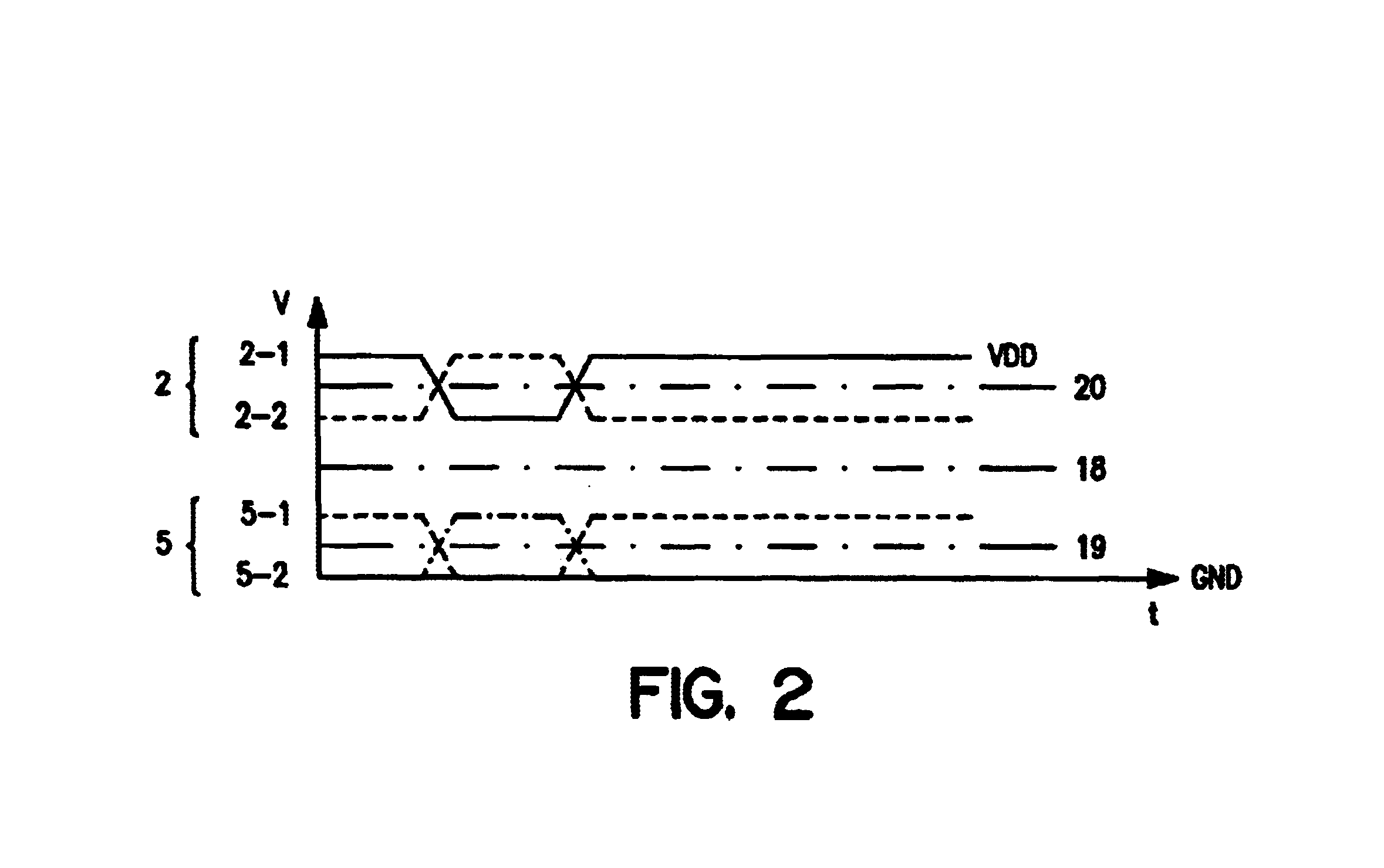

Low-voltage differential-signalling output buffer with pre-emphasis

InactiveUS6288581B1Multiple input and output pulse circuitsPulse automatic controlLow voltageEngineering

A low-voltage differential signaling (LVDS) output buffer has an improved eye pattern. The LVDS buffer has two parallel stages. A primary stage generates enough current to generate a first voltage drop across a load resistor. At higher frequencies, parasitic capacitive coupling reduces this first voltage drop, closing the eye pattern. A boost stage generates an additional boost current through the load resistor, adding to the voltage drop and opening the eye pattern. The boost stage is coupled to the outputs by link transistors that are enabled by a pre-emphasis signal generated by resetable pulse generators. When outputs switch, the pre-emphasis signal pulses the link transistors on, adding the boost current. At high frequencies, the pulse generators are reset before the pre-emphasis signal ends. The boost current is continuously added at high frequencies, but at low frequencies the boost current only occurs during the pre-emphasis period after outputs switch.

Owner:DIODES INC

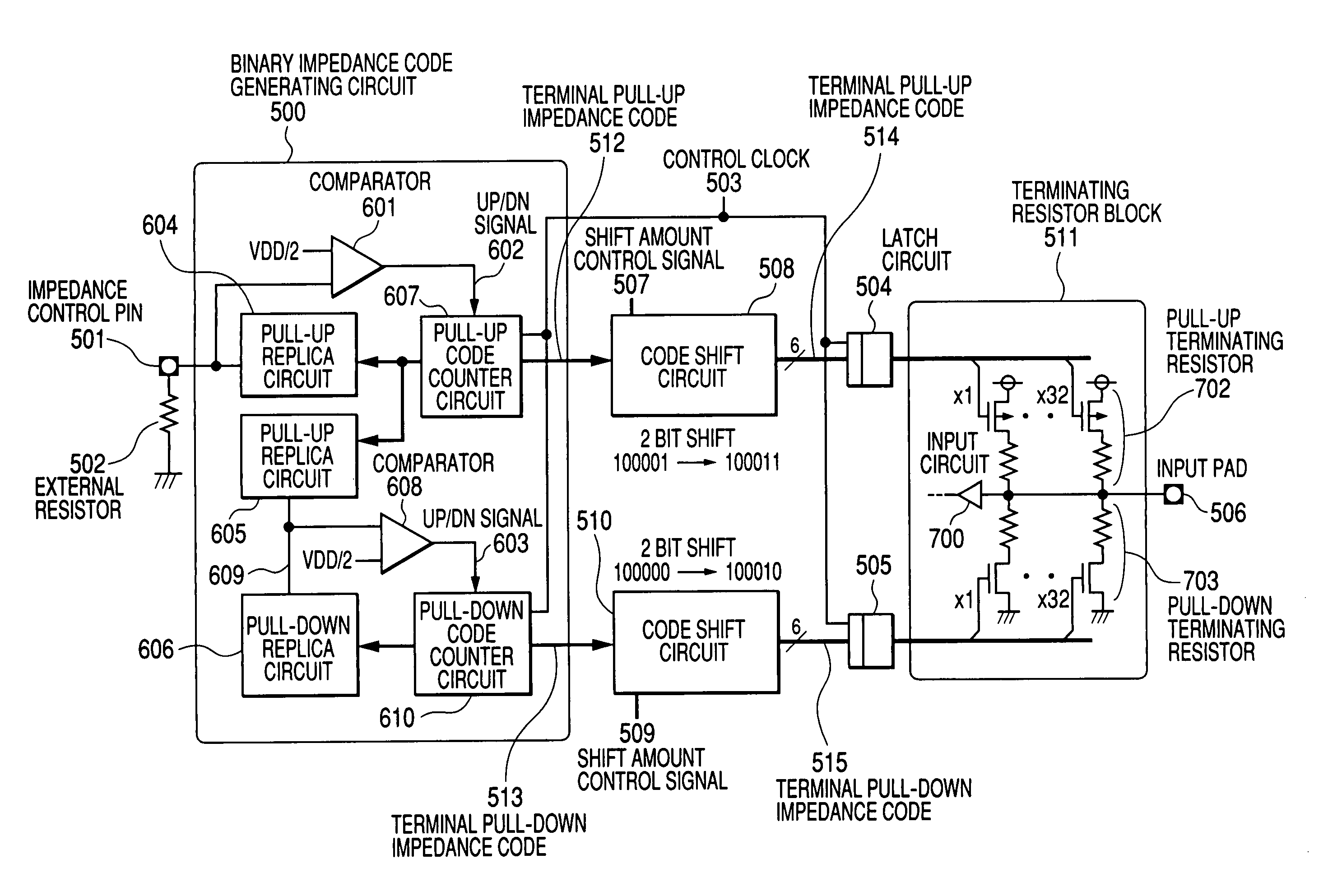

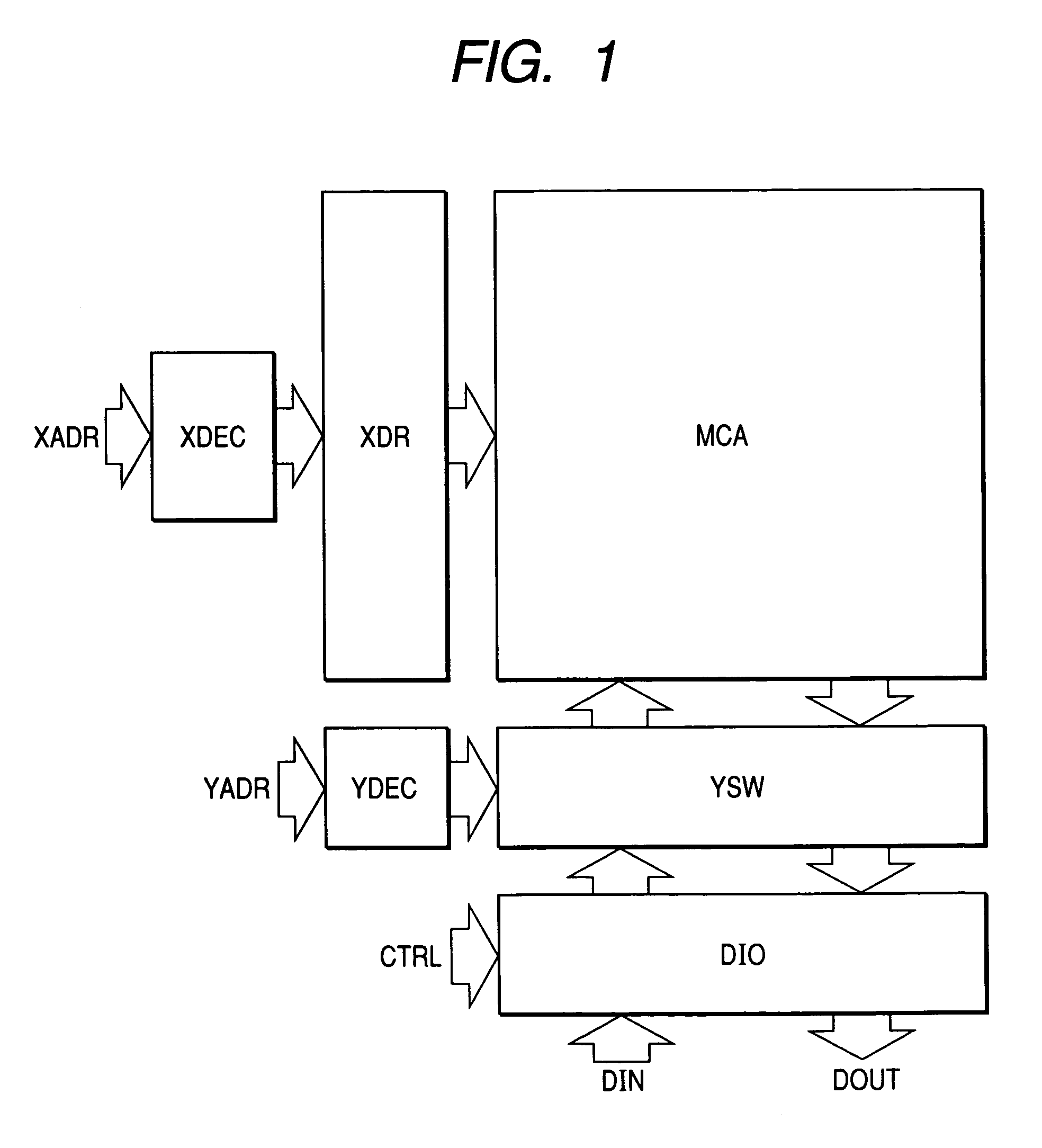

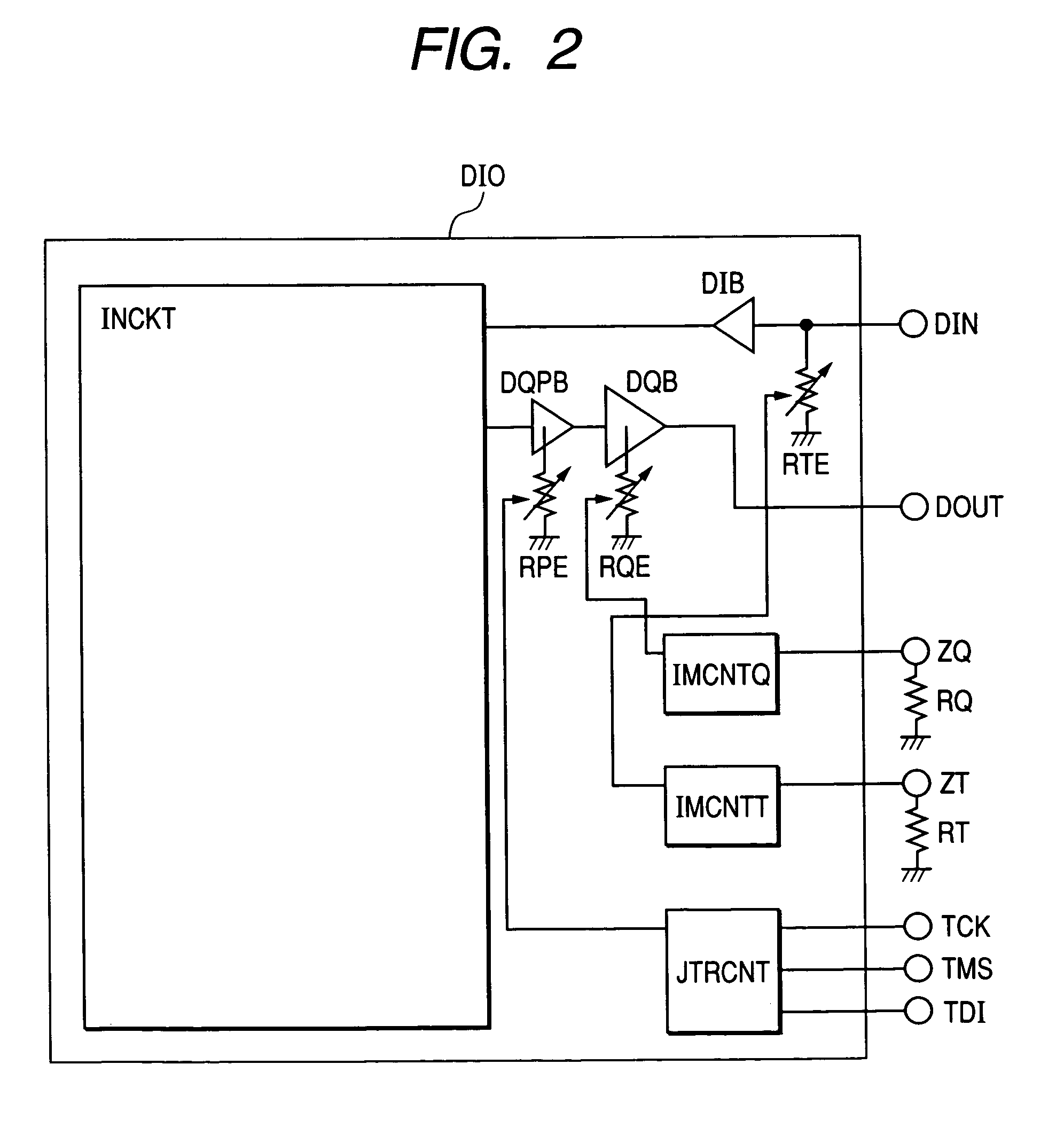

Semiconductor integrated circuit device

InactiveUS7038486B2Improve accuracyReduce yieldInput/output impedence modificationReliability increasing modificationsElectrical resistance and conductanceEngineering

A plurality of sets of circuits are provided, each of which generates an impedance code through the use of an impedance control circuit in association with a resistive element connected to an external terminal, and each of which varies the impedance in accordance with such an impedance code. The impedance control circuit includes an impedance comparator which is formed equivalently to the resistive element and the plurality of sets of circuits, and which performs an impedance comparison with each of a plurality of replica circuits to form an up signal that increases the impedance and a down signal that decreases the impedance. Counters are provided adjacent to the individuals of the plurality of sets of circuits to thereby generate the impedance codes in response to the up signal and the down signal.

Owner:RENESAS ELECTRONICS CORP

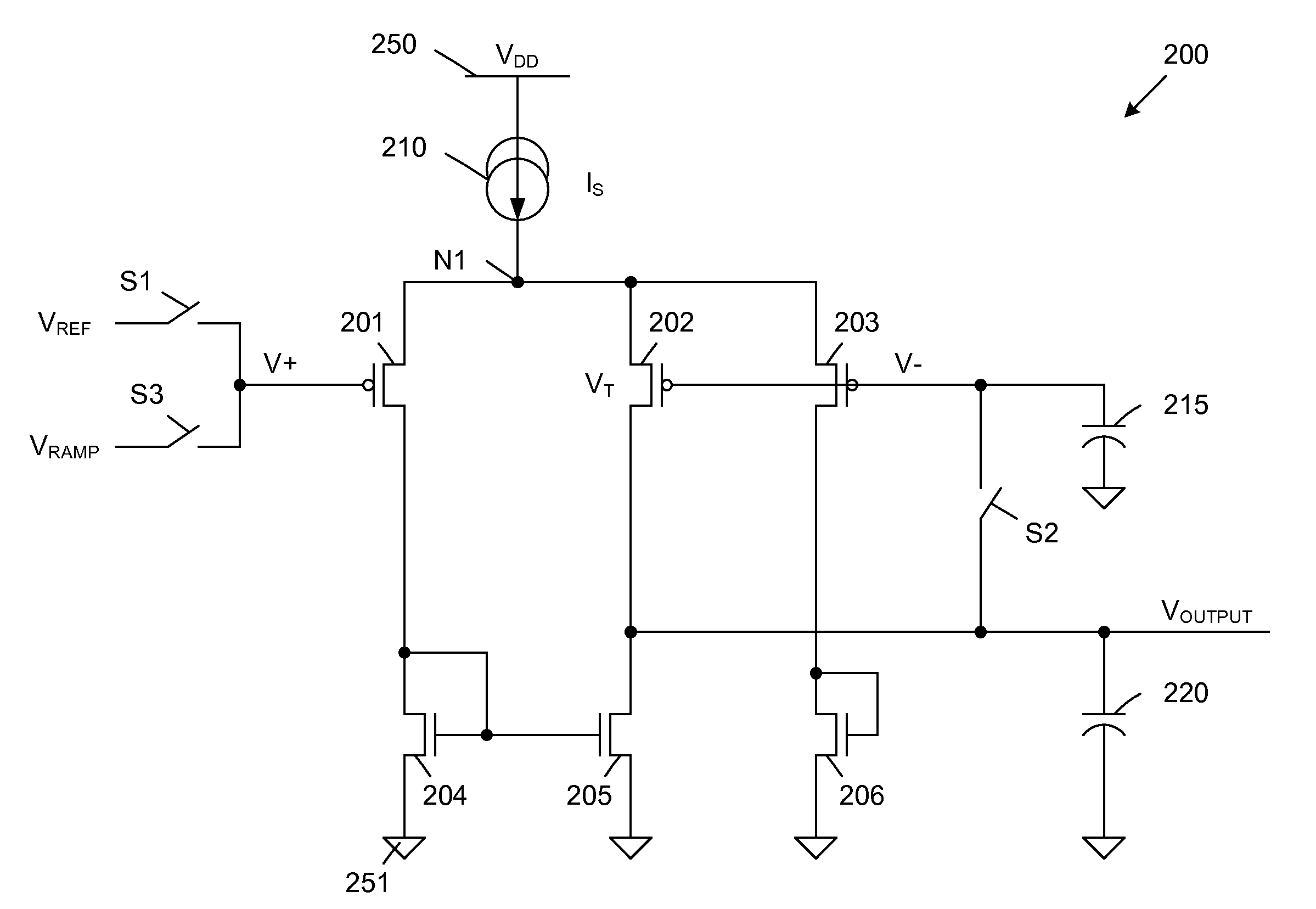

Comparator with low supplies current spike and input offset cancellation

ActiveUS20090033370A1Multiple input and output pulse circuitsInstant pulse delivery arrangementsOffset cancellationComparators circuits

A current control circuit is coupled in parallel with the current paths of a differential comparator circuit to ensure that a substantially constant current is drawn from a current source during all operating phases of a comparator. The current control circuit is biased by a reference voltage, which is also used to bias a V− input terminal of the differential comparator circuit. The reference voltage is stored by a sample capacitor, which is charged by applying the reference voltage to a V+ input terminal of the differential comparator circuit while coupling an output terminal of the differential comparator circuit to the sample capacitor in a unity feedback configuration.

Owner:TOWER SEMICONDUCTOR

Equalizer with controllably weighted parallel high pass and low pass filters and receiver including such an equalizer

ActiveUS20070201546A1Multiple-port networksMultiple input and output pulse circuitsCMOSHigh-pass filter

Owner:LATTICE SEMICON CORP

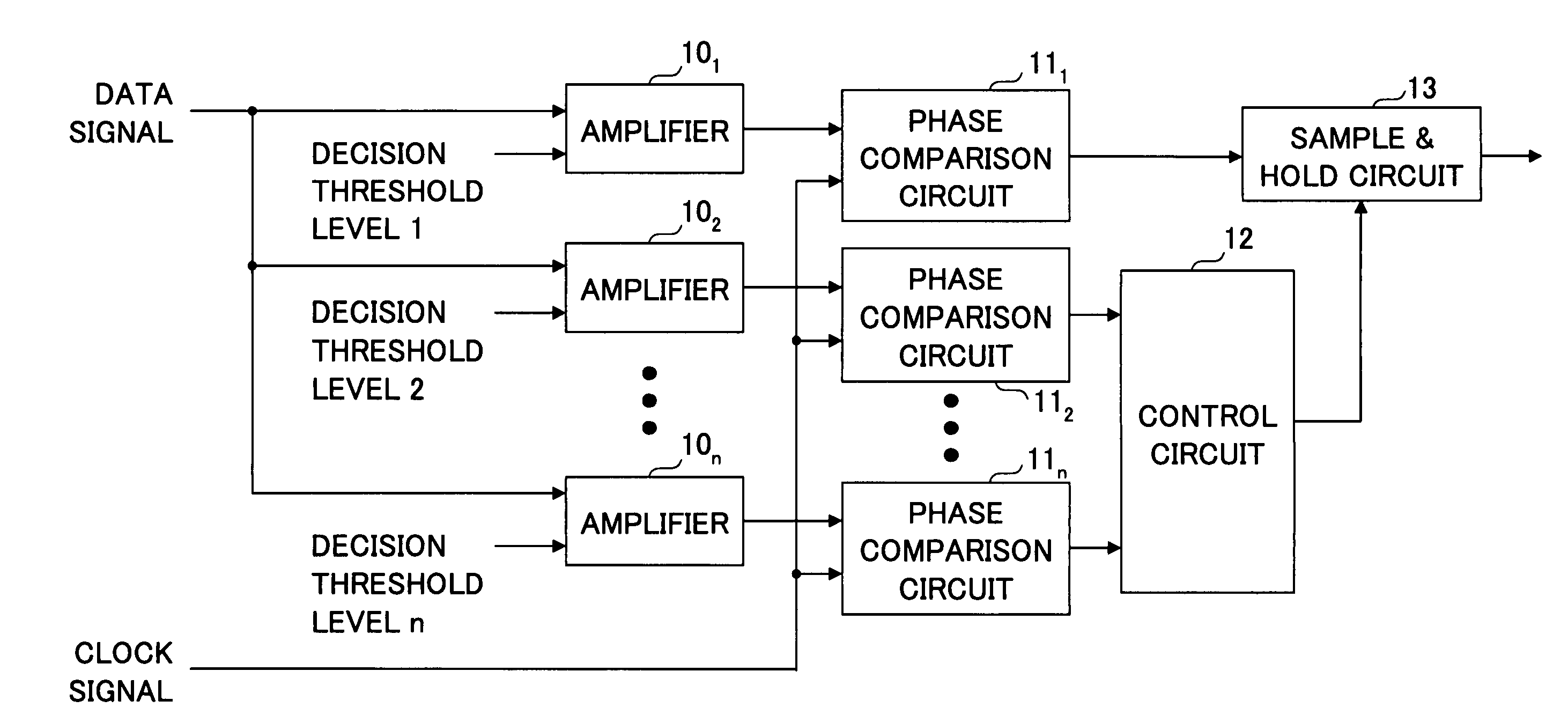

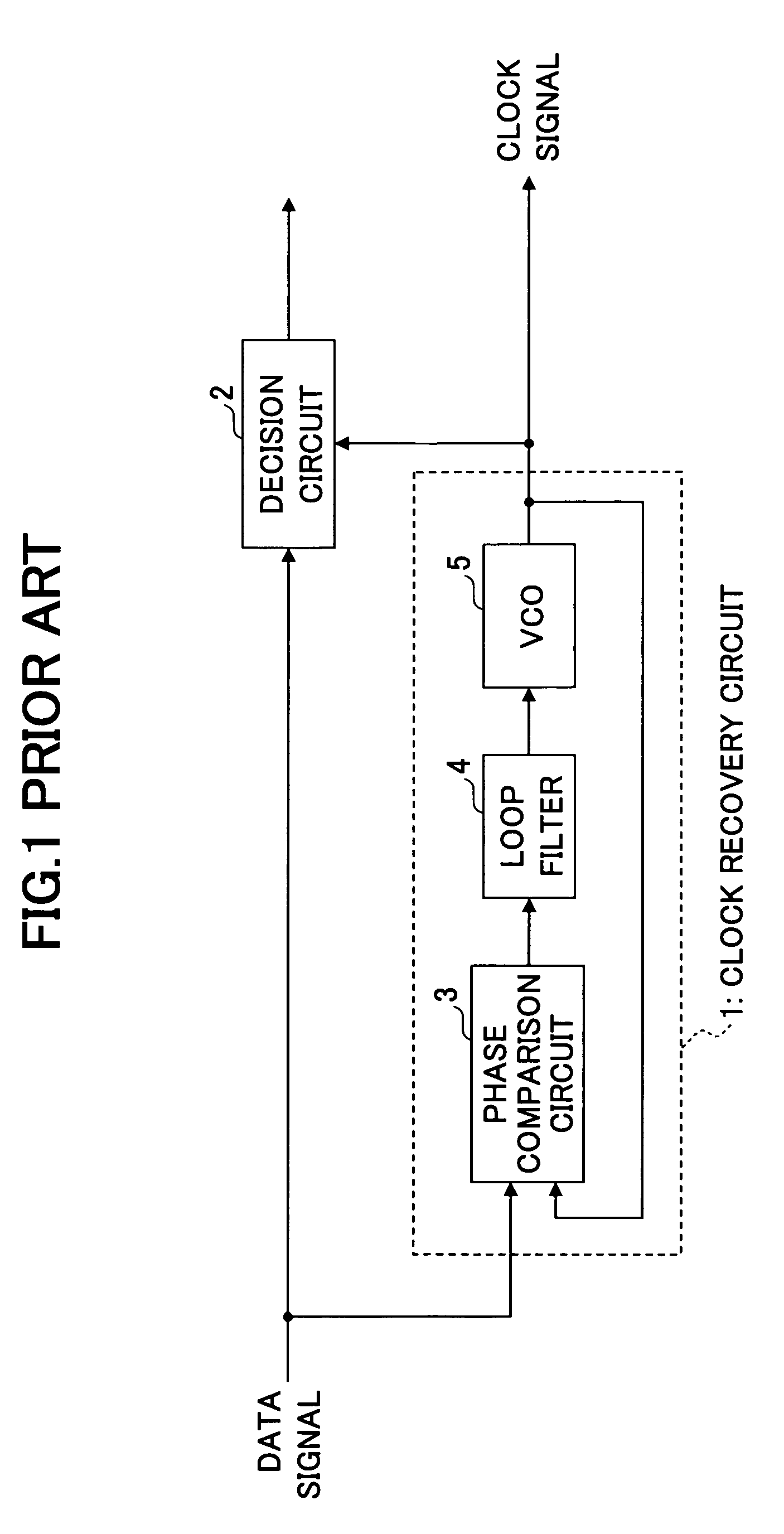

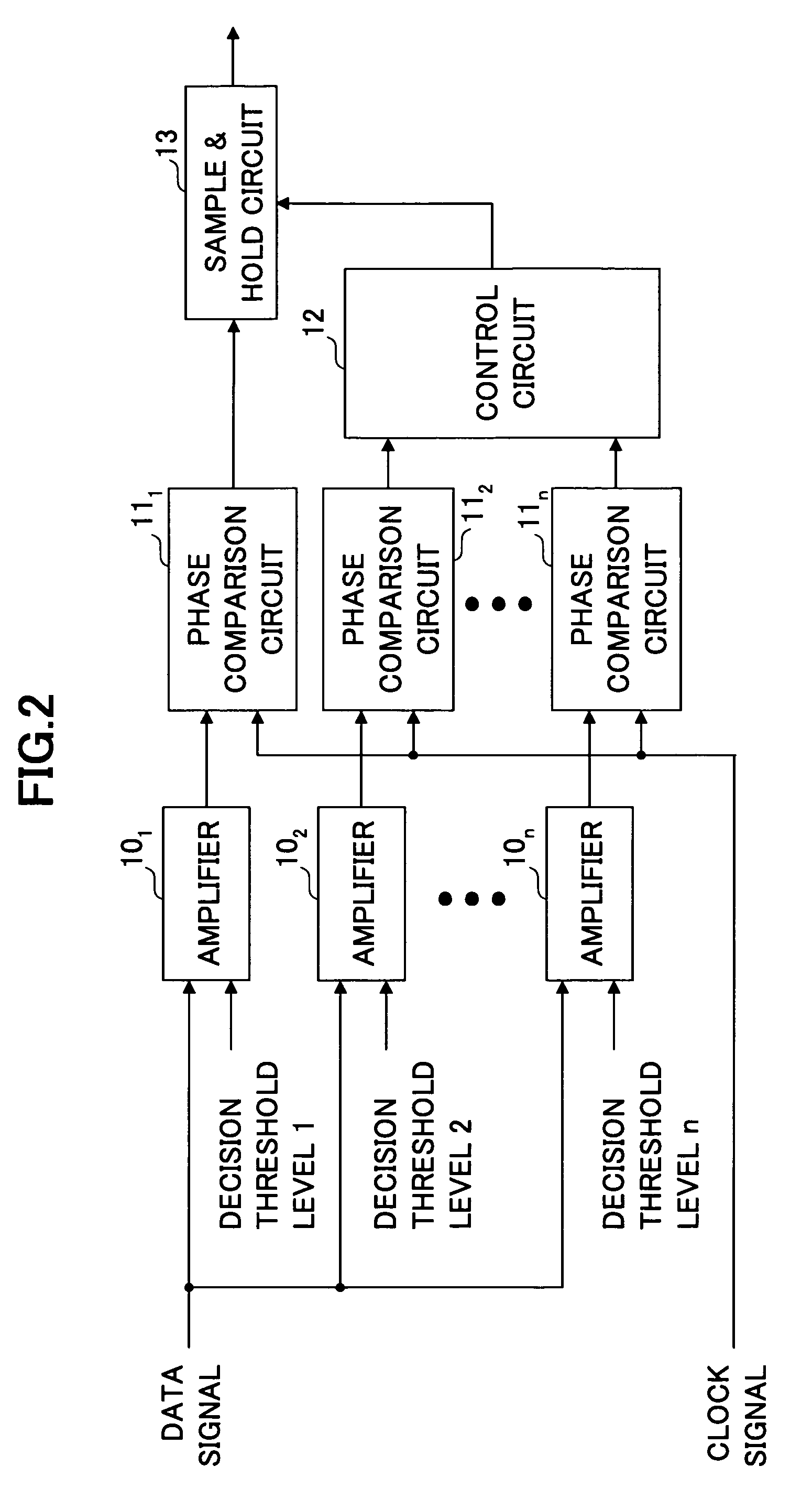

Phase comparison circuit and clock recovery circuit

InactiveUS20050220182A1Correction of phase differenceCancel noiseMultiple input and output pulse circuitsPulse automatic controlPhase differenceClock recovery

A phase comparison circuit for outputting a phase difference signal indicating a phase difference between a data signal and a clock signal is disclosed. The disclosed phase comparison circuit includes: a detection part for outputting a plurality of signals indicating phases of the data signal according to different decision threshold levels; a phase comparison part for outputting phase difference signals each indicating a phase difference between a signal in the plurality of signals output from the detection part and the clock signal; and a control part for determining whether to output a particular phase difference signal in the phase difference signals by using the whole or a part of the phase deference signals.

Owner:FUJITSU LTD

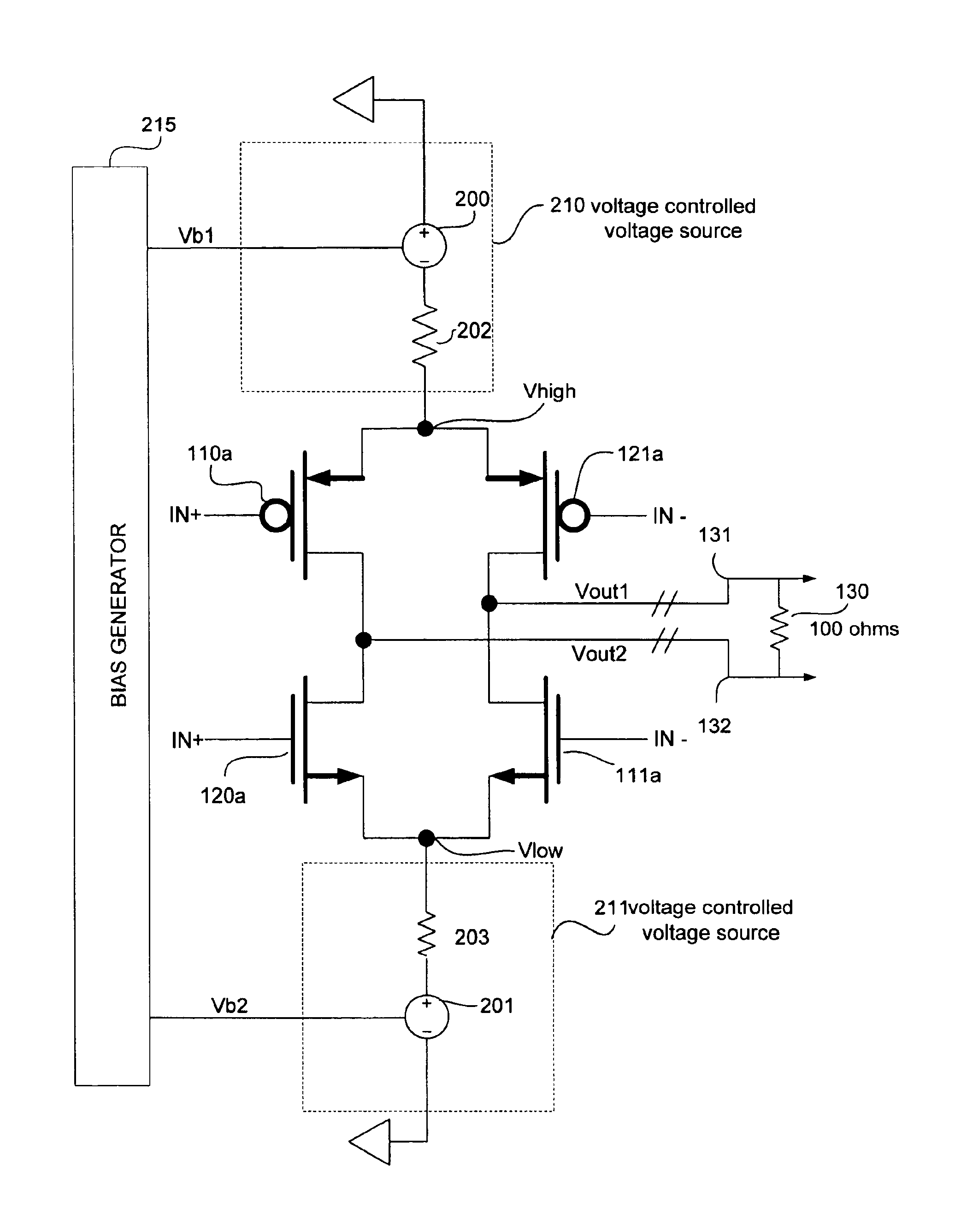

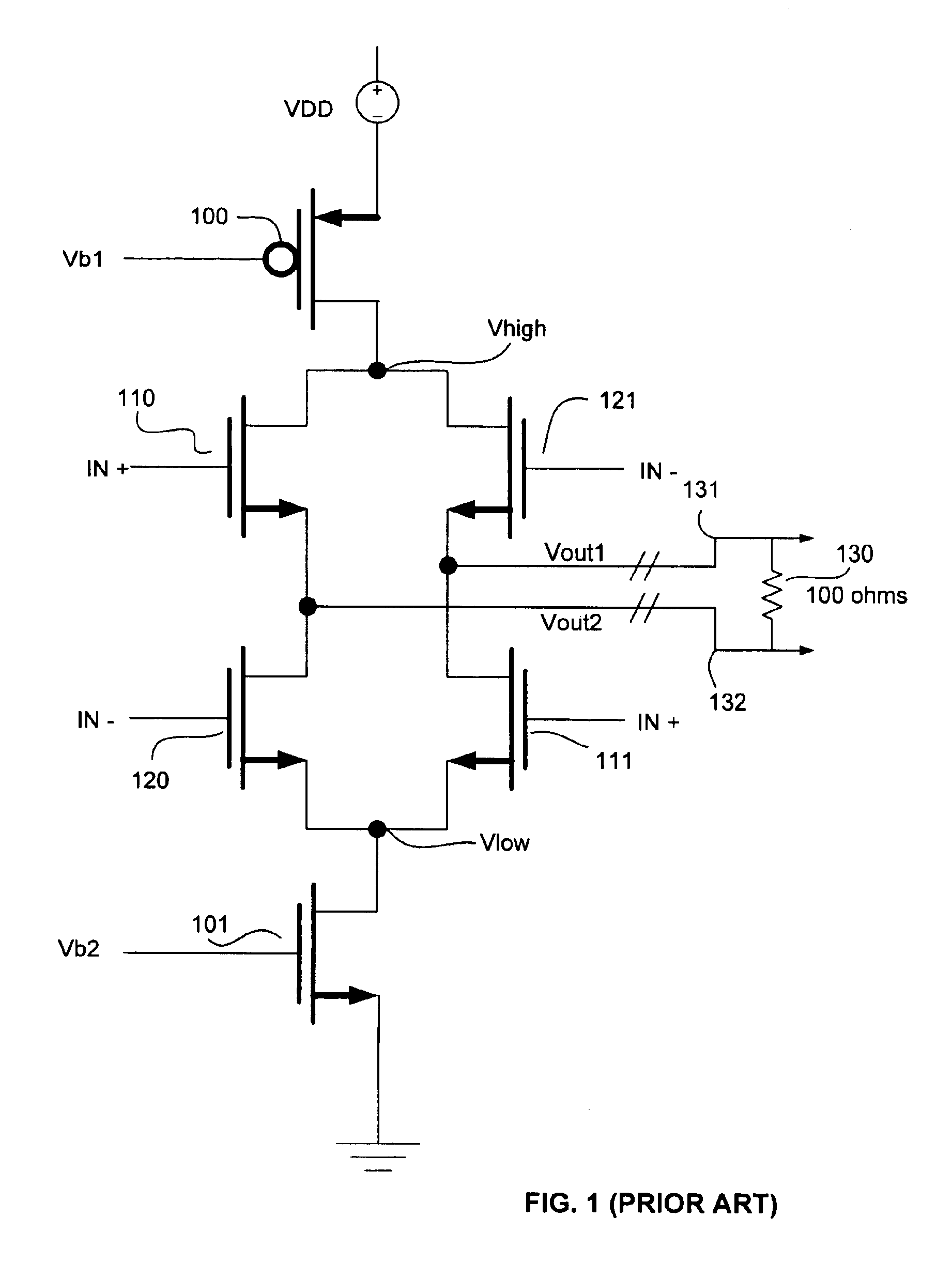

Voltage mode differential driver and method

InactiveUS6867618B2Lower impedanceMultiple input and output pulse circuitsLogic circuits characterised by logic functionVoltage sourceVoltage control

Owner:AVAGO TECH INT SALES PTE LTD

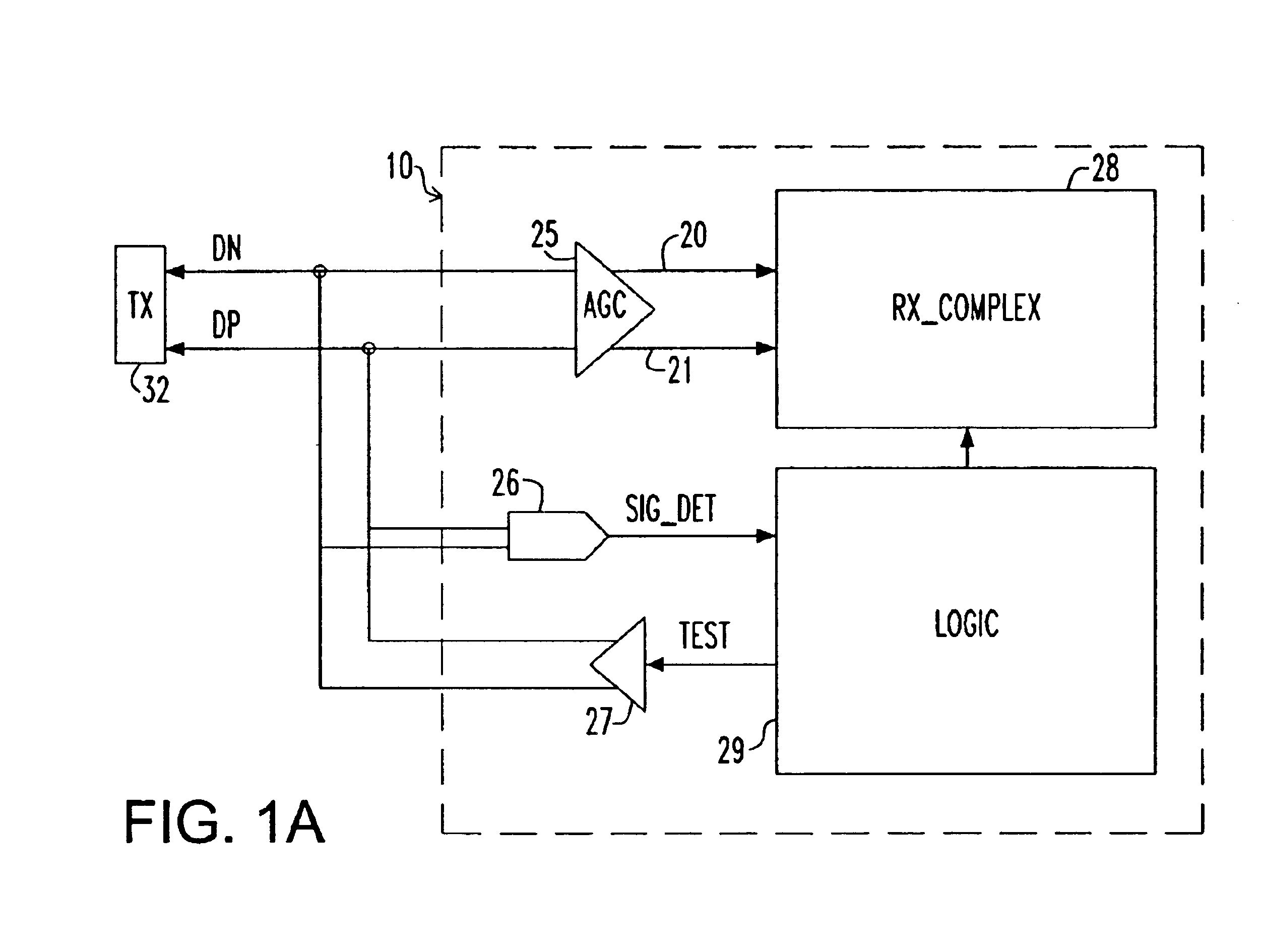

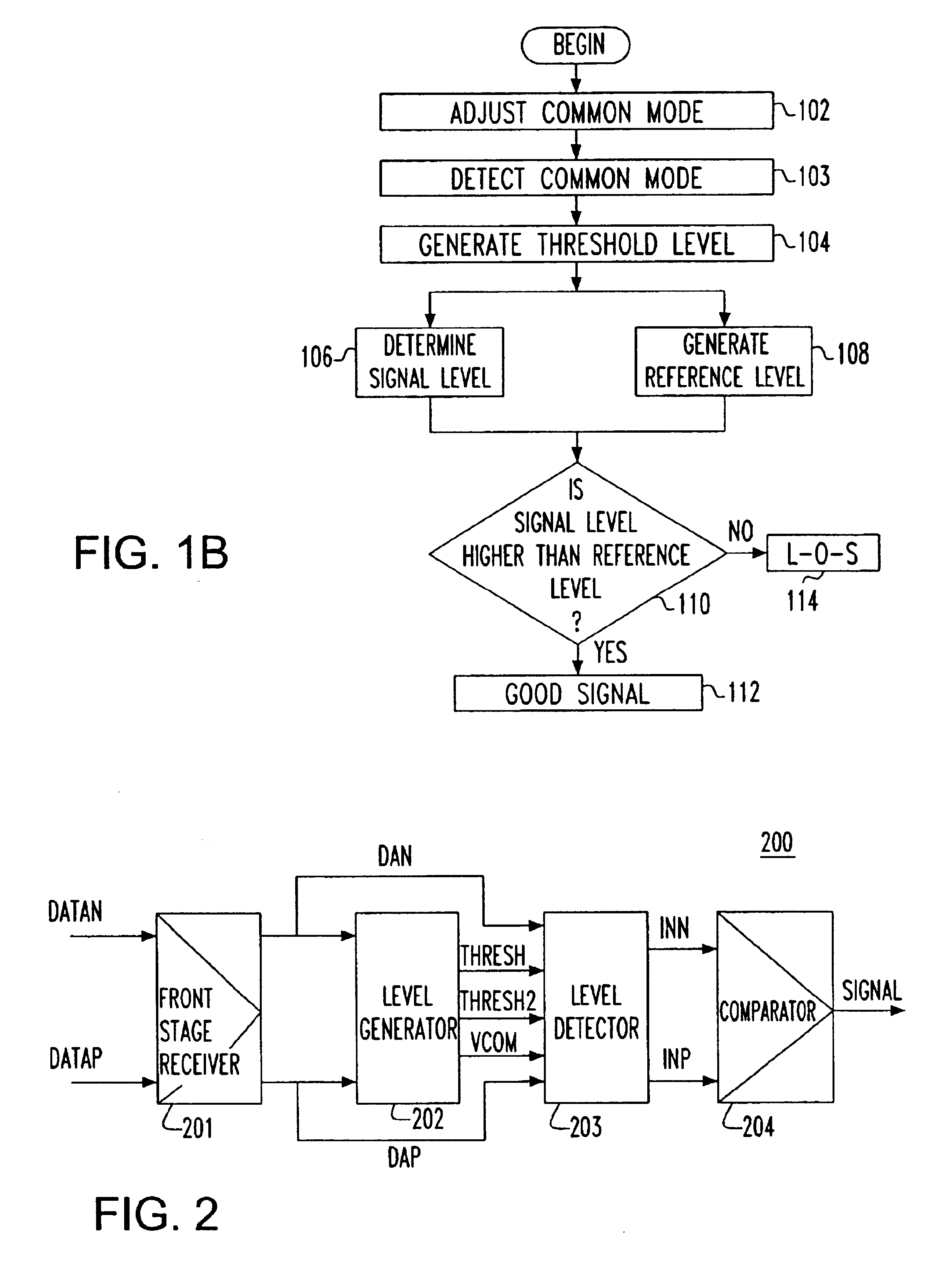

Apparatus and method for detecting loss of high-speed signal

InactiveUS6897712B2Multiple input and output pulse circuitsPulse train pattern monitoringDifferential signalingTime segment

An apparatus and method is provided for detecting loss of differential signal carried by a pair of differential signal lines. According to the method, a common mode level is detected from voltages on the pair of differential signal lines. A threshold level is generated, referenced to the detected common mode level. A signal level is generated from the voltages on the pair of differential signal lines, the signal level being averaged over a first period of time. From the threshold level and the detected common mode level a reference level is generated, the reference level being averaged over a second period of time longer than then the first period of time. The signal level is compared to the reference level to determine if a signal is present on the pair of differential signal lines.

Owner:MARVELL ASIA PTE LTD

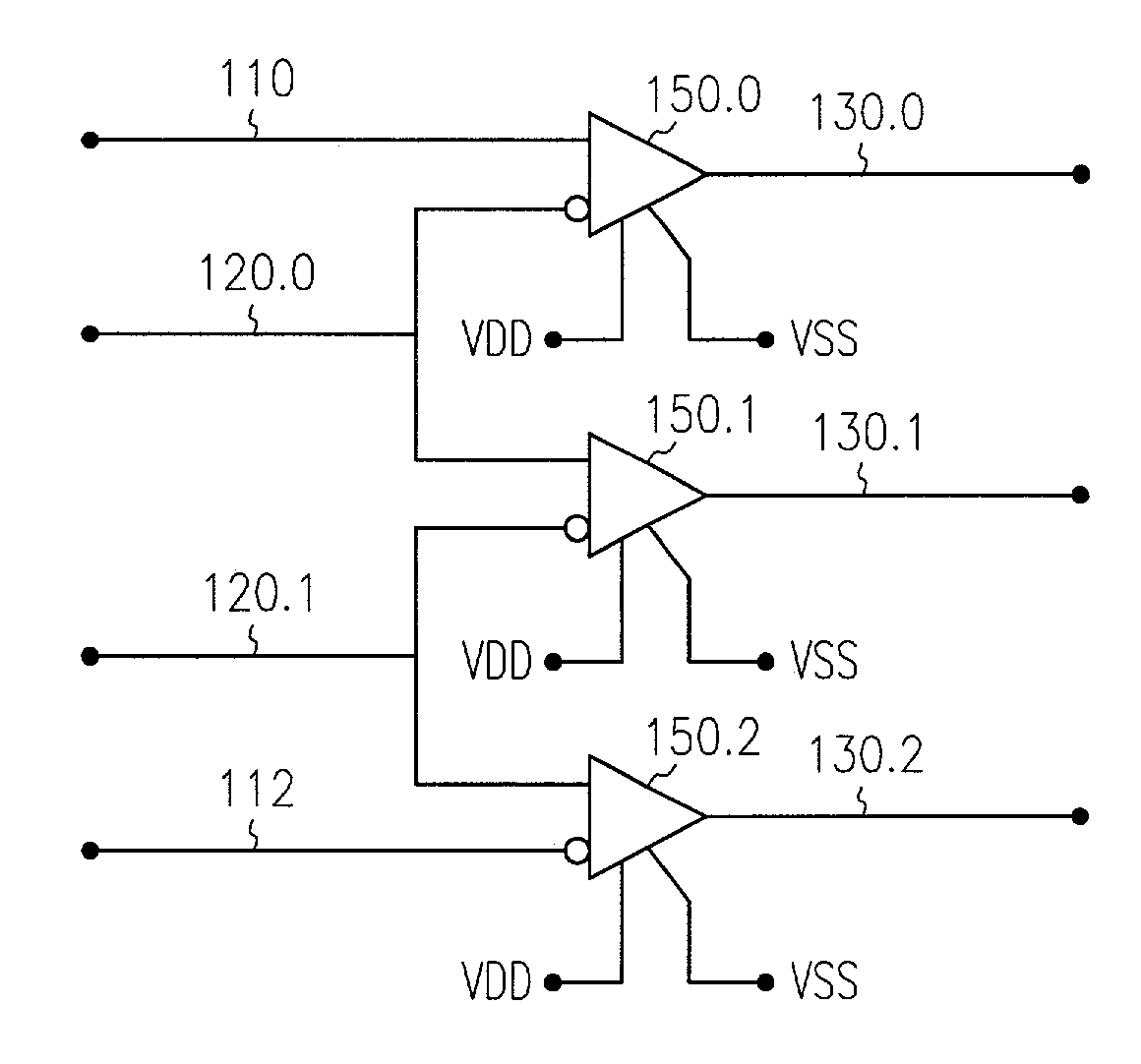

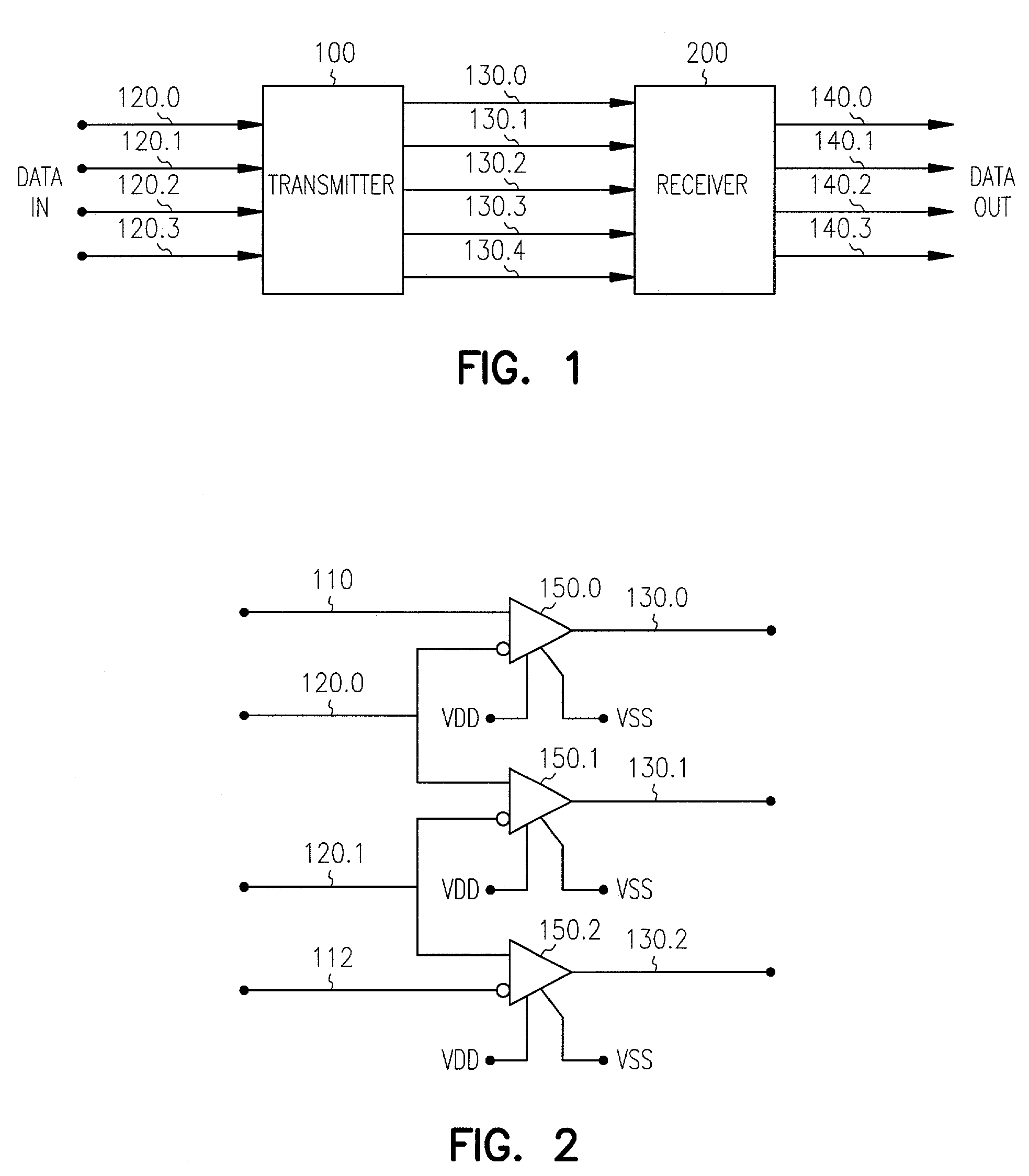

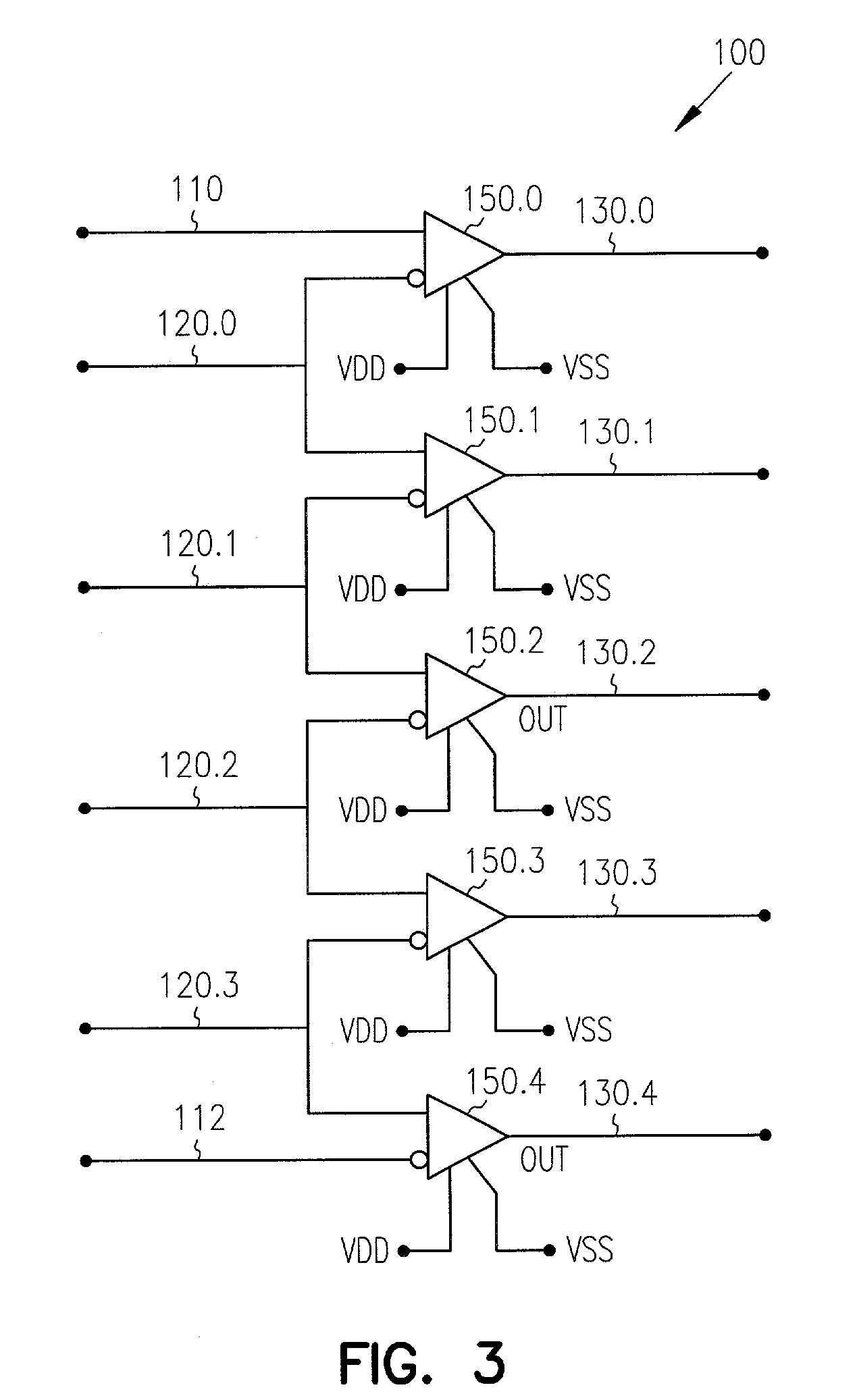

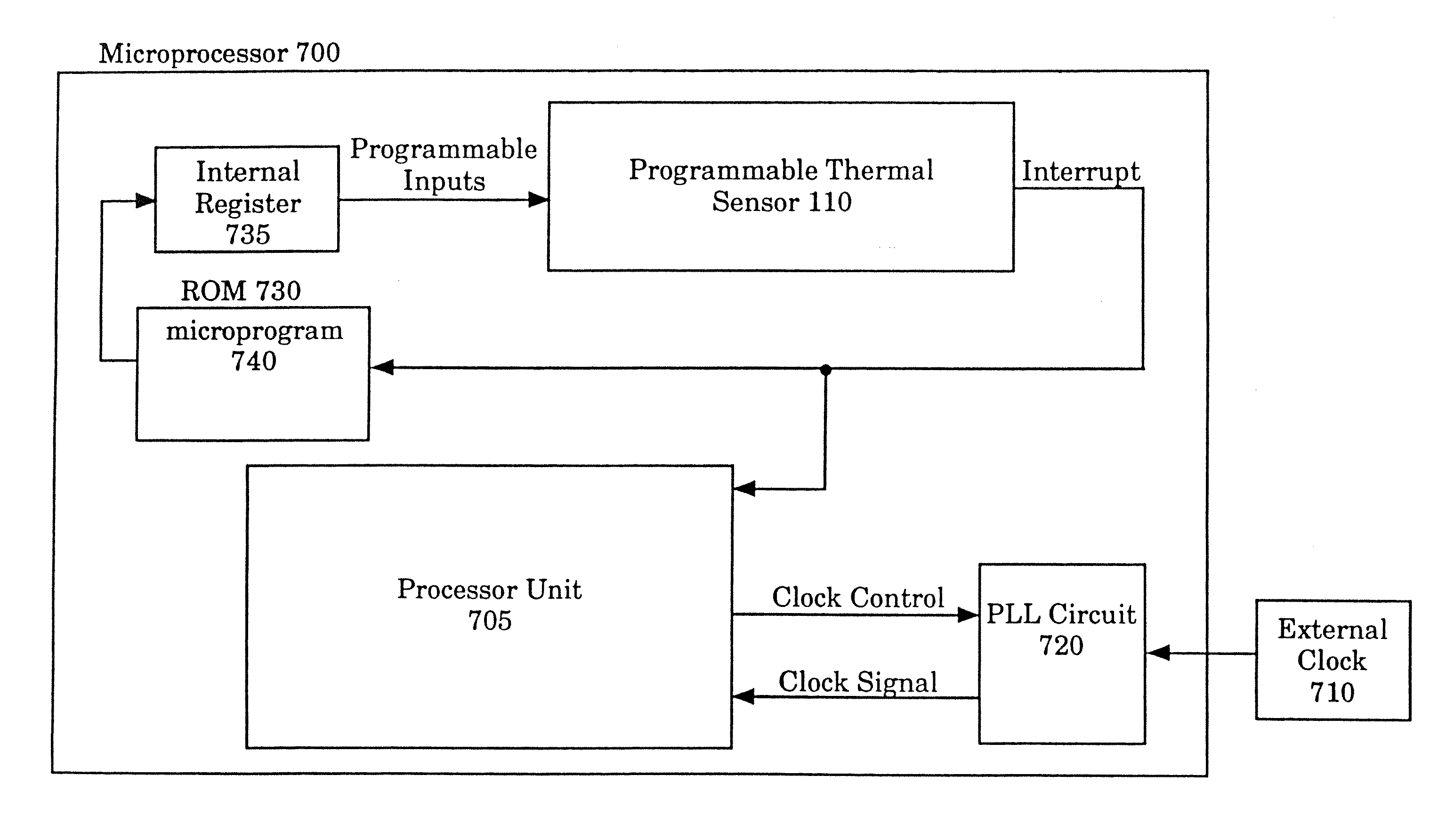

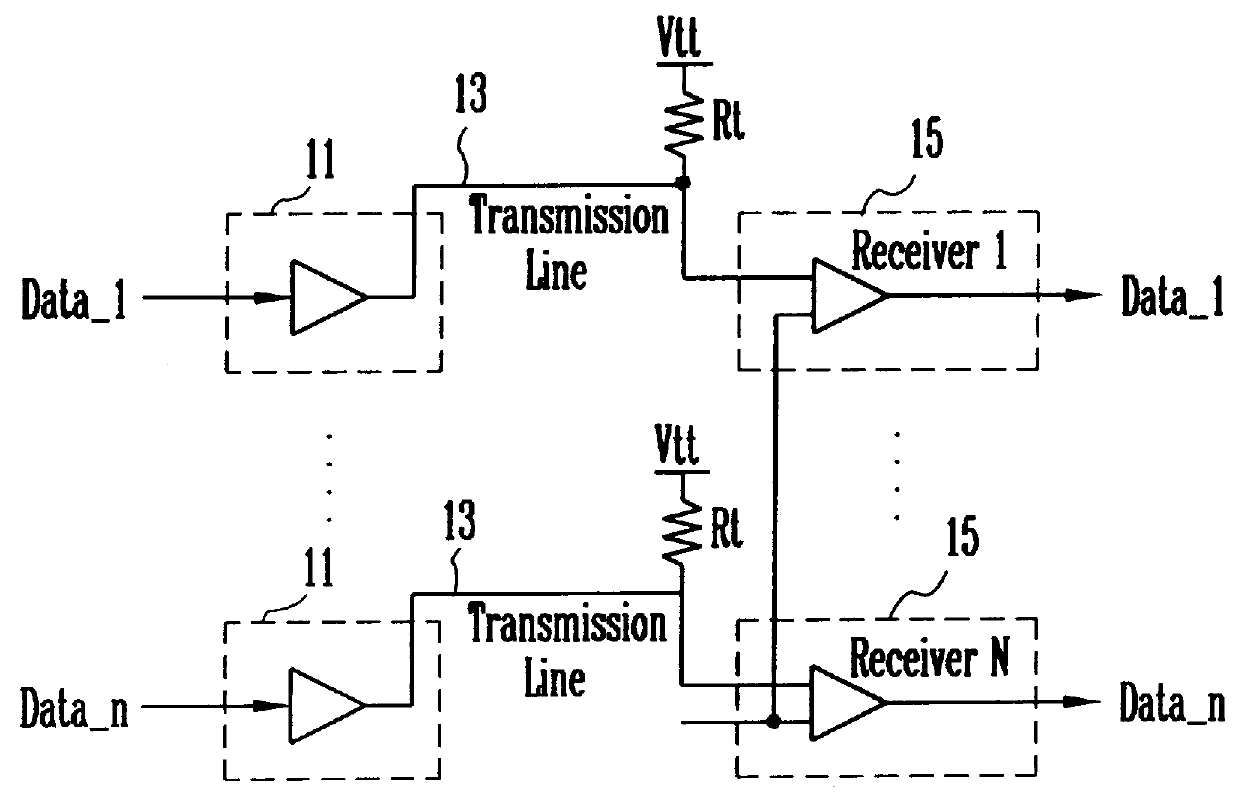

Spacial derivative bus encoder and decoder

InactiveUS7167523B2Reduce noiseReduce power consumptionMultiple input and output pulse circuitsChannel dividing arrangementsData signalBus encoding

A method and apparatus for providing efficient and accurate electronic data transmission of information on a data bus in the presence of noise. Data signals are received on a plurality of input lines by a spacial derivative encoder. The spacial derivative encoder encodes the signals and transmits them to a receiver having a spacial derivative decoder. The spacial derivative decoder then decodes the signals. Minimal overhead is required as for n input lines only n+1 lines are needed to transmit each of the encoded signals.

Owner:MORGAN STANLEY +1

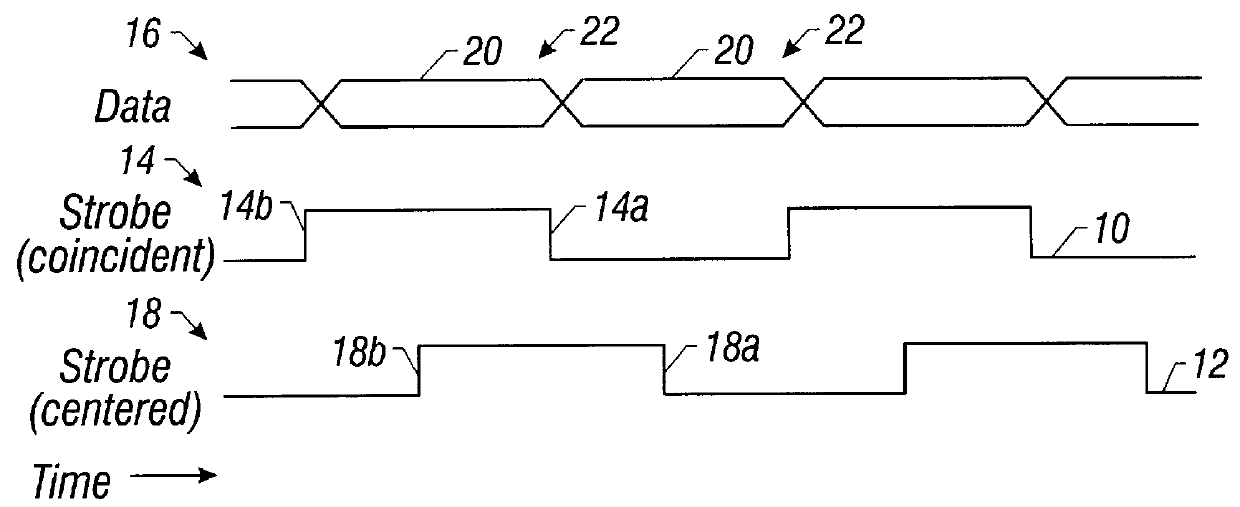

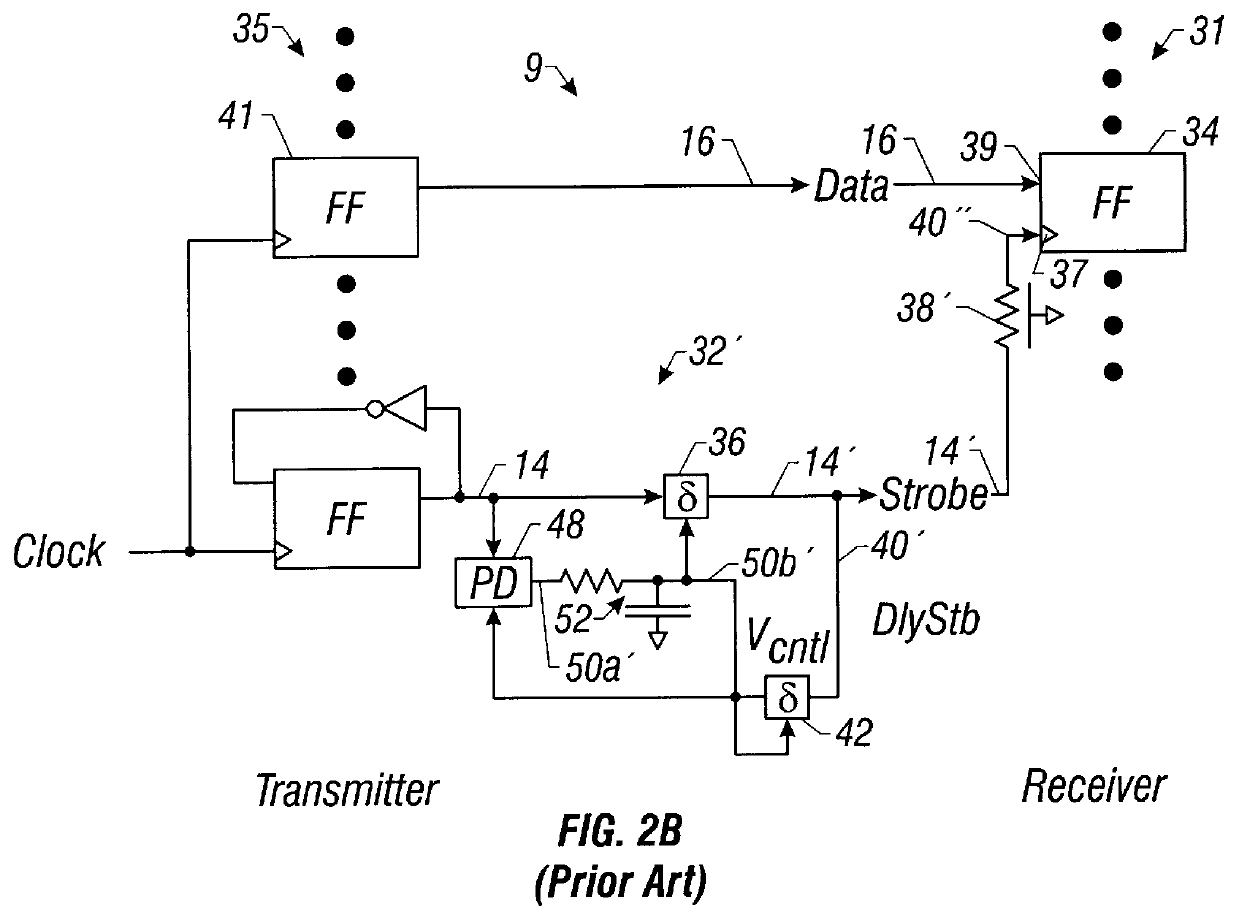

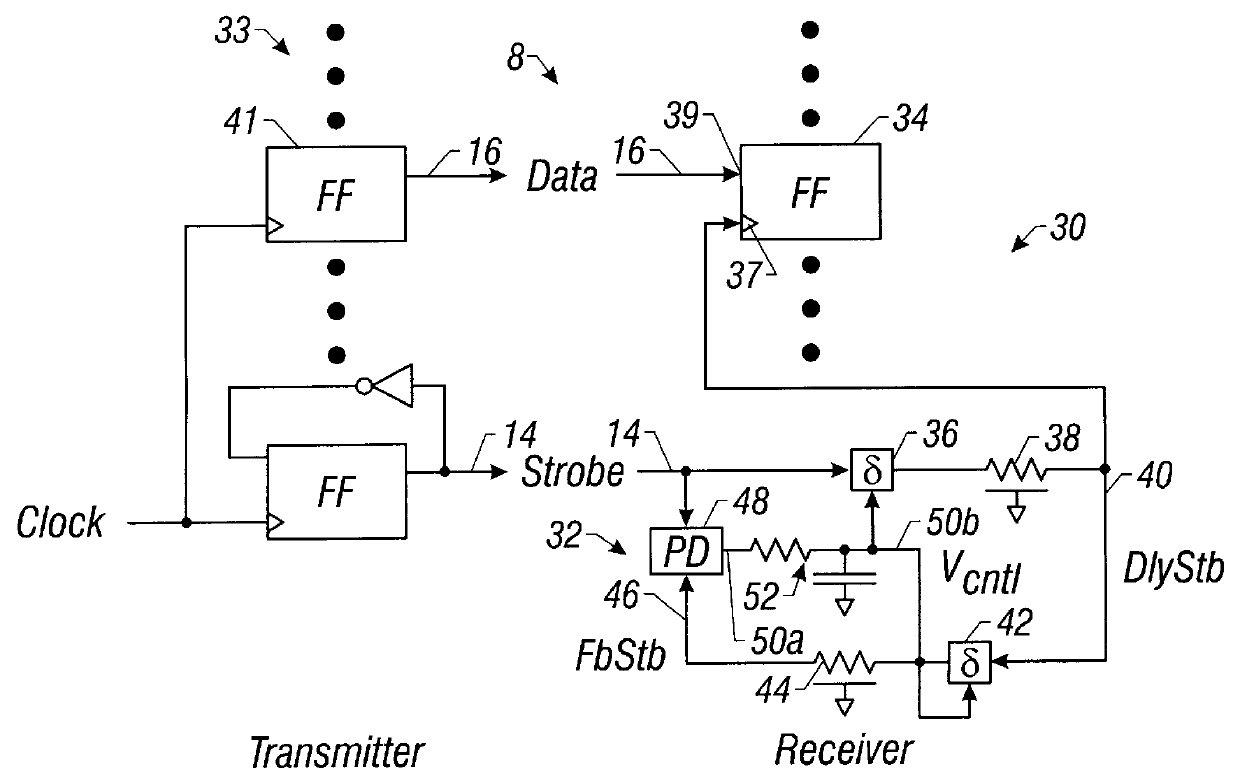

Timing control for input/output testability

InactiveUS6085345AMultiple input and output pulse circuitsPulse automatic controlPhase differenceDelay-locked loop

Circuitry added to chips that use source synchronous techniques reduces difficulties associated with testing the chips. The circuitry increases the ability to use source synchronous techniques for data transmission. The circuitry is implemented in a delayed-lock loop (DLL) in either a transmitter (driver) or a receiver. The DLL measures the phase difference between a strobe signal and a delayed strobe signal. The DLL can be externally controlled by a source selectable input which allows the delay of the delayed strobe signal to be varied to test Tsetup and Thold in the receiver without varying the timings of the strobe signal and the data signals supplied to the chips. A timing measurement circuit having the strobe signal, the delayed strobe signal, and reference signals as inputs may be used to calibrate the phase difference between the strobe signal and delayed strobe signal.

Owner:INTEL CORP

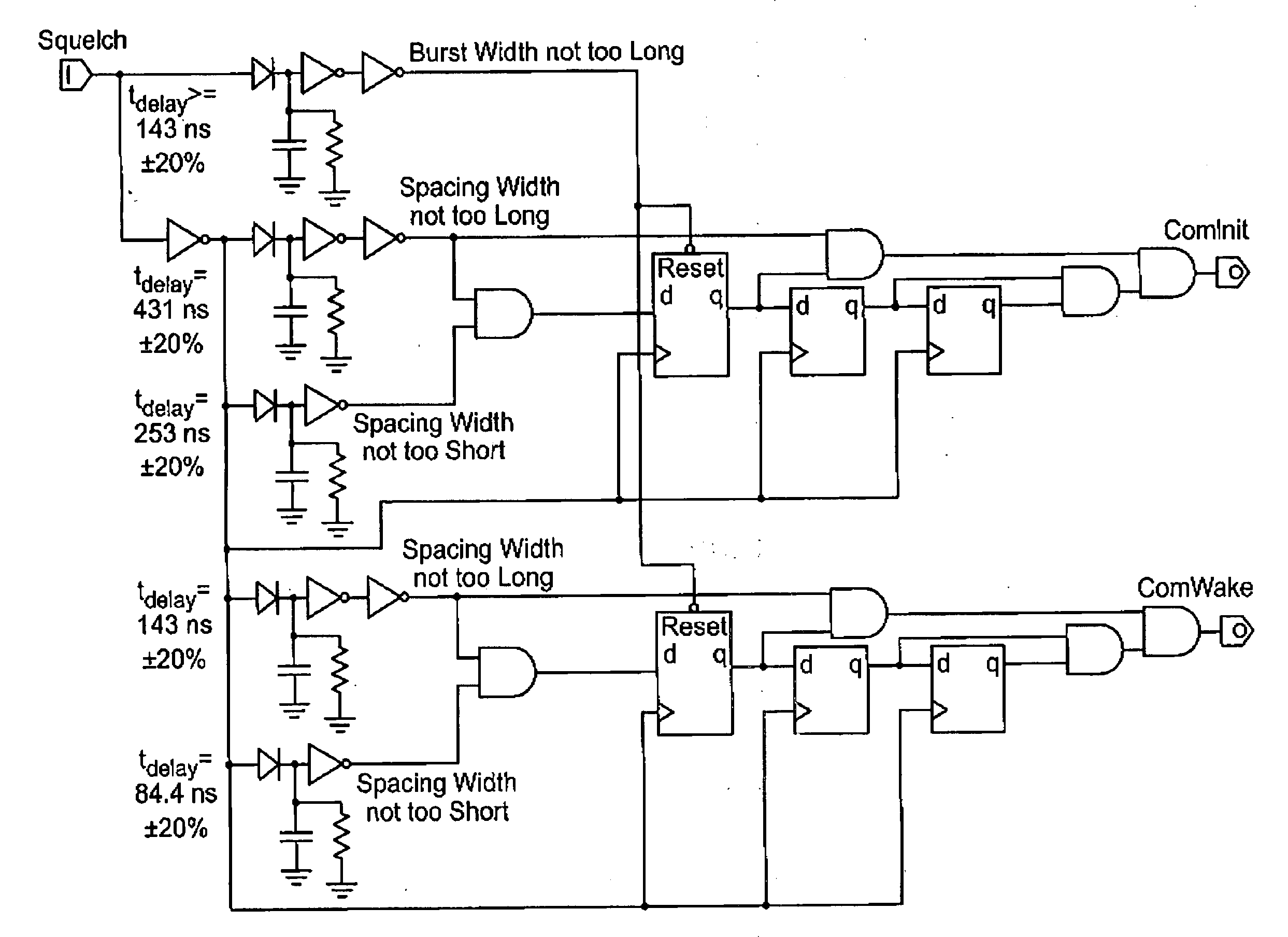

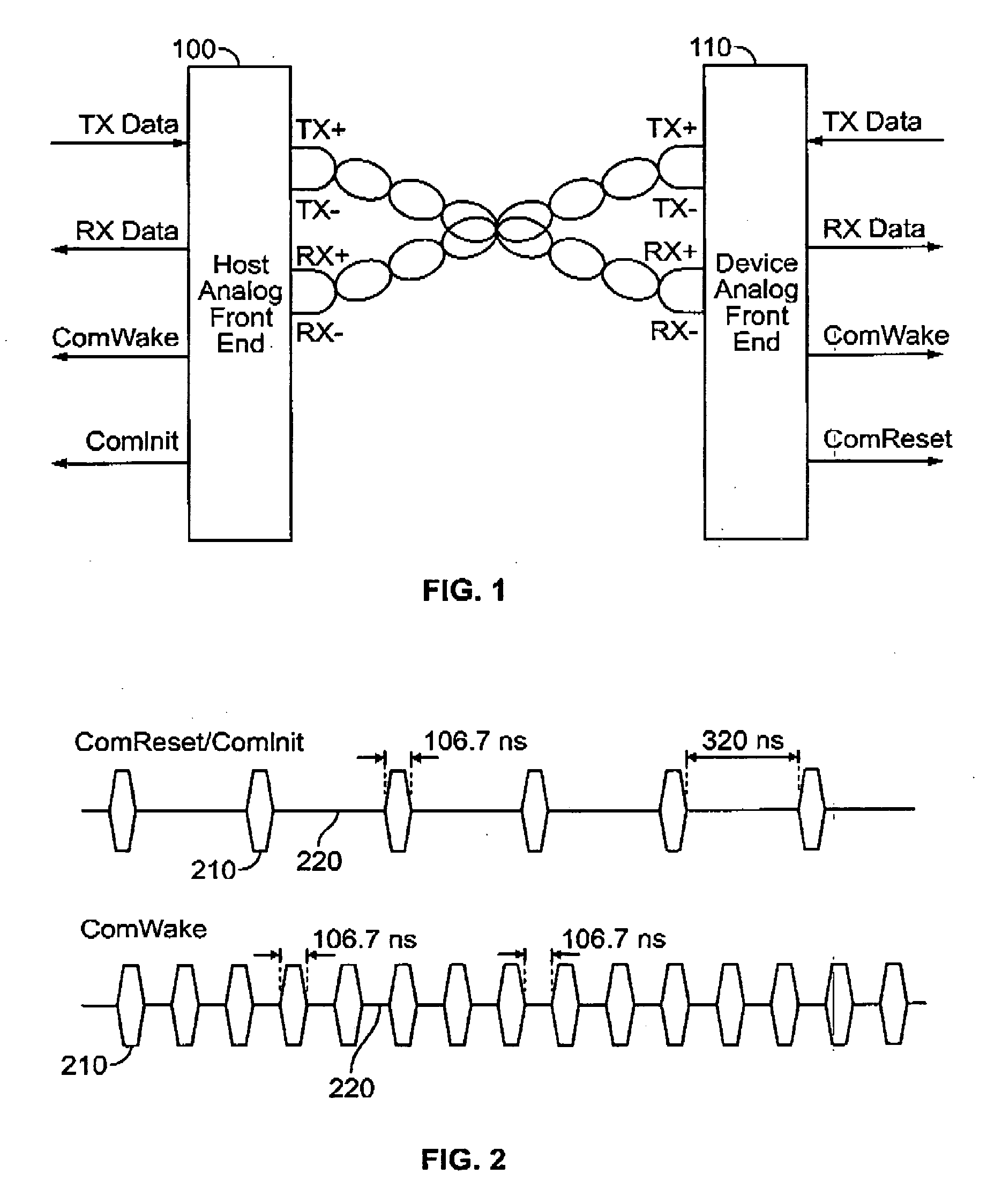

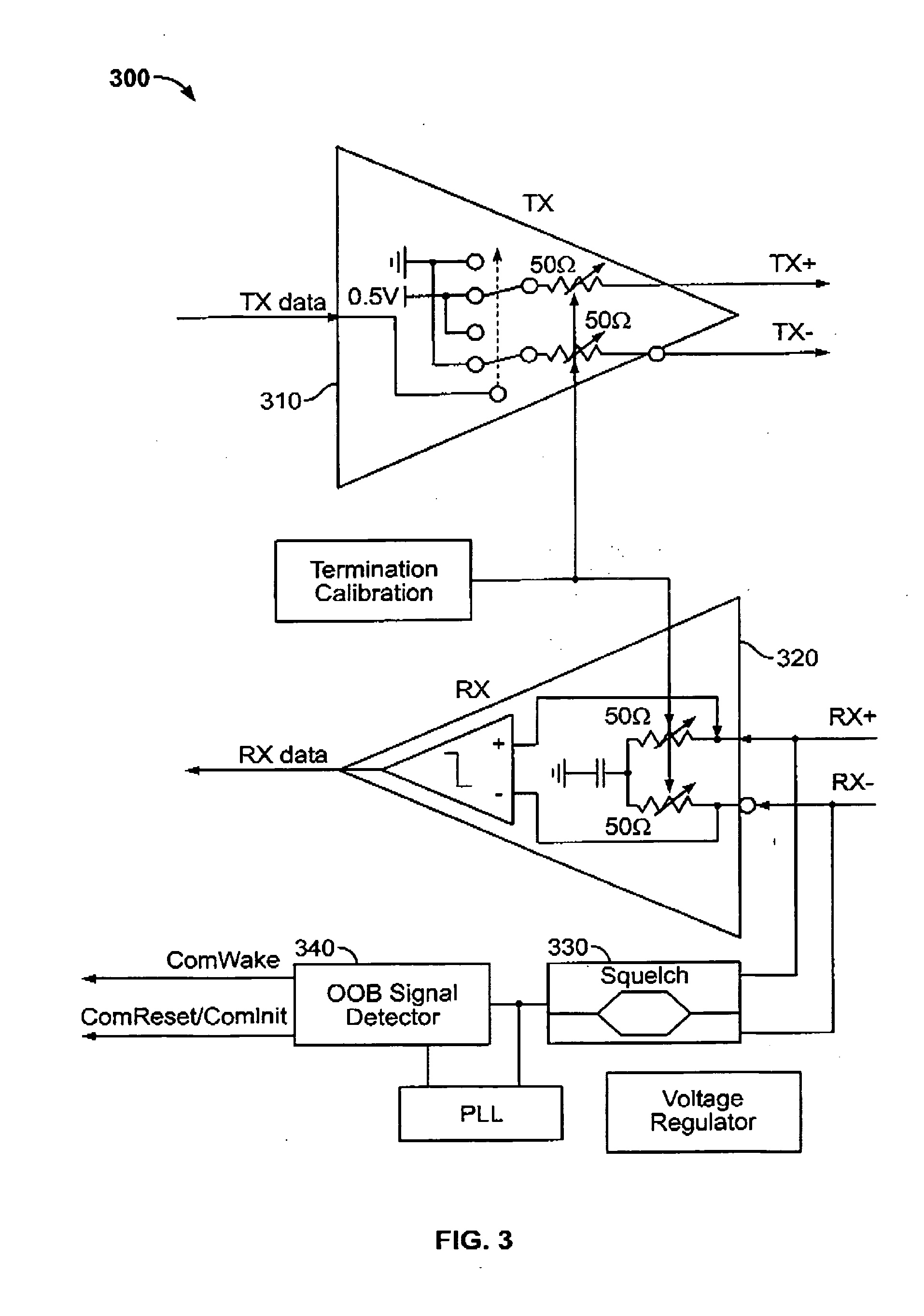

Apparatus and method for selectively enabling and disabling a squelch circuit across AHCI and SATA power states

An apparatus and a method are provided for selectively enabling and disabling a squelch circuit in a Serial Advanced Technology Attachment (SATA) host or SATA device while maintaining proper operation of the host and device. An apparatus and method are provided which allow the squelch circuit to be selectively enabled and disabled across SATA power states (PHY Ready, Partial, and Slumber) and in Advanced Host Controller Interface (AHCI) Listen mode.

Owner:INTEL CORP

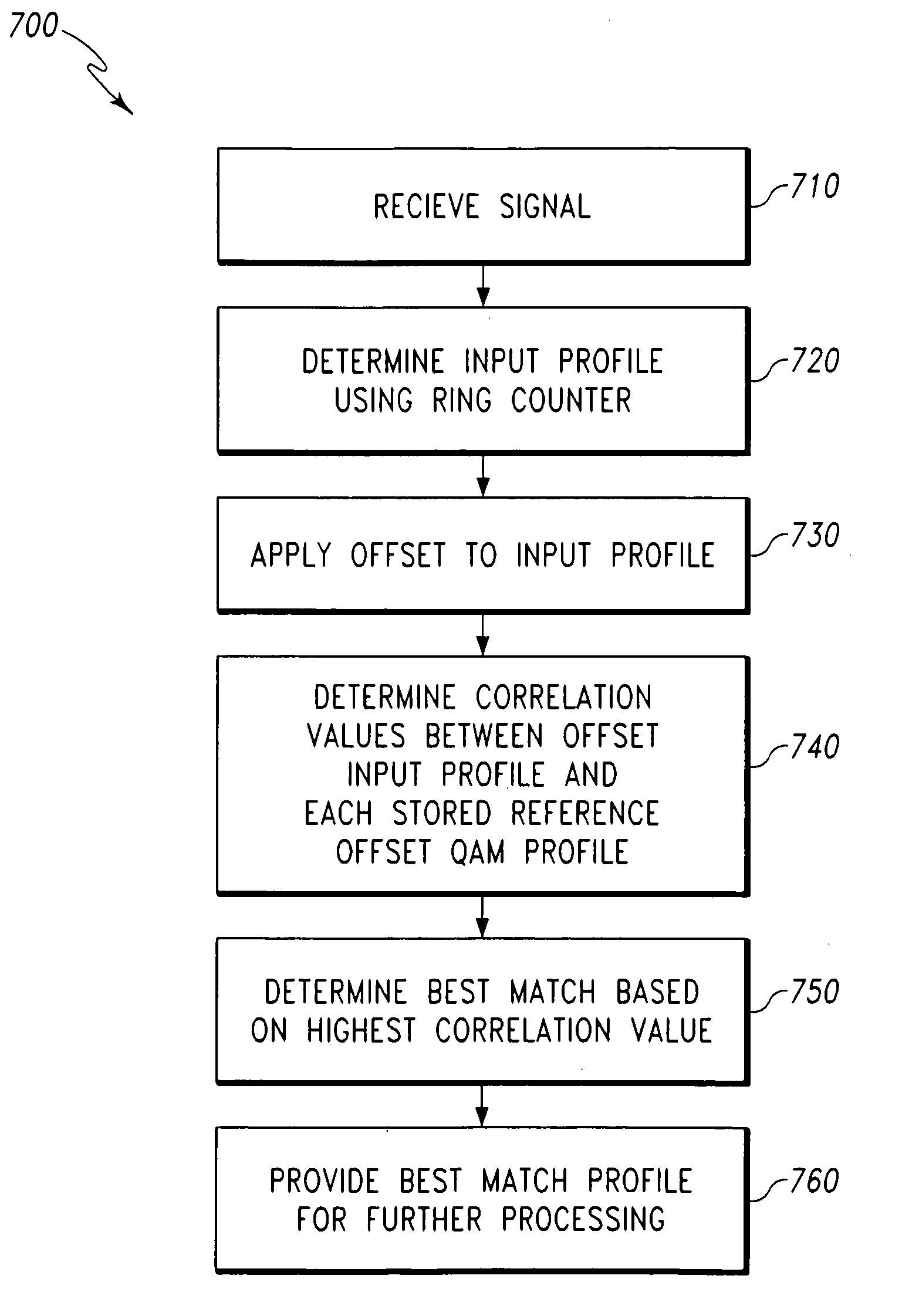

Apparatus and method for determination of signal format

InactiveUS20110074500A1Multiple input and output pulse circuitsMultiple modulation transmitter/receiver arrangementsRing counterSignal analyzer

The determination of the signal modulation format for a channel is an important aspect of the operation of a signal receiver. A method (700) is described including the steps of receiving (710) a signal, comparing (720) a sample of the received signal to a first threshold value and a second threshold value, creating (720) a signal profile based on the comparison, and selecting (750) a modulation format for the received signal based on the signal profile. An apparatus (500) is also described including a ring counter (510) that receives a sample of an input signal, compares the sample to a first threshold value and a second threshold value, and creates a signal profile for the input signal, a signal profiler (550) that compares the signal profile for the input signal to at least two reference profiles, and a detector (560) that determines a modulation format for the input signal based on the comparison in the signal profiler (550).

Owner:MAGNOLIA LICENSING LLC

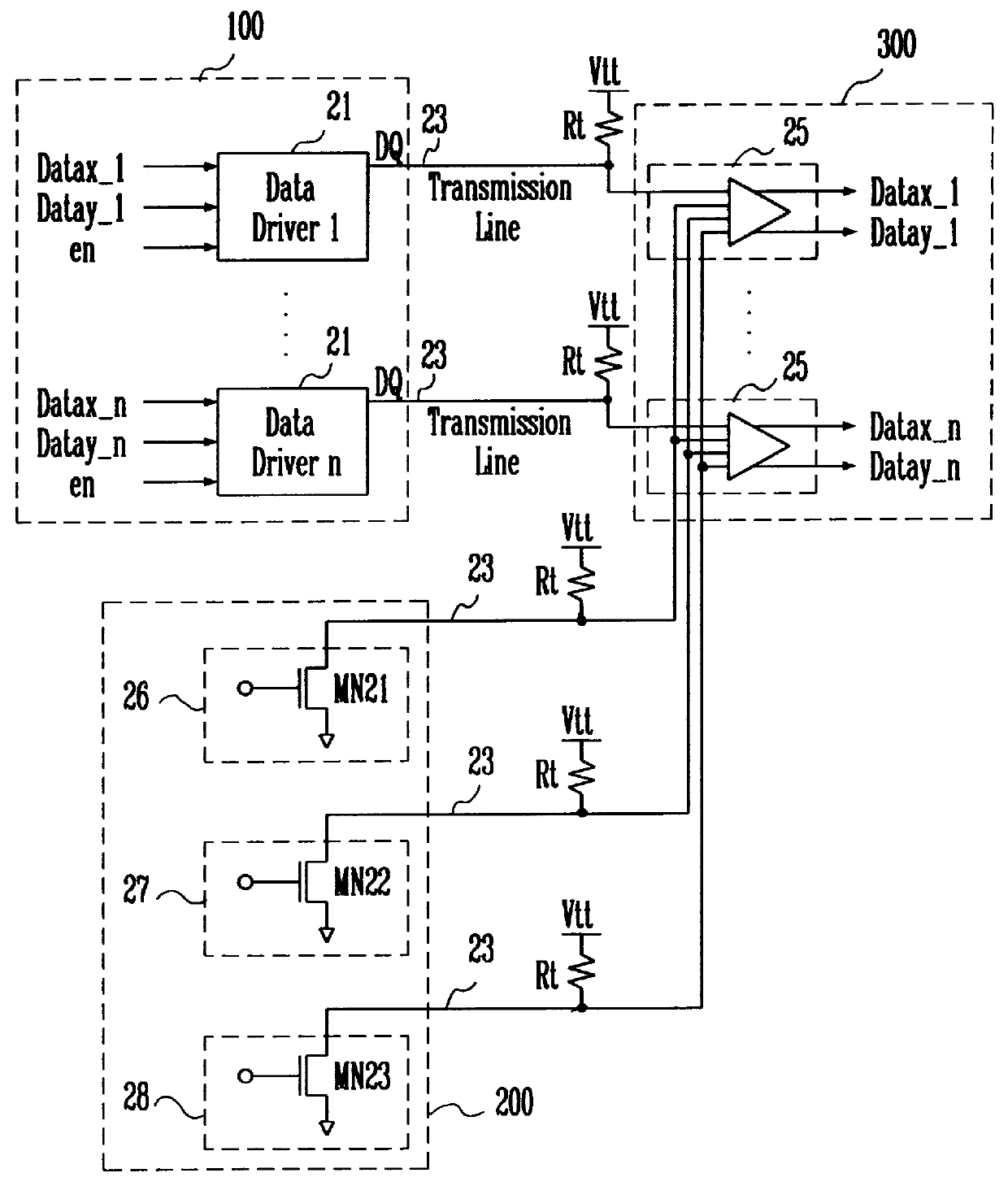

High speed interface apparatus

InactiveUS6140841AElectric signal transmission systemsElectric analogue storesThree levelData signal

The present invention discloses a much higher speed interface apparatus which comprises a data driving means for decoding two-bit data signals using them as inputs to output four-level data signals; a reference voltage generating means for generating three-level reference voltages to discriminate the voltage levels of the four-level data signals; and a receiver means for comparing the four-level data signals and the three-level reference voltage signals using them as inputs and for encoding the resulting signals to output two data signals.

Owner:HYUNDAI ELECTRONICS IND CO LTD

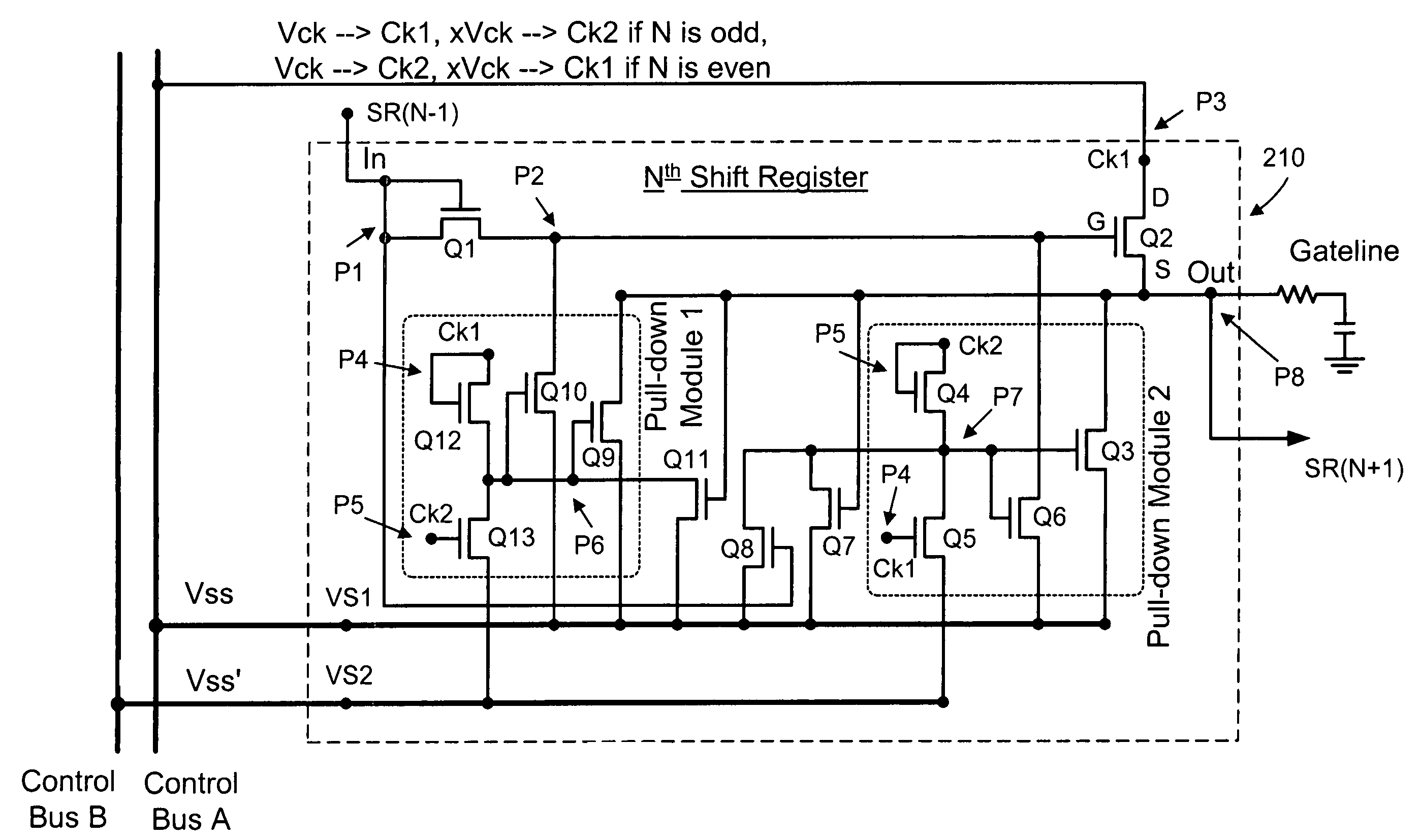

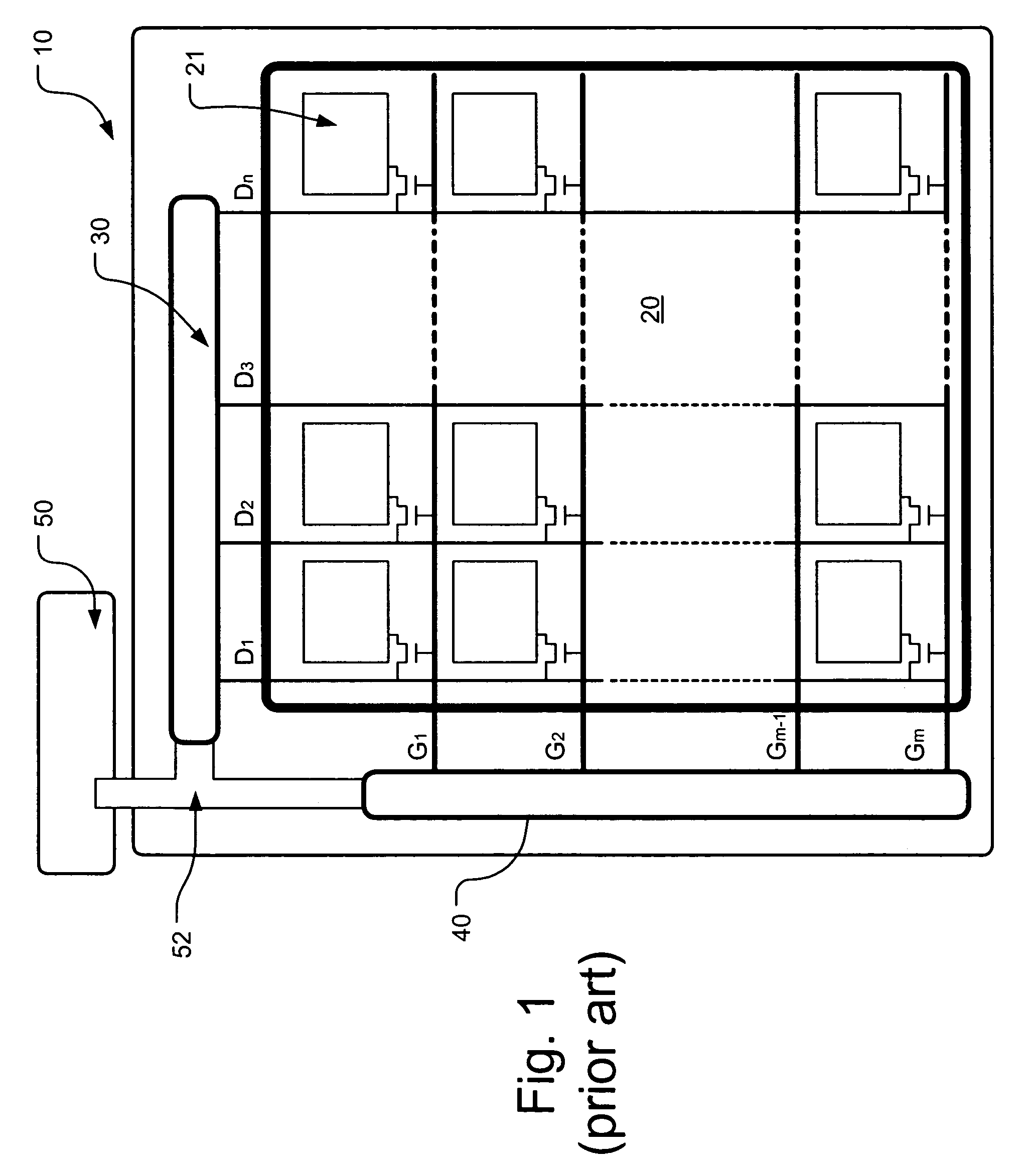

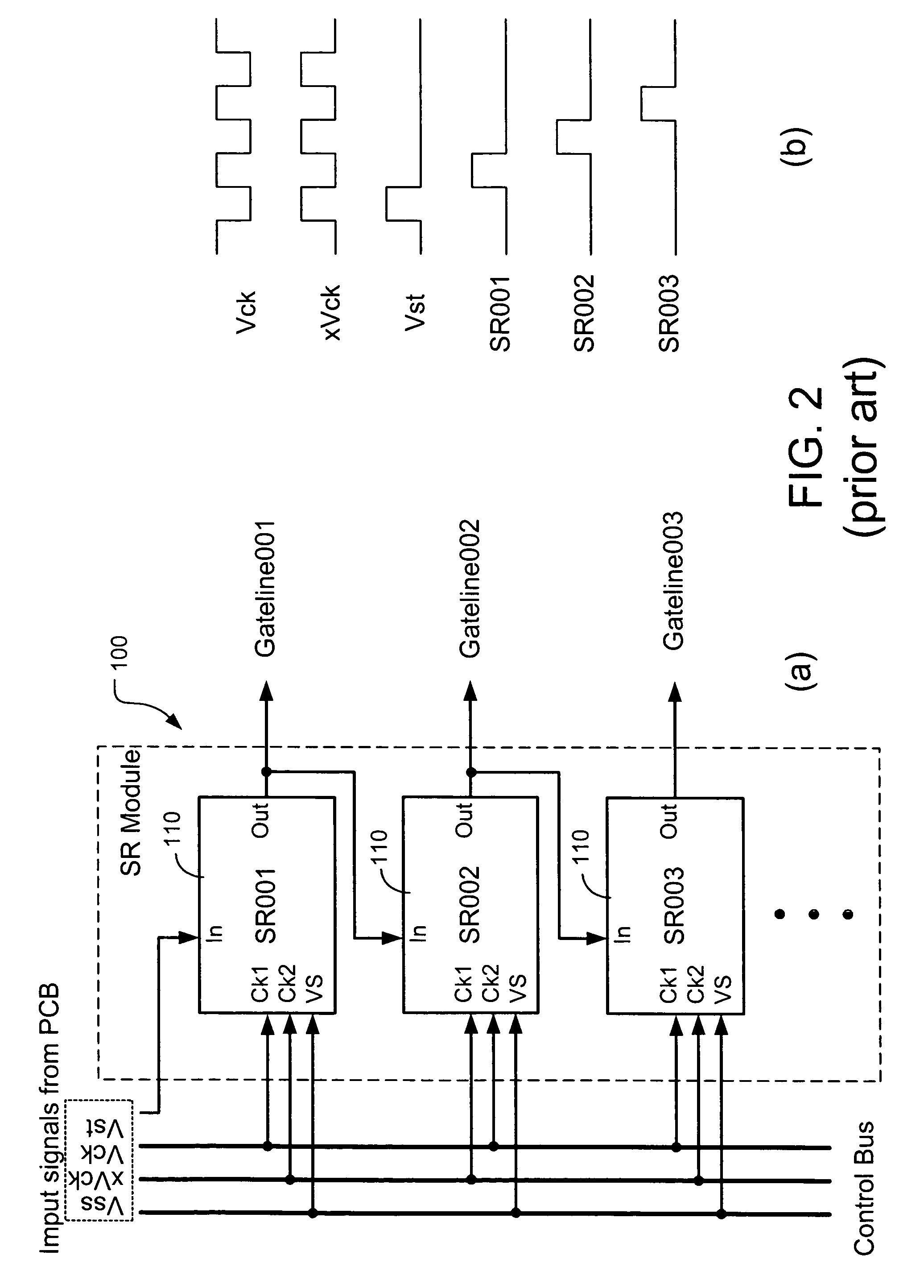

Gate line drivers for active matrix displays

ActiveUS7310402B2Reduce stepsMultiple input and output pulse circuitsDigital storageShift registerActive matrix

Owner:OPTRONIC SCI LLC

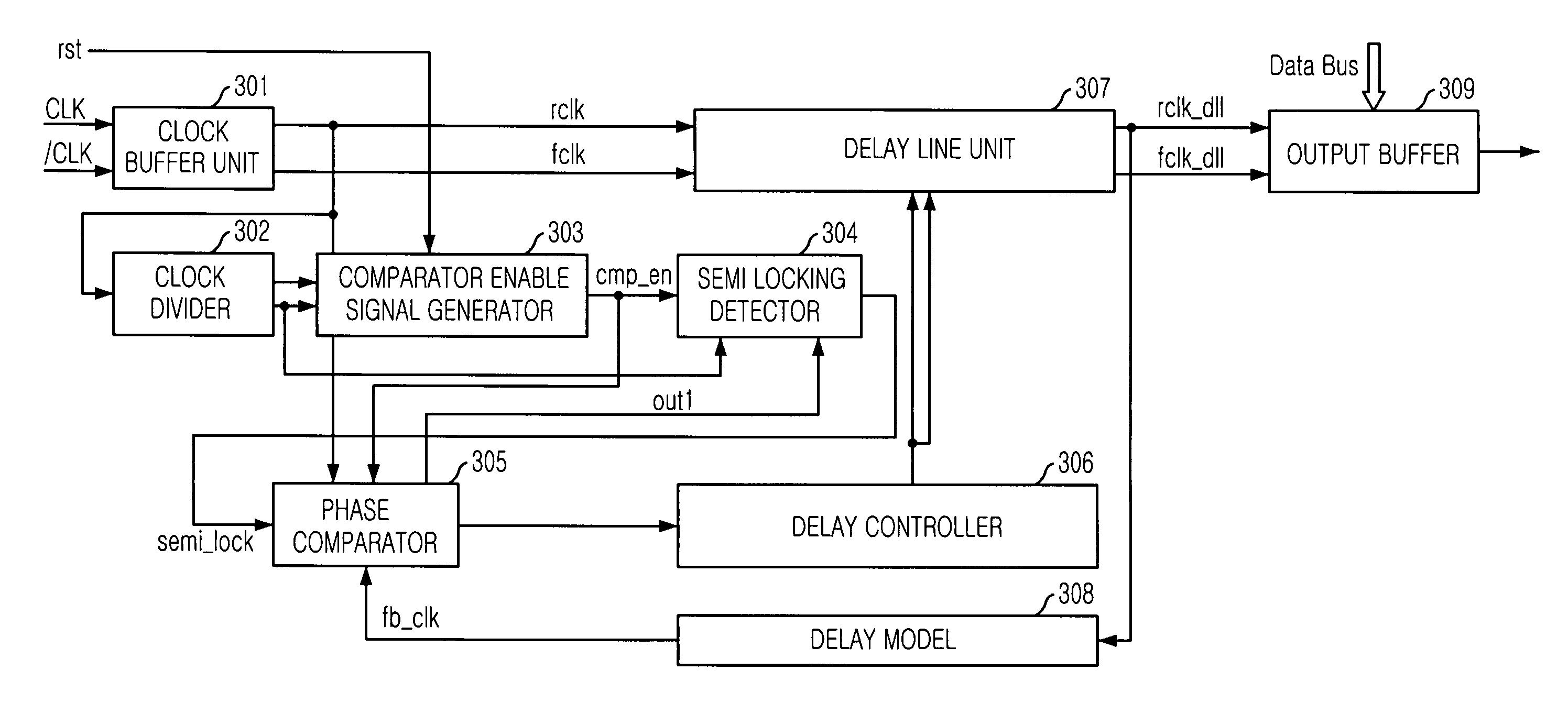

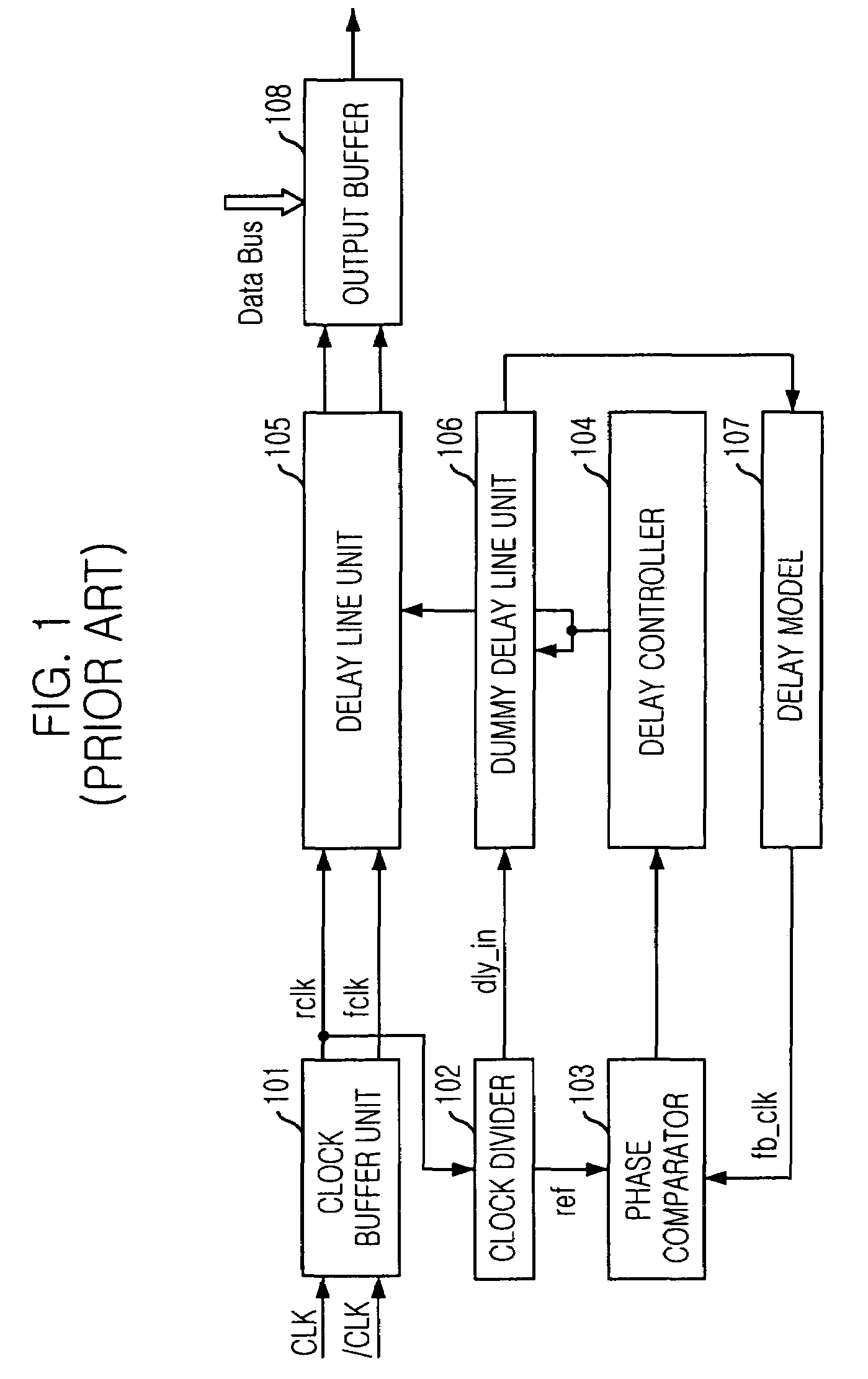

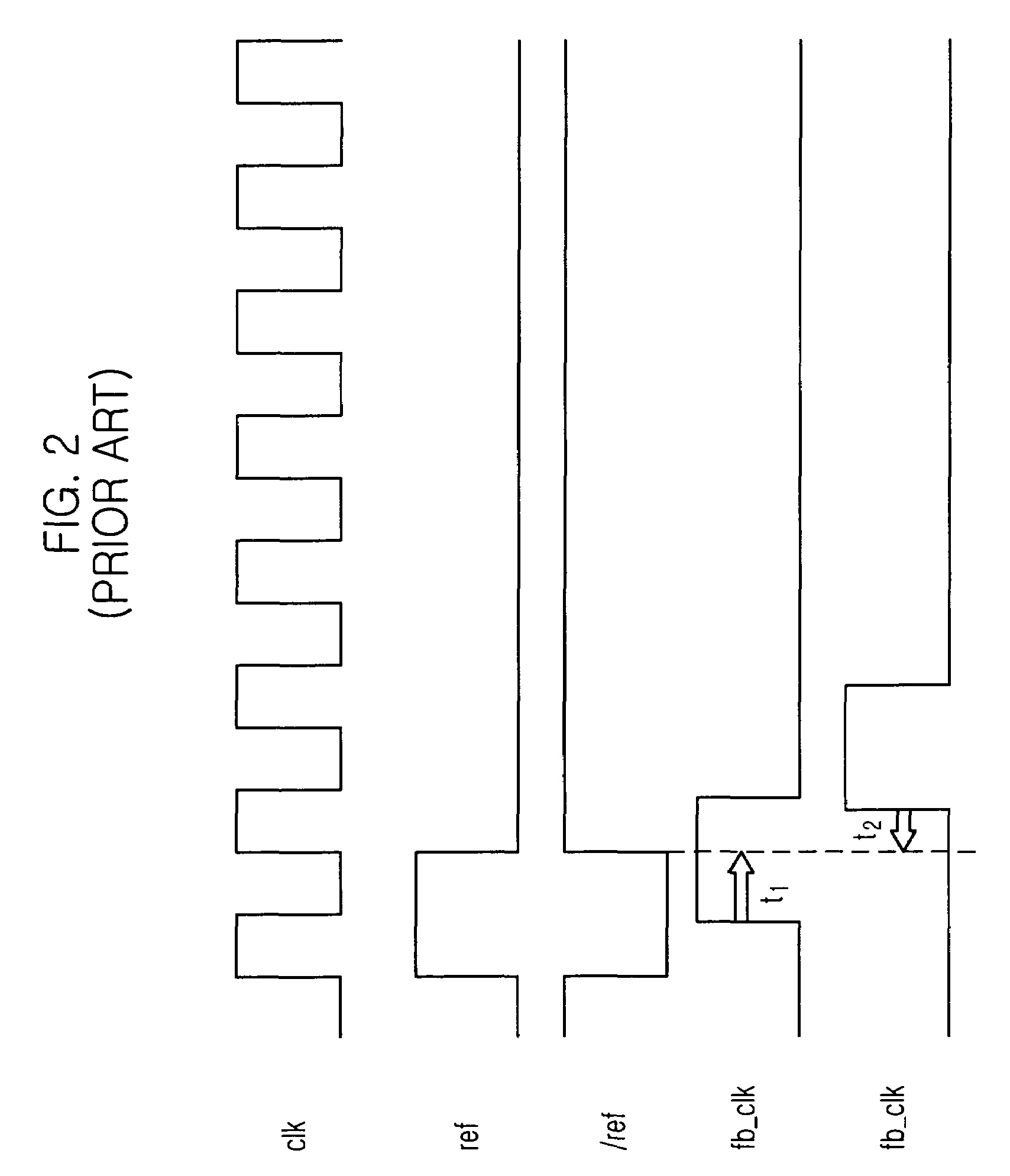

Delay locked loop in semiconductor memory device and its clock locking method

ActiveUS6989700B2Increase working frequencyGuaranteed uptimeMultiple input and output pulse circuitsPulse automatic controlOutput compareDelay-locked loop

A delay locked loop (DLL) for generating a delay locked clock signal, including: a comparator enable signal generator for generating a comparator enable signal in response to a reset signal and a plurality of clock divided signals; a semi locking detector for generating a semi locking detection signal in response to the comparator enable signal; a phase comparator enabled by the comparator enable signal for receiving a rising edge clock signal and a feed-backed clock signal in order to compare phases of the rising edge clock signal and the feed-backed clock signal and output the comparison result; and a DLL generator for generating the delay locked clock signal in response to the comparison result, wherein the comparator enable signal is generated by enlarging a pulse width of the reset signal by a predetermined amount.

Owner:SK HYNIX INC

Low voltage differential signaling device with feedback compensation

ActiveUS7030656B2Reliability increasing modificationsMultiple input and output pulse circuitsCurrent mirrorImaging Signal

A low voltage different signaling (LVDS) includes an LVDS transmitter and an LVDS receiver. The LVDS transmitter includes a feedback compensation circuit, which adjusts and stabilizes the analog image signal to be transmitted to the LVDS receiver according to the voltage difference of the analog image signal and a base signal. The feedback compensation circuit includes a voltage-to-current converting circuit and a pair of current mirror circuits.

Owner:VIA TECH INC

Differential to single-ended logic converter

InactiveUS6924668B2Easy to implementMultiple input and output pulse circuitsLogic circuits characterised by logic functionEngineeringSignal transition

The present invention is a converter stage for converting a differential logic input signal and a corresponding common mode differential logic signal each having a first single-ended logic signal and a complementary second single-ended logic signal into a single-ended logic output signal. The converter stage comprises a first and a second differential stage each having a first and a second MOS transistor and a first and second current source for the differential stages. According to the invention the current sources are controlled by the voltage level which is centered between the mid-potentials of the common mode level differential logic signal and the mid-potential of the differential logic input signal.

Owner:LONGITUDE SEMICON S A R L

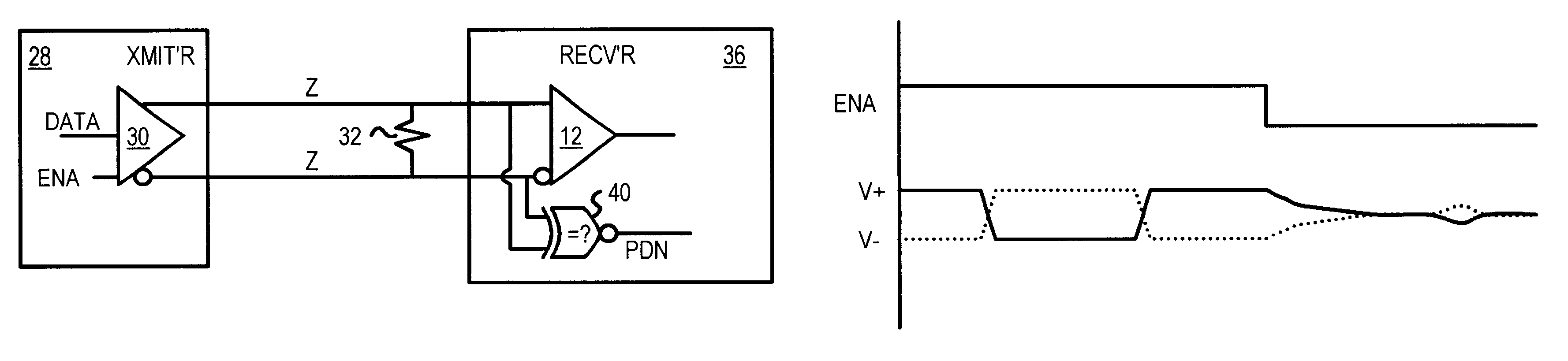

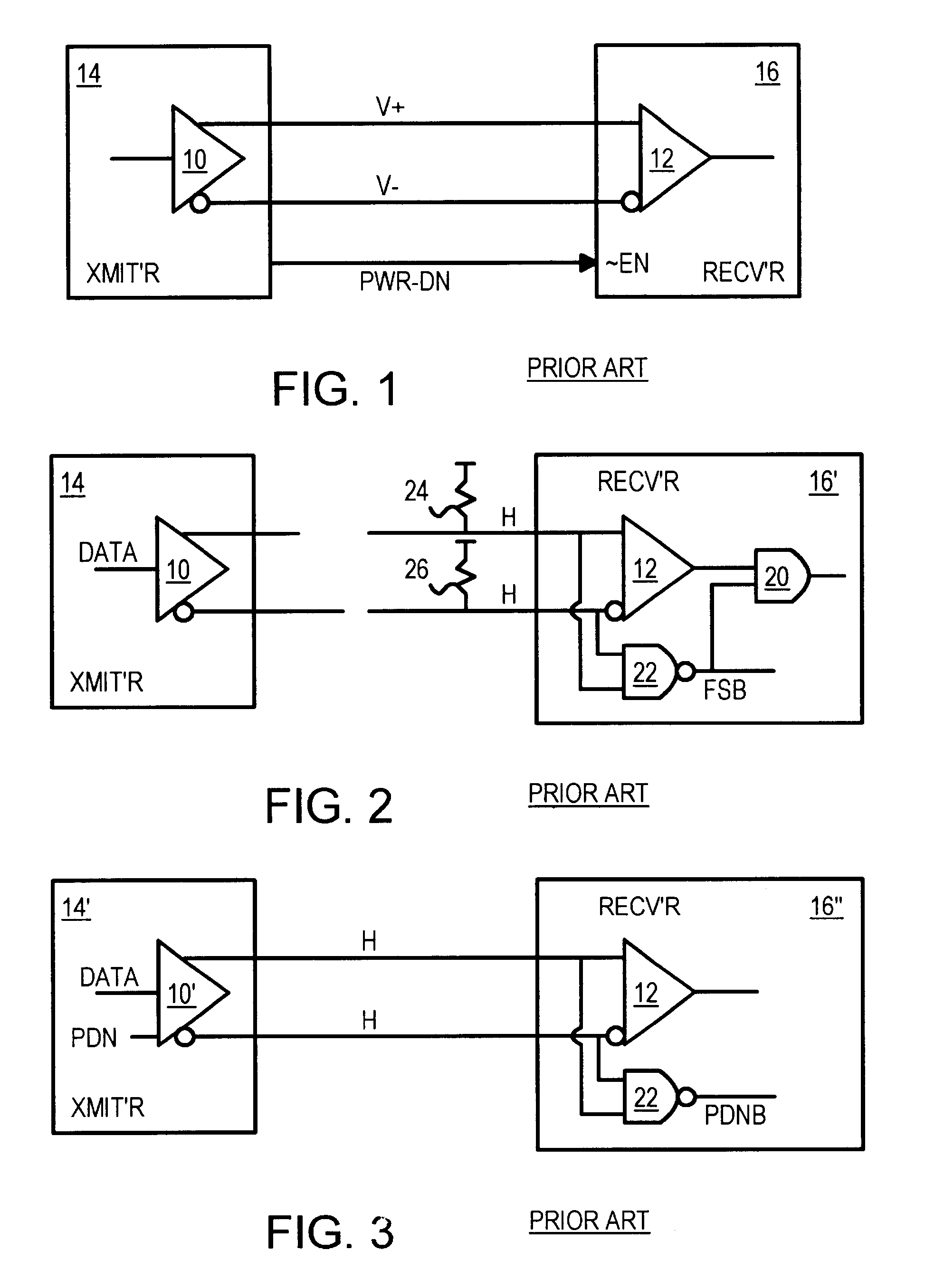

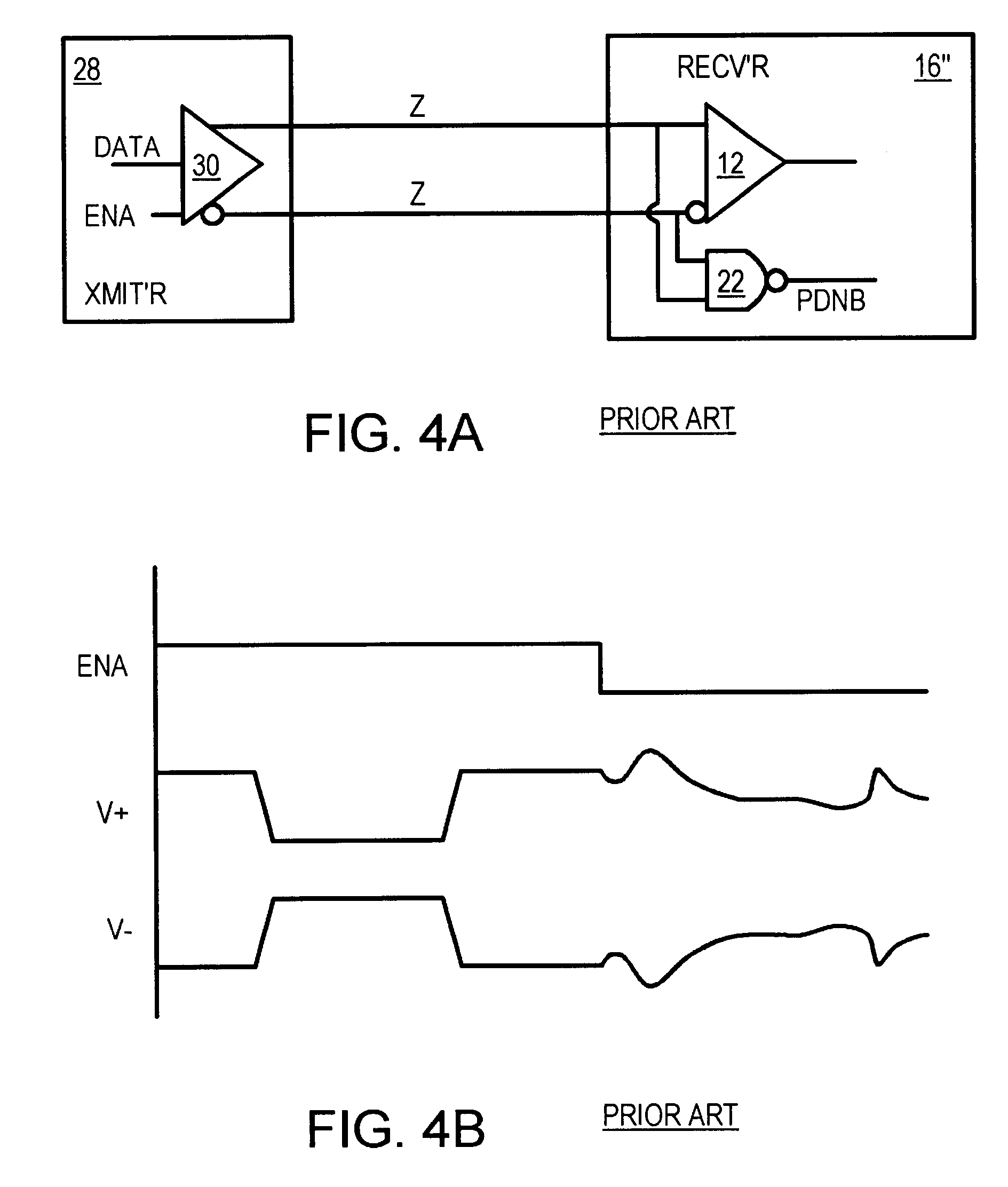

Power down mode signaled by differential transmitter's high-Z state detected by receiver sensing same voltage on differential lines

InactiveUS6593801B1Energy efficient ICTMultiple input and output pulse circuitsElectricityDifferential line

A power-down signal is encoded into a differential pair of lines between two chips. When the differential transmitter powers down, it enters a high-impedance state and floats the differential lines A shunt resistor between a pair of differential lines equalize the voltages on the differential lines so they float to a same voltage when a differential transmitter is disabled and enters a high-impedance state. The condition of equal voltages on the differential lines is detected by an equal-voltage detector that generates a power-down signal when the differential lines are at equal voltages for a period of time. The period of time can be greater than the cross-over time during normal switching to prevent false power-downs during normal switching. Standard differential drivers can signal power-down using the high-impedance state, which is detected by equal voltages on the differential lines. A sensitive dual-differential amplifier and a simpler detector are disclosed.

Owner:DIODES INC

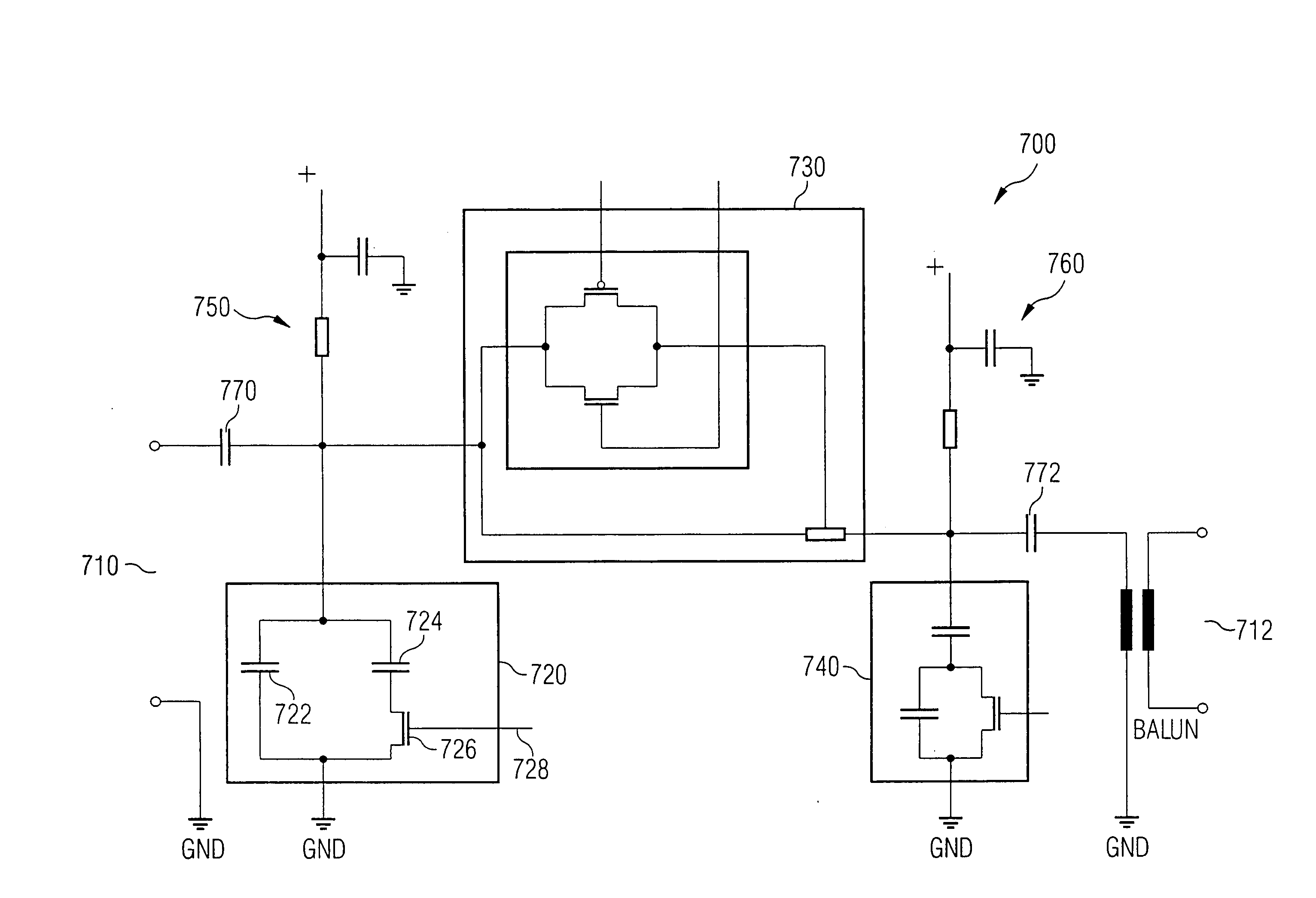

Matching network

InactiveUS20070155347A1Quick switchImproving Impedance MatchingMultiple-port networksResonant long antennasAudio power amplifierHigh frequency power

A matching network for matching an antenna to a transmitter or receiver comprises an input port for receiving high-frequency power, an output port and a switchable impedance transformation circuit, which is connected between the input port and the output port. The impedance transformation circuit comprises a CMOS switch in a high-frequency path, which has a first switching state and a second switching state. The impedance transformation circuit is implemented to match a first impedance applied to the output port to a first predetermined impedance in the first switching state, and to match a second impedance applied to the output port to a second predetermined impedance in the second switching state. The inventive matching network allows a particularly good utilization of power provided by a transmitting amplifier or an antenna.

Owner:INFINEON TECH AG

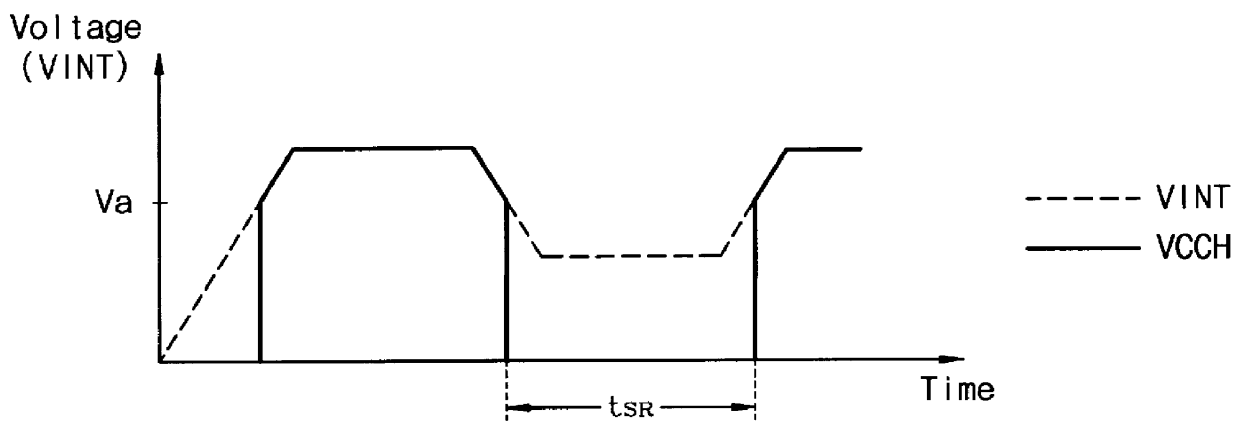

Power-up detection circuit of a semiconductor device

InactiveUS6104221AMultiple input and output pulse circuitsPulse automatic controlDevice materialEngineering

Disclosed is a power-up detection circuit of a semiconductor device which generates an output signal enabling an activation of the semiconductor device to be maintained only when an internal power voltage is more than a predetermined voltage level. In the power-up detection circuit, a level detection section is provided for detecting a level of the internal power voltage to generate a first level detection signal when the internal power voltage is less than the predetermined voltage level and to generate a second level detection signal when the internal power voltage is not less than the predetermined voltage level. And, an output driver is provided for enabling the internal circuits to be at inactive state in response to the first level detection signal, and generating the output signal having the same waveform as the internal power voltage in response to the second level detection signal.

Owner:SAMSUNG ELECTRONICS CO LTD

![Low voltage differential signaling [LVDS] driver with pre-emphasis Low voltage differential signaling [LVDS] driver with pre-emphasis](https://images-eureka.patsnap.com/patent_img/74b8f4ad-e594-484b-88fa-38de88ef32f9/US06977534-20051220-D00000.png)

![Low voltage differential signaling [LVDS] driver with pre-emphasis Low voltage differential signaling [LVDS] driver with pre-emphasis](https://images-eureka.patsnap.com/patent_img/74b8f4ad-e594-484b-88fa-38de88ef32f9/US06977534-20051220-D00001.png)

![Low voltage differential signaling [LVDS] driver with pre-emphasis Low voltage differential signaling [LVDS] driver with pre-emphasis](https://images-eureka.patsnap.com/patent_img/74b8f4ad-e594-484b-88fa-38de88ef32f9/US06977534-20051220-D00002.png)