Patents

Literature

483 results about "NOR gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The NOR gate is a digital logic gate that implements logical NOR - it behaves according to the truth table to the right. A HIGH output (1) results if both the inputs to the gate are LOW (0); if one or both input is HIGH (1), a LOW output (0) results. NOR is the result of the negation of the OR operator. It can also in some senses be seen as the inverse of an AND gate. NOR is a functionally complete operation—NOR gates can be combined to generate any other logical function. It shares this property with the NAND gate. By contrast, the OR operator is monotonic as it can only change LOW to HIGH but not vice versa.

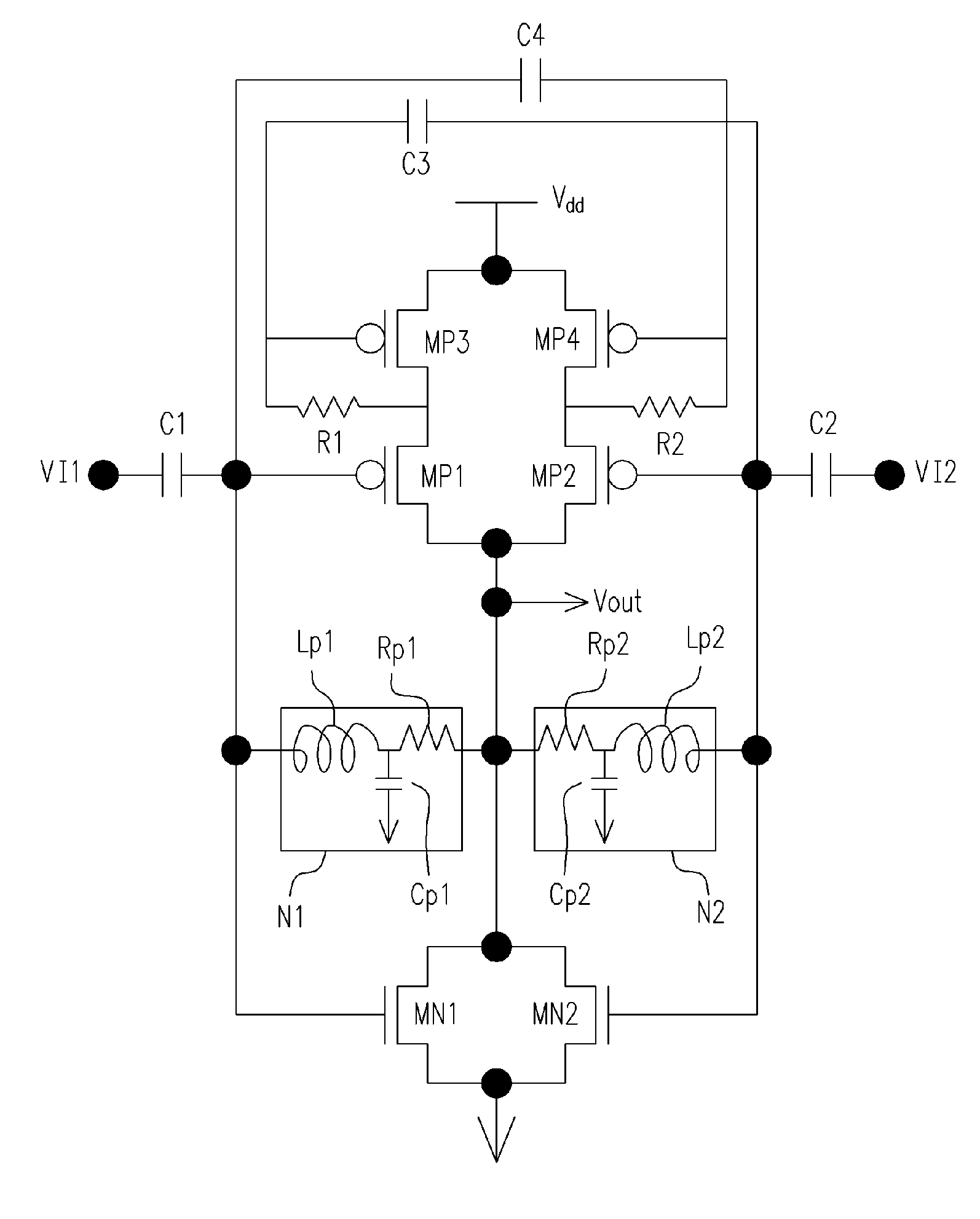

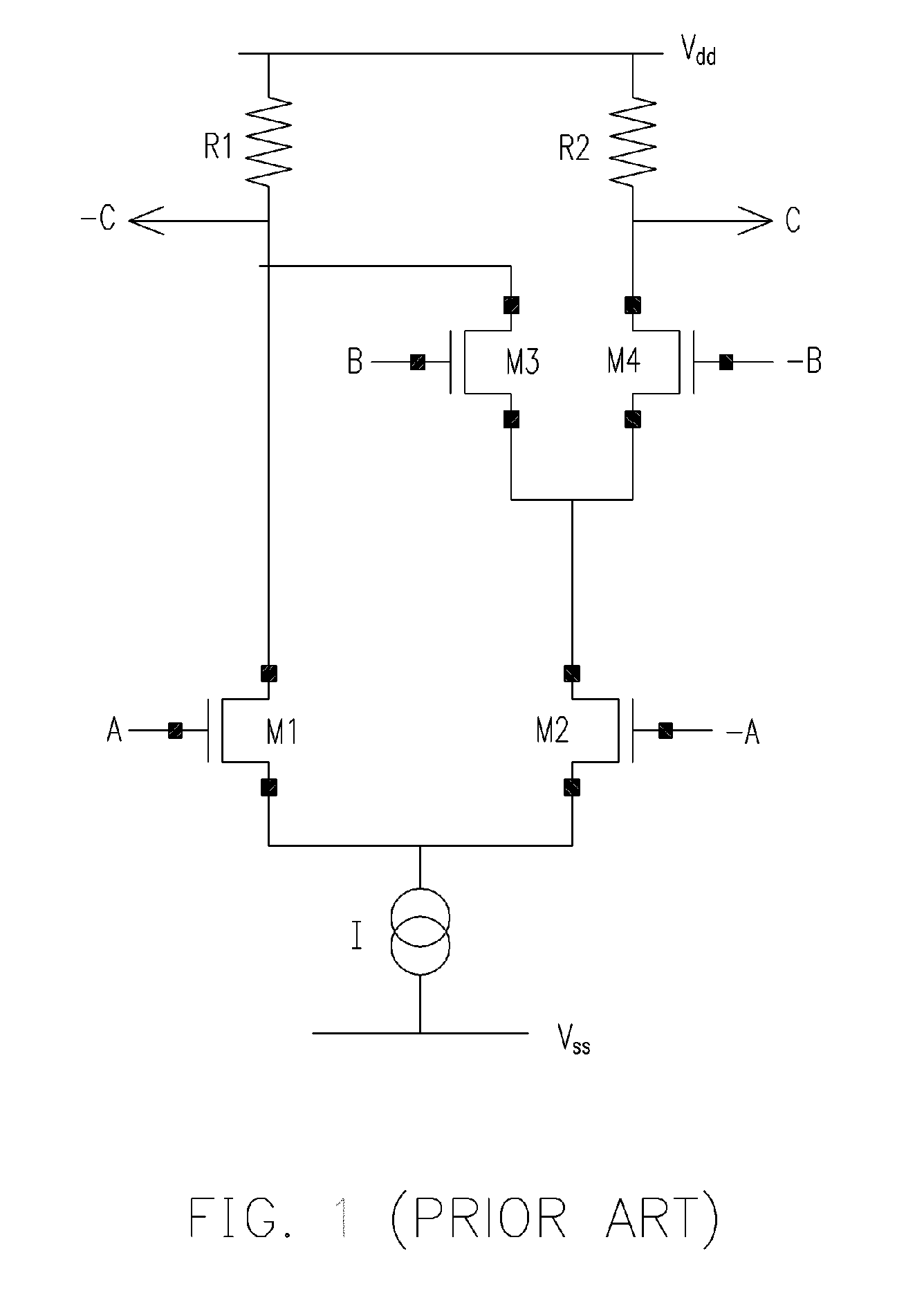

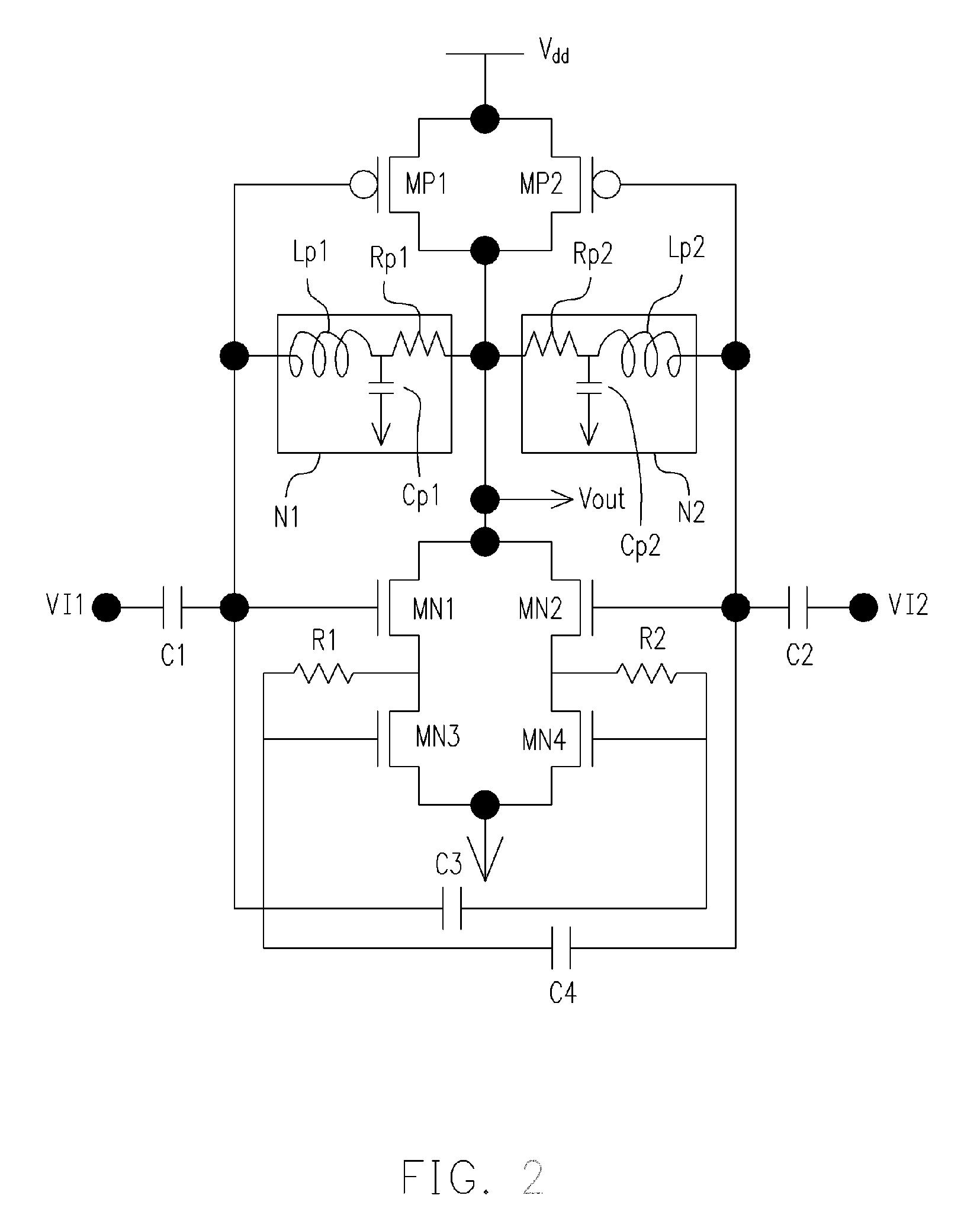

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

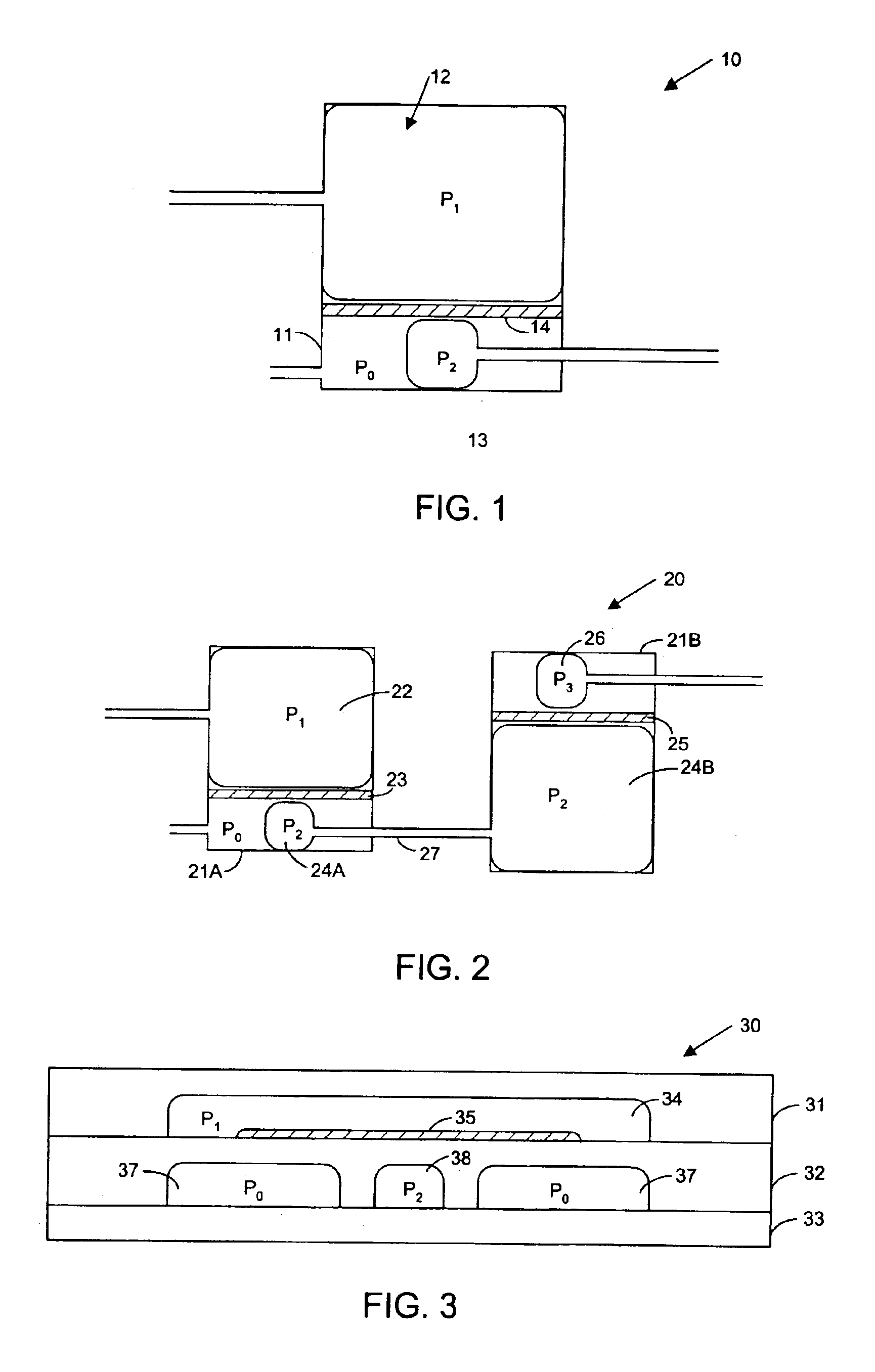

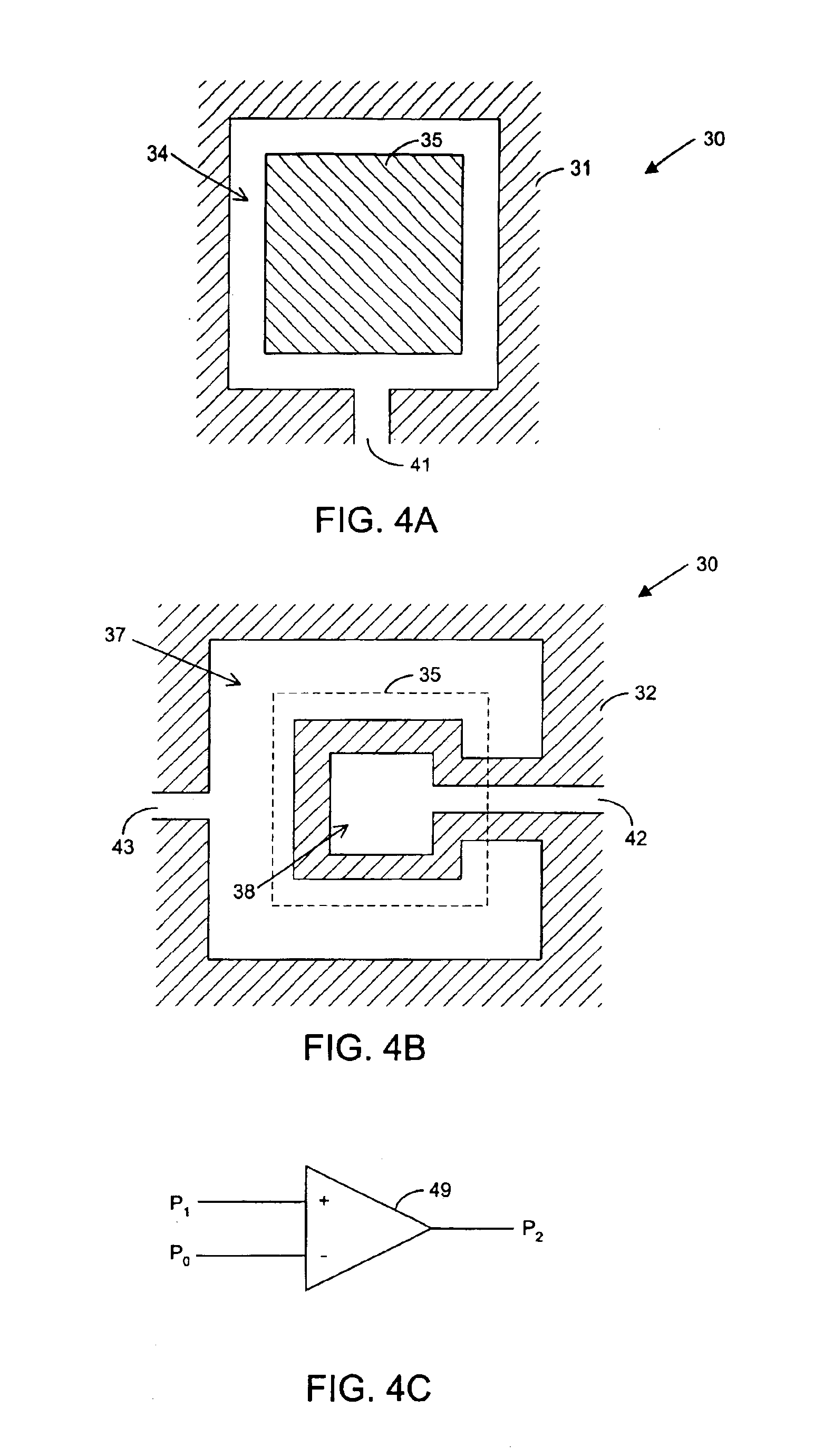

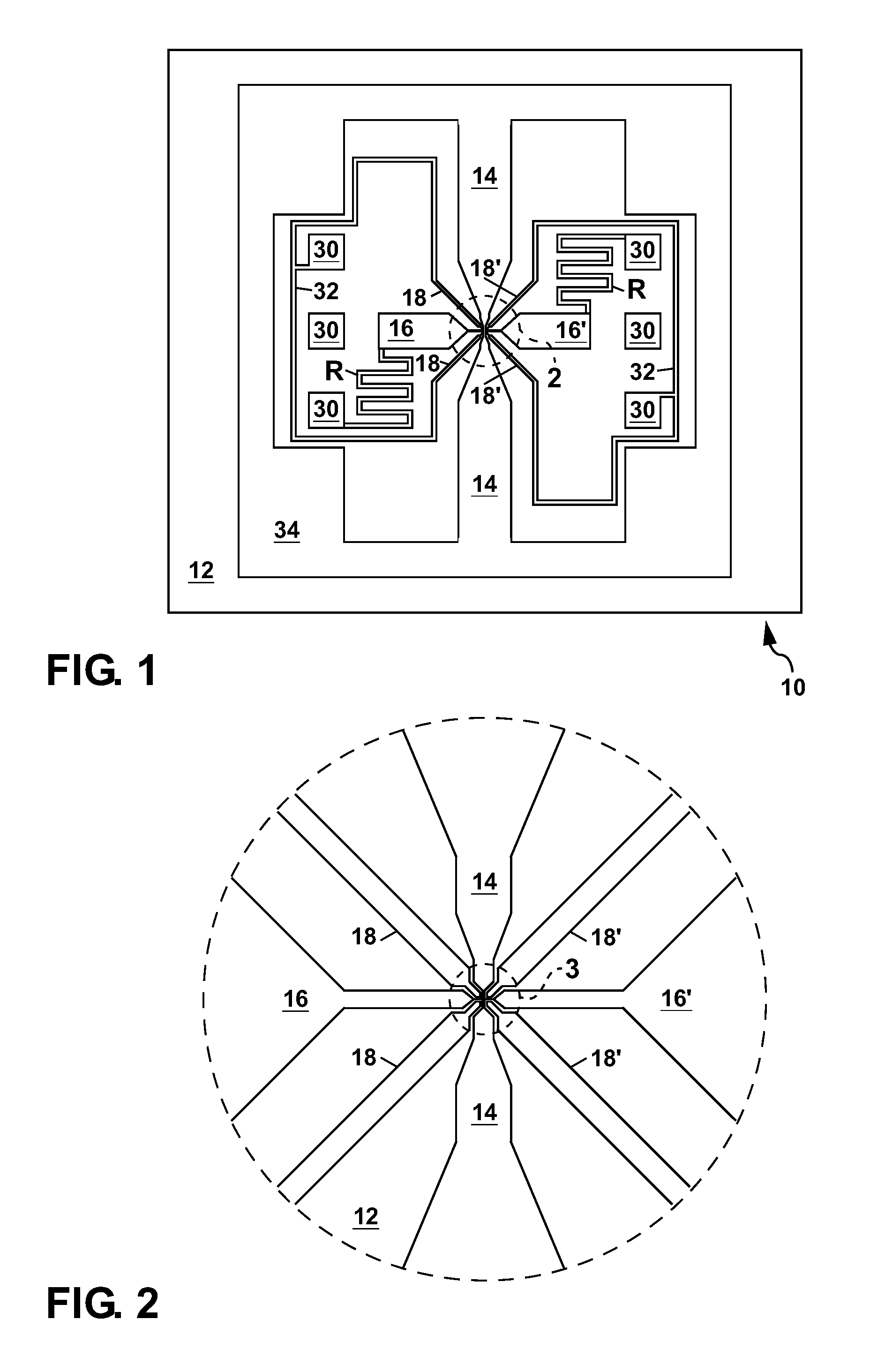

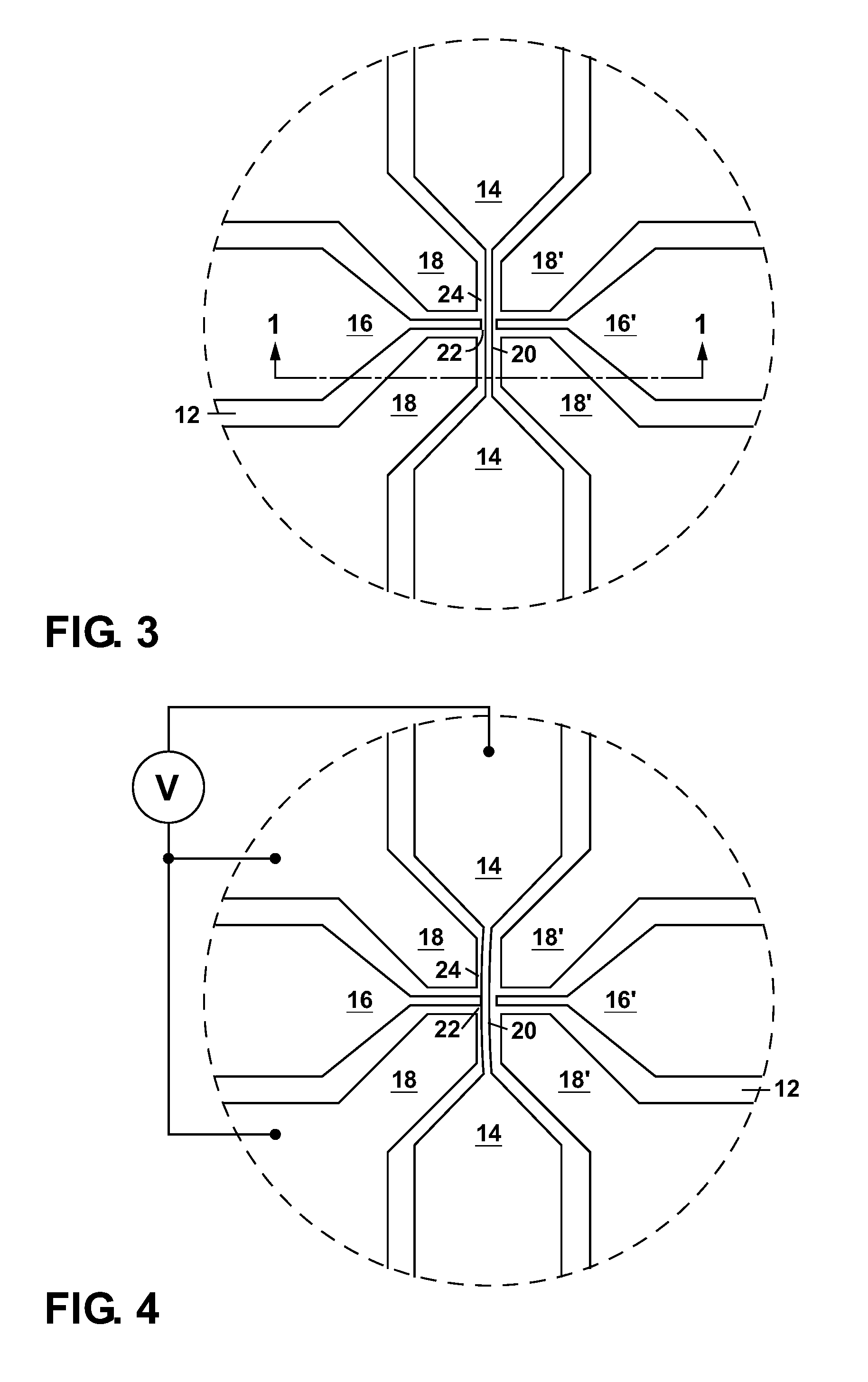

Microfabricated fluidic circuit elements and applications

InactiveUS6953058B2Macroscopic control lines exiting the chip are minimized or eliminatedGeometric CADOperating means/releasing devices for valvesFluidicsNOR gate

The present invention provides microfabricated fluidic systems and methods. Microfabricated fluidic devices of the present invention include switches that can be opened and closed to allow or block the flow of fluid through a channel in response to the pressure level in a gate of the switch. The microfabricated fluidic switches may be coupled together to perform logic functions and Boolean algebra, such as inverters, AND gates, NAND, gates, NOR gates, and OR gates. The logic gates may be coupled together to form flip-flops that latch signals. The present invention also includes microfabricated fluidic pressure multipliers that increase the pressure in a second chamber relative to a first chamber. Microfabricated fluidic devices of the present invention also include pressure sources. A pressure source of the present includes a pump coupled to a reservoir through unidirectional valves. The pressure source may be high pressure source or a low pressure source. Microfabricated fluidic devices of the present invention may also include devices that perform analog functions such as switching regulator.

Owner:FLUIDIGM CORP

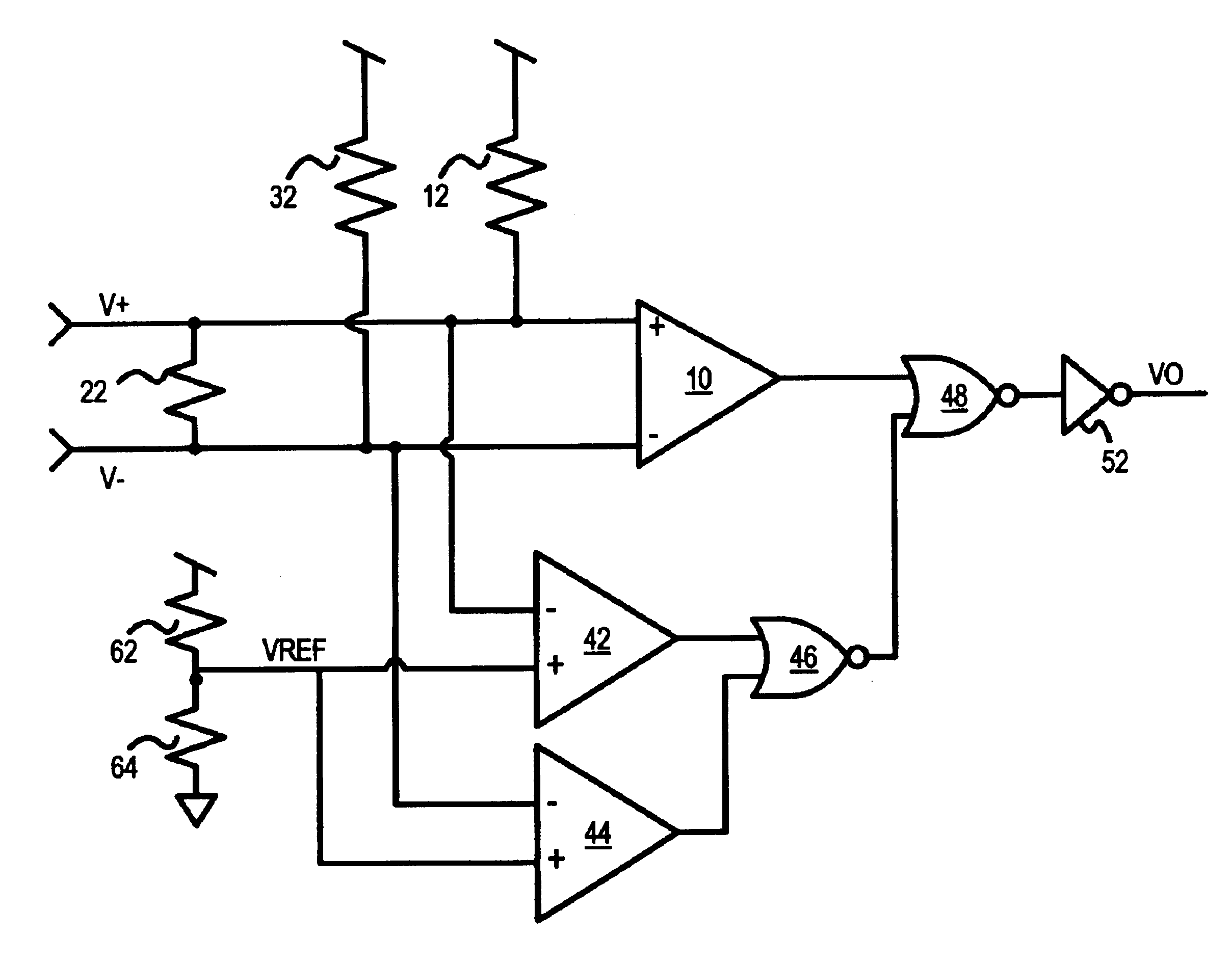

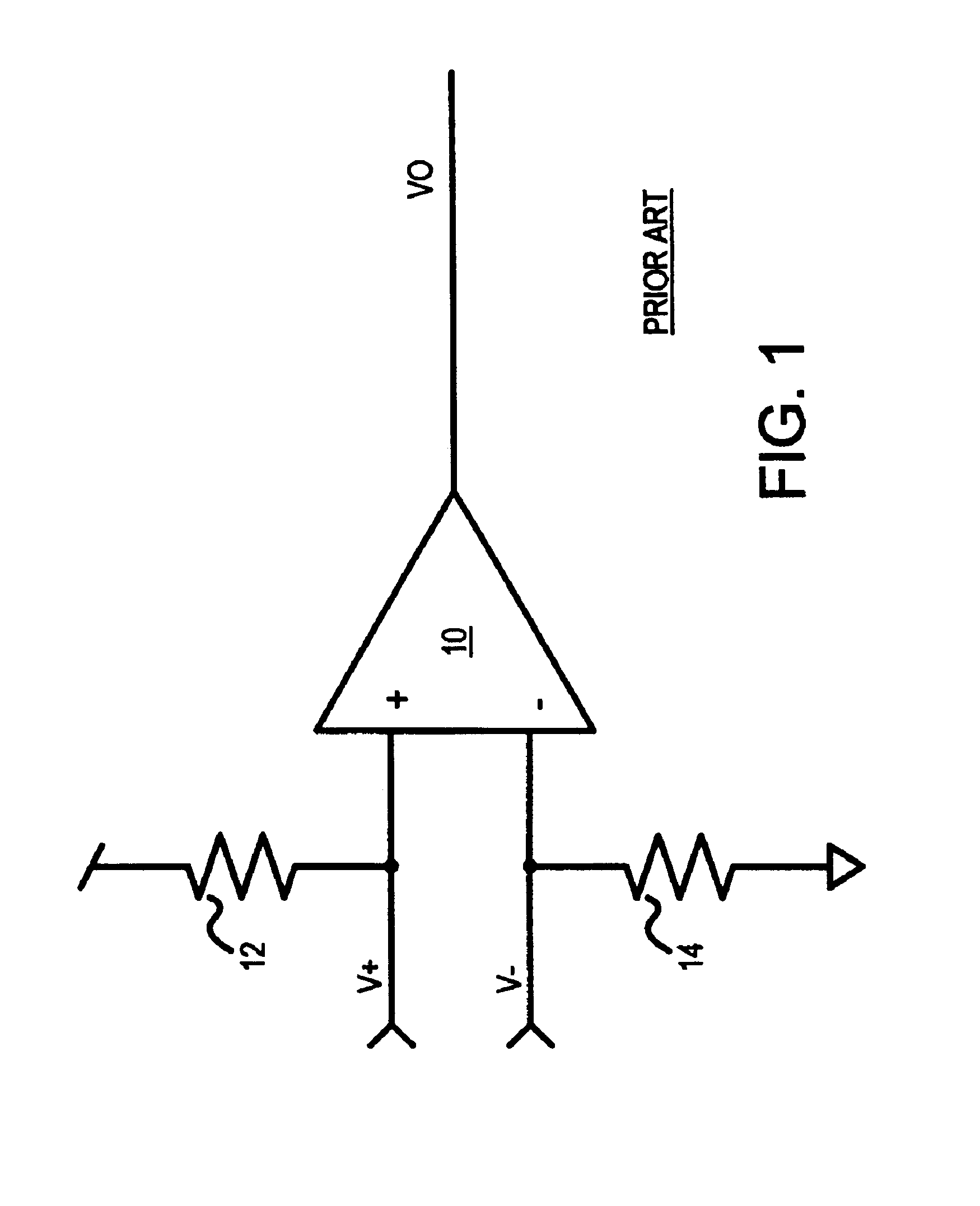

Active fail-safe detect circuit for differential receiver

InactiveUS6288577B1Multiple input and output pulse circuitsFail-safe circuitsNOR gateDifferential signaling

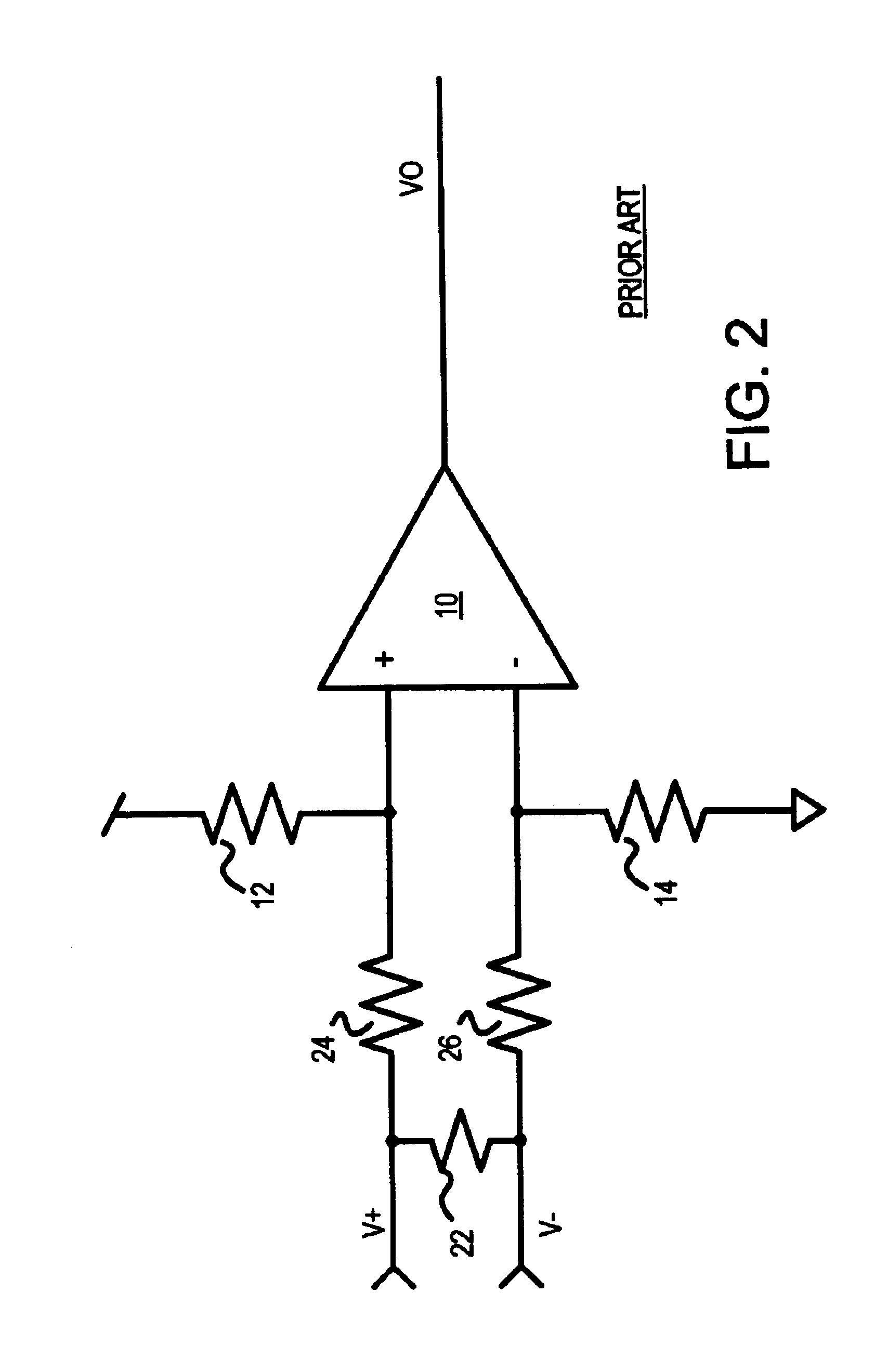

A fail-safe circuit for a differential receiver can tolerate high common-mode voltages. An output from a differential amplifier that receives a V+ and a V- differential signal can be blocked by a NOR gate when the fail-safe condition is detected, such as when the V+, V- lines are open. Pullup resistors pull V+, V- to Vcc when an open failure occurs. A pair of comparators receive a reference voltage on the non-inverting input. Once comparator outputs a high when the V+ line is above the reference voltage, and the other comparator outputs a high when the V- line is above the reference voltage. When both V+ and V- are above the reference voltage, the NOR gate blocks the output from the differential amplifier, providing a fail-safe. Since the reference voltage is very close to Vcc, a high common-mode bias can exist on V+, V- without falsely activating the fail-safe circuit.

Owner:DIODES INC

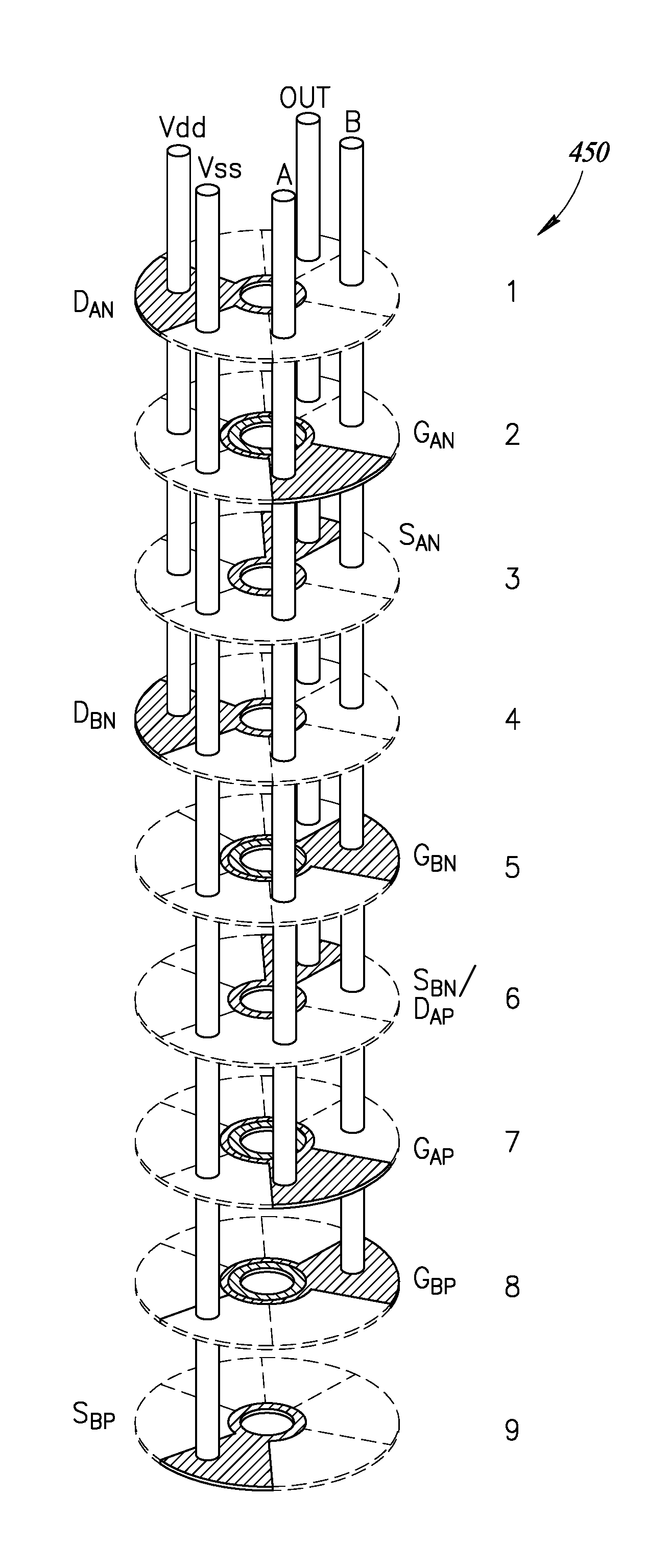

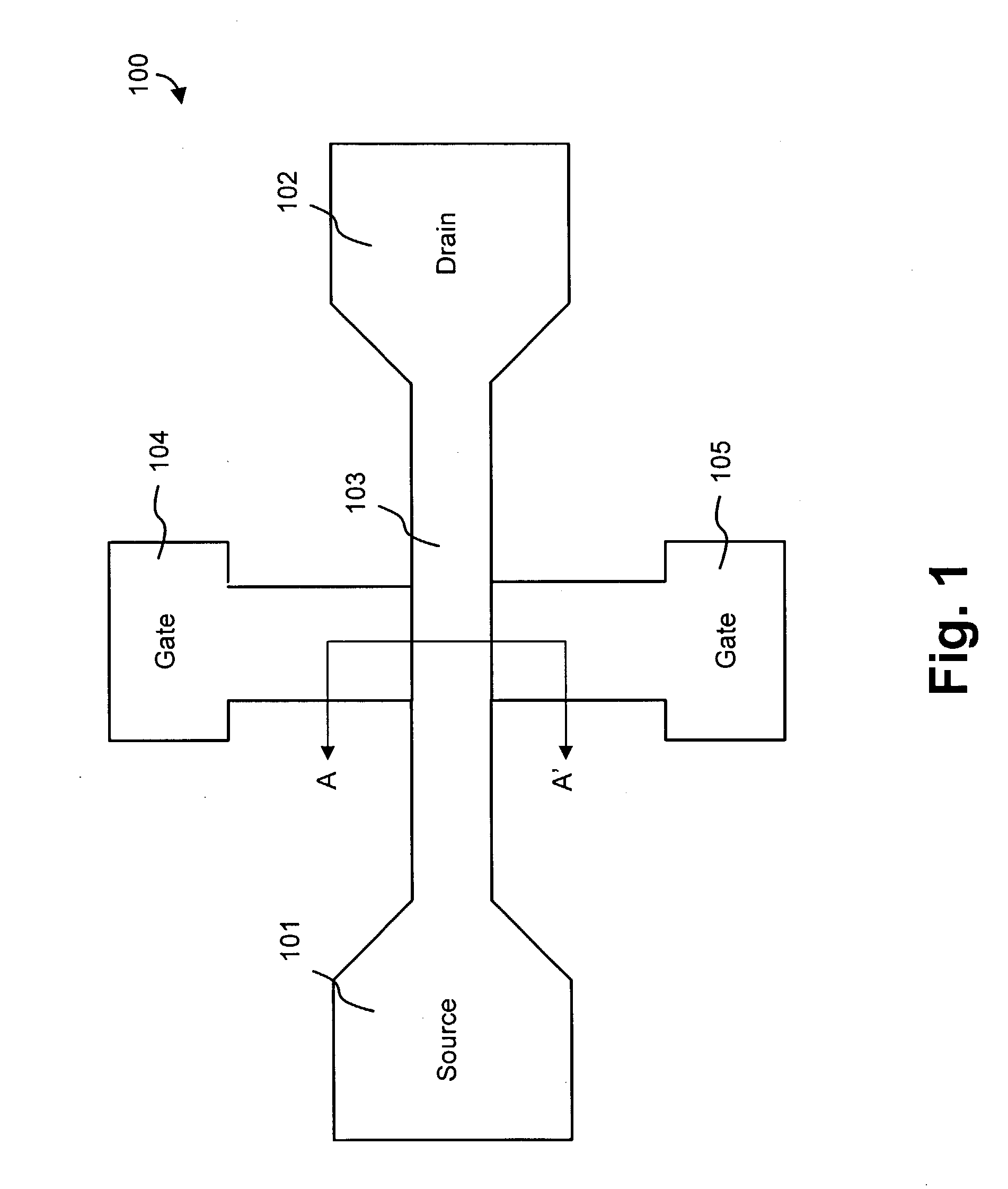

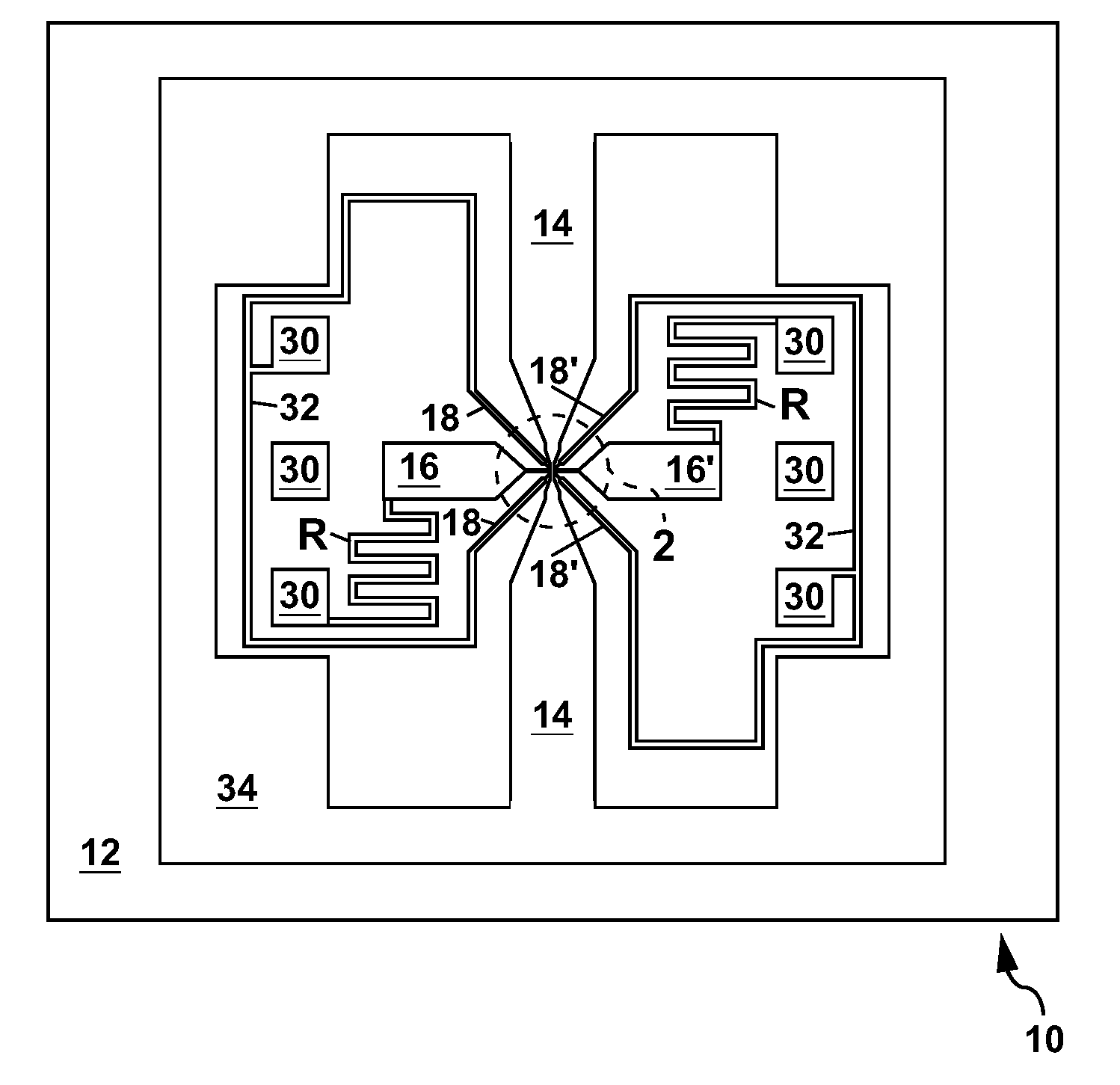

Modular interconnects for gate-all-around transistors

ActiveUS20170005106A1Facilitates building complexImprove compactionTransistorSemiconductor/solid-state device detailsNanowireNOR gate

A modular interconnect structure facilitates building complex, yet compact, integrated circuits from vertical GAA FETs. The modular interconnect structure includes annular metal contacts to the transistor terminals, sectors of stacked discs extending radially outward from the vertical nanowires, and vias in the form of rods. Extension tabs mounted onto the radial sector interconnects permit signals to fan out from each transistor terminal. Adjacent interconnects are linked by linear segments. Unlike conventional integrated circuits, the modular interconnects as described herein are formed at the same time as the transistors. Vertical GAA NAND and NOR gates provide building blocks for creating all types of logic gates to carry out any desired Boolean logic function. Stacked vertical GAA FETs are made possible by the modular interconnect structure. The modular interconnect structure permits a variety of specialized vertical GAA devices to be integrated on a silicon substrate using standard CMOS processes.

Owner:STMICROELECTRONICS SRL

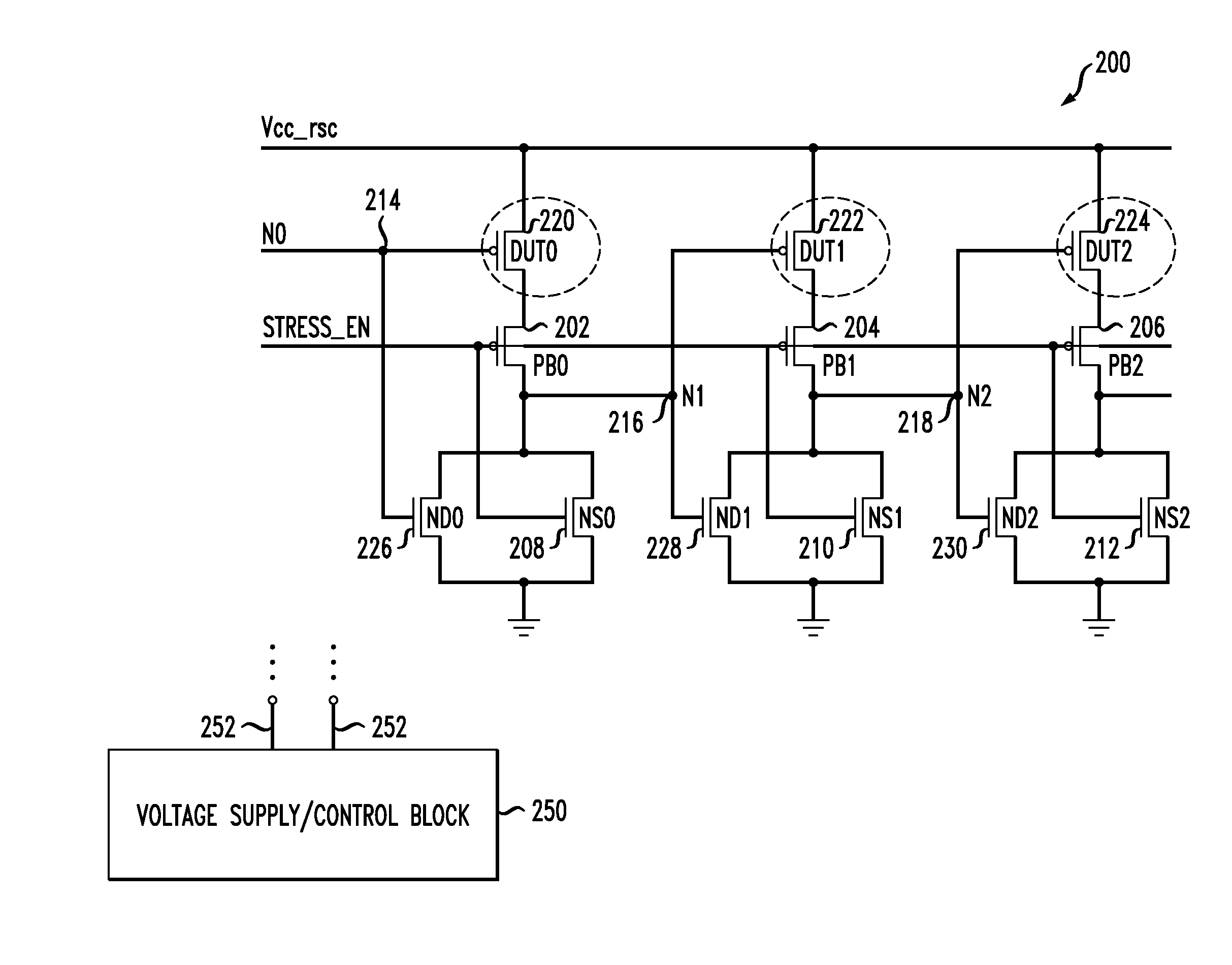

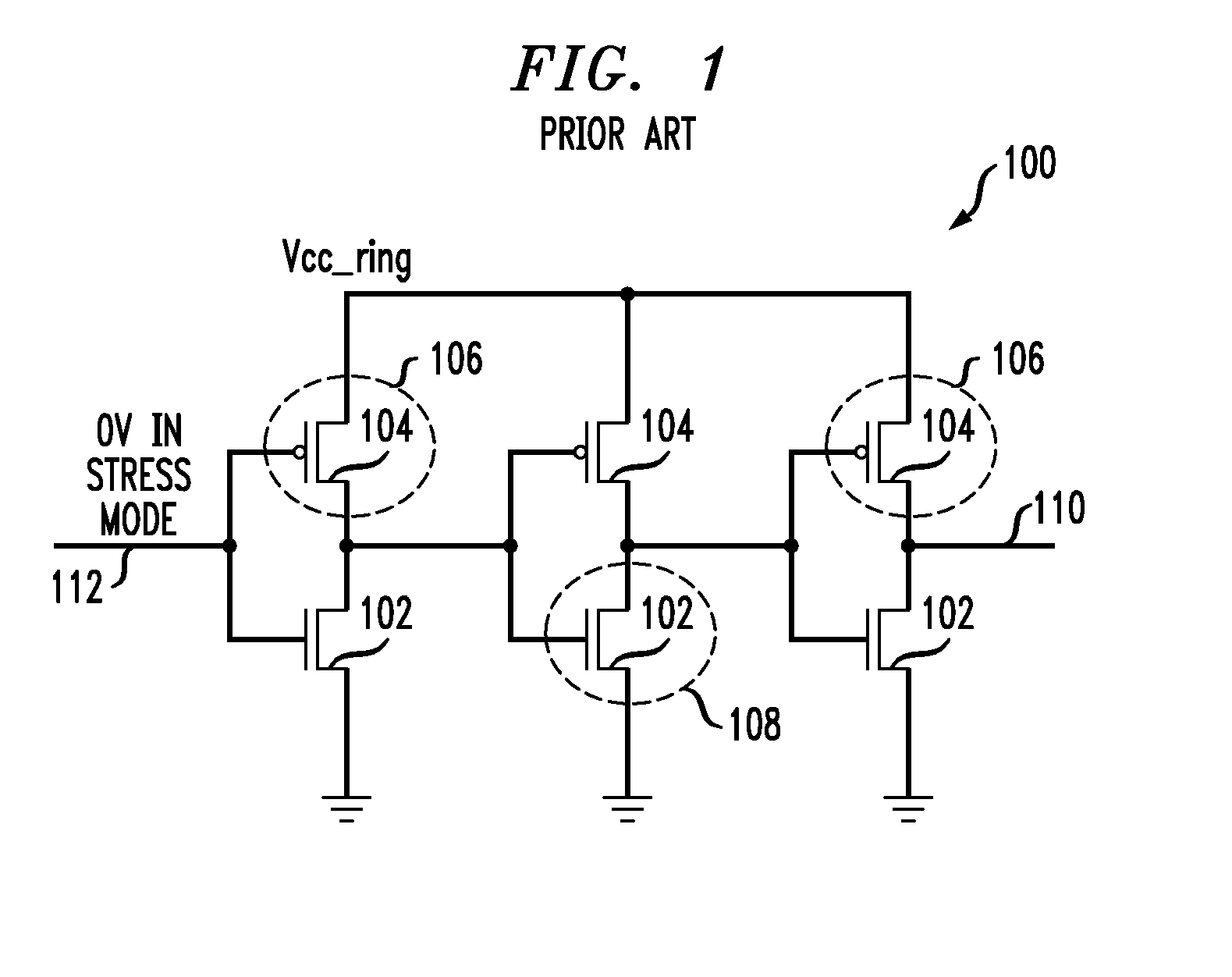

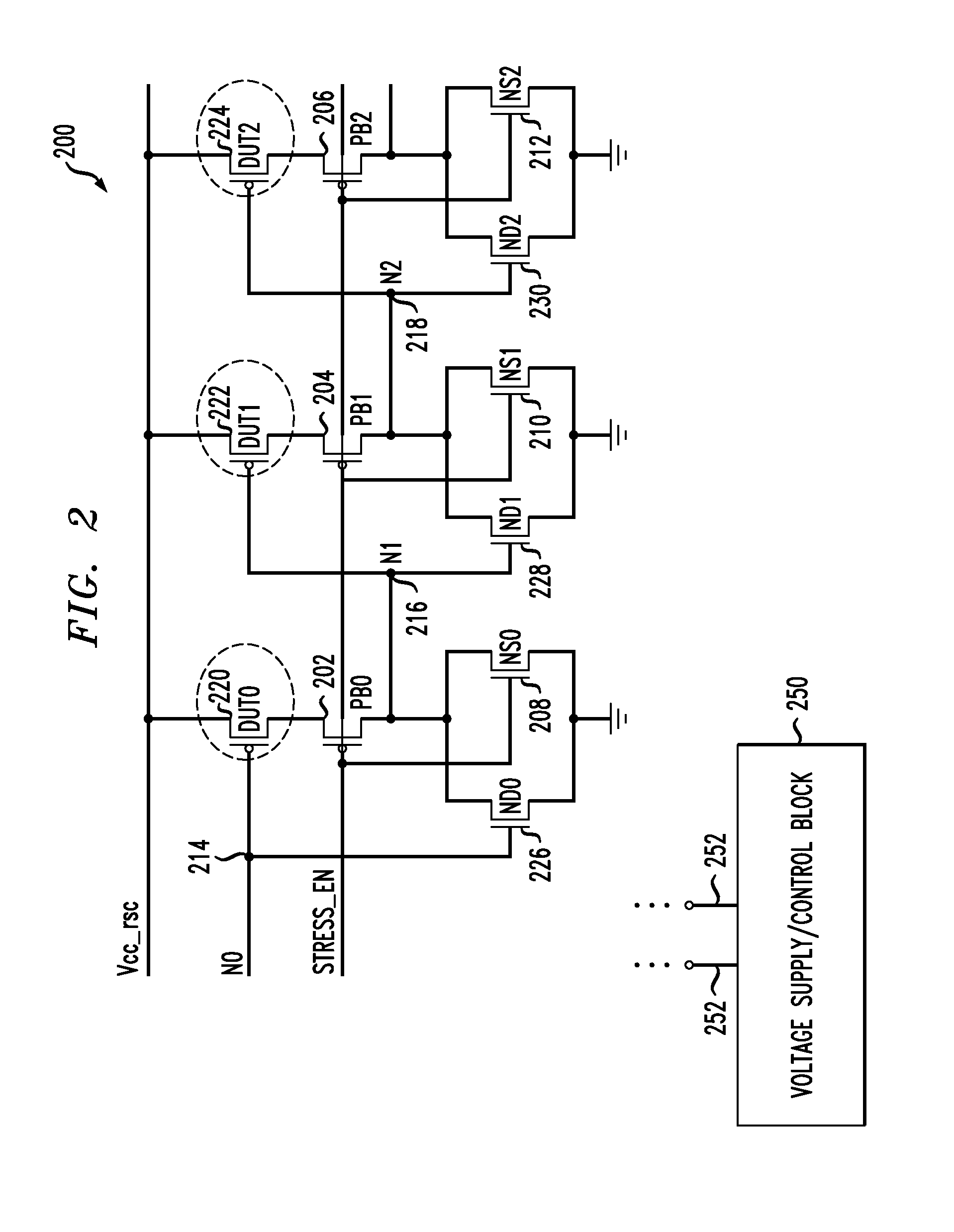

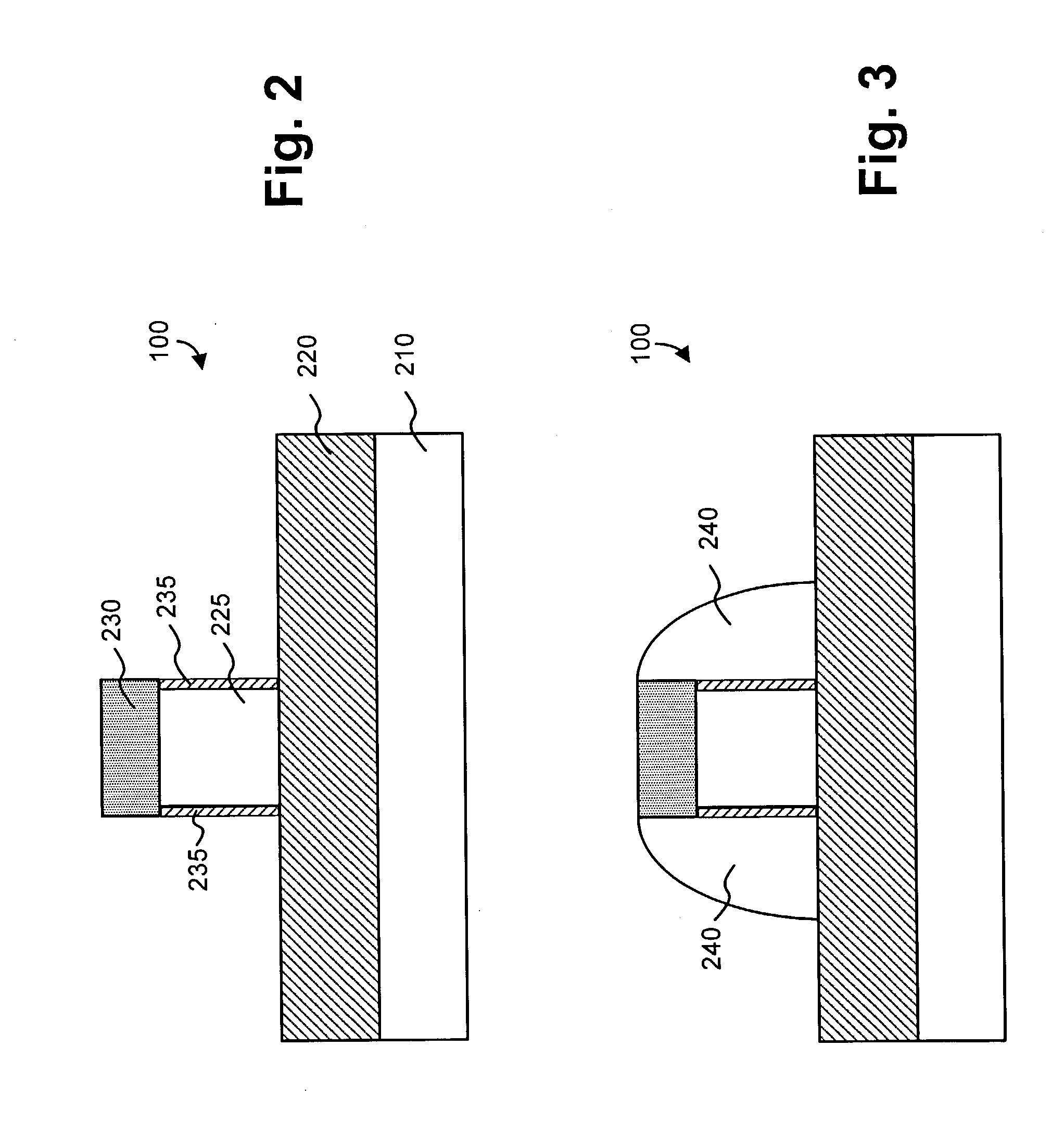

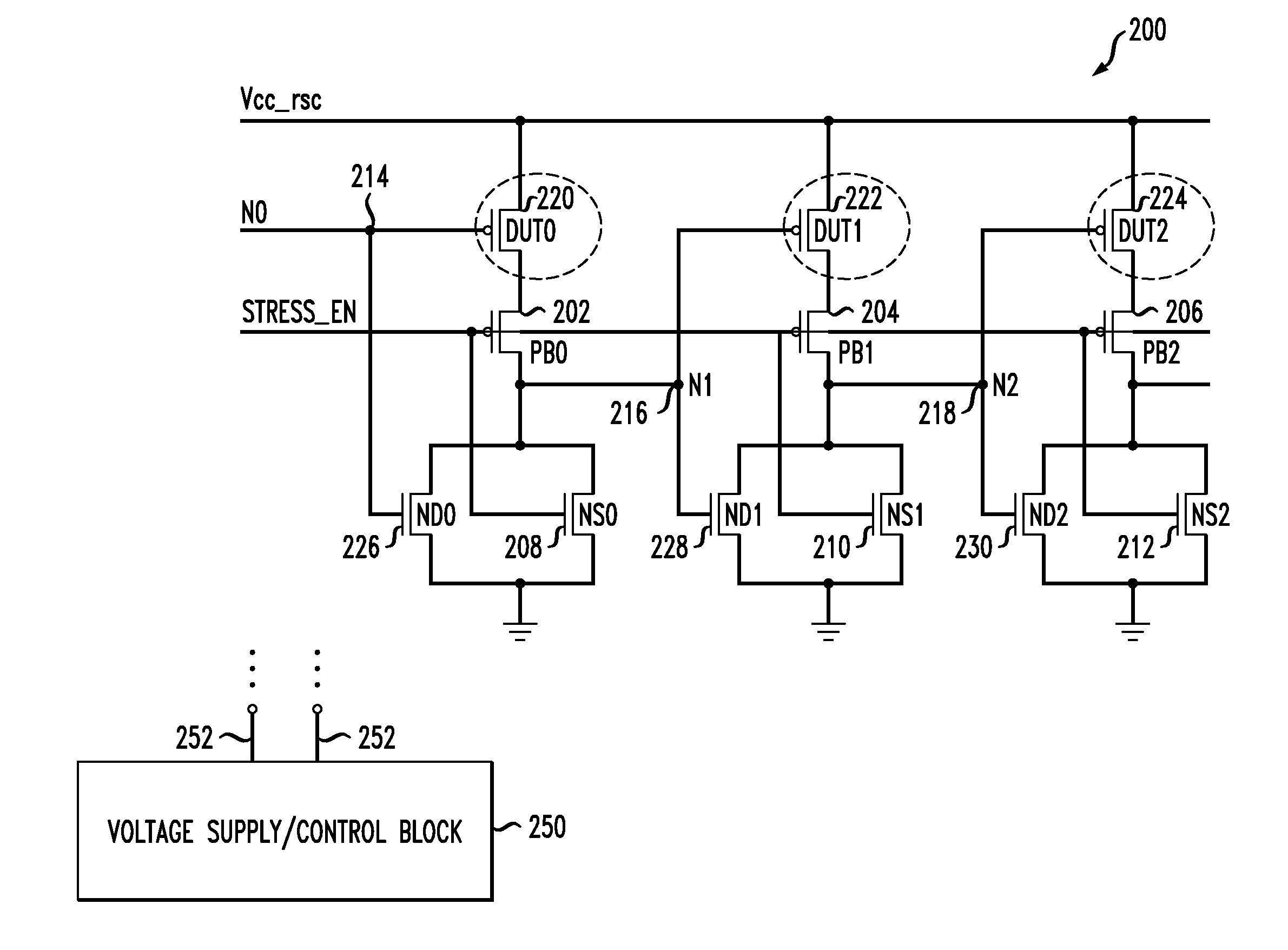

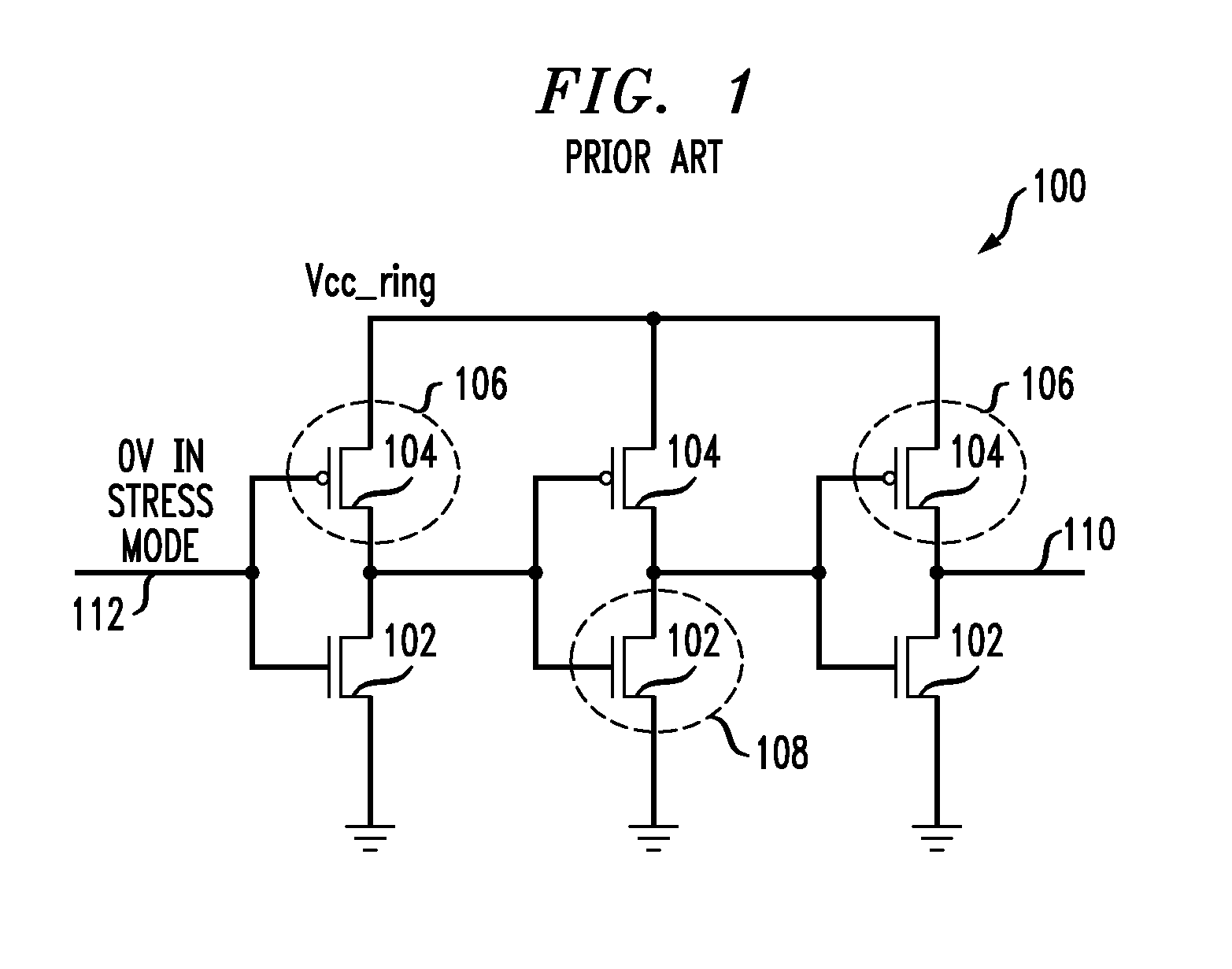

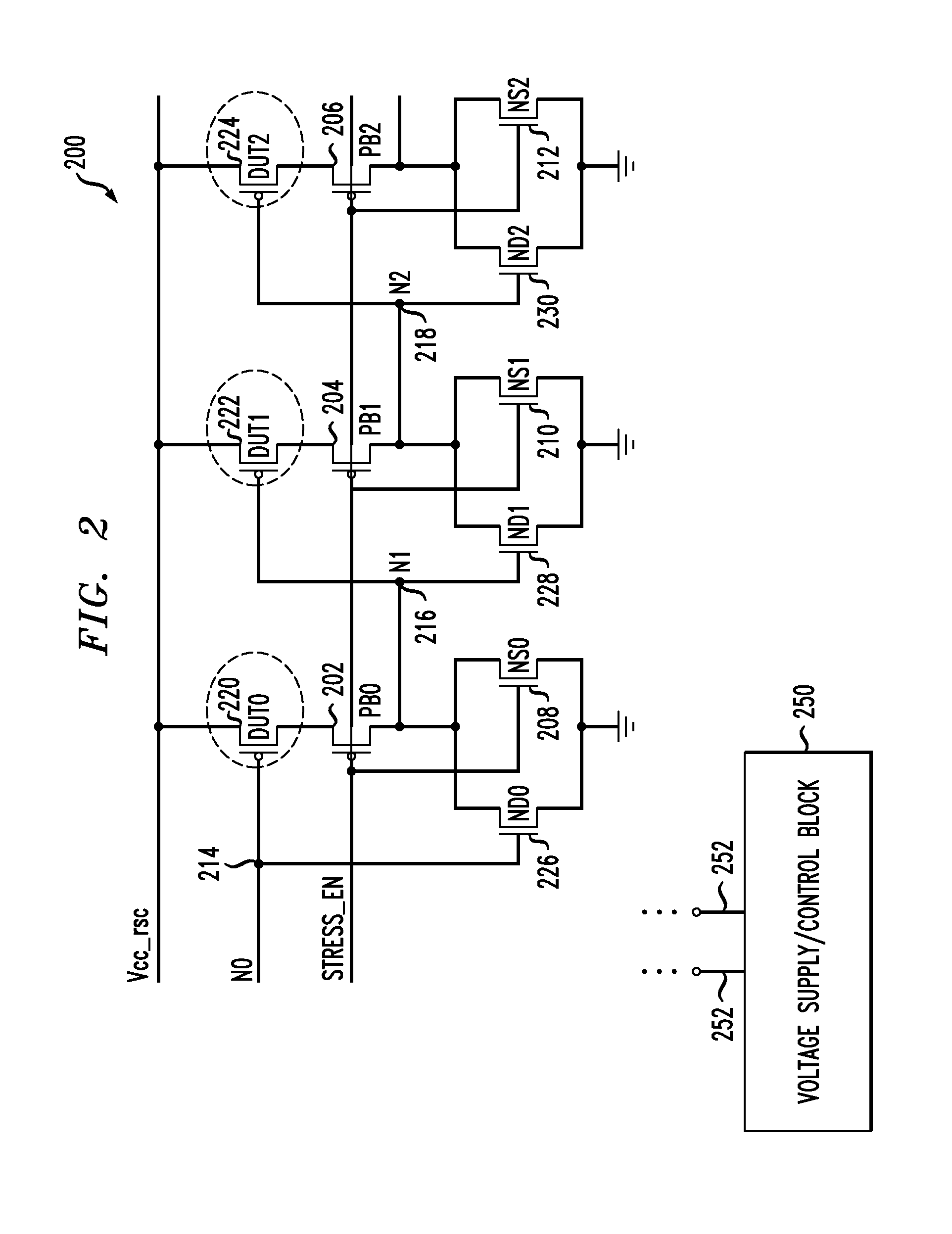

Circuits and design structures for monitoring nbti (negative bias temperature instability) effect and/or pbti (positive bias temperature instability) effect

ActiveUS20090189703A1High power supply voltageResistance/reactance/impedencePulse generation by logic circuitsNOR gateNAND gate

A ring oscillator has an odd number of NOR-gates greater than or equal to three, each with first and second input terminals, a voltage supply terminal, and an output terminal. The first input terminals of all the NOR-gates are interconnected, and each of the NOR-gates has its output terminal connected to the second input terminal of an immediately adjacent one of the NOR-gates. During a stress mode, a voltage supply and control block applies a stress enable signal to the interconnected first input terminals, and an increased supply voltage to the voltage supply terminals. During a measurement mode, this block grounds the interconnected first input terminals, and applies a normal supply voltage to the voltage supply terminals. Also included are an analogous NAND-gate based circuit, a circuit combining the NAND- and NOR-aspects, a circuit with a ring oscillator where the inverters may be coupled directly or through inverting paths, and circuits for measuring the bias temperature instability effect in pass gates.

Owner:GLOBALFOUNDRIES US INC

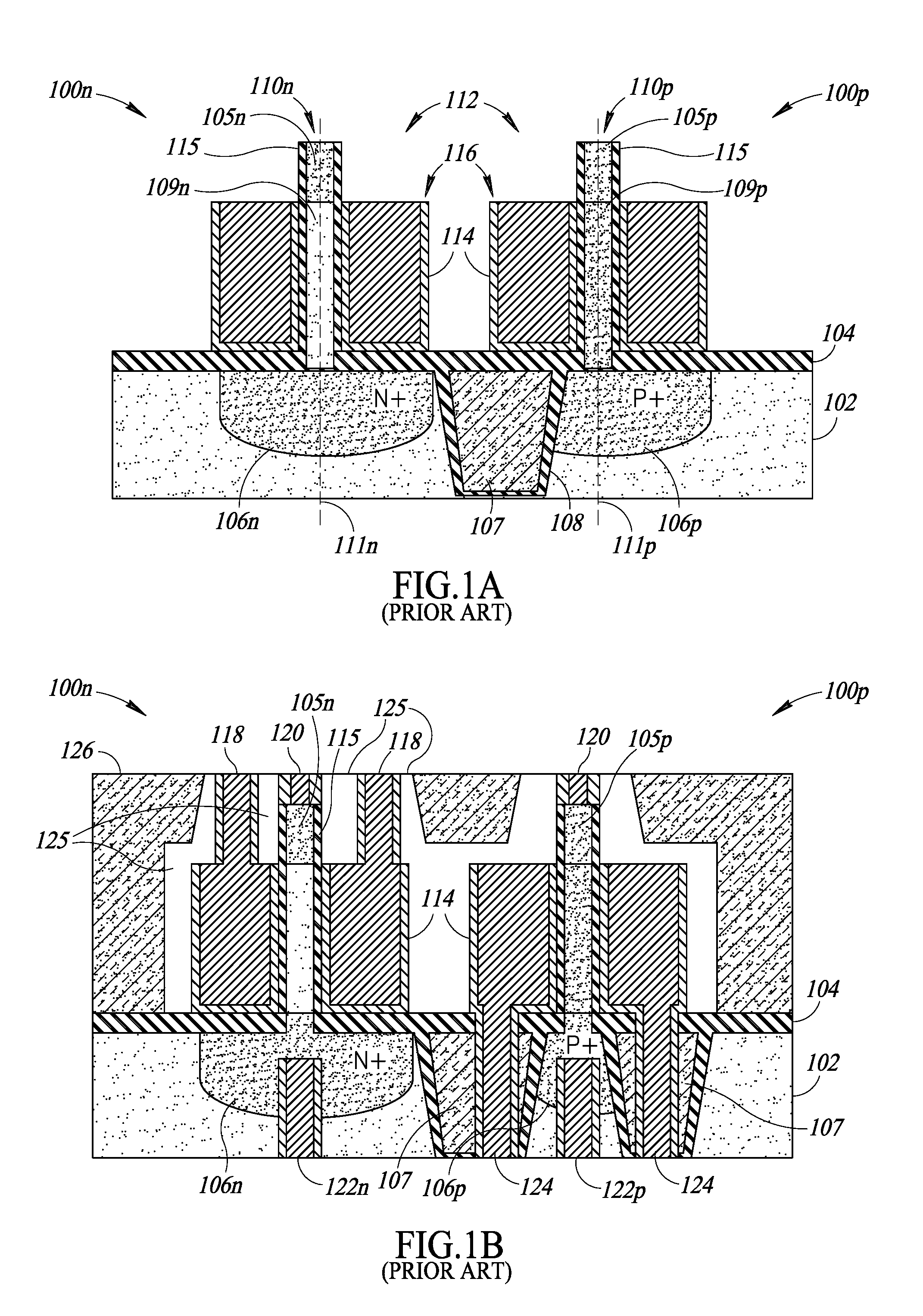

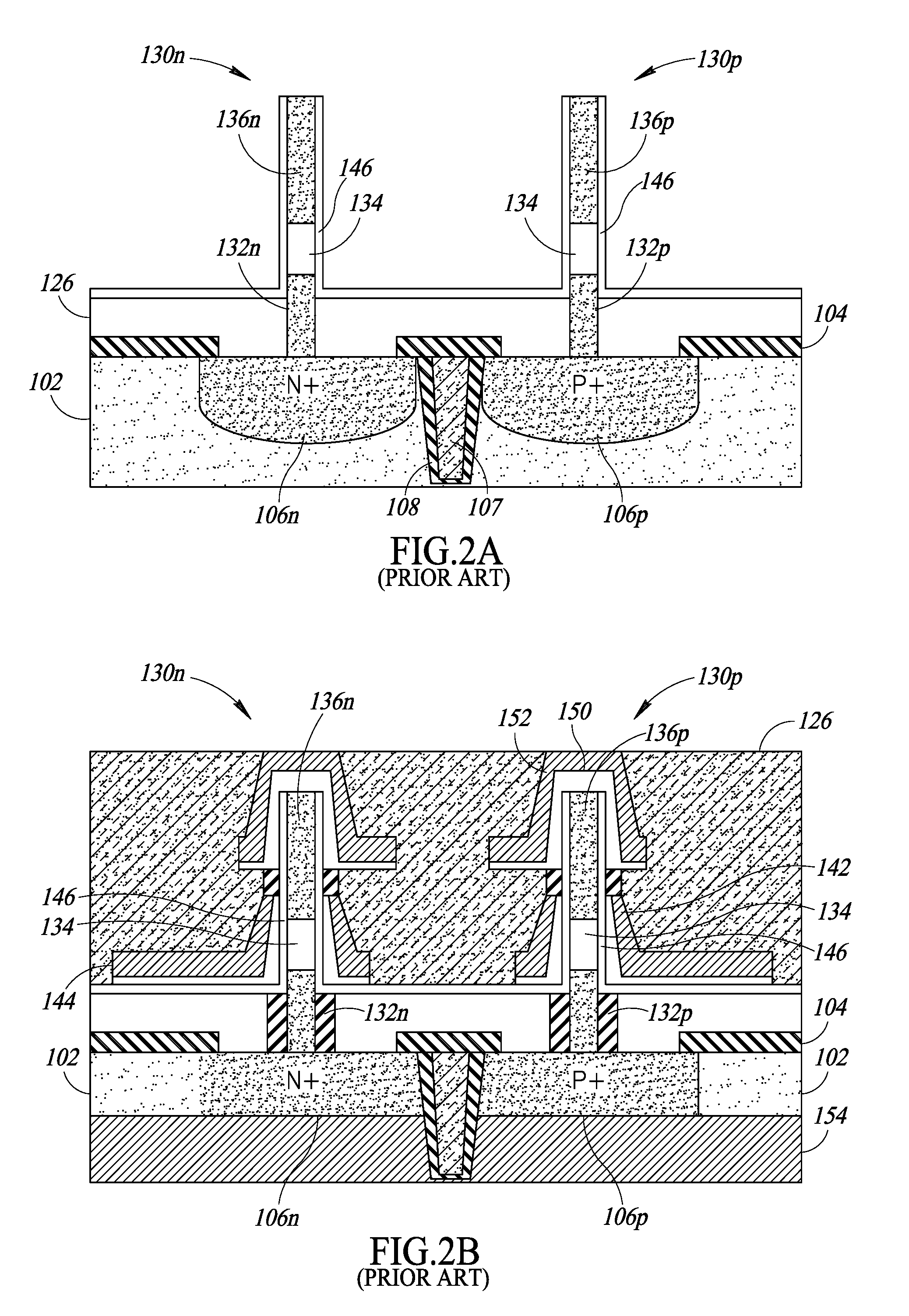

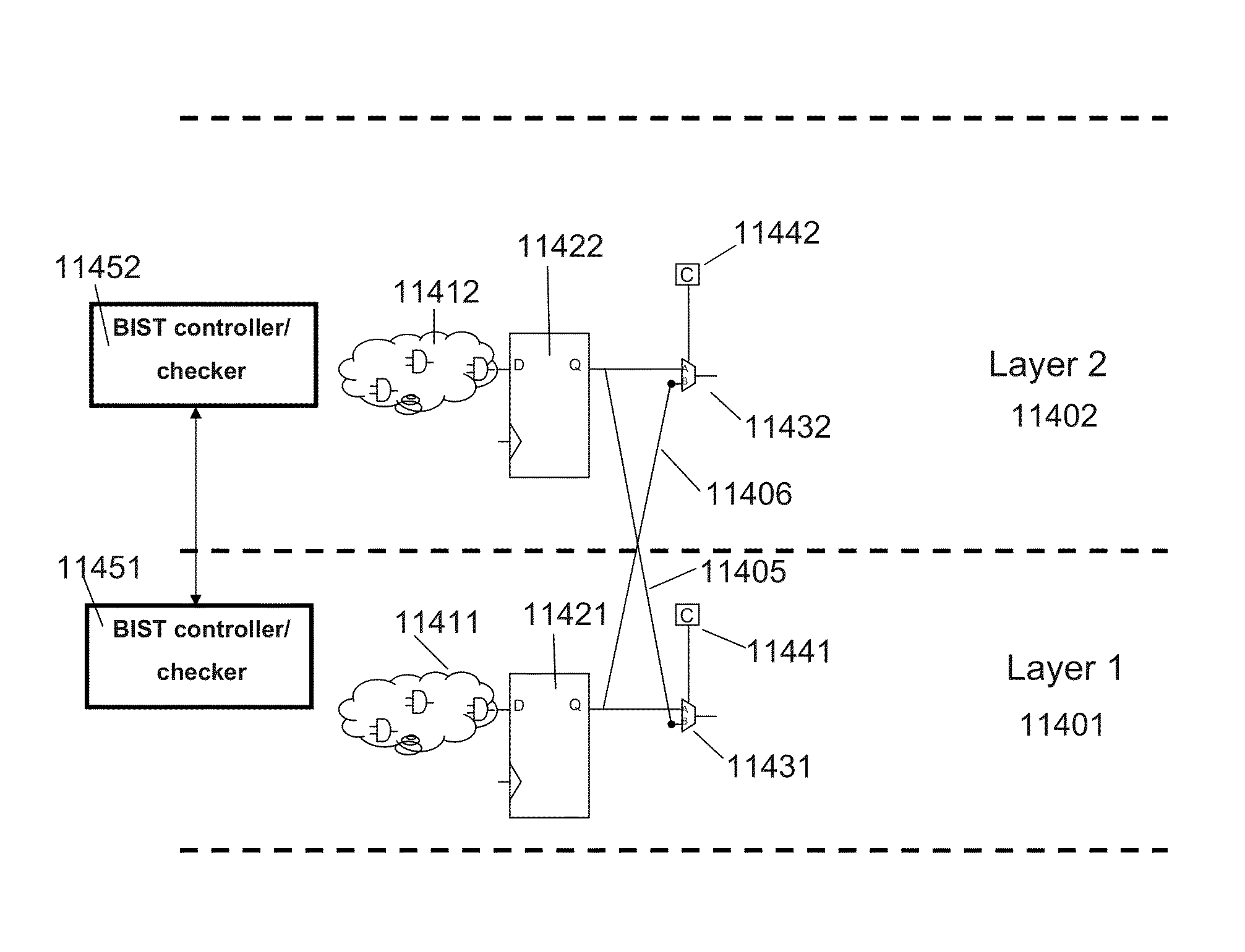

Semiconductor device and structure

ActiveUS8362482B2Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device testing/measurementDevice materialNOR gate

A semiconductor device including a first layer including first transistors, wherein first logic circuits are constructed by the first transistors, and wherein the first logic circuits include at least one of Inverter, NAND gate, or NOR gate; and a second layer overlaying said first layer, the second layer including second transistors, wherein second logic circuits are constructed by the second transistors; wherein each logic circuit in the first logic circuits has inputs and at least one first output, the inputs are connected to the second logic circuits; wherein each logic circuit in the second logic circuits has a second output, and wherein the first transistors include first selectors adapted to selectively replace at least one of the at least one first outputs with at least one of the second outputs.

Owner:SAMSUNG ELECTRONICS CO LTD

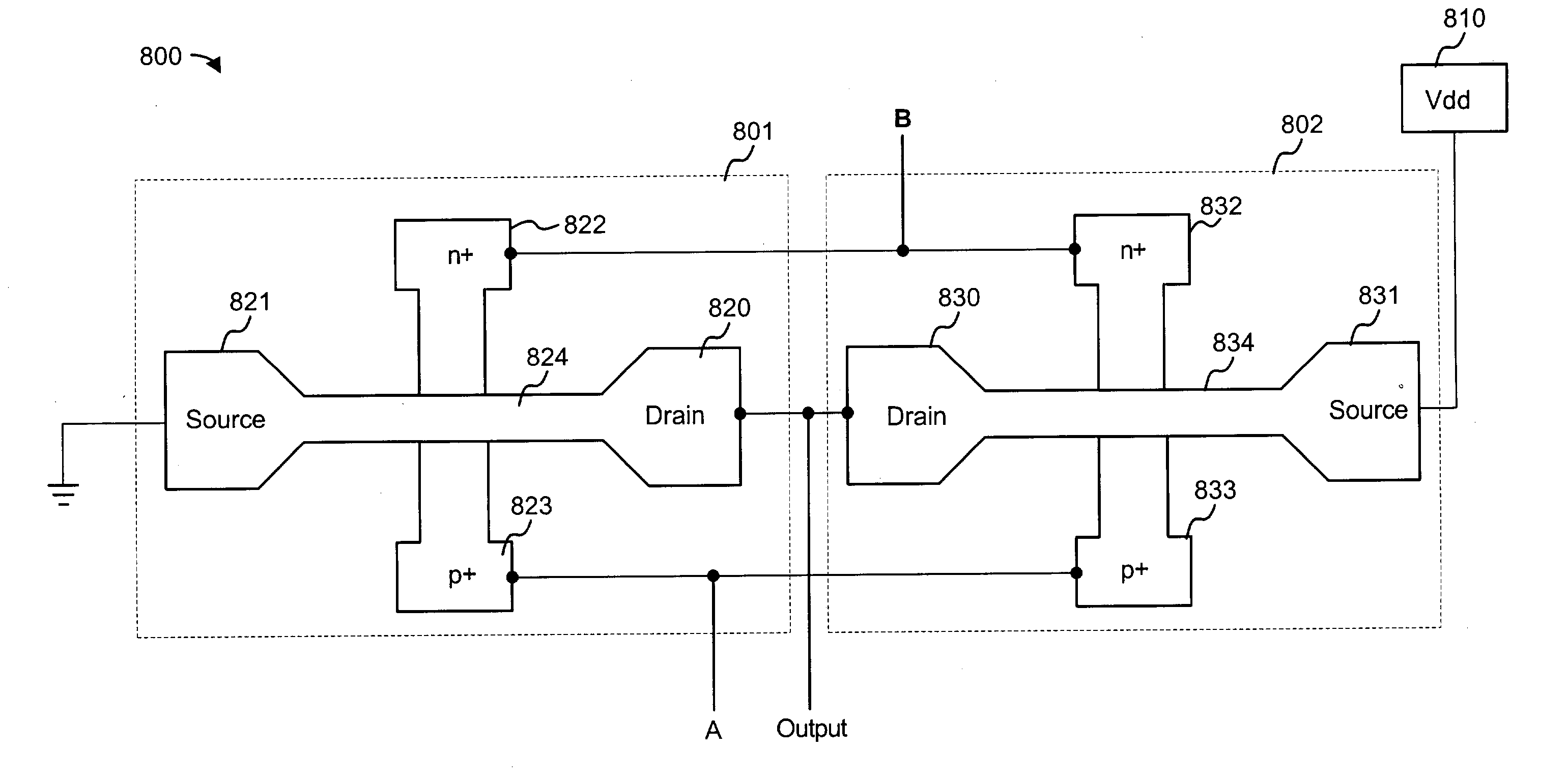

Two transistor nor device

A NOR gate includes is constructed with two asymmetric FinFET type transistors instead of the conventional four-transistor NOR gate. The reduction in the number of transistors from four down to two allows for significant improvements in integrated semiconductor circuits.

Owner:GLOBALFOUNDRIES US INC

Circuits and design structures for monitoring NBTI (negative bias temperature instability) effect and/or PBTI (positive bias temperature instability) effect

A ring oscillator has an odd number of NOR-gates greater than or equal to three, each with first and second input terminals, a voltage supply terminal, and an output terminal. The first input terminals of all the NOR-gates are interconnected, and each of the NOR-gates has its output terminal connected to the second input terminal of an immediately adjacent one of the NOR-gates. During a stress mode, a voltage supply and control block applies a stress enable signal to the interconnected first input terminals, and an increased supply voltage to the voltage supply terminals. During a measurement mode, this block grounds the interconnected first input terminals, and applies a normal supply voltage to the voltage supply terminals. Also included are an analogous NAND-gate based circuit, a circuit combining the NAND- and NOR-aspects, a circuit with a ring oscillator where the inverters may be coupled directly or through inverting paths, and circuits for measuring the bias temperature instability effect in pass gates.

Owner:GLOBALFOUNDRIES US INC

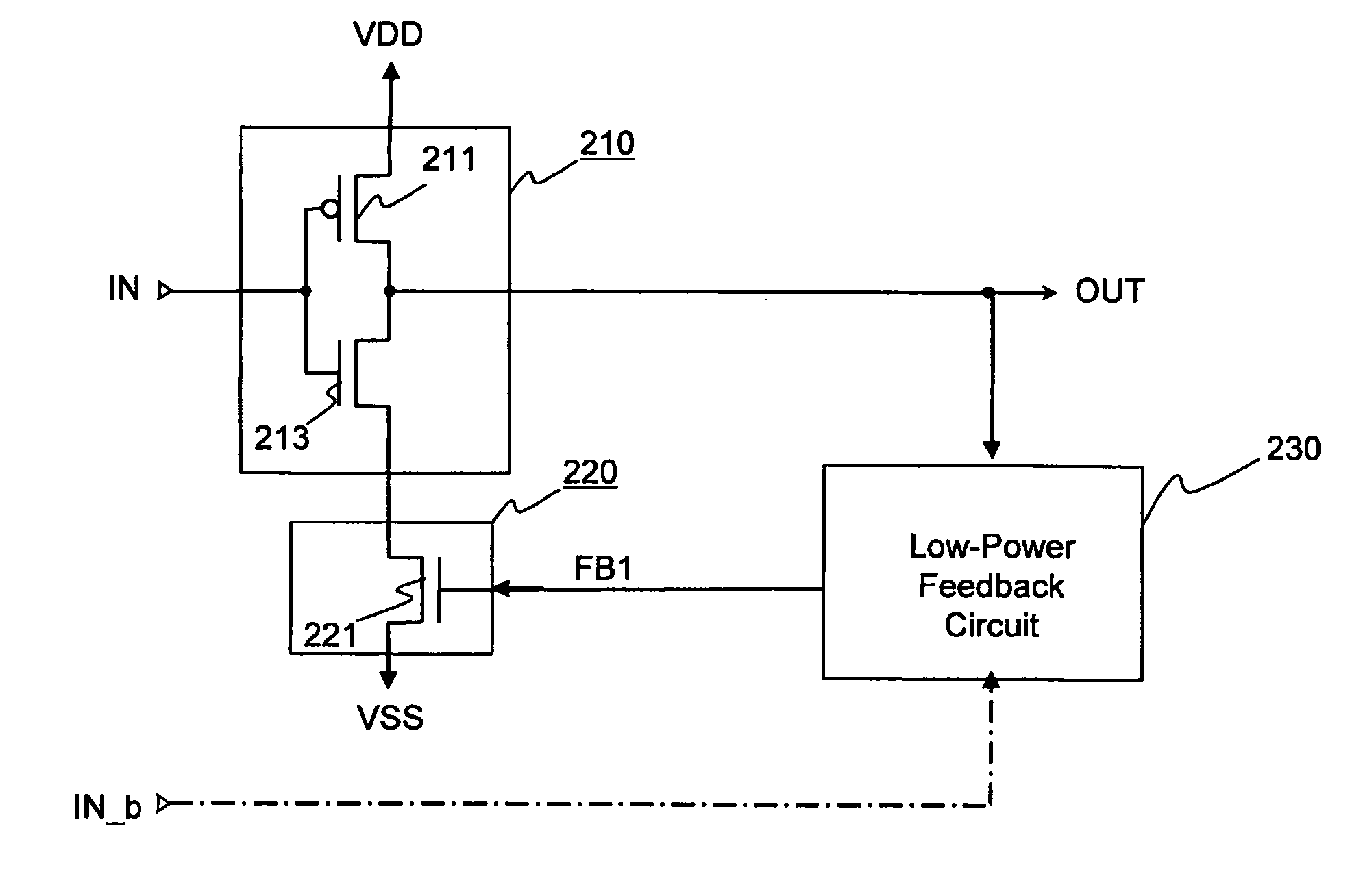

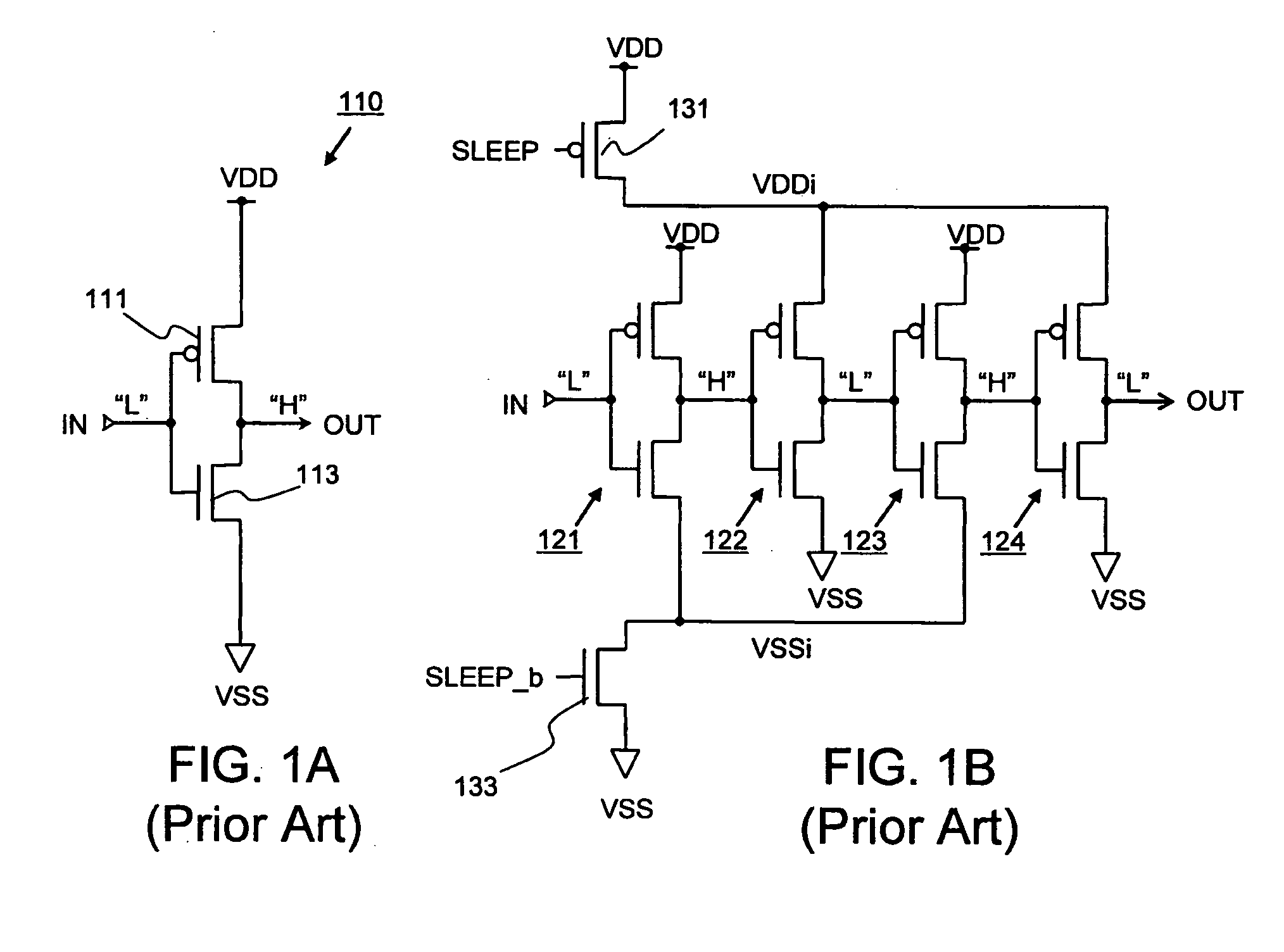

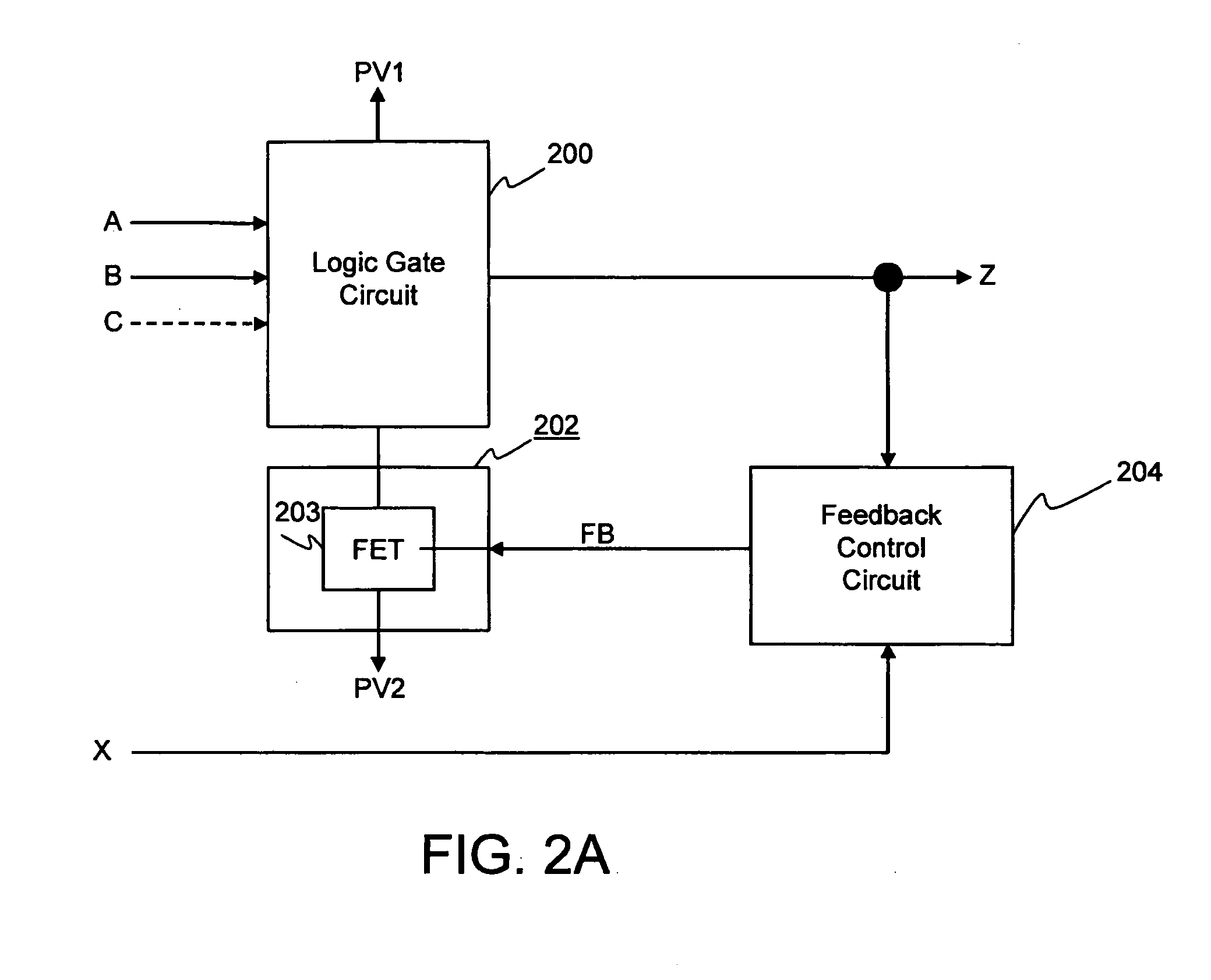

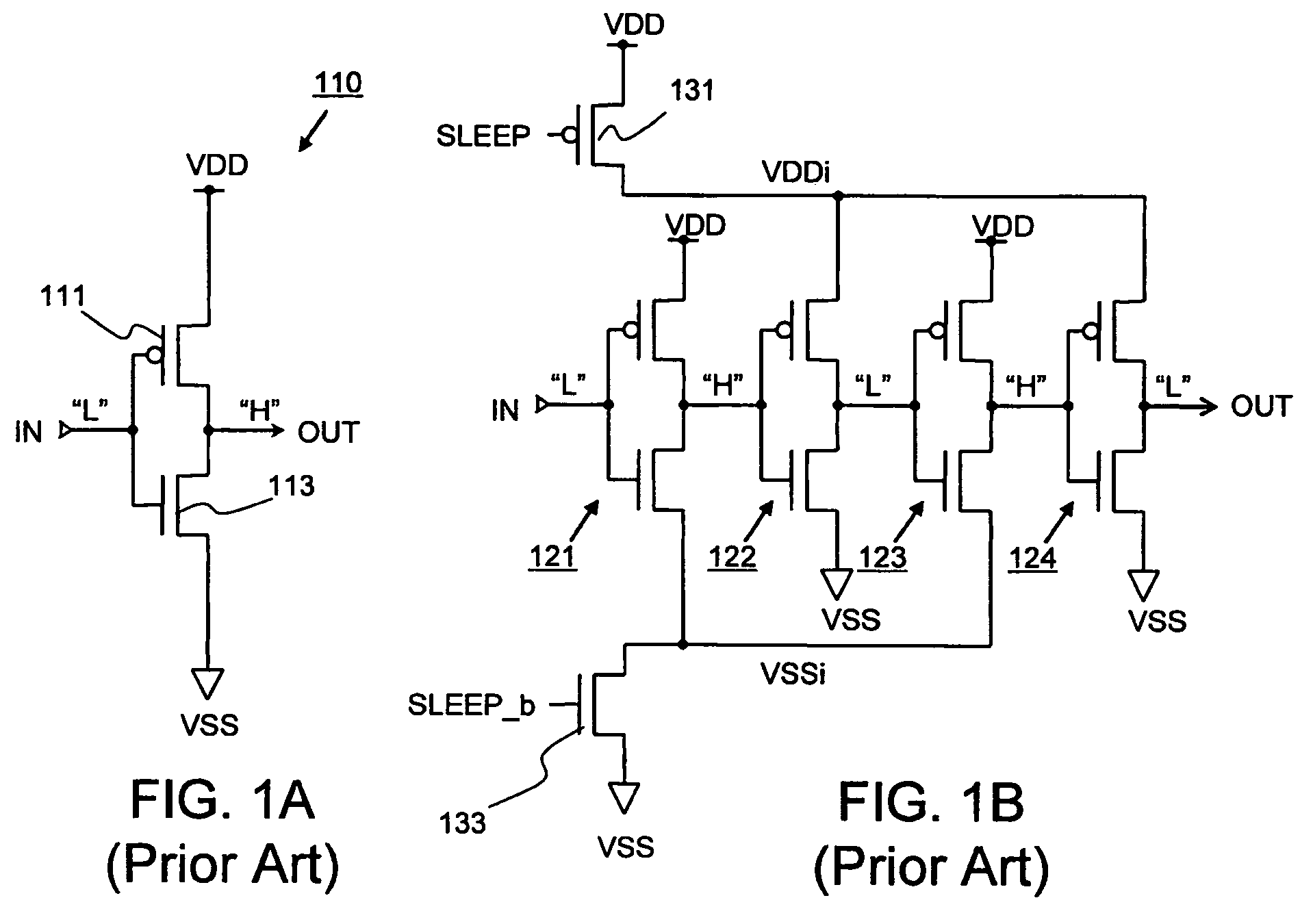

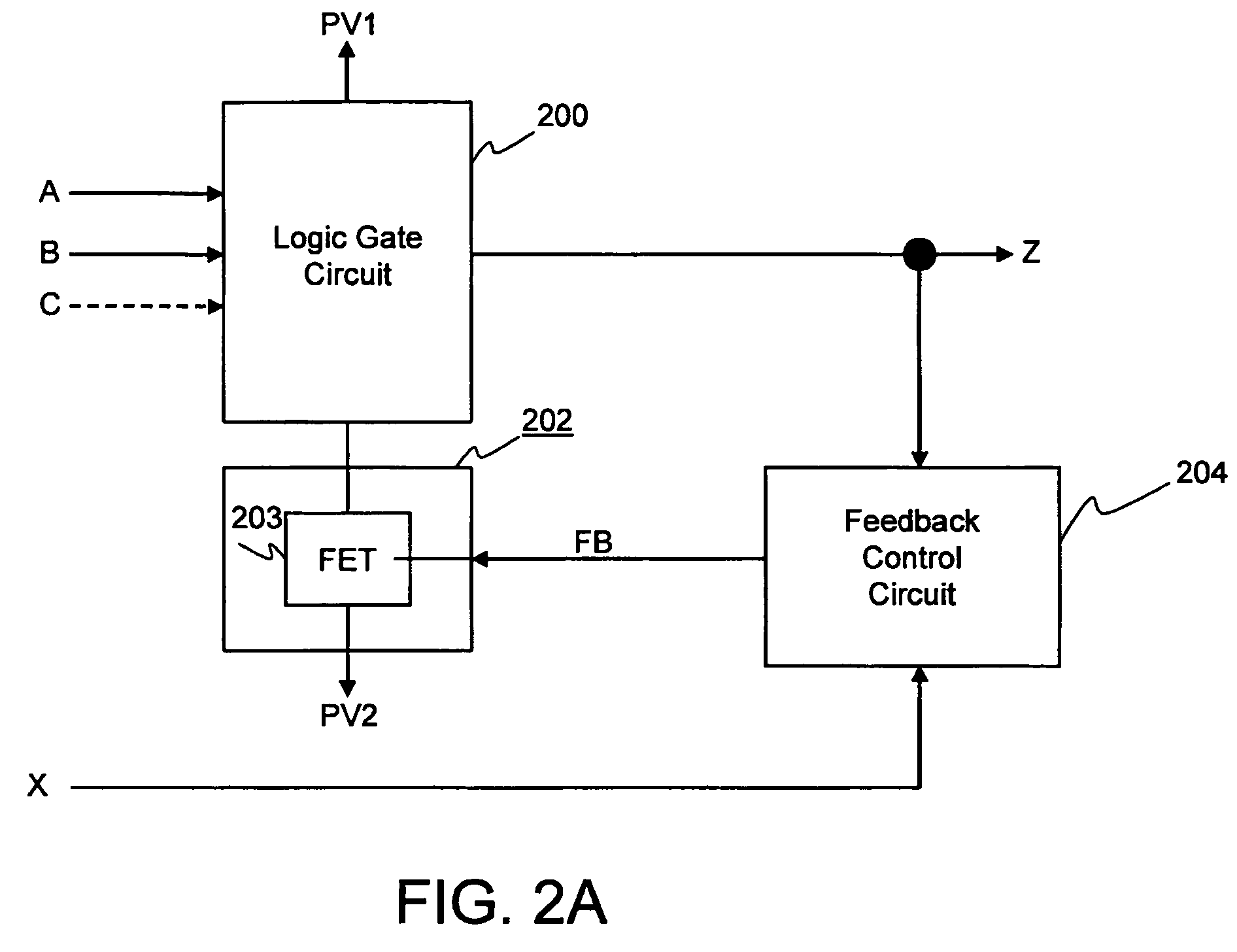

Semiconductor integrated circuit having current leakage reduction scheme

InactiveUS20070075743A1Reduce power consumptionIncrease speedTransistorReliability increasing modificationsCMOSNOR gate

A semiconductor integrated circuit includes a CMOS controlled inverter consisting of series-connected PMOS and NMOS transistors. The source of the NMOS transistor is coupled to a ground line through an additional NMOS transistor for power gating of voltage VSS. The source of the PMOS transistor can be coupled to a power supply line through an additional PMOS transistor for power gating of voltage VDD. The inverter receives an input signal IN and its complementary version that has transitioned earlier than the input signal. In response to the input signal, the inverter produces an output signal. A NAND gate that receives the output signal and the complementary input signal controls the power gating NMOS transistor. A NOR gate that receives the output signal and the complementary input signal controls the power gating PMOS transistor. The power gating to the CMOS inverter is performed by feedback of the output signal and the complementary input signal, with the result that current leakage reduction through the CMOS controlled inverter is achieved. A self leakage reduction with power gating transistors is applicable to another type of logic gates such as NAND, NOR and Exclusive-OR, AND, OR.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Nanoeletromechanical switch and logic circuits formed therefrom

A nanoelectromechanical (NEM) switch is formed on a substrate with a source electrode containing a suspended electrically-conductive beam which is anchored to the substrate at each end. This beam, which can be formed of ruthenium, bows laterally in response to a voltage applied between a pair of gate electrodes and the source electrode to form an electrical connection between the source electrode and a drain electrode located near a midpoint of the beam. Another pair of gate electrodes and another drain electrode can be located on an opposite side of the beam to allow for switching in an opposite direction. The NEM switch can be used to form digital logic circuits including NAND gates, NOR gates, programmable logic gates, and SRAM and DRAM memory cells which can be used in place of conventional CMOS circuits, or in combination therewith.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

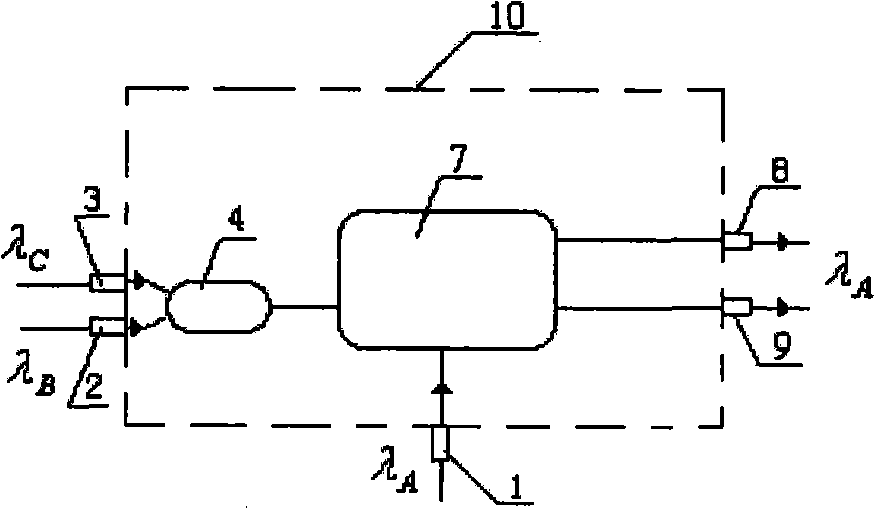

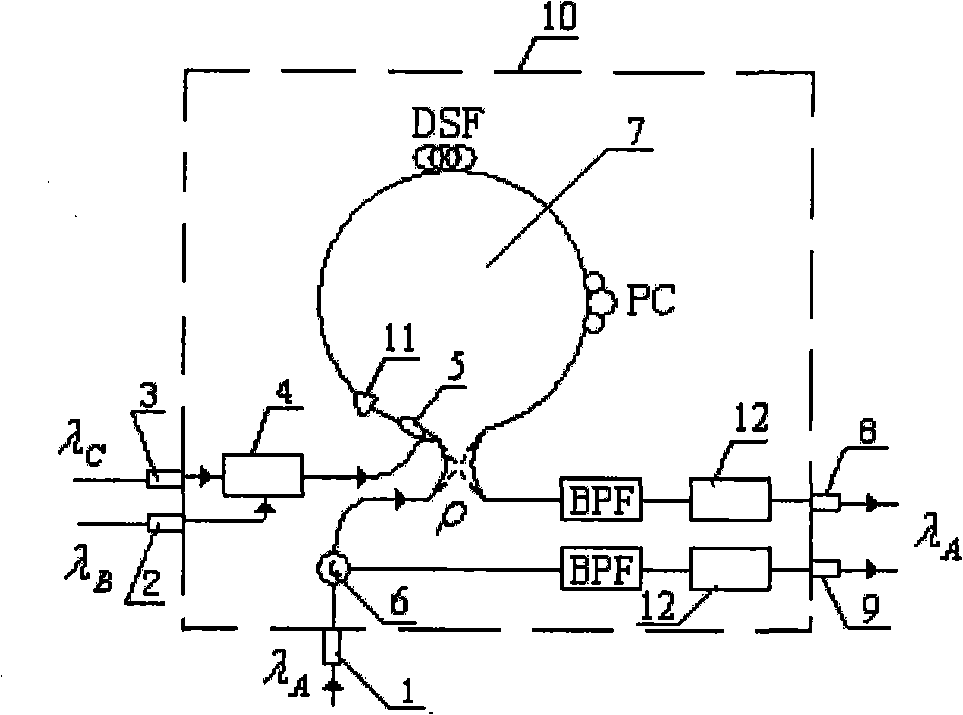

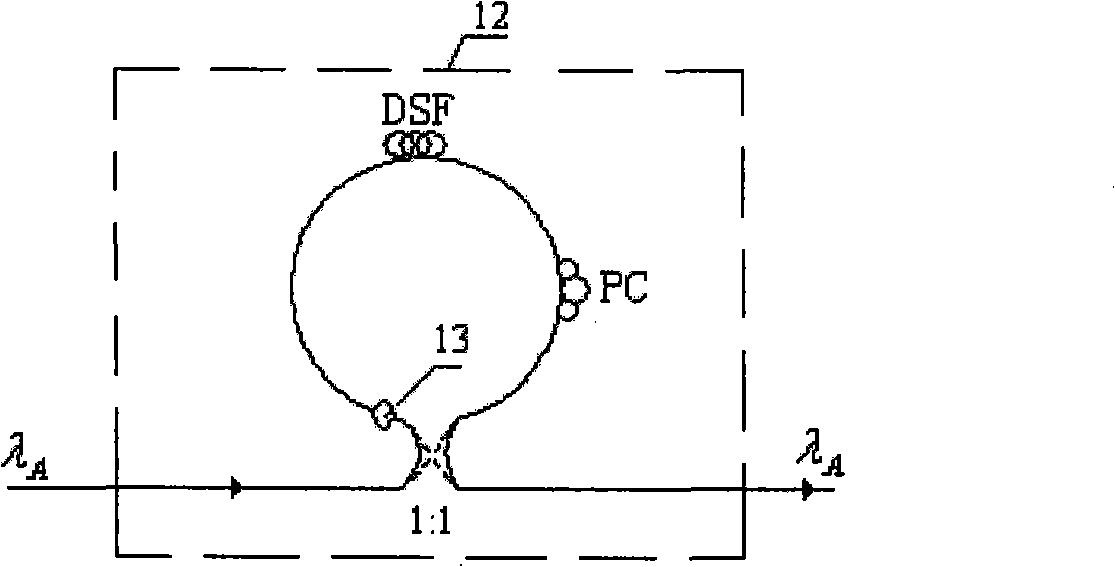

Full-optical logic gate

InactiveCN101526715AReduce the incident light powerReduce Sagnac loop lengthLogic circuits using opto-electronic devicesNon-linear opticsControl signalNOR gate

The invention relates to a full-optical logic gate (10), which can be reused to achieve opposite phase operations of an AND gate, an OR gate, an NOT gate, an NAND gate, an NOR gate, an XOR gate, an XNOR gate and combination thereof, and can also achieve a half adder. The full-optical logic gate comprises light input ports (2, 3) for receiving two control light signals respectively, a light input port (1) for receiving a synchronous light clock signal, a light output port (8) for outputting the result for expressing logic application, and a light output port (9) for outputting opposite phase operation. The full-optical logic gate is characterized by comprising a light combination device (4) and a nonlinear optical device (7), wherein the light combination device (4) is used for combining the two control light signals to generate corresponding combined signals with a wavelength division multiplexer or a polarization beam combiner; and the nonlinear optical device (7) is used for receiving the combined signals and the synchronous light clock signal and emitting two paths of light output signals mutual in opposite phase operations. The full-optical logic function depends on the characteristic of the nonlinear optical device, wherein the characteristic is selected so that the power of the output signals and the light power of the clock signal are redistributed and associated through the selected logic function.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

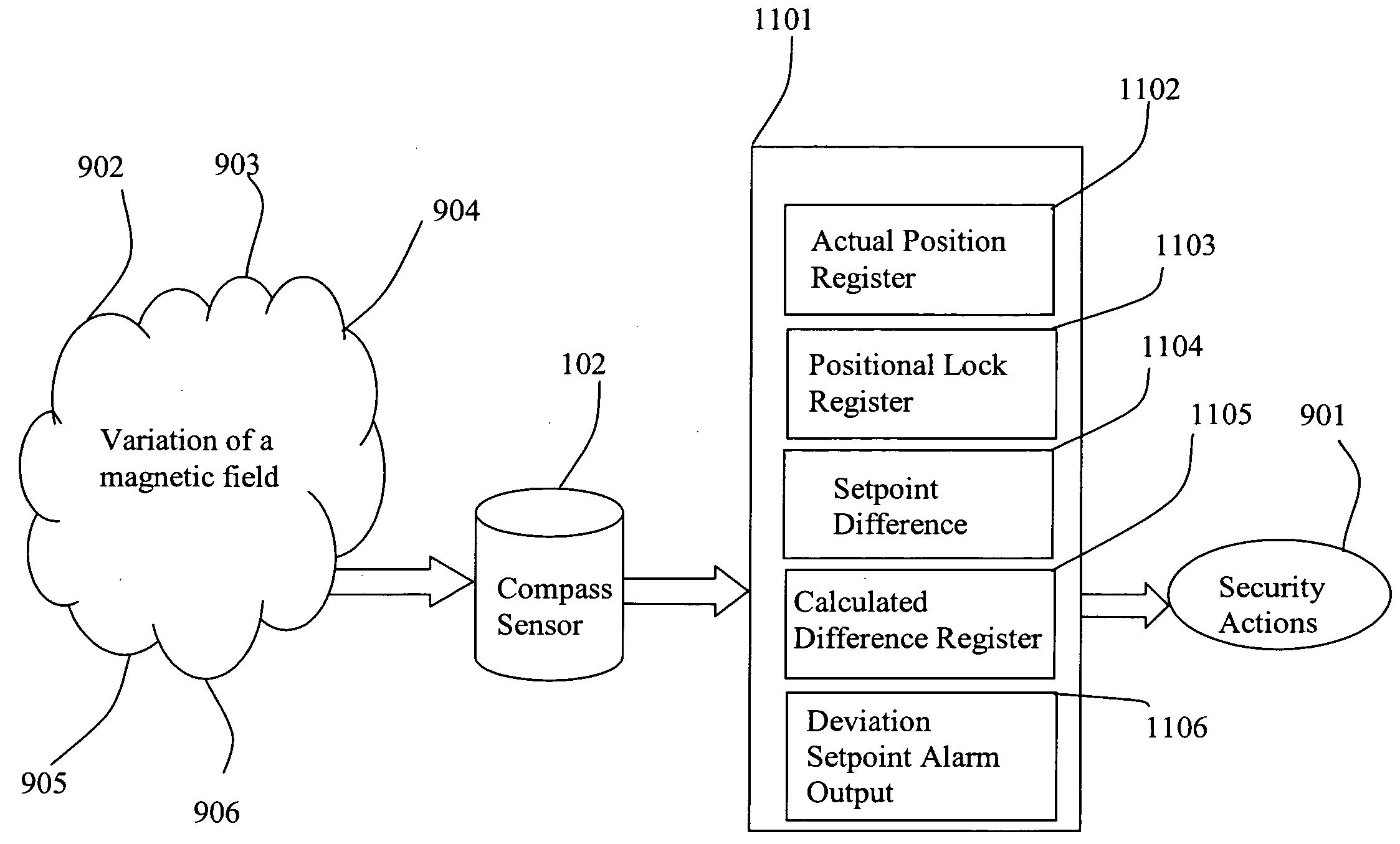

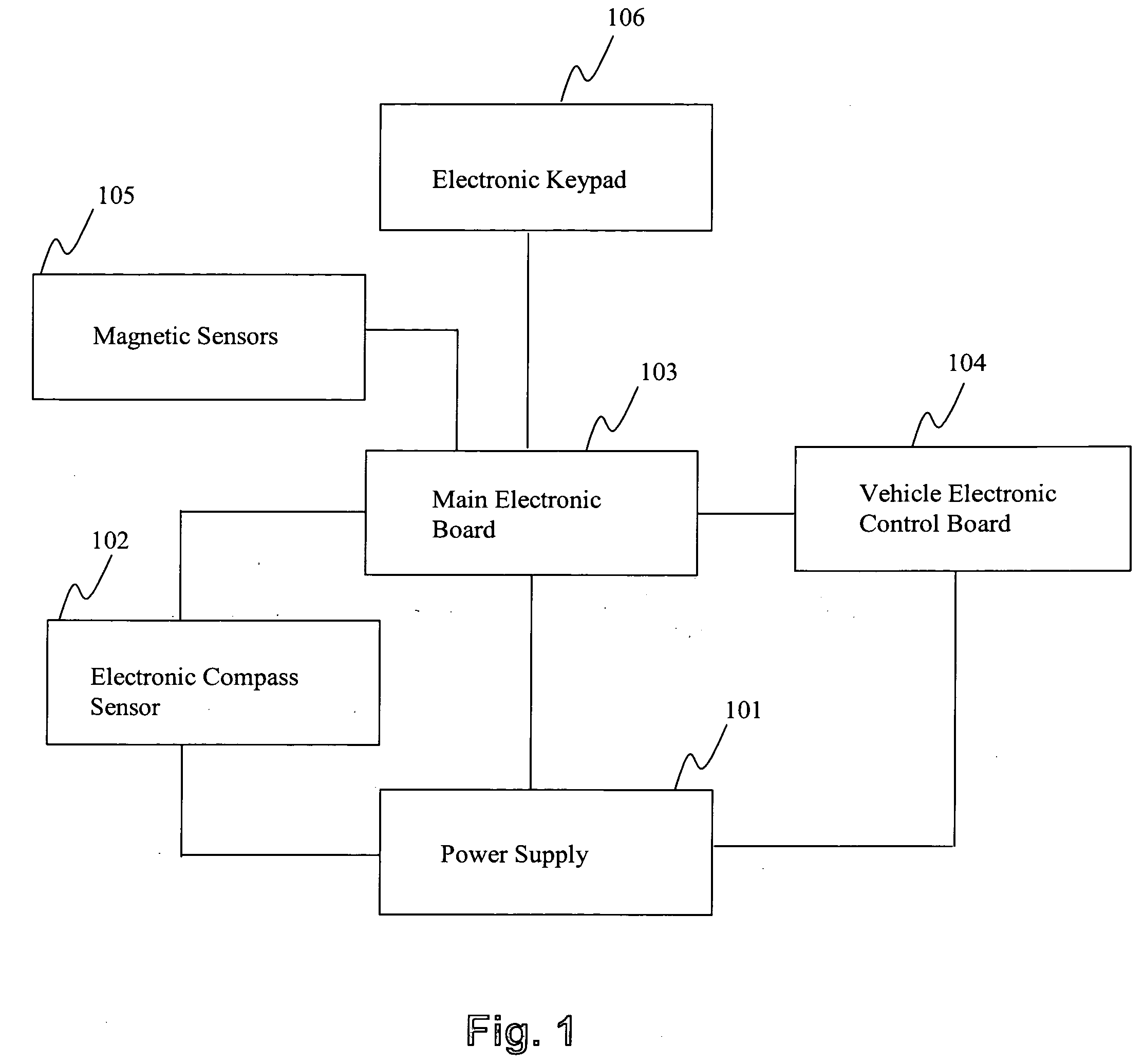

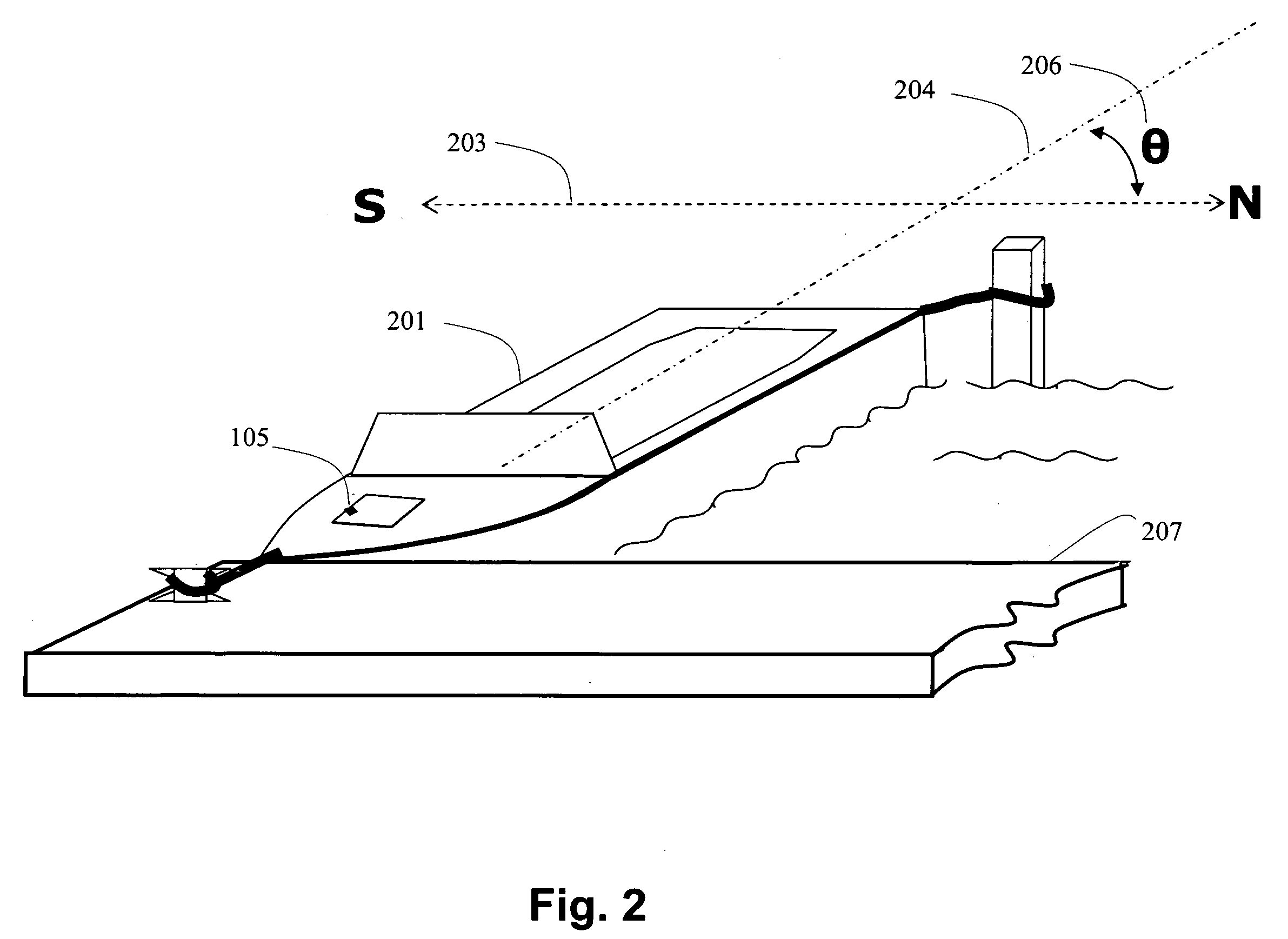

Magnetic field based alarm system

An embodiment of the present technology provides an apparatus, comprising at least one compass sensor and at least one main electronic board capable of determining a mismatch from said compass sensor and further sending a signal to a at least one vehicle control board to activate at least one security action. The present technology also provides for a security method, comprising determining at least one variation in a magnetic field with at least one magnetic sensor, amplifying said variation by at least one electronic amplifier, processing said variation by a least one electronic board and receiving said processed variation by a vehicle control board to trigger at least one security action in an alarm system. The technology also comprises an alarm circuit, further comprising an electronic compass sensor to sample an incoming magnetic field and output a signal an electronic board to receive said signal and comprise a plurality of NOR gates, transistors, resistors, capacitors, operational amplifiers, wherein said electronic board is capable of processing said signal and a vehicle control board to receive said processed signal to trigger at least one security action in an alarm system.

Owner:SOSA HECTOR

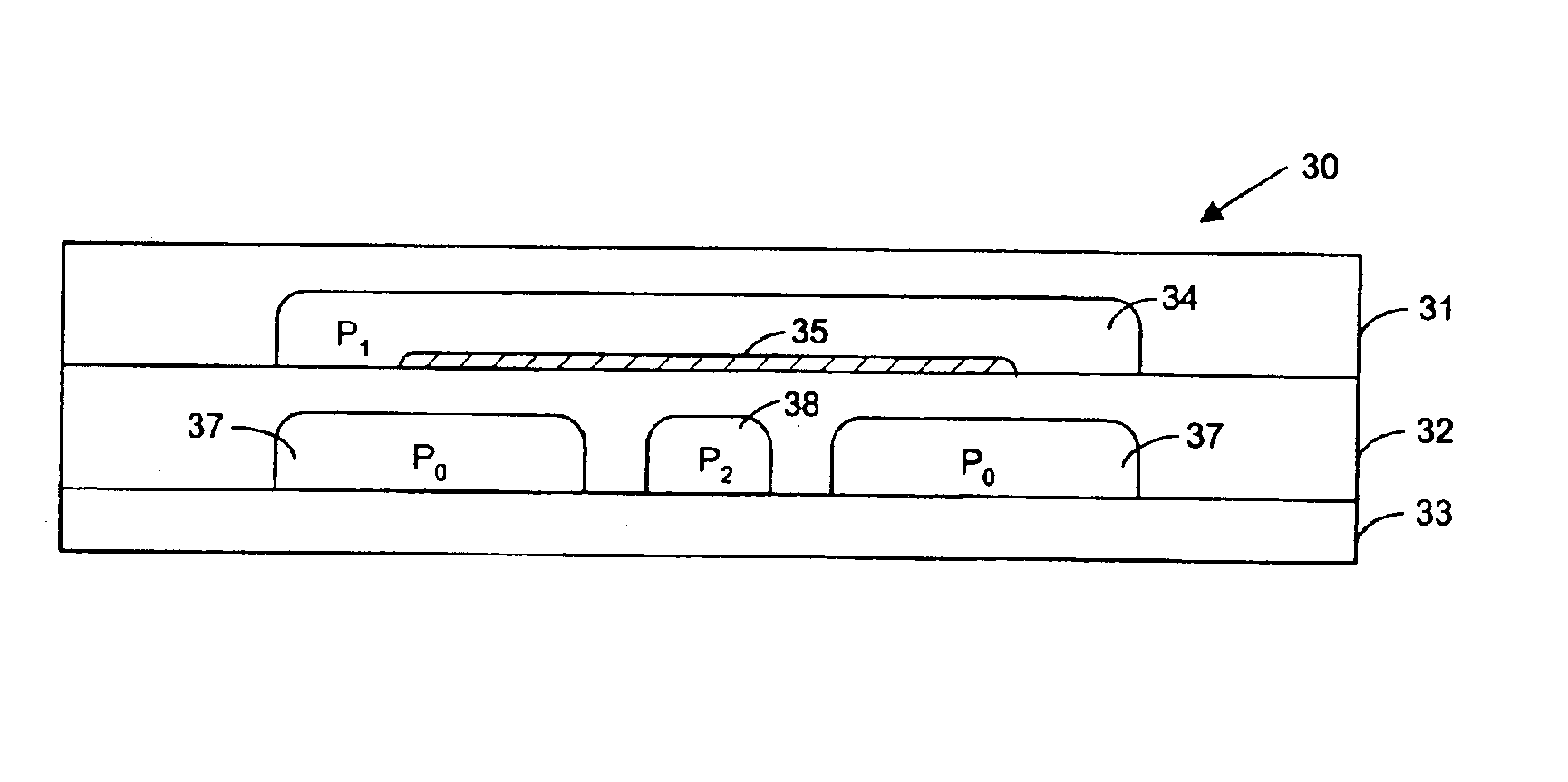

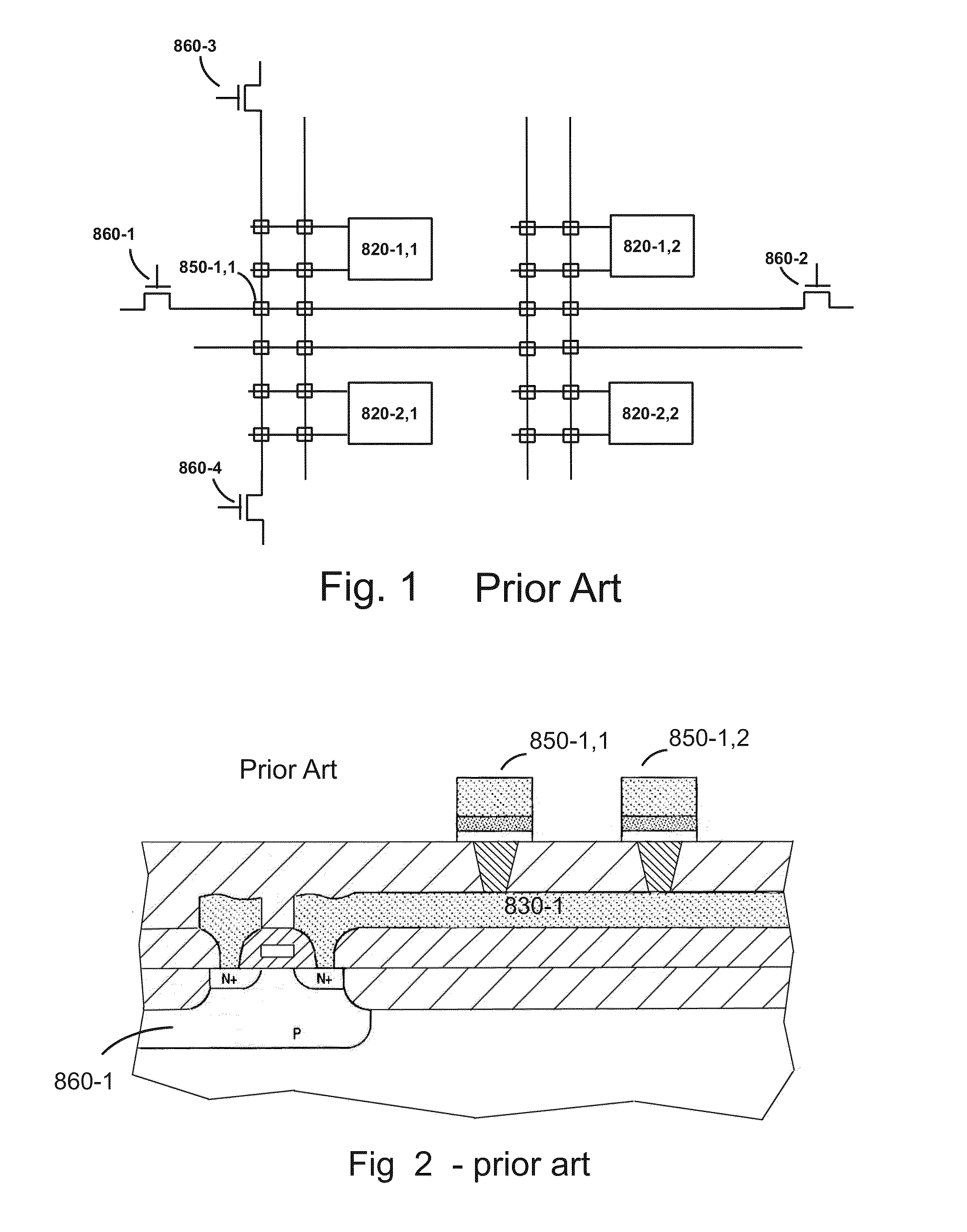

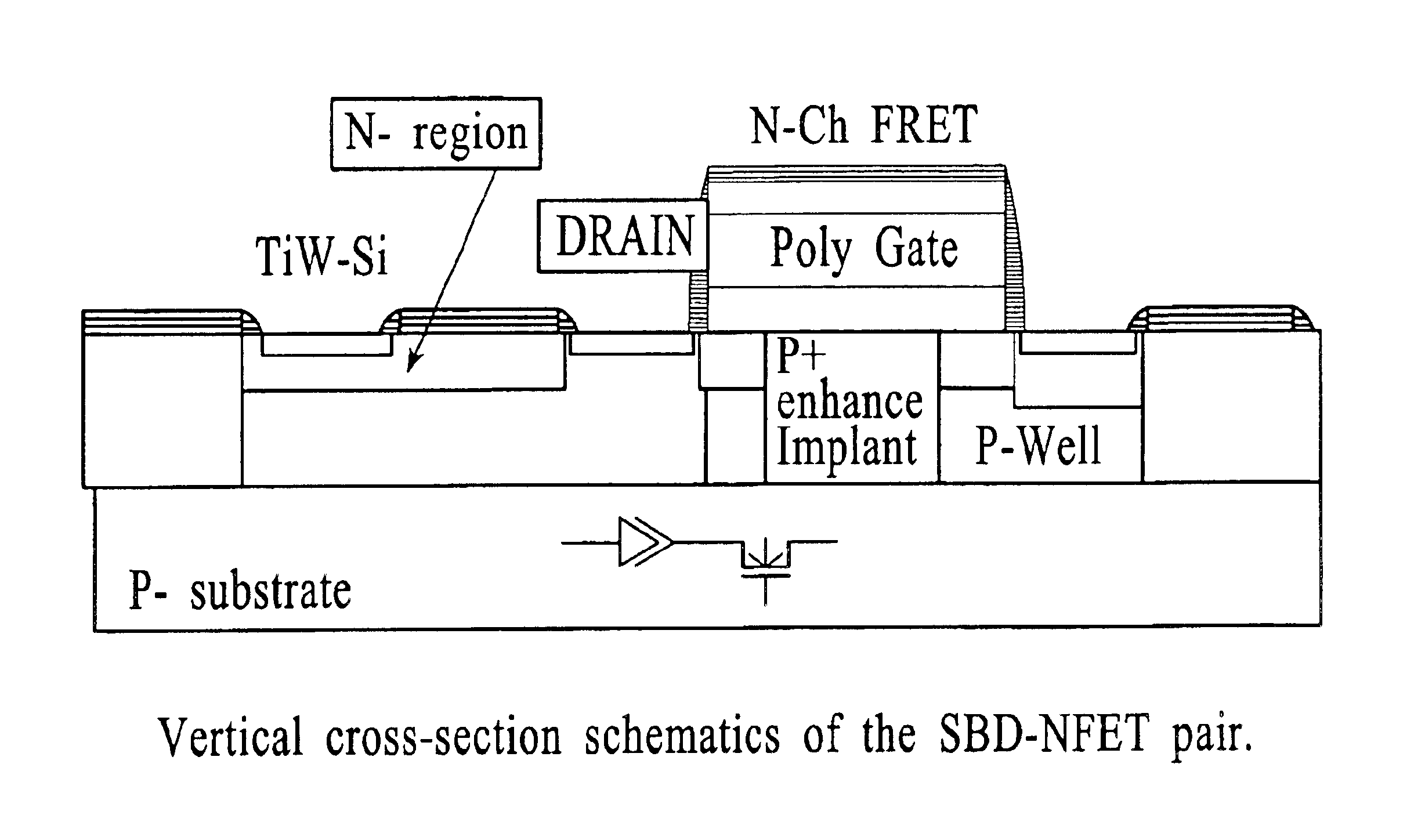

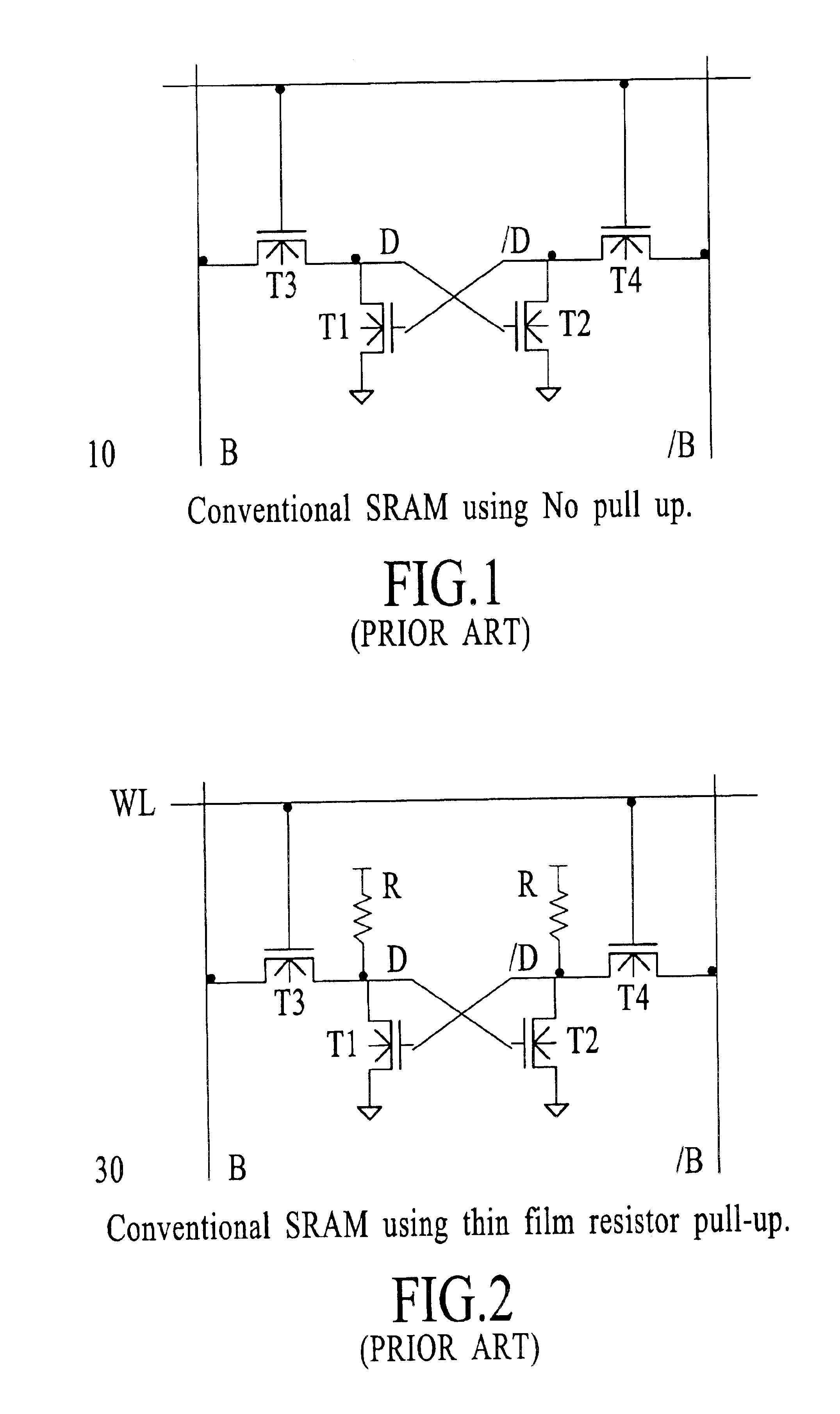

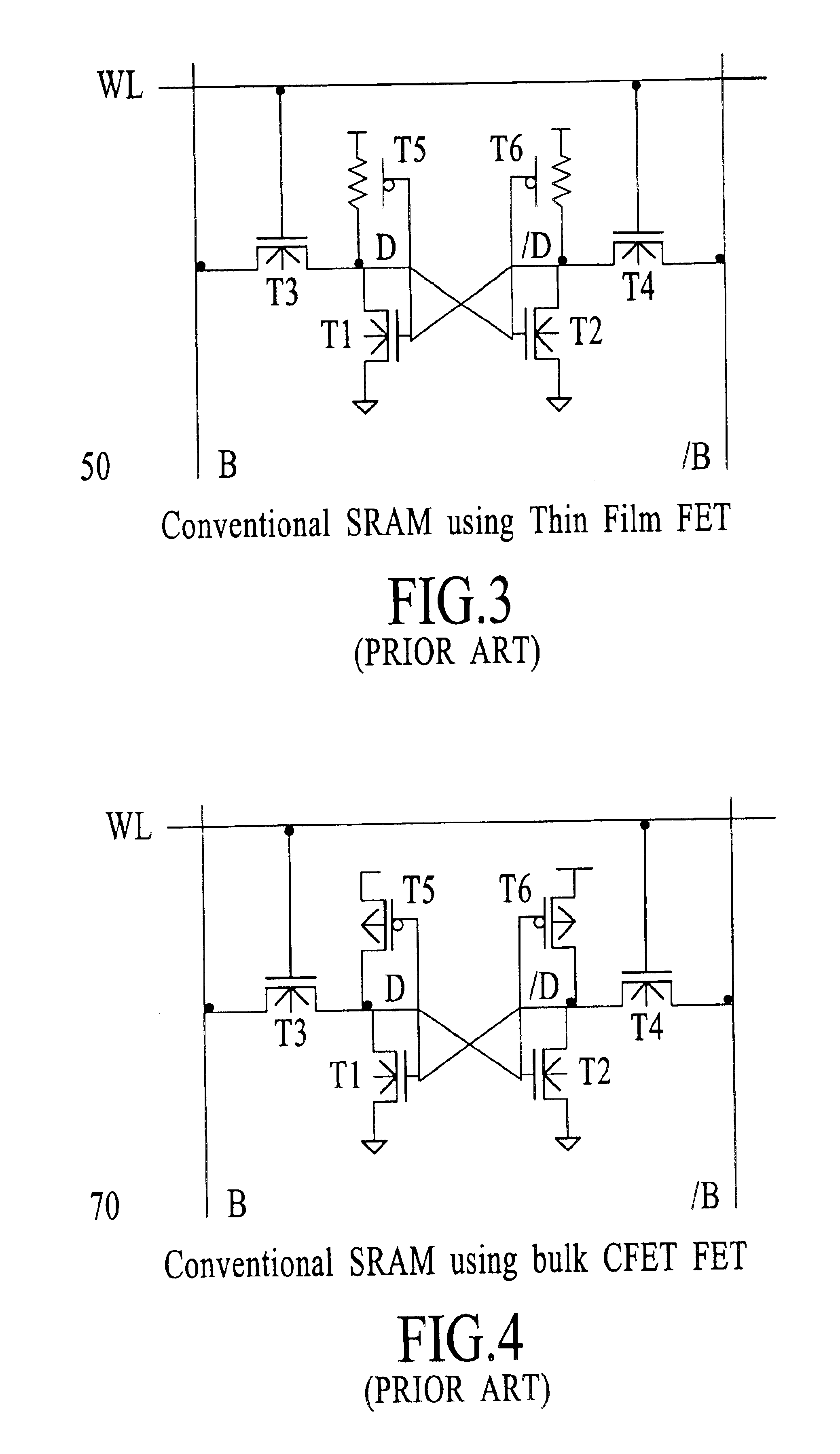

Schottky diode static random access memory (DSRAM) device, a method for making same, and CFET based DTL

InactiveUS6852578B2Stable load curveRapid designTransistorSemiconductor/solid-state device manufacturingCapacitanceLevel shifting

A high speed, low power Static Random Access Memory (SRAM) Array, which includes a 4T cell with two integrated Schottky Barrier Diodes (SBD) is provided. In a preferred embodiment, the cell bulk area and speed advantage is 30%, and AC power saving is 75% compared with the 6T CFET cell. The physical construct of the 4T cell saves capacitance in all critical nodes intra or inter cell wise, eliminates pass transistors, reduces the well noises. Typical embodiment uses a 0.15-um-rule based layout, and 1.5V supports operation at 5 ns cycles. SBD are used extensively with CFET to form a CMOS version of the Diode Transistor Logic circuitry. Generic control functions can be implemented including NAND / NOR gates, level shifting, decoding, voltage generator, ESD and latch-up protection, leakage control, and dynamic VT setting while in operation. Product applications include DRAM, SRAM, PLD, DRAM, CAM, Flash, Computing, Networking, and Communication devices as standalone system component or embedded into any ASIC.

Owner:SCHOTTKY LSI

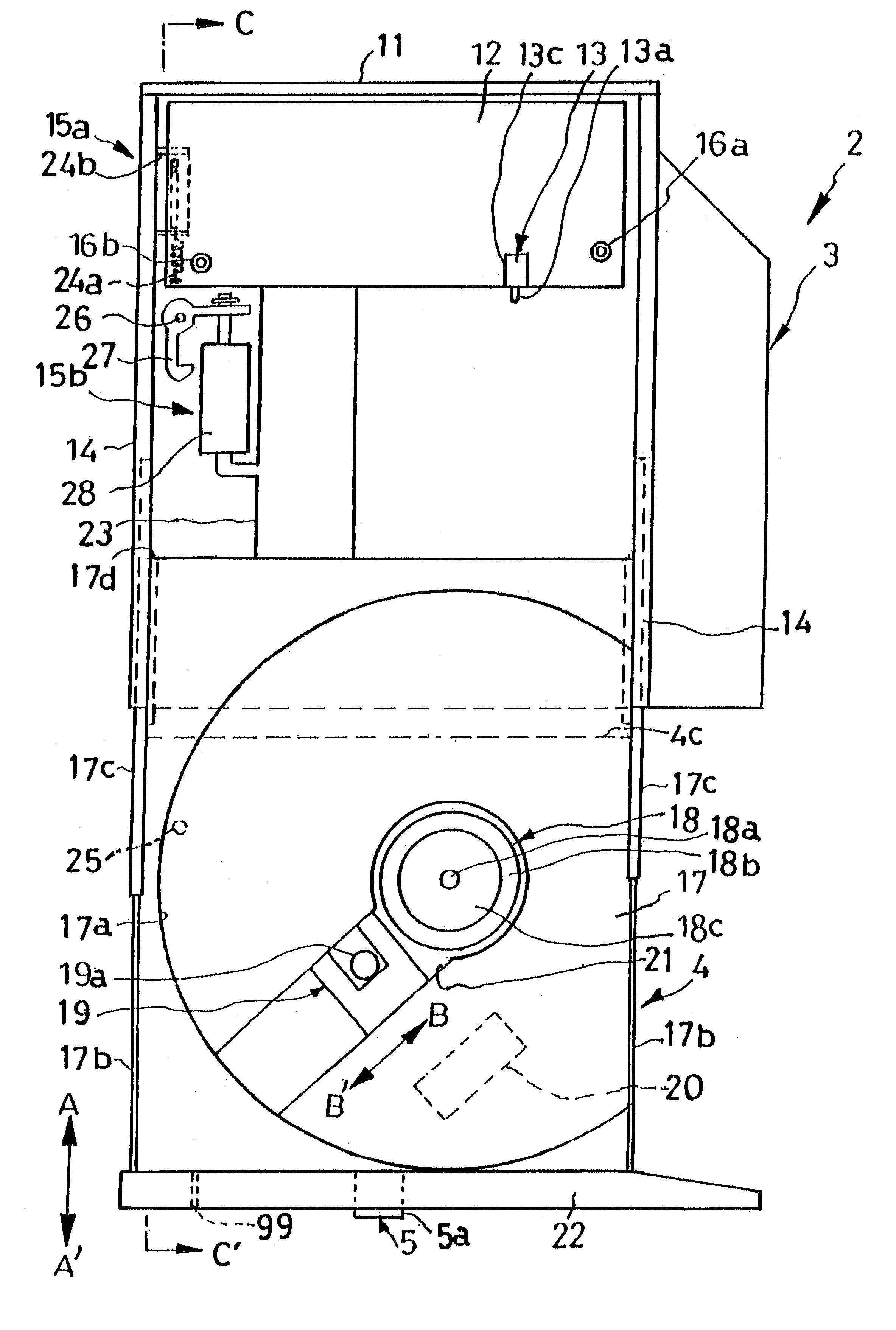

Data conversion apparatus with safety circuit

InactiveUS6426873B1Easy constructionPositive in operationLogic circuits characterised by logic functionDigital data processing detailsMotor driveElectric machine

A CD-ROM drive (2) is disclosed which has a safety circuit (40). The safety circuit (40) includes a NOR gate (51) having one input connected to a disk motor drive control signal terminal (48) of a system controller (31), and another input connected to the output (P1) of a sensor (13). The system controller (31) puts out a signal that goes low for activating a motor (18) and high for inactivating the same. The motor (18) is set into rotation when the NOR gate (51) is high, and out of rotation when the NOR gate is low. When the sensor (13) is high, however, the NOR gate (51) goes low, stopping the motor (18), regardless of the other input to the NOR gate from the system controller (31).

Owner:TEAC CORP

Large loading split I/O driver with negligible crowbar

ActiveUS7317333B1Easy to controlPower reduction in field effect transistorsPulse automatic controlDriver circuitNOR gate

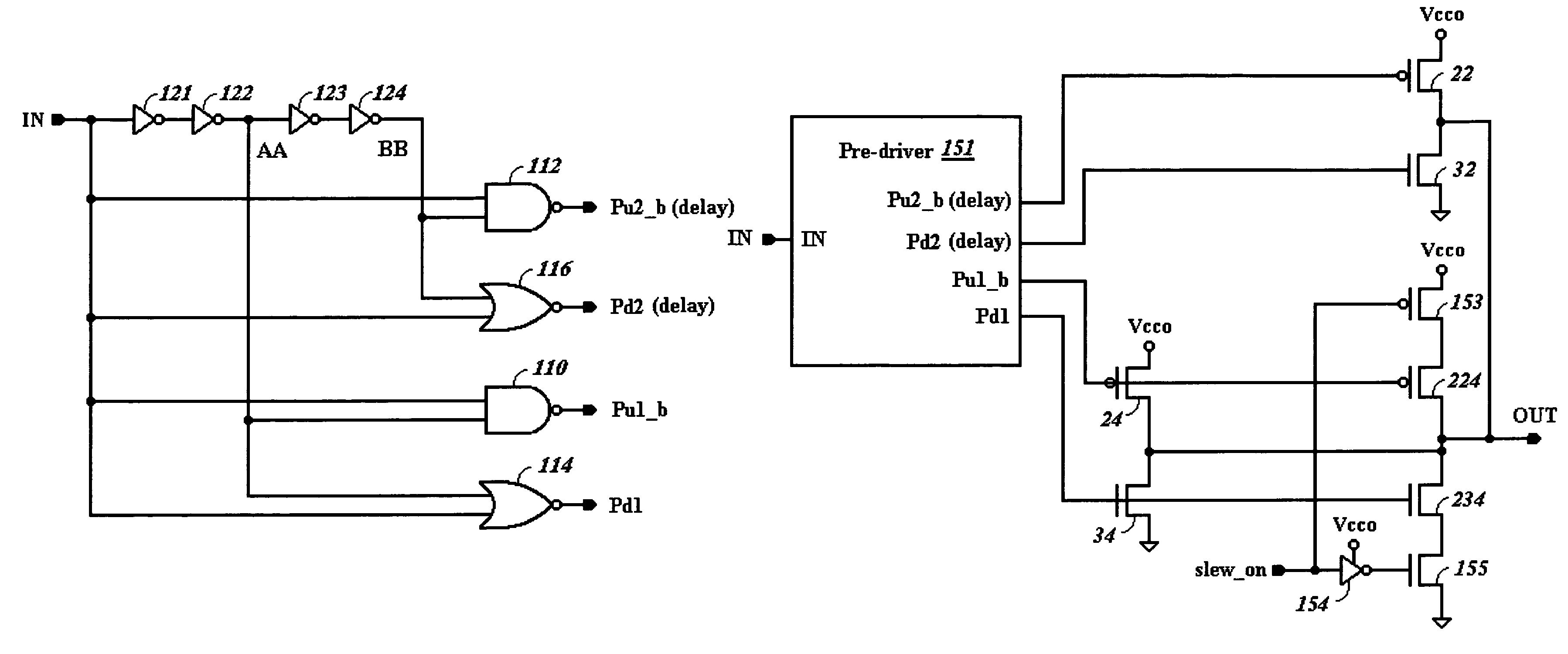

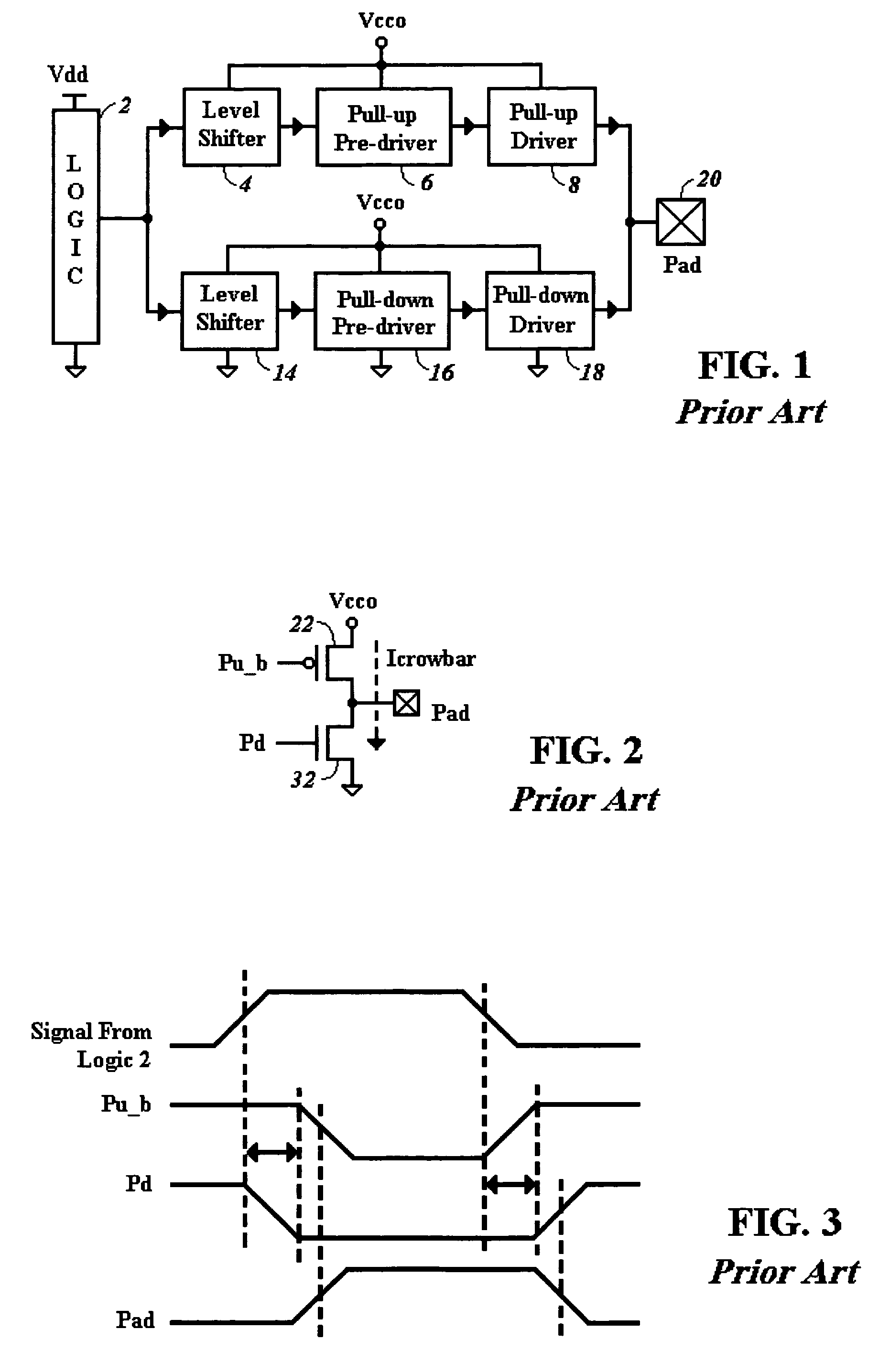

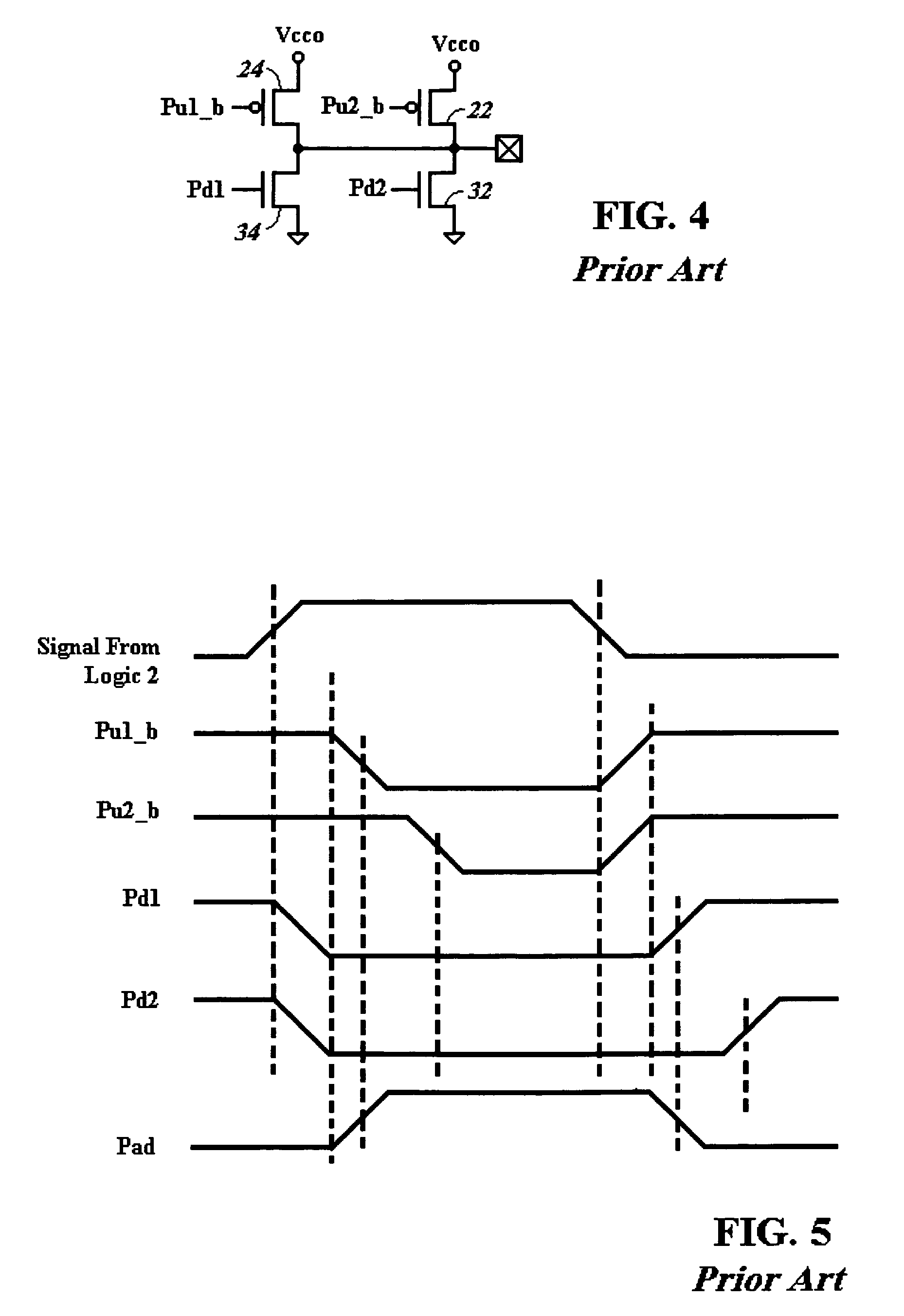

A pre-driver for large I / O pull-up and pull-down transistors is provided so that the I / O pull-up and pull-down transistors do not experience crowbar current, and the pre-driver circuit likewise does not experience crowbar current or require large driver transistors. One pre-driver circuit includes two NAND gates and two NOR gates with delay circuitry provided by two series inverters from a data input to a first node, and two additional series inverters from the first node to a second node. A further pre-driver circuit includes feedback from the pre-driver outputs to ensure its NMOS and PMOS transistors do not turn on together to create crowbar, while allowing faster switching. With the pre-driver circuit embodiments, a conventional level shifter can be used. Further with the pre-driver circuitry, slew rate control can be provided in the pull-up and pull-down driver circuitry, rather than in the pre-driver circuitry.

Owner:XILINX INC

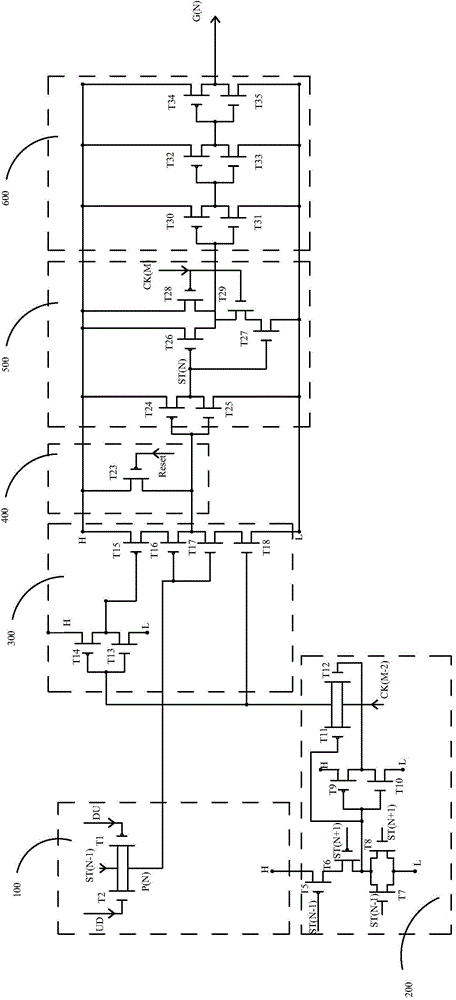

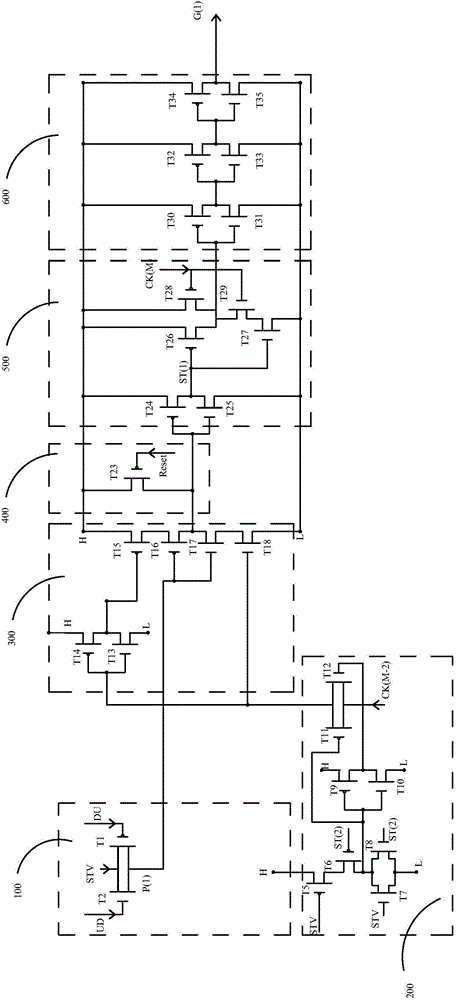

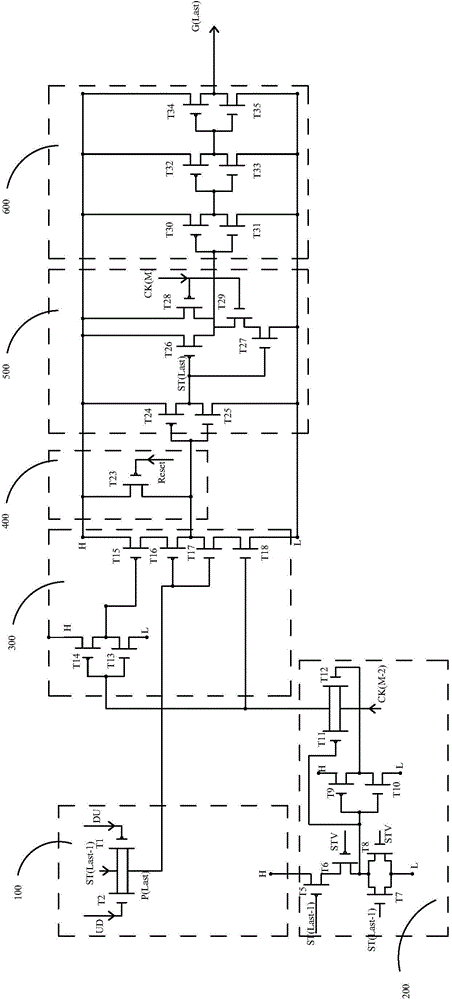

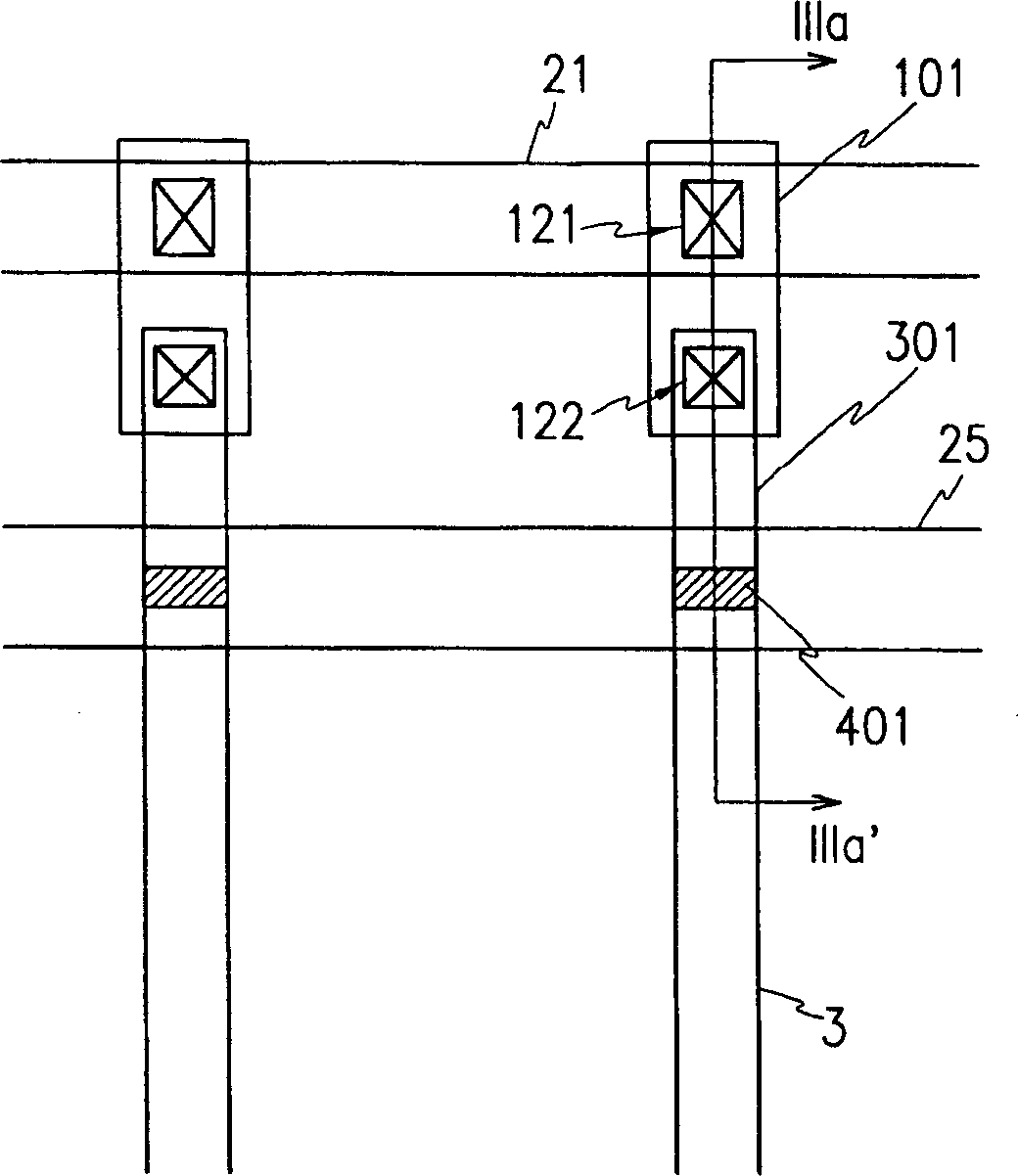

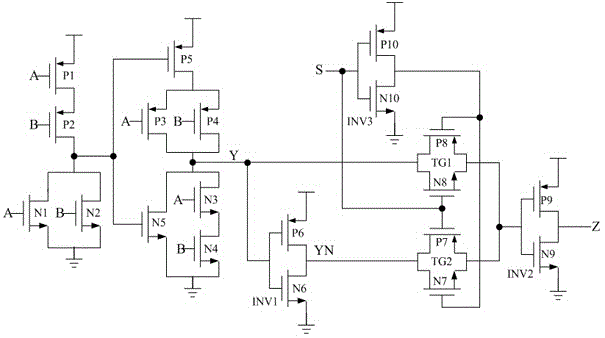

GOA circuit of low-temperature polycrystalline silicon thin film transistor

ActiveCN104464659AImprove performanceReduce the numberStatic indicating devicesElectricityTransmission gate

The invention provides a GOA circuit of a low-temperature polycrystalline silicon thin film transistor. The GOA circuit is used for forward scan transmission and comprises a plurality of cascaded GOA units, N is set to be a positive integer, a plurality of N-type transistors and a plurality of P-type transistors are adopted in the N class GOA unit, and the N class GOA unit comprises a transmission part (100), a transmission control part (200), a data storage part (300), a data clearing part (400), an output control part (500) and an output buffering part (600). Signals are transmitted between the upper and lower levels through a transmission gate, converted through an NOR gate logical unit and an NAND gate logical unit and stored and transmitted through a timing sequence phase inverter and a phase inverter, the problems that an LTPS single type TFT device is poor in circuit stability and large in power consumption, and the single type GOA circuit TFT leaks electricity are solved, the performance of the circuit is optimized, and the ultra-narrow frame or frameless design can be achieved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

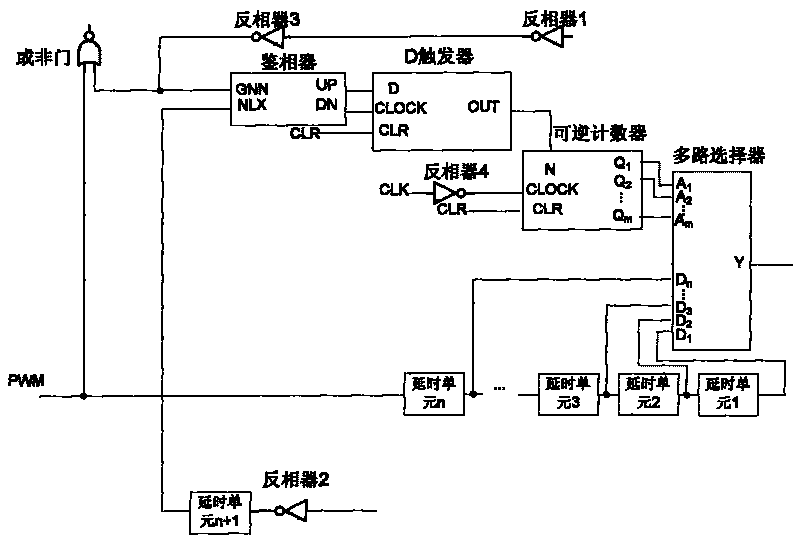

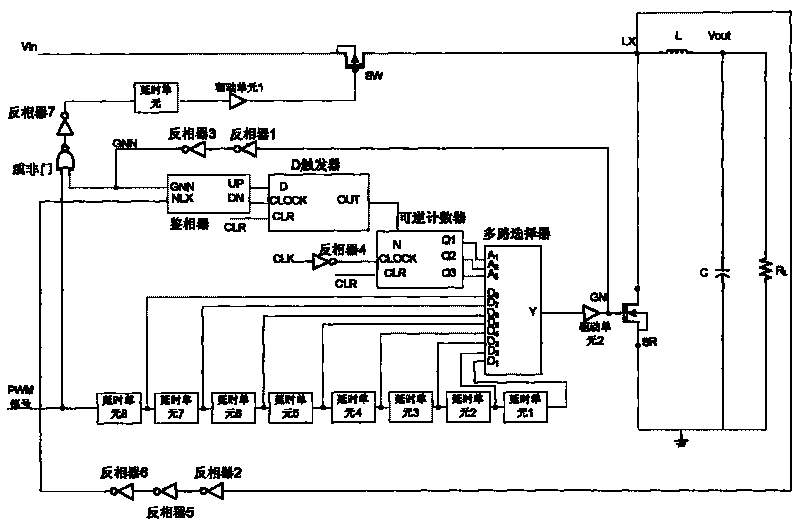

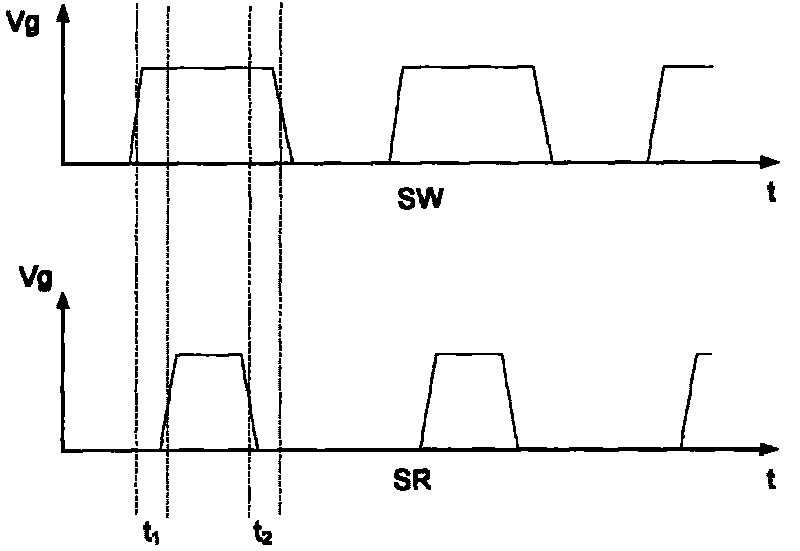

Digital self-adaptive dead-time control circuit

InactiveCN101694992AImprove efficiencyReliability increasing modificationsAc-dc conversion without reversalDiscriminatorDead time

The invention relates to a digital self-adaptive dead-time control circuit, belonging to the electronic technical field and relating to an integrated circuit technology and power conversion and motor-driving circuits which adopt a synchronous rectification technology. The digital self-adaptive dead-time control circuit comprises a phase discriminator, a D-trigger, a reversible counter, an n-to-1 multiple selector, (n+1) delay units, two low-flip level inverters, two common inverters and an NOR gate. The phase demodulation comparison of starting signals of an NMOS transistor SR is continued to control the reversible counter to carry out add-subtract count, so as to adjust a delay time unit and control the multiple selector to start the NMOS transistor SR in a suitable clock to further realize the self-adaptive adjustment of dead time. The invention not only avoids the simultaneous conduction of two power tubes caused by overshot dead time, but also avoids the conduction of a body diode caused by overlong dead time, thereby decreasing additional loss caused by the unsuitably set dead time and improving the whole efficiency of the power converter.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

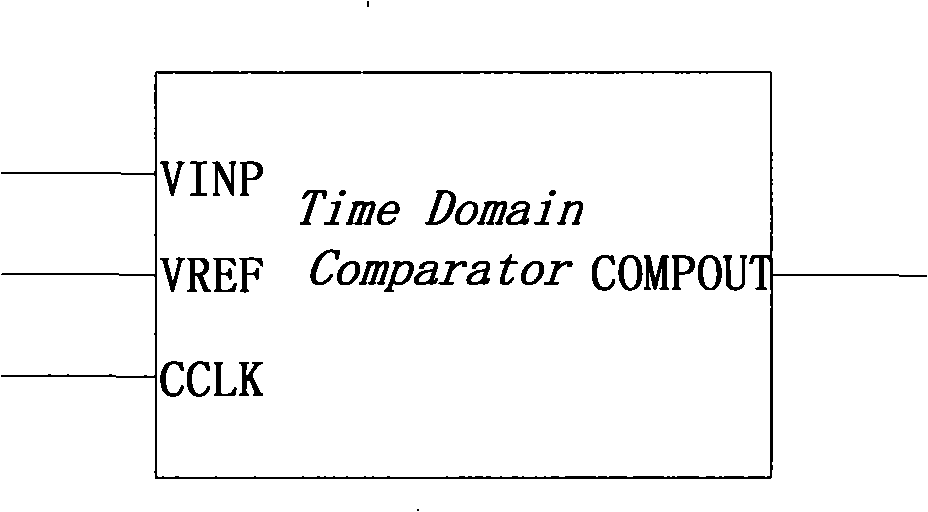

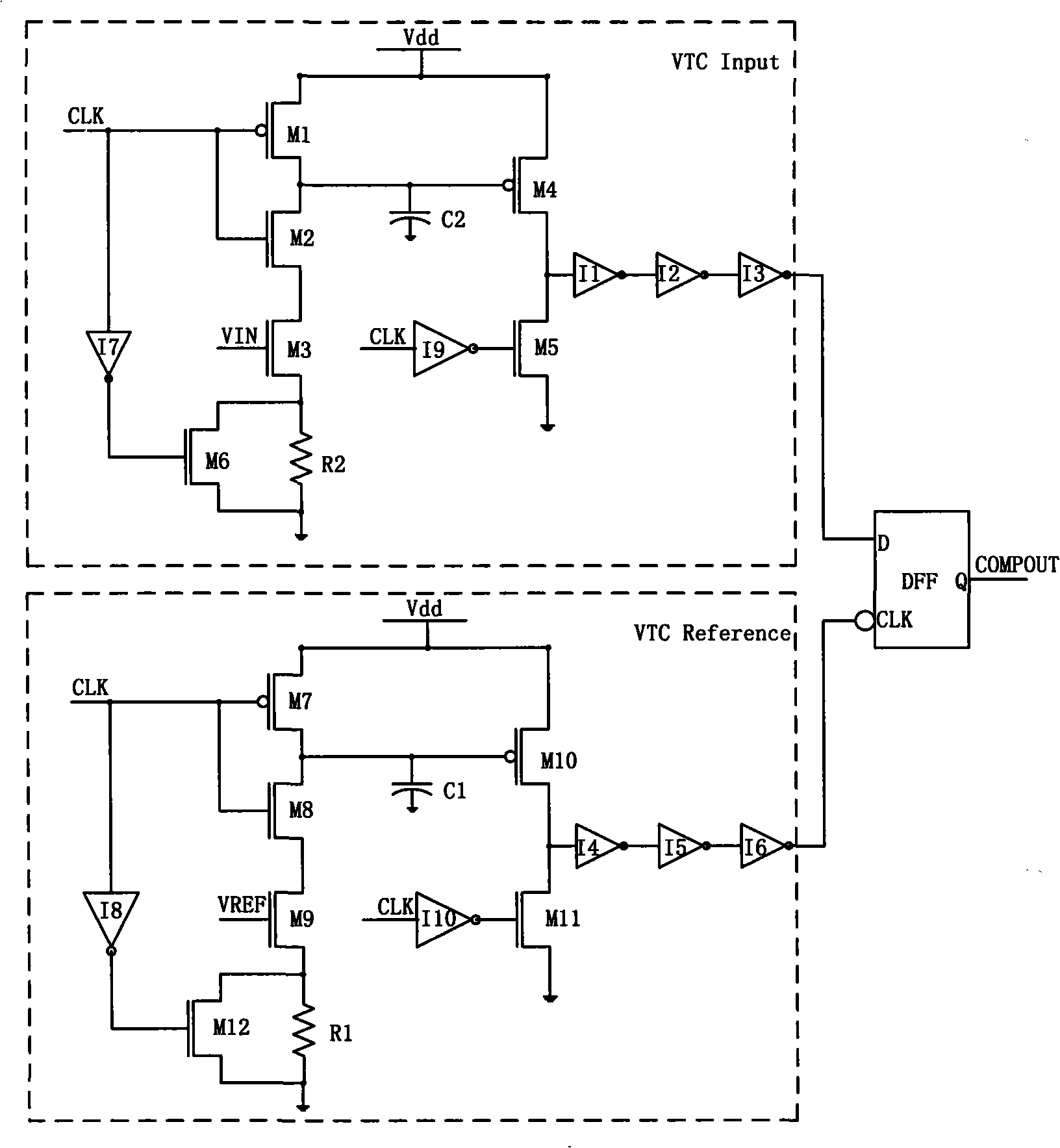

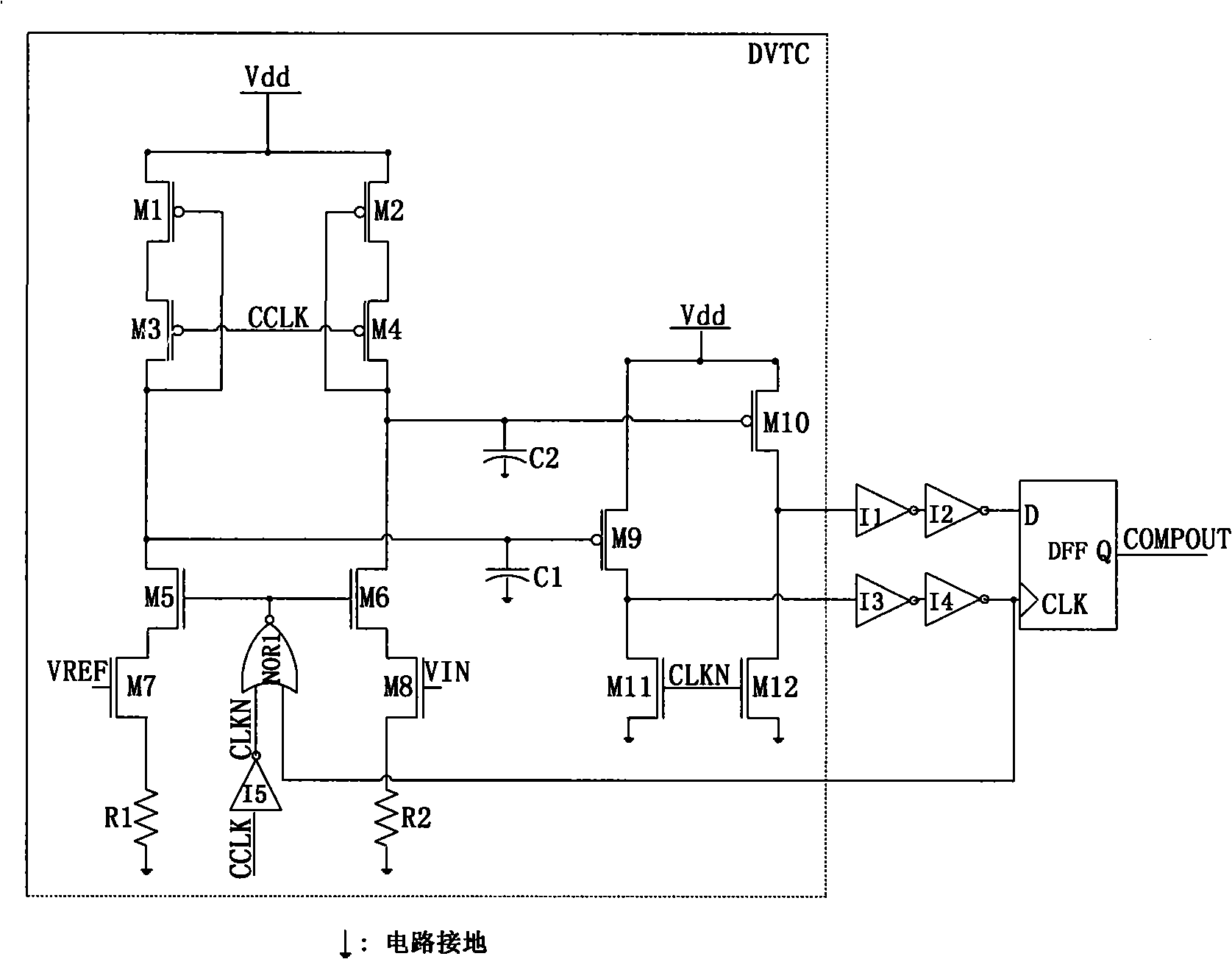

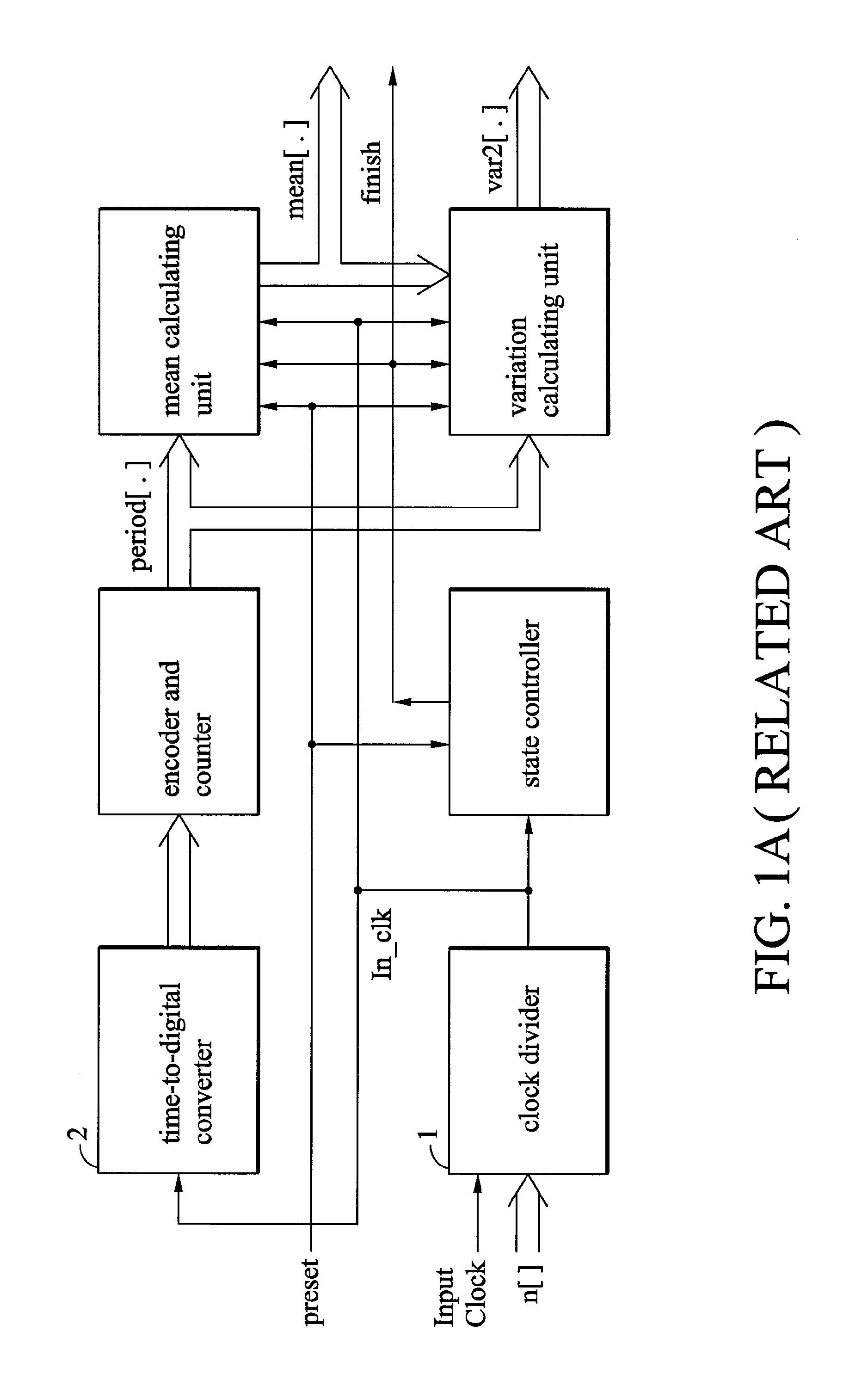

Ultra-low power consumption comparer based on time domain

InactiveCN101320975AWork fasterAnalogue/digital conversionElectric signal transmission systemsCapacitanceTime domain

A ultralow power dissipation analog to digital converter based on the time domain belongs to the field of the ultralow power dissipation analog to digital converter, characterized in that, on the basis of the available voltage-time converter VTC, an inversion signal CLKN and a feedback signal of reference output or a NOR gate NOR1 are controlled by a clock control signal CCLK, to cause the discharging process with different speed of the capacitance C1, the capacitance C2 to be interrupted, thereby accordingly advancing the working speed of the comparator.

Owner:TSINGHUA UNIV

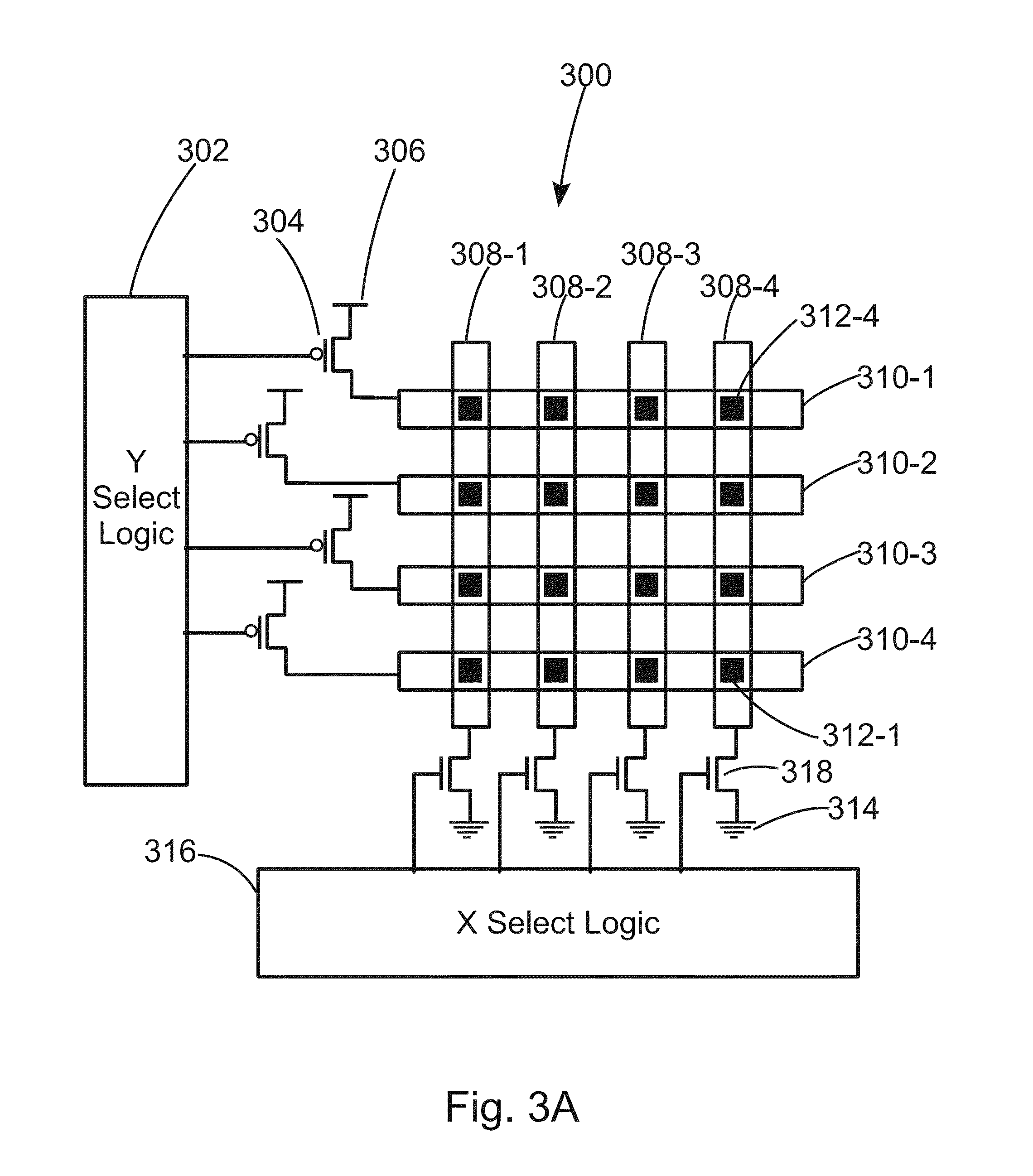

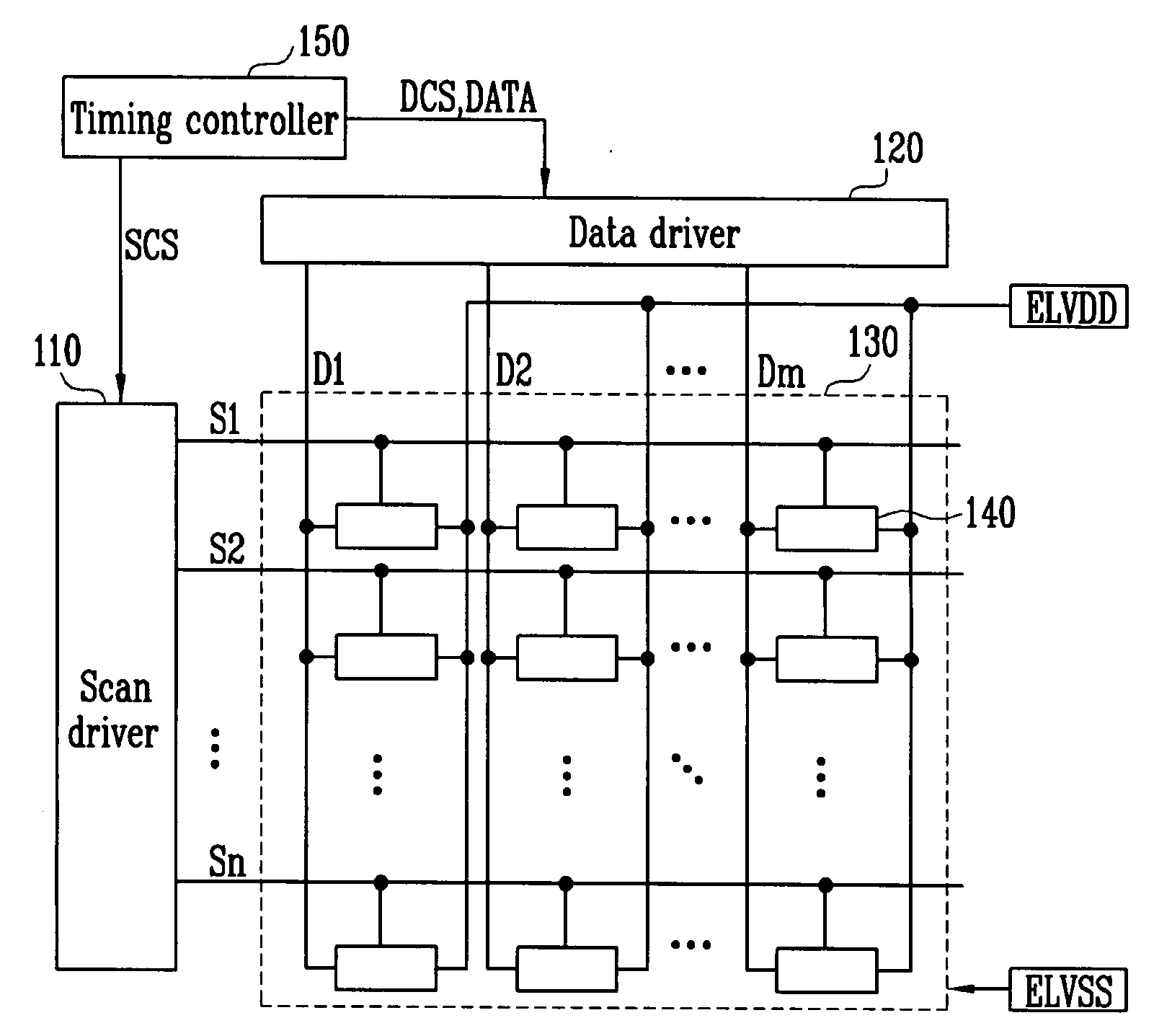

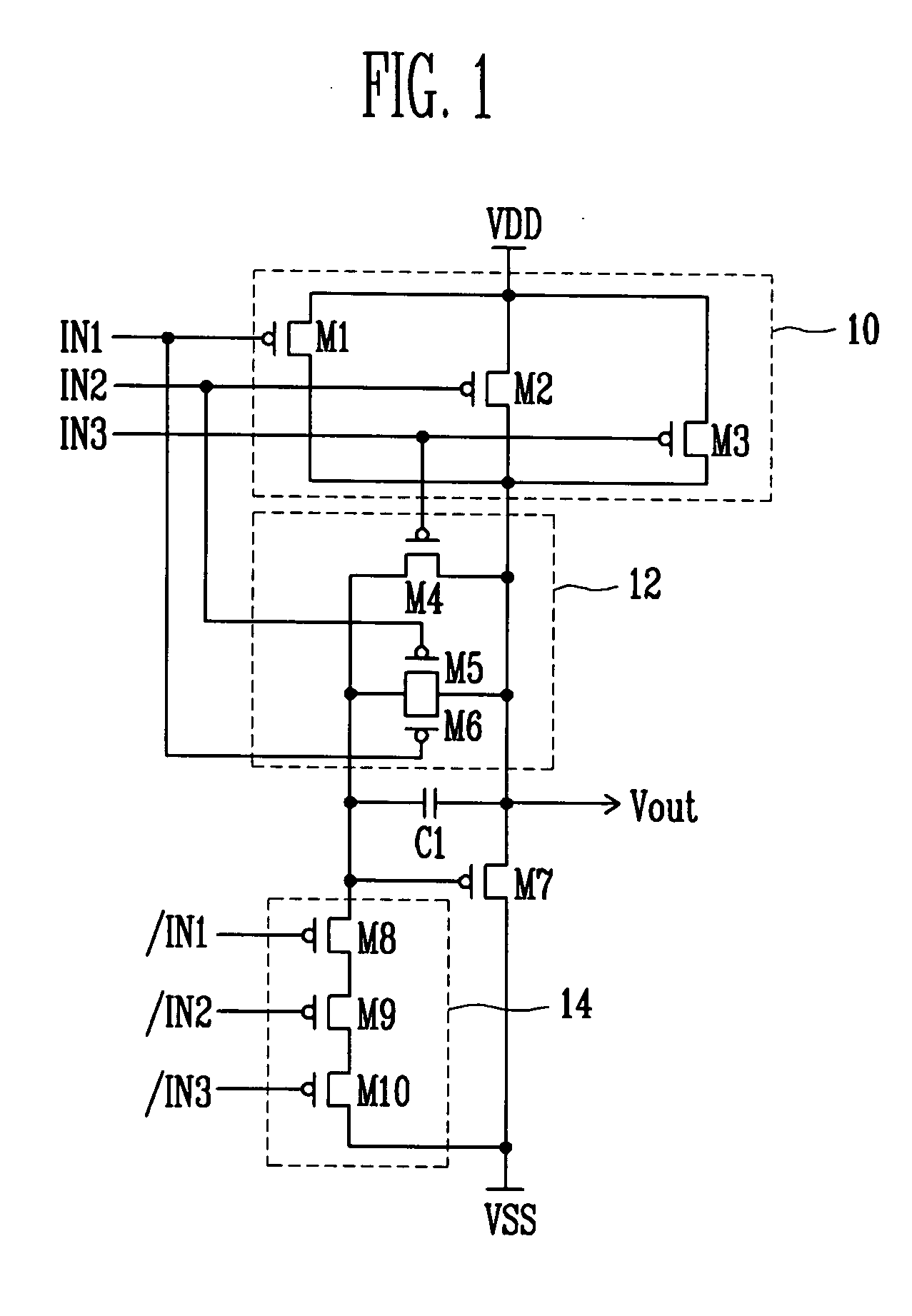

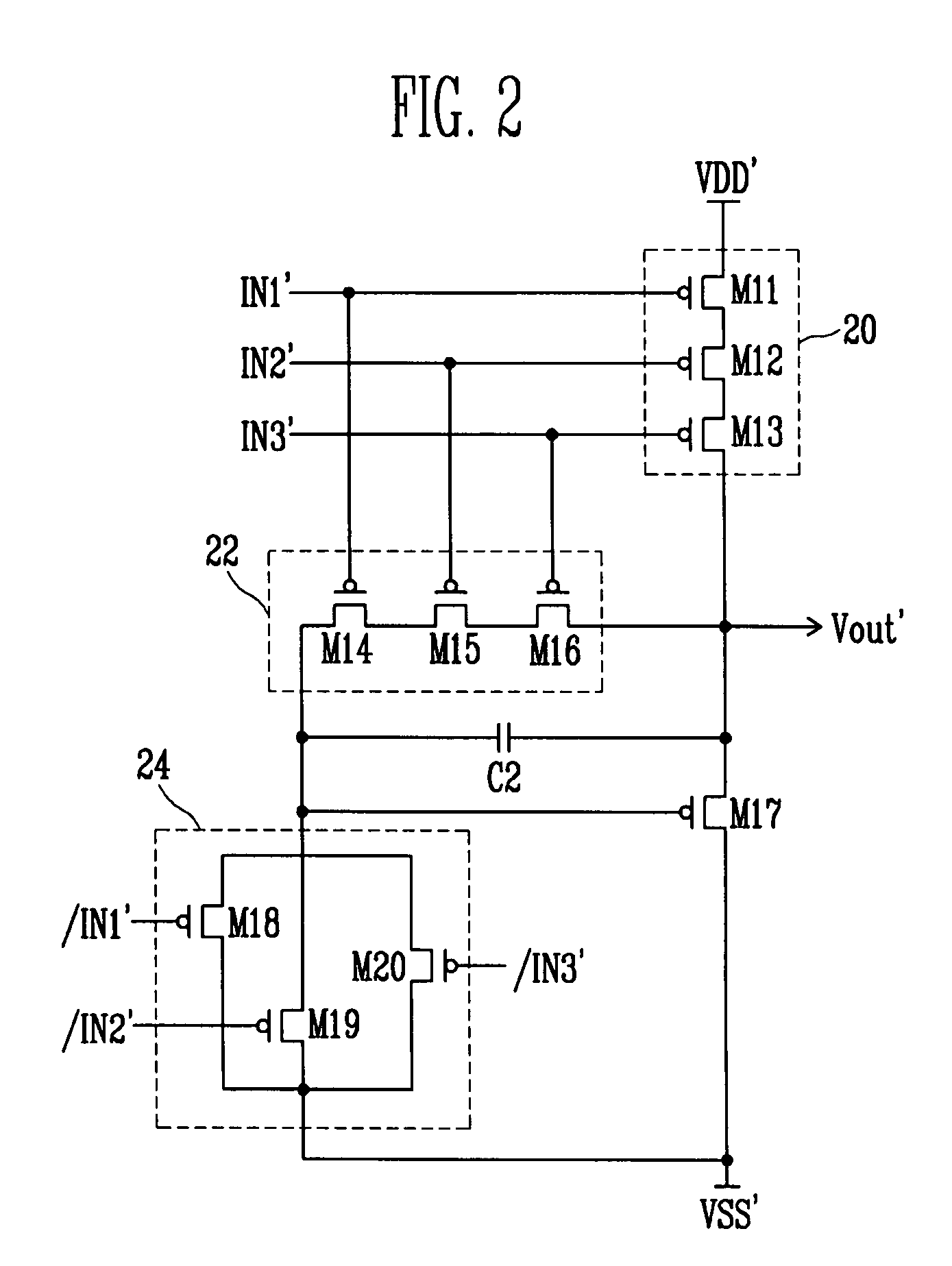

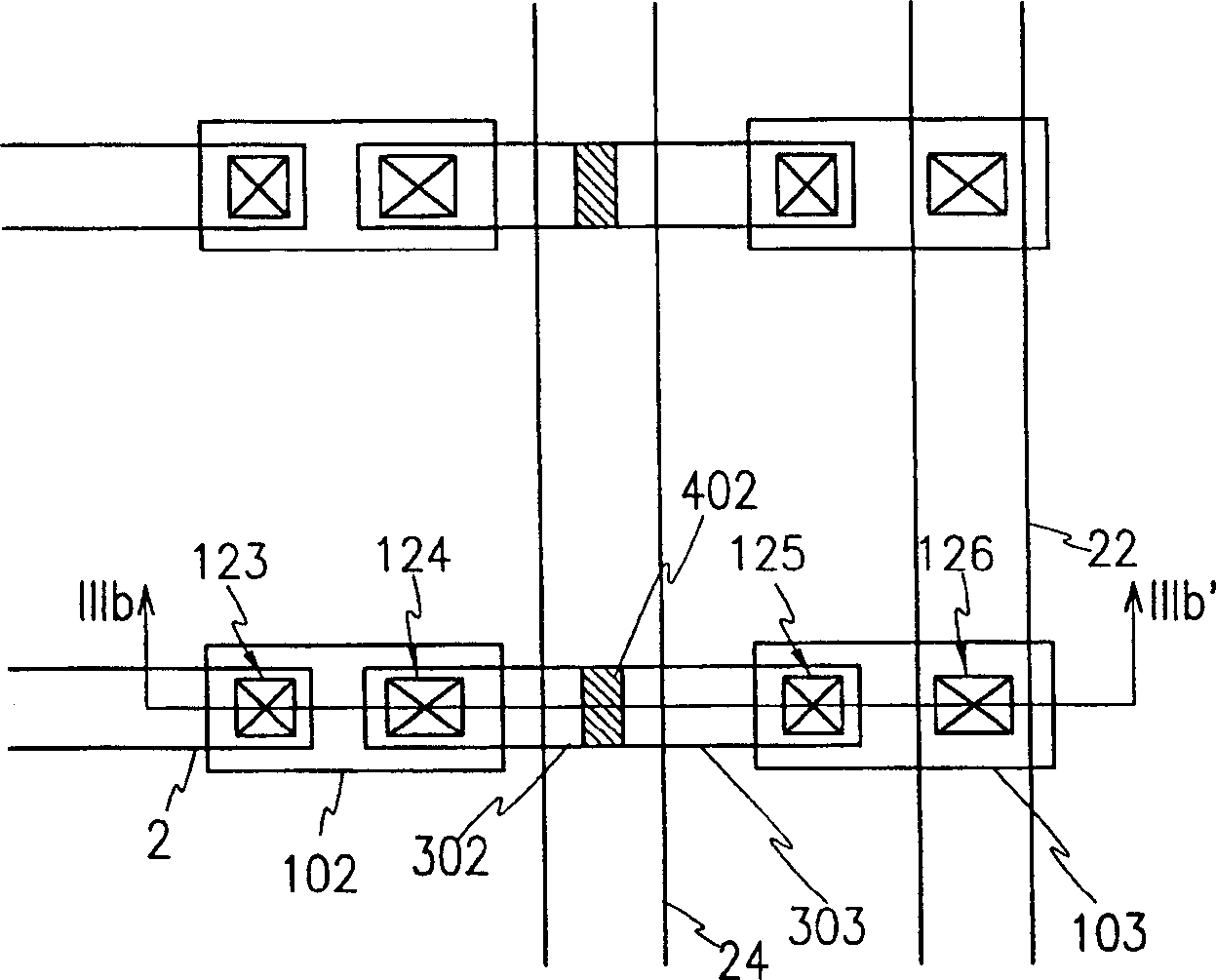

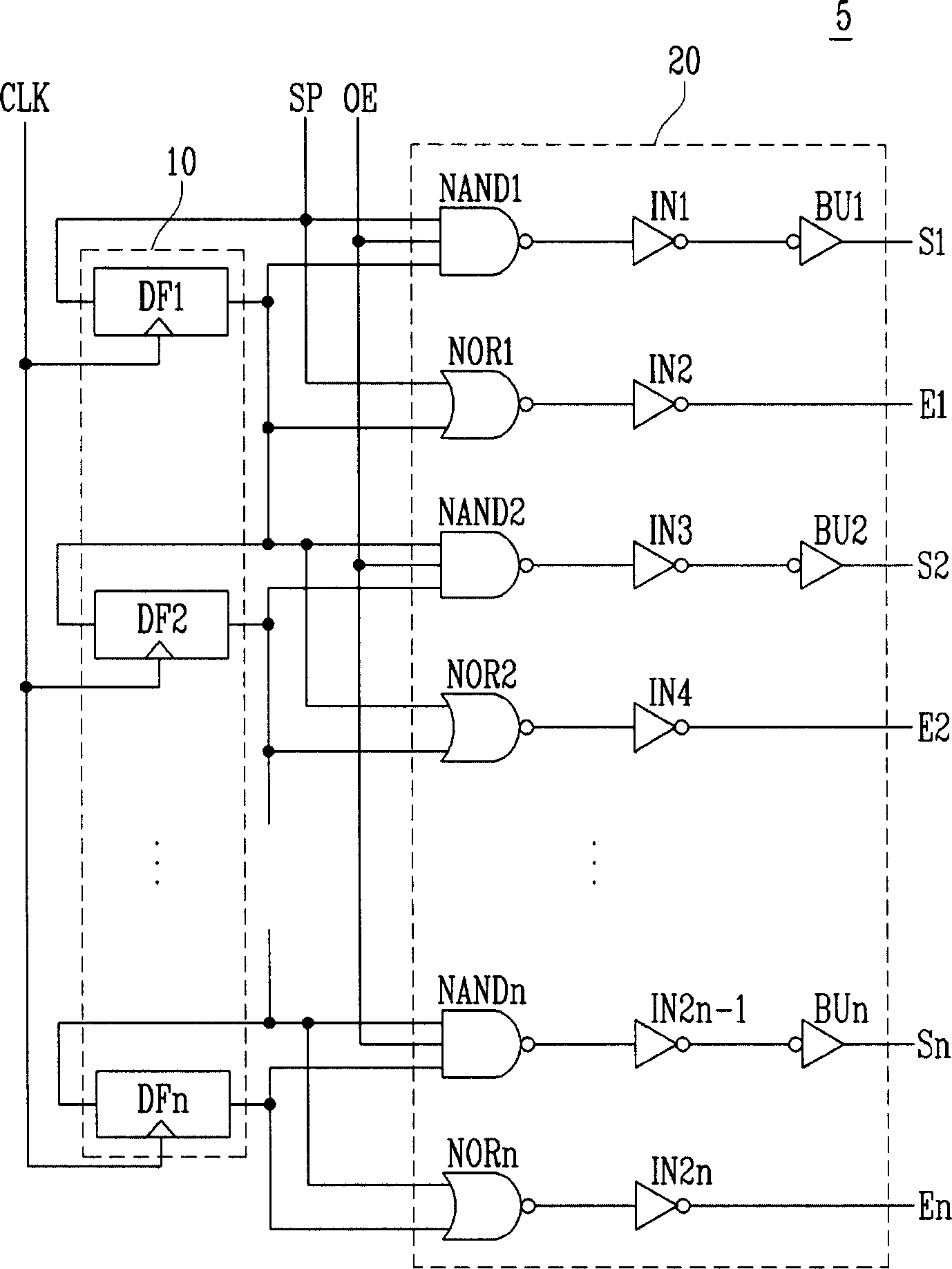

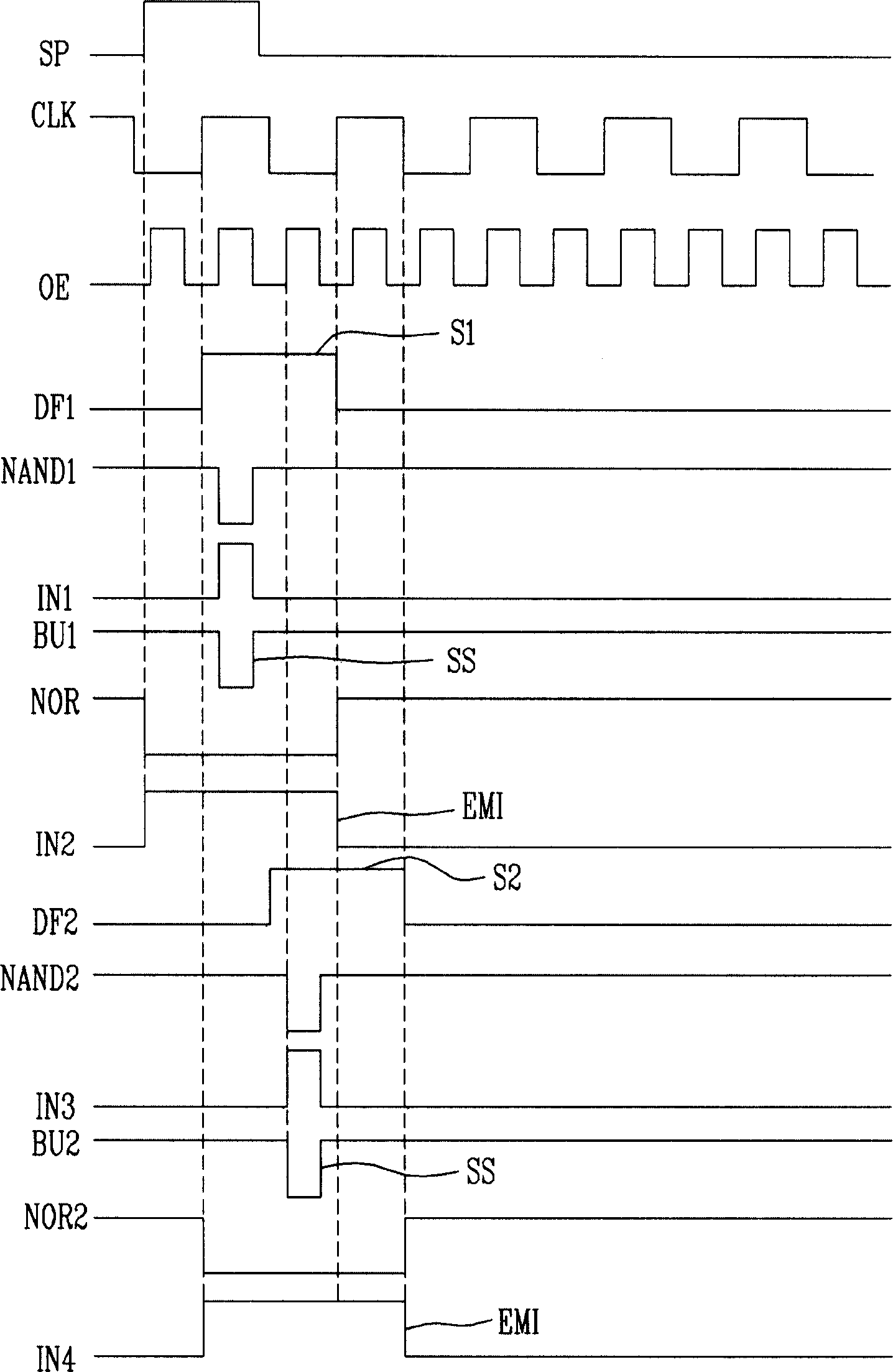

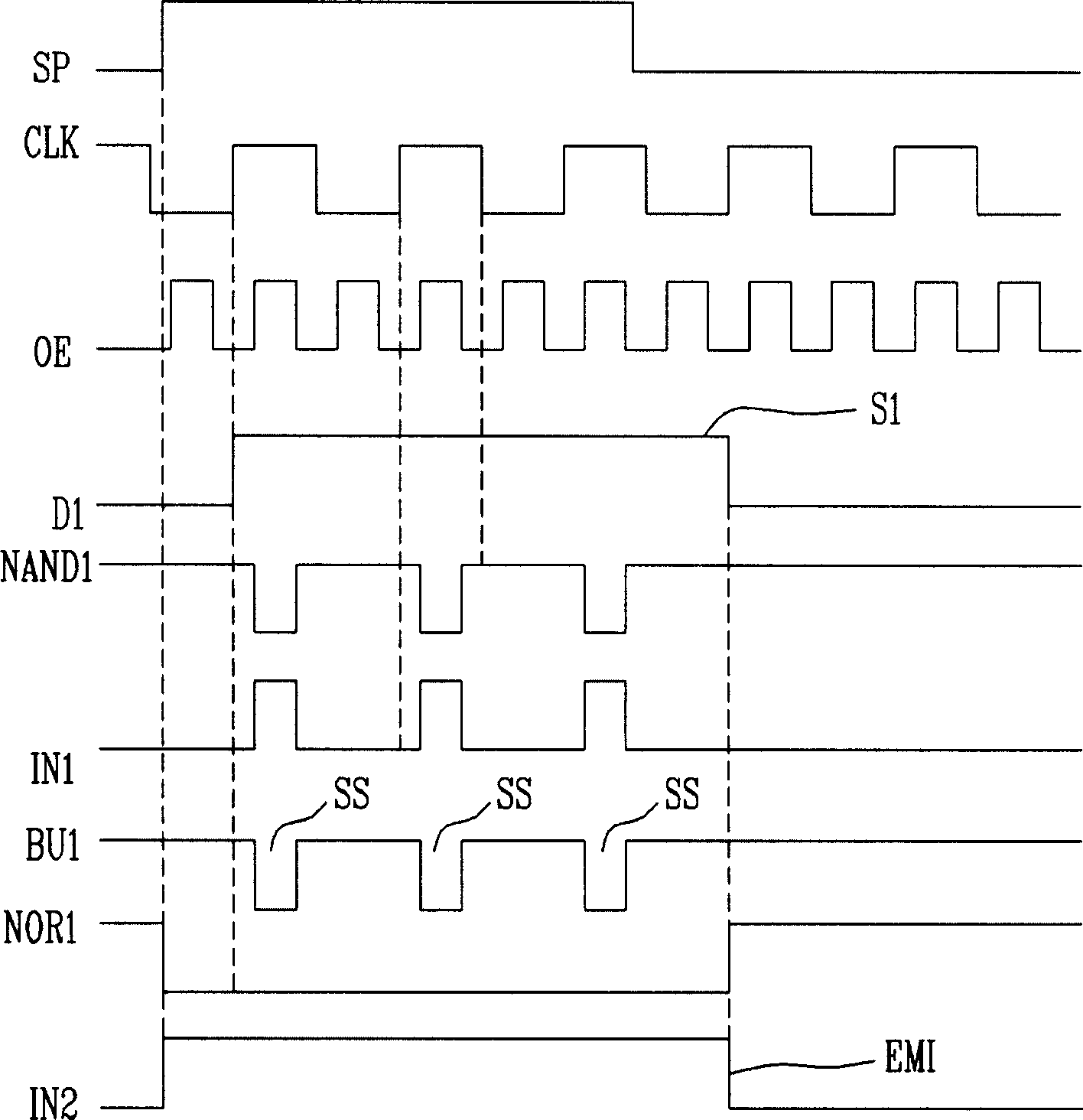

Logic gate, scan driver and organic light emitting diode display using the same

InactiveUS20080036712A1Logic circuits characterised by logic functionCathode-ray tube indicatorsScan lineNOR gate

An organic light emitting diode display, including pixel circuits coupled to respective data lines and scan lines, a data driver configured to supply data signals to the data lines, and a scan driver configured to provide scan signals to the scan lines, wherein the scan driver includes at least one decoder including a plurality of NOR gates, the decoder configured to provide a first plurality of signals, and a plurality of NAND gates coupled to respective scan lines, the NAND gates being configured to perform a NAND operation on the first plurality of signals and to provide scan signals to the scan lines, wherein all transistors in each of the NOR gates and each of the NAND gates are a same type of MOS transistor.

Owner:SAMSUNG DISPLAY CO LTD

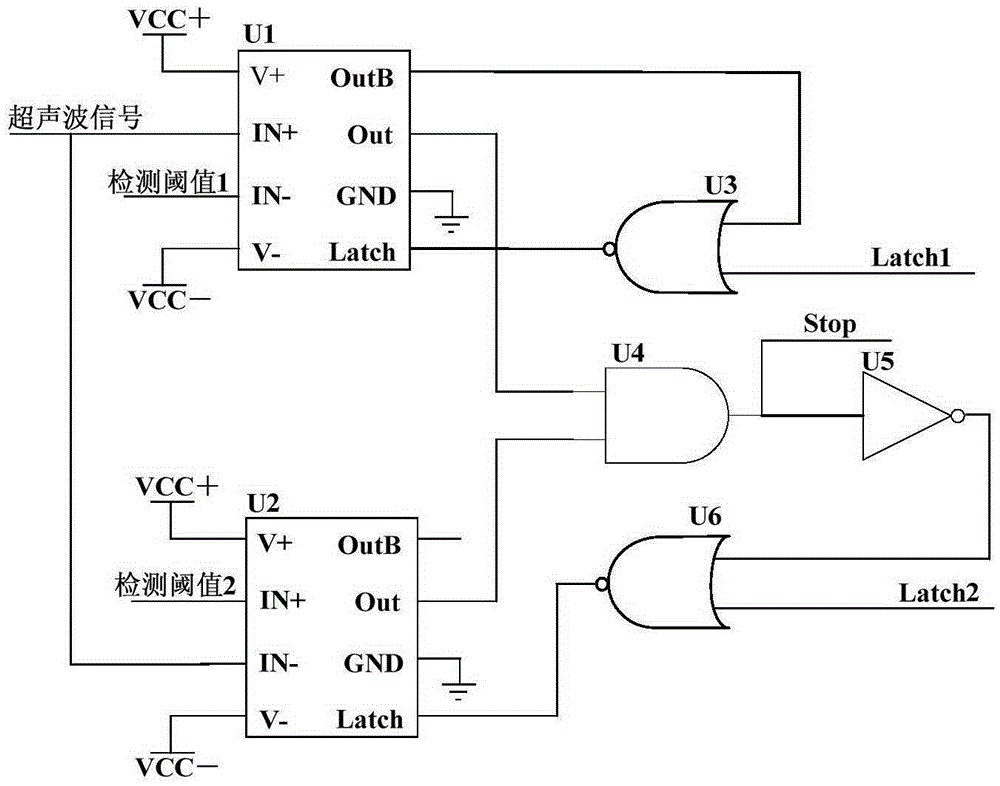

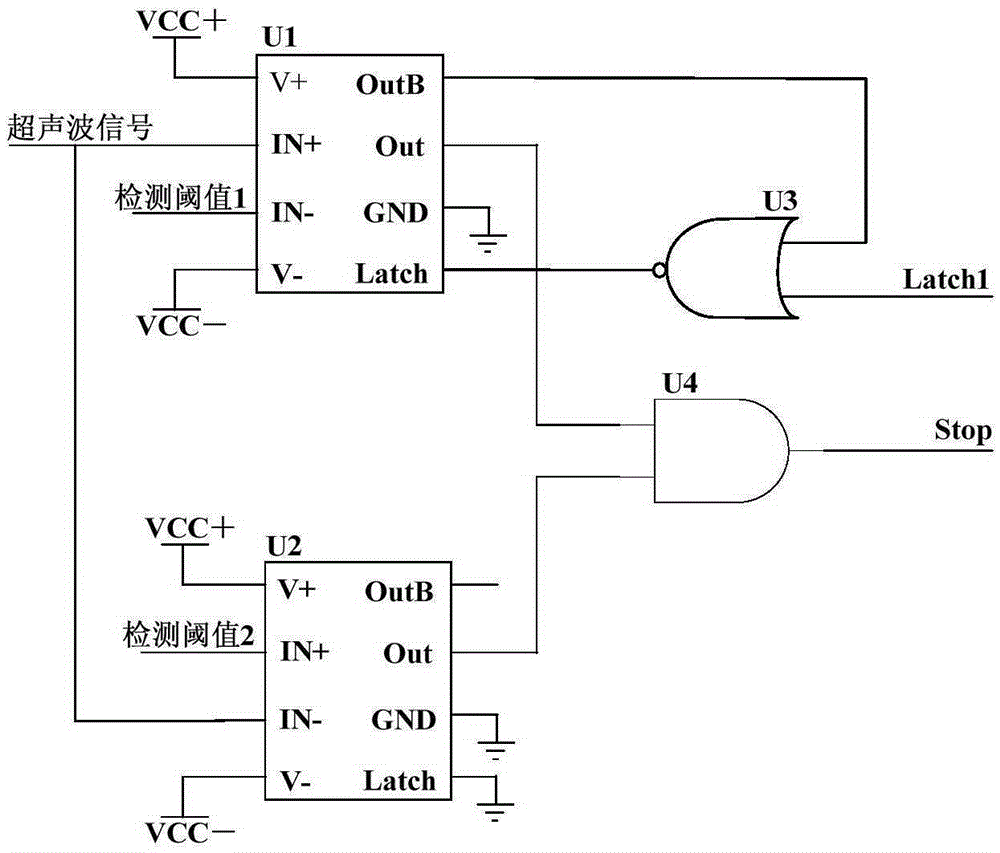

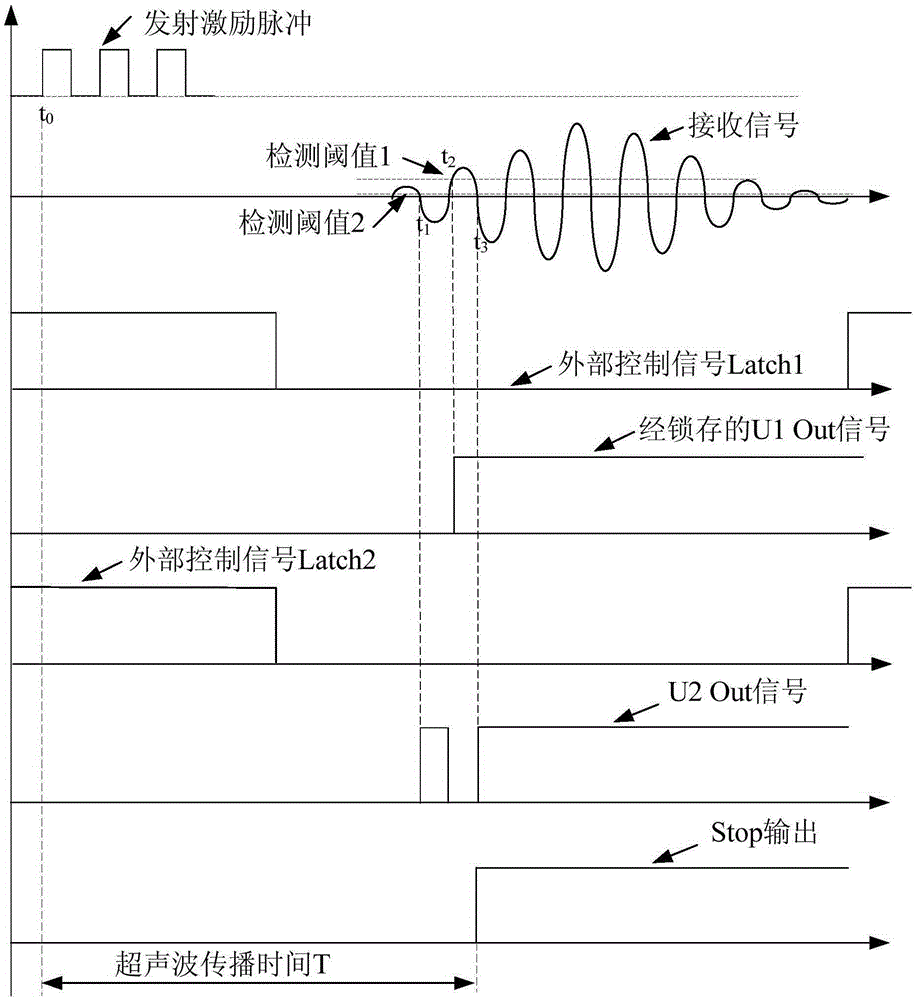

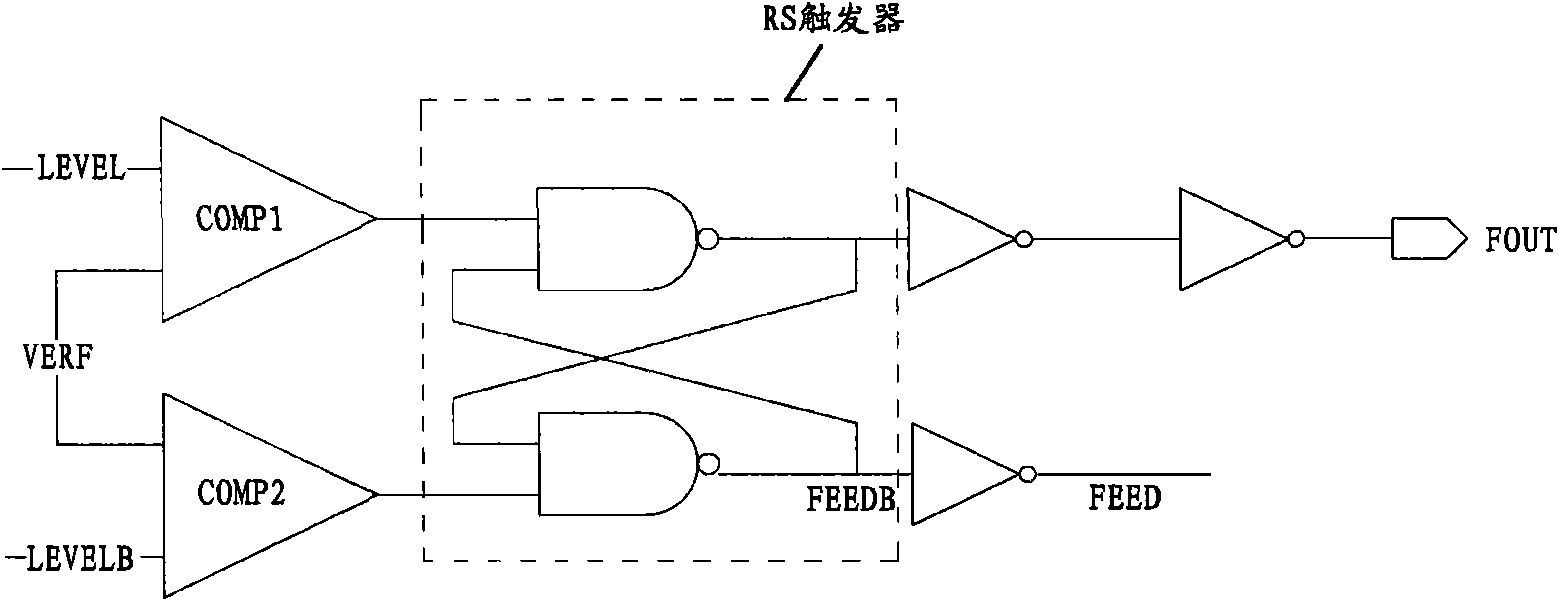

Double-threshold detection circuit of ultrasonic wave signal propagation time, and detection method

ActiveCN105300508AAvoid errorsAccurate measurementSubsonic/sonic/ultrasonic wave measurementVolume/mass flow measurementNOR gateControl signal

The invention relates to a double-threshold detection circuit of ultrasonic wave signal propagation time, and a detection method. The detection circuit comprises a first comparator, a second comparator, a first NOR gate, an AND gate, a NOT gate and a second NOR gate. First threshold signals are 0.2 to 0.5V; second threshold signals are 0 to 20mV; first external control signals are overturned into low level after emission pulses are emitted for 80 to 100[mu]s; and second external control signals are overturned into low level or high level after the emission pulses are emitted for 80 to 100[mu]s. The circuit provided by the invention has the following advantages: errors caused by influences exerted by fluid temperature and viscosity on ultrasonic waves in fluid propagation are avoided, and measurement of the propagation time is more accurate; and a NOT gate U5 and a NOR gate U6 can be omitted and the Latch pin of the first comparator U1 is connected with GND, such that detection processing and generation of multiple stop timing enabling functions can also be realized, the circuit can be further simplified, and the reliability is improved.

Owner:BEIJING INST OF CONTROL ENG

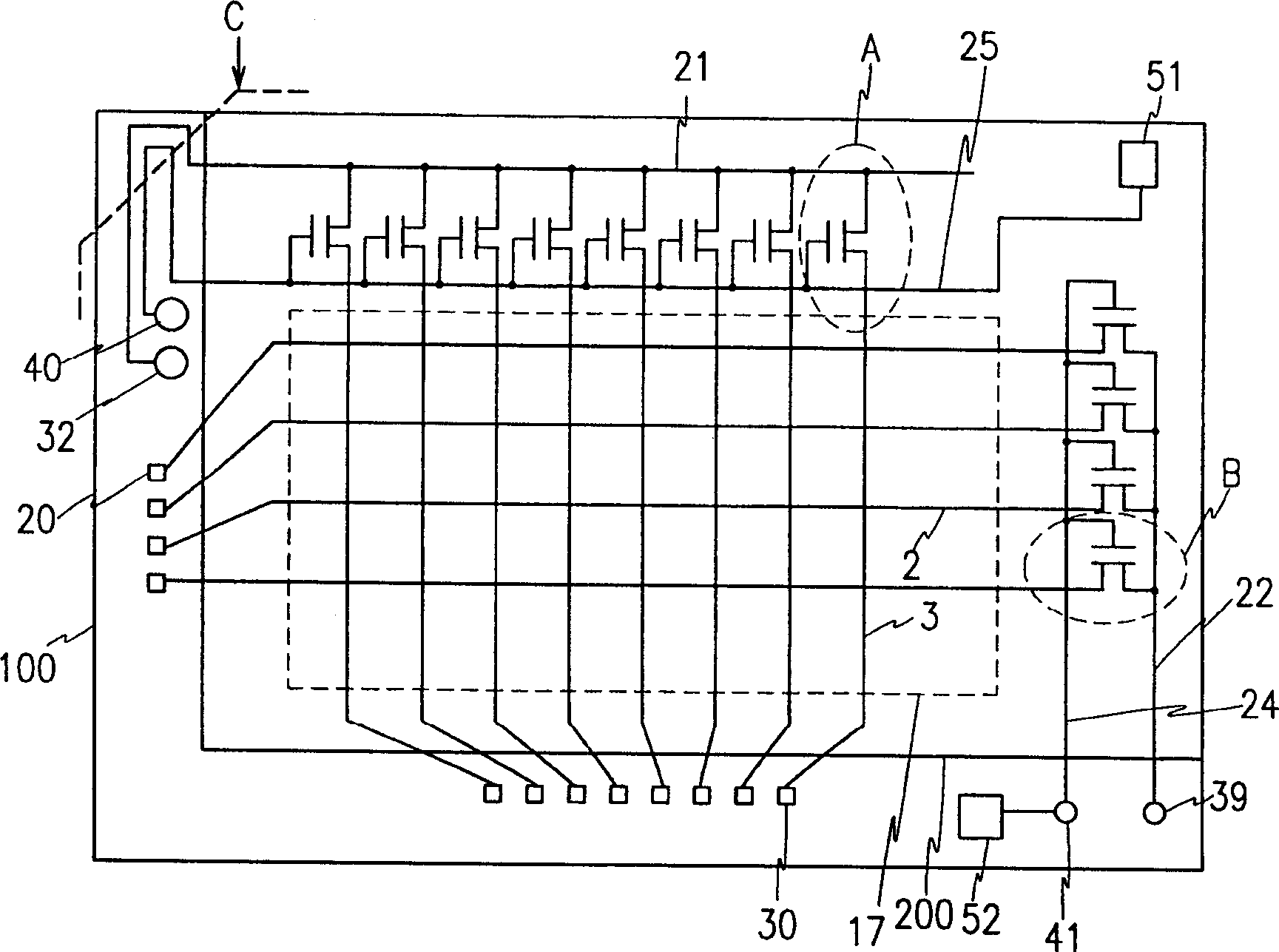

Film transistor array panel with visual checking device and its checking method

A plurality of gate lines and a plurality of data lines intersecting the gate lines to define a display area are formed on an insulating substrate including a display area and a surrounding area. On the surrounding area, a gate driving circuit connected to the gate lines and a logic circuit for VI interposed between the gate driving circuit and the gate line and having several first to third NOR gates are formed. A first input terminal of the first NOR gate of the logic circuit for VI is connected to an output terminal of the gate driving circuit, and a second input terminal thereof is connected to a CON1 terminal, and an output terminal thereof is connected to a first input terminal of the second or the third NOR gate. A second input terminal of the second NOR gate is connected to a CON2 terminal and an output terminal thereof is connected to the gate lines in odd number. A second input terminal of the NOR gate is connected to a CON3 terminal and an output terminal thereof is connected to the gate lines in even number.

Owner:SAMSUNG DISPLAY CO LTD

Scan driver, organic light emitting display using the same, and method of driving the organic light emitting display

The invention discloses an embodiment of a scan driver, which can freely adjust the width of an emission control signal. An embodiment of the scan driver includes: a shift register configured to sequentially shift the start pulse in response to a clock signal to generate a sampling pulse; a NOR gate connected to each emission control line and configured to The emission control signal is generated in response to at least two sampling pulses; and the NAND gate is connected to each scanning line to generate scanning signals in response to the at least two sampling pulses. At least one of the two sampling pulses input to the NAND gate is input through an inverter. Therefore, the width of the start pulse is controllable to freely adjust the width of the emission control signal. Therefore, the brightness of an organic light emitting display employing the scan driver can be freely adjusted.

Owner:SAMSUNG DISPLAY CO LTD

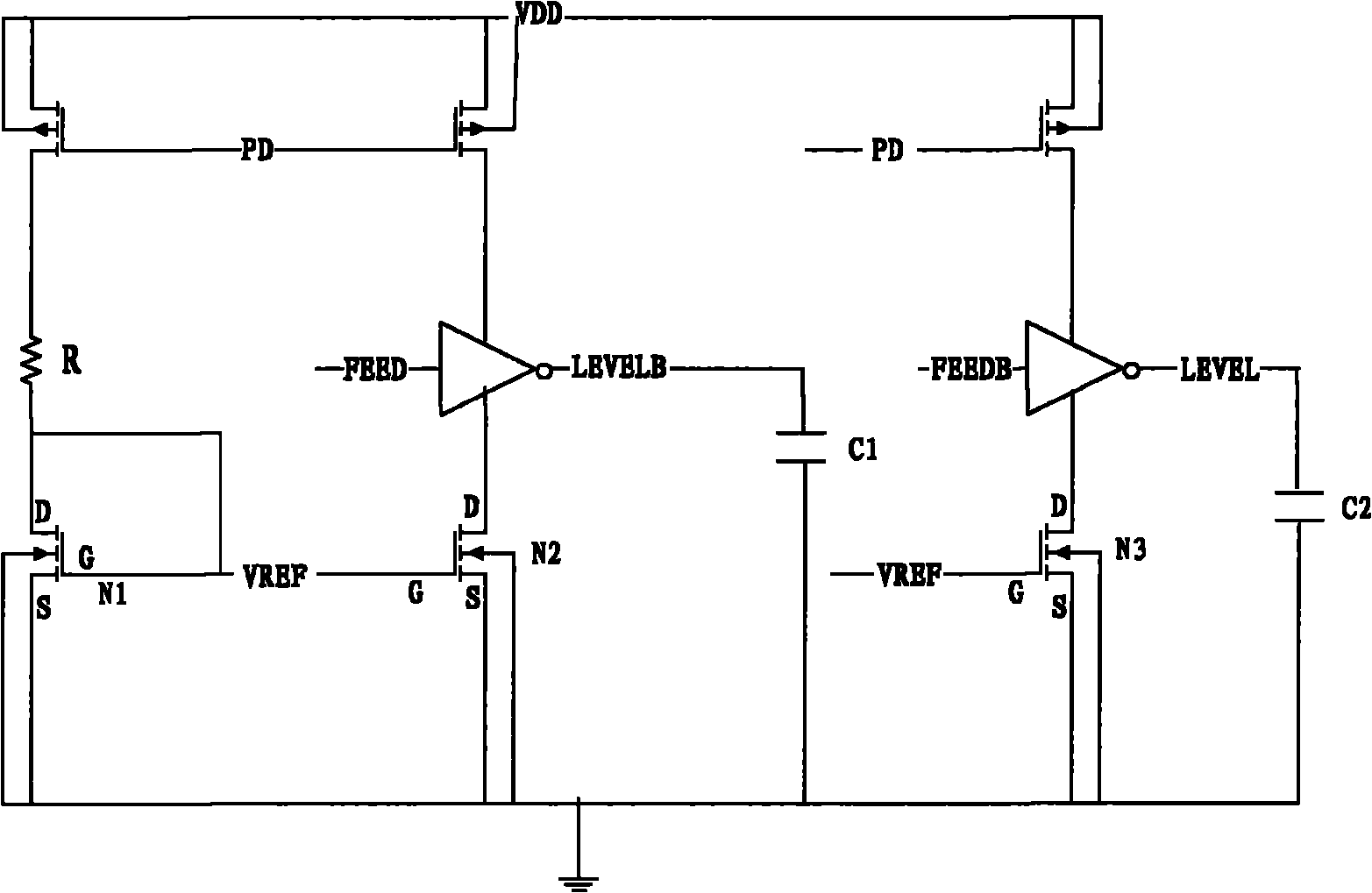

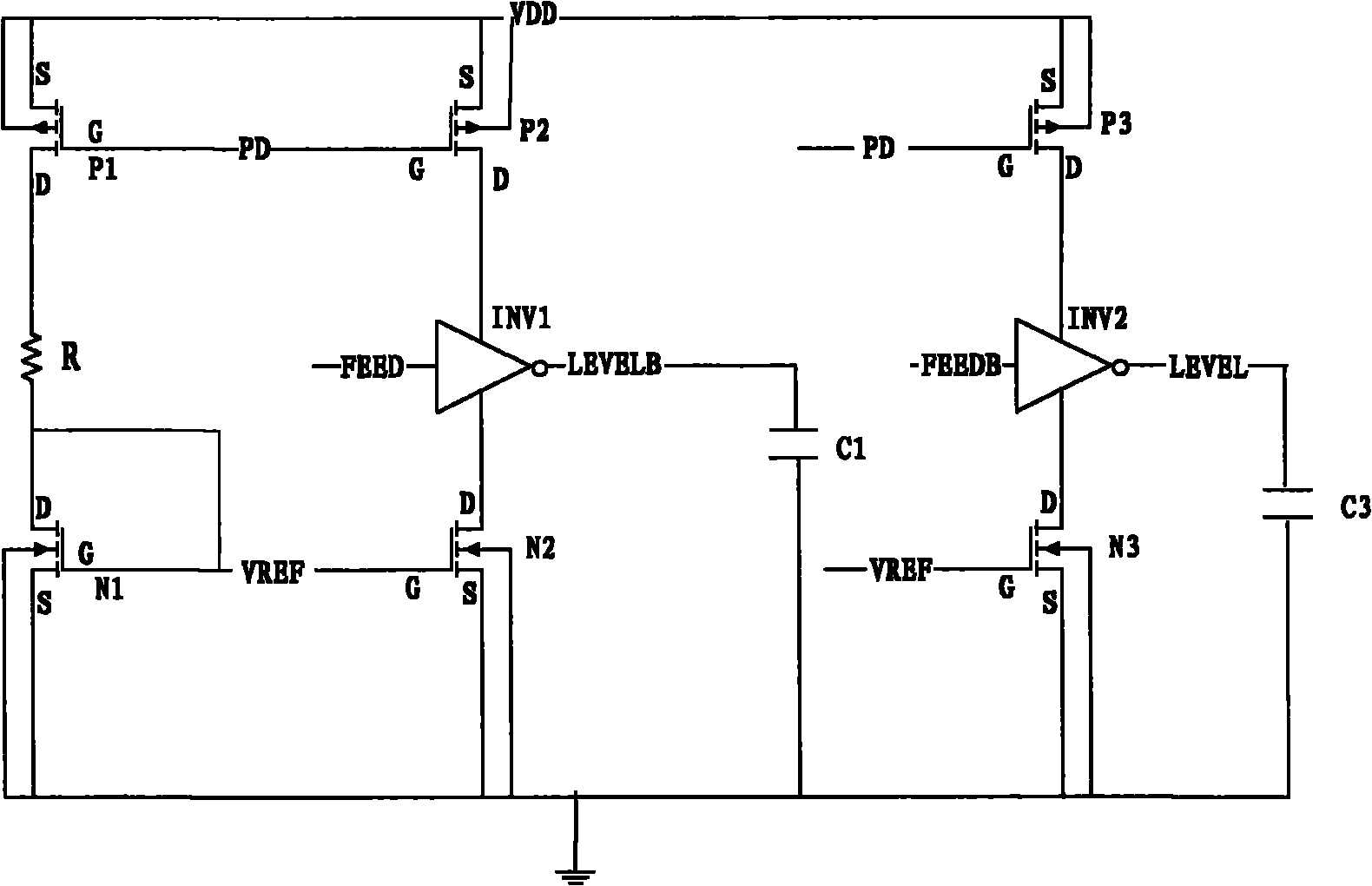

Resistance capacitance (RC) oscillator with low power consumption

The invention provides a resistance capacitance (RC) oscillator with low power consumption, which can generate clock control signals with a duty ratio of which the accuracy is increased required by an internal circuit. The RC oscillator comprises a bias circuit, a first inverter, a second n-channel metal oxide semiconductor (NMOS) transistor, a first capacitor, a second inverter, a third NMOS transistor, a second capacitor, a third inverter, a fourth inverter, a fifth inverter, a sixth inverter, an RS trigger, a nor gate and a fourth NMOS transistor, wherein the bias circuit comprises a resister and a first NMOS transistor; a first input end and a second input end of the RS trigger are respectively connected with a first input end and a second input end of the nor gate; the output end of the nor gate is connected with a grid electrode of the fourth NMOS transistor; a first output end of the RS trigger is connected with a drain electrode of the fourth NMOS transistor; and the source electrode of the fourth NMOS transistor is grounded.

Owner:SAMSUNG SEMICON CHINA RES & DEV +1

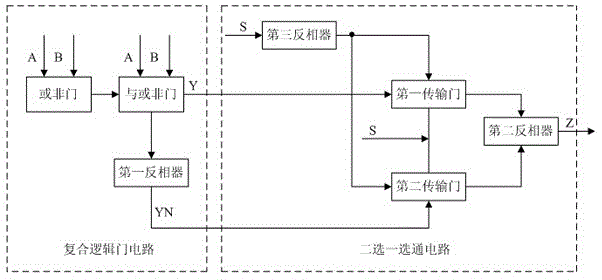

Circuit capable of realizing multiplexing of exclusive-OR gate or XNOR gate

ActiveCN105471425AReduce power consumptionReduce in quantityLogic circuits characterised by logic functionMultiplexingExclusive or

The invention discloses a circuit capable of realizing multiplexing of an exclusive-OR gate or an XNOR gate, belonging to the technical field of integrated circuits. The circuit comprises a compound logic gate circuit and an either-or gating circuit which are cascaded; the compound logic gate circuit comprises a NOR gate unit, an AND-OR-NOT gate unit and a first phase inverter, an input end of the NOR gate unit and the input end of the AND-OR-NOT gate unit are respectively connected with two paths of input signals, an output end of the NOR gate unit is connected with a control end of the AND-OR-NOT gate unit, the output end of the AND-OR-NOT gate unit is connected with the input end of the first phase inverter and outputs an exclusive-OR operation result, and the output end of the first phase inverter outputs an XNOR operation result; and the either-or gating circuit performs gating on an exclusive-OR gate unit composed of the NOR gate unit and the AND-OR-NOT gate unit, or an XNOR gate unit composed of the NOR gate unit, the AND-OR-NOT gate unit and the first phase inverter. The circuit provided by the invention realizes simple multiplexing of the exclusive-OR gate or XNOR gate circuit, reduces the number of transistors of the whole circuit system, and consequently reduces the layout area and circuit power consumption.

Owner:WUXI XINXIANG ELECTRONICS TECH

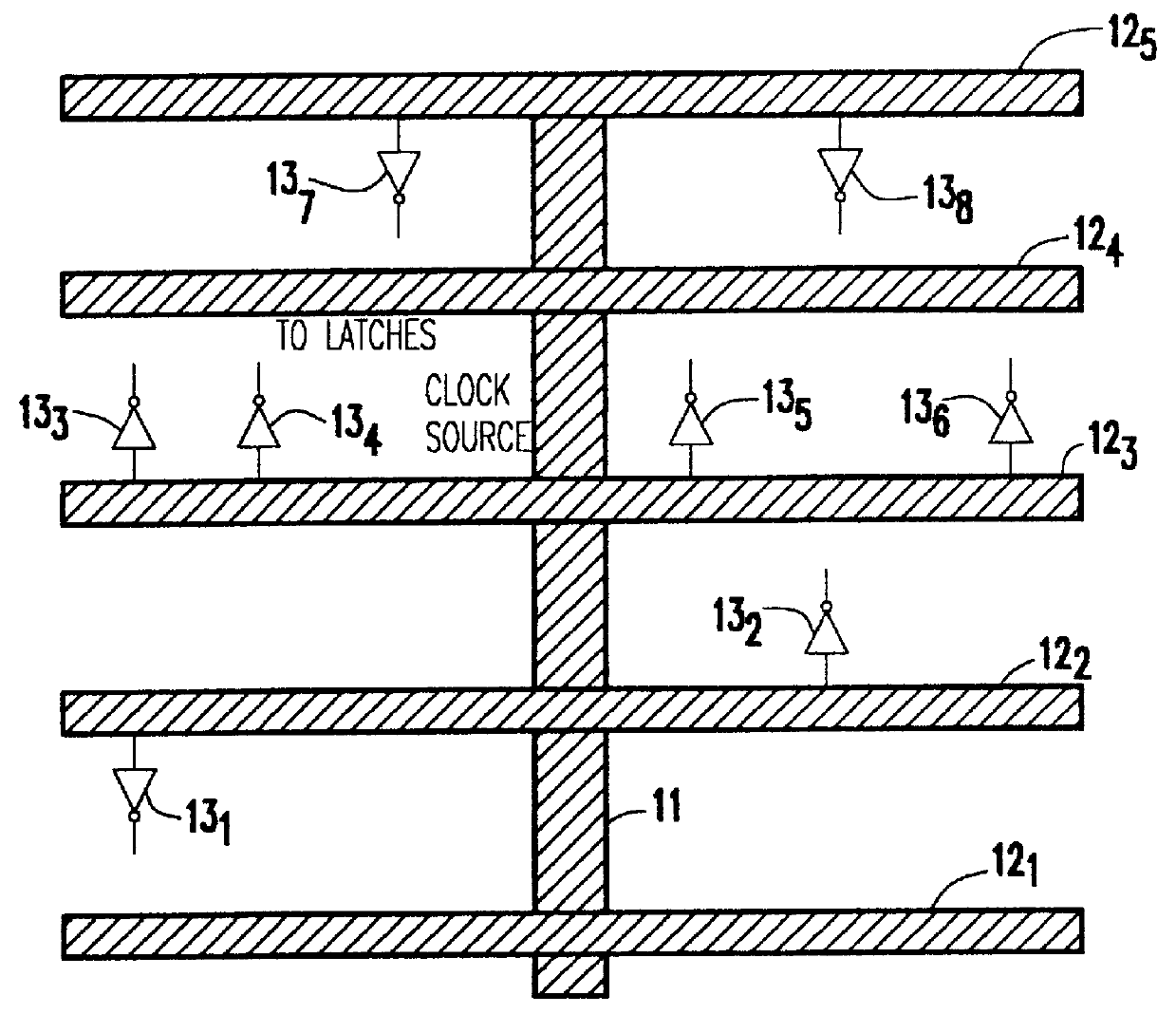

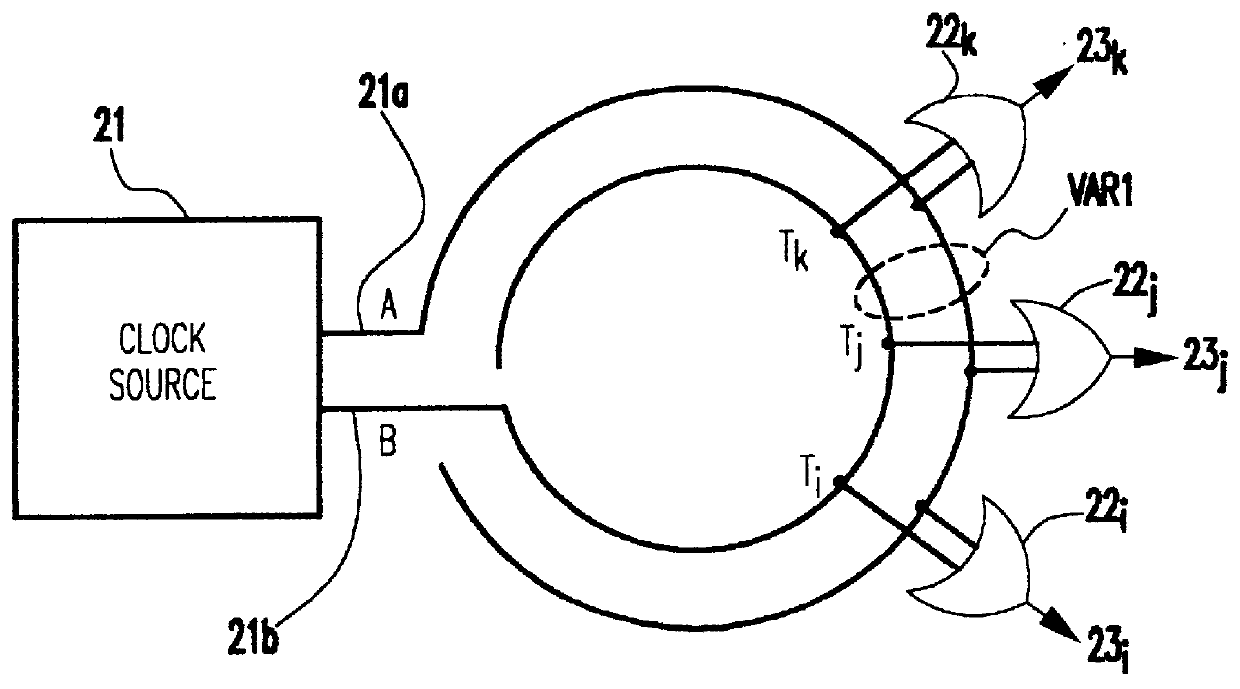

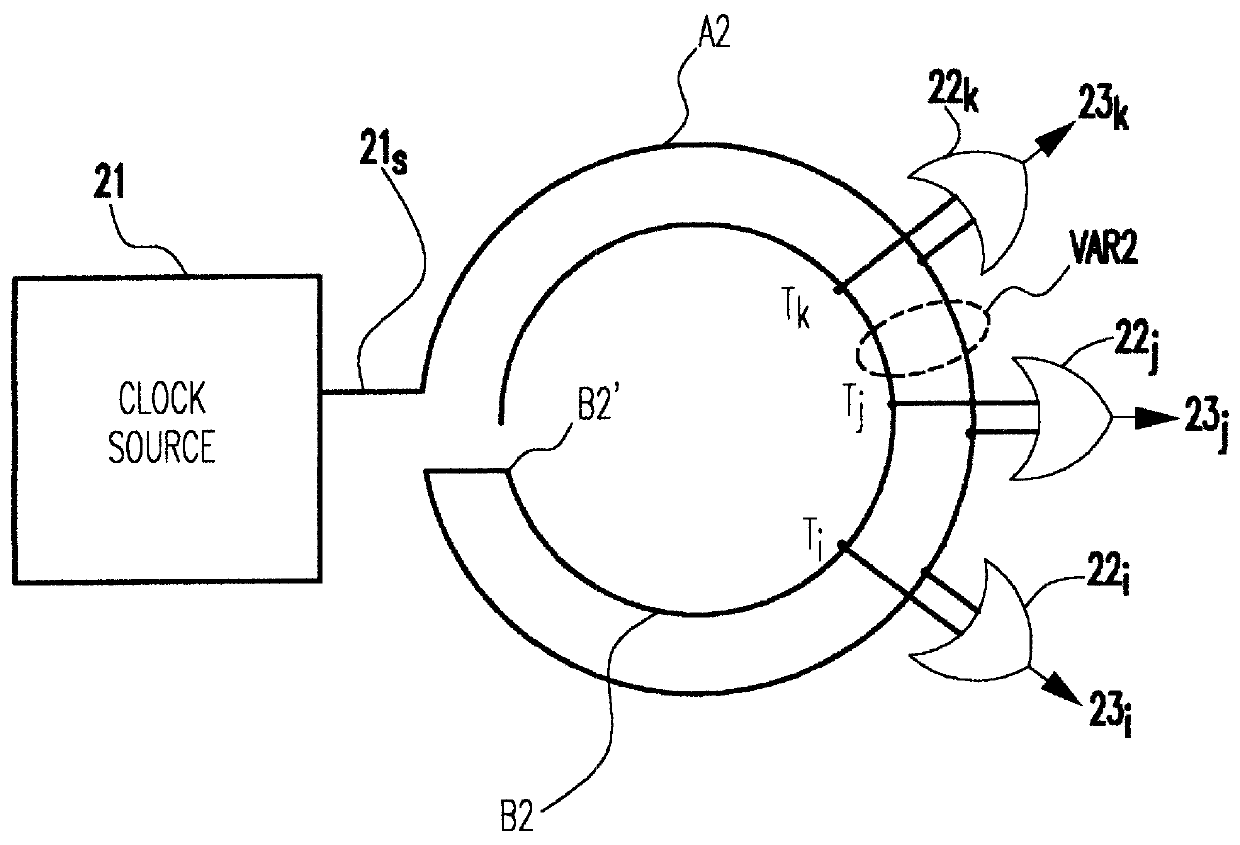

Clock distribution network with dual wire routing

InactiveUS6144224AMinimizing clock skewsModerate power consumptionDelay lines pulse generationSolid-state devicesNOR gateDistribution networks

A new clock distribution network design for VLSI circuits which effectively reduces skew without the area and power penalty associated with prior clock designs. Two wires emanating from the clock in opposite directions or, alternatively, two wires connected in series and running parallel, are used to route clock signals from the clock source to the next routing segment. The next routing segment routes clock signals to the tapping point near the circuit component by two emanated wires from the previous routing segment. Clock signals from the routing segments are fed through two-input NOR gates (alternatively, two-input NAND gates) to the clock pins. The clock signal arrival time is roughly equal to the simultaneous switching gate delay plus the average arrival times from the two paths, which turns out approximately the same across different tapping points, thus minimizing clock skews. Narrow wires may be used for routing, resulting in moderate power consumption.

Owner:IBM CORP

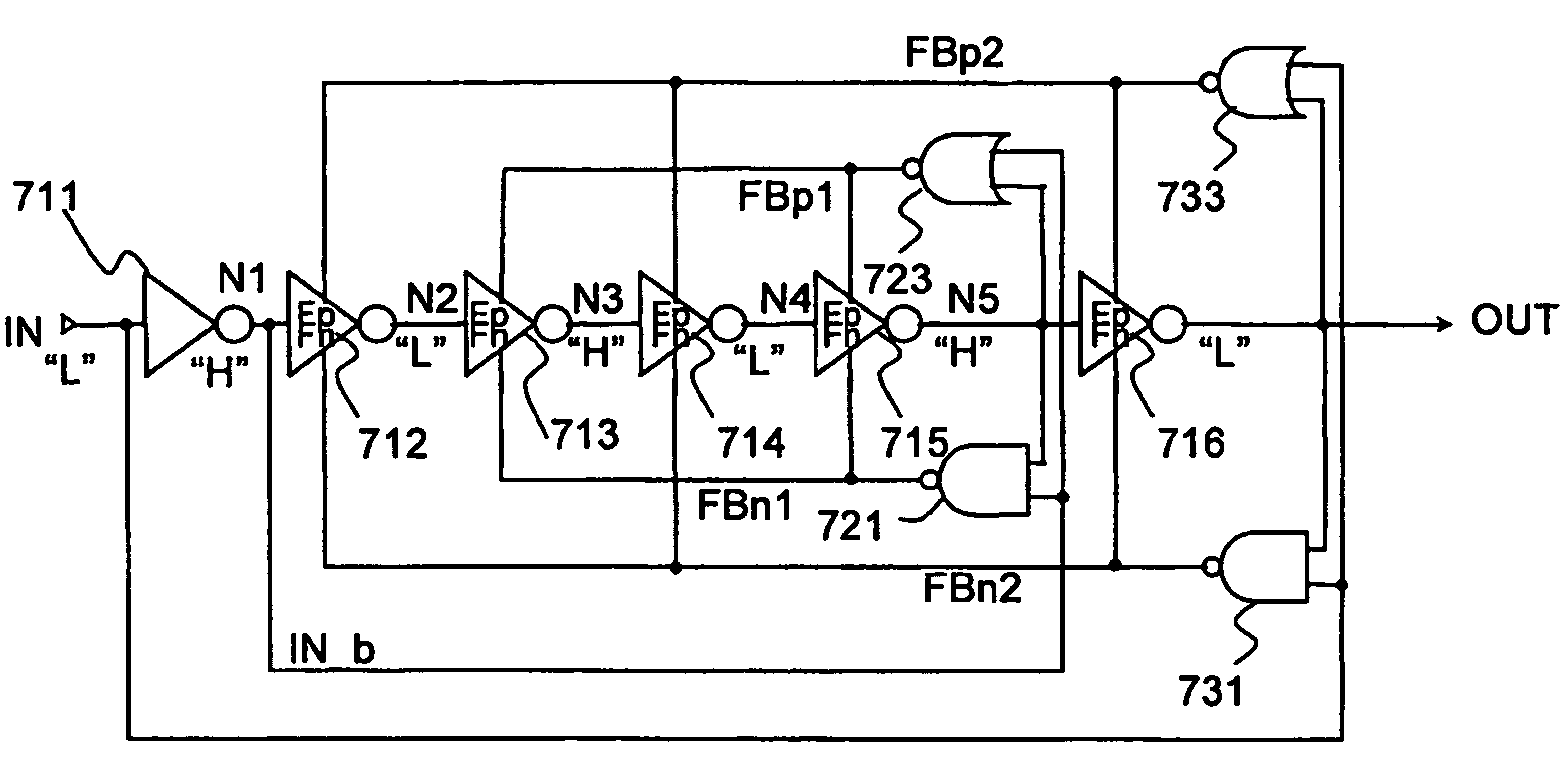

Semiconductor integrated circuit having current leakage reduction scheme

InactiveUS7292061B2Reduce power consumptionIncrease speedTransistorReliability increasing modificationsExclusive orNAND gate

A semiconductor integrated circuit includes a CMOS controlled inverter consisting of series-connected PMOS and NMOS transistors. The source of the NMOS transistor is coupled to a ground line through an additional NMOS transistor for power gating of voltage VSS. The source of the PMOS transistor can be coupled to a power supply line through an additional PMOS transistor for power gating of voltage VDD. The inverter receives an input signal IN and its complementary version that has transitioned earlier than the input signal. In response to the input signal, the inverter produces an output signal. A NAND gate that receives the output signal and the complementary input signal controls the power gating NMOS transistor. A NOR gate that receives the output signal and the complementary input signal controls the power gating PMOS transistor. The power gating to the CMOS inverter is performed by feedback of the output signal and the complementary input signal, with the result that current leakage reduction through the CMOS controlled inverter is achieved. A self leakage reduction with power gating transistors is applicable to another type of logic gates such as NAND, NOR and Exclusive-OR, AND, OR.

Owner:CONVERSANT INTPROP MANAGEMENT INC

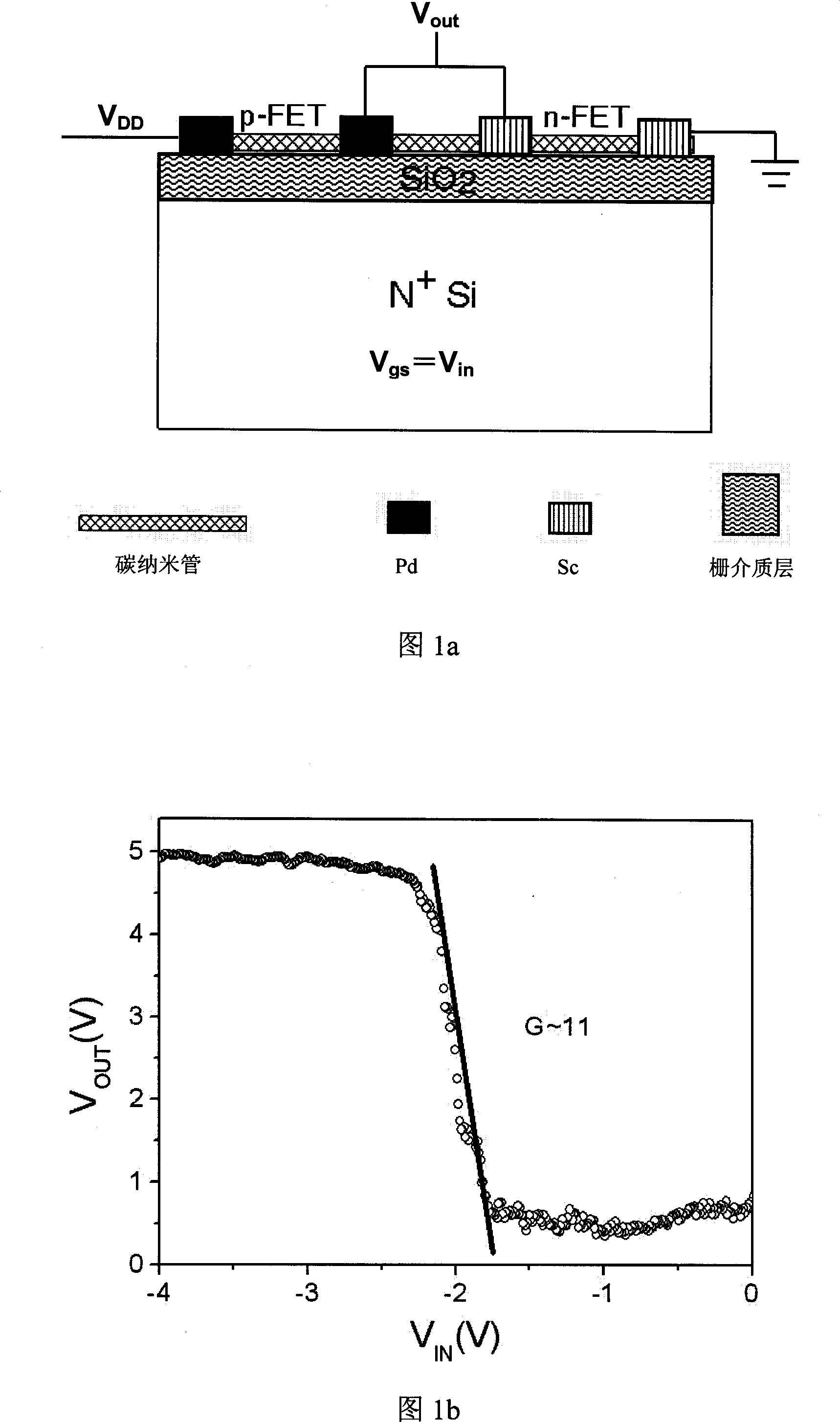

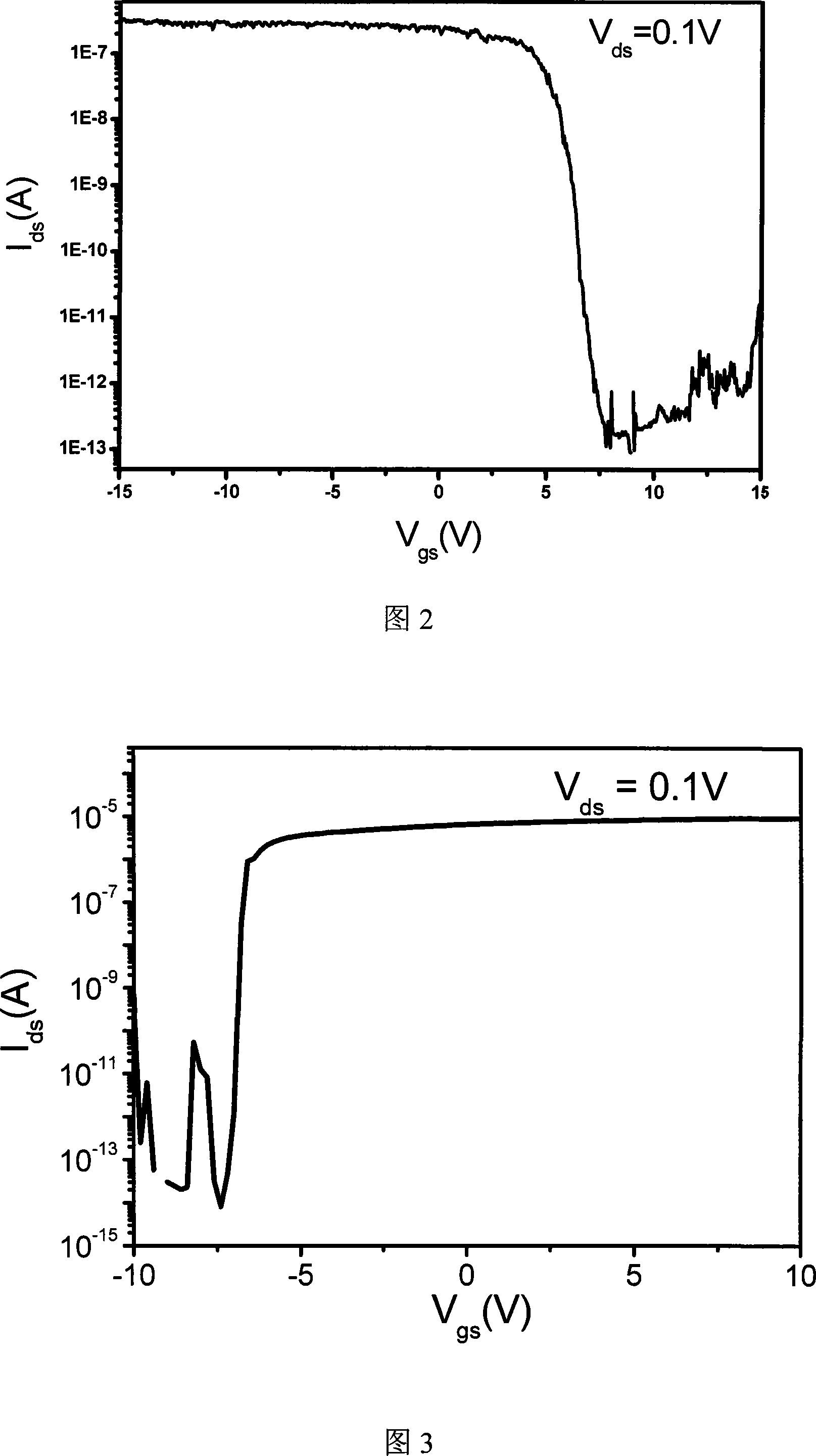

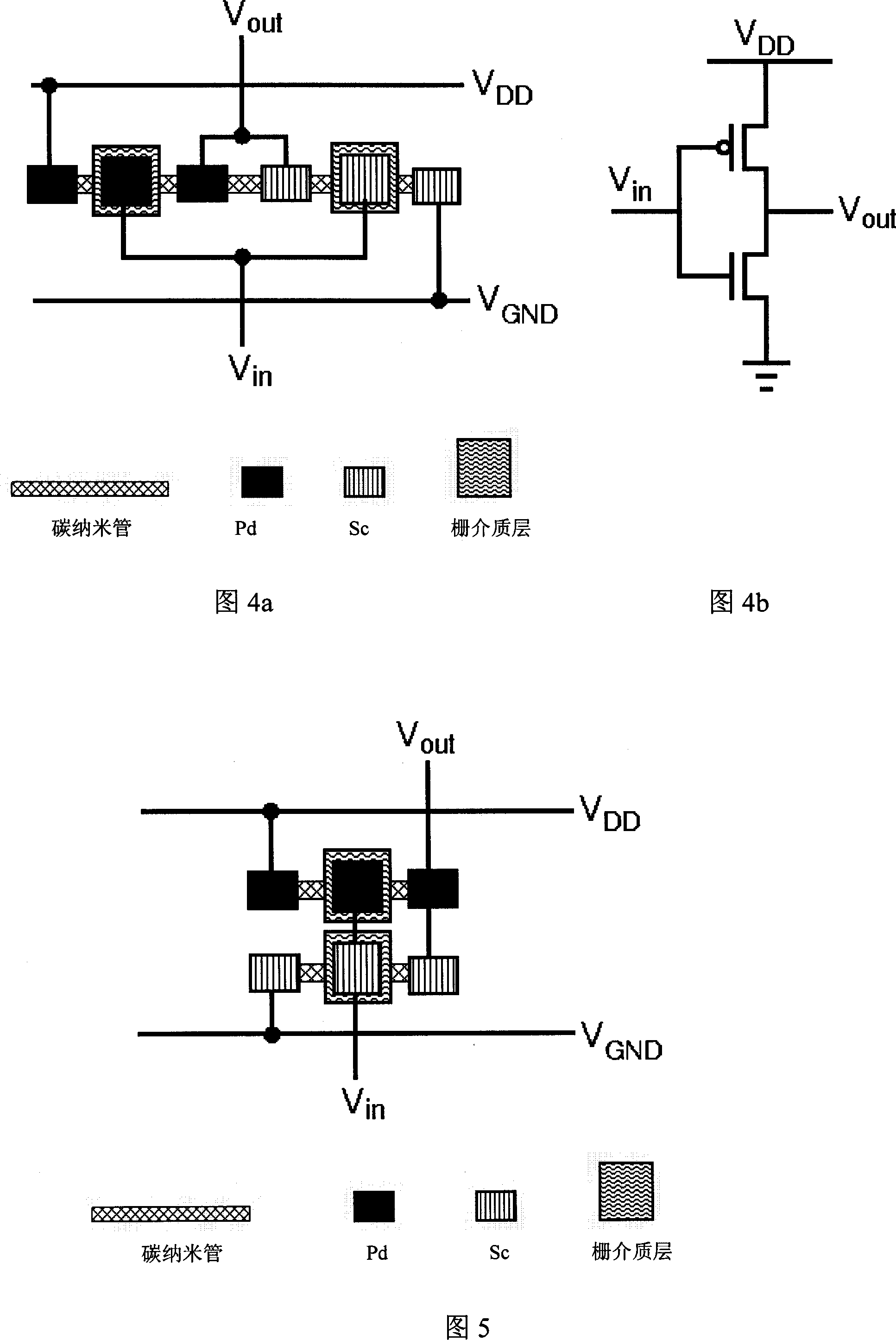

CMOS circuit based on semi-conductor nano material and preparation therefor

ActiveCN101136408AGuaranteed uniformityImprove performanceTransistorSemiconductor/solid-state device manufacturingCMOSValence band

This invention puts forward a simple preparing and integrating method for realizing high performance CMOS circuit not doped on one-dimensional semiconductor nm material, in which, the p-type field effect transistor in the CMOS circuit is realized by controlling a metal electrode of high power function to exchange electrons with the valence band of carbon nm tube or other one-dimensional nm materials, the n-type field effect transistor is realized by controlling a metal electrode of low power function to exchange electrons with the conduction band of a carbon nm tube or other one-dimensional semiconductor nm materials directly, besides, this invention applies a back grid and a top grid to realize a basic logic circuit or even more complicated logic circuit of inverters, AND-NOT gates, NOR gates and full-adders.

Owner:PEKING UNIV

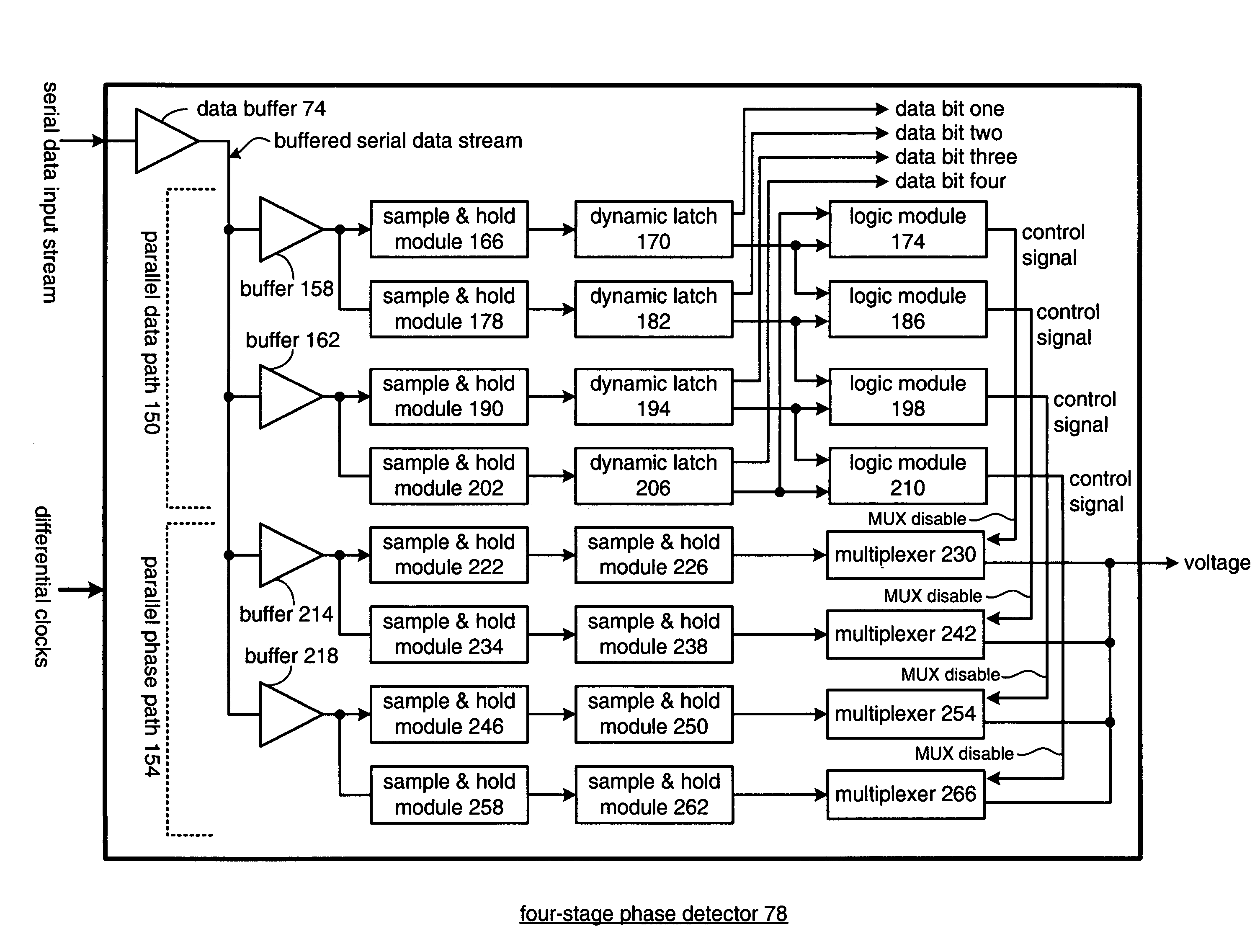

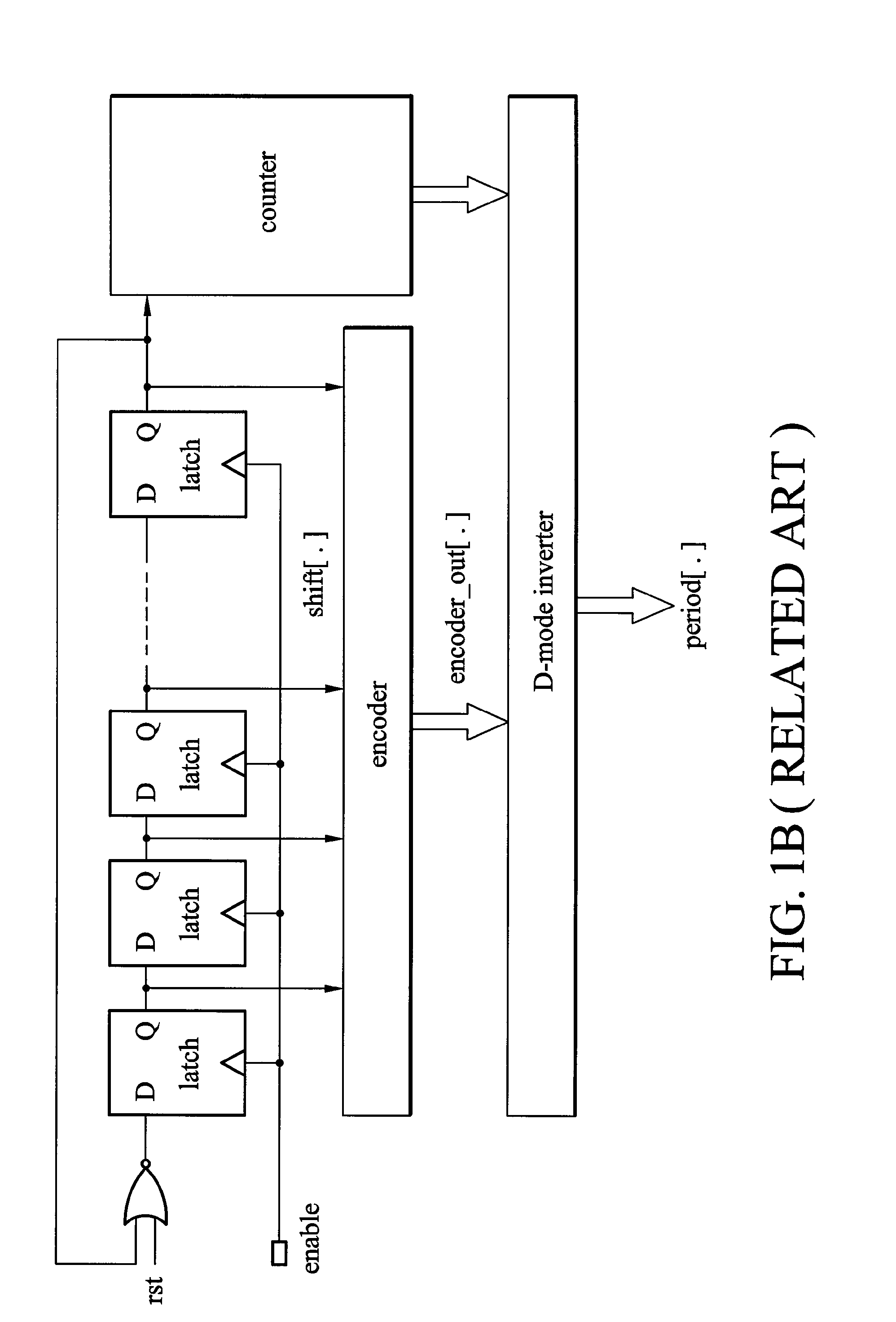

Multi-stage phase detector

ActiveUS7466787B1Reduce operating rateReduce loadPulse automatic controlOscillations comparator circuitsPhase detectorControl signal

A multi-stage phase detector (four stages in one described embodiment) comprises a plurality of data paths and phase paths that are buffered from a received serial data input stream to reduce loading. Each data path recovers a data bit and further functions as a transition detector to detect consecutive data bits having similar logic states. An exclusive NOR gate in the data path produces a control signal to disable a multiplexer in the phase path when two data bits have similar logic states. Each phase path produces a sample of a serial data input stream and produces the sample to a multiplexer for coupling to a transconductance module. The multiplexer output is coupled to or decoupled from the transconductance module by the control signal from the data path to maintain phase-lock.

Owner:XILINX INC

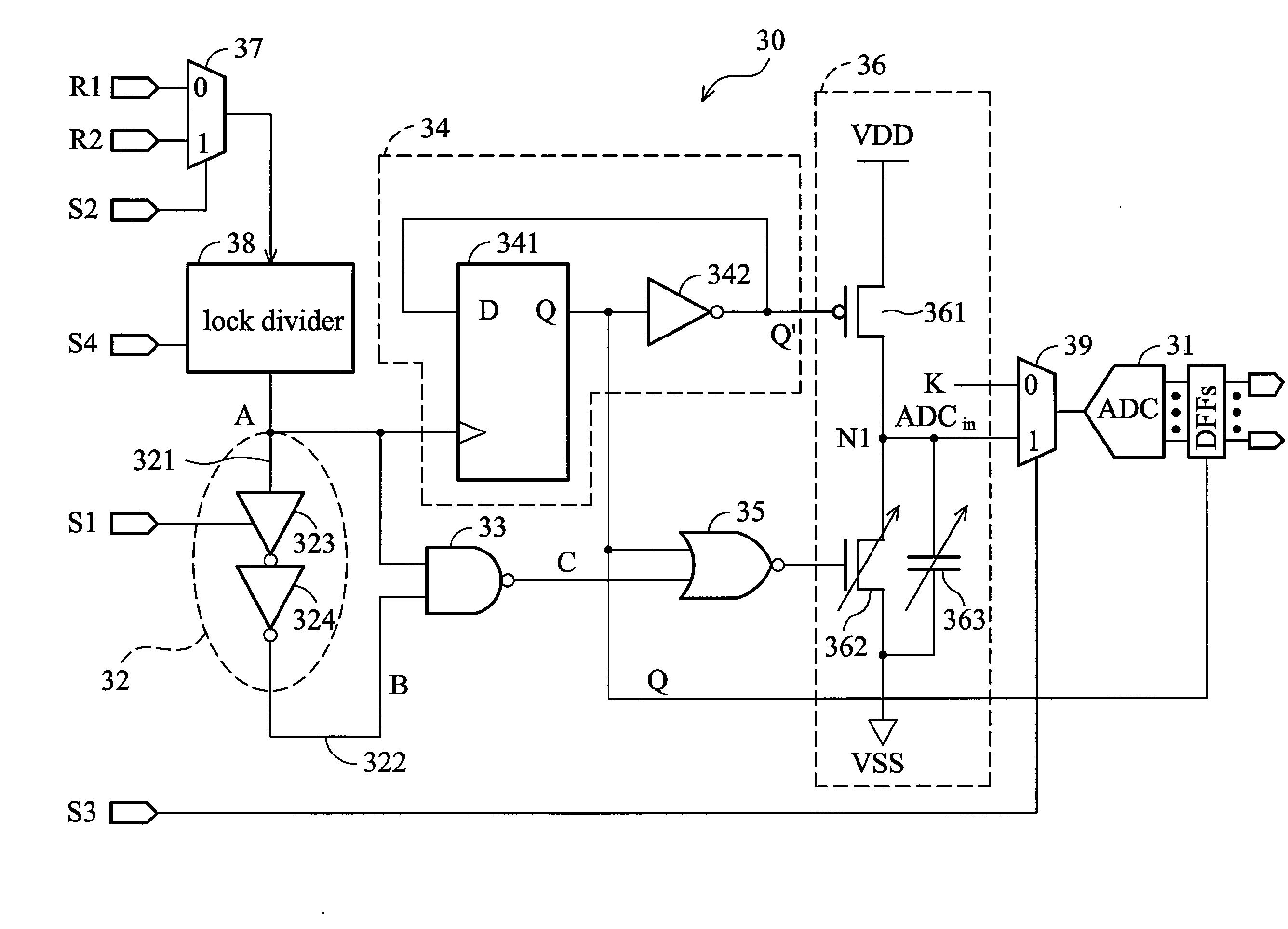

Built-in self test circuit for analog-to-digital converter and phase lock loop and the testing methods thereof

InactiveUS20080125990A1High measurement accuracyElectric signal transmission systemsNoise figure or signal-to-noise ratio measurementNOR gateA d converter

A BIST circuit for testing both an analog-to-digital converter and a phase lock loop includes a controllable delay circuit, a NAND gate, a dividing circuit, a NOR gate and a charge / discharge circuit. The invention reduces the period of the signal under test, converts its pulse width to voltage and measures the output via an ADC. The clock jitter becomes sensitive through a delay cancellation method, thus, the accuracy is improved. The invention further comprises all testing procedure for period jitters of a PLL and static characteristics of an ADC. The test error caused by process variation can be corrected by a controllable delay circuit such that the error determination of the test result is prevented.

Owner:FARADAY TECH CORP

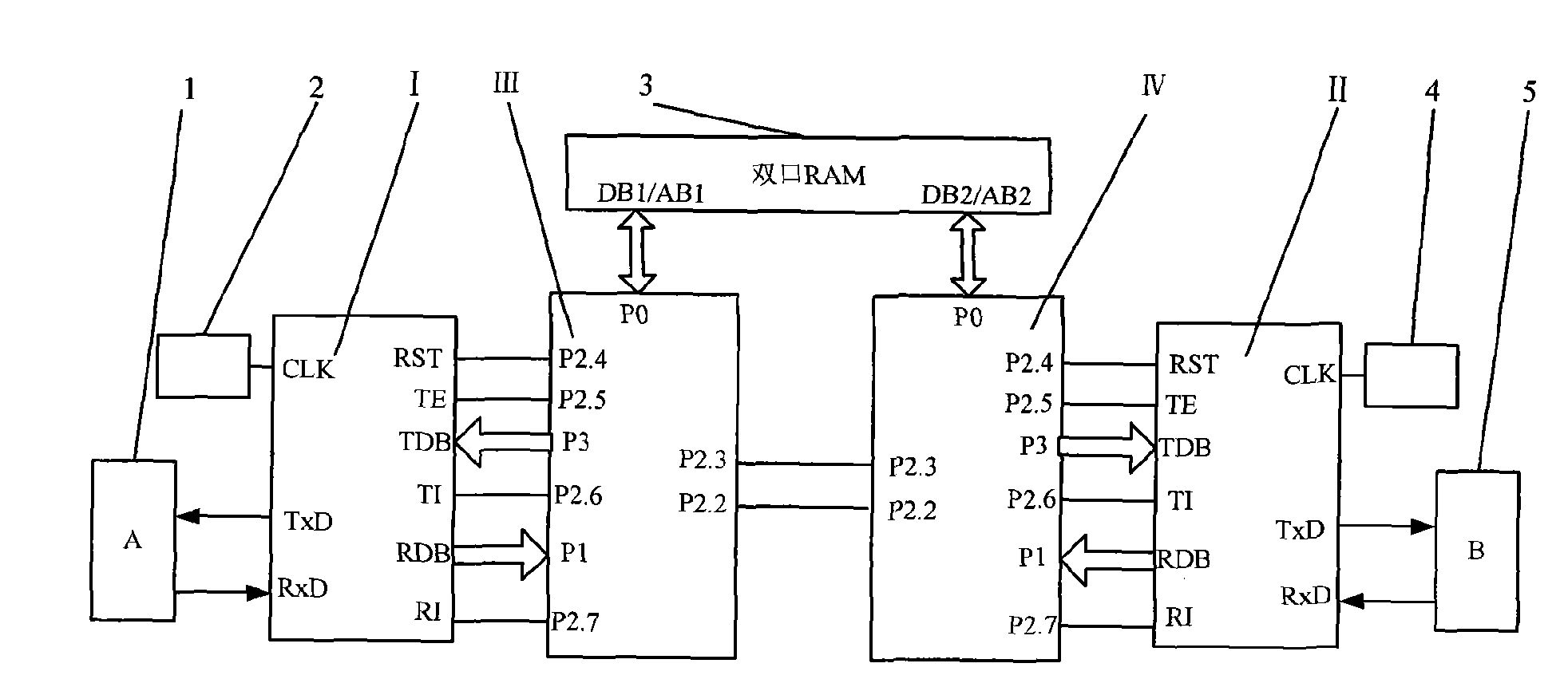

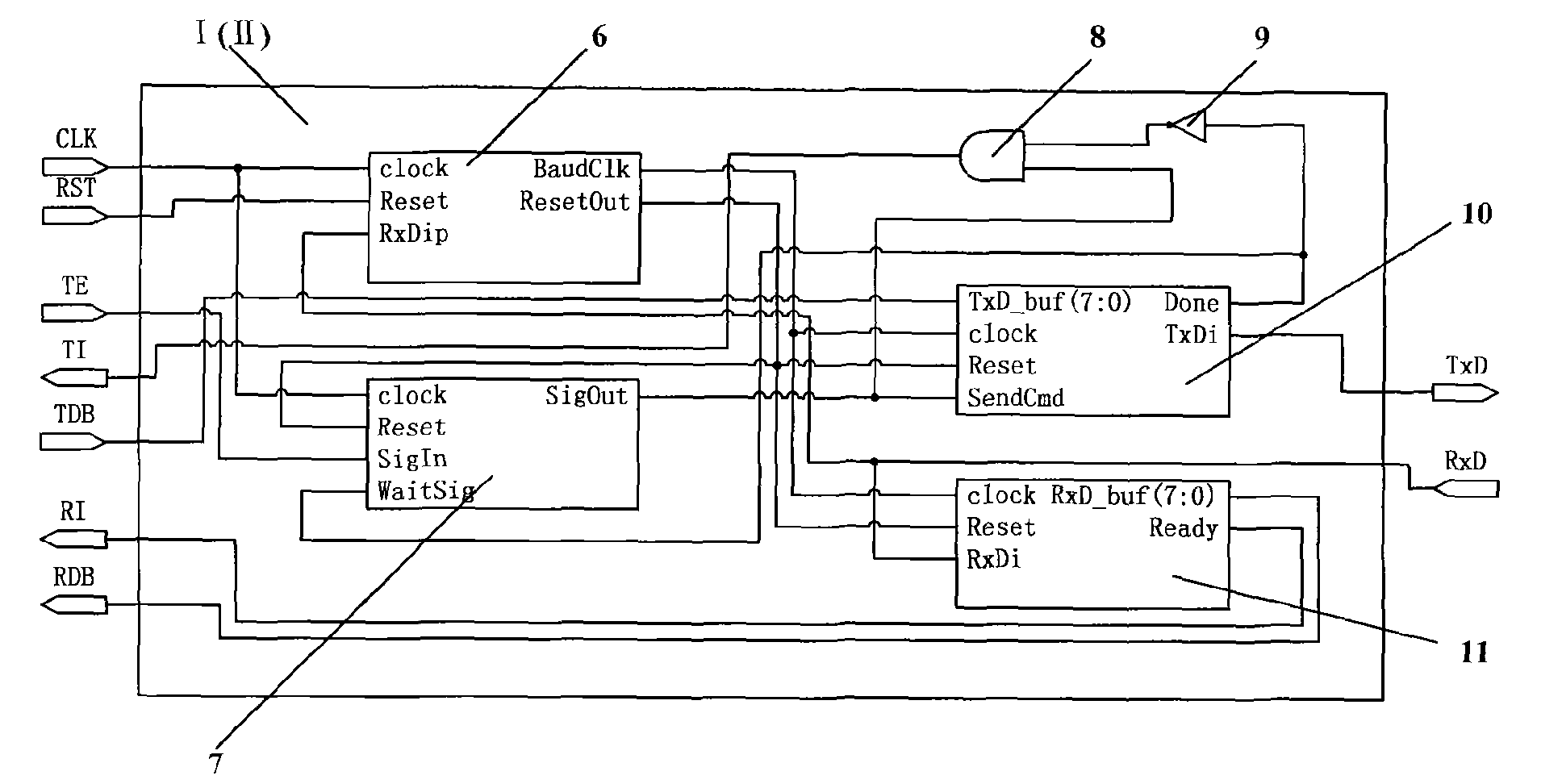

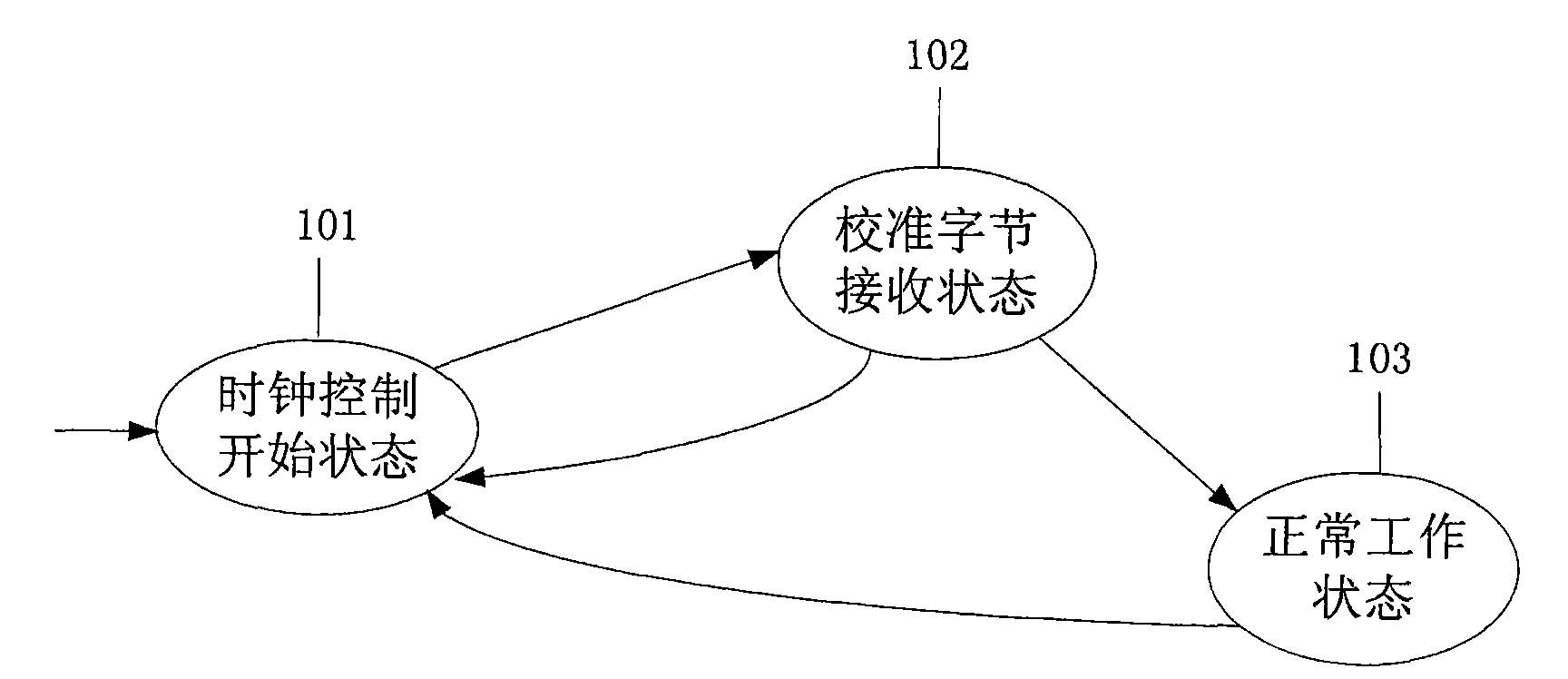

Manufacturing method of baud rate self-adaptive serial communication repeater

InactiveCN101551786ANovel structureHigh communication speedDigital computer detailsSpecial data processing applicationsMicrocontrollerData treatment

The invention provides a manufacturing method of a baud rate self-adaptive serial communication repeater, belonging to the field of electronic communication, and particularly relating to the manufacturing method of the baud rate self-adaptive serial communication repeater. The method adopts a data processing mode of connecting a first microcontroller and a second microcontroller with a double-port RAM so as to connect the first microcontroller with a first baud rate self-adaptive serial communication device through a signal line, and connect the second microcontroller with a second baud rate self-adaptive serial communication device through the signal line. The interior modules of the first baud rate self-adaptive serial communication device and the second baud rate adaptive serial communication device comprises a baud rate self-adaptive generator, a signal converter, a parallel-serial data receiving shifter, a serial-parallel data sending shifter, logic and gate and logic and nor gate which are all manufactured by adopting programming devices. The repeater has the characteristics of novel structure, stable communication, high speed, automatic recognition of data speed on a bus, double-port RAM as a shared memory, flexible and convenient interface and easy control; in addition, the repeater has good maintainability and expansibility and low cost.

Owner:DALIAN UNIV OF TECH