Patents

Literature

391 results about "Fan-out" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital electronics, the fan-out is the number of gate inputs that the output of a logic gate drives. In most designs, logic gates are connected to form more complex circuits. While no logic gate input can be fed by more than one output, it is common for one output to be connected to several inputs. The technology used to implement logic gates usually allows a certain number of gate inputs to be wired directly together without additional interfacing circuitry. The maximum fan-out of an output measures its load-driving capability: it is the greatest number of inputs of gates of the same type to which the output can be safely connected.

Intelligent probe card architecture

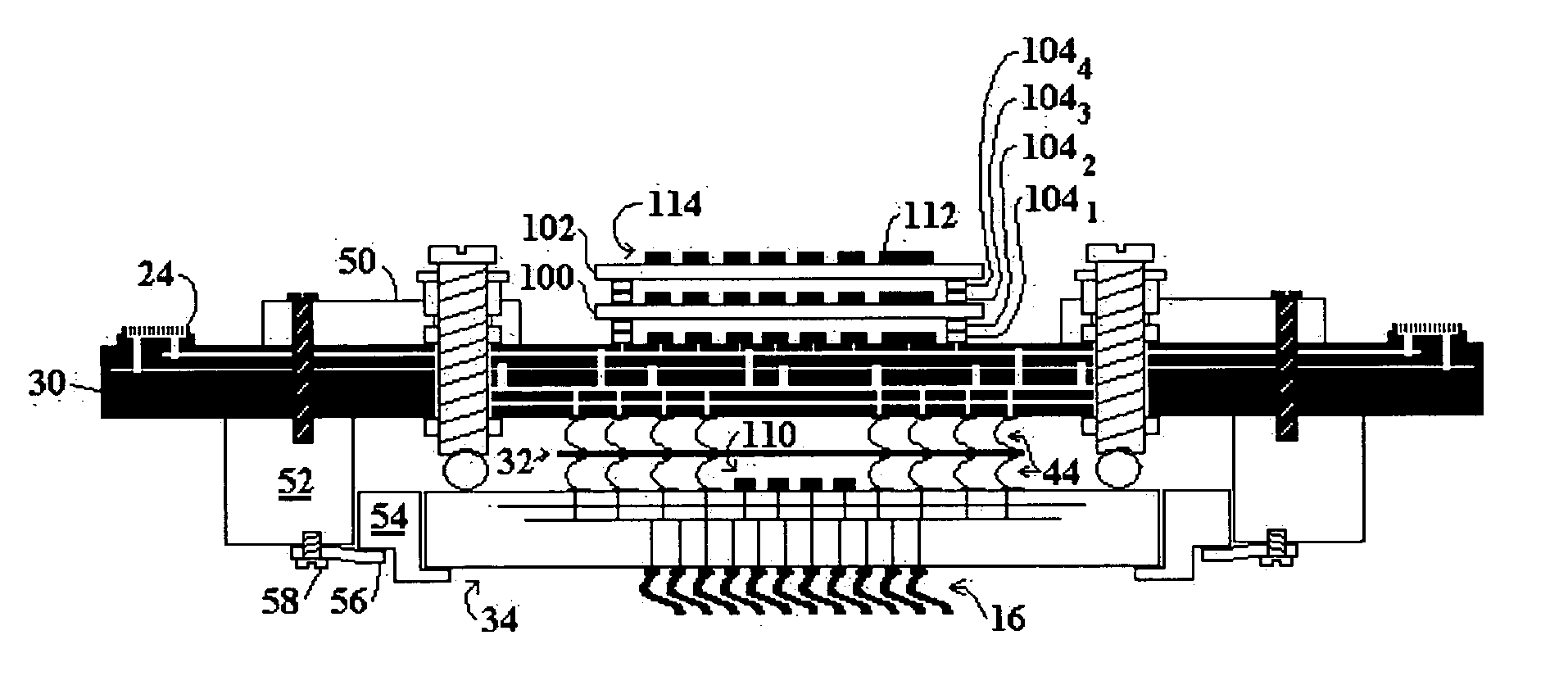

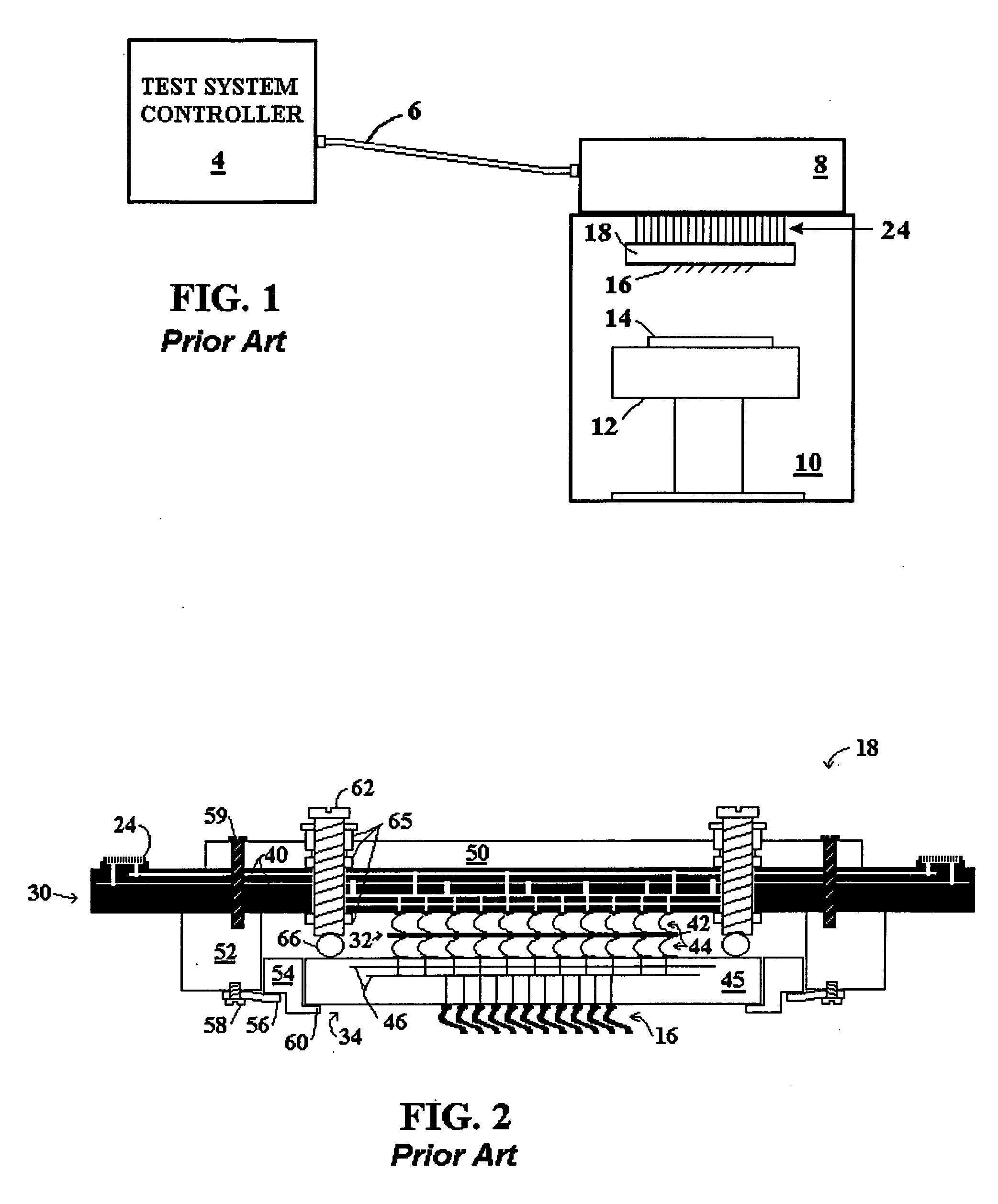

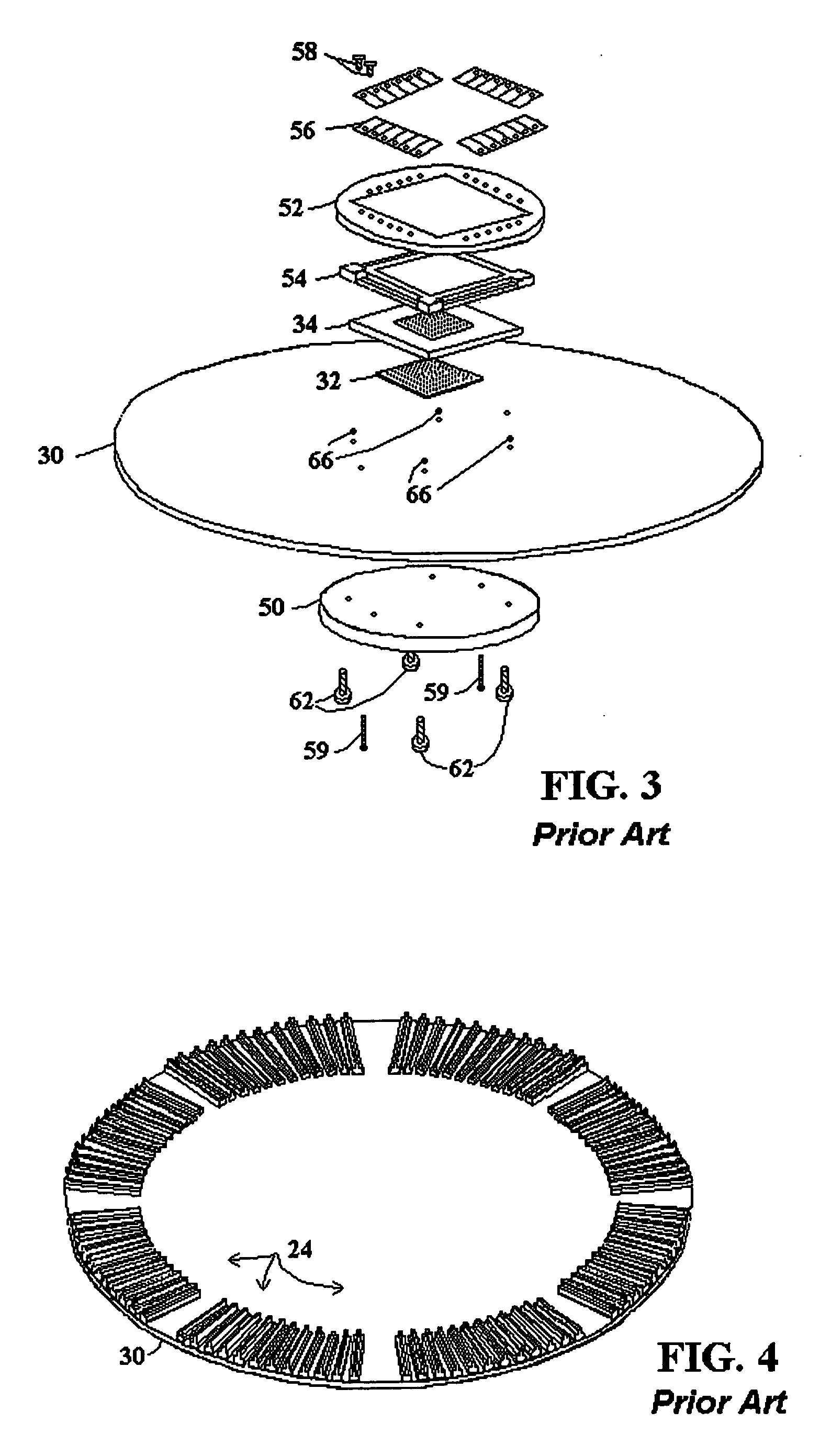

ActiveUS20050237073A1Digital circuit testingOverload protection arrangementsElectrical resistance and conductanceProbe card

A probe card for a wafer test system is provided with a number of on board features enabling fan out of a test system controller channel to test multiple DUTs on a wafer, while limiting undesirable effects of fan out on test results. On board features of the probe card include one or more of the following: (a) DUT signal isolation provided by placing resistors in series with each DUT input to isolate failed DUTs; (b) DUT power isolation provided by switches, current limiters, or regulators in series with each DUT power pin to isolate the power supply from failed DUTs; (c) self test provided using an on board micro-controller or FPGA; (d) stacked daughter cards provided as part of the probe card to accommodate the additional on board test circuitry; and (e) use of a interface bus between a base PCB and daughter cards of the probe card, or the test system controller to minimize the number of interface wires between the base PCB and daughter cards or between the base PCB and the test system controller.

Owner:FORMFACTOR INC

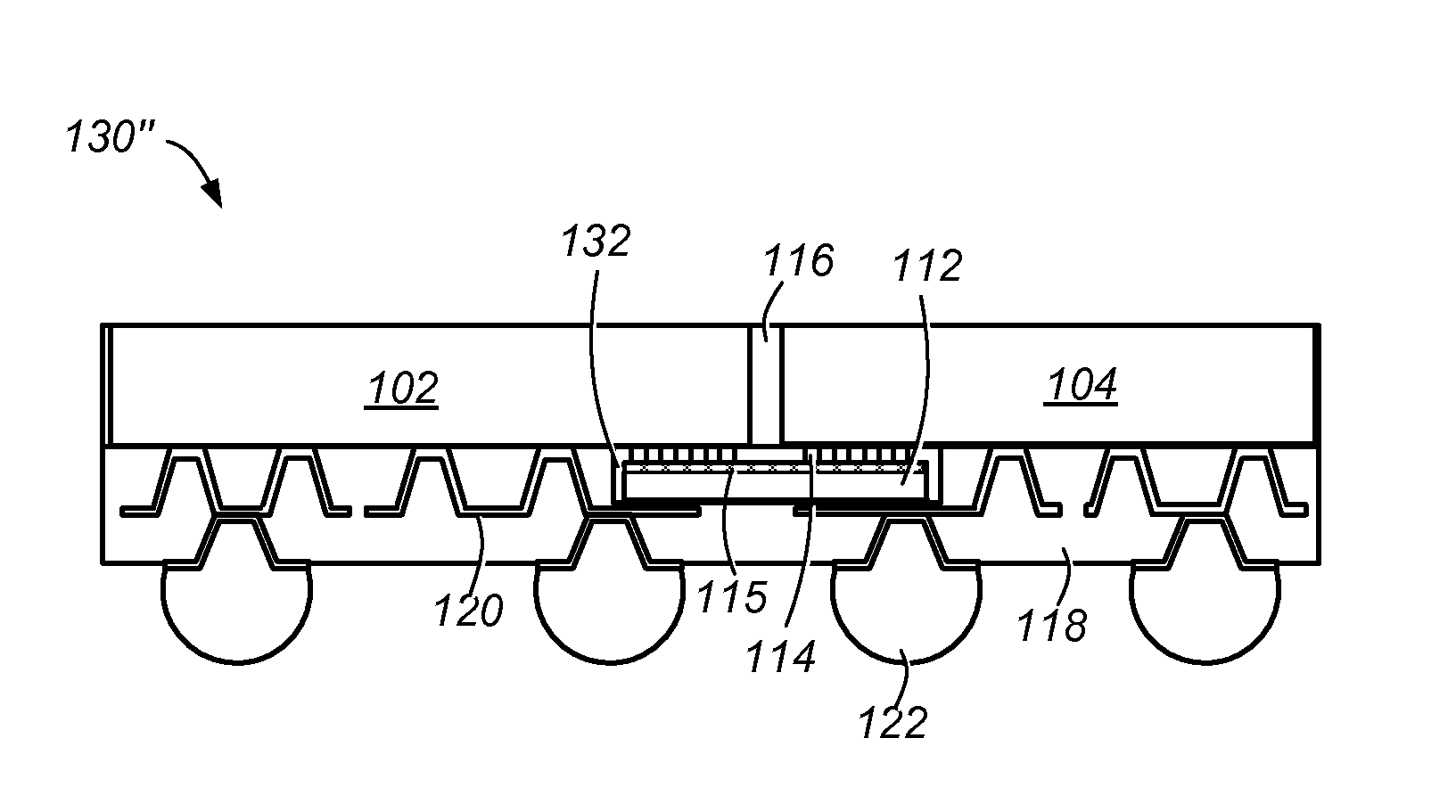

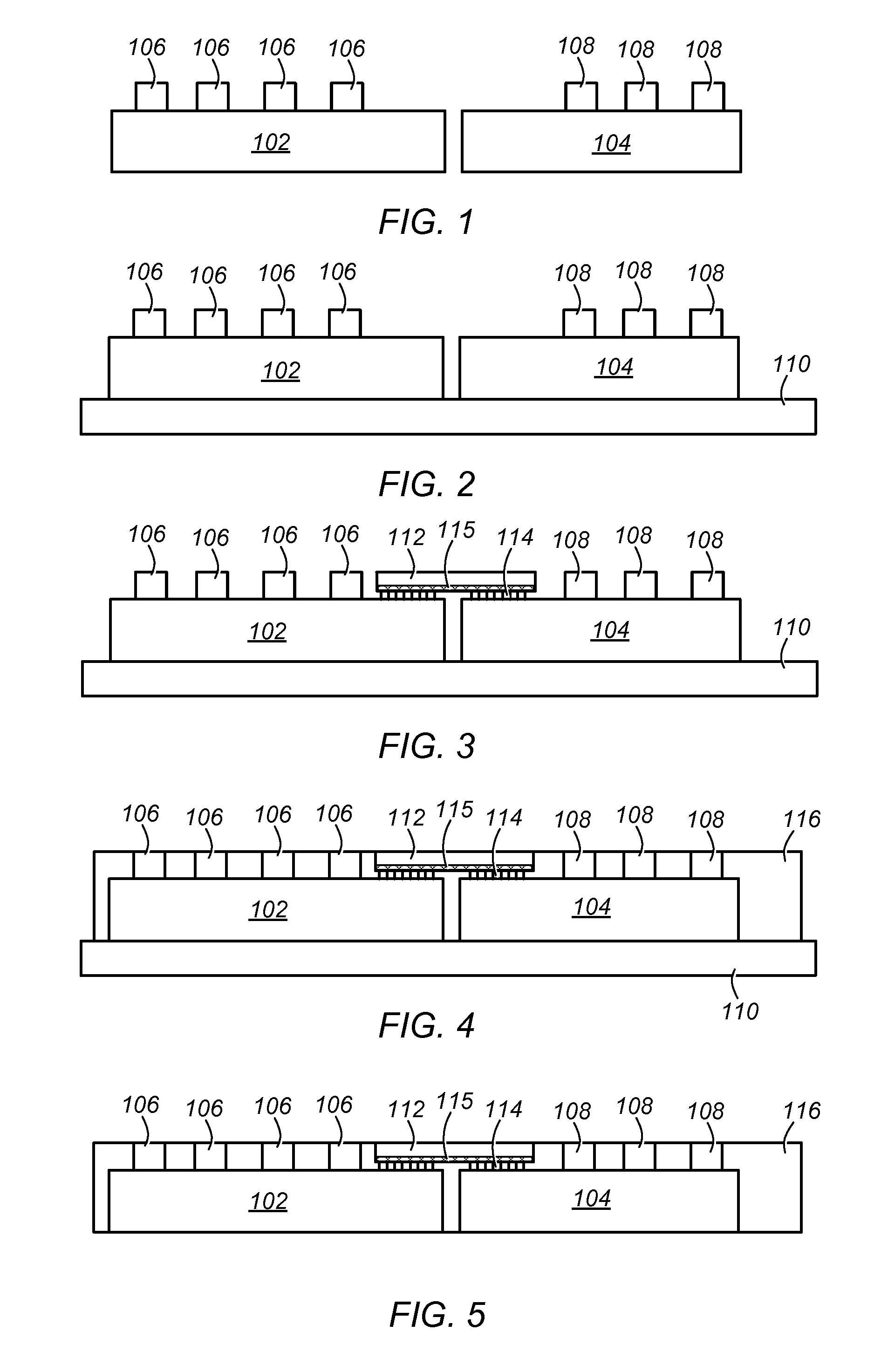

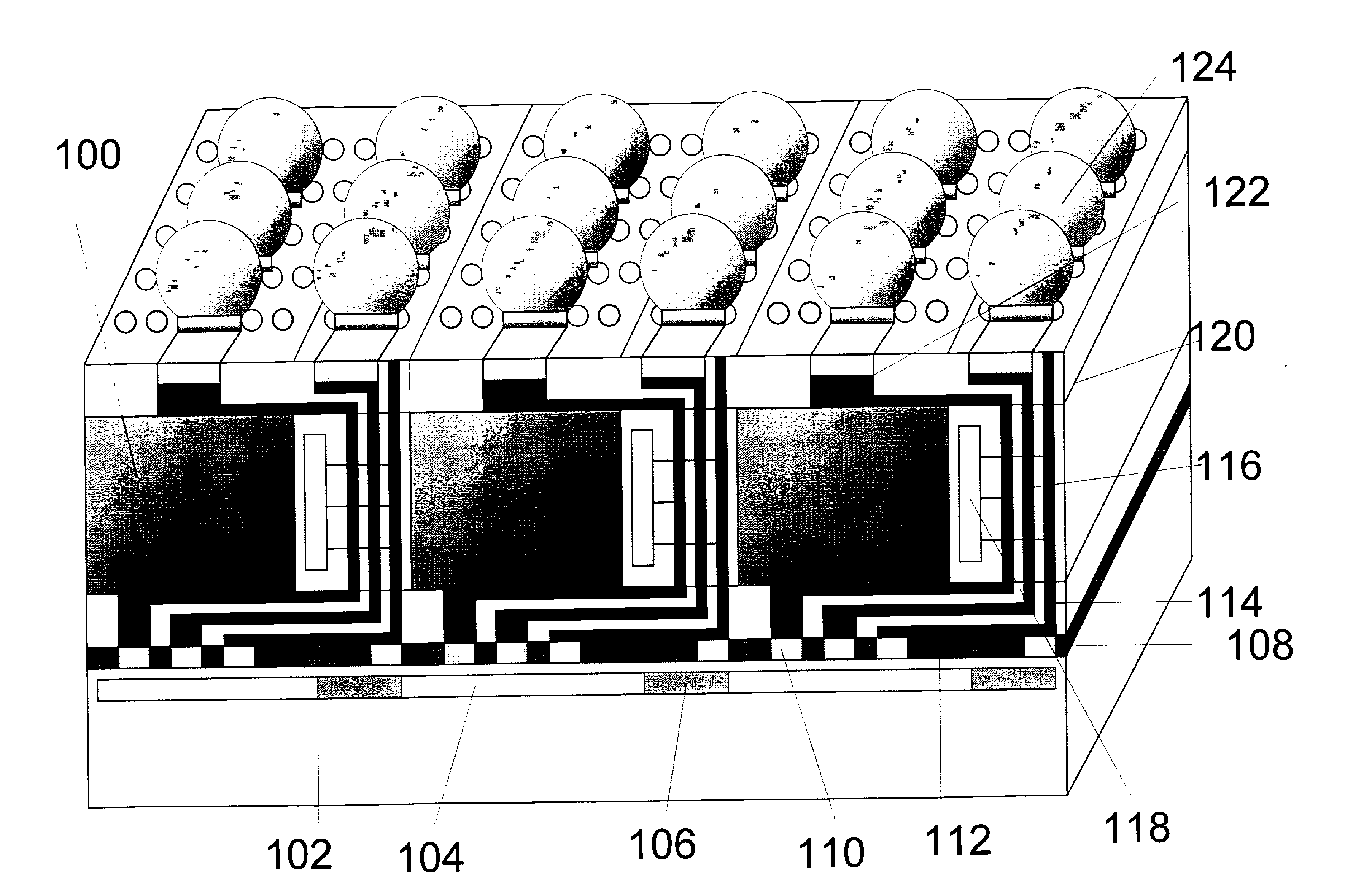

Integrated structures and methods of fabrication thereof with fan-out metallization on a chips-first chip layer

InactiveUS20080315391A1Printed circuit assemblingCross-talk/noise/interference reductionDielectricContact pad

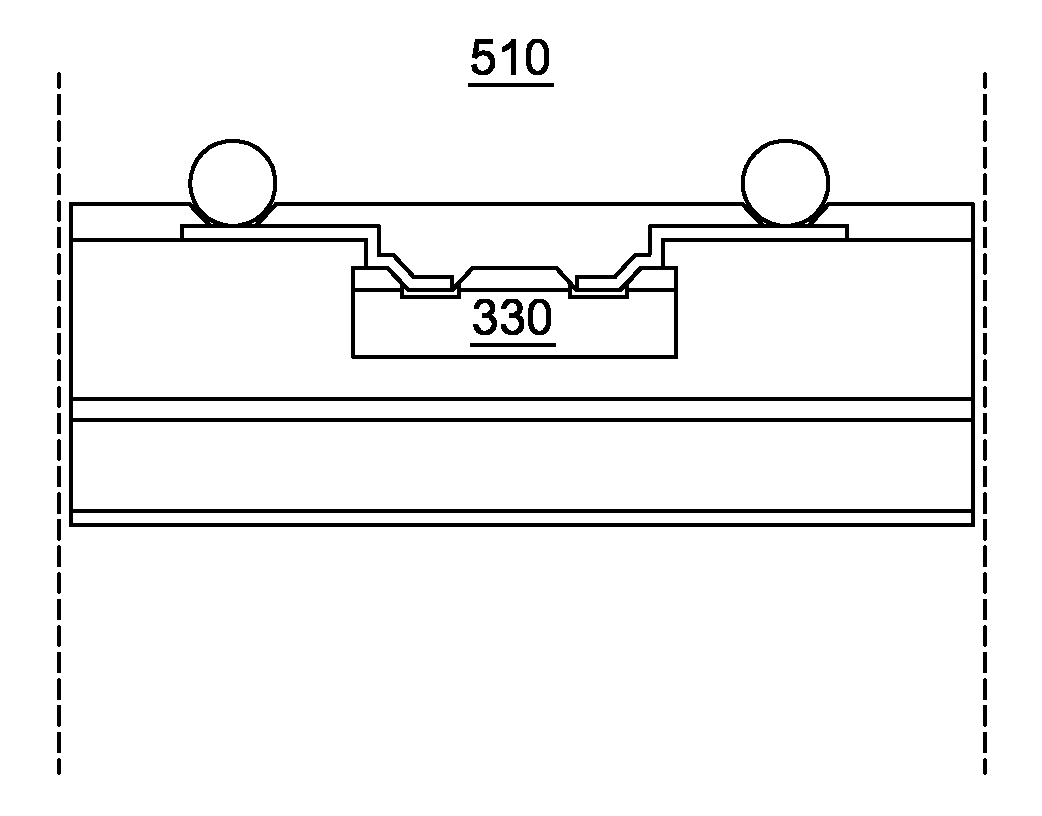

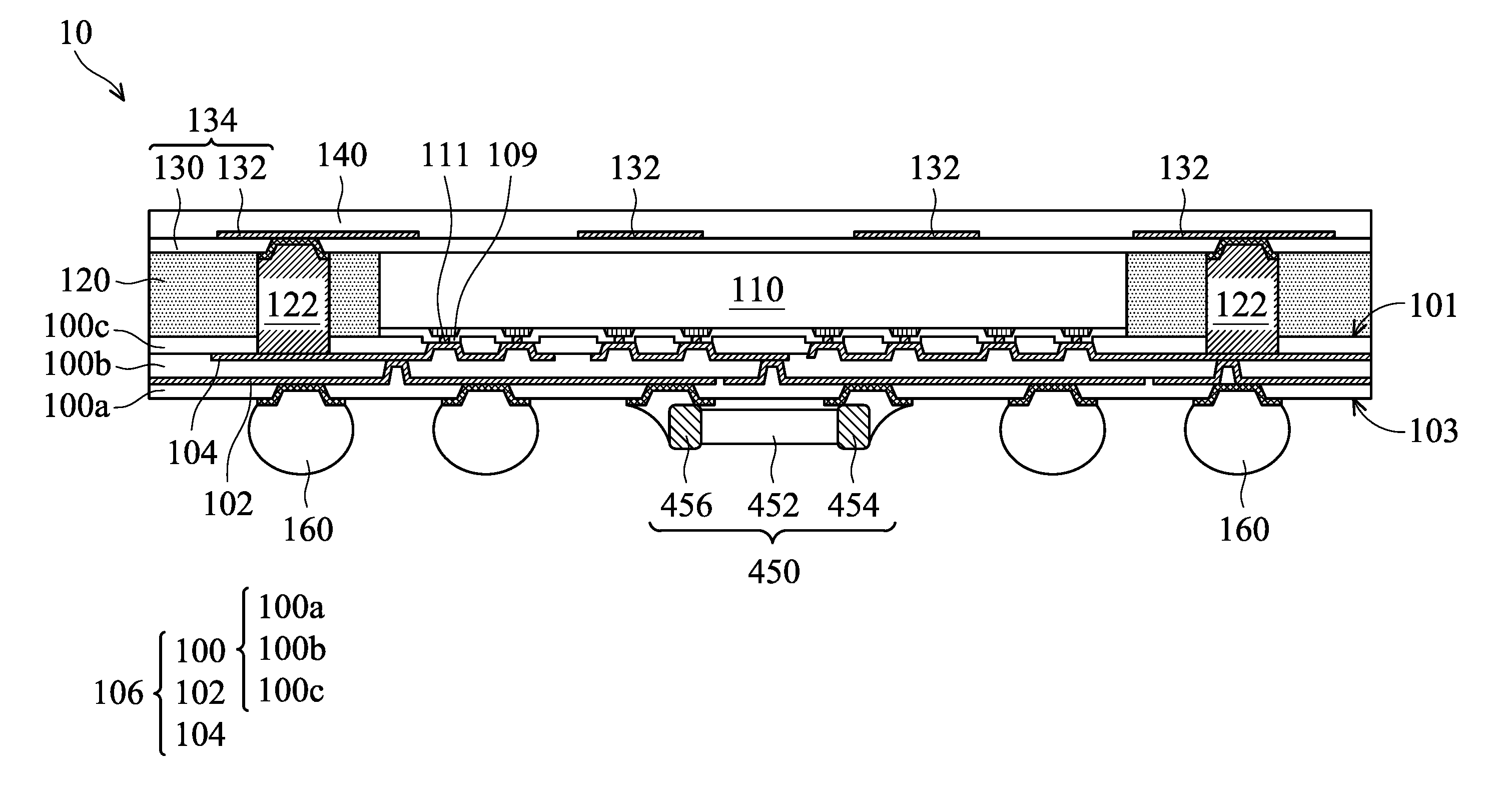

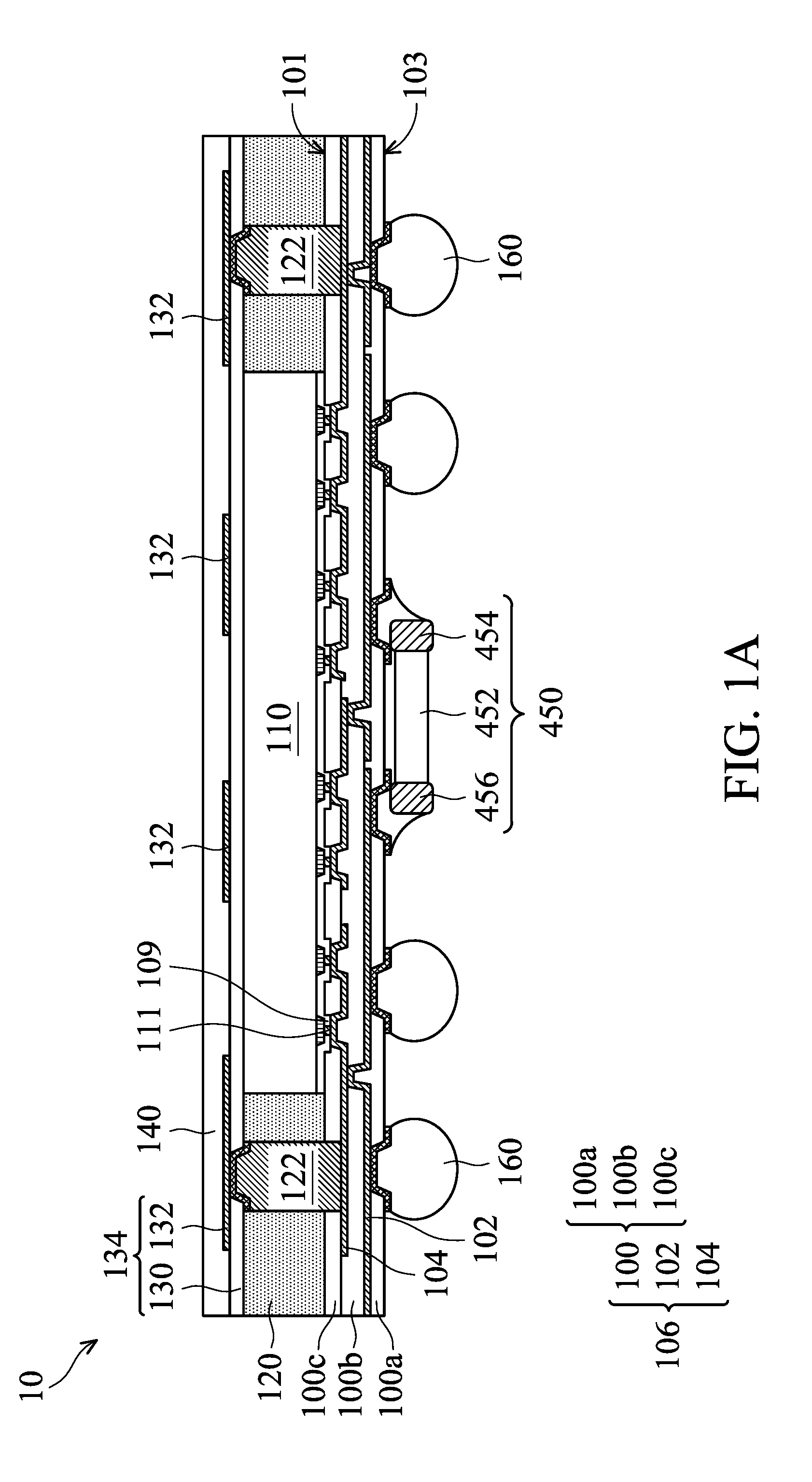

Electronic modules and methods of fabrication are provided implementing a first metallization level directly on a chips-first chip layer. The chips-first layer includes chips, each with a pad mask over an upper surface and openings to expose chip contact pads. Structural dielectric material surrounds and physically contacts the side surfaces of the chips, and has an upper surface which is parallel to an upper surface of the chips. A metallization layer is disposed over the front surface of the chips-first layer, residing at least partially on the pad masks of the chips, and extending over one or more edges of the chips. Together, the pad masks of the chips, and the structural dielectric material electrically isolate the metallization layer from the edges of the chips, and from one or more electrical structures of the chips in the chips-first layer.

Owner:EPIC TECH INC

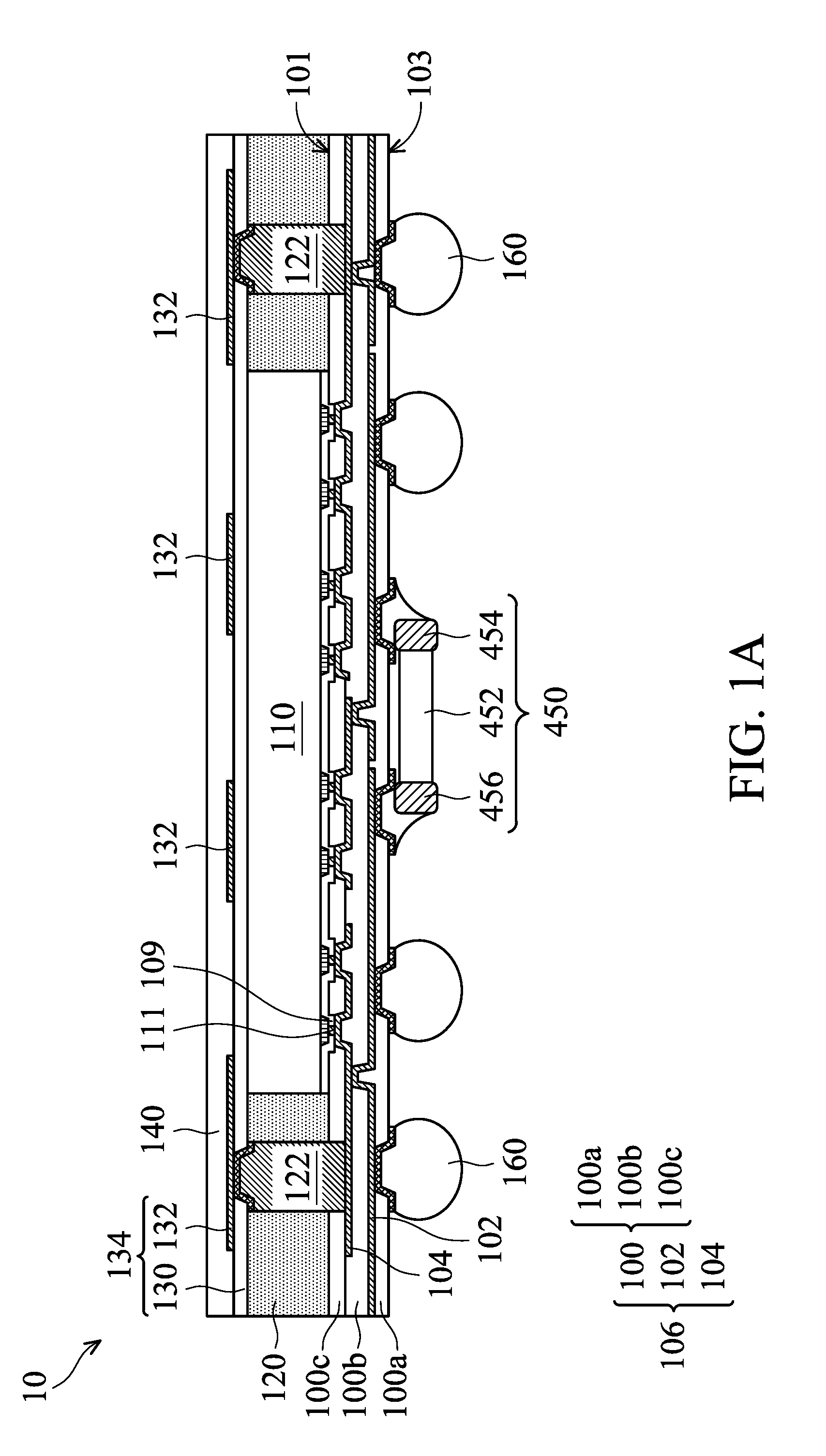

Fan-out package structure including antenna

InactiveUS20170040266A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

The invention provides a semiconductor package assembly. The semiconductor package assembly includes a first semiconductor package including a first redistribution layer (RDL) structure having a first surface and a second surface opposite to the first substrate. The first RDL structure includes a plurality of first conductive traces close to the first surface of the first RDL structure. An antenna pattern is disposed close to the second surface of the first RDL structure. A first semiconductor die is disposed on the first surface of the first RDL structure and electrically coupled to the first RDL structure. A plurality of conductive structures is disposed on the first surface of the first RDL structure and electrically coupled to the first RDL structure. The plurality of conductive structures is spaced apart from the antenna pattern through the plurality of first conductive traces of the first RDL structure.

Owner:MEDIATEK INC

Fan-out package structure including antenna

InactiveUS20160329299A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

A semiconductor package structure including a first semiconductor package is provided. The first semiconductor package includes a first semiconductor package including a first redistribution layer (RDL) structure having a first surface and a second surface opposite thereto. A first semiconductor die and a first molding compound that surrounds the first semiconductor die are disposed on the first surface of the first RDL structure. An IMD structure having a conductive layer with an antenna pattern or a conductive shielding layer is disposed on the first molding compound and the first semiconductor die.

Owner:MEDIATEK INC

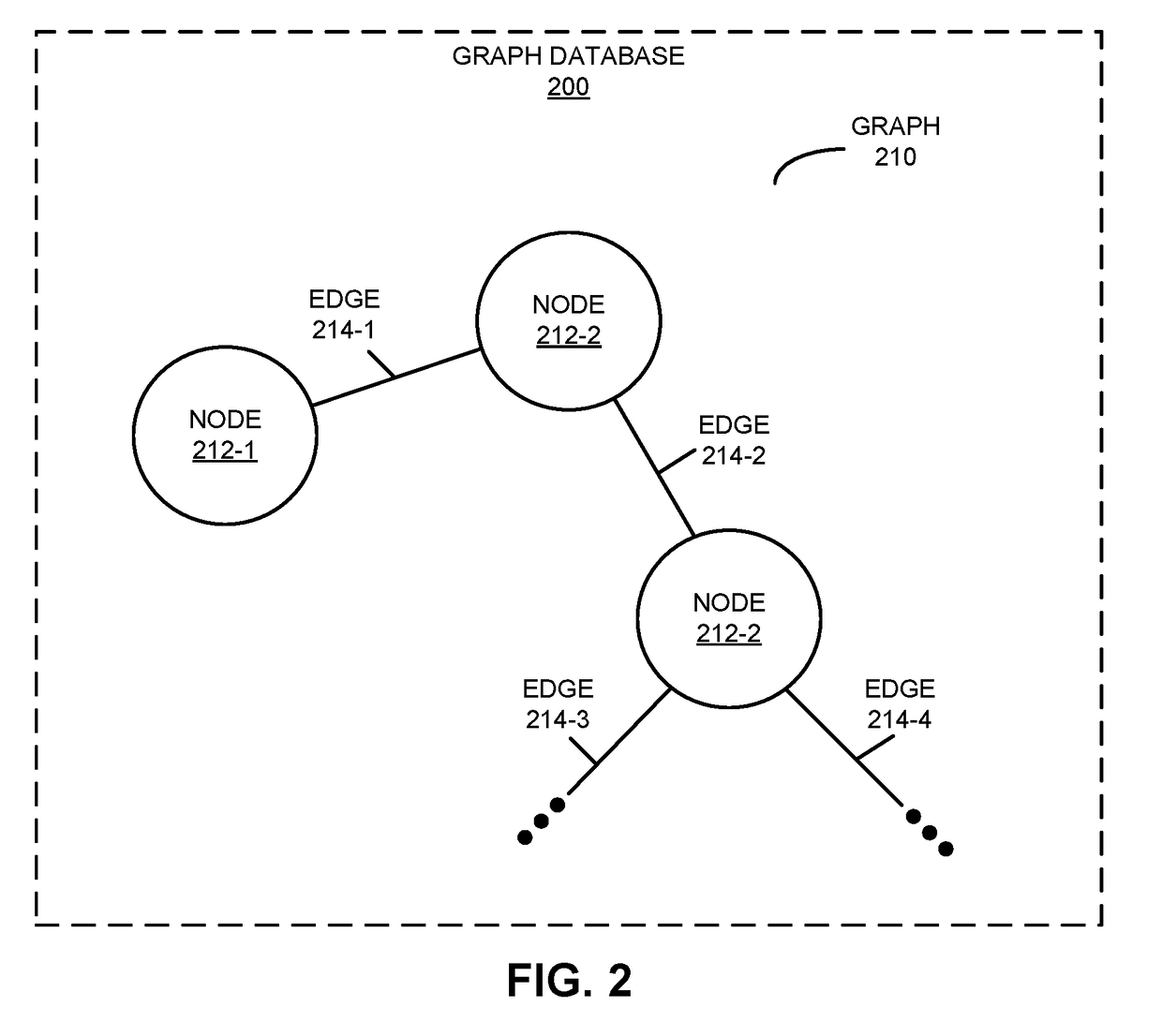

Fan-out control in scalable distributed data stores

InactiveUS20170262551A1Database distribution/replicationRelational databasesGraphicsScalable distributed

The disclosed embodiments provide a system for processing data. During operation, the system identifies a query type of a query of a graph database storing a graph, wherein the graph comprises nodes, edges between pairs of nodes, and predicates. Next, the system determines, based on the query type, a number of clusters on which the graph database is replicated for fanning out of the query. The system then selects a set of storage nodes in the determined number of clusters for processing of the query. Finally, the system generates a fan-out of the query to the selected storage nodes.

Owner:MICROSOFT TECH LICENSING LLC

Fan out wafer level package using silicon bridge

InactiveUS20150364422A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

A semiconductor device package includes a logic die coupled to a memory die in a side-by-side configuration on a redistribution layer (e.g., the logic die and the memory die are substantially adjacent). A silicon bridge may be used to interconnect the logic die and the memory die. The silicon bridge may be positioned between the die and the redistribution layer. The silicon bridge and the redistribution layer may be coupled to the lower (active) surfaces of the logic die and the memory die. The package may be formed using a wafer level process that forms a plurality of packages simultaneously.

Owner:APPLE INC

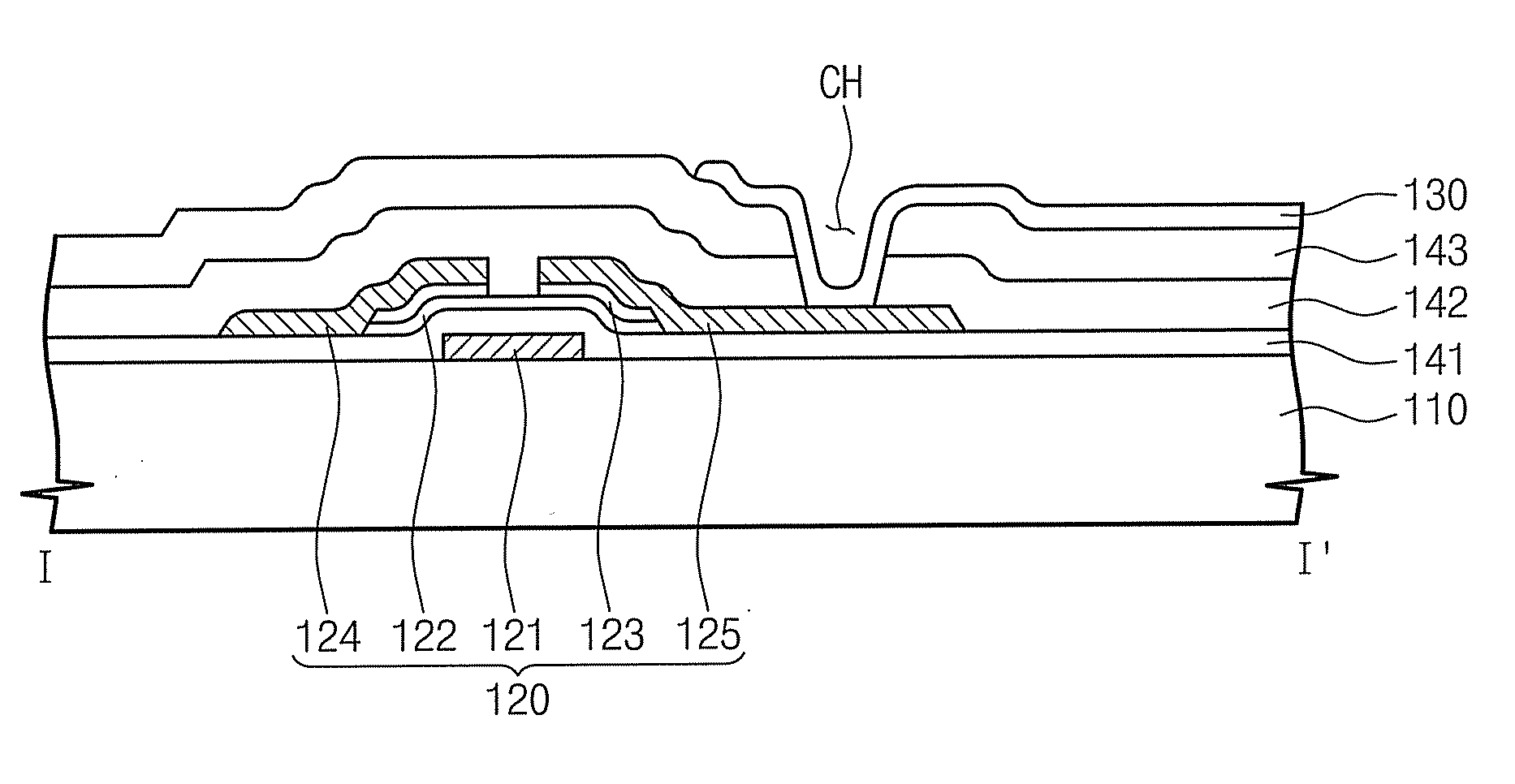

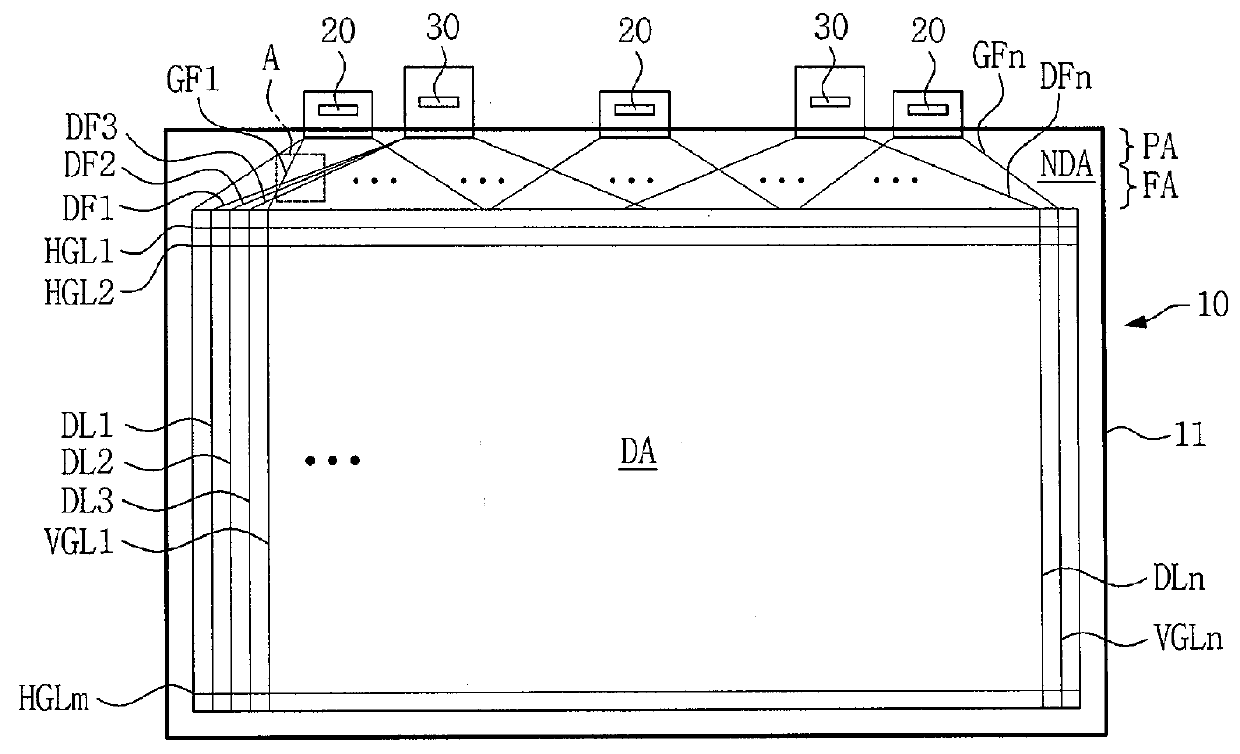

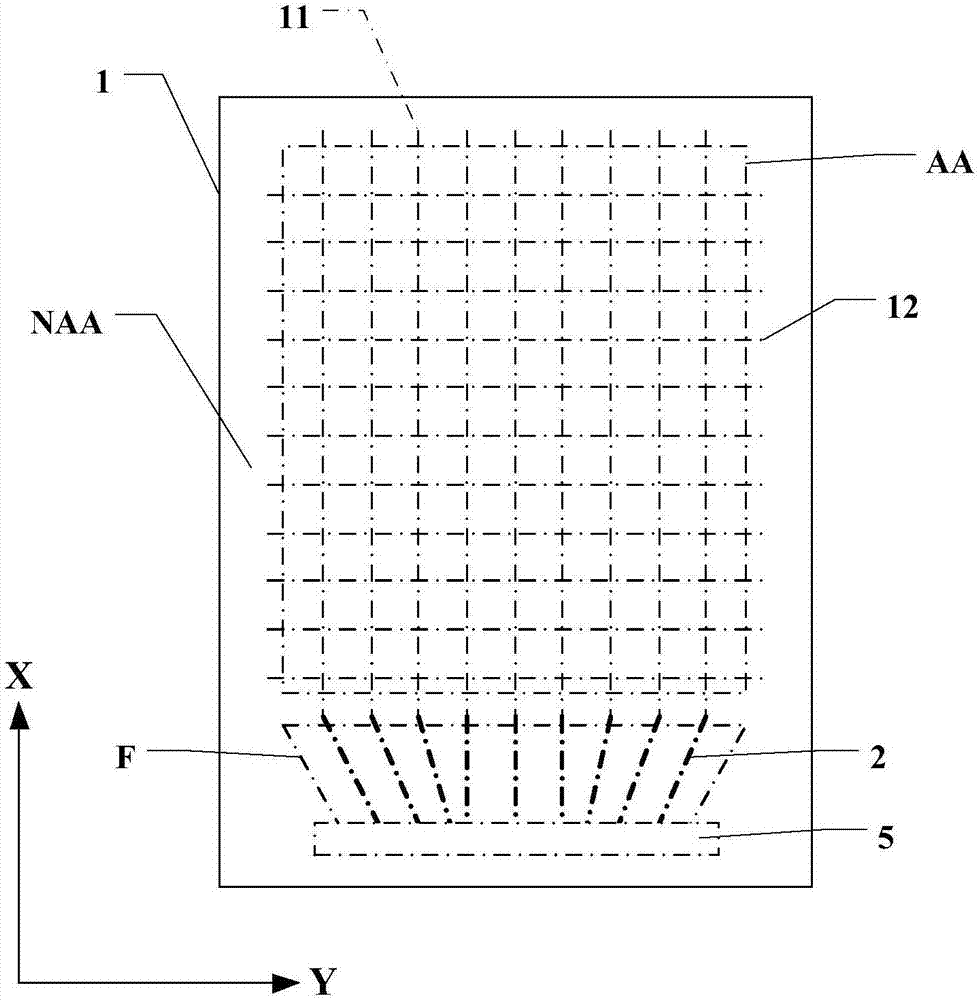

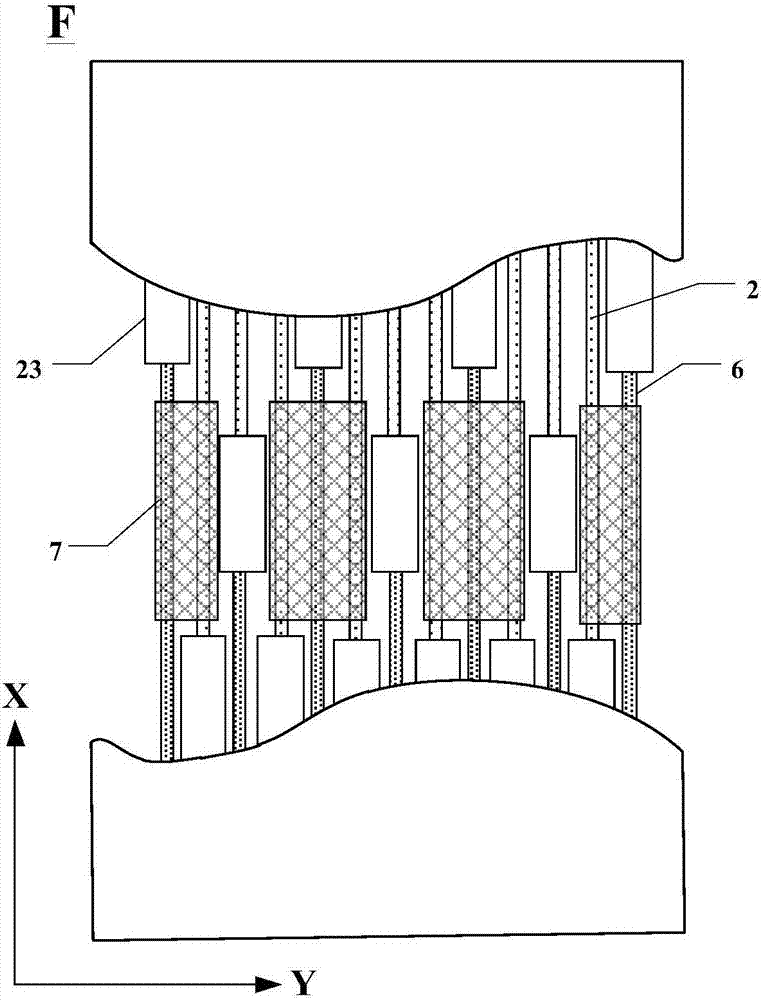

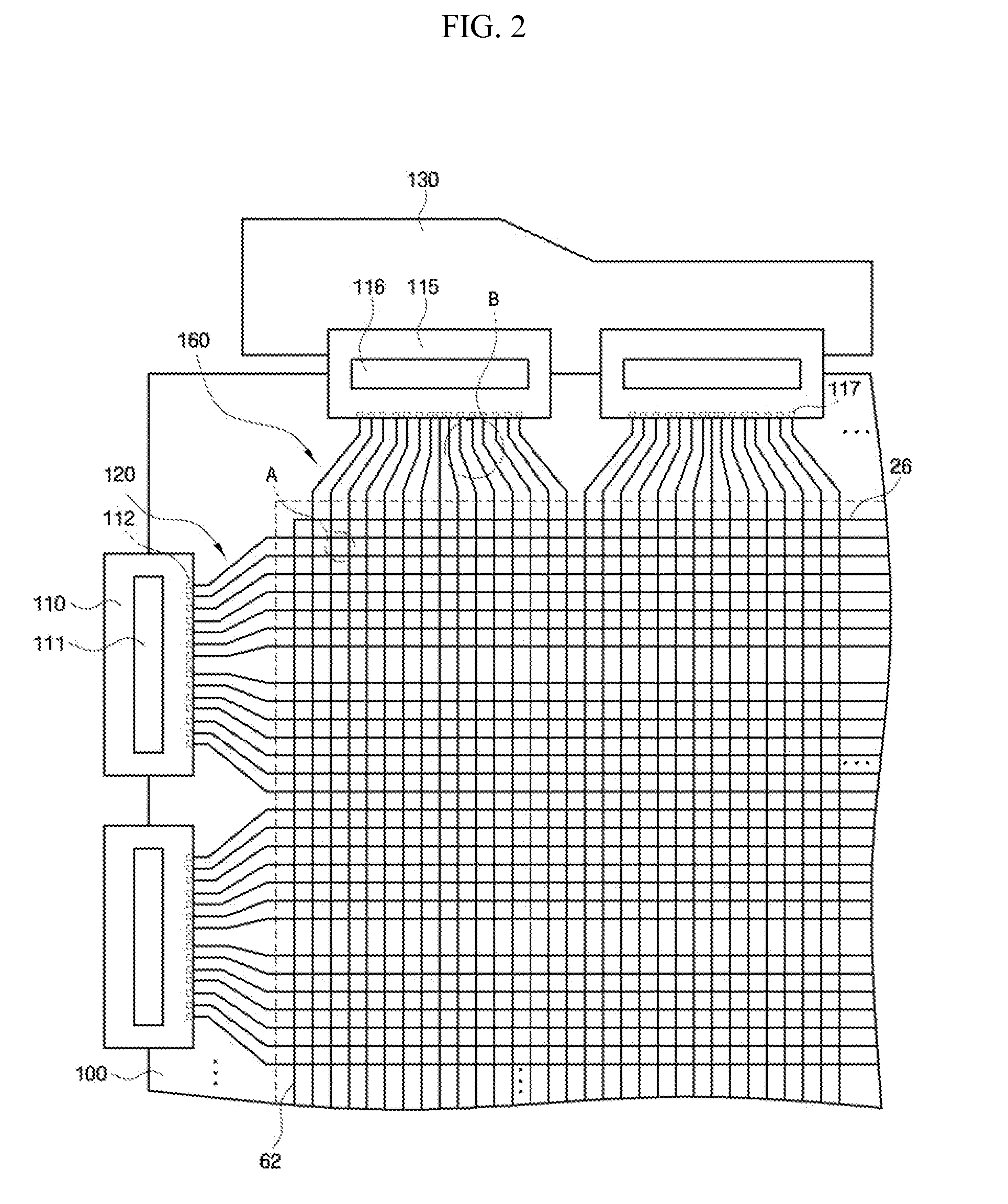

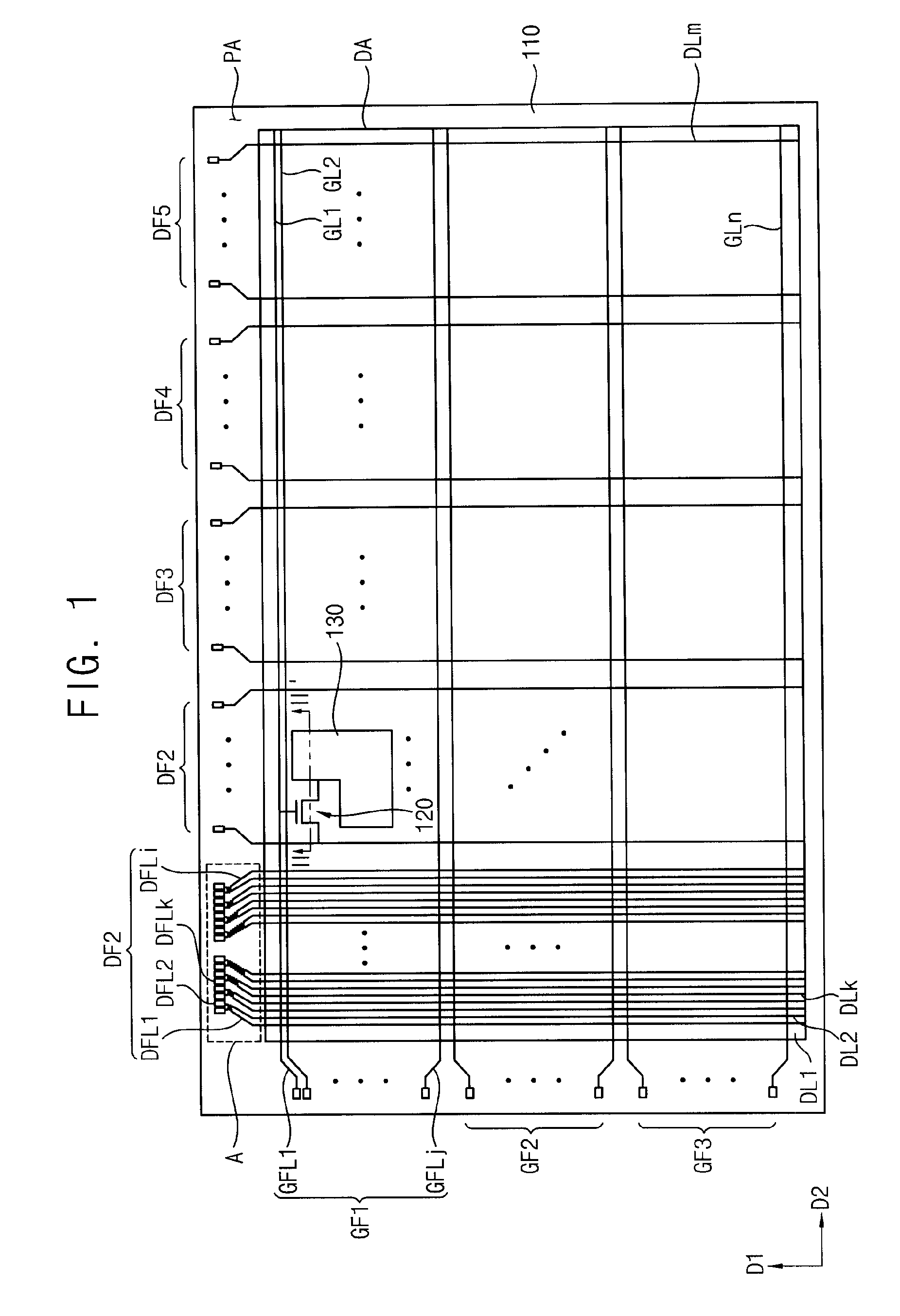

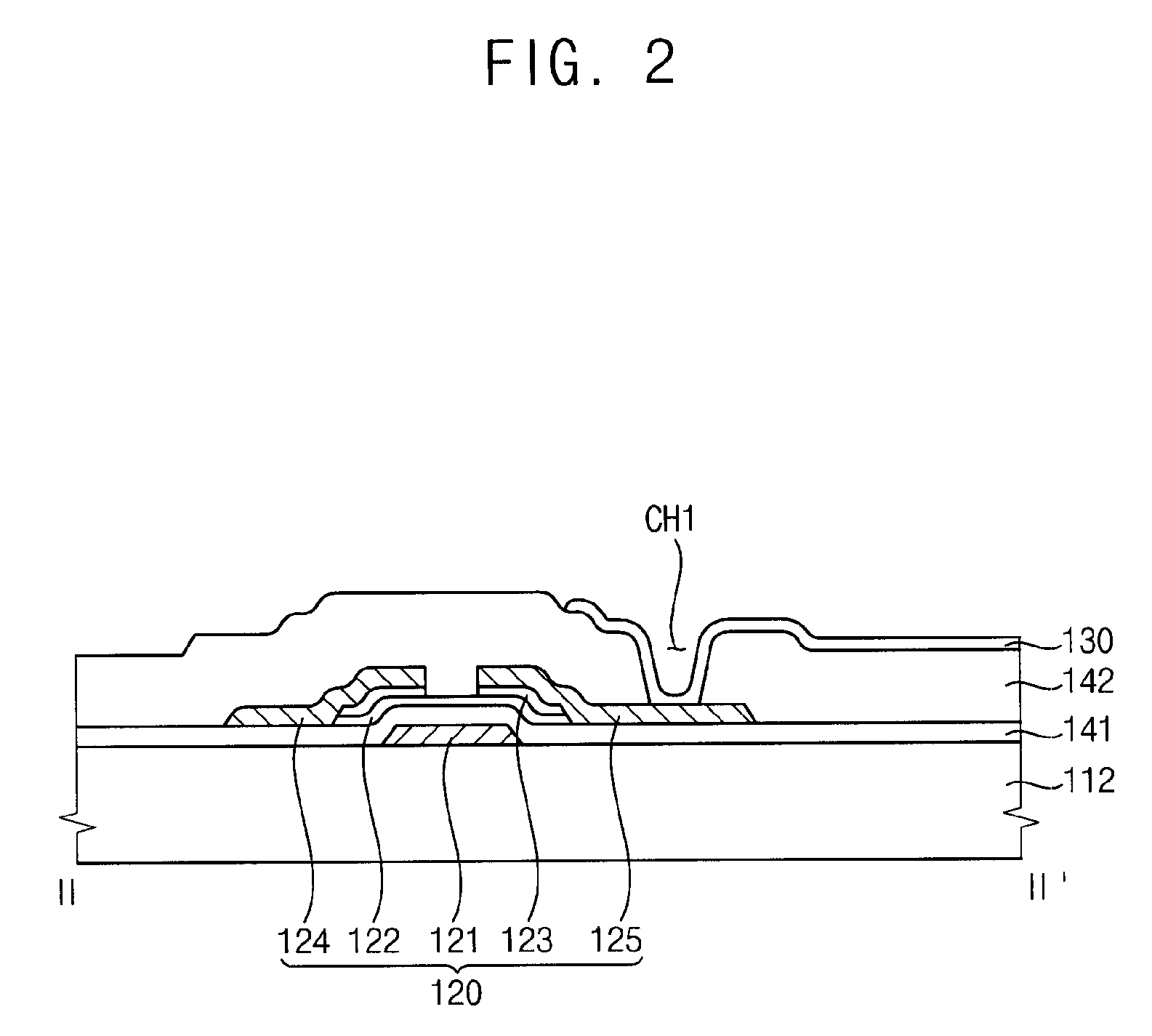

Array substrate, display apparatus having the same

ActiveUS20080203391A1Avoid delayImprove display qualityStatic indicating devicesSolid-state devicesPixel arraySignal lines

An array substrate includes a base substrate which includes a display area and a peripheral area adjacent to the display area, a plurality of fan-out lines arranged in the peripheral area to receive a driving signal from an exterior source, at least one fan-out line among the plurality of fan-out lines arranged on a different layer from a layer on which remaining fan-out lines of the plurality of fan-out lines are arranged, a plurality of signal lines arranged in the display area to receive the driving signal from the plurality of fan-out lines and a pixel array arranged in the display area to receive the driving signal from the plurality of signal lines.

Owner:SAMSUNG DISPLAY CO LTD

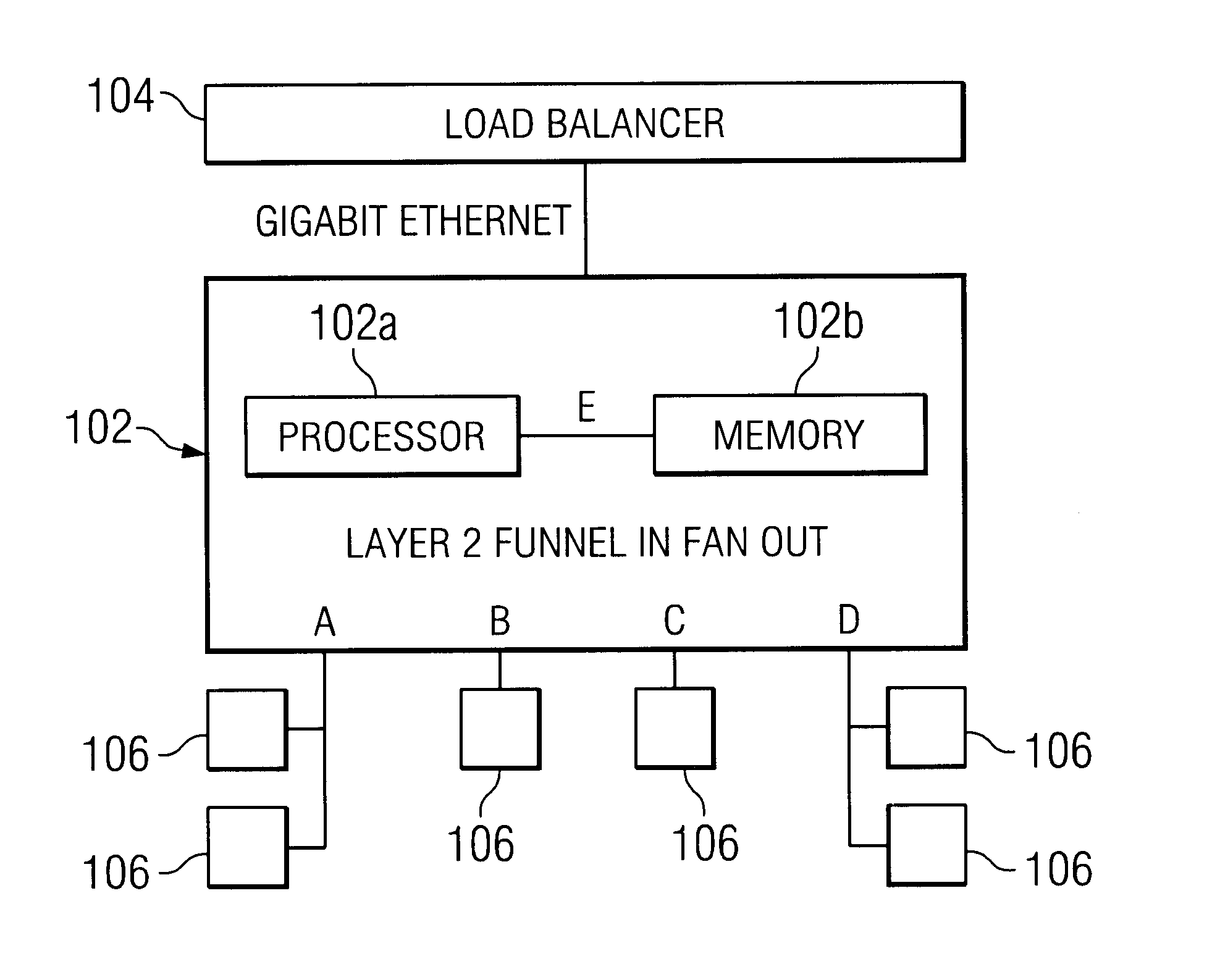

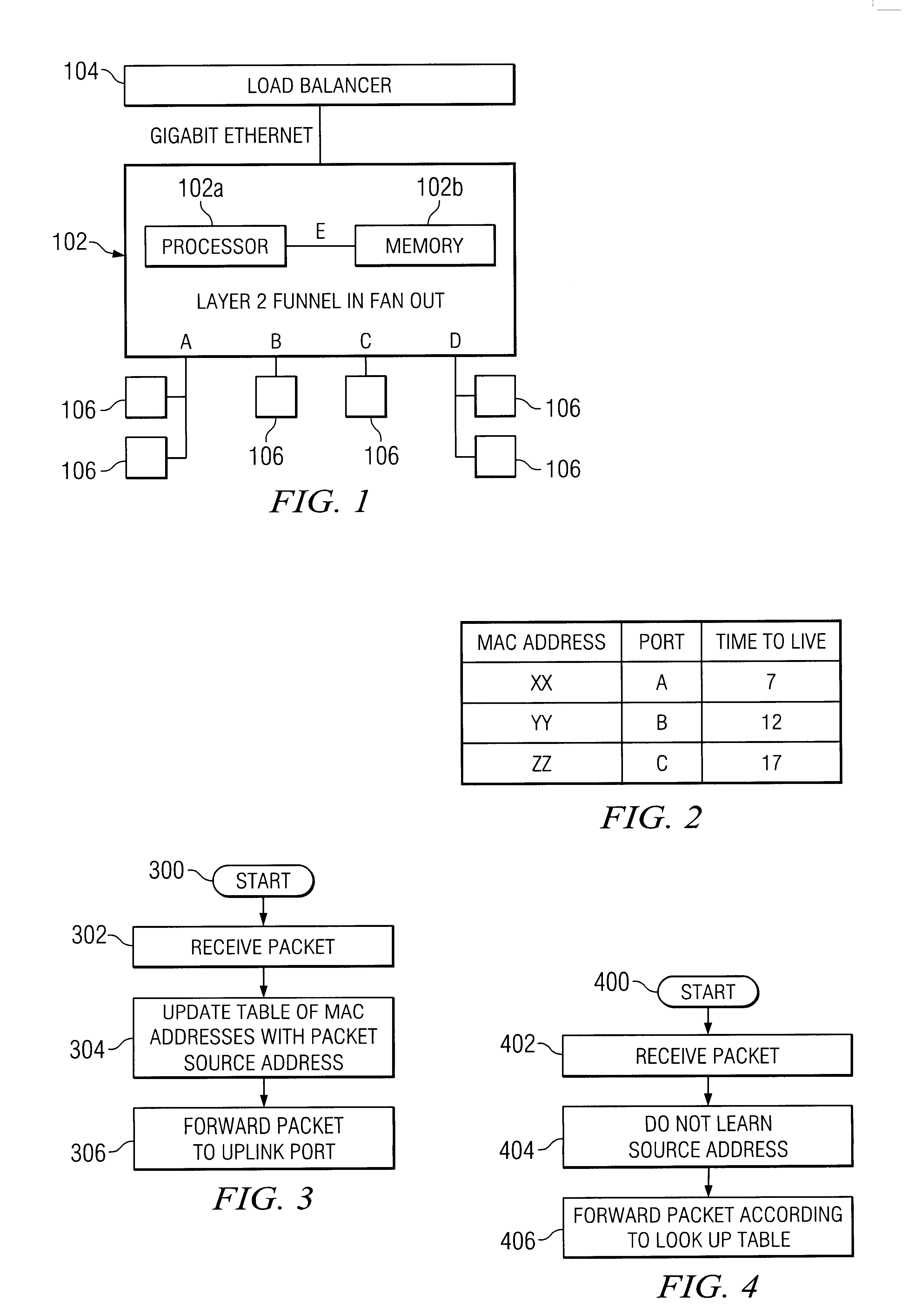

Layer 2 funnel in fan out network device

InactiveUS6850529B1Time-division multiplexData switching by path configurationComputer hardwareData rate

A funnel in fan out network device includes a fast uplink port operating at a first data rate. A plurality of slow ports operate at a second data rate. The second data rate is slower than the first data rate. A processor is configured to direct a packet received on one of the slower ports directly to the fast uplink port without looking up the destination address of the packet.

Owner:CISCO TECH INC

4d device process and structure

InactiveUS20110170266A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringUltra high density

a 4D device comprises a 2D multi-core logic and a 3D memory stack connected through the memory stack sidewall using a fine pitch T&J connection. The 3D memory in the stack is thinned from the original wafer thickness to no remaining Si. A tounge and groove device at the memory wafer top and bottom surfaces allows an accurate stack alignment. The memory stack also has micro-channels on the backside to allow fluid cooling. The memory stack is further diced at the fixed clock-cycle distance and is flipped on its side and re-assembled on to a template into a pseudo-wafer format. The top side wall of the assembly is polished and built with BEOL to fan-out and use the T&J fine pitch connection to join to the 2D logic wafer. The other side of the memory stack is polished, fanned-out, and bumped with C4 solder. The invention also comprises a process for manufacturing the device. In another aspect, the invention comprises a 4D process and device for over 50× greter than 2D memory density per die and an ultra high density memory.

Owner:IBM CORP

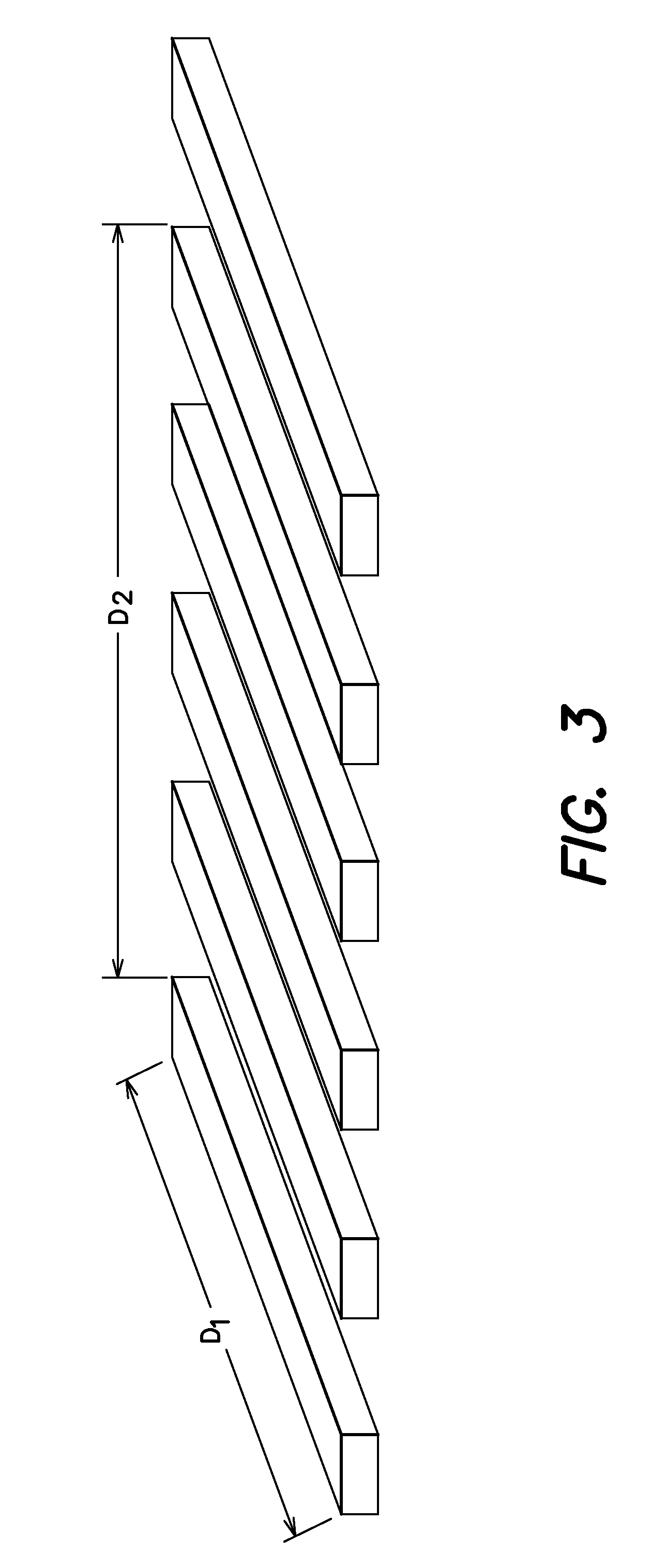

Optimization of critical dimensions and pitch of patterned features in and above a substrate

A die is formed with different and optimized critical dimensions in different device levels and areas of those device levels using photolithography and etch techniques. One aspect of the invention provides for a memory array formed above a substrate, with driver circuitry formed in the substrate. A level of the memory array consists of, for example, parallel rails and a fan-out region. It is desirable to maximize density of the rails and minimize cost of lithography for the entire memory array. This can be achieved by forming the rails at a tighter pitch than the CMOS circuitry beneath it, allowing cheaper lithography tools to be used when forming the CMOS, and similarly by optimizing lithography and etch techniques for a device level to produce a tight pitch in the rails, and a more relaxed pitch in the less-critical fan-out region.

Owner:SANDISK TECH LLC

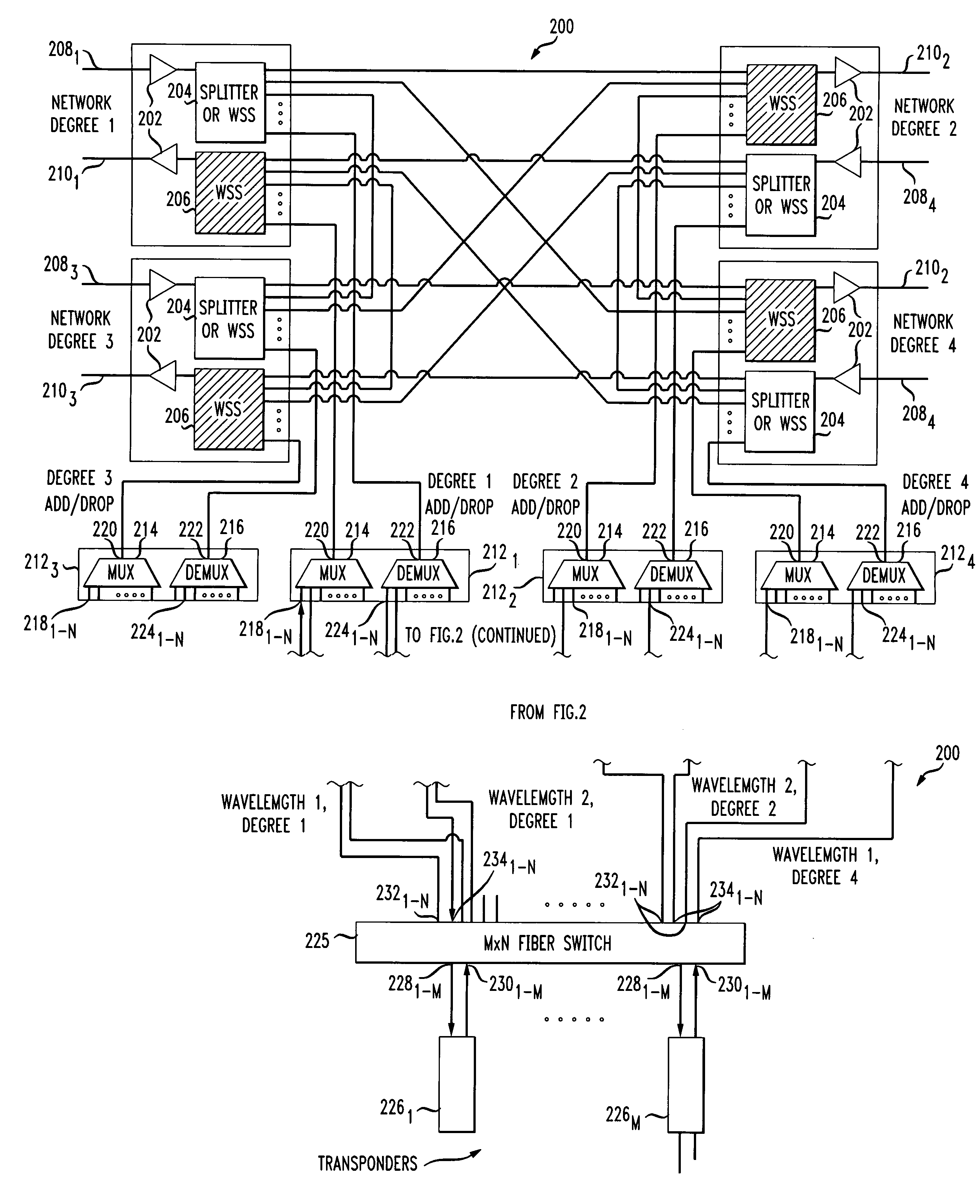

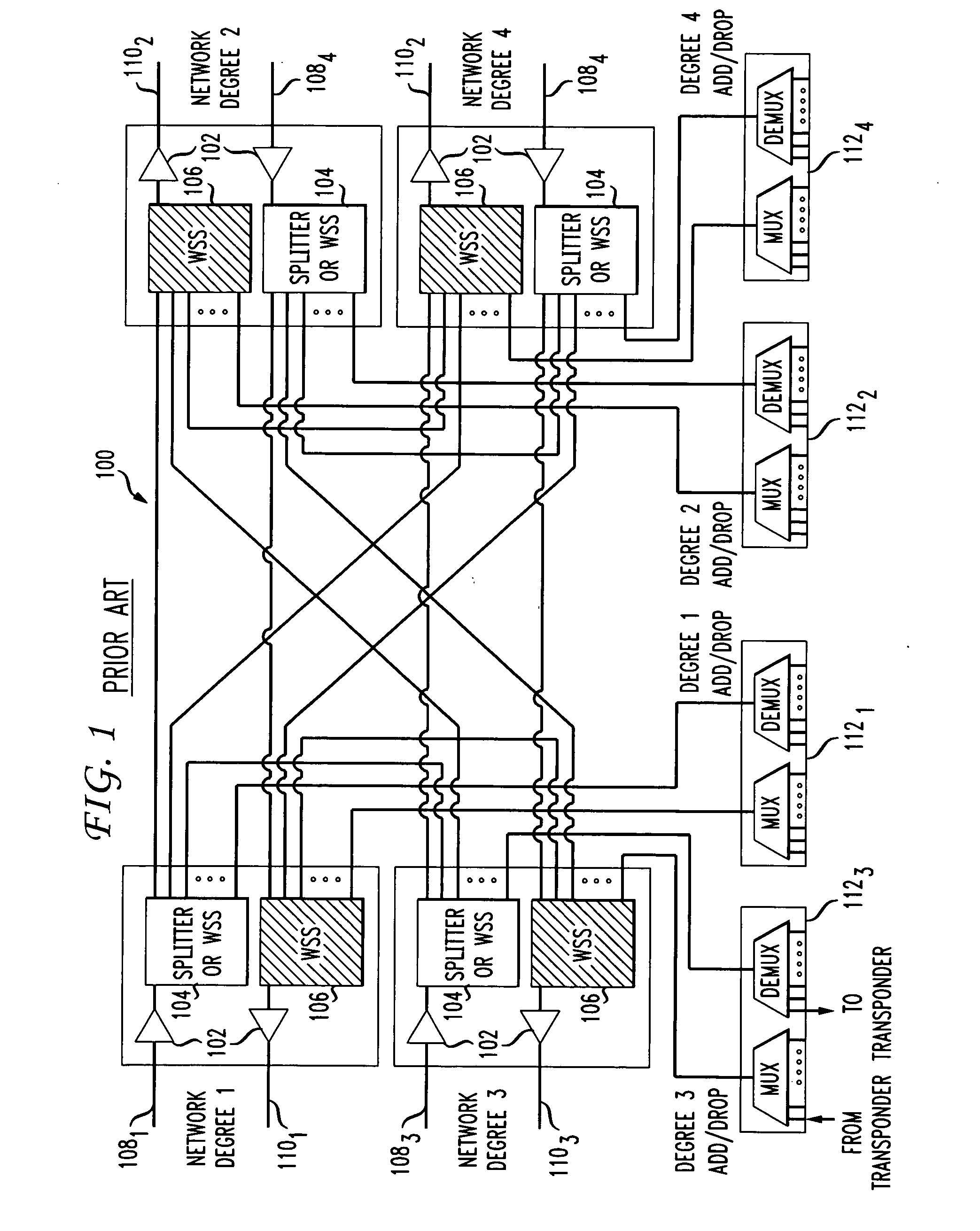

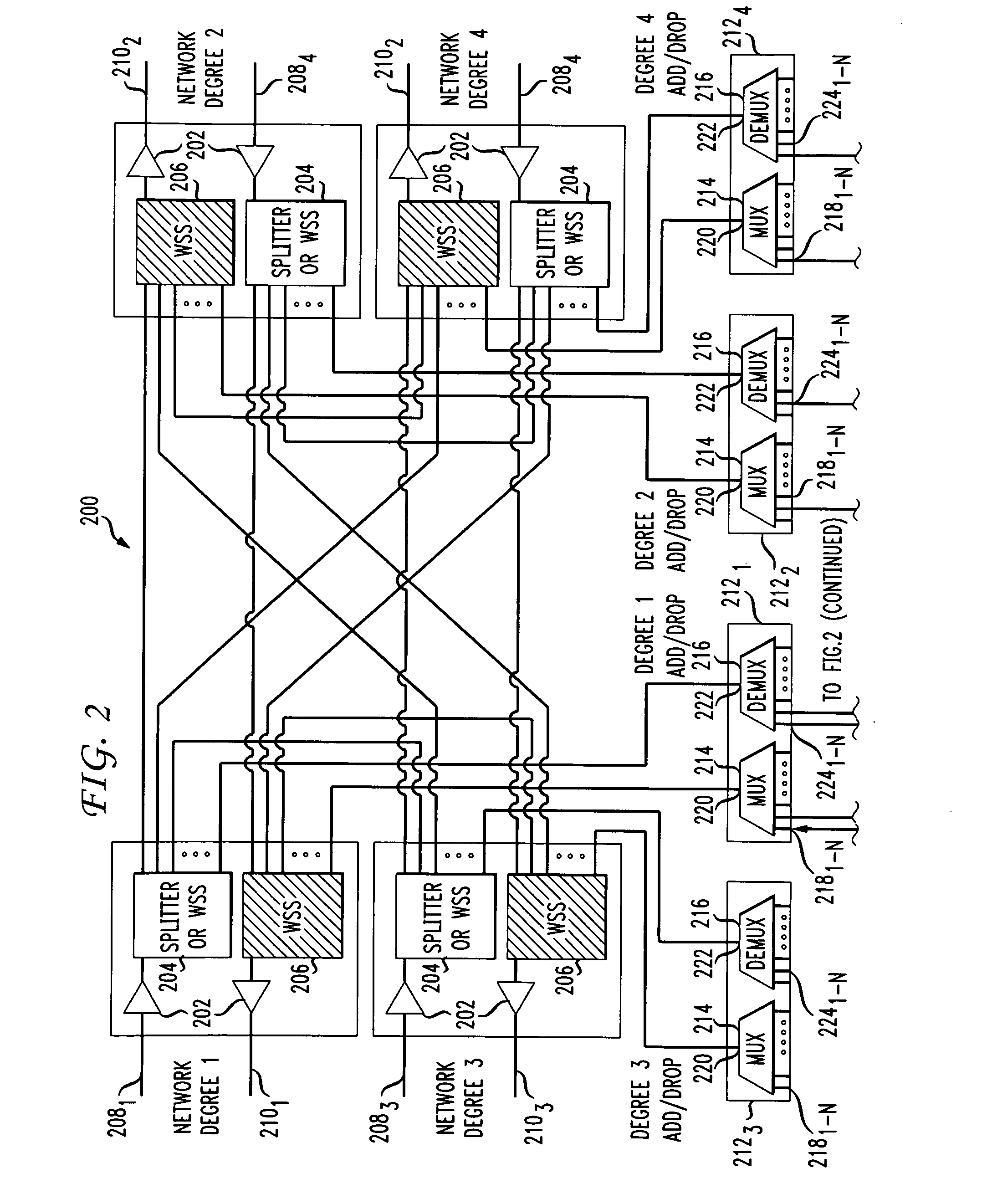

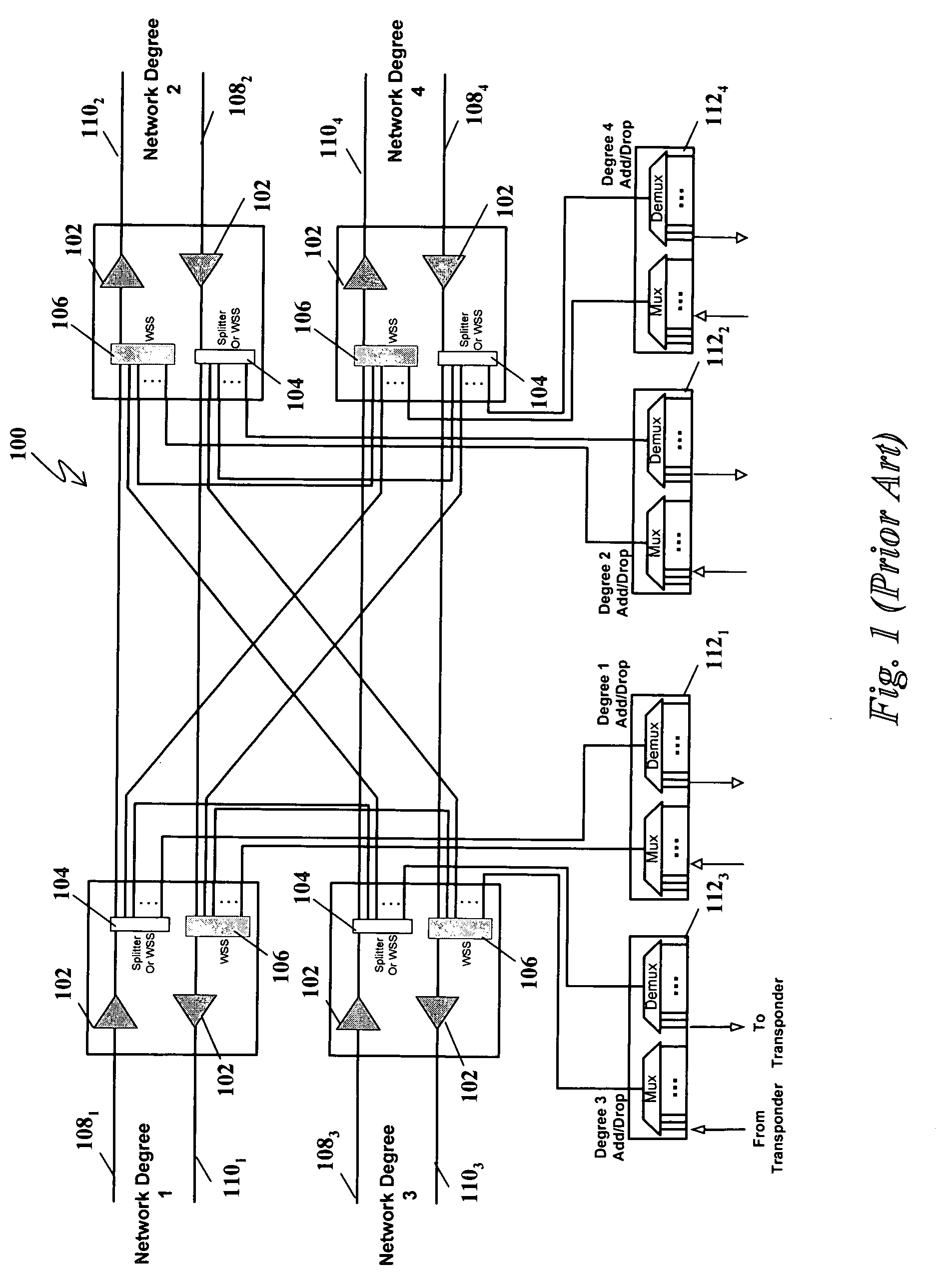

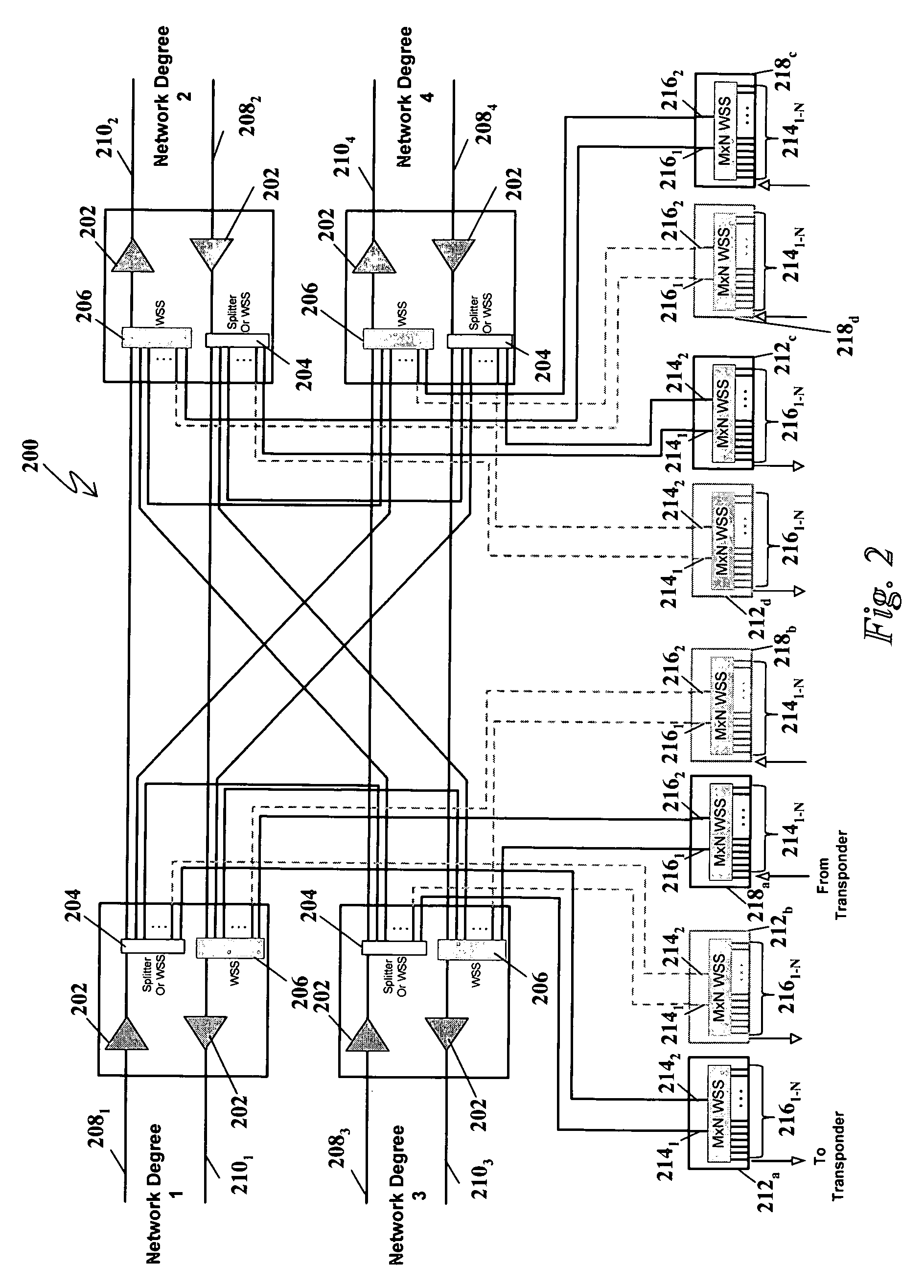

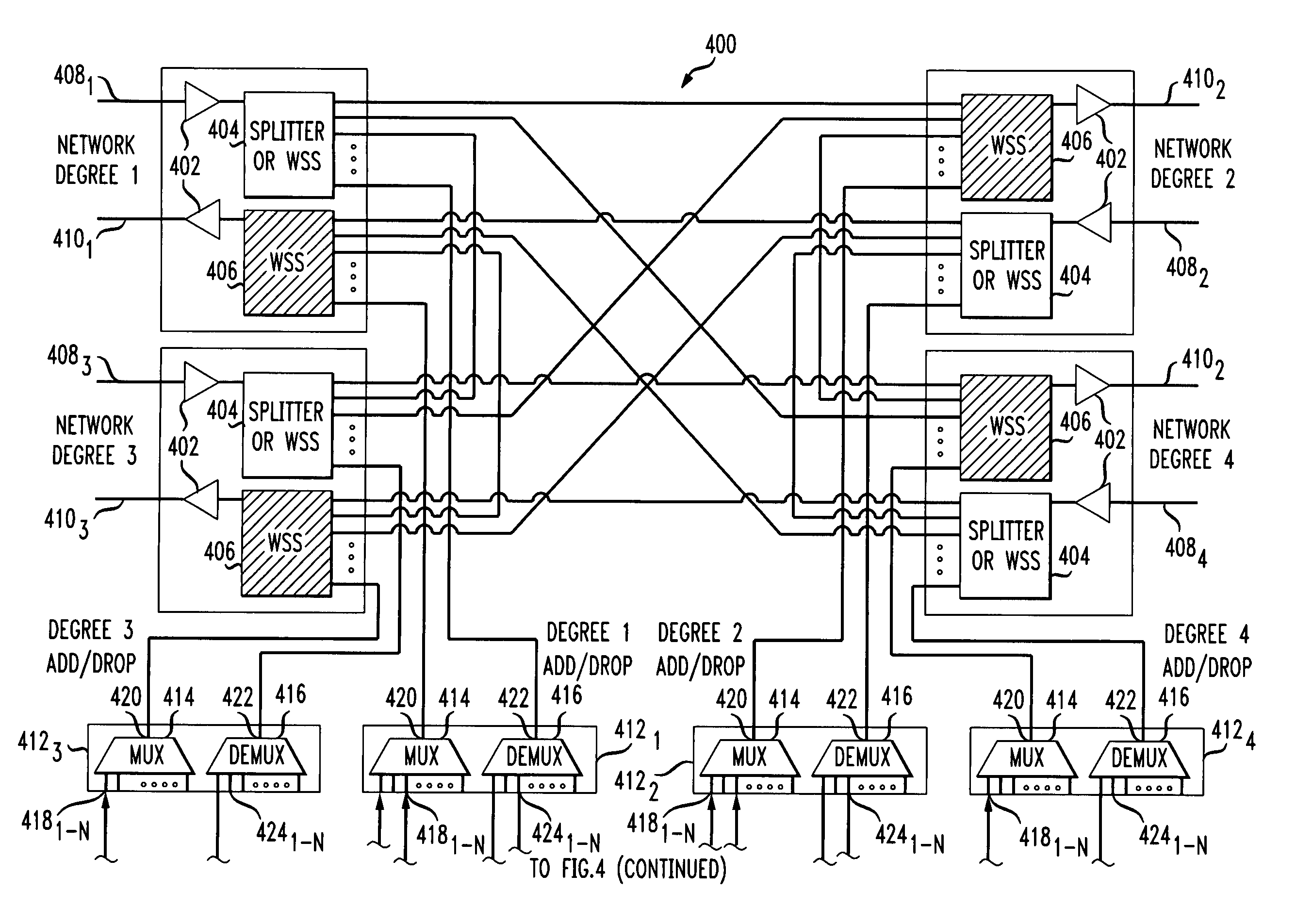

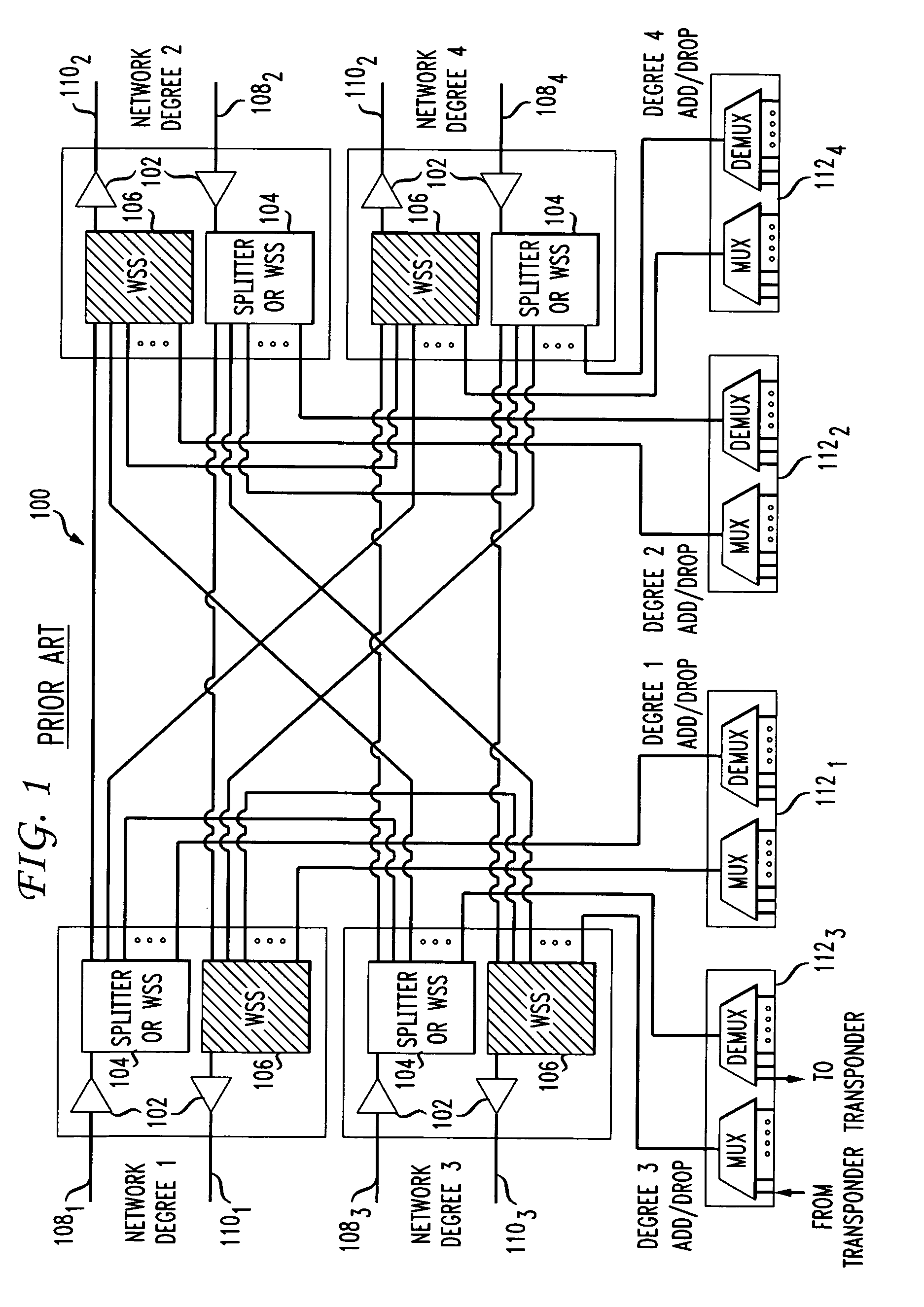

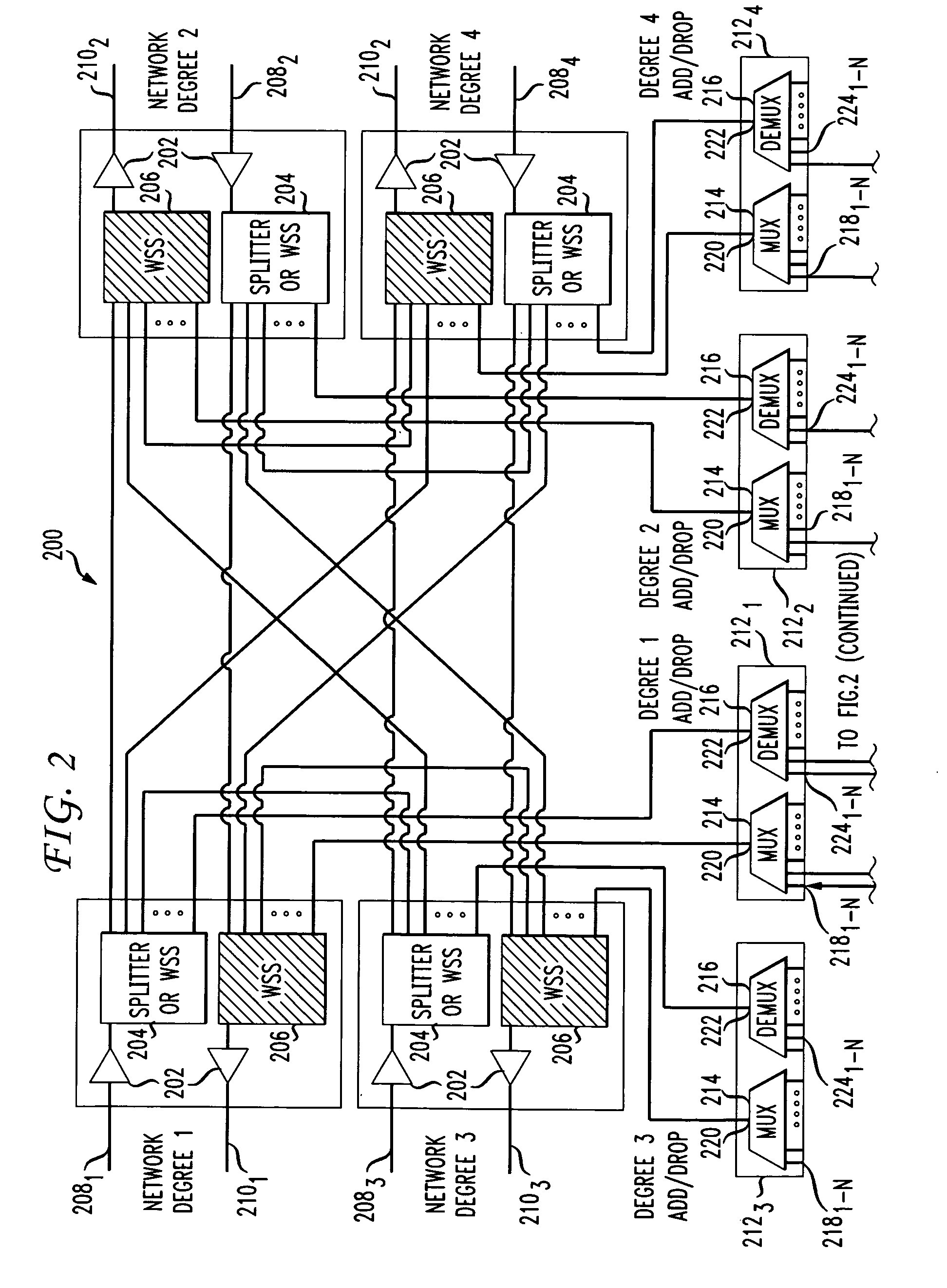

Methods for dynamic wavelength add/drop in a ROADM optical network

ActiveUS20100142961A1Multiplex system selection arrangementsWavelength-division multiplex systemsFiberMultiplexer

A system and method for dynamically adding / dropping wavelengths in a reconfigurable optical add-drop multiplexer (ROADM) transport network is disclosed. The system includes at least one optical transponder, a plurality of optical fan-out devices, each arranged to receive an input signal from a network degree and coupled to at least one of a plurality of optical fan-in devices, each optical fan-in device arranged to output a signal to a network degree, the optical fan-out devices comprising at least one wavelength selective switch and the optical fan-in devices comprising at least one wavelength selective switch, the optical fan-out devices and optical fan-in devices being connected so as to enable signals input from each of the plurality of network degrees to be switched to another network degree of the plurality of network degrees; a plurality of demultiplexers for locally dropping selected wavelengths; a plurality of multiplexers for locally adding selected wavelengths; and at least one fiber switch interposed between the at least one optical transponder and the plurality of demultiplexers and multiplexers. The fiber switch is coupled to wavelengths and degrees that are allocated for a bandwidth-on-demand application. Other configurations include additional fan-in and fan-out devices interposed between a mux / demux assembly and the optical transponders to support wavelength redistribution applications.

Owner:AT&T INTPROP I L P

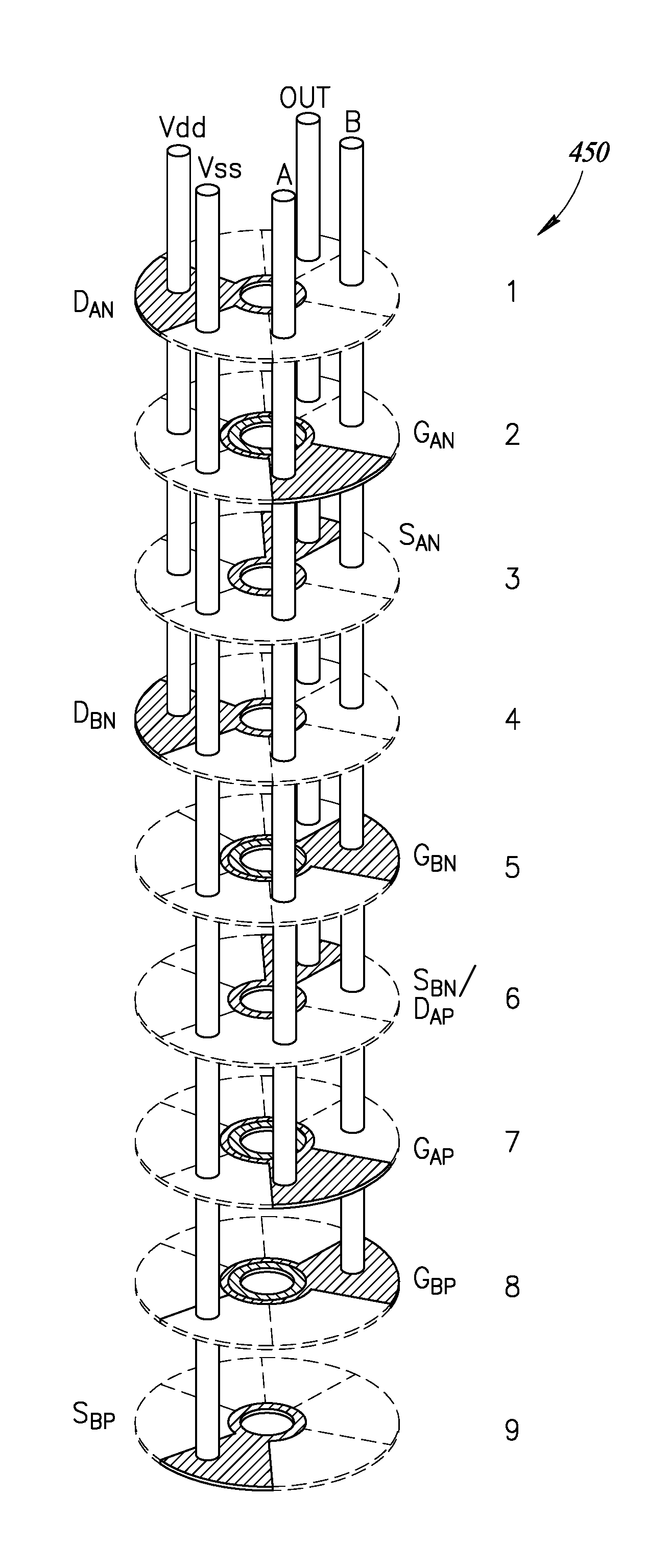

Modular interconnects for gate-all-around transistors

ActiveUS20170005106A1Facilitates building complexImprove compactionTransistorSemiconductor/solid-state device detailsNanowireNOR gate

A modular interconnect structure facilitates building complex, yet compact, integrated circuits from vertical GAA FETs. The modular interconnect structure includes annular metal contacts to the transistor terminals, sectors of stacked discs extending radially outward from the vertical nanowires, and vias in the form of rods. Extension tabs mounted onto the radial sector interconnects permit signals to fan out from each transistor terminal. Adjacent interconnects are linked by linear segments. Unlike conventional integrated circuits, the modular interconnects as described herein are formed at the same time as the transistors. Vertical GAA NAND and NOR gates provide building blocks for creating all types of logic gates to carry out any desired Boolean logic function. Stacked vertical GAA FETs are made possible by the modular interconnect structure. The modular interconnect structure permits a variety of specialized vertical GAA devices to be integrated on a silicon substrate using standard CMOS processes.

Owner:STMICROELECTRONICS SRL

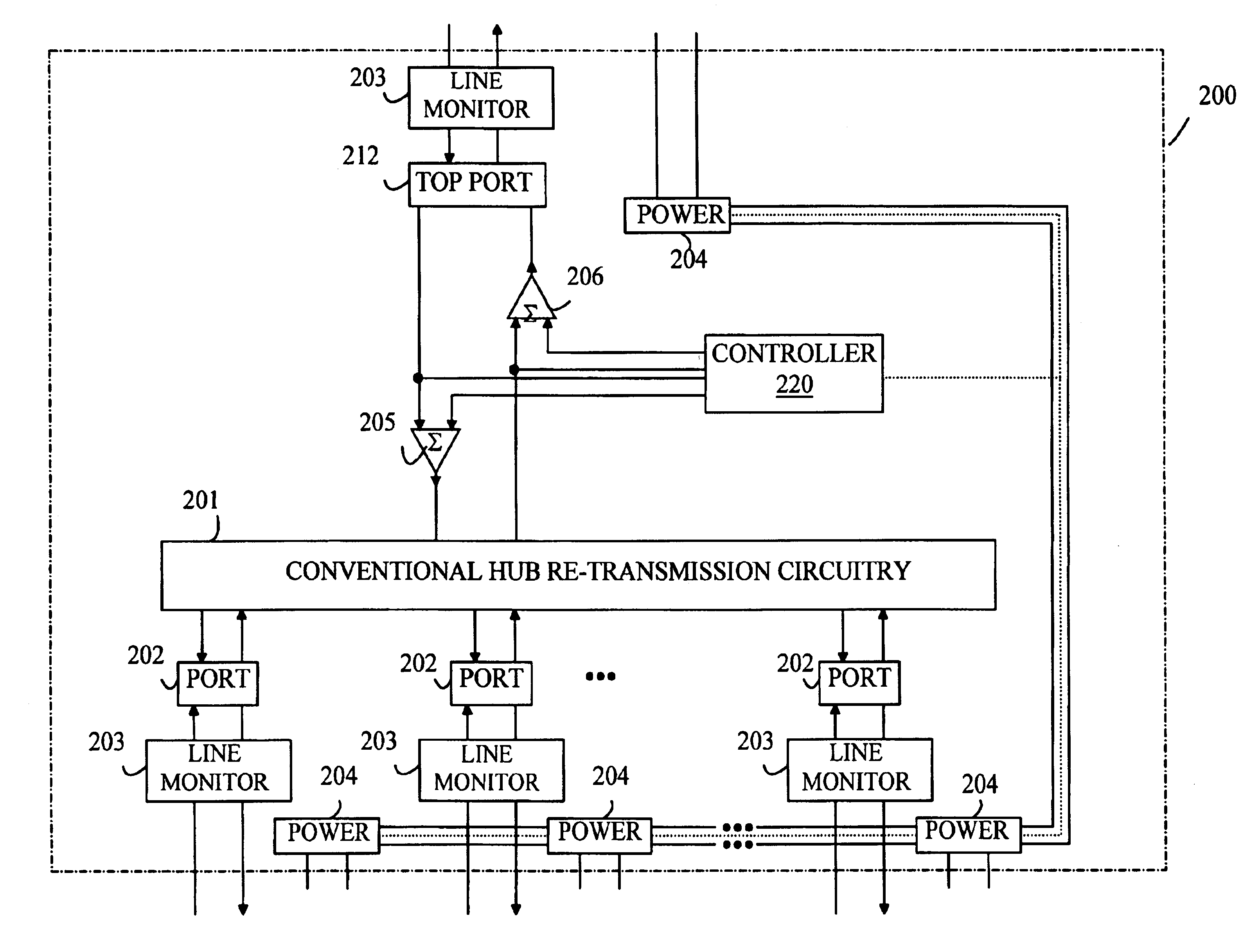

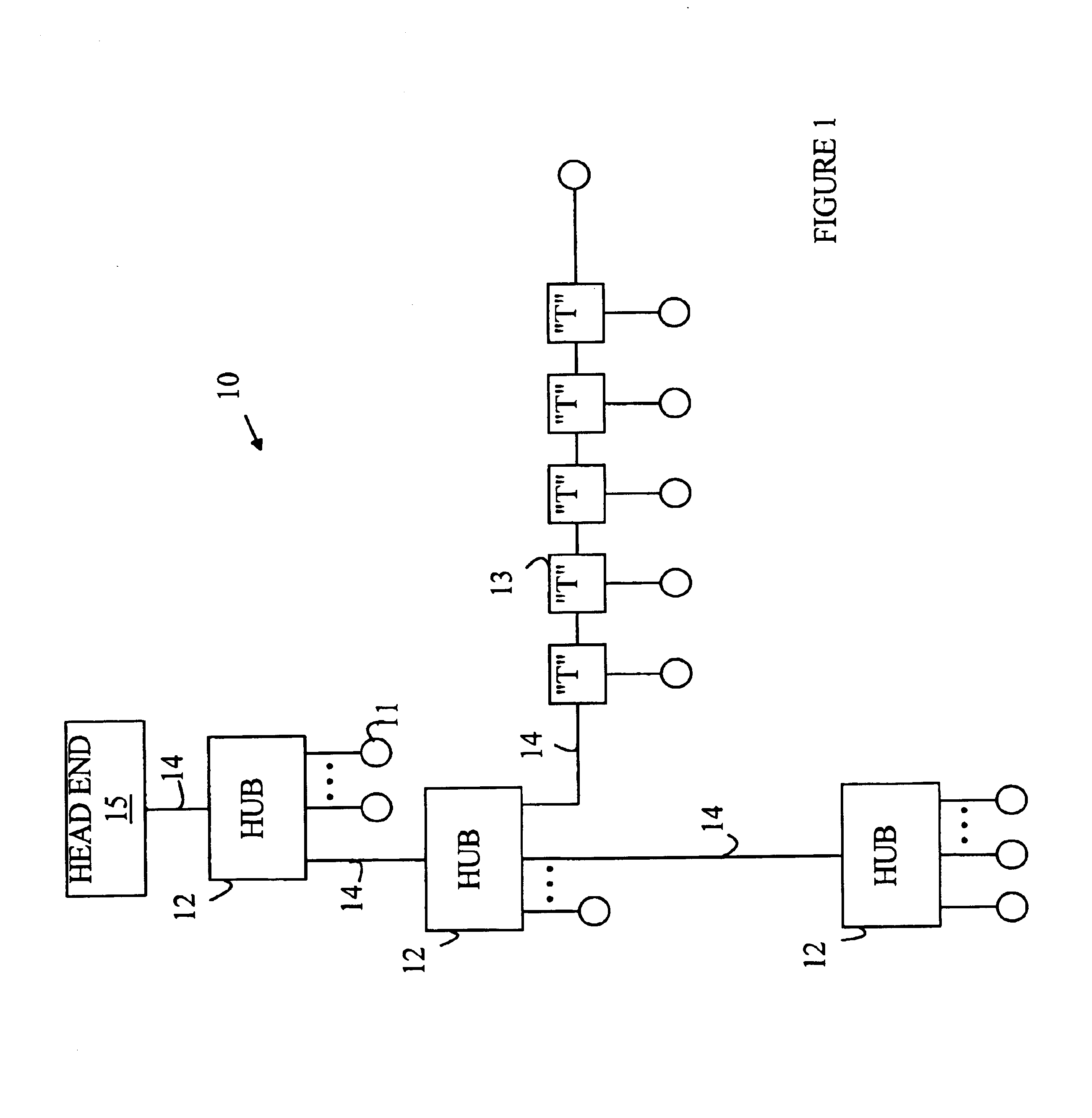

Computer network adapted for industrial environments

InactiveUS6889095B1Thermoelectric device with peltier/seeback effectElectric controllersControl storeSignal on

A network for connecting a plurality of devices and the components used in constructing the network. The network includes at least one fan-out device for connecting the devices to each other. The fan-out device includes a controller, a top port and a plurality of downstream ports. The controller monitors messages received by the ports and generates messages that are sent via the ports. The network also includes a plurality of network cables, one per port. The network preferably utilizes a cabling system that includes twisted pairs for communicating the messages via the Ethernet protocol and power conductors for distributing power to the various network devices. The fan-out device includes one power component associated with each of the ports. Each power component provides connections between the power lines in the network capble and the ports of the fan-out device. The power components are used to power the devices on the network and to monitor the power lines for problems. Switching circuitry in the power components allows the fan-out device to isolate cable runs connected thereto that have shorts or other problems. The fan-out device preferably stores a device identification number that the controller transmits on all of the ports in response to a message received on one of the downstream ports. The controller also generates a signal on the top port that causes any device connected to the fan-out device via the top port to ignore the message. One embodiment of the fan-out device provides a hub that is transparent to Ethernet protocols while not introducing the jitter into the signals associated with the re-transmission and synchronization functions performed by conventional hubs.

Owner:AGILENT TECH INC

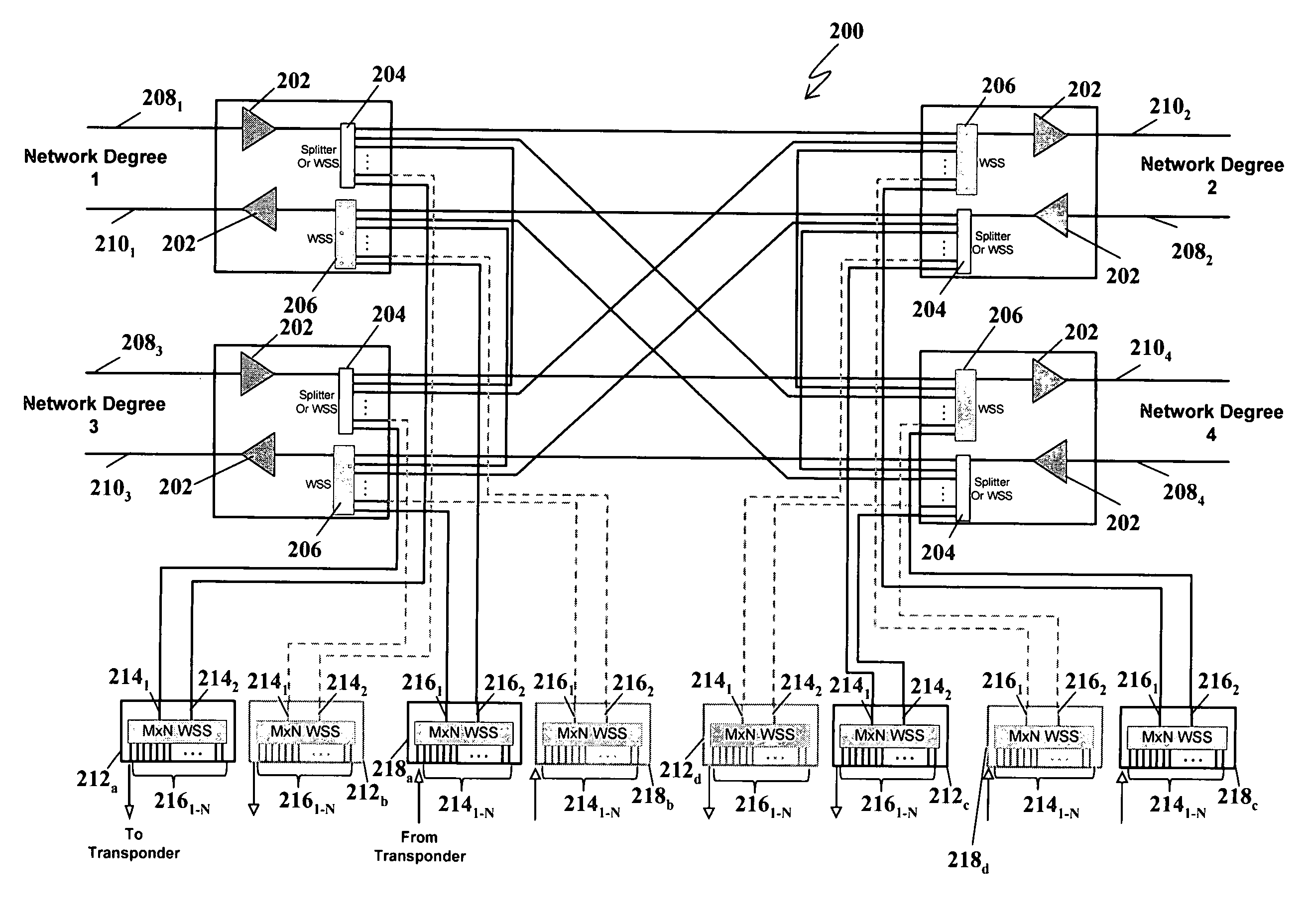

Shared, Colorless Add/Drop Configuration for a ROADM Network using MxN Wavelength Swithches

InactiveUS20100202778A1Wavelength-division multiplex systemsOptical light guidesLength waveTransmission network

A system and method for dynamically adding / dropping wavelengths in a reconfigurable optical add-drop multiplexer (ROADM) transport network is disclosed. The system includes a plurality of M×N wavelength selective switches (WSS) for locally dropping selected wavelengths at a node, where each M×N WSS has M inputs connected to optical fan-out devices in each of M network degrees, and a plurality of M×N wavelength selective switches for locally adding selected wavelengths to a node, where each M×N WSS has M outputs connected to optical fan-in devices in each of M network degrees. Several expedients of M×N wavelength selective switches comprising M switching elements for use in the system are also disclosed.

Owner:AT&T INTPROP I L P

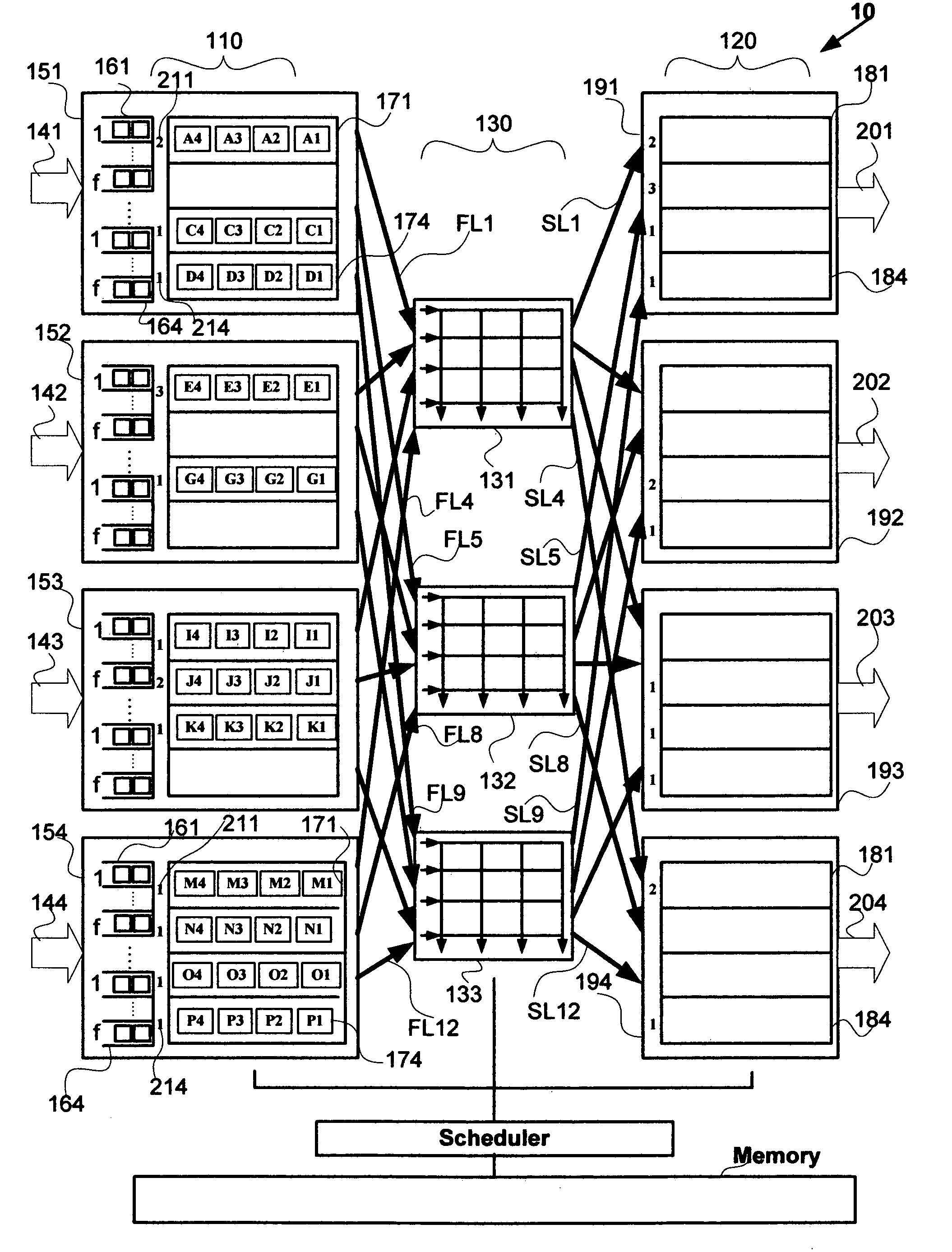

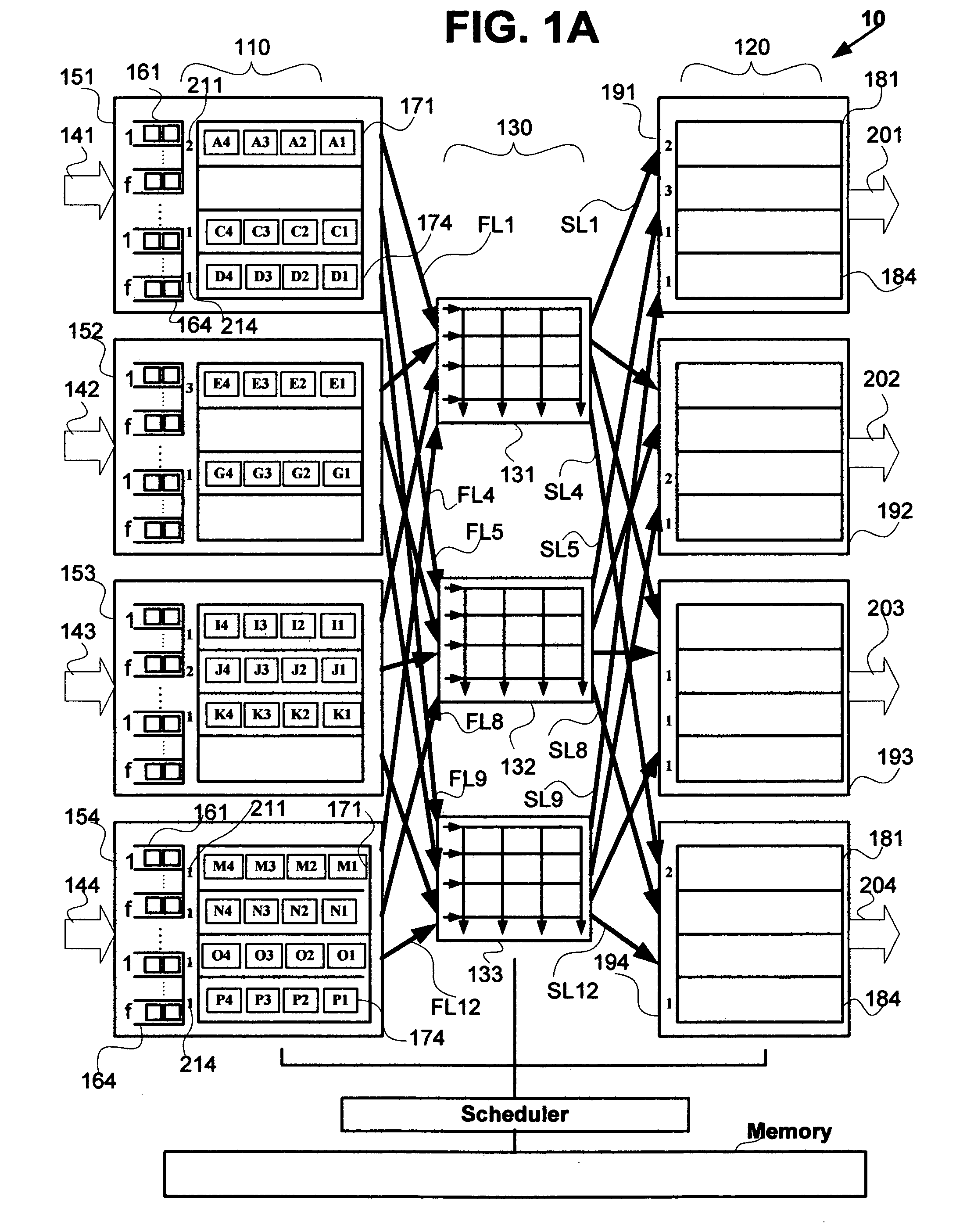

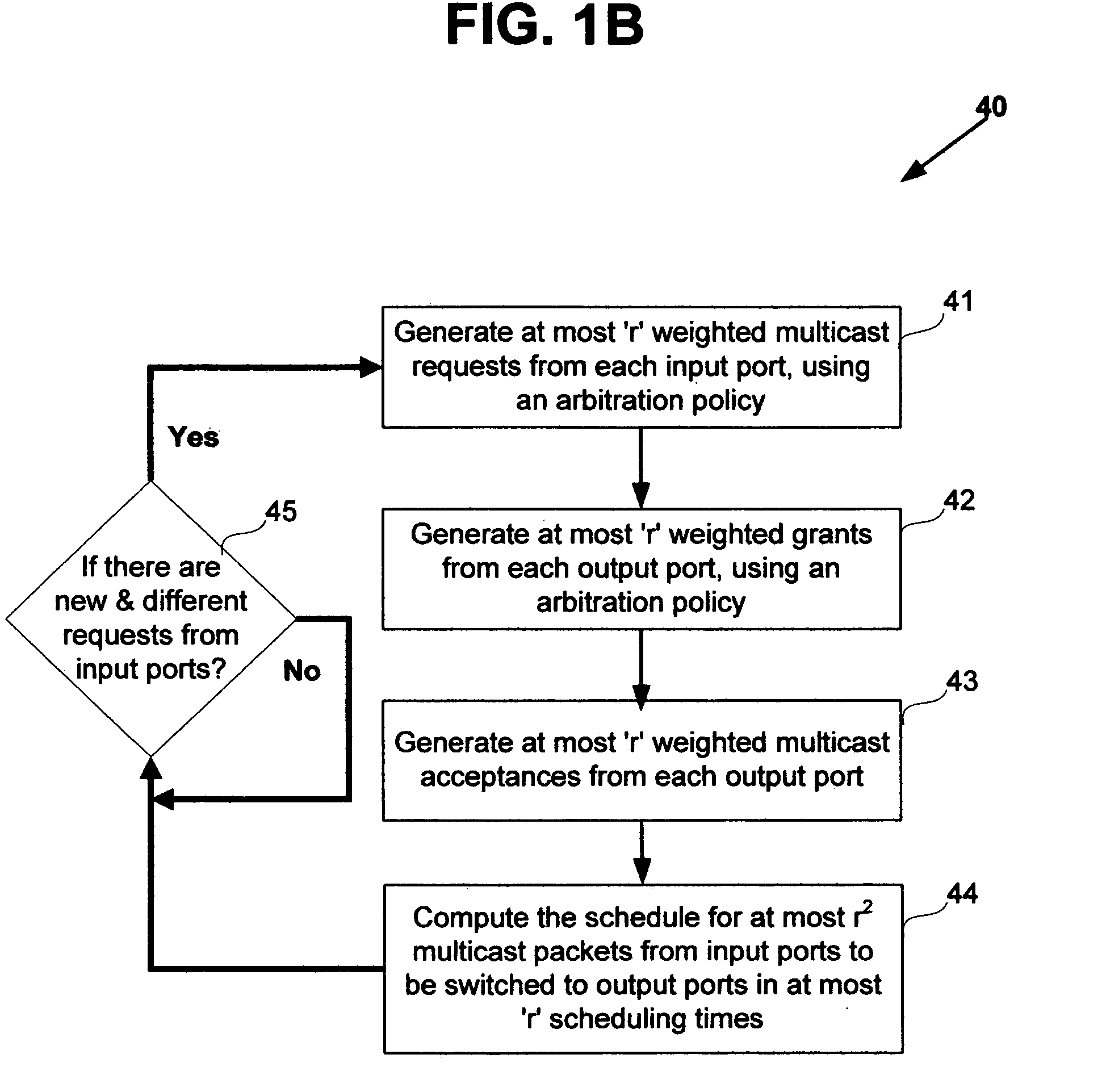

Nonblocking and deterministic multirate multicast packet scheduling

InactiveUS20070053356A1Guaranteed bandwidthGuaranteed LatencyData switching by path configurationSwitching timeMulti rate

A system for scheduling multirate multicast packets through an interconnection network having a plurality of input ports, a plurality of output ports, and a plurality of input queues, comprising multirate multicast packets with rate weight, at each input port is operated in nonblocking manner in accordance with the invention by scheduling corresponding to the packet rate weight, at most as many packets equal to the number of input queues from each input port to each output port. The scheduling is performed so that each multicast packet is fan-out split through not more than two interconnection networks and not more than two switching times. The system is operated at 100% throughput, work conserving, fair, and yet deterministically thereby never congesting the output ports. The system performs arbitration in only one iteration, with mathematical minimum speedup in the interconnection network. The system operates with absolutely no packet reordering issues, no internal buffering of packets in the interconnection network, and hence in a truly cut-through and distributed manner. In another embodiment each output port also comprises a plurality of output queues and each packet is transferred corresponding to the packet rate weight, to an output queue in the destined output port in deterministic manner and without the requirement of segmentation and reassembly of packets even when the packets are of variable size. In one embodiment the scheduling is performed in strictly nonblocking manner with a speedup of at least three in the interconnection network. In another embodiment the scheduling is performed in rearrangeably nonblocking manner with a speedup of at least two in the interconnection network. The system also offers end to end guaranteed bandwidth and latency for multirate multicast packets from input ports to output ports. In all the embodiments, the interconnection network may be a crossbar network, shared memory network, clos network, hypercube network, or any internally nonblocking interconnection network or network of networks.

Owner:TEAK TECH

Display device

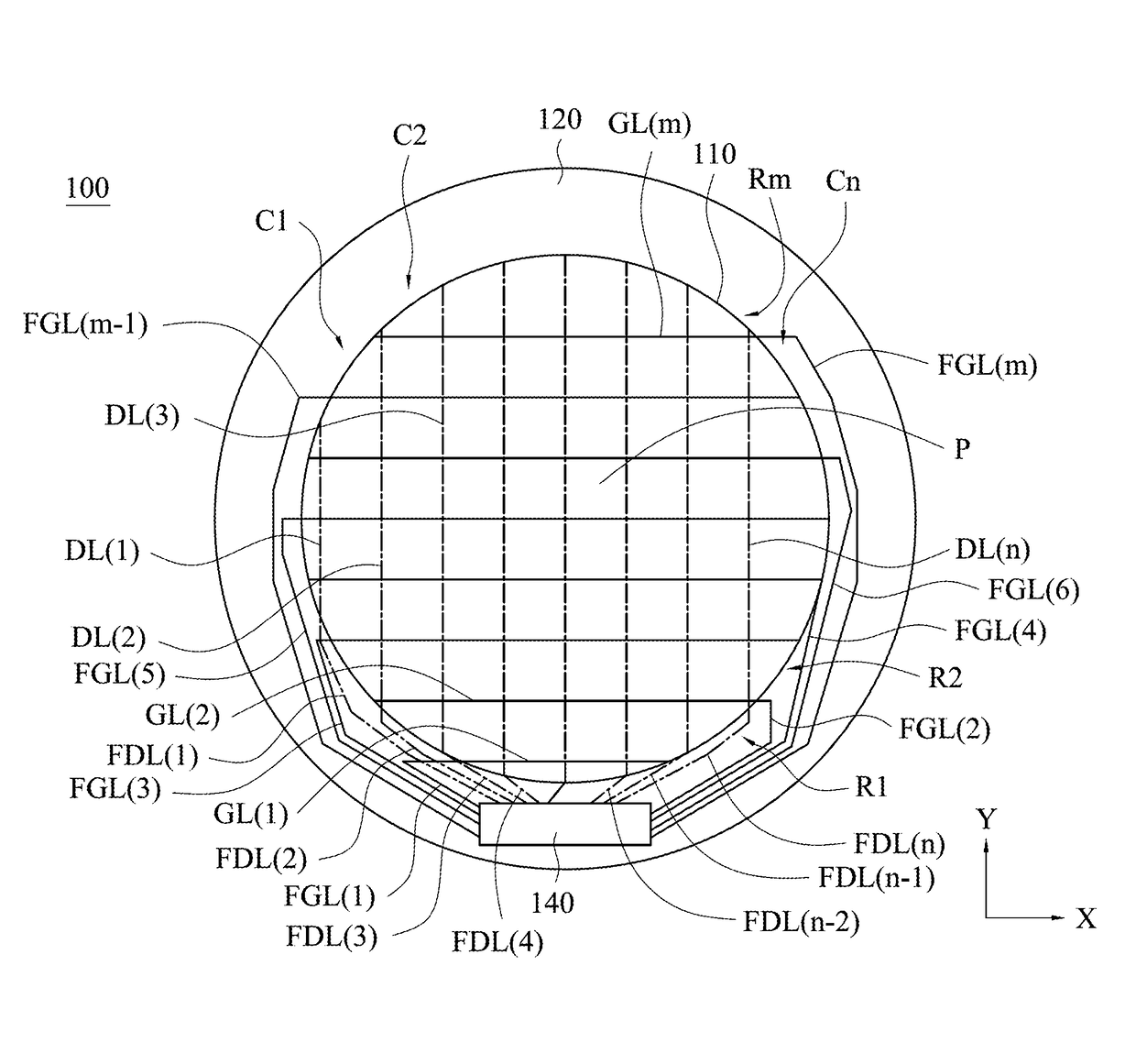

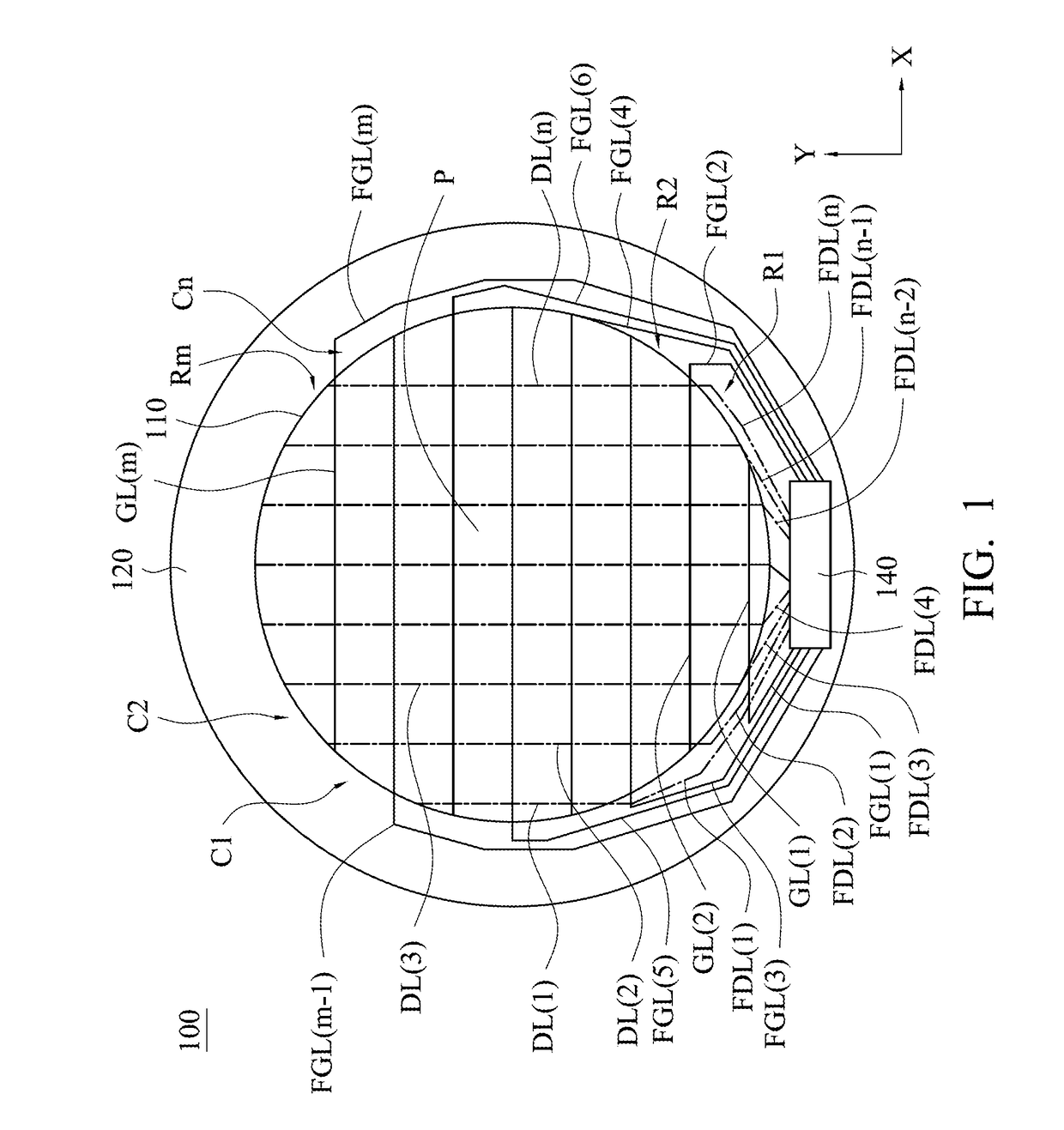

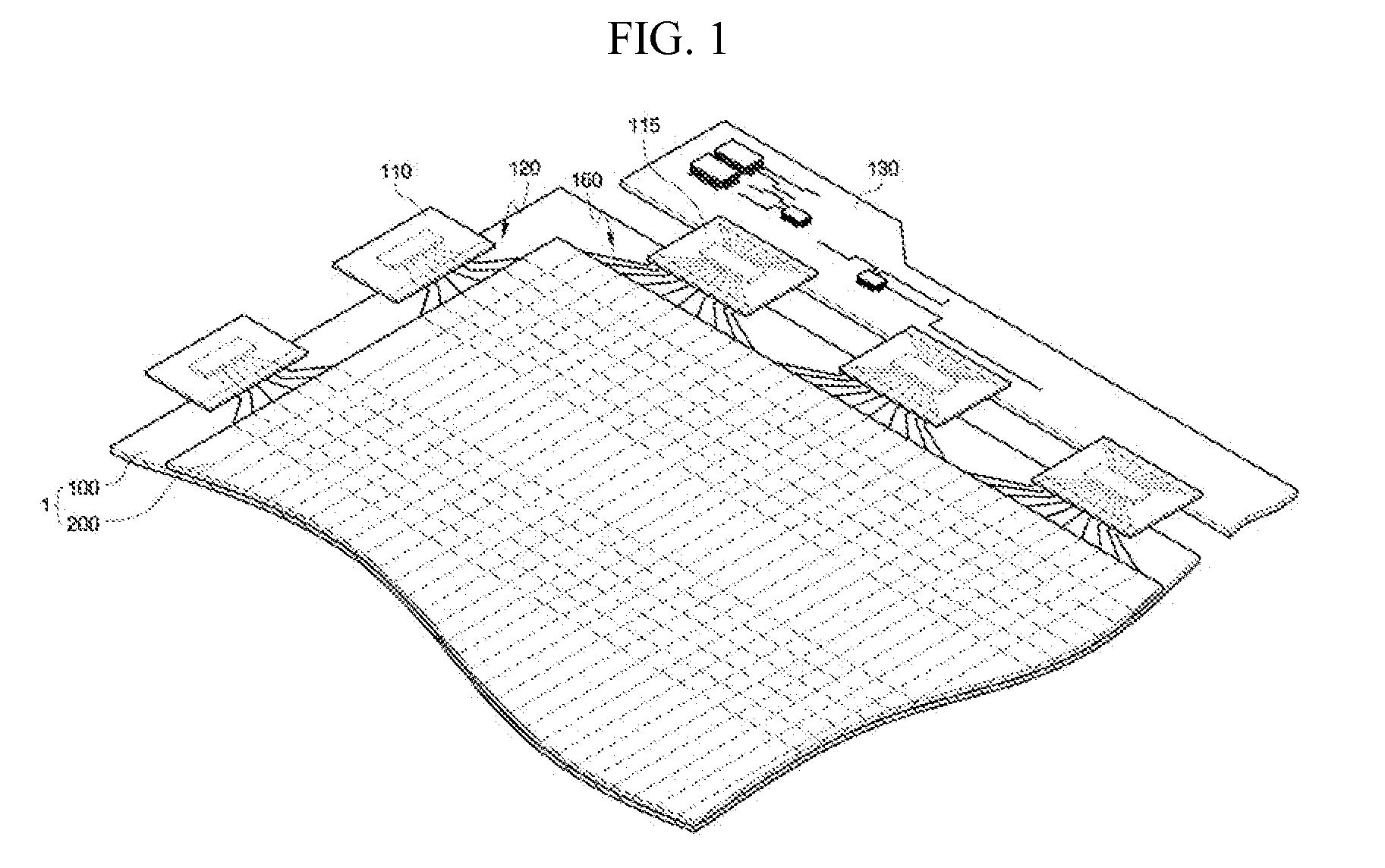

InactiveUS20170309644A1Display device is narrowedNarrow bezelStatic indicating devicesSolid-state devicesDisplay deviceEngineering

The display device includes a display area, a non-display area, pixel structures, gate lines, data lines, first fan-out conductive lines, second fan-out conductive lines and a driving circuit. The shape of the display area is non-rectangular. The pixel structures, the gate lines and the data lines are disposed in the display area. The first fan-out conductive lines are disposed in the non-display area, and are coupled to the gate lines. The second fan-out conductive lines are disposed in the non-display area, and are coupled to the data lines. The driving circuit is coupled to the first fan-out conductive lines and the second fan-out conductive lines. The first fan-out conductive lines and the second fan-out conductive lines are formed in at least three different conductive layers.

Owner:HANNSTAR DISPLAY CORPORATION

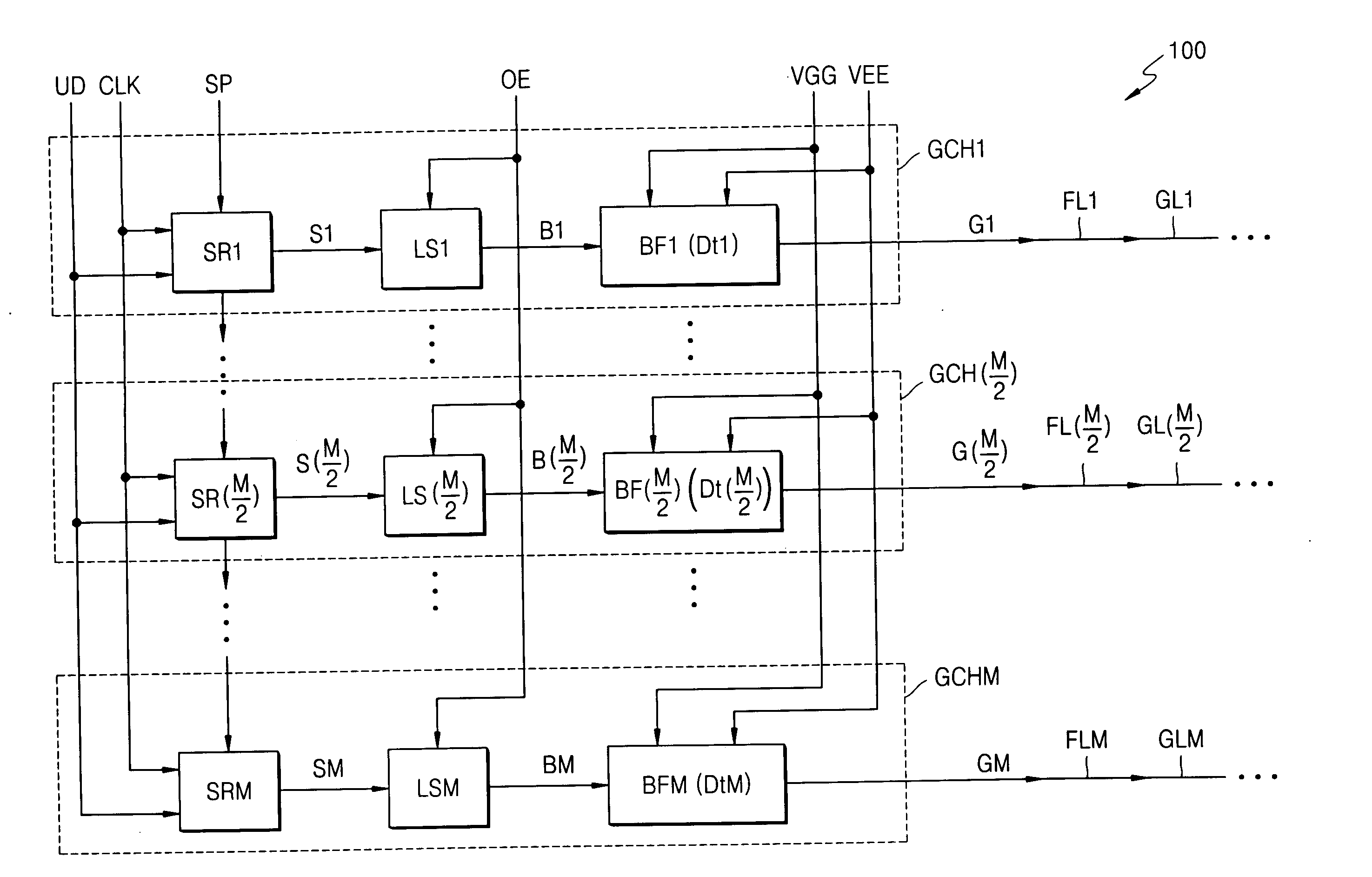

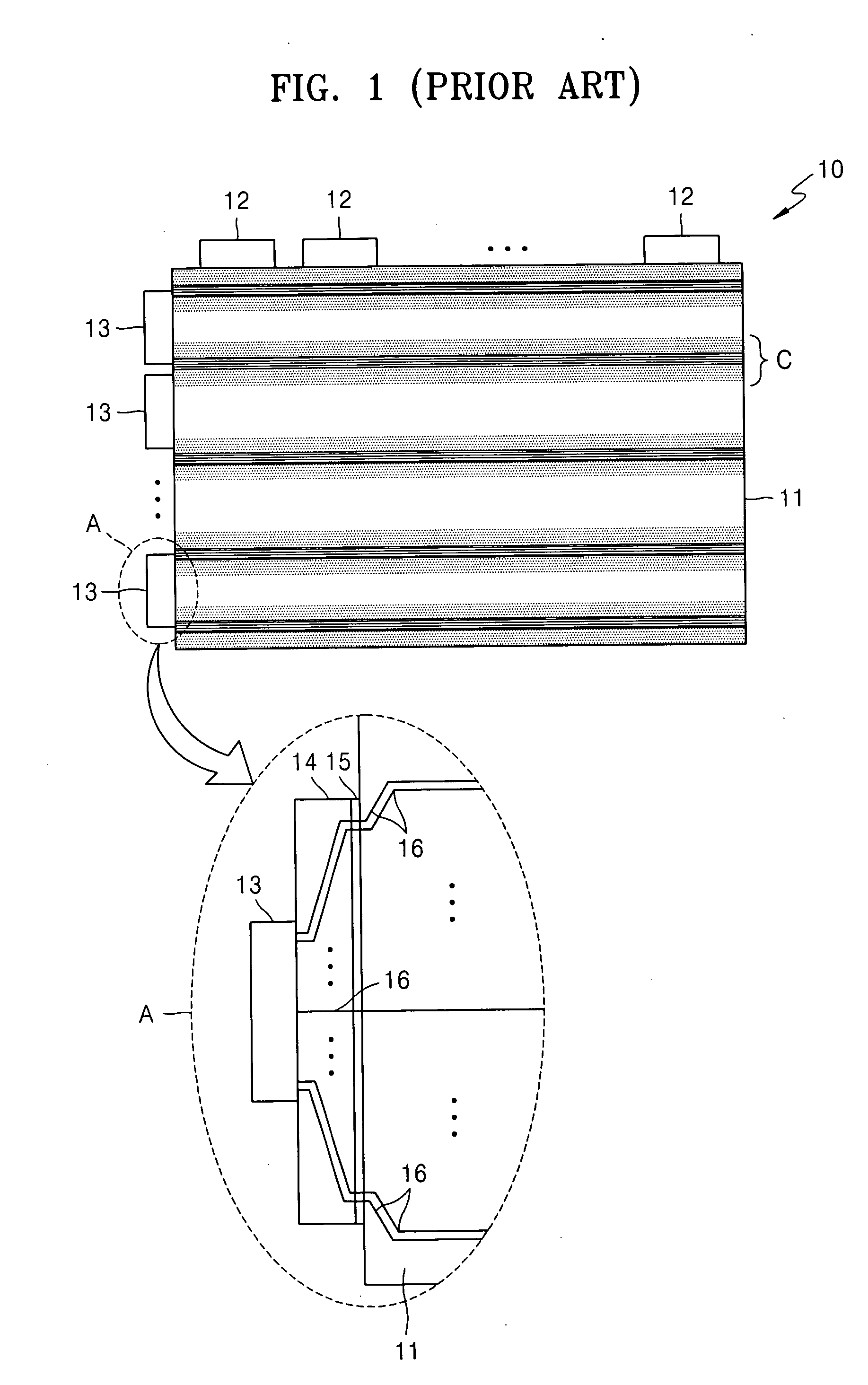

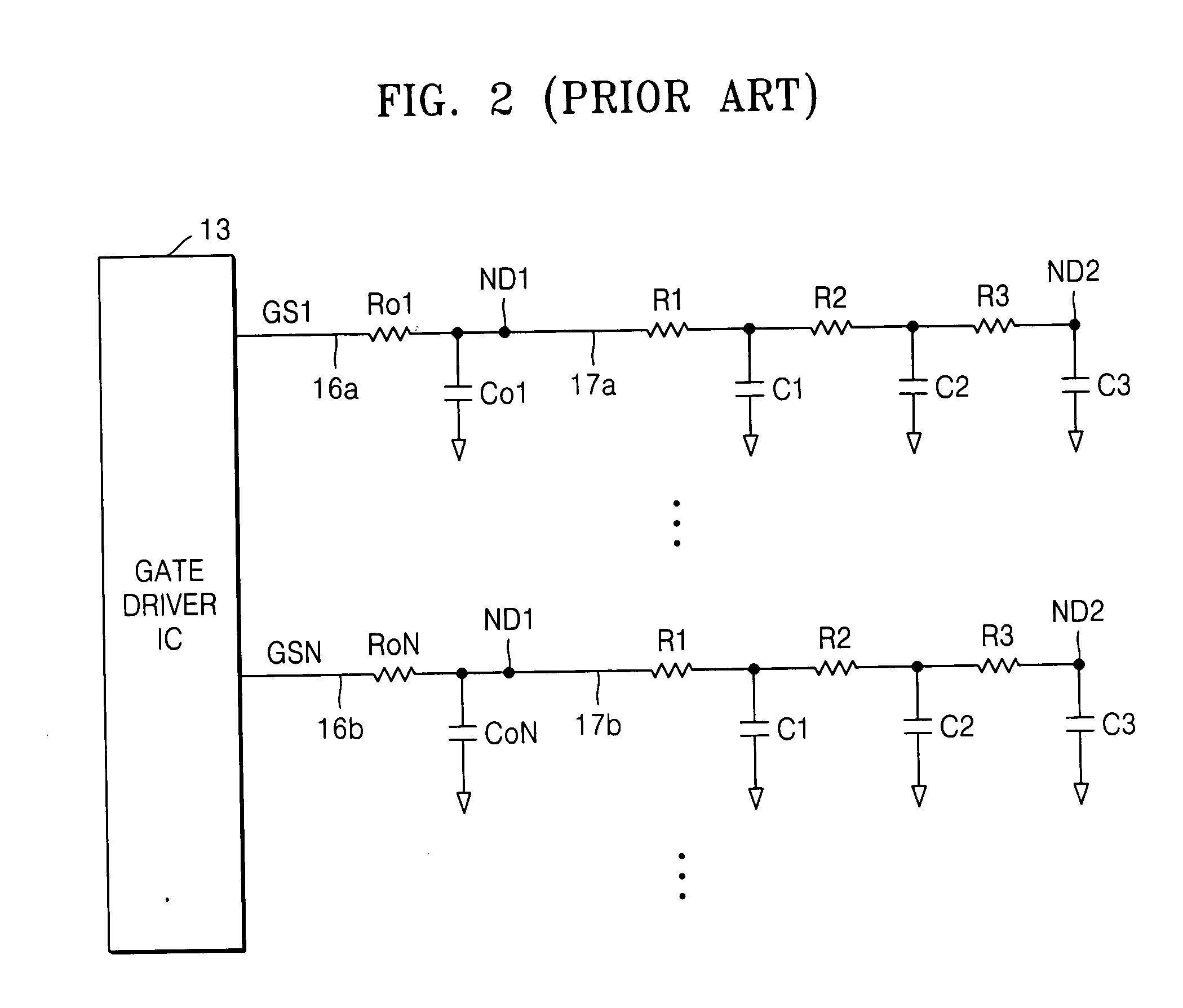

Gate line driver circuits for LCD displays

InactiveUS20060114216A1High degreeStatic indicating devicesNon-linear opticsElectrical resistance and conductanceLiquid-crystal display

A liquid crystal display (LCD) includes an LCD panel having a plurality of rows of pixel elements therein and a corresponding plurality of gate lines coupled to the plurality of rows of pixel elements. A gate line driver is also provided. The gate line driver is electrically coupled to the plurality of gate lines by a corresponding plurality of fan-out lines having unequal lengths and unequal resistance values. The gate line driver includes at least first and second buffers coupled to first and second ones of the plurality of fan-out lines, respectively. The first and second buffers having unequal pull-up impedances that inversely compensate for the unequal resistance values of the first and second ones of the plurality of fan-out lines.

Owner:SAMSUNG ELECTRONICS CO LTD

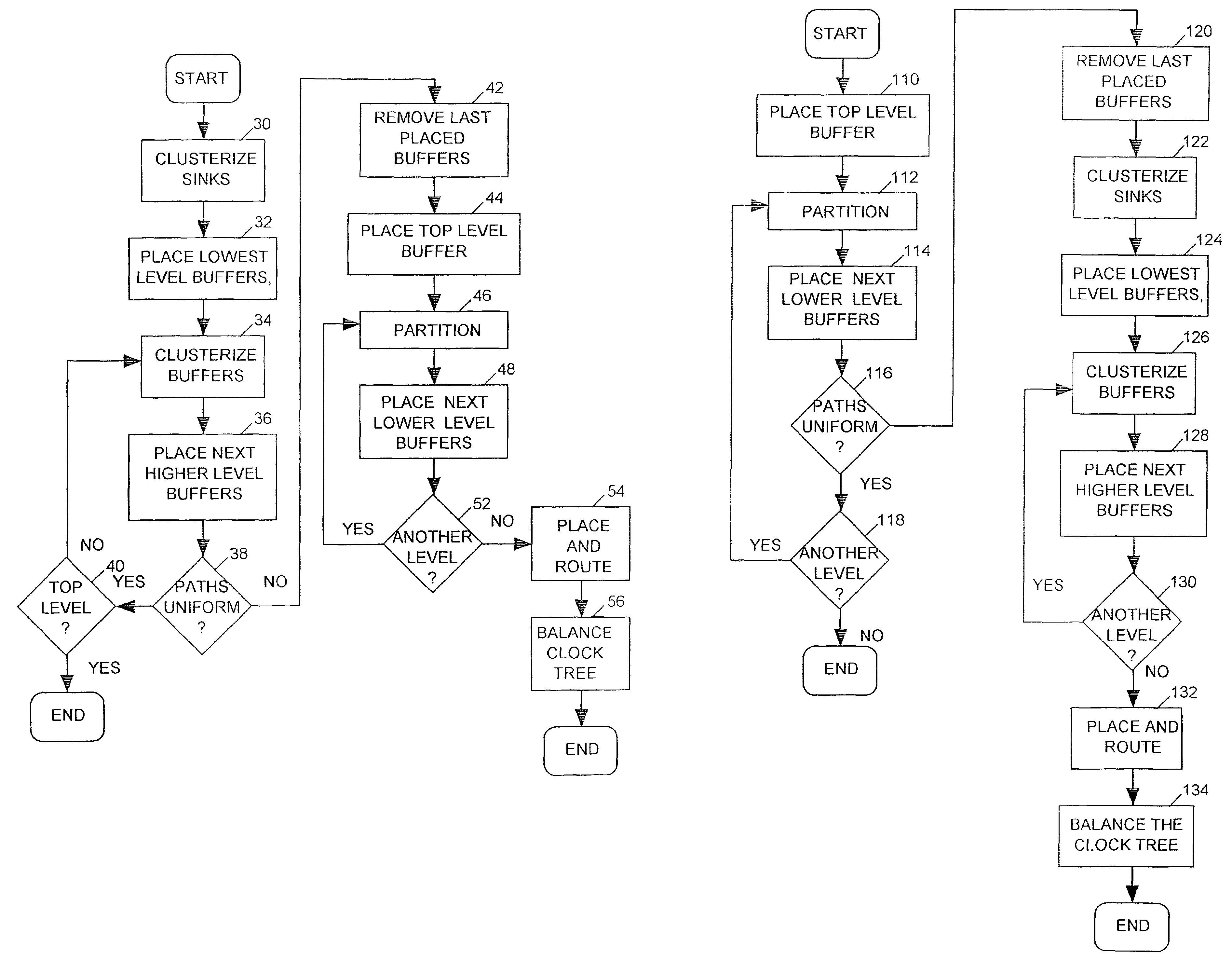

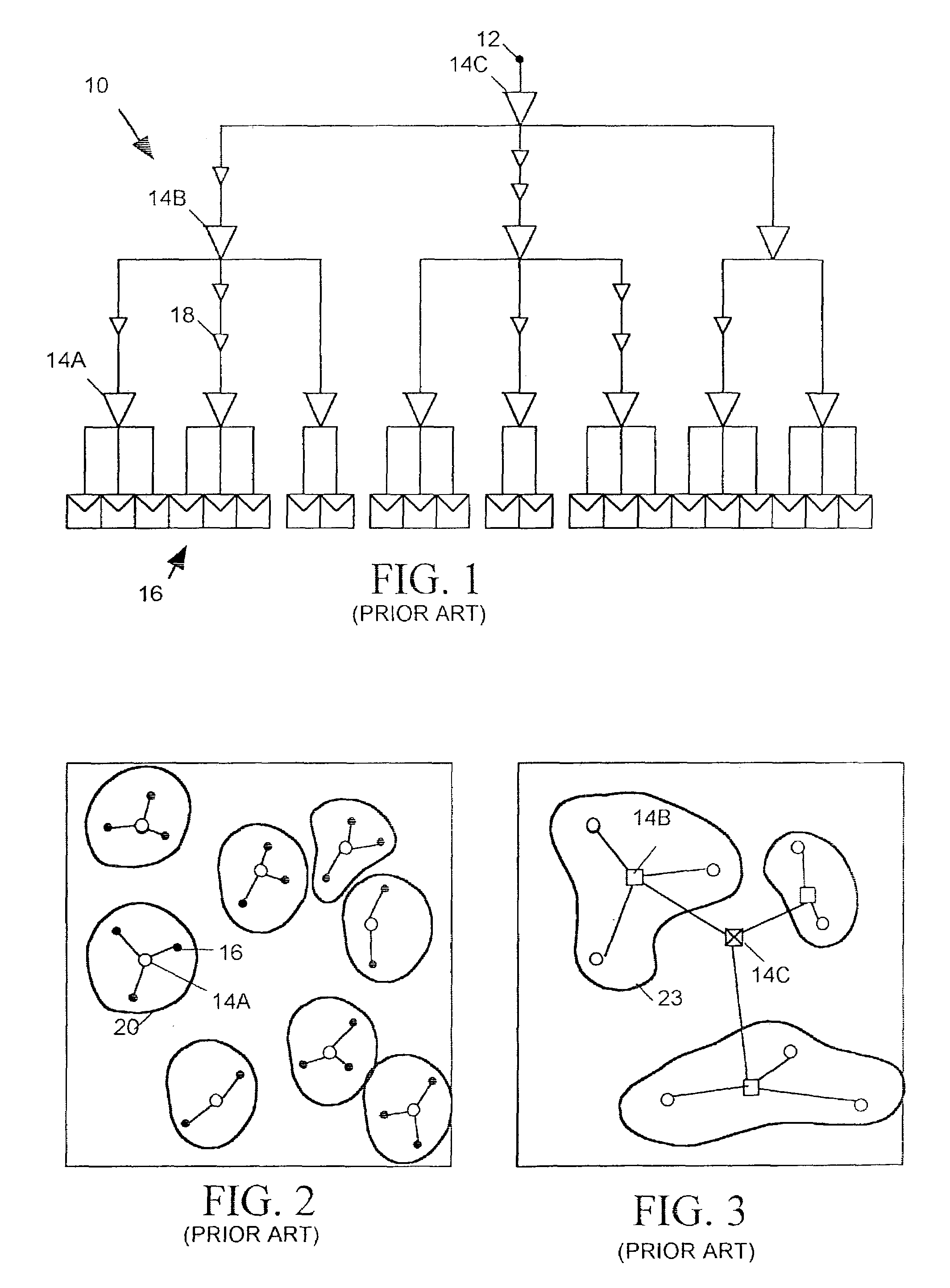

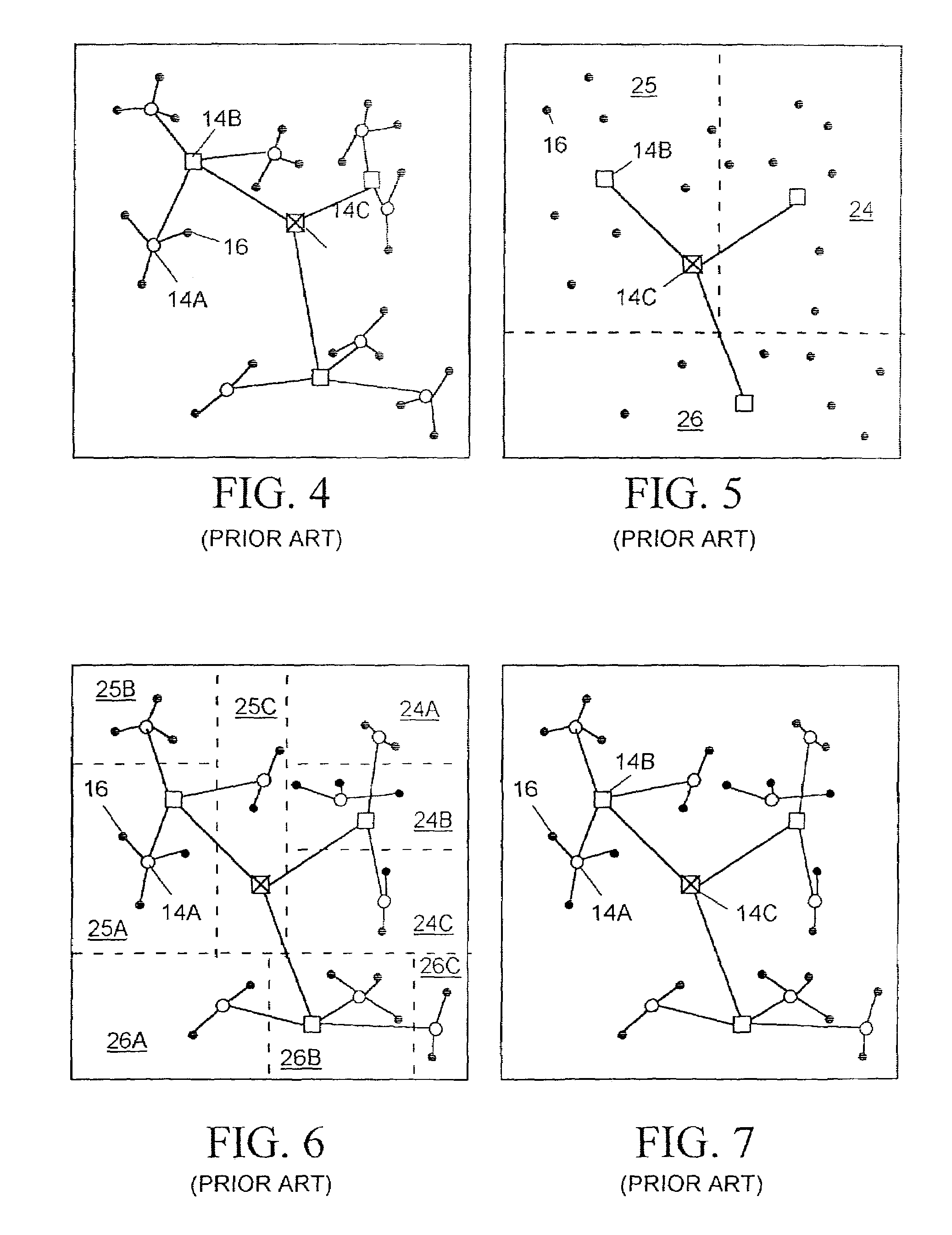

Two-stage clock tree synthesis with buffer distribution balancing

InactiveUS7051310B2Improve uniformityUniform signalElectrical apparatusCAD circuit designParallel computingClock tree synthesis

A clock tree synthesis (CTS) tool determines how to position a hierarchy of buffers for fanning out a clock signal to clocked devices (“sinks”) within an integrated circuit (IC). The tool first clusterizes the sinks and places a lowest level fan-out buffer near each cluster. The tool then iteratively places progressively higher level buffers by clusterizing a last-placed buffer level and then placing a next higher level buffer near the centroid of each lower level buffer cluster, until the tool has placed buffers at a mid-level for which variation in path distances between that level and a next higher buffer level exceeds a predetermined limit. The CTS tool then places a top level buffer at the centroid of the mid-level buffers, divides the layout into partitions, each containing a similar number of mid-level buffers, and then places a second-highest level buffer in each partition. The CTS iteratively places each next lower buffer level by dividing each partition into progressively smaller partitions and placing progressively lower level buffers in each smaller partition until it places buffers at a level having sufficient number of buffers to drive the mid-level buffers.

Owner:CADENCE DESIGN SYST INC

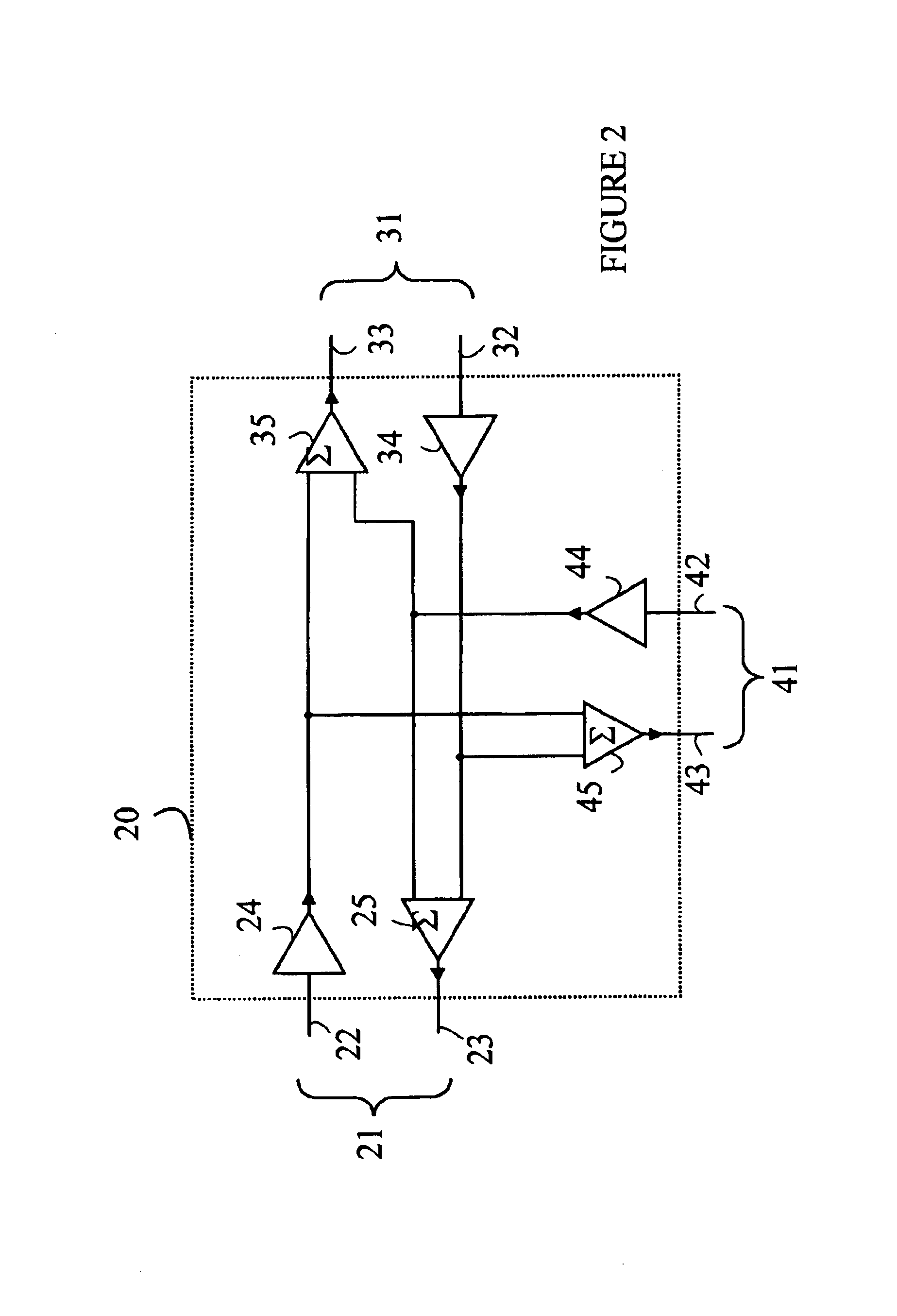

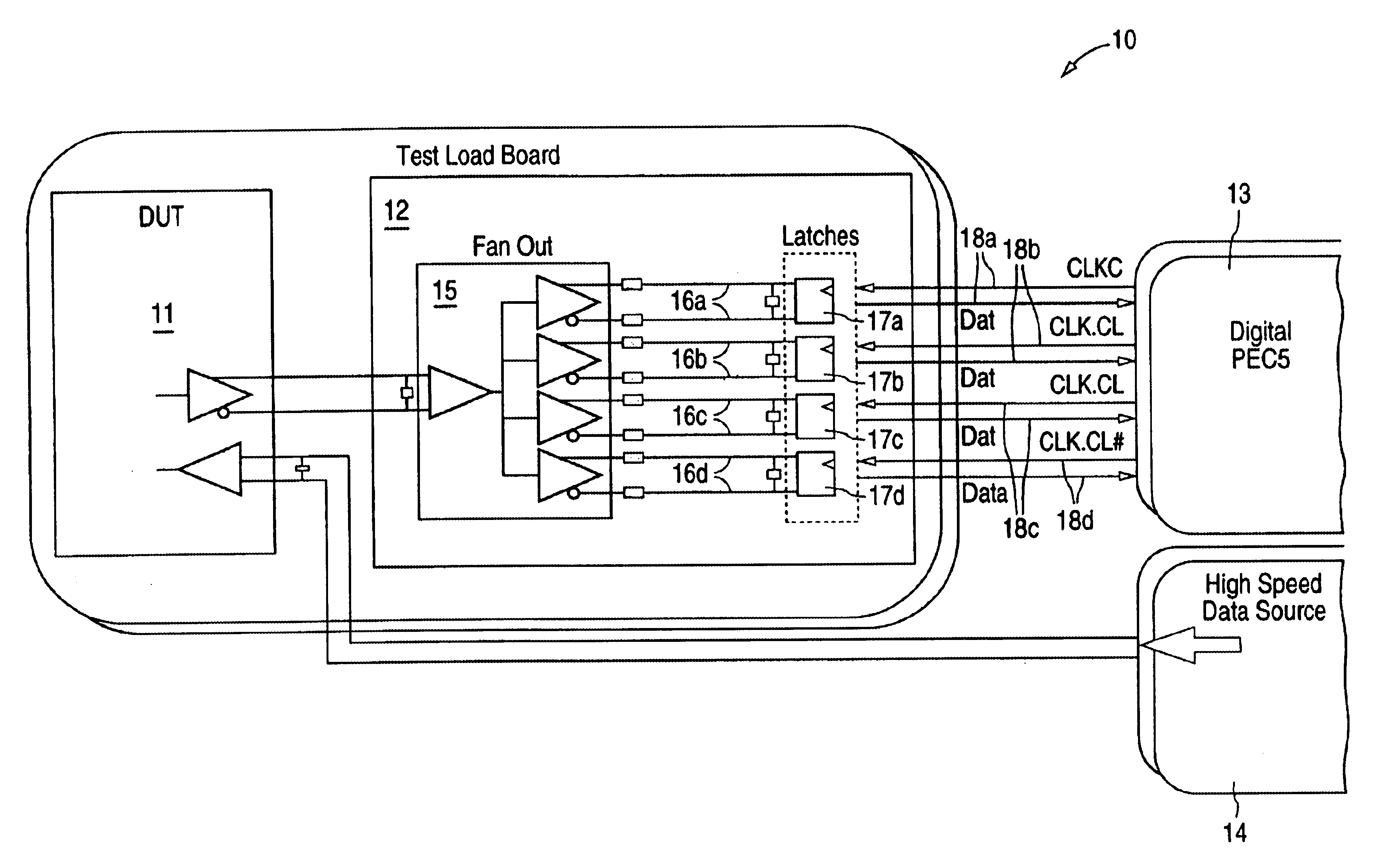

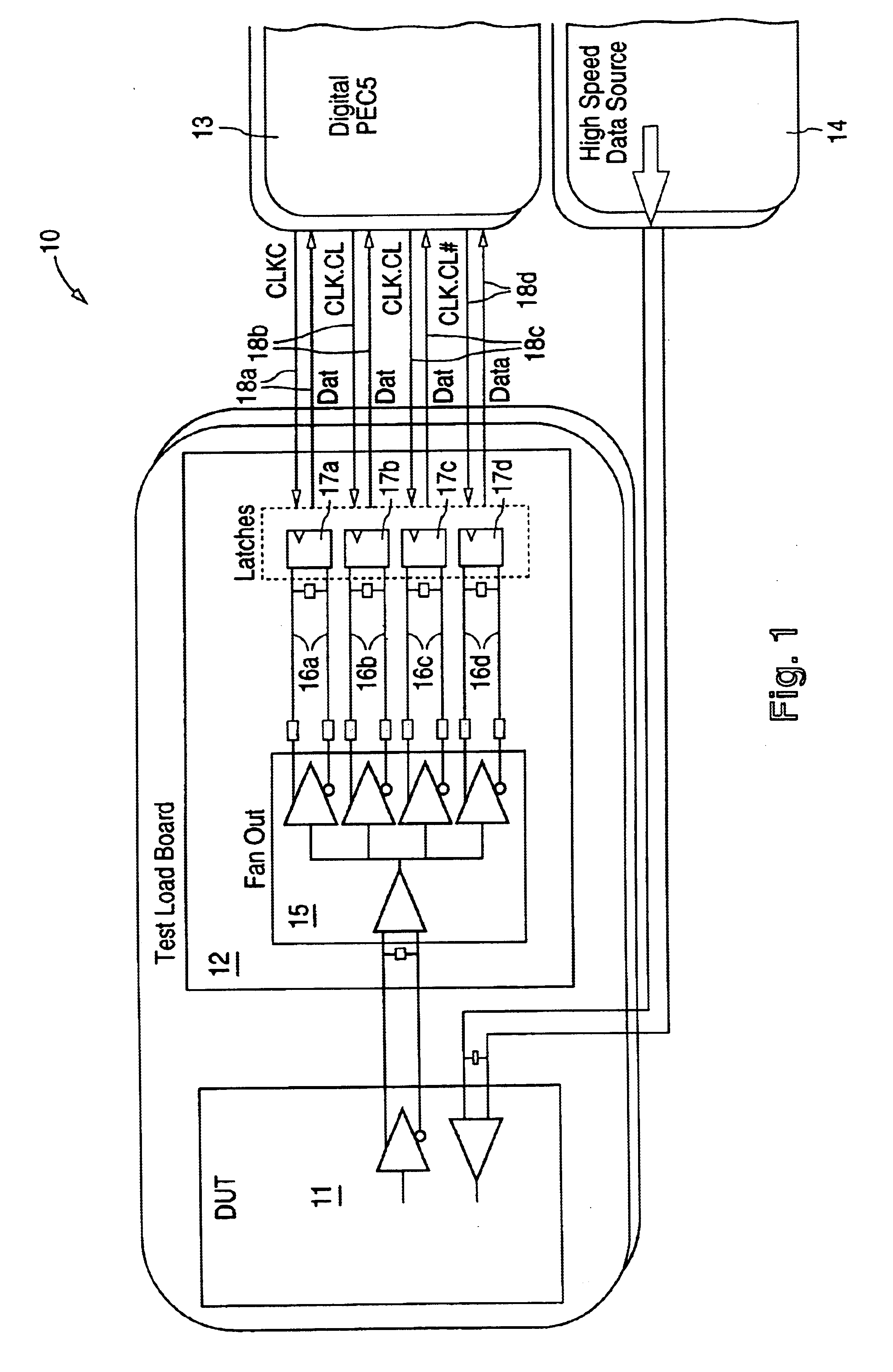

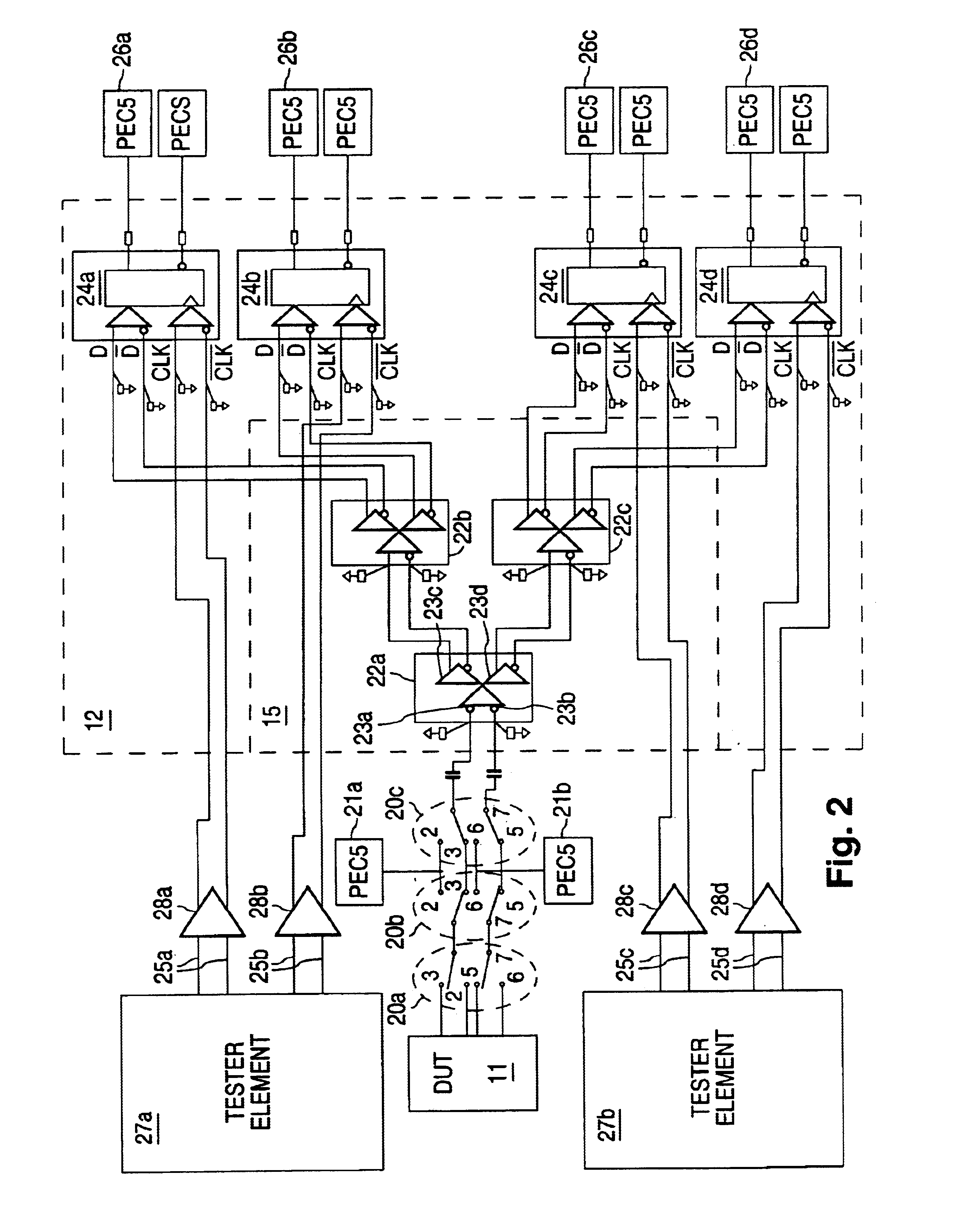

Method and apparatus for high speed IC test interface

InactiveUS6859902B1Save the total testing timeEffective real-time captureDigital circuit testingError detection/correctionData streamCommunication device

A testing method and circuit used to test high-speed communication devices on Automatic Test Equipment—ATE. The method and circuit provide a solution to testing very high speed (2.5 Gbps and above) integrated circuits. The circuit fans out the data streams from the output of the Device Under Test (DUT) to multiple tester channels which under-sample the streams. The testing method and circuit also allow for the injection of jitter into to the DUT at the output of the DUT. The skipping of data bits inherent in multi-pass testing is avoided by duplicating the tester resources to achieve effective real-time capture (saving test time and improving Bit Error Rate). Moreover the circuit synchronizes different DUTs with the timing of ATE hardware independent of DUT output data. Also, a calibration method is used compensate for differing trace lengths and propagation delay characteristics of test circuit components.

Owner:CREDENCE SYSTEMS

Dynamic wavelength service over a ROADM optical network

A system and method for dynamically adding / dropping wavelengths in a reconfigurable optical add-drop multiplexer (ROADM) transport network to form a wave division multiplexing virtual private network is disclosed. The system includes at least one optical transponder, a plurality of optical fan-out devices, each arranged to receive an input signal from a network degree and coupled to at least one of a plurality of optical fan-in devices, each optical fan-in device arranged to output a signal to a network degree, the optical fan-out devices comprising at least one wavelength selective switch and the optical fan-in devices comprising at least one wavelength selective switch, the optical fan-out devices and optical fan-in devices being connected so as to enable signals input from each of the plurality of network degrees to be switched to another network degree of the plurality of network degrees; a plurality of demultiplexers for locally dropping selected wavelengths; a plurality of multiplexers for locally adding selected wavelengths; and at least one customer-dedicated fiber switch interposed between the at least one optical transponder and the plurality of demultiplexers and multiplexers. The fiber switch is coupled to wavelengths and degrees that are allocated for a bandwidth-on-demand application. Other configurations include additional fan-in and fan-out devices interposed between a mux / demux assembly and the optical transponders to support wavelength redistribution applications.

Owner:AT&T INTPROP I L P

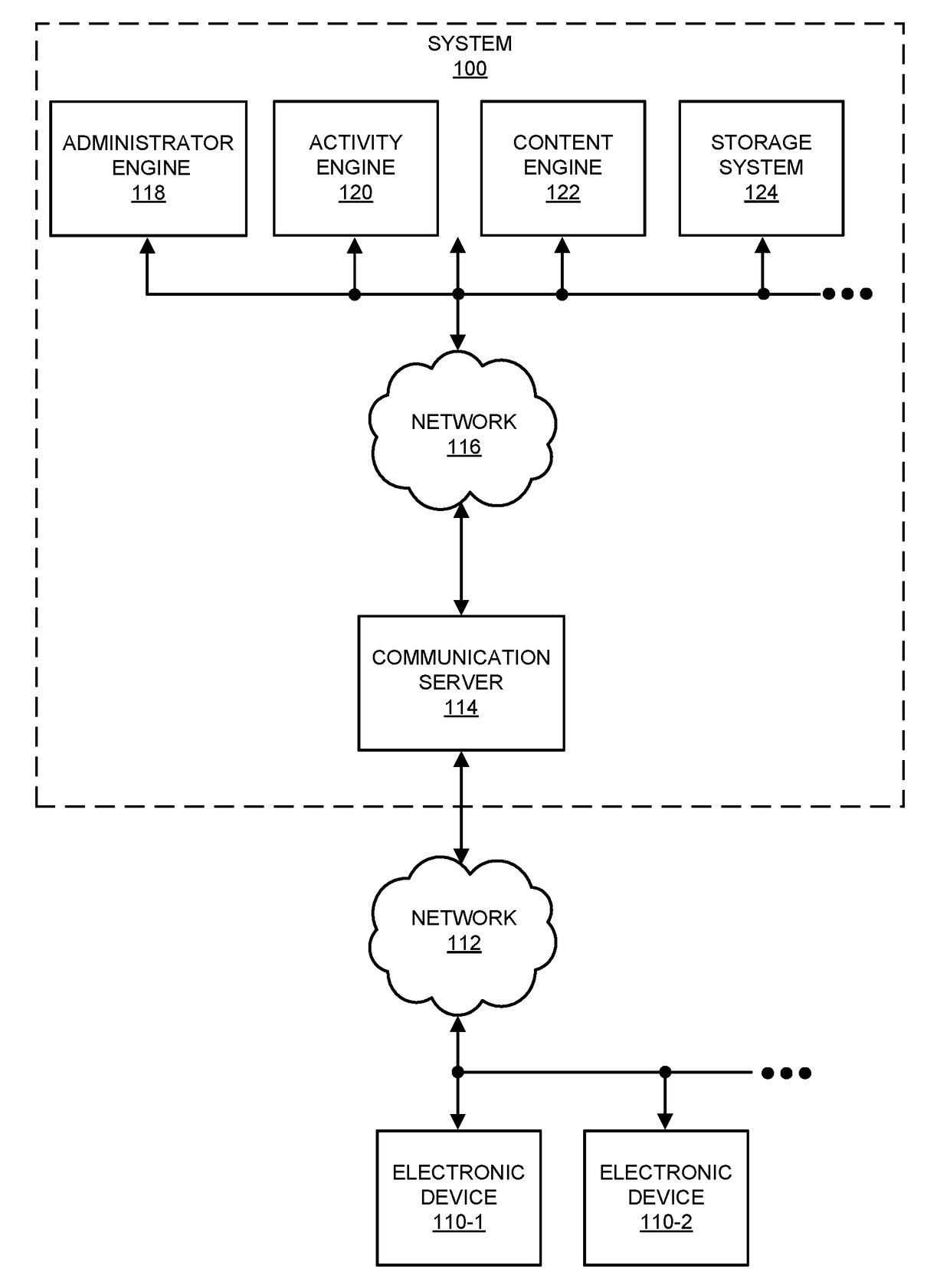

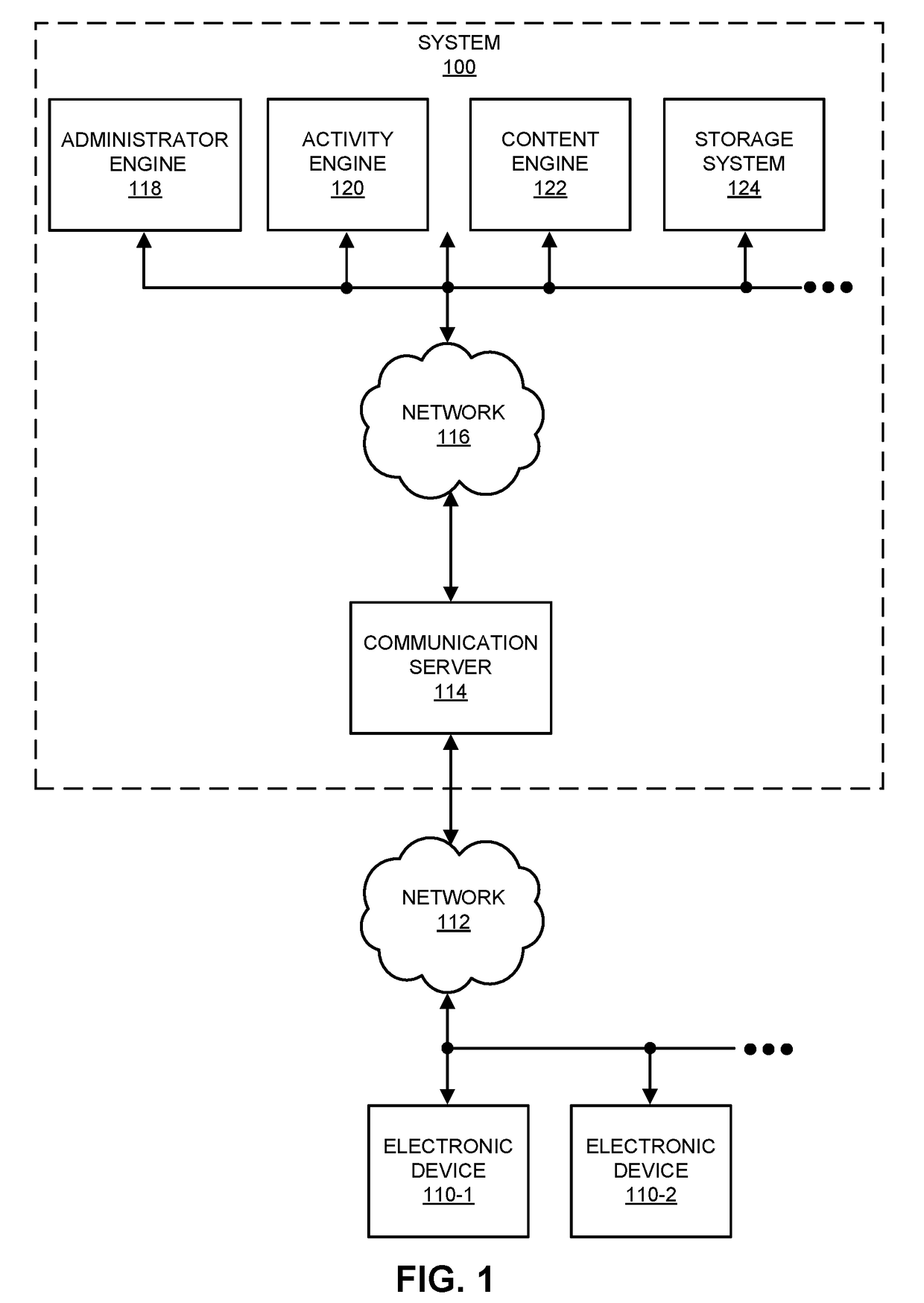

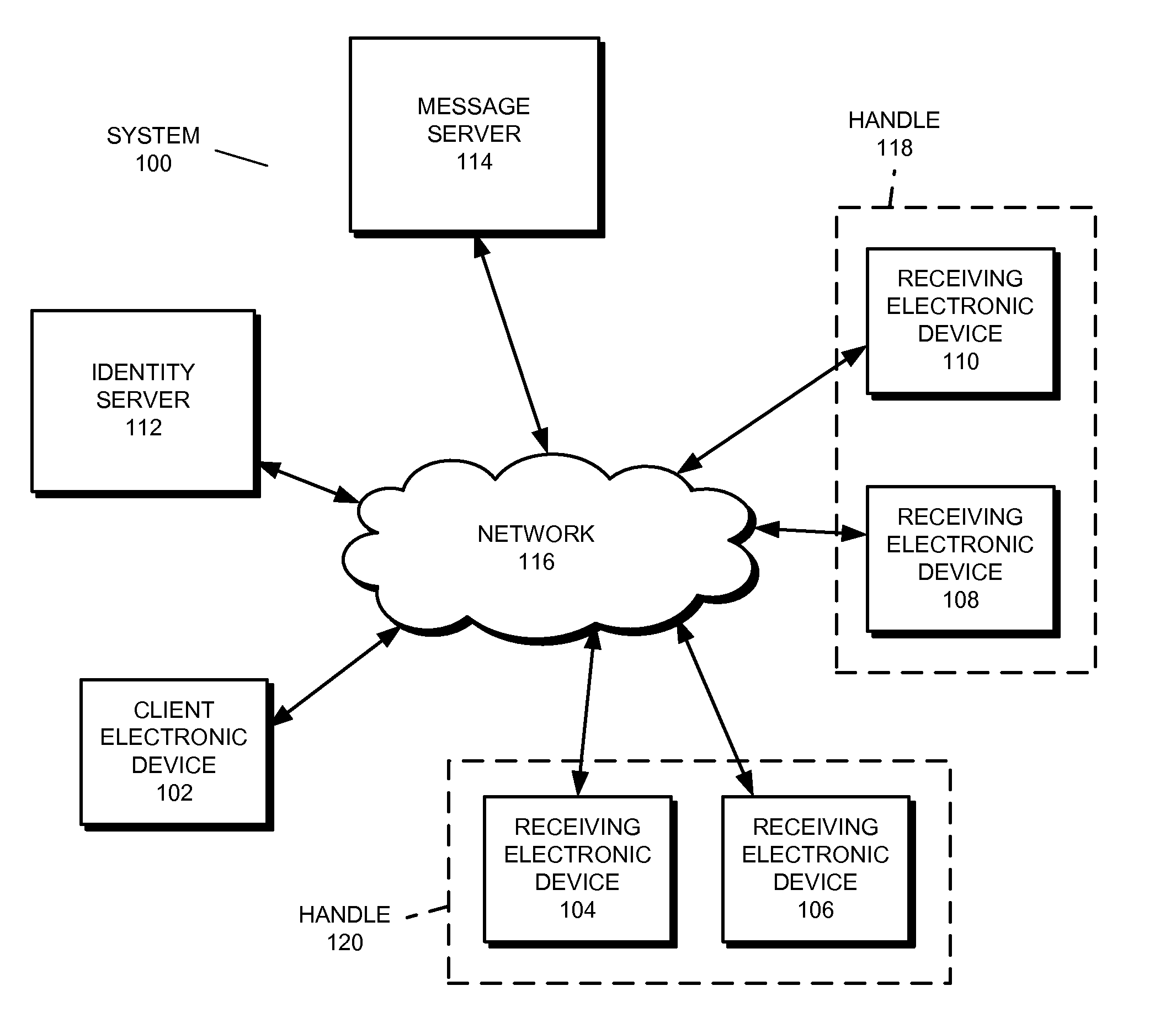

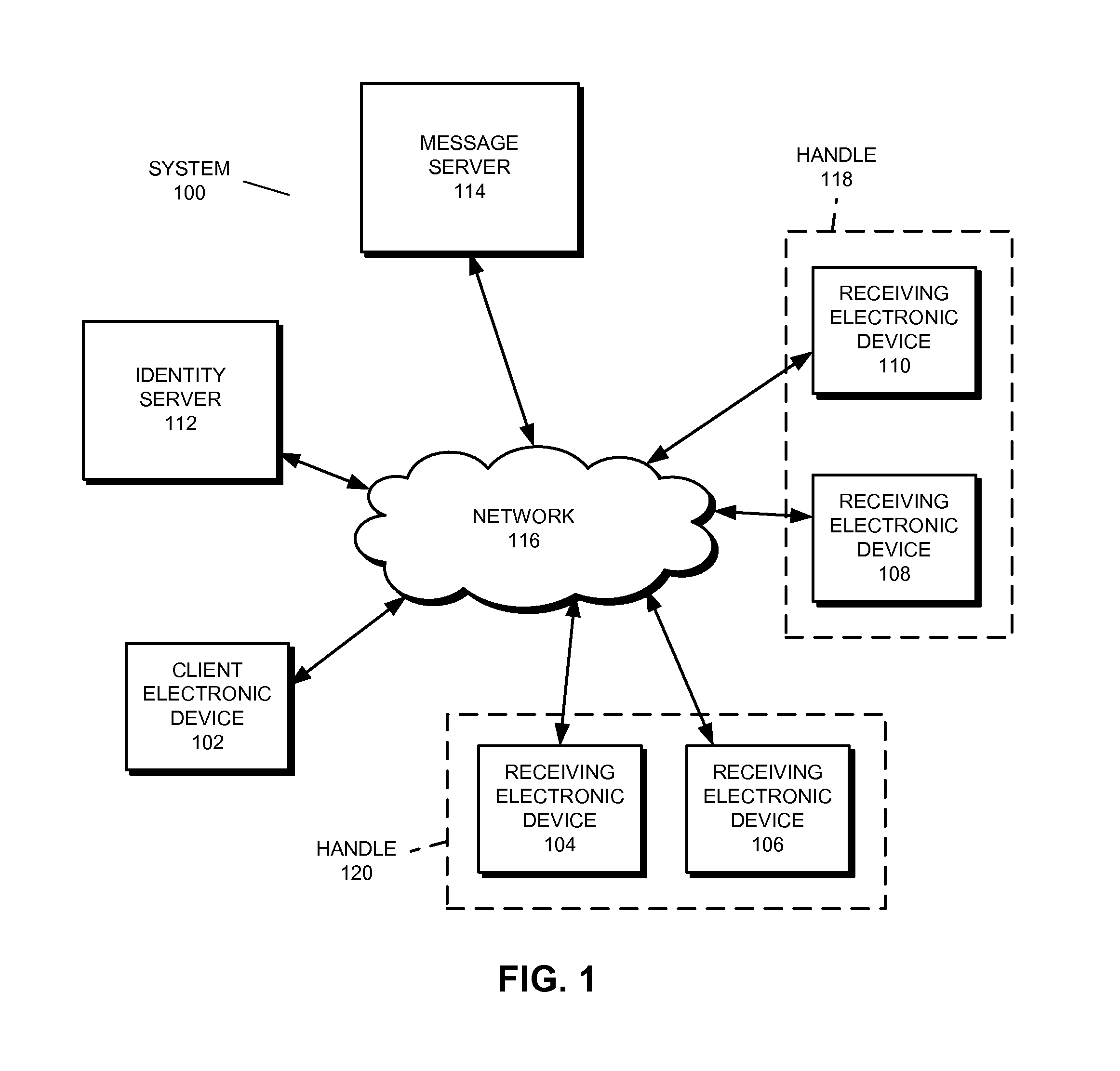

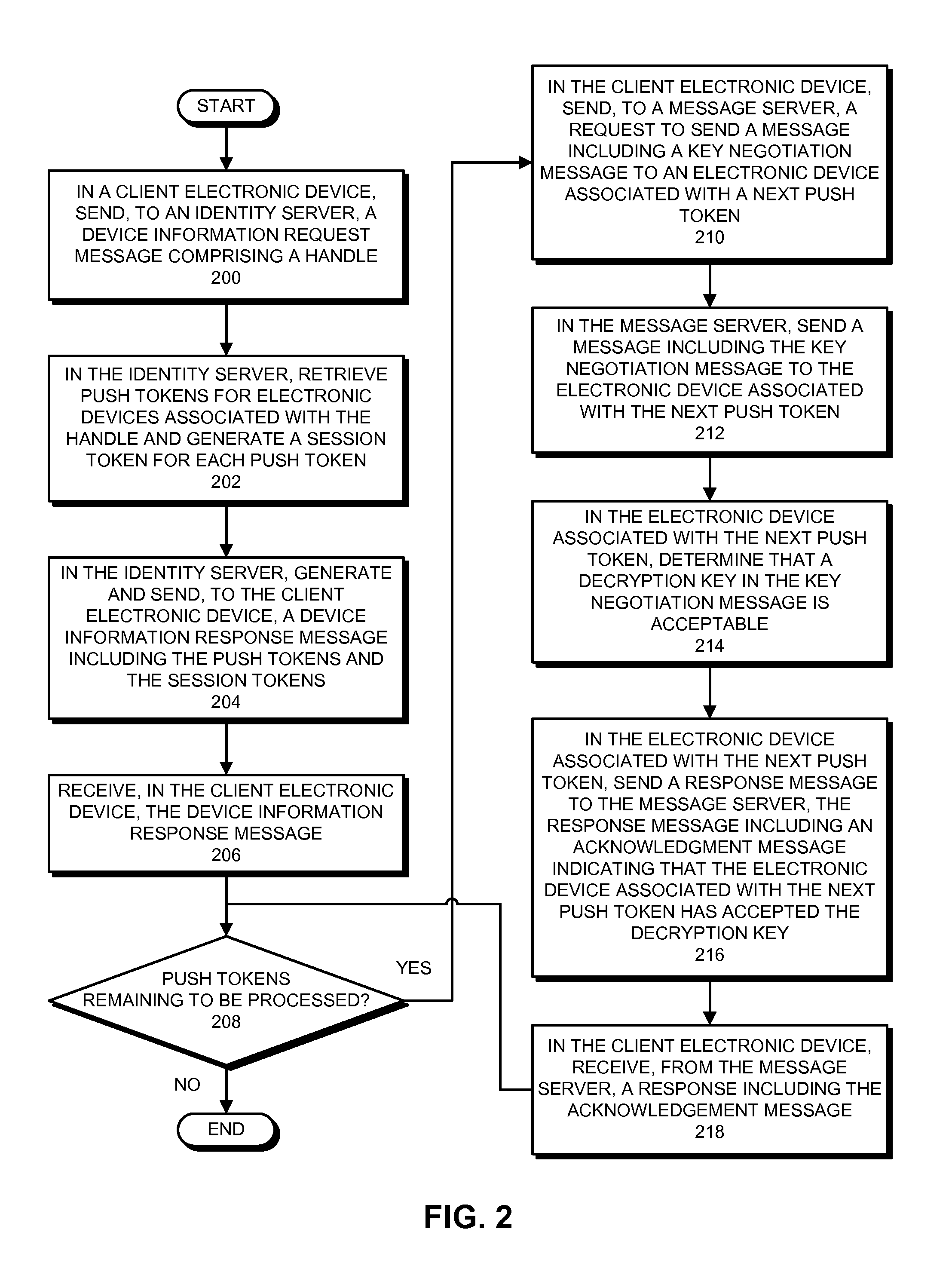

Sending messages to multiple receiving electronic devices using a message server

ActiveUS20150350119A1Key distribution for secure communicationData switching networksComputer hardwareElectronic equipment

The described embodiments include a message server that is configured to send, to multiple receiving electronic devices, corresponding messages that each include a payload acquired from a single request message received from a client electronic device. In these embodiments, the request message received from the client electronic device includes a push token for each of the receiving electronic devices and the payload. Upon receiving the request message, the message server generates, for a receiving electronic device associated with each push token, a message that includes the payload. The message server then sends each message to the corresponding receiving electronic device. In this way, the message server “fans out,” to the multiple receiving electronic devices, corresponding messages that each include the payload from the single request message.

Owner:APPLE INC

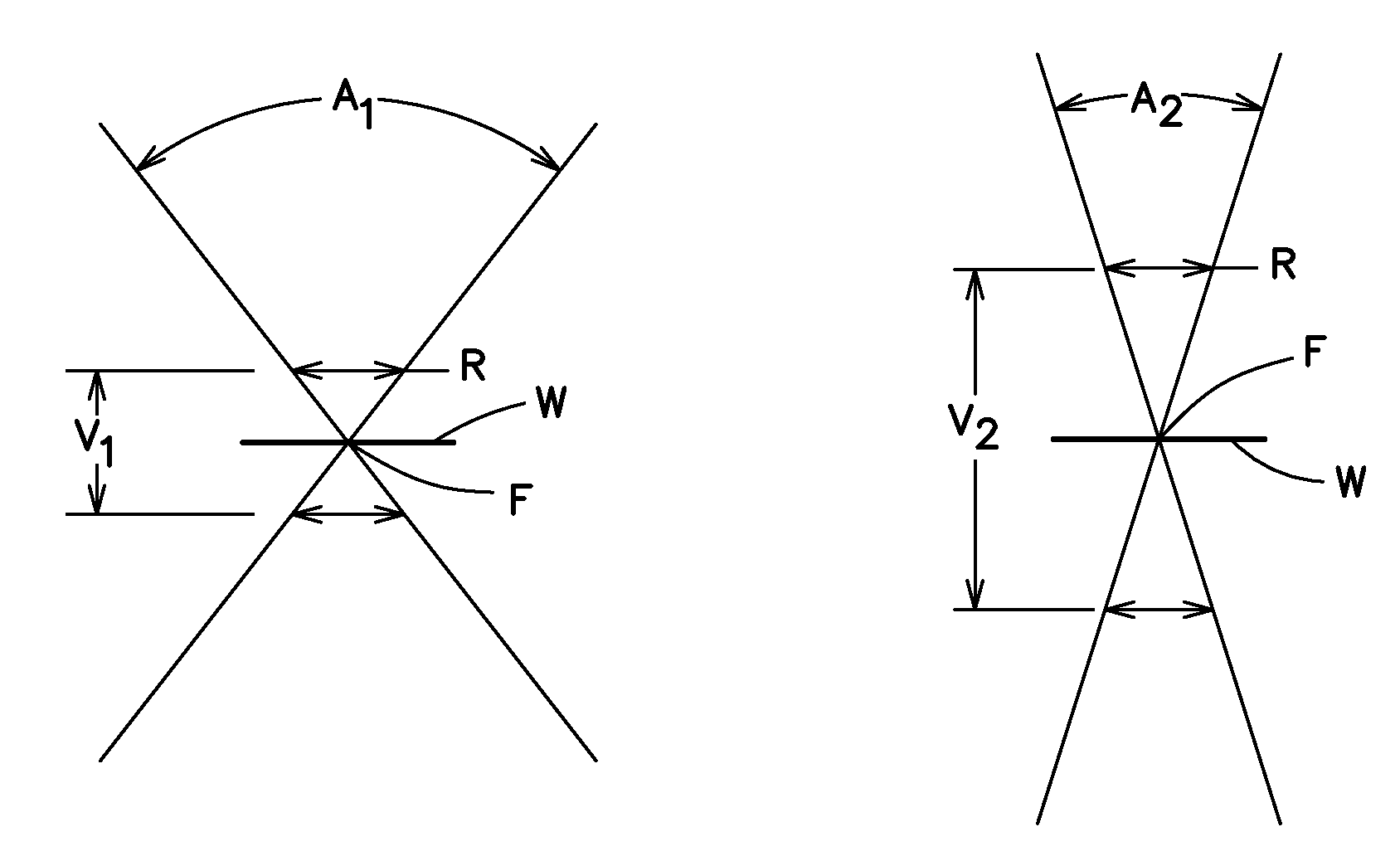

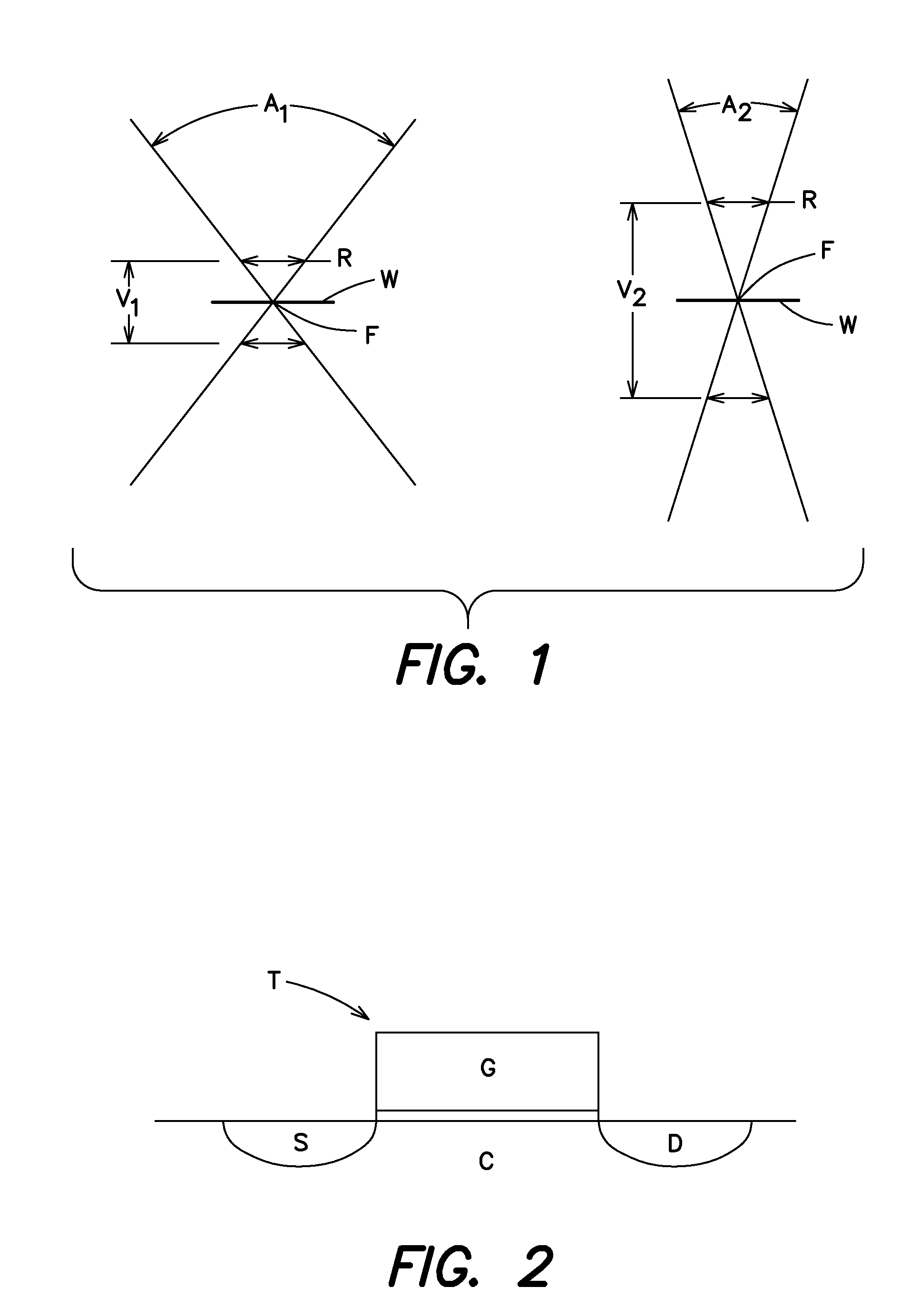

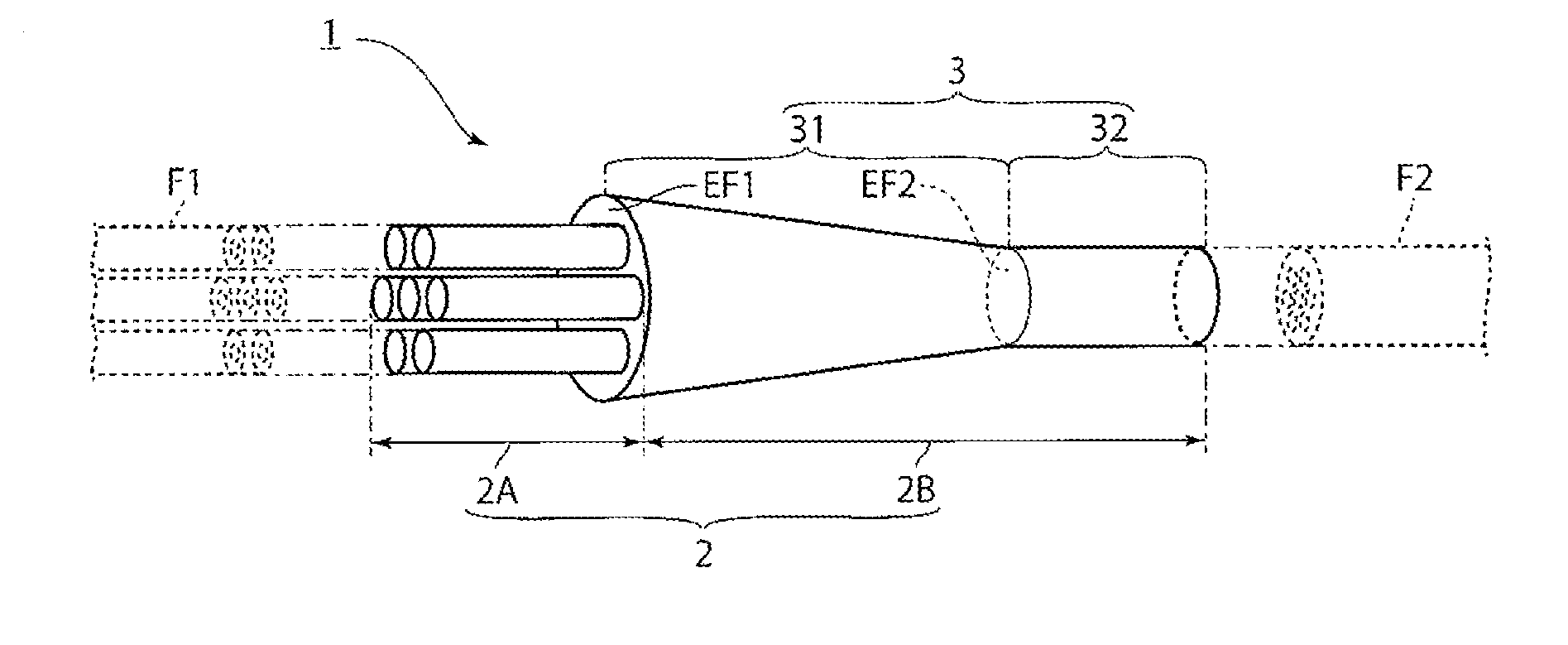

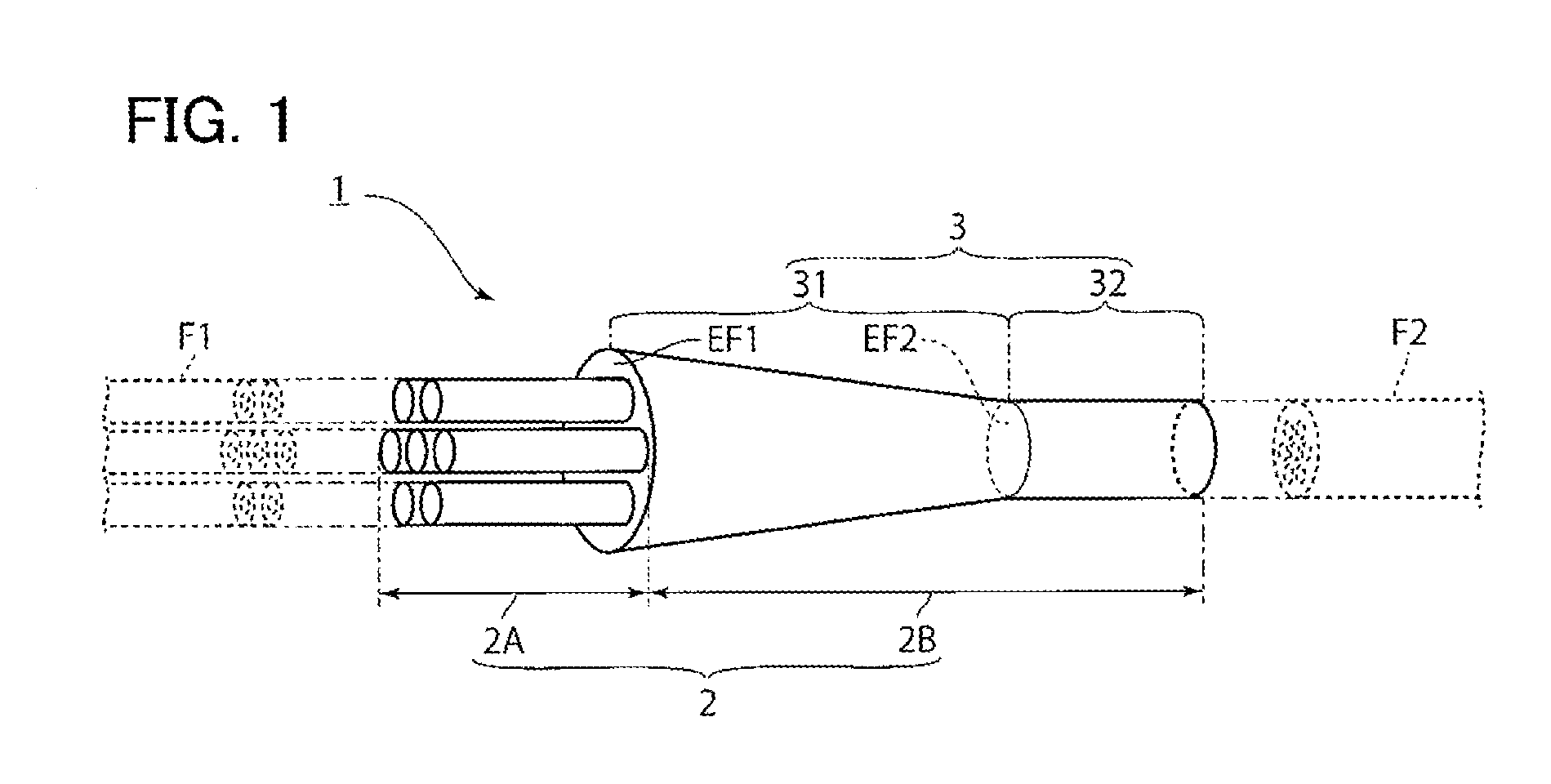

Optical fan-in/fan-out device

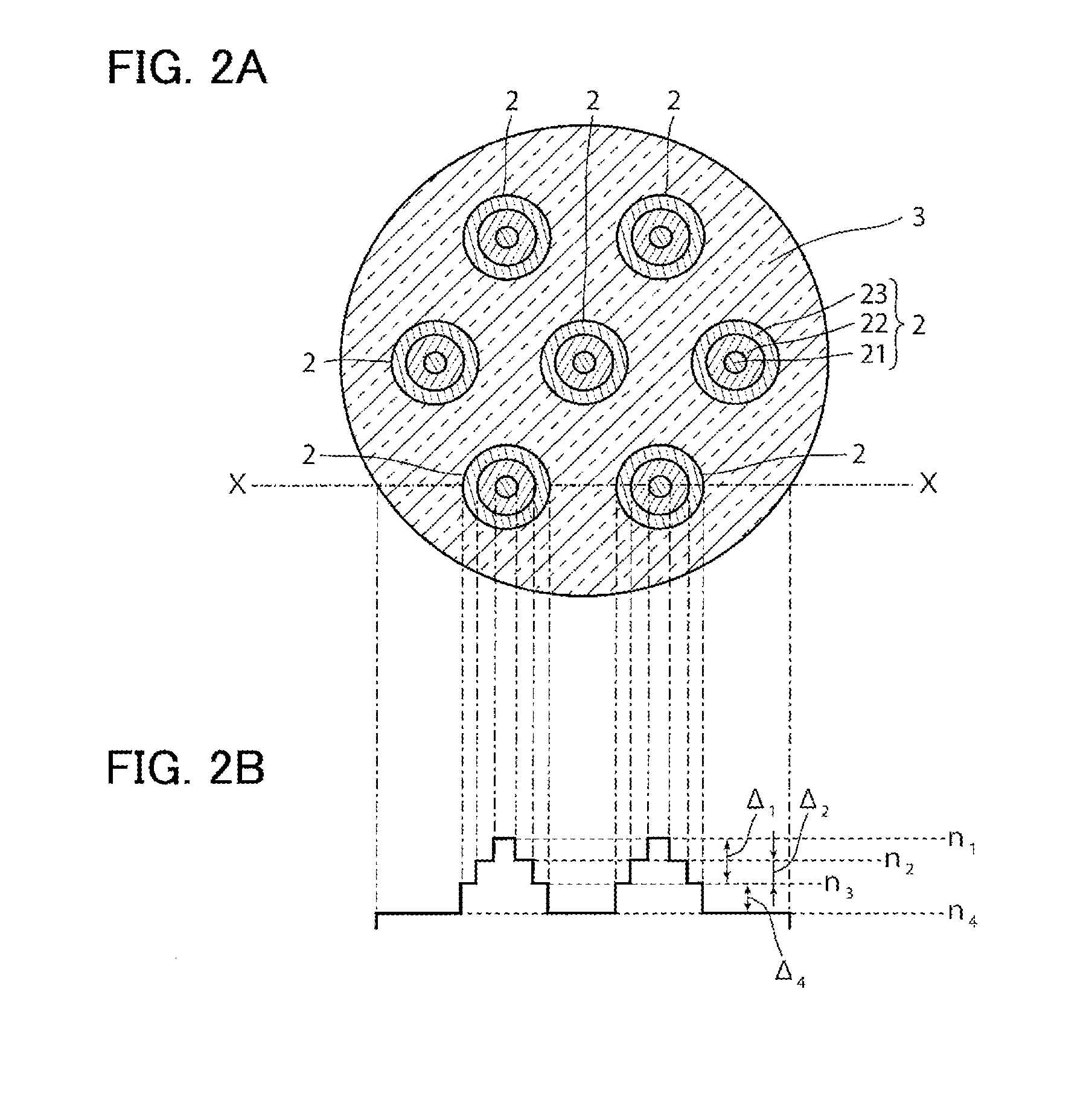

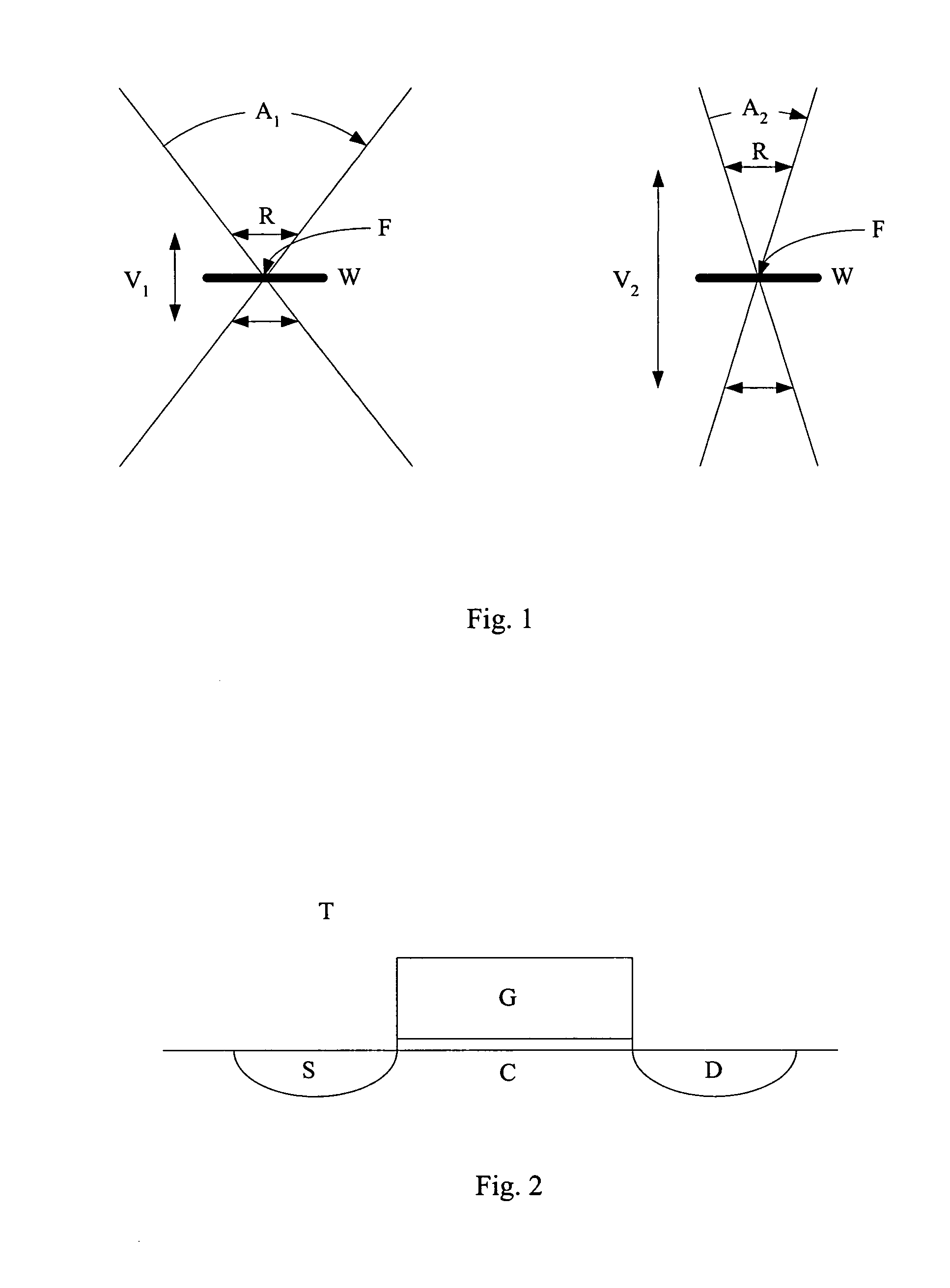

ActiveUS20140010508A1Reduce lossesOptical fibre with multilayer core/claddingMulticore optical fibreRelative refractive indexFan-out

A radius of a first core 21 in a large-diameter end surface EF1 of a tapered portion 31 is denoted by r1S, a radius of a second core 22 is denoted by r2S, a relative refractive index difference of the first core 21 with respect to a clad 23 is denoted by Δ1, a relative refractive index difference of the second core 22 with respect to the clad 23 is denoted by Δ2, a refractive index volume of the first core 21 is denoted by V1S, and a refractive index volume of the second core 22 is denoted by V2S, r2S / r1S is set to be 3 or more and 5 or less, V2S / V1S is set to be 1.07r22−13.5 or more and 1.07r22−11.5 or less, and r2S / r1S is set to be −3×Δ1 / Δ2+10 or more.

Owner:THE FUJIKURA CABLE WORKS LTD +1

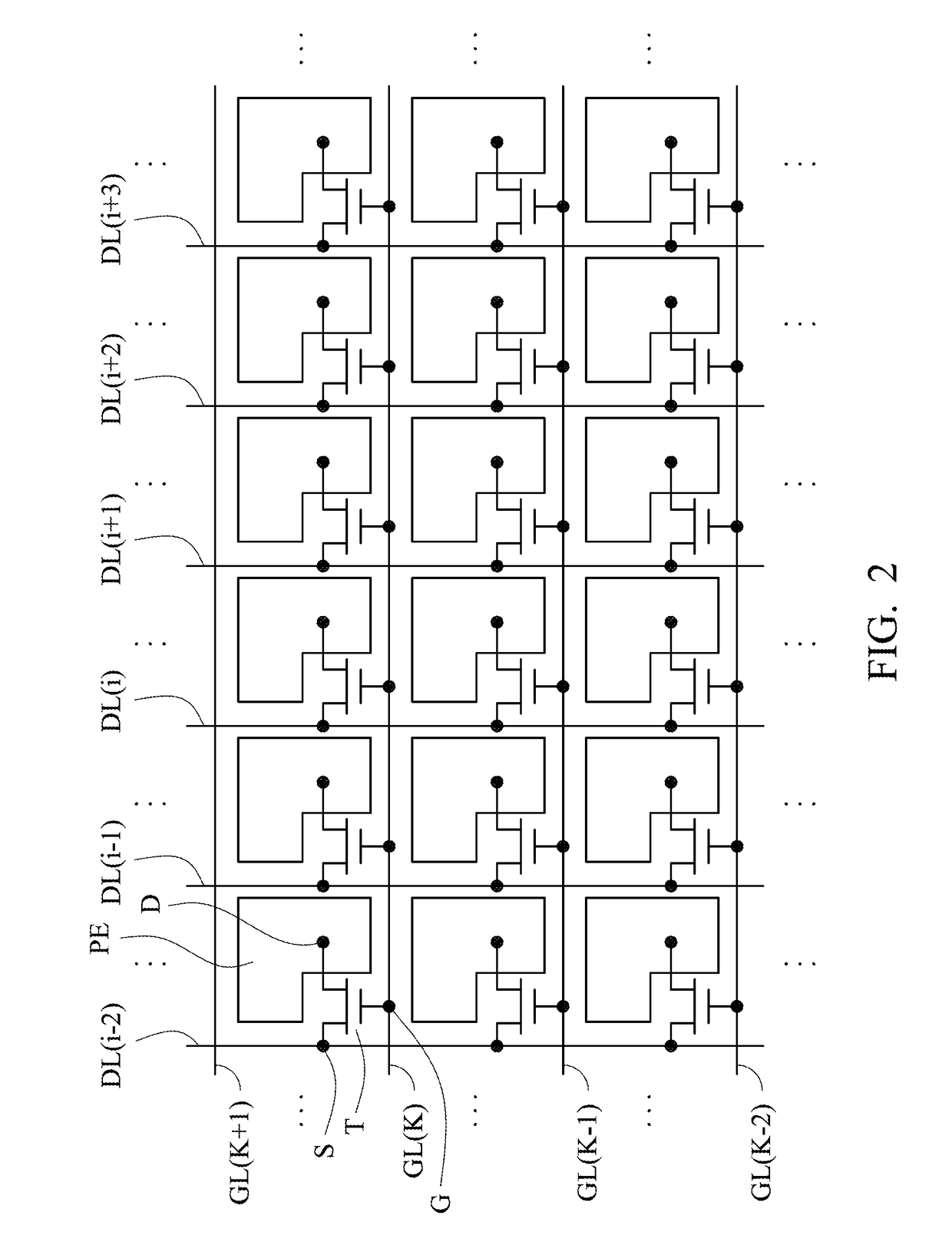

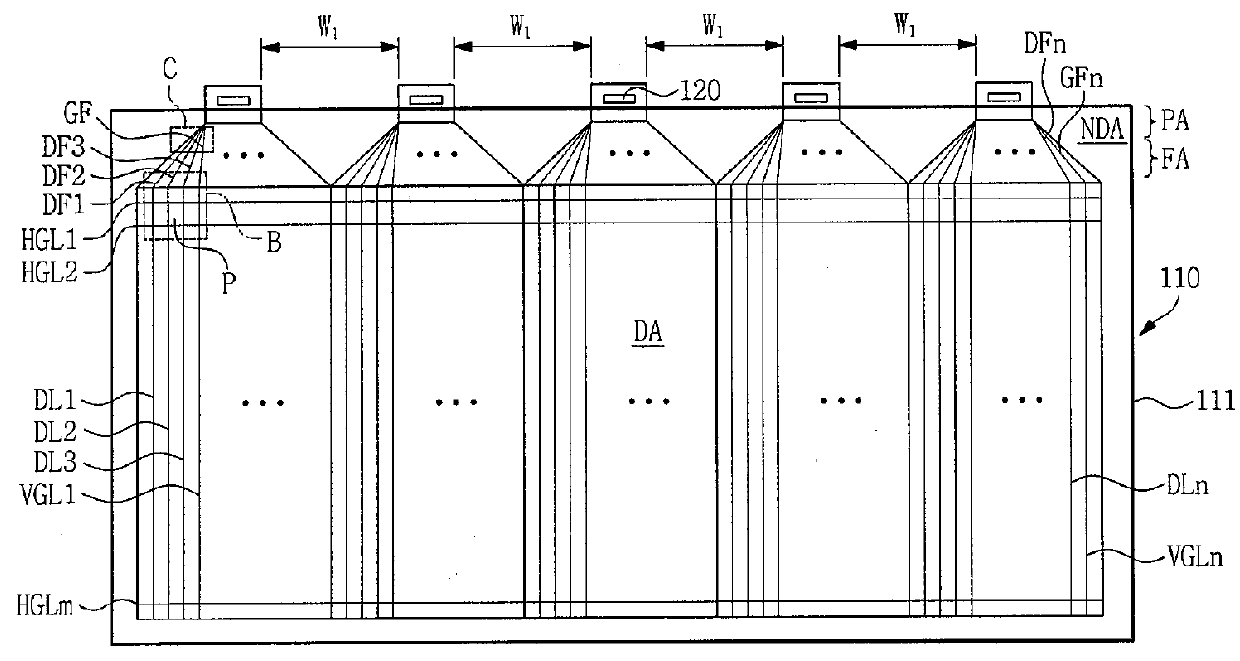

Display panel and display device having the same

ActiveUS20160035307A1Eliminate delaysSemiconductor/solid-state device detailsSolid-state devicesDisplay deviceComputer science

A display device includes: a substrate partitioned into a display area including a plurality of pixels for displaying images thereon and a non-display area around the display area; a plurality of first gate lines and a plurality of data lines extended in one direction on the display area; a plurality of pads on one side of the non-display area; a plurality of gate fan-out lines, each coupling one of the first gate lines and a corresponding one of the pads; and a plurality of data fan-out lines, each coupling one of the data lines and a corresponding one of the pads, wherein the gate fan-out lines and the data fan-out lines may be alternately disposed.

Owner:SAMSUNG DISPLAY CO LTD

Array substrate and display panel

ActiveCN107085333ANot short circuitedStatic indicating devicesNon-linear opticsElectricityDriving circuit

The invention provides an array substrate. The array substrate has a display area and a non-display area surrounding the display area, and the display area is provided with gate lines and data lines; the array substrate further includes a fan-out area, at least one signal line and at least one binding terminal, wherein the fan-out area is arranged in the non-display area, the signal lines extend in the first direction, the first direction points to the fan-out area from the display area, the binding terminals are used for binding a drive circuit, the first terminal of each binding terminal is electrically connected with the corresponding signal line, and the second terminals of binding terminals are electrically connected with test terminals through first leading wires; the signal lines or the first leading wires are arranged among the binding terminals, the signal lines or the first leading wires in a region among the binding terminals are covered with a layer of covering electrodes, and the covering electrodes are electrically insulated with the signal lines or the first leading wires.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Optimization of critical dimensions and pitch of patterned features in and above a substrate

A die is formed with different and optimized critical dimensions in different device levels and areas of those device levels using photolithography and etch techniques. One aspect of the invention provides for a memory array formed above a substrate, with driver circuitry formed in the substrate. A level of the memory array consists of, for example, parallel rails and a fan-out region. It is desirable to maximize density of the rails and minimize cost of lithography for the entire memory array. This can be achieved by forming the rails at a tighter pitch than the CMOS circuitry beneath it, allowing cheaper lithography tools to be used when forming the CMOS, and similarly by optimizing lithography and etch techniques for a device level to produce a tight pitch in the rails, and a more relaxed pitch in the less-critical fan-out region.

Owner:SANDISK TECH LLC

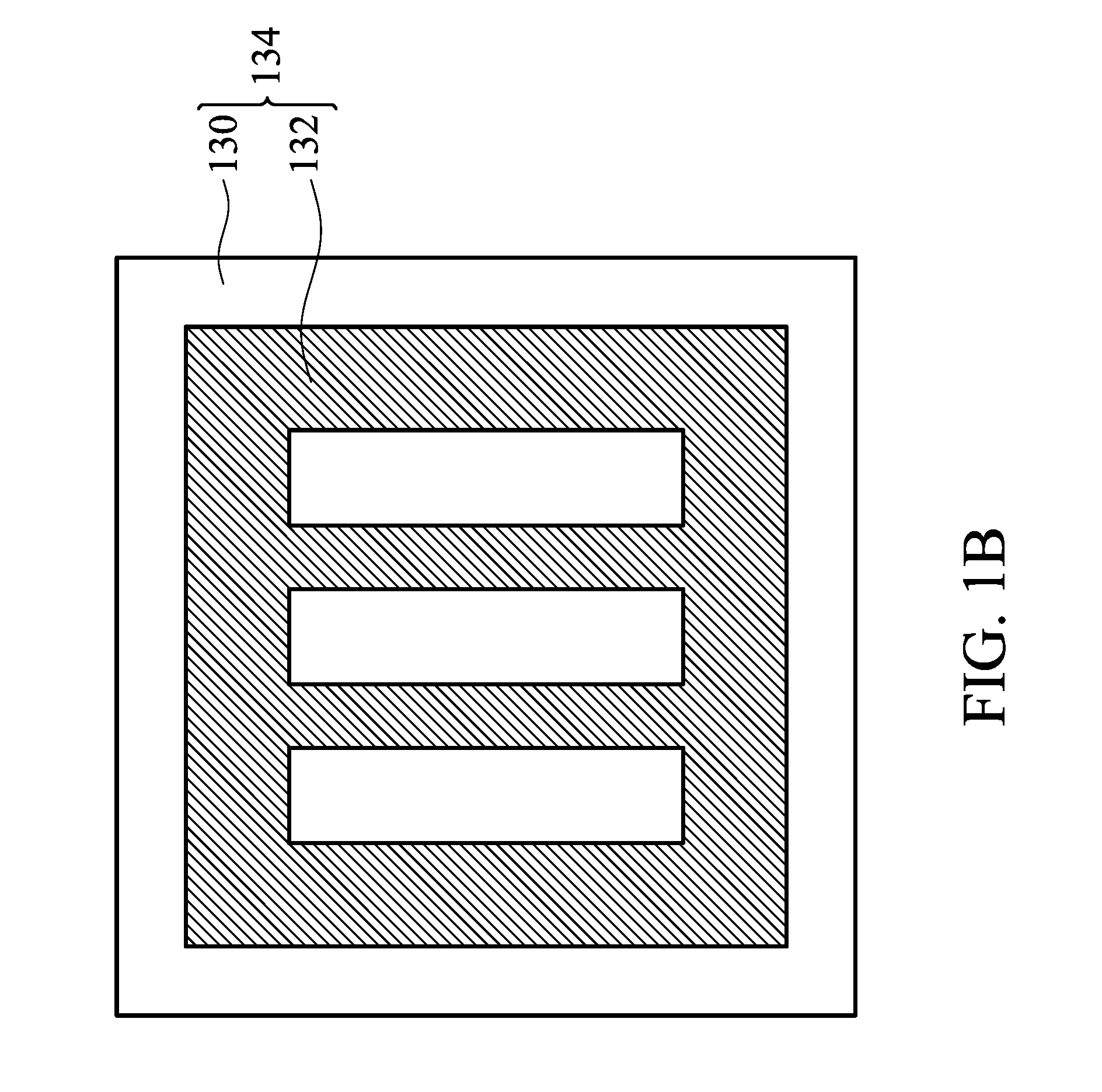

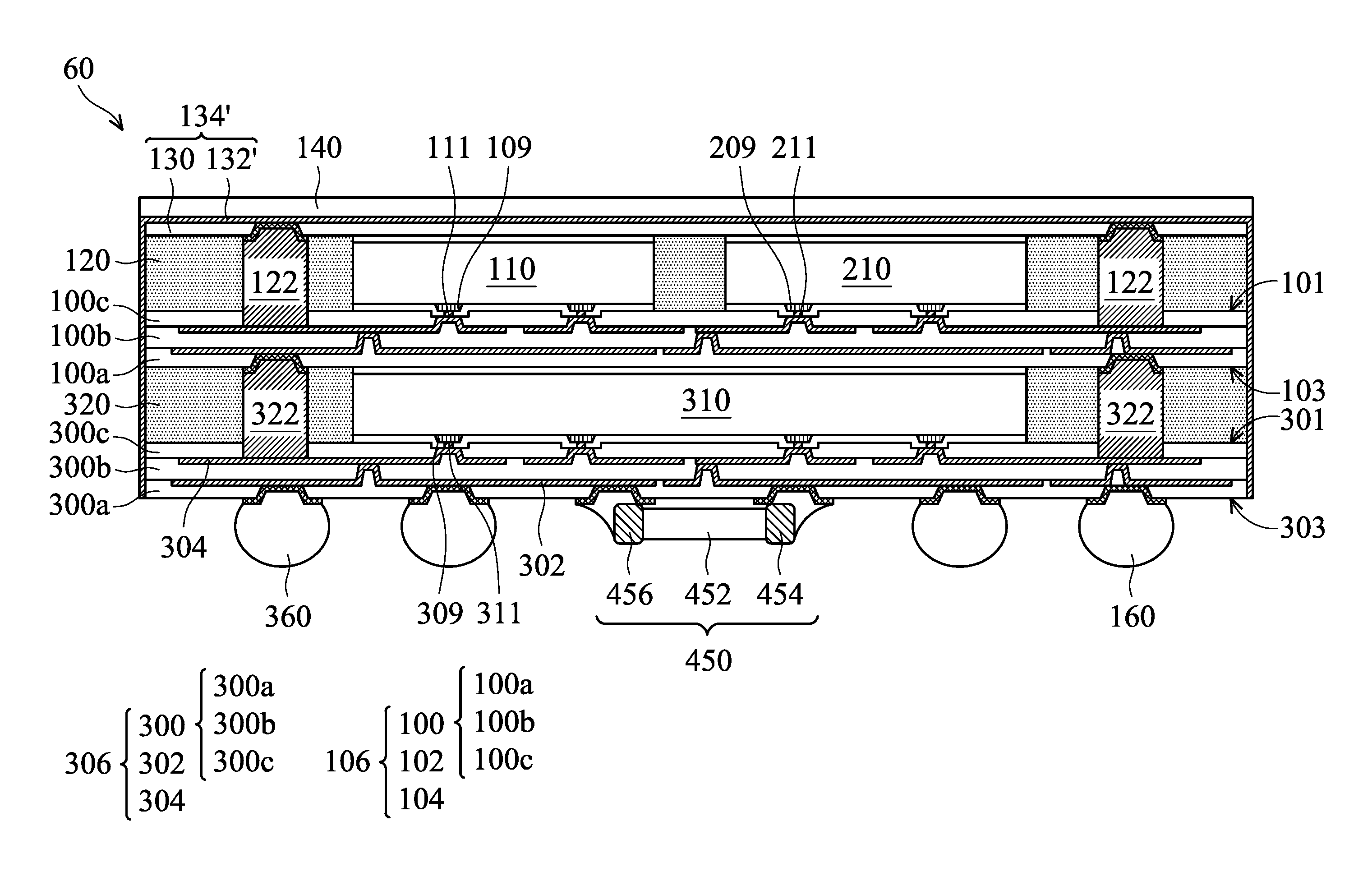

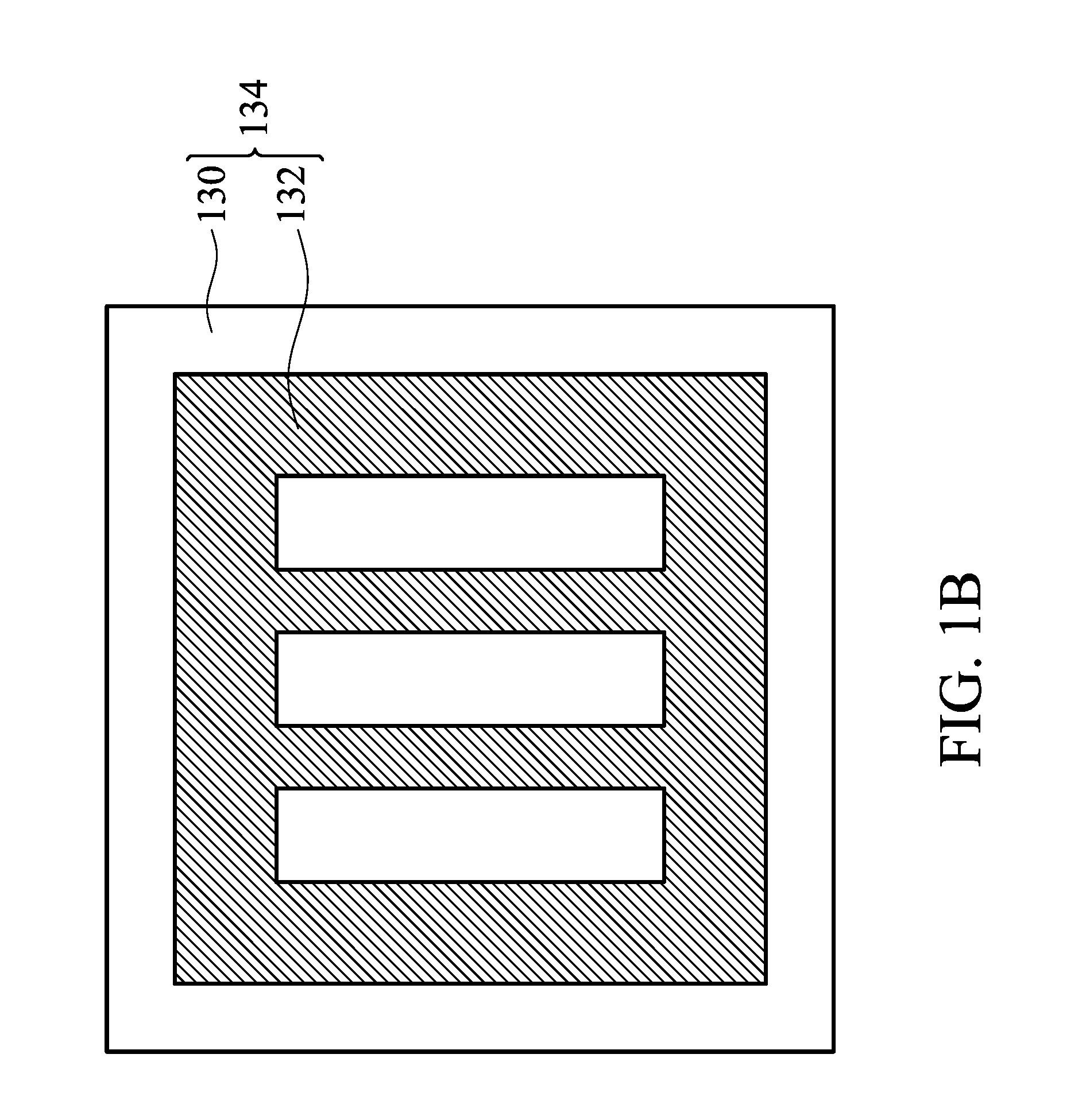

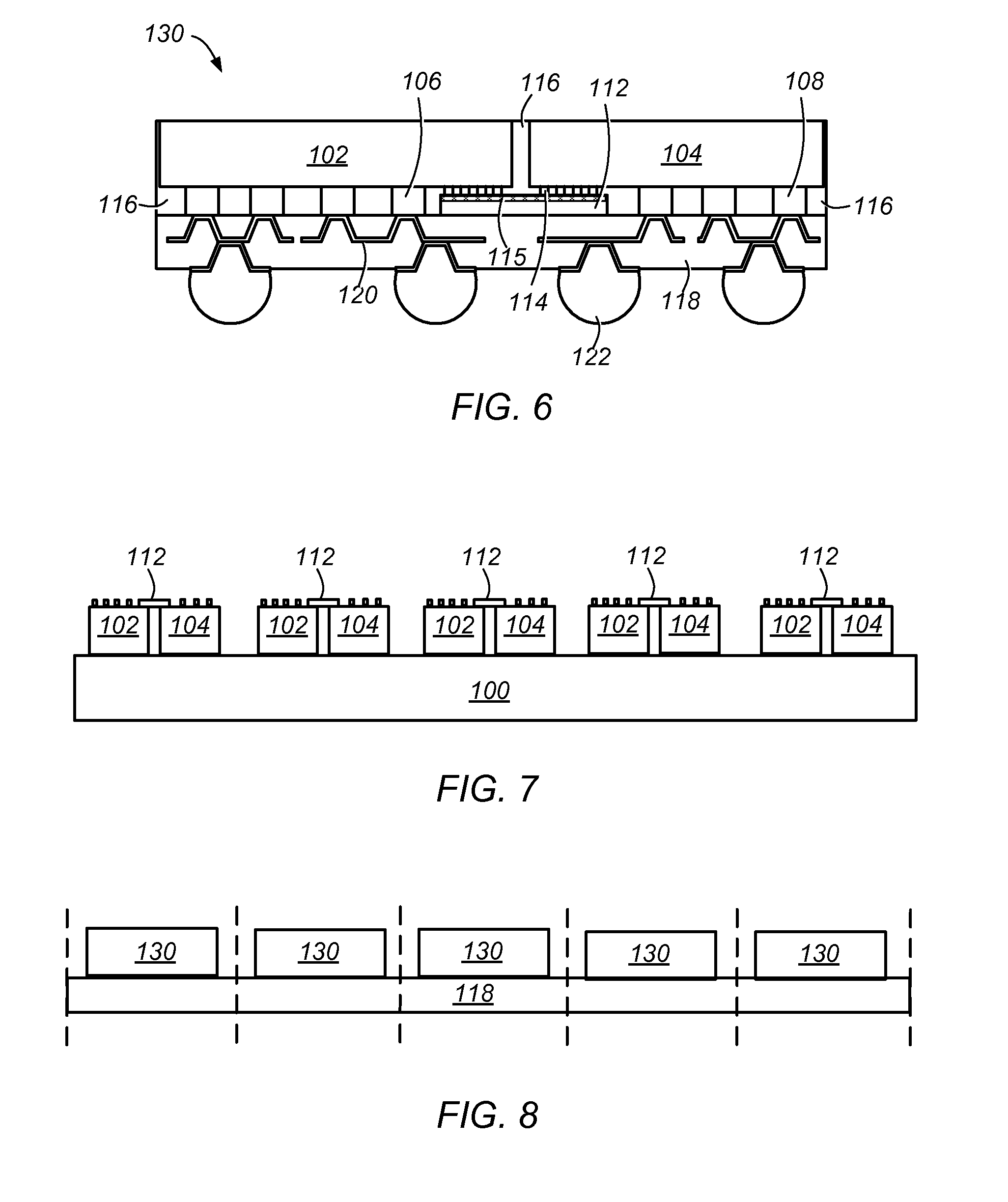

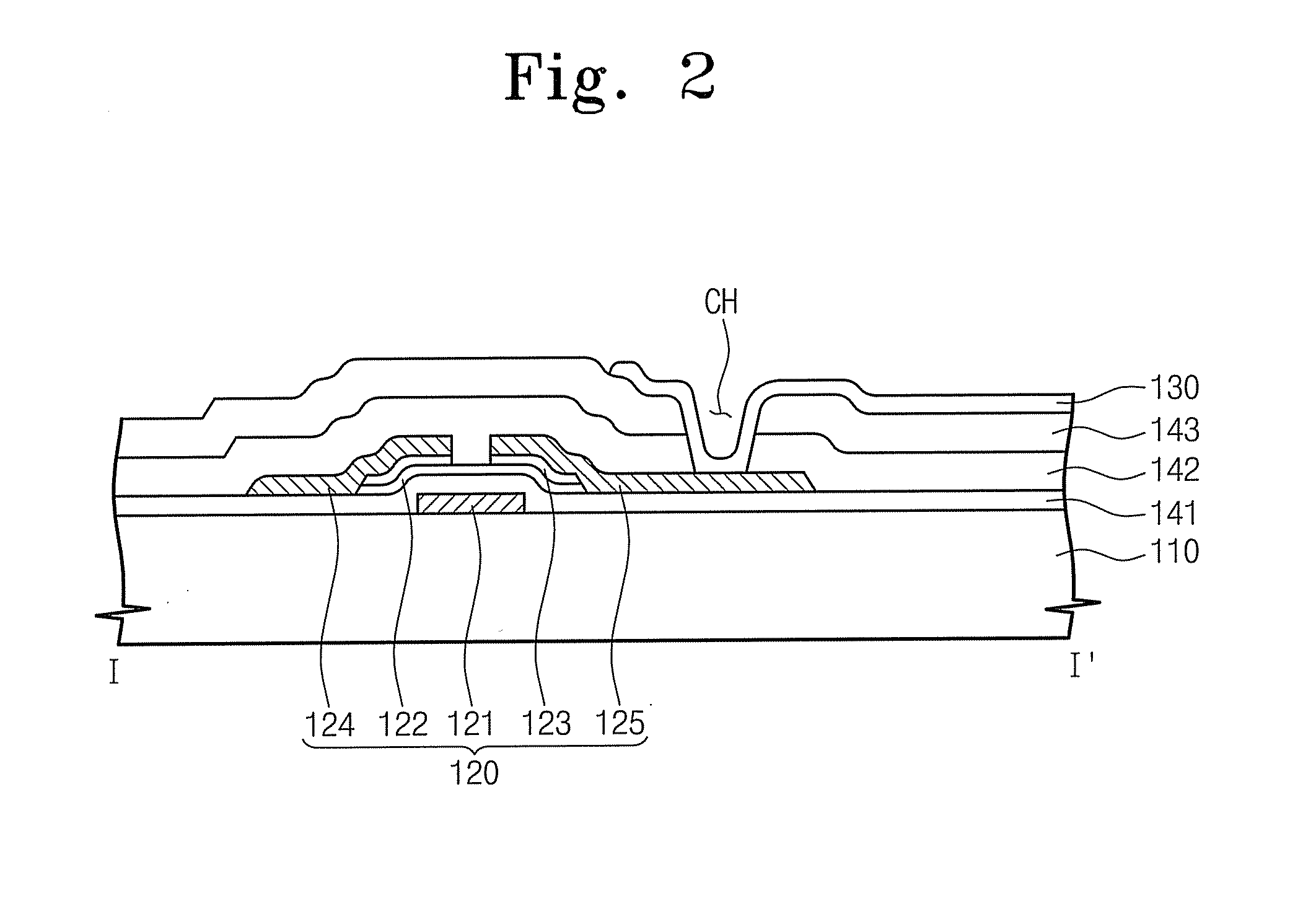

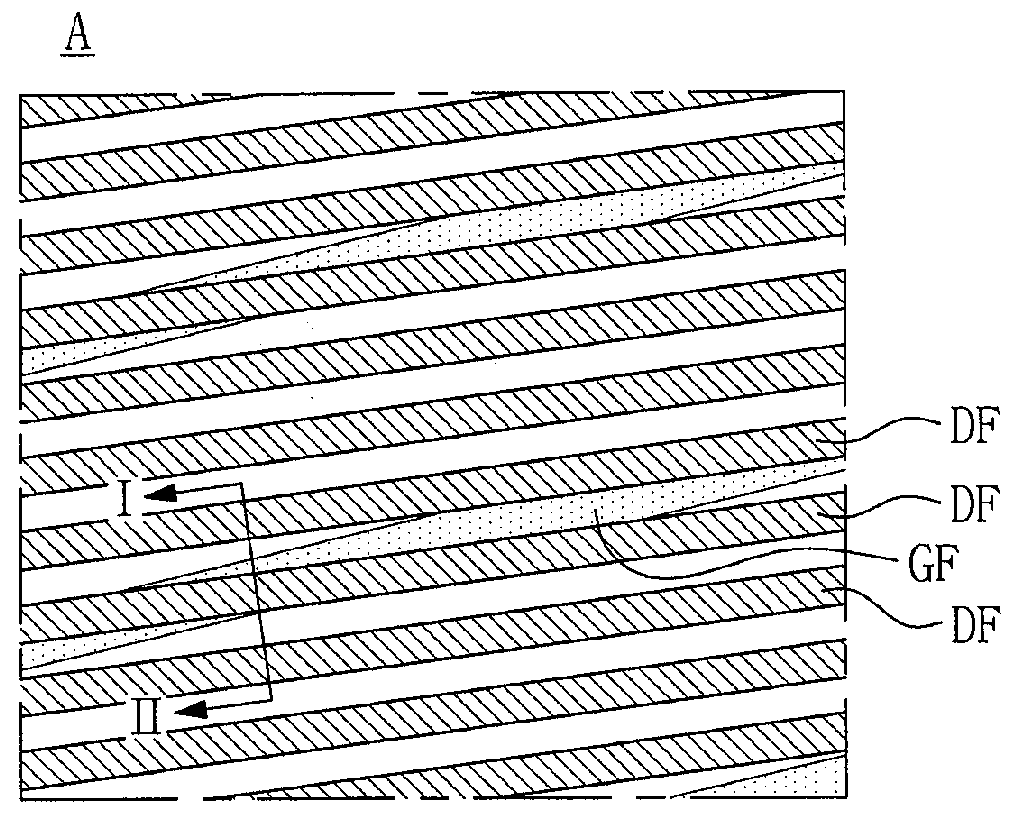

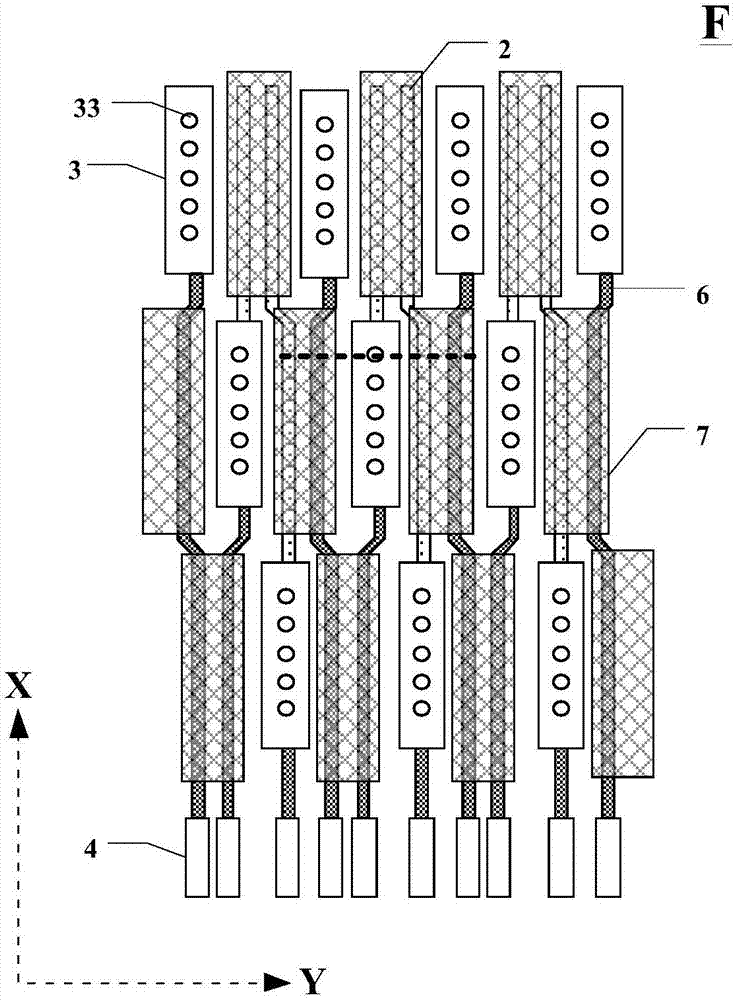

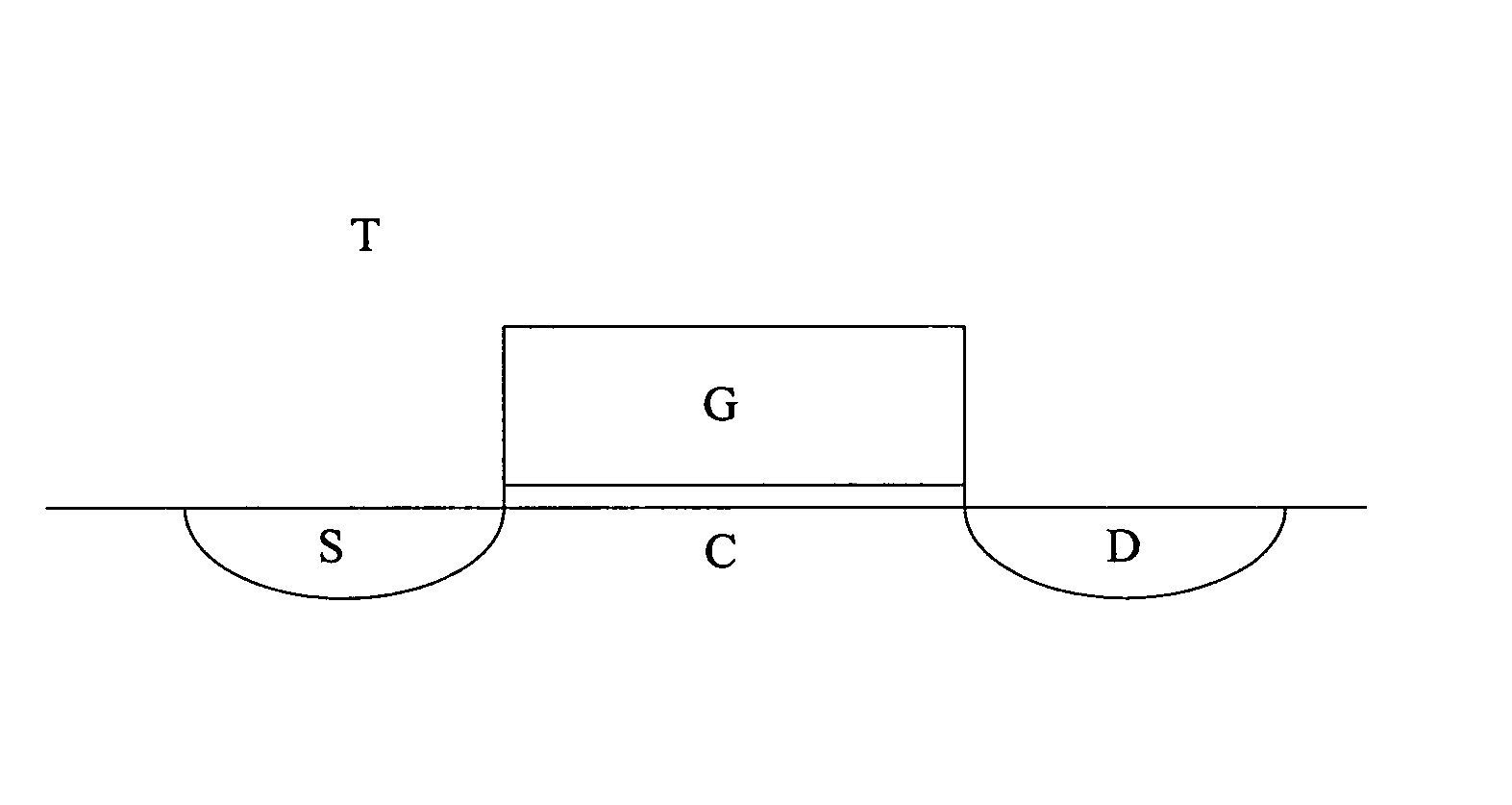

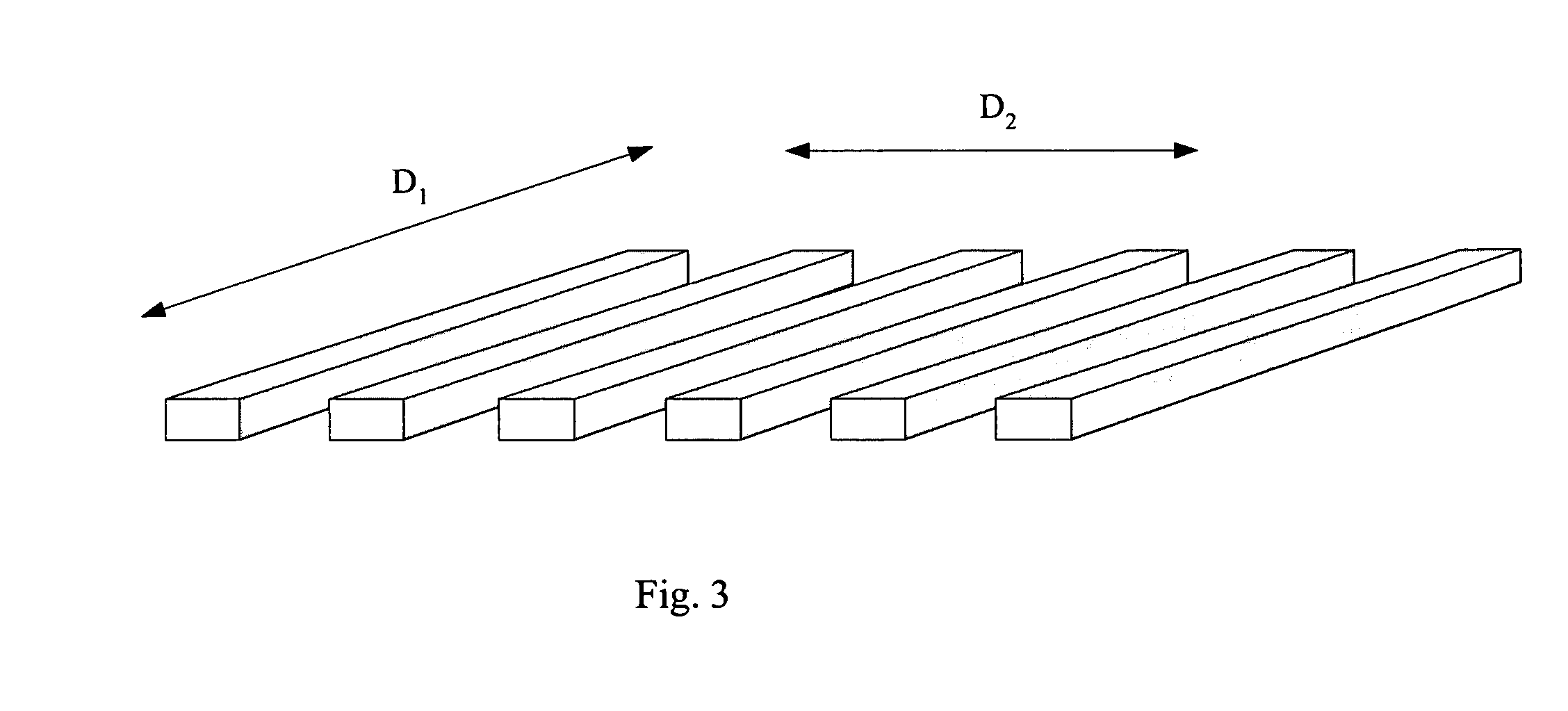

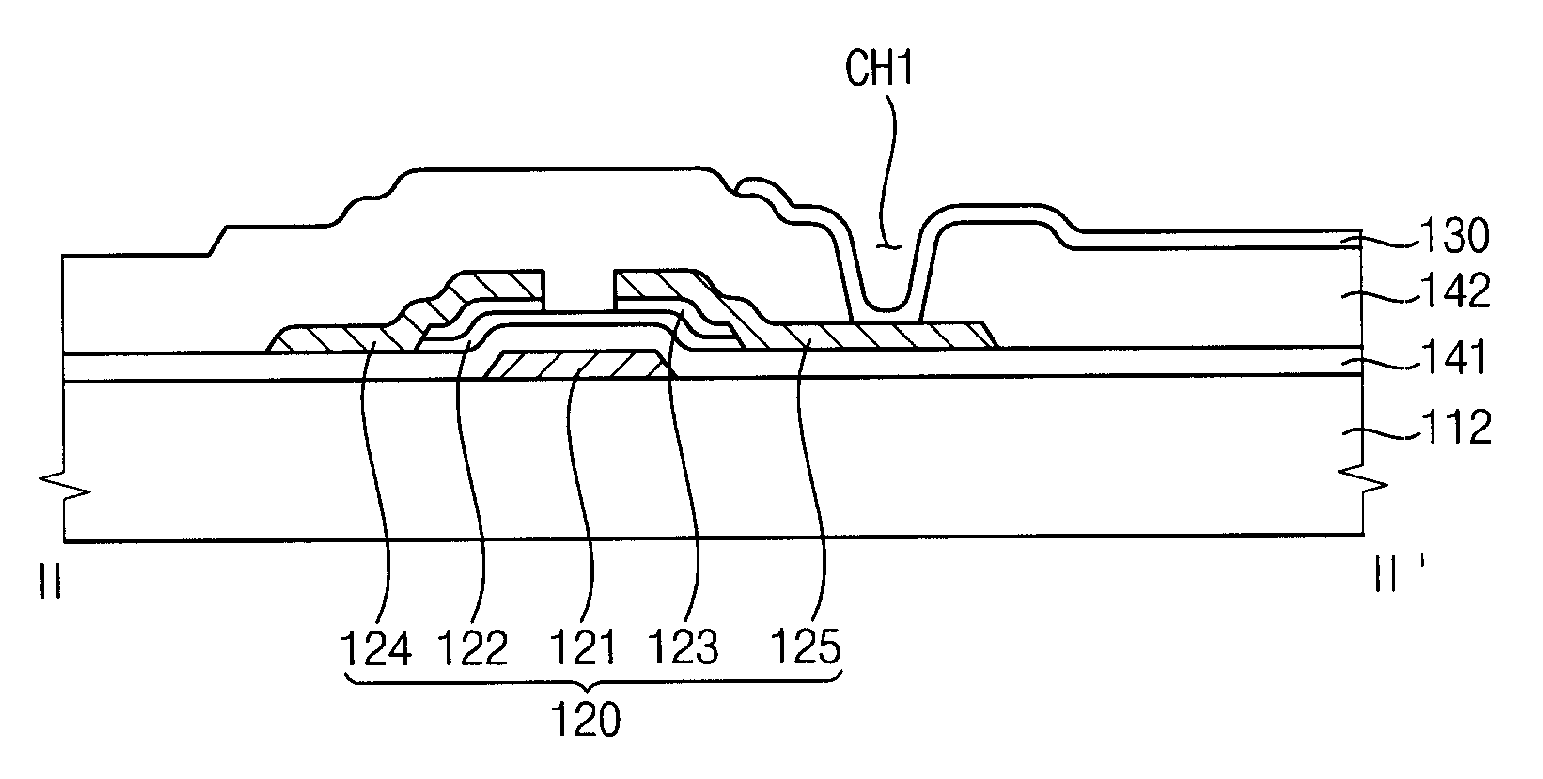

Fan-out unit and thin-film transistor array substrate having the same

ActiveUS20100155729A1Minimum channel resistance non-uniformityEfficient space utilizationTransistorPrinted circuit aspectsElectrical resistance and conductanceEngineering

A fan-out unit which can control a resistance difference among channels with efficient space utilization and a thin-film transistor (TFT) array substrate having the fan-out unit are presented. The fan-out unit includes: an insulating substrate; a first wiring layer which is formed on the insulating substrate and connected to a pad; a second wiring layer which is formed on the insulating substrate and connected to a TFT; and a resistance controller which is connected between the first wiring layer and the second wiring layer and includes a plurality of first resistors extending parallel to the first wiring layer and a plurality of second resistors extending perpendicular to the first resistors and alternately connecting to the first resistors, wherein the first resistors are longer than the second resistors.

Owner:SAMSUNG DISPLAY CO LTD

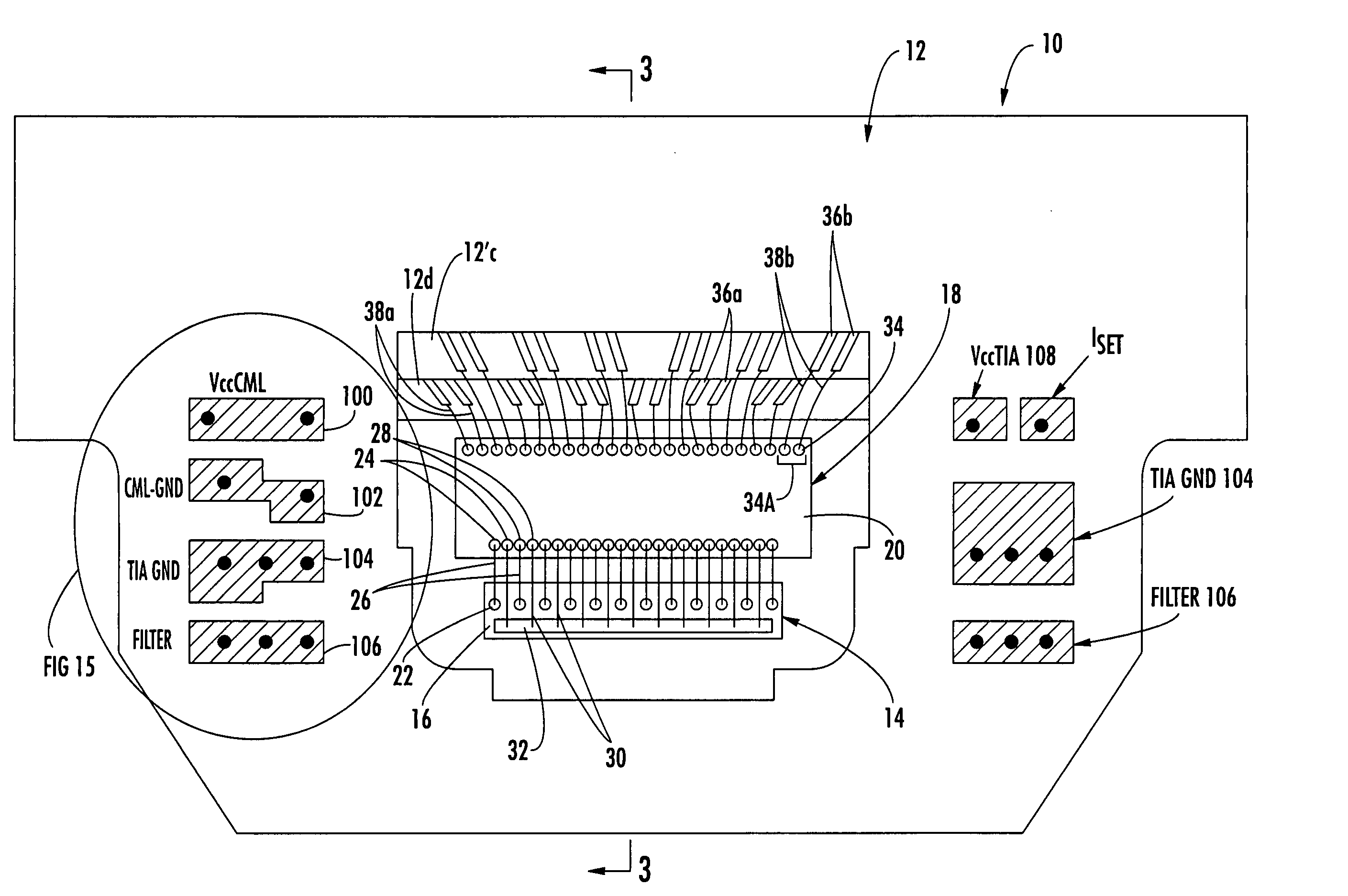

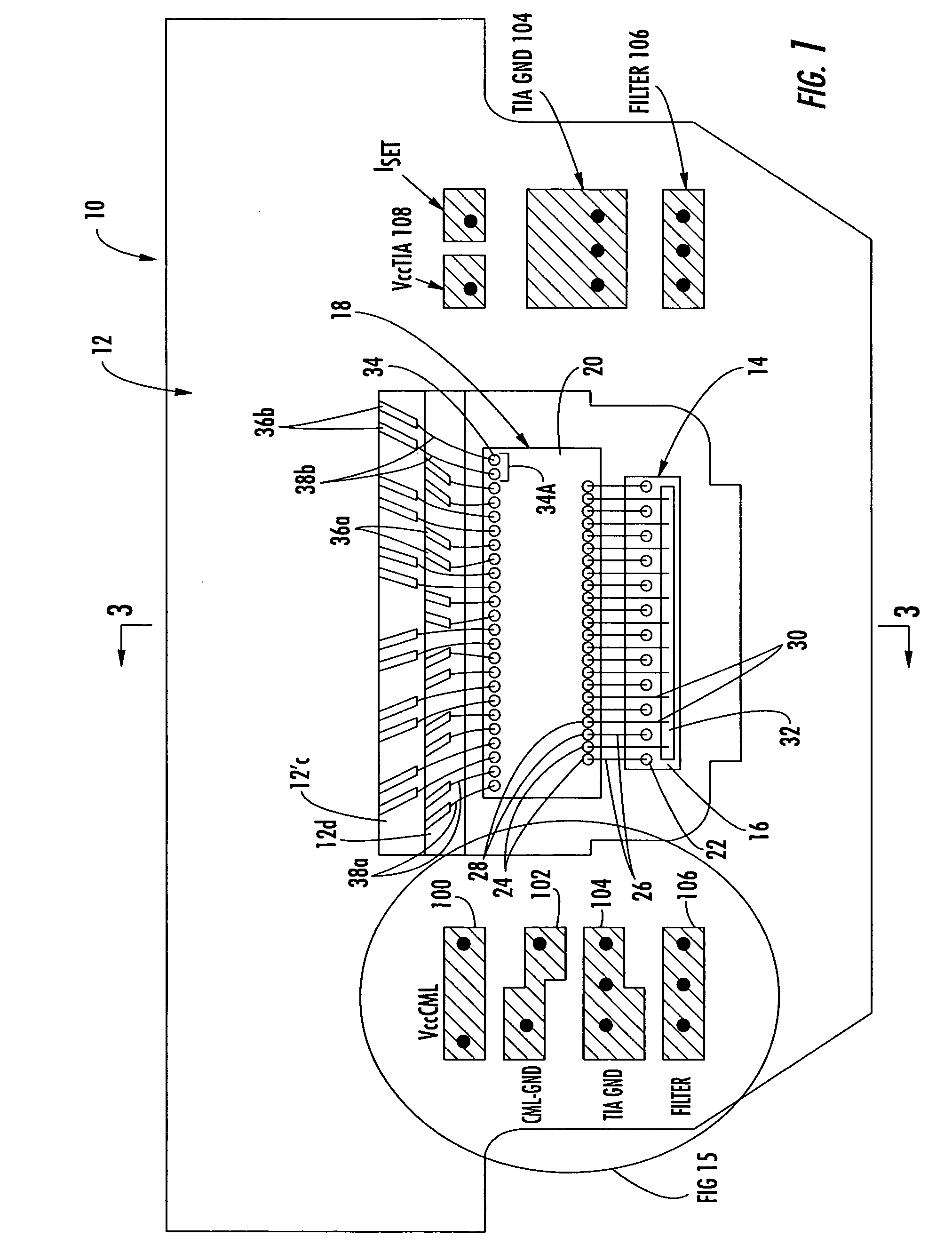

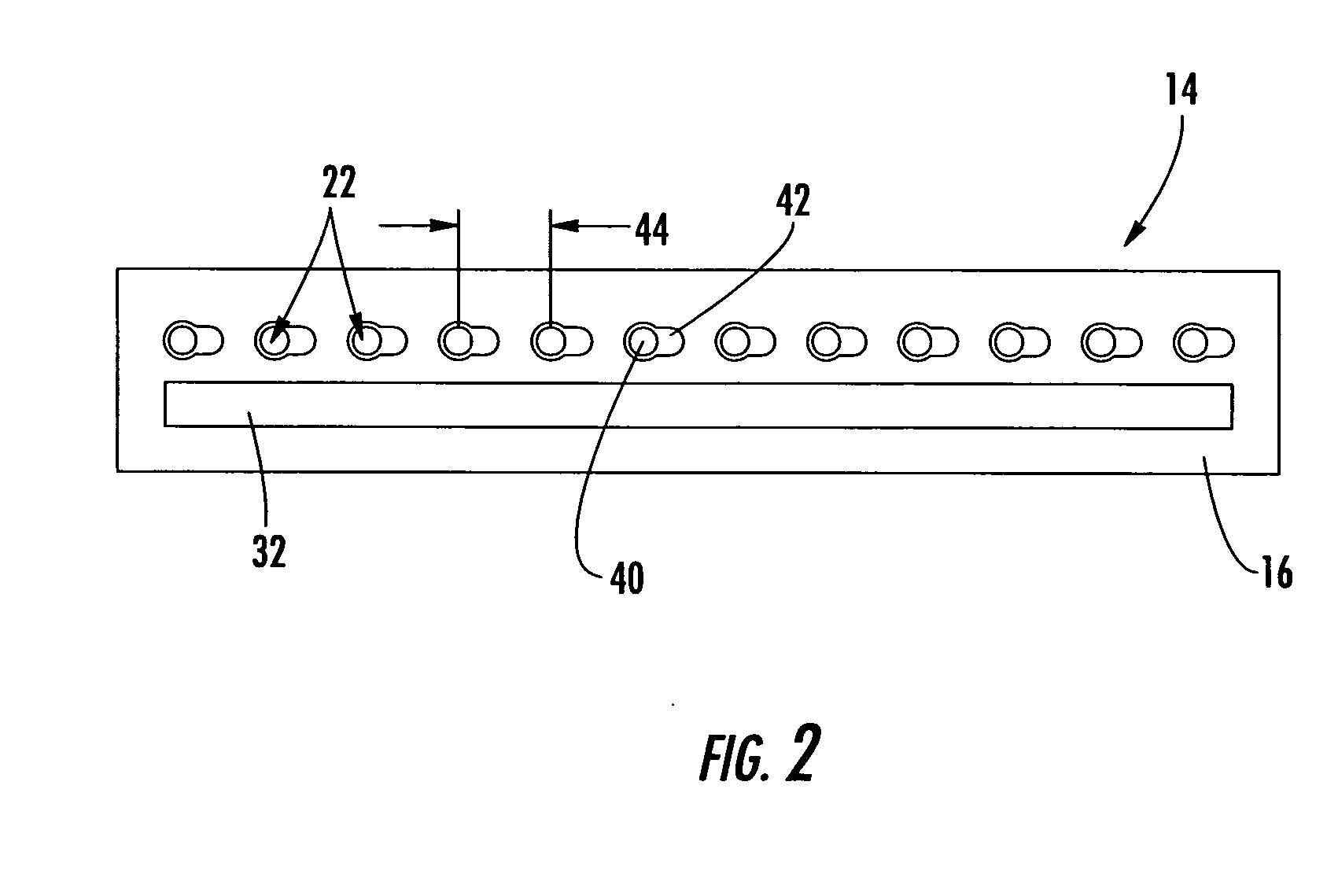

Arrayed receiver optical sub-assembly including layered ceramic substrate for alleviation of cross-talk and noise between channels

InactiveUS20050213994A1Electromagnetic receiversOptical light guidesCapacitancePhotovoltaic detectors

A receiver optical subassembly (ROSA) includes a photodetector array and a transimpedance amplifier (TIA) array. In each data channel, the photodetector is wire bonded to a corresponding input pad of the TIA array. A ground pad is disposed between adjacent input pads and connected to a ground plane via an isolated bonding strip on the photodetector array in order to alleviate crosstalk between the channels. The output data channels of the TIA are tightly spaced at the output pads of the TIA and are fanned out on the ceramic to increase the spacing of the data channels as they extend from the TIA. The ROSA includes the use of embedded capacitance to reduce crosstalk and noise by decoupling reference planes formed within the multilayer ceramic substrate. Input and output ground planes of the TIA are separated in the vicinity of the TIA and coupled on a ceramic layer spaced farther from the TIA, to alleviate crosstalk.

Owner:OPTICAL COMM PRODS

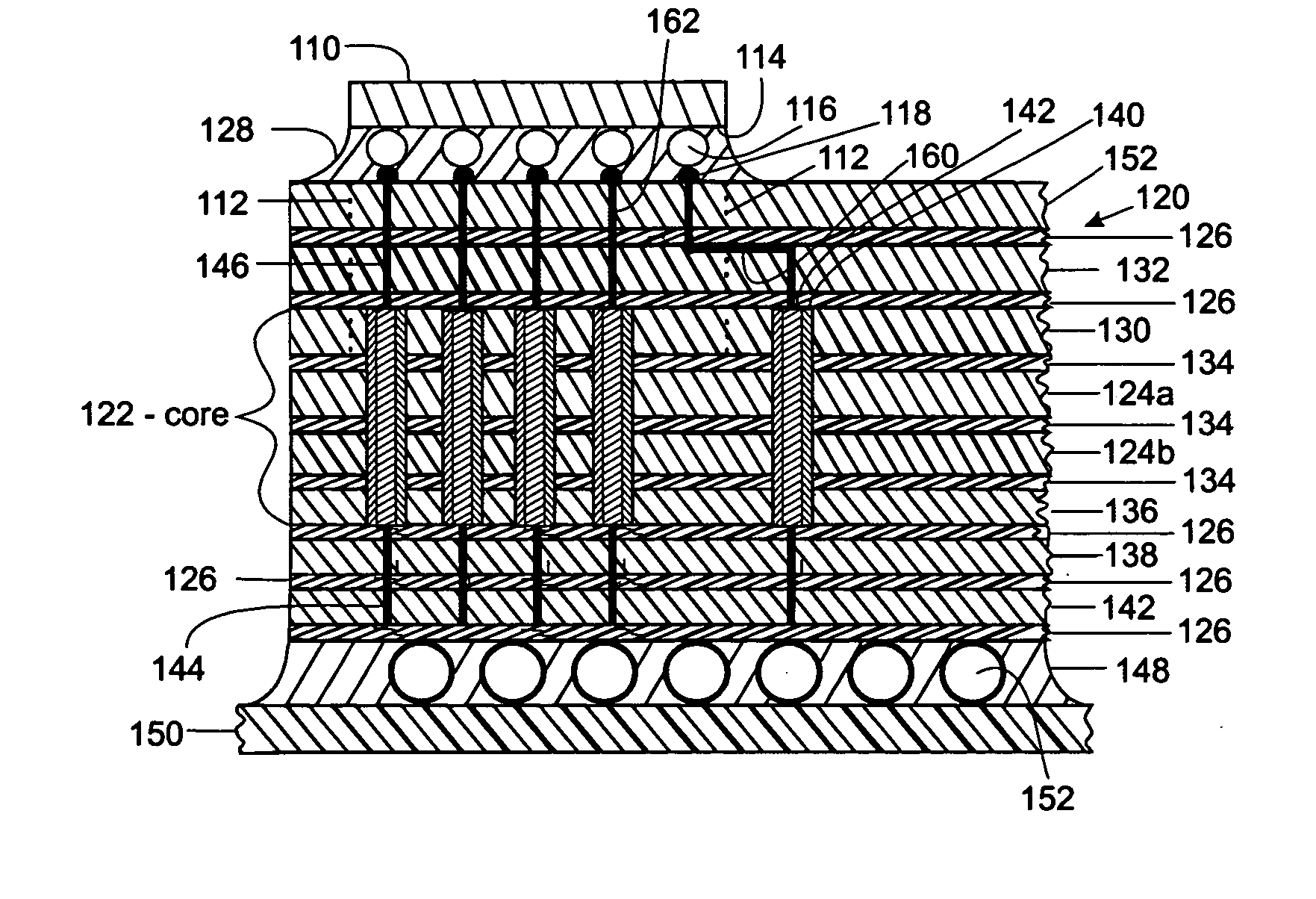

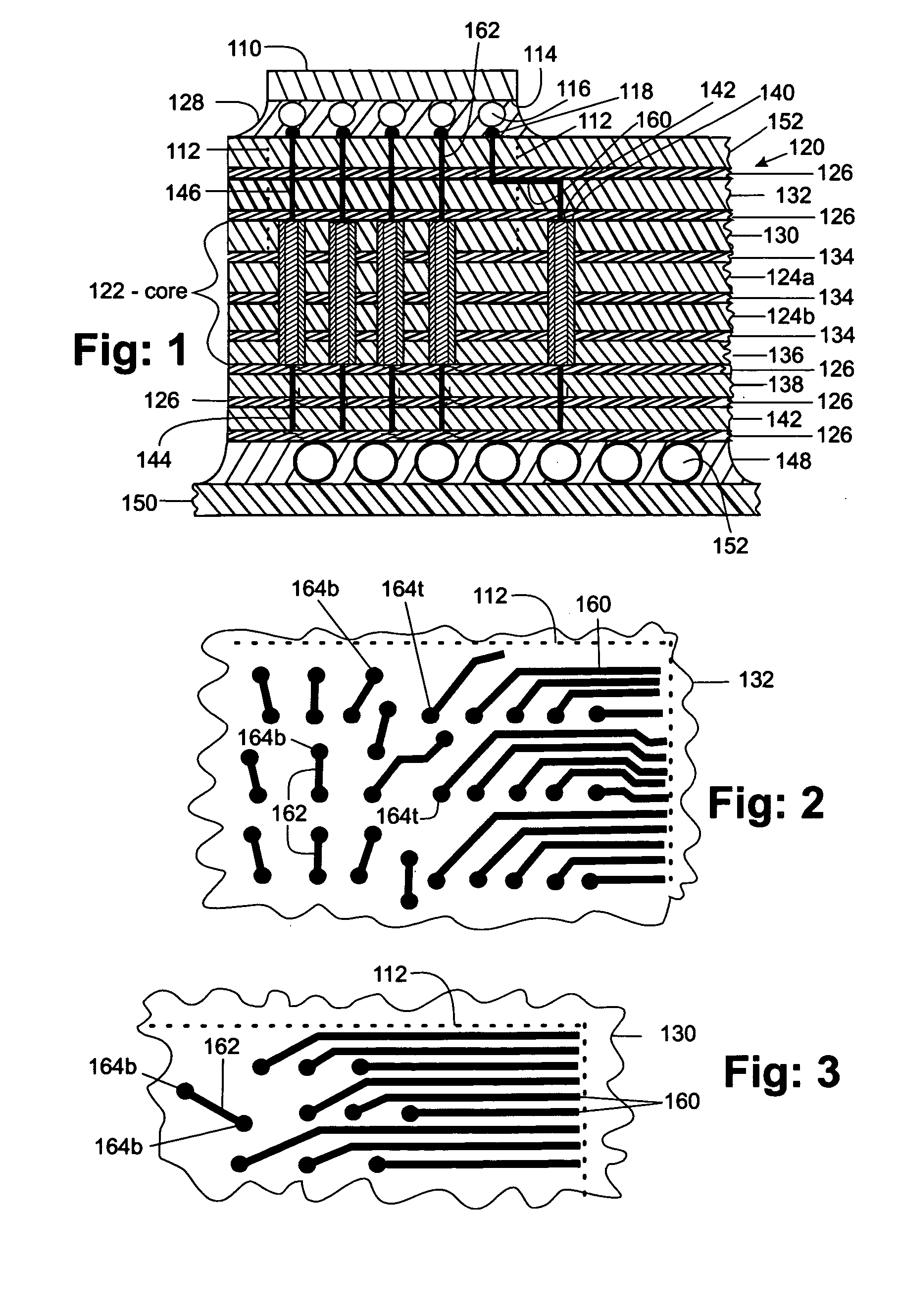

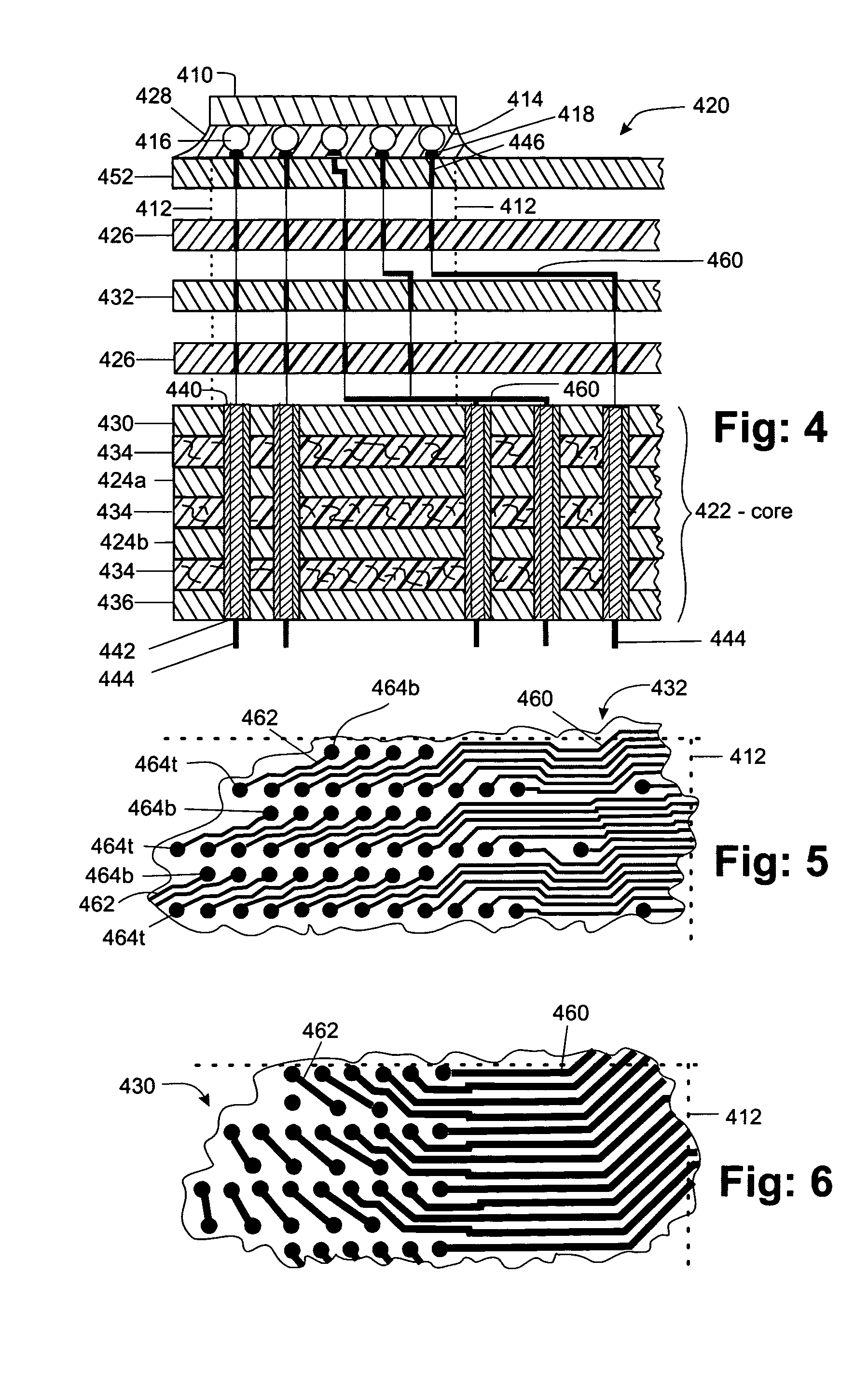

High wireability microvia substrate

InactiveUS20050104221A1Reduce chip sizeMaintaining wireability densitySemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor chipHemt circuits

The escape of signals from a semiconductor chip to a printed wiring board in a flip chip / ball grid array assembly is improved by repositioning the signals from the chip through the upper signal layers of the carrier. This involves fanning out the circuit lines through the chip carrier from the top surface that communicates with the chip, through the core to the bottom surface where signals exit the carrier to the printed wiring board. This fanning out is achieved by making better utilization of the surface area of the signal planes between the core and the chip. The signals are fanned out on each of the top signal planes so that many more of the signals are transmitted through the vias in the core to the bottom signal planes where they can escape outside of the footprint area of the chip thereby increasing the density of circuits escaping the footprint area.

Owner:IBM CORP

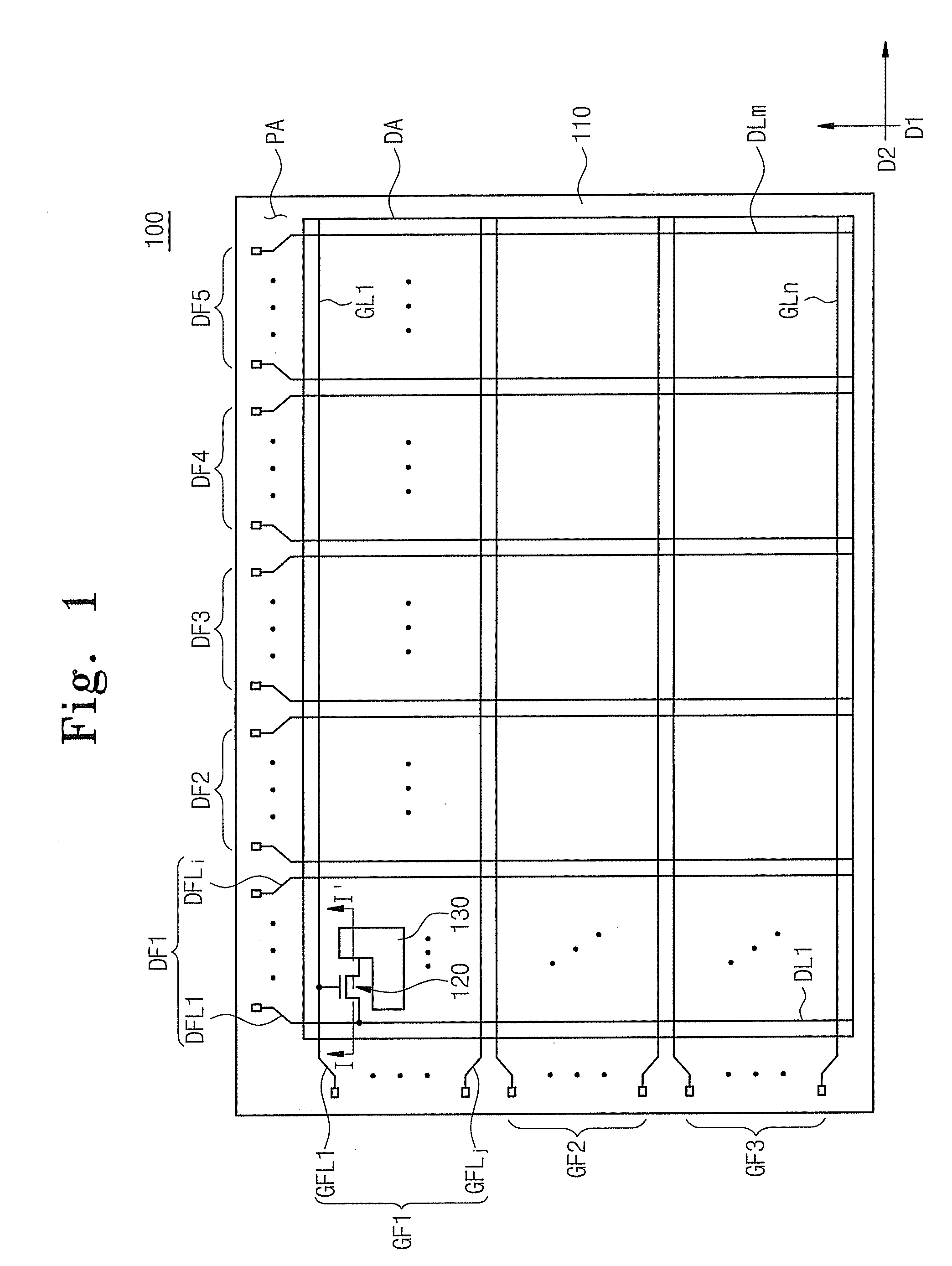

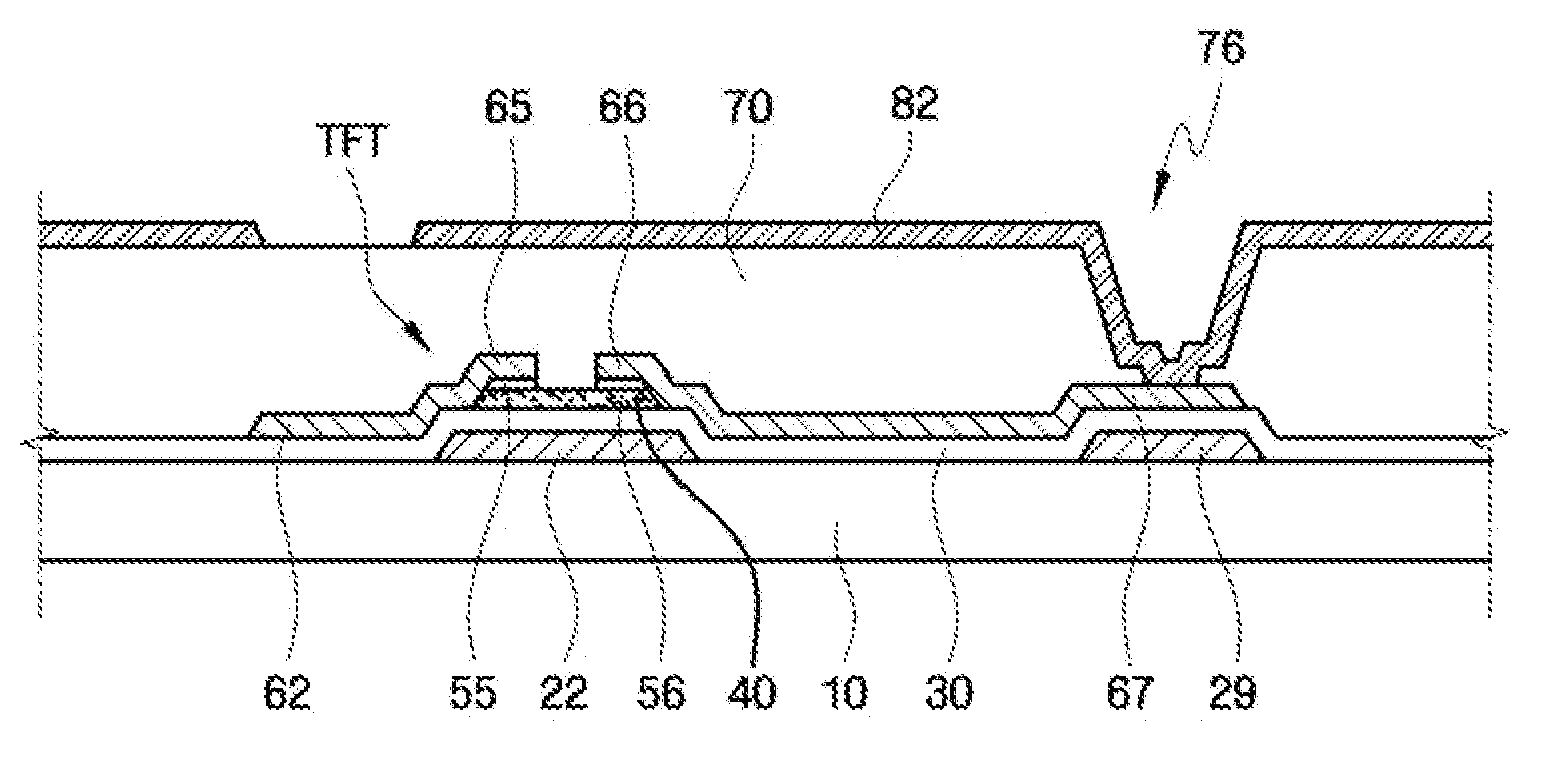

Thin film transistor substrate and method of manufacturing the same

A thin film transistor substrate includes an insulating plate, a plurality of fan-out lines arranged on the insulating plate and including at least a pair of adjacent fan-out lines, a plurality of signal lines connected to the plurality of fan-out lines, and a plurality of thin film transistors connected to the plurality of signal lines. The adjacent fan-out lines partially overlap with each other, and each overlapping area of the adjacent fan-out lines is the same.

Owner:SAMSUNG DISPLAY CO LTD

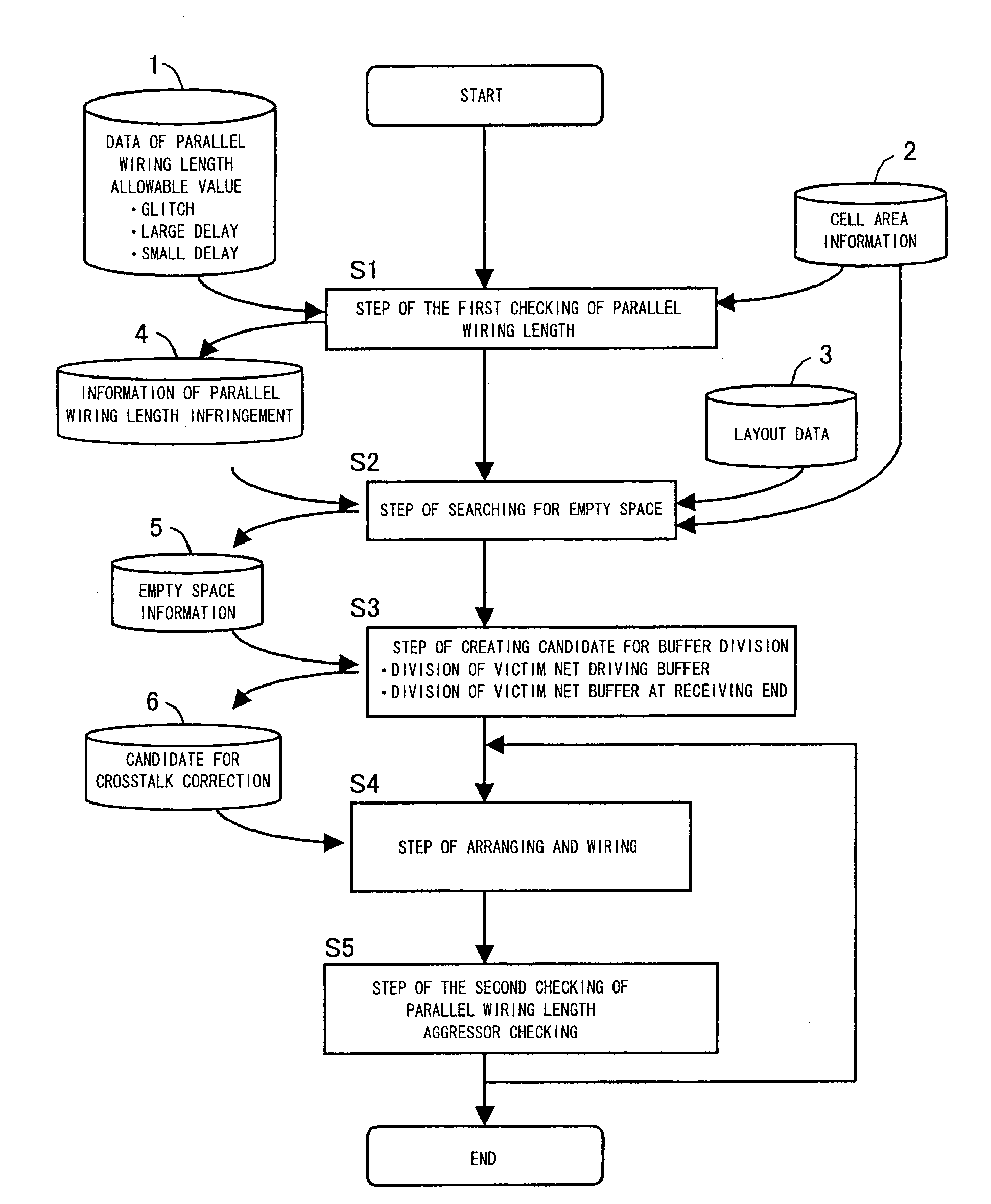

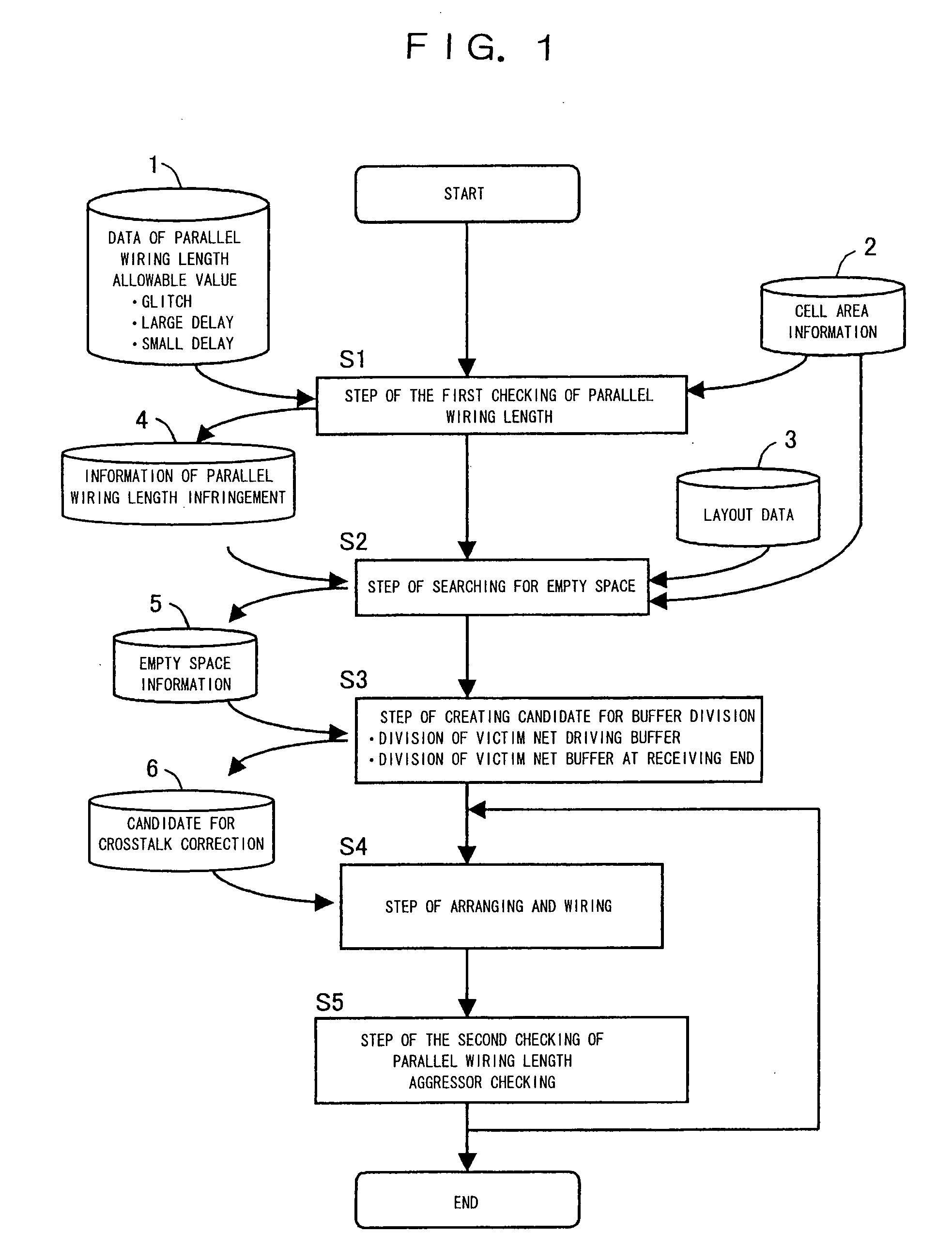

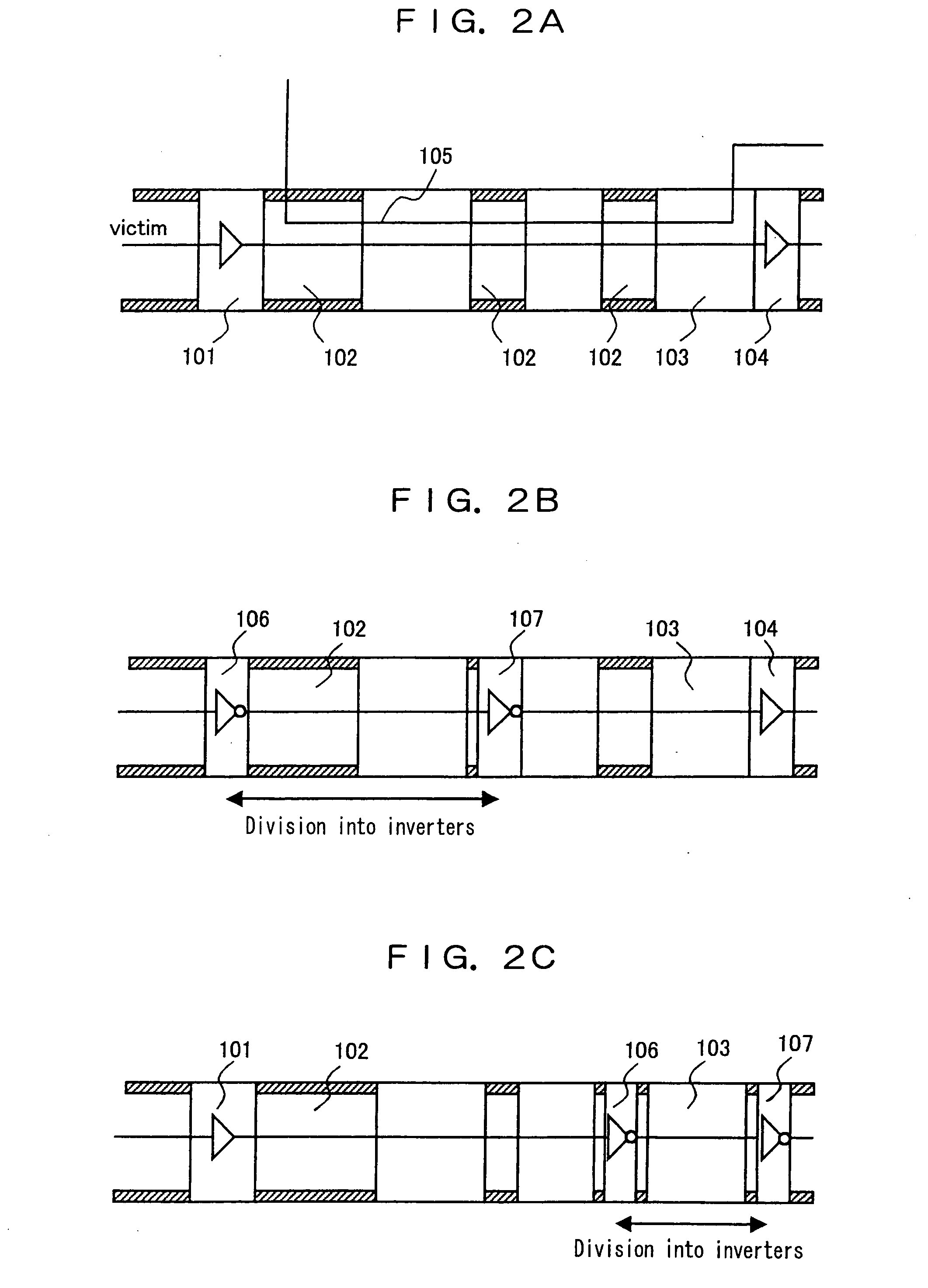

Method for correcting crosstalk

InactiveUS20060015834A1Increasing areaIncreasing consumptionSemiconductor/solid-state device testing/measurementSolid-state devicesCapacitanceSnubber

Owner:SOCIONEXT INC