Patents

Literature

37results about How to "Increasing area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

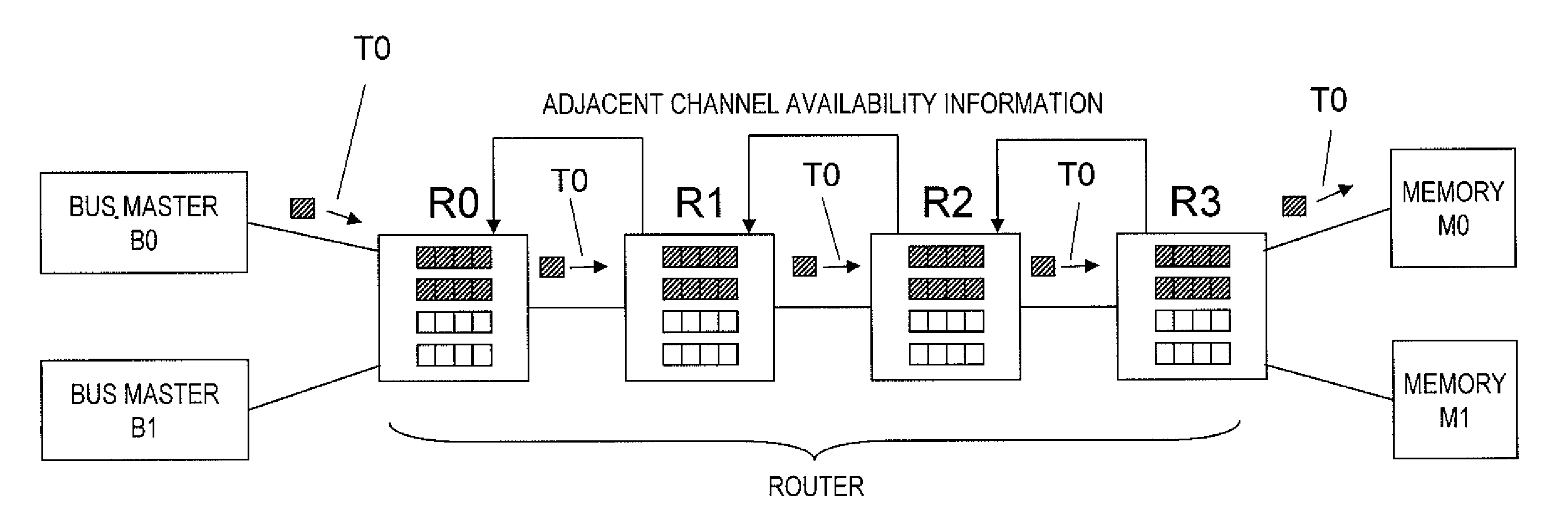

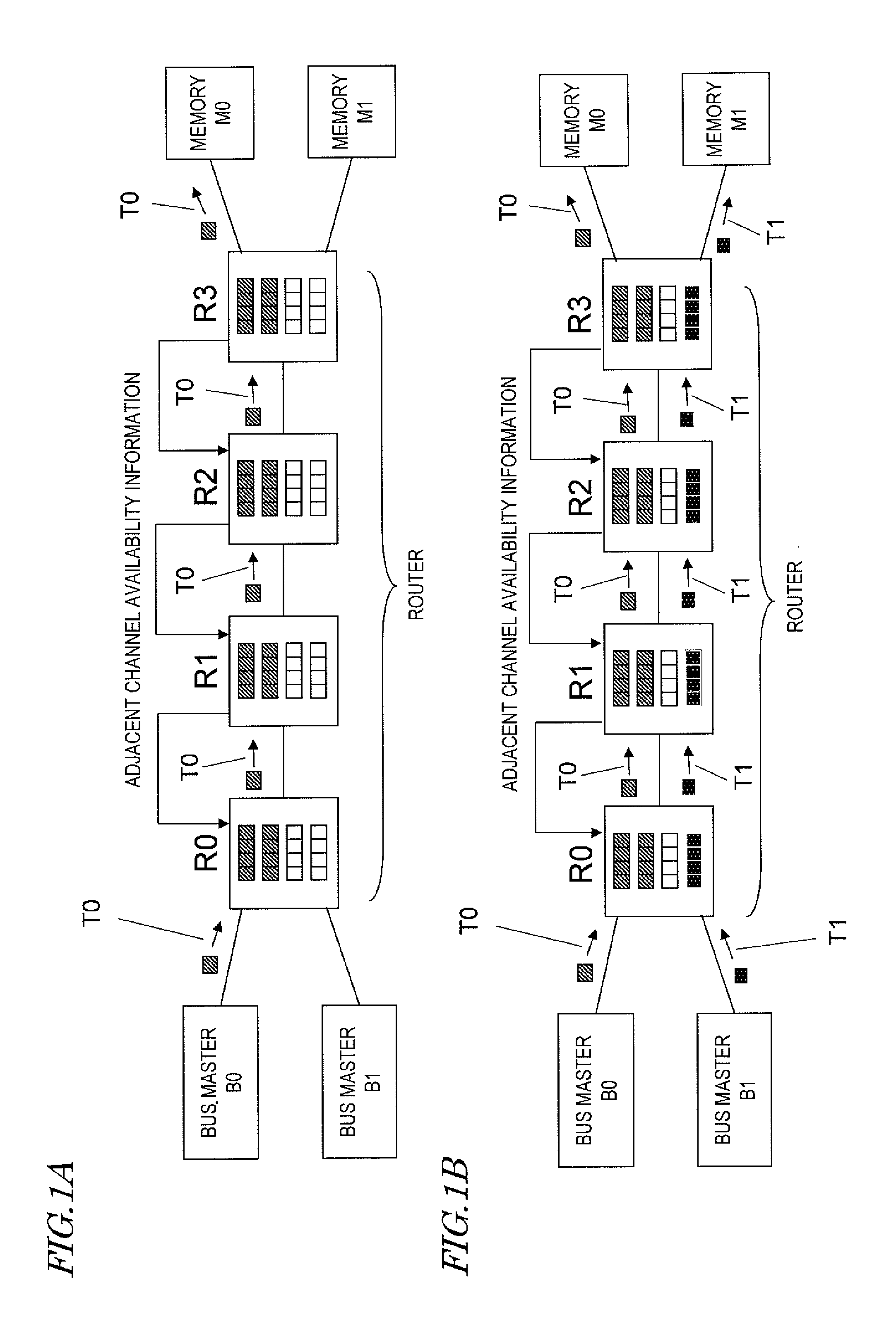

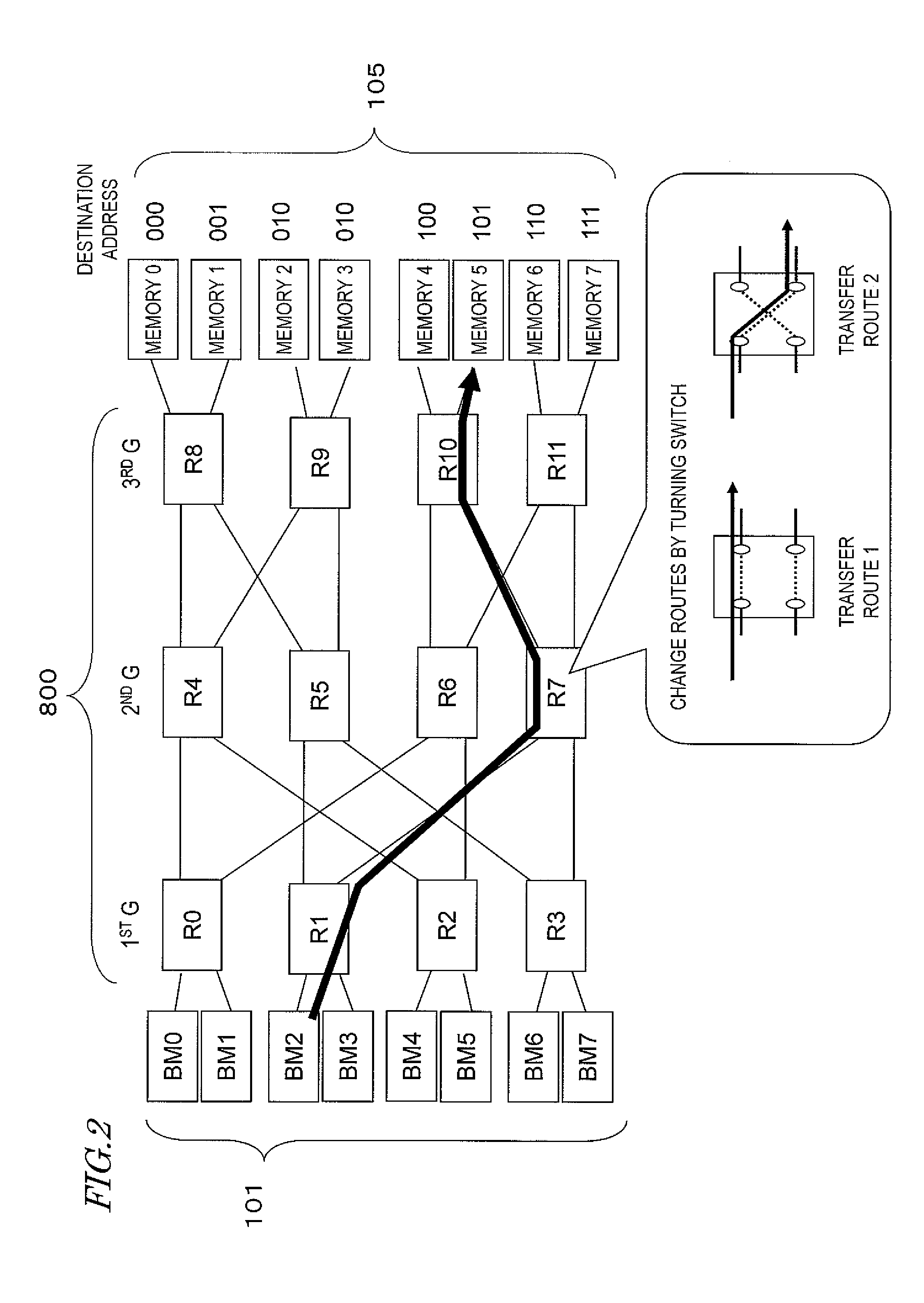

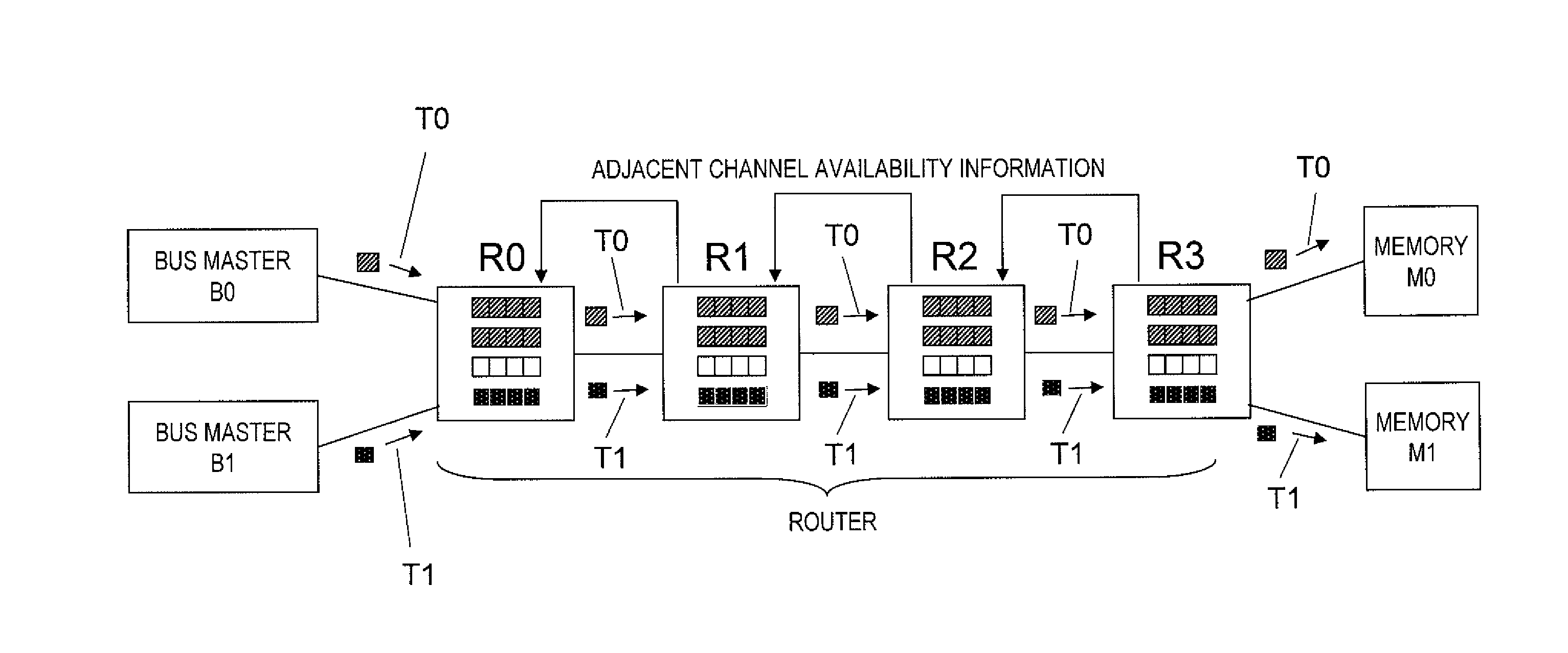

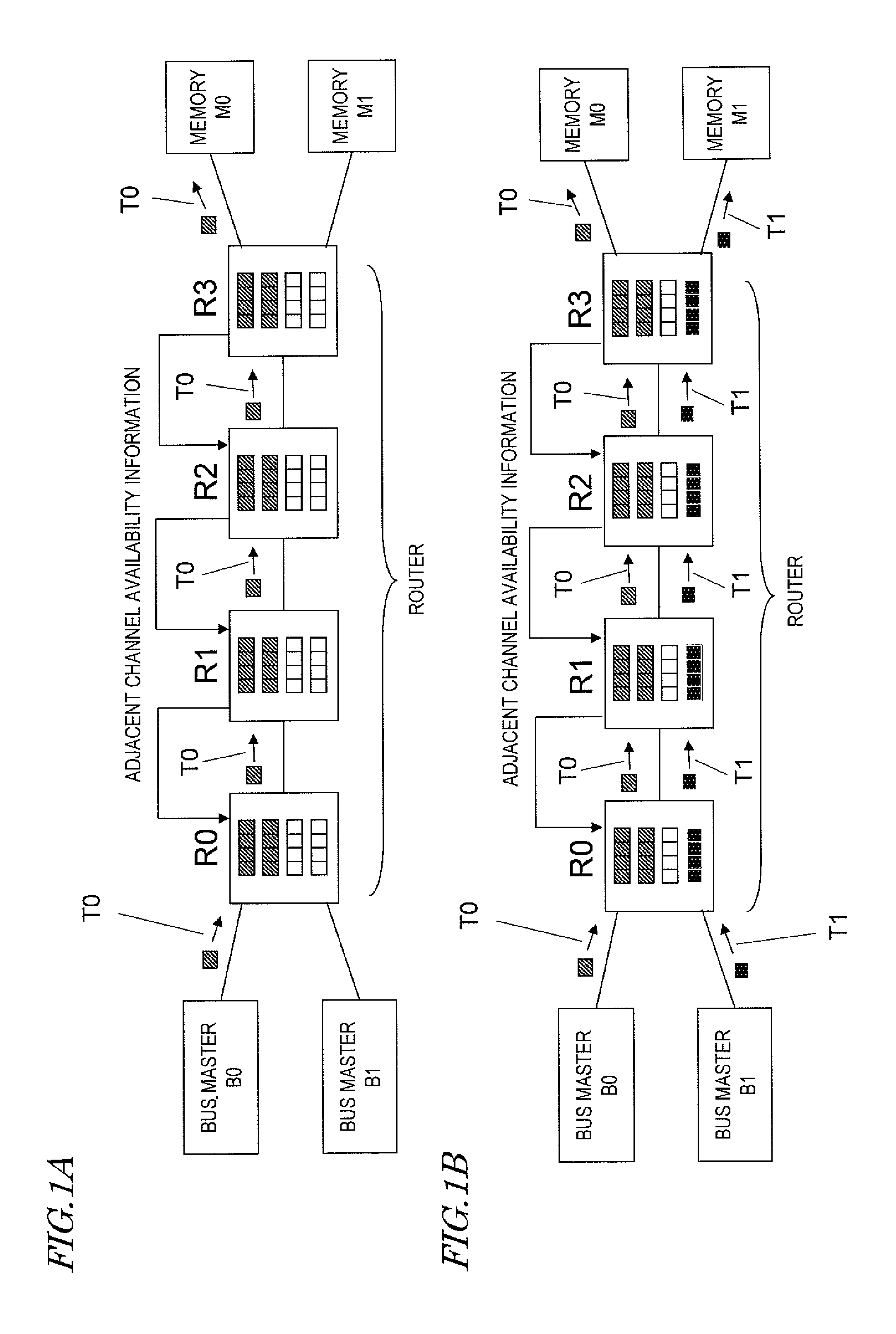

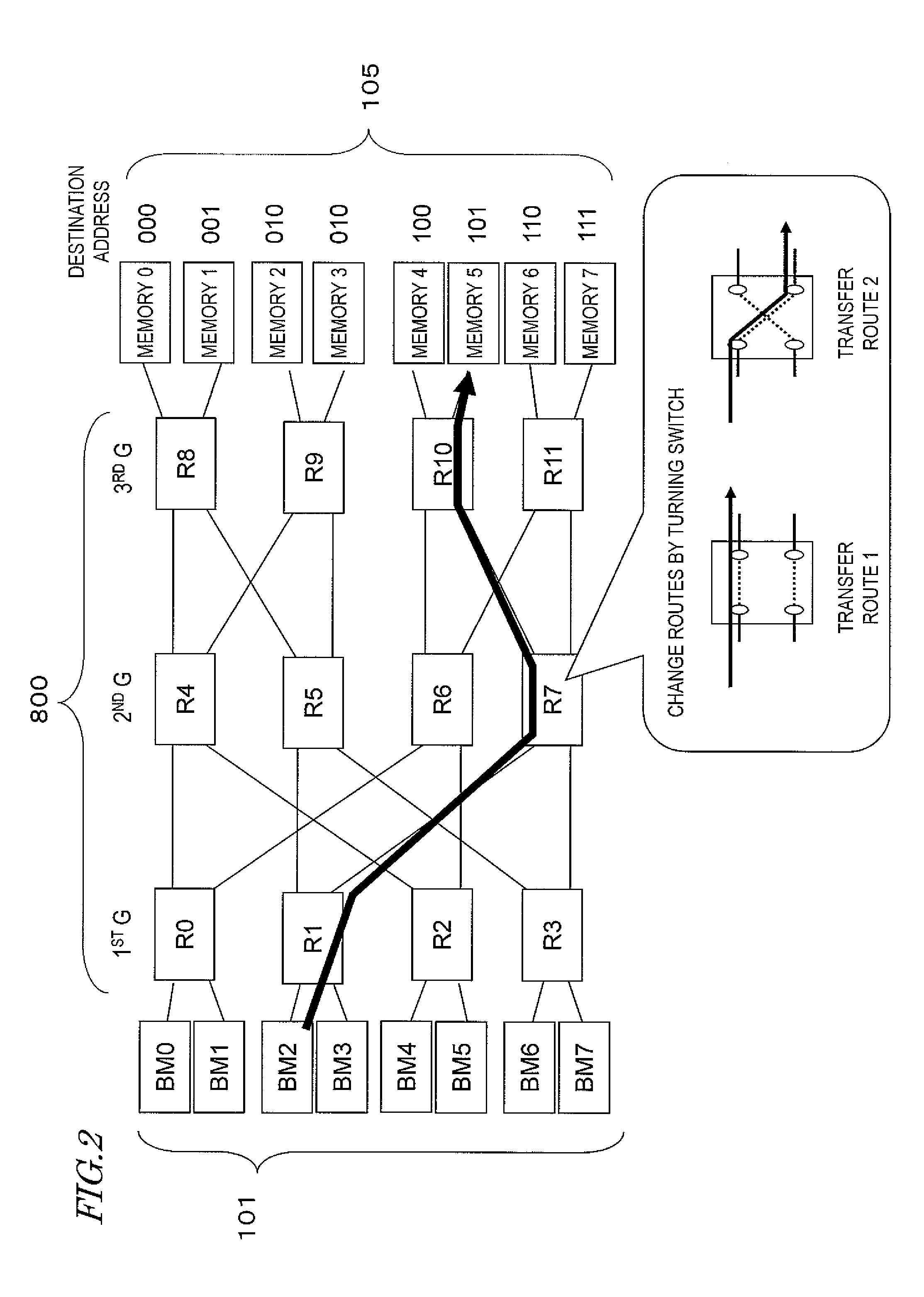

Router, method for controlling router, and program

ActiveUS20130028083A1Impede flow of trafficImprove transmission performanceError preventionTransmission systemsOperating system

An router includes: a plurality of data storage sections configured to store input data; and an arbiter configured to compare the availability of at least one of the plurality of data storage sections with respect to data that is stored in that data storage section and that shares at least a part of a transmission path to the availability of another data storage section in an adjacent router with respect to that data that also shares at least that part of the transmission path, thereby determining, based on a result of the comparison, whether or not to output that data.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

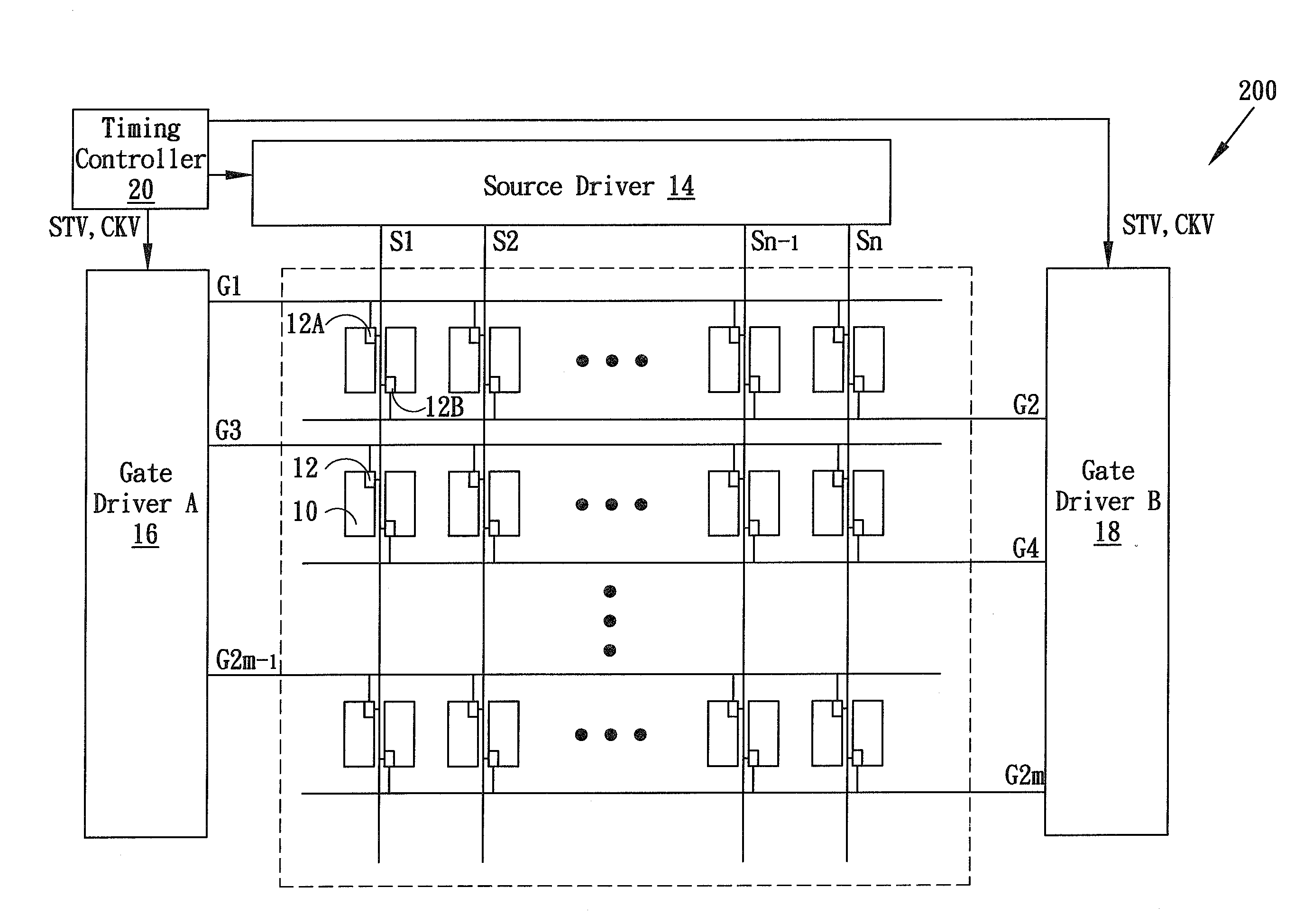

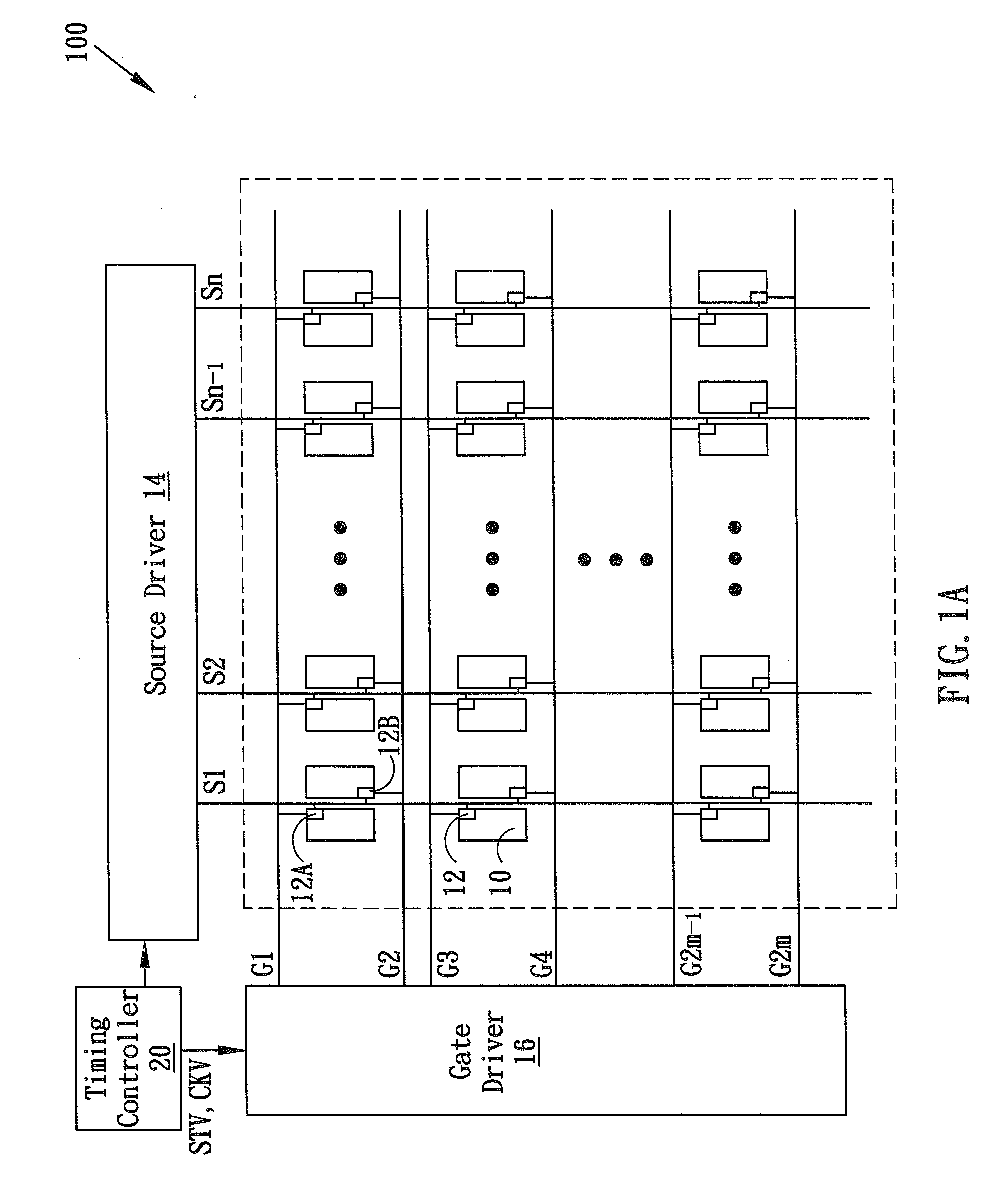

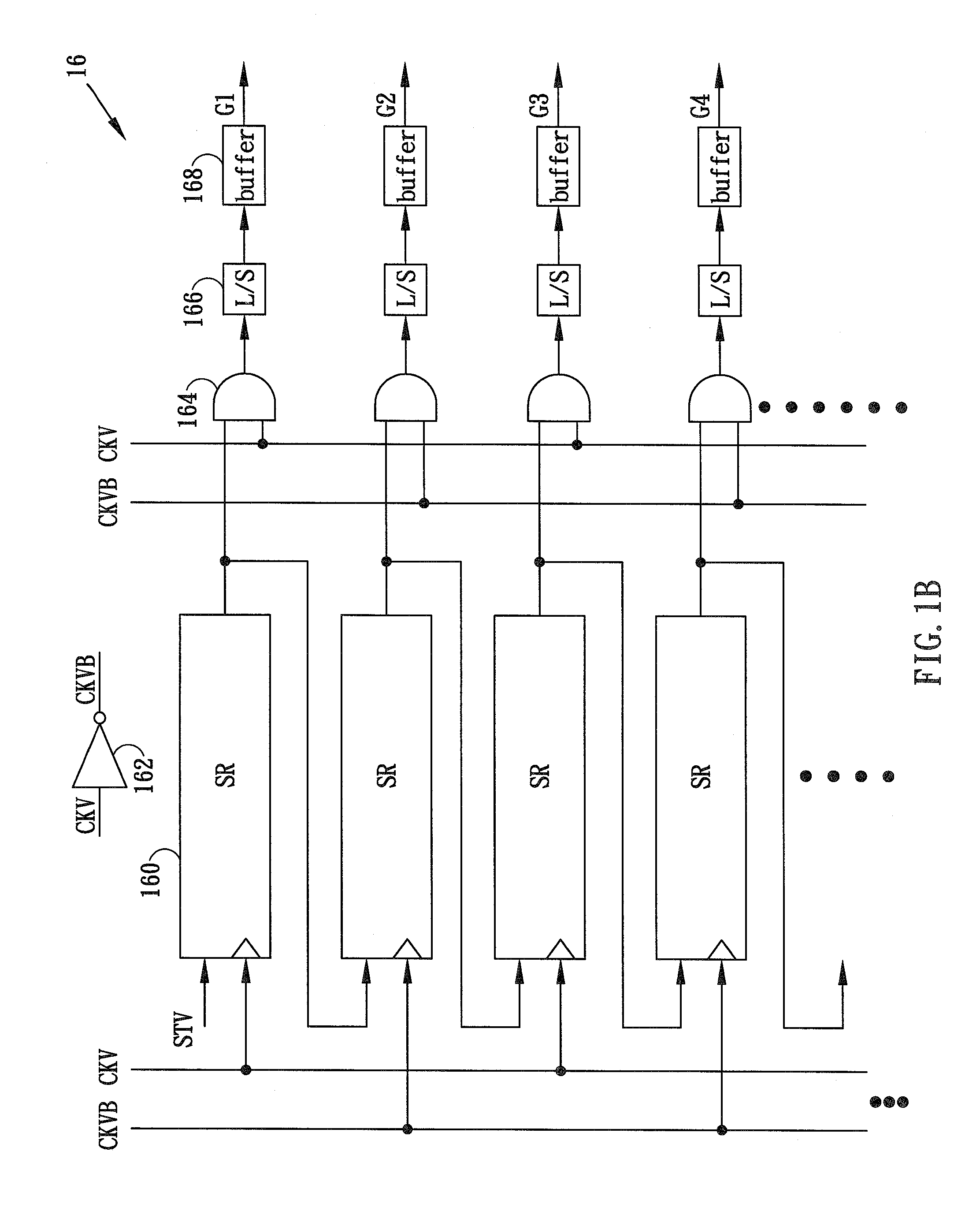

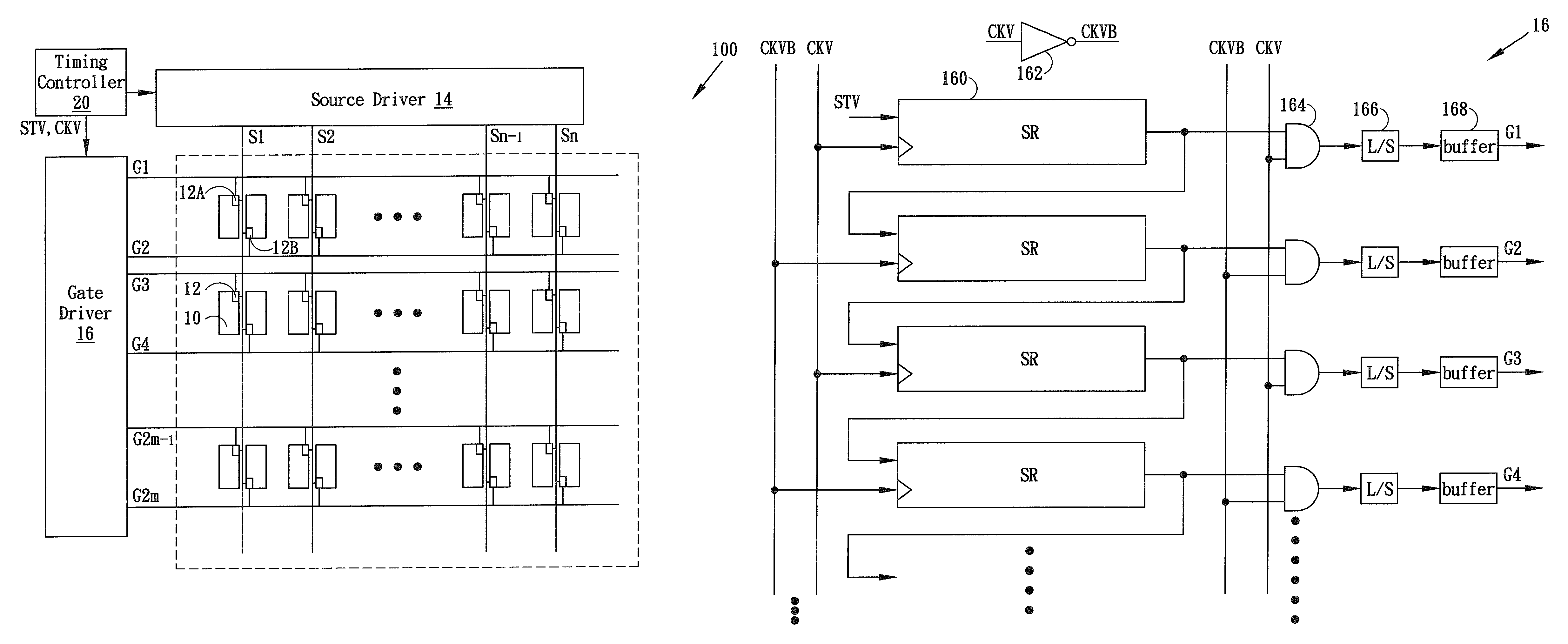

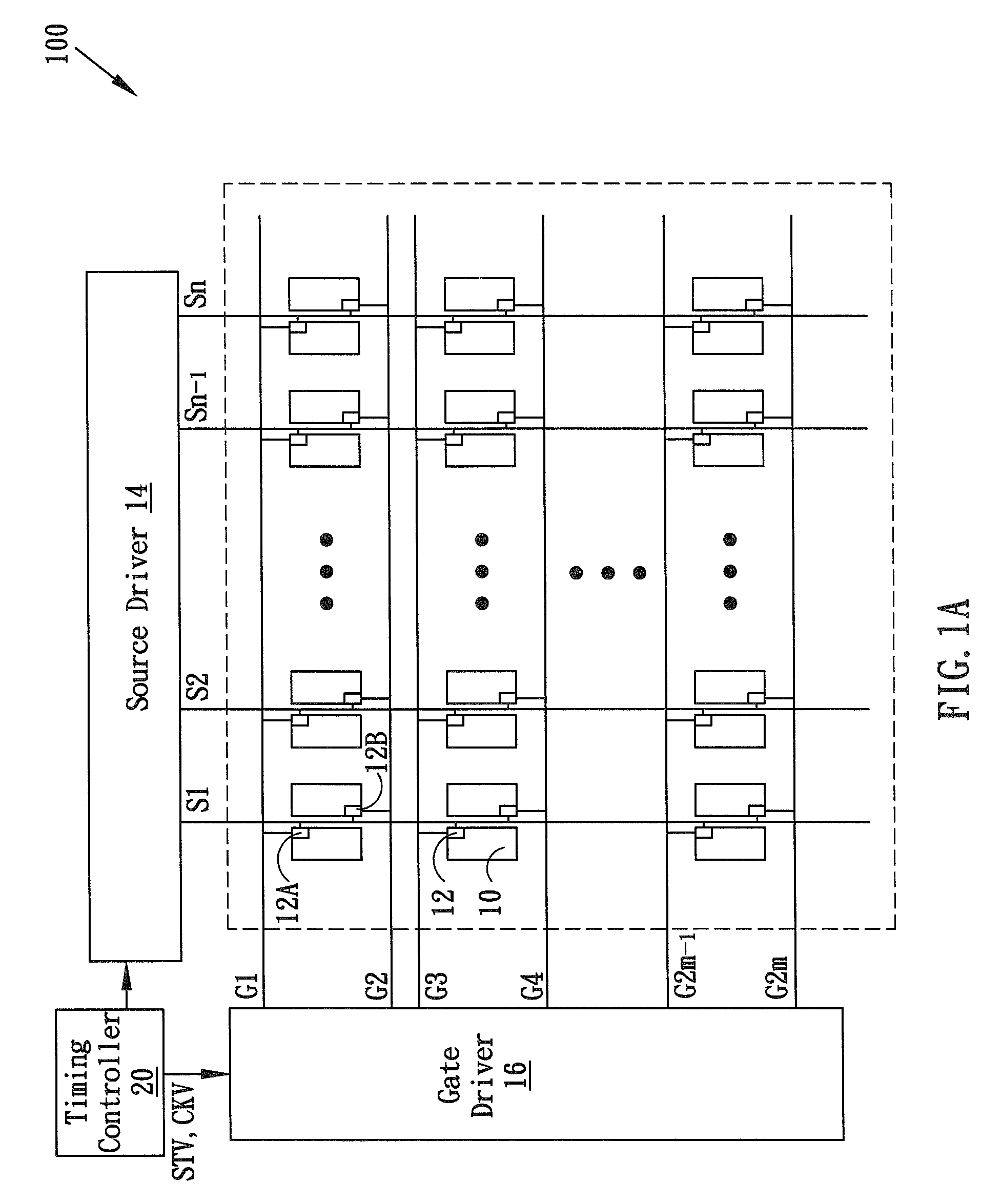

Gate Driving Waveform Control

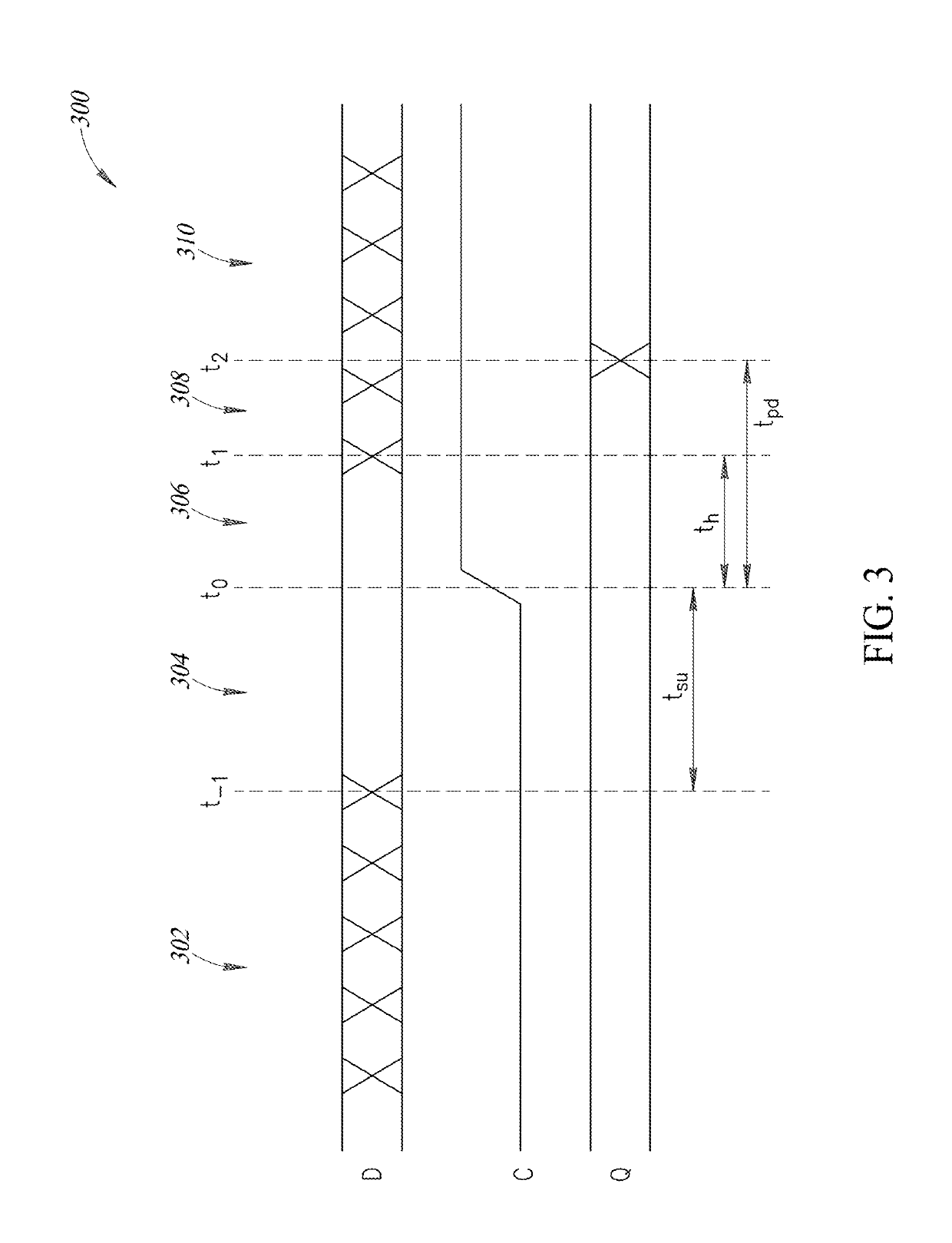

ActiveUS20090278782A1Increasing complexityIncreasing areaCathode-ray tube indicatorsInput/output processes for data processingShift registerLiquid-crystal display

A gate driver and associated method for a double gate liquid crystal display (LCD) is disclosed. A gate driving signal generating circuit, such as coupled shift registers, generates the gate driving signals in response to horizontal synchronization signal. In one embodiment, a phase control circuit, such as logic AND gates, is coupled to receive the outputs of the shift registers for determining phase relationship between the outputs of the shift registers and the horizontal synchronization signal.

Owner:HIMAX TECH LTD

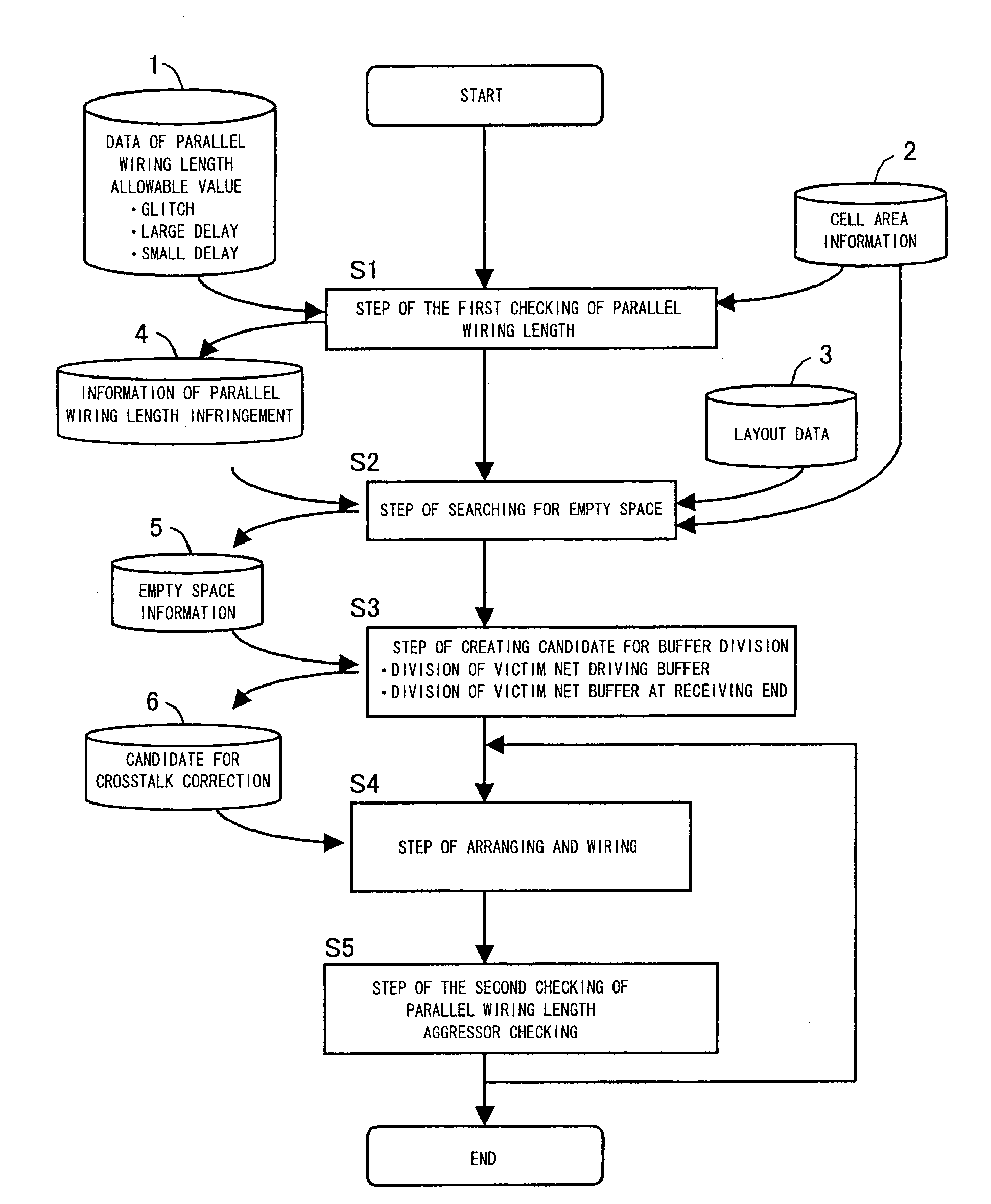

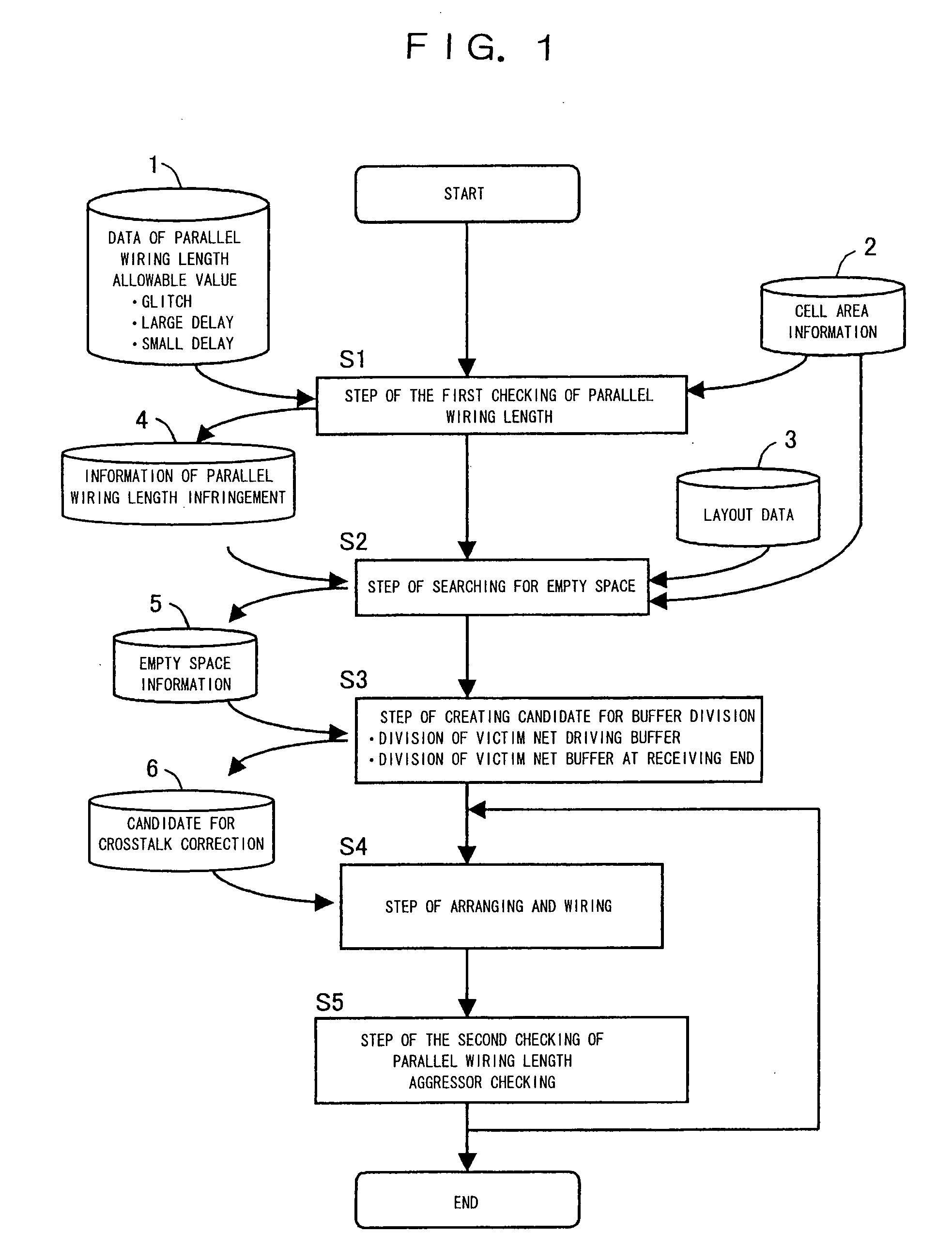

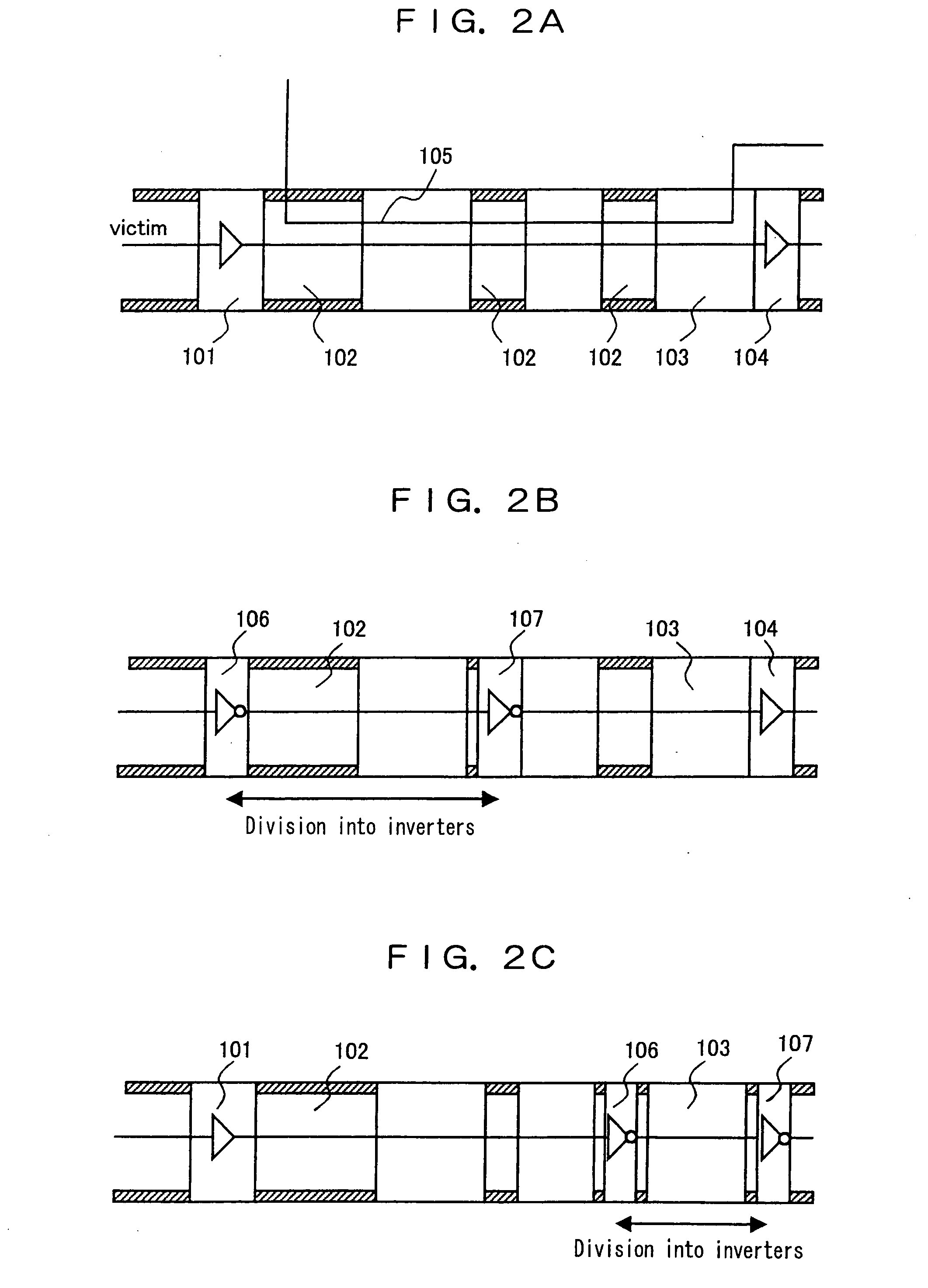

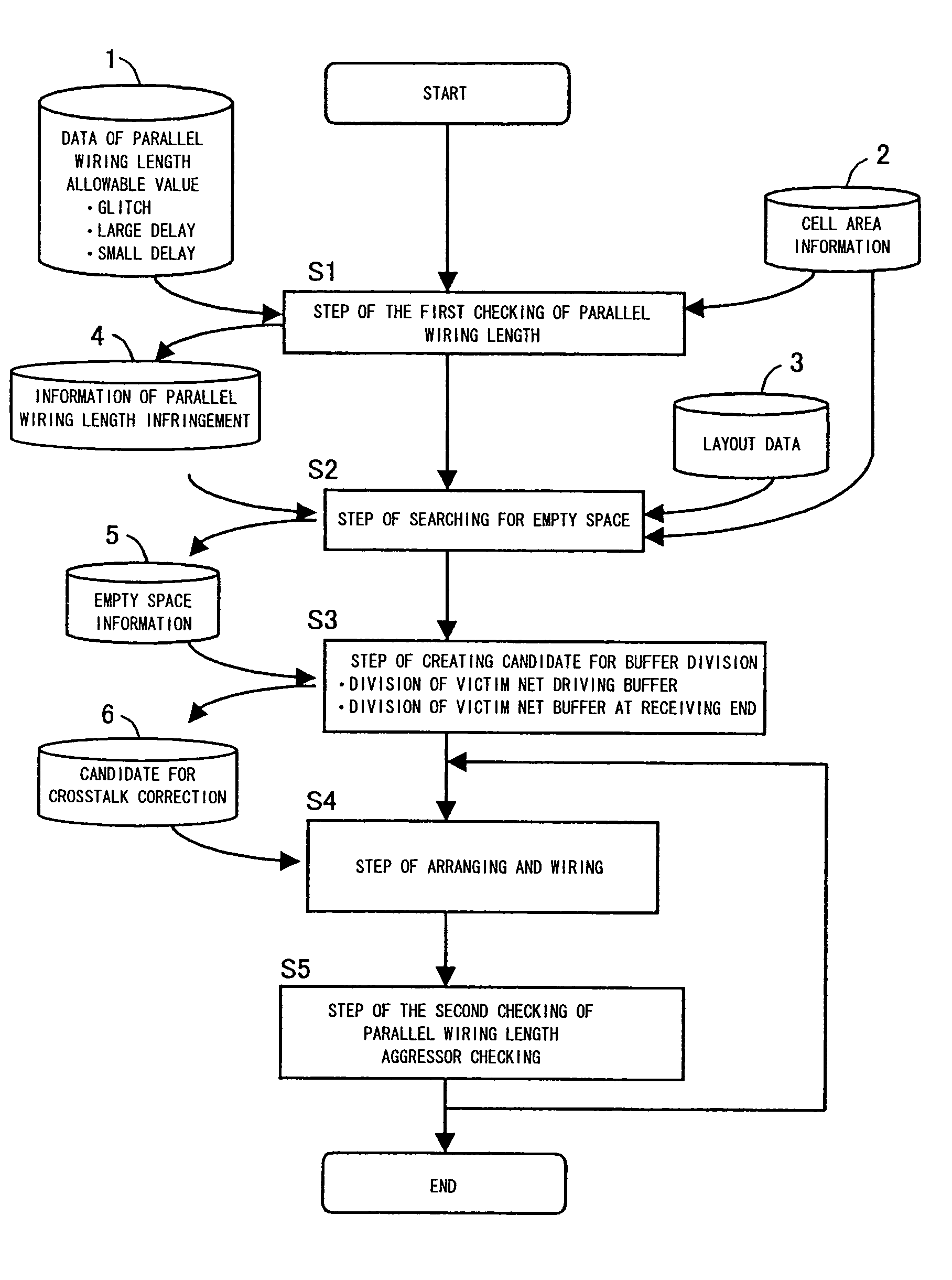

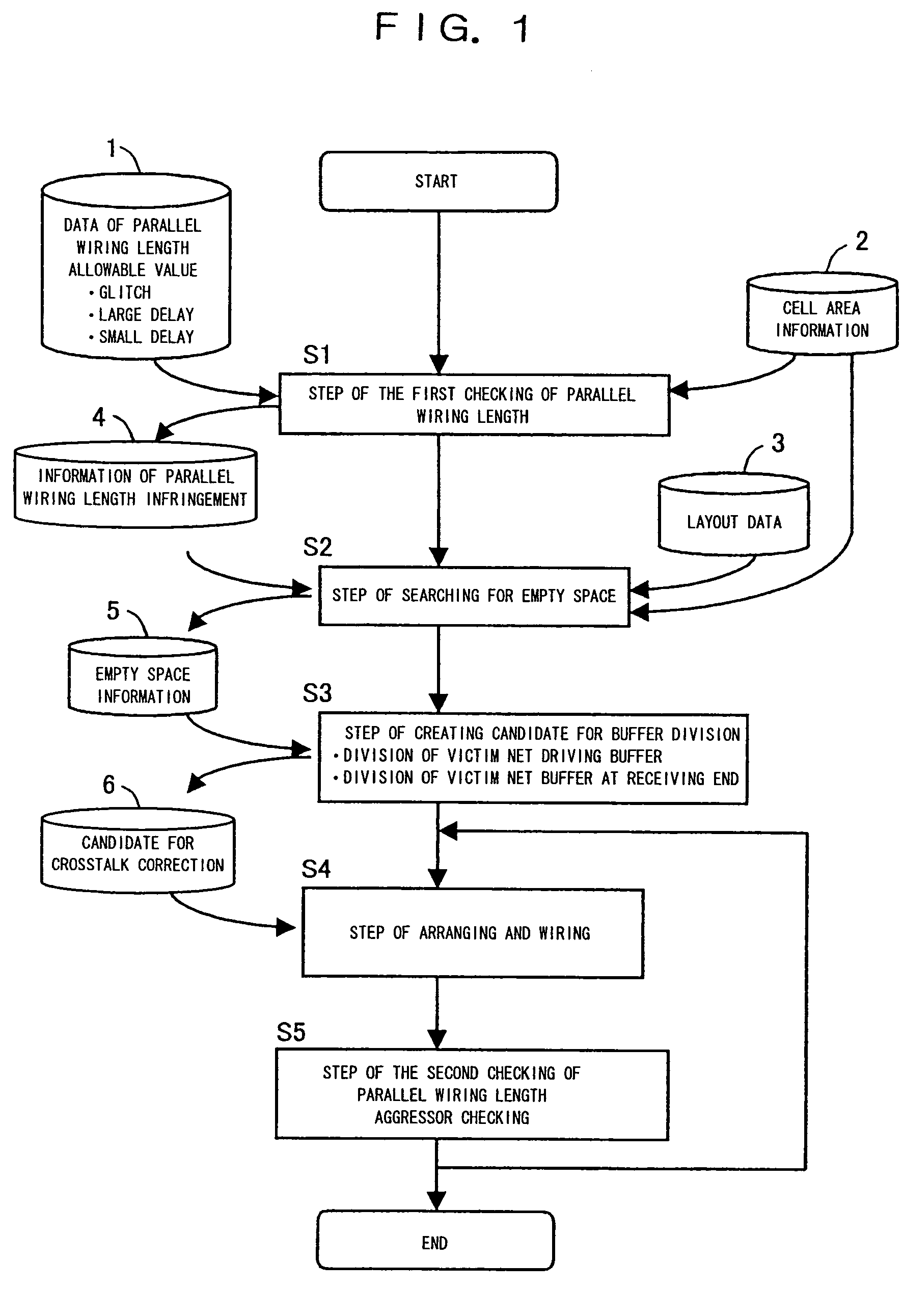

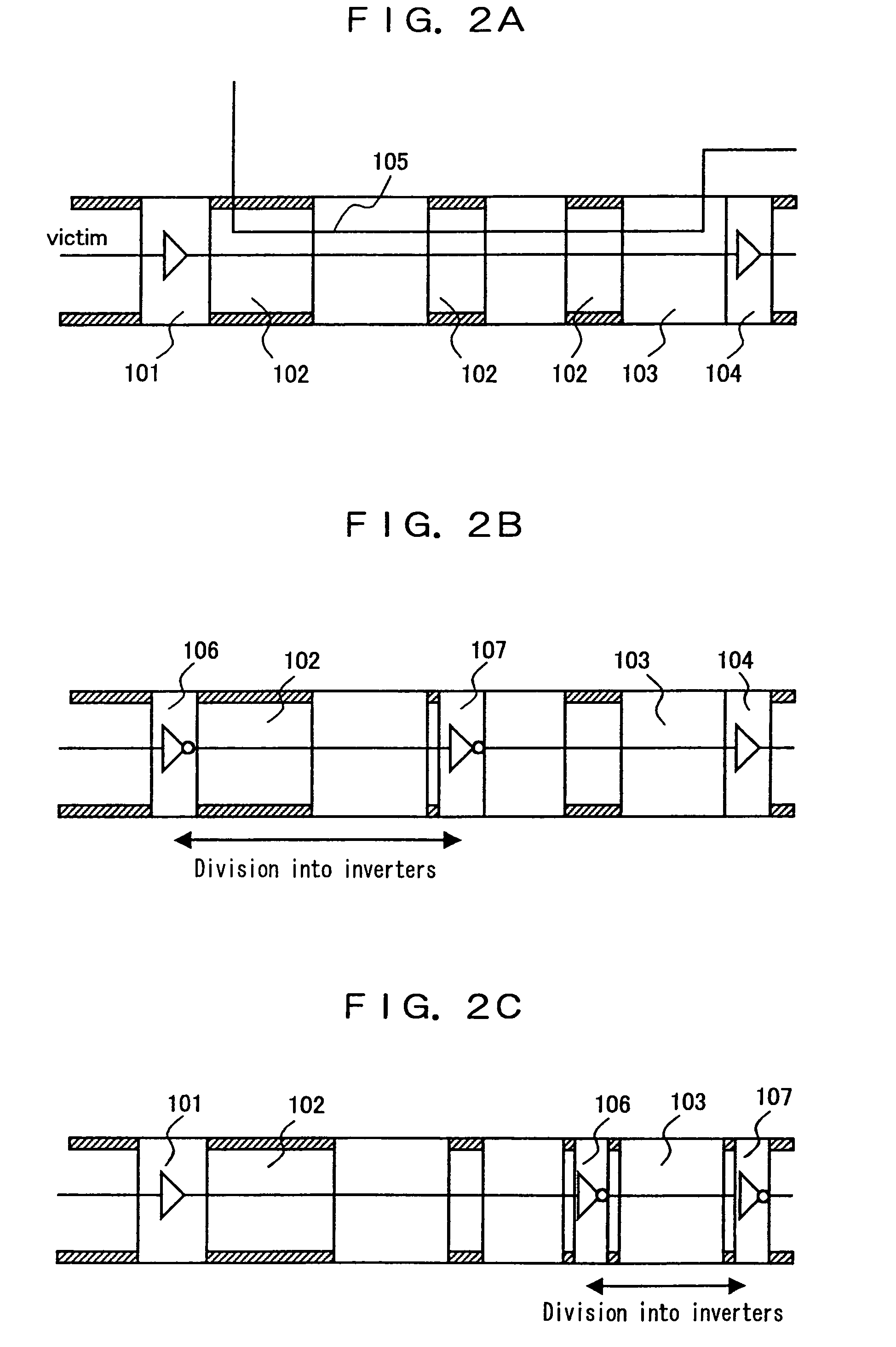

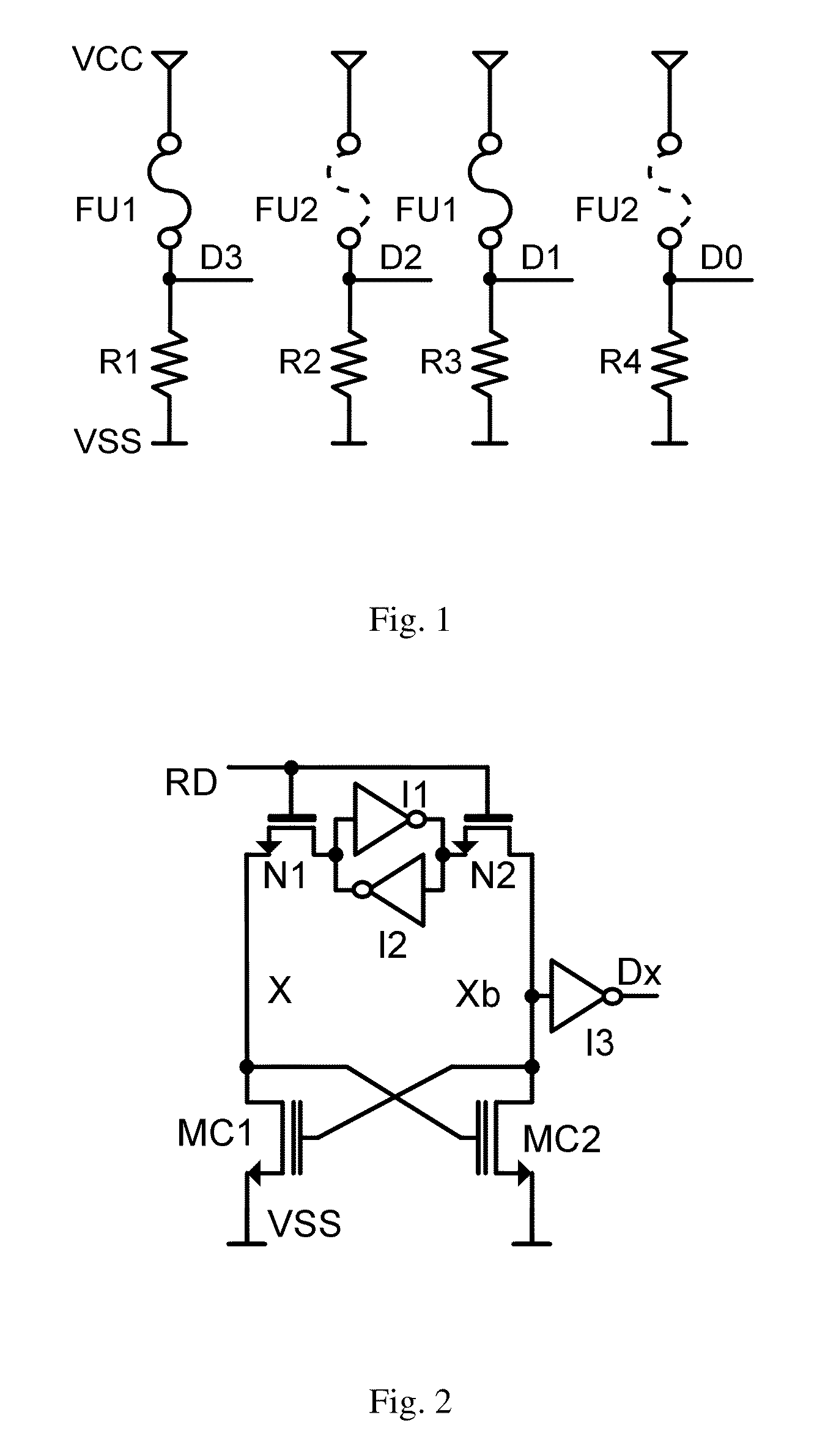

Method for correcting crosstalk

InactiveUS20060015834A1Increasing areaIncreasing consumptionSemiconductor/solid-state device testing/measurementSolid-state devicesCapacitanceSnubber

Owner:SOCIONEXT INC

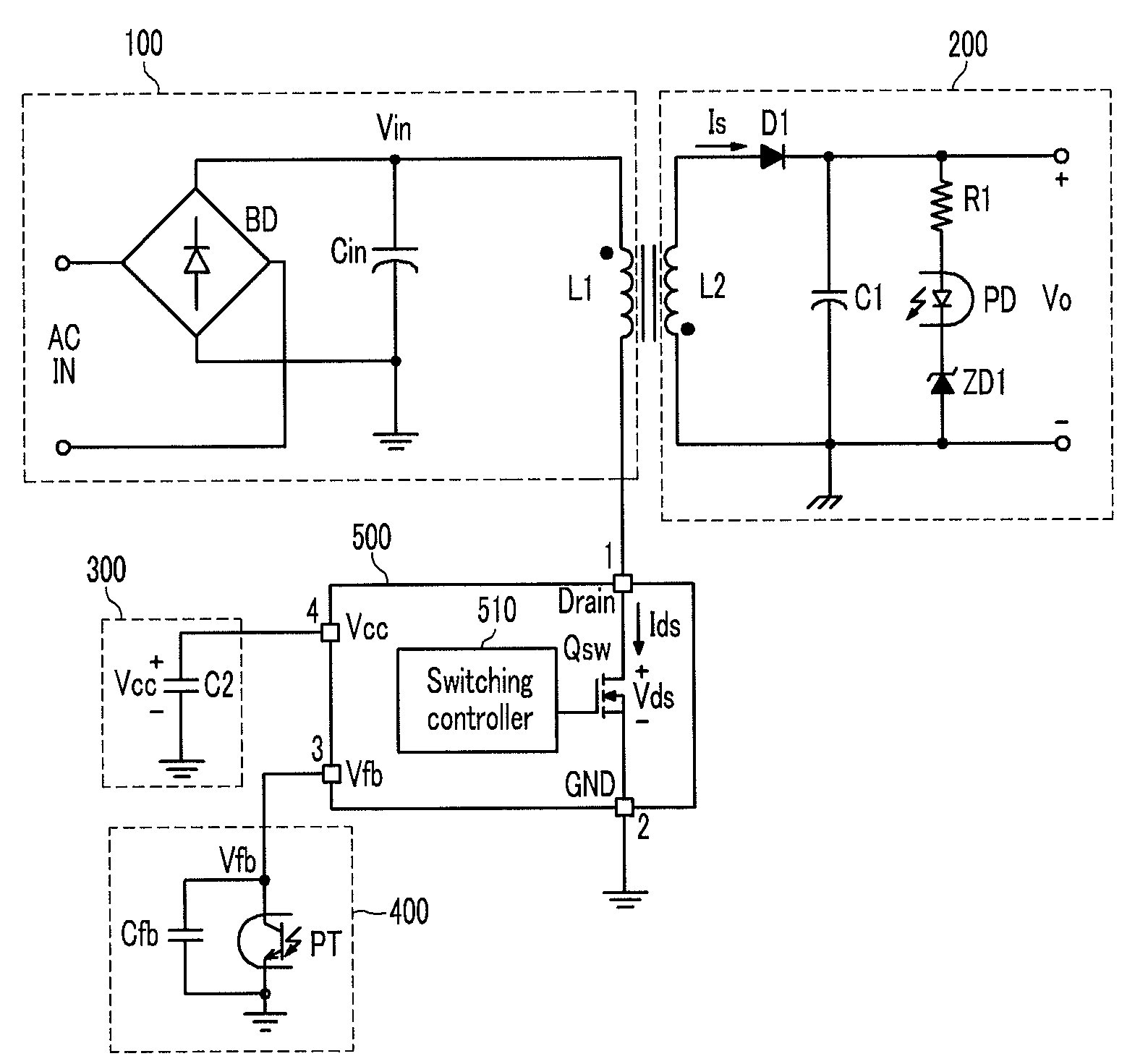

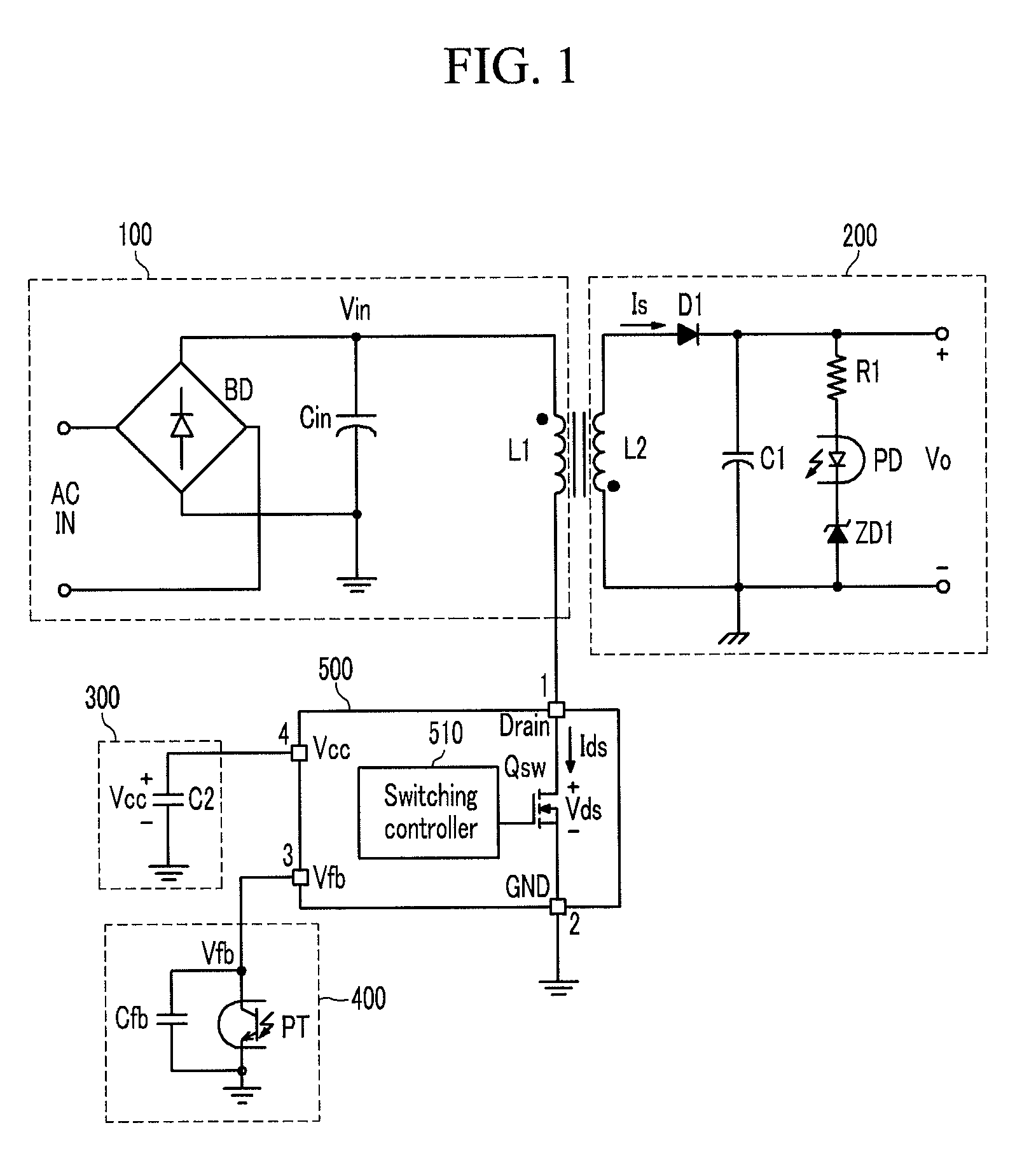

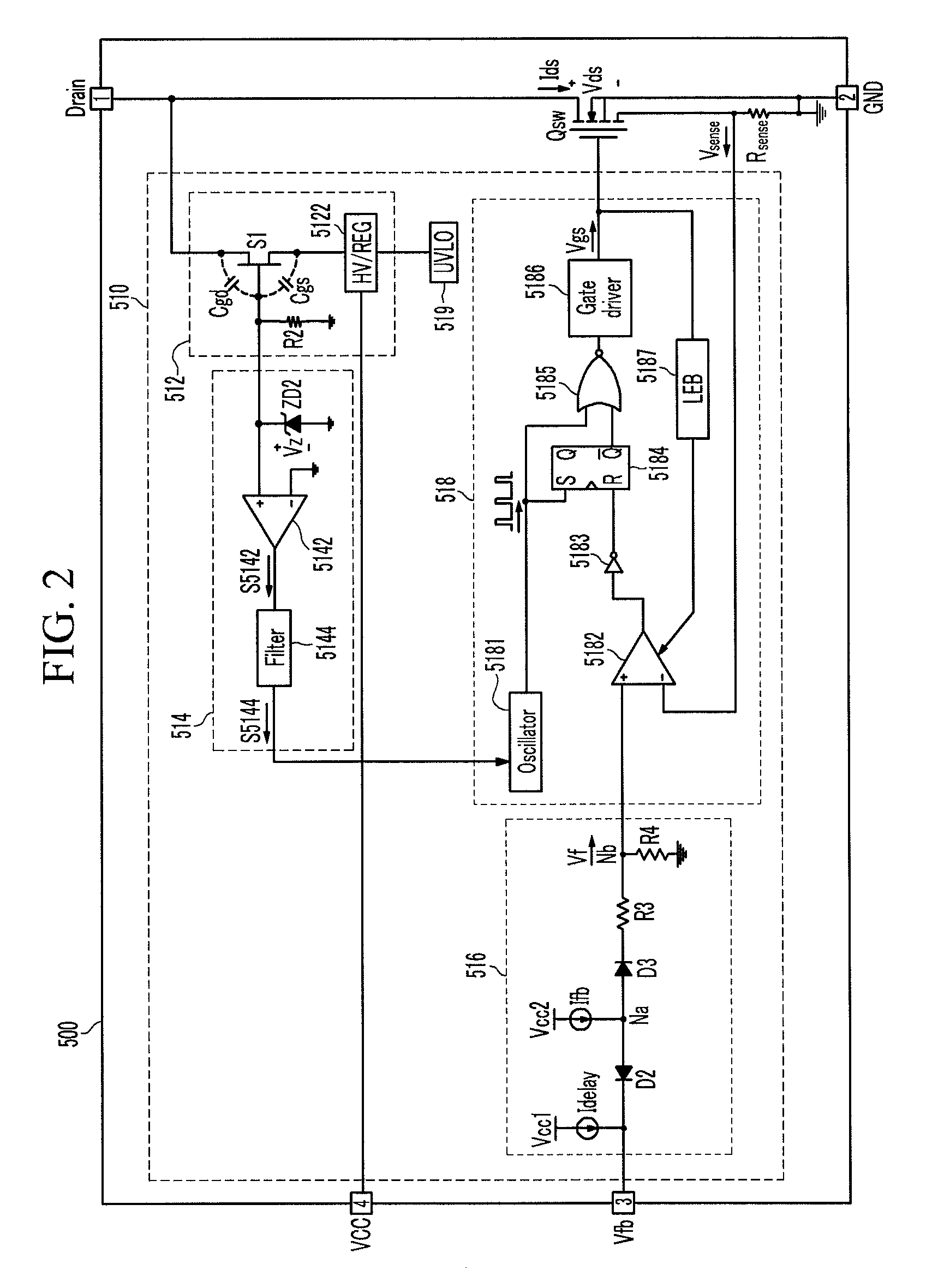

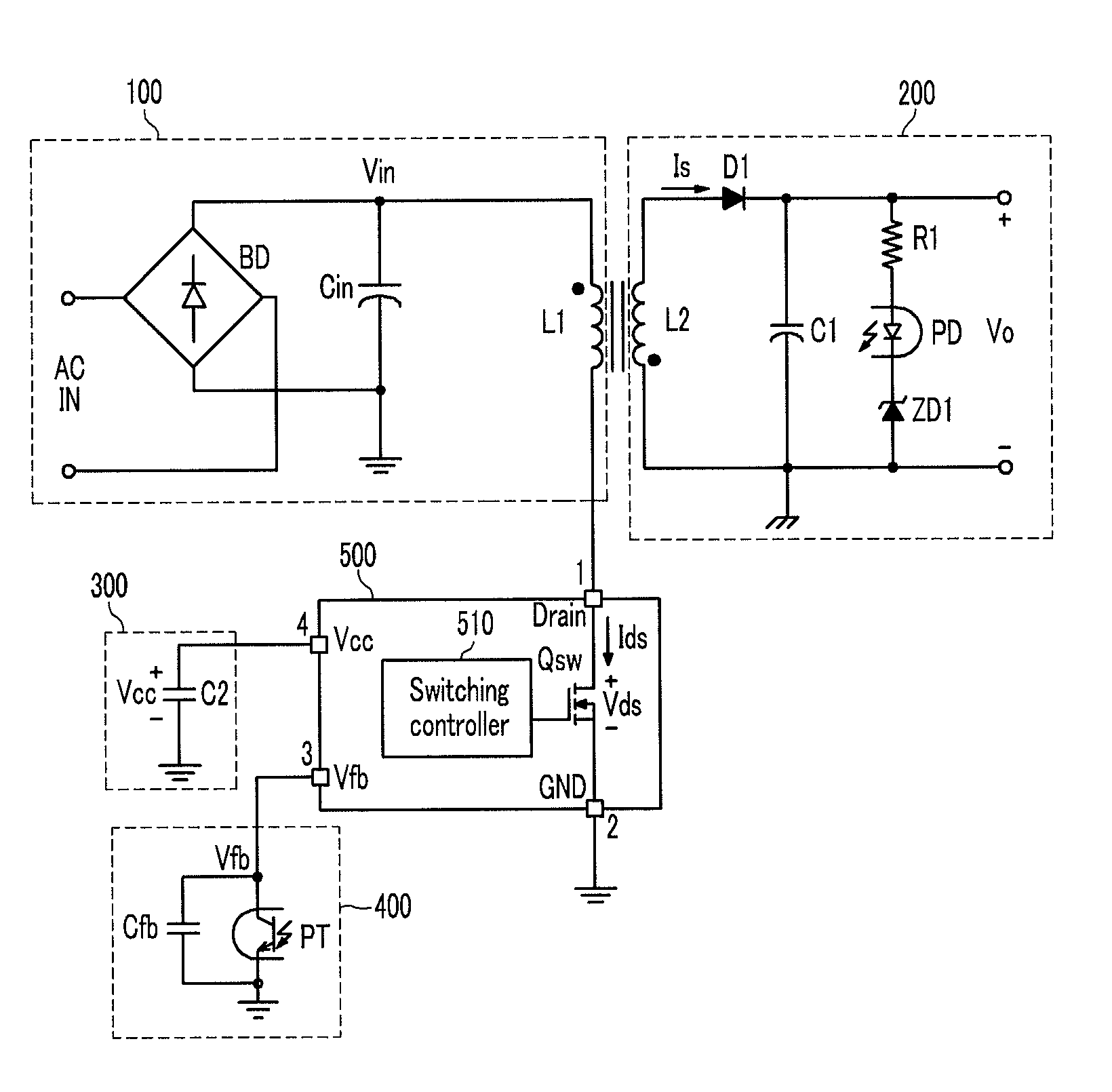

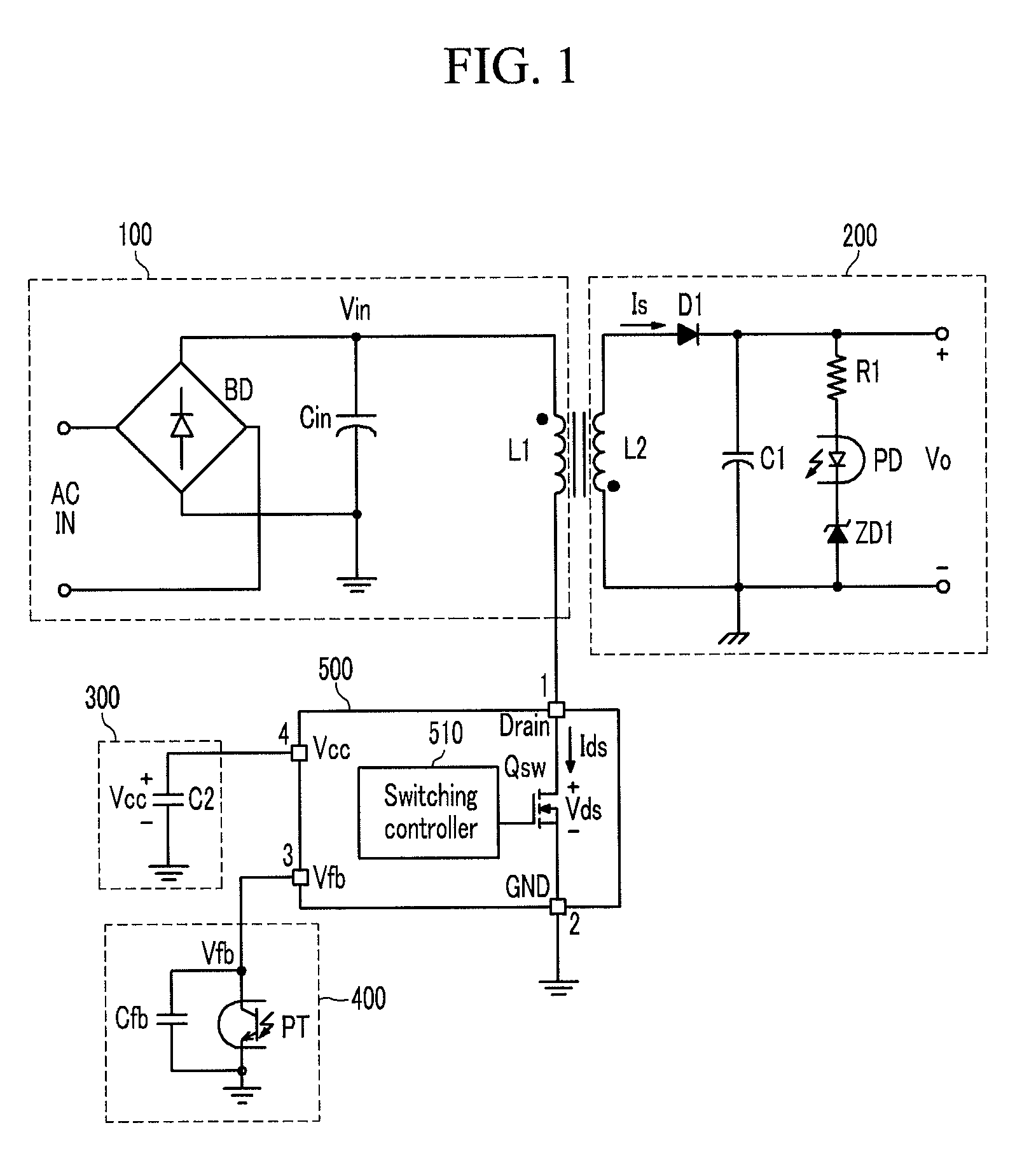

Converter

ActiveUS20090296437A1Increasing areaIncreasing costAc-dc conversion without reversalEfficient power electronics conversionResonanceWave shape

A converter is provided including: a first switch; an energy transmitting element for converting input energy into output energy according to the switching of the first switch; and a switching controller for detecting a time when a voltage between a first terminal and a second terminal of the first switch reaches a valley of a resonance waveform, and actuating the first switch corresponding to one of the detected valleys of the resonance waveform. The switching controller includes: a valley detector for changing the state of the output signal whenever a voltage between a first terminal and a second terminal of the first switch reaches a valley of the resonance waveform; and a PWM controller for actuating the first switch corresponding to an output signal of the valley detector.

Owner:SEMICON COMPONENTS IND LLC

Converter that actuates a switch corresponding to a detected valley of a resonance waveform

ActiveUS8259471B2Increasing areaIncreasing costAc-dc conversion without reversalEfficient power electronics conversionResonanceTransverter

A converter is provided including: a first switch; an energy transmitting element for converting input energy into output energy according to the switching of the first switch; and a switching controller for detecting a time when a voltage between a first terminal and a second terminal of the first switch reaches a valley of a resonance waveform, and actuating the first switch corresponding to one of the detected valleys of the resonance waveform. The switching controller includes: a valley detector for changing the state of the output signal whenever a voltage between a first terminal and a second terminal of the first switch reaches a valley of the resonance waveform; and a PWM controller for actuating the first switch corresponding to an output signal of the valley detector.

Owner:SEMICON COMPONENTS IND LLC

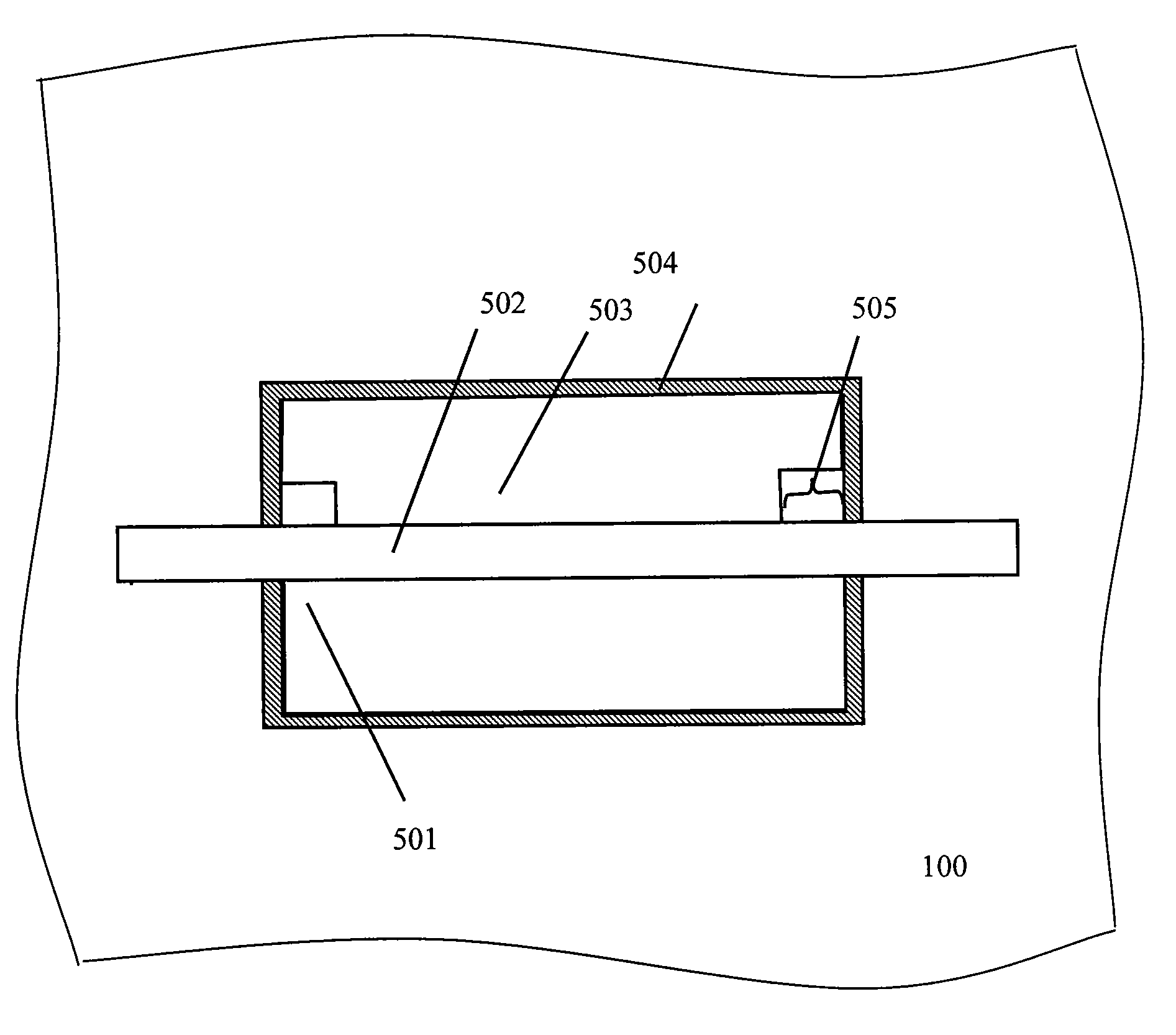

Semiconductor resistor

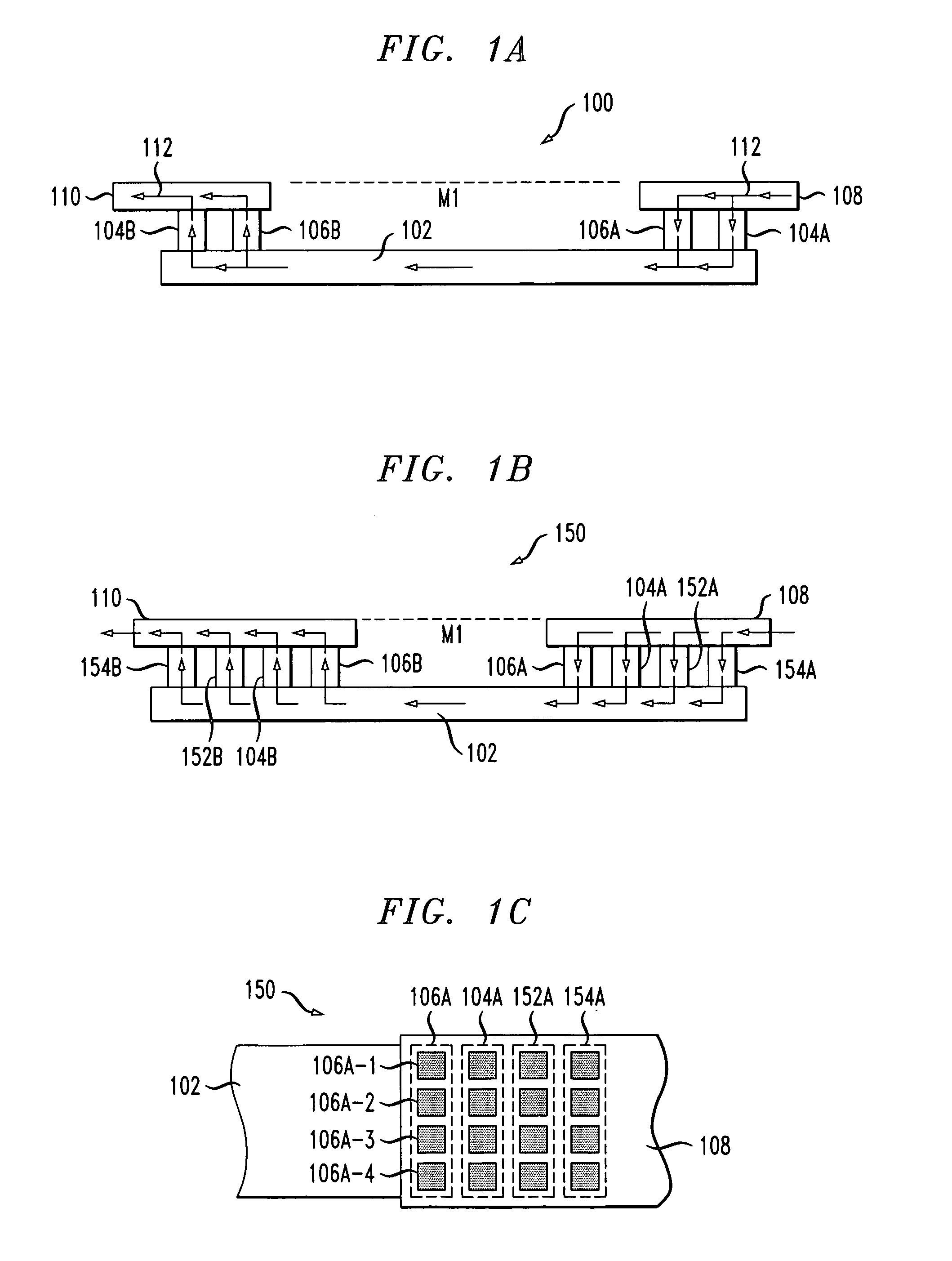

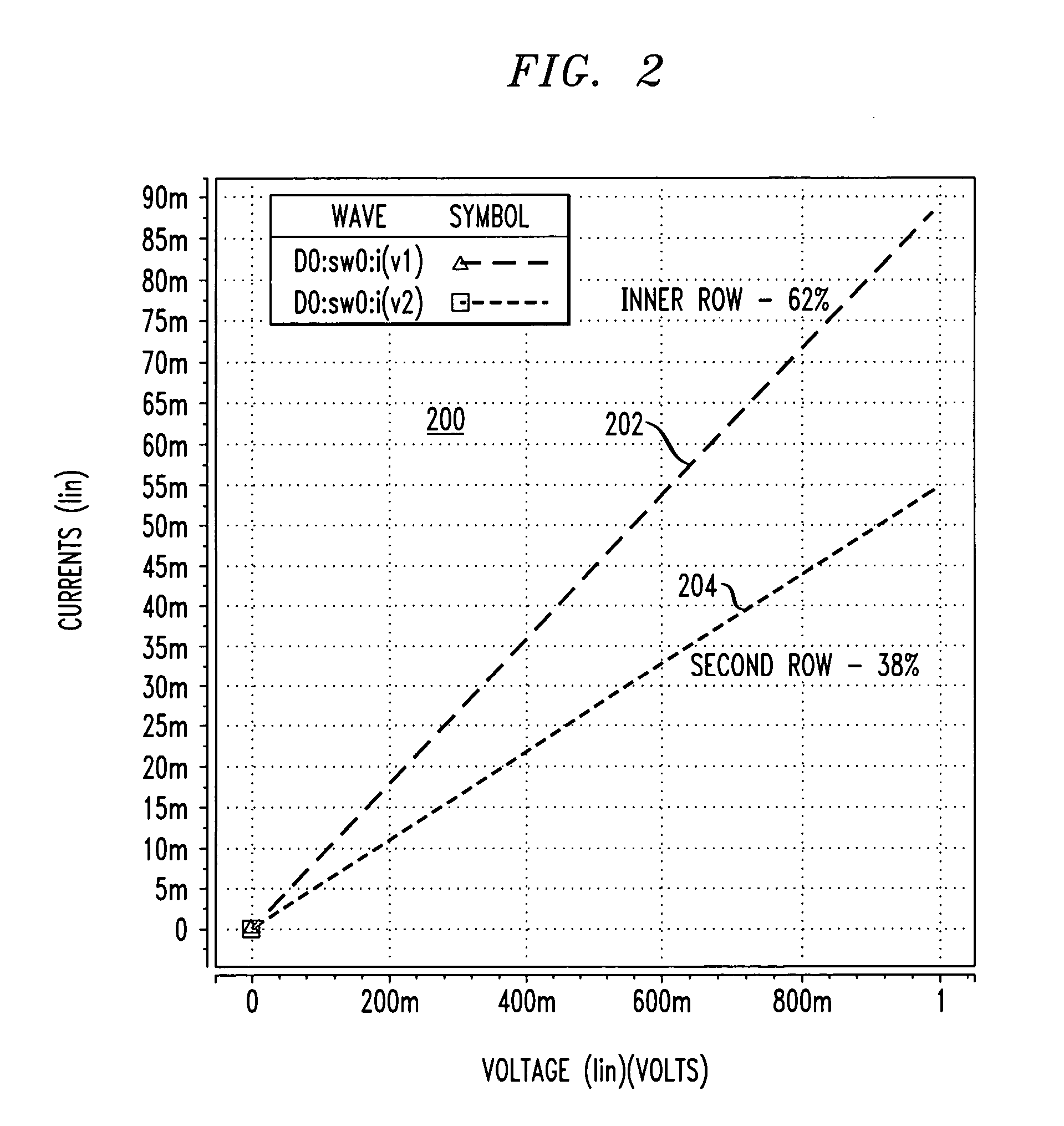

ActiveUS20050168319A1Increasing areaIncreasing costResistor terminals/electrodesSemiconductor/solid-state device detailsCurrent distributionEngineering

A semiconductor resistor comprises a resistor body formed on a semiconductor substrate and first and second conductive terminals electrically connected to the resistor body at opposite ends thereof. The semiconductor resistor further includes at least first and second conductive paths between at least one of the first and second conductive terminals and the resistor body. The at least one conductive terminal is configured such that a resistance of the at least one conductive terminal between the at least first and second conductive paths is substantially matched to a resistance of the resistor body between the at least first and second conductive paths. In this manner, a current distribution between the at least first and second conductive paths is substantially matched.

Owner:BELL SEMICON LLC

Method for correcting crosstalk

InactiveUS6983436B2Without increase area and power consumptionIncreasing areaSemiconductor/solid-state device testing/measurementSolid-state devicesData bufferVIT signals

In a semiconductor integrated circuit, there is provided a method for correcting crosstalk, which exerts an influence via coupling capacitance between wiring by the signal transitions between adjacent wiring, comprising the step of creating a candidate for buffer division, the step of creating a candidate for cell movement, or the step of victim net logic synthesis. Thereby, the crosstalk is corrected through the buffer division, the cell movement, or an increase of elements in number by logic decomposition, logic inversion and a change of fan-outs in number.

Owner:SOCIONEXT INC

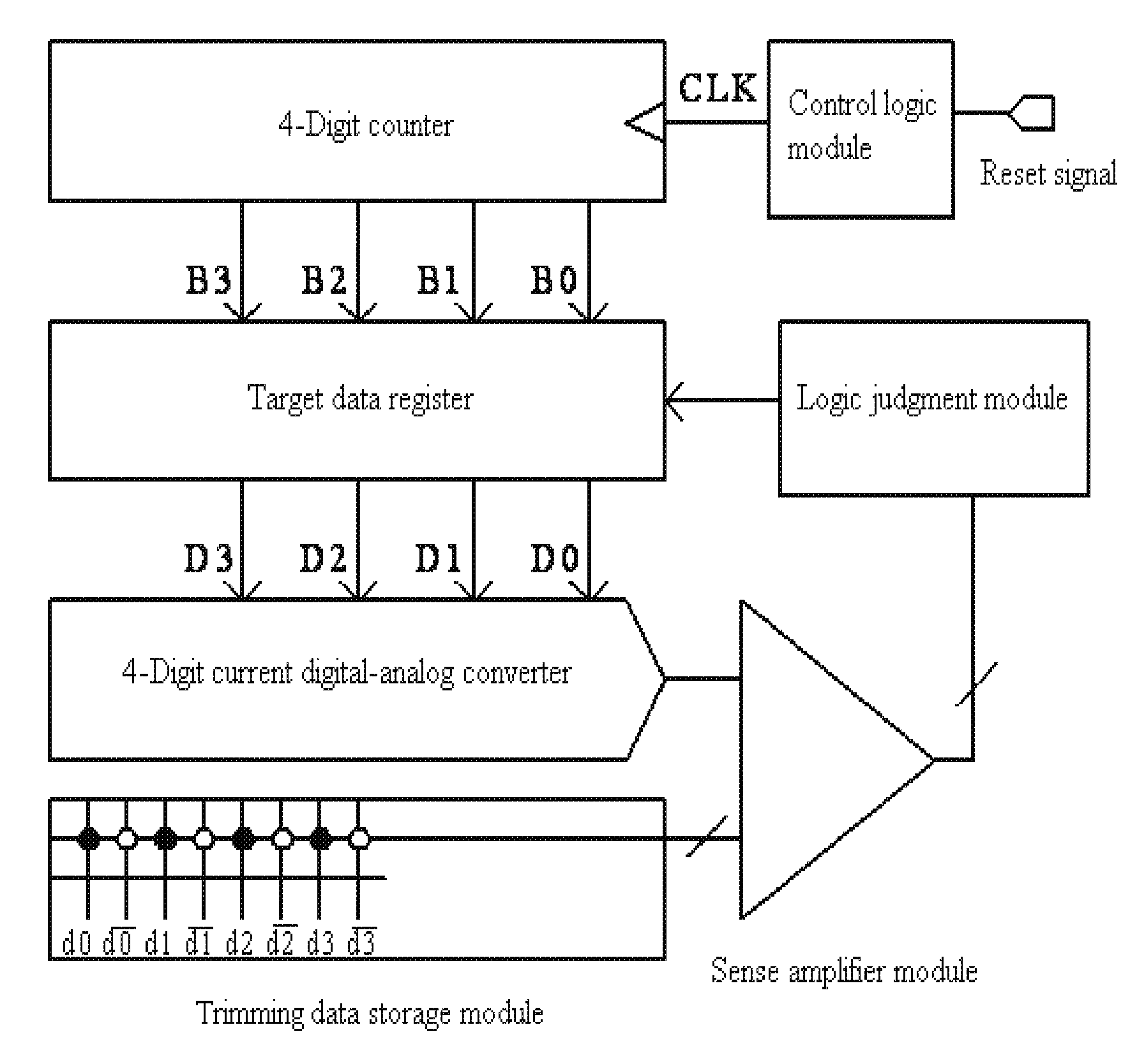

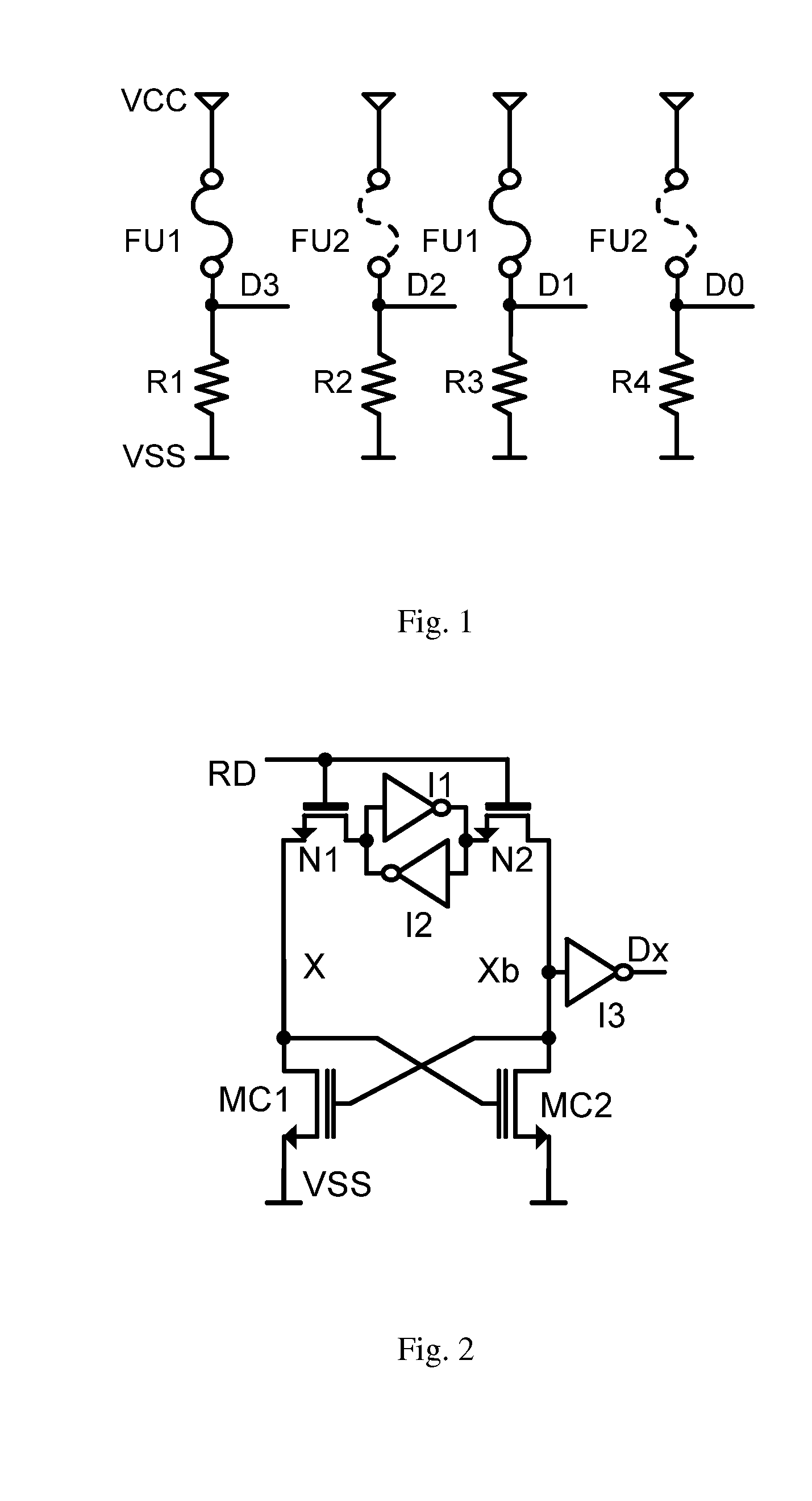

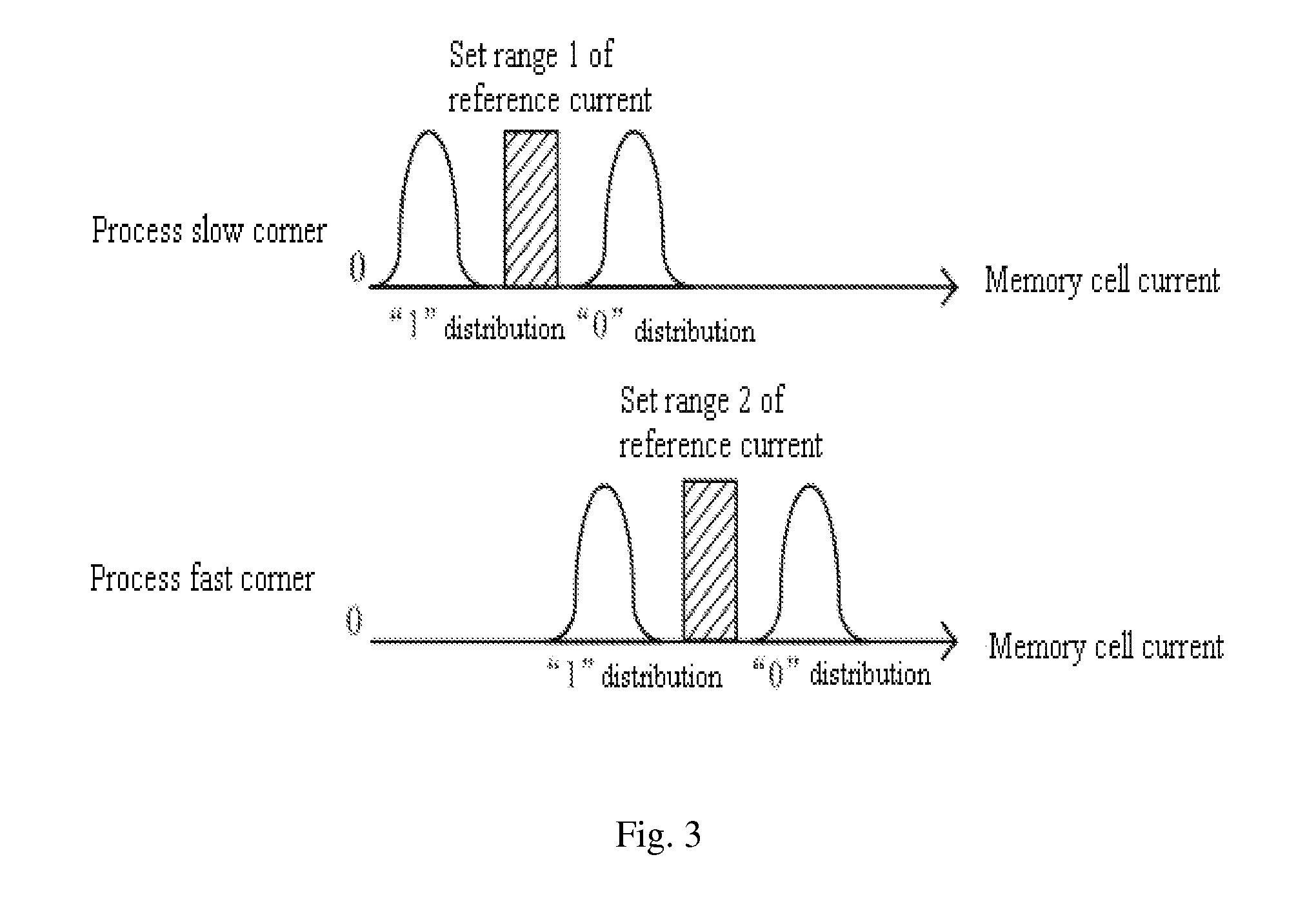

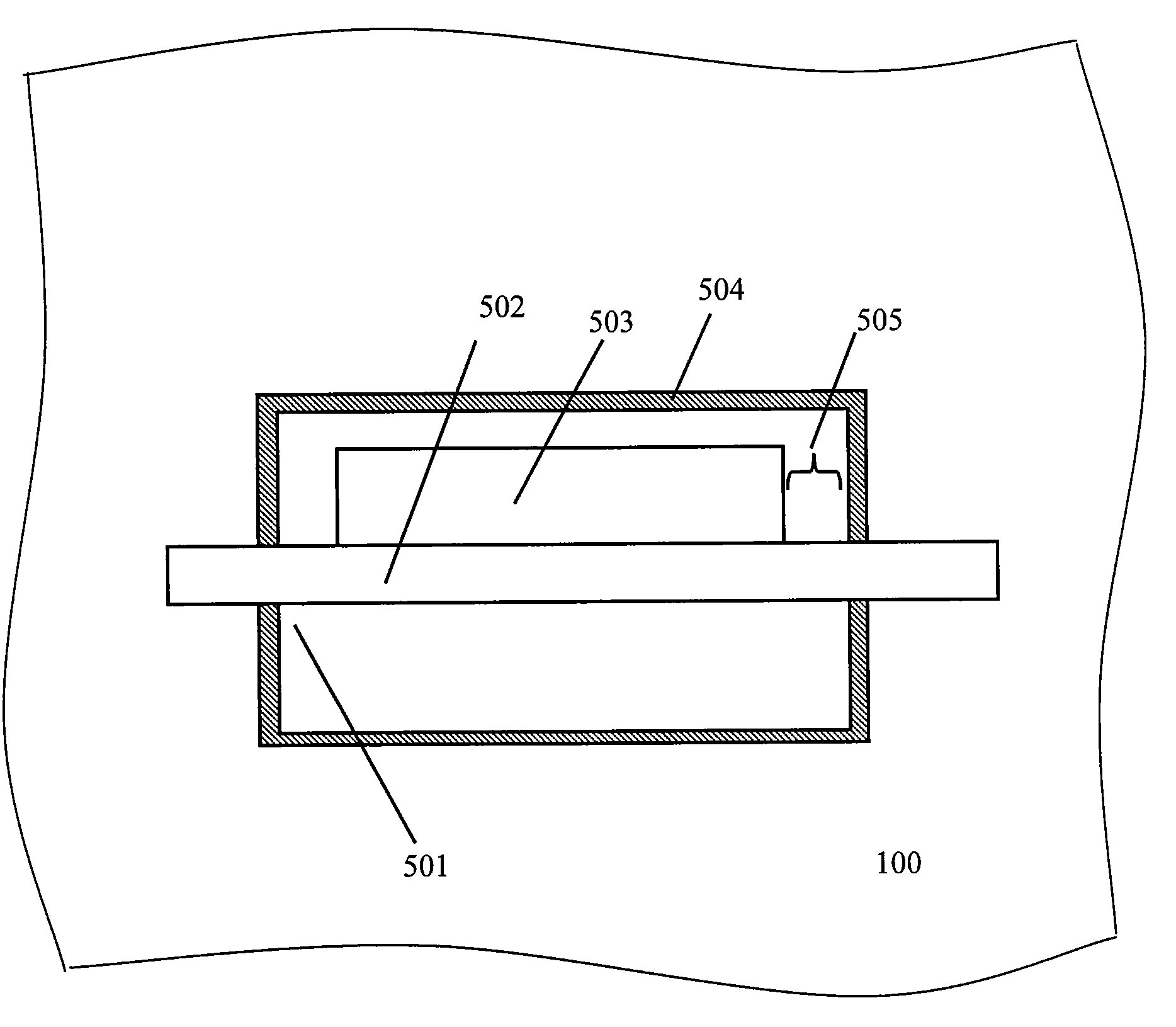

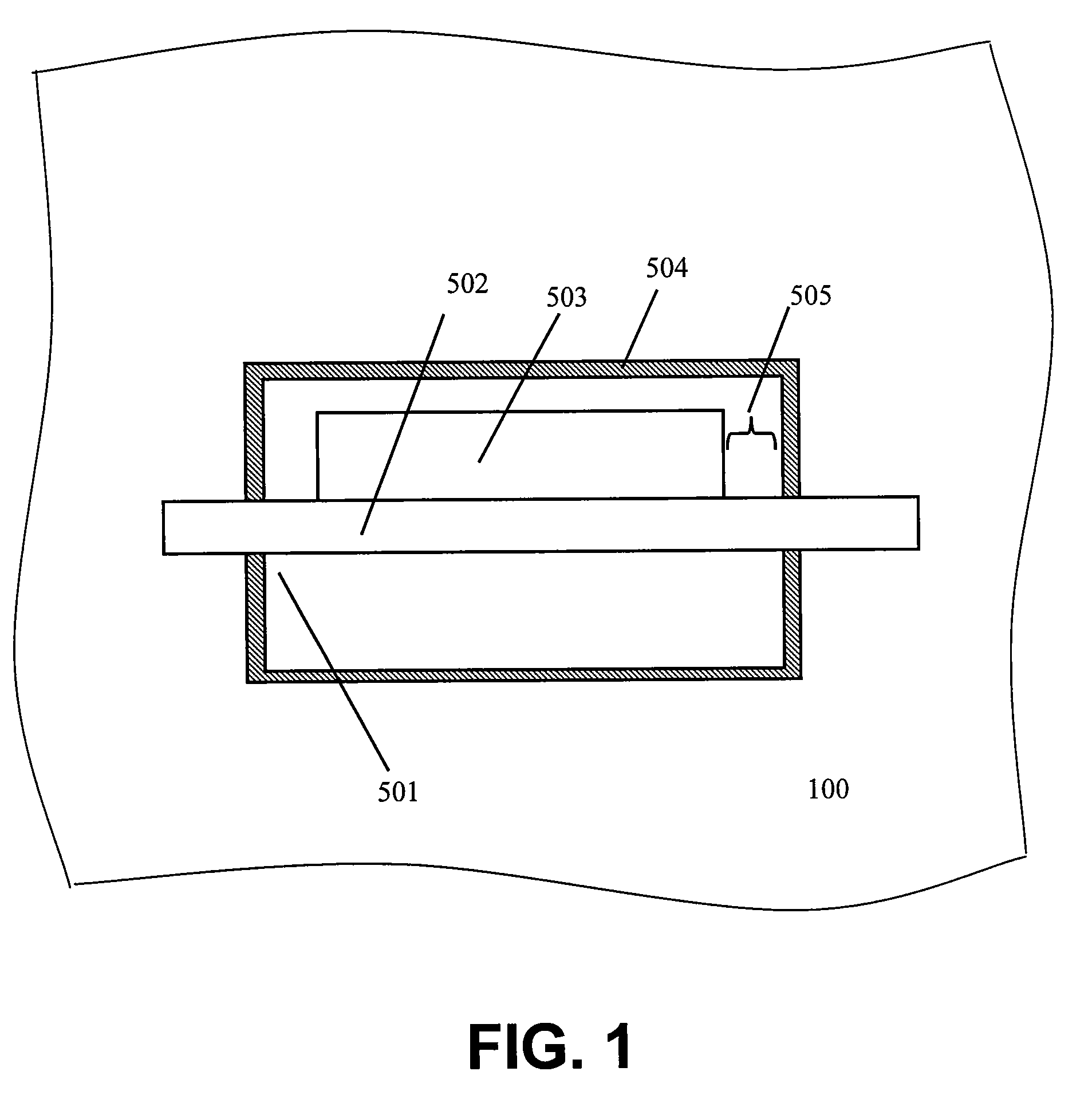

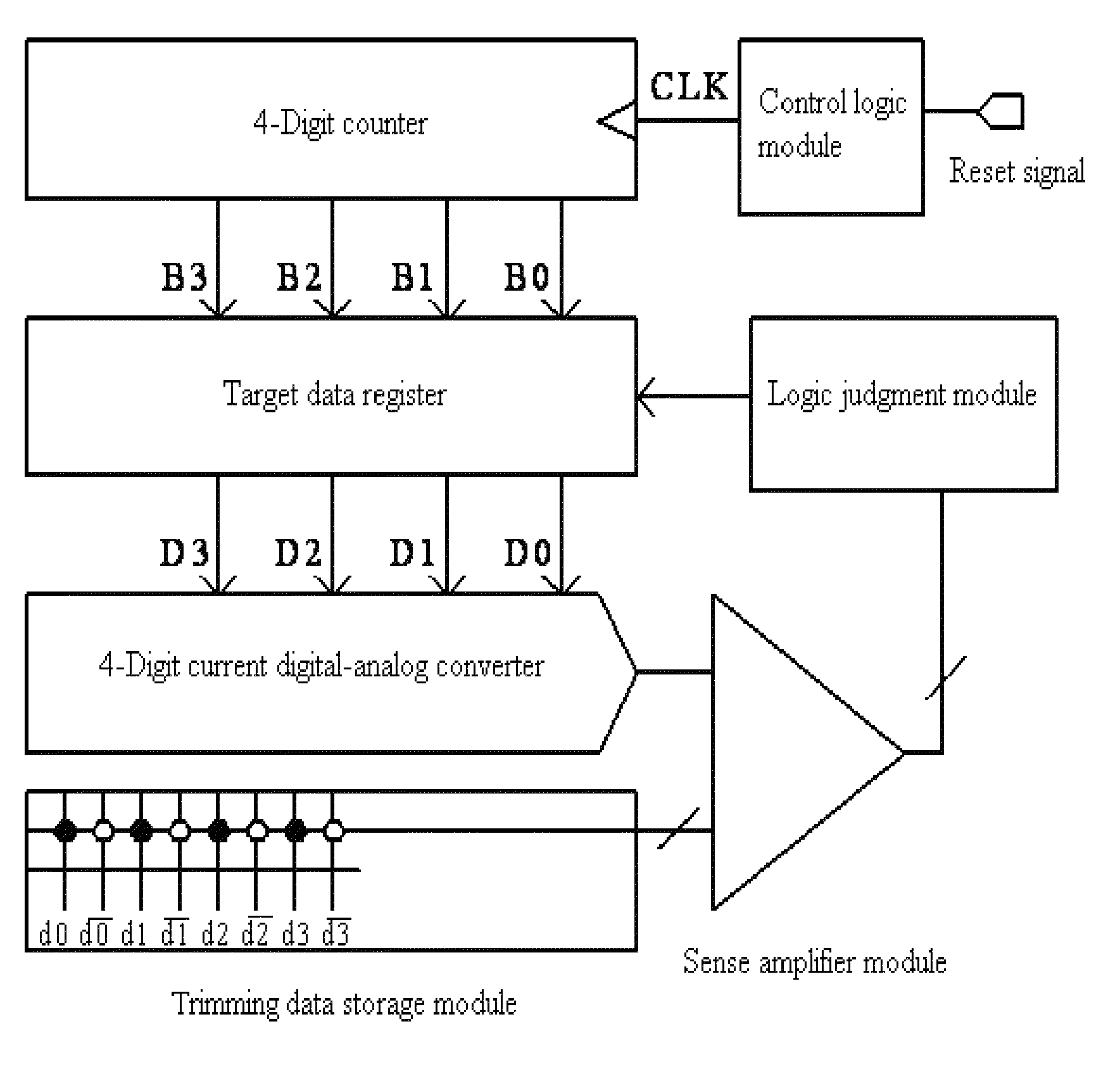

Selfcalibration method and circuit of nonvolatile memory and nonvolatile memory circuit

ActiveUS20100014363A1Increasing area costIncreasing circuit areaRead-only memoriesDigital storageAudio power amplifierReference current

The present invention discloses a selfcalibration method of a reading circuit of a nonvolatile memory, by which trimming data having recorded a reference current are stored in a bit-pair form into the memory and regulate a sense amplifier, and a value of the reference current is obtained according to the trimming data when “0” and “1” in the outputted trimming data have the same quantities. The present invention further discloses a selfcalibration circuit of the nonvolatile memory, which includes a trimming data storage module, a sense amplifier module, a logic judgment module, and a scanning module. The present invention furthermore discloses a nonvolatile memory circuit, which includes a memory cell array and the selfcalibration circuit of the reading circuit of the nonvolatile memory. The present invention, not requiring an additional fuse or differential unit, can solve a deadlock problem securely and reliably without increasing circuit area and test cost, and be widely applied to OTP, MTP and EEPROM of various processes or various nonvolatile memories such as Flash EEPROM, MRAM, and FeRAM, improving reliability of the memory effectively.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

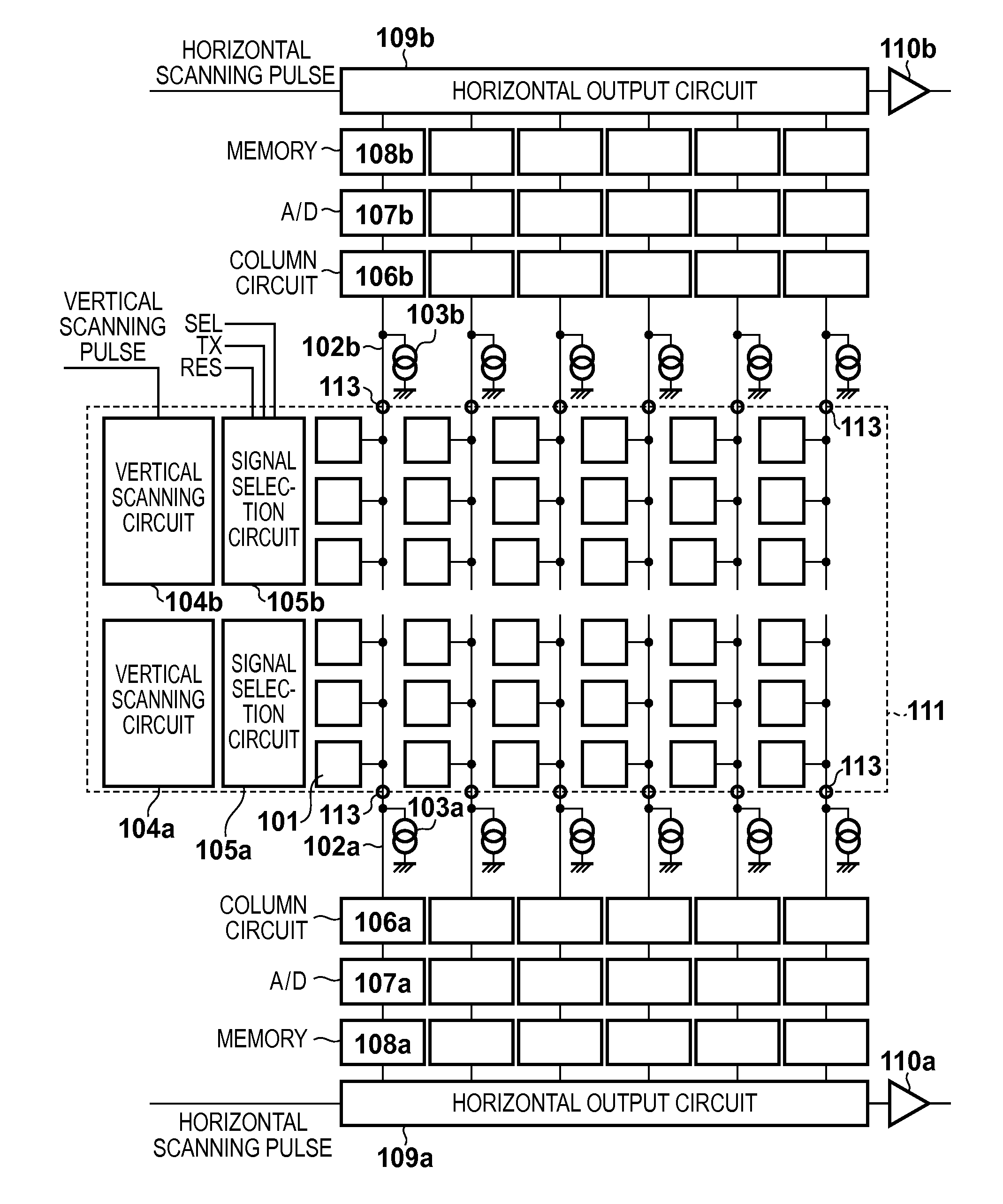

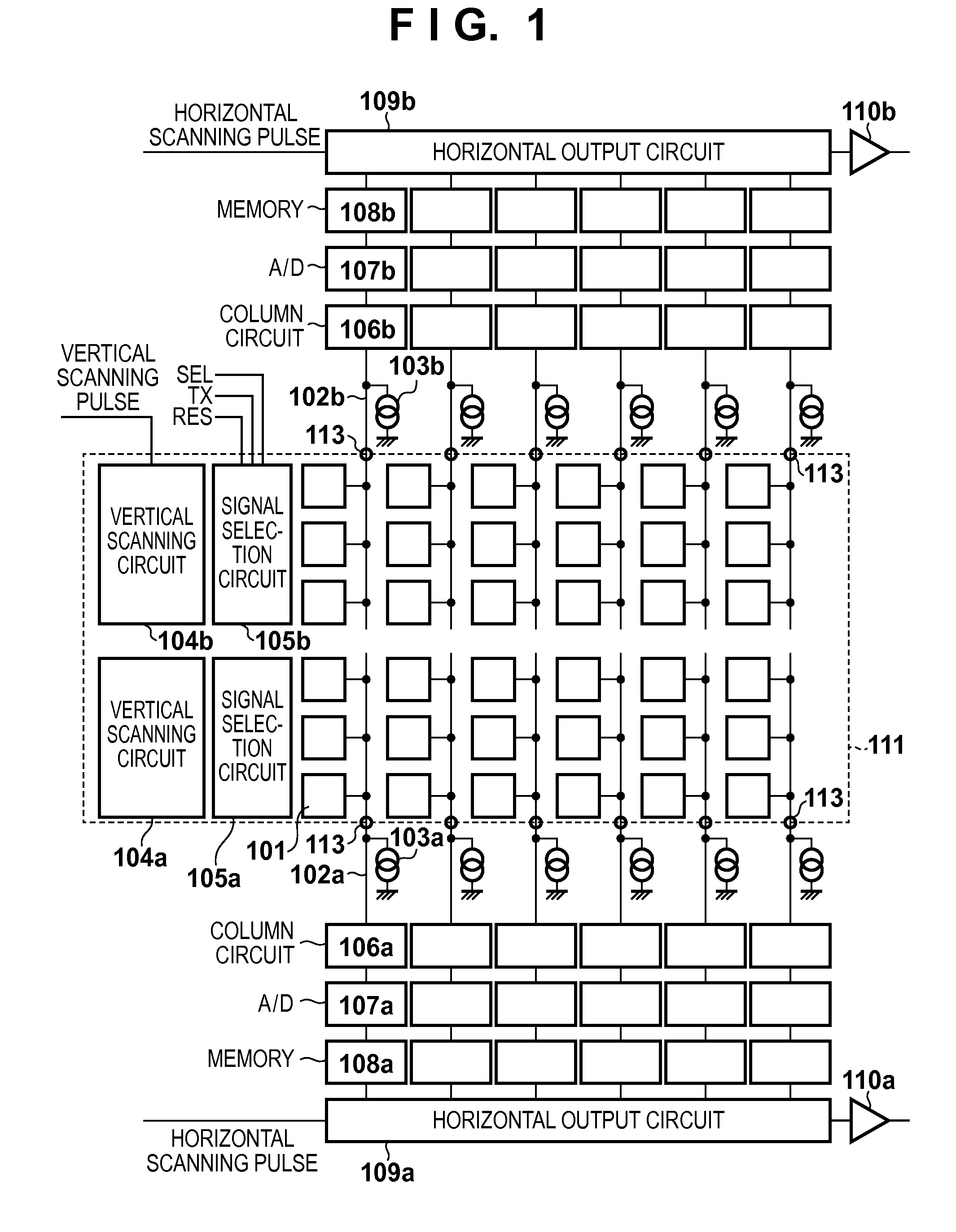

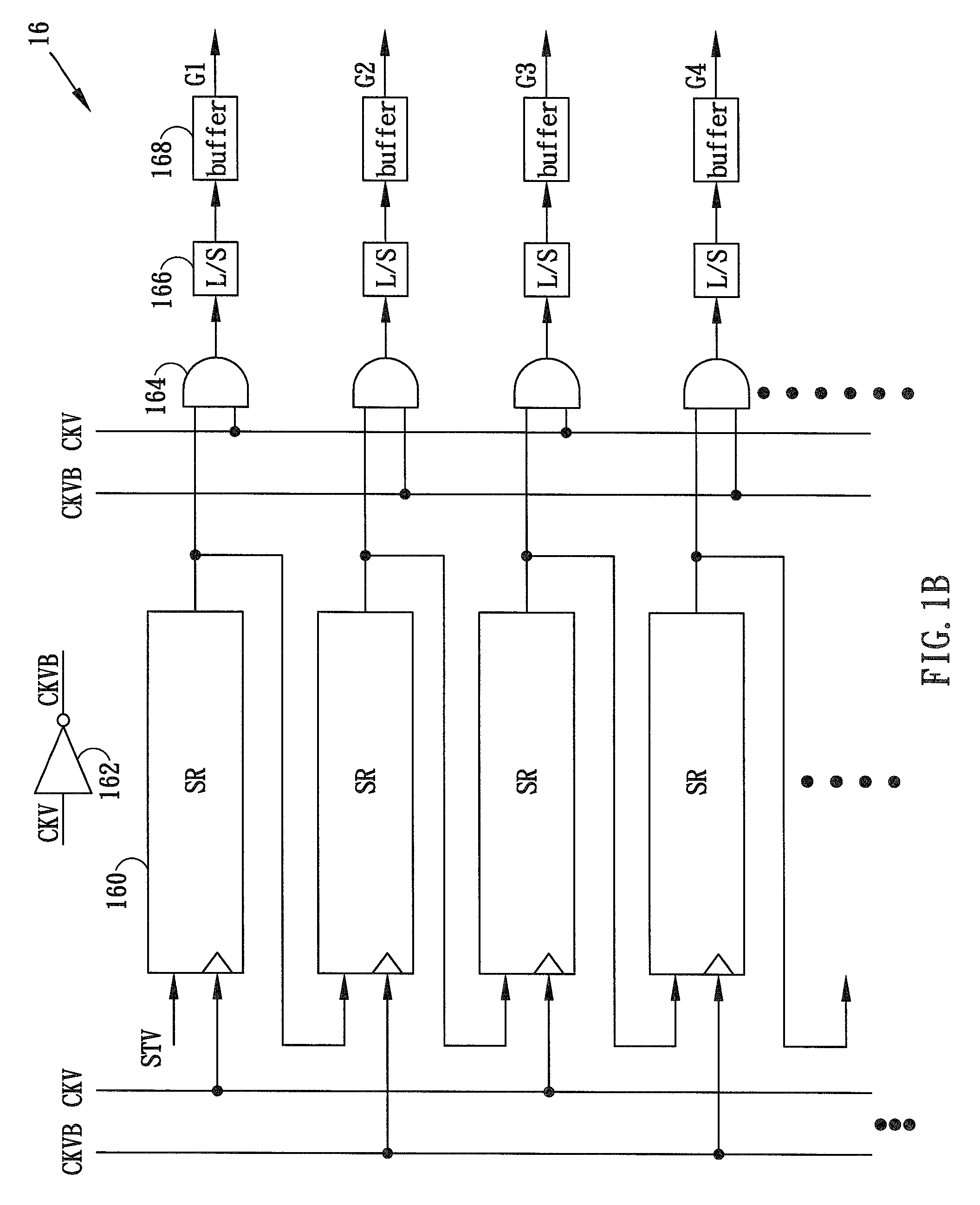

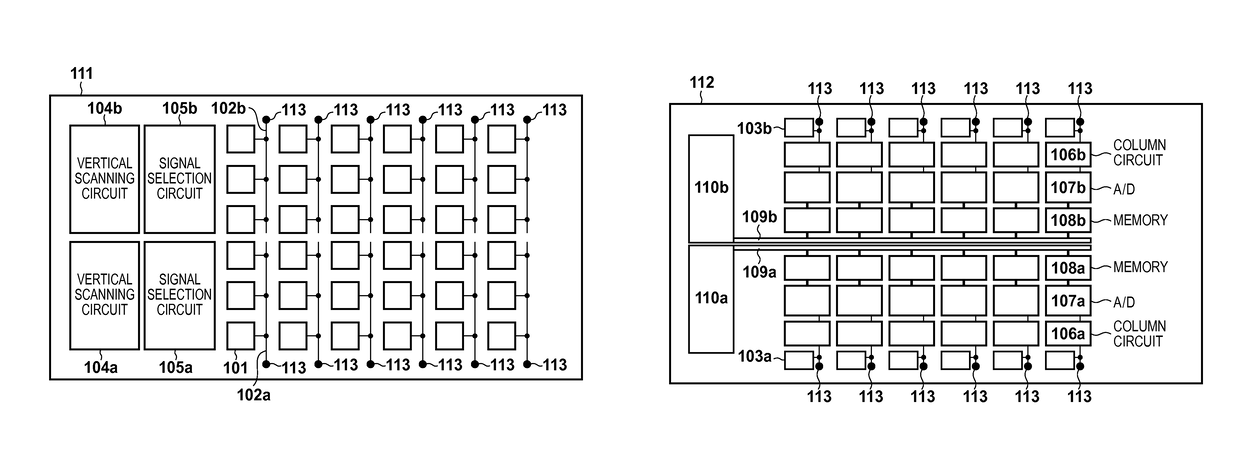

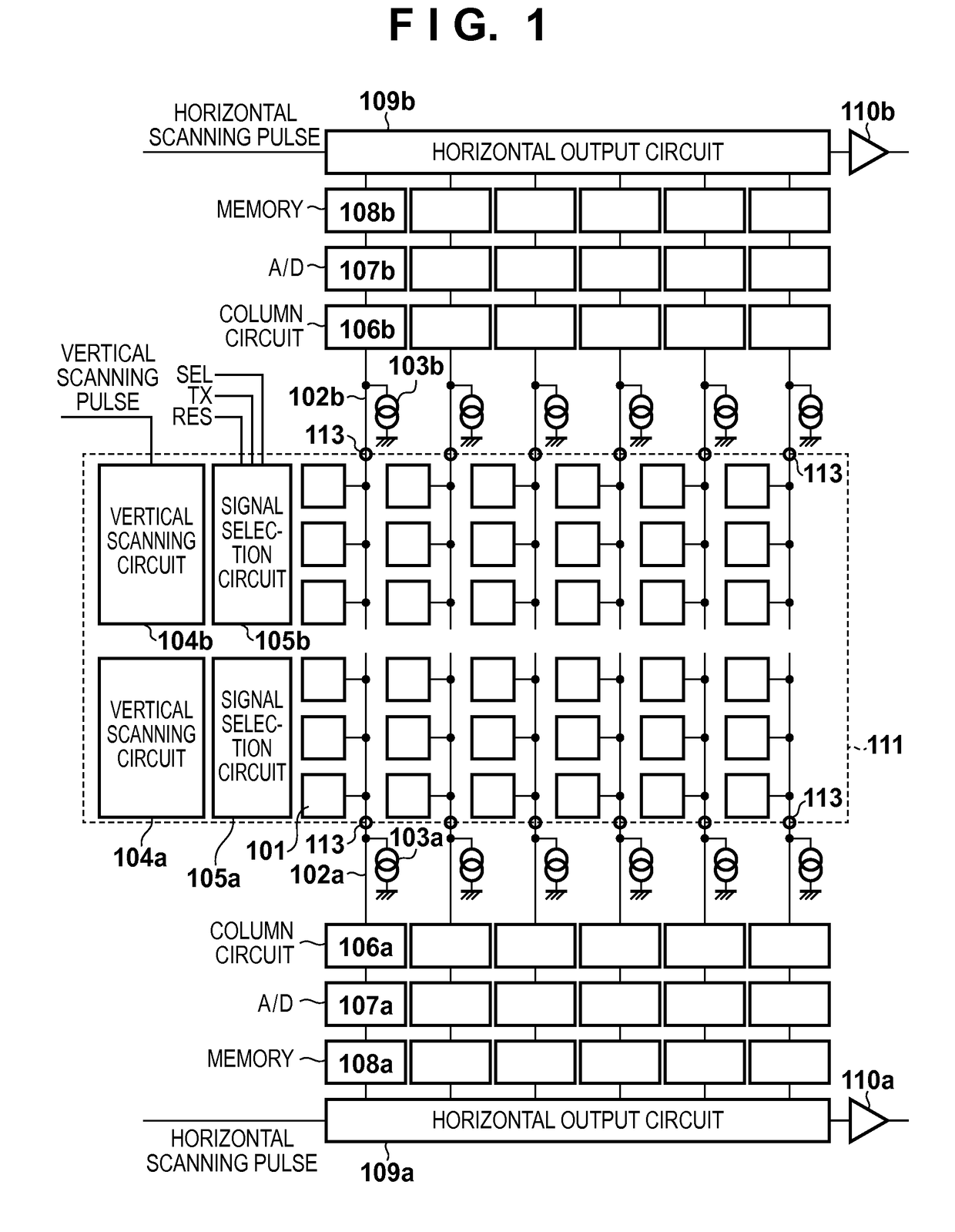

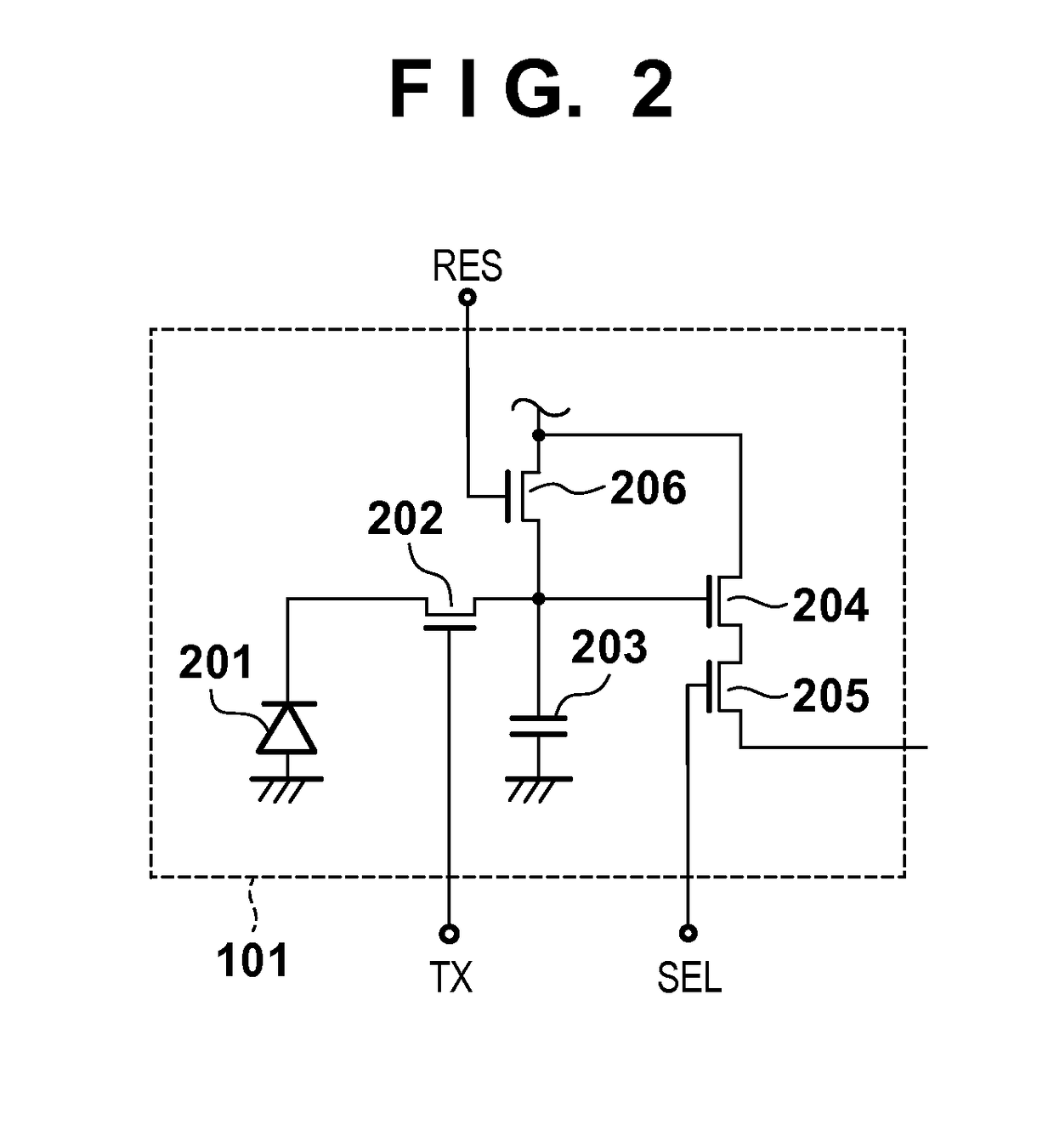

Image sensor, image capturing apparatus, and cellular phone

ActiveUS20160156861A1Run at high speedQuality improvementTelevision system detailsSolid-state devicesComputer hardwareSemiconductor

An image sensor comprises: a first semiconductor including a plurality of pixels two-dimensionally arranged, and a plurality of divided output lines, in a first direction, configured to read out pixel signals from the plurality of pixels in the first direction; and a second semiconductor including a plurality of signal processing units, corresponding to the plurality of output lines, respectively, configured to process the readout pixel signals, and a readout unit configured to read out the signals output from the signal processing units in a second direction, wherein the first semiconductor and the second semiconductor are stacked, and the plurality of output lines and the plurality of signal processing units are connected in correspondence with each other.

Owner:CANON KK

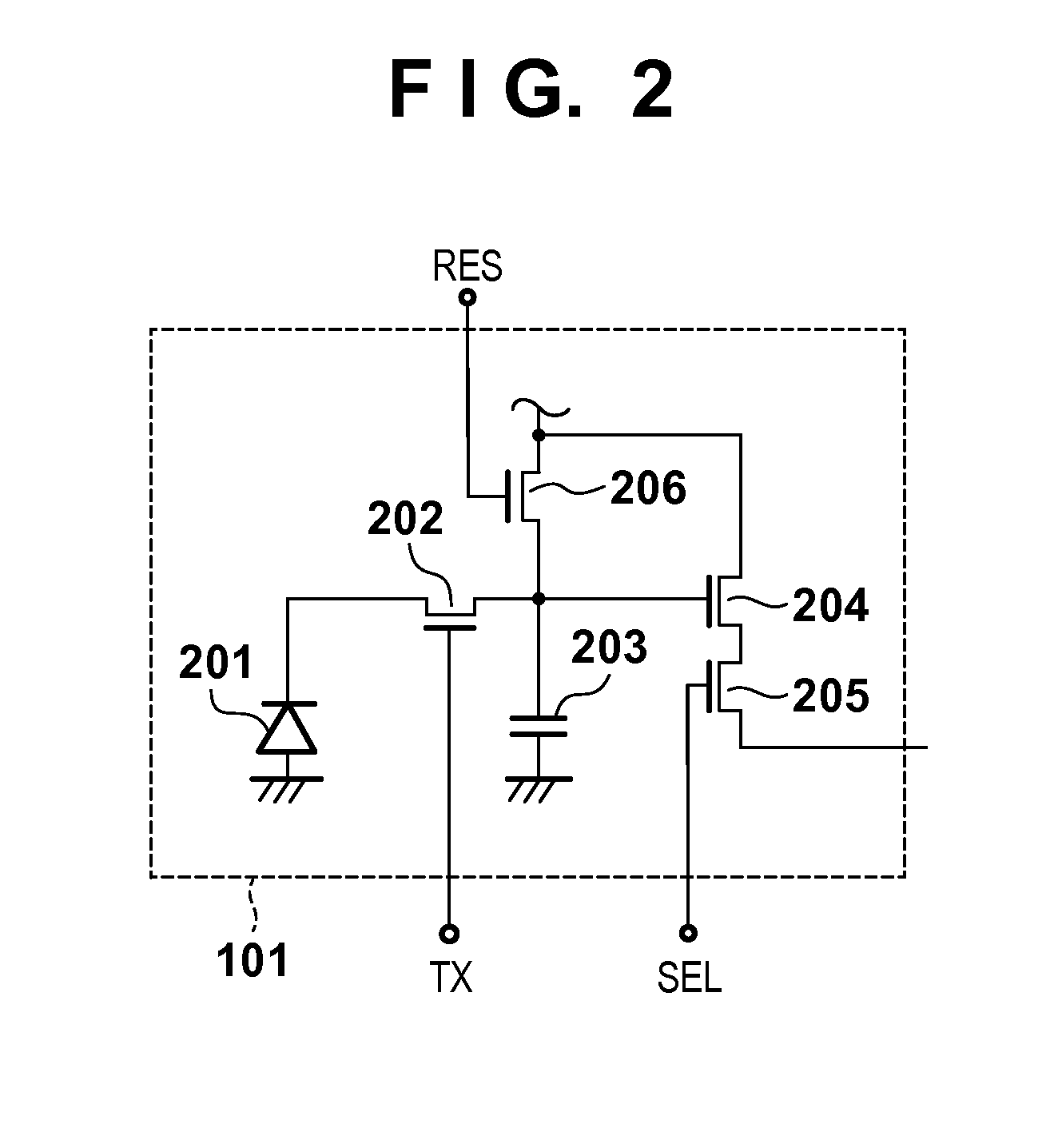

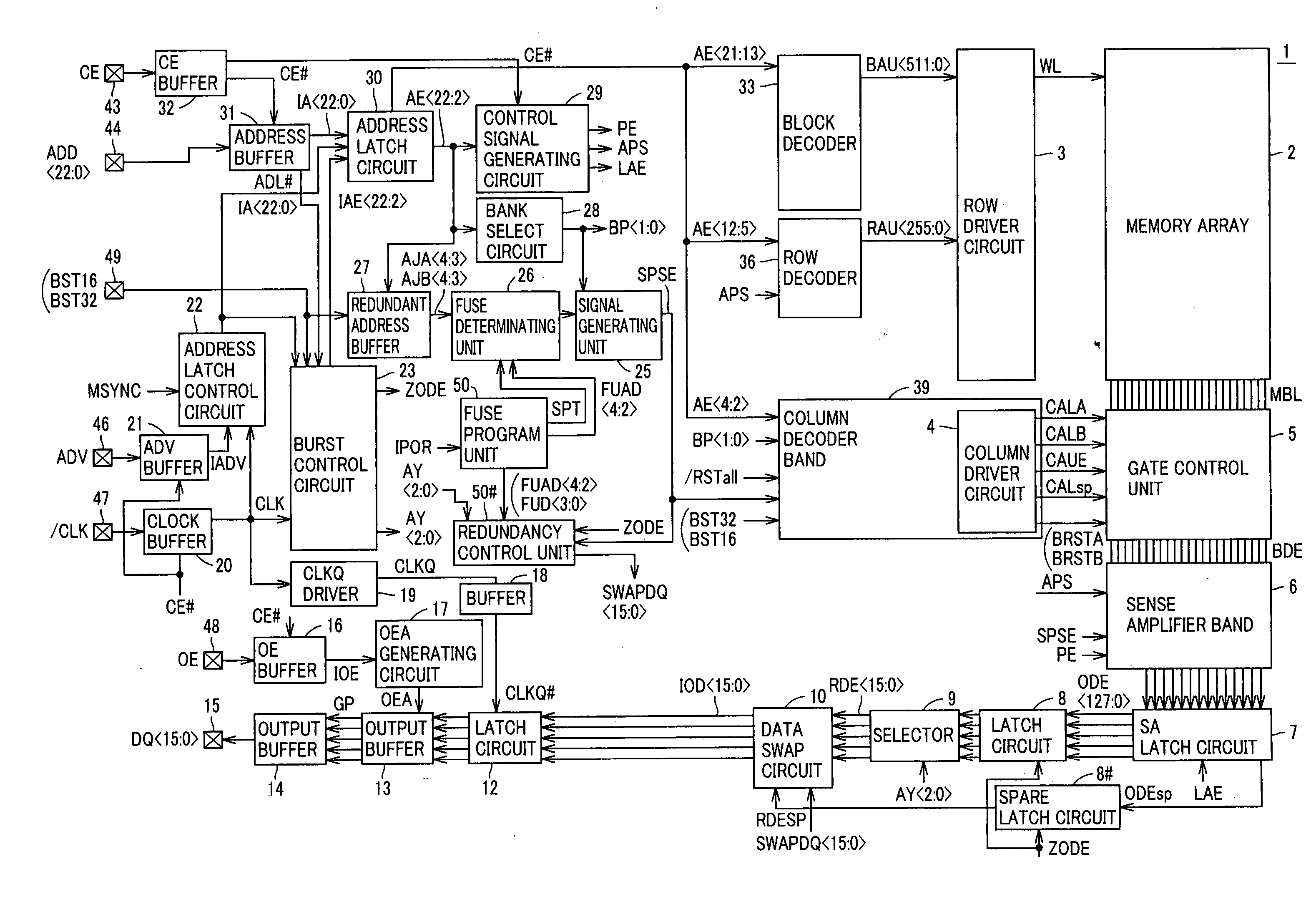

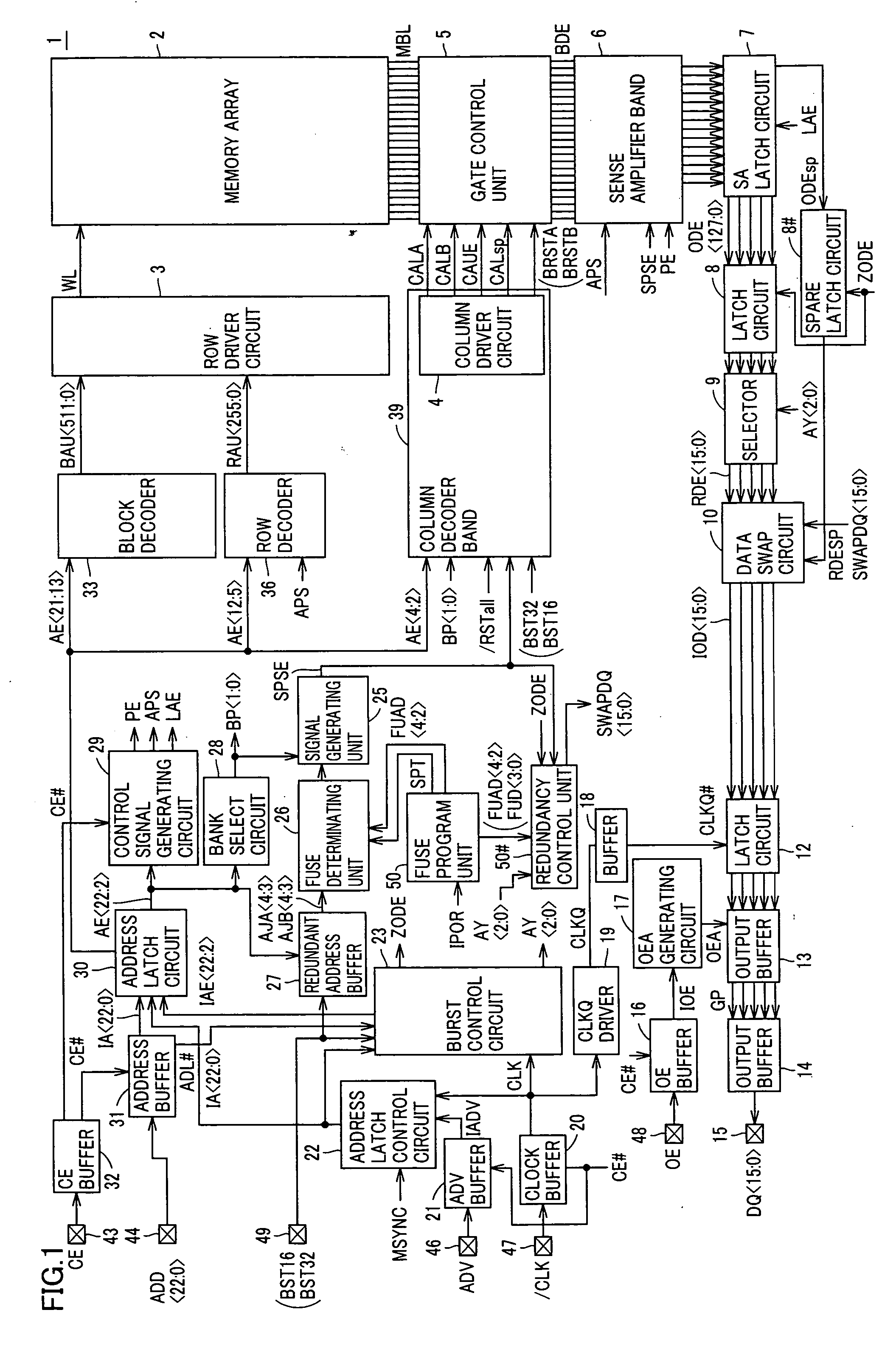

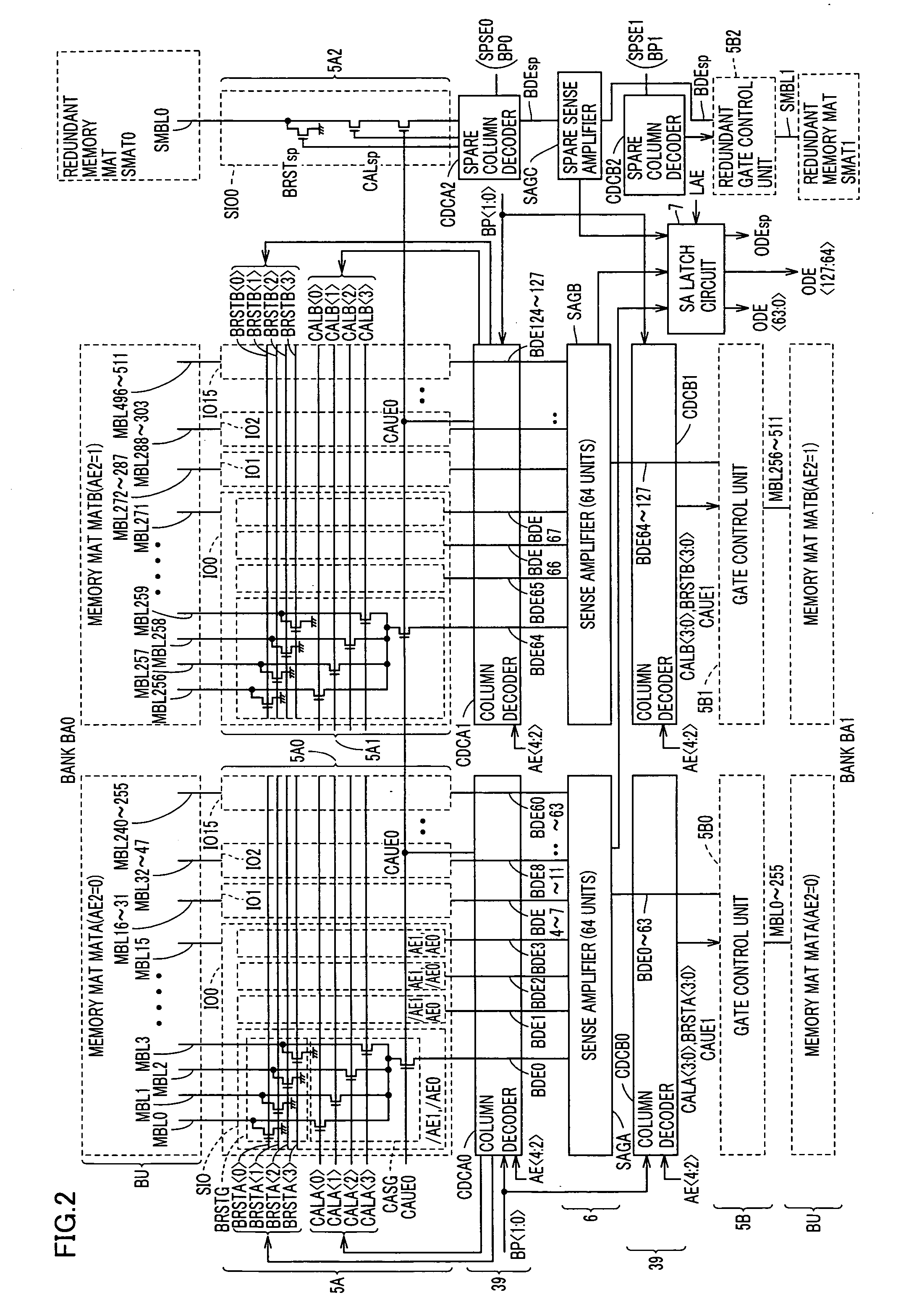

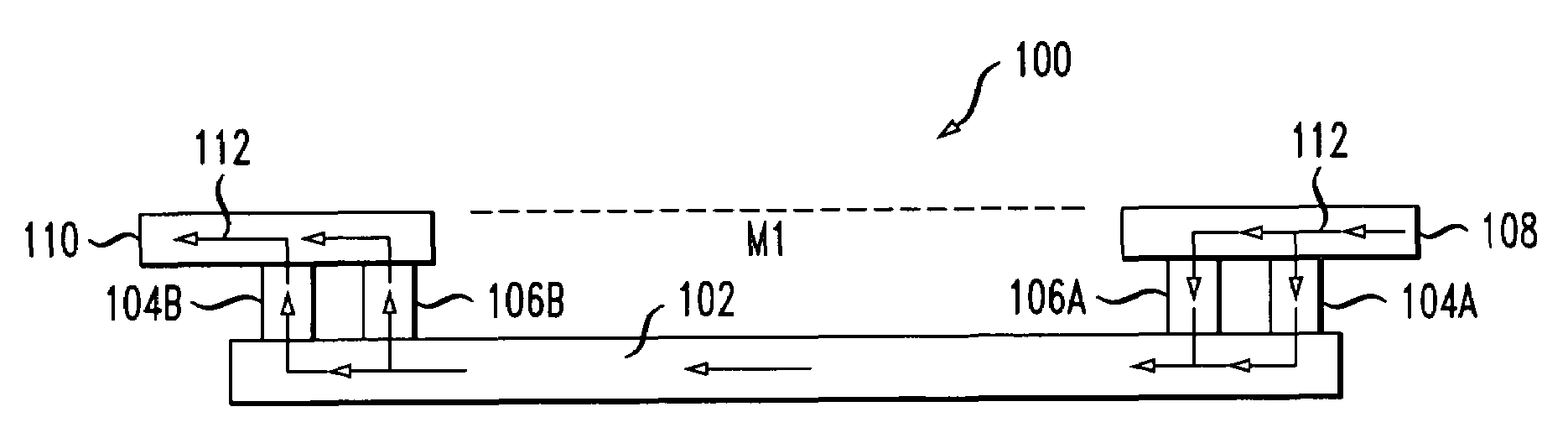

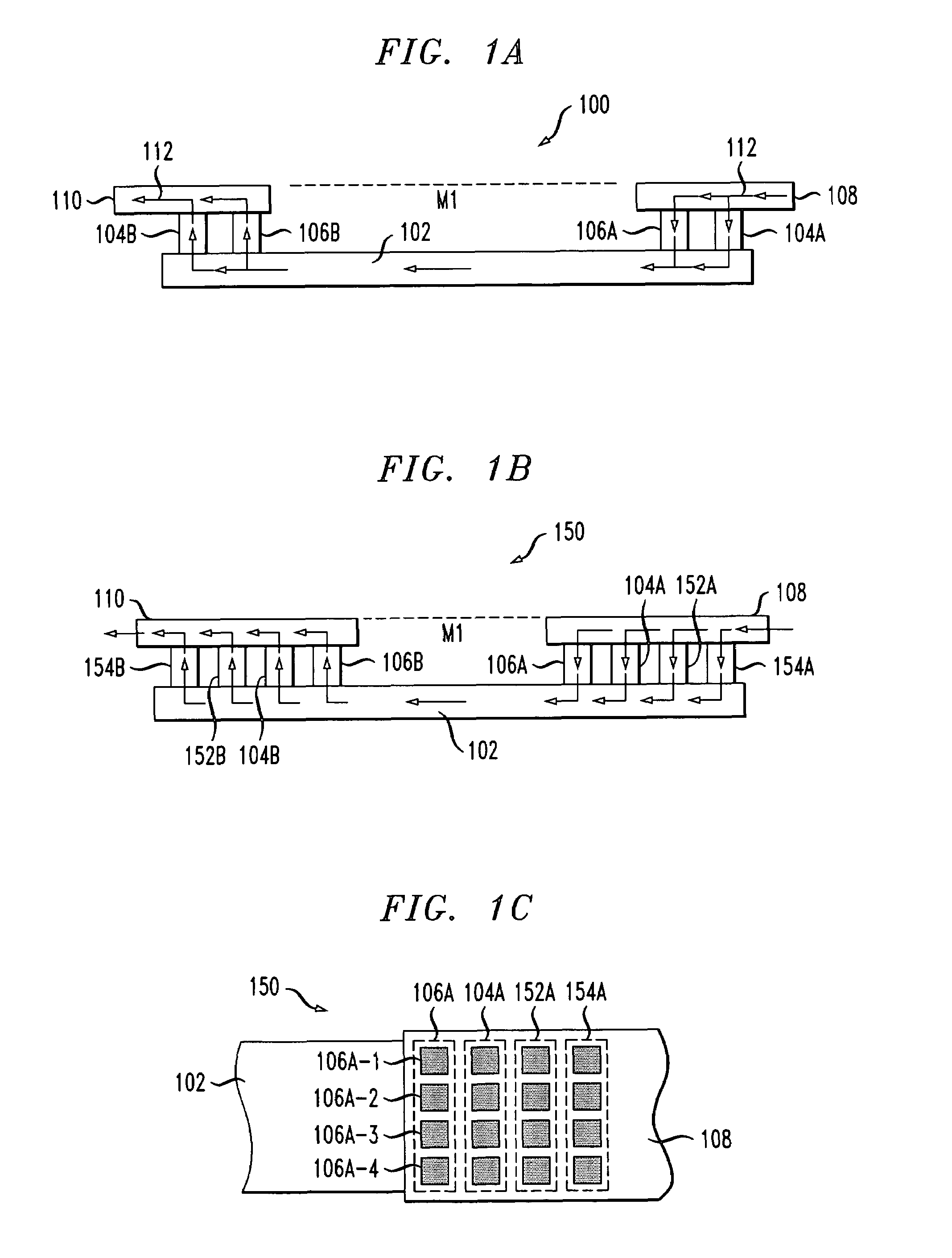

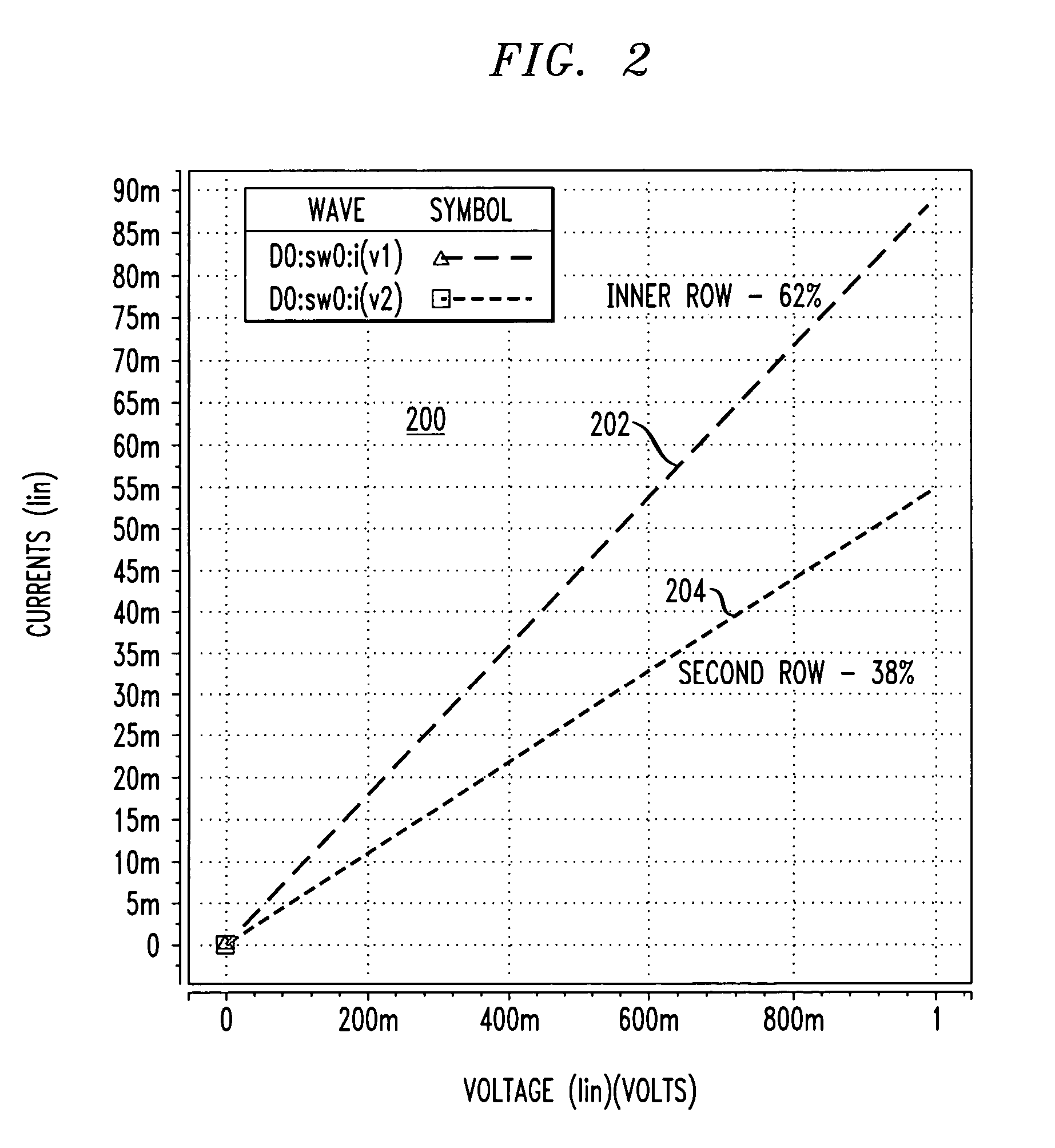

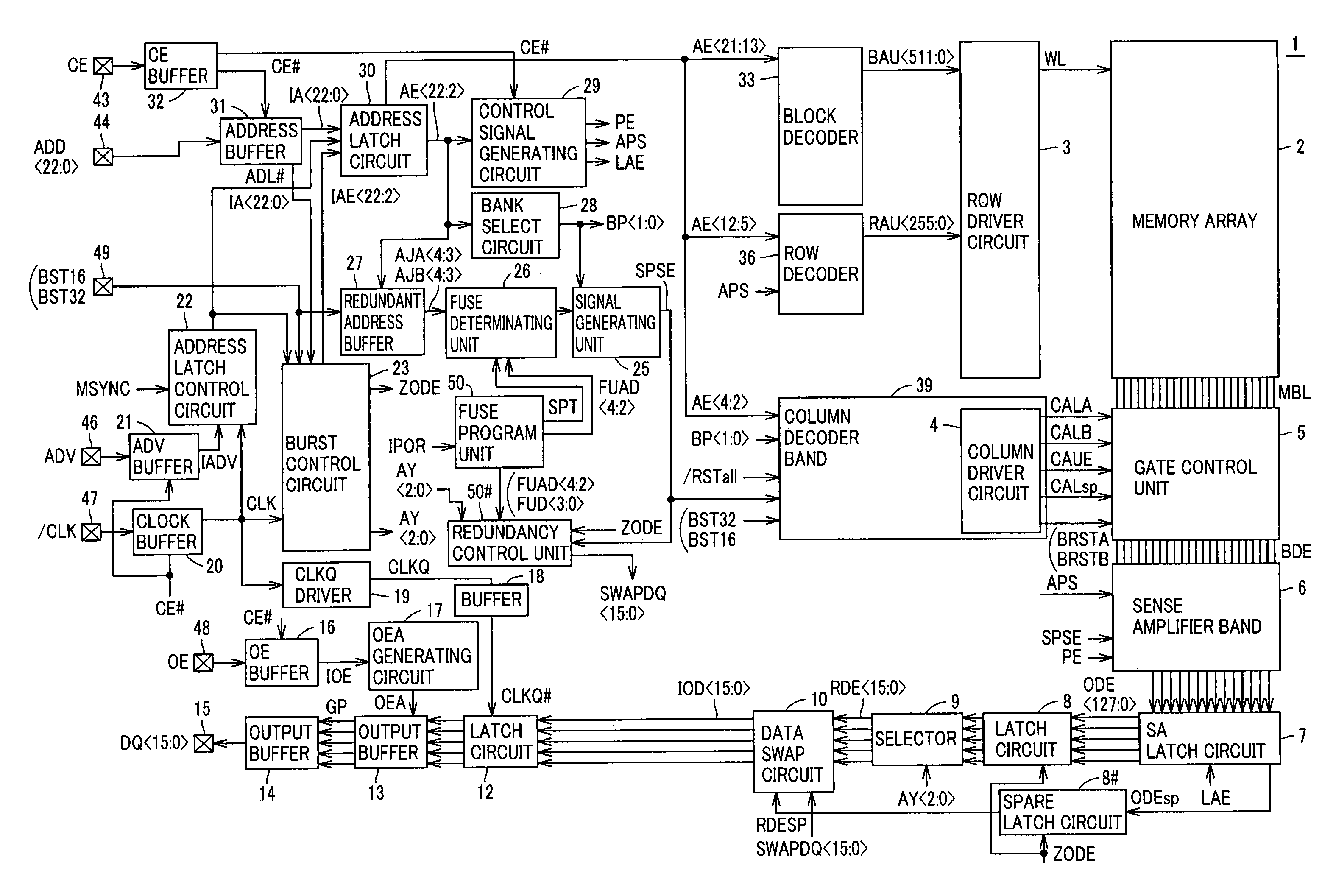

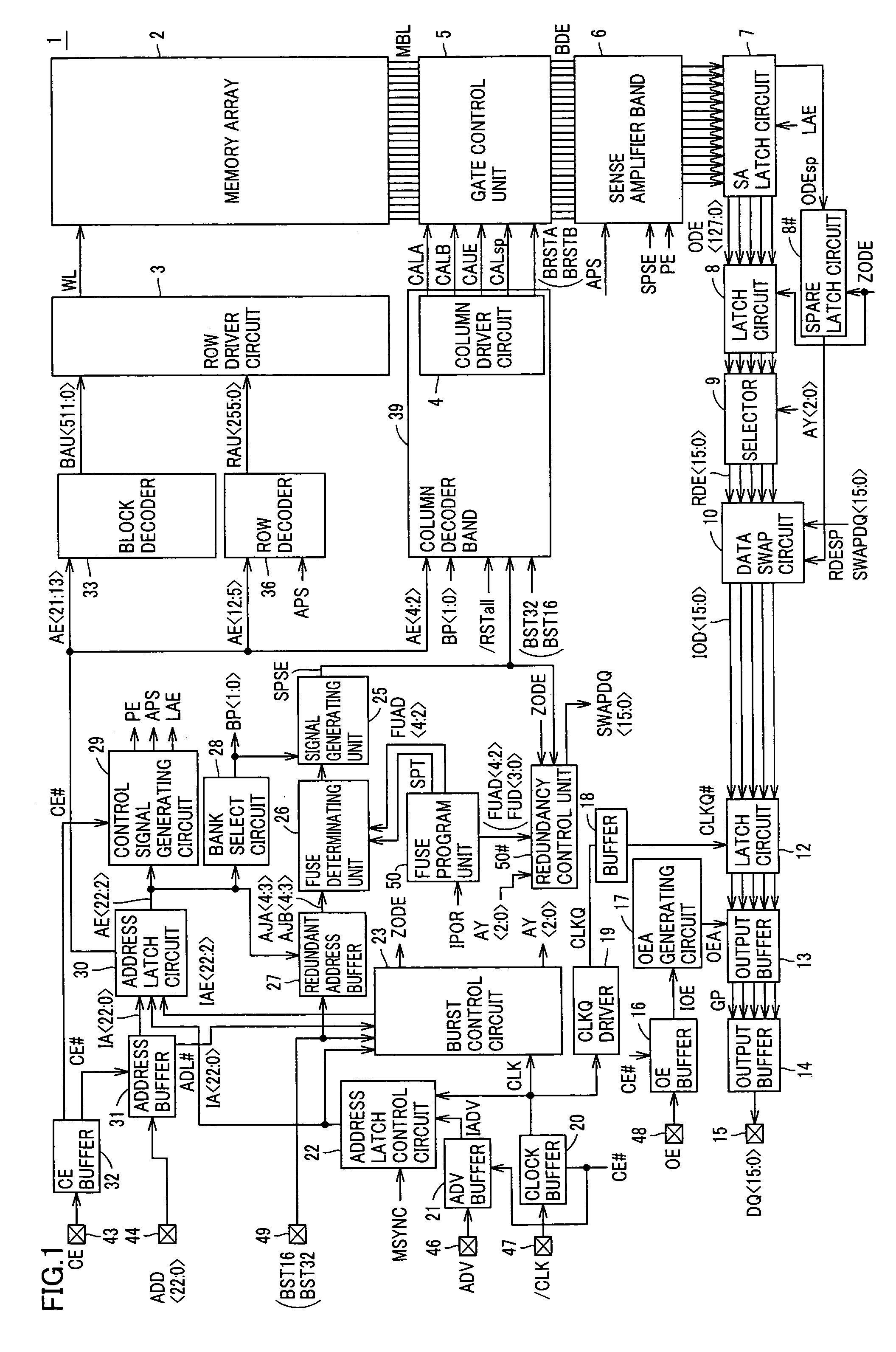

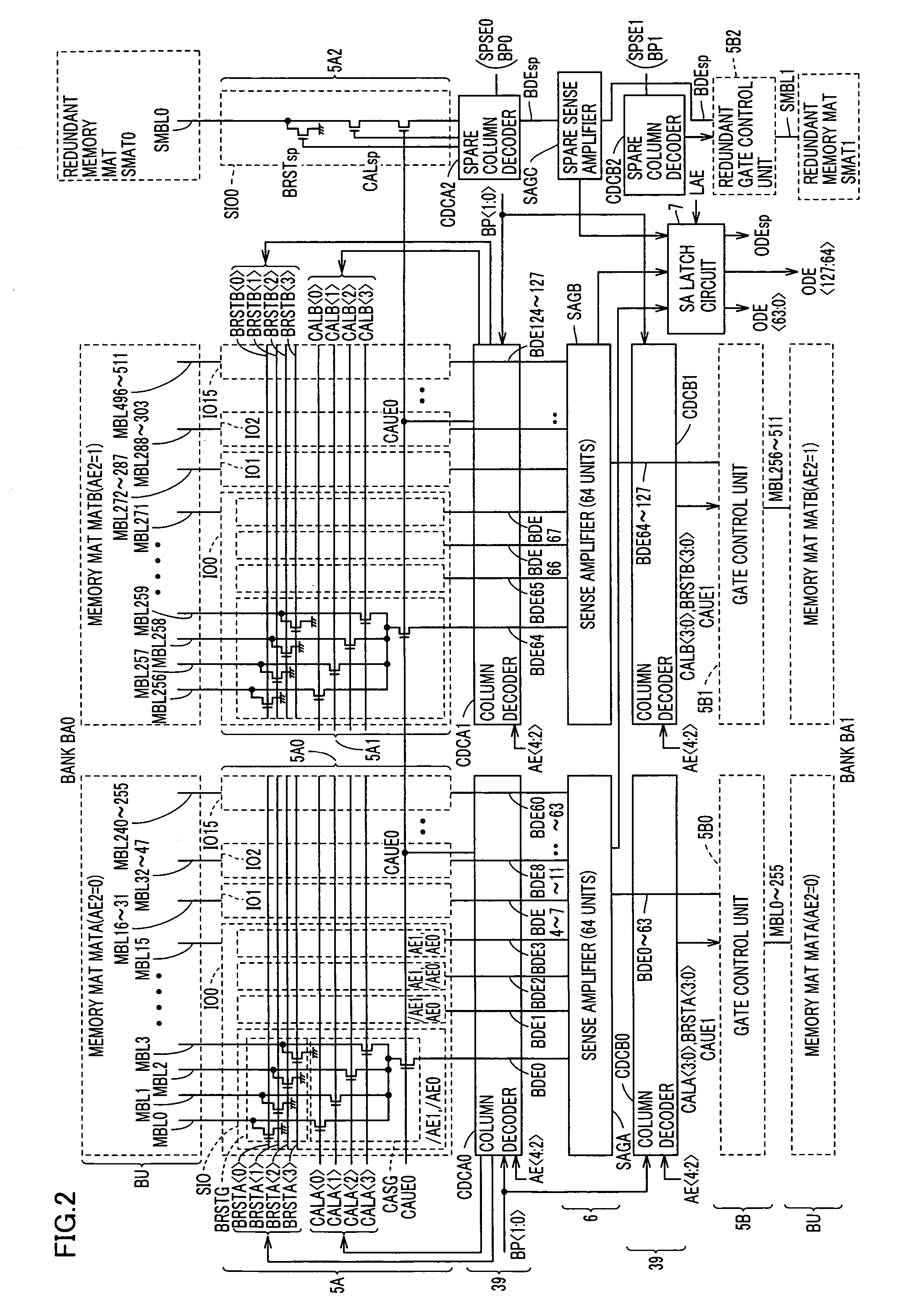

Semiconductor memory device for improving access time in burst mode

ActiveUS20050057996A1Increasing areaIncreasing consumptionRead-only memoriesDigital storageAccess timeSemiconductor

A semiconductor memory device is disclosed. A block unit is divided into memory mats based on an internal address. In the case where the internal address is “1”, data are read in ascending order in accordance with a start address from the memory mat, while the internal address is incremented by an address conversion circuit thereby to select a 4-word block including the words next selected from the memory mat. At the same time, the internal address is incremented based on the start address, so that the period for reading each word included in the lowest order of 4-word block can be secured. In the process, the address next to be input can be decoded.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device

InactiveUS20090050966A1Increasing areaIncreasing stepTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

In order to suppress an off leak current of an off transistor for ESD protection, in an NMOS for ESD protection whose isolation region has a shallow trench structure, a drain region is placed apart from the shallow trench isolation region so as not to be in direct contact with the shallow trench isolation region in a region where the drain region of the NMOS transistor for ESD protection is adjacent to at least a gate electrode of the NMOS transistor for ESD protection.

Owner:ABLIC INC

Semiconductor resistor

ActiveUS7034653B2Increasing areaIncreasing costResistor terminals/electrodesSemiconductor/solid-state device detailsCurrent distributionSemiconductor

A semiconductor resistor comprises a resistor body formed on a semiconductor substrate and first and second conductive terminals electrically connected to the resistor body at opposite ends thereof. The semiconductor resistor further includes at least first and second conductive paths between at least one of the first and second conductive terminals and the resistor body. The at least one conductive terminal is configured such that a resistance of the at least one conductive terminal between the at least first and second conductive paths is substantially matched to a resistance of the resistor body between the at least first and second conductive paths. In this manner, a current distribution between the at least first and second conductive paths is substantially matched.

Owner:BELL SEMICON LLC

Semiconductor device

ActiveUS20090050967A1Sufficient ESD protection functionIncreasing occupation areaTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

In a semiconductor device including an n-type metal oxide semiconductor transistor for electrostatic discharge protection surrounded by a shallow trench for device isolation, in order to suppress the off-leak current in an off state, there is formed, in the vicinity of the drain region of the NMOS transistor for ESD protection, an n-type region receiving a signal from an external connection terminal via a p-type region in contact with the drain region of the NMOS transistor for ESD protection.

Owner:ABLIC INC

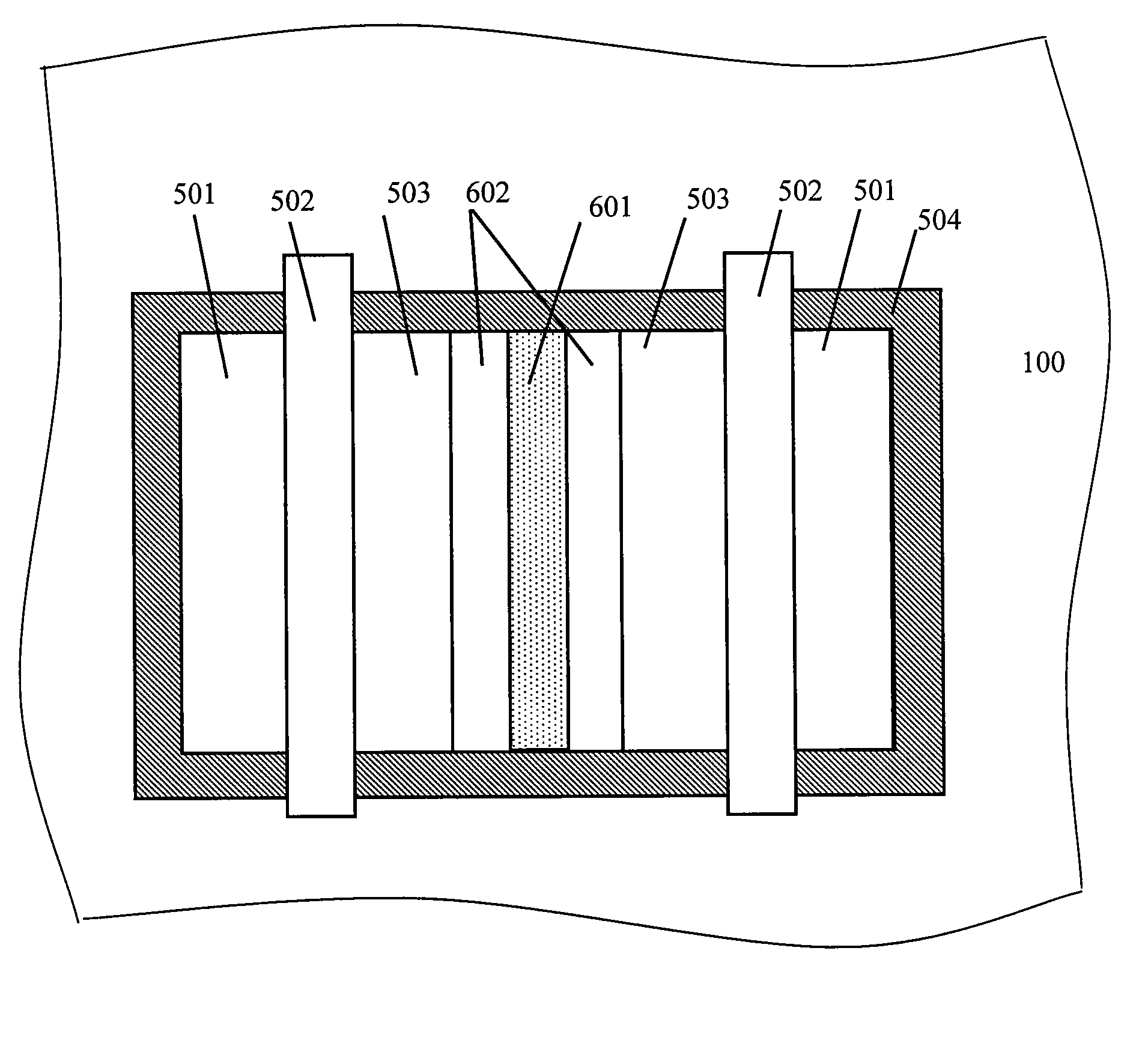

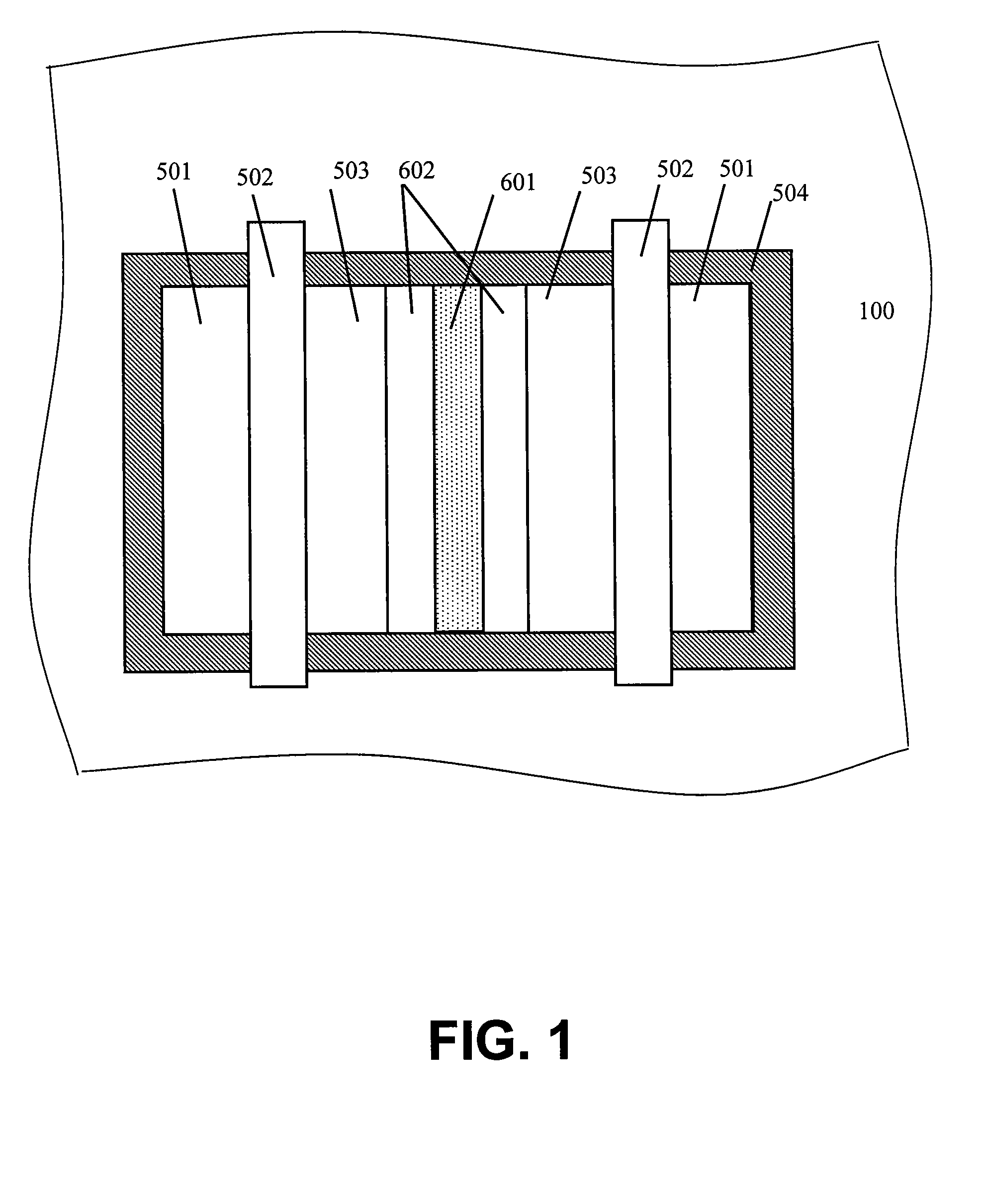

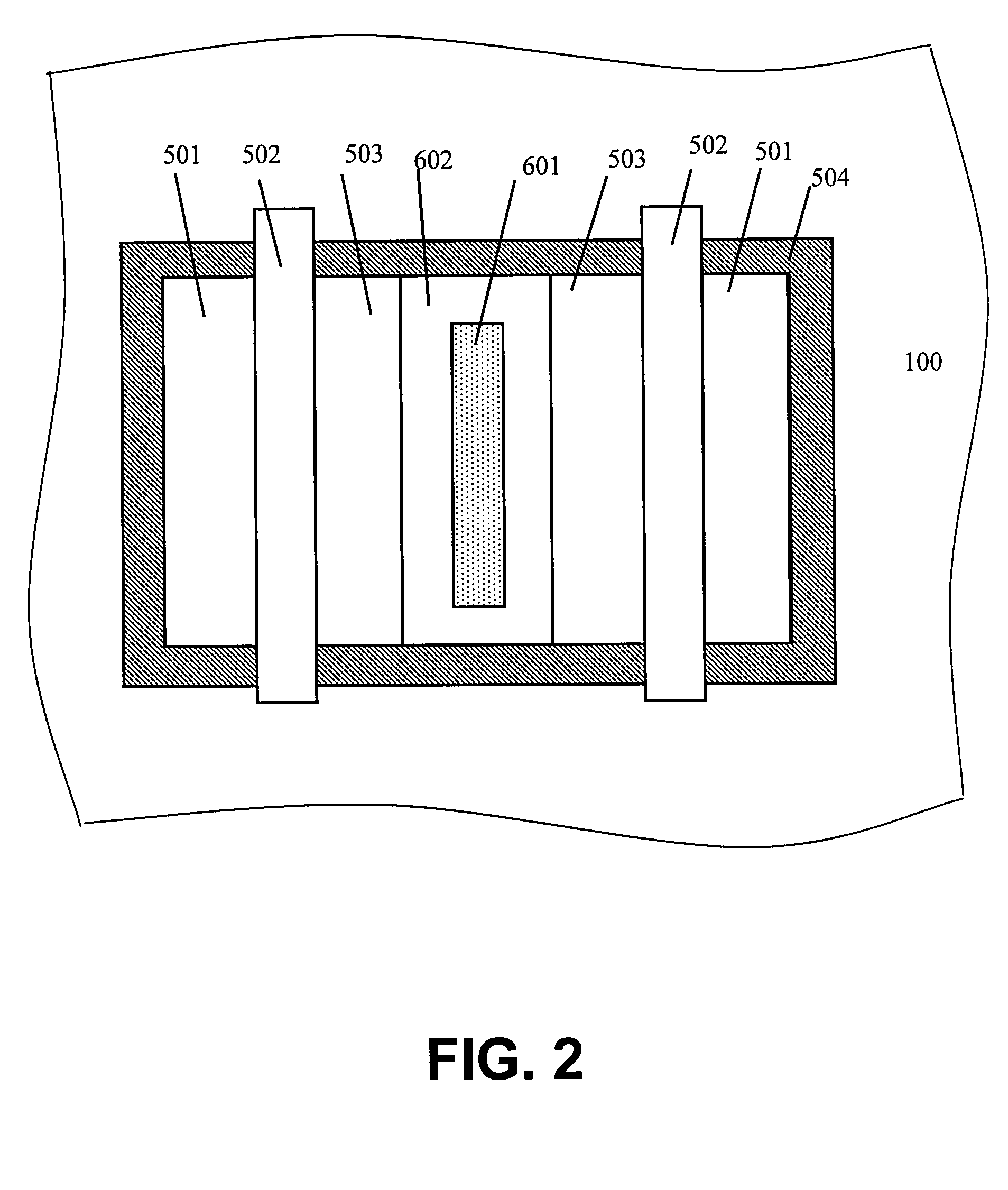

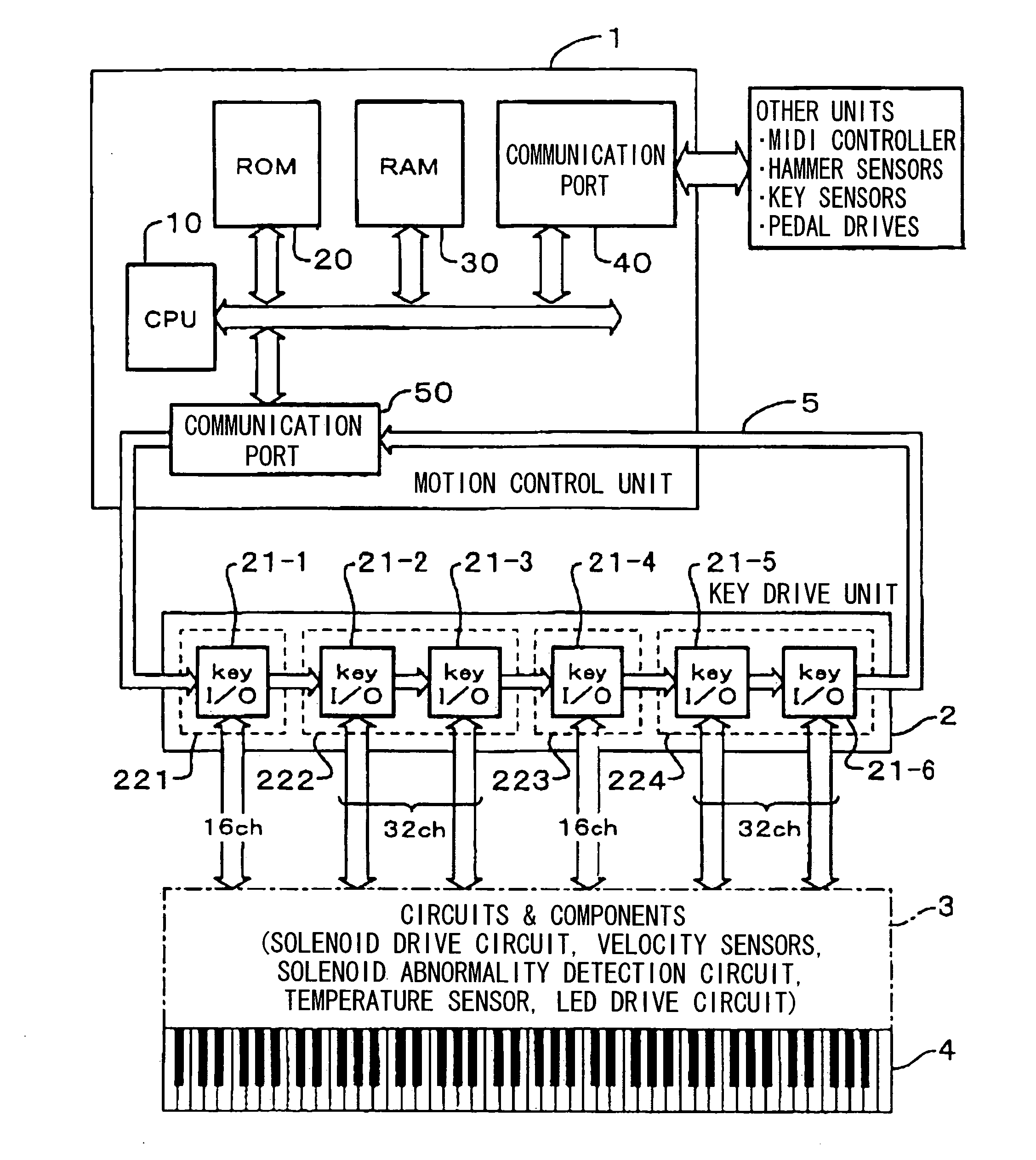

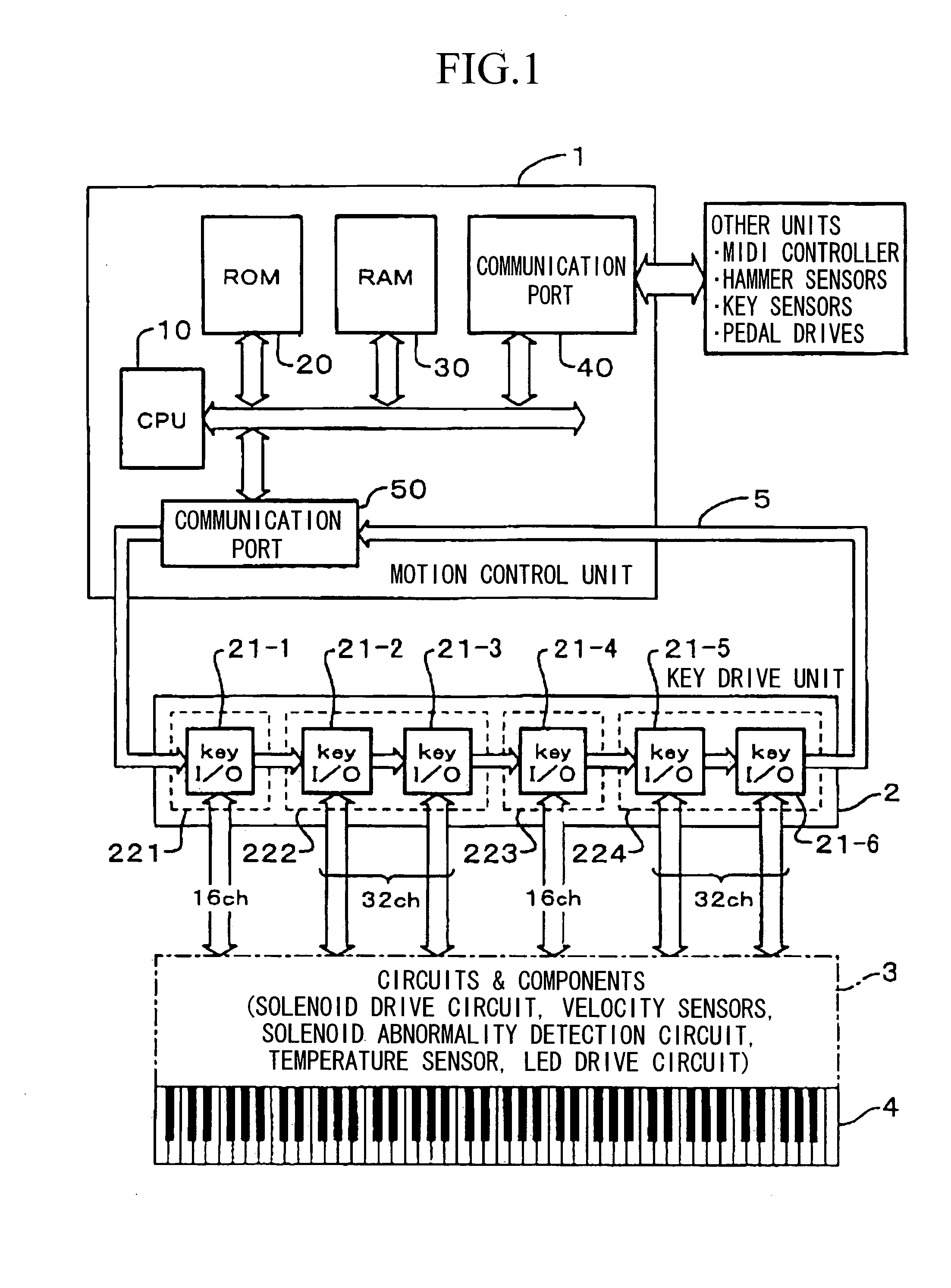

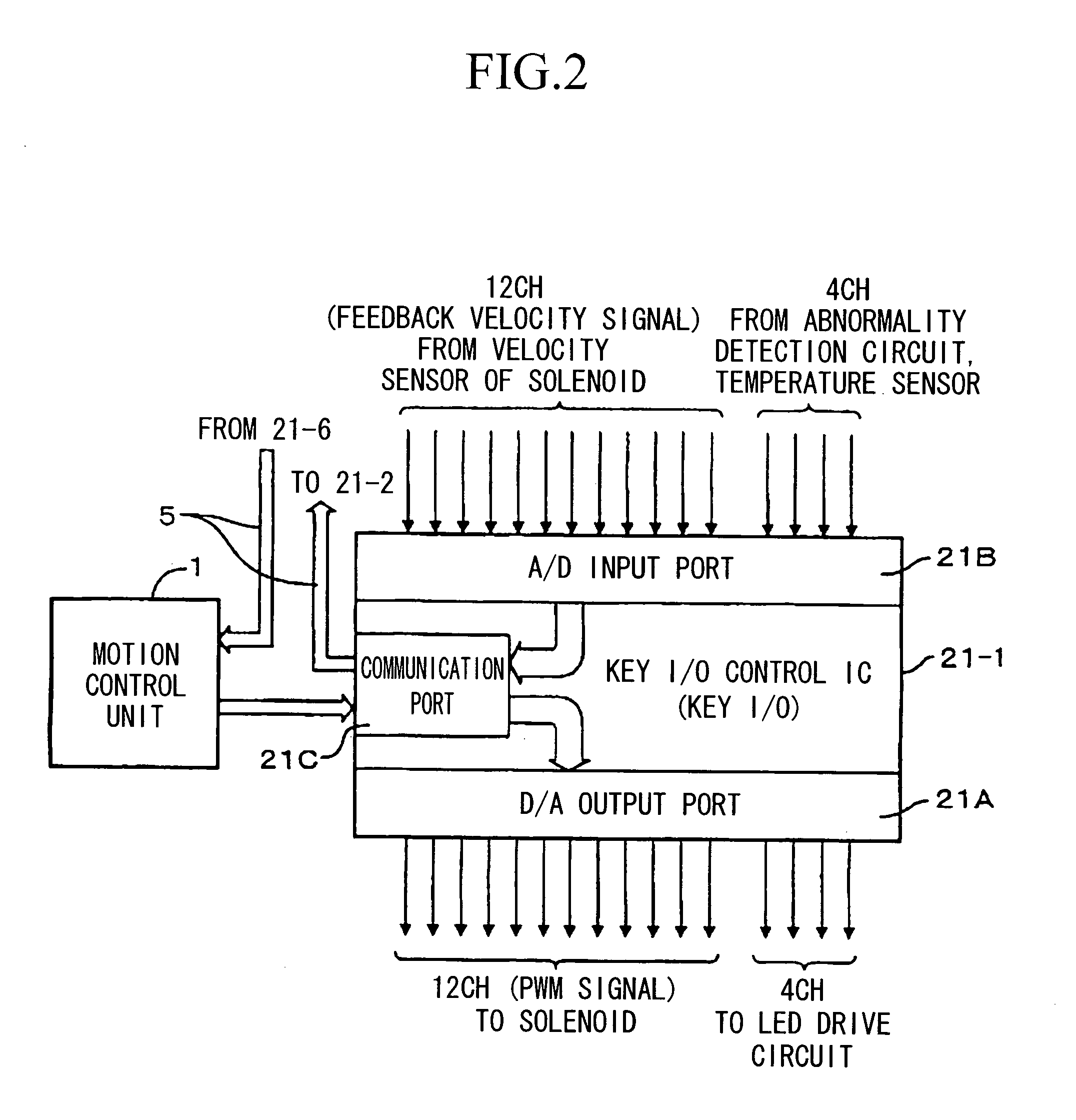

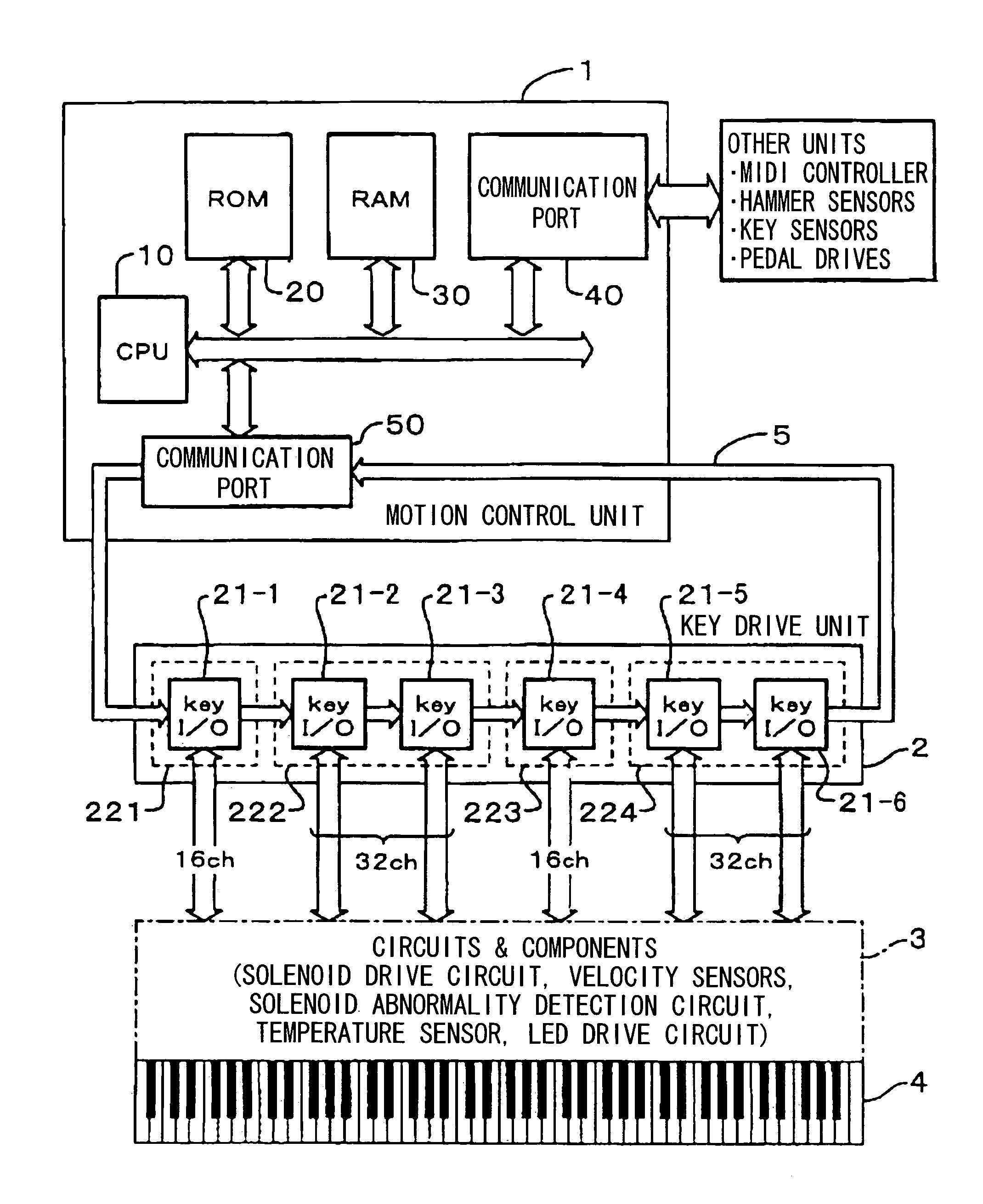

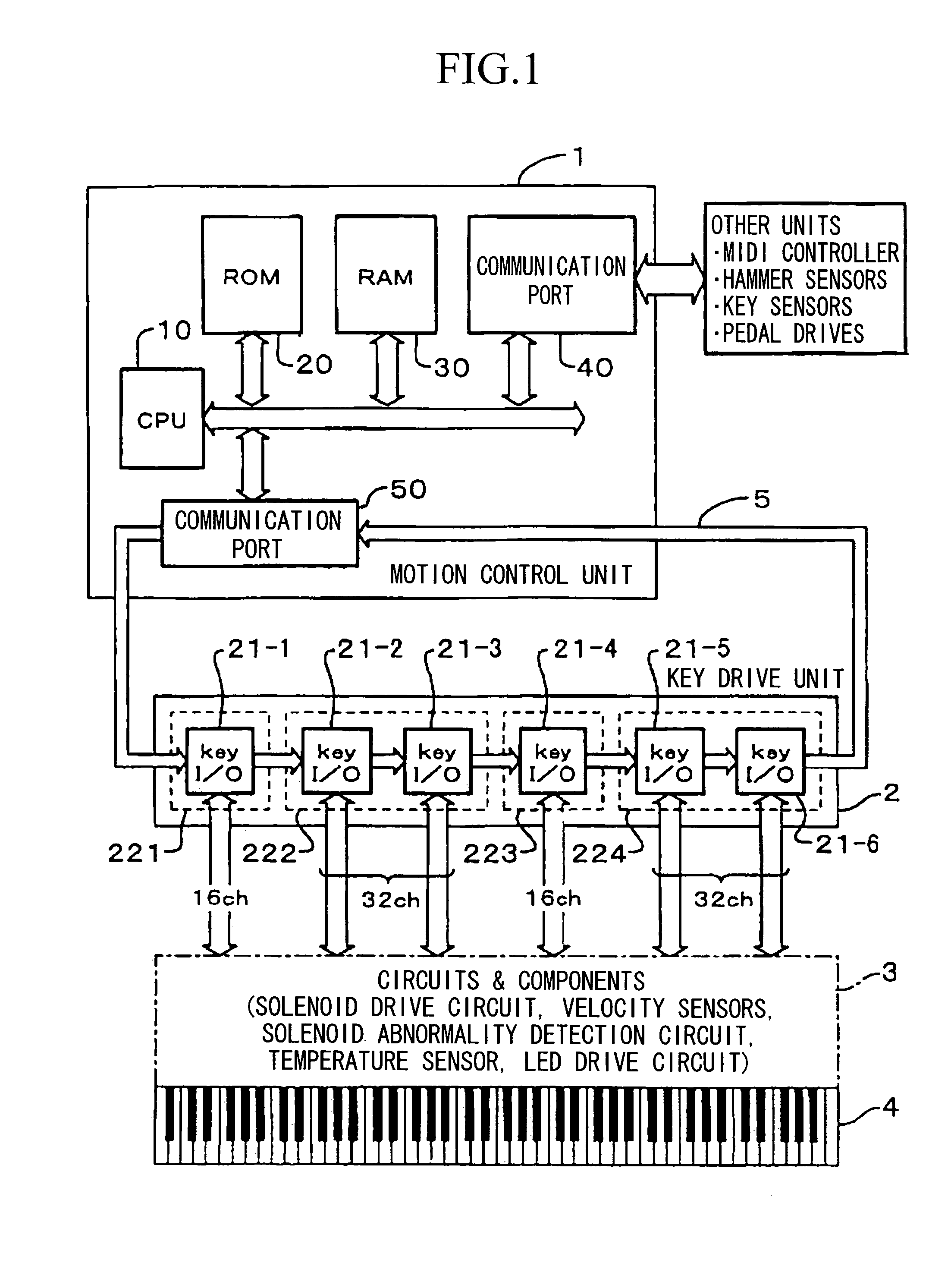

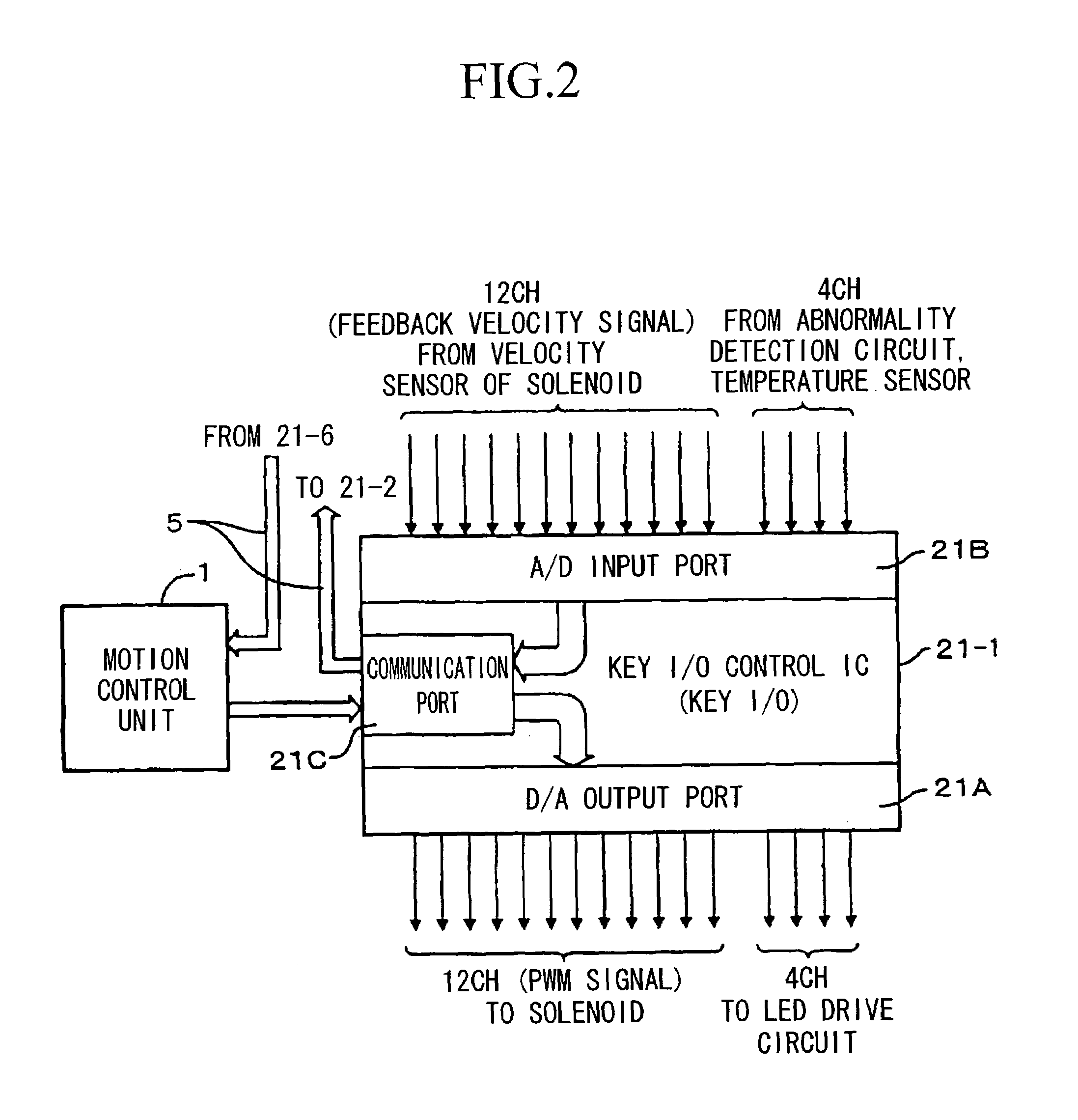

Performance operator control apparatus

ActiveUS20050132871A1Easy to useIncreasing areaElectrophonic musical instrumentsAutomatic musical instrumentsPianoEngineering

A performance operator control apparatus adapted to a player piano comprises a motion control unit and a key drive unit comprising a plurality of key I / O control ICs in connection with keys of a keyboard, which are driven by solenoids so as to realize automatic performance, wherein upon detection of electrification abnormality of solenoids or temperature abnormality, LEDs are turned on to indicate the abnormality. The key I / O control ICs receive velocity signals regarding the solenoids so as to perform feedback controls on the keys in the automatic performance. In addition, unoccupied channels of the key I / O control ICs, which are not assigned to the keys and sensors, are used to input monitoring signals and to output inspection signals. Herein, the abnormality is determined based on the difference between pre-inspection data and post-inspection data, which are transferred using a loop connection channel of the key I / O control IC.

Owner:YAMAHA CORP

Semiconductor memory device for improving access time in burst mode

ActiveUS7123538B2Increasing areaIncreasing consumptionRead-only memoriesDigital storageAccess timeSemiconductor

A semiconductor memory device is disclosed. A block unit is divided into memory mats based on an internal address. In the case where the internal address is “1”, data are read in ascending order in accordance with a start address from the memory mat, while the internal address is incremented by an address conversion circuit thereby to select a 4-word block including the words next selected from the memory mat. At the same time, the internal address is incremented based on the start address, so that the period for reading each word included in the lowest order of 4-word block can be secured. In the process, the address next to be input can be decoded.

Owner:RENESAS ELECTRONICS CORP

Self-calibration method of a reading circuit of a nonvolatile memory

ActiveUS8184490B2Increasing areaIncreasing costRead-only memoriesDigital storageAudio power amplifierComputer module

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

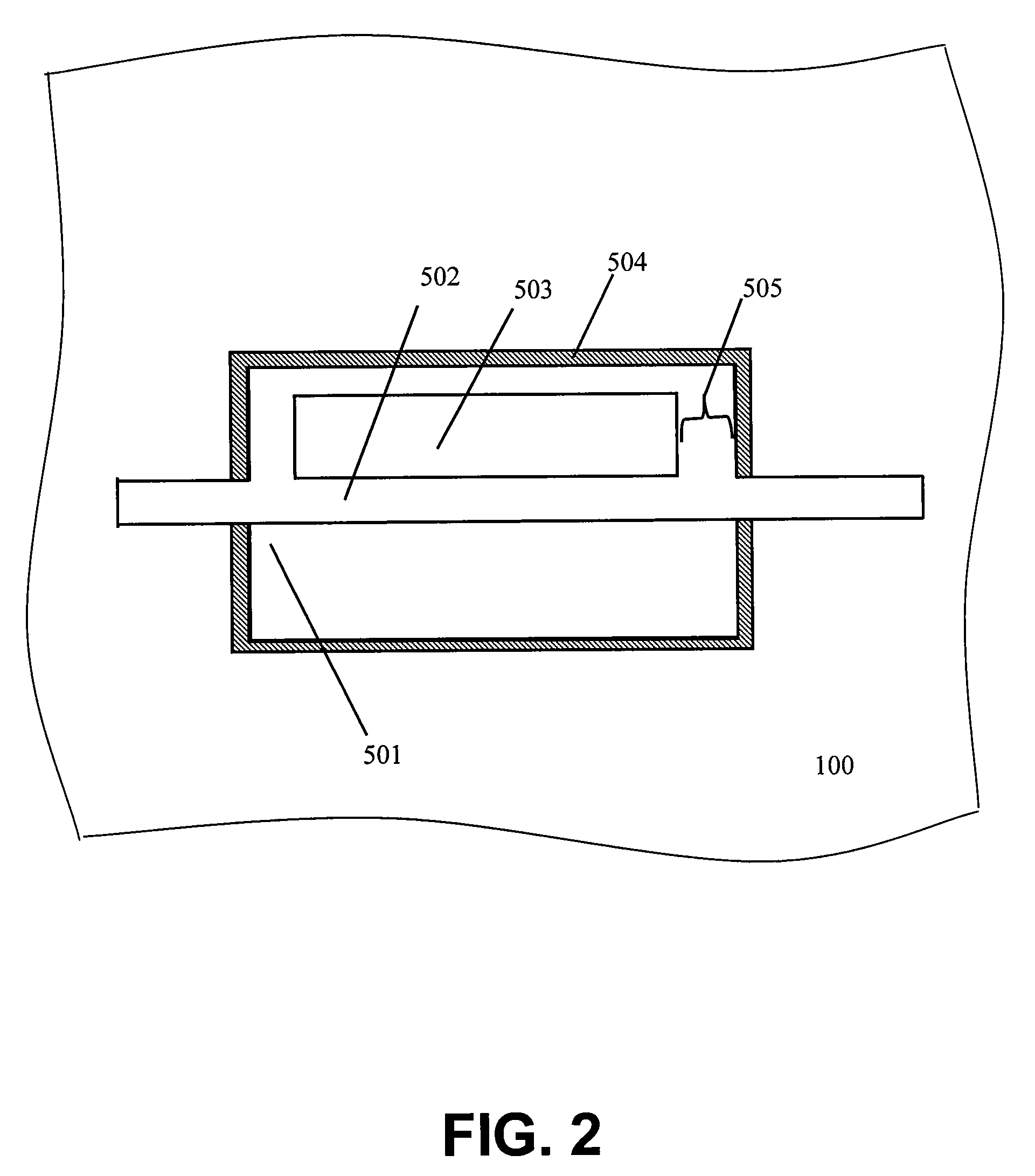

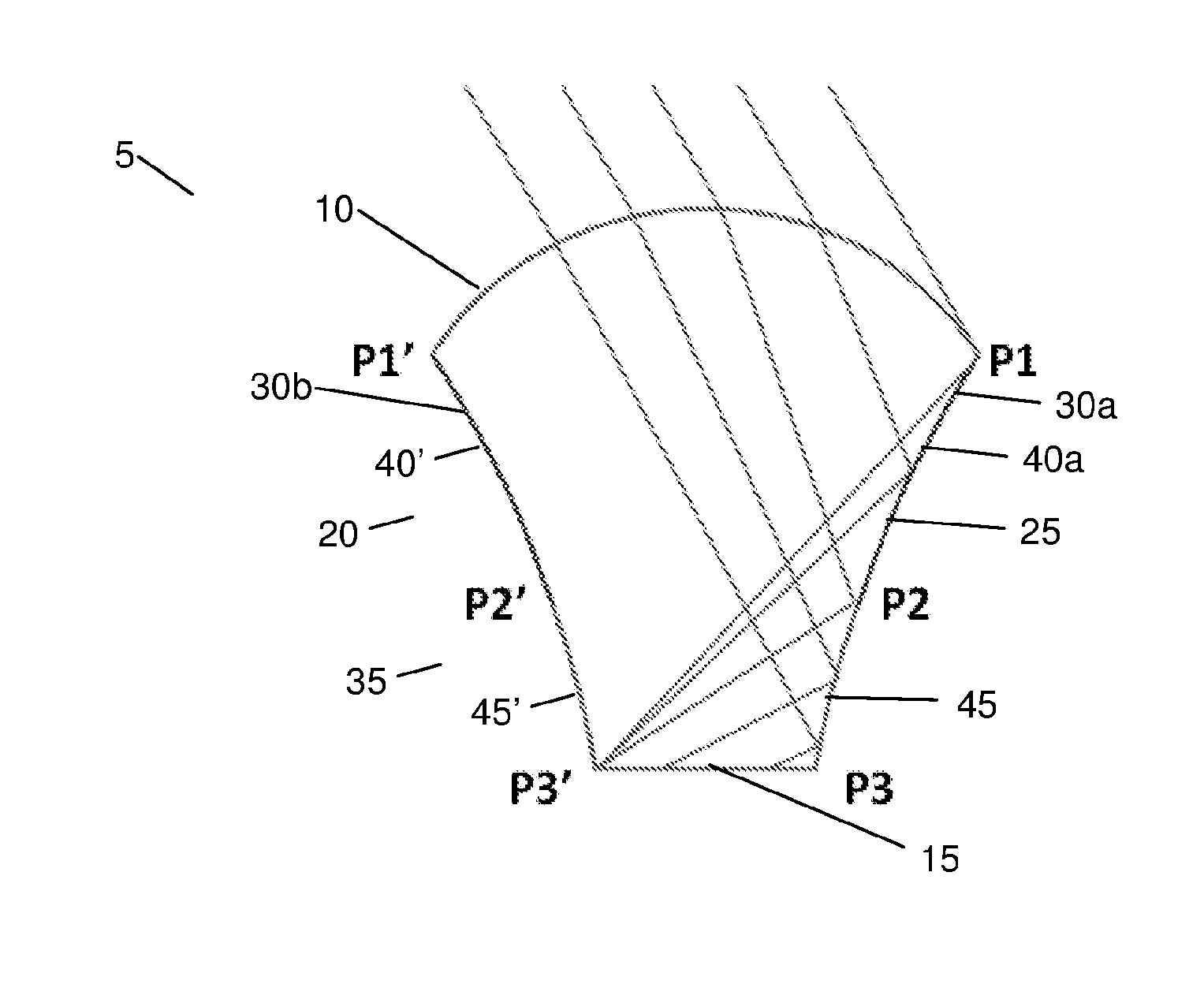

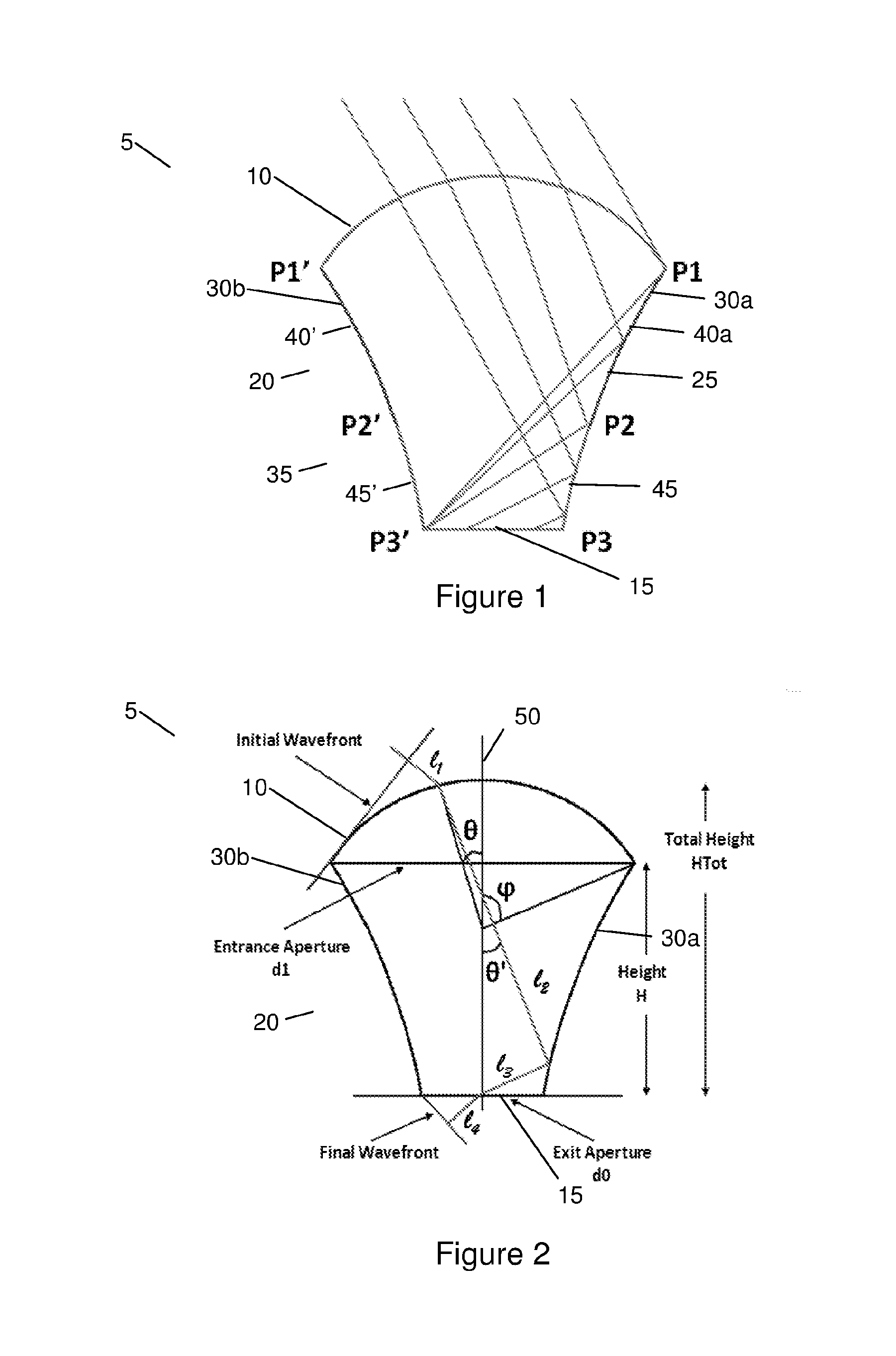

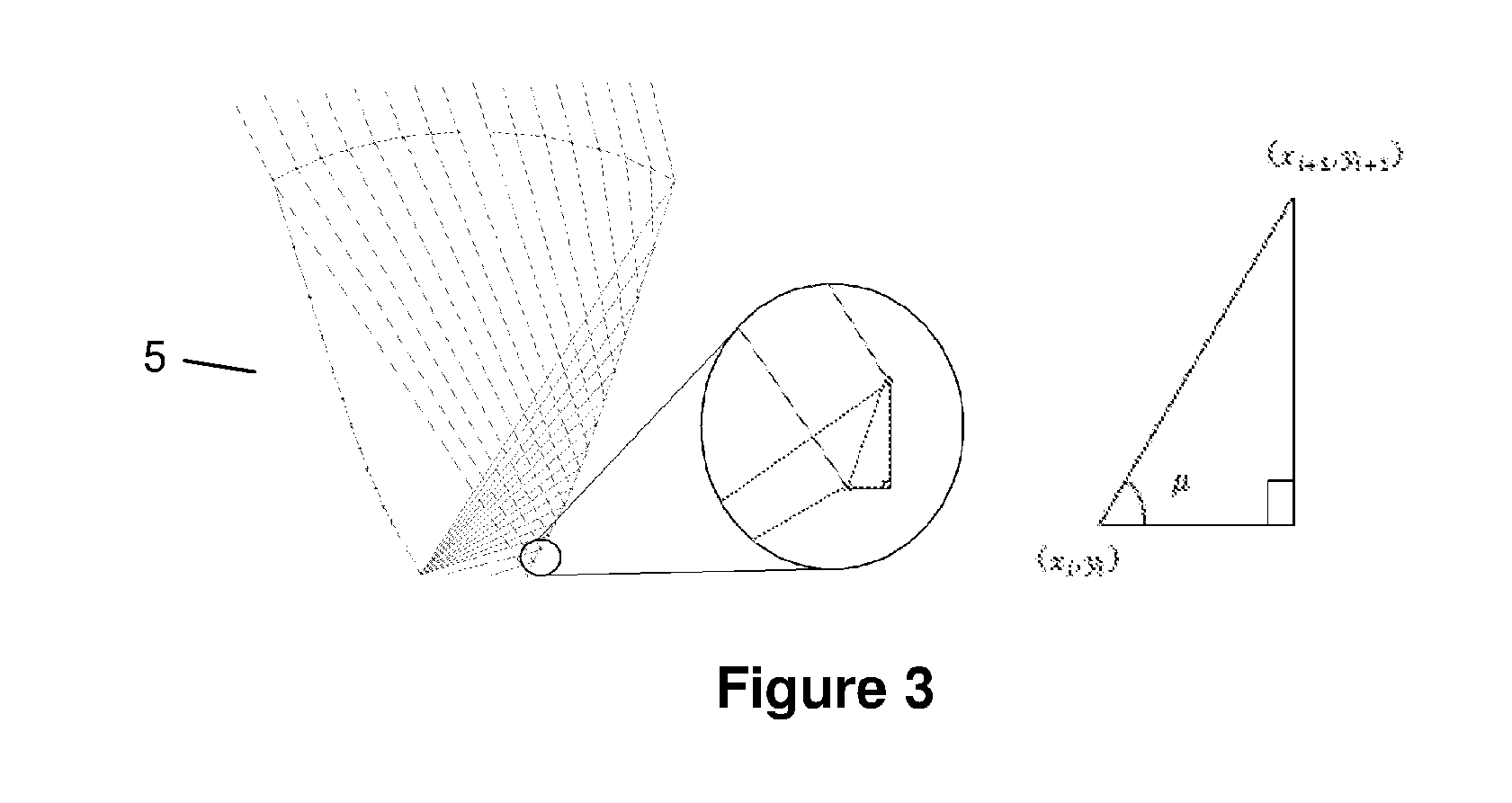

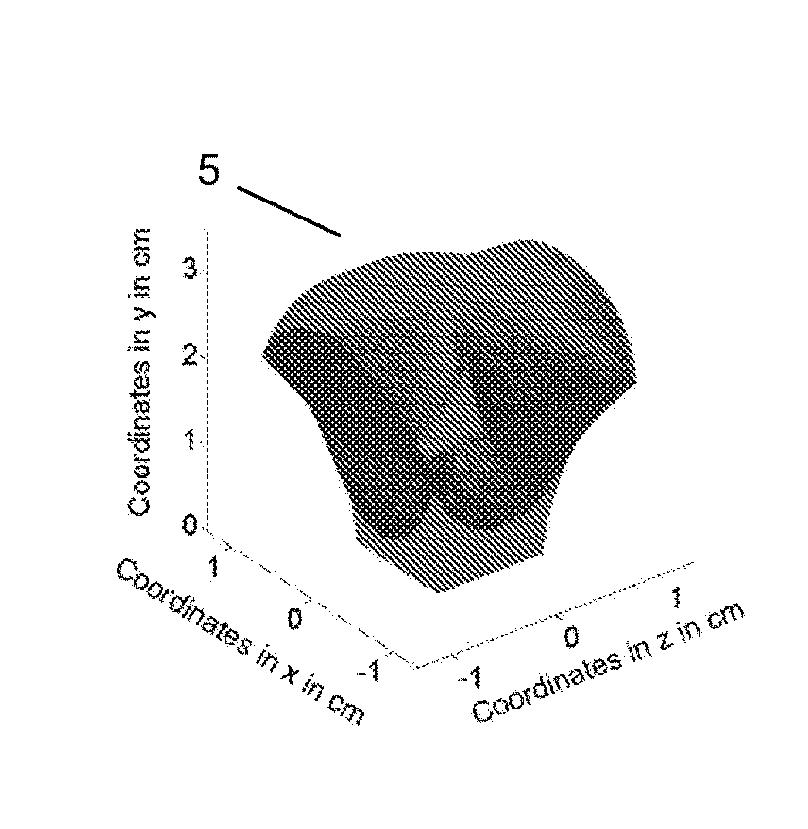

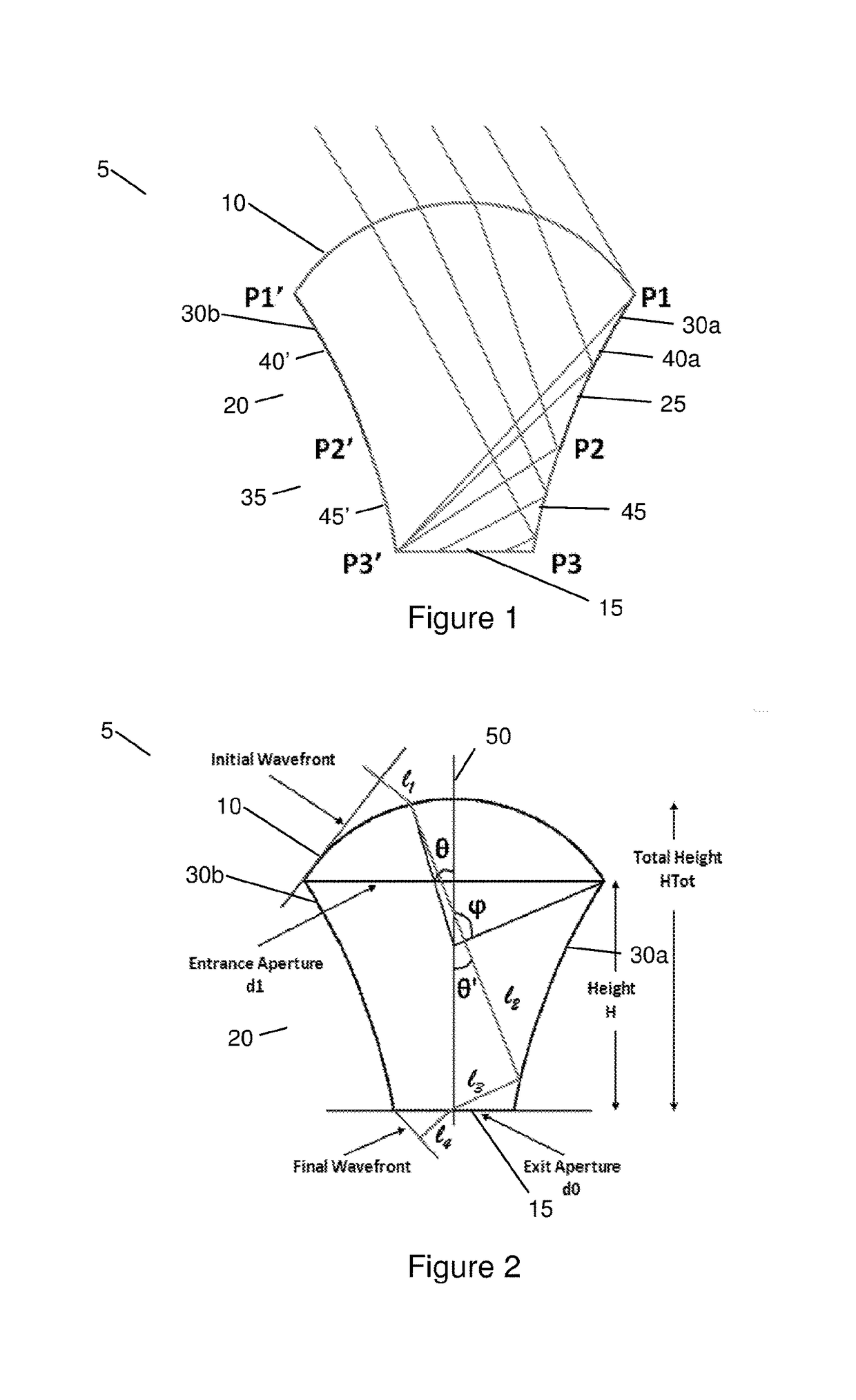

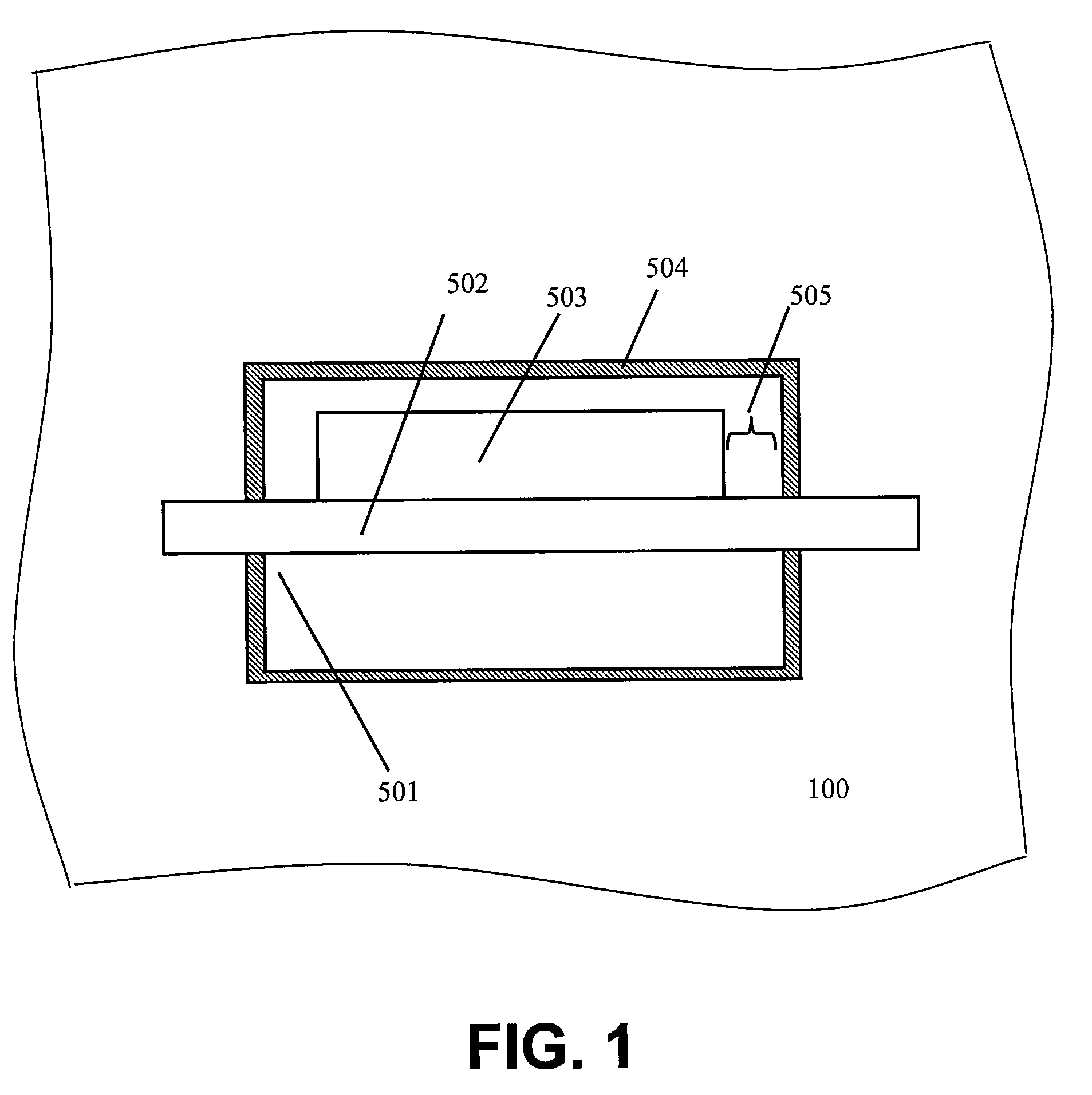

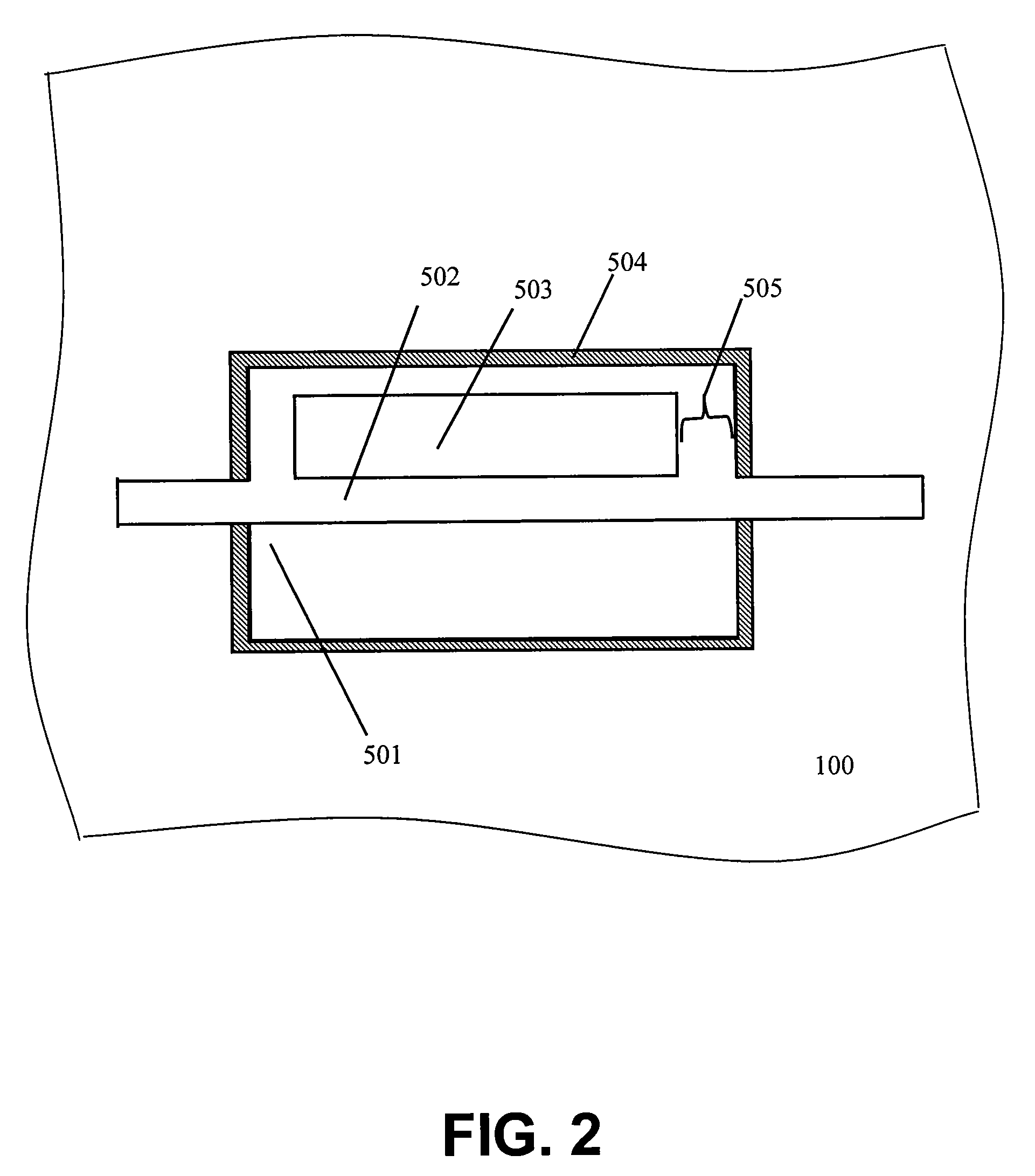

Optical element

ActiveUS20140345689A1Enhanced radiationHigh sensitivitySolar heating energyCondensersOptical radiationOptics

An optical element and associated methods for generating an optical element and apparatus comprising the optical element, wherein the optical element comprises a first surface (10), a second surface (15), and a side wall structure (25) between the first and second surfaces. The side wall structure has an internally reflecting profile such that optical radiation incident on the first surface at an angle less than or equal to an acceptance angle and then incident on the side wall structure is internally reflected to the second surface by the side wall structure. In a first cross section of the optical element, the side wall structure has a first internally reflecting profile and / or the first surface has a first cross sectional profile. In a second cross section that is rotated relative to the first cross section, the side wall structure has a second internally reflecting profile and / or the first surface has a second cross sectional profile, wherein the second internally reflecting profile of the side wall structure and / or the second cross sectional profile of the first surface is different from the first internally reflecting profile of the side wall structure and / or the first cross sectional profile of the first surface.

Owner:UNIV COURT OF GLASGOW CALEDONIAN UNIV

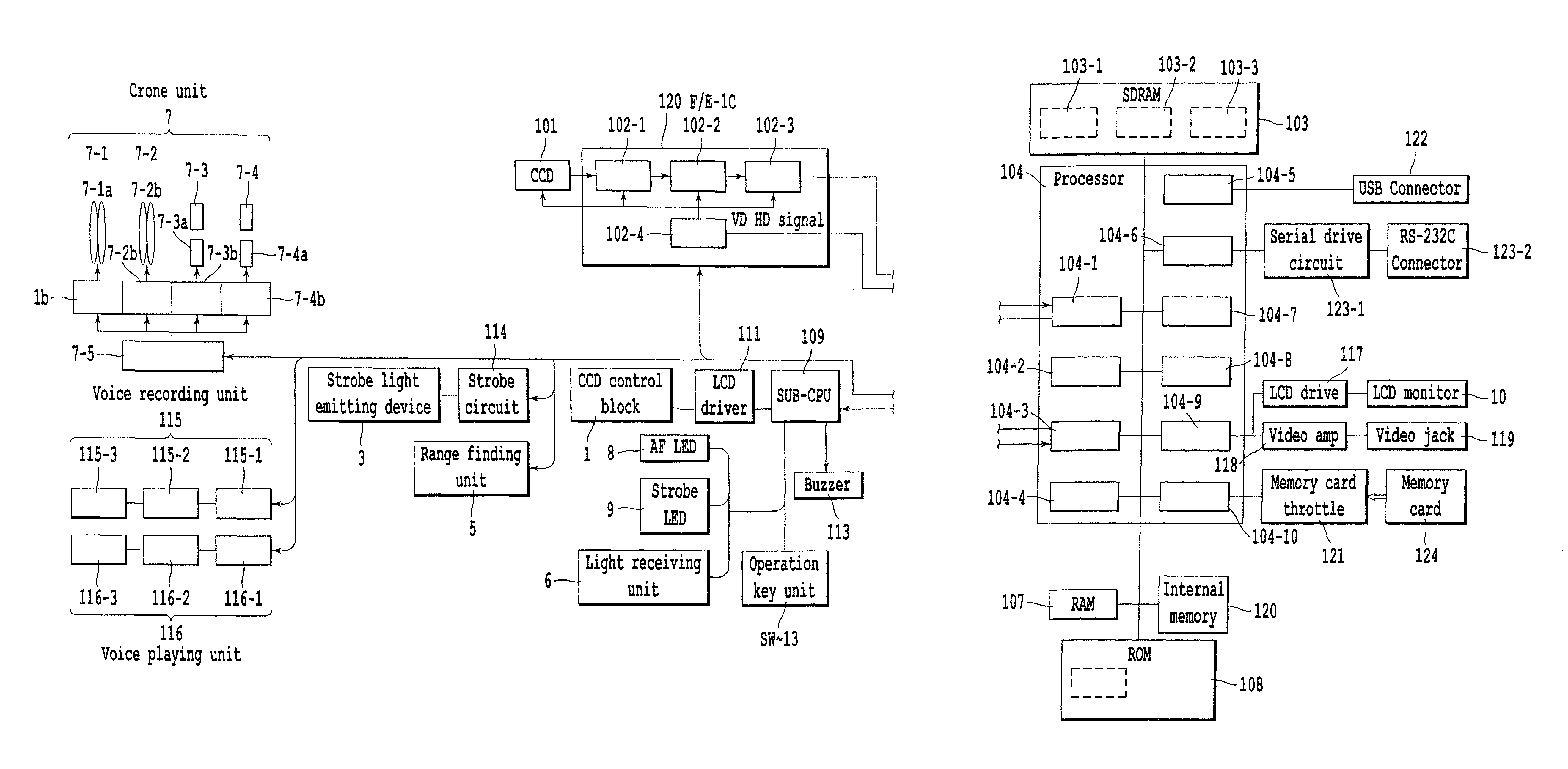

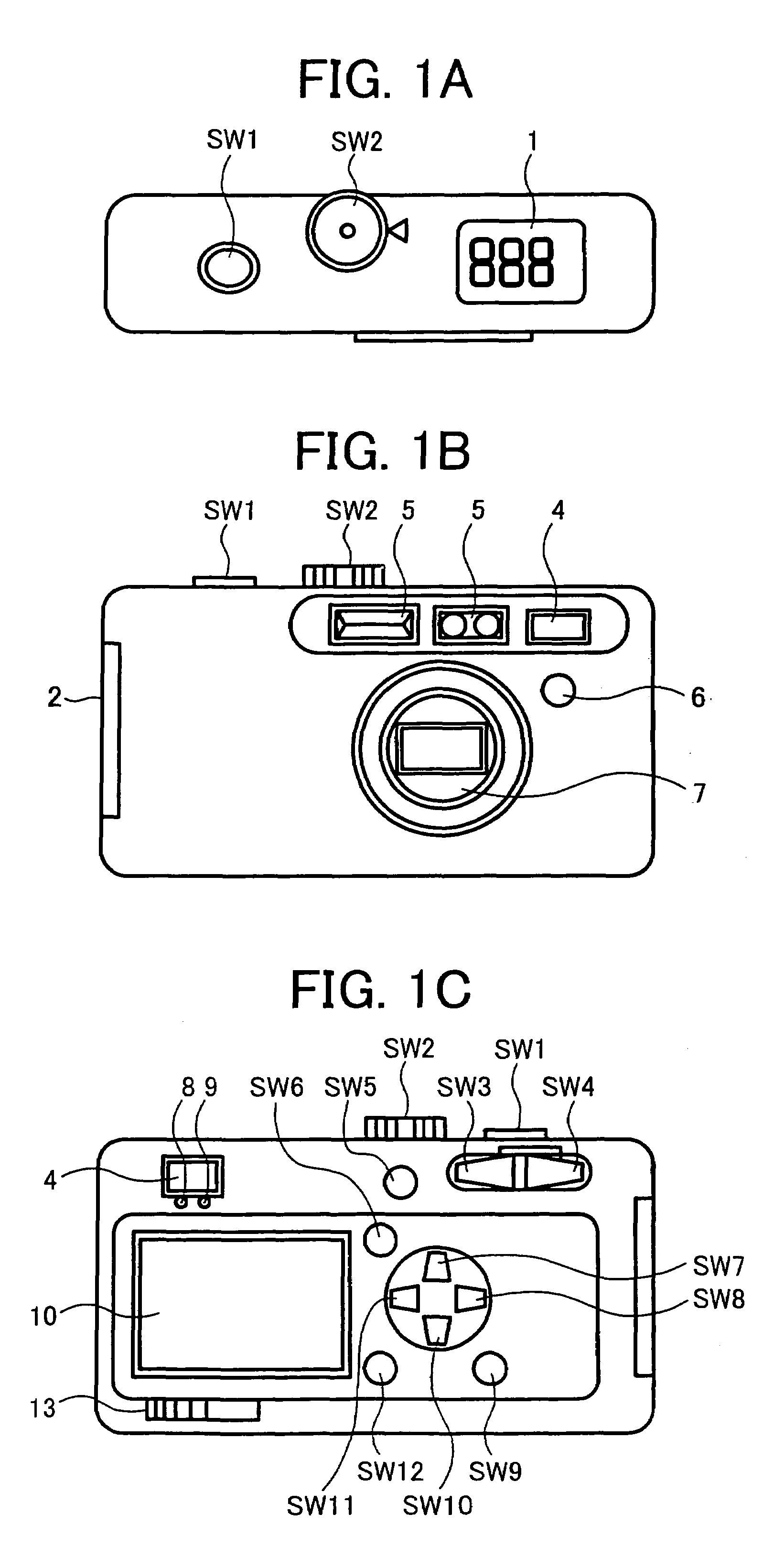

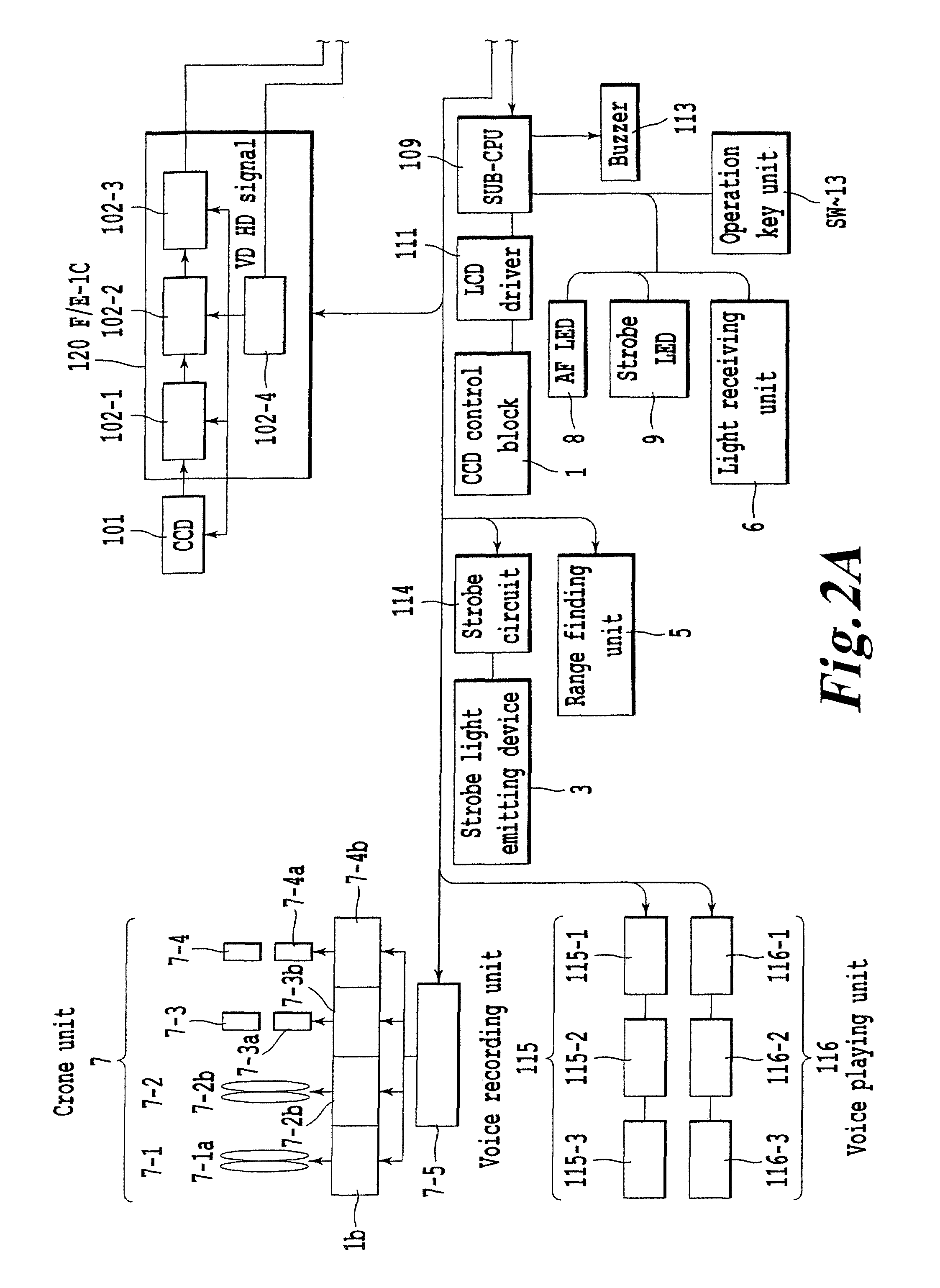

Imaging apparatus and imaging method for reducing release time lag

InactiveUS7589782B2Increased power consumptionRelease operation can be shortenedTelevision system detailsTelevision system scanning detailsRelease timeExposure period

An imaging apparatus includes an exposure period setup part for generating a timing signal, an image pick up device control part for controlling an operation of image pick up device, a timing part for measuring an elapsed time from the exposure period timing signal, and an imaging apparatus control part for controlling the image pick up device control part and the exposure period setup part. The timing part measures the elapsed time from the exposure period timing signal right after a release operation to the beginning of exposure setup operation by the exposure period setup part, and if a time from the measured elapsed time to the generation of the calculated next exposure period timing signal is equal or greater than a predetermined time, the imaging apparatus control part shortens the time till the generation of the next exposure period timing signal from a regular exposure period.

Owner:RICOH KK

Router, method for controlling router, and program

ActiveUS9426099B2Increasing size and numberAvoid flowError preventionTransmission systemsOperating system

An router includes: a plurality of data storage sections configured to store input data; and an arbiter configured to compare the availability of at least one of the plurality of data storage sections with respect to data that is stored in that data storage section and that shares at least a part of a transmission path to the availability of another data storage section in an adjacent router with respect to that data that also shares at least that part of the transmission path, thereby determining, based on a result of the comparison, whether or not to output that data.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

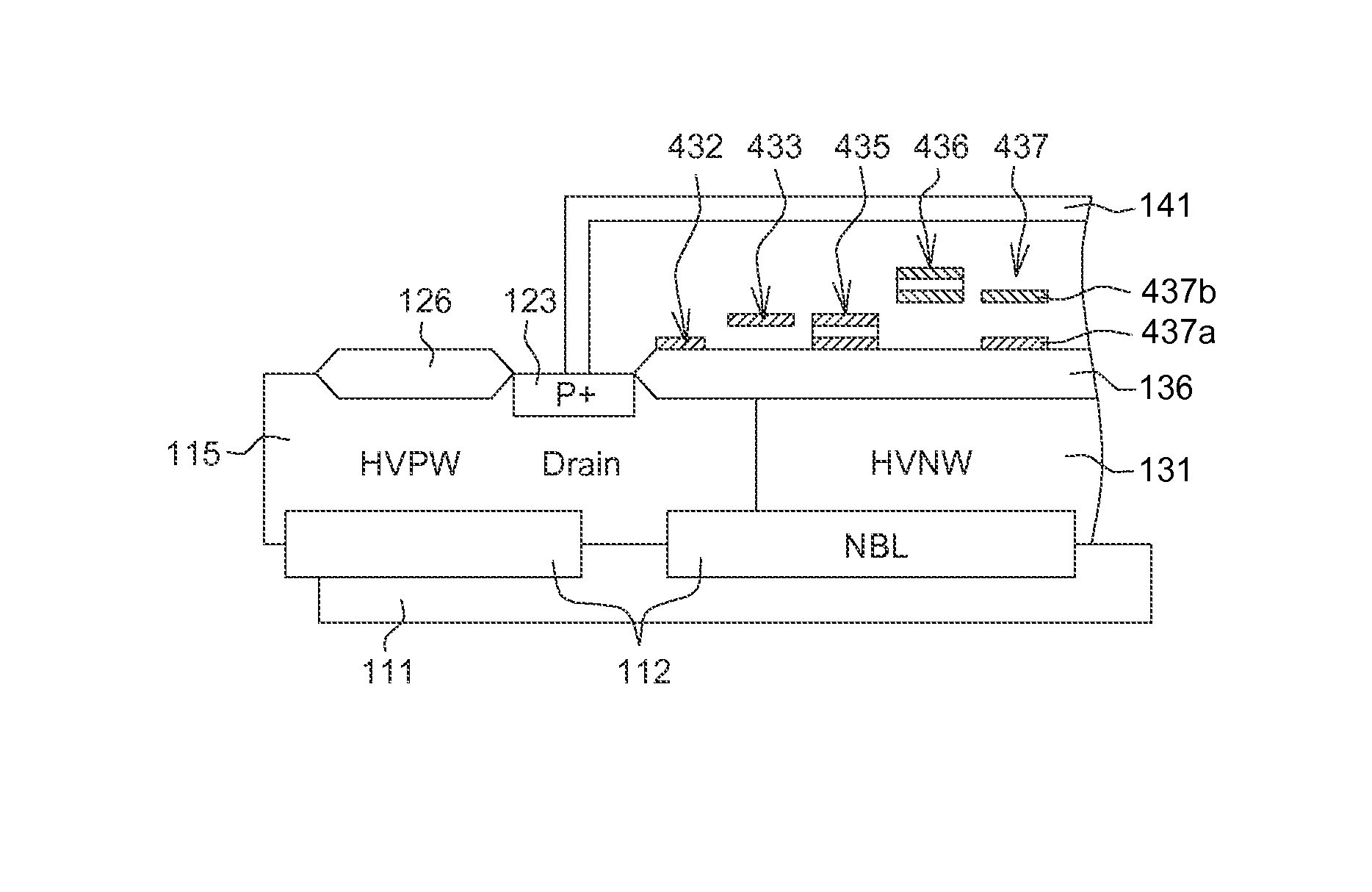

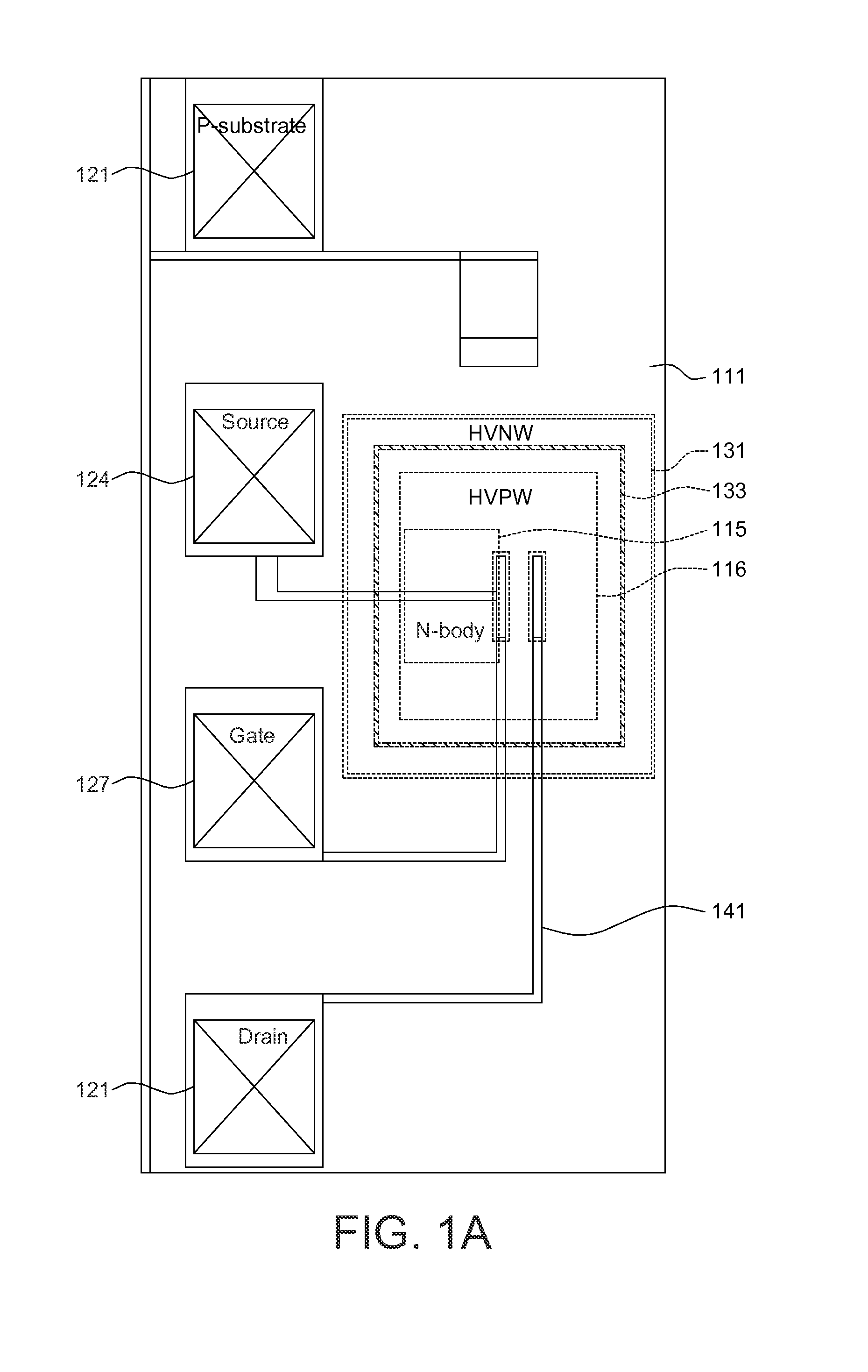

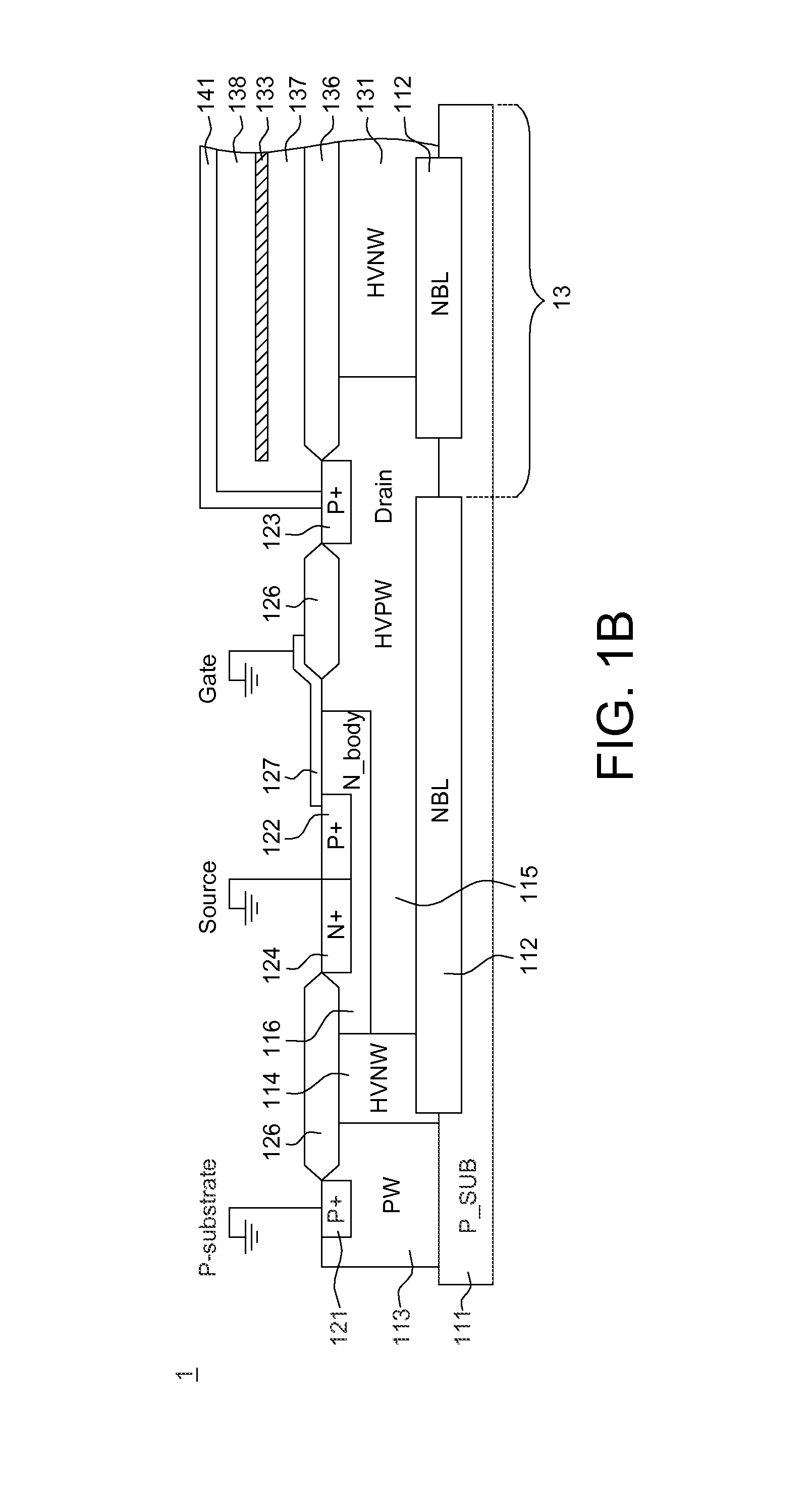

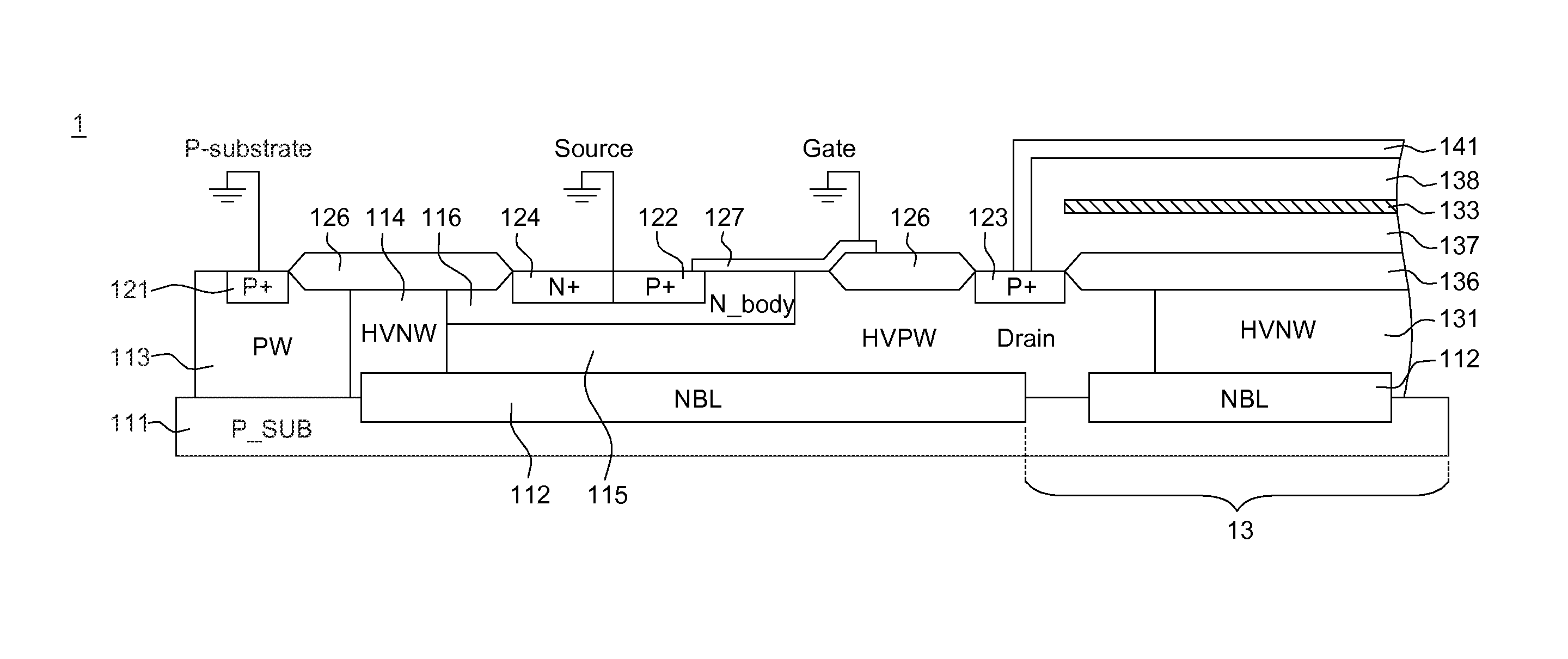

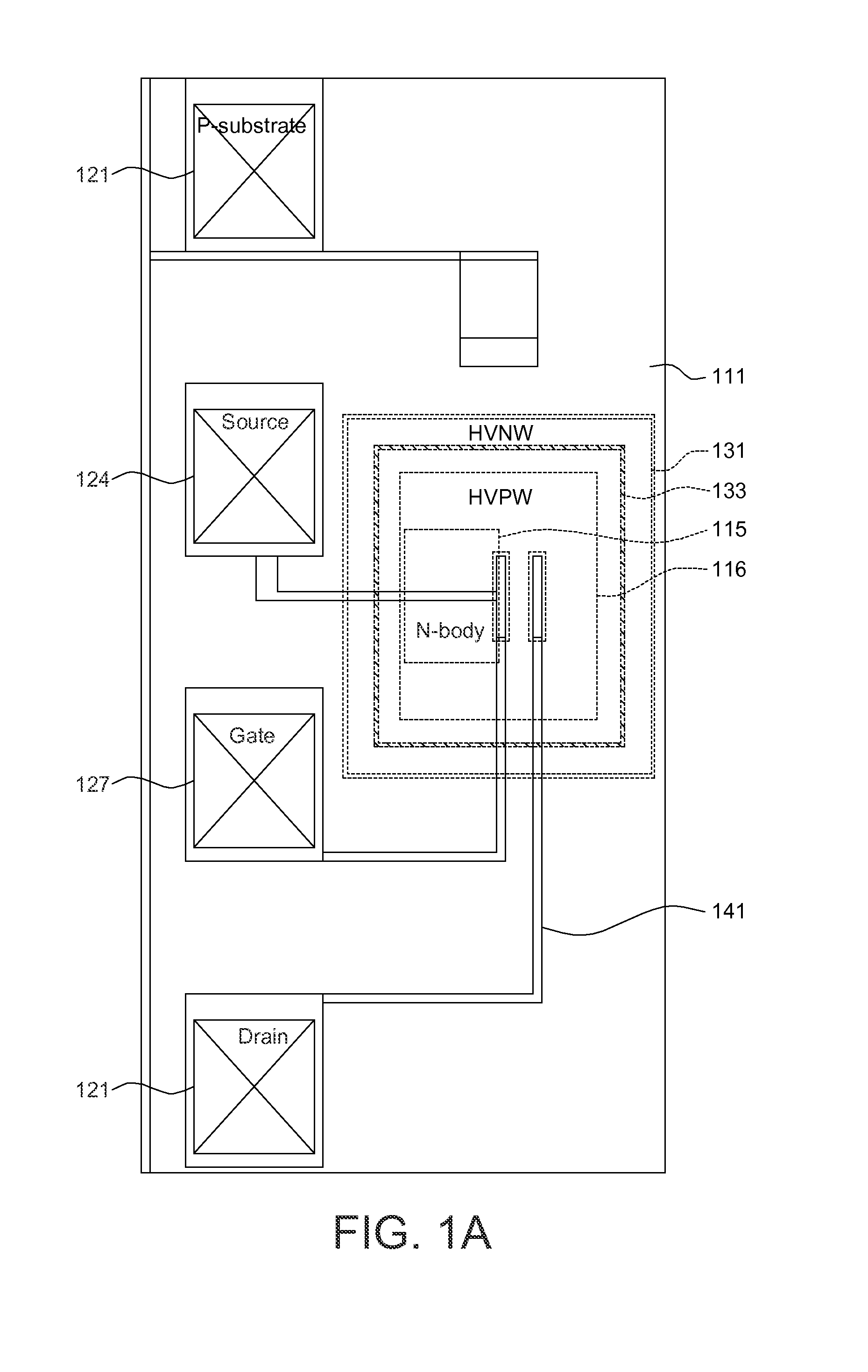

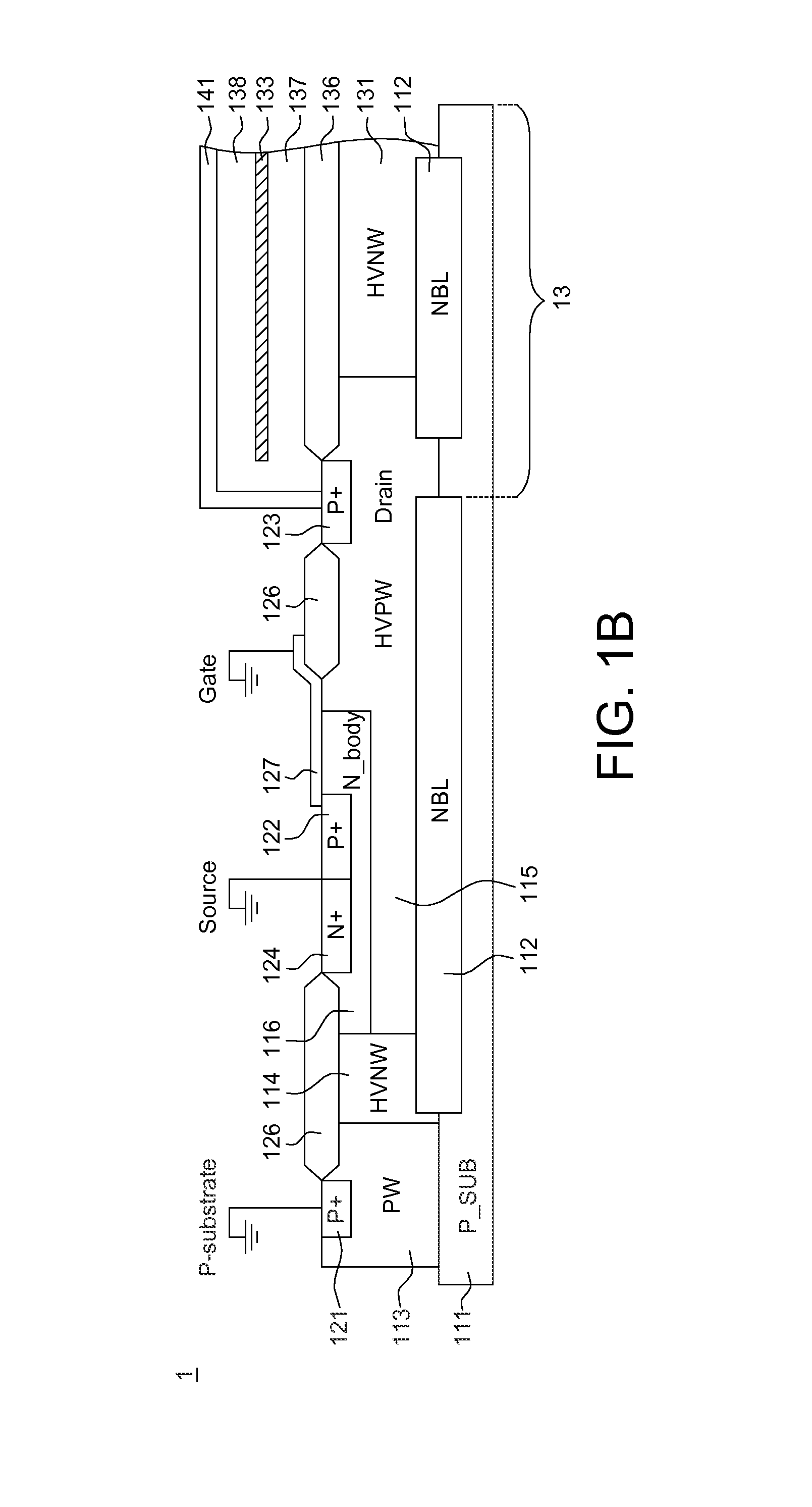

Field device and method of operating high voltage semiconductor device applied with the same

ActiveUS20140077866A1Increasing costIncreasing device areaElectronic switchingElectric pulse generator detailsElectricityHigh pressure

A field device and method of operating high voltage semiconductor device applied with the same are provided. The field device includes a first well having a second conductive type and second well having a first conductive type both formed in the substrate (having the first conductive type) and extending down from a surface of the substrate, the second well adjacent to one side of the first well and the substrate is at the other side of the first well; a first doping region having the first conductive type and formed in the second well, the first doping region spaced apart from the first well; a conductive line electrically connected to the first doping region and across the first well region; and a conductive body insulatively positioned between the conductive line and the first well, and the conductive body correspondingly across the first well region.

Owner:MACRONIX INT CO LTD

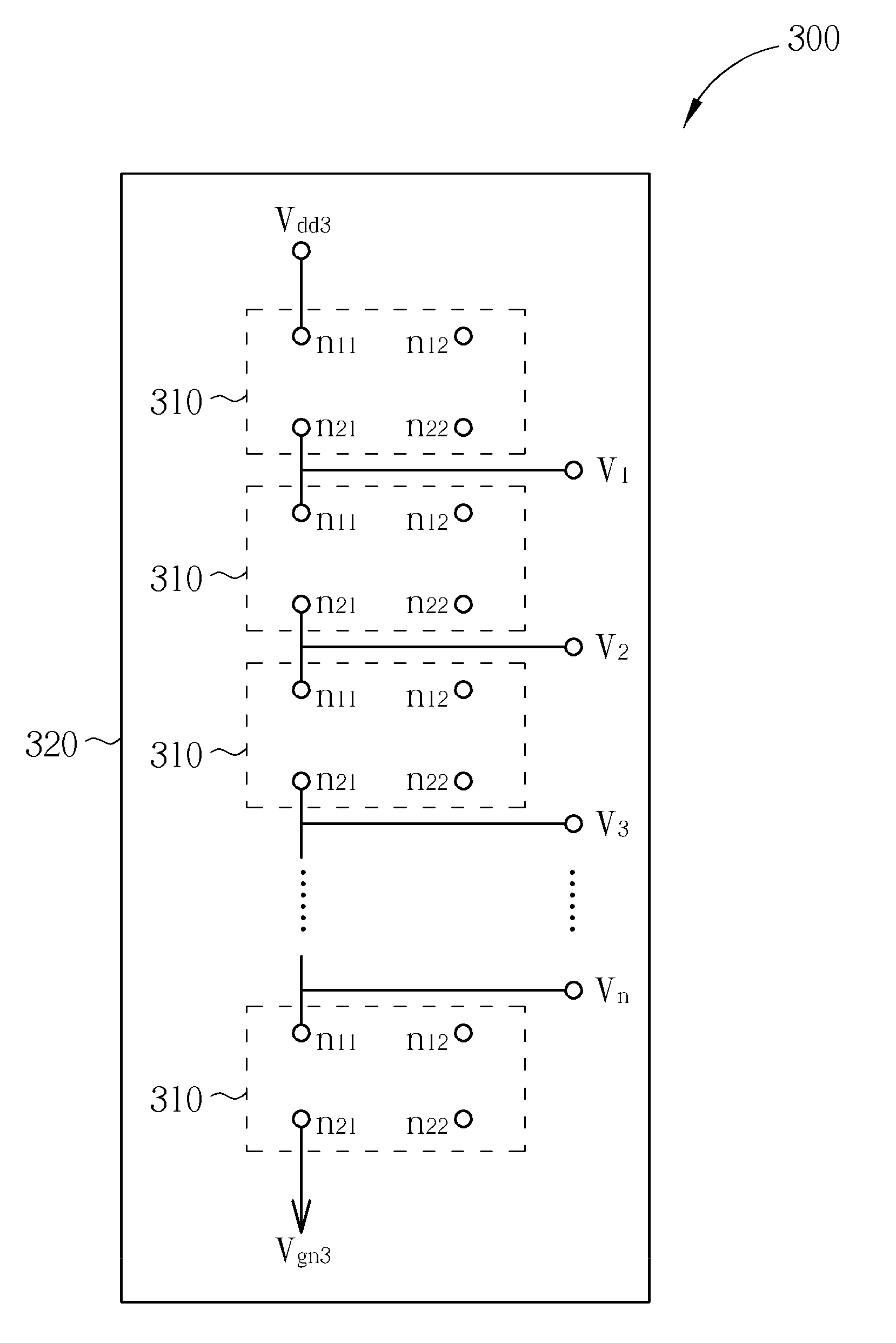

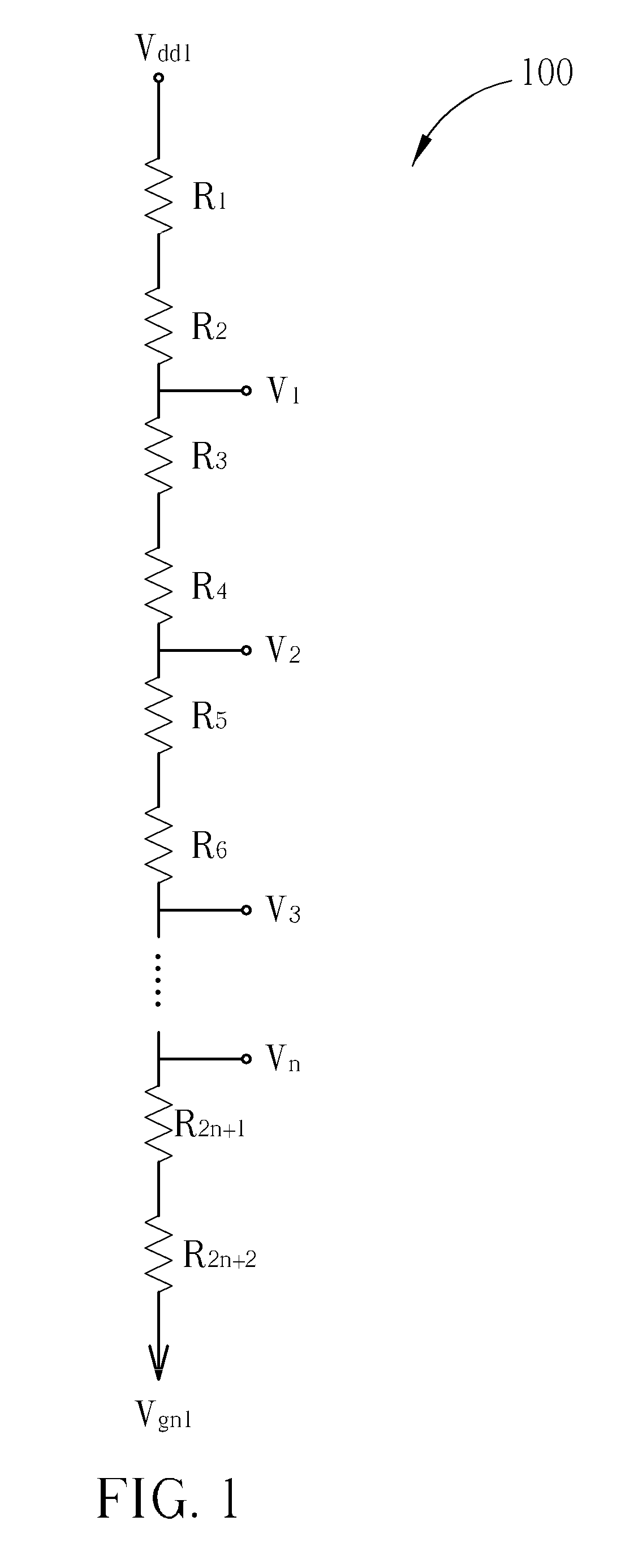

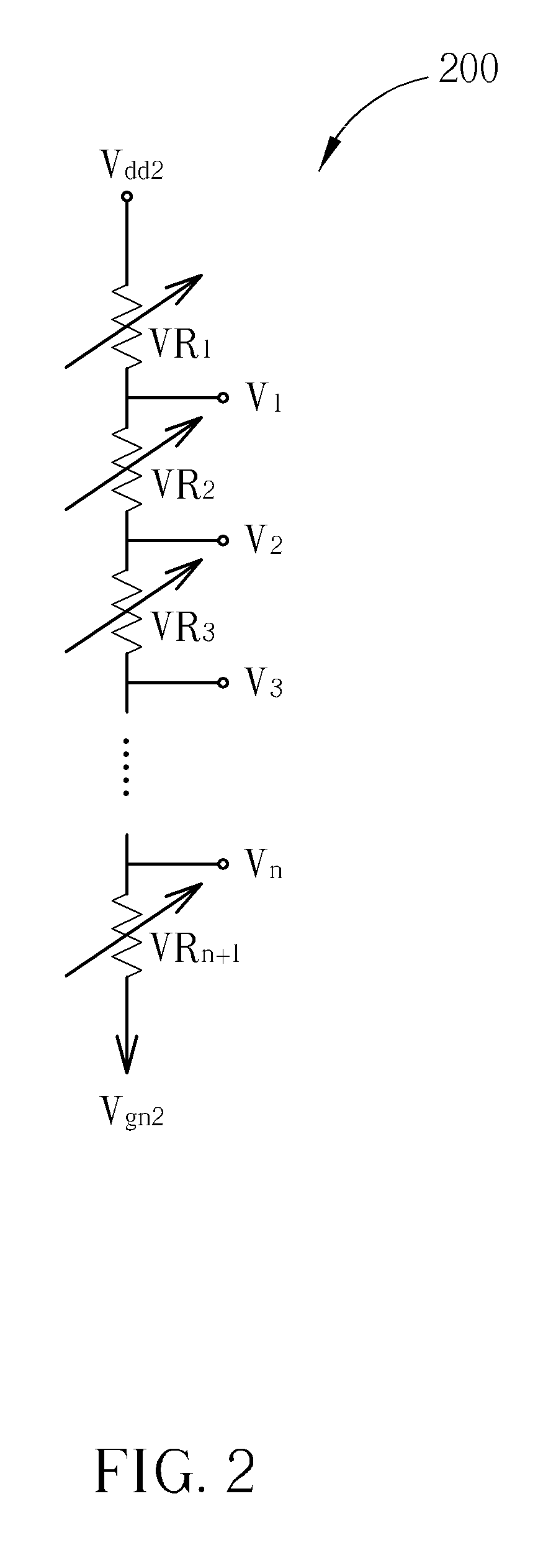

Resistive module, voltage divider and related layout methods

InactiveUS20090262053A1Increasing areaIncreasing costOther resistor networksElongated resistive elementElectricityVoltage divider

Owner:CHUNGHWA PICTURE TUBES LTD

Field device and method of operating high voltage semiconductor device applied with the same

ActiveUS8896061B2Increasing areaIncreasing costElectronic switchingElectric pulse generator detailsElectricityEngineering

A field device and method of operating high voltage semiconductor device applied with the same are provided. The field device includes a first well having a second conductive type and second well having a first conductive type both formed in the substrate (having the first conductive type) and extending down from a surface of the substrate, the second well adjacent to one side of the first well and the substrate is at the other side of the first well; a first doping region having the first conductive type and formed in the second well, the first doping region spaced apart from the first well; a conductive line electrically connected to the first doping region and across the first well region; and a conductive body insulatively positioned between the conductive line and the first well, and the conductive body correspondingly across the first well region.

Owner:MACRONIX INT CO LTD

Performance operator control apparatus

ActiveUS7259319B2Easy to useIncreasing areaElectrophonic musical instrumentsVibration measurement in fluidPianoMagnetic valve

A performance operator control apparatus adapted to a player piano comprises a motion control unit and a key drive unit comprising a plurality of key I / O control ICs in connection with keys of a keyboard, which are driven by solenoids so as to realize automatic performance, wherein upon detection of electrification abnormality of solenoids or temperature abnormality, LEDs are turned on to indicate the abnormality. The key I / O control ICs receive velocity signals regarding the solenoids so as to perform feedback controls on the keys in the automatic performance. In addition, unoccupied channels of the key I / O control ICs, which are not assigned to the keys and sensors, are used to input monitoring signals and to output inspection signals. Herein, the abnormality is determined based on the difference between pre-inspection data and post-inspection data, which are transferred using a loop connection channel of the key I / O control IC.

Owner:YAMAHA CORP

Gate driving waveform control

InactiveUS9129576B2Increasing complexityIncreasing areaCathode-ray tube indicatorsInput/output processes for data processingShift registerLiquid-crystal display

A gate driver and associated method for a double gate liquid crystal display (LCD) is disclosed. A gate driving signal generating circuit, such as coupled shift registers, generates the gate driving signals in response to horizontal synchronization signal. In one embodiment, a phase control circuit, such as logic AND gates, is coupled to receive the outputs of the shift registers for determining phase relationship between the outputs of the shift registers and the horizontal synchronization signal.

Owner:HIMAX TECH LTD

Image sensor, image capturing apparatus, and cellular phone

ActiveUS9621830B2Increasing areaIncreasing costTelevision system detailsSolid-state devicesElectrical conductorComputer science

An image sensor comprises: a first semiconductor including a plurality of pixels two-dimensionally arranged, and a plurality of divided output lines, in a first direction, configured to read out pixel signals from the plurality of pixels in the first direction; and a second semiconductor including a plurality of signal processing units, corresponding to the plurality of output lines, respectively, configured to process the readout pixel signals, and a readout unit configured to read out the signals output from the signal processing units in a second direction, wherein the first semiconductor and the second semiconductor are stacked, and the plurality of output lines and the plurality of signal processing units are connected in correspondence with each other.

Owner:CANON KK

Optical element

ActiveUS9910253B2Enhanced radiationHigh sensitivitySolar heating energySolar heat devicesOptical radiationOptics

An optical element and associated methods for generating an optical element and apparatus comprising the optical element, wherein the optical element comprises a first surface (10), a second surface (15), and a side wall structure (25) between the first and second surfaces. The side wall structure has an internally reflecting profile such that optical radiation incident on the first surface at an angle less than or equal to an acceptance angle and then incident on the side wall structure is internally reflected to the second surface by the side wall structure. In a first cross section of the optical element, the side wall structure has a first internally reflecting profile and / or the first surface has a first cross sectional profile. In a second cross section that is rotated relative to the first cross section, the side wall structure has a second internally reflecting profile and / or the first surface has a second cross sectional profile, wherein the second internally reflecting profile of the side wall structure and / or the second cross sectional profile of the first surface is different from the first internally reflecting profile of the side wall structure and / or the first cross sectional profile of the first surface.

Owner:UNIV COURT OF GLASGOW CALEDONIAN UNIV

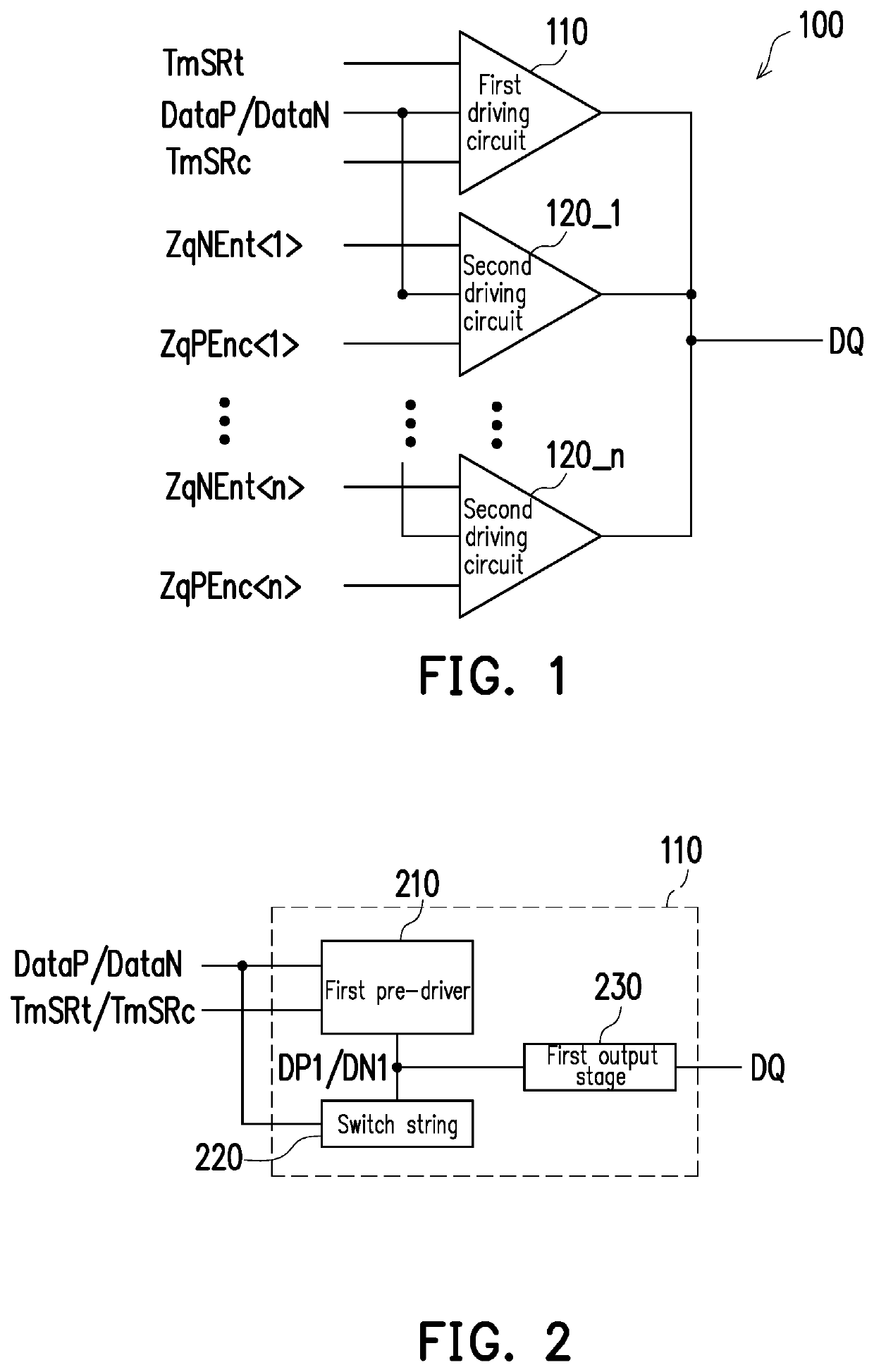

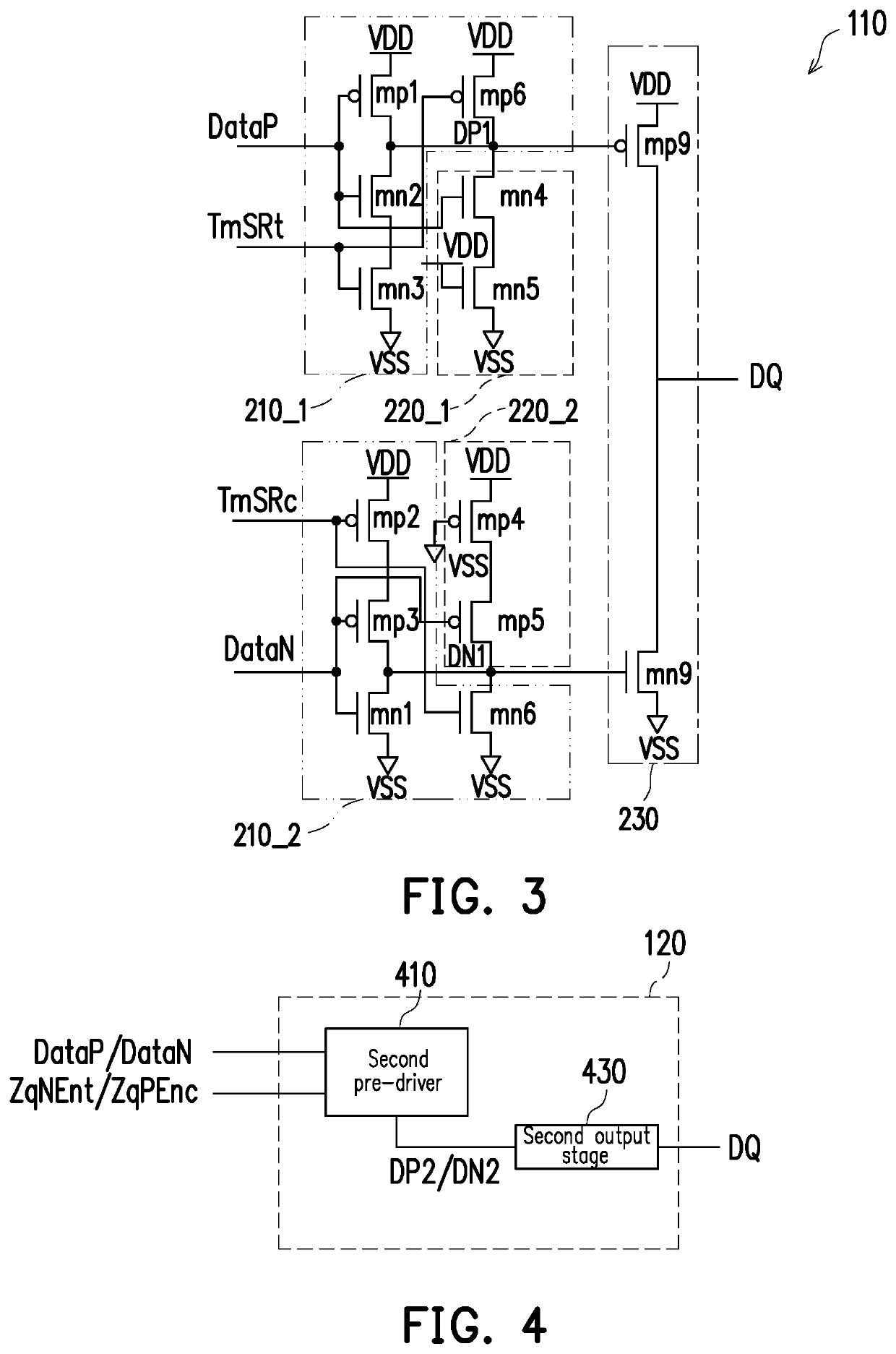

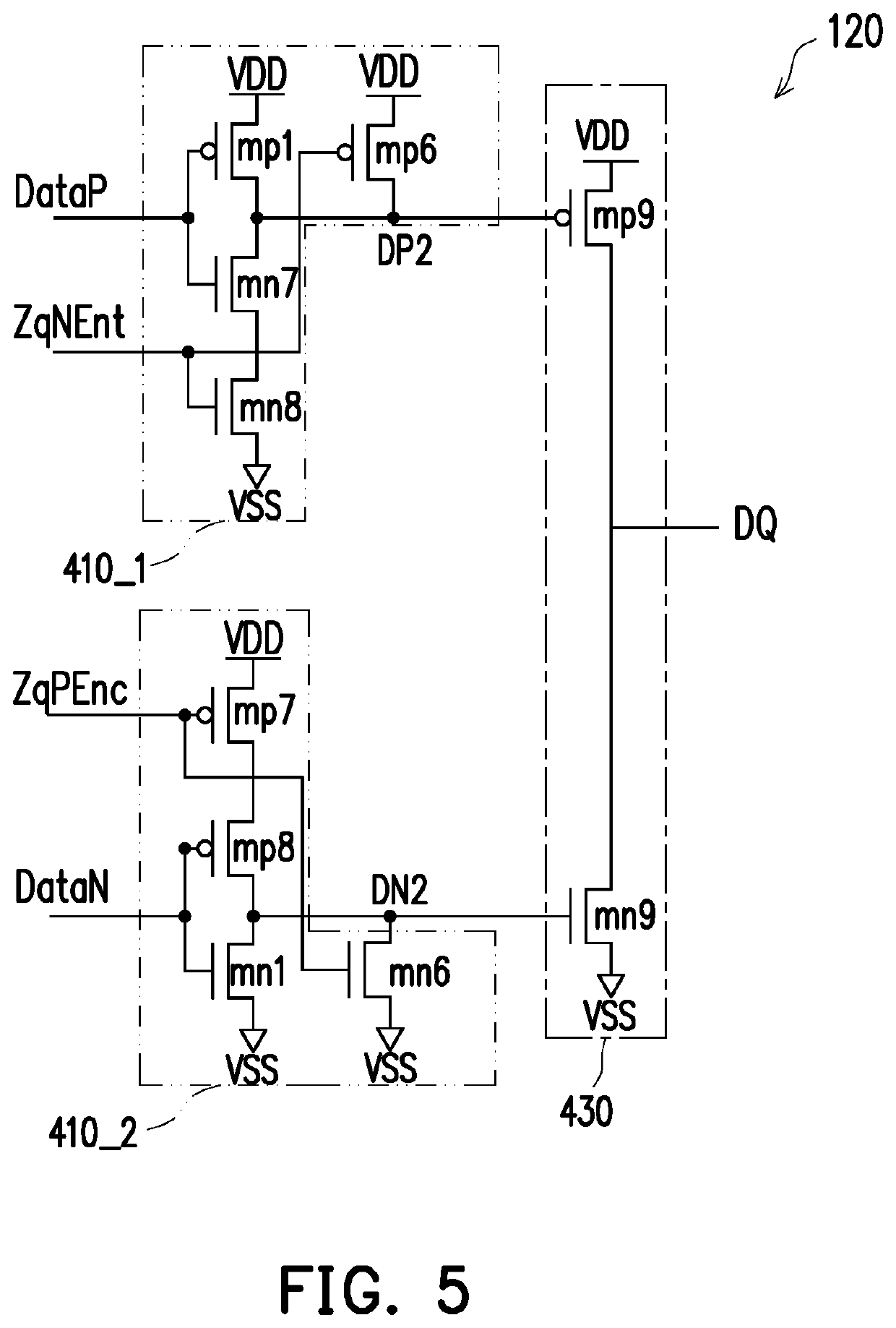

Off-chip driver

ActiveUS20200075060A1Increasing layout areaIncreasing power consumptionReliability increasing modificationsDigital storageControl signalData signal

An off-chip driver including a first driving circuit is provided. The first driving circuit is used to adjust a slew rate of the off-chip driver. The first driving circuit includes a first pre-driver, a switch string, and a first output stage. The first pre-driver receives a read signal and a first pre-driver control signal. The switch string is configured to perform a voltage division operation in cooperation with the first pre-driver on a power supply voltage according to the read signal, so as to generate a first output stage control signal. The first output stage generates a data signal according to the first output stage control signal.

Owner:WINBOND ELECTRONICS CORP

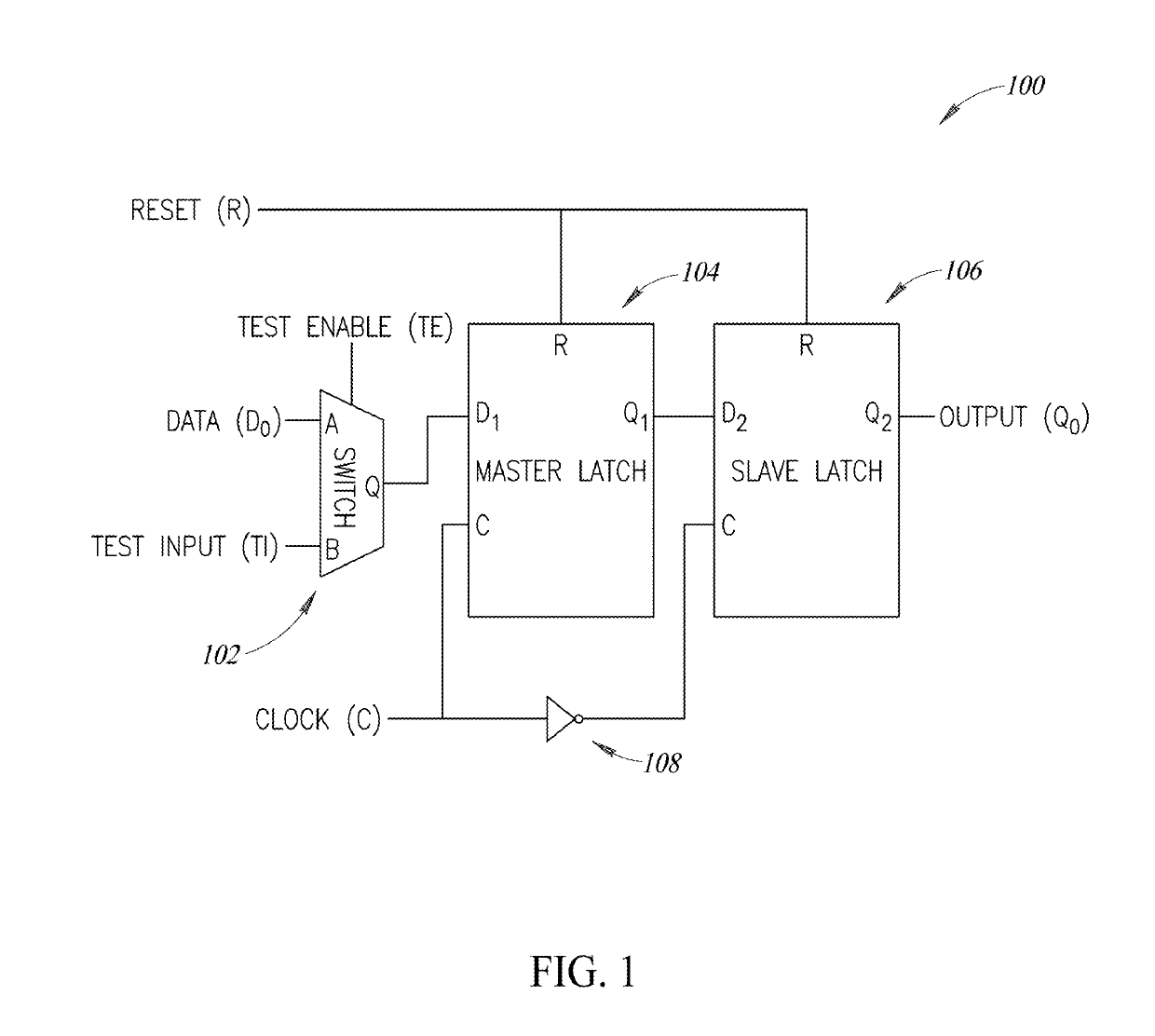

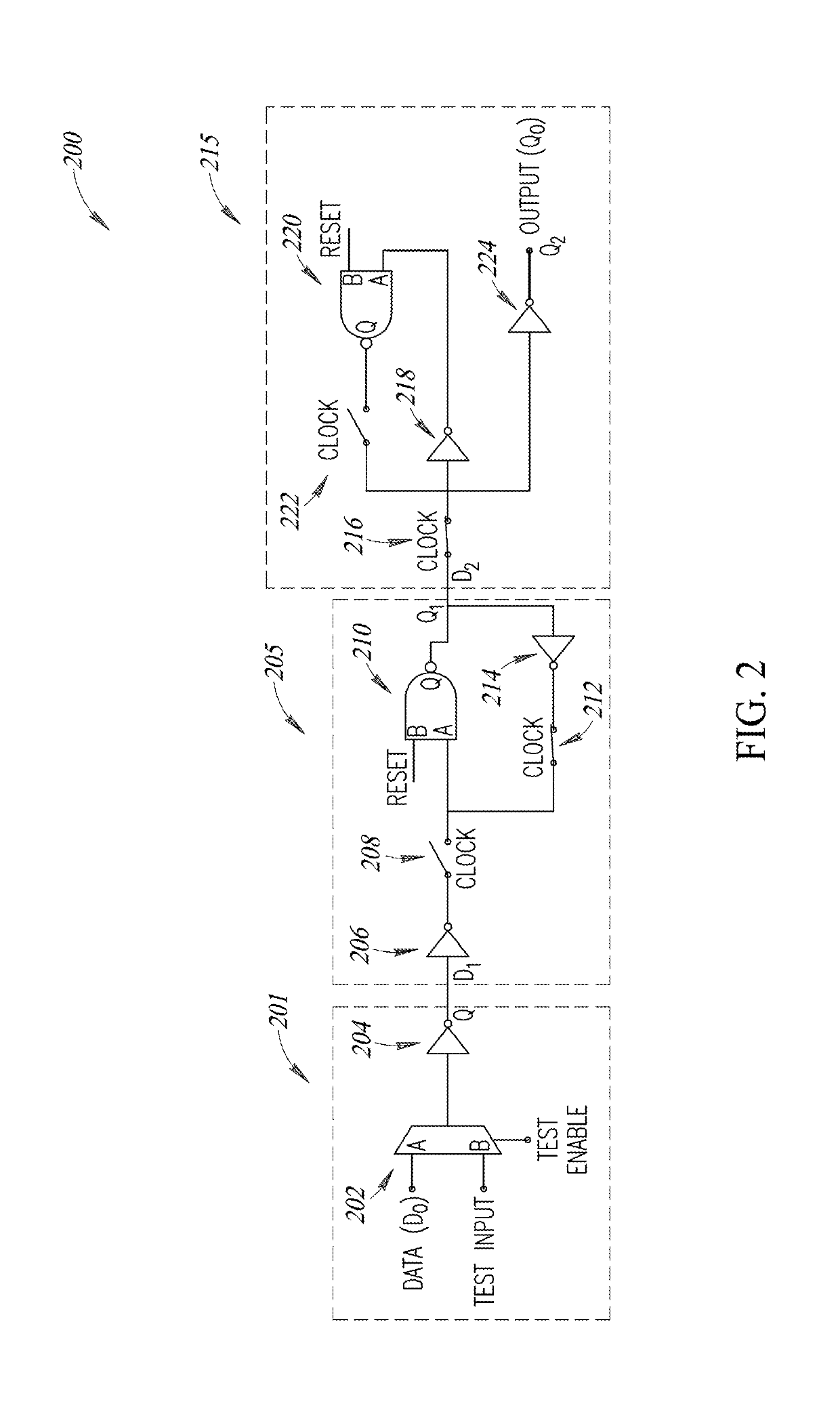

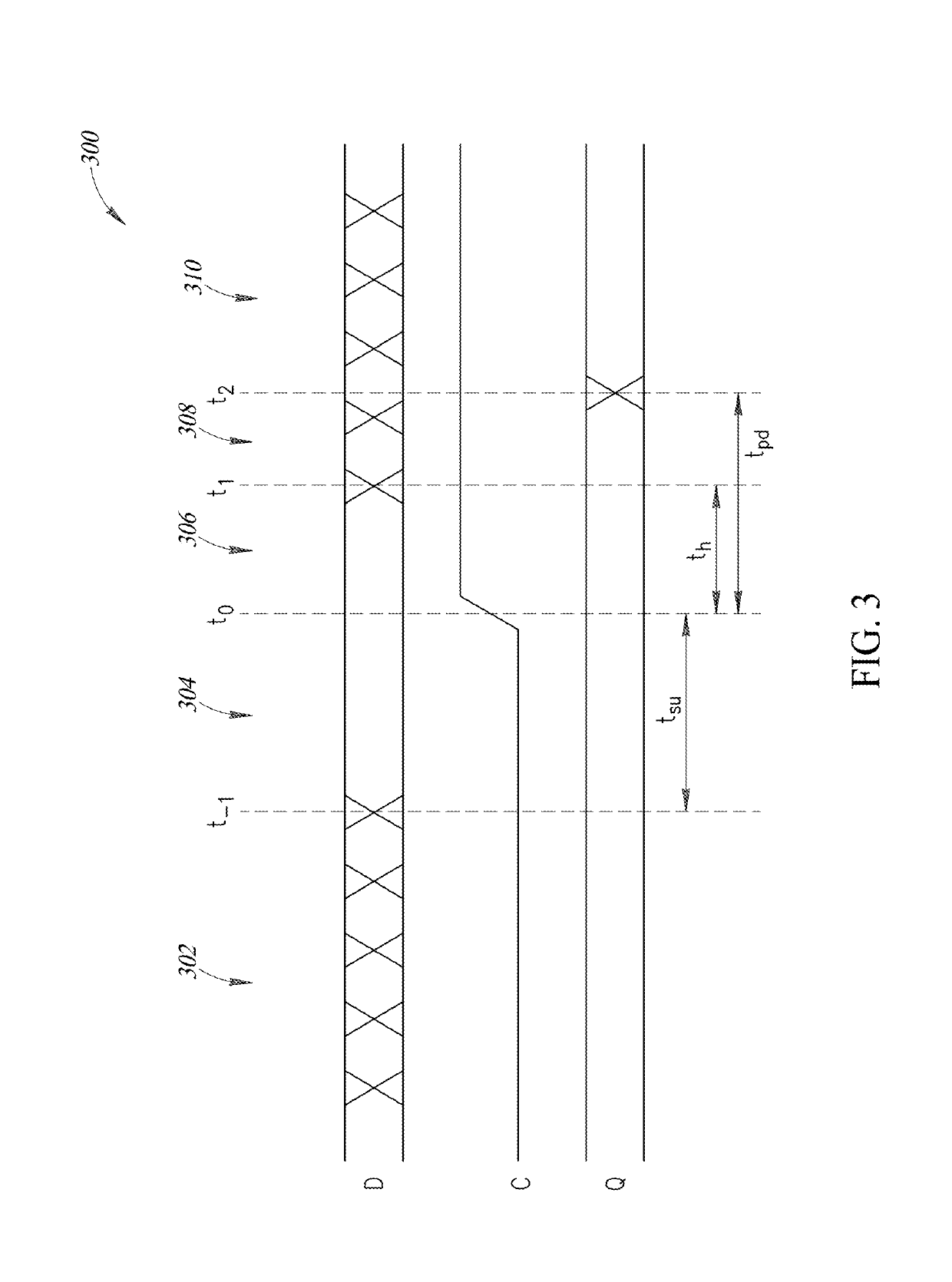

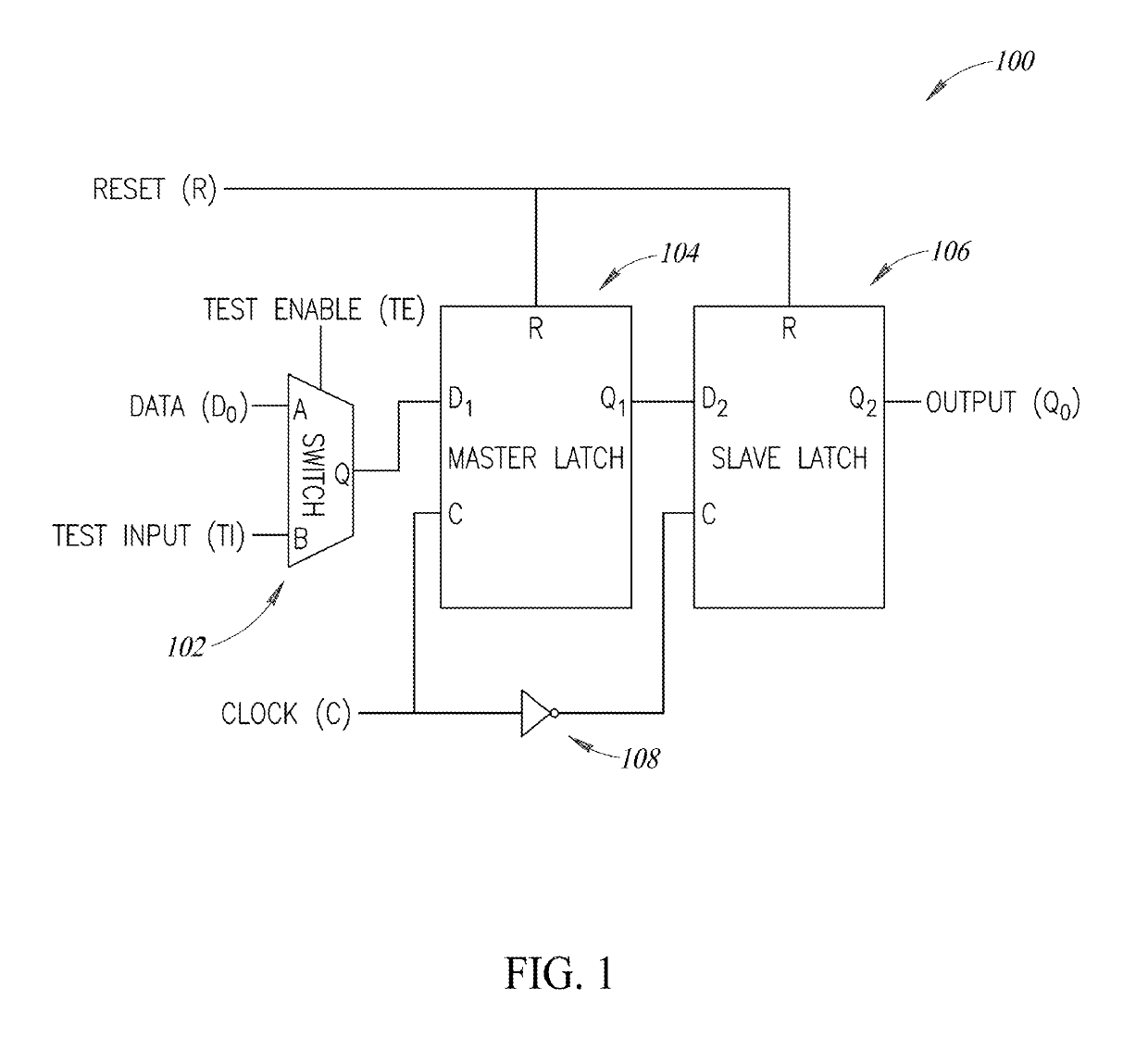

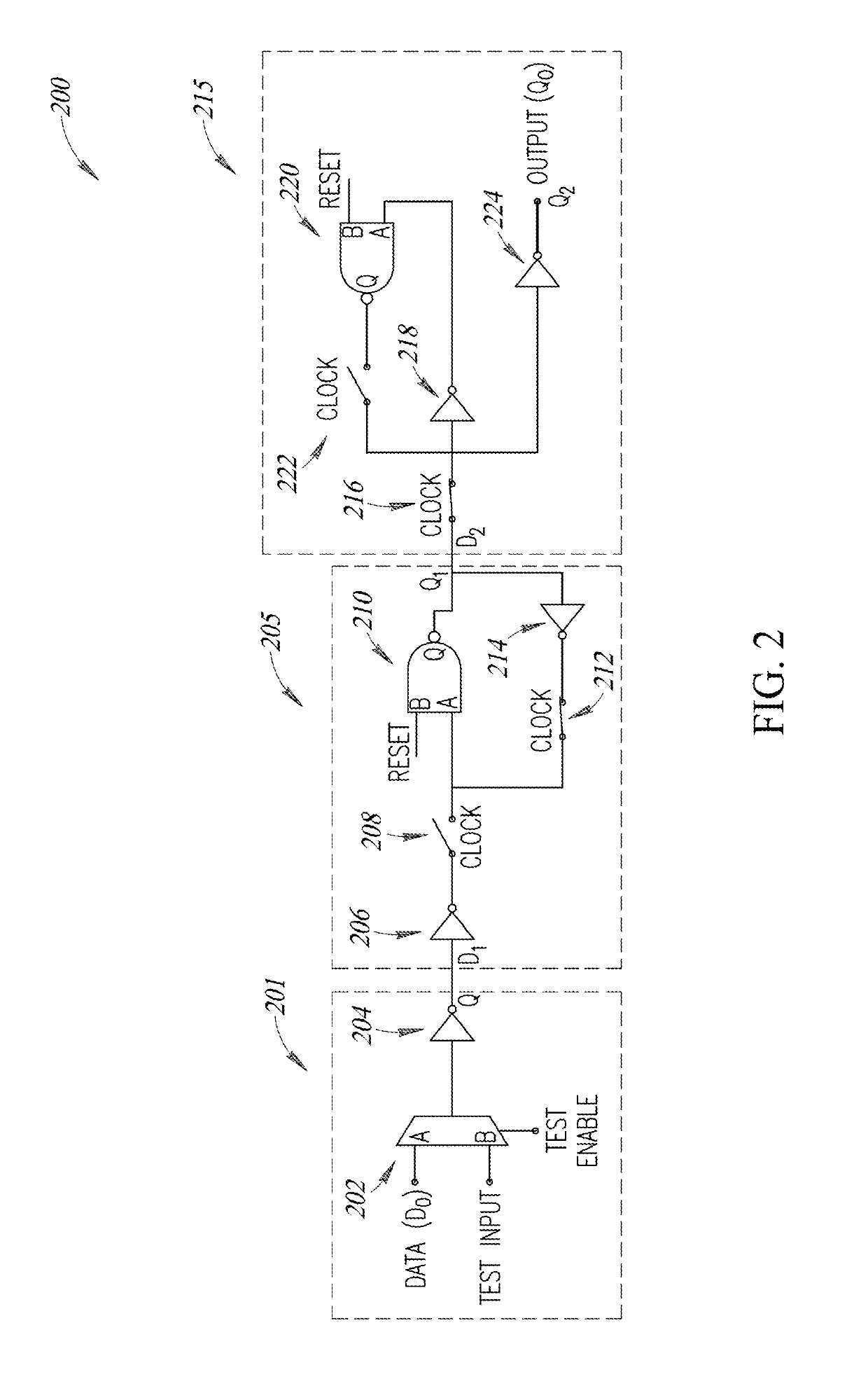

Low voltage, master-slave flip-flop

ActiveUS10277207B1Increasing area consumptionIncreasing circuit areaRead-only memoriesDigital storageLow voltageMemory circuits

The present disclosure is directed to a master-slave flip-flop memory circuit having a partial pass gate transistor at the input of the master latch. The partial pass gate transistor includes a pull-up clock enabled transistor for selectively coupling a high output of a test switch to the input of the master latch. The input of the master latch is also directly coupled to a low output of the test switch around the partial pass gate. In addition, a revised circuit layout is provided in which the master latch has three inverters. A first inverter is coupled to the input of the master latch. Second and third inverters are coupled to an output of the first inverter, with the second inverter having an output coupled to the input of the first inverter, and the third inverter having an output coupled to an output of the master latch. The first and second inverters are clock enabled, and the third inverter is reset enabled.

Owner:STMICROELECTRONICS INT NV

Semiconductor device

InactiveUS8907443B2Increasing areaIncreasing stepTransistorSemiconductor/solid-state device detailsPower semiconductor deviceDevice material

In order to suppress an off leak current of an off transistor for ESD protection, in an NMOS for ESD protection whose isolation region has a shallow trench structure, a drain region is placed apart from the shallow trench isolation region so as not to be in direct contact with the shallow trench isolation region in a region where the drain region of the NMOS transistor for ESD protection is adjacent to at least a gate electrode of the NMOS transistor for ESD protection.

Owner:ABLIC INC

Low voltage, master-slave flip-flop

ActiveUS20190273484A1Increase variabilityHigh voltageRead-only memoriesDigital storageLow voltageDirect coupling

The present disclosure is directed to a master-slave flip-flop memory circuit having a partial pass gate transistor at the input of the master latch. The partial pass gate transistor includes a pull-up clock enabled transistor for selectively coupling a high output of a test switch to the input of the master latch. The input of the master latch is also directly coupled to a low output of the test switch around the partial pass gate. In addition, a revised circuit layout is provided in which the master latch has three inverters. A first inverter is coupled to the input of the master latch. Second and third inverters are coupled to an output of the first inverter, with the second inverter having an output coupled to the input of the first inverter, and the third inverter having an output coupled to an output of the master latch. The first and second inverters are clock enabled, and the third inverter is reset enabled.

Owner:STMICROELECTRONICS INT NV