Patents

Literature

255 results about "Logic synthesis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, logic synthesis is a process by which an abstract specification of desired circuit behavior, typically at register transfer level (RTL), is turned into a design implementation in terms of logic gates, typically by a computer program called a synthesis tool. Common examples of this process include synthesis of designs specified in hardware description languages, including VHDL and Verilog. Some synthesis tools generate bitstreams for programmable logic devices such as PALs or FPGAs, while others target the creation of ASICs. Logic synthesis is one aspect of electronic design automation.

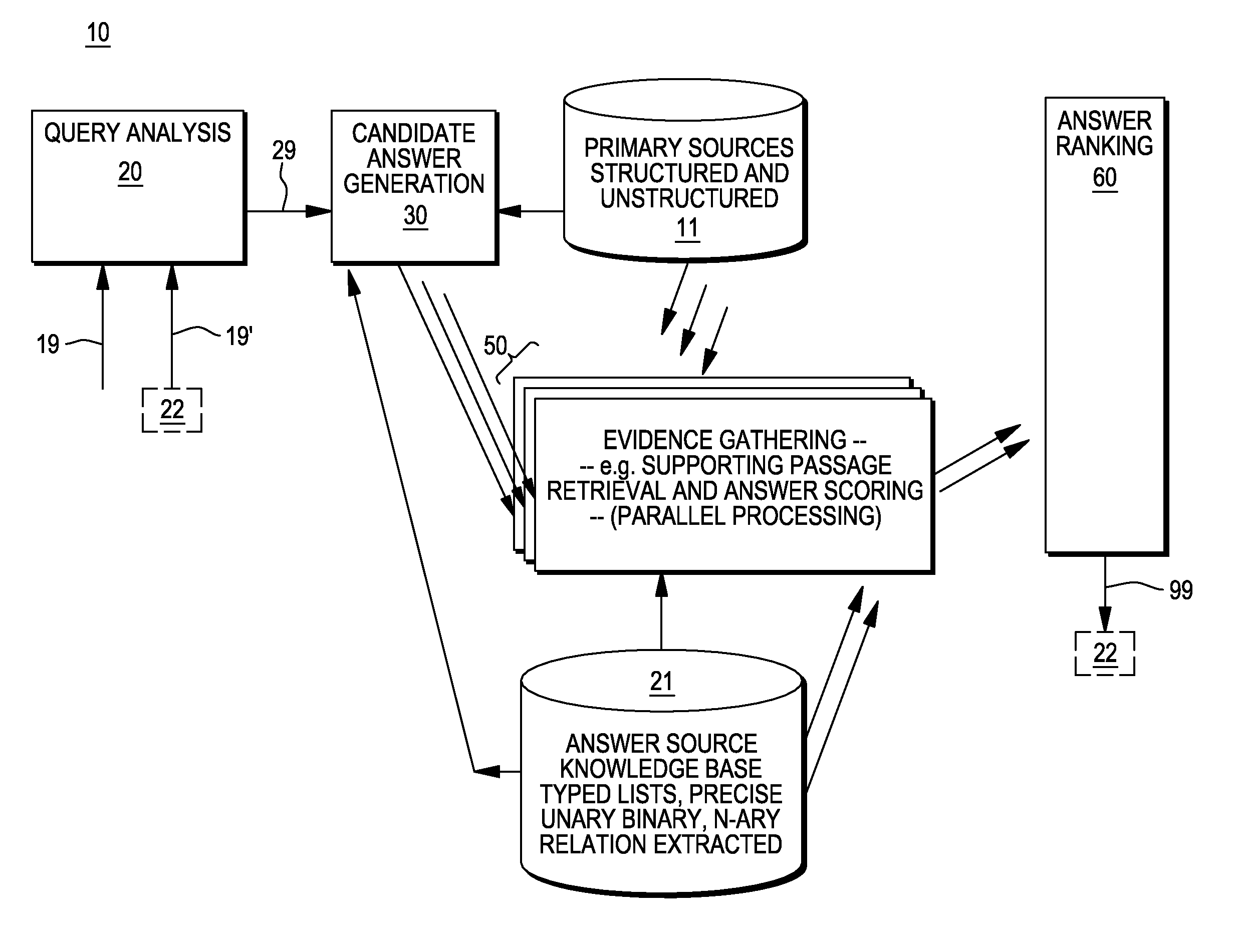

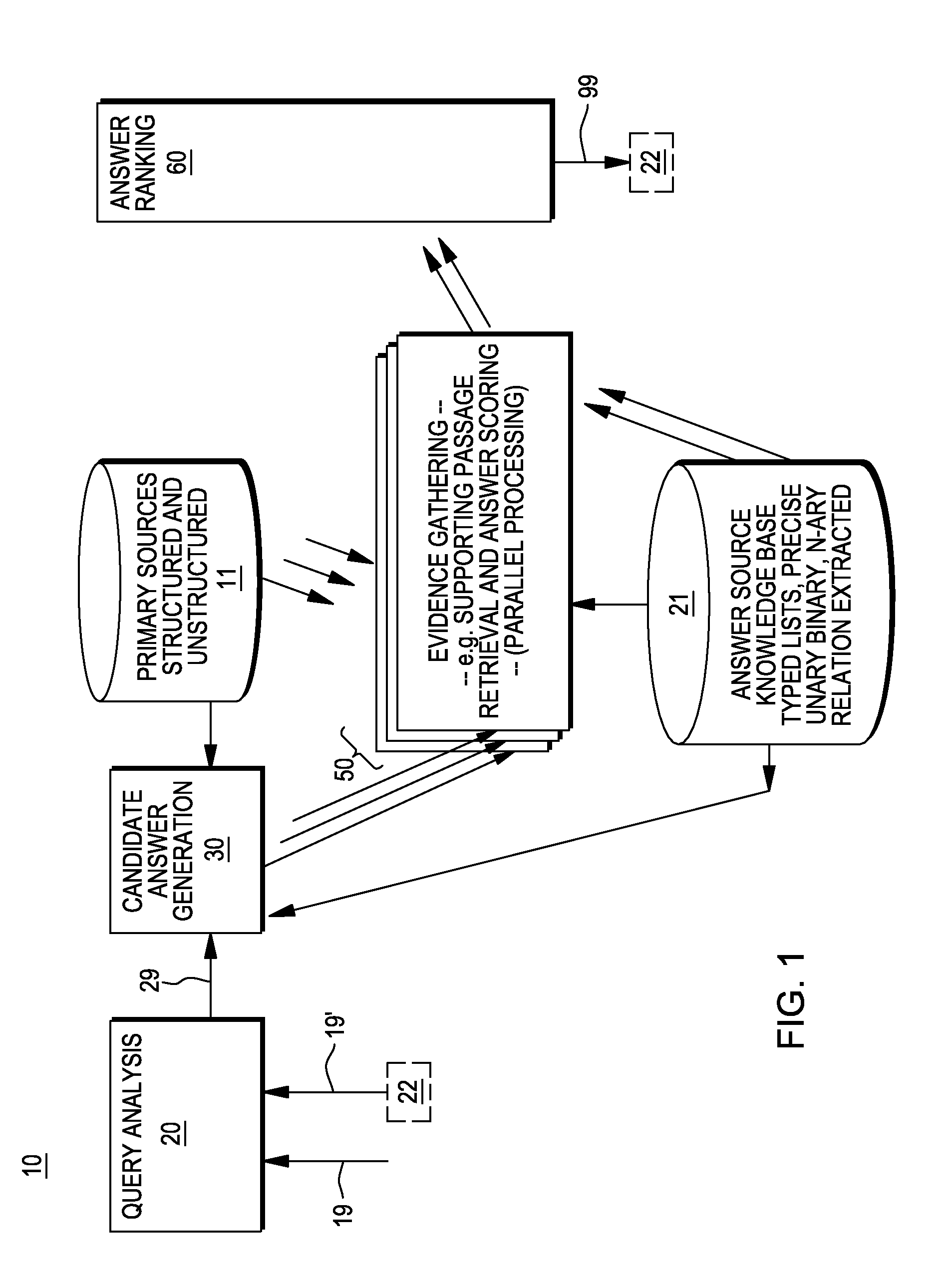

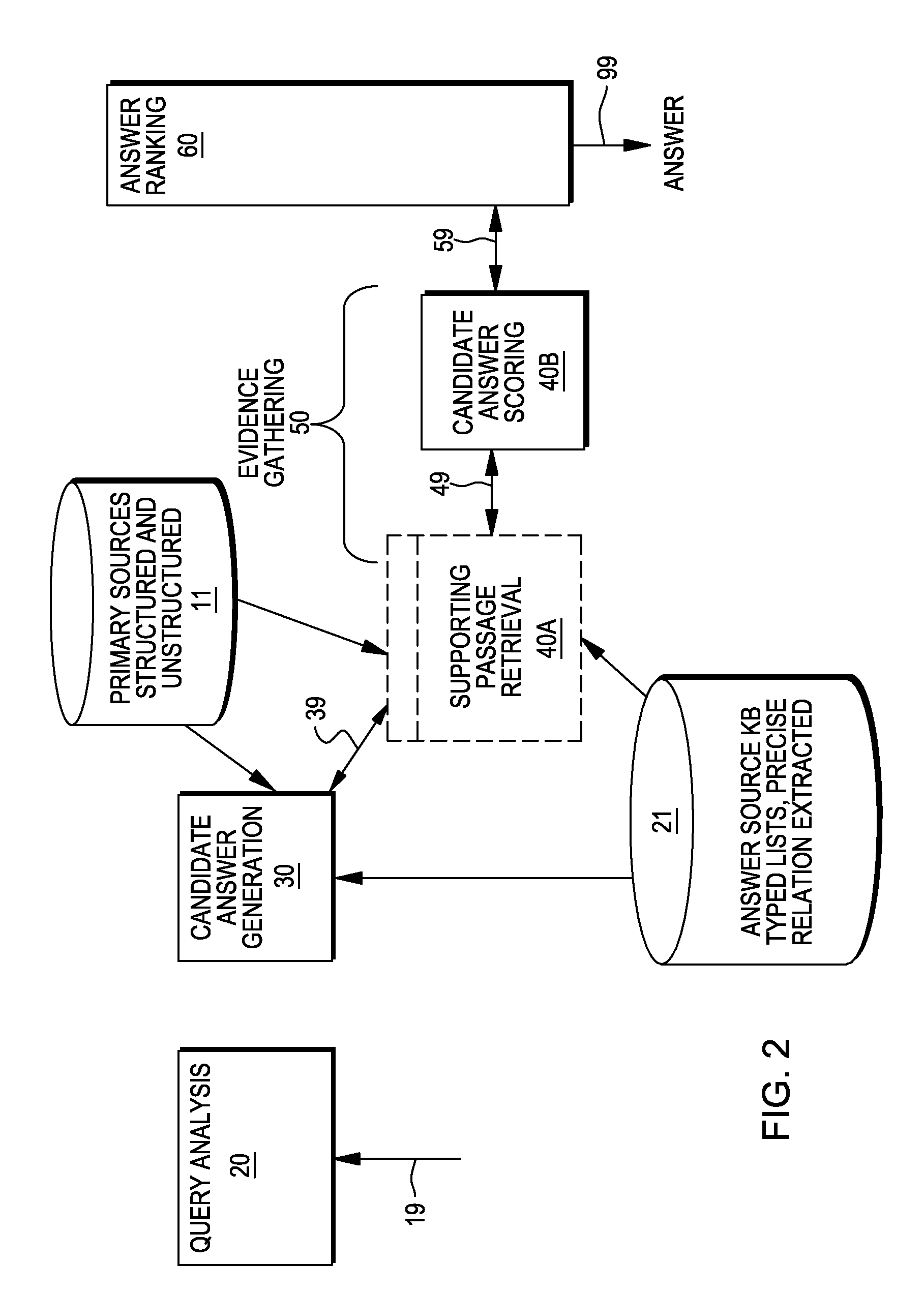

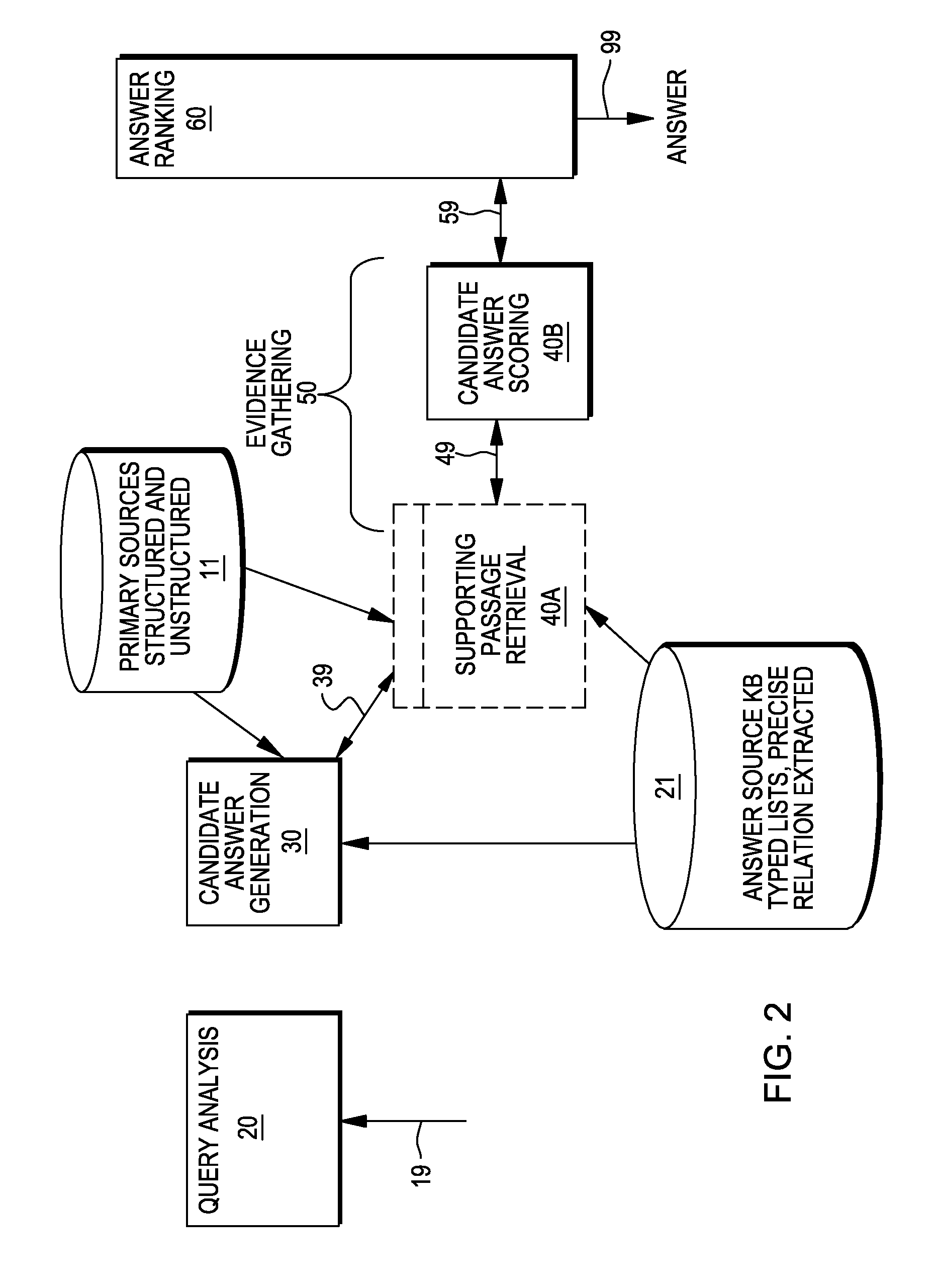

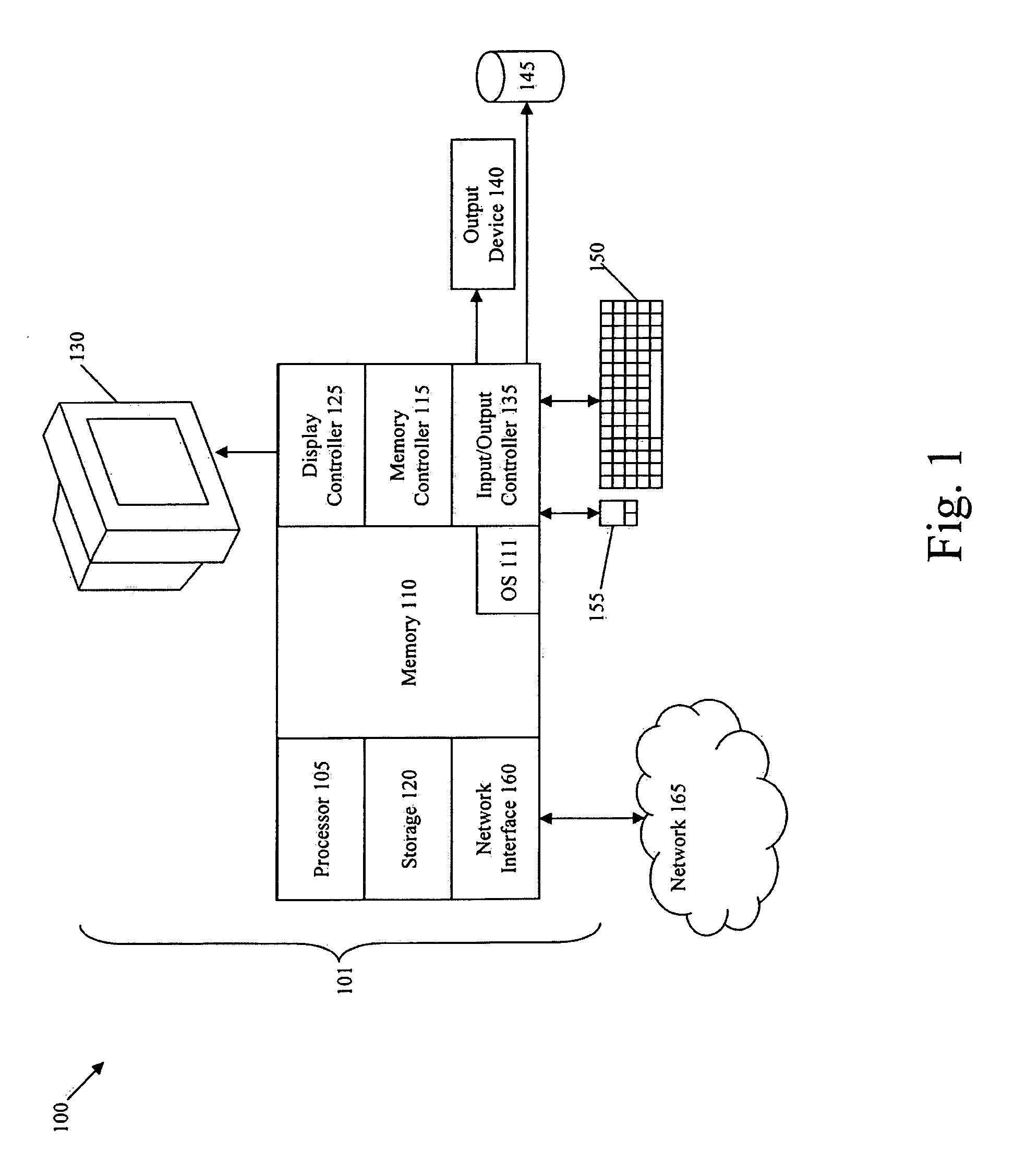

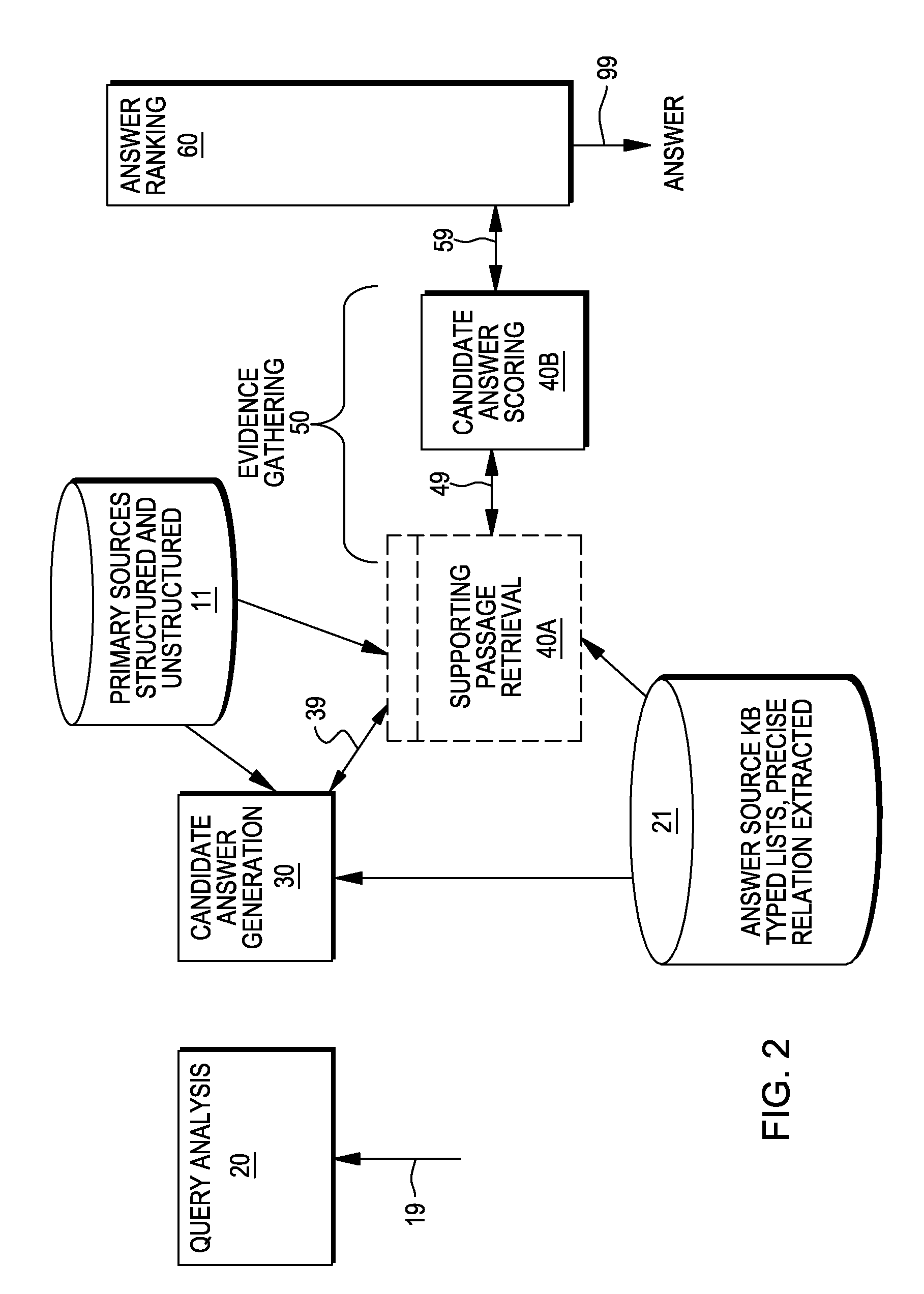

Providing answers to questions using logical synthesis of candidate answers

A method, system and computer program product for generating answers to questions. In one embodiment, the method comprises receiving an input query, decomposing the input query into a plurality of different subqueries, and conducting a search in one or more data sources to identify at least one candidate answer to each of the subqueries. A ranking function is applied to each of the candidate answers to determine a ranking for each of these candidate answers; and for each of the subqueries, one of the candidate answers to the subquery is selected based on this ranking. A logical synthesis component is applied to synthesize a candidate answer for the input query from the selected the candidate answers to the subqueries. In one embodiment, the procedure applied by the logical synthesis component to synthesize the candidate answer for the input query is determined from the input query.

Owner:IBM CORP

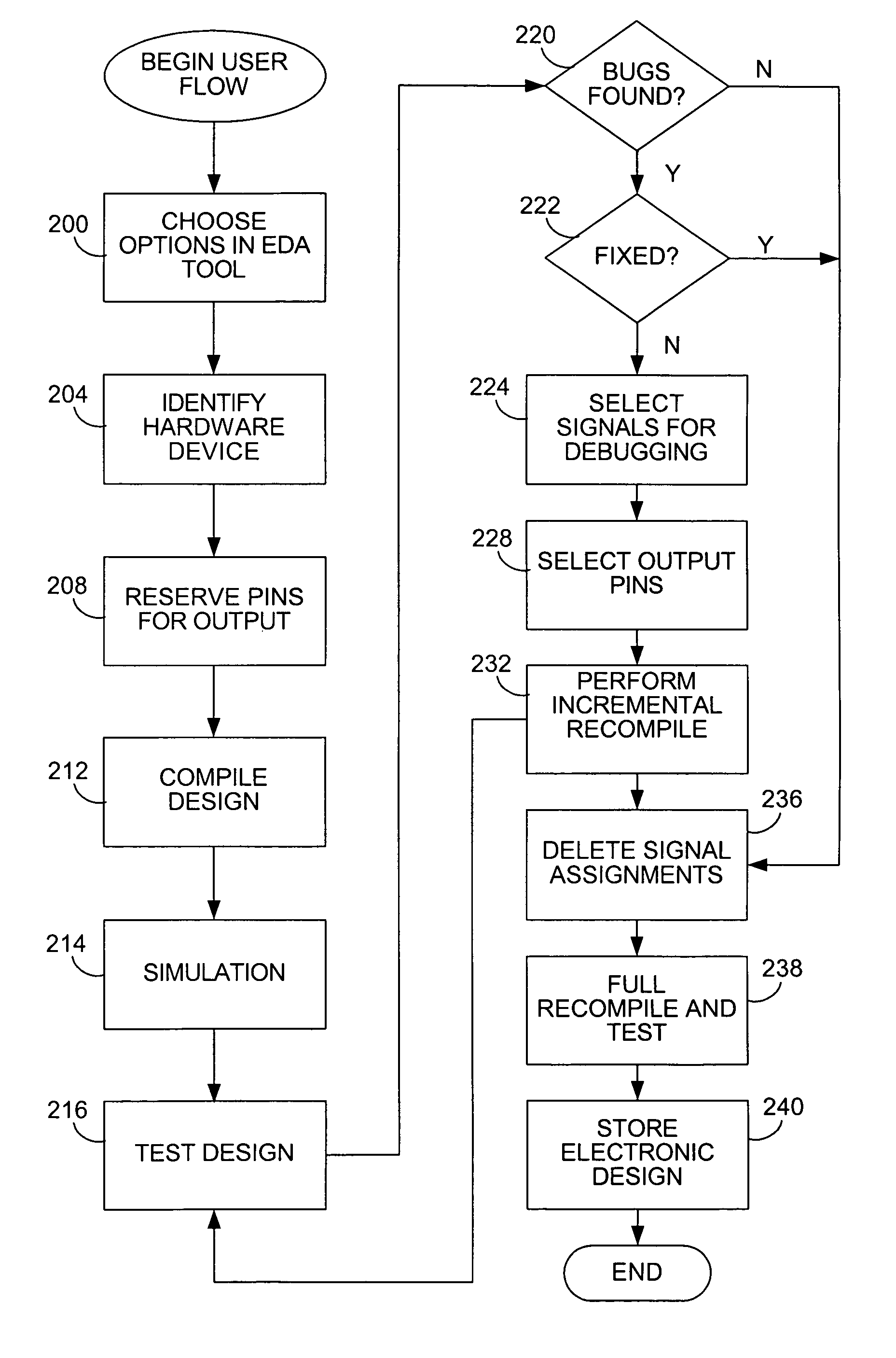

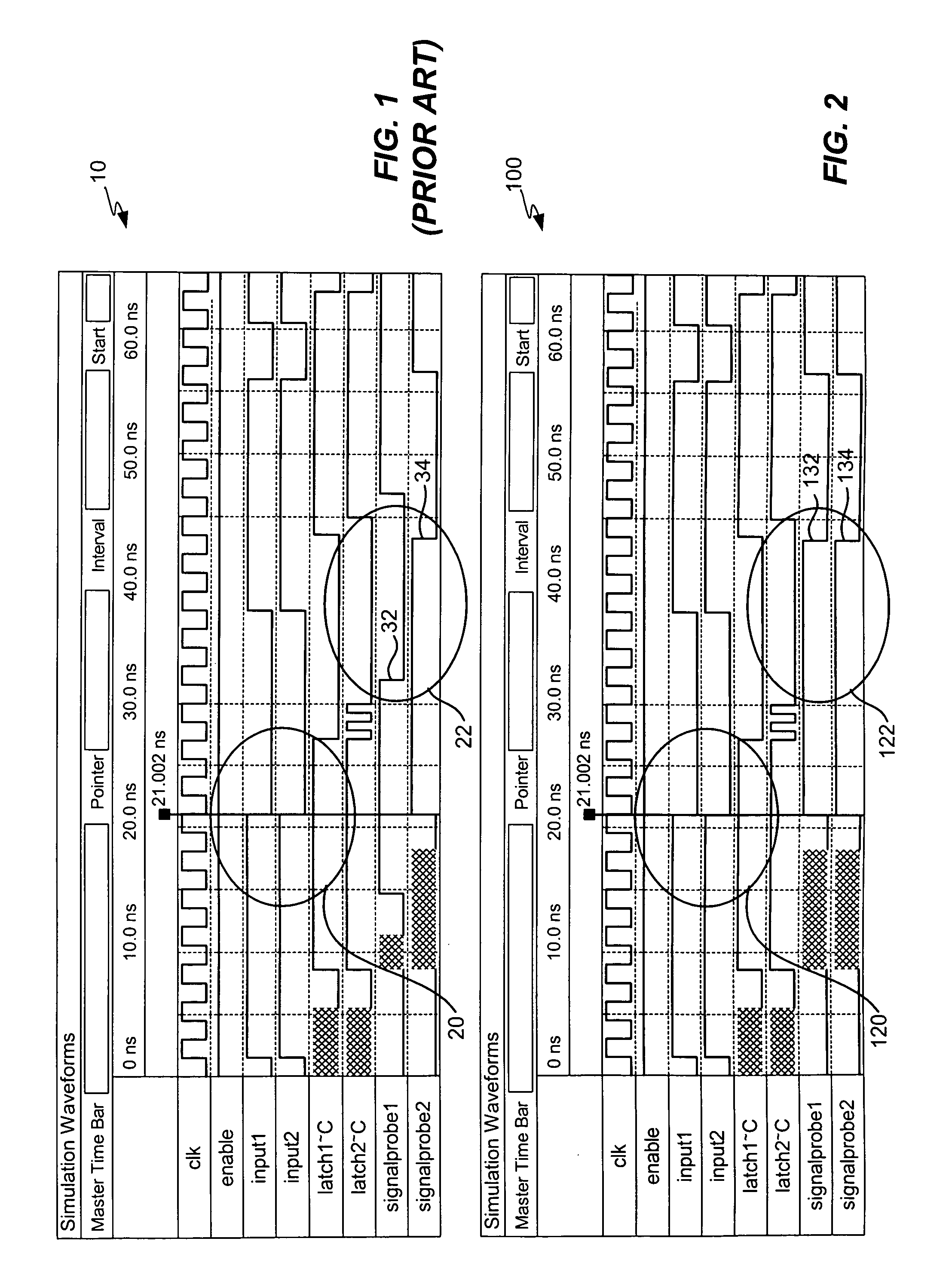

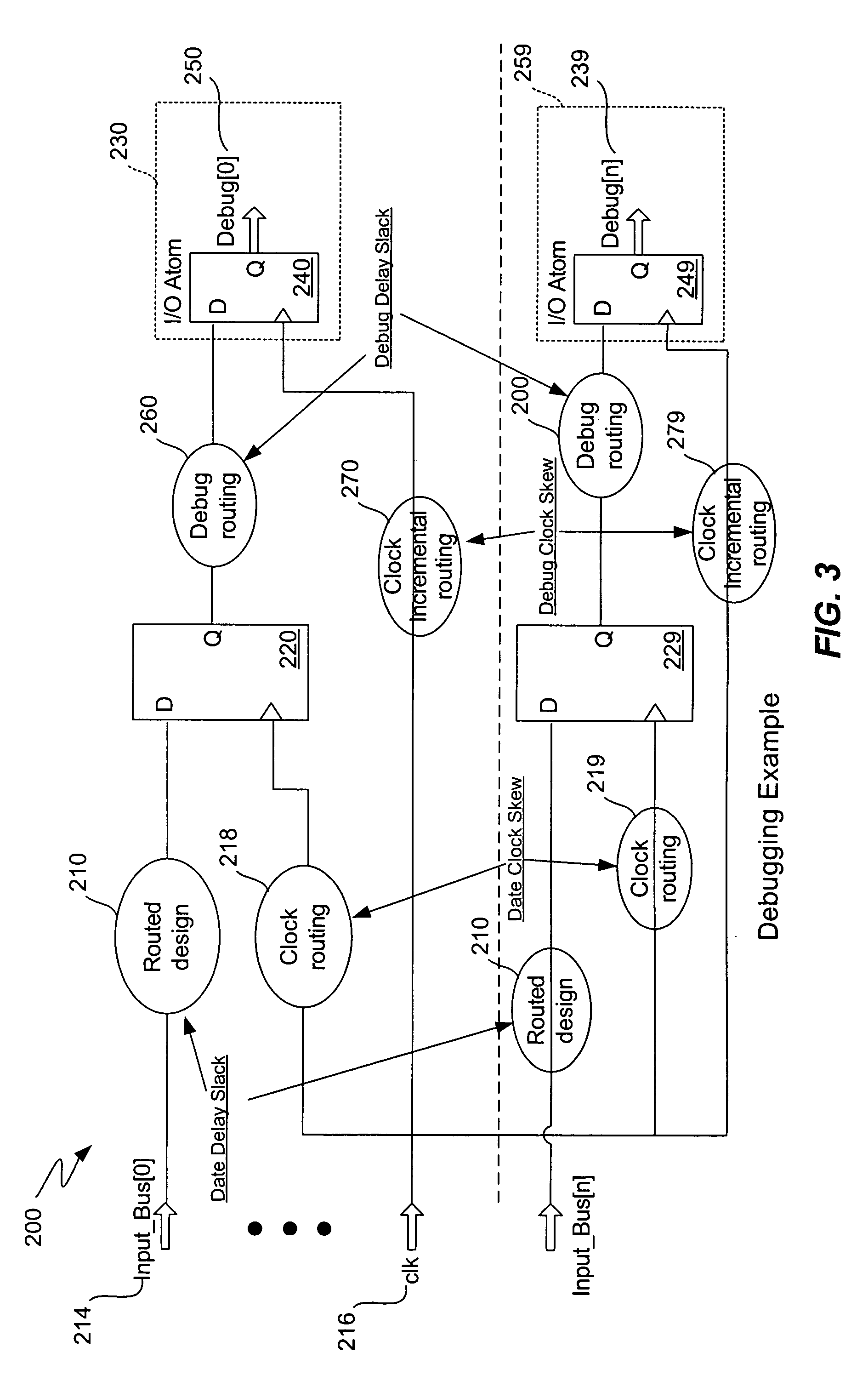

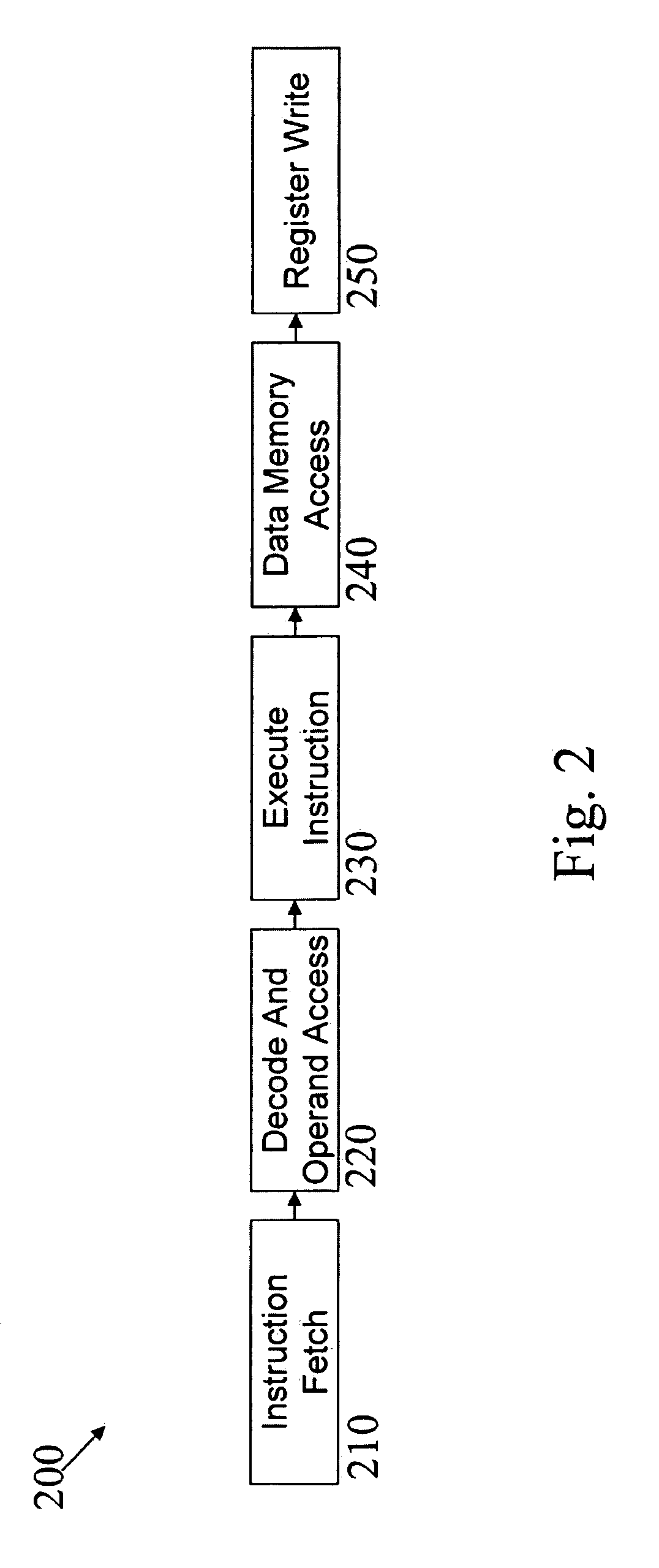

Chip debugging using incremental recompilation and register insertion

InactiveUS7206967B1Efficient solutionError detection/correctionElectrical testingComputer architectureProcessor register

While debugging, a user chooses an incremental recompile. Internal signals of interest and output pins are selected, and a number of additional registers are chosen to insert in the path of each internal signal. A clock is selected for the registers. An incremental recompile of the compiled design compiles a routing from each internal signal to an output pin via the added registers. The database building and logic synthesis stages are skipped. The post-fitting logical netlist and routing netlist are retrieved. The new registers are created and the internal signal is connected to the output pin atom in the logical netlist. The fitter places and routes the connections to create a new routing netlist and then the new routing netlist is output into a programming output file (POF) in a form suitable for programming the PLD. The original routing netlist is undisturbed. The user views the internal signals at the output pins chosen. The user may iterate through this process many times in order to debug the PLD. The debugging assignments may be deleted.

Owner:ALTERA CORP

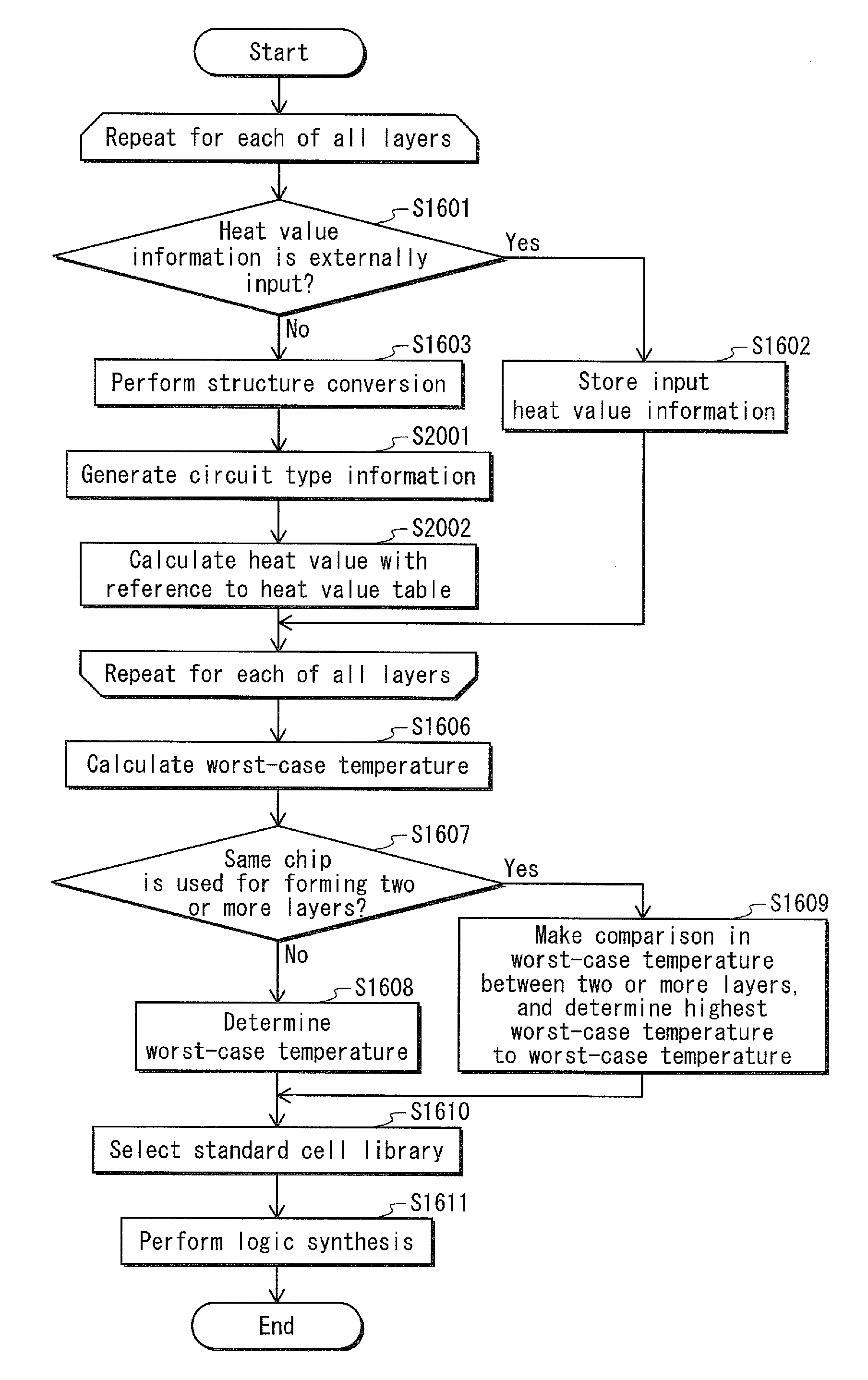

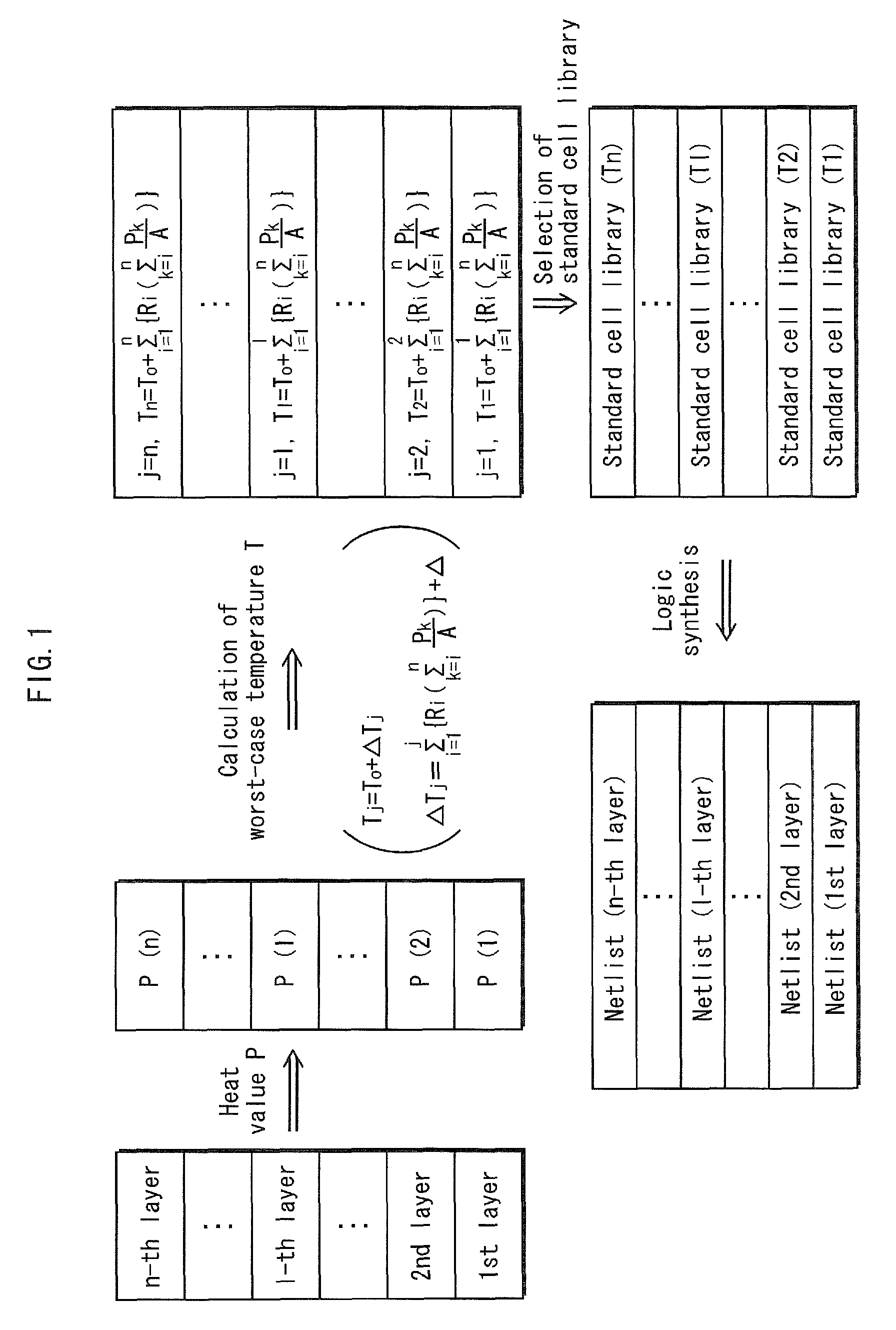

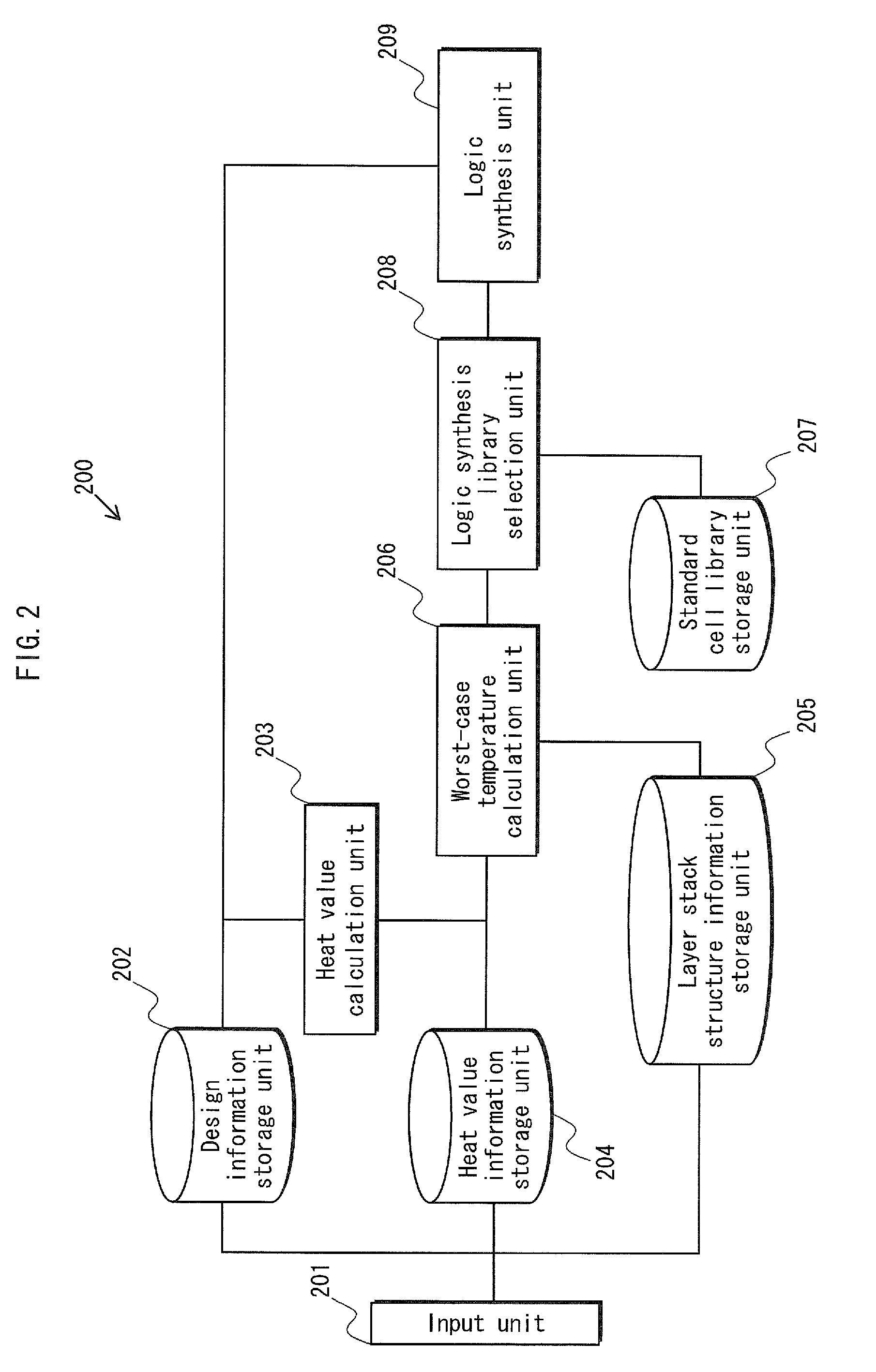

Three-dimensional integrated circuit design device, three-dimensional integrated circuit design, method, and program

InactiveUS8566762B2Increase the areaReduce power consumptionSolid-state devicesComputer aided designEngineeringThree-dimensional integrated circuit

A worst-case temperature calculation unit calculates, based on heat value information of each layer of a three-dimensional integrated circuit to be designed and stack structure information of the three-dimensional integrated circuit, a worst-case temperature of a layer during operation that is targeted for logic synthesis. A logic synthesis library selection unit selects a library appropriate for the calculated worst-case temperature. A logic synthesis unit performs logic synthesis on the targeted layer with use of the selected library.

Owner:PANASONIC CORP

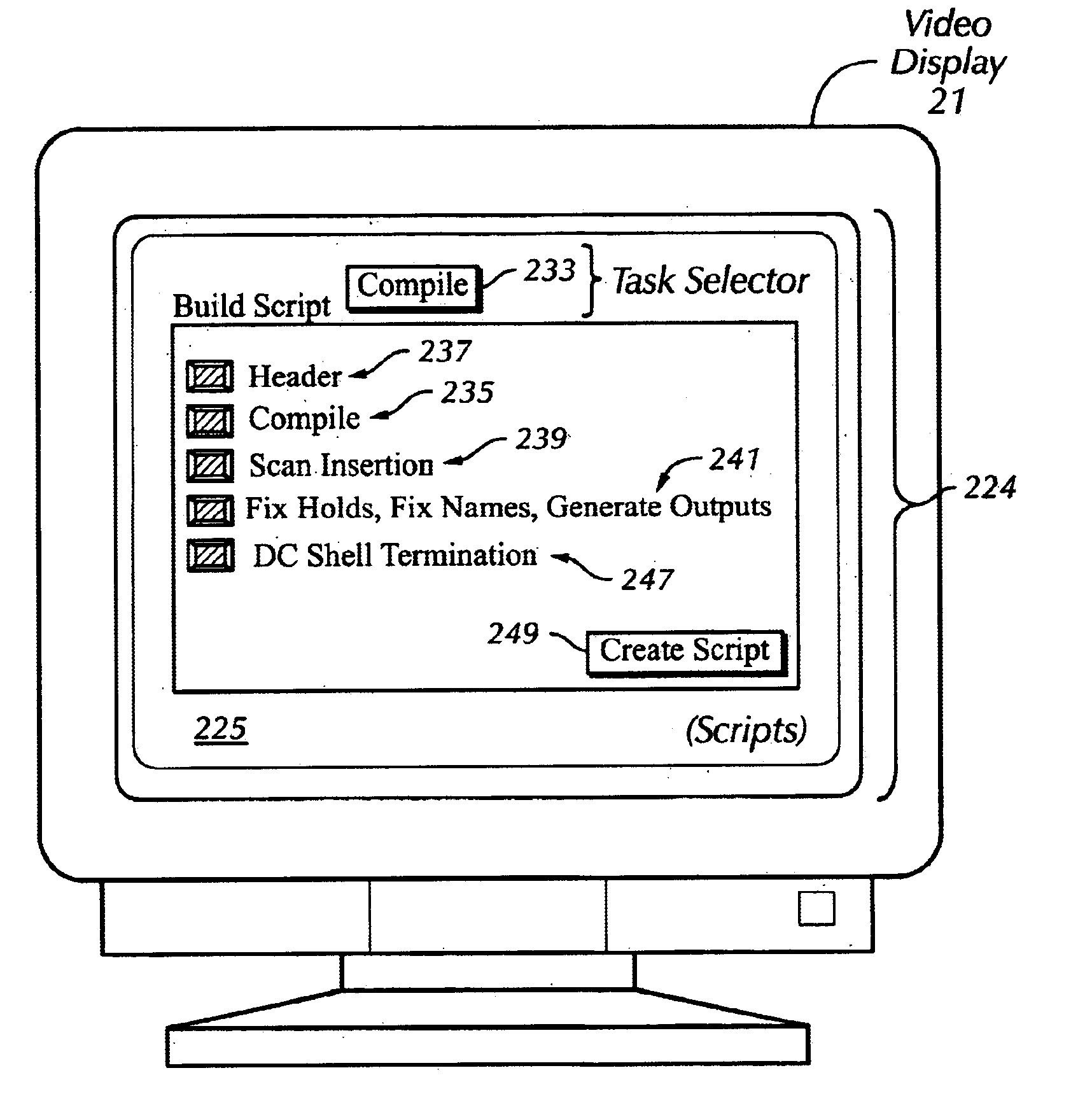

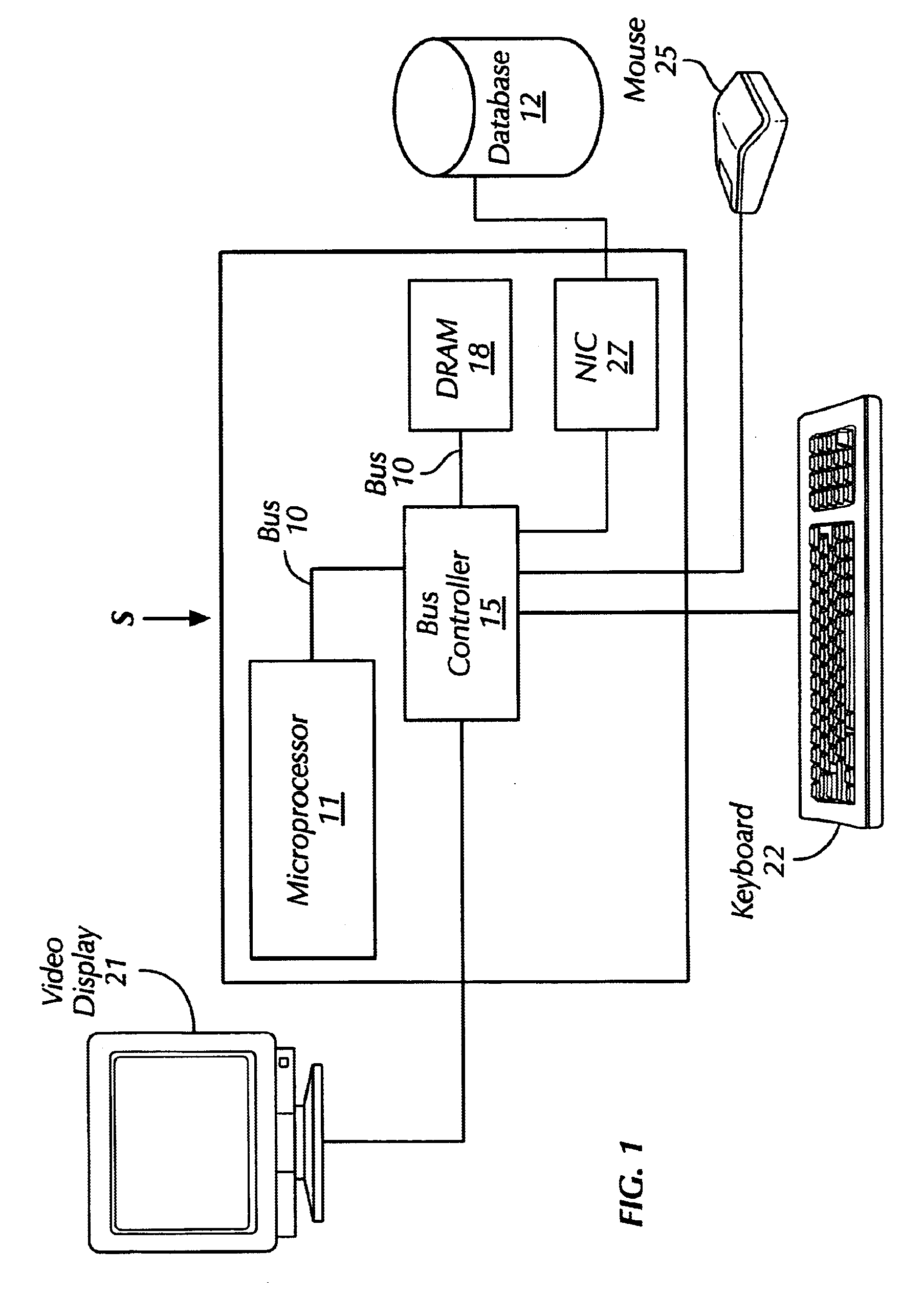

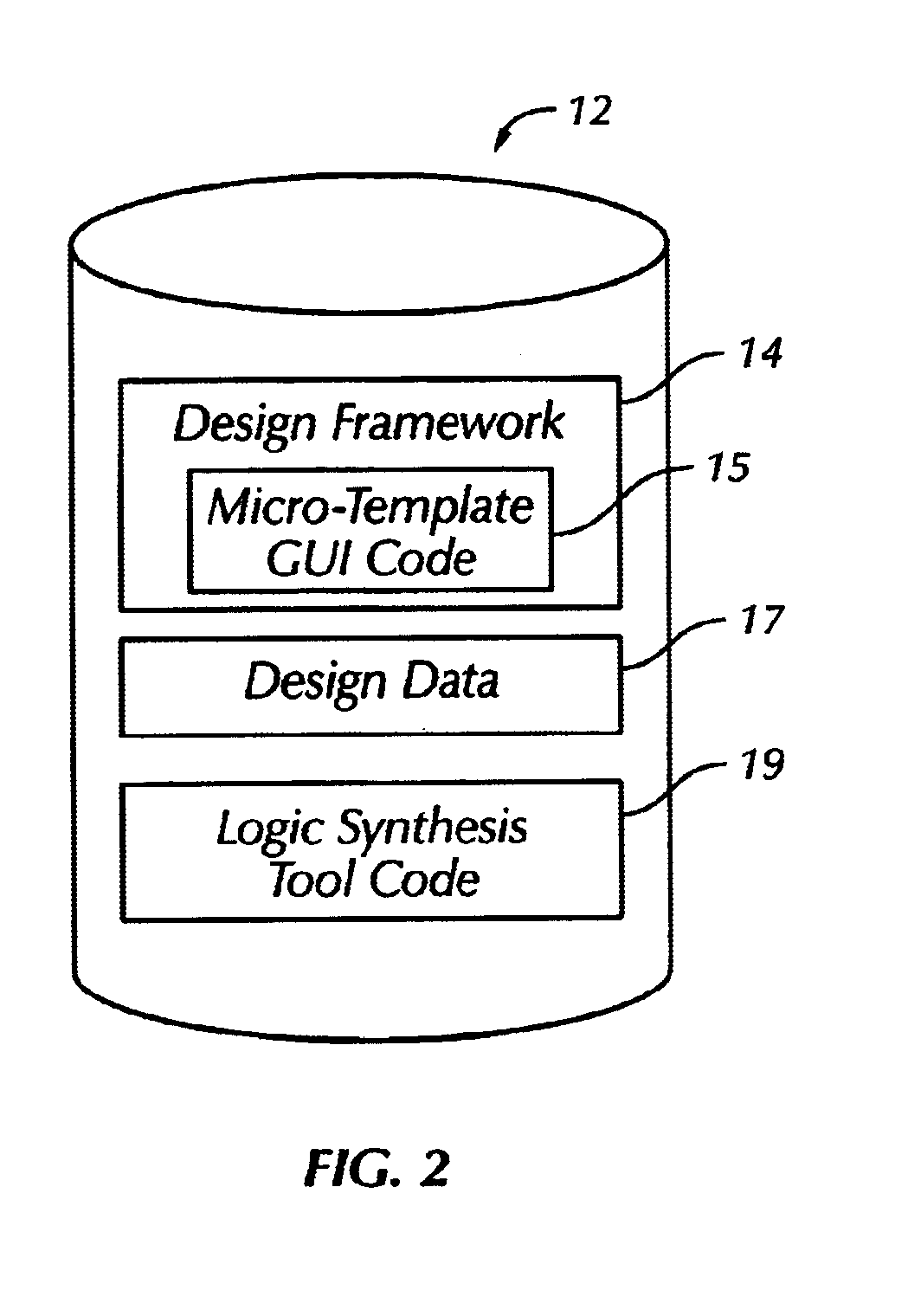

Methodology and graphical user interface for building logic synthesis command scripts using micro-templates

InactiveUS6697880B1Shorten the compositing timeSoftware engineeringSpecific program execution arrangementsGraphicsGraphical user interface

A template for a logic synthesis command script is broken into smaller and functionally independent templates termed "micro-templates." Using micro-templates, logic synthesis time may be significantly reduced. Each micro-template may correspond to a particular synthesis operation and may be enabled or disabled. Where synthesis of a particular set of synthesis operations is desired, the micro-templates corresponding to those synthesis operations are enabled.

Owner:GLOBALFOUNDRIES INC

Multiple-valued logic circuit architecture; supplementary symmetrical logic circuit structure (SUS-LOC)

InactiveUS6133754AEasy to copyEasy transferPower consumption reductionLogic circuits characterised by logic functionMany-valued logicLogic synthesis

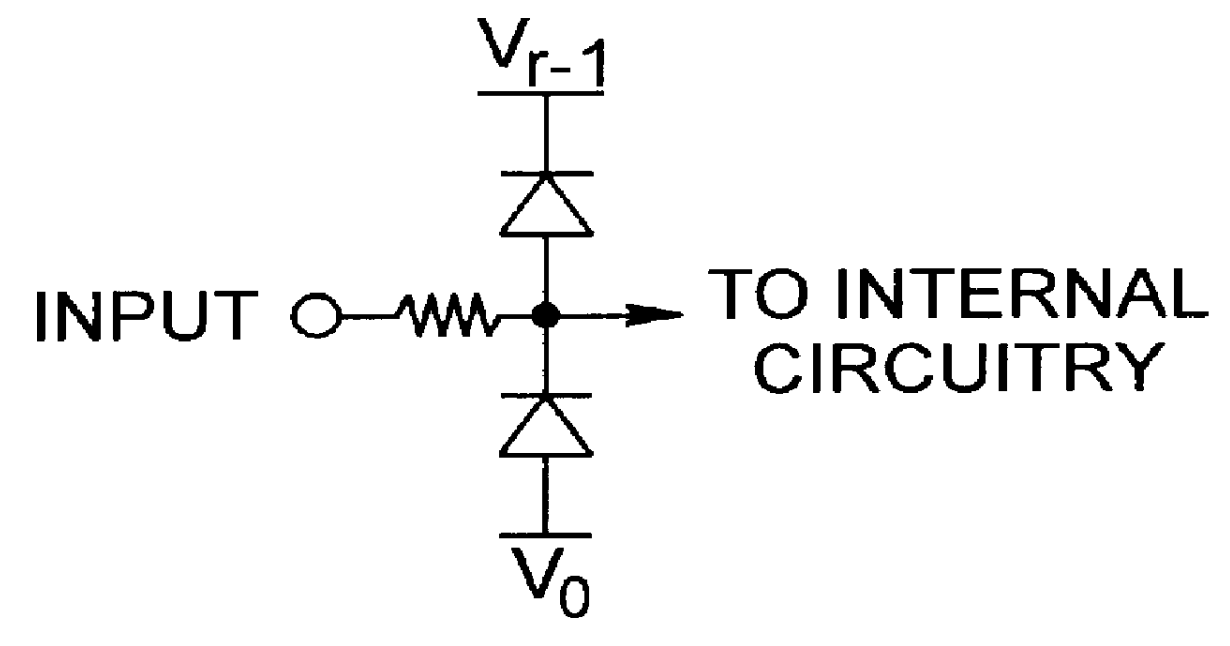

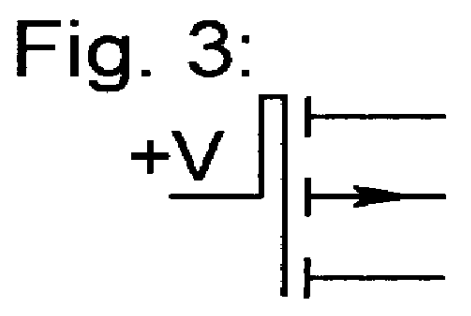

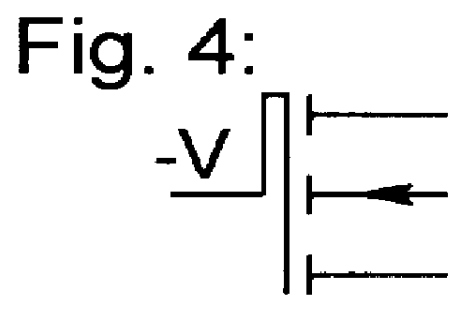

Circuit structure and resulting circuitry for multiple-valued logic. The circuit structure allows the design and fabrication of any r-valued logic function of n-places where r is an integer greater than 1 and n is an integer greater than 0. This structure is called SUpplementary Symmetrical LOgic Circuit structure (SUS-LOC). In circuits incorporating SUS-LOC, circuit branches are realized that uniquely deliver circuit response and output. For some circuits, and due to the operating characteristics of the switch elements, additional circuit elements, or stages, must be incorporated to prevent "back biasing." SUS-LOC is fully active. Only active elements perform logic synthesis and those components not directly related to logic synthesis, such as resistors and / or other passive loads, are relegated the task of circuit protection. The fabrication of r-valued, multi-valued, or multiple-valued logic circuits, designed using the definitions of the SUS-LOC structure can be accomplished with known techniques, materials, and equipment.

Owner:OMNIBASE LOGIC

Linear and non-linear genetic algorithms for solving problems such as optimization, function finding, planning and logic synthesis

InactiveUS20020169563A1Biological testingSpecial data processing applicationsAlgorithmGenetic algorithm

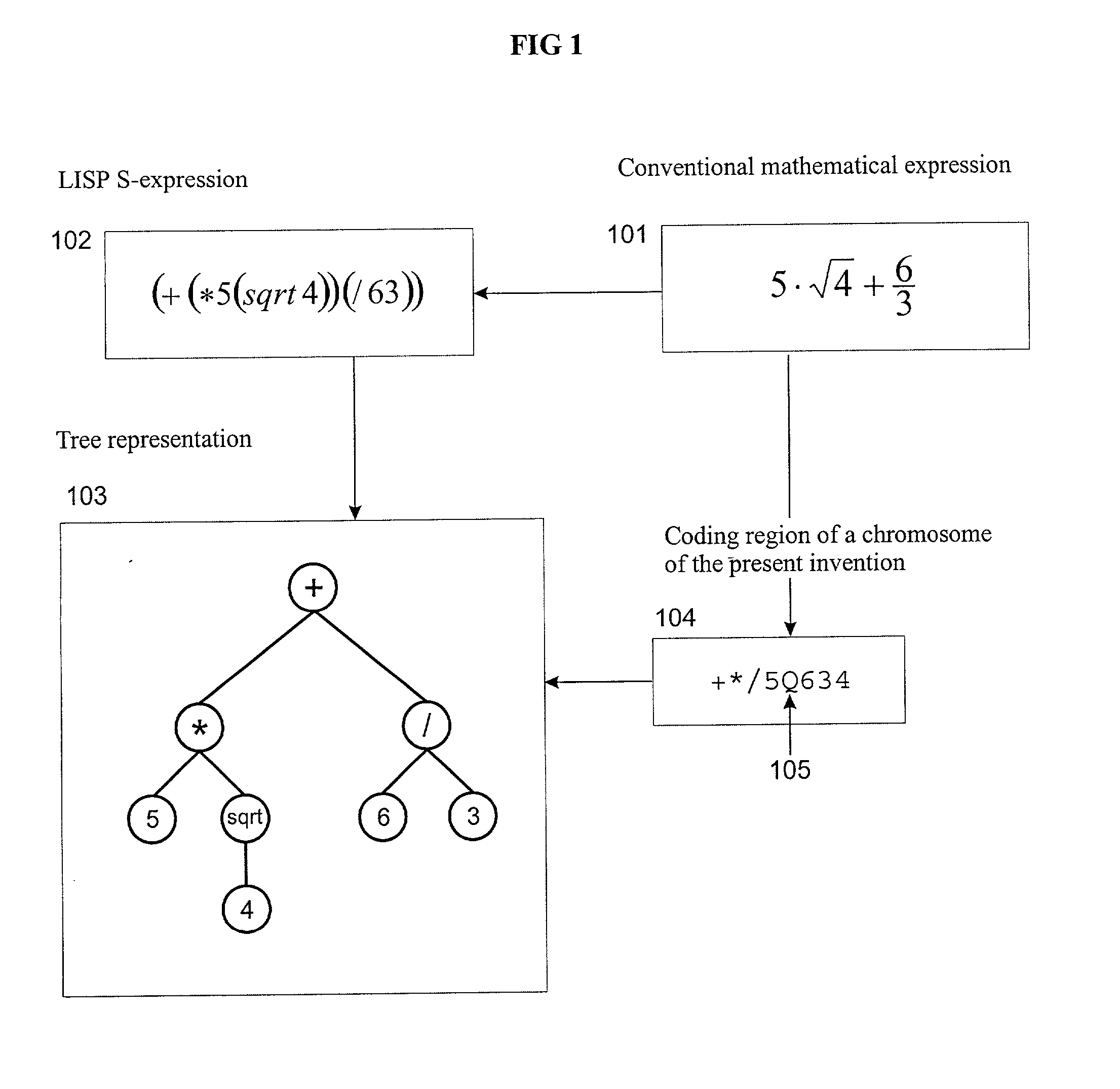

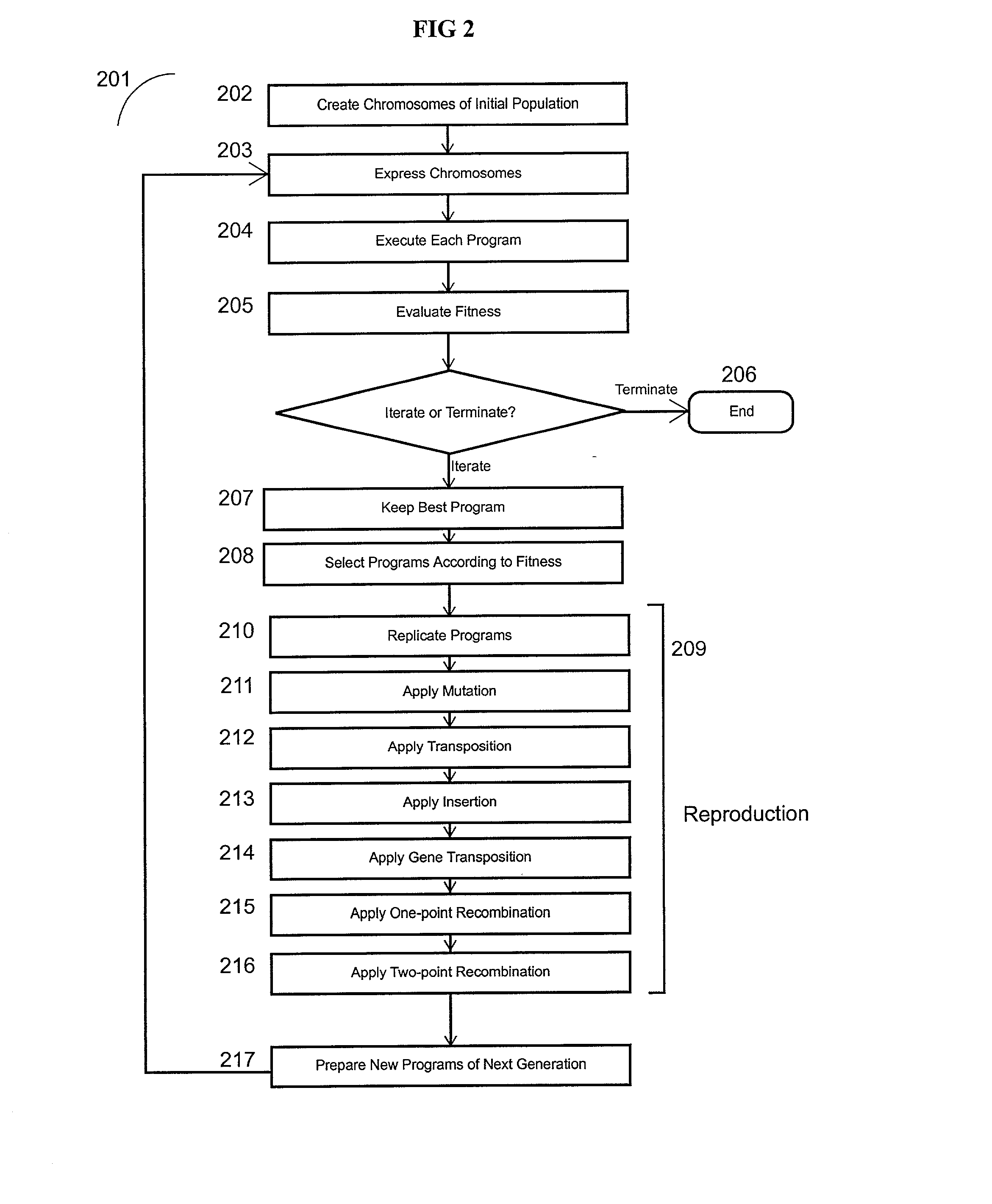

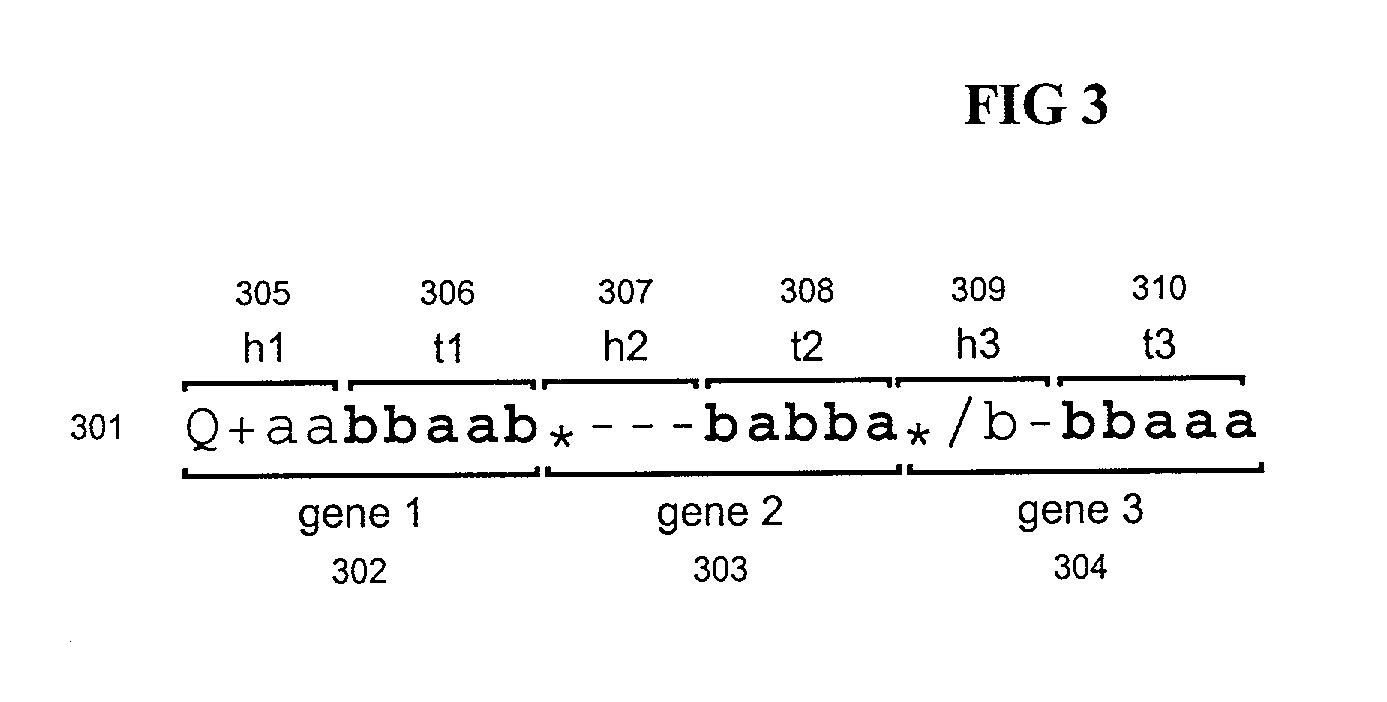

The present invention is a mixed (linear and non-linear) genetic algorithm capable of learning and inventing. An initial population of linear chromosomes (linear entities) composed of genes containing the functions and arguments to a problem, is created and expressed as non-linear entities called expression trees. The non-linear entities are then executed, producing results. Then the results are assigned values and the respective individuals (linear entities and respective non-linear entities) are selected to reproduce according to these values. During reproduction, the linear entity or chromosome is subjected to one or several operators, namely, mutation, one-point recombination, two-point recombination, transposition, insertion and gene transposition. This way, new individuals are created which are in their turn executed, initializing a new cycle which is repeated as many times as necessary to discover a solution to the problem.

Owner:DE CARVALHO FERREIRA MARIA CANDIDA

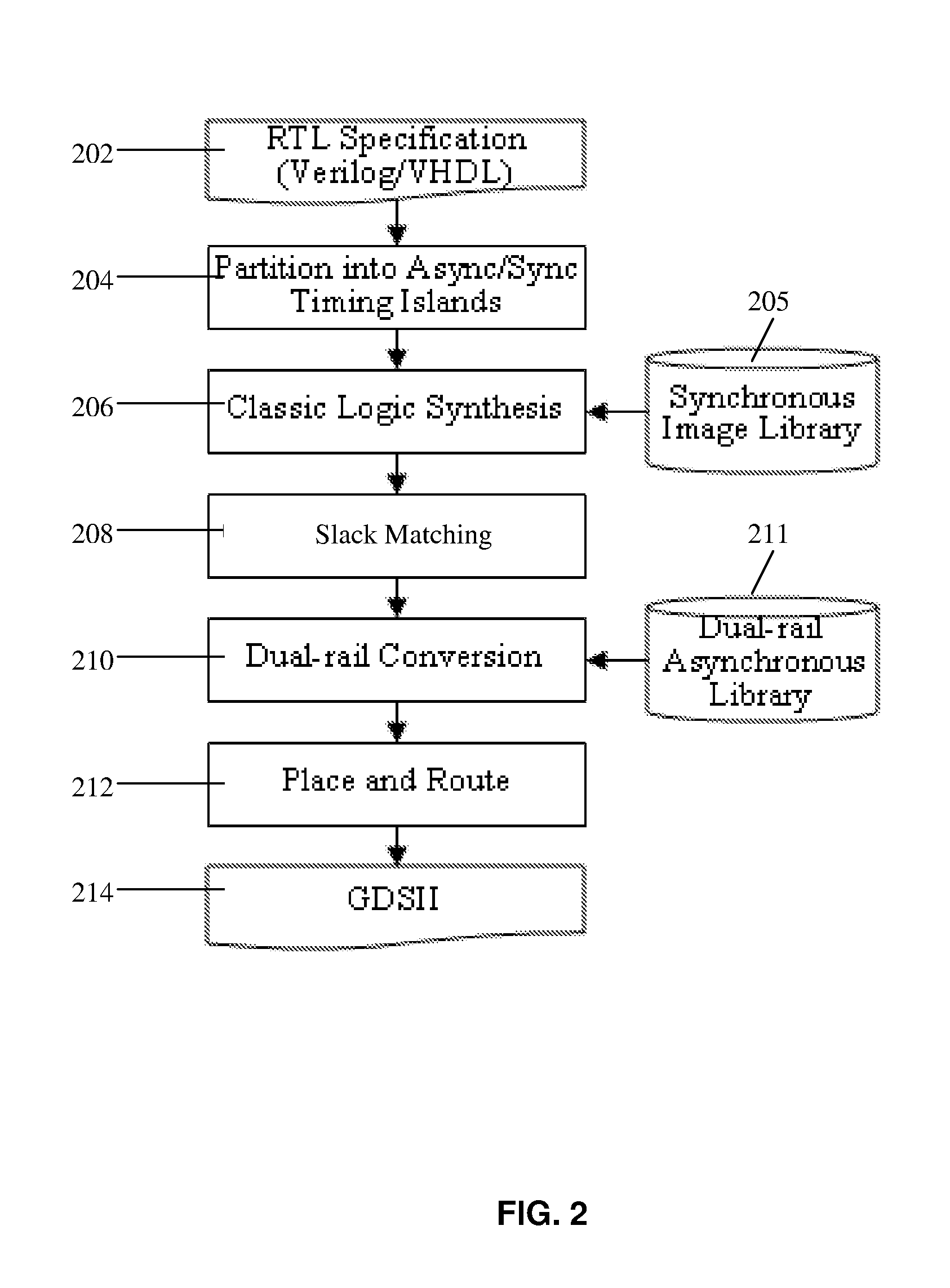

Logic synthesis of multi-level domino asynchronous pipelines

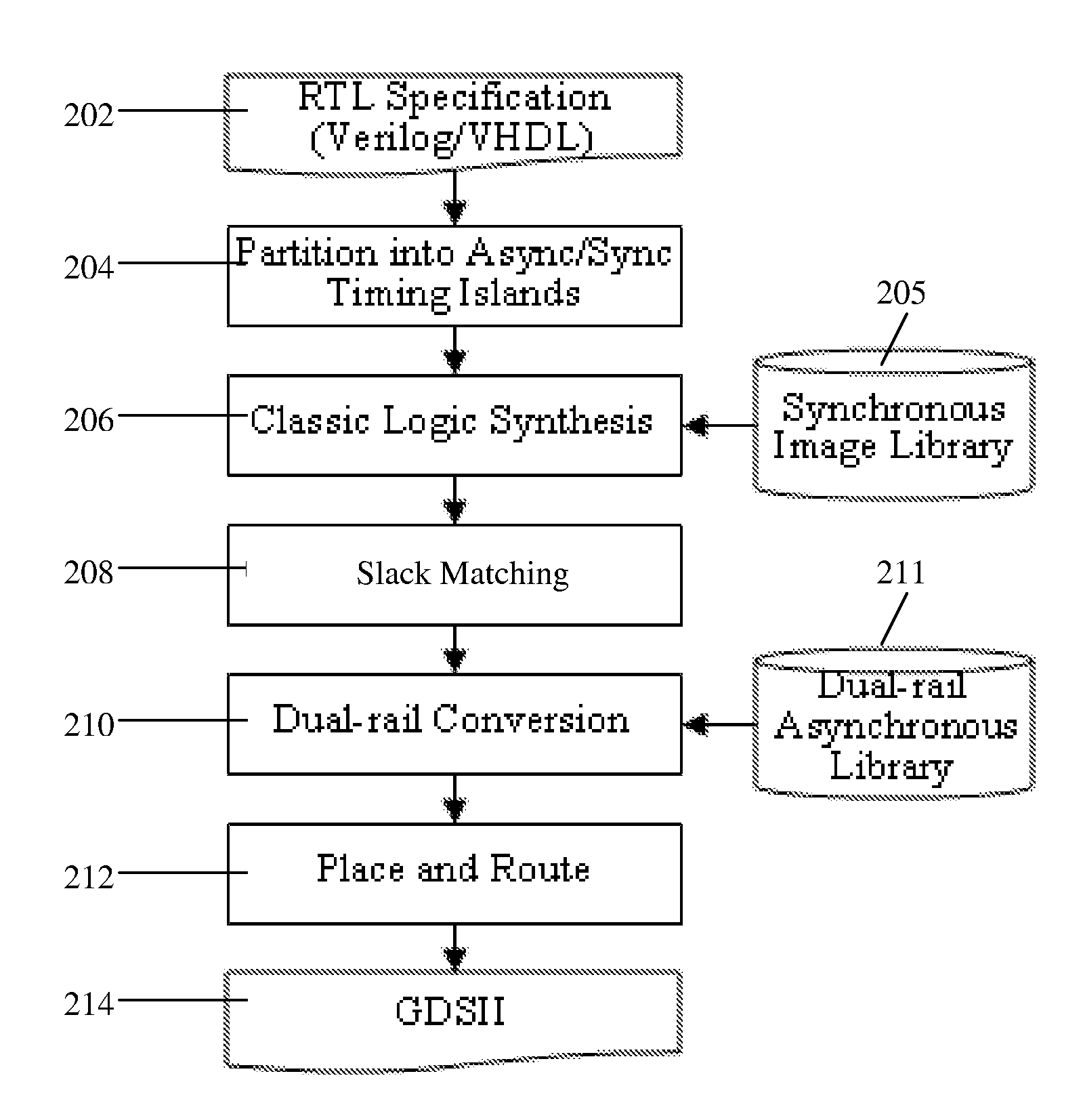

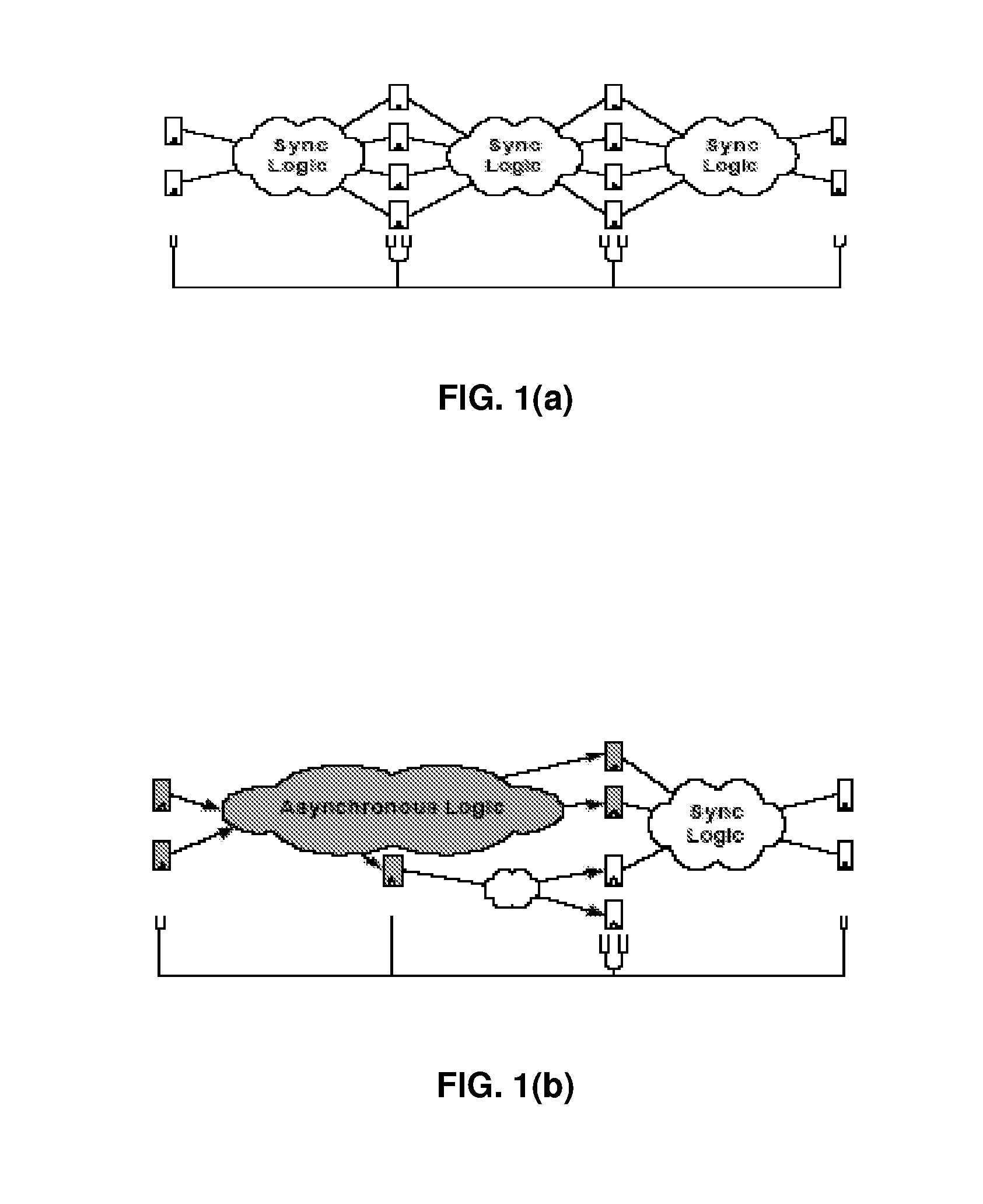

InactiveUS20090217232A1Reduce overheadNo impact on the level of performanceCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceLogic synthesis

Owner:INTEL CORP

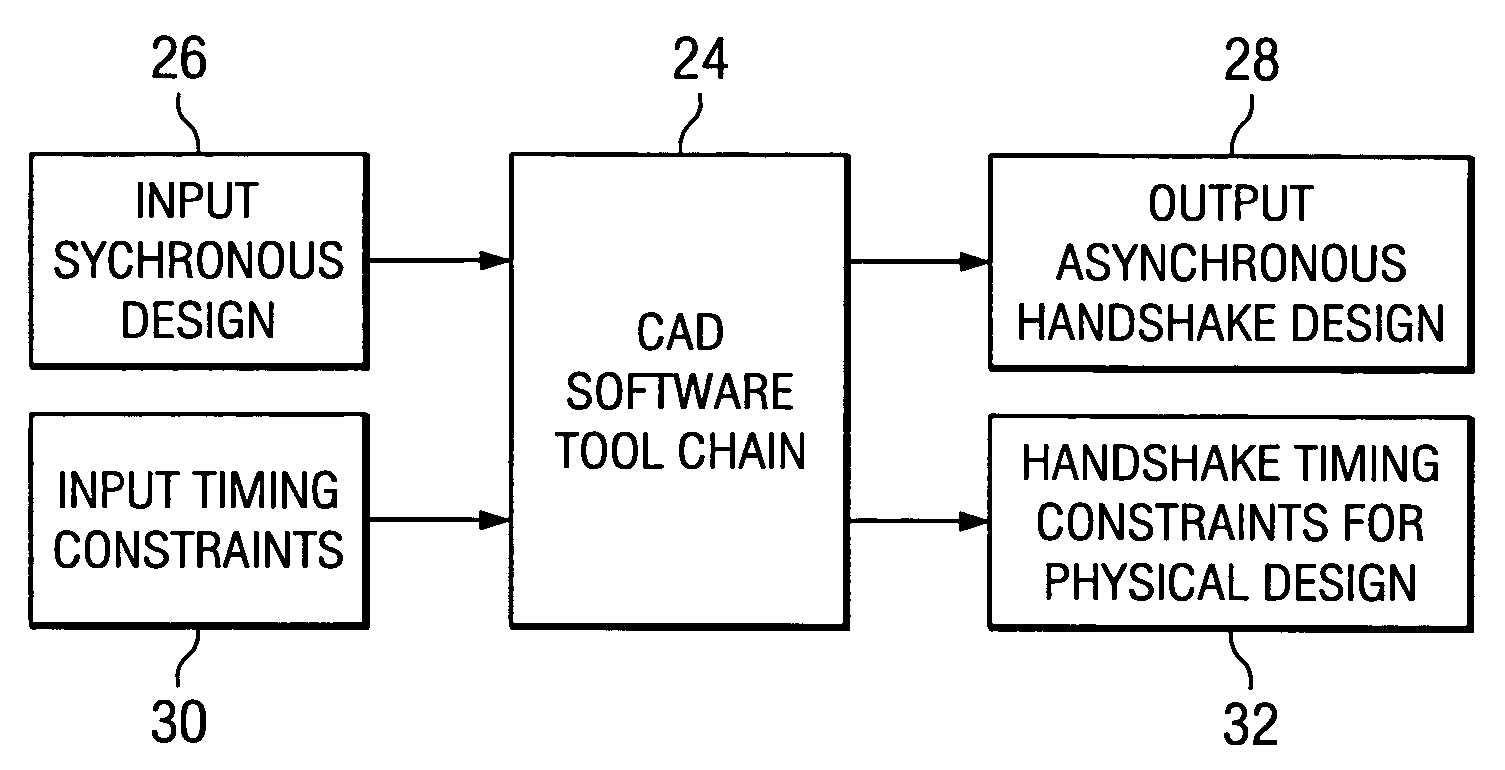

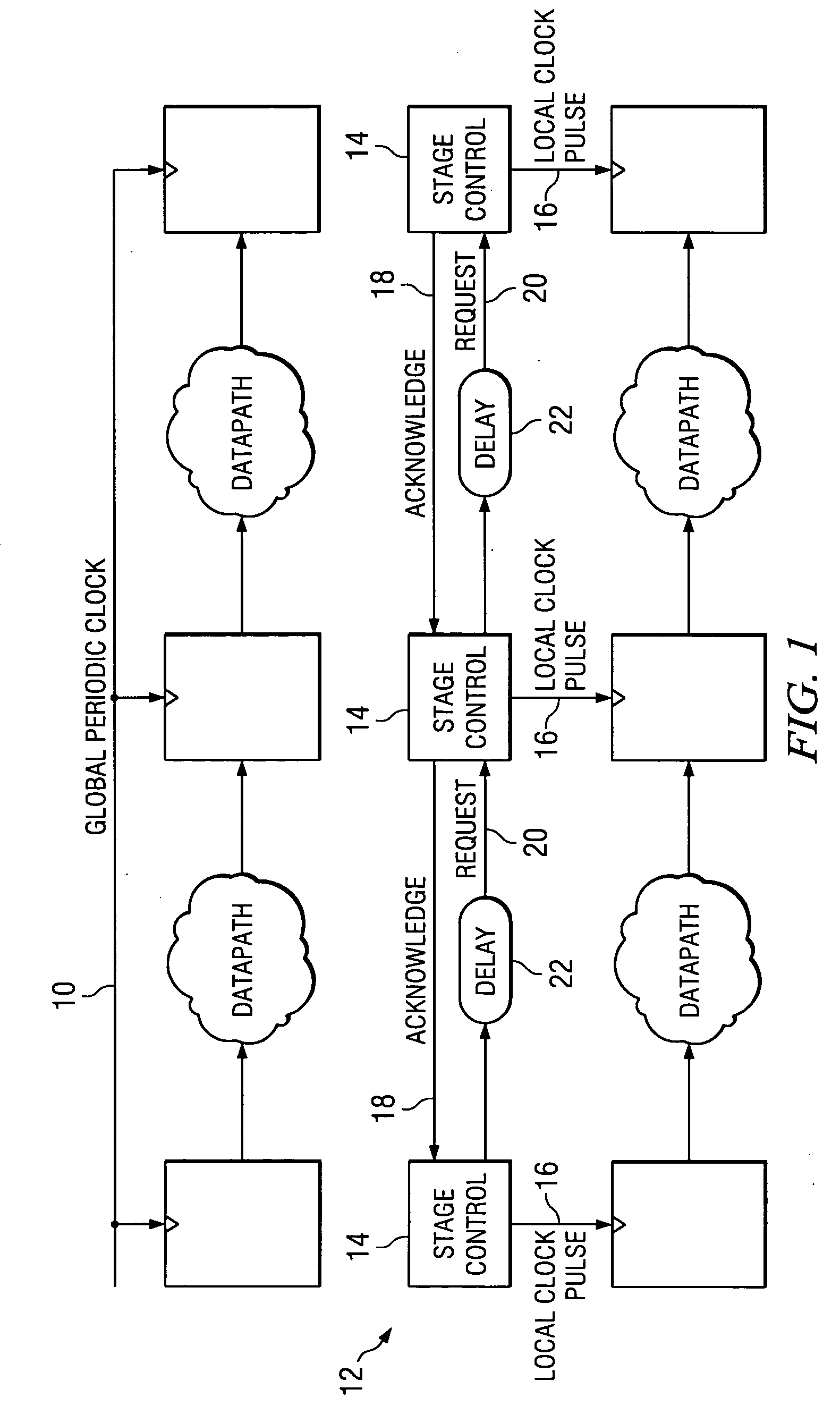

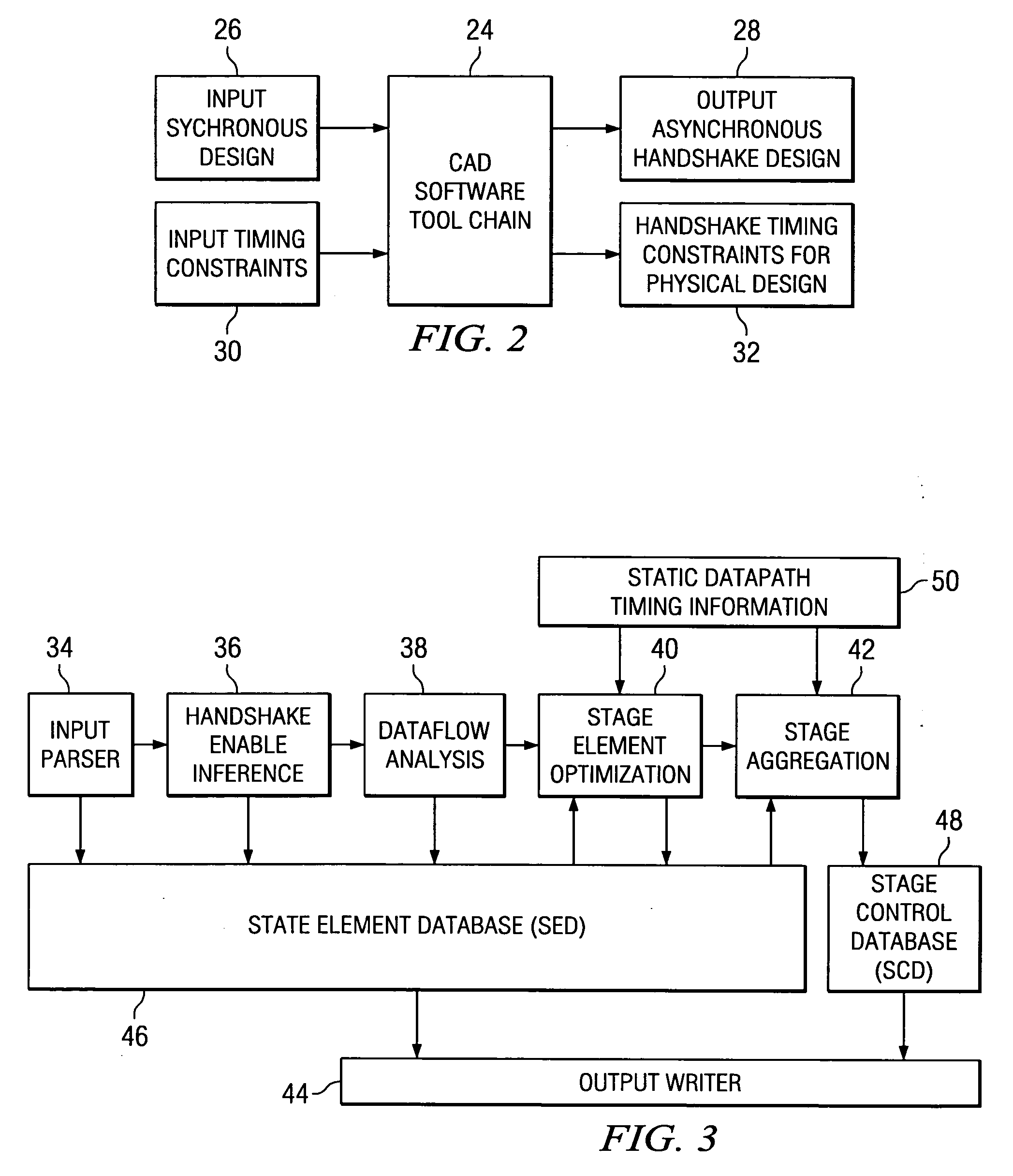

System & method for asynchronous logic synthesis from high-level synchronous descriptions

ActiveUS20050160392A1CAD circuit designSoftware simulation/interpretation/emulationHandshake circuitsLogic synthesis

A method for generating an equivalent asynchronous handshake circuit from a synchronous description of its intended behavior.

Owner:TEXAS INSTR INC

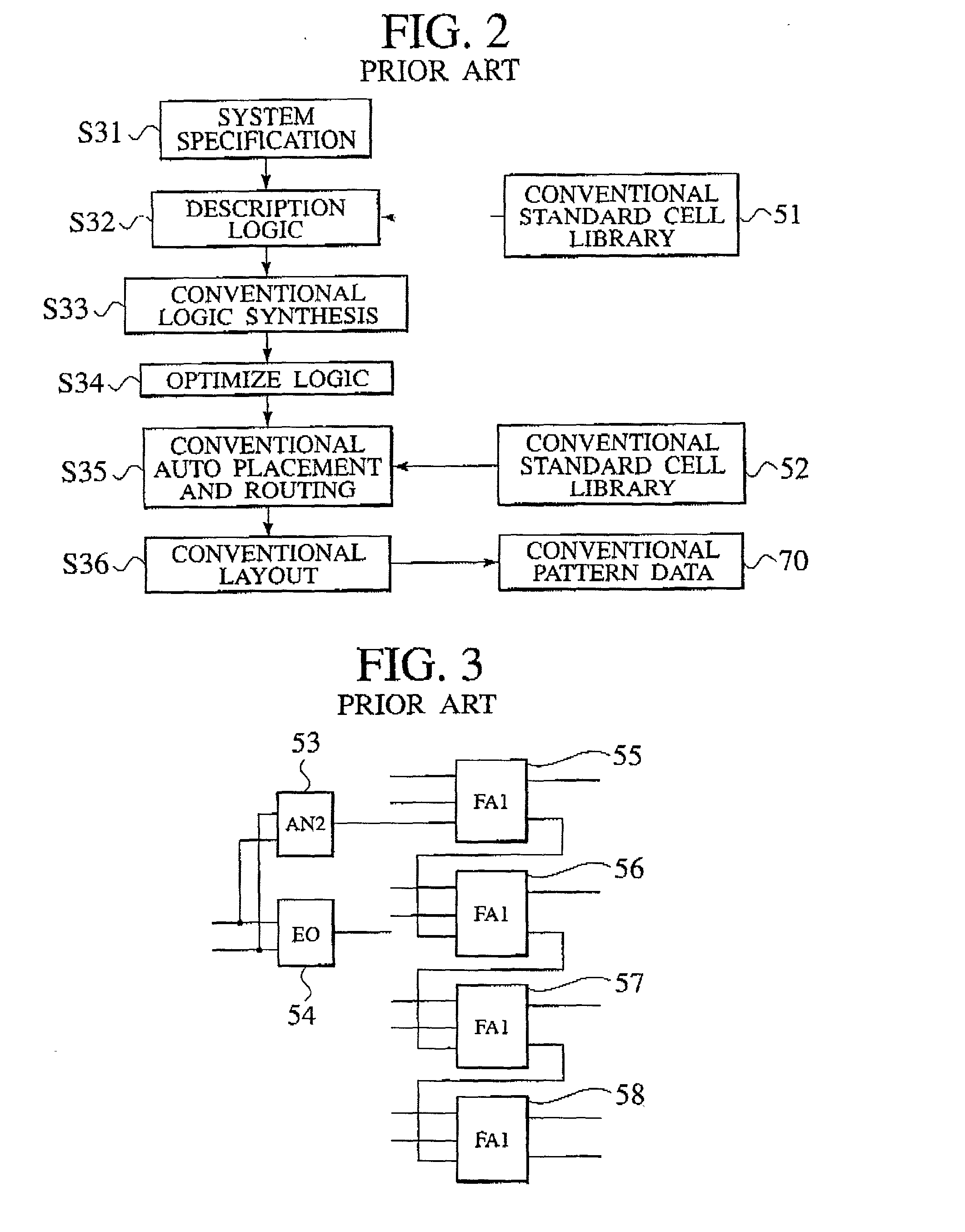

Development method for integrated circuits, program storage medium for storing the development method for integrated circuits, and concurrent development system, development program, and development method of ASIC and programmable logic device

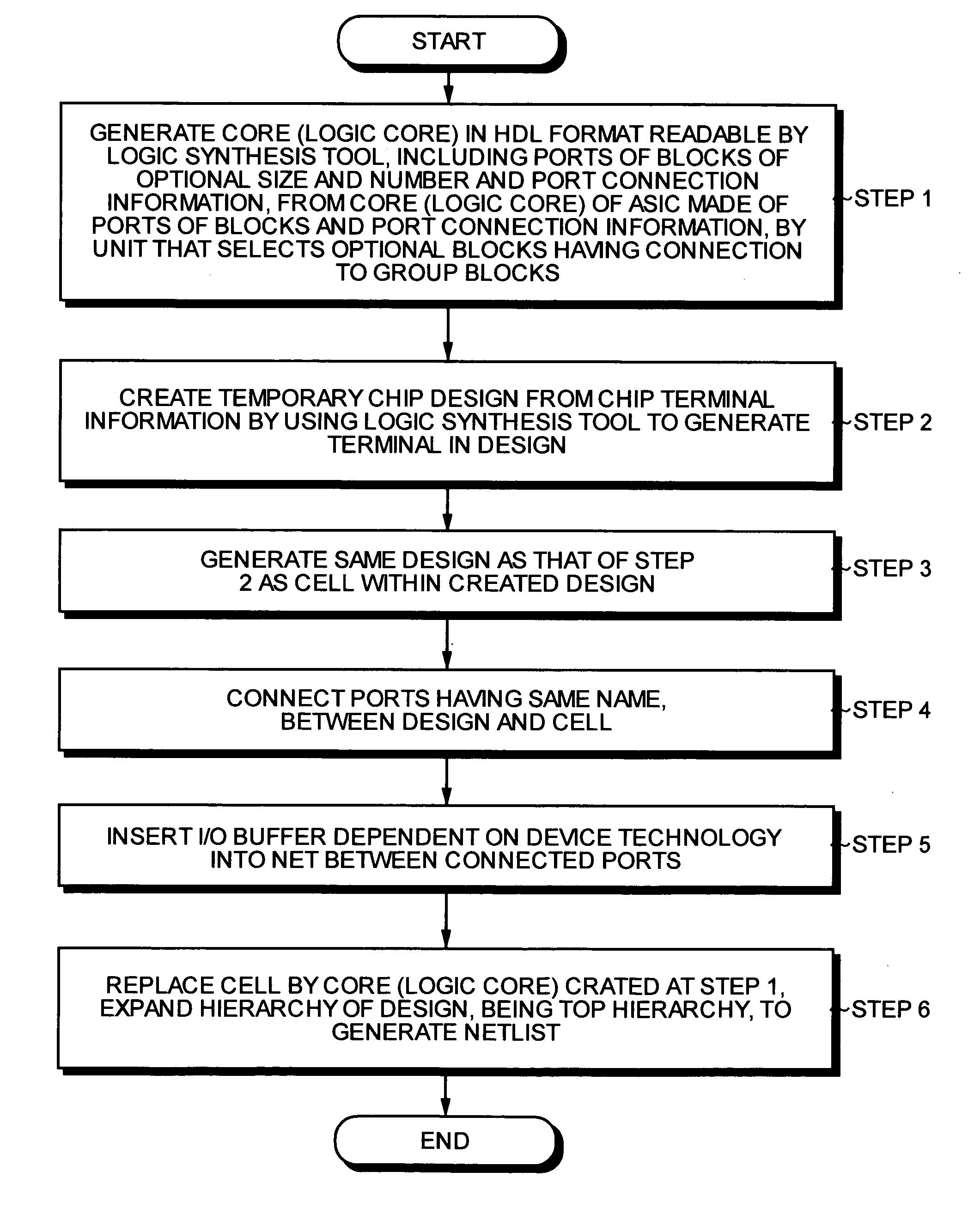

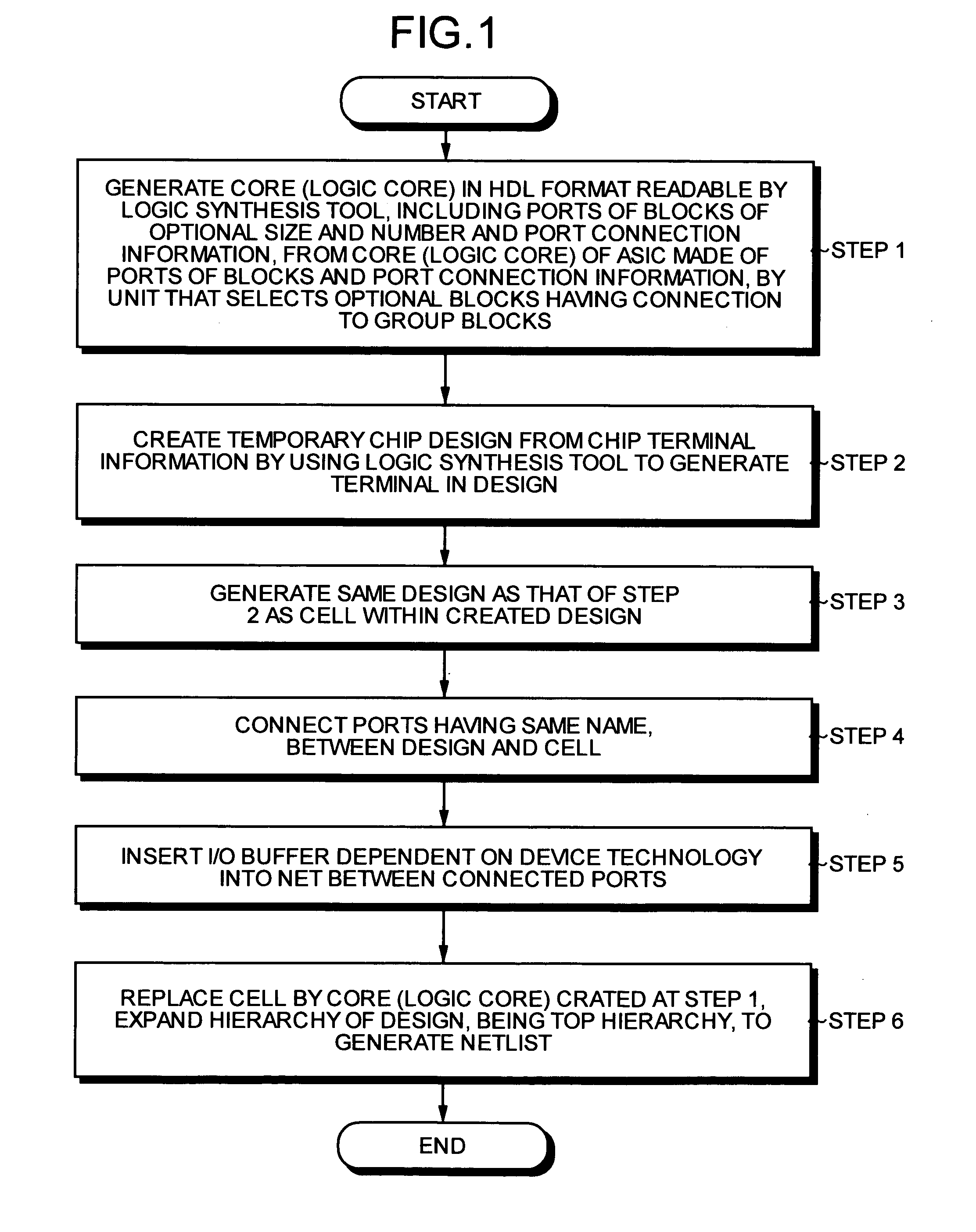

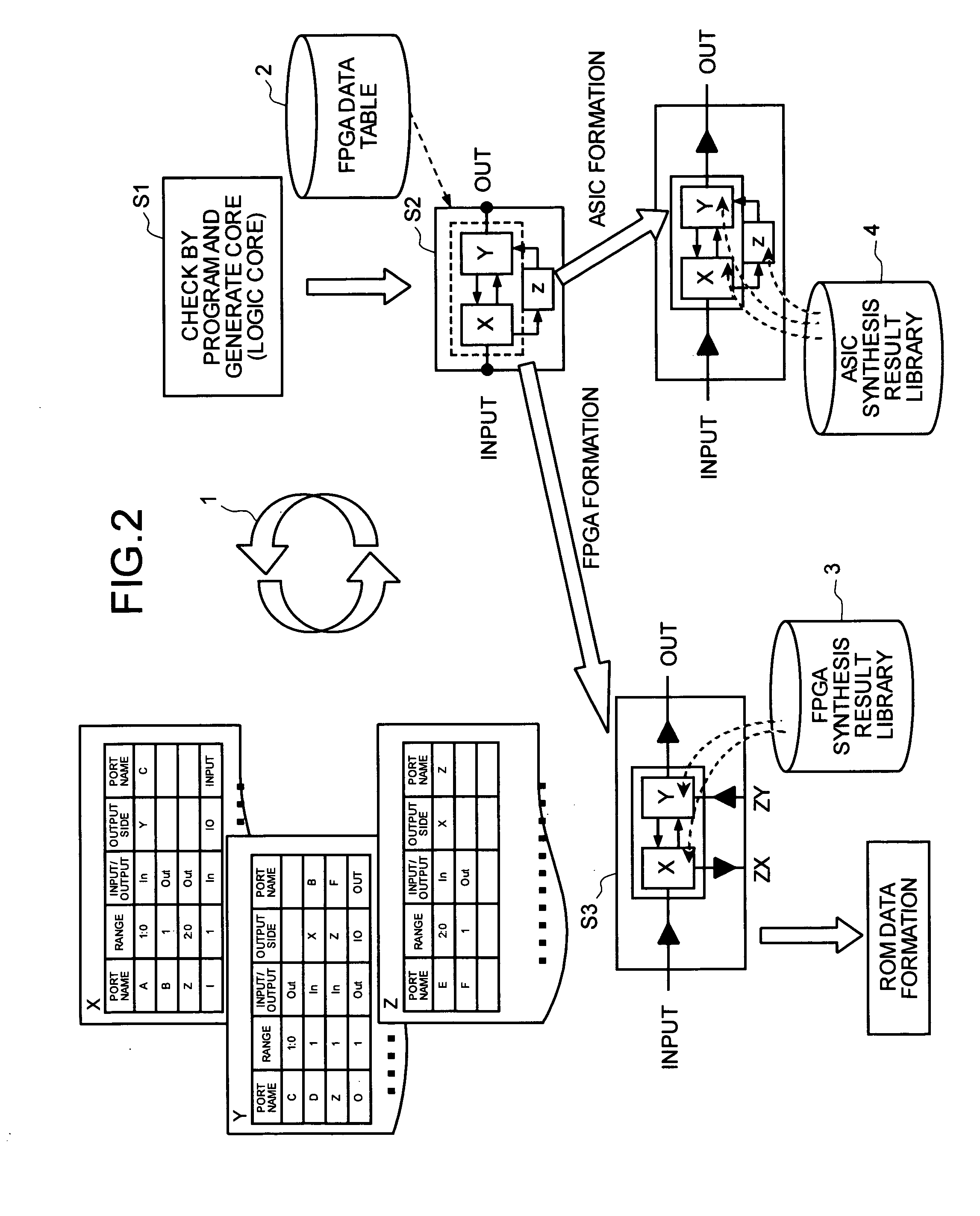

InactiveUS20050071787A1Keep in touchAvoid repetitionSemiconductor/solid-state device manufacturingCAD circuit designComputer architectureLevel structure

A method for developing integrated circuits includes generating a core (logic core) in an HDL format readable by a logic synthesis tool, from an ASIC core (logic core) made of ports of blocks and port connection information, creating a temporary chip design from chip terminal information to generate a terminal in the temporary chip design, generating a design identical to that created, as a cell within the design created, connecting a design port with a cell port, wherein a name of the design port is identical to a name of the cell port, inserting an I / O buffer, depending on the device technology, into a net between the ports connected, replacing the cell by the core (logic core) created to gerate a netlist, and expanding a hierarchy of the design, being the top hierarchy.

Owner:FUJITSU LTD

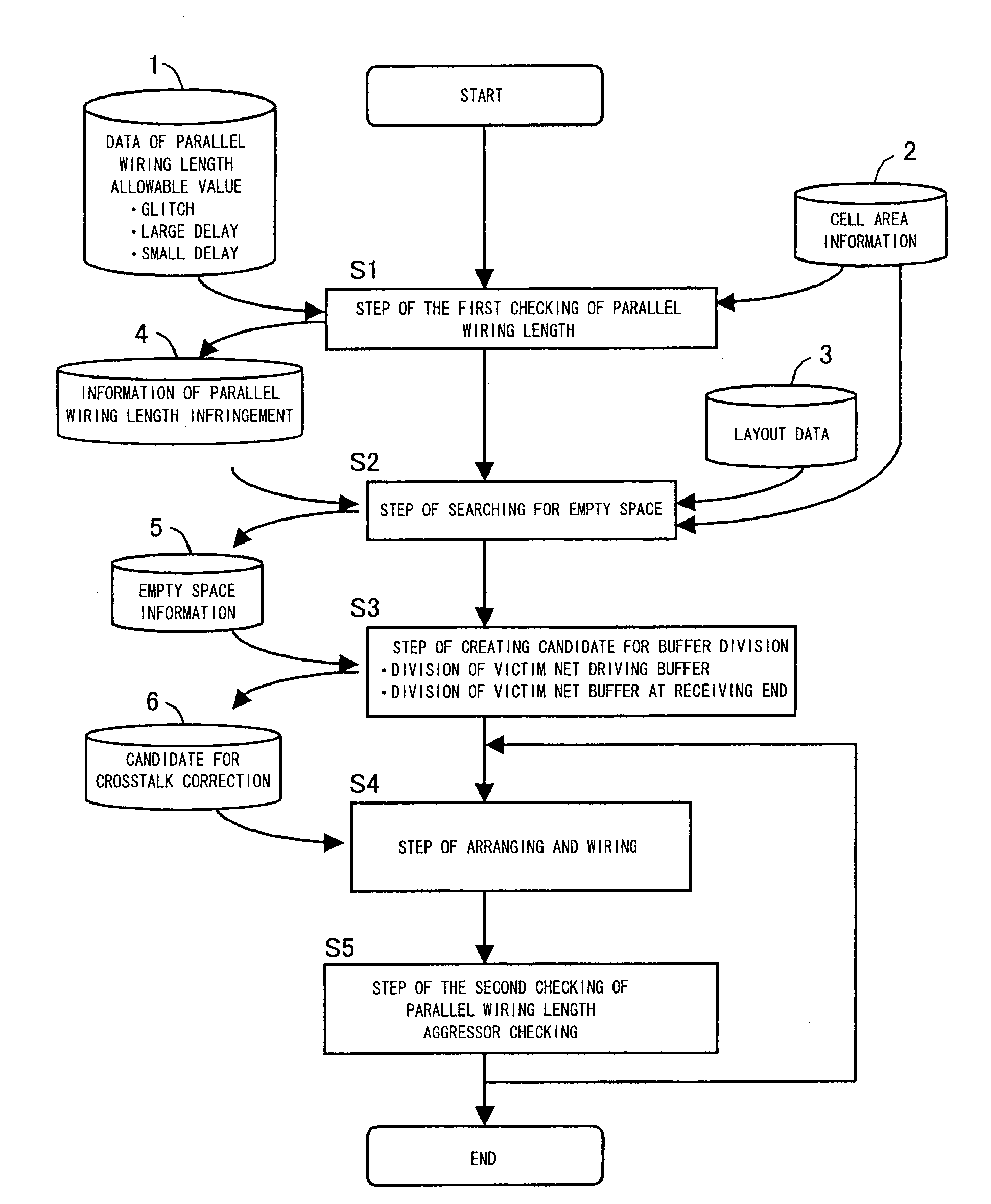

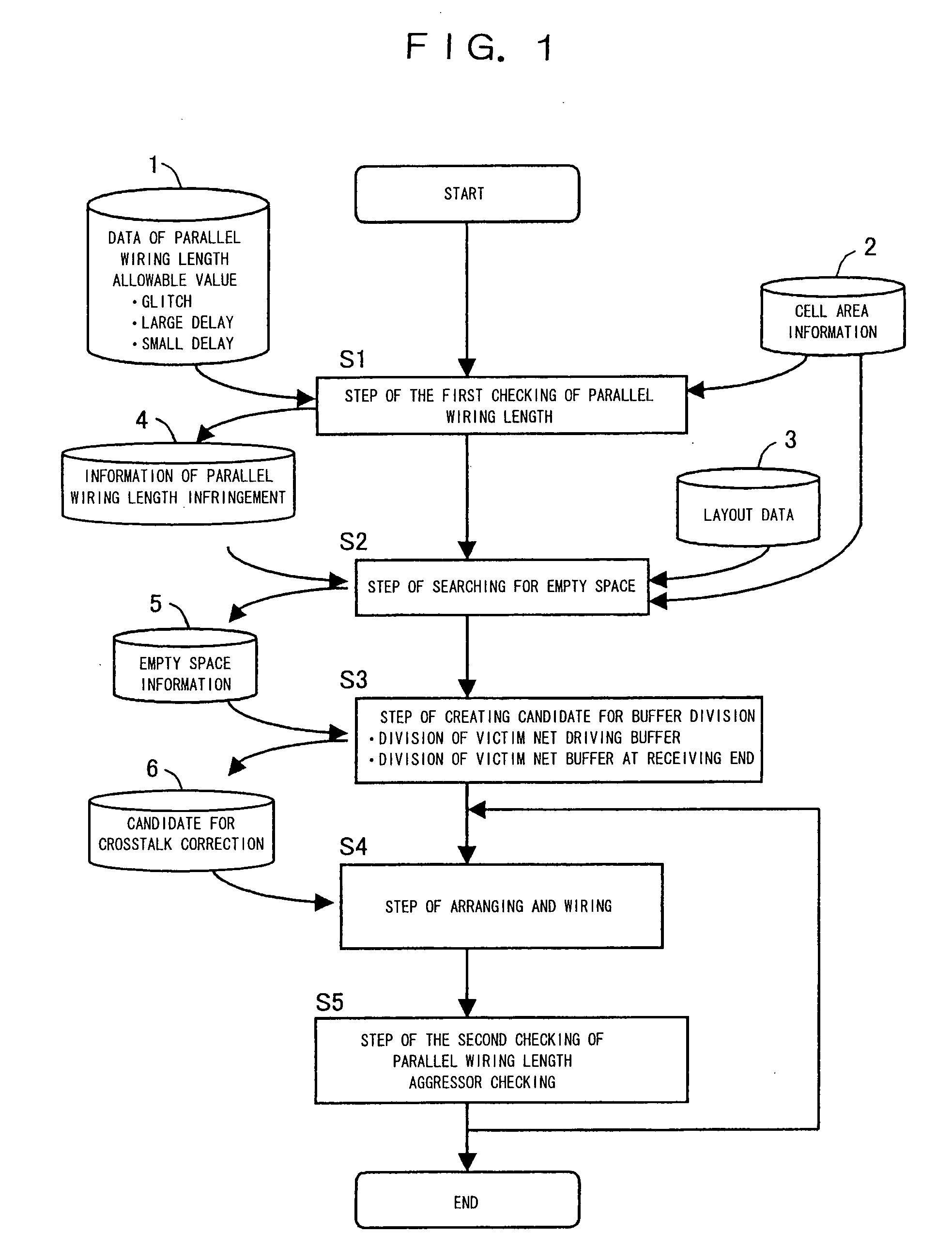

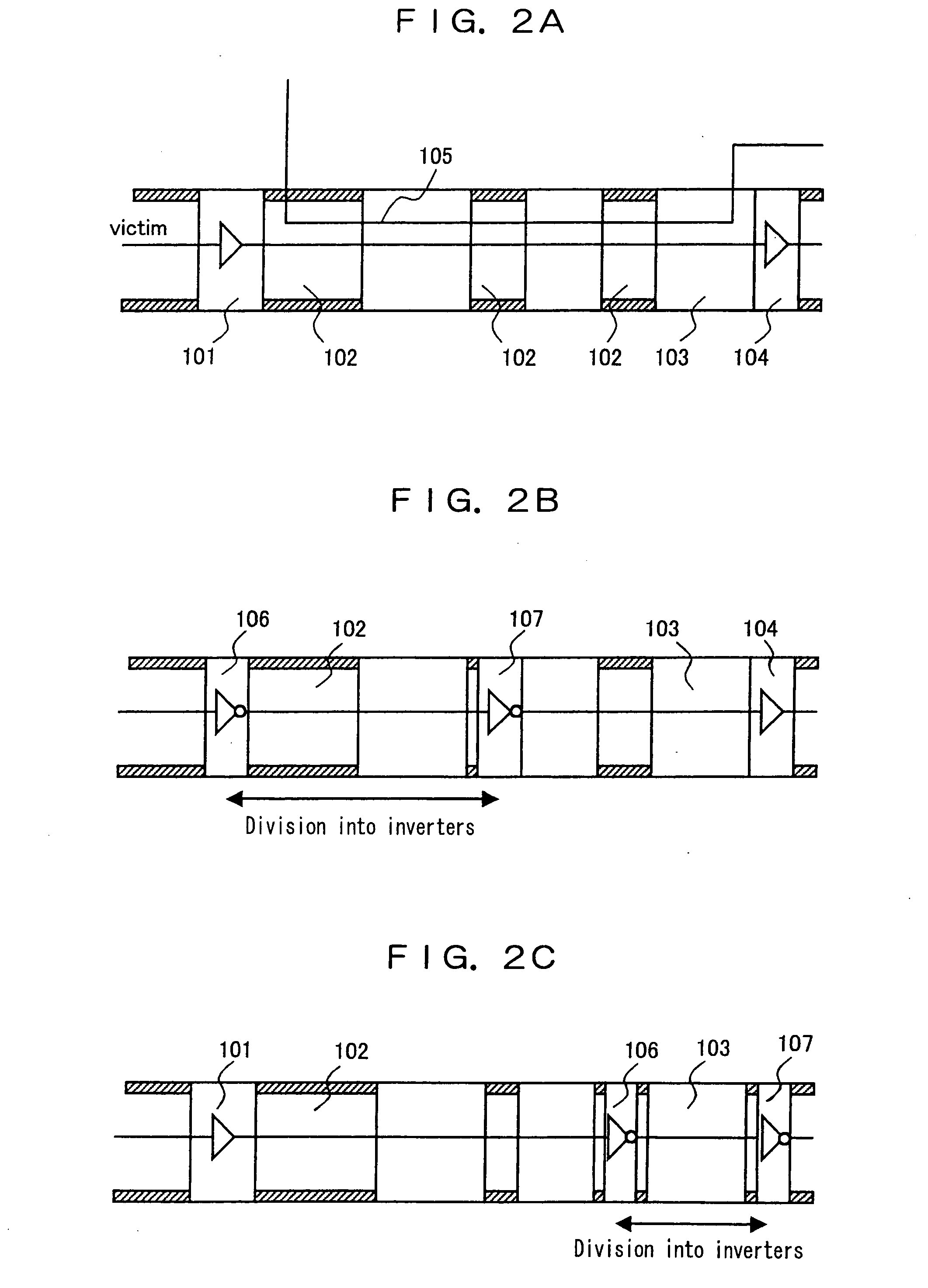

Method for correcting crosstalk

InactiveUS20060015834A1Increasing areaIncreasing consumptionSemiconductor/solid-state device testing/measurementSolid-state devicesCapacitanceSnubber

Owner:SOCIONEXT INC

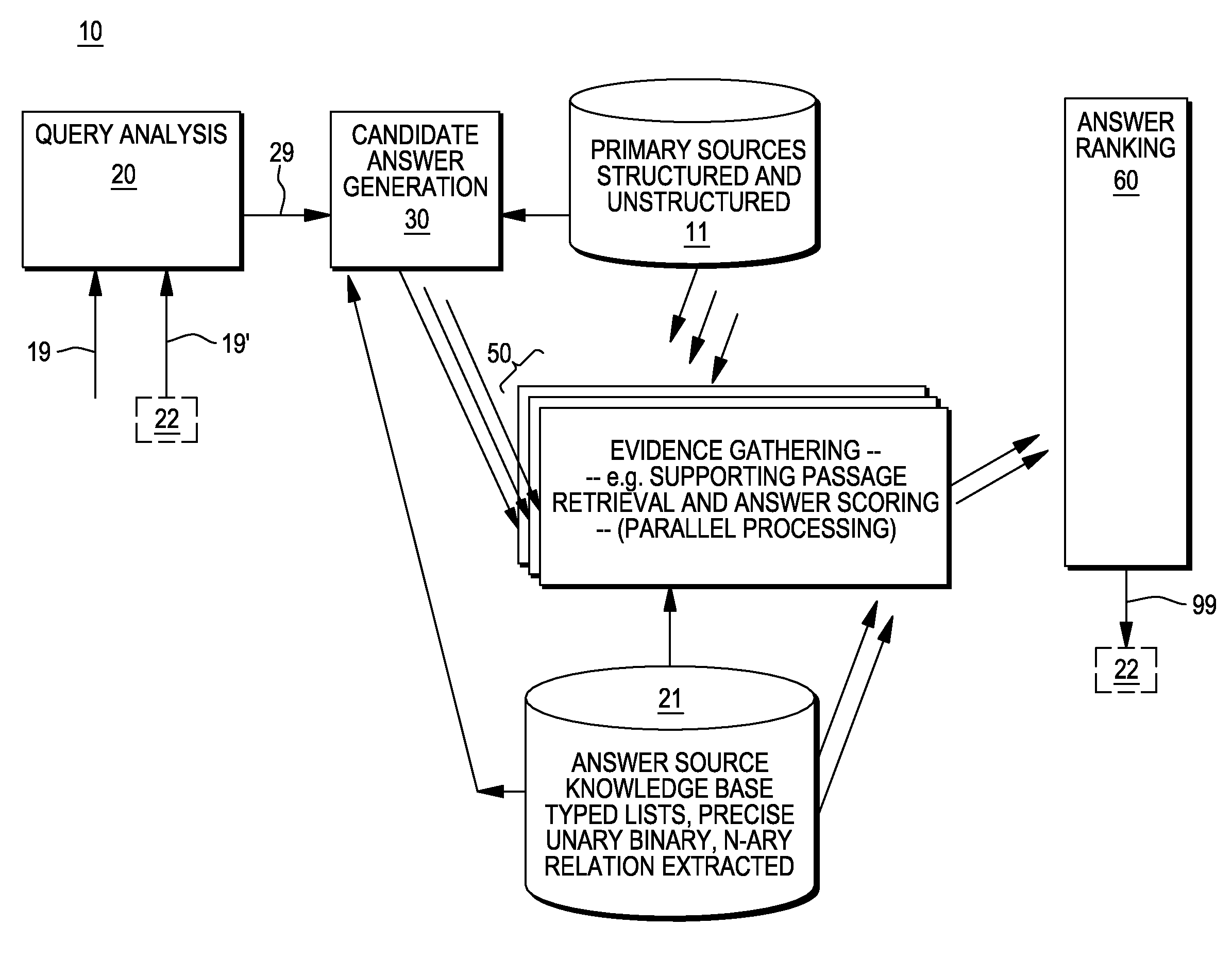

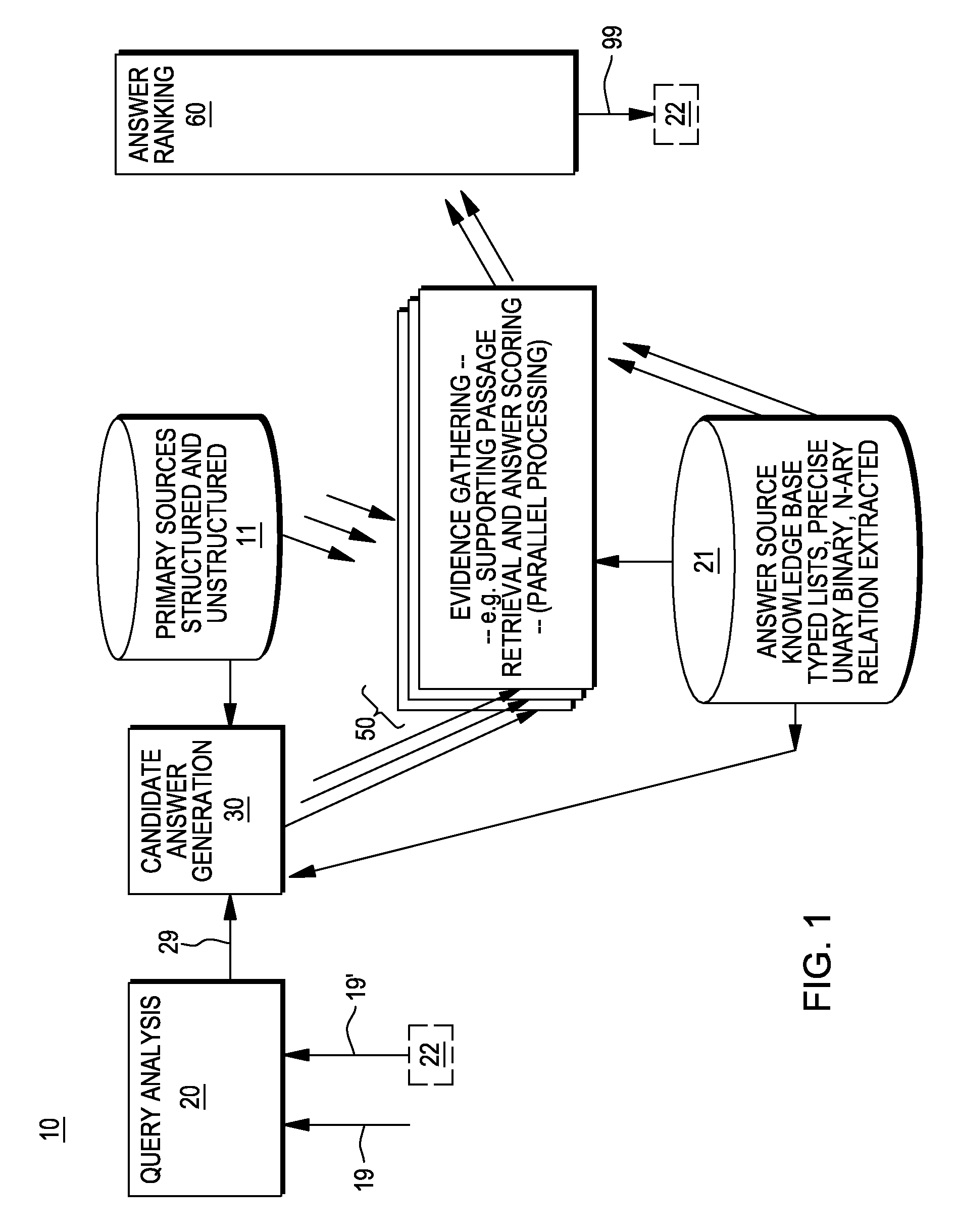

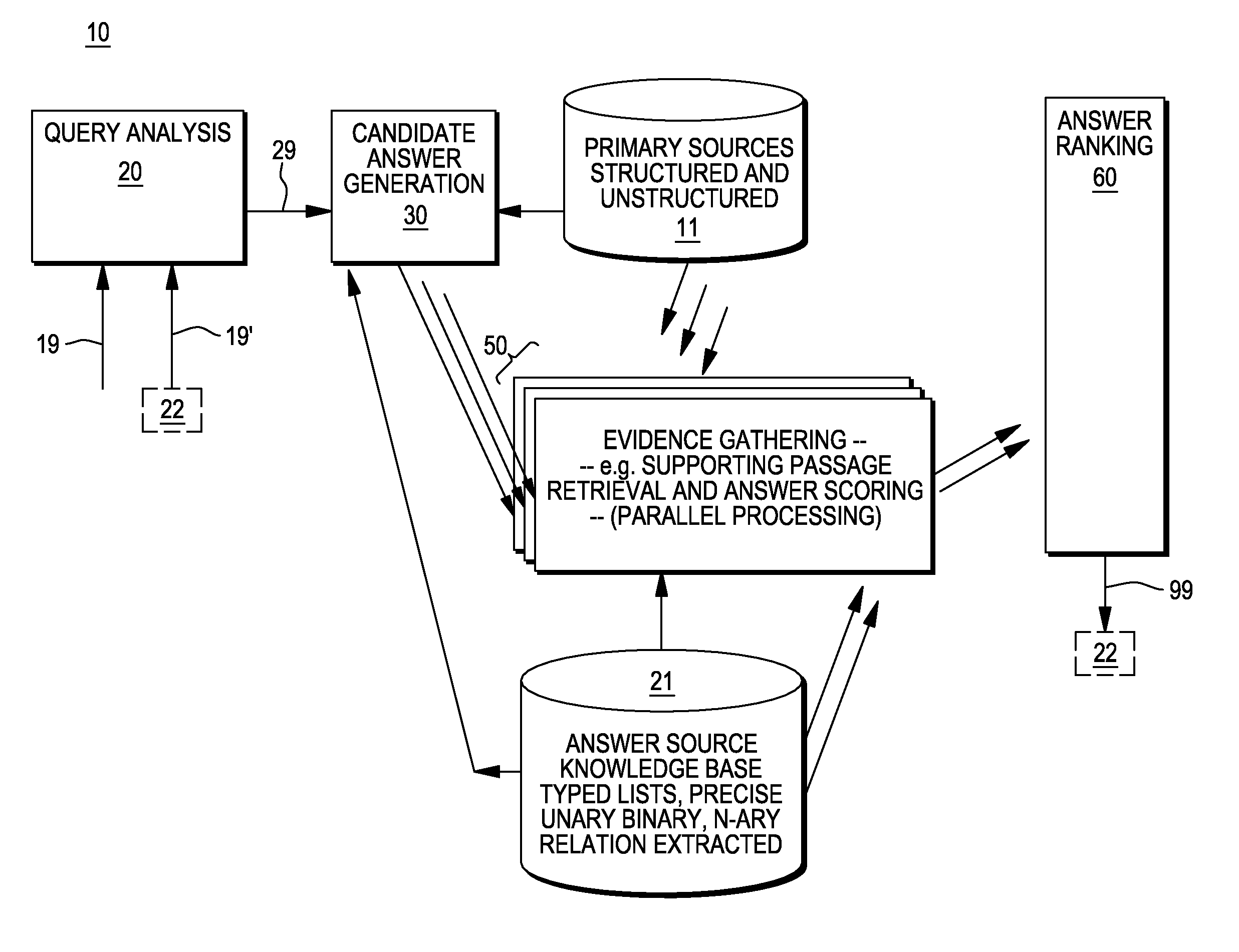

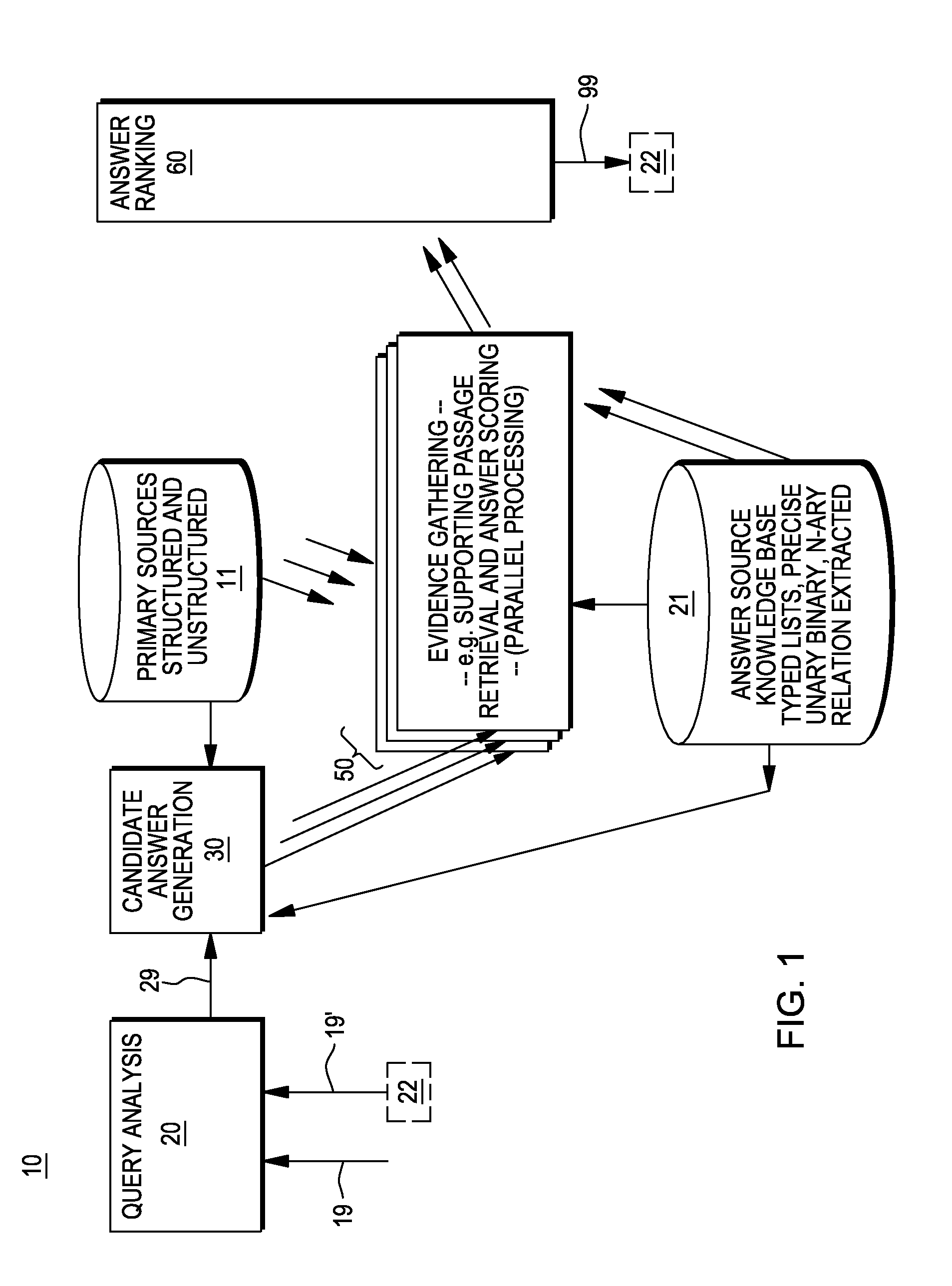

Providing answers to questions using logical synthesis of candidate answers

A method, system and computer program product for generating answers to questions. In one embodiment, the method comprises receiving an input query, decomposing the input query into a plurality of different subqueries, and conducting a search in one or more data sources to identify at least one candidate answer to each of the subqueries. A ranking function is applied to each of the candidate answers to determine a ranking for each of these candidate answers; and for each of the subqueries, one of the candidate answers to the subquery is selected based on this ranking. A logical synthesis component is applied to synthesize a candidate answer for the input query from the selected the candidate answers to the subqueries. In one embodiment, the procedure applied by the logical synthesis component to synthesize the candidate answer for the input query is determined from the input query.

Owner:IBM CORP

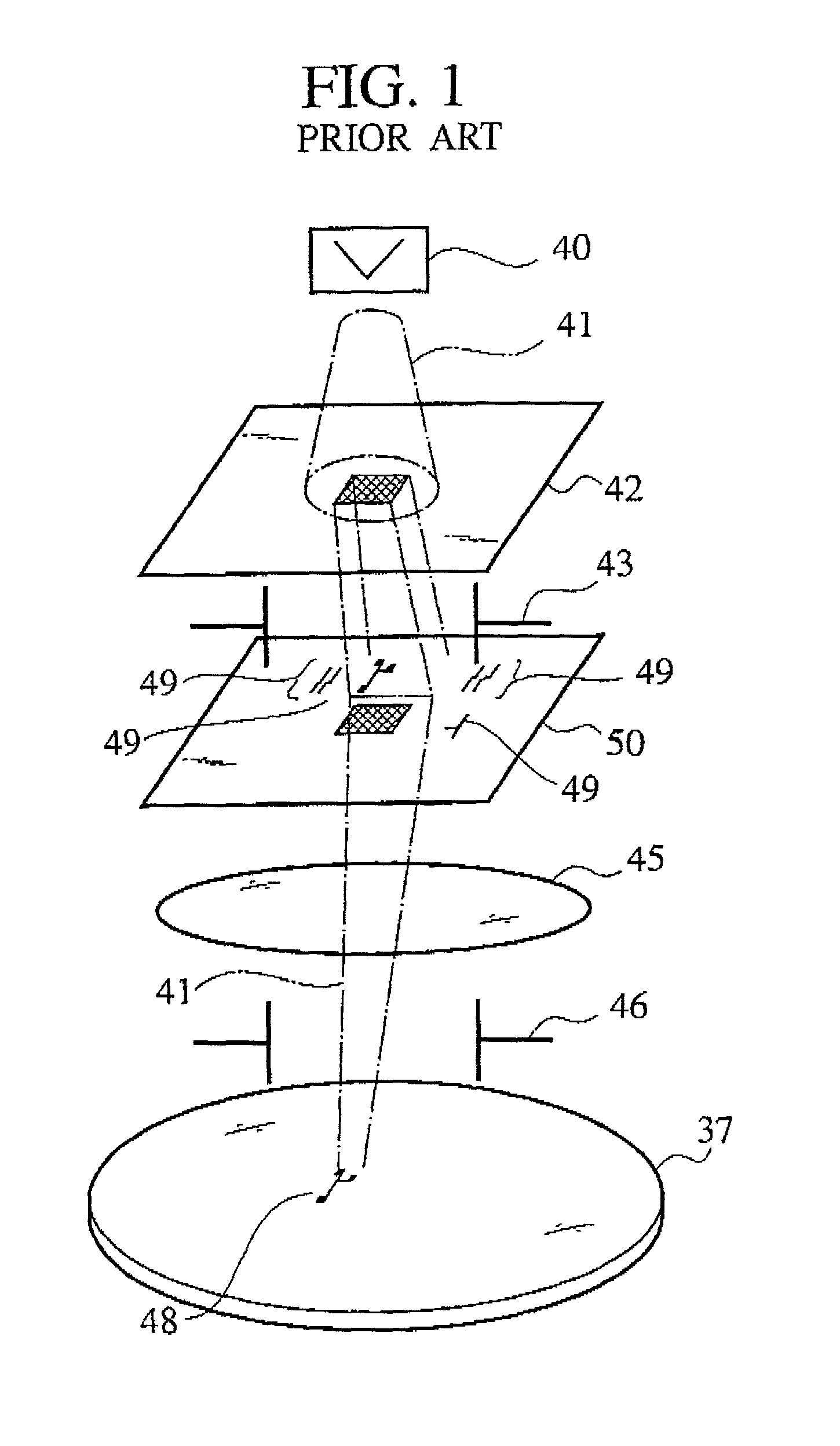

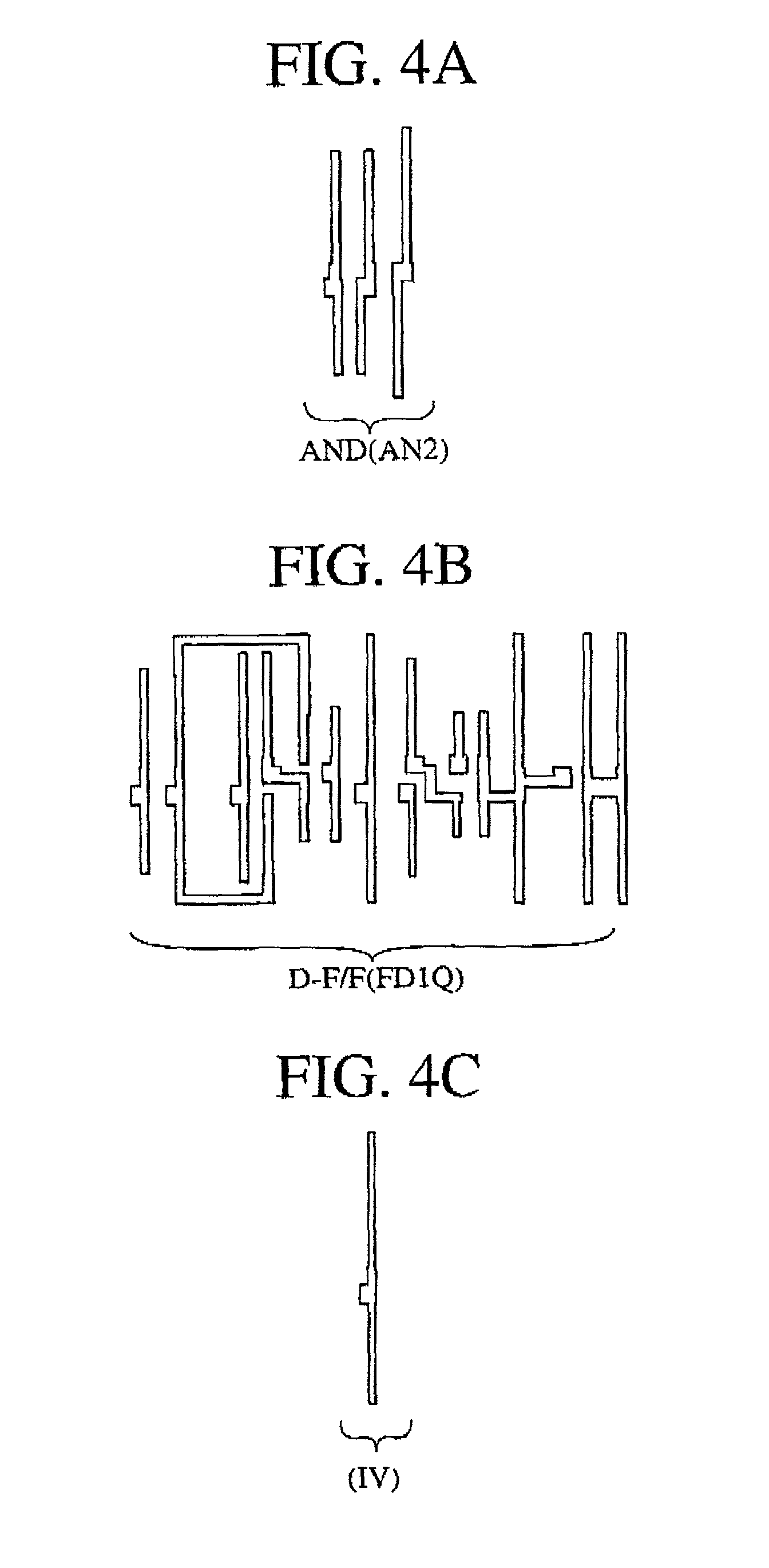

Exposure pattern data generation apparatus associated with standard cell library and charged beam exposure

Logic synthesis is conducted for CP apertures 44 using standard cells corresponding to shaping holes 4 used in logic design of a system and placed at first placement positions on the respective CP apertures 44. A CP aperture 44 used for exposure is selected from among the CP apertures for which logic synthesis has been conducted. Second placement positions of the standard cells on a substrate which standard cells correspond to the shaping holes 4 provided on the selected CP aperture 44 and wiring routes the standard cells are calculated.

Owner:KK TOSHIBA

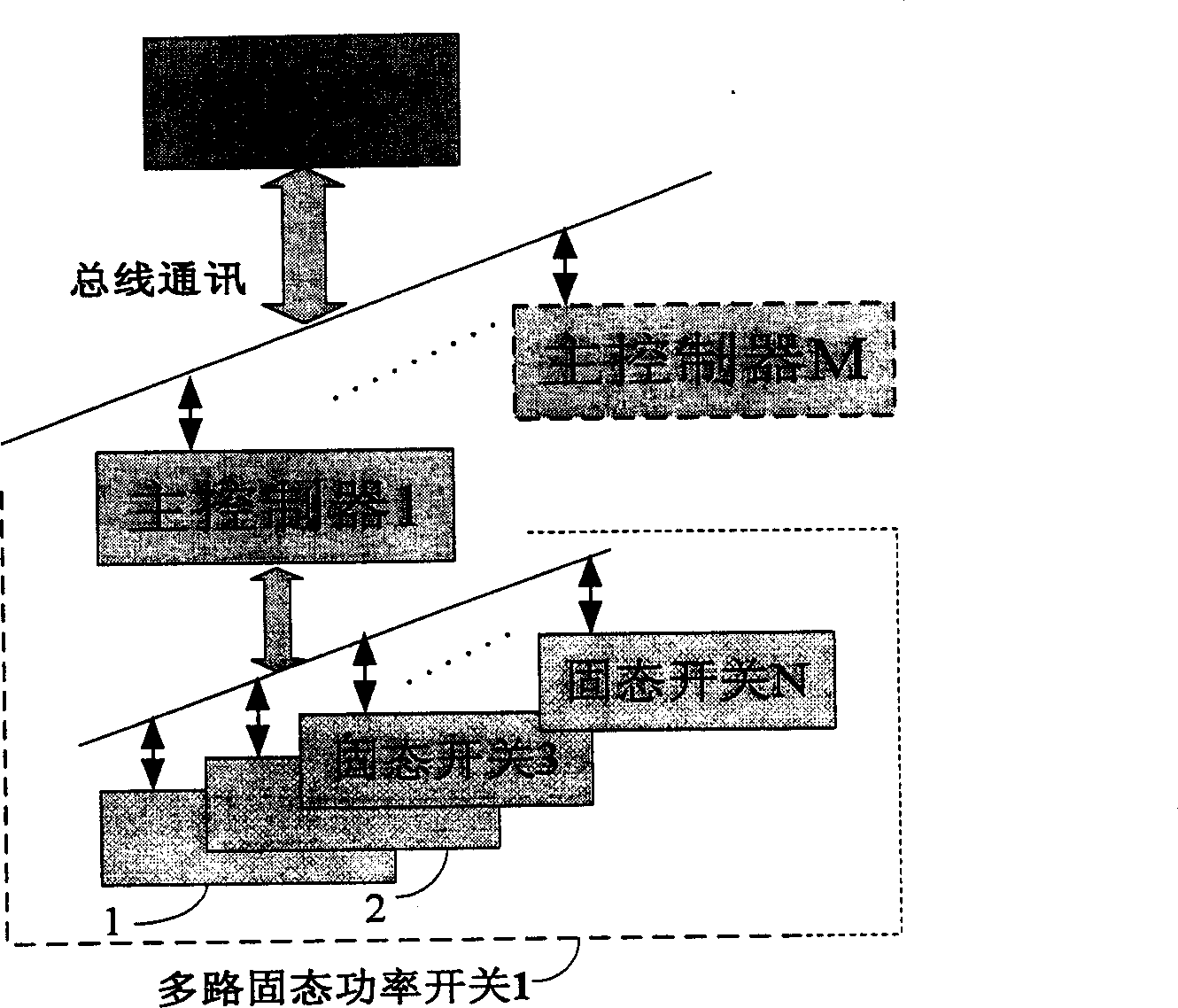

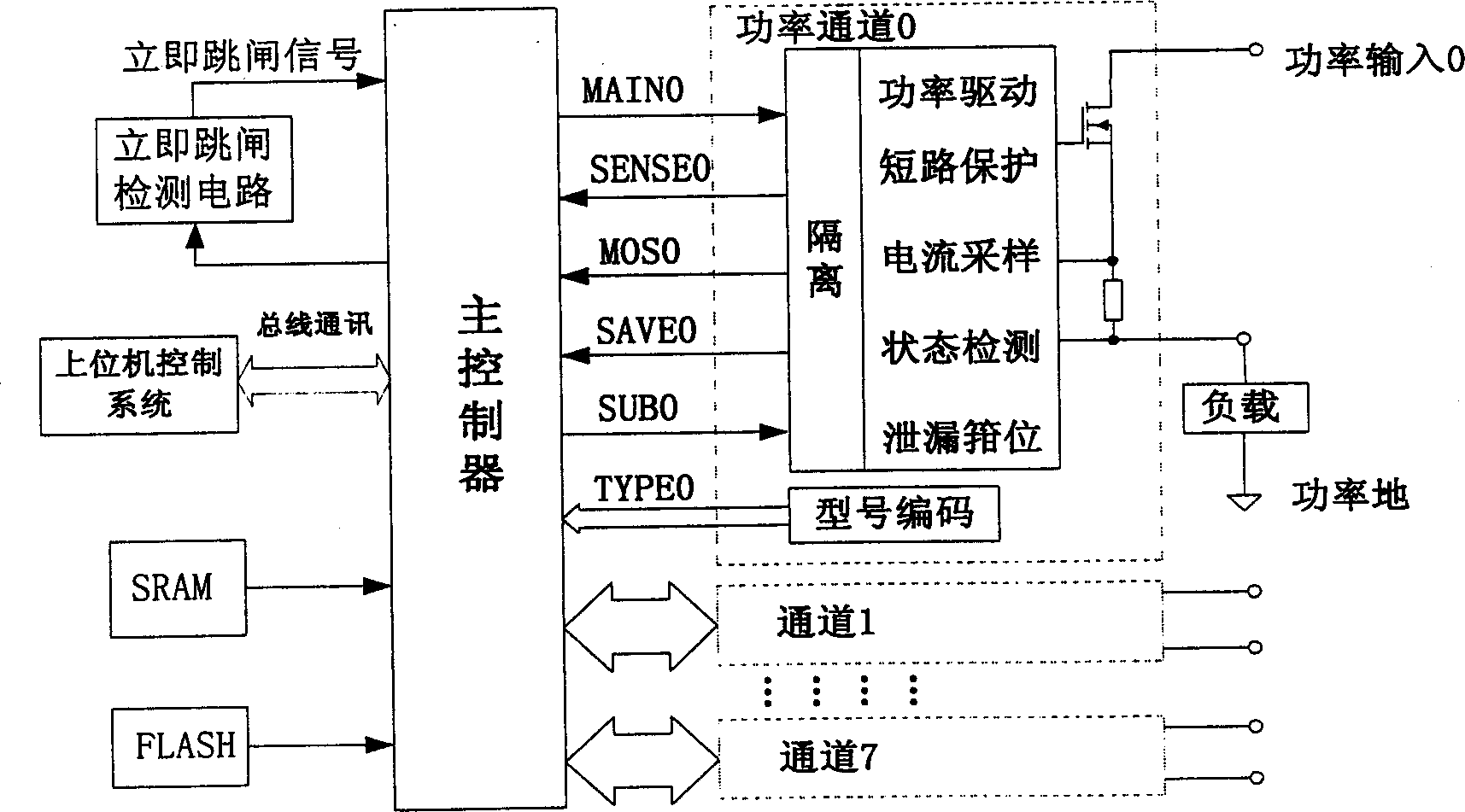

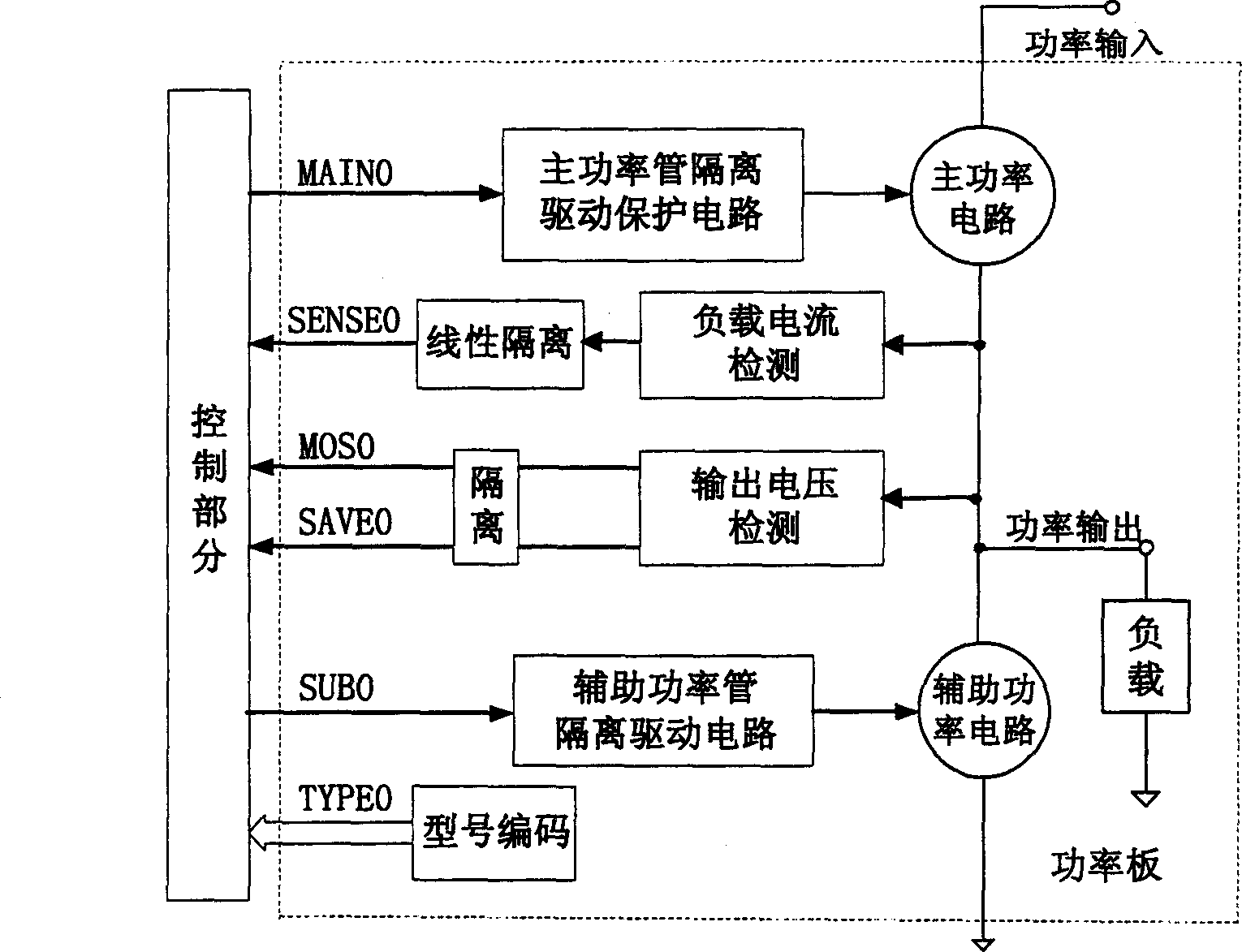

Multipath solid-state power switch digitized integration controlling method

ActiveCN1801560AEasy to controlLow integrationComputer controlElectronic switchingControl signalProgrammable logic device

The solid power switch control method uses MPU and PLD for integrated control and management, and completes the communication with bus of up machine. Wherein, using MPU to integrated control and protect the I2T and PLD to logic synthesize control signals of all channels; using level-control magnetic isolation drive protective circuit with voltage bootstrapping function; sharing one high-frequency demodulation signal for multipath drive; using rating code function to make MPU online recognize rating of every power plate and distinguish different I2T tripping curve. This invention increases power density of solid power switch, and reduces volume and weight.

Owner:SHANGHAI AVIATION ELECTRIC

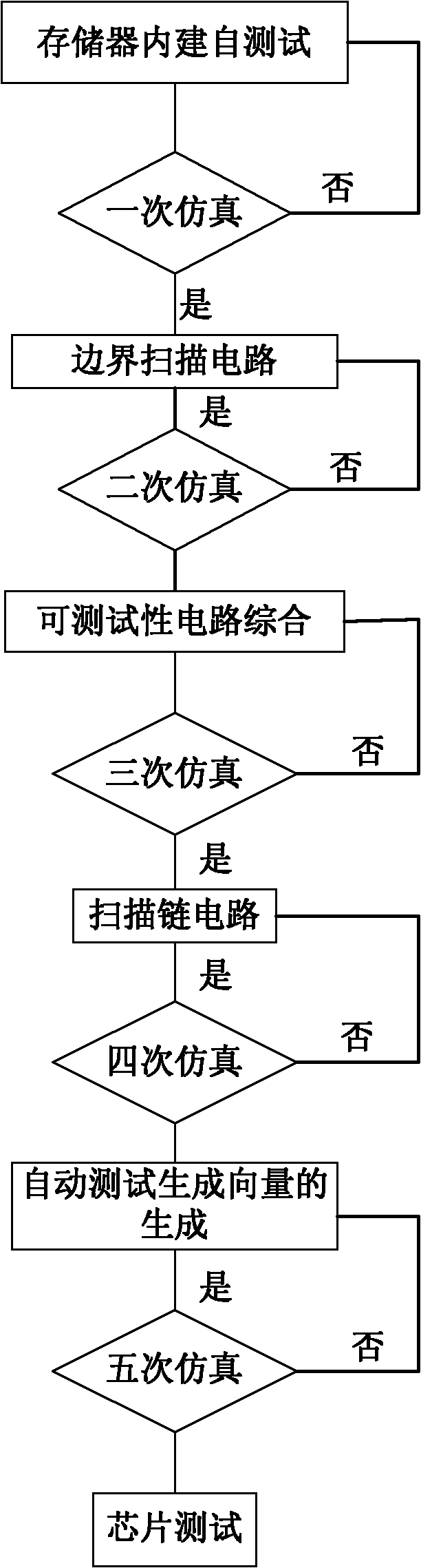

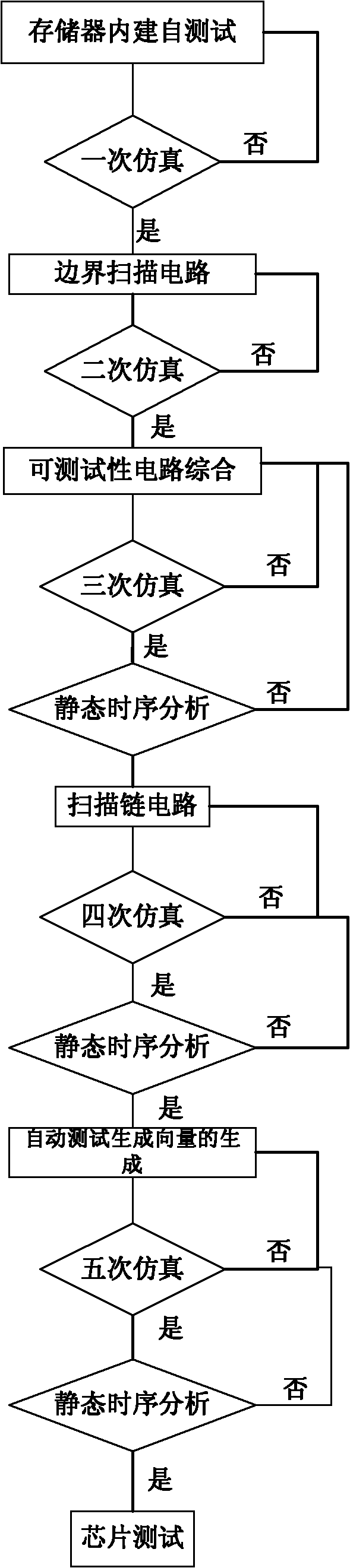

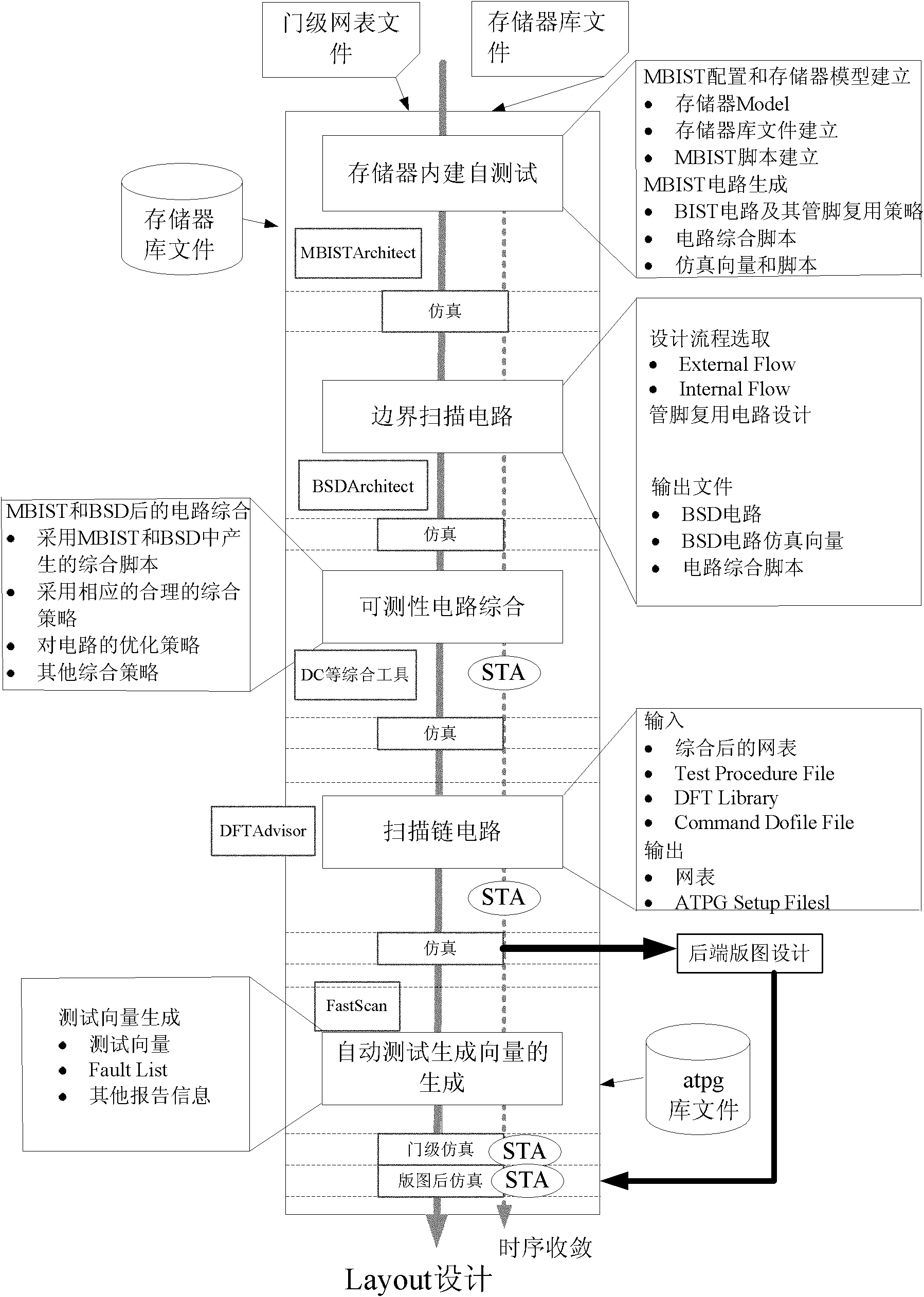

Method for designing testability of chip

ActiveCN102081689AHigh degree of automationSpecial data processing applicationsDesign for testingComputer architecture

The invention relates to a method for designing testability of a chip, which comprises the steps: (1) insertion of a built-in self test circuit of a memory; (2) insertion of a boundary scan circuit; (3) integration of a testability circuit; (4) insertion of a scan chain circuit; and (5) generation of automatic test generated vectors. In order to solve the technical problems that in the traditional chip design process, a set of complete and systematical method in test methods aiming at different test objects is not available, tools such as a DFT (diagnostic function test) tool, a logic synthesis tool, a circuit simulation tool and the like are not joined and the design program is complicated, the invention provides the process guarantee for automation of the DFT design and complete and systematical correctness of the DFT design.

Owner:西安翔腾微电子科技有限公司

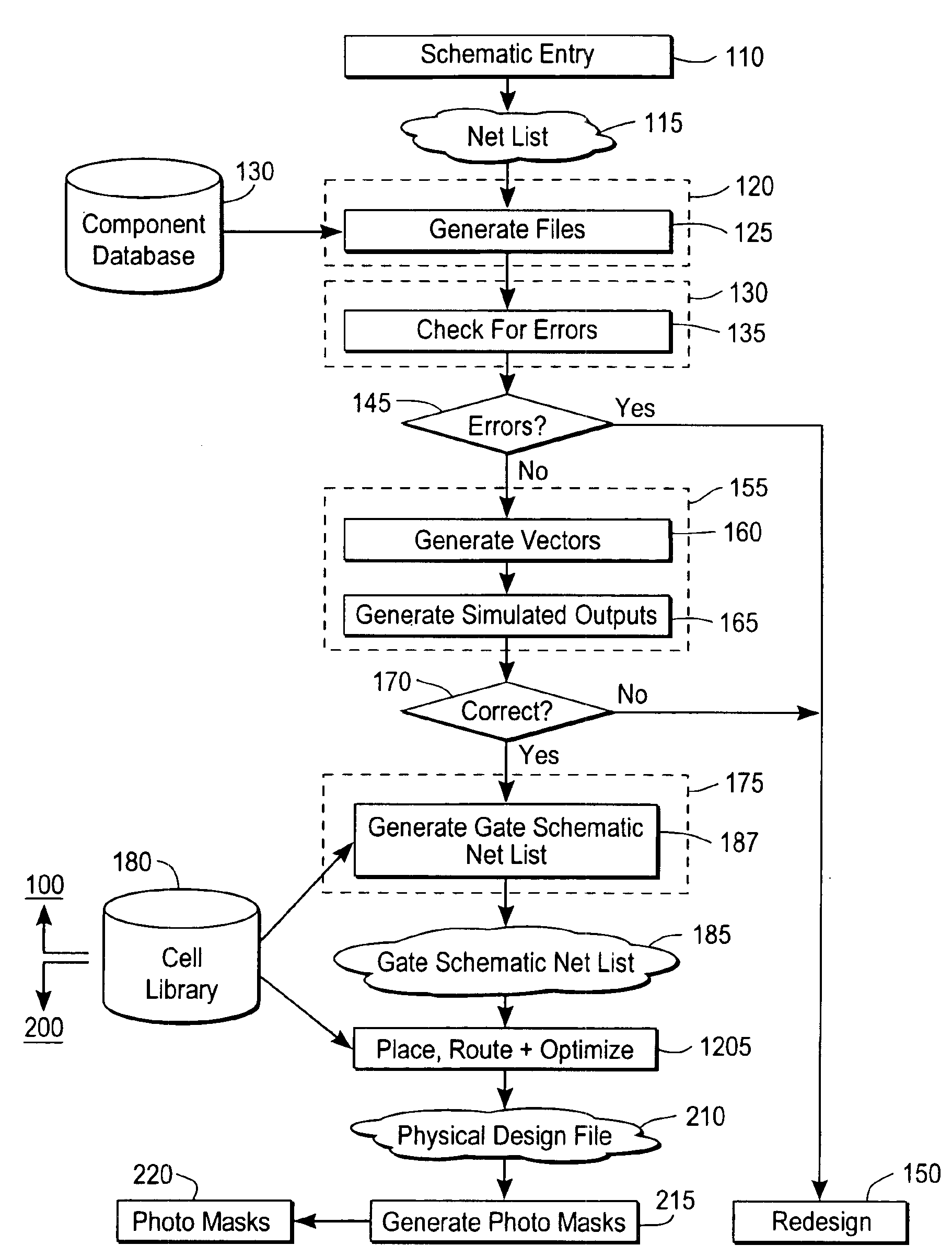

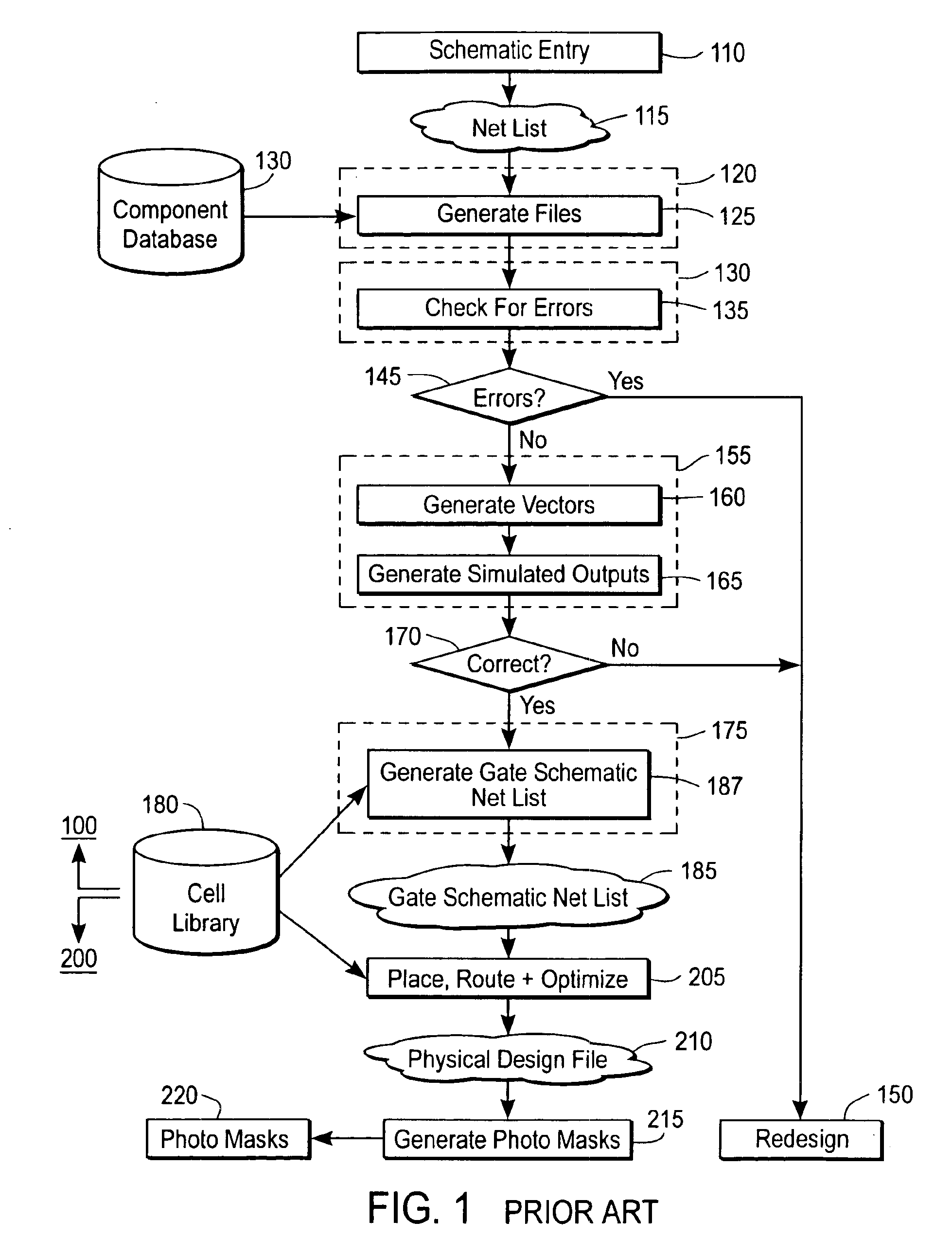

Method for rapid estimation of wire delays and capacitances based on placement of cells

InactiveUS6931610B1Method is fastComputer aided designSoftware simulation/interpretation/emulationCapacitanceEngineering

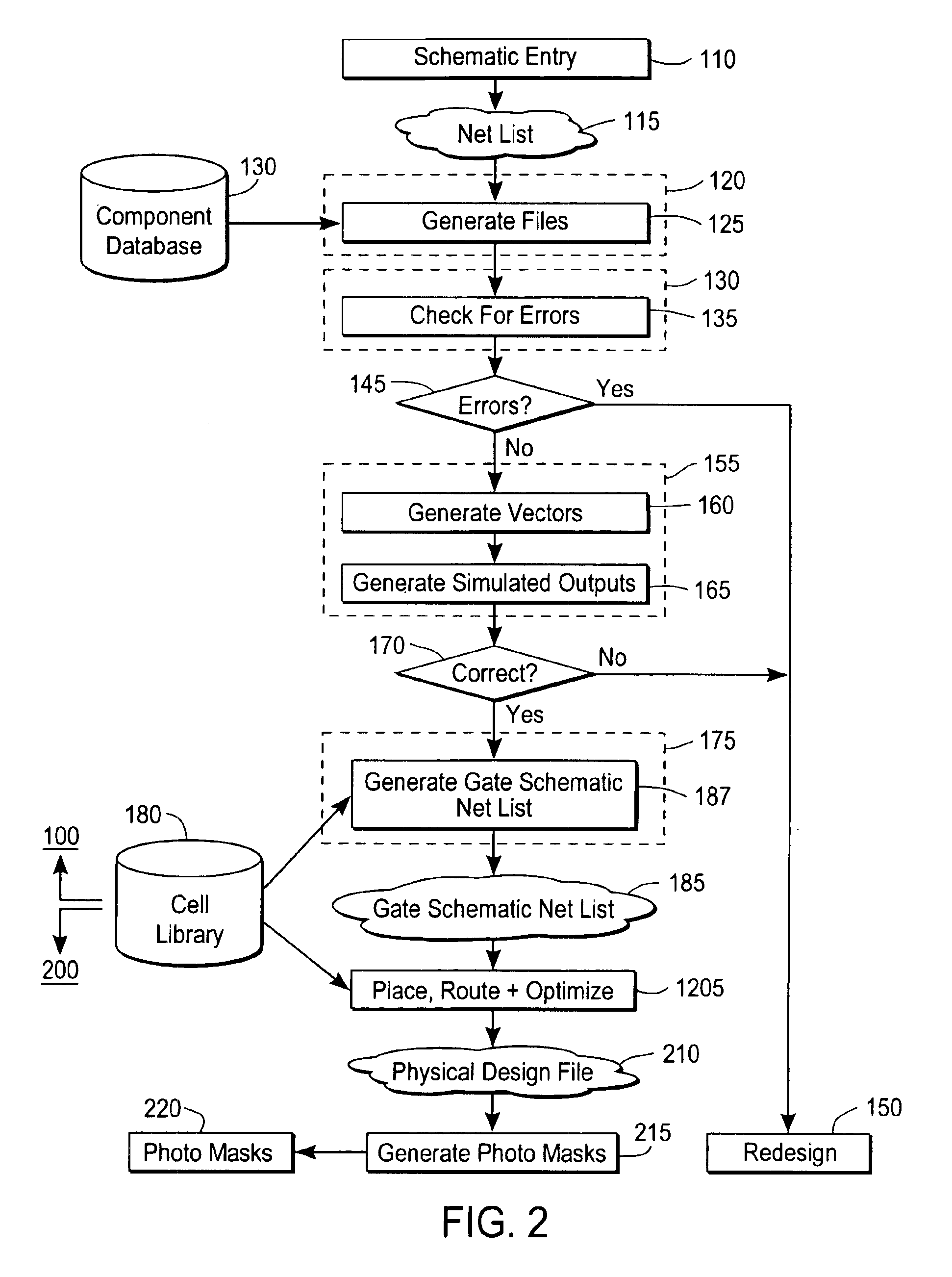

A fast method of estimating capacitances and wire delays in an integrated circuit design is based on placement information such as that contained in a gate schematic net list from a logic synthesis tool. A simple tree topology called a spine tree is constructed to connect the pins of the net as an approximation of actual connections therein. Capacitance is extracted for this topology assuming a worst case scenario, and Elmore delays are computed for the wire delays based on the worst-case capacitances. The method takes linear time as a function of the number of pins in the net and is much faster than using a Steiner tree method in this context.

Owner:MAGMA DESIGN AUTOMATION

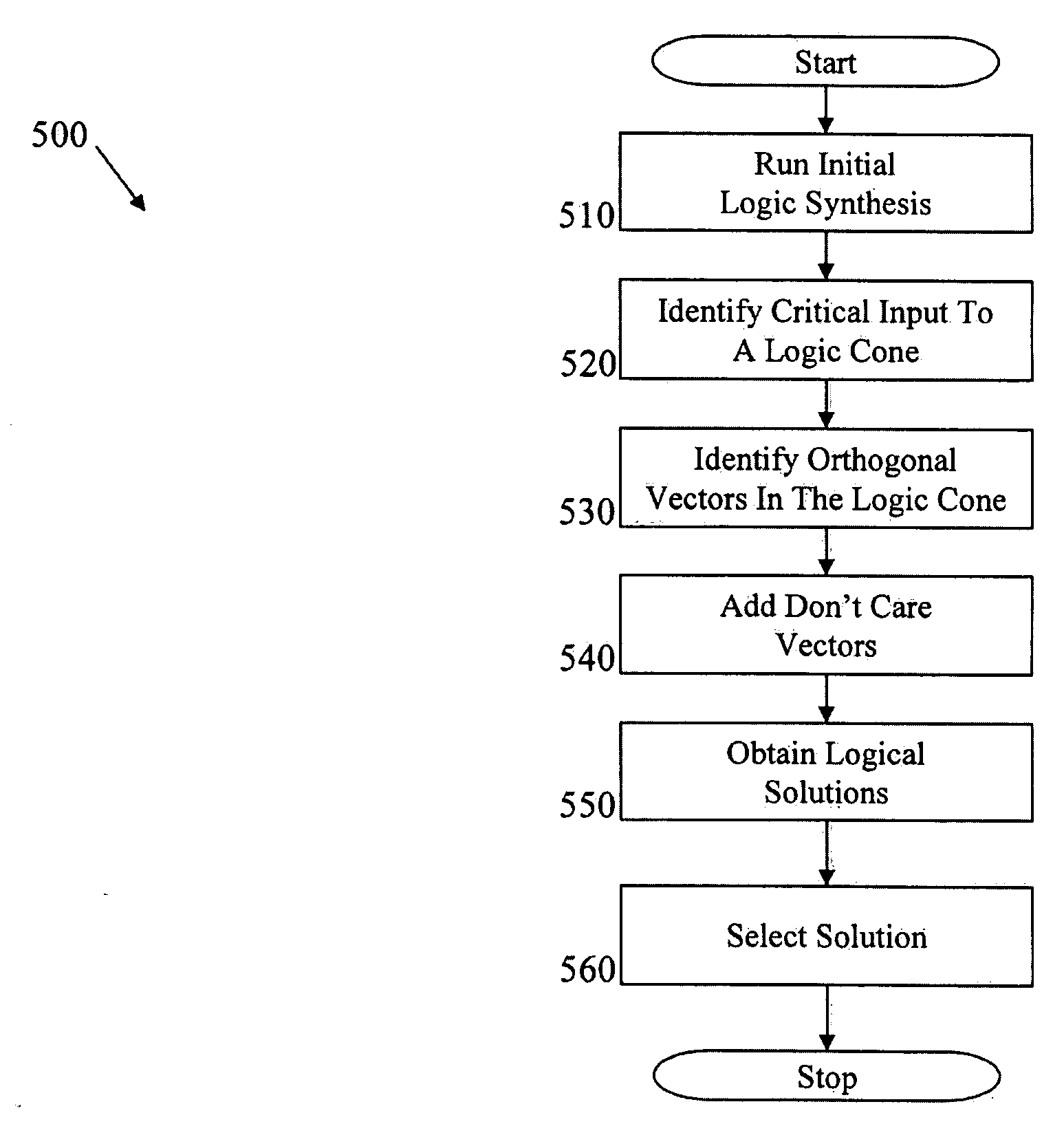

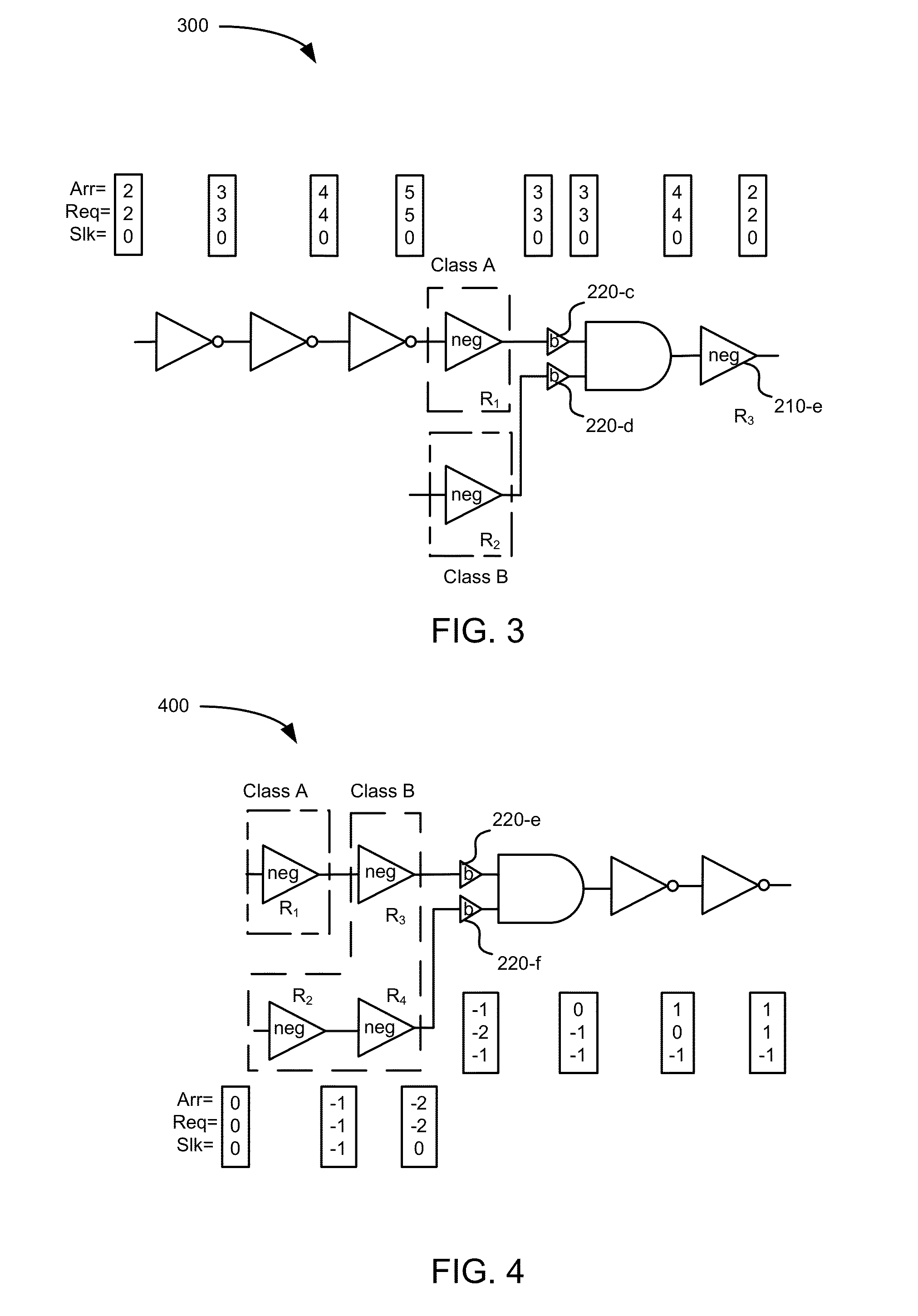

Method, system and computer program product for exploiting orthogonal control vectors in timing driven systems

InactiveUS20090241084A1Limited orthogonalityComputer aided designSpecial data processing applicationsControl vectorTheoretical computer science

Systems, methods and computer program products for exploiting orthogonal control vectors in timing driven systems. An exemplary embodiment includes running an initial logic synthesis run on the system, identifying critical inputs to a logic cone related to the run, identifying orthogonal vectors in the logic cone, adding vectors to the logic cone, obtaining logical solutions and selecting a solution from the logical solutions.

Owner:GLOBALFOUNDRIES INC

Logic power optimization algorithm

InactiveUS6658634B1Reduce wasted powerCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceLogic network

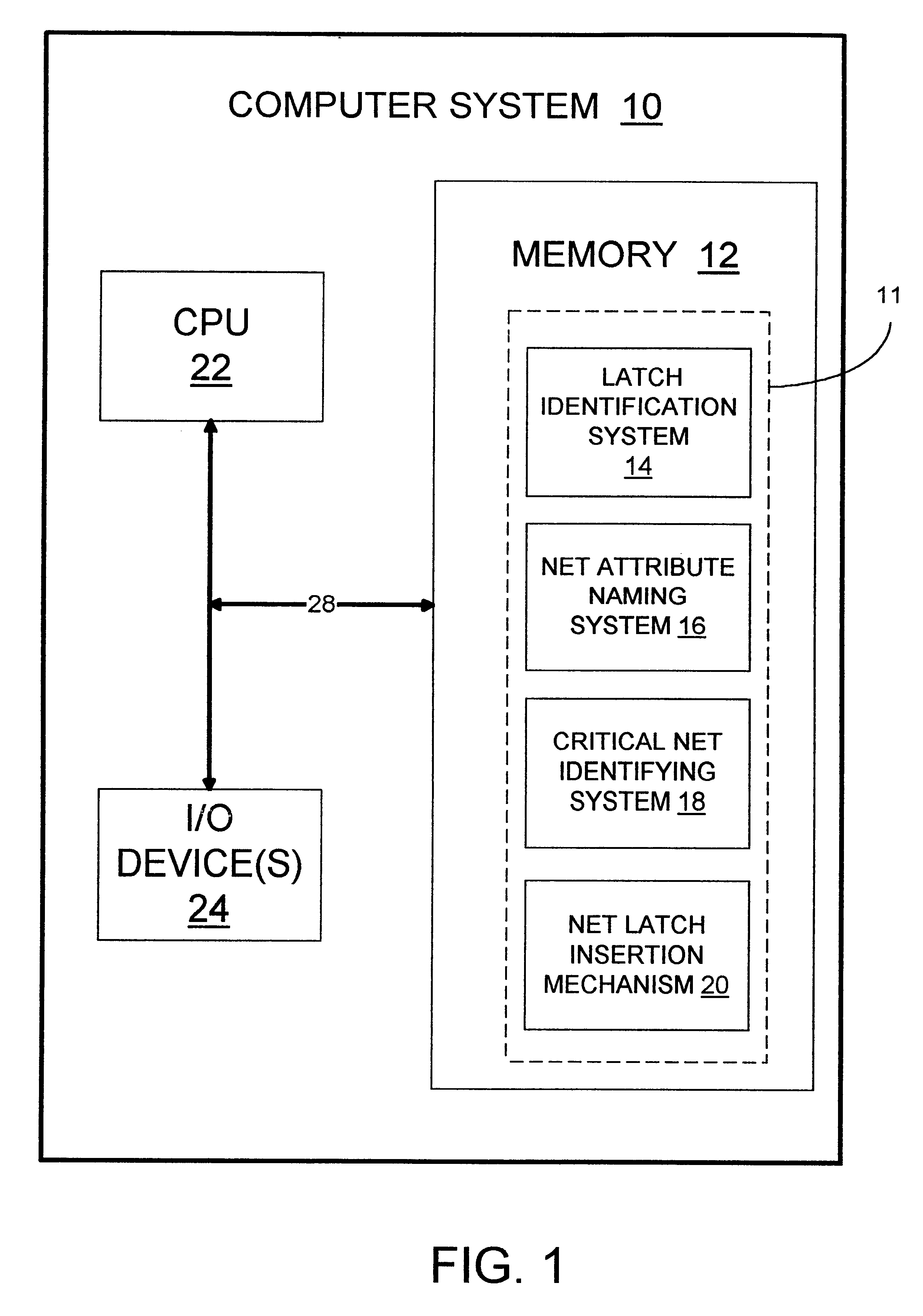

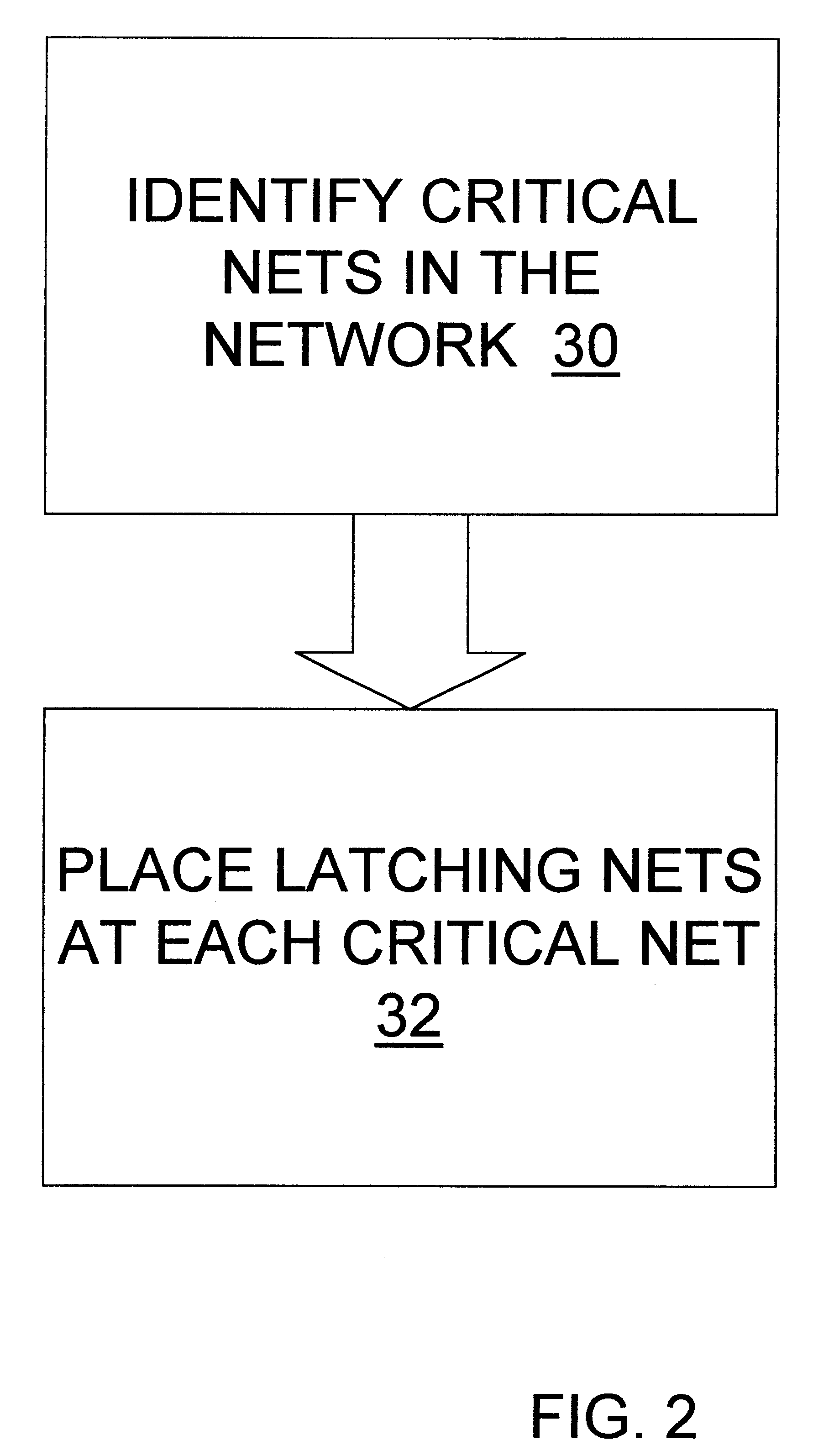

Disclosed is a system and method for eliminating the unnecessary toggling of logic in a logic network. The method and system can be incorporated directly into logic synthesis software, or may be implemented manually. Provided is a mechanism for identifying critical nets and then inserting net latches at the critical nets wherein each net latch is controlled by an enable signal that also controls a related output latch. Each net latch is comprised of a circuit which can on command hold static the last logic level on a given logic node.

Owner:GOOGLE LLC

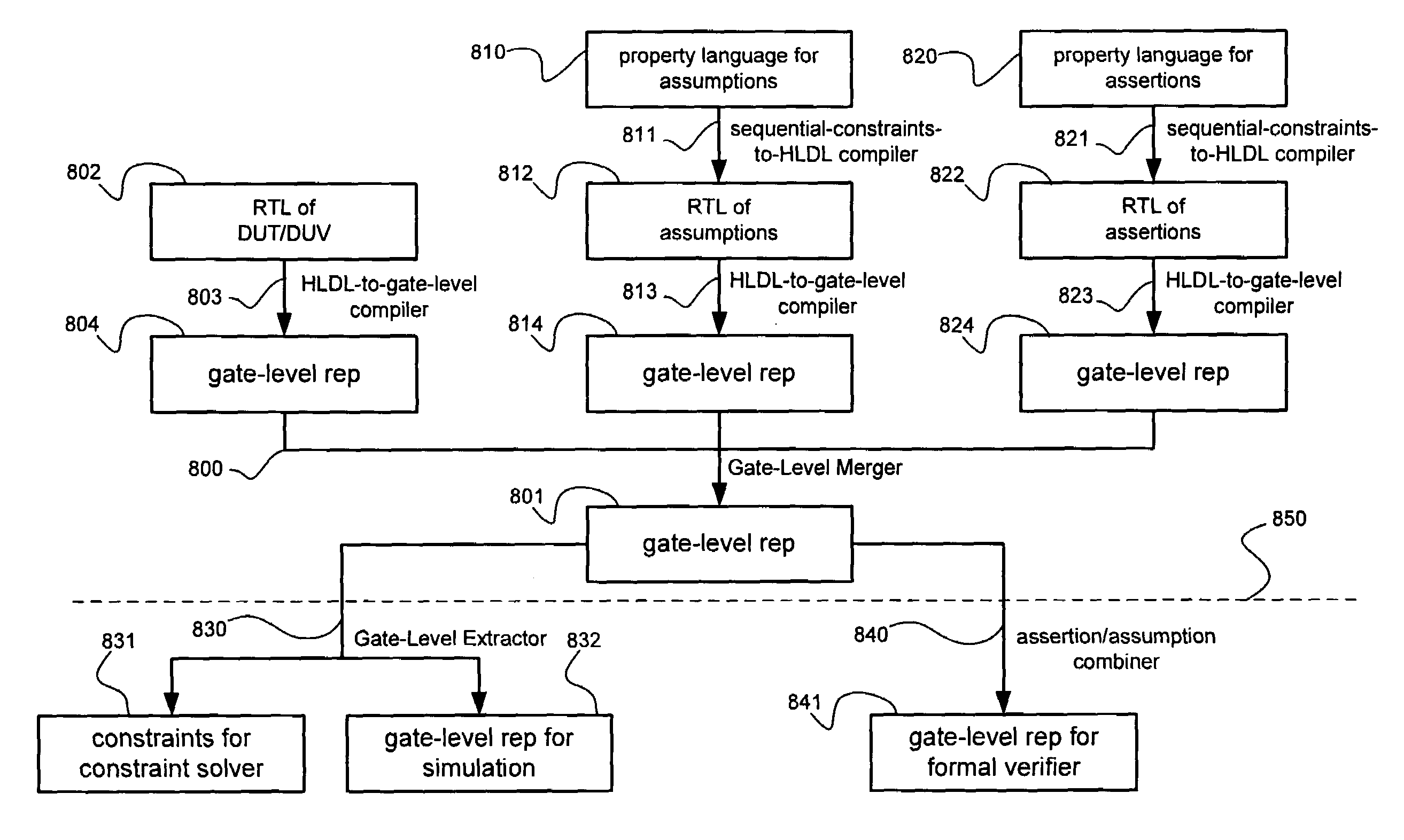

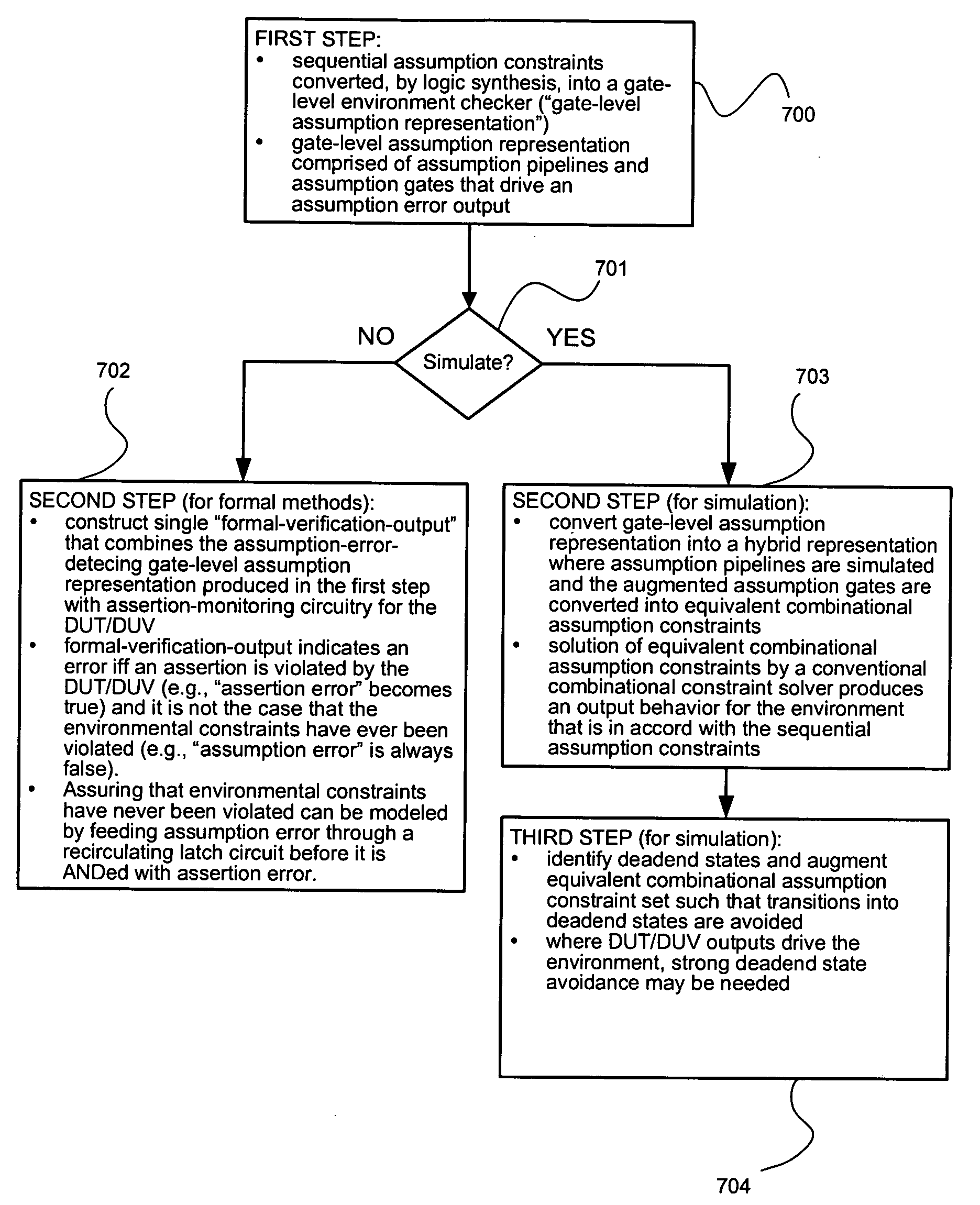

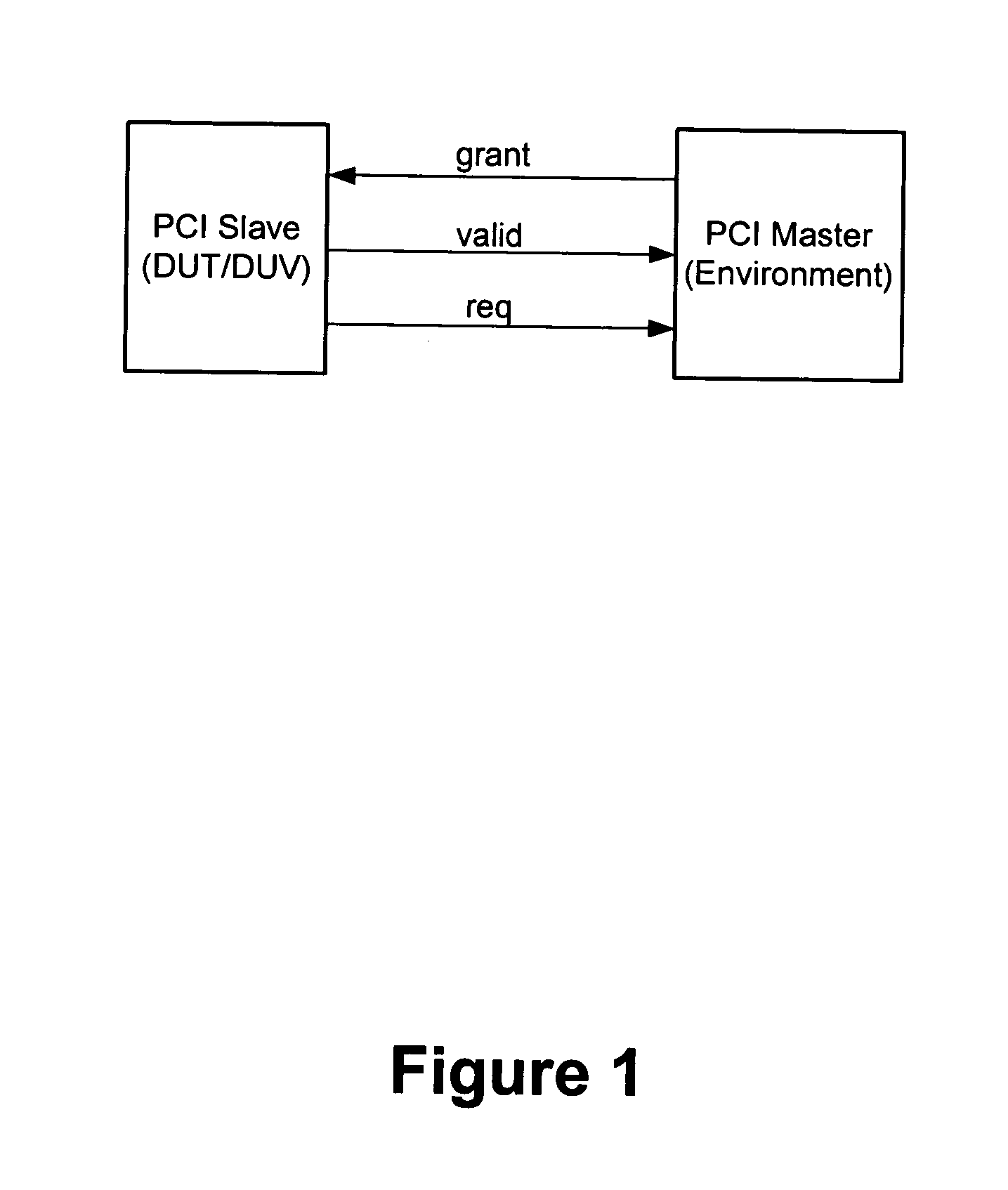

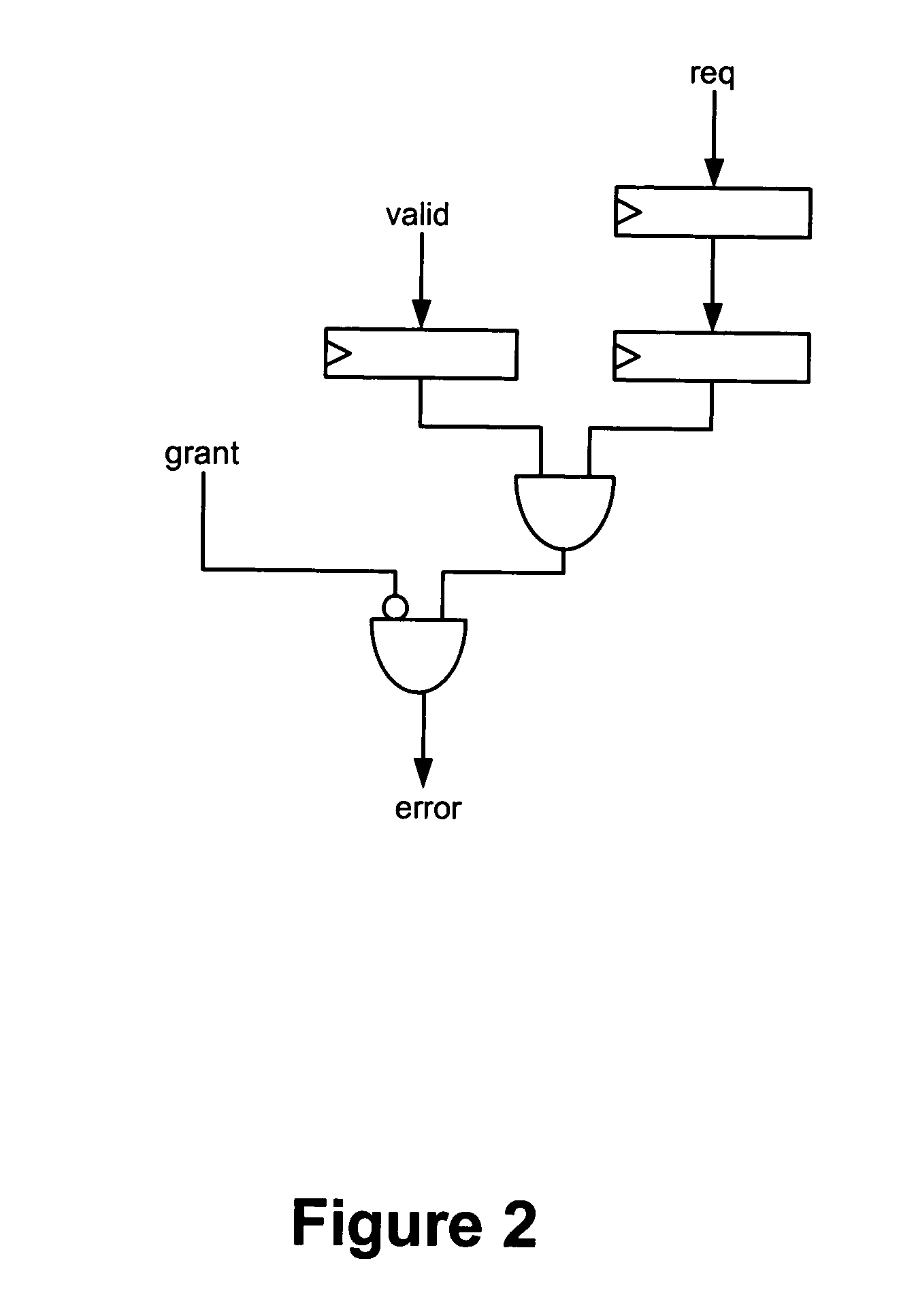

Method and apparatus for solving sequential constraints

ActiveUS7076753B2Computer aided designSoftware simulation/interpretation/emulationLogic synthesisCircuit design

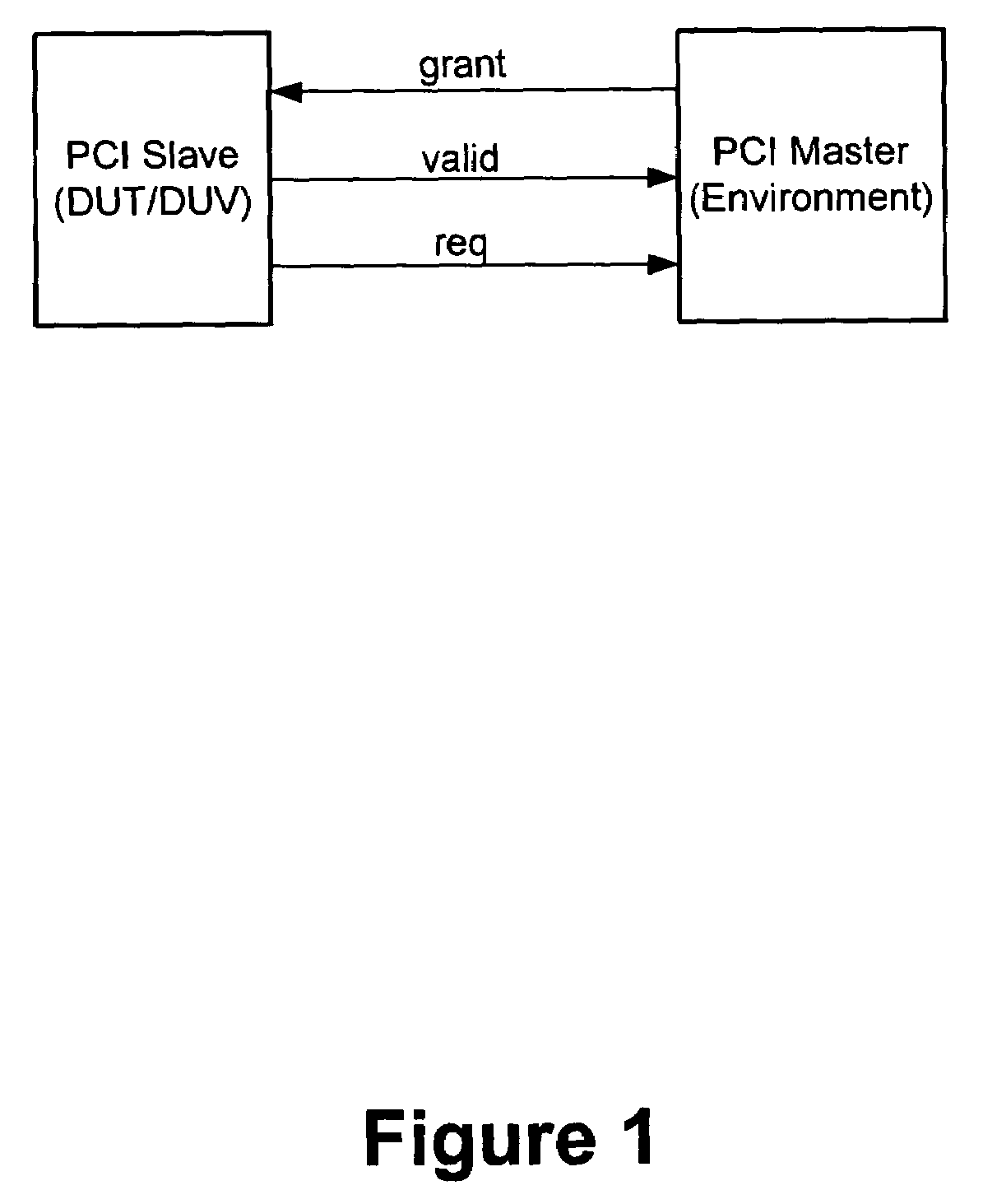

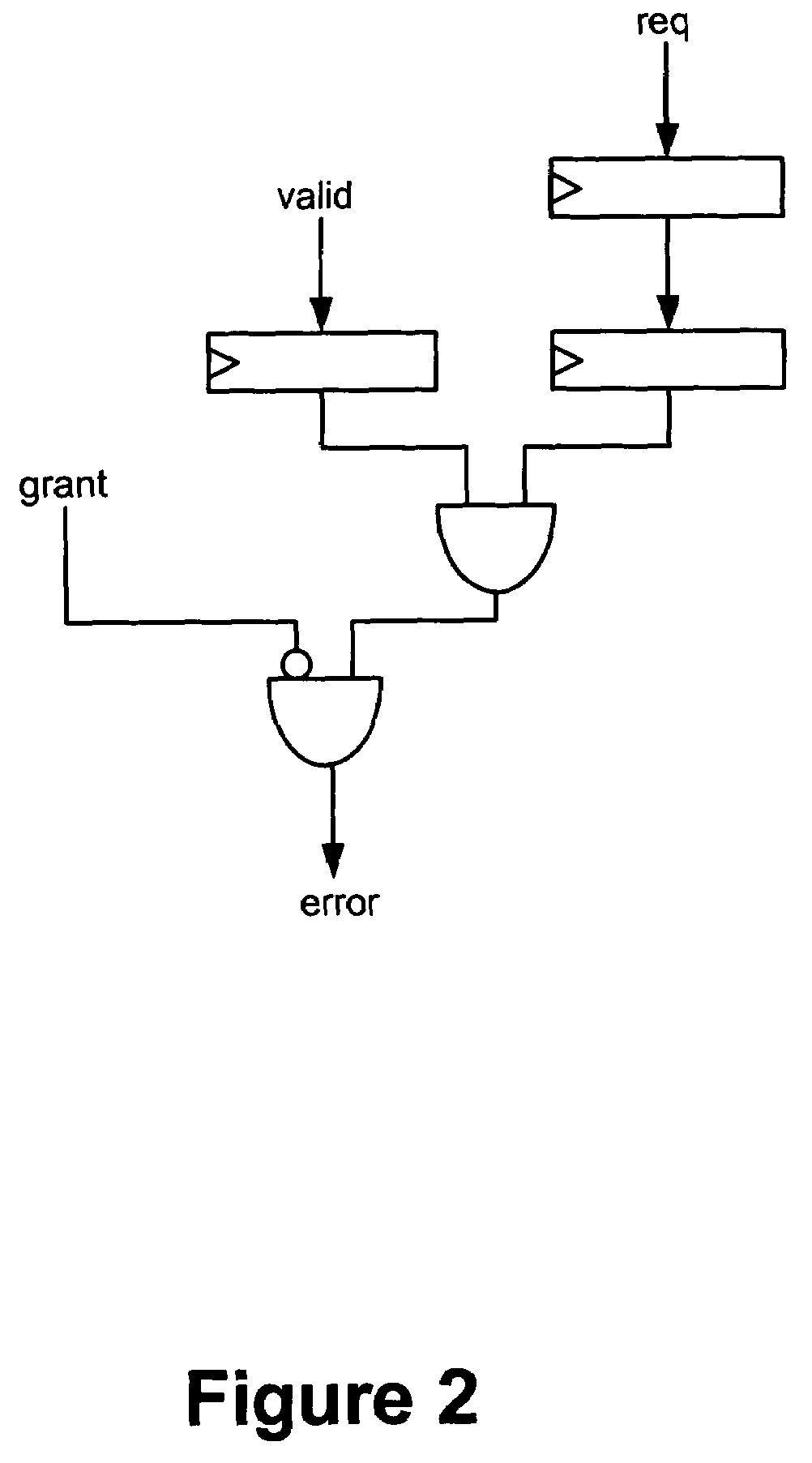

Relates to automatic conversion of assumption constraints, used in circuit design verification, that model an environment for testing a DUT / DUV, where the assumptions specify sequential behavior. Such assumptions are converted, with the use of logic synthesis tools, into a gate-level representation. For formal verification, a verification output is constructed from the gate-level representation and DUT / DUV assertion-monitoring circuitry. A formal verifier seeks to prove the verification output cannot indicate a design error. For simulation verification, the gate-level representation is converted into a hybrid representation comprising pipelines and combinational constraints. During simulation, the pipelines hold state information necessary for a solution, of the combinational constraints, to be in accord with the sequential assumption constraints. For certain sequential assumption constraints, the combinational constraints are insufficient to insure avoidance of deadend states. In a deadend state, an assumption is violated. A method is presented for augmenting the combinational constraints to avoid deadend states.

Owner:SYNOPSYS INC

Providing answers to questions using logical synthesis of candidate answers

A method, system and computer program product for generating answers to questions. In one embodiment, the method comprises receiving an input query, decomposing the input query into a plurality of different subqueries, and conducting a search in one or more data sources to identify at least one candidate answer to each of the subqueries. A ranking function is applied to each of the candidate answers to determine a ranking for each of these candidate answers; and for each of the subqueries, one of the candidate answers to the subquery is selected based on this ranking. A logical synthesis component is applied to synthesize a candidate answer for the input query from the selected the candidate answers to the subqueries. In one embodiment, the procedure applied by the logical synthesis component to synthesize the candidate answer for the input query is determined from the input query.

Owner:INT BUSINESS MASCH CORP

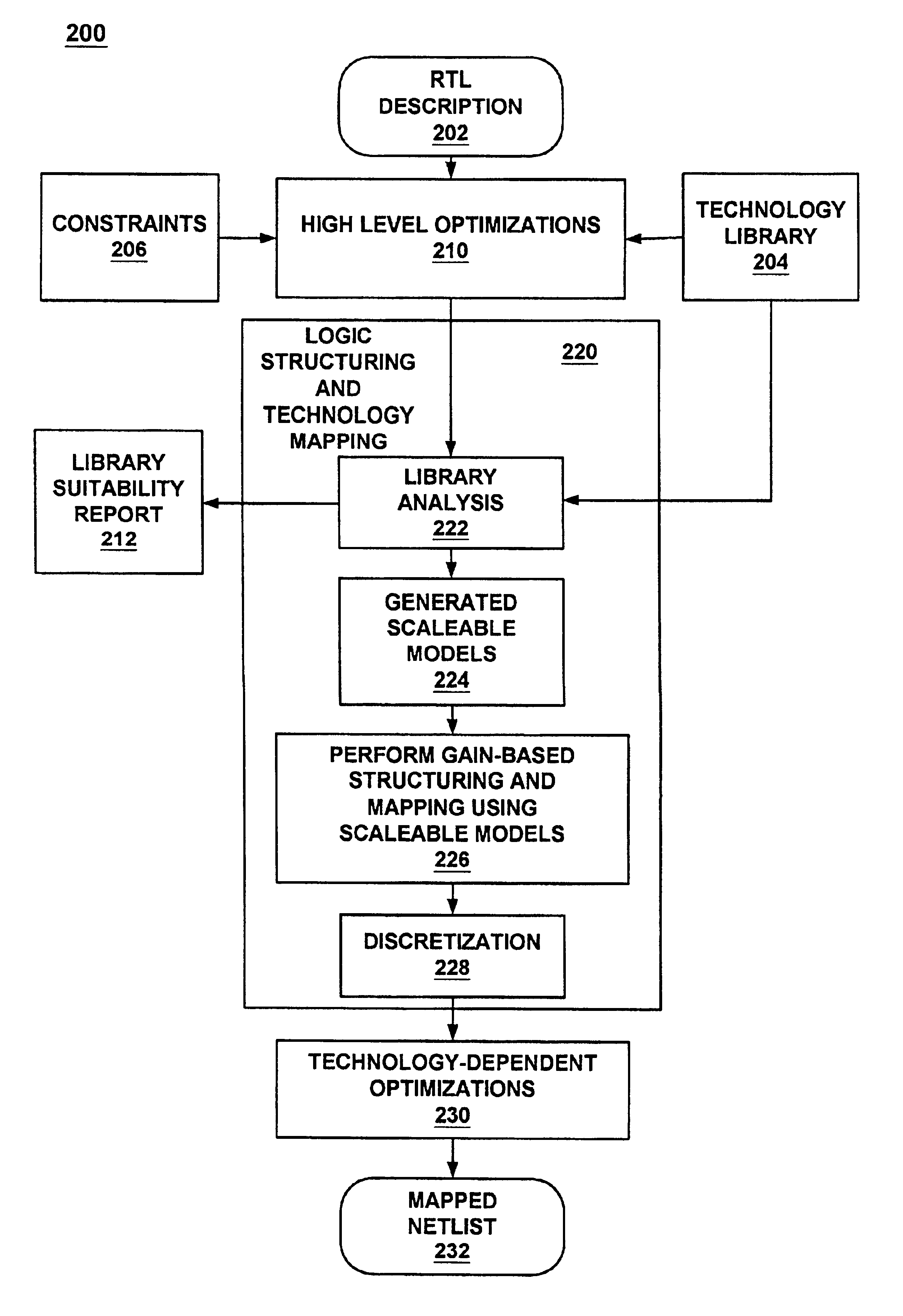

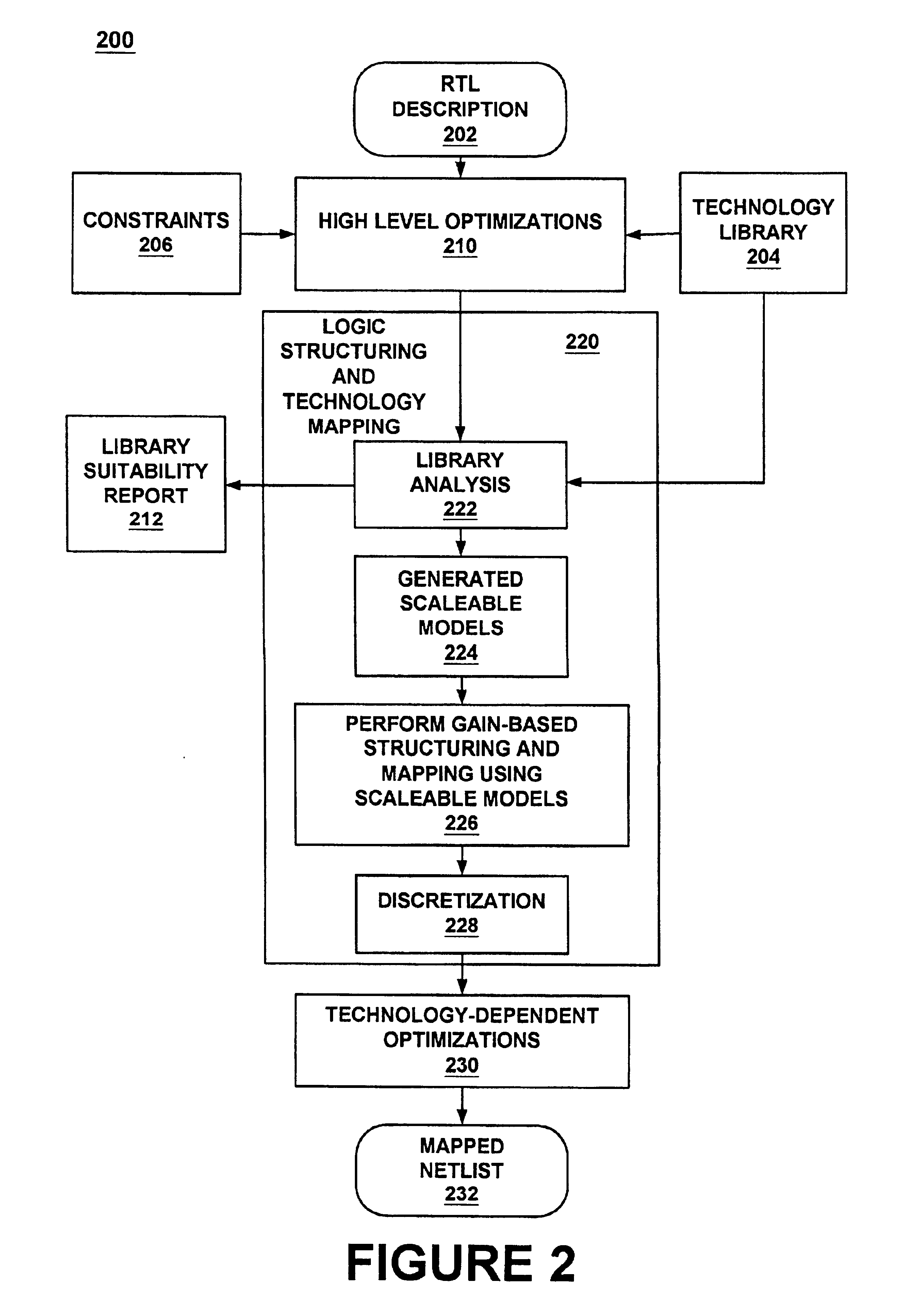

Non-linear, gain-based modeling of circuit delay for an electronic design automation system

InactiveUS6912702B1CAD circuit designSoftware simulation/interpretation/emulationCapacitanceTechnology dependent

A non-linear, gain-based modeling of circuit delay within an electronic design automation system. The present invention provides a scalable cell model for use in early logic structuring and mapping for the design of integrated circuits. The scalable cell model includes a four dimensional delay model accepting input slew and gain and providing delay and output slew. By eliminating output loading as a requirement for delay computations, the scalable model of the present invention can effectively be used to provide accurate delay information for early logic synthesis processes, e.g., that precede technology dependent optimizations where the actual load of a cell is unknown. This scalable cell model considers: the impact of transition times on delay; complex gates having different input capacitances for different input pins; the impact of limited discrete cell sizes in the technology library; and design rules, e.g., maximum capacitance and maximum transition associated with gates. A technology library is analyzed and clustering is performed to select a cluster of cells for each cell group of a common functionality. A nominal input slew value is computed for all cells and a scaling factor is computed for each cell of each cluster. From each cluster, a four dimensional gain-based non-linear scalable cell model (look-up table) is generated. A default gain is computed for each scalable cell model and an area model and an input pin capacitance model are generated for each scalable cell model.

Owner:SYNOPSYS INC

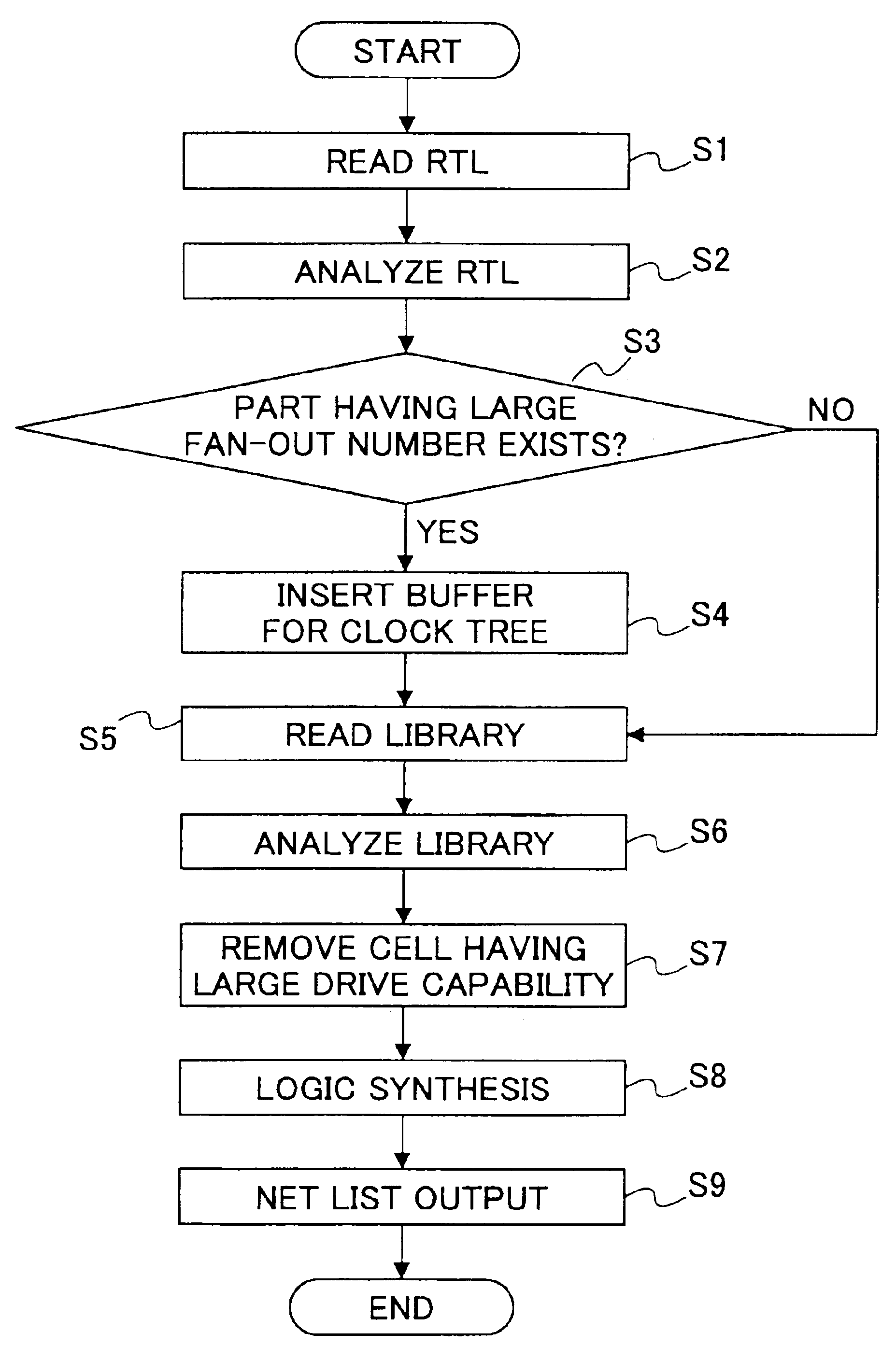

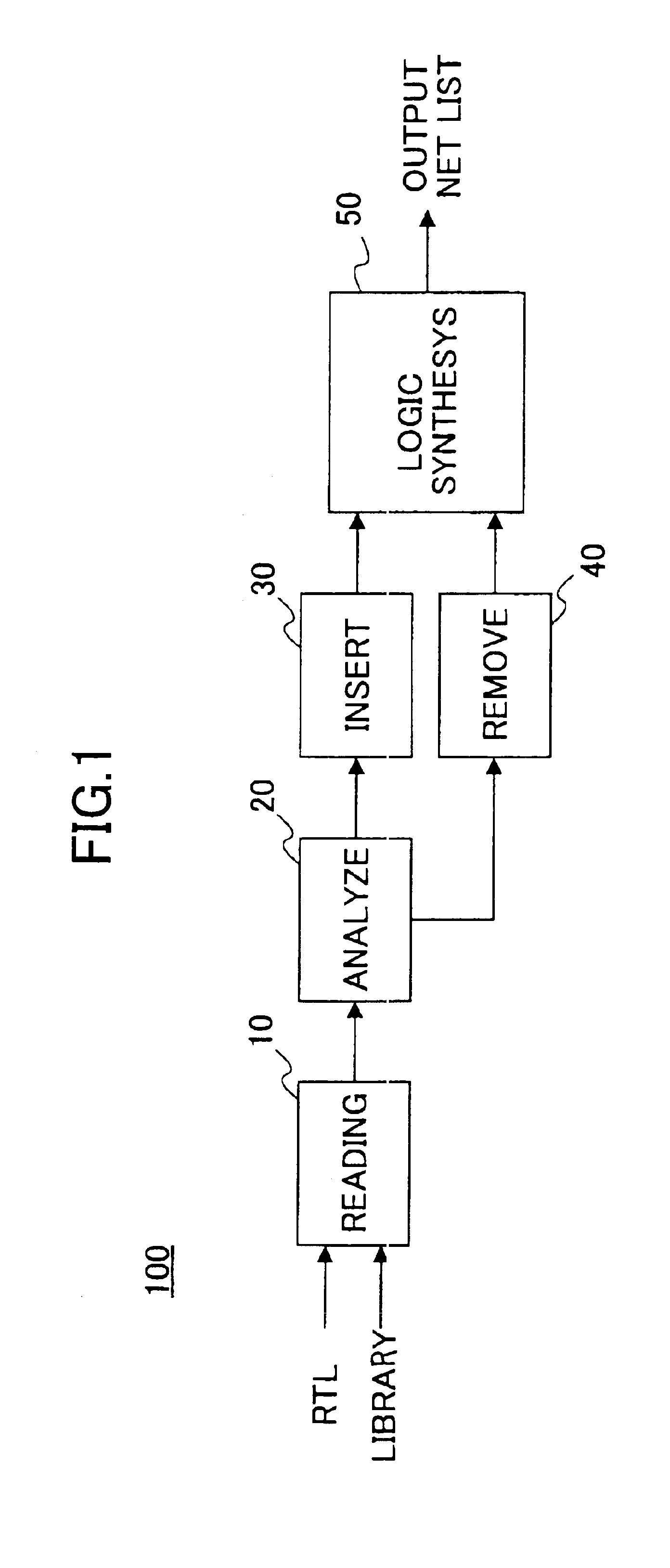

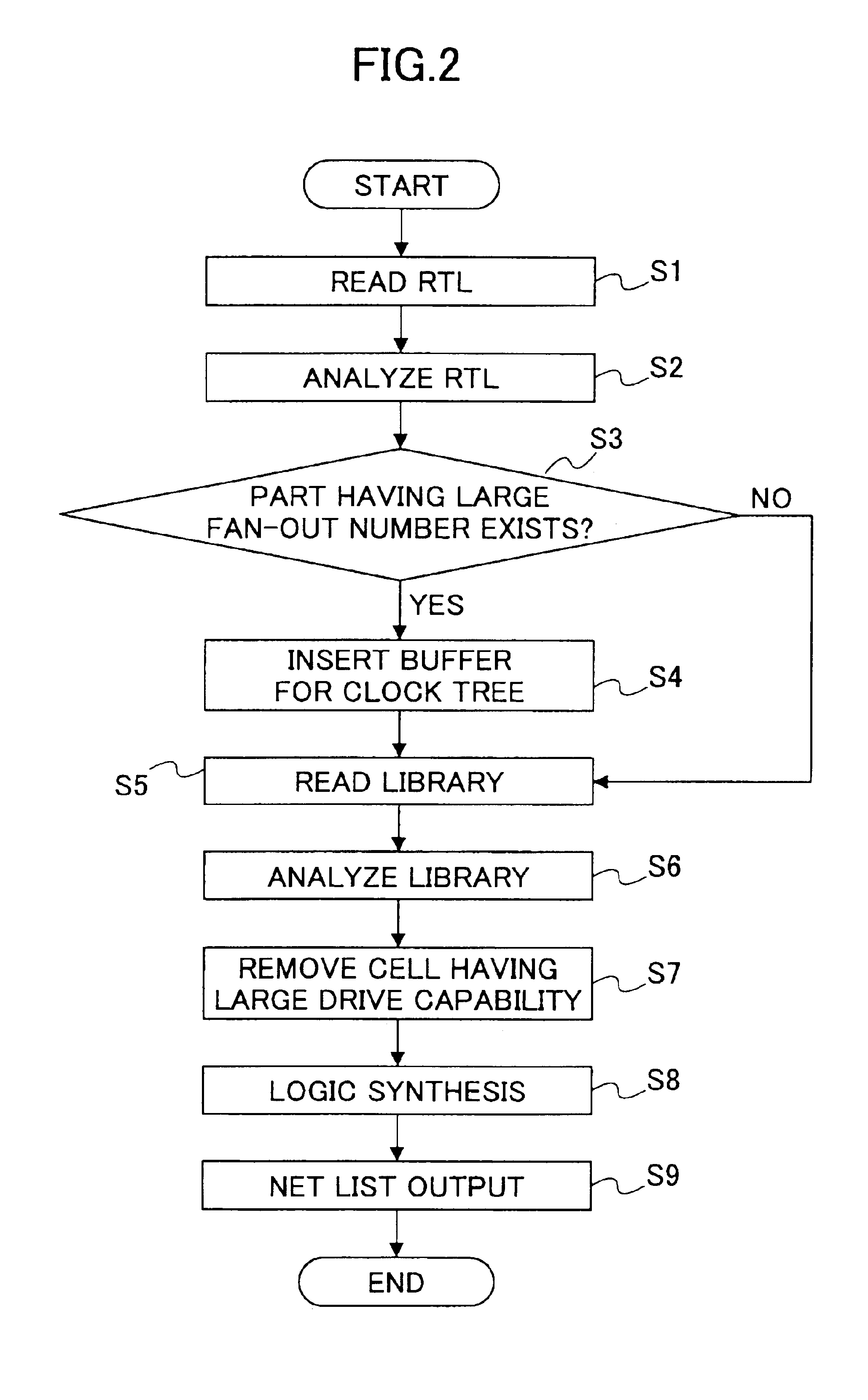

Logic synthesis device and logic synthesis method

InactiveUS6910202B2Unnecessary loadUnnecessary load can be avoidedSemiconductor/solid-state device manufacturingComputer aided designSynthesis methodsTheoretical computer science

An analysis part analyzes a description of a logic design; an extraction part extracts a part of the description of the logic design having a fan-out number beyond a predetermined value, based on the analysis; an insertion part inserts a buffer for clock tree synthesis for performing an adjustment on the part extracted by said extracting part, the adjustment being performed at a time of subsequent layout process; and a logic synthesis part performs logic synthesis on the description of the logic design obtained after the insertion performed by said inserting part.

Owner:RICOH KK

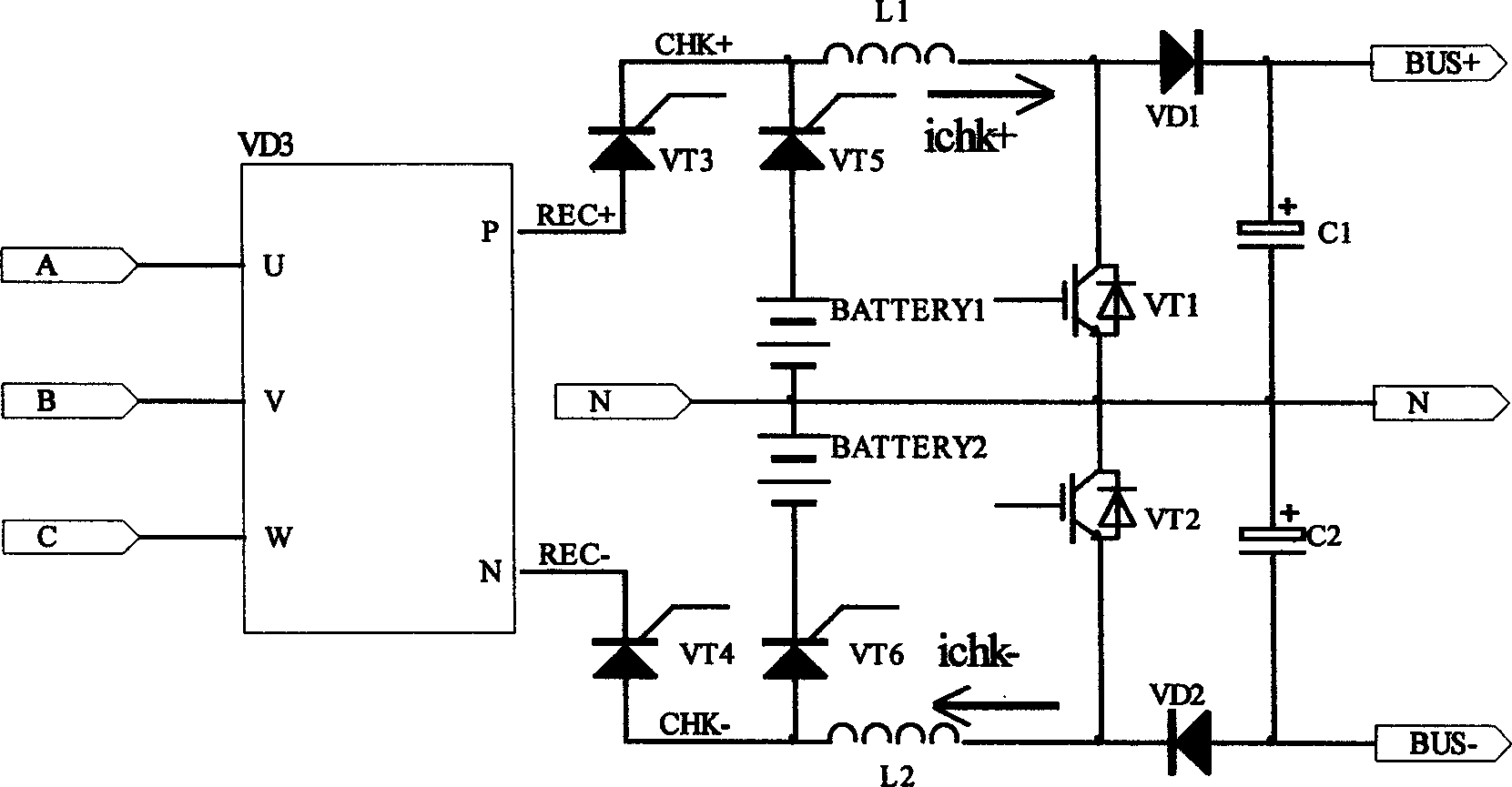

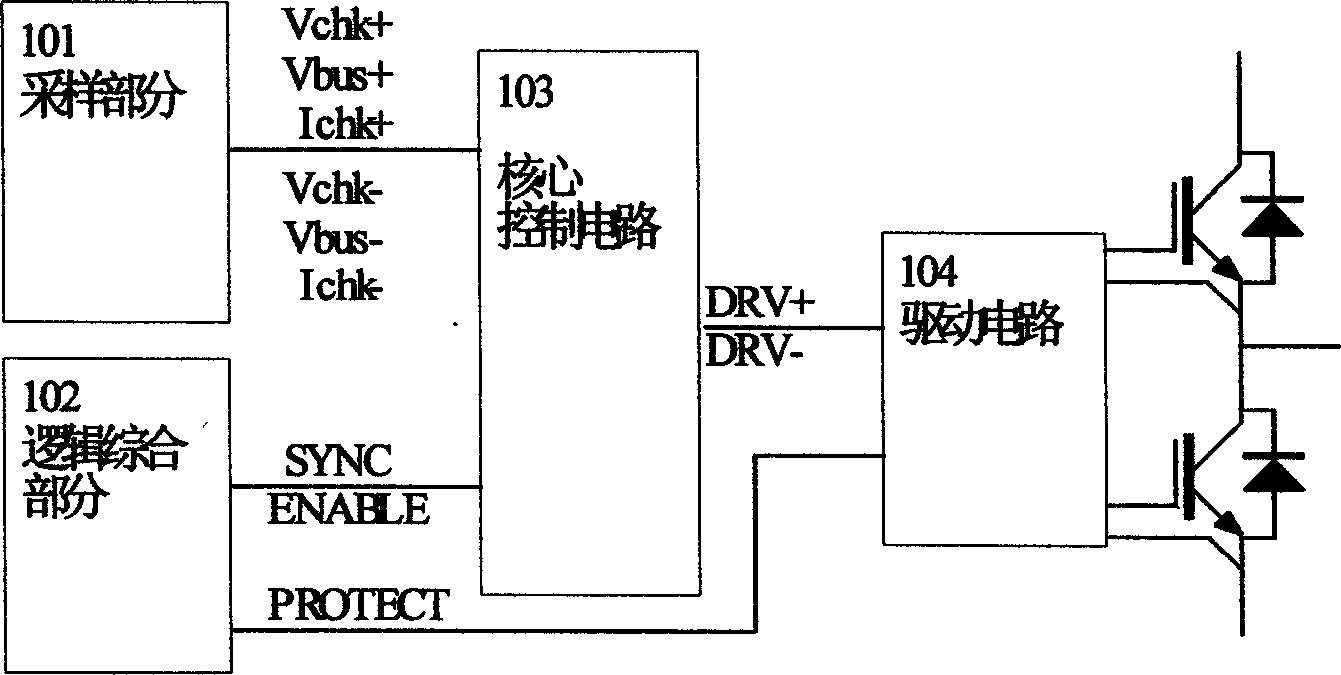

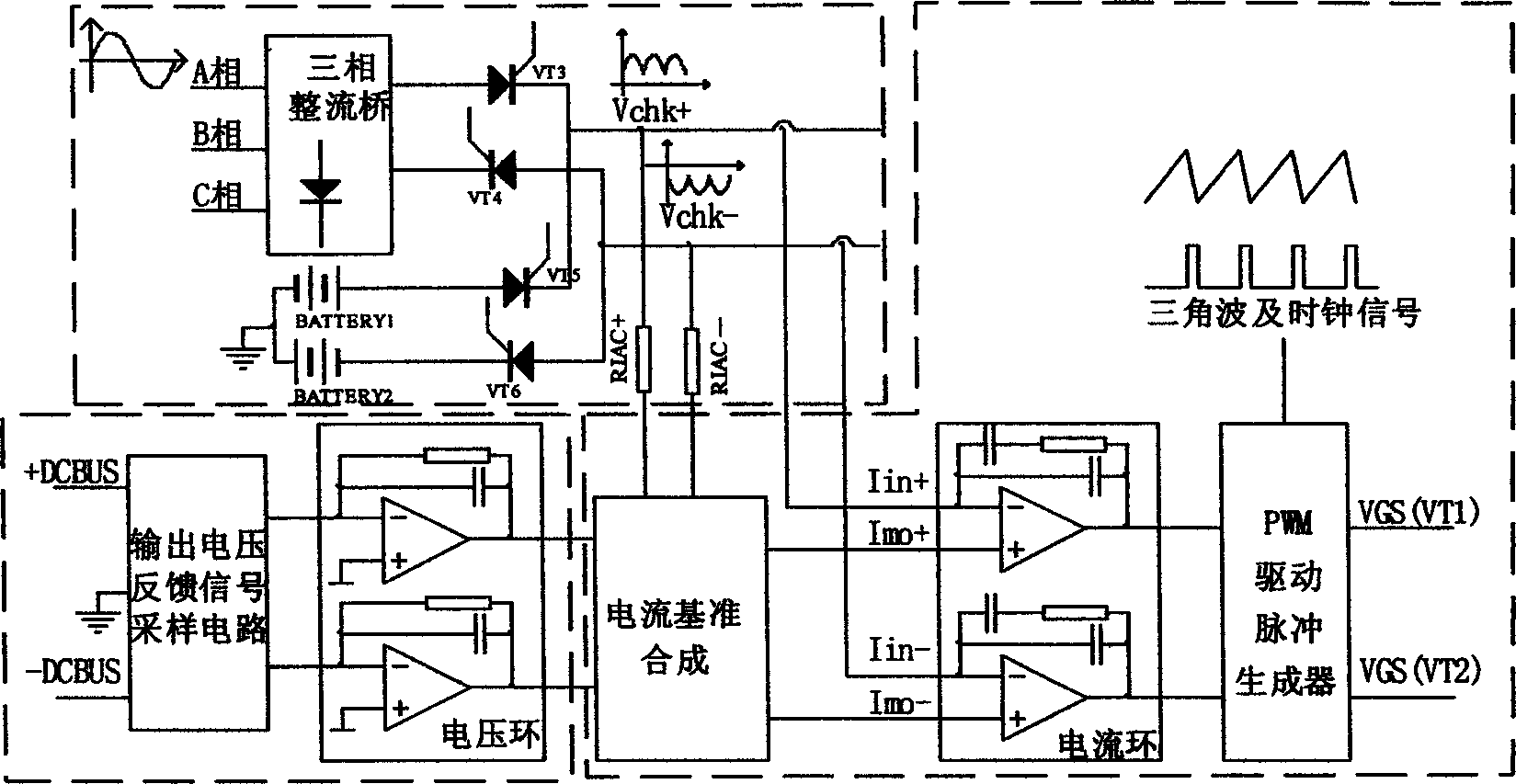

Circuit providing output in three electrical levels for correcting two-phase power factor

InactiveCN1540848AReduce weight and sizeReduce complexityEfficient power electronics conversionEnergy industryThree-phasePerformance index

The disclosed correcting circuit and control device possesses features of small size and weight, low complex degree, excellent performance index being suitable to larger power. Circuit providing output in three electrical levels for correcting three-phase power factor includes: triphase rectification bridge VD3, power switch 'VT3, VT4, VT5, VT6', voltage boosting main tube 'VTl, VT2' voltage boosting diodes 'VDl, VD2' etc. Controlling device includes signal sempling unt, logic synthesis unit, core control unit and drive unit.

Owner:ZTE CORP

Method and apparatus for solving sequential constraints

ActiveUS20050138585A1Strong constraintComputer aided designSoftware simulation/interpretation/emulationLogic synthesisCircuit design

Relates to automatic conversion of assumption constraints, used in circuit design verification, that model an environment for testing a DUT / DUV, where the assumptions specify sequential behavior. Such assumptions are converted, with the use of logic synthesis tools, into a gate-level representation. For formal verification, a verification output is constructed from the gate-level representation and DUT / DUV assertion-monitoring circuitry. A formal verifier seeks to prove the verification output cannot indicate a design error. For simulation verification, the gate-level representation is converted into a hybrid representation comprising pipelines and combinational constraints. During simulation, the pipelines hold state information necessary for a solution, of the combinational constraints, to be in accord with the sequential assumption constraints. For certain sequential assumption constraints, the combinational constraints are insufficient to insure avoidance of deadend states. In a deadend state, an assumption is violated. A method is presented for augmenting the combinational constraints to avoid deadend states.

Owner:SYNOPSYS INC

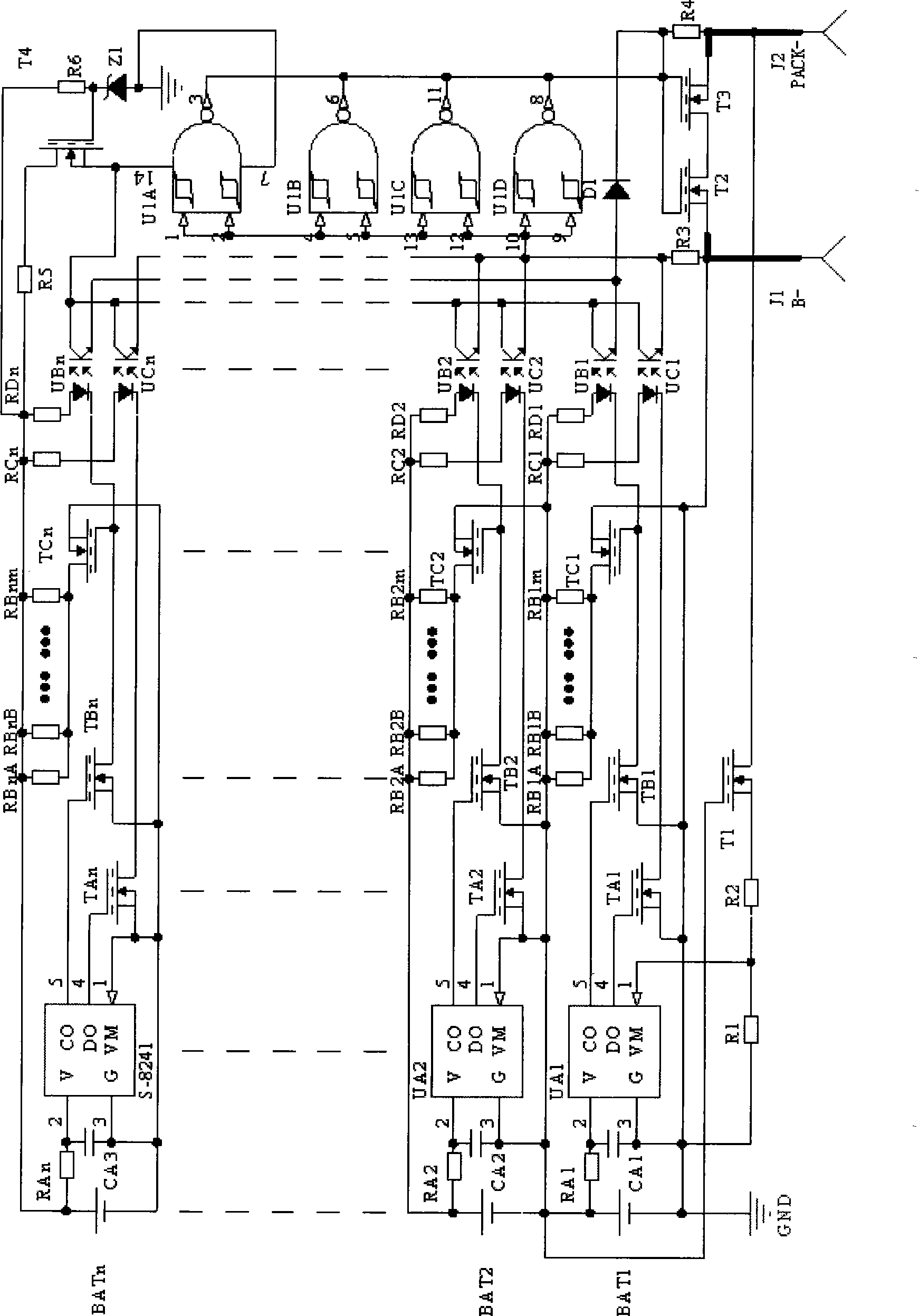

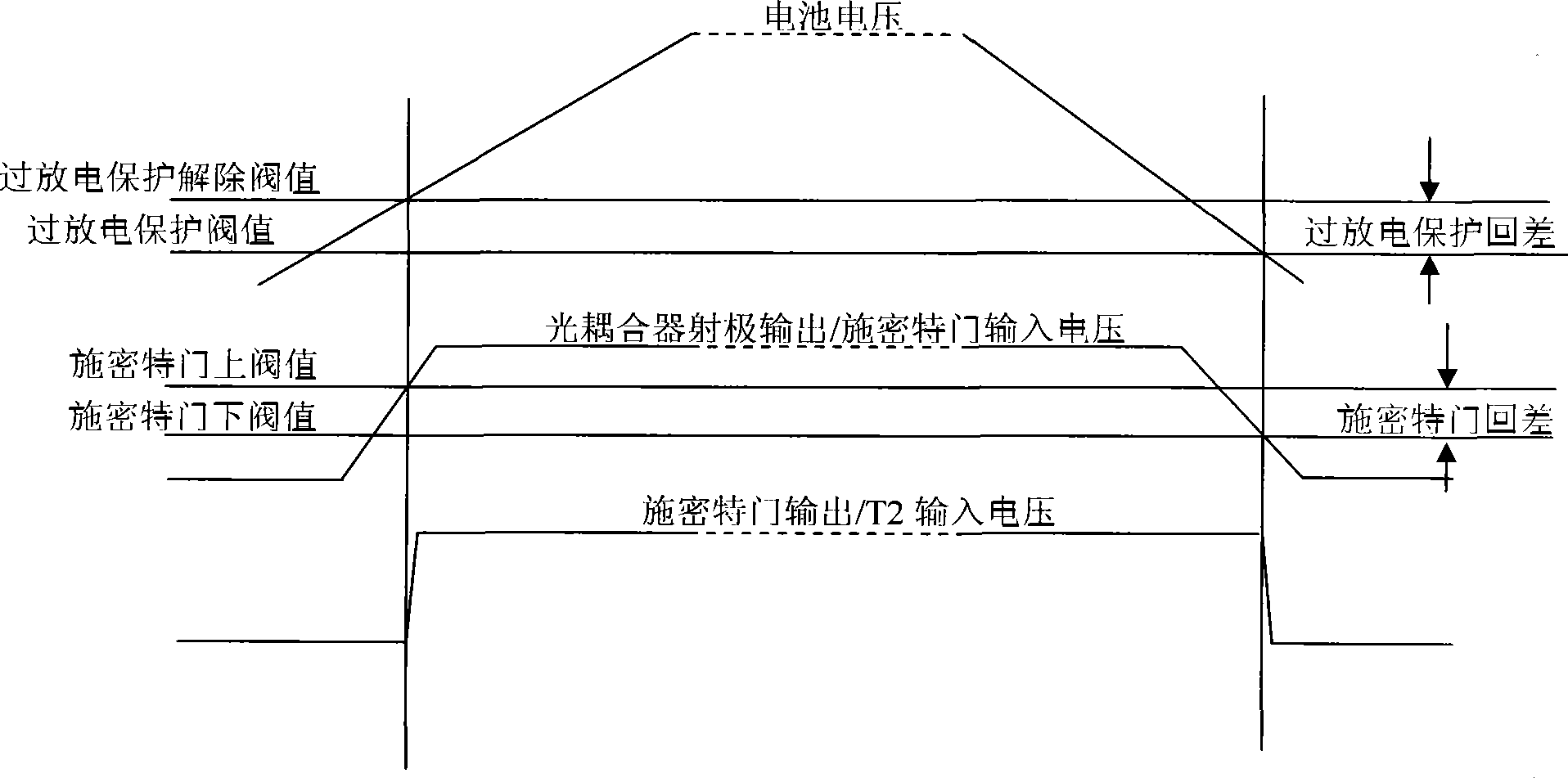

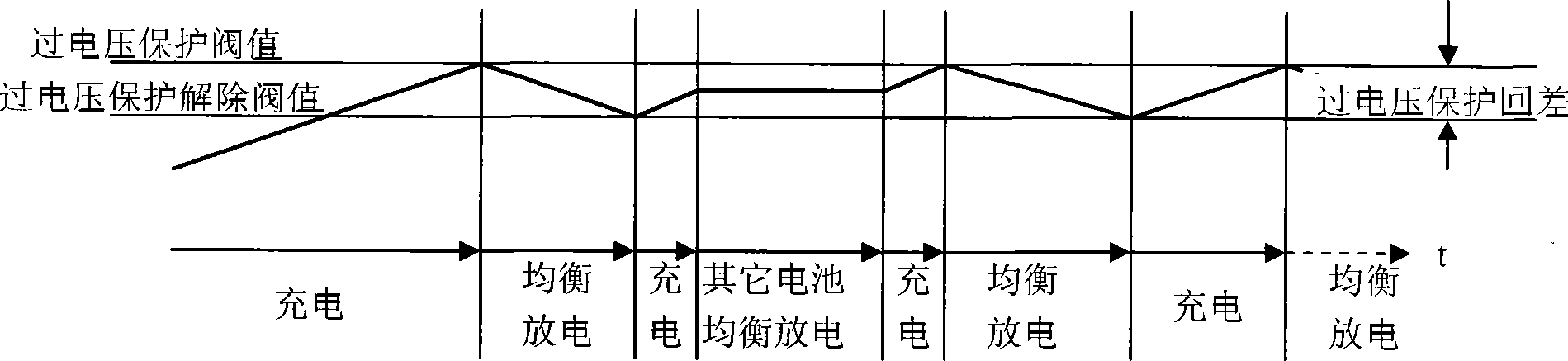

Cascade combined protection equilibrium module for large-capacity lithium ion battery

InactiveCN101442209AReduce self-consumption currentImprove detection accuracyBatteries circuit arrangementsEmergency protective circuit arrangementsMOSFETControl signal

The invention provides a series combination protecting-balancing module for high-capacity lithium ion batteries, which adopts a special micropower integrated circuit of a single lithium ion battery as a detection controller of individual battery voltage, reduces consumable current, and obtains high-precision detection voltage. Optical couplers are driven through a MOSFET, so as to realize the logic synthesis and level transfer of the charge-discharge protection control signals of every individual battery, and a Schmidt trigger circuit is adopted to reshape a total discharge control signal. The sampling of the current value and voltage limitation of a loading loop are realized through a MOSFET source follower circuit, and the multilevel current and short-circuit detecting function of a special integrated circuit is utilized to realize over-current and short-circuit protection and state keeping. The power supply of a control loop is realized by use of a whole-set electricity taking mode, so as to guarantee the consumable current balance of every individual battery; and an intermittent balance control mode is realized by utilizing the voltage-delay return difference of charging-protection staring-releasing control signals.

Owner:WEIHAI KEYIDA ELECTRONICS

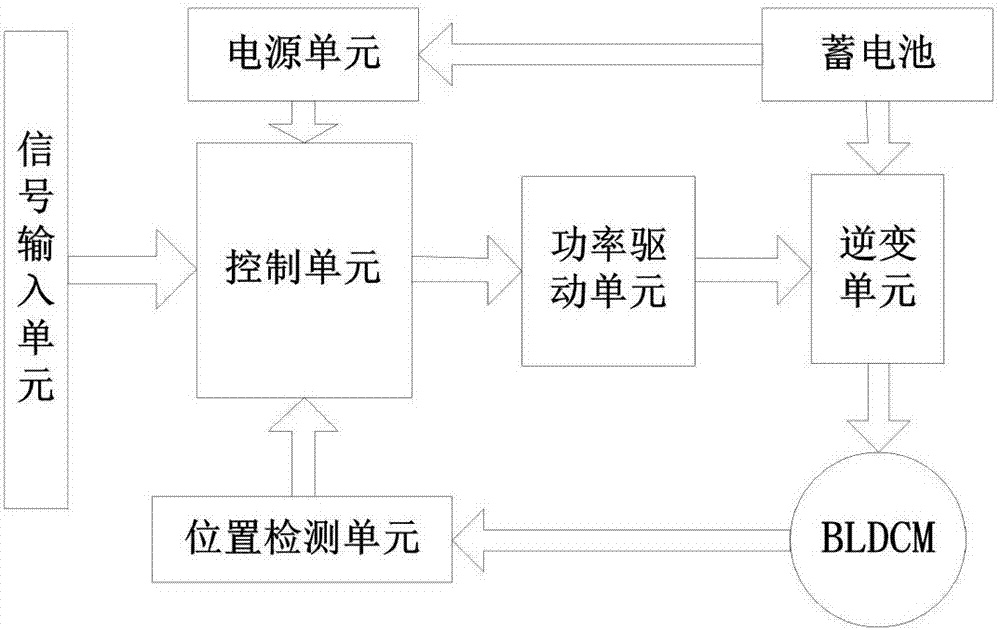

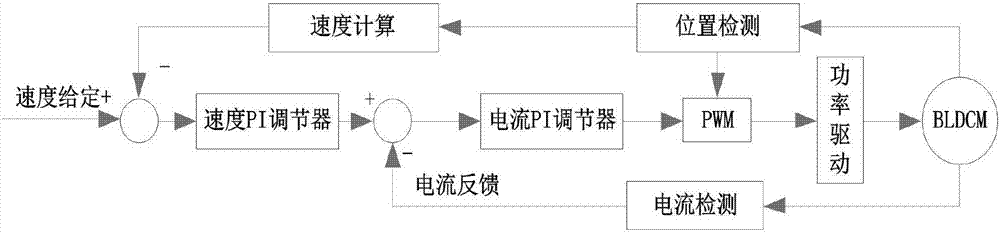

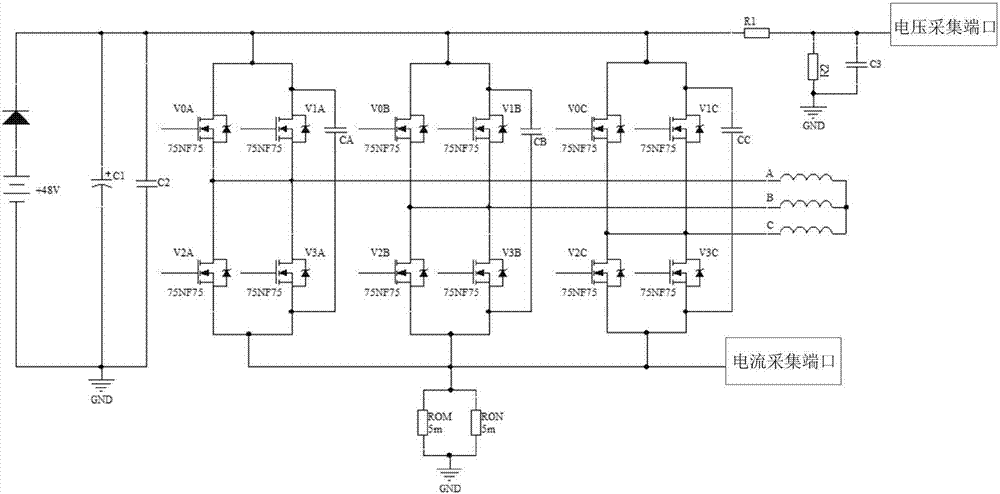

Electric vehicle permanent magnet DC brushless motor controller and control method

ActiveCN107086827ARealize self-lockingImprove efficiencyElectronic commutatorsOvervoltageBrushless motors

The invention discloses an electric vehicle permanent magnet DC brushless motor controller and a control method. The electric vehicle permanent magnet DC brushless motor controller comprises a control unit, a power driving unit, an inverter unit and BLDCM, a position detection unit and a signal input unit; subjects various input signals to logic synthesis in order to provide various control signals for a driving circuit; generates a PWM signal with a corresponding duty cycle in order to adjust the rotating speed of a motor, realizes motor self-locking by changing a driving timing sequence; and achieves overcurrent, undervoltage, and overvoltage fault protection functions. While guaranteeing the normal operation of an electric vehicle, the electric vehicle permanent magnet DC brushless motor controller improves the efficiency of the motor and a storage battery, saves energy, is simple in hardware structure, low in cost, perfect in function and high in reliability, and has high application and promotion values.

Owner:HUBEI UNIV OF AUTOMOTIVE TECH

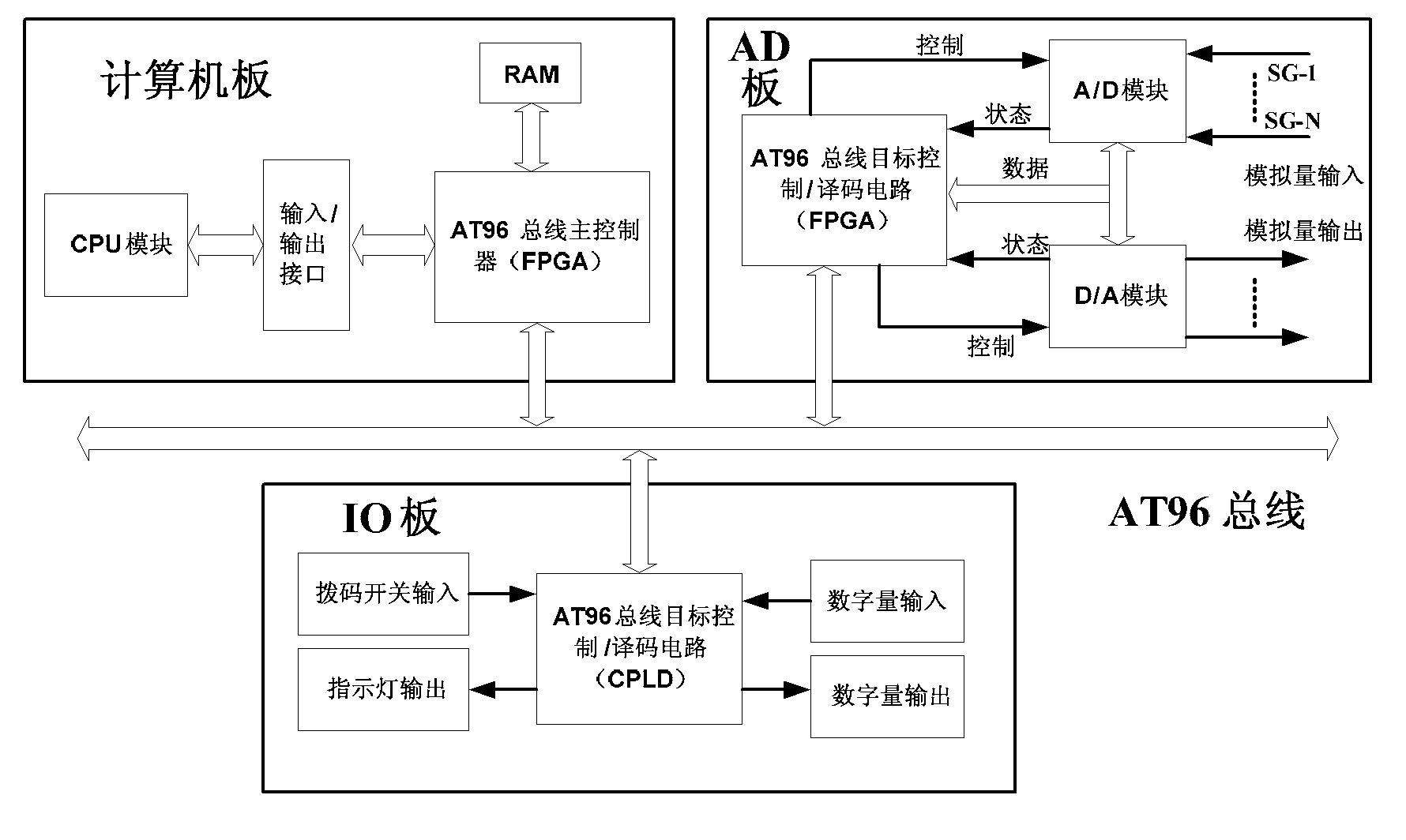

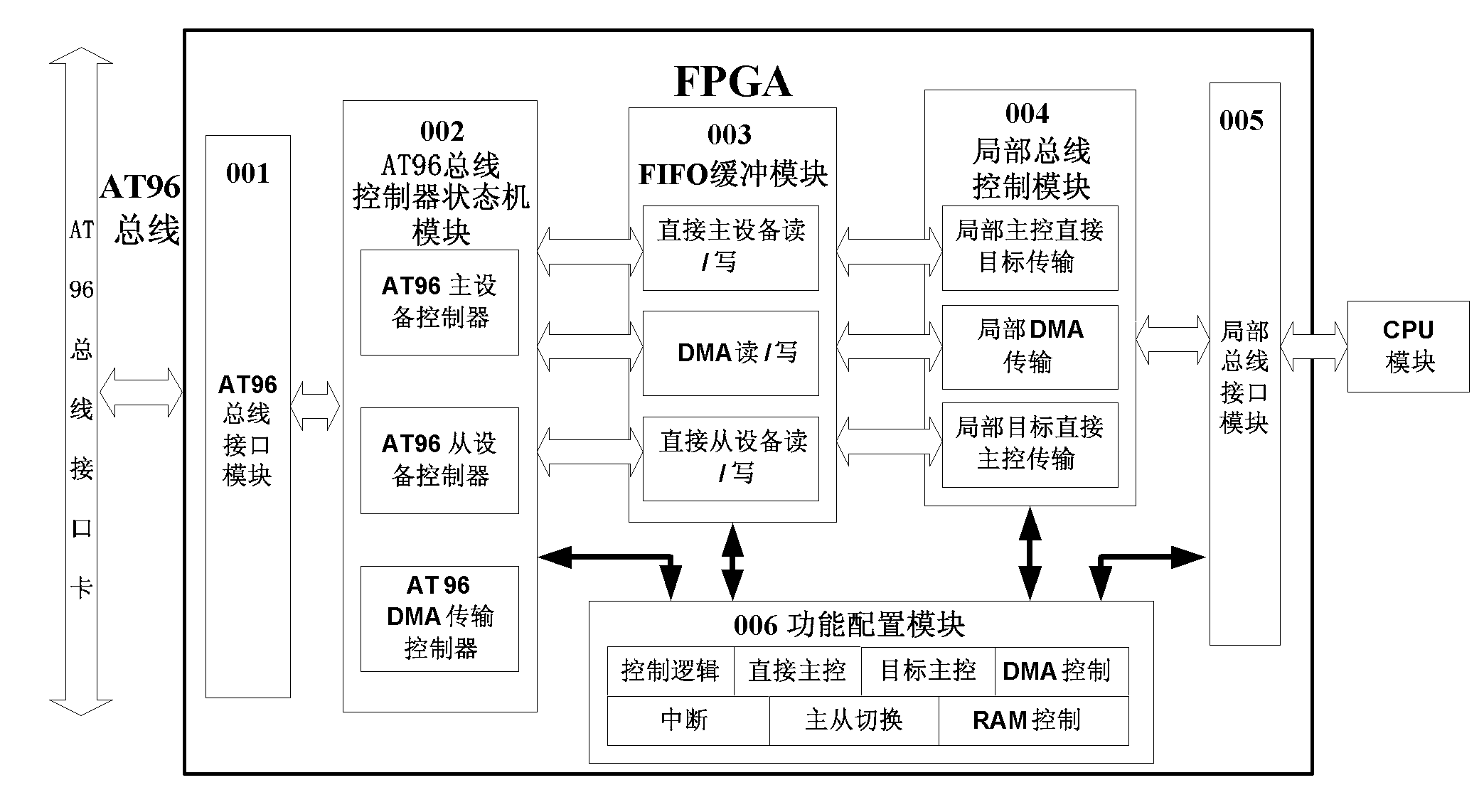

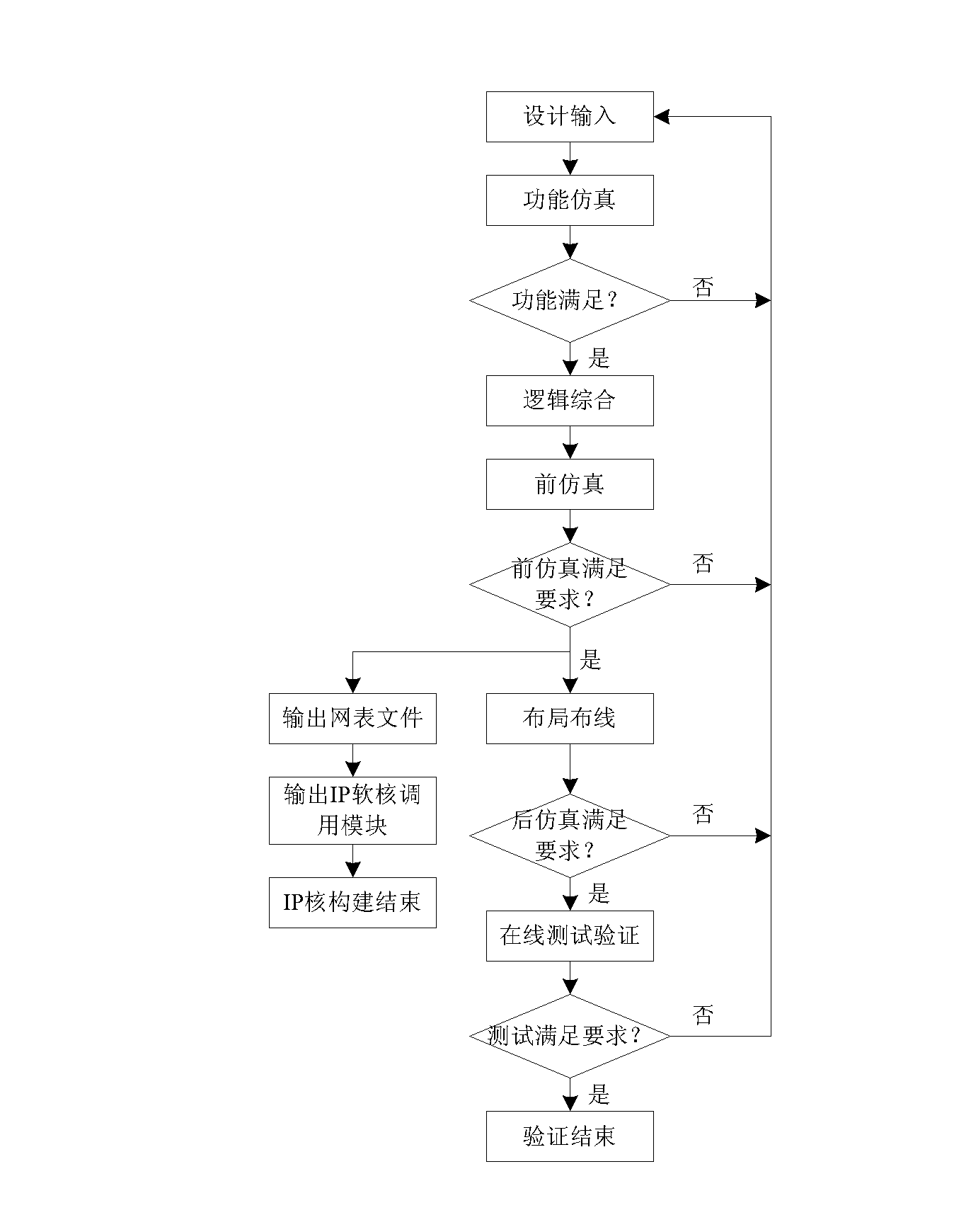

AT96 bus controller IP (internet protocol) core based on FPGA (field programmable gate array) and construction method thereof

InactiveCN102184148AReduce loadFlexible designElectric digital data processingInternet protocol suiteComputer module

The invention relates to an AT96 bus controller IP (internet protocol) core based on an FPGA (field programmable gate array), which comprises an AT96 bus interface module, an AT96 bus controller state machine module, a FIFO (first in, first out) cache module, a local bus control module, a local bus interface module and a function configuration module, wherein one end of the AT96 bus interface module is connected to an AT96 bus interface card while the other end is connected to the AT96 bus controller state machine module; the AT96 bus controller state machine module is connected to the FIFO cache module; the FIFO cache module is connected to the local bus control module; the local bus control module is connected to the local bus interface module; and the function configuration module is connected to later four modules. A construction method for the AT96 bus controller IP core based on FPGA comprises the following six steps: 1) design input; 2) function simulation; 3) logic composition; 4) pre-simulation; 5) a table file output; and 6) an IP core calling module output.

Owner:BEIHANG UNIV

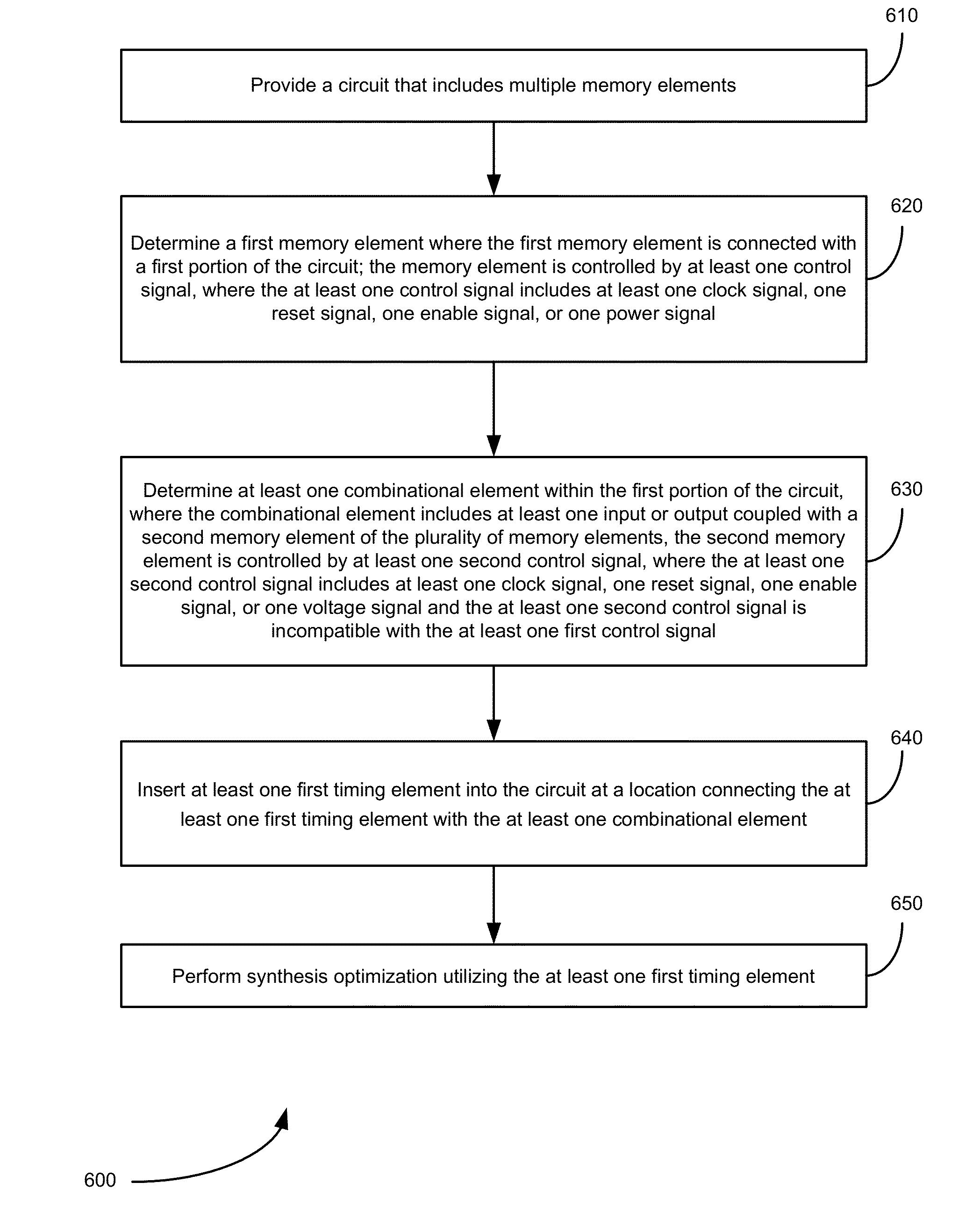

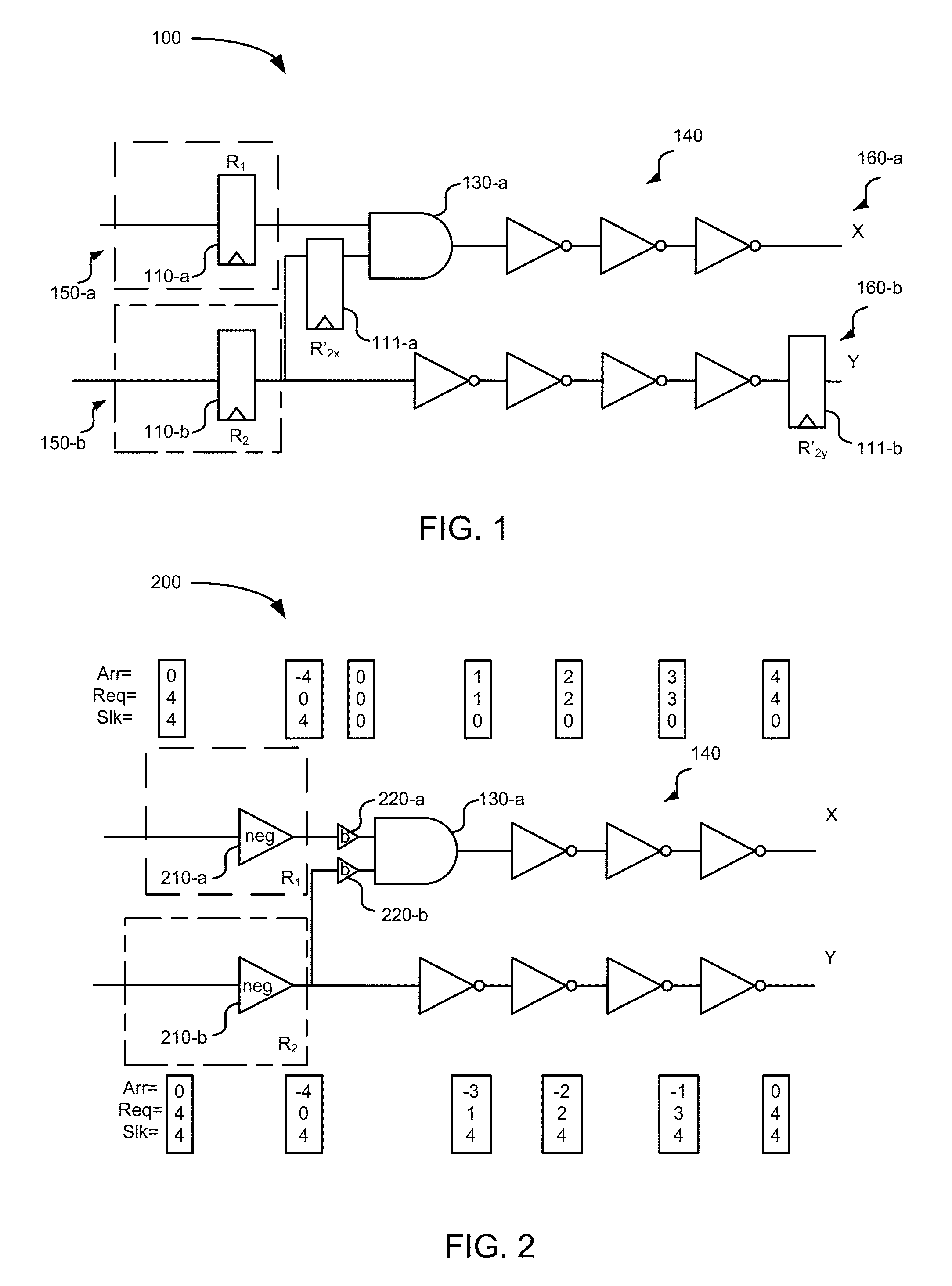

Boundary buffers to model register incompatibility during pre-retiming optimization

ActiveUS8423939B1Improve featuresRetardation valueComputer aided designSoftware simulation/interpretation/emulationControl signalComputer science

Methods, systems, and machine-readable storage medium for logic synthesis that adjust a timing model of a circuit are provided. A first memory element from multiple memory elements of the circuit may be determined, where the first memory element is connected with a first portion of the circuit and is controlled by at least one first control signal. A combinational element within the first portion of the circuit may be determined. The combinational element may include at least one input or output coupled with a second memory element. The second memory element may be controlled by at least one second control signal. The second control signal may be incompatible with the first control signal. A first timing element may be inserted into the circuit at a location connecting the first timing element with the combinational element. A synthesis optimization may be performed utilizing the at least one first timing element.

Owner:CADENCE DESIGN SYST INC

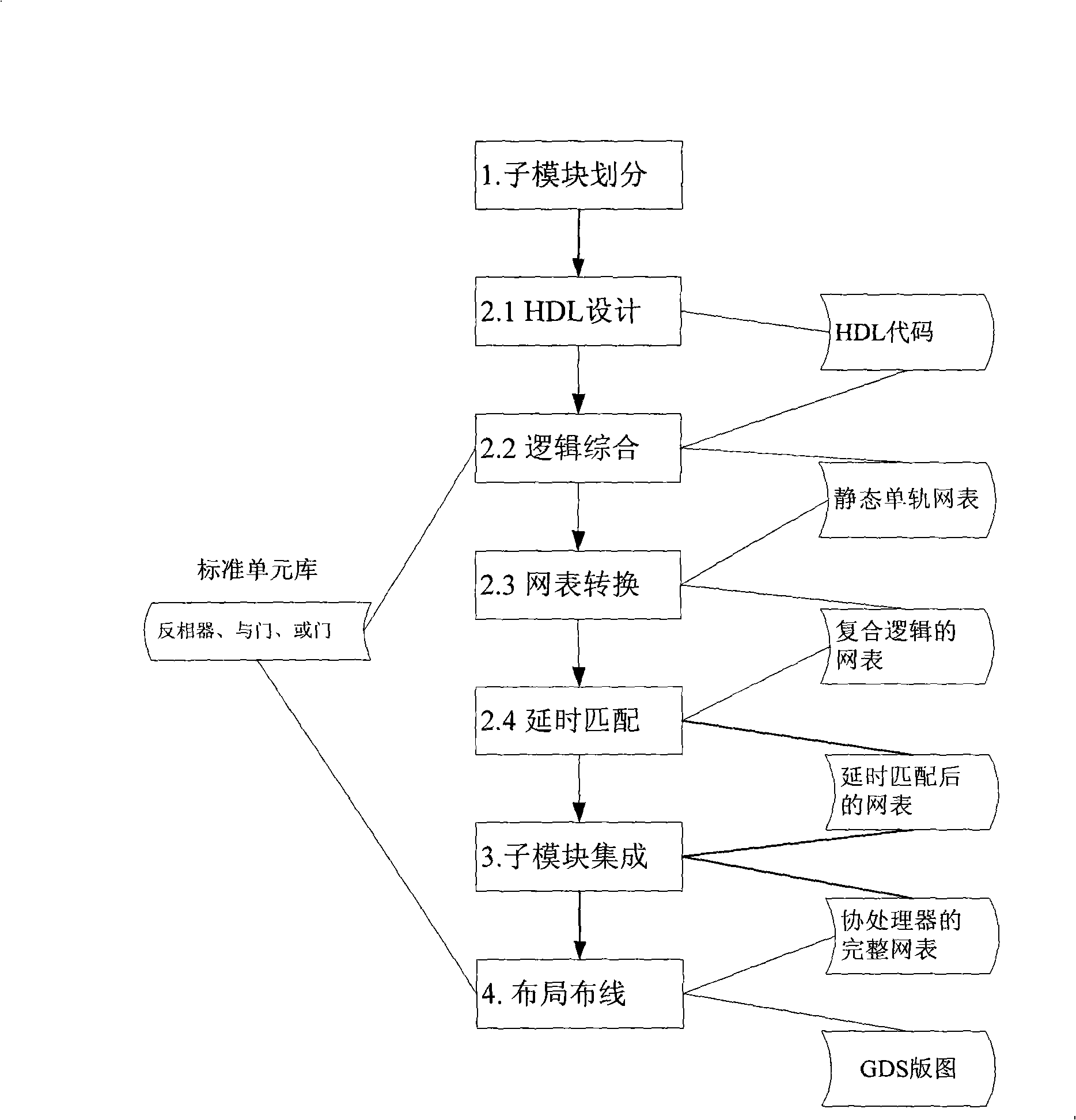

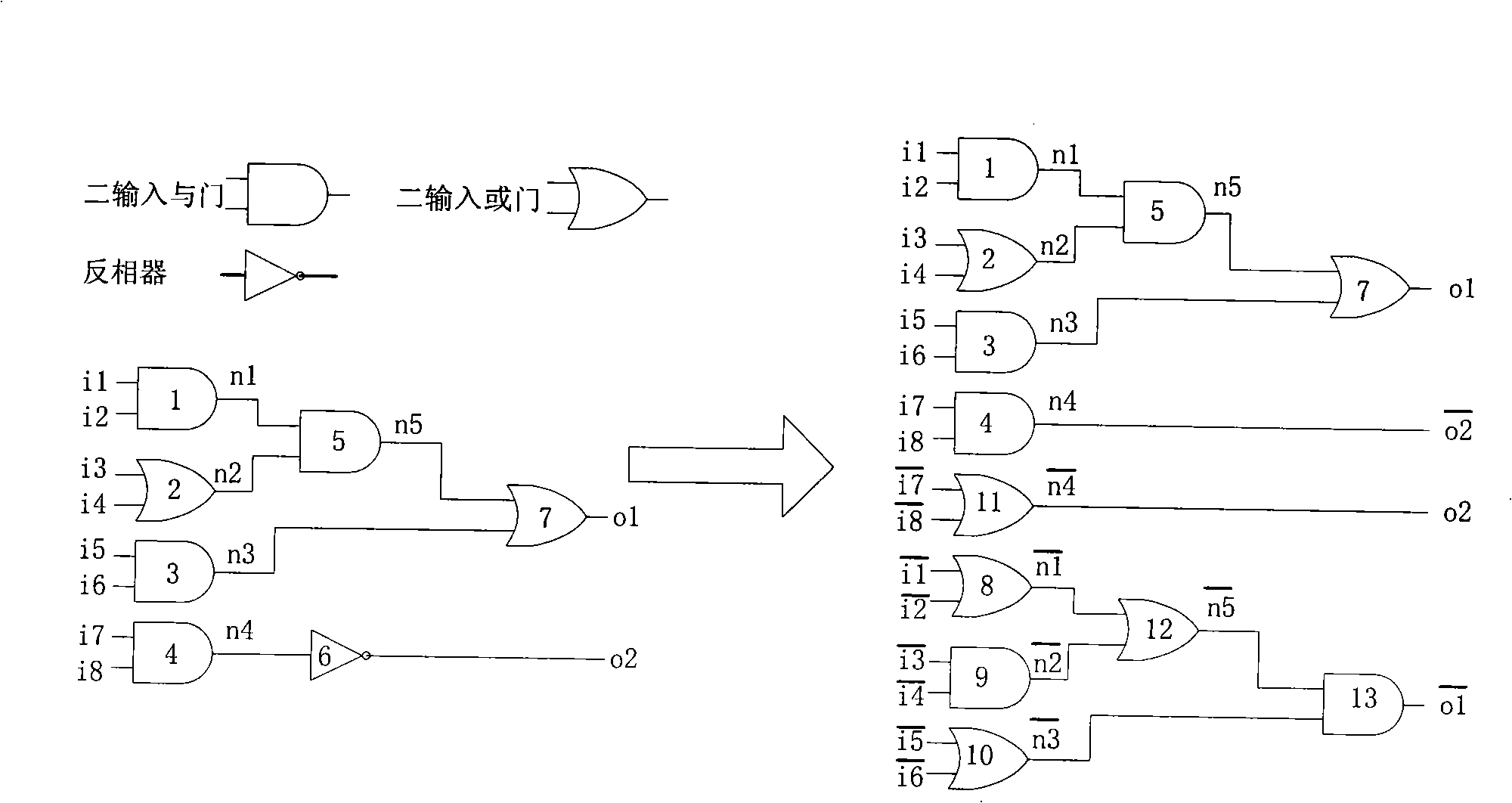

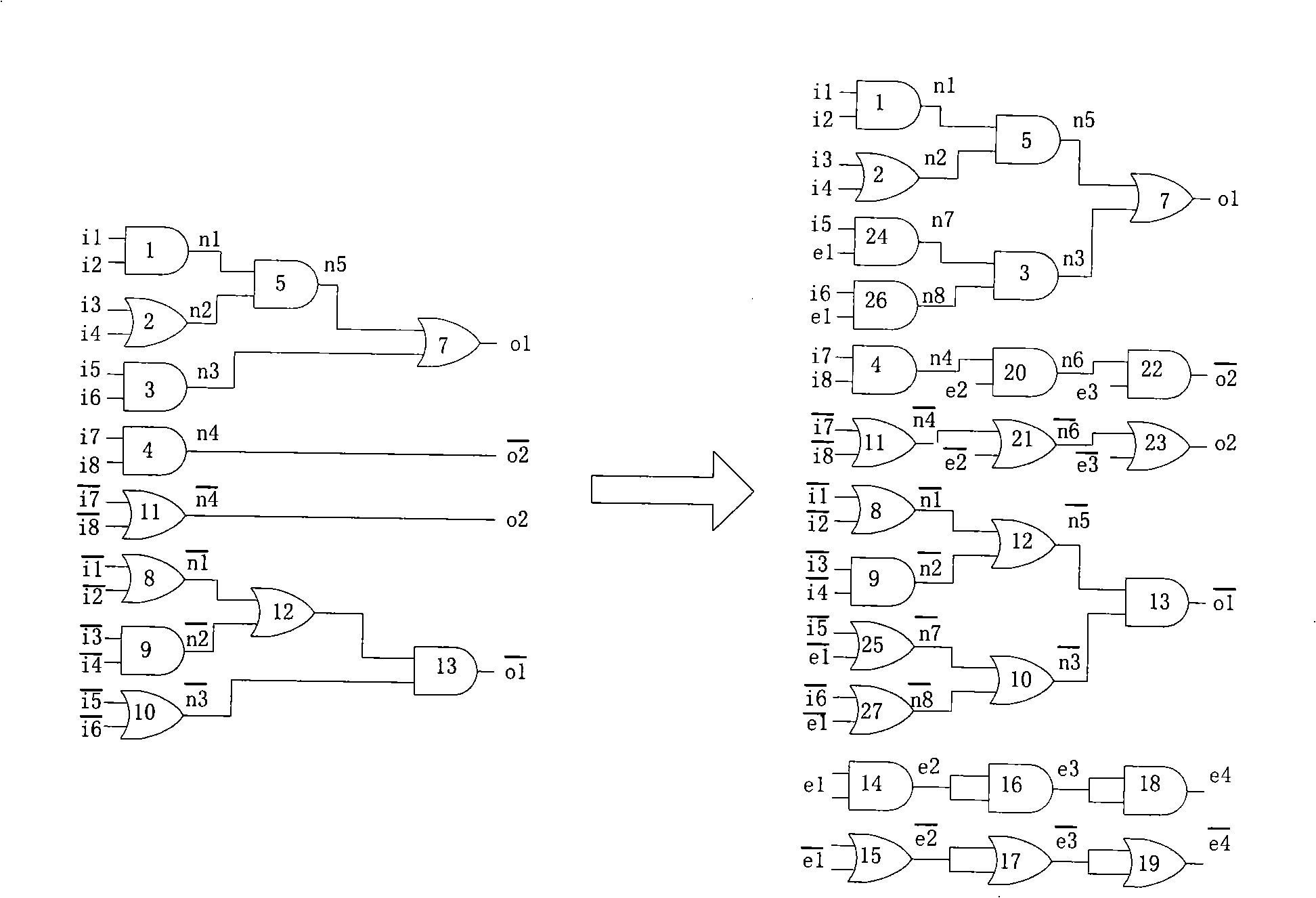

Design method of asynchronous block cipher algorithm coprocessor

InactiveCN101350038AHigh anti-power consumption attack protection capabilityGood constant power consumptionEncryption apparatus with shift registers/memoriesSpecial data processing applicationsCoprocessorMonorail

The invention discloses a method for designing an asynchronous block cipher algorithm coprocessor, wherein the technical problem which should be solved is to provide the method for designing the asynchronous block cipher algorithm coprocessor. The technical scheme comprises: taking each round of iteration in the block cipher algorithm as an independent submodule, adopting HDL to design each submodule, carrying out logic synthesis to each submodule, obtaining a static monorail net list, transforming the static monorail net list into a composite logic net list which is composed of two inputs which are complementary and doors and / or the doors, carrying out delay matching to each submodule, adding a delay matching module with same delay with the submodule, guaranteeing that the delays of signal input to signal output of each submodule are same, guaranteeing that the input reach time with the doors and / or the doors is same, connecting each submodule in turn, obtaining a complete net list, carrying out rear placement and routing, and obtaining a GDS layout. The coprocessor which is designed through adopting the method has higher power consumption attack resisting and protection ability and simultaneously has high operation performance and low power consumption features.

Owner:NAT UNIV OF DEFENSE TECH

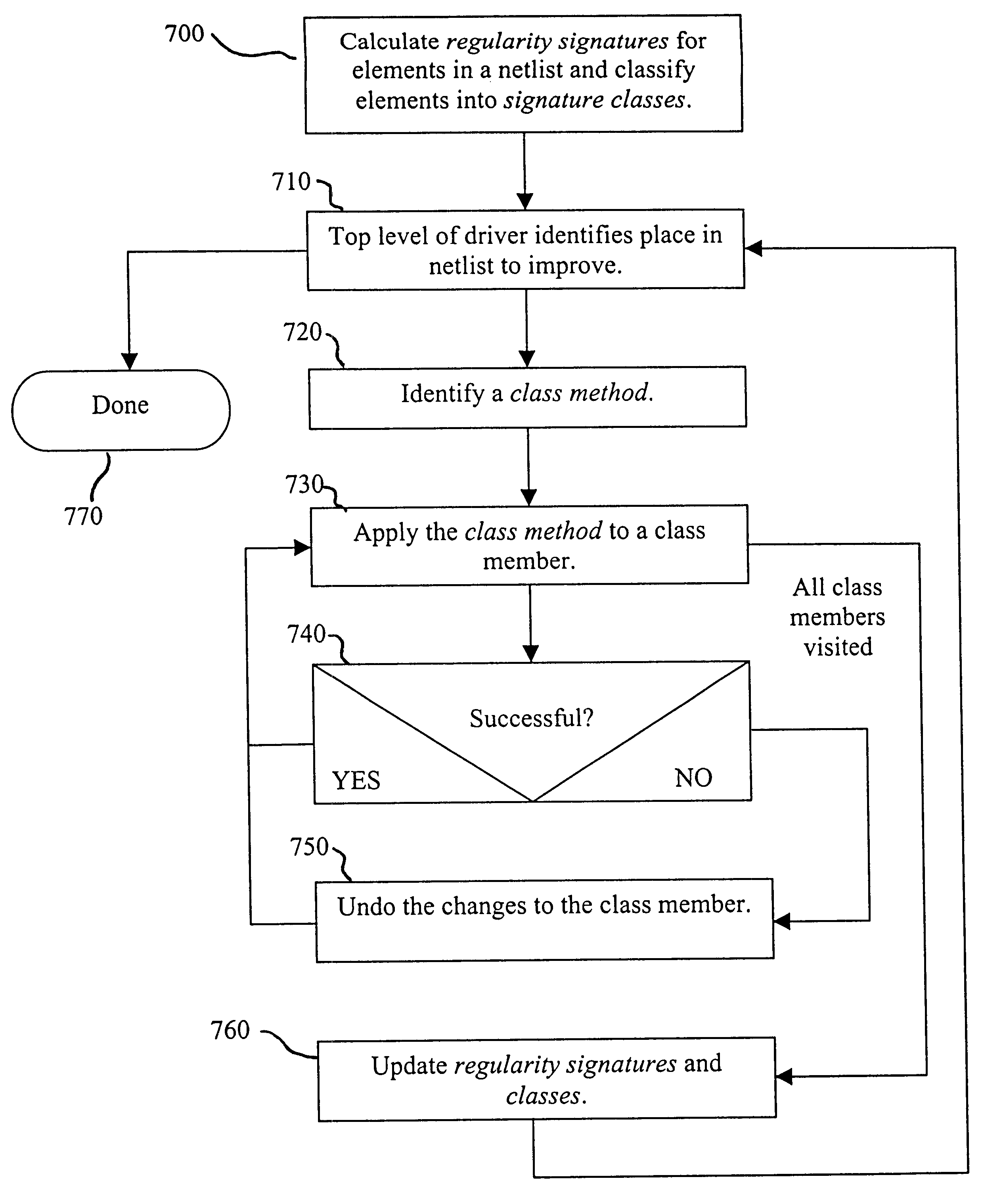

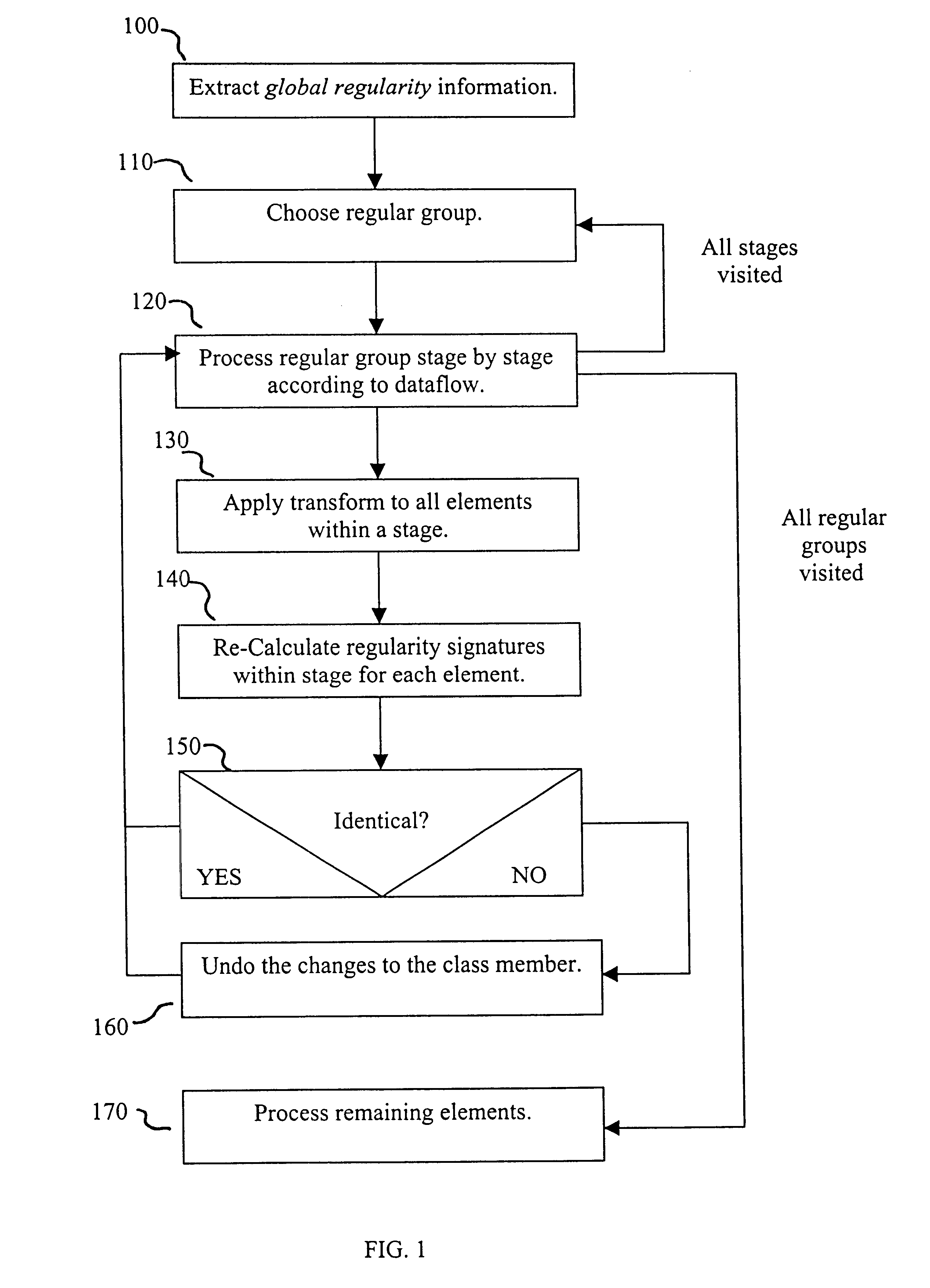

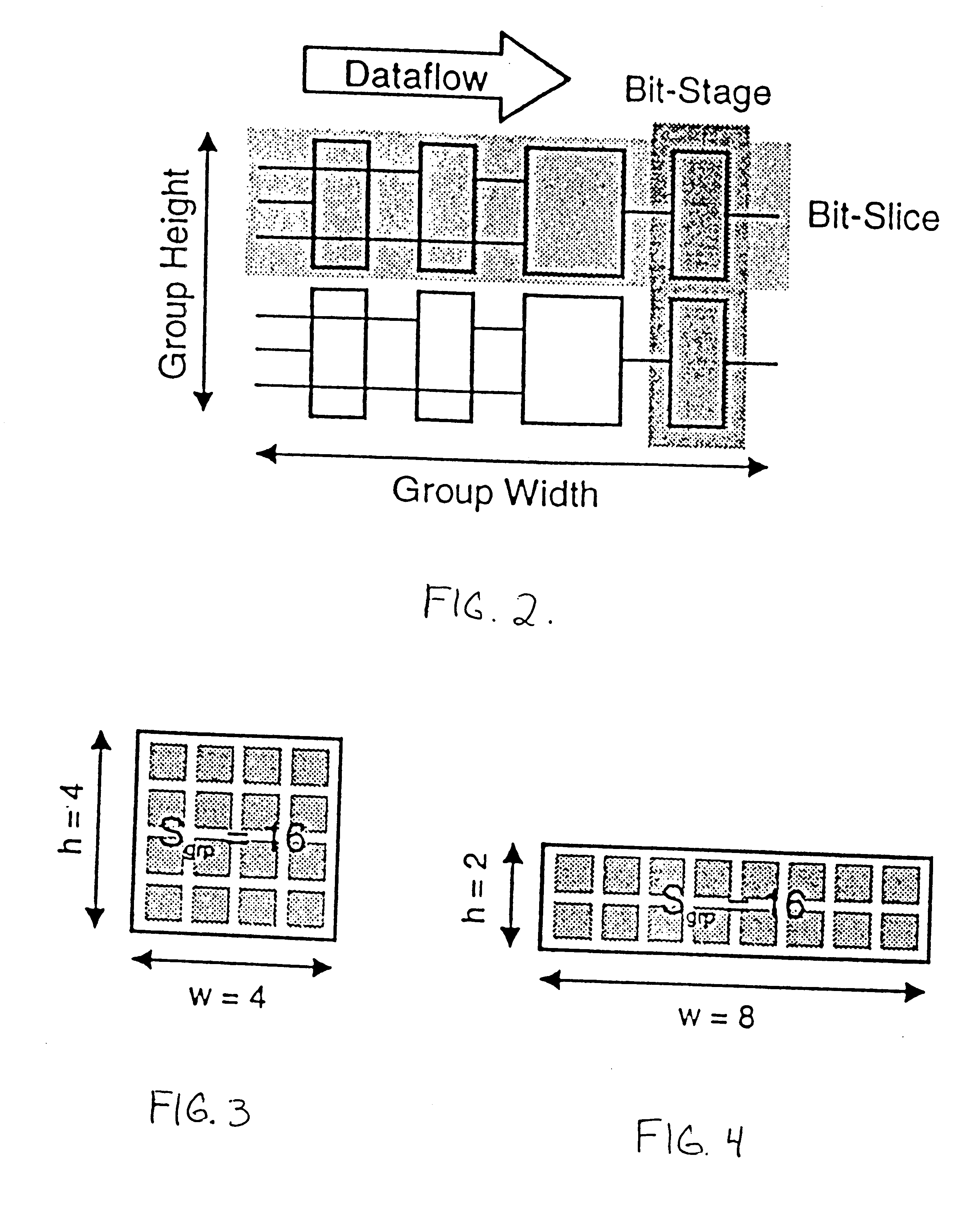

Method for preserving regularity during logic synthesis

InactiveUS6557159B1Preserving regularityImproved netlistComputer aided designSoftware simulation/interpretation/emulationData miningLogic synthesis

The present invention concerns a method for maintaining regularity in a netlist during logic synthesis. The method determines a global regularity for the netlist. The method determines a group of elements in the netlist having similar regularity signatures. Further, the method applies a transform to the group of elements.

Owner:IBM CORP

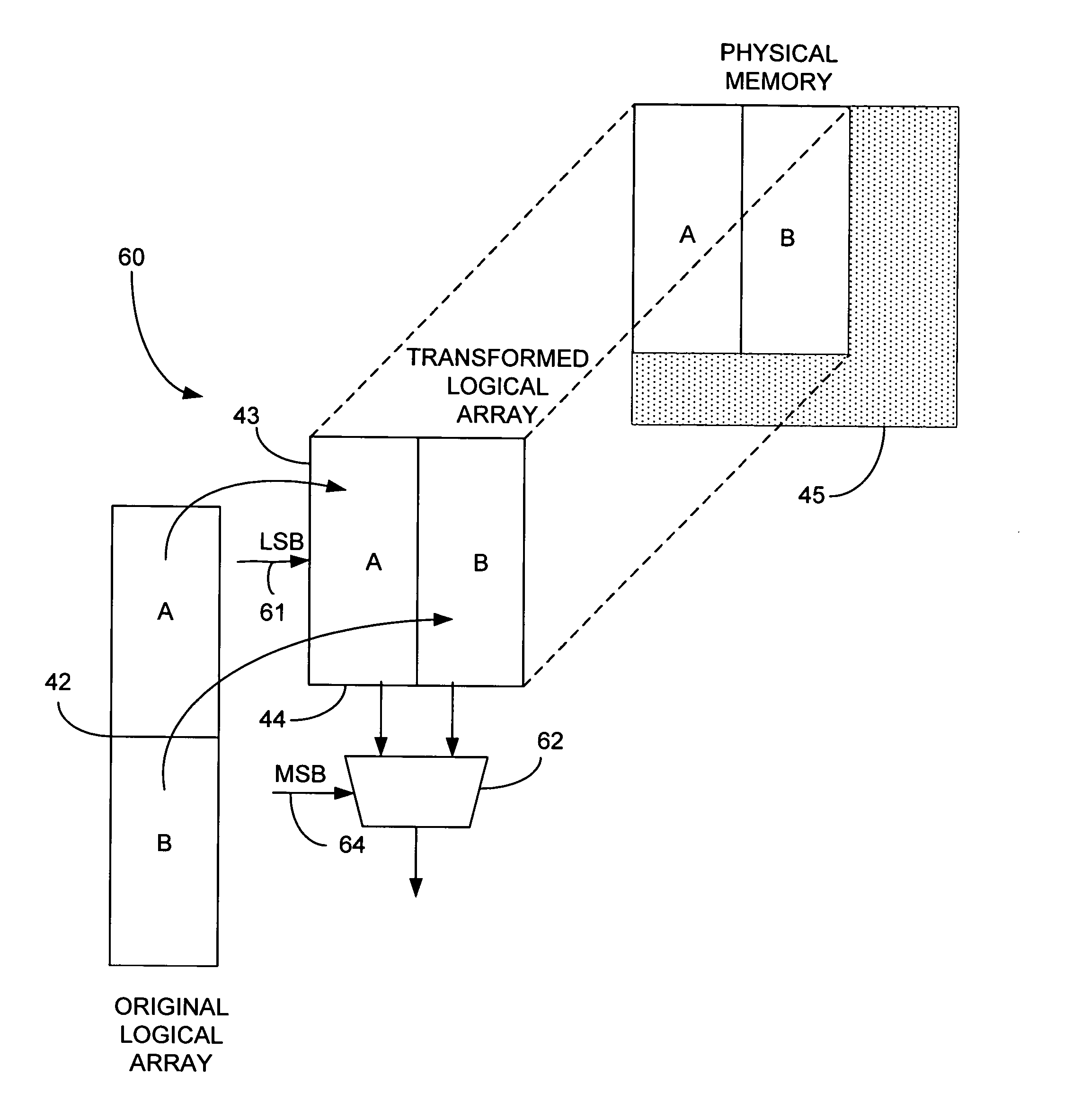

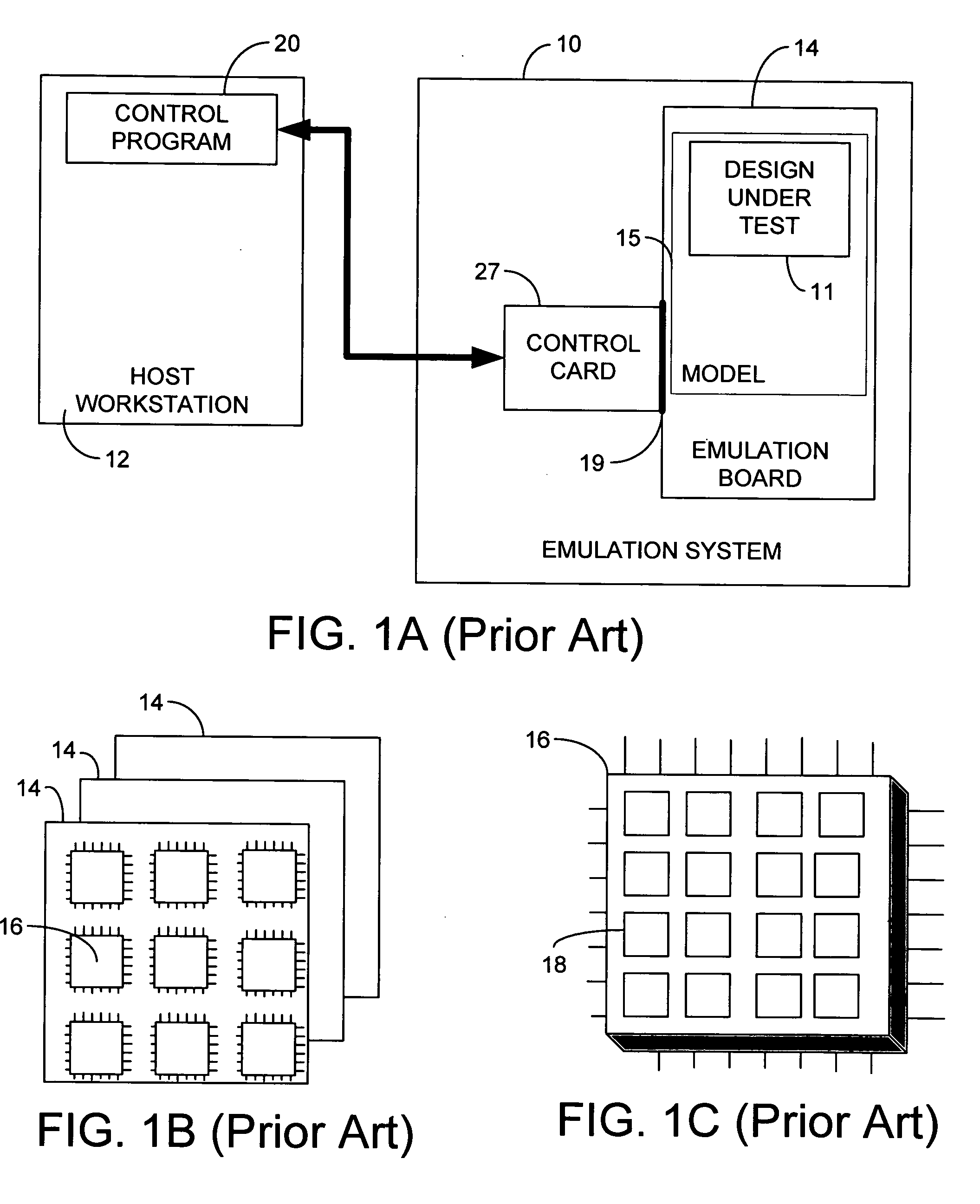

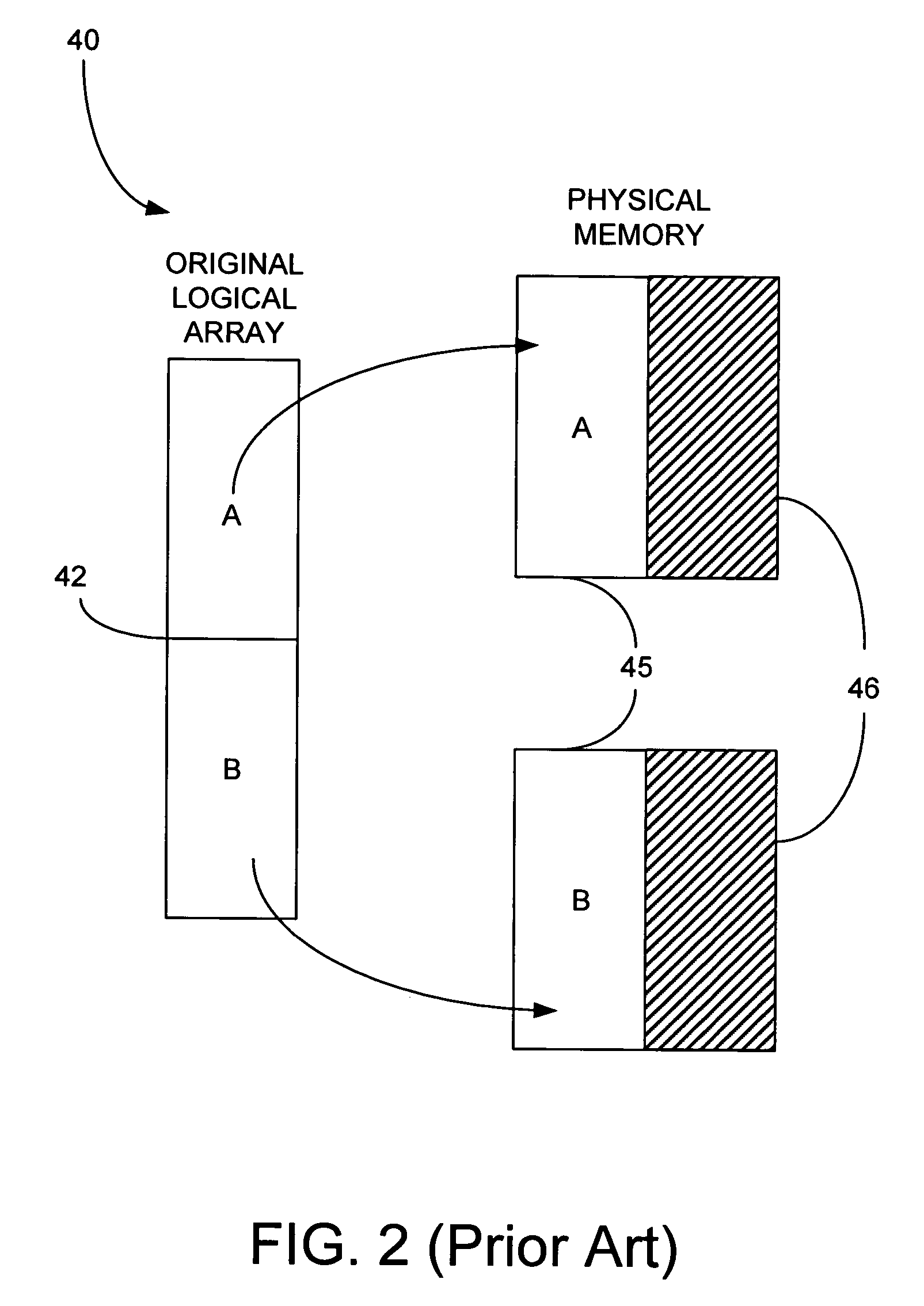

Method and apparatus to increase the usable memory capacity of a logic simulation hardware emulator/accelerator

InactiveUS20050256696A1Efficient use ofIncrease memory capacityComputer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceRunning time

A method, apparatus and program product are provided for increasing the usable memory capacity of a logic simulation hardware emulator. The present invention performs an additional logic synthesis operation during model build to transform an original logical array within a logic model into a transformed logical array, such that a row within the transformed logical array includes a plurality of merged logical array rows from the original logical array. The invention further modifies read and write port logic surrounding the transformed logical array during the logic synthesis operation to support read and write accesses during model emulation run time.

Owner:IBM CORP