Method for designing testability of chip

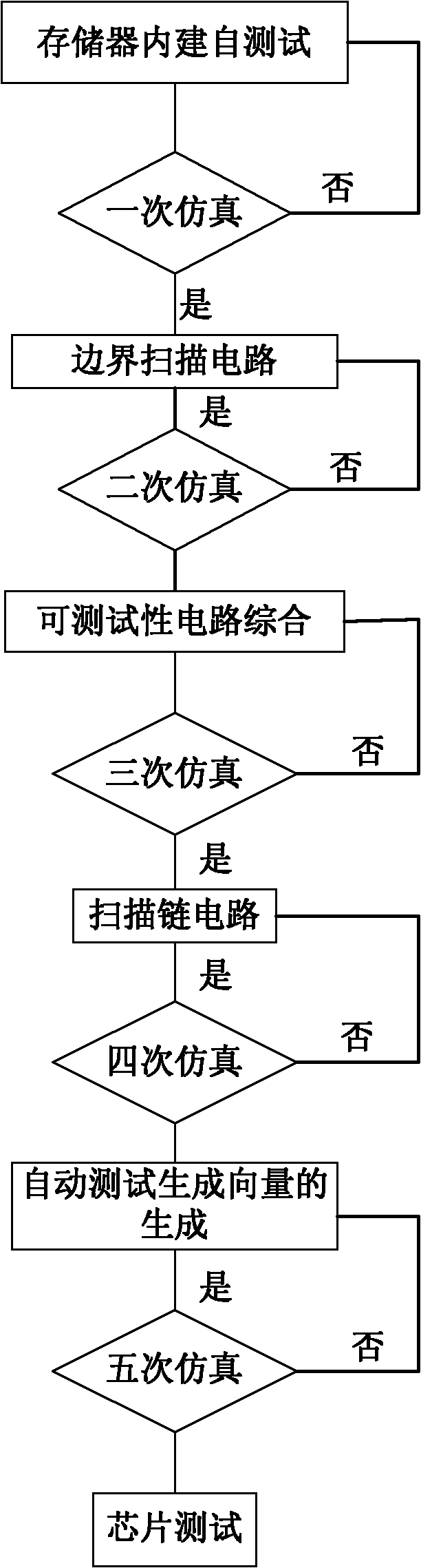

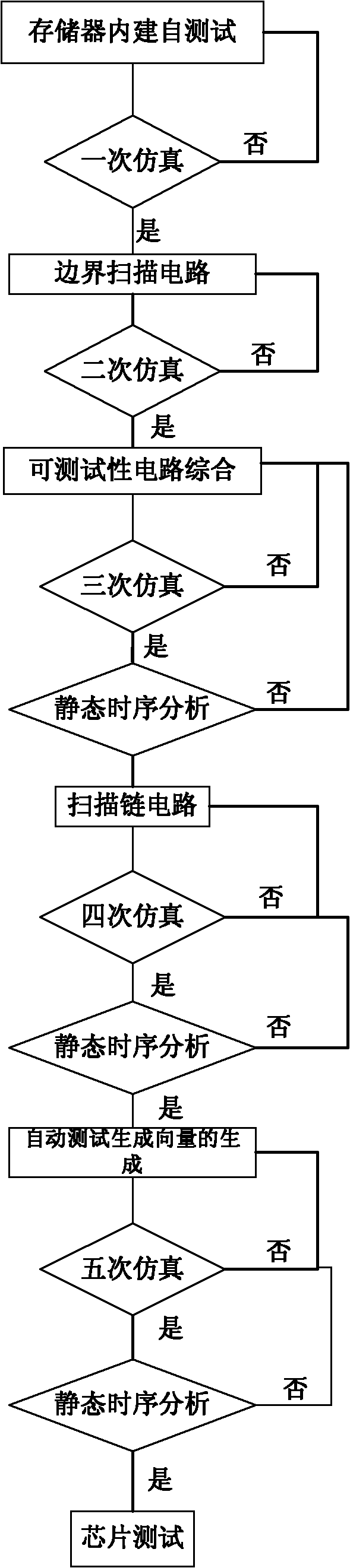

A design method and testing technology, applied in the field of DFT insertion, simulation and static timing analysis, logic synthesis, can solve the test method without a complete system, DFT tools, logic synthesis tools, circuit simulation and other tools can not achieve connection, design Program complexity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

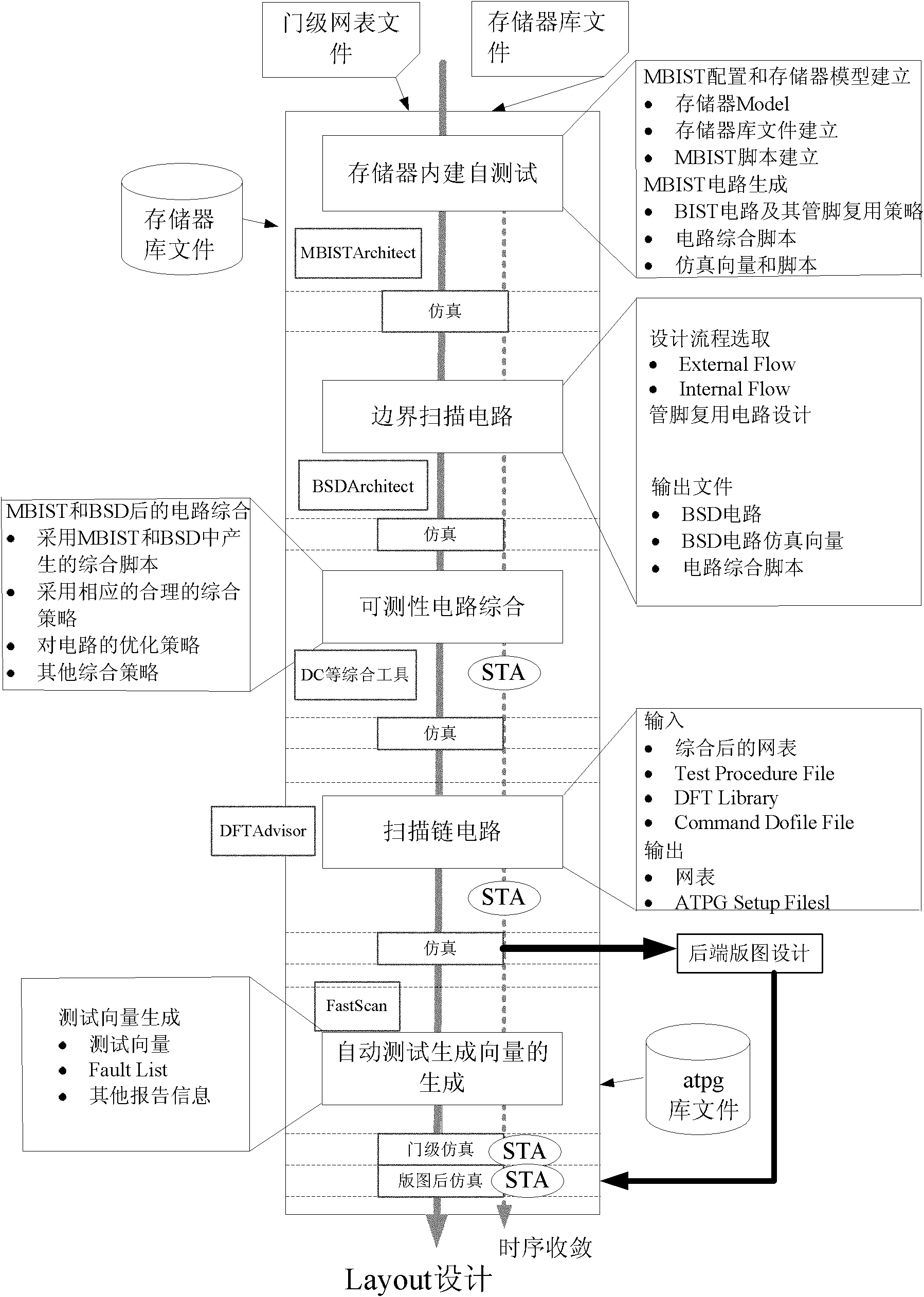

[0122] This process is mainly based on Mentor's DFT tools (MBISTArchitect, BSDArchitect, FastScan, DFTAdvisor), Synopsys' DC synthesis tool, Mentor's simulation tool ModelSim and other tools to complete a typical SoC-based DFT design and test vector production and simulation.

[0123] (1) Synthesize the RTL code into a gate-level netlist file based on the process library using synthesis tools from companies such as SynopSys.

[0124] (2) Write the storage library files required by Mentor's MBISTArchitect. After these two steps are completed, the preparation for DFT design is completed.

[0125] (3) Use the MBISTArchitect tool memory built-in self-test circuit of Mentor Company to insert the MBIST circuit. The specific implementation script is:

[0126] mbistarchitect. / netlist / mydesign_fix_timing.v-verilog\

[0127] -top mydesign_top \

[0128] -lverilog . / libs / *.v\

[0129] -logfile mbist.log-replace\

[0130] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More