Patents

Literature

280 results about "Verilog" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Verilog, standardized as IEEE 1364, is a hardware description language (HDL) used to model electronic systems. It is most commonly used in the design and verification of digital circuits at the register-transfer level of abstraction. It is also used in the verification of analog circuits and mixed-signal circuits, as well as in the design of genetic circuits. In 2009, the Verilog standard (IEEE 1364-2005) was merged into the SystemVerilog standard, creating IEEE Standard 1800-2009. Since then, Verilog is officially part of the SystemVerilog language. The current version is IEEE standard 1800-2017.

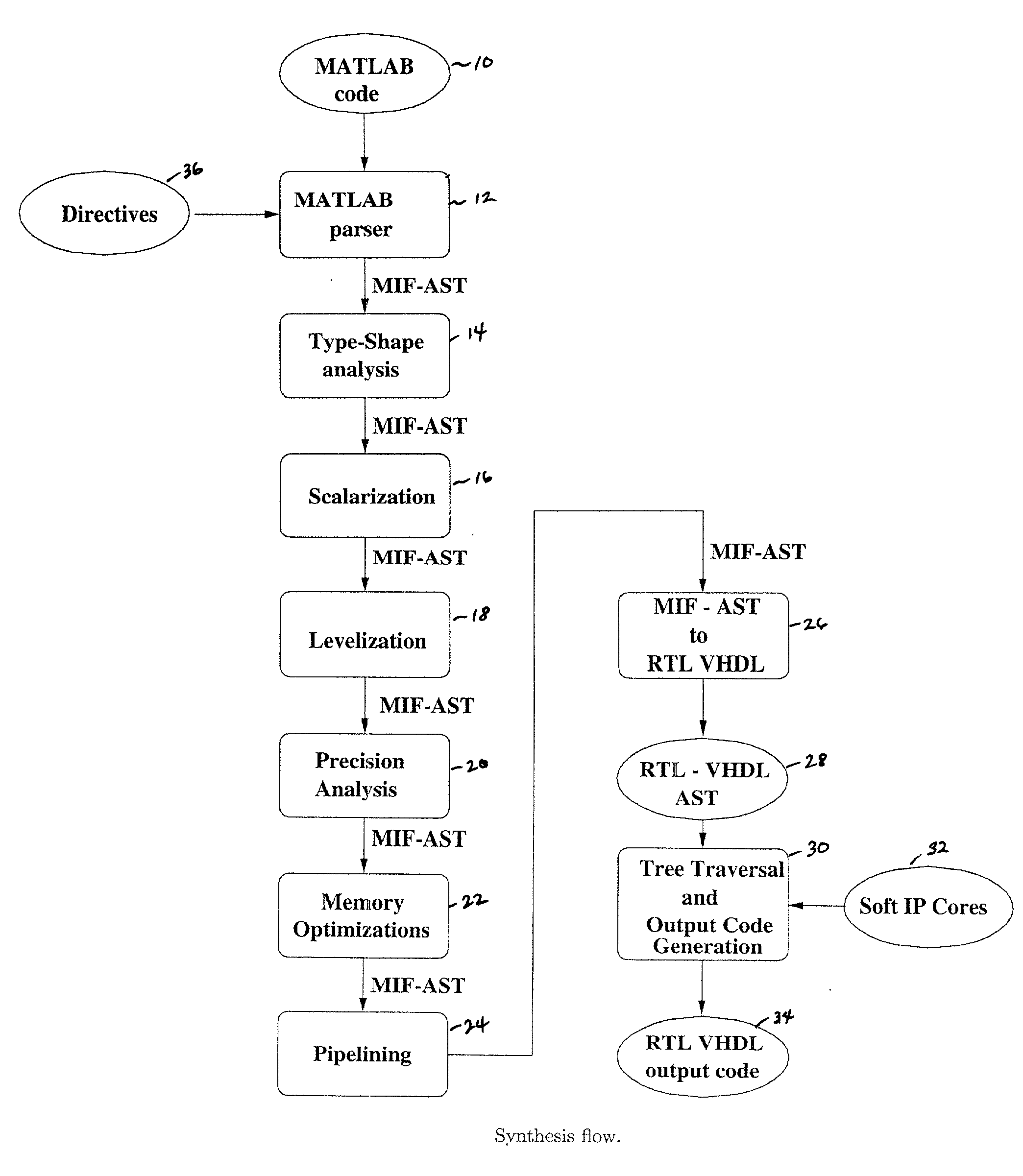

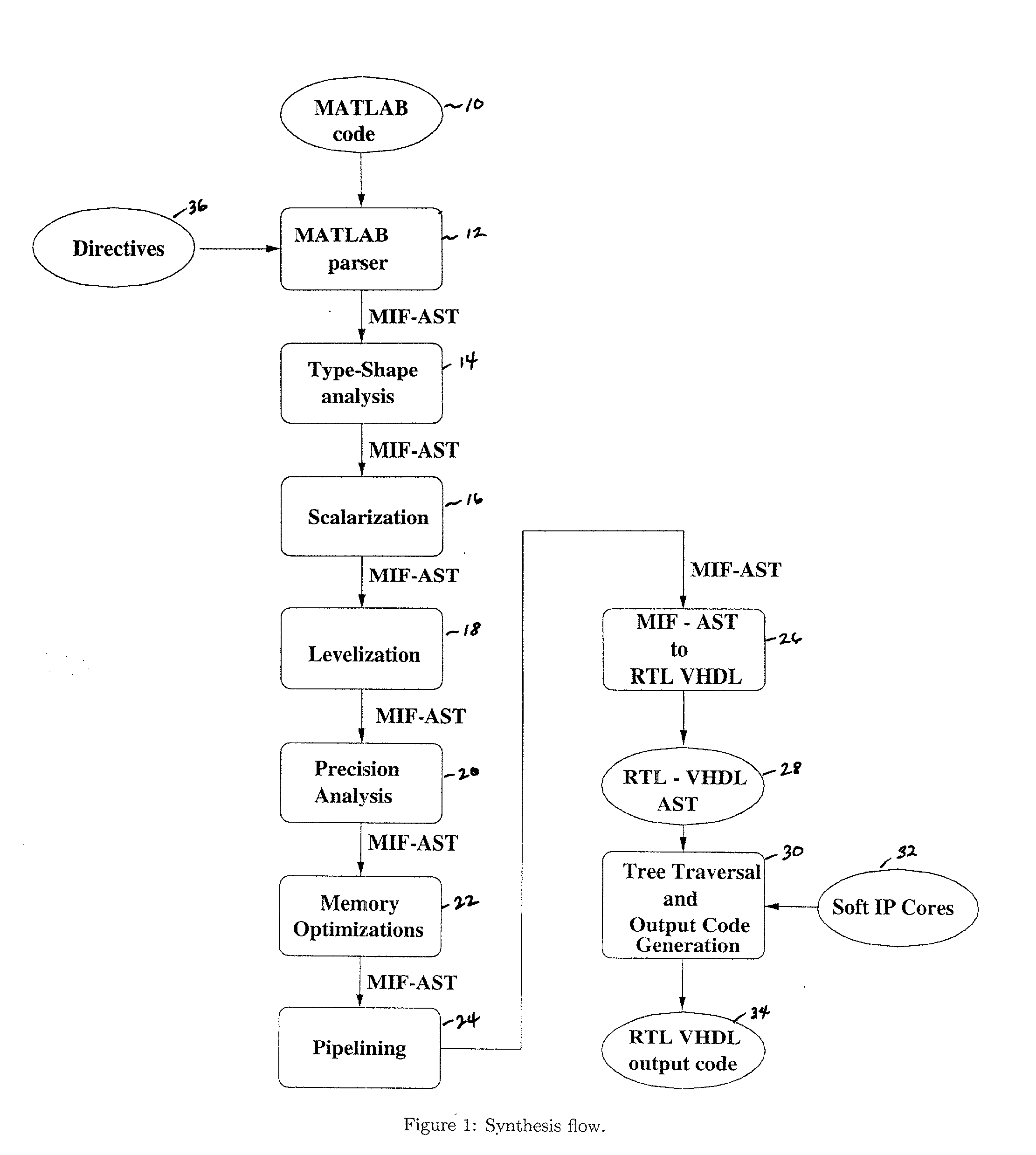

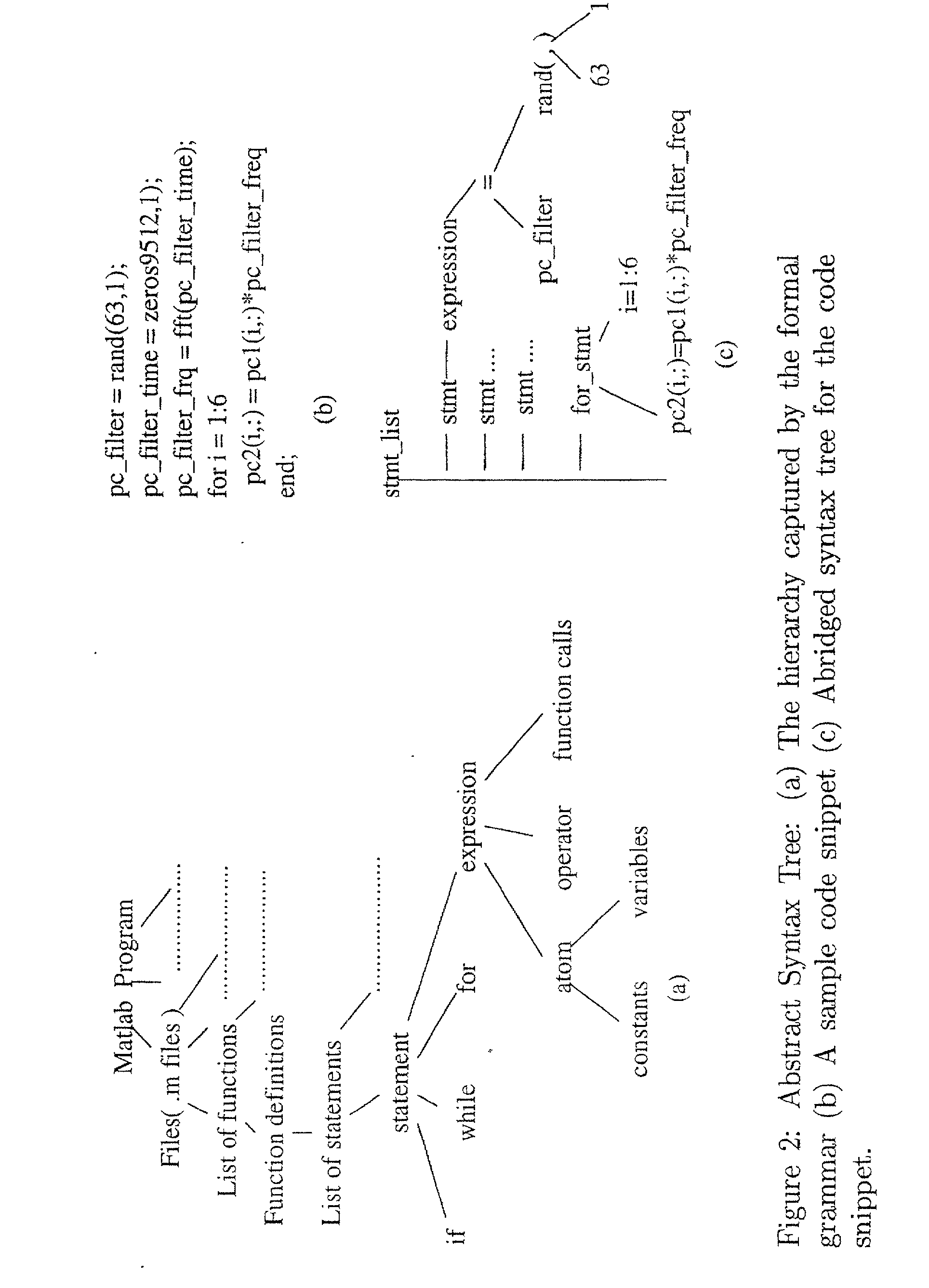

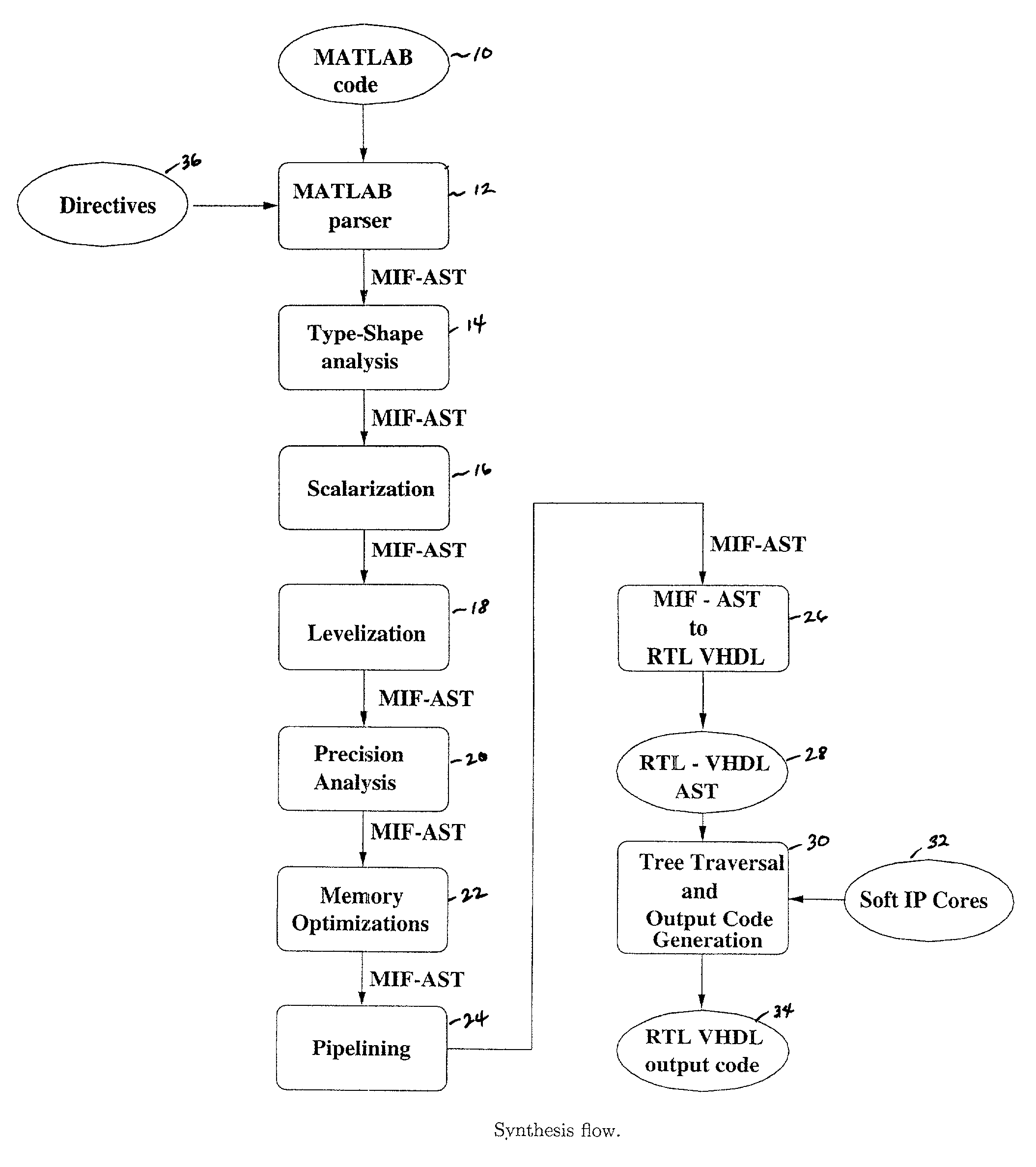

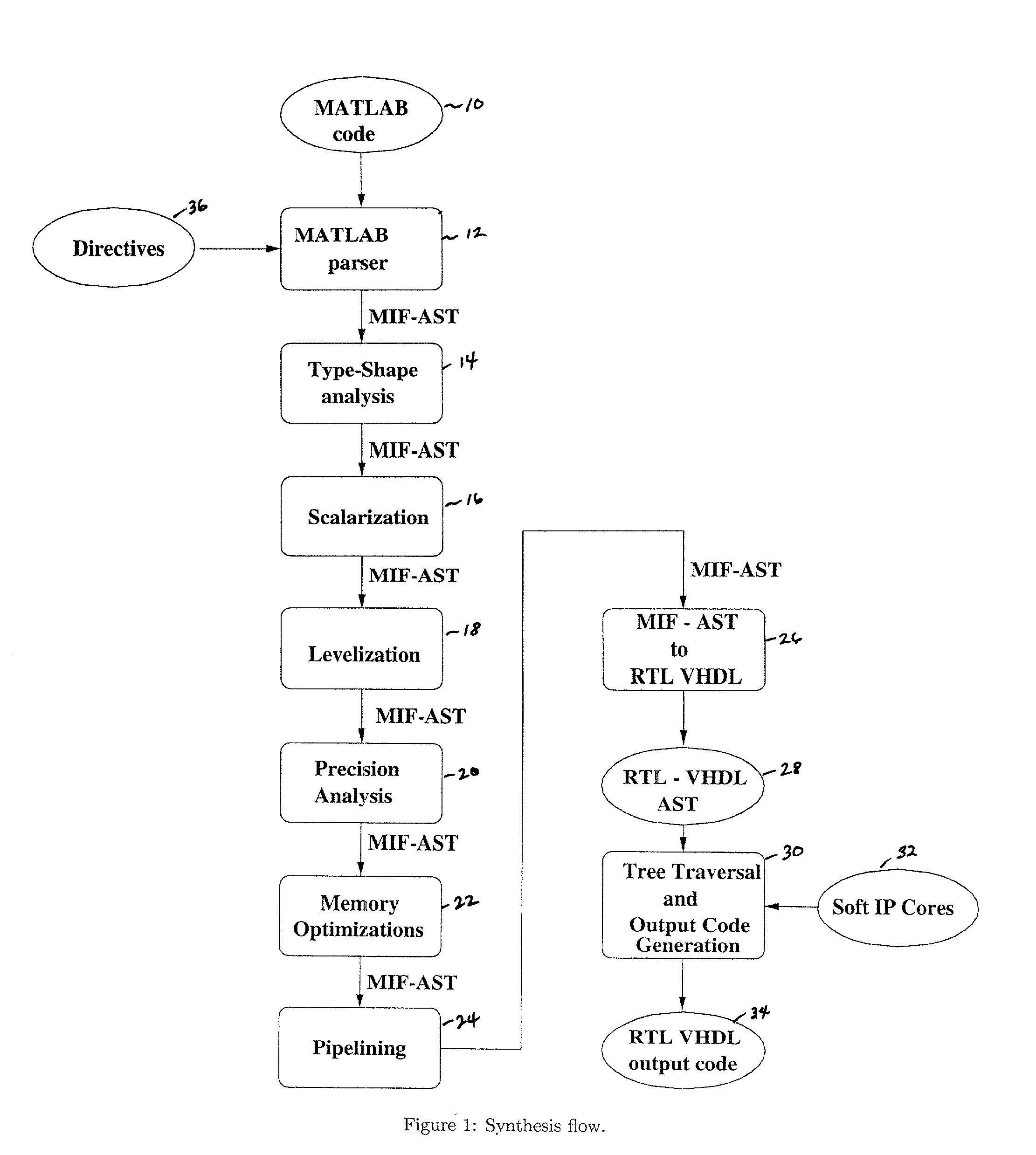

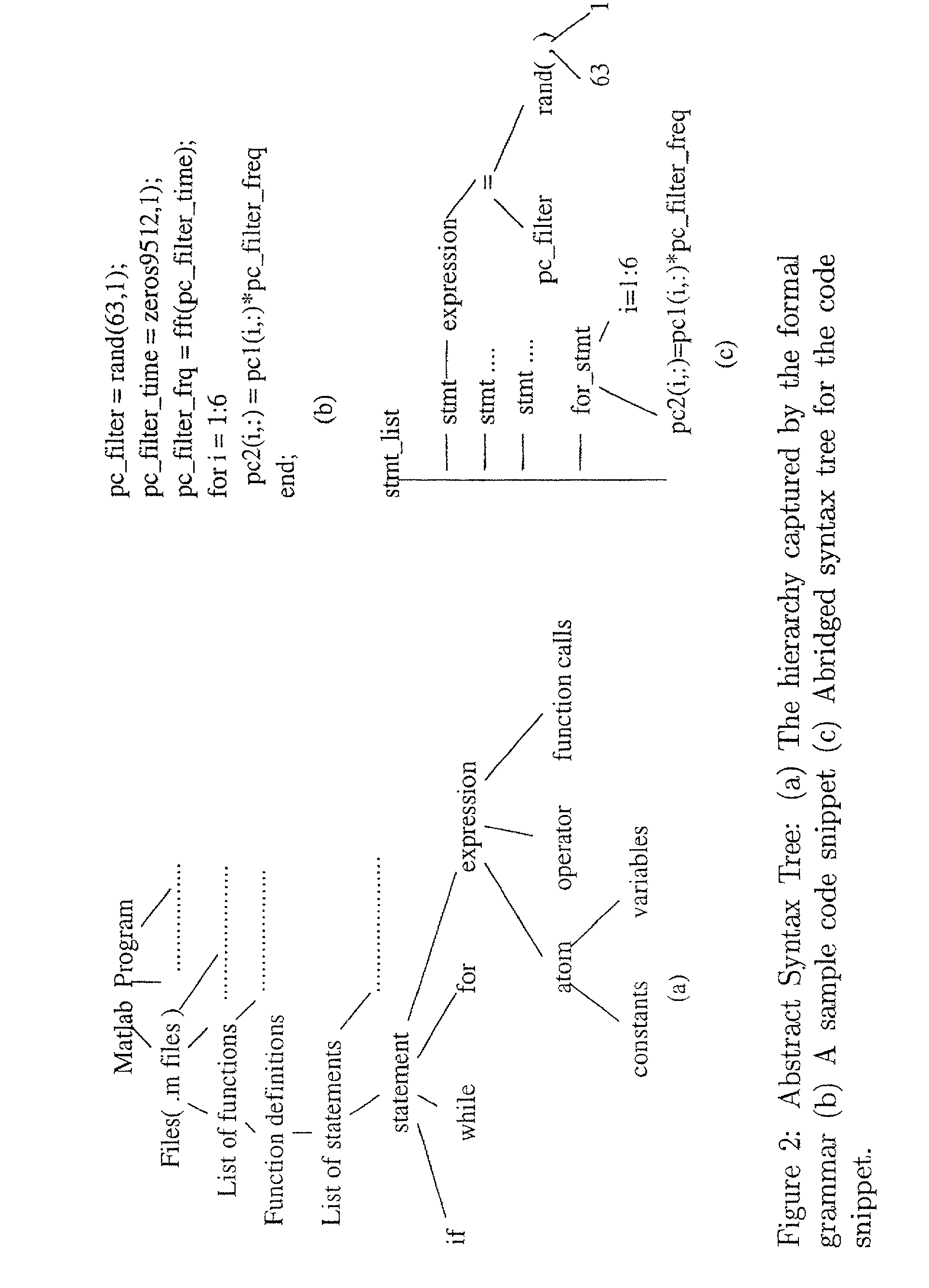

Method and apparatus for automatically generating hardware from algorithms described in matlab

Digital circuit is synthesized from algorithm described in the MATLAB programming language. A MATLAB program is compiled into RTL-VHDL, which is synthesizable using system-specific tools to develop ASIC or FPGA configuration. Intermediate transformations and optimizations are performed to obtain highly optimized description in RTL-VHDL or RTL Verilog of given MATLAB program. Optimizations include levelization, scalarization, pipelining, type-shape analysis, memory optimizations, precision analysis and scheduling.

Owner:NORTHWESTERN UNIV

Method and apparatus for automatically generating hardware from algorithms described in MATLAB

Digital circuit is synthesized from algorithm described in the MATLAB programming language. A MATLAB program is compiled into RTL-VHDL, which is synthesizable using system-specific tools to develop ASIC or FPGA configuration. Intermediate transformations and optimizations are performed to obtain highly optimized description in RTL-VHDL or RTL Verilog of given MATLAB program. Optimizations include levelization, scalarization, pipelining, type-shape analysis, memory optimizations, precision analysis and scheduling.

Owner:NORTHWESTERN UNIV

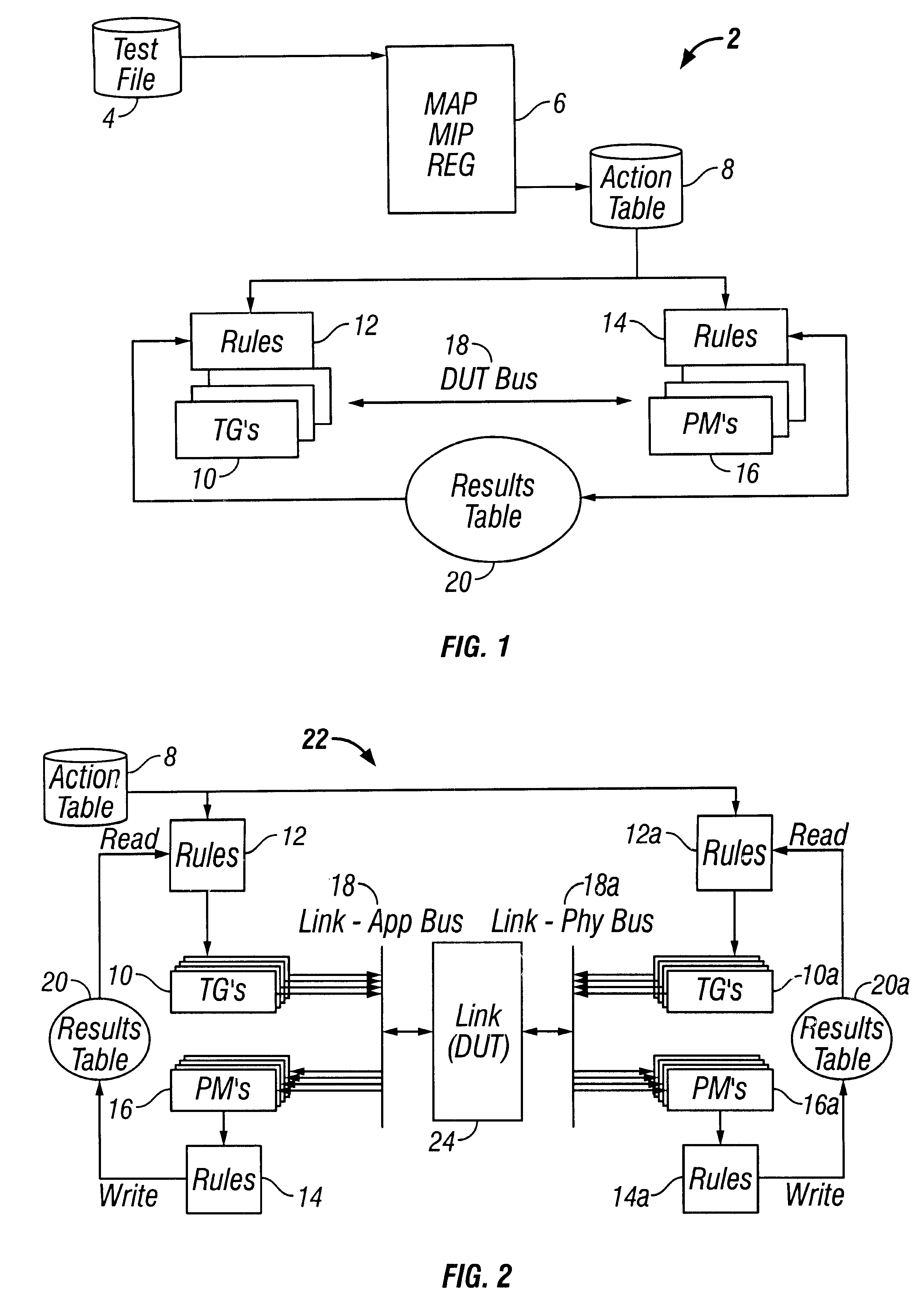

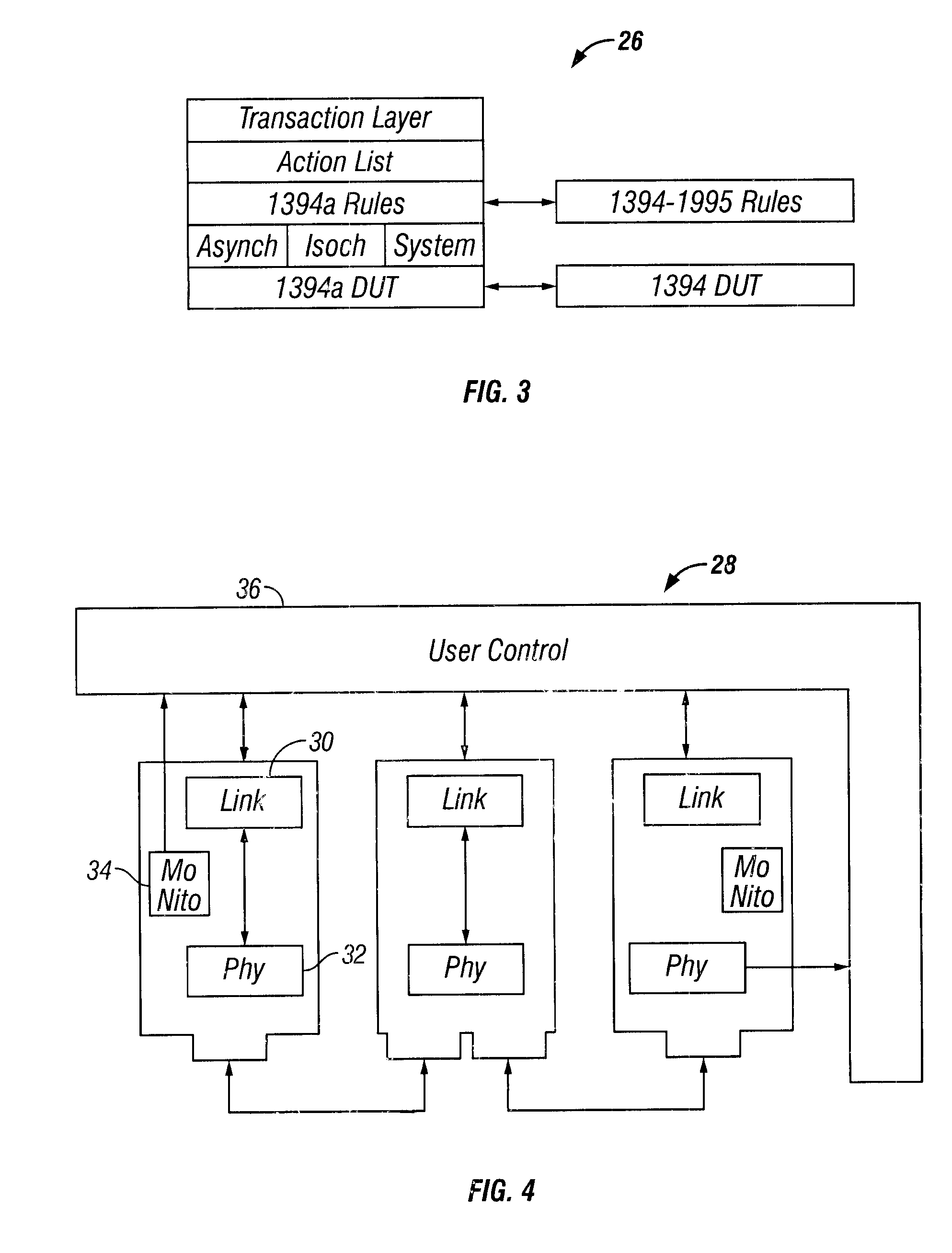

Device and method for testing a device through resolution of data into atomic operations

InactiveUS6457152B1Improve throughputElectronic circuit testingError detection/correctionClosed loopVerilog

A method of testing a device includes monitoring an output of the device, wherein the output is generated by the device in response to an applied test command; and resolving the output into atomic operations, wherein the atomic operations are substantially the smallest constituent operations which are substantially independent of the device. The method is used to provide a simple, comprehensive test environment that effectively tests 1394a and 1394-1995 designs, for example, in Verilog. The test environment contains rules which completely characterize the behavior of different 1394 bus protocols as defined by the IEEE specifications. The test environment provides portability between different devices under test and between different protocols, automated closed-loop reconciliation of test commands and protocol requirements, topology independence, and out-of-order execution of instructions or relative sequencing. The test environment further allows failure injection, and separate and independent design of the device and a test system.

Owner:SYNOPSYS INC

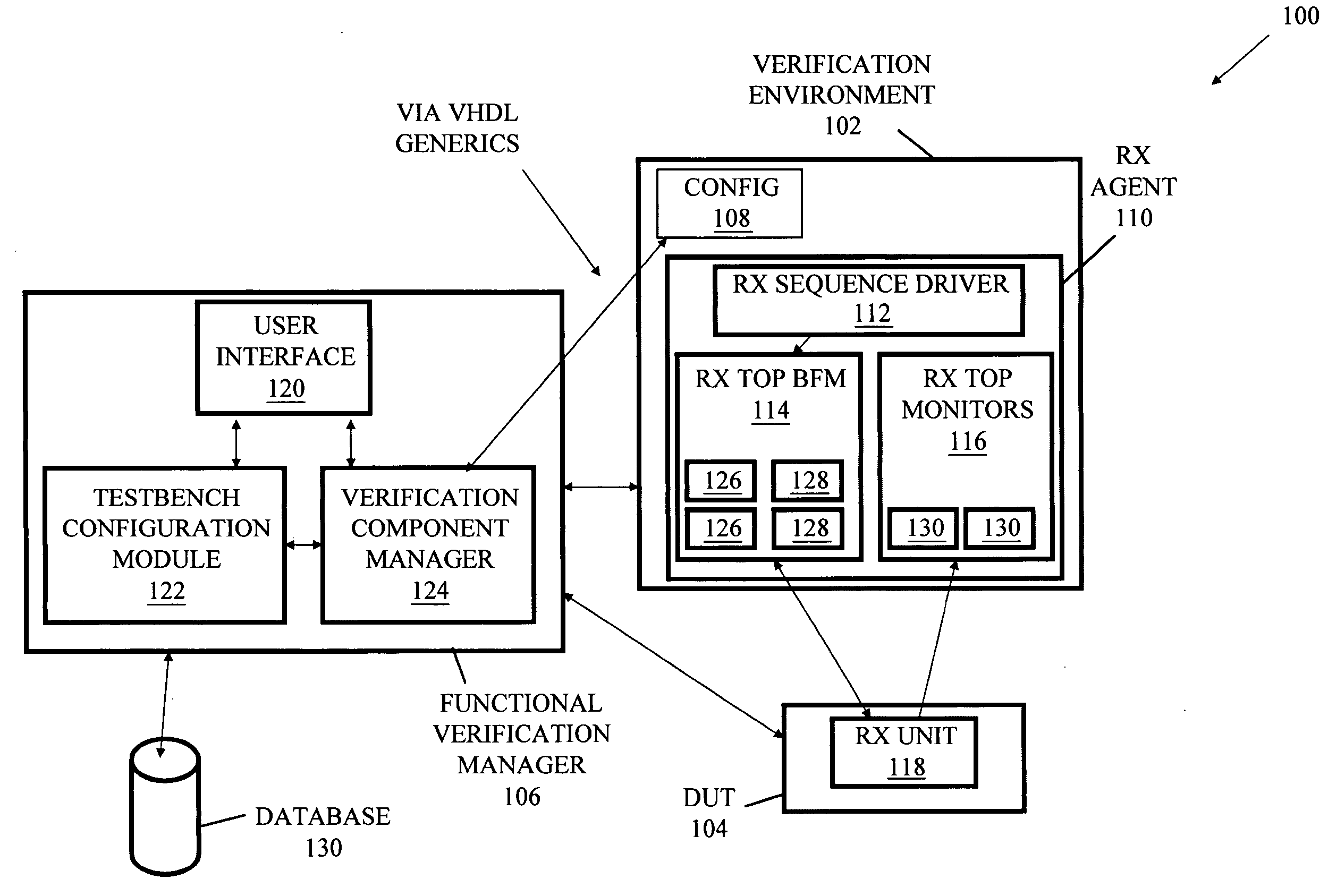

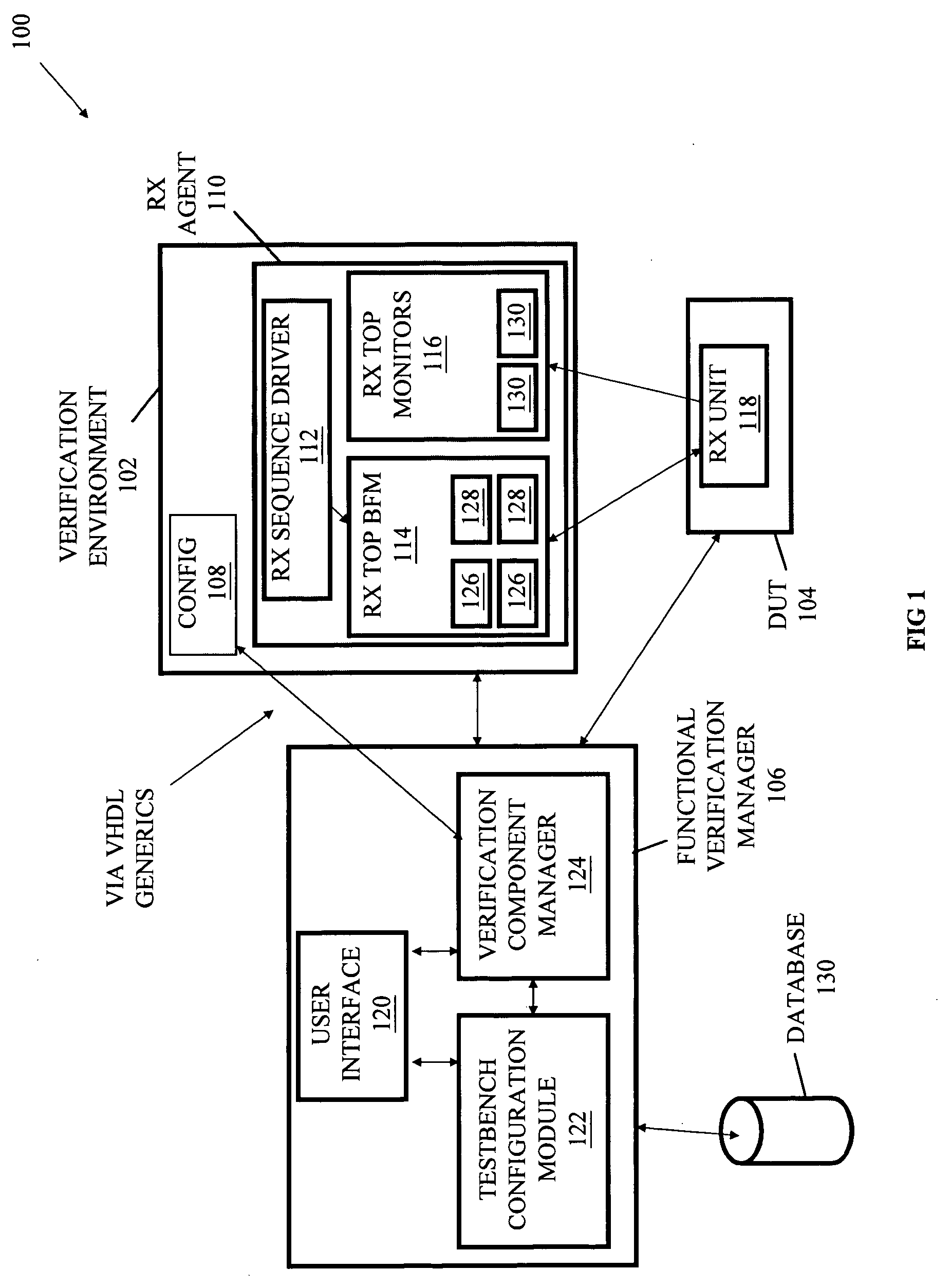

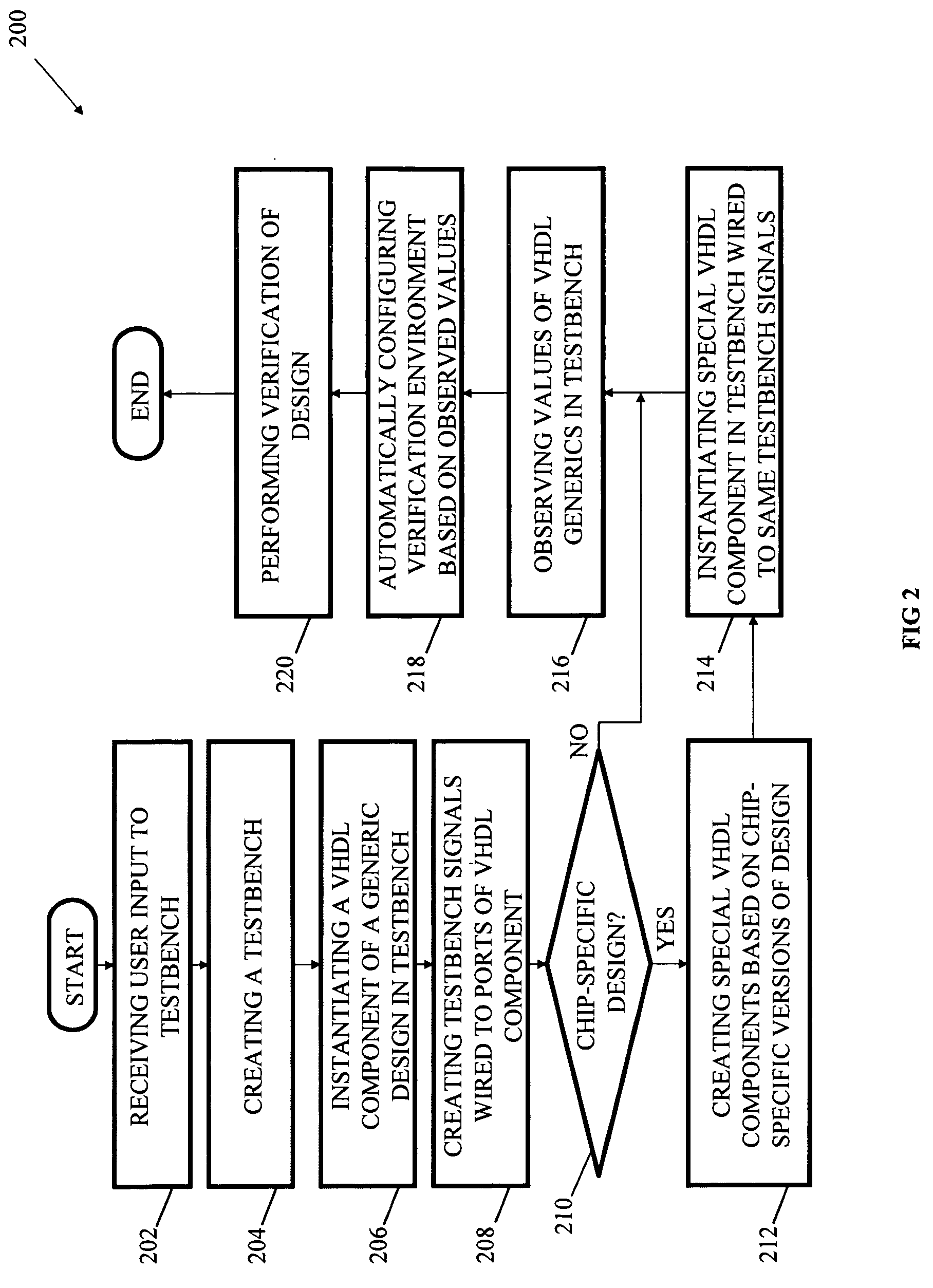

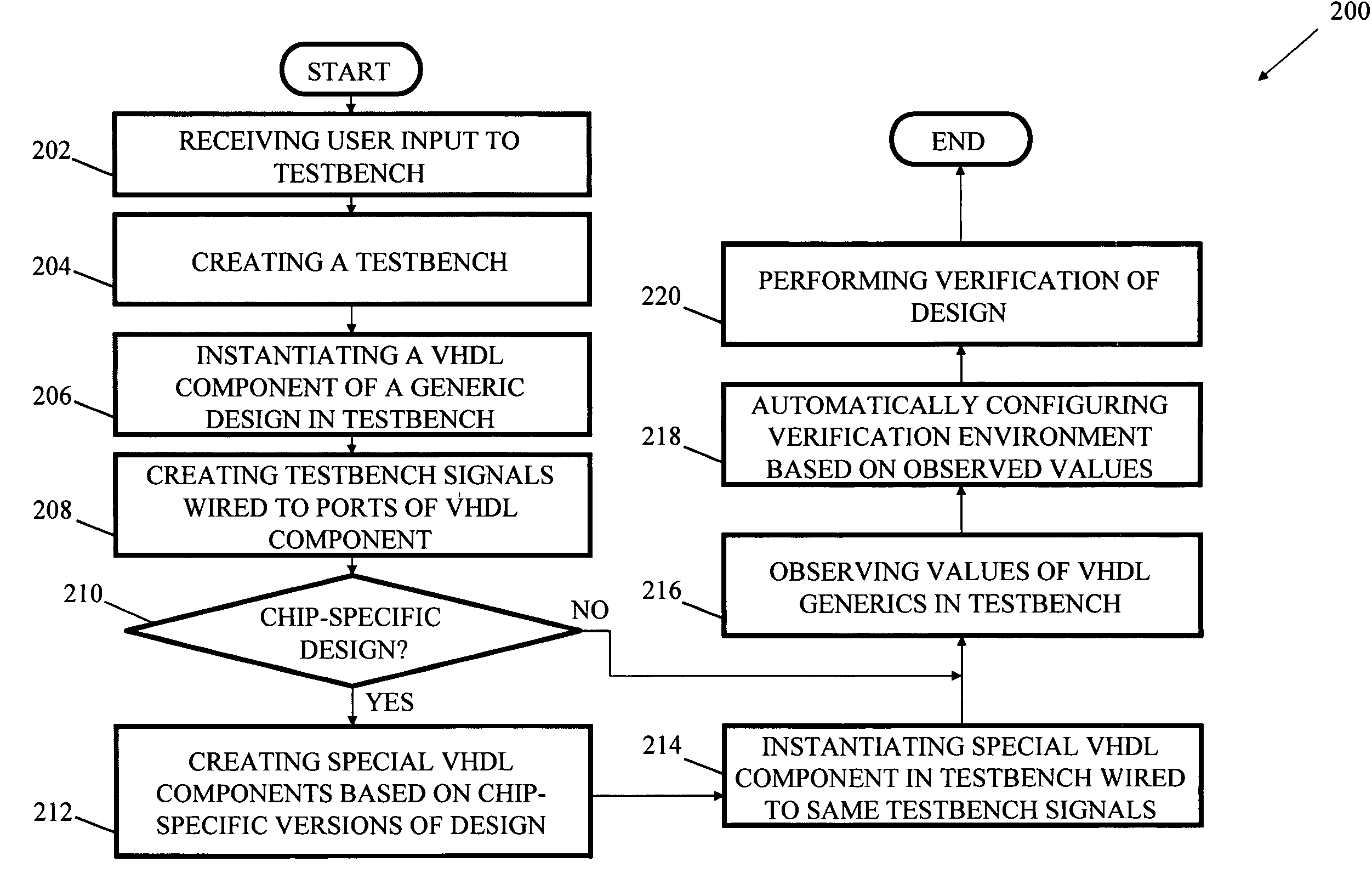

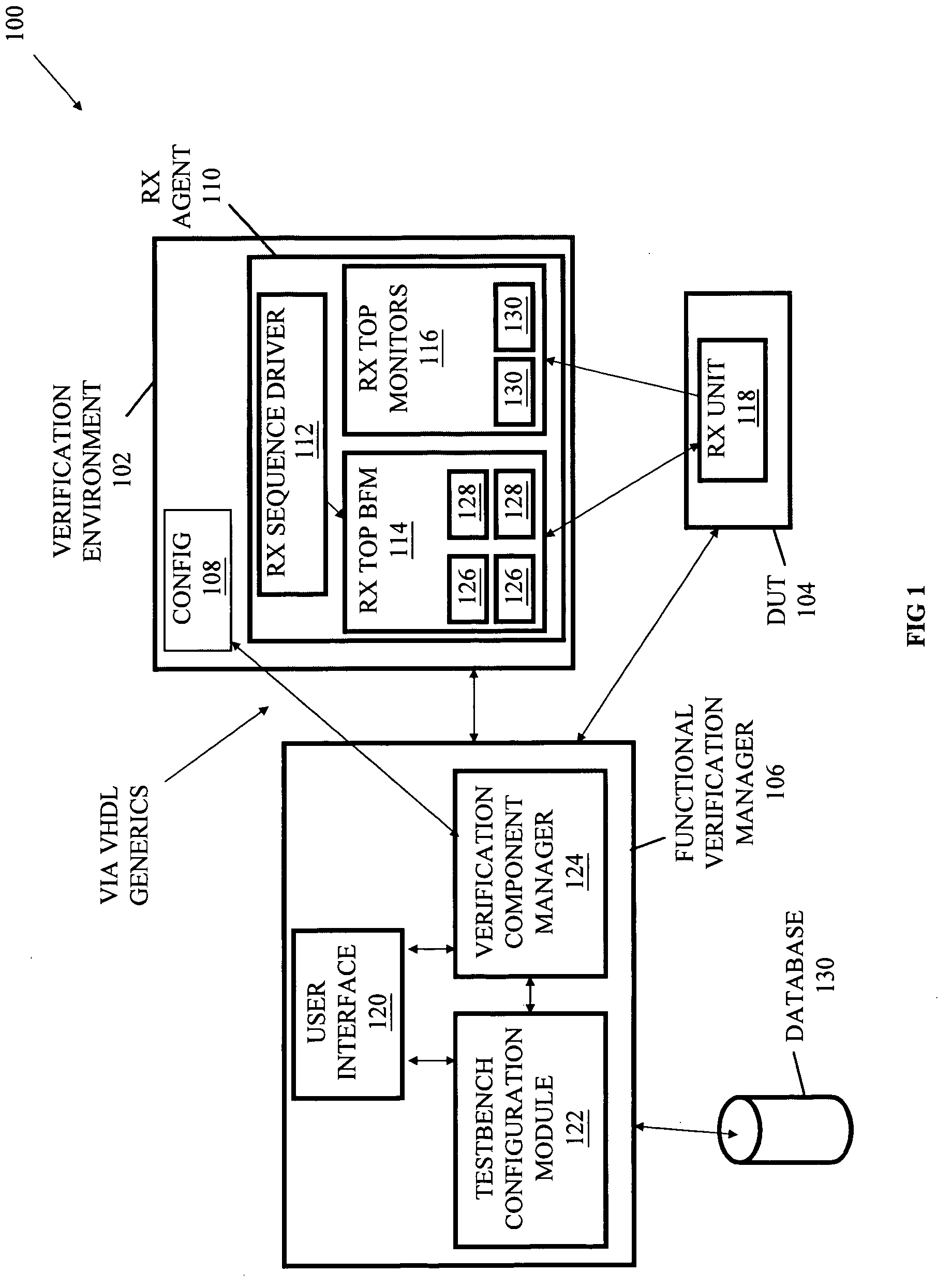

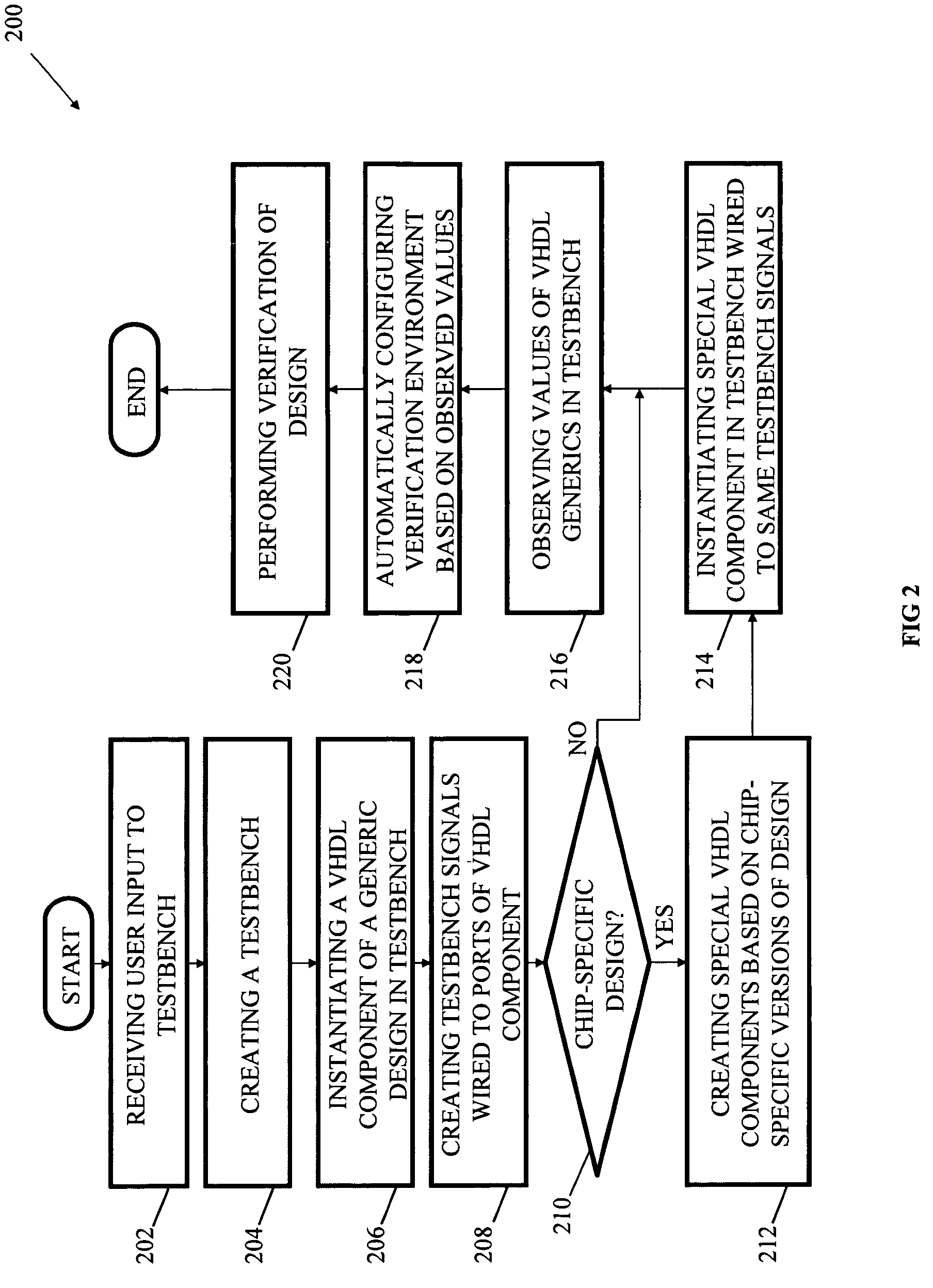

Methods, systems and media for managing functional verification of a parameterizable design

InactiveUS20060190871A1Electrical testingComputer programmed simultaneously with data introductionComputer architectureAuto-configuration

Methods, systems, and media for managing functional verification of a parameterizable design are disclosed. Embodiments include a system having a testbench configuration module adapted to configure a testbench, the testbench having testbench signals and one or more instantiated components having a plurality of ports of a generic design, where the testbench signals are wired to the plurality of ports. The testbench may also have one or more instantiated special components based on chip-specific versions of the design where the special components are wired to the same ports as the generic design. The system may also include a functional verification manager that, through a component module, observes values in the testbench and automatically configure a verification environment based on the observed values, including automatic insertion of checkers at different levels of hierarchy. The testbench may be a VHDL or Verilog testbench in some embodiments.

Owner:GLOBALFOUNDRIES INC

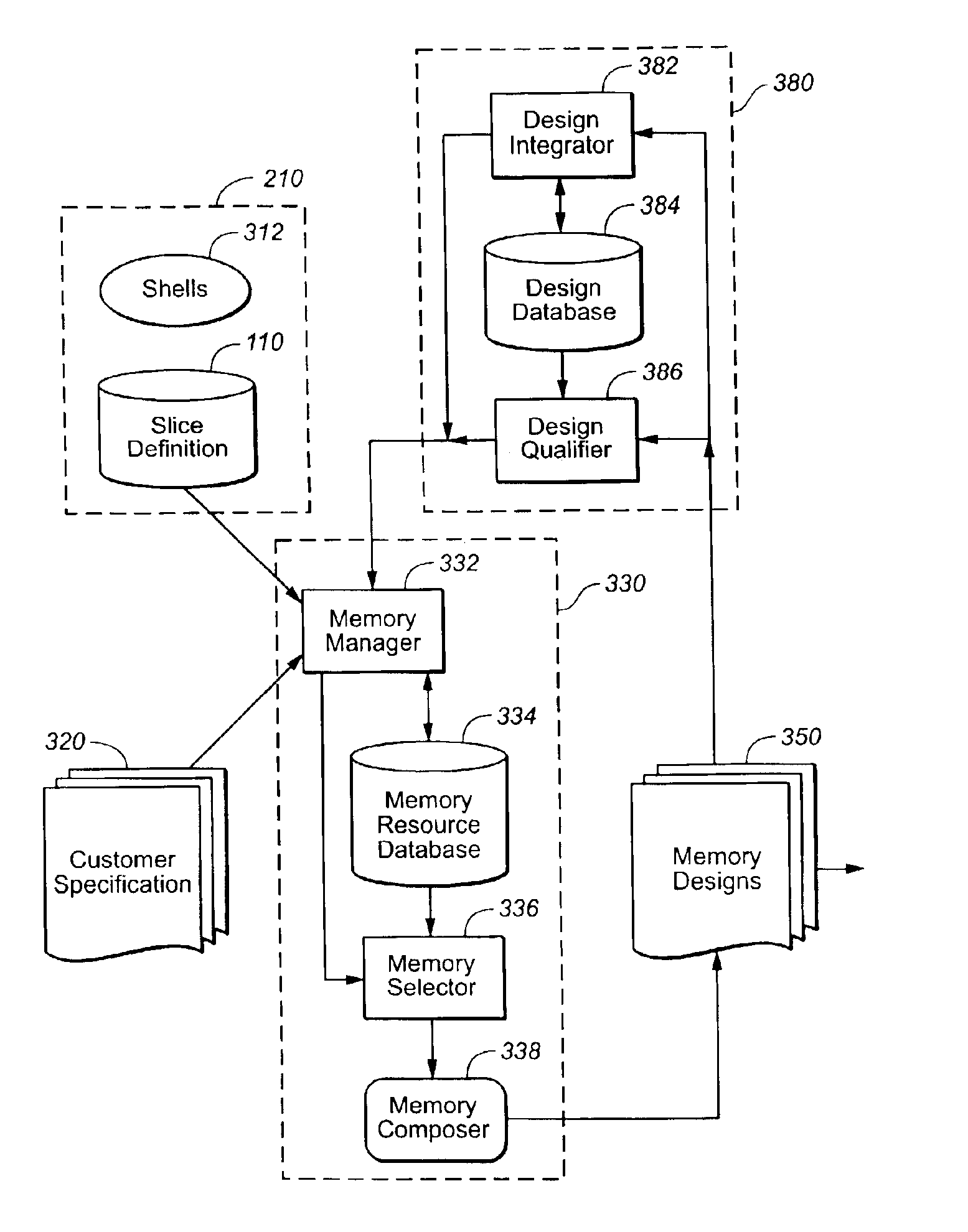

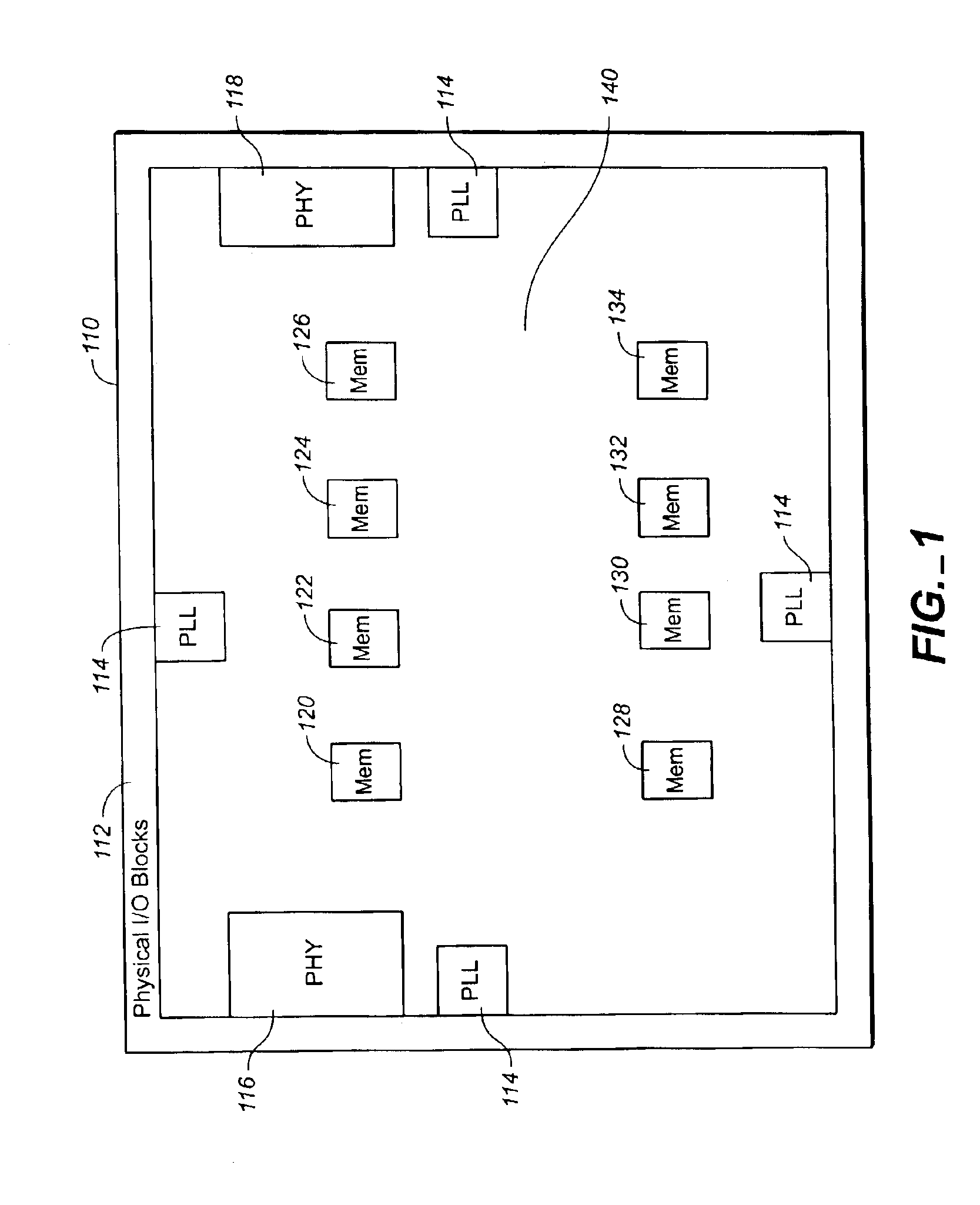

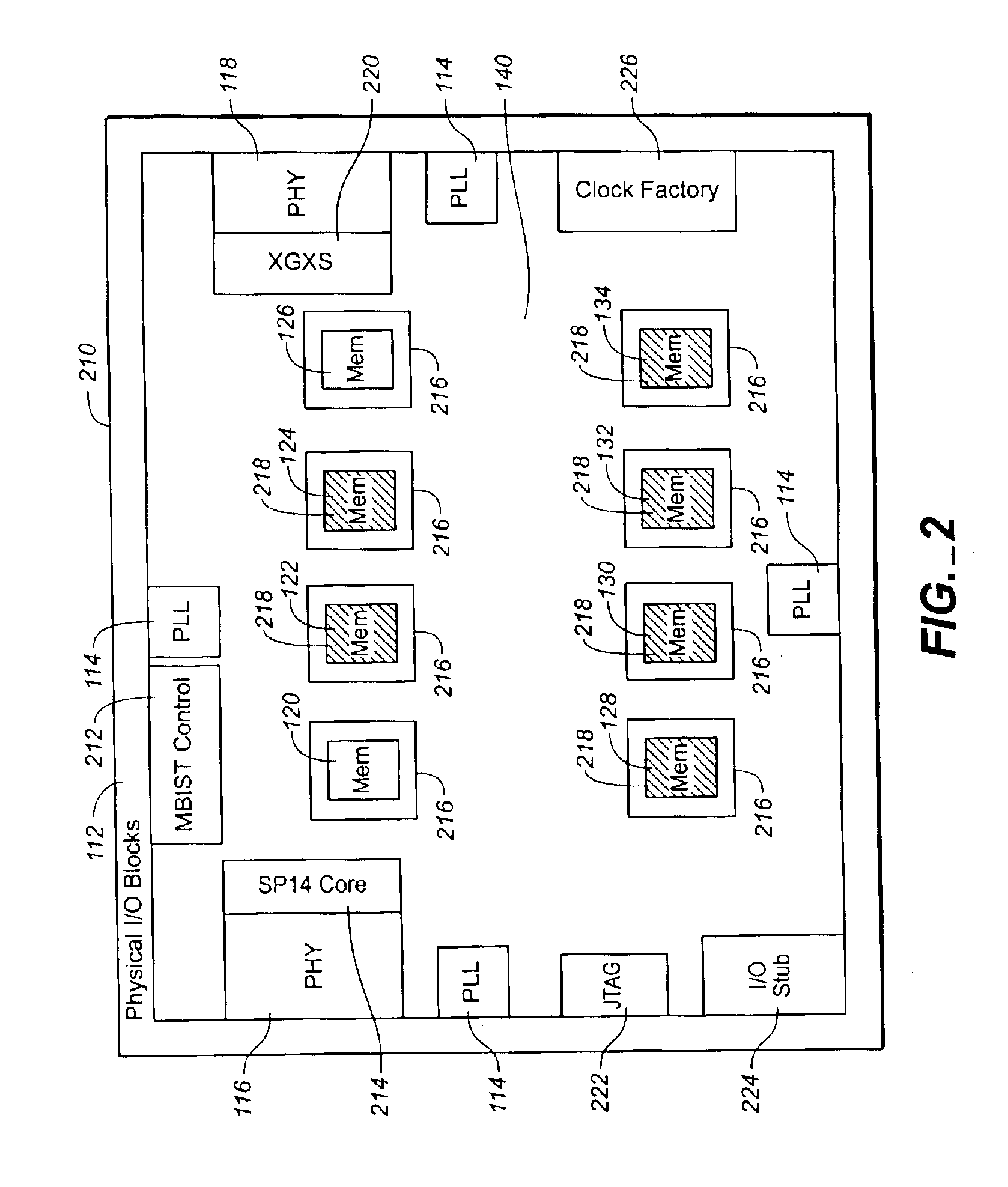

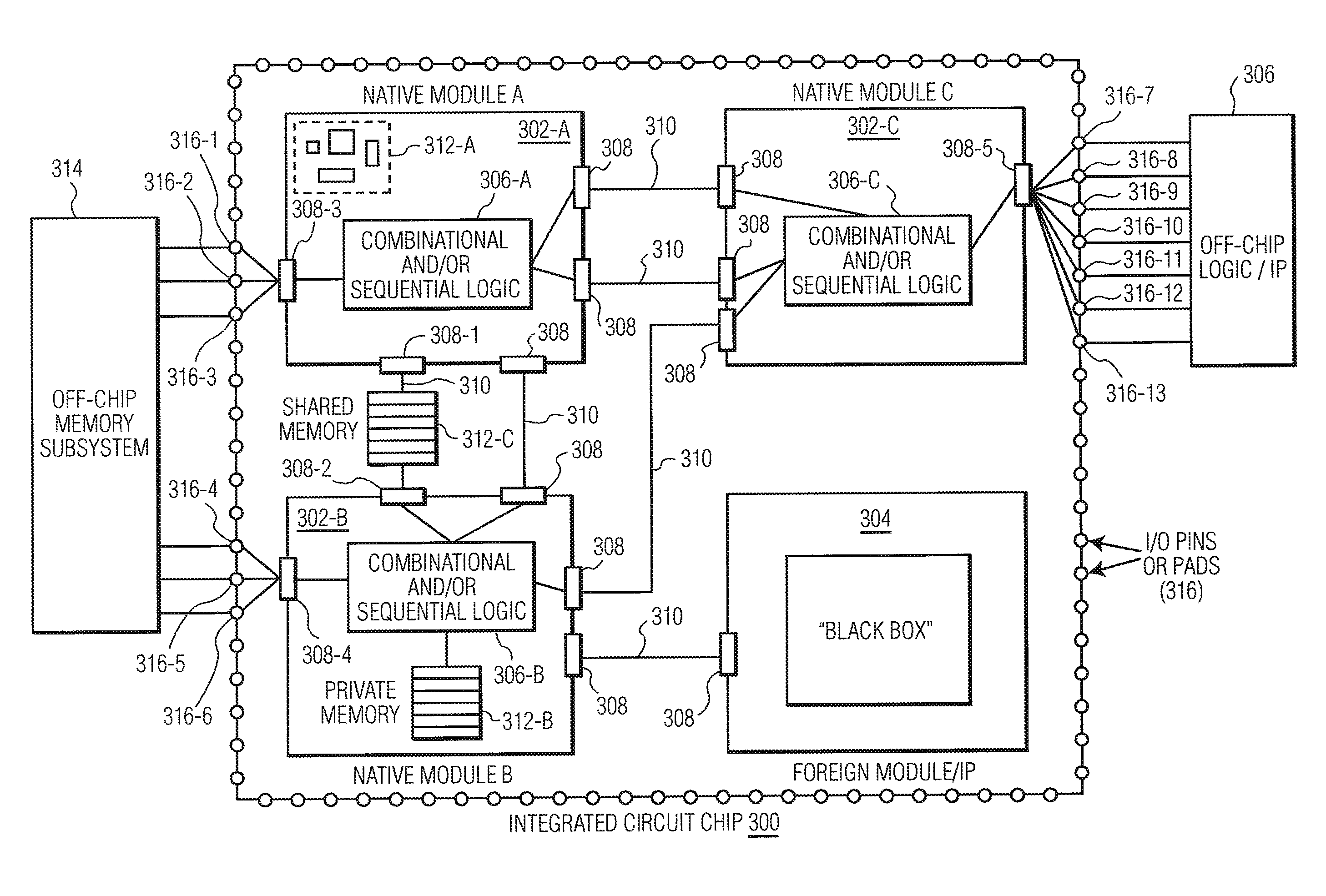

Automated selection and placement of memory during design of an integrated circuit

InactiveUS7069523B2Solid-state devicesSemiconductor/solid-state device manufacturingIntegratorComputer architecture

A tool for designing integrated circuits that optimizes the placement and timing of memory blocks within the circuit. Given a manufactured slice that has a number of blocks already diffused and logically integrated, the memory generation tool herein automatically considers the available diffused memory and the gate array of the slices to configure and optimize them into a customer's requirements for memory. The memory generation tool has a memory manager, a memory resource database, a memory resource selector, and a memory composer. Together these all interact to generate memories from the available memories within the memory resource database. The memory composer actually generates the RTL logic shells for the memories, and outputs the memory designs in Verilog, VHDL, or other tool synthesis language. Once a memory is created, it is tested. Upon successful testing, the memory manager updates the memory resource database to indicate the successfully tested memory is no longer available as a resource for the generation of further memories. A design integrator may review the memory designs output and further integrate the memory, its timing, testing, etc. with other blocks and functions of the integrated circuit.

Owner:BELL SEMICON LLC

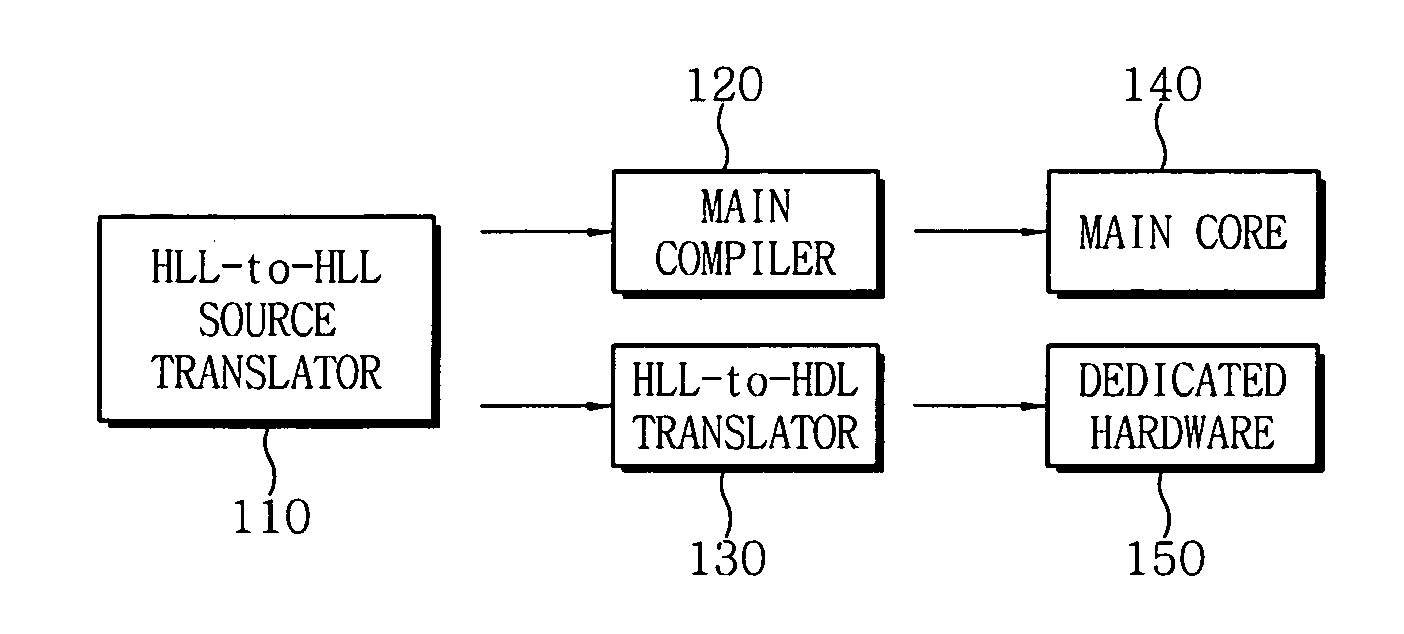

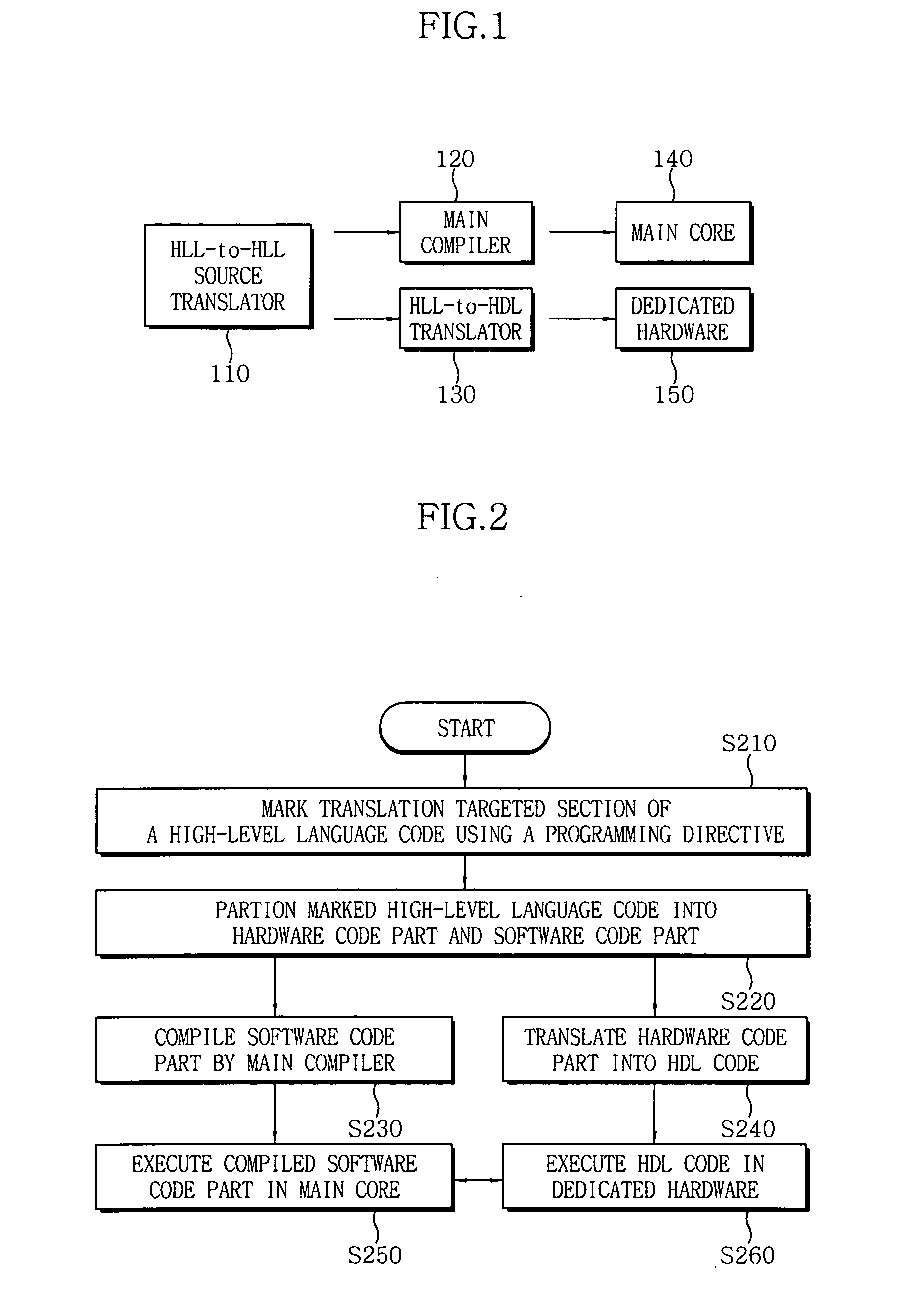

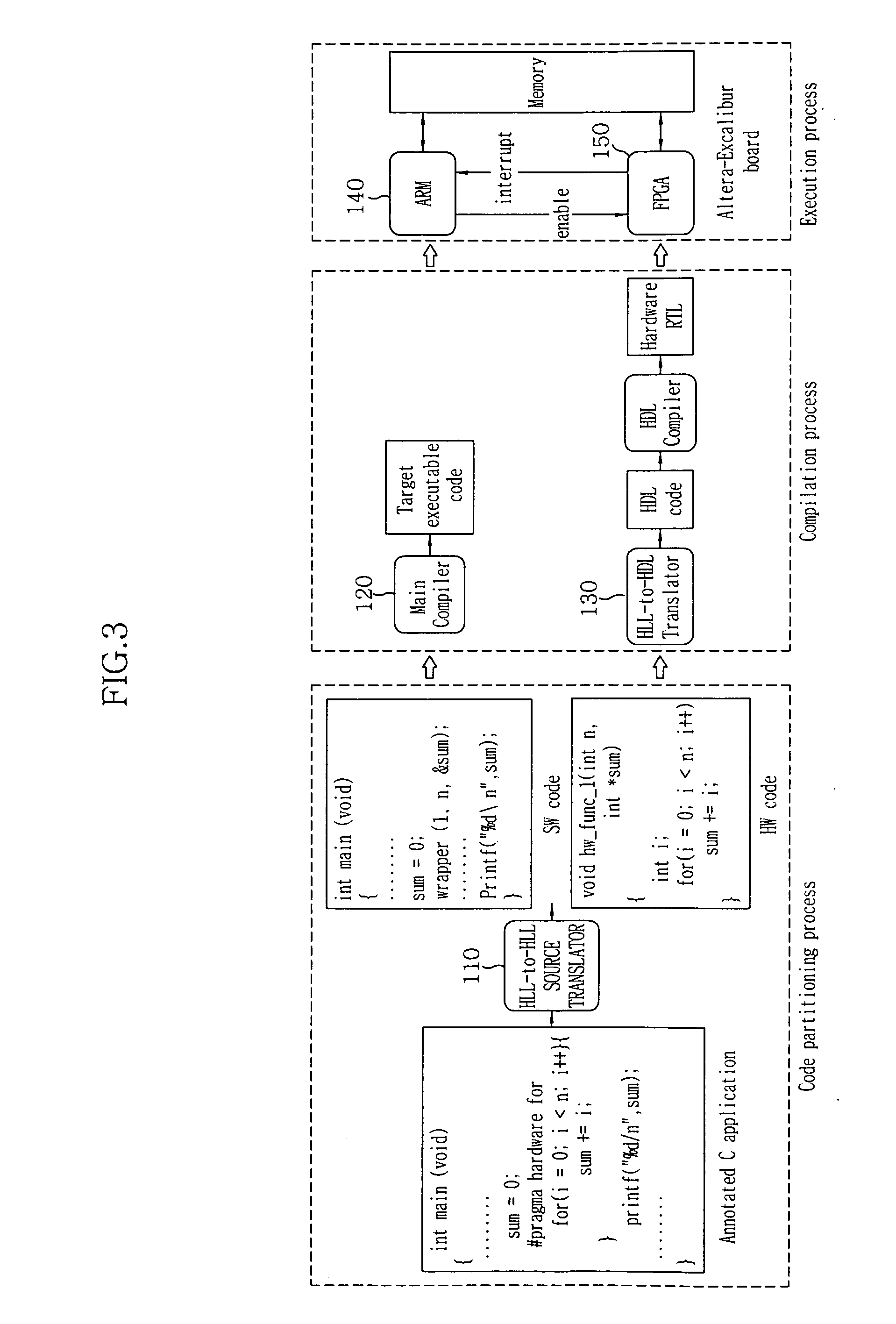

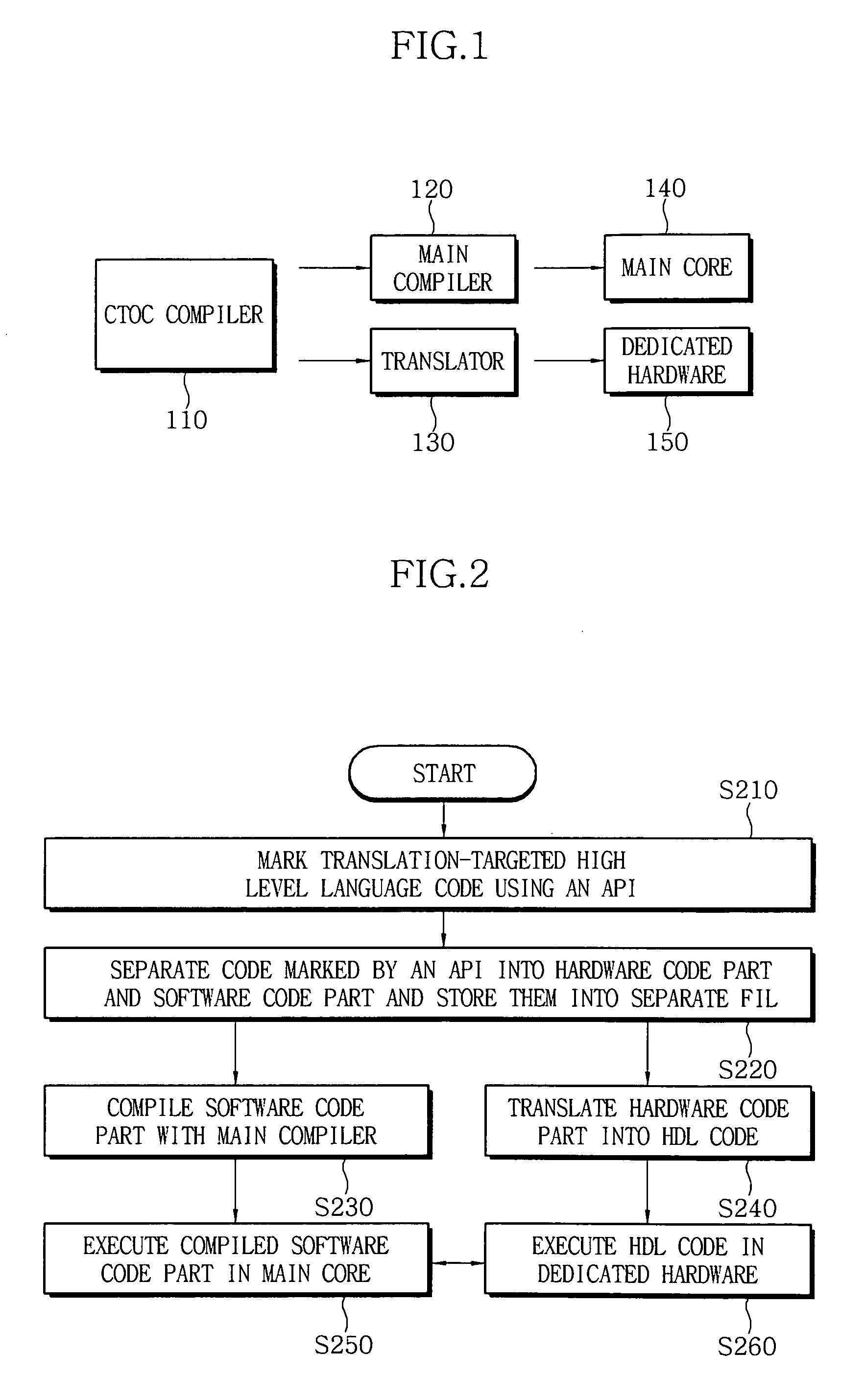

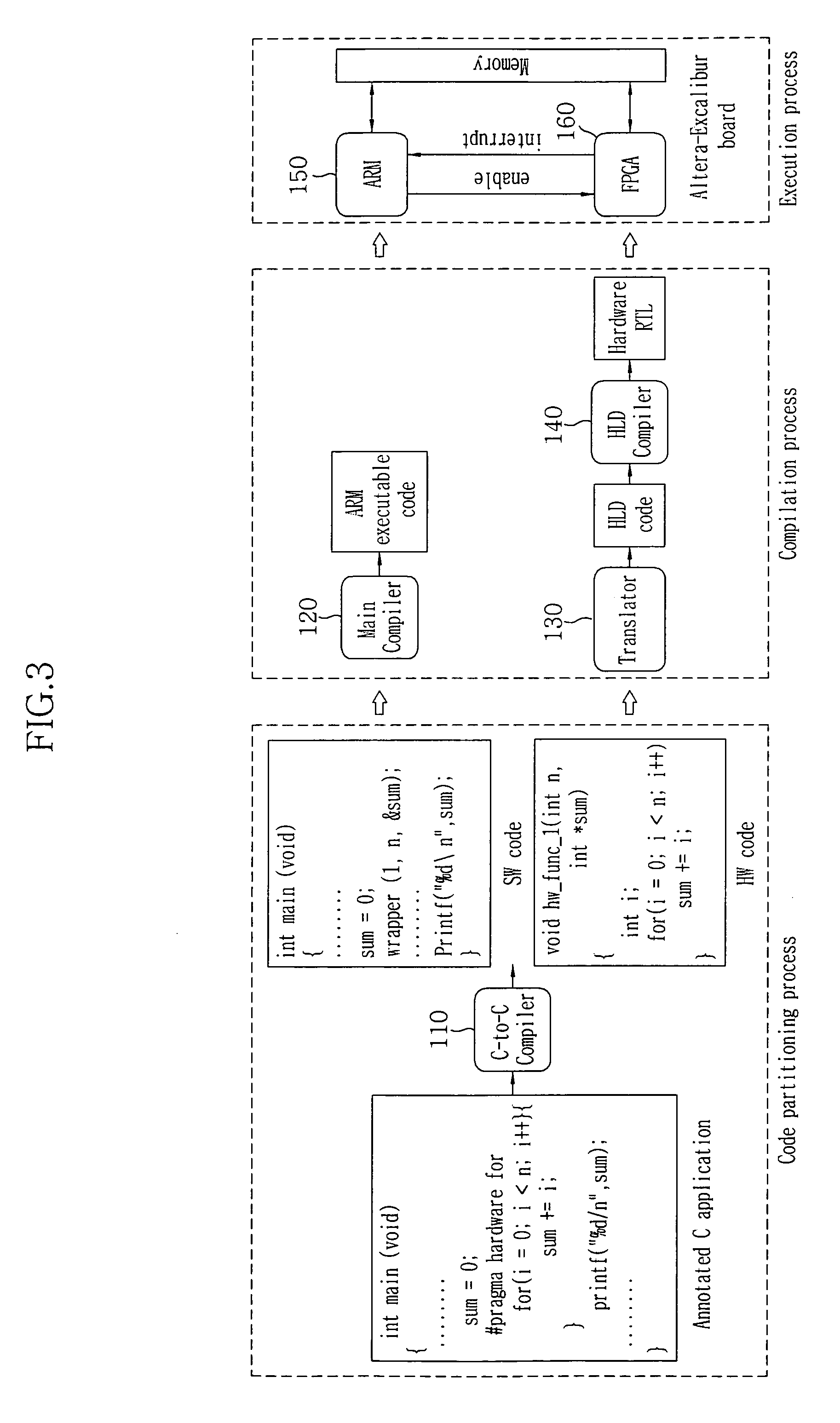

System and method for translating high-level programming language code into hardware description language code

The present invention is directed to a method and system for translating a high-level language (HLL) code such as C, C++, Fortran, Java or the like into a HDL code such as Verilog or VHDL which requires no modification in the original HLL source code, while supporting a cross call between software and hardware, and even recursive calls in hardware. The system includes: a HLL-to-HLL source translator which reads user programming directive from a translation-targeted high-level language code marked with the user directive, and separates the translation-targeted high-level language code into a hardware code part and a software code part; a main compiler which compiles the software code part; a HLL-to-HDL translator which includes the front-end and middle-end of the main compiler and a HDL backend; a main core which executes the compiled software code part; and a dedicated hardware which executes the HDL code.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

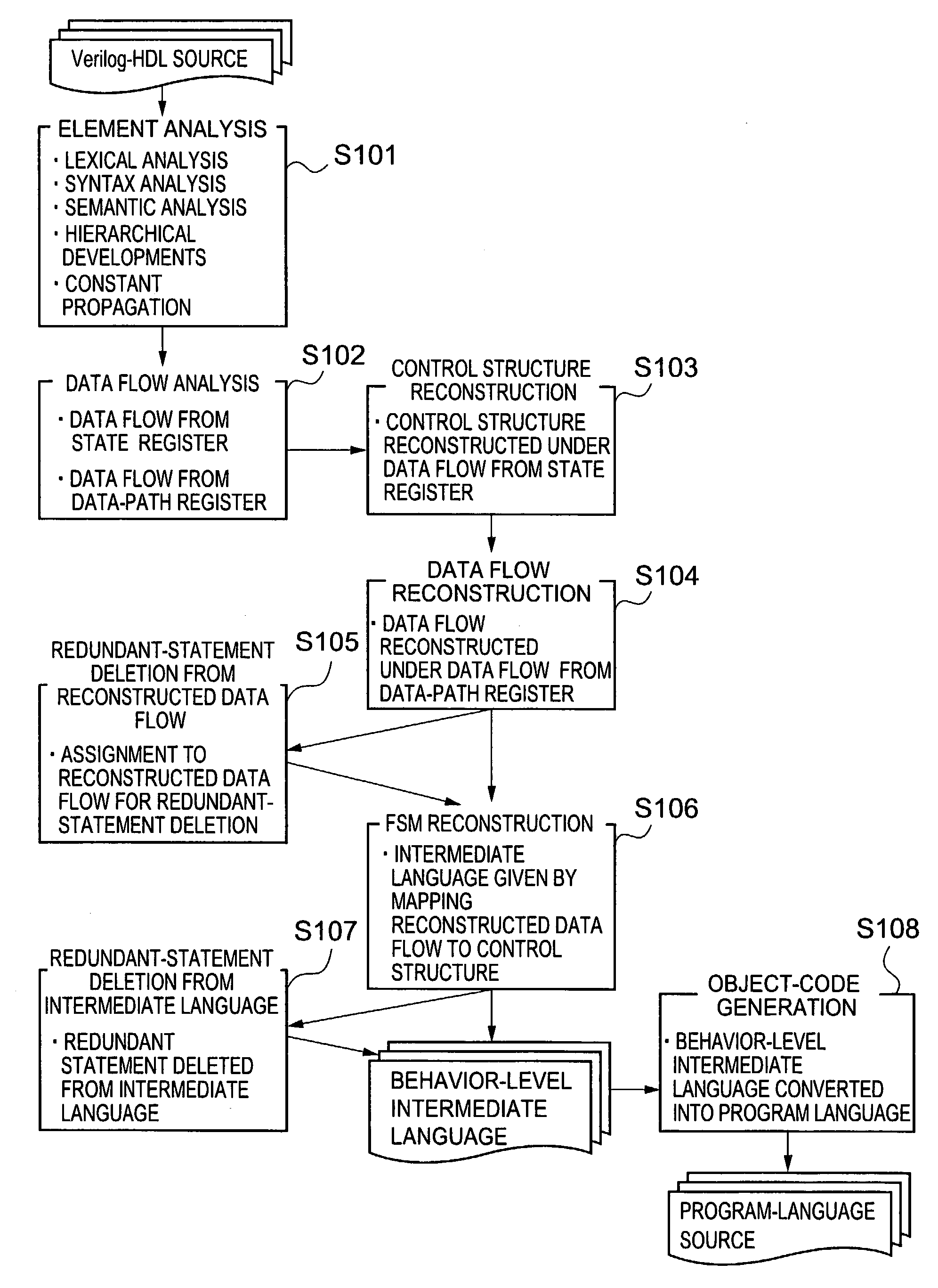

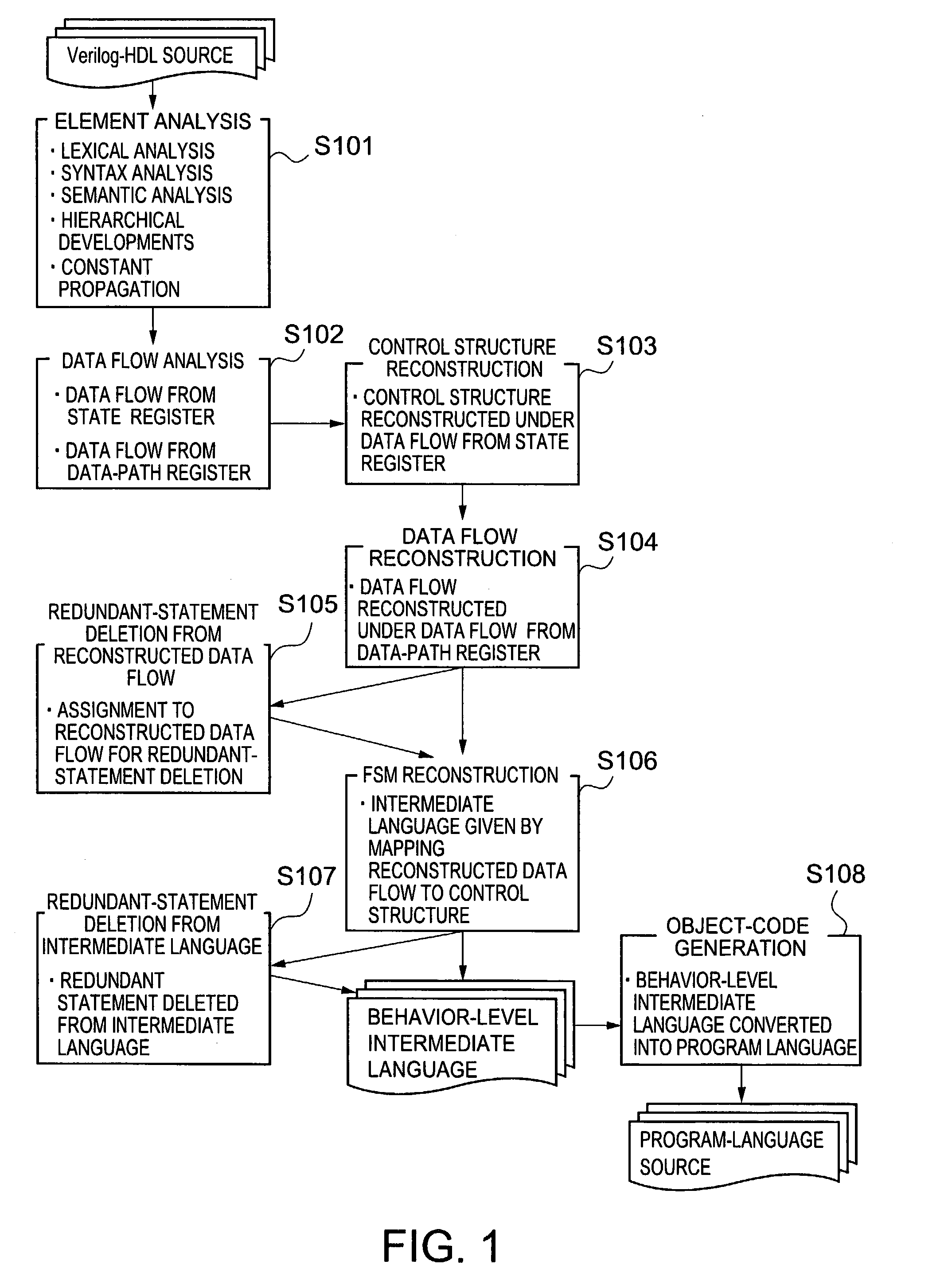

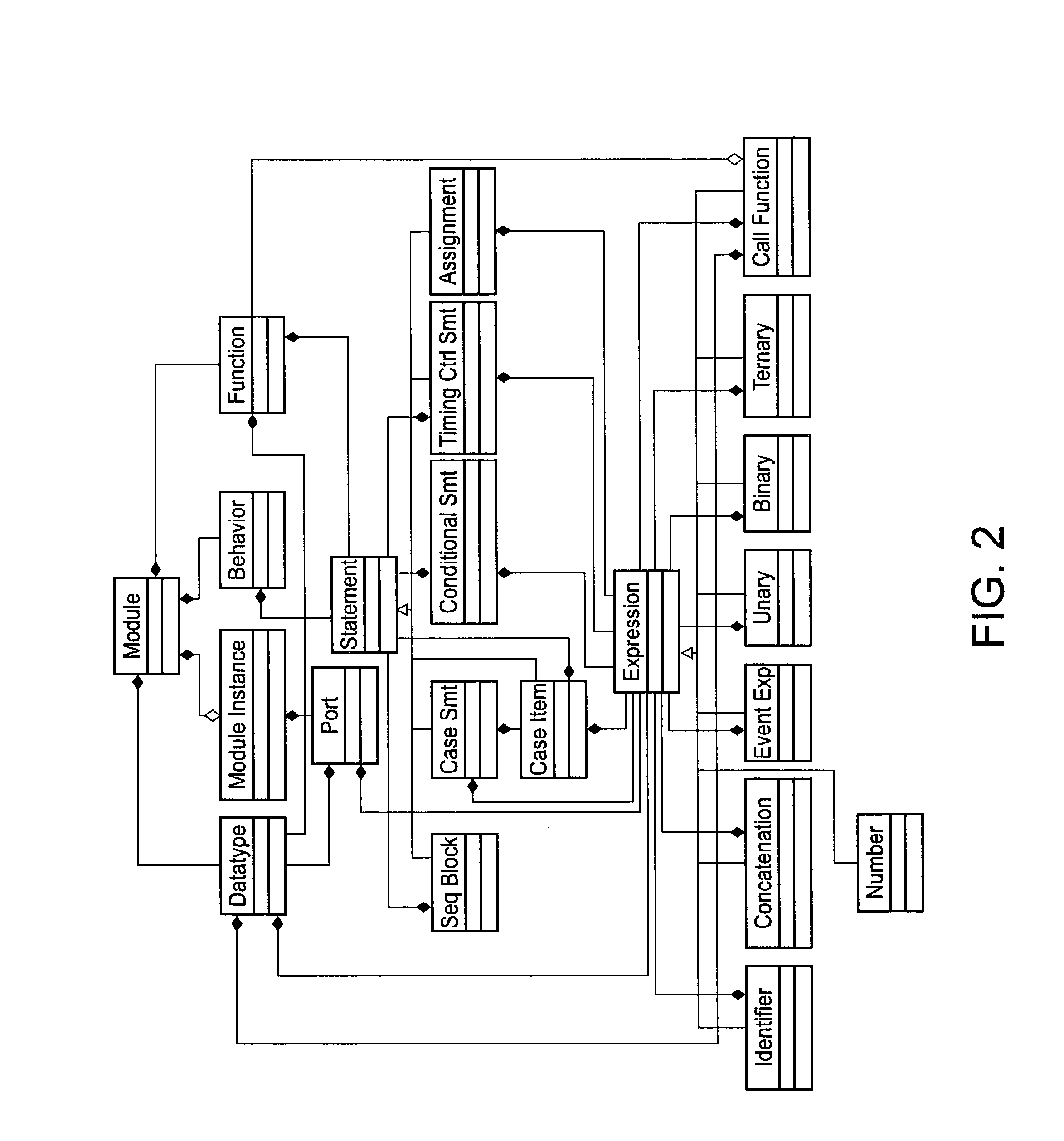

Hardware-operation description conversion method and program therefor

InactiveUS6996788B2CAD circuit designSoftware simulation/interpretation/emulationData streamAnalysis data

A verilog-HDL source at the register-transfer level (RTL) is converted into a programming language executable on computer. Constructed in an analyzing of elements is a data structure corresponding to the elements of the verilog-HDL source. Created in an analyzing of a data-flow are a first data flow from a state register and a second flow from data-path register. Reconstructed in a reconstructing of a control-structure is the first data flow. Reconstructed in a reconstructing of a data-path is the second data flow so that the reconstructed second data is constituted only by circuitry operating in each state of the control structure. Each reconstructed data flow is mapped in each state of the control structure in a combining of the control-structure / data-flow, to output an behavior-level intermediate language. The intermediate language is converted into a programming language in a generating of an object-code.

Owner:KK TOSHIBA

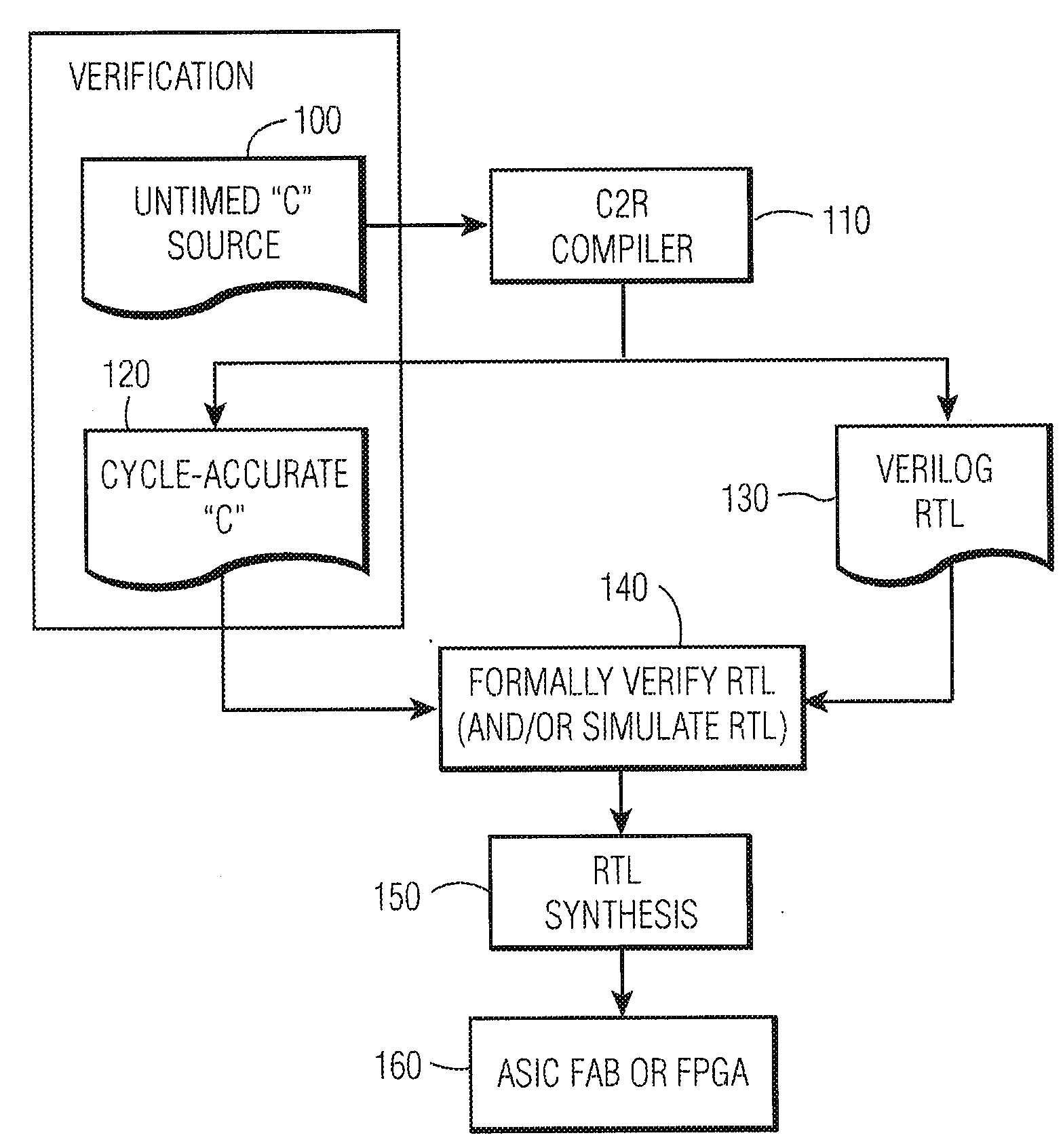

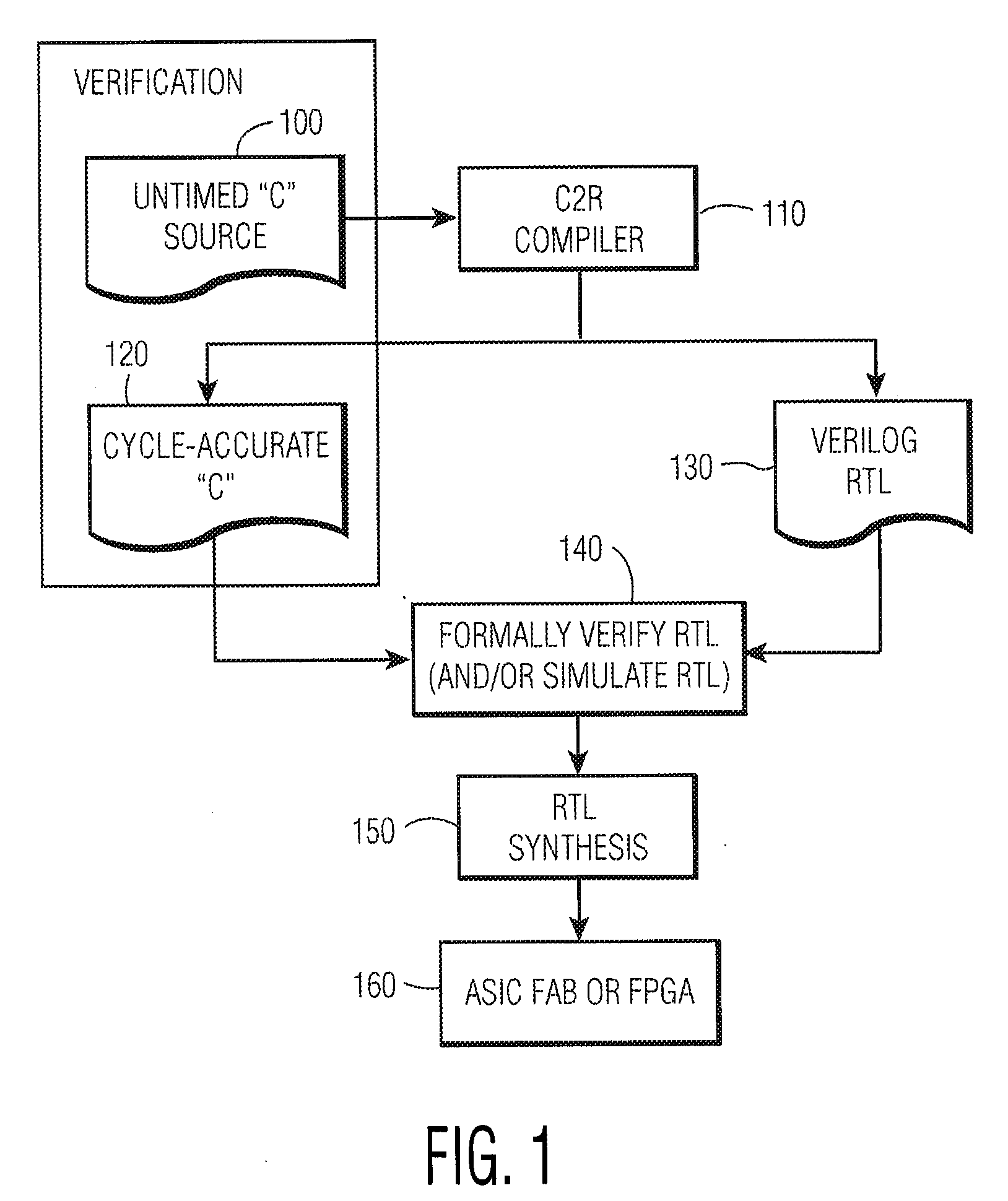

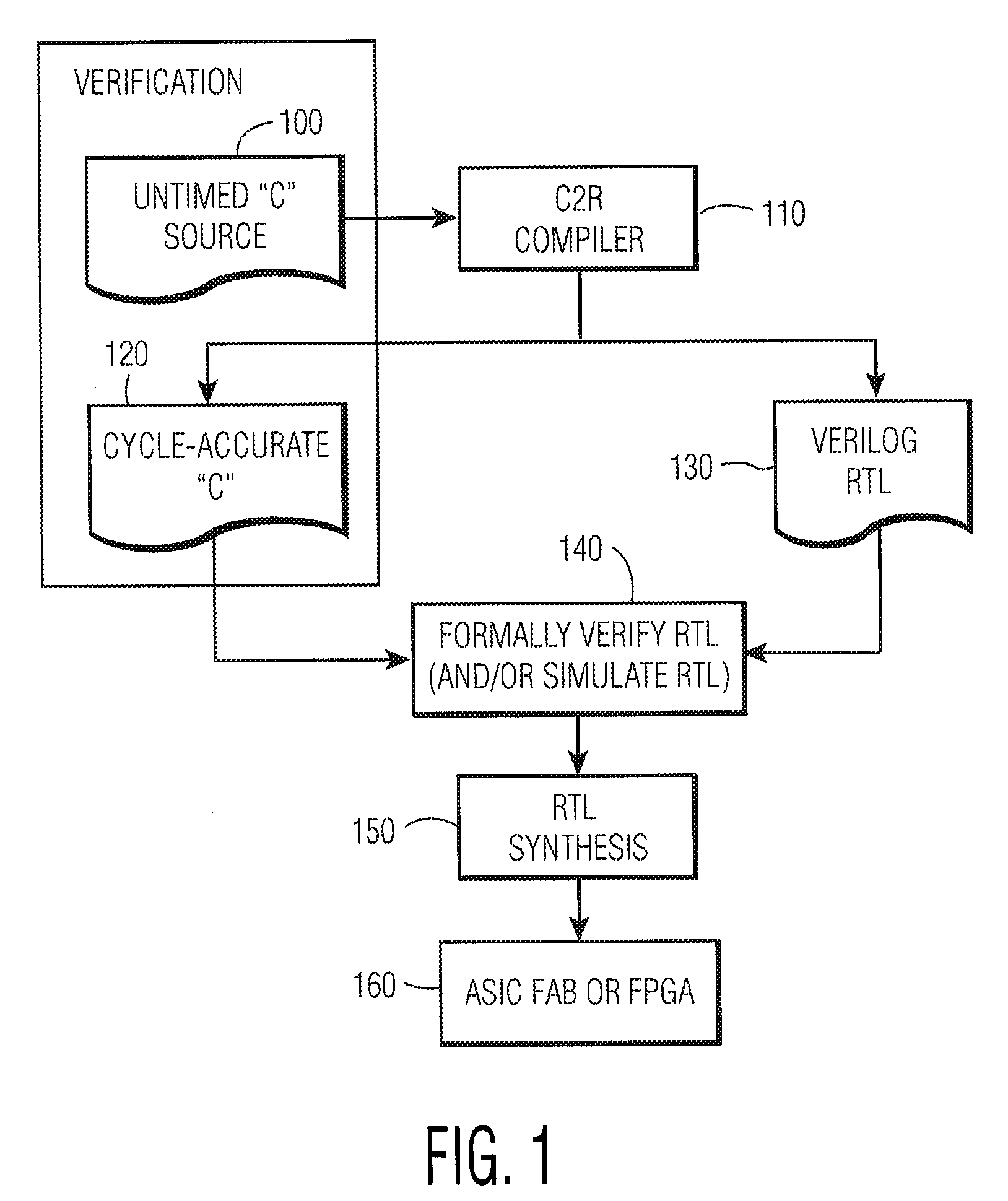

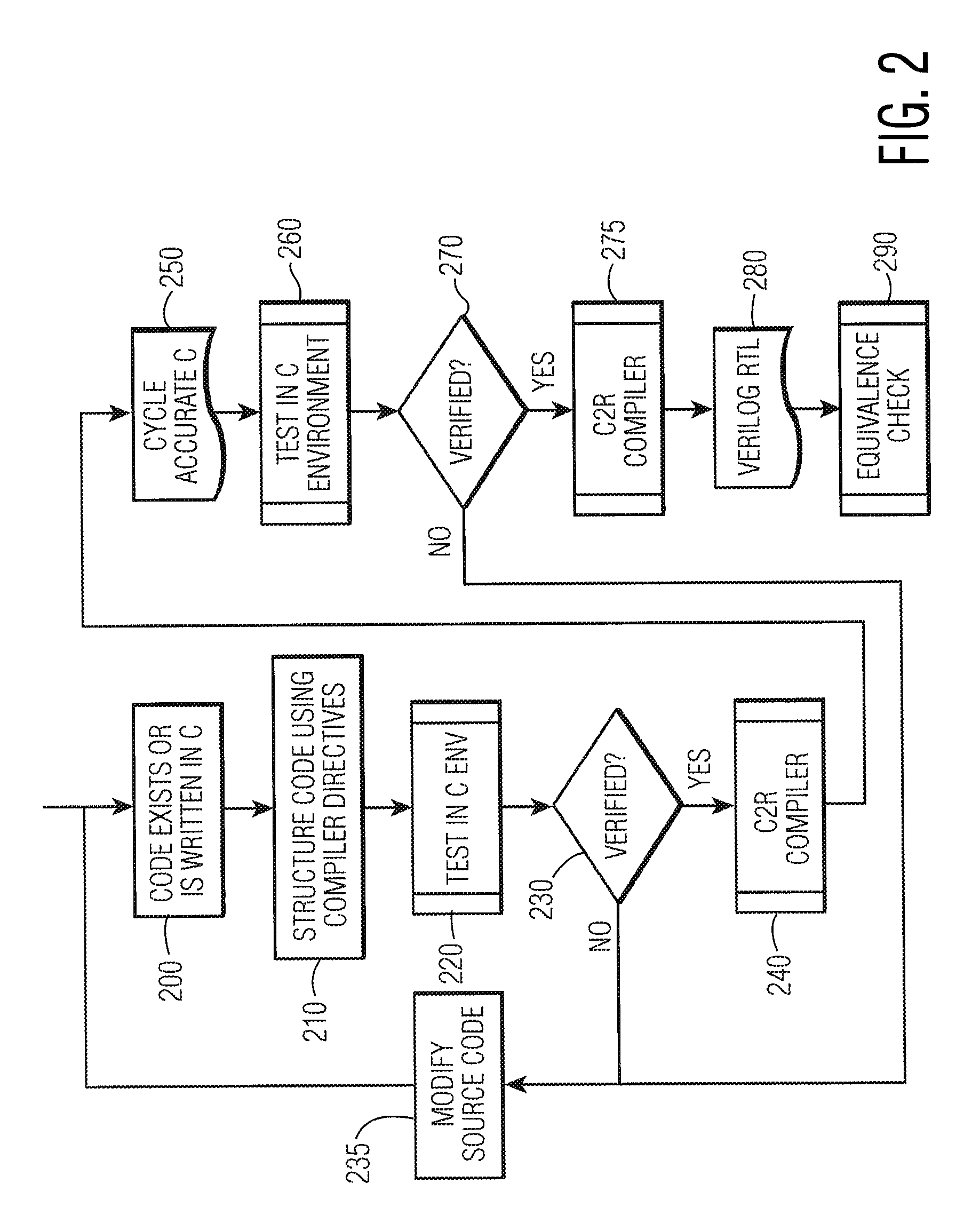

System and method for converting software to a register transfer (RTL) design

ActiveUS20090144690A1Analogue computers for electric apparatusCAD circuit designComputer architectureProcessor register

A method for converting a C-type programming language program to a hardware design, where the said program is an algorithmic representation of one or more processes. The C-type programming language program is compiled into a hardware description language (HDL) synthesizable design. The compiler categorizes variables as using either implicit memory or custom memory. Different accessor functions are used depending on which type of memory is used. The programming language may use ANSI C and the HDL may be Verilog Register Transfer Level (RTL). The hardware device generated from the HDL synthesizable design may be an Application-Specific Integrated Circuit (ASIC) or a Field Programmable Gate Array (FPGA).

Owner:EXAR CORP

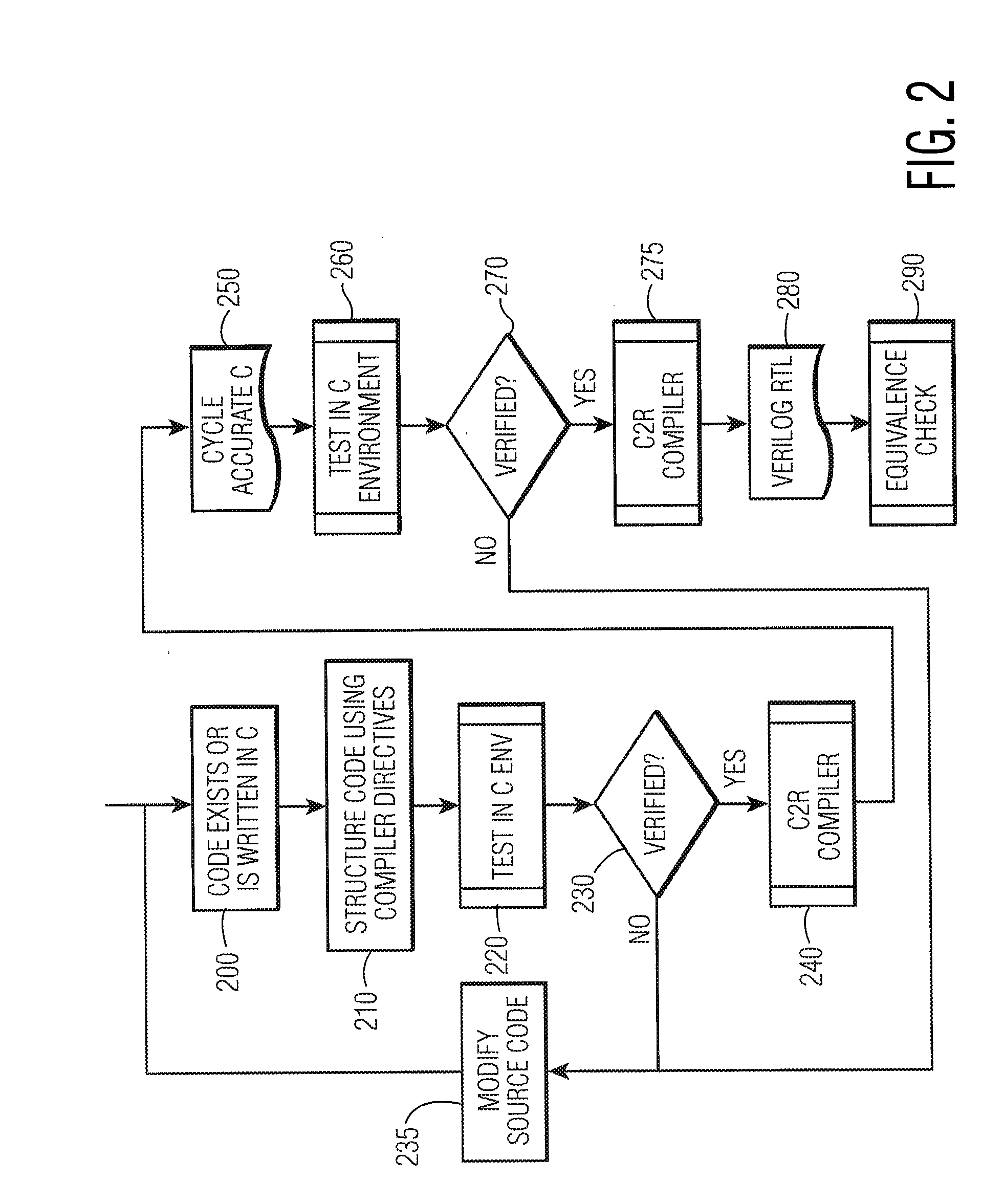

Izhikevich neural network synchronous discharging simulation platform based on FPGA

InactiveCN104615909AIncrease flexibilityEasy to operateSpecial data processing applicationsControl signalNetwork model

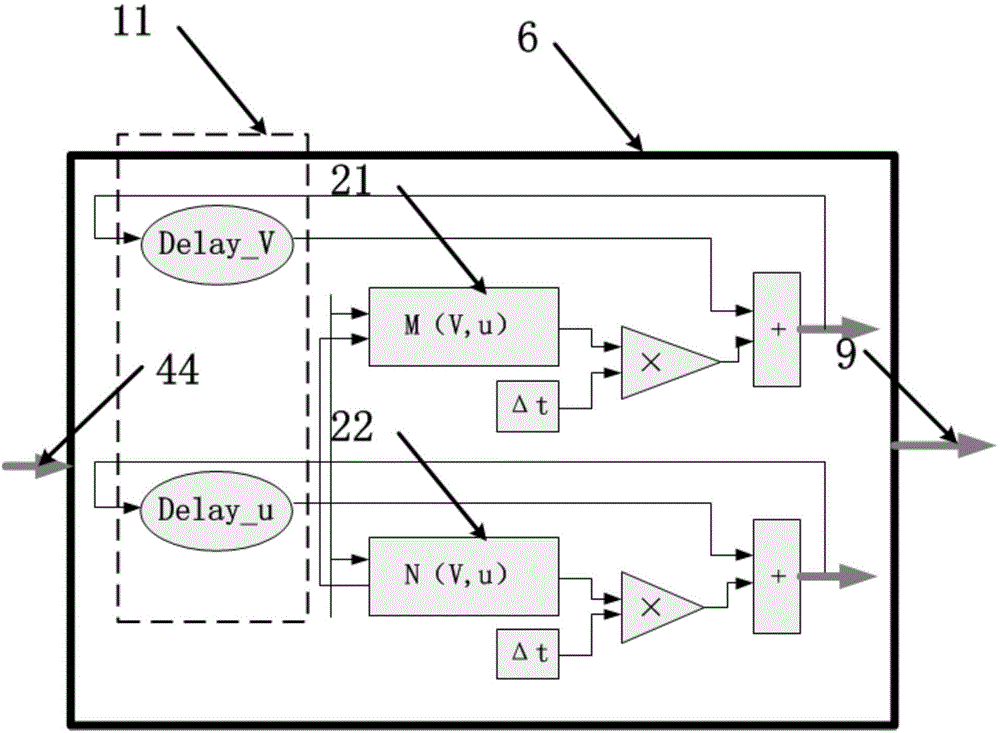

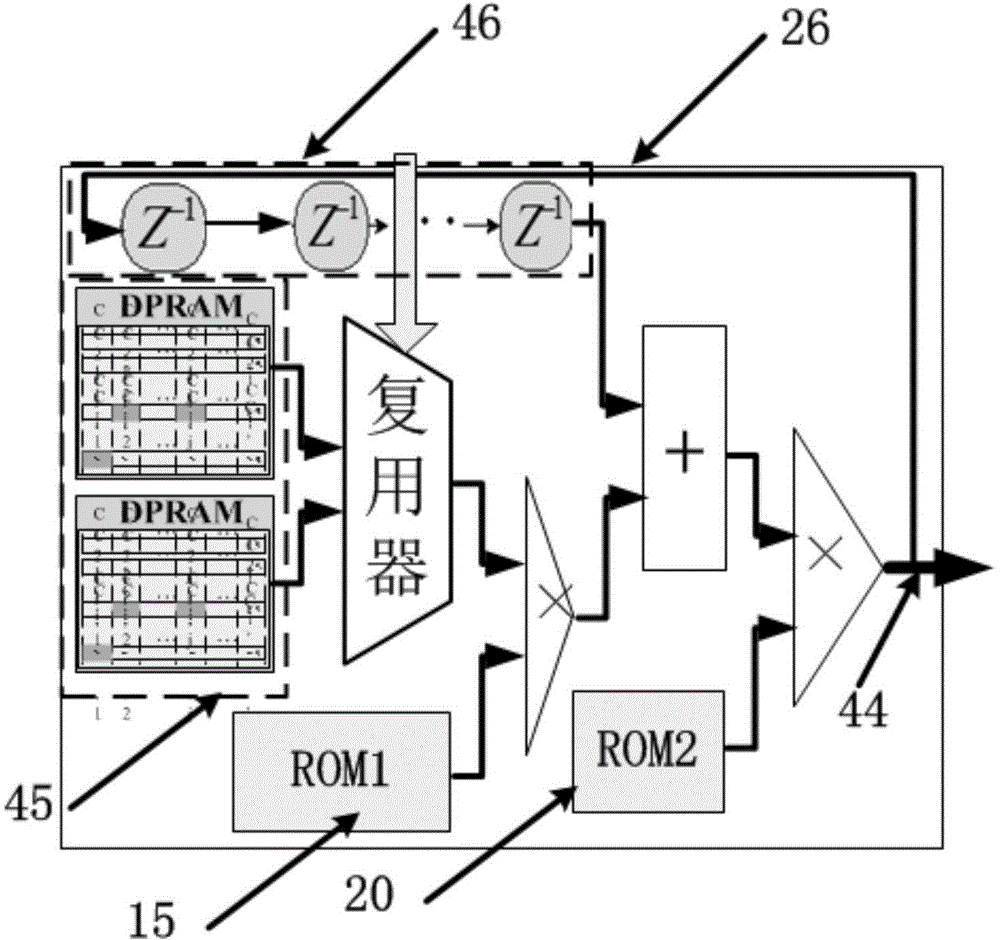

The invention provides an Izhikevich neural network synchronous discharging simulation platform based on an FPGA. The simulation platform comprises an FPGA neural network computing processor and an upper computer which are connected with each other. The FPGA neural network computing processor comprises an FPGA chip, an off-chip memorizer array and an Ethernet communication module, wherein the FPGA chip receives an upper computer control signal output by the off-chip memorizer array, and receives a presynaptic membrane potential signal output by the off-chip memorizer array. The upper computer is in communication with the FPGA chip and the off-chip memorizer array through a VB programming realization man-machine operating interface and the Ethernet communication module, and a neural network model is established on the FPGA chip through Verilog HDL language programming. The Izhikevich neural network synchronous discharging simulation platform has the advantages that the hardware modeling of the phenotype and physiological type neural network model is achieved through an animal-free experiment serving as a biological neural network on the basis of an FPGA neural network experiment platform conducting computation at a high speed, and the consistency with true biological nerve cells on the time scale can be achieved.

Owner:TIANJIN UNIV

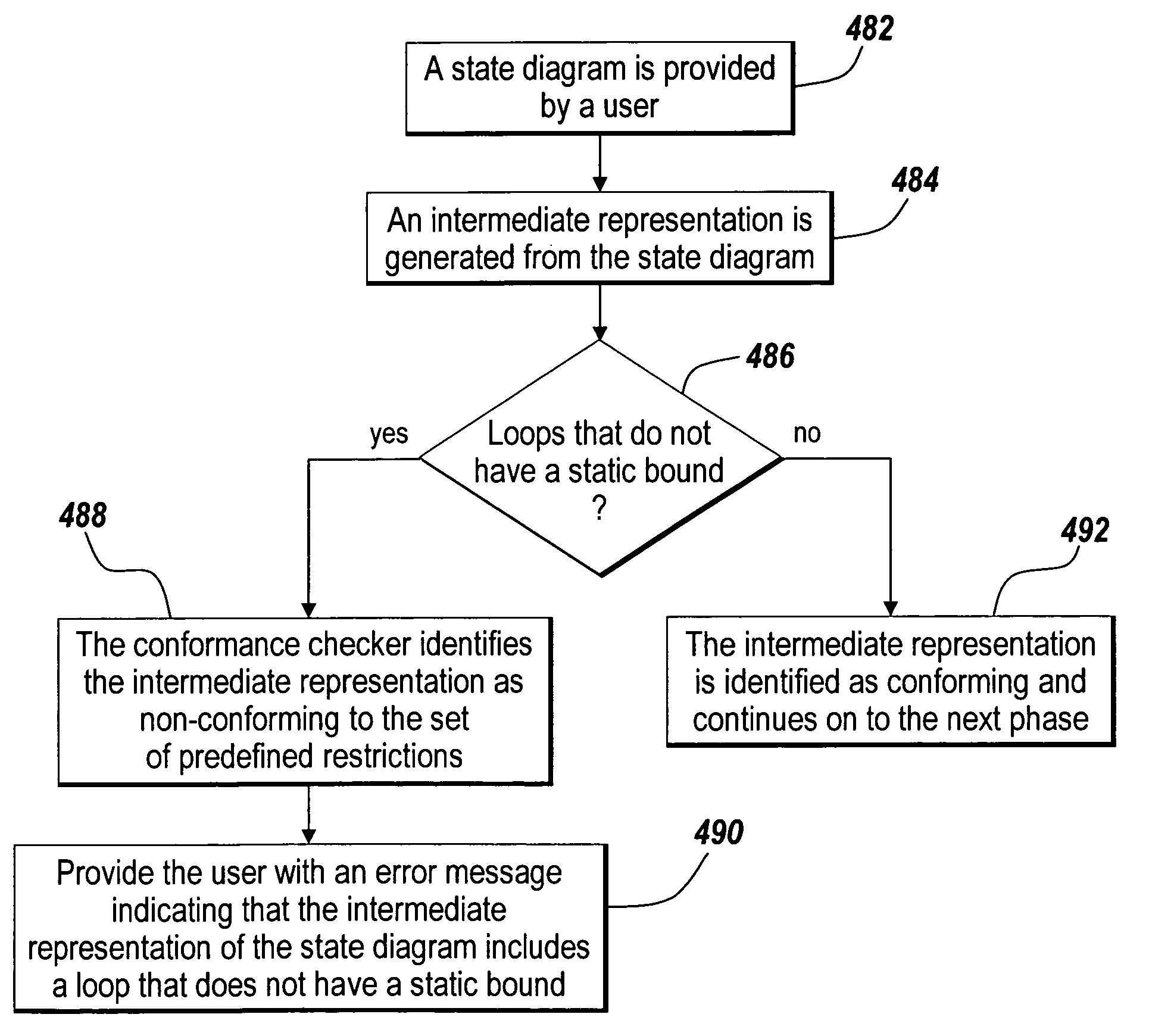

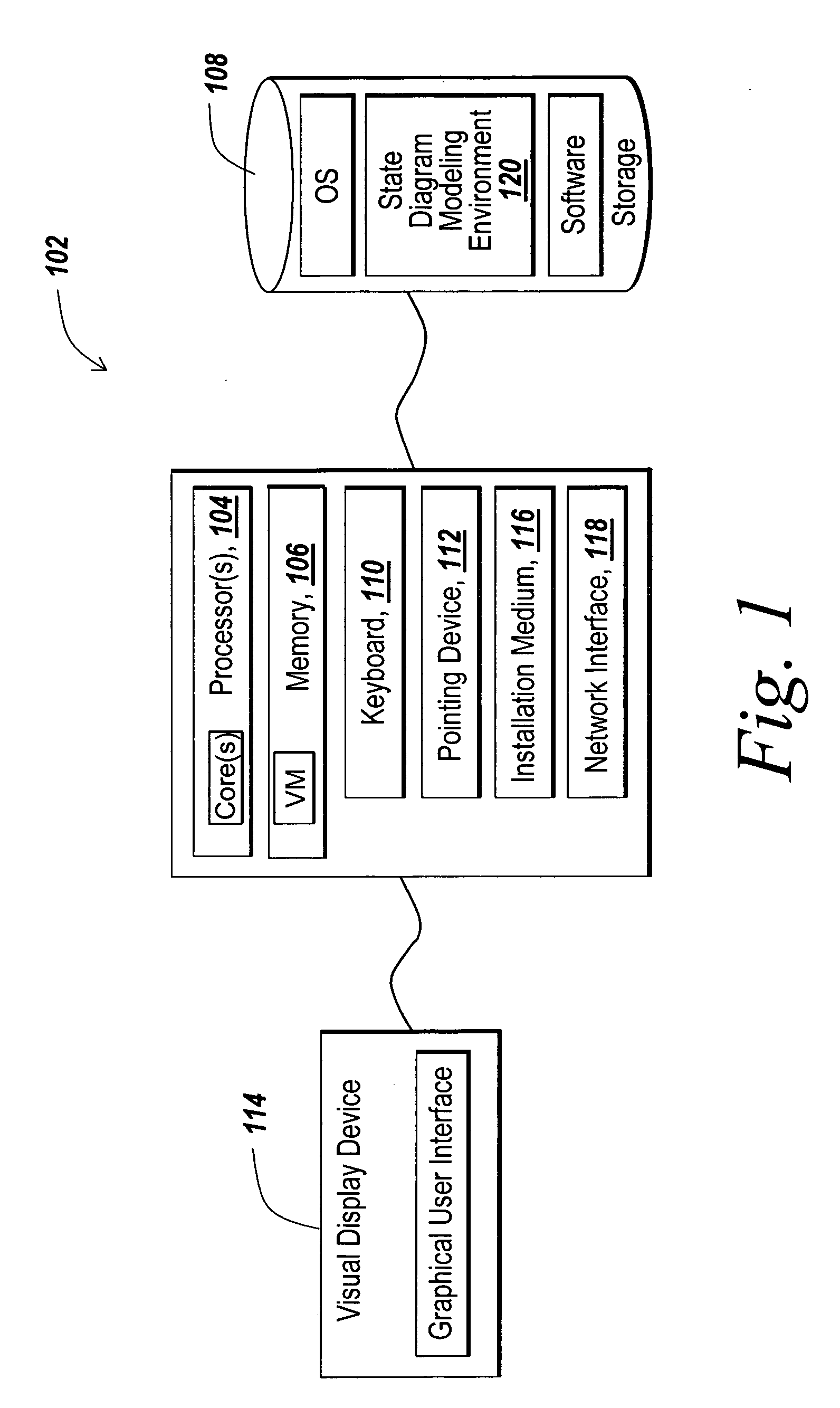

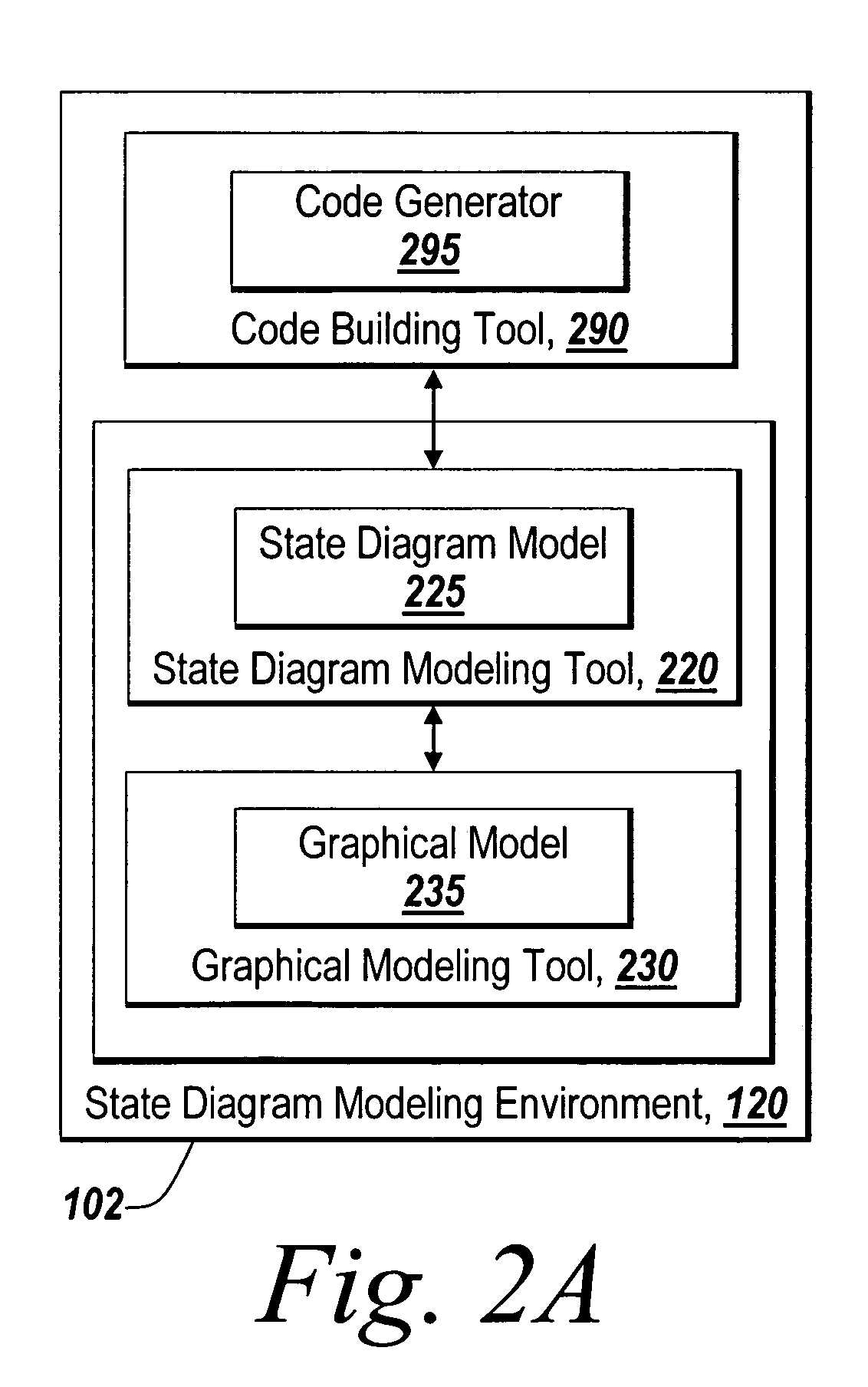

Hardware description language code generation from a state diagram

The present invention provides a state diagramming environment in a computing device that enables the conversion of a state diagram into a hardware description language. To achieve this conversion, the present invention generates an intermediate representation of the state diagram. The intermediate representation is checked against a set of predefined restrictions for compliance. The state diagramming environment converts the intermediate representation of the state diagram into a hardware description language, such as VHDL or Verilog.

Owner:THE MATHWORKS INC

System and method for converting software to a register transfer (RTL) design

ActiveUS7904850B2Analogue computers for electric apparatusCAD circuit designComputer architectureTerm memory

A method for converting a C-type programming language program to a hardware design, where the said program is an algorithmic representation of one or more processes. The C-type programming language program is compiled into a hardware description language (HDL) synthesizable design. The compiler categorizes variables as using either implicit memory or custom memory. Different accessor functions are used depending on which type of memory is used. The programming language may use ANSI C and the HDL may be Verilog Register Transfer Level (RTL). The hardware device generated from the HDL synthesizable design may be an Application-Specific Integrated Circuit (ASIC) or a Field Programmable Gate Array (FPGA).

Owner:EXAR CORP

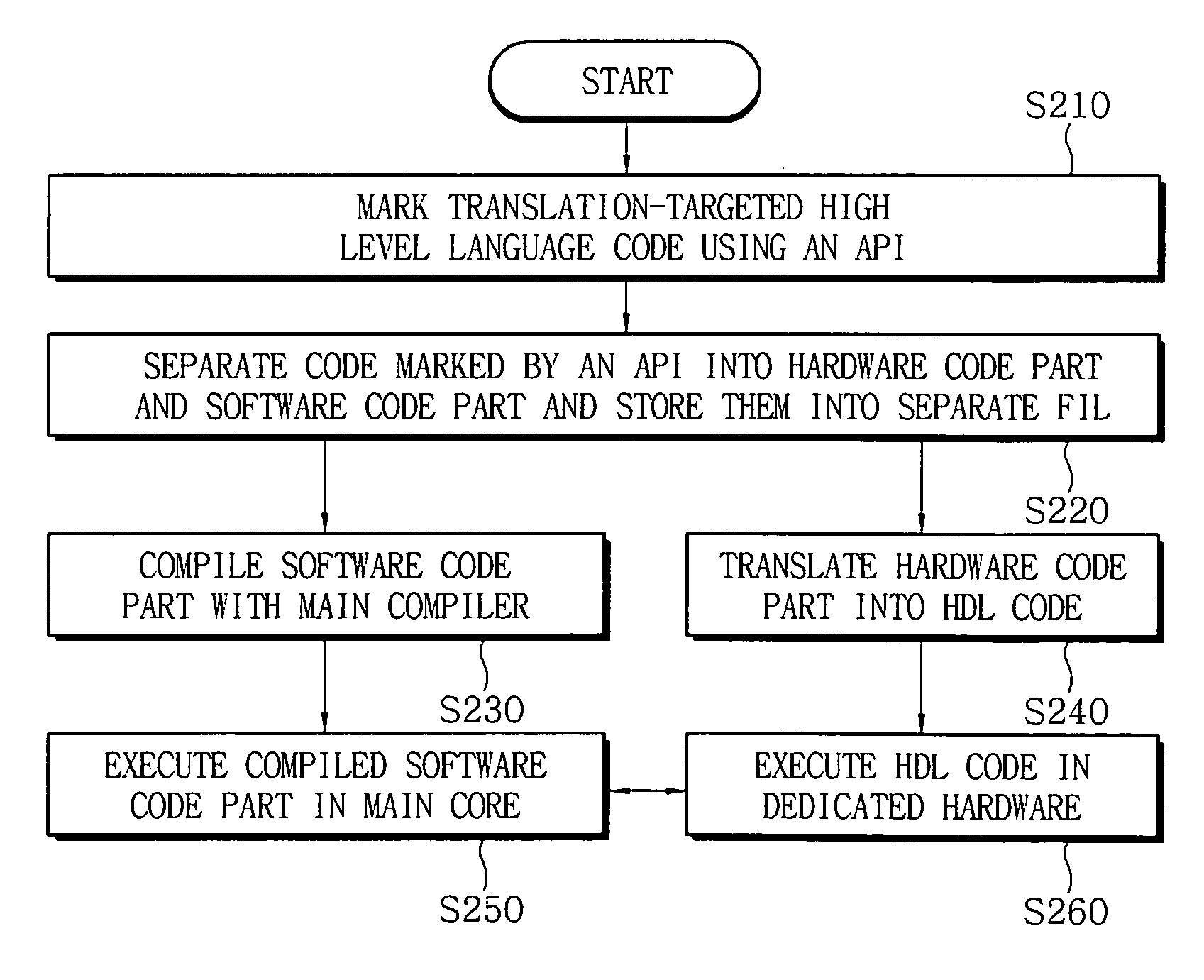

System and Method for translating high programming level languages code into Hardware Description Language code

The present invention is directed to a method and system for translating a high programming level language code such as C, C++, Fortran, Java or the like into a HDL code such as Verilog or VHDL. The system includes: a C-to-C source translator which reads user API from a translation-targeted high level language code marked with the user API, separates the translation-targeted high level language code into a hardware code part and a software code part, and stores the hardware code part and the software code part in separate files; a main compiler which compiles the stored software code part; a translator which translates the stored hardware code part into a HDL code including one or more block modules and one top module; a main core which executes the compiled software code part; and a dedicated hardware which executes the HDL code.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

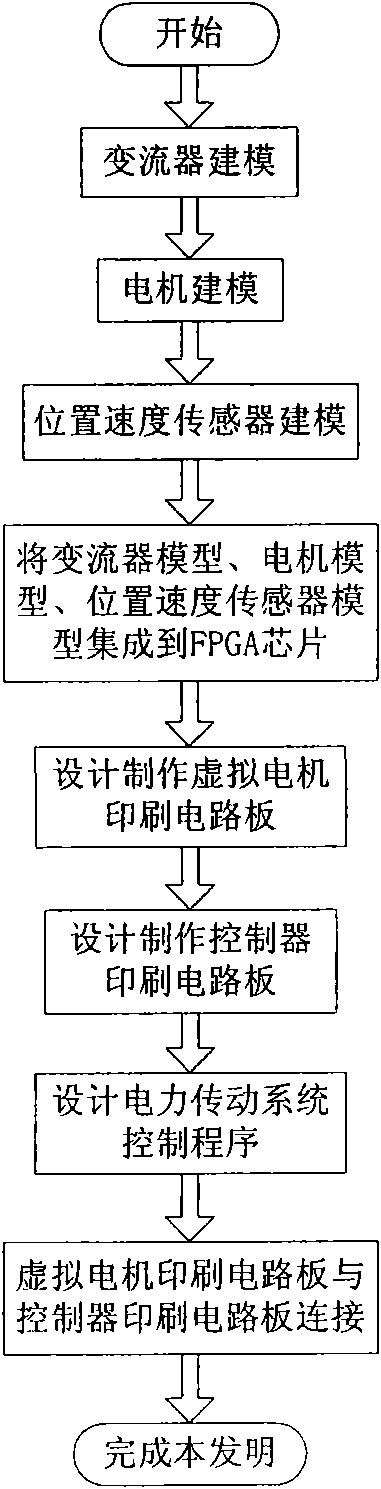

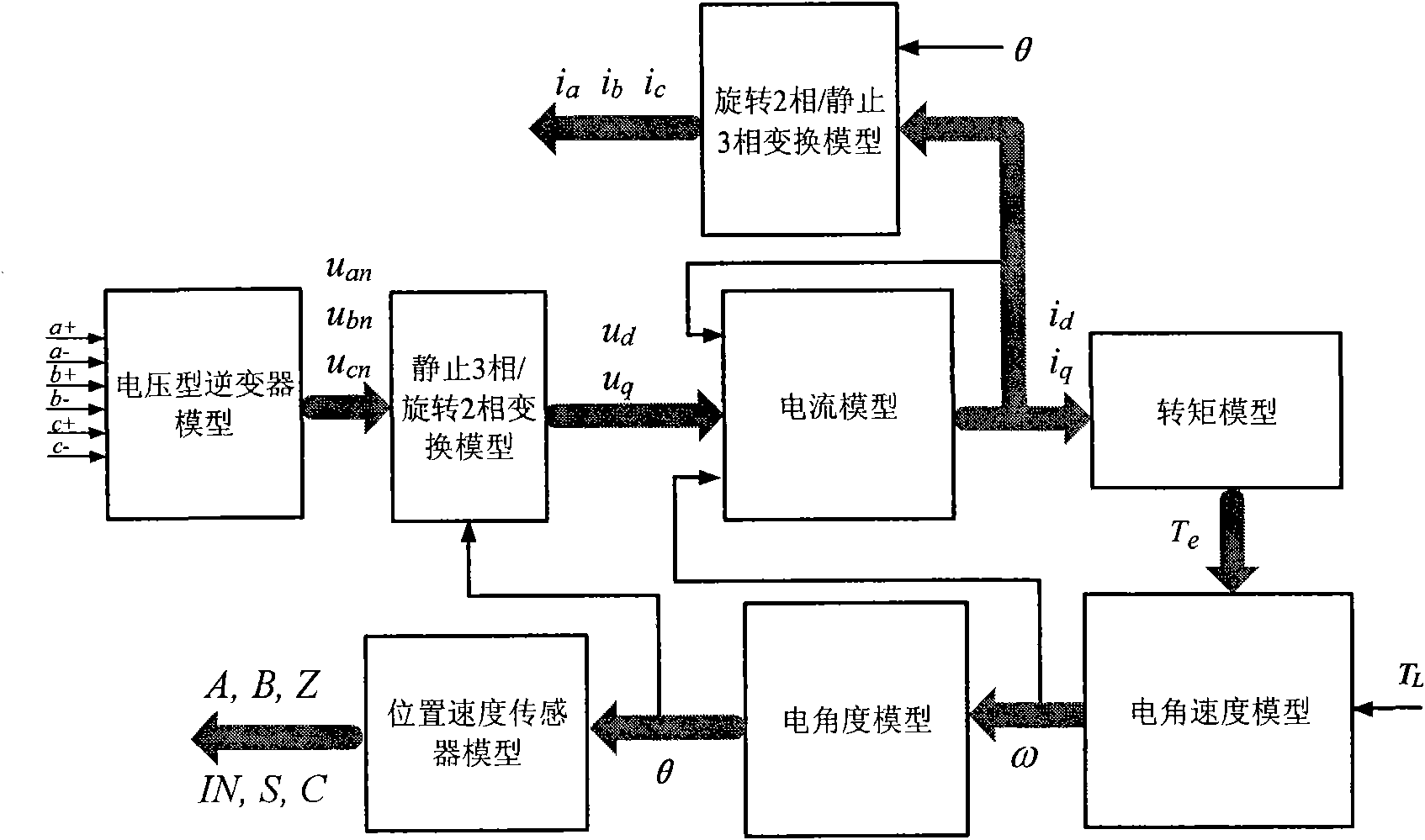

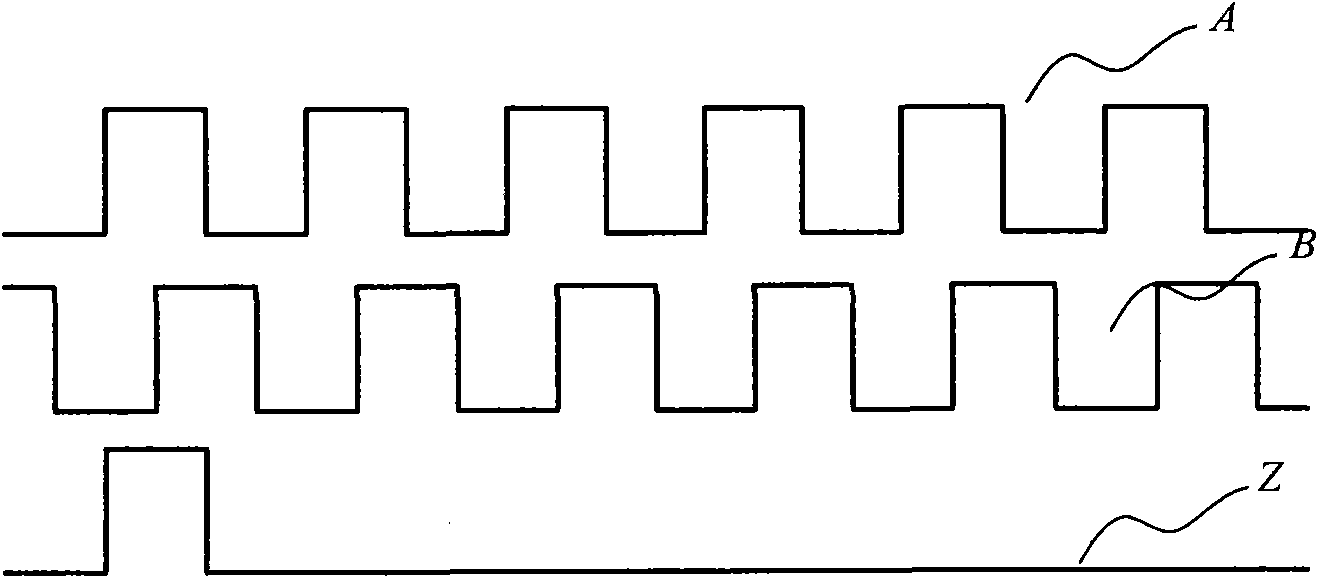

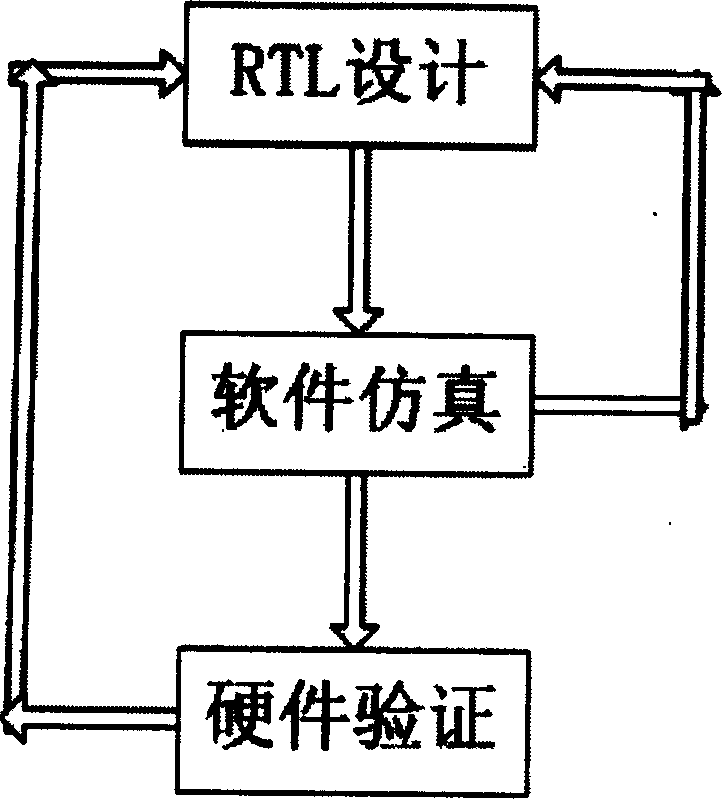

Building method for electric drive system hardware-in-the-loop simulation device

InactiveCN102012674AReal-time simulationImprove real-time performanceAC motor controlSimulator controlReal-time simulationElectric drive

The invention relates to a building method for an electric drive system hardware-in-the-loop simulation device. A converter, a motor and a position and speed sensor in a power transmission system are modeled through a hardware description language Verilog HDL and then are integrated into a field programmable gate array (FPGA) chip. The FPGA chip and an interface circuit form a virtual motor printed circuit board. The virtual motor printed circuit board is connected with an electric drive system controller printed circuit board to form the electric drive system hardware-in-the-loop simulation device. By the method, hardware-in-the-loop real-time simulation on an electric drive system can be performed and the quick development and product test of the electric drive system can be realized; moreover, the method has the characteristics of energy conservation, safety and low cost.

Owner:SHANGHAI UNIV

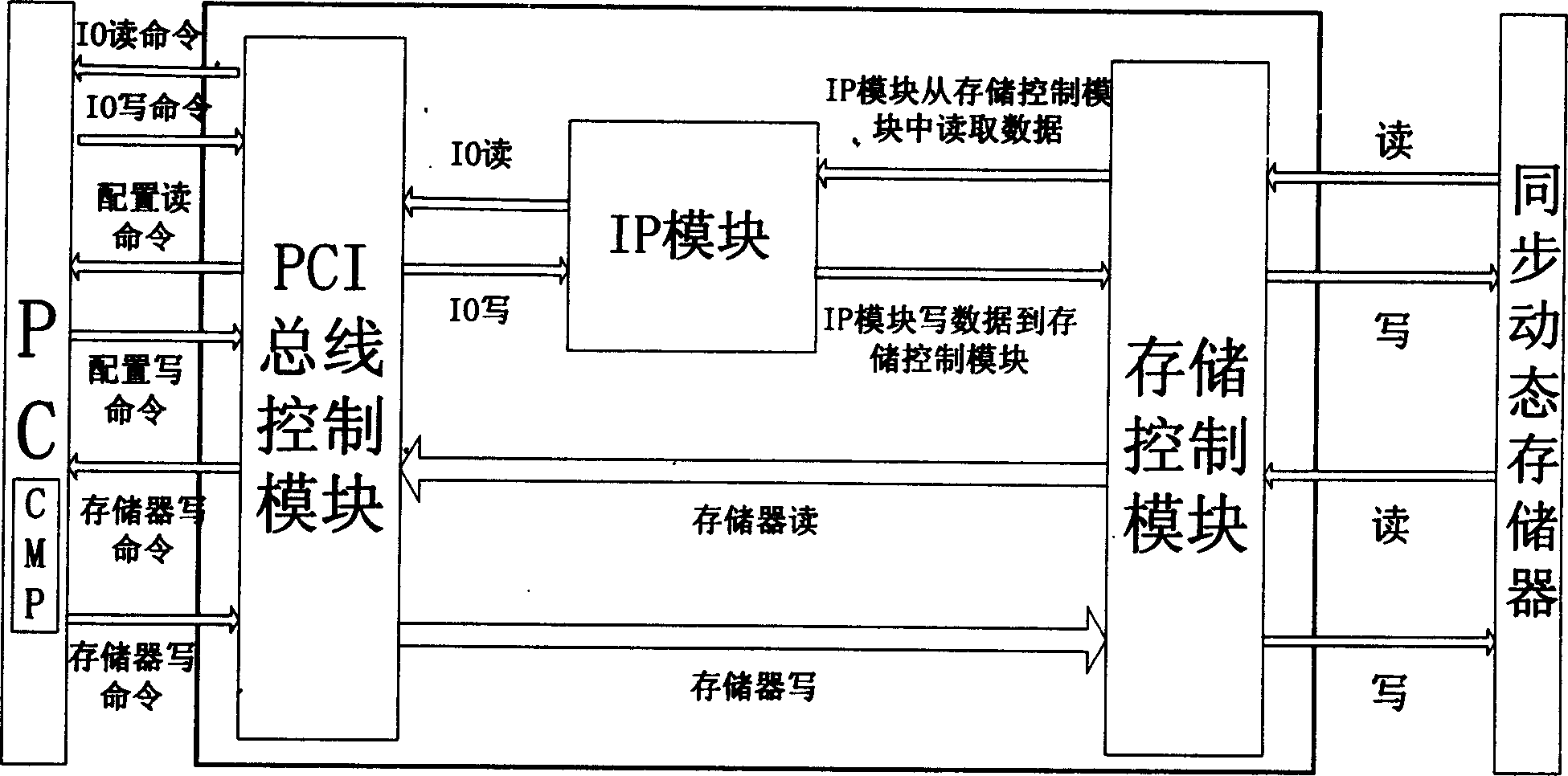

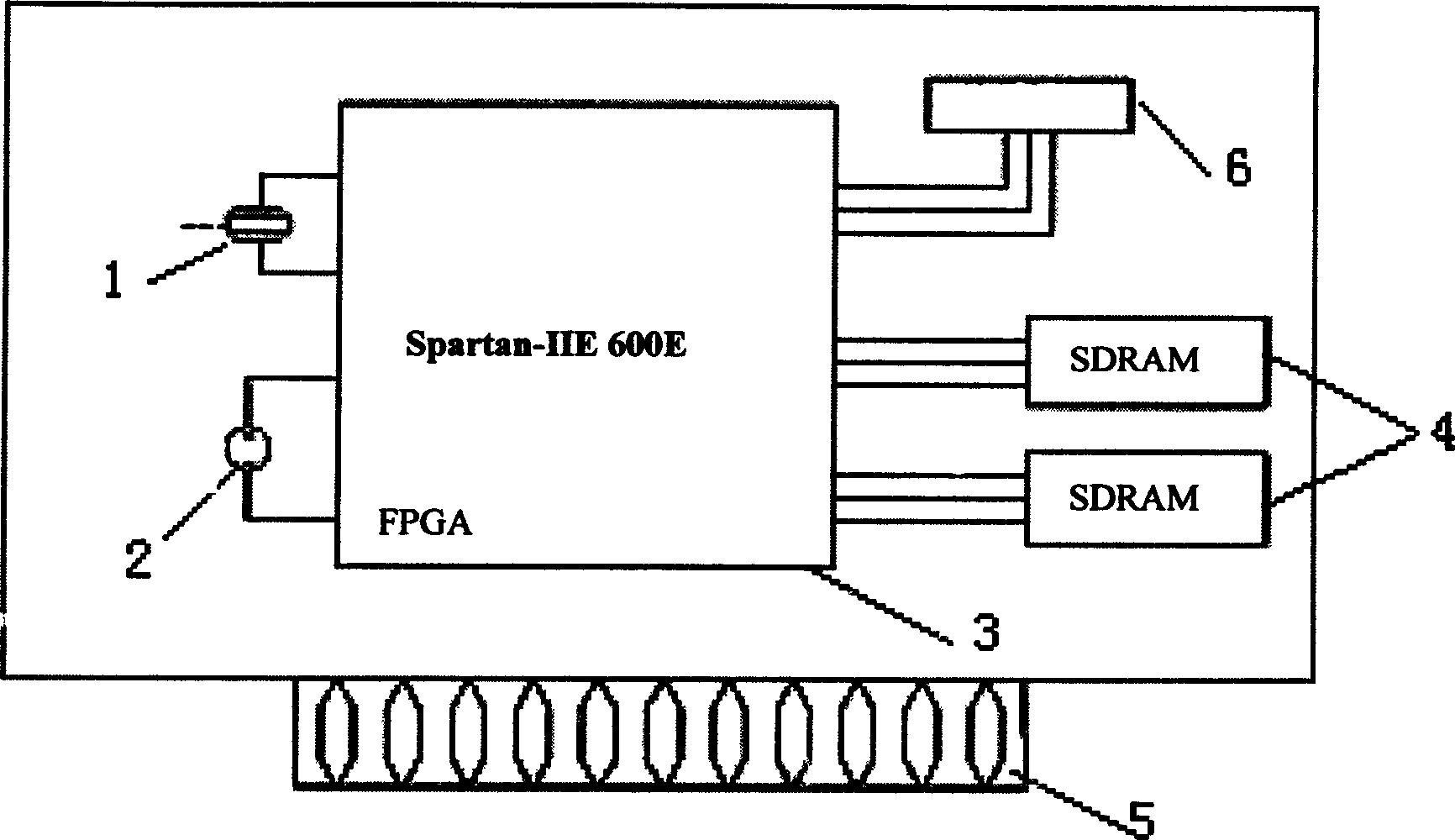

IP nuclear simulation confirmation platform based on PCI bus and proving method thereof

InactiveCN1609862ASimple structureReasonable designError detection/correctionSpecial data processing applicationsComputer hardwareValidation methods

The IP kernel simulating verification platform based on PCI bus includes crystal vibrator, DC voltage regulator, FPGA, programming interface, SDRAM and PCI interface. The verification process includes describing IP kernel system in Verilog HDL language, interconnecting the top layer simulating modules with PCI bus, interconnecting hardware modules with internal bus the same as that in SoC inside the chip, embedding verified IP kernel into the verification platform, and controlling the platform to test IP kernel in PC. The present invention has verification platform with simple structure and convenient use, and verification process capable of simulating effectively SoC environment of IP, utilizing FPGA and PC in the hardware verification of IP, real-time creating test data for IP kernel to test and real-time accessing the register and memory inside IP kernel to obtain the verification finishing data.

Owner:SOUTH CHINA UNIV OF TECH

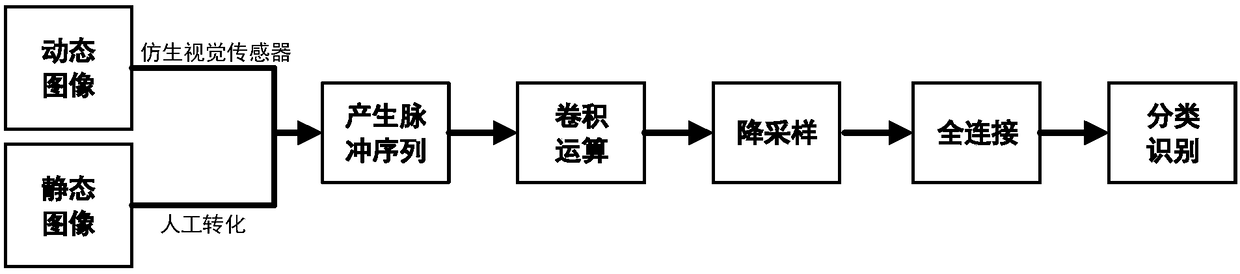

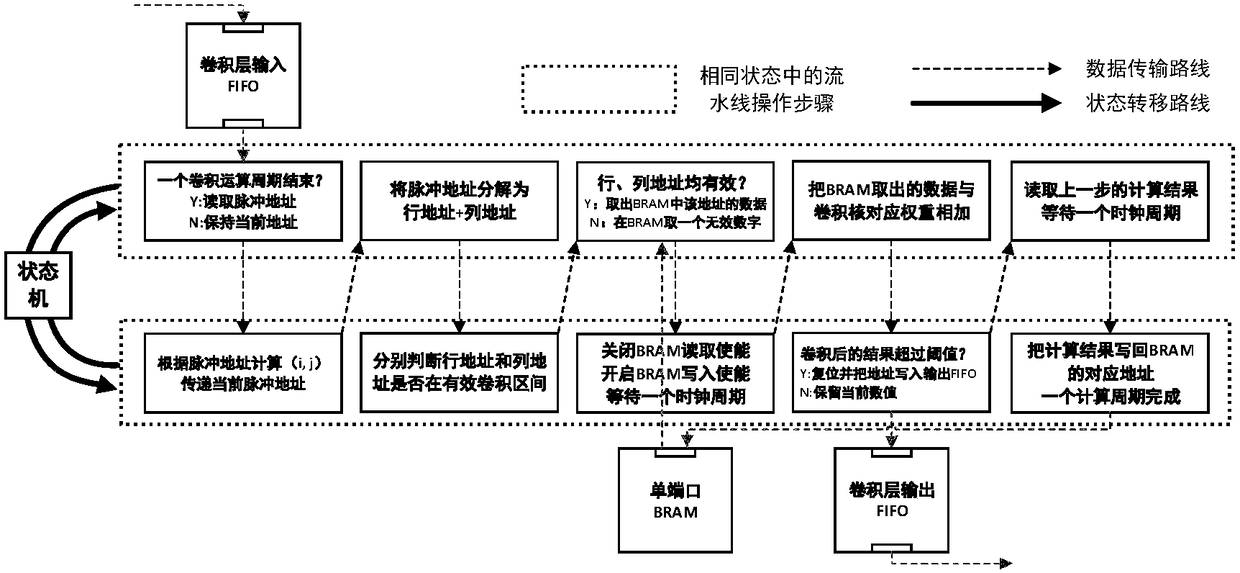

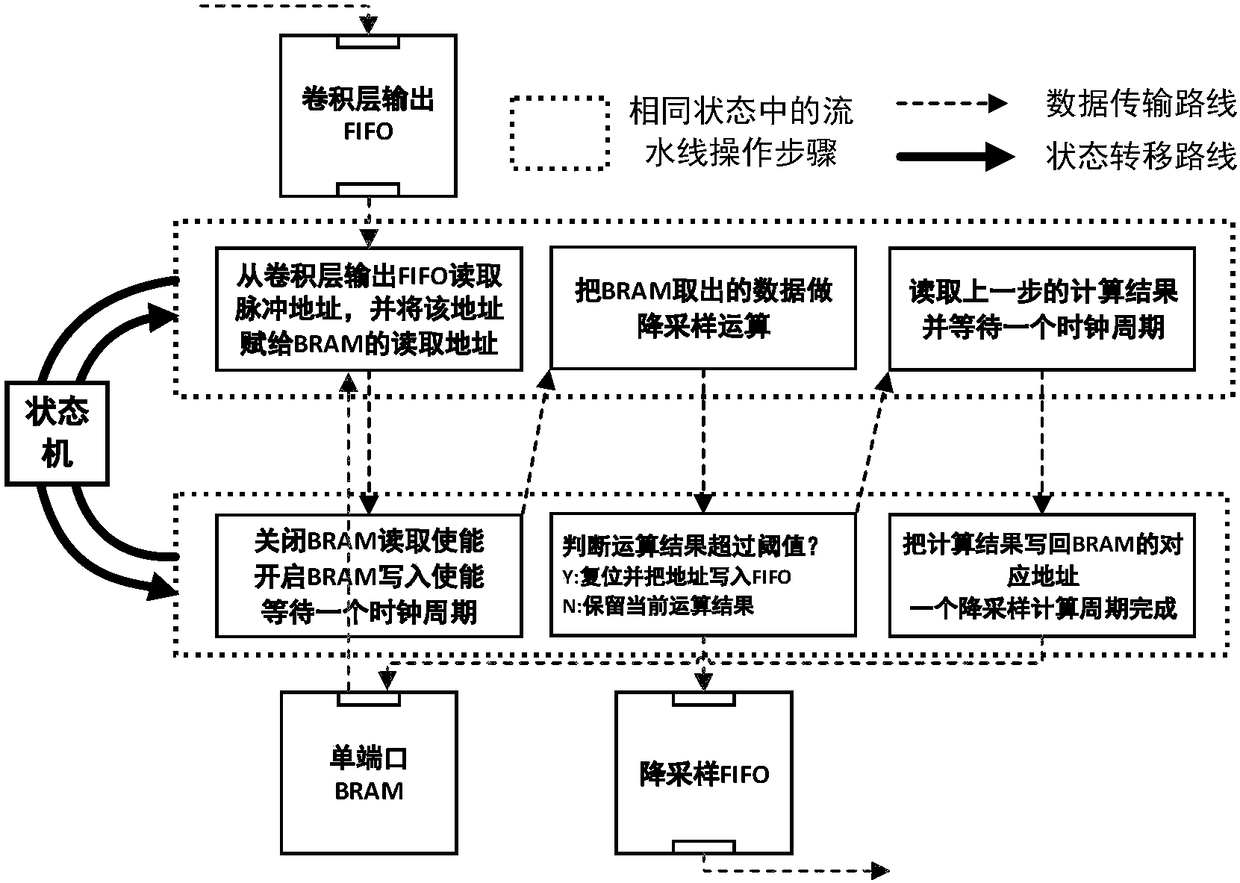

Image recognition method based on FPGA customized pulse neural network

ActiveCN108470190AImprove accuracyFast recognitionCharacter and pattern recognitionNeural architecturesPattern recognitionNerve network

The invention discloses an image recognition method based on an FPGA customized pulse neural network and performs image recognition by customizing a convolutional pulse neural network on an FPGA platform; the convolutional pulse neural network includes a convolutional layer, a downsampling layer, a full joint layer and a classification layer; the image recognition method includes processes of: pulse sequence generation, convolution operation, downsampling, full joint, and classification and recognition; the specific adopted development platform is Xilinx FPGA development board Virtex-7, the adopted development software is Vivado, and the programming language is Verilog. The method can recognize the pulse sequence information that the numerical neural network cannot recognize, and has the advantages of a faster recognition speed, a higher accuracy rate and lower power consumption in the high speed scene.

Owner:PEKING UNIV

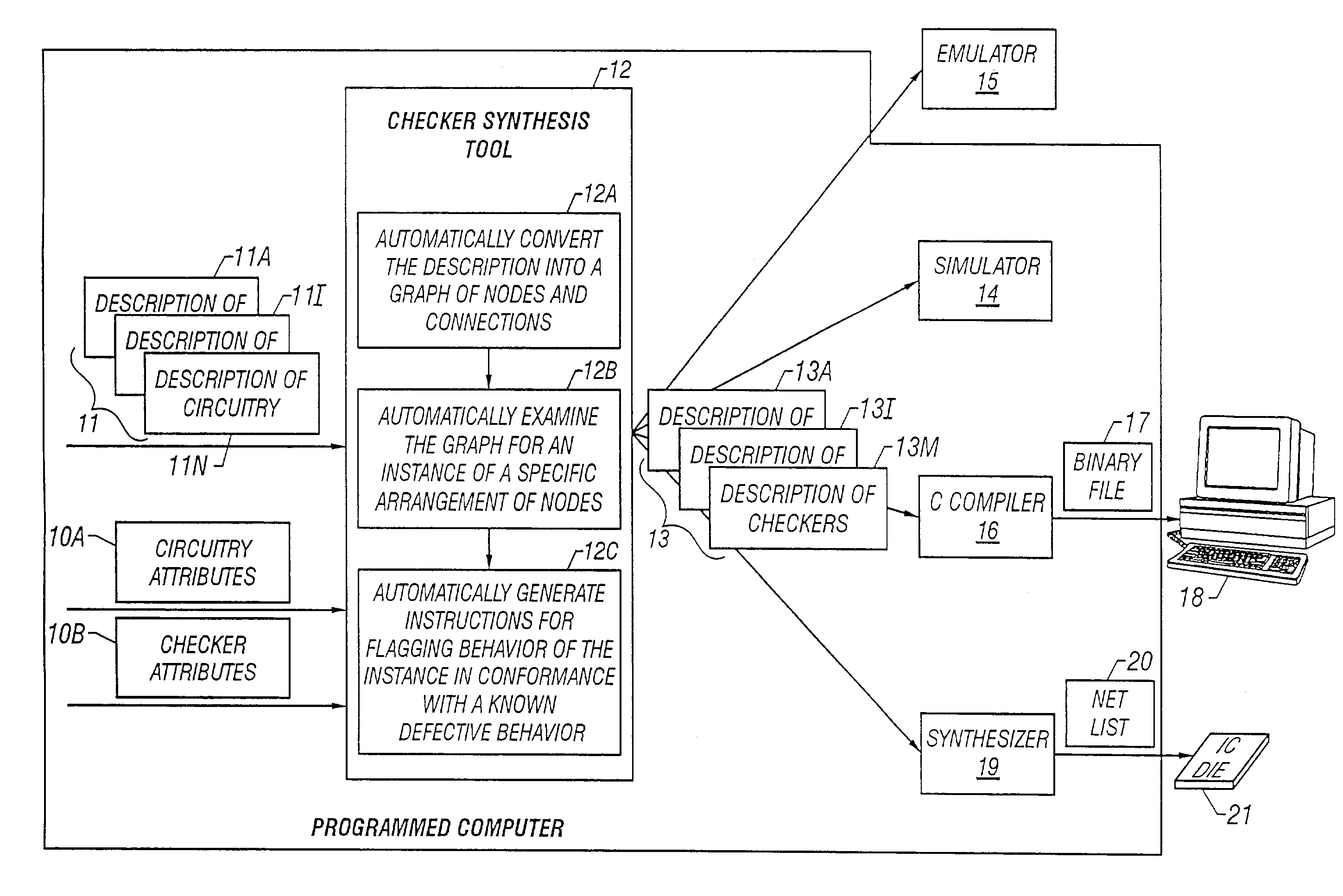

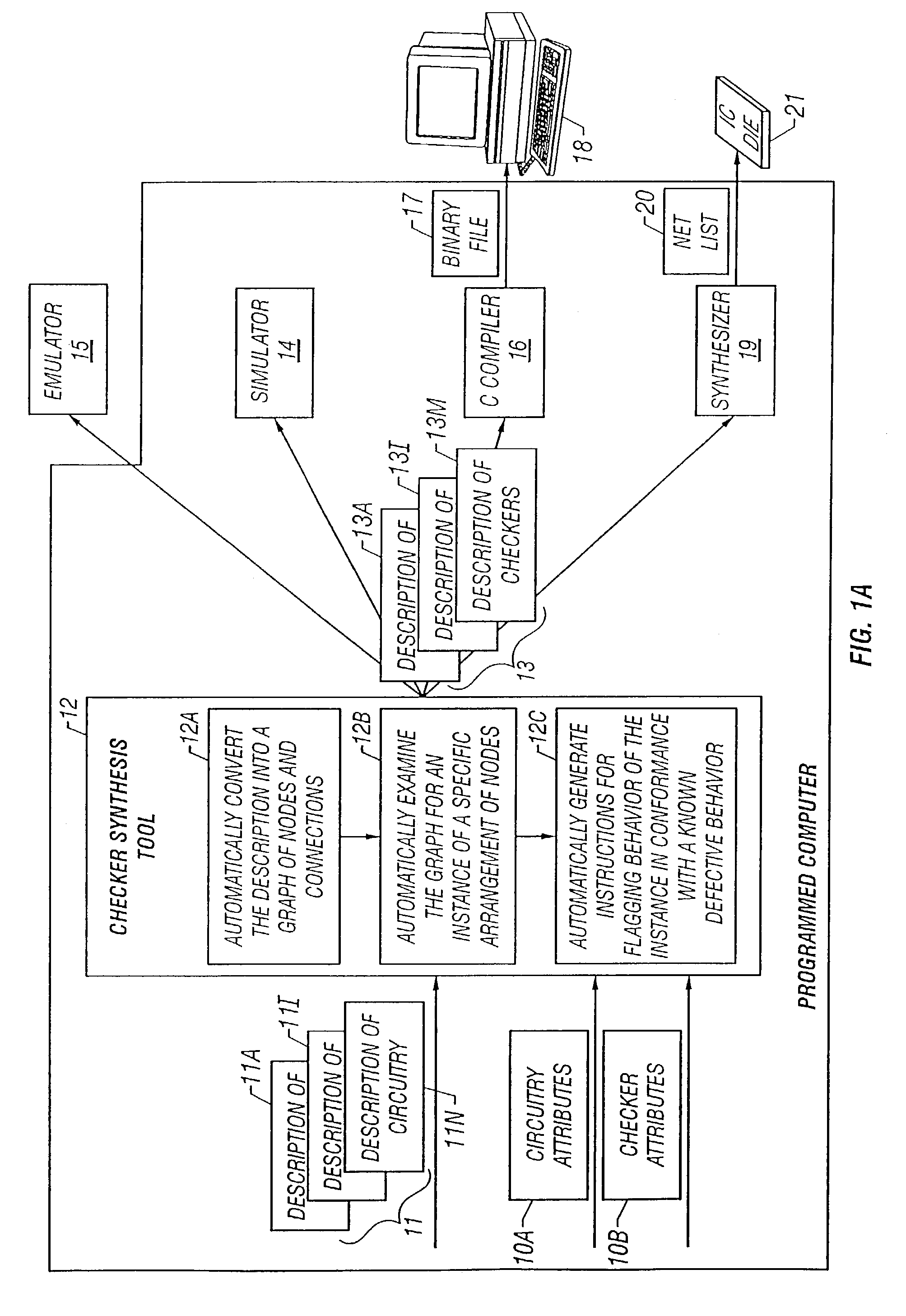

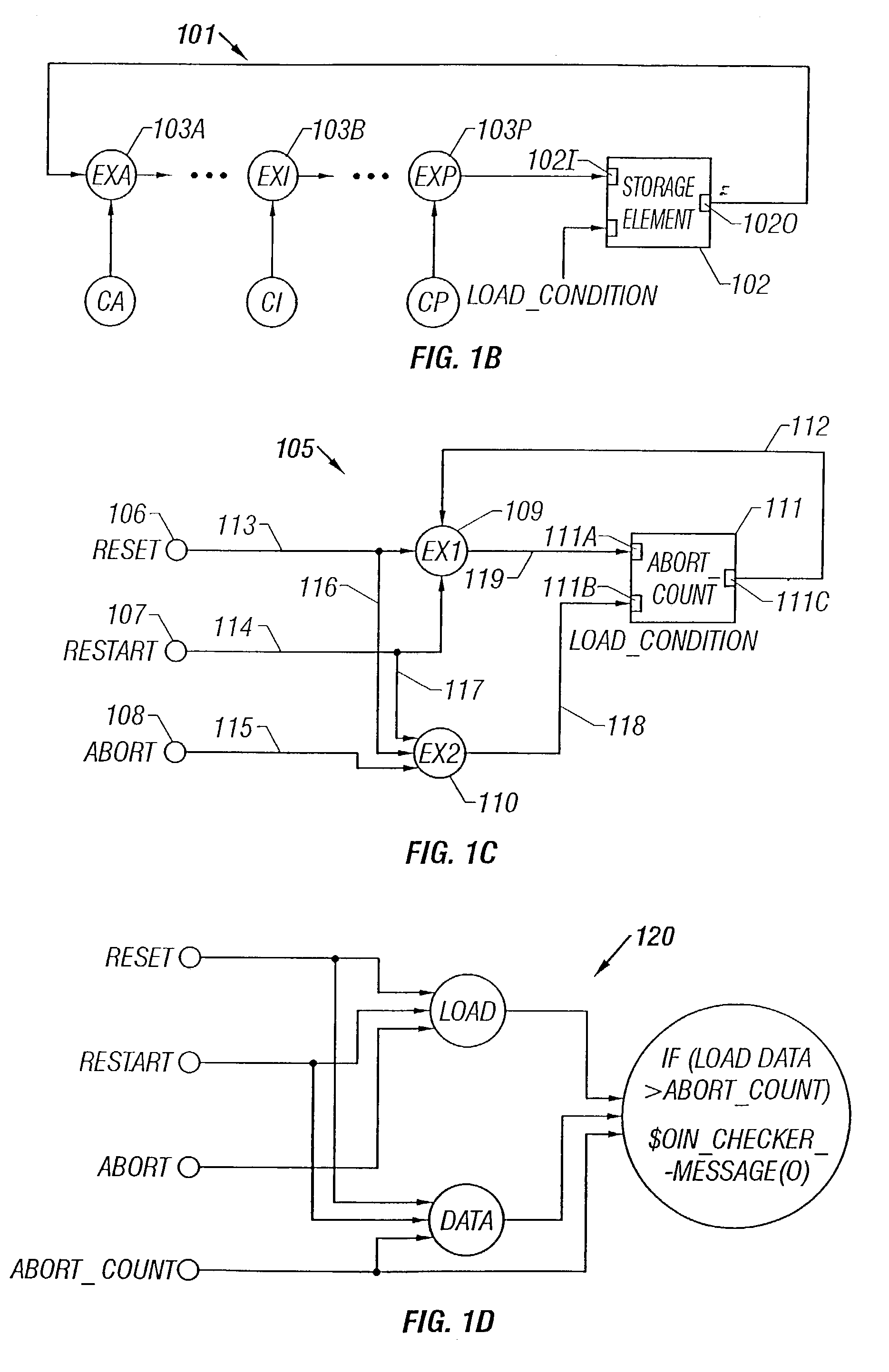

Method for automatically generating checkers for finding functional defects in a description of circuit

InactiveUS7007249B2Eliminate generationEliminating diagnosisAnalogue computers for electric apparatusCAD circuit designGraphicsProcessor register

A programmed computer generates descriptions of circuits (called “checkers”) that flag functional defects in a description of a circuit undergoing functional verification. The programmed computer automatically converts the circuit's description into a graph, automatically examines the graph for instances of a predetermined arrangement of nodes and connections, and automatically generates instructions that flag a behavior of a device represented by the instance in conformance with a known defective behavior. The checkers can be used during simulation or emulation of the circuit, or during operation of the circuit in a semiconductor die. The circuit's description can be in Verilog or VHDL and the automatically generated checkers can also be described in Verilog or VHDL. Therefore, the checkers can co-simulate with the circuit, monitoring the simulated operation of the circuit and flagging defective behavior. The programmed computer can automatically determine load conditions of registers in the circuit and automatically generate checkers to flag data loss in the registers. Some of the checkers may use signals generated by other checkers.

Owner:MENTOR GRAPHICS CORP

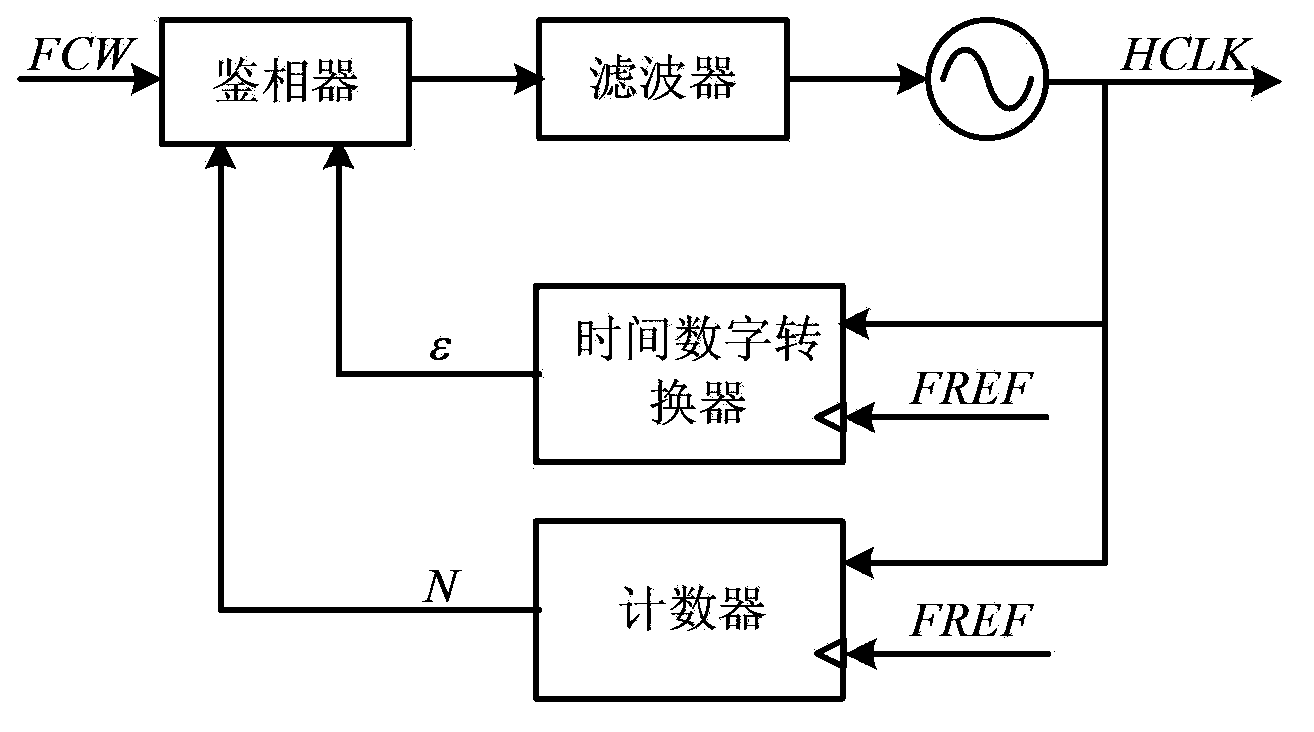

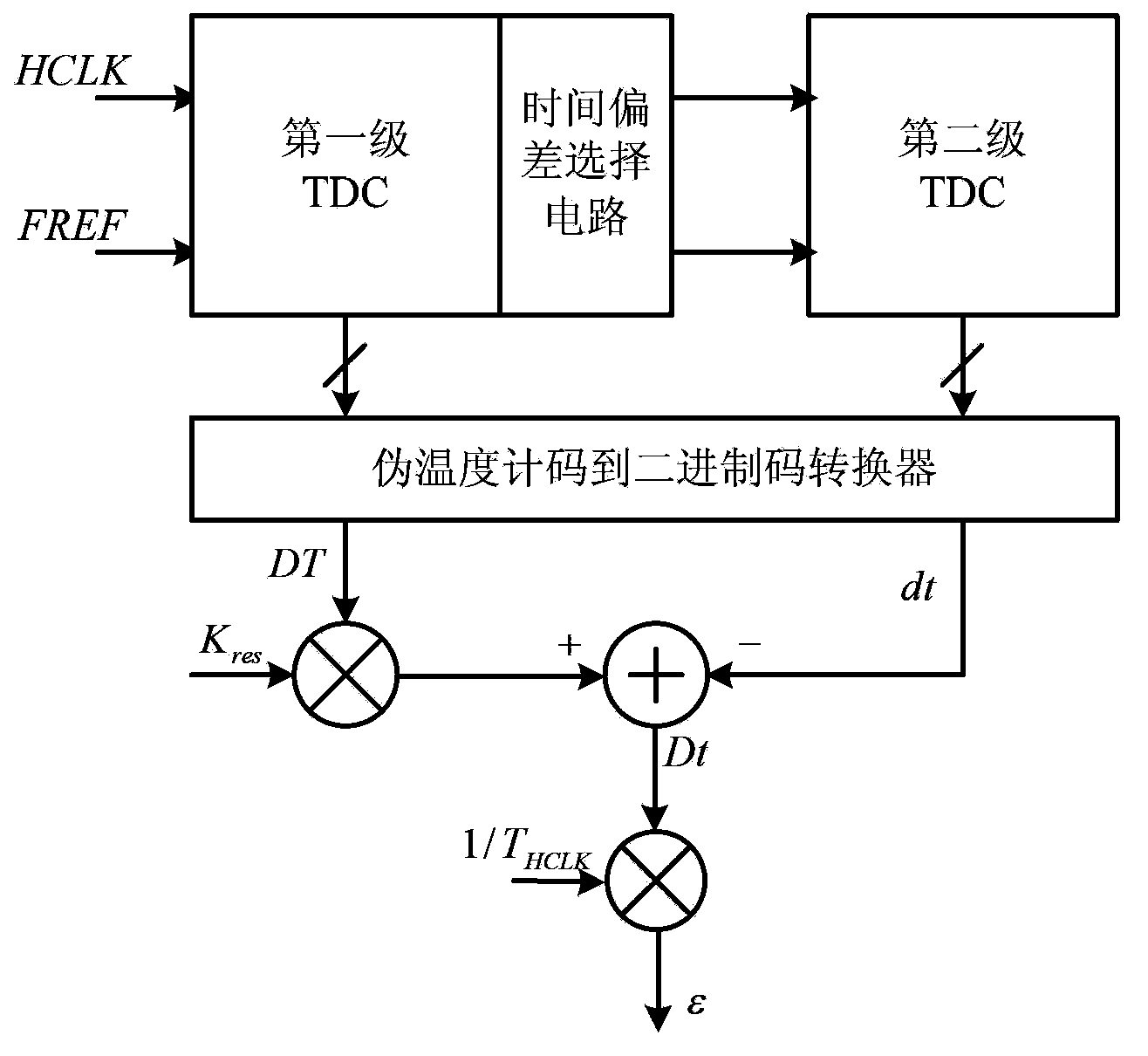

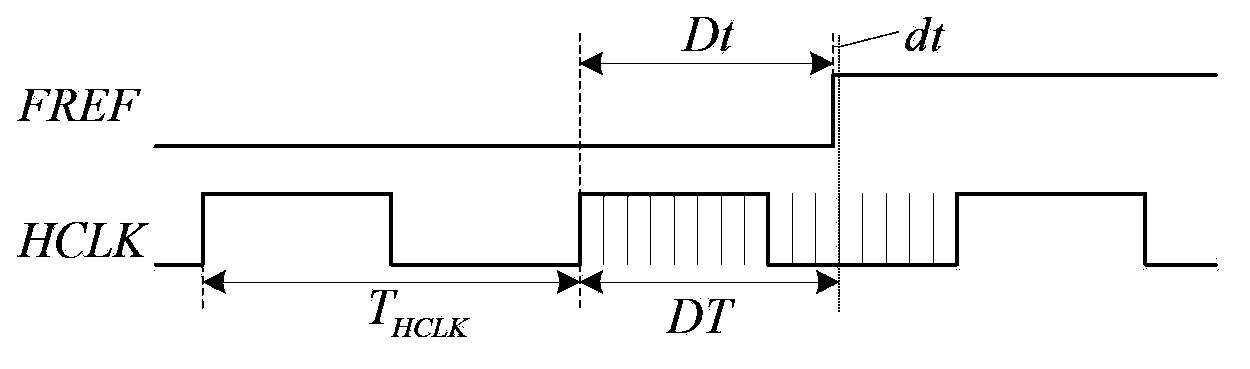

Two-stage time-to-digital converter

InactiveCN103684467AAdapt to needsHigh resolutionAnalogue/digital conversionElectric signal transmission systemsDigital down converterFull custom

The invention belongs to the field of microelectronics and time measurement, and particularly relates to a two-stage time-to-digital converter. The circuits of the converter can be applied to all digital phase-locked loops (ADPLL) with high frequency wide bands. According to the two-stage time-to-digital converter of the invention, the combination of semi custom and full custom is adopted, and two-stage time-to-digital converter comprises a first-stage quantizing structure, a time deviation selection circuit, a second-stage quantizing structure and a decoding circuit, wherein the first-stage quantizing structure adopts a buffer delay chain for coarse quantization; the time deviation selection circuit is composed of a selective signal generator, a delay chain and a multiplexer; the second-stage quantizing structure adopts a Vernier delay chain using a buffer as a basic unit to carry out fine quantization, and a duplication chain comprising a first-stage buffer chain simultaneously multiplexes the Vernier delay chain for measurement of a resolution ratio; the decoding circuit corresponds to a quantization scheme to realize transformation from pseudo thermometer codes to binary codes; the selective signal generator and the decoding circuit are realized by Verilog semi-custom, and the rest are realized by full-custom. The two-stage time-to-digital converter of the invention can be applied to ADPLL with the high frequency wide bands so as to realize time-to-digital conversion with high resolution and linearity.

Owner:FUDAN UNIV

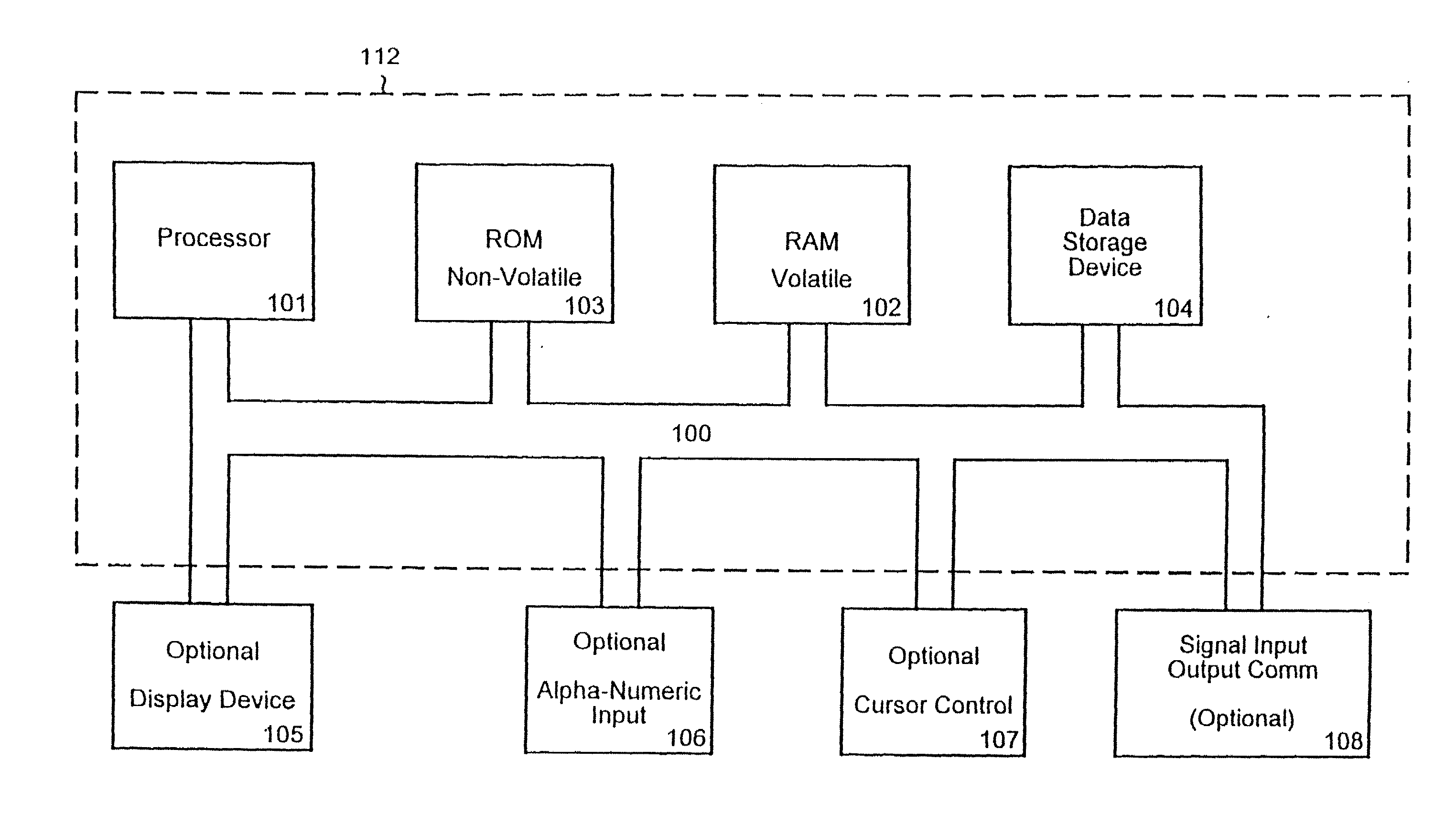

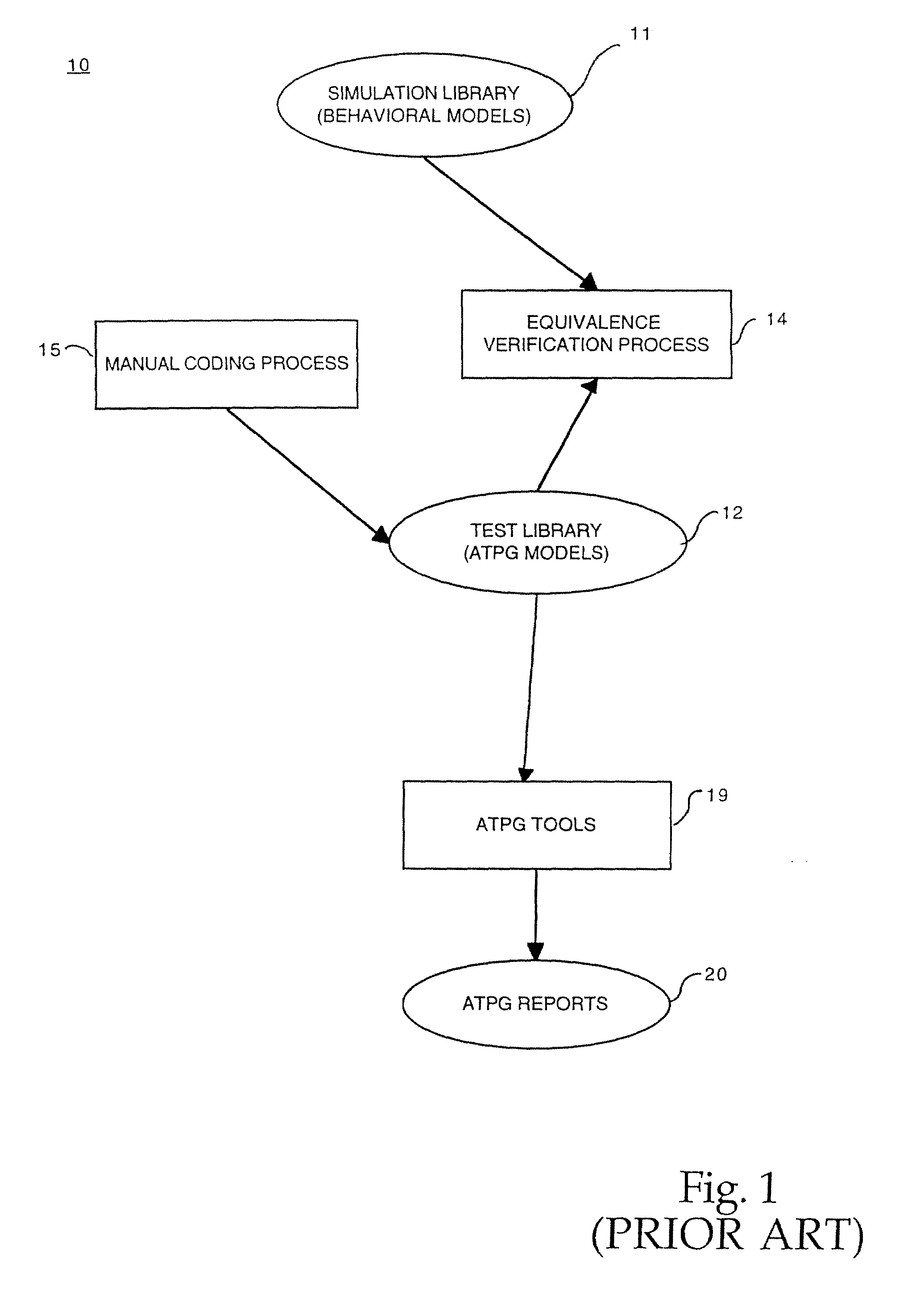

Method and system for generating an atpg model of a memory from behavioral descriptions

InactiveUS20040167764A1Tedious, time-consuming, error-prone and difficult tasksFacilitate the processDigital circuit testingCAD circuit designRandom access memoryTheoretical computer science

Abstract of the Disclosure 42Method and system for constructing a structural model of a memory for use in ATPG (Automatic Test Pattern Generation). Behavioral models of memories of simulation libraries are re-coded into simplified behavioral models using behavioral hardware description language (e.g., Verilog). Simplified behavioral models are automatically converted into structural models that include ATPG memory primitives. Structural models are stored for subsequent access during pattern generation. In another embodiment for modeling random access memories (RAMs), the ATPG memory primitives include memory primitives, data bus primitives, address bus primitives, read-port primitives and macro output primitives. In another embodiment for modeling content addressable memories (CAMs), the ATPG memory primitives include memory primitives, compare port primitives and macro output primitives. Functional equivalence between simplified behavioral models and simulation models can be verified with the same behavioral hardware description language simulator (e.g., Verilog). Another advantage is complicated memories, such as CAMs, can be accurately modeled for ATPG.

Owner:SYNOPSYS INC

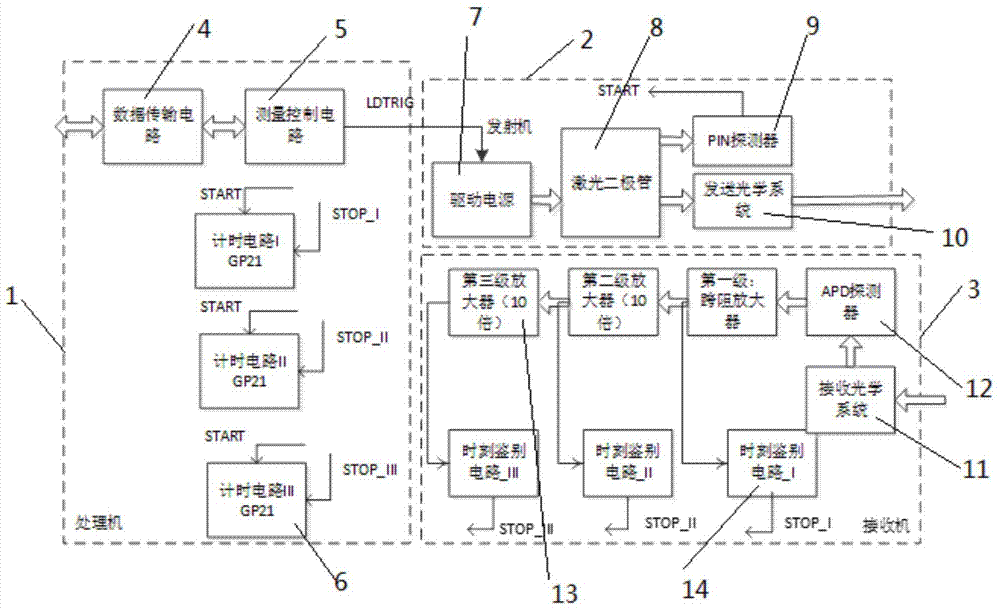

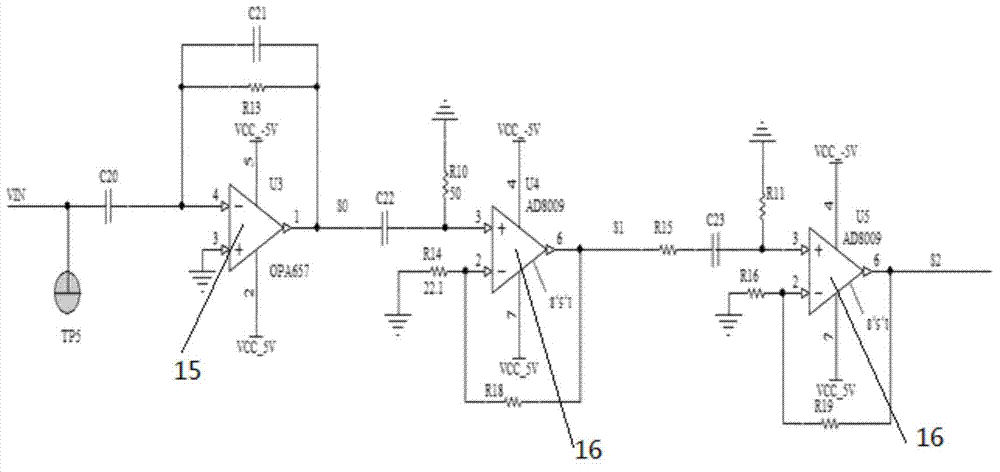

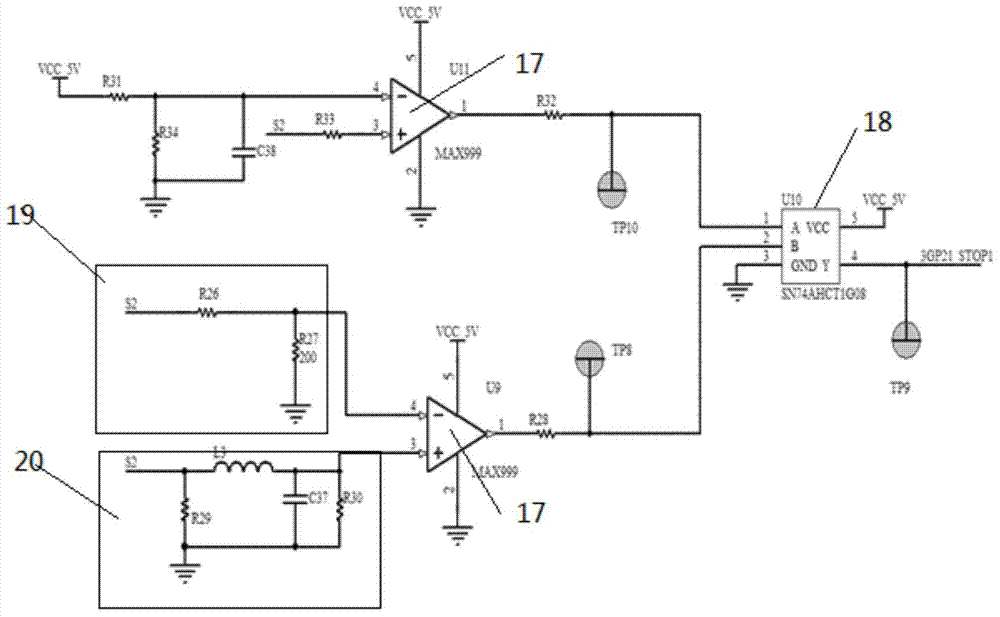

Circuit for expanding range of pulse laser short-range dynamic gain

InactiveCN104777470AGuaranteed ranging accuracyExtended Dynamic Gain RangeWave based measurement systemsDiscriminatorThree stage

The invention discloses a circuit for expanding a range of pulse laser short-range dynamic gain. When echo signals pass through a three-stage amplification circuits, voltage signals amplified at each stage are input into a time discriminator circuit; an STOP signal is generated after the discrimination of the time discriminator circuit and is input into a corresponding timing circuit formed by TDC-GP21; finally discrimination and optimization by a measurement controller formed by FPGA according to the designed Verilog HDL codes and three TDC-GP21 measurement time intervals are carried out, thereby calculating the flight distance of laser. The circuit has the advantages that the dynamic range of the laser radar short-range distance measurement is expanded, the distance measurement accuracy is improved, and the circuit is capable of controlling the laser radar short-range gain without the introduction of STC or AGC circuits.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI

Methods, systems and media for managing functional verification of a parameterizable design

InactiveUS7237210B2Electrical testingComputer programmed simultaneously with data introductionAuto-configurationComputer architecture

Methods, systems, and media for managing functional verification of a parameterizable design are disclosed. Embodiments include a system having a testbench configuration module adapted to configure a testbench, the testbench having testbench signals and one or more instantiated components having a plurality of ports of a generic design, where the testbench signals are wired to the plurality of ports. The testbench may also have one or more instantiated special components based on chip-specific versions of the design where the special components are wired to the same ports as the generic design. The system may also include a functional verification manager that, through a component module, observes values in the testbench and automatically configure a verification environment based on the observed values, including automatic insertion of checkers at different levels of hierarchy. The testbench may be a VHDL or Verilog testbench in some embodiments.

Owner:GLOBALFOUNDRIES INC

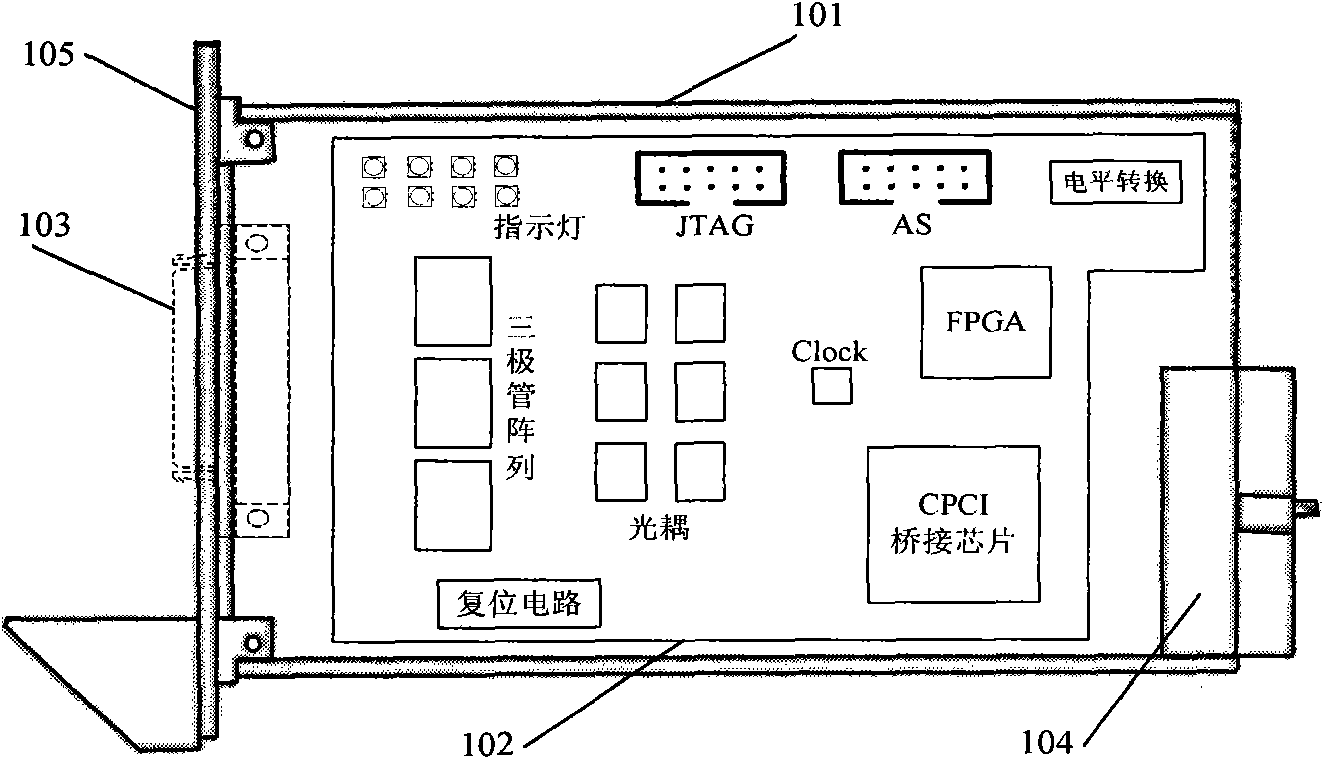

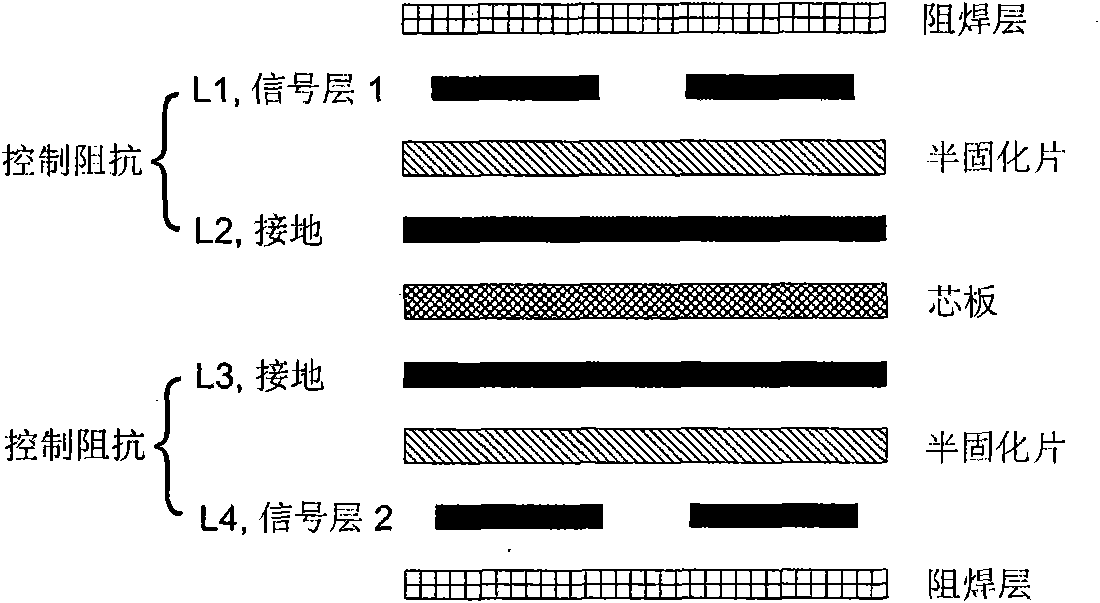

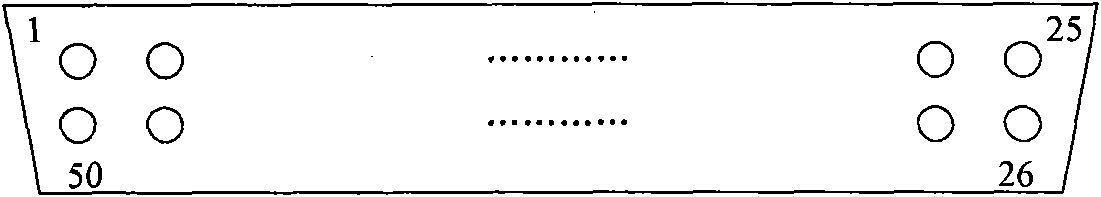

BMCH protocol data transceiver module based on CPCI bus

InactiveCN101963948AAchieve receptionRealize sendingElectric digital data processingTransceiverComputer module

The invention relates to a BMCH protocol data transceiver module based on a CPCI bus, comprising a hardware module and an FPGA program, wherein the hardware module comprises an impedance control circuit board, an electronic component, an SCSI50 signal gang socket, a standard CPCI bus connector and a standard 3U Eurocard board card front panel; the impedance control circuit board and the electronic component are the core functional carriers of the invention and are divided into five functional units, i.e. an FPGA unit, a CPCI bus unit, a BMCH protocol transmitting and conditioning unit, a BMCH protocol receiving and conditioning unit and an assistant unit; and the FPGA program comprises a BMCH protocol data receiver module, a BMCH protocol data transmitter module and a self-checking functional module and is programmed and developed by Verilog HDL. The invention has stable performance and high reliability and can carry out continuous transmission of the BMCH protocol data of large data volume for a long term; CPCI bus data transmission has a DMA function, practical bus transmission rate can reach 80MB / s, and no frames are lost by high-speed continuous transmission; and the BMCH bus signal has strong driving capability and long transmission distance. The invention has simple structure, low cost and convenient use.

Owner:BEIHANG UNIV

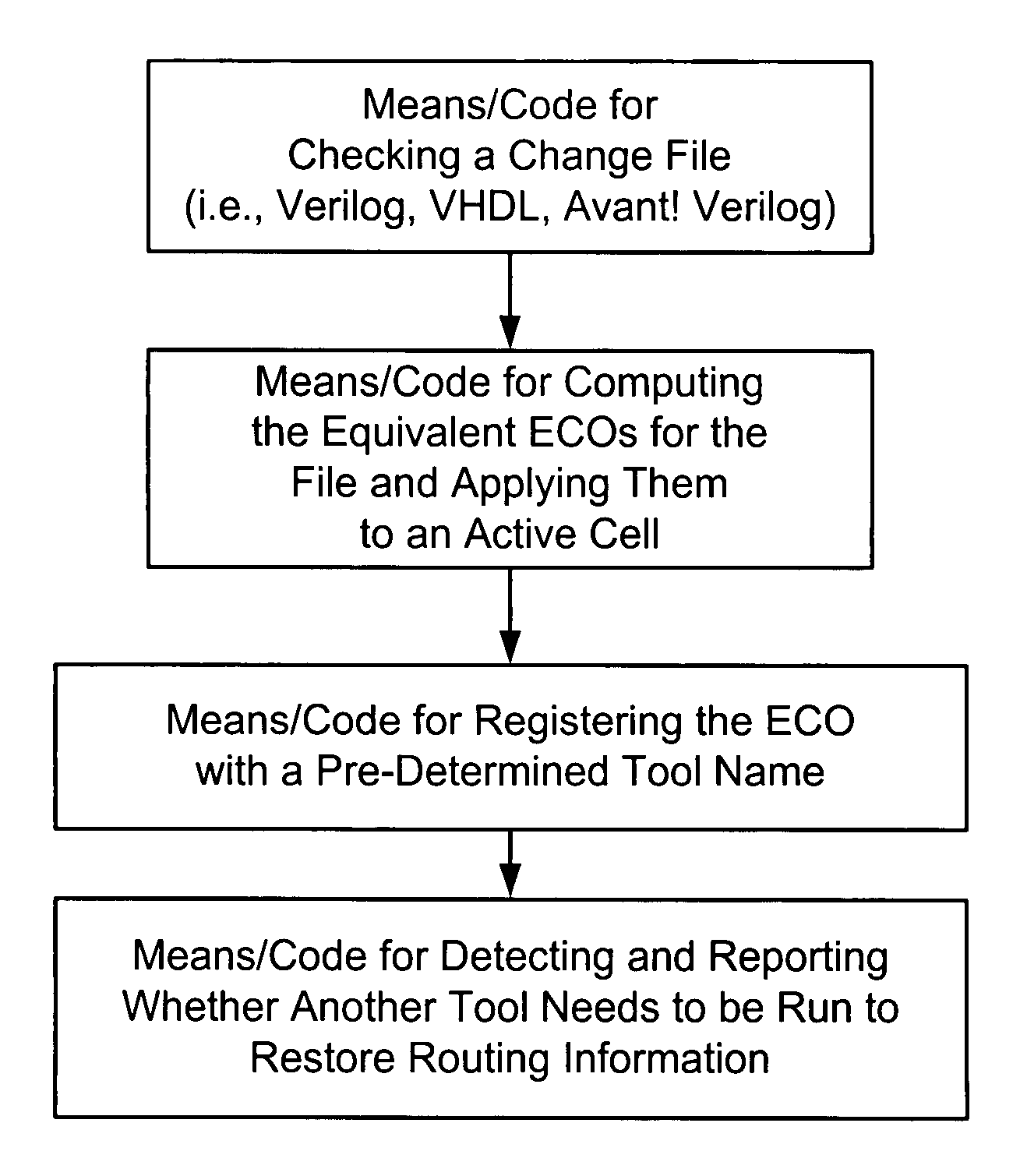

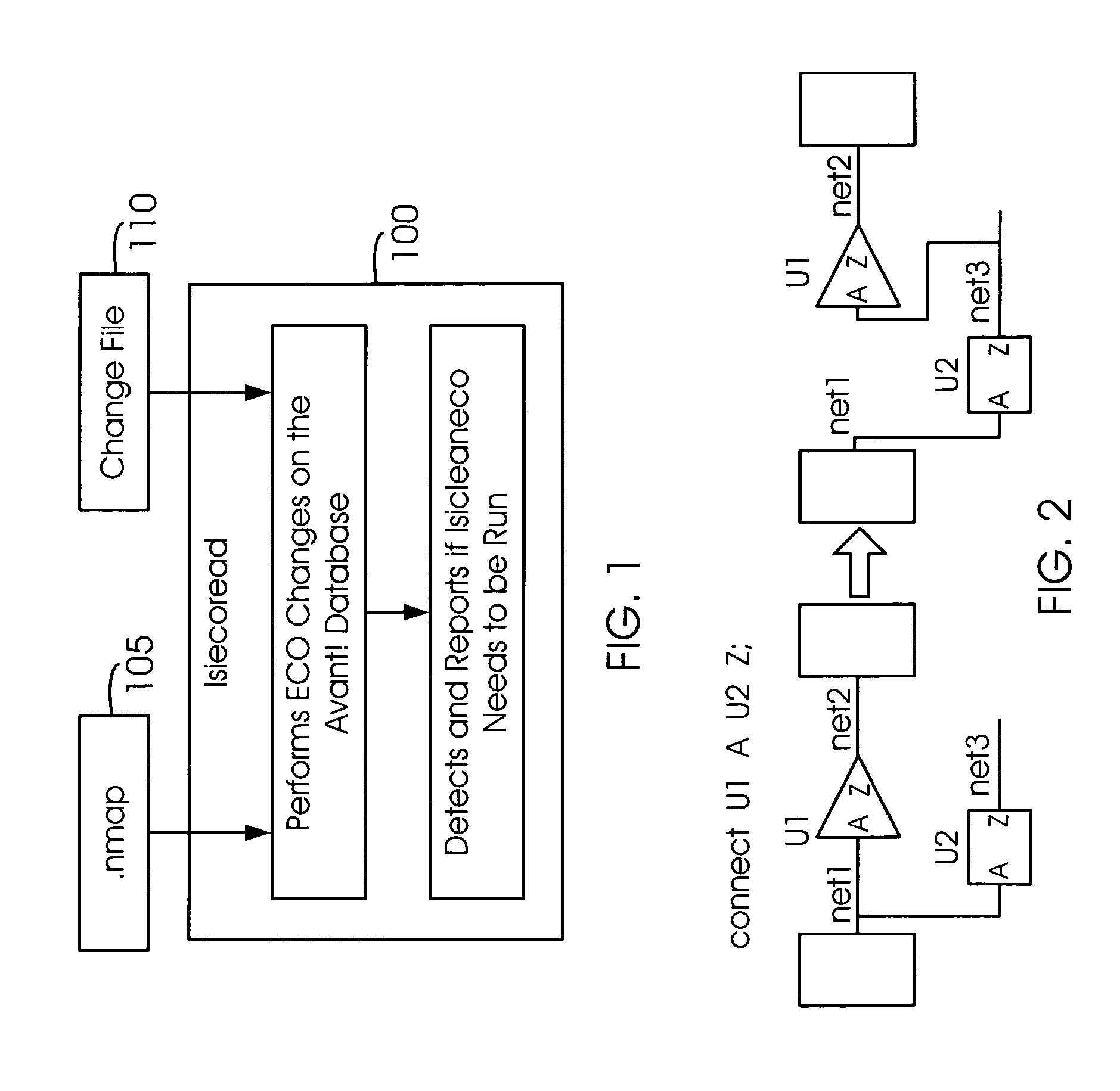

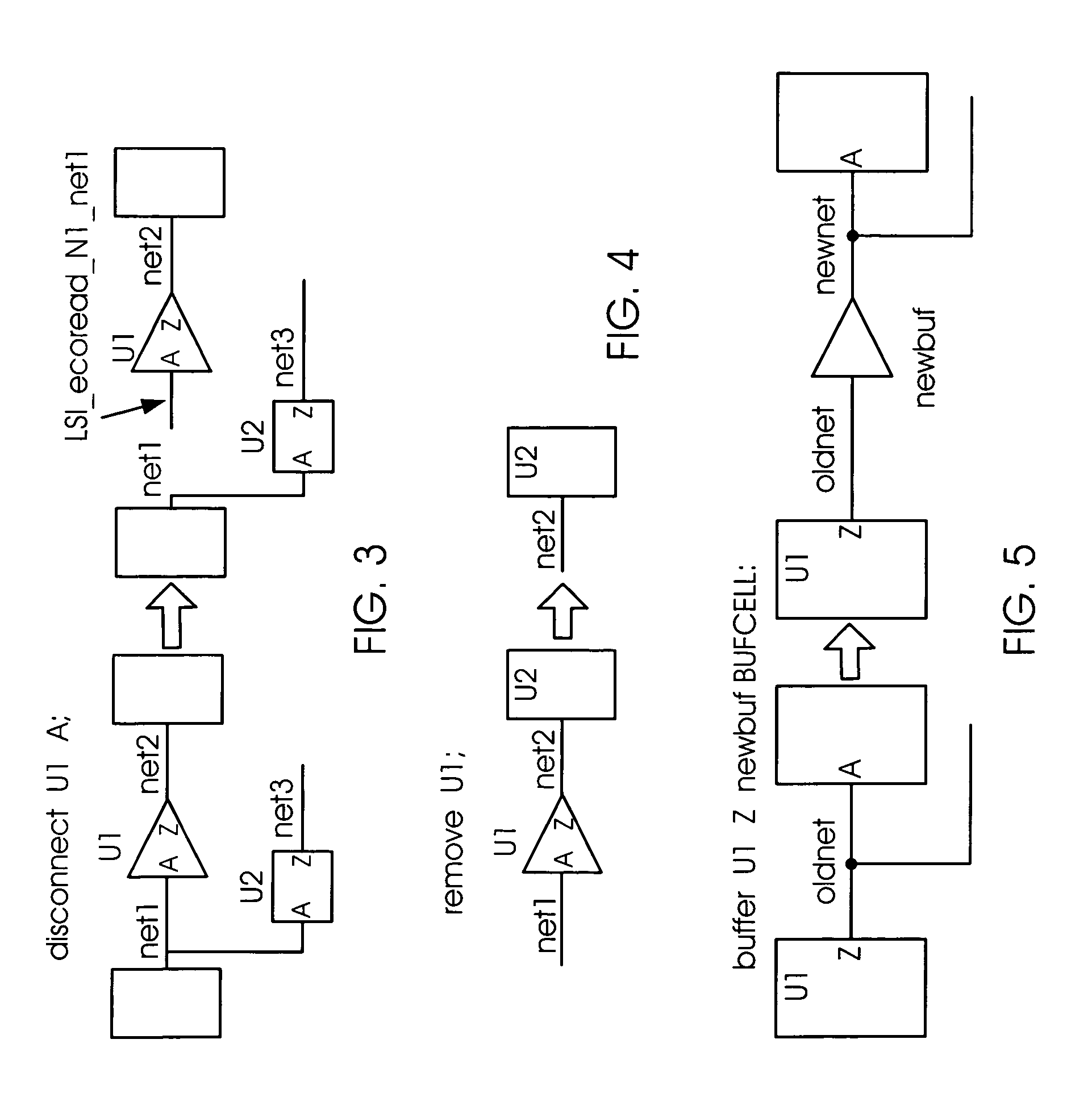

Method and apparatus for implementing engineering change orders

ActiveUS7007248B2Easy to learnEasy maintenanceData processing applicationsDigital data processing detailsApplication engineeringActive cell

Owner:BELL SEMICON LLC

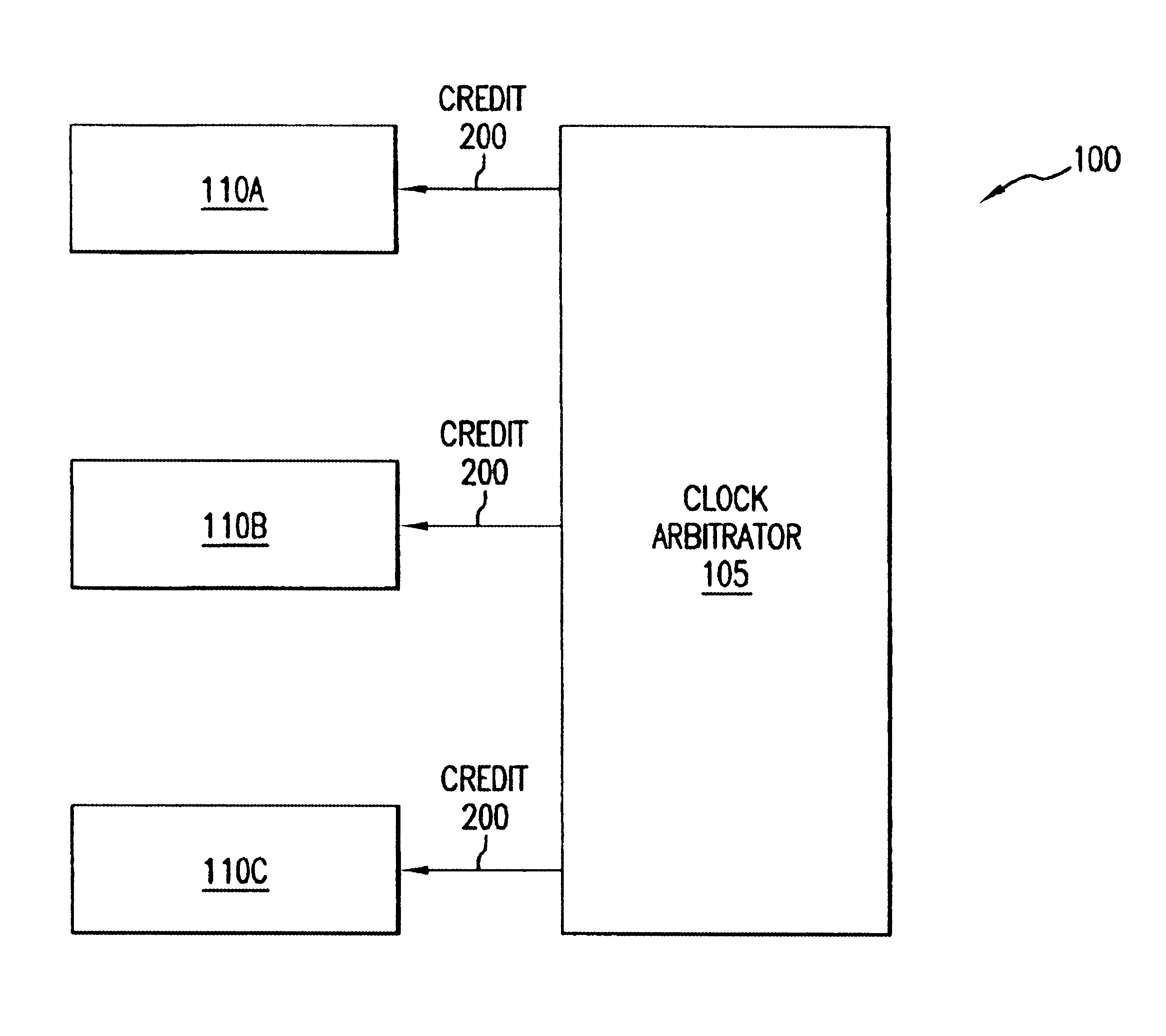

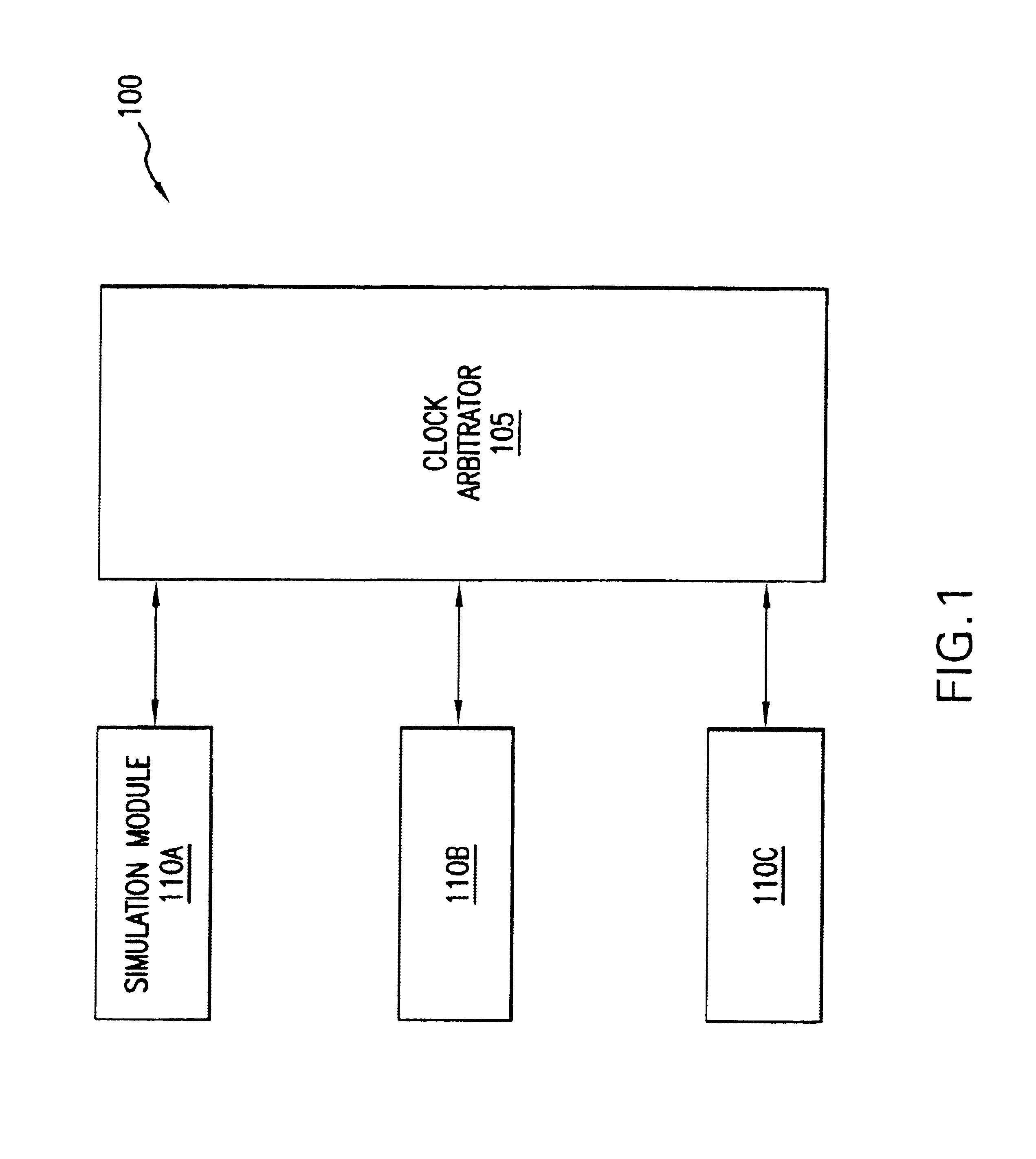

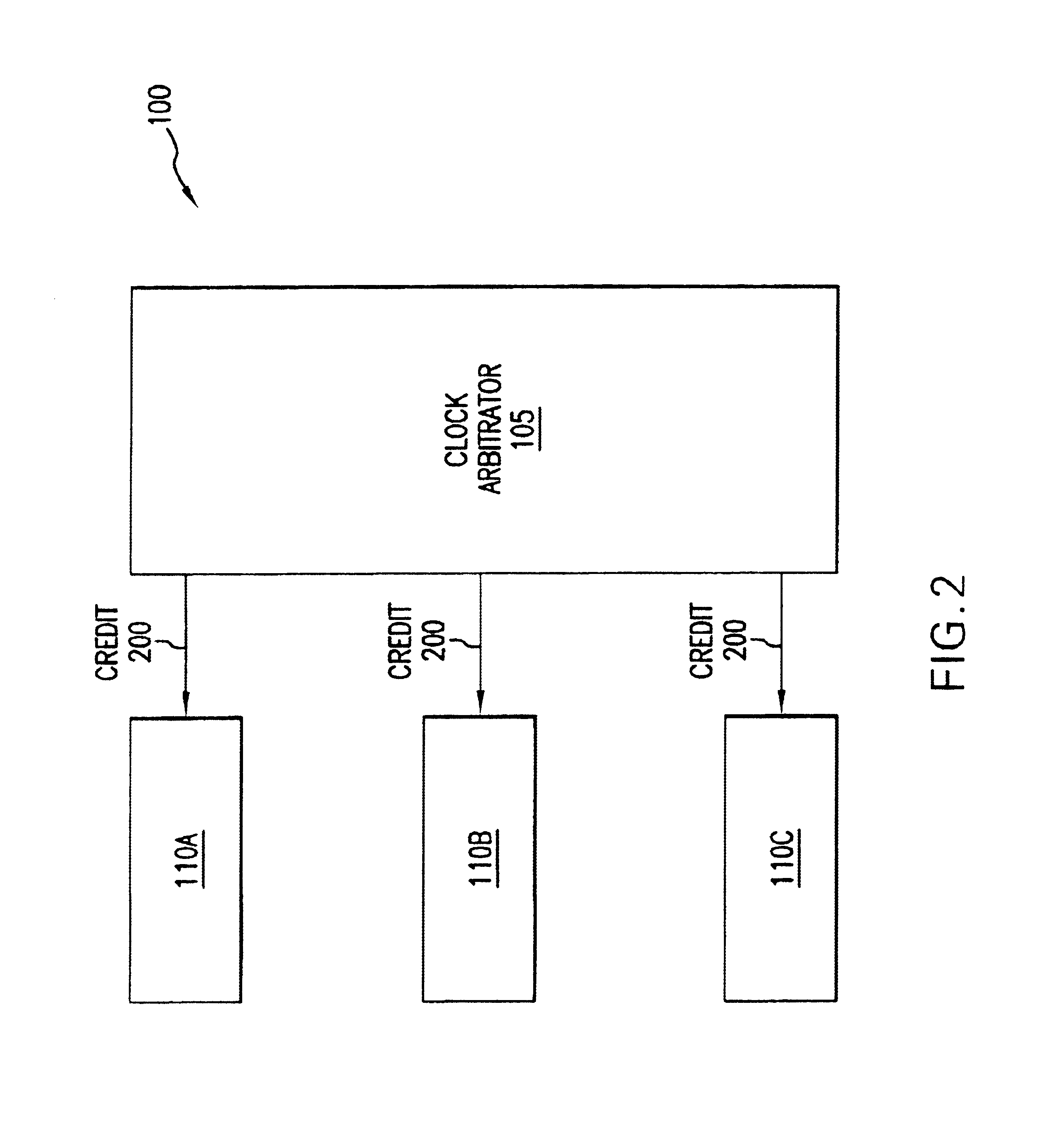

Synchronization of hardware simulation processes

InactiveUS6879948B1Rapid and efficient mannerDetecting faulty computer hardwareCAD circuit designComputer scienceTest bench

A system, method, and computer program product is presented for simulating a system of hardware components. Each component is simulated in a hardware definition language such as VERILOG. Each component is represented as a simulated device under test (DUT) that is incorporated into a simulation module. The invention synchronizes the simulation modules by issuing clock credit to each simulation module. Each simulation module can only operate when clock credit is available, and can only operate for some number of clock cycles corresponding to the value of the clock credit. Operation is said to consume the clock credit. After a simulation module has consumed its clock credit, its DUT halts. Once every simulation module has consumed its clock credit and halted, another clock credit can be issued. This allows checkpointing of the operation of each DUT and simulates parallelism of the DUTs using executable images of manageable size. A given DUT can include two or more subsets of logic that each require a clock signal having a different rate. Such subsets of the logic of a DUT are referred to as clock domains. The appropriate clock signals are created by a test bench component of the simulation module. The test bench creates a master clock signal for the DUT. The test bench then divides this clock signal to produce clock signals applied to the clock domains of the DUT. The test bench can be created through automated means by providing a system specification that defines the inputs (including clocks) and outputs of a DUT. This allows a test bench specific to the DUT to be created.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

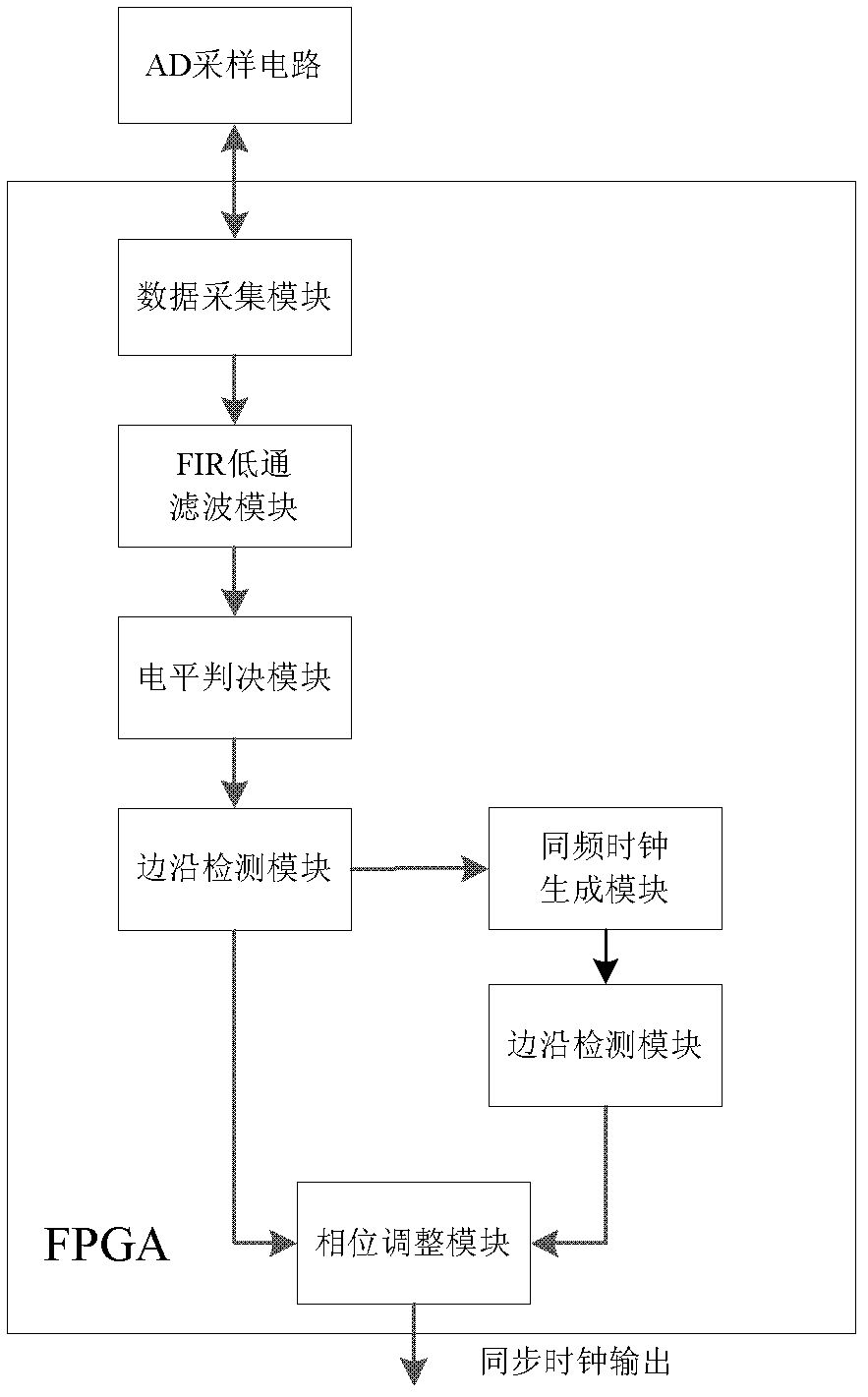

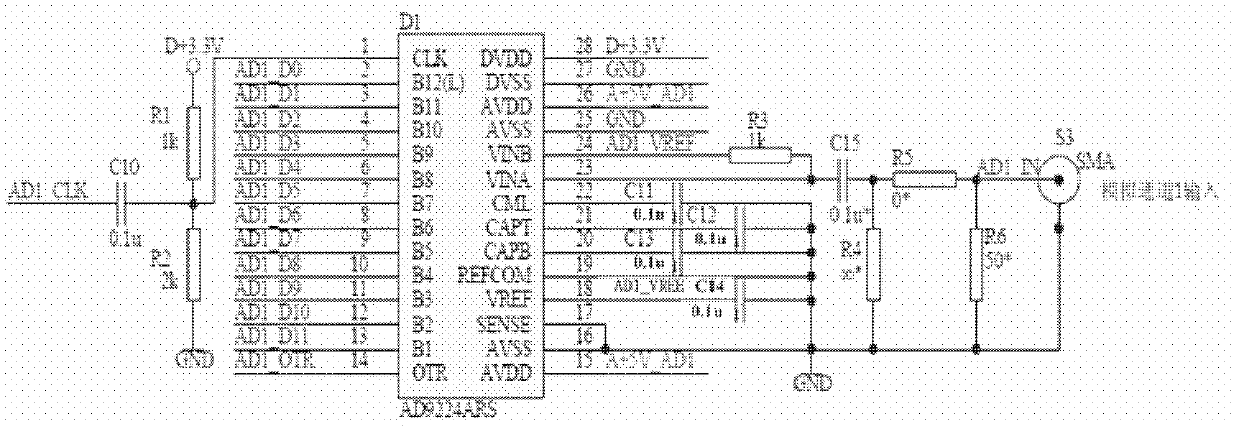

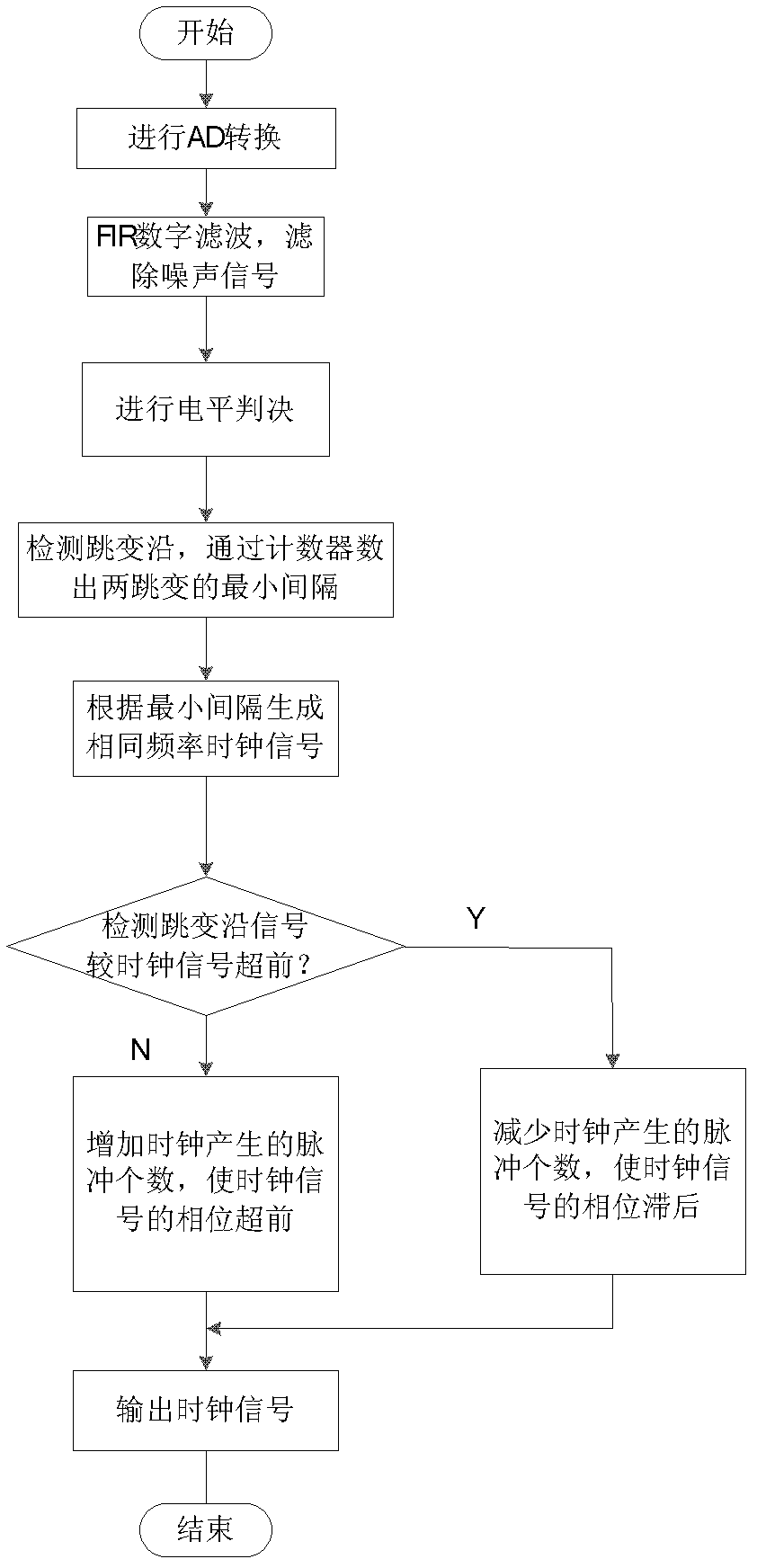

Noise adding signal synchronization clock extraction device based on FPGA (field programmable gate array)

InactiveCN102611447AImprove noise immunityGood for high speedPulse automatic controlFinite impulse responseLow-pass filter

The invention discloses a noise adding signal synchronization clock extraction device based on an FPGA (field programmable gate array), belonging to the field of communication control. The noise adding signal synchronization clock extraction device comprises an AD (analog-digital) sampling circuit, a data acquisition module, an FIR (finite impulse response) low-pass filter module, a level judgment module, an edge detection module, a common-frequency clock generation module and a phase adjusting module, wherein the data acquisition module, the FIR (finite impulse response) low-pass filter module, the level judgment module, the edge detection module, the common-frequency clock generation module and the phase adjusting module are realized in the FPGA. According to the noise adding signal synchronization clock extraction device based on the FPGA, both data acquisition and data processing are realized by hardware, and the advantage of hardware acceleration is brought into full play; and on an FPGA platform, a verilog language is used for programming, a system is modularized, a 150-order FIR low-pass filter is designed, the rising and falling edges of a filtered signal are detected, a cycle of a synchronized signal is obtained, then the synchronized signal is extracted by a synchronizing phase, and the advantages of good noise resistance, high speed and high precision of the system are achieved.

Owner:NORTHEASTERN UNIV

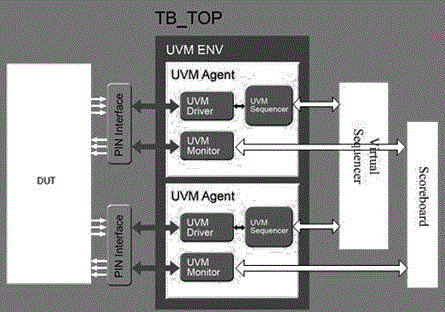

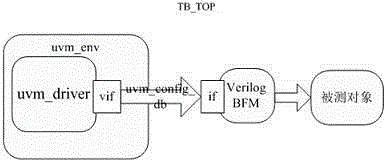

Method for constructing UVM verification component by utilizing existing Verilog BFM

ActiveCN104461812AReduce modificationAvoid affecting the verification progressFunctional testingVerilogComputer engineering

The method discloses a method for constructing a UVM verification component by utilizing an existing Verilog BFM and belongs to the field of computer construction verification. The method comprises the steps that the existing Verilog BFM is transformed; the transformed Verilog BFM is integrated into a UVM verification environment. According to the method, the existing bus model can be used in the new UVM environment without too much modification, so that existing resources are effectively utilized, the number of codes needing to be modified is the smallest, the time is saved to the maximum degree, the verification cycle is greatly shortened, and the situation that errors caused by a verification platform itself affect verification progress is avoided.

Owner:SHANDONG LANGCHAO YUNTOU INFORMATION TECH CO LTD

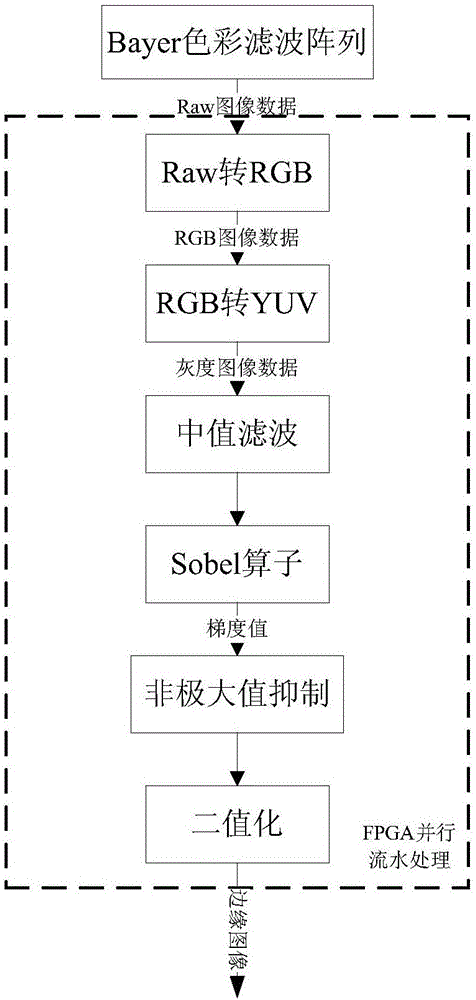

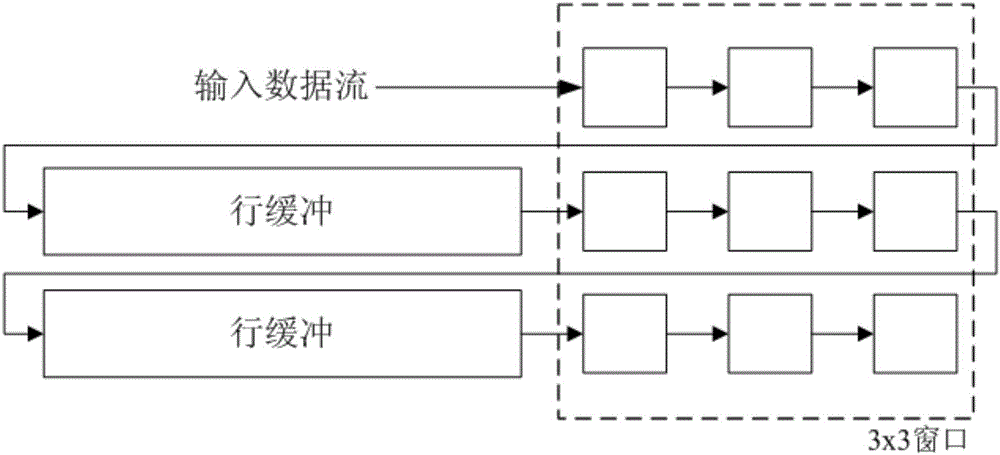

High-resolution image accelerated processing method based on parallel pipeline mechanism

InactiveCN106447597AEfficient executionHigh speed executionProcessor architectures/configurationDetails involving image processing hardwareRgb imageHigh resolution image

The invention discloses a high-resolution image accelerated processing method based on a parallel pipeline mechanism. The method is realized by utilizing the FPGA parallel pipeline processing mechanism. The method comprises the following steps: S1) carrying out color interpolation on a RAW-format image generated through a Bayer color filter array (CFA) through a 3*3 template of a bilinear method to obtain RGB image data, and converting the RGB image data into a YUV color space and extracting a Y component therein to obtain a grayscale image; S2) removing spot noise in the grayscale image obtained in the step 1) through a median value filtering method; and S3) carrying out gray gradient calculation on each point on the grayscale image obtained after spot noise removing through a sobel operator, carrying out non-maximum suppression on gradient amplitude results and realizing edge thinning, and finally, carrying out binaryzation on the result thereof to extract edge information of the grayscale image. The advantages are that, by combining FPGA parallel processing and pipeline structure features and by utilizing Verilog DHL (hardware description language) to compile an image processing unit of the FPGA, high-efficiency high-speed execution of an image processing algorithm is realized.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

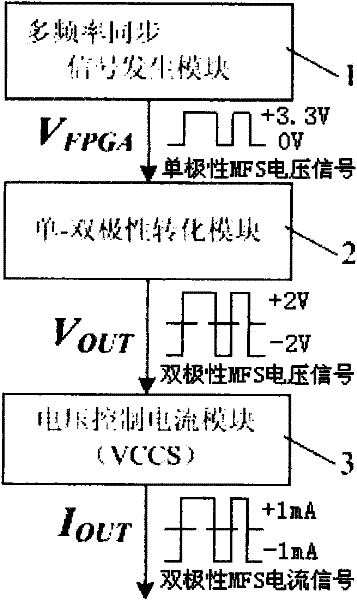

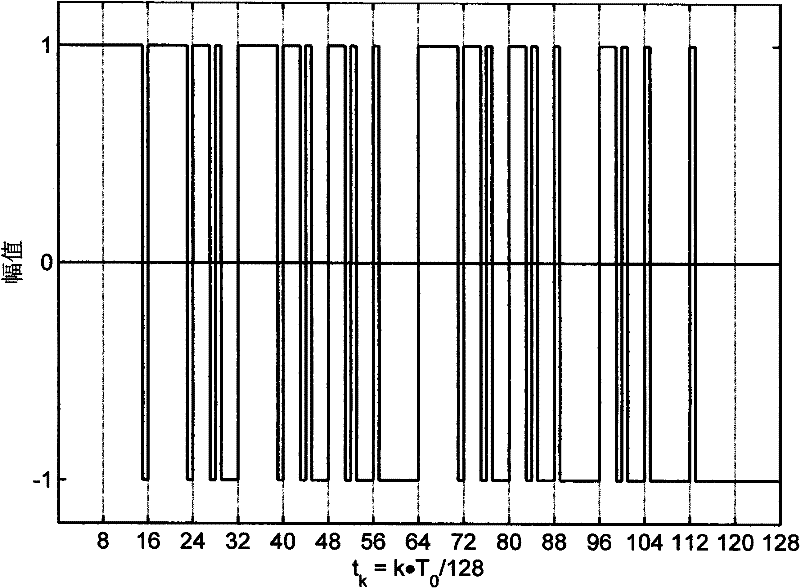

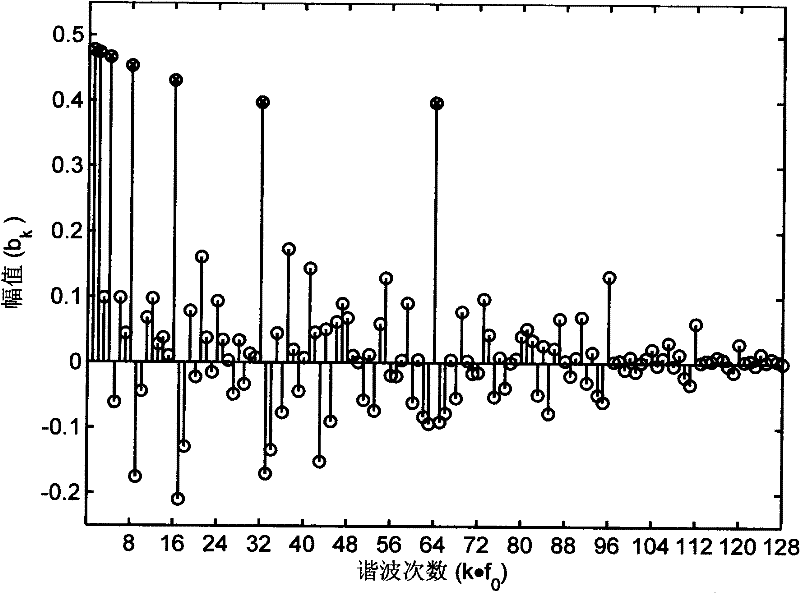

Multifrequency synchronous excitation current source used in bio-electrical impedance frequency spectrum measurement

InactiveCN102048537AImprove stabilityIncrease output impedanceDiagnostic recording/measuringSensorsFrequency spectrumFinite-state machine

The invention discloses a multifrequency synchronous excitation current source used in bio-electrical impedance frequency spectrum measurement, which comprises a multifrequency synchronous signal generating module, a unipolar-bipolar conversion module, and a voltage control current source module in sequential connection, wherein the multifrequency synchronous signal generating module adopts an FPGA (Field Programmable Gate Array) as a carrier, performs hardware programming through utilizing a Verilog HDL (Hardware Description Language), generates unipolar MFS voltage signal V FPGA based on finite state machine principles, and inputs the signal V FPGA to the unipolar-bipolar conversion module; the unipolar-bipolar conversion module is used for converting unipolar MFS voltage signal V FPGA into symmetric bipolar MFS voltage signal V OUT, and inputting the signal V FPGA into the voltage control current source module; and the voltage control current source module is used for converting the bipolar MFS voltage signal V OUT output by the unipolar-bipolar conversion module into bipolar MFS current signal IOUT and directly exerting the bipolar MFS current signal IOUT onto a tested biomass target receiving BIS (Bispectral) measurement. The multifrequency synchronous excitation current source provided by the invention lays a foundation for the realization of BIS multifrequency synchronous measurement.

Owner:XIAN UNIV OF TECH

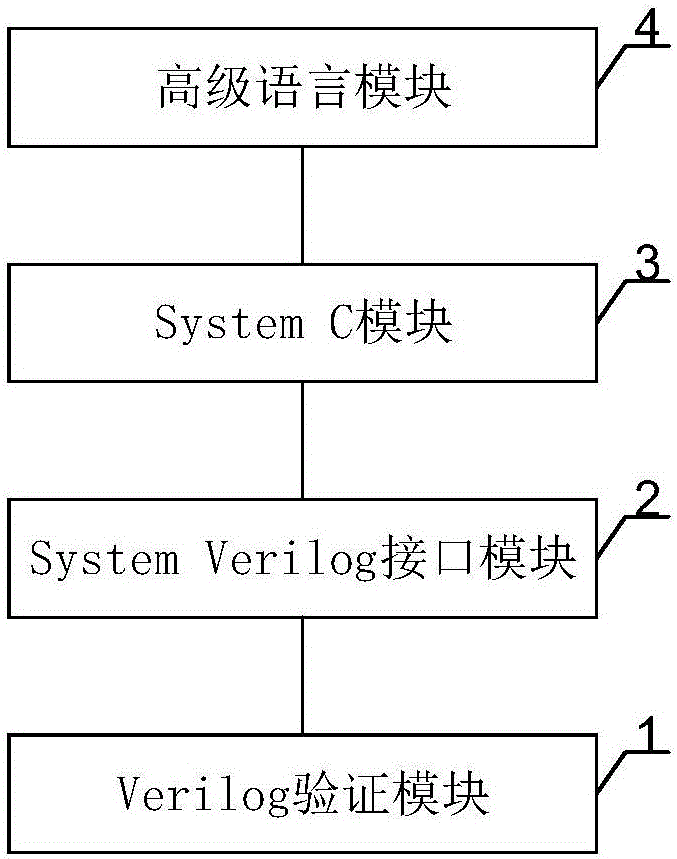

Simulation verification system

ActiveCN106682370AMeet the needs of simulation verificationImprove test efficiencyDesign optimisation/simulationSpecial data processing applicationsTest efficiencyData information

The invention discloses a simulation verification system. The simulation verification system comprises a Verilog verification module, a System Verilog interface module, a System C module and a high-level language module. The Verilog verification module is used for instantiating RTL codes and obtaining first state information and further used for receiving time sequence control information returned by the System Verilog interface module to achieve simulation verification on a chip. The System Verilog interface module is used for processing the first state information to obtain second state information and further used for sending the time sequence control information returned by the System C module. The System C module is used for providing multiple language models and obtaining transaction-level data information and language call instructions according to the second state information and the corresponding language models and further used for generating and sending the time sequence control information according to an algorithm returned by the high-level language model. The high-level language model is used for obtaining and returning corresponding algorithms according to the transaction-level data information and the language call instructions. The application range is wide, and the testing efficiency and the precision of the testing result are improved.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

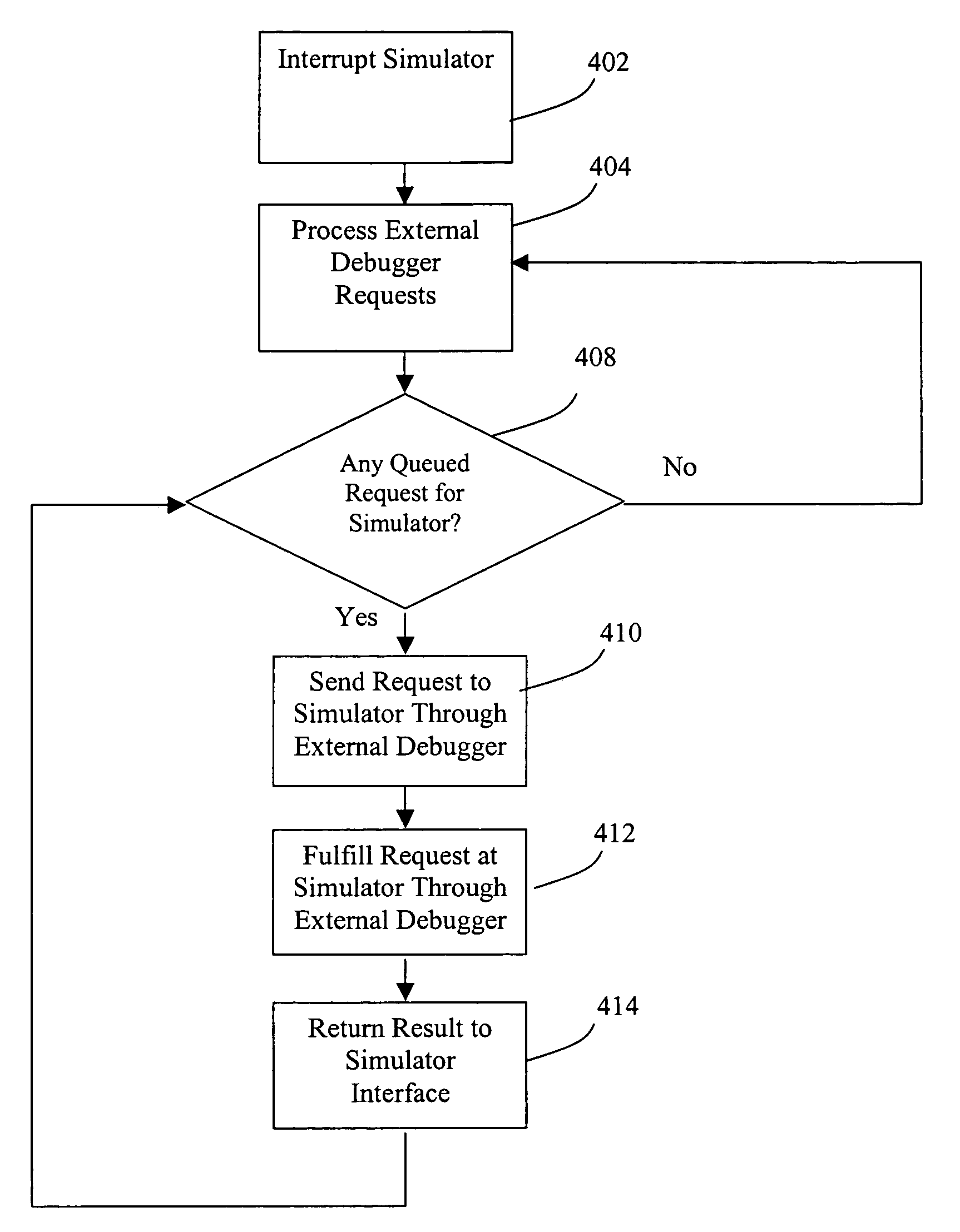

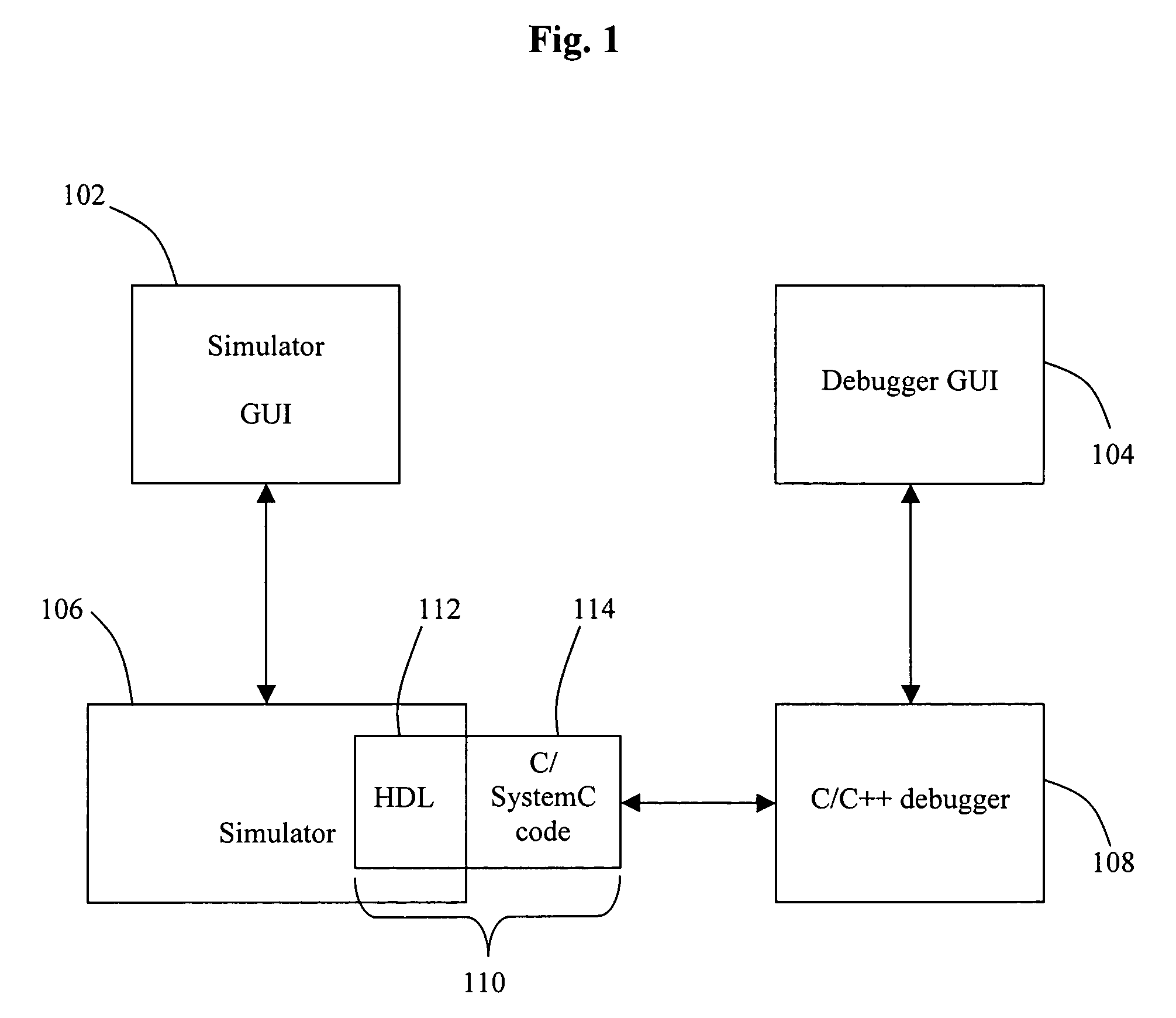

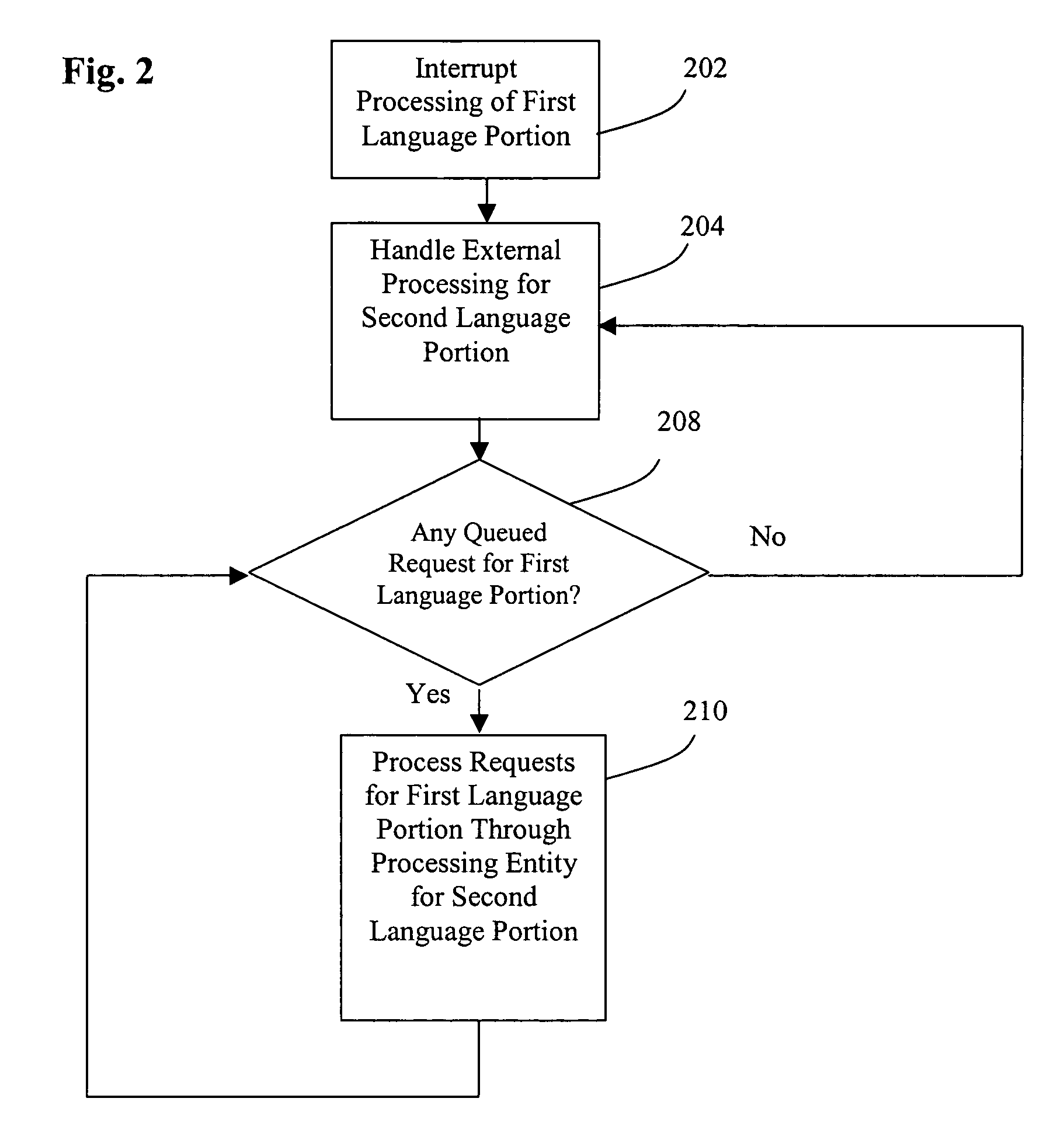

Mechanism and method for simultaneous processing and debugging of multiple programming languages

Disclosed is a method, mechanism, and computer usable medium for simultaneous processing or debugging of multiple programming languages. A particularly disclosed approach provides a method and mechanism for resolving the issue of simultaneous debugging of hardware represented by an HDL, e.g., Verilog or VHDL, and software, e.g., represented by C, C++, SystemC code. This approach overcomes the problem of the HDL portion of the design being inaccessible when C, C++ or SystemC code is debugged.

Owner:CADENCE DESIGN SYST INC

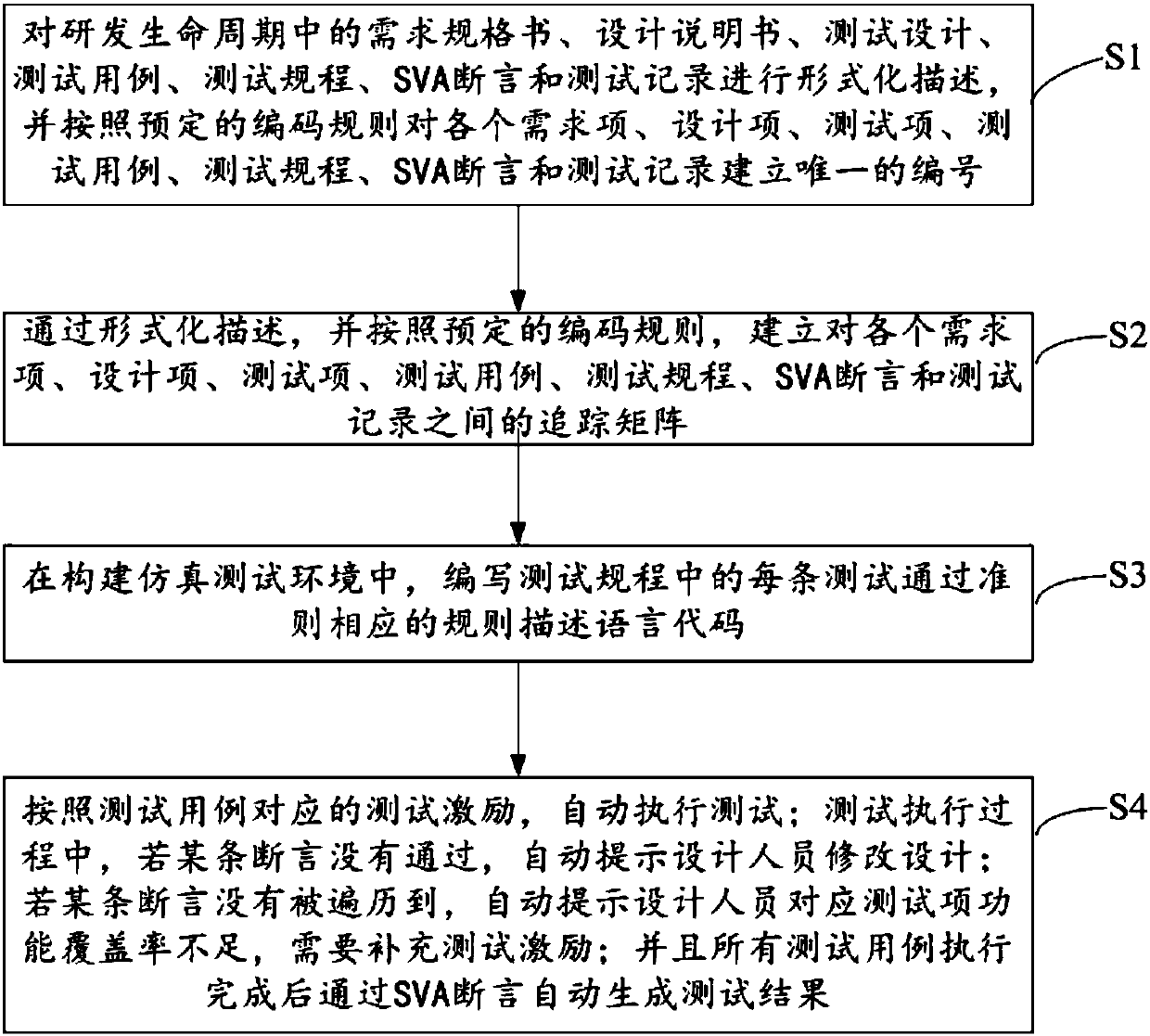

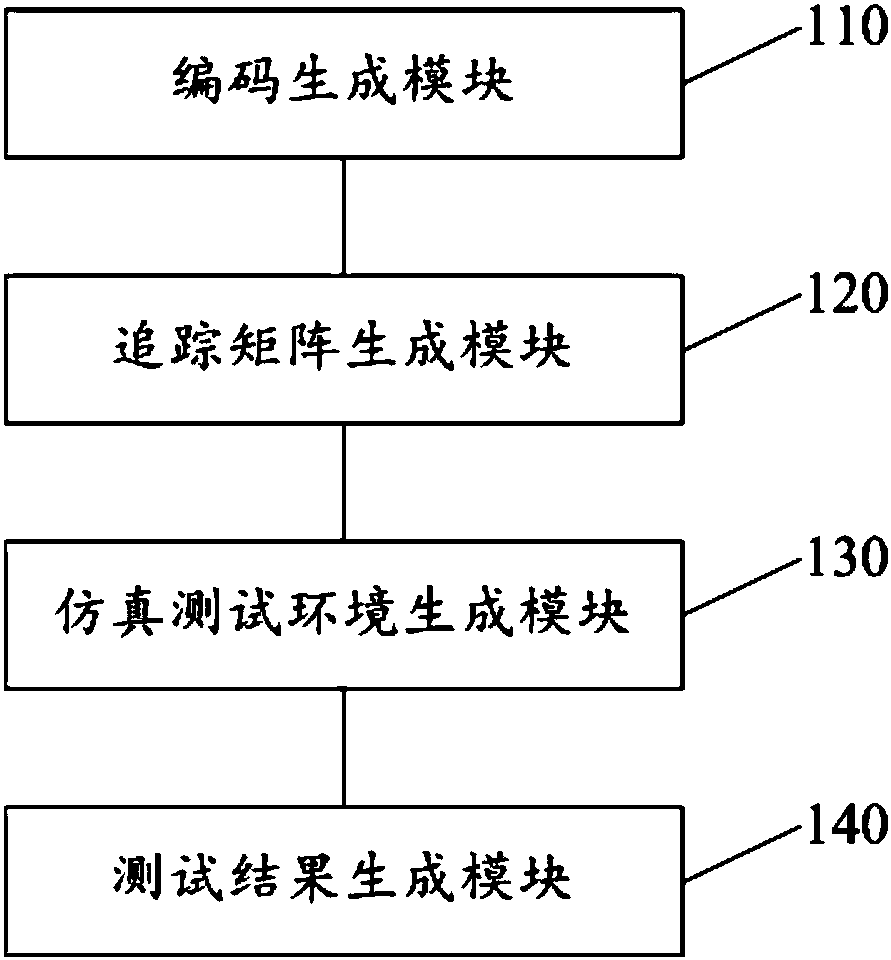

Statistical method and device of programmable-logic simulation test function coverage

ActiveCN107797929AImprove test activity completenessImprove completenessSoftware testing/debuggingComputer architectureDependability

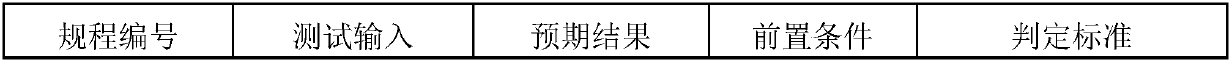

The invention belongs to the technical field of safety level instrument control system simulation tests, aims to solve the technical problem that simulation test function coverage in the prior art cannot be accurately obtained, and provides a statistical method and device which can effectively increase programmable-logic simulation test function coverage. The statistical method includes: S1, carrying out formalized description on demand items in an HPD (HDL (hardware description language)-programmed device) demand specification book, and establishing a unique number for each demand item according to a predetermined coding rule; S2, establishing a tracking matrix of a to-be-tested system; S3, writing SVA (System Verilog Assertion) code corresponding to each test passing criterion in test regulations; and S4, automatically generating a test result through SVA after execution is completed according to test excitation corresponding to test cases. The function coverage can be visually represented through adding effective tracking and monitoring on a coding link in a simulation test process, and the simulation test process of programmable logic is enabled to be more rigorous and more accord with a requirement of high reliability.

Owner:CHINA TECHENERGY +1