Patents

Literature

100results about How to "High-speed execution" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

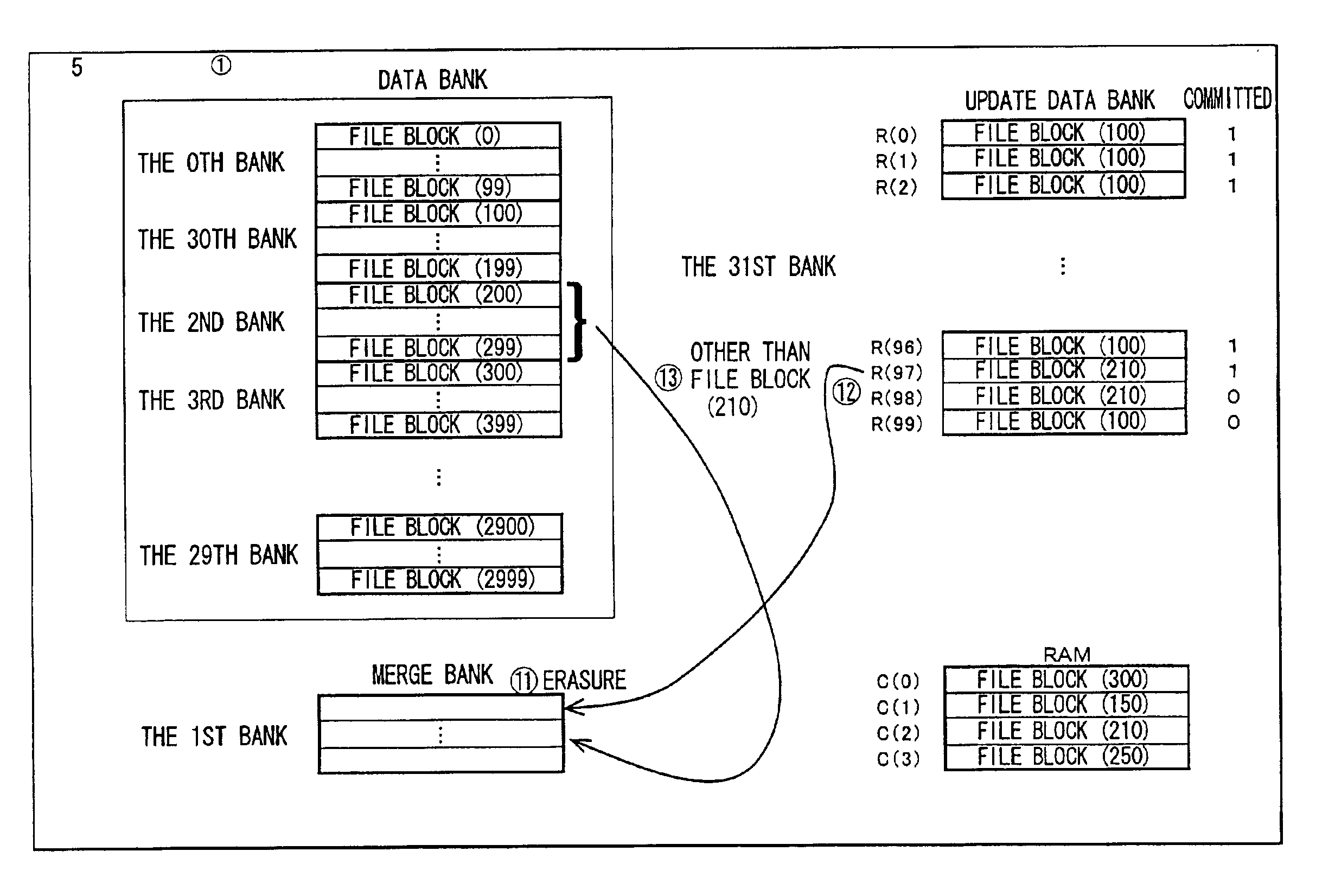

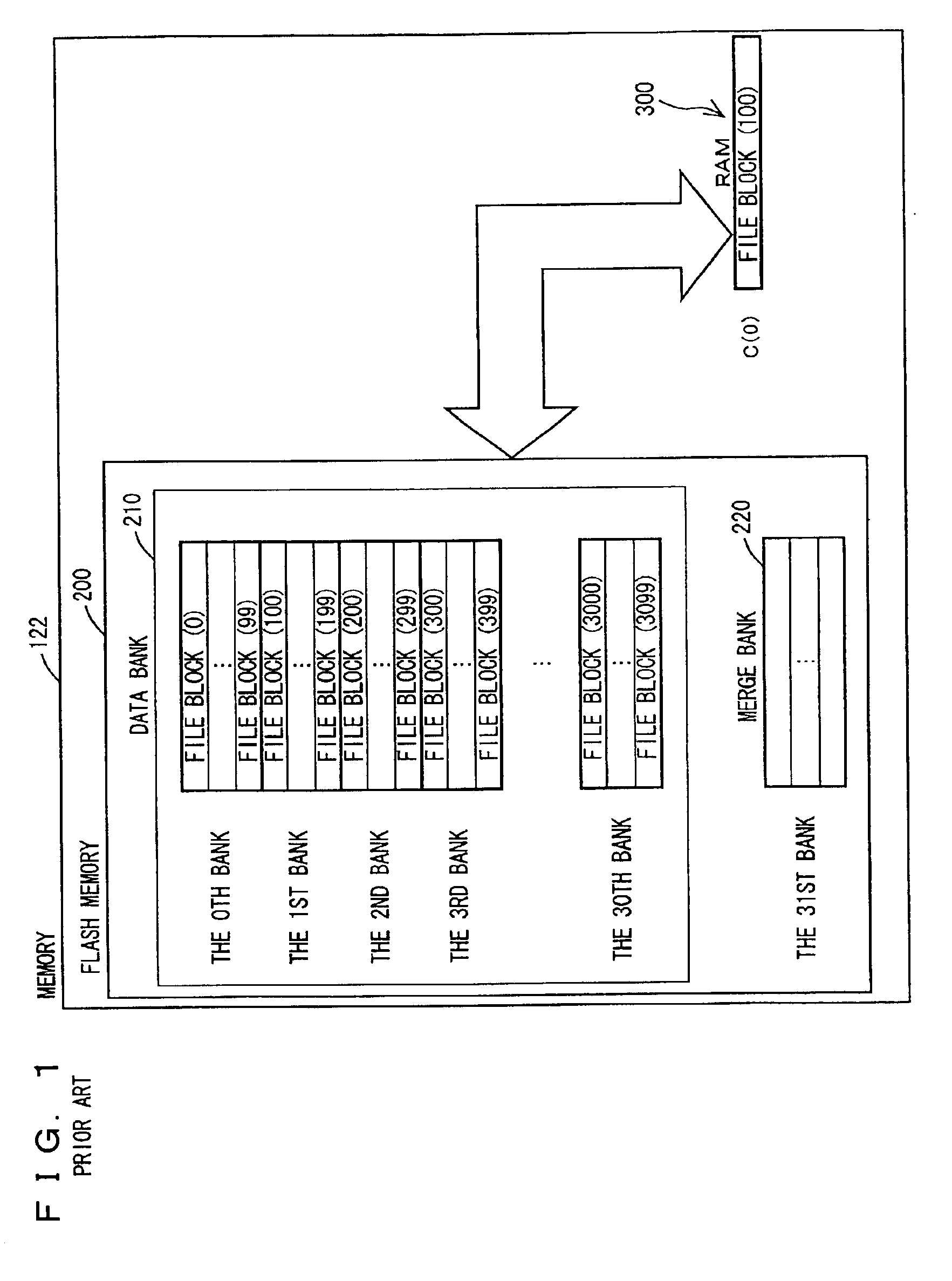

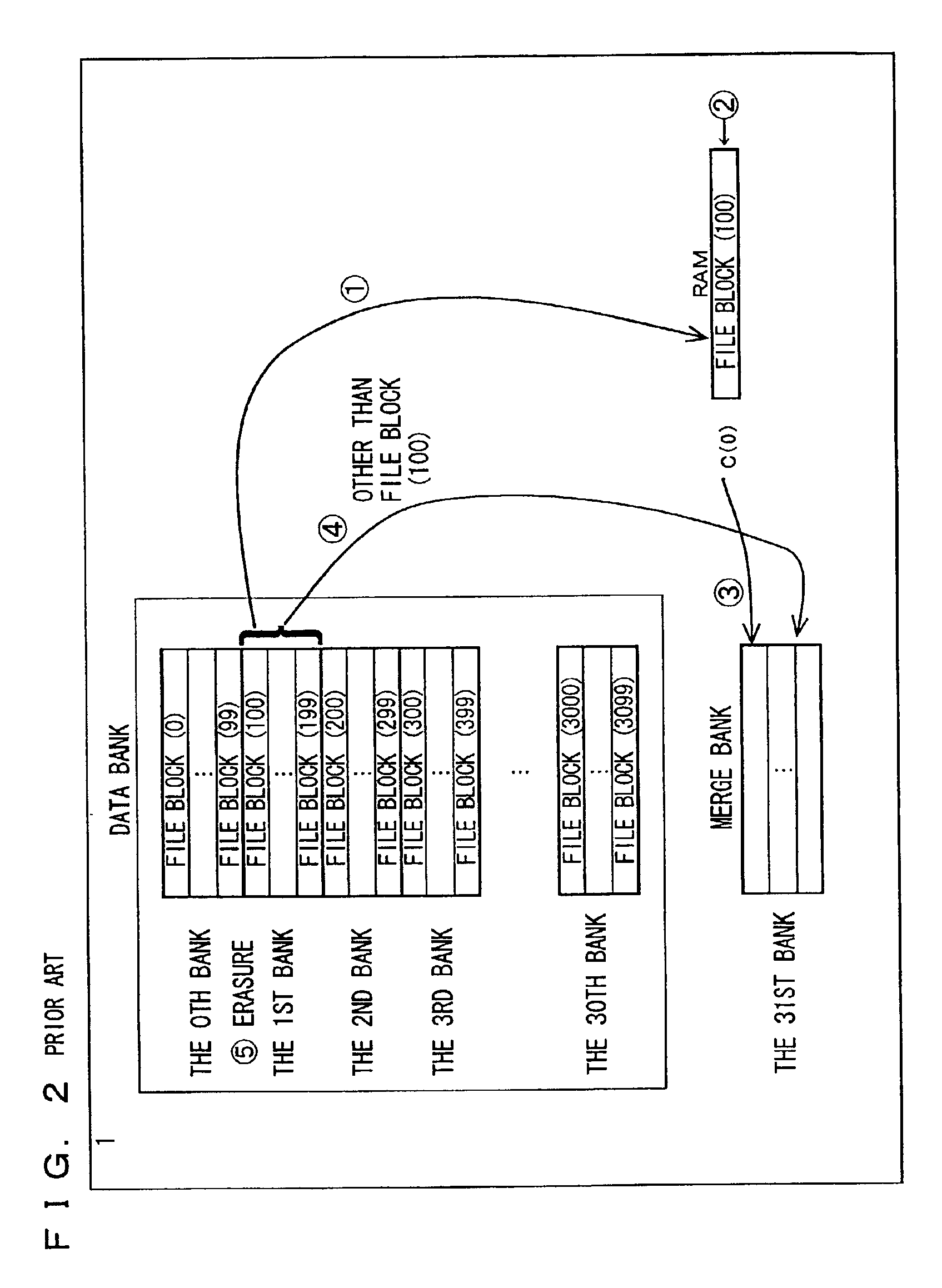

File system including non-volatile semiconductor memory device having a plurality of banks

InactiveUS6871259B2Increase speedHigh-speed executionMemory architecture accessing/allocationMemory loss protectionFile systemData storing

A flash memory includes a data bank having a plurality of banks, a merge bank, and an update data bank. A file system using the flash memory includes a unit storing update data corresponding to a data rewrite command into the update data bank, a unit selecting the latest update data for each block from update data stored in the update data bank when the update data bank becomes full, and a processing unit processing the latest update data. The processing unit includes a unit storing latest update data into a merge bank, a unit selecting data associated with the latest update data from the data bank to store the selected data into the merge bank, and a unit setting the merge bank as a new data bank.

Owner:RENESAS ELECTRONICS CORP

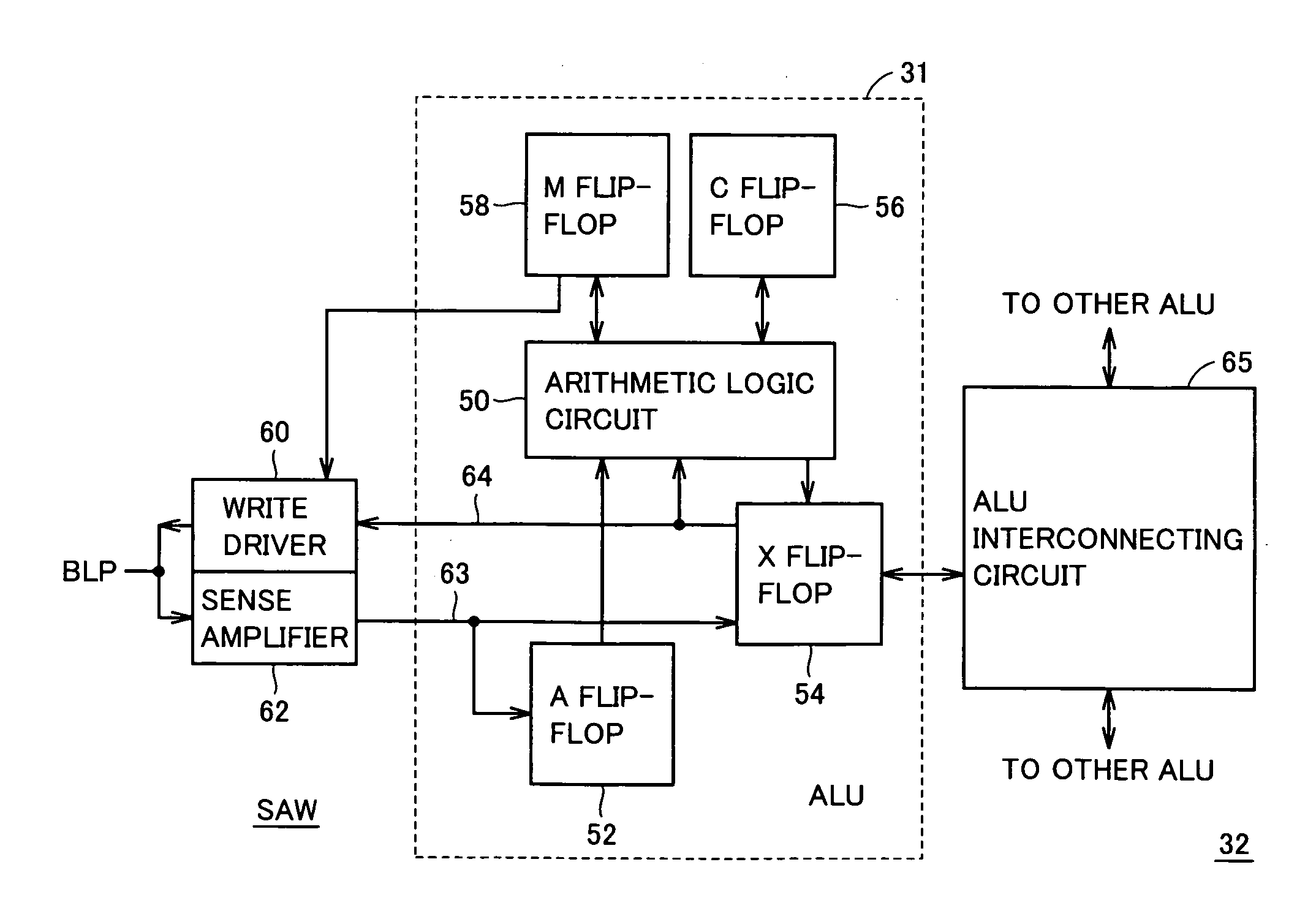

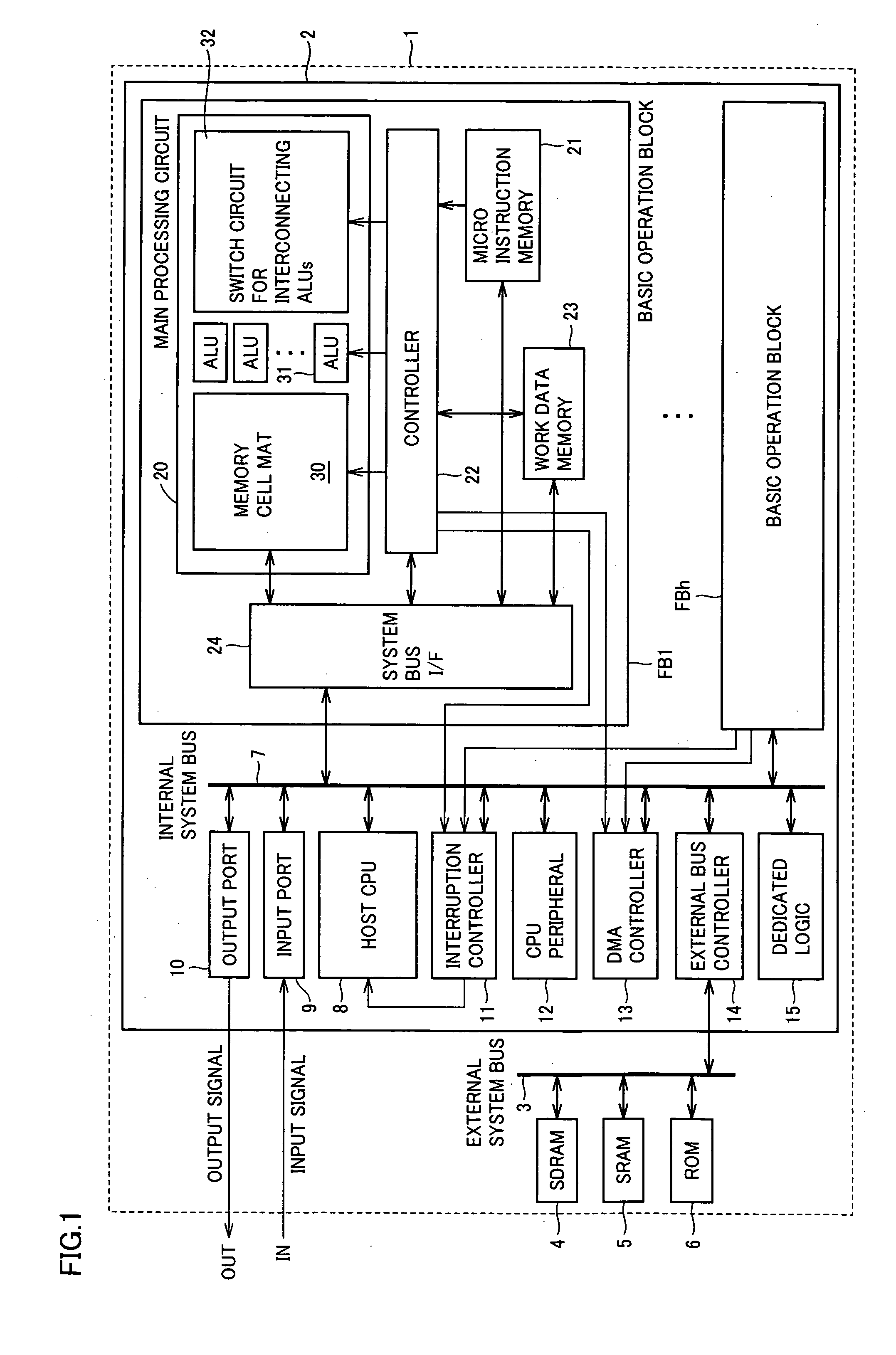

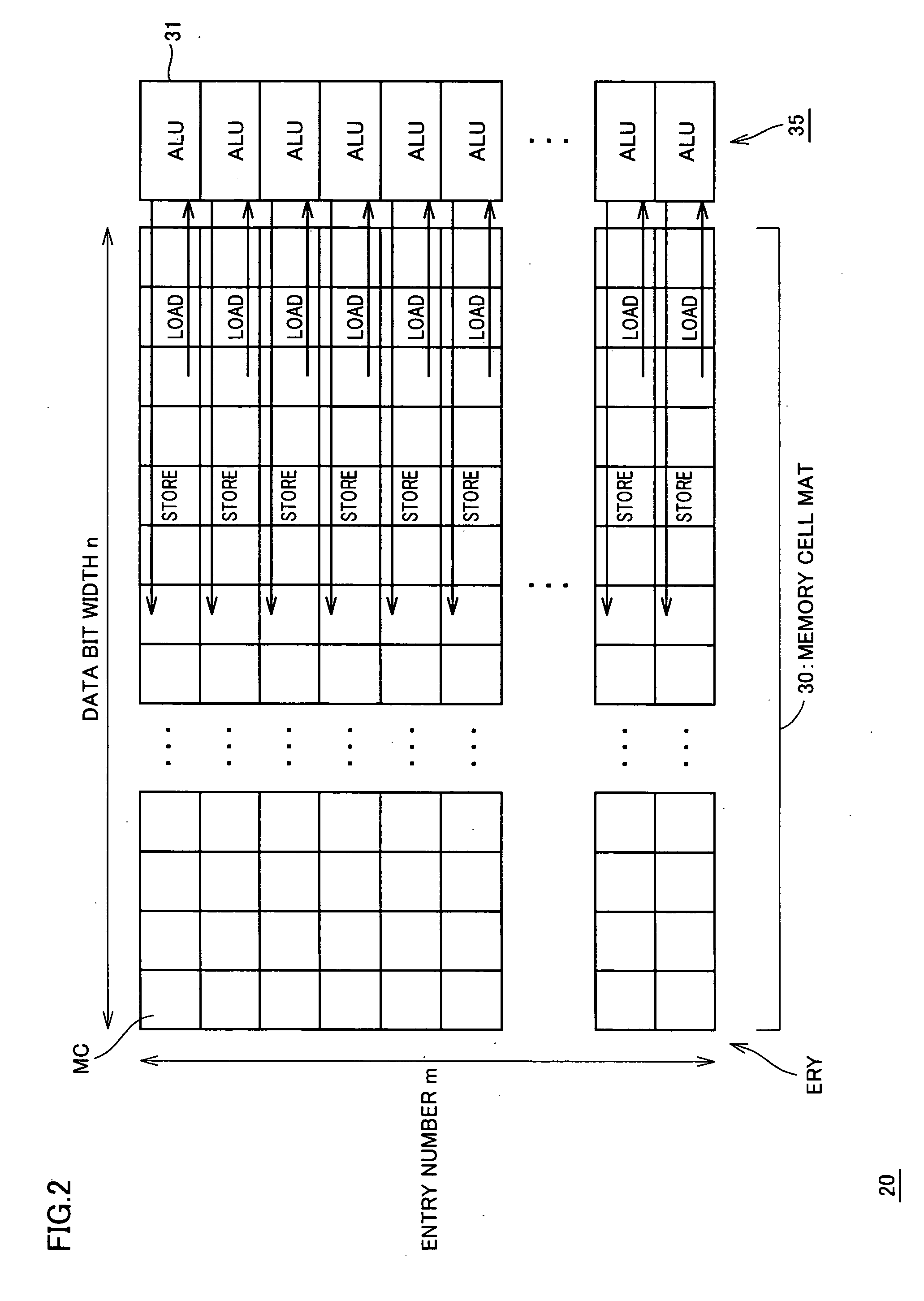

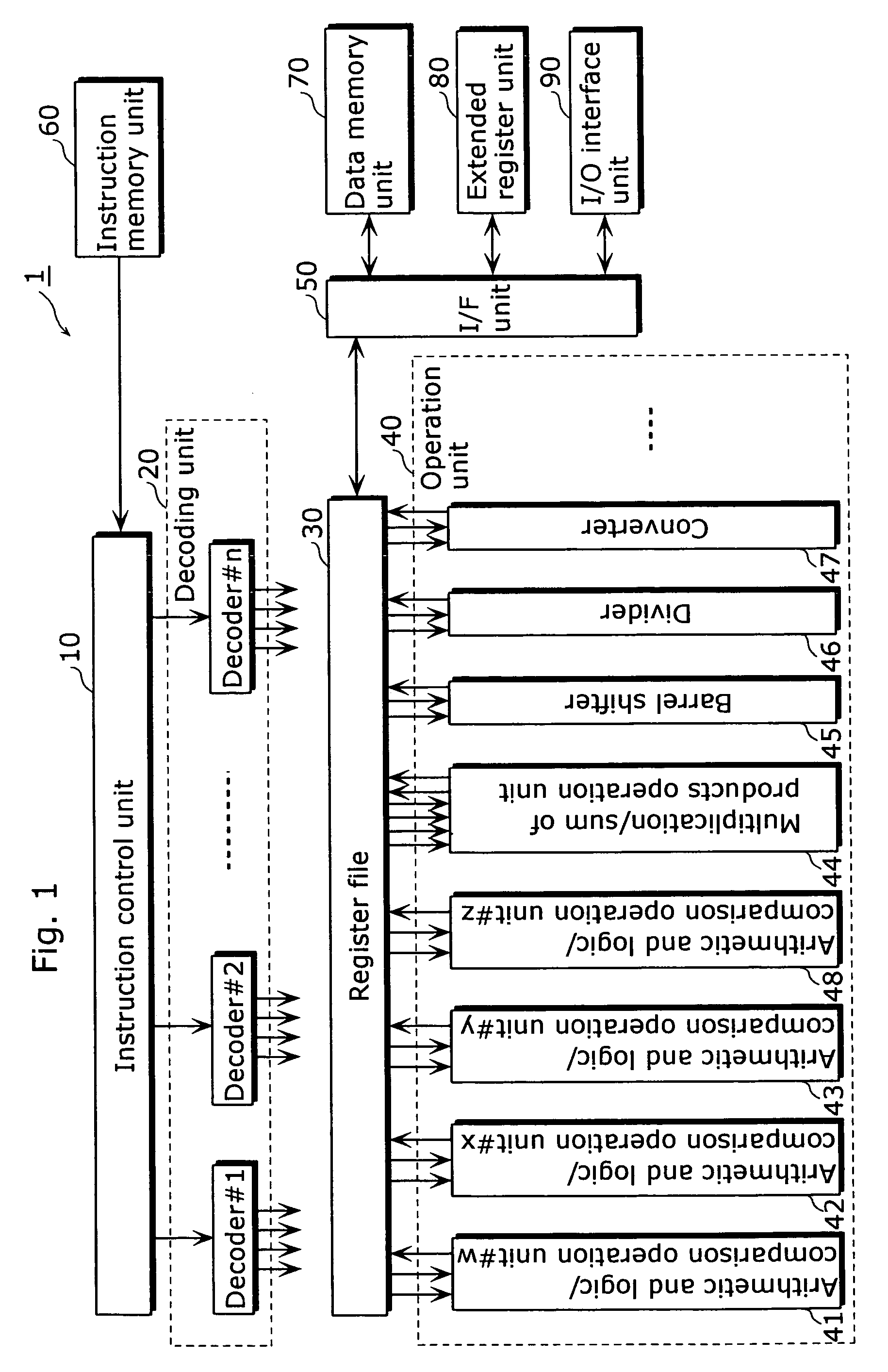

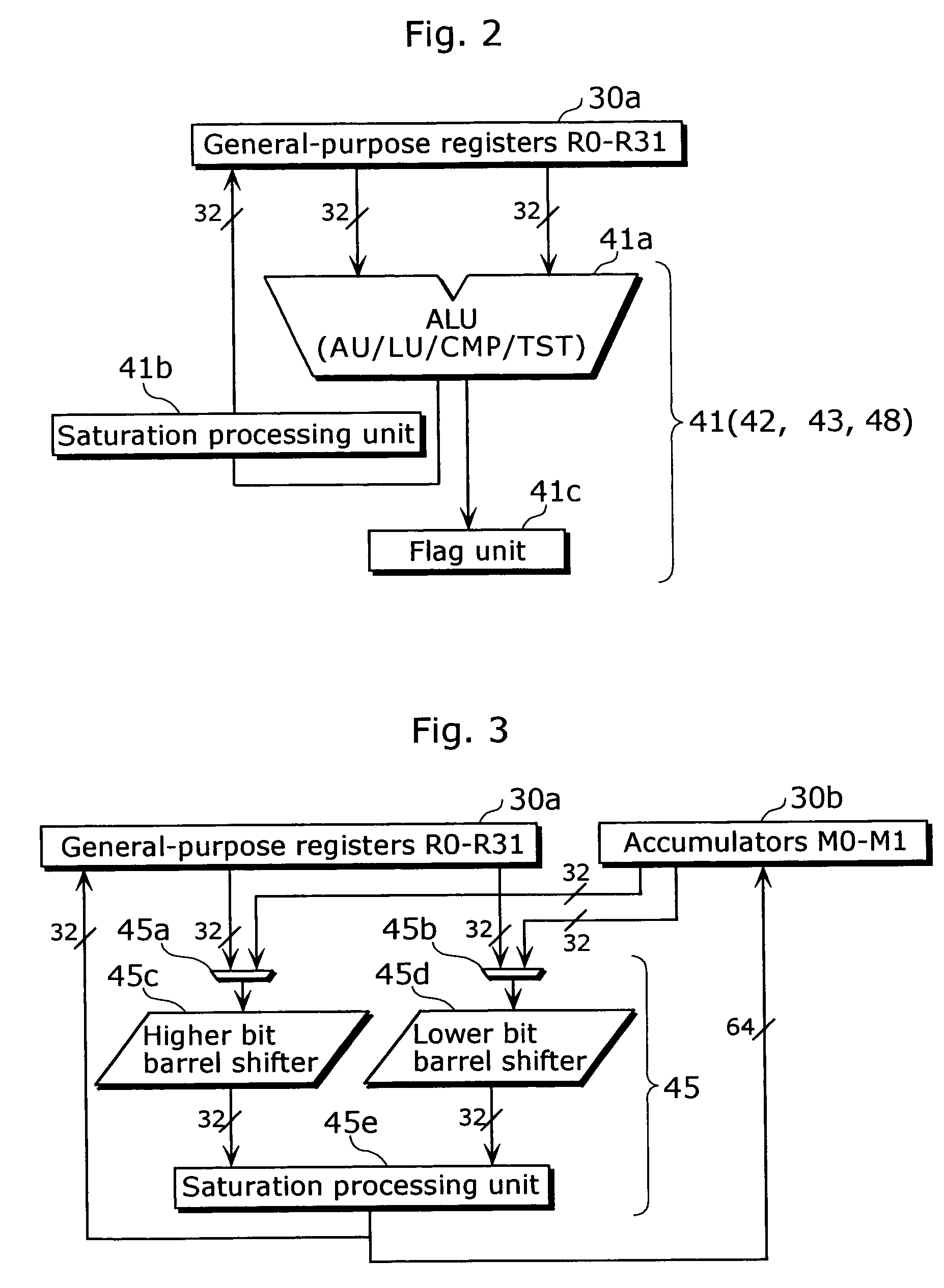

Semiconductor signal processing device

InactiveUS20060101231A1Increase speedBig amount of dataSingle instruction multiple data multiprocessorsSpecific program execution arrangementsInstruction memoryParallel computing

An instruction for an arithmetic / logic operation to a main processing circuit is stored in the form of a micro program in a micro instruction memory, and the operation of the main processing circuit is controlled in accordance with the micro program, under the control of a controller. In the main processing circuit, a memory mat is divided into entries each storing data of a plurality of bits, and for each entry, a processor (ALU) is arranged. Arithmetic / logic operations are performed entry-parallel and in bit-serial manner between each entry and the associated ALU. In accordance with the micro program control method, a large amount of data can be processed efficiently. Thus, a processing device that efficiently performs an arithmetic / logic operation on a large amount of data at high speed is provided.

Owner:RENESAS TECH CORP

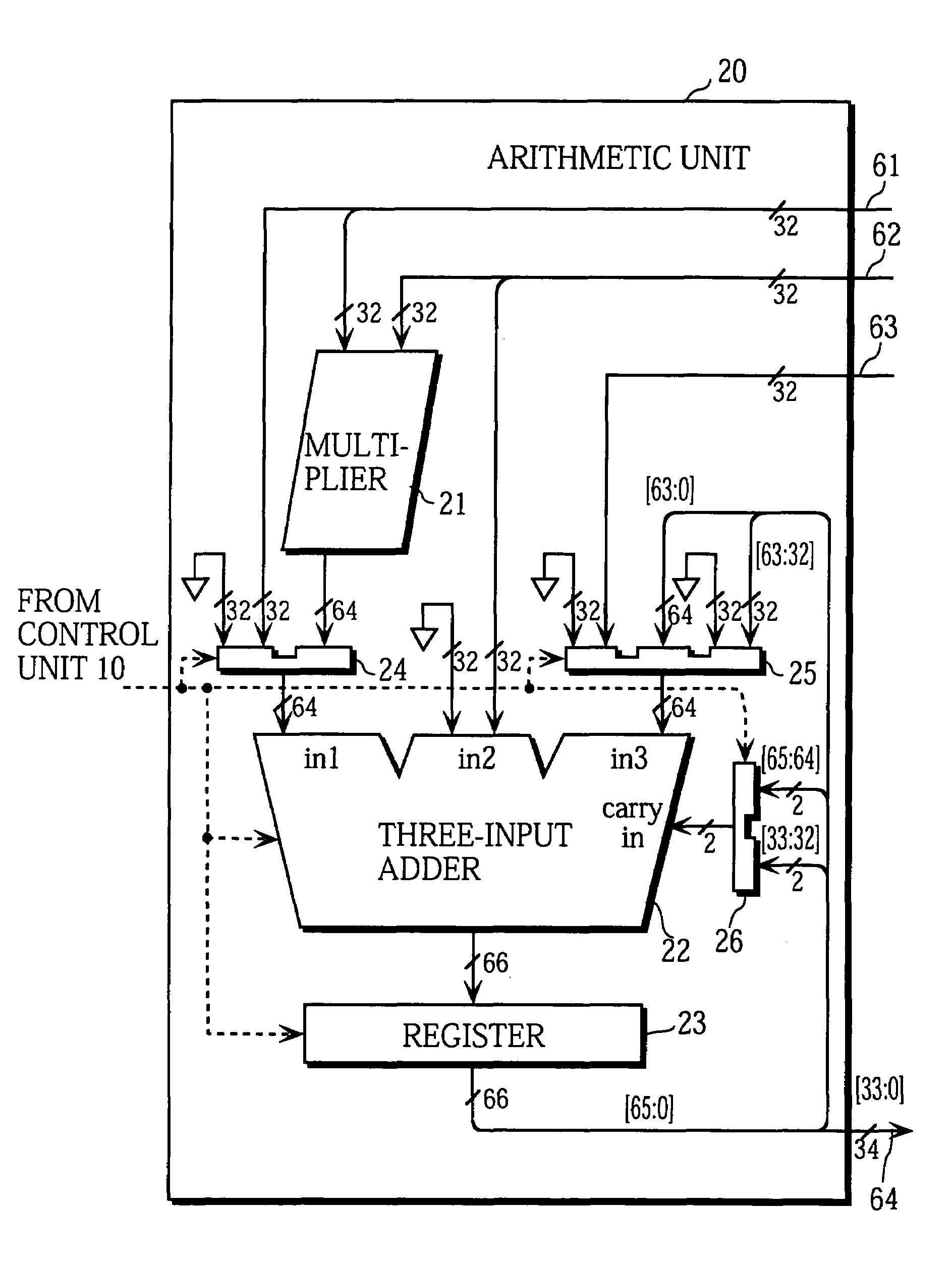

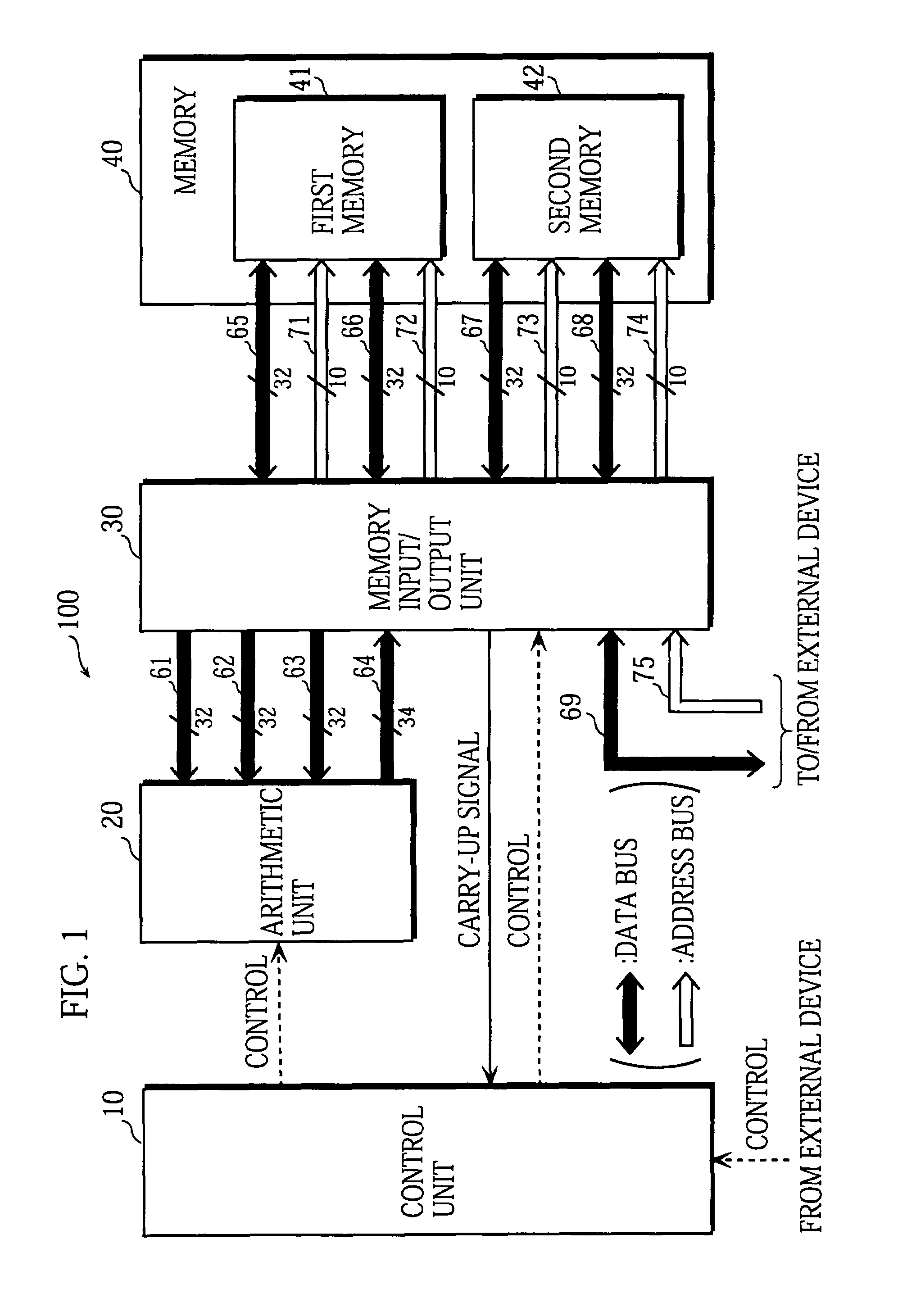

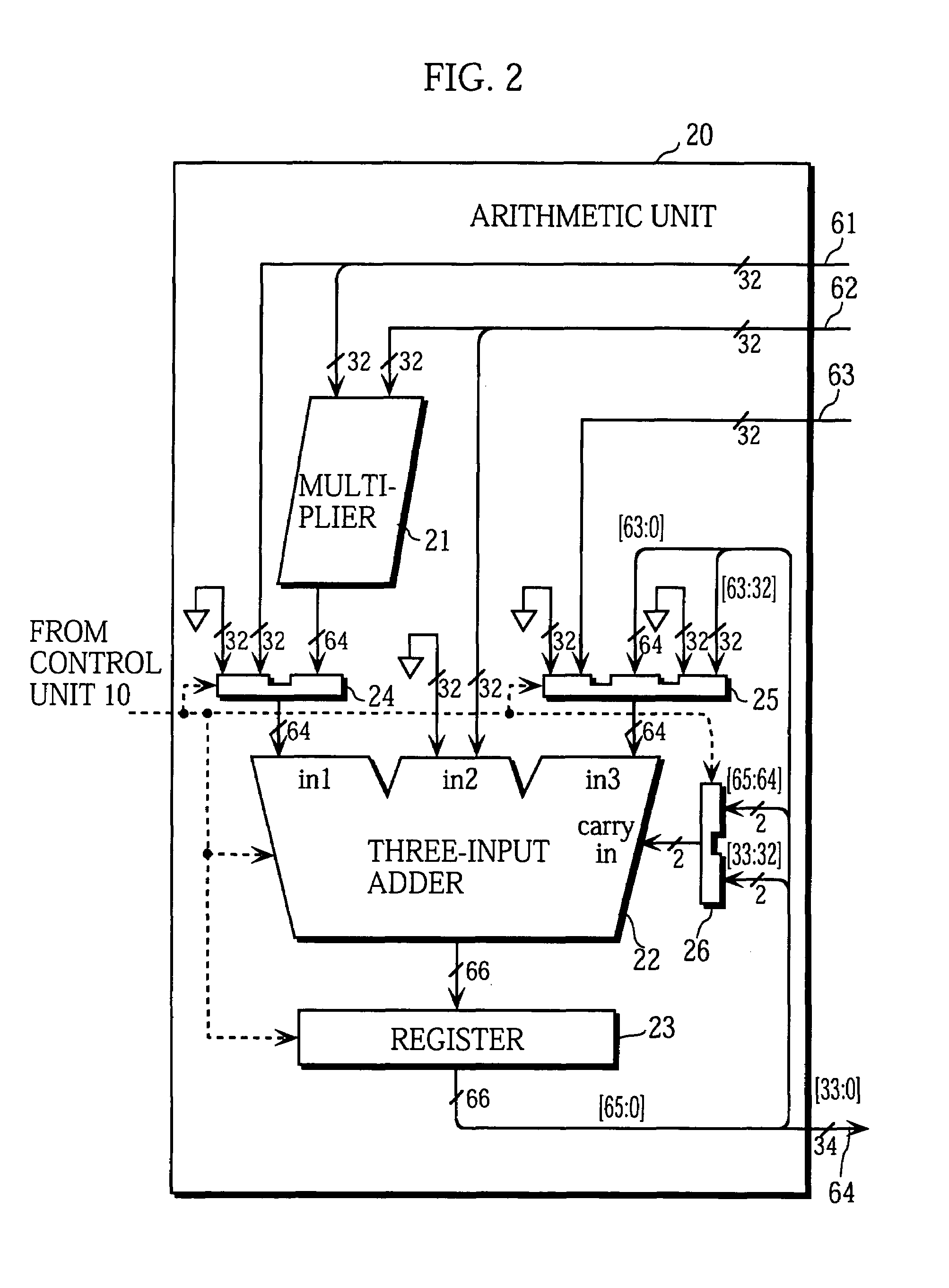

Multi-word arithmetic device for faster computation of cryptosystem calculations

InactiveUS6963644B1Good flexibilityHigh-speed executionPublic key for secure communicationDigital computer detailsCryptosystemMontgomery reduction

Owner:PANASONIC CORP

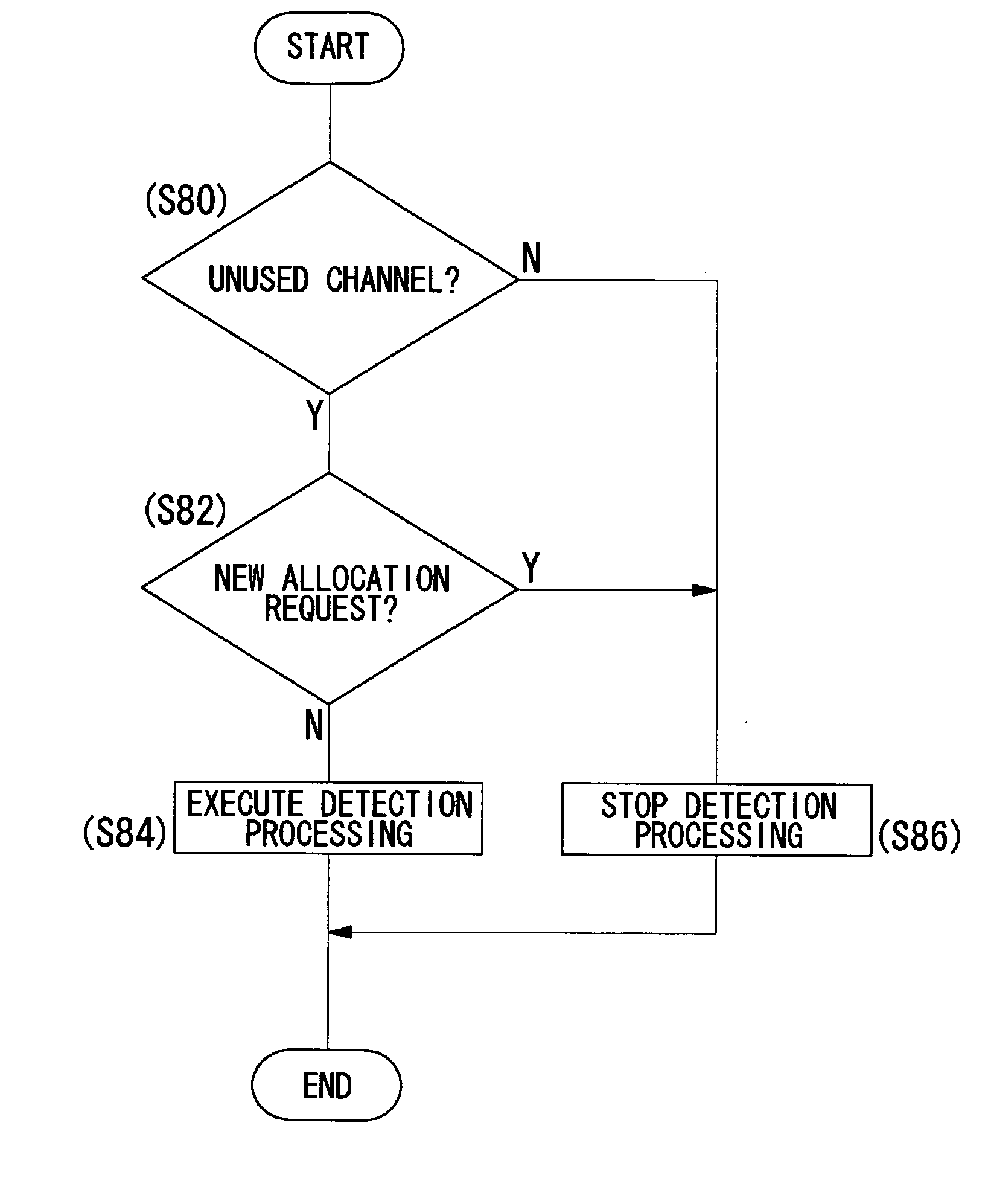

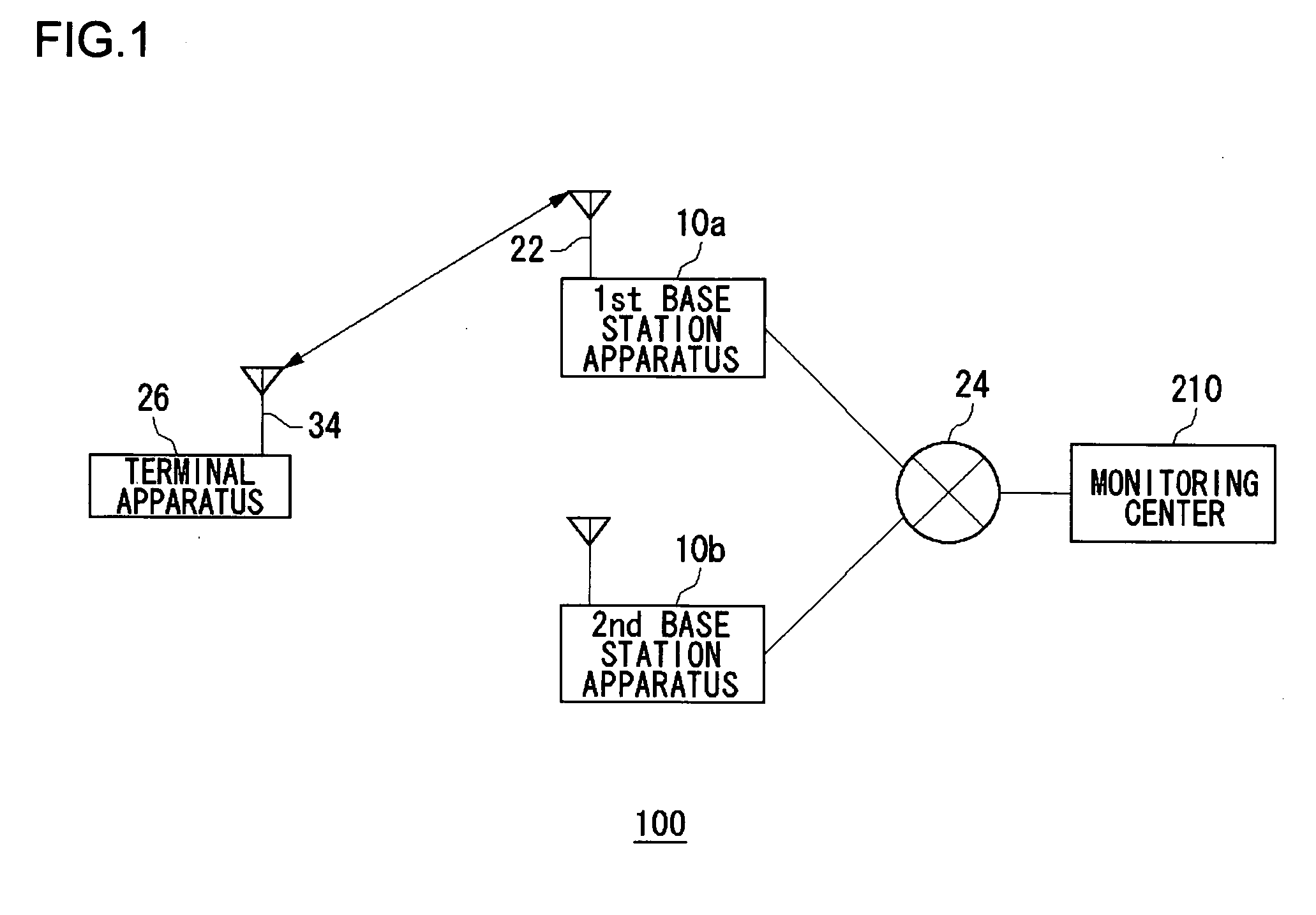

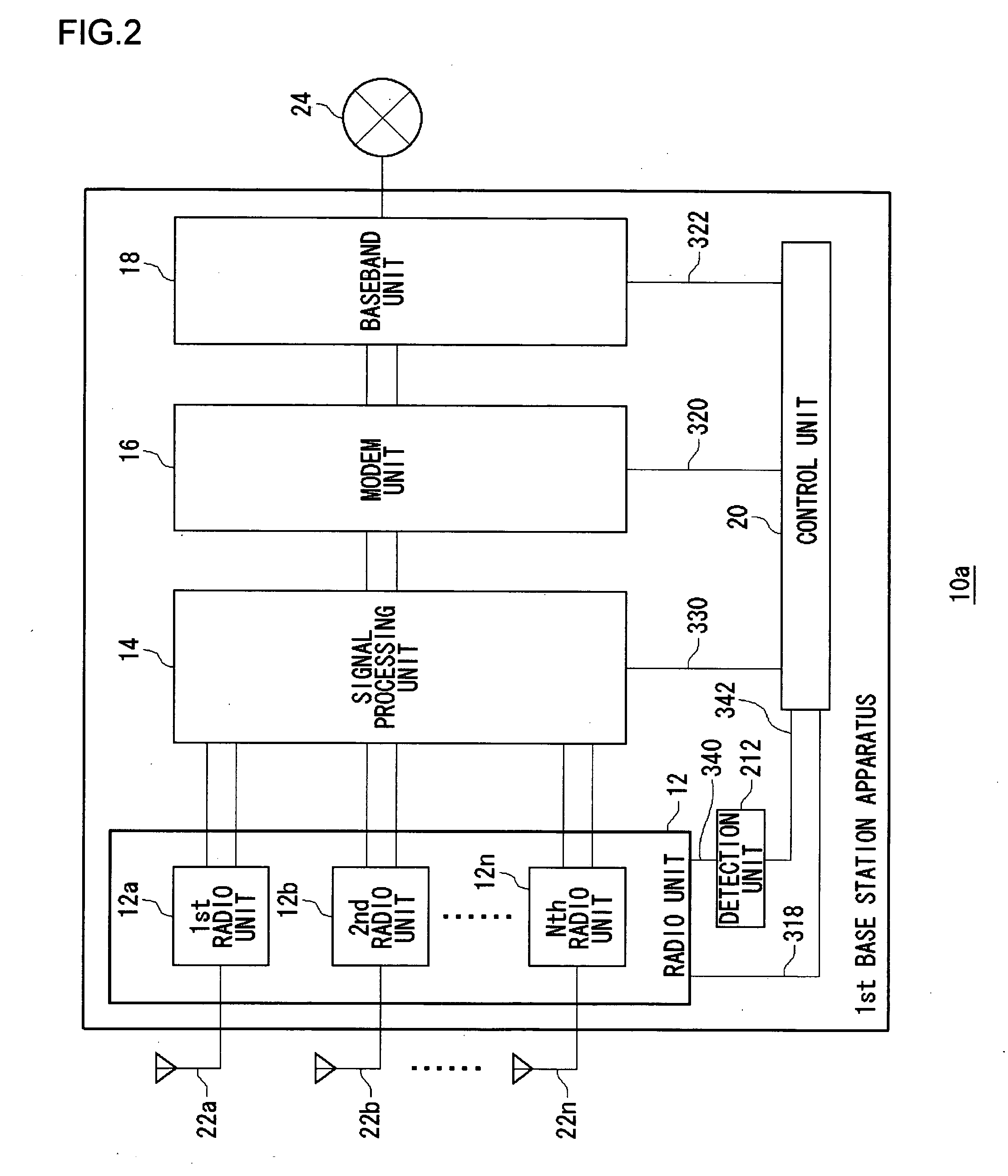

Malfunction detection method and base station apparatus utilizing the same

InactiveUS20060003773A1Improve scaleLittle effectSpatial transmit diversityReceivers monitoringEngineeringComparator

A measuring unit inputs a detection received signal and measures a received RSSI value as the detection received signal. A first comparator inputs a plurality of received RSSI values measured by the measuring unit and compares them with a predetermined threshold value. A signal difference deriving unit derives a relative relationship among the plurality of RSSI values. A second comparator compares the relative relationship with a predetermined value. If the first comparator and the second comparator detect any malfunction, a decision unit receives notification accordingly from the first comparator and the second comparator and finally judges the malfunction of communication functions associated therewith.

Owner:KYOCERA CORP

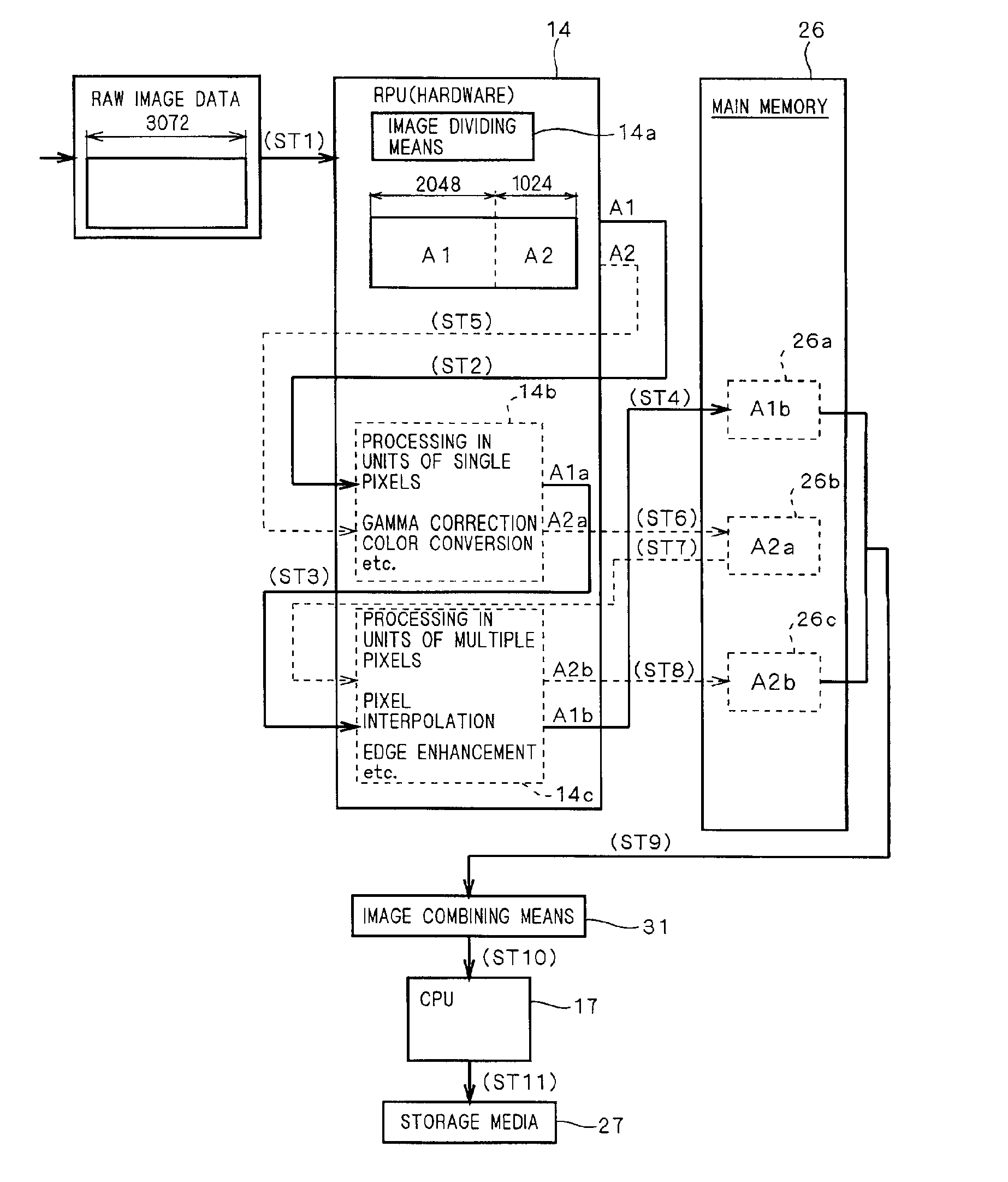

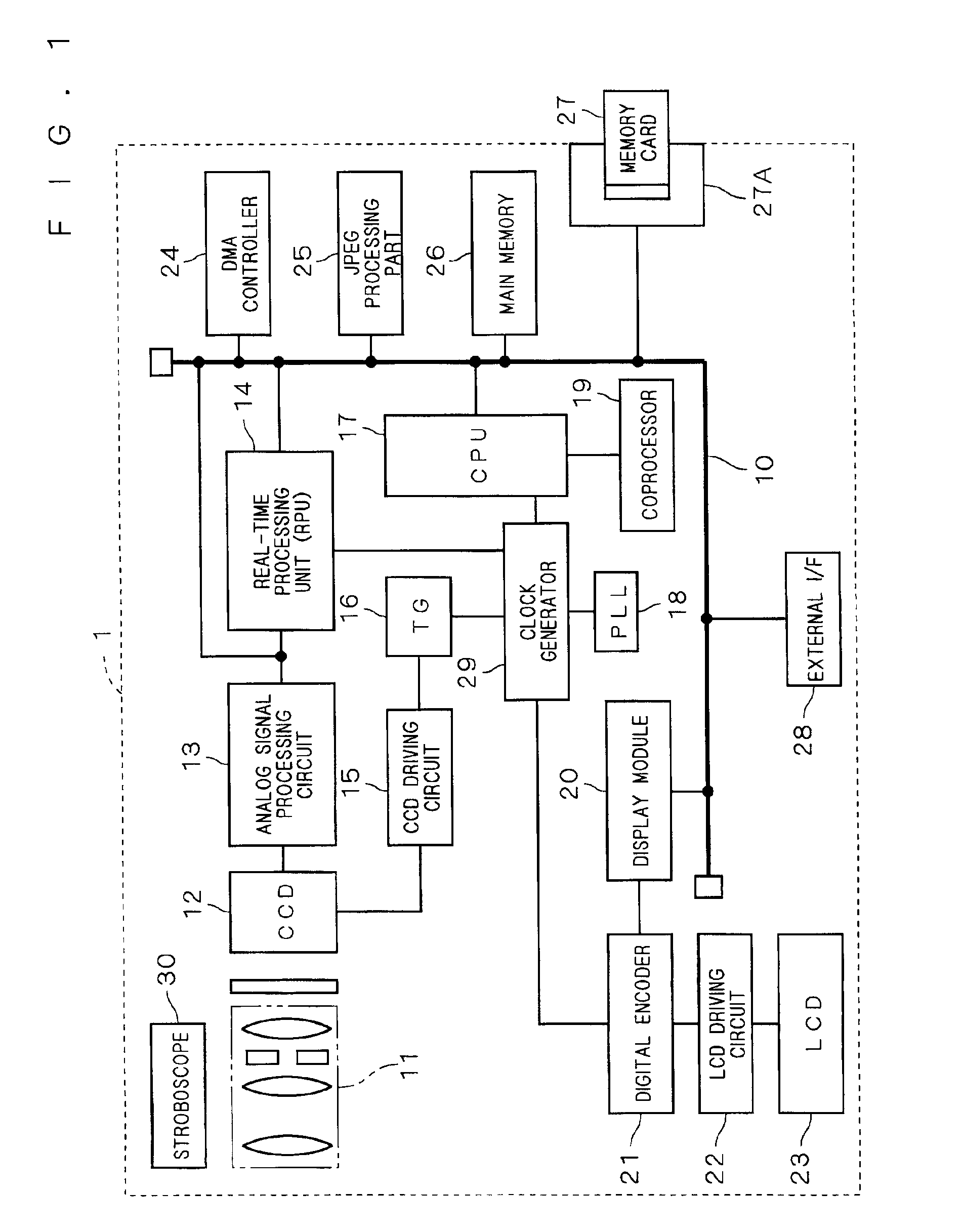

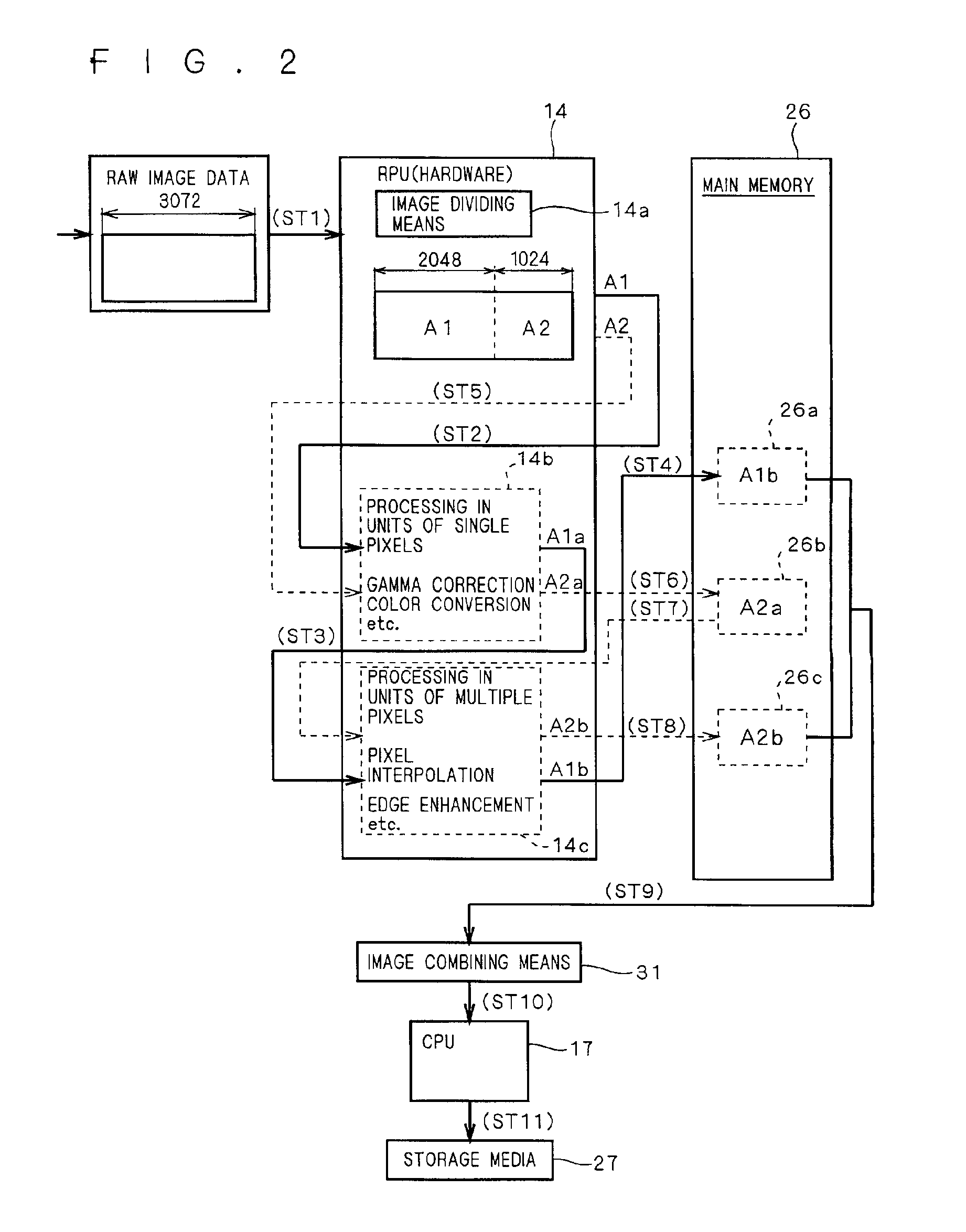

Image processor

ActiveUS6944358B2Low costReduce processing timeTelevision system detailsGeometric image transformationImaging processingComputer graphics (images)

Image dividing means of an RPU divides raw image data into divided image data A1 having 2048 horizontal pixels and A2 having 1024 horizontal pixels. The divided image data A1 is continuously processed in single pixel processing means and multiple pixel processing means and thereafter transferred to and stored in a buffer. The divided image data A2 is processed in the single pixel processing means and thereafter transferred to and temporarily stored in another buffer. The multiple pixel processing means reads and processes divided image data A2a stored in this buffer and thereafter transfers and stores the same to and in still another buffer. Image combining means reads divided image data A1b and A2b stored in the buffers and combines the same with each other. Thus, an image processing time and a cost can be reduced even if raw image data having horizontal pixels in a number exceeding the capacity of a line memory is received.

Owner:MEGACHIPS

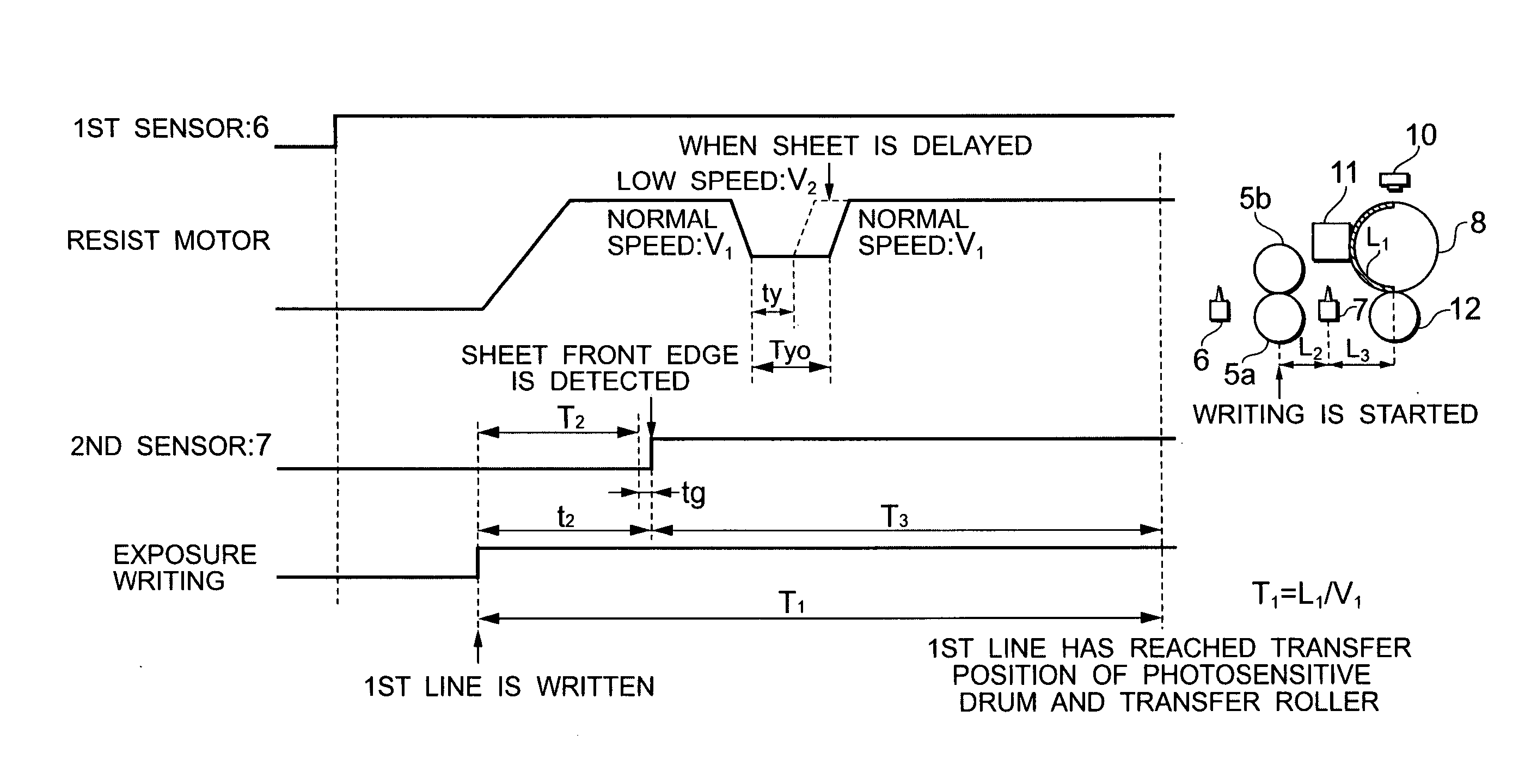

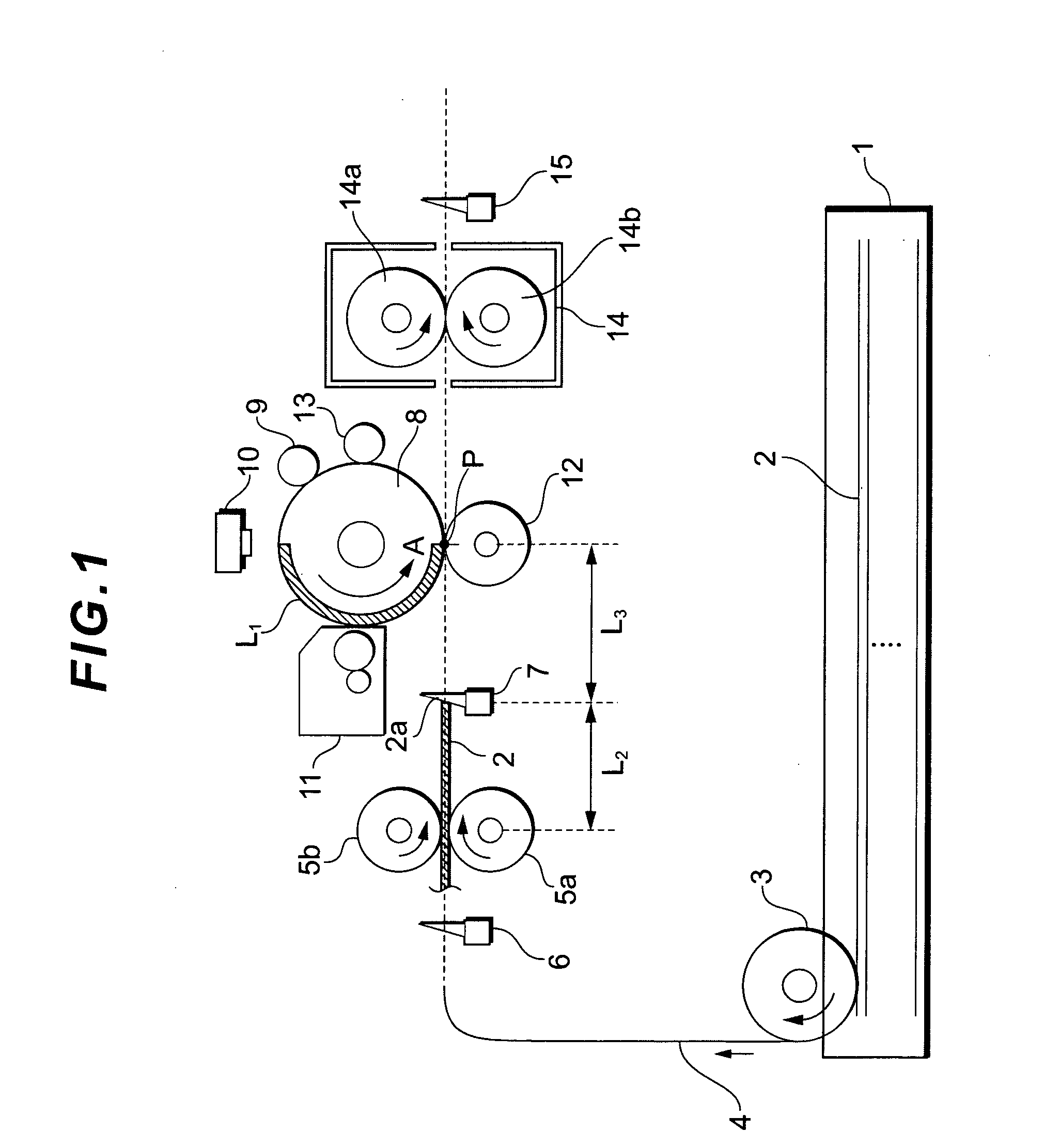

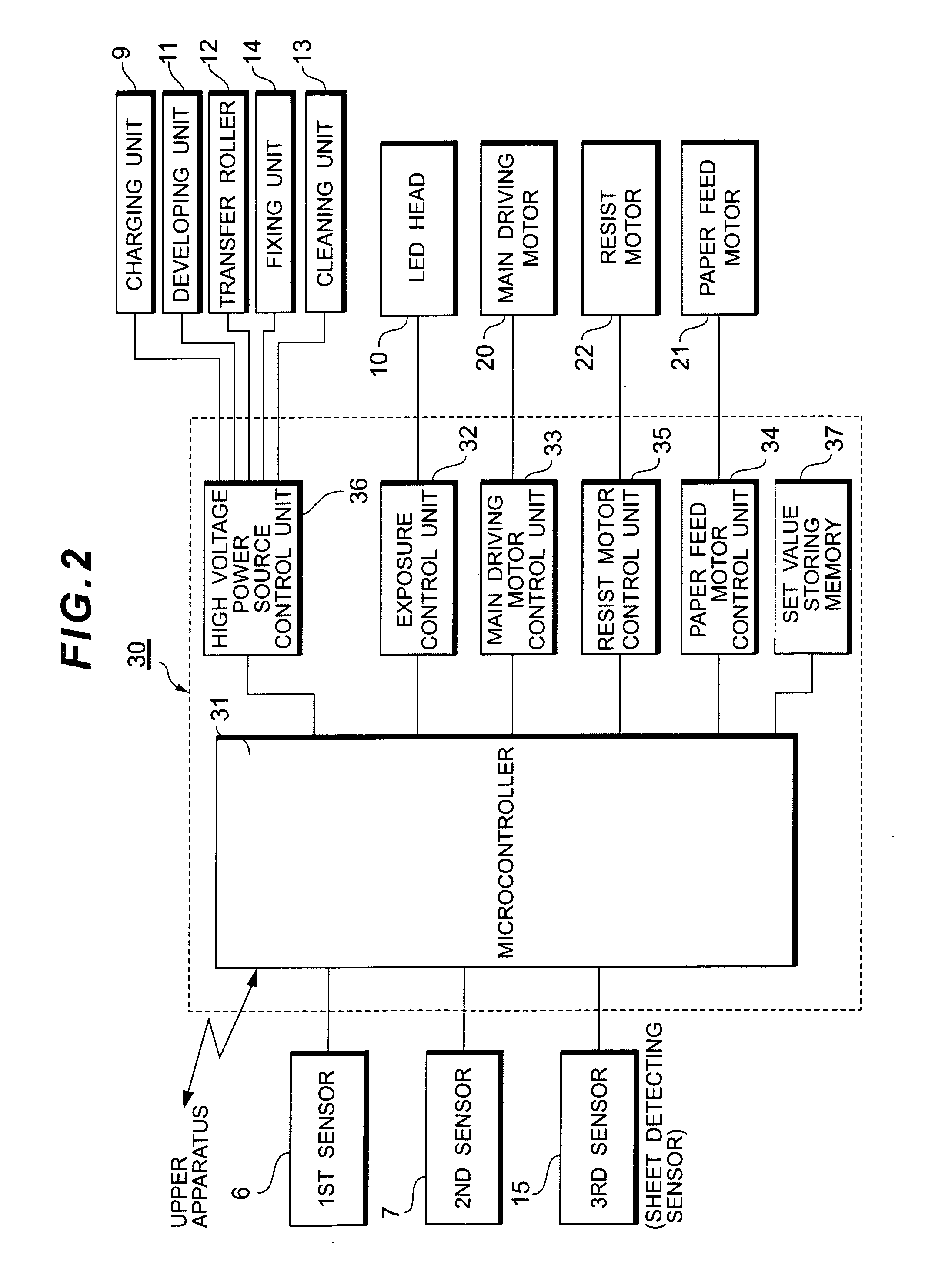

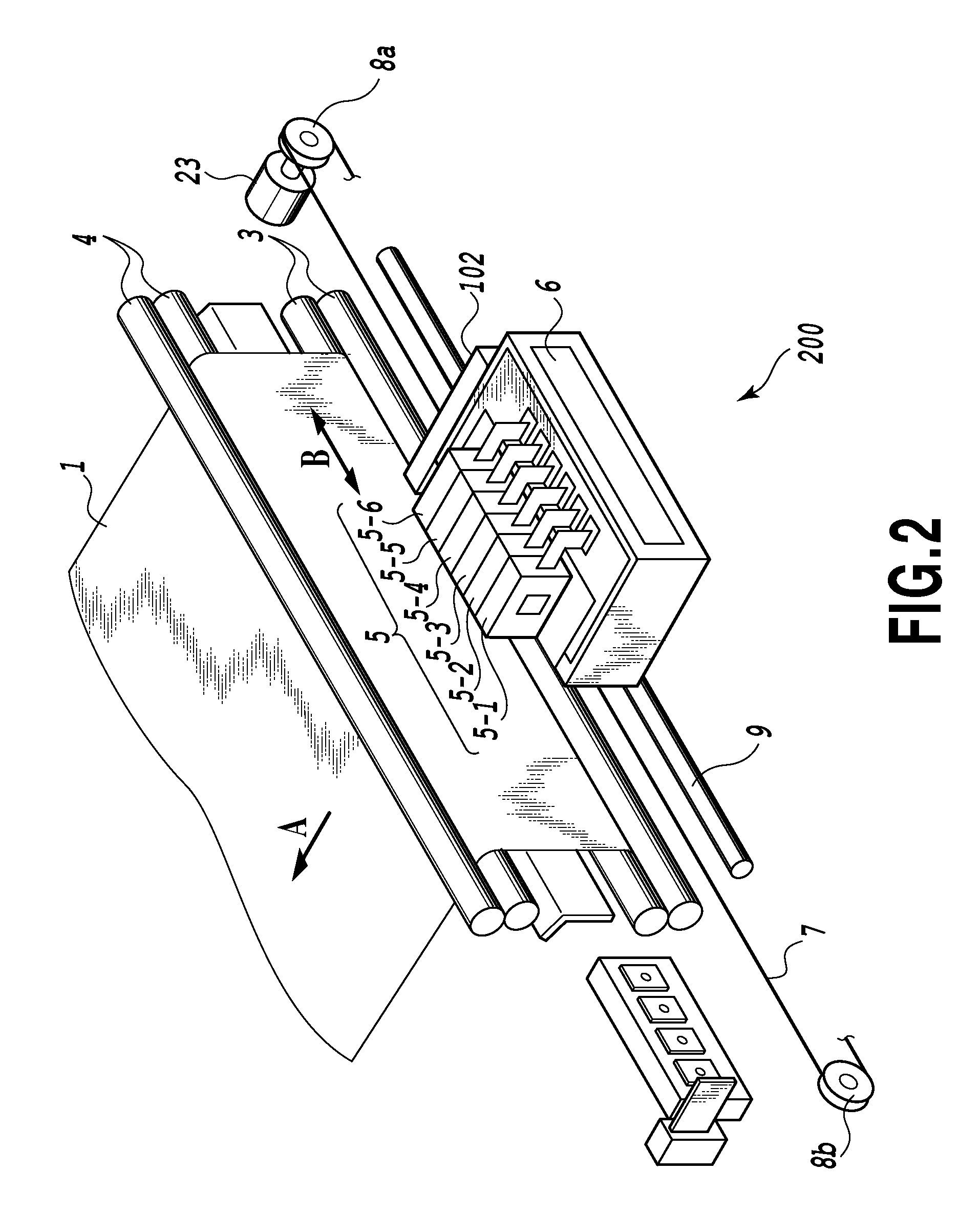

Image recording apparatus and its control method

ActiveUS20050254870A1High speedHigh-speed executionElectrographic process apparatusImage recordingTime of arrival

After a skew of a sheet as a recording medium is corrected by correcting a sheet curve, exposure writing on a photosensitive drum is started synchronously with re-driving of resist rollers. When a sheet front edge is detected by a sensor, sheet conveyance is continued while adjusting a sheet conveying speed when an exposure start position reaches a transfer position at a pressure contact point between the drum and a transfer roller, thereby adjusting the time of arrival at the transfer position. A time / distance interval between the preceding and subsequent sheets are shortened, a conveying path is shortened, and the whole apparatus is miniaturized. Print processing efficiency is raised and stable printing without a variation is executed. A transfer start position of the sheet is made to accurately coincide with the exposure start position of the drum, thereby realizing a high print processing speed.

Owner:OKI ELECTRIC IND CO LTD

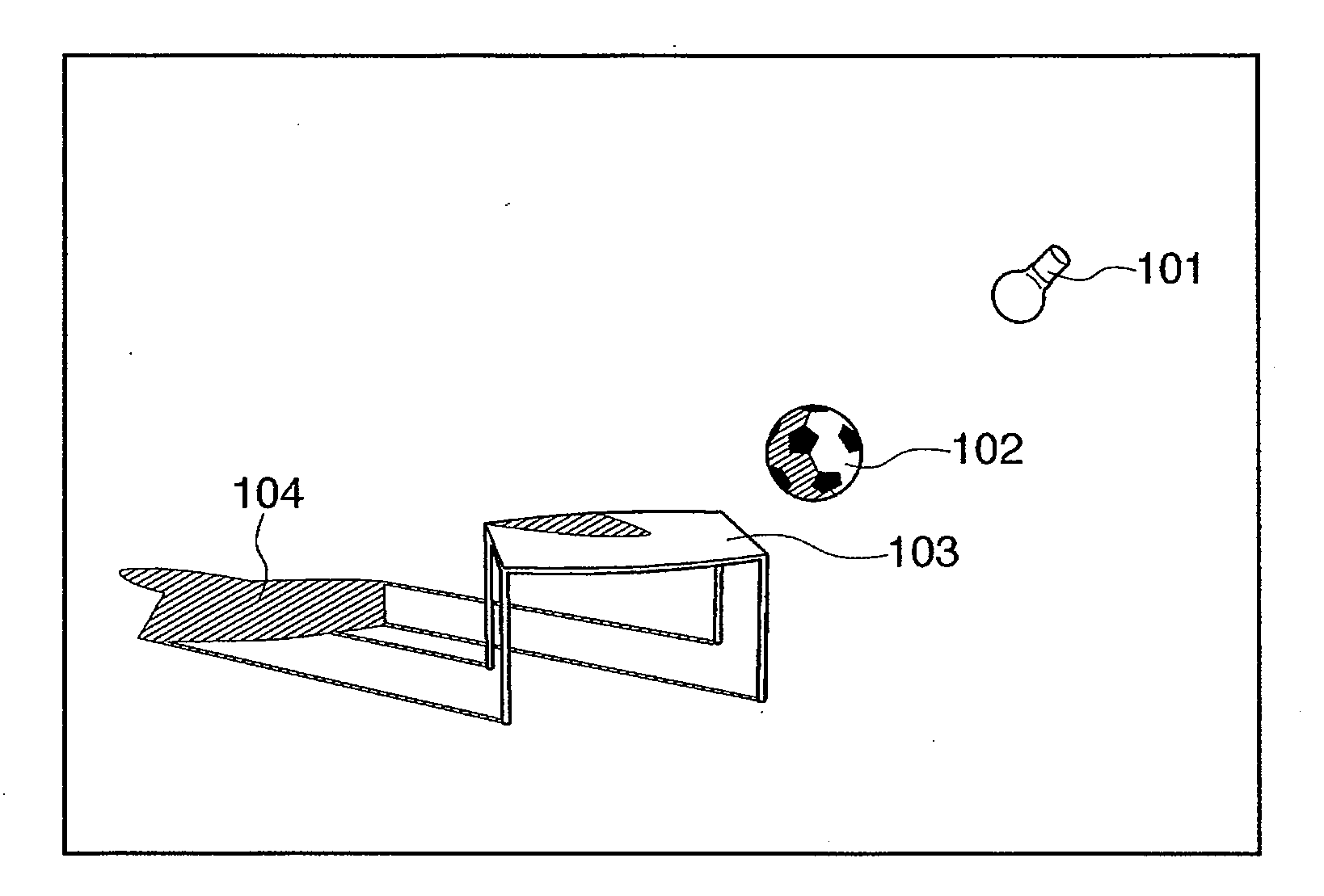

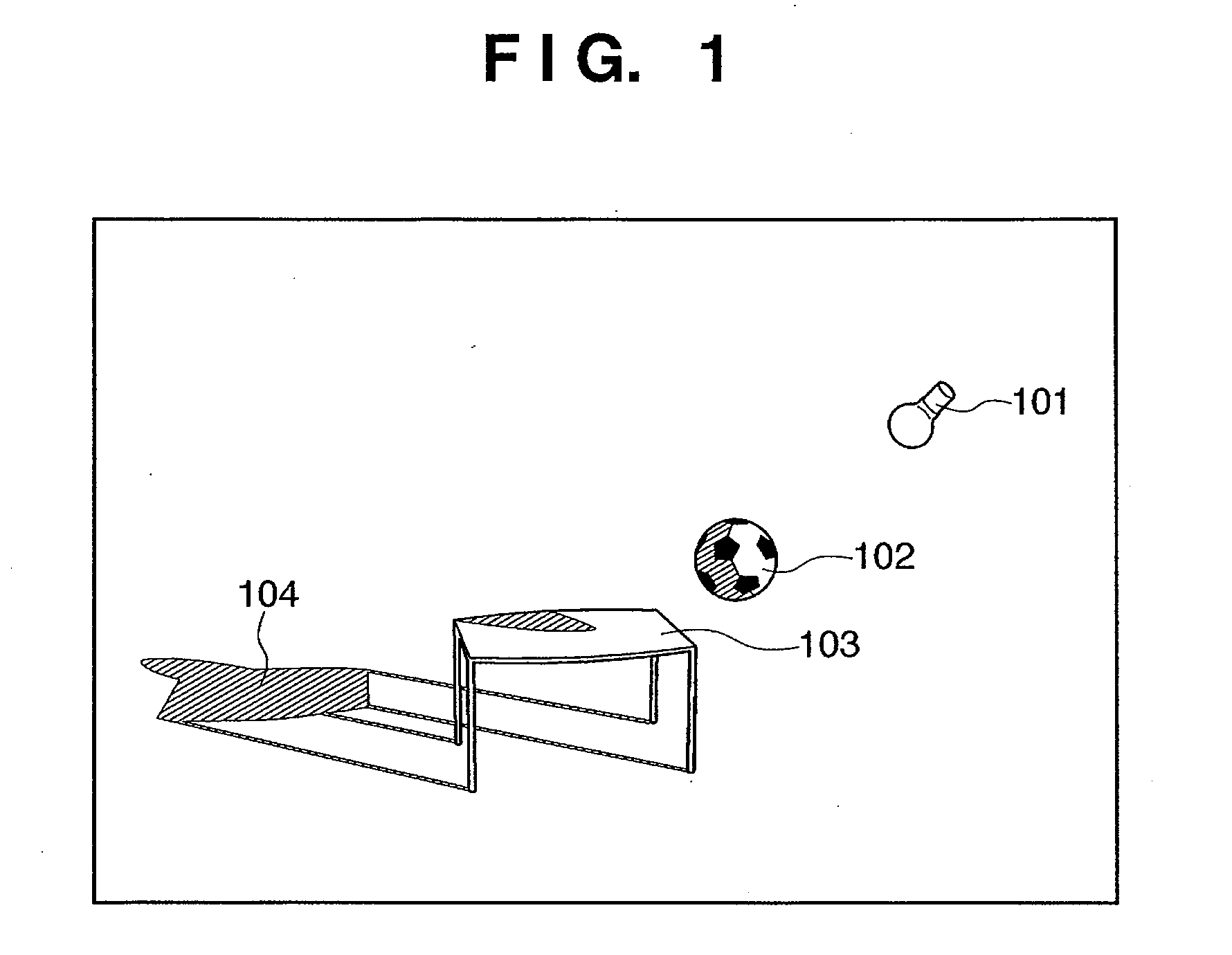

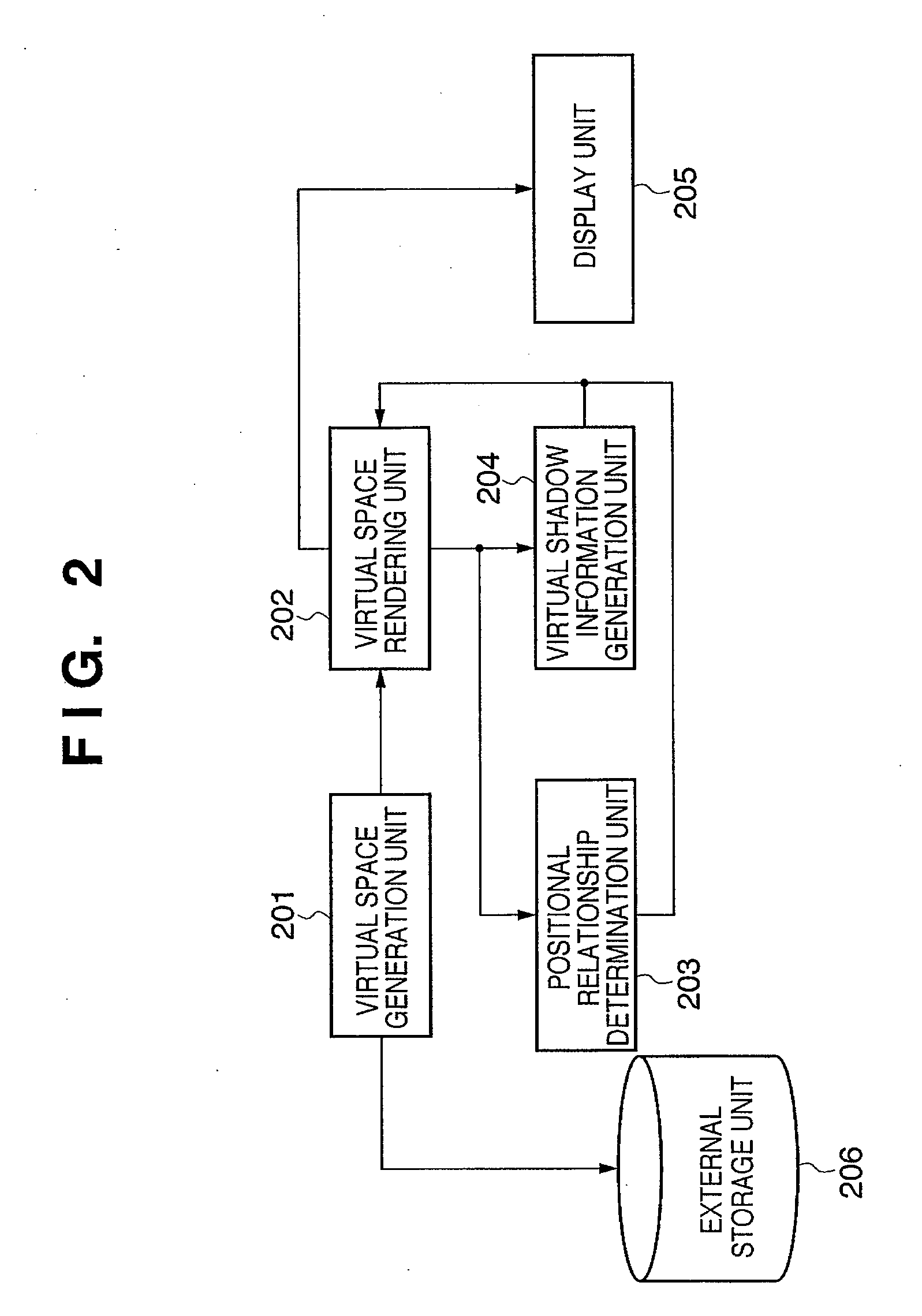

Image processing apparatus and method of controlling operation of same

ActiveUS20080231631A1Increase speedHigh-speed execution3D-image rendering3D modellingImaging processingComputer graphics (images)

In an image processing method of determining the positional relationship among virtual objects in virtual space and generating a virtual shadow of the virtual objects, a plurality of virtual objects are rendered in a first plane to which a first axis passing through a virtual light source is normal, and the positional relationship among the plurality of virtual objects is determined based upon the result of rendering acquired. Shadow information of the plurality of virtual objects is generated using the result of acquired rendering.

Owner:CANON KK

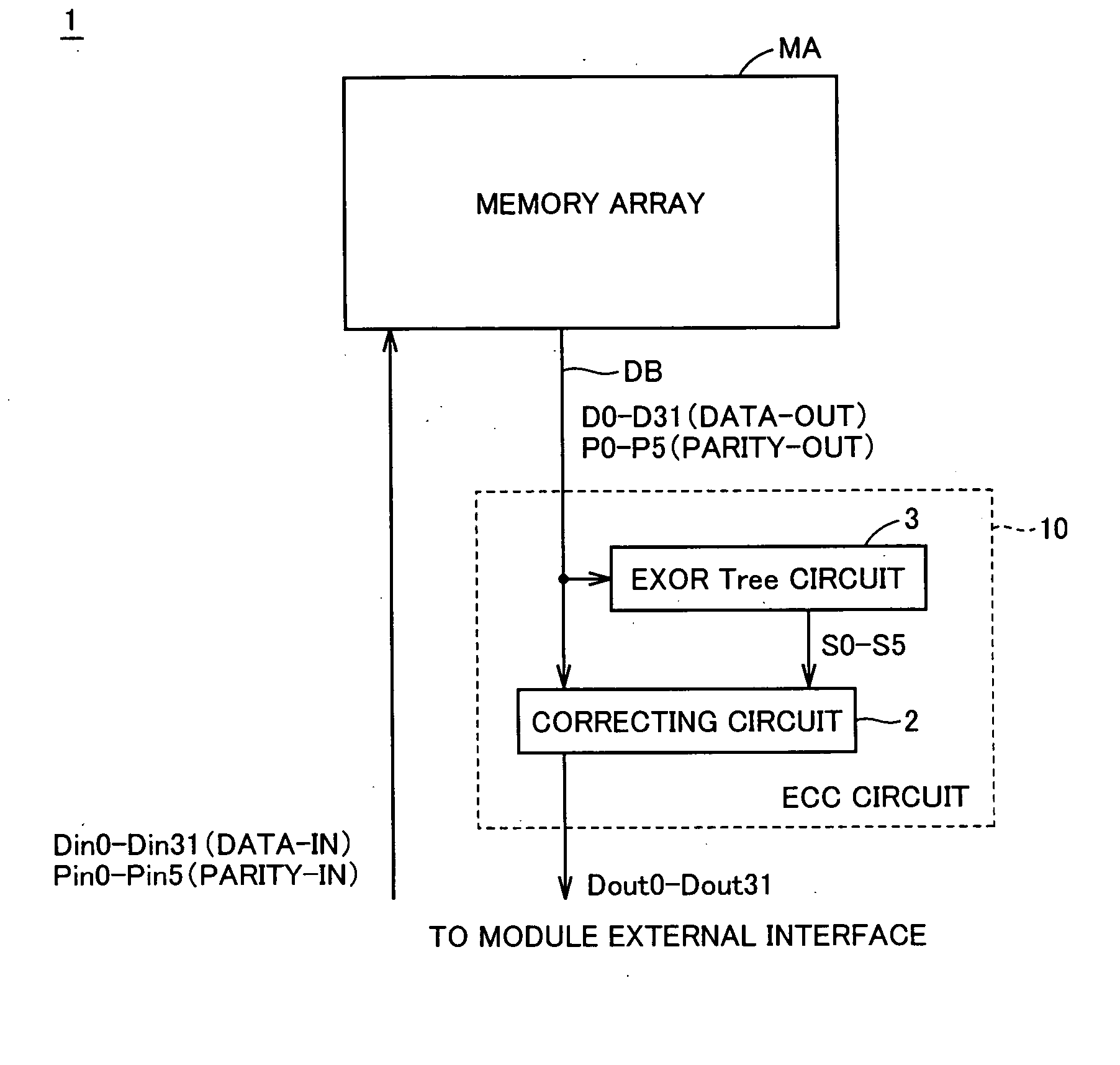

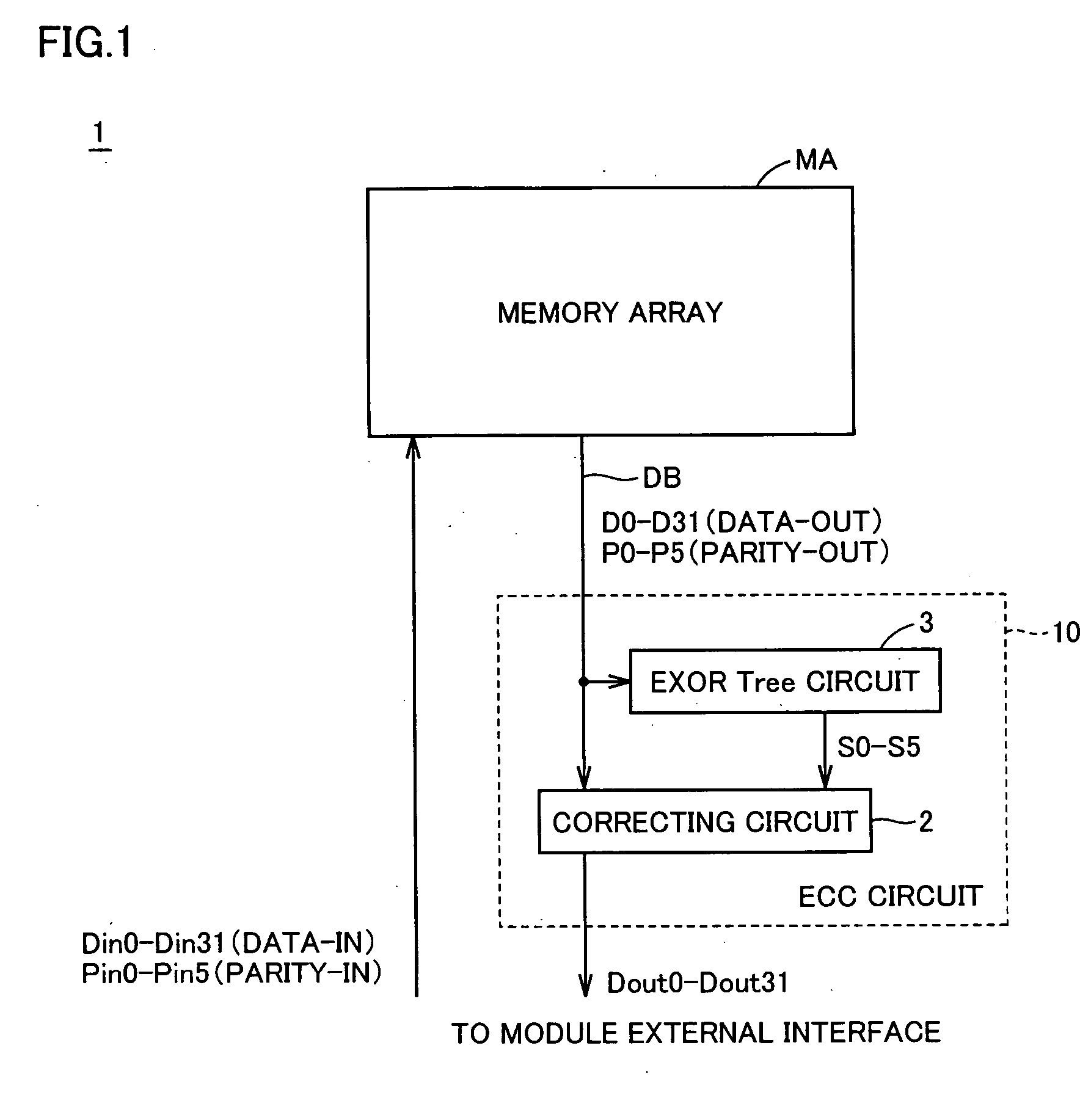

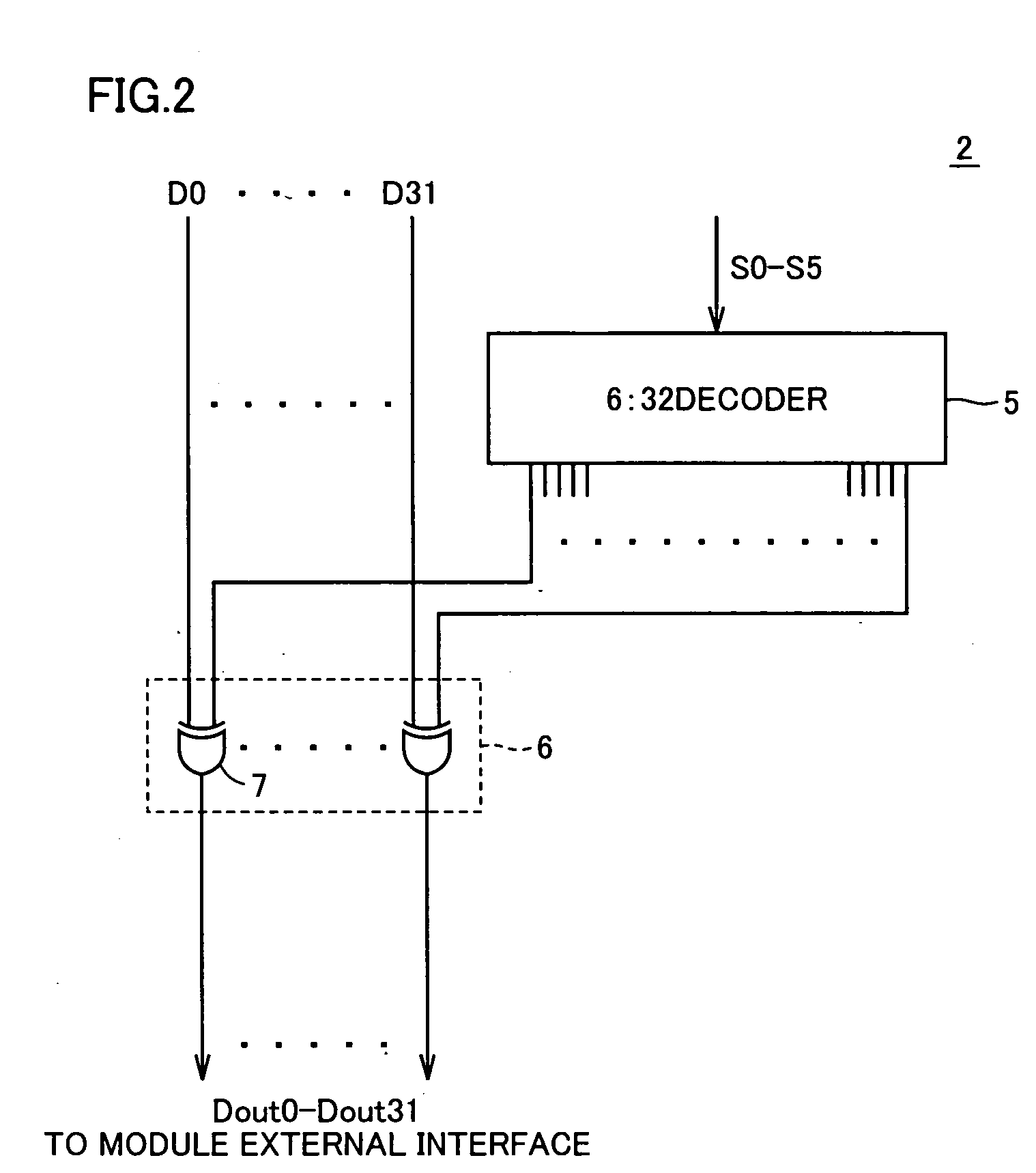

Semiconductor device improving error correction processing rate

ActiveUS20050289441A1Improving error correction processing rateReduce areaError detection/correctionCode conversionExclusive orP channel

In an exclusive OR circuit (XOR gate) constituting an ECC circuit, the drivability of P channel MOS transistors is set larger than the drivability of N channel MOS transistors. Accordingly, the speed of the logic level of an output node being set to an H level from an L level identified as a reset state is increased than the case where the drivability is set equal. Thus, the time required to output a syndrome from a plurality of stages of XOR gates can be reduced to allow execution of error correction processing at high speed.

Owner:RENESAS ELECTRONICS CORP

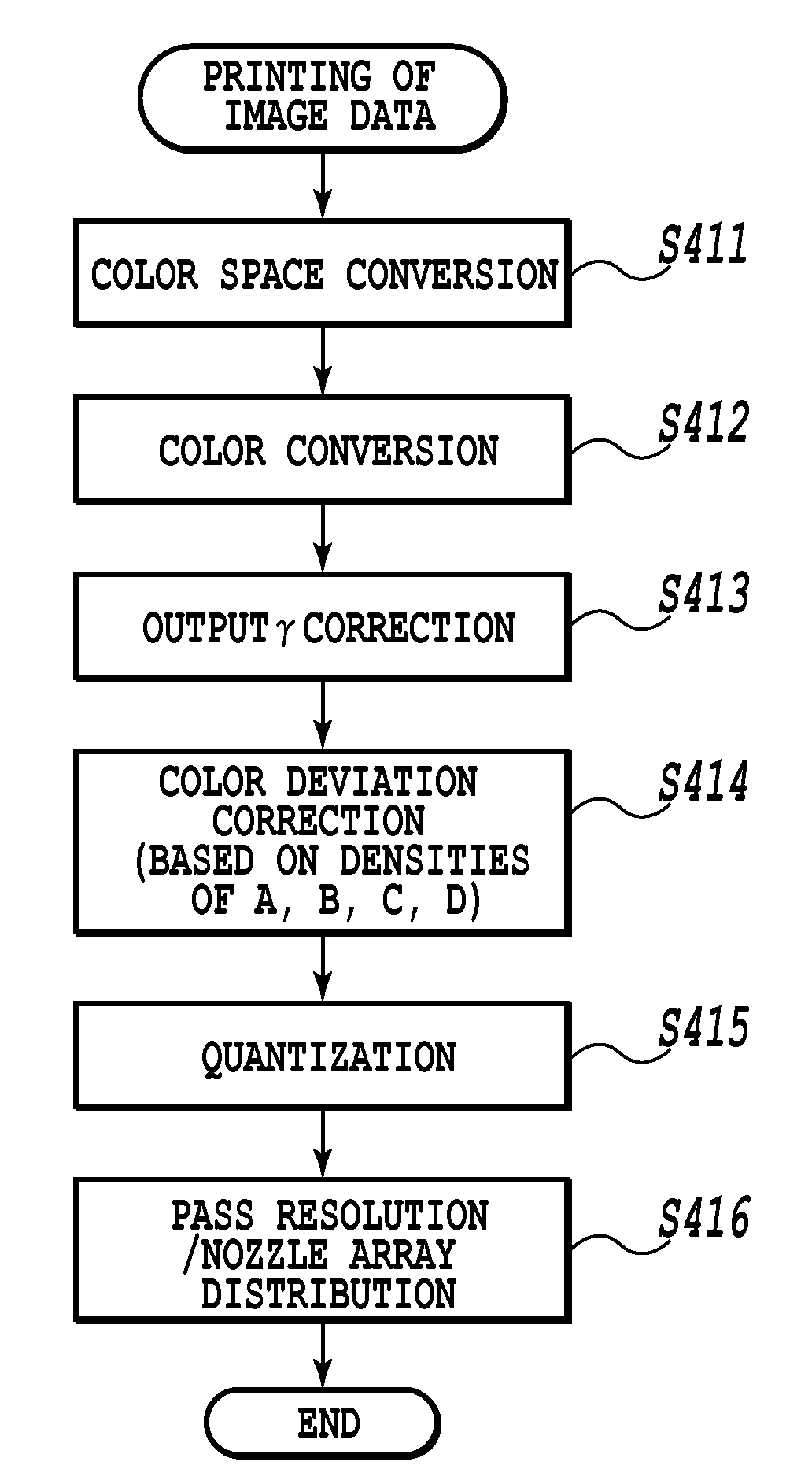

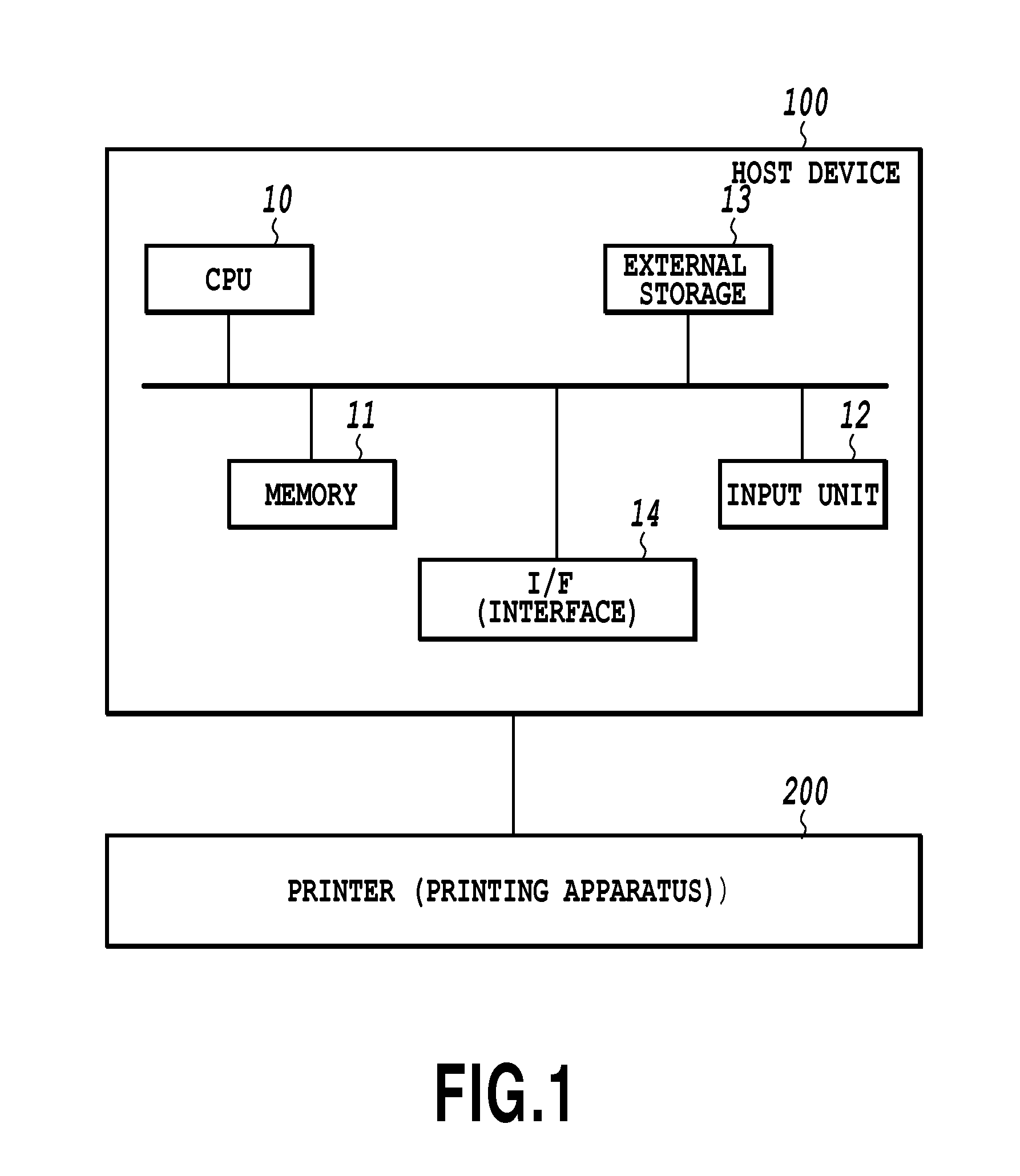

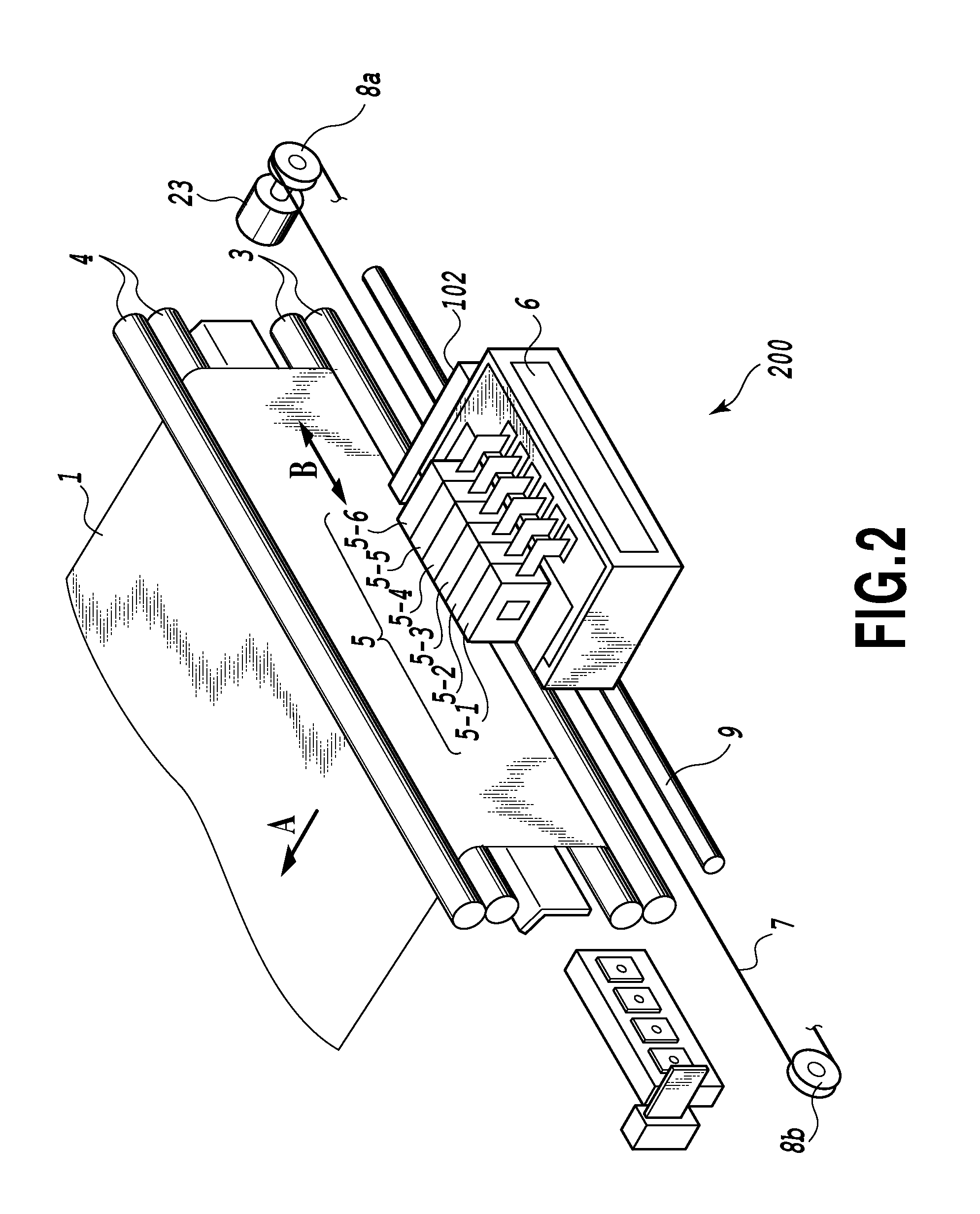

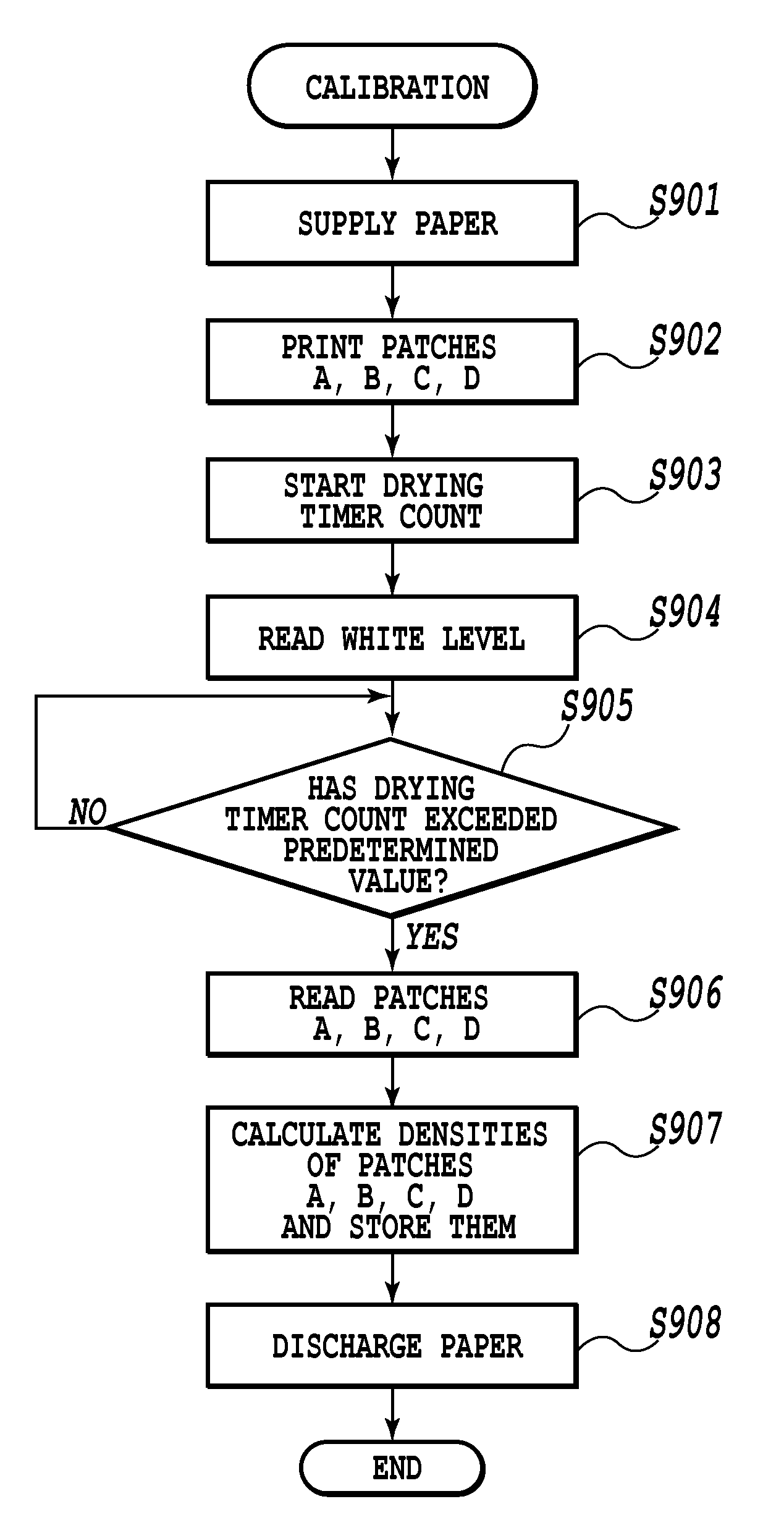

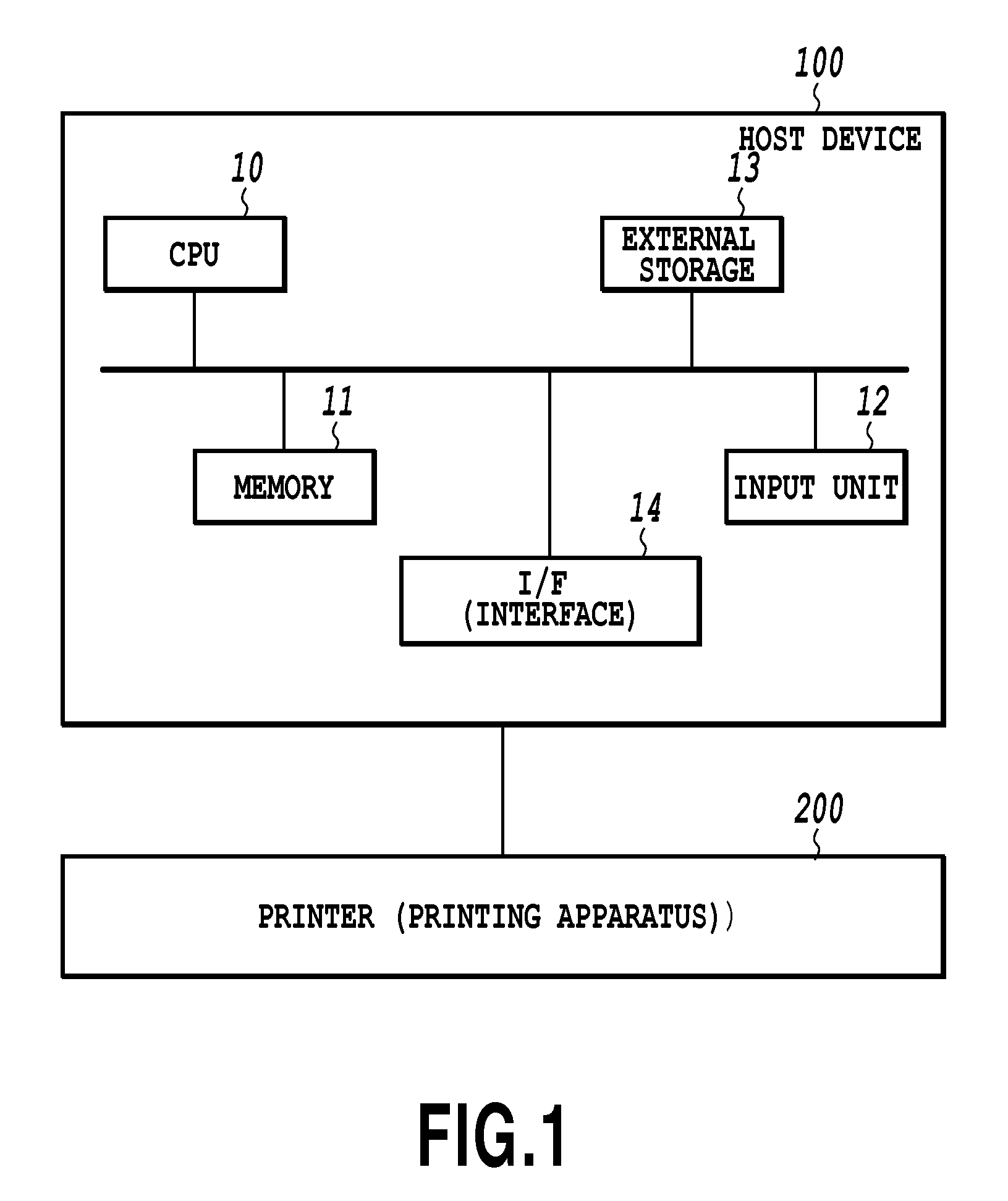

Printing apparatus and calibration method

A printing apparatus and a calibration method are provided which, by using a small-capacity memory, can perform a high-speed calibration processing on data used to eject ink of the same color from a plurality of nozzle arrays. By ejecting ink of the same color from the plurality of nozzle arrays, patch is printed and, based on the printed result of the patch, a content of a print data correction processing is changed.

Owner:CANON KK

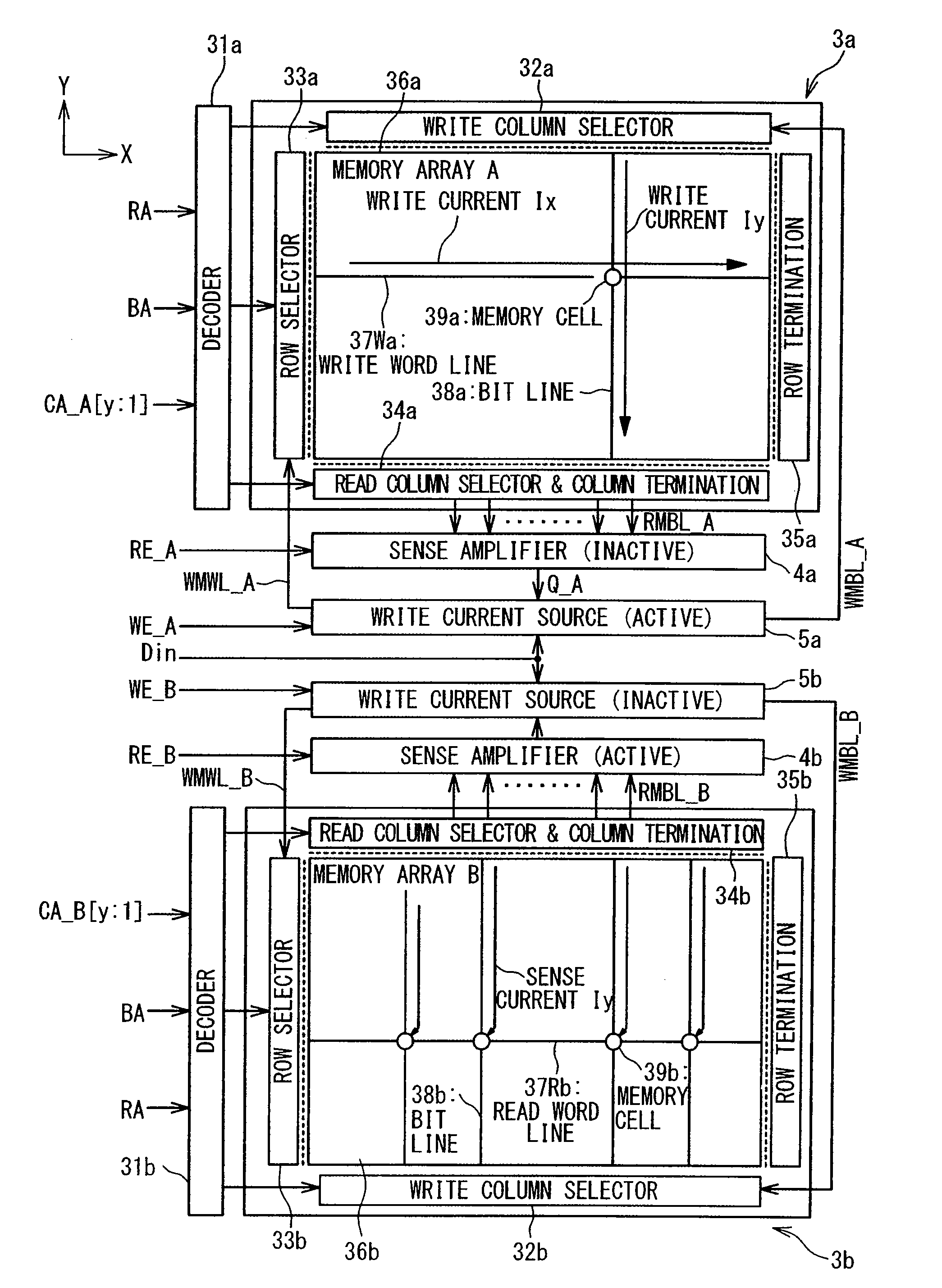

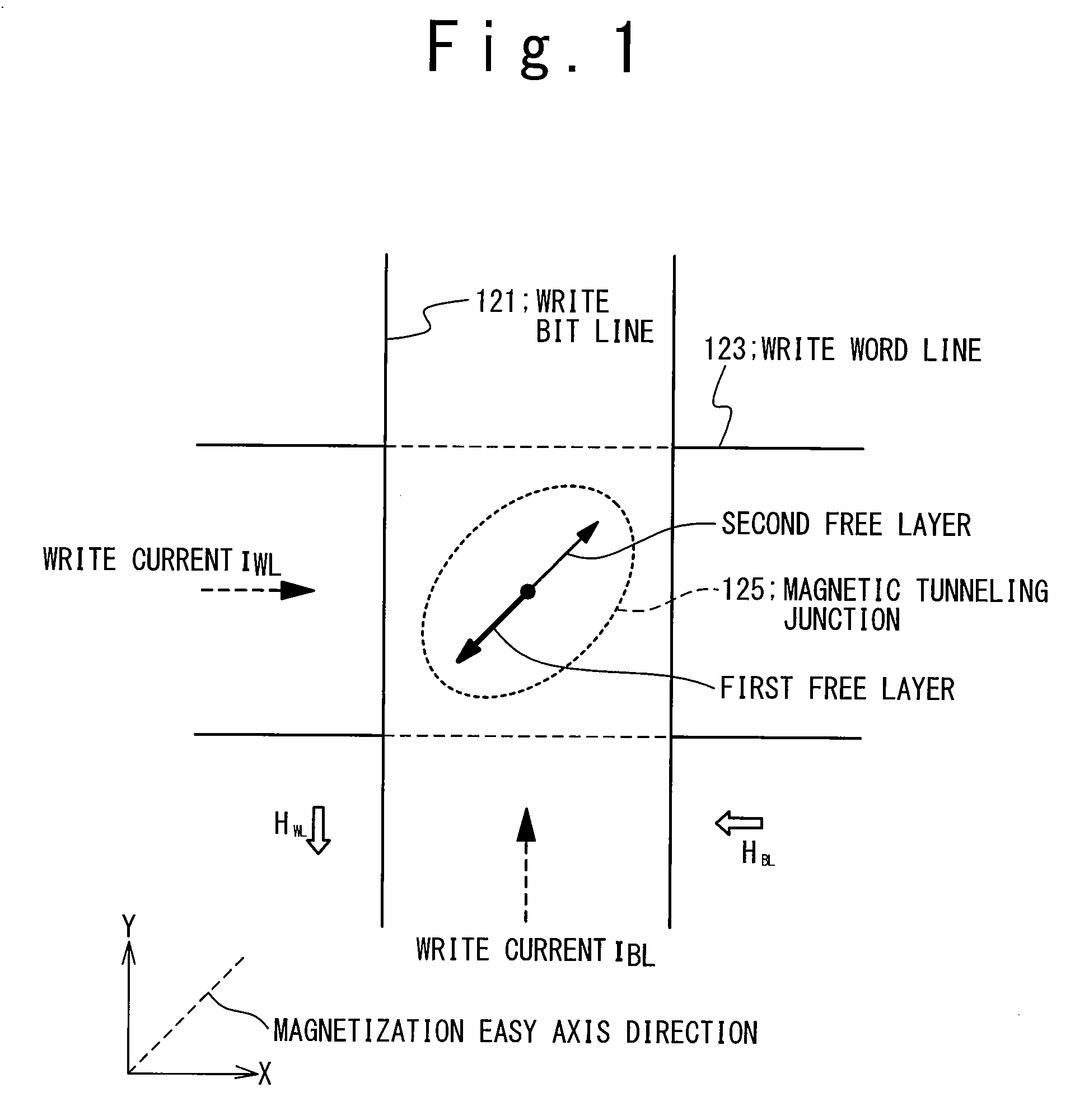

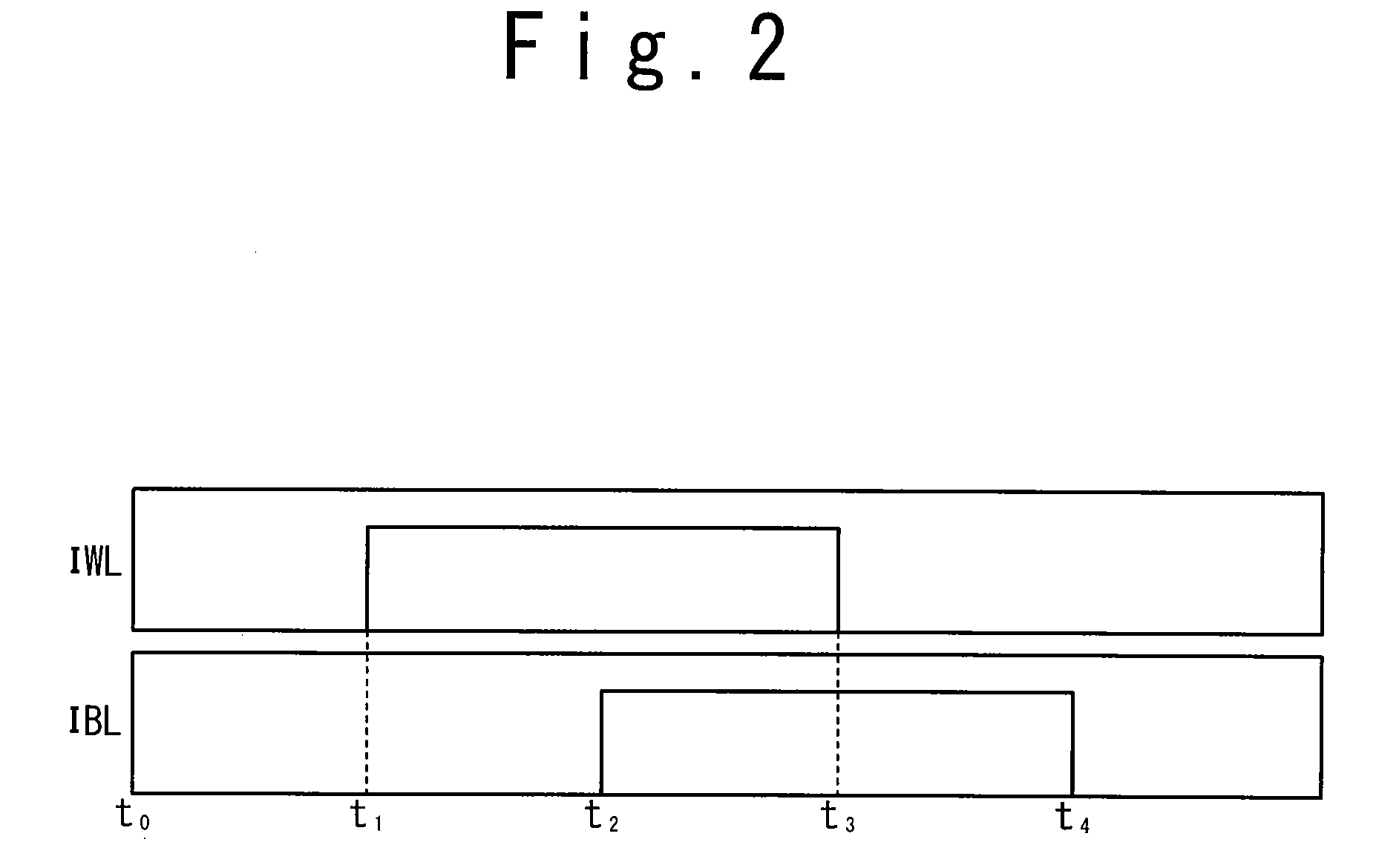

Toggle Magnetic Random Access Memory and Write Method of Toggle Magnetic Random Access Memory

ActiveUS20090010044A1Increase speedIncrease the areaDigital storageStatic random-access memoryRandom access memory

A toggle magnetic random access memory includes a first memory array, a second memory array and a controller. The first memory array includes a plurality of first memory cells including magnetoresistive elements. The second memory array includes a plurality of second memory cells including magnetoresistive elements and differs from the first memory array in write wirings used for writing. The controller controls the first memory array and the second memory array such that a first state in which a first burst write operation in the first memory array is executed and a second state in which a second burst write operation in the second memory array is executed are alternately executed in a continuous burst write mode. Accordingly, the continuous burst write operation can be executed at the high speed without any drop in the reliability and any increase in the circuit area.

Owner:NEC CORP

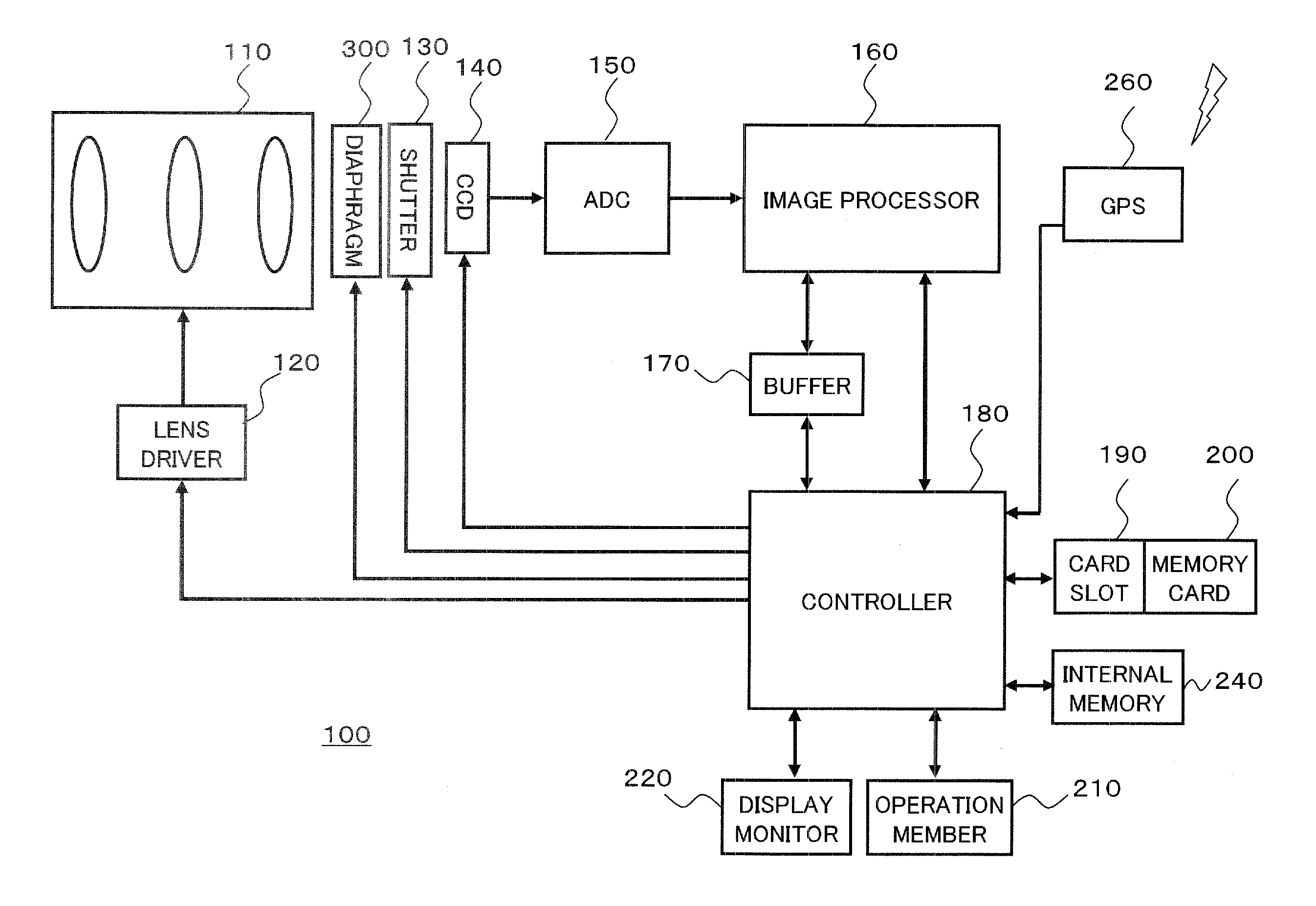

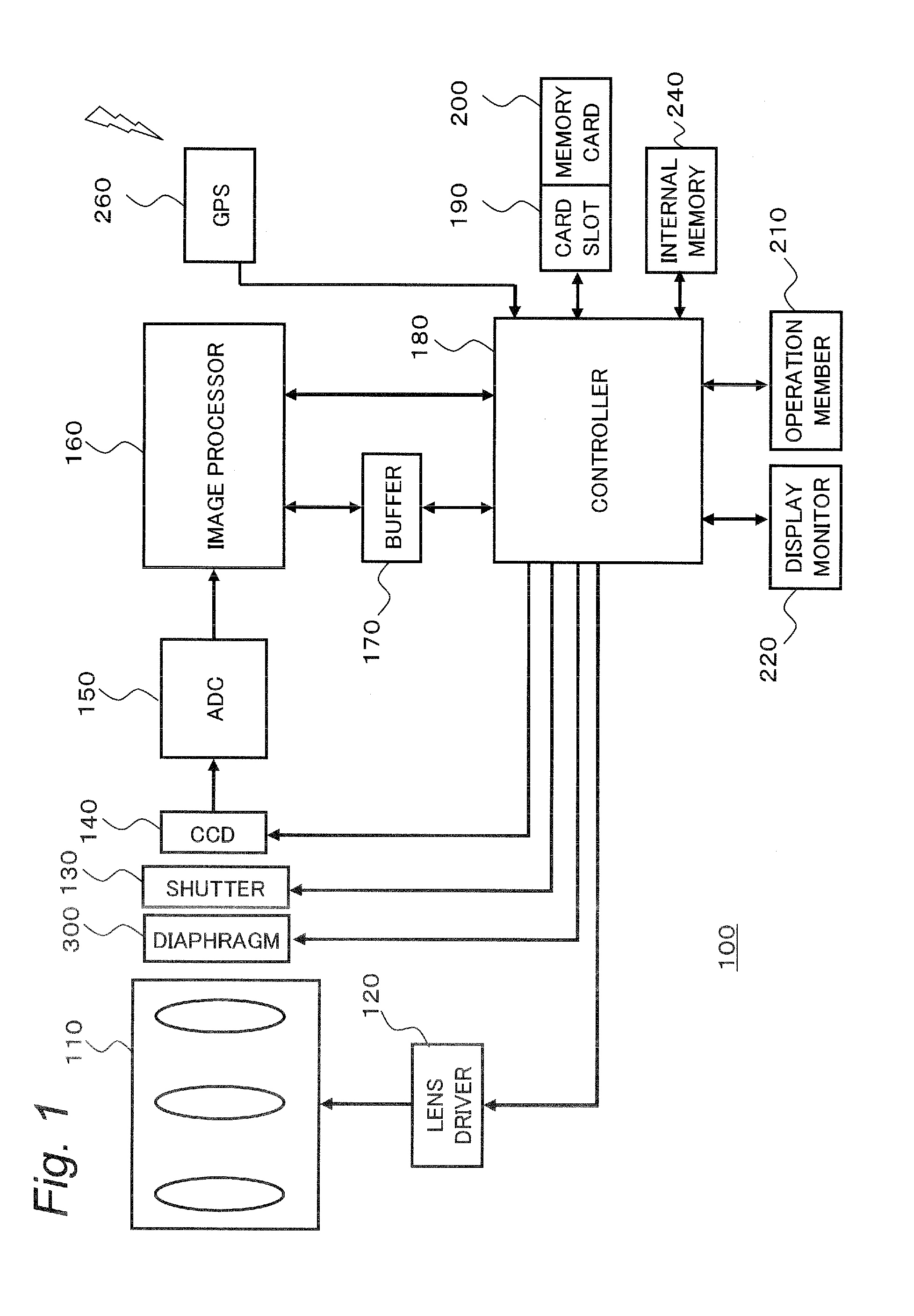

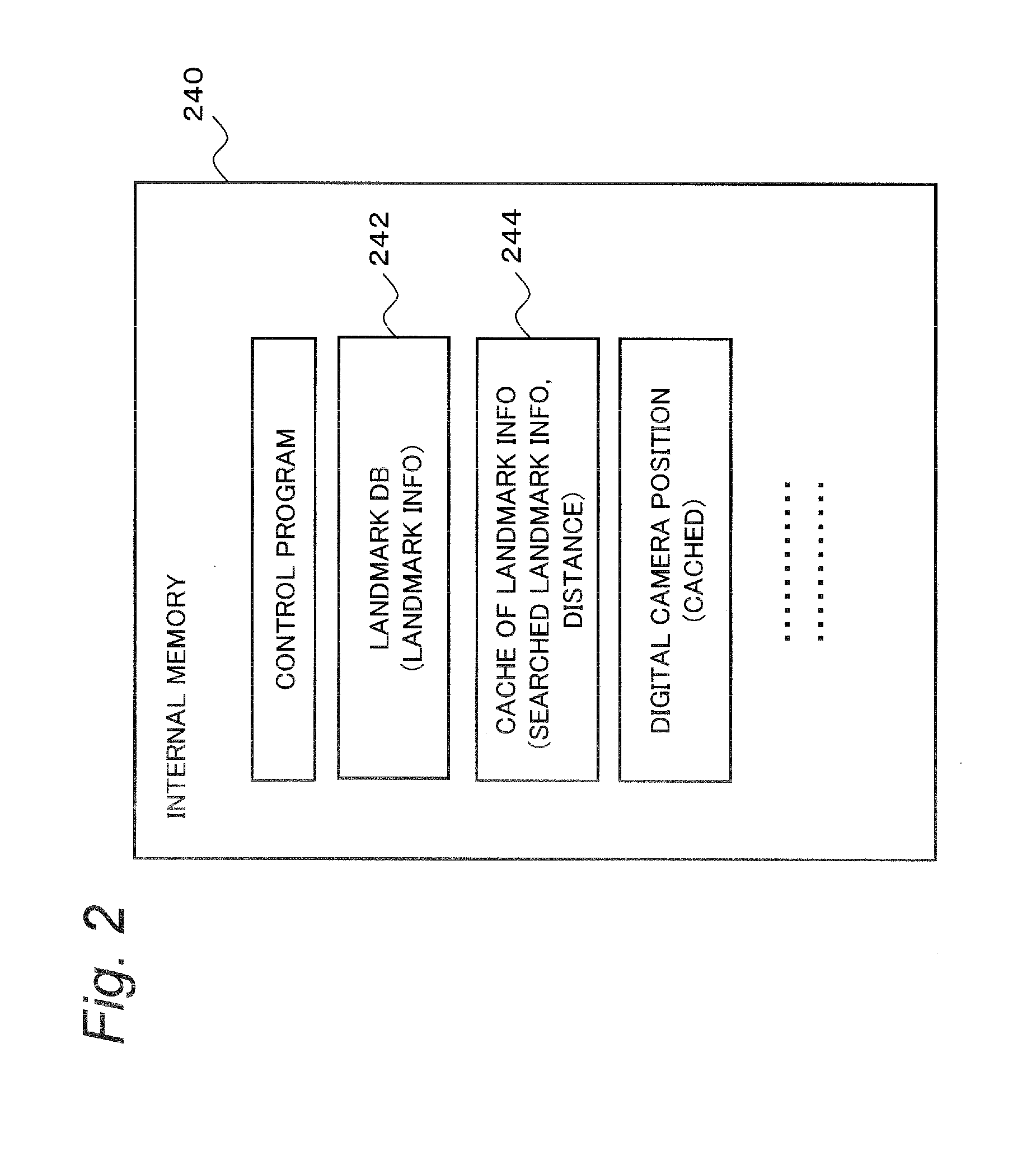

Landmark search apparatus, electronic apparatus and imaging apparatus having the same, and landmark search method

InactiveUS20110213798A1Increase speedExact searchDigital data processing detailsMetadata still image retrievalImaging equipmentStorage cell

A landmark search apparatus includes a position obtaining unit configured to obtain a current position of the object, a first storage unit configured to store landmark information including a name of a landmark and position information of the landmark related to the name, an retrieving unit configured to retrieve the landmark information from the first storage unit based on the obtained current position, a second storage unit configured to store the retrieved landmark information as retrieved landmark information, and a determining unit configured to determine whether the retrieved landmark information is valid, based on the current position of the object, and a distance between a position of the subject at the time of storing the retrieved landmark information in the second storage unit and the landmark indicated by the retrieved landmark information.

Owner:IMAGE PROCESSING TECH

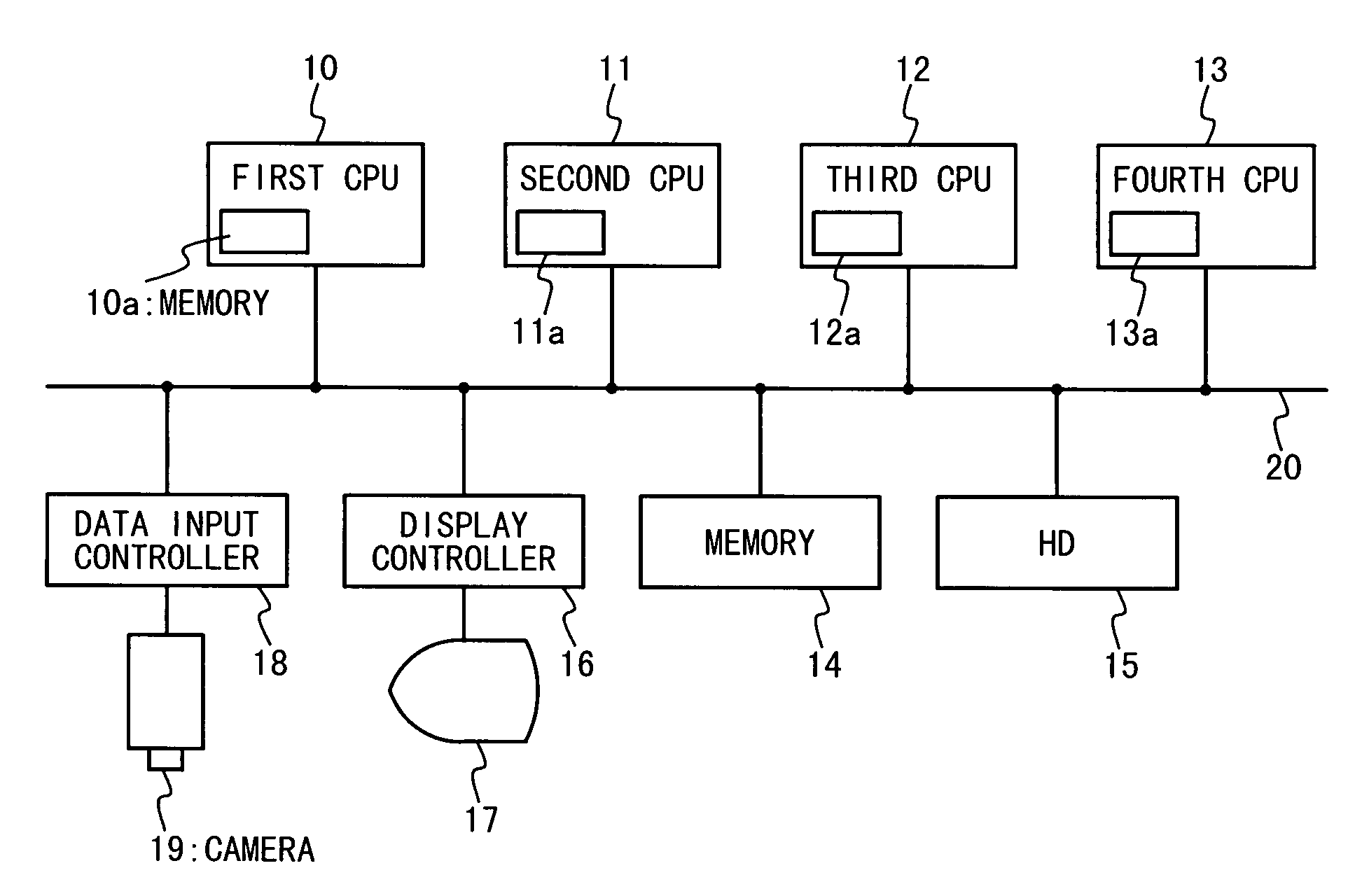

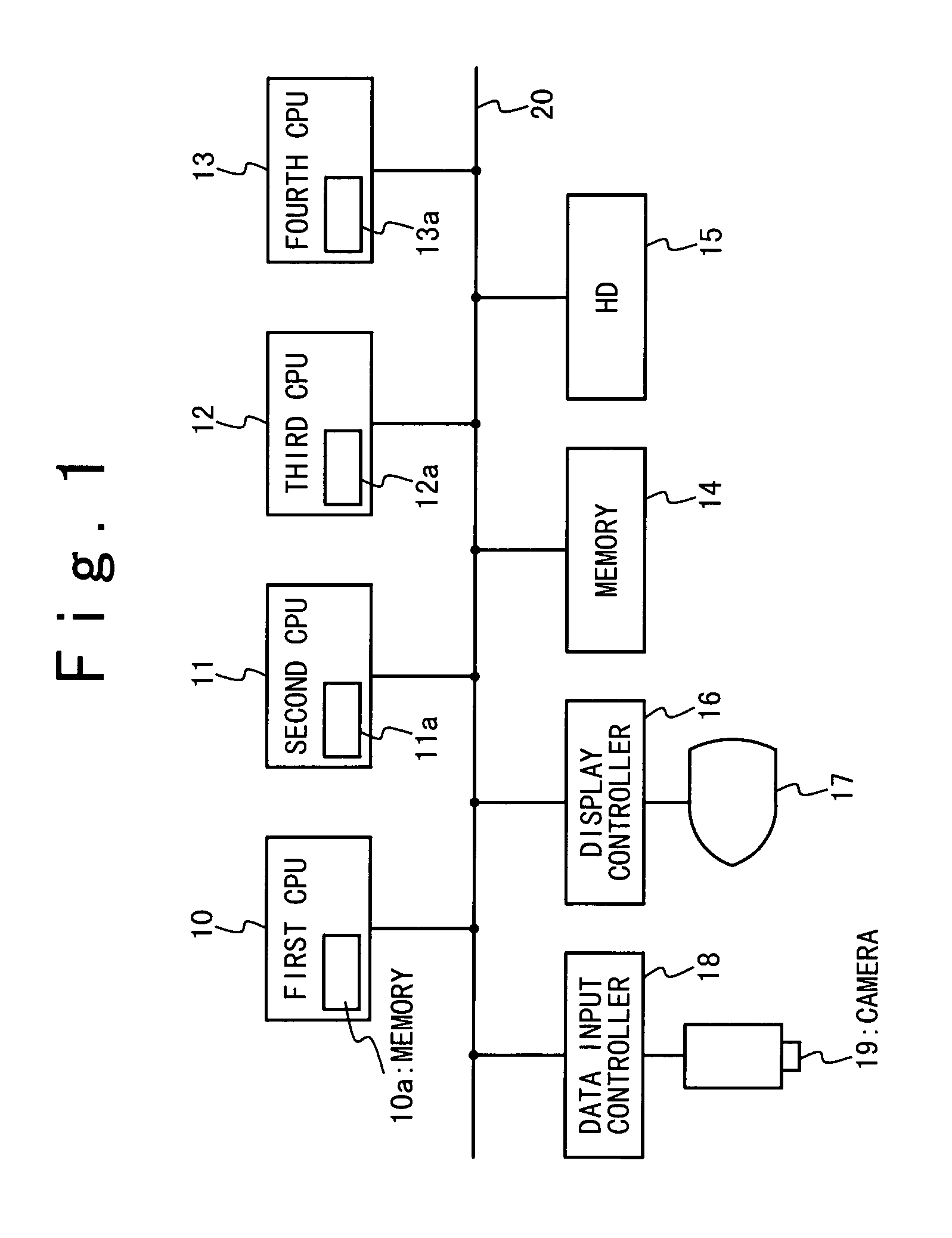

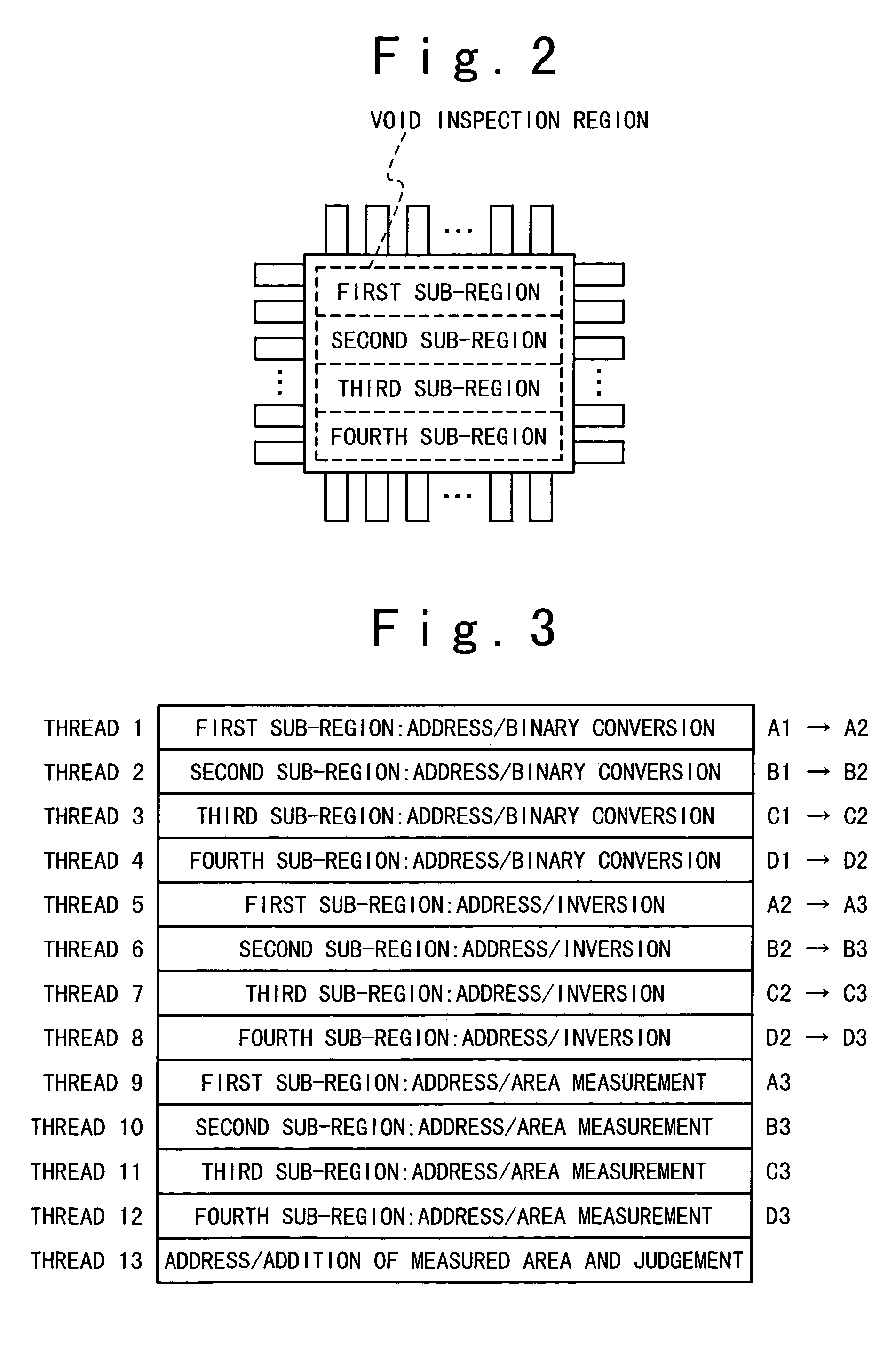

Appearance inspection apparatus and method in which plural threads are processed in parallel

InactiveUS6987894B2Simple configurationIncrease speedDigital circuit testingSemiconductor/solid-state device testing/measurementParallel processingHigh velocity

An appearance inspection apparatus is composed of a memory 14, a thread generator and a plurality of CPUs 10 to 13. The memory 14 stores image data of an appearance of an IC. The thread generator generates a thread in which a procedure is described for independently processing the image data stored in the memory 14 and storing the processing result into the memory 14. The plurality of CPUs 10 to 13 for executing the plurality of threads generated by the thread generator, in parallel. Thus, this can provide an appearance inspection apparatus and an appearance inspection method that can execute an appearance inspection at a high speed, irrespectively of a simple configuration.

Owner:RENESAS ELECTRONICS CORP

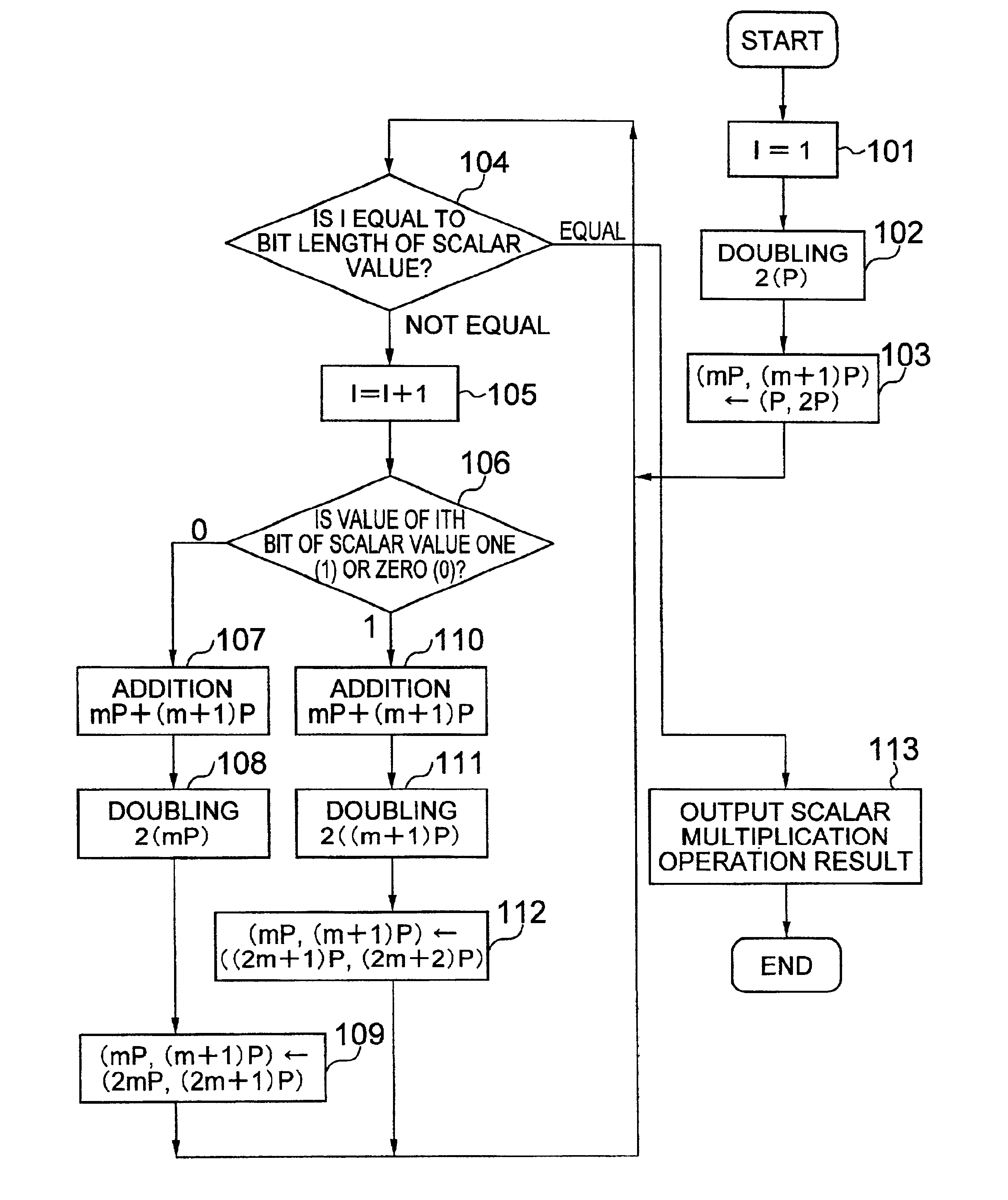

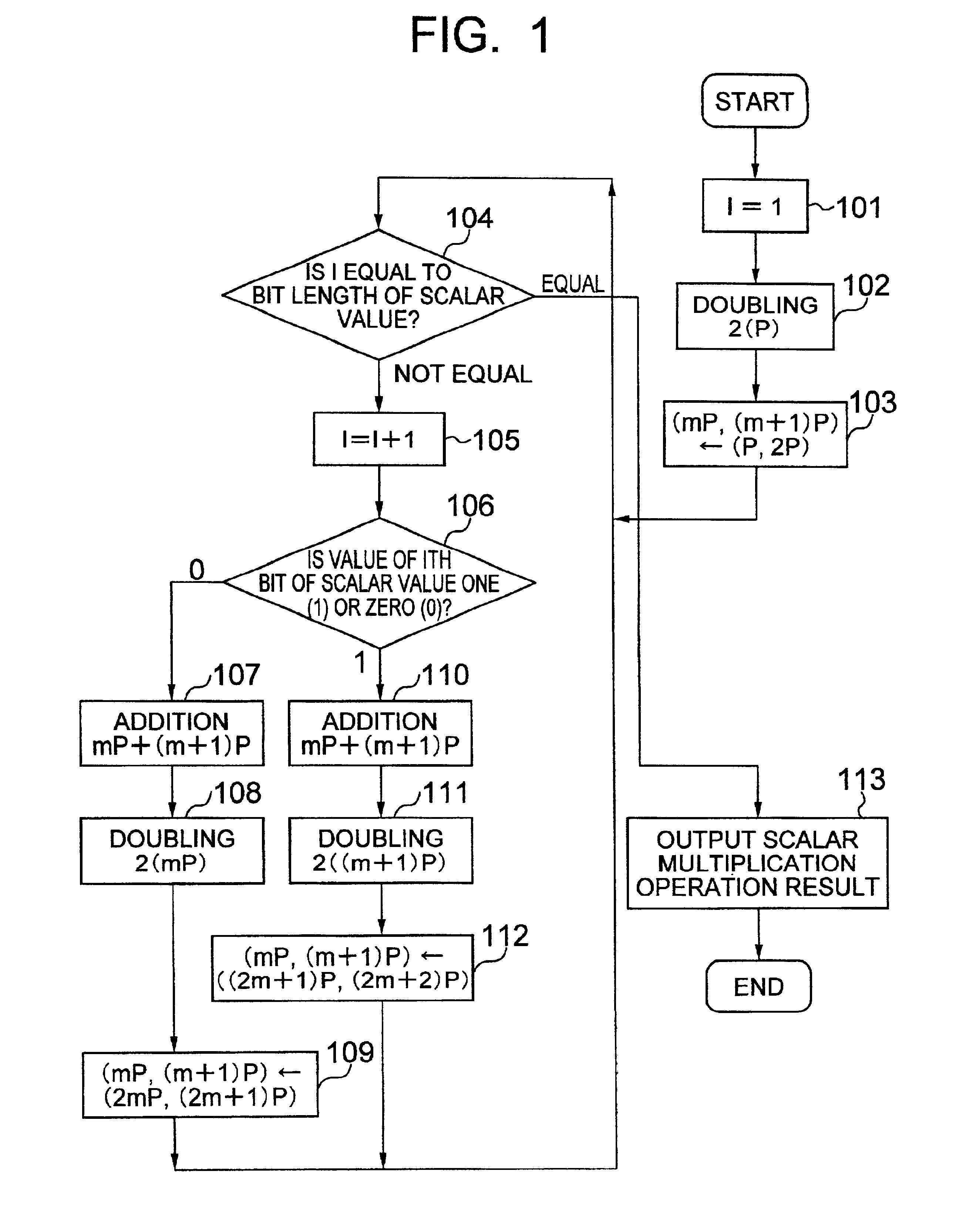

Method of calculating multiplication by scalars on an elliptic curve and apparatus using same and recording medium

InactiveUS7046801B2Increase speedCryptographic processing can be made in speedSecret communicationComputations using residue arithmeticComputer hardwareScalar Value

A cryptographic processing method in which dependence of cryptographic processing process and secret information on each other is cut off; and in which, when a scalar multiplied point is calculated from a scalar value and a point on an elliptic curve in an elliptic curve cryptosystem, a value of a bit of the scalar value is judged; and in which operations on the elliptic curve are executed a predetermined times and in a predetermined order without depending on the judged value of the bit.

Owner:HITACHI LTD

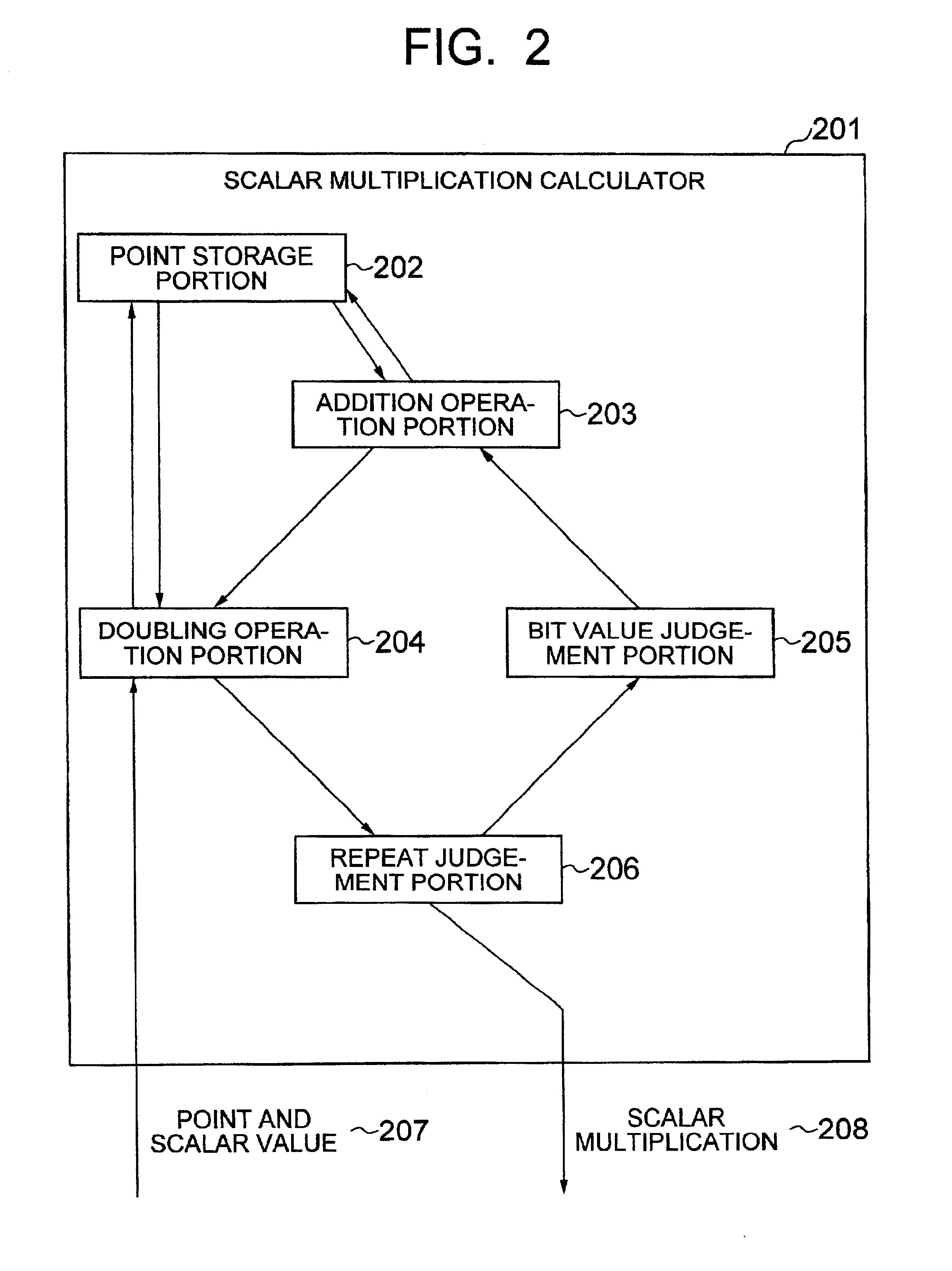

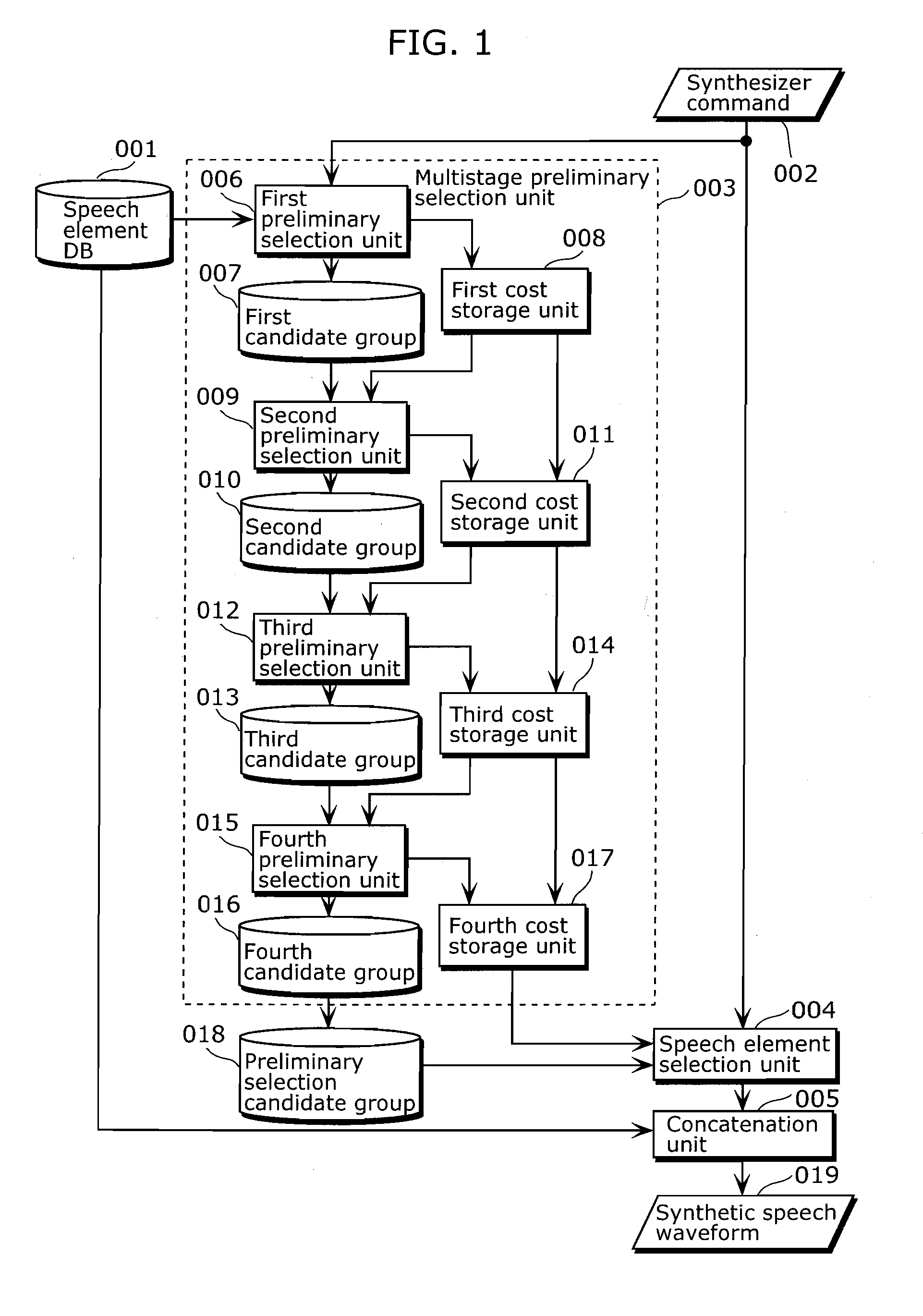

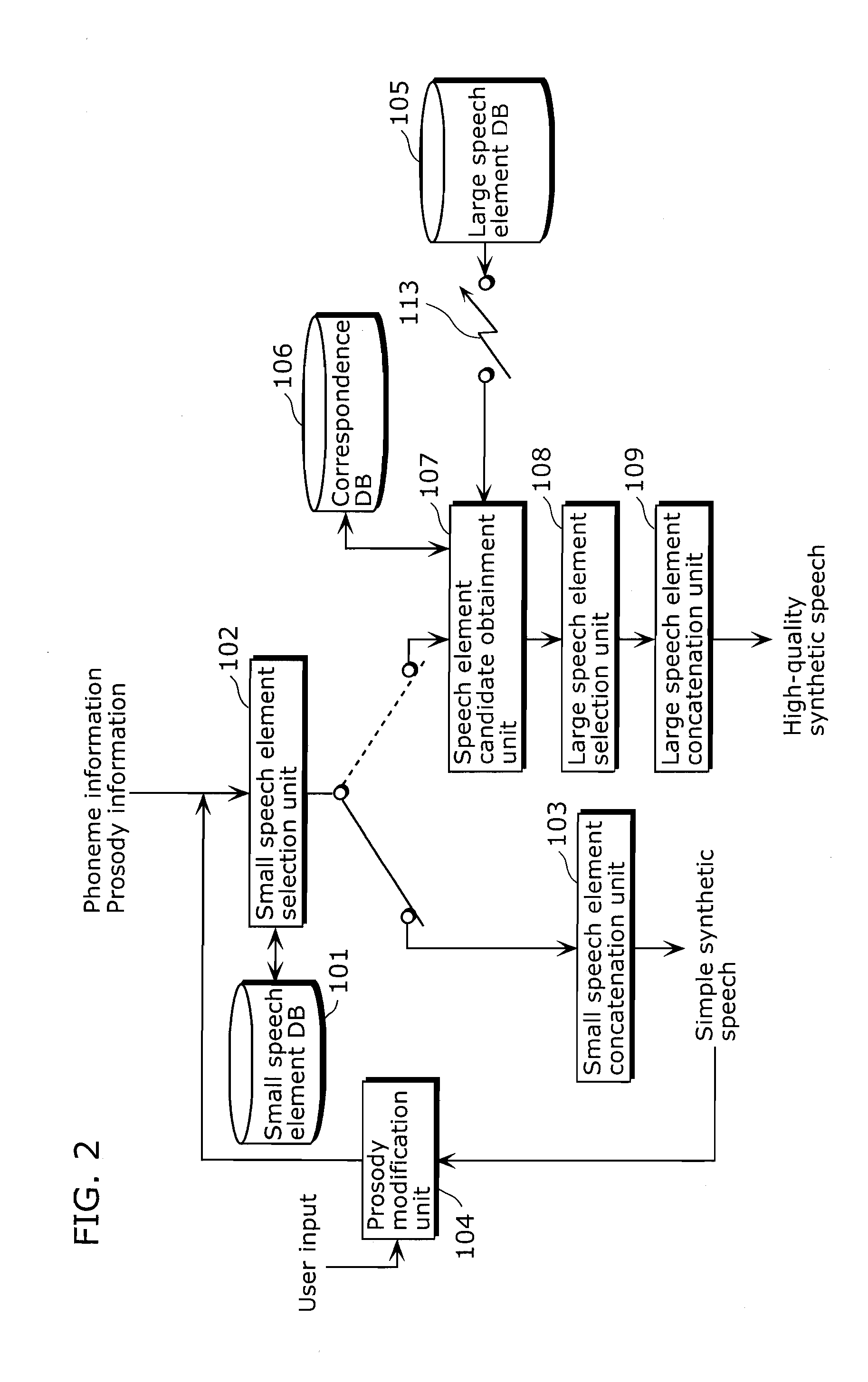

Speech synthesizer

InactiveUS20090254349A1Increase speedSimple contentSpecial data processing applicationsSpeech synthesisSpeech synthesisSpeech sound

A speech synthesizer can execute speech content editing at high speed and generate speech content easily. The speech synthesizer includes a small speech element DB (101), a small speech element selection unit (102), a small speech element concatenation unit (103), a prosody modification unit (104), a large speech element DB (105), a correspondence DB (106) that associates the small speech element DB (101) with the large speech element DB (105), a speech element candidate obtainment unit (107), a large speech element selection unit (108), and a large speech element concatenation unit (109). By editing synthetic speech using the small speech element DB (101) and performing quality enhancement on an editing result using the large speech element DB (105), speech content can be generated easily on a mobile terminal.

Owner:PANASONIC CORP

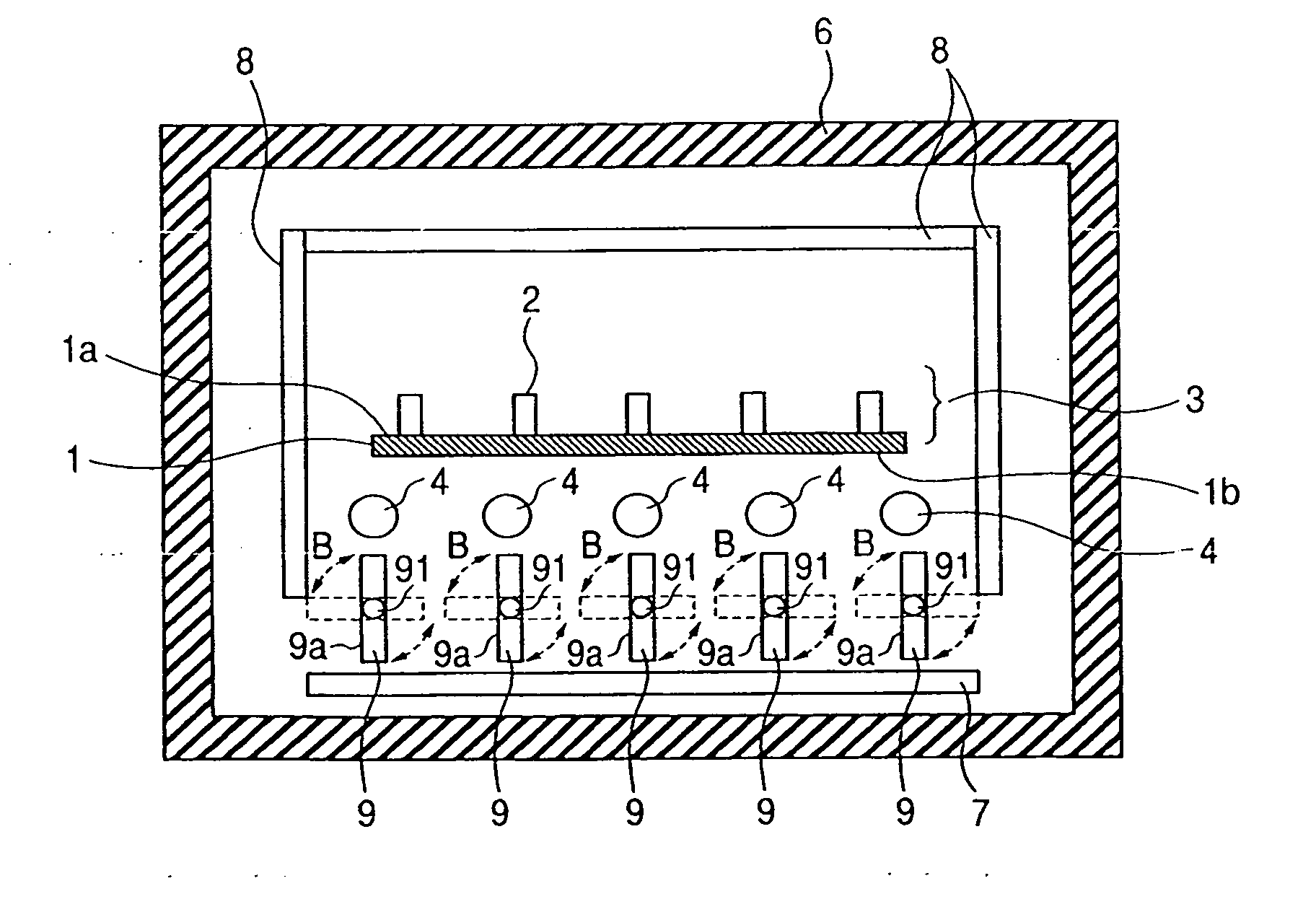

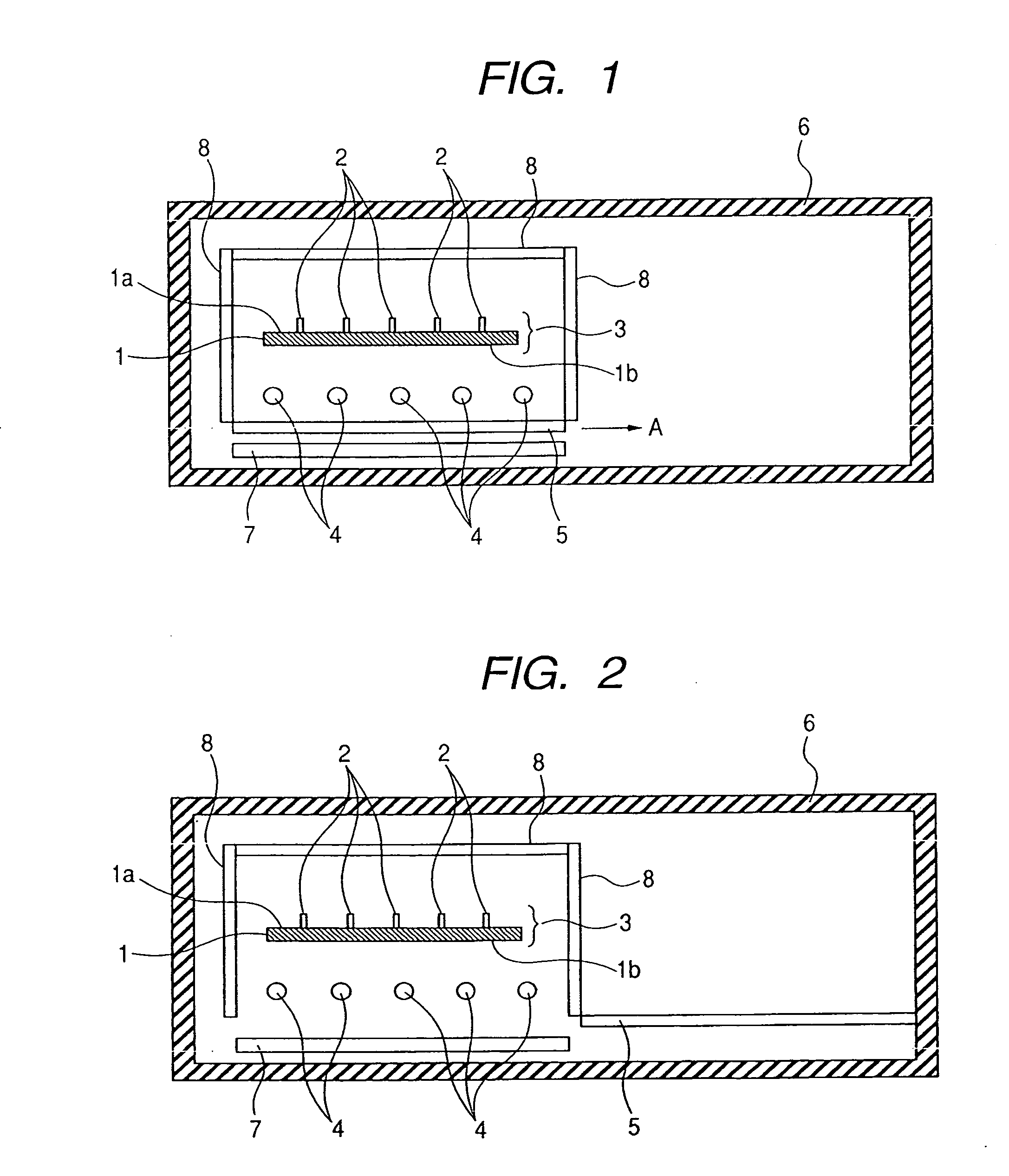

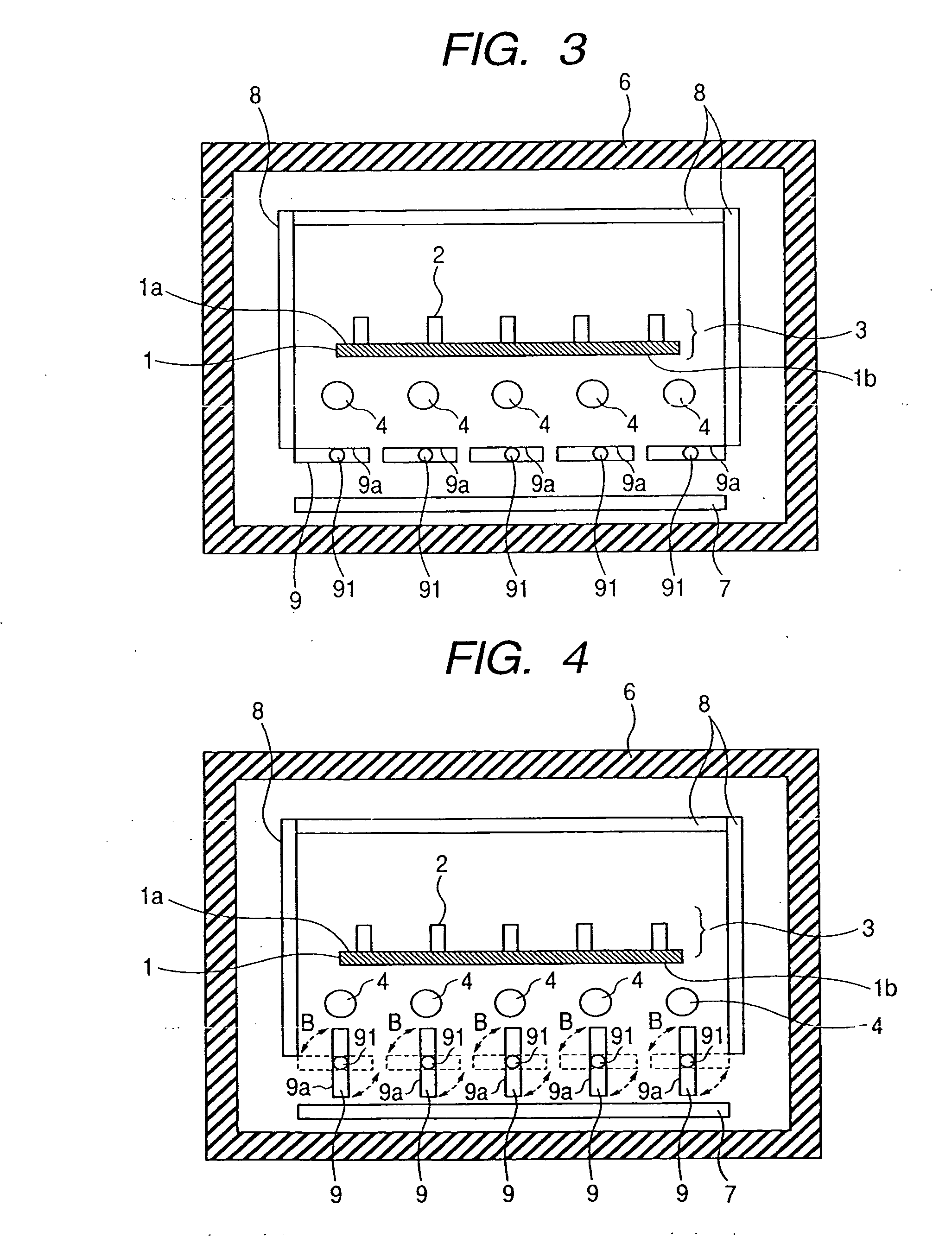

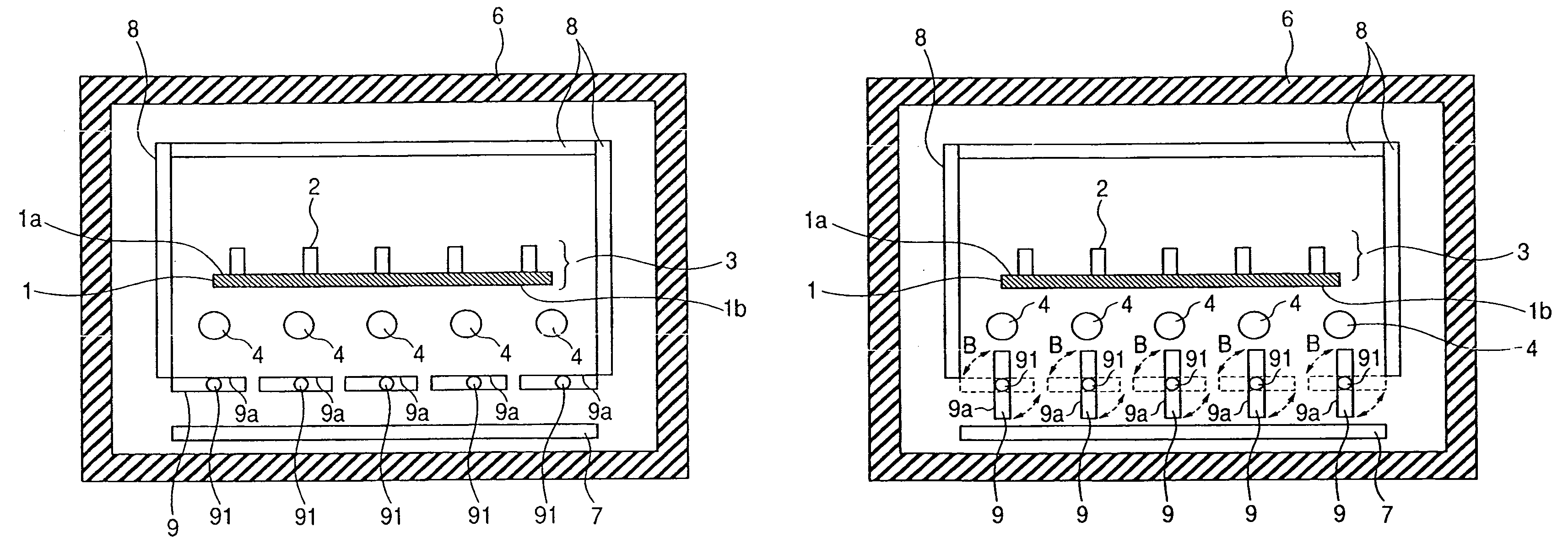

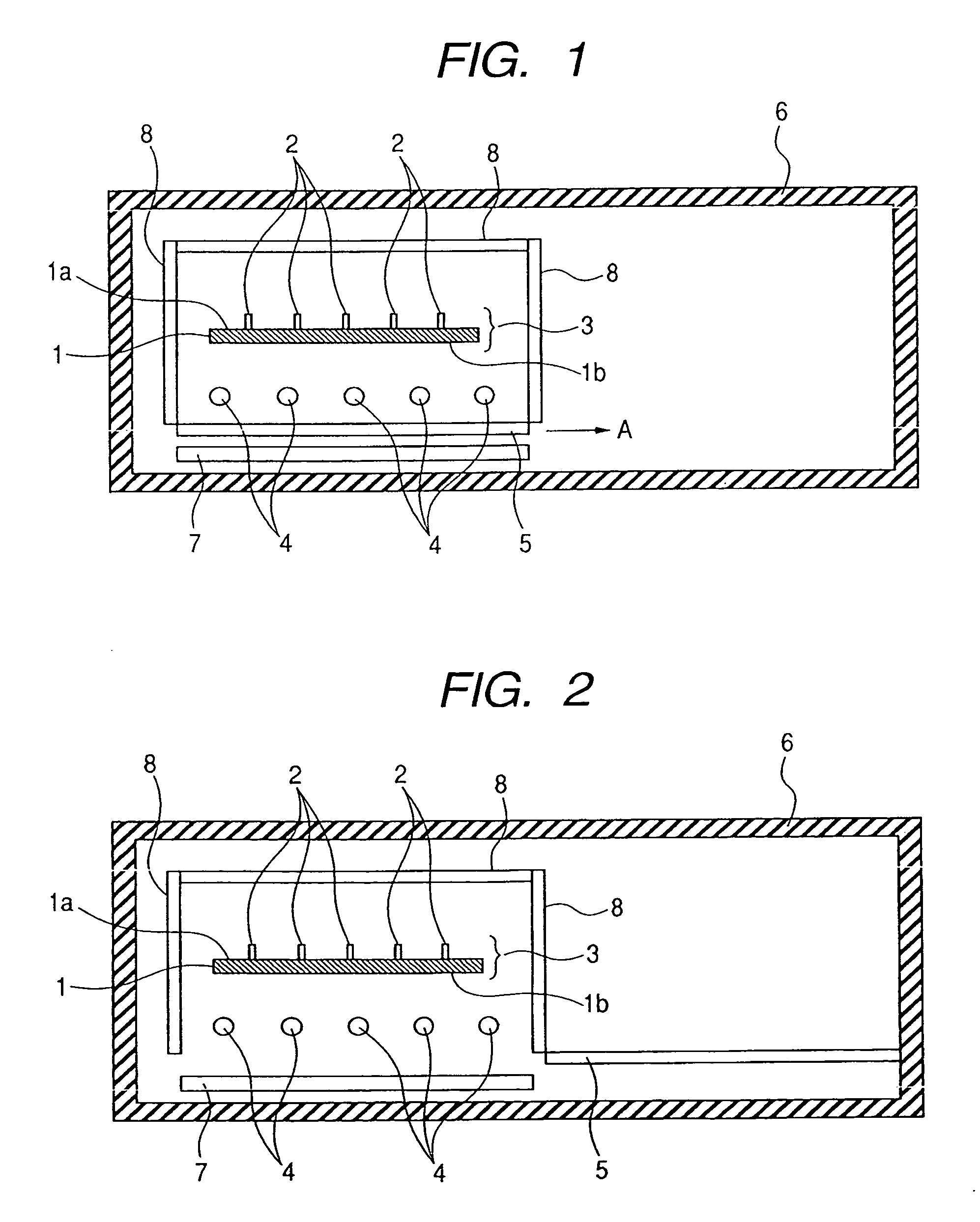

Heating/cooling method, manufacturing method of image displaying apparatus, heating/cooling apparatus, and heating/cooling processing apparatus

InactiveUS20050034850A1Increase speedHigh-speed executionBaking ovenSemiconductor/solid-state device manufacturingComputer graphics (images)Method of images

A heating / cooling method, a manufacturing method of an image displaying apparatus, a heating / cooling apparatus, and a heating / cooling processing apparatus, in which the heating and cooling of a substrate can be executed at a high speed are provided.

Owner:CANON KK

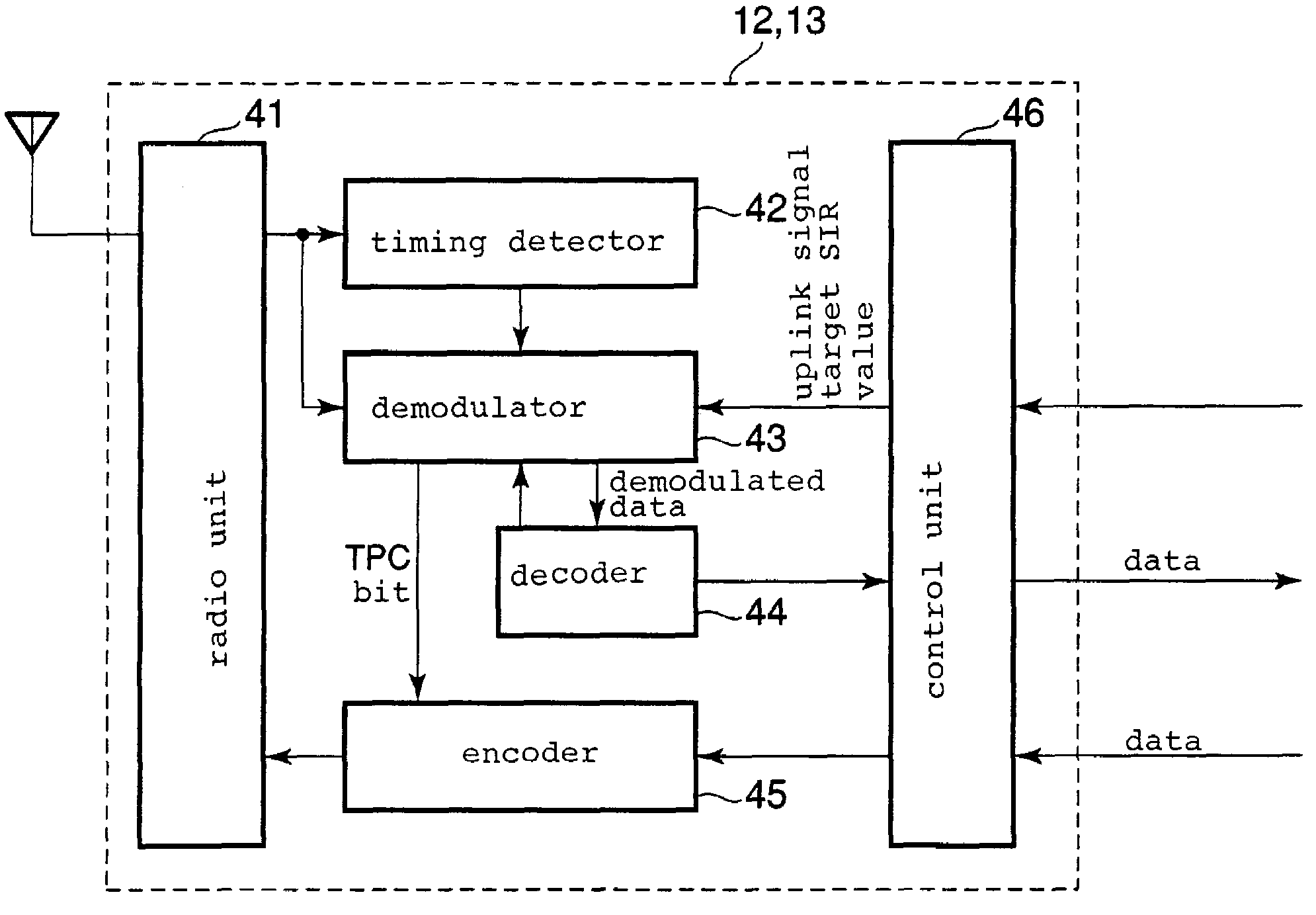

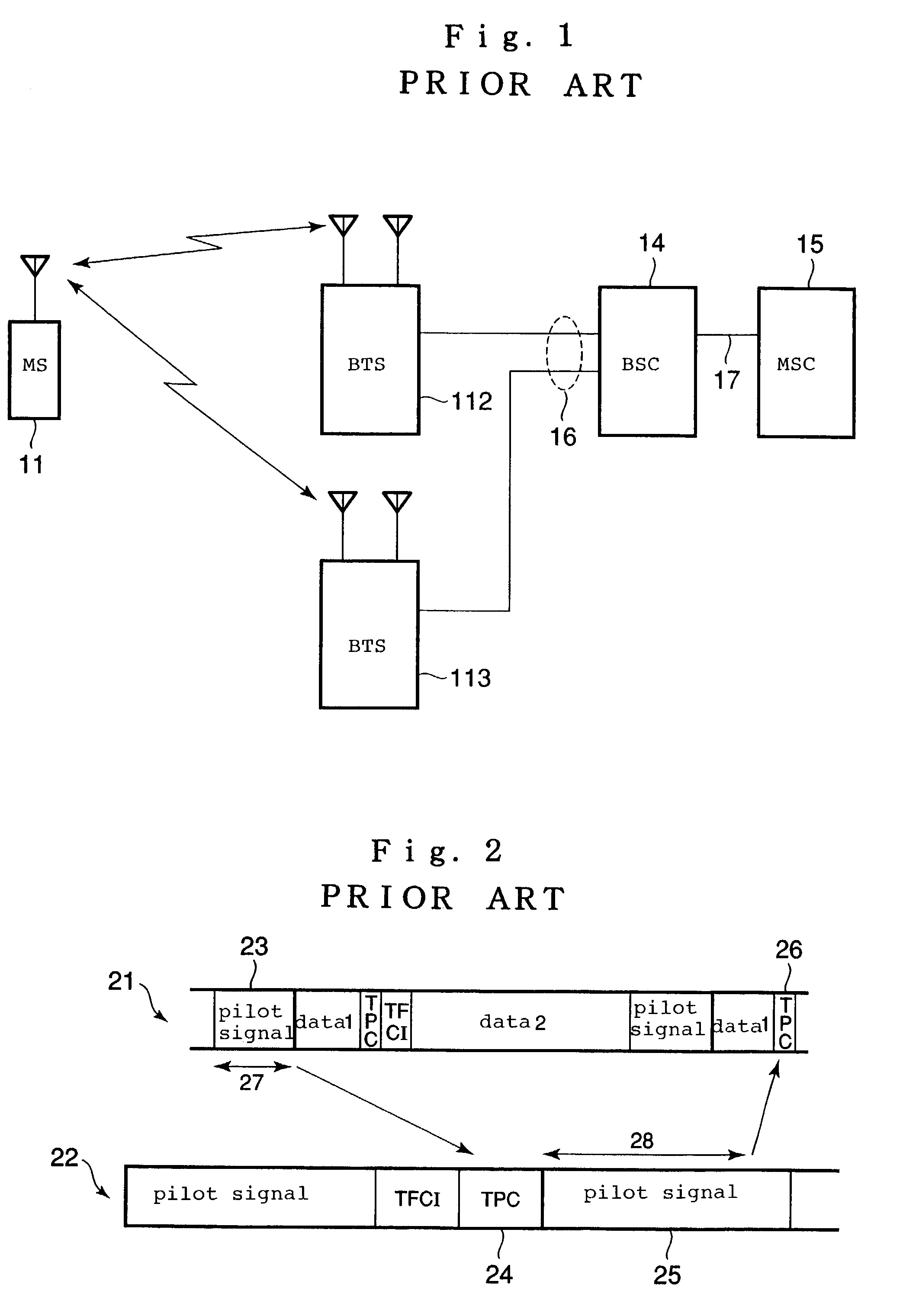

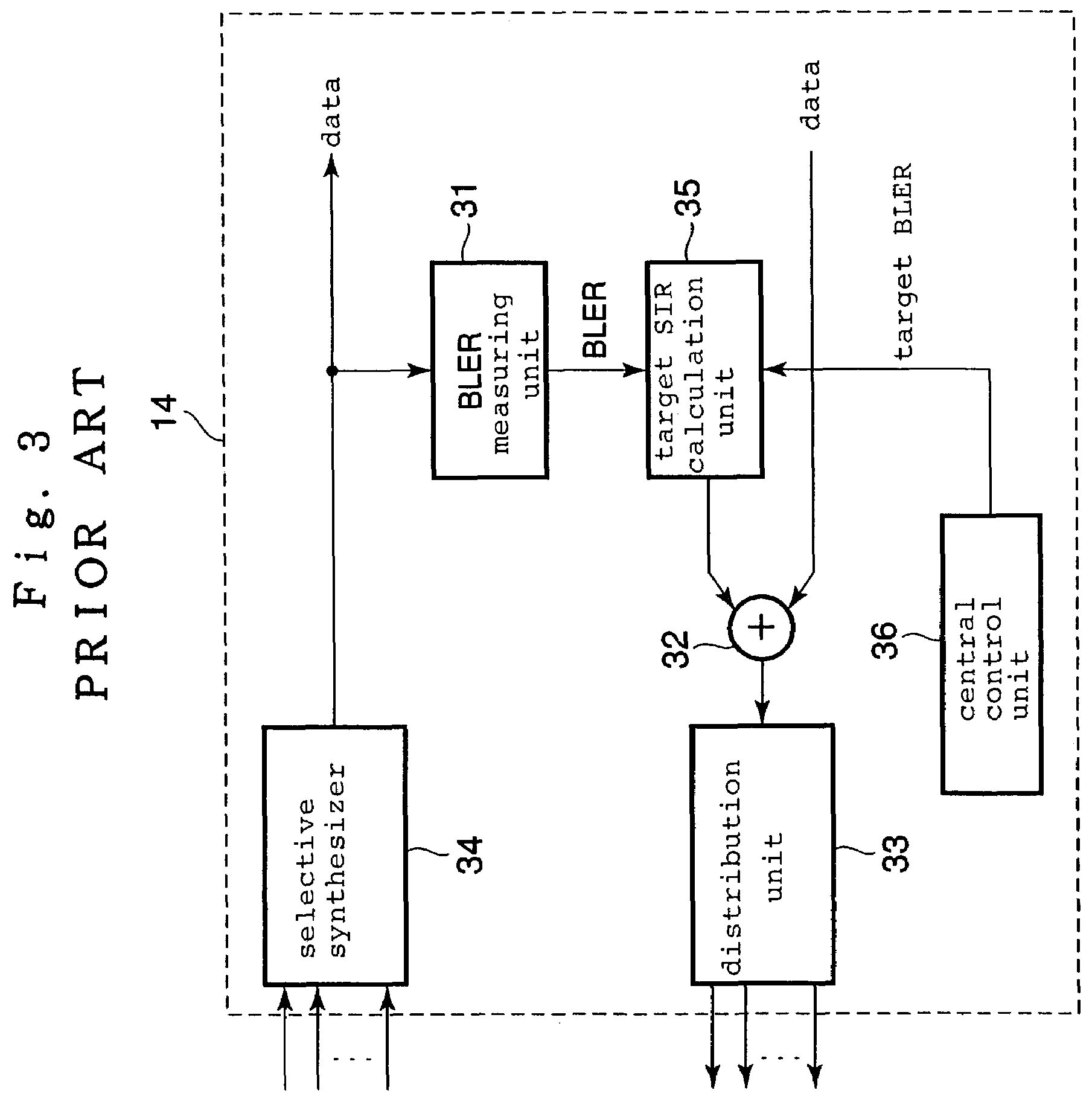

CDMA mobile communication system in which updating of a reference value for controlling closed-loop transmission power is realized in a base transceiver station

InactiveUS7203510B2Inhibit deteriorationHigh-speed executionPower managementResonant long antennasTransceiverCommunications system

A CDMA mobile communication system is disclosed in which a reference value, an uplink signal SIR value, which is used in a closed-loop transmission power control is updated in base transceiver stations. The uplink signal target SIR value is updated independently at base transceiver stations and not at the base station controller. At the base transceiver station, when a decoder detects a loss of synchronization of a user signal from a mobile station, a demodulator adds a step value ΔSIR that has been set in advance to the uplink signal SIR value that has been reported from the base station controller to obtain an uplink signal target SIR provisional value. When this uplink signal target SIR provisional value is smaller than an uplink signal target SIR maximum value that has been set in advance, the uplink signal target SIR value is updated to the uplink signal target SIR provisional value.

Owner:NEC CORP

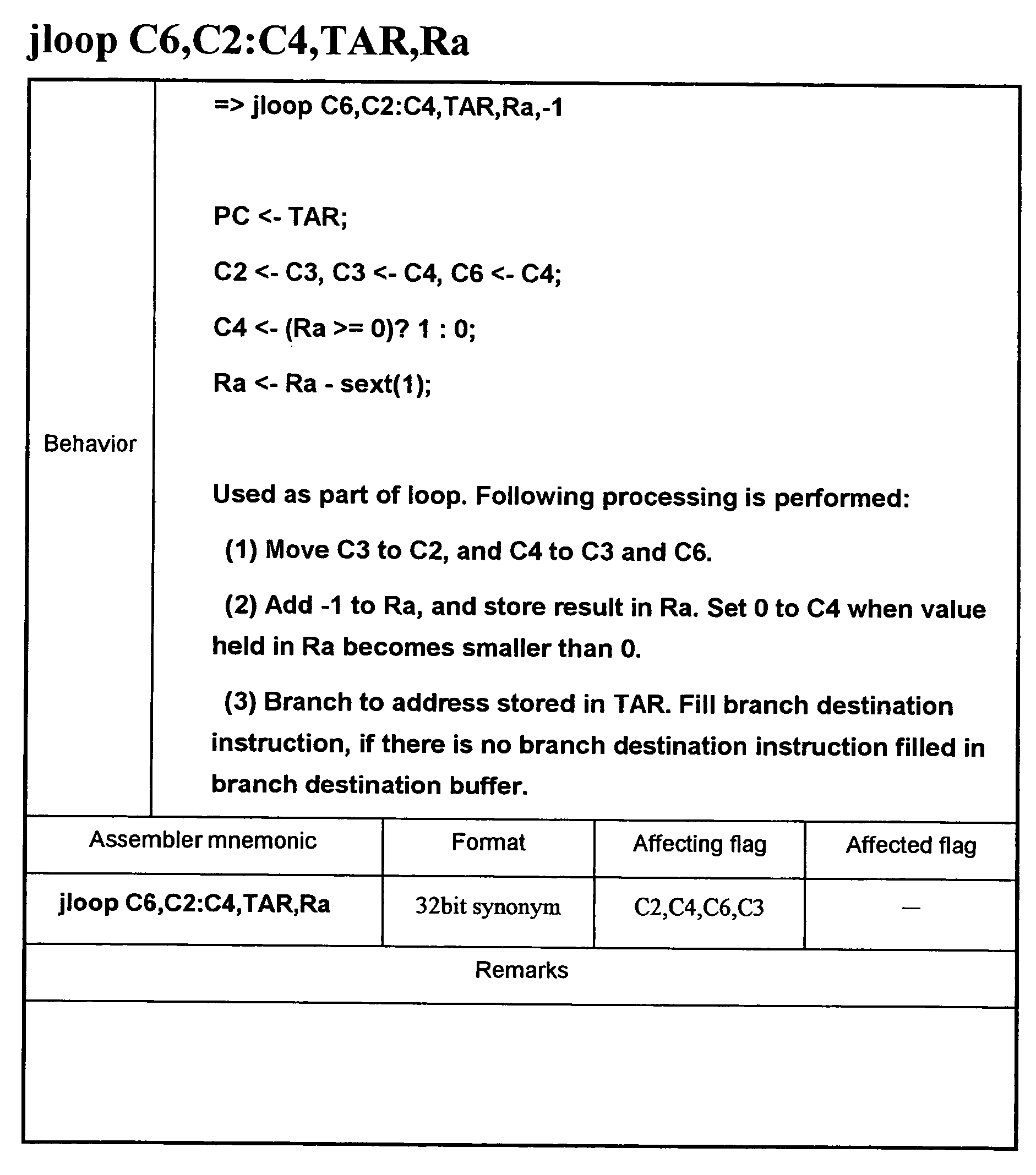

Processor and compiler for decoding an instruction and executing the decoded instruction with conditional execution flags

InactiveUS7380112B2Increase speedReduce the amount of powerSoftware engineeringDigital computer detailsCompilerConditional execution

The present invention provides a processor which has a small-scale circuit and is capable of executing loop processing at a high speed while consuming a small amount of power. When the processor decodes an instruction “jloop C6,C1:C4,TAR,Ra”, the processor (i) sets a conditional flag C4 to 0 when the value of a register Ra is smaller than 0, (ii) moves the value of a conditional flag C2 to a conditional flag C1, moves the value of a conditional flag C3 to the conditional flag C2, and moves the value of the conditional flag C4 to the conditional flags C3 and C6, (iii) adds −1 to the register Ra and stores the result into the register Ra, and (iv) branches to an address specified by a branch register (TAR). When not filled with a branch target instruction, the jump buffer will be filled with a branch target instruction.

Owner:PANASONIC CORP

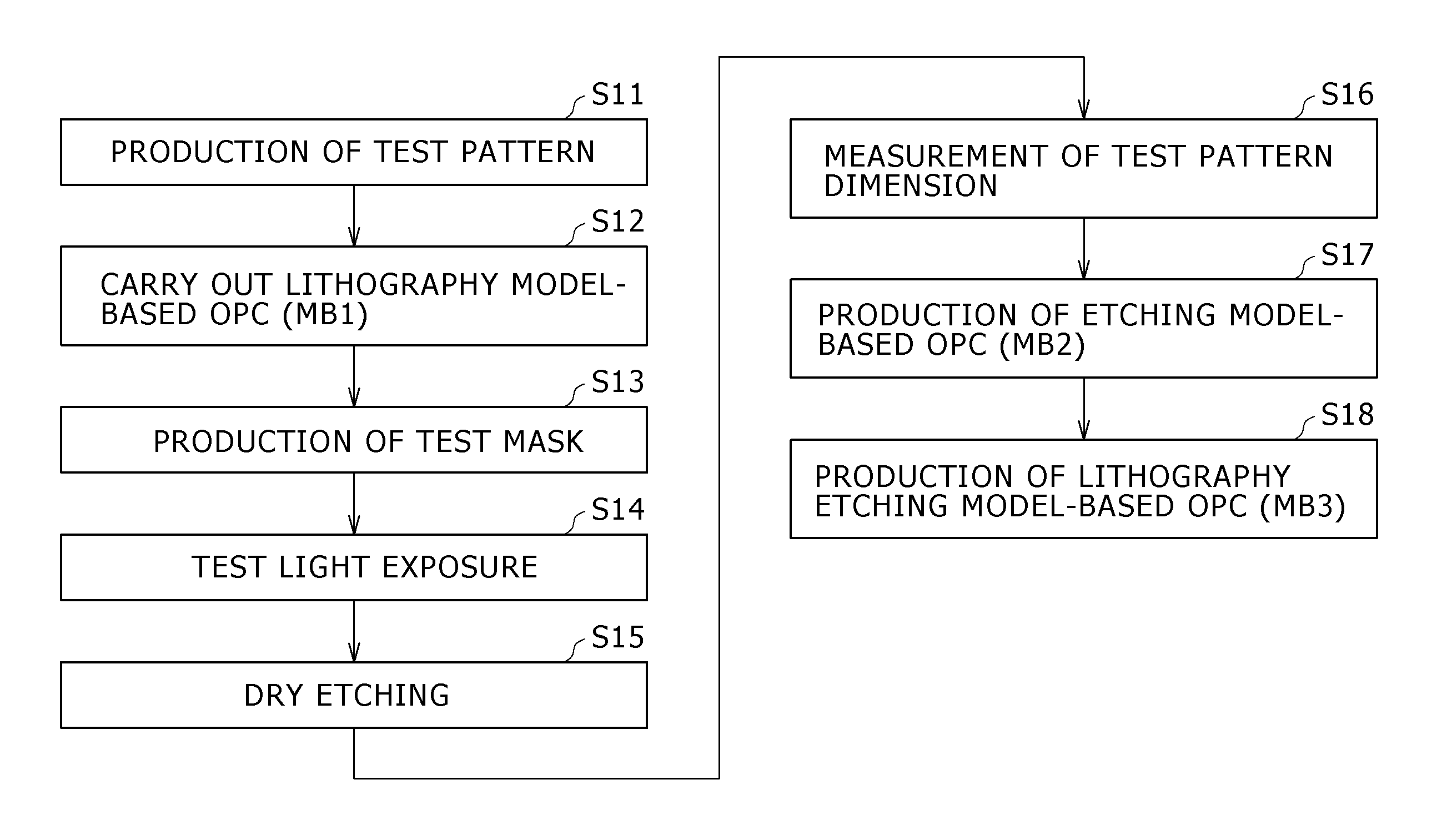

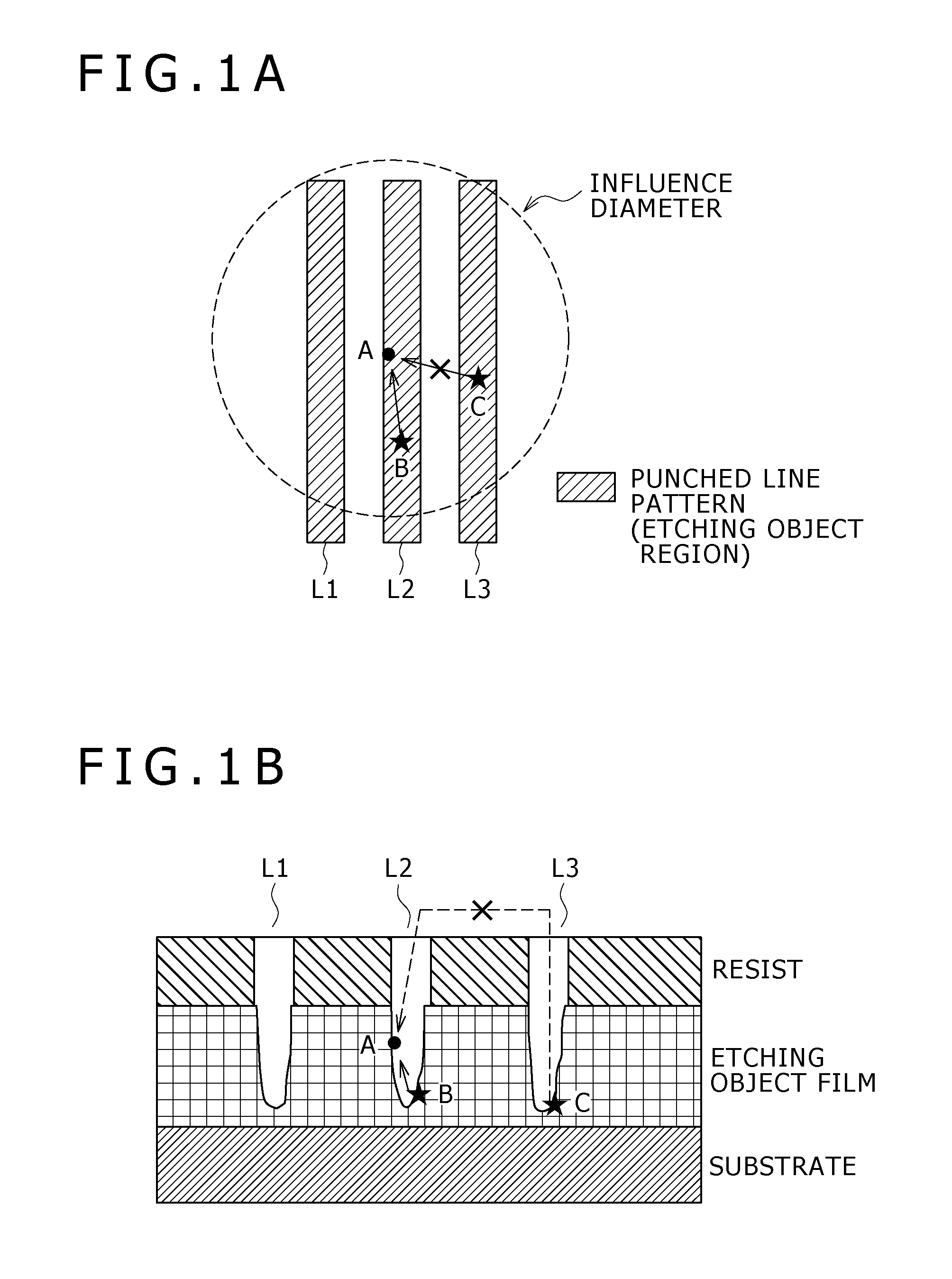

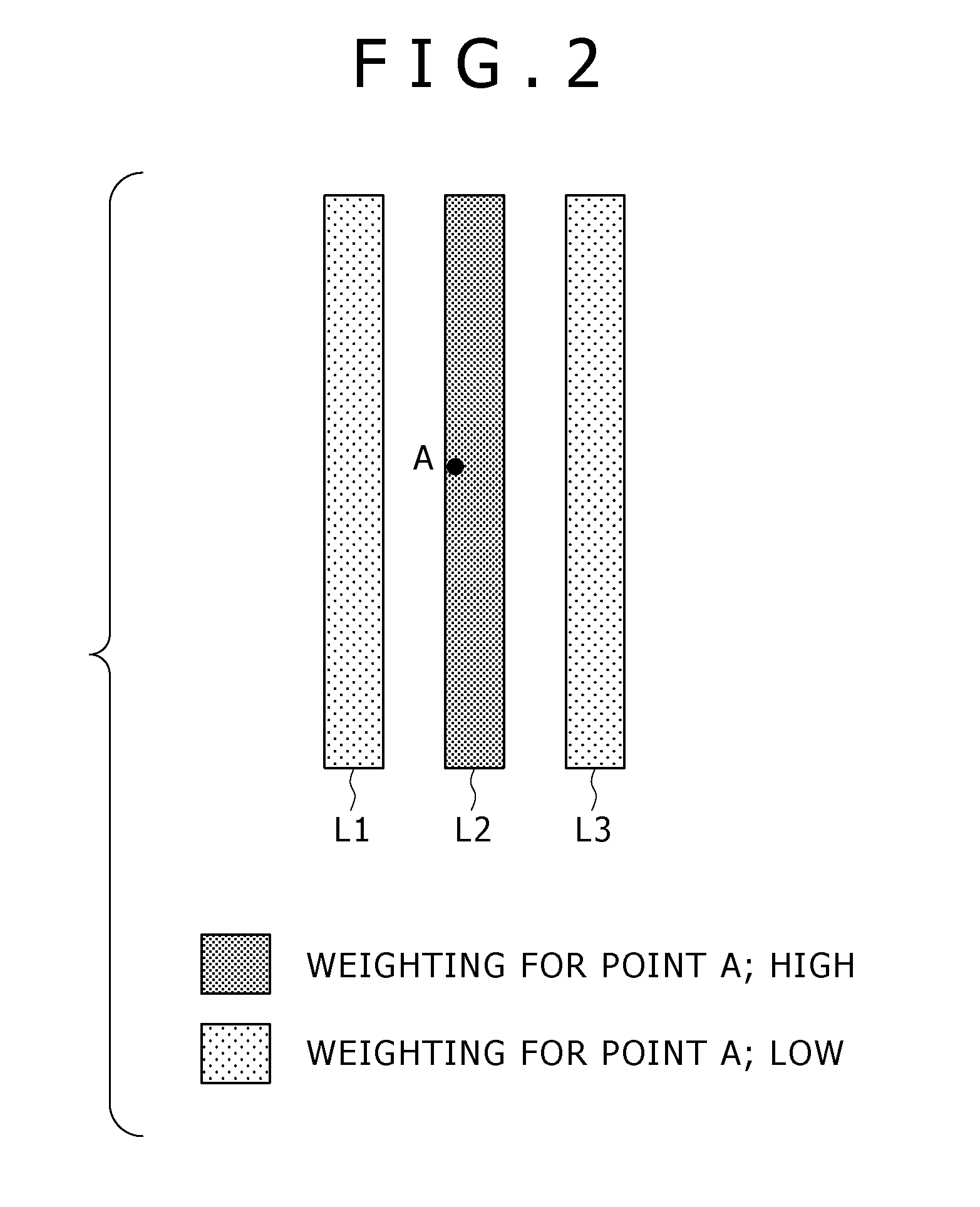

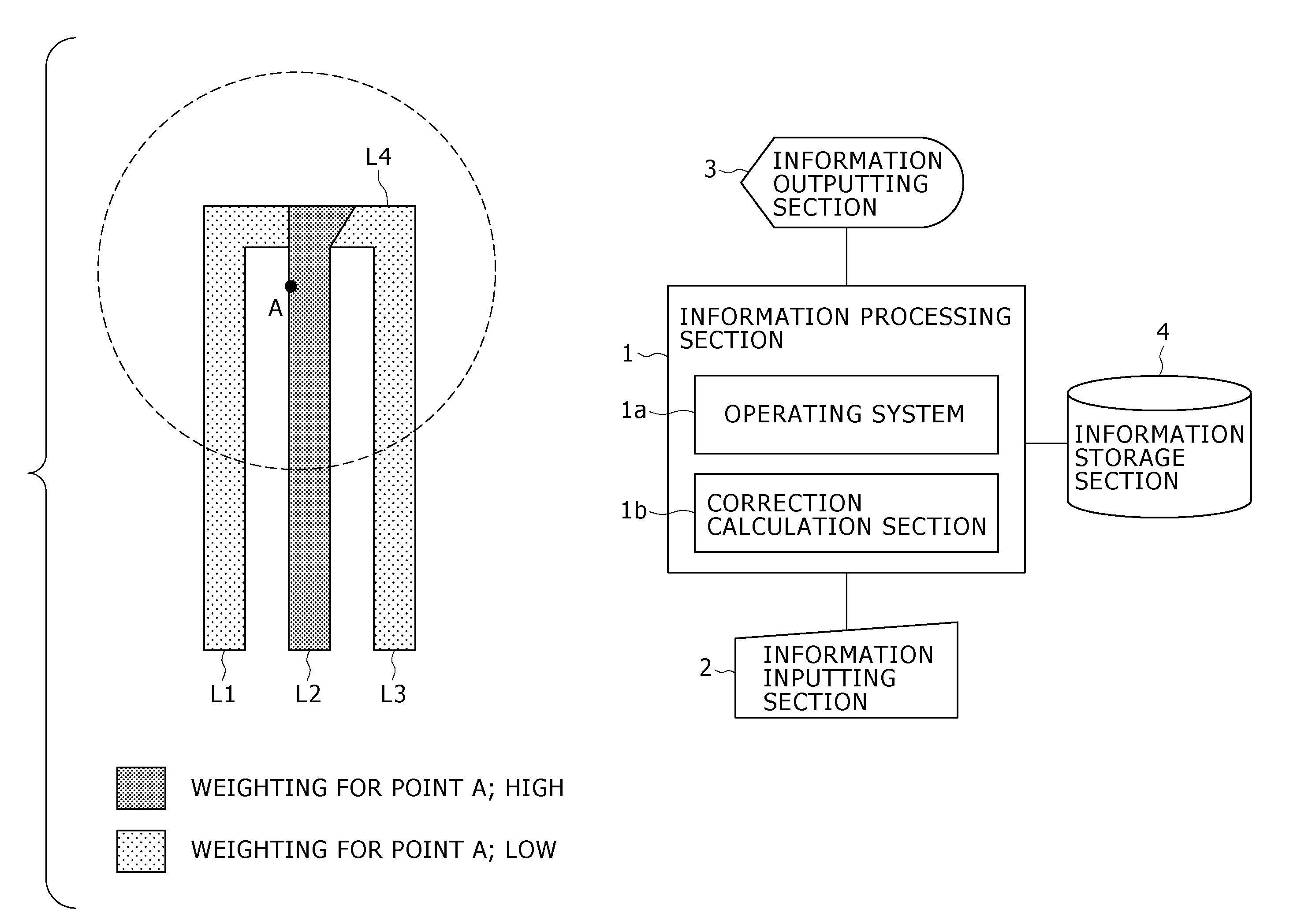

Pattern correction apparatus, pattern correction program, pattern correction method and fabrication method for semiconductor device

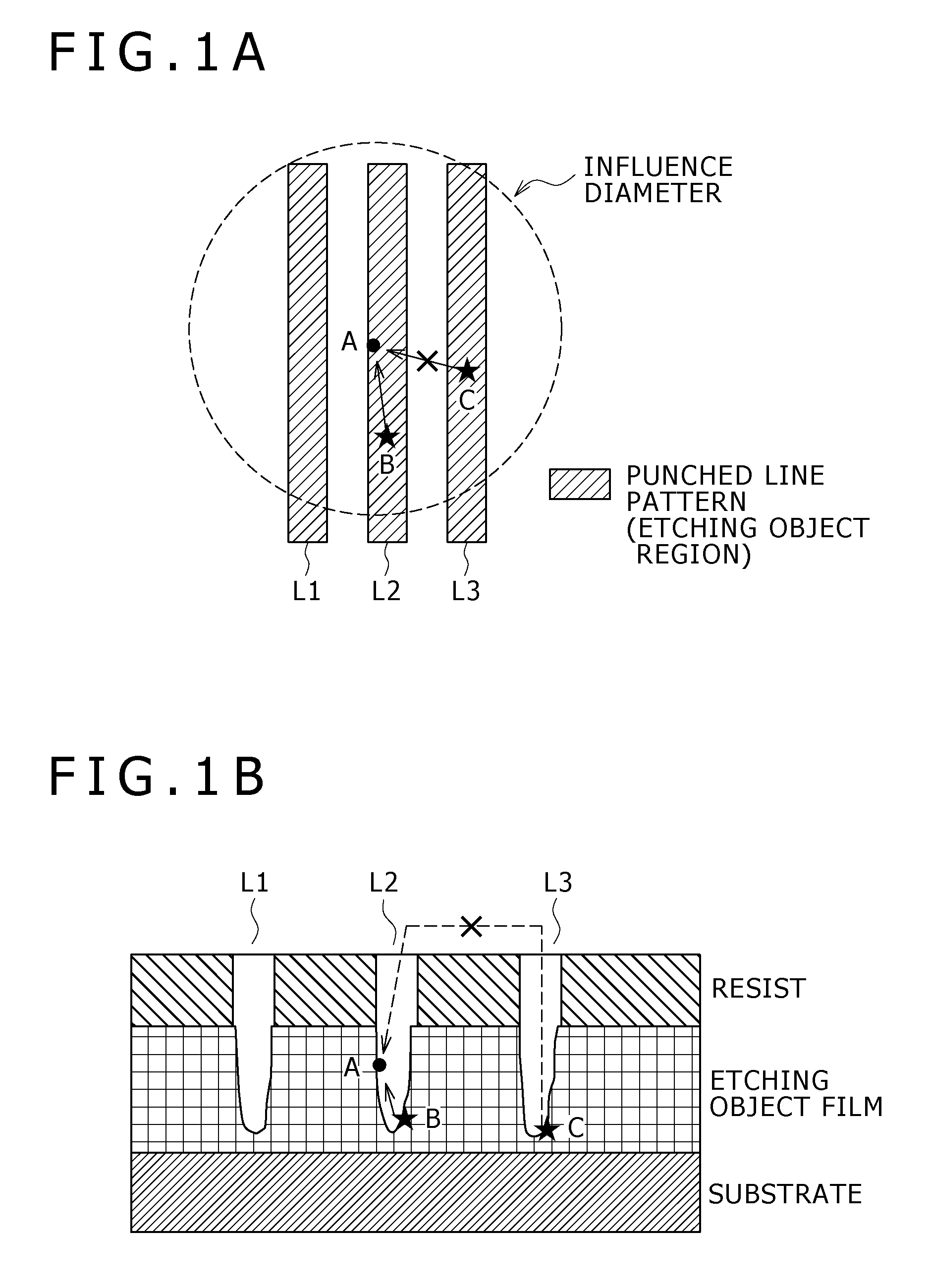

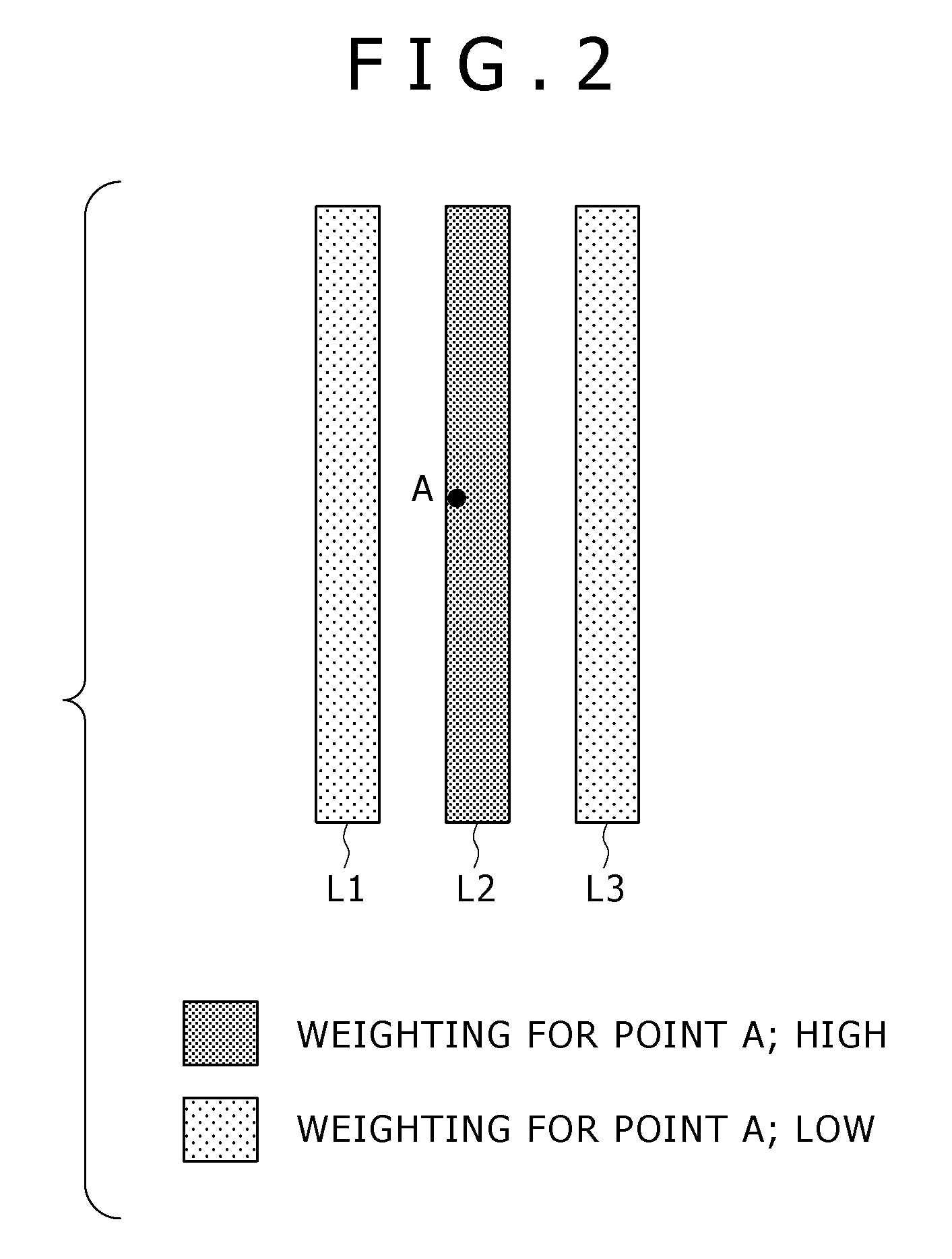

InactiveUS20080178141A1High degree of accuracyHigh weightSolid-state devicesSemiconductor/solid-state device manufacturingPoint setDesign pattern

A pattern correction apparatus for performing both of optical proximity effect correction and process proximity effect correction with regard to a design pattern includes: a correction calculation means configured to perform correction calculation by two-dimensional model-based optical proximity effect correction for each of sampling points set on pattern edges which form the design pattern; the correction calculation means performing the correction calculation which involves weighting with a two-dimensional distribution of the pattern edges around the sampling point taken into consideration; the weighting being performed such that a high weight is applied to a region in which reaction products which can have an influence on the sampling point are produced but a low weight is applied to any other region.

Owner:SONY CORP

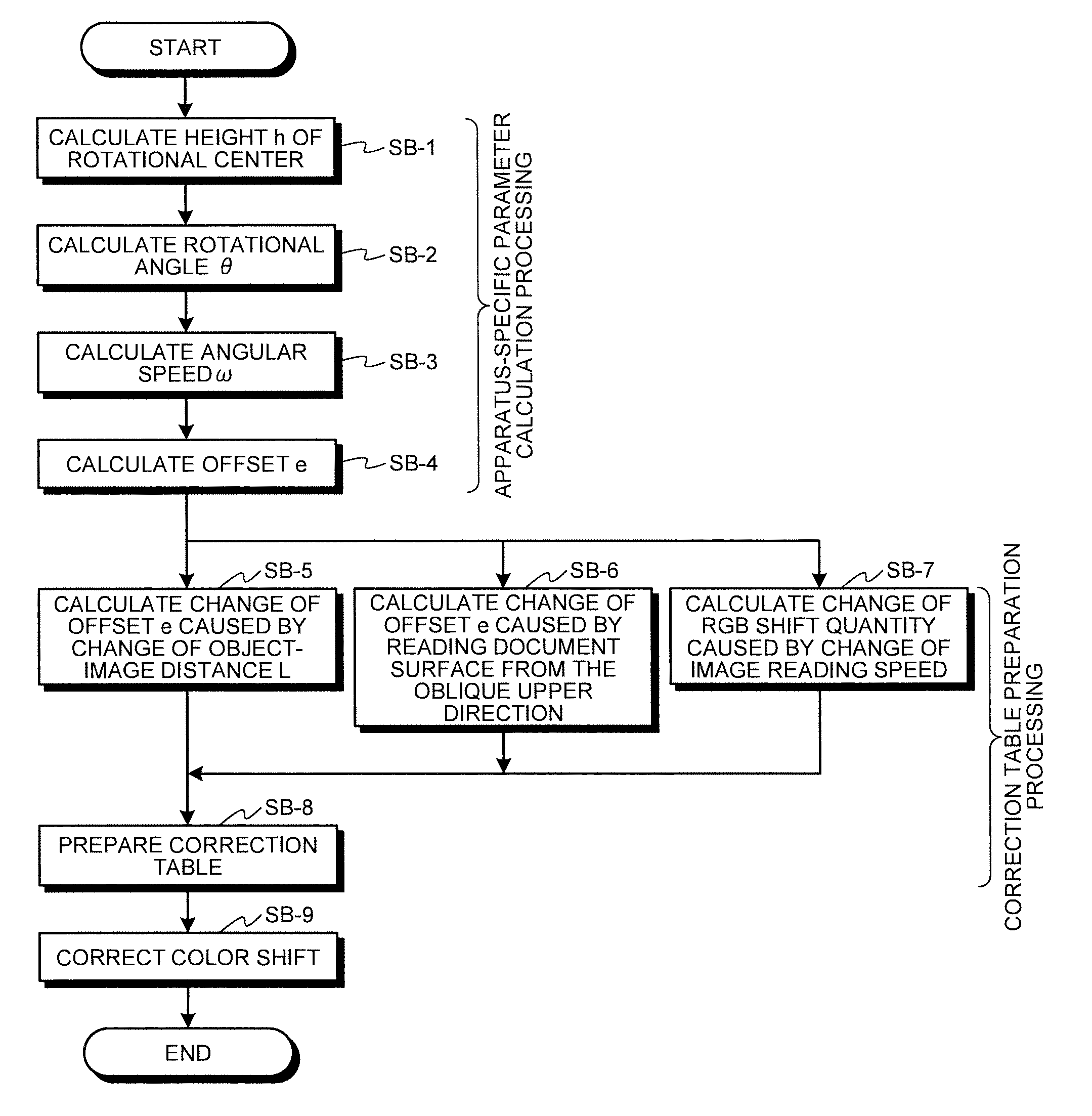

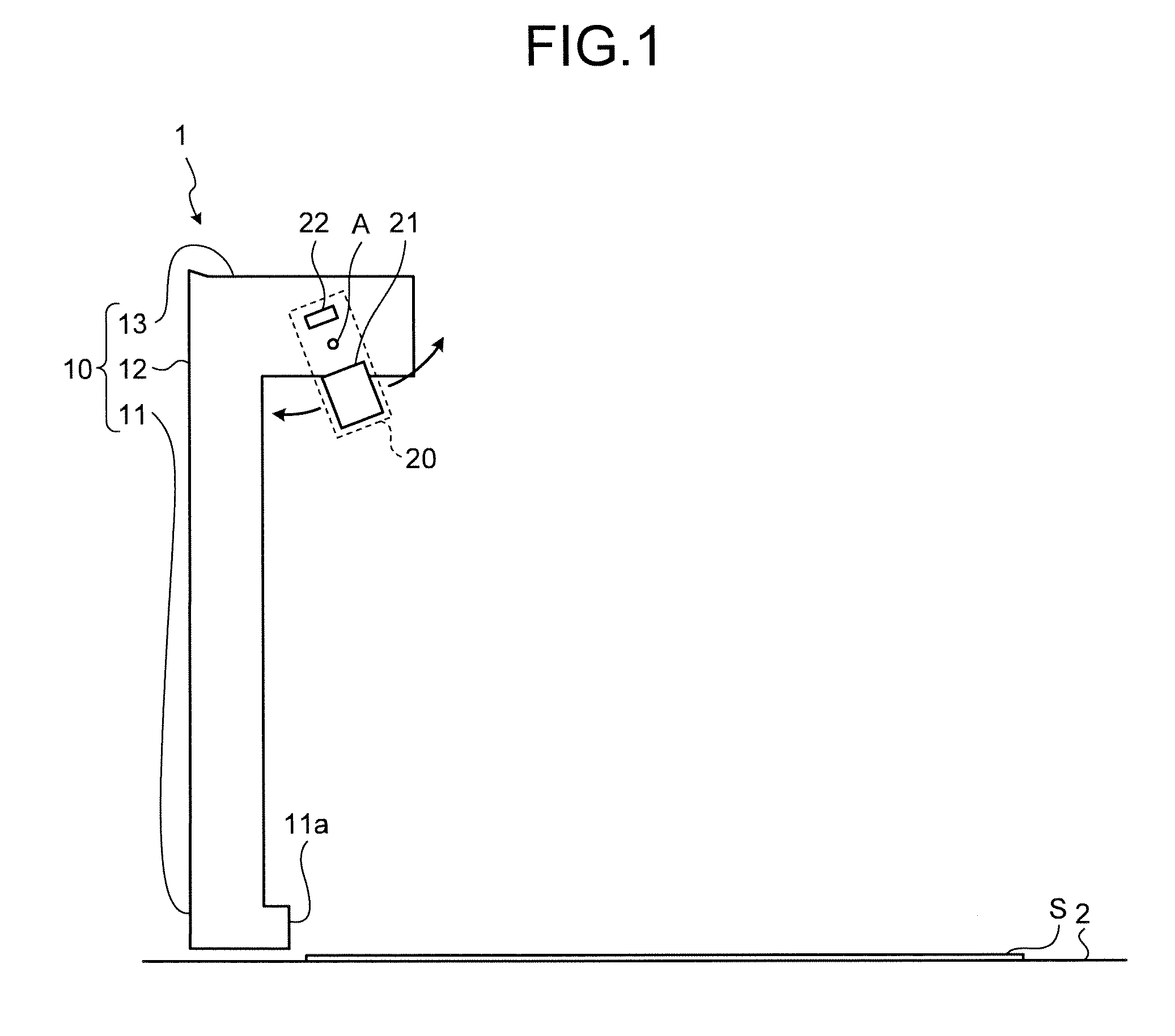

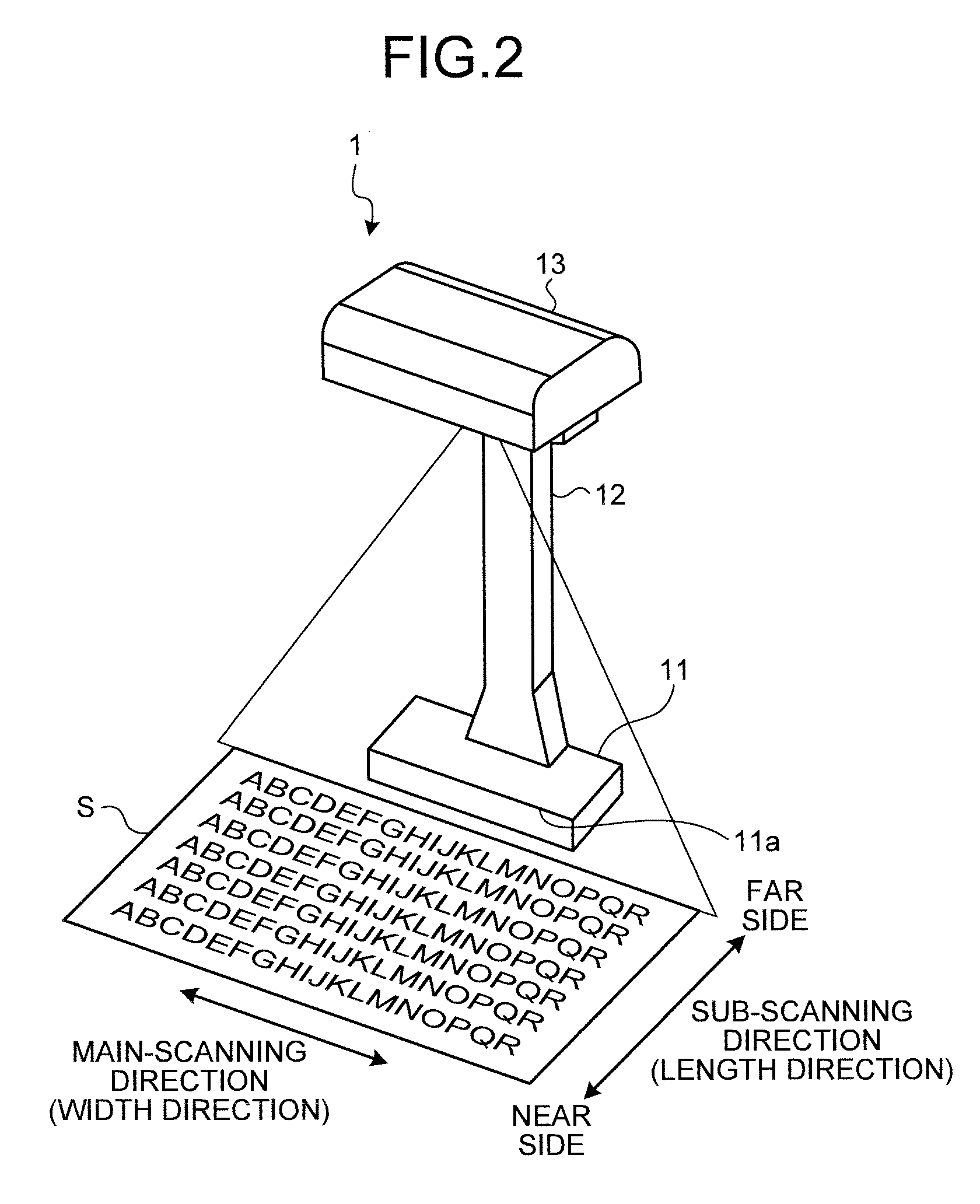

Image-reading apparatus, image processing method, and computer program product

ActiveUS20120320437A1Solve problemsIncrease speedColour-separation/tonal-correctionPictoral communicationImaging processingColor shift

An image-reading apparatus, includes a variation acquiring unit that acquires a variation of a distance or an angle between a medium to be read and an imaging unit or a light source, and a color shift correcting unit that calculates a color shift between the medium and the imaging unit or the light source based on the variation acquired by the variation acquiring unit and corrects the color shift.

Owner:PFU LTD

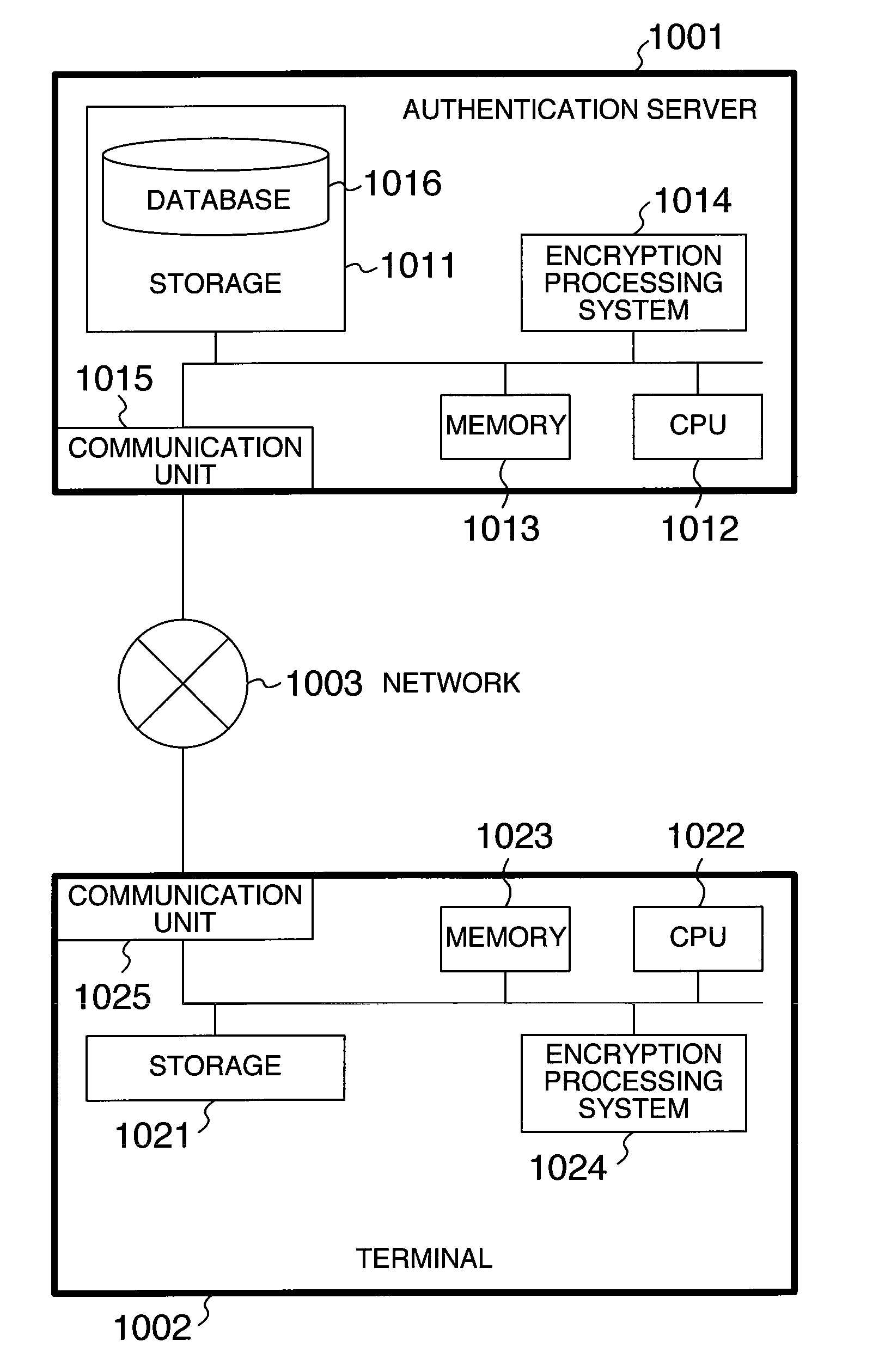

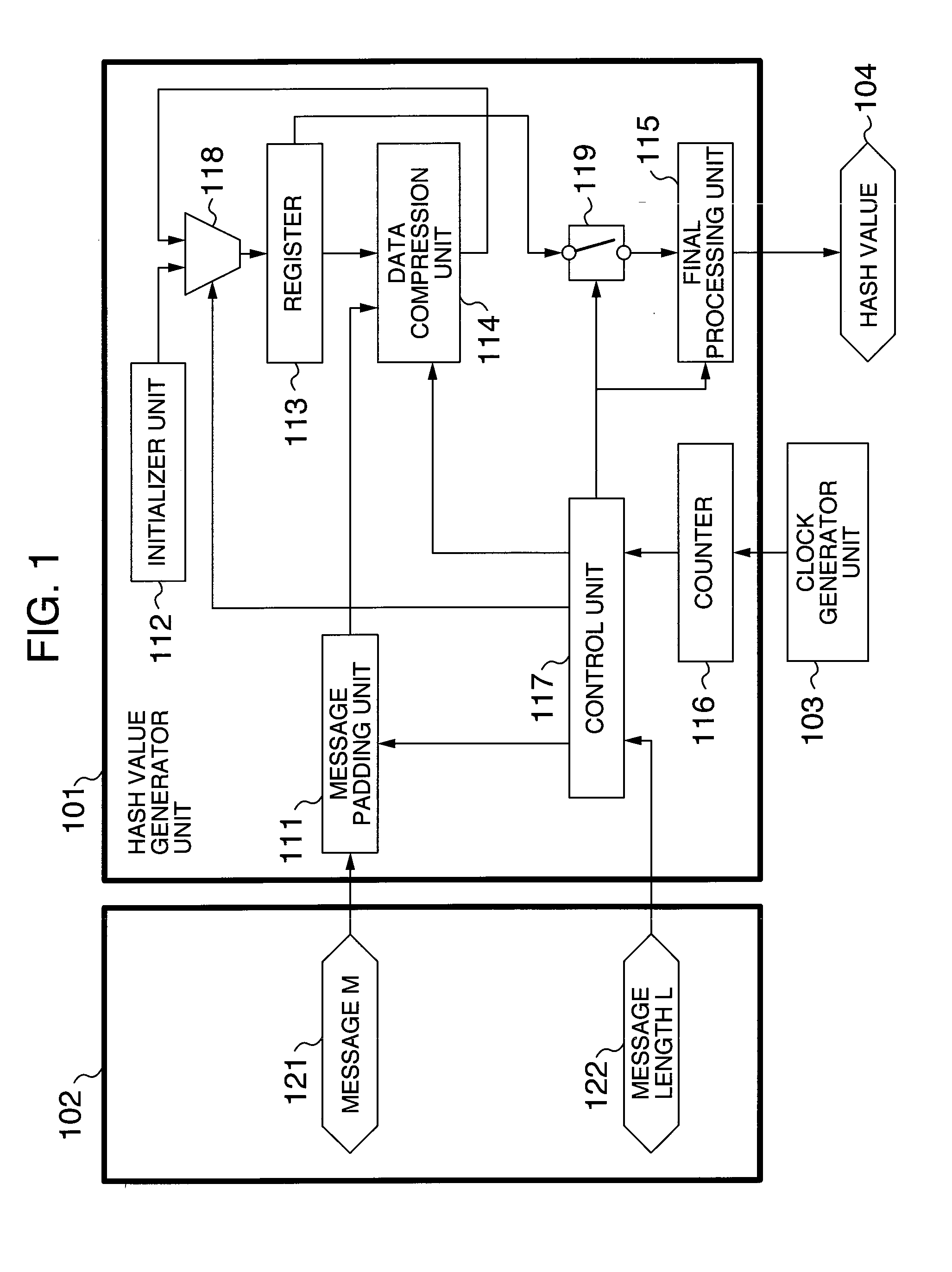

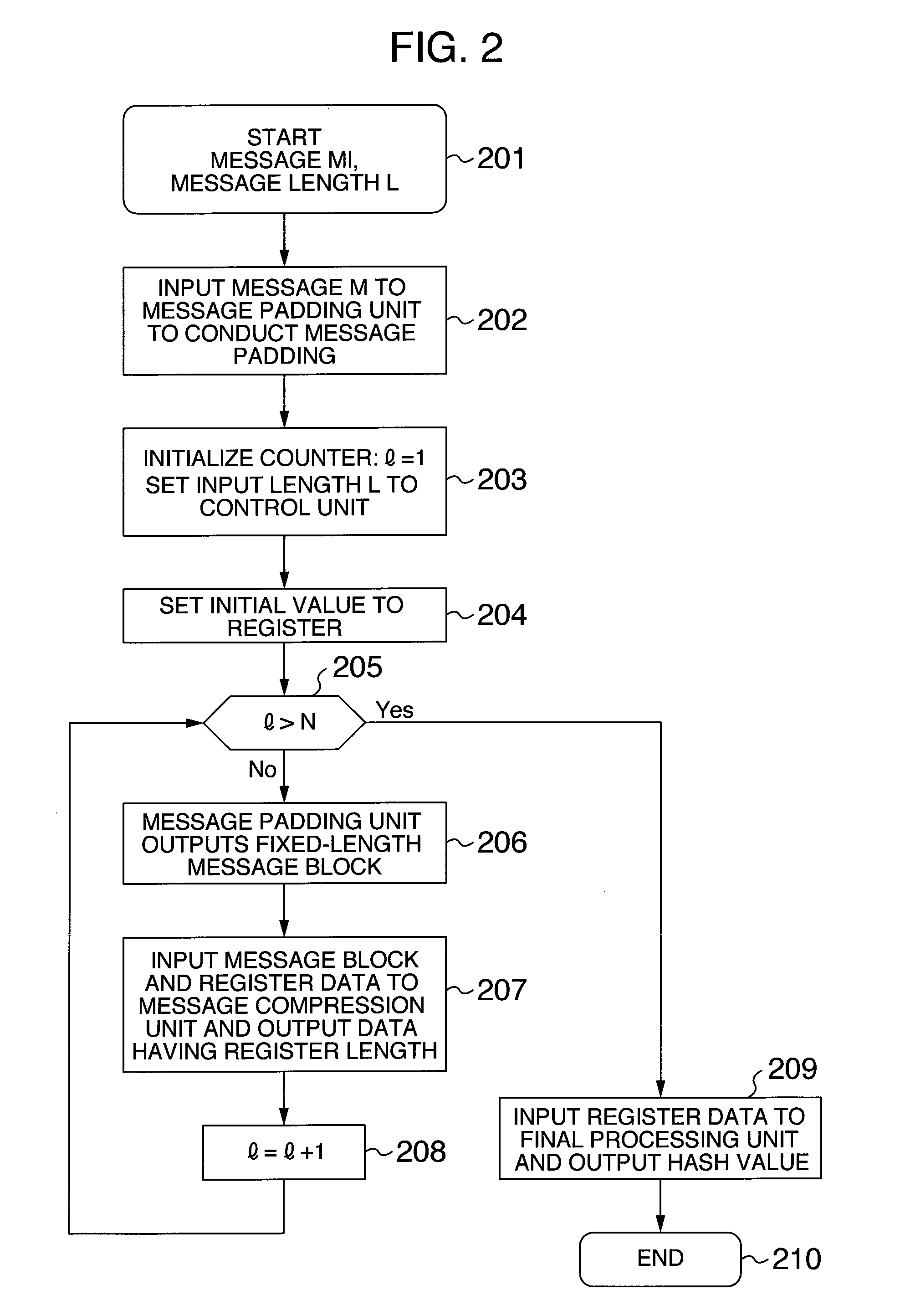

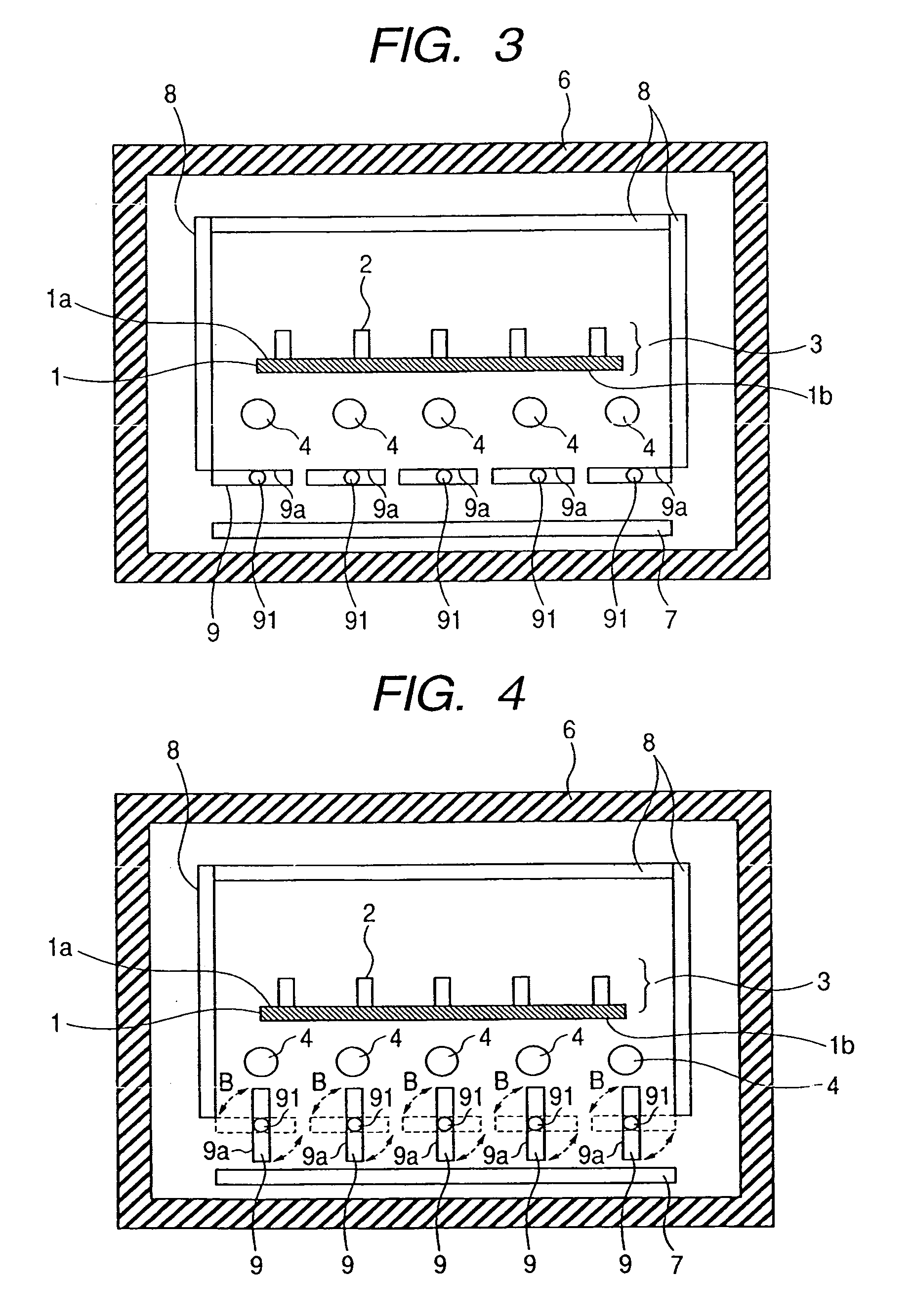

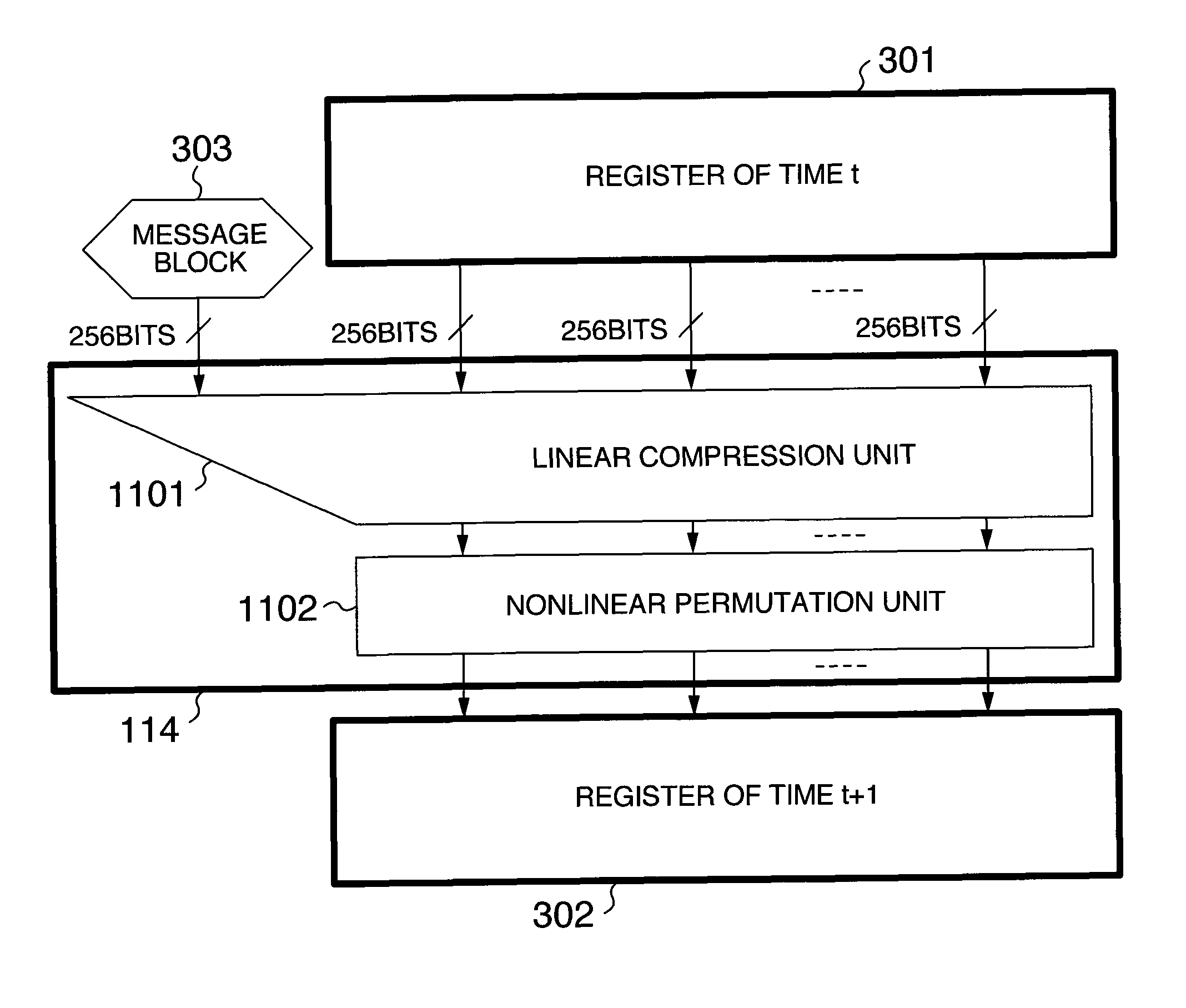

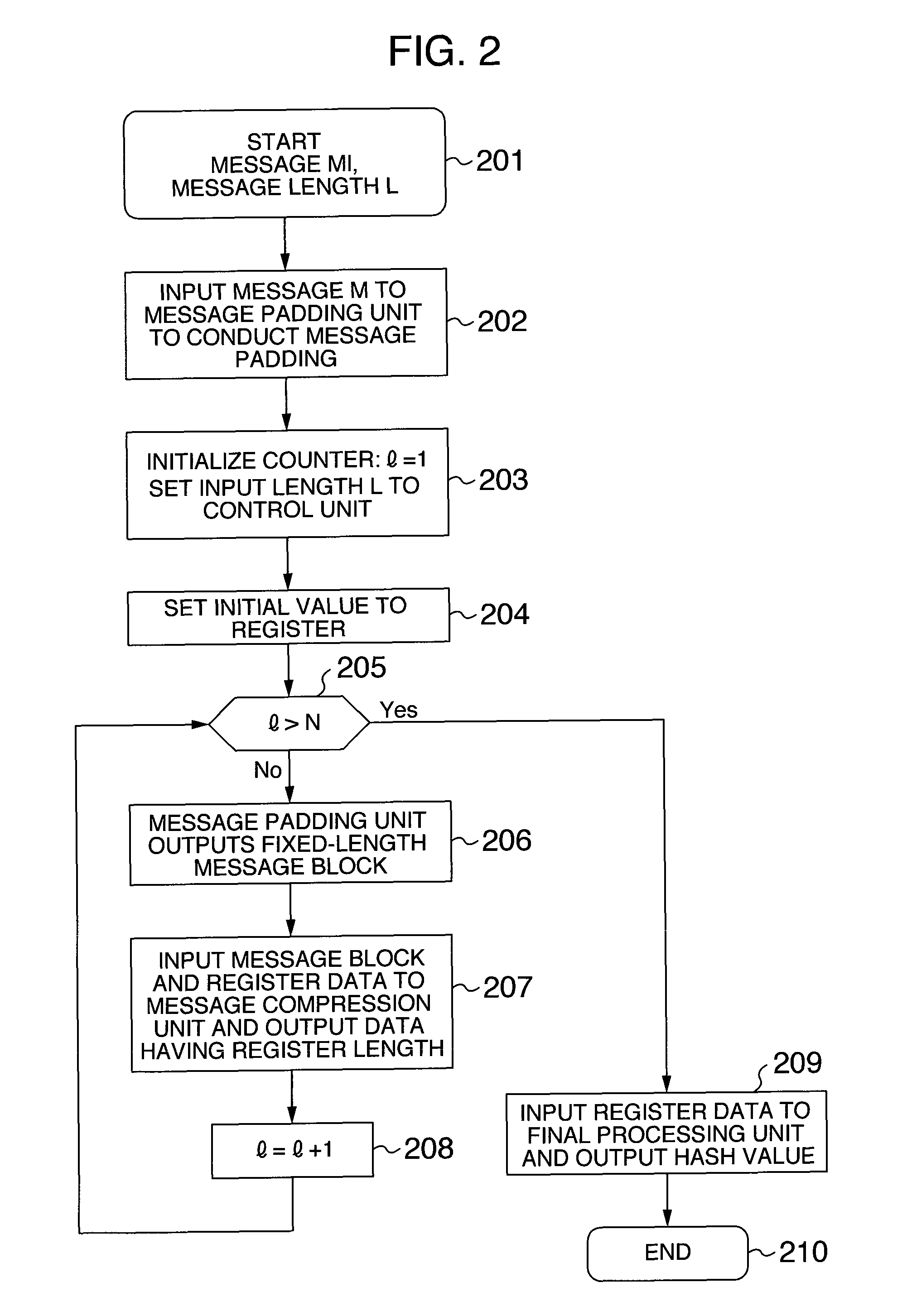

Hash value generator

InactiveUS20100049986A1Increase speedHigh-speed executionUser identity/authority verificationSecret communicationComputer hardware

To achieve high safety, large-sized nonlinear permutation is employed; however, the larger permutation processing is, the more the period of time required for the processing is, which hence is not efficient. There is provided a hash value generation method or a hash value generator which has the following aspects and which is highly safe and is capable of executing processing at a high speed.1. As a message insertion method, there is employed a linear conversion in which the insertion message affects all subblocks.2. An internal state is divided into a plurality of subblocks, and nonlinear permutation is conducted in each subblock unit.3. Additionally, the linear conversion of item 1 above may be configured such that each subblock of the internal state affects the subblocks of the output.

Owner:HITACHI LTD

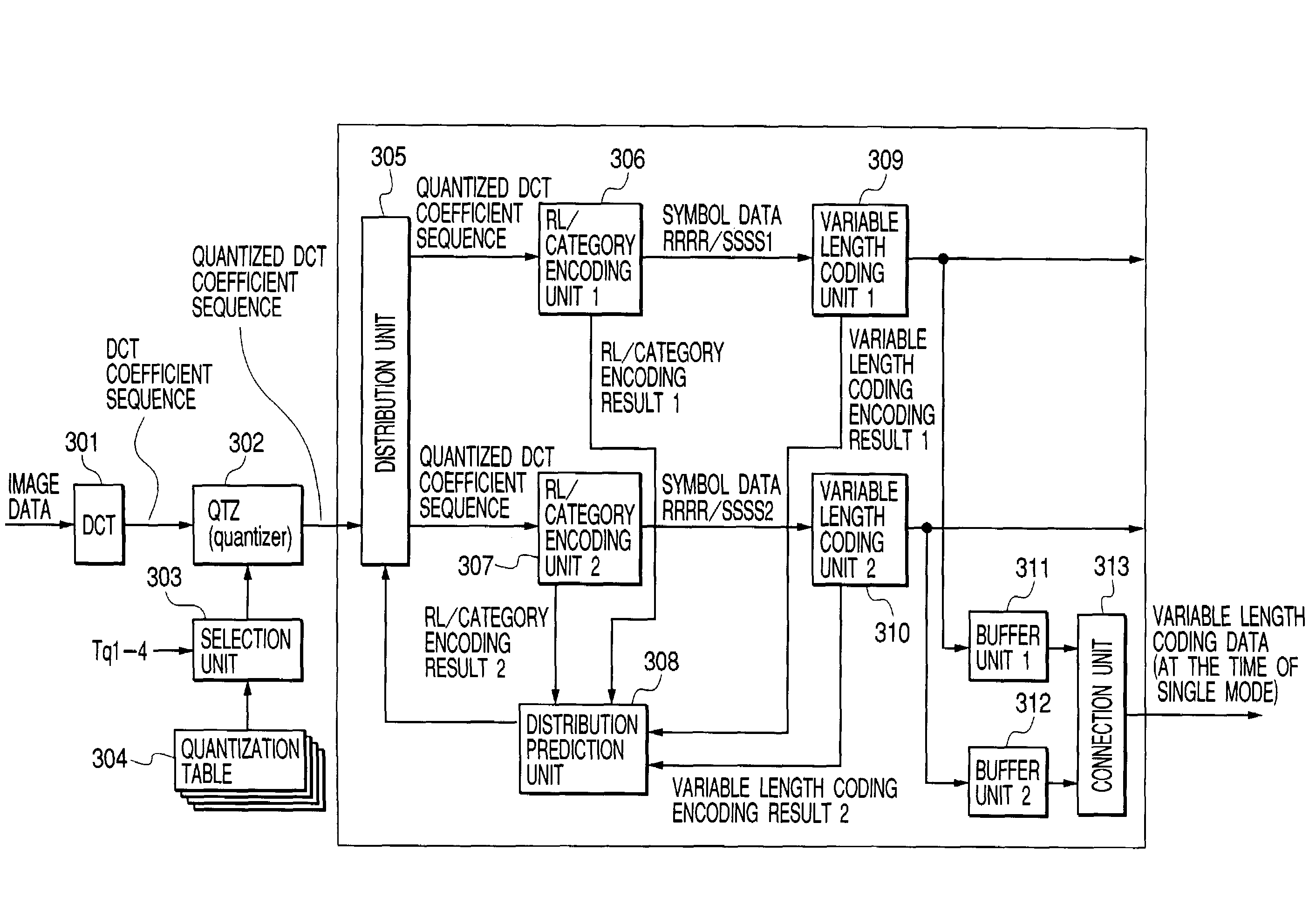

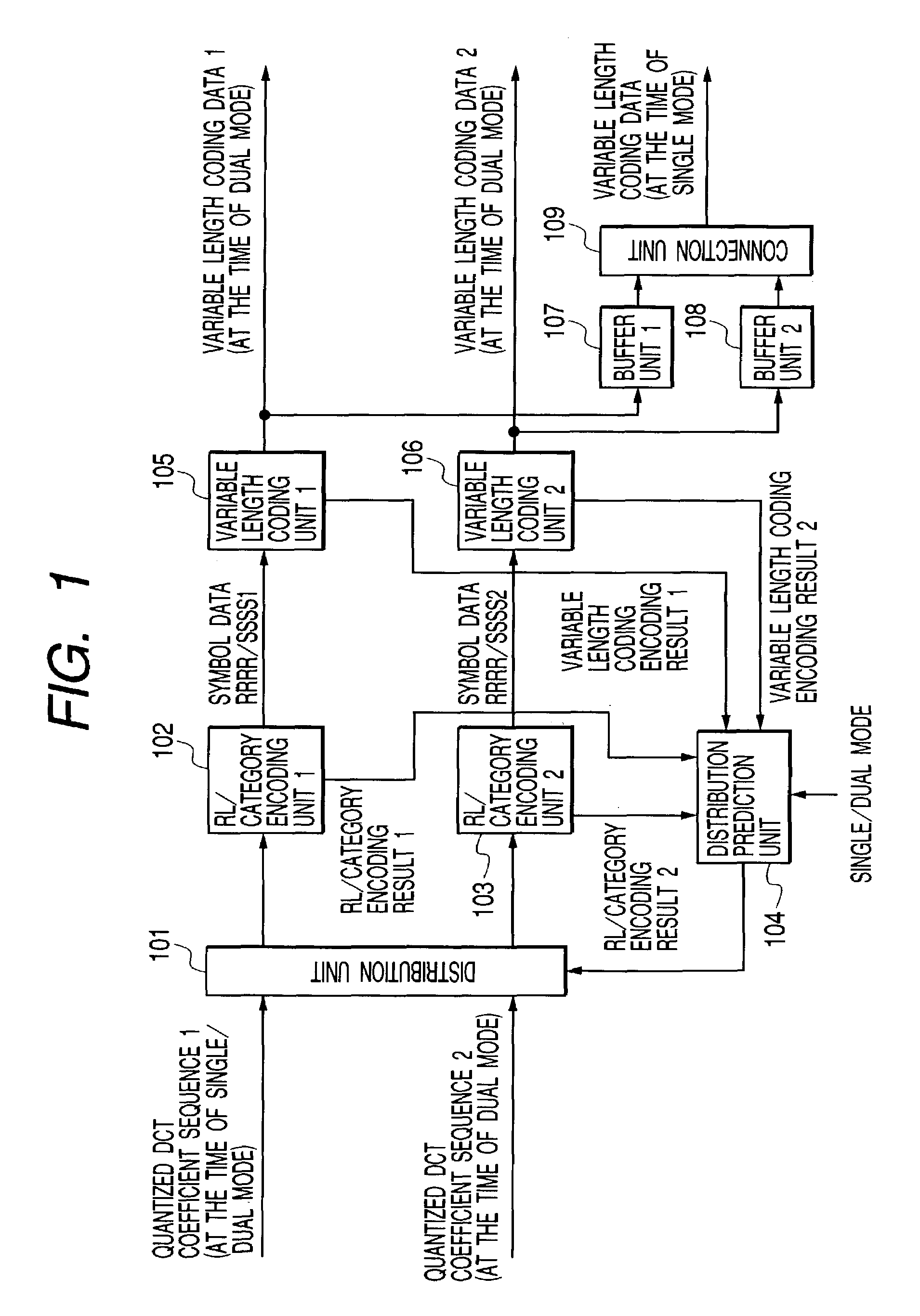

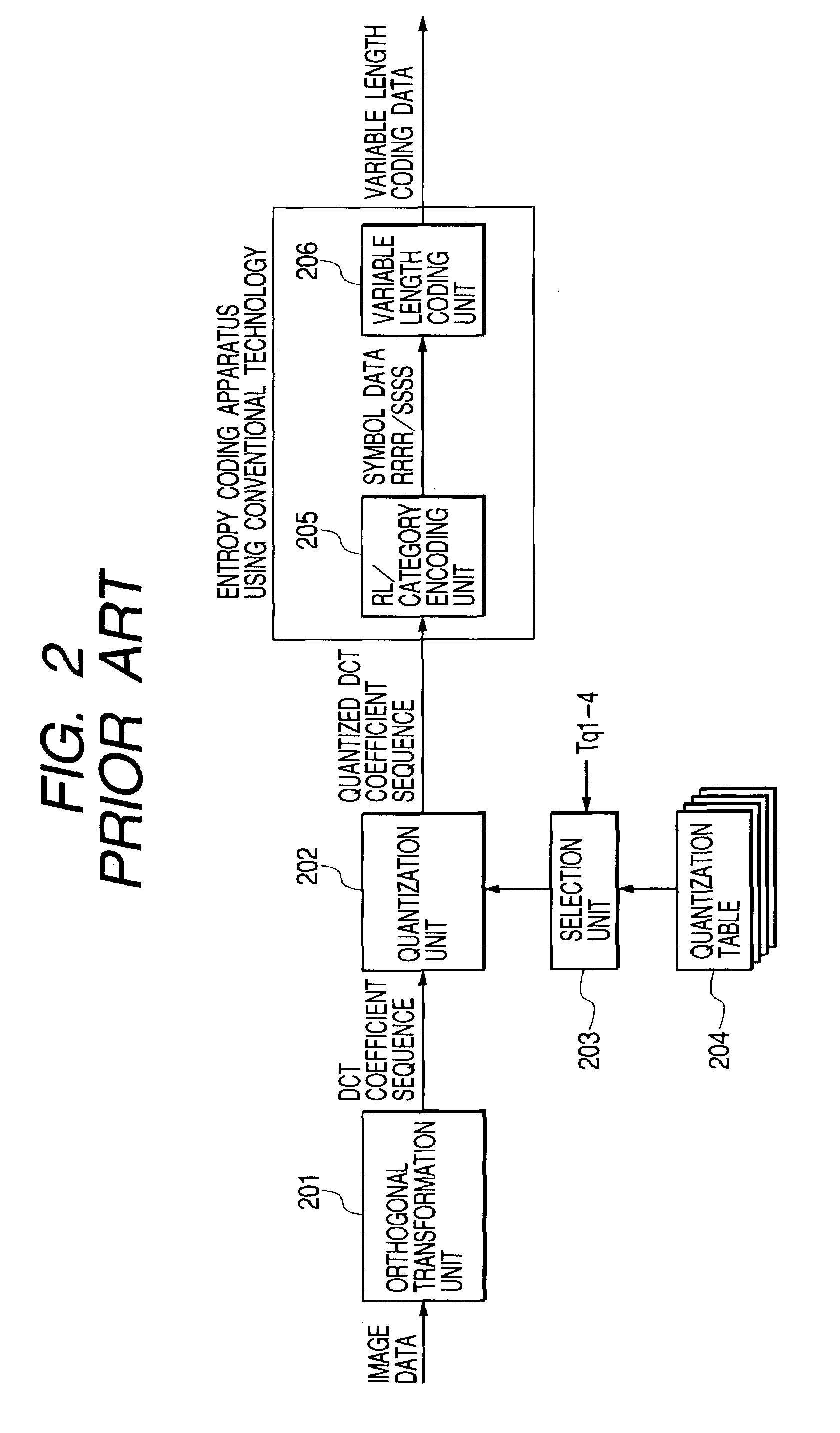

Entropy coding apparatus

InactiveUS7224844B2Increase speedEasy to operateCode conversionImage codingOrthogonal transformationComputer science

For the entropy coding of image data after subjected to orthogonal transforation and quantization, a plurality of entropy coding units are provided in parallel. The plurality of entropy coding units can be operated efficiently and the entropy coding can be executed at high speed. In order to realize these operations, for example, an entropy coding apparatus has: an orthogonal transformation unit for performing an orthogonal transformation of image data; a quantization unit for quantizing coefficients obtained by the orthogonal transformation; N entropy coding units for entropy-coding the quantized coefficients output from the quantization unit; a distribution unit for selecting one of the N entropy coding units for each quantized coefficient and supplying the quantized coefficient to the selected entropy coding unit; and a prediction unit for monitoring a coding state of each of the N entropy coding units and predicting an optimum one of the N entropy coding units for a succeeding quantized coefficient in accordance with monitor results.

Owner:CANON KK

Printing apparatus and calibration method

Owner:CANON KK

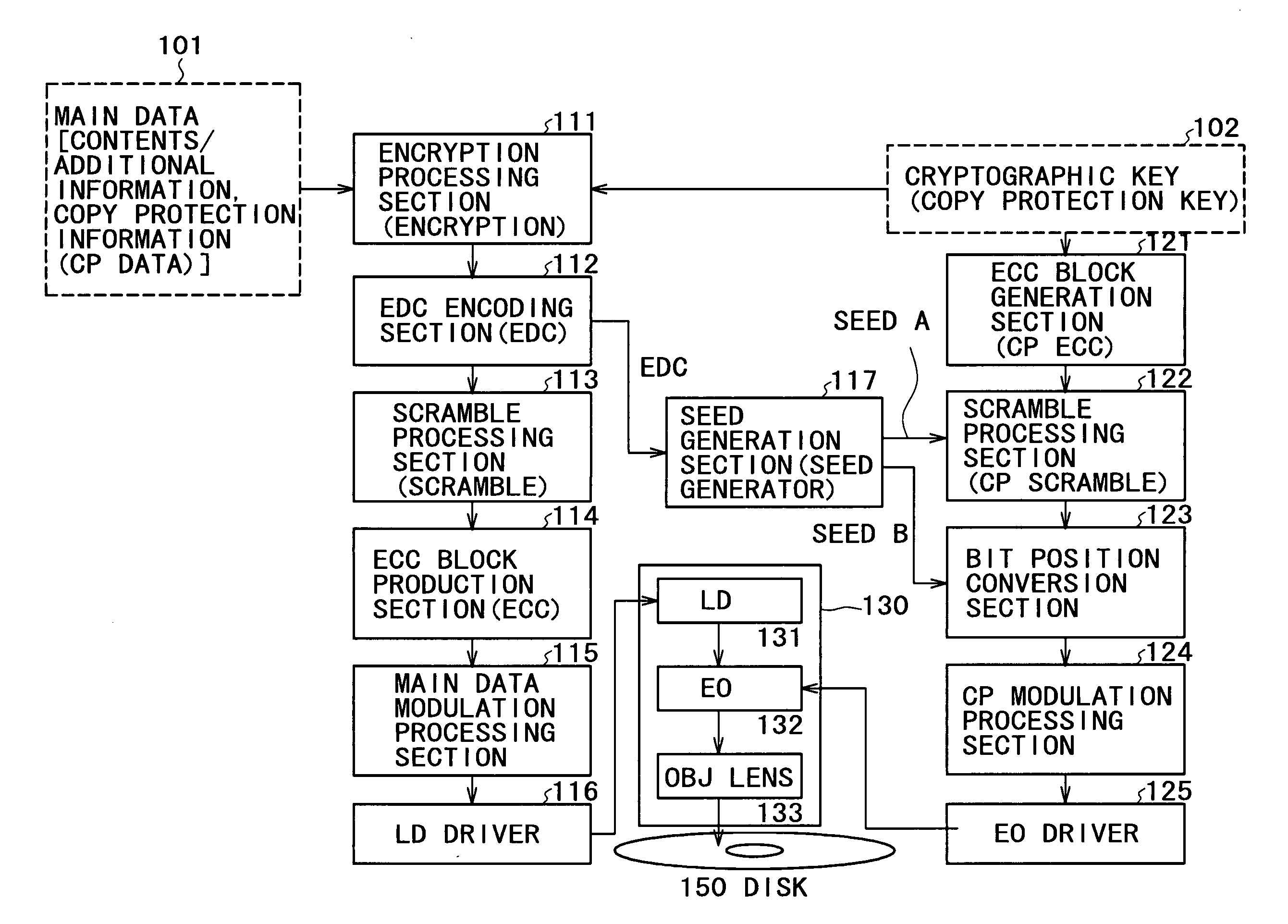

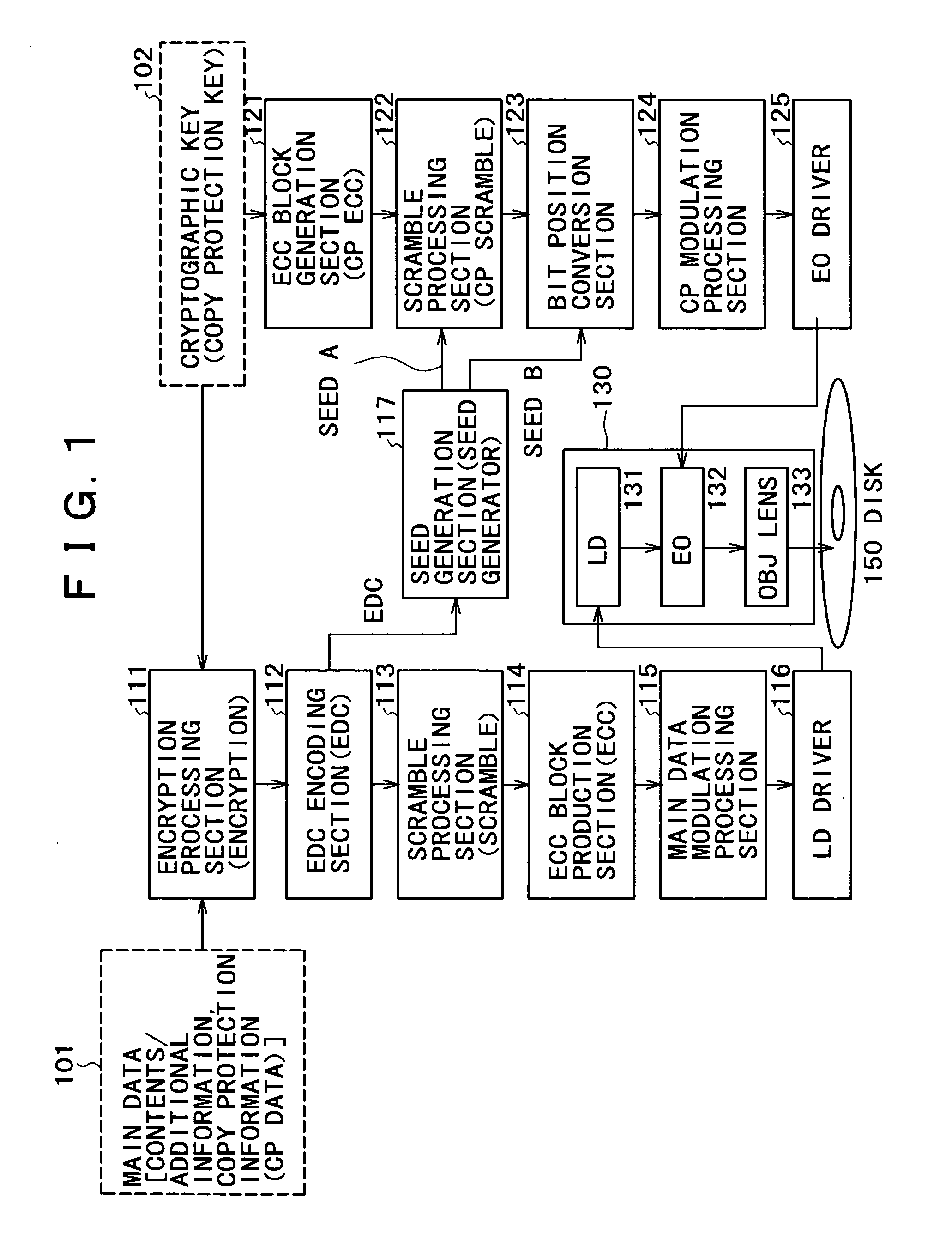

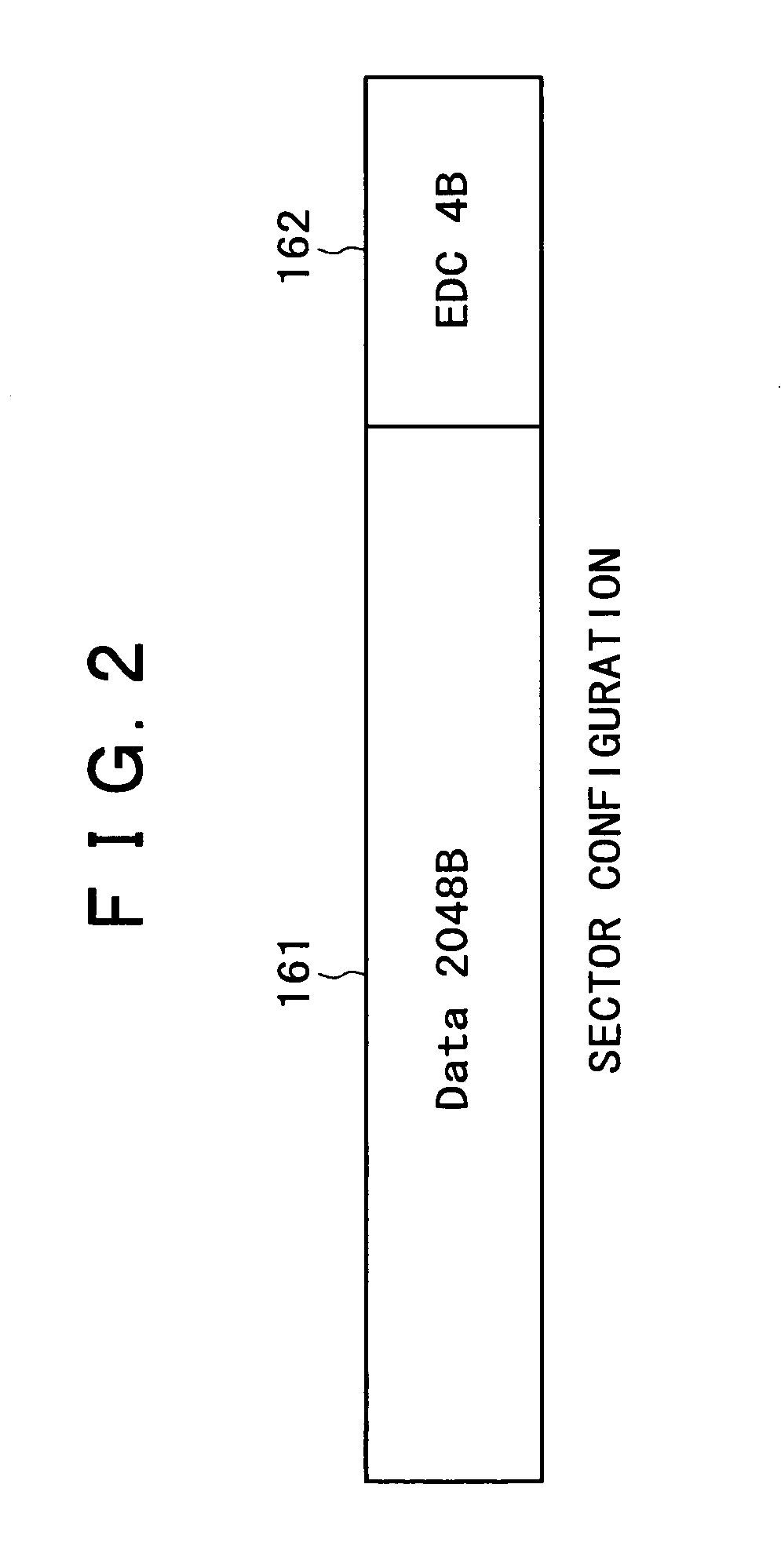

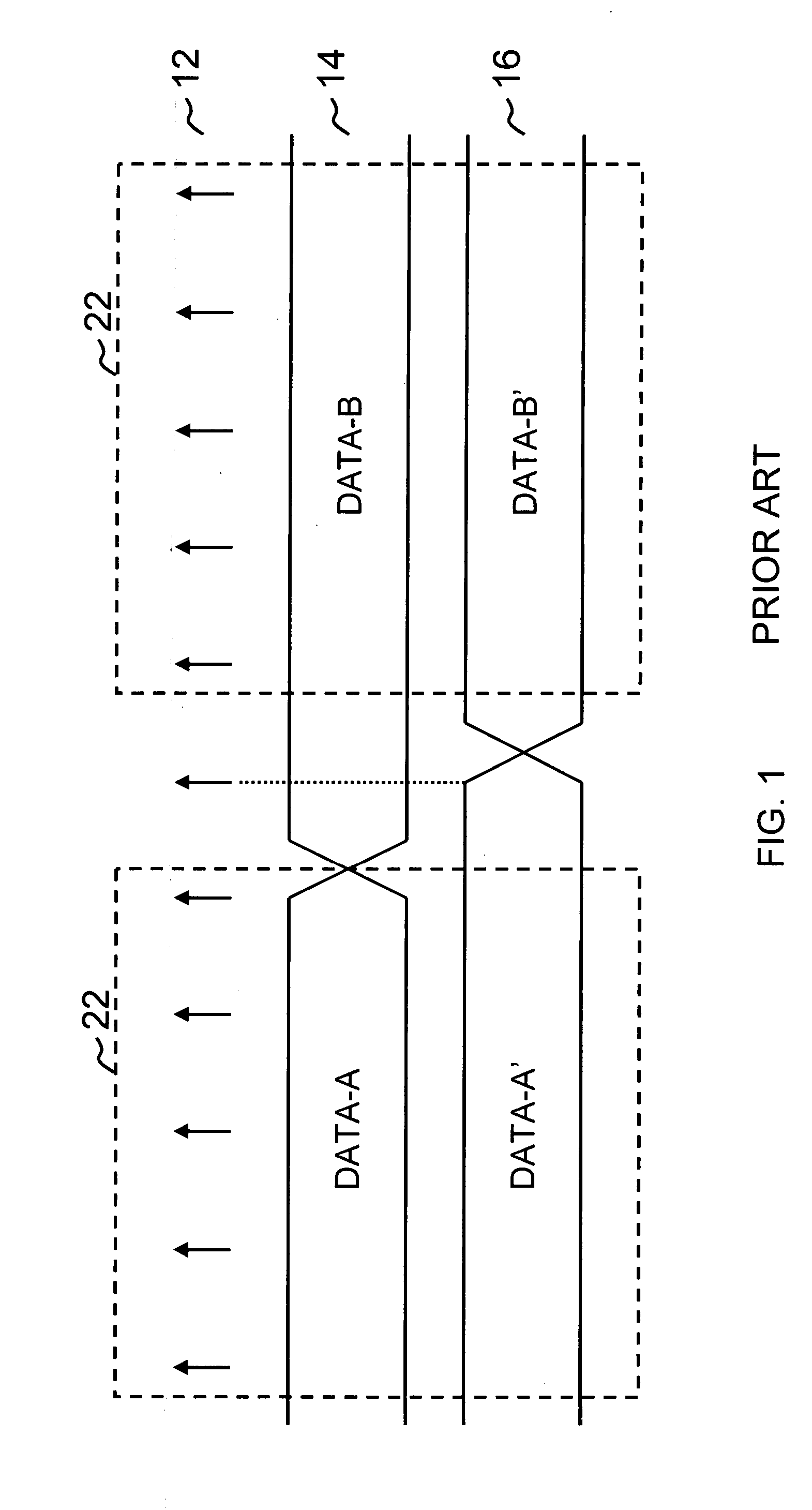

Information recording processing apparatus, information reproduction processiing apparatus, information recording medium, information recording processing method, information reproduction processing method, and computer program

InactiveUS20050089162A1Efficient data reproductionIncrease speedKey distribution for secure communicationElectronic circuit testingCopy protectionData recording

An information recording and / or reproduction processing apparatus is provided. The information recording and / or reproduction processing apparatus is provided by which additional information such as copy protection information is recorded as encrypted data on an information recording medium and also a cryptographic key is recorded such that the difficulty in analysis thereof is promoted. Where additional information such as copy protection information is encrypted and recorded and also a cryptographic key for the encrypted additional information is recorded together, a seed is generated based on an error correction code set corresponding to the additional information. Then, a scrambling or bit position conversion process in which random numbers generated based on the seed are applied is executed for the cryptographic key data, and resulting cryptographic key data is recorded on an information recording medium. Upon such recording, the additional information is recorded as pit information while the cryptographic key data is recorded as wobble data. The cryptographic key has an increased difficulty in analysis and allows achievement of an efficient data reproduction process.

Owner:SONY CORP

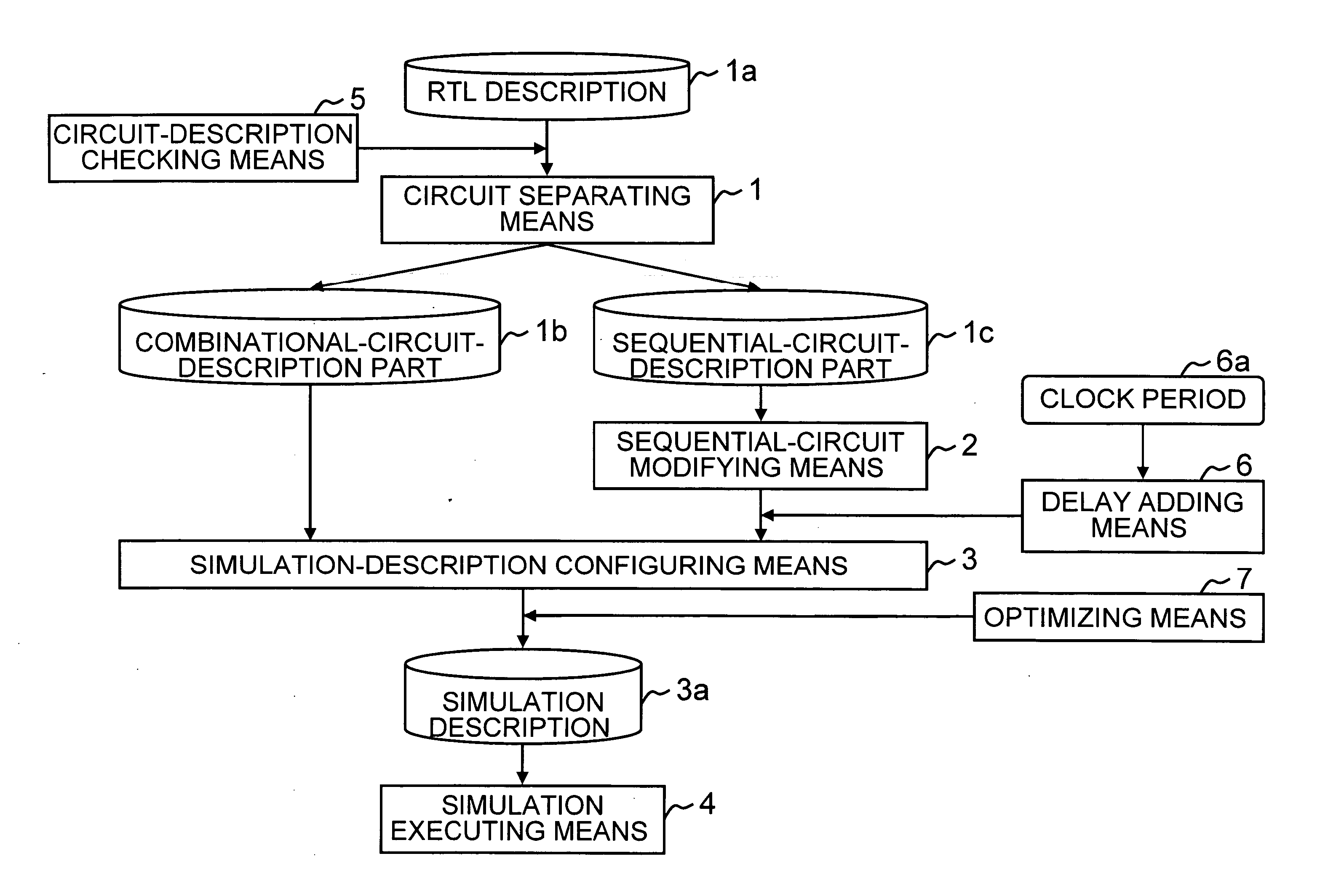

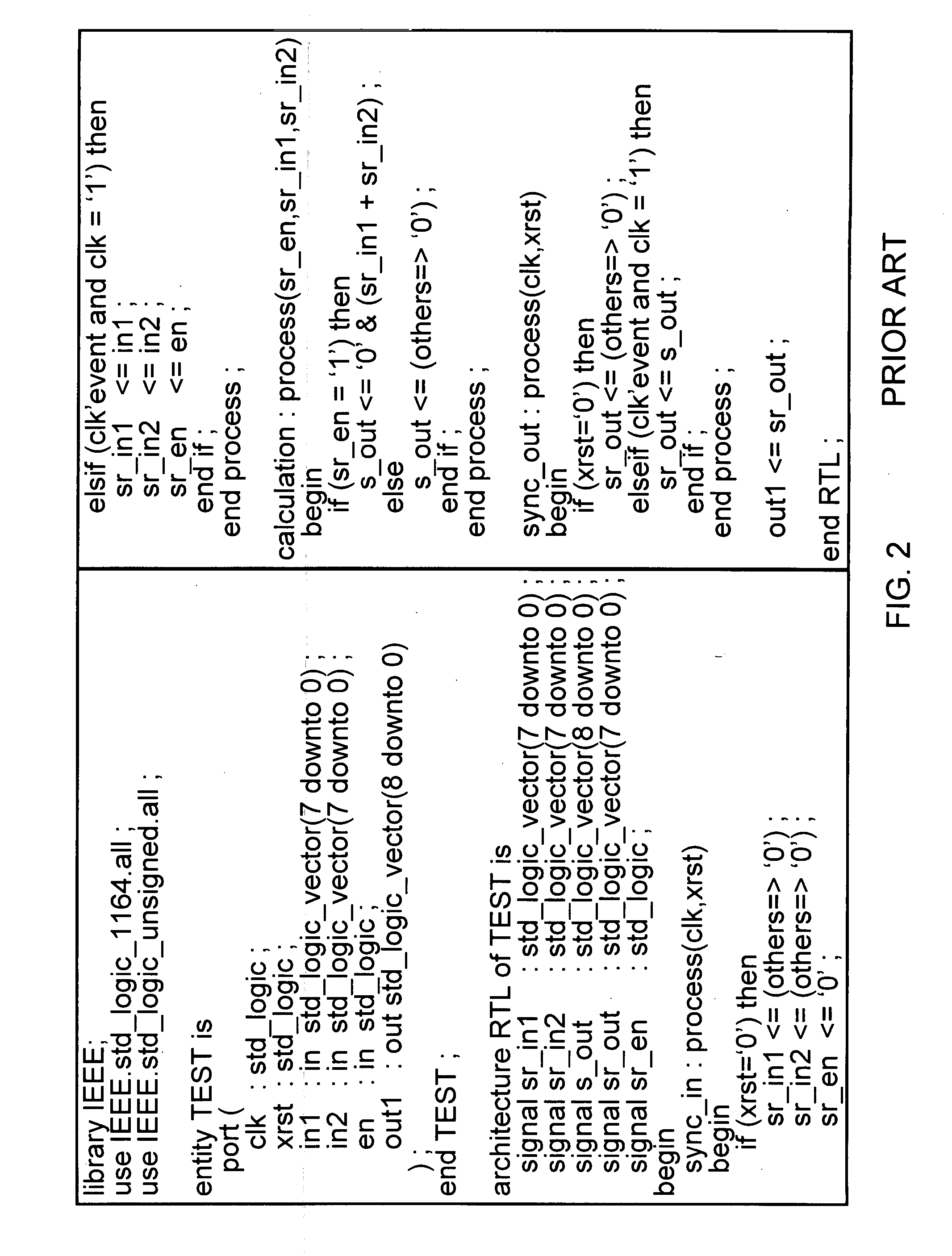

Apparatus for handling register-transfer-level description, method thereof, and program storage medium storing program thereof

InactiveUS20080071514A1Reduce loadImprove simulation speedCAD circuit designSpecial data processing applicationsTheoretical computer scienceRegister-transfer level

A circuit description is separated into sequential-circuit descriptions as a sequential-circuit-description part and combinational-circuit descriptions as a combinational-circuit-description part. The sequential-circuit-description part is modified and converted into combinational-circuit descriptions. A simulation description is configured with the combinational-circuit-description part and the combinational-circuit descriptions converted from the sequential-circuit-description part. This arrangement can generate a simulation description that does not contain a sequential-circuit description requiring an arithmetic operation at each clock event and that allows the number of arithmetic operations to be reduced. This is because, during simulation, the arithmetic operation is triggered by an update of input variables other than a clock, rather than being triggered by a clock event.

Owner:FUJITSU LTD

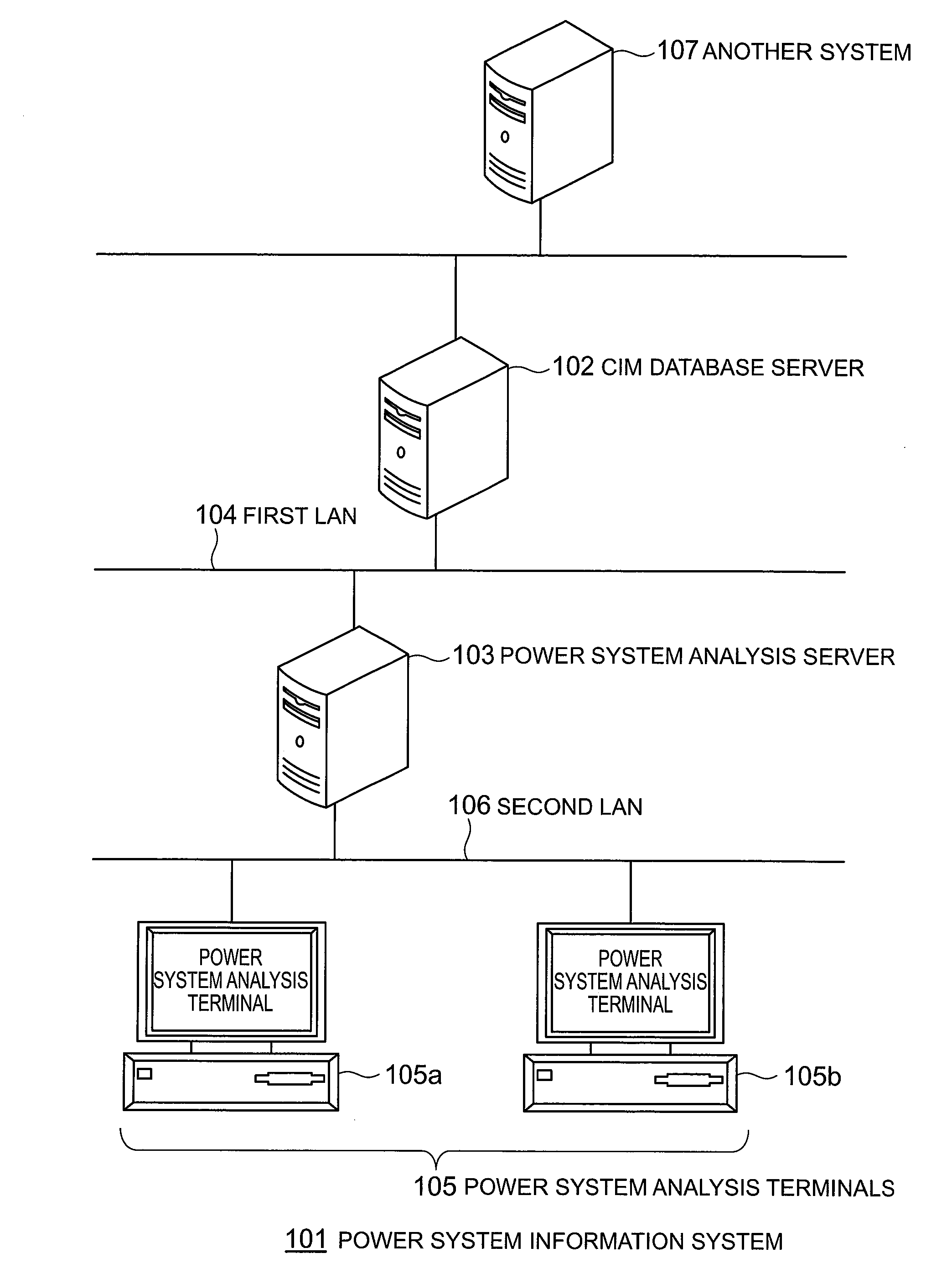

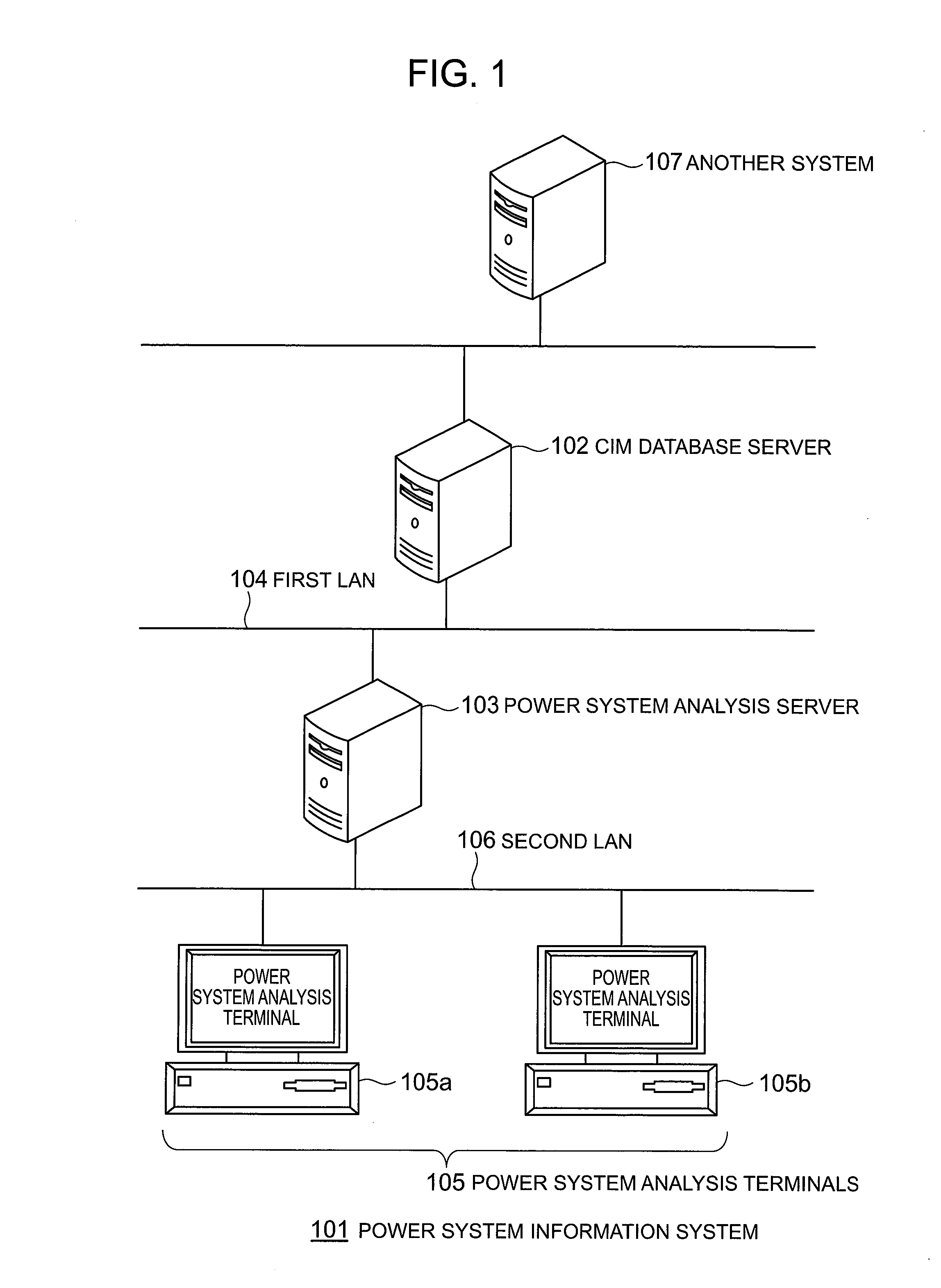

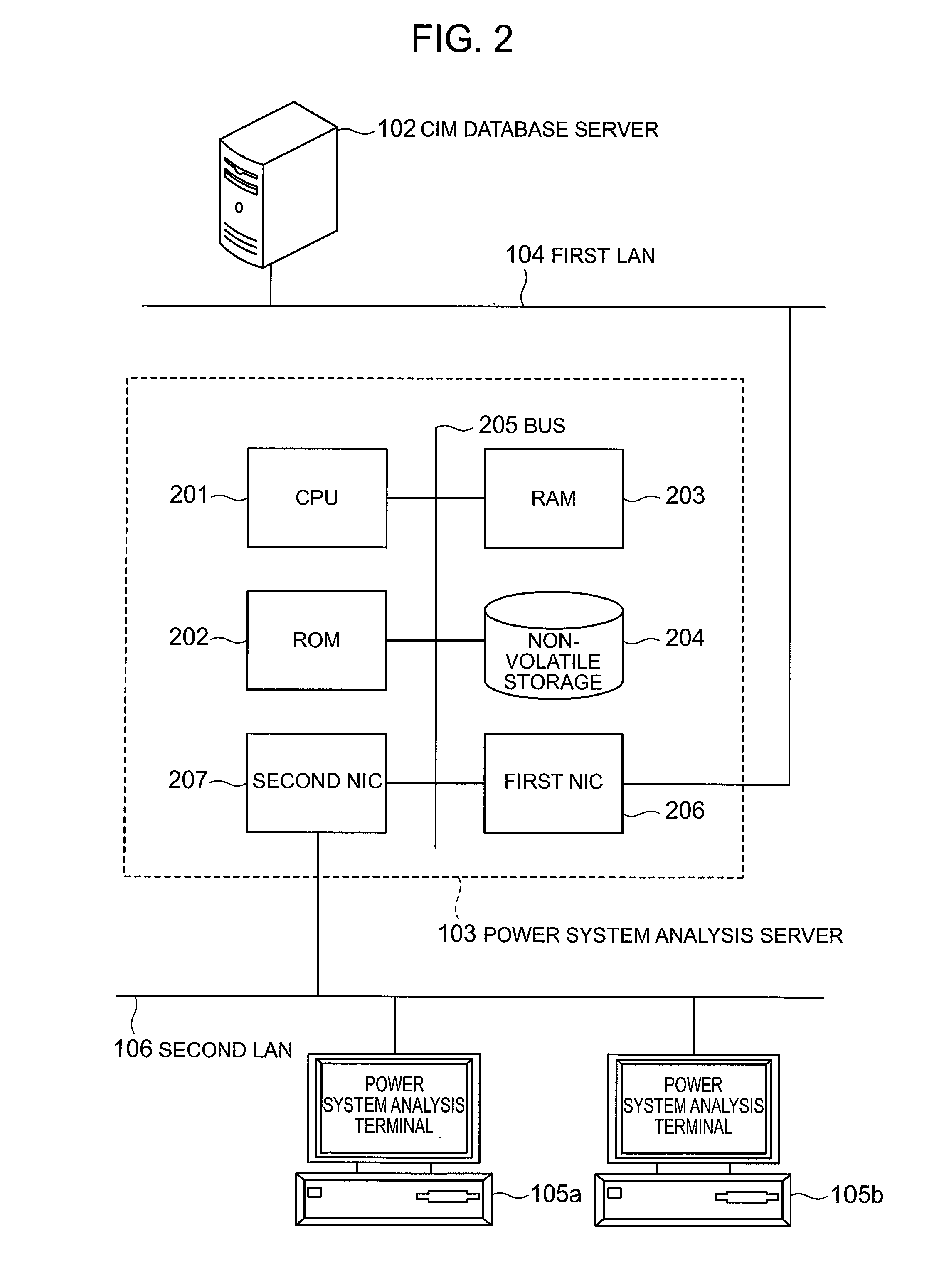

Conversion method, program and system of power system data models

ActiveUS20140122051A1Improve versatilityShorten speedAnalogue computers for nuclear physicsDesign optimisation/simulationSystems analysisDatabase server

A power system data model conversion method, a power system data model conversion system and a power system data model conversion program which are to perform a fast power system analysis and used for a power system analysis capable of reducing inconsistency with another information system, wherein all instances used for the power system analysis are read out from a CIM database server which is commonly used on a power system information system, and a connected relation between instances is constructed while performing recursive retrieval. And, conversion processing of the data model is performed to integrate information necessary for the power system analysis and dispersed to extend over the plural classes of a CIM data model into one class.

Owner:HITACHI LTD

Proximity effect correction with regard to a semiconductor circuit design pattern

InactiveUS7689968B2Increase weightImprove accuracySolid-state devicesSemiconductor/solid-state device manufacturingComputer scienceDesign pattern

A pattern correction apparatus for performing both of optical proximity effect correction and process proximity effect correction with regard to a design pattern includes: a correction calculation means configured to perform correction calculation by two-dimensional model-based optical proximity effect correction for each of sampling points set on pattern edges which form the design pattern; the correction calculation means performing the correction calculation which involves weighting with a two-dimensional distribution of the pattern edges around the sampling point taken into consideration; the weighting being performed such that a high weight is applied to a region in which reaction products which can have an influence on the sampling point are produced but a low weight is applied to any other region.

Owner:SONY CORP

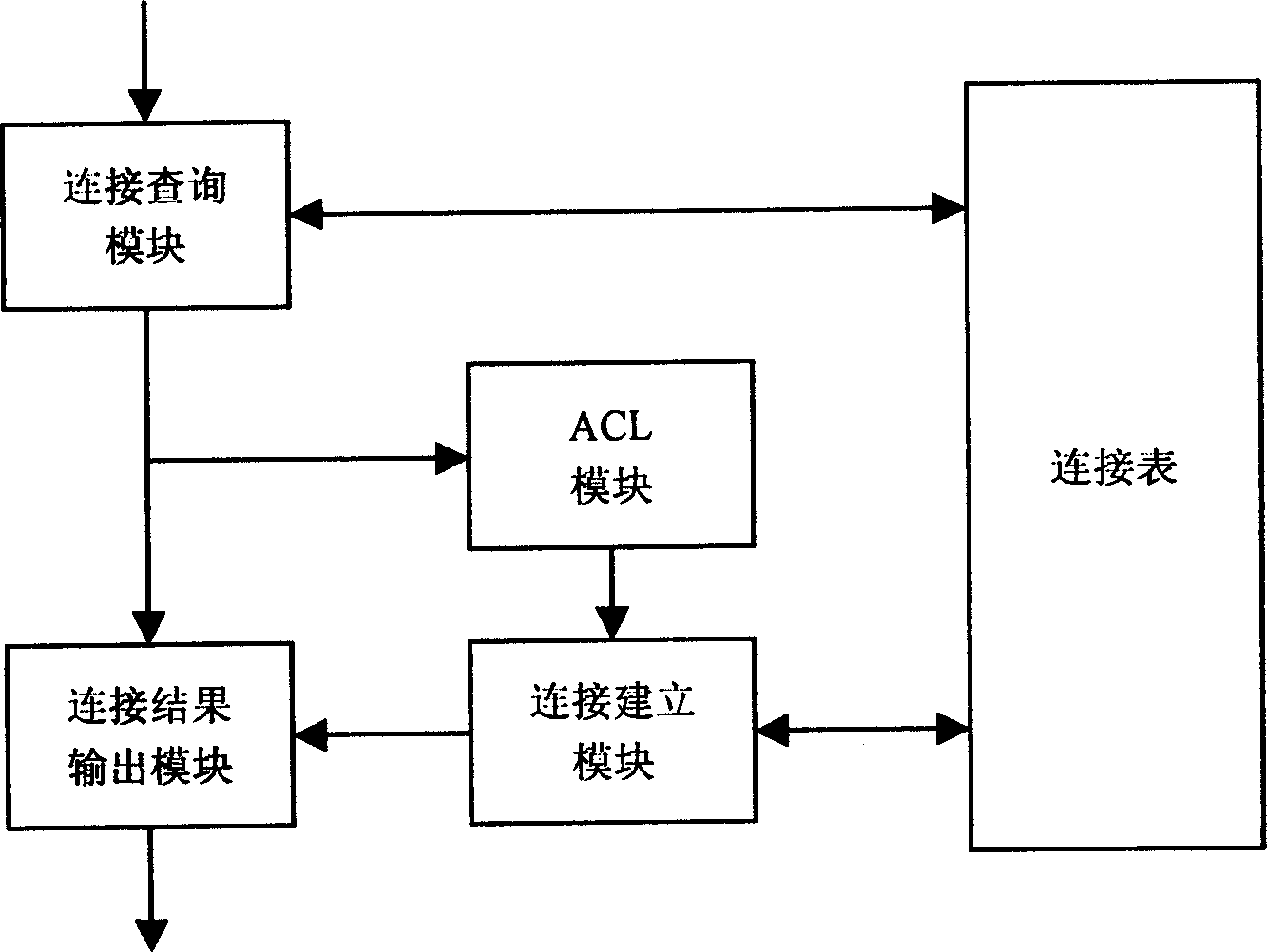

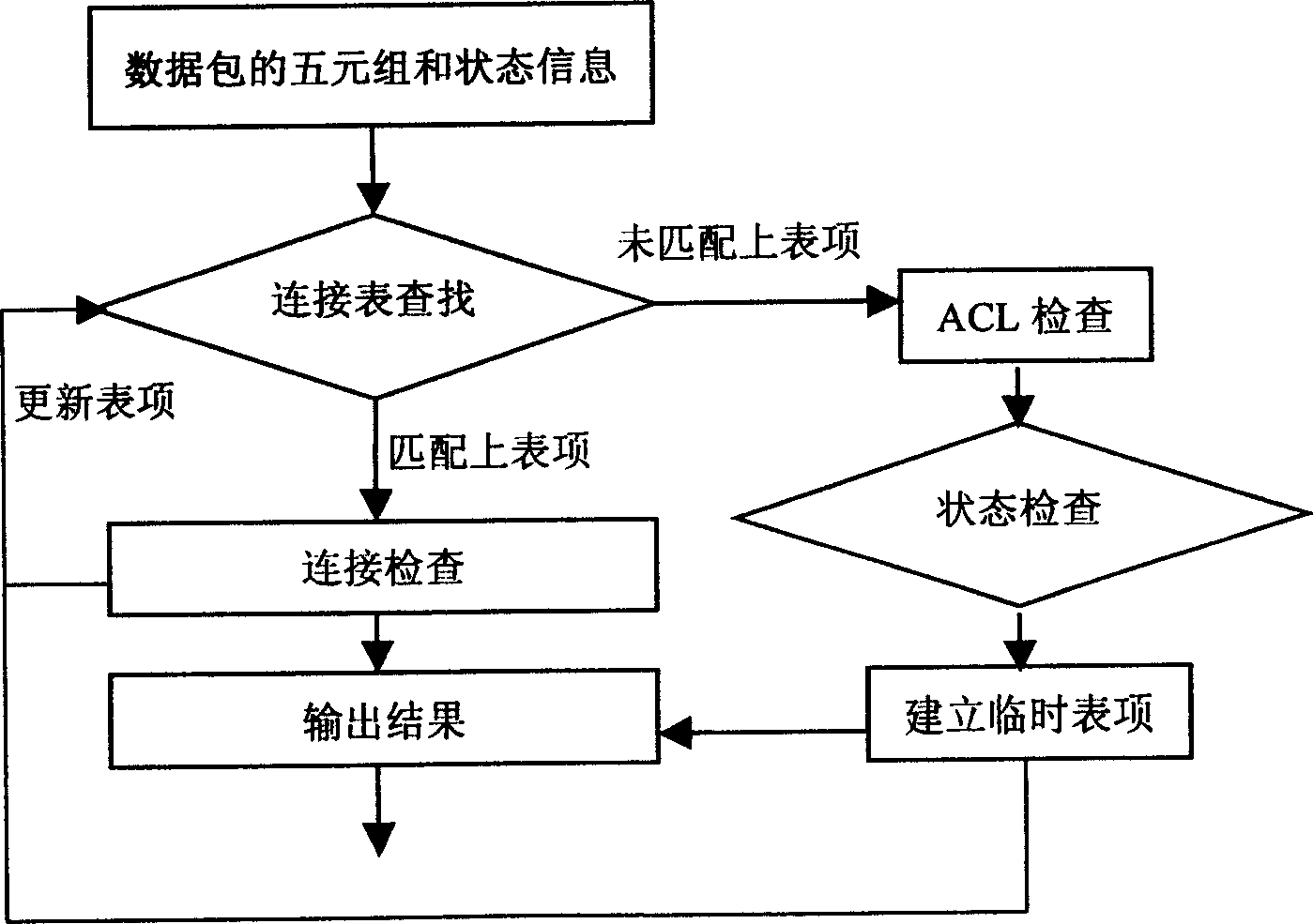

Establishment of TCP data flow connection by hardware

InactiveCN1819557AImprove reading and writing efficiencyHigh speed executionData switching networksData streamNetwork packet

The invention provides a hardware method for building a TCP data stream connection. A hardware module is used to make deep analysis for the data packet, and in term of quintuple and state information to build communication connection for the packet. When using the hardware connection, each functional module works independently so that opening the TCP connection doesn't reduce the efficiency of other modules. Meanwhile RAM read writing speed by hardware is also very high to make the data format of read writing able to be simplified.

Owner:四川南山之桥微电子有限公司

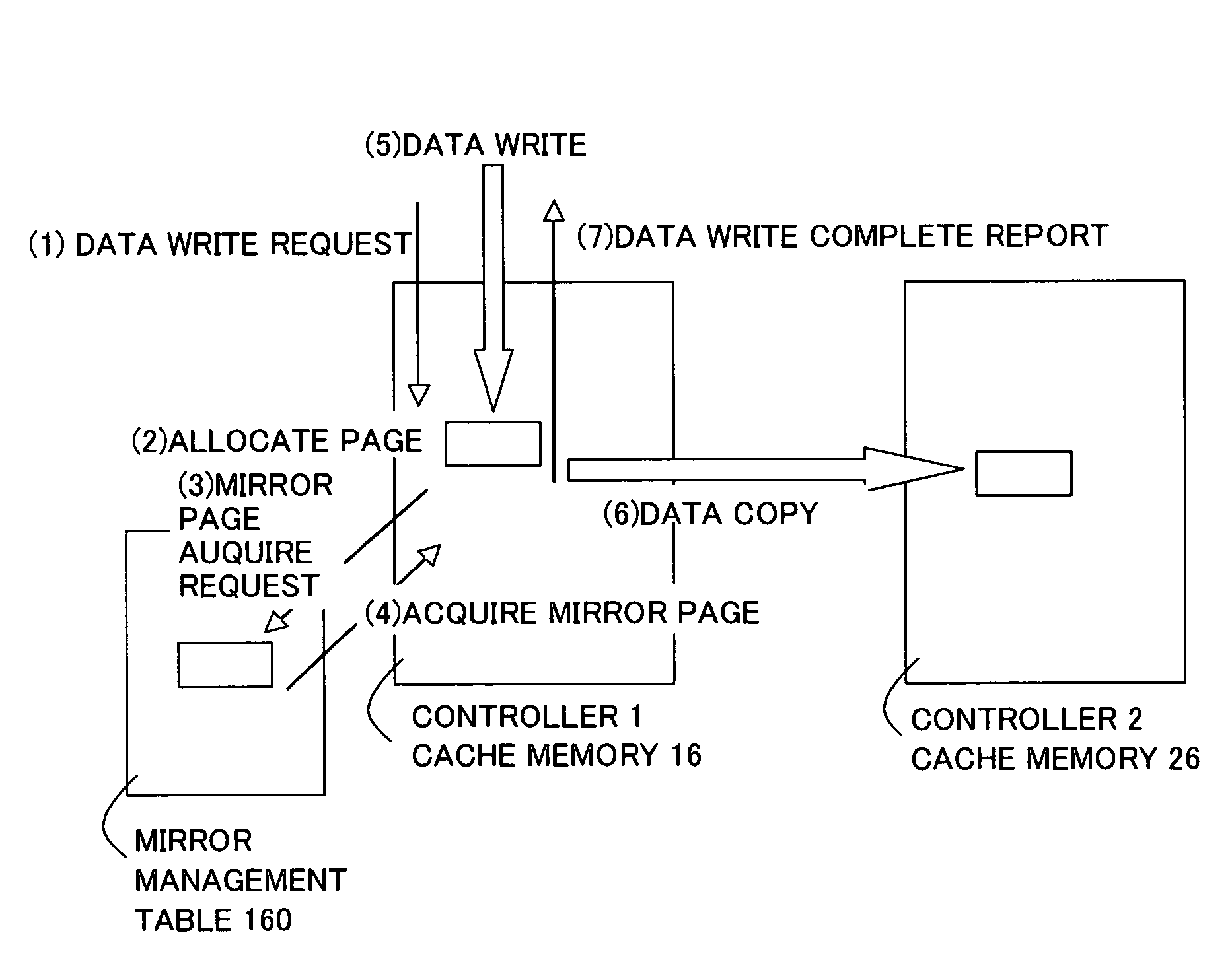

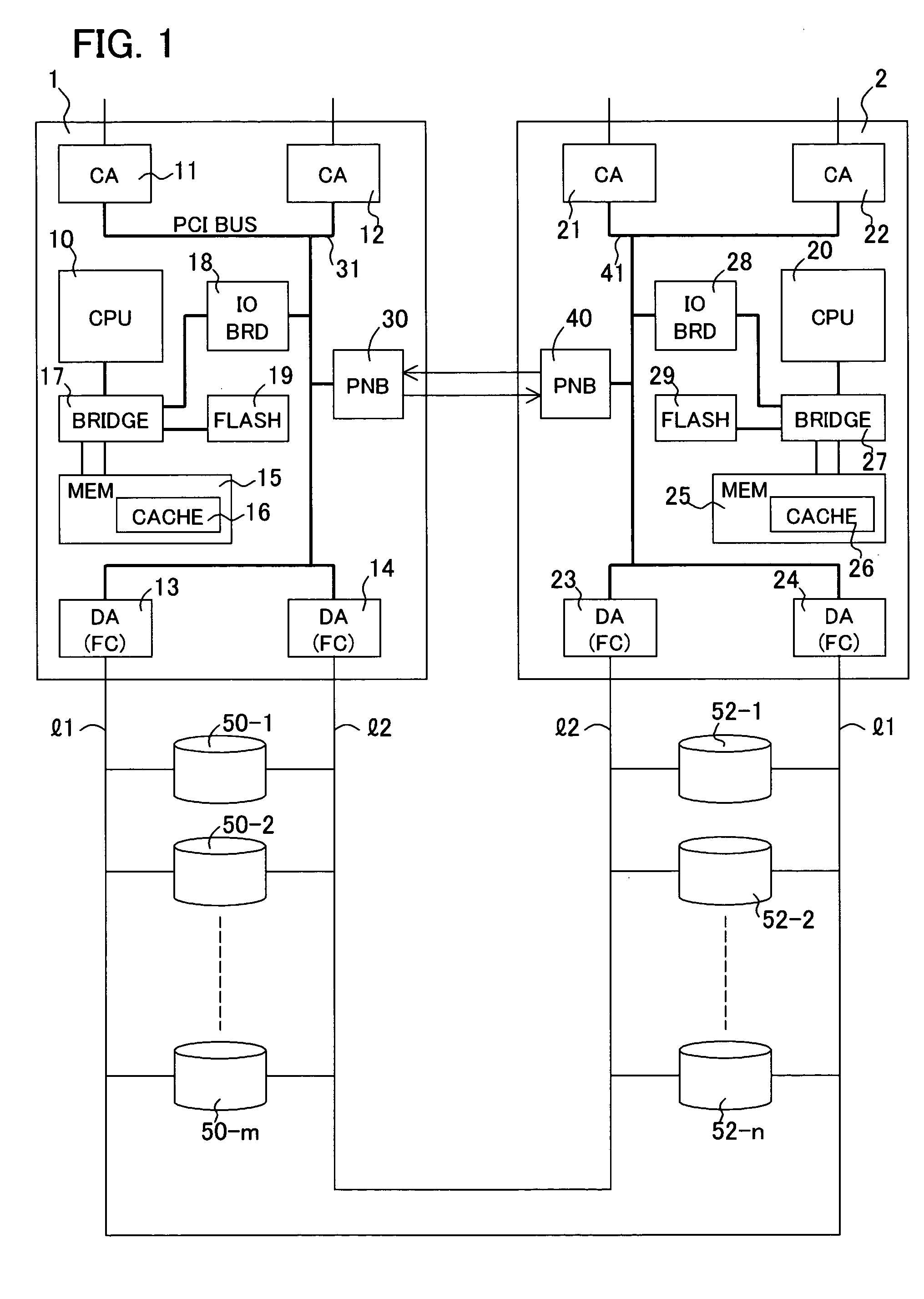

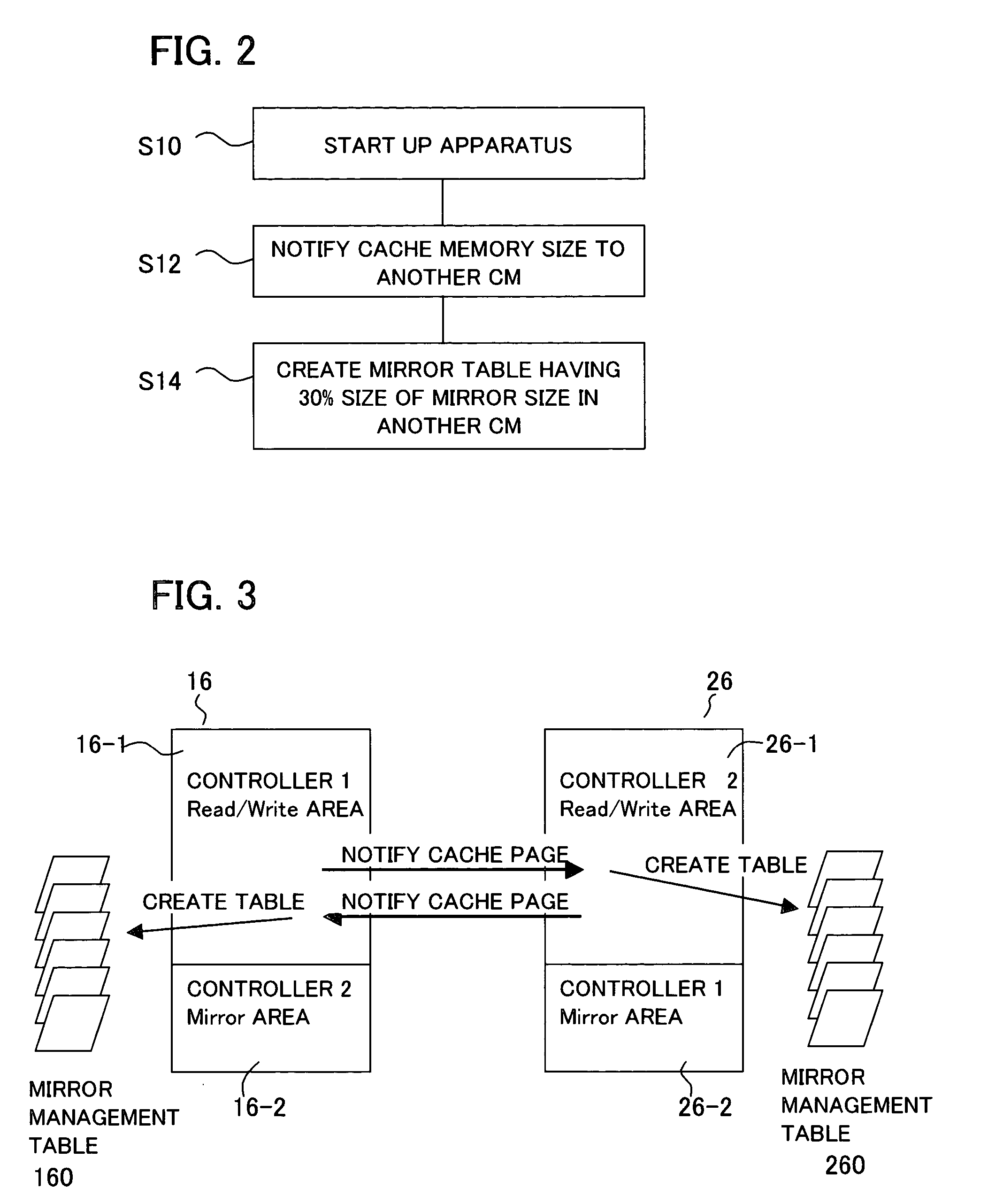

Storage control apparatus and control method thereof

ActiveUS7421538B2Reduce control loadReduce loadInput/output to record carriersMemory loss protectionOperating systemControl equipment

A storage control apparatus controls physical disks according to the host access using a pair of controllers, while mirroring processing is decreased when data is written to a cache memory and high-speed operation is enabled. The mirror management table is created with allocating the mirror area of the cache memory of the other controller, and acquisition of a mirror page of the cache memory of the other controller is executed referring to the mirror management table without an exchange of mirror page acquisition messages between the controllers.

Owner:FUJITSU LTD

Heating/cooling method, manufacturing method of image displaying apparatus, heating/cooling apparatus, and heating/cooling processing apparatus

InactiveUS7383875B2Increase speedHigh-speed executionBaking ovenSemiconductor/solid-state device manufacturingComputer graphics (images)Method of images

Owner:CANON KK

Hash value generator

InactiveUS8108682B2Increase speedHigh-speed executionUser identity/authority verificationSecret communicationComputer hardwareHigh velocity

To achieve high safety, large-sized nonlinear permutation is employed; however, the larger permutation processing is, the more the period of time required for the processing is, which hence is not efficient. There is provided a hash value generation method or a hash value generator which has the following aspects and which is highly safe and is capable of executing processing at a high speed.1. As a message insertion method, there is employed a linear conversion in which the insertion message affects all subblocks.2. An internal state is divided into a plurality of subblocks, and nonlinear permutation is conducted in each subblock unit.3. Additionally, the linear conversion of item 1 above may be configured such that each subblock of the internal state affects the subblocks of the output.

Owner:HITACHI LTD