Patents

Literature

275 results about "Register-transfer level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital circuit design, register-transfer level (RTL) is a design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those signals.

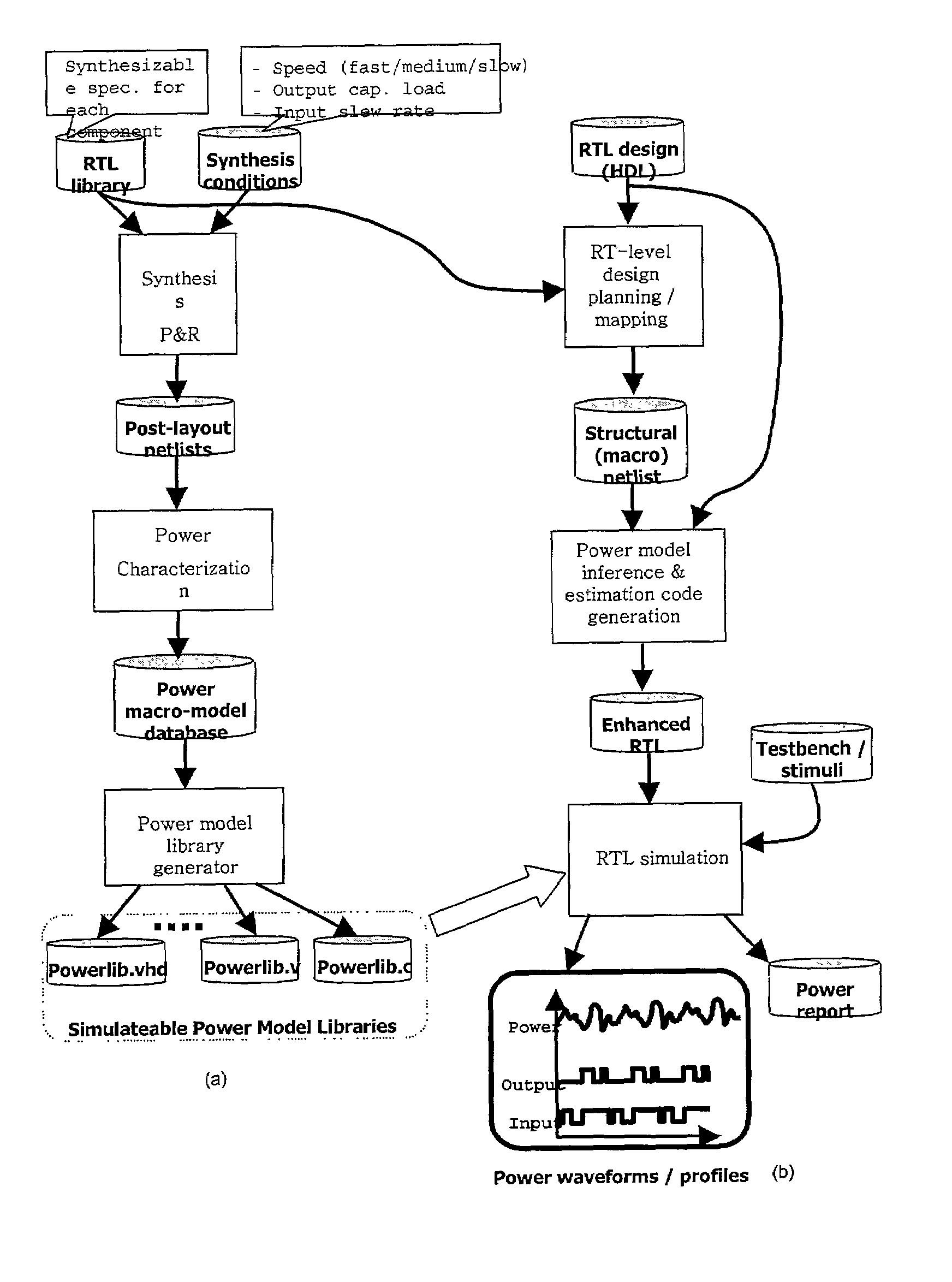

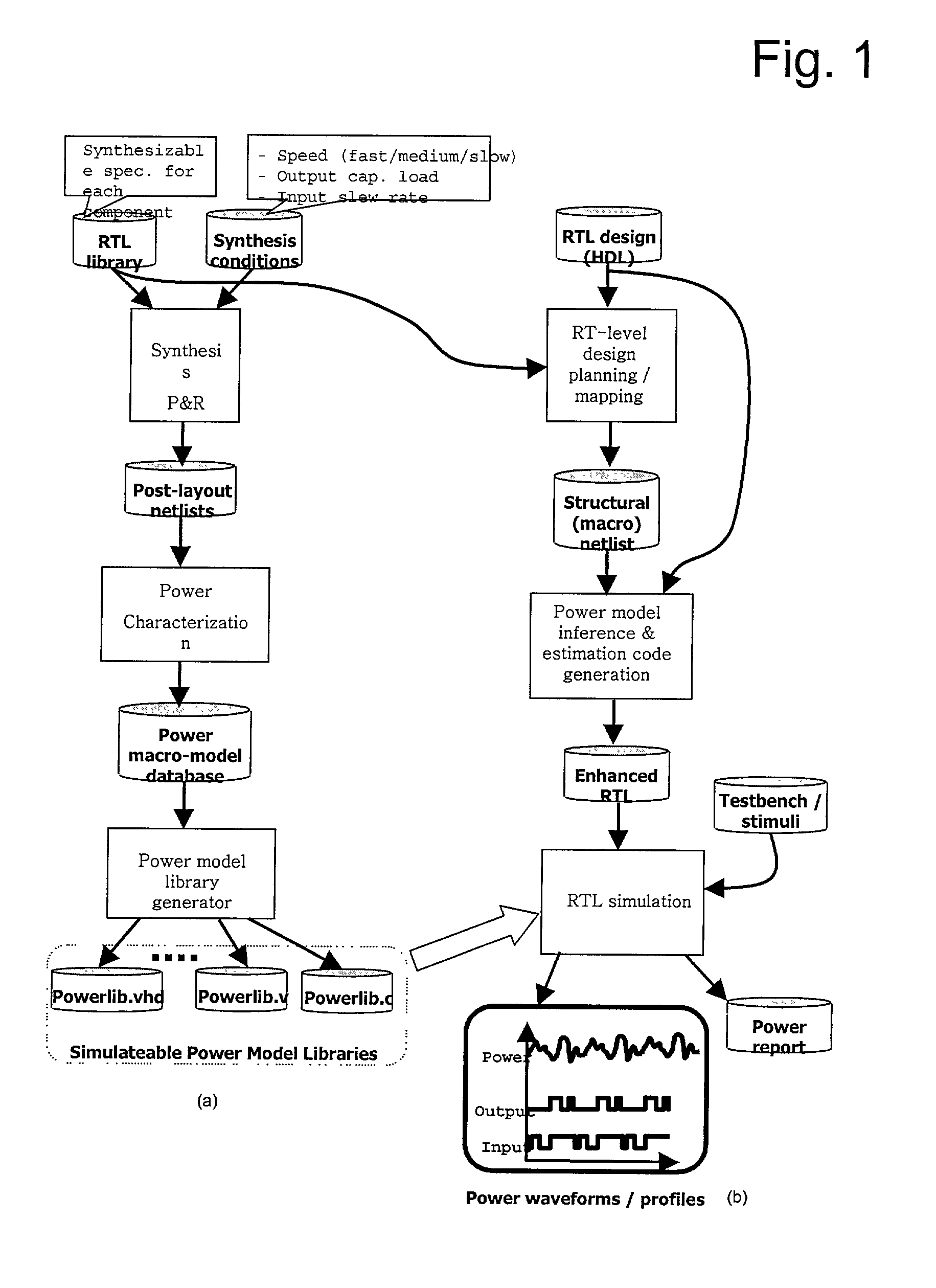

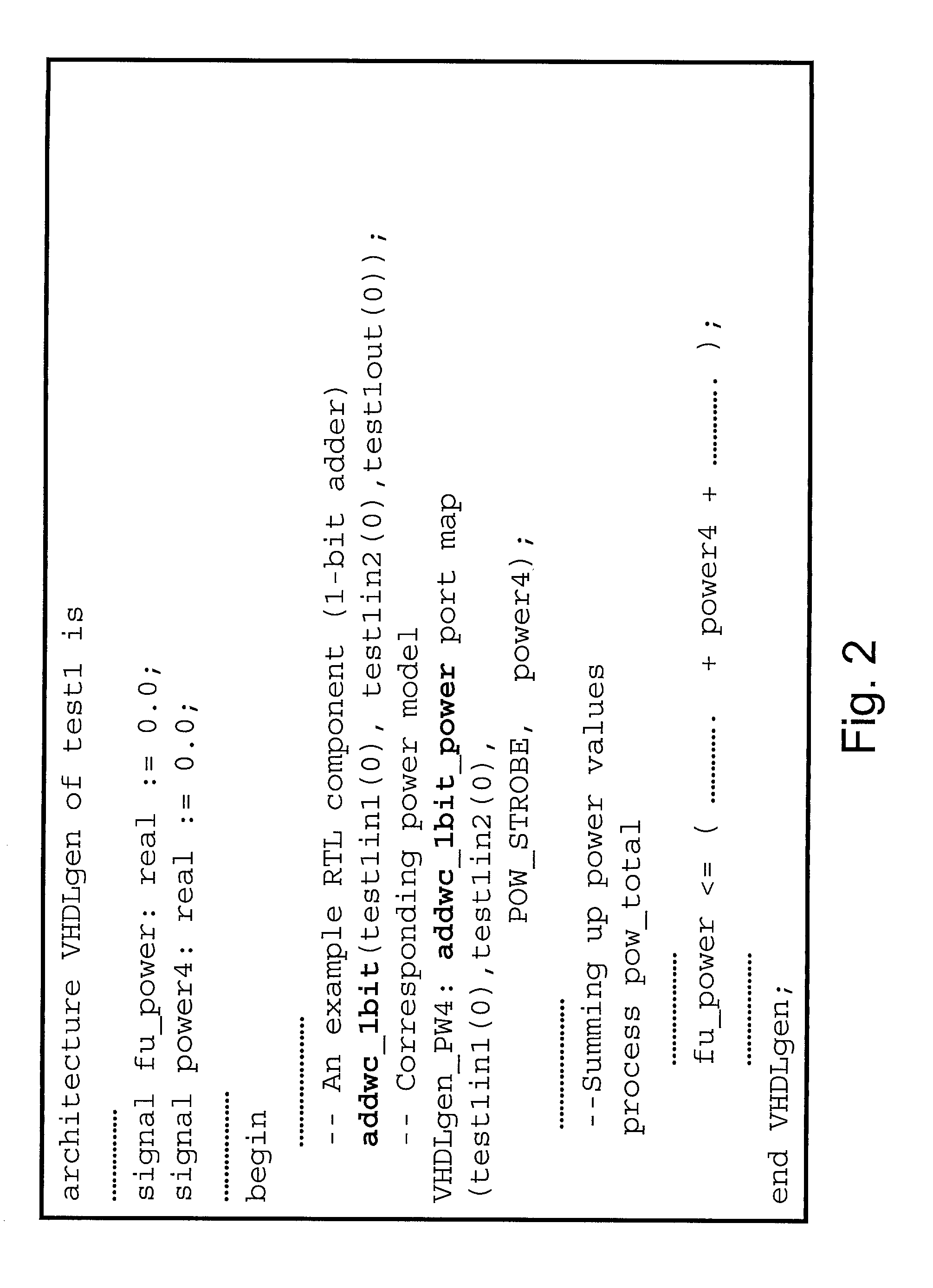

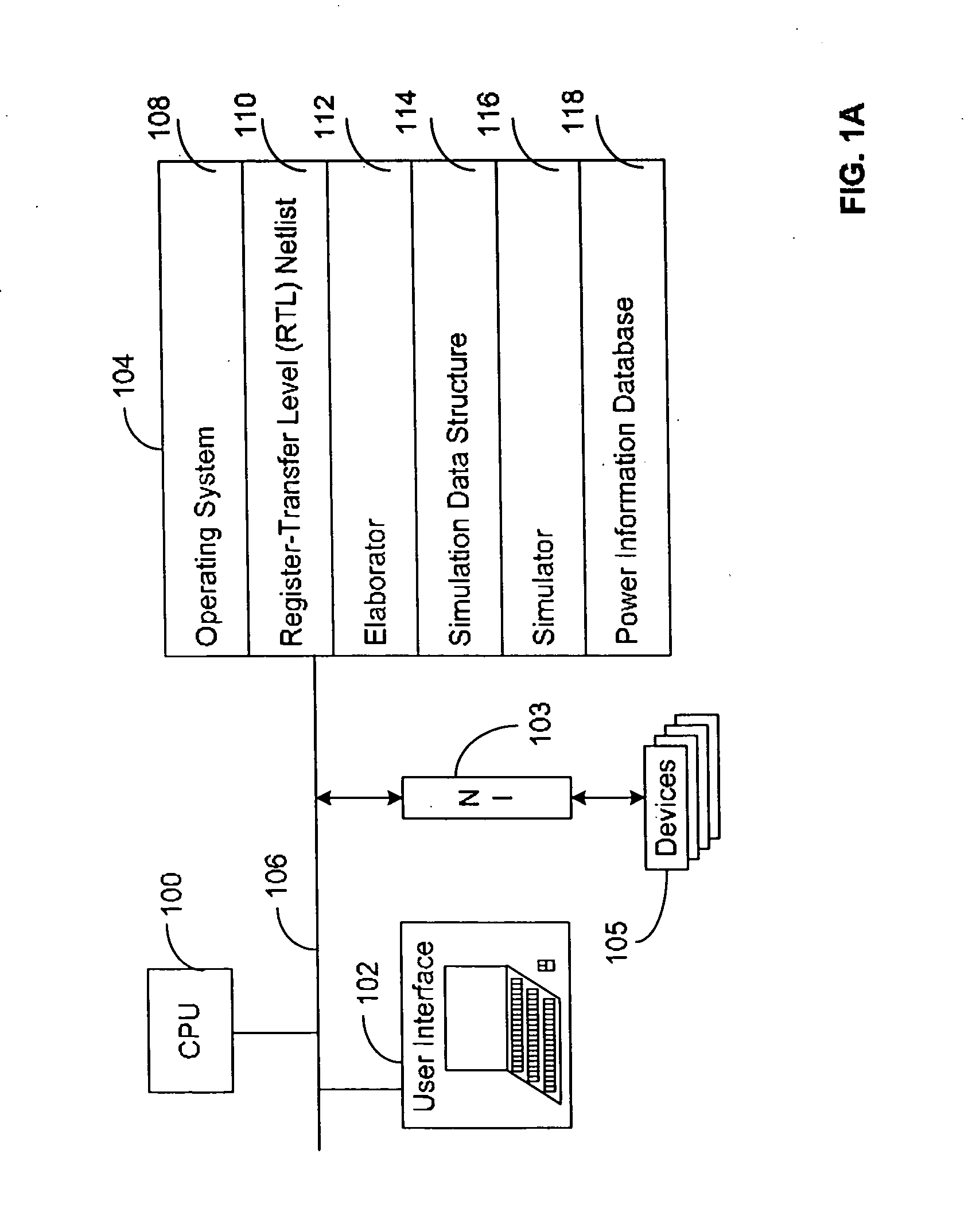

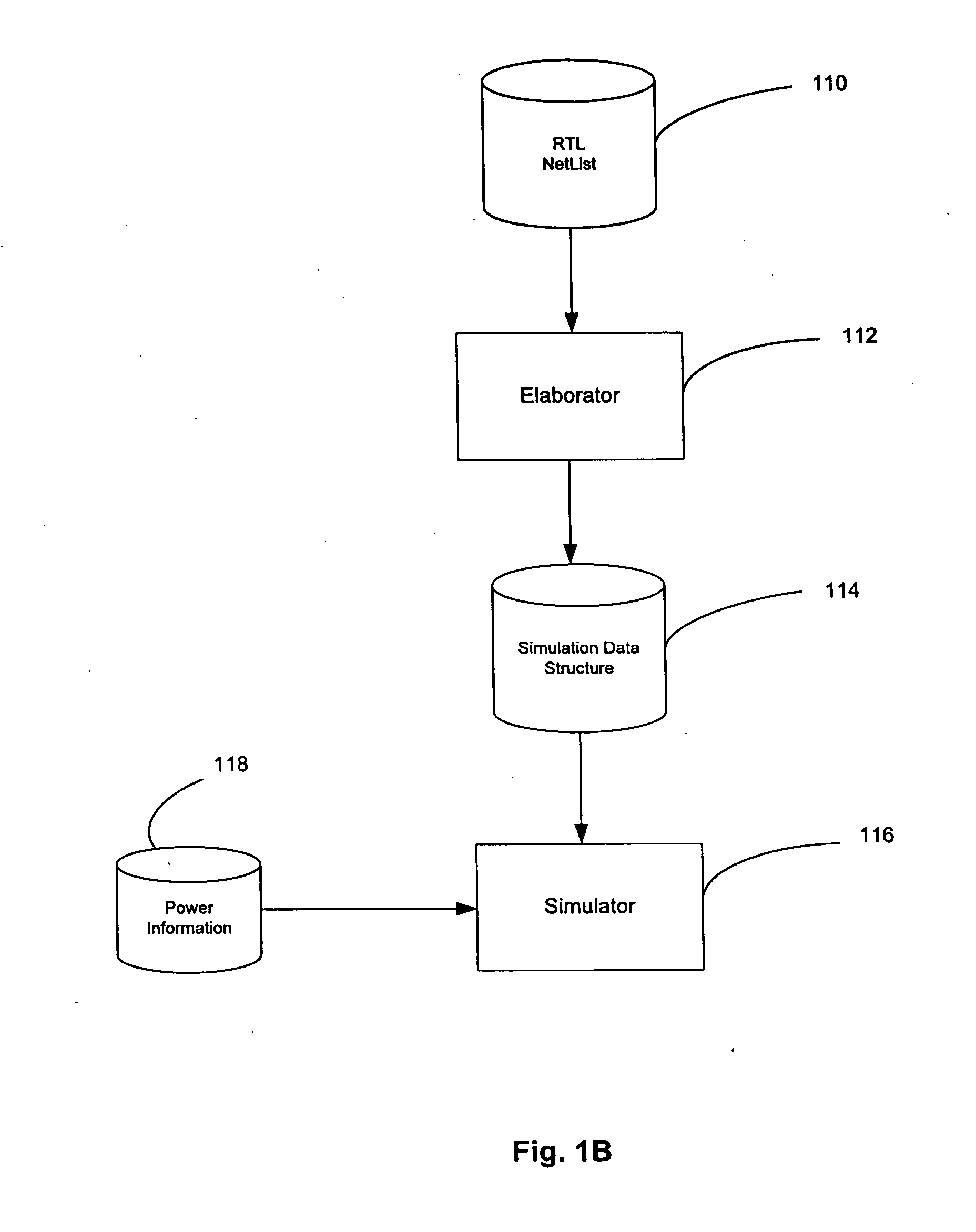

Method and apparatus for efficient register-transfer level (RTL) power estimation

InactiveUS7134100B2Accelerating power estimationEnhanced RTL descriptionCAD circuit designSoftware simulation/interpretation/emulationComputer scienceDelay calculation

Techniques for accelerating power estimation for a circuit comprising generating an RTL description of the circuit. A power model enhanced RTL description of the circuit is generated. A simulator is selected. The power model enhanced RTL description is modified to make it more friendly to the simulator. The simulator is run to estimate the power consumed by the circuit. Techniques using delayed computation and partitioned sampling are also provided. Power estimation systems using the above techniques area also provided.

Owner:NEC CORP

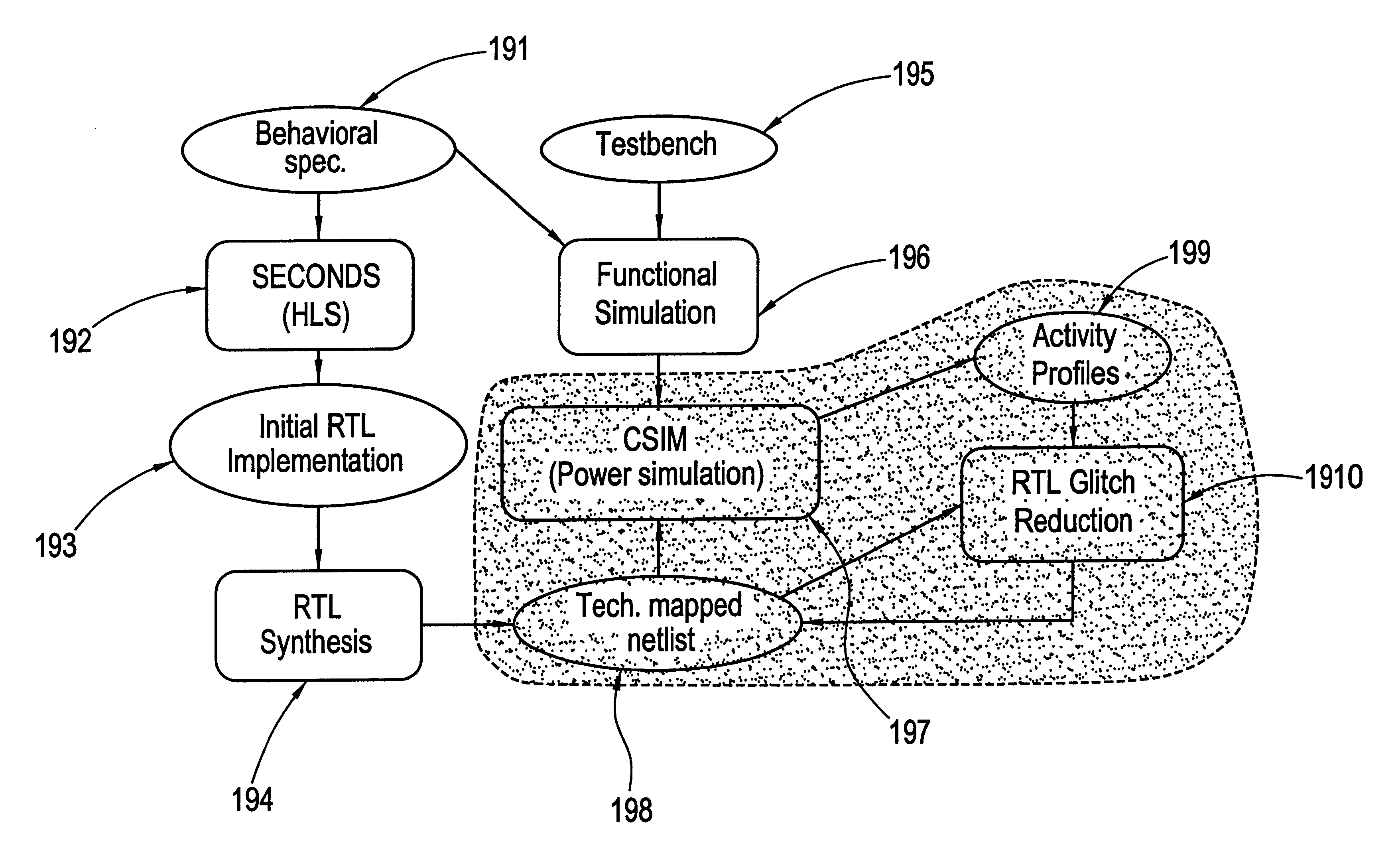

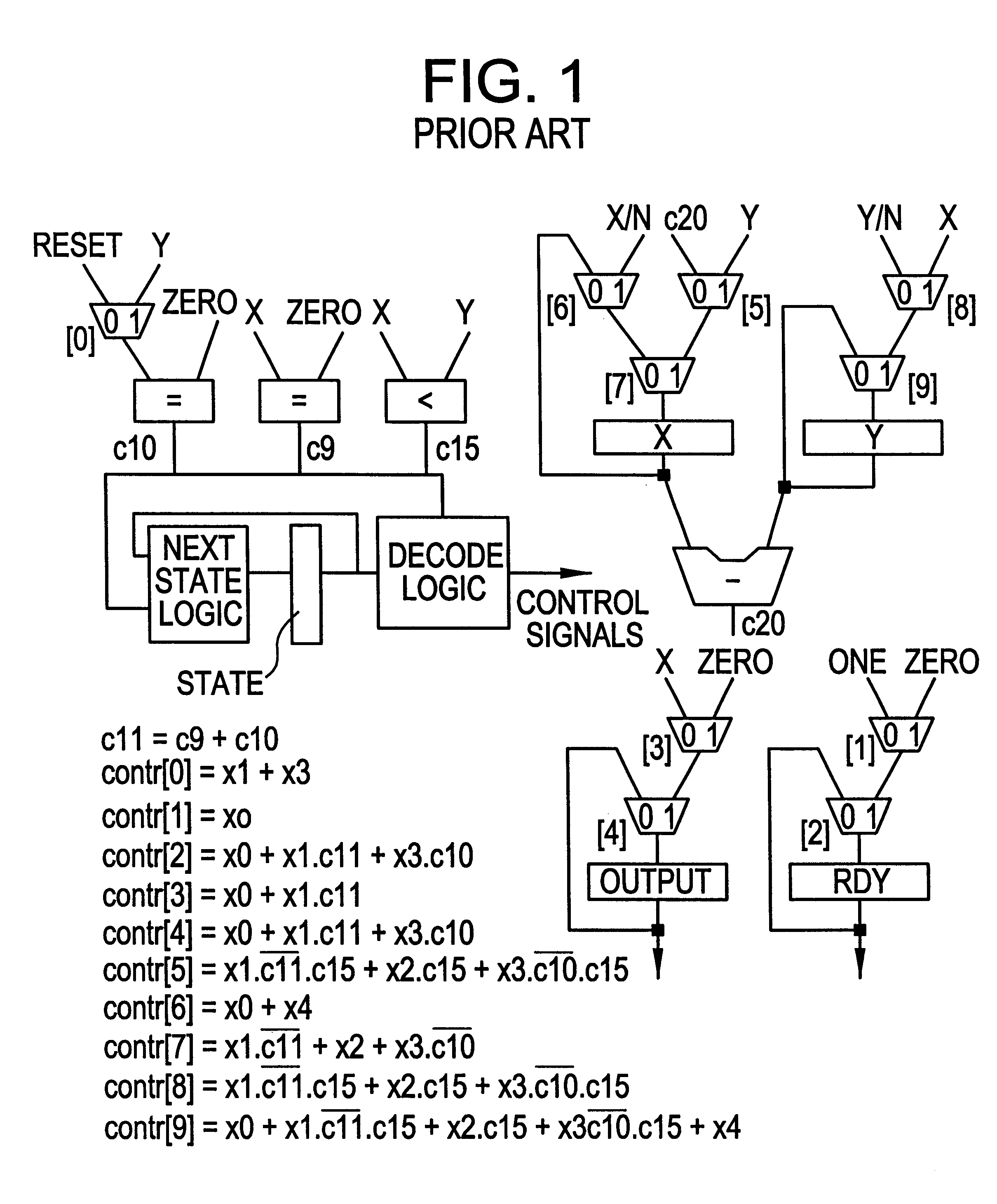

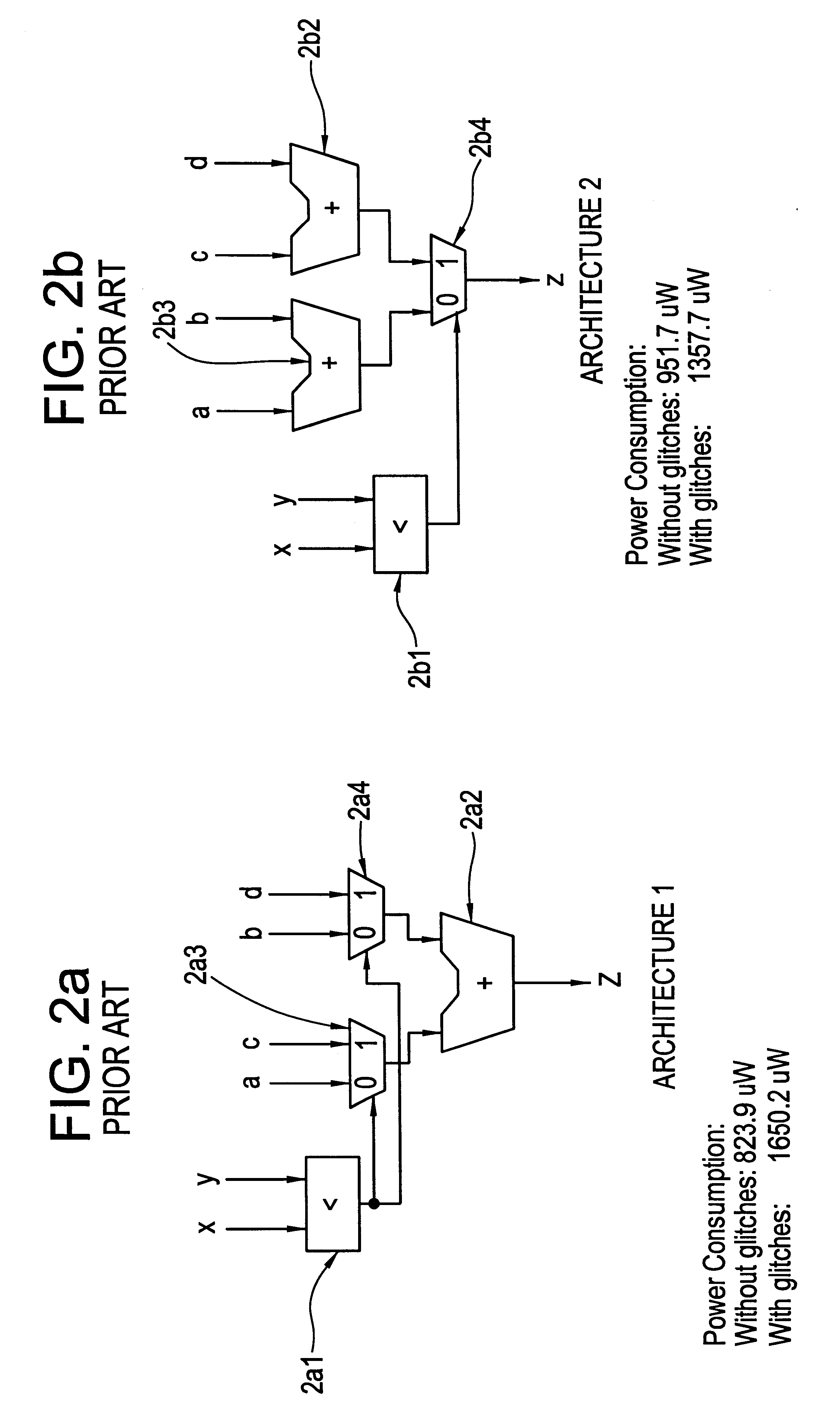

Register transfer level power optimization with emphasis on glitch analysis and reduction

InactiveUS6324679B1Reduce power consumptionLogic circuits characterised by logic functionDigital data processing detailsDatapath circuitsPathPing

A method and apparatus for design-for-low-power of register transfer level (RTL) controller / data path circuits that implement control-flow intensive specifications. The method of the invention focuses on multiplexer networks and registers which dominate the total circuit power consumption and reduces generation and propagation of glitches in both the control and data path parts of the circuit. Further the method reduces glitching power consumption by minimizing propagation of glitches in the RTL circuit through restructuring multiplexer networks (to enhance data correlations and eliminate glitchy control signals), clocking control signals, and inserting selective rising / falling delays, in order to kill the propagation of glitches from control as well as data signals. To reduce power consumption in registers, the clock inputs to registers are gated with conditions derived by an analysis of the RTL circuit, ensuring that glitches are not introduced on the clock signals.

Owner:NEC CORP

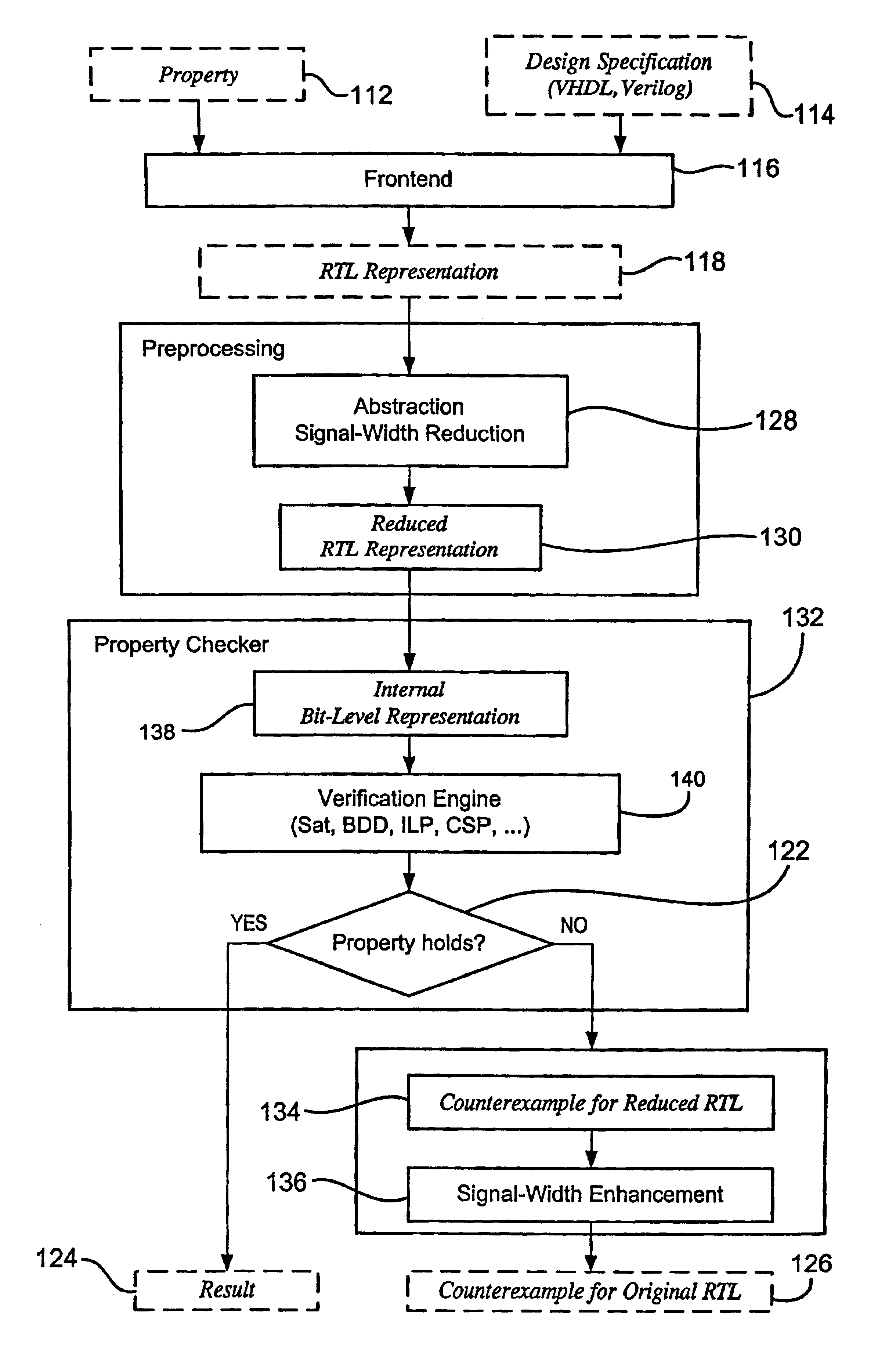

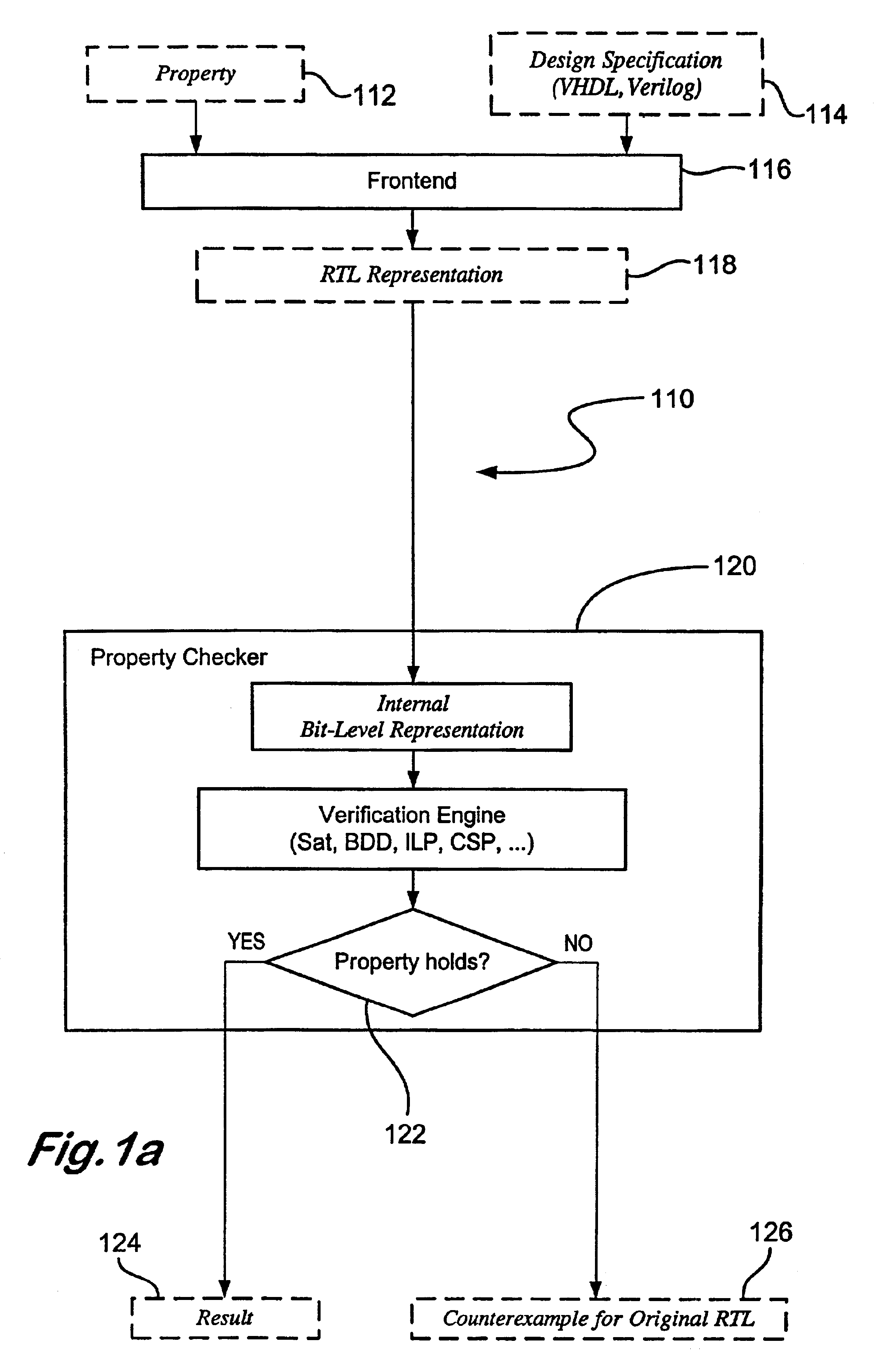

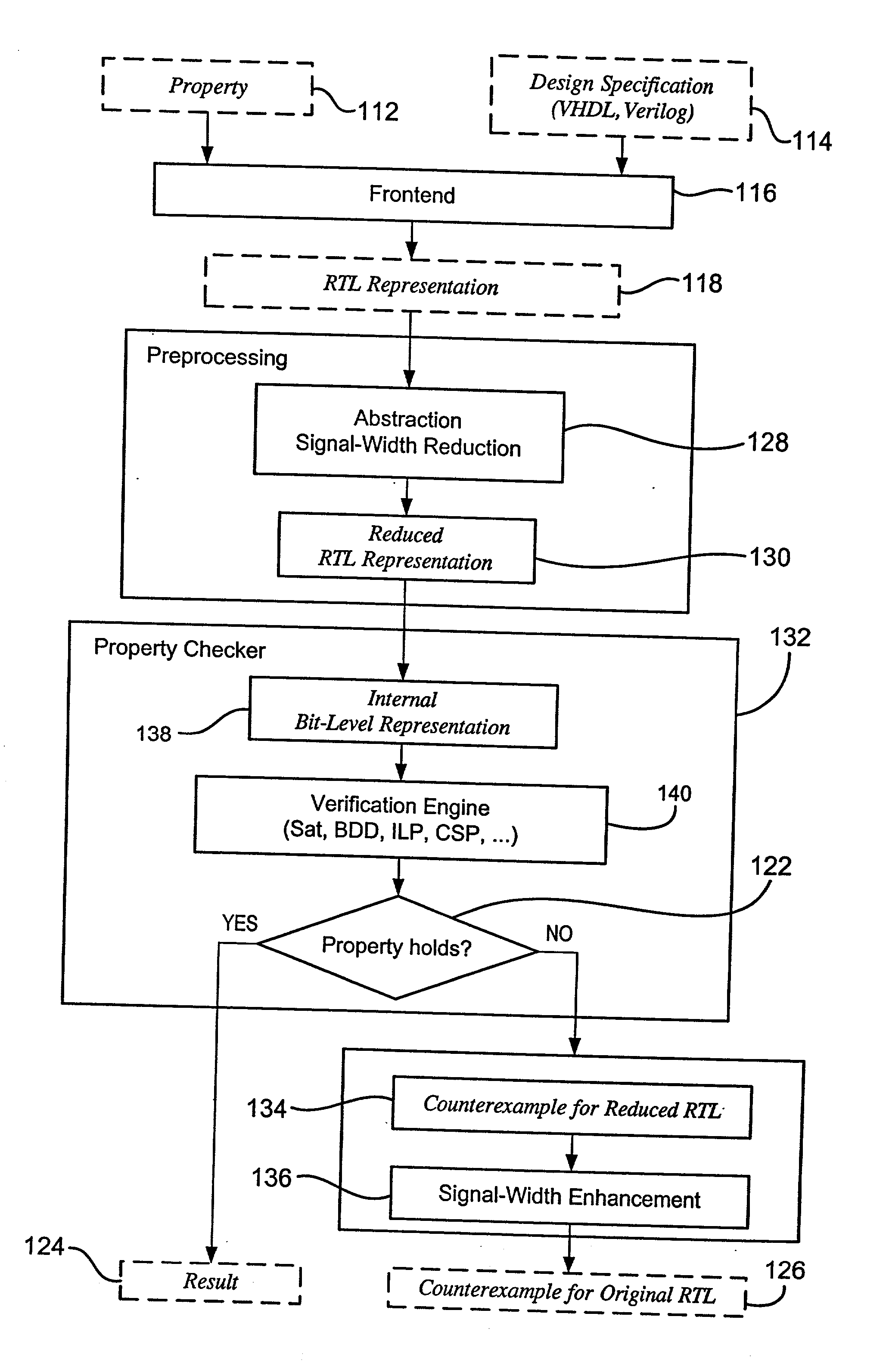

Method of circuit verification in digital design

InactiveUS6728939B2Reduce designEasy to understandComputer aided designSoftware simulation/interpretation/emulationComputer architectureValidation methods

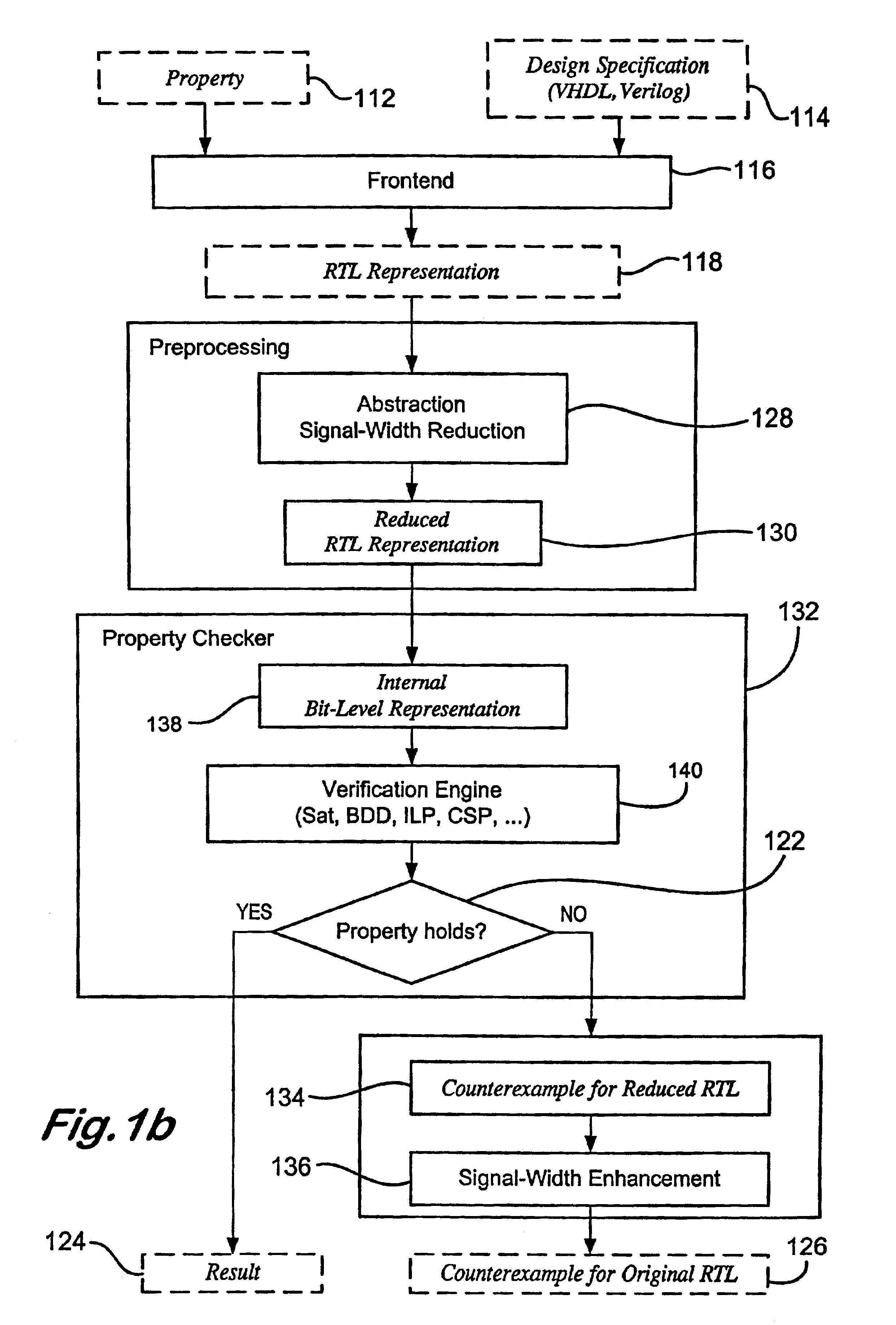

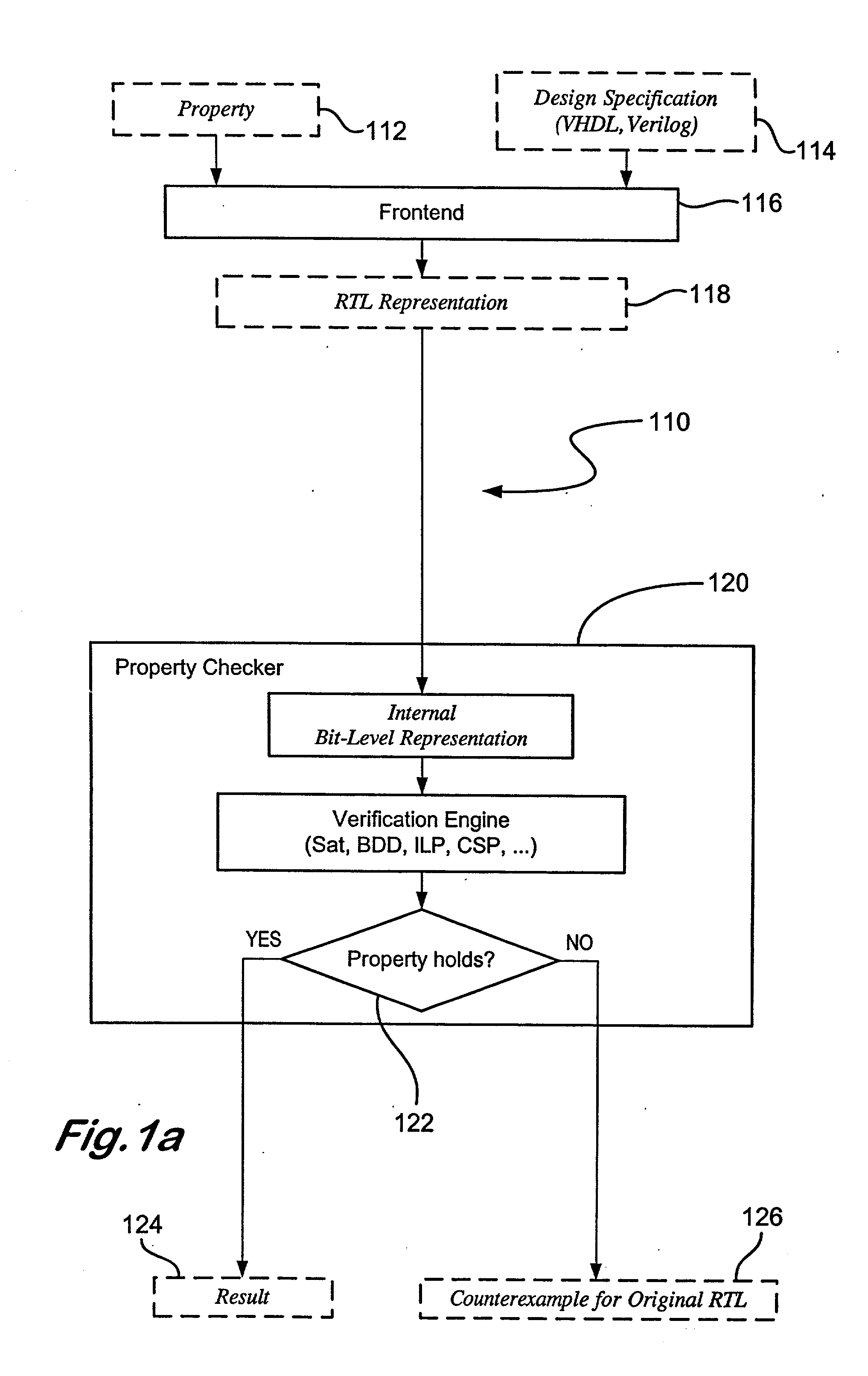

The present invention relates to a method of circuit verification in digital design and in particular, relates to a method of register transfer level property checking to enable the same. Today's electrical circuit designs frequently contain up to several million transistors, and circuit designs need to be checked to ensure that circuits operate correctly. Formal methods for verification are becoming increasingly attractive since they confirm design behavior without exhausting simulating a design. A digital circuit design verification method, prior to a property checking process for each property of a non-reduced RTL model, determines a reduced RTL model which retains specific signal properties of a non-reduced RTL model which are to be checked. A linear signal width reduction causes an exponential reduction of the induced state space. Reducing state space sizes in general goes hand in hand with reduced verification runtimes, thus speeding up verification tasks.

Owner:ONESPIN SOLUTIONS

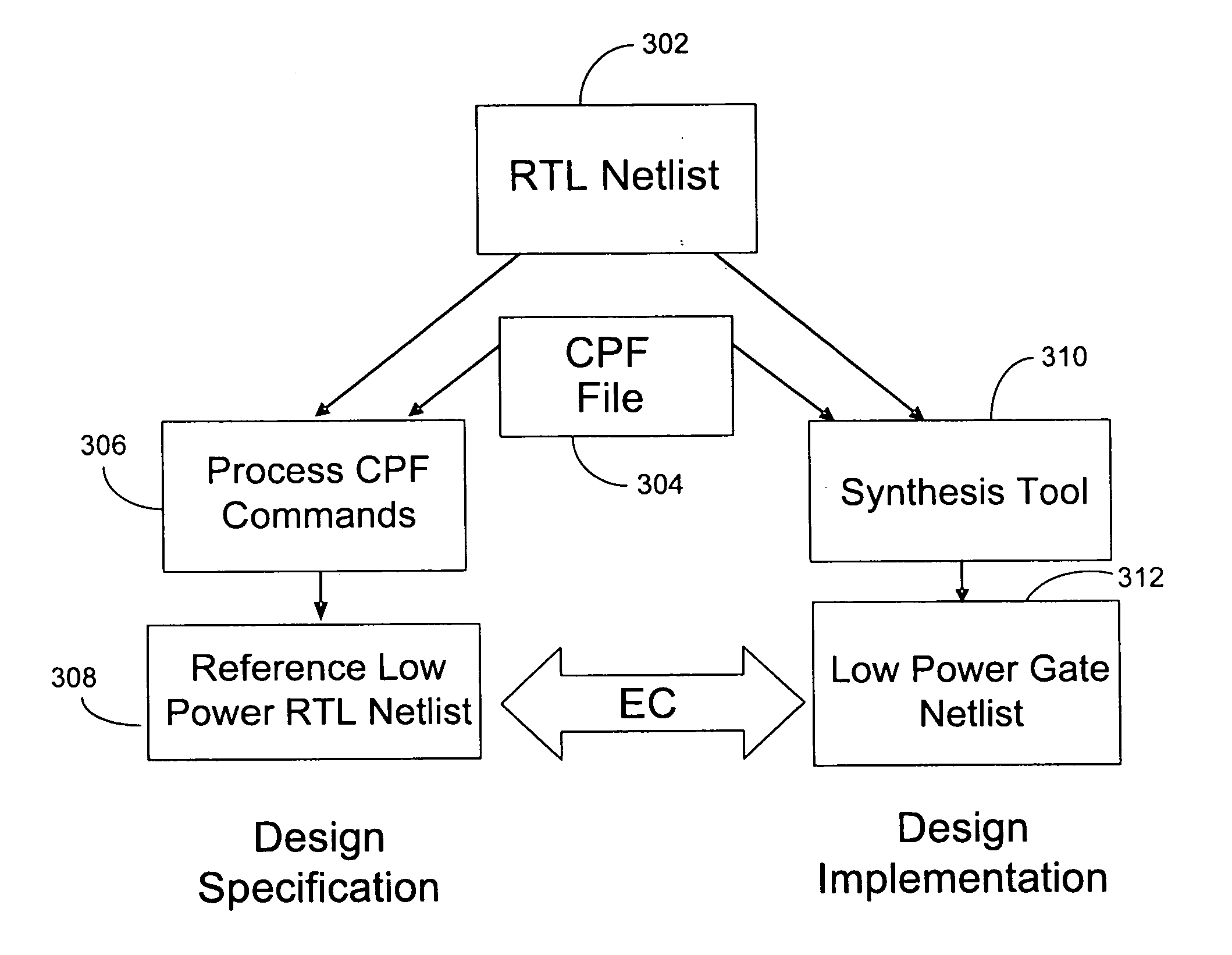

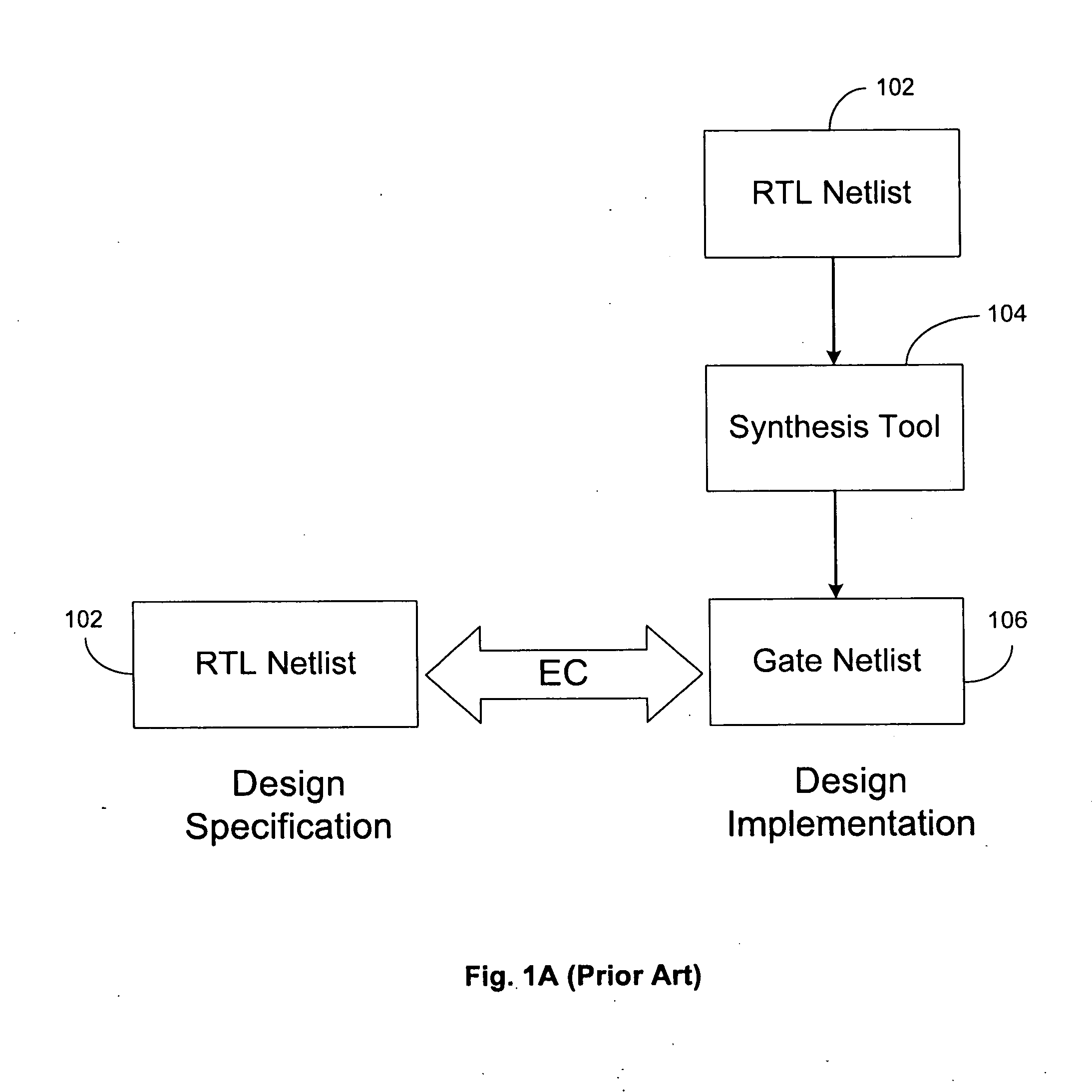

Method and system for equivalence checking of a low power design

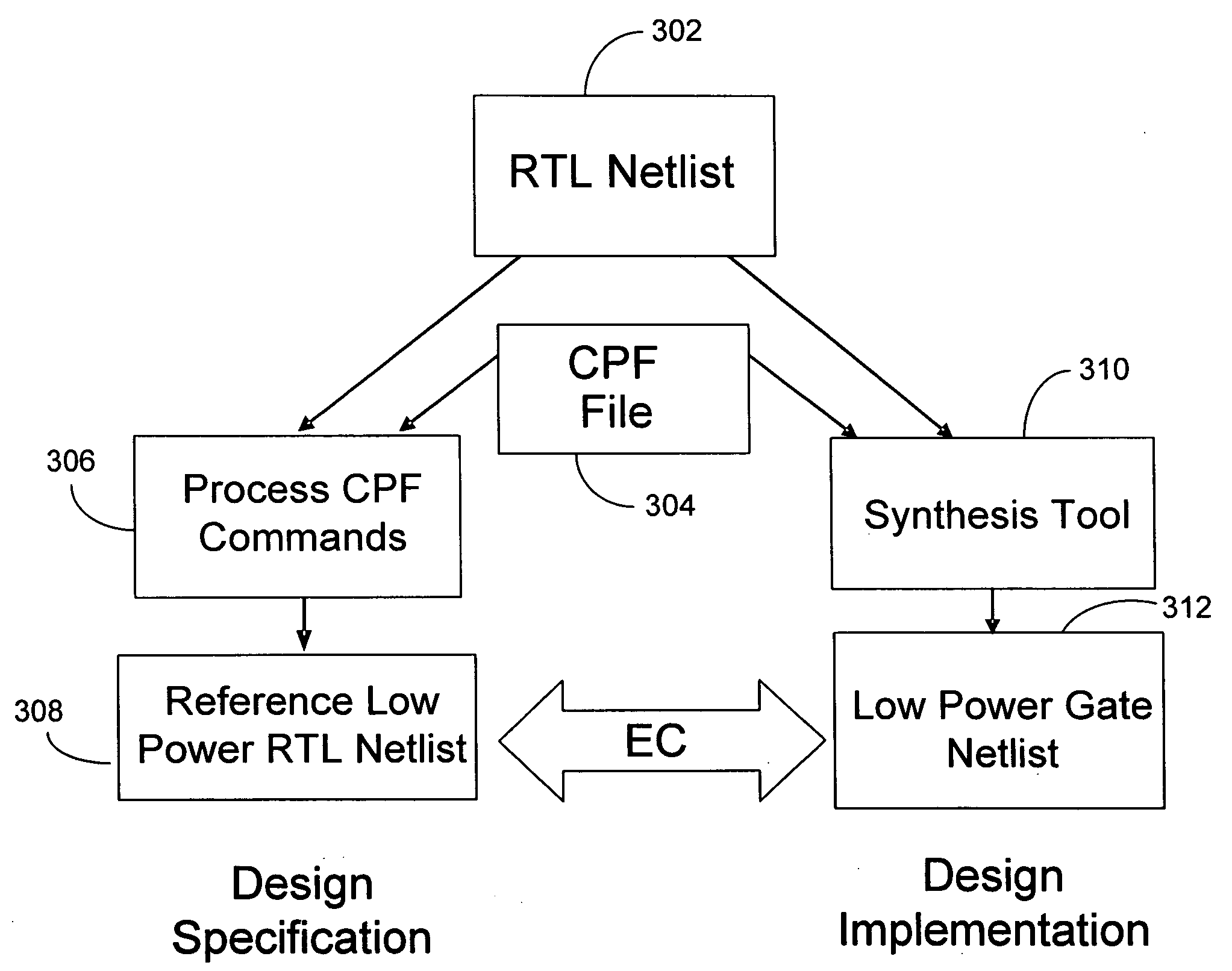

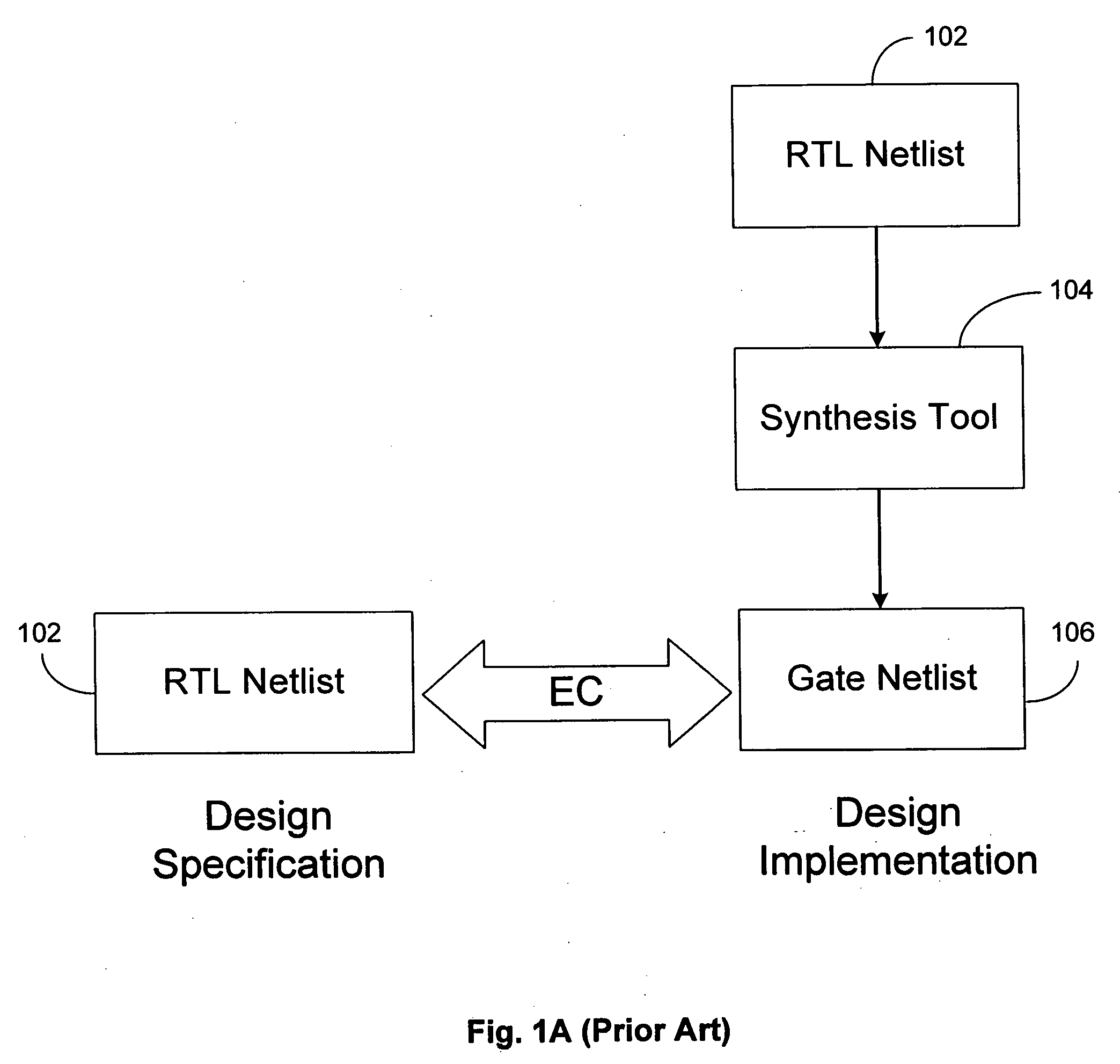

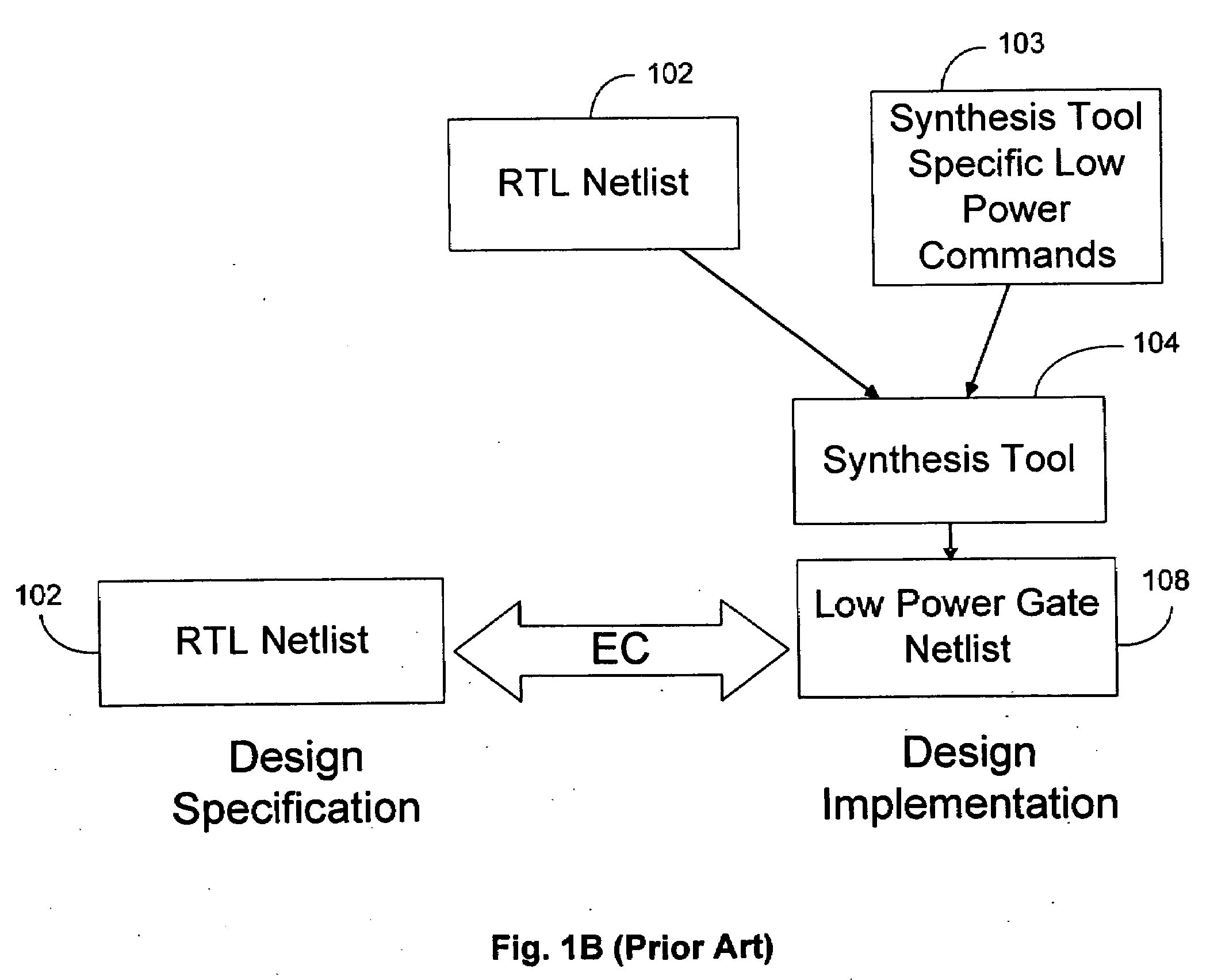

ActiveUS20080127014A1CAD circuit designSoftware simulation/interpretation/emulationProcessor registerEngineering

Method and system for equivalence checking of a low power design are disclosed. The method includes receiving a register-transfer level (RTL) netlist representation of a circuit, receiving a power specification file for describing power requirements of the circuit, creating a low power gate netlist for representing a design implementation of the circuit using the RTL netlist and the power specification file, creating a reference low power RTL netlist for representing a design specification of the circuit using the RTL netlist and the power specification file, and performing equivalence checking between the low power gate netlist and the reference low power RTL netlist. The method further includes annotating low power information described in the power specification file into the reference low power RTL netlist, and creating low power logic in the reference low power RTL netlist.

Owner:CADENCE DESIGN SYST INC

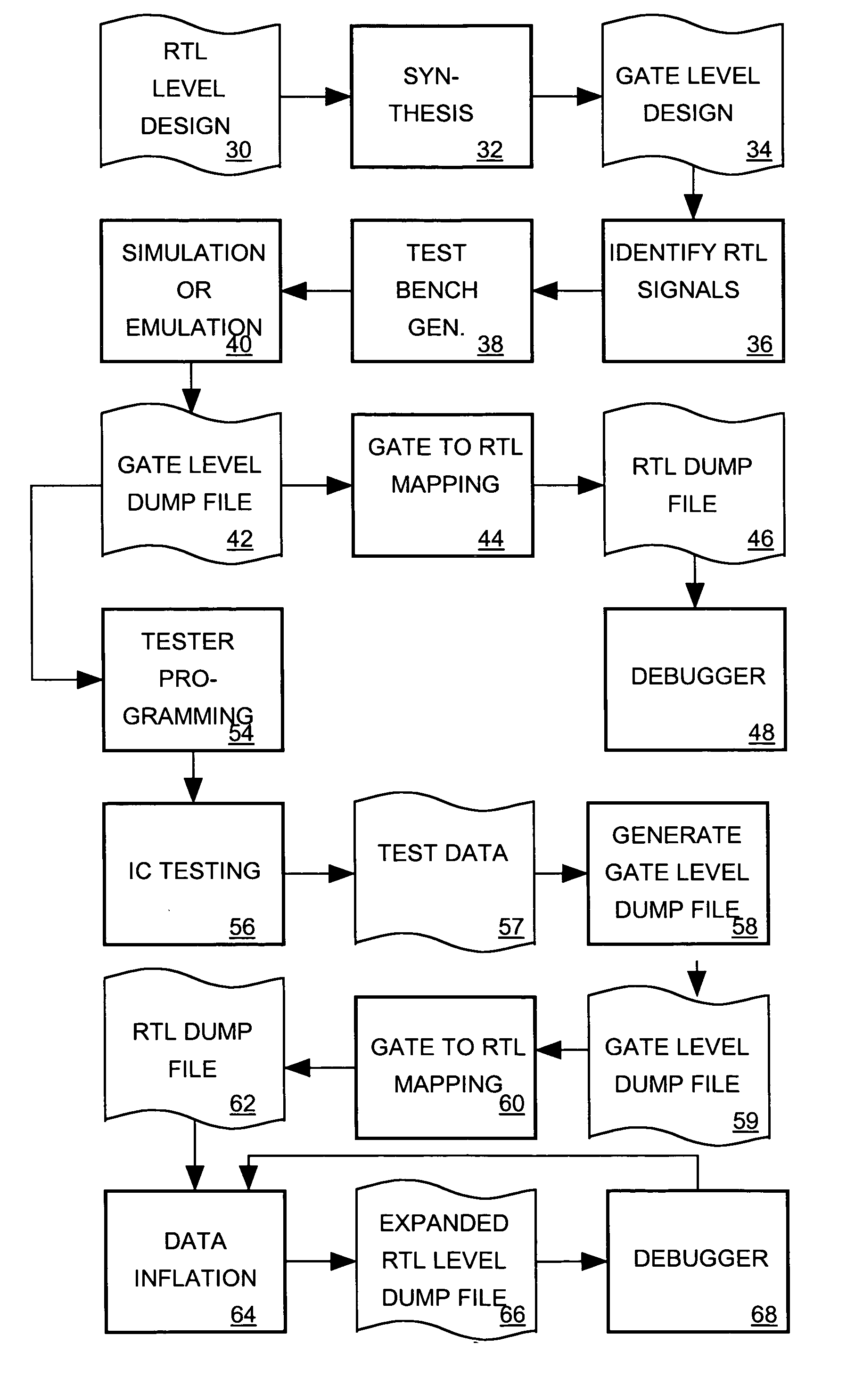

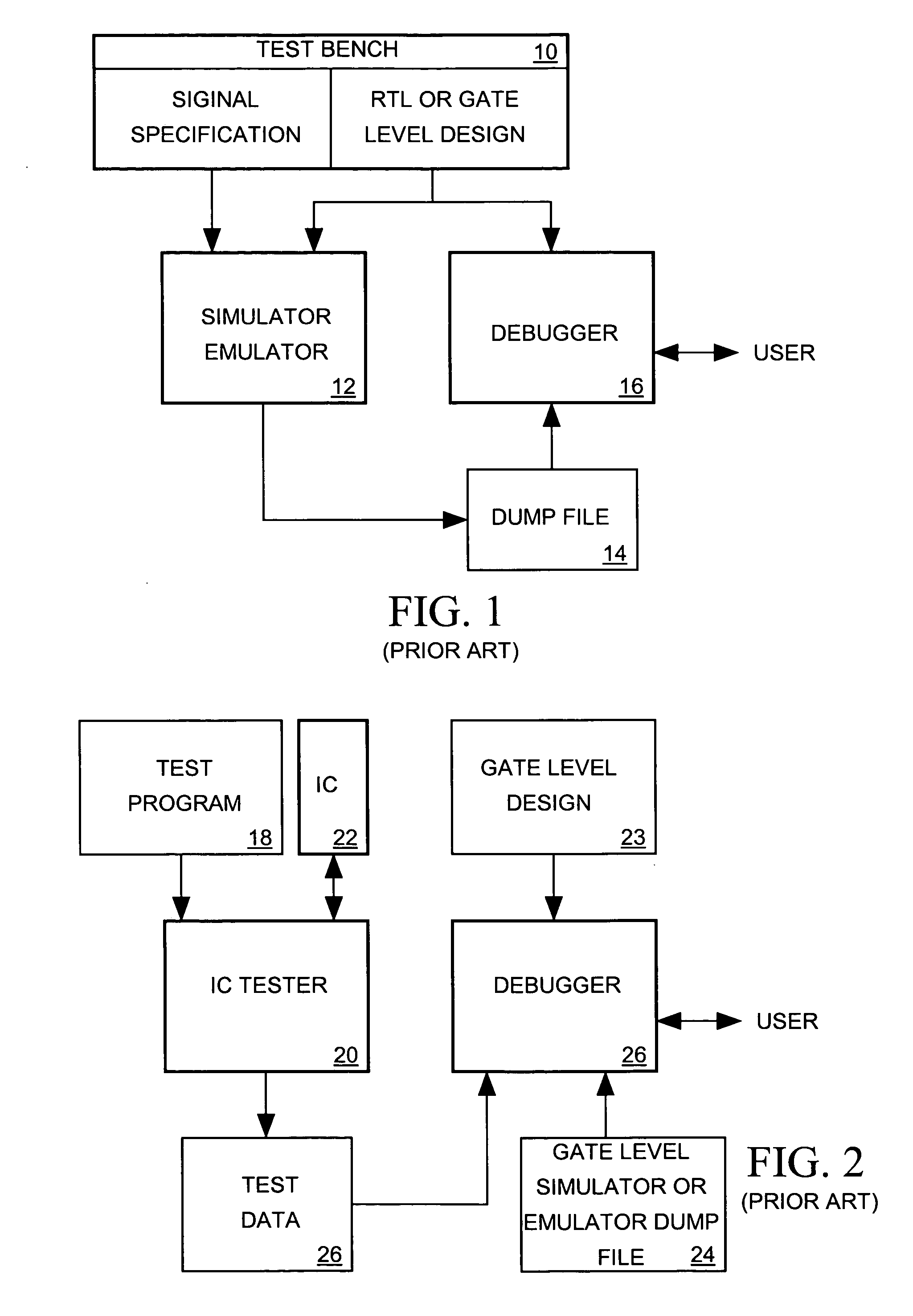

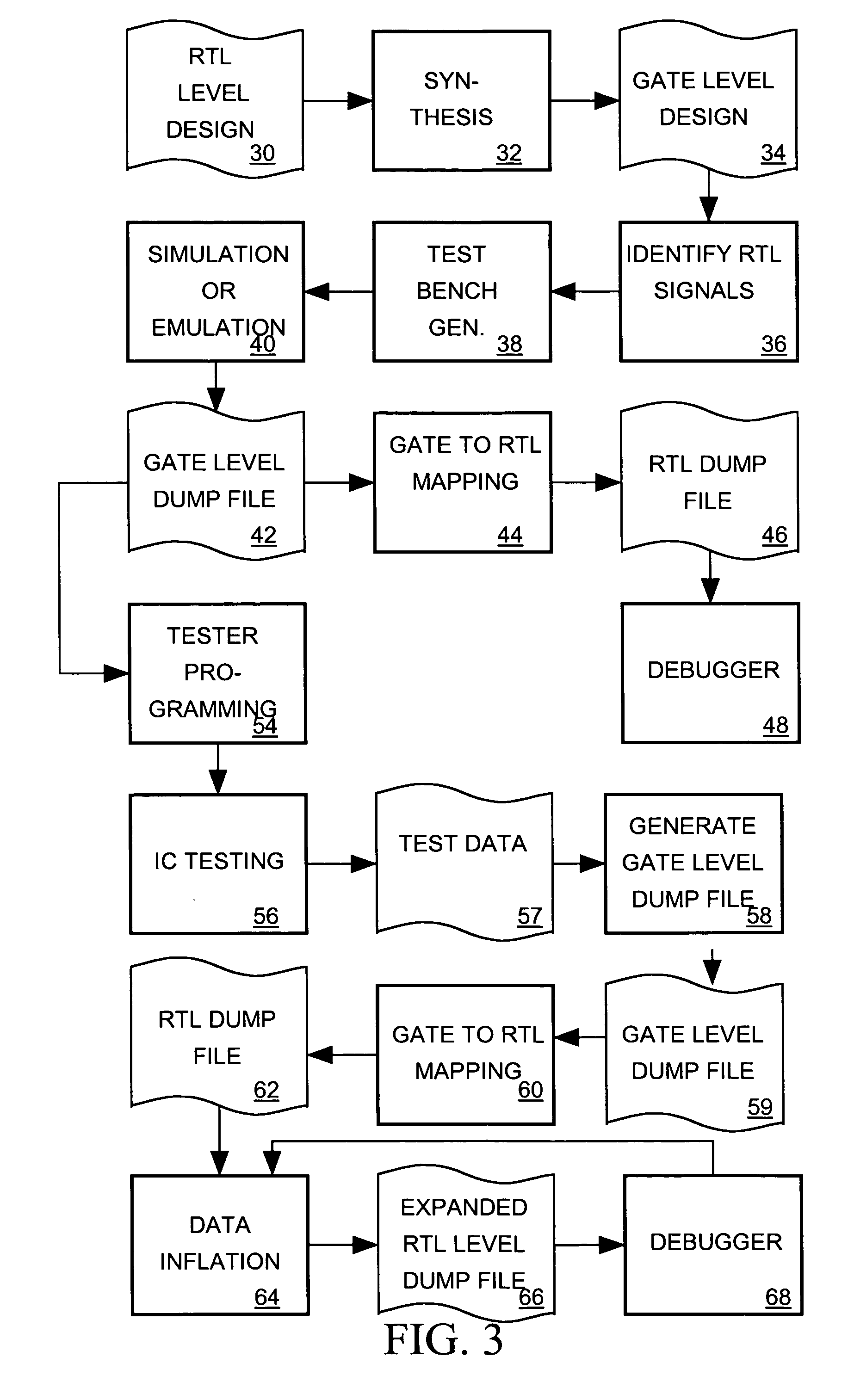

Debugging system for gate level IC designs

ActiveUS20070174805A1Easy to understandSimplify the commissioning processSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareComputer architectureComputer-aided

A register transfer level (RTL) IC design describing a IC as comprising a plurality of logic blocks communicating via signals and using a high level language to describe the logic blocks according to the logical relationships between signals they receive and signals they generate. A computer-aided synthesizer processes an RTL IC design to produce a gate level design for the IC describing its logic blocks as comprising instances of cells communicating via signals. A synthesizer or emulator processes the gate level design to produce a gate level dump file referencing signals of the gate level design and indicating how those signals behave in response to time-varying signals supplied as inputs to the IC. The gate level dump file is converted into an RTL dump file referencing signals of the RTL design and indicating how those signals behave. A debugger processes the RTL dump file to produce displays depicting the RTL design and behavior of signals indicated by the RTL dump file. Thus while the IC is simulated or emulated at the gate level of the design to produce waveform data for a debugger, the gate level-to-RTL dump file conversion process enables a designer debug the more familiar RTL design based on the gate level simulation or emulation results.

Owner:SYNOPSYS INC

Method of circuit verification in digital design

InactiveUS20020138812A1Reduce designEasy to understandComputer aided designSoftware simulation/interpretation/emulationComputer architectureCircuit design

The present invention relates to a method of circuit verification in digital design and in particular relates to a method of register transfer level property checking to enable the same. Today's electrical circuit designs frequently contain up to several million transistors and circuit designs need to be checked to ensure that circuits operate correctly. Formal methods for verification are becoming increasingly attractive since they confirm design behavior without exhaustively simulating a design. The present invention provides a digital circuit design verification method wherein, prior to a property checking process for each property of a non-reduced RTL model, a reduced RTL model is determined, which reduced RTL model retains specific signal properties of a non-reduced RTL model which are to be checked. A linear signal width reduction causes an exponential reduction of the induced state space. Reducing state space sizes in general goes hand in hand with reduced verification runtimes, and thus speeding up verification tasks.

Owner:ONESPIN SOLUTIONS

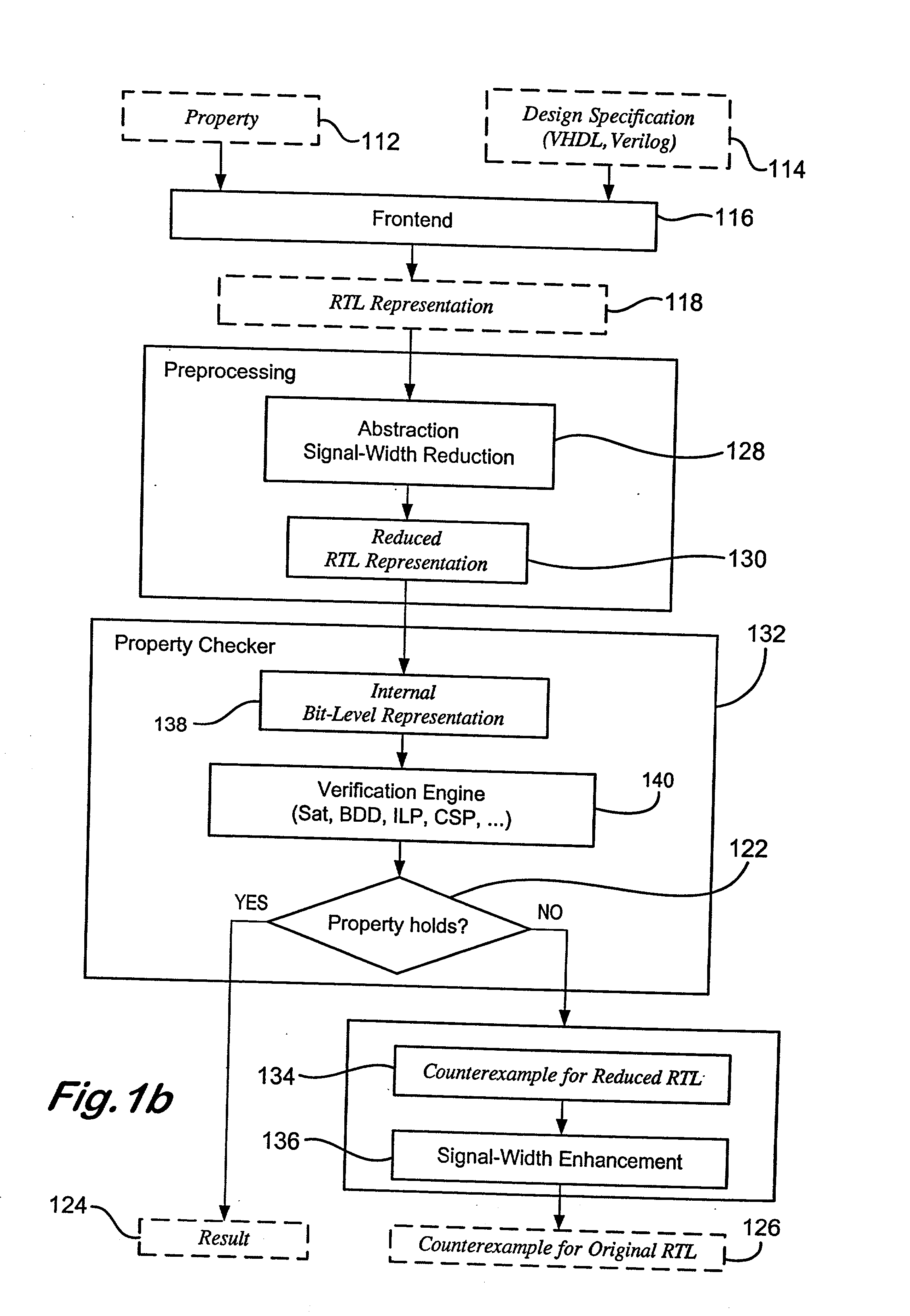

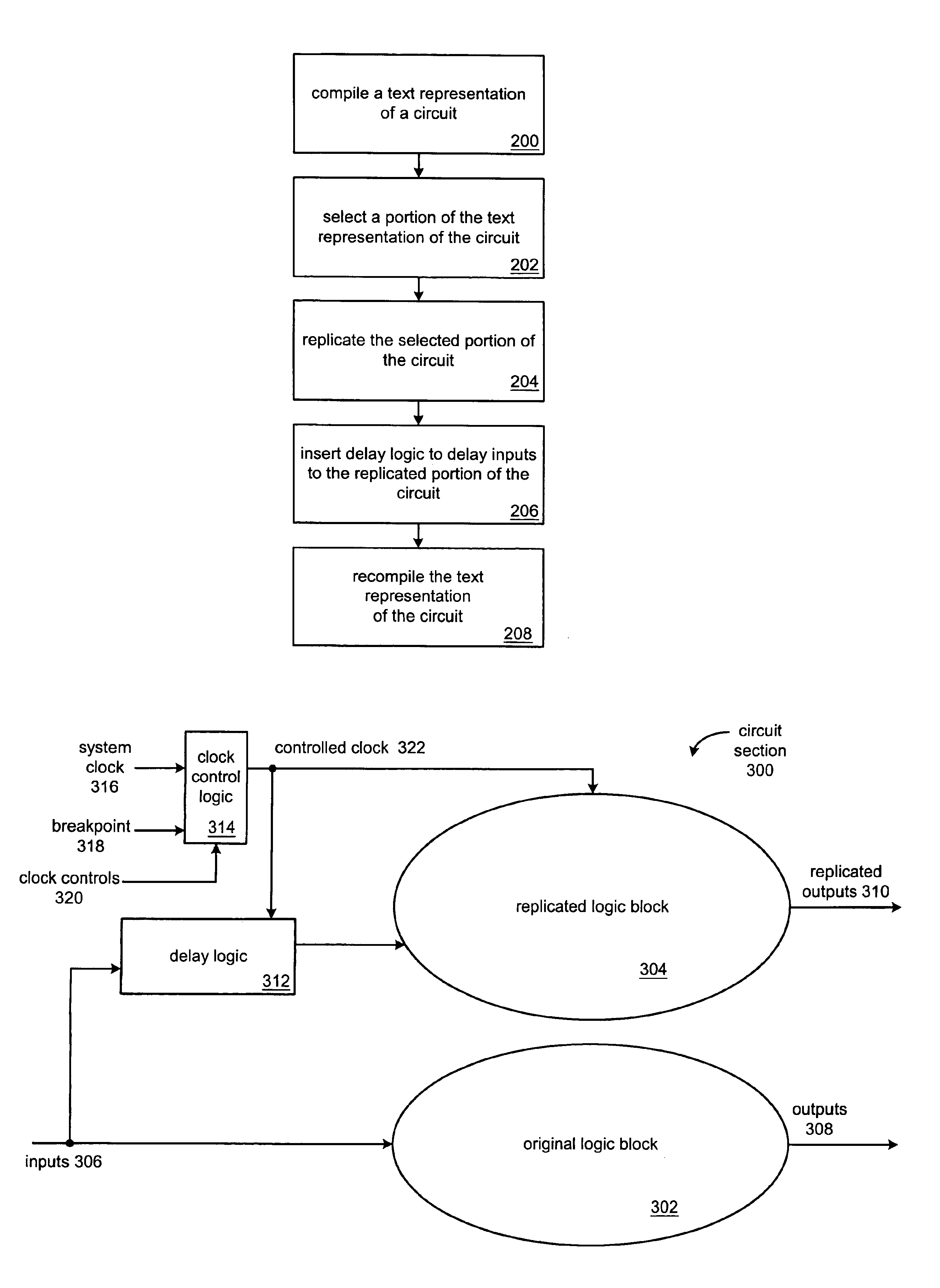

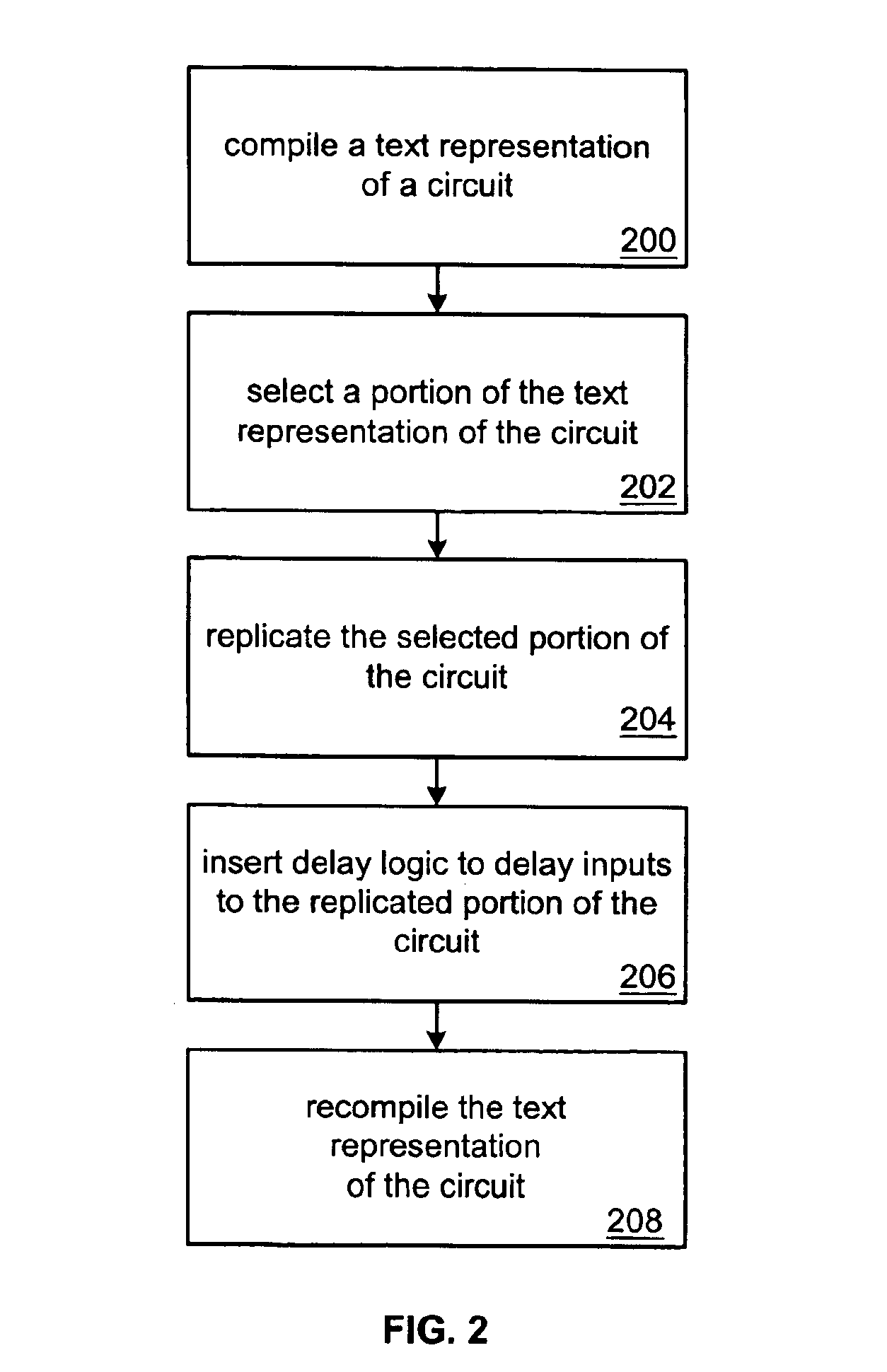

Method and system for debugging using replicated logic

InactiveUS6904576B2Digital circuit testingSemiconductor/solid-state device manufacturingComputer architectureProcessor register

A method and apparatus is provided to debug using replicated logic. A text representation of a circuit is compiled to generate a first register transfer level (RTL) netlist. The netlist may be mapped to a target architecture, such as a field programmable gate array (FPGA). The netlist may be used to program an FPGA to create a prototype board for debugging. After debug, a portion of the circuit that a designer would like to analyze is selected. The selected portion of the circuit is replicated. Delay logic is inserted to delay the inputs into the replicated portion of the circuit. The text representation of the circuit is recompiled to generate a second RTL netlist. The second RTL netlist may be mapped to a target architecture, such as a FPGA or application specific integrated circuit (ASIC).

Owner:SYNOPSYS INC

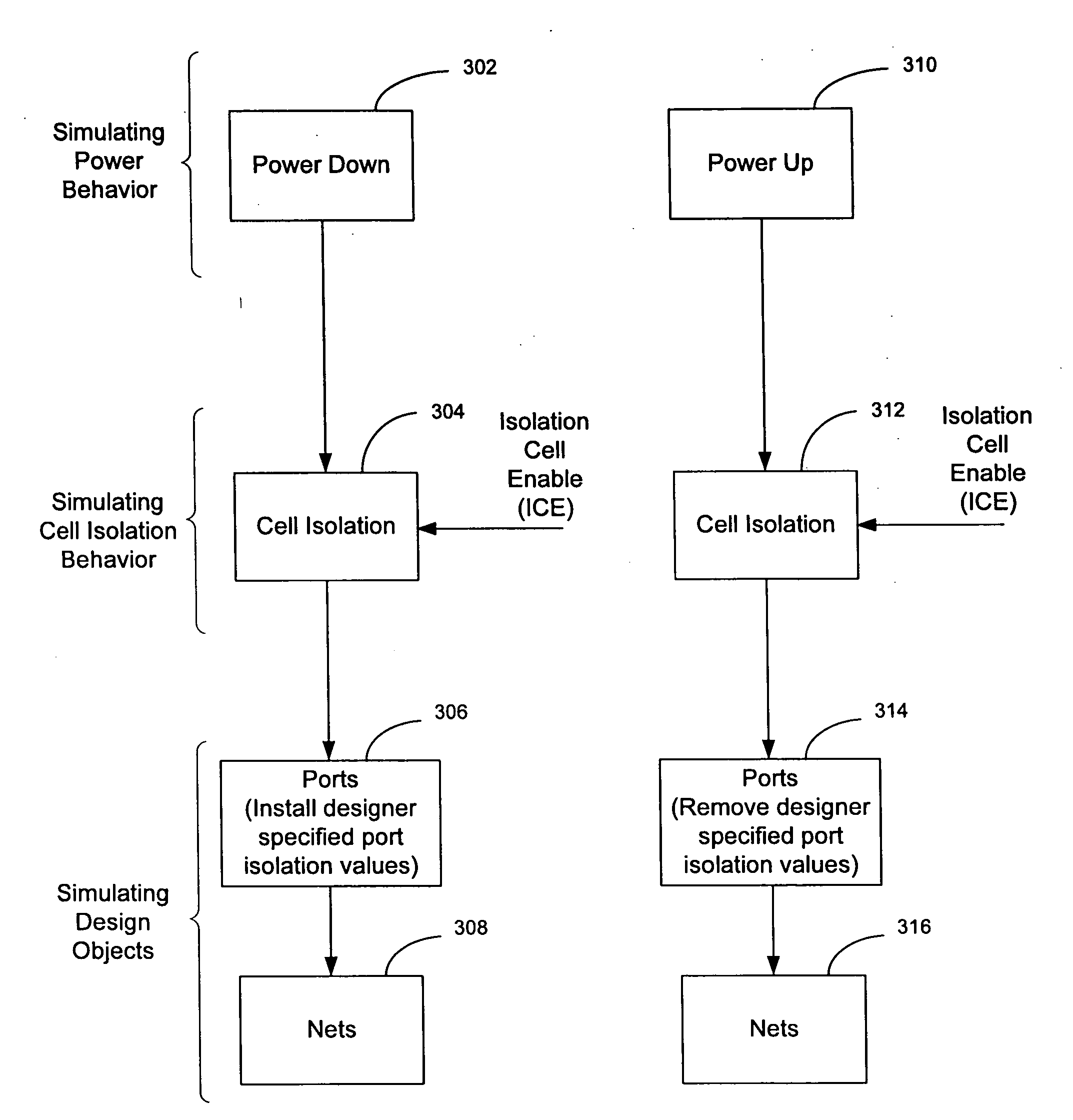

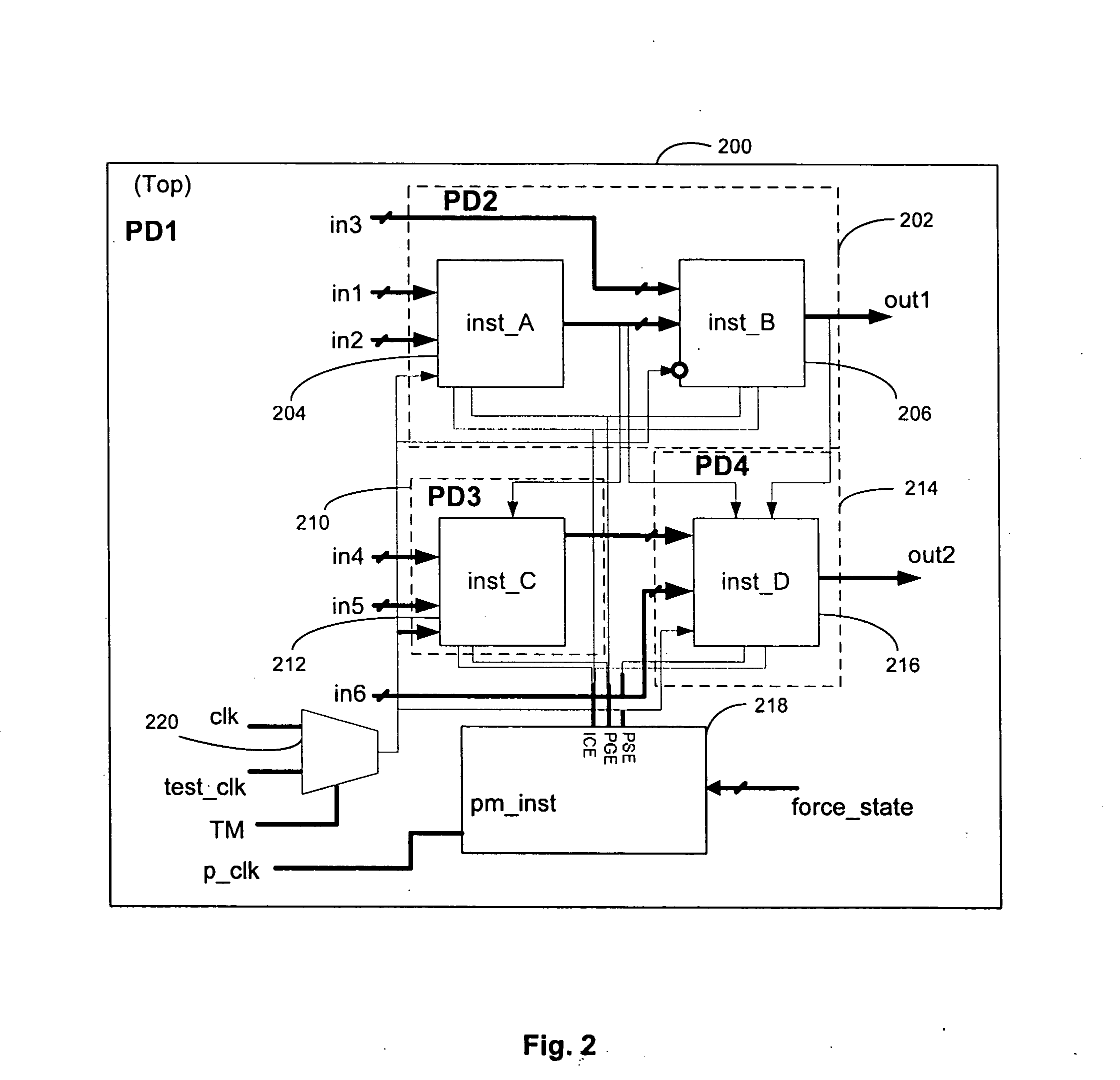

Simulation of power domain isolation

ActiveUS20070245278A1CAD circuit designSoftware simulation/interpretation/emulationControl signalProcessor register

Method and system for simulating isolation of a power domain are disclosed. The method includes receiving a netlist description of the circuit that is represented in a register-transfer-level (RTL) design environment, receiving power information specifications of the circuit, associating the plurality of power domains and the power information specifications in the RTL design environment, where the plurality of power domains are controlled by a set of power control signals through a power manager logic, isolating a power domain among the plurality of power domains for simulation, and simulating isolation behavior of the power domain in response to variations in power applied to the power domain.

Owner:CADENCE DESIGN SYST INC

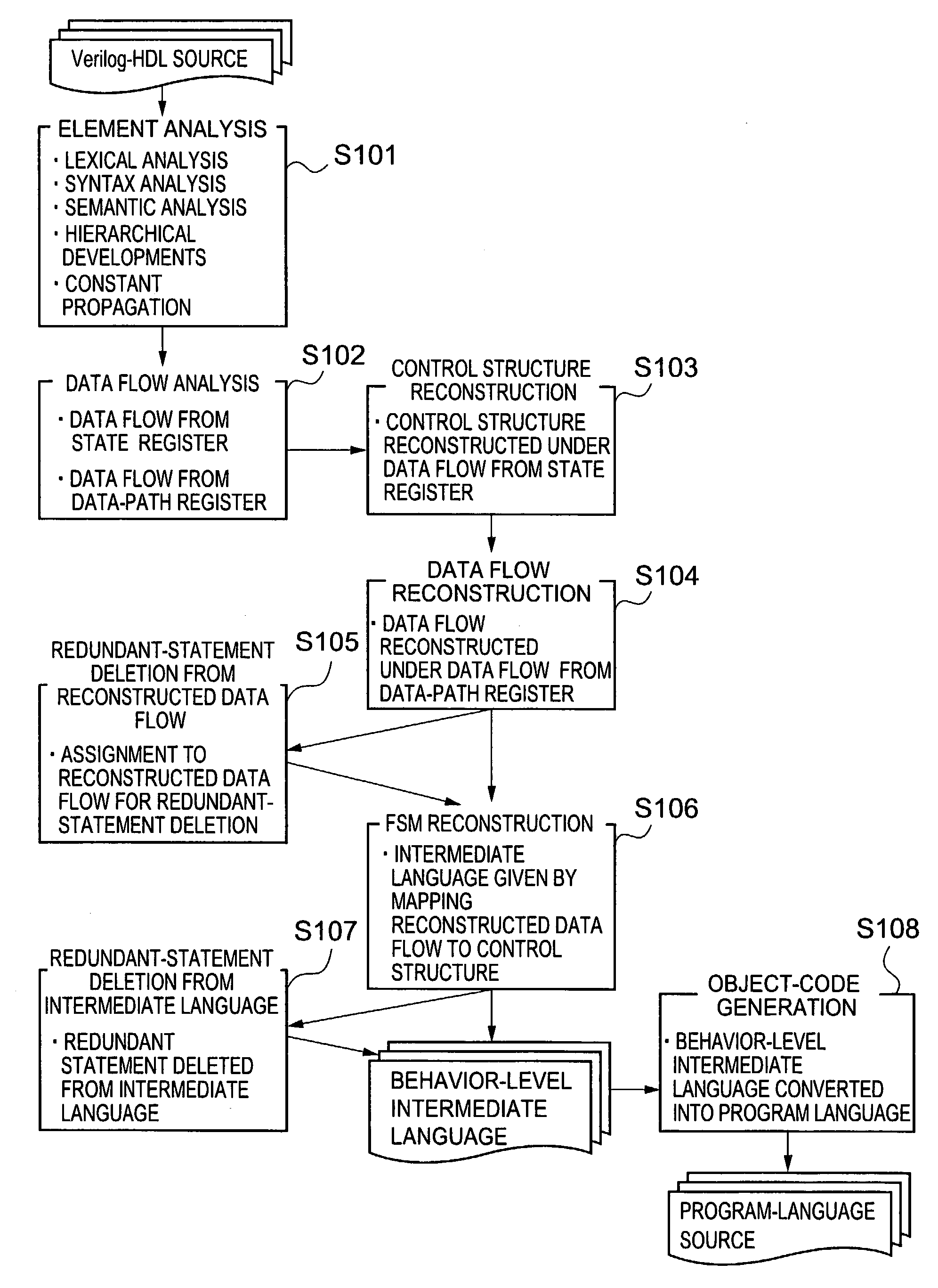

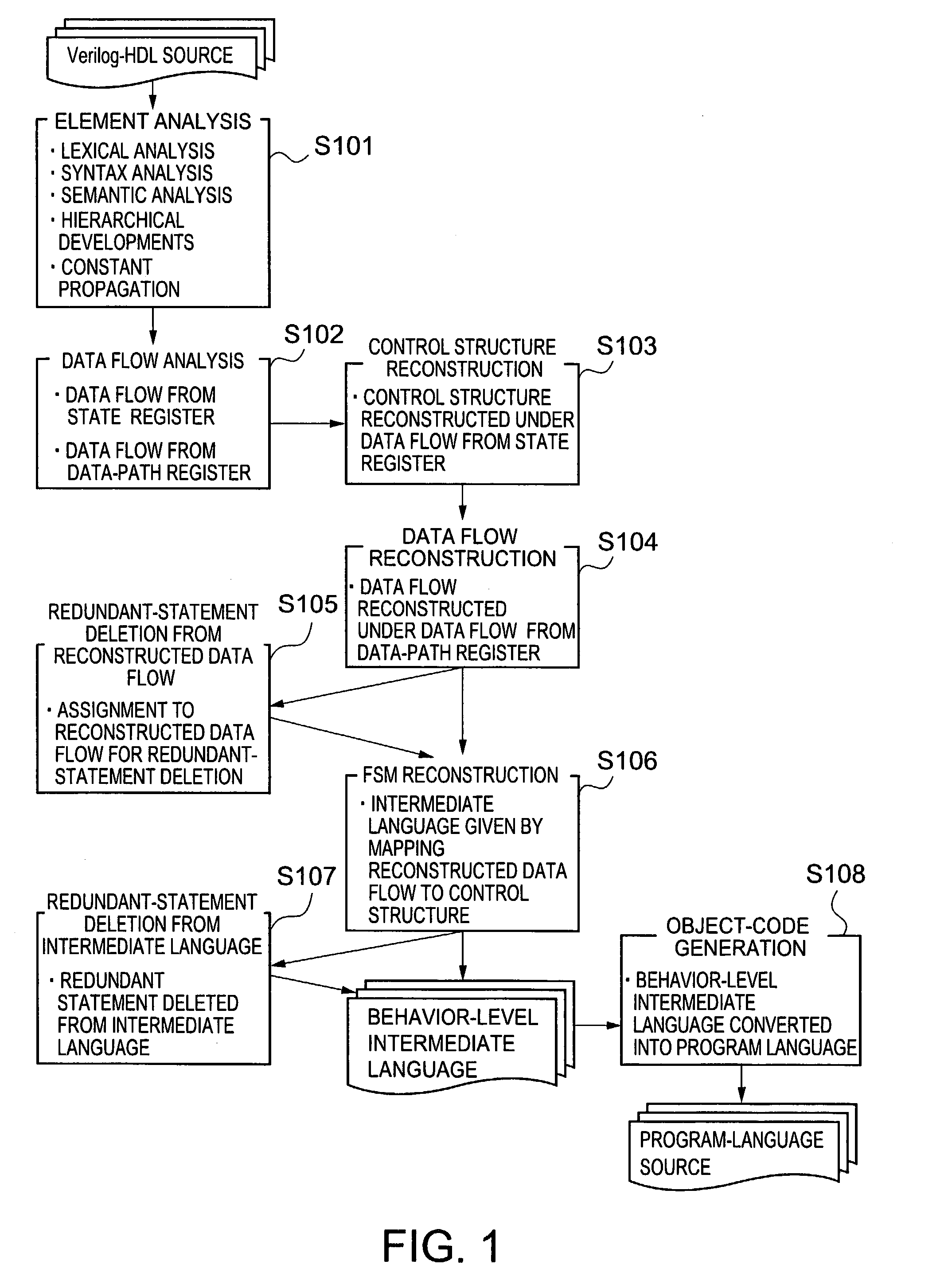

Hardware-operation description conversion method and program therefor

InactiveUS6996788B2CAD circuit designSoftware simulation/interpretation/emulationData streamAnalysis data

A verilog-HDL source at the register-transfer level (RTL) is converted into a programming language executable on computer. Constructed in an analyzing of elements is a data structure corresponding to the elements of the verilog-HDL source. Created in an analyzing of a data-flow are a first data flow from a state register and a second flow from data-path register. Reconstructed in a reconstructing of a control-structure is the first data flow. Reconstructed in a reconstructing of a data-path is the second data flow so that the reconstructed second data is constituted only by circuitry operating in each state of the control structure. Each reconstructed data flow is mapped in each state of the control structure in a combining of the control-structure / data-flow, to output an behavior-level intermediate language. The intermediate language is converted into a programming language in a generating of an object-code.

Owner:KK TOSHIBA

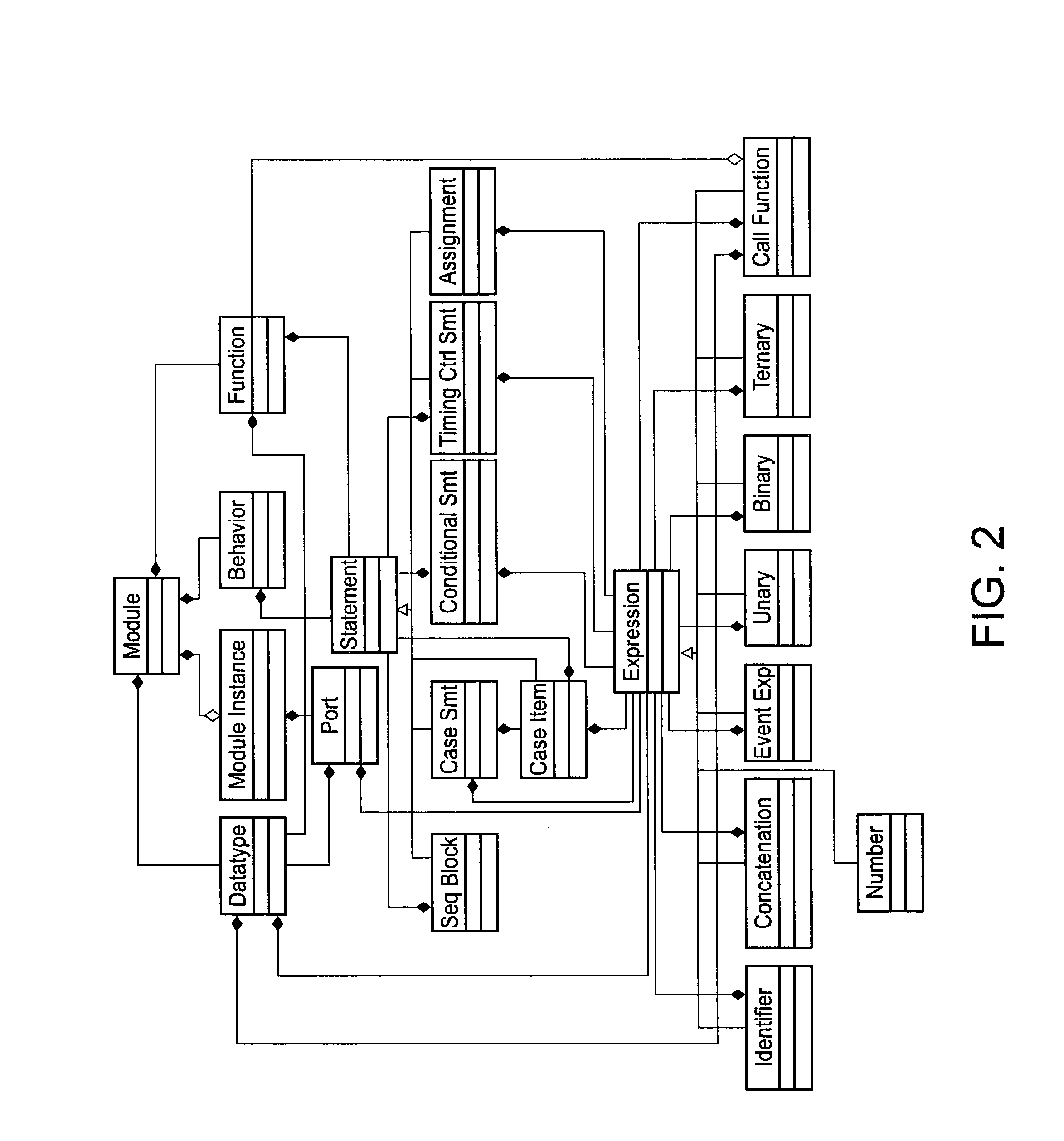

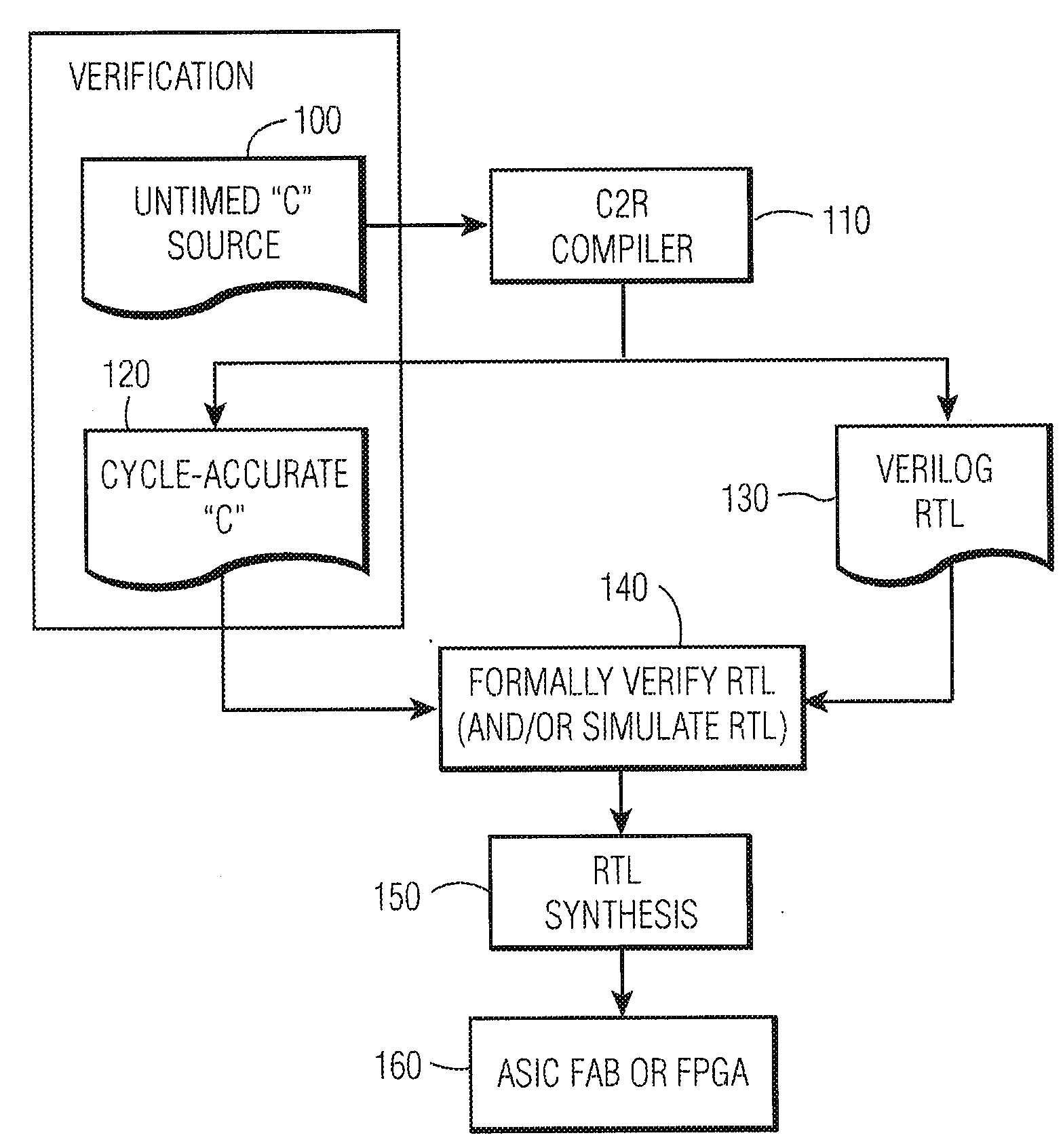

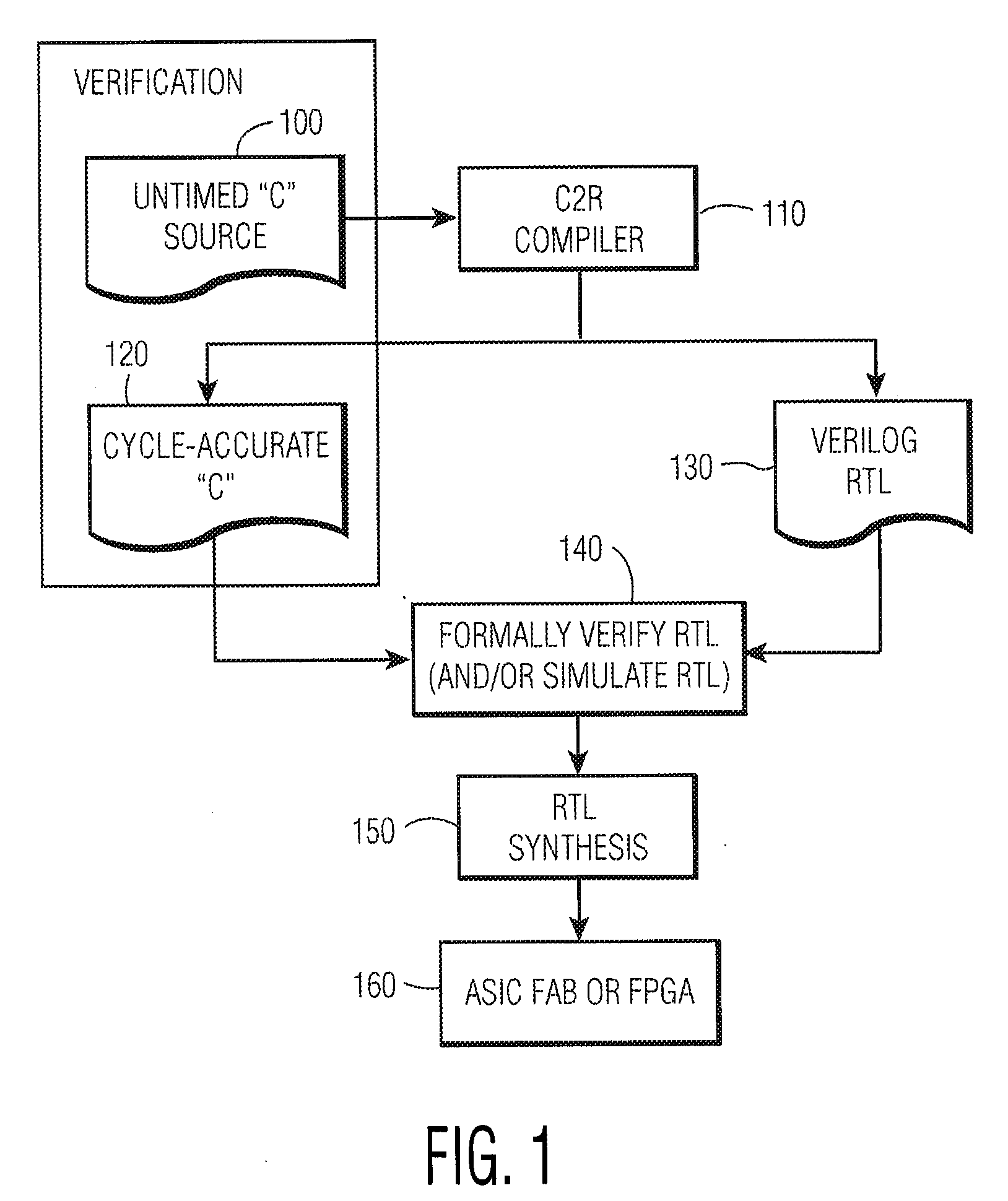

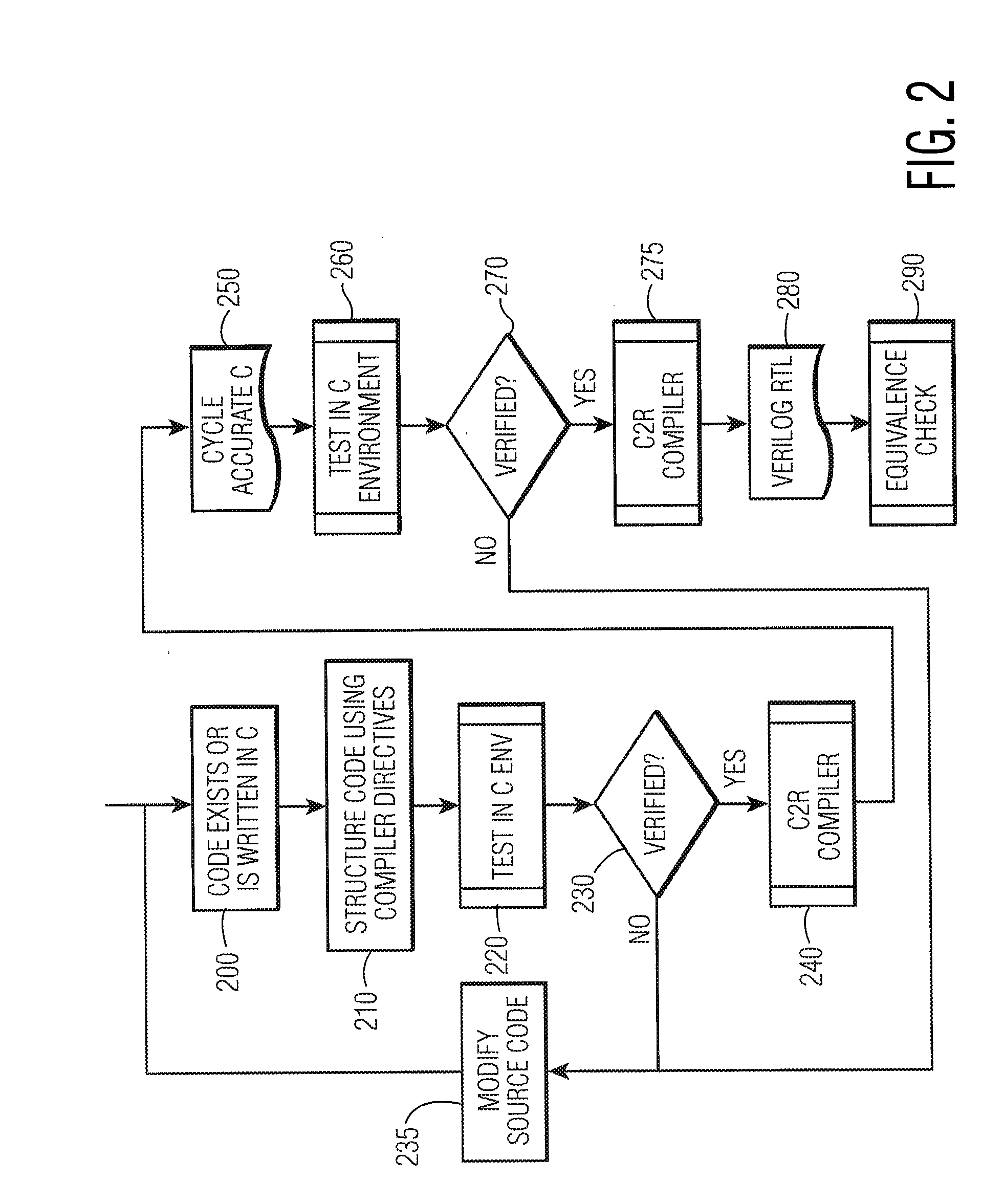

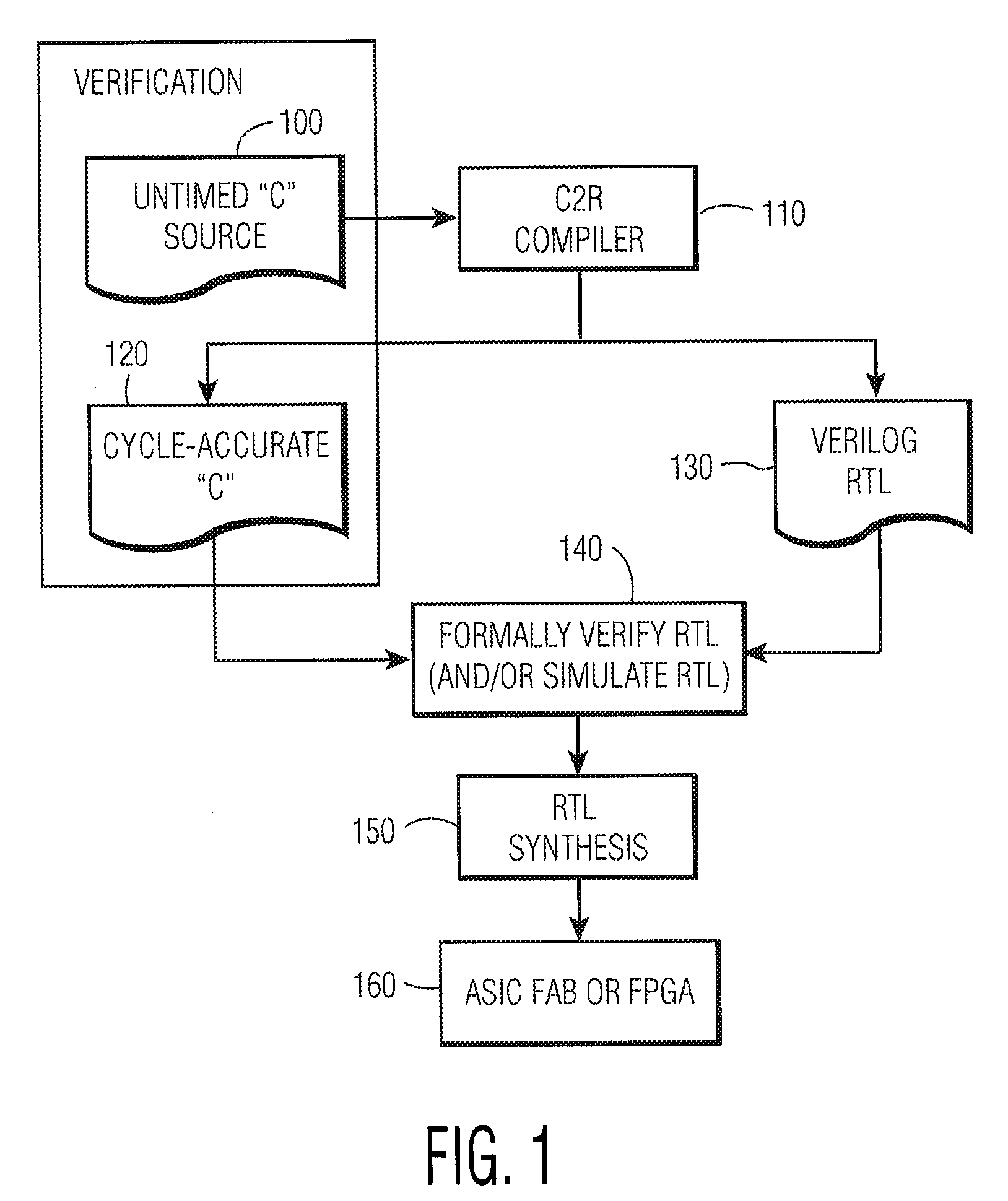

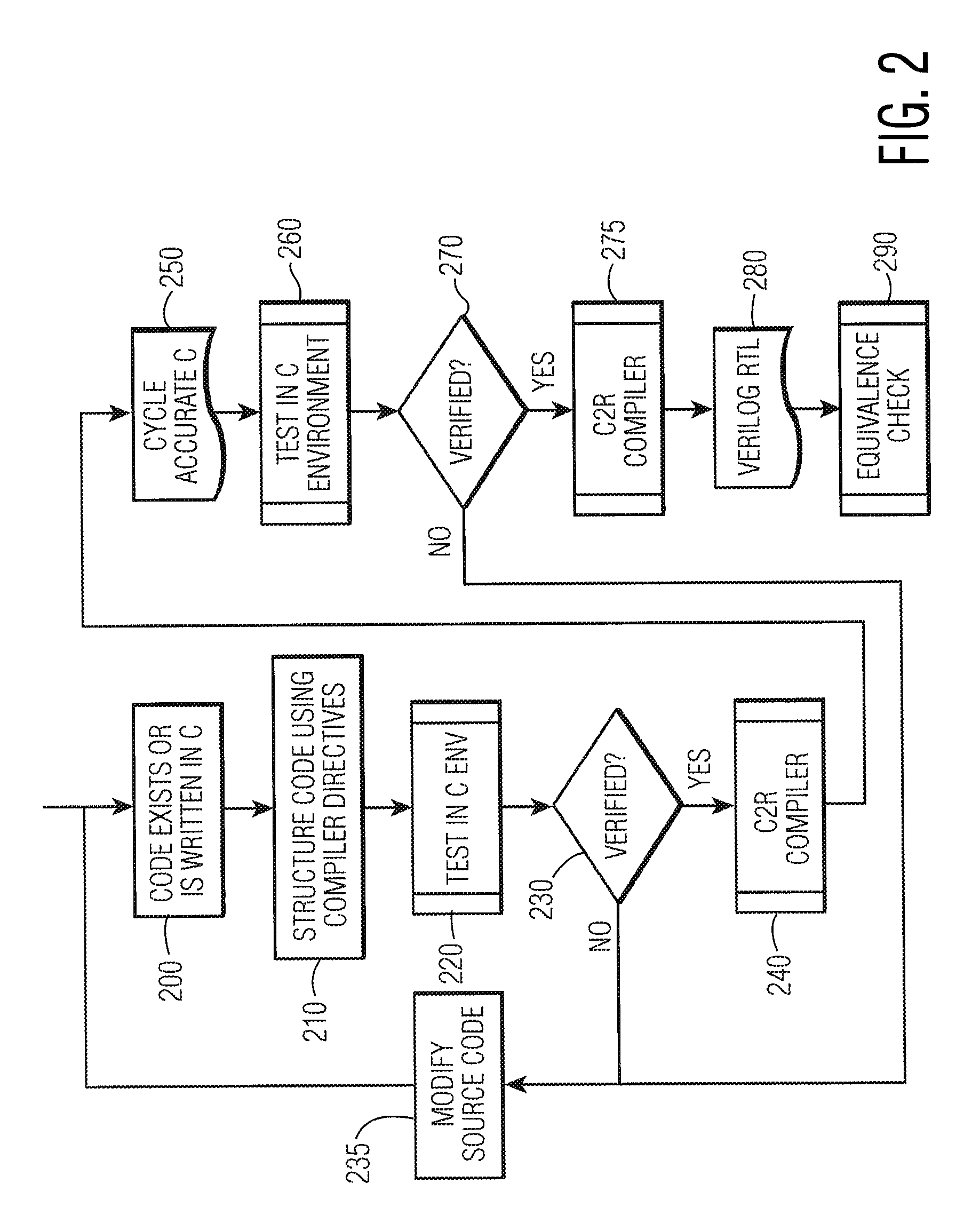

System and method for converting software to a register transfer (RTL) design

ActiveUS20090144690A1Analogue computers for electric apparatusCAD circuit designComputer architectureProcessor register

A method for converting a C-type programming language program to a hardware design, where the said program is an algorithmic representation of one or more processes. The C-type programming language program is compiled into a hardware description language (HDL) synthesizable design. The compiler categorizes variables as using either implicit memory or custom memory. Different accessor functions are used depending on which type of memory is used. The programming language may use ANSI C and the HDL may be Verilog Register Transfer Level (RTL). The hardware device generated from the HDL synthesizable design may be an Application-Specific Integrated Circuit (ASIC) or a Field Programmable Gate Array (FPGA).

Owner:EXAR CORP

Method and system for verifying power specifications of a low power design

ActiveUS20080127015A1CAD circuit designSoftware simulation/interpretation/emulationProcessor registerComputer compatibility

Method and system for verifying power specifications of a low power design are disclosed. The method includes receiving a register-transfer level (RTL) netlist representation of the low power design, receiving a power specification file for describing power requirements of the low power design and verifying the power specification file in accordance with the RTL netlist representation of the low power design. The method further includes verifying completeness, compatibility, and consistency of power requirements for the low power design.

Owner:CADENCE DESIGN SYST INC

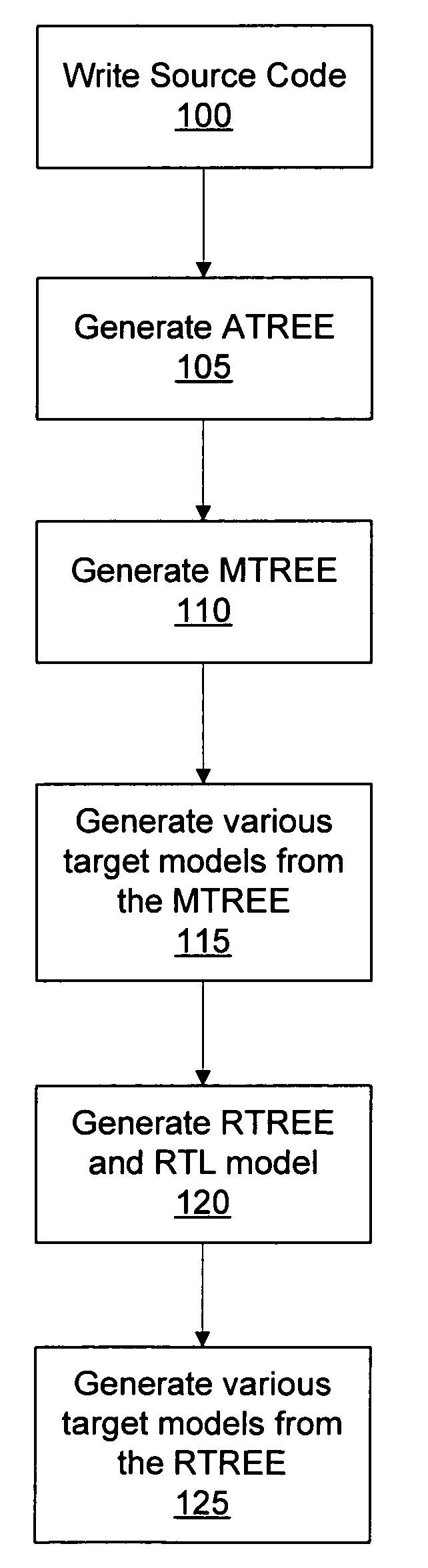

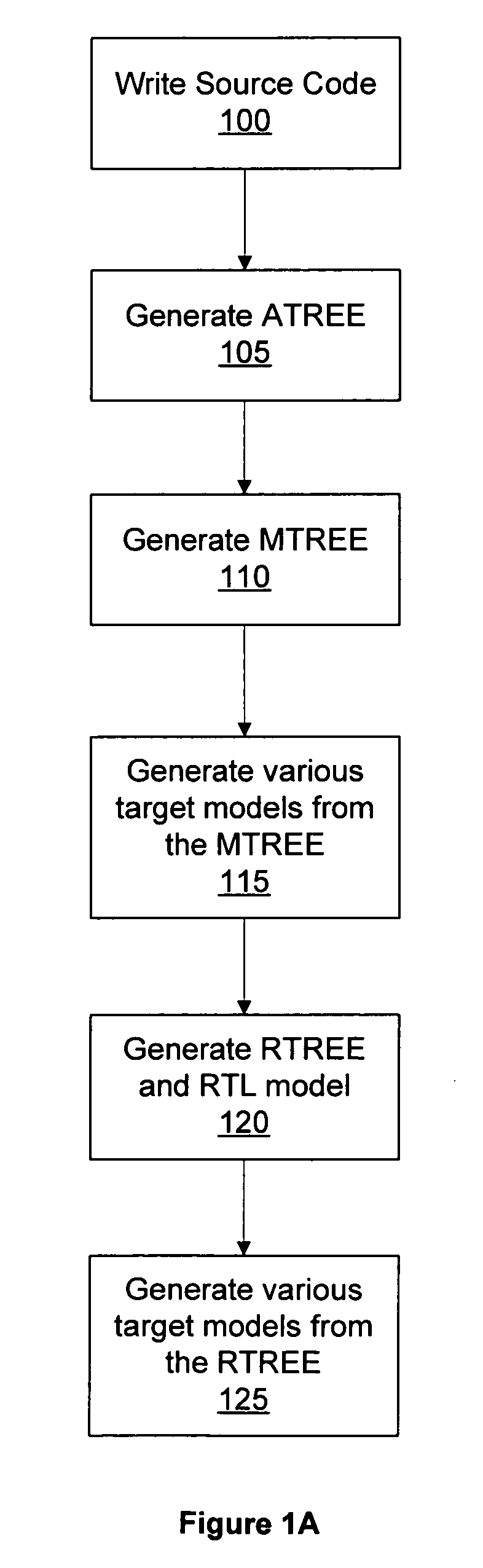

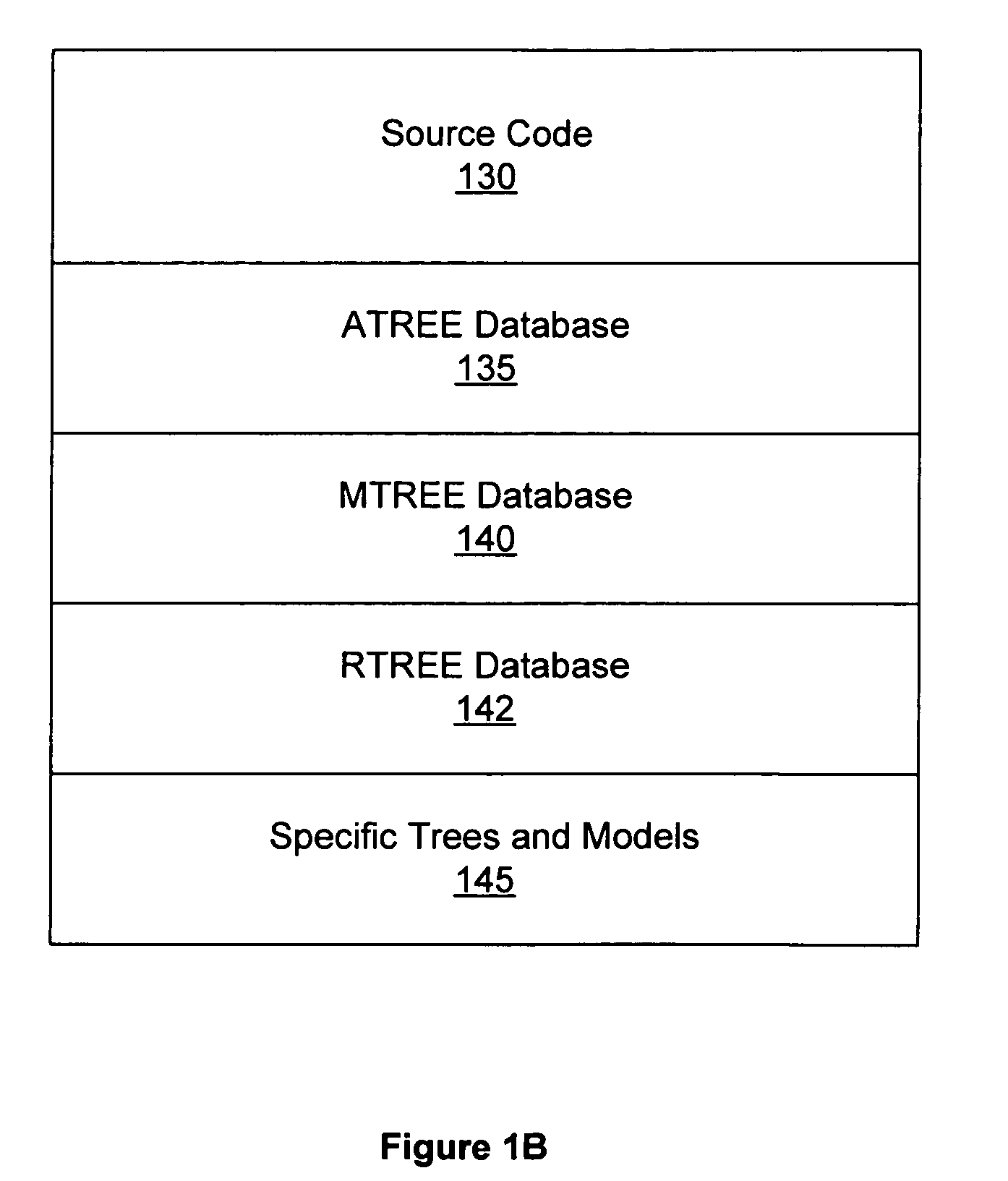

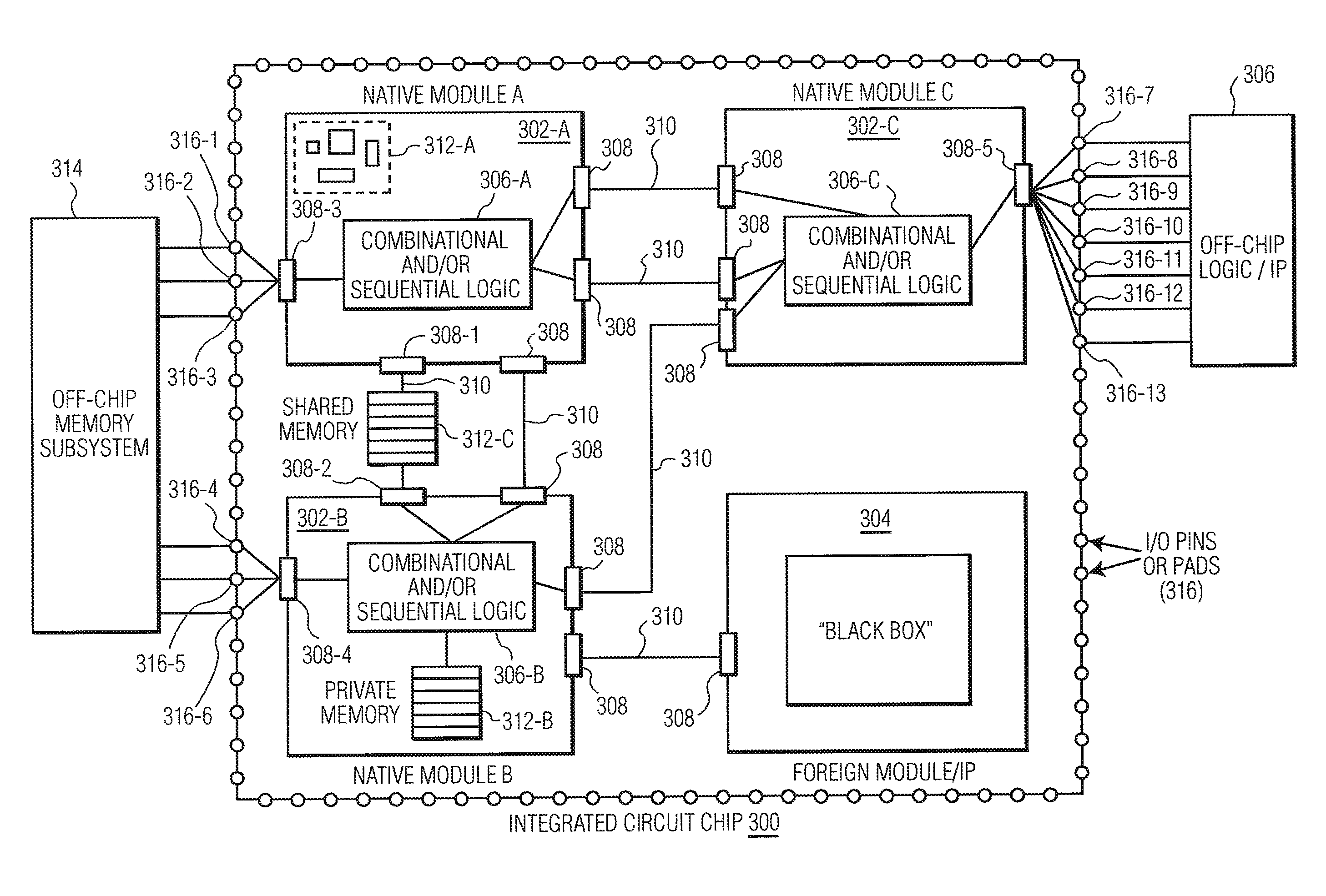

Building integrated circuits using a common database

InactiveUS7363610B2Improved performance per watt of power consumptionCAD circuit designSoftware simulation/interpretation/emulationComputer architectureHigh-level programming language

Systems and methods for designing and generating integrated circuits using a high-level language are described. The high-level language is used to generate performance models, functional models, synthesizable register transfer level code defining the integrated circuit, and verification environments. The high-level language may be used to generate templates for custom computation logical units for specific user-determined functionality. The high-level language and compiler permit optimizations for power savings and custom circuit layout, resulting in integrated circuits with improved performance per watt of power consumption.

Owner:NVIDIA CORP

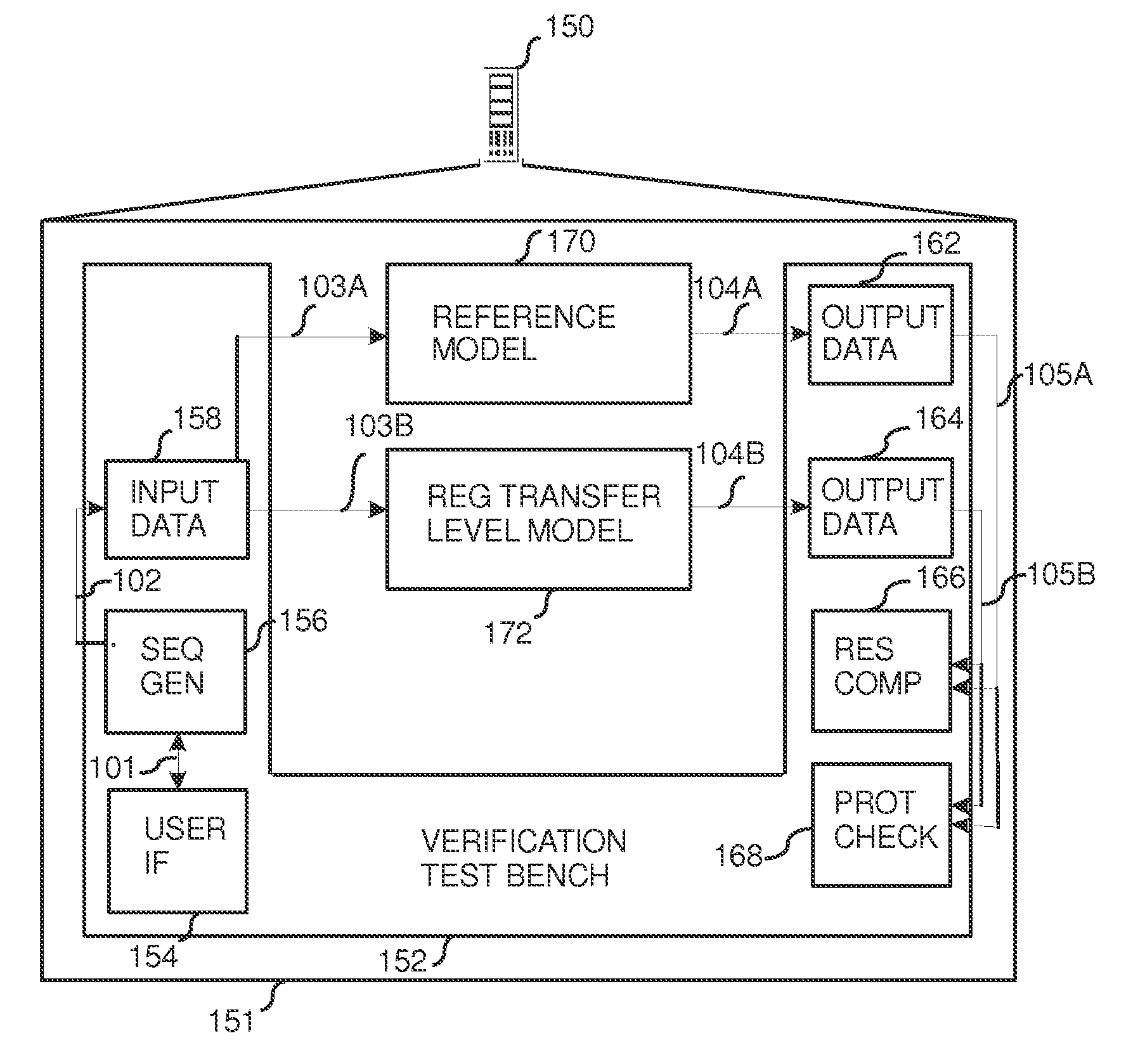

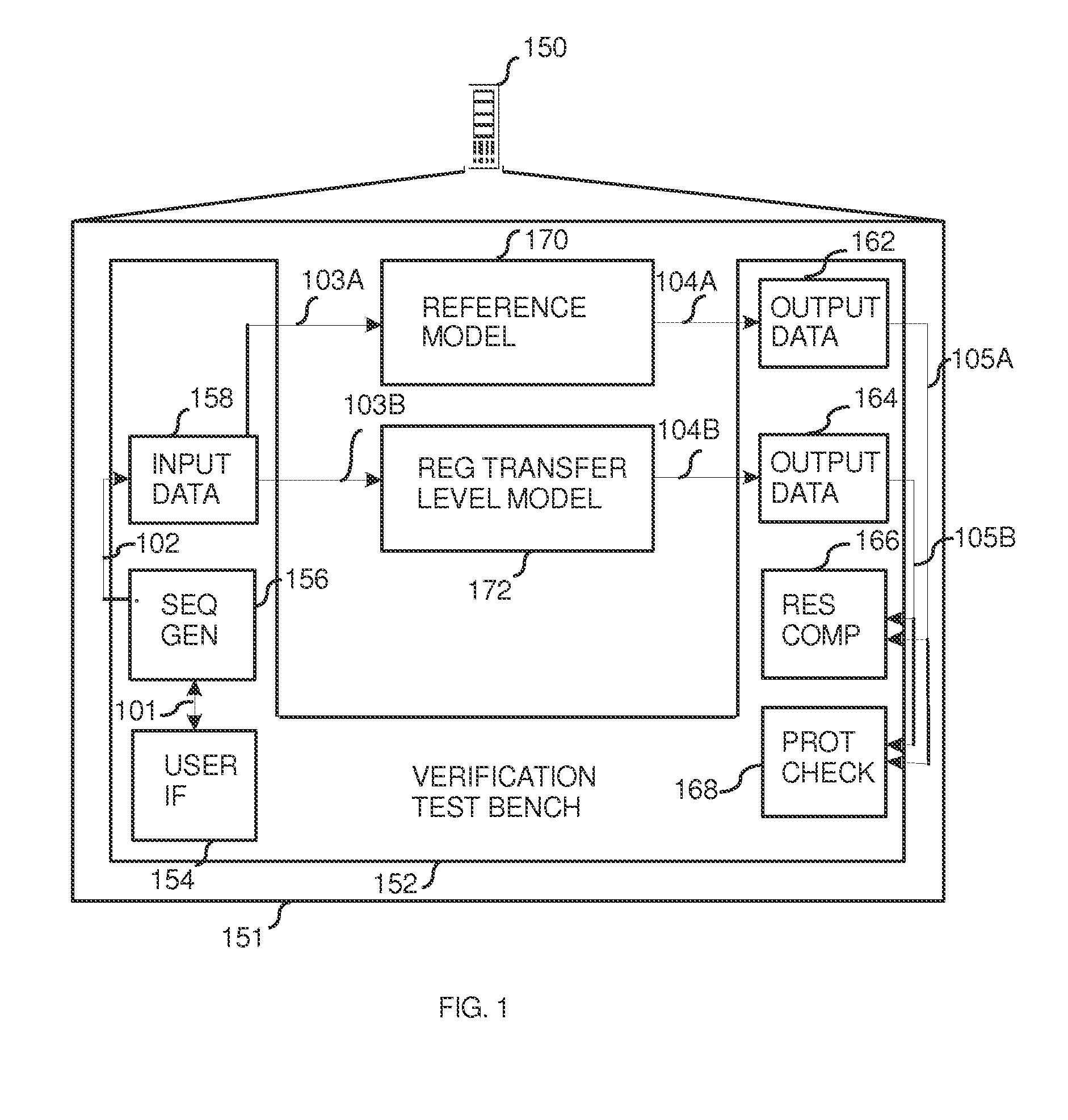

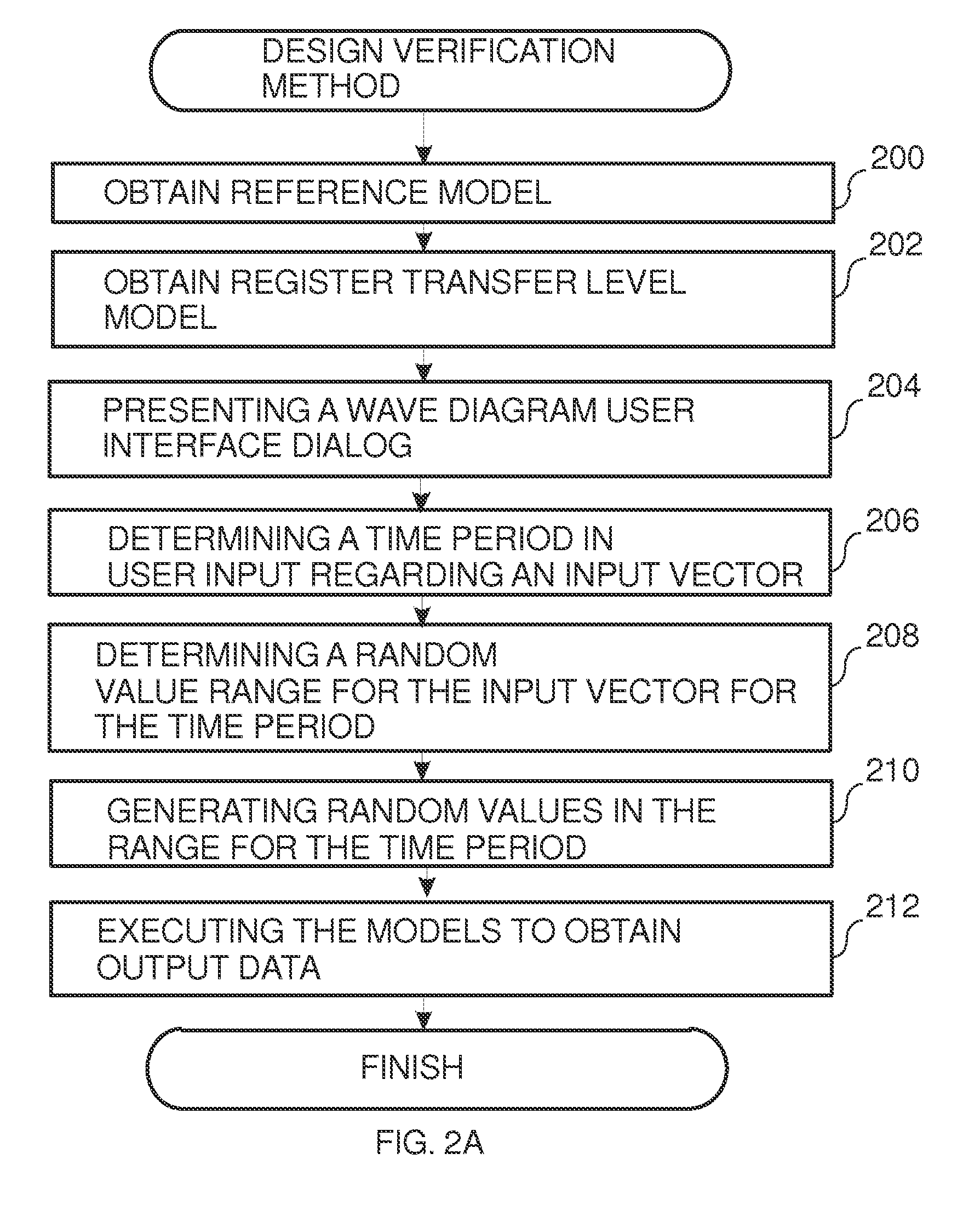

Method for integrated circuit design verification in a verification environment

InactiveUS20110055780A1Easy to testQuality improvementElectrical testingSoftware simulation/interpretation/emulationReference modelProcessor register

The invention relates to a method. In the method a reference model and a register transfer level model are obtained to a test bench. To a user is presented at least one wave diagram in a user interface on a display of an apparatus. A time interval associated with an input vector is determined based on a first type of user input. A random number range is associated with the time interval based on a second type of user input. The generation of an input data file is started for at least one test case for the reference model and the register transfer level model. Random numbers within the random number range are generated, the random numbers being stored within the input data file. The test cases are executed using either of the models.

Owner:VENELL MARTTI

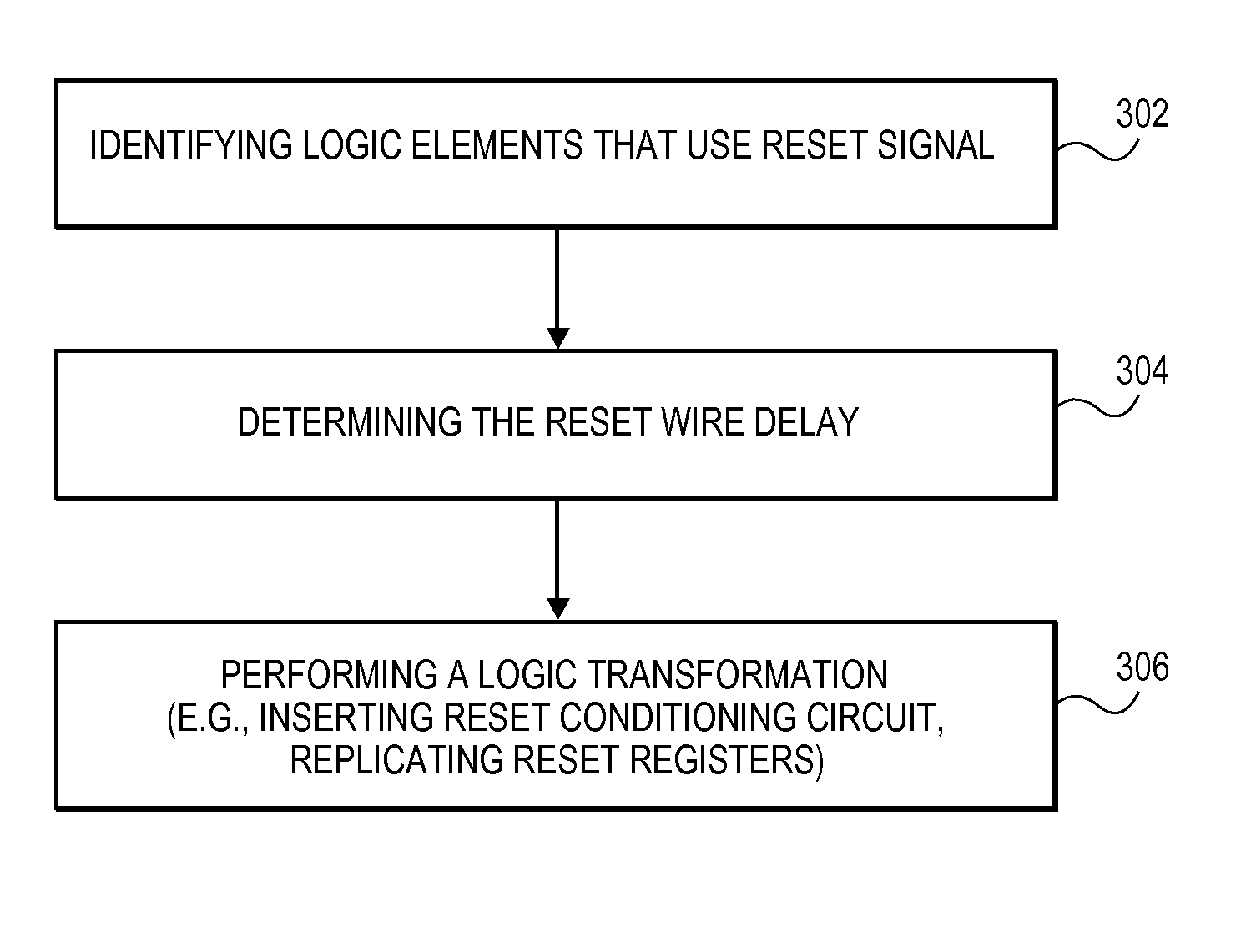

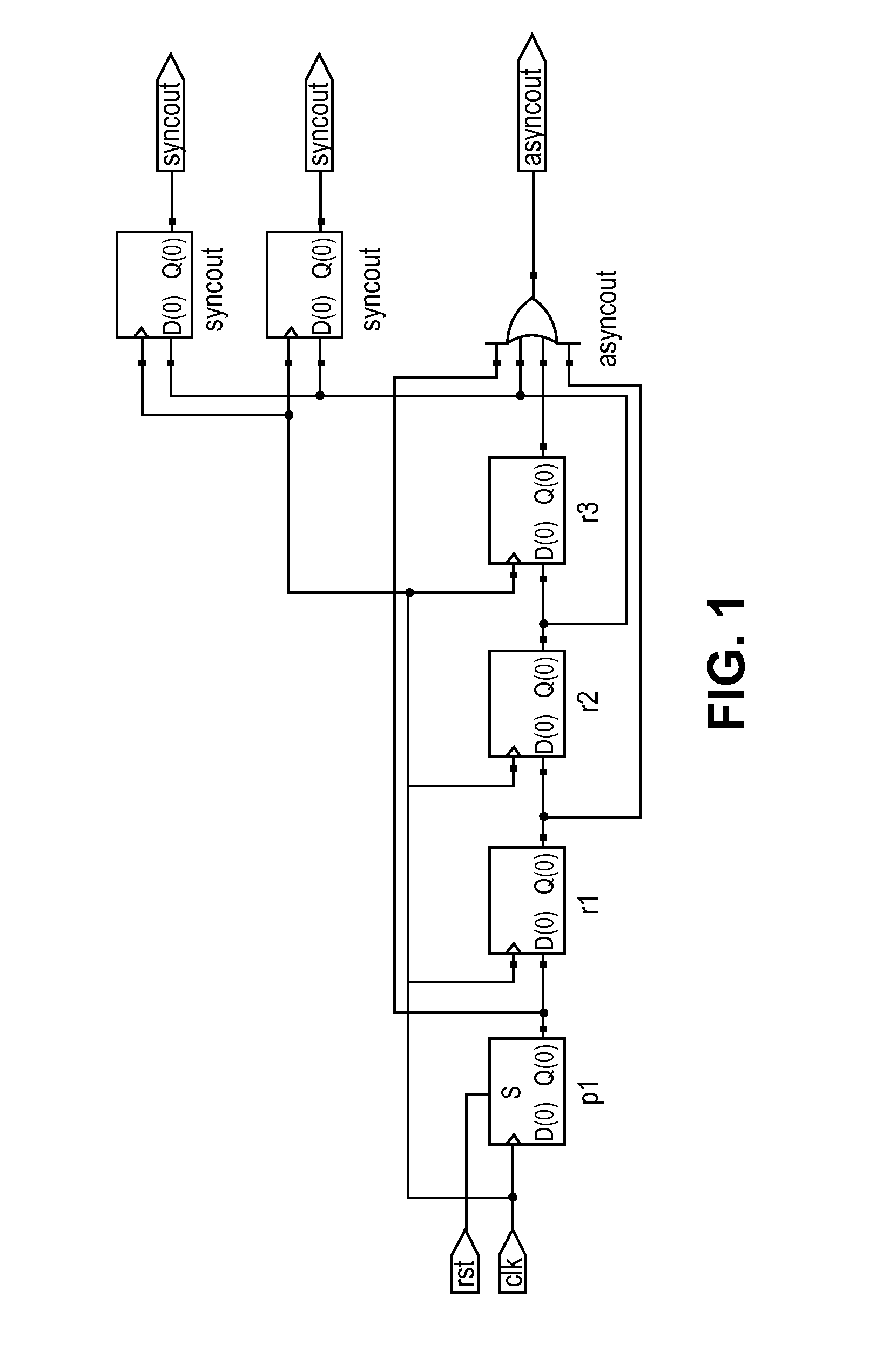

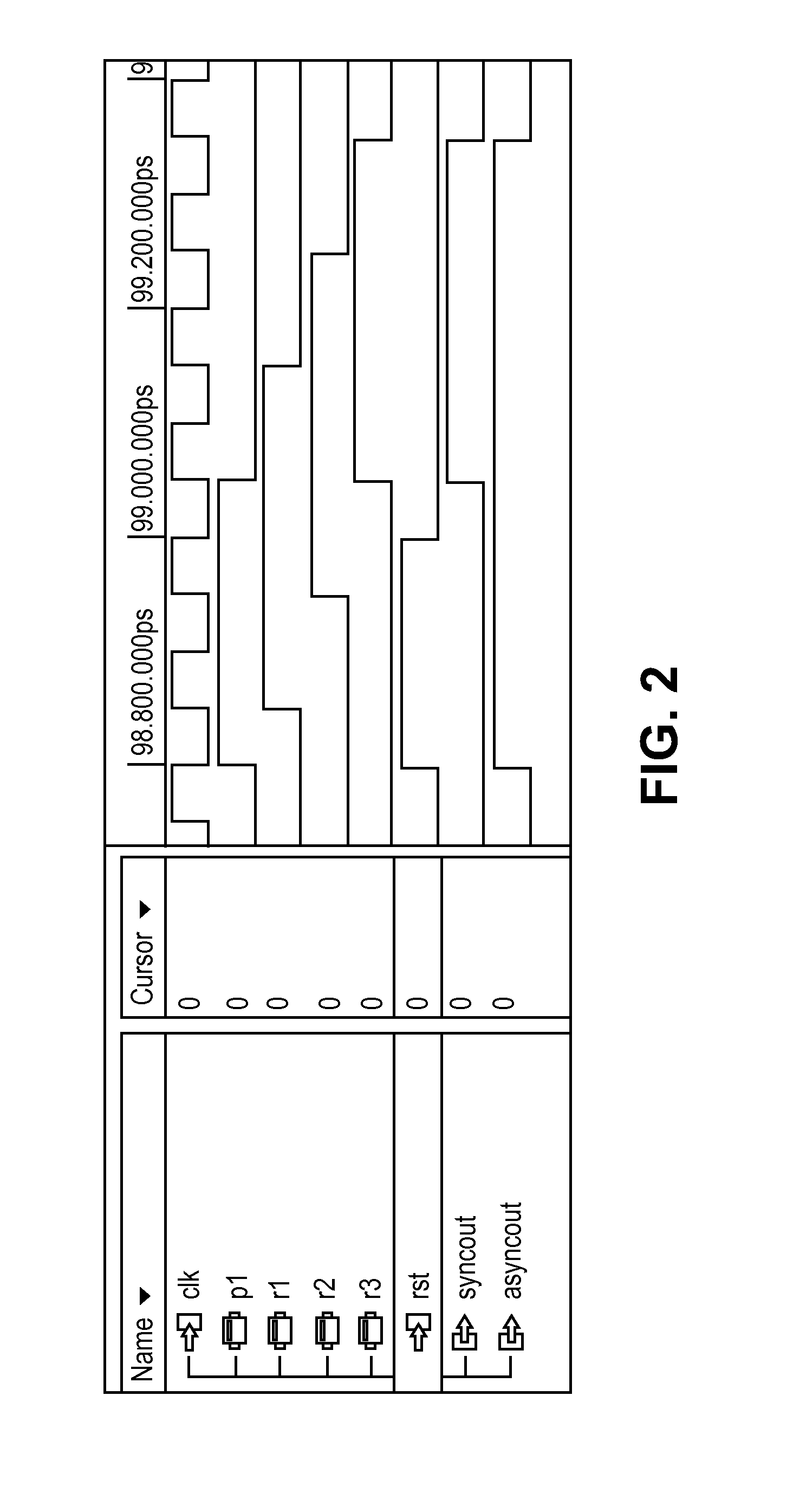

Methods and apparatuses for reset conditioning in integrated circuits

ActiveUS7594211B1Reduce metastability problemReliable signalData resettingComputer aided designPropagation delayProcessor register

Embodiments of the present invention disclose methods and apparatuses to reduce metastability problem related to propagation delay of reset signals in integrated circuits, with preferred applications in automatic physical synthesis for RTL (register transfer level) netlist. In an embodiment, a reset conditioning circuit is inserted into the original integrated circuit to make the reset behavior more reliable to avoid unpredictable states, especially for the de-assertion state of the reset signal. The reset conditioning circuit can provide an asynchronous reset signal output with extended duration so that all the load registers employing asynchronous reset signal will get the reset properly. Further, the reset conditioning circuit can modify the timing of the reset signal so that its de-assertion edge is synchronized with a rising clock edge. In another embodiment, the reset conditioning circuit replicates a synchronous reset signal to provide a reset signal closer to loads or registers at a plurality of circuit modules or partitions. The generation of the reset conditioning circuit is well suitable for physical synthesis of RTL netlists, especially for automatic physical synthesis.

Owner:SYNOPSYS INC

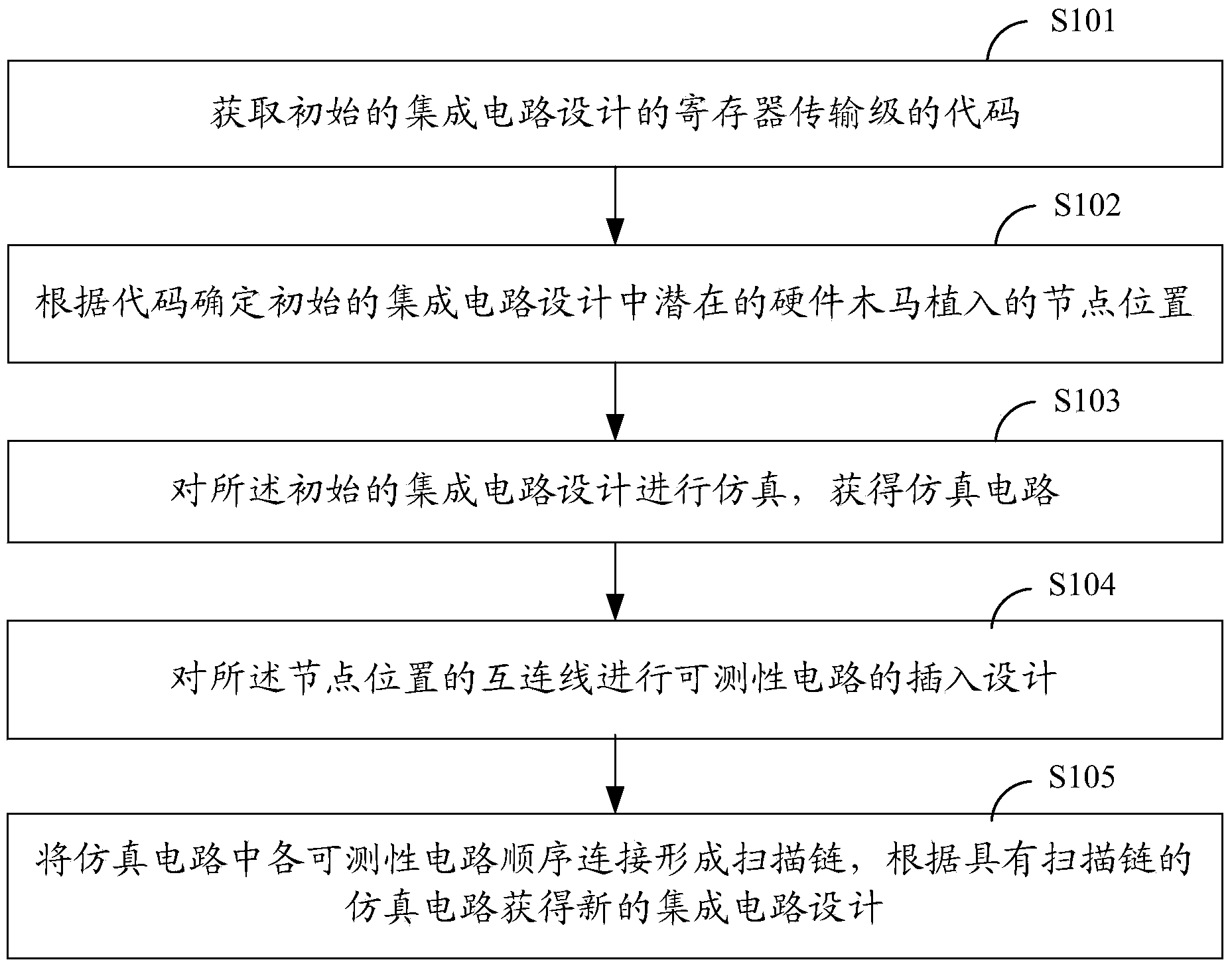

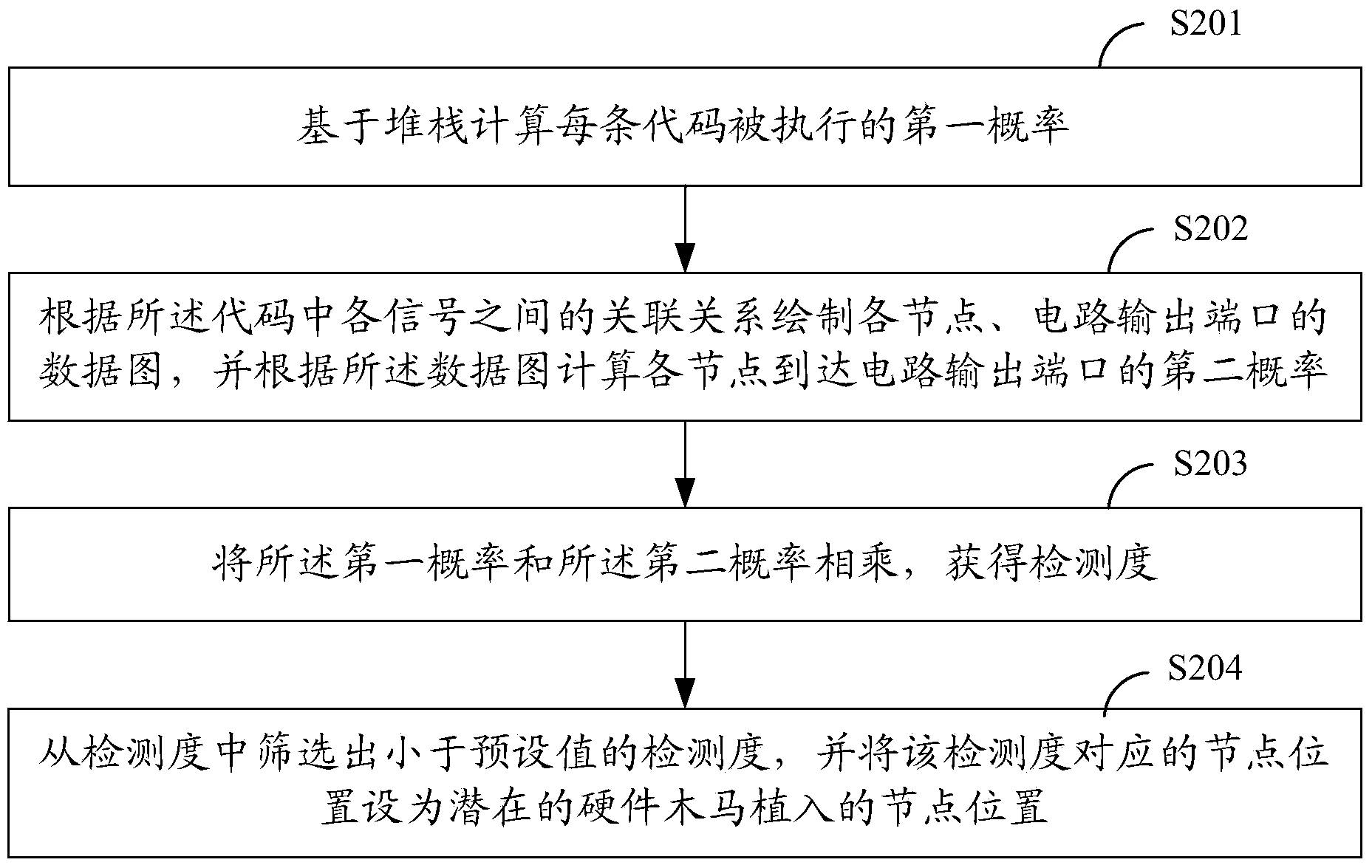

Design method of integrated circuit and hardware trojan detection method

ActiveCN104239616ALow costReduce overheadPlatform integrity maintainanceSpecial data processing applicationsHardware TrojanProcessor register

The invention relates to a design method of an integrated circuit and a hardware trojan detection method. The design method comprises the following steps of acquiring a code of a register transfer level of an initial integrated circuit design; confirming a node position embedded by a potential hardware Trojan in the initial integrated circuit design according to the code; simulating the initial integrated circuit design to obtain a simulating circuit; computing the logic value probability of an interconnection line of the node position in the simulating circuit, and carrying out insertion design of testability circuits on the interconnection line of the node position according to the logic value probability; sequentially connecting the testability circuits in the simulating circuit to form a scan chain, and acquiring a new integrated circuit design according to the simulating circuit with the scan chain, wherein the scan chain is used for detecting the position of the hardware trojan of the integrated circuit according to the input test signals and the output results. According to the integrated circuit designed by the scheme of the invention, the position of the hardware trojan can be found, and the cost is reduced.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

System and method for converting software to a register transfer (RTL) design

ActiveUS7904850B2Analogue computers for electric apparatusCAD circuit designComputer architectureTerm memory

A method for converting a C-type programming language program to a hardware design, where the said program is an algorithmic representation of one or more processes. The C-type programming language program is compiled into a hardware description language (HDL) synthesizable design. The compiler categorizes variables as using either implicit memory or custom memory. Different accessor functions are used depending on which type of memory is used. The programming language may use ANSI C and the HDL may be Verilog Register Transfer Level (RTL). The hardware device generated from the HDL synthesizable design may be an Application-Specific Integrated Circuit (ASIC) or a Field Programmable Gate Array (FPGA).

Owner:EXAR CORP

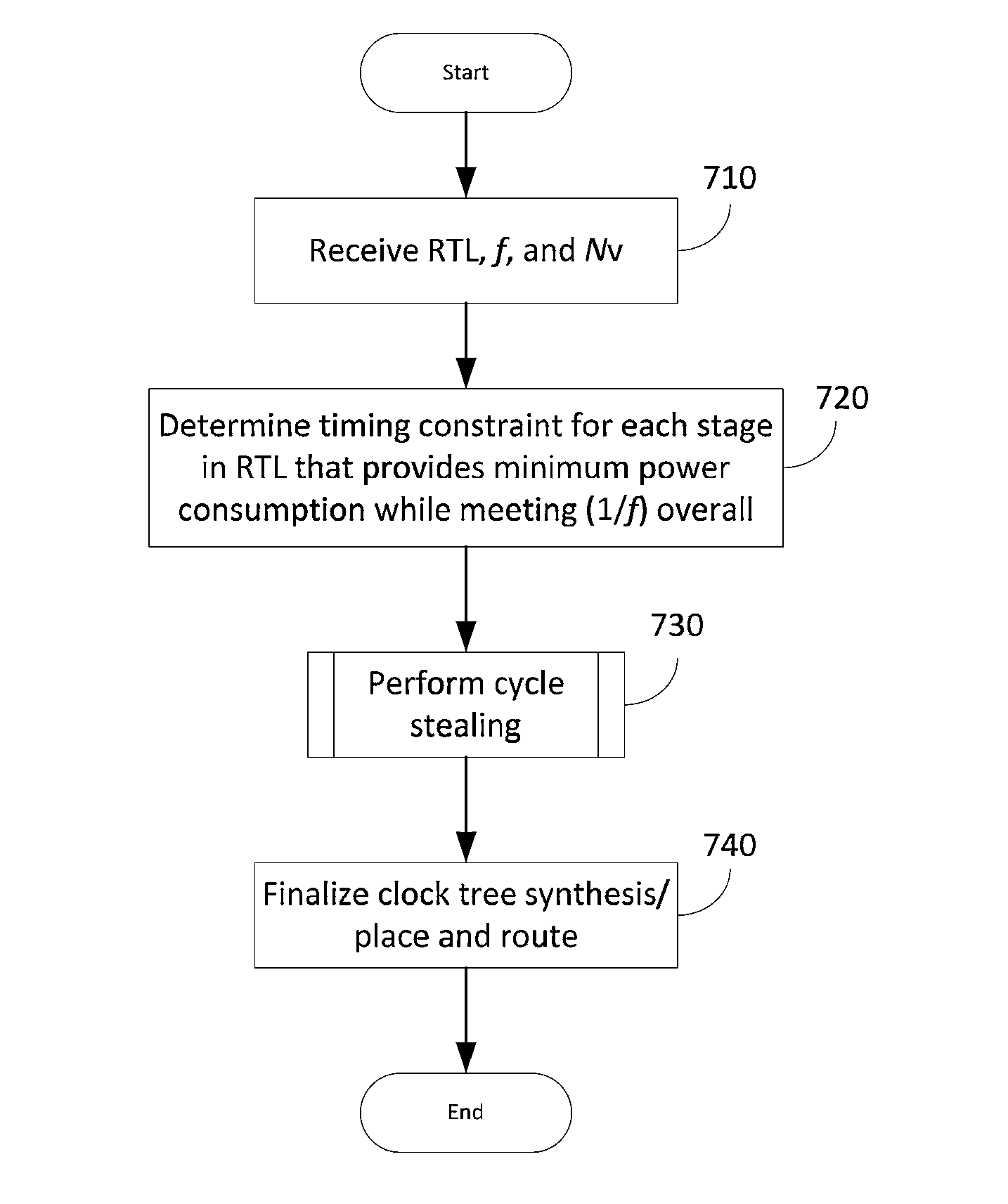

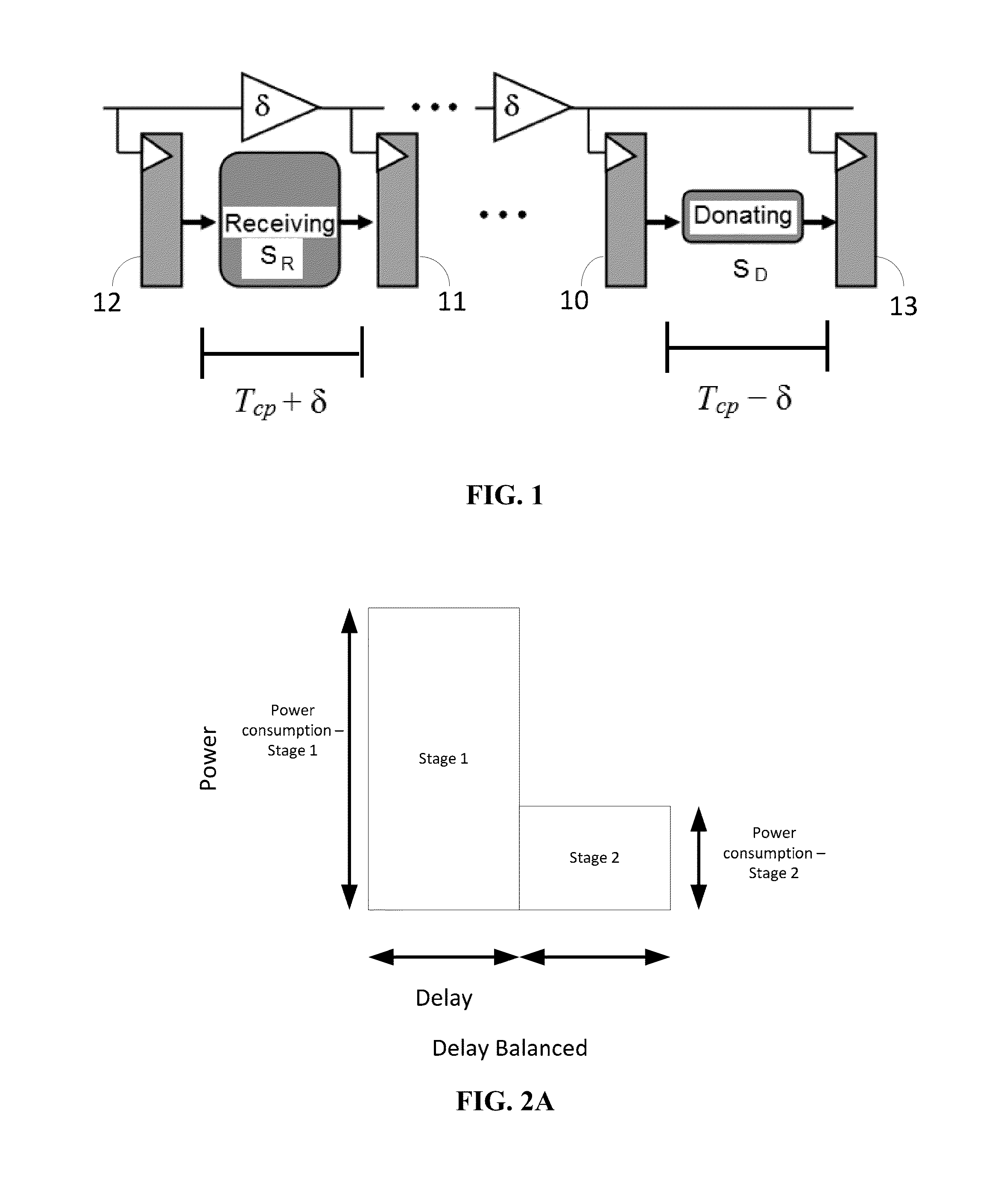

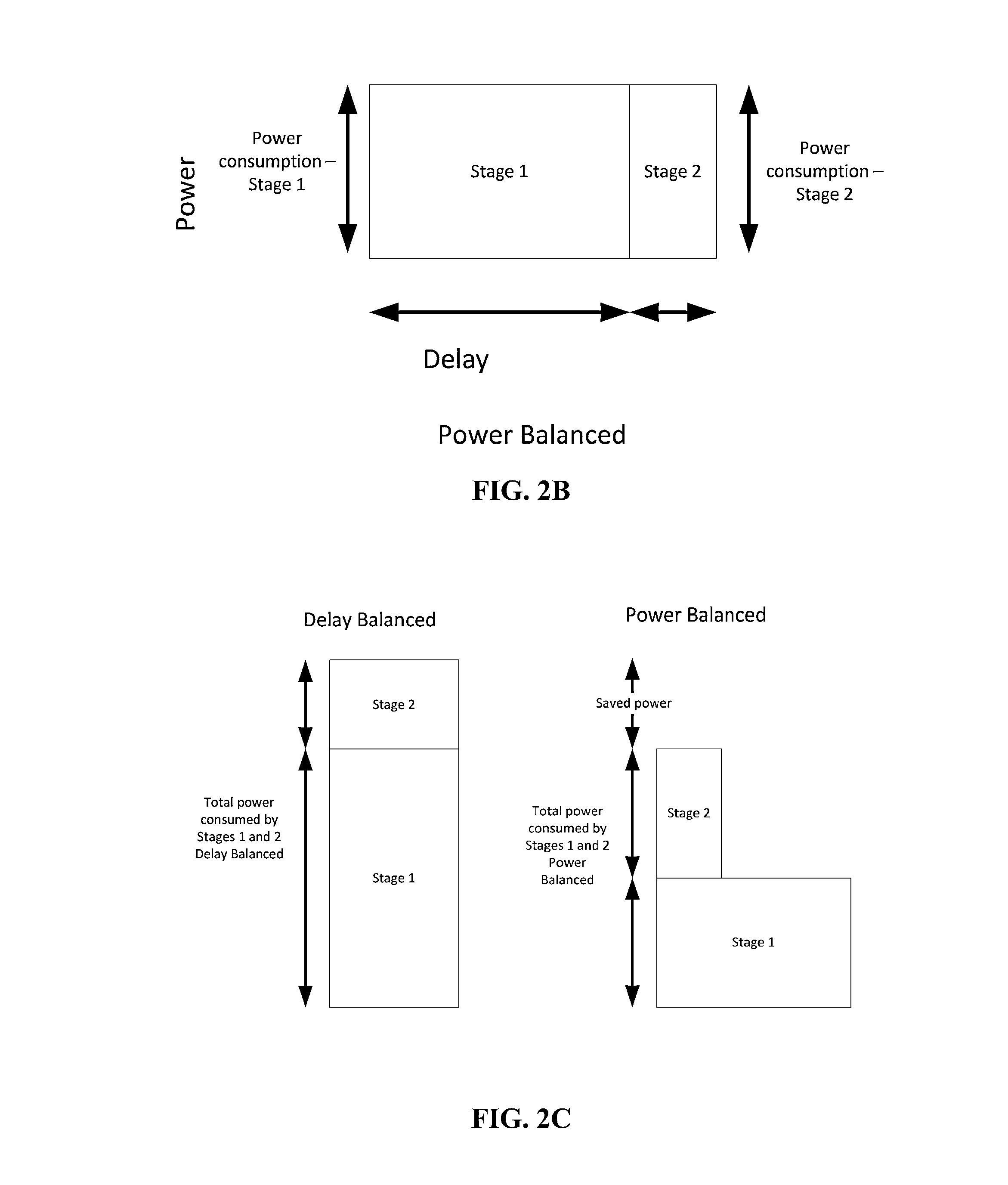

Power balanced pipelines

InactiveUS20130111425A1Reduce power disparitySmall and less leakyCAD circuit designSoftware simulation/interpretation/emulationOperational systemPower balancing

Power balancing techniques are provided for improving power efficiency of pipelined processors. A design-level implementation can be incorporated during synthesis of pipeline clocks in which a register transfer level (RTL) code, operating frequency, and available voltage domains are used to perform cycle time stealing with, and optimize for, power efficiency. A test-level implementation can be incorporated during testing of a chip in which delay and power measurements are used to perform calculations based on cycle time stealing and optimization of power efficiency. The calculations are then used to perform voltage scaling and / or adjust tunable delay buffers. Process variations may also be corrected during test time. A run-time approach can be incorporated for dynamic power balancing in which the operating system keeps track of one or more performance indicators such as a count of floating point instructions and uses a look-up table to provide the appropriate delays.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

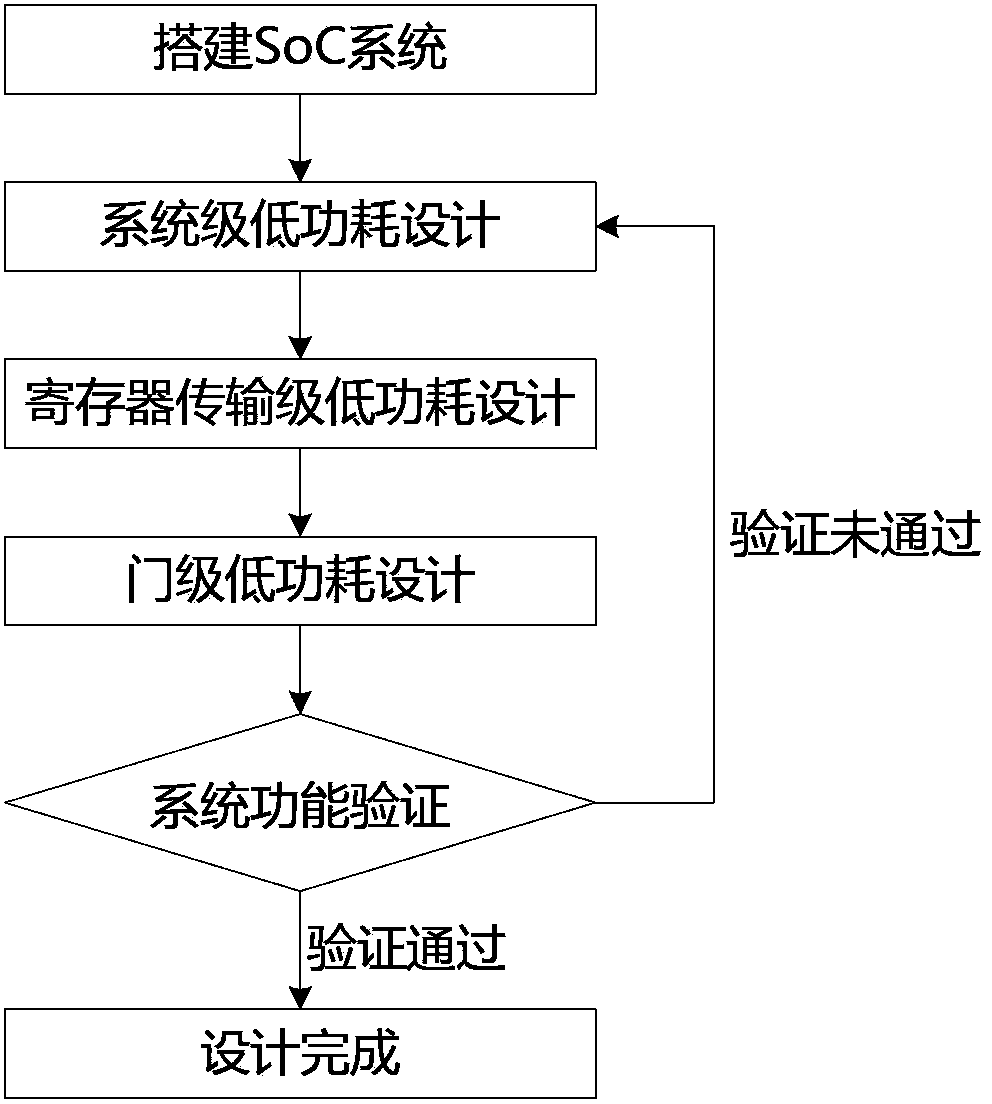

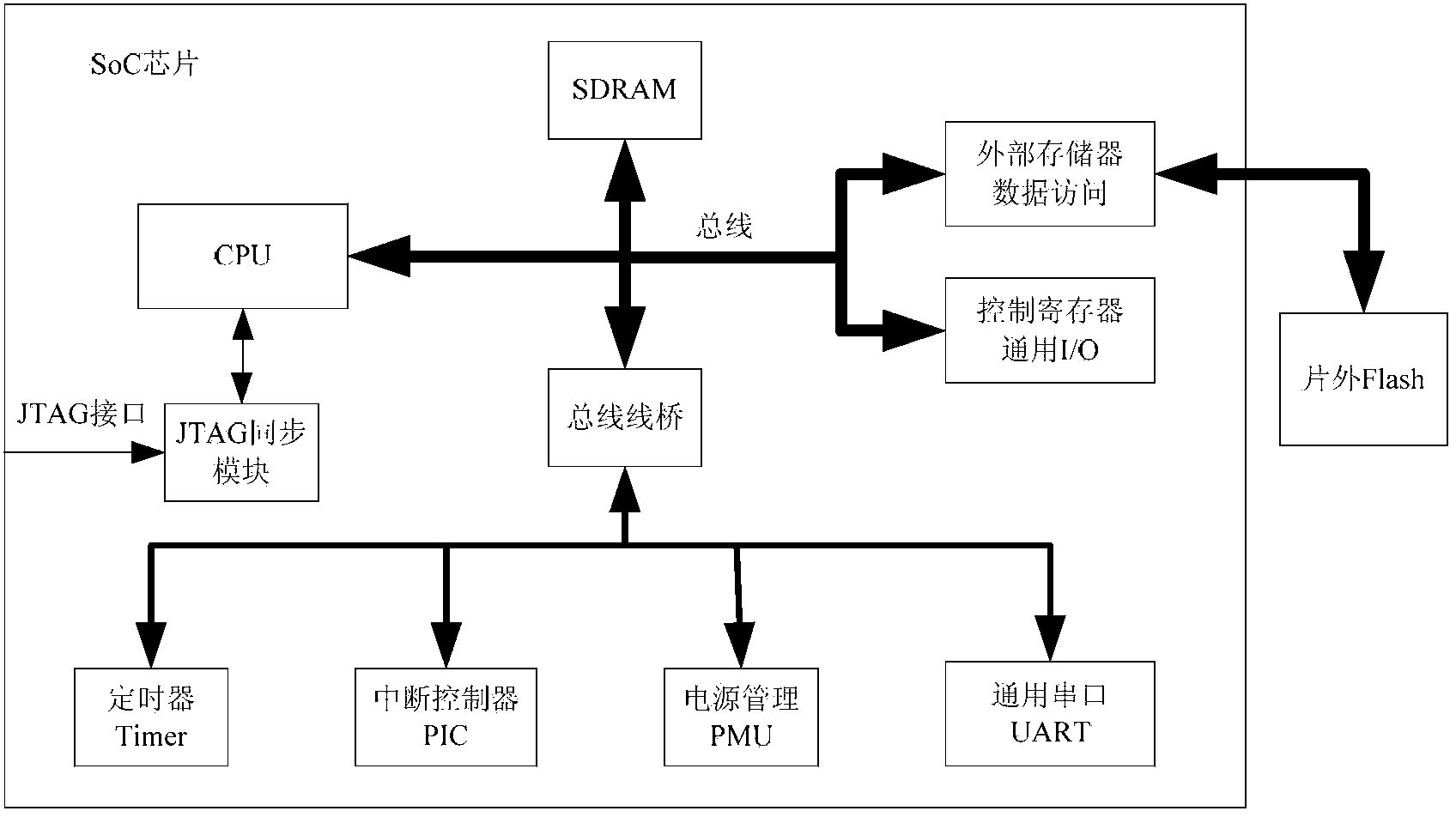

Multi-level collaborative low-power design method

ActiveCN103412990AEasy to optimizeConvenience trade-offPower supply for data processingSpecial data processing applicationsLow-power electronicsEngineering

A multi-level collaborative low-power design method includes firstly establishing an SoC (system on chip); secondly, completing a system-level low-power design; thirdly, completing a register transfer-level low-power design; fourthly, completing a gate-level low-power design; and fifthly, completing system function verification. The design method is operated from the top to the bottom, results of power optimization of each level are overlapped, the low-power design is performed at multiple levels collaboratively, and optimization and choosing of power can be performed better as required; the power of the entire system is lowered, meanwhile, normal functions can be guaranteed, and effect of lowering the power is more significant.

Owner:BEIHANG UNIV

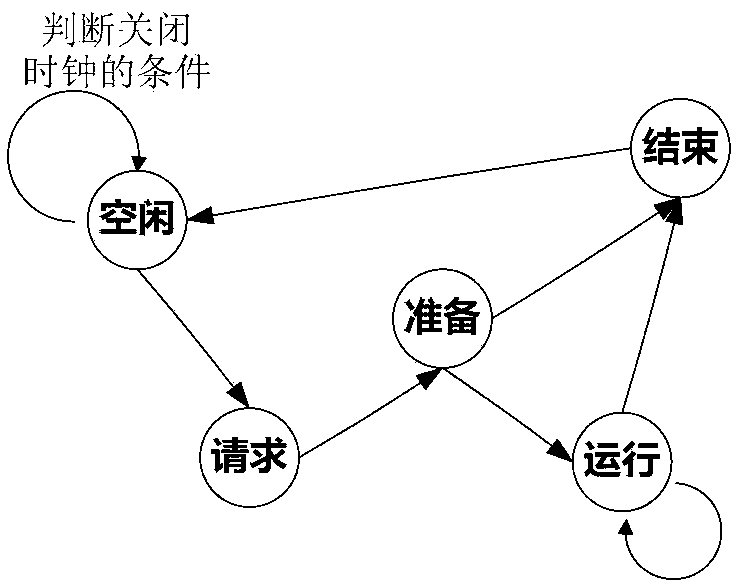

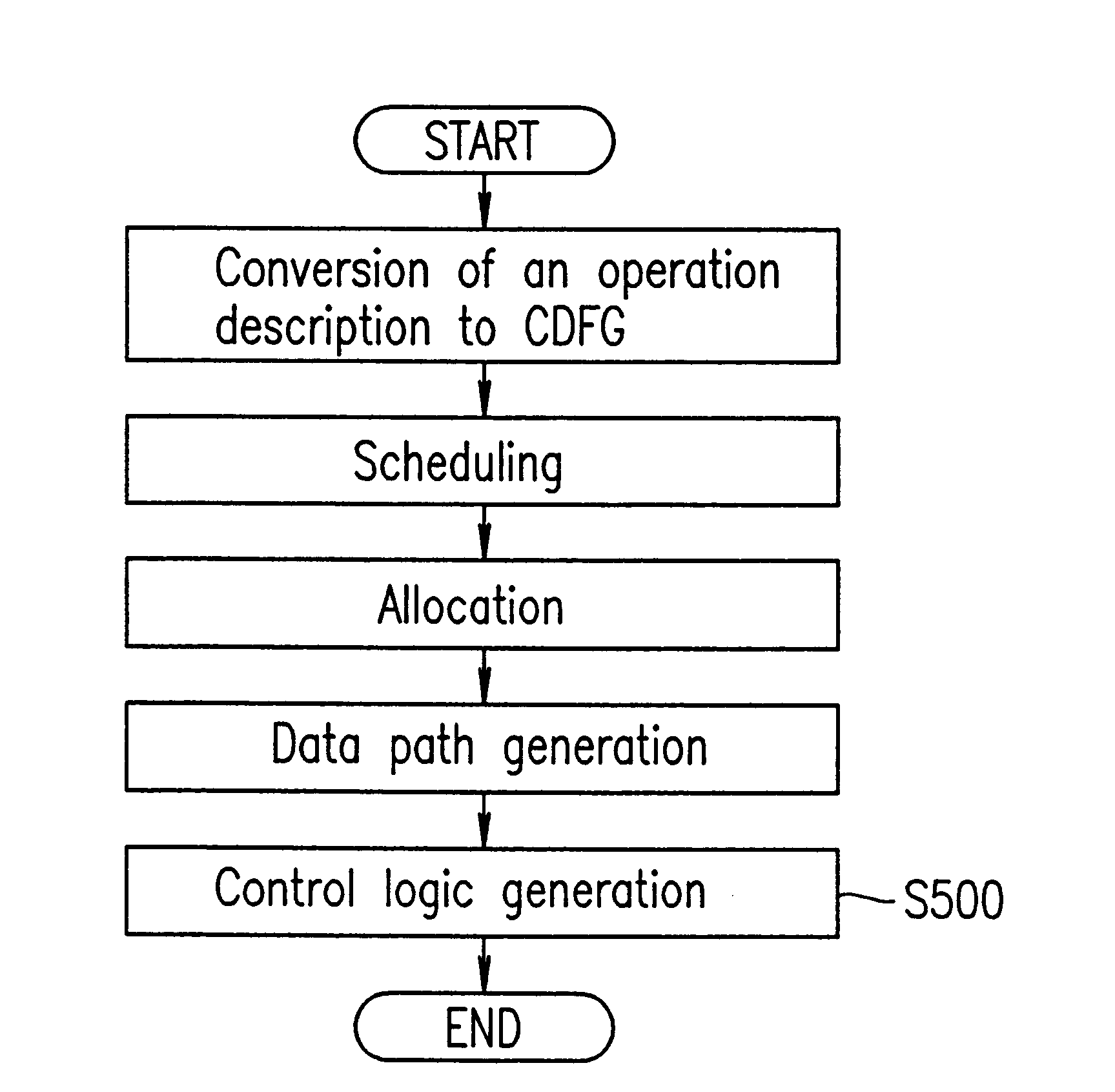

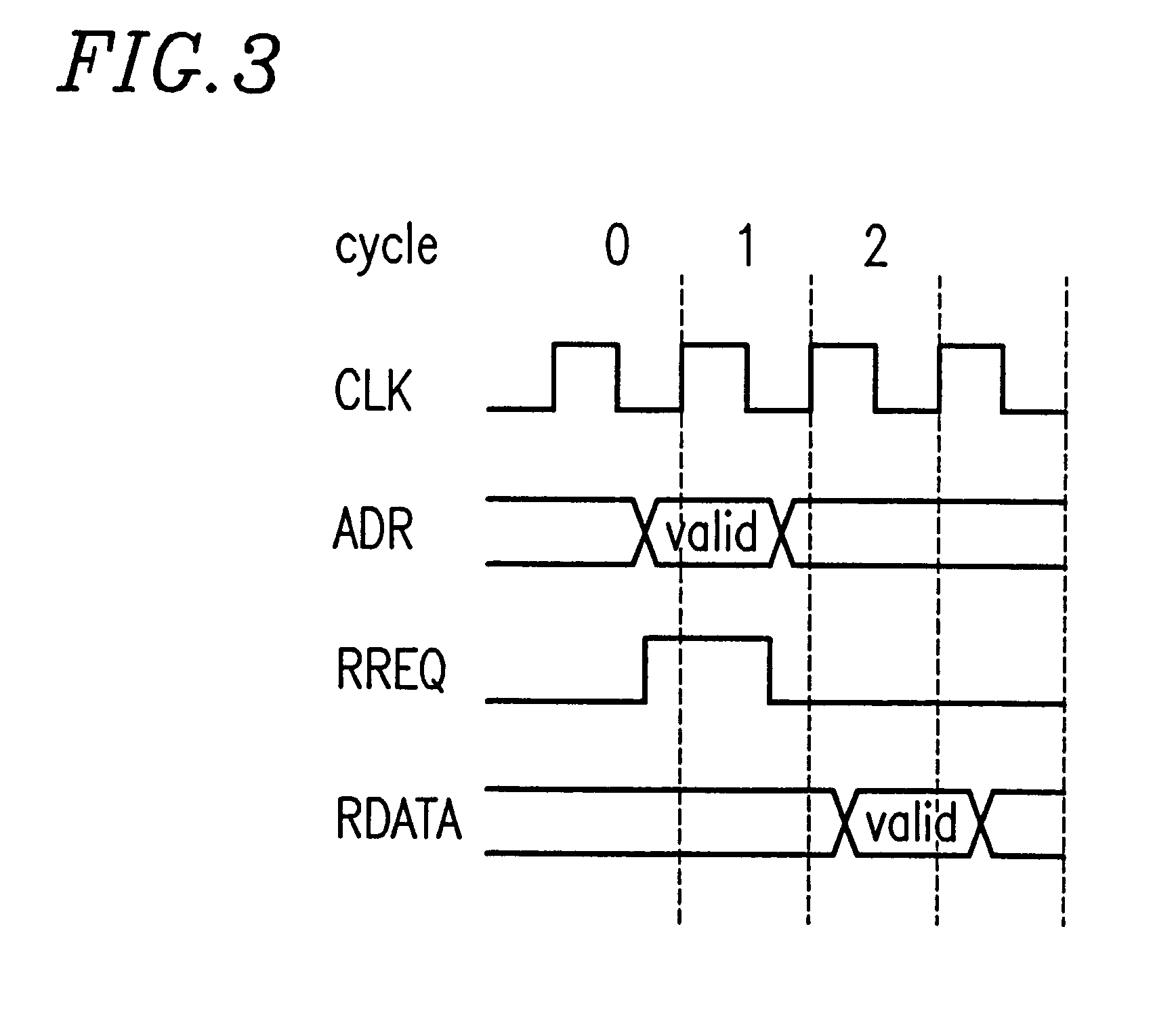

High level synthesis method, thread generated using the same, and method for generating circuit including such threads

A high level synthesis method for generating a logic circuit of a register transfer level from an operation description includes a control data flowgraph generation stage; a scheduling stage; an allocation stage; a data path generation stage; and a control logic generation stage. When generating a thread sharing a common memory with another thread operating in parallel therewith, a memory access request is represented by a node of a control data flowgraph so as to perform scheduling, and a control logic is generated. The control logic outputs a memory access request signal to a common memory interface in a state corresponding to a step to which the node is scheduled, and keeps the state until a memory access request acceptance signal from the common memory interface is changed to be active.

Owner:SHARP KK

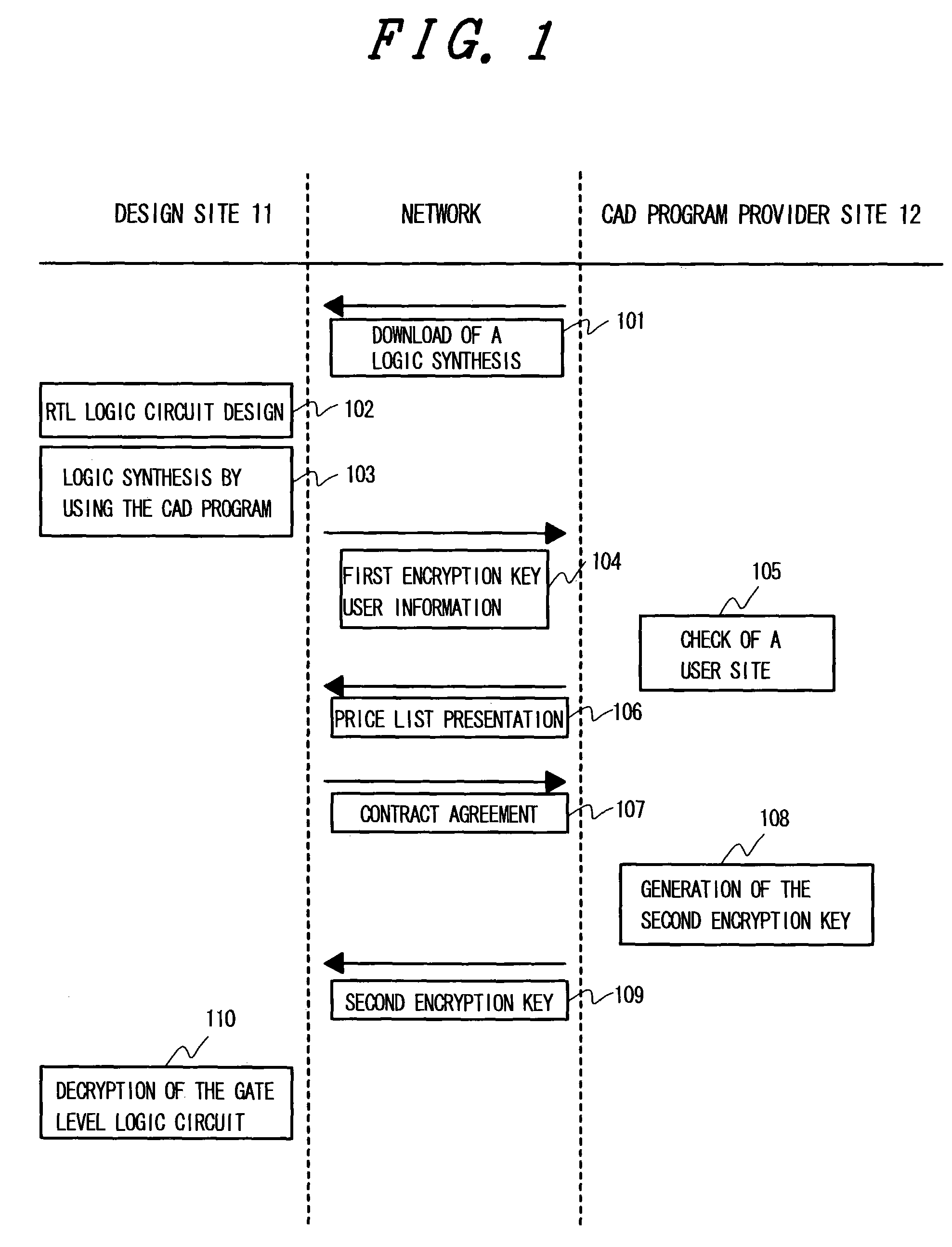

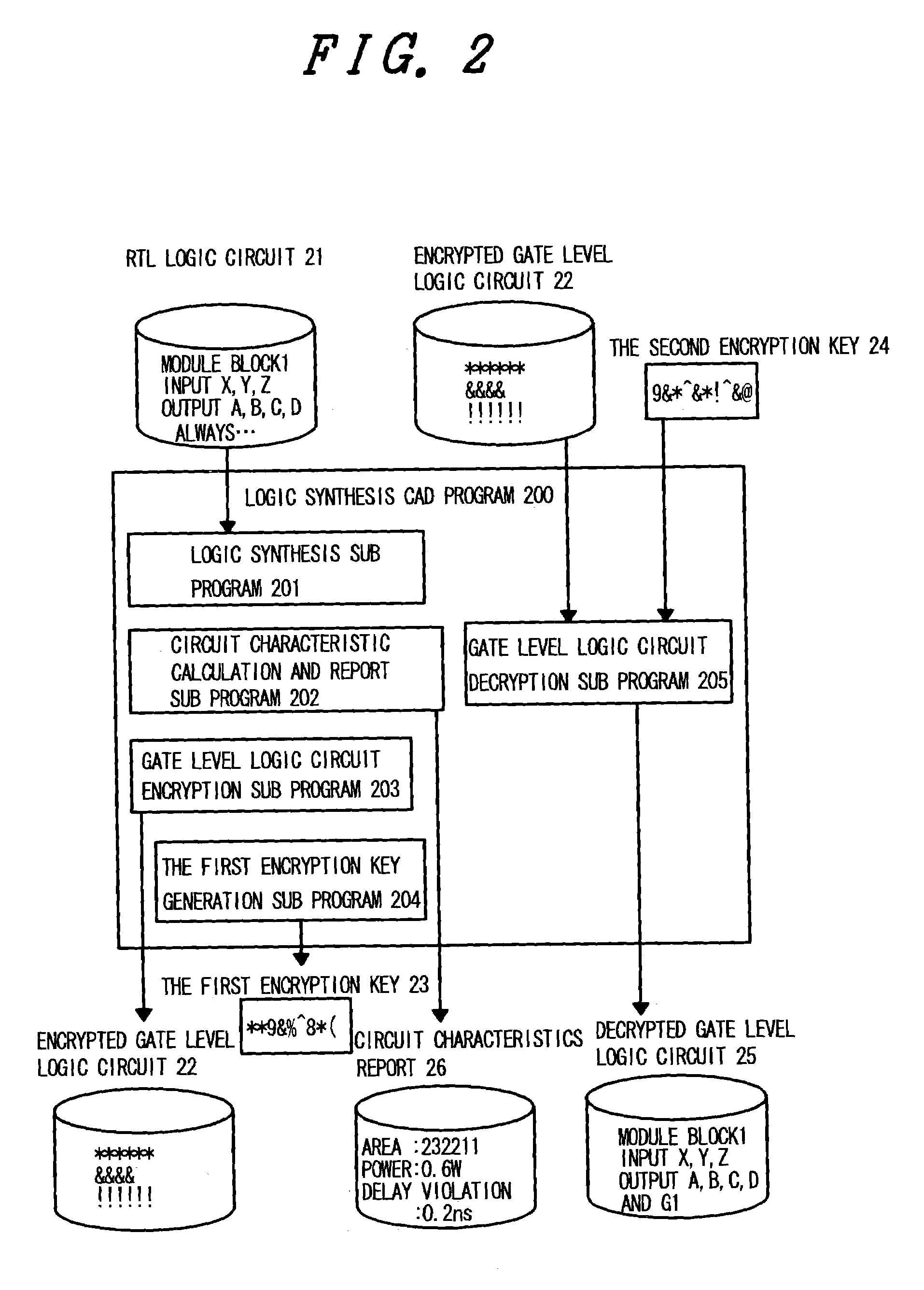

Method for designing logic circuit and CAD program

InactiveUS7111258B2Low costShort timeKey distribution for secure communicationCAD circuit designProcessor registerDesign phase

A method for designing a logic circuit and a CAD program which allow a logic circuit with desired performance to be designed in a short period of time by suppressing the elongation of a logic design period for achieving a circuit area, an operating speed, power consumption, and the like as target specifications are provided at low cost. Shorter-period and lower-cost design is accomplished by allowing a user to use a high-performance logic synthesis CAD program at no charge if he only checks circuit characteristics resulting from synthesis and collecting a fee if the user is satisfied with the resulting circuit characteristics and intends to use a gate level logic circuit. In a design phase which receives a register transfer level or operation level logic circuit and synthesizes a gate level logic circuit, desired circuit characteristics are obtainable in a short period of time at low cost.

Owner:HITACHI LTD

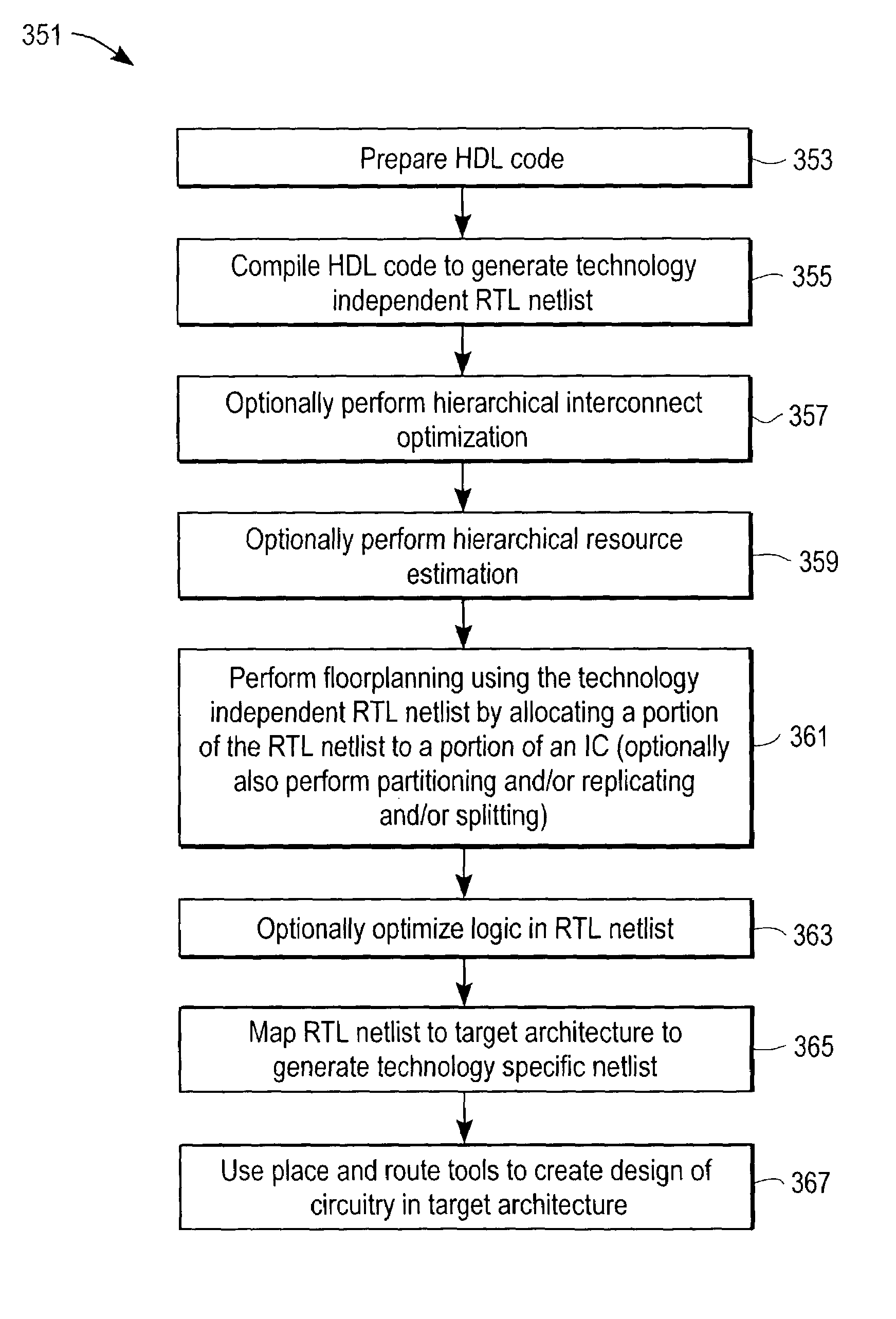

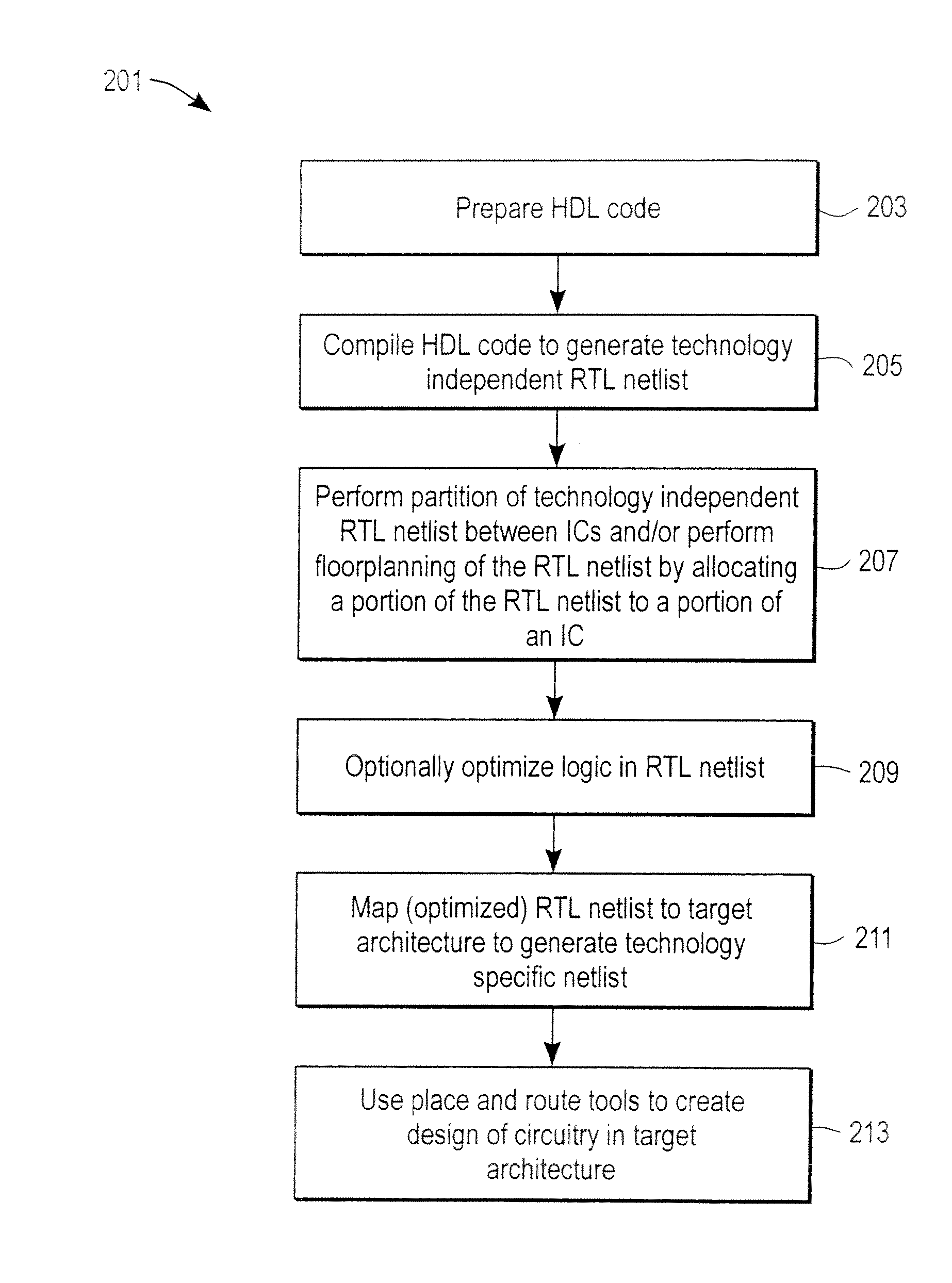

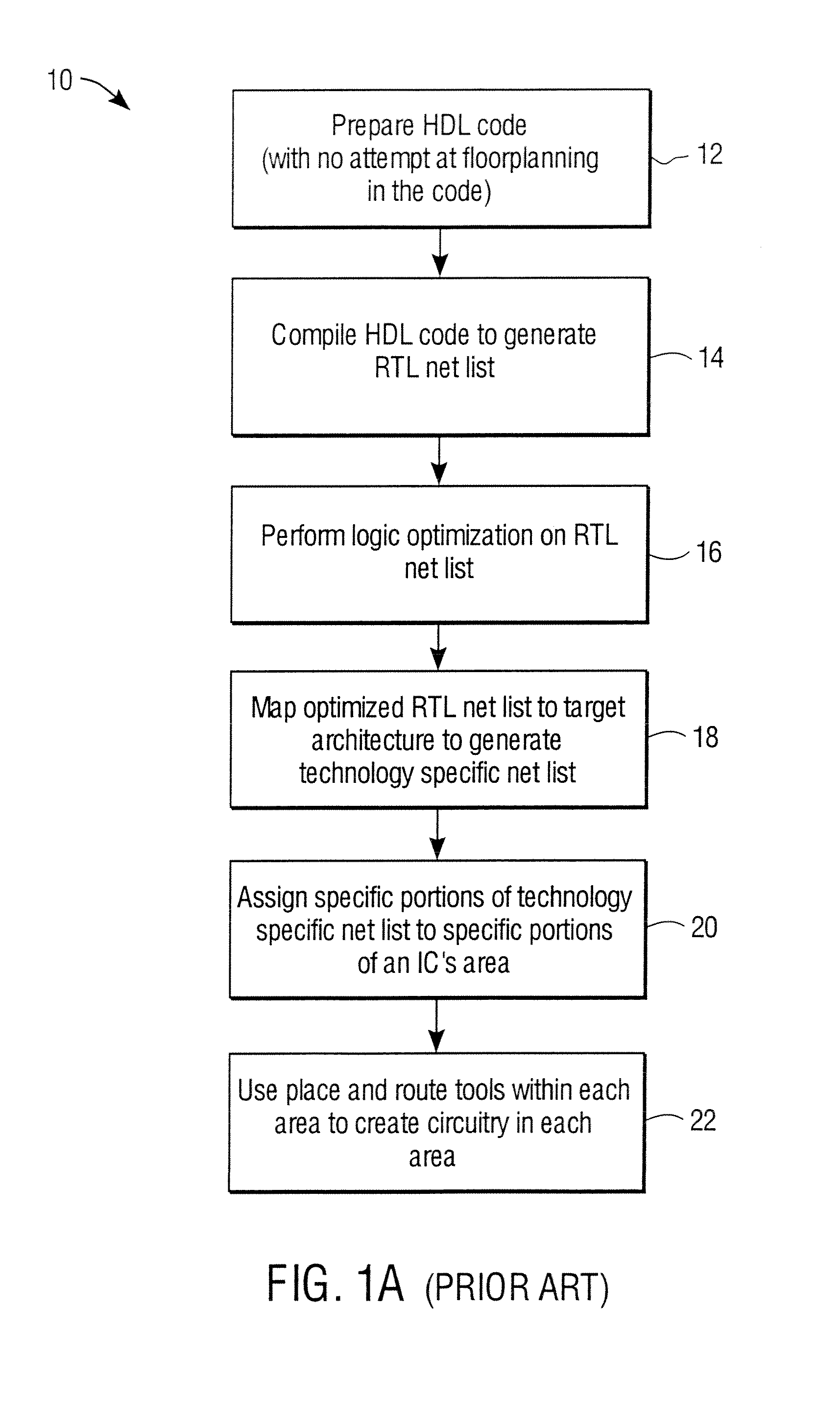

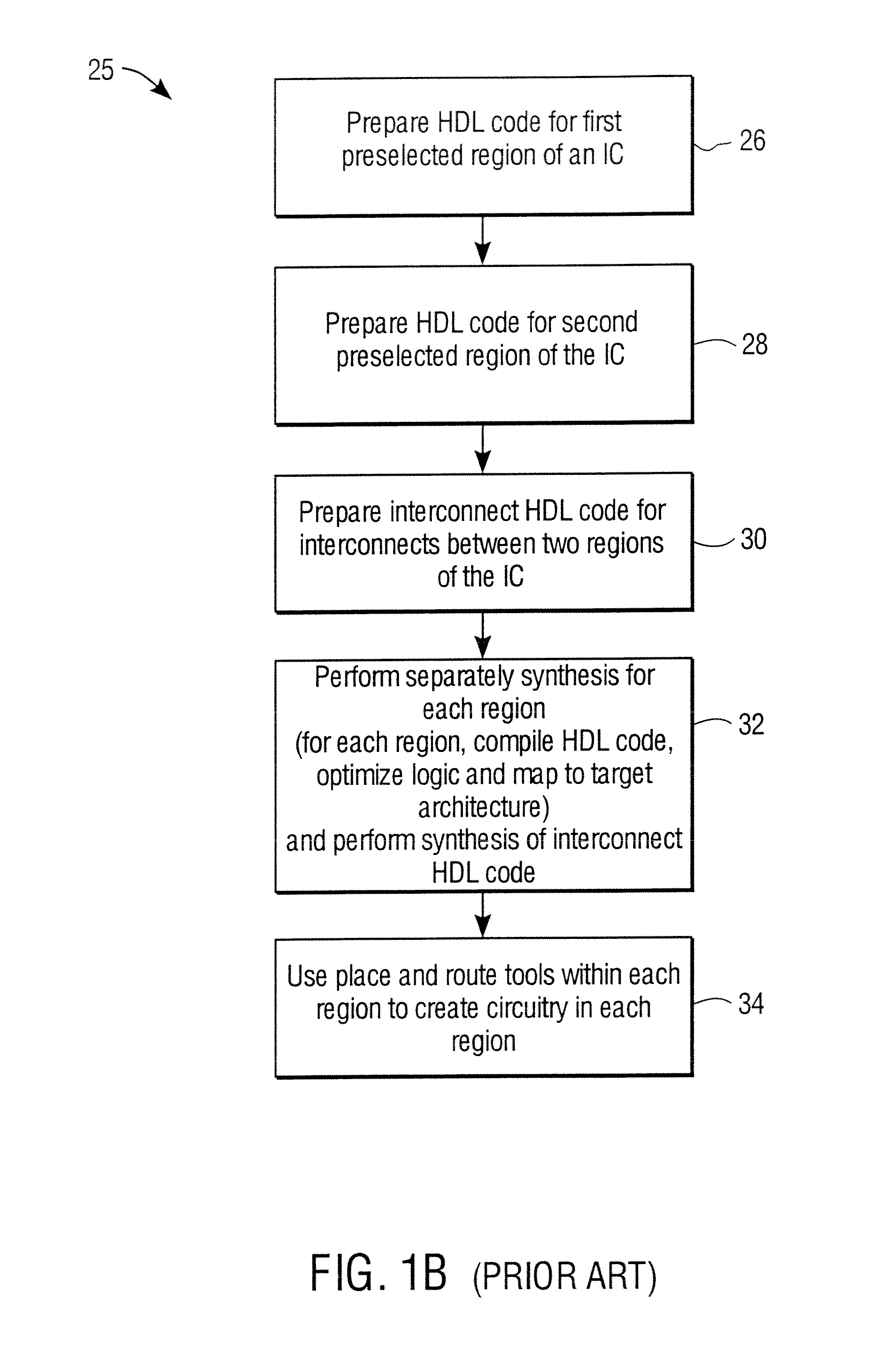

Methods and apparatuses for designing integrated circuits

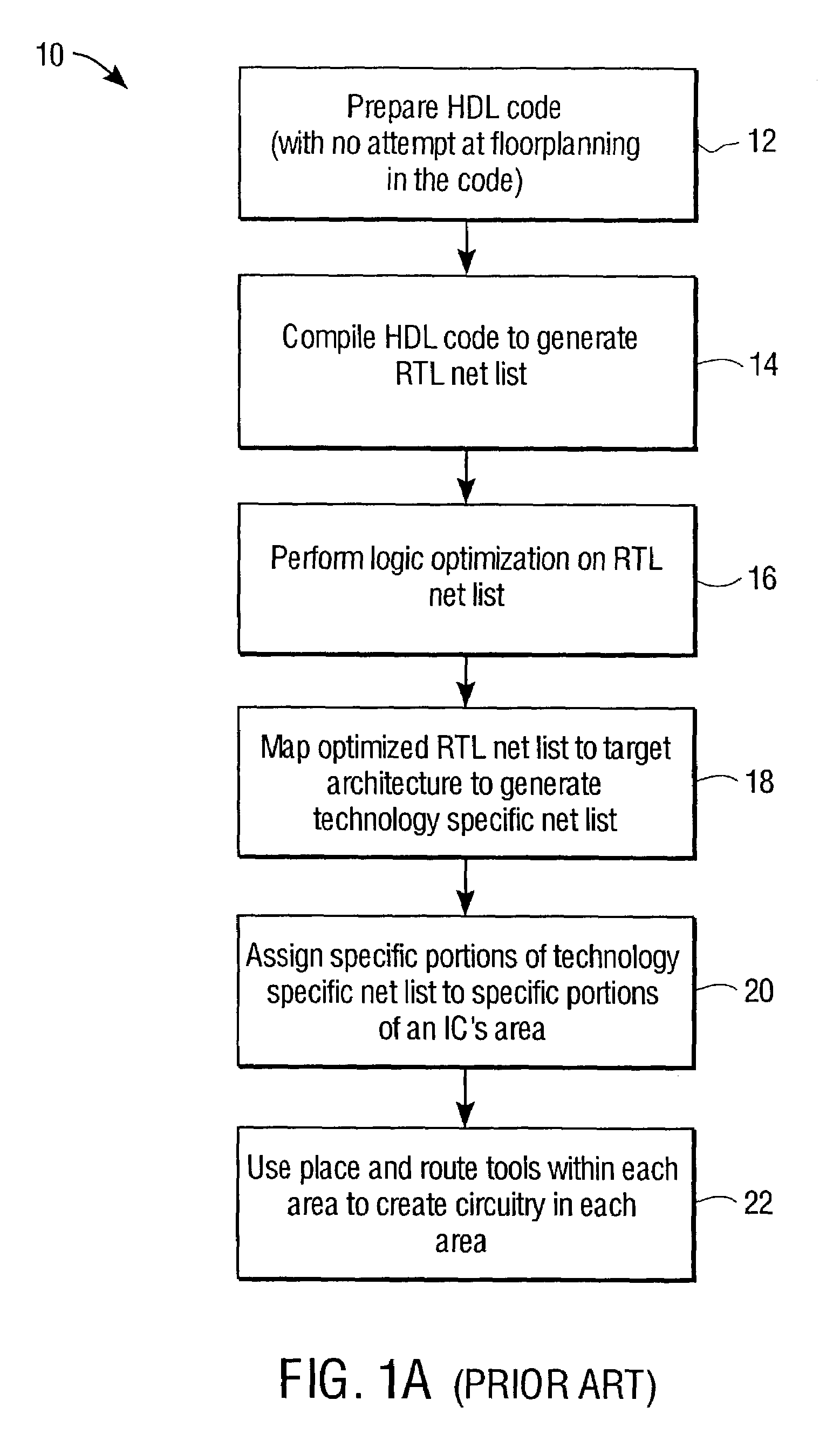

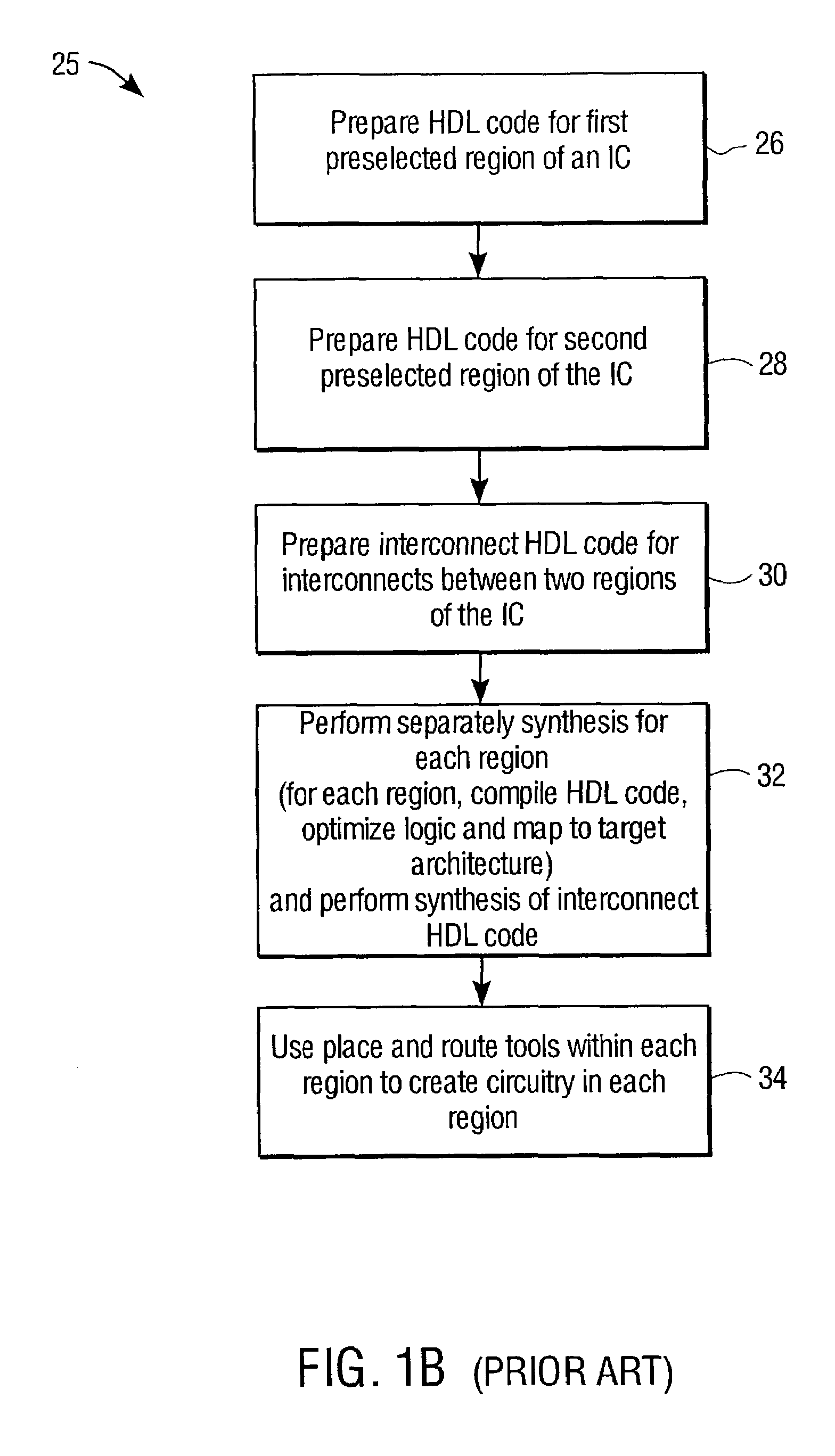

InactiveUS7010769B2CAD circuit designSoftware simulation/interpretation/emulationComputer architectureNetlist

Methods and apparatuses for designing an integrated circuit. In one example of a method, a hardware description language (HDL) code is compiled to produce a technology independent RTL (register transfer level) netlist. A portion of an area of the IC is allocated to a specific portion of the technology independent RTL netlist. In a typical implementation of this method, the allocation restricts circuitry created from the specific portion to the portion of the IC.

Owner:SYNOPSYS INC

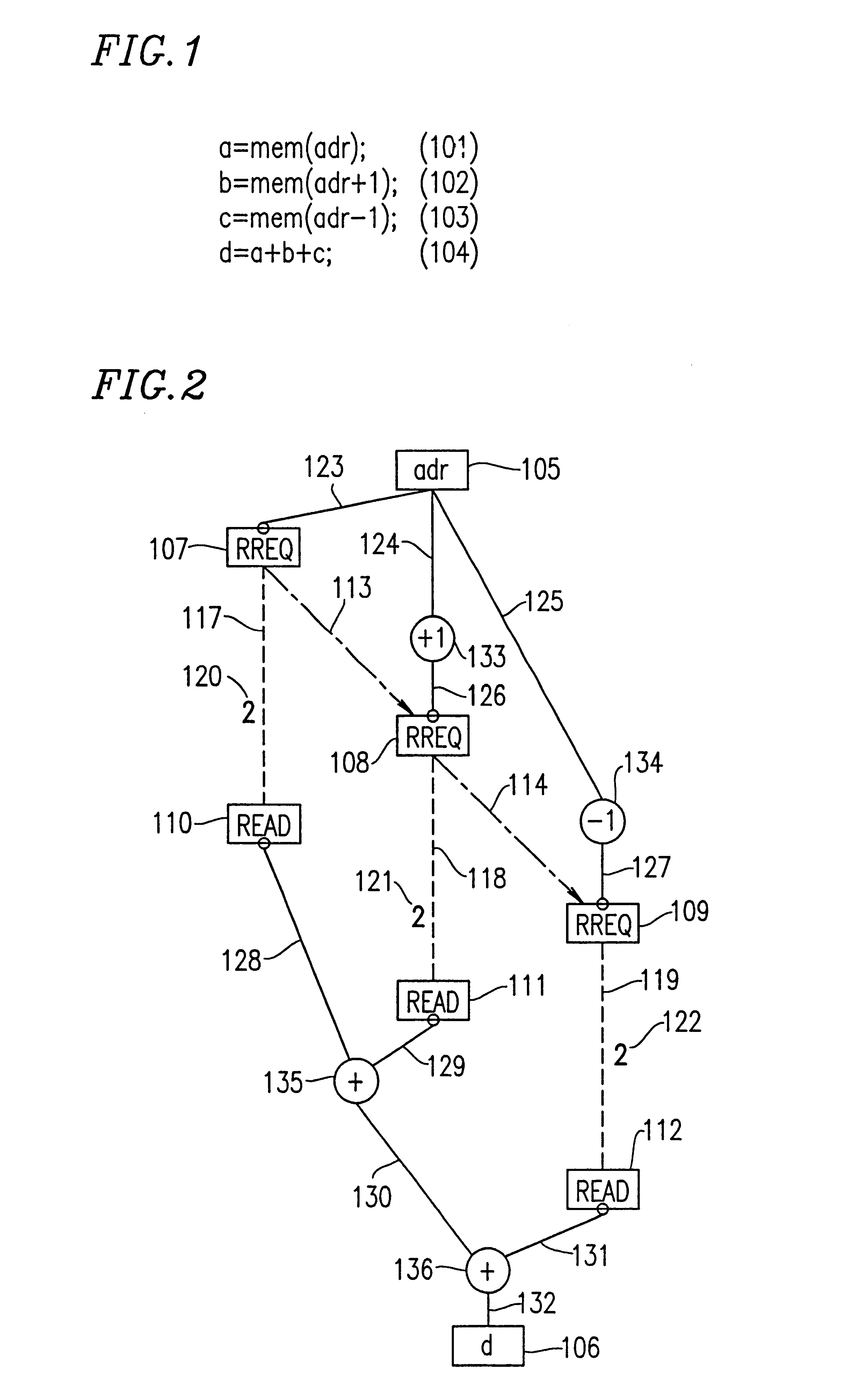

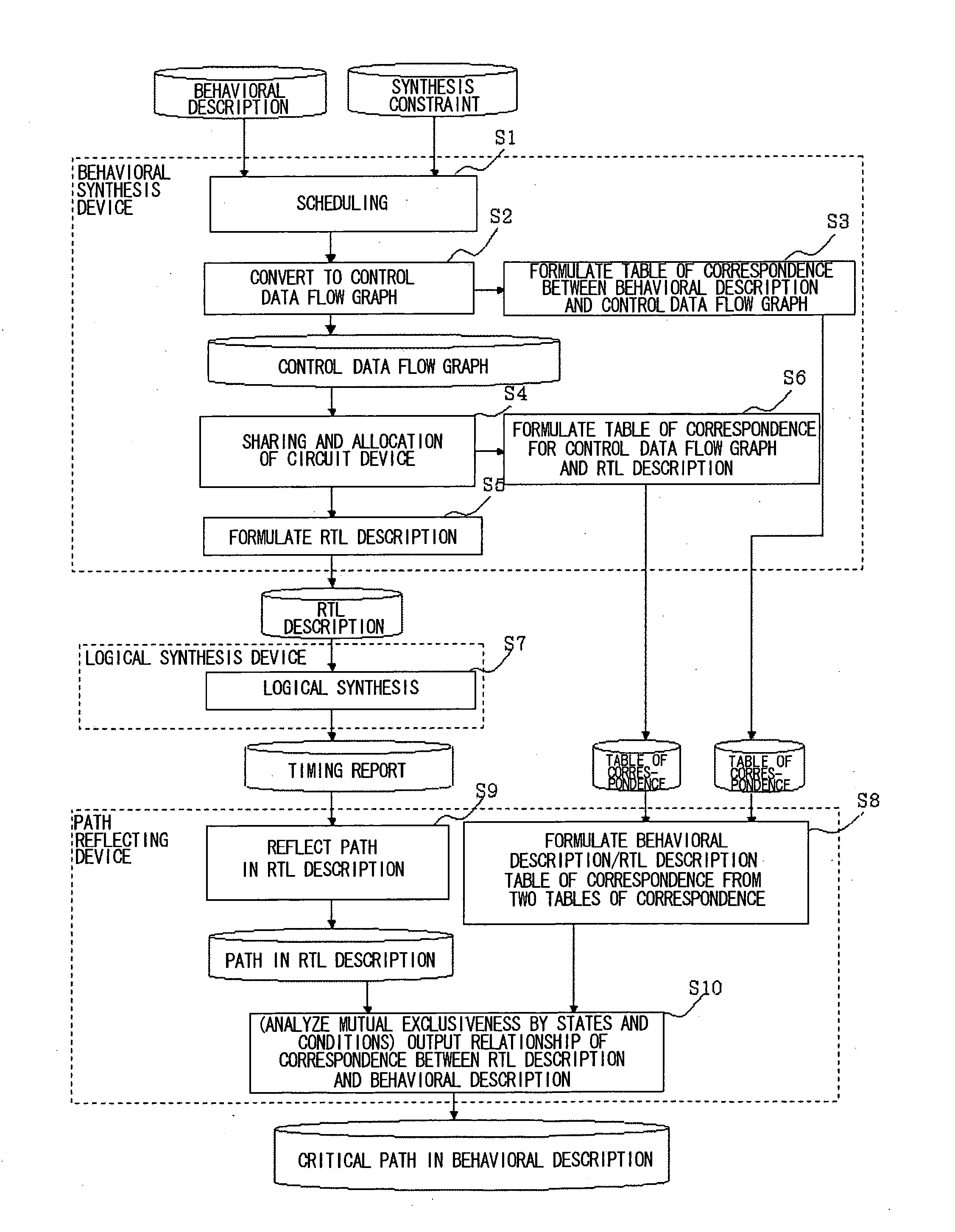

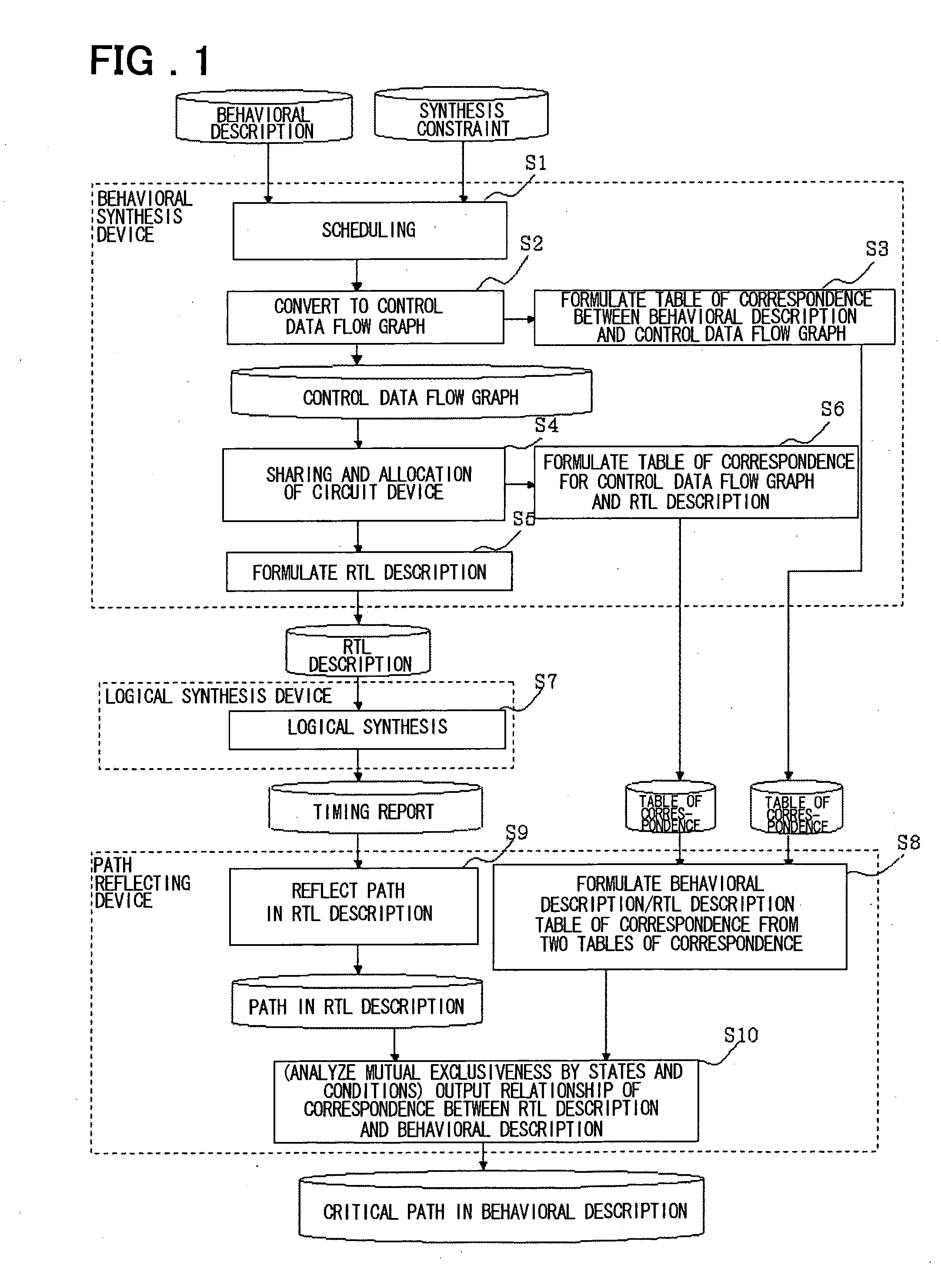

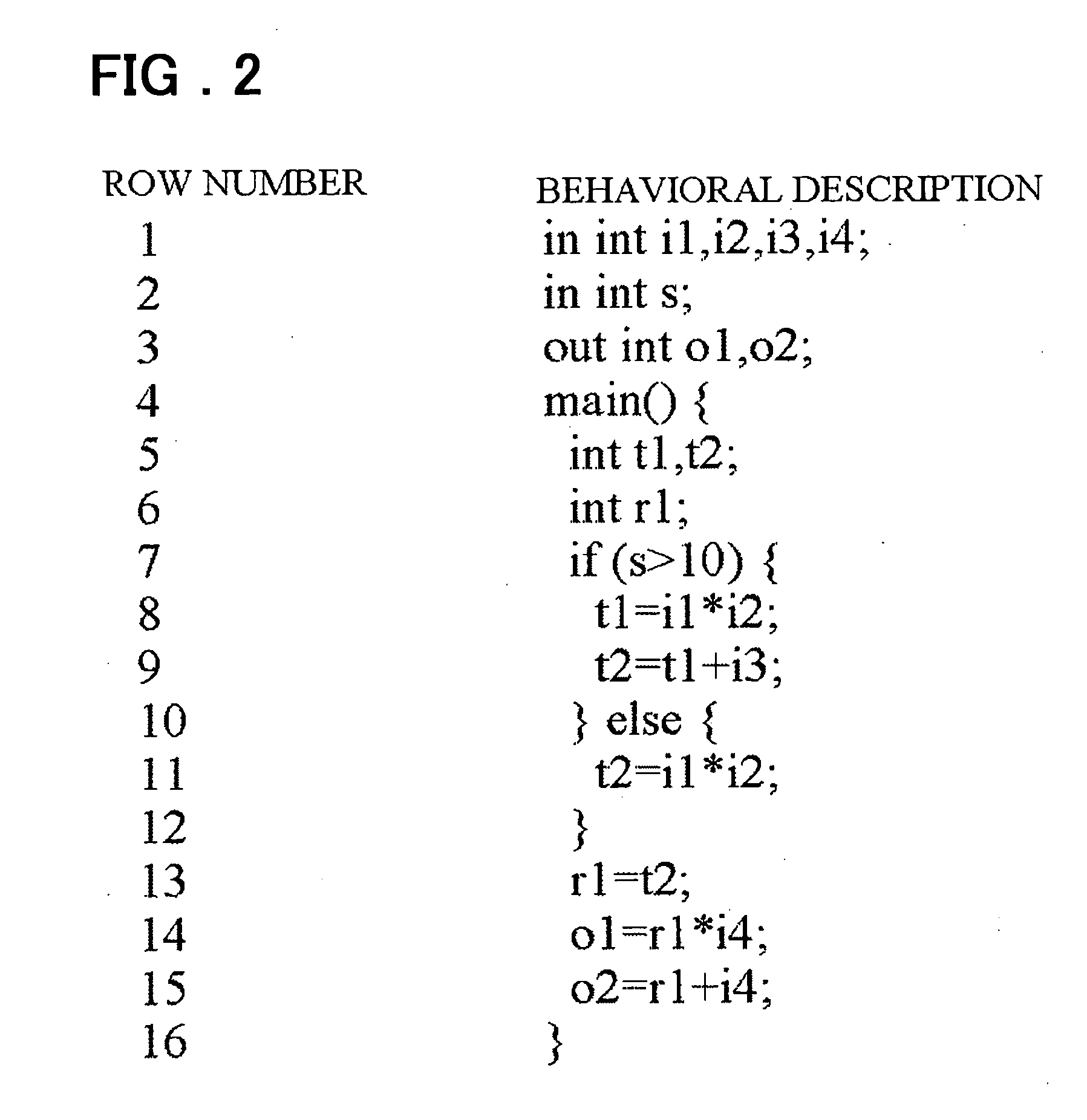

Method, apparatus and program for determining the relationship of correspondence between register transfer level description and behavioral description

InactiveUS20060225022A1Improve design productivityImprove efficiencyCAD circuit designSoftware simulation/interpretation/emulationArithmetic processing unitTheoretical computer science

The relationship of correspondence between the RTL description and the behavioral description is extracted with ease. A behavioral synthesis device analyzes how the scheduling, preparation of a control data flow graph and the sharing of arithmetic processing units and registers are carried out. The behavioral synthesis device then formulates a table of correspondence to show the relationship of correspondence between the RTL description and the CDFG and a table of correspondence to show the relationship of correspondence between the CDFG and the behavioral description. A path determining device couples these tables of correspondence to generate a table of correspondence determining the relationship of correspondence between the RTL description and the behavioral description. The path determining device reflects a path of interest in the RTL description. The path determining device then outputs the behavioral description, corresponding to the RTL description, so that the behavioral description will be uniquely determined by the states of the FSM possessed by the RTL description and by the conditional branching in the behavioral description.

Owner:NEC ELECTRONICS CORP

Methods and apparatuses for designing integrated circuits

InactiveUS20070288871A1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureNetlist

Methods and apparatuses for designing an integrated circuit. In one example of a method, a hardware description language (HDL) code is compiled to produce a technology independent RTL (register transfer level) netlist. A portion of an area of the IC is allocated to a specific portion of the technology independent RTL netlist. In a typical implementation of this method, the allocation restricts circuitry created from the specific portion to the portion of the IC.

Owner:SYNOPSYS INC

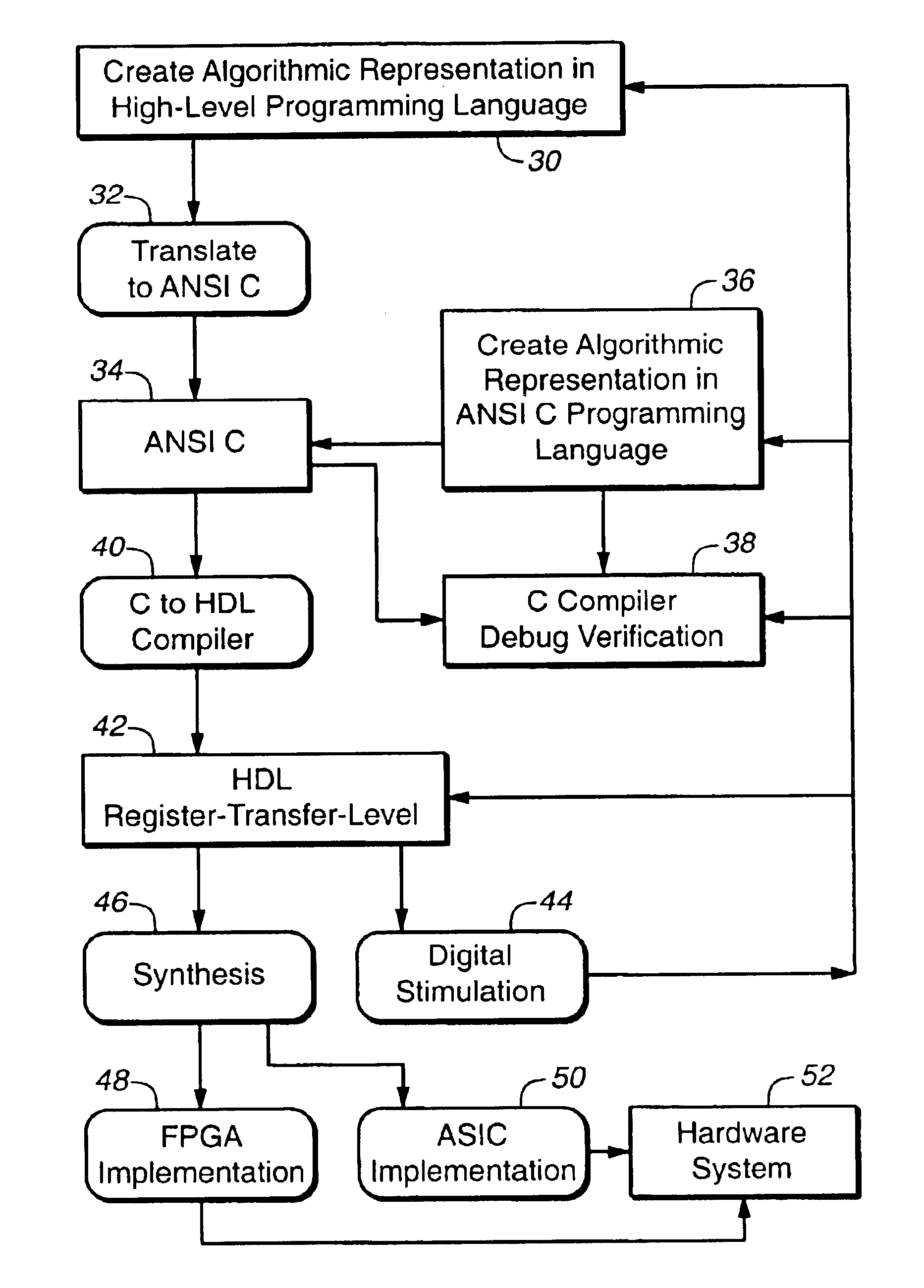

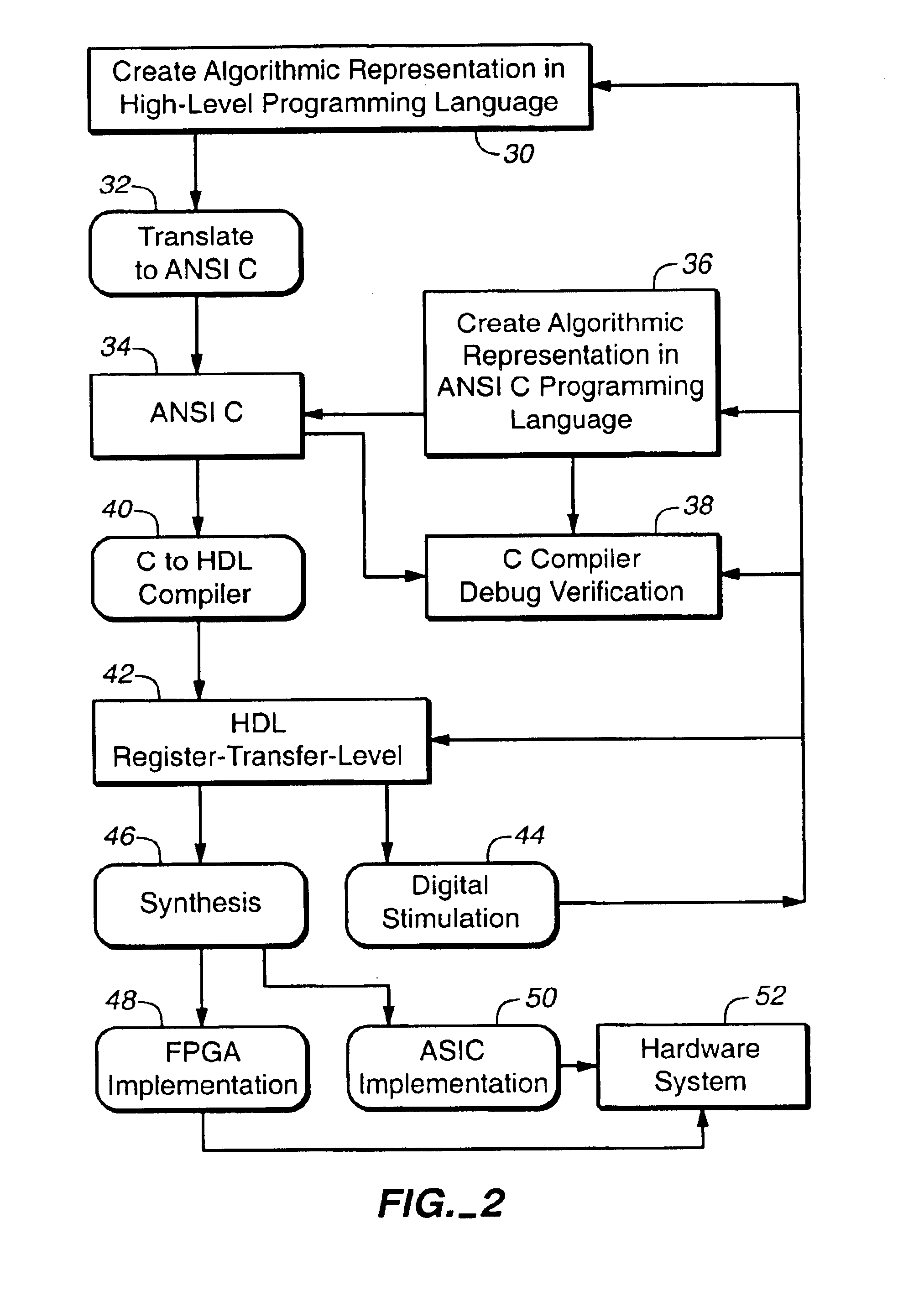

System for converting hardware designs in high-level programming languages to hardware implementations

A computer aided hardware design system for enabling design of an actual hardware implementation for a digital circuit using a high-level algorithmic programming language. The system converts an algorithmic representation for a hardware design initially created in the high-level programming language, such as ANSI C, to a hardware design implementation, such as an FPGA or other programmable logic or an ASIC. The C-type program representative of the hardware design is compiled into a register transfer level (RTL) hardware description language (HDL) that can be synthesized into a gate-level hardware representation. The system additionally enables simulation of the HDL design to verify design functionality. Finally, various physical design tools can be utilized to produce an actual hardware implementation. The system also permits the use of other non-C-type high-level programming languages by first translating to a C-type program. In contrast to previous hardware design tools, the system compiles all C-type programming language features, including pointers and structures, into synthesizable HDL.

Owner:SYNOPSYS INC

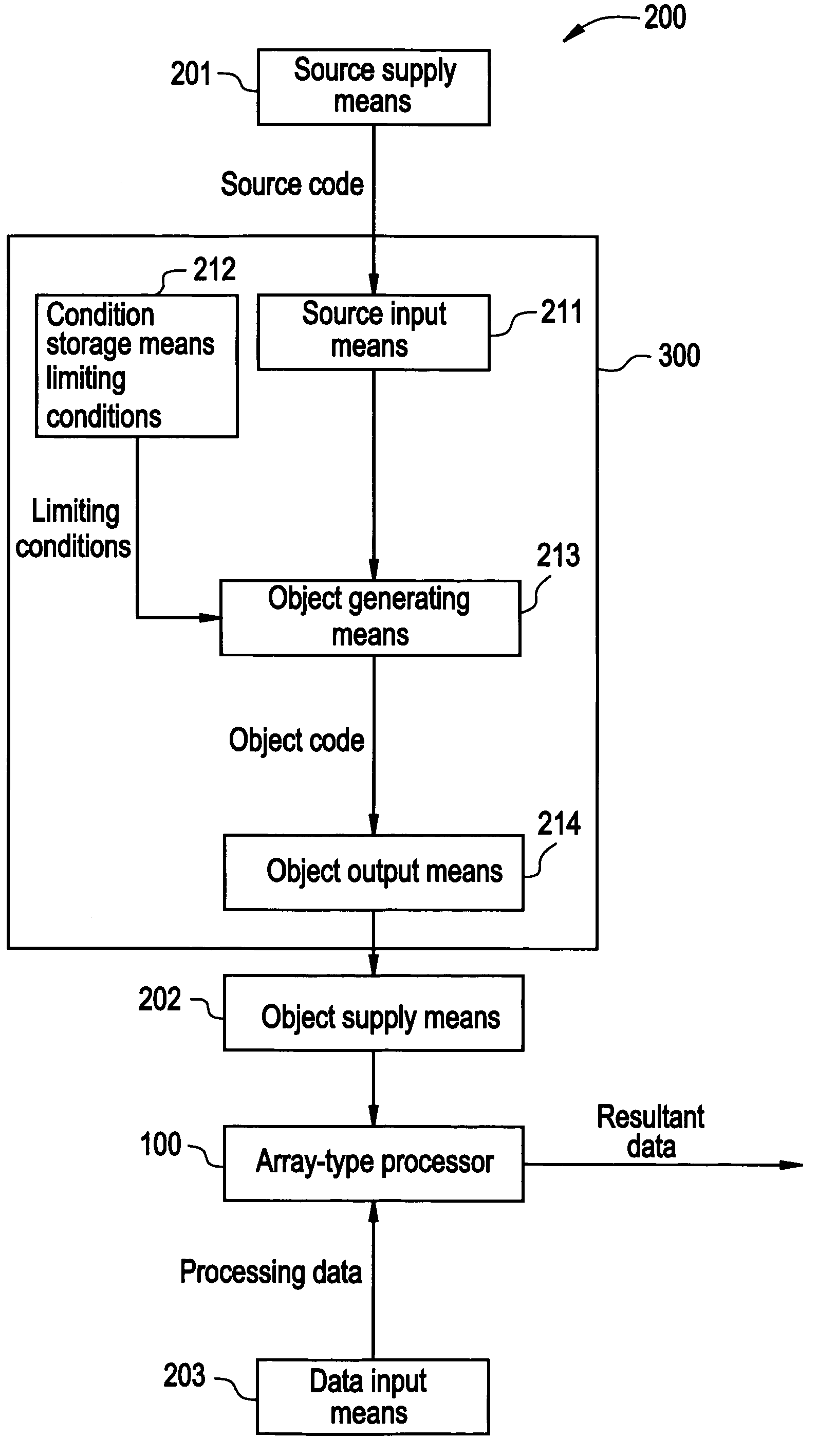

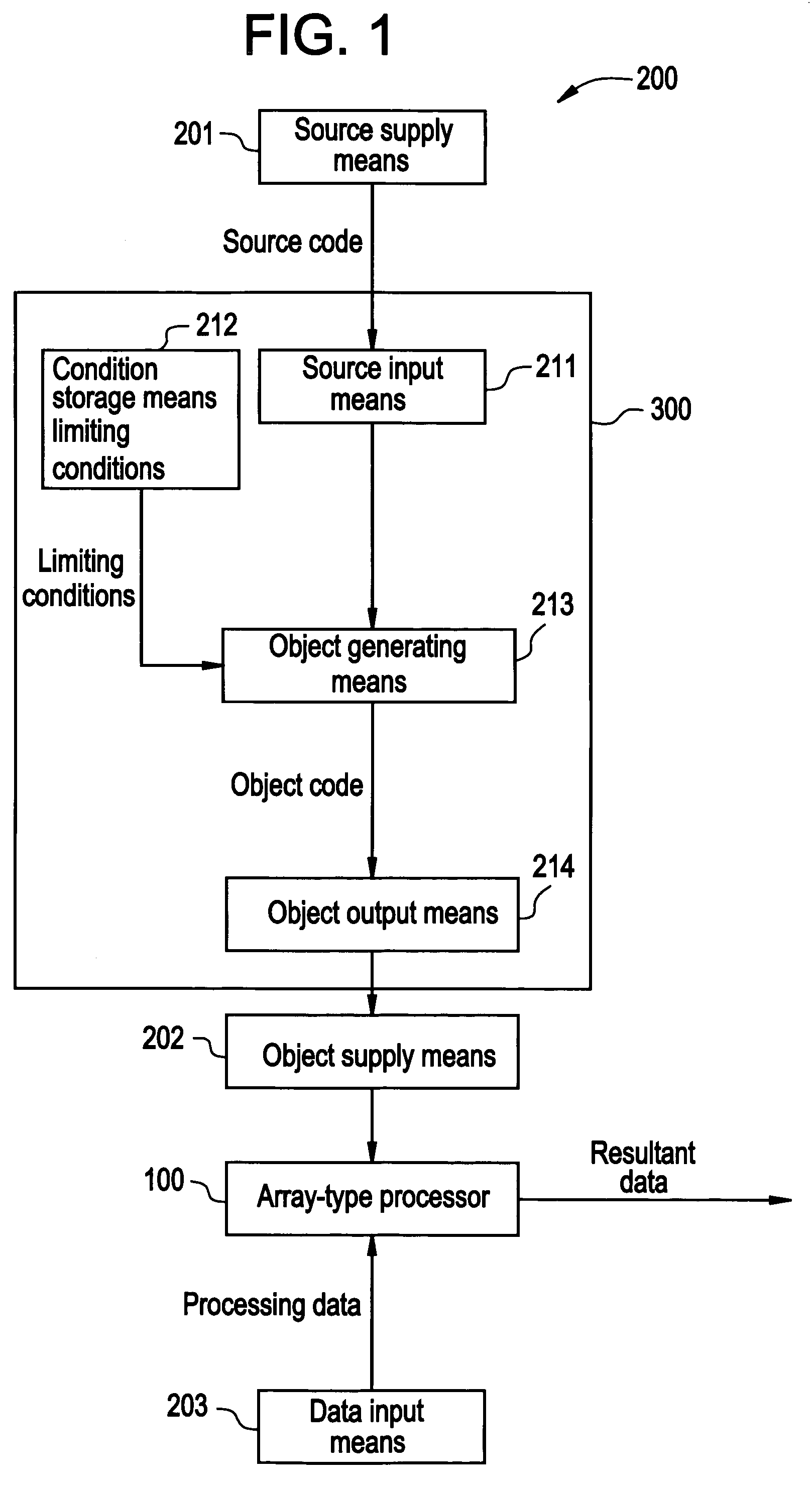

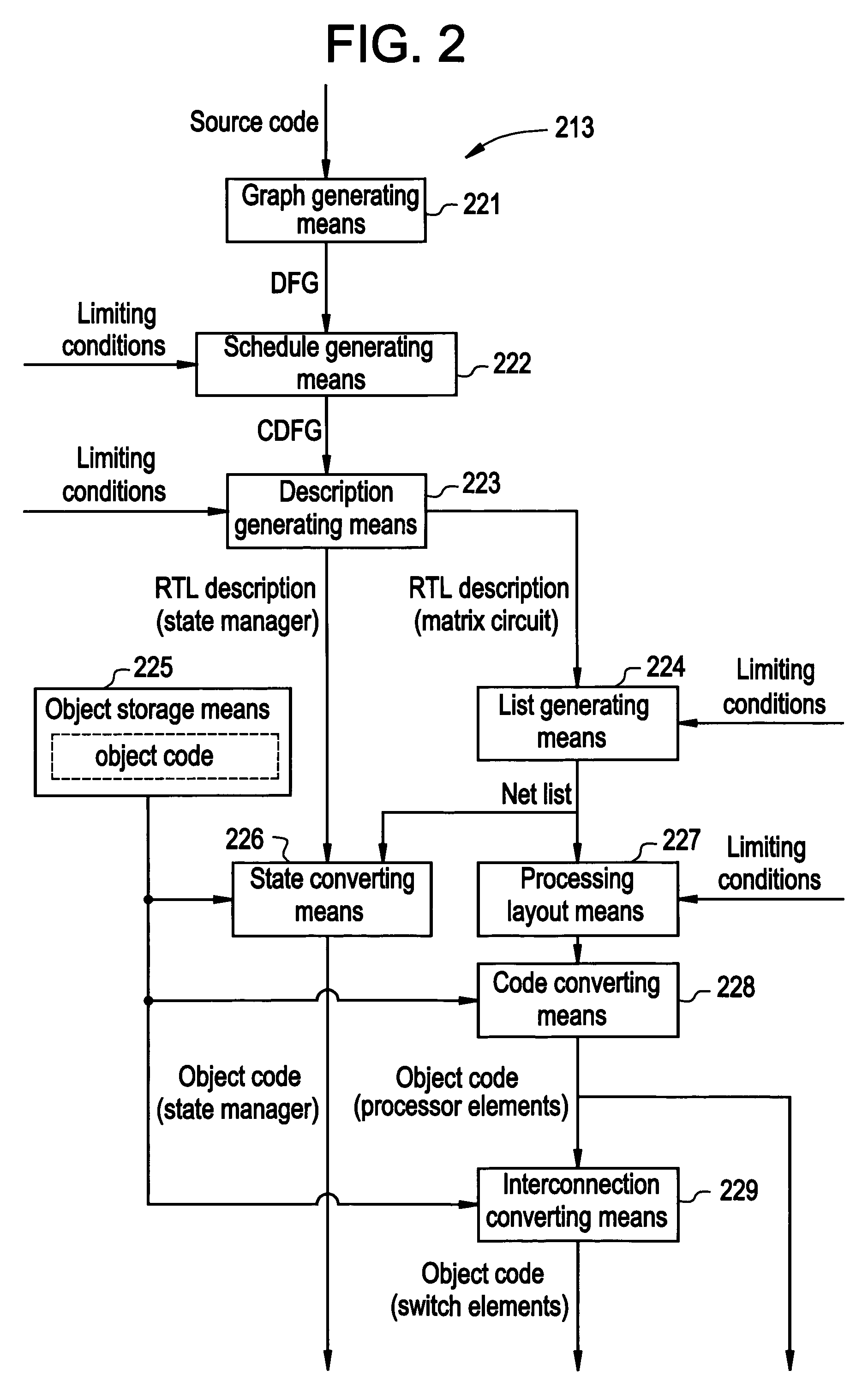

Data processing apparatus and method for generating the data of an object program for a parallel operation apparatus

An object code for sequentially switching contexts of processing circuits arrayed in a matrix in a parallel operation apparatus is generated from a general source code descriptive of operation of the parallel operation apparatus. A Data Flow Graph (DFG) is generated from the source code descriptive of operation of the parallel operation apparatus according to limiting conditions, registered in advance, representing a physical structure, etc. of the parallel operation apparatus, and scheduled in a Control Data Flow Graph (CDFG). An Register Transfer Level (RTL) description is generated from the CDFG, converting a finite-state machine into an object code and converting a data path into a net list. An object code of the processing circuits is generated in each context from the net list.

Owner:NEC CORP

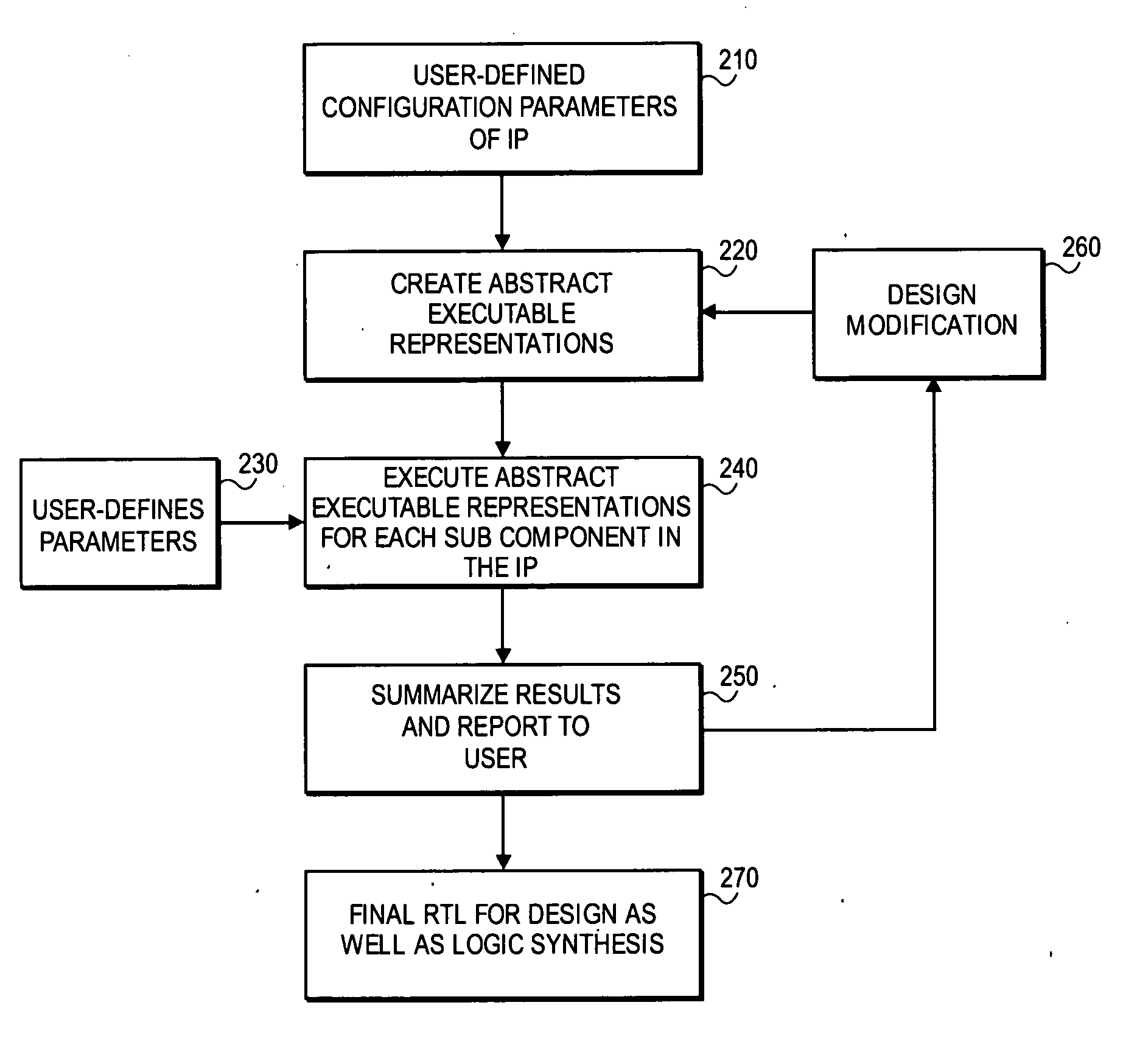

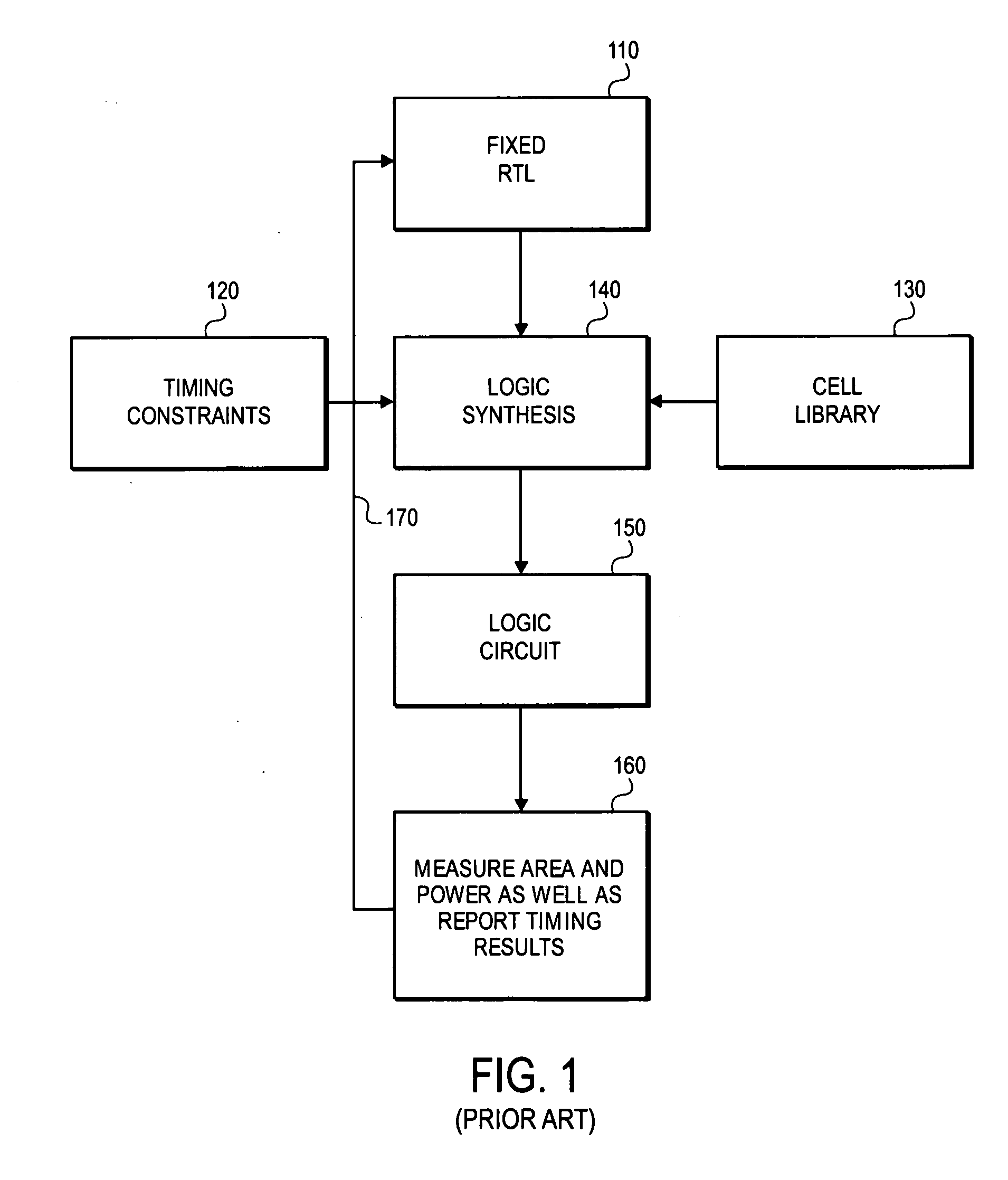

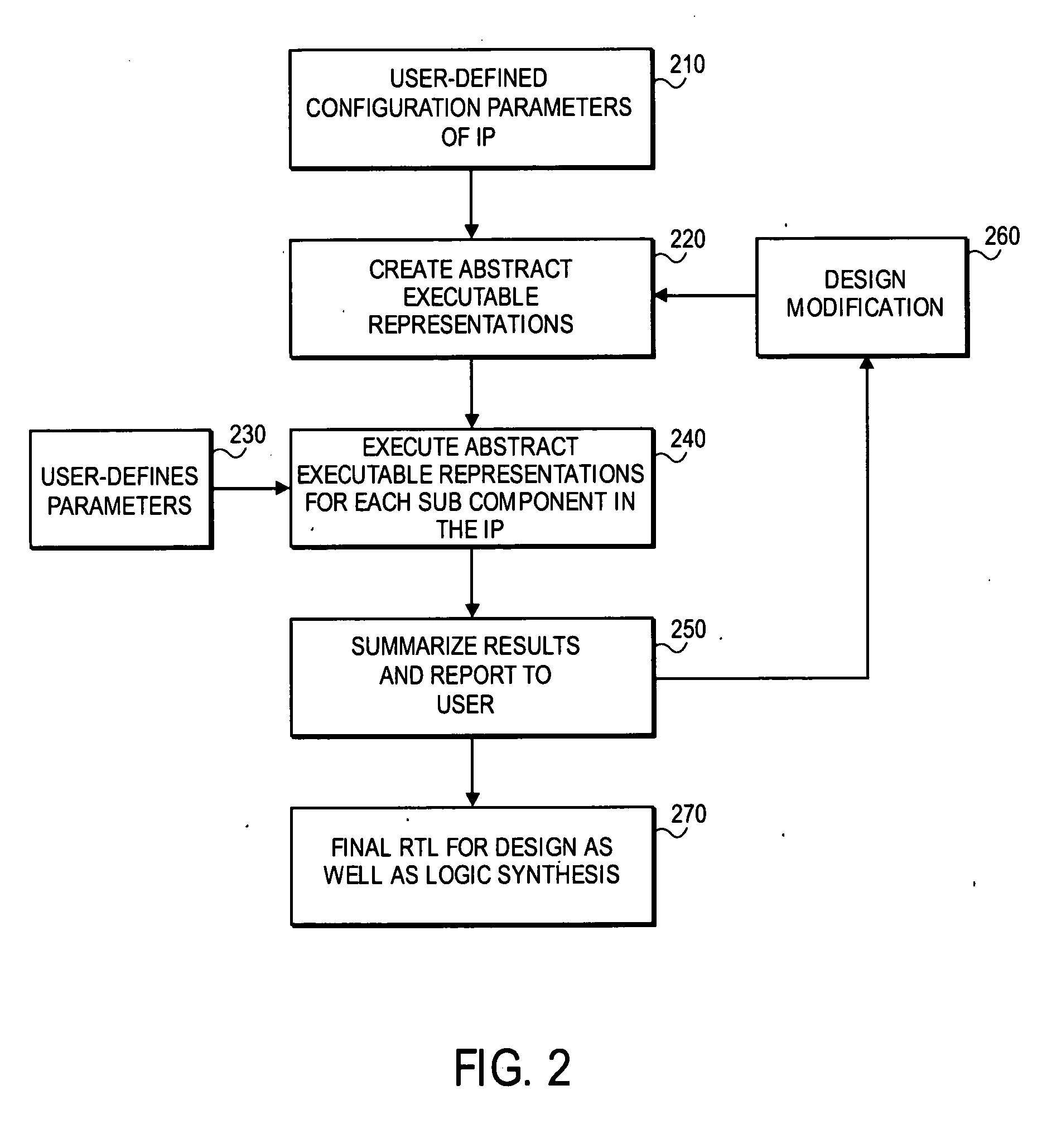

Various methods and apparatuses for estimating characteristics of an electronic system's design

Methods and apparatuses are described for an Intellectual Property (IP) Generator for estimating timing, area, and power characteristics of an electronic system design. The IP Generator receives a user-supplied file having data describing a configuration of an IP design having multiple levels of hierarchy. The IP Generator also receives user-supplied technology parameters and data-flow information. The IP generator correlates estimated timing, area, and power characteristics for each IP sub component based on the user supplied technology parameters, data-flow information and configuration parameters. The IP generator reports the timing, area, and power estimates to a user via a graphic user interface prior to a transformation of a Register Transfer Level (RTL) design into the gate-level circuit design.

Owner:META PLATFORMS TECH LLC

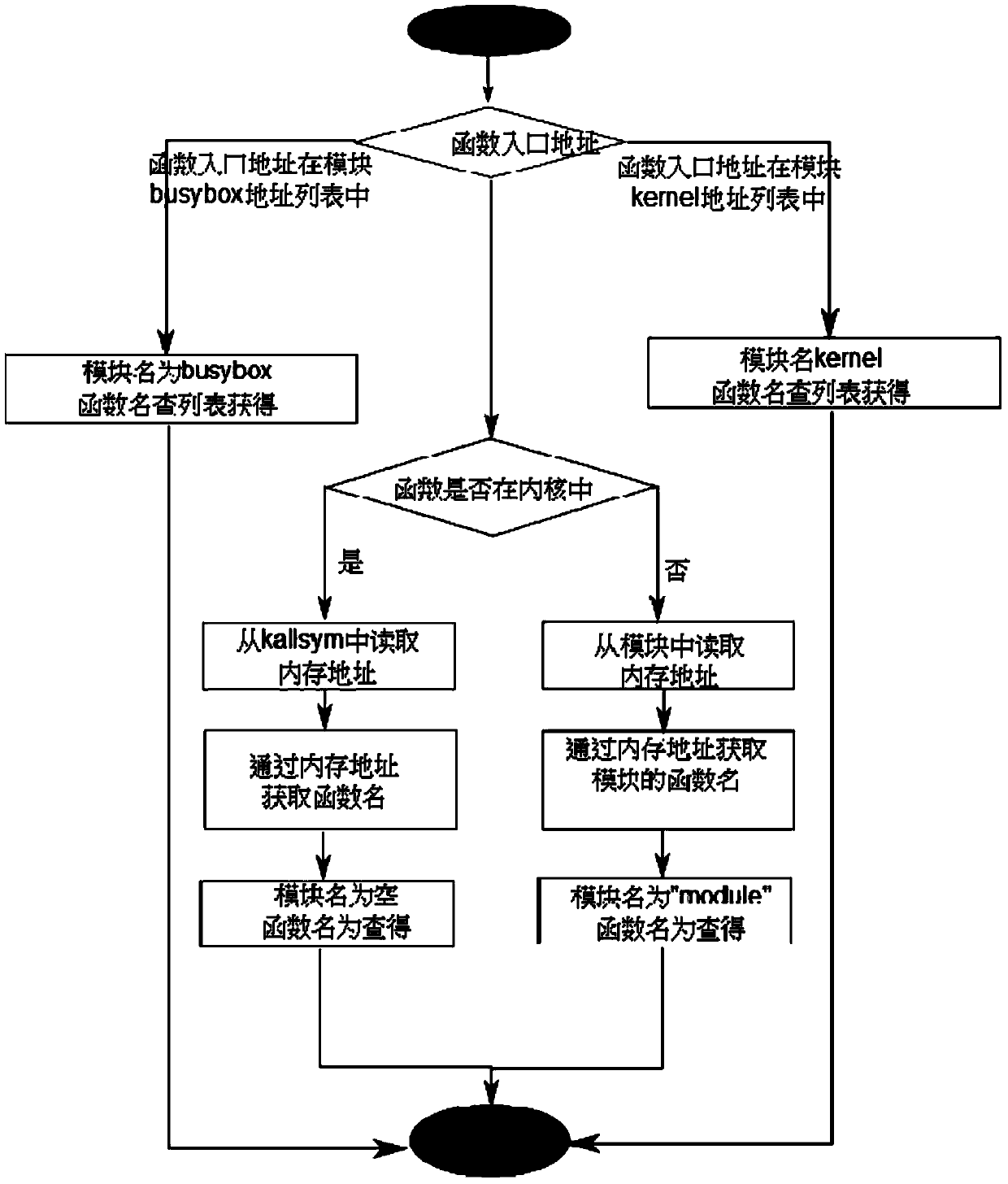

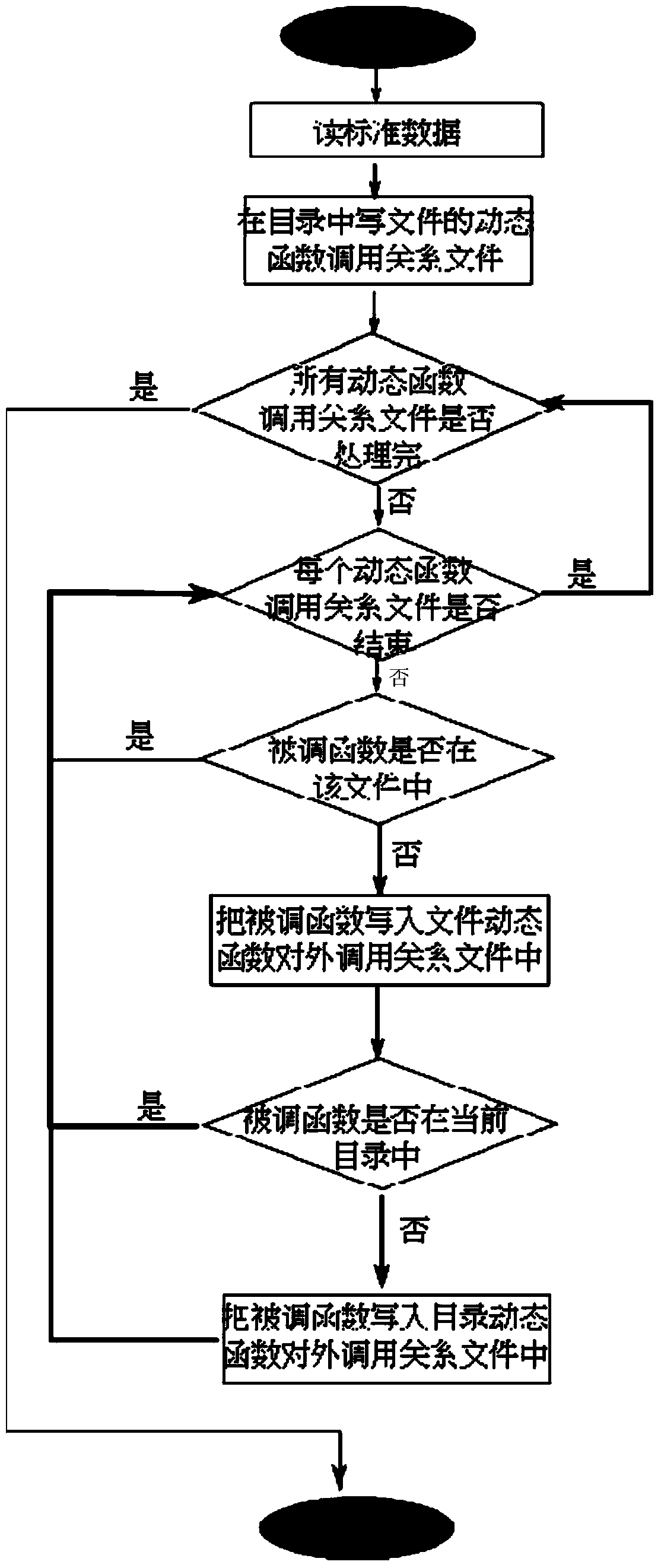

Method for determining dynamic function call relation based on register transfer languages

The invention discloses a method for determining a dynamic function call relation based on register transfer languages, mainly aiming to solve the problems in design that a call relation of a function pointer and a loadable module function cannot be analyzed through a static function call relation. The method includes: detecting function call executing events during system operation, if call instructions are detected, analyzing function names corresponding to function entry addresses called through the instructions, performing statistics on number of the instructions and outputting the function names, call occurrence time, subordinate process numbers, subordinate threading numbers, subordinate stack top pointers and module numbers prior to storing to a trace data file; if the detected instructions are return instructions, outputting time, the subordinate process numbers, the subordinate threading numbers and the subordinate stack top pointers to the track data file; processing the track data file to acquire the data format with predetermined standard, transmitting the track data file to a static function call relation generating device so as to generate a dynamic function call graph describing the function call relation.

Owner:TSINGHUA UNIV

Tool to create a reconfigurable interconnect framework

ActiveUS20180189424A1Reduce power consumptionImproves data reuseMathematical modelsKernel methodsComputer architectureProcessor register

Embodiments are directed towards a method to create a reconfigurable interconnect framework in an integrated circuit. The method includes accessing a configuration template directed toward the reconfigurable interconnect framework, editing parameters of the configuration template, functionally combining the configuration template with a plurality of modules from an IP library to produce a register transfer level (RTL) circuit model, generating at least one automated test-bench function, and generating at least one logic synthesis script. Editing parameters of the configuration template includes confirming a first number of output ports of a reconfigurable stream switch and confirming a second number of input ports of the reconfigurable stream switch. Each output port and each input port has a respective architectural composition. The output port architectural composition is defined by a plurality of N data paths including A data outputs and B control outputs. The input port architectural composition is defined by a plurality of M data paths including A data inputs and B control inputs.

Owner:STMICROELECTRONICS SRL

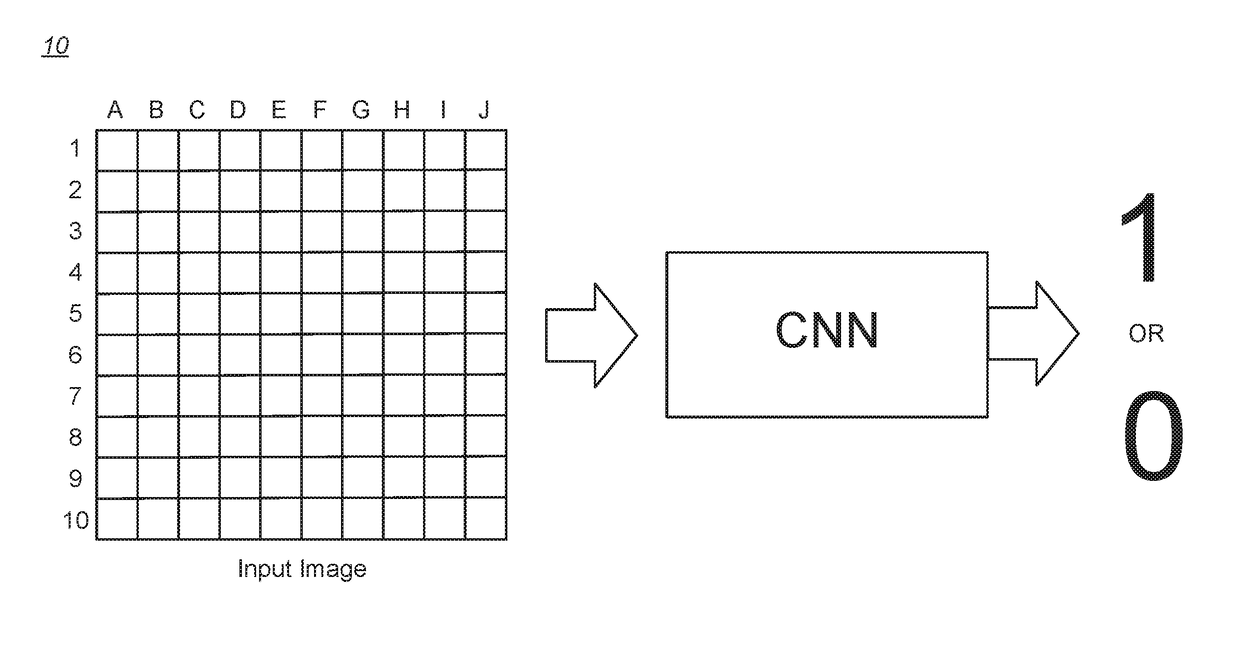

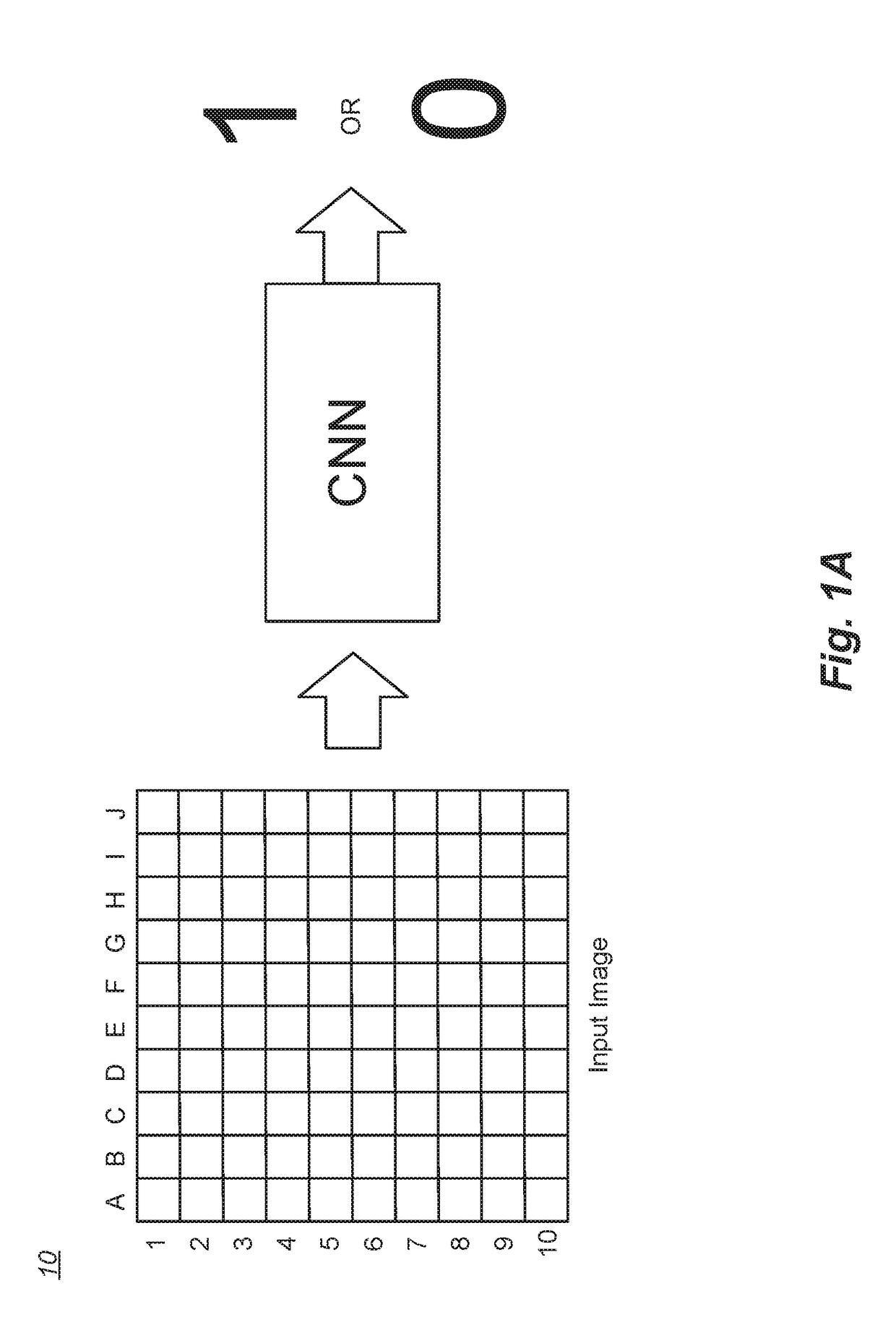

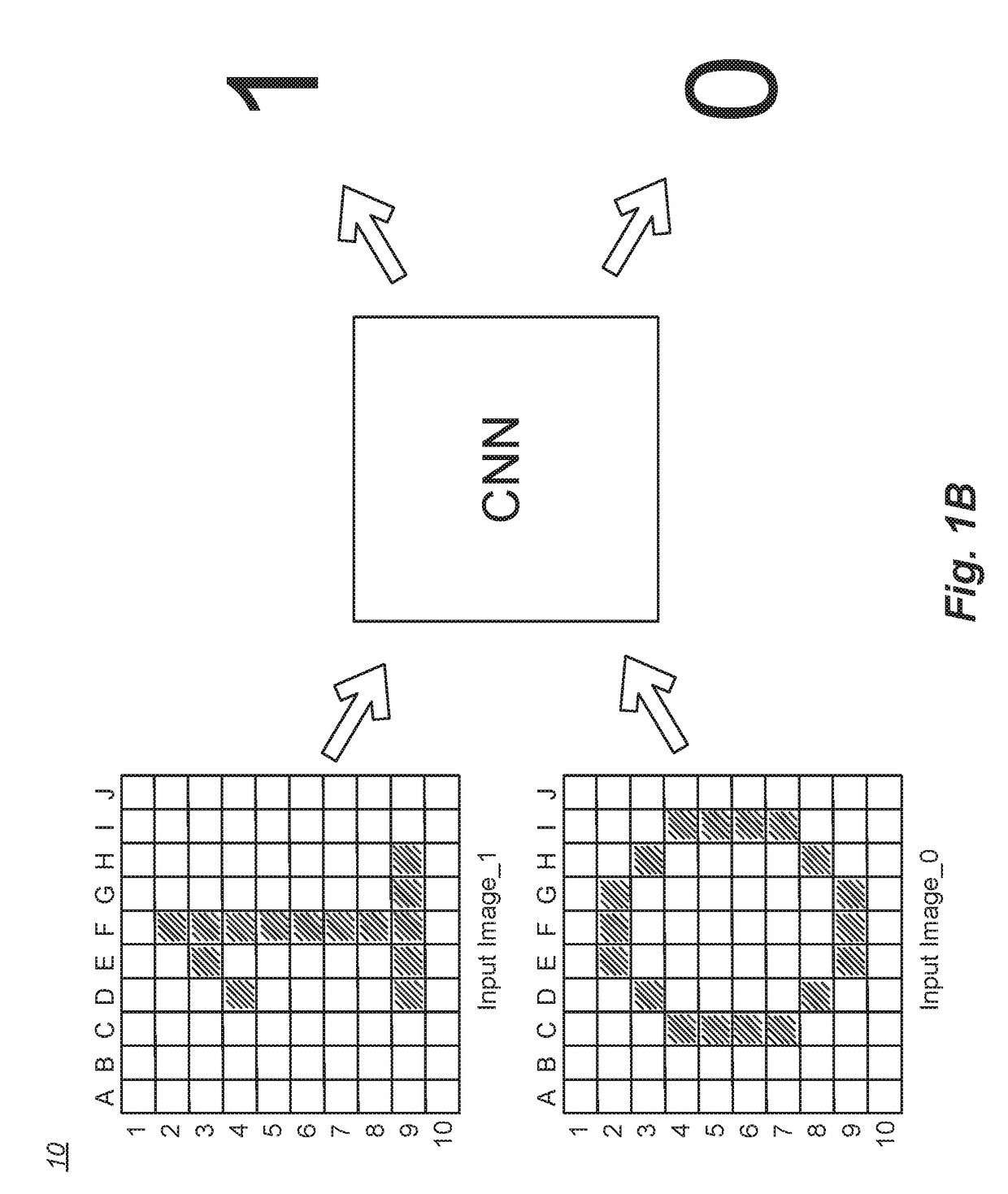

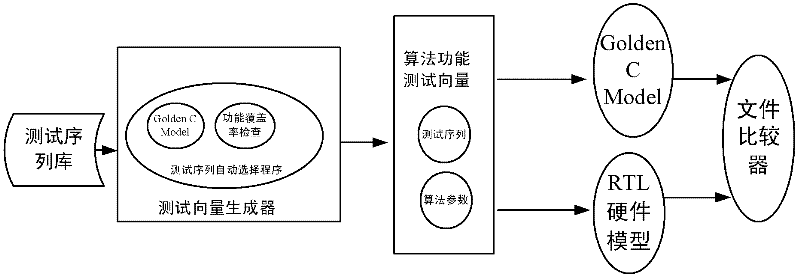

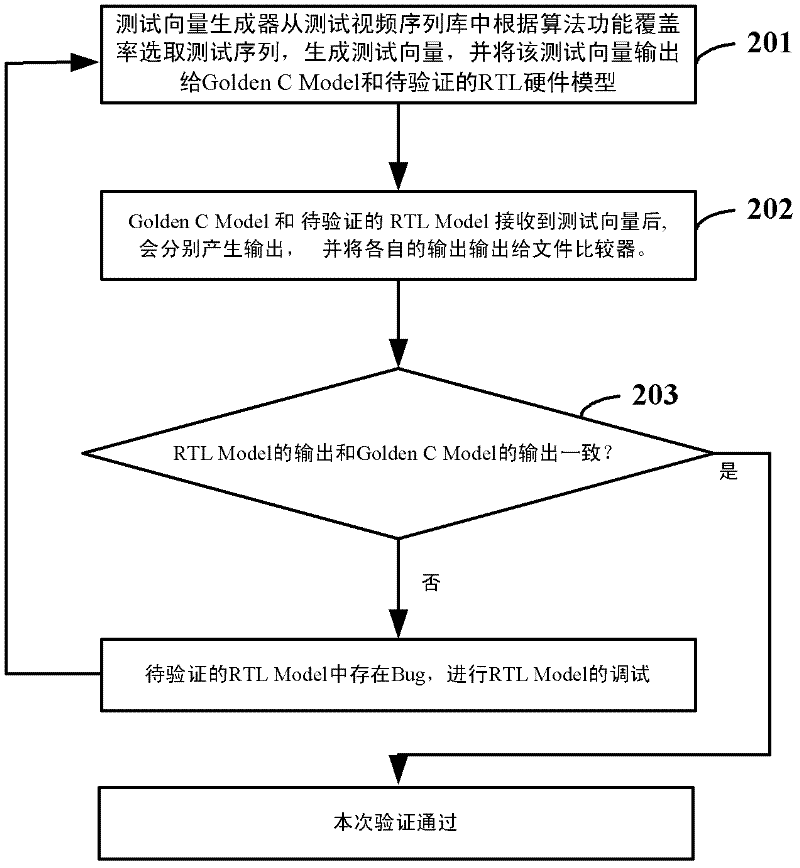

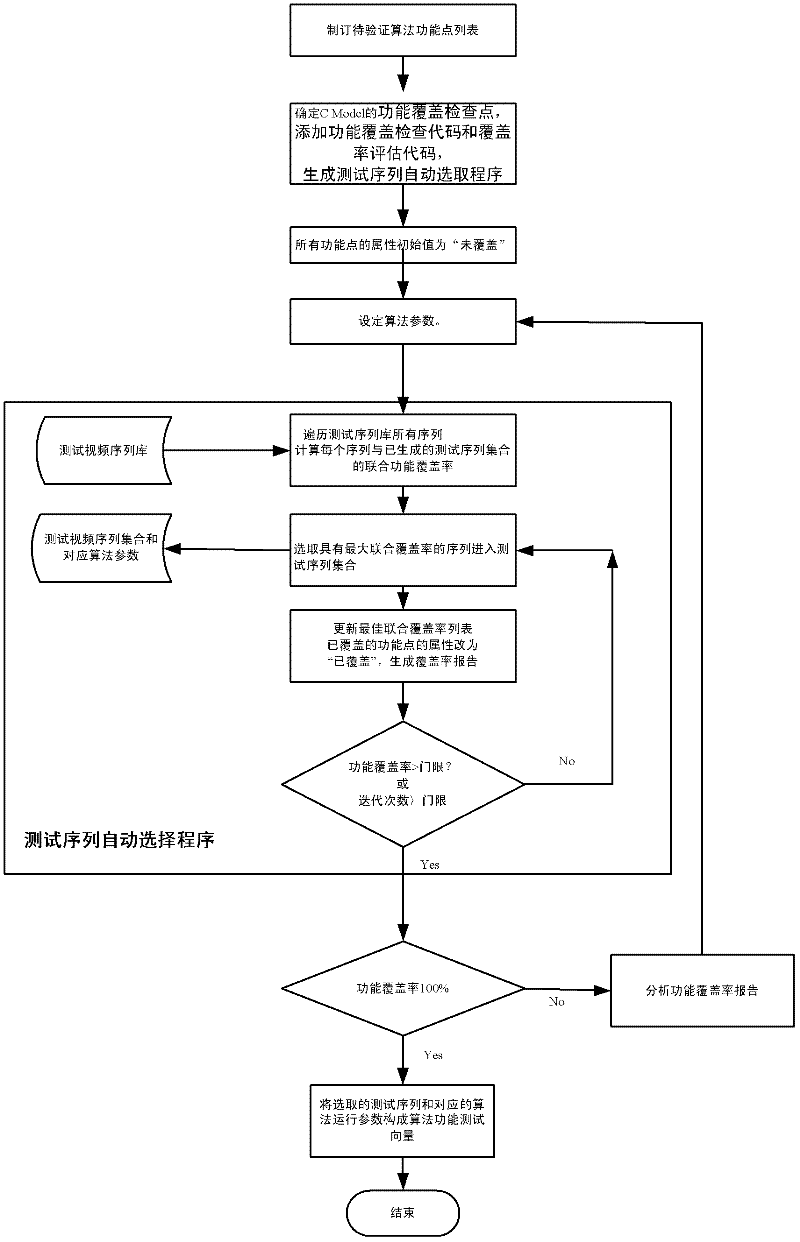

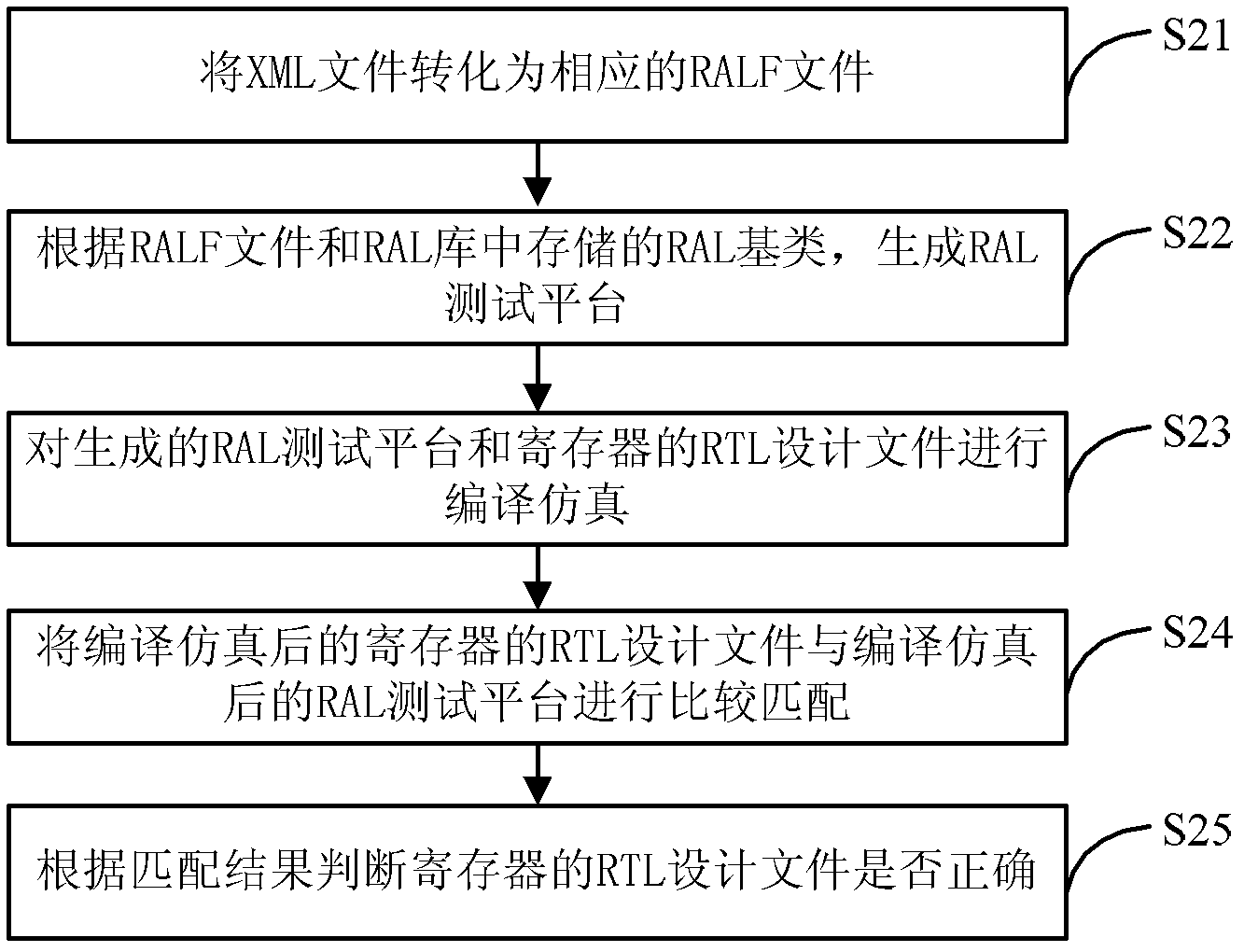

System and method for verifying register transfer level (RTL) hardware

ActiveCN102567165AImprove verification efficiencyImprove accuracyFunctional testingProcessor registerVideo sequence

The invention discloses a system and a method for verifying register transfer level (RTL) hardware of a video algorithm. The system comprises a test video sequence library, a test vector generator, a golden C language model, an RTL hardware model to be verified and a file comparator, wherein the test video sequence library is used for storing a test sequence required by verifying the design of the RTL hardware of the video algorithm; the test vector generator is used for selecting the test sequence from the test video sequence library according to the functional coverage of the algorithm, generating a test vector and outputting the test vector to the golden C language model and the RTL hardware model to be verified; the golden C language model and the RTL hardware model to be verified are used for respectively generating output after receiving the test vector and outputting the respective output to the file comparator; and the file comparator is used for comparing whether the output of the golden C language model is consistent with the output of the RTL hardware model to be verified or not, indicating that the RTL hardware passes verification if the outputs are consistent, and indicating that the RTL hardware does not pass verification if the outputs are inconsistent. By the system and the method, the efficiency and correctness of verifying the design of the RTL hardware of the video algorithm are improved.

Owner:北京集朗半导体科技有限公司

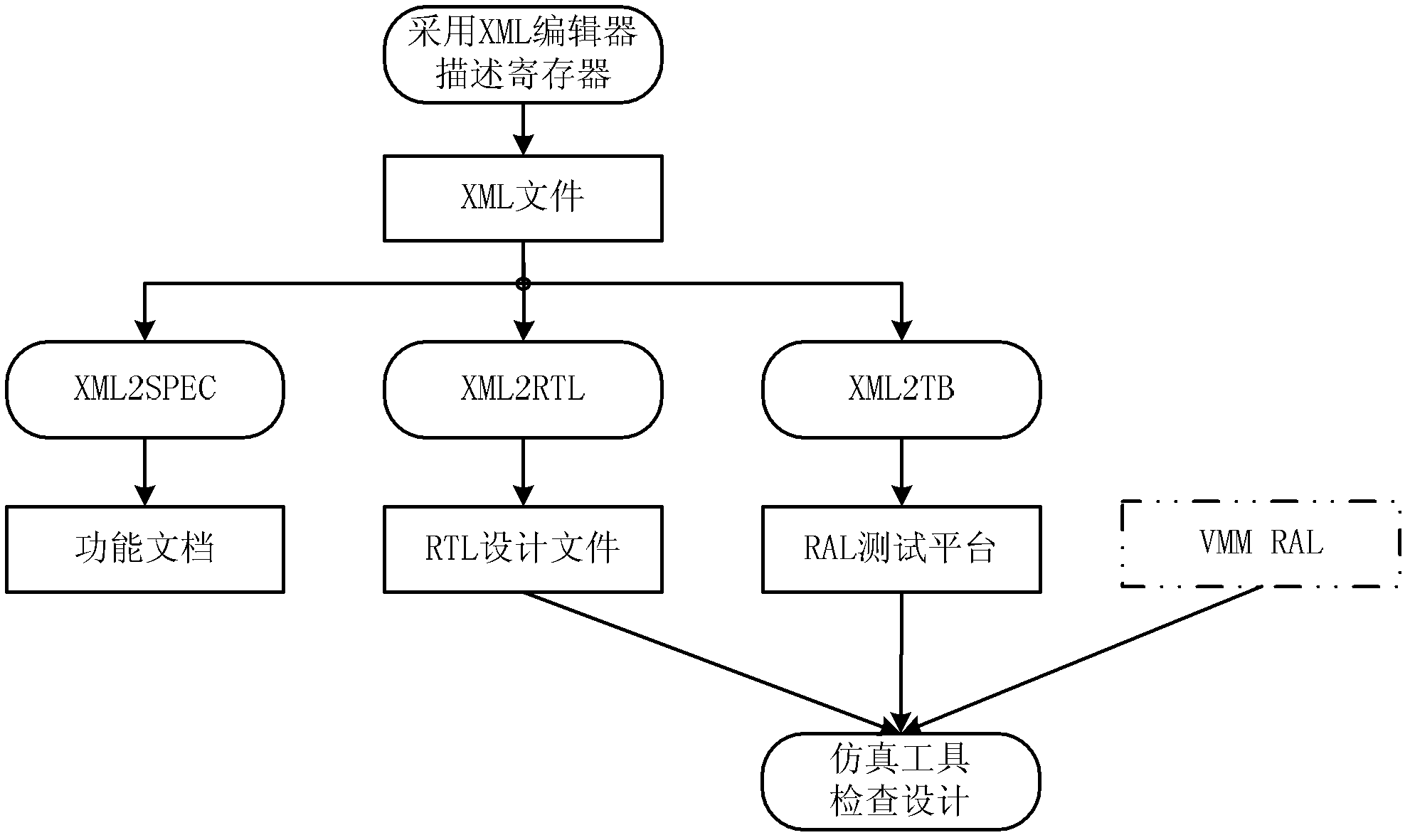

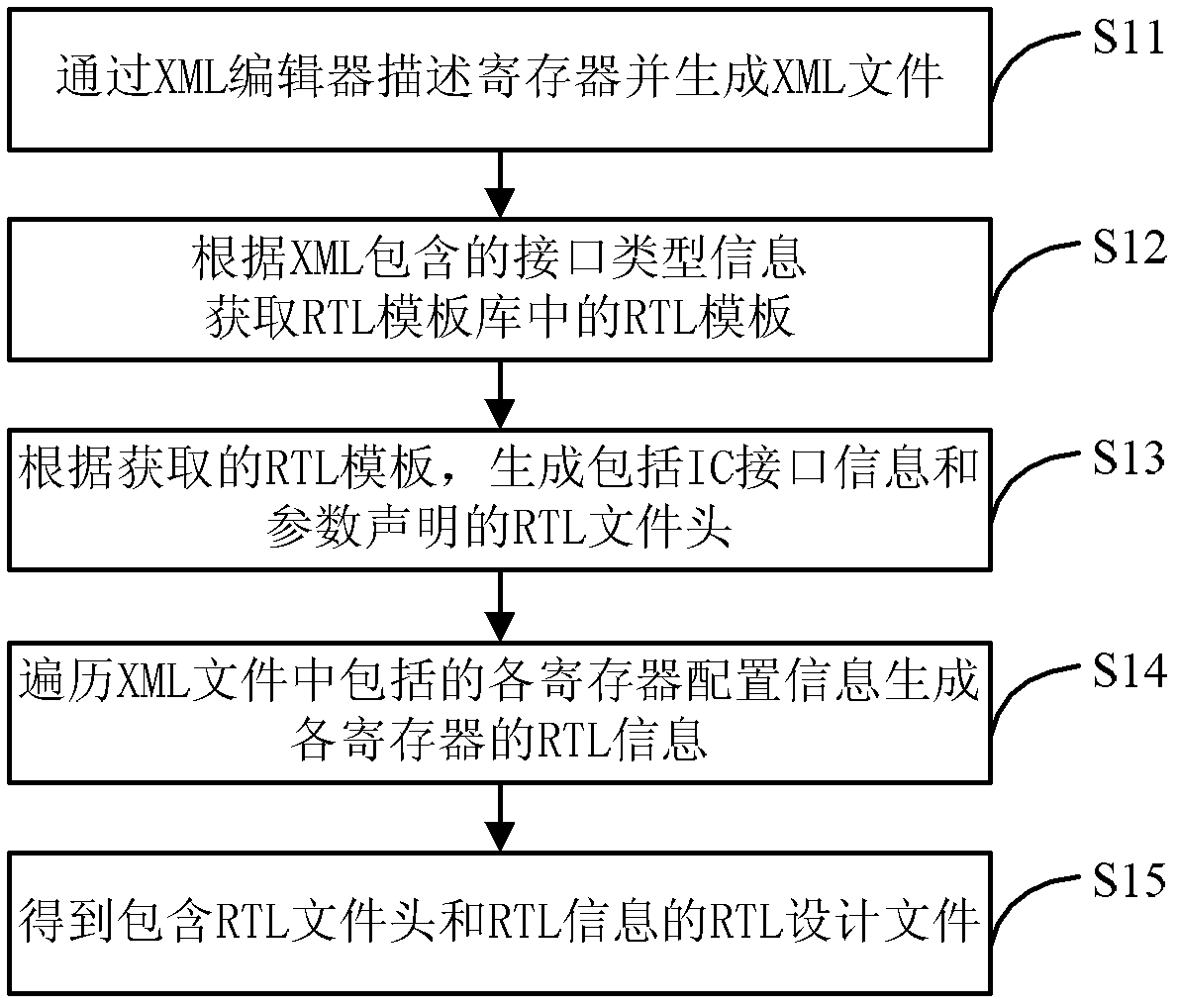

Register designing method and register designing device in integrated circuit designing process

ActiveCN102592023AAvoid the problem of difficult and cumbersome design and maintenanceReduce Design DefectsSpecial data processing applicationsRegister allocationComputer architecture

The invention discloses a register designing method in an integrated circuit designing process. The register designing method comprises the steps of generating an XML (Xtensible Markup Language) file including register configuration information by an XML editor; according to the type of a register interface included in the register configuration information, obtaining an RTL (Register Transfer Level) template in an RTL template base; according to the obtained RTL template and the register configuration information, generating an RTL file header including the register interface information and the parameter declaration; traversing all the register configuration information included in the XML file to generate RTL information of all the registers; and obtaining an RTL designing file including the RTL file header and the RTL information. According to the register designing method of the invention, the IC (Integrated Circuit) designing defects are reduced, and the designing success rate is increased.

Owner:GUANGDONG NUFRONT COMP SYST CHIP