Patents

Literature

31 results about "Glitch removal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

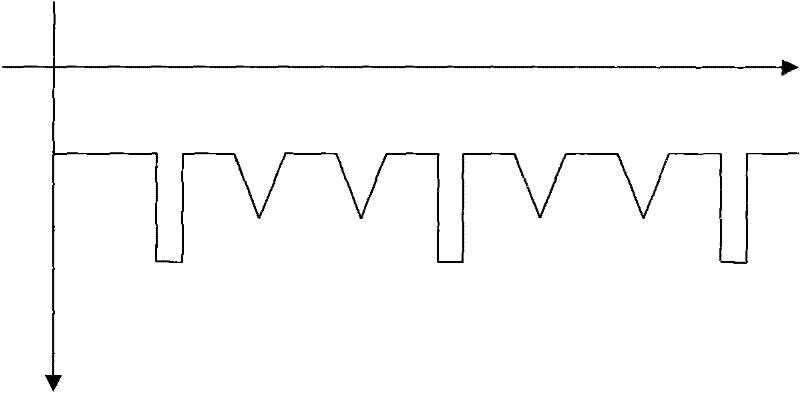

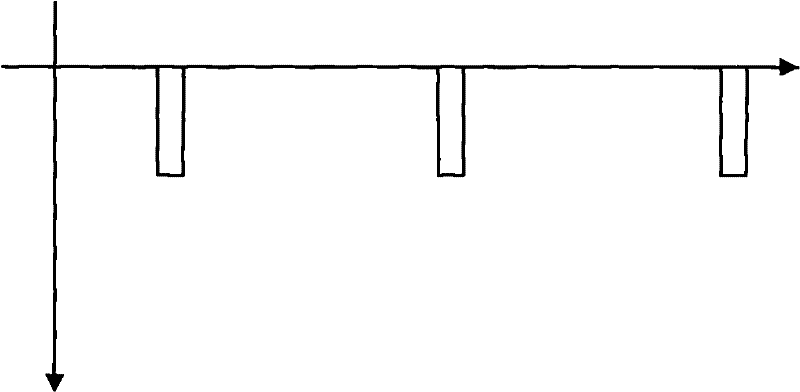

Glitch removal is the elimination of glitches—unnecessary signal transitions without functionality—from electronic circuits. Power dissipation of a gate occurs in two ways: static power dissipation and dynamic power dissipation. Glitch power comes under dynamic dissipation in the circuit and is directly proportional to switching activity. Glitch power dissipation is 20%-70% of total power dissipation and hence glitching should be eliminated for low power design.

Register transfer level power optimization with emphasis on glitch analysis and reduction

InactiveUS6324679B1Reduce power consumptionLogic circuits characterised by logic functionDigital data processing detailsDatapath circuitsPathPing

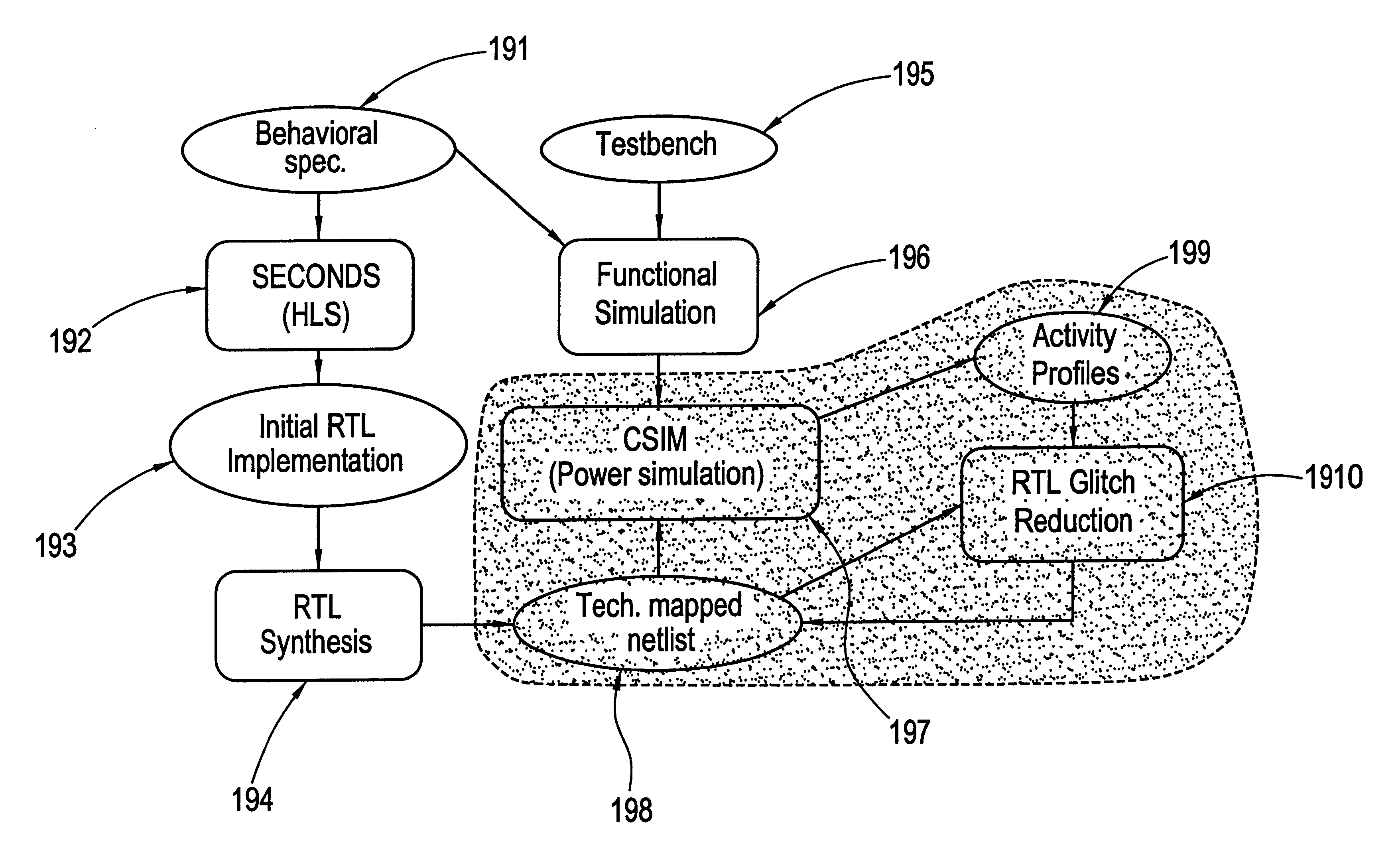

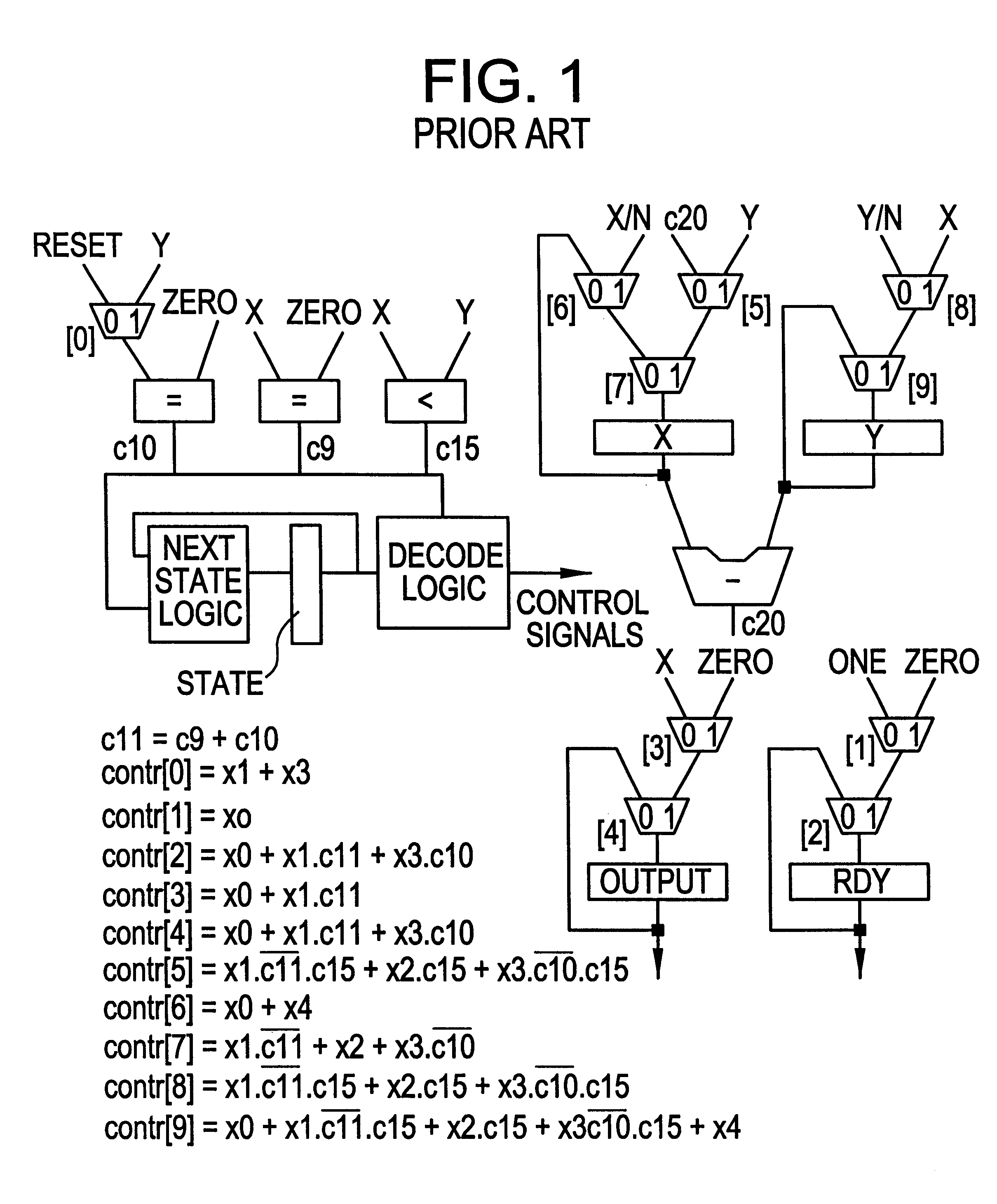

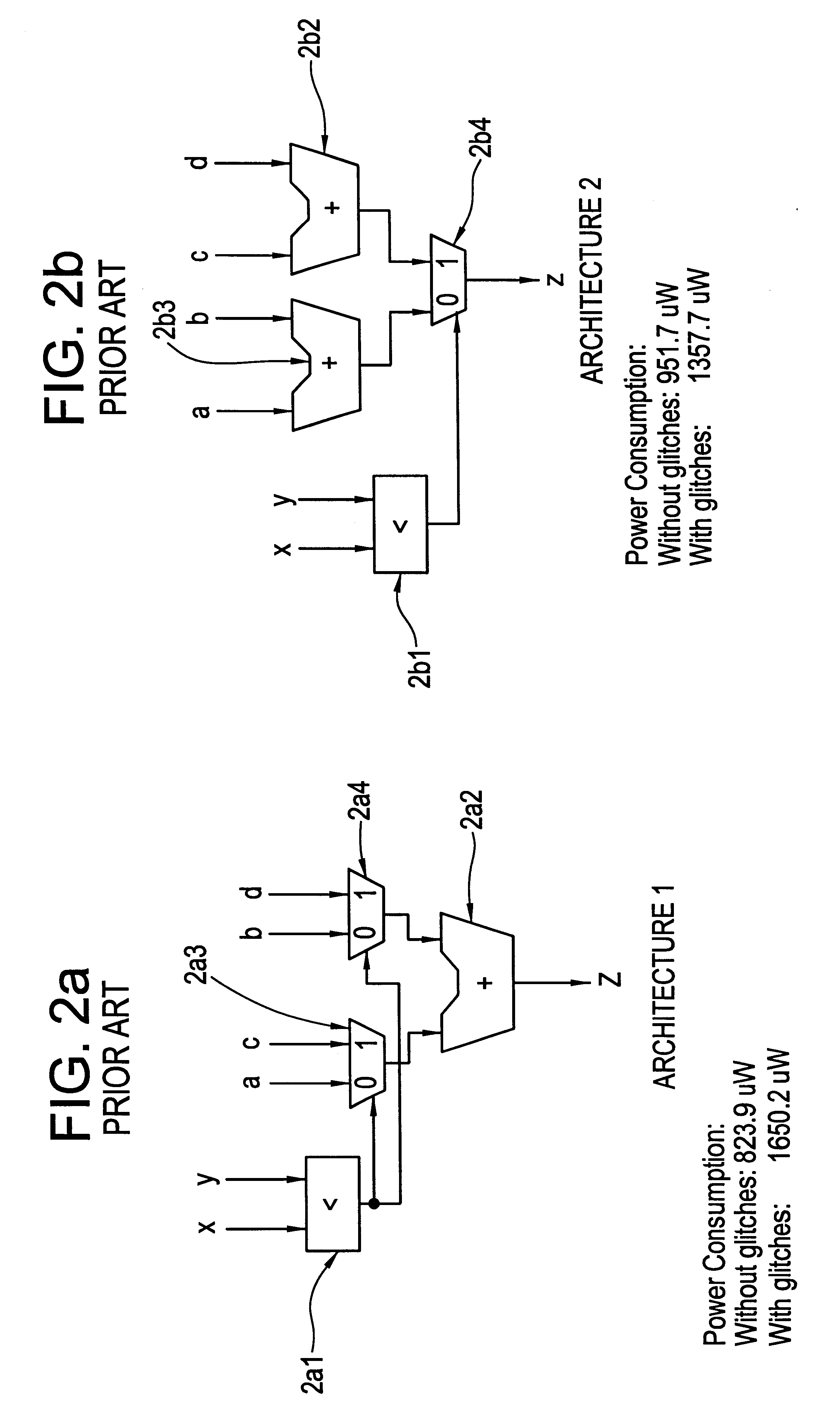

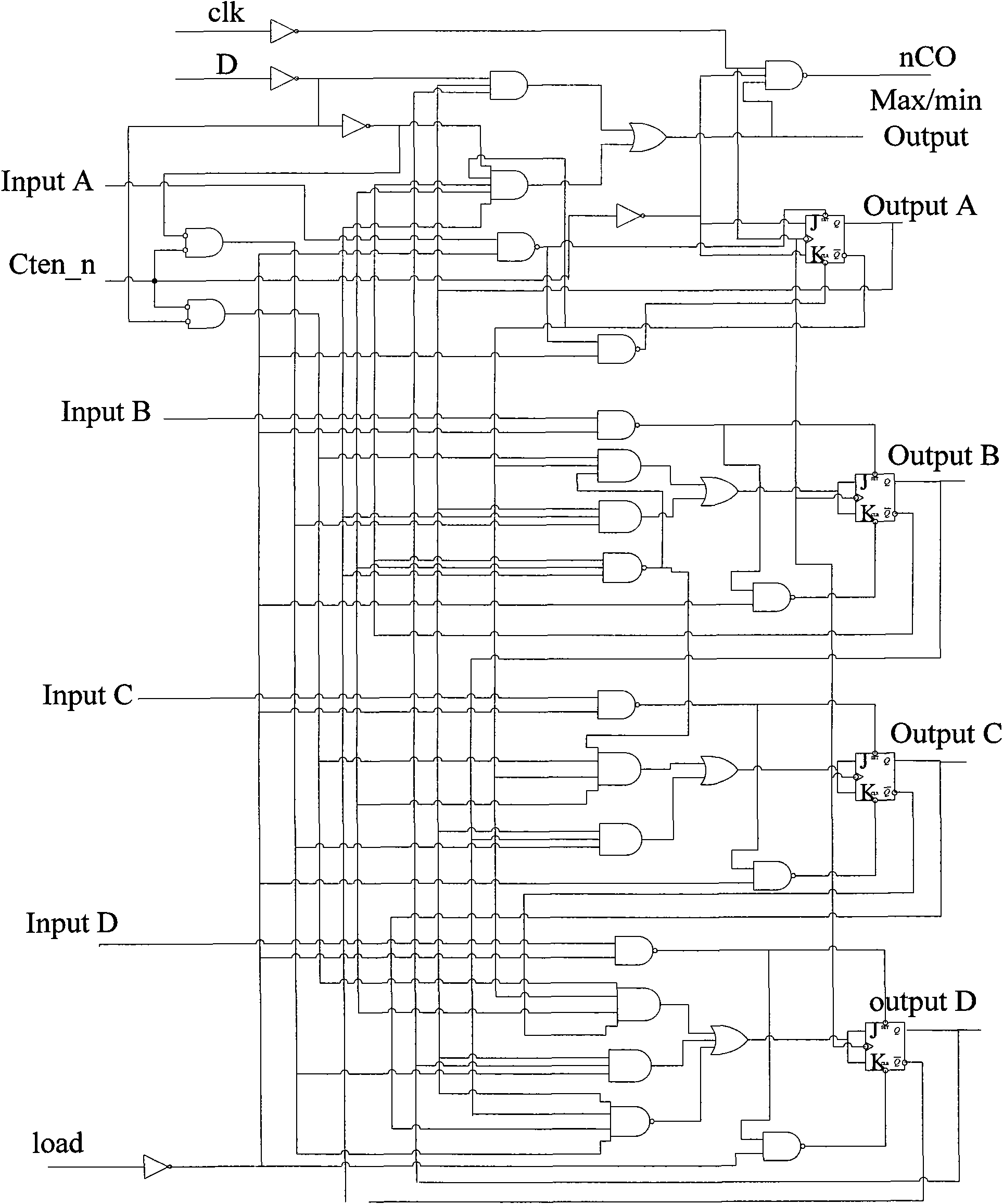

A method and apparatus for design-for-low-power of register transfer level (RTL) controller / data path circuits that implement control-flow intensive specifications. The method of the invention focuses on multiplexer networks and registers which dominate the total circuit power consumption and reduces generation and propagation of glitches in both the control and data path parts of the circuit. Further the method reduces glitching power consumption by minimizing propagation of glitches in the RTL circuit through restructuring multiplexer networks (to enhance data correlations and eliminate glitchy control signals), clocking control signals, and inserting selective rising / falling delays, in order to kill the propagation of glitches from control as well as data signals. To reduce power consumption in registers, the clock inputs to registers are gated with conditions derived by an analysis of the RTL circuit, ensuring that glitches are not introduced on the clock signals.

Owner:NEC CORP

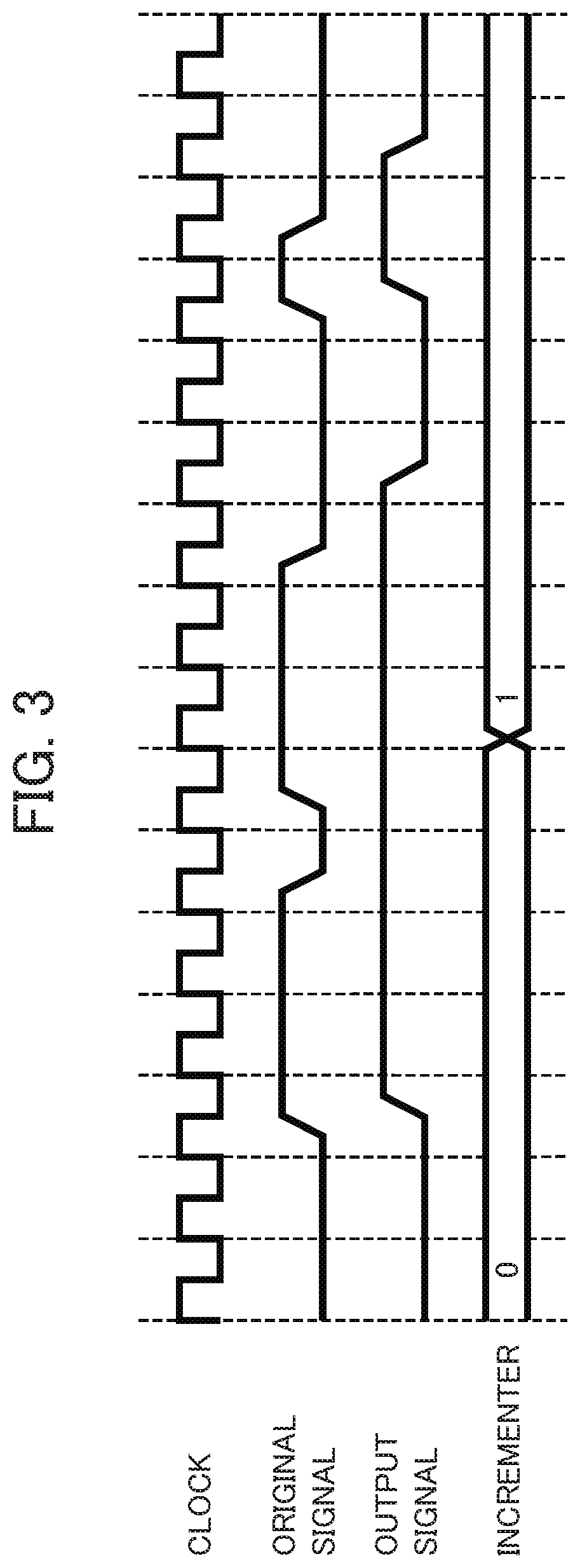

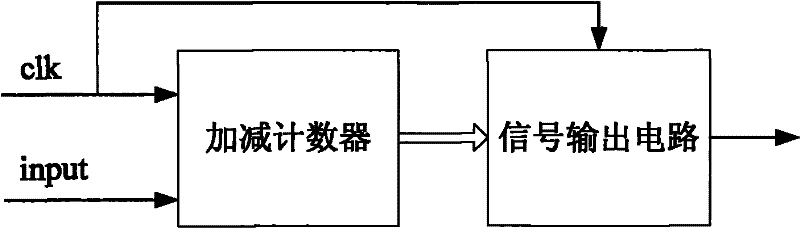

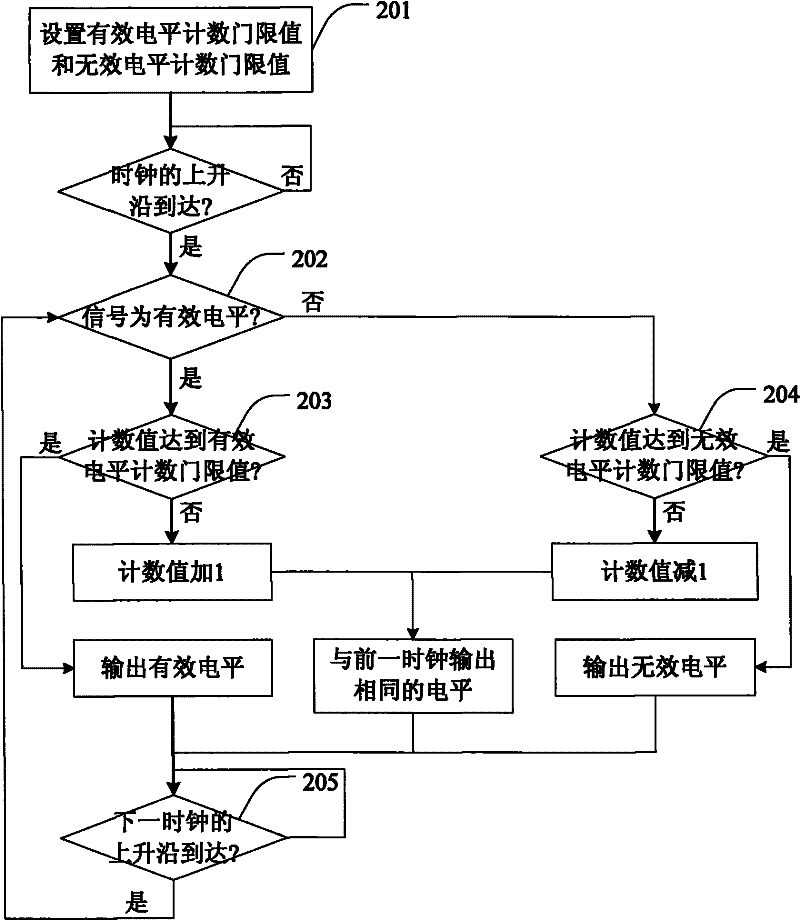

Method and device for eliminating signal noise

ActiveCN101568237ARemove completelyReduce difficultyPulse descriminationLogic circuit coupling/interface arrangementsComputer scienceGlitch removal

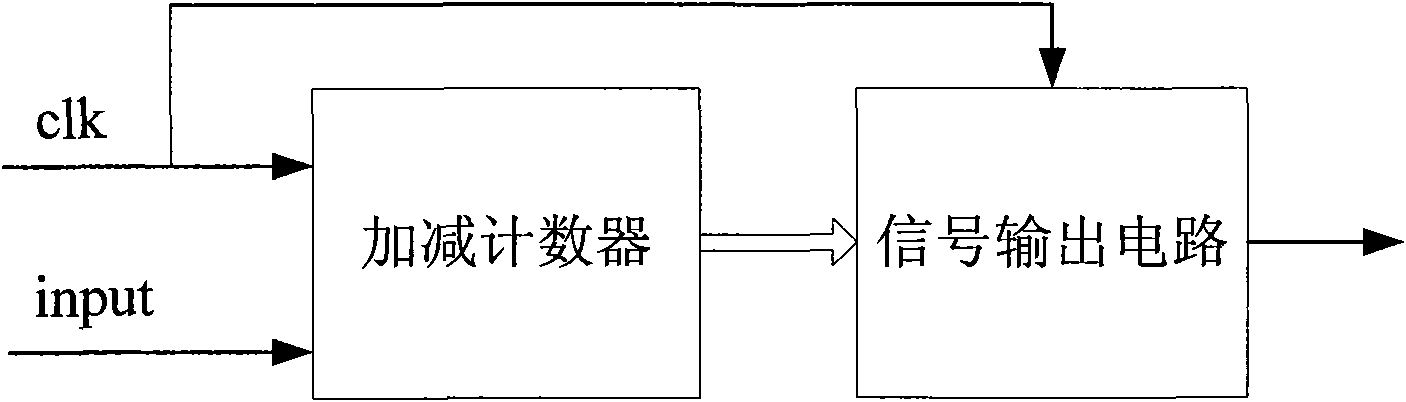

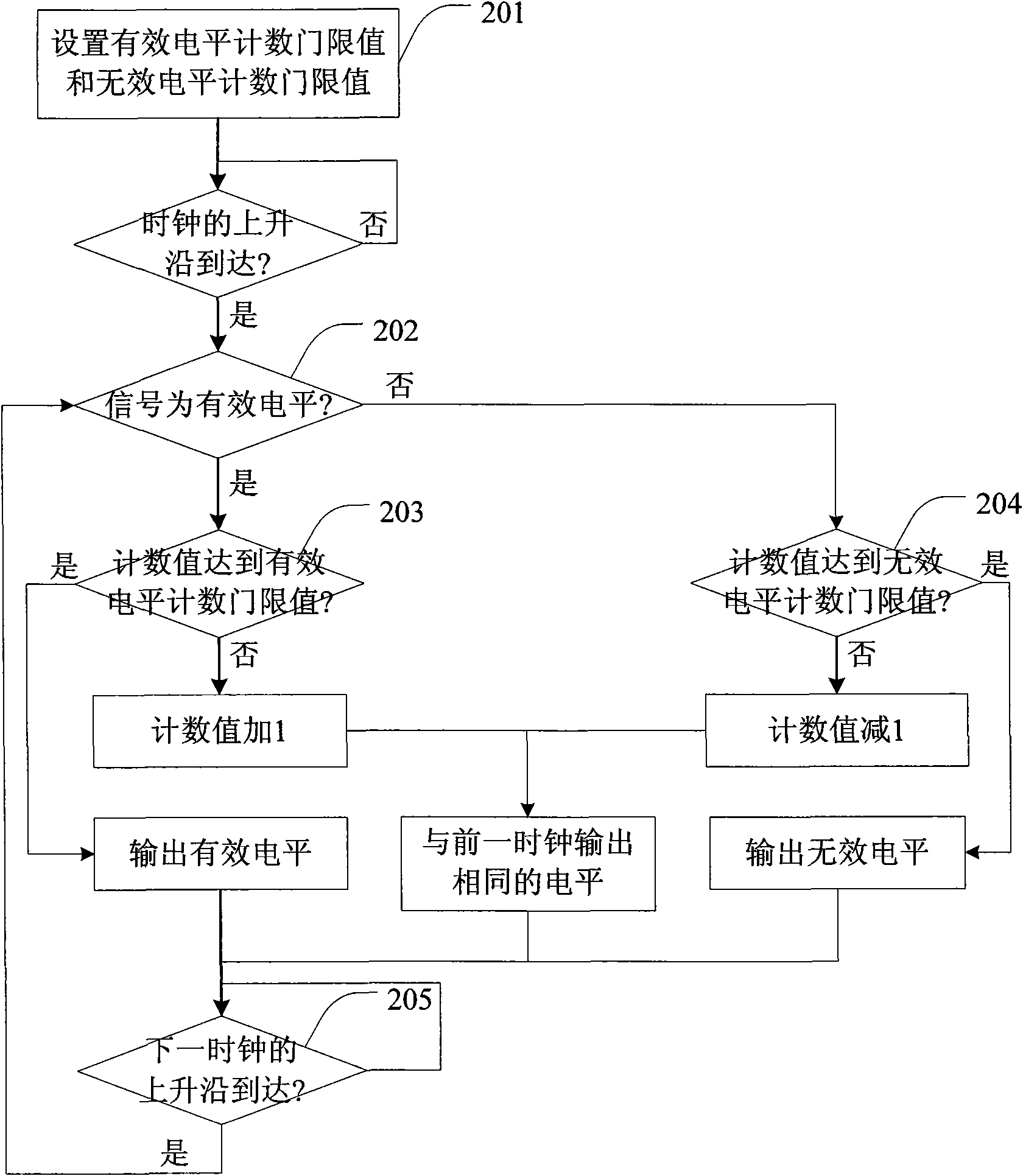

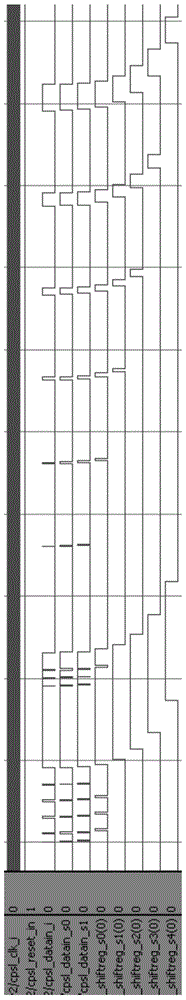

The invention discloses a method and device for eliminating signal noise, the device includes a backward-forward counter and a signal output circuit; the method for eliminating signal noise has the following steps: 1) setting valid and invalid level counting thresholds; 2) receiving the signal with signal noise needed to be eliminated by the backward-forward counter and beginning to count; when the rising edge of each clock arrives, if the signal is an valid electrical level, adding one on the current counting value, otherwise subtracting one; and the counting value does not increase / decrease until it reaches to a valid / invalid level counting threshold; meanwhile, the signal output circuit outputs signal without noise according to the counting value: when the rising edge of each clock arrives, if the counting value is a valid / invalid level counting threshold, then outputting valid / invalid level; if the counting value is between the valid and invalid level counting threshold, keeping the output equal to the output of the previous clock. The device provided by the invention can thoroughly eliminate wide noise, stably output signal without noise, and which is simple to be realized, thereby improving reliability of the system.

Owner:ZTE CORP

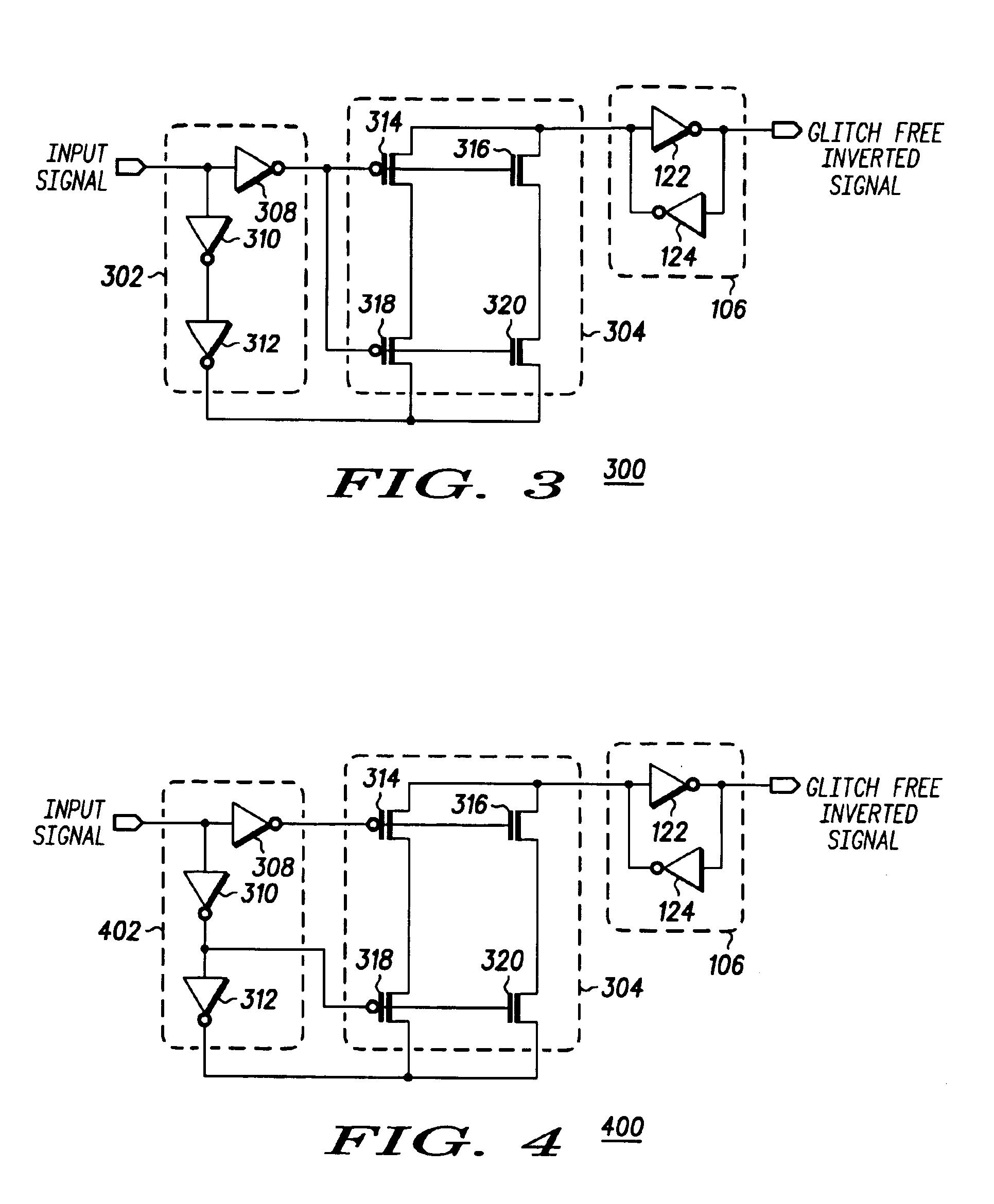

Glitch removal circuit

InactiveUS6894540B1Duration/width modulated pulse demodulationOscillations generatorsEngineeringGlitch removal

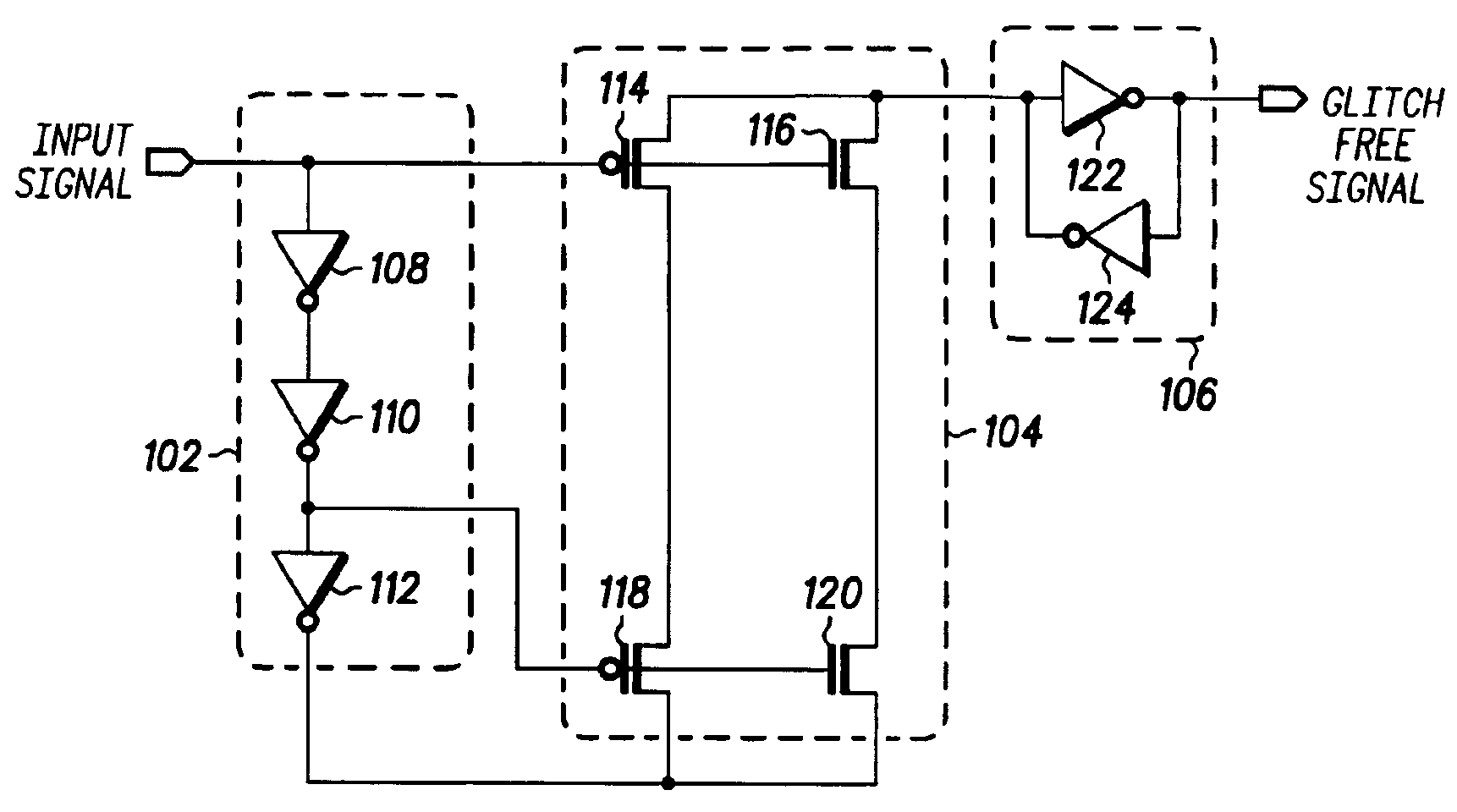

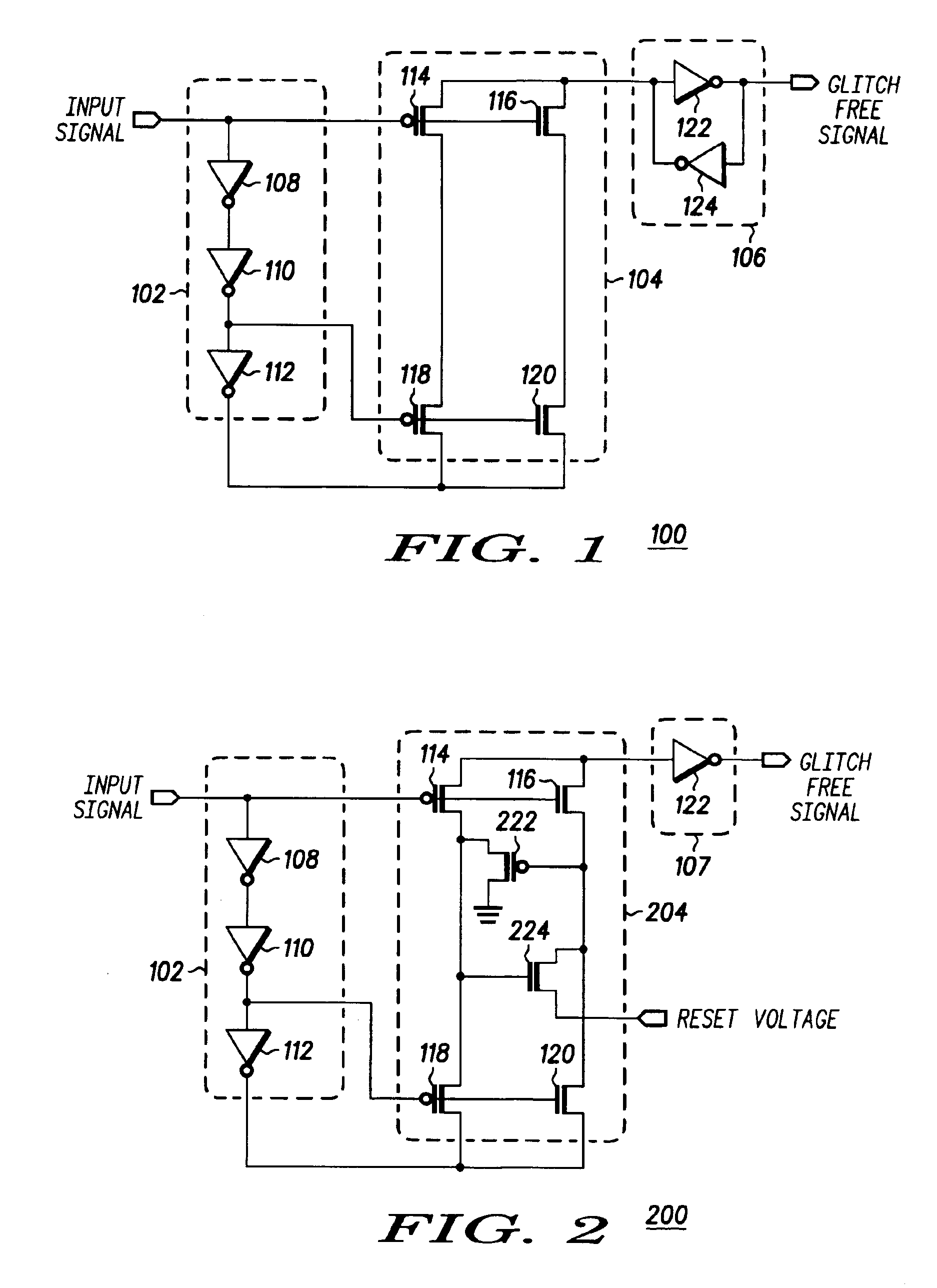

A glitch removal circuit that removes both positive and negative glitches from an input signal includes a delay circuit, a glitch blocking circuit, and a latch circuit. The delay circuit receives the input signal and introduces a delay into it. The glitch blocking circuit is coupled to the delay circuit, and includes two NMOS transistors and two PMOS transistors. The glitch blocking circuit receives the input signal and the delayed input signal and blocks the input signal if there is a glitch in it. The latch circuit is coupled to the output of the glitch blocking circuit. The latch circuit inverts the output of the glitch blocking circuit and stores the output on a continuous basis. The latch circuit provides glitch free signal as the output.

Owner:NORTH STAR INNOVATIONS

Circuit and method for glitch correction

InactiveUS20080258835A1Easy to operateEfficient detectionAngle modulation detailsBoundary crossingGlitch

Correction of glitches output from a delta-sigma modulator is accomplished using an integer boundary crossing detector and a FIR filter. The detector monitors a portion of an input to the modulator. The detector recognizes a transition from an all 1's bit pattern to an all 0's bit pattern or vice versa as representative of potential for a glitch to be present on the output of the modulator. The detector responsively generates condition detection output. Receipt of such condition detection output triggers the generation of a correction signal by the filter. The correction signal is, at least substantially similar, in magnitude but opposite in sign from to the expected glitch at the output of the modulator. The correction signal is added to the output of the modulator to substantially eliminate the glitch.

Owner:CONVERSANT INTPROP MANAGEMENT INC

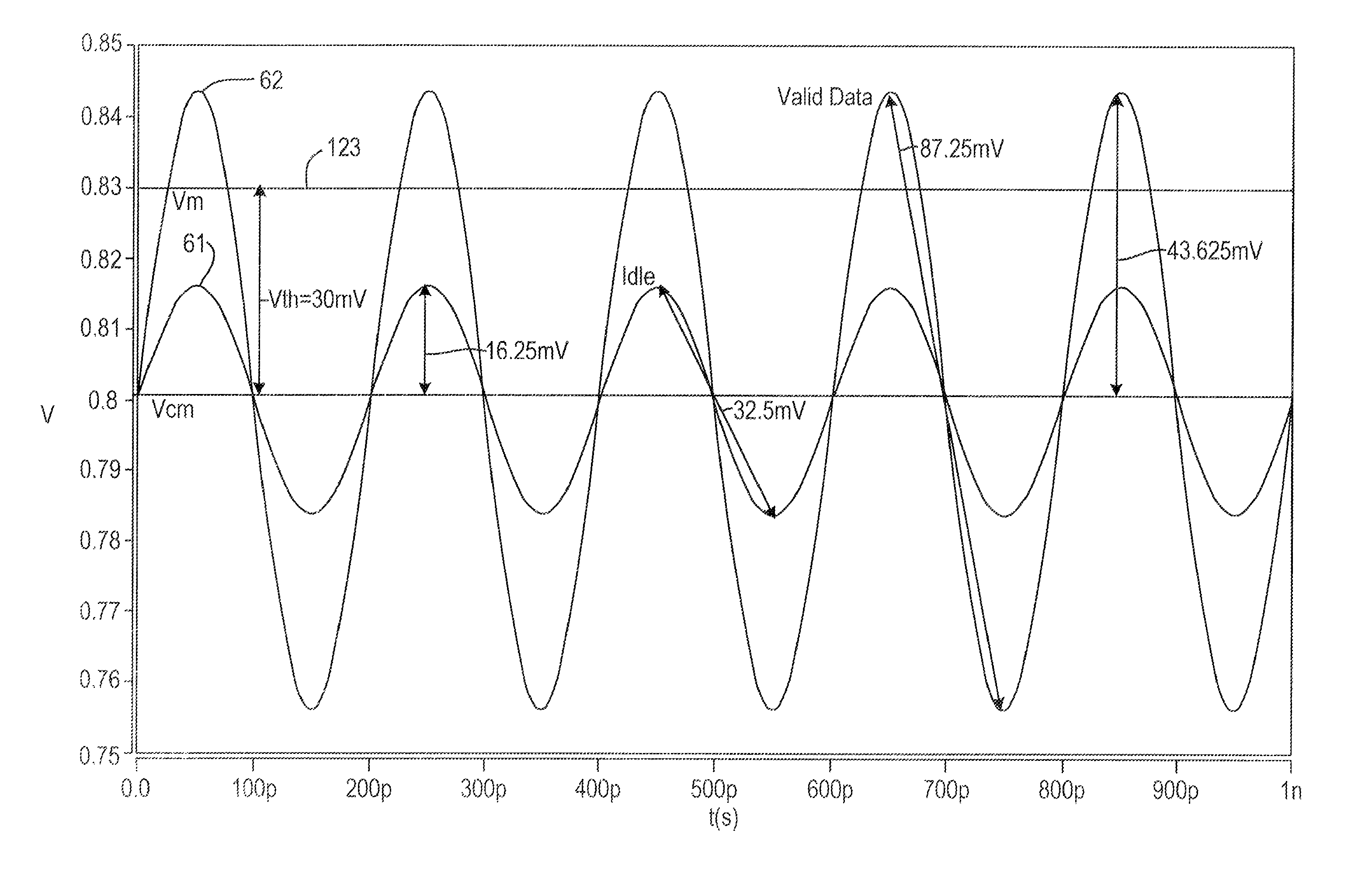

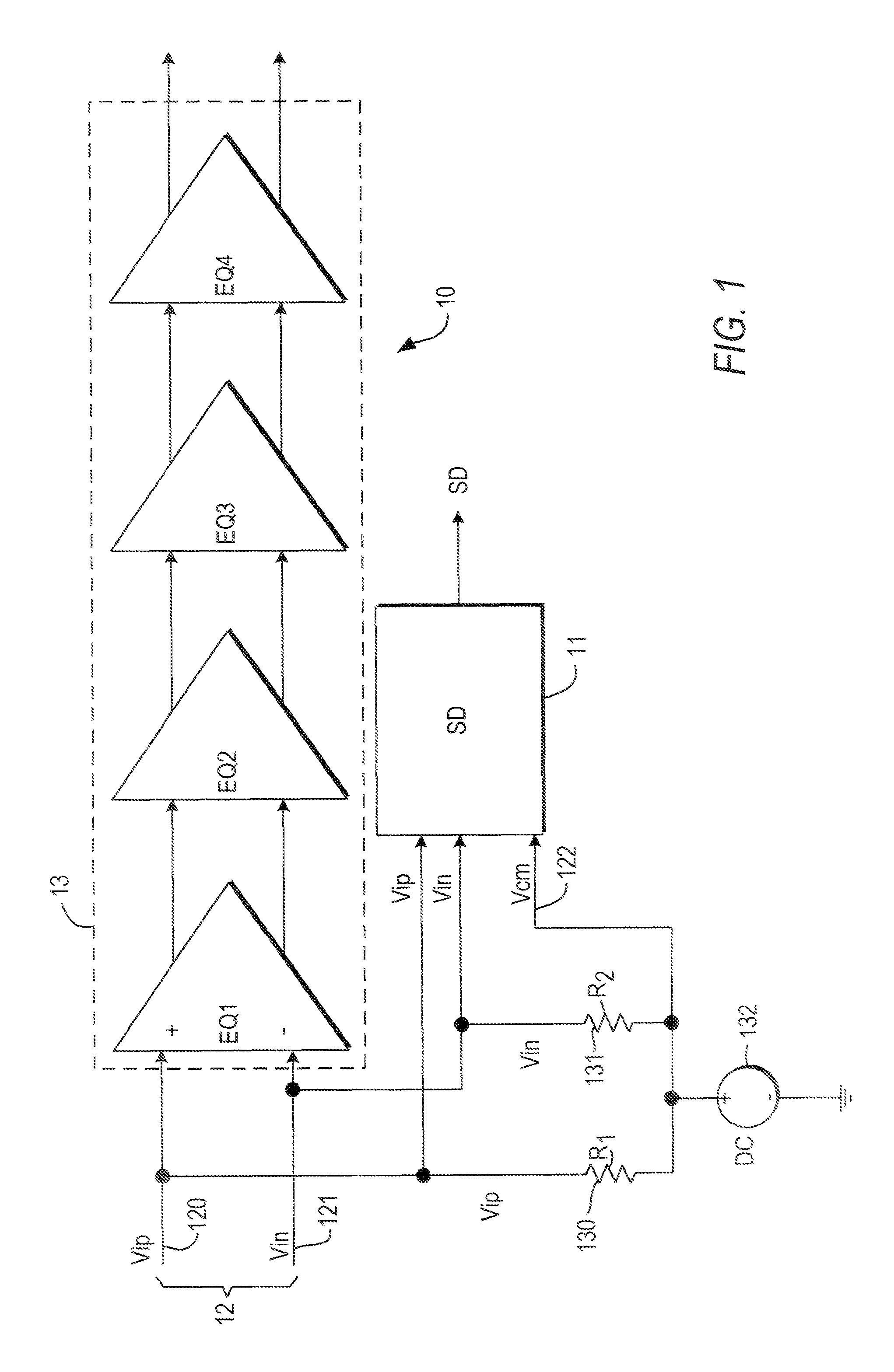

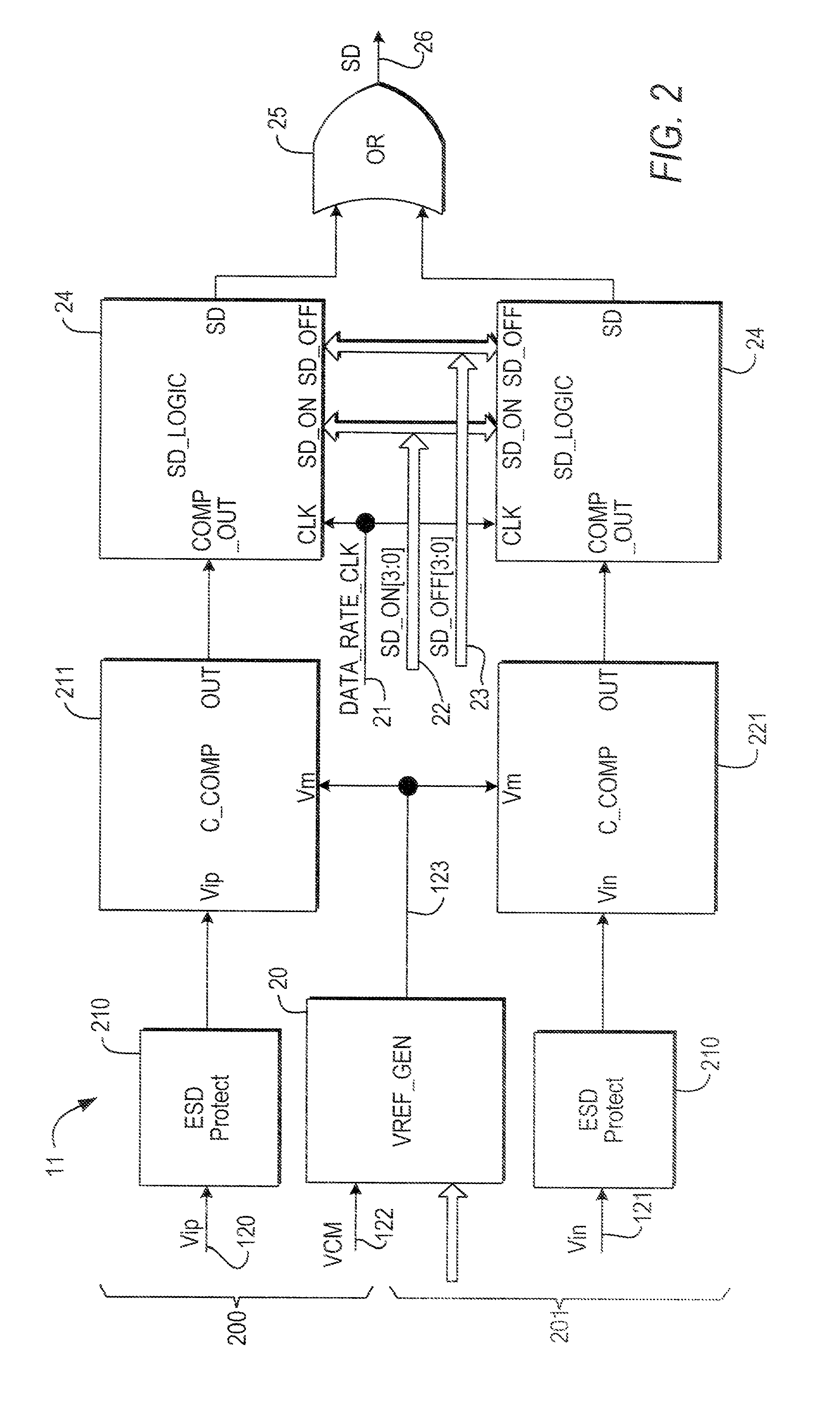

High-speed signal detect for serial interface

InactiveUS7812591B1Precise processReduce the impactAnalogue/digital conversionMultiple input and output pulse circuitsSerial digital interfaceVoltage reference

More accurate signal detection circuitry in serial interfaces, particularly on a programmable integrated circuit device, such as a PLD, includes a high-speed, high-resolution, high-bandwidth comparator, along with digital filtering, to reduce the effect of process, temperature or supply variations. The comparator is used to compare a direct input signal with a programmable reference voltage, and, in a preferred embodiment, can detect the signal level within 8 mV accuracy. The output of the comparator may then be digitally filtered. Preferably, both a high-pass digital filter and a low-pass analog filter may be used to eliminate glitches and low-frequency noise. Preferably, the digital filters are programmable to adjust the sensitivity to noise. The filtered output is then latched and output to indicate receipt or loss of signal. This signal detect circuitry can operate reliably at data rates as high as 7 Gbps.

Owner:ALTERA CORP

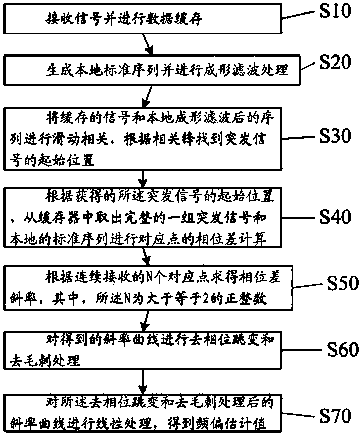

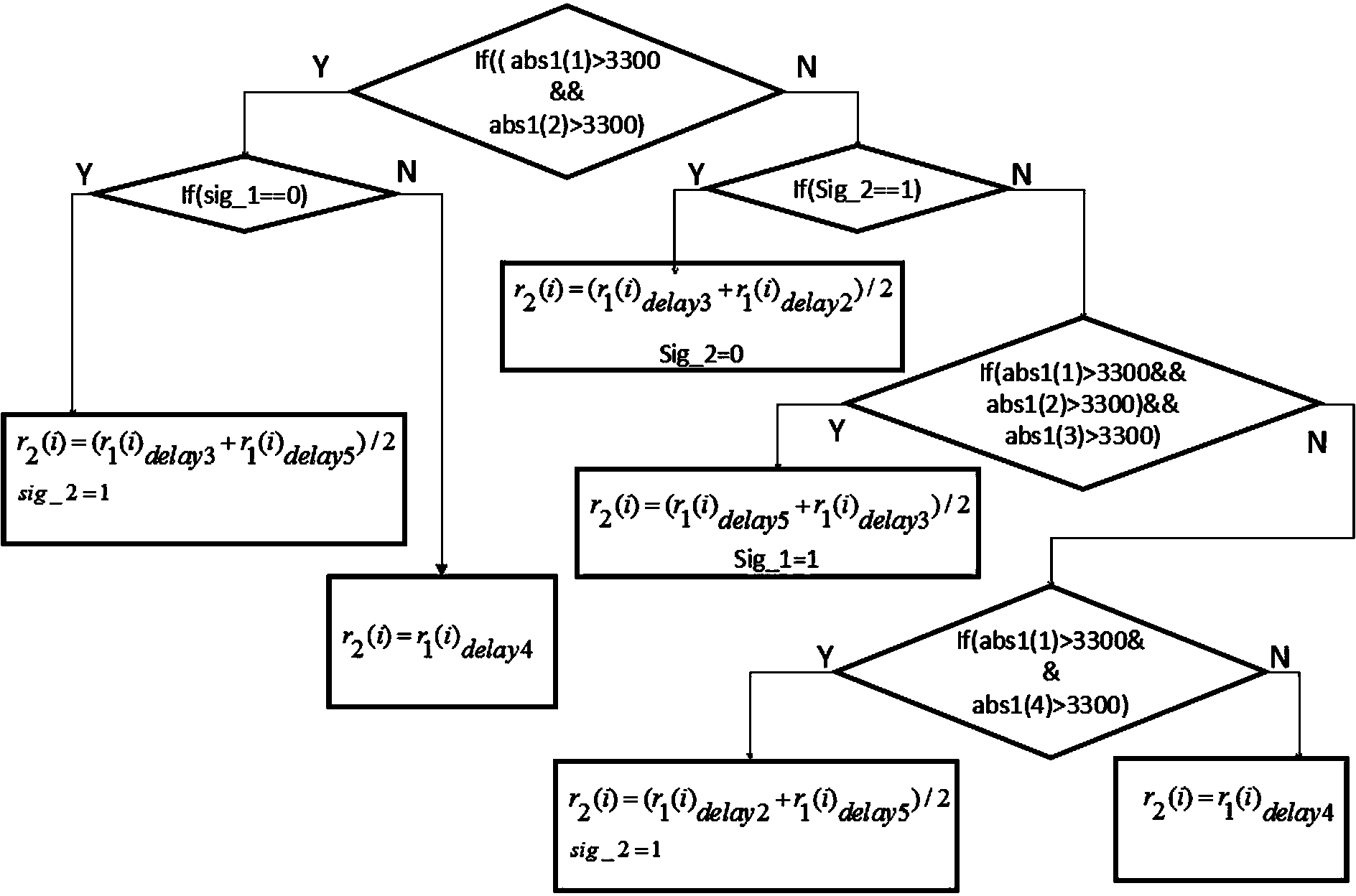

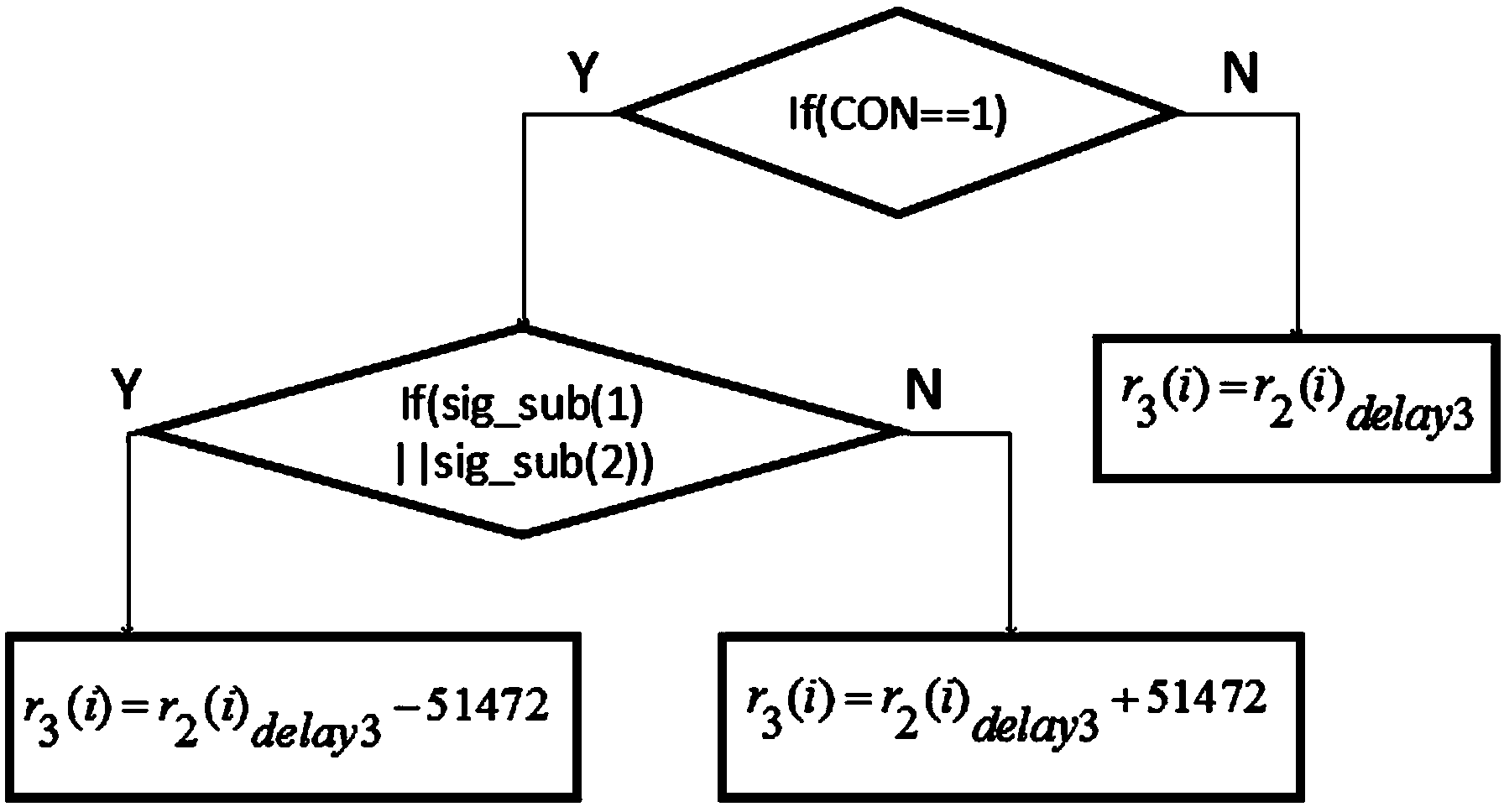

Burst signal frequency deviation correction method applied to satellite phones

ActiveCN104378317AAvoid dependenceSolve the technical problem that the frequency offset estimation will be inaccurateBaseband system detailsPhase differenceLocal sequence

The invention discloses a burst signal frequency deviation correction method applied to satellite phones. The method comprises the steps that signals are received, and data caching is carried out on the signals; local standard sequences are generated, and shaping filtering is carried out on the local standard sequences; sliding correlation is carried out on the cached signals and local sequences obtained after shaping filtering, and the initial positions of burst signals are found according to correlation peaks; according to the obtained initial positions of the burst signals, a complete set of burst signals are taken out of a cache, and phase difference calculation of corresponding points of the burst signals and the local standard sequences is carried out; the phase difference slope is worked out according to N corresponding points received continuously, phase jump removal and glitch removal are carried out on an obtained slope curve, linear processing is carried out on a slope curve obtained after phase jump removal and glitch removal, and then a frequency deviation estimated value is obtained. The method eliminates dependence on channel estimation in the prior art and is accurate in frequency deviation estimation.

Owner:CHENGDUSCEON TECH

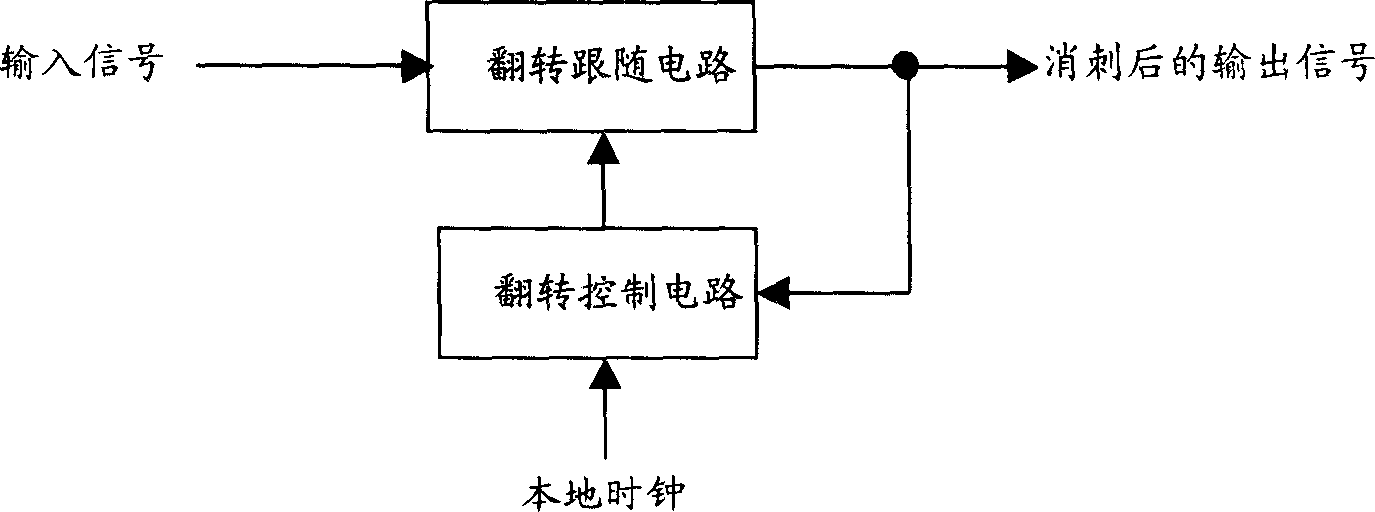

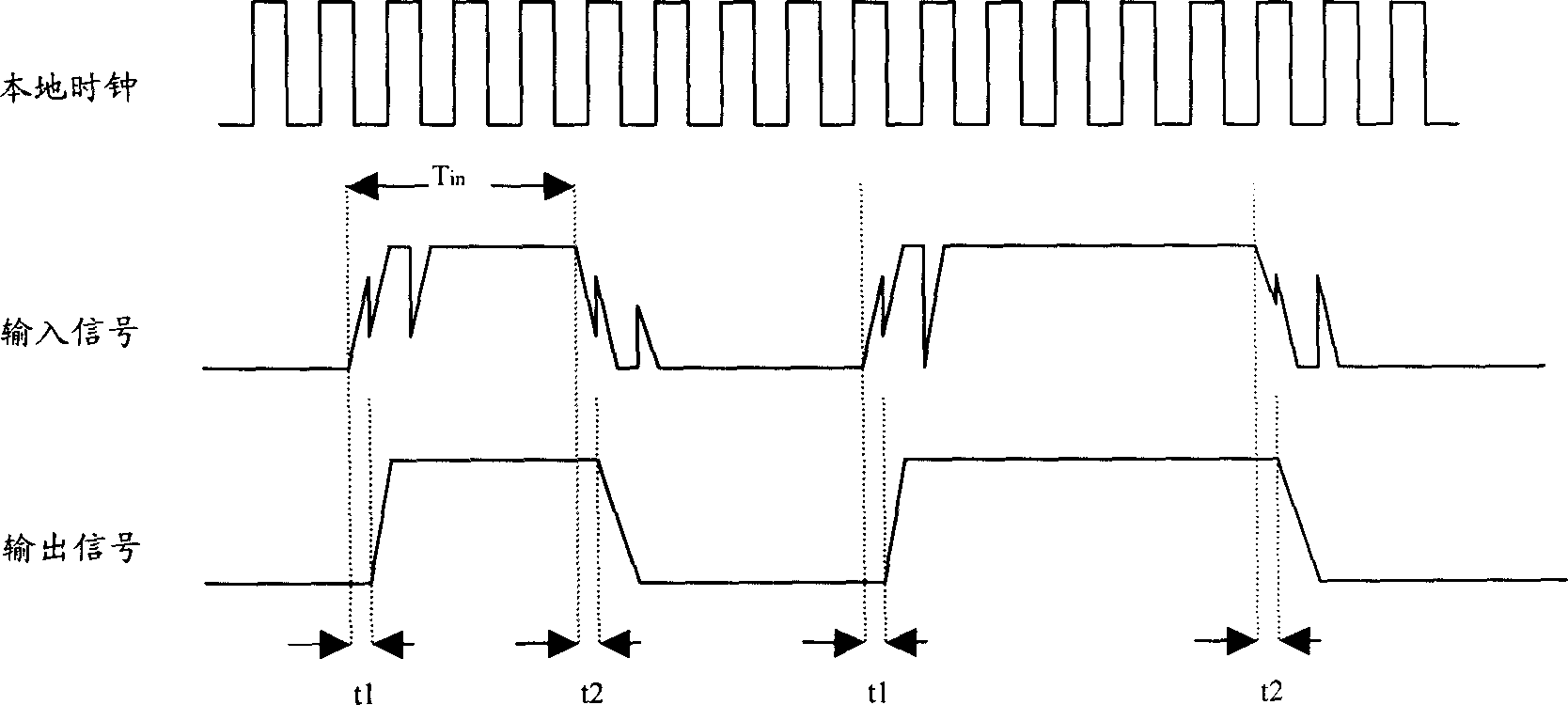

Burr removing device and method

A method for removing bur off includes automatically closing turnover function by turnover follow-up circuit when turnover output level is turned over, having a preset time delay under control of turnover control circuit then starting turnover function of turnover follow-up circuit. The device for realizing said method is also disclosed.

Owner:HUAWEI TECH CO LTD

Vibration key-phase signal preprocessing method of turbo generator set

InactiveCN101915605AEliminate distractionsPrecise key phase square wave signalSubsonic/sonic/ultrasonic wave measurementUsing electrical meansPretreatment methodEngineering

The invention relates to a vibration key-phase signal preprocessing method of a turbo generator set in a large-scale thermal power plant. The method comprises the following steps of: eliminating burr interference through voltage triggering; meanwhile, further eliminating the burr interference in key-phase pulses by means of the optoelectronic isolation of an integrated circuit; and finally shaping square waves. The processing method proposed by the invention can effectively eliminate various burr interferences, obtain accurate key-phase square-wave signals, achieve the aim of processing the key-phase signals of different kinds of sensors in different power plants and provide a site with key-phase signals which are more accurate and convenient to analyze.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING) +1

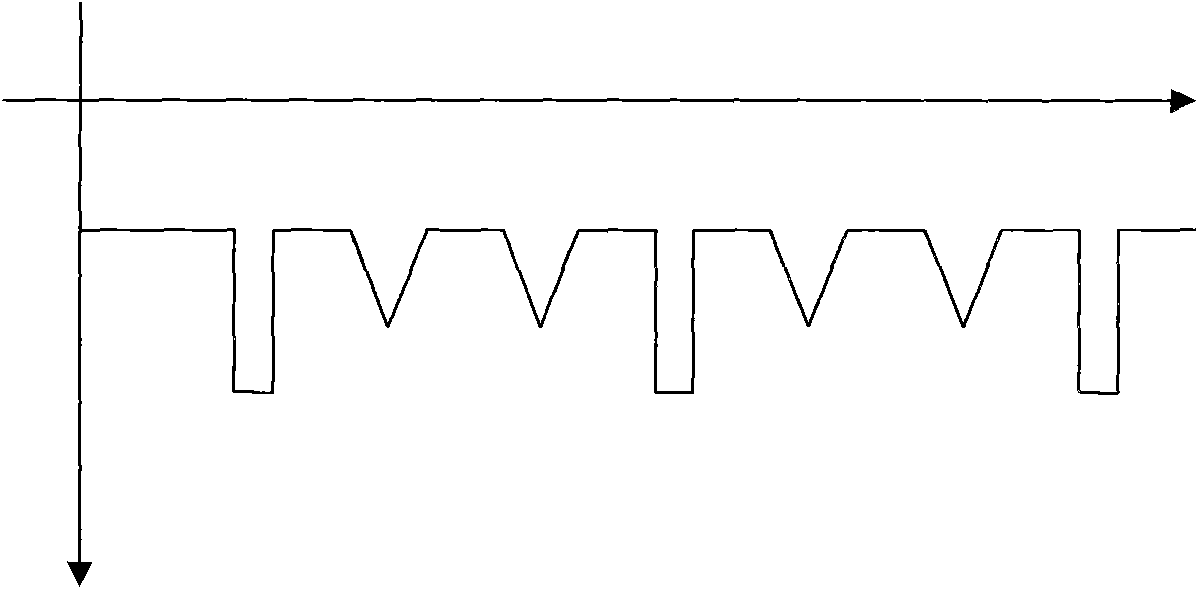

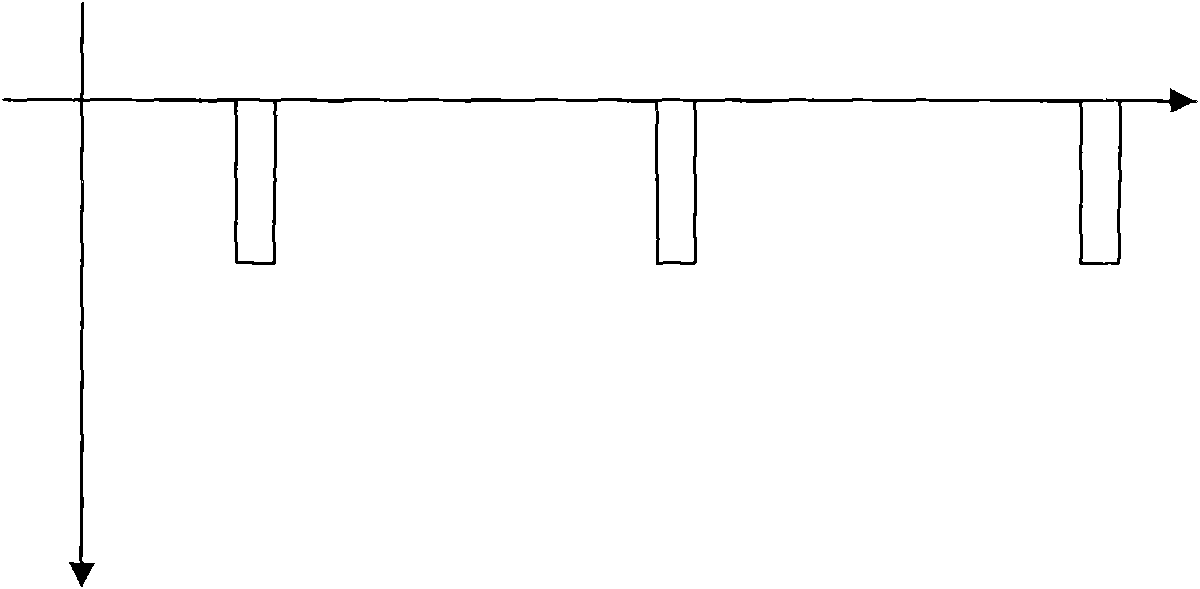

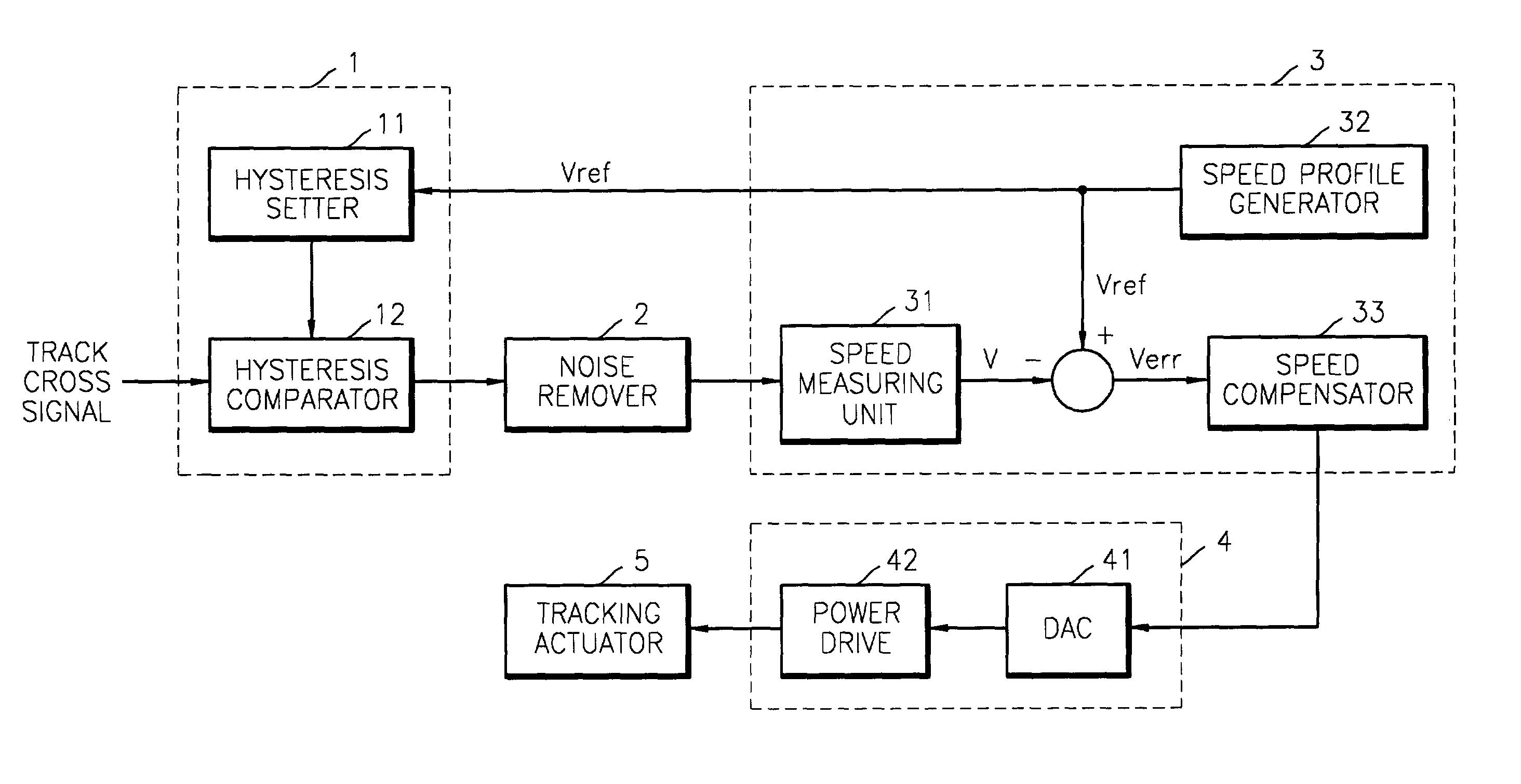

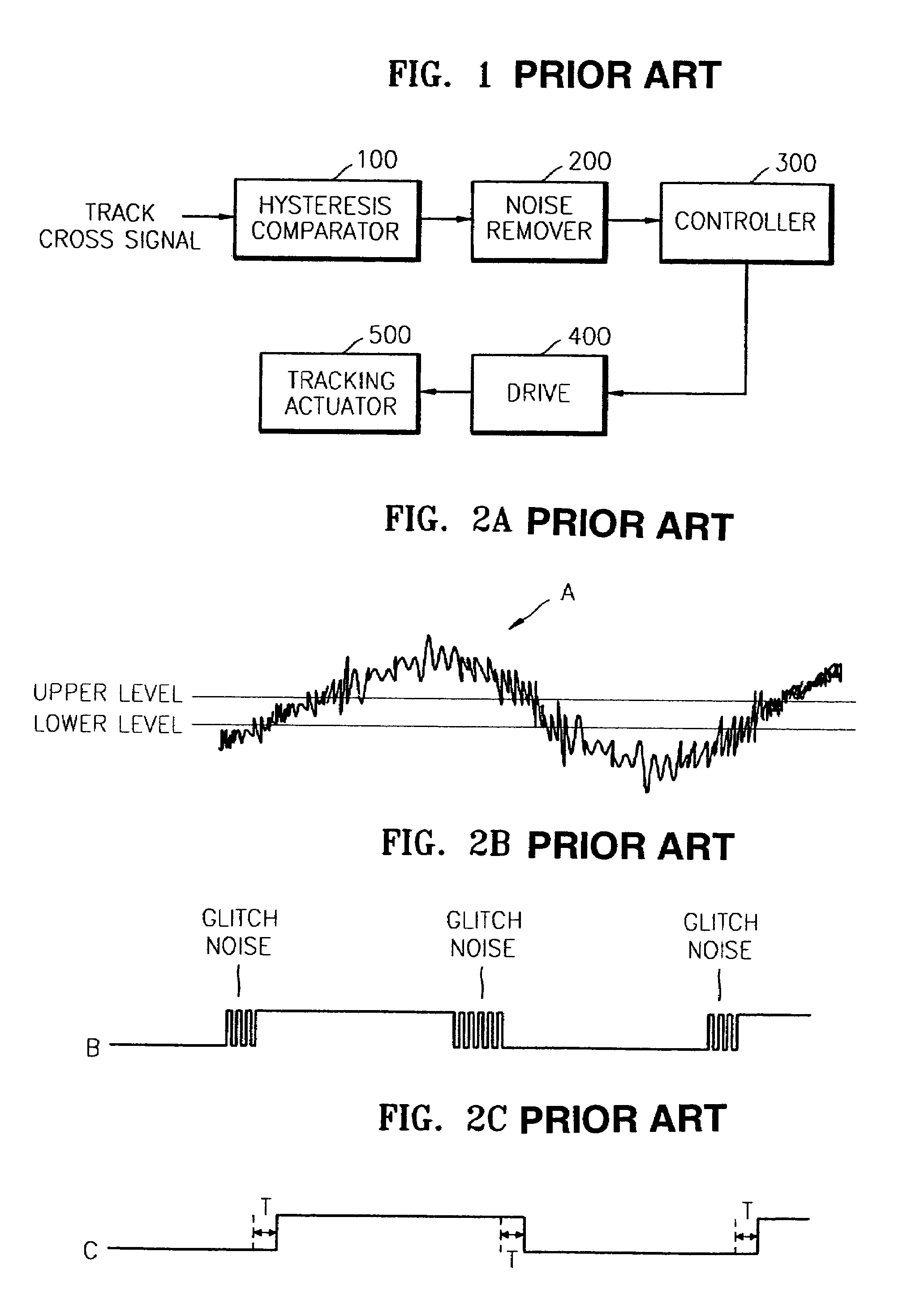

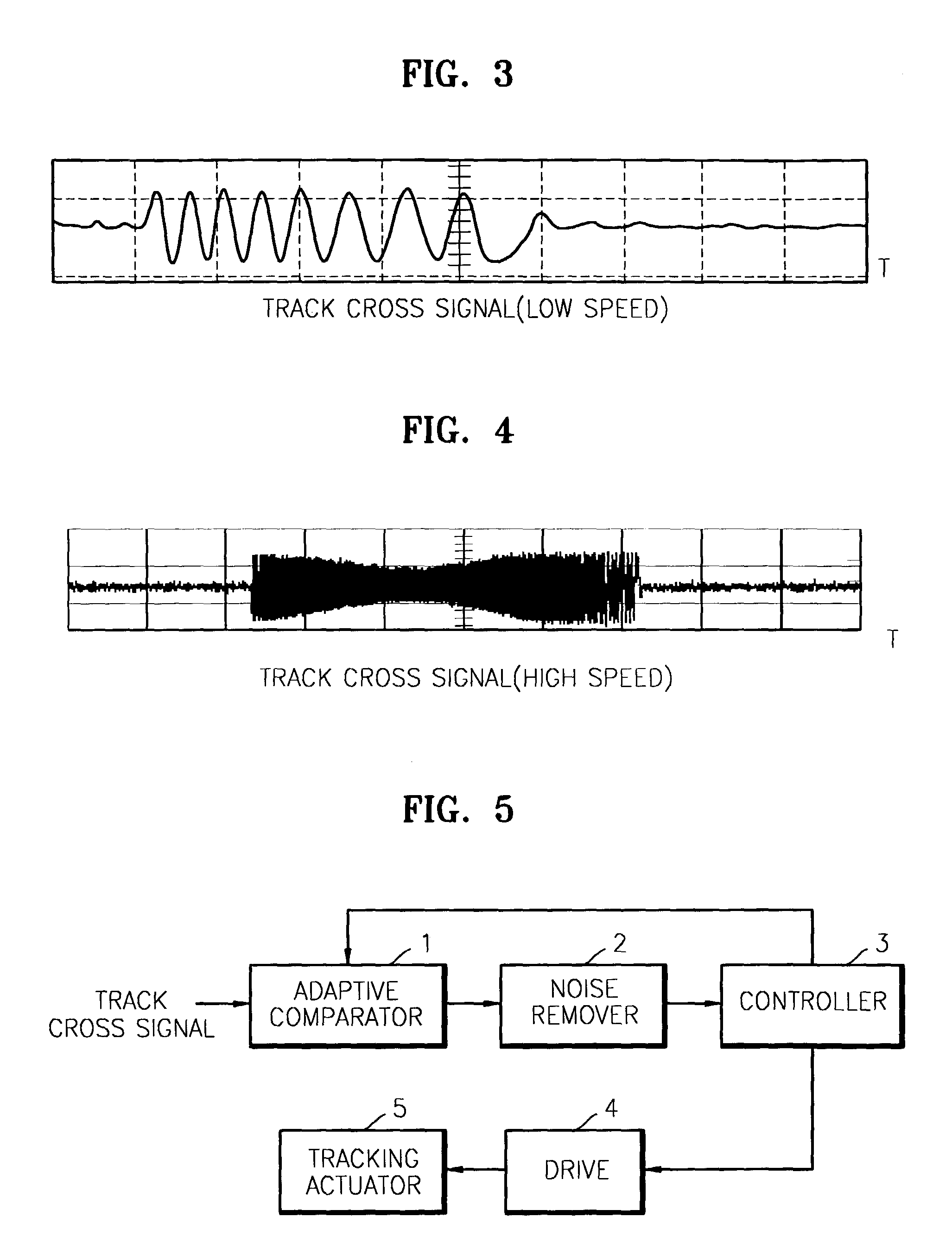

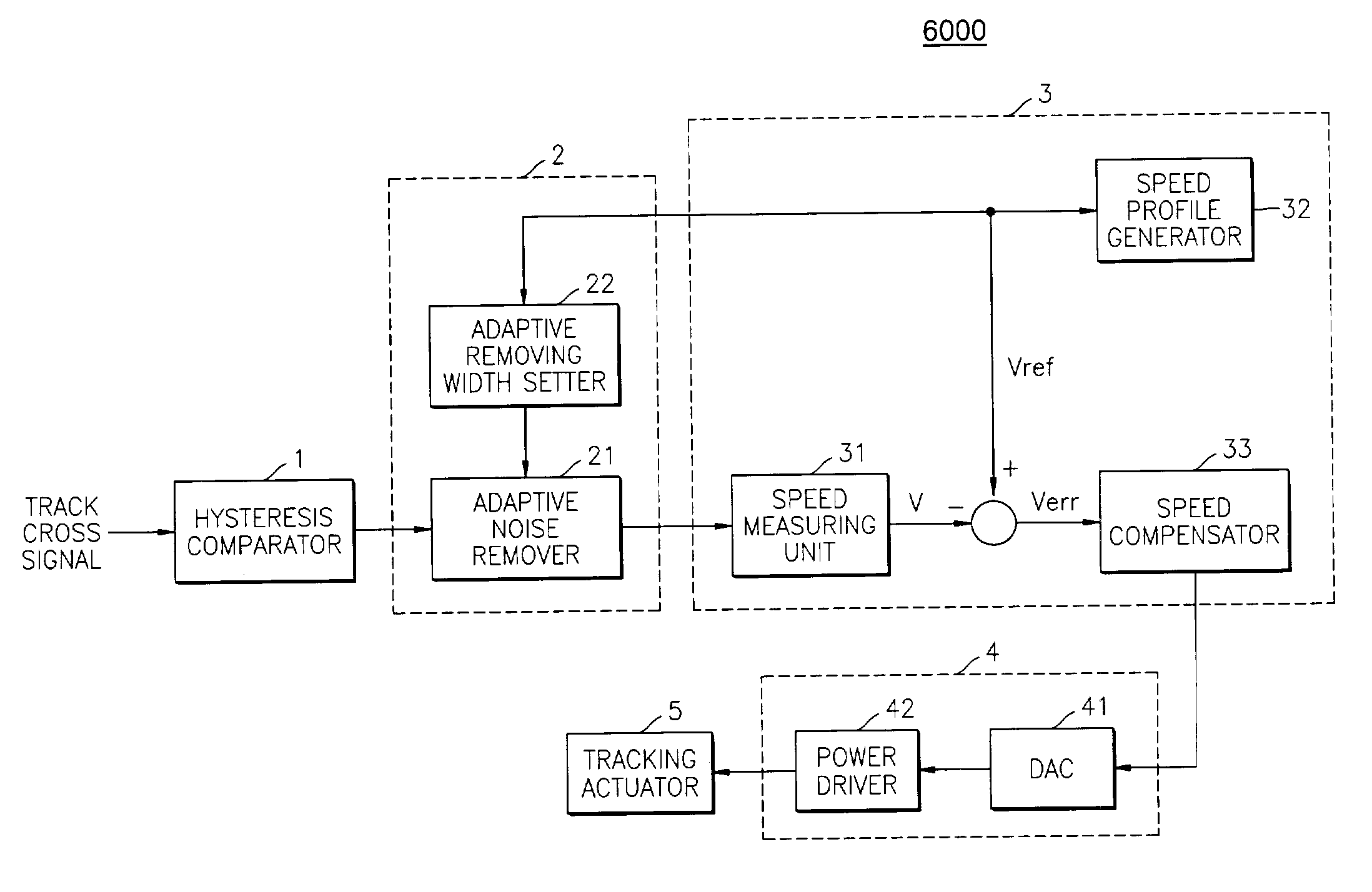

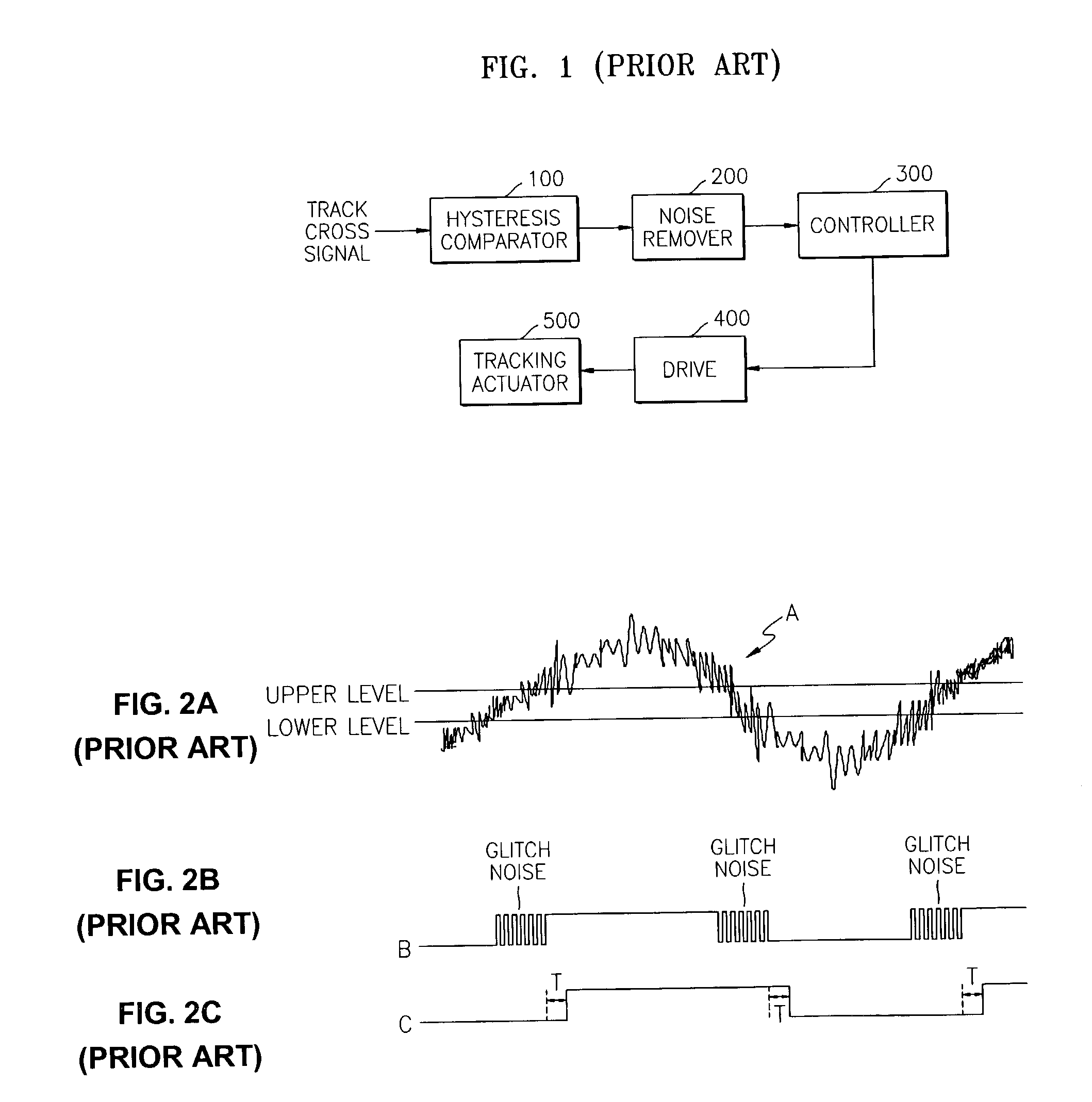

Method and apparatus for canceling glitch noise from track crossing signal

InactiveUS7136329B2Cancel noiseEffectively removing noiseModification of read/write signalsSignal processing for reducing noiseHysteresisEngineering

Provided are a method and apparatus for canceling noise from a track cross signal, a method for controlling an optical disc drive, an optical disc drive, and an optical disc reproducing apparatus. The method for removing noise from a track cross signal includes (a) removing noise from the track cross signal by binarizing the track cross signal with reference to hysteresis set values that are determined according to a command speed for a tracking actuator; and (b) removing glitch noise from the binarized track cross signal based on a predetermined time value. Accordingly, it is possible to effective remove noise to obtain information regarding the precise speed and position of a desired track.

Owner:SAMSUNG ELECTRONICS CO LTD

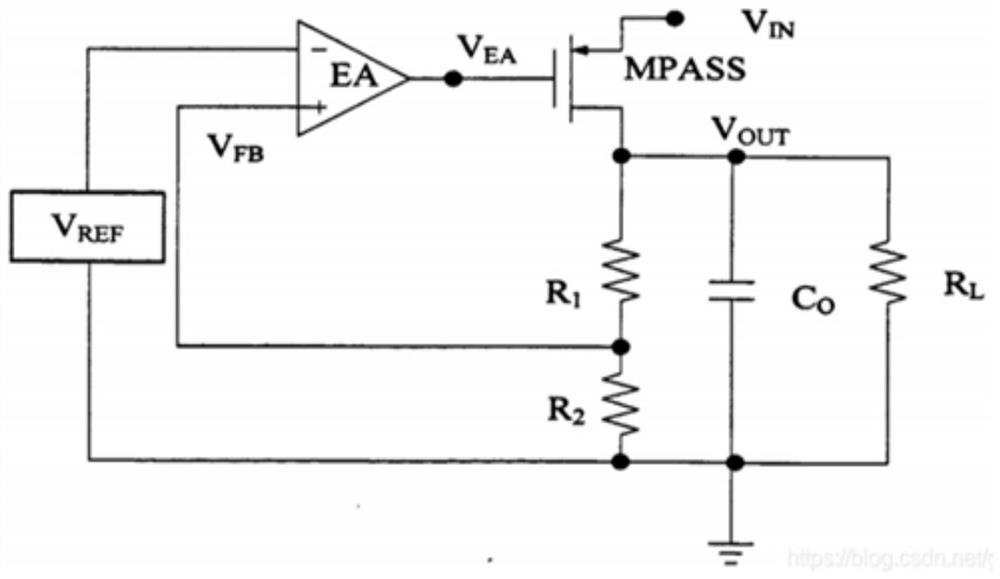

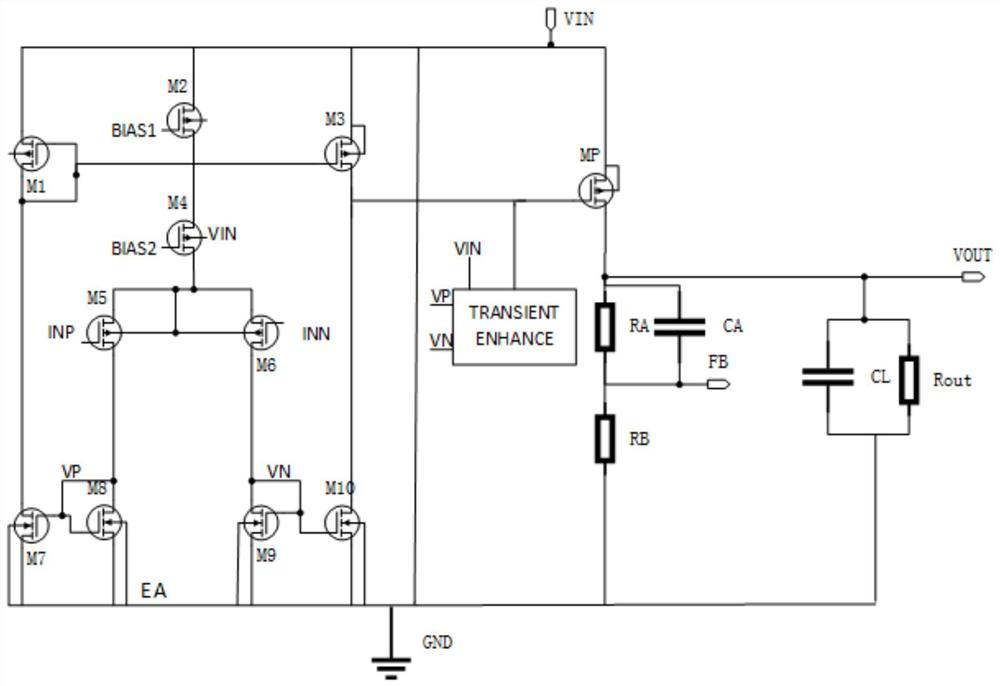

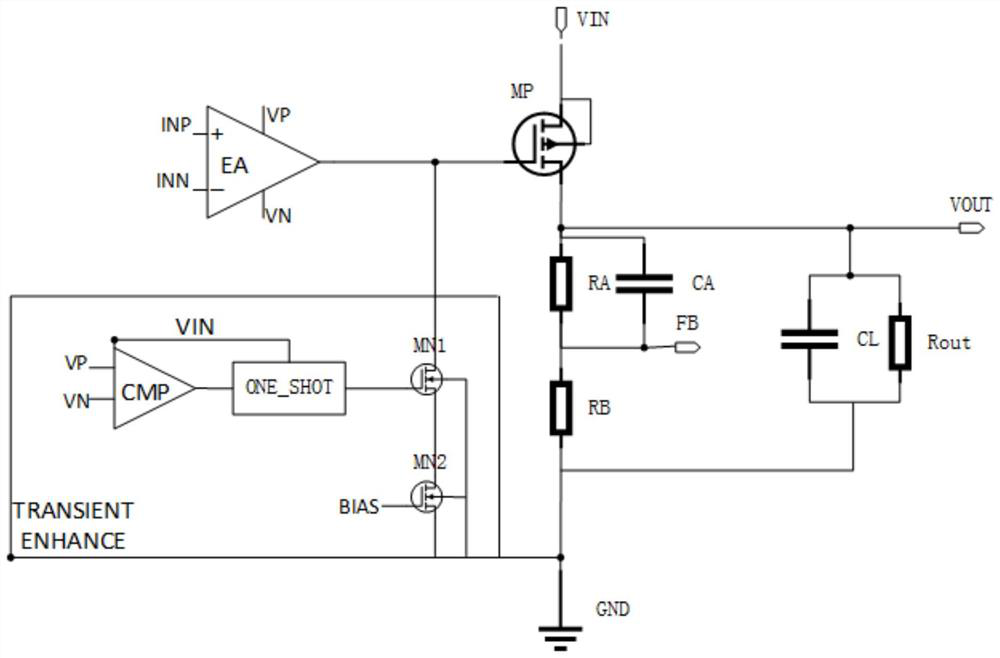

Novel transient response enhanced LDO

PendingCN112732000AEnhanced Load Transient ResponseImproved noise immunityElectric variable regulationCapacitanceHemt circuits

The invention provides a novel transient response enhanced LDO. The novel transient response enhanced LDO comprises an error amplifier EA, an adjusting tube MP, feedback resistor networks RA and RB, a feedback capacitor CA, a load capacitor CL and a load resistor Rout. A transient response enhancement circuit TRANSIENT ENHANGCE is connected between the error amplifier EA and the grid electrode of the adjusting tube MP, and the TRANSIENT ENHANGCE comprises a hysteresis comparator, an ONE_SHOT and two NMOS tubes MN1 and MN2. The hysteresis comparator is used for collecting and comparing the drain voltage of the input differential pair transistor of the error amplifier EA, burrs of the obtained comparison result are eliminated through the ONESHOT, and the anti-noise performance of transient enhancement is improved. And the grid voltage of the adjusting tube MP is adjusted through the NMOS tube, so that the effect of enhancing the transient response of the load is achieved.

Owner:BRITE SEMICON SHANGHAI CORP

Method and apparatus for canceling glitch noise from track cross signal

InactiveUS7042812B2Cancel noiseSignal processing for reducing noiseRecord information storageActuatorOrbit

A method and apparatus for canceling noise from track cross signal includes binarizing the track cross signal with reference to at least two reference values, and removing noise from the binarized track cross signal based on a command speed according to which a tracking actuator moves a pickup. Accordingly, it is possible to remove noise from a track cross signal so as to obtain information regarding precise speed of track searching or position on the track, irrespective of the searching speed.

Owner:SAMSUNG ELECTRONICS CO LTD

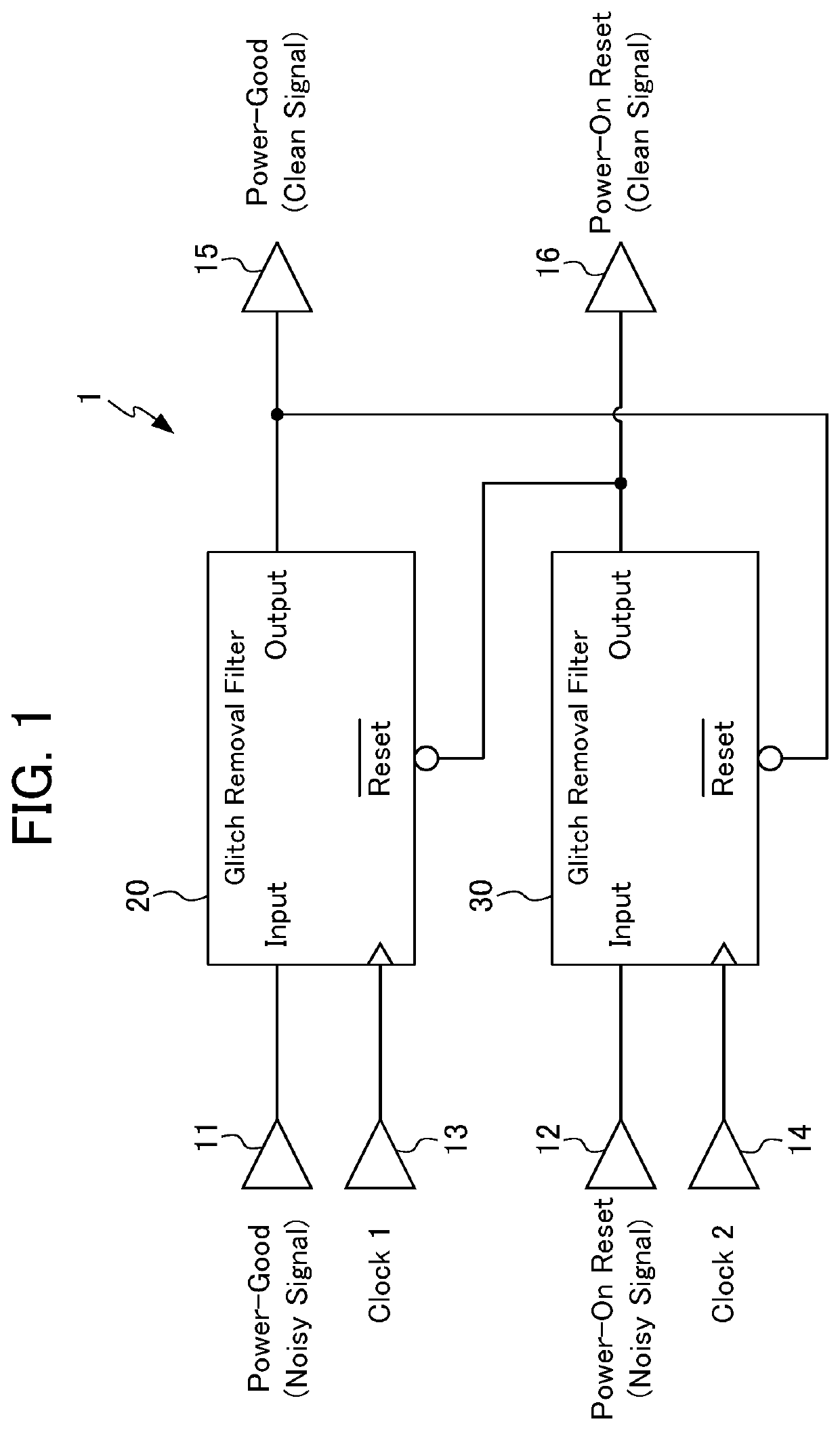

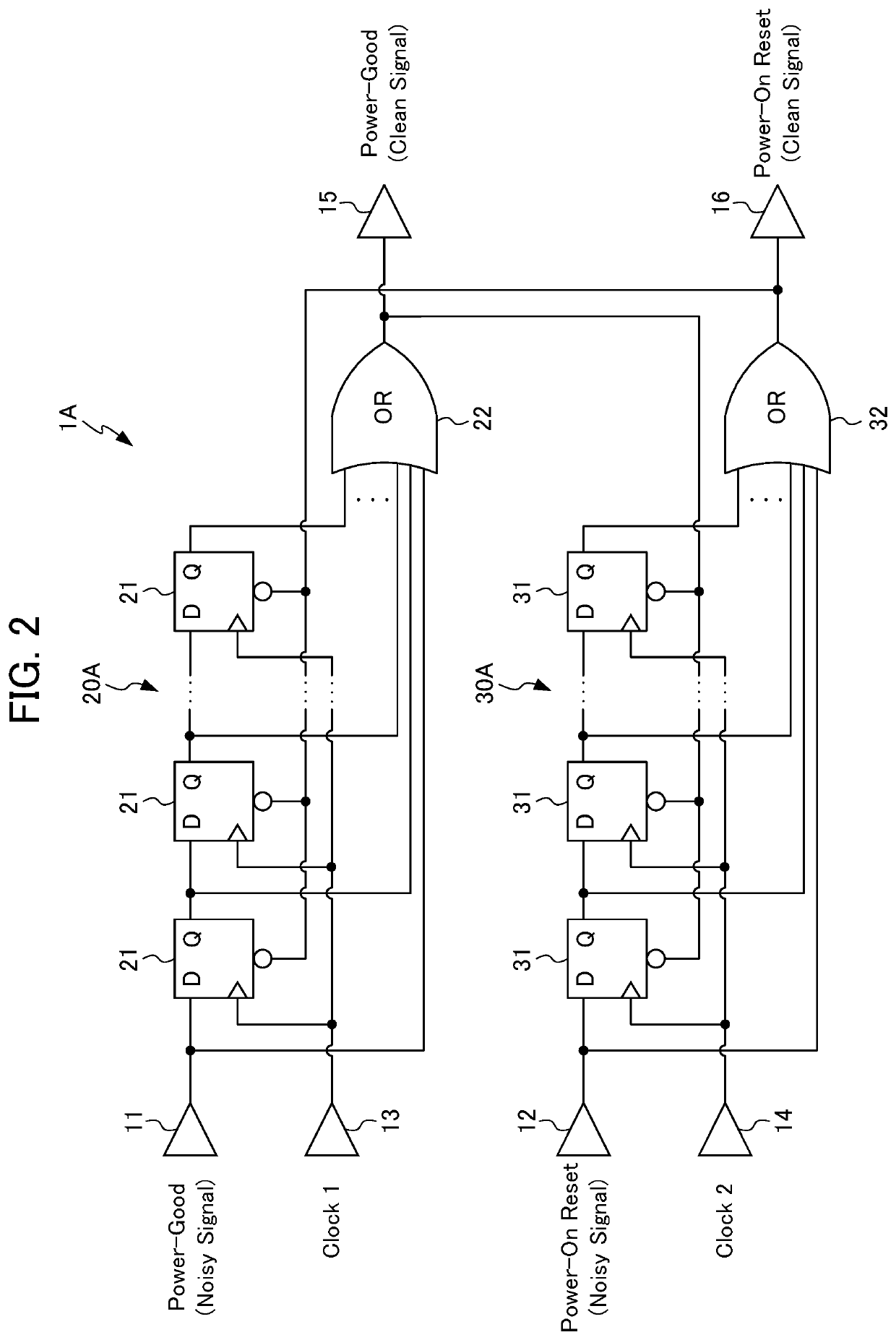

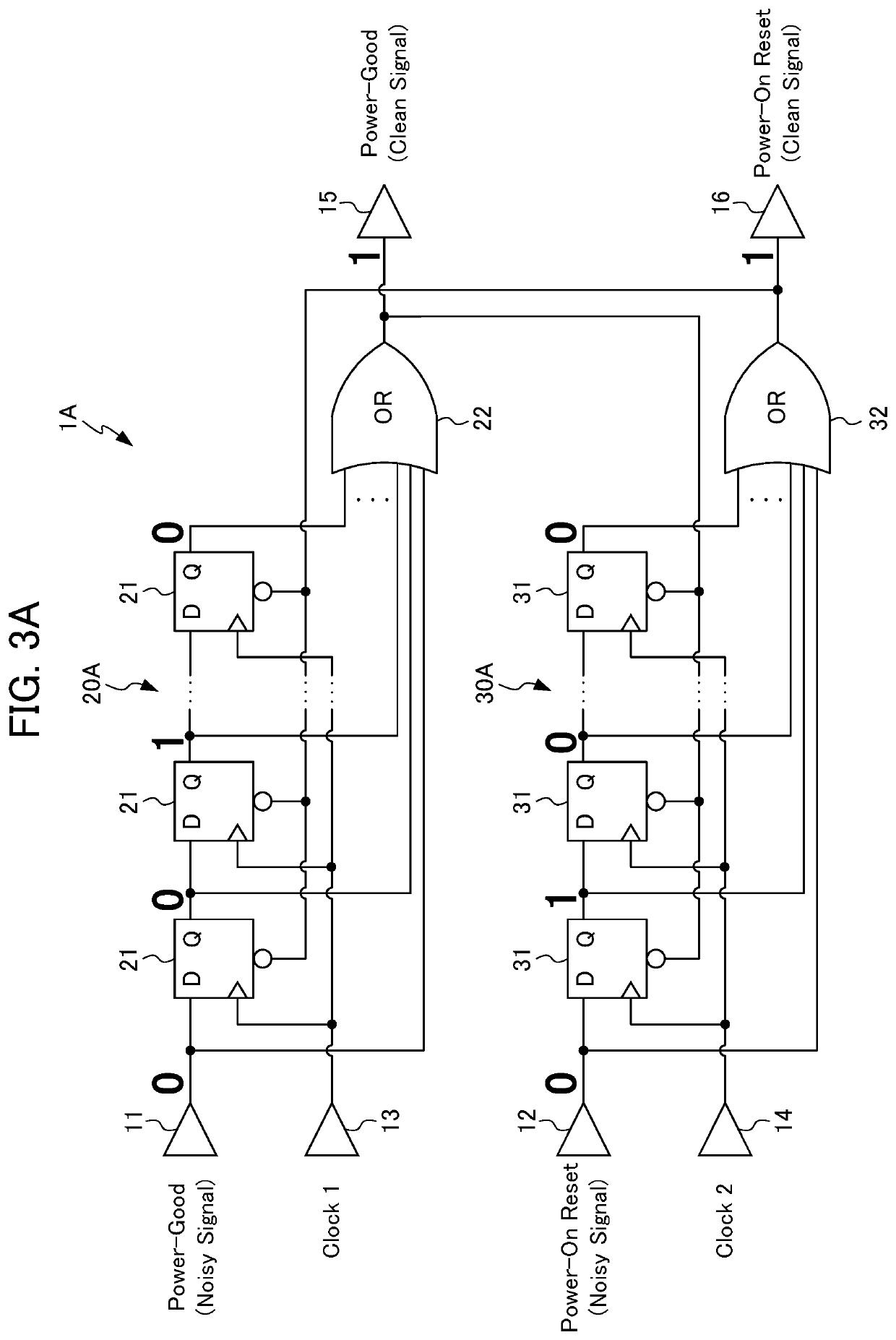

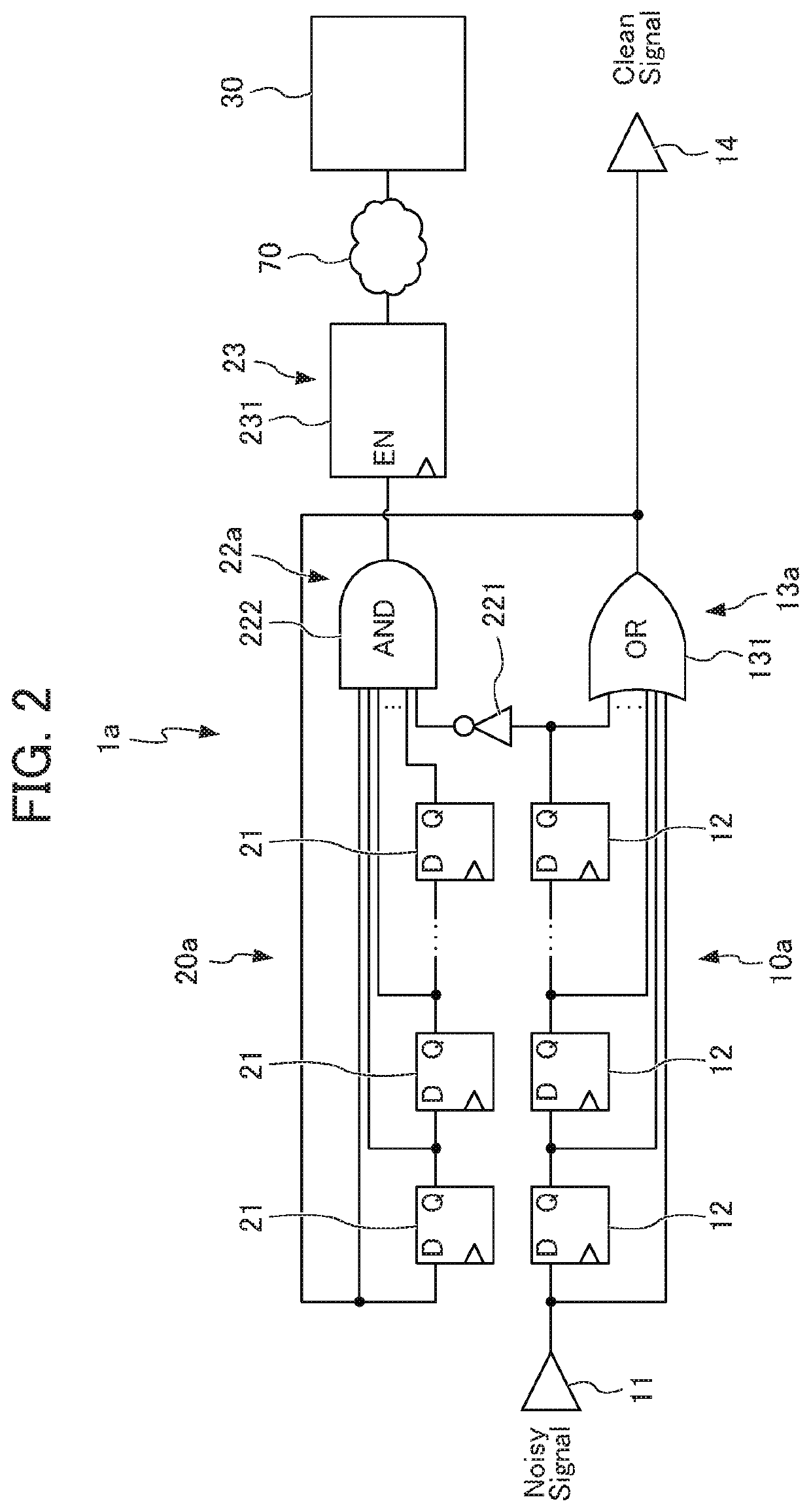

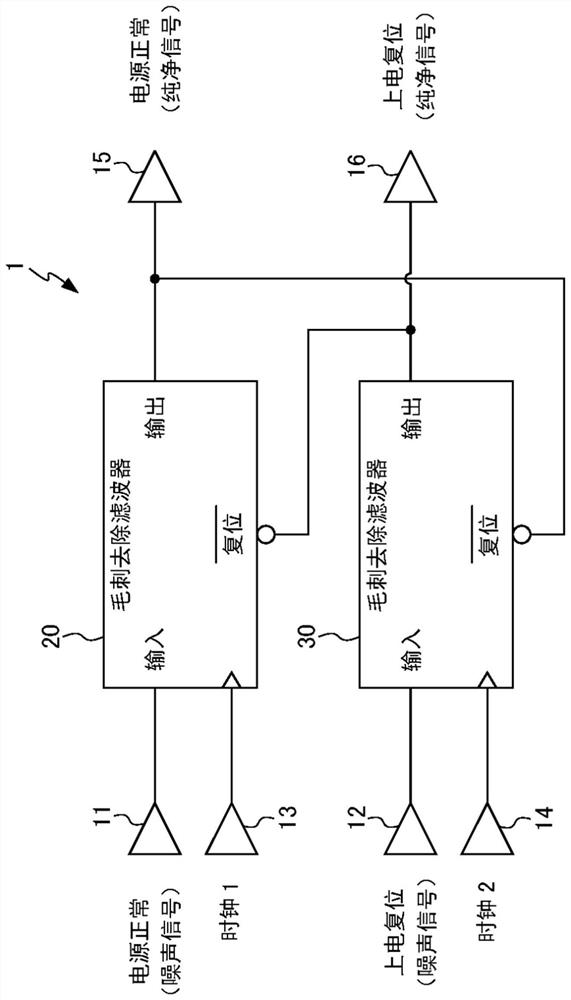

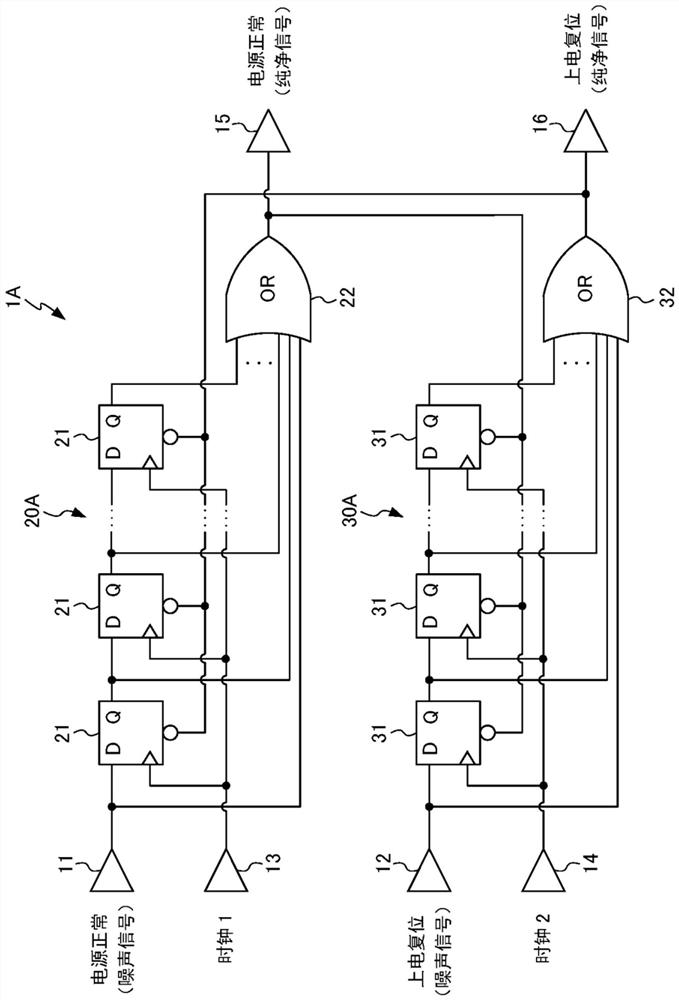

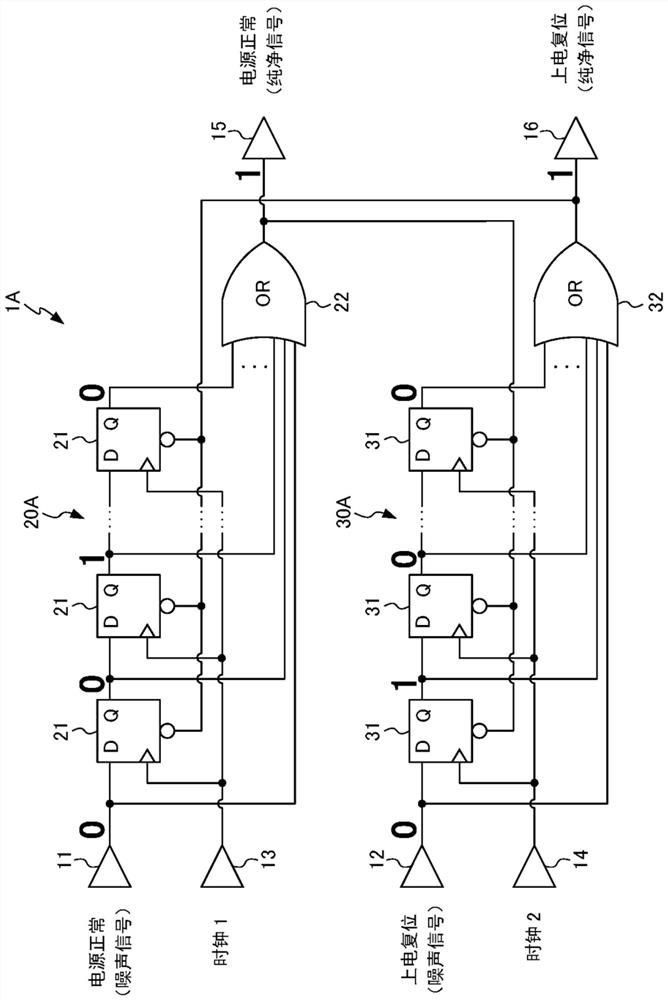

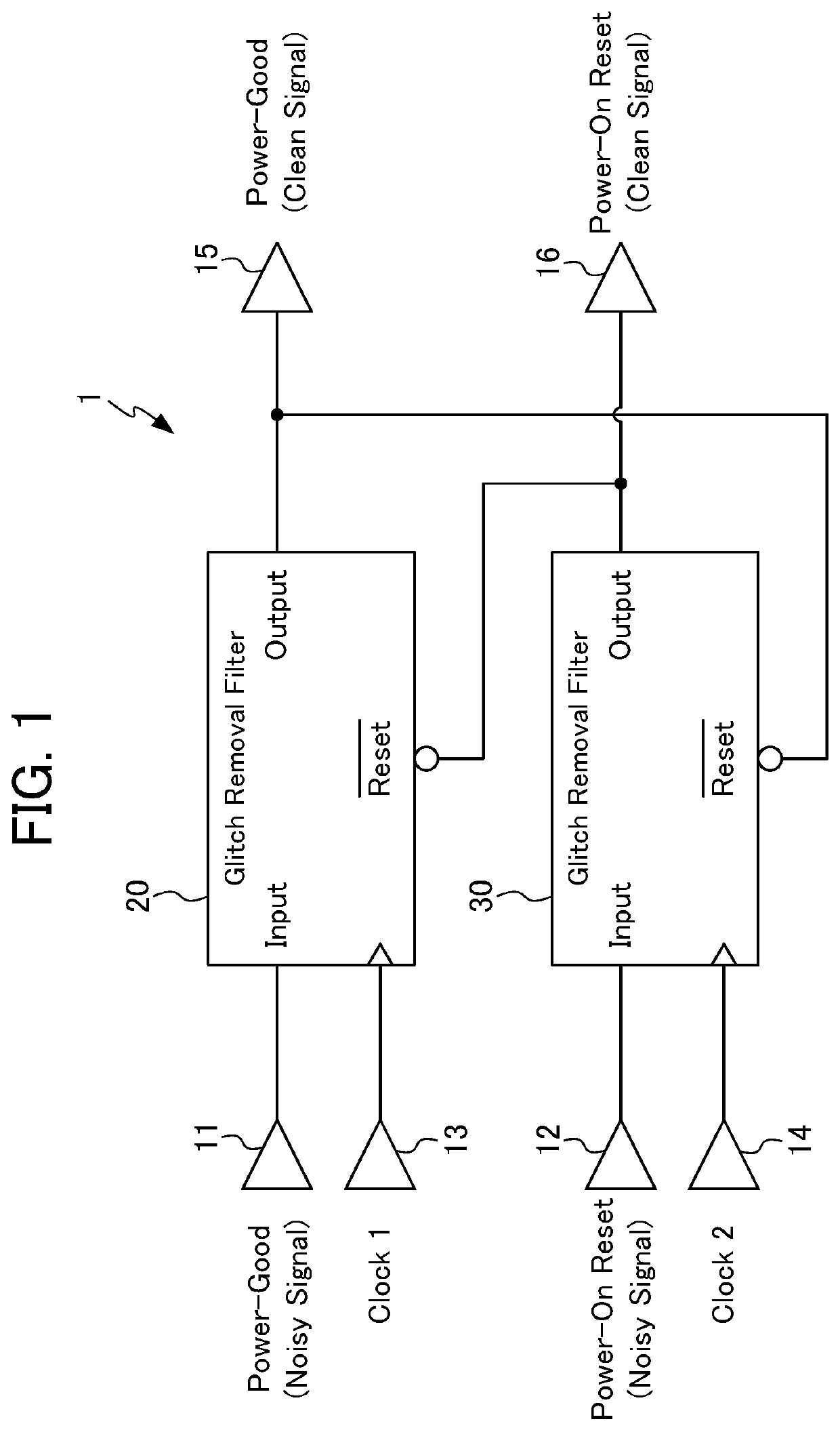

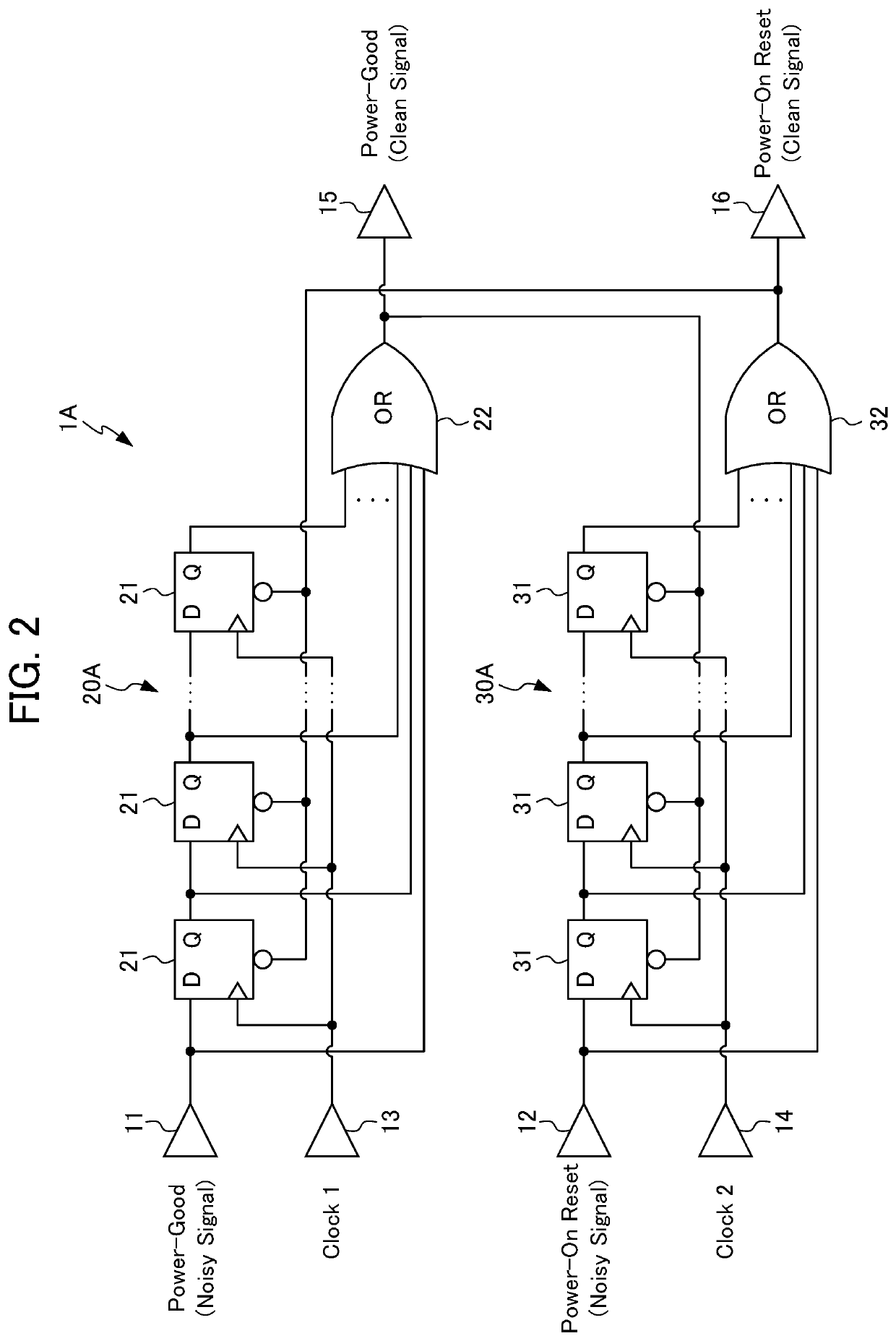

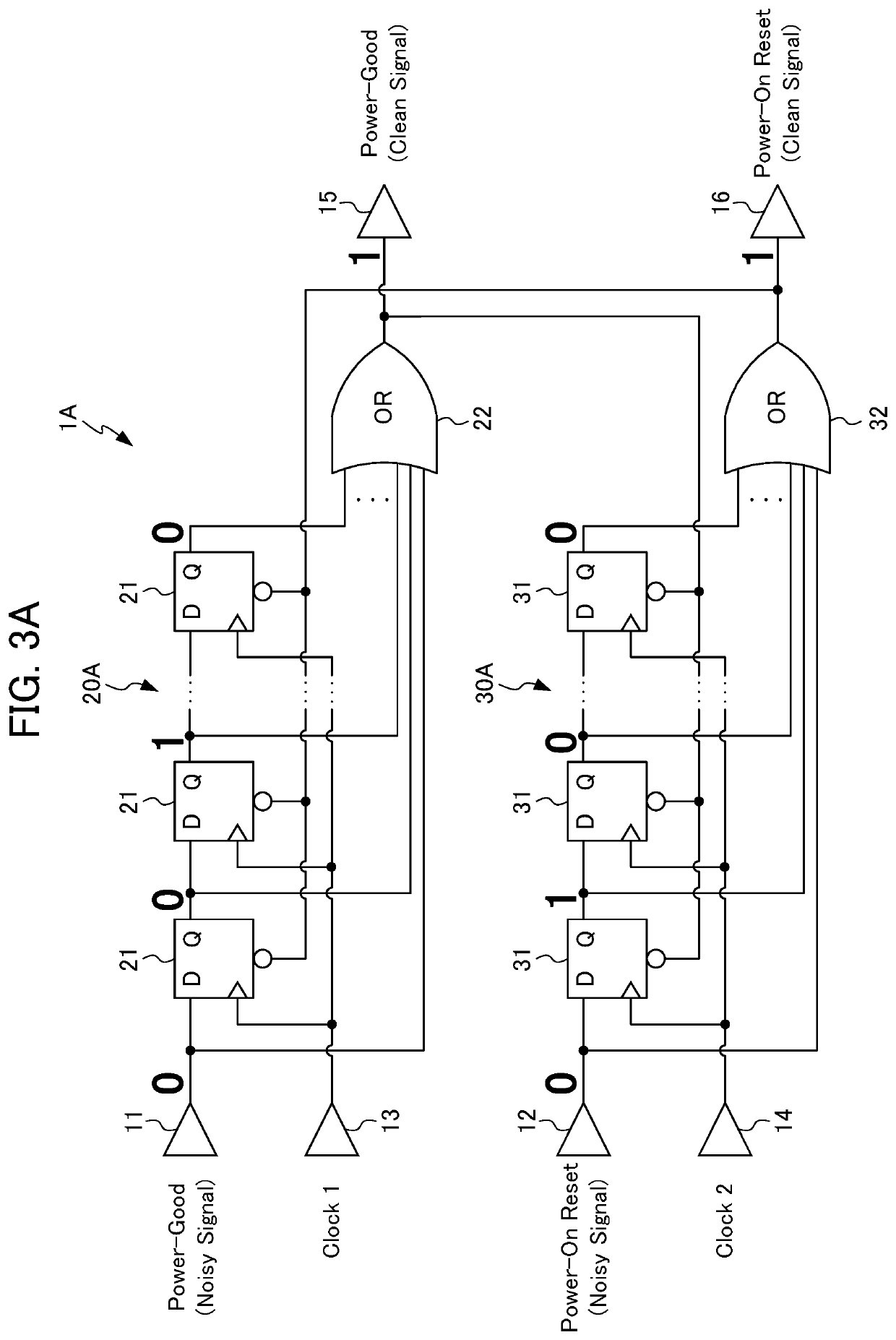

Glitch removal circuit and electronic device

ActiveUS20200280305A1Removing glitch noiseRemove noisePulse shapingVoltage/temperature variation compensationPower-on resetHemt circuits

A glitch removal circuit removes glitch noise contained in a Power-good signal and a Power-on Reset signal, and includes: a first glitch removal unit that operates according to a first clock signal, and removes glitch noise from a Power-good signal; and a second glitch removal unit that operates according to a second clock signal, and removes glitch noise from a Power-on Reset signal, in which the first glitch removal unit is configured so as to be initialized according to an output signal of the second glitch removal unit, and the second glitch removal unit is configured so as to be initialized according to an output signal of the first glitch removal unit.

Owner:FANUC CORP

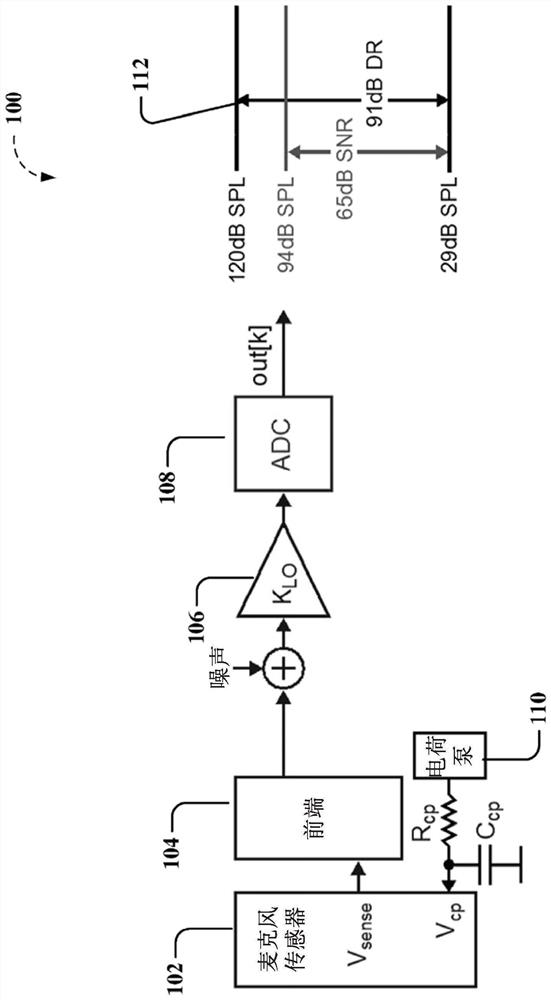

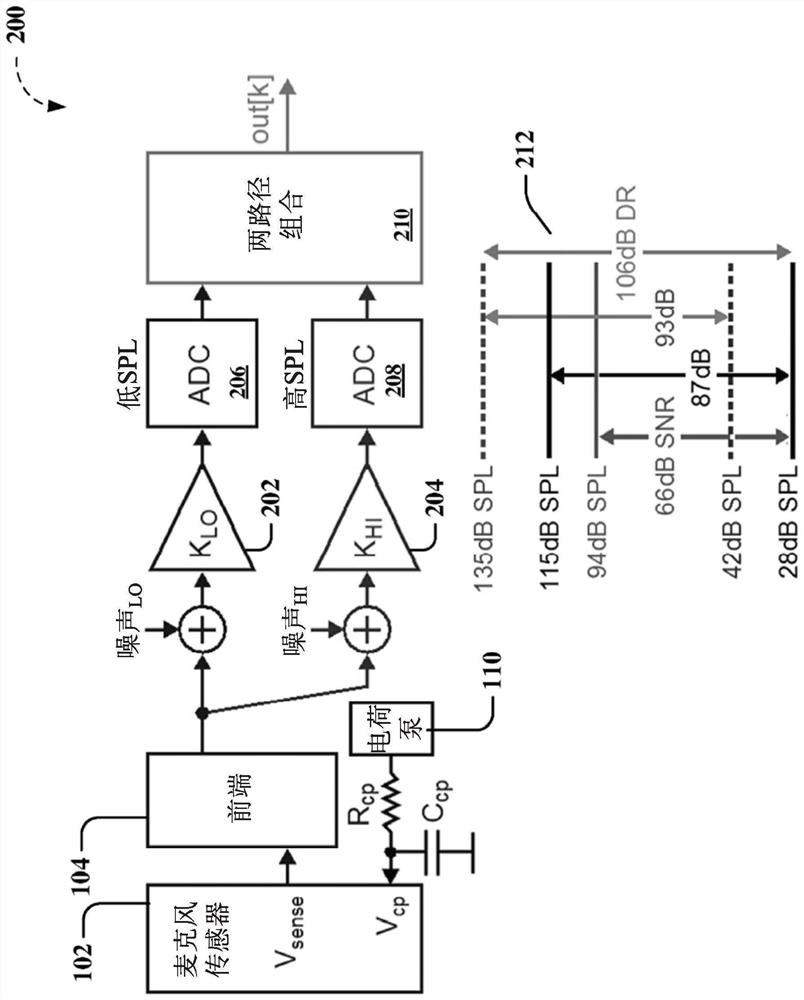

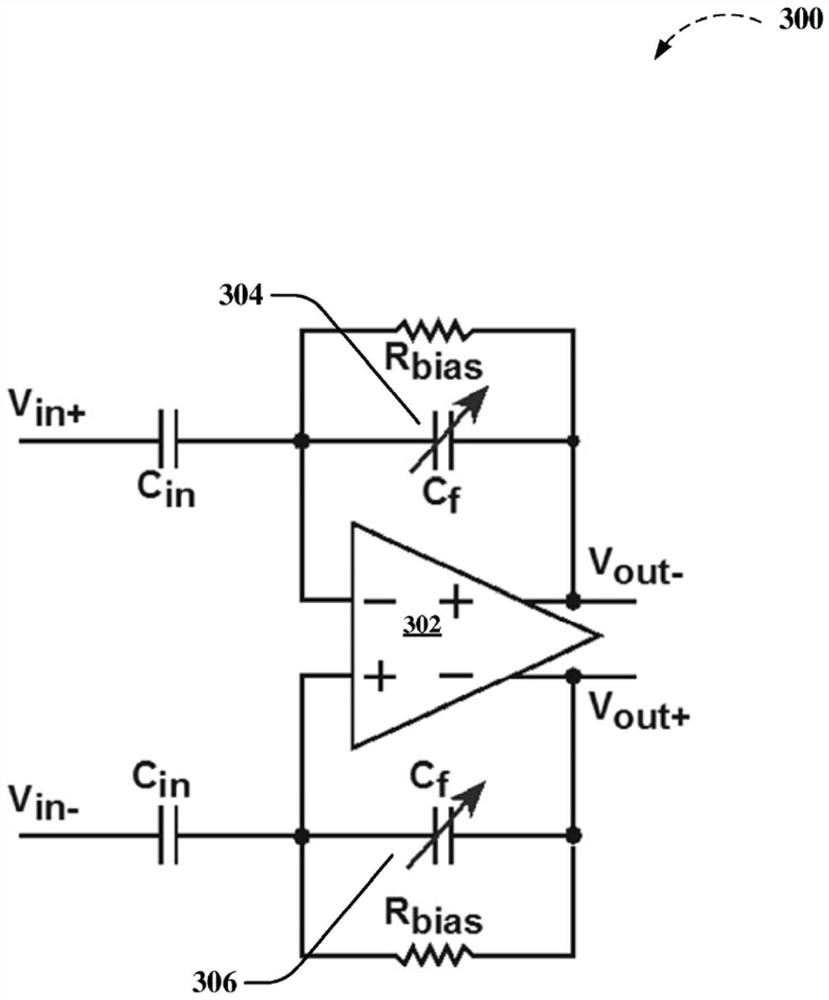

Adaptive analog to digital converter (ADC) multipath digital microphones

Exemplary multipath digital microphone described herein can comprise exemplary embodiments of adaptive ADC range multipath digital microphones, which allow low power to be achieved for amplifiers or gain stages, as well as for exemplary adaptive ADCs in exemplary multipath digital microphone arrangements described herein, while still providing a high DR digital microphone systems. Further non-limiting embodiments can comprise an exemplary glitch removal component configured to minimize audible artifacts associated with the change in the gain of the exemplary adaptive ADCs.

Owner:INVENSENSE

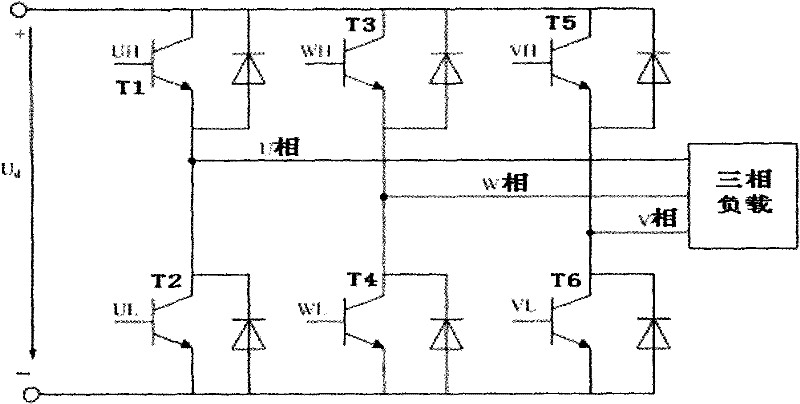

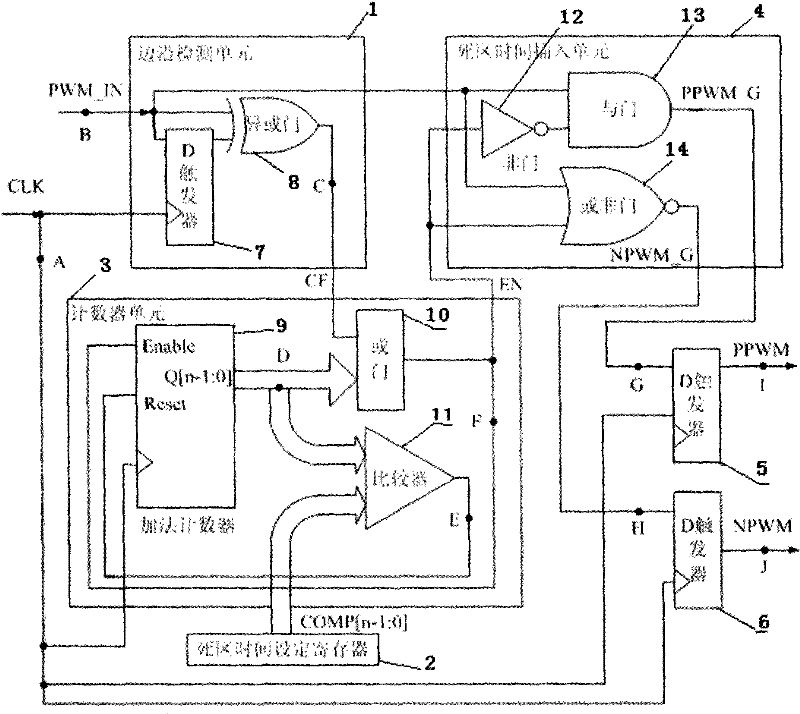

PWM (Pulse-Width Modulation) complementary output method of inserting variable dead zone time

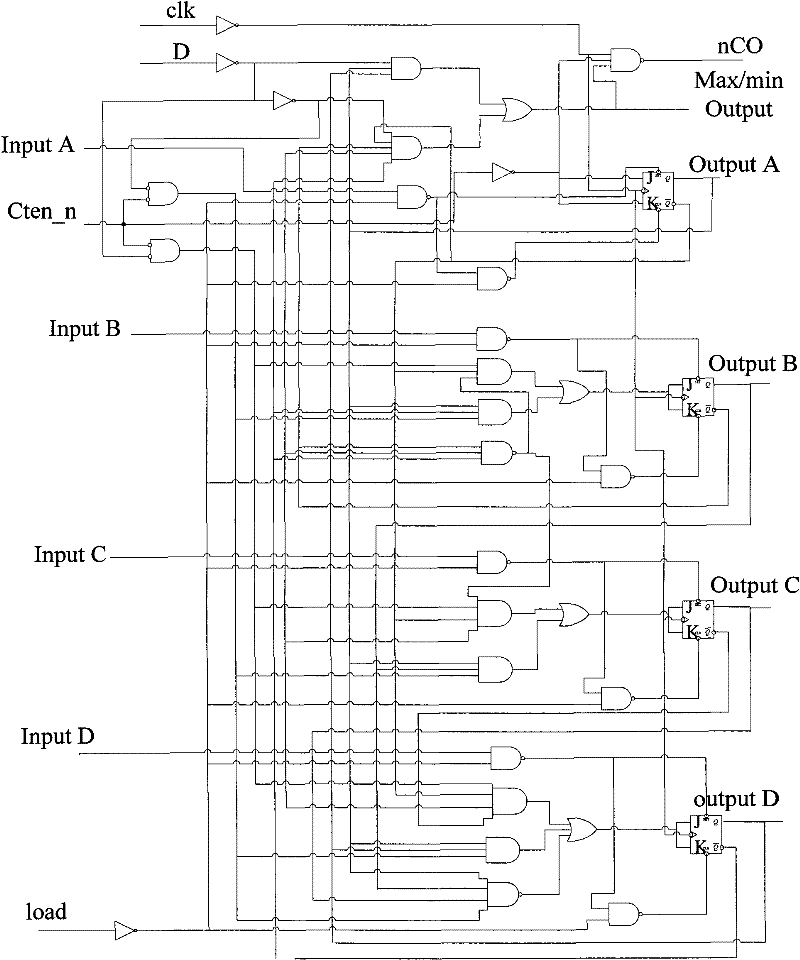

The invention relates to a PWM (Pulse-Width Modulation) complementary output method of inserting variable dead zone time, which belongs to a control technology of a three-phase bridge type inverter circuit and is realized by three groups of same control circuits. Each group of circuit comprises an edge detecting unit, a dead zone time setting register, a counting unit, a dead zone time inserting unit and two D triggers for outputting complementary signals. The edge detecting unit firstly detects a PWM input signal, and generates an edge change mark signal CF when the waveform changes. A 'or' relation is established among phases of an output value of a counter, and then a 'or' relation is established with the CF to obtain an enabling control signal of the counter. In the counter unit, whena counted value is equal to a set value, the counted value is synchronized and reset to 0. The dead zone time inserting unit modifies the PWM input signal according to EN (European Norm), the dead zone is inserted into the PWM input signal, and burr is eliminated by the D trigger to obtain a complementary PWM signal to output. The invention has simple circuit, and is suitable to be integrated to a microcontroller provided with a PWM waveform generator, and the dead zone time can be adjusted in a wide range.

Owner:SHANDONG UNIV

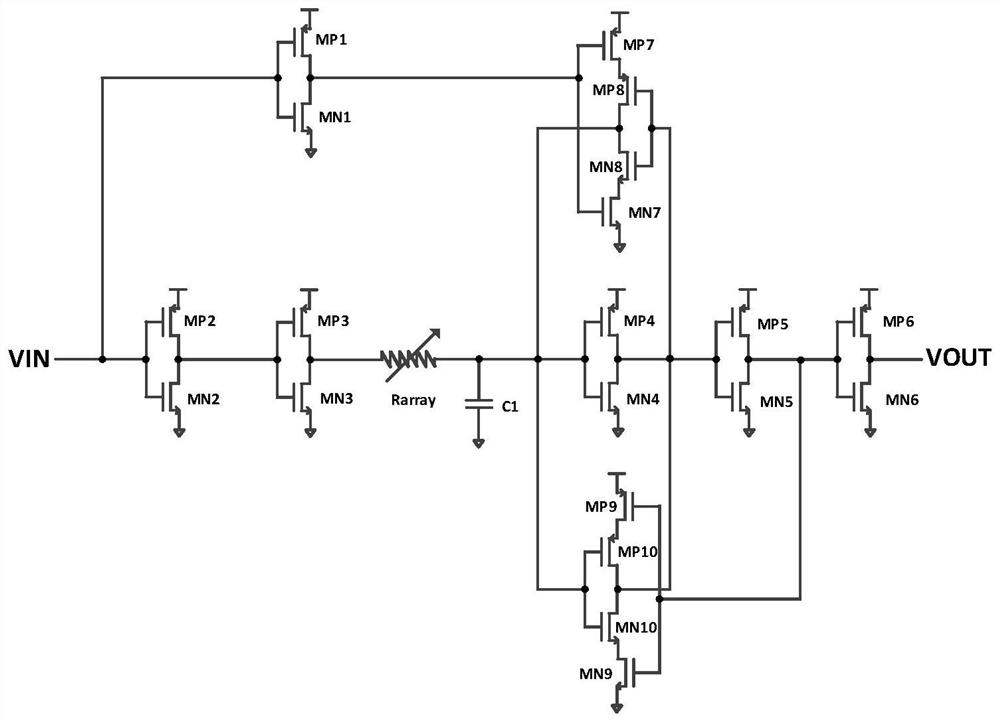

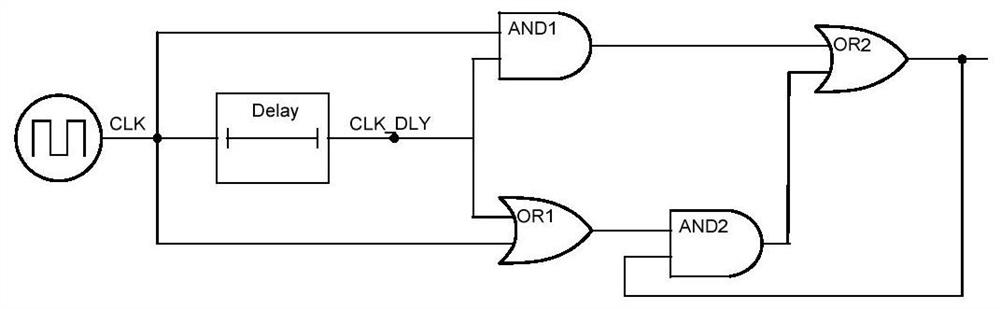

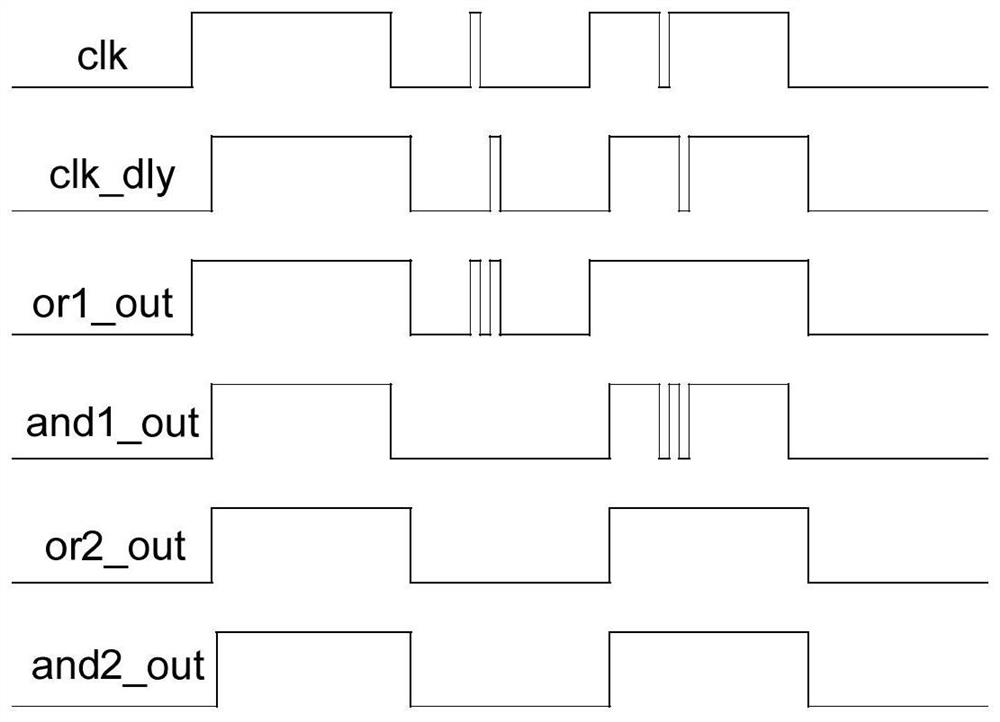

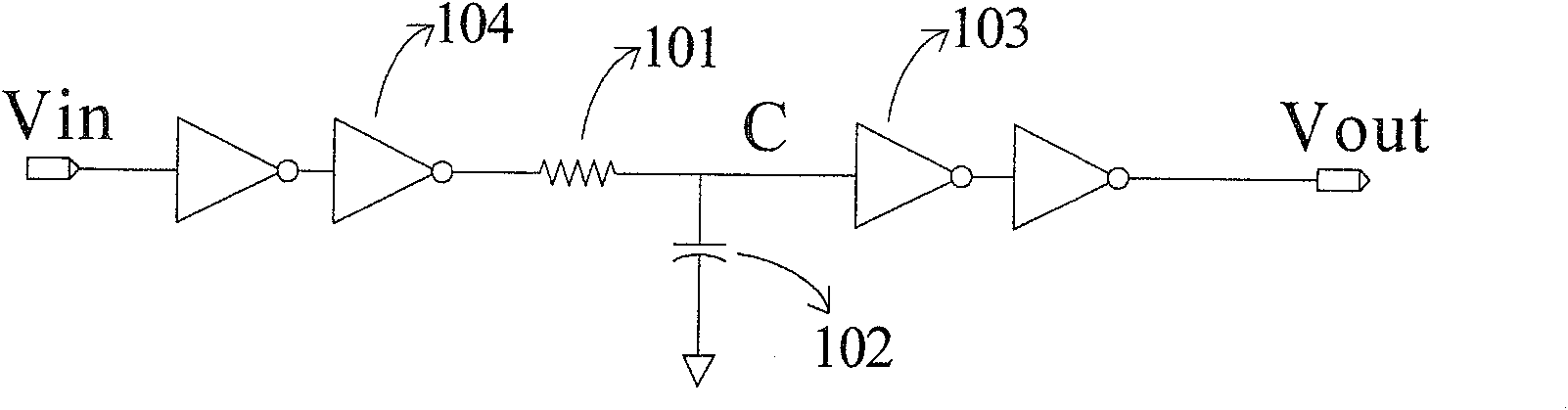

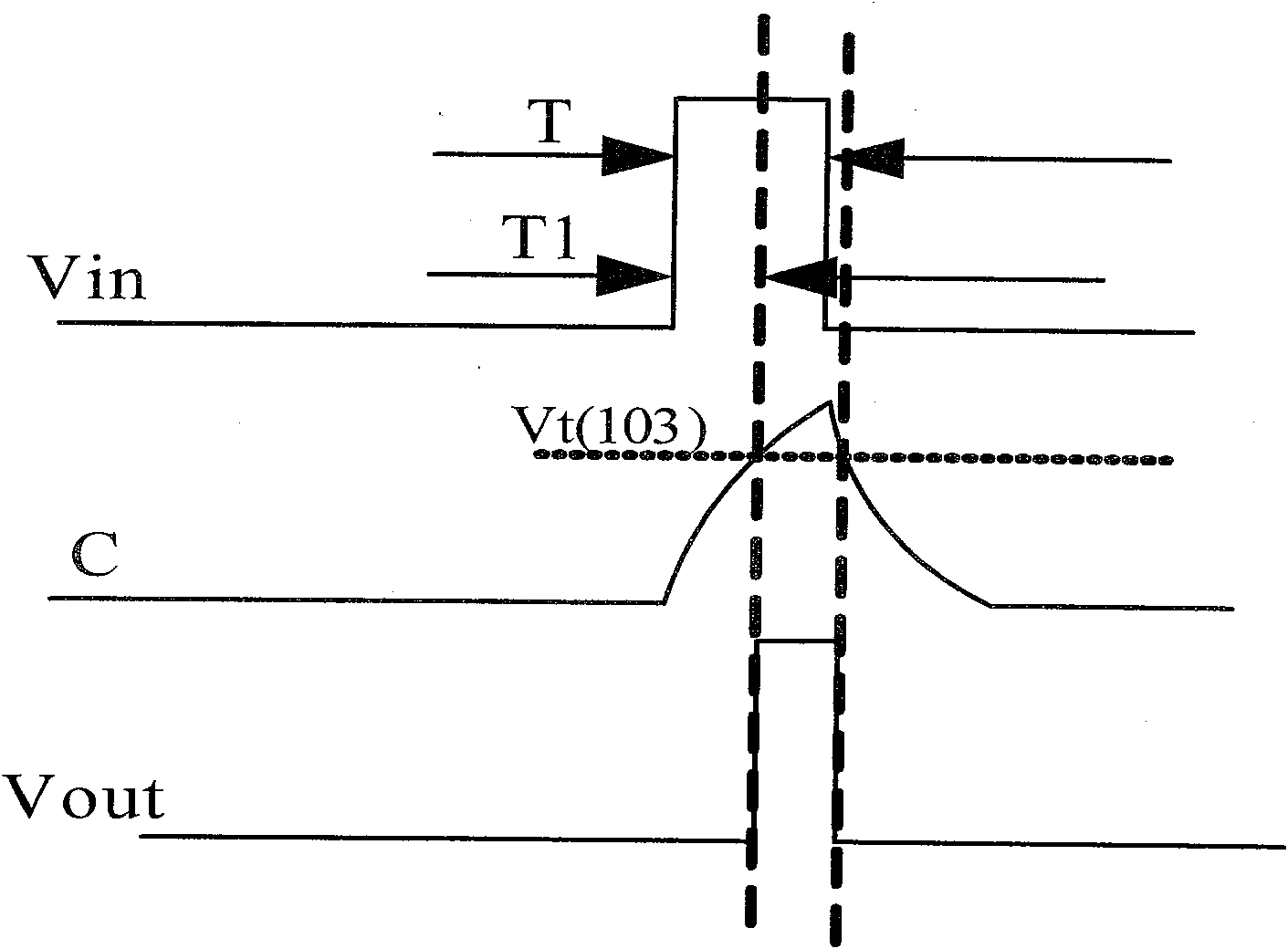

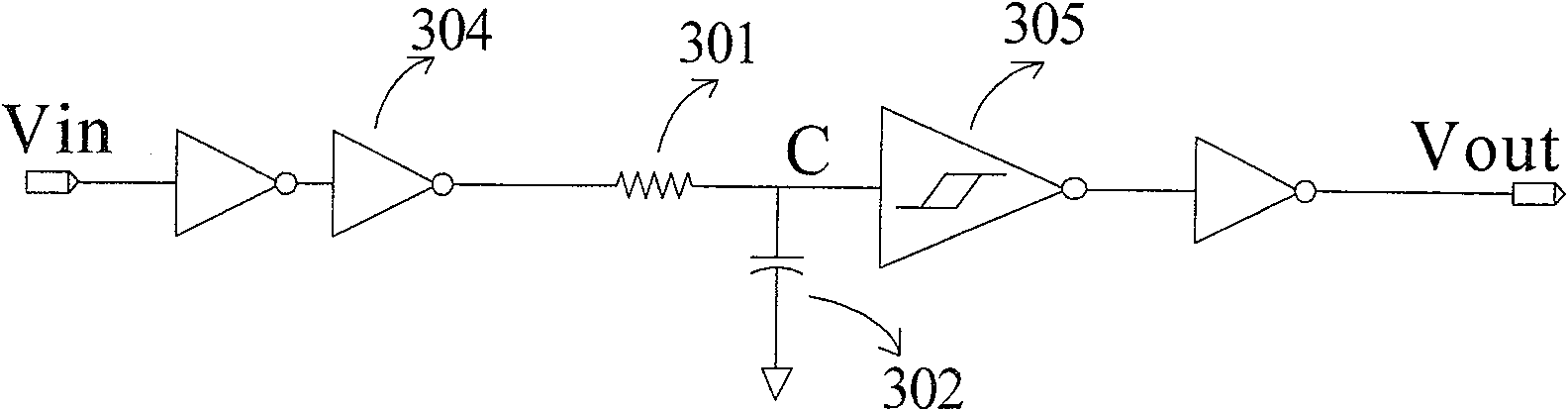

Digital signal glitch elimination circuit and glitch elimination method

PendingCN112003593AEliminate bindingLogic circuits characterised by logic functionPulse manipulationCapacitanceHemt circuits

The invention provides a digital signal glitch elimination circuit, which comprises an analog elimination circuit, and is characterized in that the analog elimination circuit comprises an MOS inverter, an MOS nested inverter, a resistor array and a capacitor. The output end of the analog elimination circuit is electrically connected with a digital elimination circuit, a signal link unit and a logic processing unit are arranged in the digital elimination circuit, the signal link unit is used for carrying out delay processing on an input digital signal, and the logic processing unit is used forcarrying out logic operation on the digital signal subjected to delay processing. The analog elimination circuit is used for eliminating digital signal glitches whose glitch time width is smaller thanan input clock signal period, and the digital elimination circuit is used for eliminating digital signal glitches whose glitch time width is larger than the input clock signal period and outputting the digital signal glitches as OUT. Through the combination of the analog elimination circuit and the digital elimination circuit, burrs generated in the digital signal transmission process are eliminated, and the circuit has the advantages of being capable of eliminating high-level and low-level burrs at the same time, programmable in burr elimination time width, small in area and the like.

Owner:SHANGHAI CHIPANALOG MICROELECTRONICS LTD

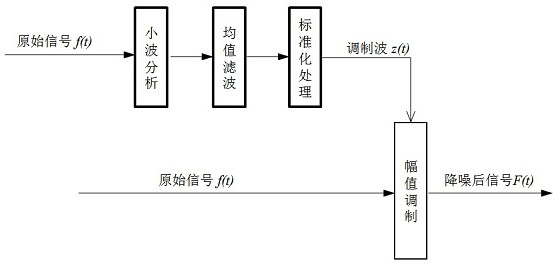

Digital signal processing method for eliminating glitch interference signals

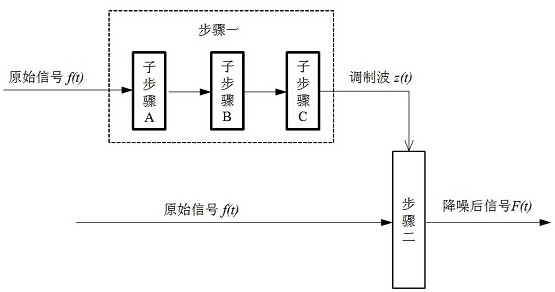

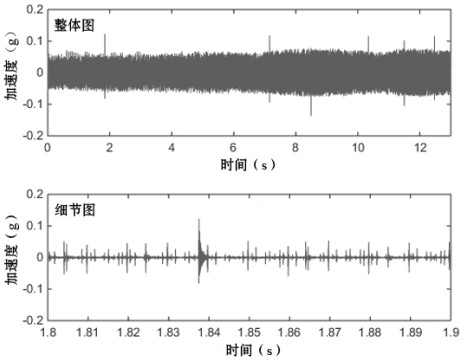

PendingCN112329591AAvoid direct deliveryCharacter and pattern recognitionDigital signal processingPhase difference

The invention discloses a digital signal processing method for eliminating glitch interference signals, and the method comprises the steps: sequentially carrying out the wavelet analysis, mean filtering and standardization of an original signal, and enabling an obtained result signal to serve as a modulation wave. And then the modulated wave is used for amplitude modulation of an original signal,amplitude modulation not only effectively suppresses the amplitude of a glitch interference signal in the original signal, but also does not generate a phase difference, so that the phase of the signal after noise reduction is consistent with that of the original signal. The noise reduction effect of the method not only gives full play to the good effect of mean filtering in the aspect of eliminating glitch signals, but also avoids the direct transmission of waveform phase difference generated by mean filtering, so that the phase of the denoised signal is consistent with that of the original signal. Therefore, the method has no phase difference between the denoised signal and the original signal.

Owner:CHENGDU KAITIAN ELECTRONICS

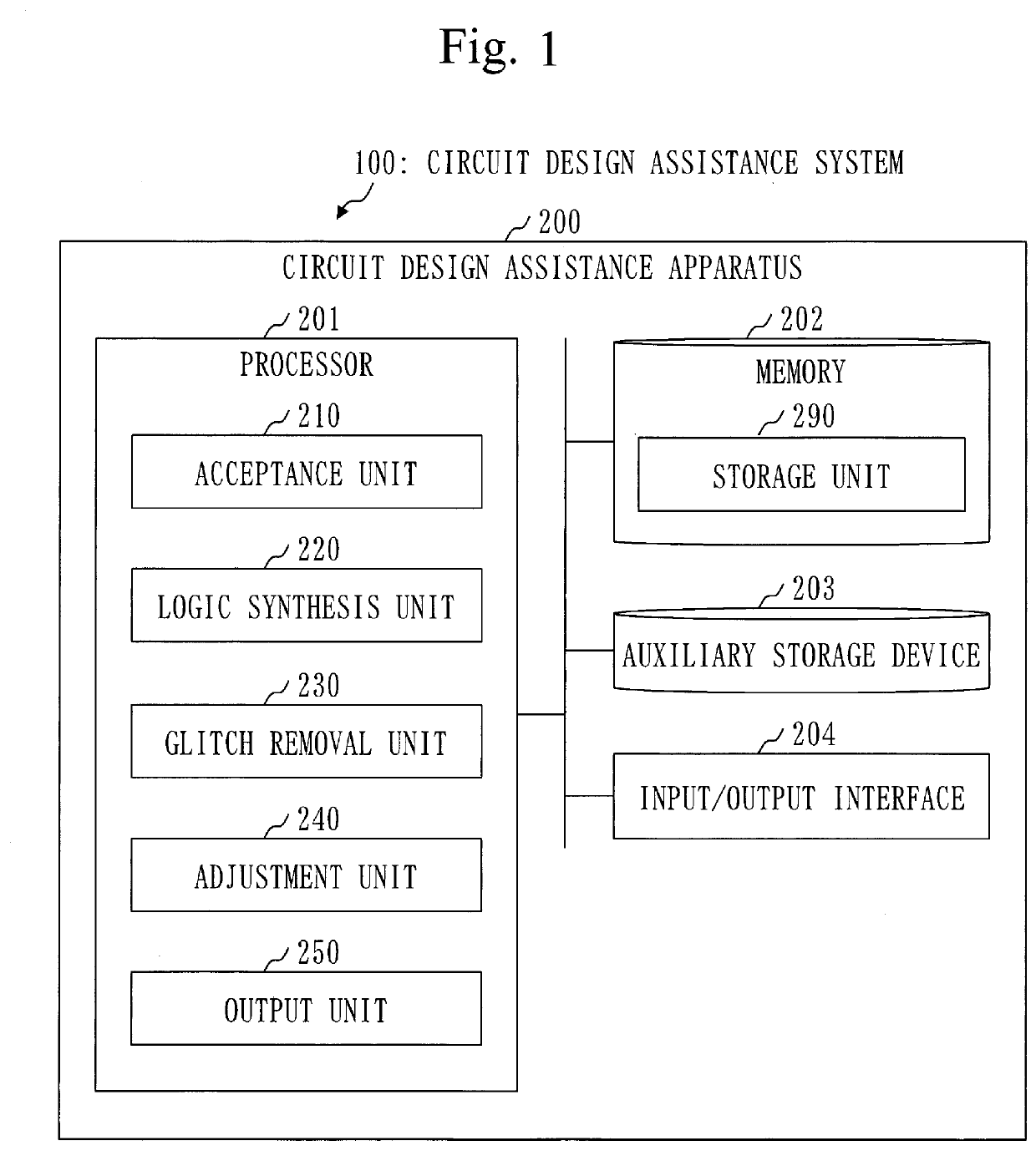

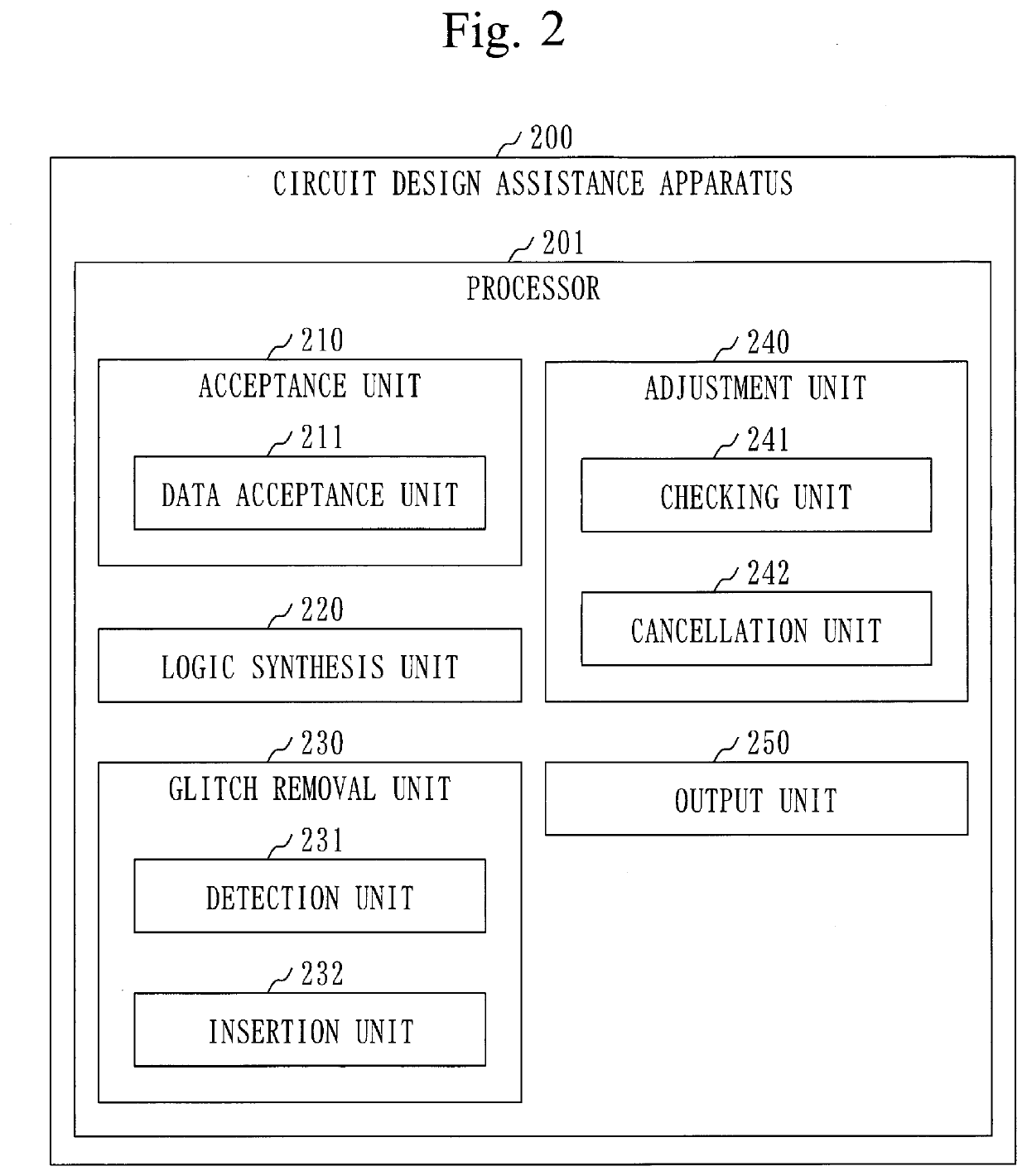

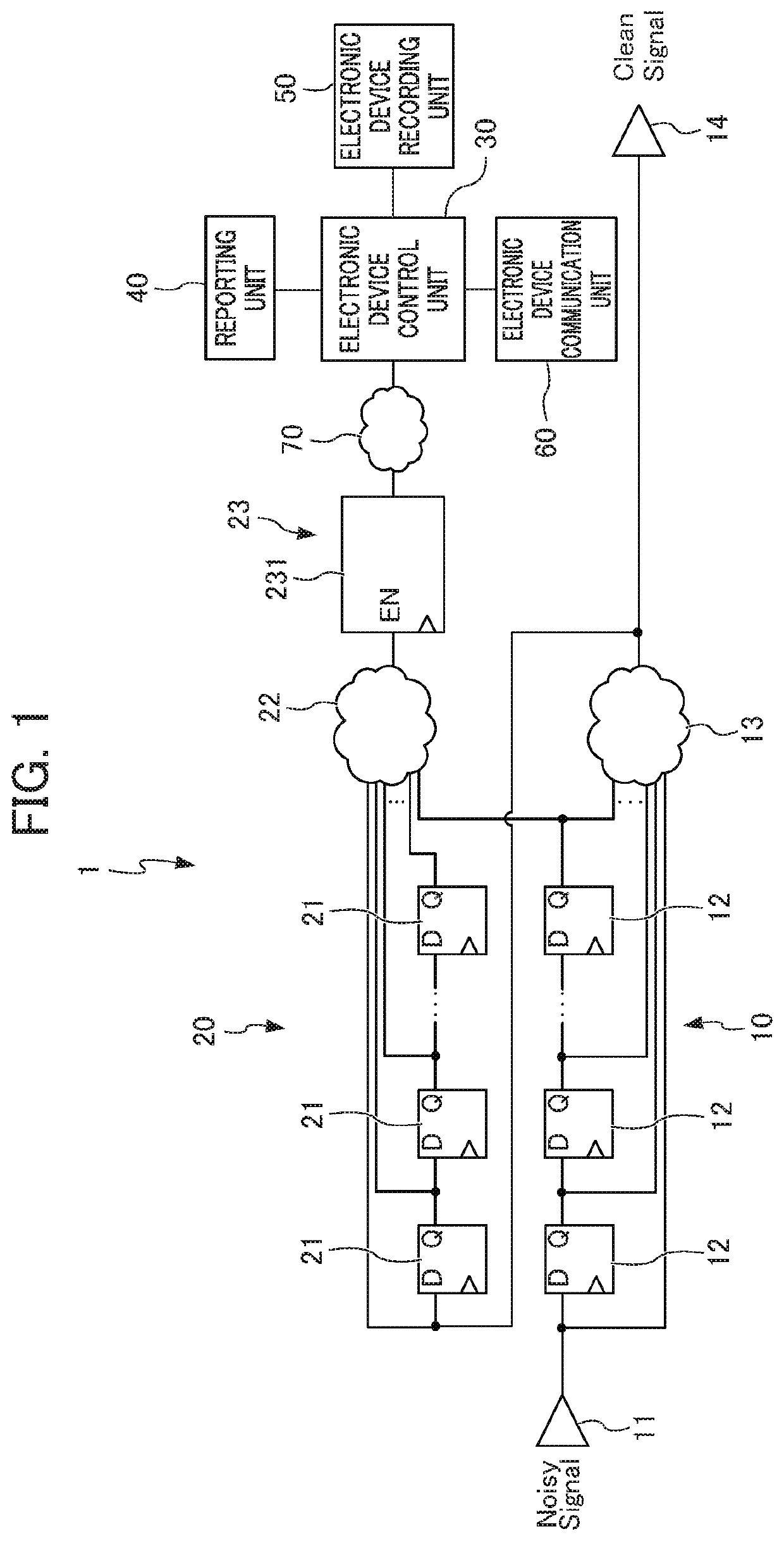

Circuit design assistance system and computer readable medium

ActiveUS20210224448A1Eliminate burrsCAD circuit designSpecial data processing applicationsSoftware engineeringHemt circuits

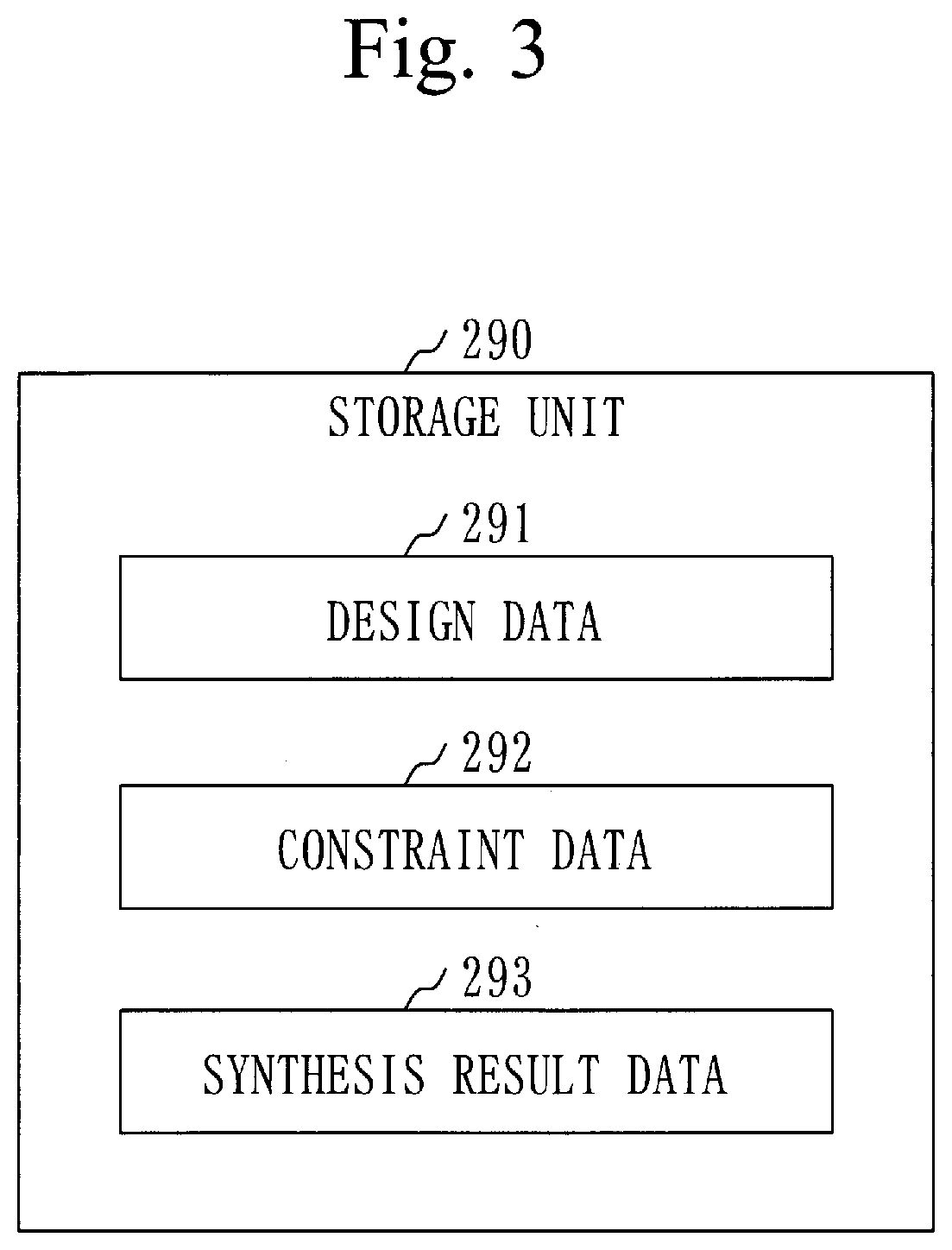

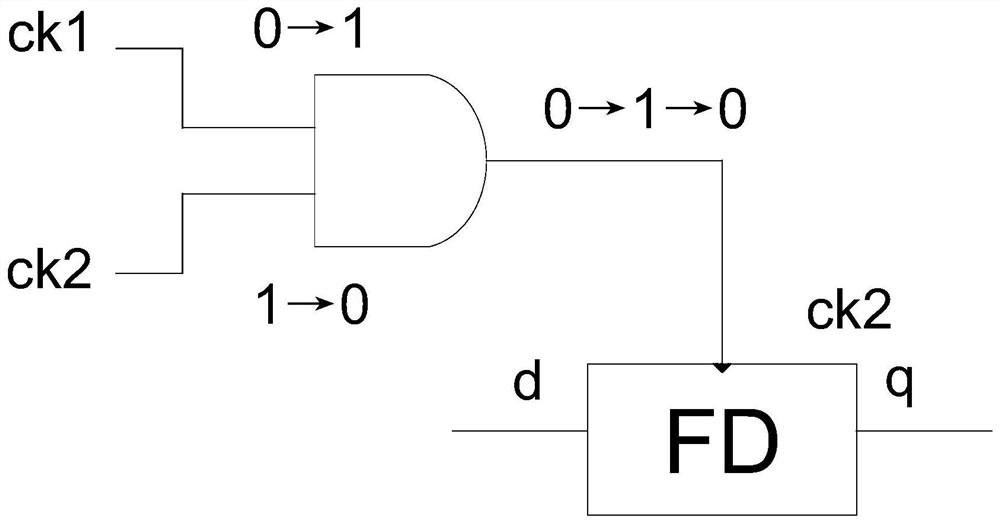

A detection unit (231) detects, based on synthesis result data obtained by logic synthesis on design data of a target circuit, a predicted place where a glitch is predicted to occur in the target circuit. An insertion unit (232) inserts a glitch removal circuit in an output side of the predicted place by making a change to at least one of the synthesis result data and the design data.

Owner:MITSUBISHI ELECTRIC CORP

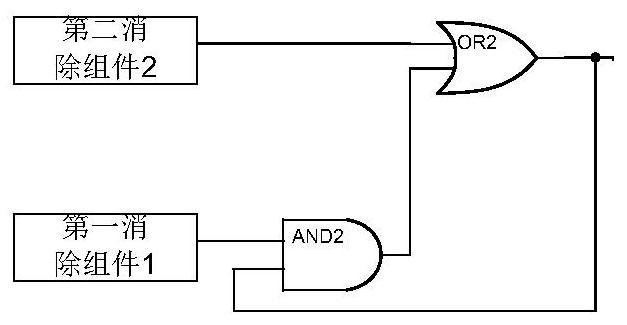

Burr eliminating circuit

ActiveCN113676163AAvoid it happening againEliminate burrsPulse manipulationSoftware engineeringInverter

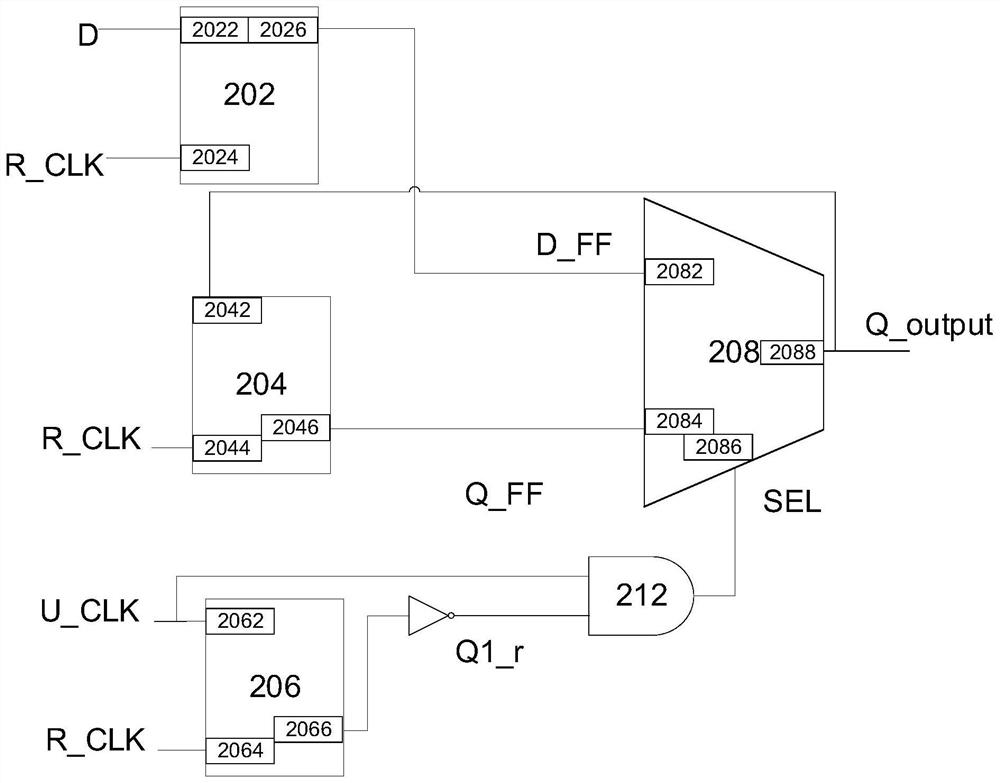

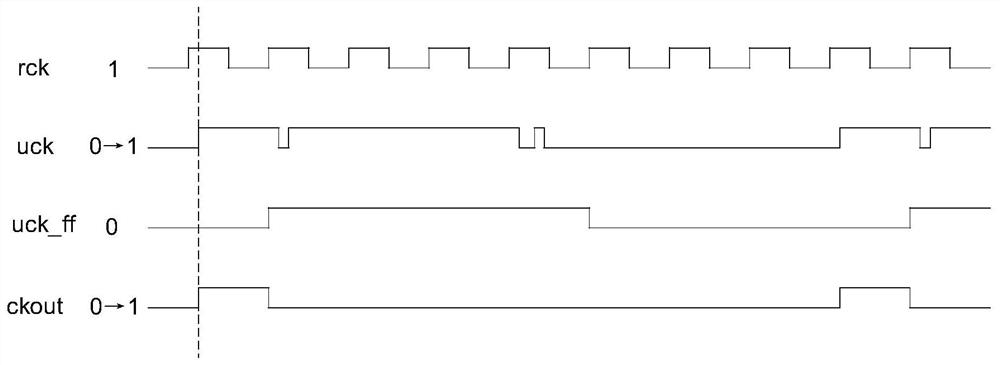

The invention provides a burr eliminating circuit, which comprises a first latch, a second latch, a selector and a third latch, and is characterized in that the selector comprises a first input end, a second input end, a gating input end and a gating output end, wherein the first latch comprises a first data input end for receiving data, a first clock input end for receiving a first clock, and a first data output end connected to the first input end; the second latch comprises a second data input end connected with the gating output end, a second clock input end used for receiving the first clock, and a second data output end connected to the second input end; the third latch comprises a third data input end used for receiving the second clock, a third clock input end used for receiving the first clock and a third data output end connected to a phase inverter, the phase inverter and the second clock serve as input of an AND gate unit, and the output end of the AND gate unit is connected to the gating input end.

Owner:芯华章科技股份有限公司

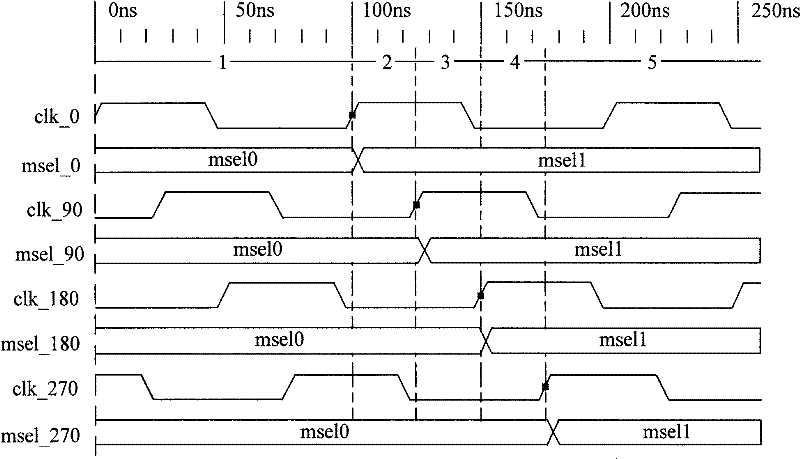

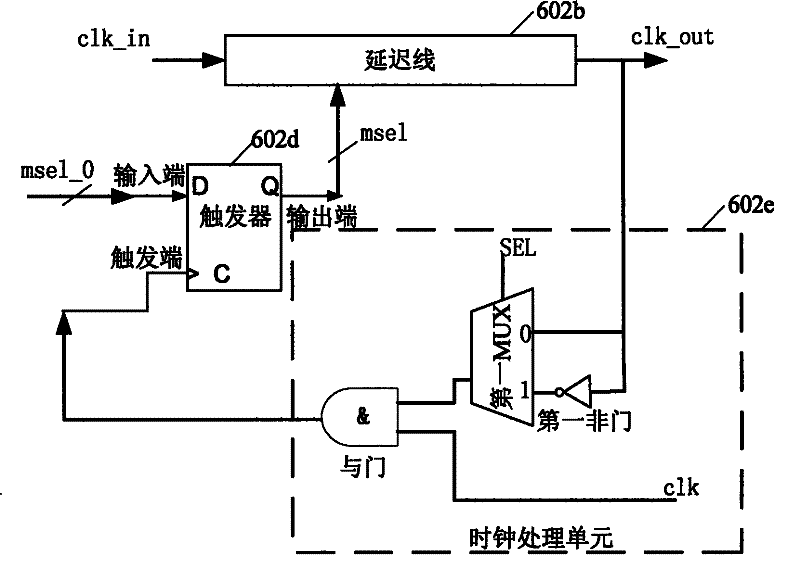

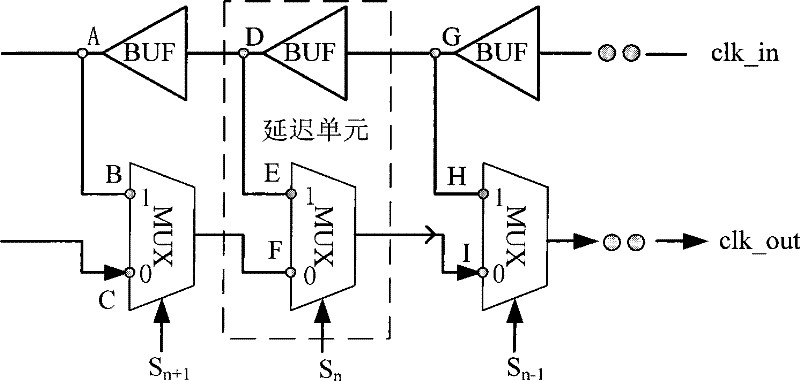

Digital phase-locked loop and method for burr elimination

The invention discloses a digital phase-locked loop and a method for eliminating spike, belonging to electronic technology field. The digital phase-locked loop includes a trigger and delay lines. the method includes the steps that the trigger receives a delayed clock signal outputted by the delay line from a triggering end, and receives signals of a first delay unit selection end in the delay line from an input end, wherein the selection end of the first delay unit is on a state 1 before triggering the trigger; the trigger samples the signal of the first delay unit selection end using delayedclock signal, and outputs signal after sampling to the selection end of a second delay unit in the delay line, wherein the selection end of the second delay unit is on the state 1 after triggering the trigger. By means of sampling the signal of the selection end of the first delay unit using delayed clock signal by the trigger and using the sampling signal as the signal of the selection end of the second delay unit, the invention avoids the spike caused by jump variation while updating delay module on the clock edge.

Owner:HUAWEI TECH CO LTD

Method and device for eliminating signal noise

The invention discloses a method and device for eliminating signal noise, the device includes a backward-forward counter and a signal output circuit; the method for eliminating signal noise has the following steps: 1) setting valid and invalid level counting thresholds; 2) receiving the signal with signal noise needed to be eliminated by the backward-forward counter and beginning to count; when the rising edge of each clock arrives, if the signal is an valid electrical level, adding one on the current counting value, otherwise subtracting one; and the counting value does not increase / decreaseuntil it reaches to a valid / invalid level counting threshold; meanwhile, the signal output circuit outputs signal without noise according to the counting value: when the rising edge of each clock arrives, if the counting value is a valid / invalid level counting threshold, then outputting valid / invalid level; if the counting value is between the valid and invalid level counting threshold, keeping the output equal to the output of the previous clock. The device provided by the invention can thoroughly eliminate wide noise, stably output signal without noise, and which is simple to be realized, thereby improving reliability of the system.

Owner:ZTE CORP

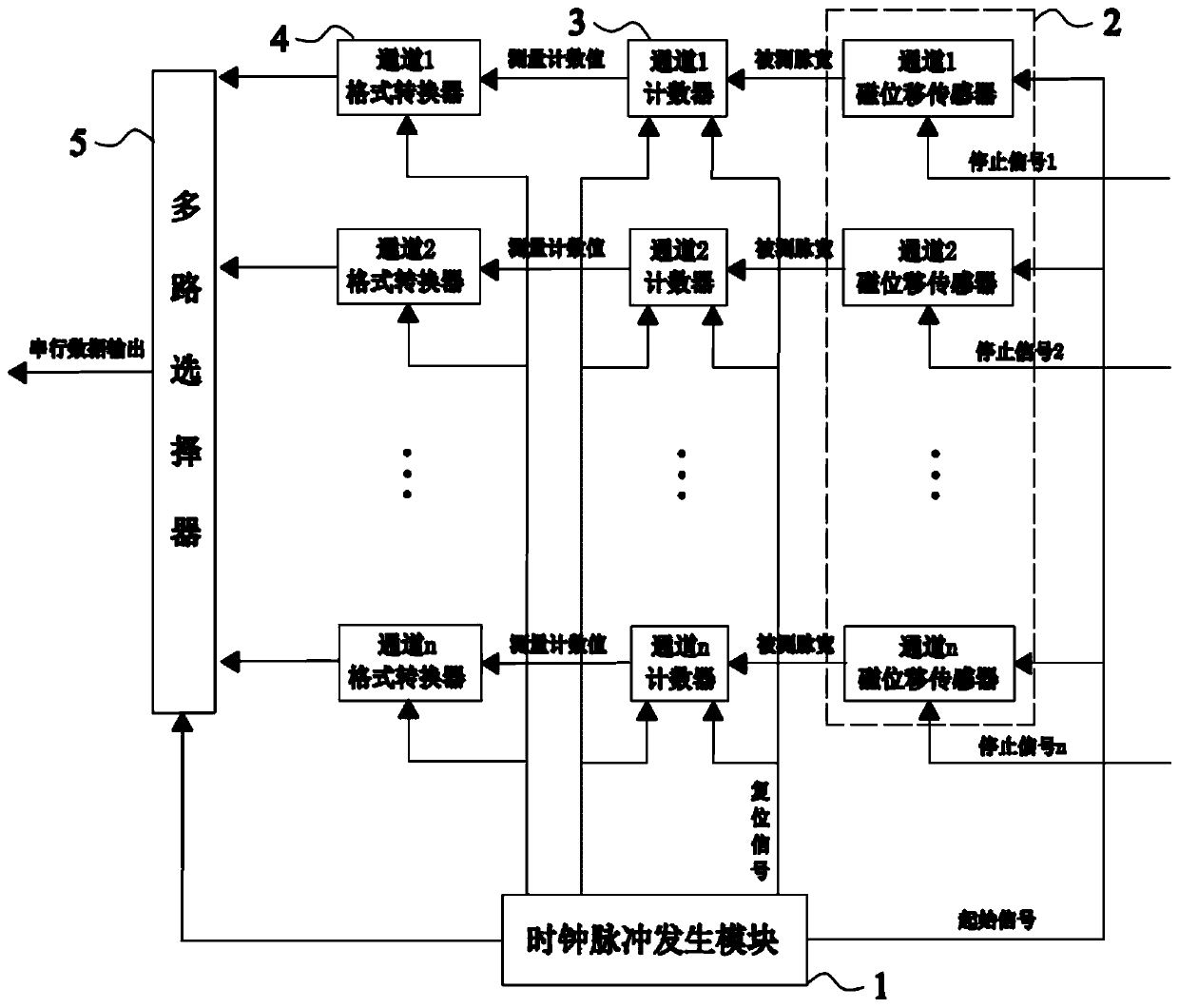

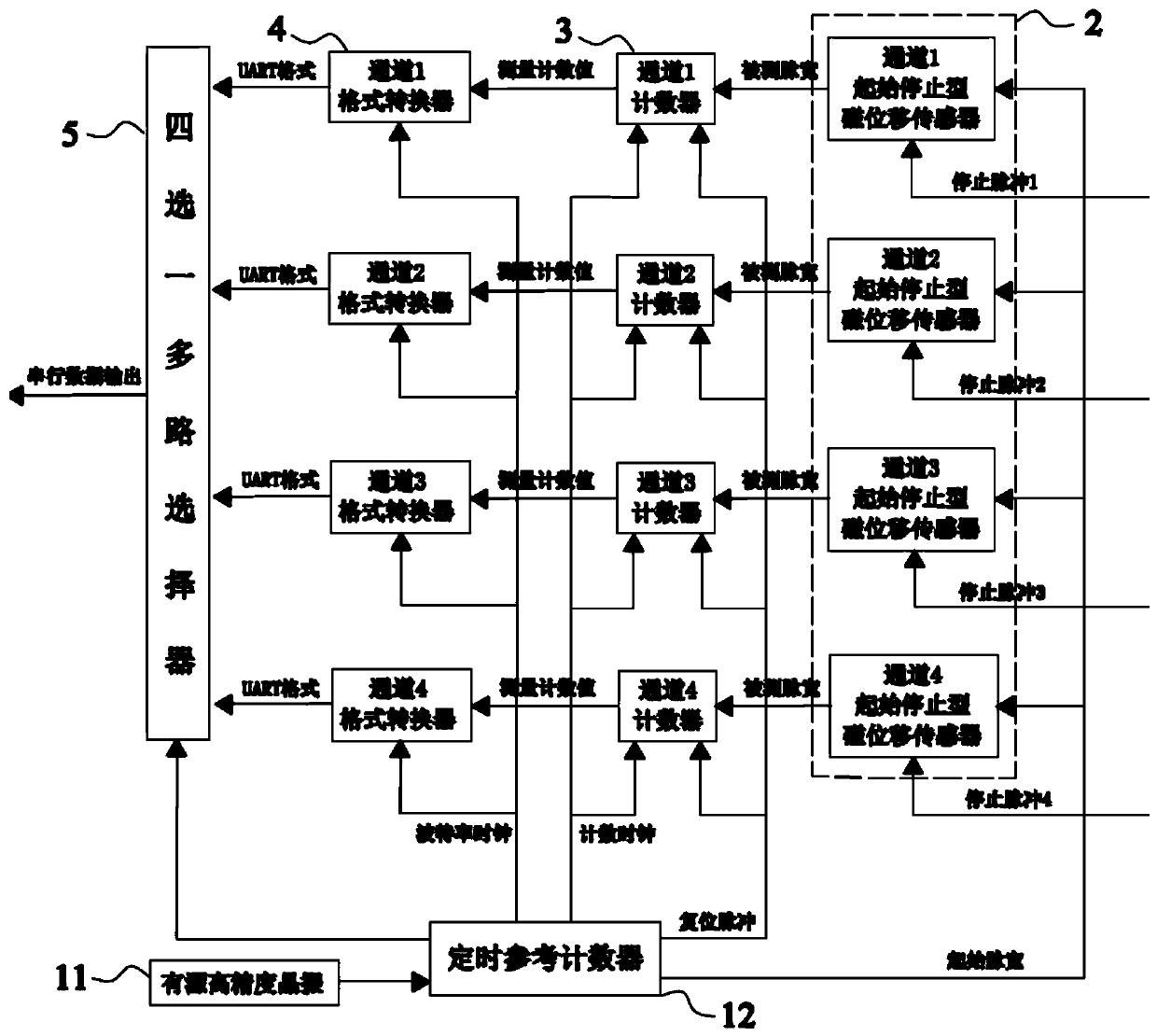

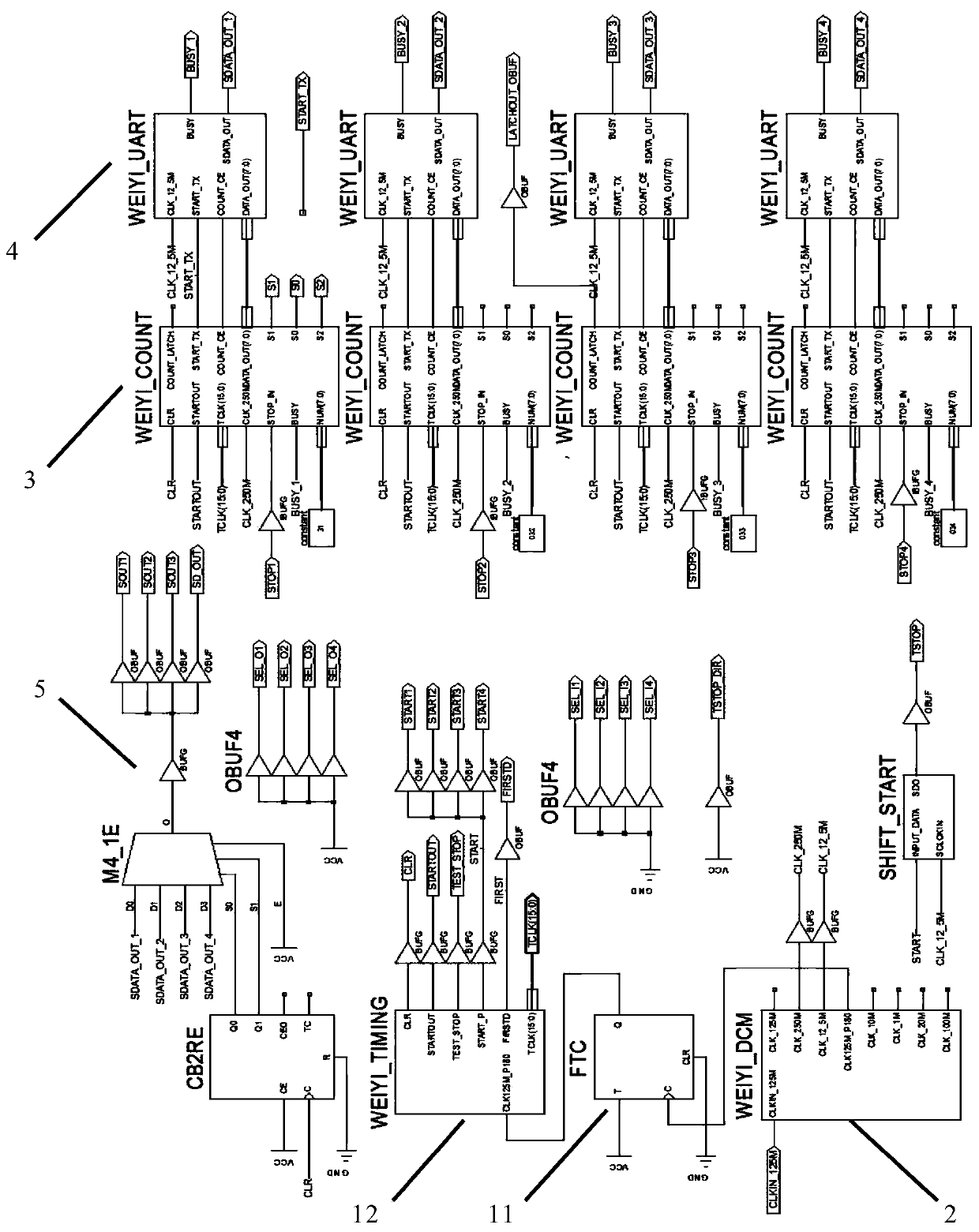

A system for eliminating burrs of magnetic displacement sensors in rail status monitoring

ActiveCN108917572BSynchronous Logic TimingHigh measurement accuracyUsing electrical meansComplete dataData acquisition

The present invention provides a system for eliminating a burr phenomenon of a magnetic displacement sensor during rail state monitoring. The entire system can be integrated on an FPGA chip; each magnetic displacement sensor is controlled by a clock pulse generation module to carry out data collection in different monitoring periods, and convert the format and complete data output in the next monitoring period. Through the above design, the delay and synchronization in the measurement engineering can be strictly controlled, so that the magnetic displacement measurement accuracy only depends onthe high-speed, high-stability, high-precision clock reference and design algorithm, thereby avoiding the problems of complexity, instability, temperature drift and requirement for calibration when the traditional analog magnetic displacement sensor processes the low-level signals, and greatly improving the measurement precision. Since the whole system is synchronized to one clock, the logic timing sequences in the system are synchronized, thereby realizing time-sharing serial output of multichannel data in different measurement periods, which can prevent logic competition and remove the burrs.

Owner:南京城铁信息技术有限公司

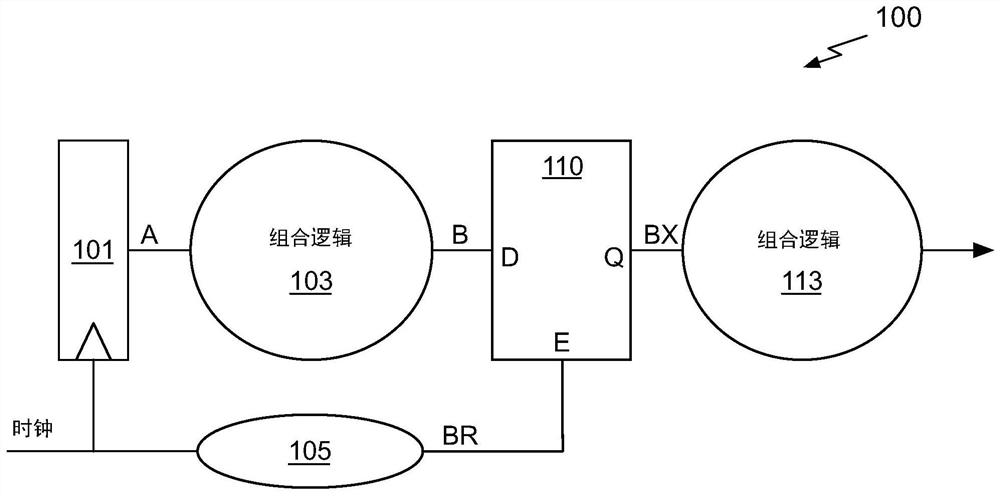

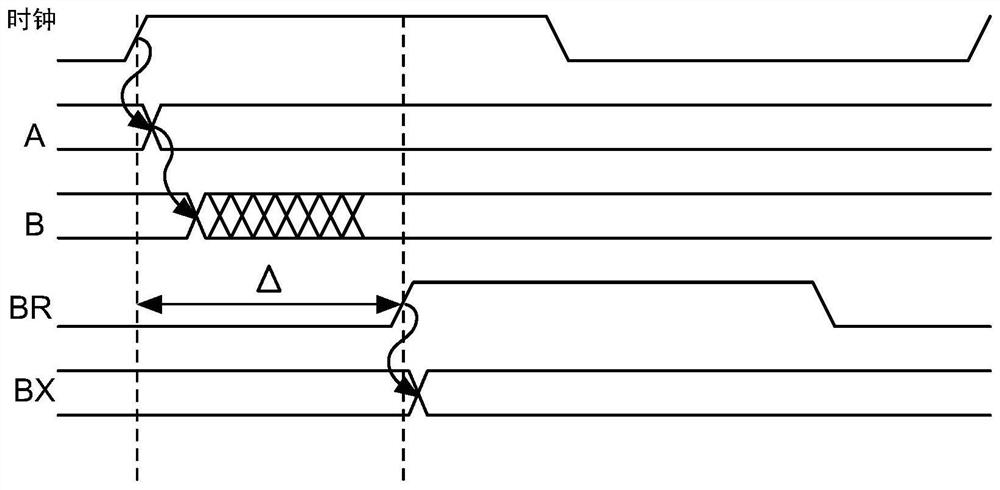

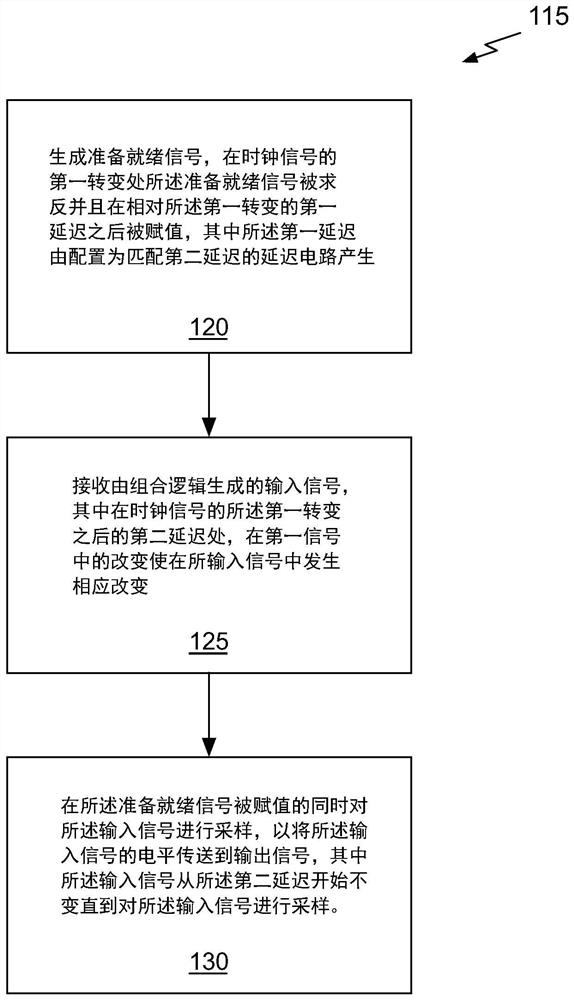

Glitch-free multiplexer and glitch transmission prevention

When a signal glitches, logic receiving the signal may change in response, thereby charging and / or discharging nodes within the logic and dissipating power. Providing a glitch-free signal may reduce the number of times the nodes are charged and / or discharged, thereby reducing the power dissipation. A technique for eliminating glitches in a signal is to insert a storage element that samples the signal after it is done changing to produce a glitch-free output signal. The storage element is enabled by a 'ready' signal having a delay that matches the delay of circuitry generating the signal. The technique prevents the output signal from changing until the final value of the signal is achieved. The output signal changes only once, typically reducing the number of times nodes in the logic receiving the signal are charged and / or discharged so that power dissipation is also reduced.

Owner:NVIDIA CORP

Glitch removal circuit and electronic device

PendingCN111628754APulse shapingVoltage/temperature variation compensationPower-on resetHemt circuits

Owner:FANUC LTD

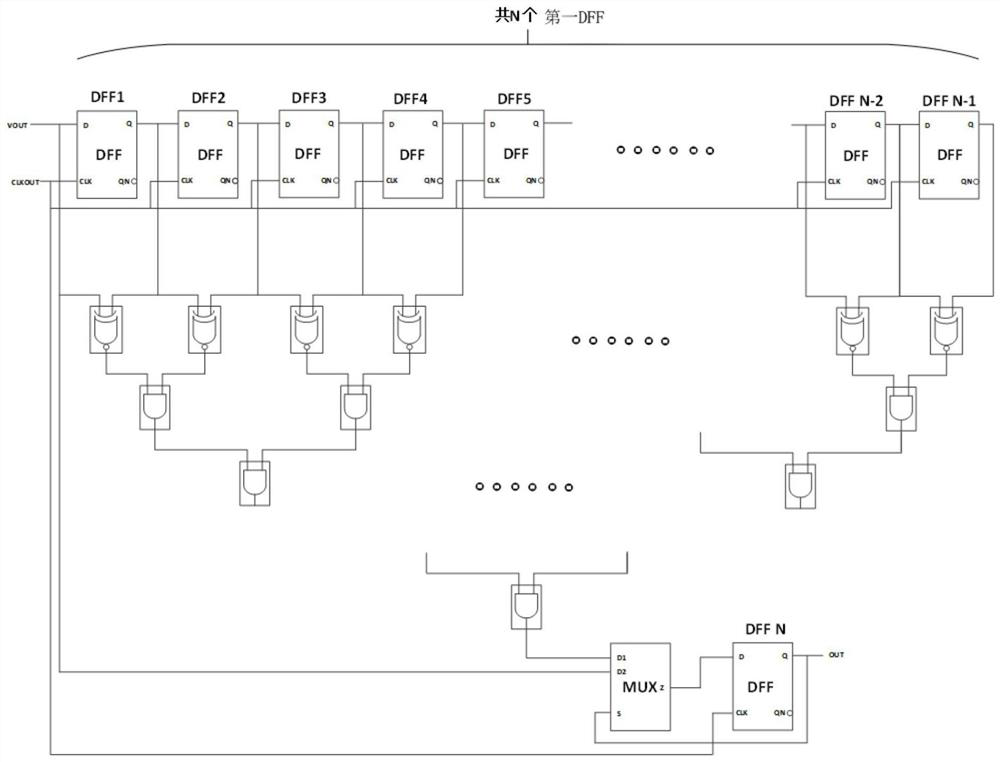

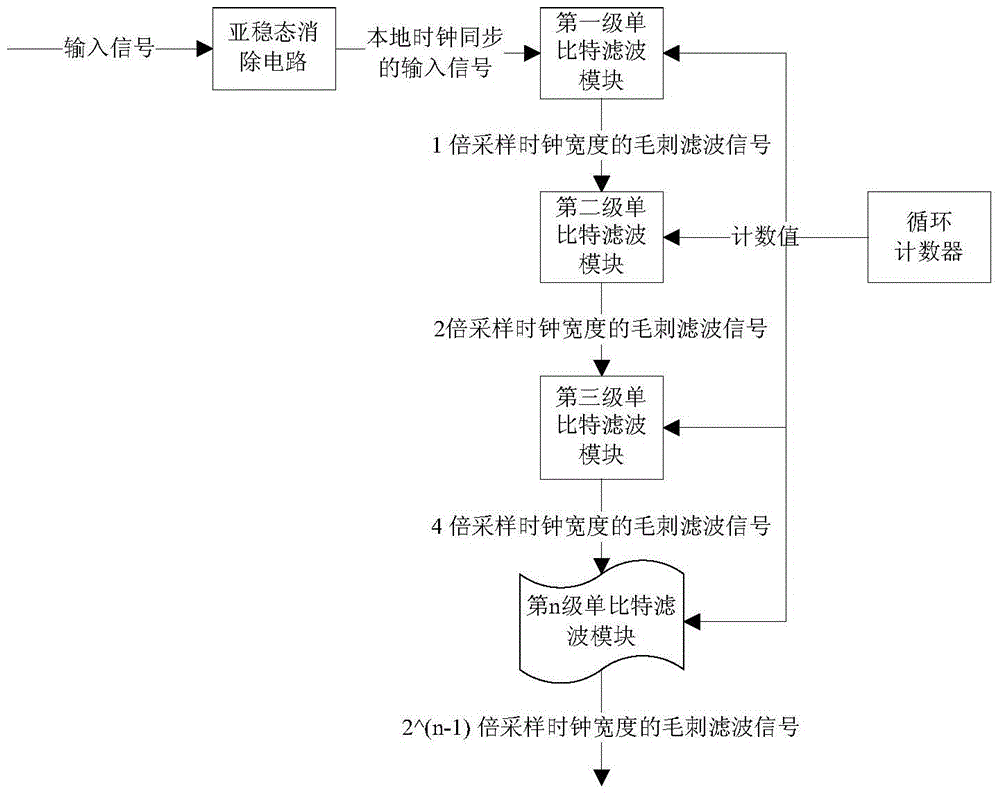

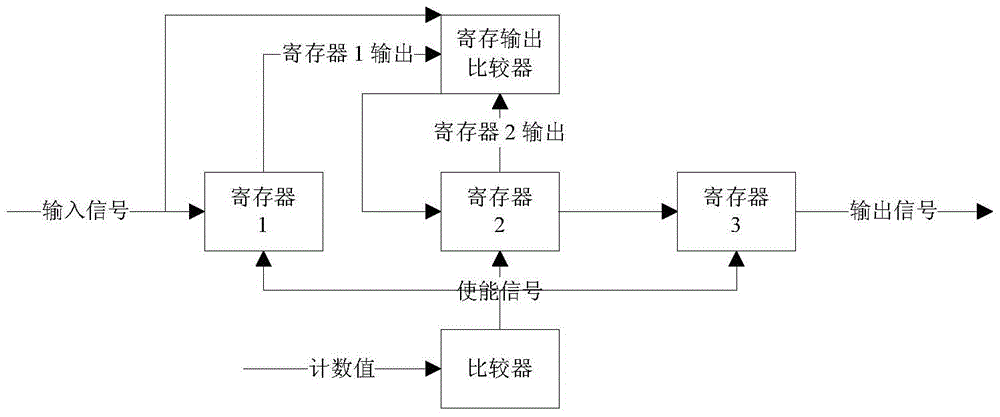

A Serial Cascaded Single-bit Filter Structure for Eliminating Glitch Signals

ActiveCN104065361BPhase independentImprove general performancePulse shapingOriginal dataComputer module

The invention relates to a serially cascaded single-bit filter structure for eliminating spur signals, comprising: a serially cascaded single-bit filter module, a loop counter circuit, a metastable elimination circuit; a serially cascaded single-bit filter module The filter module further includes a first-level single-bit filtering module, a second-level single-bit filtering module, a third-level single-bit filtering module... an nth-level single-bit filtering module; The original data disturbed by the glitch signal is recovered from each sampled data, and the design of eliminating glitch signals of different widths is realized by cascading single-bit filters in series, and the pulse signals of different sampling clock widths are filtered out step by step; The traditional equal time interval sampling scheme cannot correctly restore the insufficiency of the equal time interval glitch signal, and a general glitch signal elimination circuit is realized.

Owner:BEIJING RES INST OF SPATIAL MECHANICAL & ELECTRICAL TECH

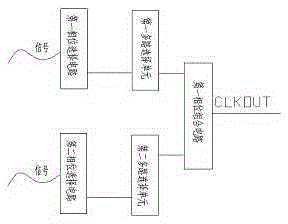

High-precision clock phase control circuit

InactiveCN105406841AHigh precisionIncrease flexibilitySingle output arrangementsPulse shapingComputer hardwareSignal quality

The invention discloses a high-precision clock phase control circuit, relating to the field of electronic circuits. The high-precision clock phase control circuit comprises a multi-phase clock generation circuit module and a programmable phase selection circuit module, wherein the clock generation circuit module comprises a plurality of phase selection circuits, and each phase selection circuit comprises at least one selection unit and at least one protection unit; the programmable phase selection circuit module comprises a plurality of many-way selection units and phase combination circuits, and each many-way selection unit is respectively communicated with each phase combination circuit. According to the high-precision clock phase control circuit, the multi-phase clock generation circuit module and the programmable phase selection circuit module are combined, so that the high-precision clock phase control circuit has the advantages of simple structure, low cost, high sensitivity and higher precision, and the specific clock switching method can be used for eliminating burr phenomena, and the signal quality and precision are improved.

Owner:WUHU RUIXIN ELECTRONICS TECH CO LTD

Clock detection circuit and method

The invention relates to a clock detection circuit and method, and the circuit comprises a glitch elimination unit, a first counter, a second counter, and a detection unit, and the glitch elimination unit is used for inputting a to-be-detected clock signal, and eliminating the glitch of the to-be-detected clock signal, so as to obtain a first signal; the first counter records a first jump edge parameter of the first signal; the second counter records a second jump edge parameter, with the same type as the first jump edge parameter, of the second signal; the second signal is synchronized with the first signal after being synchronized; the detection unit judges whether the first jump edge parameter and the second jump edge parameter are the same or not and outputs a signal used for detecting whether burrs exist in the to-be-detected clock signal or not according to the judgment result. Whether burrs exist in the clock signal to be detected or not is detected by comparing the jump edge parameters of the clock signal without the burrs and the original clock signal without the burrs, the clock signal to be detected can be used for detection, an external clock is not needed, and the detection precision is improved.

Owner:GREE ELECTRIC APPLIANCES INC +1

A burr judgement and elimination circuit

InactiveCN100576743CEnsure safe workSingle output arrangementsPulse descriminationFeedback controlComputer science

The present invention discloses a burr eliminating circuit which comprises a delay module which is used for detecting the width of the burr and a delay output module for eliminating the burr problem generated in specific condition. The delay module is connected with a feedback control circuit module. The delay module controls the feedback control circuit module to reset with an accelerated speed when the burr is detected and sets with an accelerated speed when the valid data is detected. The circuit of the invention totally satisfies the functions of determining and eliminating the burr and can expands the width of the valid narrow pulsewidth signal to a safe width for securing the safe operation.

Owner:CHIPHOMER TECH SHANGHAI

Glitch removal circuit and electronic device

ActiveUS10903826B2Remove noisePulse shapingVoltage/temperature variation compensationPower-on resetHemt circuits

A glitch removal circuit removes glitch noise contained in a Power-good signal and a Power-on Reset signal, and includes: a first glitch removal unit that operates according to a first clock signal, and removes glitch noise from a Power-good signal; and a second glitch removal unit that operates according to a second clock signal, and removes glitch noise from a Power-on Reset signal, in which the first glitch removal unit is configured so as to be initialized according to an output signal of the second glitch removal unit, and the second glitch removal unit is configured so as to be initialized according to an output signal of the first glitch removal unit.

Owner:FANUC LTD

Vibration key-phase signal preprocessing method of turbo generator set

InactiveCN101915605BEliminate distractionsPrecise key phase square wave signalSubsonic/sonic/ultrasonic wave measurementUsing electrical meansEngineeringGlitch removal

The invention relates to a vibration key-phase signal preprocessing method of a turbo generator set in a large-scale thermal power plant. The method comprises the following steps of: eliminating burr interference through voltage triggering; meanwhile, further eliminating the burr interference in key-phase pulses by means of the optoelectronic isolation of an integrated circuit; and finally shaping square waves. The processing method proposed by the invention can effectively eliminate various burr interferences, obtain accurate key-phase square-wave signals, achieve the aim of processing the key-phase signals of different kinds of sensors in different power plants and provide a site with key-phase signals which are more accurate and convenient to analyze.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING) +1