Glitch-free multiplexer and glitch transmission prevention

A circuit and decoder technology, applied in the direction of pulse technology, pulse processing, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

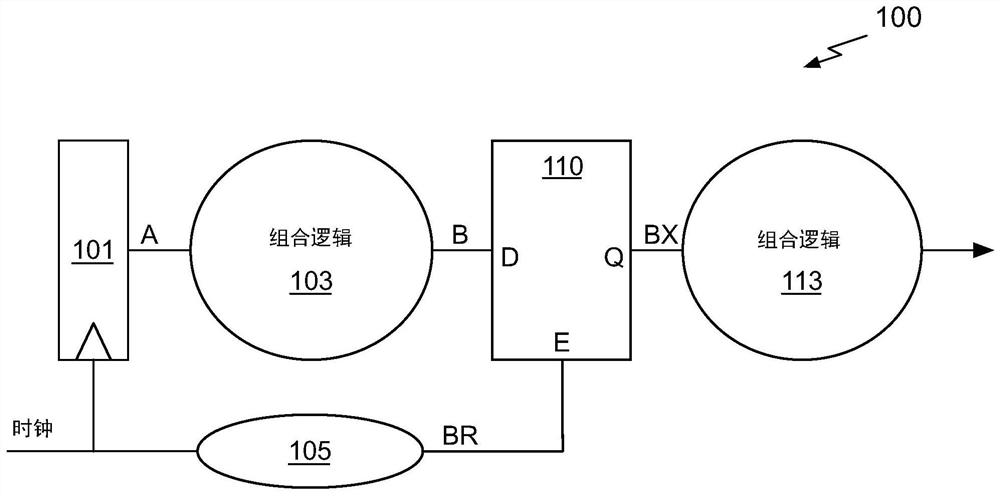

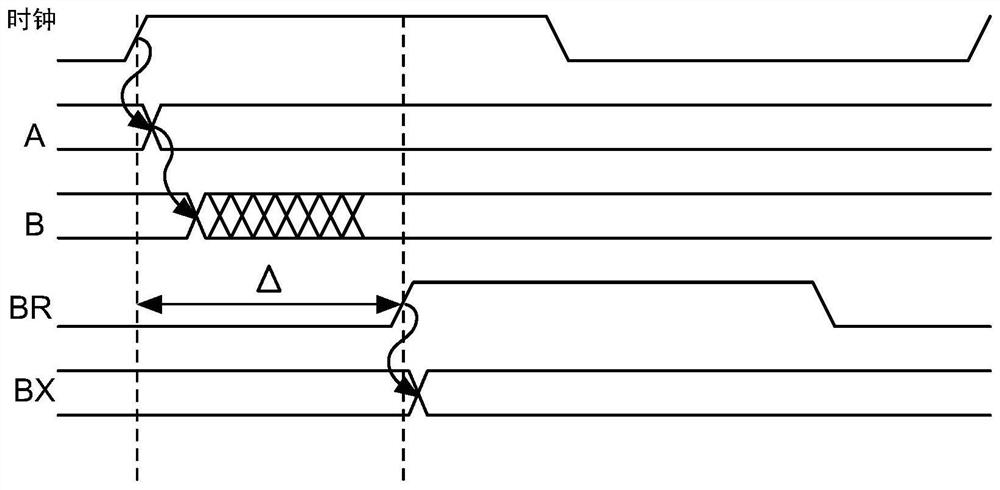

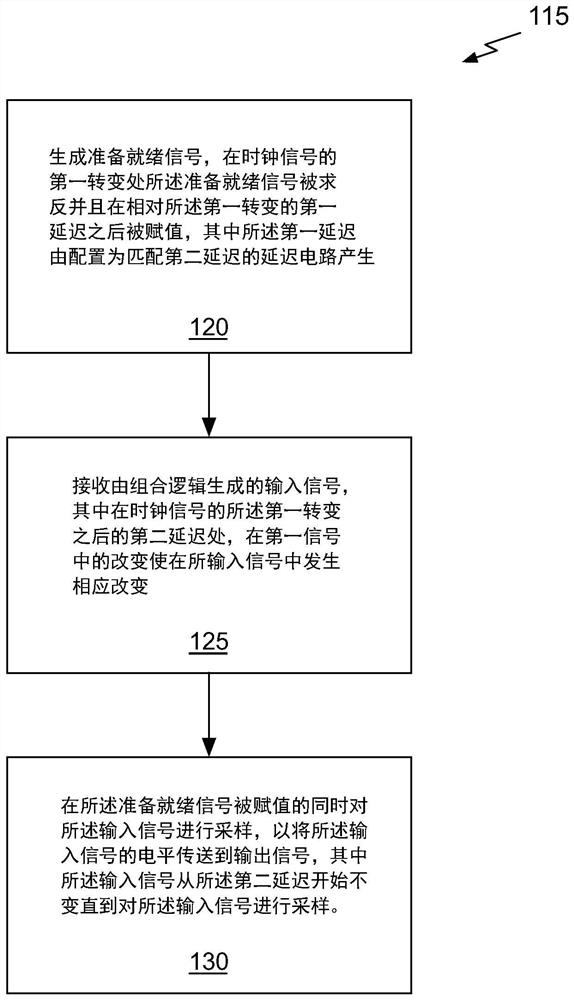

[0029] In response to the changed data and selection input, the output of the multi-transistor can change multiple times before stabilizing to the final state. In the context described below, the change is a transition of the voltage level that identifies it as a different state. For example, the change is identified as an assigned state compared to the reverse or not assigned state. In another example, the change is a transition from a high level to a low level or from a low level to a high level. In the context described below, a stable or constant level can vary while the range of voltage values identified as the same state (eg, logic is true or logic is fake).

[0030] Multiple changes in the output of the multiplexers are considered to be burrs, and the combined logic of the received output can respond by charging and / or discharging and dissipating power by charging and / or discharging and dissipating power by charging and / or discharging and dissipating power by chargi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More