Patents

Literature

2704results about "Logic circuits characterised by logic function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method for determination of a horizontal minimum of digital values

ActiveUS8650232B2Logic circuits characterised by logic functionComputation using non-contact making devicesComputer science

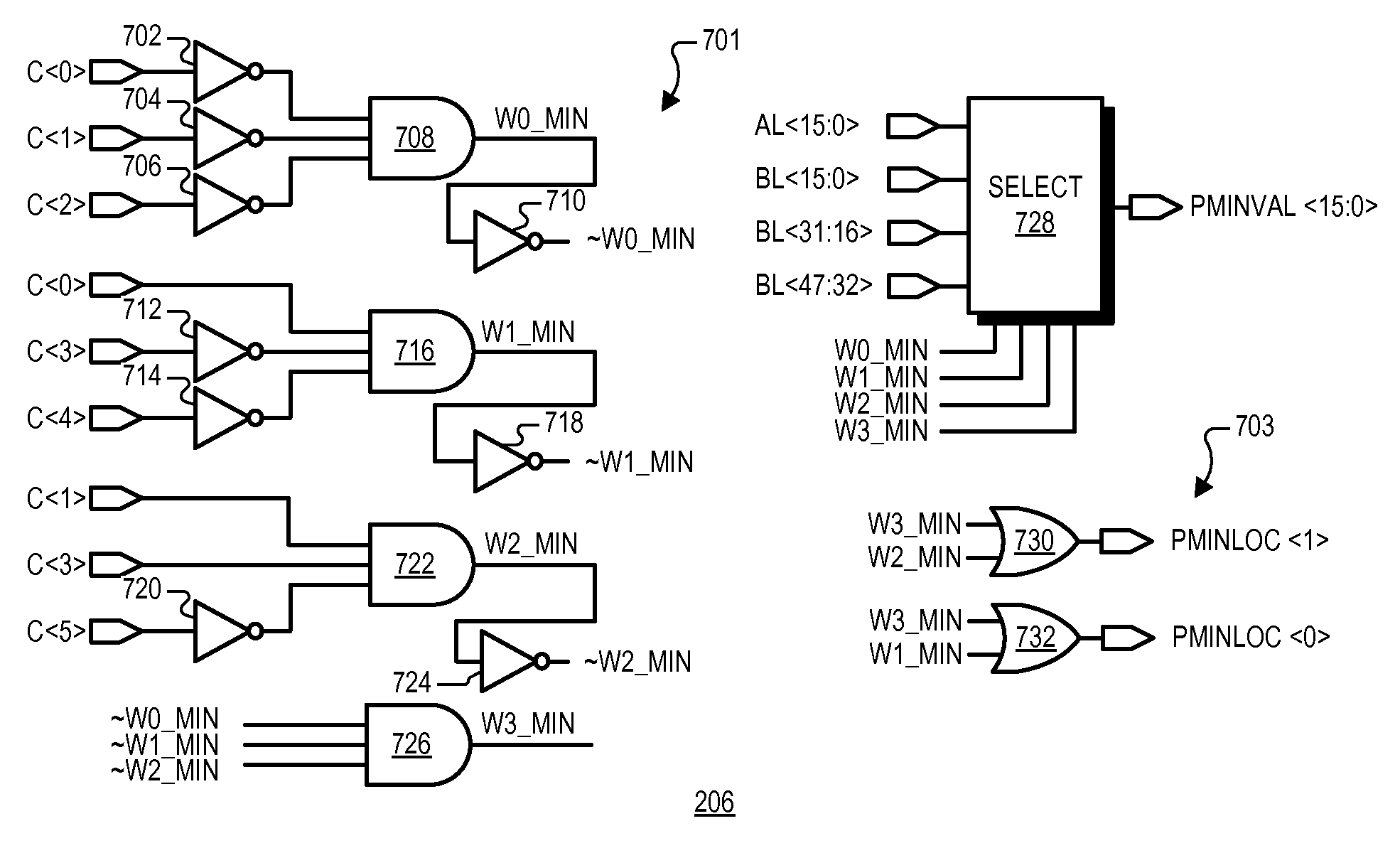

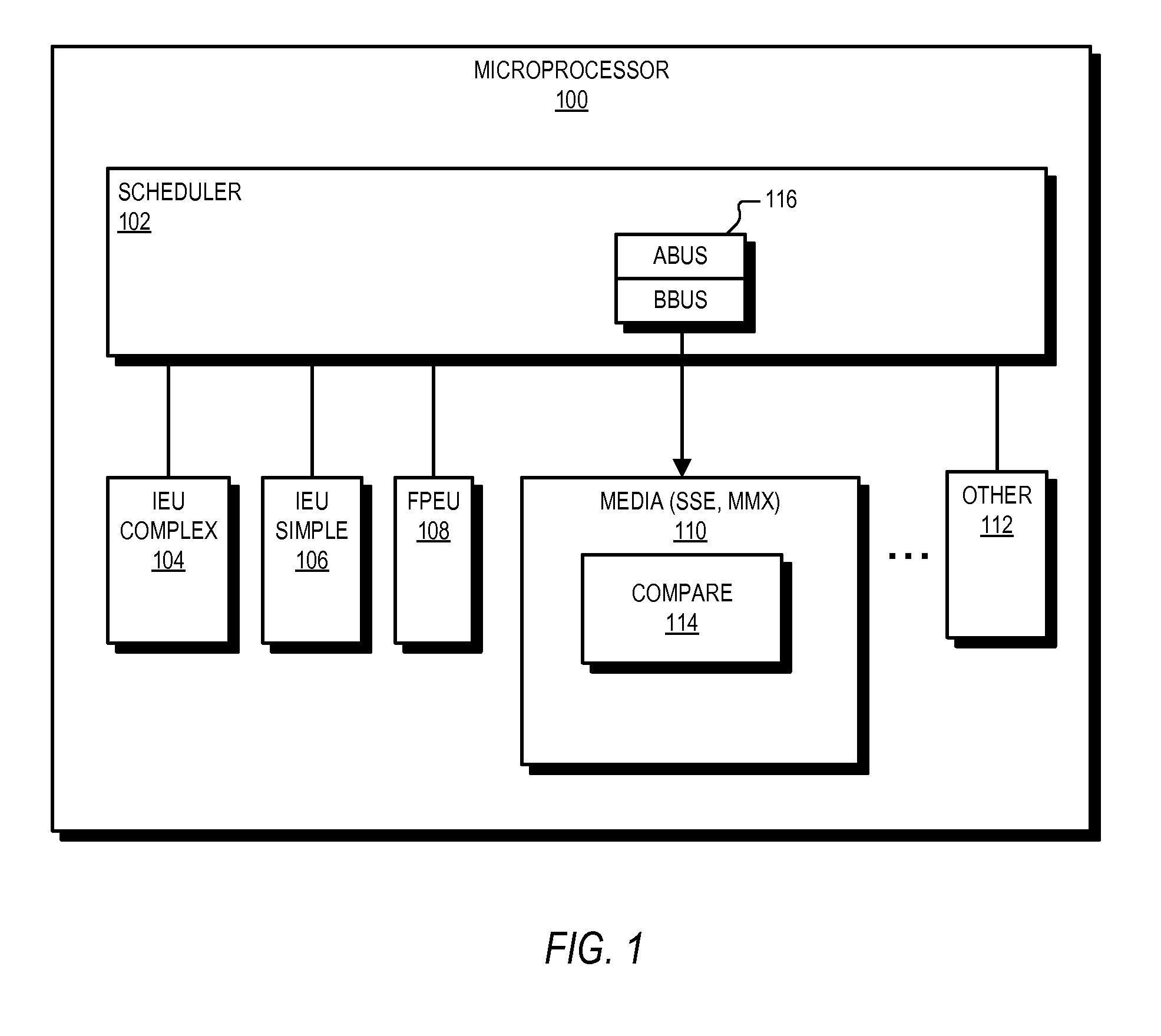

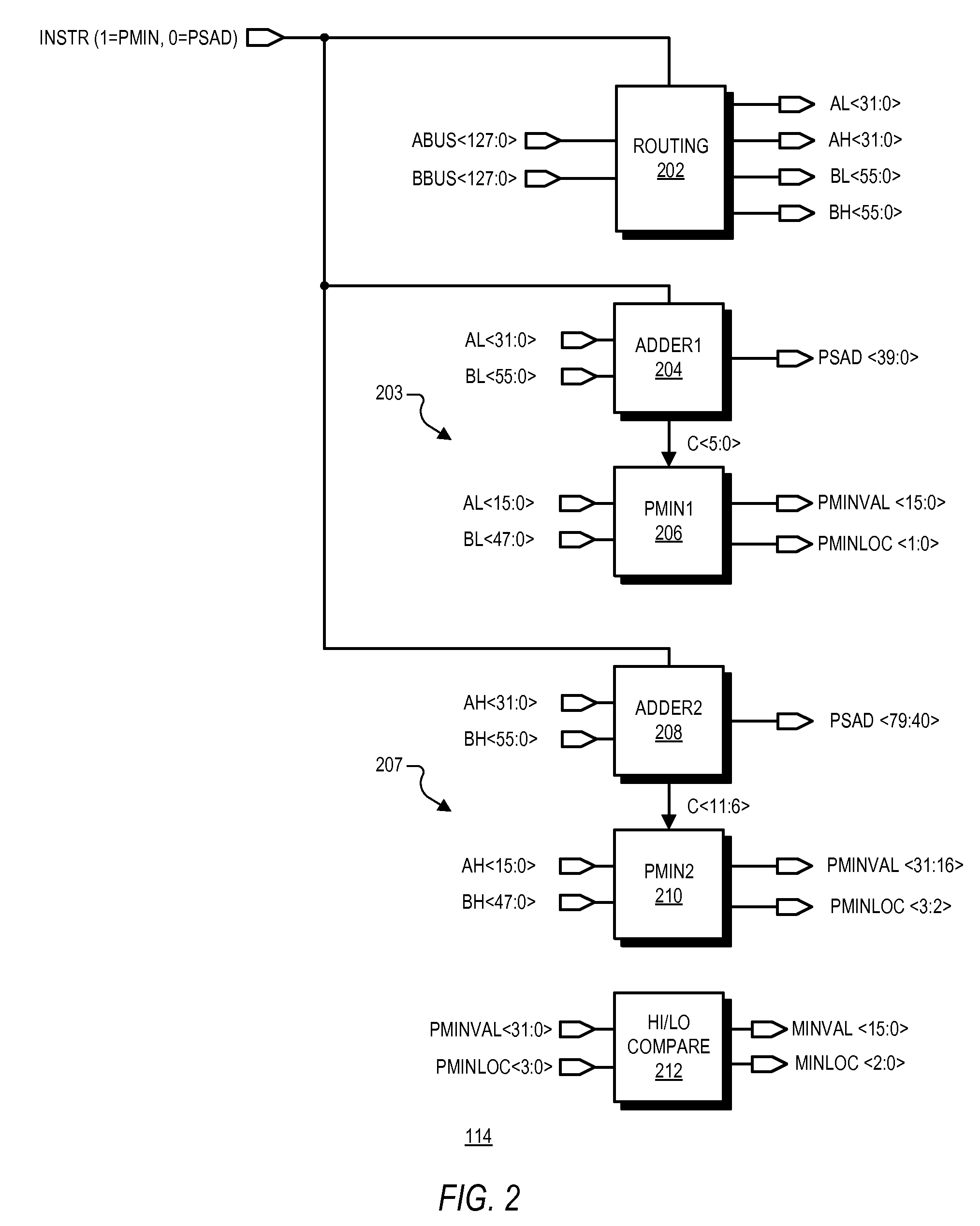

A system for fast determination of a horizontal minimum of multiple digital values including a difference circuit and a compare circuit. The difference circuit may include first and second adders in which the first adder compares upper bits of a first digital value with upper bits of a second digital value and provides a first carry output and a propagate output. The second adder compares lower bits of the first digital value with lower bits of the second digital value and provides a second carry output. The compare circuit determines whether the first digital value is greater than the second digital value based on the carry and propagate outputs. Multiple difference circuits may be used to compare each of multiple digital values with every other digital value to provide corresponding compare bits, which are then used to determine a minimum one of the digital values and its corresponding location.

Owner:VIA TECH INC

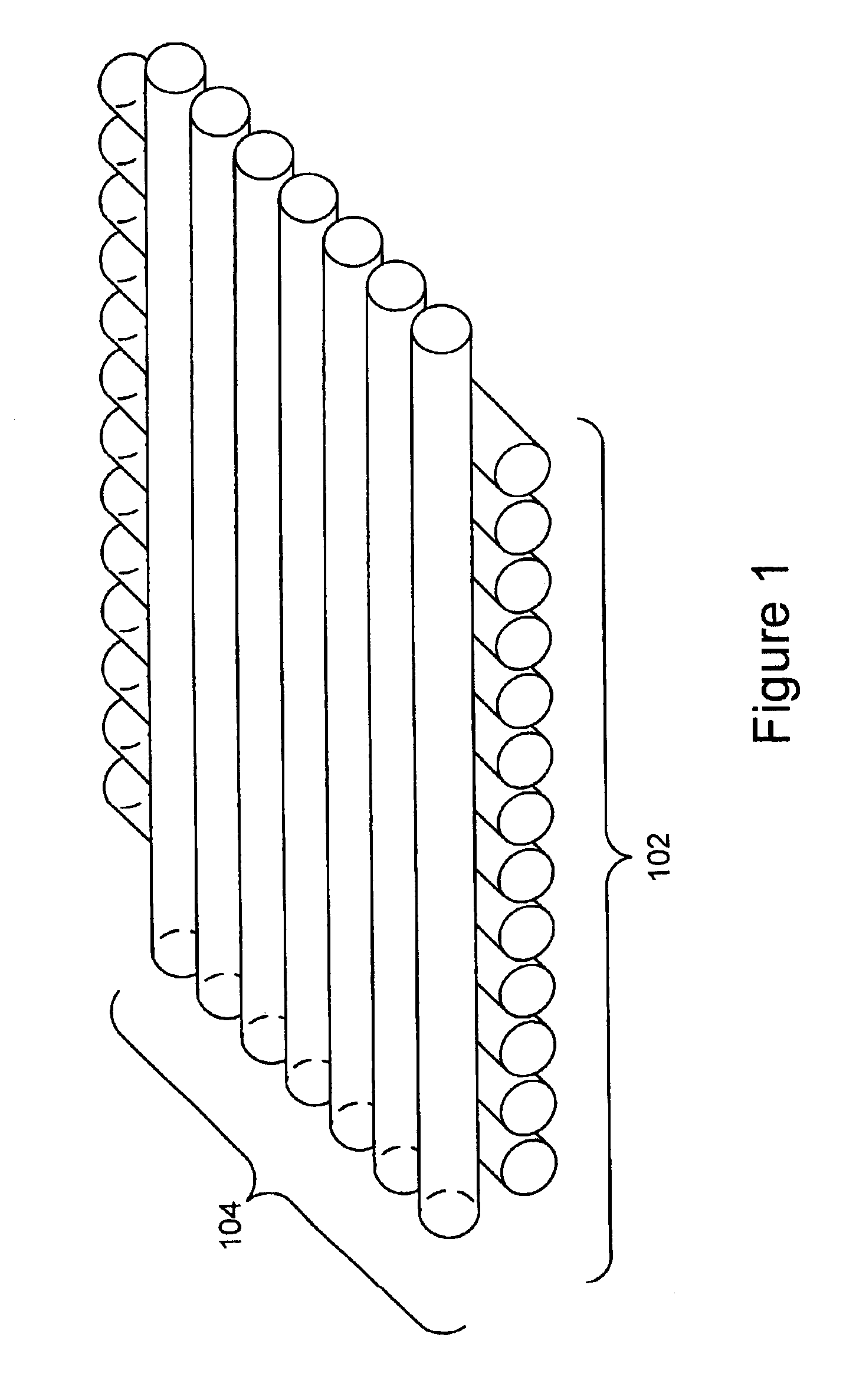

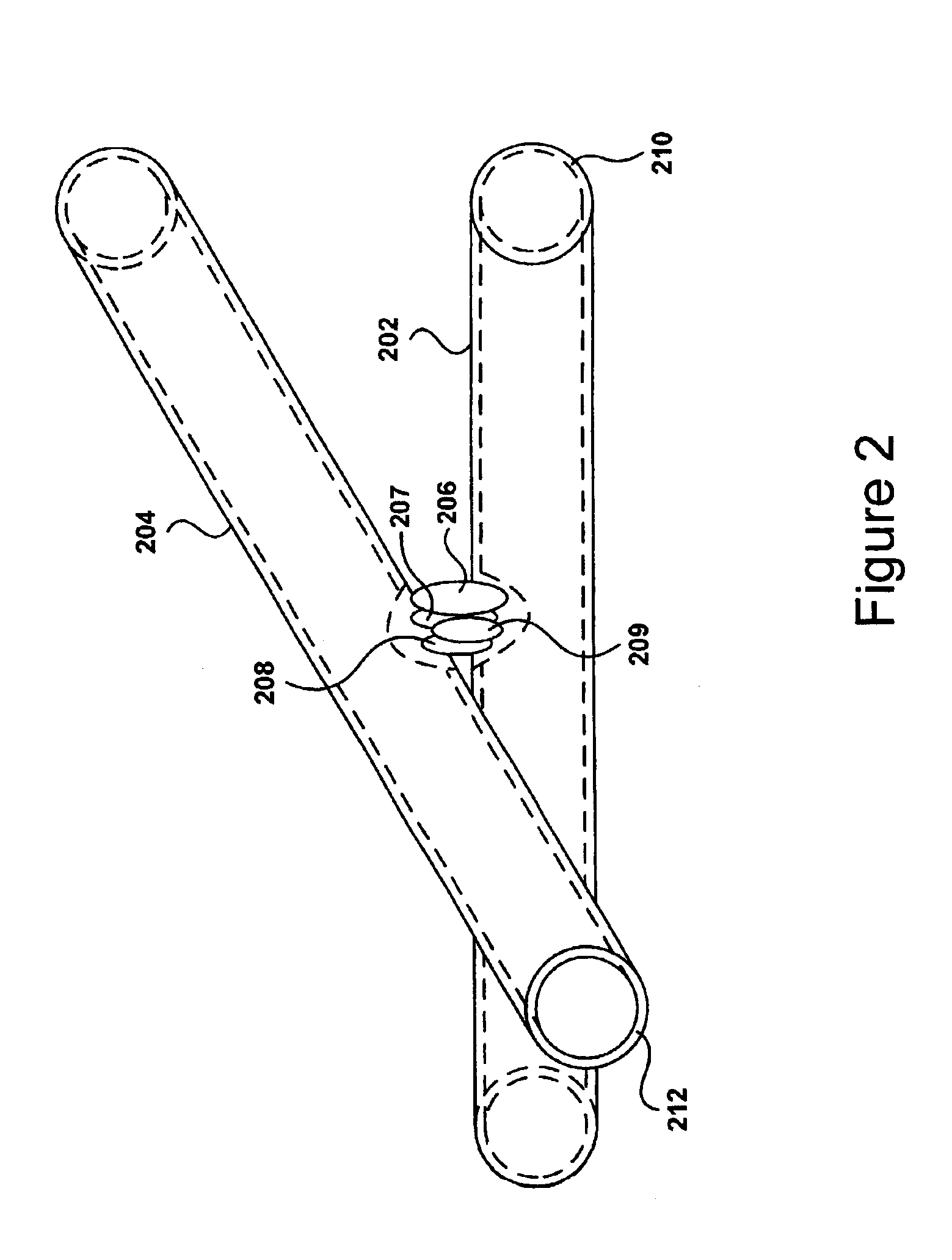

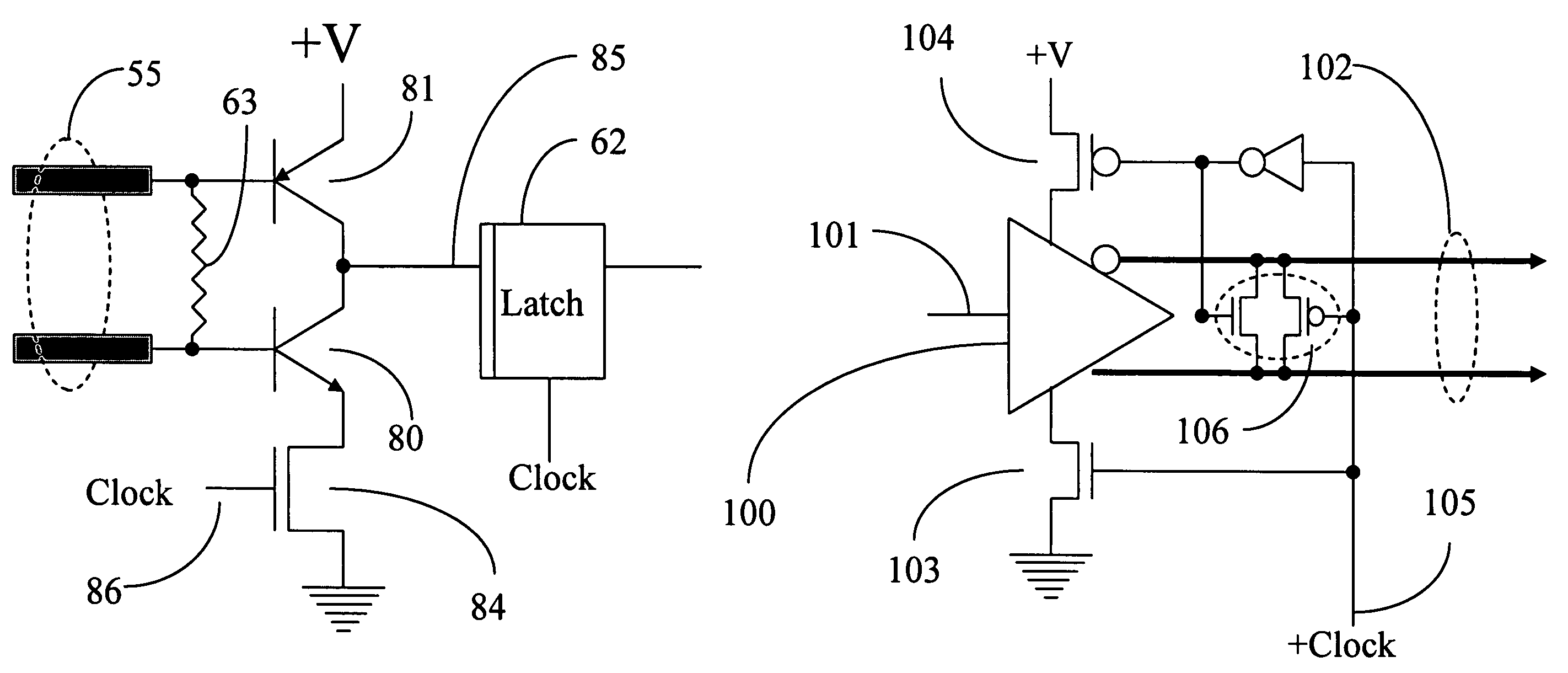

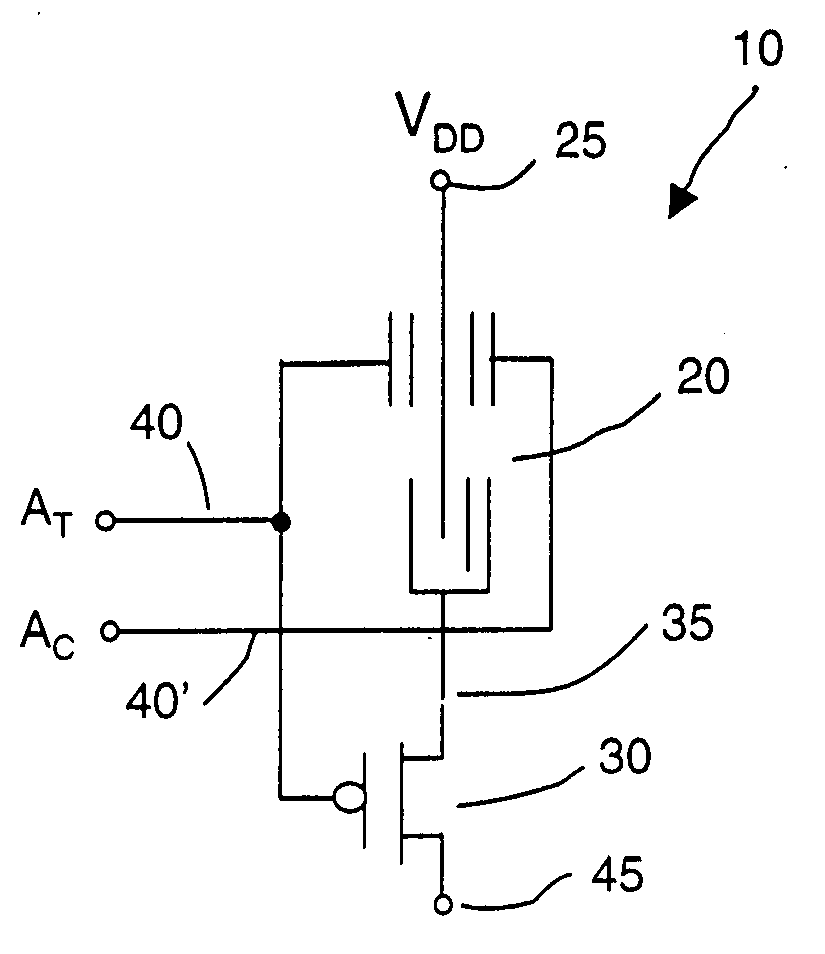

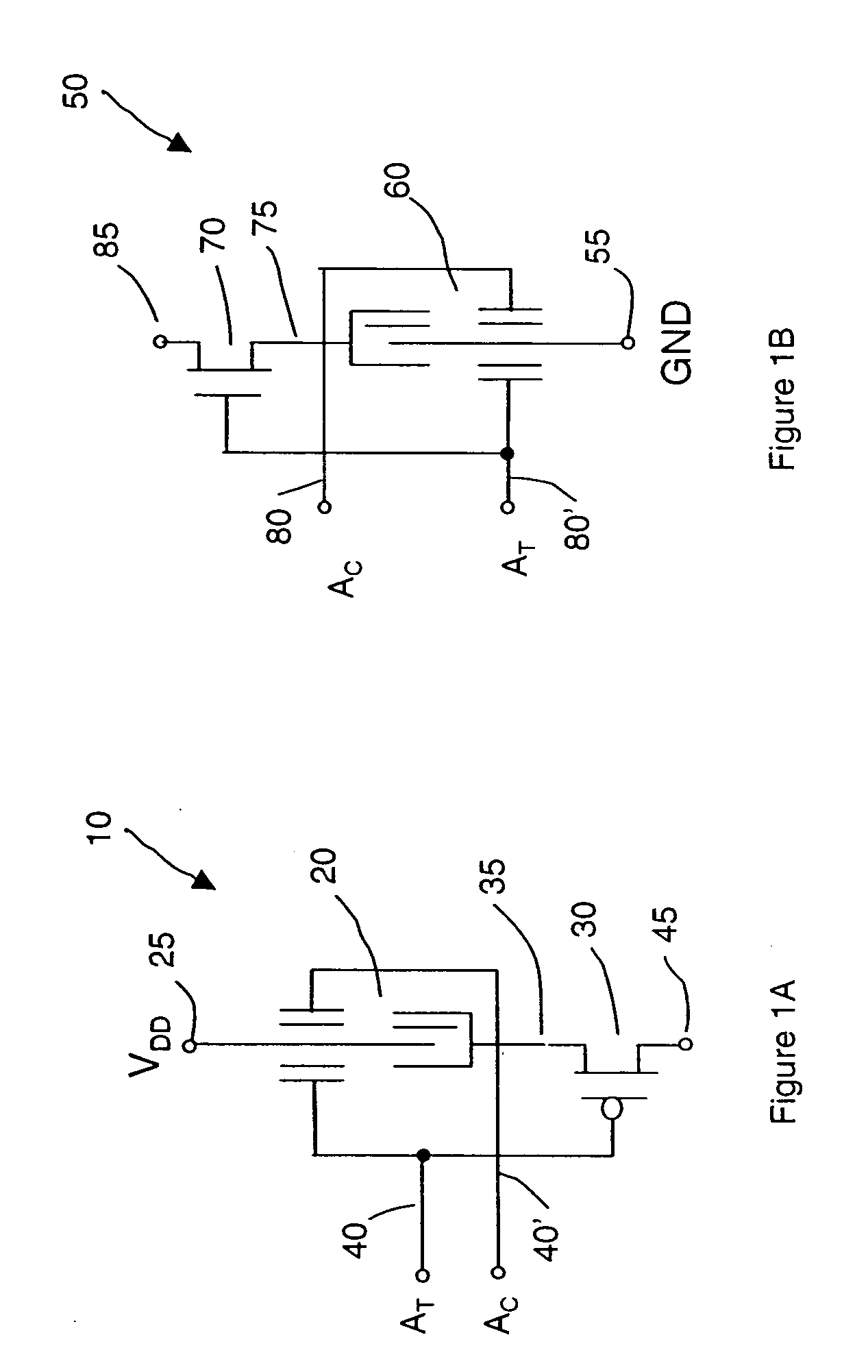

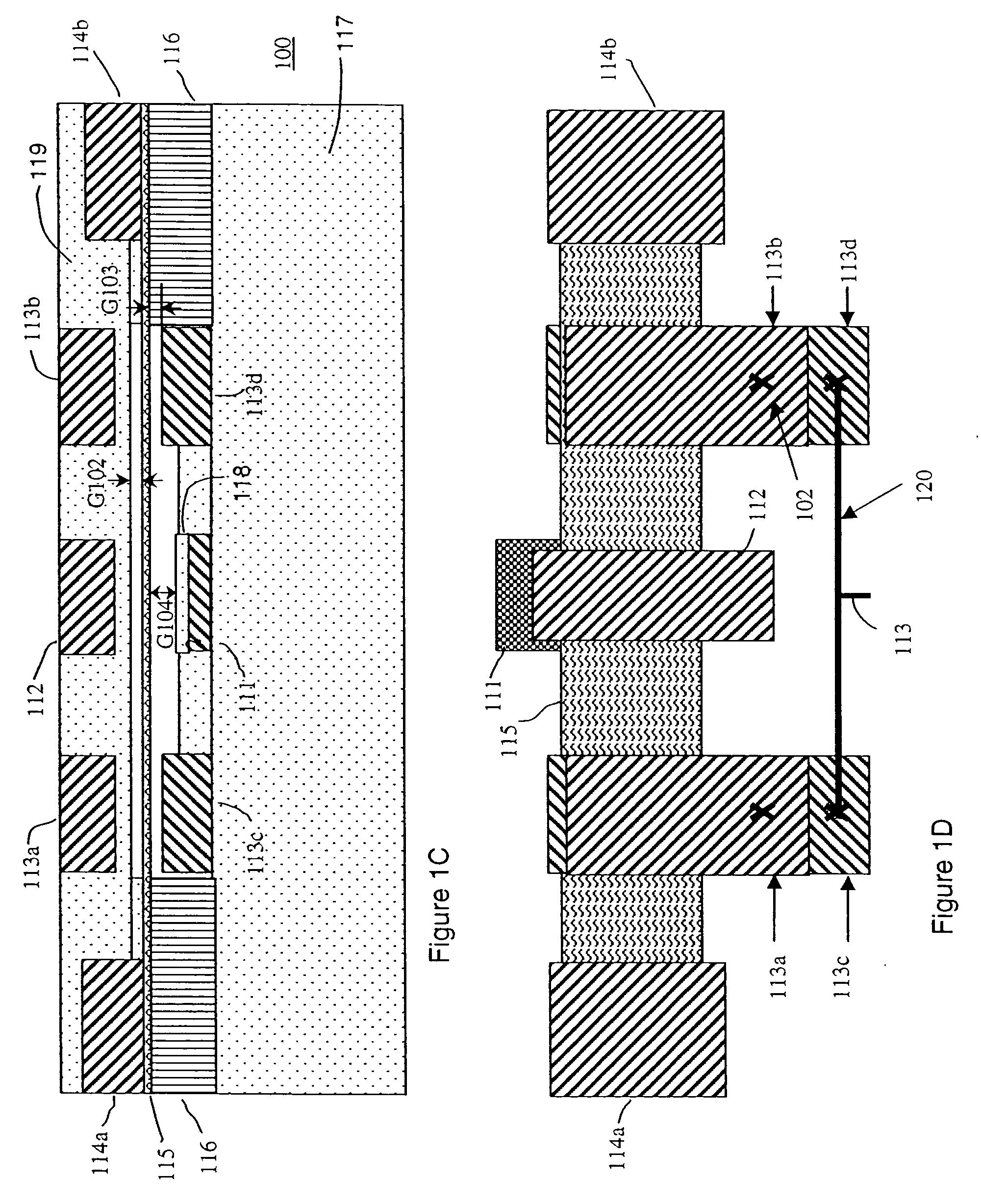

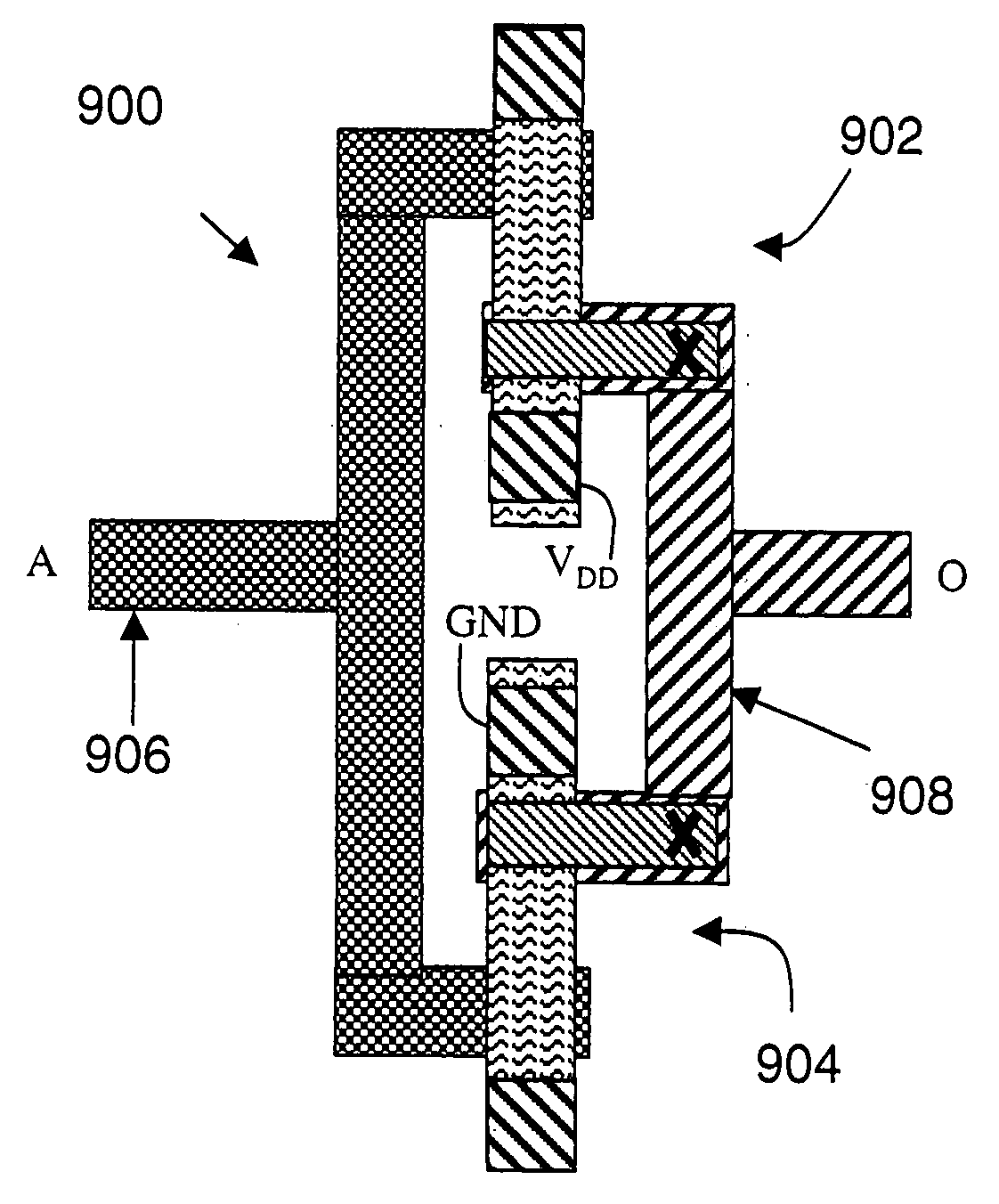

Molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits, and more complex circuits composed, in part, from molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits

InactiveUS6919740B2High densityLittle powerLogic circuits characterised by logic functionNanoinformaticsCrossbar switchNanowire

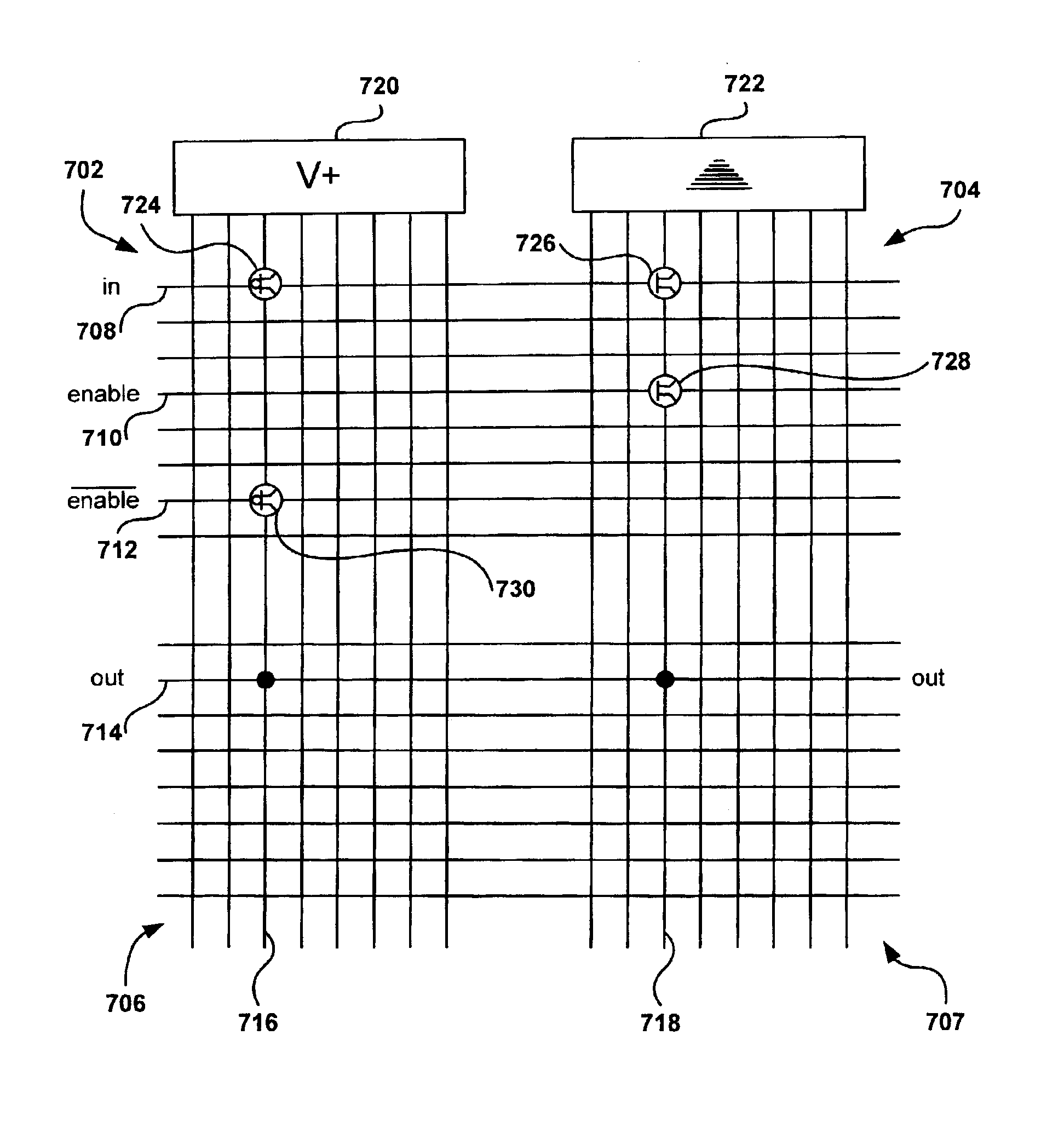

Methods for implementing familiar electronic circuits at nanoscale sizes using molecular-junction-nanowire crossbars, and nanoscale electronic circuits produced by the methods. In one embodiment of the present invention, a 3-state inverter is implemented. In a second embodiment of the present invention, two 3-state inverter circuits are combined to produce a transparent latch. The 3-state inverter circuit and transparent-latch circuit can then be used as a basis for constructing additional circuitry, including master / slave flip-flops, a transparent latch with asynchronous preset, a transparent latch with asynchronous clear, and a master / slave flip-flop with asynchronous preset. 3-state inverters can thus be used to compose latches and flip-flops, and latches and flip-flops can be used, along with additional Boolean circuitry, to compose a wide variety of useful, state-maintaining circuits, all implementable within molecular-junction-nanowire crossbars by selectively configuring junctions within the molecular-junction-nanowire crossbars.

Owner:HEWLETT PACKARD DEV CO LP

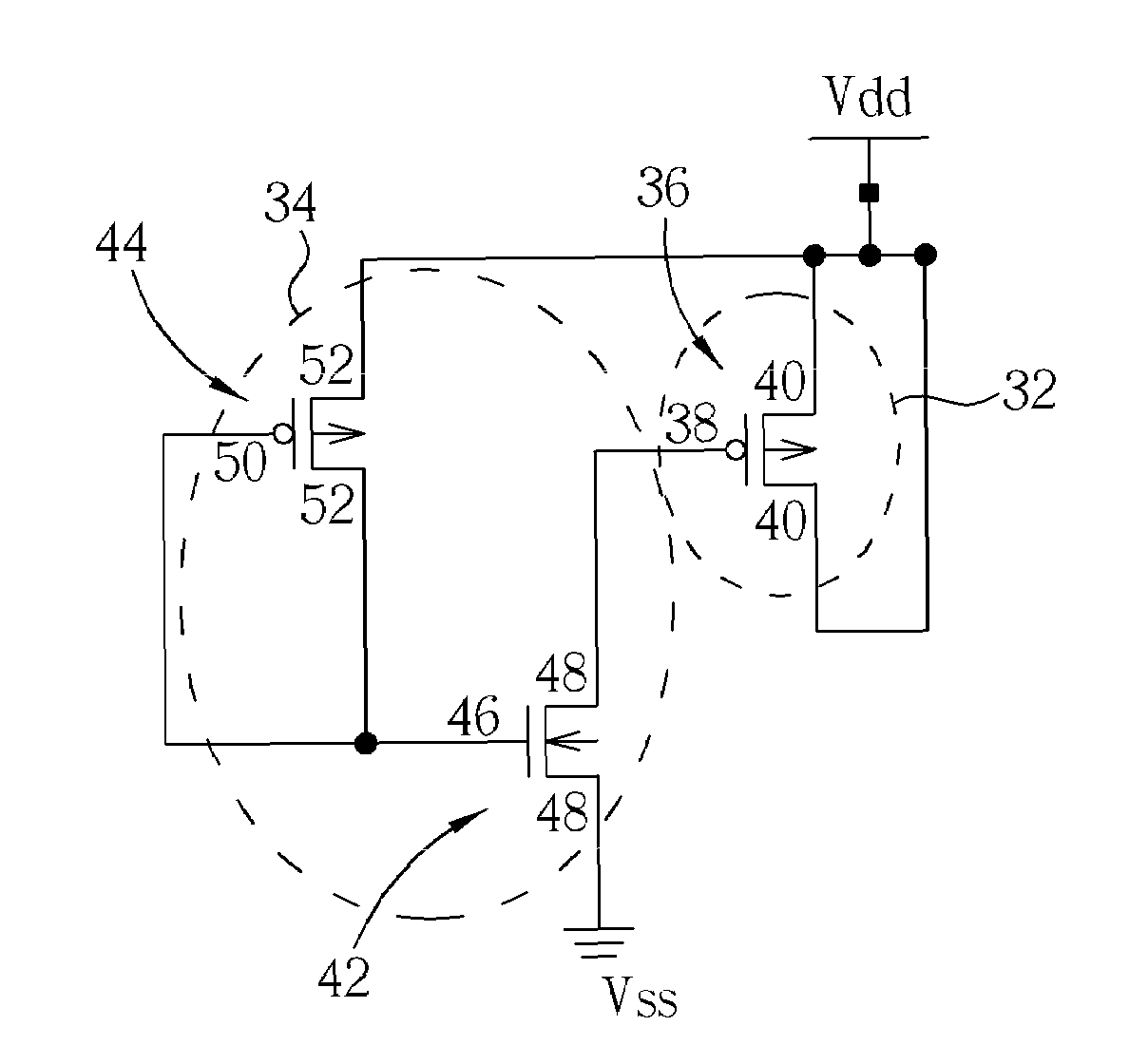

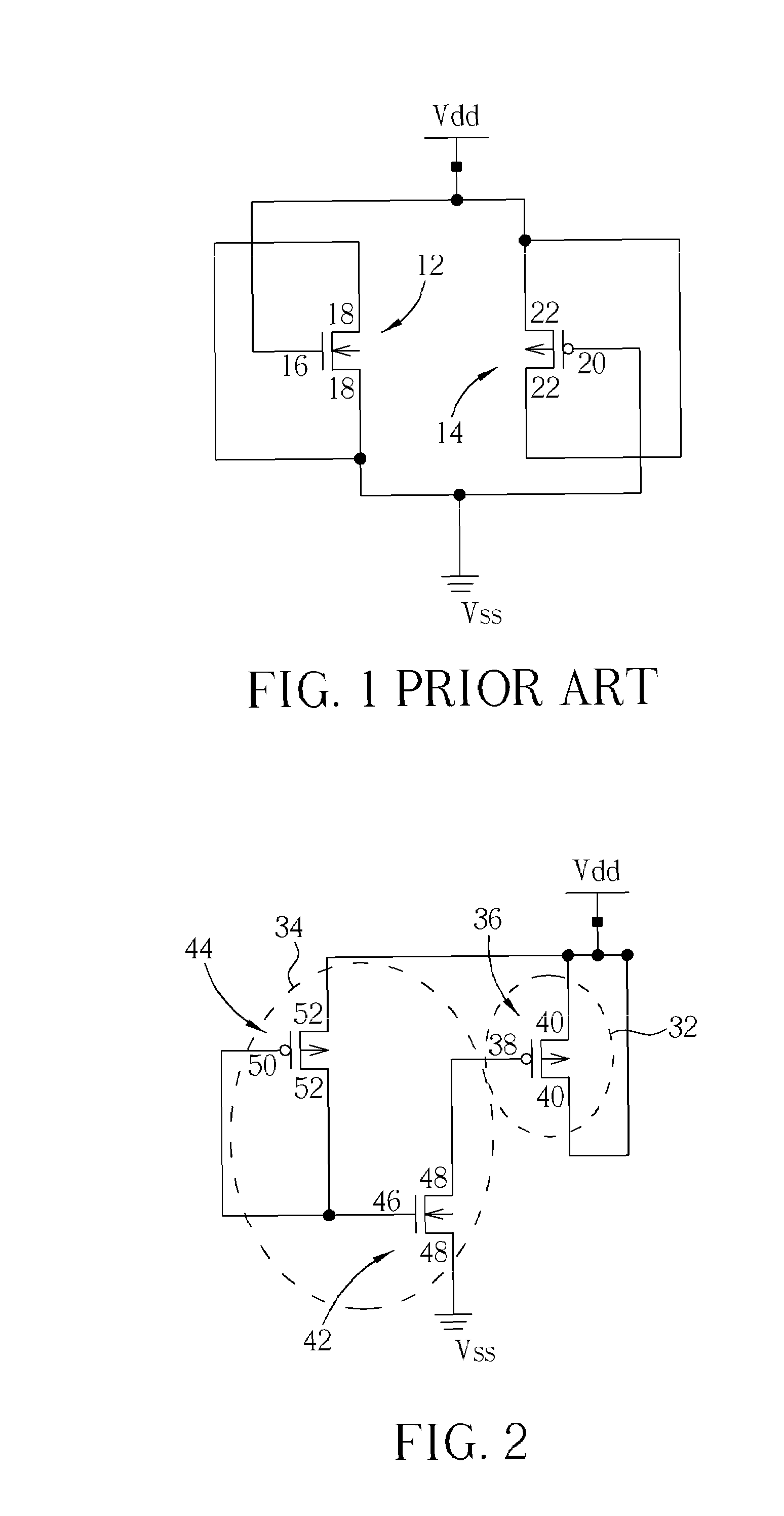

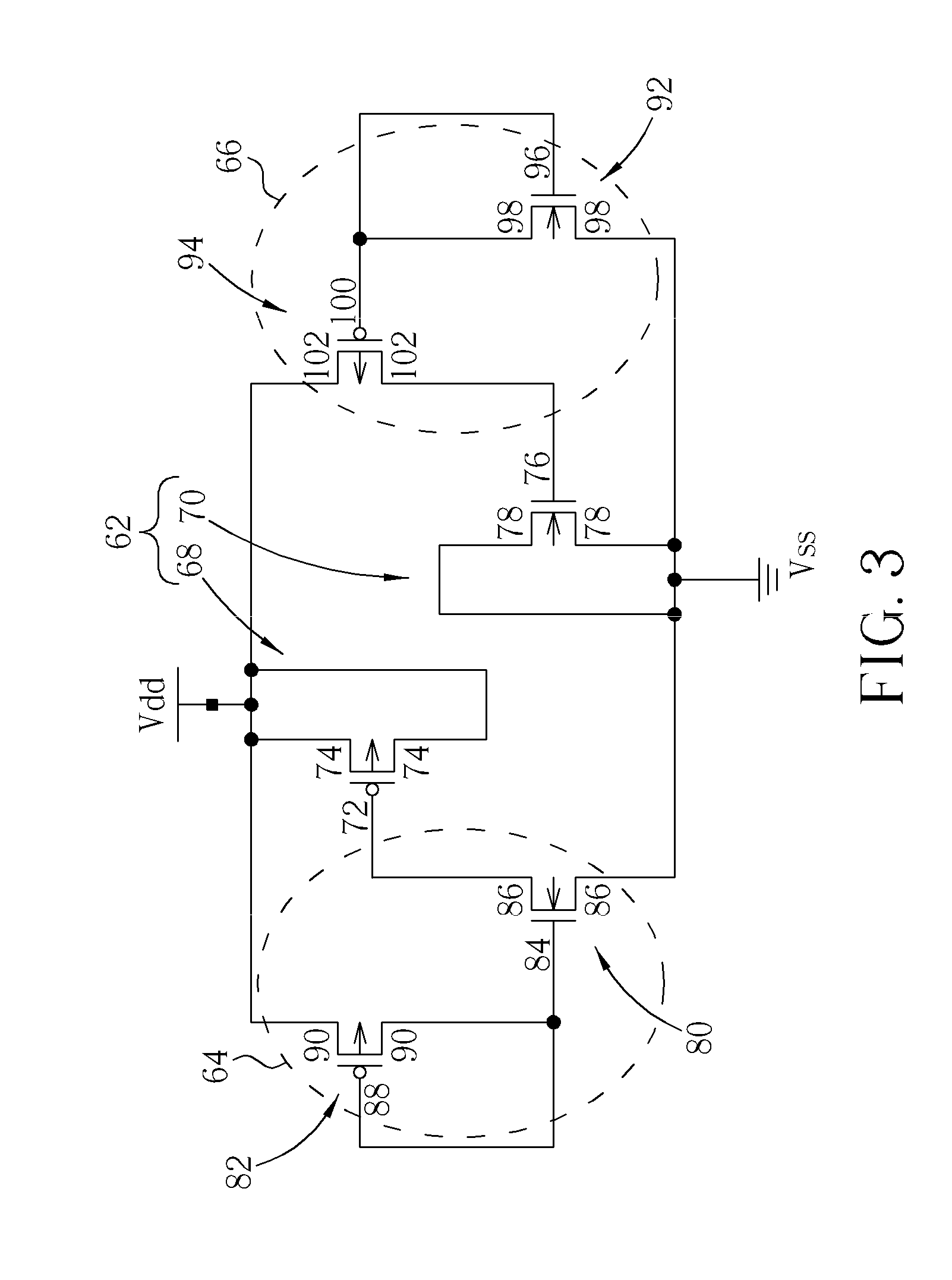

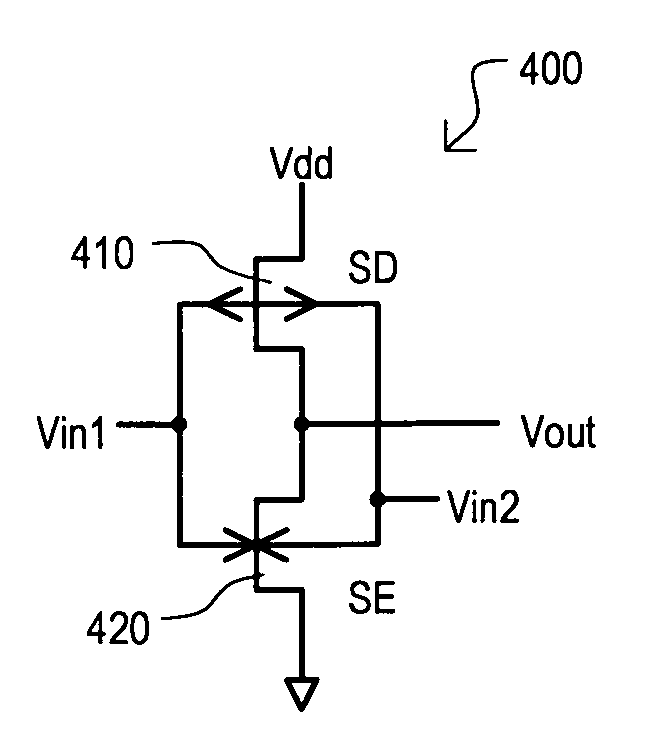

Logic circuit utilizing pass transistors and logic gate

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

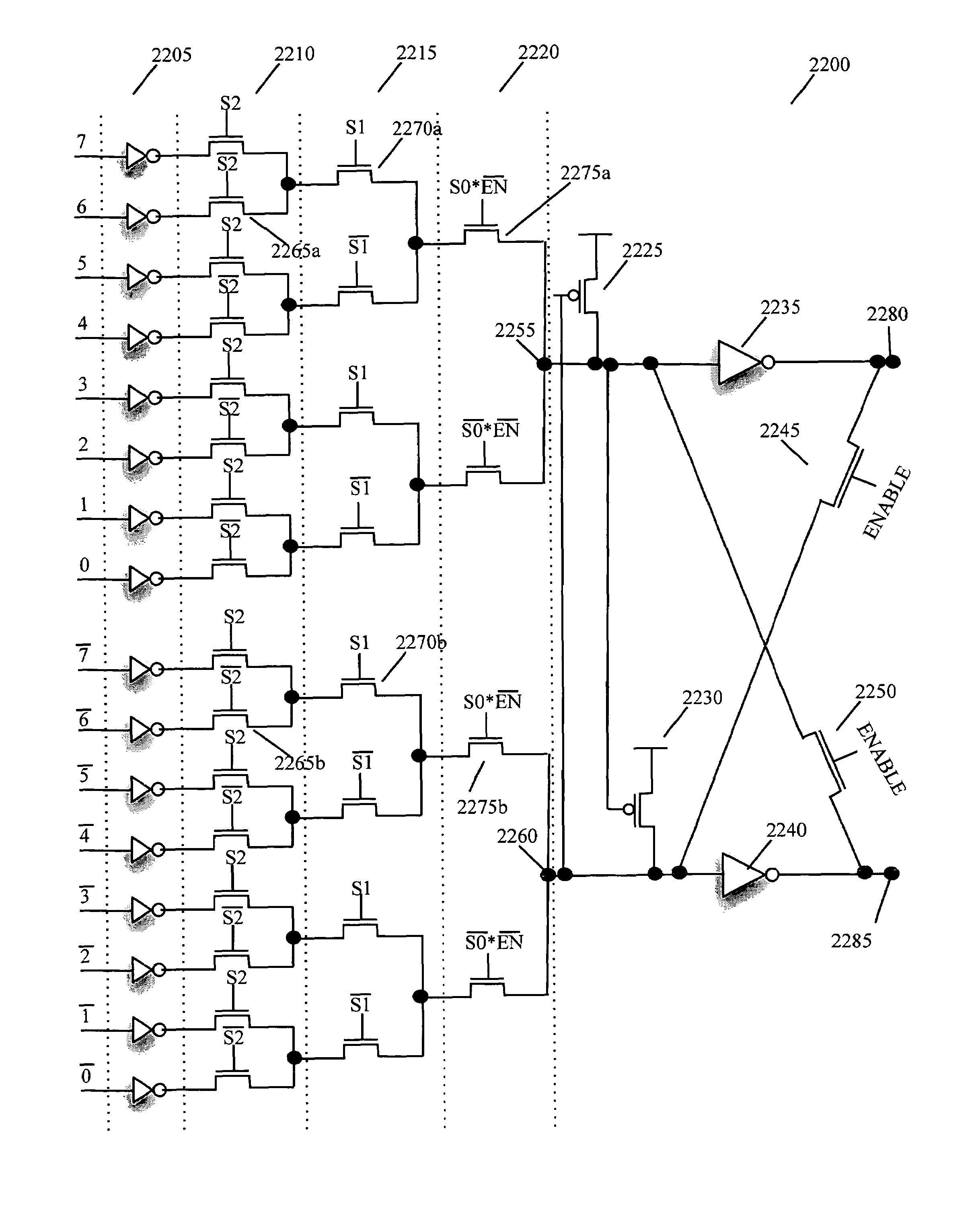

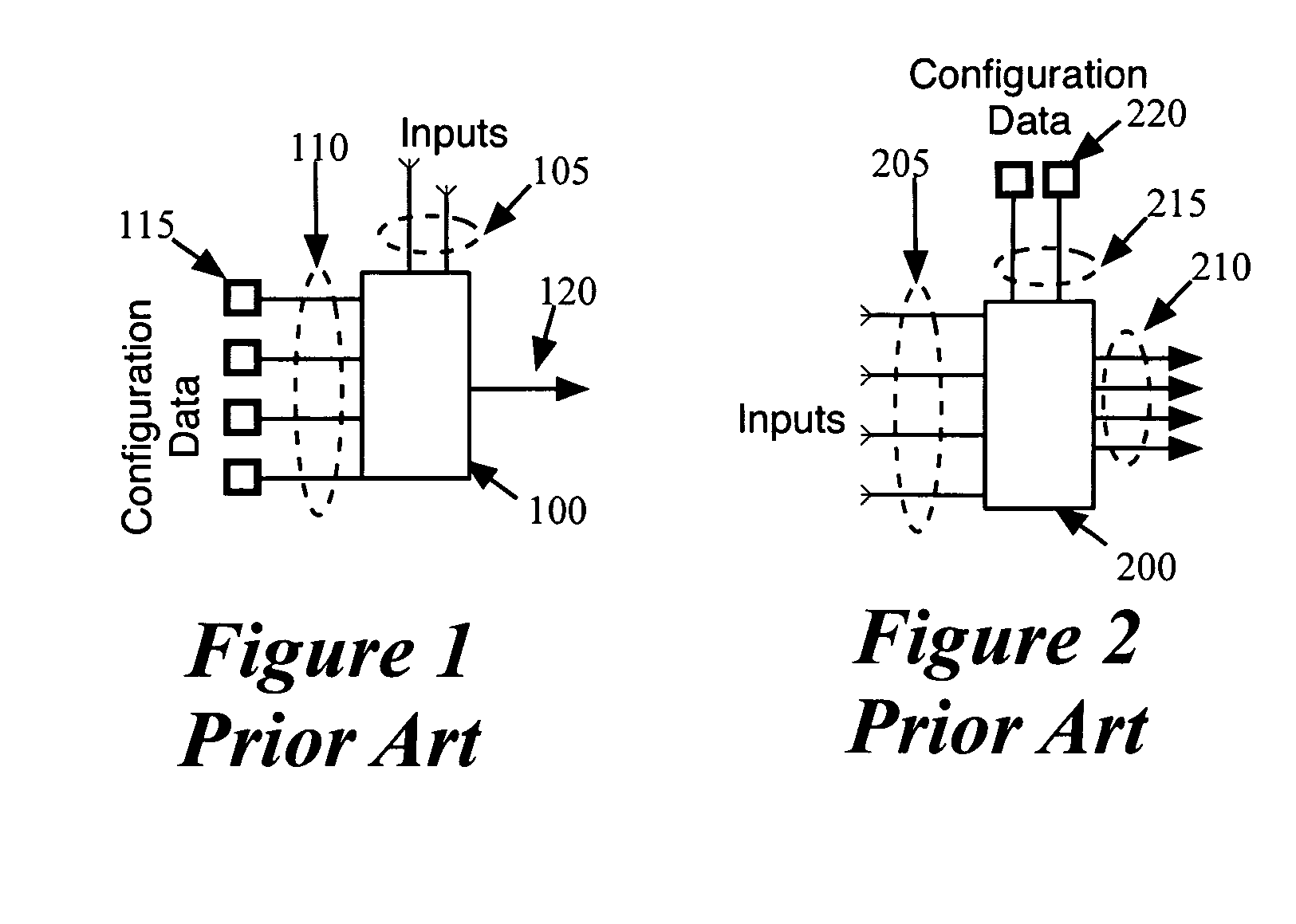

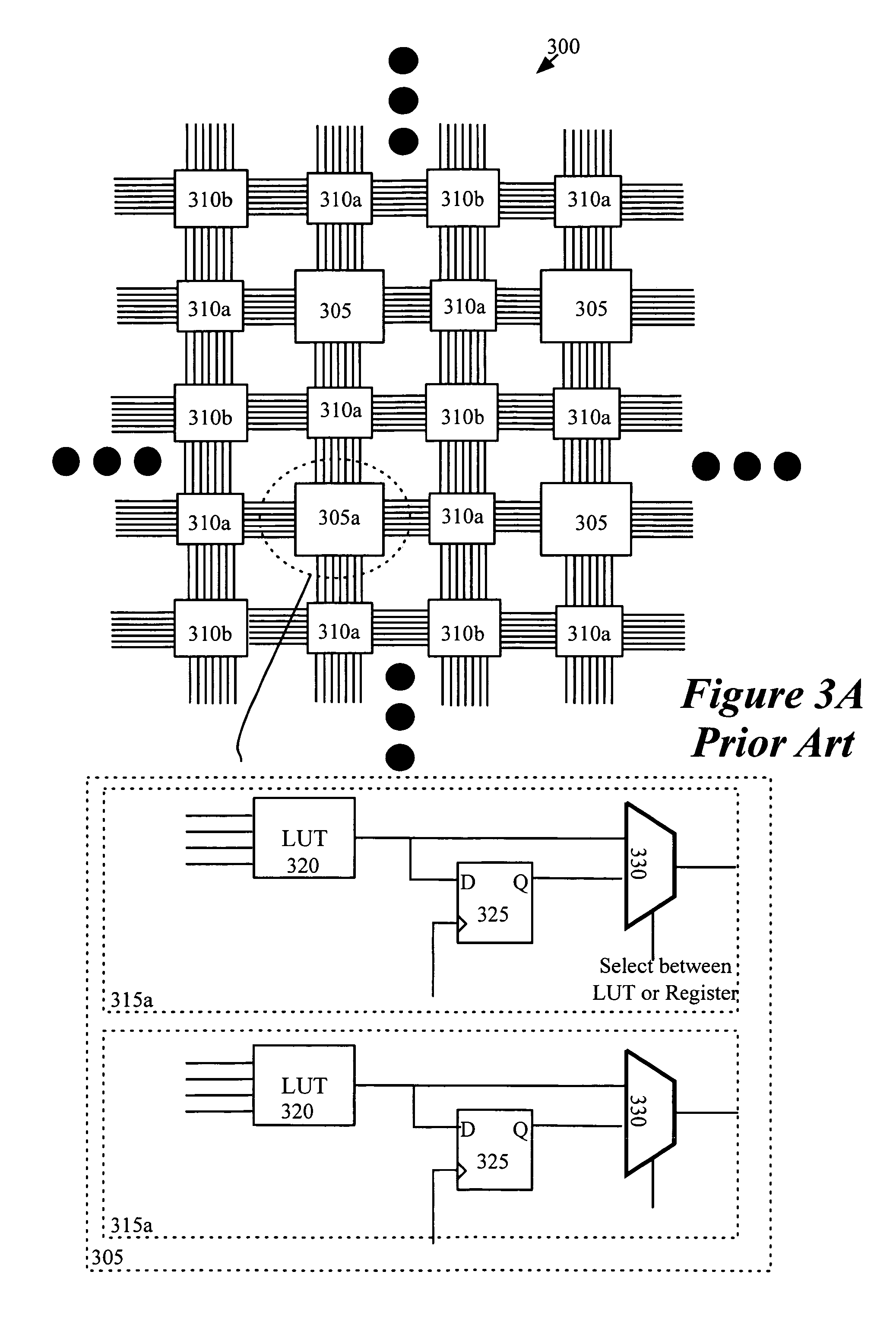

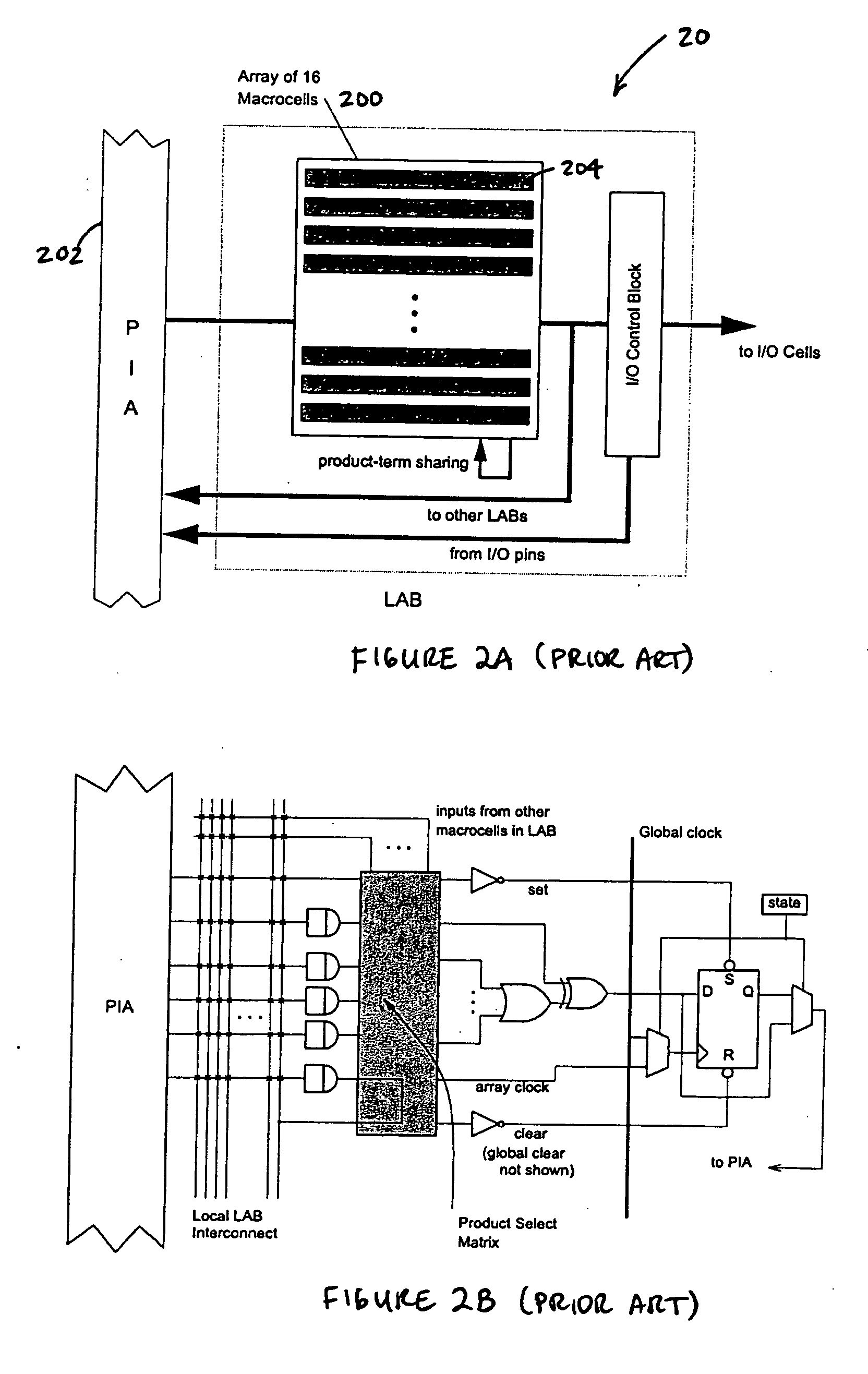

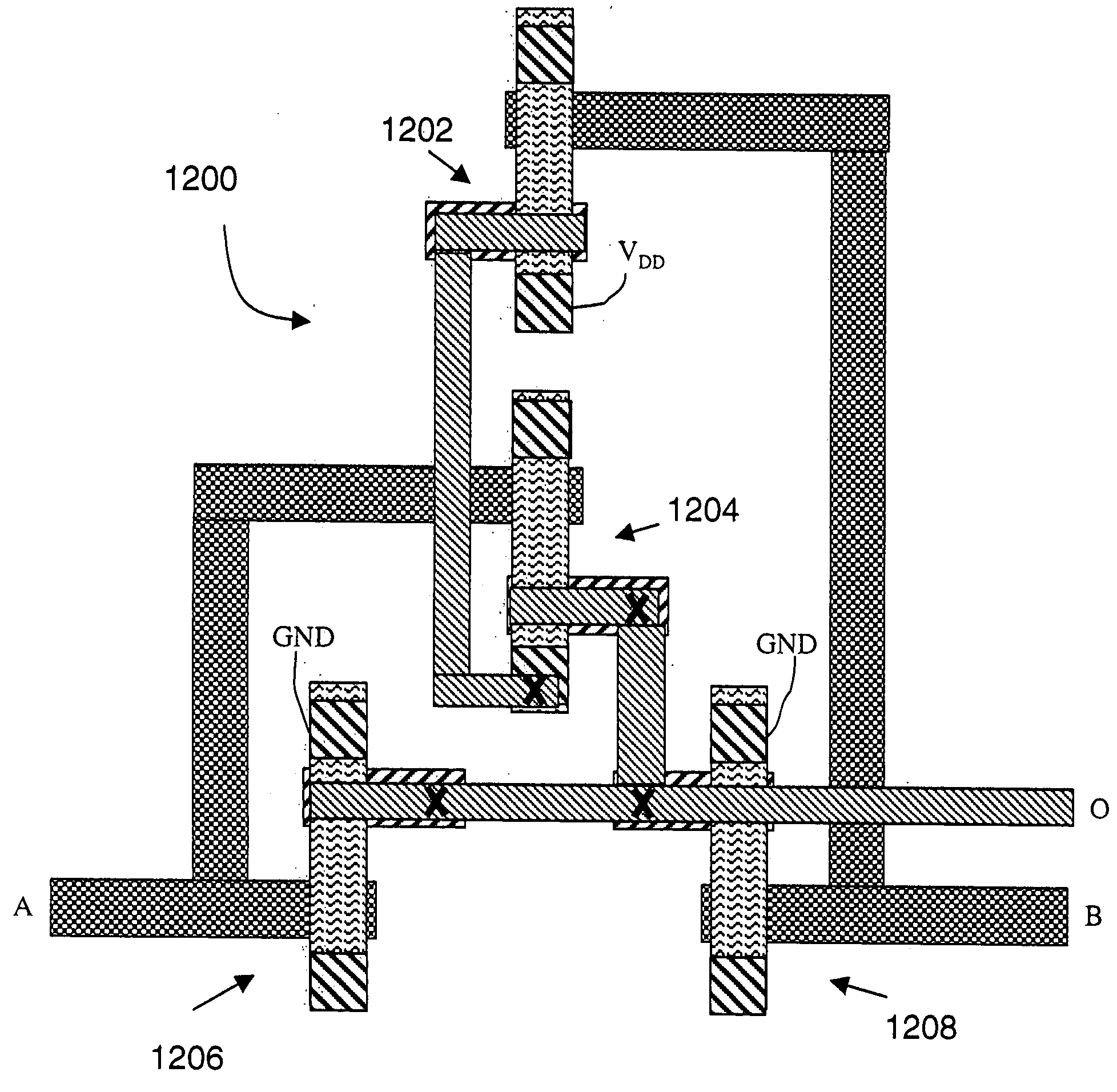

Configurable IC with interconnect circuits that also perform storage operations

InactiveUS7342415B2Logic circuits characterised by logic functionSolid-state devicesComputer scienceLogic circuitry

Owner:ALTERA CORP

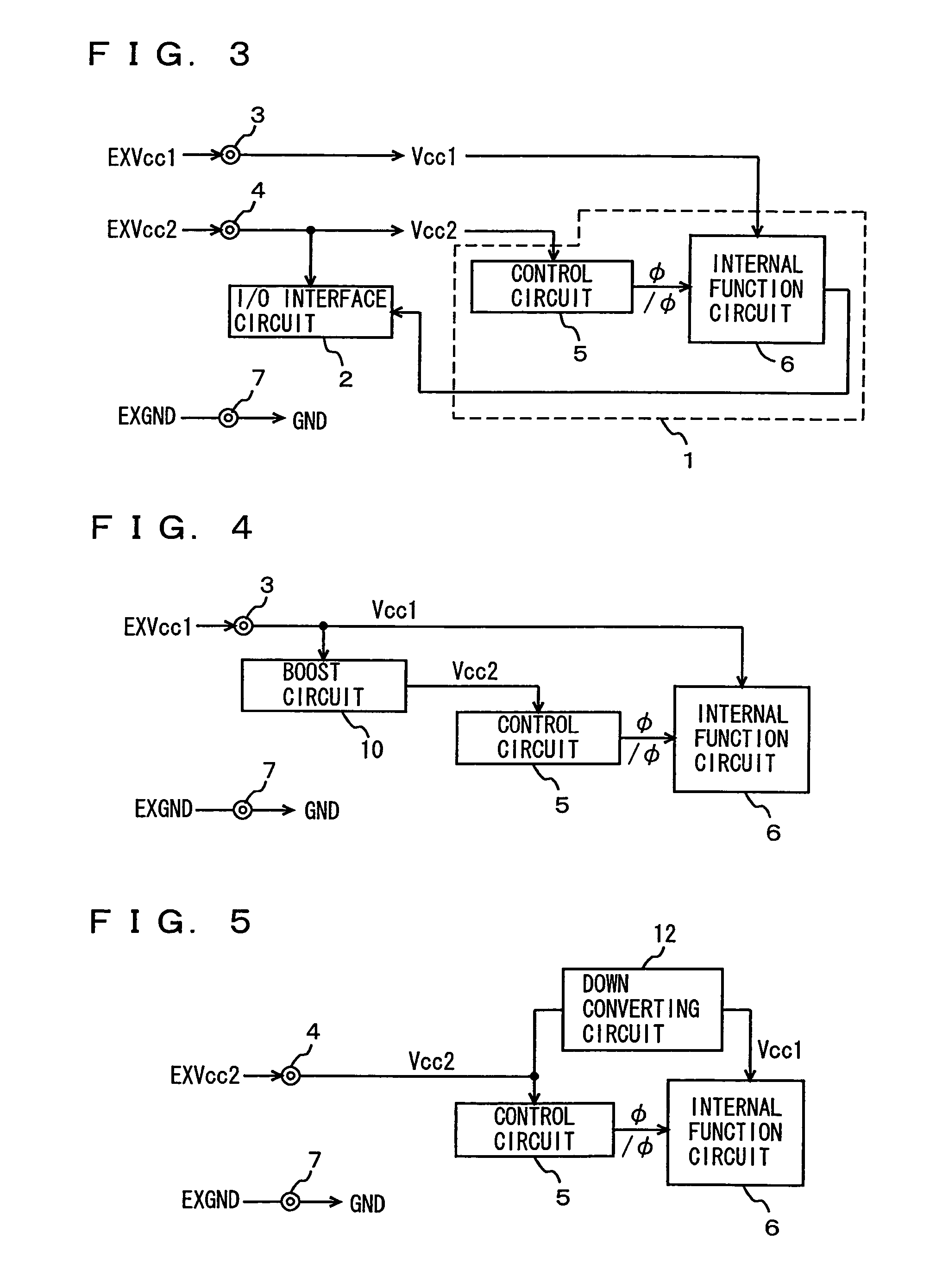

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

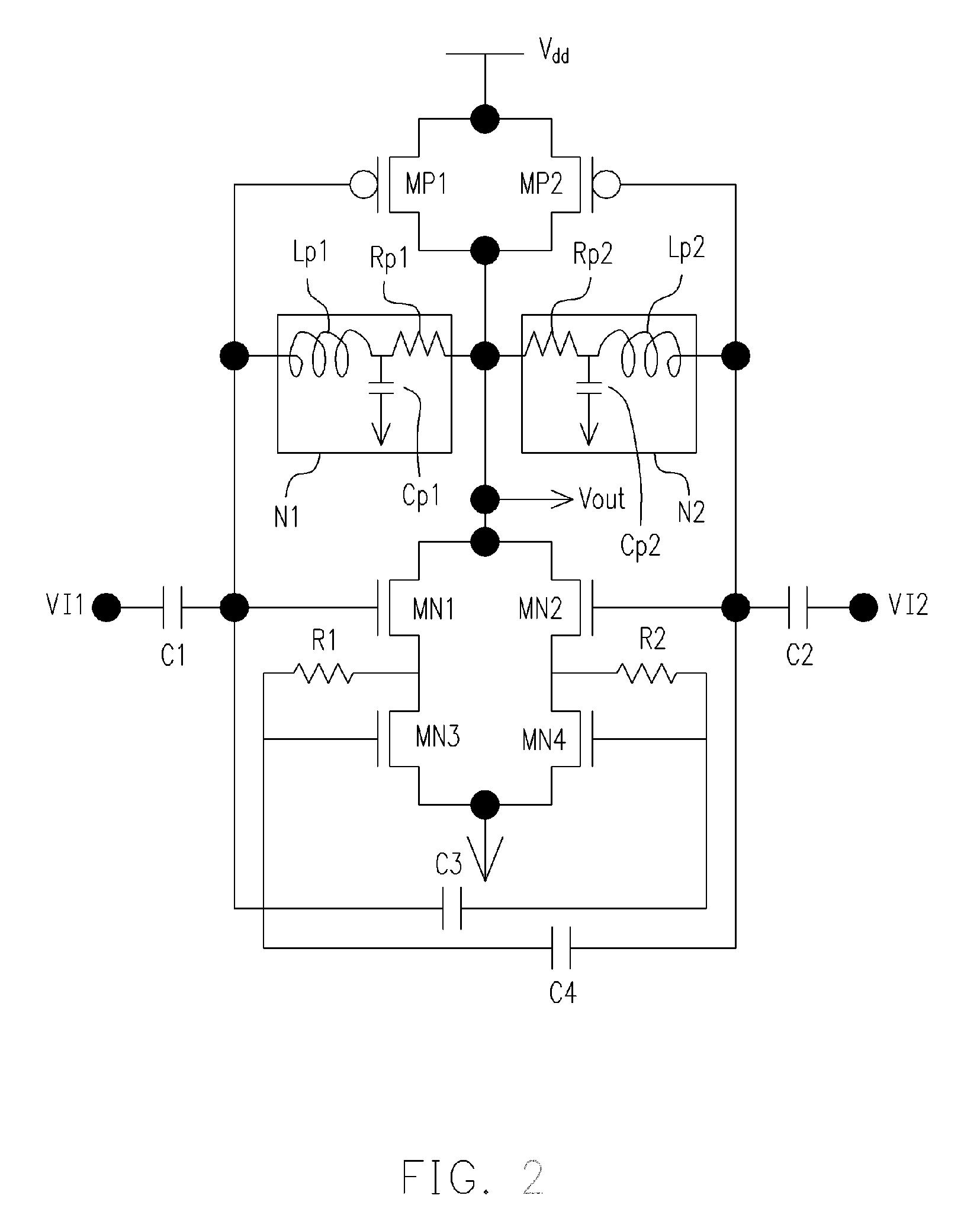

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

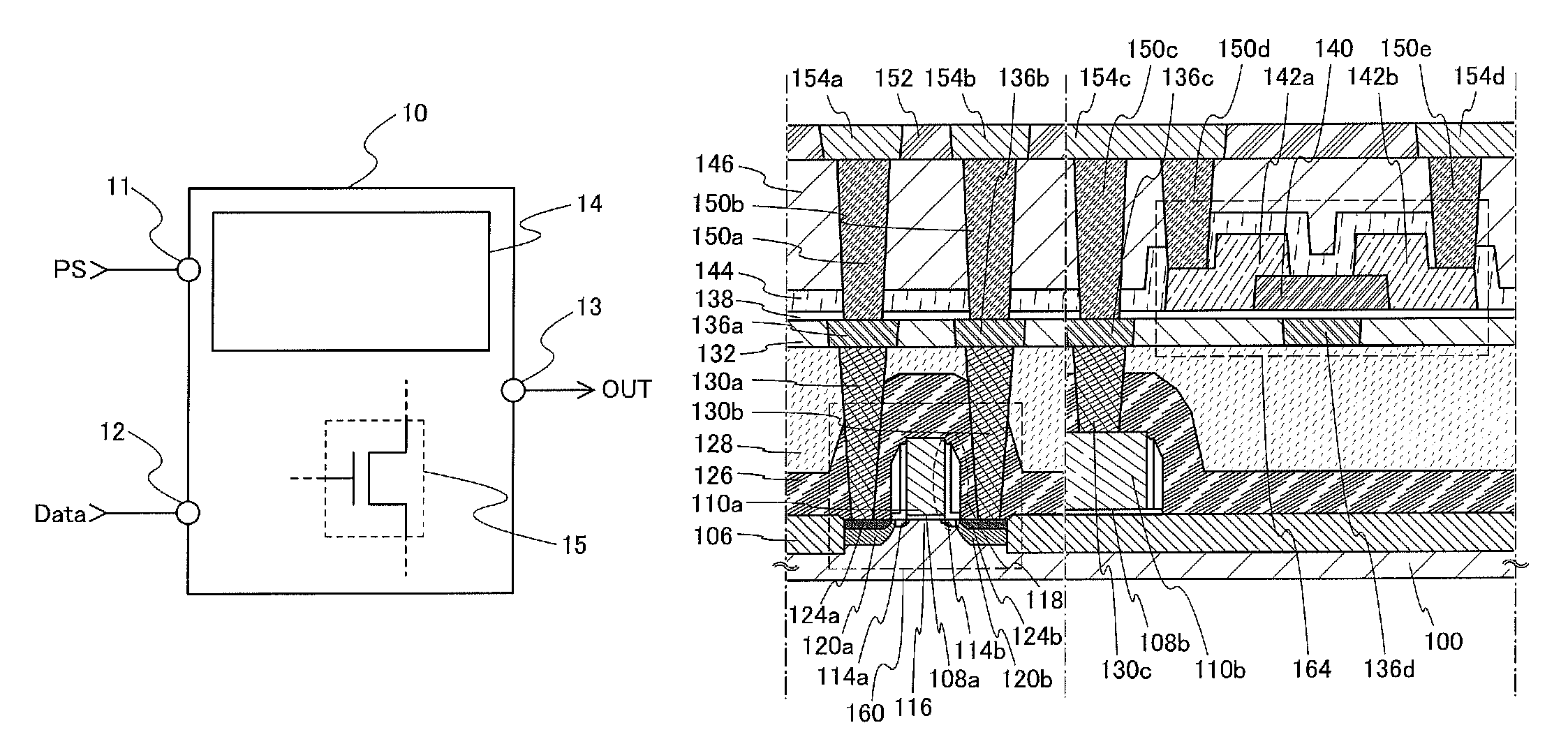

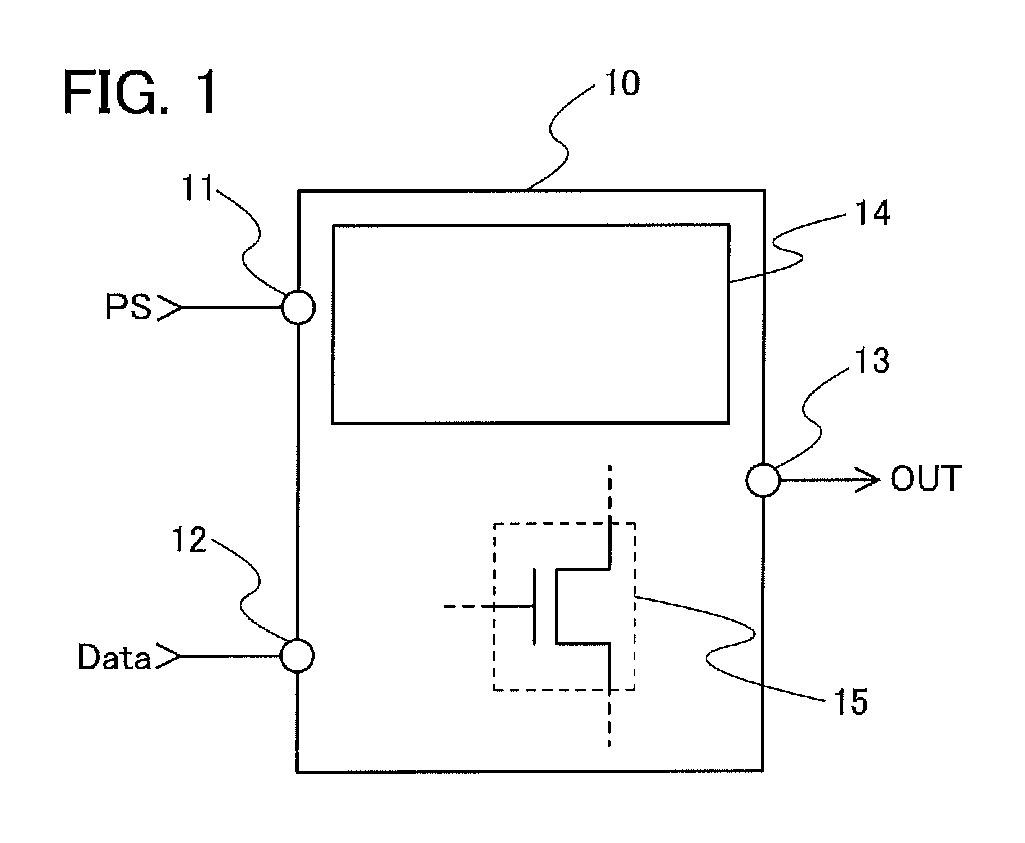

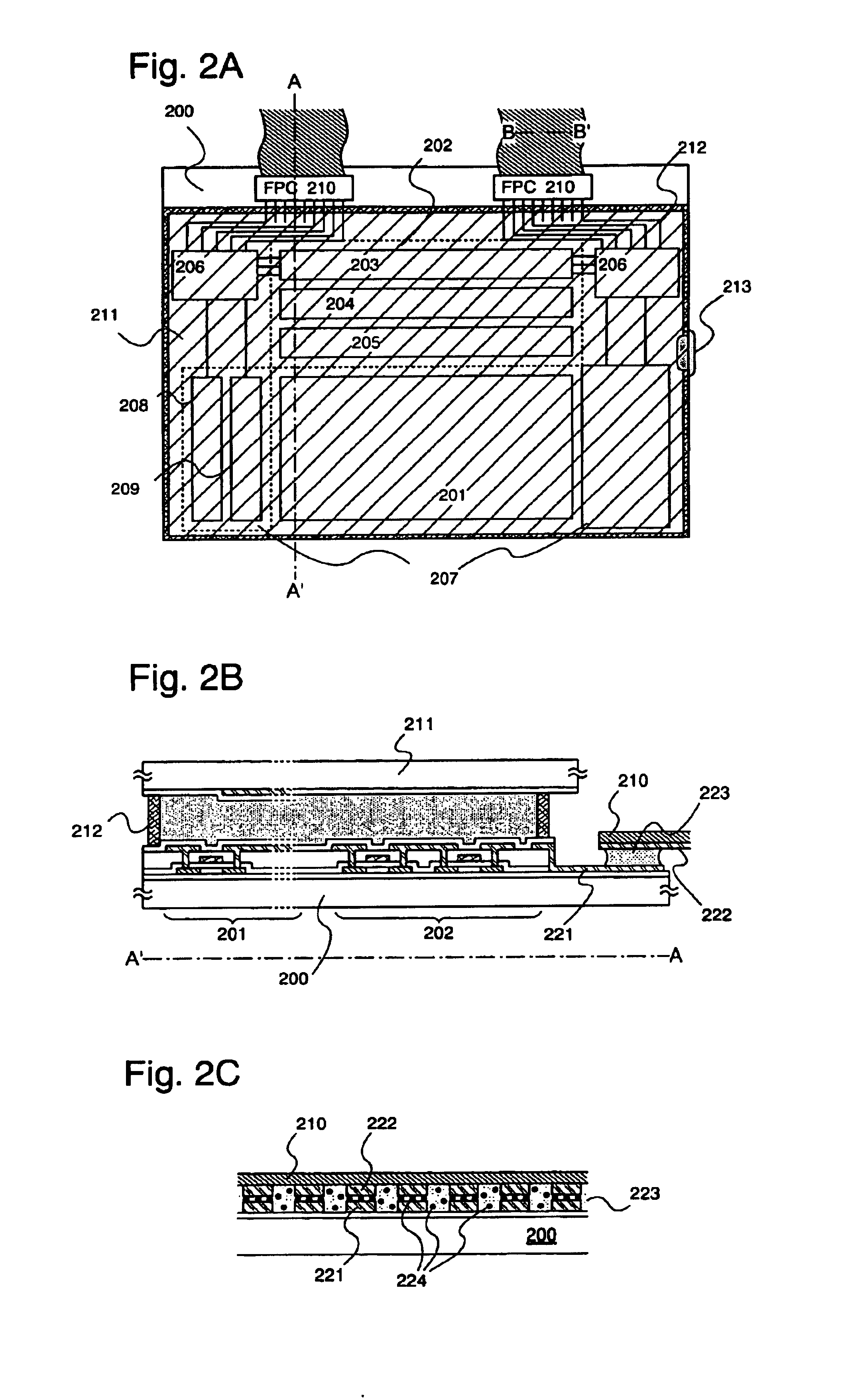

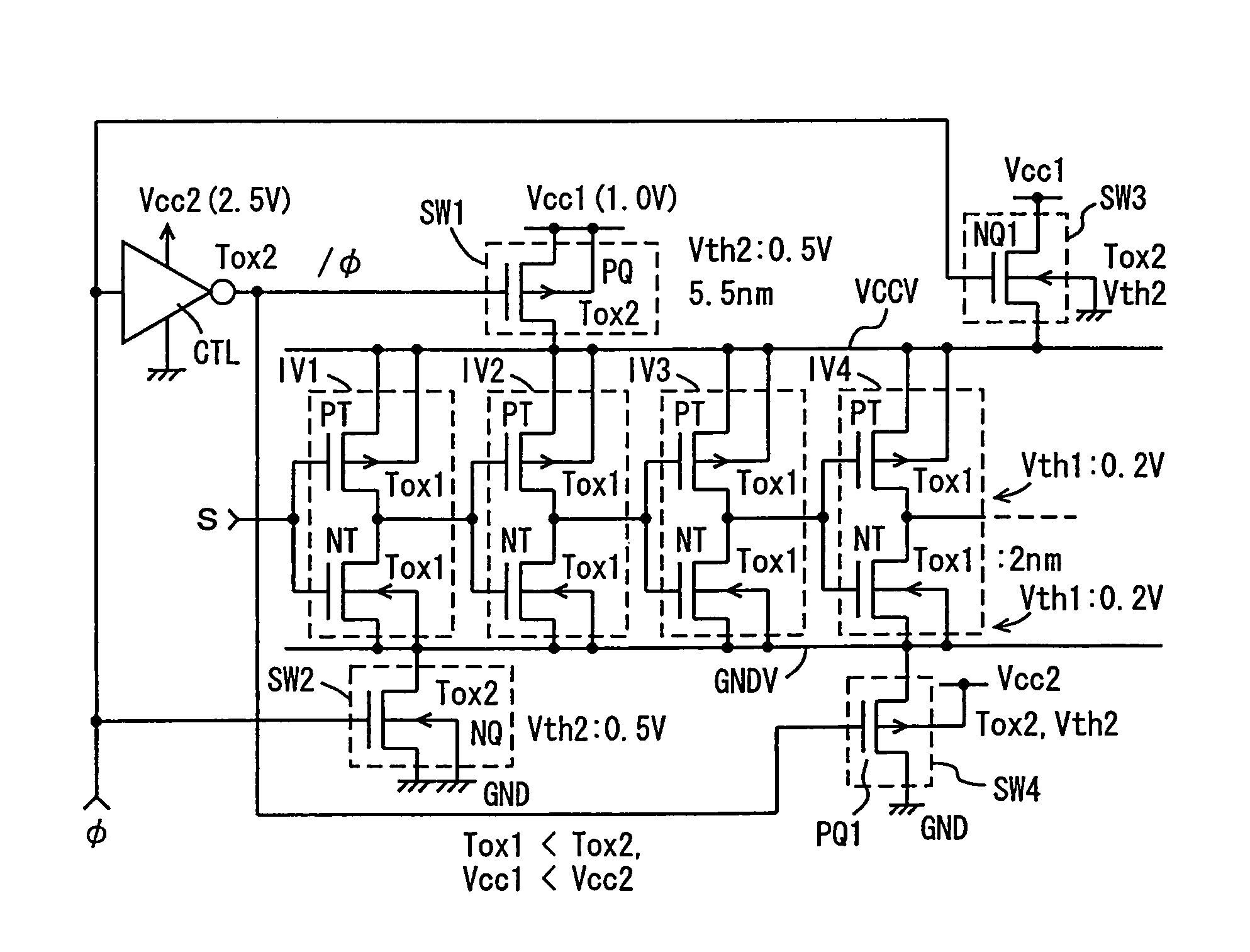

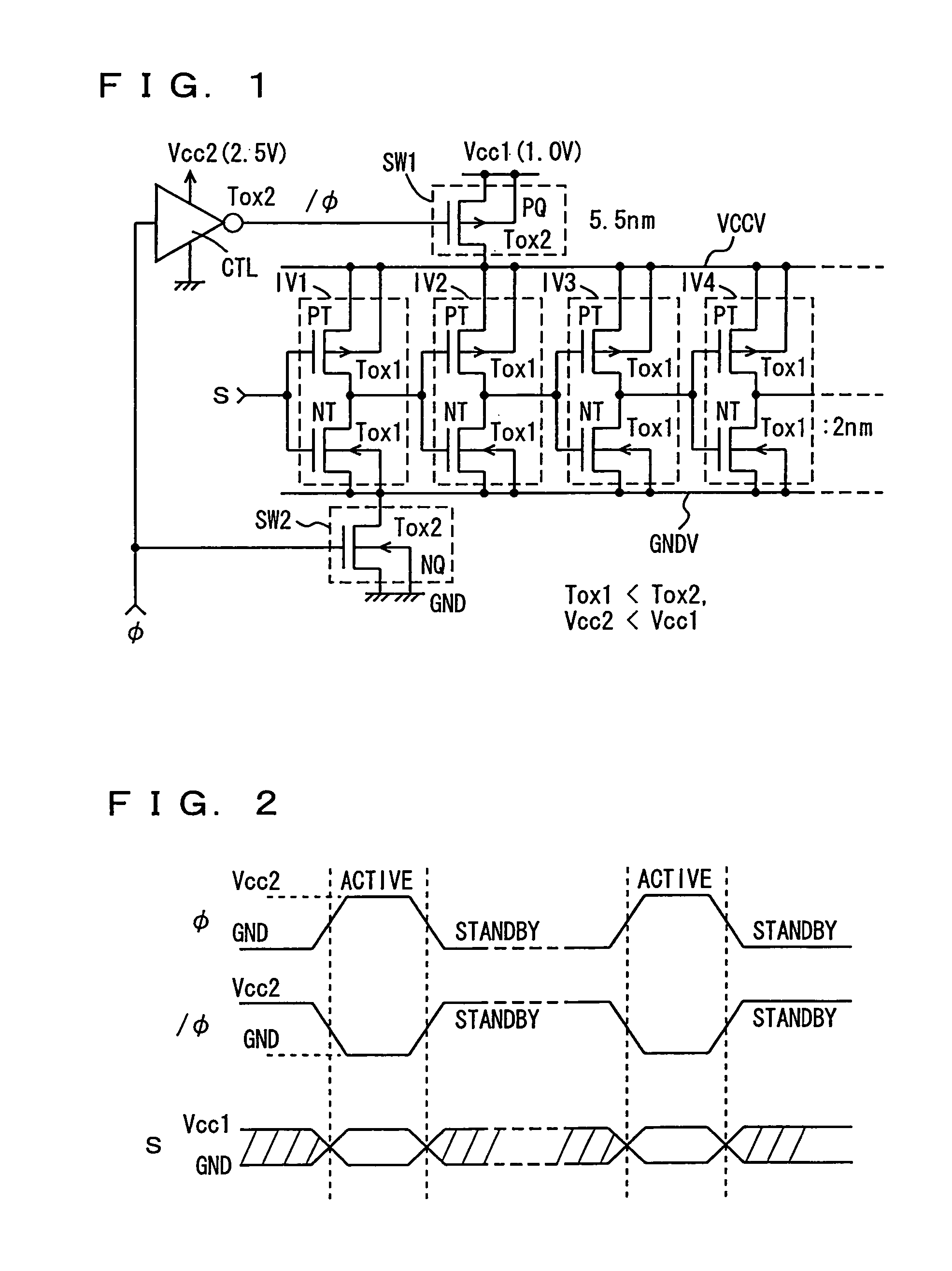

Logic circuit and semiconductor device

ActiveUS8207756B2Reduce dynamic power consumptionLeakage of highTransistorPower reduction by control/clock signalHydrogen concentrationPower semiconductor device

In a logic circuit where clock gating is performed, the standby power is reduced or malfunction is suppressed. The logic circuit includes a transistor which is in an off state where a potential difference exists between a source terminal and a drain terminal over a period during which a clock signal is not supplied. A channel formation region of the transistor is formed using an oxide semiconductor in which the hydrogen concentration is reduced. Specifically, the hydrogen concentration of the oxide semiconductor is 5×1019 (atoms / cm3) or lower. Thus, leakage current of the transistor can be reduced. As a result, in the logic circuit, reduction in standby power and suppression of malfunction can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

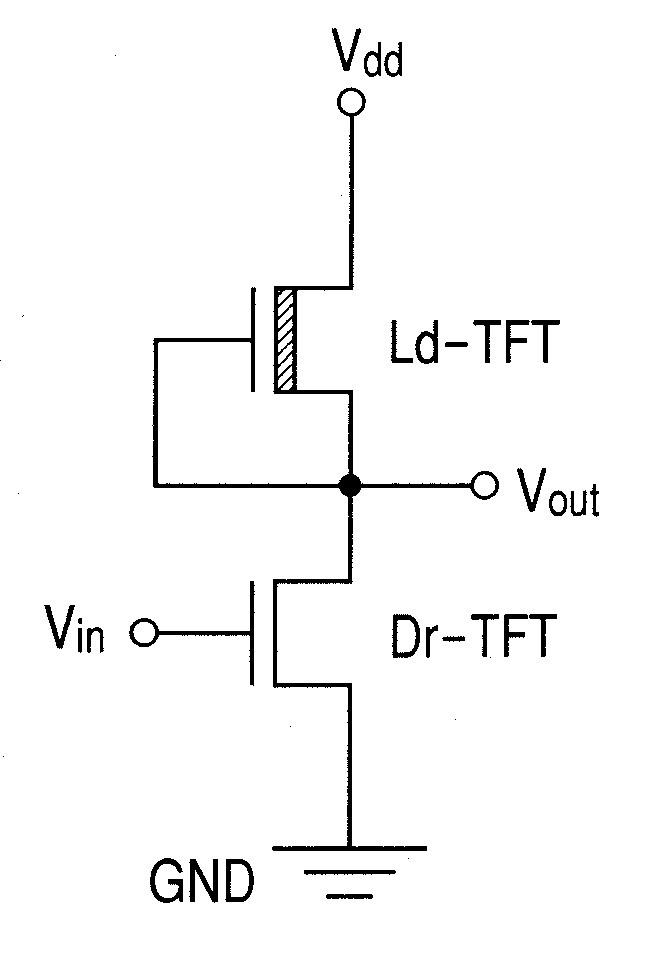

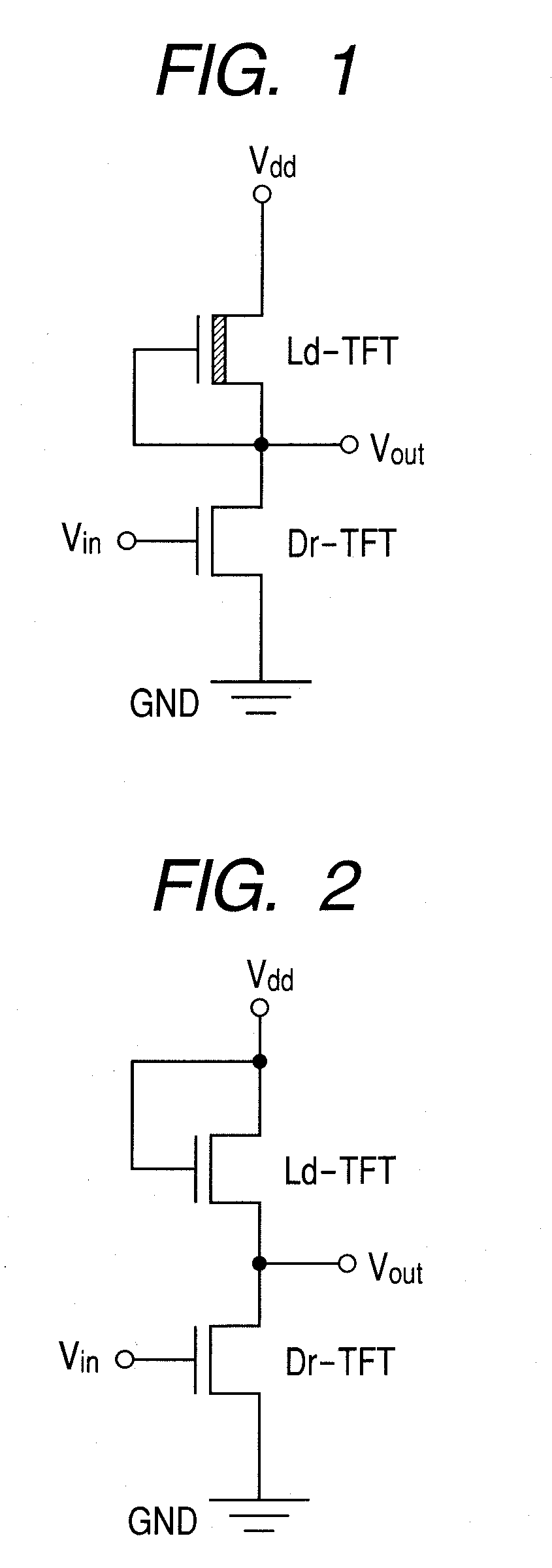

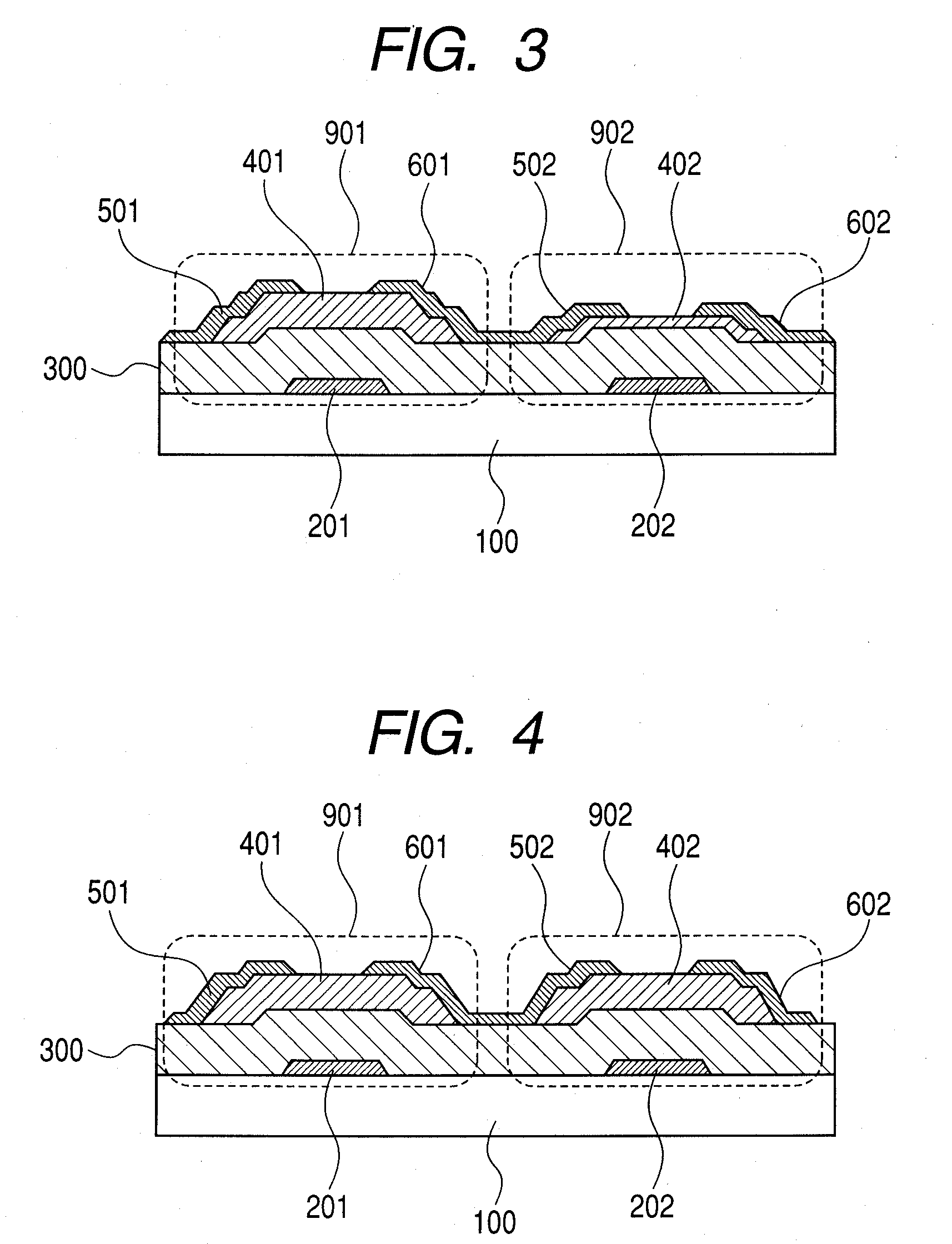

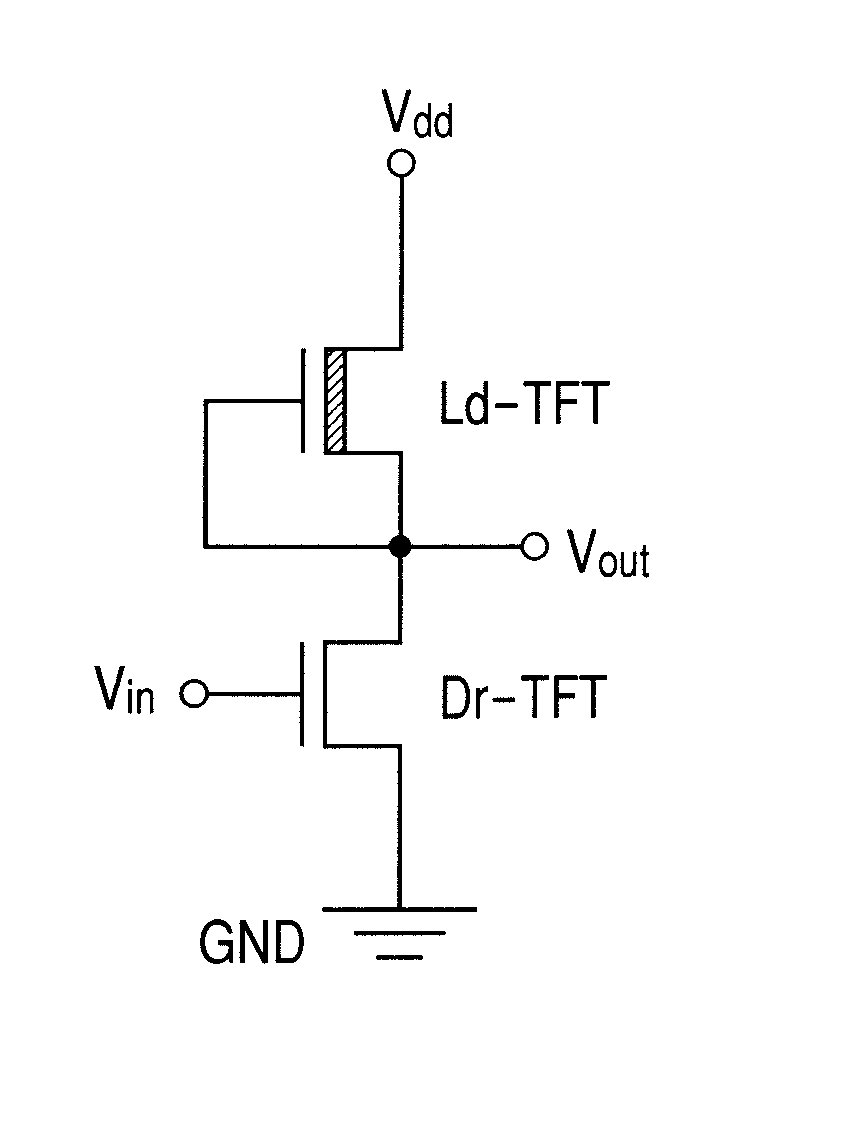

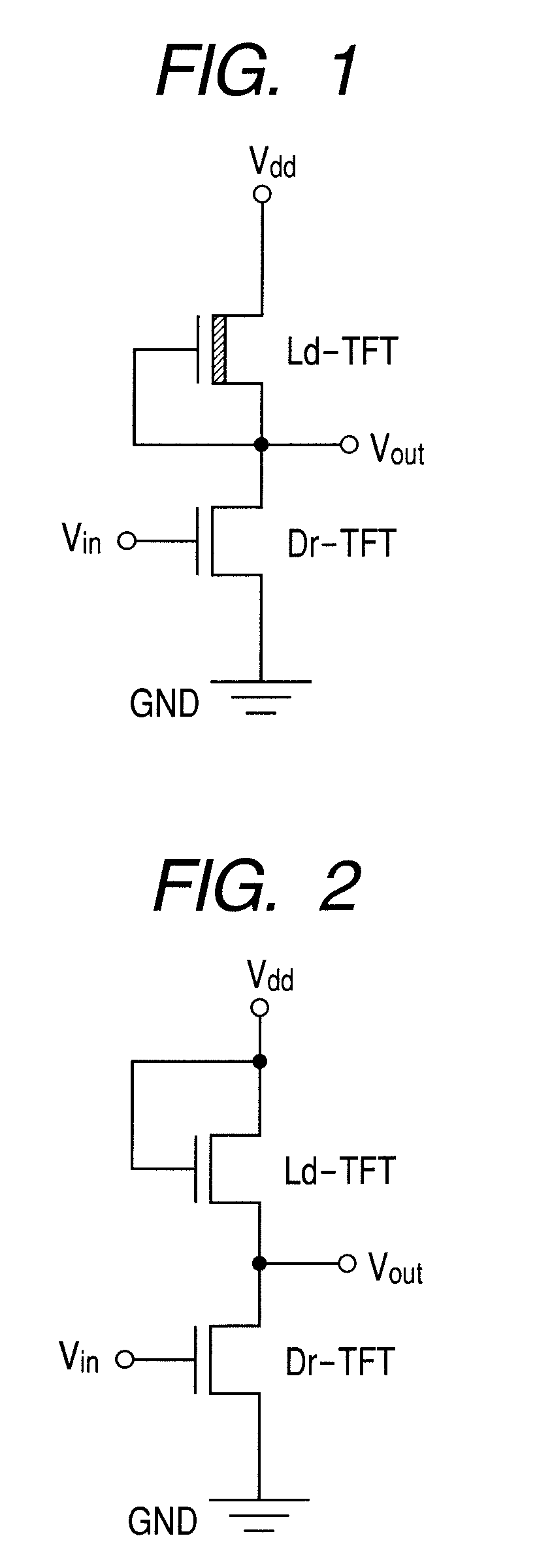

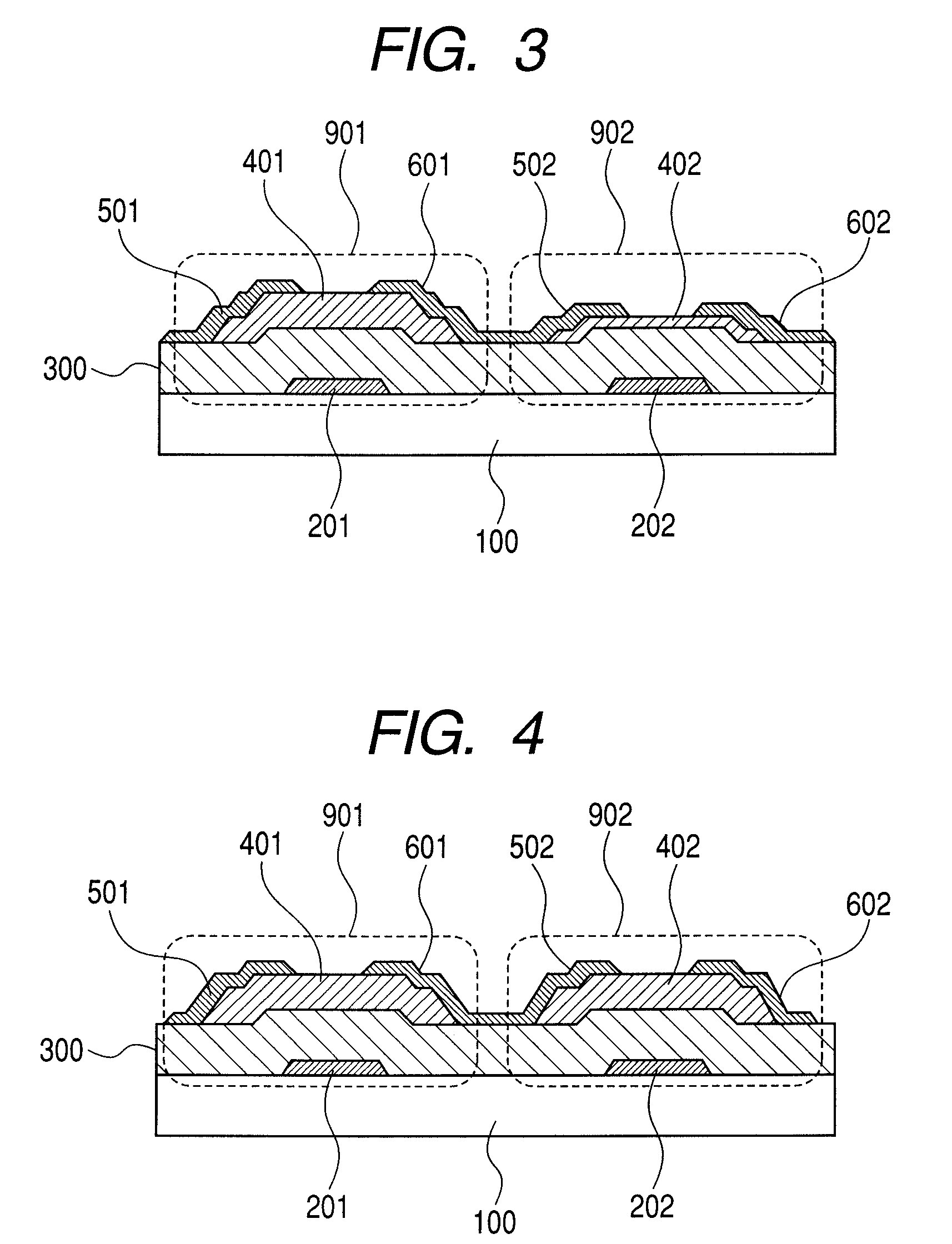

Inverter manufacturing method and inverter

ActiveUS20100085081A1Easy to manufactureIncrease the differenceLogic circuits characterised by logic functionSolid-state devicesEngineeringSemiconductor

To provide an enhancement-depletion (E / D) inverter which can be easily manufactured, in the present invention, a method of manufacturing an inverter which is composed of an oxide semiconductor in which a channel layer includes at least one element selected from In, Ga and Zn formed on a same substrate, the inverter being the E / D inverter having plural thin film transistors, is characterized by comprising the steps of: forming a first transistor and a second transistor, the thicknesses of the channel layers of the first and second transistors being mutually different; and executing heat treatment to at least one of the channel layers of the first and second transistors.

Owner:CANON KK

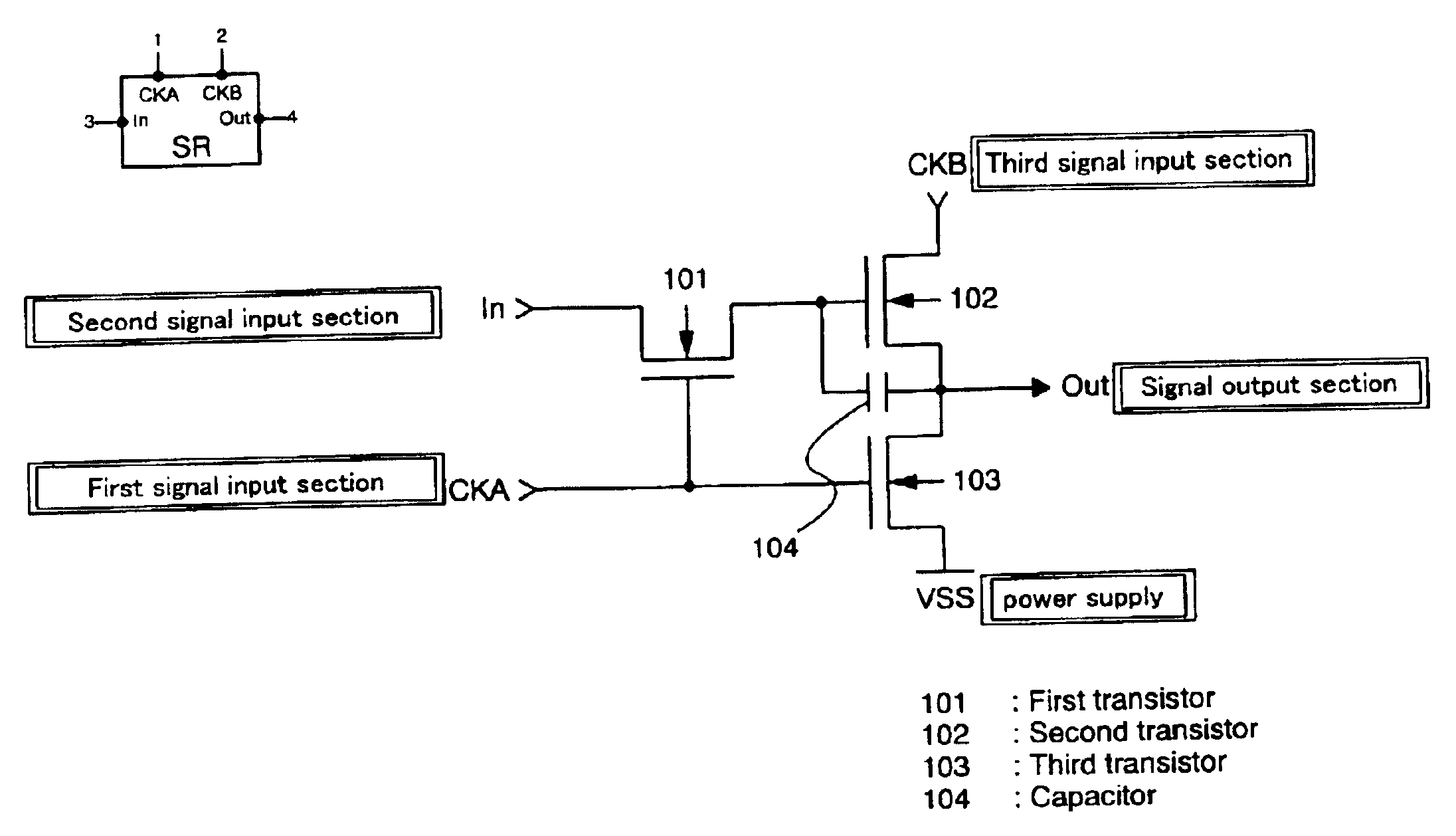

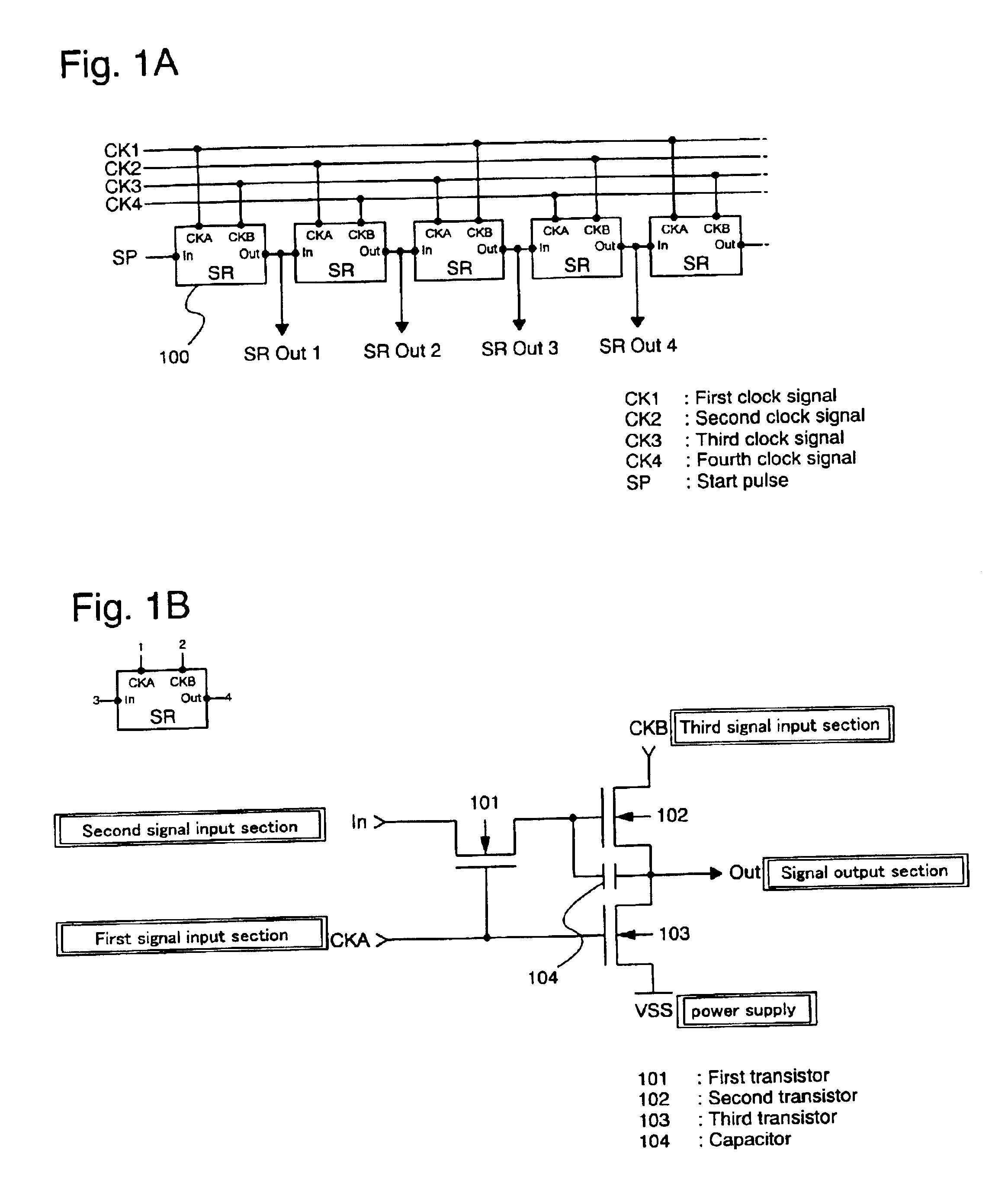

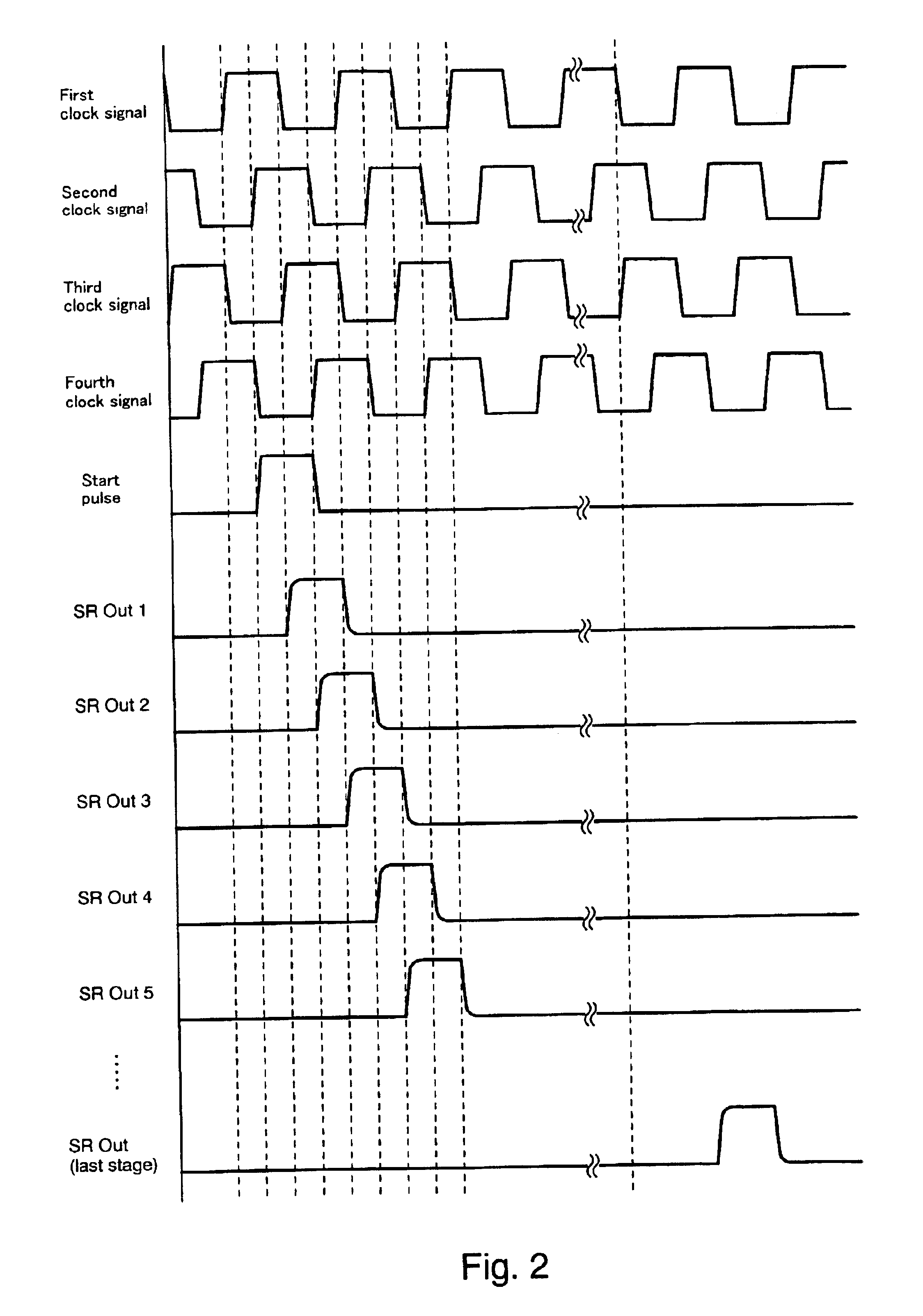

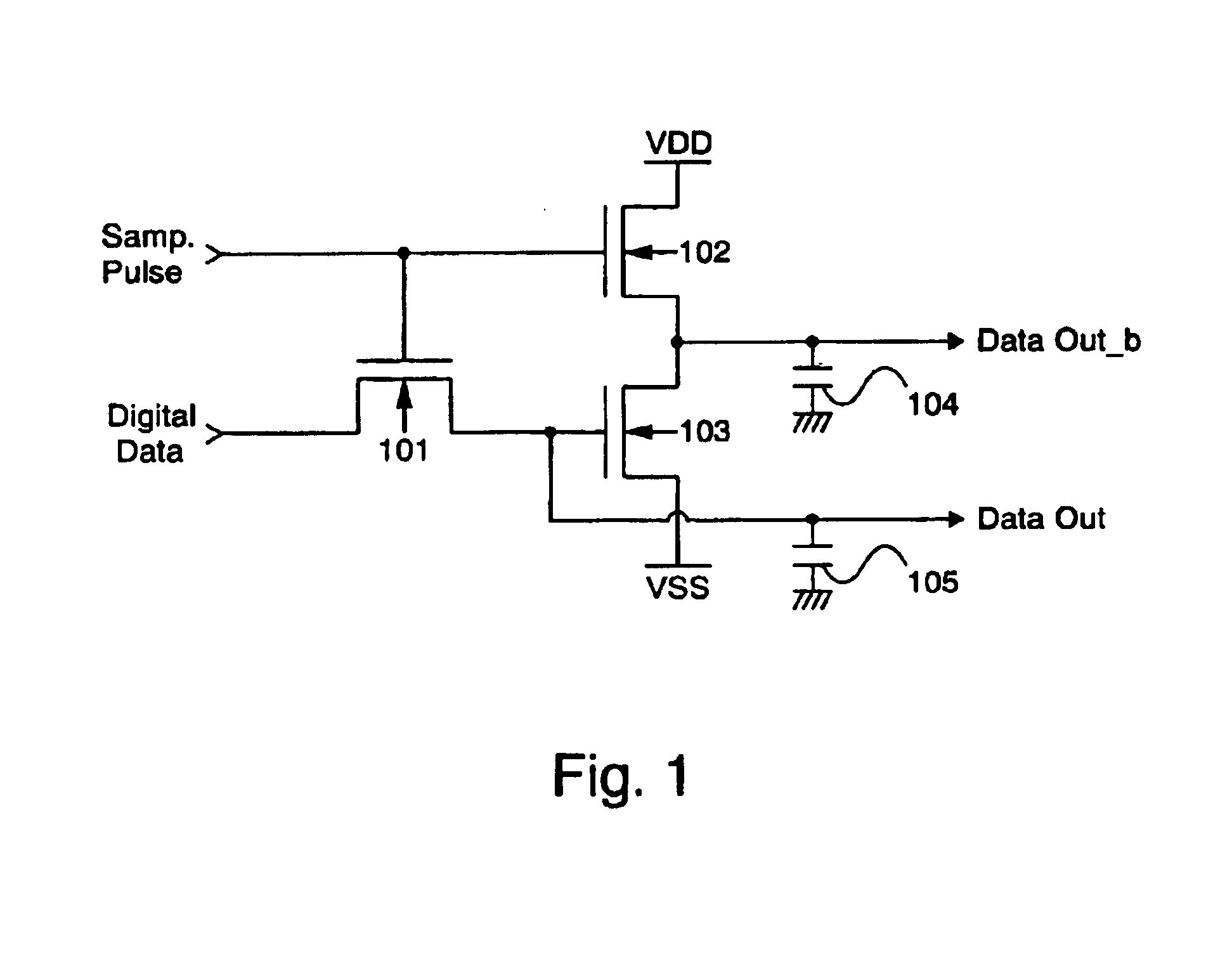

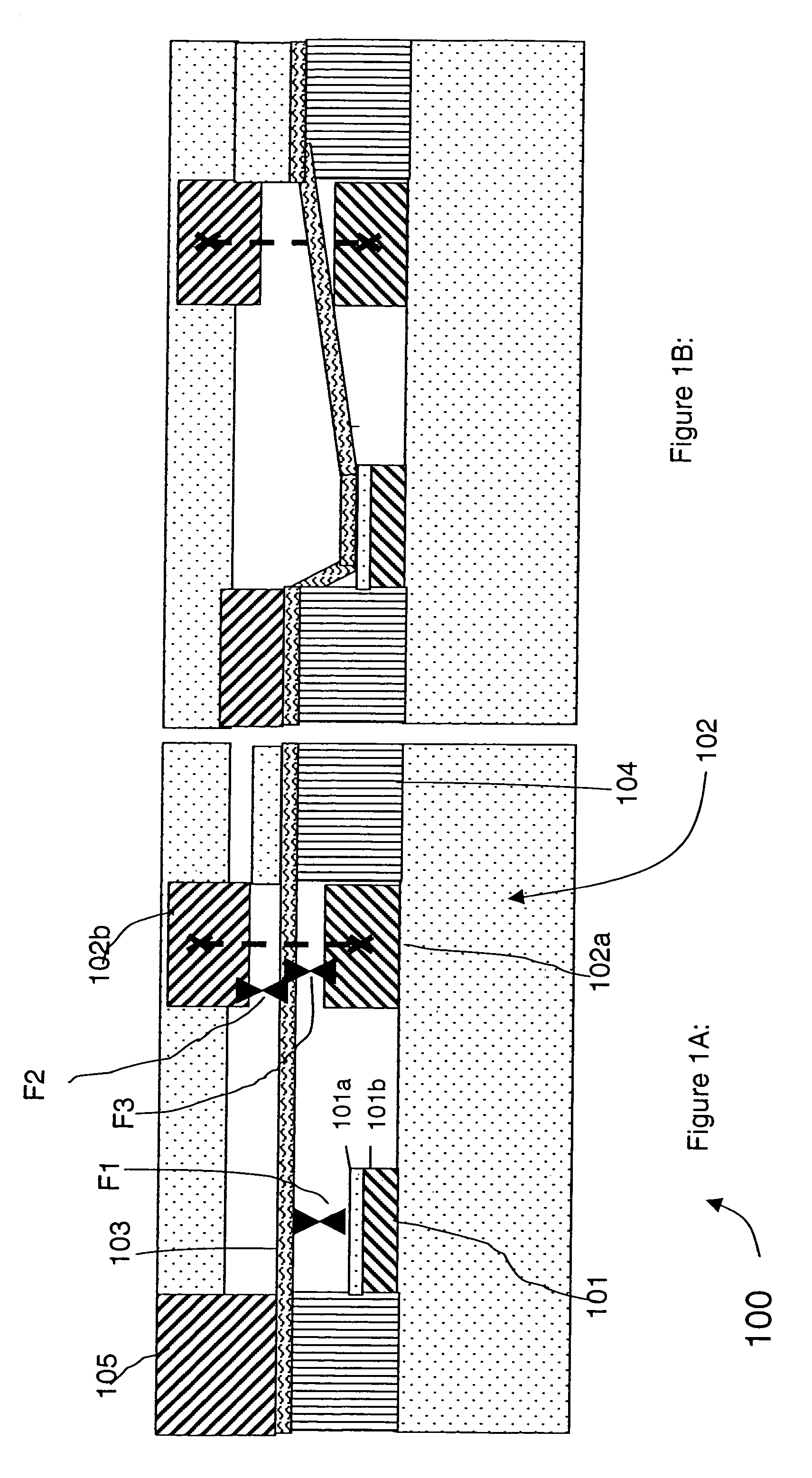

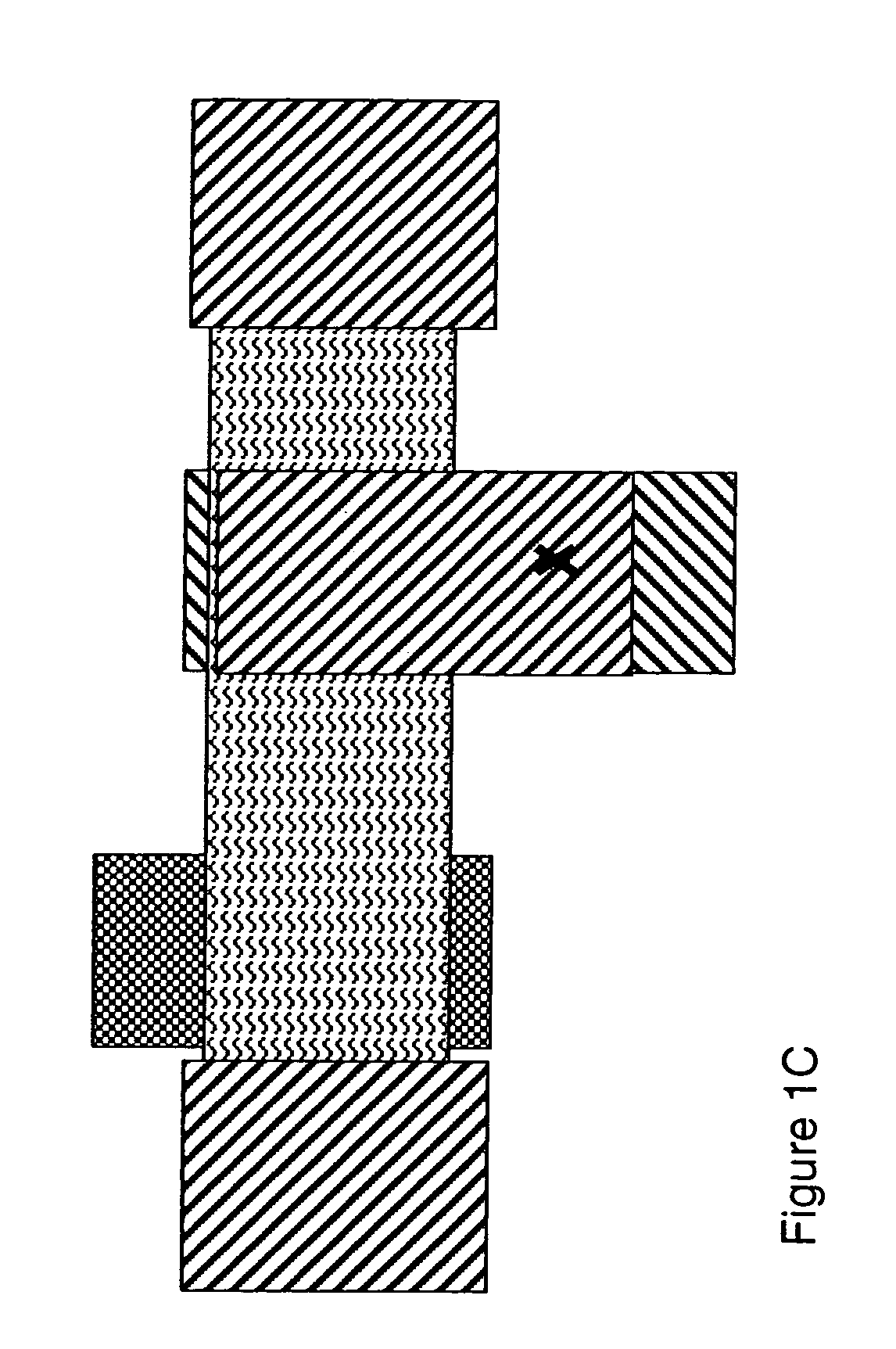

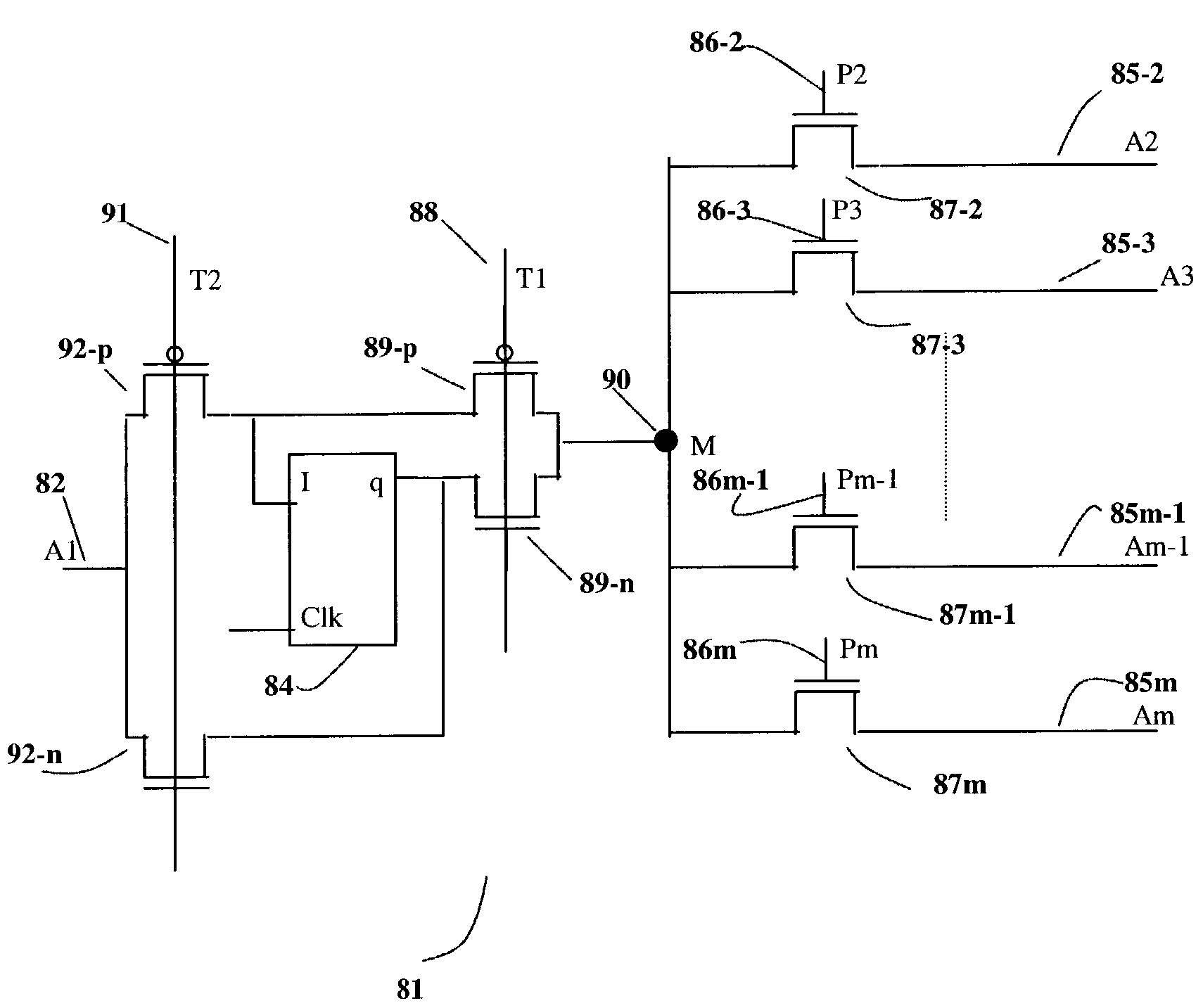

Pulse output circuit, shift register, and display device

InactiveUS6928136B2Low costReduce manufacturing stepsTransistorLogic circuits characterised by logic functionElectricityShift register

A circuit is provided which is constituted by TFTs of one conductivity type, and which is capable of outputting signals of a normal amplitude. When an input clock signal CK1 becomes a high level, each of TFTs (101, 103) is turned on to settle at a low level the potential at a signal output section (Out). A pulse is then input to a signal input section (In) and becomes high level. The gate potential of TFT (102) is increased to (VDD−V thN) and the gate is floated. TFT (102) is thus turned on. Then CK1 becomes low level and each of TFTs (101, 103) is turned off. Simultaneously, CK3 becomes high level and the potential at the signal output section is increased. Simultaneously, the potential at the gate of TFT (102) is increased to a level equal to or higher than (VDD+V thN) by the function of capacitor (104), so that the high level appearing at the signal output section (Out) becomes equal to VDD. When SP becomes low level; CK3 becomes low level; and CK1 becomes high level, the potential at the signal output section (Out) becomes low level again.

Owner:SEMICON ENERGY LAB CO LTD

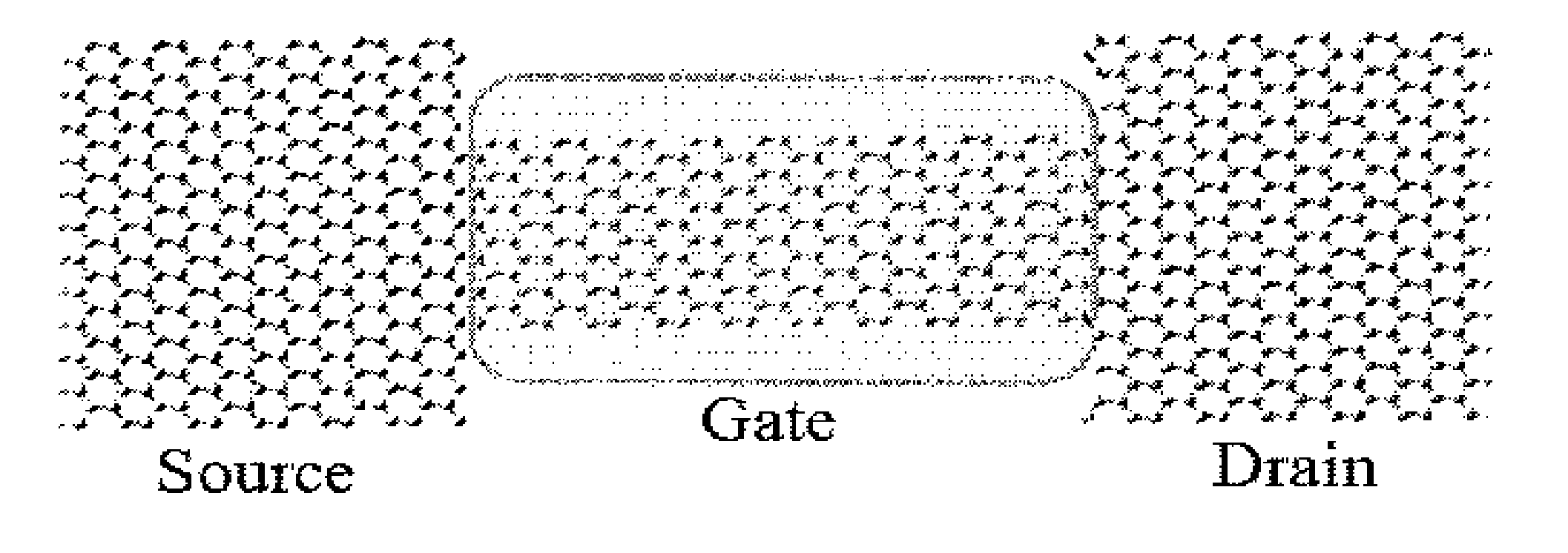

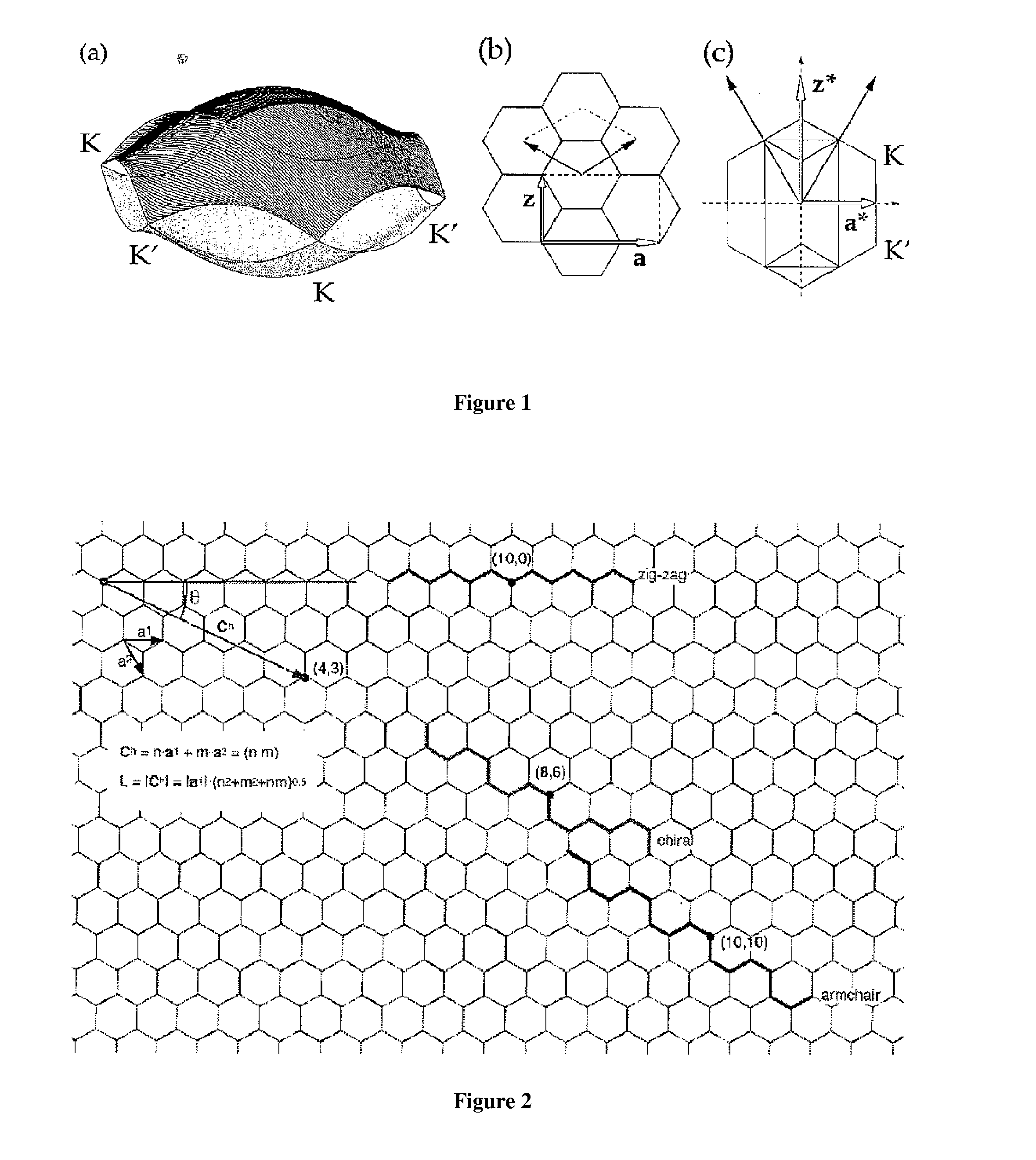

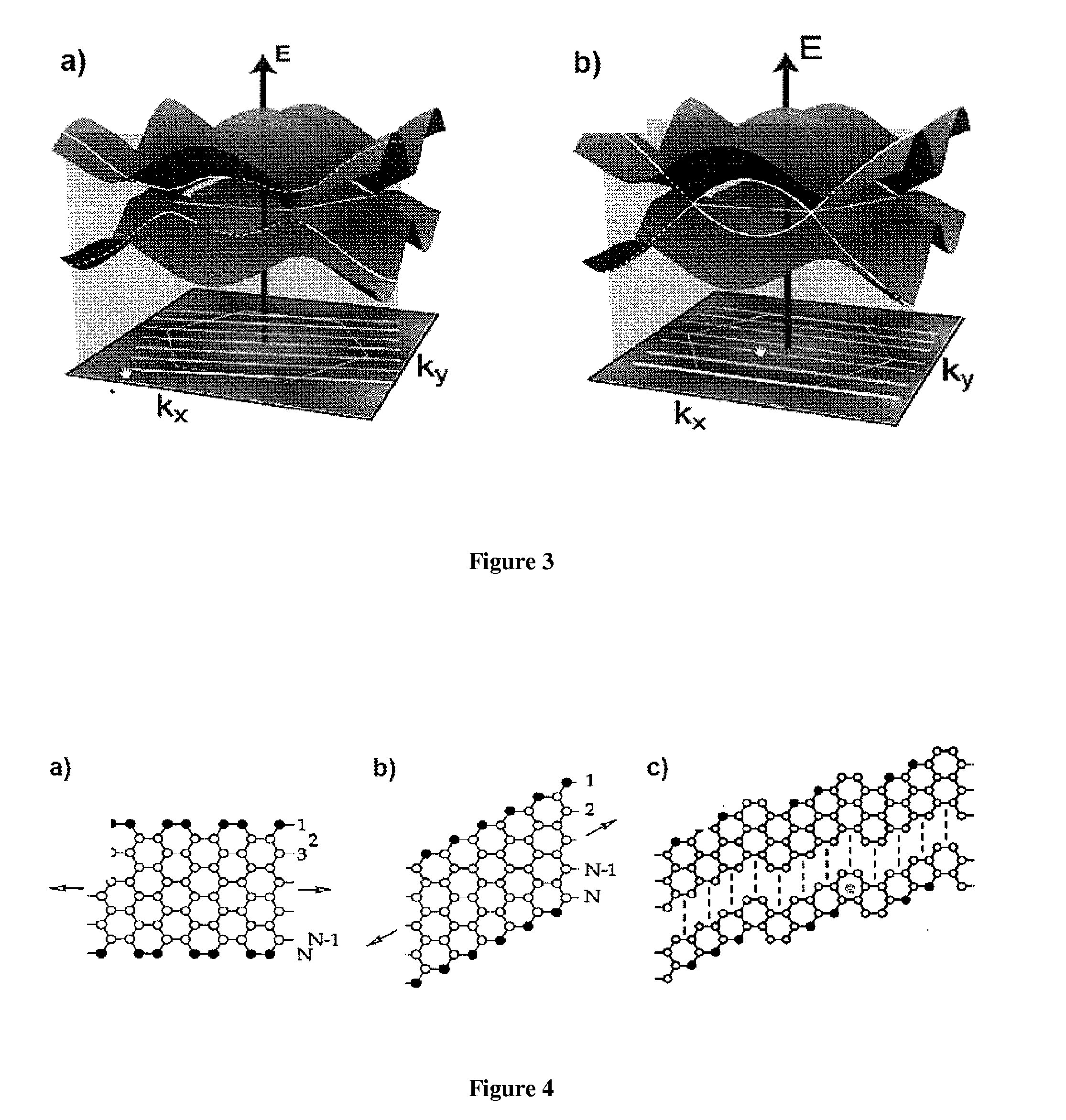

Monolithically-Integrated Graphene-Nano-Ribbon (GNR) Devices, Interconnects and Circuits

InactiveUS20090174435A1Logic circuits characterised by logic functionNanoinformaticsGraphene nanoribbonsElectronic component

The invention discloses new and advantageous uses for carbon / graphene nanoribbons (GNRs), which includes, but is not limited to, electronic components for integrated circuits such as NOT gates, OR gates, AND gates, nano-capacitors, and other transistors. More specifically, the manipulation of the shapes, sizes, patterns, and edges, including doping profiles, of GNRs to optimize their use in various electronic devices is disclosed.

Owner:UNIV OF VIRGINIA

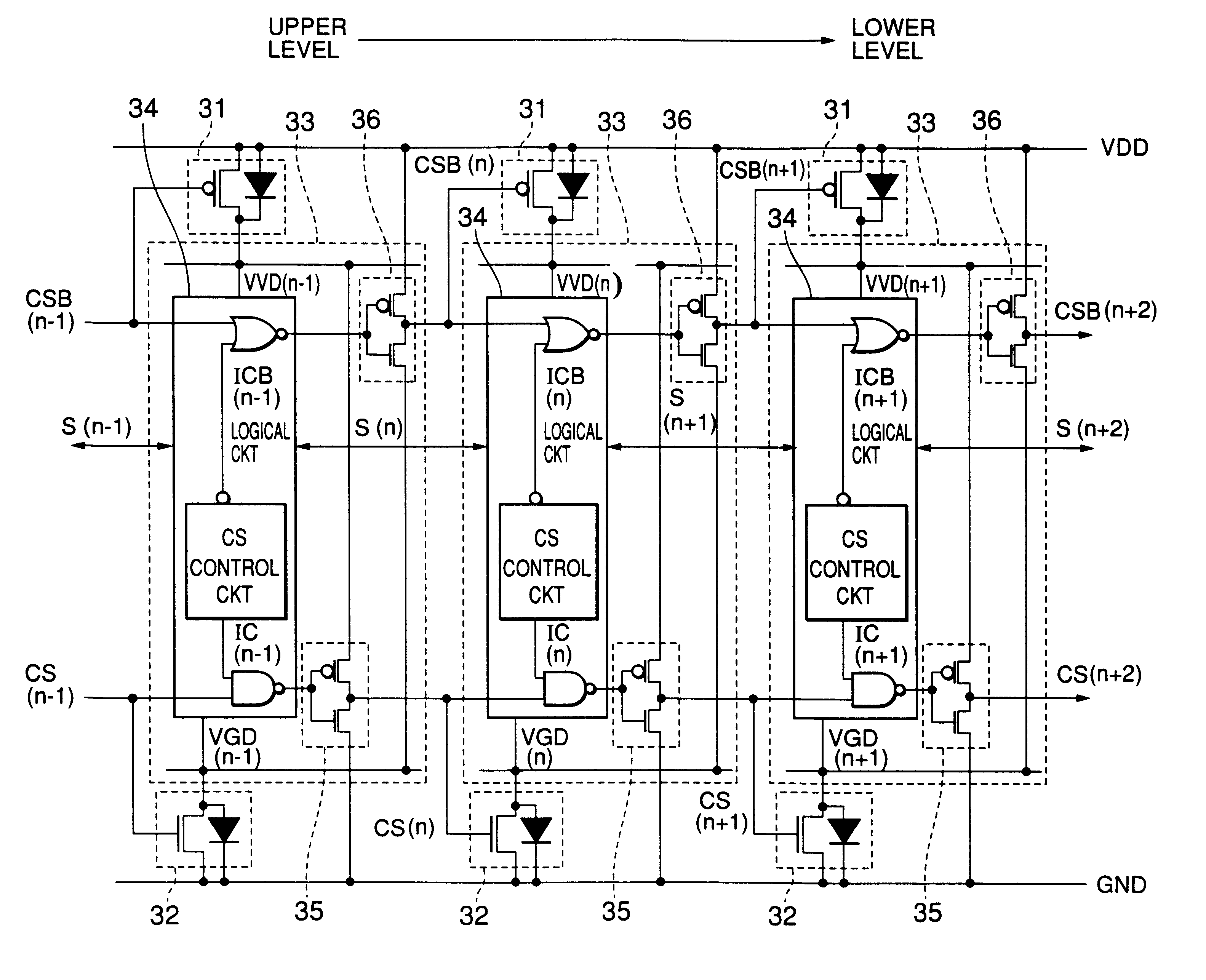

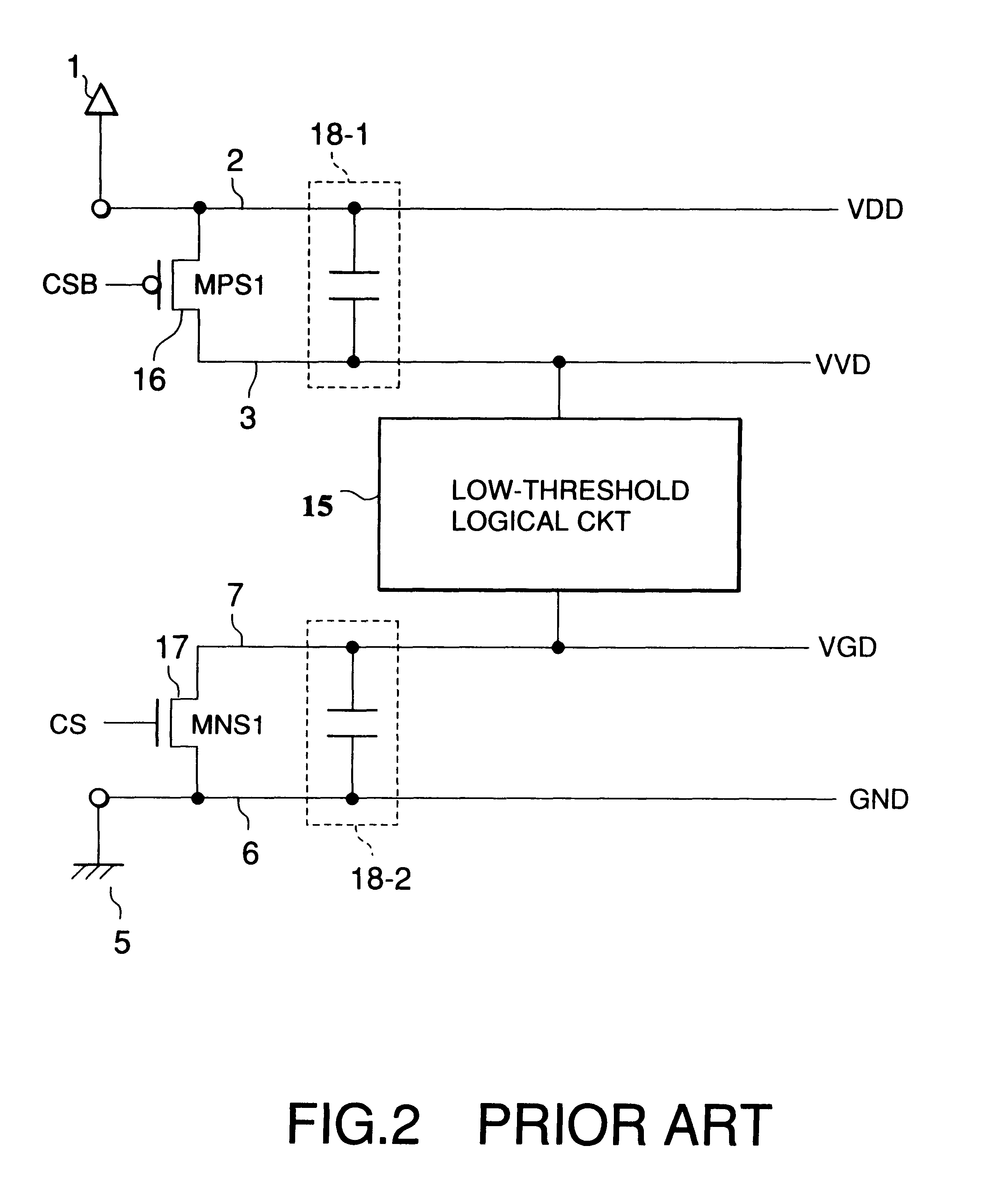

Semiconductor integrated circuit device with low power consumption and simple manufacturing steps

InactiveUS6208171B1Reduce manufacturing stepsProduction costPower reduction by control/clock signalLogic circuits characterised by logic functionPotential clampBack bias

In a semiconductor integrated circuit, a control transistor 4 and a potential clamp circuit 9 are arranged between a power supply line 2 and a virtual power supply line 3. Even in a sleeve mode where the control transistor 4 is turned off, the potential clamp circuit 9-1 clamps the virtual power supply line 3 at a certain potential to hold a potential state (high level or low level) of each node of a logical circuit. At this time, each FET forming the logical circuit is applied with a back bias so that a threshold voltage Vt becomes higher than that in an active mode. Therefore, a leakage current can be decreased. In the semiconductor integrated circuit, the threshold voltage Vt of the control transistor 4 can be selected to be equal to that of one FET of the complementary FET forming the logical circuit. Therefore, the layout area and the number of manufacturing steps can be reduced.

Owner:NEC CORP

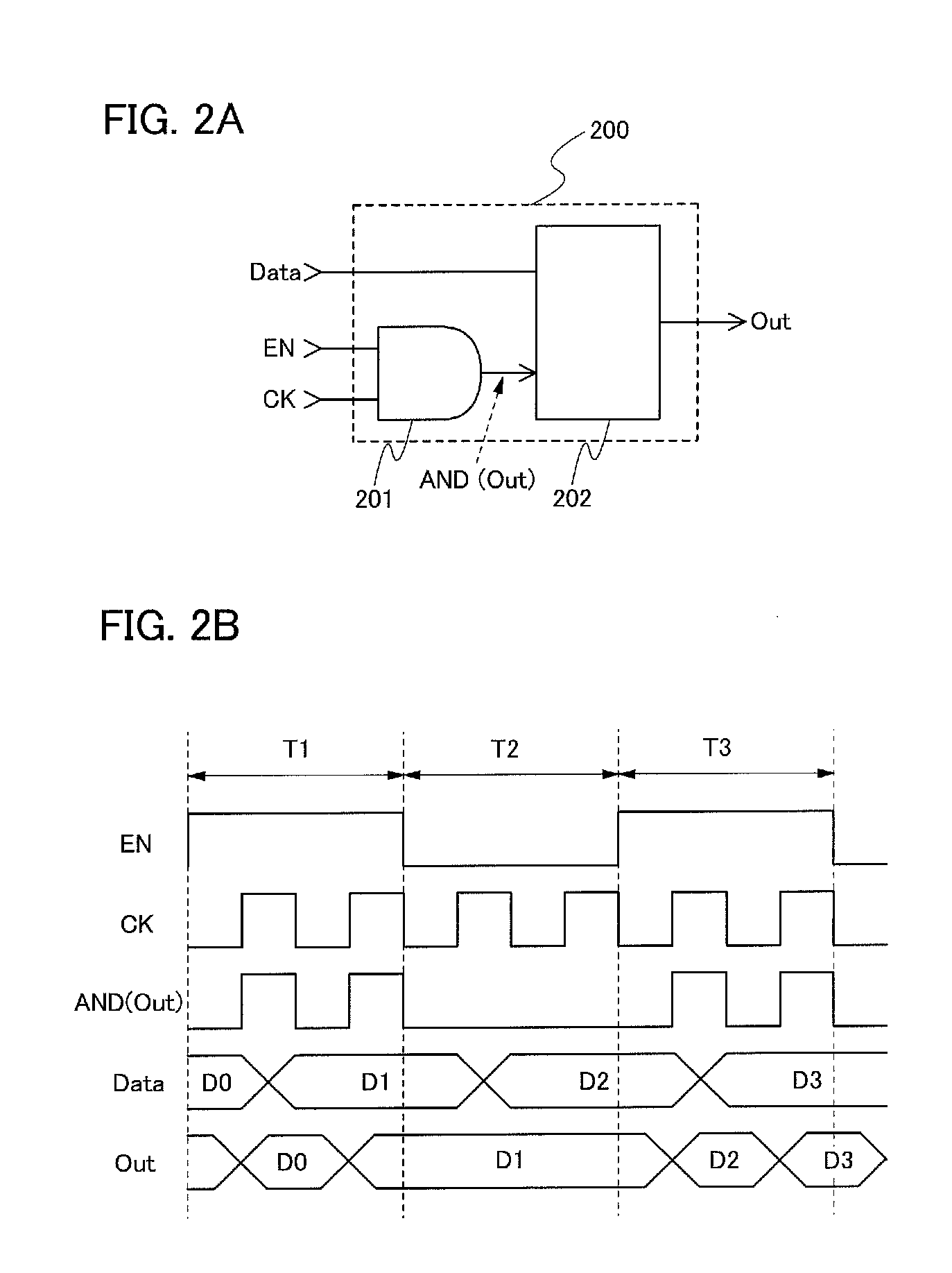

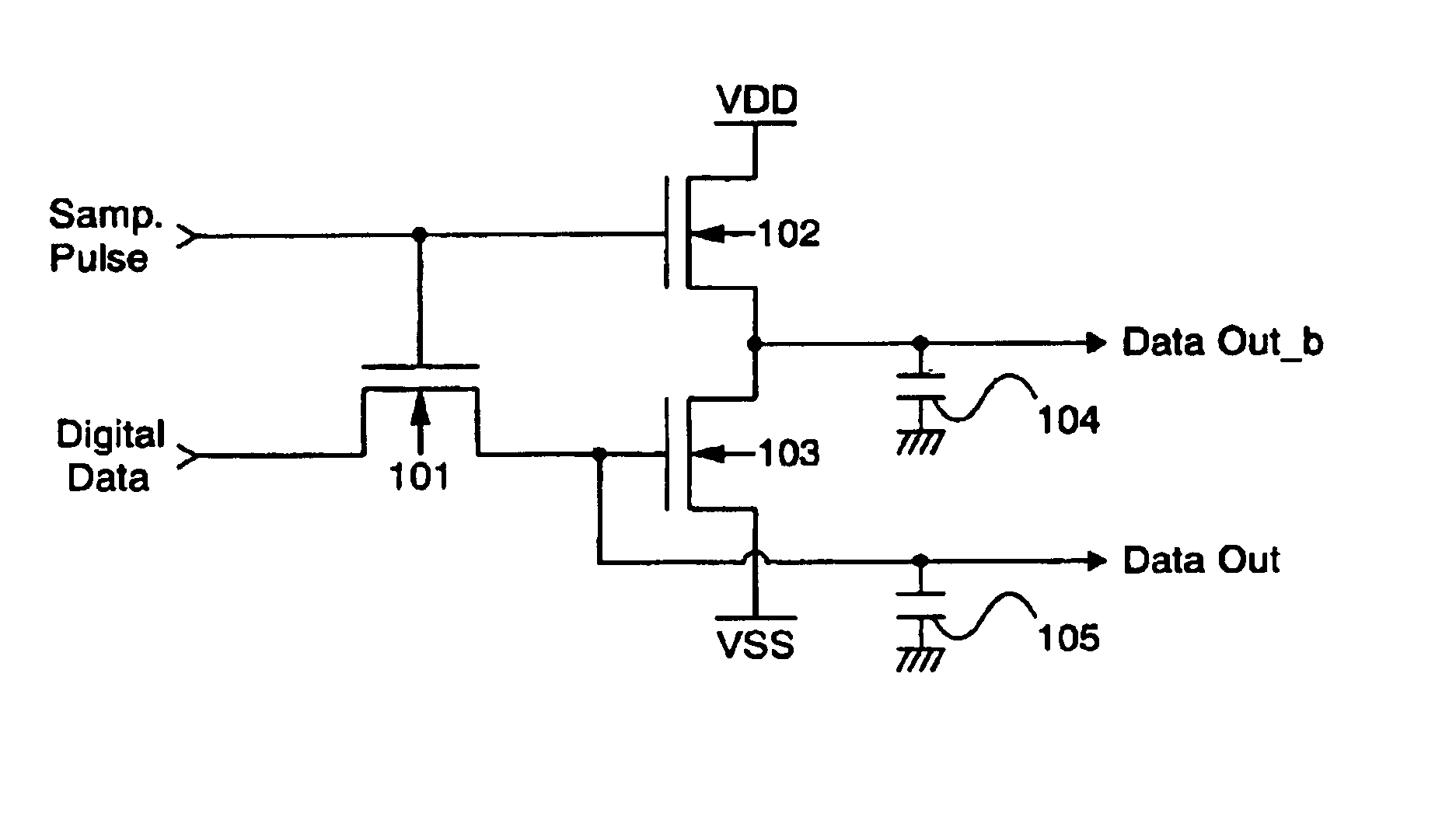

Semiconductor device and display device

InactiveUS7068076B2Obstruction is producedPower reduction in field effect transistorsLogic circuits characterised by logic functionDigital videoDevice material

A circuit capable of reducing a consumption current is provided for a digital display device composed of unipolar TFTs. There is provided a latch circuit for holding a digital video signal. According to the latch circuit, when the digital video signal is inputted to an input electrode of a TFT (101), a non-inverting output signal is outputted from an output electrode of the TFT (101) and an inverting output signal is outputted from output electrodes of TFTs (102 and 103). Two line outputs of non-inversion and inversion are obtained. Thus, when a buffer located in a subsequent stage is operated, a period for which a direct current path is produced between a high potential and a low potential of a power source can be shortened, thereby contributing to reduction in a consumption current.

Owner:SEMICON ENERGY LAB CO LTD

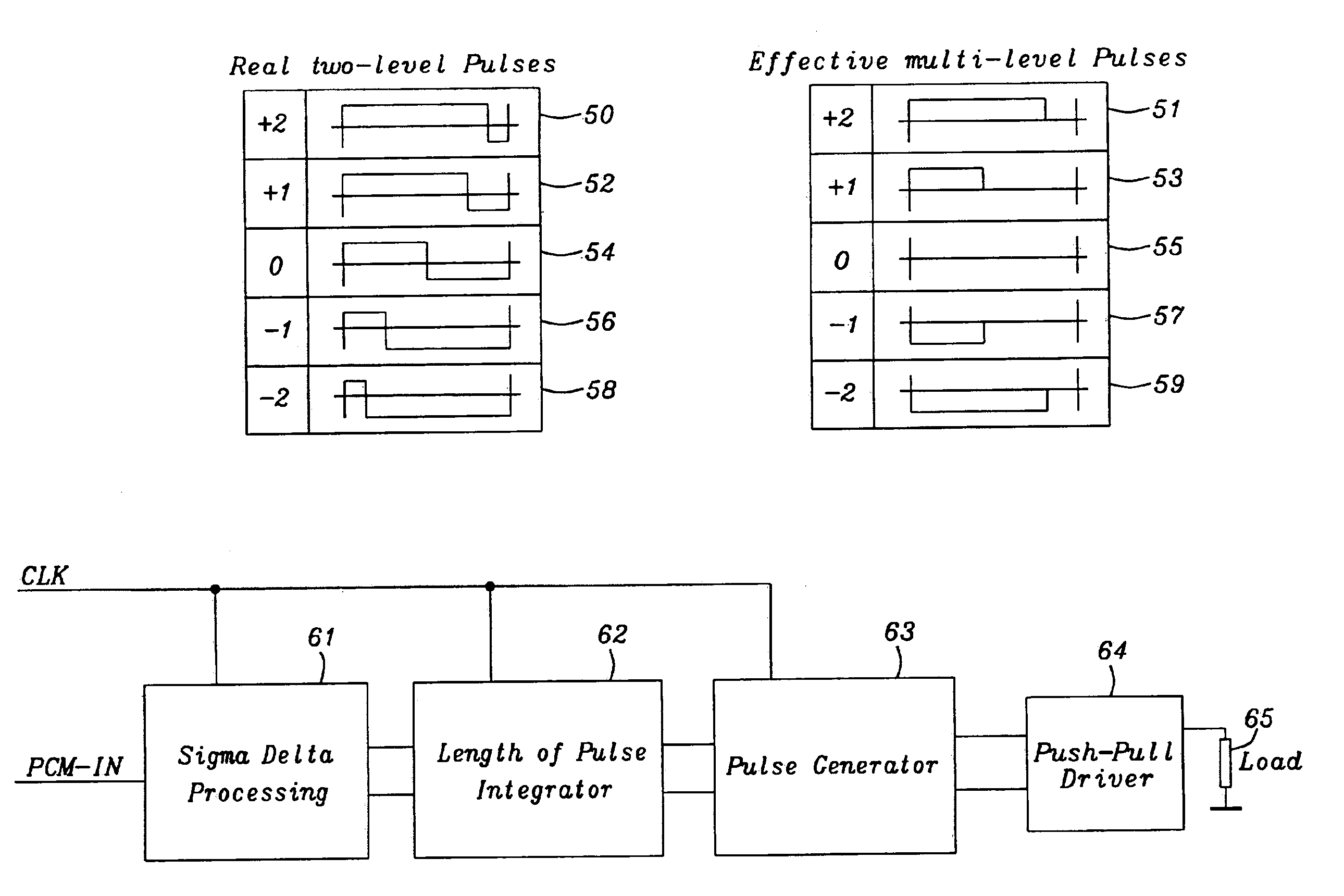

Multi-level Class-D amplifier by means of 2 physical layers

InactiveUS6842070B2Good quality output signalReduce electromagnetic interferencePush-pull amplifiersPhase-splittersSignal qualityClass-D amplifier

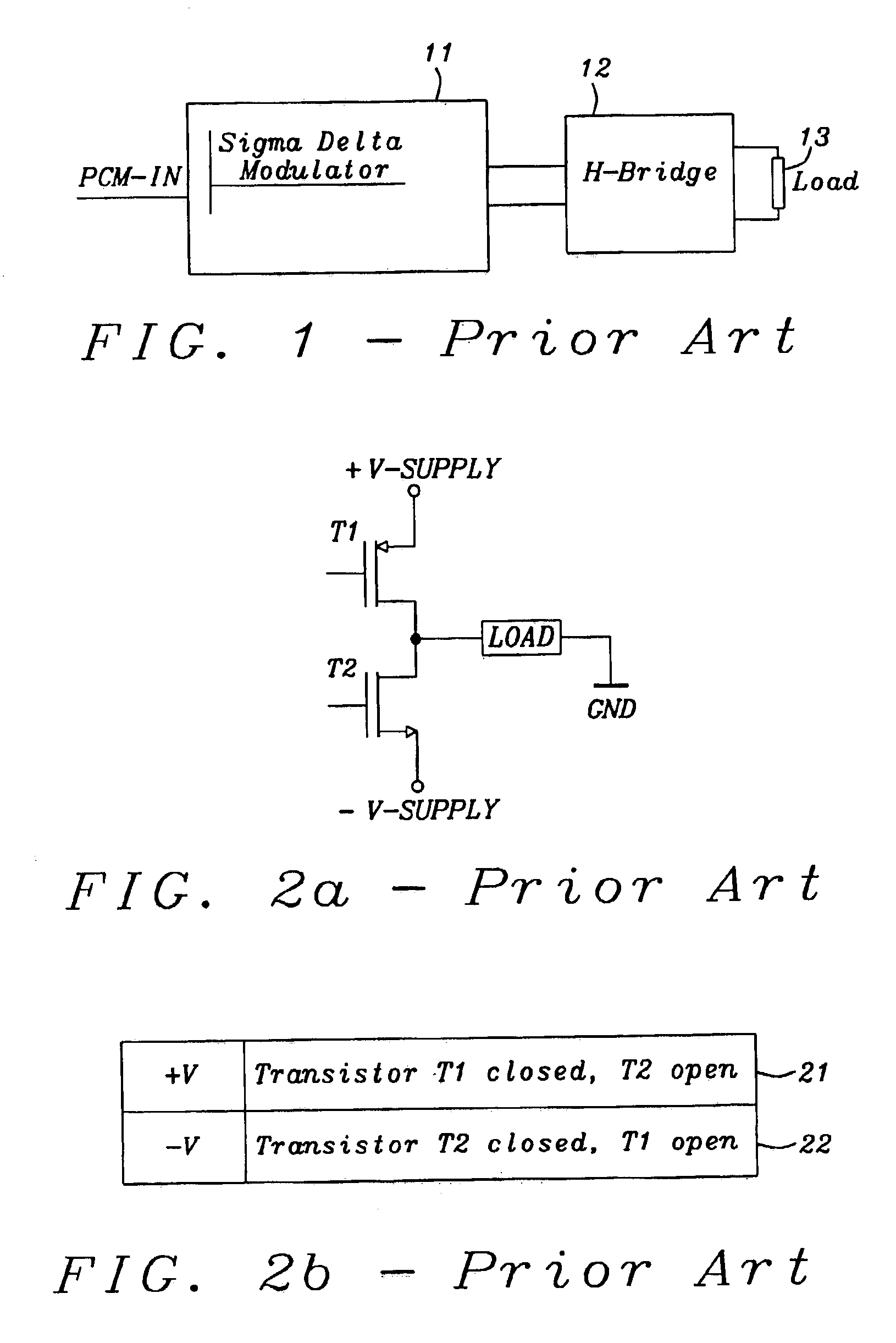

Introduce a pulse length control mechanism to generate virtual multi-level output pulses for a Class-D Amplifier, which has only 2 physical output levels. Typically a Sigma-Delta-Modulator converts the input signal into high frequency low bit rate. The disclosed invention adds functions to transform the SDM signal into pulses with equivalent multi-level time-voltage areas and adds a pulse-length-control mechanism to produce various output pulse patterns, where the summations of the positive and negative pulses, within one sampling period, result in time-voltage area values, corresponding to 3 or more digital levels. Thus the invention produces higher signal quality at lower sampling rates.

Owner:DIALOG SEMICONDUCTOR GMBH

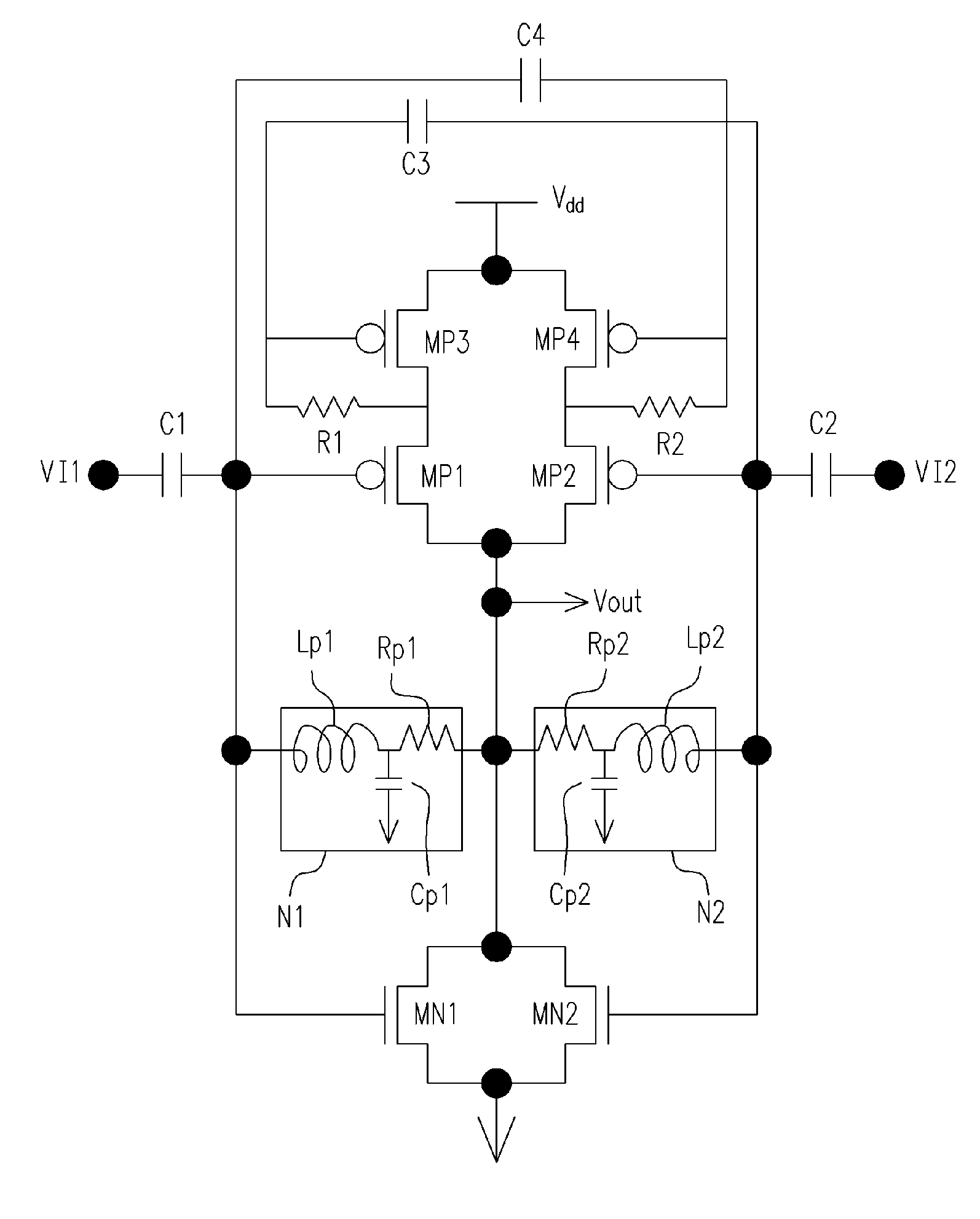

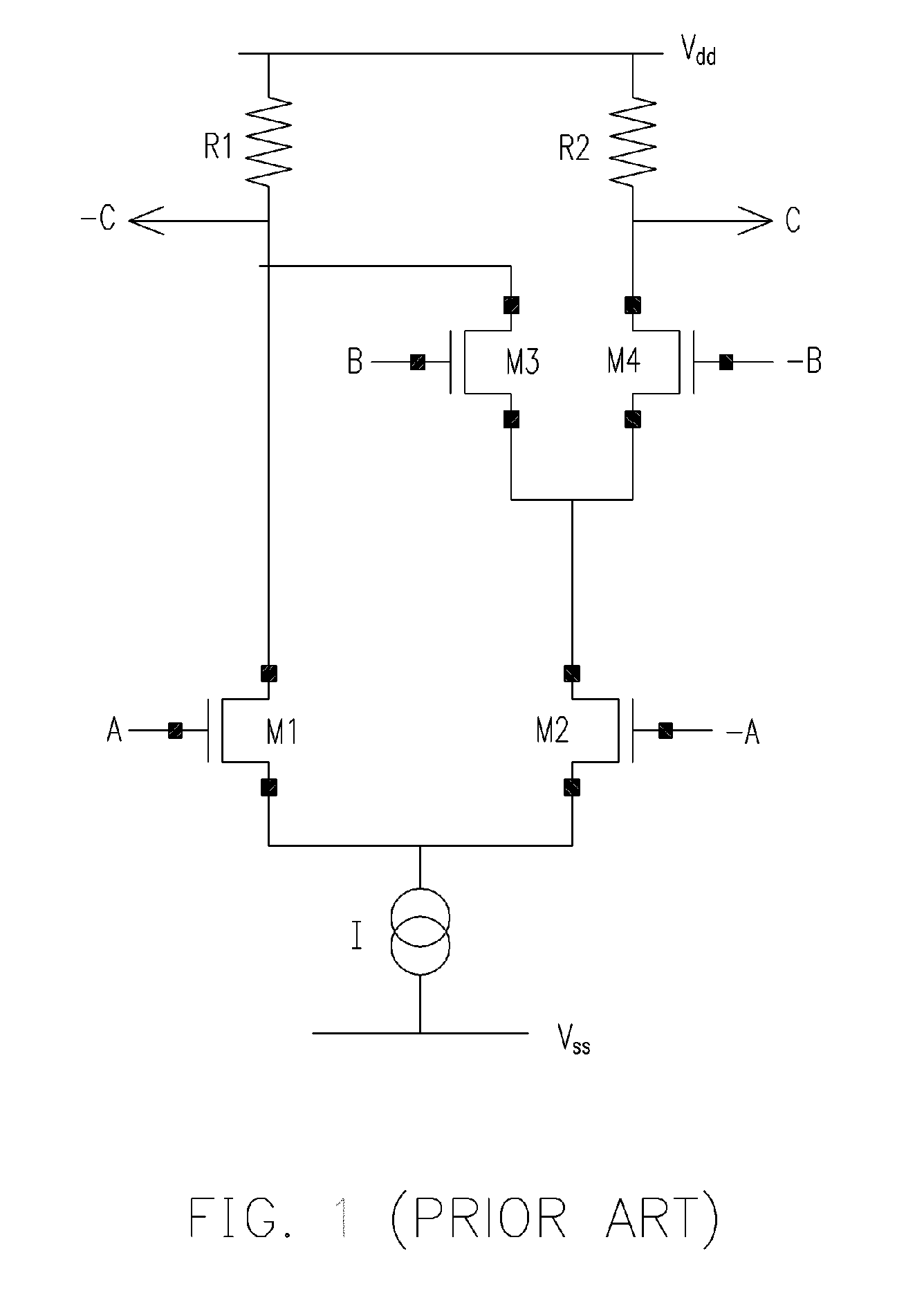

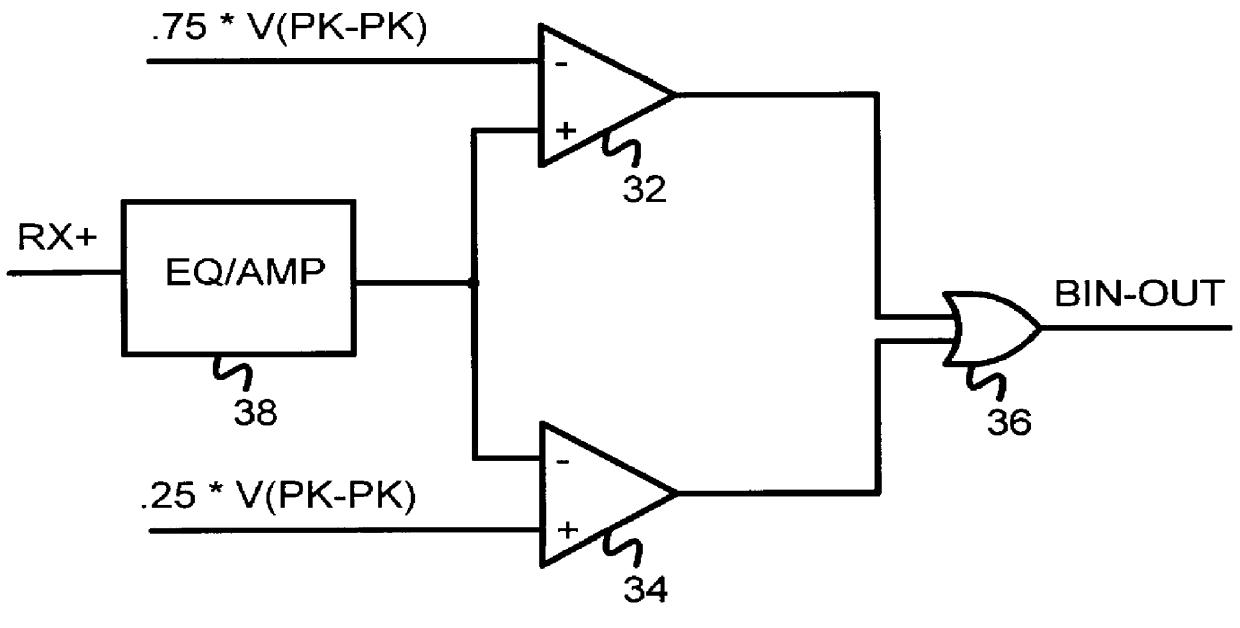

Self-biasing CMOS PECL receiver with wide common-mode range and multi-level-transmit to binary decoder

InactiveUS6049229AReduced Power RequirementsSimplify interconnect routingLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsThree levelEmitter-coupled logic

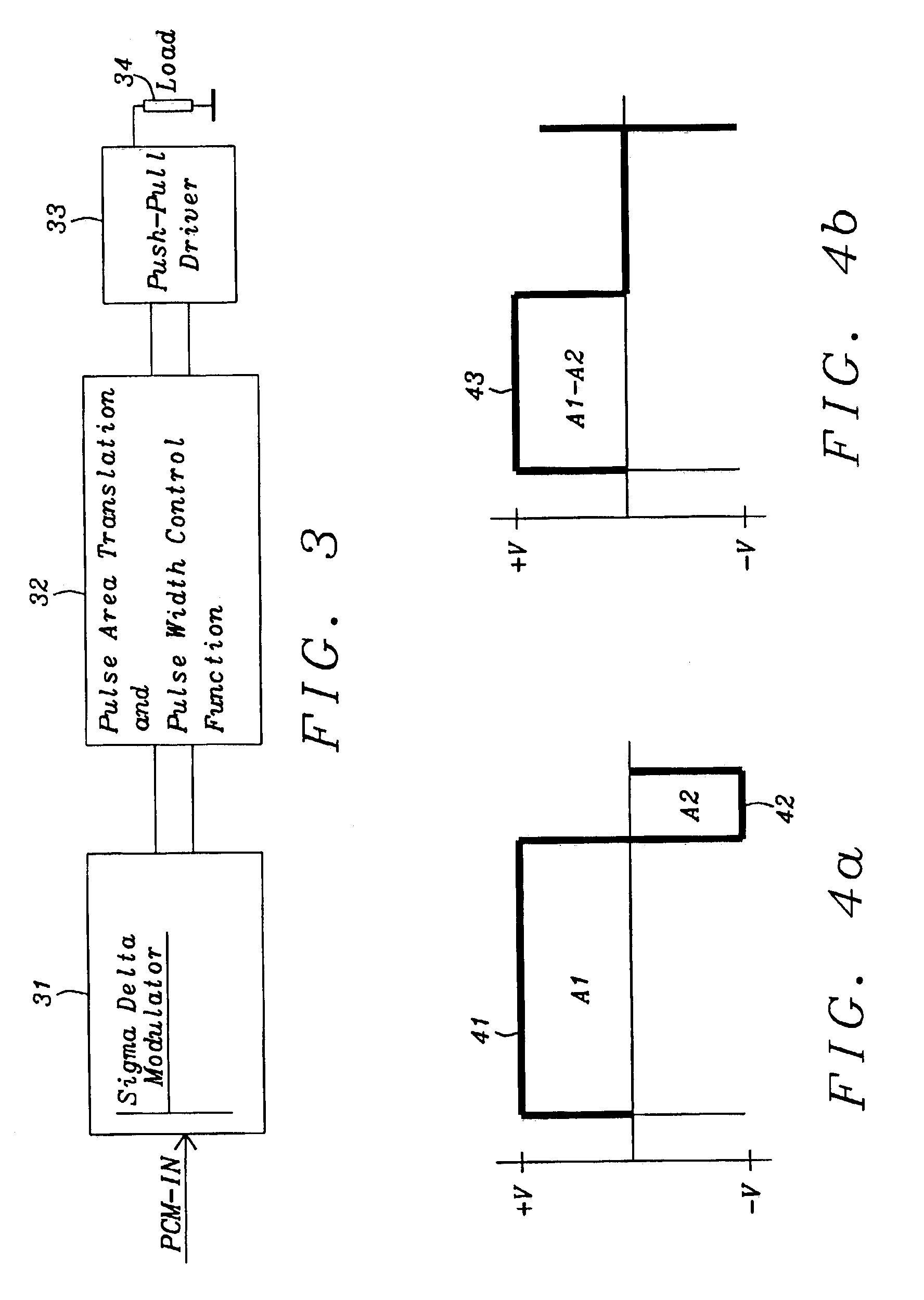

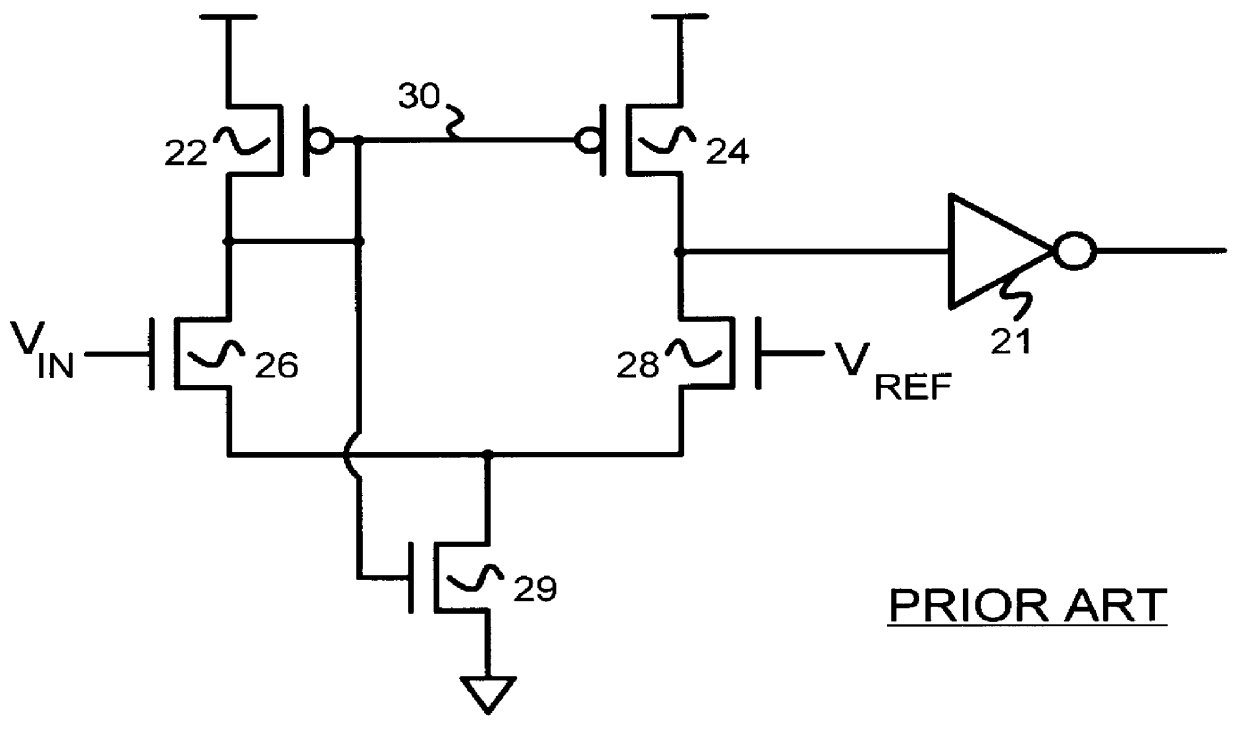

A pseudo-emitter-coupled-logic (PECL) receiver has a wide common-mode range. Two current-mirror CMOS differential amplifiers are used. One amplifier has n-channel differential transistors and a p-channel current mirror, while the second amplifier has p-channel differential transistors and an n-channel current mirror. When the input voltages approach power or ground, one type of differential transistor continues to operate even when the other type shuts off. The outputs of the two amplifiers are connected together and each amplifier receives the same differential input signals. The tail-current transistor is self-biased using the current-mirror's gate-bias. This self biasing of each amplifier eliminates the need for an additional voltage reference and allows each amplifier to adjust its biasing over a wide input-voltage range. Thus the common-mode input range is extended using self biasing and complementary amplifiers. The complementary self-biased comparators can be used for receiving binary or multi-level-transition (MLT) inputs by selecting different voltage references for threshold comparison. Using the same reference on both differential inputs eliminates a second reference for multi-level inputs having three levels. Thus binary and MLT inputs can be detected and decoded by the same decoder.

Owner:DIODES INC

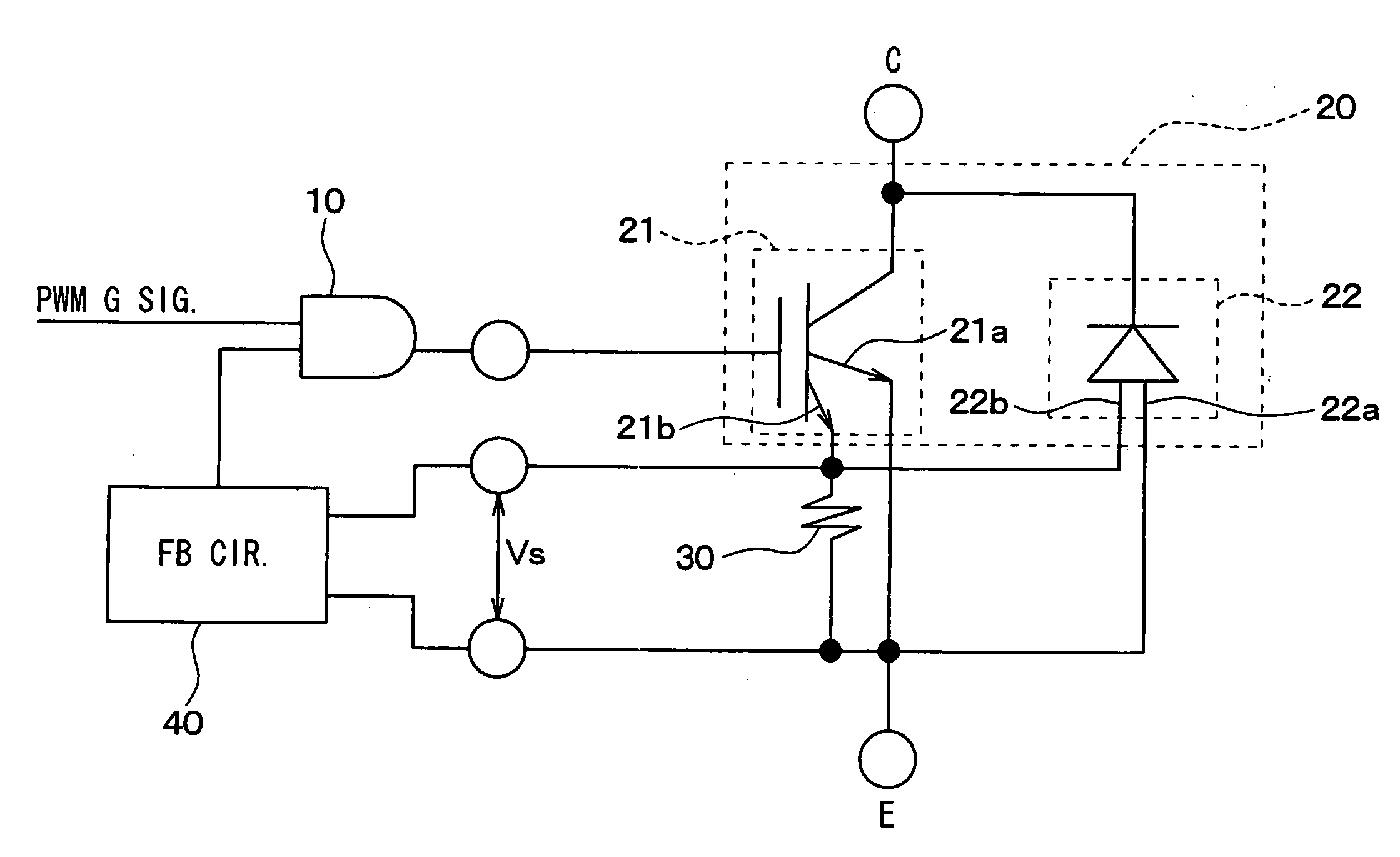

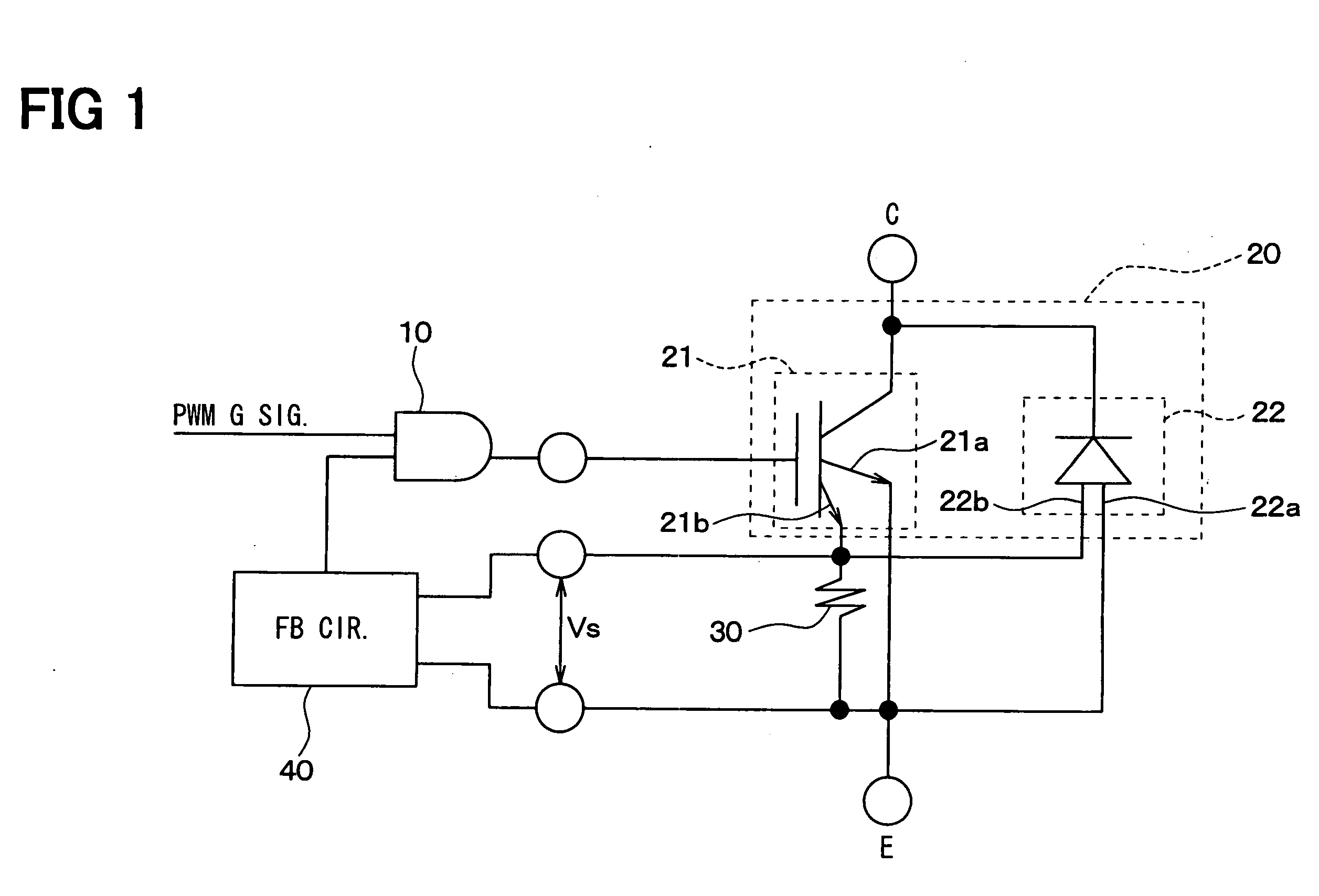

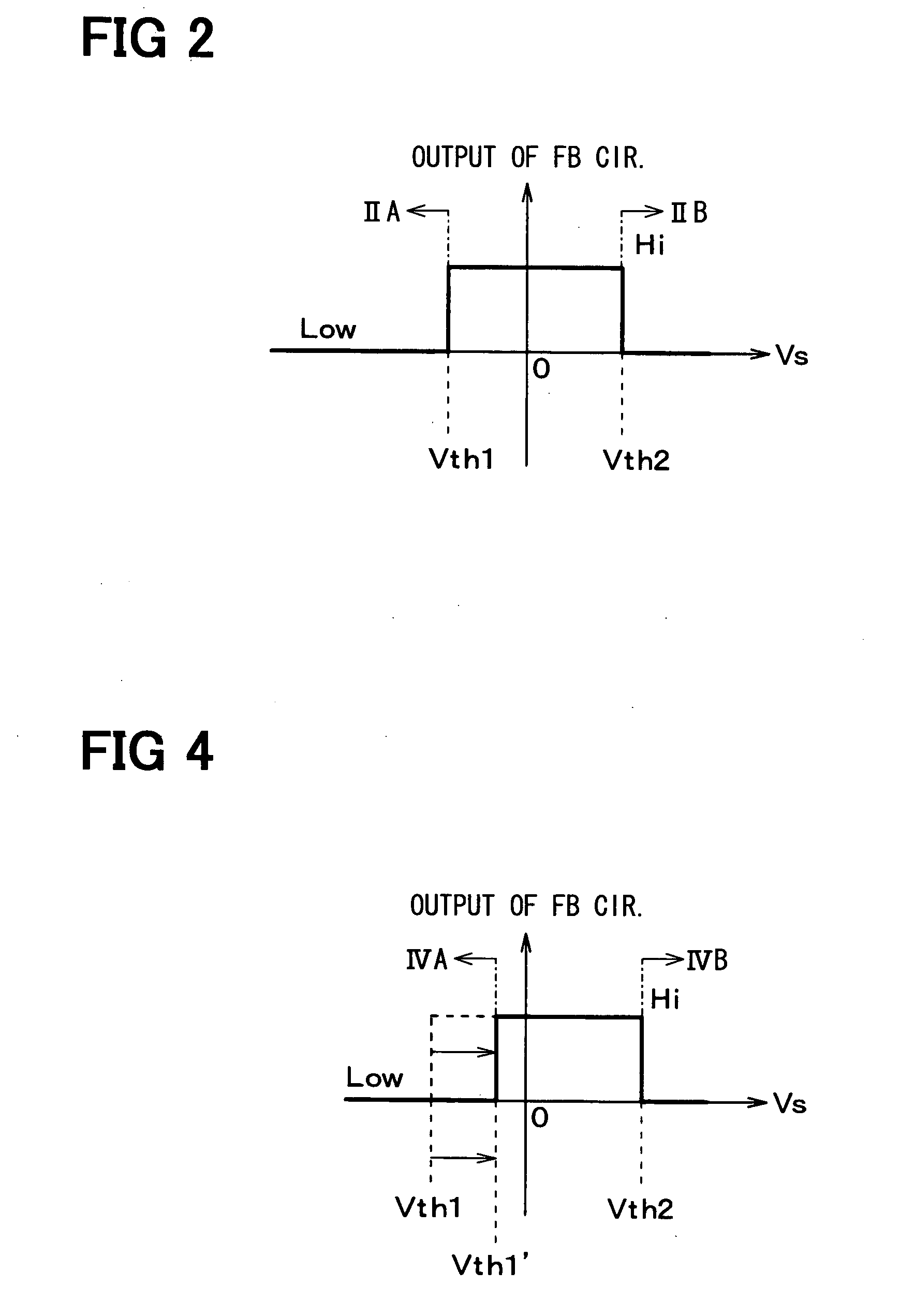

Semiconductor device having diode-built-in IGBT and semiconductor device having diode-built-in DMOS

ActiveUS20090057832A1Increase lossTransistorLogic circuits characterised by logic functionSemiconductorSemiconductor device

A semiconductor device includes: a semiconductor substrate; a diode-built-in insulated-gate bipolar transistor having an insulated-gate bipolar transistor and a diode, which are disposed in the substrate, wherein the insulated-gate bipolar transistor includes a gate, and is driven with a driving signal input into the gate; and a feedback unit for detecting current passing through the diode. The driving signal is input from an external unit into the feedback unit. The feedback unit passes the driving signal to the gate of the insulated-gate bipolar transistor when the feedback unit detects no current through the diode, and the feedback unit stops passing the driving signal to the gate of the insulated-gate bipolar transistor when the feedback unit detects the current through the diode.

Owner:DENSO CORP

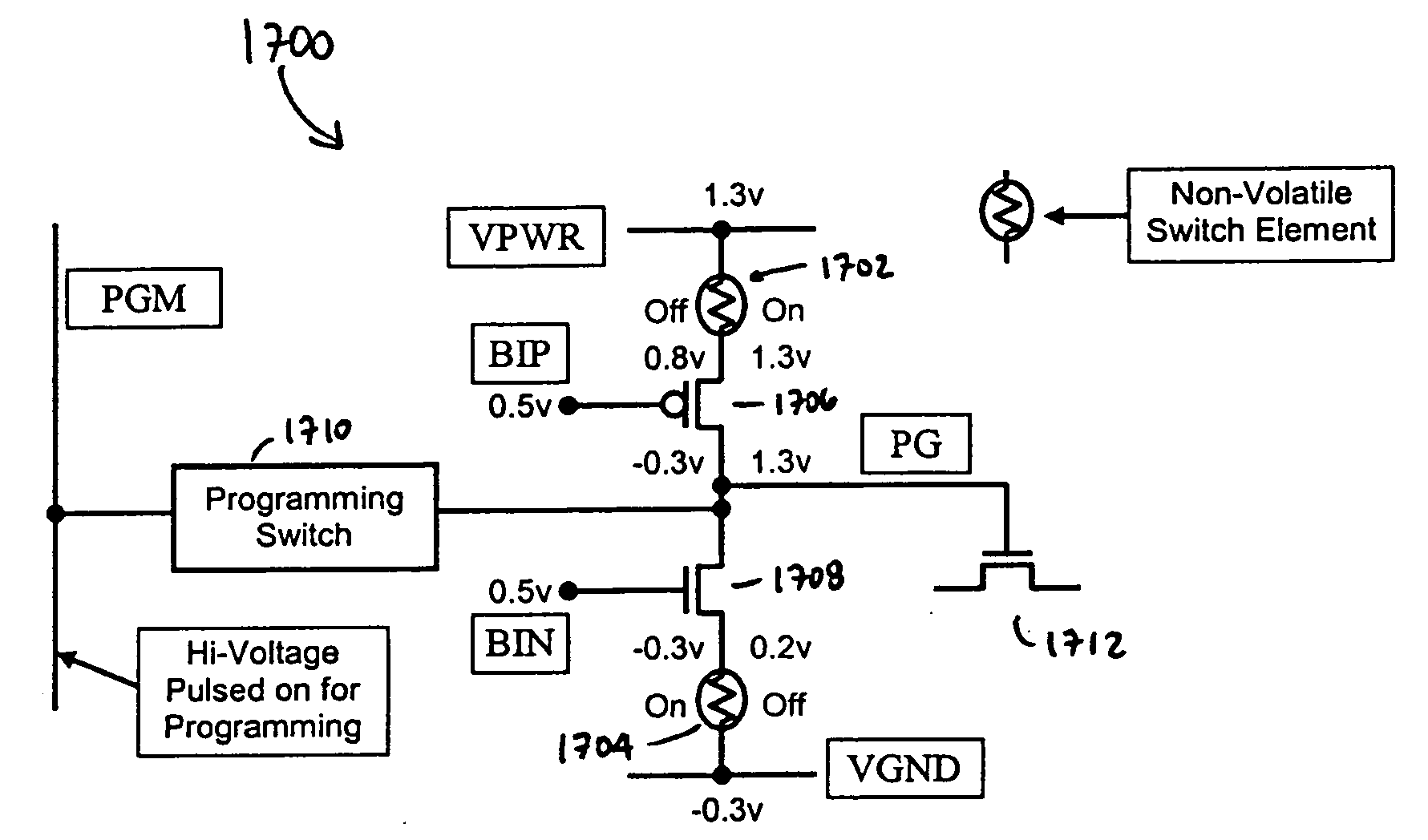

Reconfigurable logic structures

InactiveUS20070146012A1Logic circuits characterised by logic functionNanoinformaticsElectronic structurePhase-change memory

Reconfigurable electronic structures and circuits using programmable, non-volatile memory elements. The programmable, non-volatile memory elements may perform the functions of storage and / or a switch to produce components such as crossbars, multiplexers, look-up tables (LUTs) and other logic circuits used in programmable logic structures (e.g., (FPGAs)). The programmable, non-volatile memory elements comprise one or more structures based on Phase Change Memory, Programmable Metallization, Carbon Nano-Electromechanical (CNT-NEM), or Metal Nano-Electromechanical device technologies.

Owner:CSWITCH

Circuits made from nanotube-based switching elements with multiple controls

InactiveUS20050035786A1TransistorLogic circuits characterised by logic functionNanotubeElectrically conductive

Nanotube-based switching elements with multiple controls and circuits made from such. A switching element includes an input node, an output node, and a nanotube channel element having at least one electrically conductive nanotube. A control structure is disposed in relation to the nanotube channel element to controllably form and unform an electrically conductive channel between said input node and said output node. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. The control structure includes a control electrode and a release electrode, disposed on opposite sides of the nanotube channel element. The control and release may be used to form a differential input, or if the device is constructed appropriately to operate the circuit in a non-volatile manner. The switching elements may be arranged into logic circuits and latches having differential inputs and / or non-volatile behavior depending on the construction.

Owner:NANTERO

Overvoltage/undervoltage tolerant transfer gate

InactiveUS6163199AMassage combsLogic circuits characterised by logic functionOvervoltageComplementary pair

A transfer gate or pass gate circuit for transferring logic signals between nodes for a range of available high-potential supply levels. The primary transfer gate is designed to protect against potentials that either exceed either a high-potential or a low-potential level or that undershoot such potential levels. For overshoot (overvoltage) tolerance, this is achieved by coupling a NMOS transistor in parallel with a pair of PMOS transistors that are coupled in series. All three transistors are located between two nodes, either of which can be the input or the output of the transfer gate. The NMOS transistor is designed to be larger than the PMOS transistors and carries most of the transfer capability. The smaller PMOS transistors are designed to eliminate potential drops that would otherwise occur with a single NMOS transistor or with a complementary pair of transistors. For undershoot (undervoltage) tolerance, a PMOS transistor is coupled in parallel with a pair of NMOS transistors that are coupled in series.

Owner:SEMICON COMPONENTS IND LLC

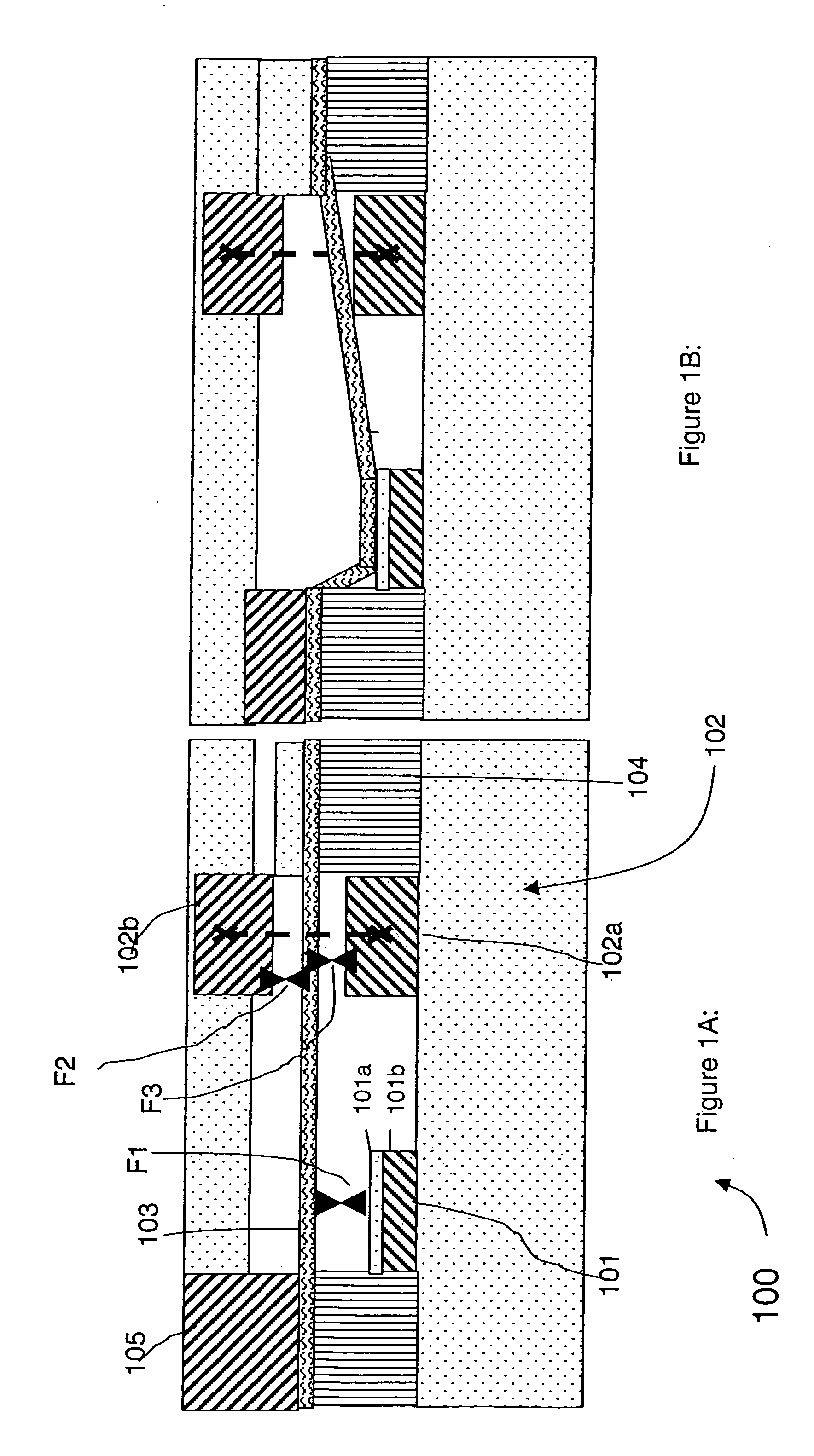

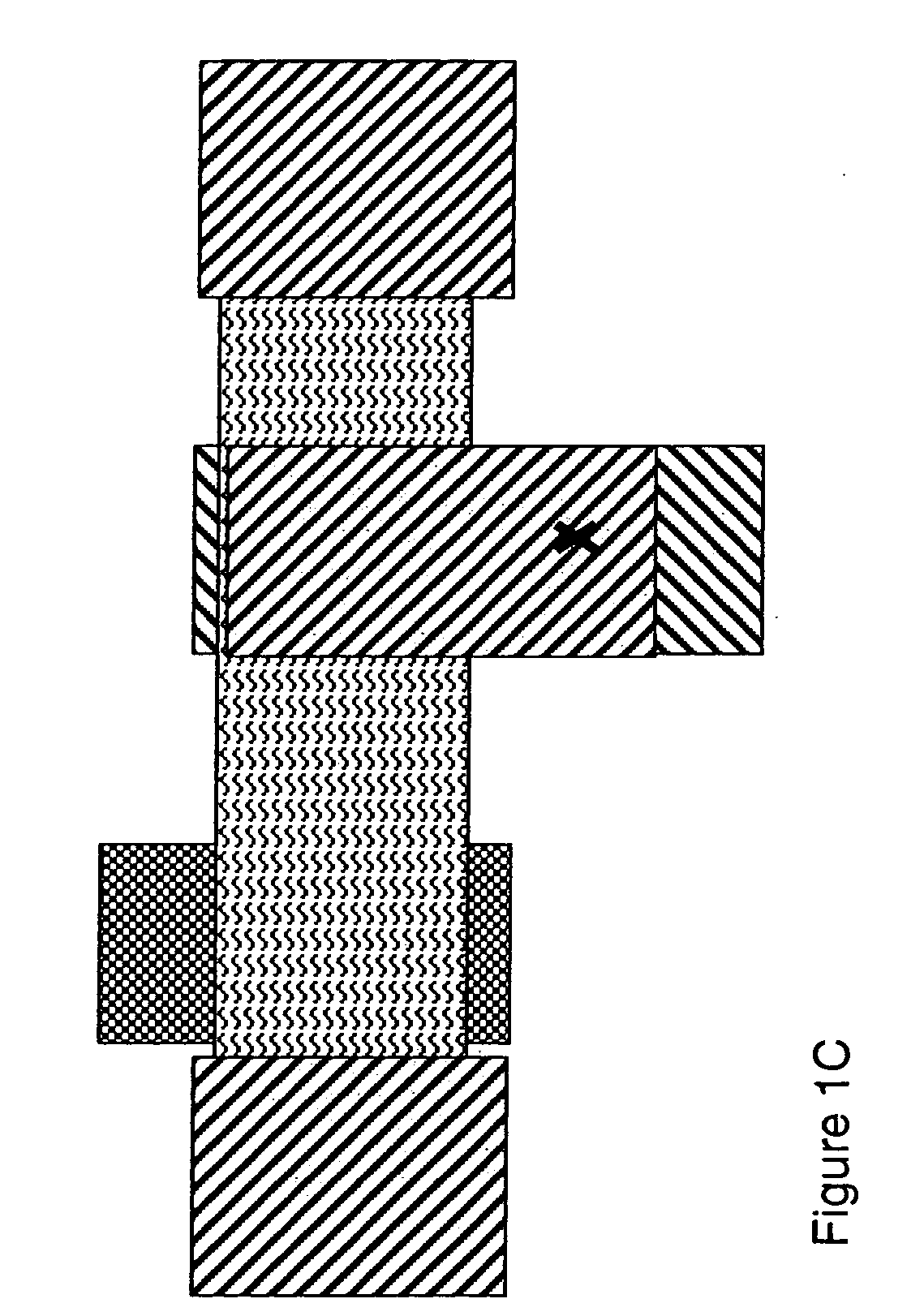

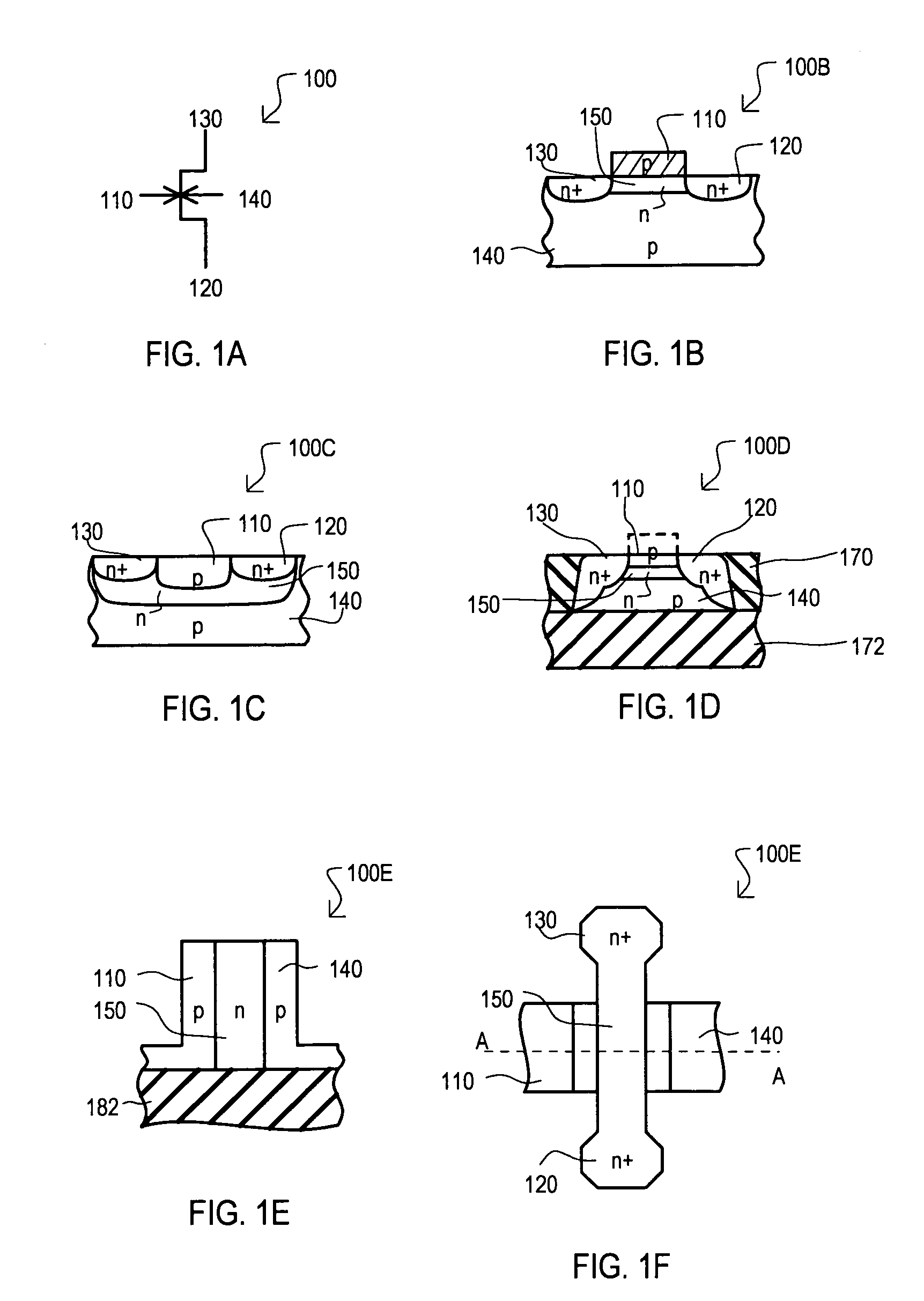

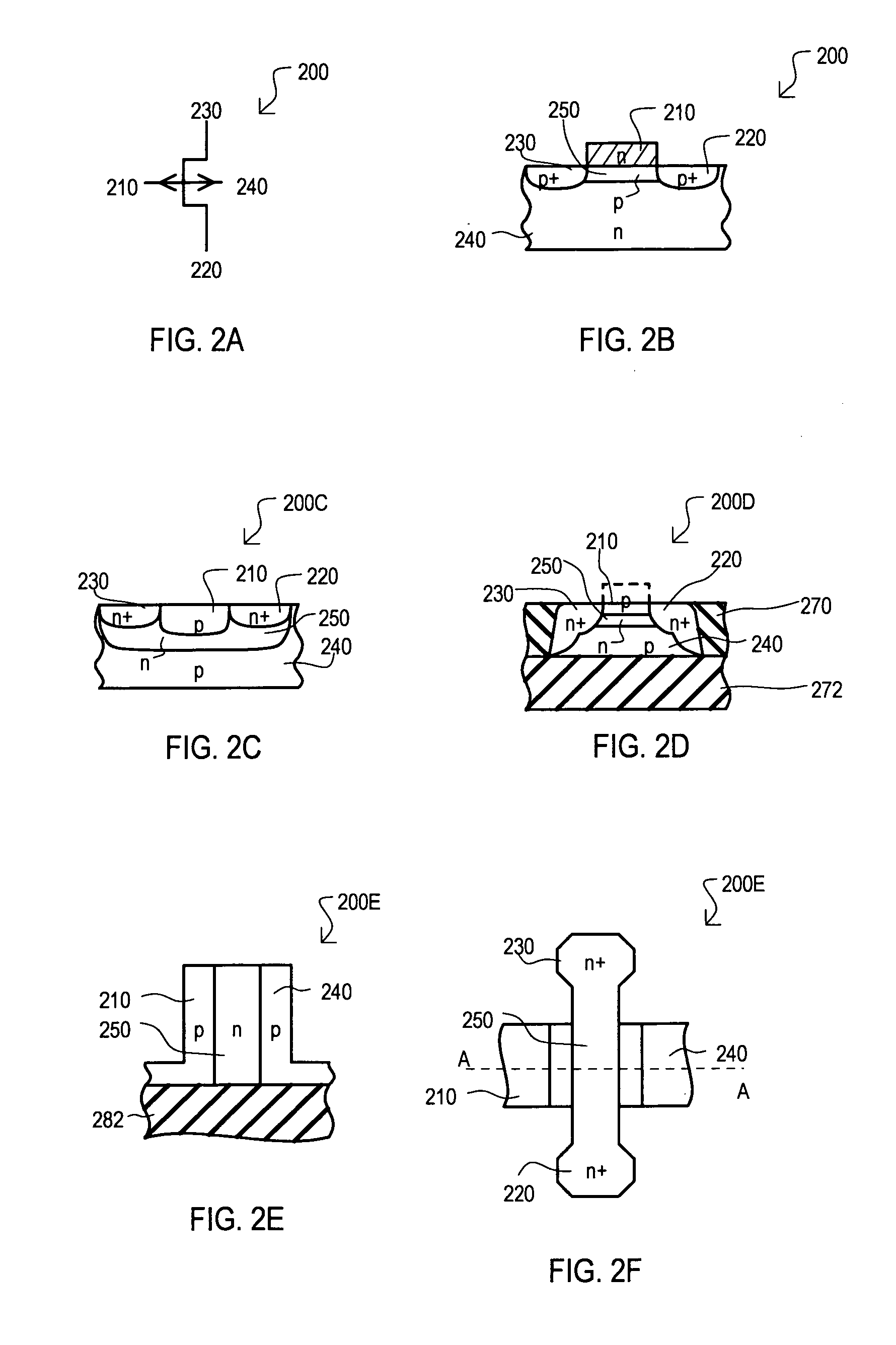

Integrated nanotube and field effect switching device

ActiveUS20060061389A1Logic circuits characterised by logic functionNanoelectromechanical switchesElectricityDevice form

Hybrid switching devices integrate nanotube switching elements with field effect devices, such as NFETs and PFETs. A switching device forms and unforms a conductive channel from the signal input to the output subject to the relative state of the control input. In embodiments of the invention, the conductive channel includes a nanotube channel element and a field modulatable semiconductor channel element. The switching device may include a nanotube switching element and a field effect device electrically disposed in series. According to one aspect of the invention, an integrated switching device is a four-terminal device with a signal input terminal, a control input terminal, a second input terminal, and an output terminal. The devices may be non-volatile. The devices can form the basis for a hybrid NT-FET logic family and can be used to implement any Boolean logic circuit.

Owner:NANTERO

Nanotube-based switching elements and logic circuits

Nanotube-based switching elements and logic circuits. Under one embodiment of the invention, a switching element includes an input node, an output node, a nanotube channel element having at least one electrically conductive nanotube, and a control electrode. The control electrode is disposed in relation to the nanotube channel element to controllably form an electrically conductive channel between the input node and the output node. The channel at least includes said nanotube channel element. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. Under another embodiment of the invention, the control electrode is arranged in relation to the nanotube channel element to form said conductive channel by causing electromechanical deflection of said nanotube channel element. Under another embodiment of the invention, the output node includes an isolation structure disposed in relation to the nanotube channel element so that channel formation is substantially invariant from the state of the output node. Under another embodiment of the invention, the isolation structure includes electrodes disposed on opposite sides of the nanotube channel element and said electrodes produce substantially the same electric field. Under another embodiment of the invention, a Boolean logic circuit includes at least one input terminal and an output terminal, and a network of nanotube switching elements electrically disposed between said at least one input terminal and said output terminal. The network of nanotube switching elements effectuates a Boolean function transformation of Boolean signals on said at least one input terminal. The Boolean function transformation includes a Boolean inversion within the function, such as a NOT or NOR function.

Owner:NANTERO

Filler circuit cell

ActiveUS7705666B1Logic circuits characterised by logic functionOscillations generatorsVoltage sourceDecoupling capacitor

A filler circuit cell is disclosed. The filler circuit cell includes a decoupled capacitor, a tie low circuit and a tie high circuit. The decoupled capacitor includes a first NMOS transistor and a first PMOS transistor, in which the source / drain of the first NMOS transistor is connected to a second voltage source and the source / drain of the first PMOS transistor is connected to a first voltage source. The tie low circuit includes a second NMOS transistor and a second PMOS transistor and the tie high circuit includes a third NMOS transistor and a third PMOS transistor.

Owner:UNITED MICROELECTRONICS CORP

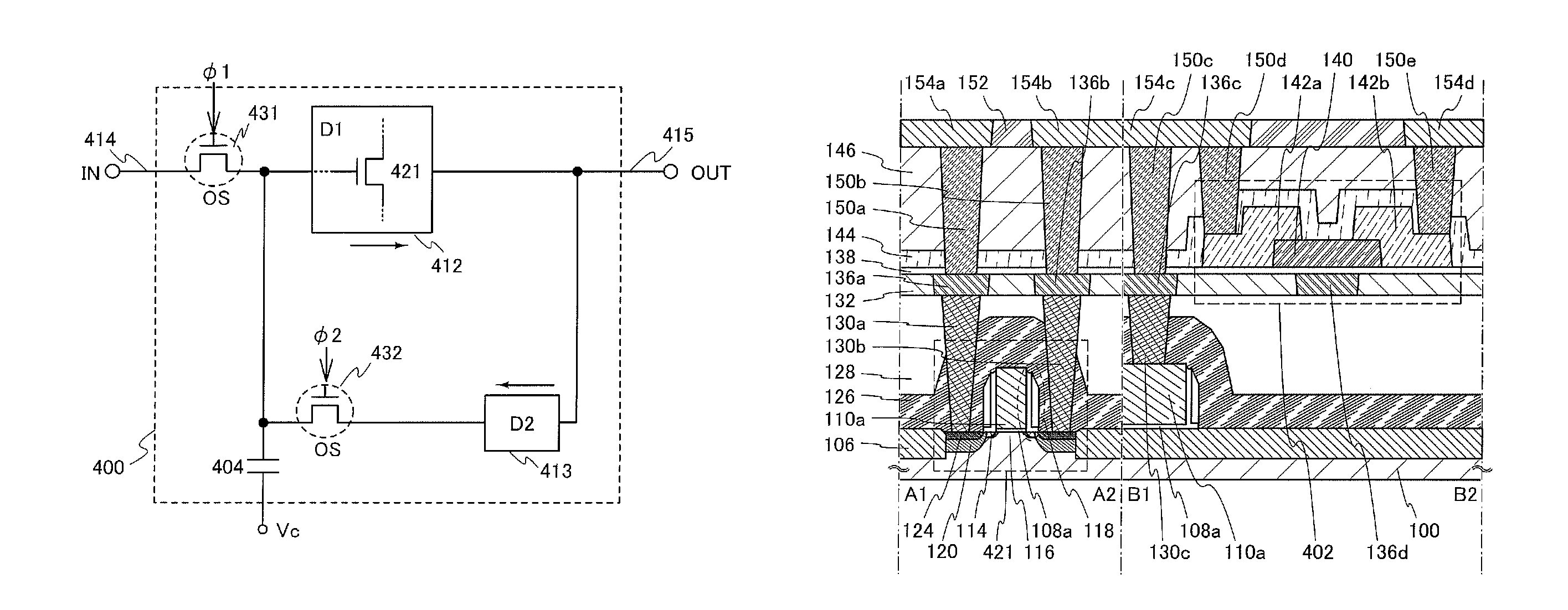

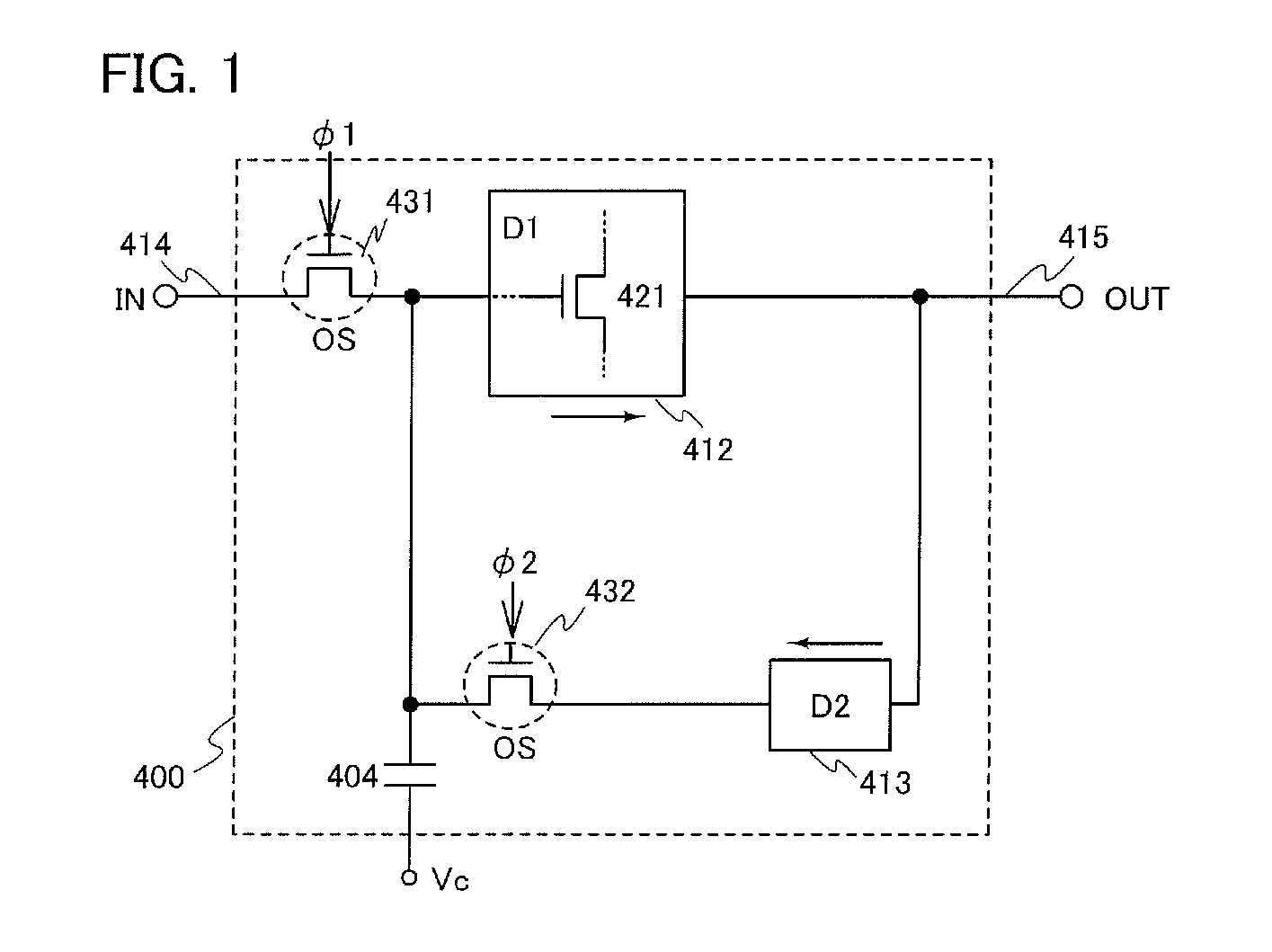

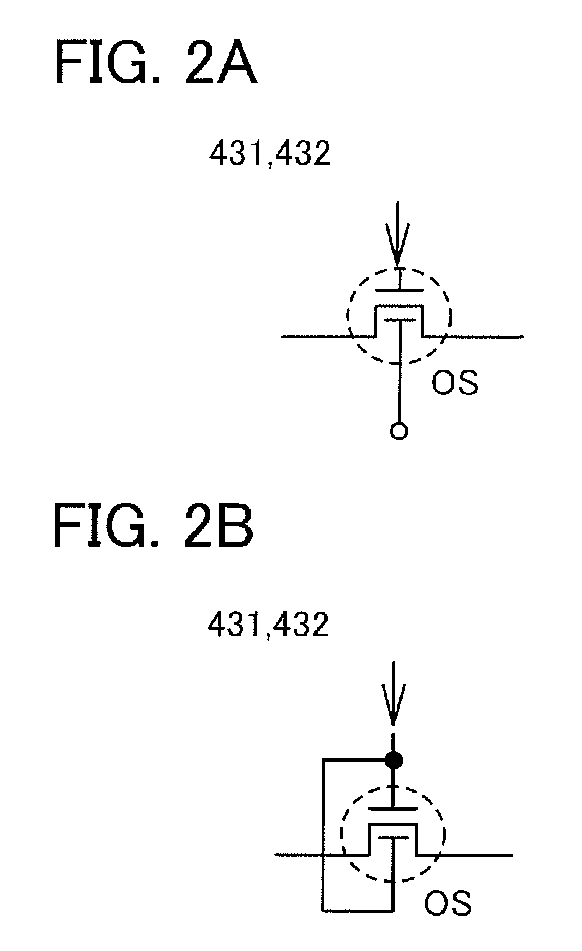

Non-volatile latch circuit and logic circuit, and semiconductor device using the same

ActiveUS8314637B2Data retentionWide temperature rangeTransistorLogic circuits characterised by logic functionSemiconductor materialsCapacitor

A novel non-volatile latch circuit and a semiconductor device using the non-volatile latch circuit are provided. The latch circuit has a loop structure in which an output of a first element is electrically connected to an input of a second element and an output of the second element is electrically connected to an input of the first element through a second transistor. A transistor using an oxide semiconductor as a semiconductor material of a channel formation region is used as a switching element, and a capacitor is provided to be electrically connected to a source electrode or a drain electrode of the transistor, whereby data of the latch circuit can be retained, and a non-volatile latch circuit can thus be formed.

Owner:SEMICON ENERGY LAB CO LTD

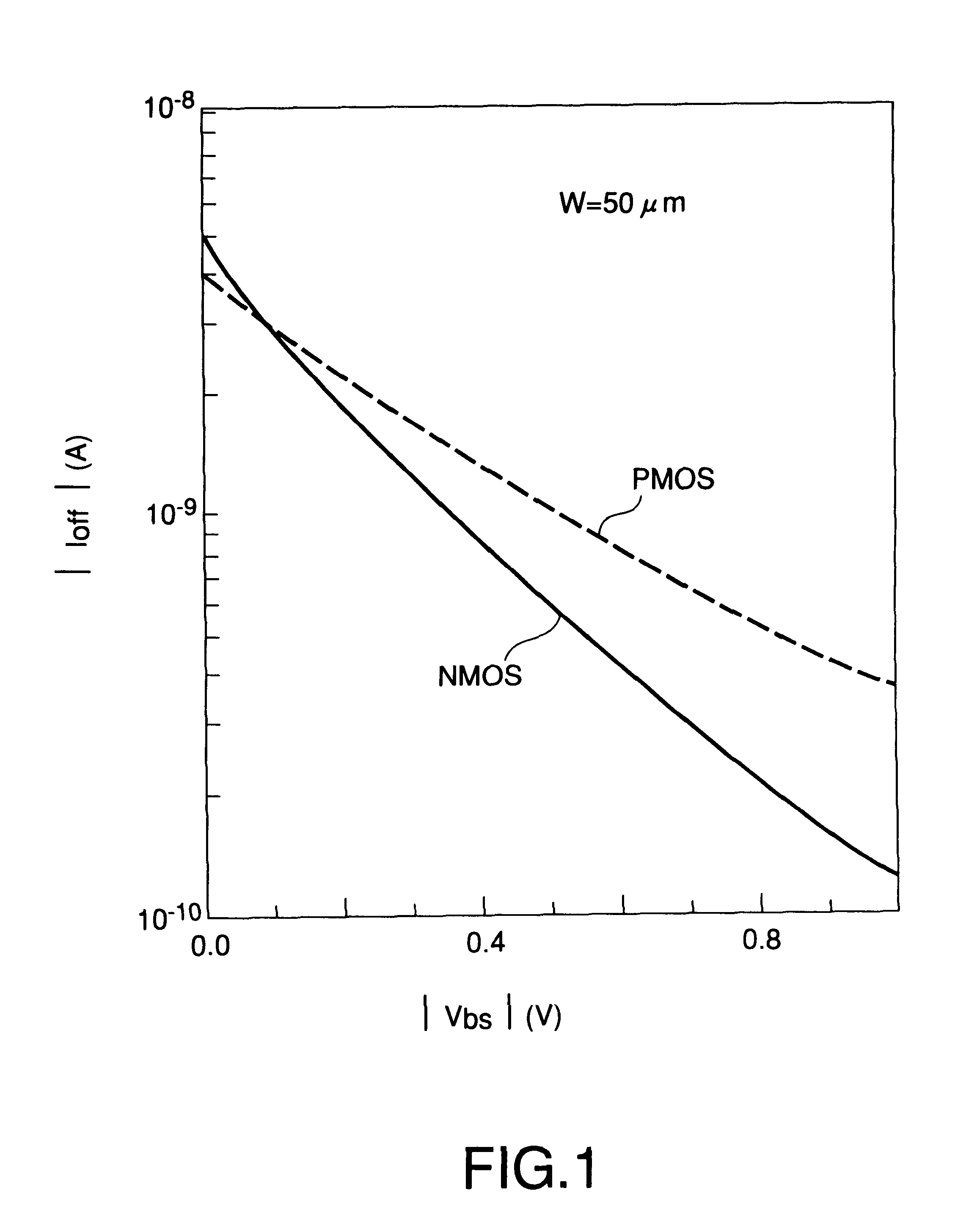

Low power consumption MIS semiconductor device

InactiveUS7355455B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

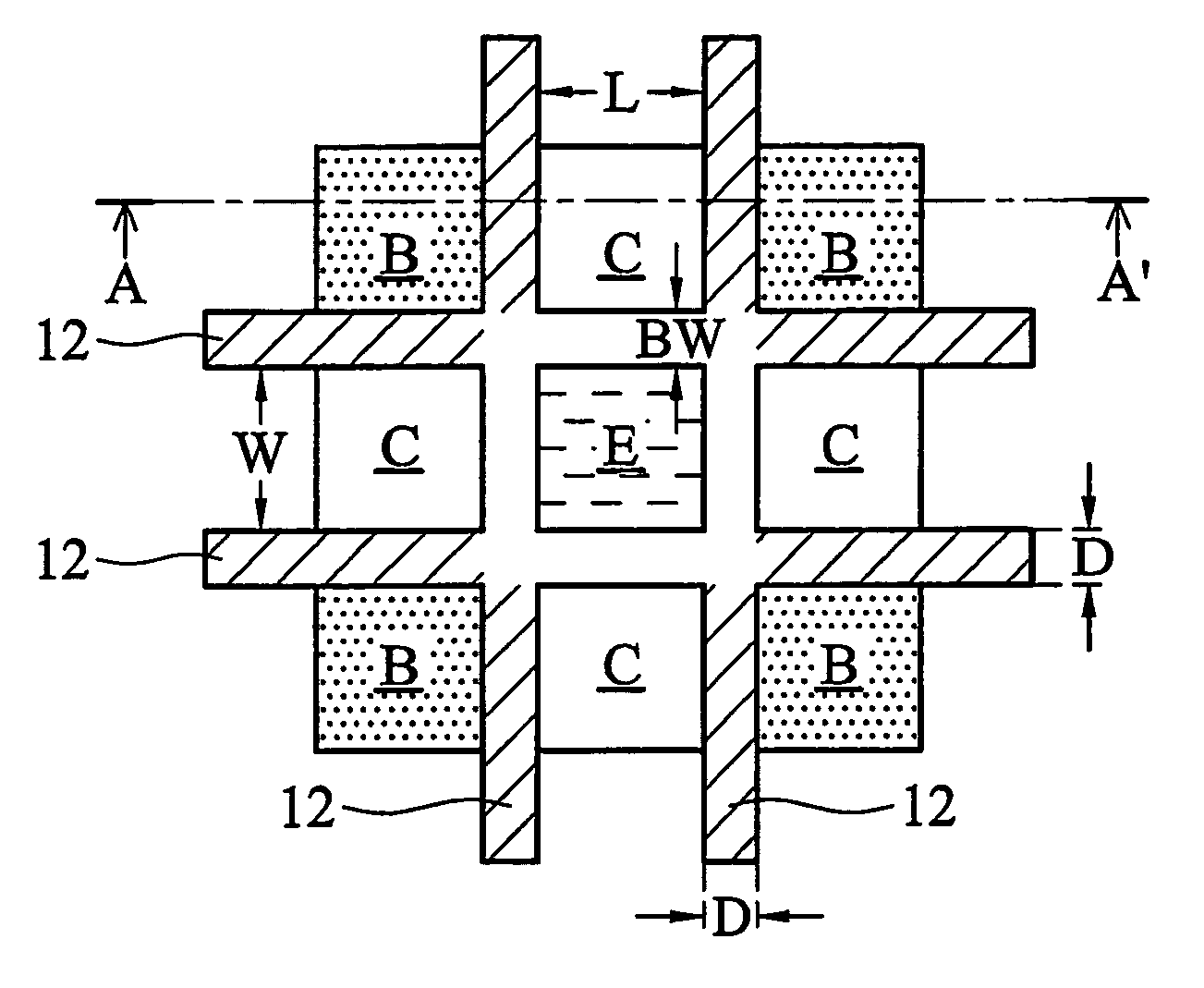

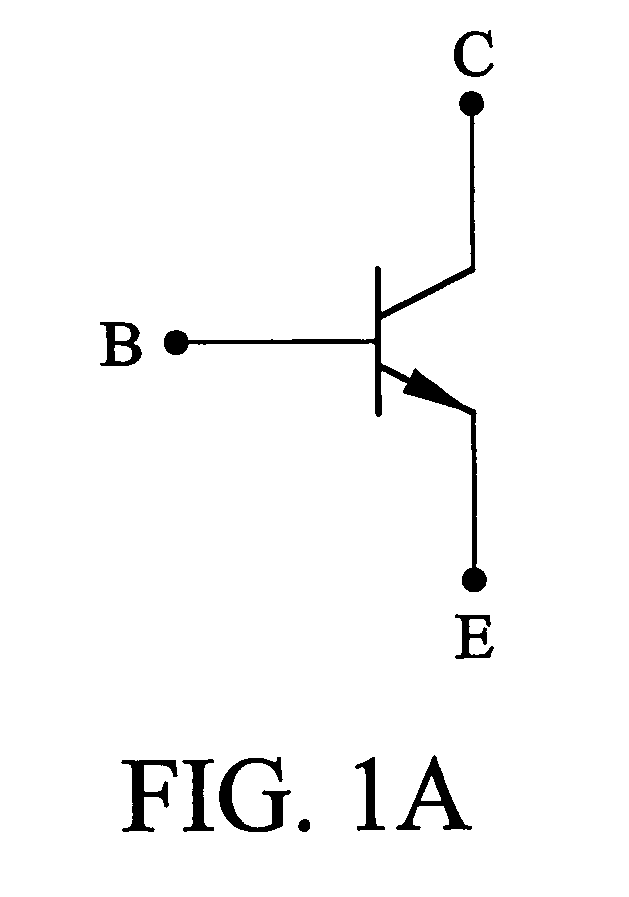

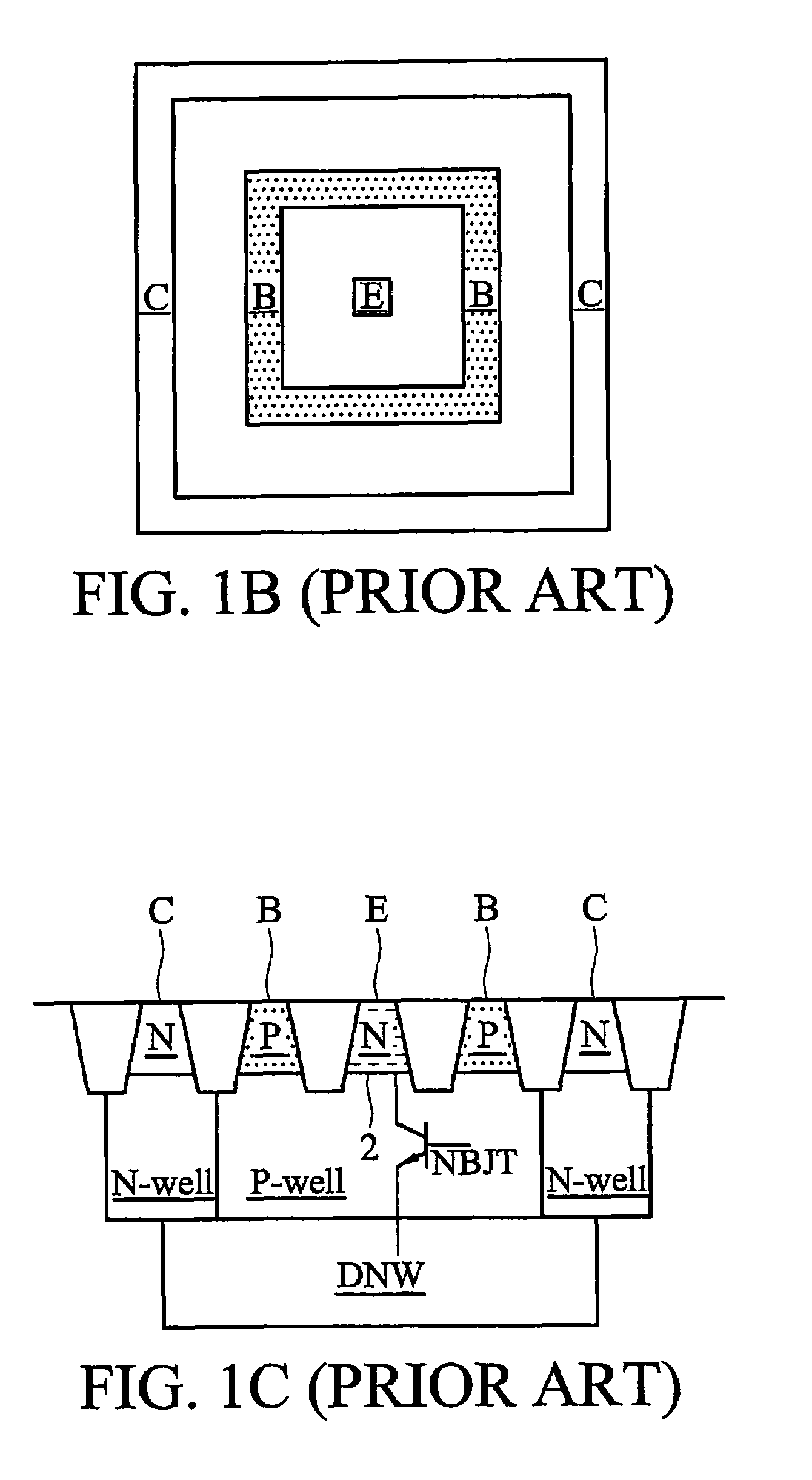

High-gain vertex lateral bipolar junction transistor

InactiveUS7701038B2Reduce parasitic effectsIncrease currentLogic circuits characterised by logic functionSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

A lateral bipolar junction transistor having improved current gain and a method for forming the same are provided. The transistor includes a well region of a first conductivity type formed over a substrate, at least one emitter of a second conductivity type opposite the first conductivity type in the well region wherein each of the at least one emitters are interconnected, a plurality of collectors of the second conductivity type in the well region wherein the collectors are interconnected to each other, and a plurality of base contacts of the first conductivity type in the well region wherein the base contacts are interconnected to each other. Preferably, all sides of the at least one emitters are adjacent the collectors, and none of the base contacts are adjacent the sides of the emitters. The neighboring emitter, collectors and base contacts are separated by spacings in the well region.

Owner:TAIWAN SEMICON MFG CO LTD

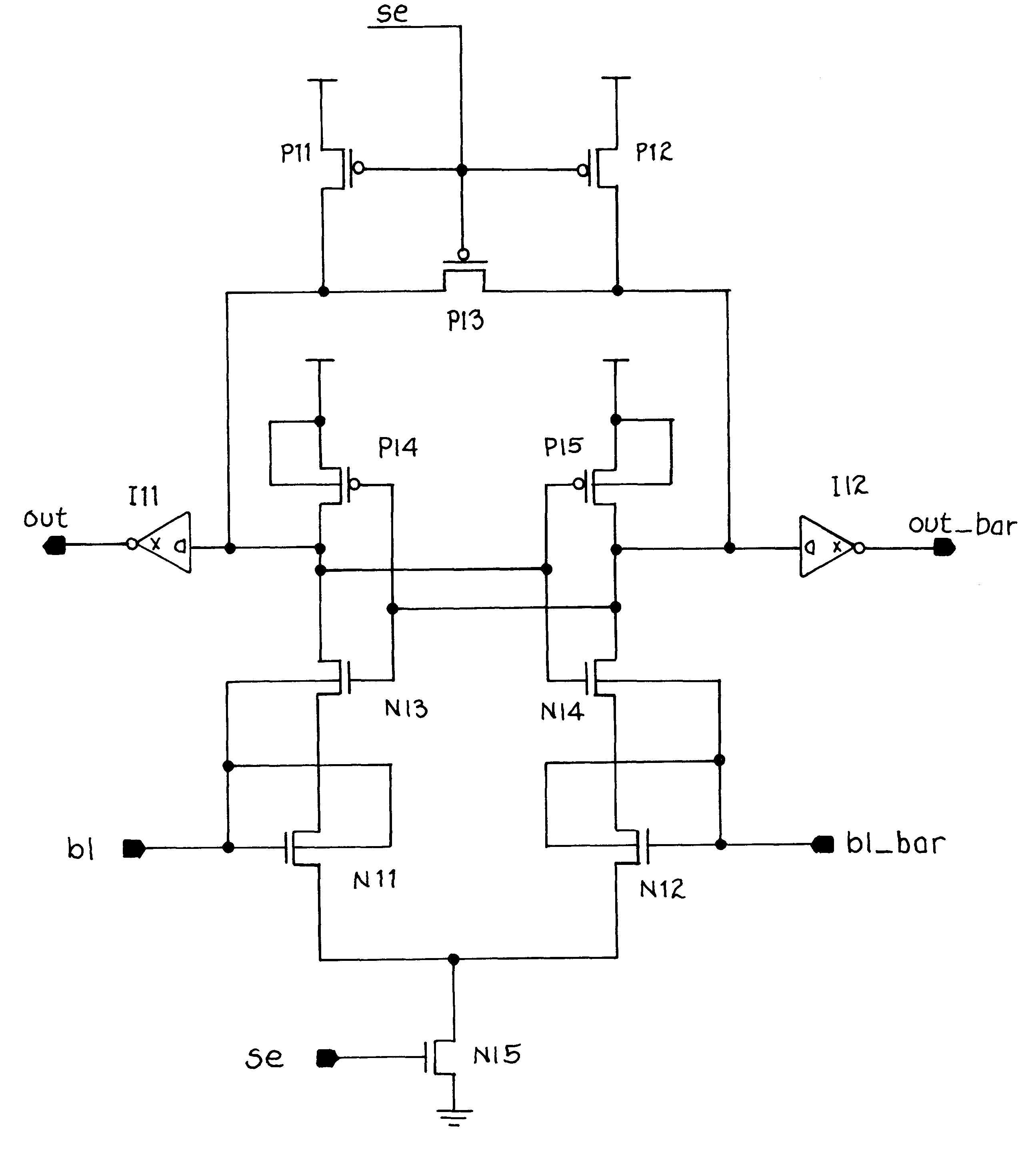

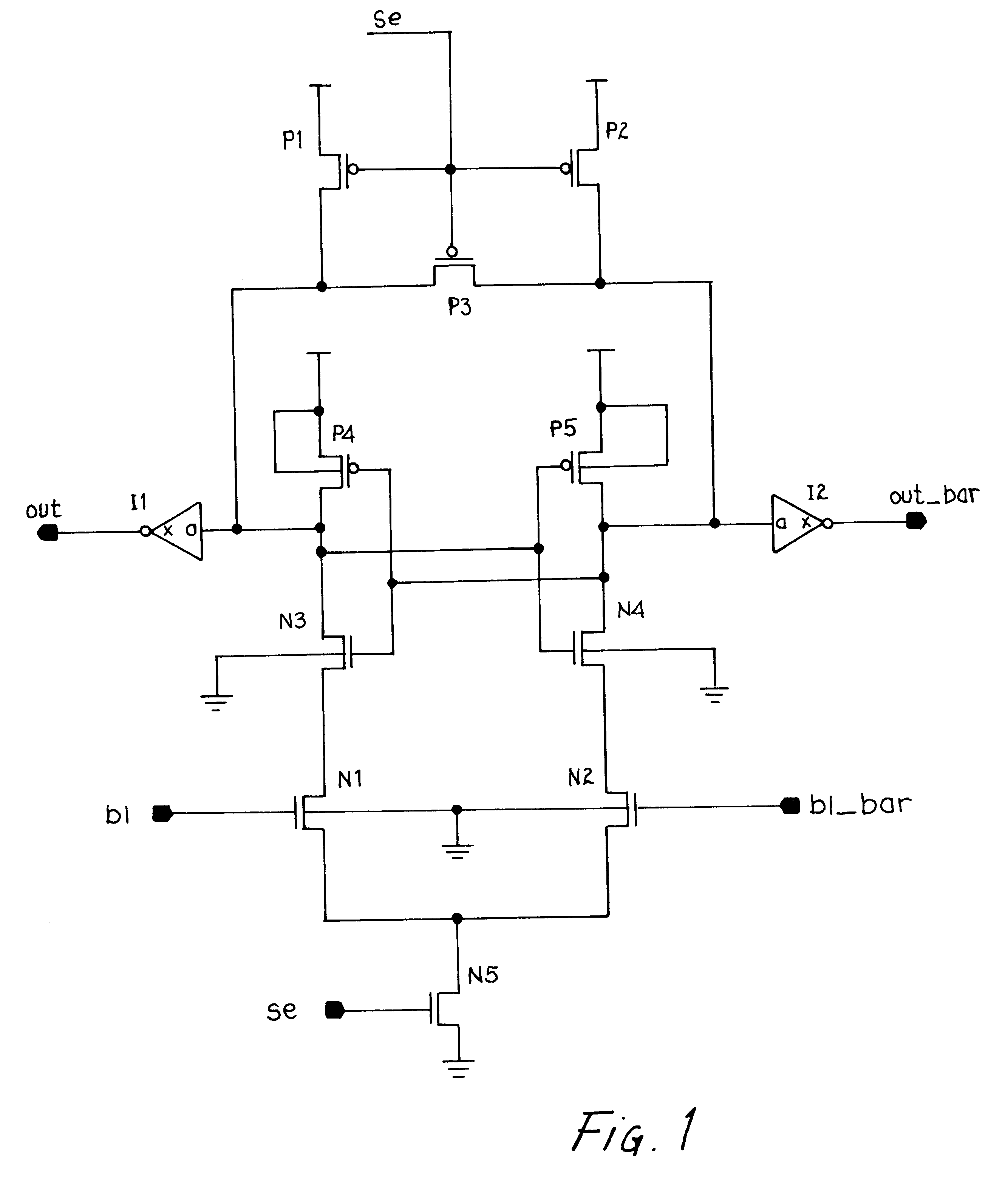

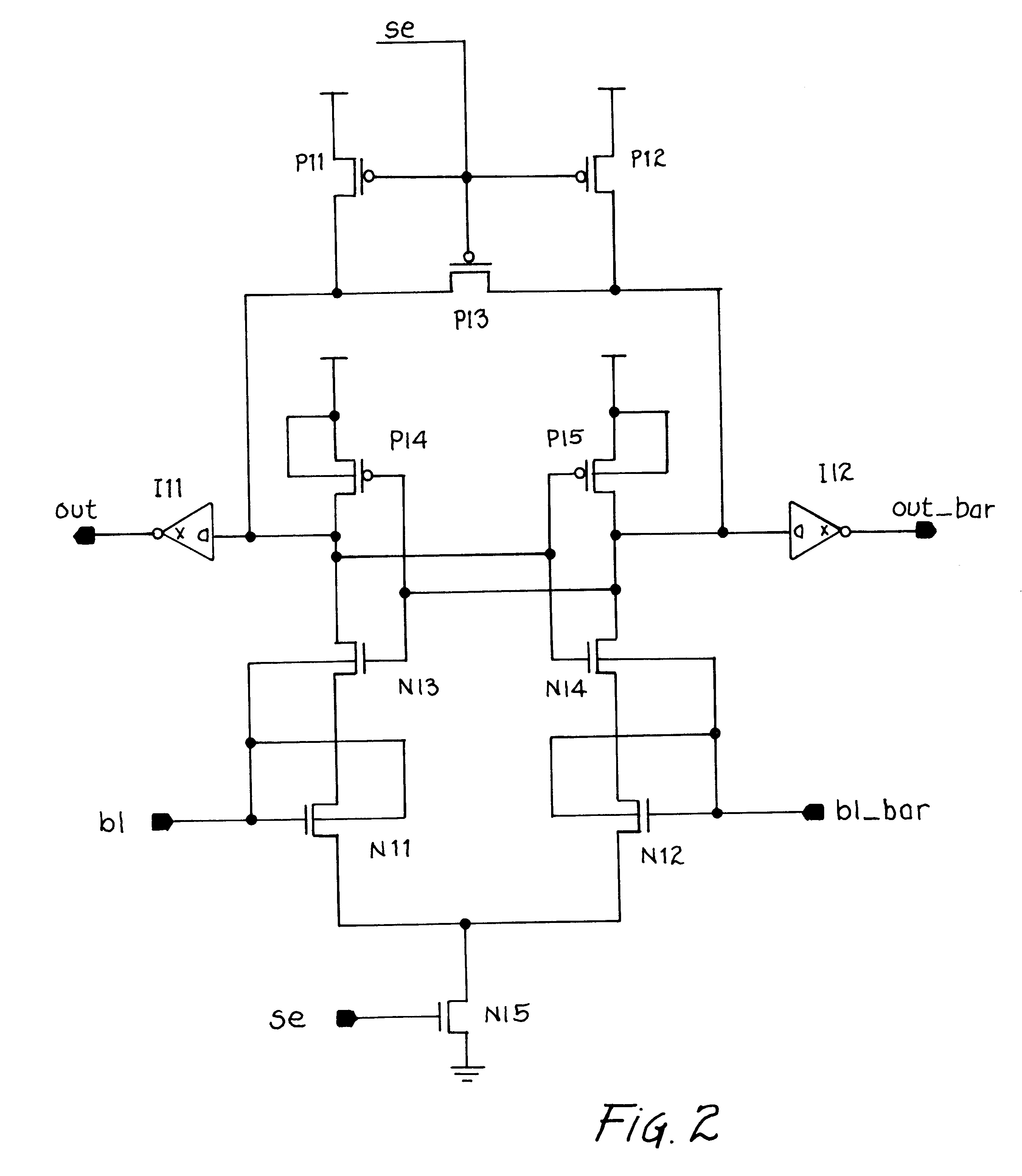

Sense amplifier and method for sensing signals in a silicon-on-insulator integrated circuit

InactiveUS6433589B1Logic circuits characterised by logic functionDigital storageAudio power amplifierSwitching time

An improved sense amplifier ad method for sensing signals in a silicon-on-insulator (SOI) integrated circuit improve the performance of semiconductor memories and other circuits implemented in SOI technology. The bodies of amplifier transistors within the sense amplifier and bodies of input transistors to the sense amplifier are coupled to corresponding input signals, eliminating the history dependance that would result from unconnected bodies, while achieving faster switching times due to a dynamically produced difference in threshold voltage of the input transistors and amplifier transistors. The switching time is improved over circuits using input transistors and amplifier transistors having statically biased bodies.

Owner:IBM CORP

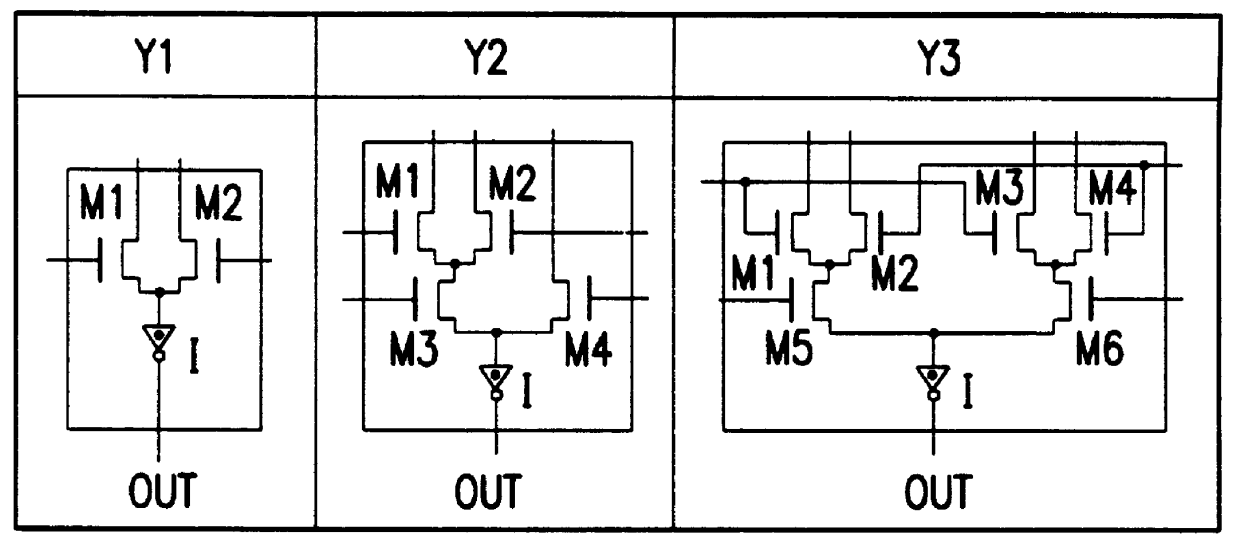

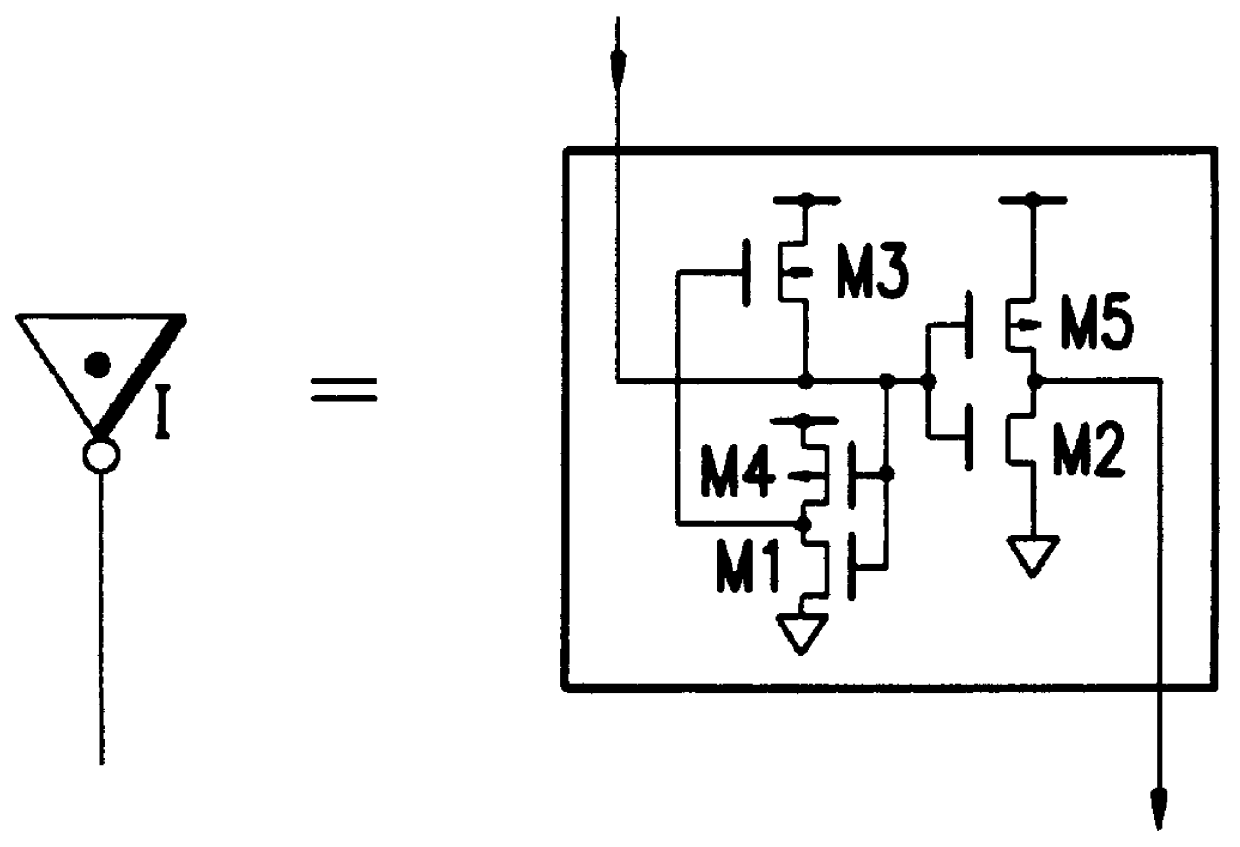

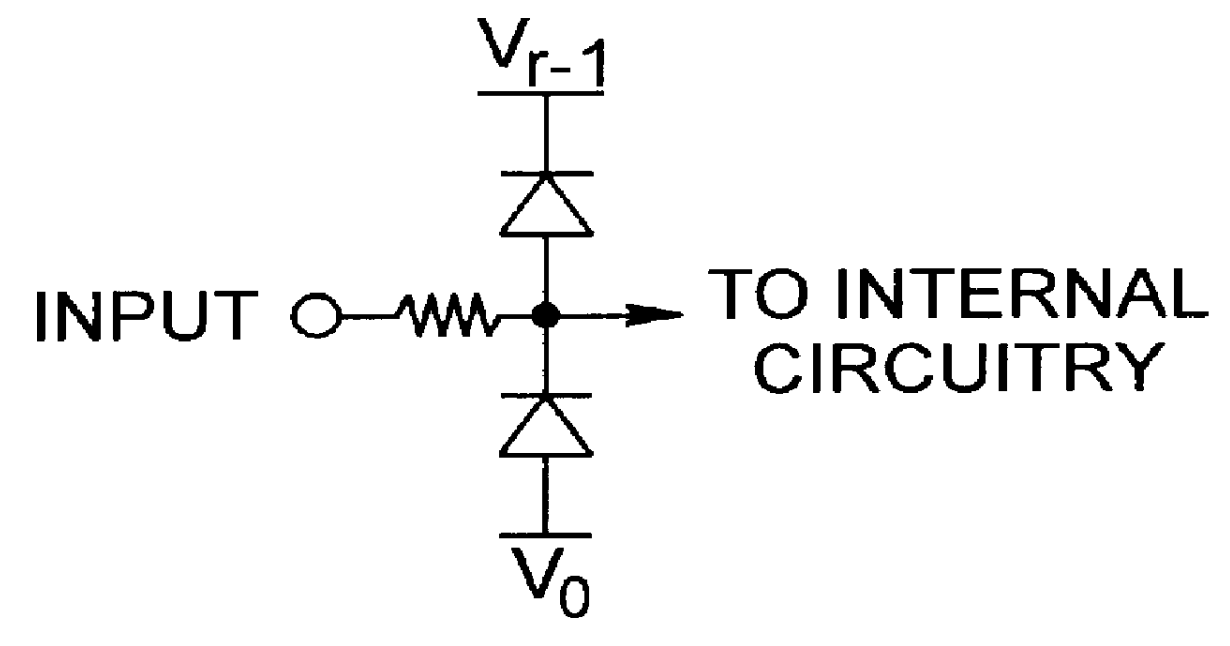

Multiple-valued logic circuit architecture; supplementary symmetrical logic circuit structure (SUS-LOC)

InactiveUS6133754AEasy to copyEasy transferPower consumption reductionLogic circuits characterised by logic functionMany-valued logicLogic synthesis

Circuit structure and resulting circuitry for multiple-valued logic. The circuit structure allows the design and fabrication of any r-valued logic function of n-places where r is an integer greater than 1 and n is an integer greater than 0. This structure is called SUpplementary Symmetrical LOgic Circuit structure (SUS-LOC). In circuits incorporating SUS-LOC, circuit branches are realized that uniquely deliver circuit response and output. For some circuits, and due to the operating characteristics of the switch elements, additional circuit elements, or stages, must be incorporated to prevent "back biasing." SUS-LOC is fully active. Only active elements perform logic synthesis and those components not directly related to logic synthesis, such as resistors and / or other passive loads, are relegated the task of circuit protection. The fabrication of r-valued, multi-valued, or multiple-valued logic circuits, designed using the definitions of the SUS-LOC structure can be accomplished with known techniques, materials, and equipment.

Owner:OMNIBASE LOGIC

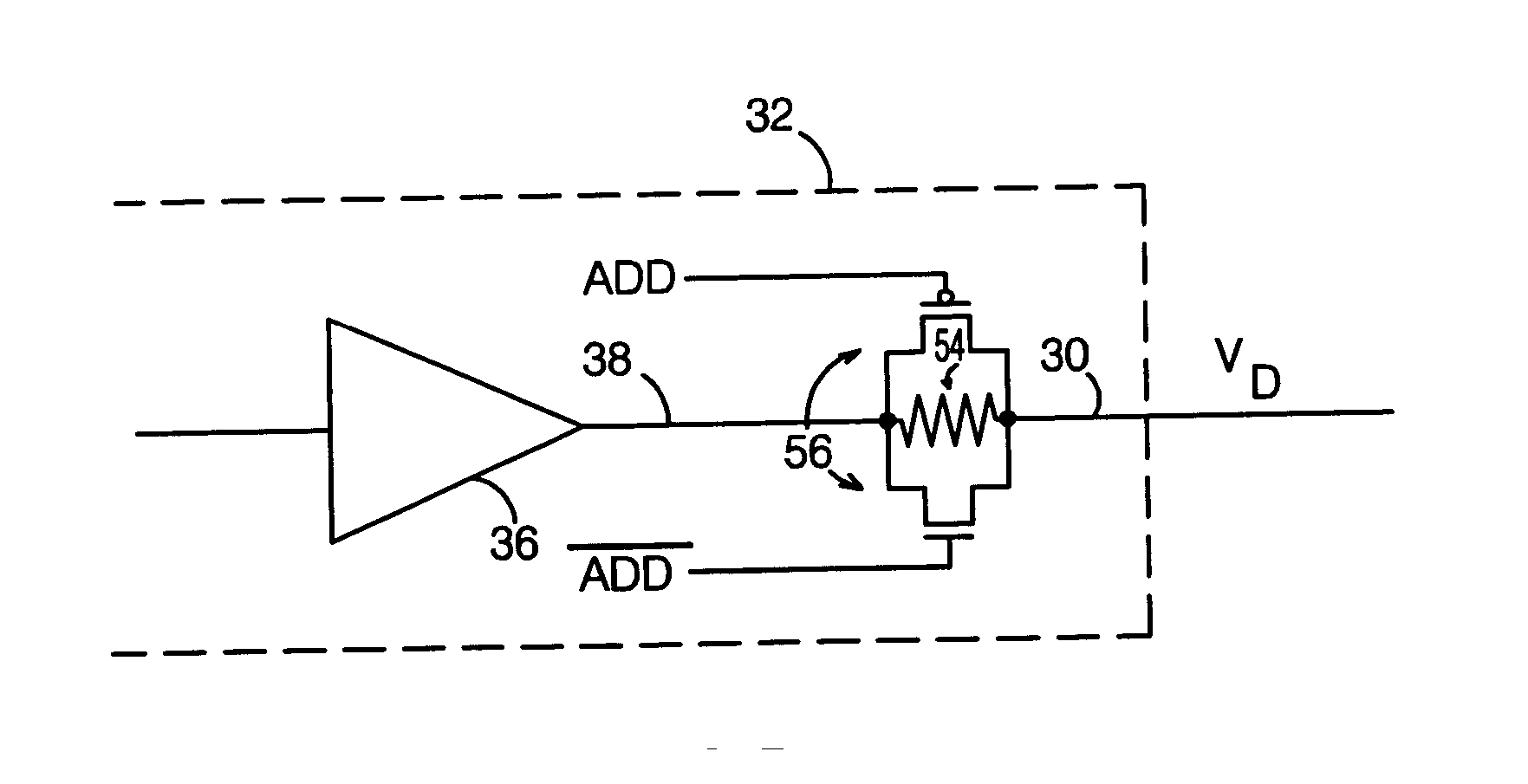

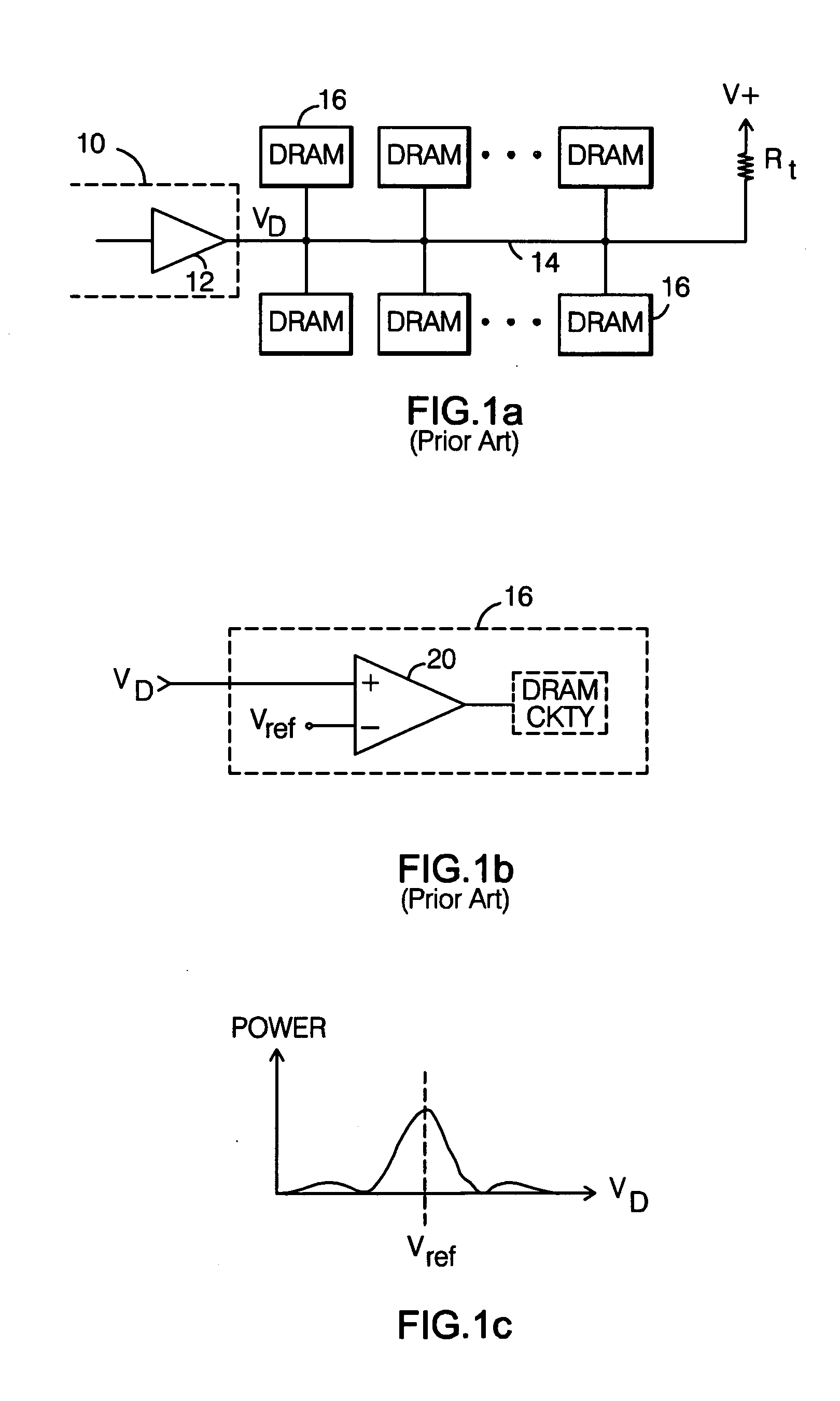

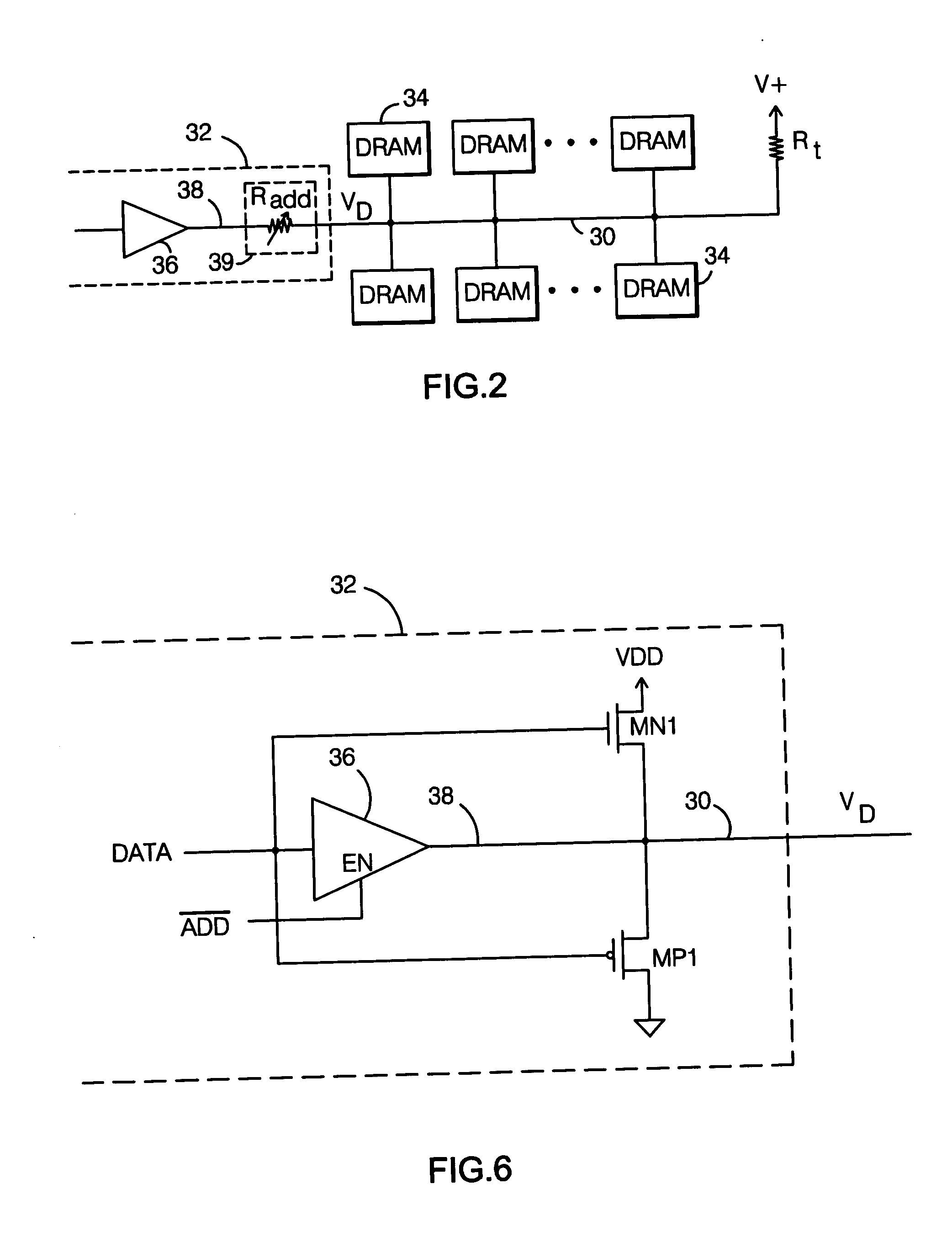

Output buffer with switchable output impedance

ActiveUS20070216445A1Reduce power consumptionAvoid unnecessary power consumptionInput/output impedence modificationReliability increasing modificationsDriver circuitNormal mode

An output buffer with a switchable output impedance designed for driving a terminated signal line. The buffer includes a drive circuit, and a means for switching the output impedance of the drive circuit between a first, relatively low output impedance when the output buffer is operated in a ‘normal’ mode, and a second output impedance which is greater than the first output impedance when operated in a ‘standby’ mode. By increasing the drive circuit's output impedance while in ‘standby’ mode, power dissipation due to the termination resistor is reduced. When used in a memory system, additional power savings may be realized by arranging the buffer such that the increased impedance in ‘standby’ mode shifts the signal line voltage so as to avoid the voltage range over which a line receiver's power consumption is greatest.

Owner:MARVELL ASIA PTE LTD

Architecture for programmable logic device

InactiveUS7154299B2Efficient use ofEfficient use of resourcesLogic circuits characterised by logic functionSolid-state devicesComputer architectureProgrammable logic device

An improved Programmable Logic Device architecture that provides more efficient utilization of resources by enabling access to defined circuit elements in the domain of any Programmable Logic Block (PLB) from any other PLB in the device, by incorporating a connecting means in the routing structure for selectively connecting the input or output of the circuit element in the domain of the PLB to the common interconnect matrix connecting all the PLBs together.

Owner:HD SILICON SOLUTIONS LLC

Inverter manufacturing method and inverter

ActiveUS8304298B2Easy to manufactureIncrease the differenceLogic circuits characterised by logic functionSolid-state devicesPower inverterSemiconductor

Owner:CANON KK

Circuit configurations having four terminal JFET devices

InactiveUS20070262793A1Logic circuits characterised by logic functionSolid-state devicesPhase detectorMultiplexer

Circuits using four terminal junction field effect transistors (JFETs) are disclosed. Such circuits can include various static and dynamic logic circuits, flip-flops, multiplexer, tri-state driver, phase detector, logic having variable speeds of operation, and / or analog circuit with such four terminal JFETs operating in a linear or nonlinear mode.

Owner:MIE FUJITSU SEMICON

Popular searches

Digital computer details Comparison of digital values Microcontrol arrangements Logic circuits using semiconductor devices Electric pulse generator Bulk negative resistance effect devices Special data processing applications Logic circuit coupling/interface arrangements Semiconductor devices Electronic switching