Patents

Literature

42 results about "Emitter-coupled logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, emitter-coupled logic (ECL) is a high-speed integrated circuit bipolar transistor logic family. ECL uses an overdriven BJT differential amplifier with single-ended input and limited emitter current to avoid the saturated (fully on) region of operation and its slow turn-off behavior. As the current is steered between two legs of an emitter-coupled pair, ECL is sometimes called current-steering logic (CSL), current-mode logic (CML) or current-switch emitter-follower (CSEF) logic.

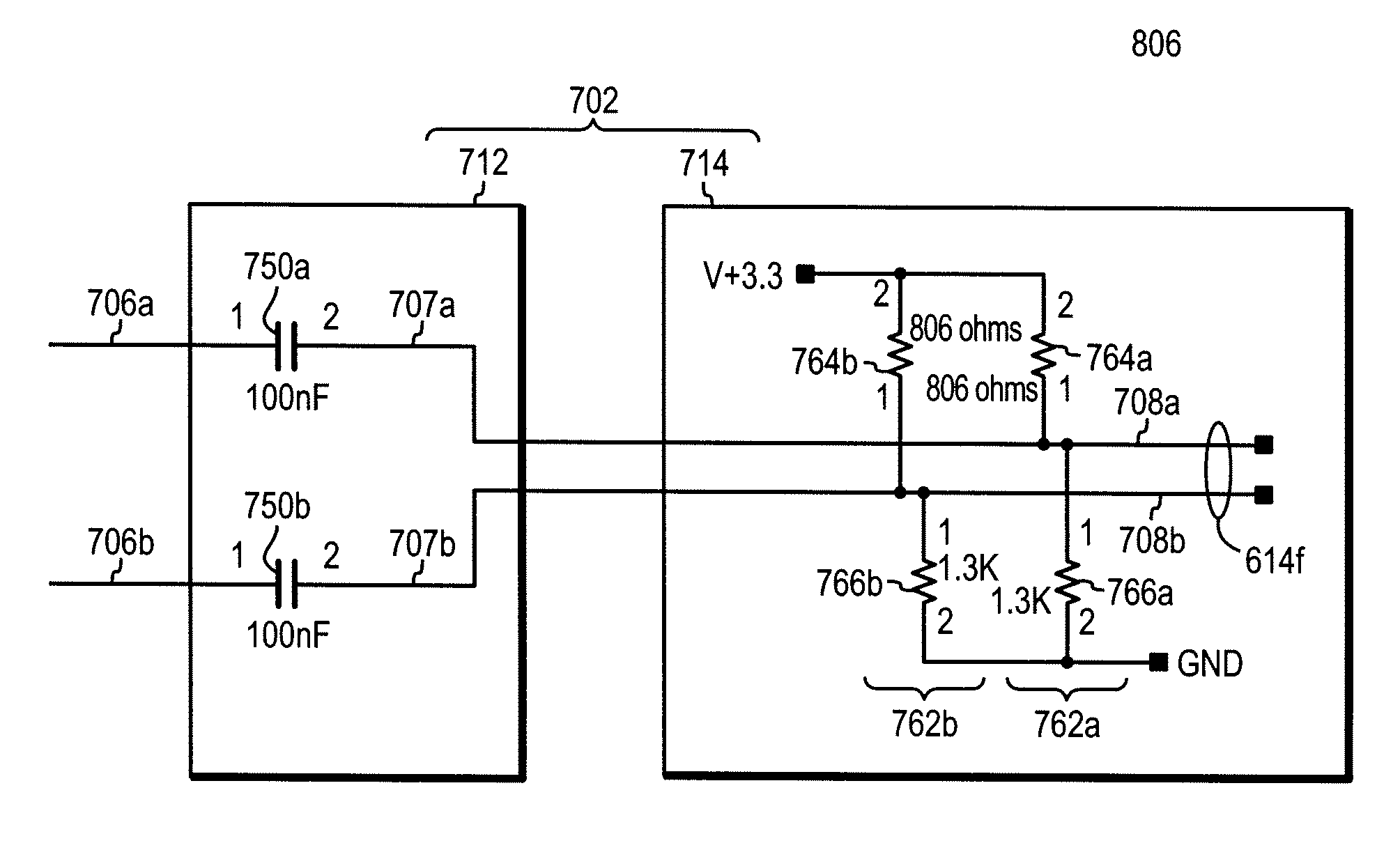

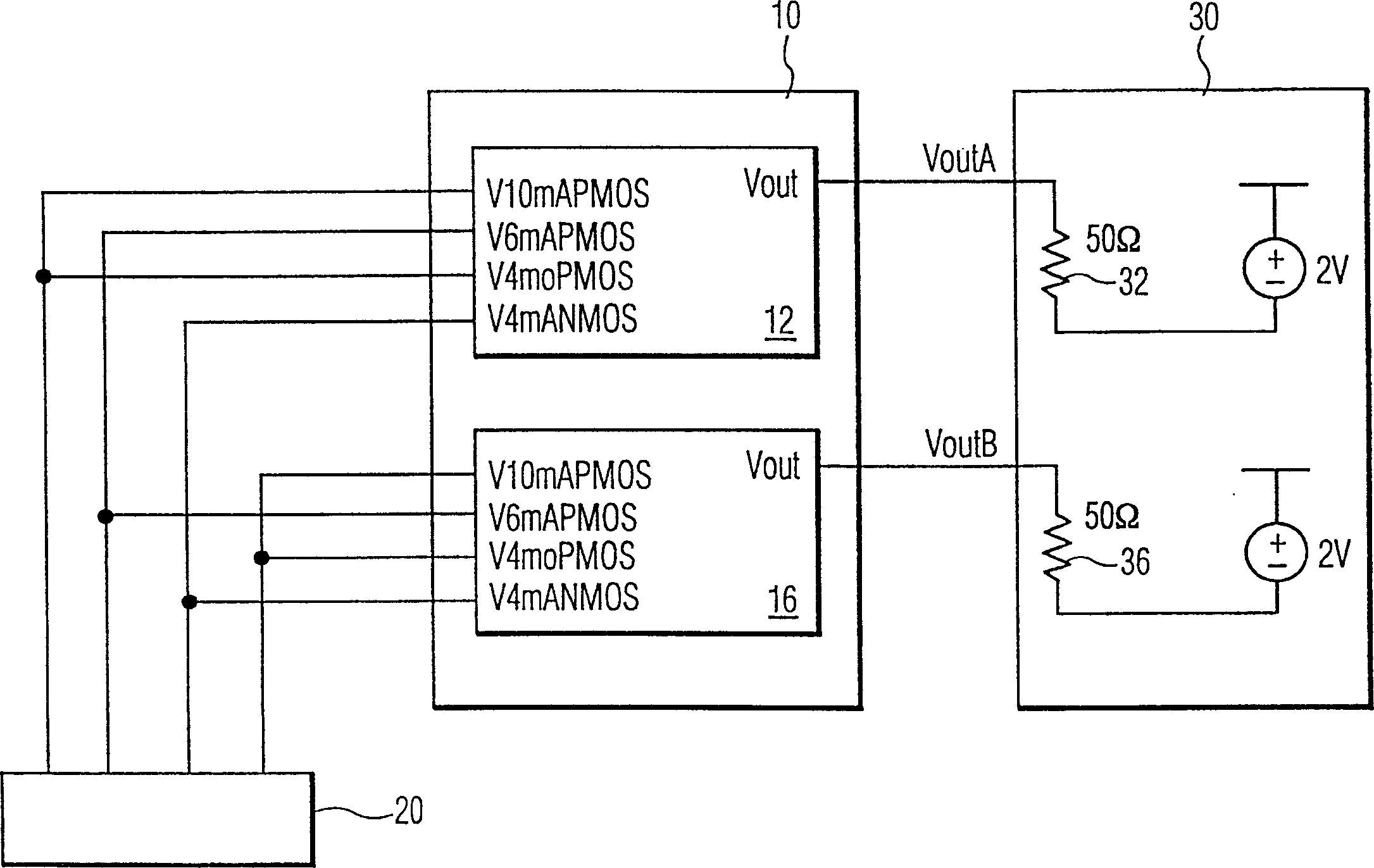

Self-biasing CMOS PECL receiver with wide common-mode range and multi-level-transmit to binary decoder

InactiveUS6049229AReduced Power RequirementsSimplify interconnect routingLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsThree levelEmitter-coupled logic

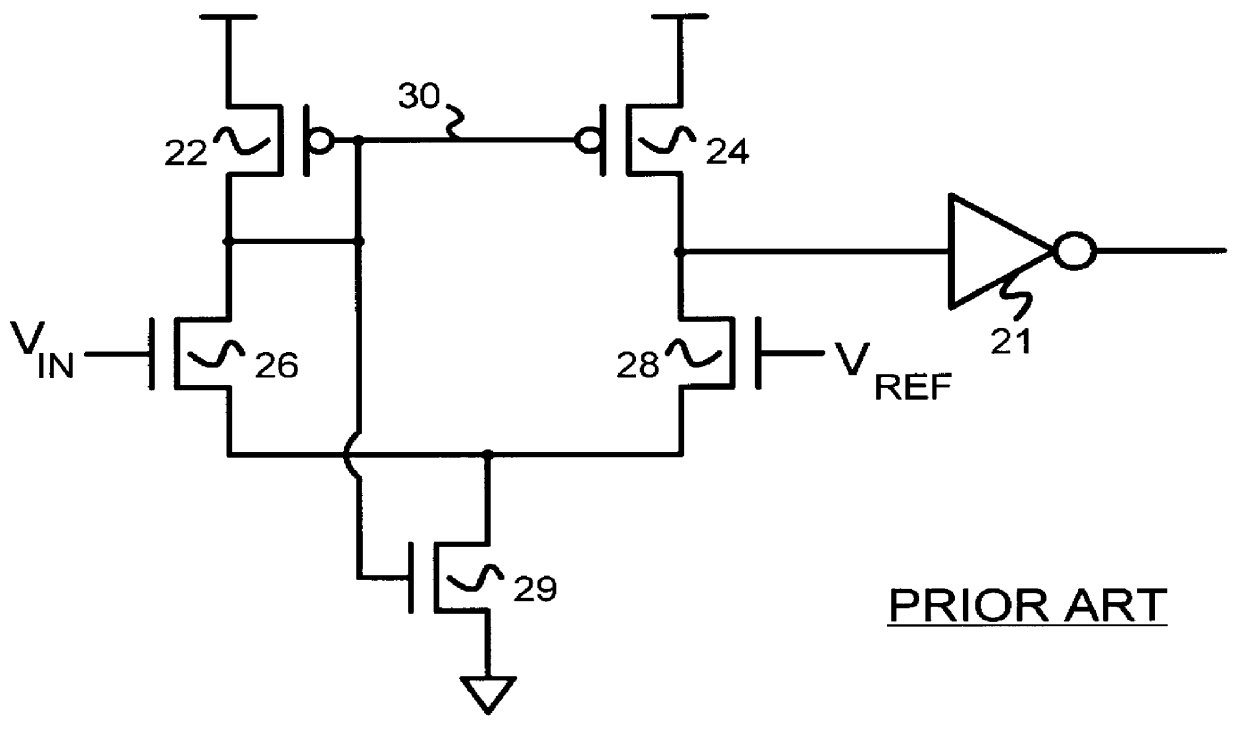

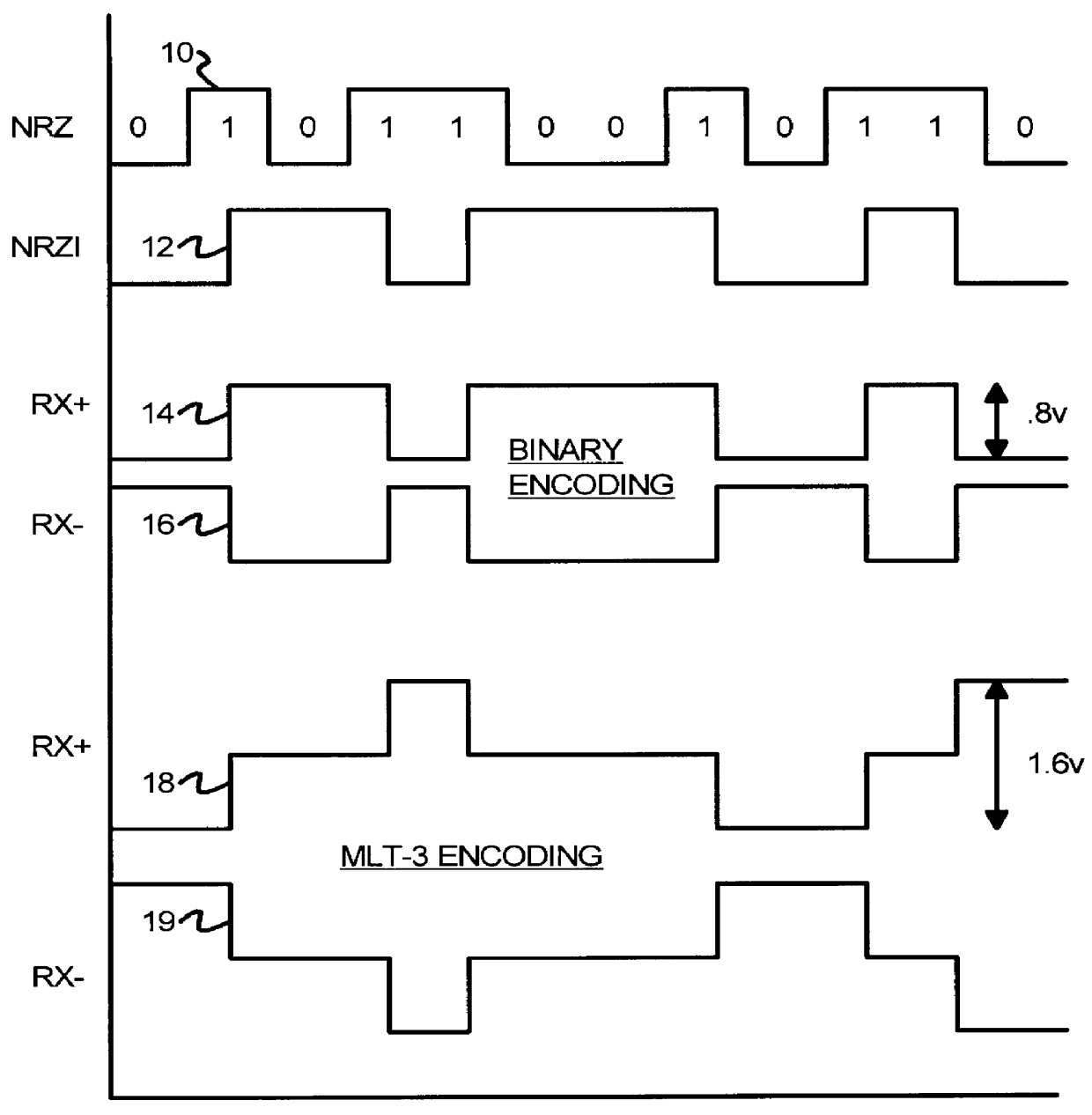

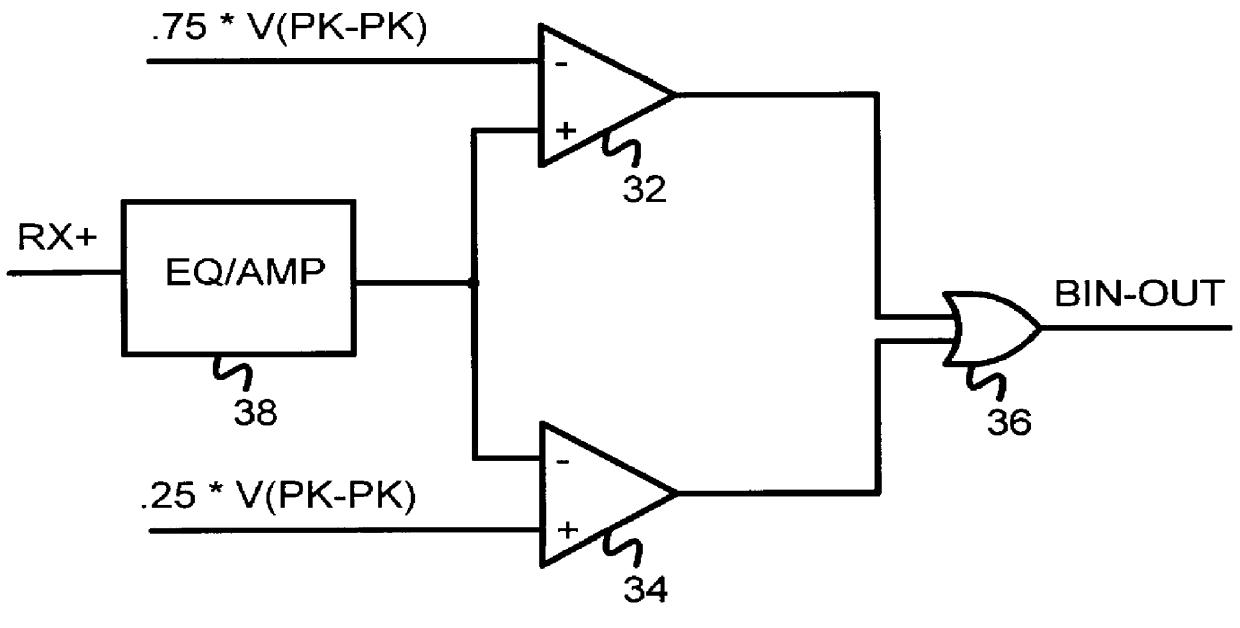

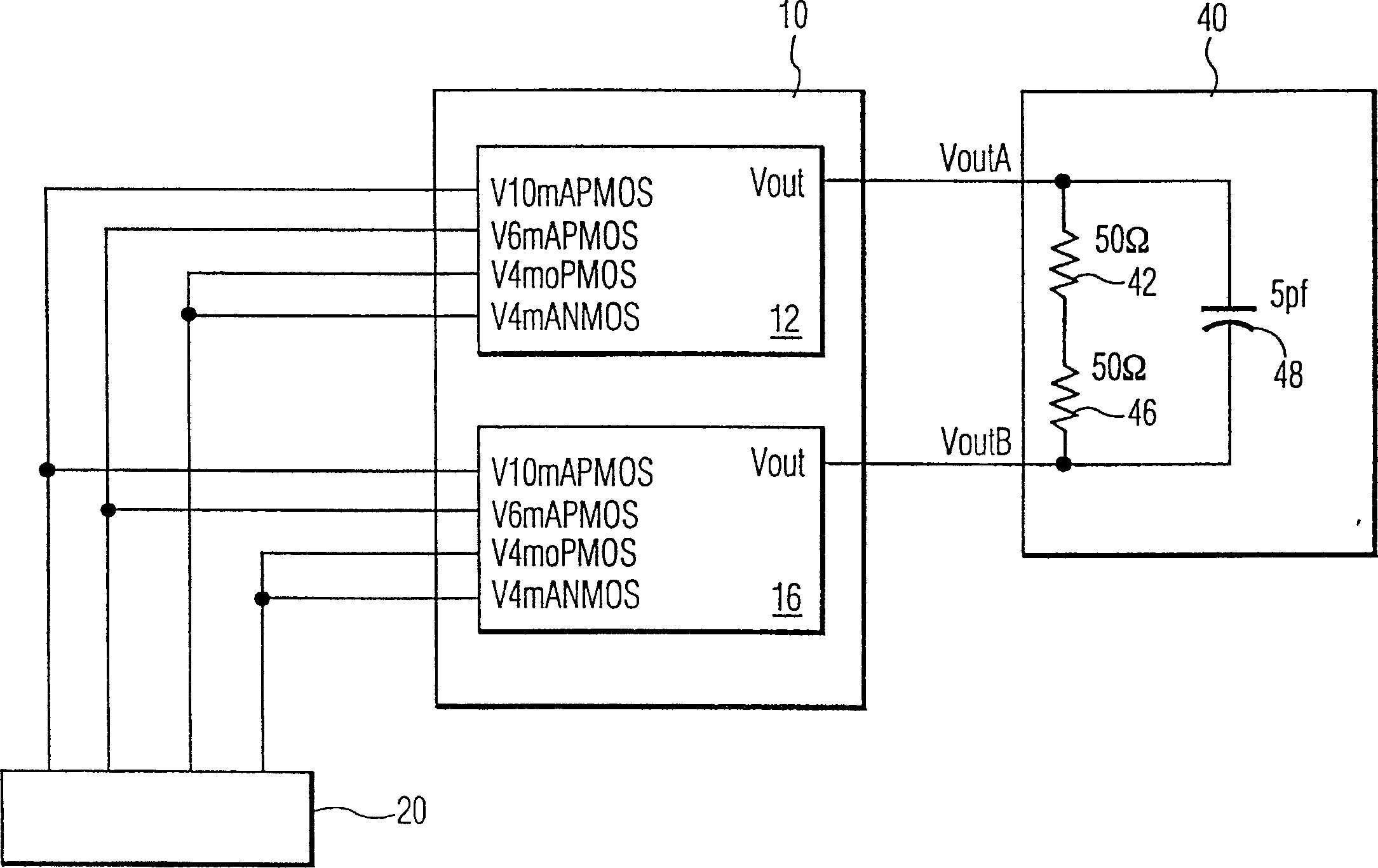

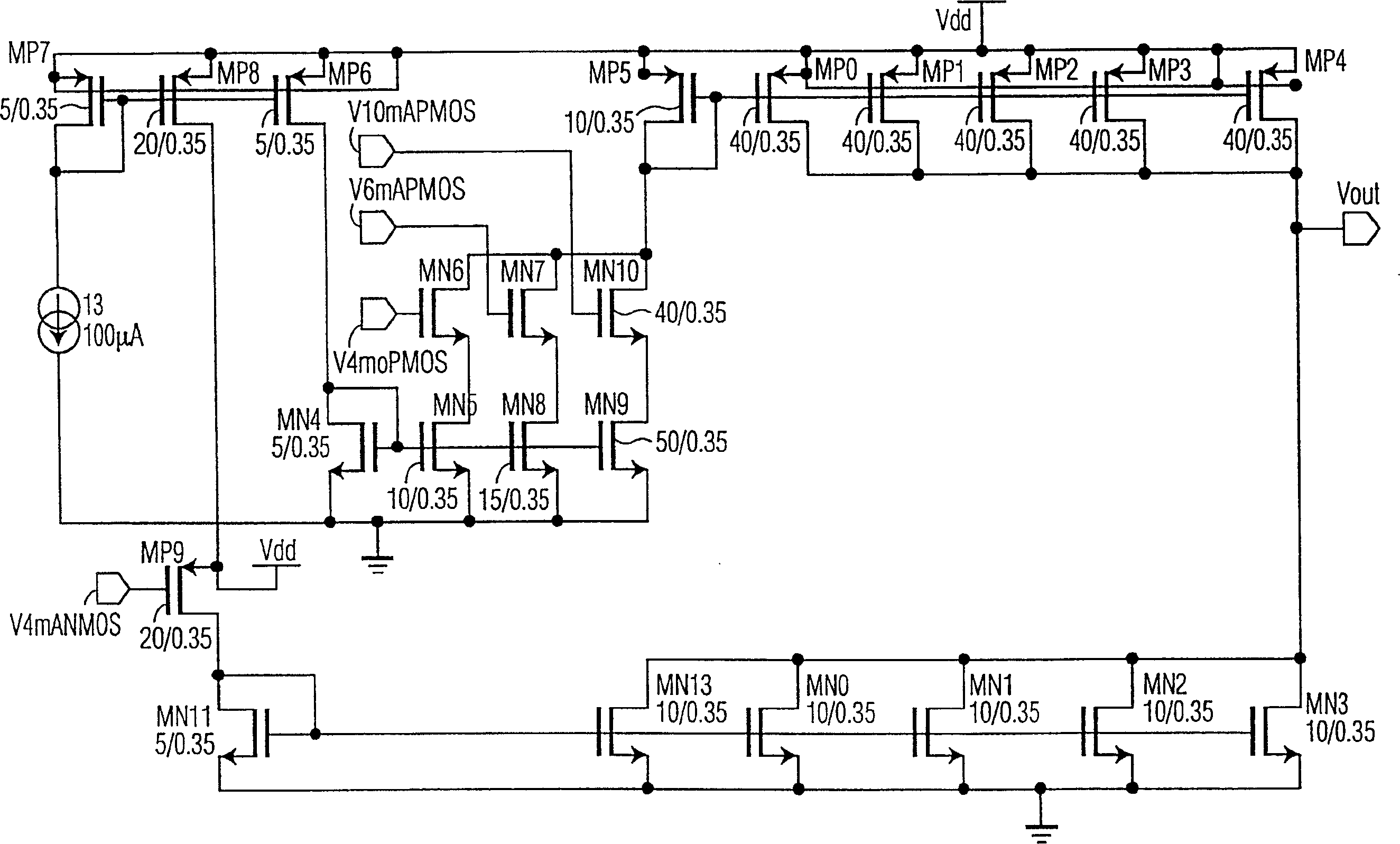

A pseudo-emitter-coupled-logic (PECL) receiver has a wide common-mode range. Two current-mirror CMOS differential amplifiers are used. One amplifier has n-channel differential transistors and a p-channel current mirror, while the second amplifier has p-channel differential transistors and an n-channel current mirror. When the input voltages approach power or ground, one type of differential transistor continues to operate even when the other type shuts off. The outputs of the two amplifiers are connected together and each amplifier receives the same differential input signals. The tail-current transistor is self-biased using the current-mirror's gate-bias. This self biasing of each amplifier eliminates the need for an additional voltage reference and allows each amplifier to adjust its biasing over a wide input-voltage range. Thus the common-mode input range is extended using self biasing and complementary amplifiers. The complementary self-biased comparators can be used for receiving binary or multi-level-transition (MLT) inputs by selecting different voltage references for threshold comparison. Using the same reference on both differential inputs eliminates a second reference for multi-level inputs having three levels. Thus binary and MLT inputs can be detected and decoded by the same decoder.

Owner:DIODES INC

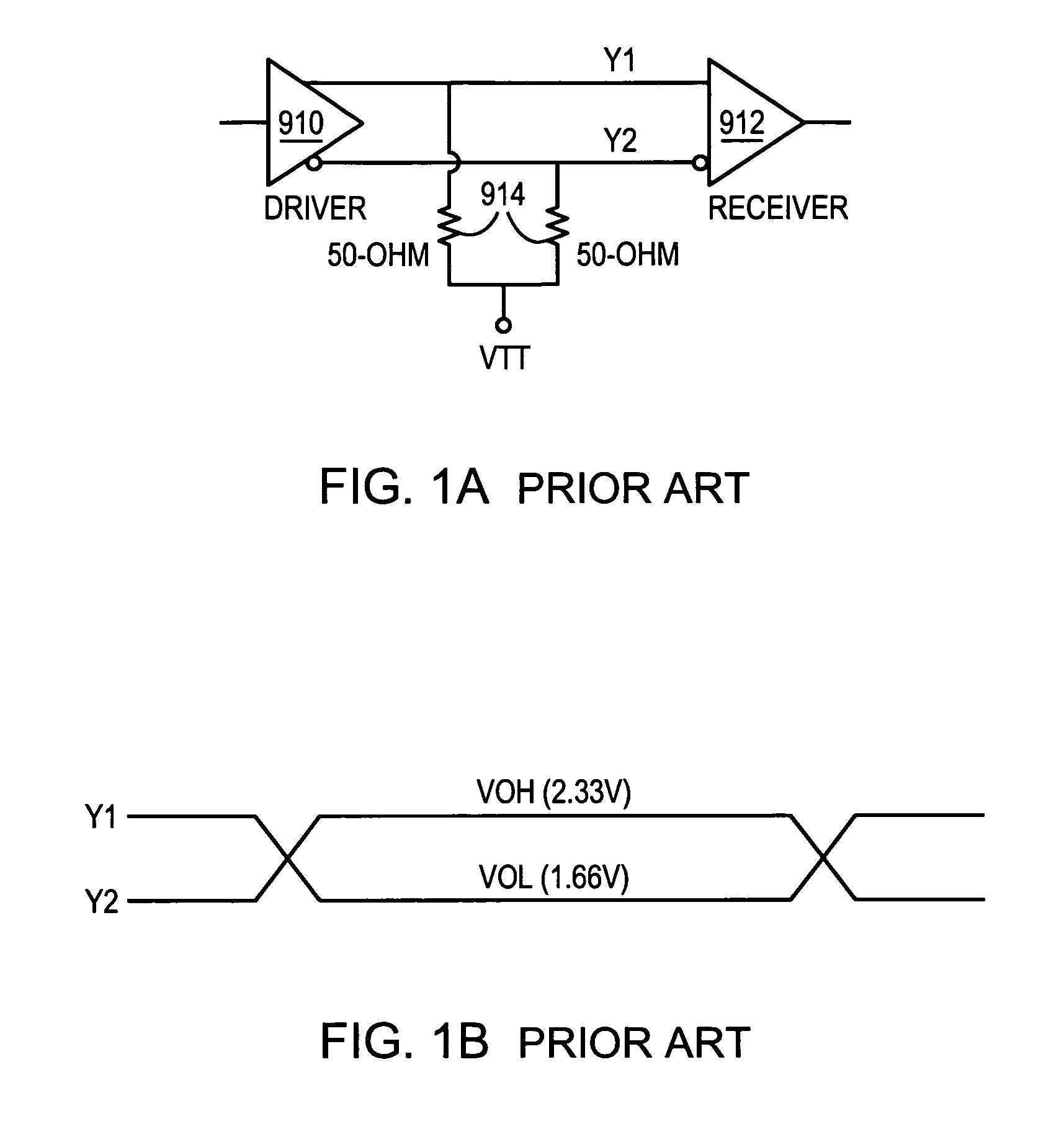

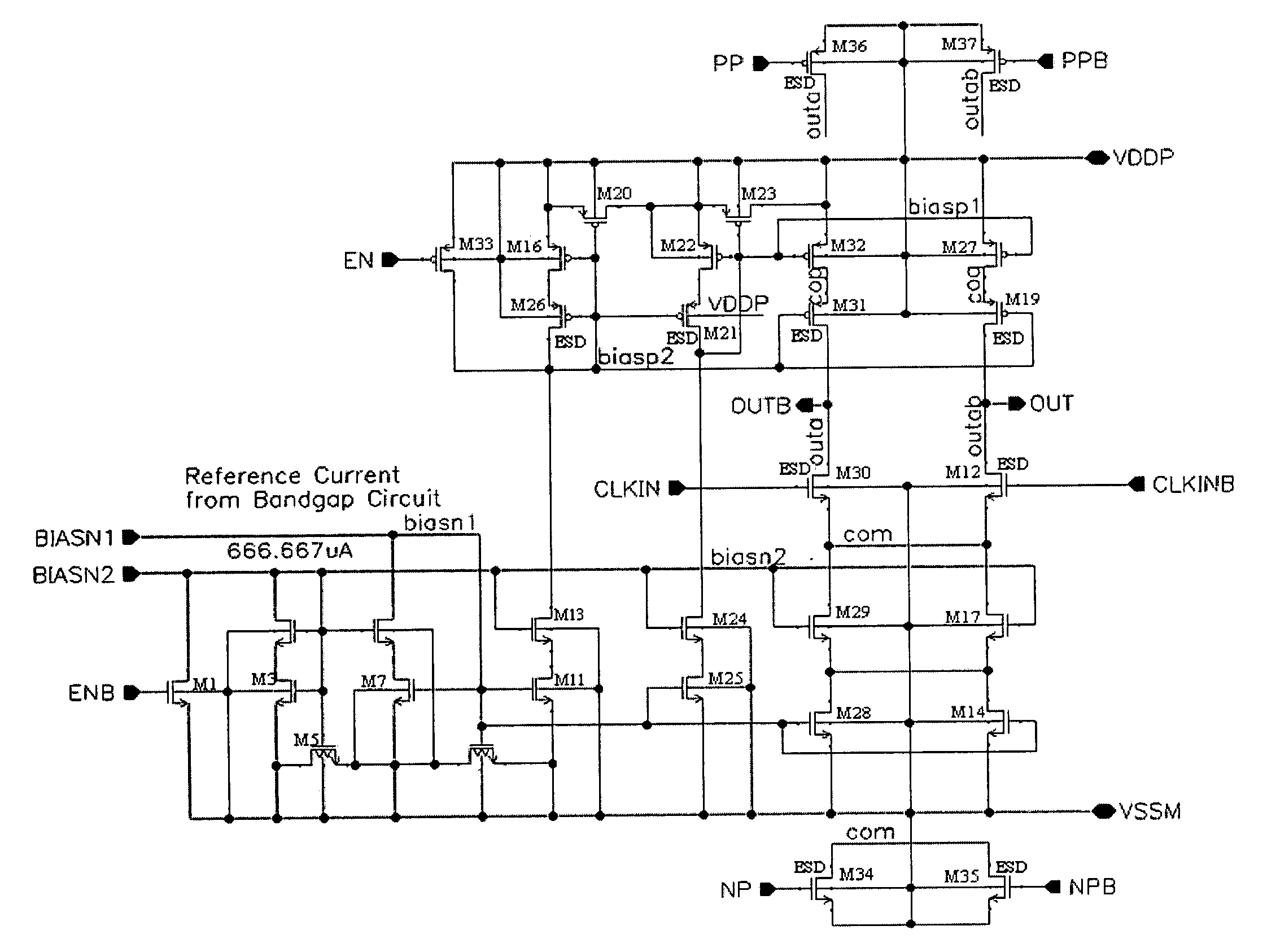

CMOS low-voltage PECL driver with initial current boost

InactiveUS6424217B1Power reduction by control/clock signalAmplifier modifications to raise efficiencyElectricityCMOS

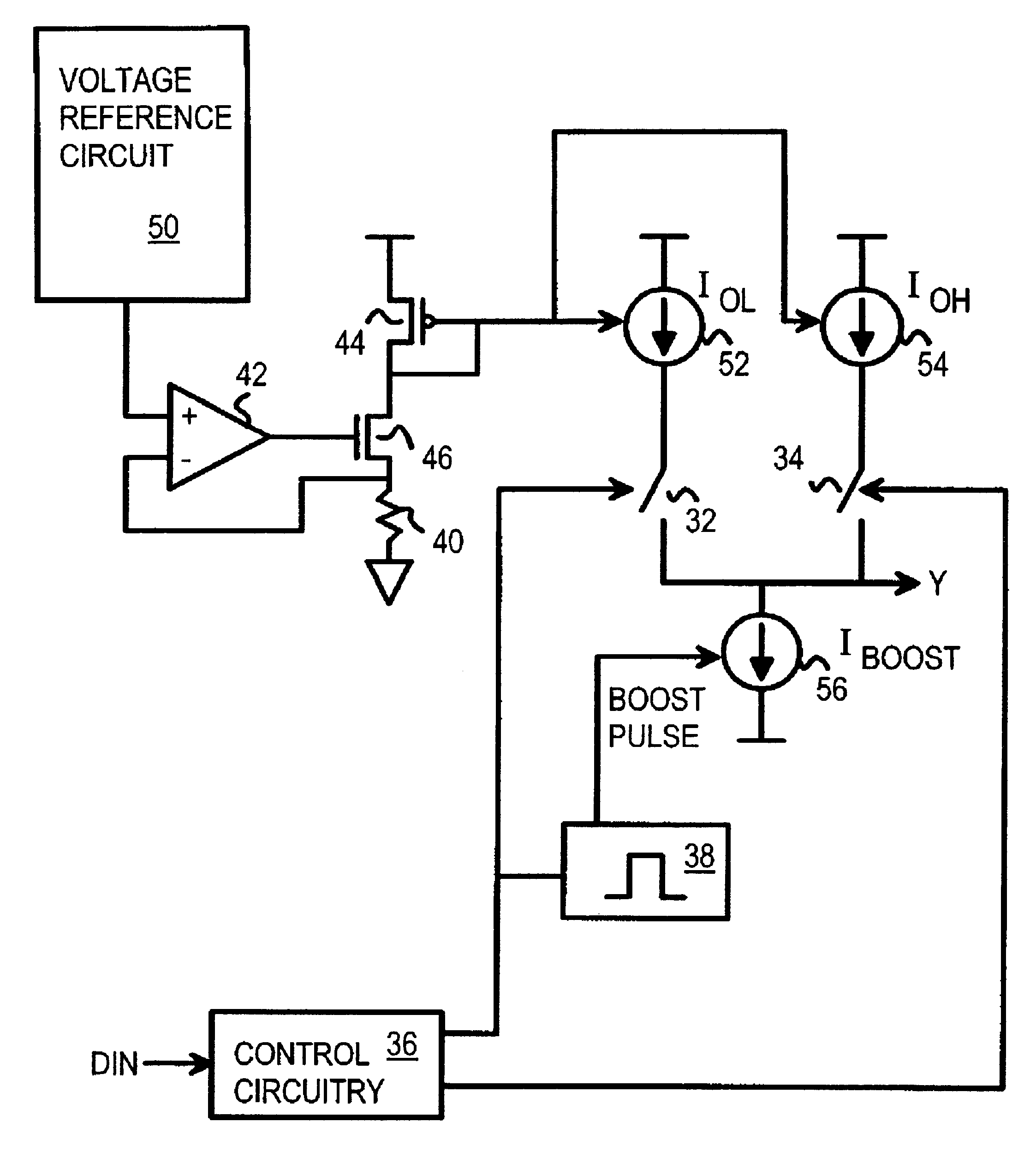

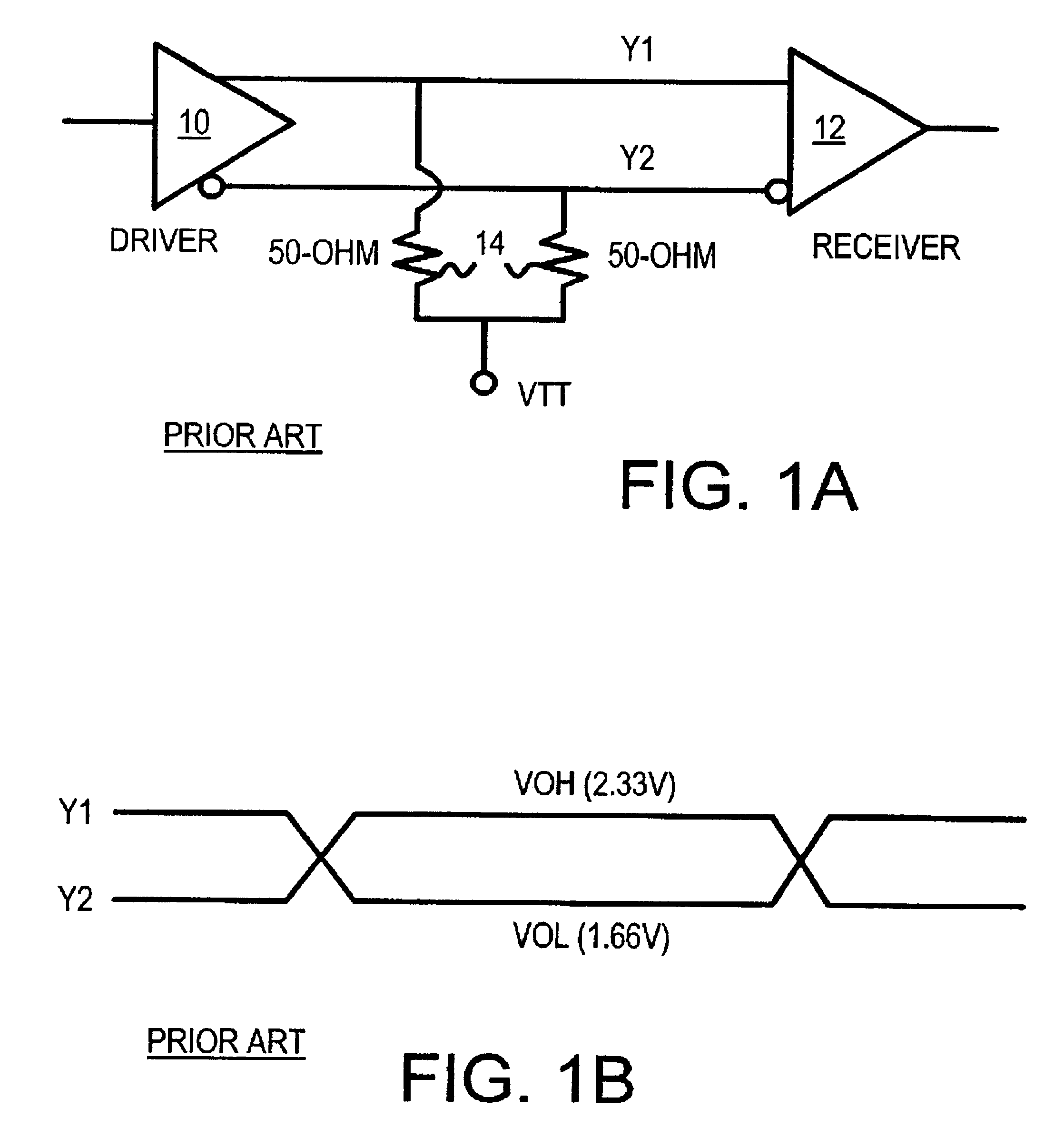

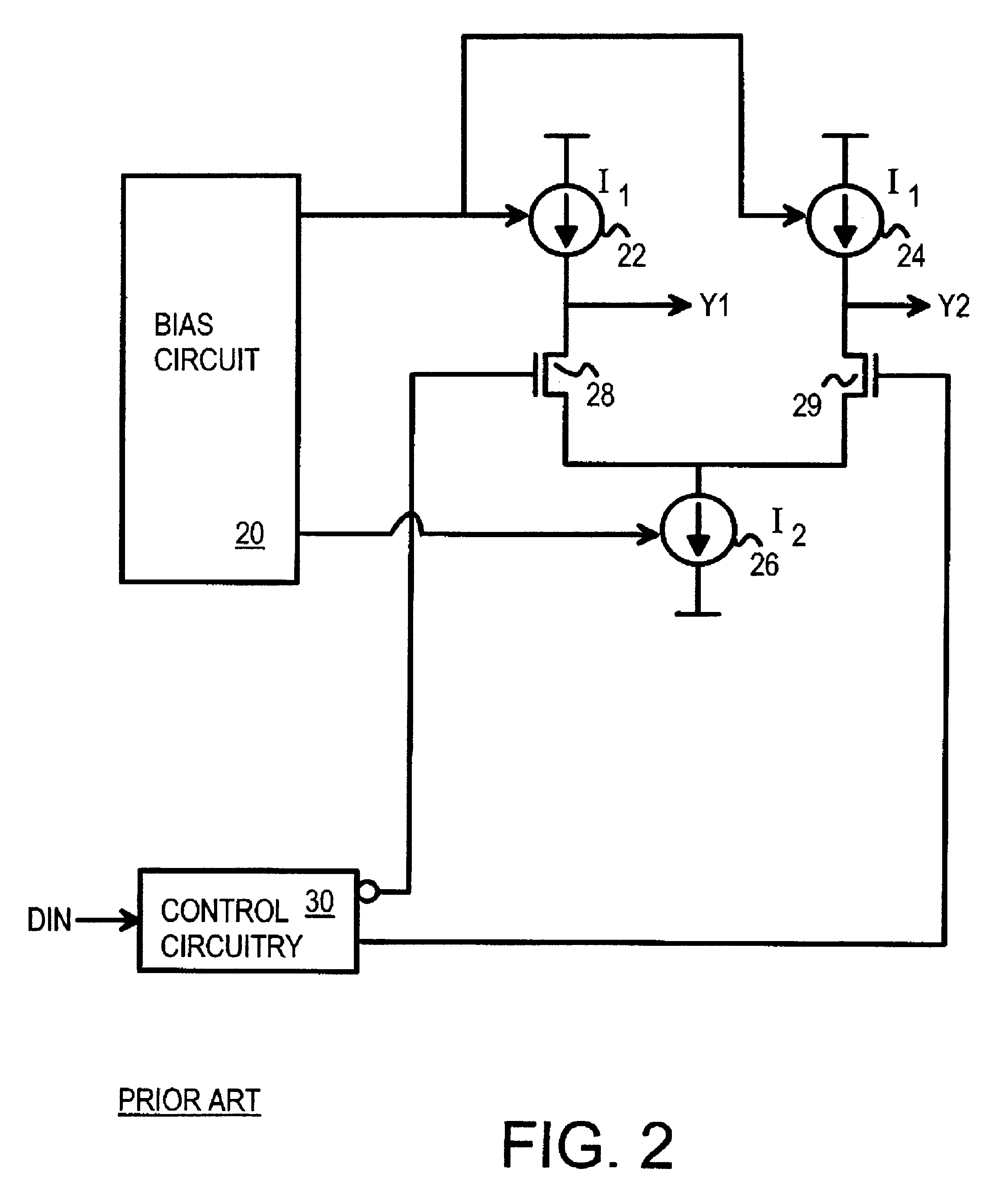

A differential amplifier has a boosted sink current that is turned on by a pulse generator when the output is driven low. This boosted sink current quickly lowers the output to the voltage-output-low VOL level. After the pulse ends, the sink current ends and power is reduced to a lower standby level. A differential pair of switches receives the true and complement data. One switch is closed when the data is true, connecting a current source that sets the standby voltage-output-high VOH level. The other switch is closed when the complement data is high, connecting another current source that sets the standby VOL level. A second differential amplifier with reversed true and complement data drives a complement output for a differential signaling transmitter, such as for a pseudo-emitter-coupled logic (PECL) driver.

Owner:DIODES INC

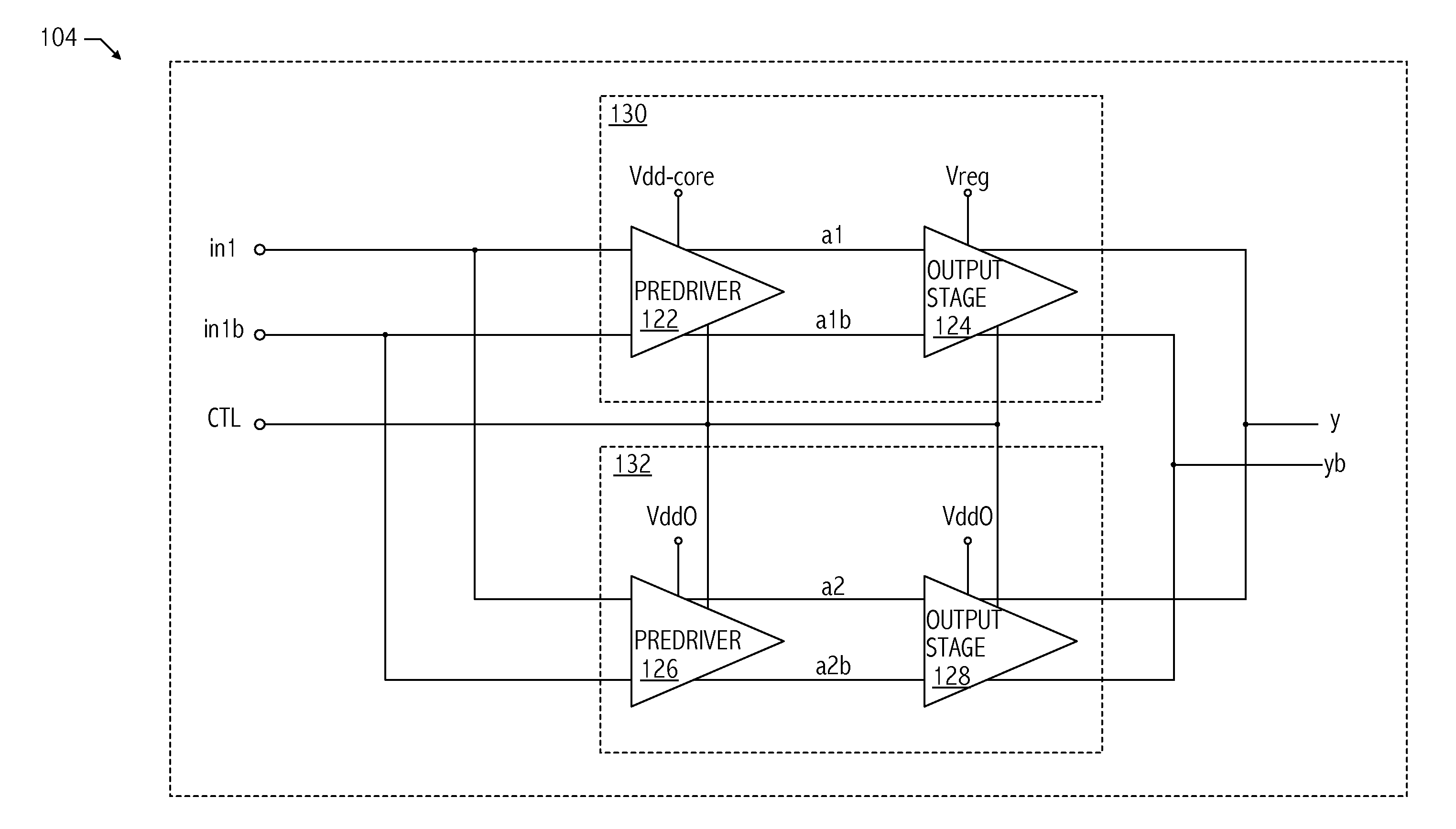

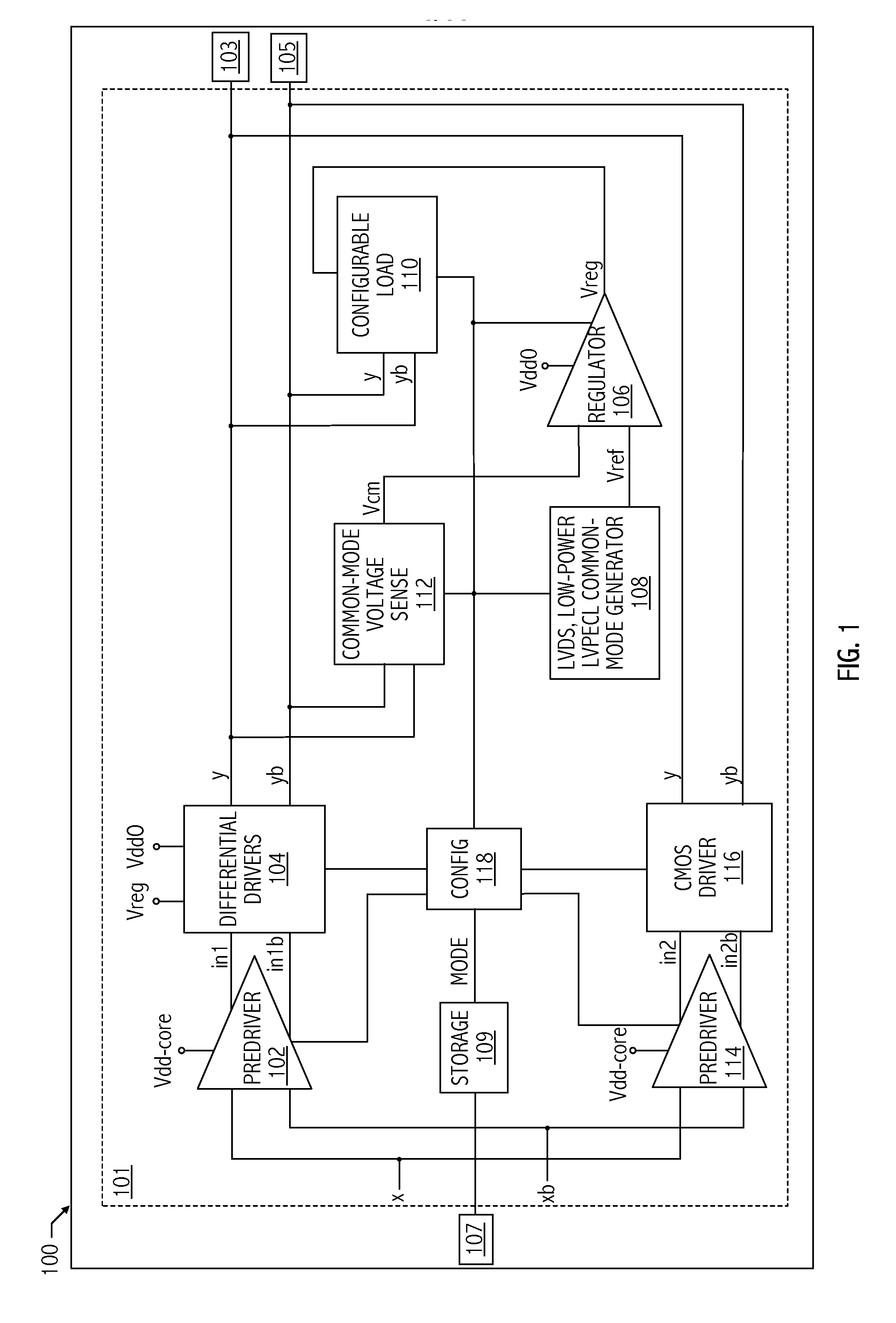

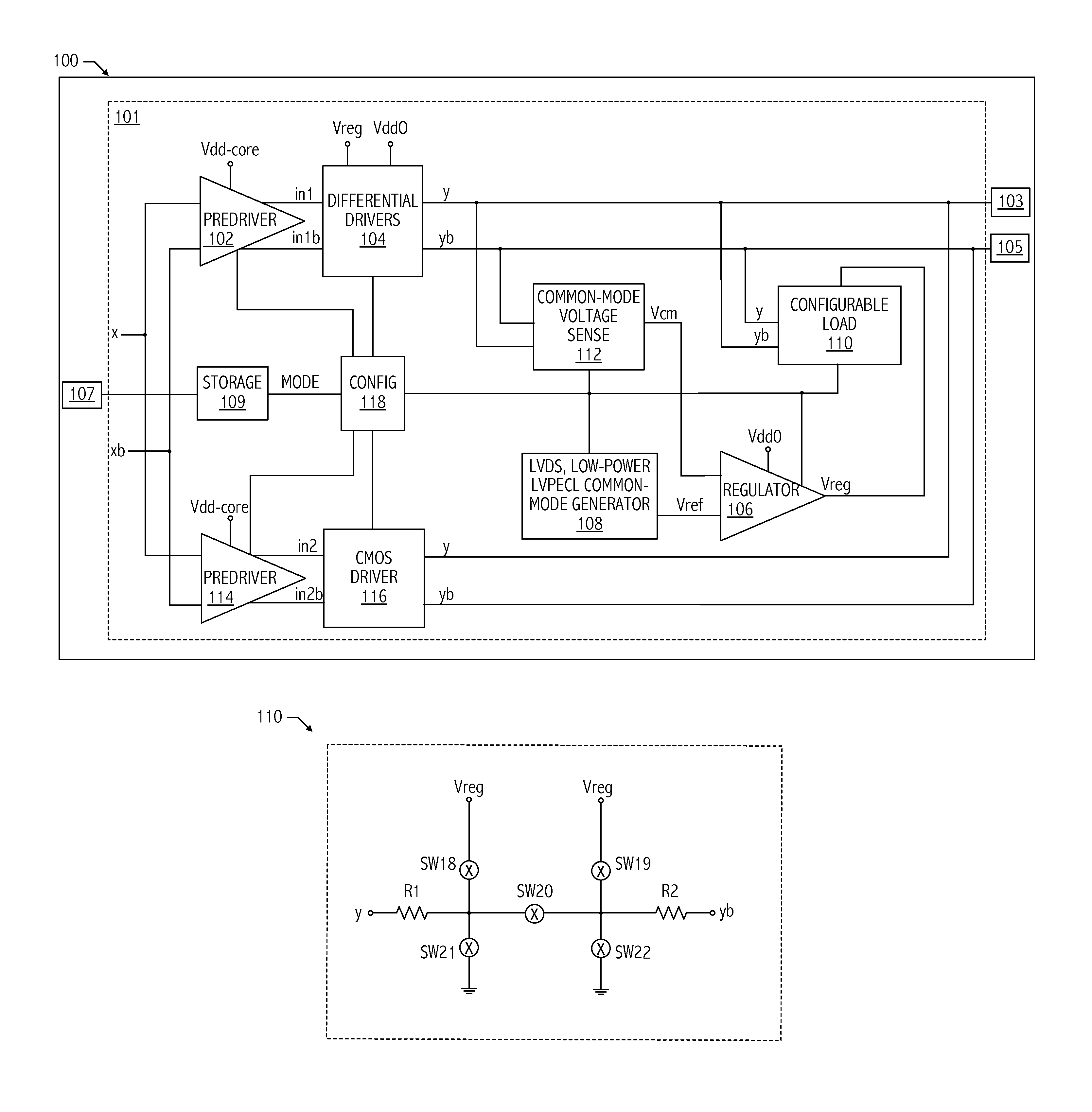

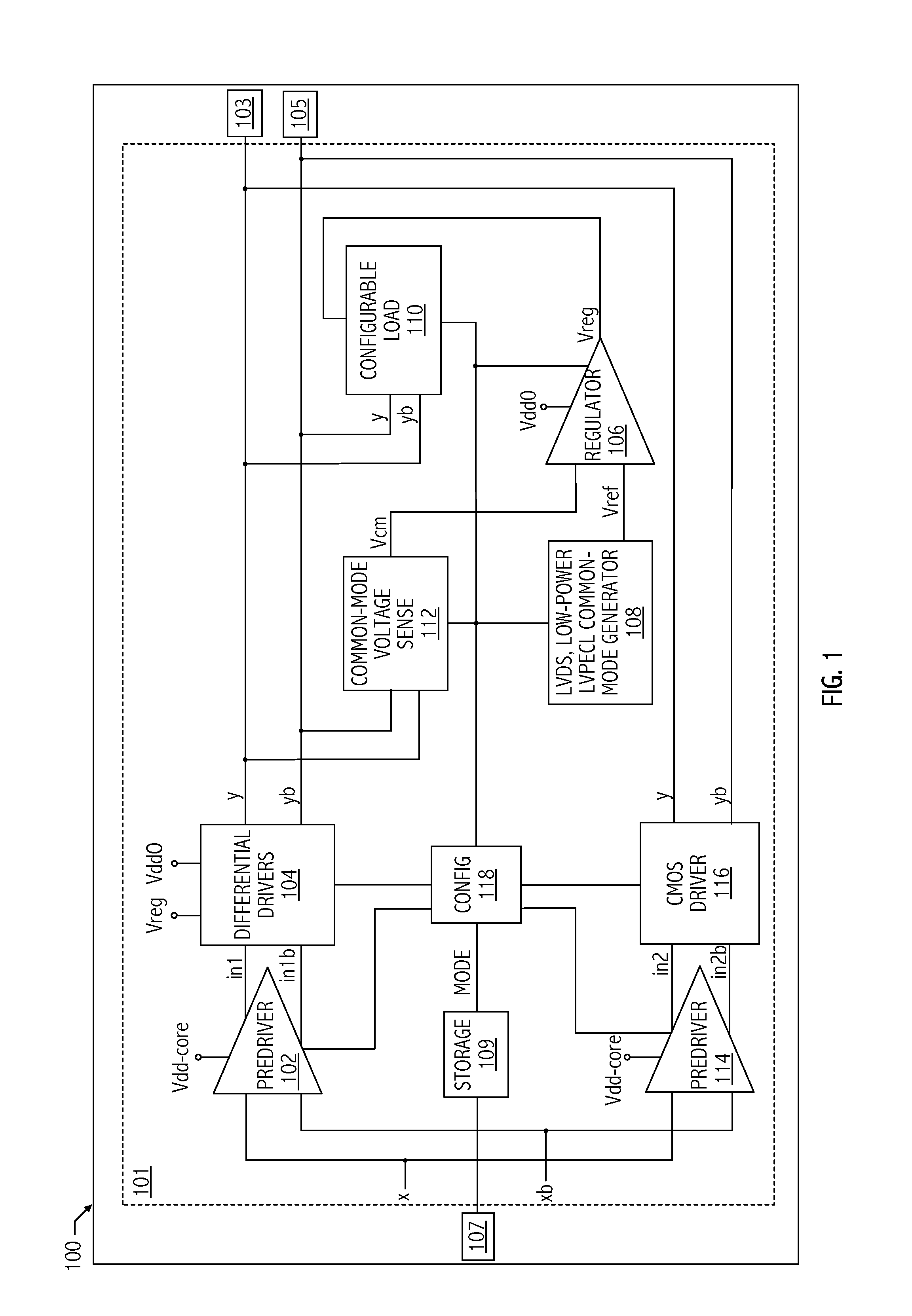

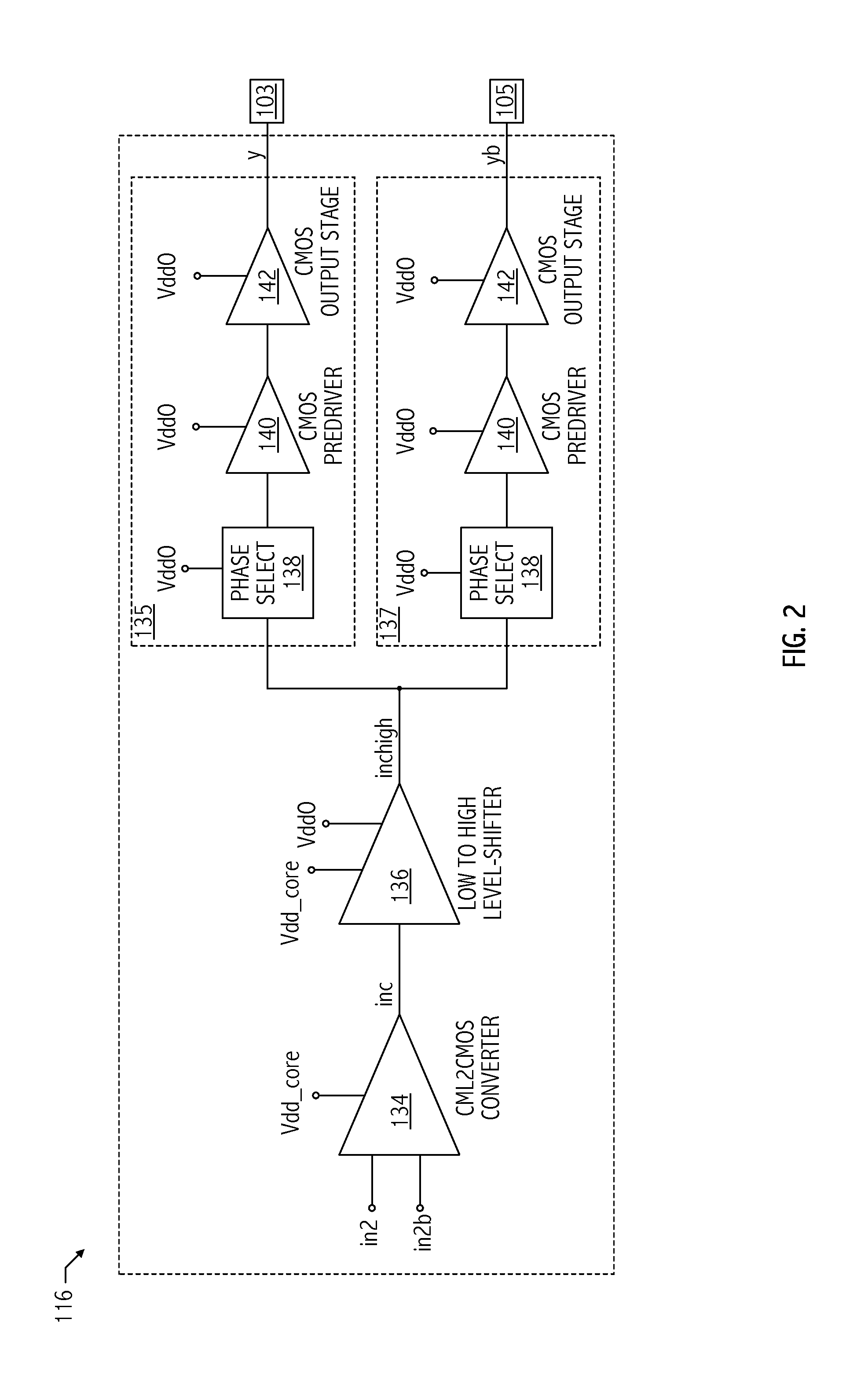

Multiple signal format output driver with configurable internal load

A multiple signal format output driver is configurable to provide a current-mode logic (CML) output signal in response to a CML value of one or more first values of the control signal. The output driver is configurable to provide a low-power, low-voltage positive emitter-coupled logic (low-power LVPECL) output signal in response to a low-power LVPECL value of the one or more first values of the control signal. The output driver is configurable to provide a low-voltage differential signaling (LVDS) output signal in response to an LVDS value of the one or more first values of the control signal. The output driver may be configurable to provide a LVPECL output signal in response to a second value of the control signal. The output driver may be configurable to provide a high-speed current steering logic (HCSL) output in response to a third value of the control signal.

Owner:SKYWORKS SOLUTIONS INC

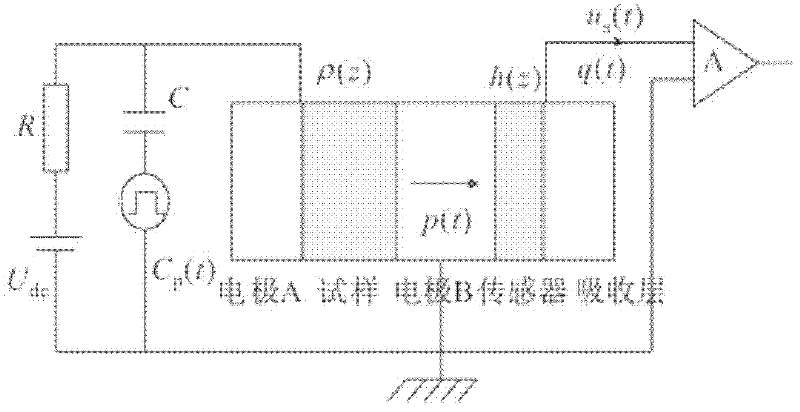

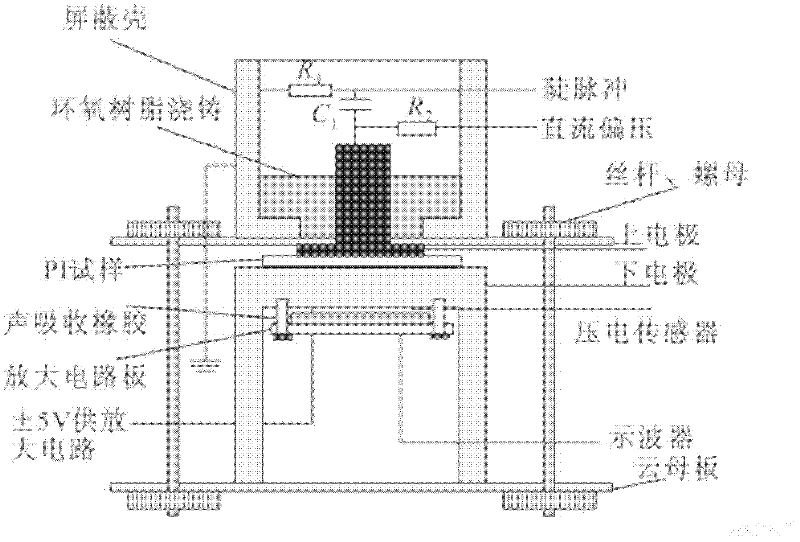

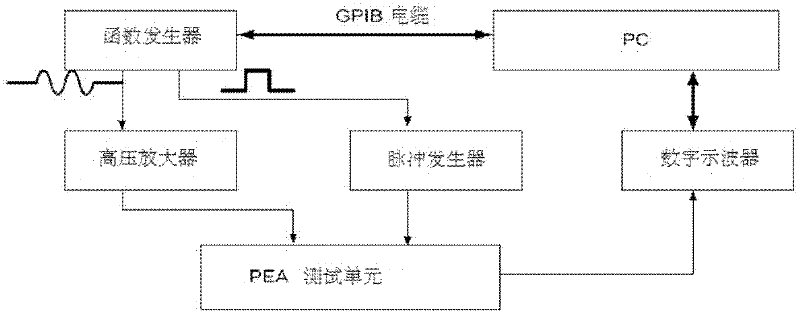

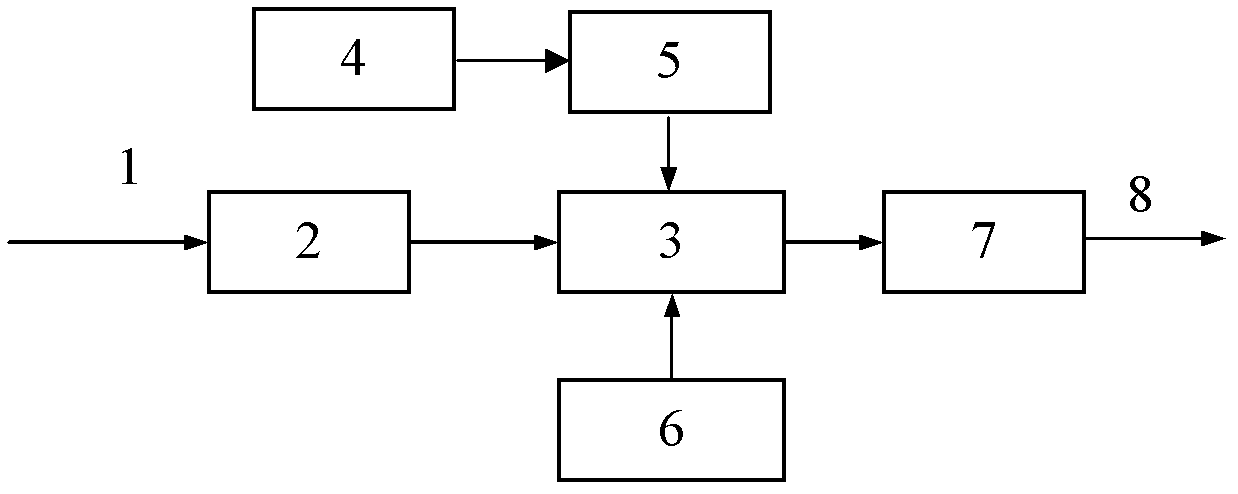

Alternating current-direct current space charge measuring system and method capable of improving pulsed electro-acoustic method

InactiveCN102654537ACreative improvementImprove signal processing capabilitiesElectrical measurementsEmitter-coupled logicData acquisition

The invention discloses an alternating current-direct current space charge measuring system capable of improving a pulsed electro-acoustic (PEA) method, comprising a pulse generator, an emitter-coupled logic integrated programming support environment (Eclipse) signal averaging controller, a high-voltage pulse generator, a PEA measuring unit, a signal generator and a processing host. The system disclosed by the invention adopts the pulse generator of 3kHz and an Eclipse high-speed data acquisition system to acquire real-time signals, so that the measuring time is obviously shortened, a good phase resolution ratio can be obtained under high-frequency voltage and low-frequency voltage and real-time measurement of space charge under the influence of alternating current-direct current voltage can be realized; and meantime, a space charge attenuation graph can more vividly reflect dynamic change of charge.

Owner:SOUTHWEST UNIVERSITY

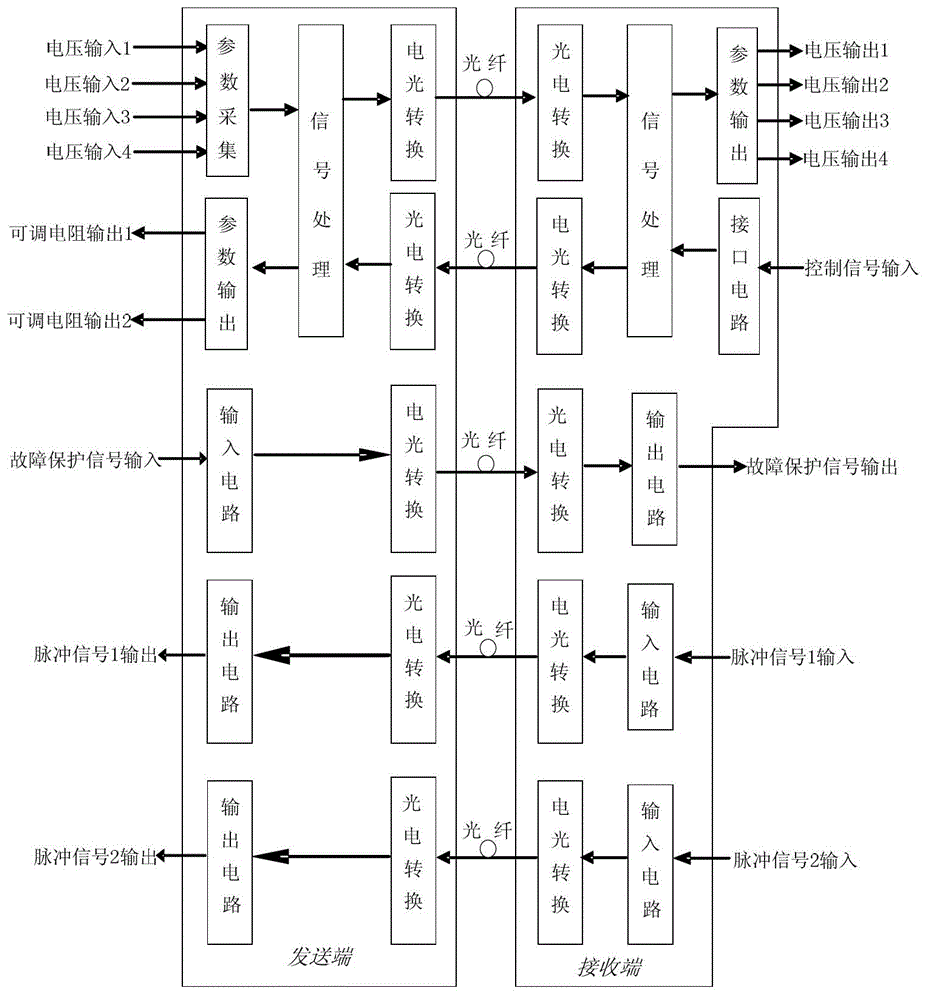

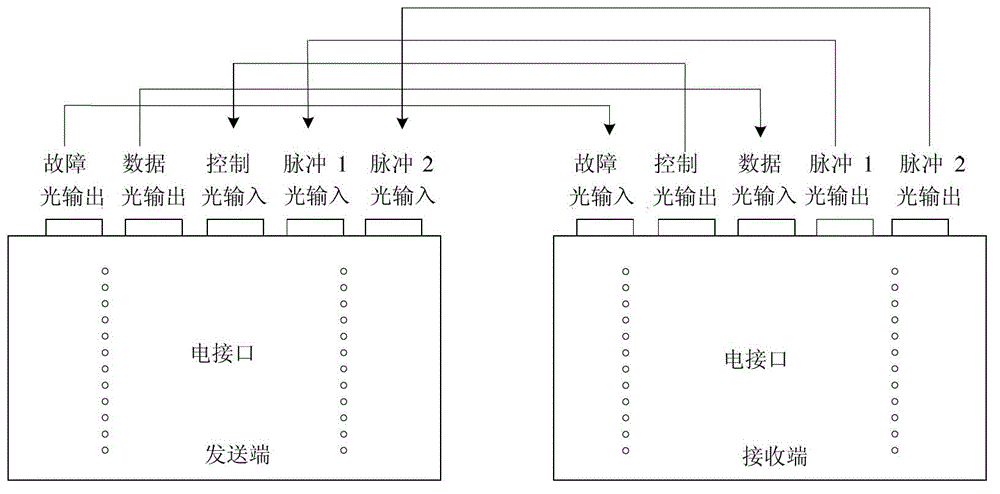

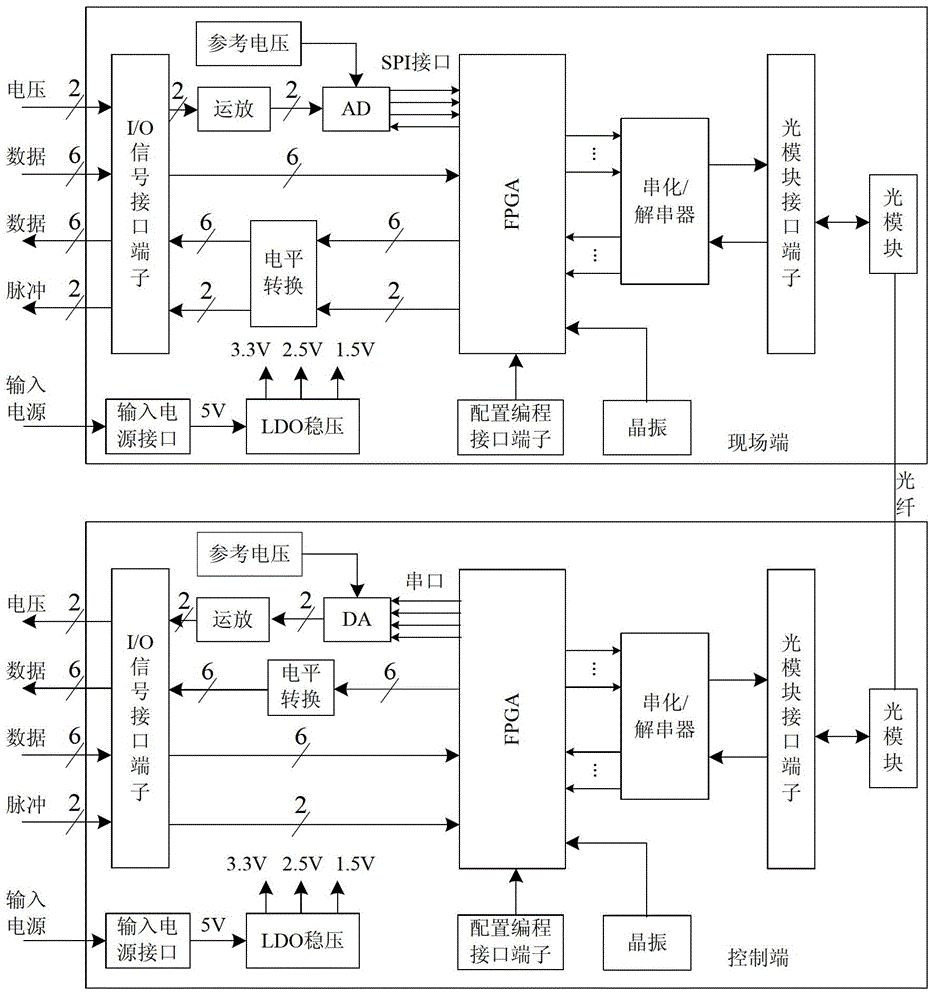

Miniaturized multi-path two-way signal optical fiber transmission component

ActiveCN102882604AReduce volumeSuitable for data transmission applicationsFibre transmissionTransistor–transistor logicAnti jamming

The invention discloses a miniaturized multi-path two-way signal optical fiber transmission component. The miniaturized multi-path two-way signal optical fiber transmission component comprises a field end and a control end which have multi-chip stack encapsulation structures; the field end is connected with the control end through a transmission optical fiber; the control end can input a plurality of voltage signals and a plurality of data signals, convert a plurality of voltage signals and a plurality of data signals into a positive emitter coupled logic (PECL) signal and transmit the PECL signal to the control end through an optical module and a transmission optical cable; the control end reduces the received PECL signal into a plurality of voltage signals and a plurality of data signals and outputs a plurality of voltage signals and a plurality of data signals; the control end also can input a plurality of transistor-transistor logic (TTL) pulse signals and a plurality of data signals, convert a plurality of TTL pulse signals and a plurality of data signals into the PECL signal, and transmit the PECL signal to the field end through the optical module and the transmission optical cable; the field end reduces the received PECL signal into a plurality of data signals and a plurality of TTL pulse signals and outputs a plurality of data signals and a plurality of TTL pulse signals, so that a plurality of two-way signals are transmitted by an optical fiber, and the anti-jamming capacity is high; and therefore, the miniaturized multi-path two-way signal optical fiber transmission component is particularly suitable for the data transmission of a modern airborne and ship-borne radar system.

Owner:8TH RES INST OF CETC

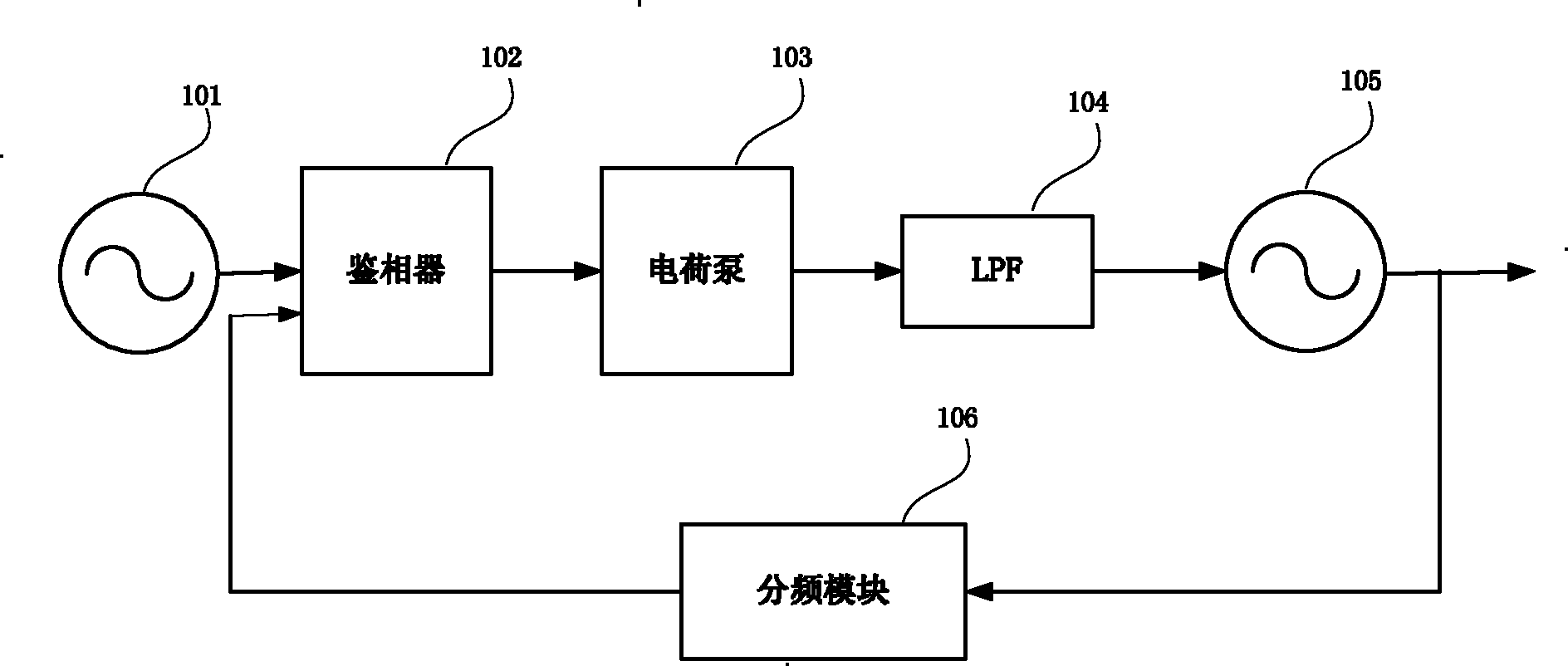

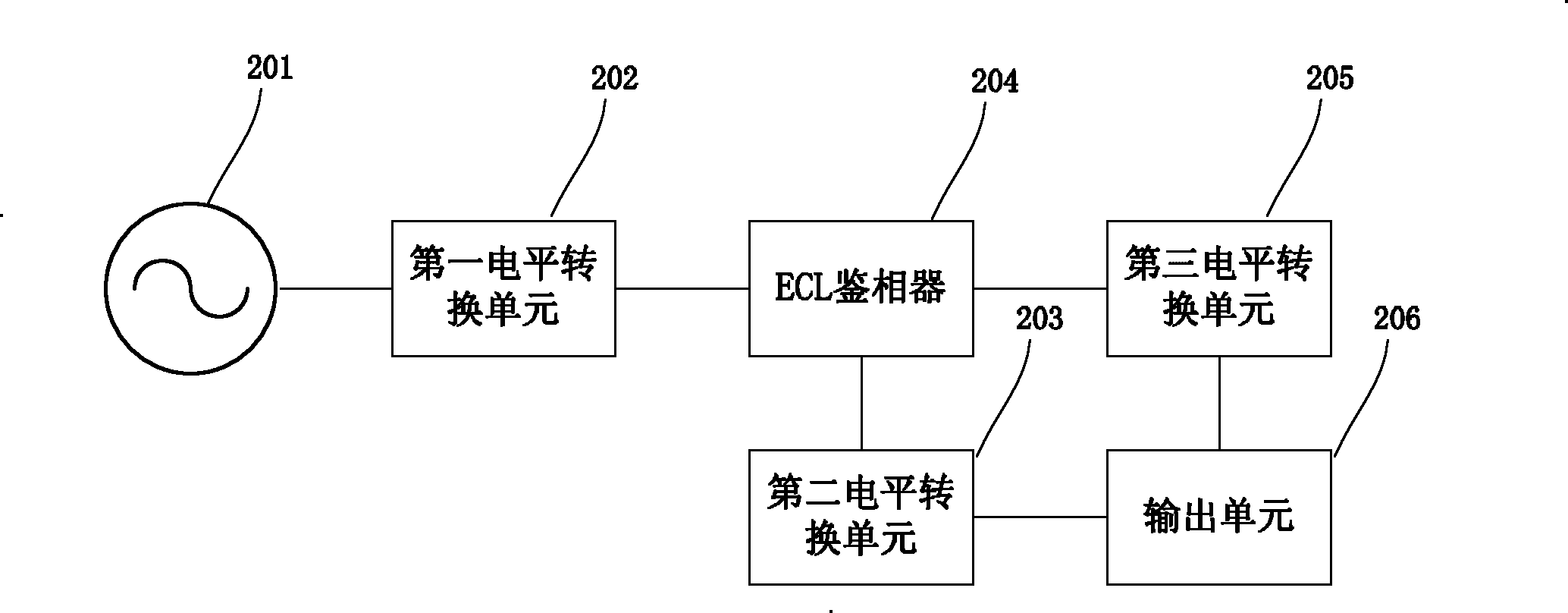

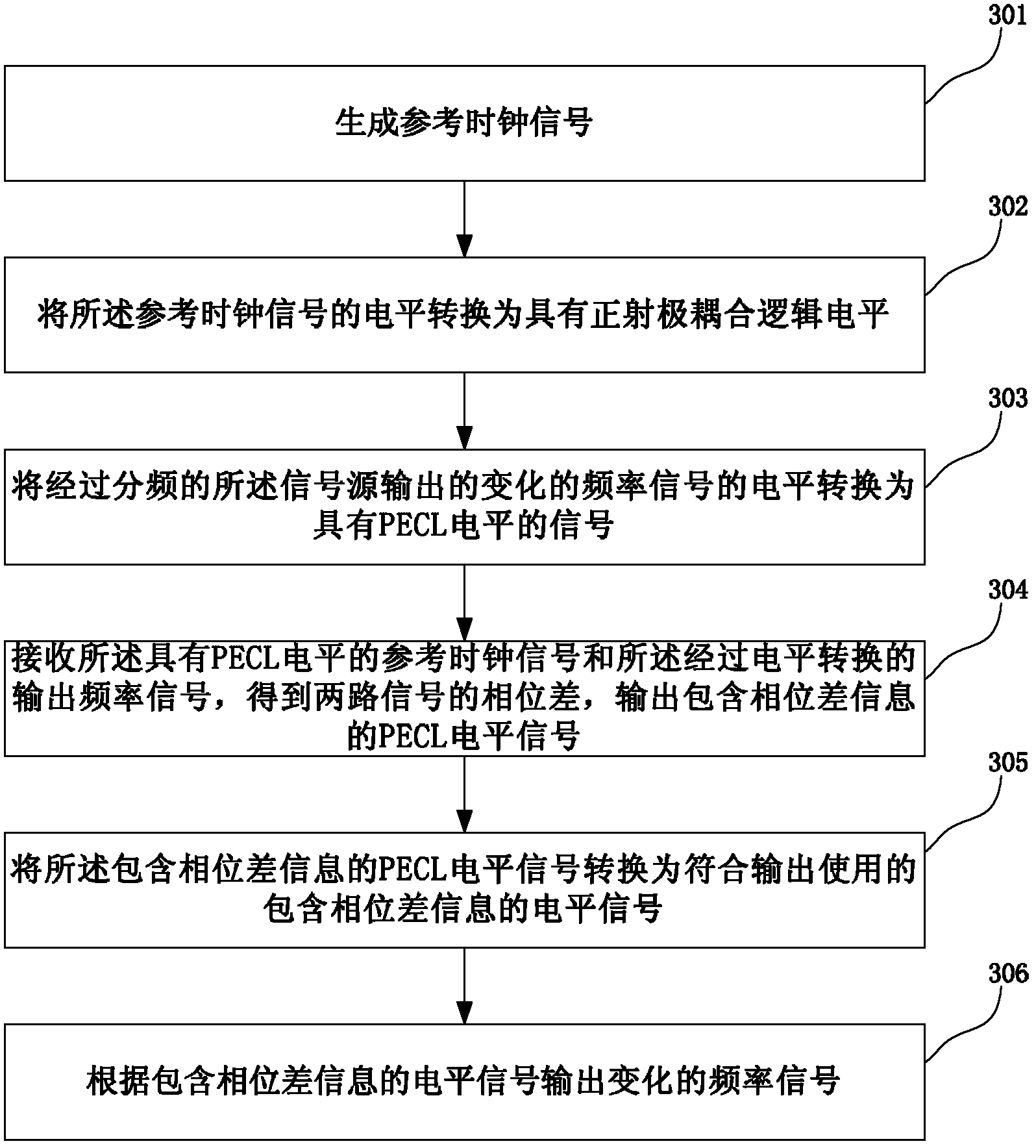

Phase-locked loop signal source with emitter coupled logic (ECL) phase discriminator and generation method thereof

ActiveCN103178842AIncrease the phase detection frequencyReduce phase noisePulse automatic controlDiscriminatorPhase noise

The invention relates to the field of testing, in particular to a phase-locked loop signal source with an emitter coupled logic (ECL) phase discriminator and a generation method thereof. The signal source comprises a reference clock unit for providing reference clock signals and the ECL phase discriminator, wherein the ECL phase discriminator is used for receiving reference clock signals of a positive emitter coupled logic (PECL) level transmitted by a first level conversion unit and variable output signals undergone frequency division processing and transmitted by a second level conversion unit and transmitting PECL level signals containing phase difference information of two paths of signals to a third level conversion unit; the third level conversion unit converts PECL level comprising phase difference information into level signals in accordance with using of an output unit; and the output unit outputs variable frequency signals according to phase difference information. By means of an embodiment of the phase-locked loop signal source with the ECL phase discriminator, the phase discrimination frequency of the signal source can be improved through the ECL phase discriminator and the level converter working in coordination with the ECL phase discriminator, and phase noises of the signal source can be further reduced.

Owner:RIGOL

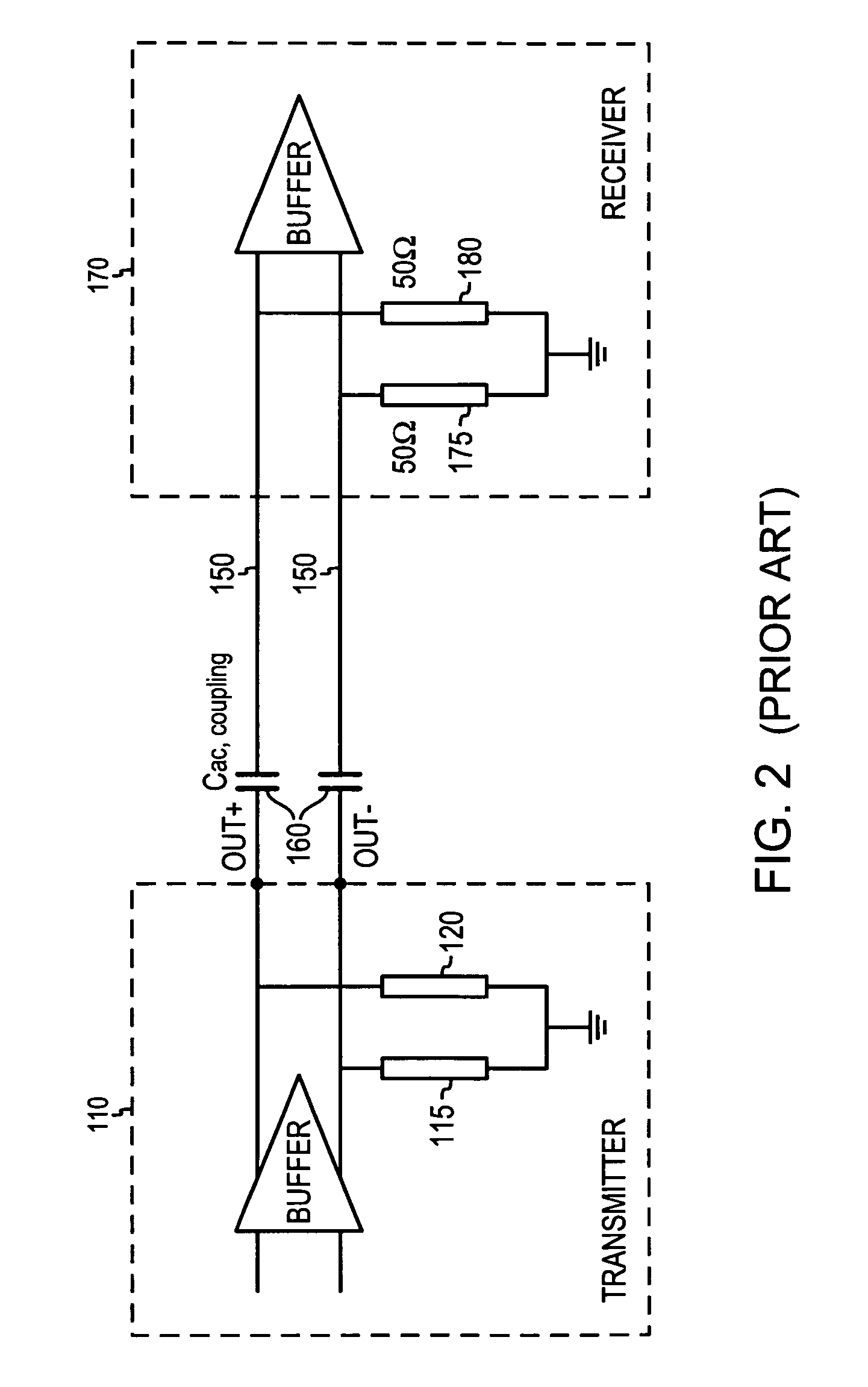

Deriving corresponding signals

ActiveUS7383373B1Low failure rateSave clock cycleReliability increasing modificationsError preventionEmitter-coupled logicVIT signals

Apparatus used in deriving corresponding signals includes first and second circuitry. The first circuitry derives, from a source-terminated first signal driven from a Peripheral Control Interface (PCI) Express compatible source, an AC-coupled second signal. The second circuitry derives, from the AC-coupled second signal, a destination-terminated DC biased third signal that drives a pseudo-emitter-coupled logic (PECL) compatible receiver.

Owner:EMC IP HLDG CO LLC

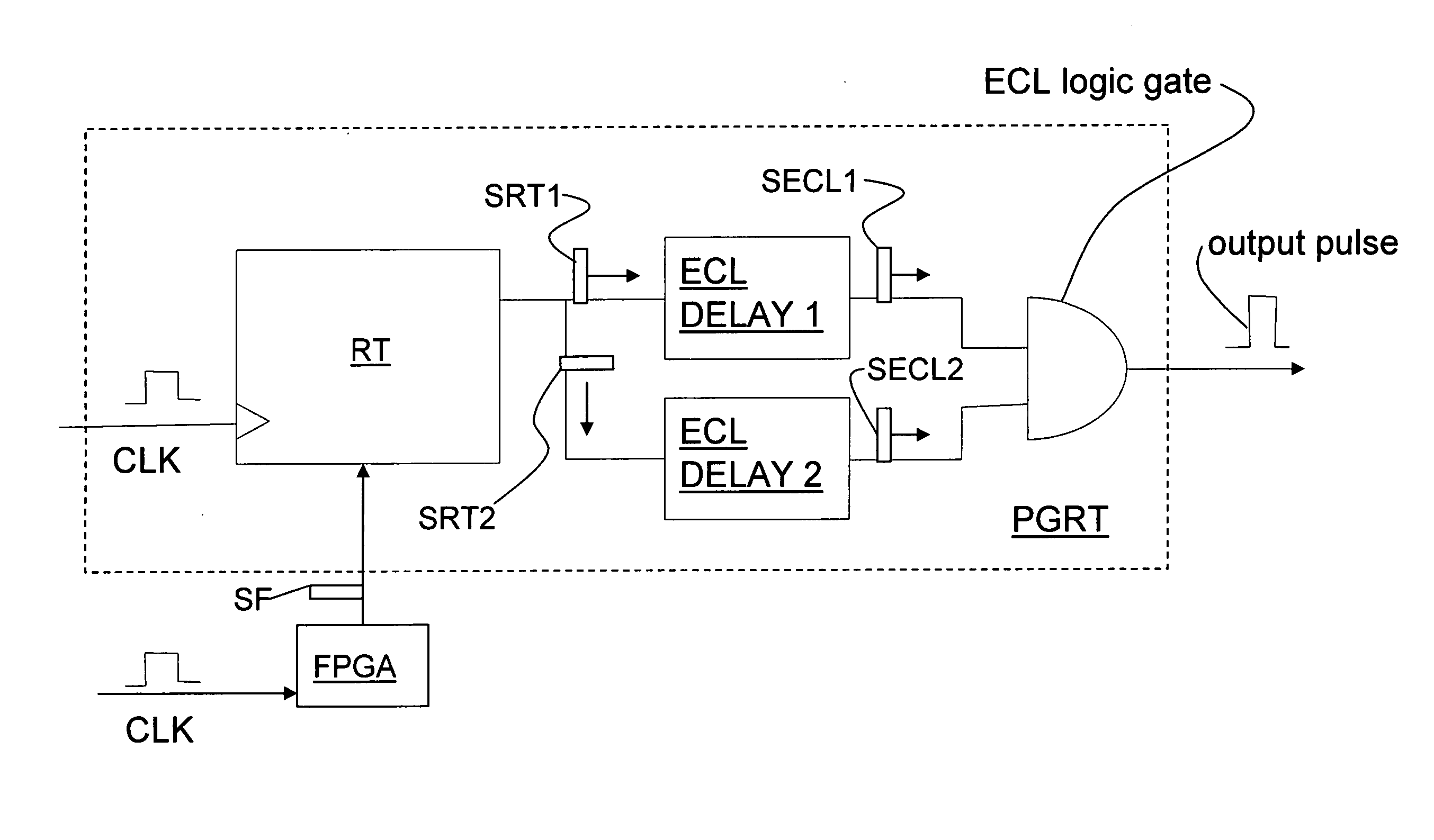

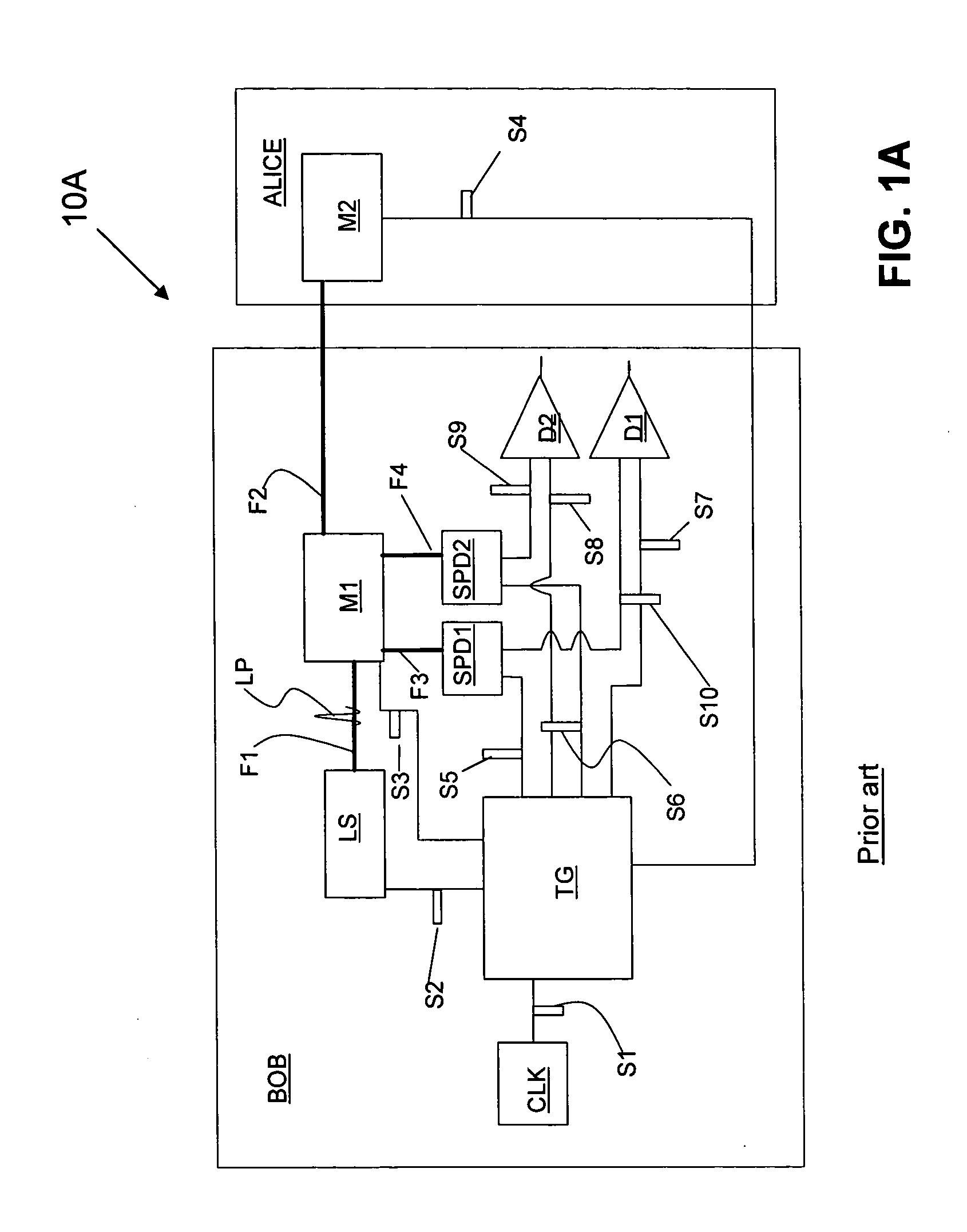

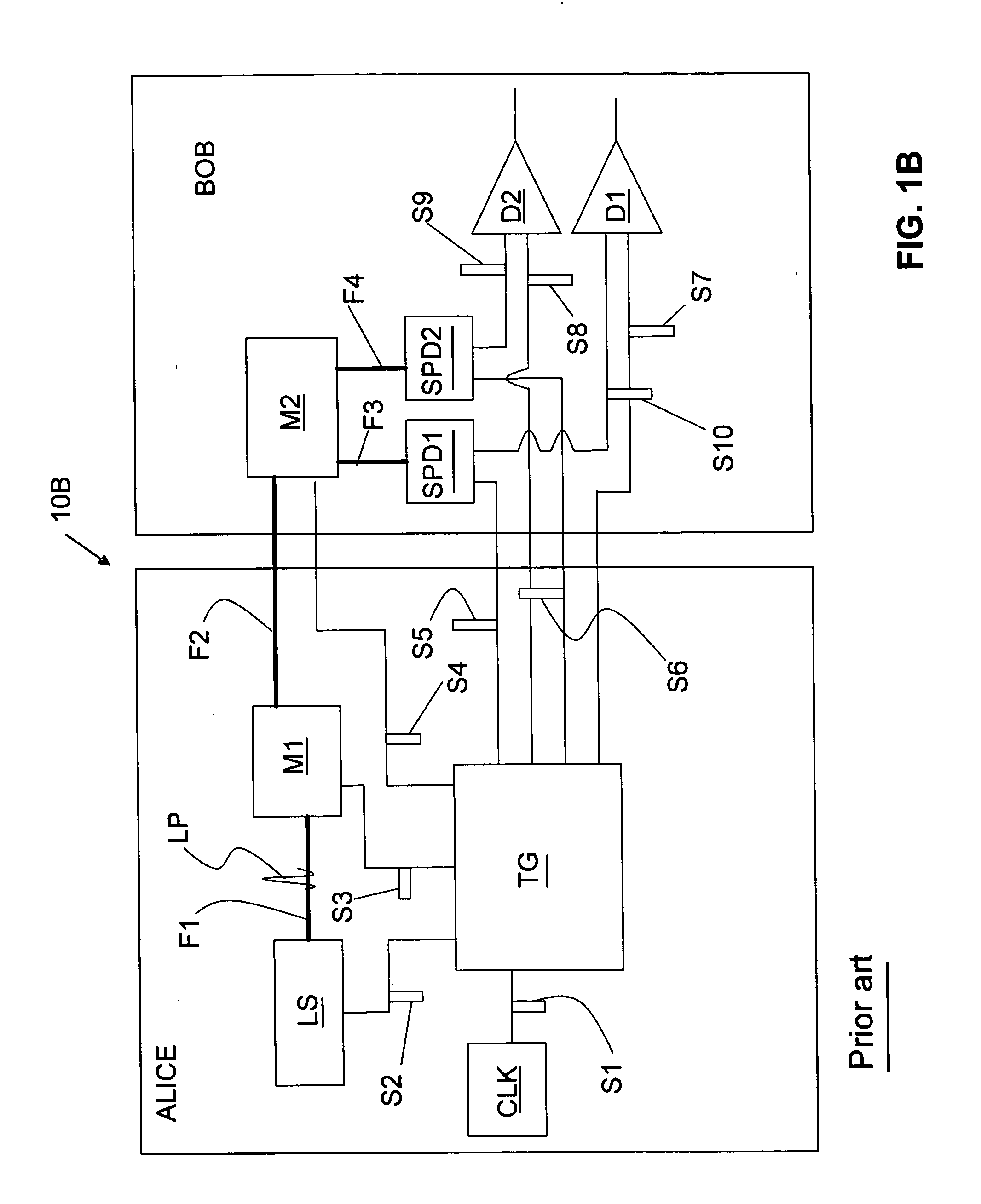

Timing error reduction in QKD systems

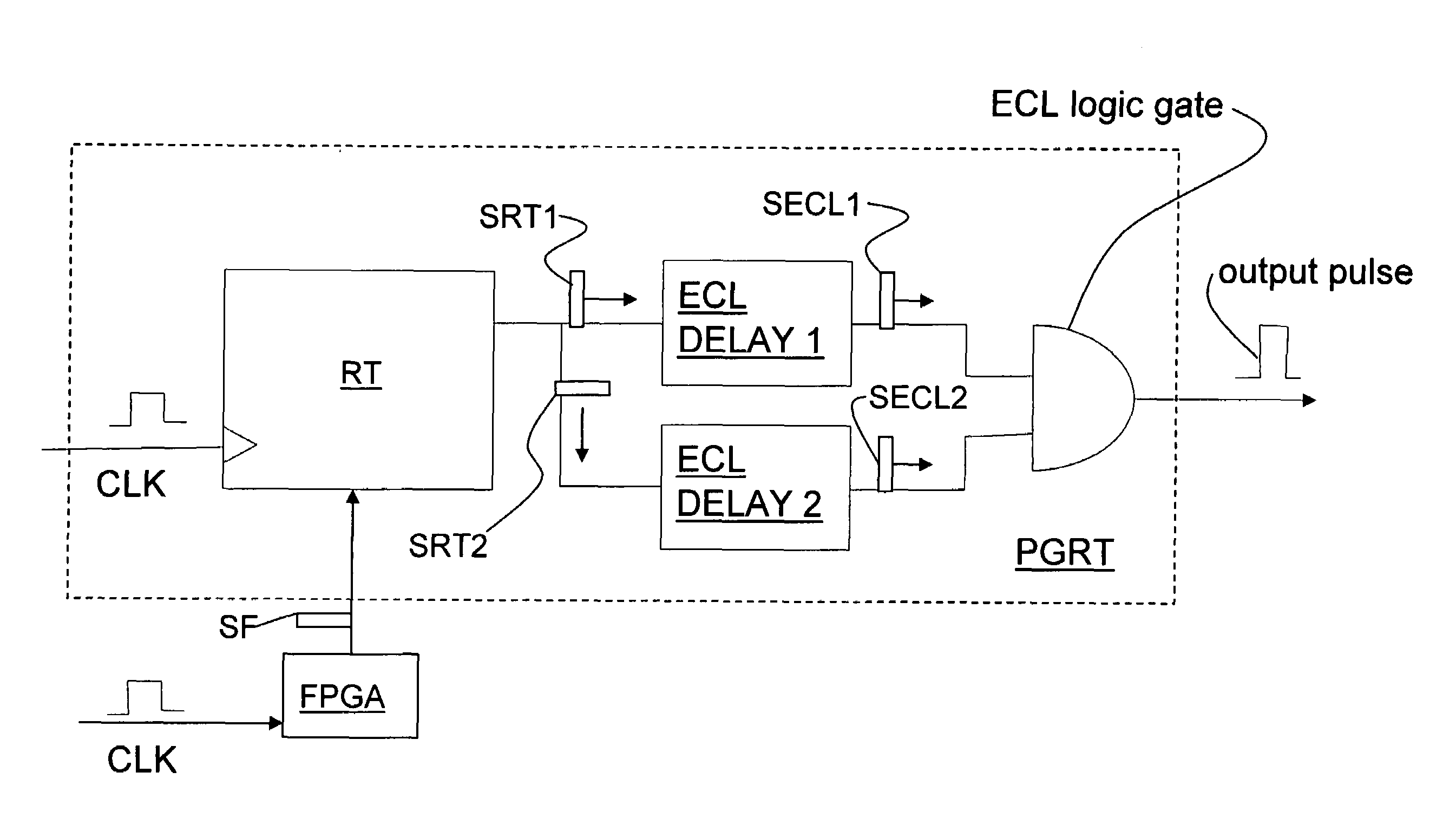

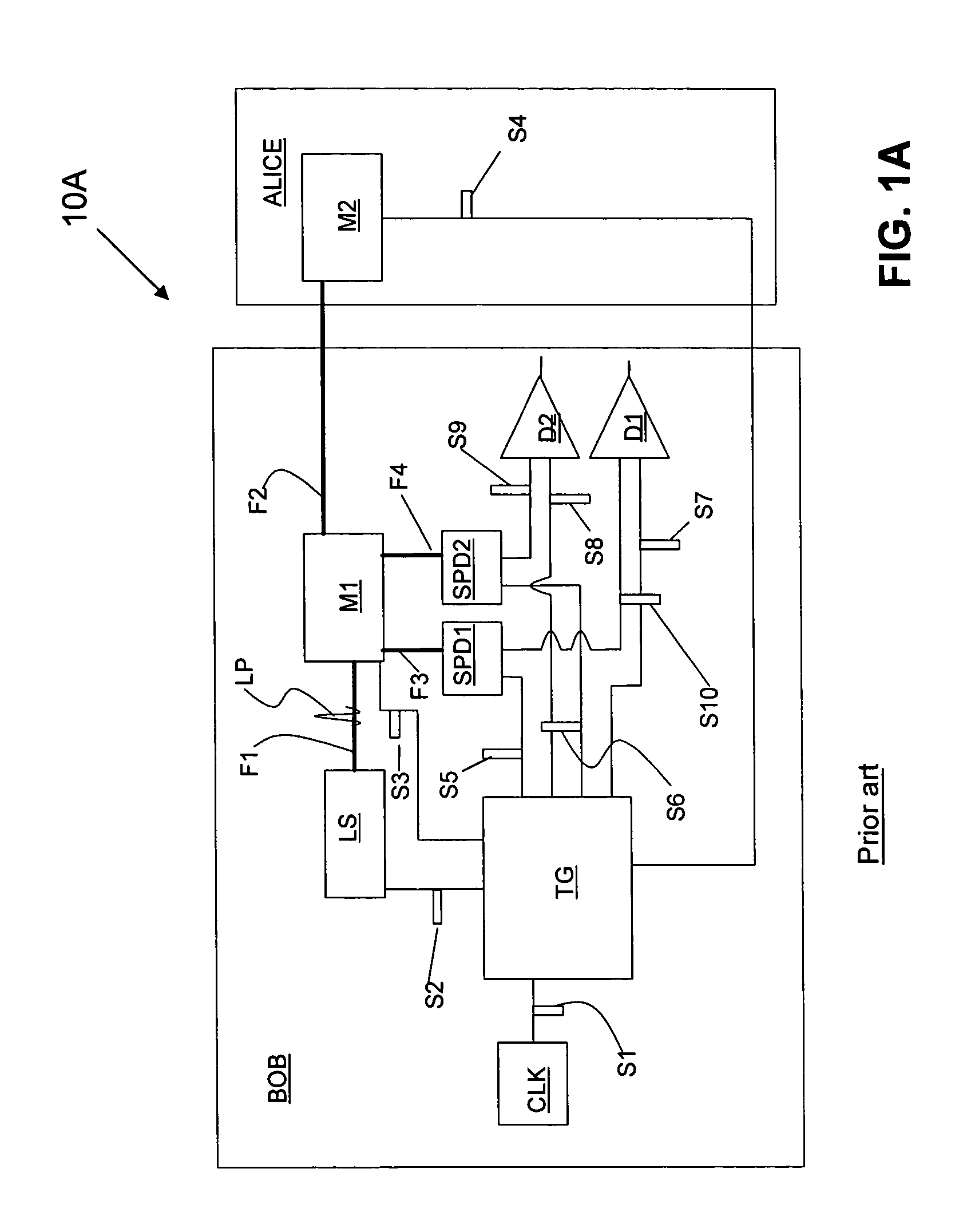

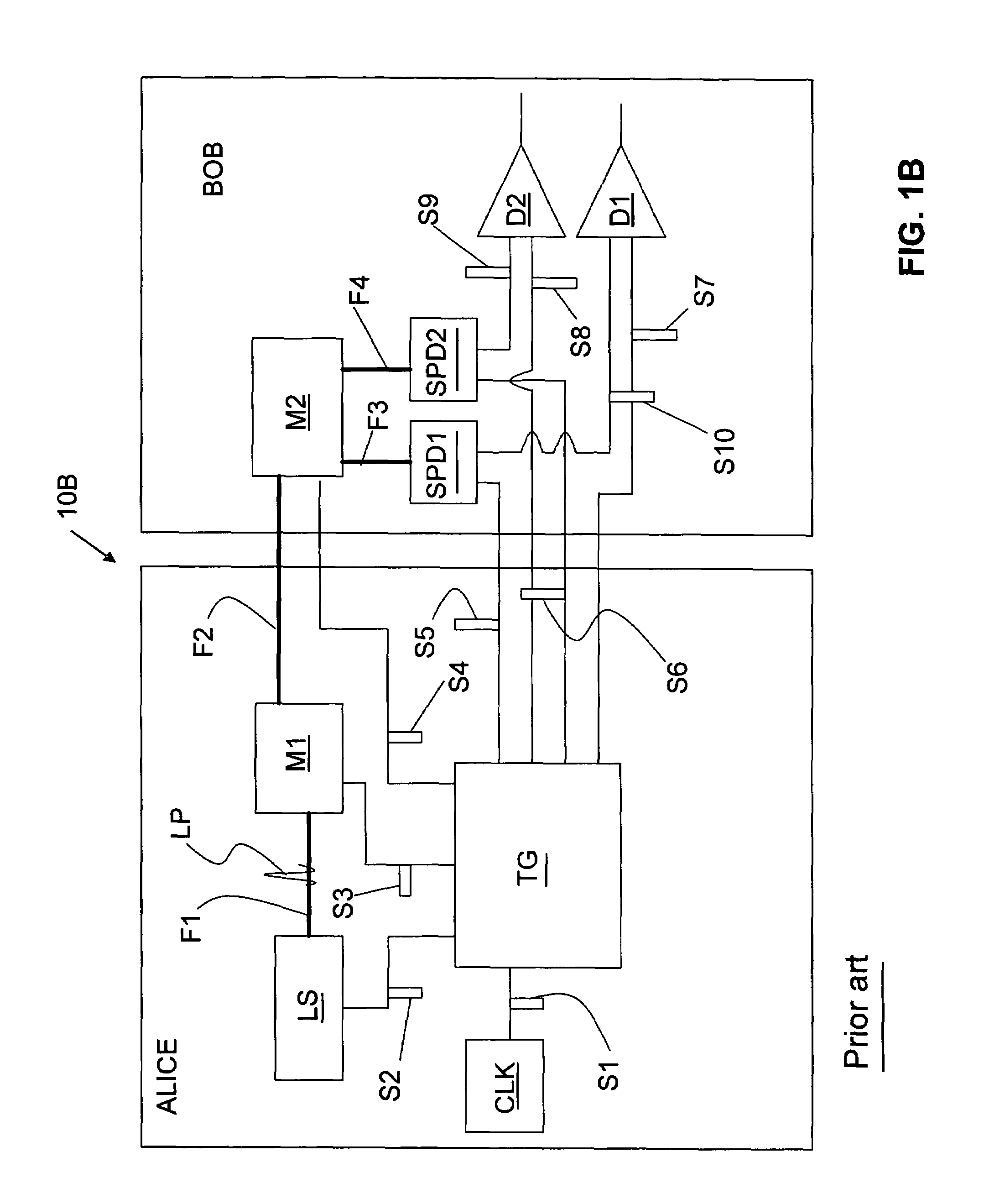

ActiveUS20060034615A1Reducing and eliminating timing errorReduce time jitterSynchronisation information channelsSynchronisation by photonic/optical meansEmitter-coupled logicEngineering

Systems and methods for reducing or eliminating timing errors in a quantum key distribution (QKD) system (100) are disclosed. The QKD system has a pulse generator with retimer (PGRT) that includes a field-programmable gate array (FPGA) (or FPGA output) which is used as a timing generator (TG). While an FPGA has the desired degree of programmability for use in a QKD system, it also suffers from undue amounts of jitter in the digital output. The present invention utilizes emitter-coupled logic (ECL) to reduce the timing jitter from the FPGA by coupling two ECL delays (ECL delay 1 and ECL delay 2) to the FPGA and to retiming block, and by using an ECL logical AND gate to set the pulse width of the various synchronization signals. An embodiment of the present invention includes multiple clock domains having individual clocks (CLK), phase-lock loops (PLLs), retiming circuits (RT) and timing generators (TG) for robust jitter reduction and hence highly accurate QKD system timing.

Owner:MAGIQ TECH INC

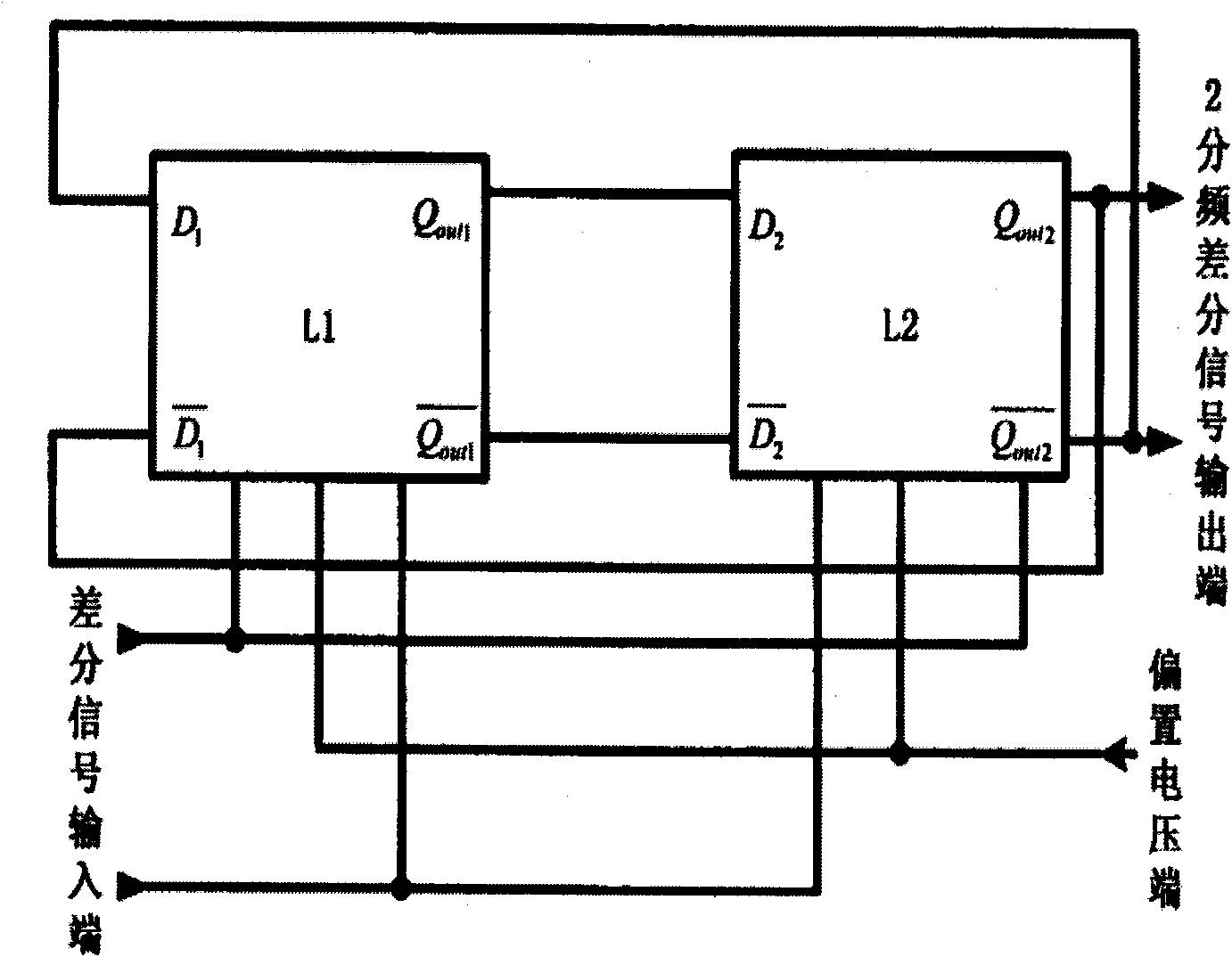

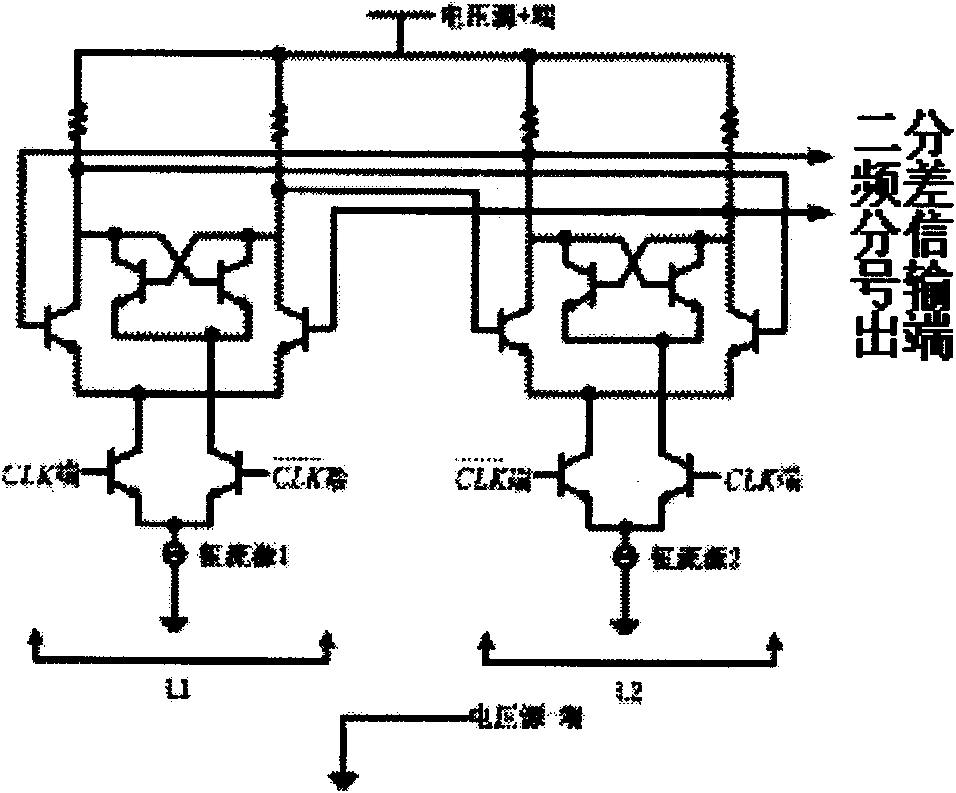

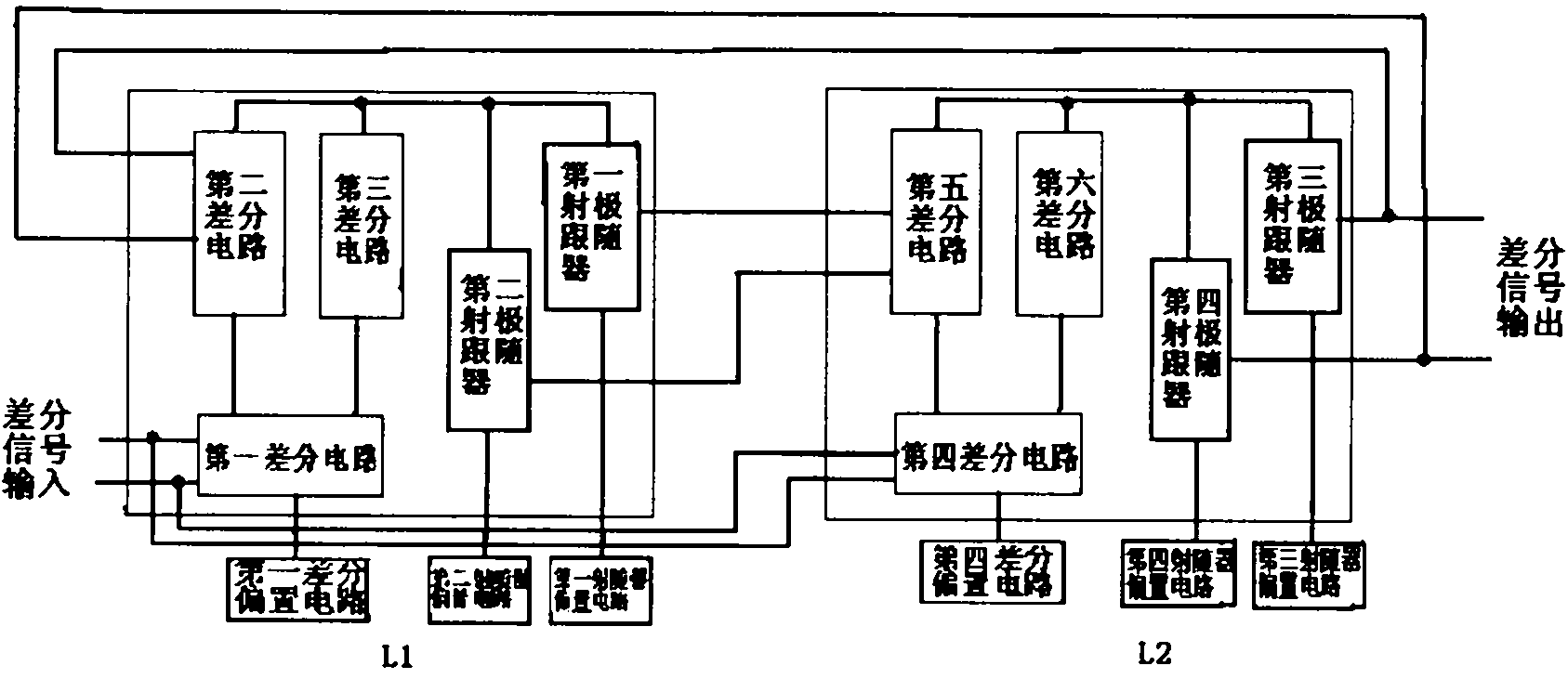

InGaP/GaAs HBT (Heterojunction Bipolar Transistor) super-high-speed frequency-halving circuit based on ECL (Emitter-Coupled Logic)

InactiveCN101854173AIncrease working frequencyImplement inputPulse automatic controlTransceiverType frequency

The invention discloses an InGaP / GaAs HBT (Heterojunction Bipolar Transistor) super-high-speed frequency-halving circuit based on ECL (Emitter-Coupled Logic), mainly solving the problems of narrower working frequency range, low frequency and high chip manufacture cost of the traditional frequency dividing circuit. The frequency-halving circuit mainly comprises six difference circuits, four emitter followers and six biasing circuits, wherein a second difference circuit and a third difference circuit are connected to a fifth difference circuit through a first emitter follower and a second emitter follower; the fifth difference circuit and a sixth difference circuit are connected to the second difference circuit through a third emitter follower and a fourth emitter follower to form a trigger with a principal and subordinate structure; and the six difference circuits and the four emitter followers form an ECL circuit. The circuit has the advantages of both the ECL and the InGaP / GaAs HBT and also has strong common-mode interference resistance, stable current gain and high working frequency and is suitable to being used as a medium-scale super-high-speed N-stage cascading 2N frequency divider and a phase locked loop type frequency synthesizer in a radio transceiver.

Owner:XIDIAN UNIV

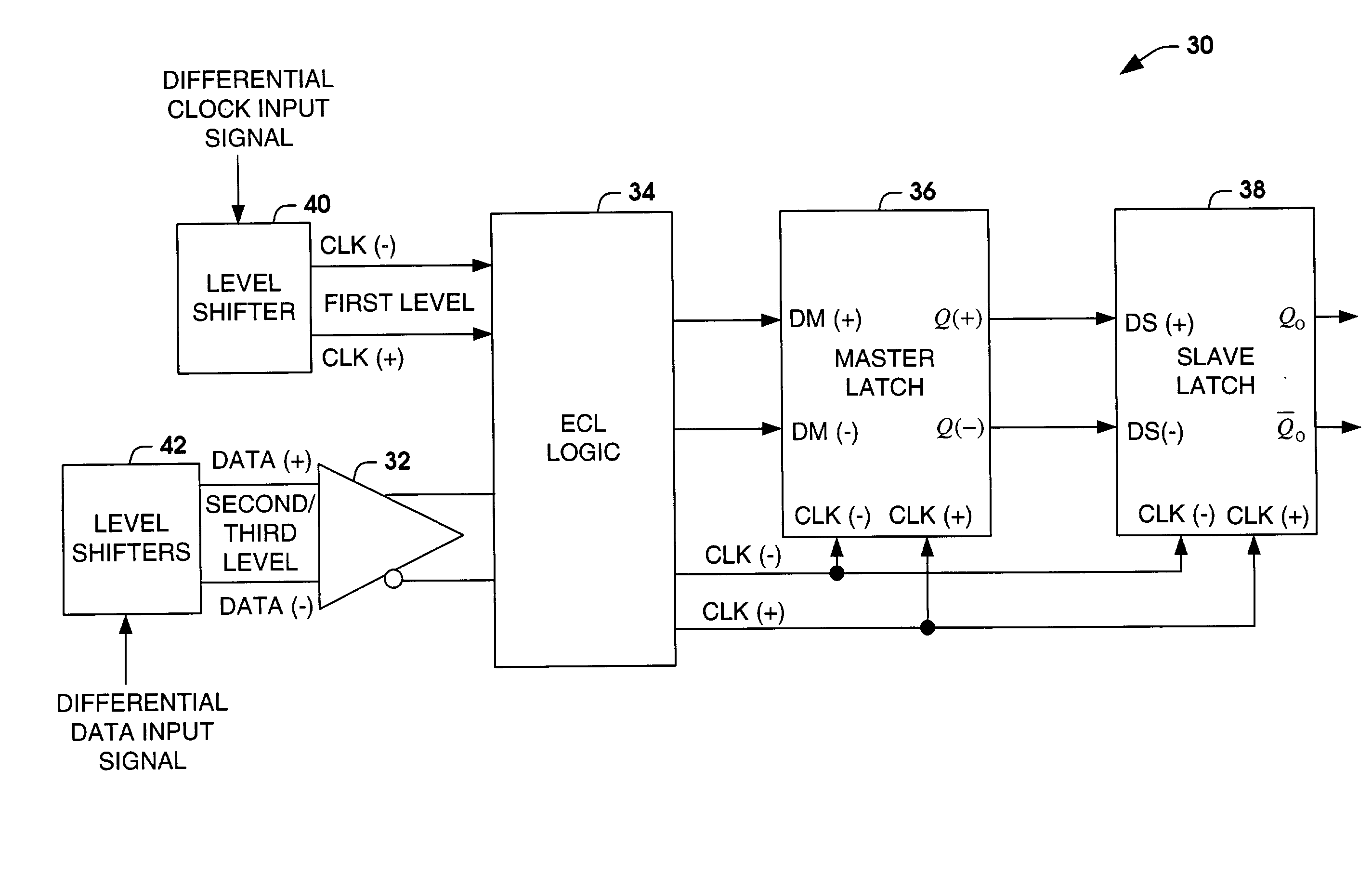

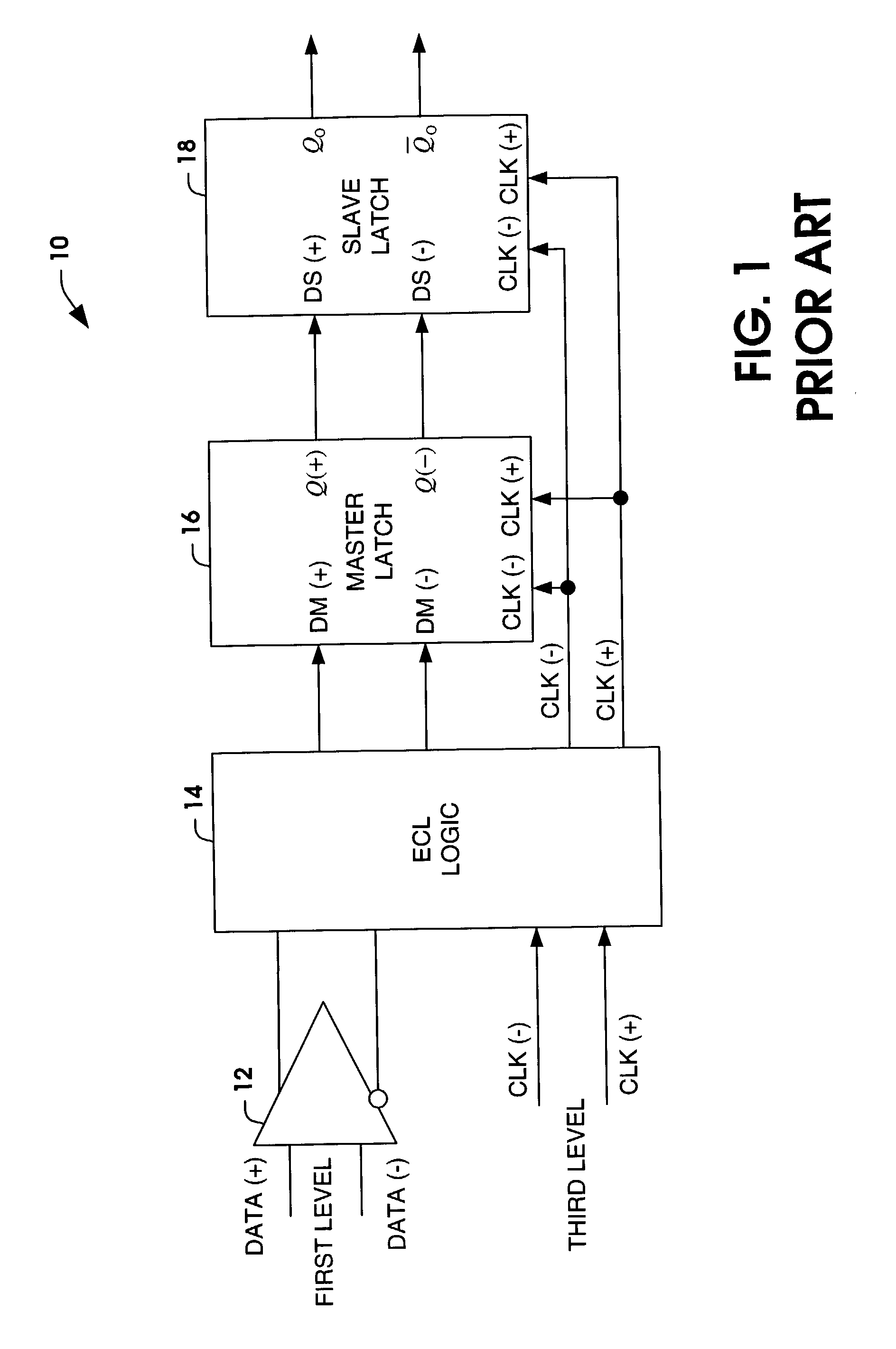

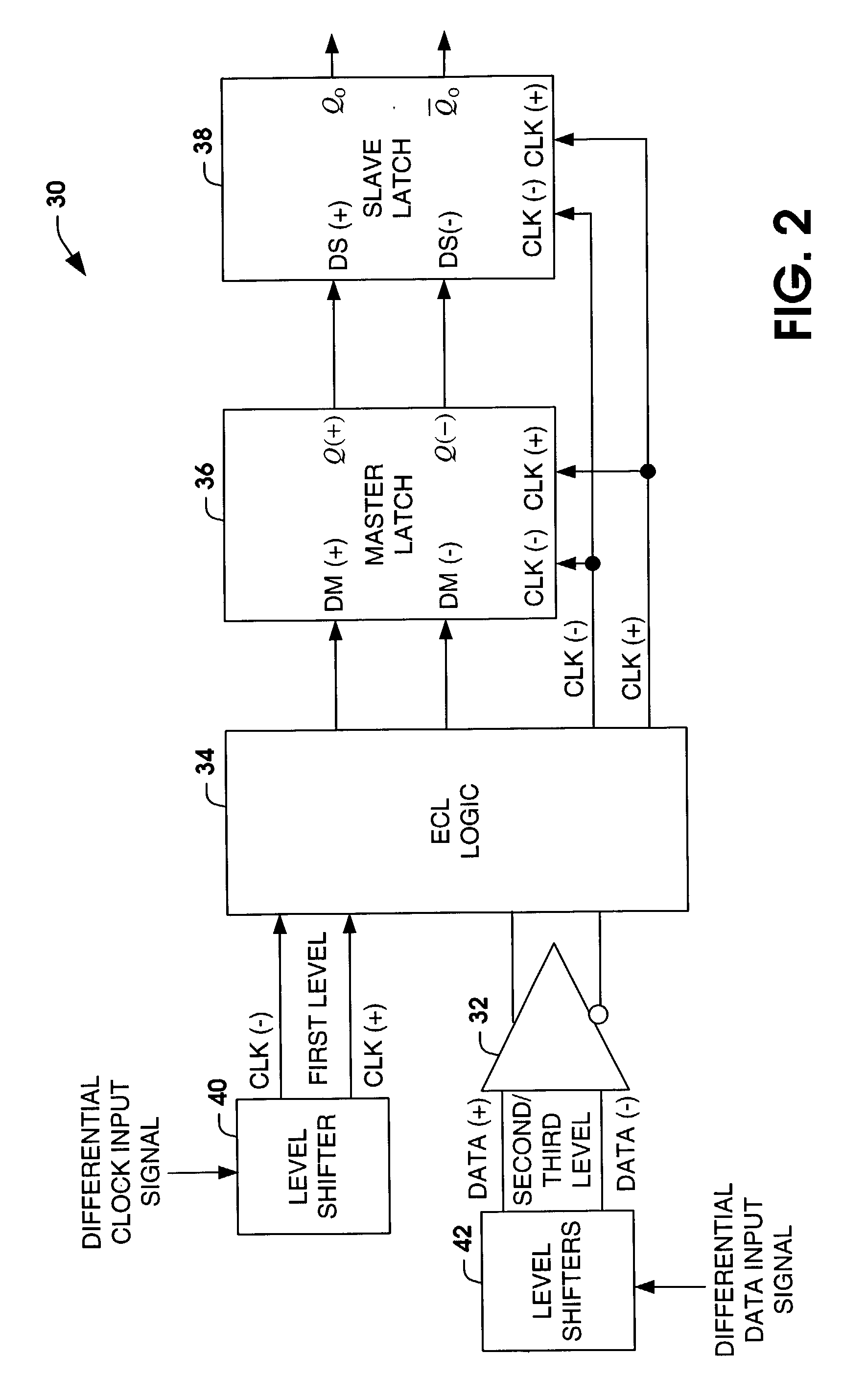

Ultra high speed flip-flop

InactiveUS6693457B2Increase data rateHigh bandwidthElectric pulse generatorLogic circuit coupling/interface arrangementsUltra high speedEmitter-coupled logic

Owner:NORTHROP GRUMMAN SYST CORP

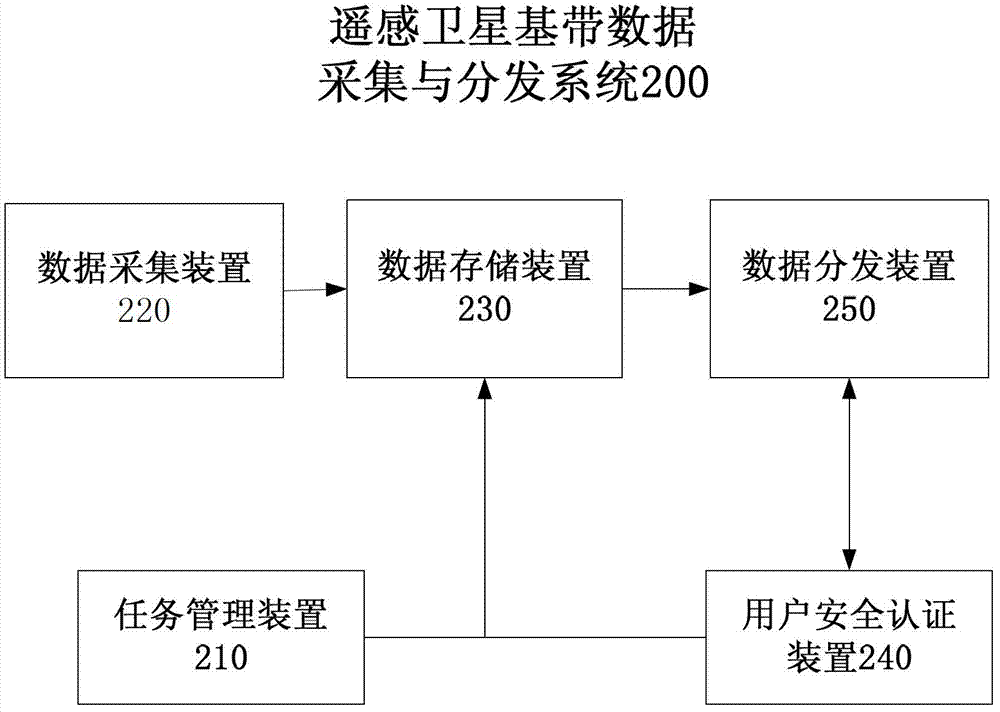

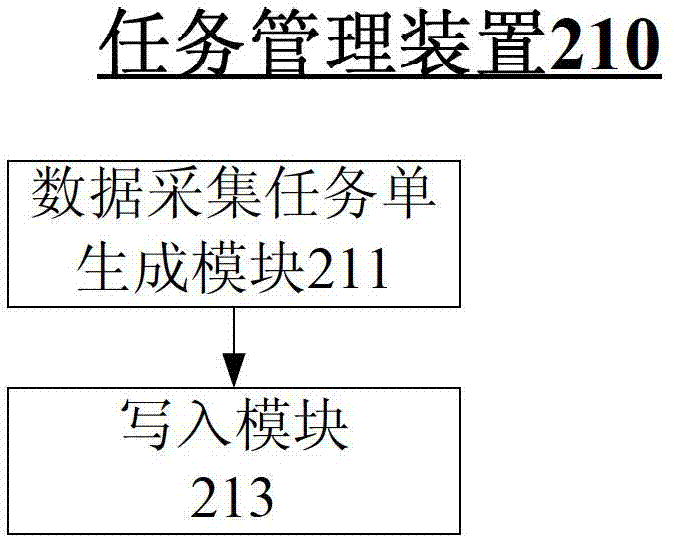

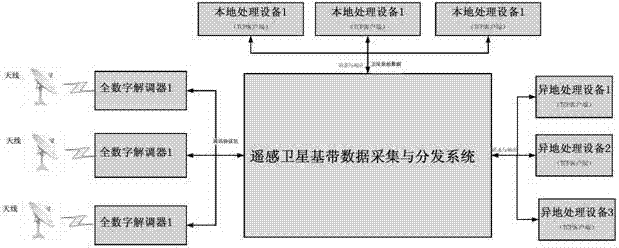

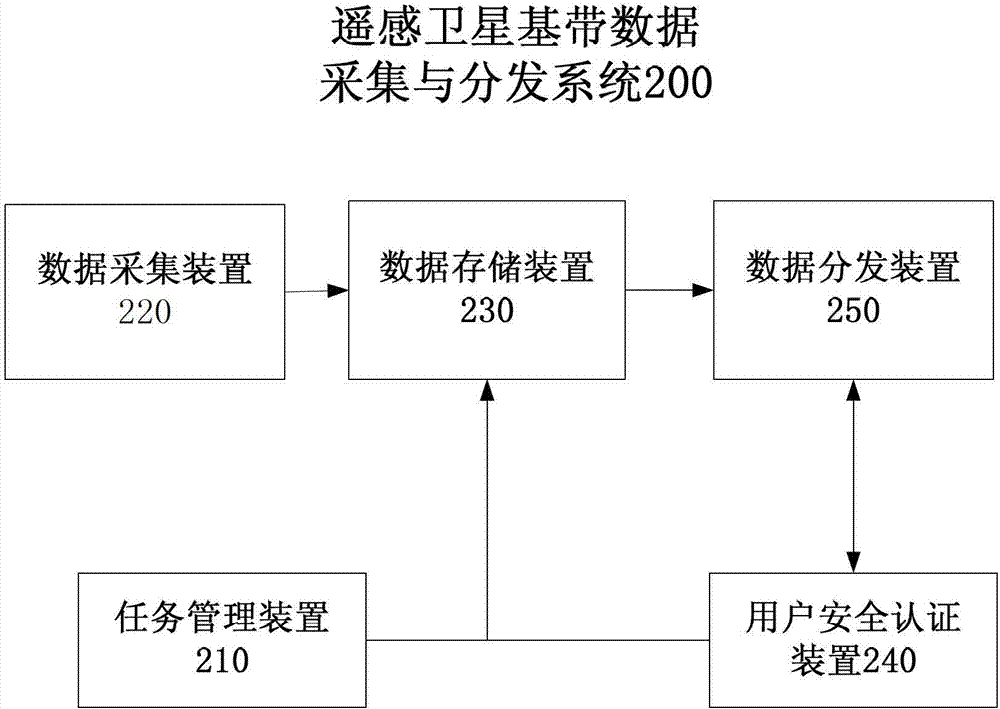

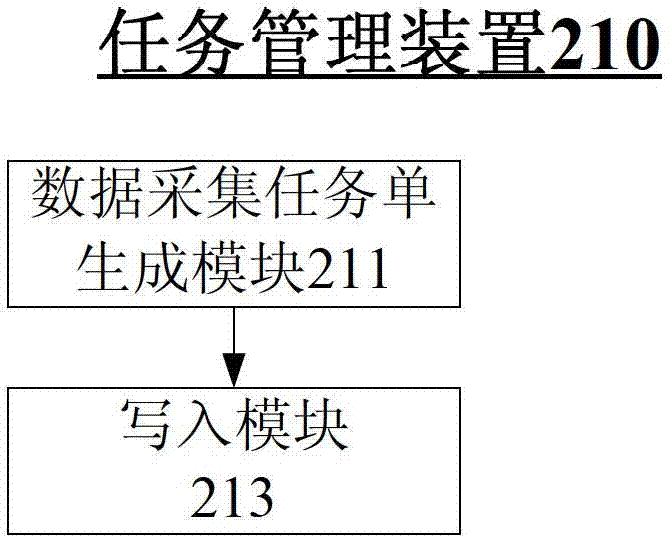

System and method for acquiring and distributing baseband data of remote sensing satellite

ActiveCN102832988AData Distribution Service SecurityThe data distribution service is activeRadio transmissionData switching networksNetwork approachData acquisition

The invention provides a system for acquiring and distributing baseband data of a remote sensing satellite. The system comprises a task management device, a data acquiring device, a data storage device and a data distributing device. When detecting a data acquisition task list, the data acquiring device acquires baseband data of the remote sensing satellite and corresponding time code information thereof from the remote sensing satellite by a fully digital demodulator via the network. The data distributing device distributes the required baseband data of the remote sensing satellite to user equipment after receiving data distribution requests of the user equipment. By the aid of the system, the baseband data of the remote sensing satellite can be acquired in real time via the network, and meanwhile, uniform data distributing services can be provided to rear-end equipment via the network, and accordingly, limits of ECL (emitter-coupled logic) signal transmission distance and special acquisition cards are eliminated.

Owner:CENT FOR EARTH OBSERVATION & DIGITAL EARTH CHINESE ACADEMY OF SCI

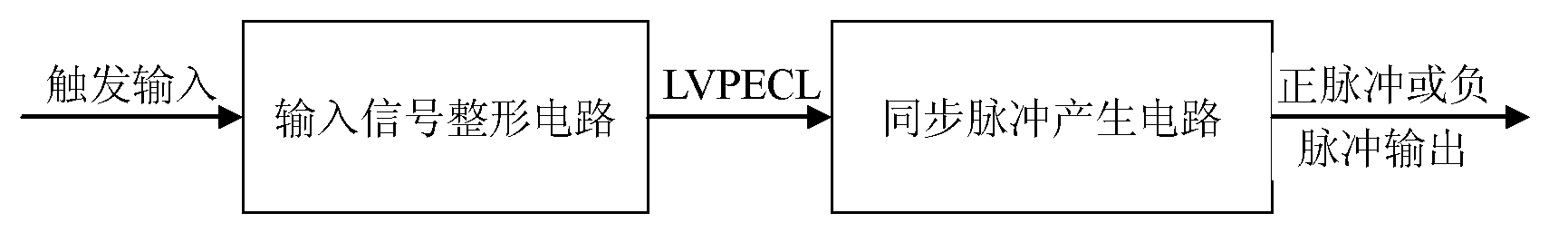

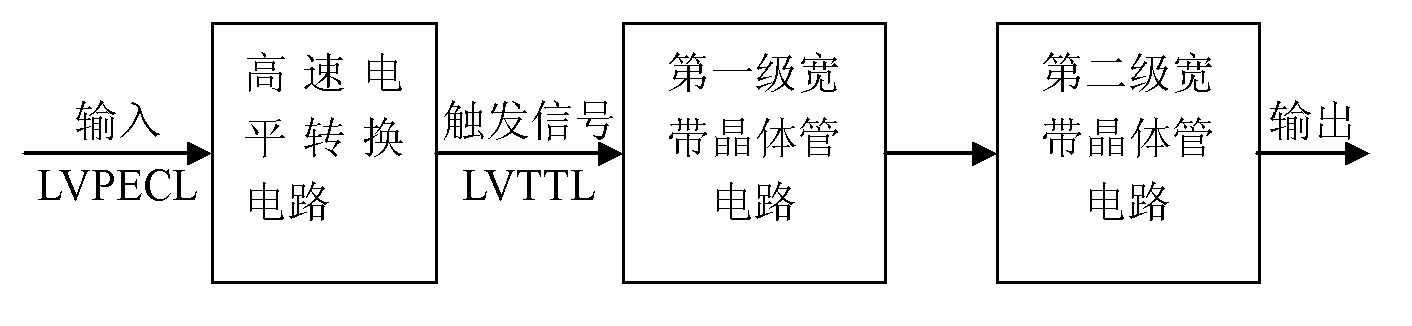

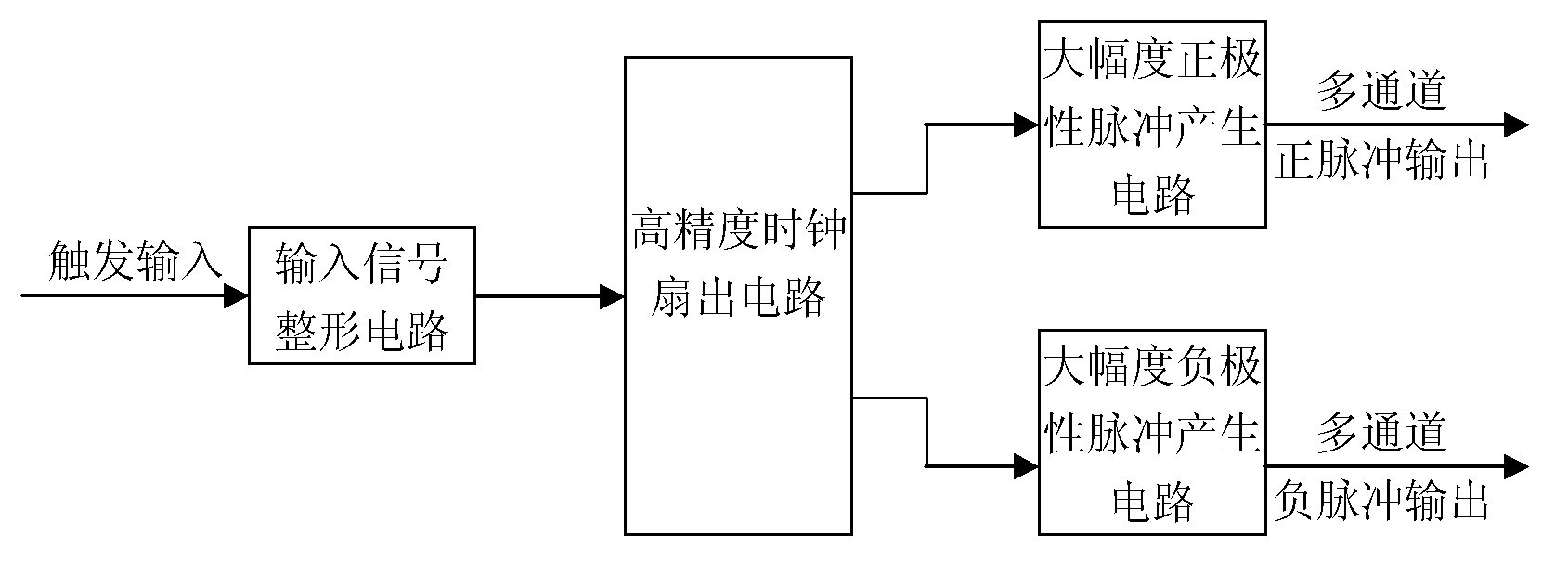

Generating device and method of large-amplitude ultra-high speed synchronization pulse

InactiveCN103066960ASimple structureReduce processing requirementsContinuous to patterned pulse manipulationPulse shapingLow voltageEmitter-coupled logic

The invention discloses a generating device of a large-amplitude ultra-high speed synchronization pulse. The generating device of the large-amplitude ultra-high speed synchronization pulse comprises an input signal shaping circuit and a synchronization pulse generating circuit, wherein the input signal shaping circuit is used for shaping input trigger pulse signal to output low voltage positive pole emitter coupling logic (LVPECL) reference level signal, and the synchronization pulse generating circuit is used for generating the large-amplitude ultra-high speed synchronization pulse with the LVPECL reference level signal as trigger signal. No transistor with an extremely high working voltage is needed in the generating device and method of a large-amplitude ultra-high speed synchronization pulse, therefore, voltage demand on a direct current voltage source is not high. Key functions of the generating device and method of a large-amplitude ultra-high speed synchronization pulse is achieved by a multilevel broadband transistor circuit which can send out positive pulse and negative pulse with pulse front smaller than 200ps and amplitude close to 15V. Meanwhile, compared with input synchronization pulse, delaying time shake of output synchronization pulse is small and smaller than 20ps.

Owner:UNIV OF SCI & TECH OF CHINA

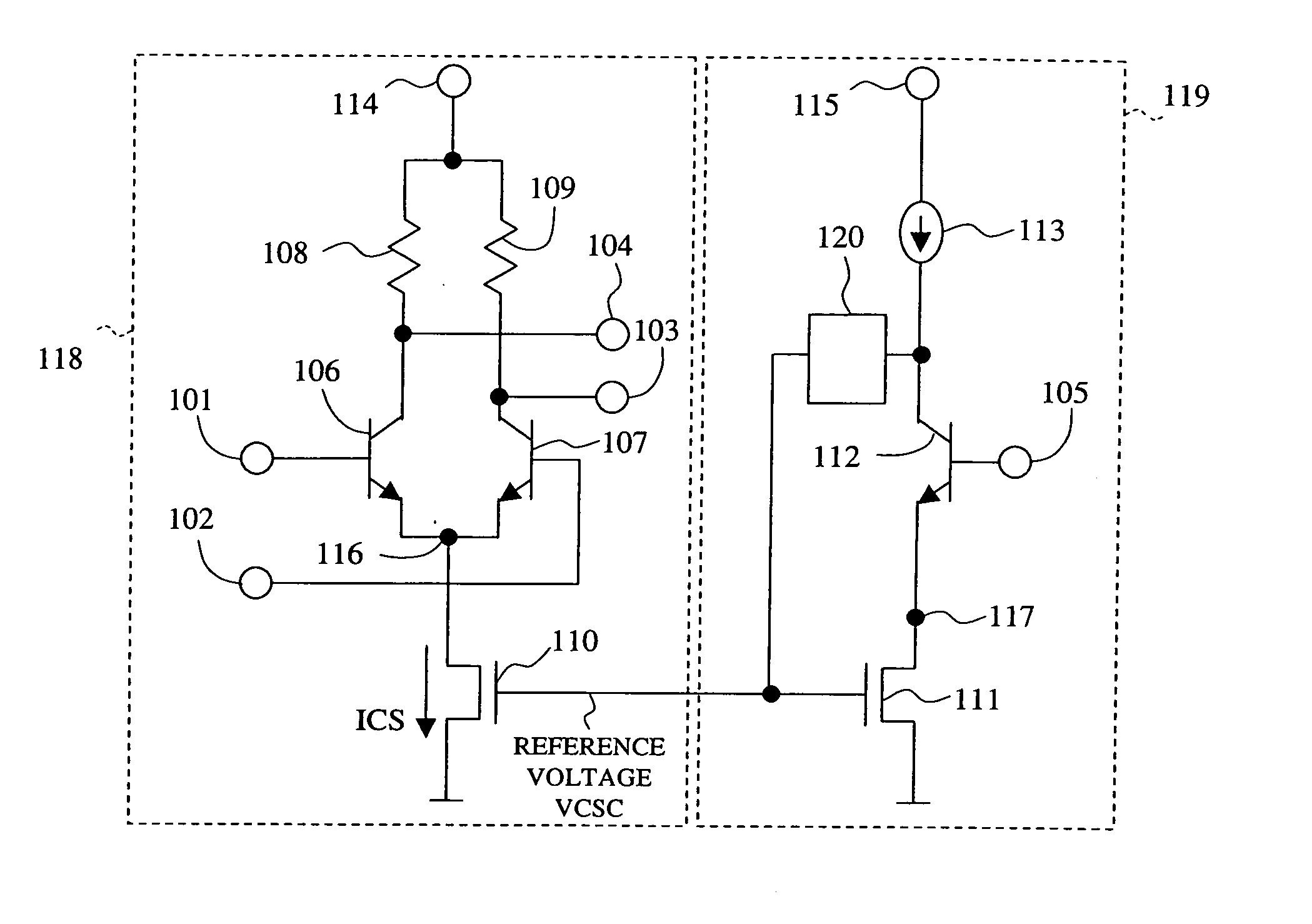

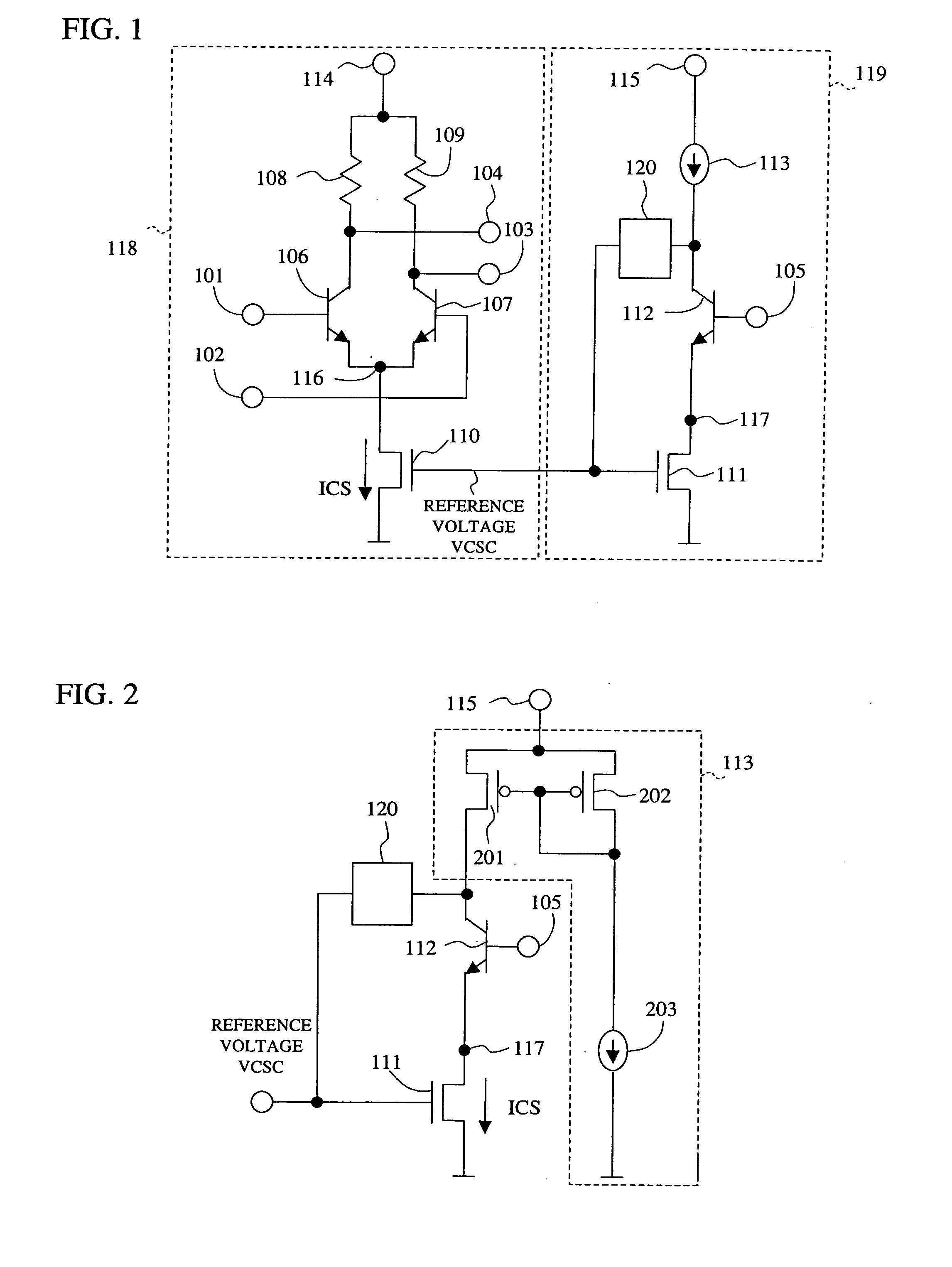

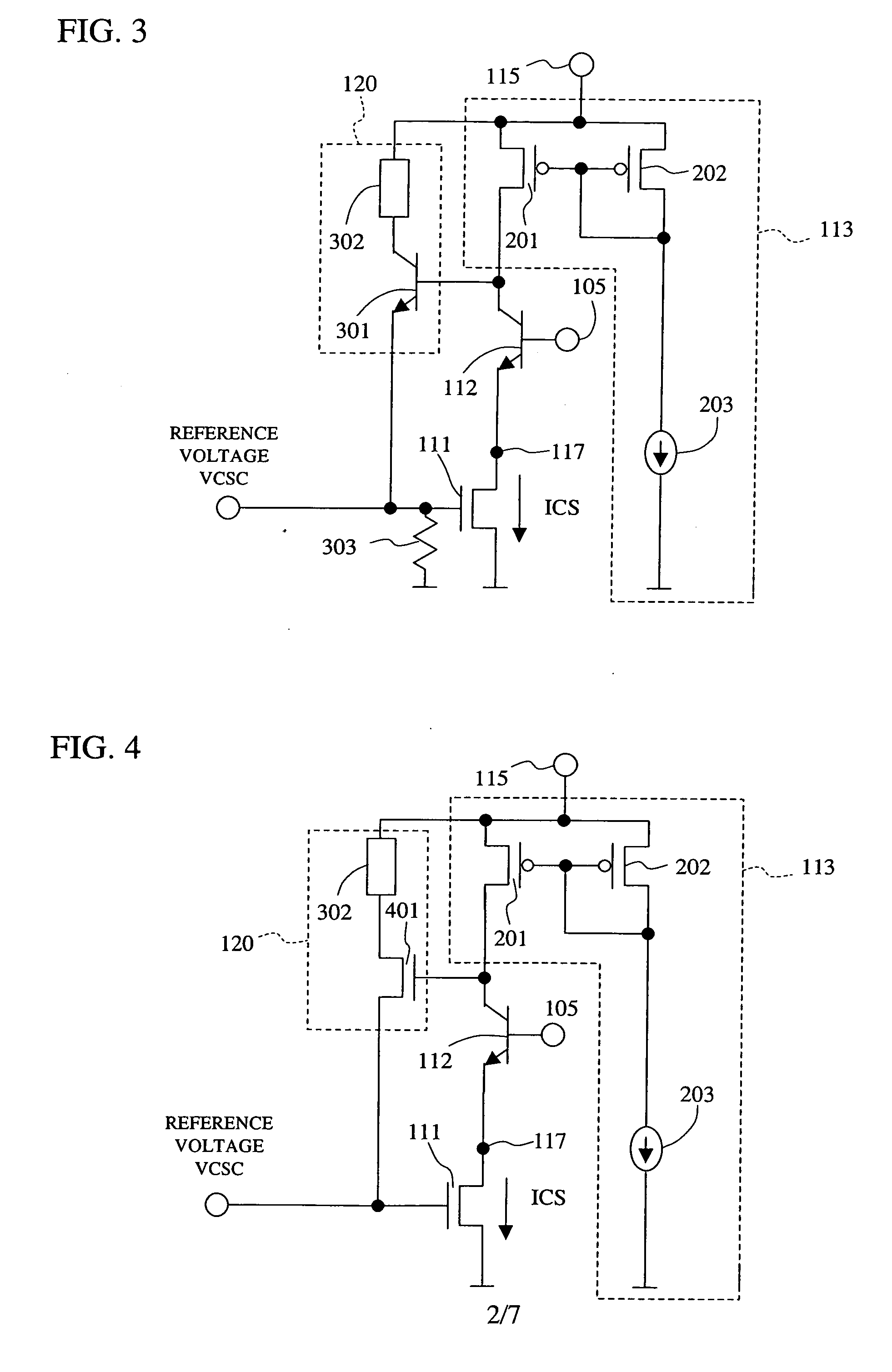

Logic circuit

InactiveUS20050068066A1Reduce power supply voltageRaise the possibilityMultiple input and output pulse circuitsLogic circuits characterised by logic functionEmitter-coupled logicVoltage reference

The power supply-voltage dependency of a current source current is reduced and the power supply voltage is lowered. The invention includes an emitter-coupled logic circuit 118 and a reference-voltage generating circuit 119 for generating a reference voltage VCSC for controlling a drain current (=current source current ICS) of a constant current-supplying n-type MOS transistor 110. The emitter-coupled logic circuit 118 comprises a current switch made up of a pair of emitter-coupled bipolar transistors 106 and 107, a constant current-supplying n-type MOS transistor 110 that is connected in series with the current switch, and resistor means 108 and 109 connected in series with the bipolar transistors 106 and 107 individually for obtaining an output voltage. The reference-voltage generating circuit 119 comprises an n-type MOS transistor 111, a bipolar transistor 112 which determines the drain voltage of the n-type MOS transistor 111, and a control circuit 120 for controlling the drain current of the n-type MOS transistor 111.

Owner:HITACHI LTD

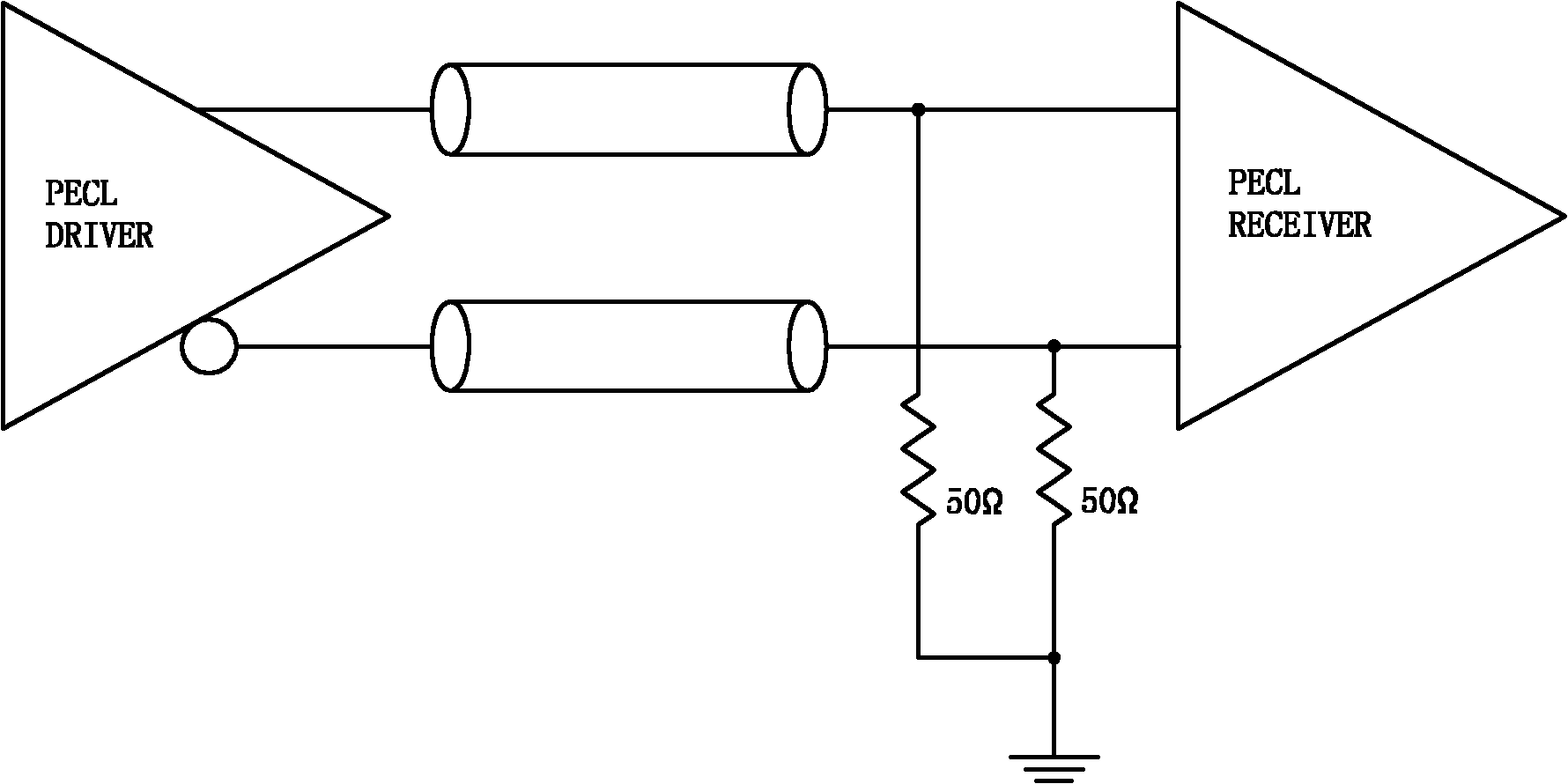

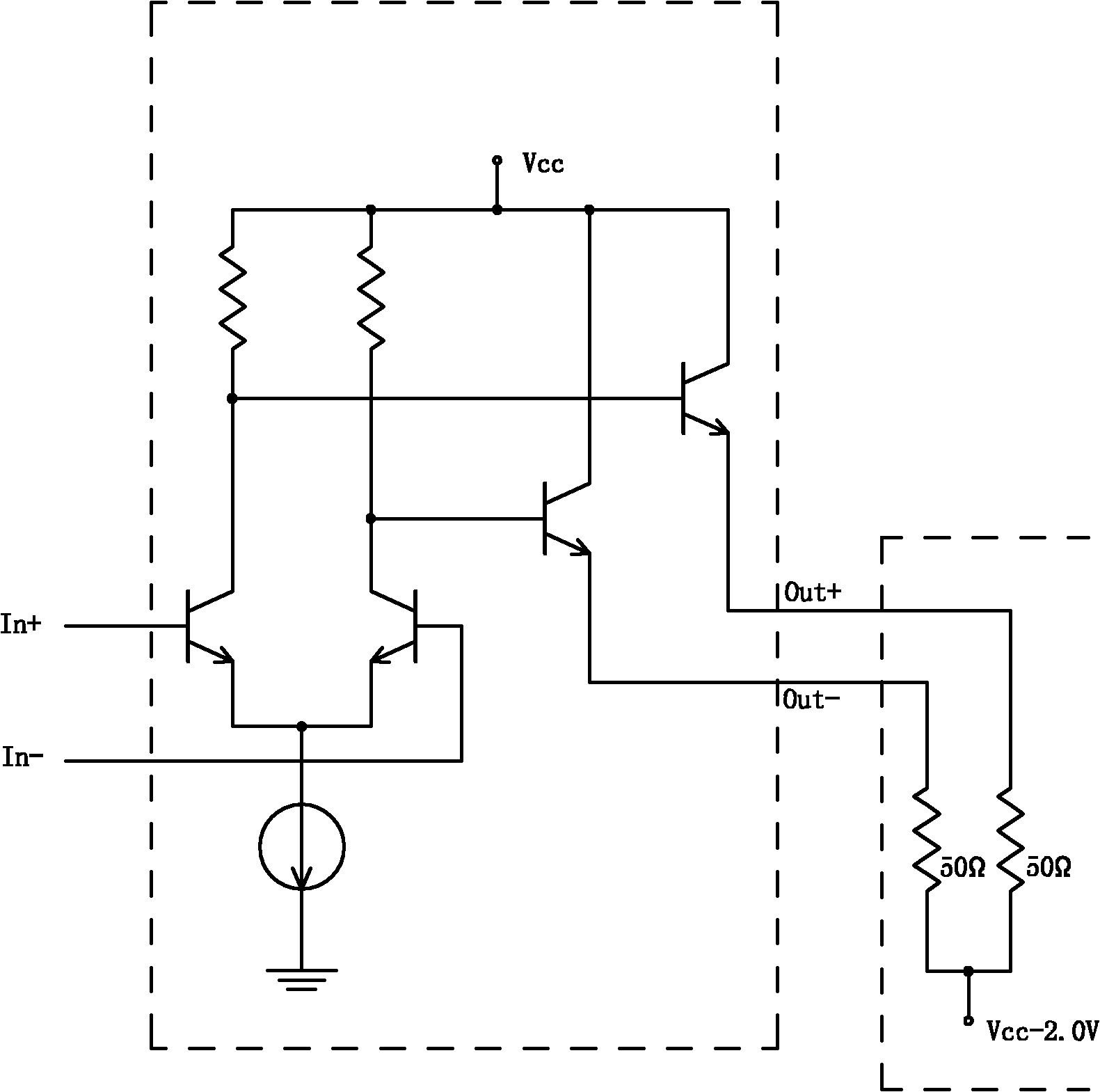

PECL (Positive Emitter Coupling Logic) level interface circuit

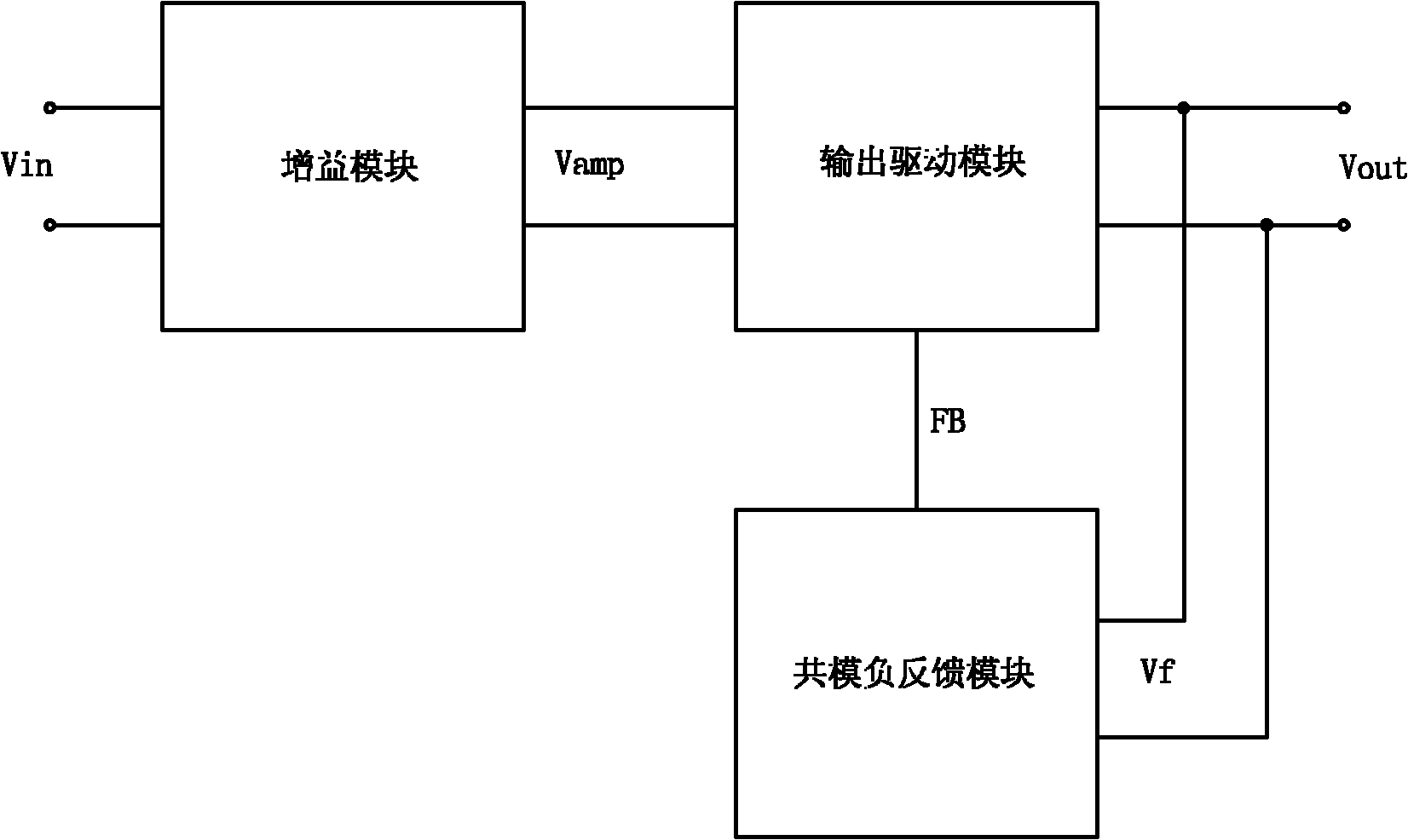

ActiveCN102088284AHigh precisionSimple structureLogic circuit coupling/interface arrangementsNegative feedbackDifferential signaling

The invention discloses a PECL (Positive Emitter Coupling Logic) level interface circuit. The circuit is characterized by comprising a gain module, an output drive module and a common-mode negative feedback module, wherein an input CMOS (Complementary Metal-Oxide-Semiconductor) differential signal is received and amplified by the gain module, is transmitted to the output drive module through the differential signal output end, and is output from the PECL level output end of the output drive module; the input end of the common-mode negative feedback module is connected in parallel to the PECL level output end, and provides a negative feedback signal to the output drive module; and the output drive module and the negative feedback module commonly perform level modification on the amplified differential signal to ensure that the final signal output from the PECL level output end fulfills the PECL level with Vcc-1.3V common-mode voltage. The PECL level interface circuit provides the common-mode negative feedback mode by the common-mode negative feedback module, and performs common-mode voltage modification on the signal in the drive module to ensure that the circuit with the CMOS process can output a signal with PECL level standard.

Owner:XIAMEN UX HIGH SPEED IC

Timing error reduction in QKD systems

ActiveUS7409162B2Reducing and eliminating timing errorReduce time jitterSynchronisation information channelsSynchronisation by photonic/optical meansTiming generatorEmitter-coupled logic

Systems and methods for reducing or eliminating timing errors in a quantum key distribution (QKD) system (100) are disclosed. The QKD system has a pulse generator with retimer (PGRT) that includes a field-programmable gate array (FPGA) (or FPGA output) which is used as a timing generator (TG). While an FPGA has the desired degree of programmability for use in a QKD system, it also suffers from undue amounts of jitter in the digital output. The present invention utilizes emitter-coupled logic (ECL) to reduce the timing jitter from the FPGA by coupling two ECL delays (ECL delay 1 and ECL delay 2) to the FPGA and to retiming block, and by using an ECL logical AND gate to set the pulse width of the various synchronization signals. An embodiment of the present invention includes multiple clock domains having individual clocks (CLK), phase-lock loops (PLLs), retiming circuits (RT) and timing generators (TG) for robust jitter reduction and hence highly accurate QKD system timing.

Owner:MAGIQ TECH INC

Multiple signal format output driver with configurable internal load

ActiveUS8823414B2Reliability increasing modificationsLogic circuits characterised by logic functionLow voltageControl signal

A multiple signal format output driver is configurable to provide a current-mode logic (CML) output signal in response to a CML value of one or more first values of the control signal. The output driver is configurable to provide a low-power, low-voltage positive emitter-coupled logic (low-power LVPECL) output signal in response to a low-power LVPECL value of the one or more first values of the control signal. The output driver is configurable to provide a low-voltage differential signaling (LVDS) output signal in response to an LVDS value of the one or more first values of the control signal. The output driver may be configurable to provide a LVPECL output signal in response to a second value of the control signal. The output driver may be configurable to provide a high-speed current steering logic (HCSL) output in response to a third value of the control signal.

Owner:SKYWORKS SOLUTIONS INC

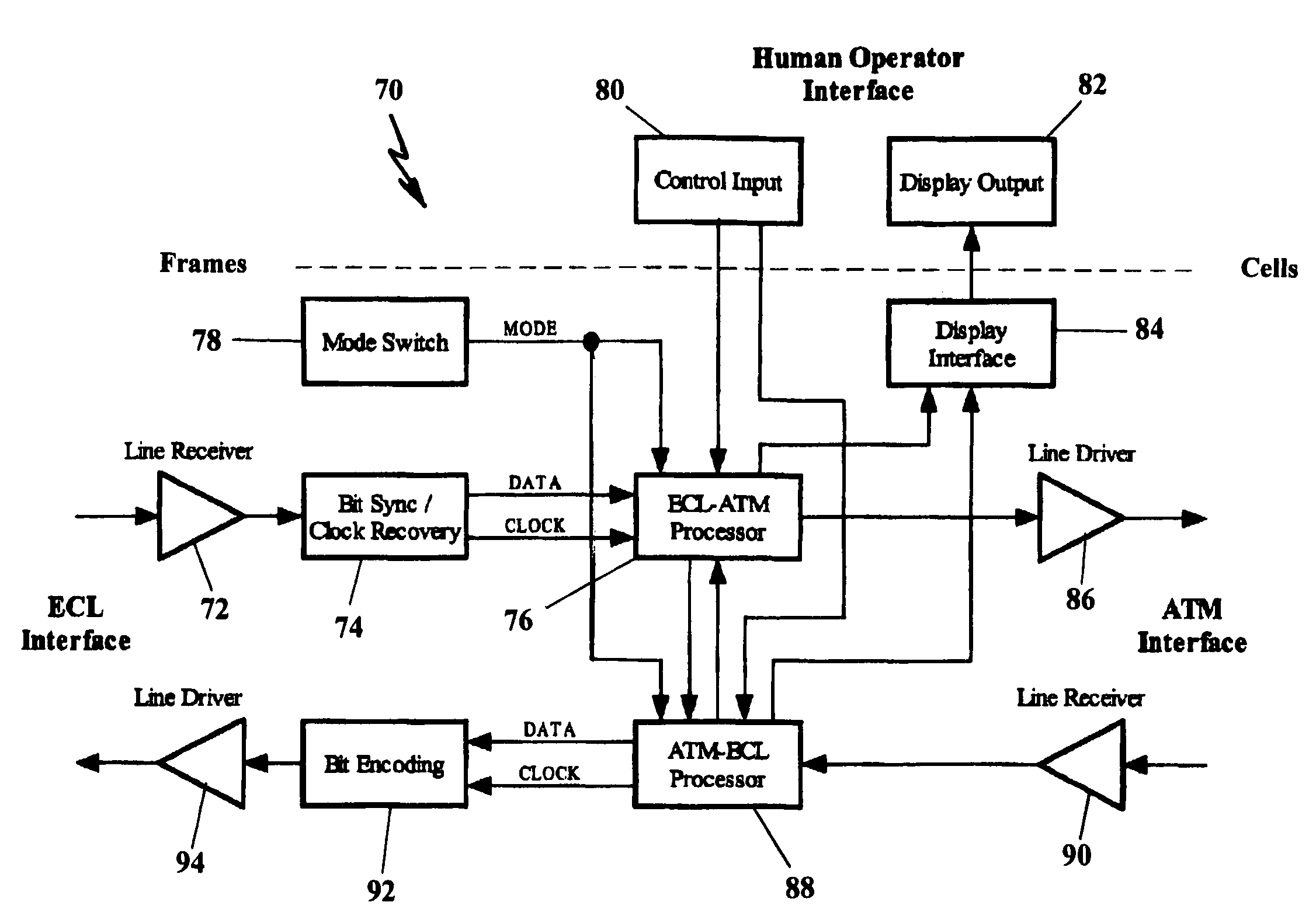

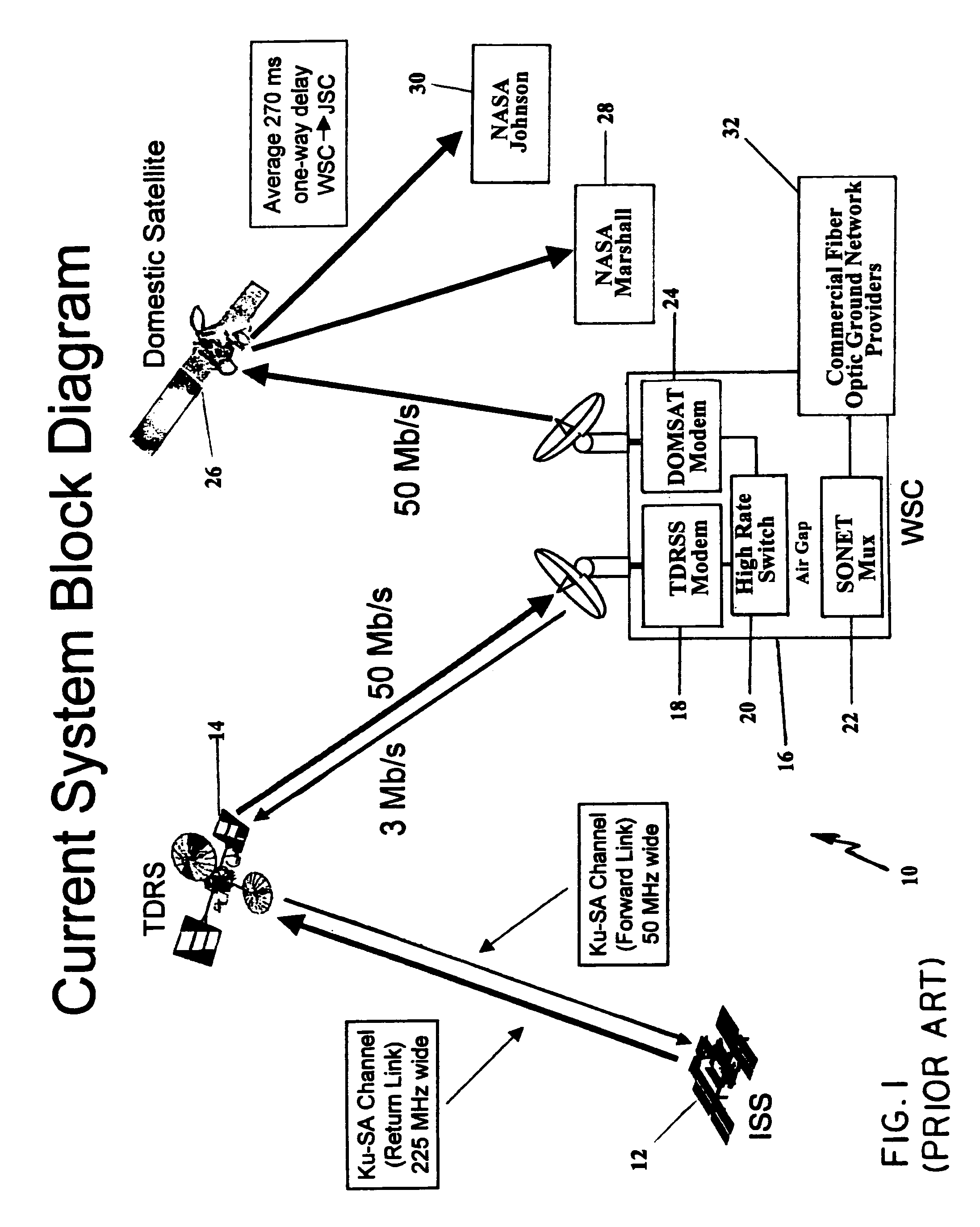

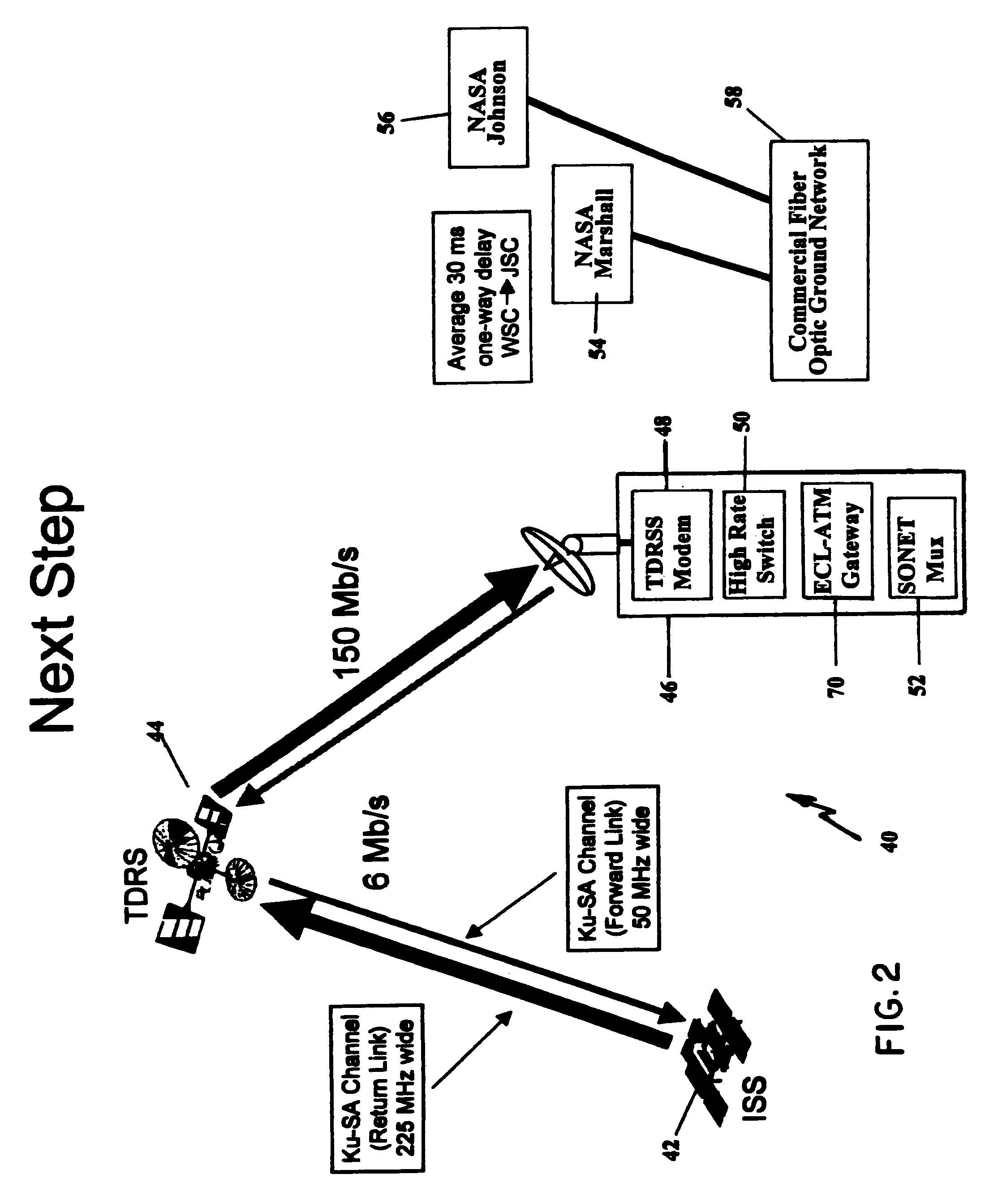

High performance ECL-to-ATM protocol network gateway

A network protocol translation device that allows serial data sent using the standard Asynchronous Transfer Mode (ATM) protocol to be used between two locations, using a satellite link or a terrestrial wireless link between the two locations. This is done by translating the standard ATM data to a standard satellite modem interface at one location, and translating the data back to the ATM format at the second (remote) location. The translation can occur at any data rate up to the available effective bandwidth of the ATM connection. The device is also capable of providing Forward Error Correction in the protocol translation. The device is functionally transparent to protocols above ATM, i.e., IP, UDP and TCP. It also interfaces with standard physical layers below ATM such as Synchronous Optical Network (SONET). At the satellite interface, the device is compatible with (but not limited to) Emitter Coupled Logic (ECL).

Owner:BEERING DAVID R

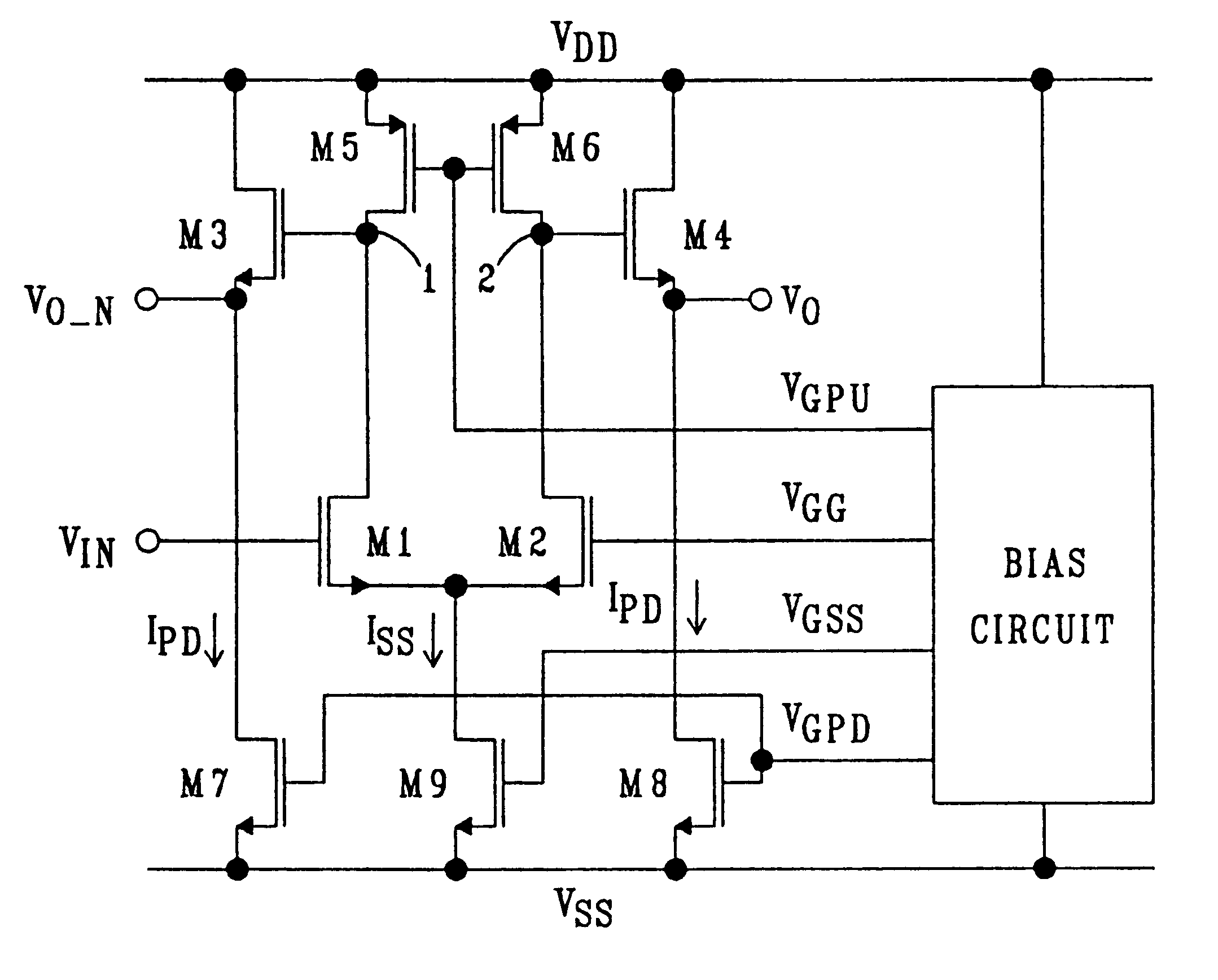

Source-coupled logic with reference controlled inputs

InactiveUS6229353B1Multiple input and output pulse circuitsInstant pulse delivery arrangementsNoise generationLow noise

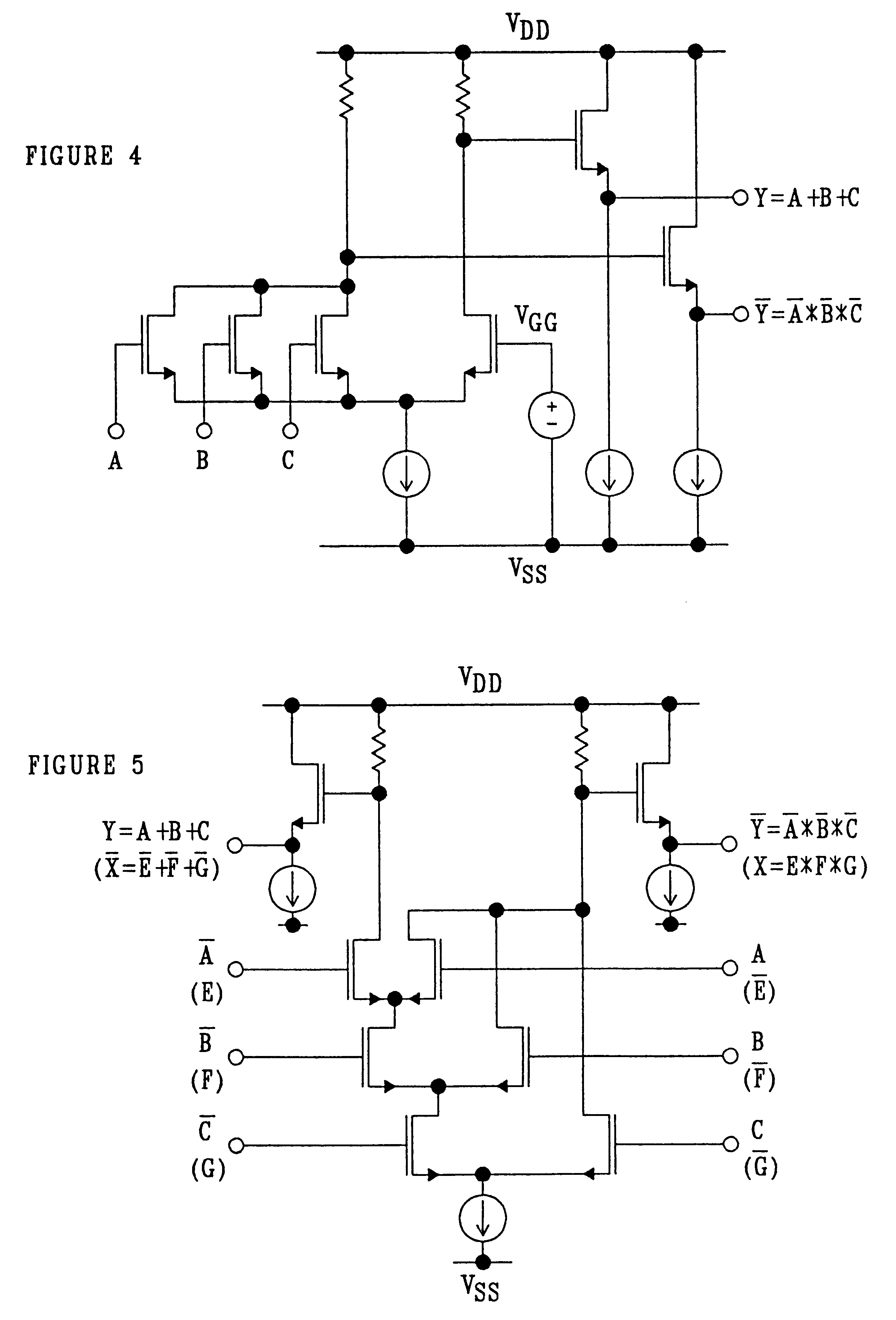

This invention relates to source-coupled logic (SCL) which is a functional derivative of emitter-coupled logic (ECL). ECL is widely recognized as having the characteristics of high speed (low propagation delay) and low power supply noise generation. The SCL of the prior art succeeds at maintaining and improving the low noise characteristics of this architecture but does not fulfill the promise of high speed that one would expect from a current-mode logic. In addition, it uses a differential form of logic that is not as flexible and easy-to-use as a reference controlled or "single-ended" logic. The SCL disclosed here has the desired high speed properties and maintains the ease of use that is a property of reference controlled ECL. In addition, the reference controlled SCL of this invention provides new capabilities that make it even more flexible than ECL in generating logical switching functions.

Owner:WERKING PAUL M

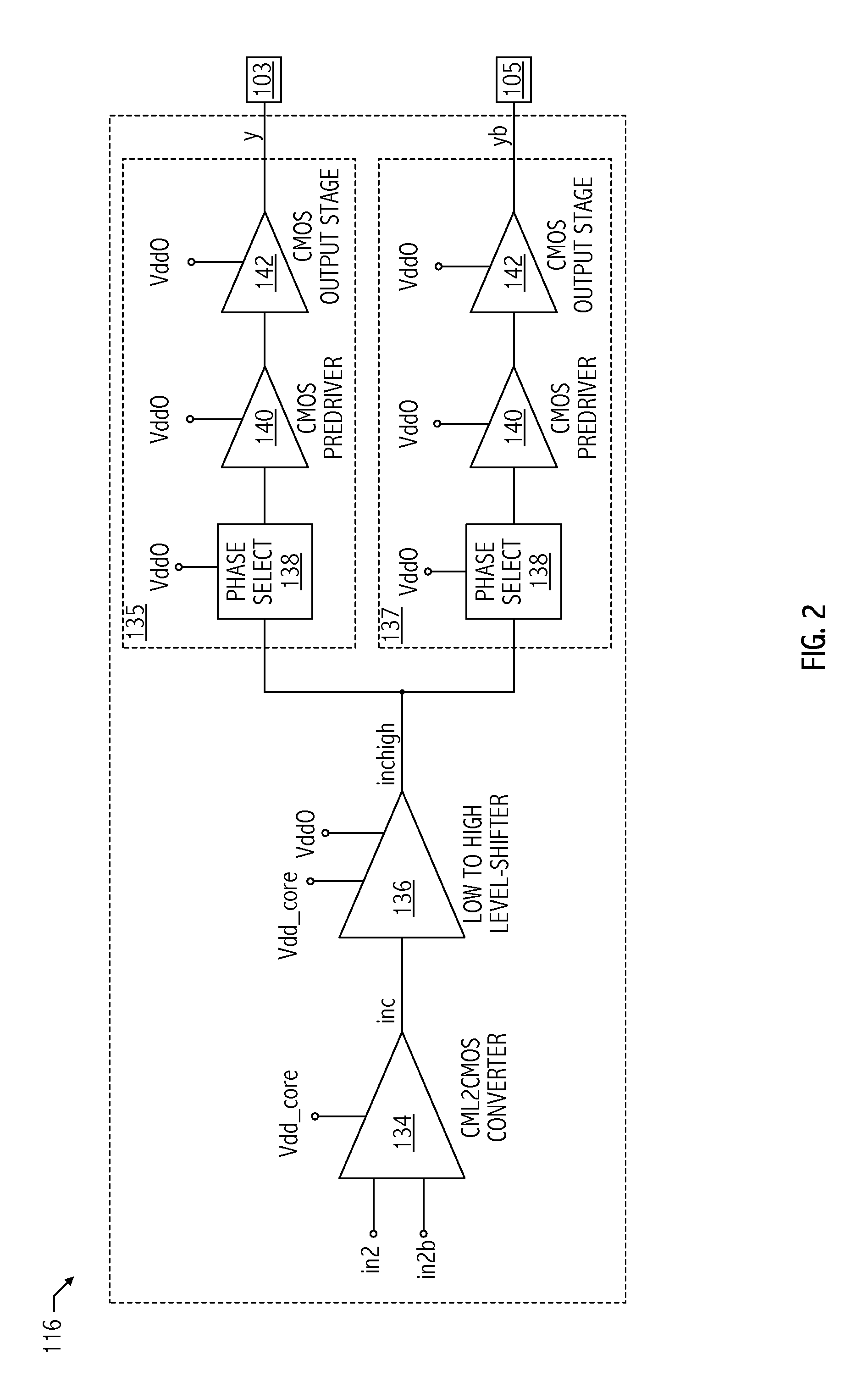

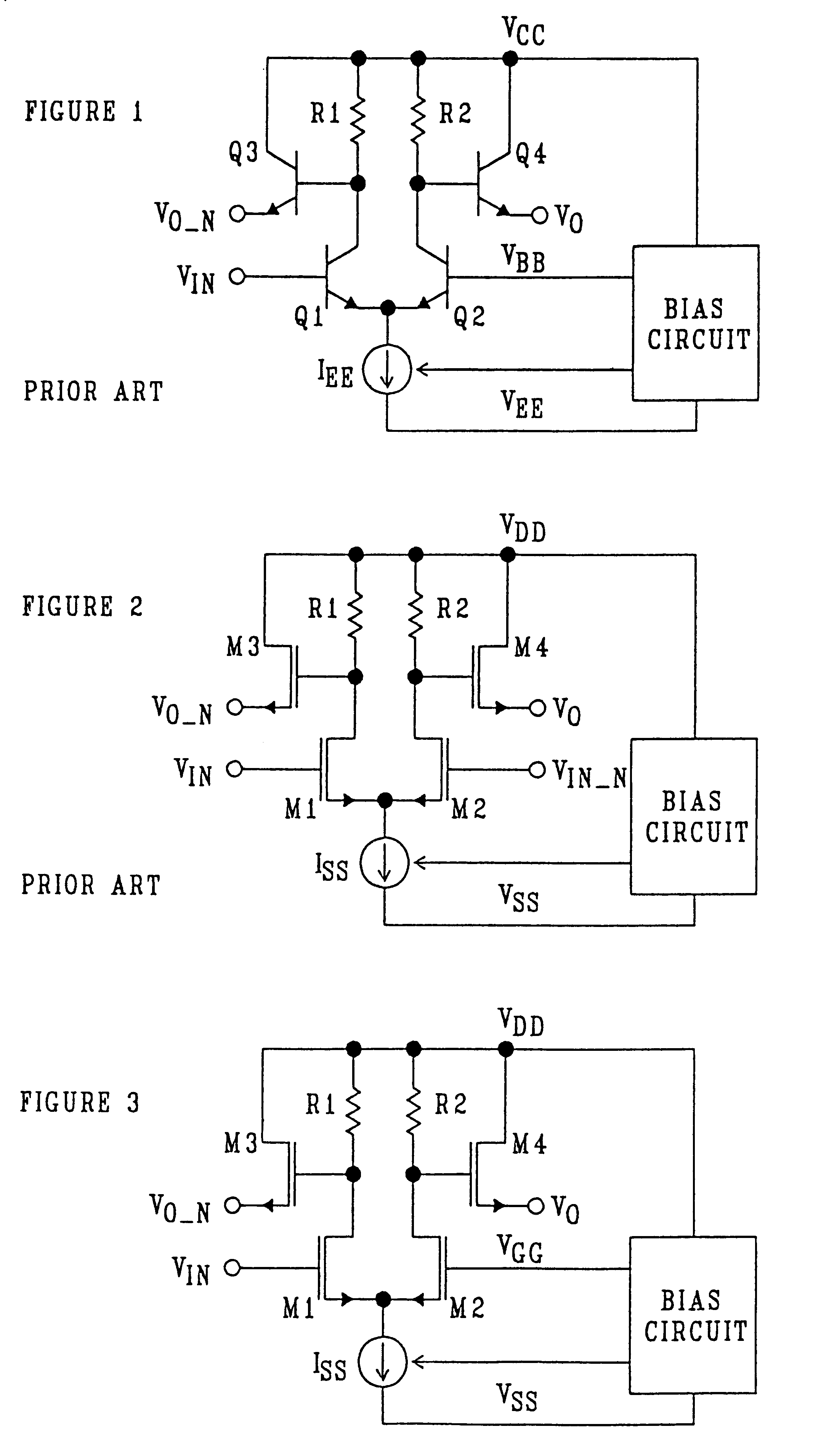

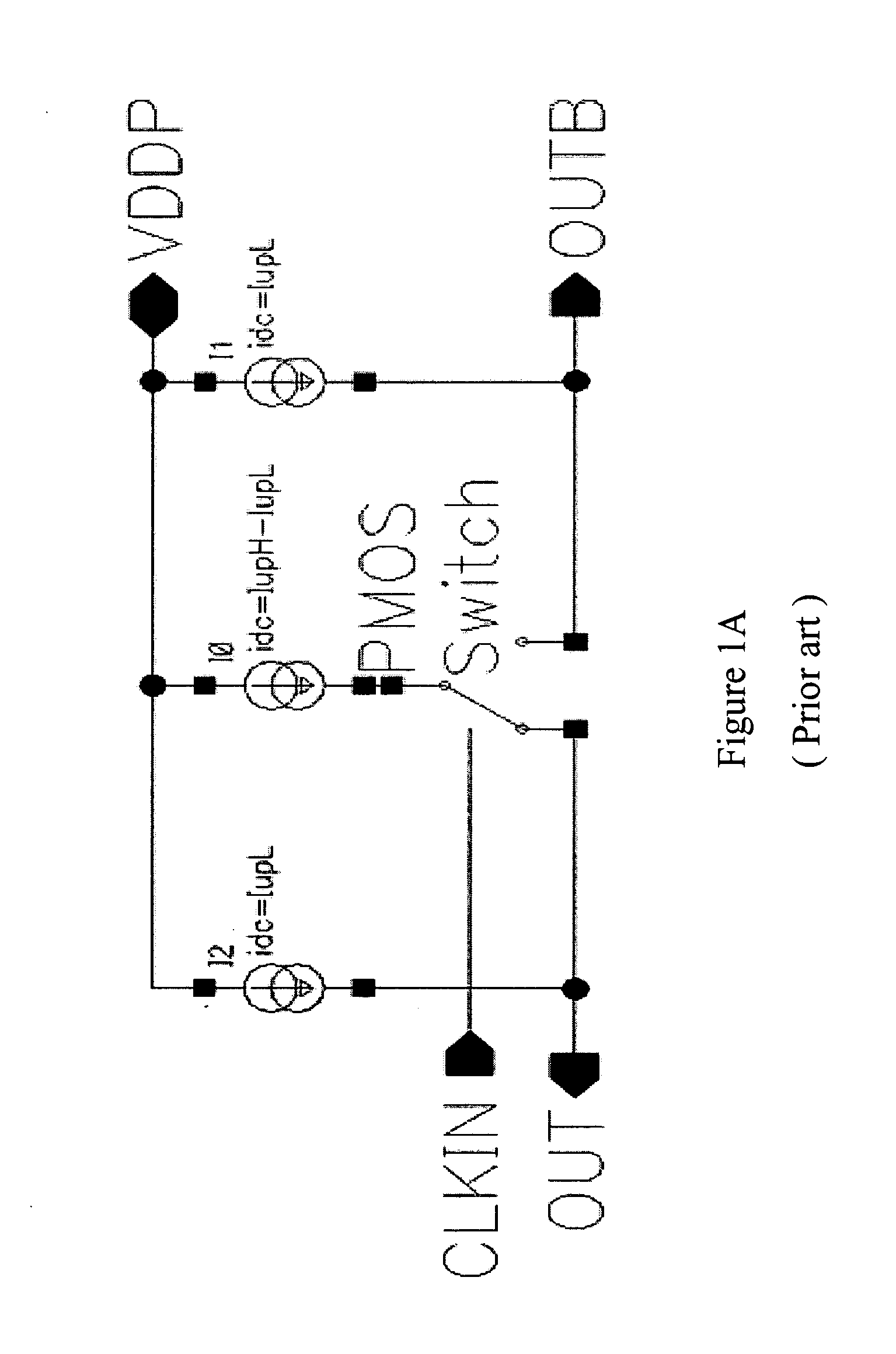

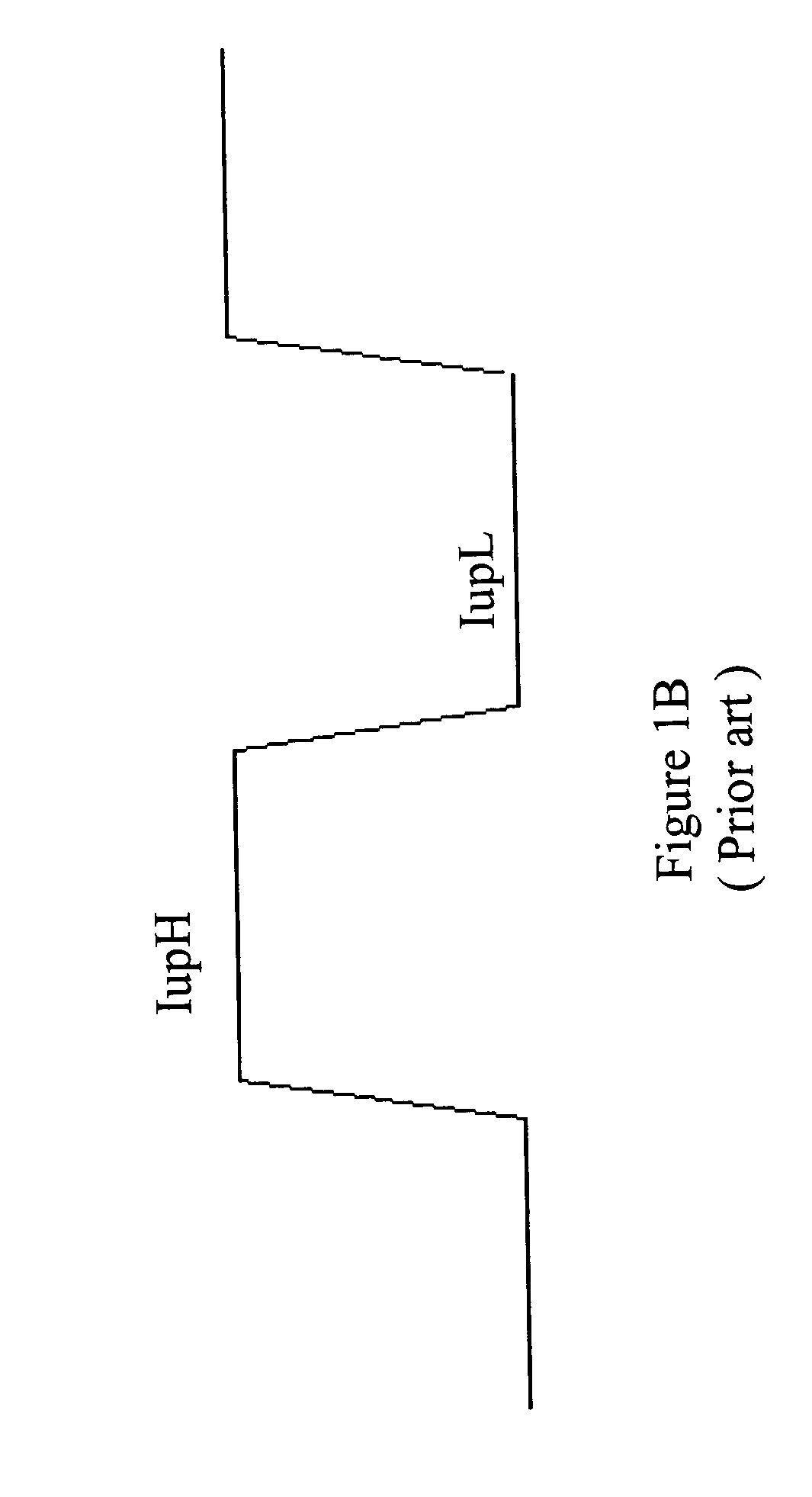

Complimentary metal oxide silicon low voltage positive emitter coupled logic buffer

ActiveUS20060158227A1High-frequency switching capabilityHigh frequency switching capabilitiesLogic circuits characterised by logic functionLogic circuit coupling/interface arrangementsCMOSMOSFET

A low voltage positive emitter coupled logic (LV-PECL) buffer fabricated in the complimentary oxide metal silicon (CMOS) process. The LV-PECL buffer in CMOS is operable for a wide frequency range from DC to frequencies as high as 800 MHZ in 0.5 um process. Synchronized feedforward logic is utilized without the need for a feedback loop. N-MOSFET's, which are faster than P-MOSFET's, are used for the implementation of switched current sources. The switched current sources deliver a pull-up current variable in time and as a result have more than two values. The pull-up current is sharply increased in value during the output waveform transition times in an impulse manner.

Owner:MICROCHIP TECH INC

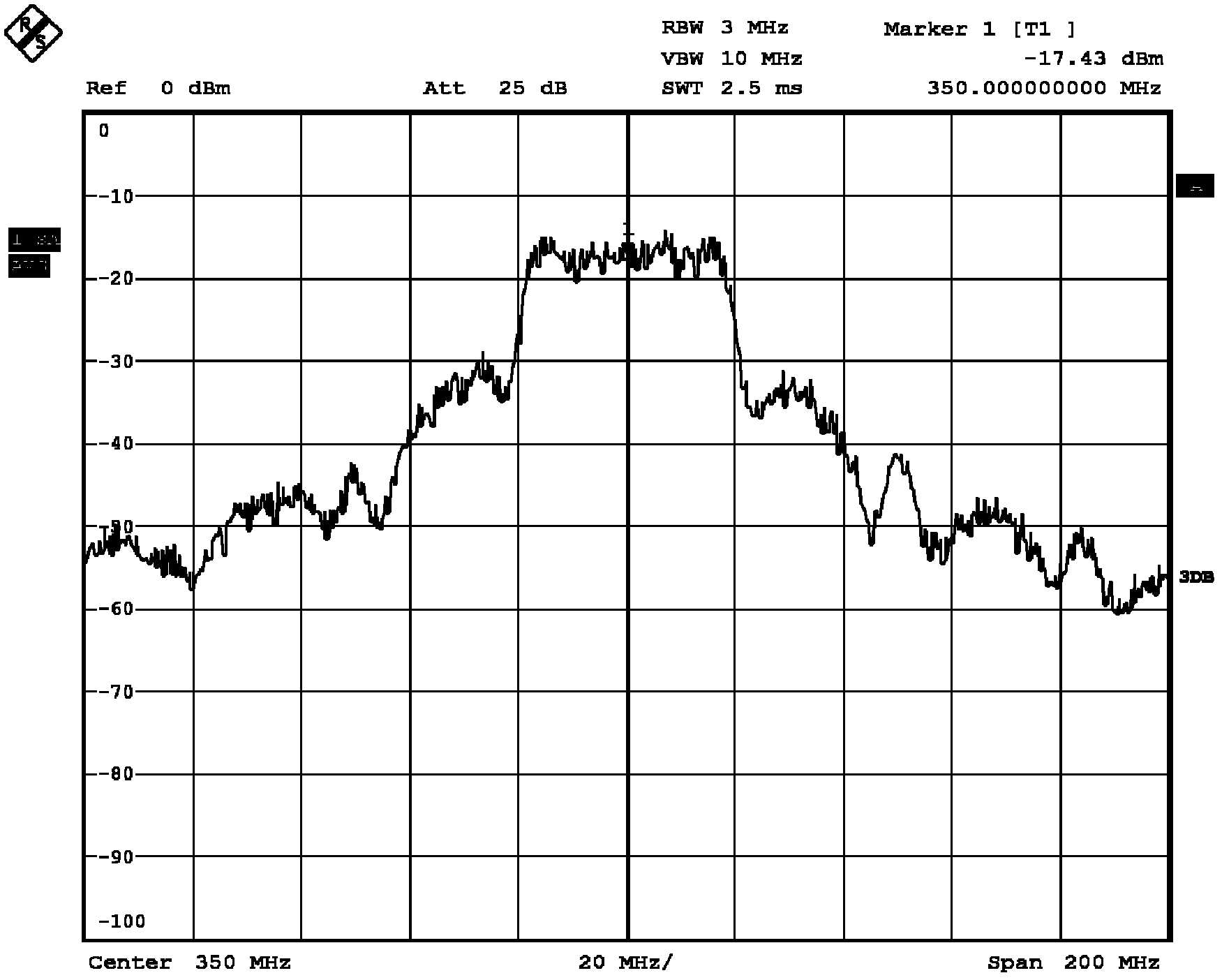

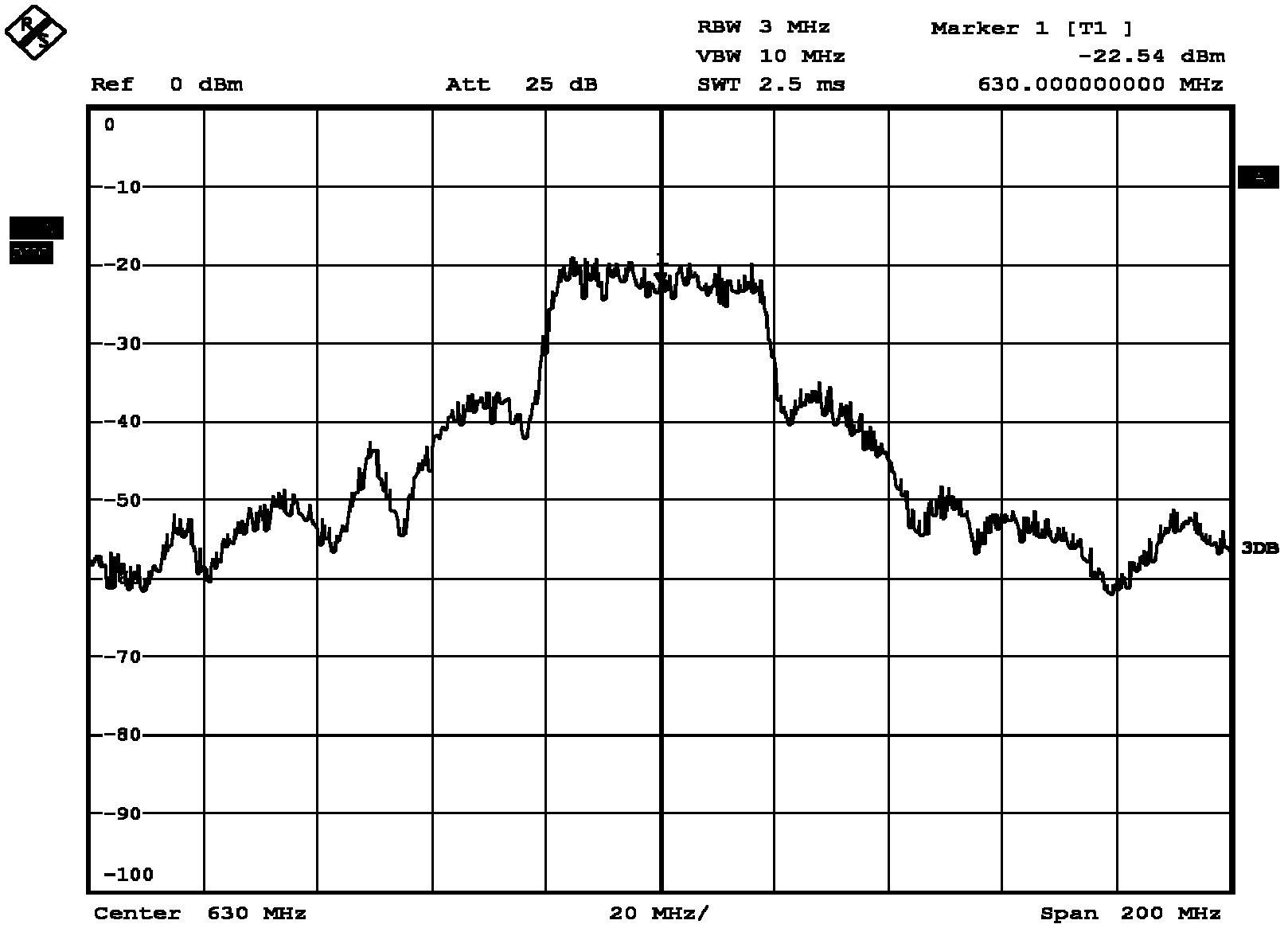

2CPFSK (continuous-phase frequency-shift keying) digital-modulation super-Nyquist application device

The invention discloses a 2CPFSK (continuous-phase frequency-shift keying) digital-modulation super-Nyquist application device. A baseband signal is output to a DDS (direct digital synthesizer) circuit through a baseband signal receiving circuit, a differential LVPECL (low voltage positive emitter coupling logic) emitter receives a clock signal of a frequency reference source to provide a reference frequency for the DDS circuit, a singlechip is configured with a DDS inner register, the frequency content of a Profile0 register is selected as the output of the DDS circuit when a receiving signal is of low level, and the frequency content of a profile1 register is selected as the output of the DDS circuit when the receiving signal is of high level; and the output of the DDS circuit is subjected to outer frequency element filtering through a band pass filter to obtain a 2CPFSK modulation signal with the required frequency. According to the 2CPFSK digital-modulation super-Nyquist application disclosed by the invention, direct output frequency can reach L wave band or can be higher, bandwidth and transmission velocity are improved, frequency conversion times of a known 2CPFSK signal emitter is reduced, and the size of the emitter is reduced.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

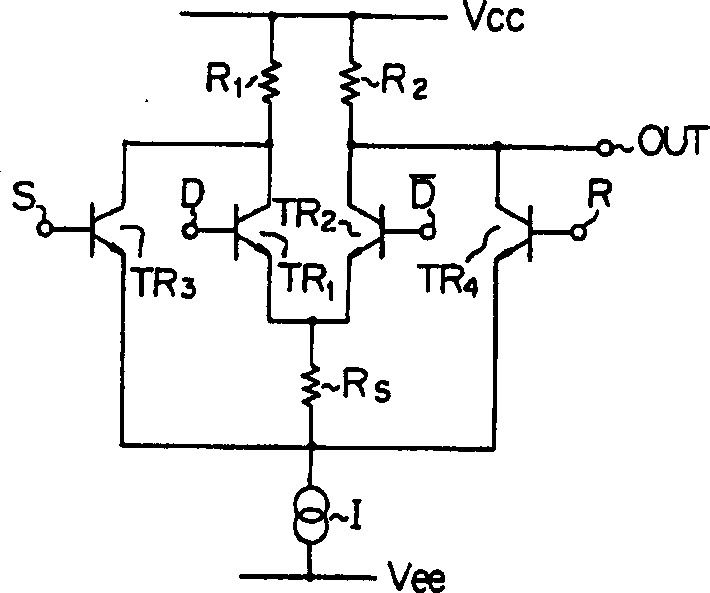

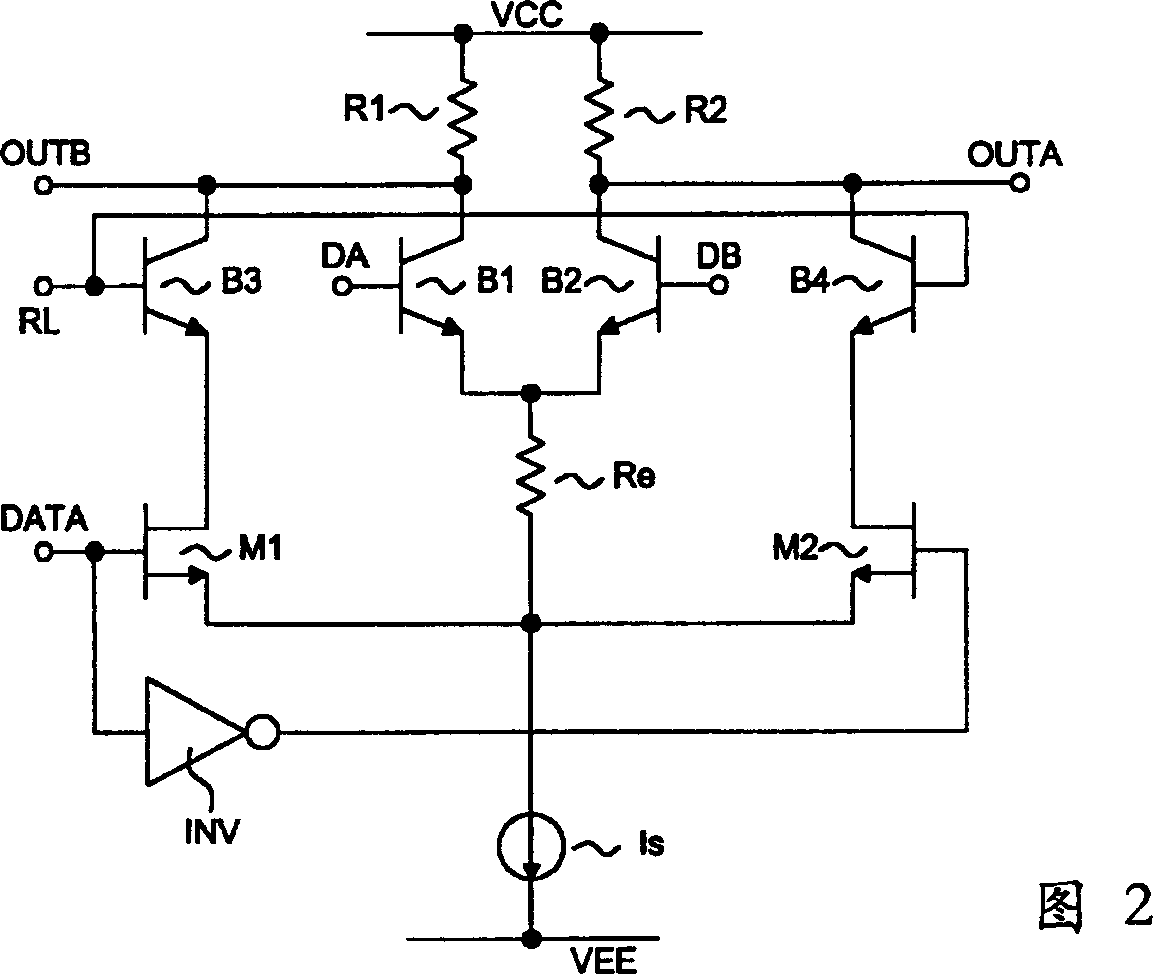

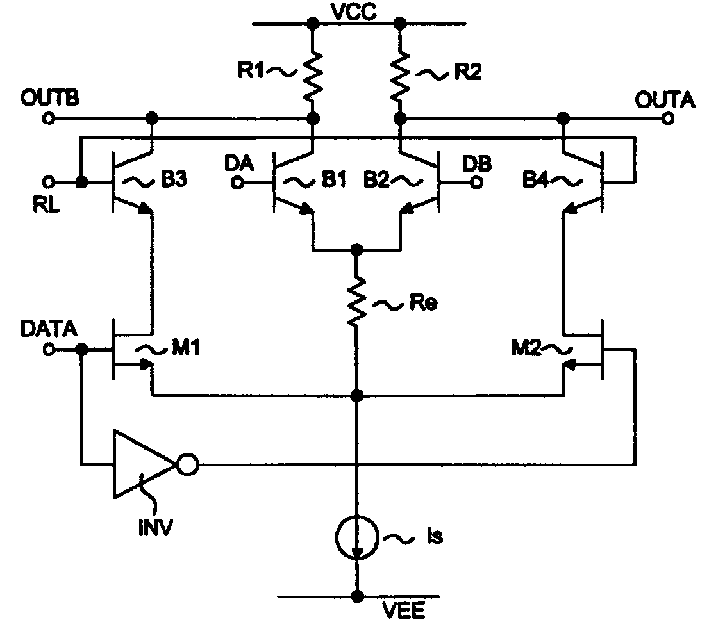

Emitter coupled logic circuit having data heavy dnty function

InactiveCN1479449AImprove the speed of data reload actionElectronic switchingLogic circuits using semiconductor devicesData controlControl signal

The circuit includes cascaded first transistor and second transistor, which are bipolar joint transistor (BJT) and field effect transistor (FET) respectively. BJT receives overloading control signal, and FET receives overloading data in order to use cascaded control of BJT and FET to overload digital overloading data on ECL circuit. Since set overloading data is received by ECL directly, thus digital overload data does not need to pass through prepositive ECL voltage level conversion treatment. Before overloading control signal acts, the overloading data can be set to transfer to FET. Thus, the FET can be set to on or off. Once overloading control signal acts, the status of output is controlled based on overloading data so as to raise data overloading acting speed of the ECL circuit.

Owner:MEDIATEK INC

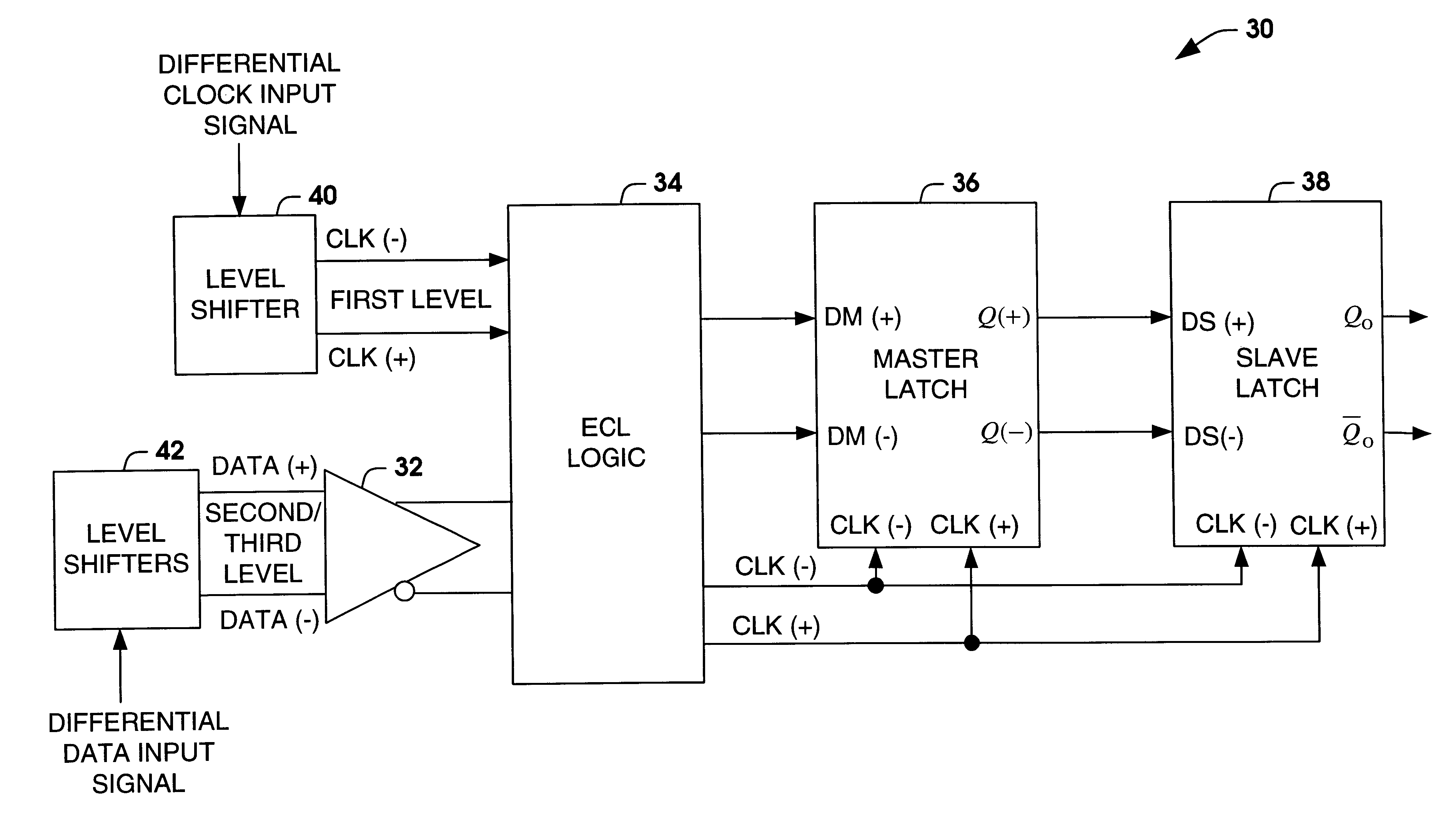

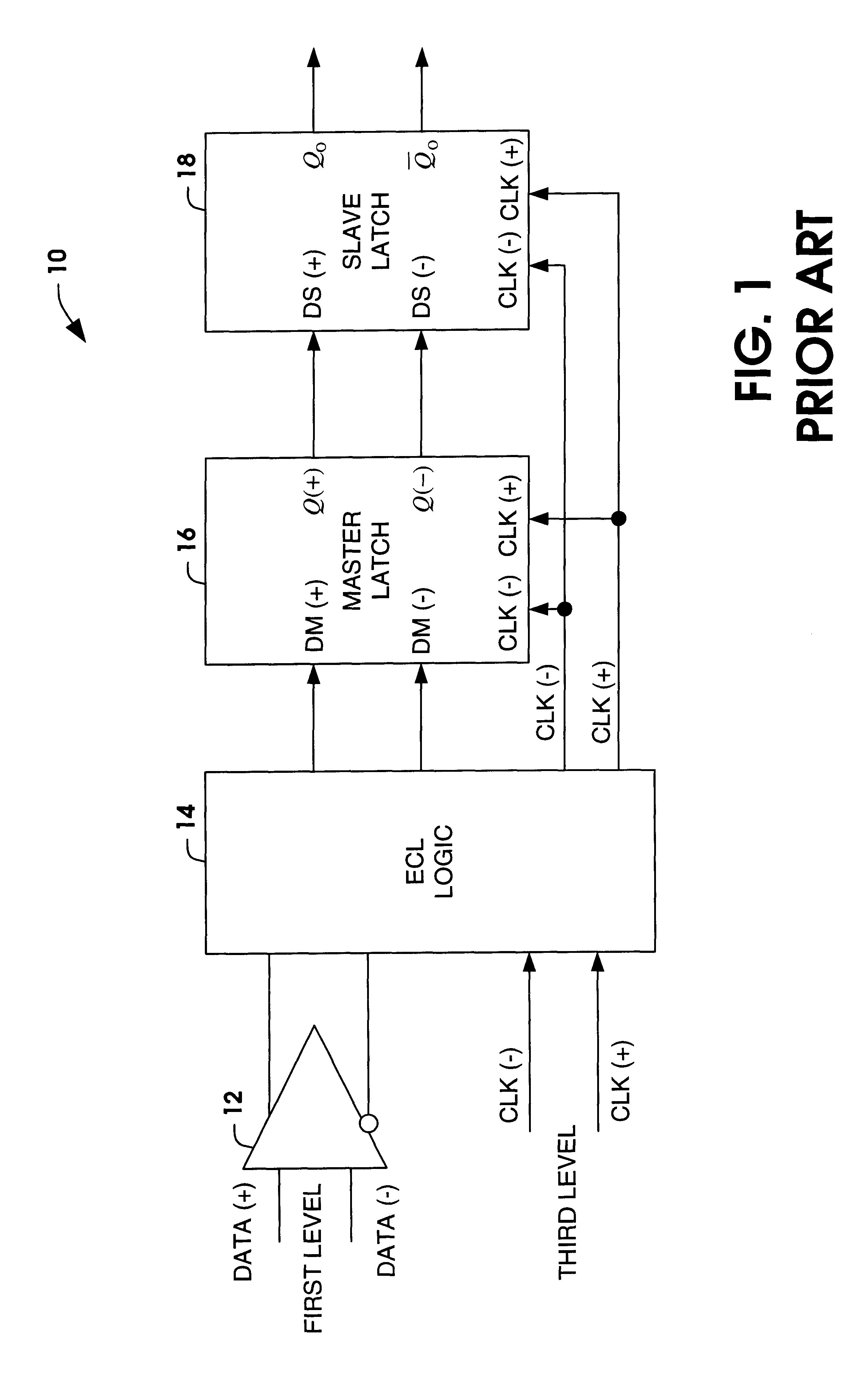

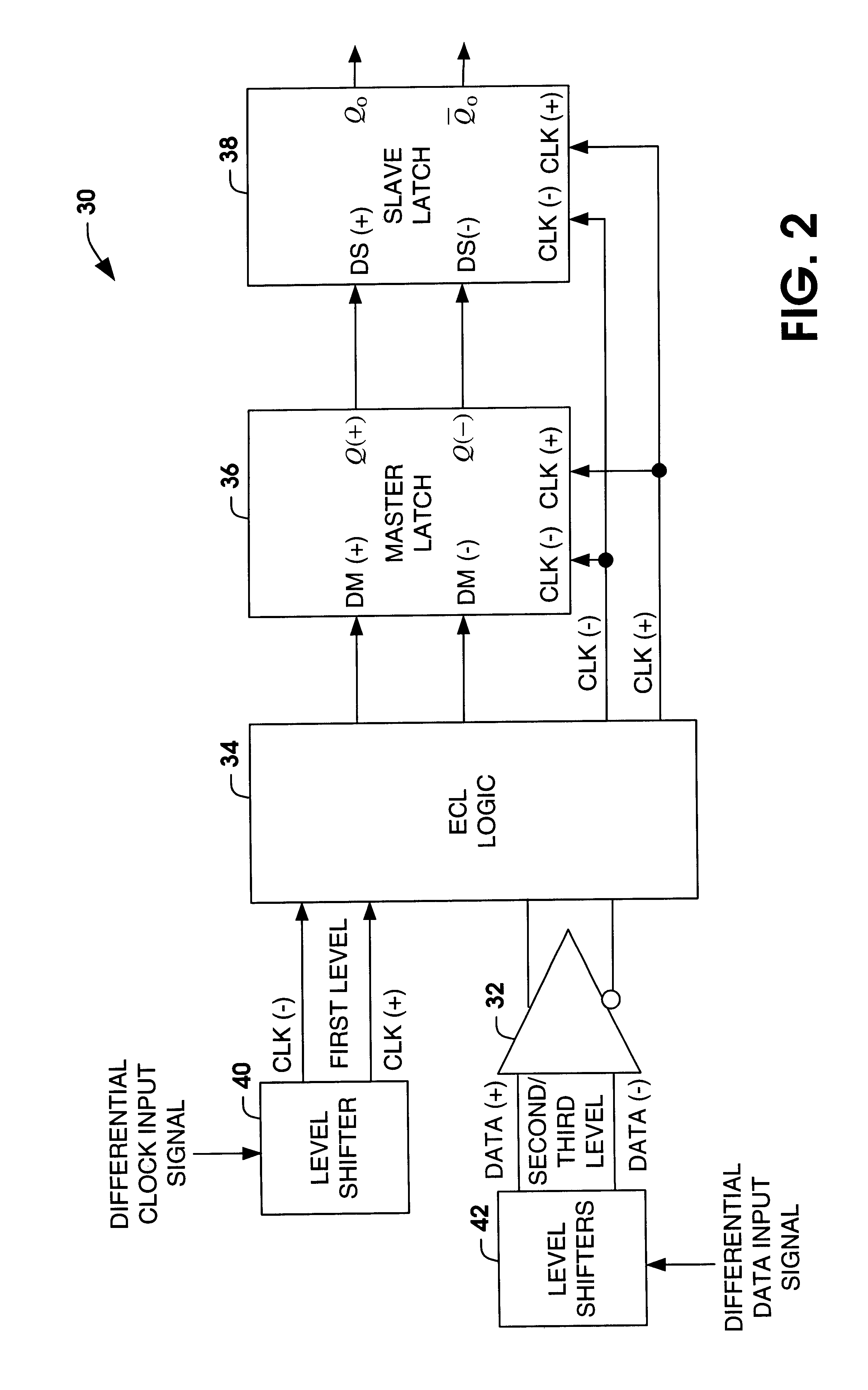

Ultra high speed flip-flop

InactiveUS20040012408A1Increase data rateHigh bandwidthElectric pulse generatorLogic circuit coupling/interface arrangementsUltra high speedEmitter-coupled logic

An ultra high speed Emitter Coupled Logic (ECL) flip-flop is provided and a method of operating the same. The ECL flip-flop provides for clock levels that operate at logic levels above the data levels. Since the clock operates at logic levels above the data, the clock experiences level shifts that are less than the level shifts of the data. Therefore, the clock will provide a higher fidelity signal relative to the conventional clock signal. The ECL flip-flop can operate at significantly higher data rates than conventional flip-flop circuitry.

Owner:NORTHROP GRUMMAN SYST CORP

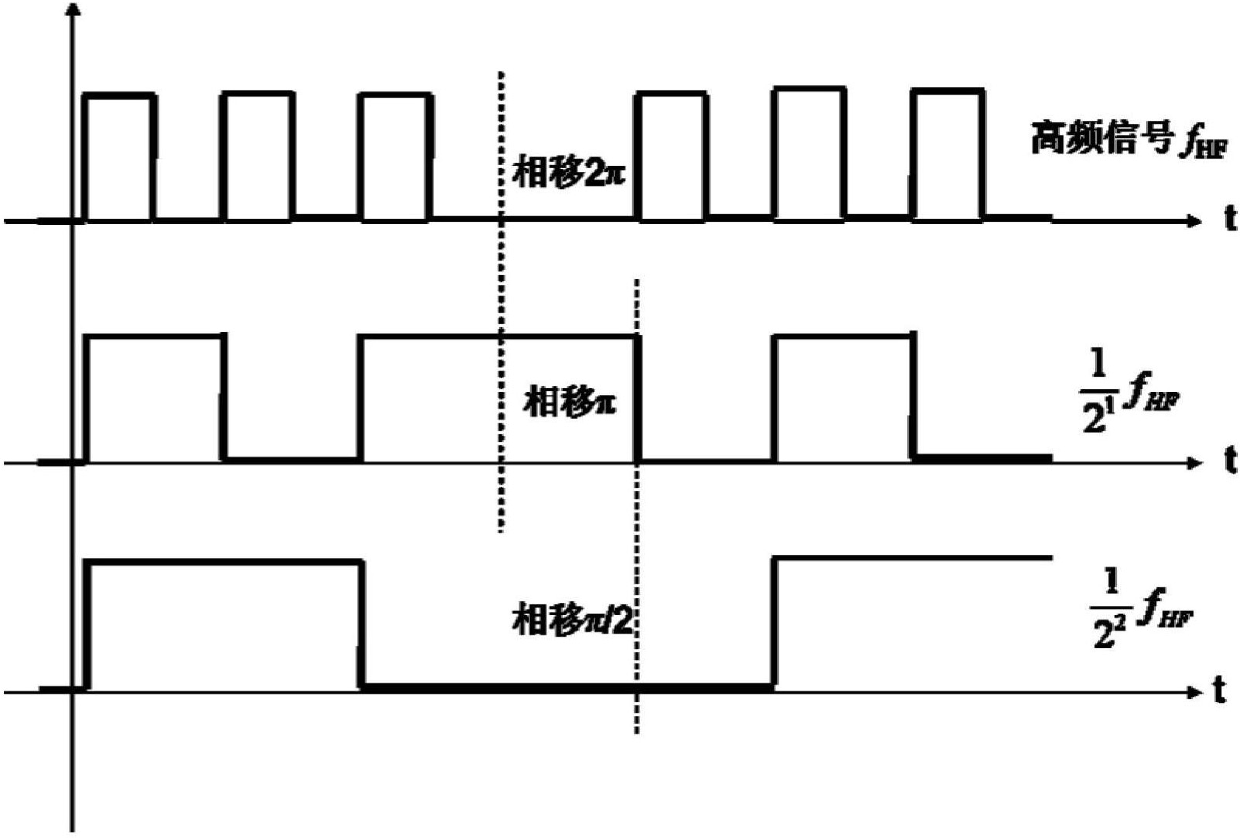

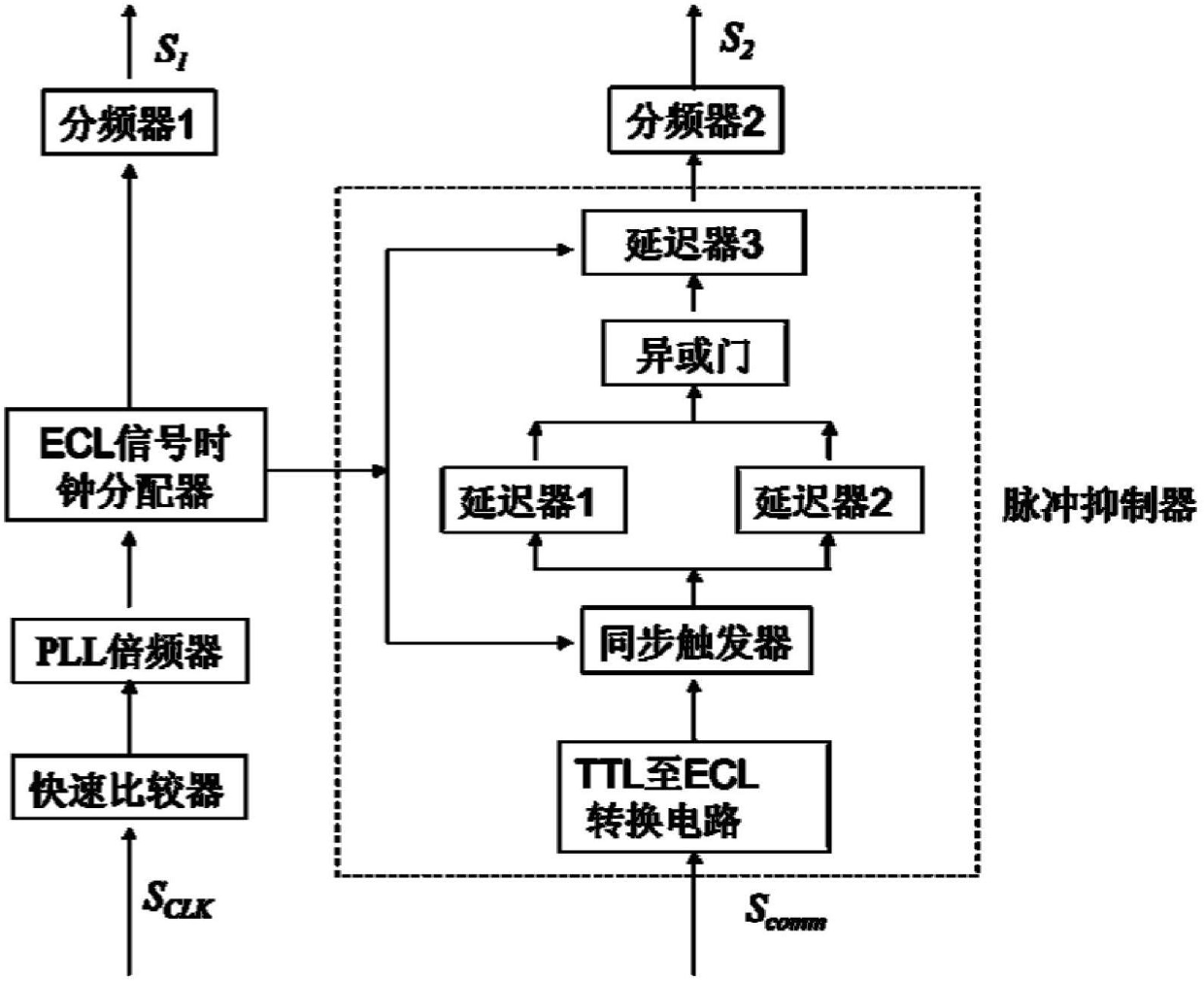

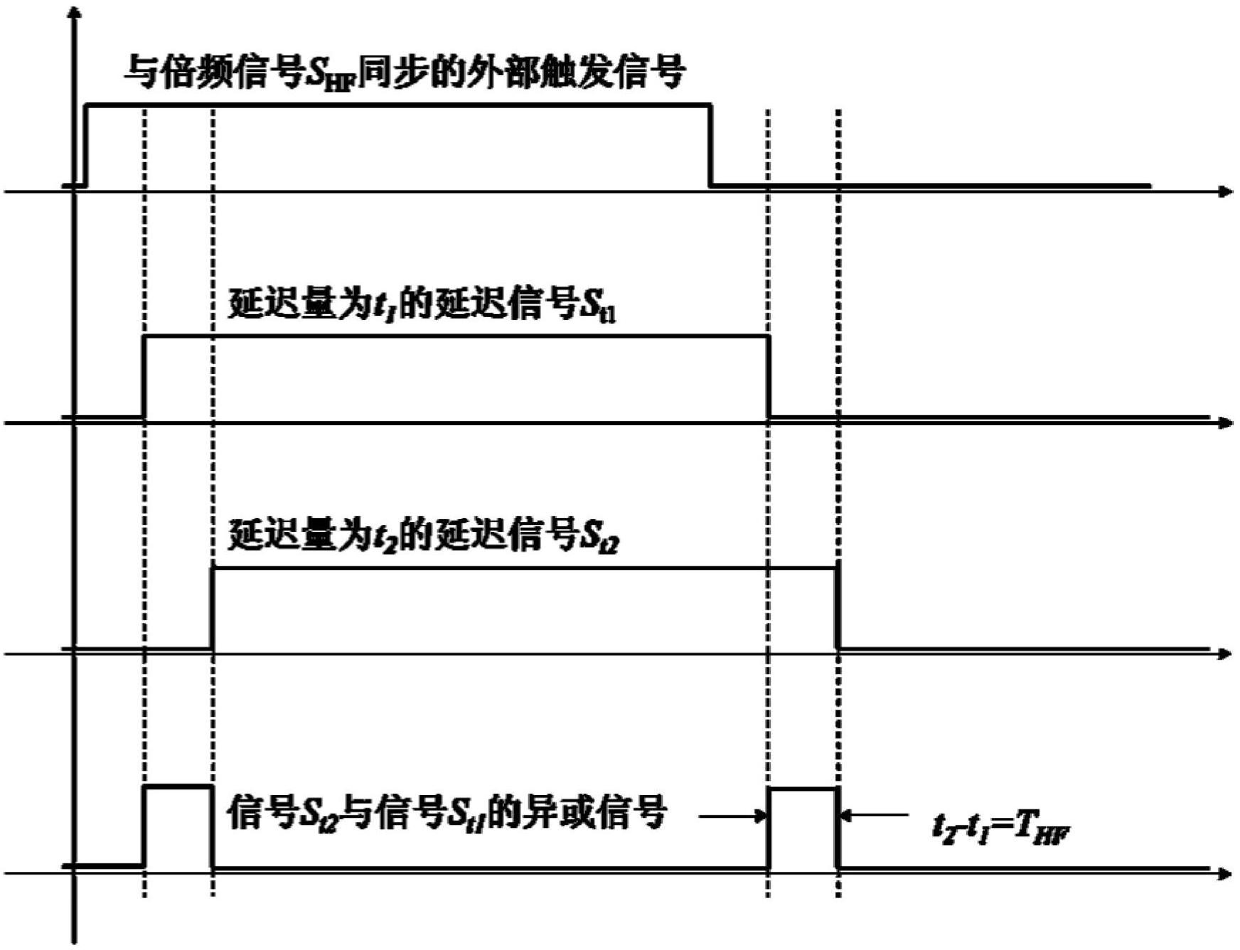

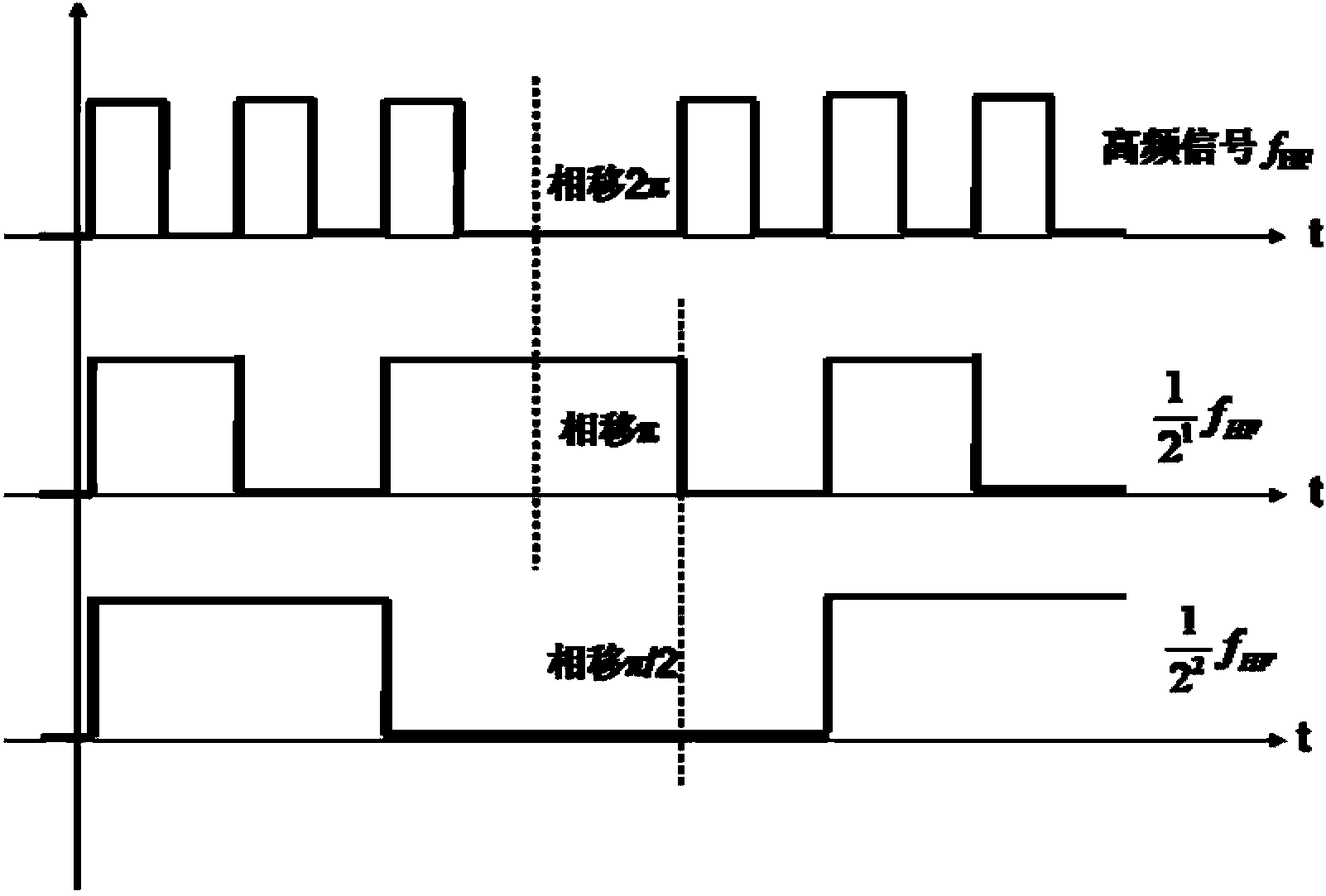

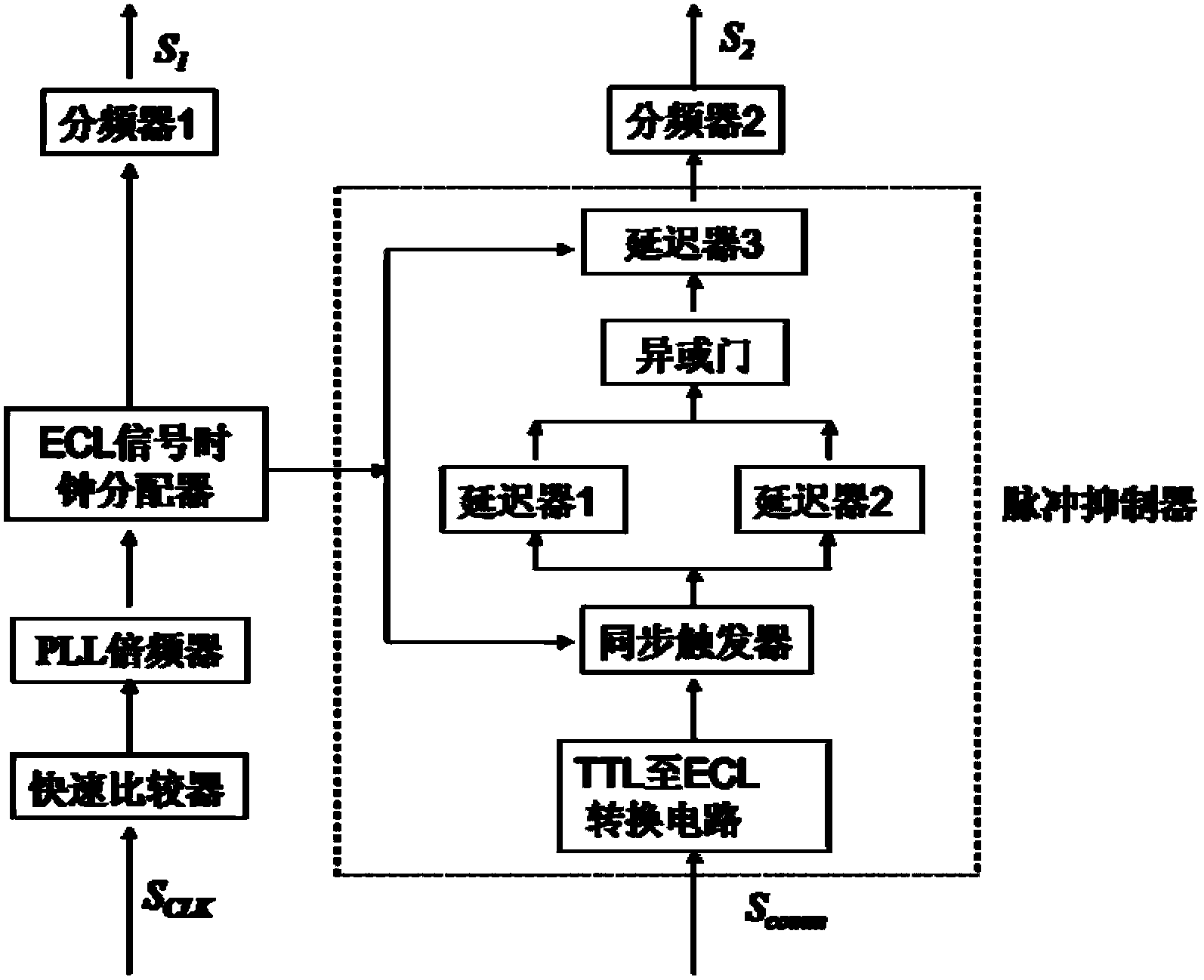

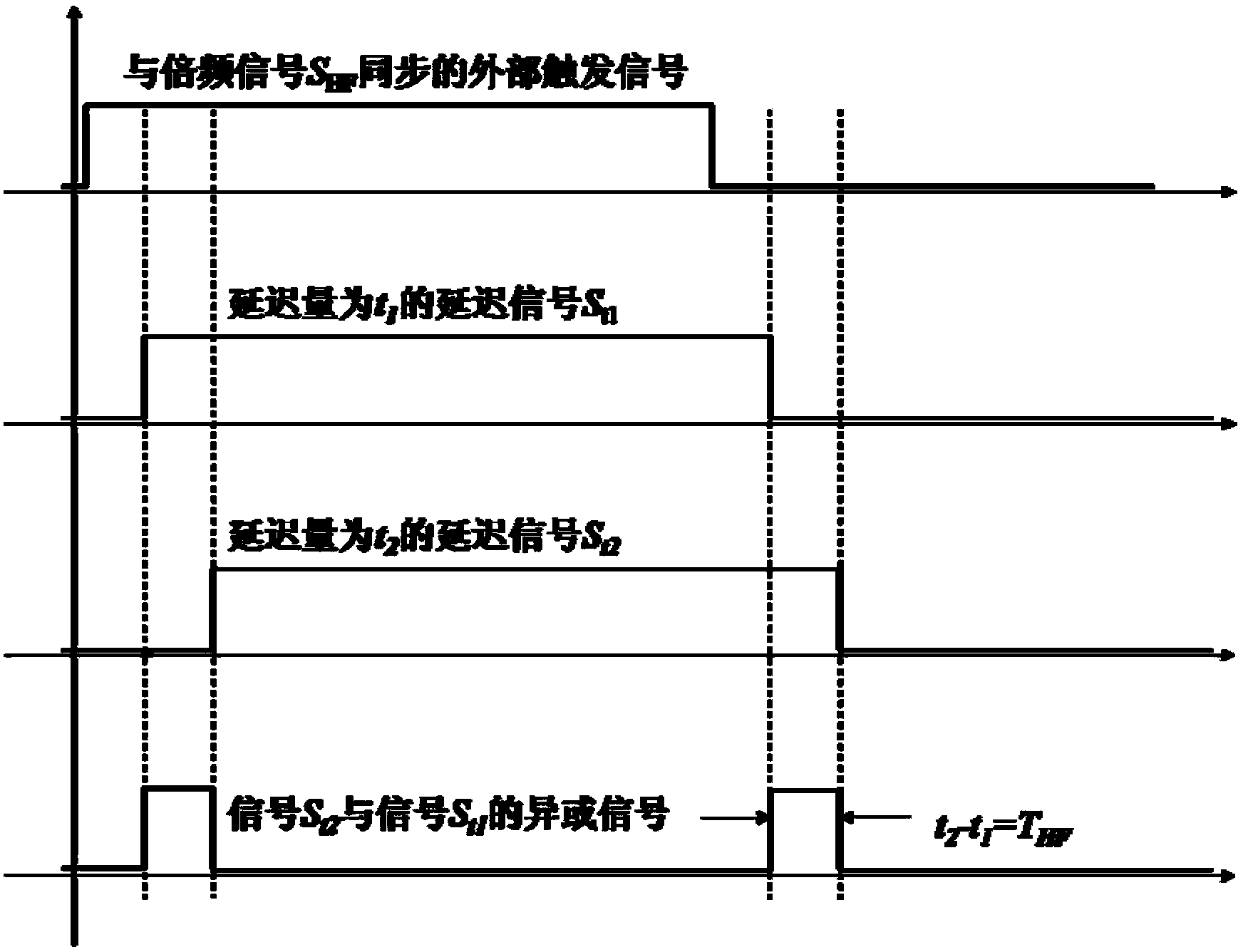

Programmable ECL (emitter coupled logic) device based high-frequency phase shift signal generation circuit

InactiveCN102664625ASimple design principleReduce volumePulse automatic controlFrequency multiplierEmitter-coupled logic

The invention discloses a programmable ECL (emitter coupled logic) device based a high-frequency phase shift signal generation circuit. The existing high-frequency signal generator is expensive and the hardware circuit is complex. The programmable ECL device based a high-frequency phase shift signal generation circuit provided by the invention comprises a rapid comparator, a PLL (phase locking loop) frequency multiplier, an ECL signal clock distributor, a pulse suppressor, a first digital frequency divider and a second digital frequency divider; the rapid comparator converts an external clock signal into a square wave signal; the PLL frequency multiplier performs frequency multiplying on the square wave signal; the ECL signal clock distributor distributes the frequency multiplying signal to two ways, one way of the frequency multiplying signal is directly subjected to frequency division through the first digital frequency divider, and the other way of frequency multiplying signal is subjected to frequency division by the second digital frequency divider after the pulse suppressor suppresses a phase shift of 2pi; the frequency dividing multiple of the first digital frequency divider and the second digital frequency divider is respectively 2, and the output signal of the first digital frequency divider has the phase shift as shown in the specification relative to the output signal of the second digital frequency divider. According to the invention, the circuit design principle is simple, and the duplicability is high.

Owner:CHINA JILIANG UNIV

System and method for acquiring and distributing baseband data of remote sensing satellite

ActiveCN102832988BData Distribution Service SecurityThe data distribution service is activeRadio transmissionData switching networksEmitter-coupled logicData acquisition

The invention provides a system for acquiring and distributing baseband data of a remote sensing satellite. The system comprises a task management device, a data acquiring device, a data storage device and a data distributing device. When detecting a data acquisition task list, the data acquiring device acquires baseband data of the remote sensing satellite and corresponding time code information thereof from the remote sensing satellite by a fully digital demodulator via the network. The data distributing device distributes the required baseband data of the remote sensing satellite to user equipment after receiving data distribution requests of the user equipment. By the aid of the system, the baseband data of the remote sensing satellite can be acquired in real time via the network, and meanwhile, uniform data distributing services can be provided to rear-end equipment via the network, and accordingly, limits of ECL (emitter-coupled logic) signal transmission distance and special acquisition cards are eliminated.

Owner:CENT FOR EARTH OBSERVATION & DIGITAL EARTH CHINESE ACADEMY OF SCI

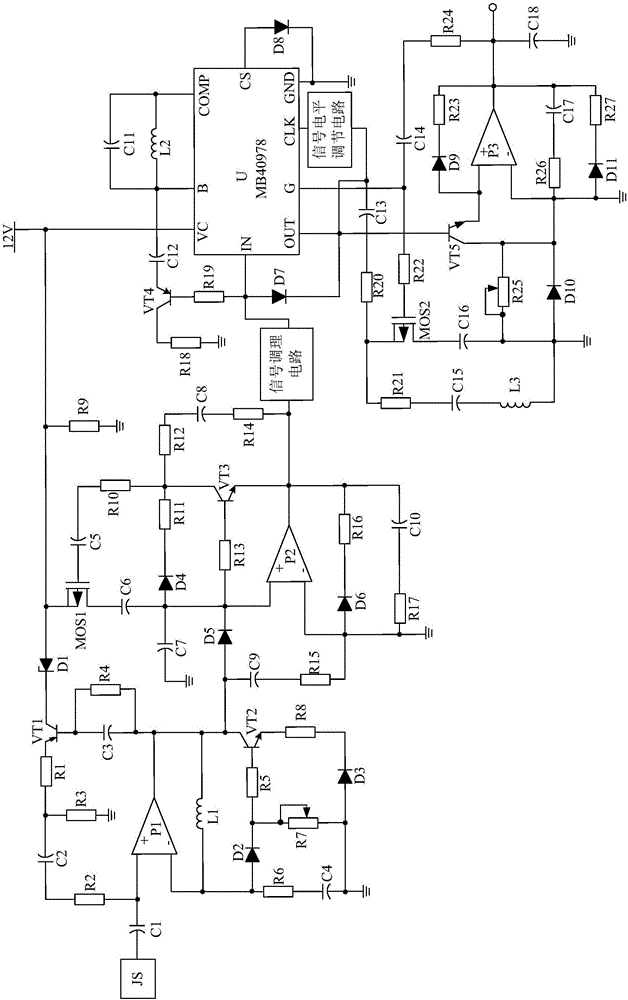

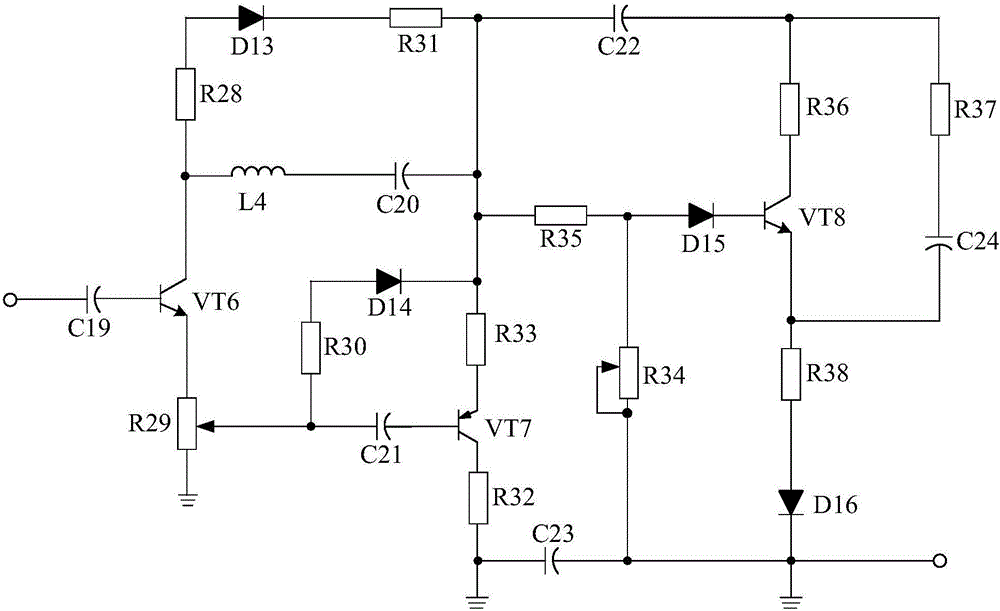

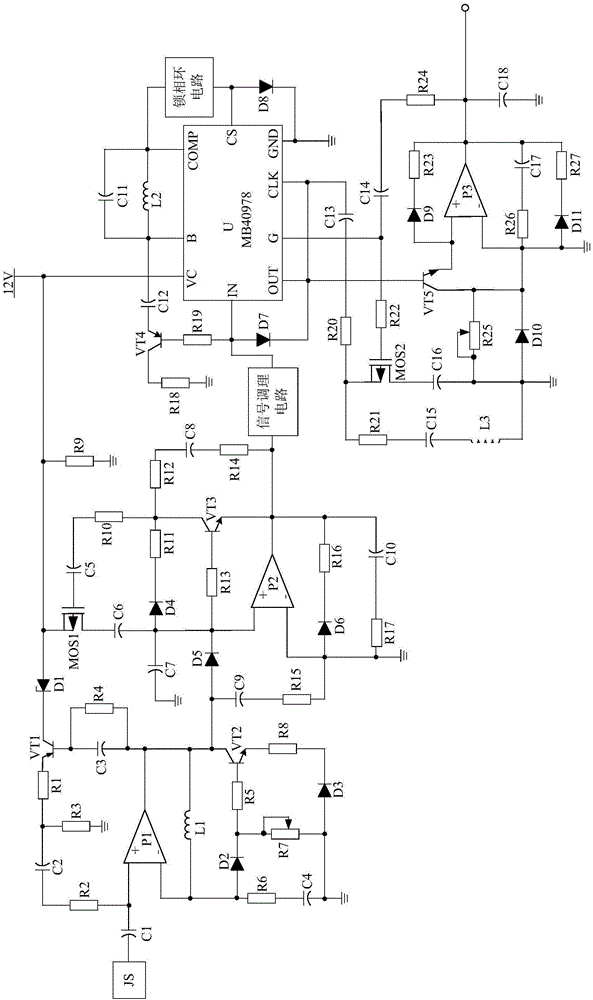

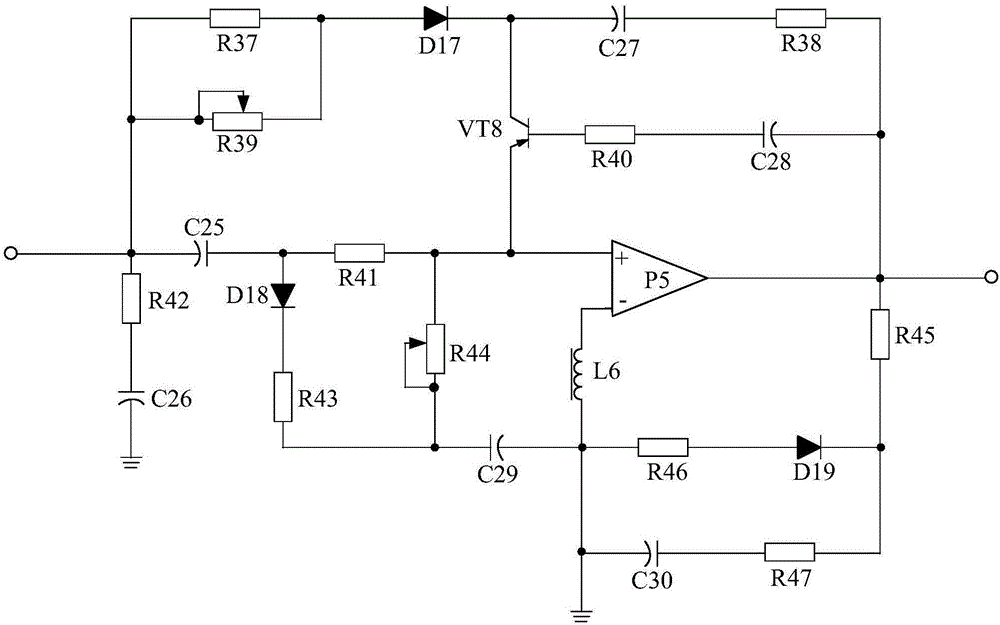

Rectangular wave modulation-type signal processing system for electrolyzer anode current measurement device

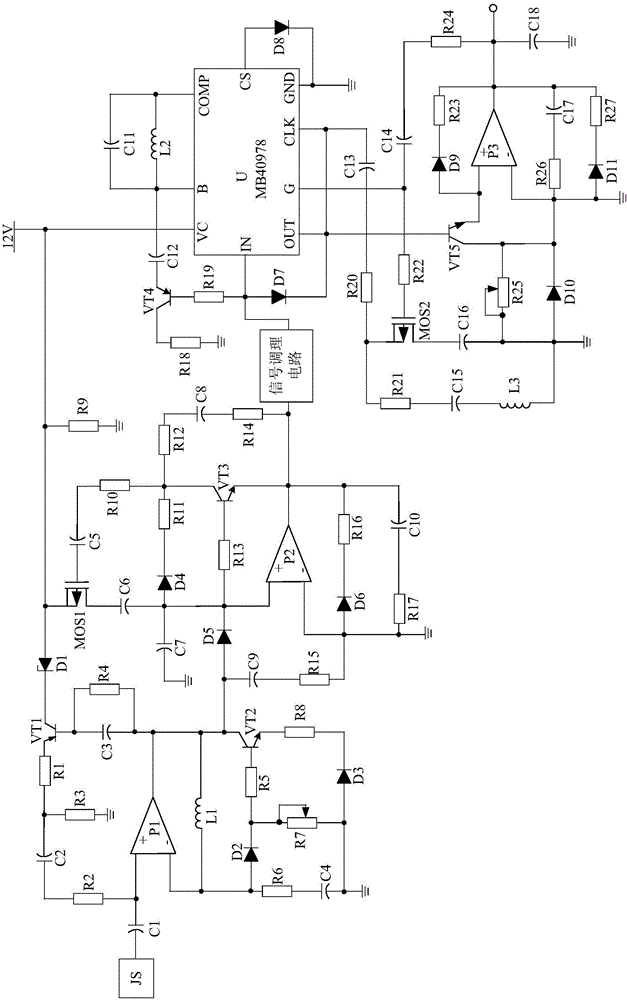

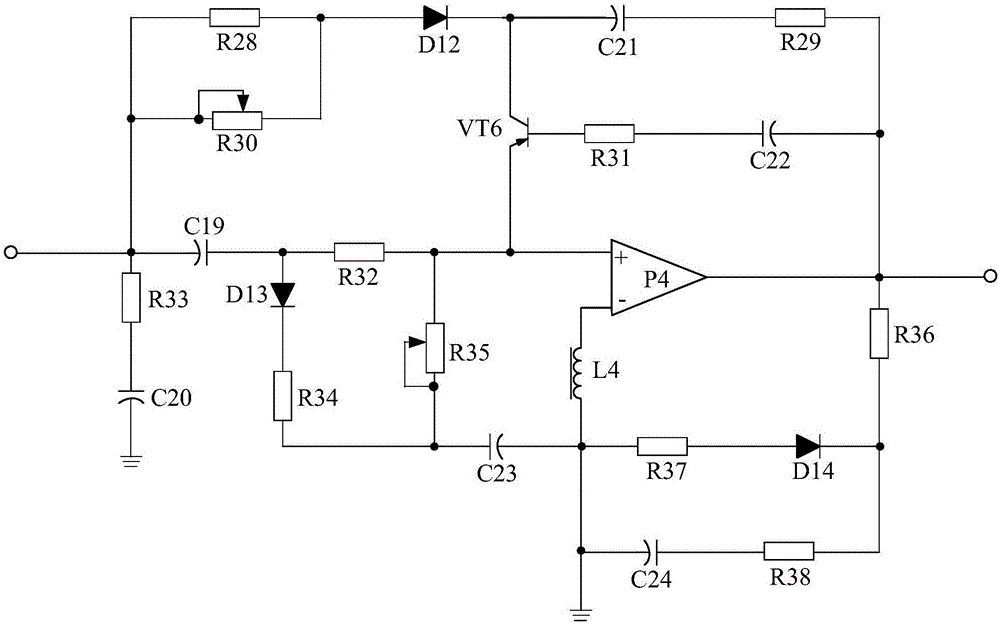

InactiveCN106226581AAccurate measurementReasonable designCurrent measurements onlyMeasurement deviceElectrolysis

The invention discloses a rectangular wave modulation-type signal processing system for an electrolyzer anode current measurement device, which is characterized by being mainly composed of a processing chip U, a signal collector JS, a triode VT4, a polar capacitor C11, a diode D8, a second-order low-pass filter circuit connected with the signal collector JS, an emitter-coupled logic circuit serially connected between the second-order low-pass filter circuit and the processing chip U, a signal conditioning circuit serially connected between the emitter-coupled logic circuit and the IN pin of the processing chip U, a linear isolation circuit connected with the OUT pin and the G pin of the processing chip U respectively, and a signal level modulation circuit serially connected between the CLK pin of the processing chip U and the linear isolation circuit. The rectangular wave modulation-type signal processing system for the electrolyzer anode current measurement device has the advantages that the design is reasonable; the overall structure is simple; the using effects are good; and accurate measurement on the current of an anode bar by the electrolyzer anode current measurement device can be well ensured.

Owner:SICHUAN HUASUO AUTOMATION INFORMATION ENGCO

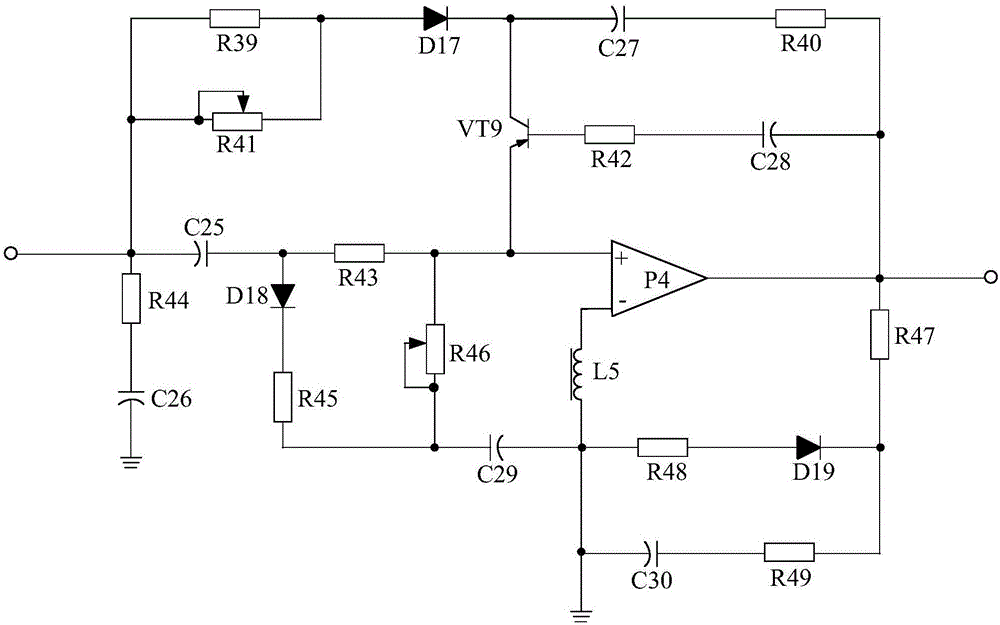

Harmonic suppression type signal processing system used for electrolytic-tank anode current measuring device

InactiveCN106249028AAccurate measurementReasonable designCurrent/voltage measurementElectrolysisMeasurement device

The invention discloses a harmonic suppression type signal processing system used for an electrolytic-tank anode current measuring device. The harmonic suppression type signal processing system is characterized by mainly comprising a processing chip U, a signal acquisition device JS, a triode VT4, a polarity capacitor C11, a diode D8, a phase-locked loop circuit serially connected between a COMP pin and a CS pin of the processing chip U, a second-order low-pass filtering circuit connected with the signal acquisition device JS, an emitter coupling logic circuit serially connected between the second-order low-pass filtering circuit and the processing chip U, a signal conditioning circuit serially connected between the emitter coupling logic circuit and an IN pin of the processing chip U, and a linear isolating circuit connected with an OUT pin, a G pin and a CLK pin of the processing chip U. The harmonic suppression type signal processing system has the advantages of reasonable design, simple overall structure and good using effect, and can ensure accurate measurement of the current of an anode rod of the electrolytic-tank anode current measuring device.

Owner:SICHUAN HUASUO AUTOMATION INFORMATION ENGCO

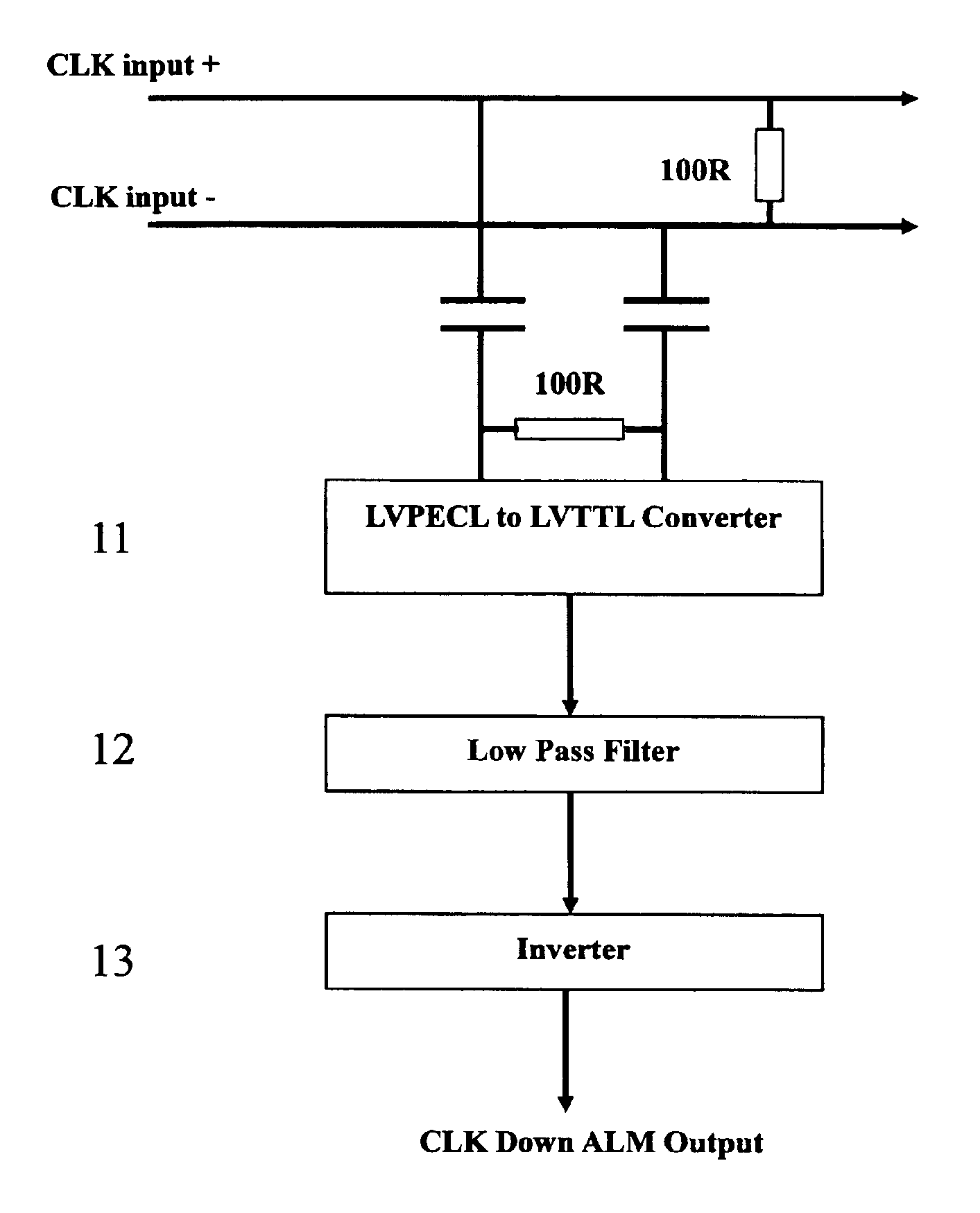

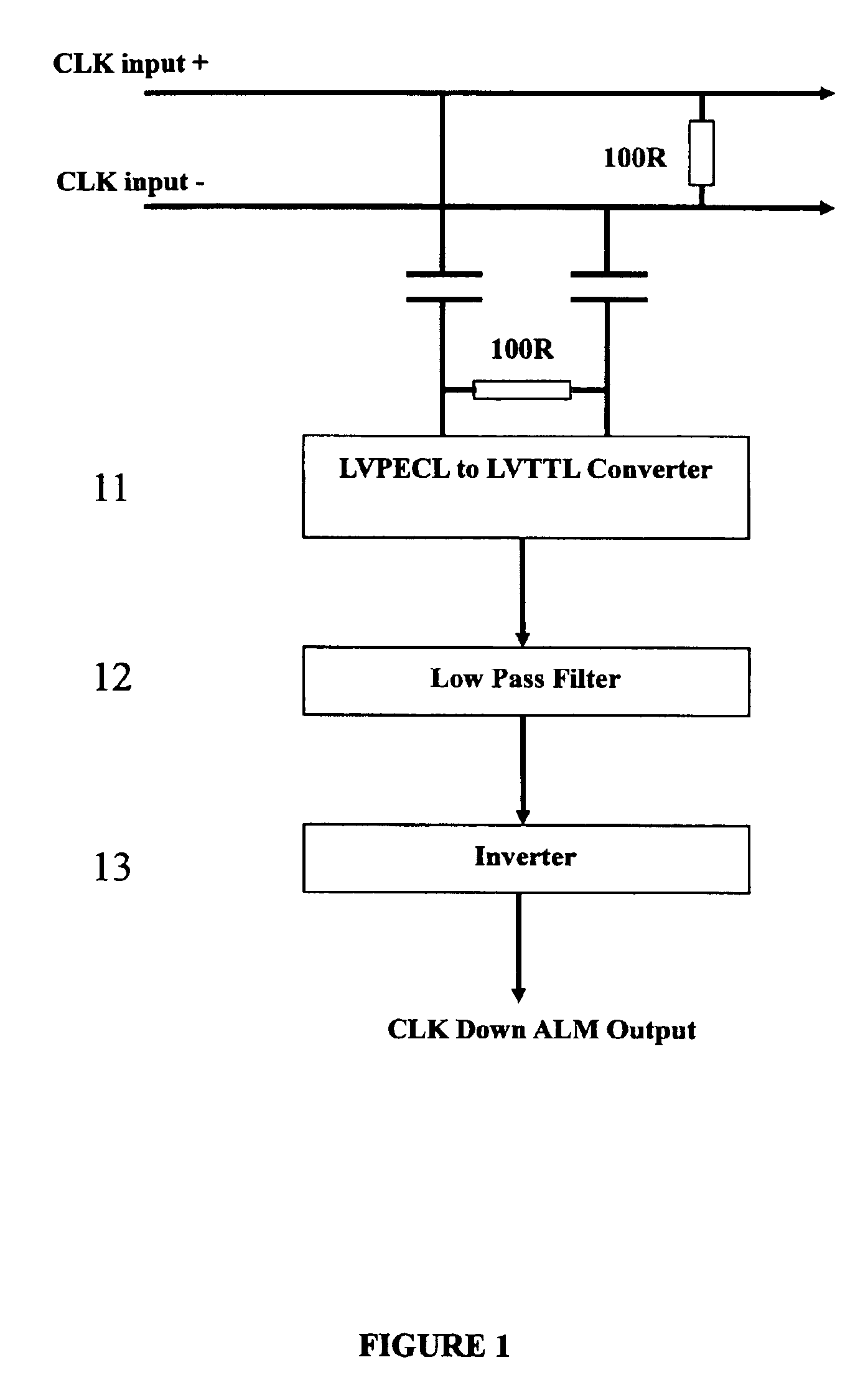

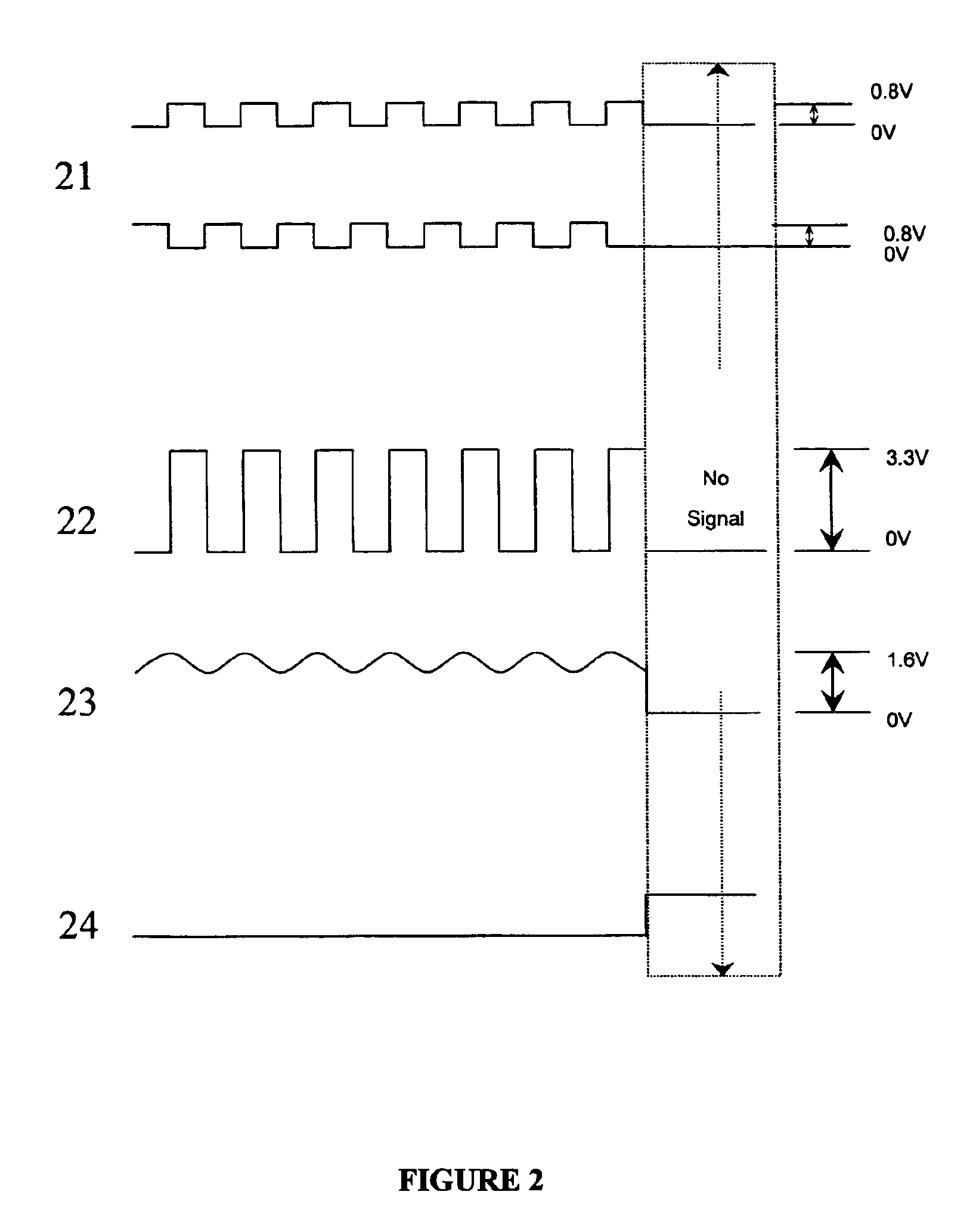

Clock down sensor

InactiveUS6919741B2Pulse train pattern monitoringGenerating/distributing signalsTransistor–transistor logicLow-pass filter

A clock down sensor mainly comprises a converter and a low-pass filter. The converter is used to convert an input signal from a PECL (Positive Emitter Coupling Logic) signal to a TTL (Transistor Transistor Logic) signal, the low pass filter is used to obtain a DC (Direct Current) level of the TTL signal. Thereby, the sensor can judge whether the clock signal is terminated according to the potential of the output signal in order to emit a warning so that a breakdown elimination inquiry can be done or automatic breakdown elimination can be processed earlier.

Owner:ASIA OPTICAL INT LTD

Programmable ECL (emitter coupled logic) device based high-frequency phase shift signal generation circuit

InactiveCN102664625BSimple design principleReduce volumePulse automatic controlProgrammable logic deviceSoftware engineering

The invention discloses a programmable ECL (emitter coupled logic) device based a high-frequency phase shift signal generation circuit. The existing high-frequency signal generator is expensive and the hardware circuit is complex. The programmable ECL device based a high-frequency phase shift signal generation circuit provided by the invention comprises a rapid comparator, a PLL (phase locking loop) frequency multiplier, an ECL signal clock distributor, a pulse suppressor, a first digital frequency divider and a second digital frequency divider; the rapid comparator converts an external clock signal into a square wave signal; the PLL frequency multiplier performs frequency multiplying on the square wave signal; the ECL signal clock distributor distributes the frequency multiplying signal to two ways, one way of the frequency multiplying signal is directly subjected to frequency division through the first digital frequency divider, and the other way of frequency multiplying signal is subjected to frequency division by the second digital frequency divider after the pulse suppressor suppresses a phase shift of 2pi; the frequency dividing multiple of the first digital frequency divider and the second digital frequency divider is respectively 2, and the output signal of the first digital frequency divider has the phase shift as shown in the specification relative to the output signal of the second digital frequency divider. According to the invention, the circuit design principle is simple, and the duplicability is high.

Owner:CHINA JILIANG UNIV

Universal positive emitter coupling logic/low voltage differential command output structure

InactiveCN1246964CLogic circuits coupling/interface using field-effect transistorsCMOSSystems design

The invention implements a Positive Emitter Coupled Logic (PECL) output using CMOS transistors that approximate the Motorola ECL characteristics into standard PECL termination schemes. By creating a PECL output using a switchable current source the PECL output can be integrated into a Low Voltage Differential Signaling (LVDS) structure. The invention allows the user to switch between PECL and LVDS outputs via control logic by enabling the specific circuit elements for each signaling technology. With this invention, the combination of two drivers on one IC device gives system designers the flexibility to use the same circuitry in two separate signaling schemes. Thus, the designers can select to use one output characteristics or the other for their designs.

Owner:NXP BV

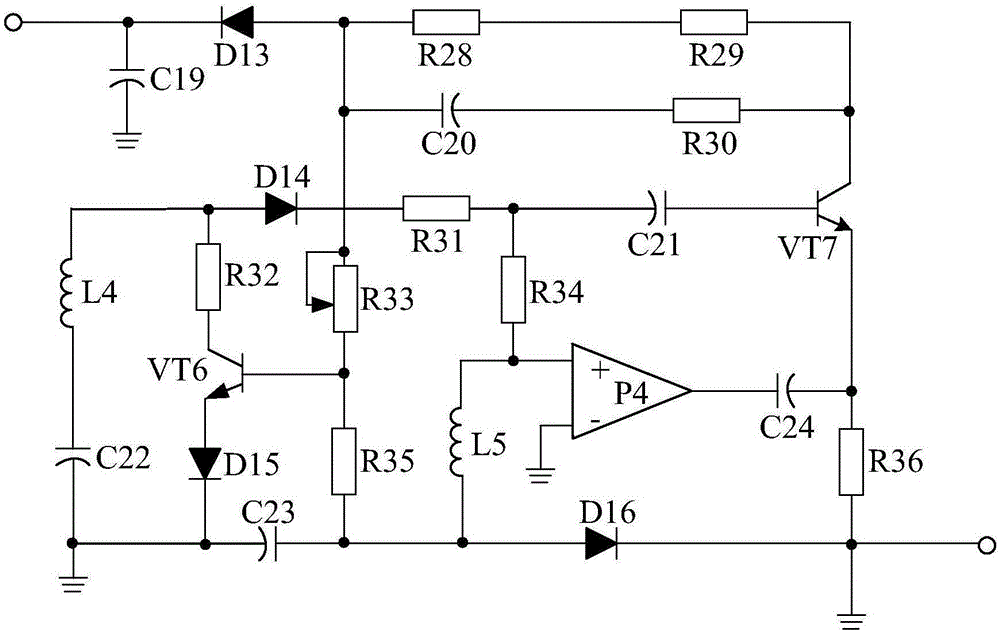

Signal conditioning type processing system for electrolytic tank anode current measurement apparatus

InactiveCN106291059AAccurate measurementReasonable designCurrent measurements onlySignal conditioning circuitsMeasurement device

The invention discloses a signal conditioning type processing system for an electrolytic tank anode current measurement apparatus. The system is characterized by mainly consisting of a processing chip U, a signal gatherer JS, a triode VT4, a polar capacitor C11, a diode D8, a second-order low-pass filtering circuit connected with the signal gatherer JS, an emitter coupled logic circuit connected in series between the second-order low-pass filtering circuit and the processing chip U, a signal conditioning circuit connected in series between the emitter coupled logic circuit and the IN pin of the processing chip U, and a linear isolation circuit connected with the OUT pin, the G pin and the CLK pin of the processing chip U. The design is reasonable, the overall structure is simple, the application effect is good, and it can be well ensured that the electrolytic tank anode current measurement apparatus measures currents of an anode bar accurately.

Owner:SICHUAN HUASUO AUTOMATION INFORMATION ENGCO