Patents

Literature

159 results about "Retiming" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

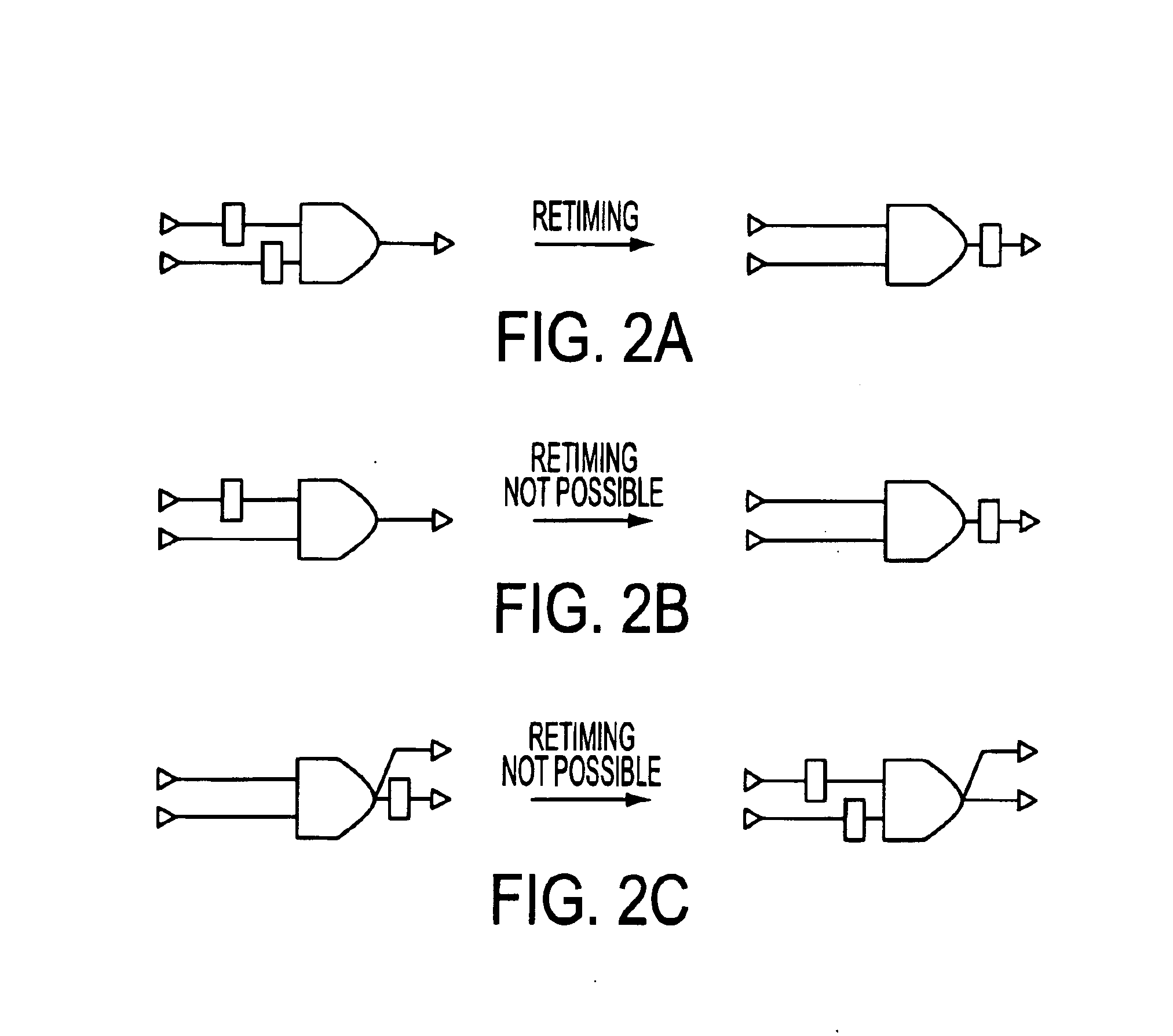

Retiming is the technique of moving the structural location of latches or registers in a digital circuit to improve its performance, area, and/or power characteristics in such a way that preserves its functional behavior at its outputs. Retiming was first described by Charles E. Leiserson and James B. Saxe in 1983.

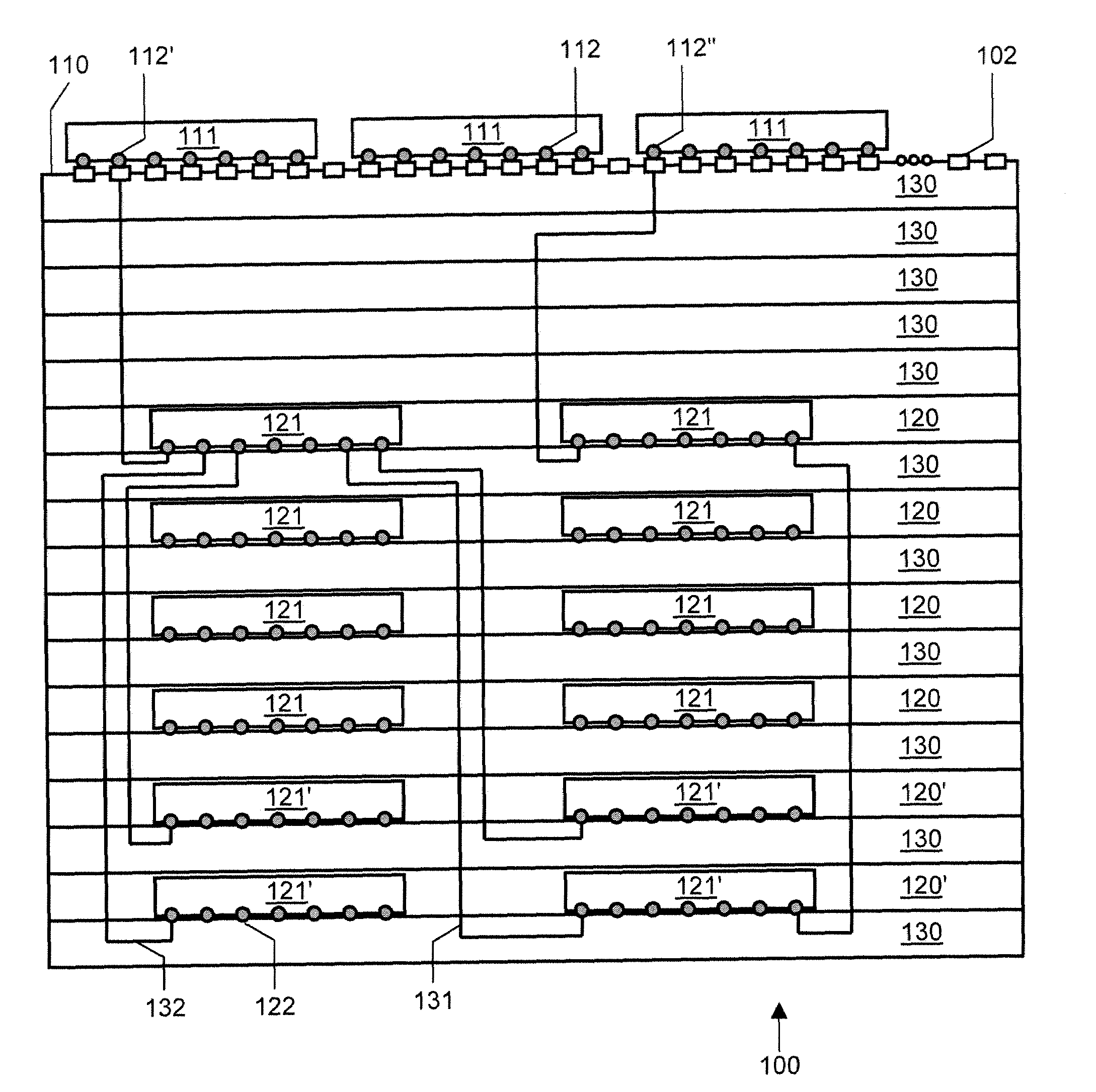

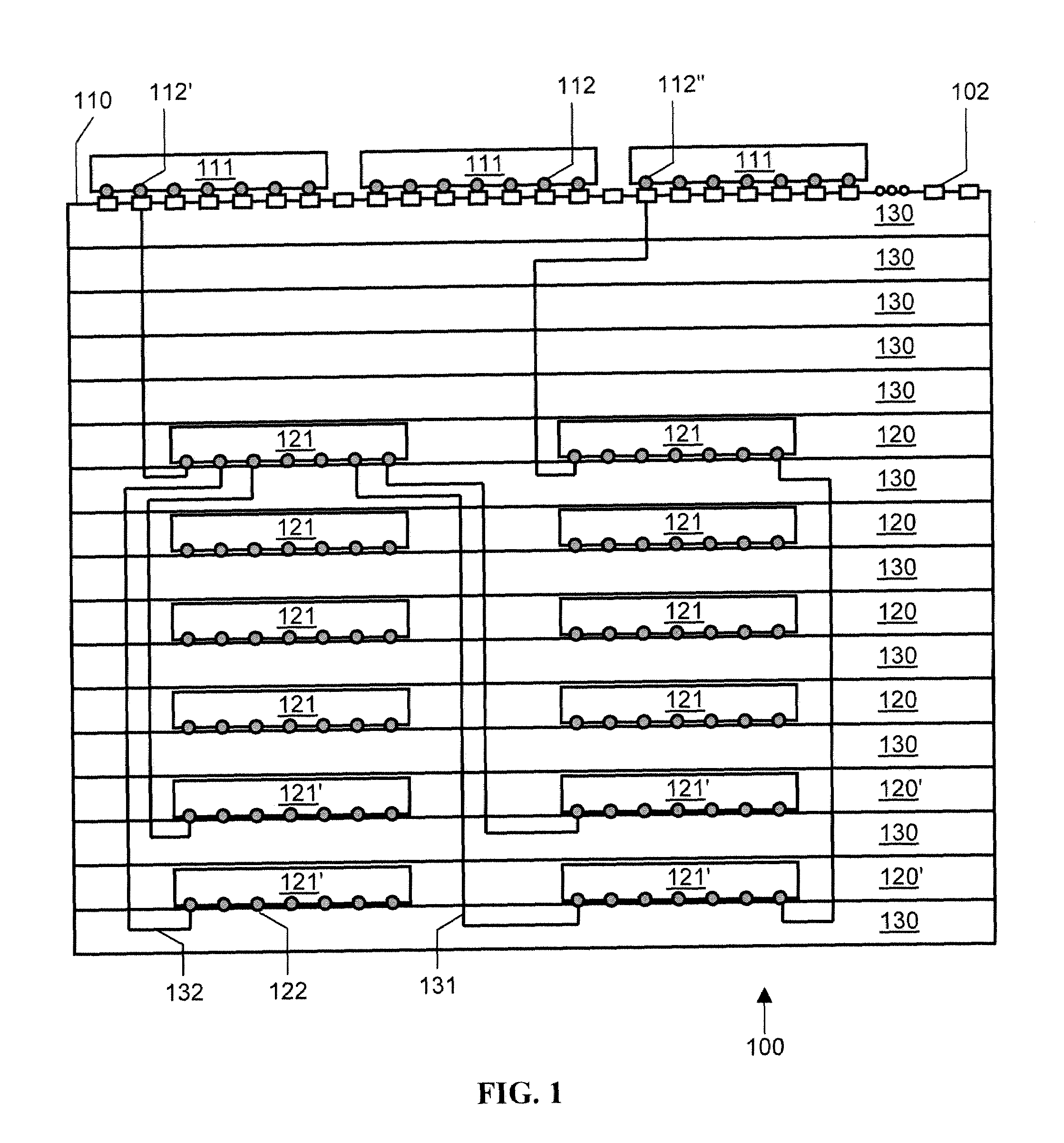

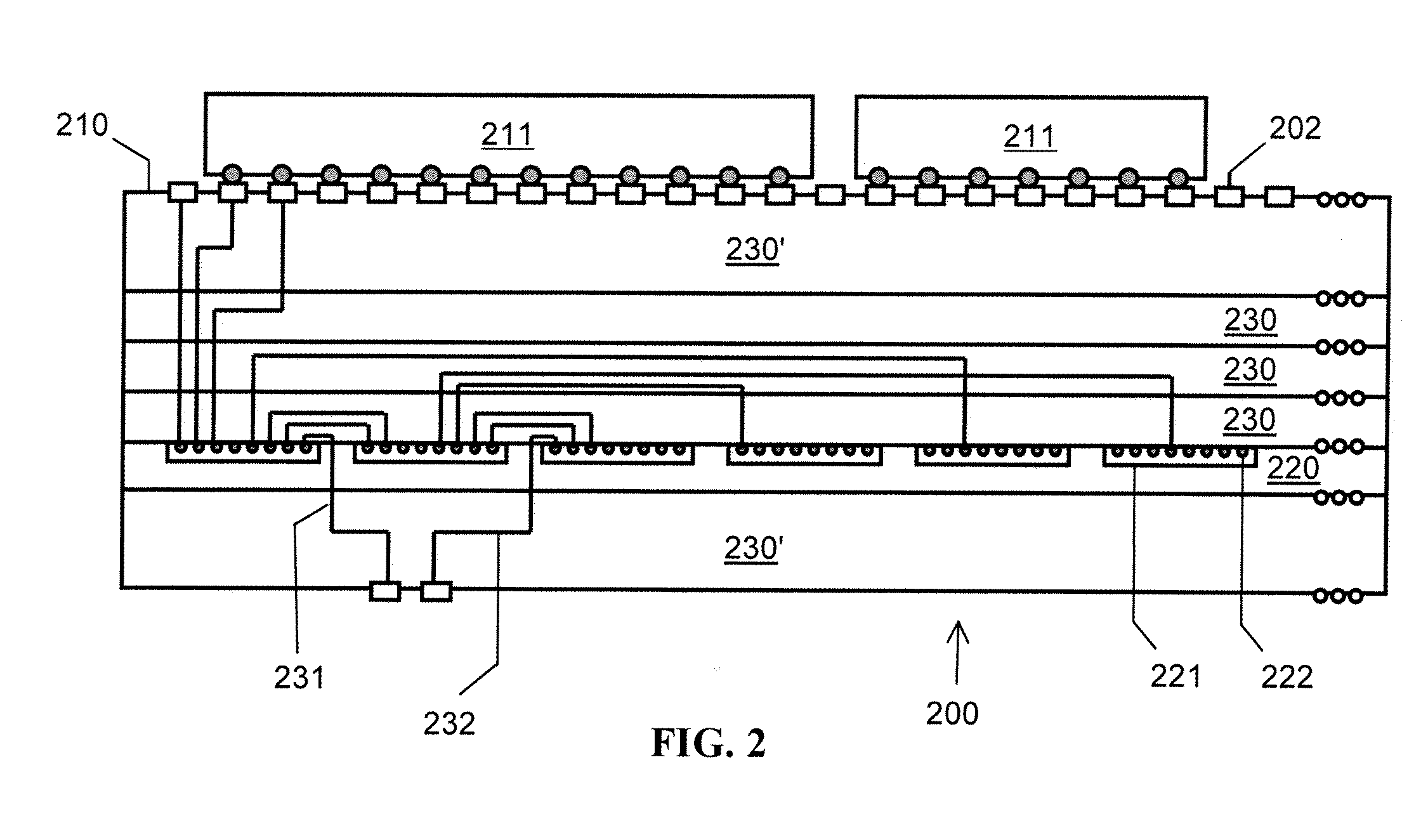

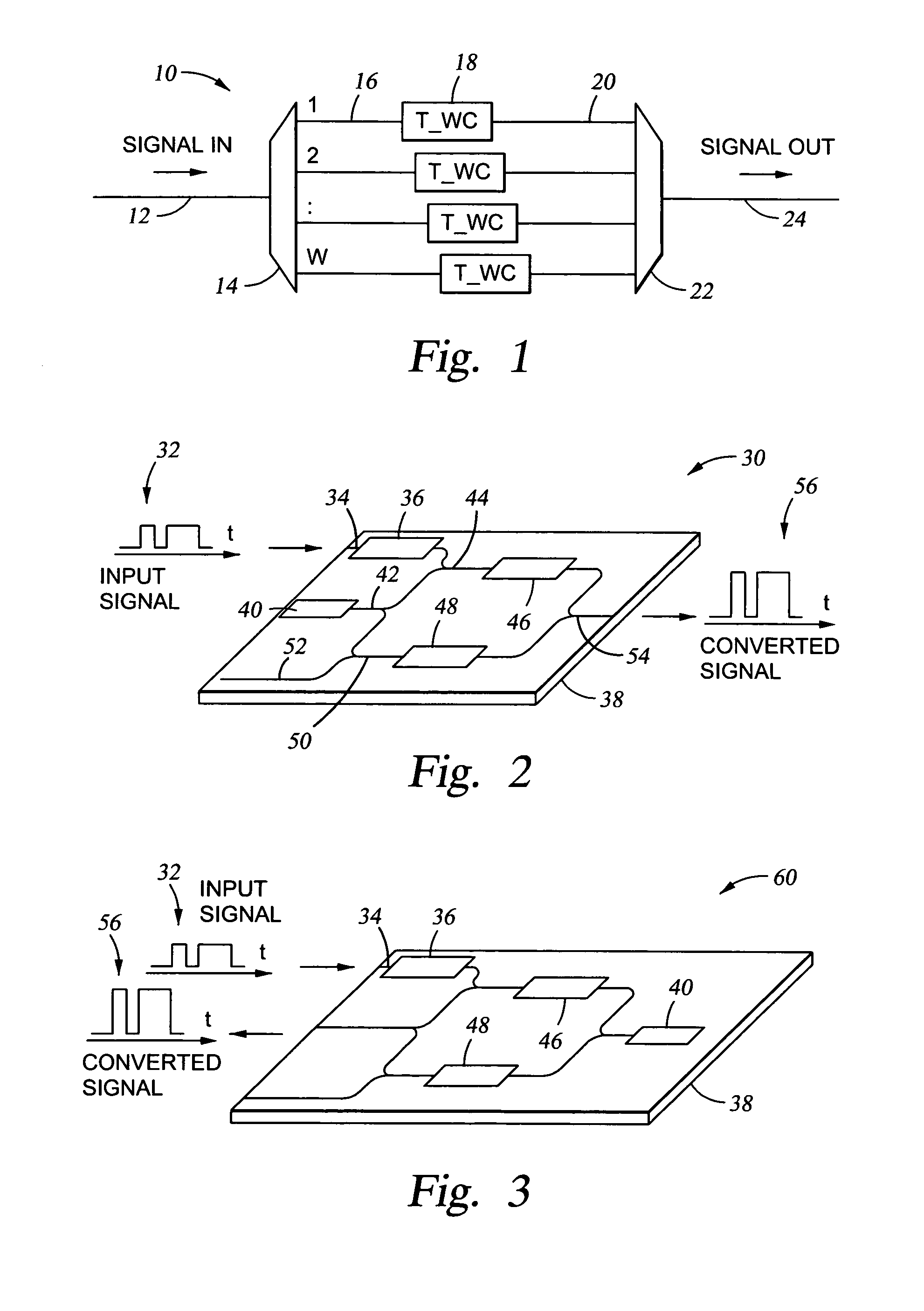

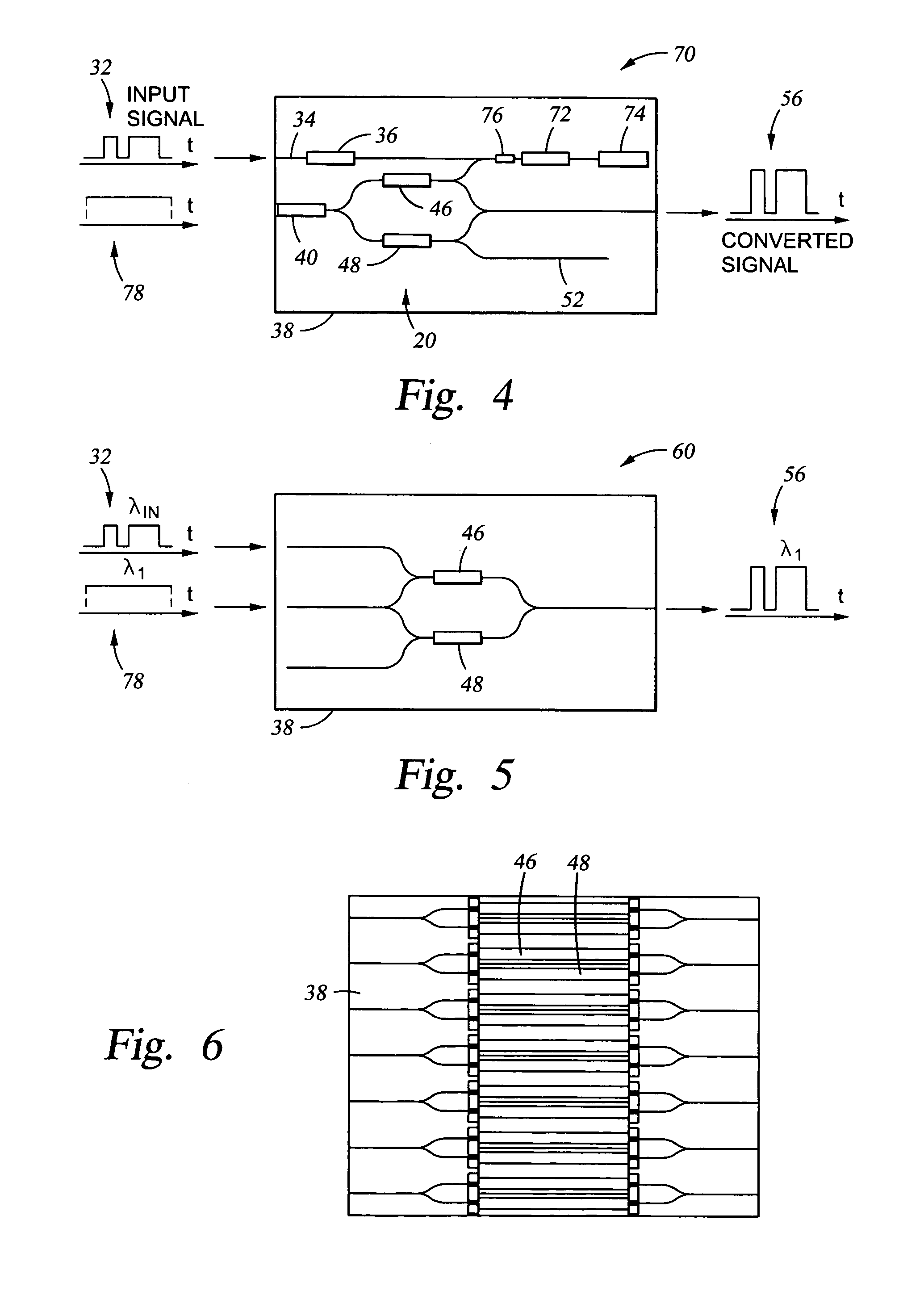

Reprogrammable circuit board with alignment-insensitive support for multiple component contact types

InactiveUS20080143379A1Semiconductor/solid-state device testing/measurementWave amplification devicesSignal conditioningContact type

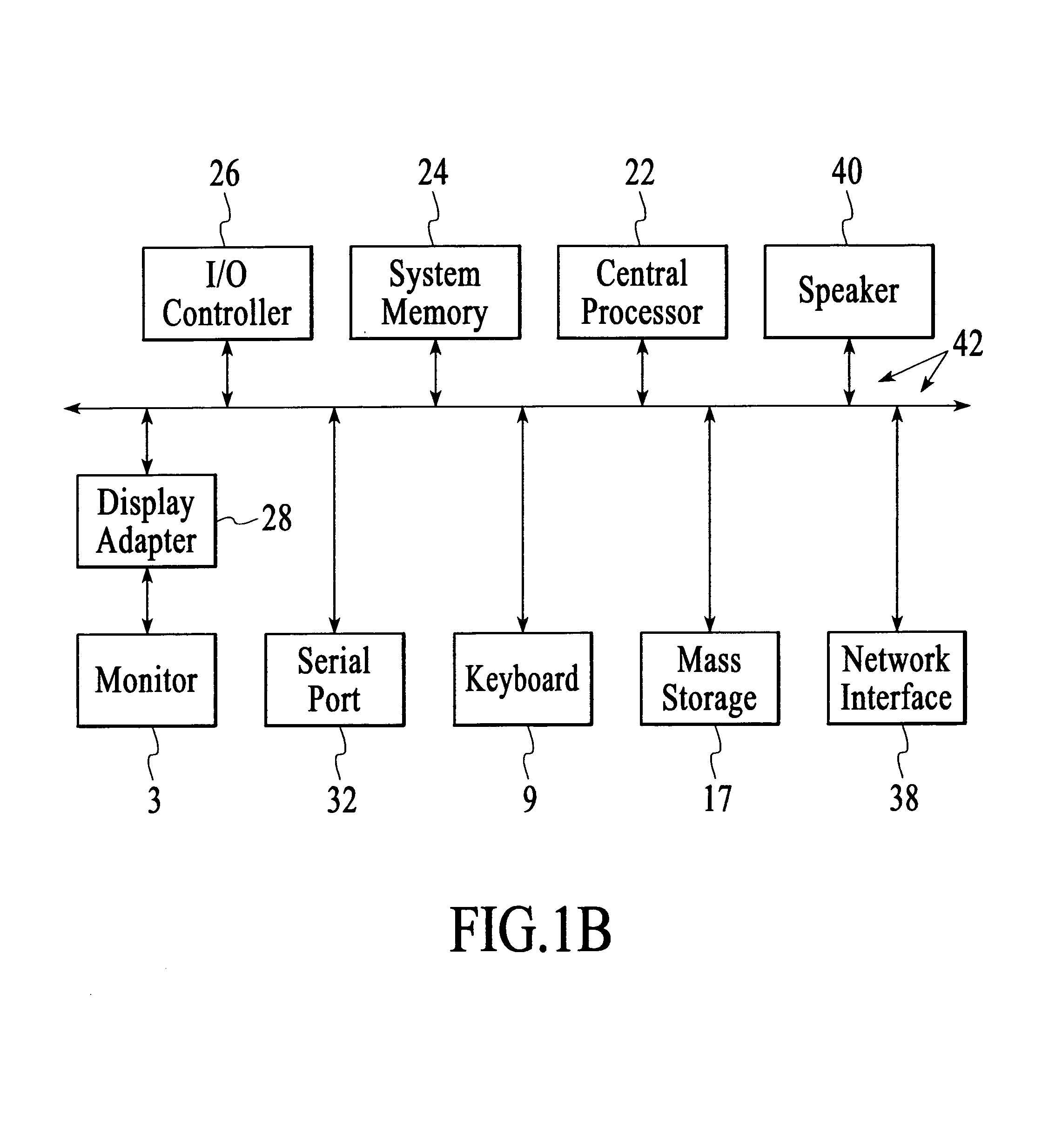

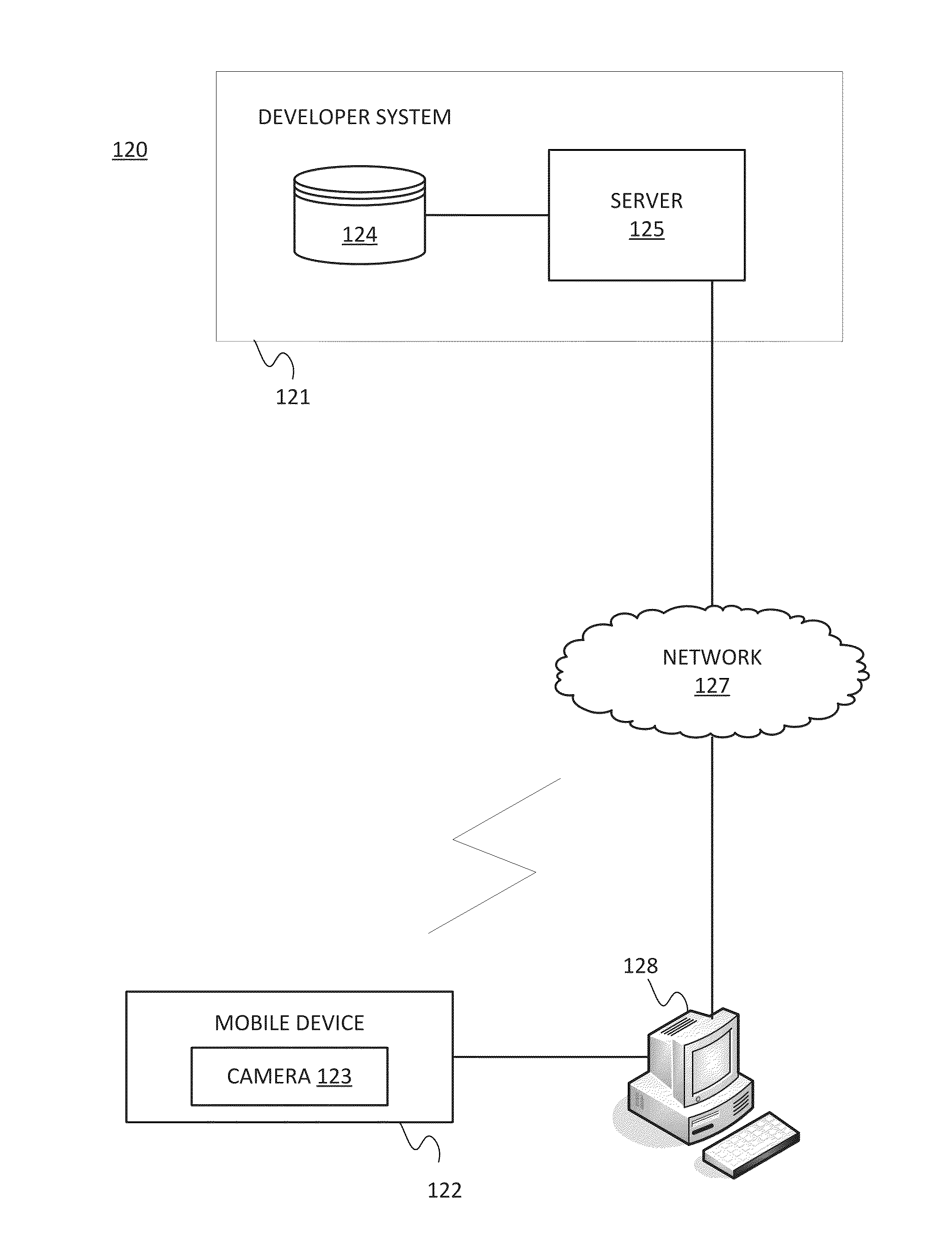

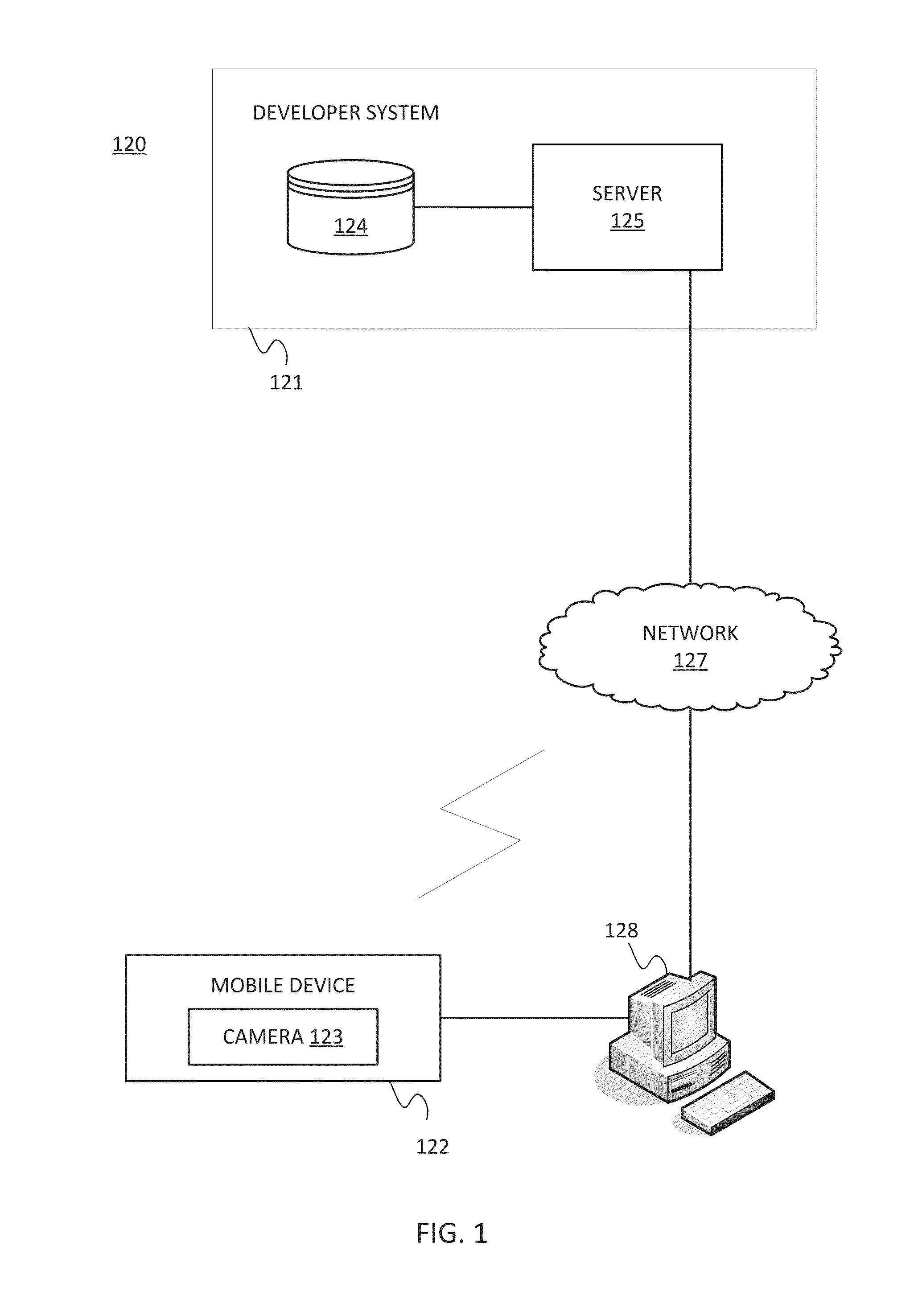

The present invention is directed to a system that programmably interconnects integrated circuit chips and other components at near-intra-chip density. The system's contact structure allows it to adapt to components with a wide variety of contact spacings and interconnection requirements, the use of releasable attachment means allows component placement to be modified as needed, the system identifies the contacts and the components to facilitate specifying the inter-component connections, and the system provides signal conditioning and retiming to minimize issues with signal integrity and signal skew.

Owner:NORMAN RICHARD

Register retiming technique

InactiveUS7120883B1High frequencySimple designCAD circuit designSoftware simulation/interpretation/emulationTrade offsEmbedded system

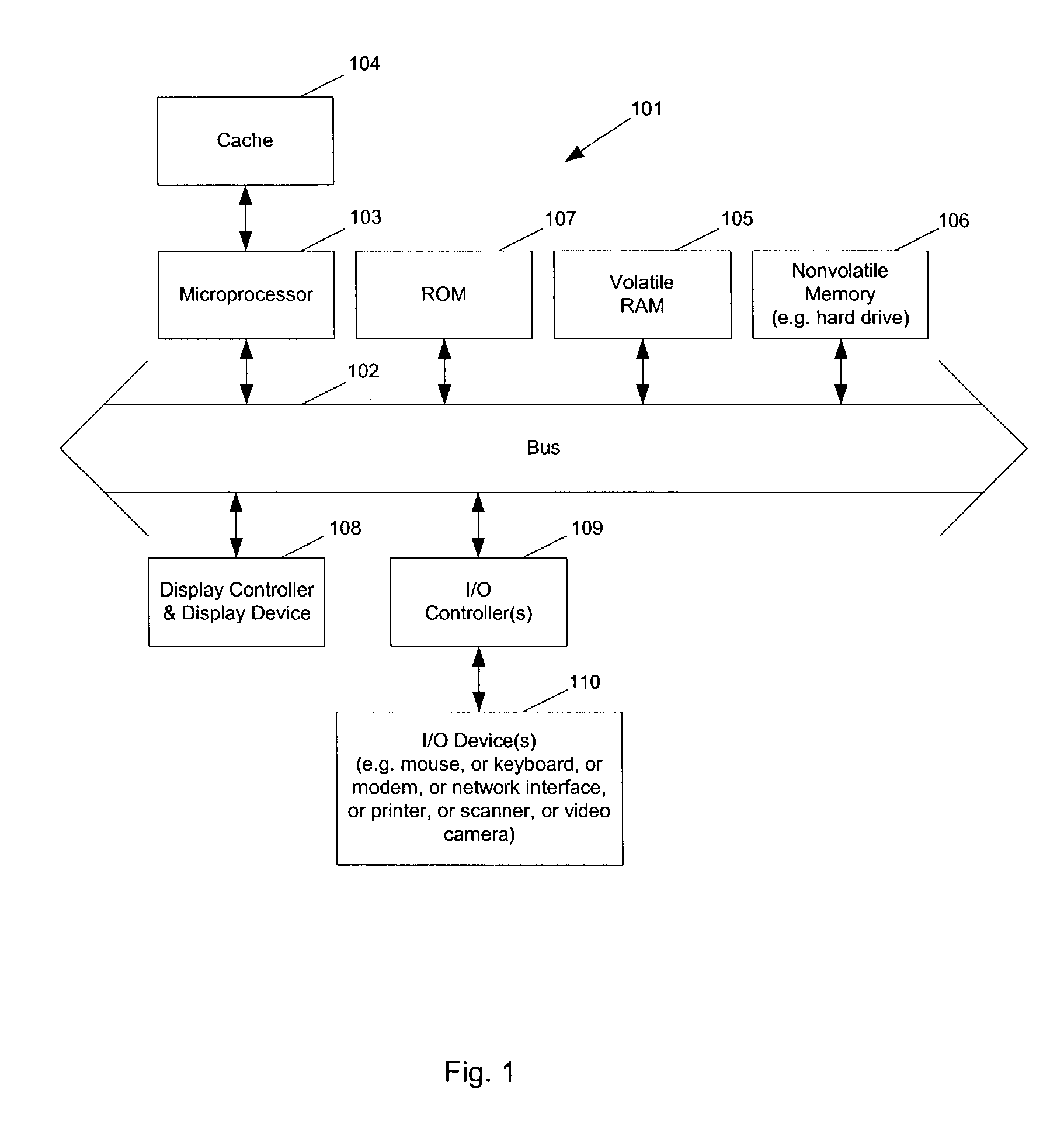

An electronic automation system performs register retiming on a logic design, which may be a logic design for a programmable logic integrated circuit. Register retiming is a moving or rearranging of registers across combinatorial logic in a design in order to improve a maximum operating frequency or fmax. In one implementation, the system includes machine-readable code, which may be stored on a computer-readable medium such as a disk, executing on a computer. The system balances timing in order to trade off delays between critical and noncritical paths. Register retiming may make changes to a design at a gate level.

Owner:ALTERA CORP

Computer system with a semi-differential bus signaling scheme

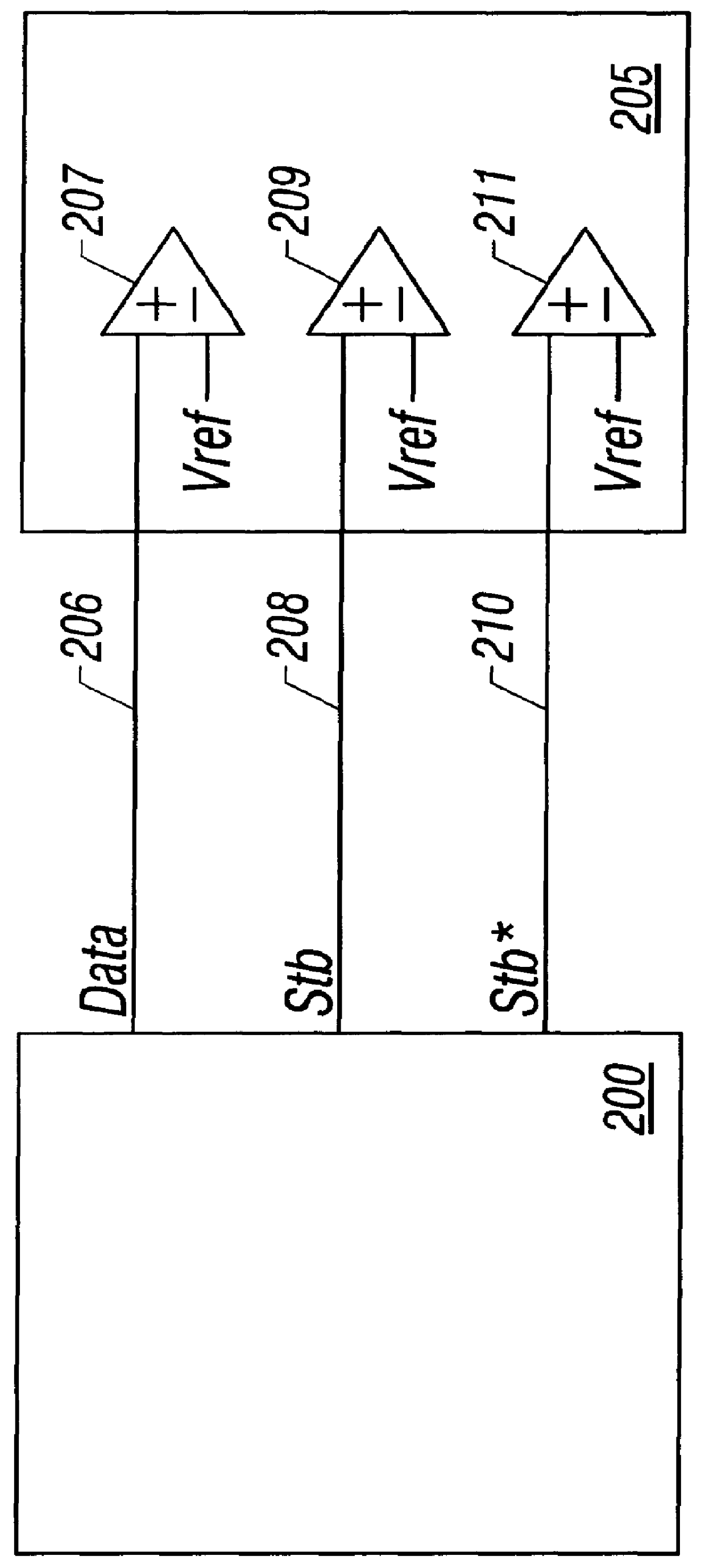

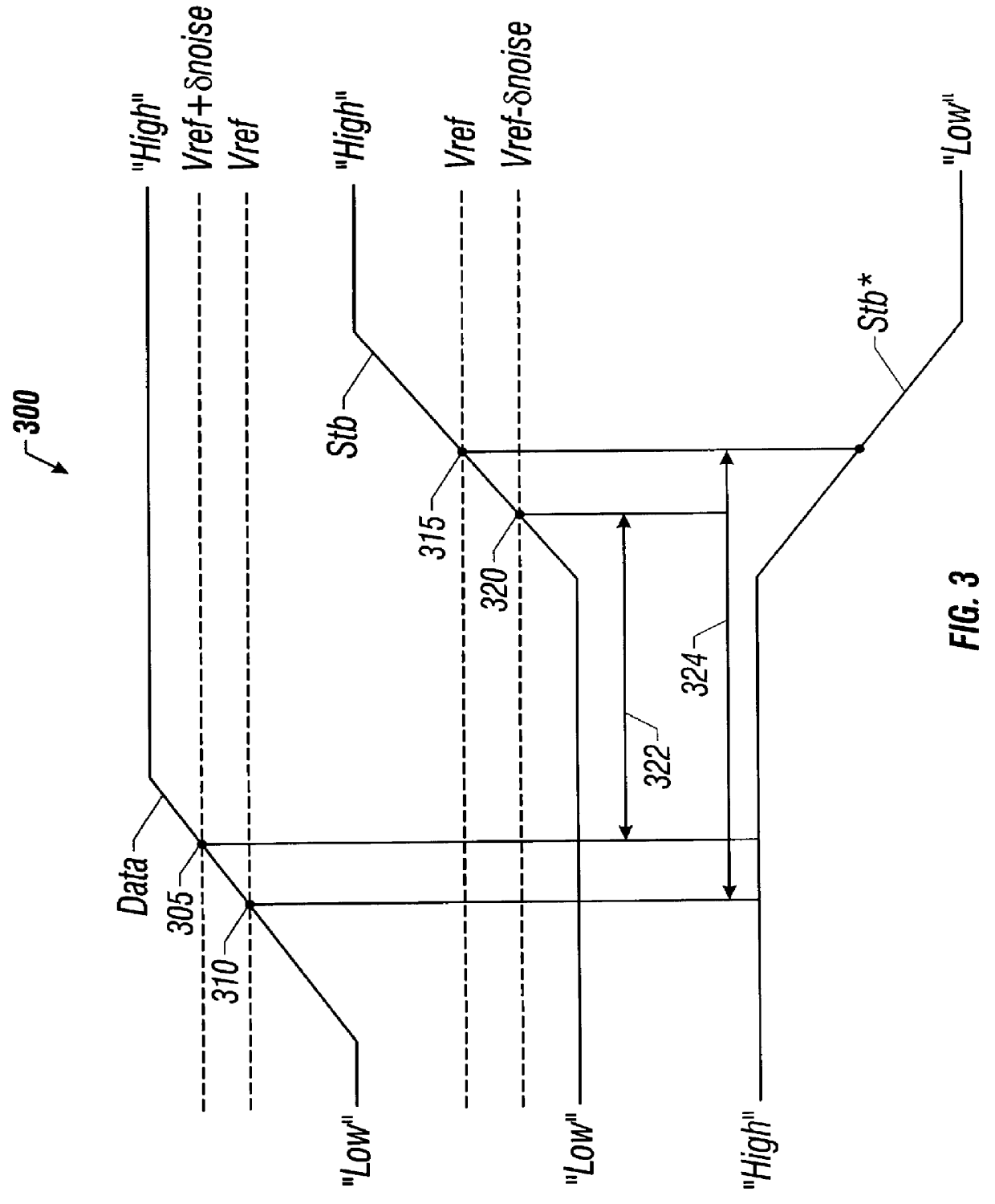

A computer system with a semi-differential bus-signaling scheme is described. The computer system includes a transmitter coupled to a common bus. The transmitter sends clock signals and a data signal to logic-comparing devices within a receiver. The logic-comparing devices compare the data signal to a reference voltage while comparing the clock signals to each other. After the comparison, the clock signals can be used to capture the data into a retiming circuit.

Owner:INTEL CORP

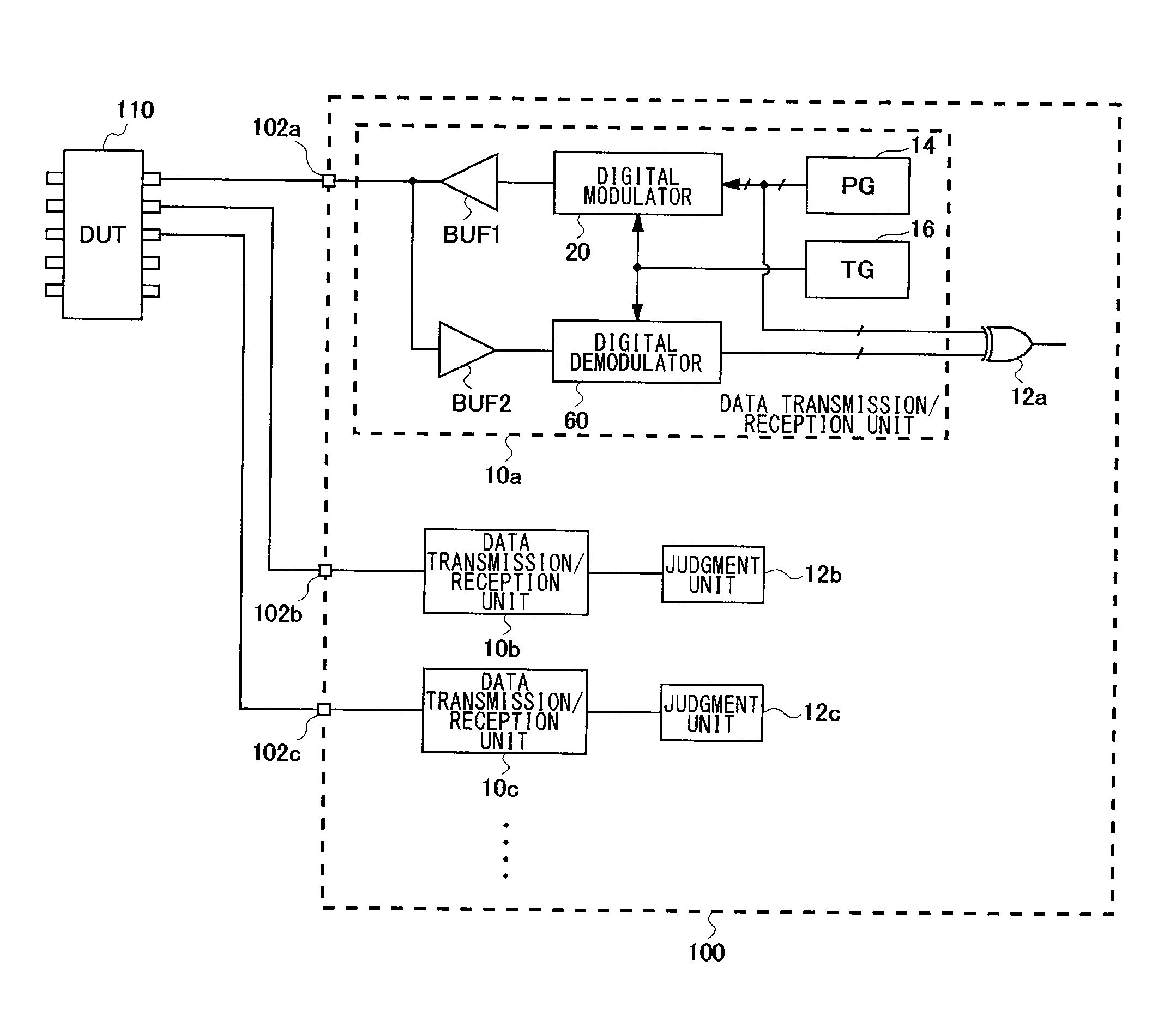

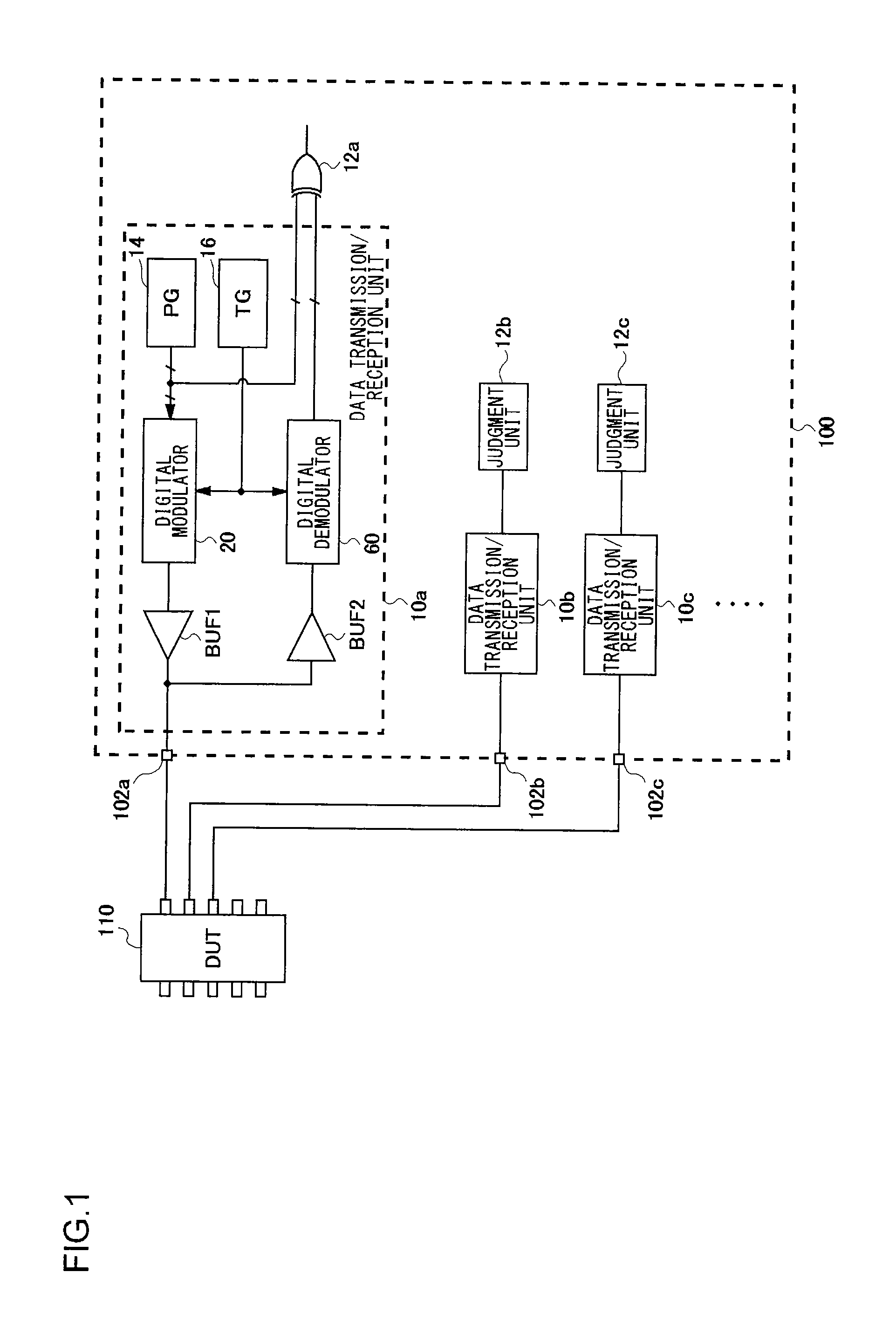

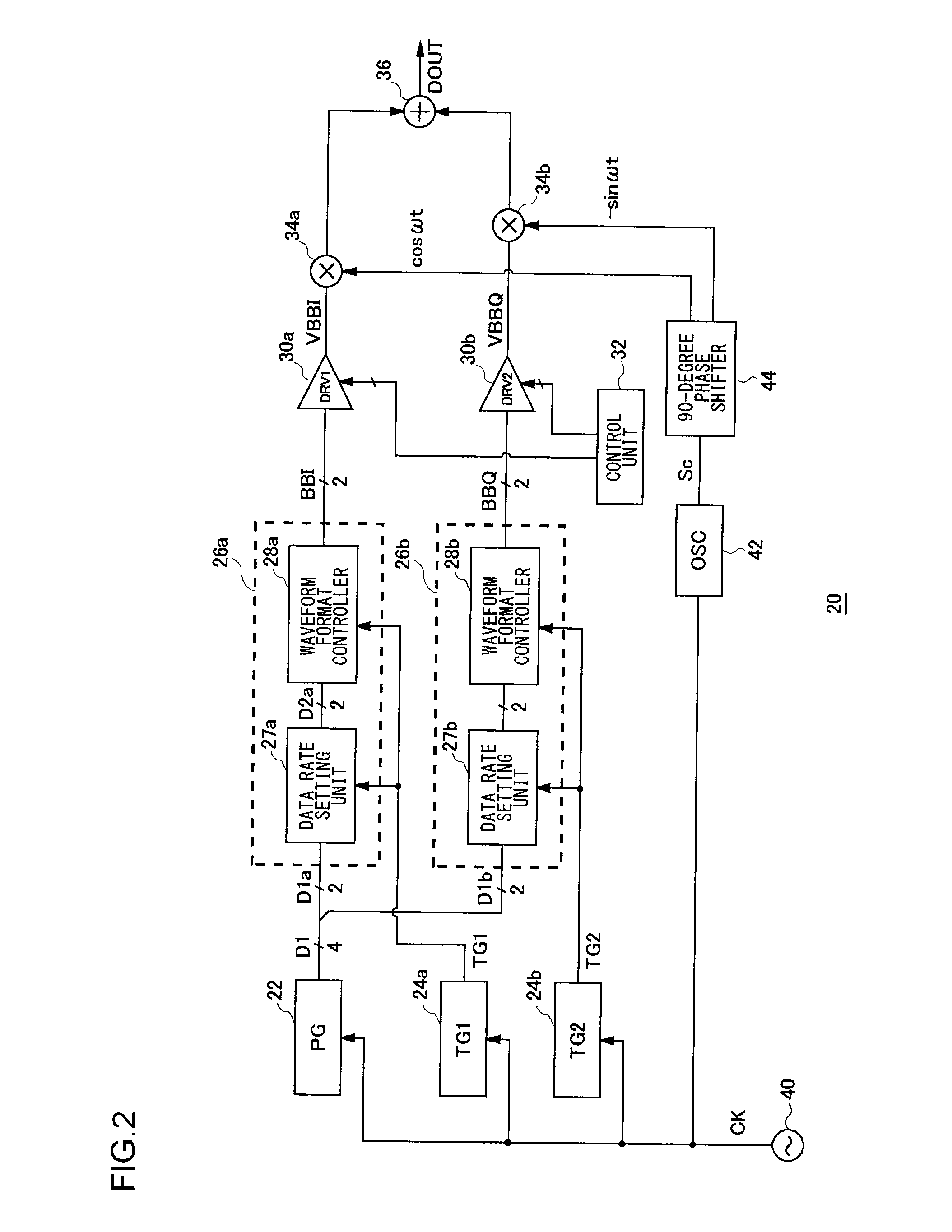

Test apparatus for digital modulated signal

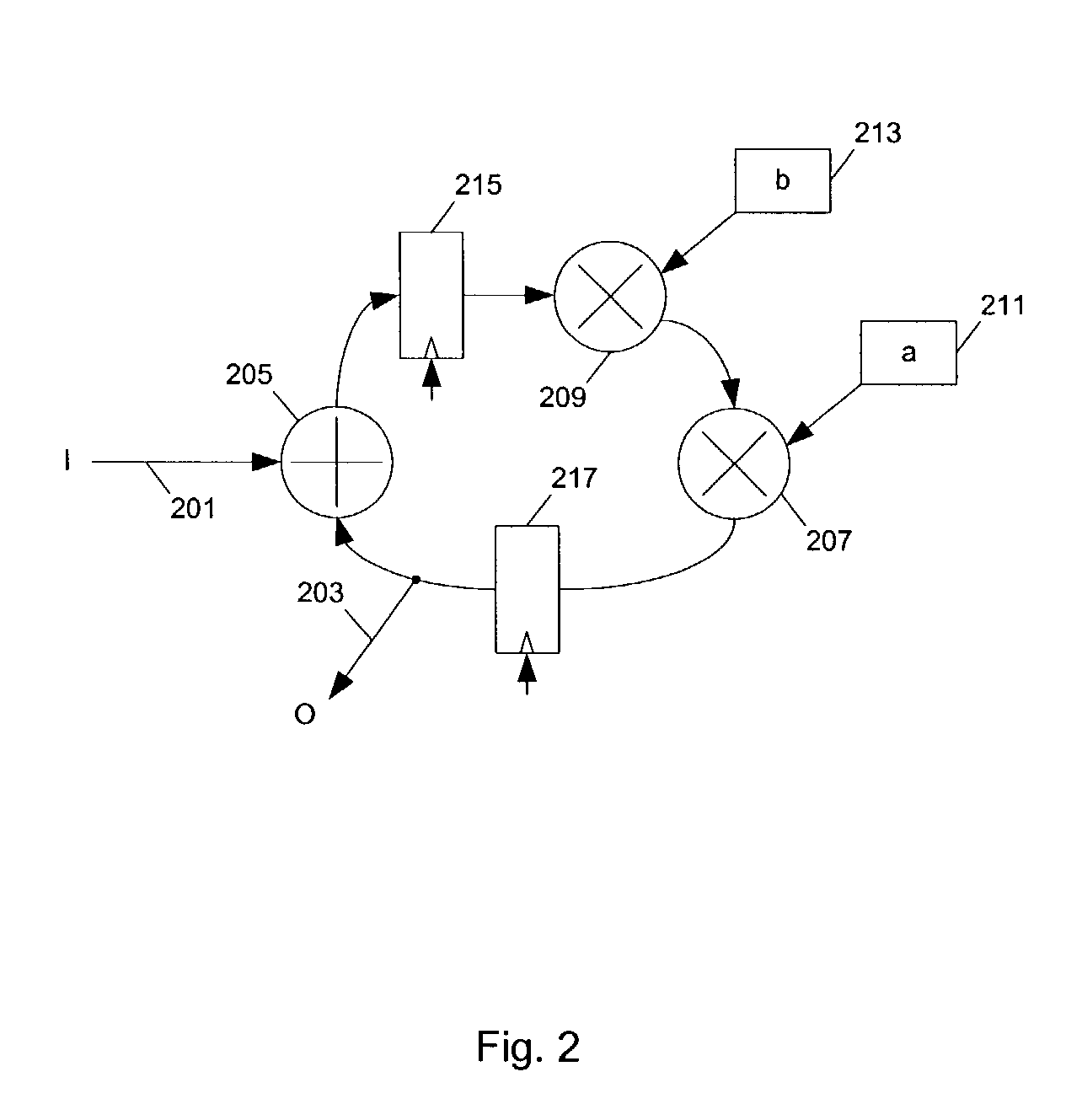

ActiveUS20100321127A1Reduce circuit sizeCalibrating non-linear distortionElectrical testingAngle modulationBinary multiplierCarrier signal

A test apparatus includes digital modulators provided in increments of multiple channels. A baseband signal generator performs retiming of data input as a modulation signal for the in-phase (quadrature) component, using a timing signal the timing of which can be adjusted, thereby generating a baseband signal. A driver generates a multi-value digital signal having a level that corresponds to the baseband signal output from the baseband signal generator. A multiplier amplitude-modulates a carrier signal with the multi-value digital signal. An adder sums the output signals of the multipliers.

Owner:ADVANTEST CORP

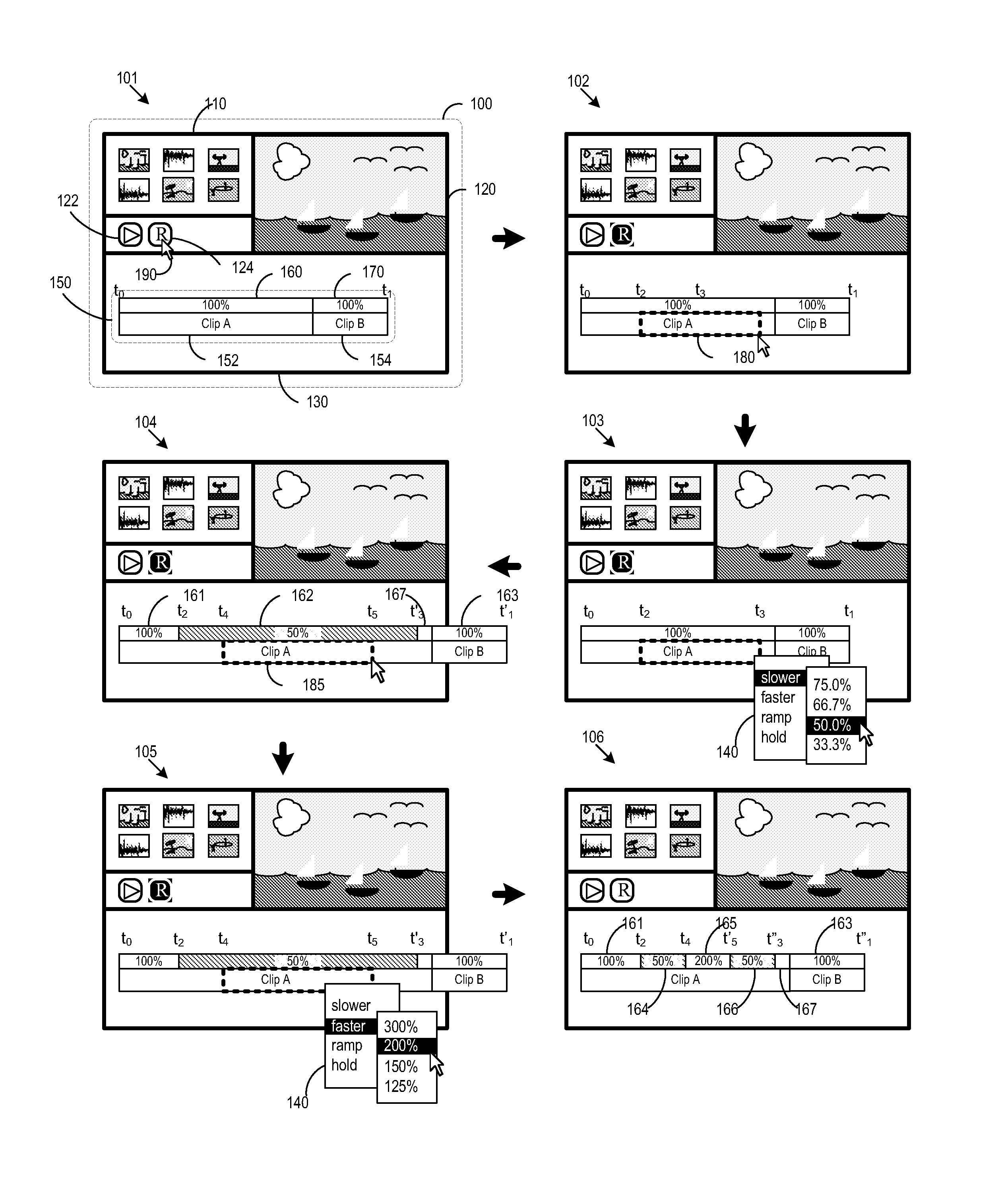

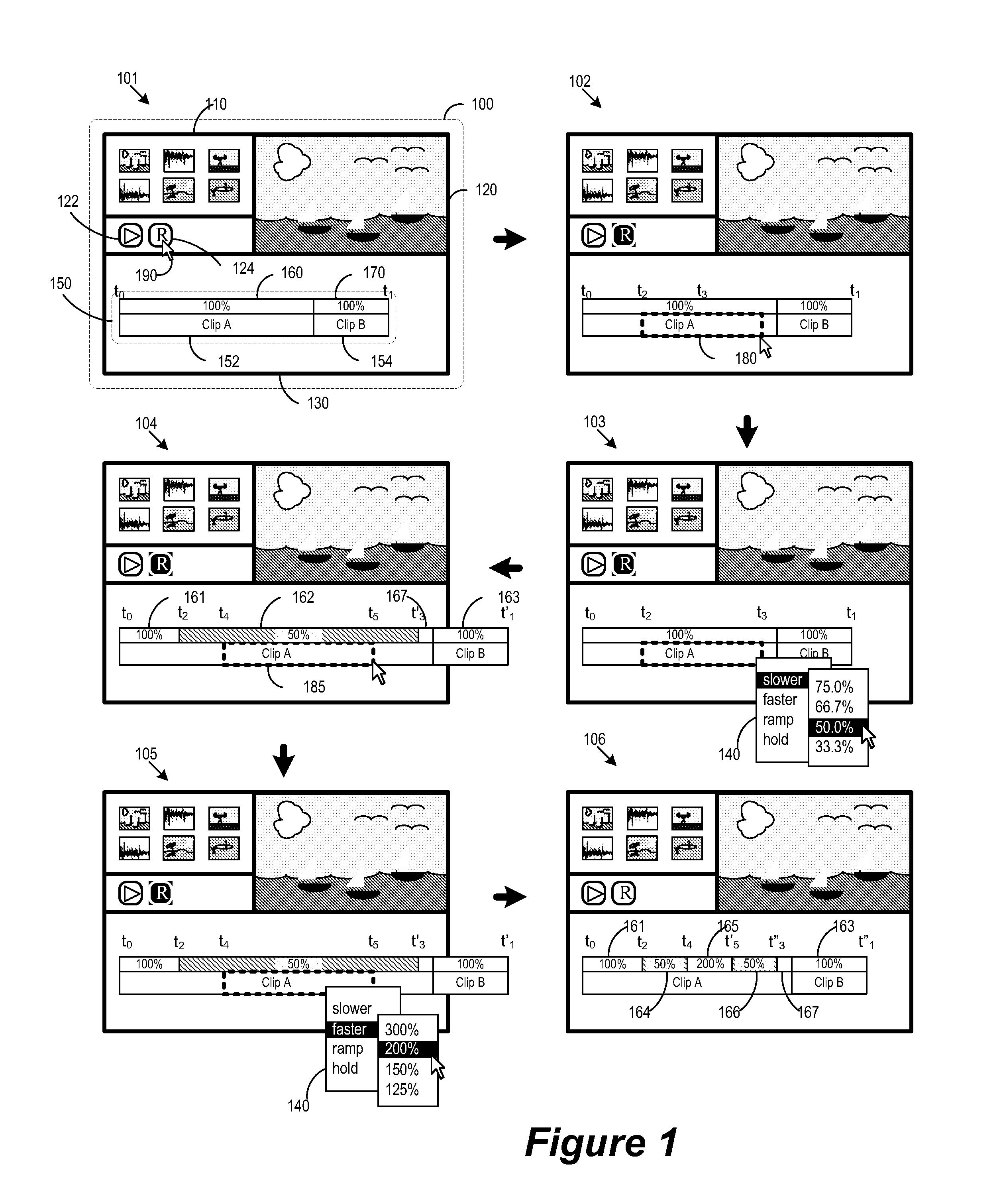

Retiming media presentations

ActiveUS20120210228A1Quick effectFaster rateVideo data browsing/visualisationElectronic editing digitised analogue information signalsComputer graphics (images)Slow speed

A novel method for retiming a portion of a media content (e.g., audio data, video data, audio and video data, etc.) in a media-editing application is provided. The media editing application includes a user interface for defining a range in order to select a portion of the media content. The media editing application performs retiming by applying a speed effect to the portion of the media content selected by the defined range. For a faster speed effect, the media editing application retimes the selected portion of the media content by sampling the media content at a faster rate. For a slower speed effect, the media editing application retimes the selected portion of the media content by sampling the content at a slower rate.

Owner:APPLE INC

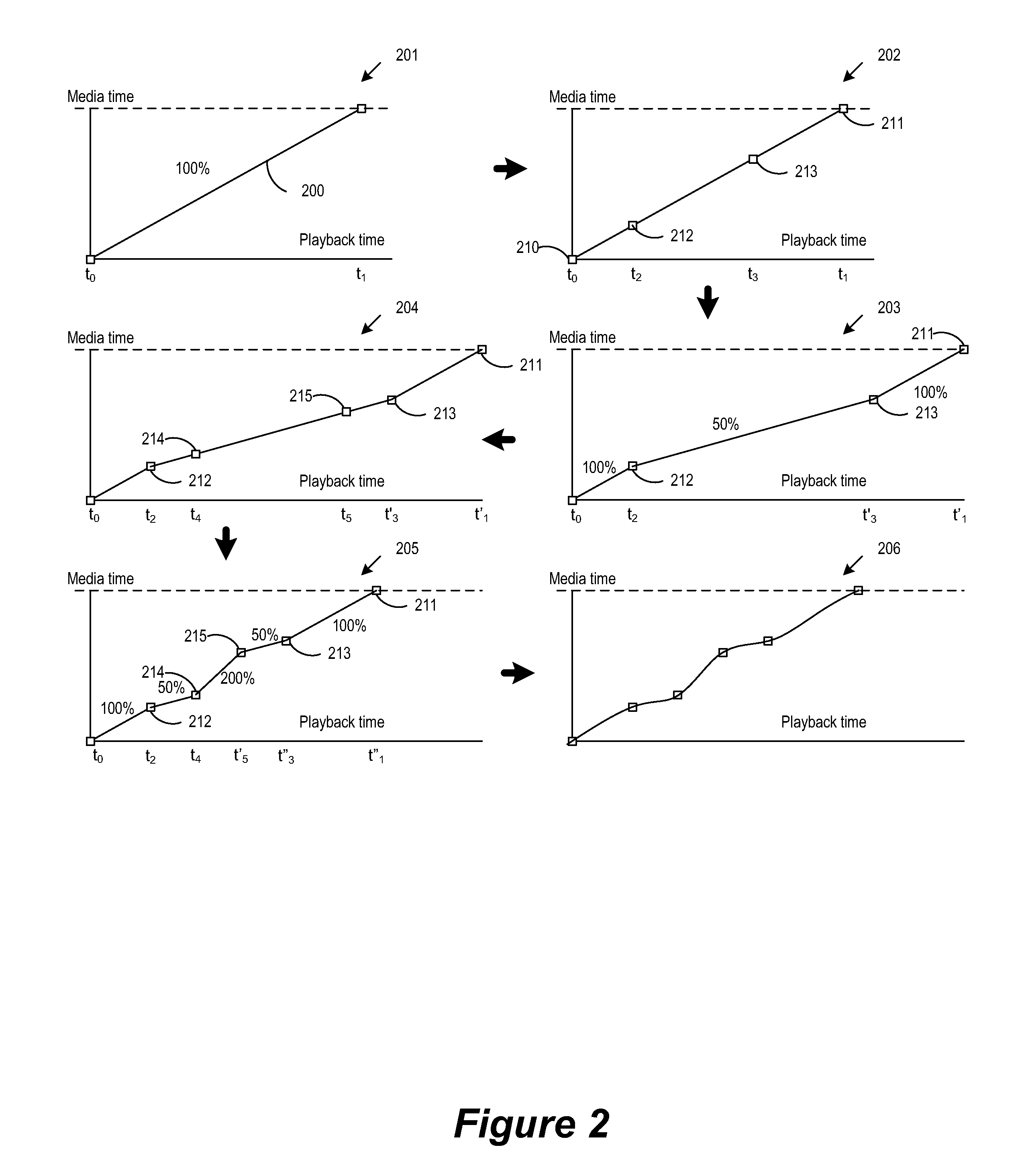

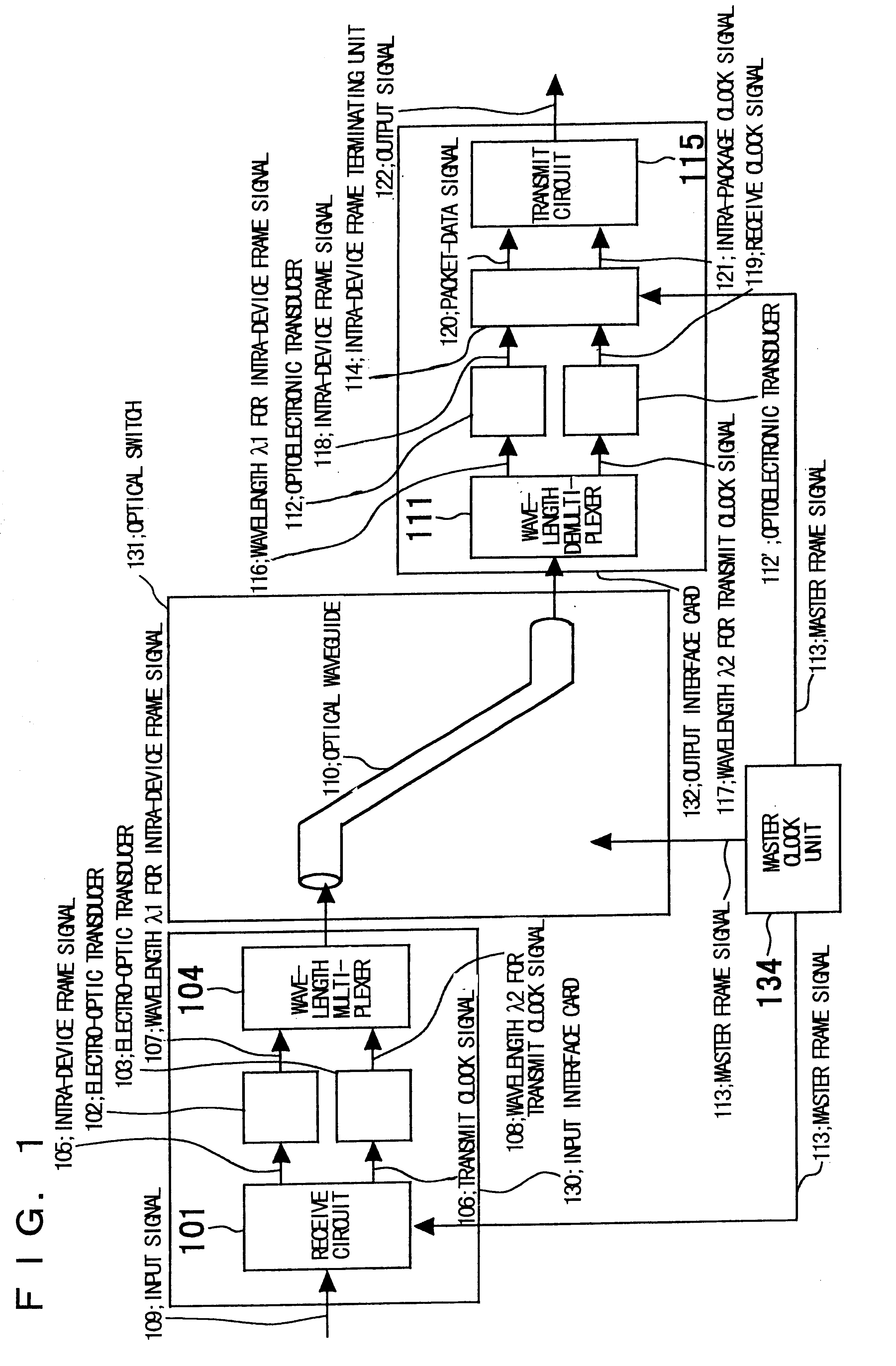

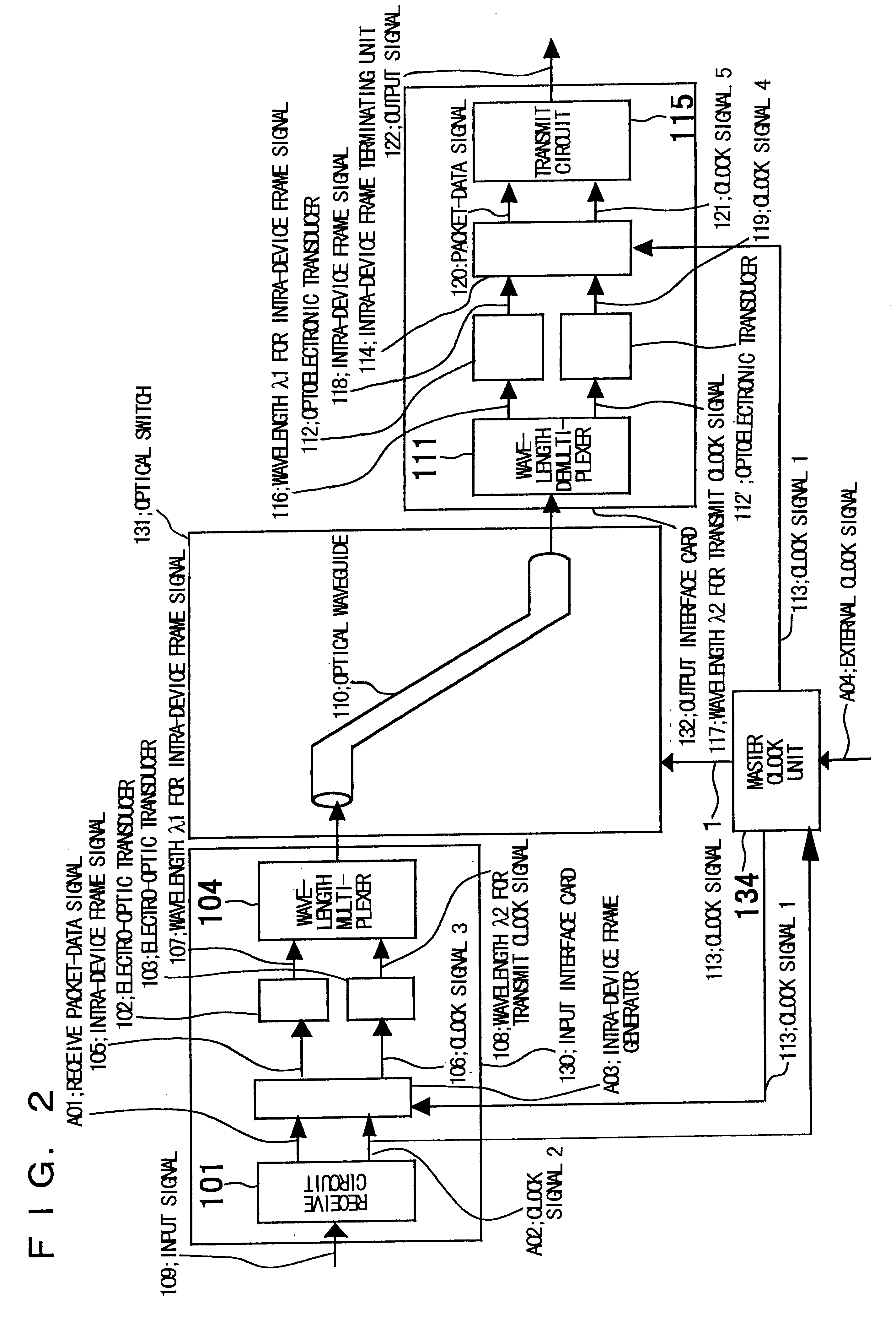

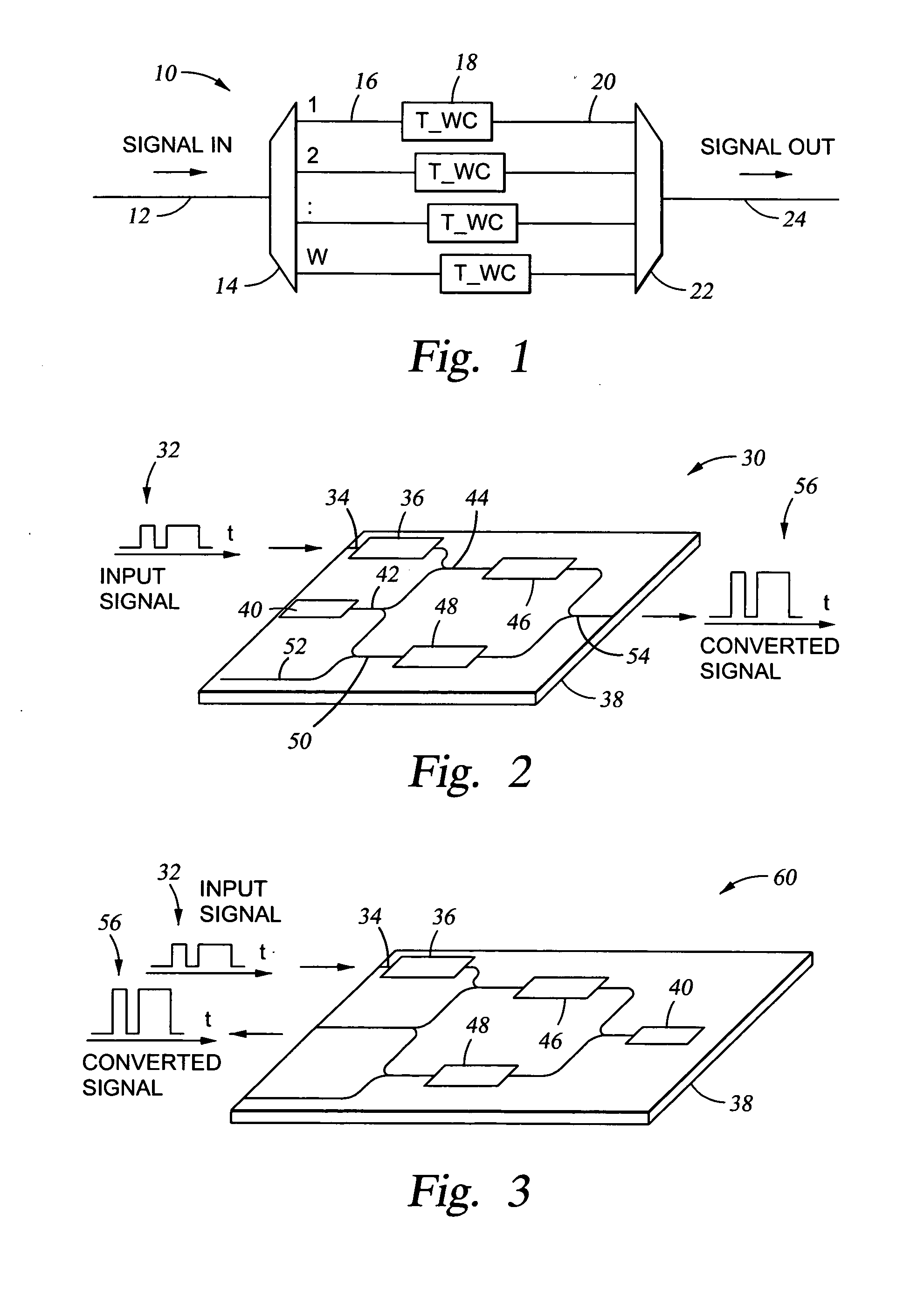

Optical packet switch

InactiveUS6512616B1Increase in sizeDevice is bulkyMultiplex system selection arrangementsTime-division optical multiplex systemsOptical packetData field

An optical packet switch uses electric circuits to implement input and output sections of an optical switch that performs packet switching. Retiming of packet data in the output section is facilitated to reduce the scale of the circuitry. In the input section a packet-data signal and a clock signal for retiming the packet data are wavelength multiplexed by a wavelength multiplexer and transferred over the same optical waveguide of the optical switch. In the output section the packet-data signal and the clock signal, which have been transferred from the same optical waveguide in the packet switch, are demultiplexed by a wavelength demultiplexer, and retiming of the packet-data signal is performed by an intra-device frame terminating unit. A frame format comprises, in addition to a flag pattern and a data field, a preamble and dummy data at the beginning and end thereof, respectively, for accommodating skew caused by transfer through the optical switch as well as a period of signal instability produced by switching of the optical switch. The packet data is transferred upon being placed in the data field of the frame format.

Owner:NEC CORP

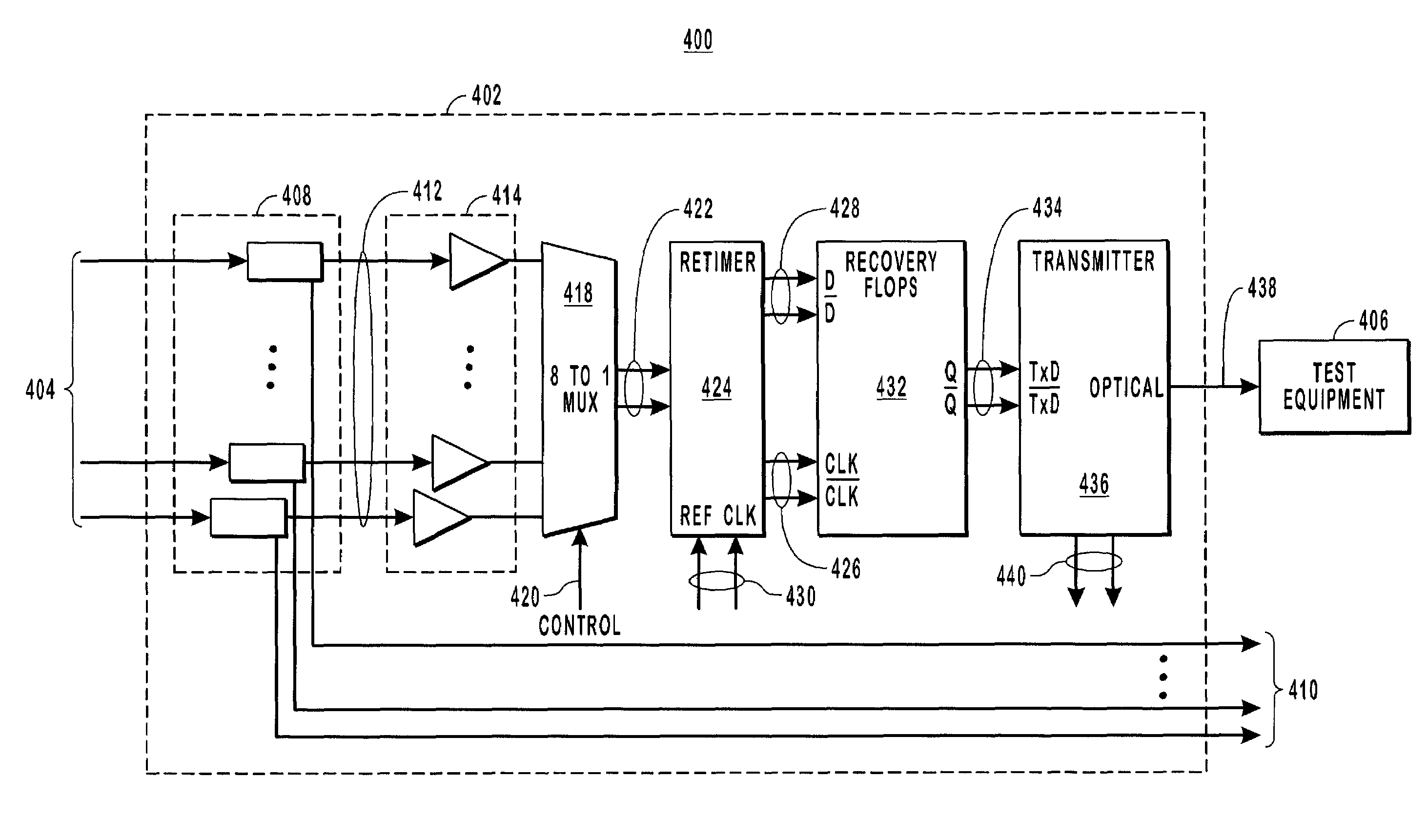

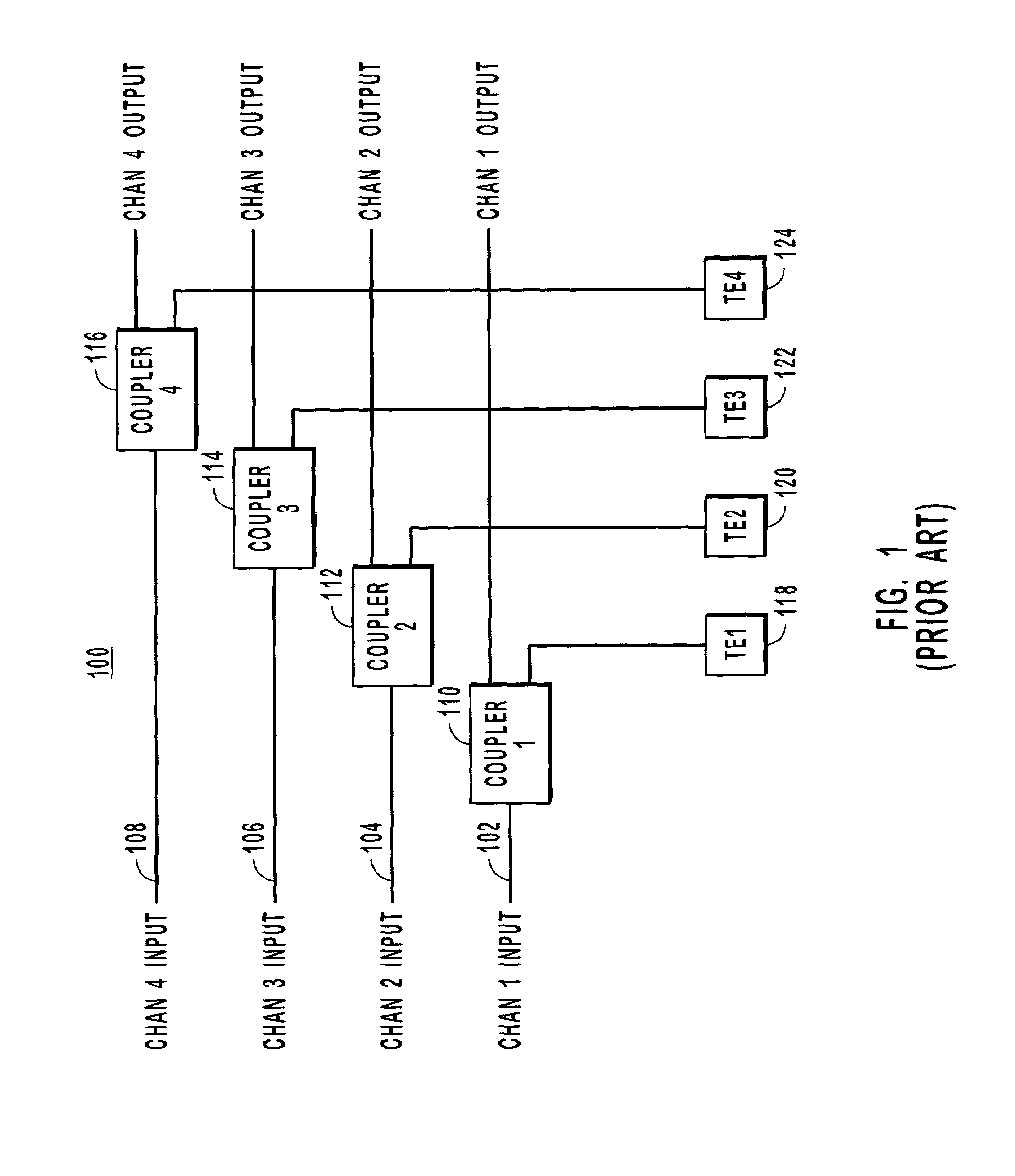

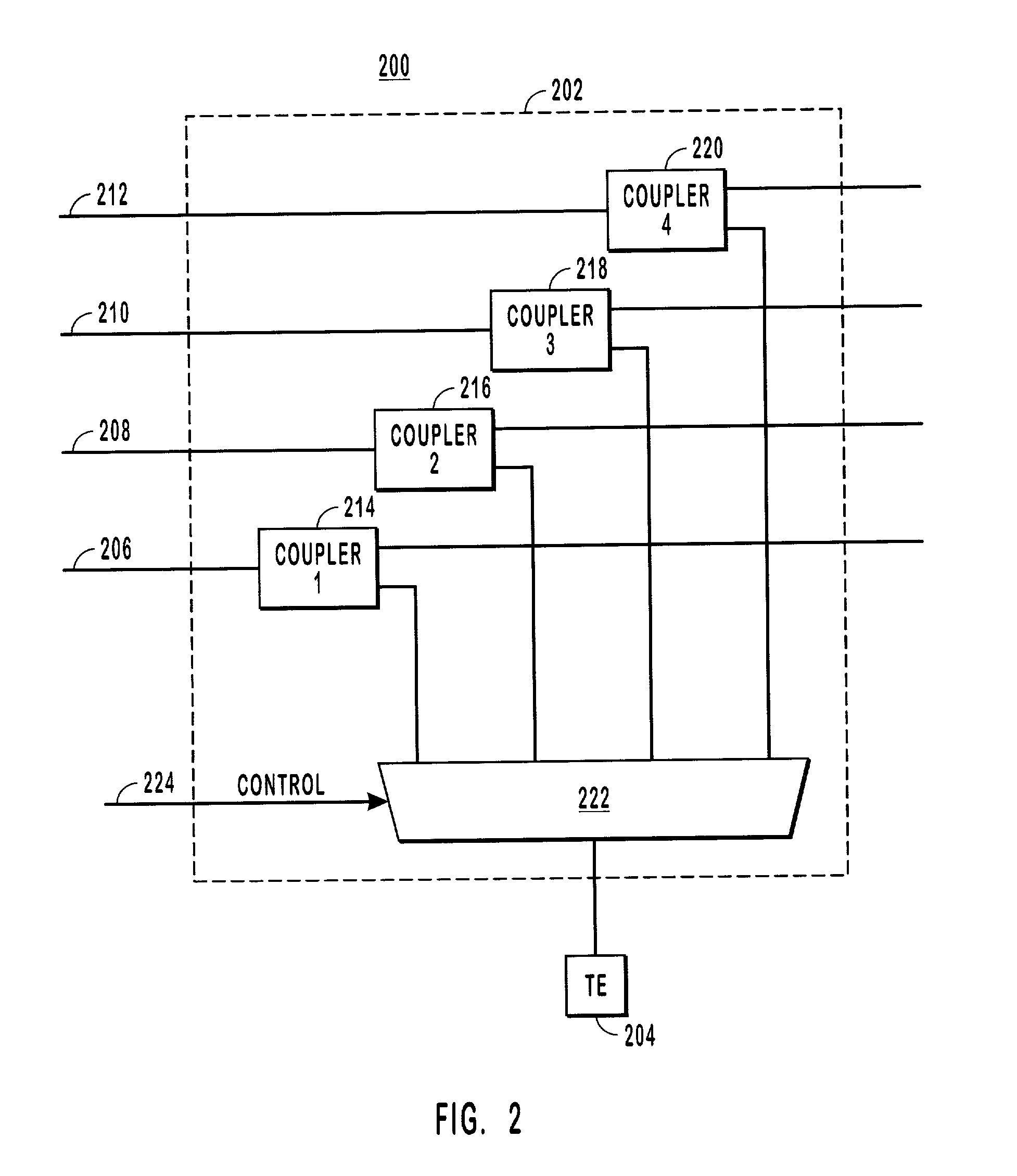

Optical channel selection and evaluation system

A system and method of selecting and viewing communication traffic transmitted over an optical channel selected from among a plurality of possible channels without disrupting the communication traffic occurring over the selected channel or other channels is presented. The system and method includes an optical channel analyzing switch which taps each of the possible plurality of channels and selects a specific channel for routing to a network analyzer. The signal on the selected channel, prior to being analyzed by the network analyzer, undergoes clock and data recovery and retiming / recombination to mitigate contamination from routing and switching the selected original signal between the signal source and the network analyzer. The retimed and recombined channel signal results in a signal, as presented to the network analyzer, which is representative of the original channel signal.

Owner:VIAVI SOLUTIONS INC

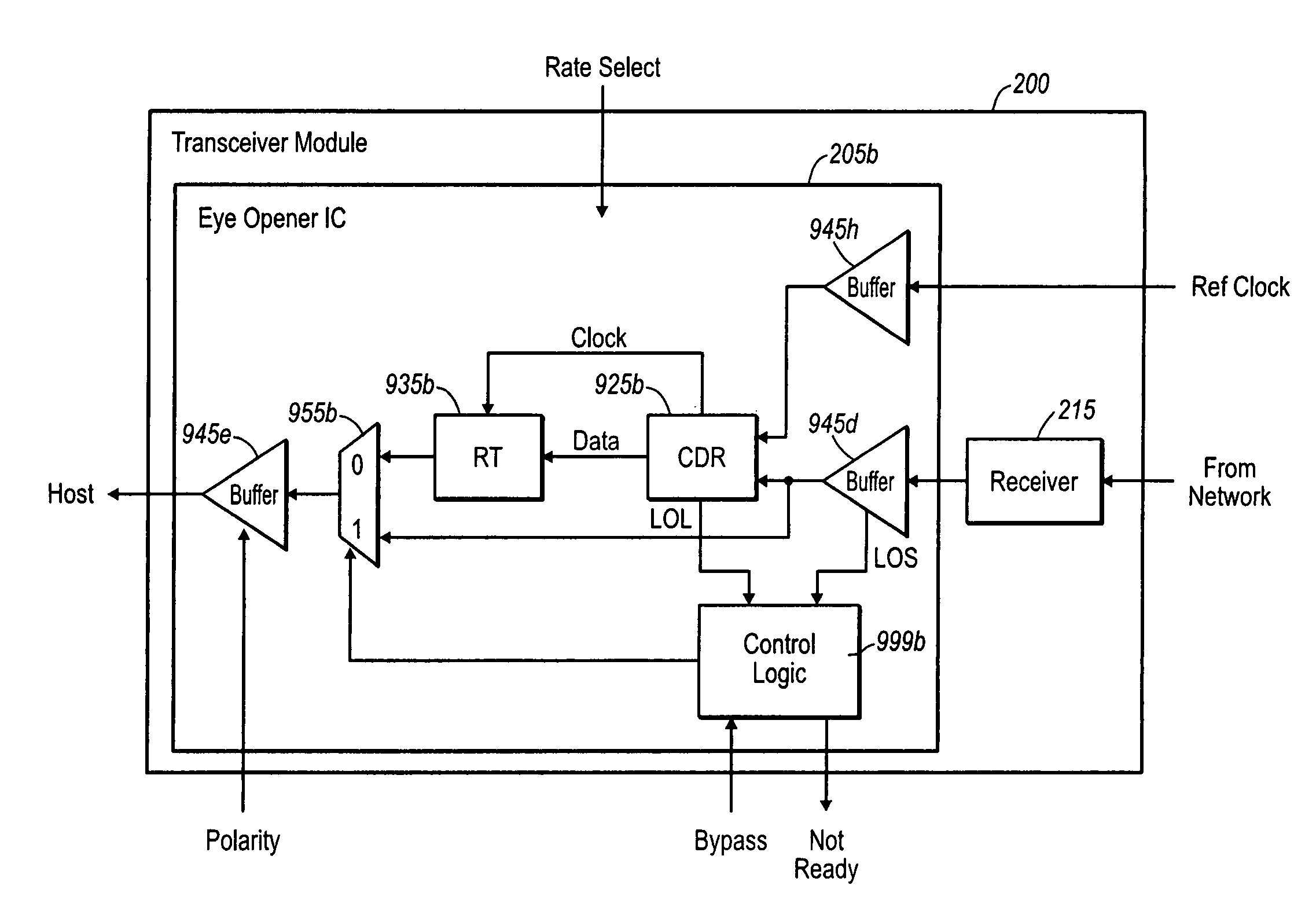

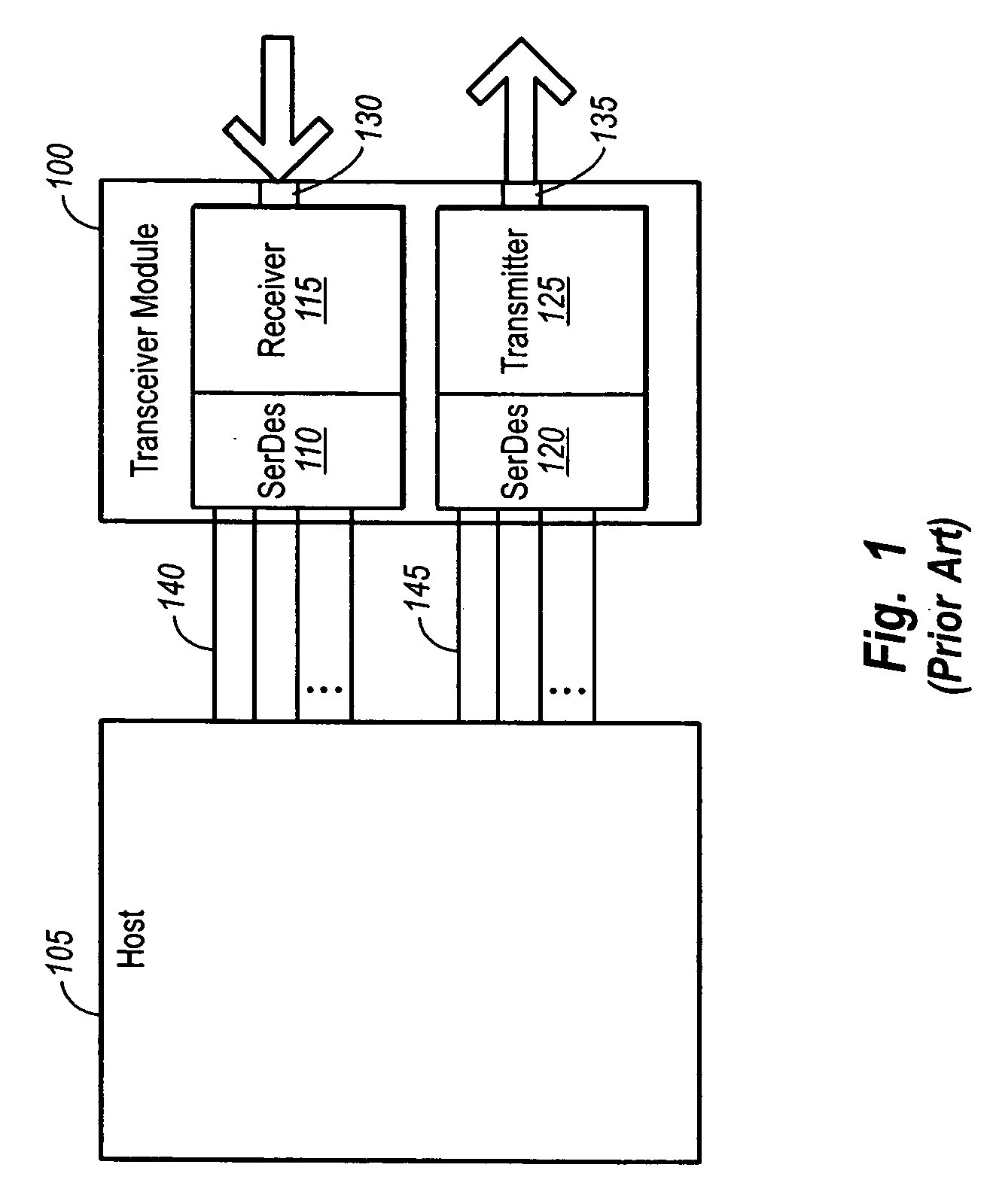

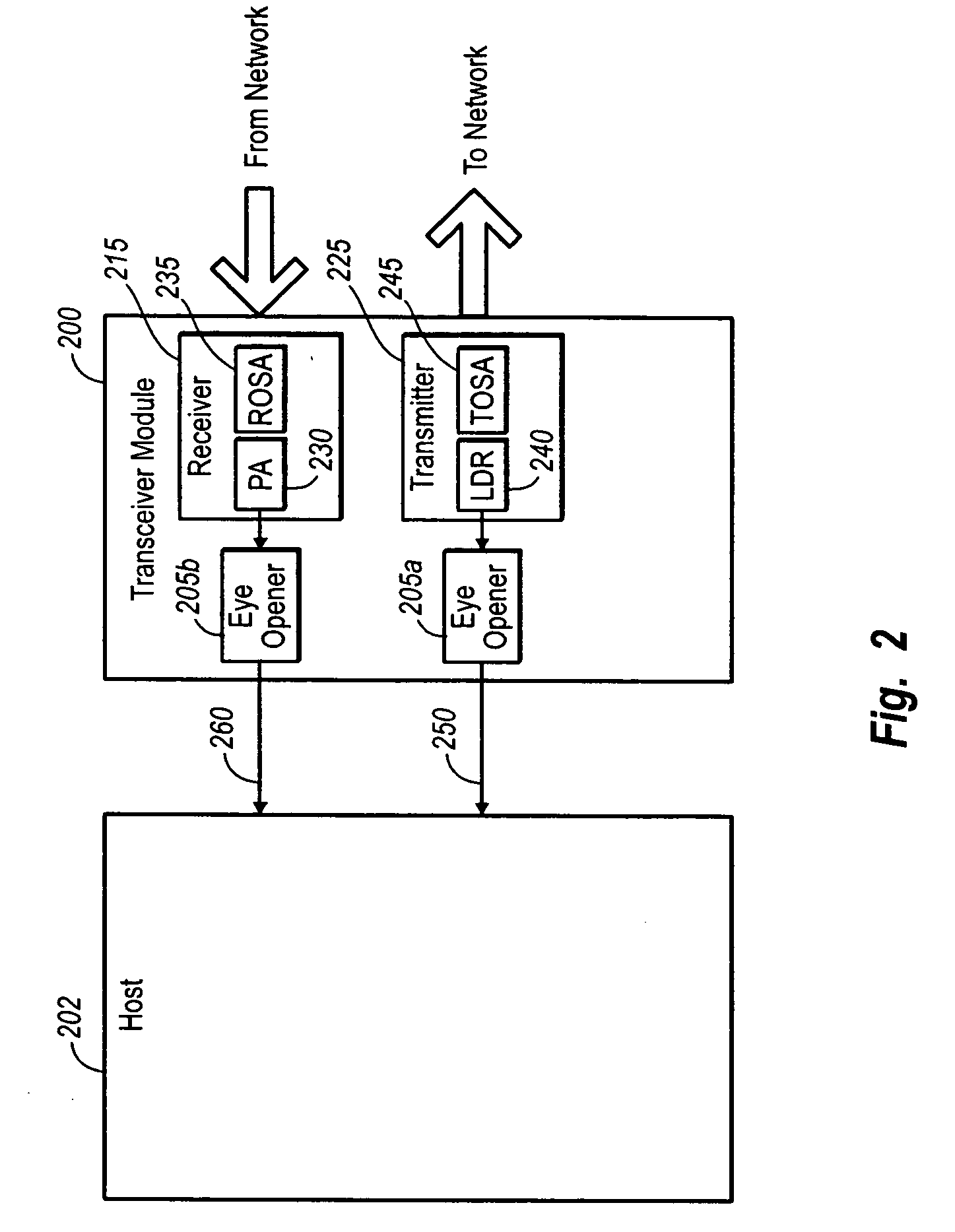

Transceiver module and integrated circuit with clock and data recovery clock diplexing

ActiveUS20050281193A1Reduce bit errorsError detection/prevention using signal quality detectorCorrect operation testingTransceiverData stream

An integrated circuit. The integrated circuit is usable in a transceiver module. The integrated circuit includes an input port that is configured to receive a data stream. A clock port on the integrated circuit is configured to receive a reference clock diplexed with another signal or voltage used by the integrated circuit. An eye opening circuit is connected to the input port and clock. The eye opening circuit is configured to retime the data stream received at the input port. An output port is connected to the eye opening circuits The output port is configured to transmit a retimed signal from the eye opening circuit to a device external to the integrated circuit. A bypass circuit is connected to the input port and the output port. The bypass circuit may selectively bypass the eye opening circuit.

Owner:II VI DELAWARE INC

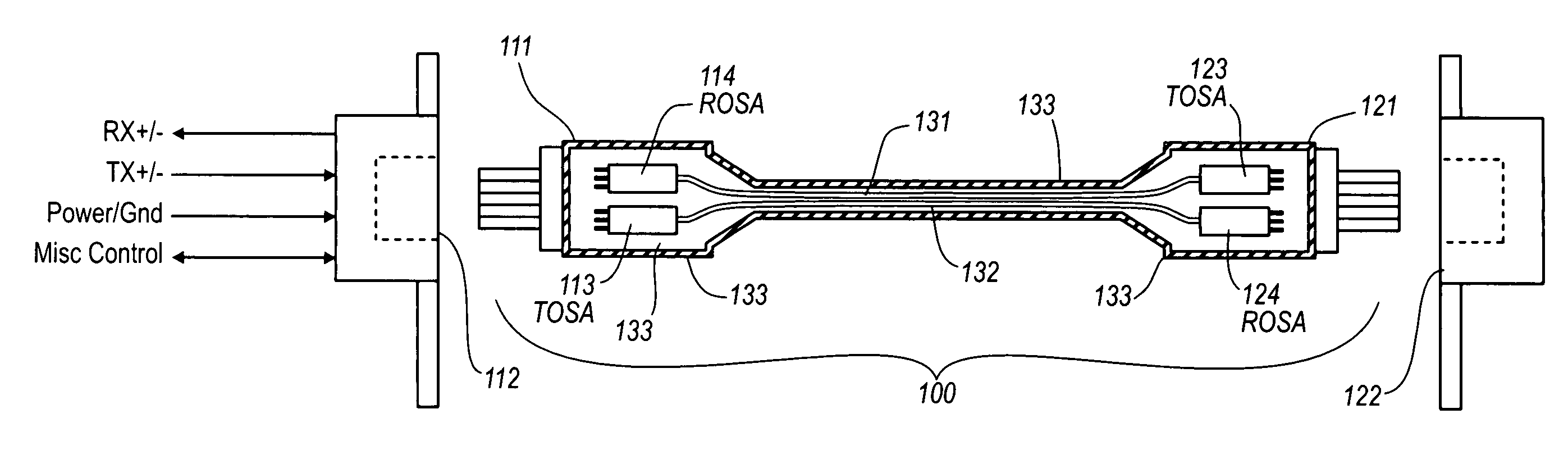

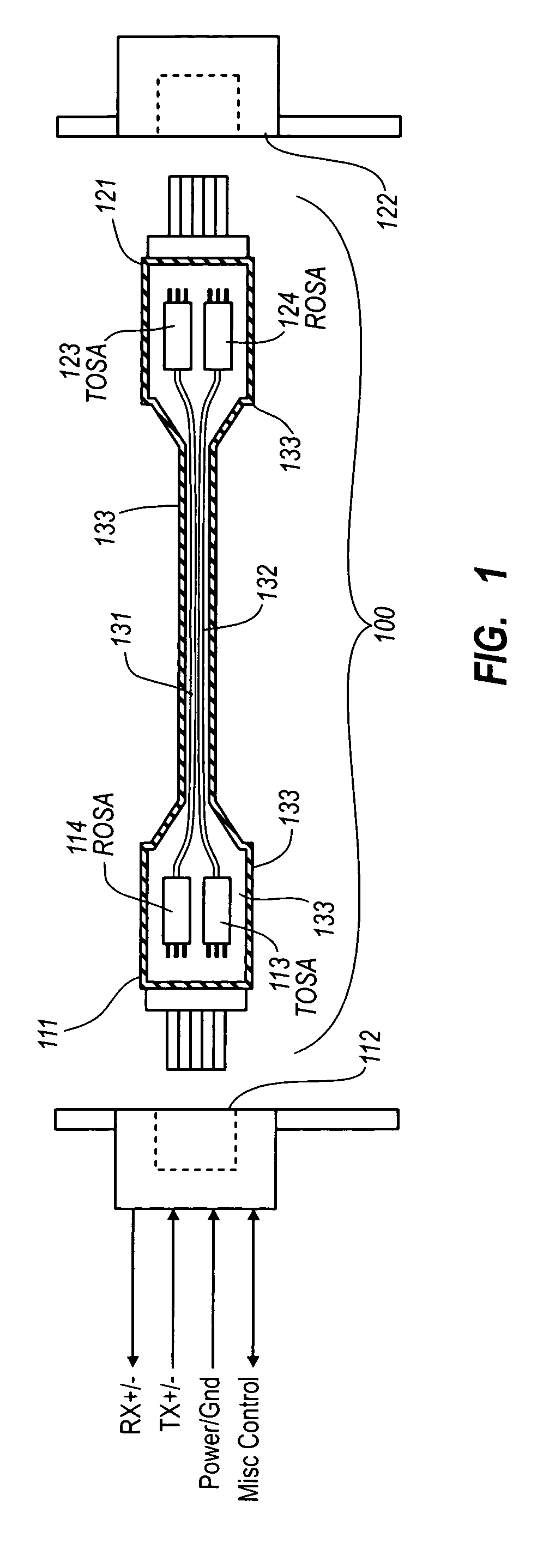

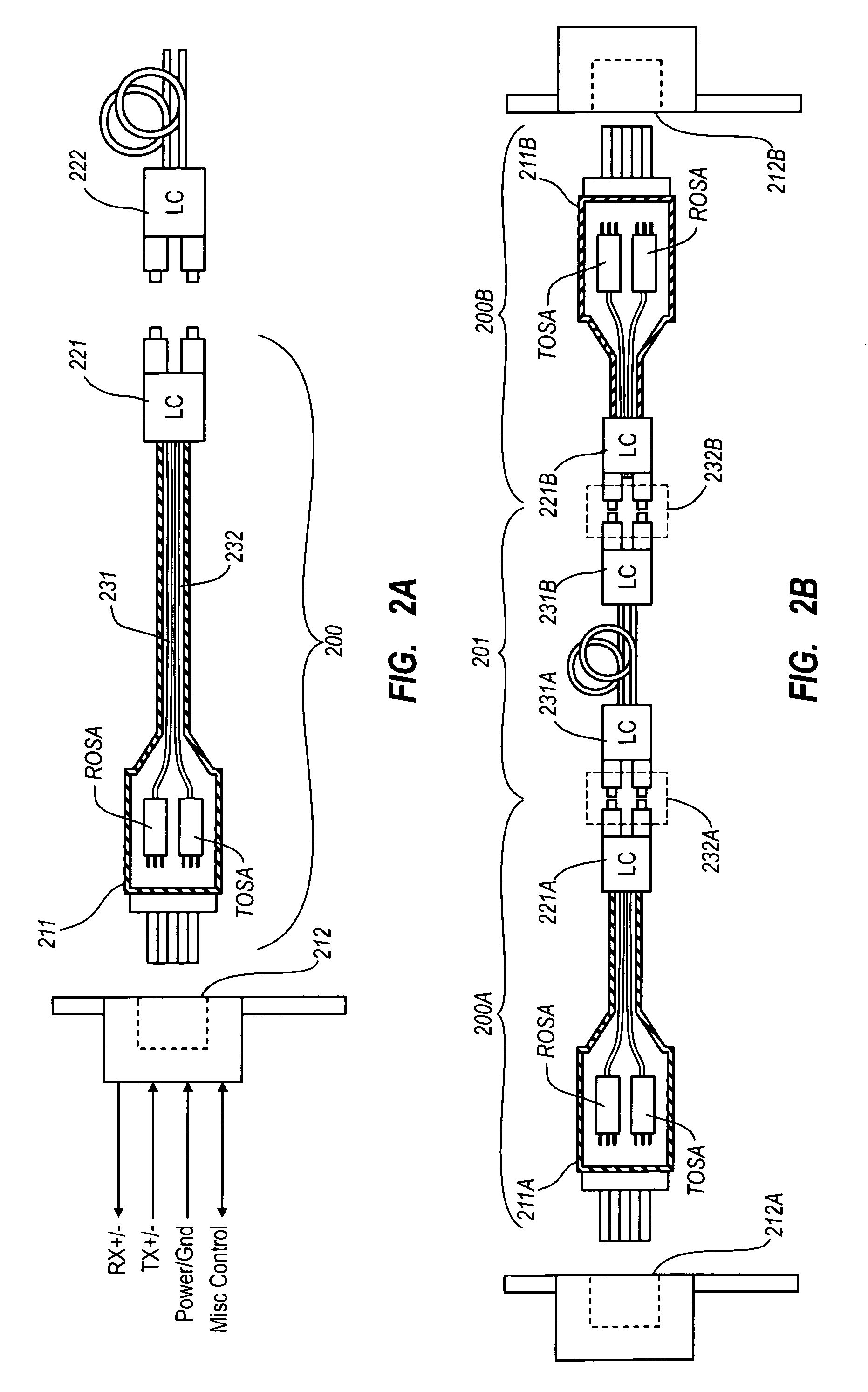

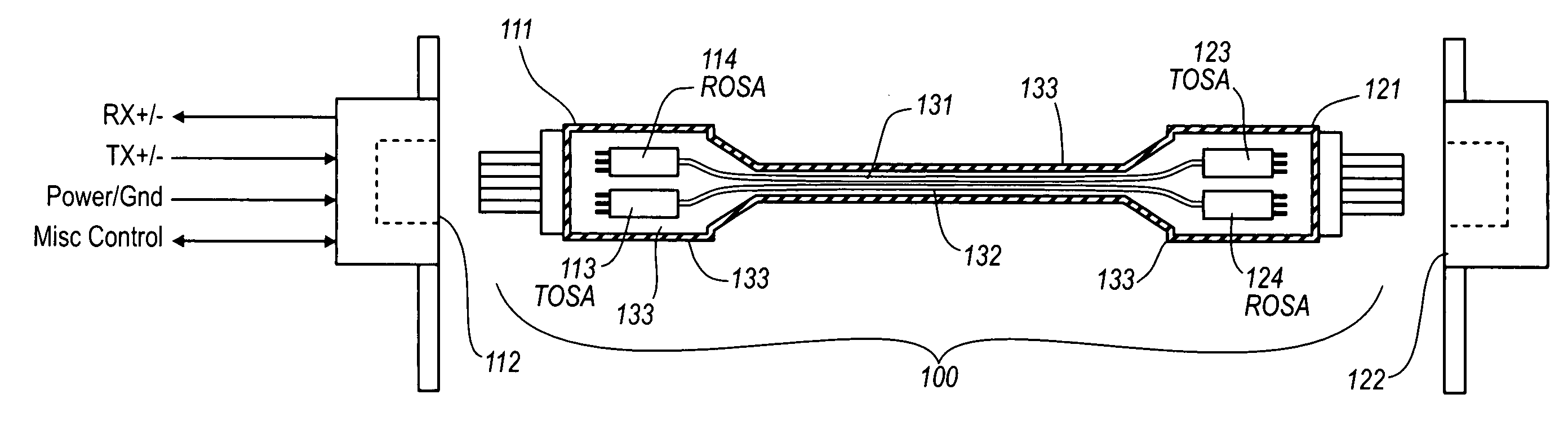

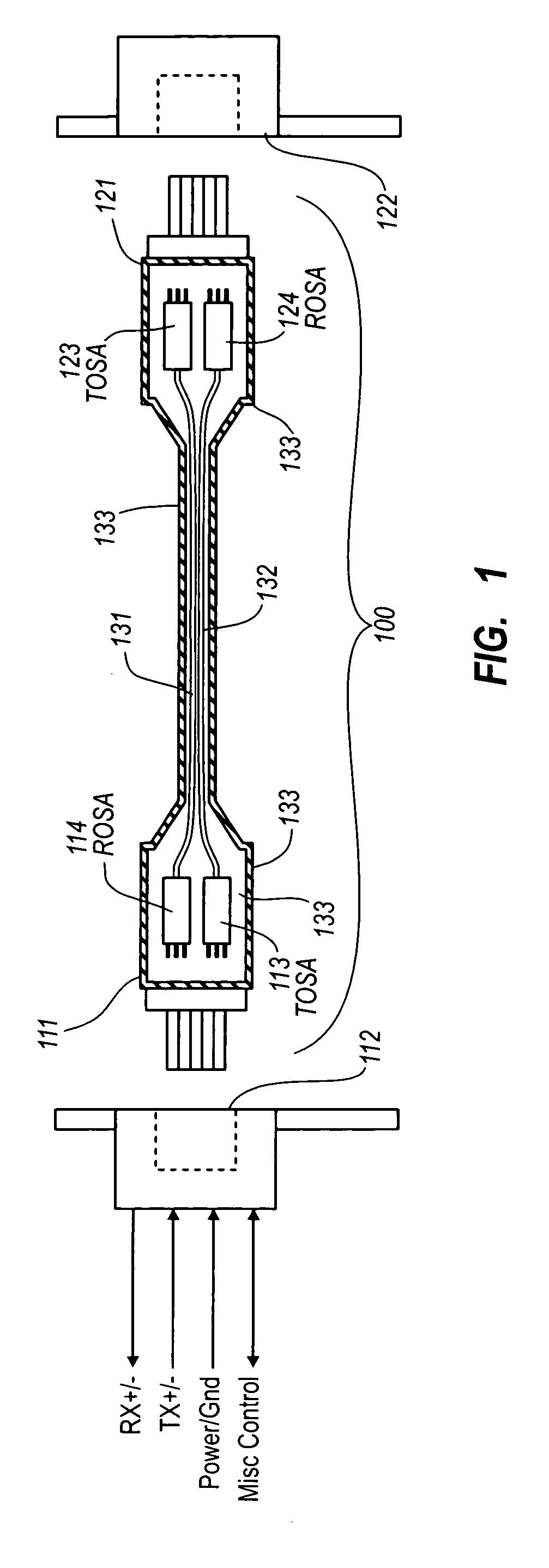

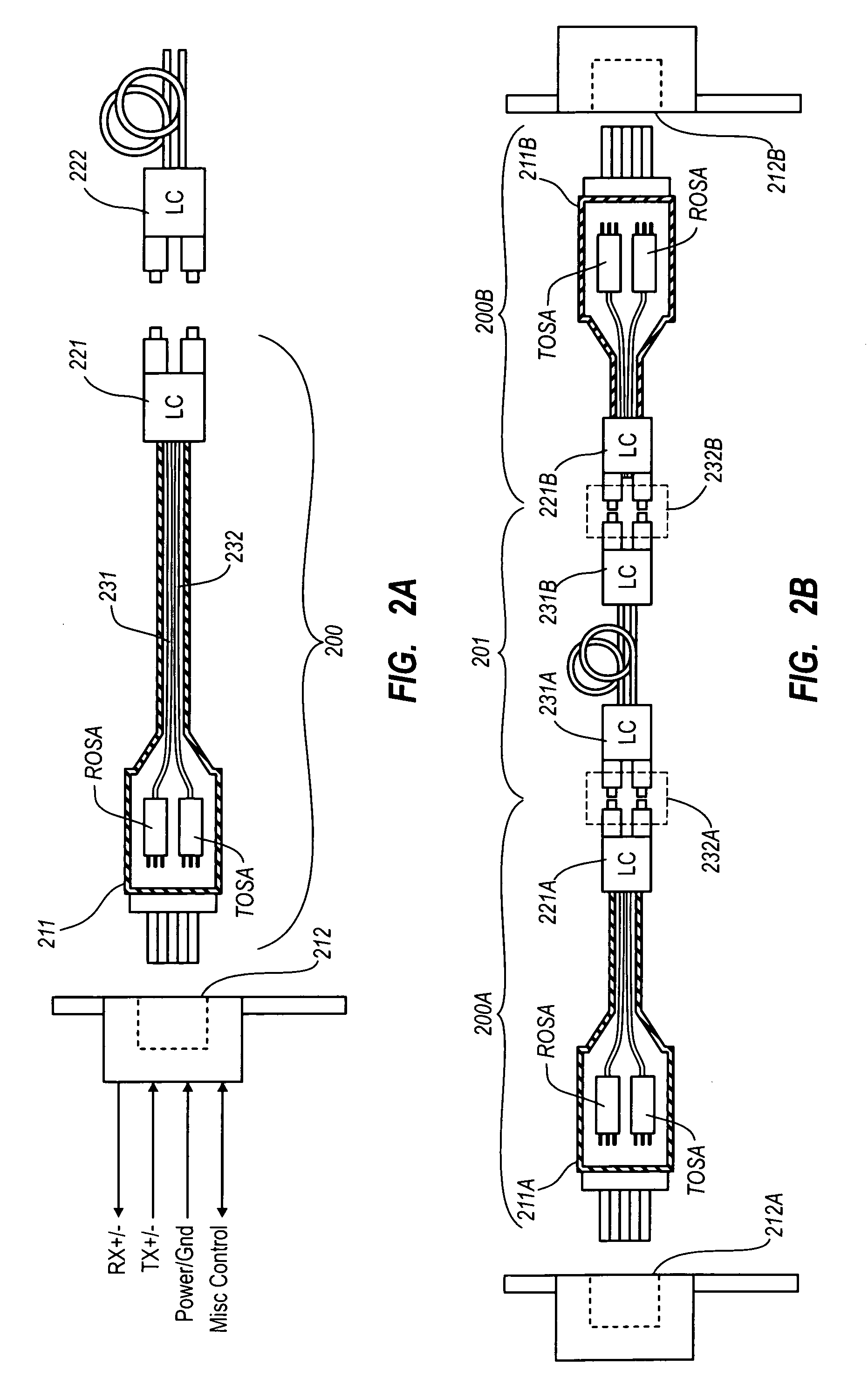

Active optical cable with integrated retiming

An active cable that is configured to communicate over much of its length using one or more optical fibers, and that includes an integrated electrical connector at least one end. The active cable includes an integrated retiming mechanism. Thus, multiple links of cable may be used while reducing the chance that the jitter will exceed allowable limits. The cable may be an electrical to optical cable, and electrical to electrical cable, or one of many other potential configurations.

Owner:II VI DELAWARE INC

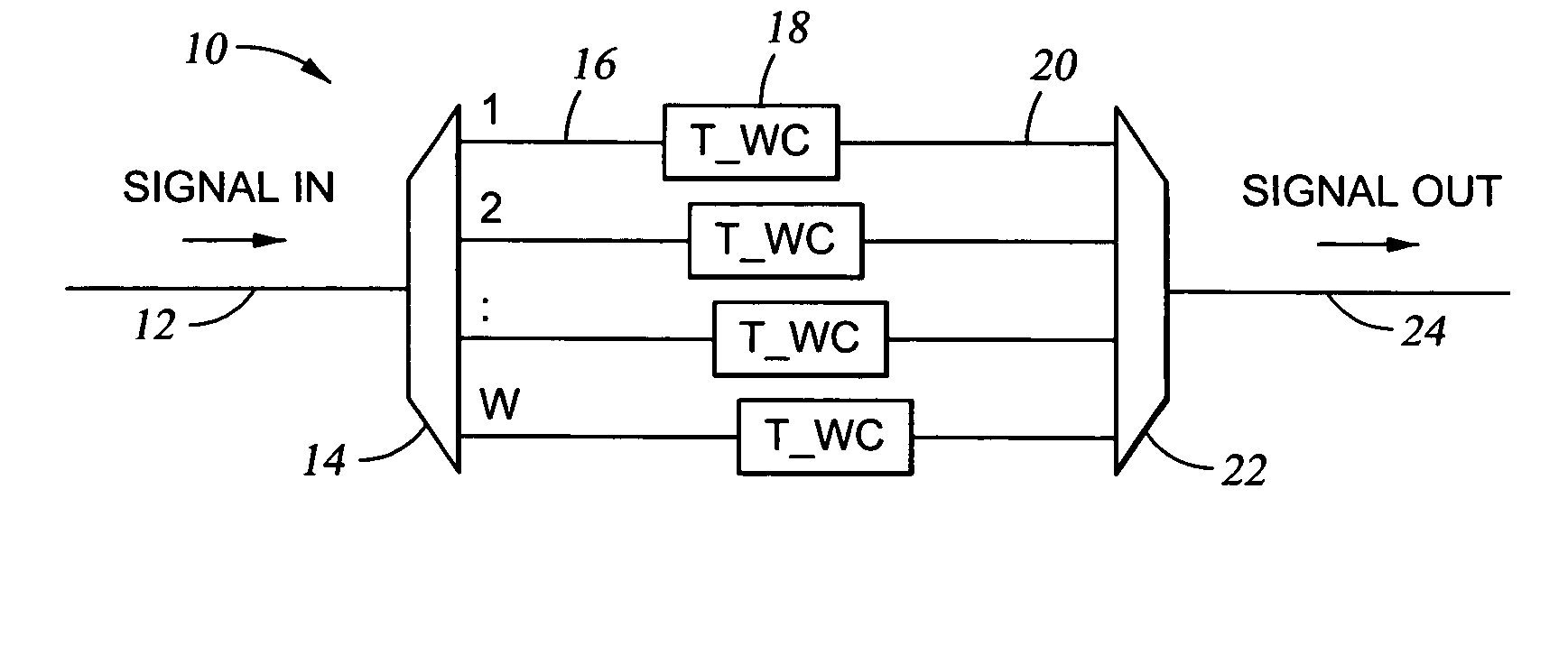

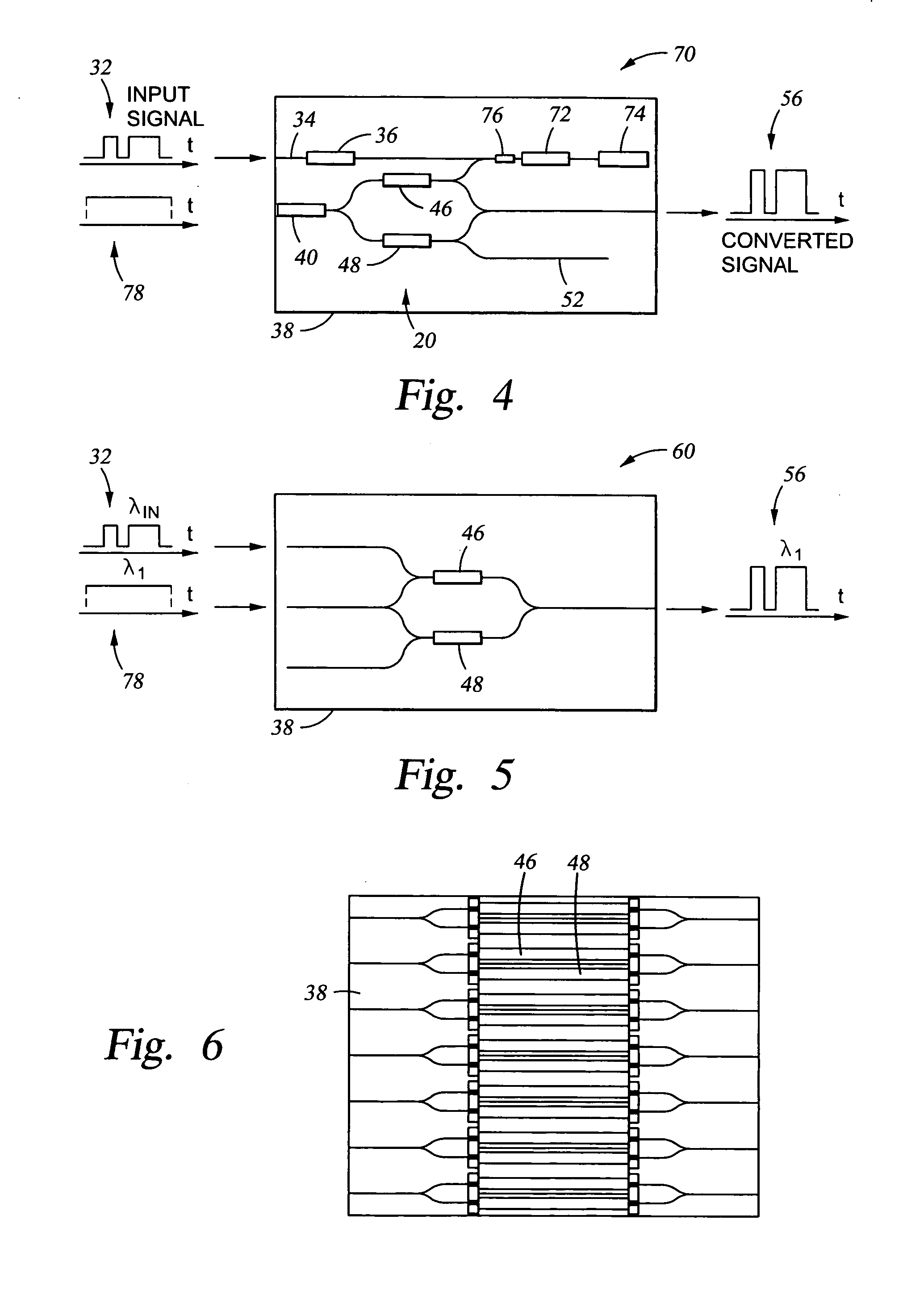

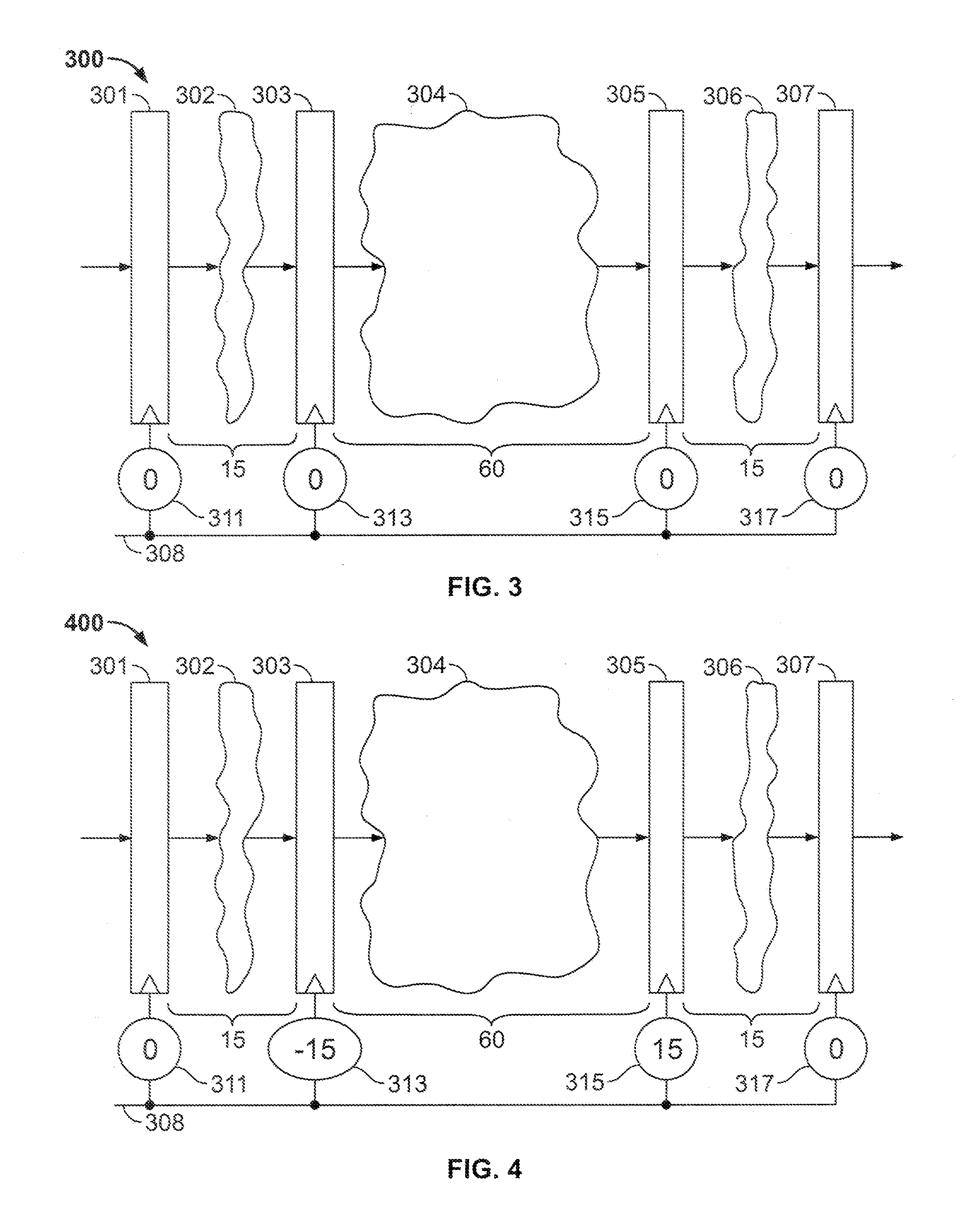

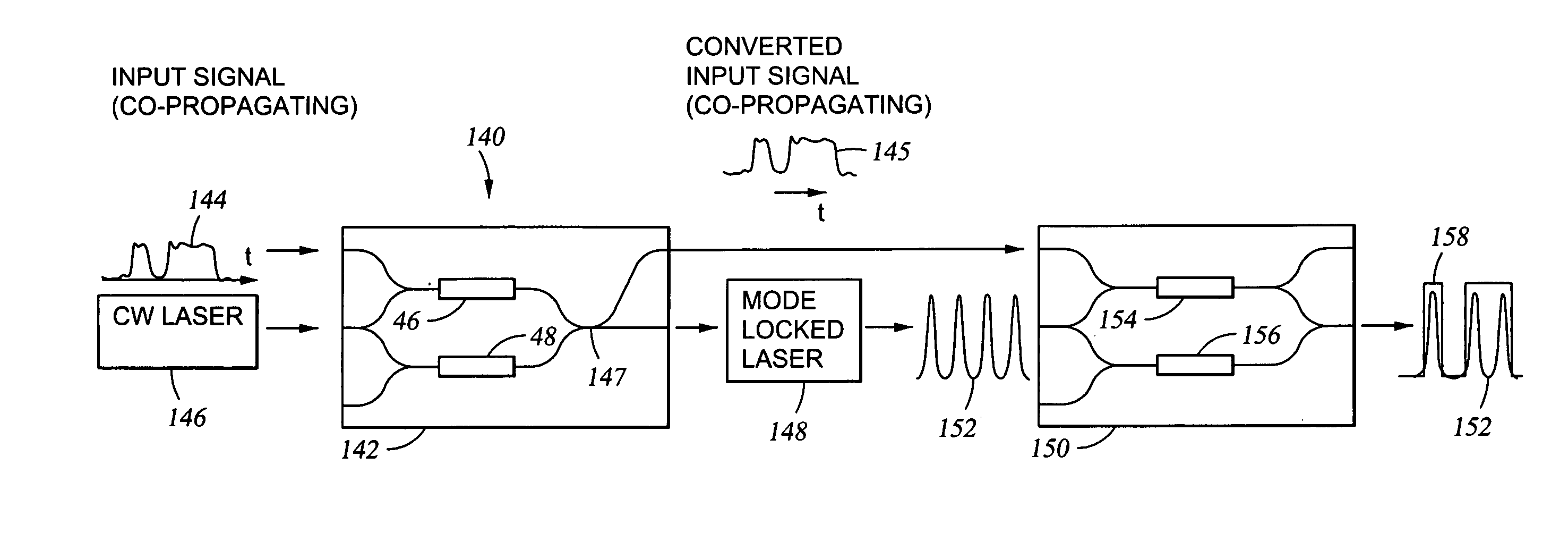

Reconfigurable multi-channel all-optical regenerators

ActiveUS20050053377A1Small and even zero changeEliminate needWavelength-division multiplex systemsElectromagnetic transmissionMach–Zehnder interferometerWaveguide

An all-optical regenerating circuit including a wavelength converter based on a Mach-Zehnder interferometer. The input signal is amplified and the interferometer adjusted to place the input signal across an entire monotonic portion of a sinusoidal transfer function to the wavelength-converted output signal. Retiming is effected by wavelength converters including pulsed laser sources of the output wavelength. A multi-wavelength regenerator may be integrated on a chip including two arrayed waveguides and an array of tunable lasers on parallel waveguides therebetween.

Owner:RGT UNIV OF CALIFORNIA

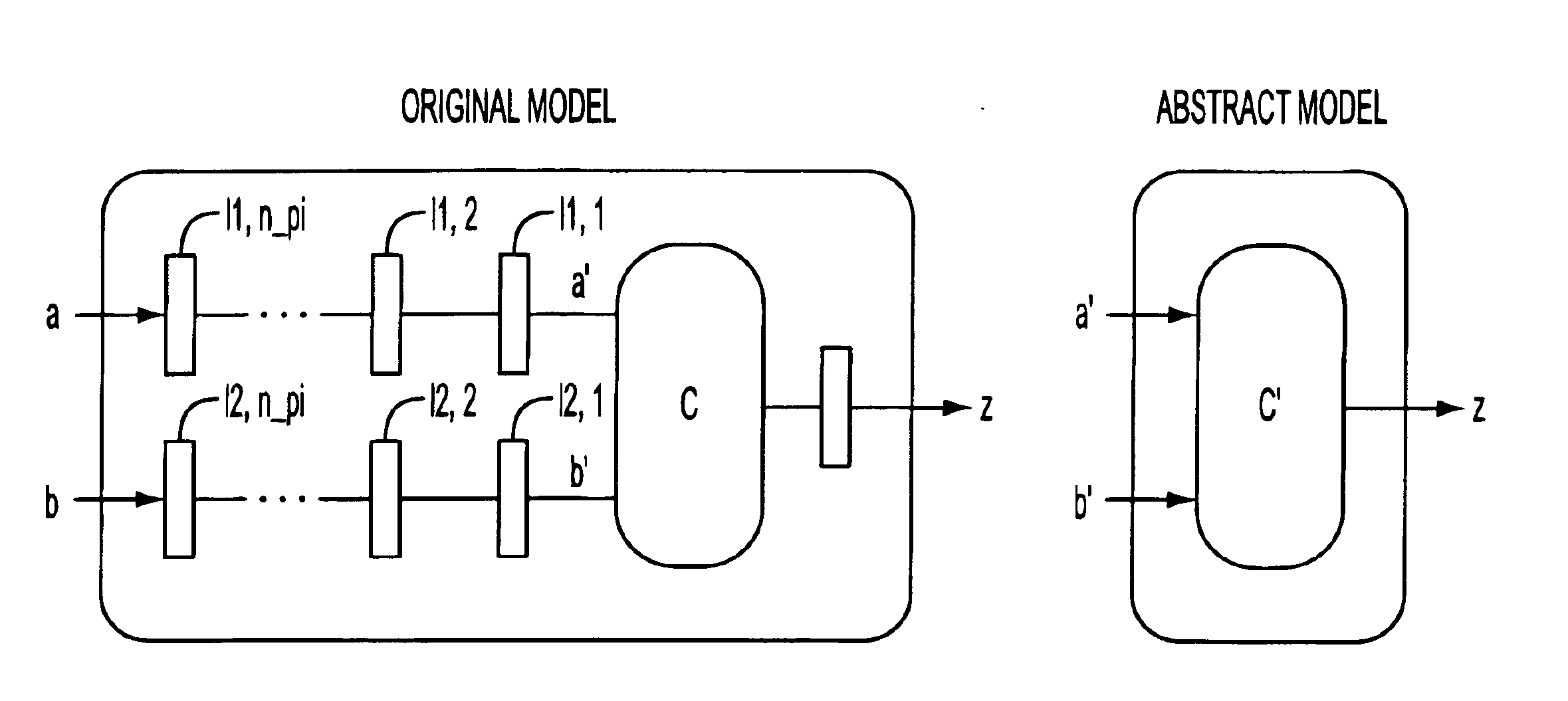

Method for design validation using retiming

InactiveUS6874135B2Minimize the numberReduce complexityDetecting faulty computer hardwareCAD circuit designDesign testingTest sequence

A method for derivation and abstraction of test models for validation of industrial designs using guided simulation is described. The method employs automatic abstractions for the test model which reduce its complexity while preserving the class of errors that can be detected by a transition tour. A method for design validation comprising generating a state-based test model of the design. The test model is abstracted by retiming and latch removal. Finally, a validation technique is applied on the abstracted test model. First, the number of internal (non-peripheral) latches in a design is minimized via retiming using a method of Maximal Peripheral Retiming (MPR). According to the MPR method, internal latches are retimed to the periphery of the circuit. Subsequently, all latches that can be retimed to the periphery are automatically abstracted in the test model. The validation technique may comprise of model checking, invariant checking or simulation using test sequences generated from the abstracted test model.

Owner:NEC CORP

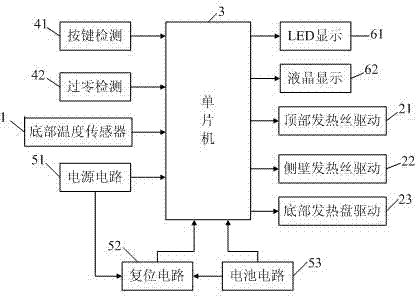

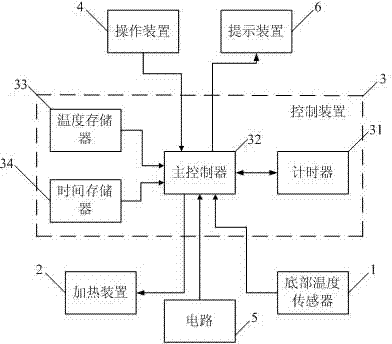

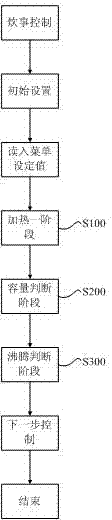

Heating control method for electrical cooking appliance

ActiveCN102949081ASolve the fragilePrevent overflowAuxillary controllers with auxillary heating devicesWarming devicesStop timeHeat control

The invention relates to a heating control method for electrical cooking equipment. The heating control method includes: continuously heating food, stopping heating til the food reaches to a first preset temperature; judging whether the heating stopping time reaches a first preset time or not; if yes, acquiring capacity of the food according to a current temperature value of the food and a preset capacity judging temperature value; heating the food and retiming after the capacity of the food is acquired, and in a preset periodic time, judging whether the food is boiling or not according to the current temperature value of the food, a periodic bottom temperature and a preset boiling judging temperature value. The electrical cooking equipment is provided with a fuzzy reasoning functional program capable of accurately controlling heating thermal power.

Owner:佛山食神网络智能科技有限公司

Retiming in a Video Sequence

InactiveUS20150221335A1Television system detailsElectronic editing digitised analogue information signalsFrame basedComputer graphics (images)

Slow motion is added to a video clip using retiming. Retiming adjusts the timing of the video. The video sequence may be stored ahead of time, modified in real time as the video is collected, or in real time as the video is played back. A memory stores a video sequence. A processor selects a subset of frames from the video sequence based on a focus frame identifier and a slow motion timing pattern. The processor generates at least one intermediate frame for insertion into the subset of frames based on the slow motion timing pattern for the video sequence and the focus frame identifier for the video sequence.

Owner:HERE GLOBAL BV

Reprogrammable circuit board with alignment-insensitive support for multiple component contact types

InactiveUS8124429B2Semiconductor/solid-state device testing/measurementWave amplification devicesSignal conditioningContact type

Owner:NORMAN RICHARD

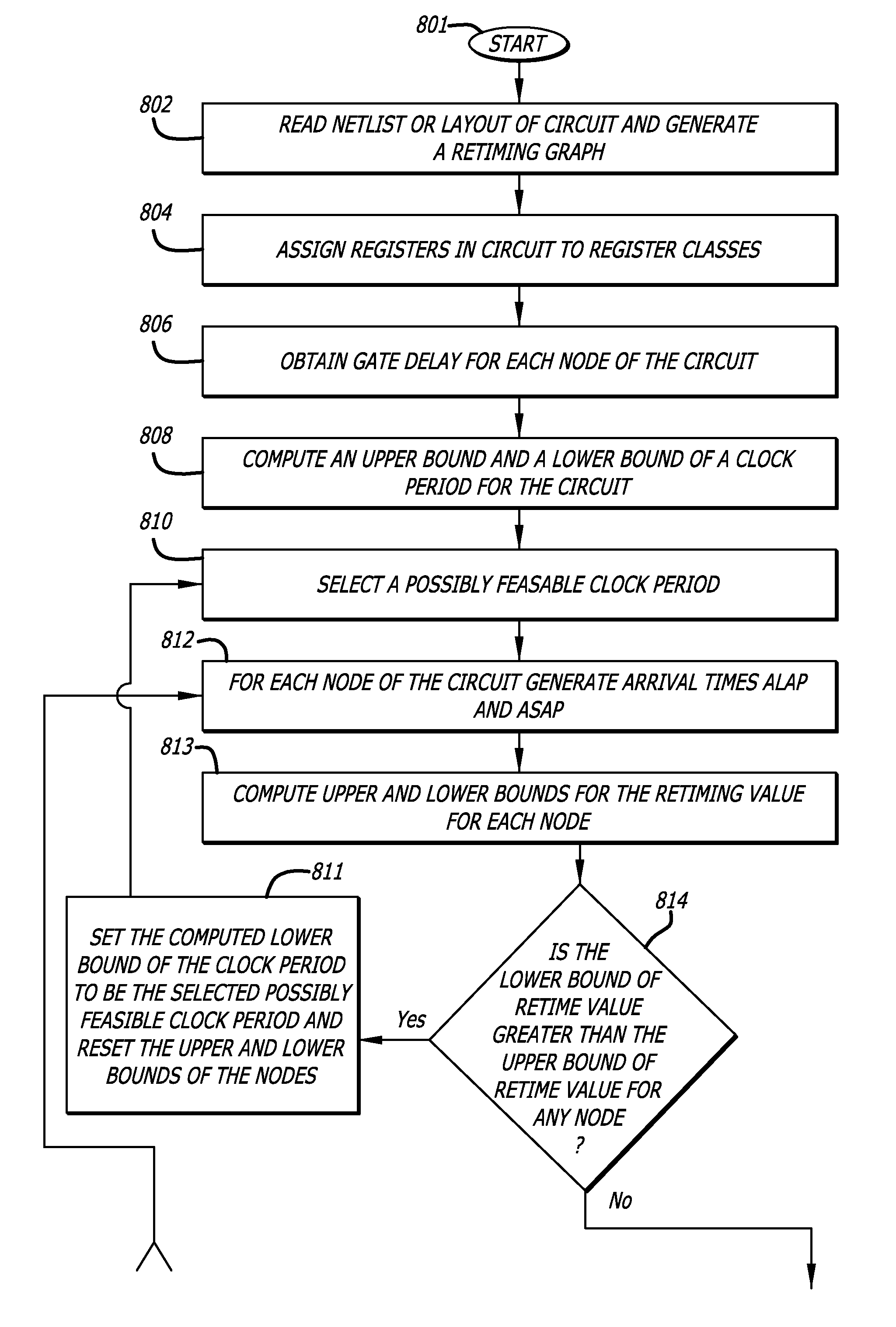

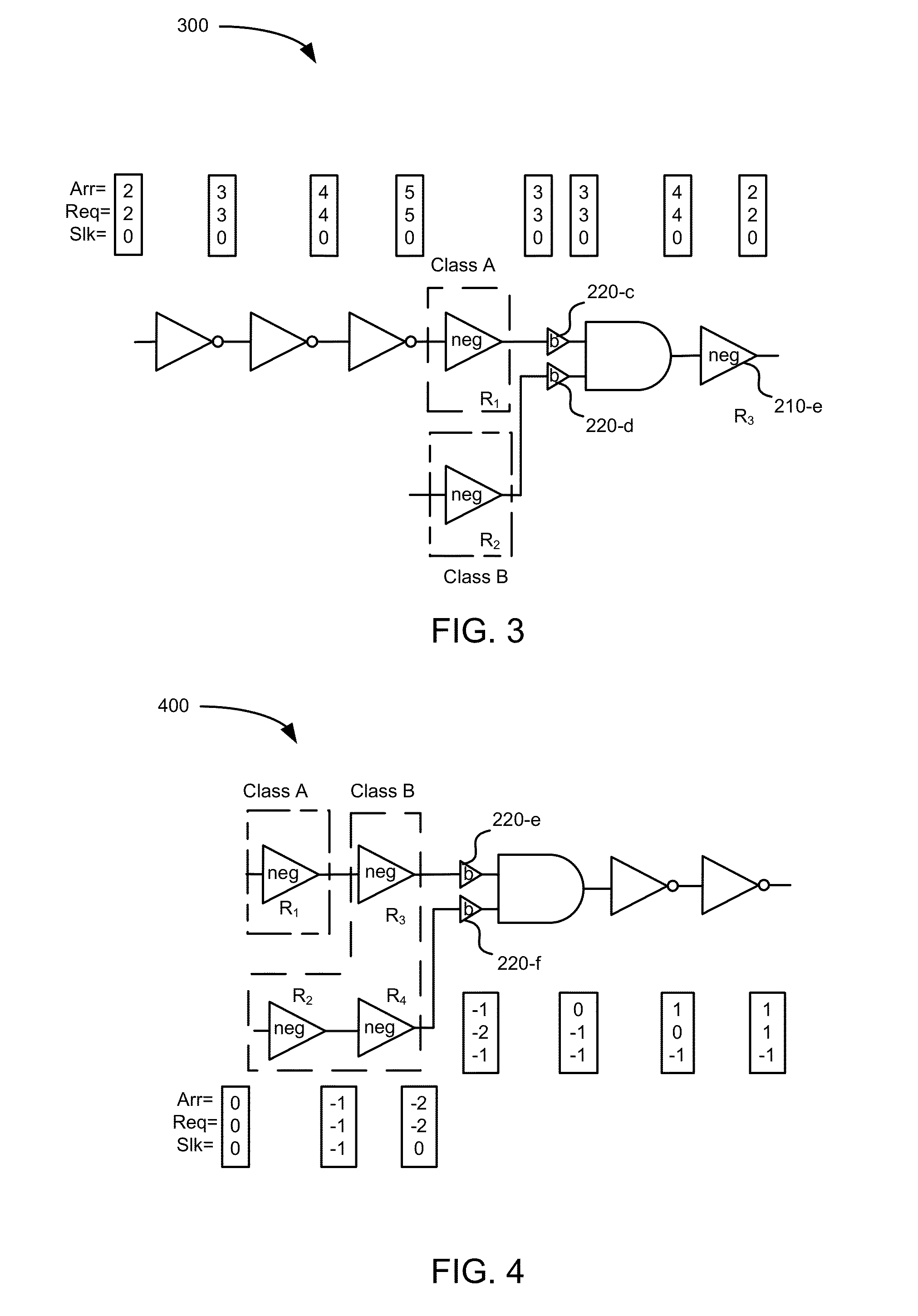

Constraint based retiming of synchronous circuits

ActiveUS7945880B1Minimizes maximum delayBalance out slackComputer aided designSoftware simulation/interpretation/emulationLower limitProcessor register

In one embodiment of the invention, a method of retiming a circuit is disclosed. The method includes computing an upper bound and a lower bound for a clock period of a clock signal to clock a circuit in response to a netlist of the circuit; selecting a potential clock period for the clock signal to clock registers of the circuit in response to the computed upper bound and the computed lower bound for the clock period; computing an upper bound and a lower bound of a retiming value for each node of the circuit to determine if a retiming of the circuit is achievable with the potential clock period; and computing the retiming value for each node of the circuit to minimize circuit area in response to the computed upper bound and the computed lower bound of the retiming value for each node.

Owner:CADENCE DESIGN SYST INC

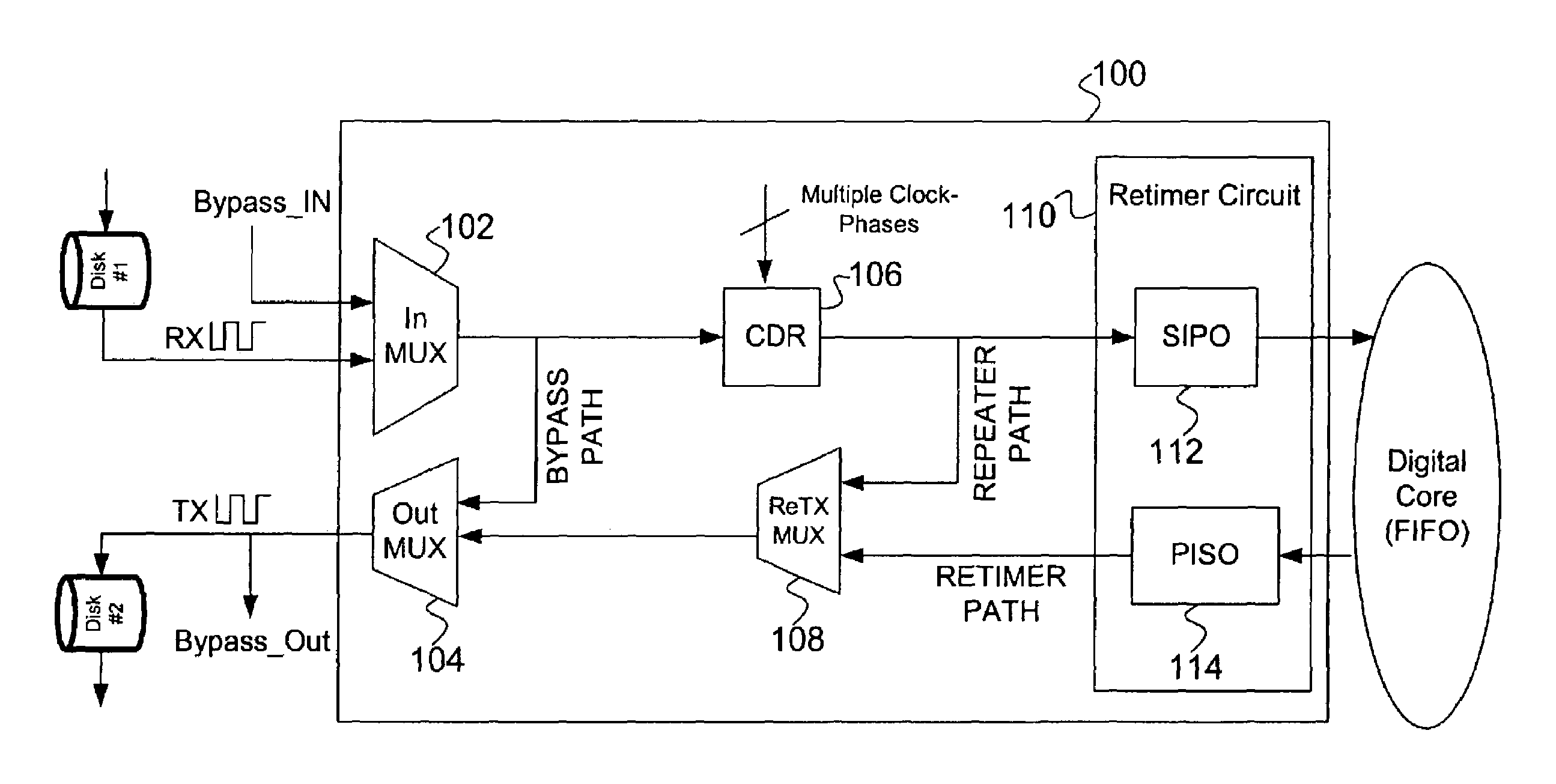

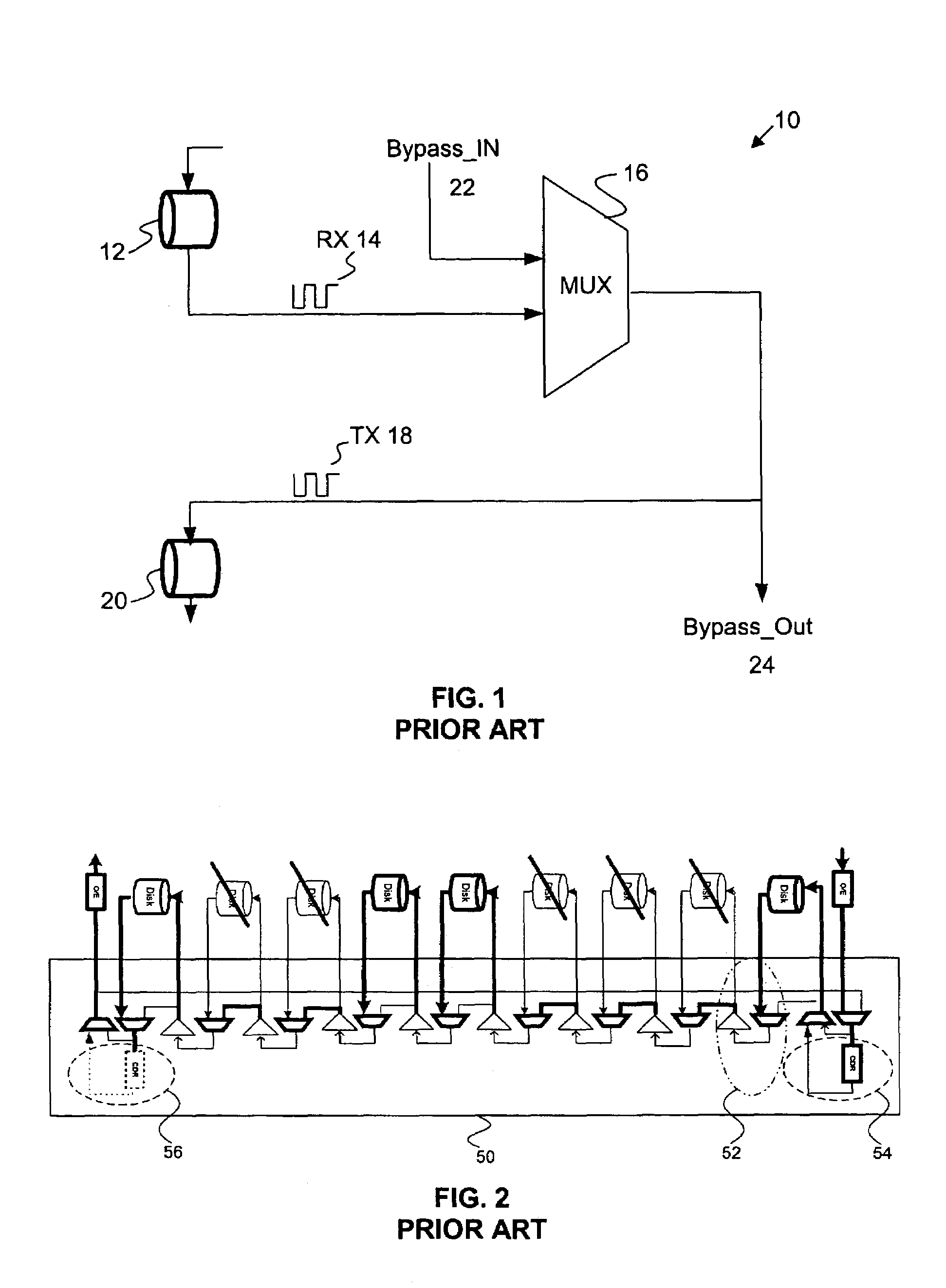

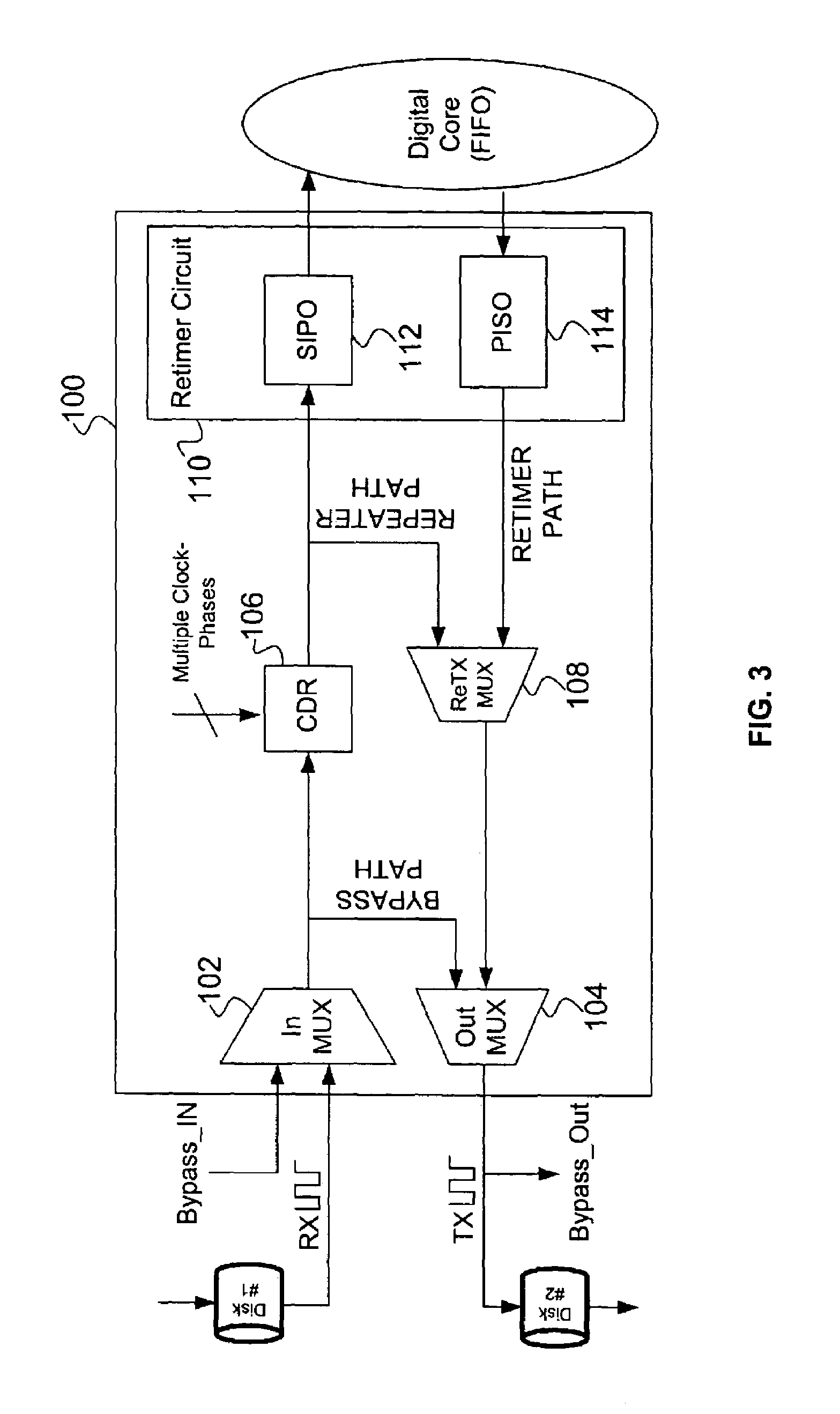

Multi-function bypass port and port bypass circuit

An architecture is provided for implementing bypass, repeater and retimer functions in high-speed multi-port SERDES bypass ports and devices. Specifically, this architecture uses clock recovery to implement a repeater function which retransmits data synchronously at a recovered-clock rate, providing very low-latency as no elastic-buffers are required to perform clock-rate compensation. It also supports a full retiming function where incoming data is retransmitted synchronously to the local-clock domain, in which case elastic-buffers are needed to compensate for differences between incoming clock and local-clock domains. The architecture disclosed herein is advantageously used for Fibre-Channel Arbitrated Loop (FCAL) applications. It can also be leveraged in other applications like Infiniband, XAUI, PCI-Express to create a single device that be used as “eye-opener” to extend reach with low-latency when operated in “repeater mode” and as retiming device when operated as “retimer-mode”. It can also perform as an amplifier with very low-latency when operated in bypass-mode.

Owner:MICROSEMI STORAGE SOLUTIONS

Register retiming technique

InactiveUS7689955B1High frequencySimple designCAD circuit designSoftware simulation/interpretation/emulationProgrammable logic deviceProcessor register

An electronic automation system performs register retiming on a logic design, which may be a logic design for a programmable logic integrated circuit. Register retiming is a moving or rearranging of registers across combinatorial logic in a design in order to improve a maximum operating frequency or fmax. In one implementation, the system includes machine-readable code, which may be stored on a computer-readable medium such as a disk, executing on a computer. The system balances timing in order to trade off delays between critical and noncritical paths. Register retiming may make changes to a design at a gate level.

Owner:ALTERA CORP

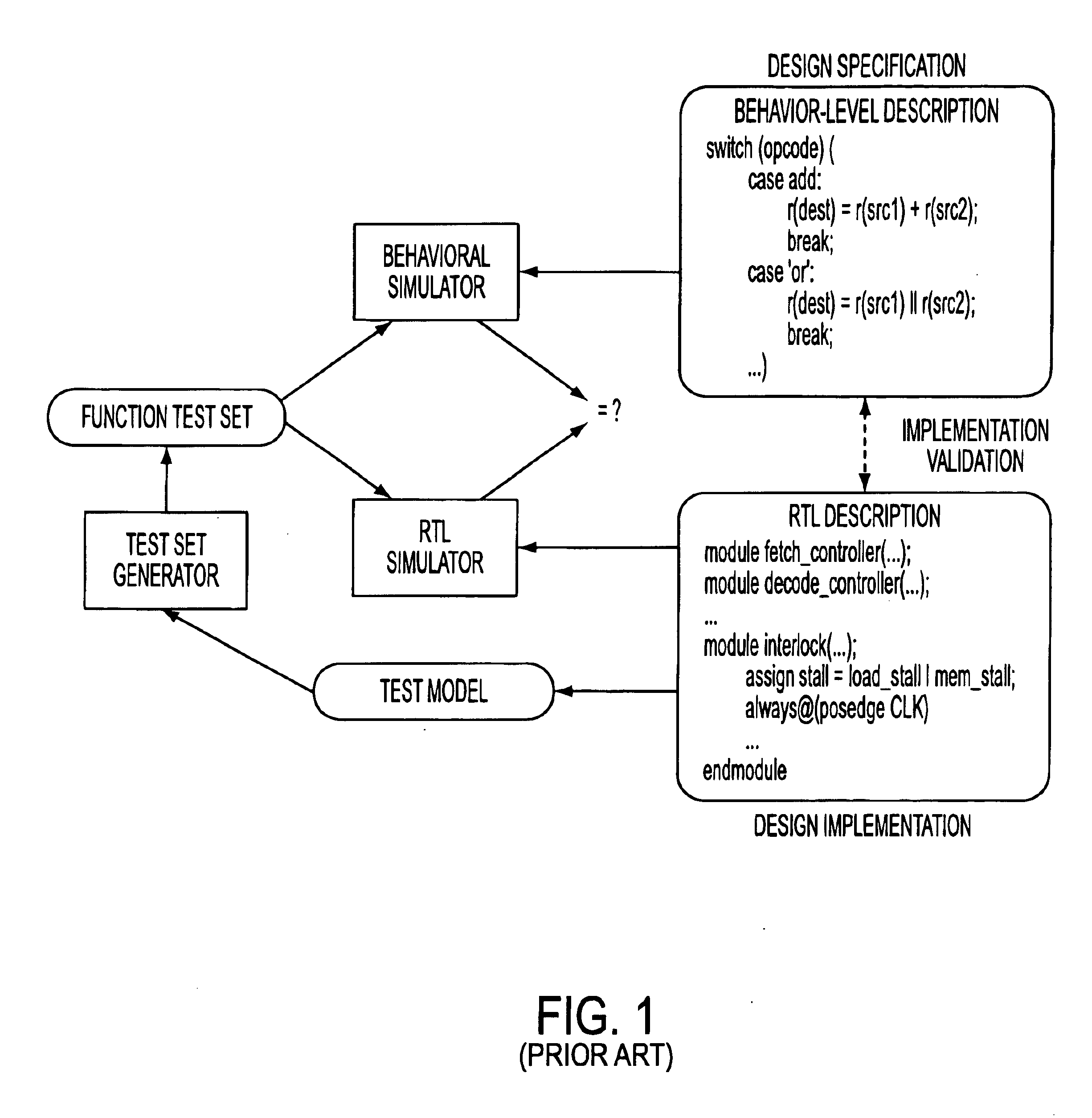

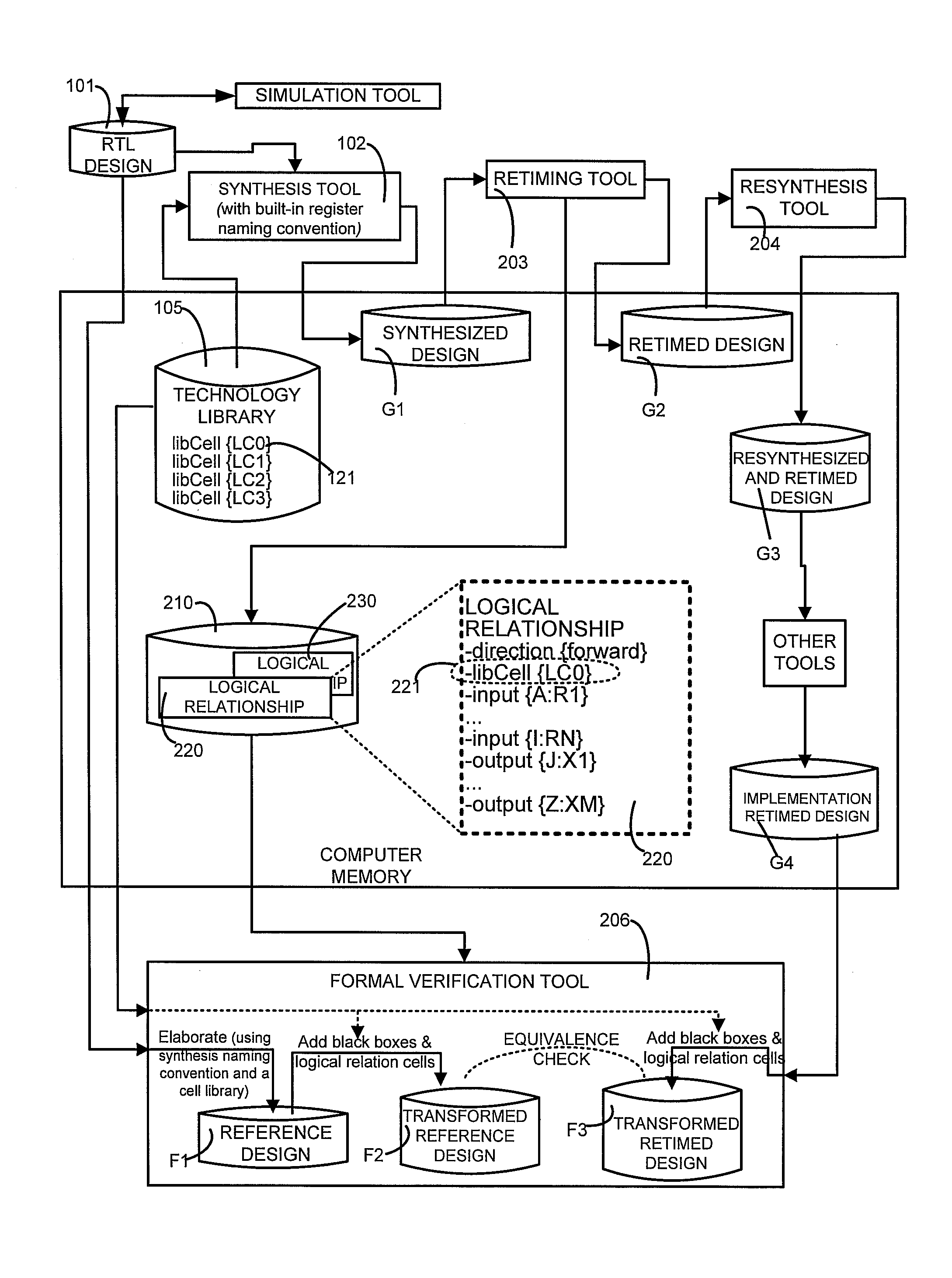

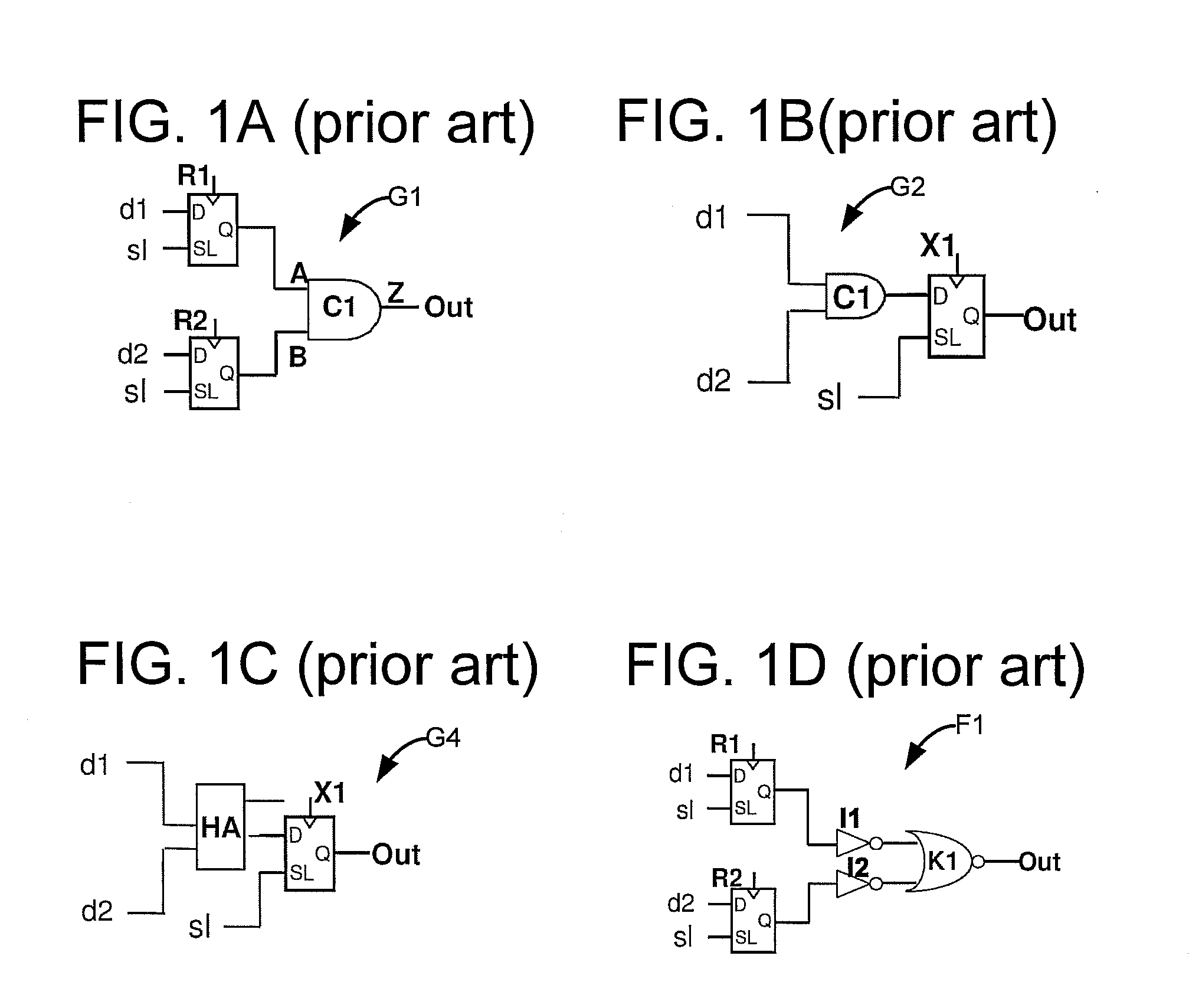

Transformation of IC designs for formal verification

ActiveUS20090293028A1Computer aided designSoftware simulation/interpretation/emulationBlack boxCombinational logic

A memory is encoded with data that represents a reference IC design, a retimed IC design, and logical relationships, wherein at least one logical relationship describes combinational logic without reference to structural information, such as actual cells that have been instantiated in the IC designs. The logical relationships are used to instantiate logic described therein, and to define one or more black boxes as being functionally inverse of the logic. Each instantiated logic and its functionally inverse black box are thereafter added to the reference IC design to obtain a transformed reference IC design. A transformed retimed IC design is also obtained by addition of the instantiated logic(s) and functionally inverse black box(es) to the retimed IC design. These two transformed IC designs are then supplied to an equivalence checker, for formal verification.

Owner:SYNOPSYS INC

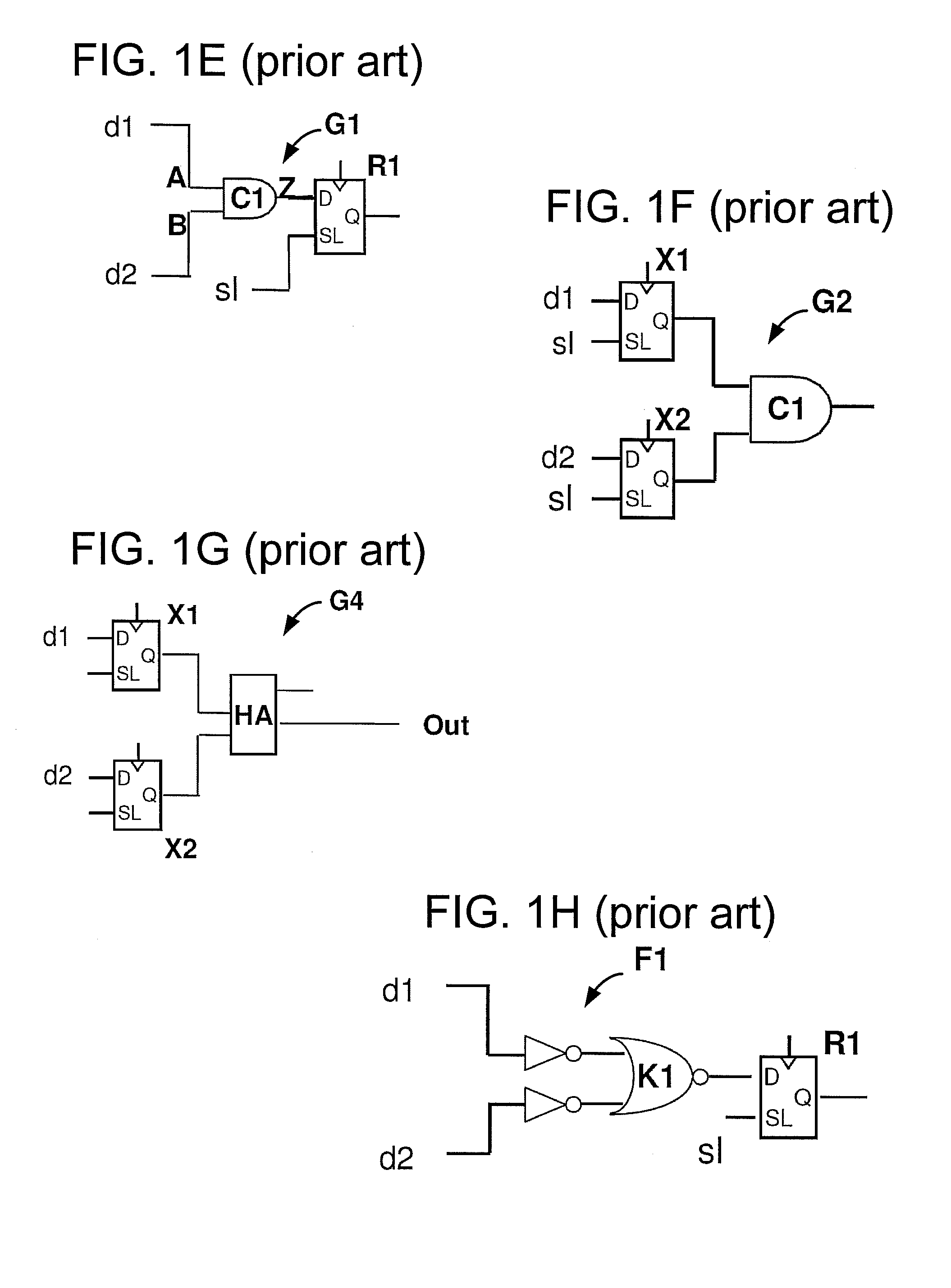

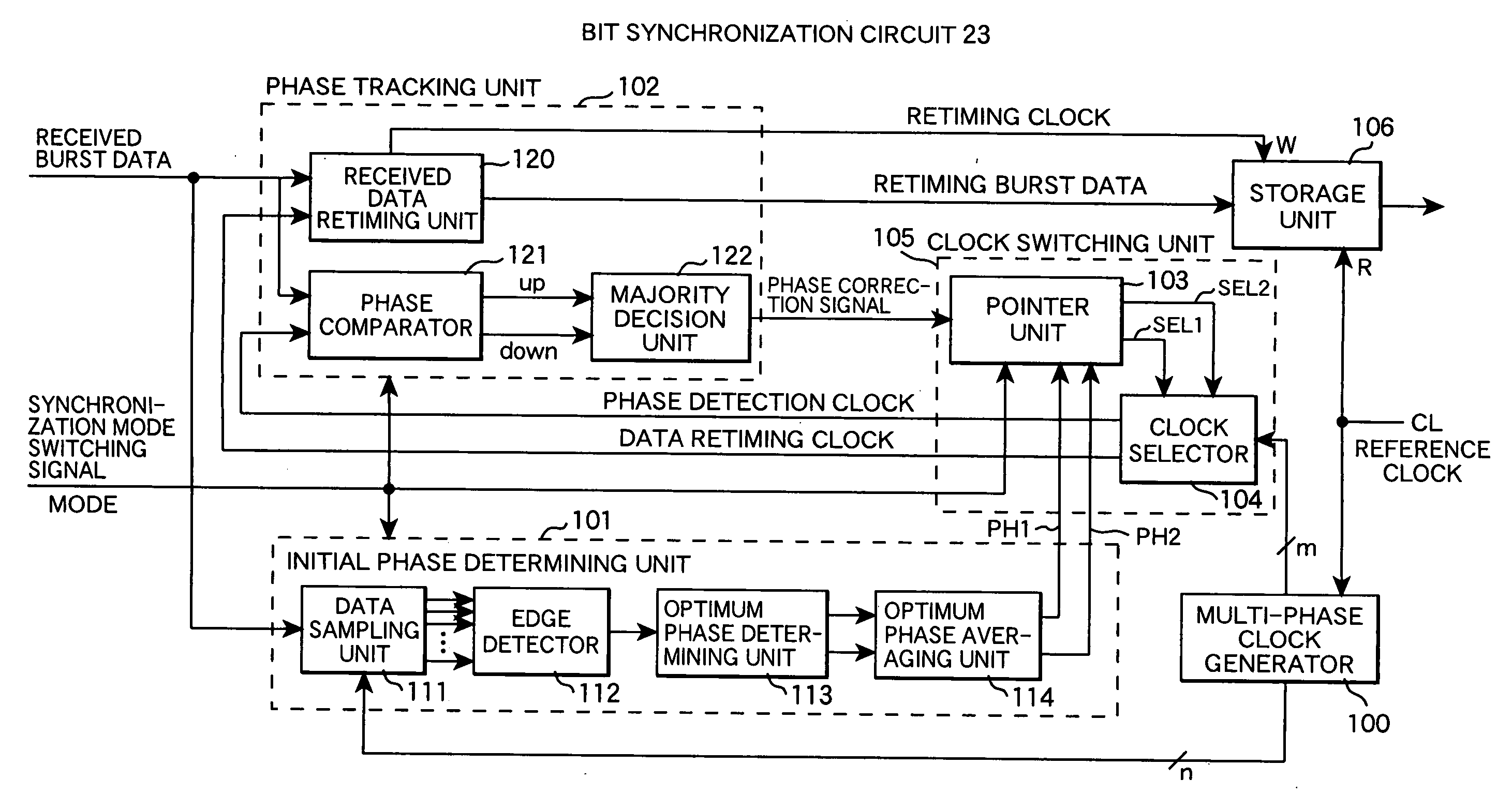

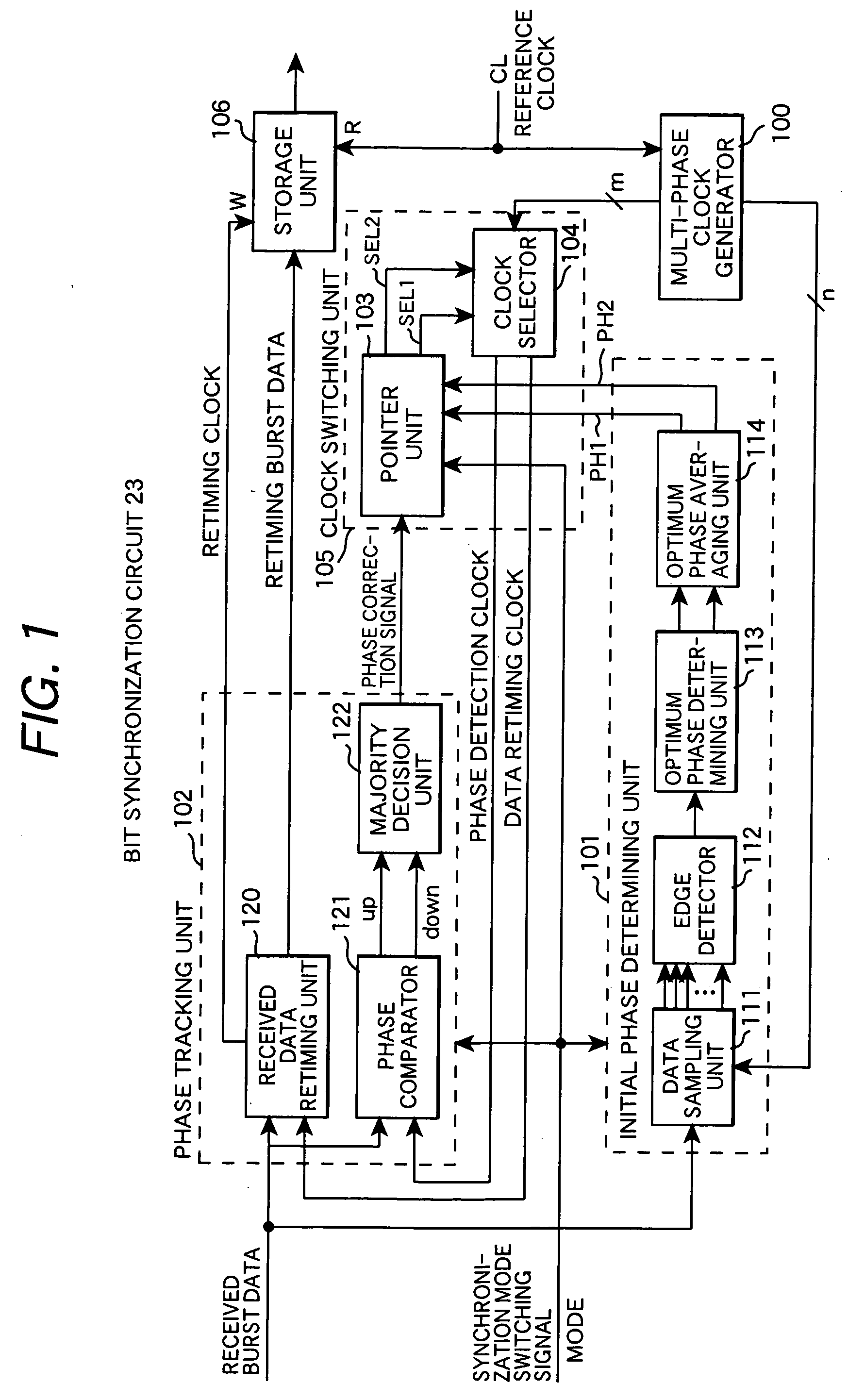

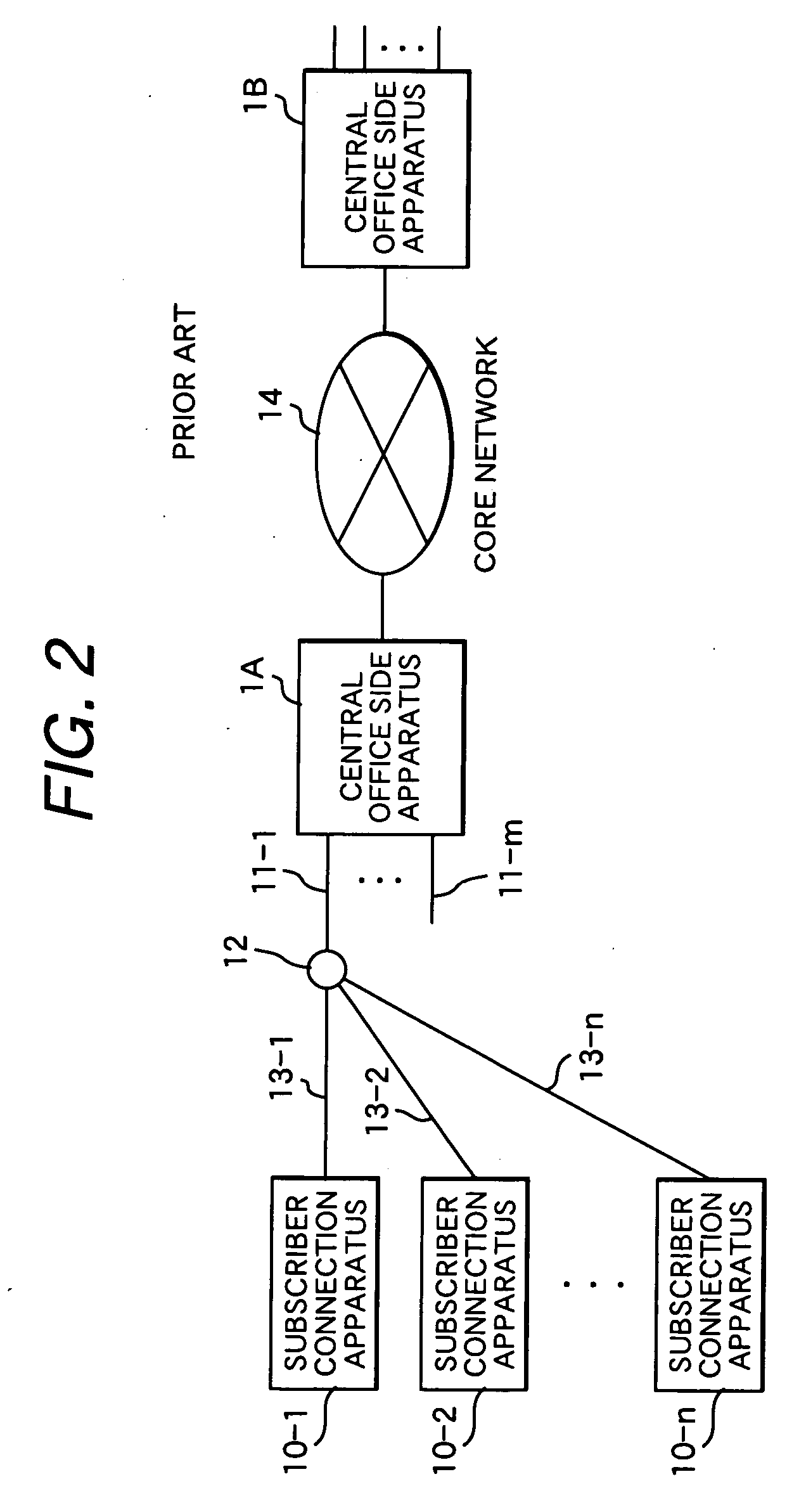

Bit synchronization circuit with phase tracking function

InactiveUS20070030937A1Reduce power consumptionQuick fixReceiver initialisationPulse automatic controlData synchronizationPhase relation

A bit synchronization circuit comprising an initial phase determining unit for rapidly determining, during a period of receiving a preamble of burst data, a clock with a phase synchronized with received burst data from among multi-phase clocks having the same frequency as an internal reference clock and a phase tracking unit for modifying the synchronized phase clock responsive to phase variation of received data during a period of receiving a payload of burst data by taking the synchronized phase clock determined by the initial phase determining unit as an initial phase. The bit synchronization circuit retimes burst data with a data retiming clock having a predetermined phase relation with the synchronized phase clock and outputs the burst data in synchronization with the internal reference clock.

Owner:HITACHI LTD

Active optical cable with integrated retiming

ActiveUS20070237471A1Reduce chanceWell formedCoupling light guidesFibre mechanical structuresElectrical connectorElectric cables

An active cable that is configured to communicate over much of its length using one or more optical fibers, and that includes an integrated electrical connector at at least one end. The active cable includes an integrated retiming mechanism. Thus, multiple links of cable may be used while reducing the chance that the jitter will exceed allowable limits. The cable may be an electrical to optical cable, and electrical to electrical cable, or one of many other potential configurations.

Owner:II VI DELAWARE INC

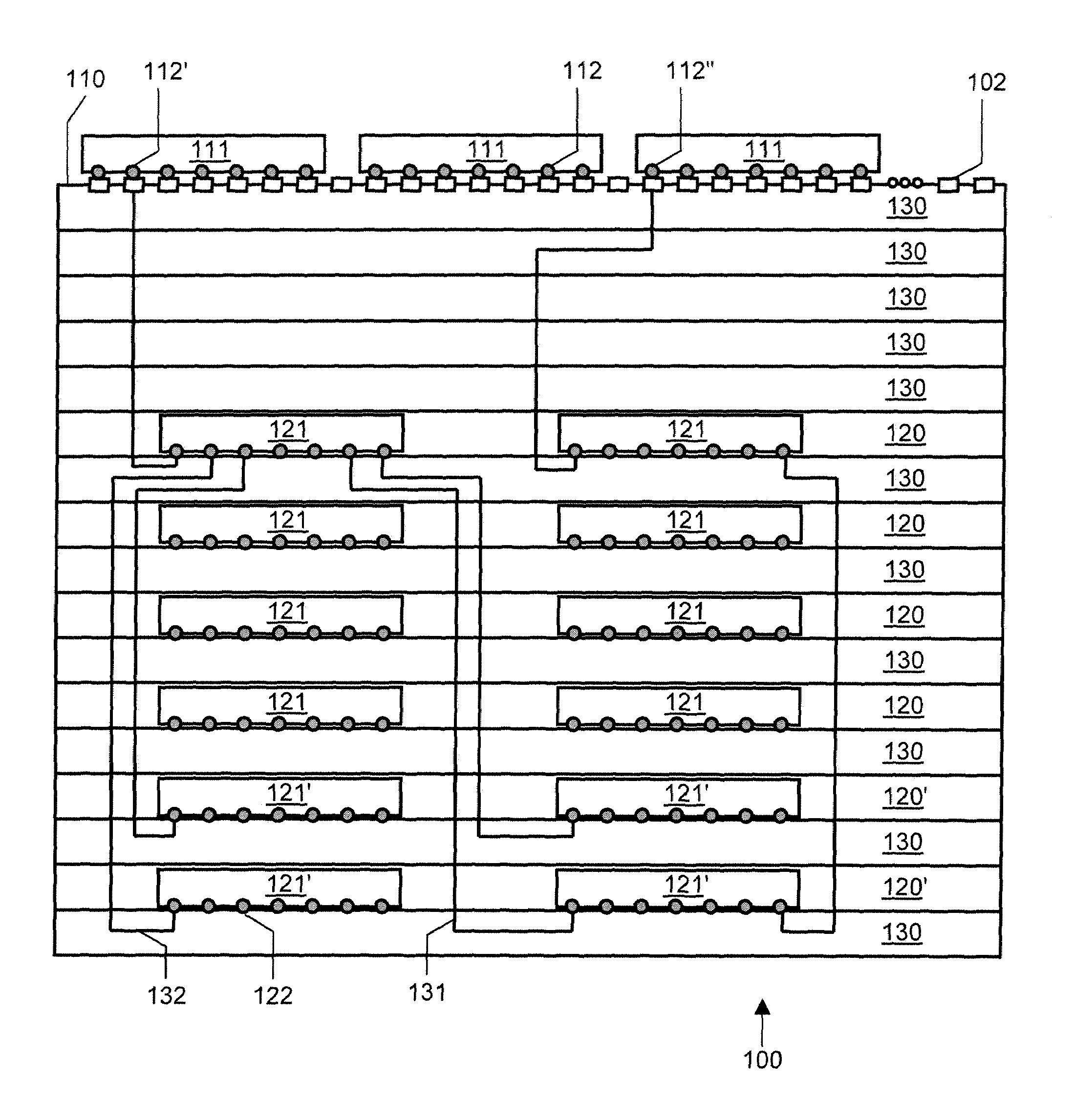

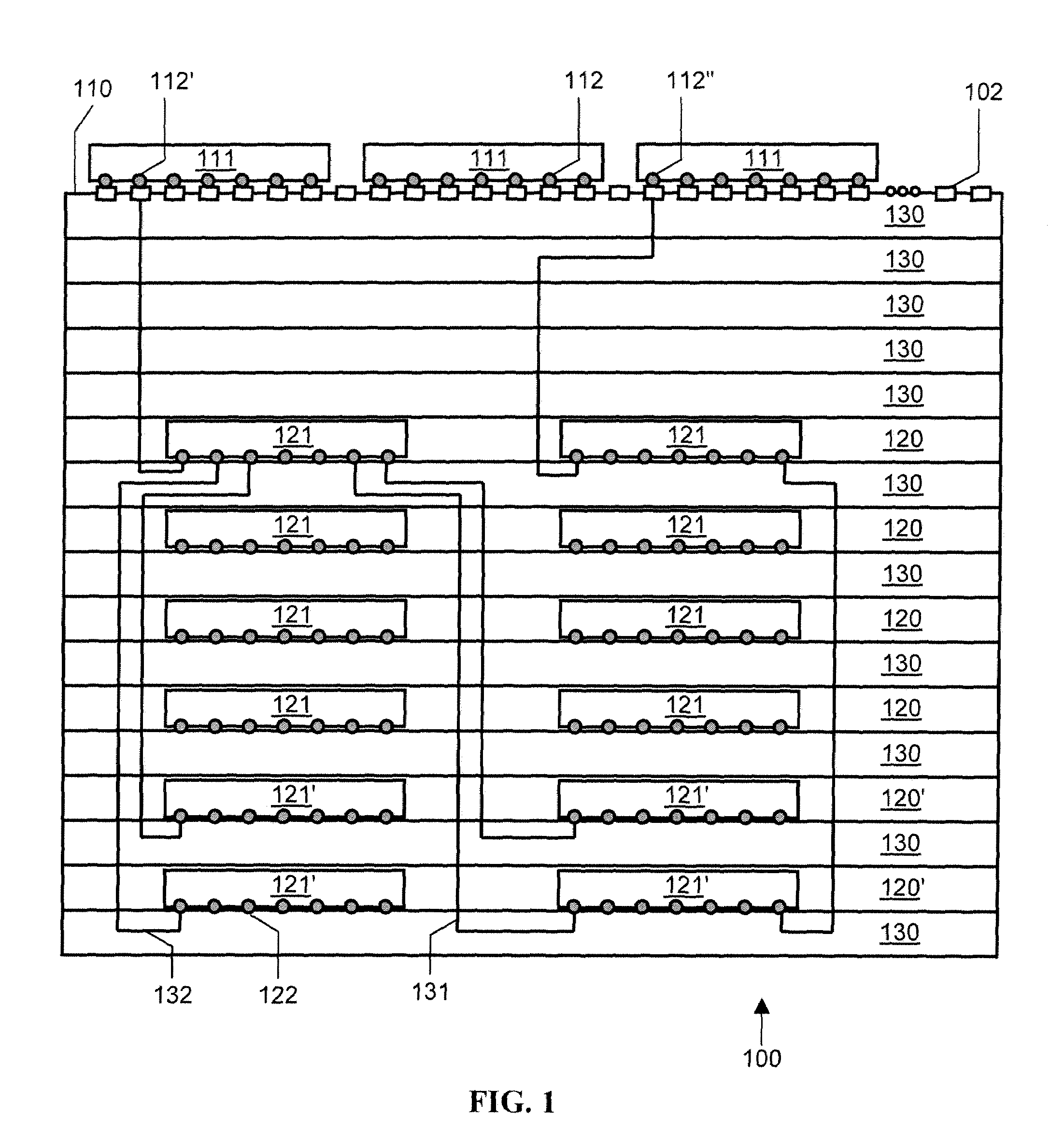

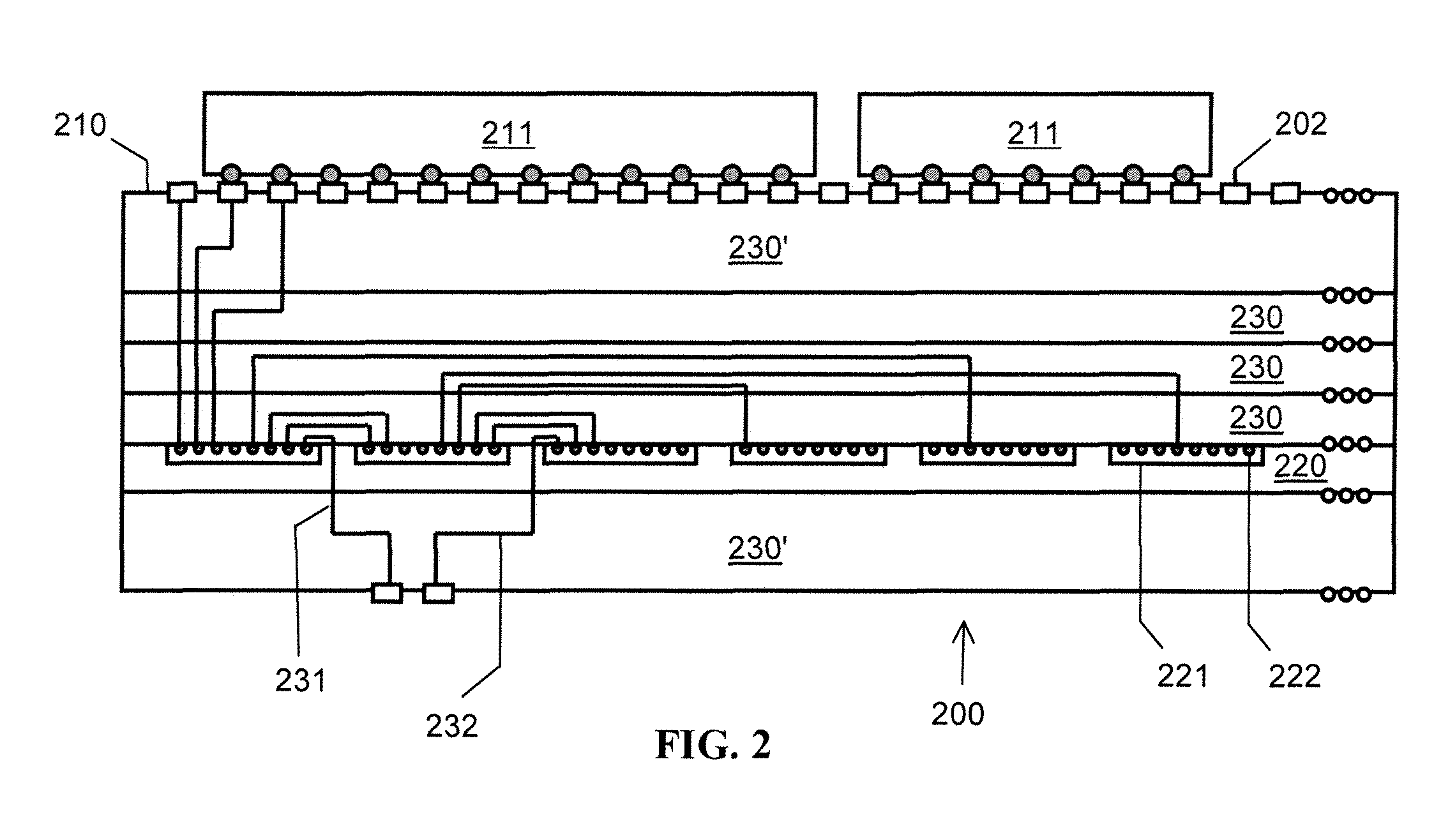

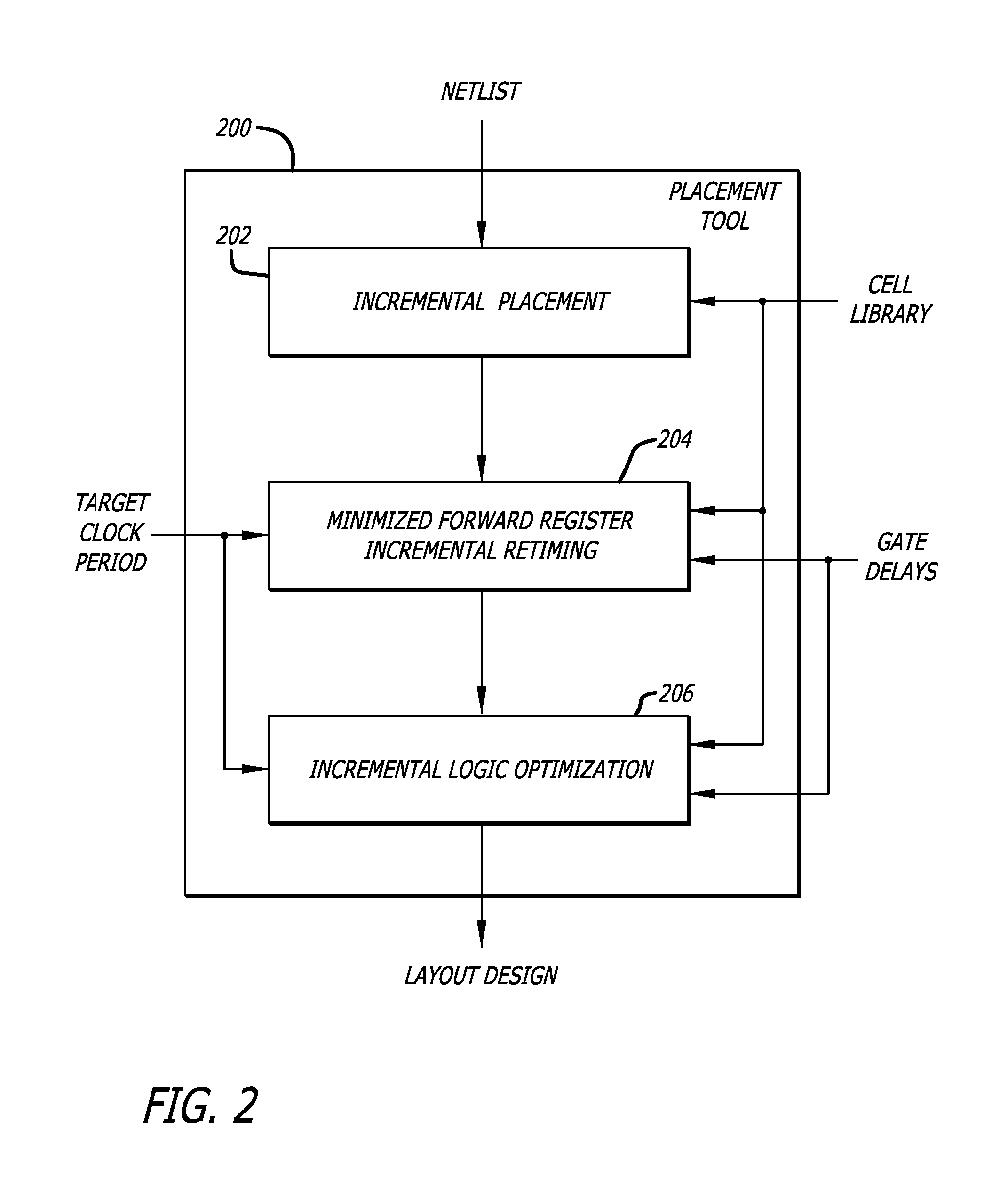

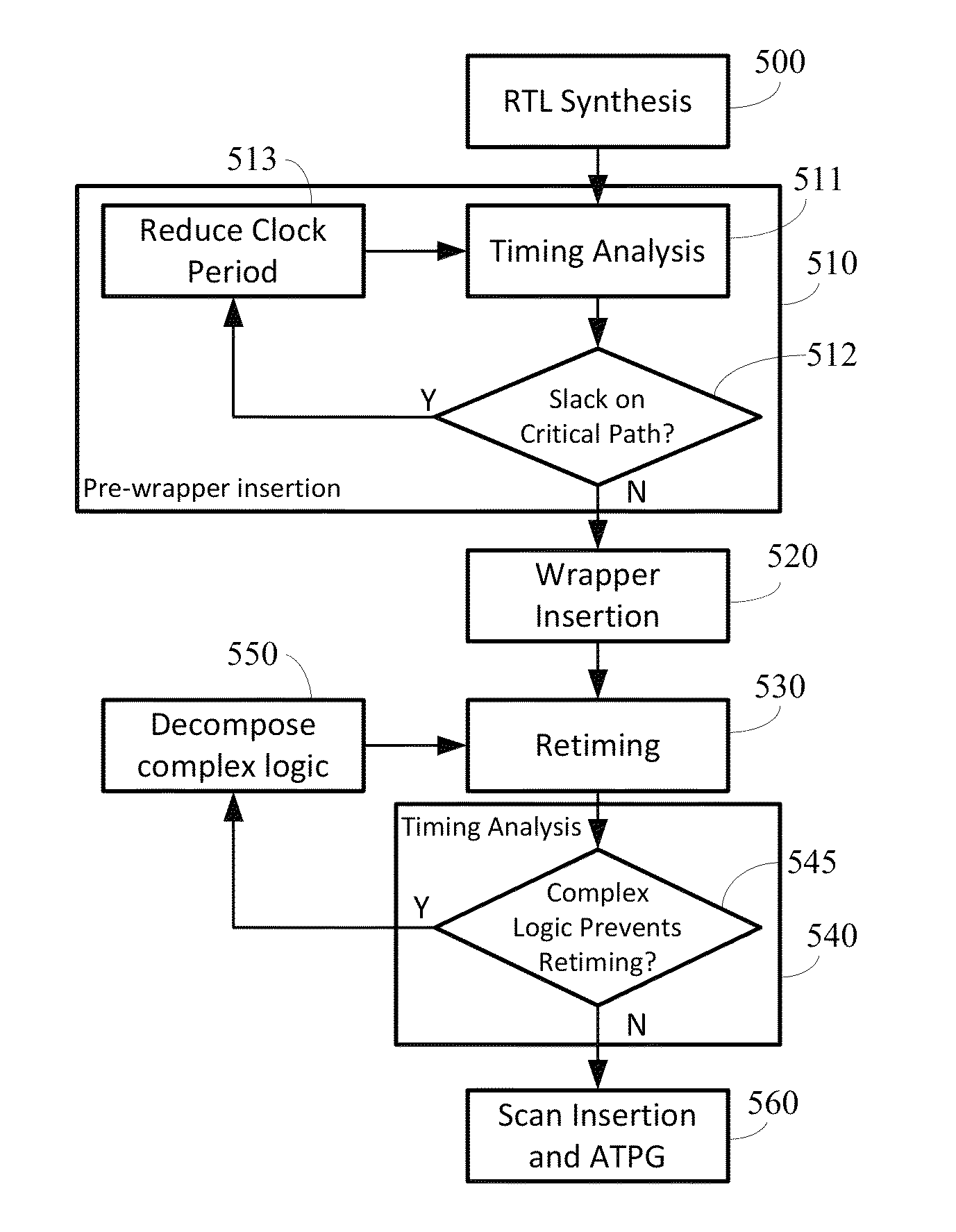

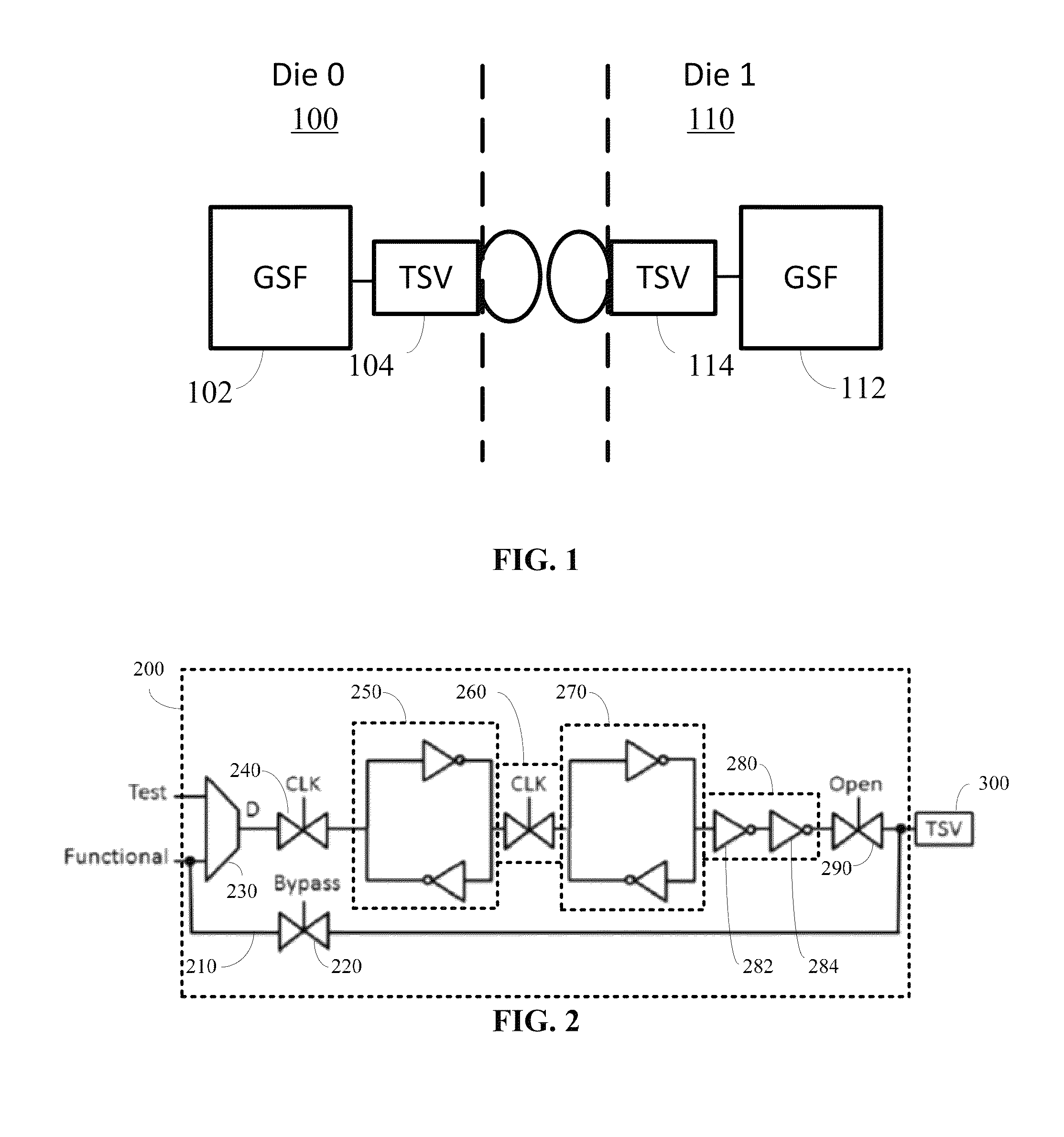

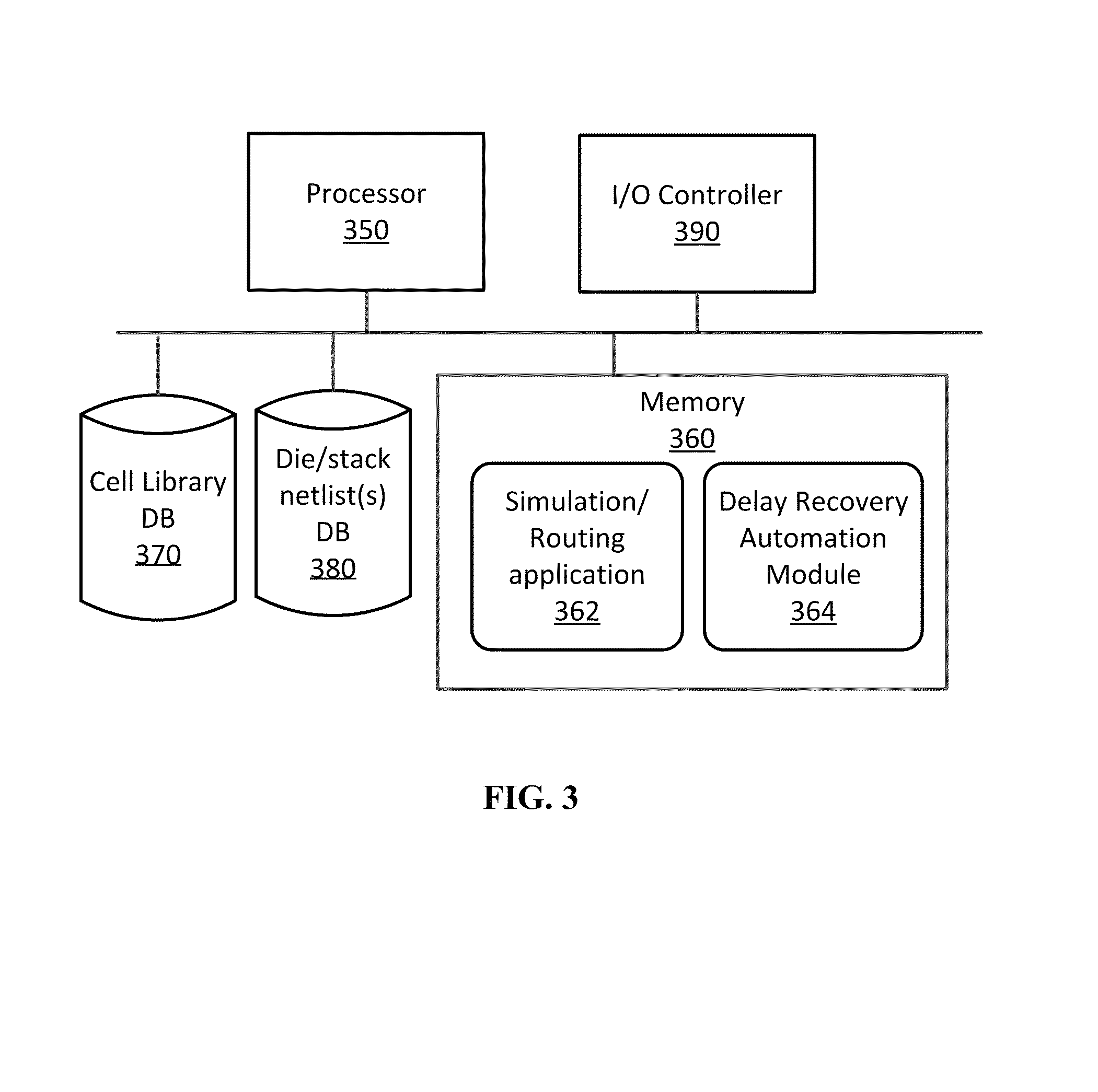

Retiming-based design flow for delay recovery on inter-die paths in 3D ICs

InactiveUS8832608B1Increase delayImprove latencyComputer aided designSpecial data processing applicationsDesign for testingDesign testing

A three dimensional (3D) stacked integrated circuit (IC) design-for-Testing (DfT) die-level wrapper boundary register having a bypass mode and design-level DfT delay recovery techniques are provided. Die wrappers that contain boundary registers at the interface between dies can be inserted into 3D ICs where the boundary registers include a gated scan flop with a bypass line passing the functional input to a through-silicon-via (TSV) in a manner avoiding the clocked stages of the gated scan flop during functional operation. A retiming process can be applied during design layout using a simulation / routing tool or standalone program to recover the additional delay added to the TSV paths by the DfT insertion. Retiming can be performed at both die and stack level, and in further embodiments, logic redistribution across adjacent dies of the stack can be performed for further delay optimization.

Owner:DUKE UNIV

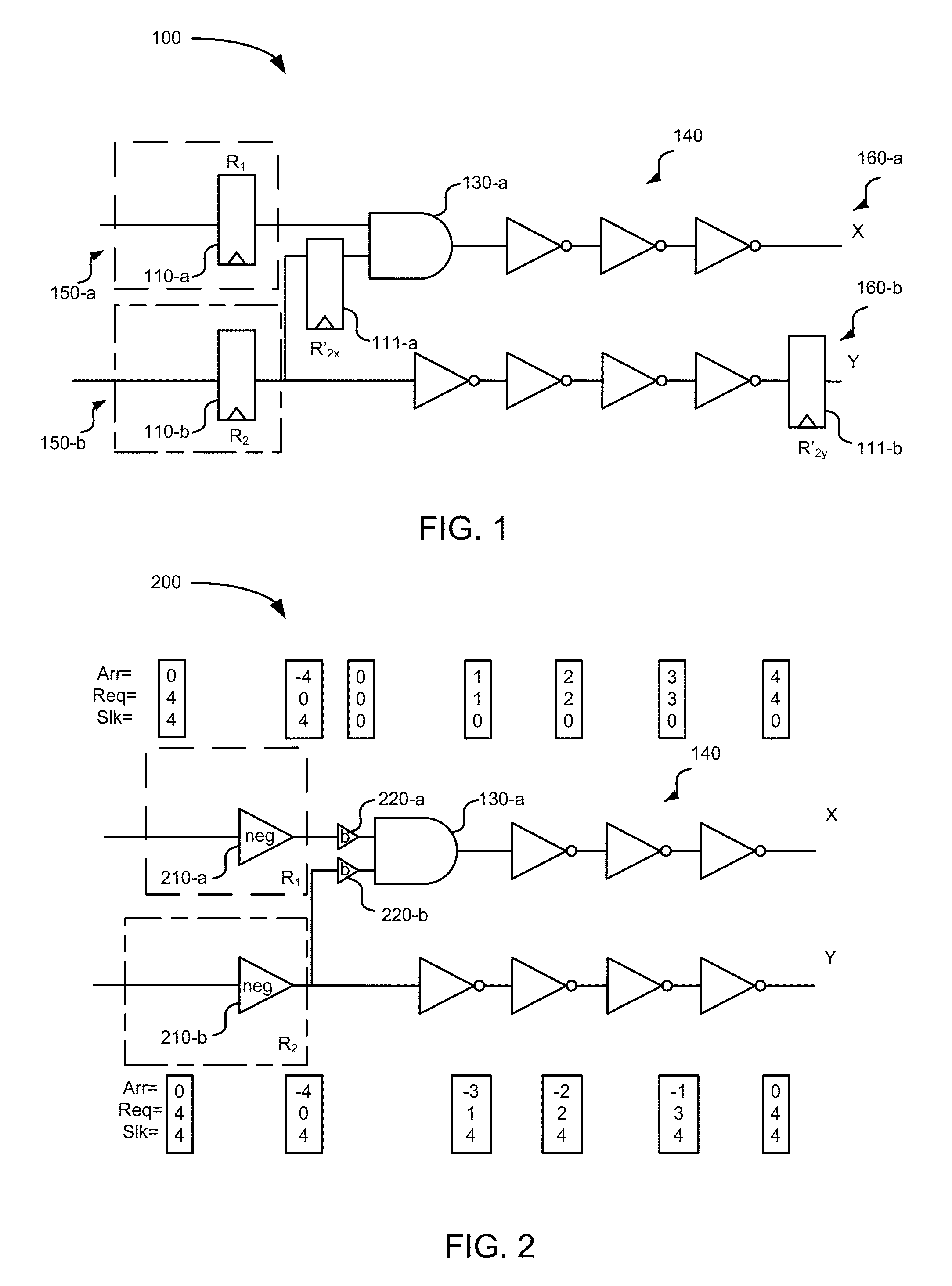

Programmable device configuration methods adapted to account for retiming

ActiveUS8677298B1Reduce delaysOptimize circuit designCAD circuit designSpecial data processing applicationsEmbedded systemIntegrated circuit

A method of configuring an integrated circuit device with a user logic design includes analyzing the user logic design to identify critical and near-critical cyclic logic paths within the user logic design, applying timing optimizations to the critical and near-critical cyclic logic paths, and retiming logic paths other than the critical and near-critical cyclic logic paths.

Owner:ALTERA CORP

Reconfigurable multi-channel all-optical regenerators

ActiveUS7099586B2Small and even zero changeEliminate needWavelength-division multiplex systemsElectromagnetic transmissionMach–Zehnder interferometerWaveguide

Owner:RGT UNIV OF CALIFORNIA

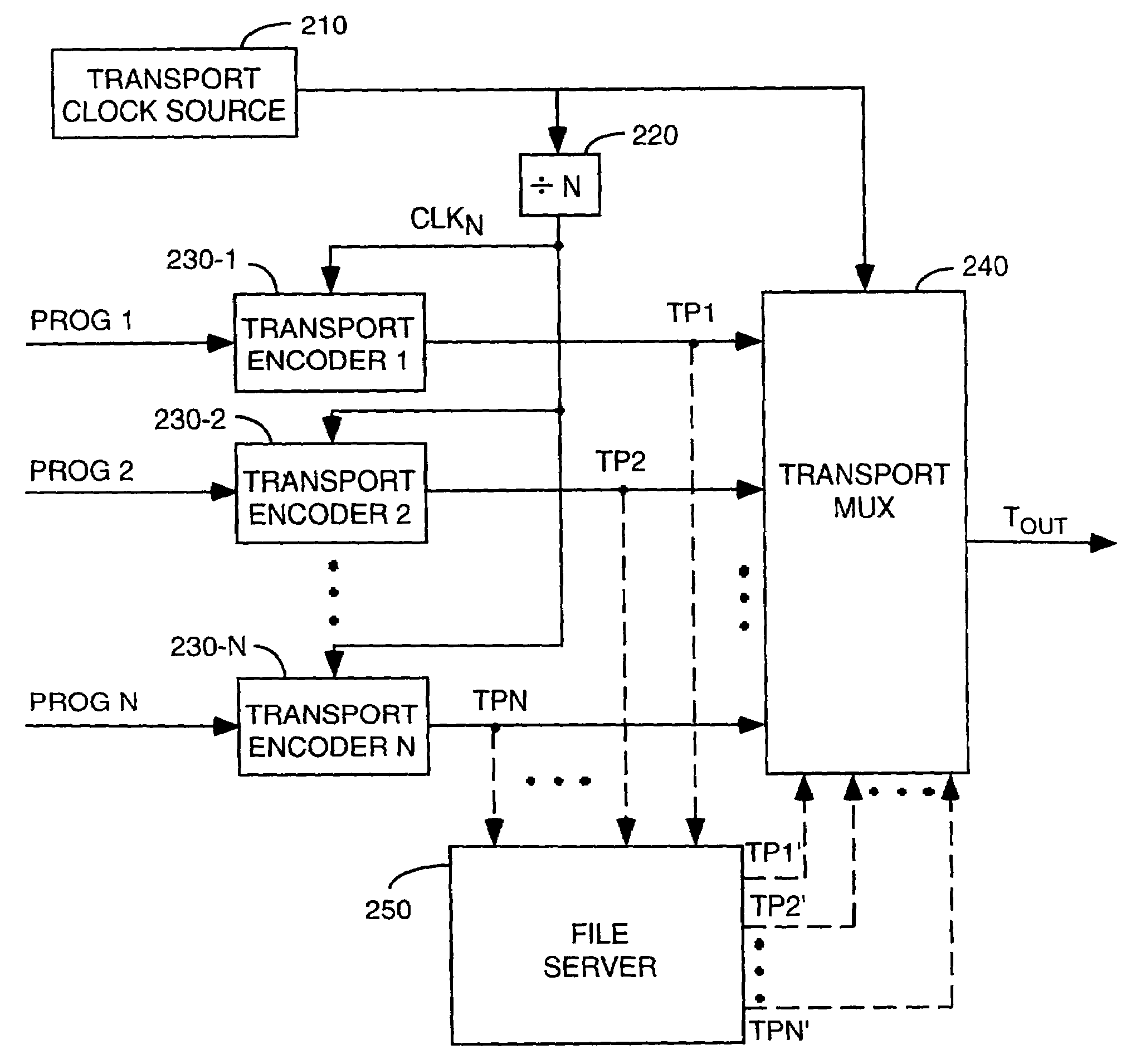

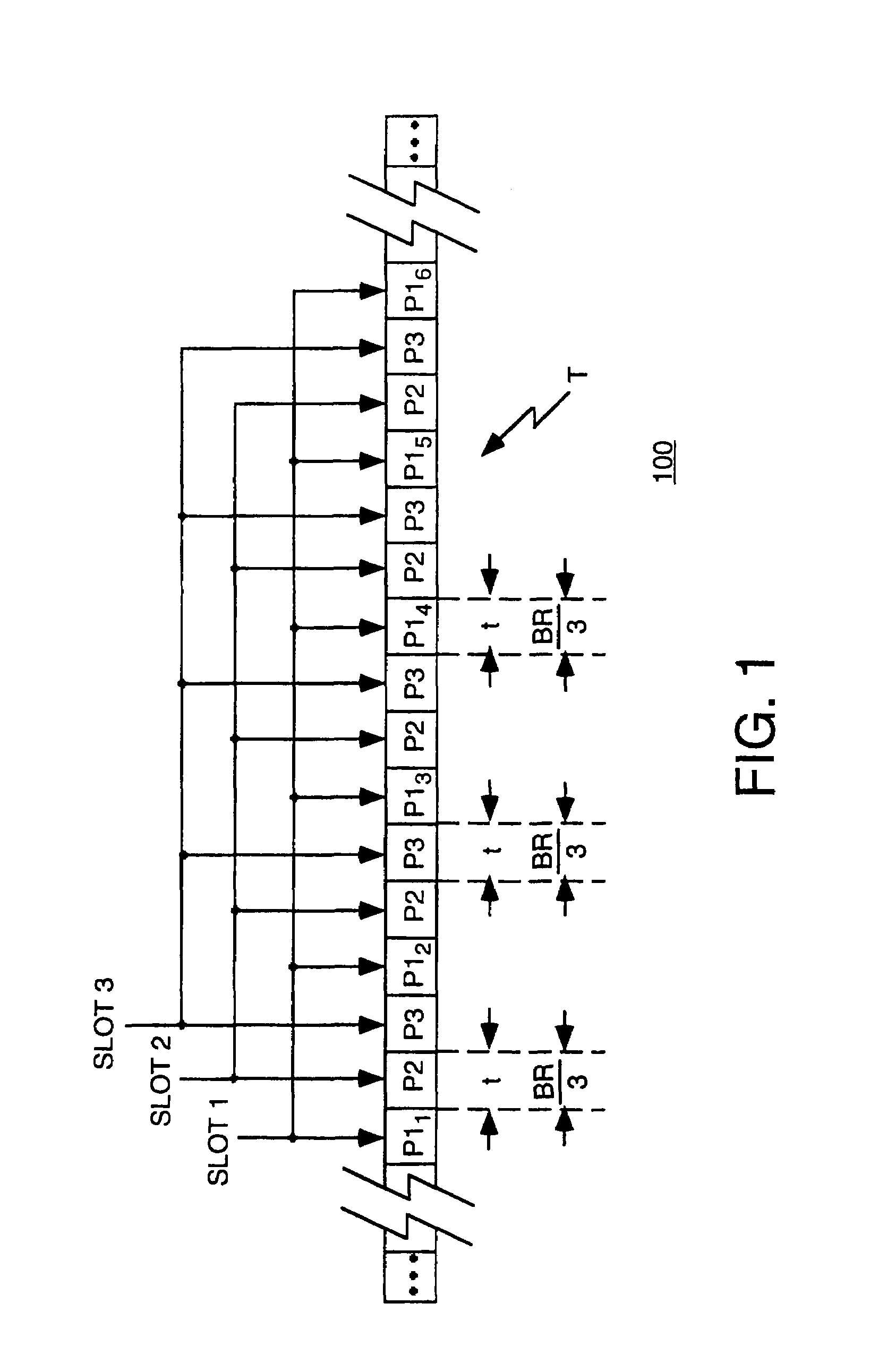

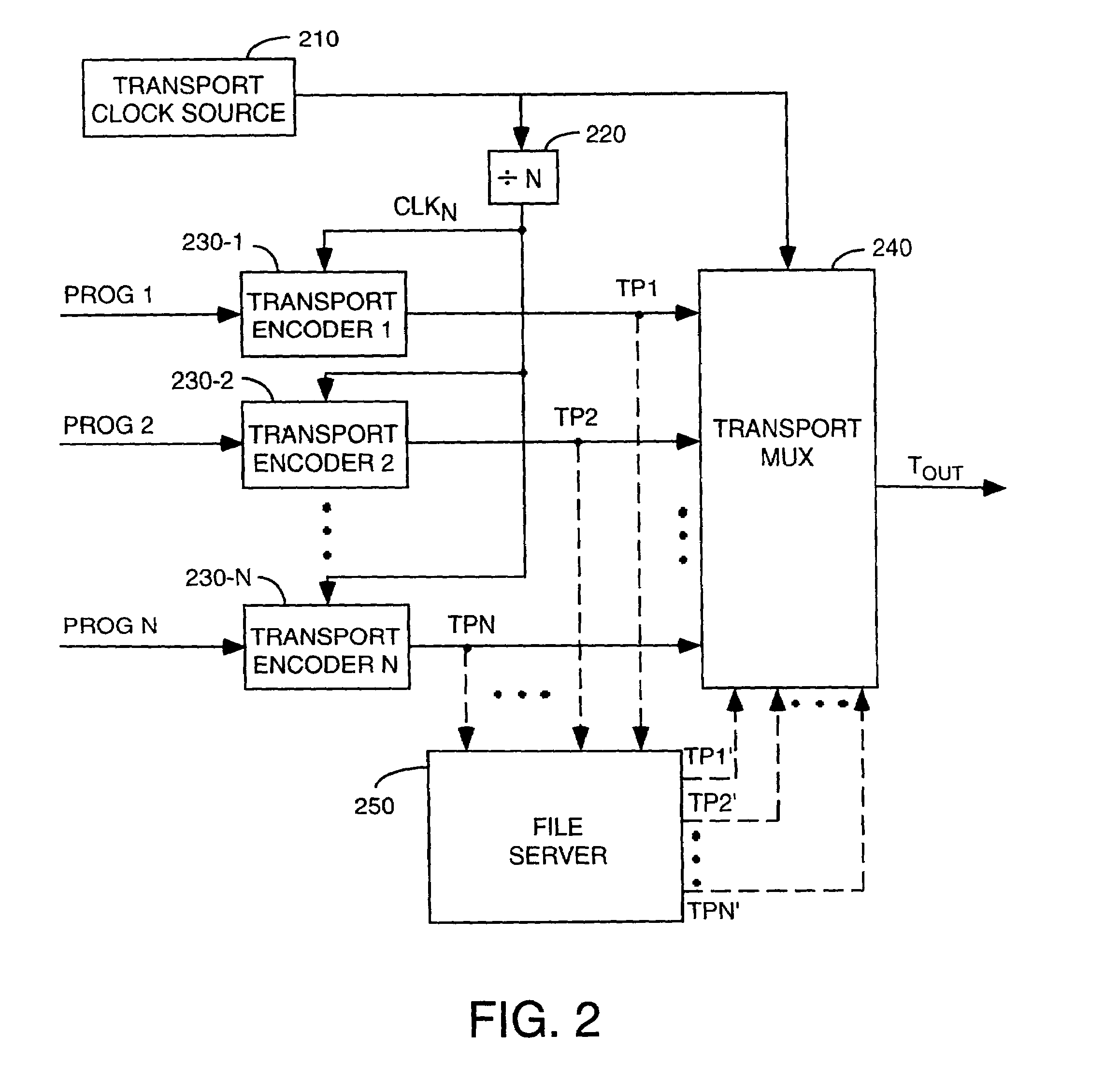

Method and apparatus for forming and utilizing a slotted MPEG transport stream

A method and apparatus for forming and processing an MPEG transport stream such that programs may be inserted into, or deleted from, the MPEG transport stream without significant retiming operations.

Owner:COX COMMUNICATIONS

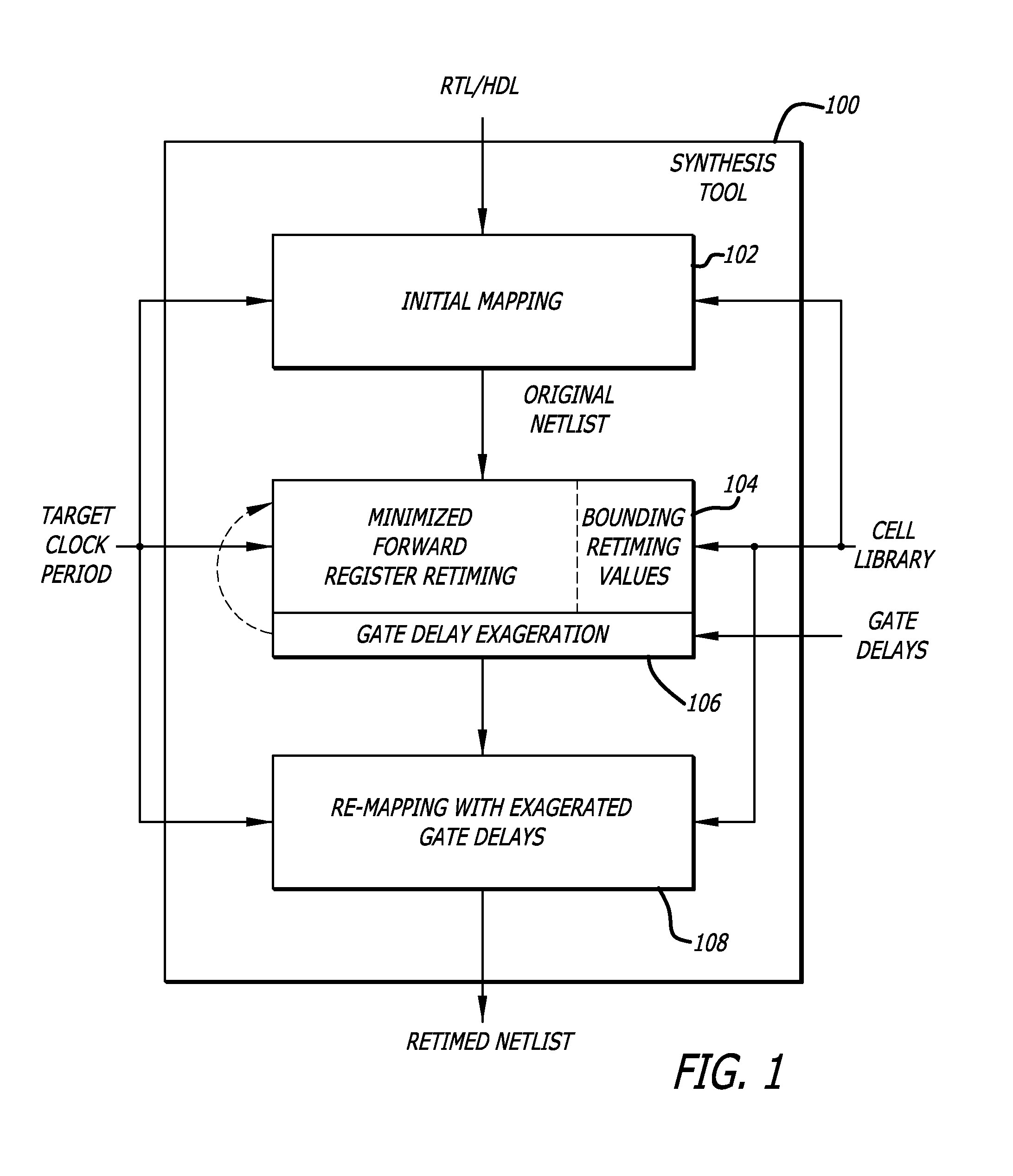

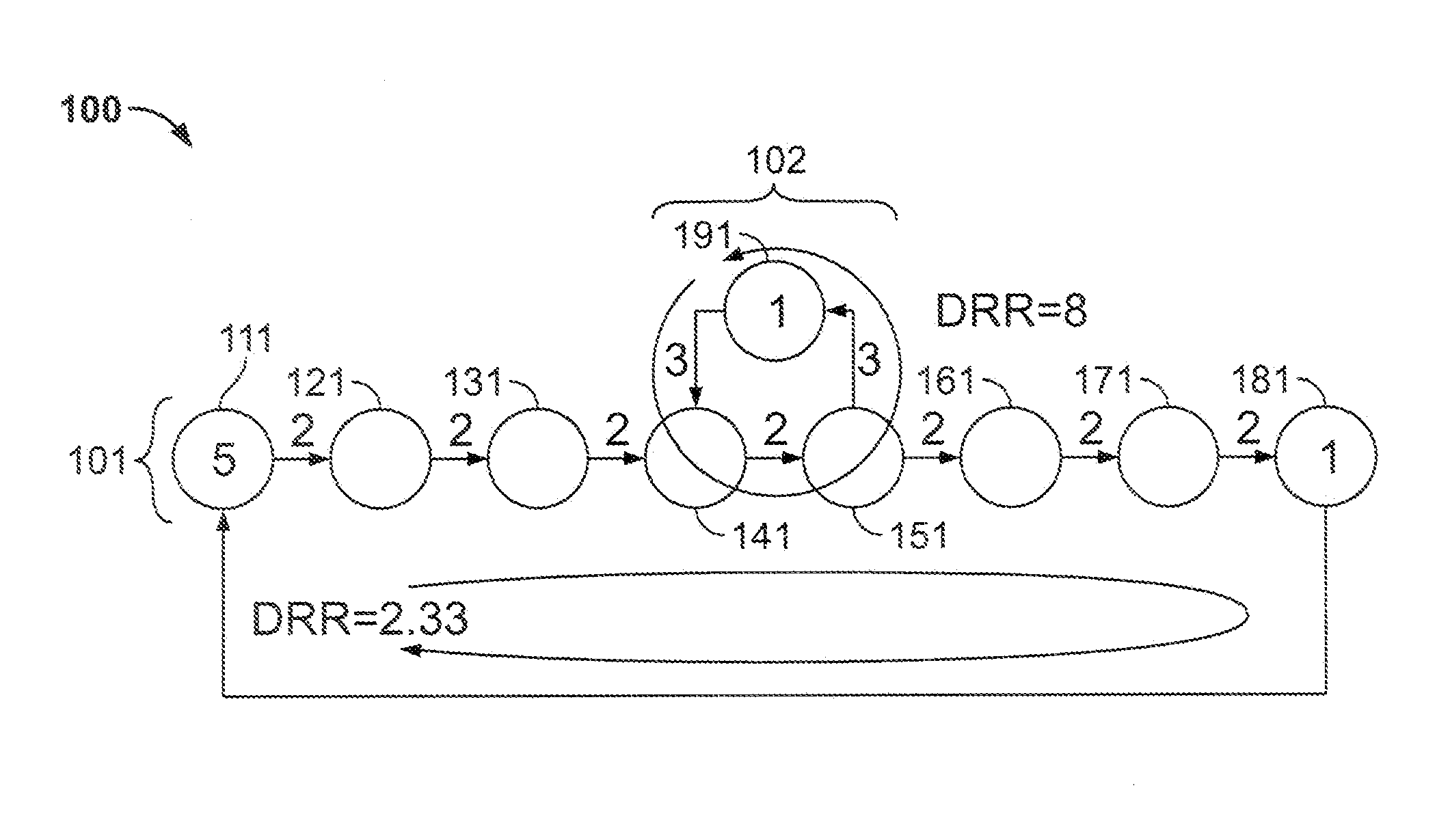

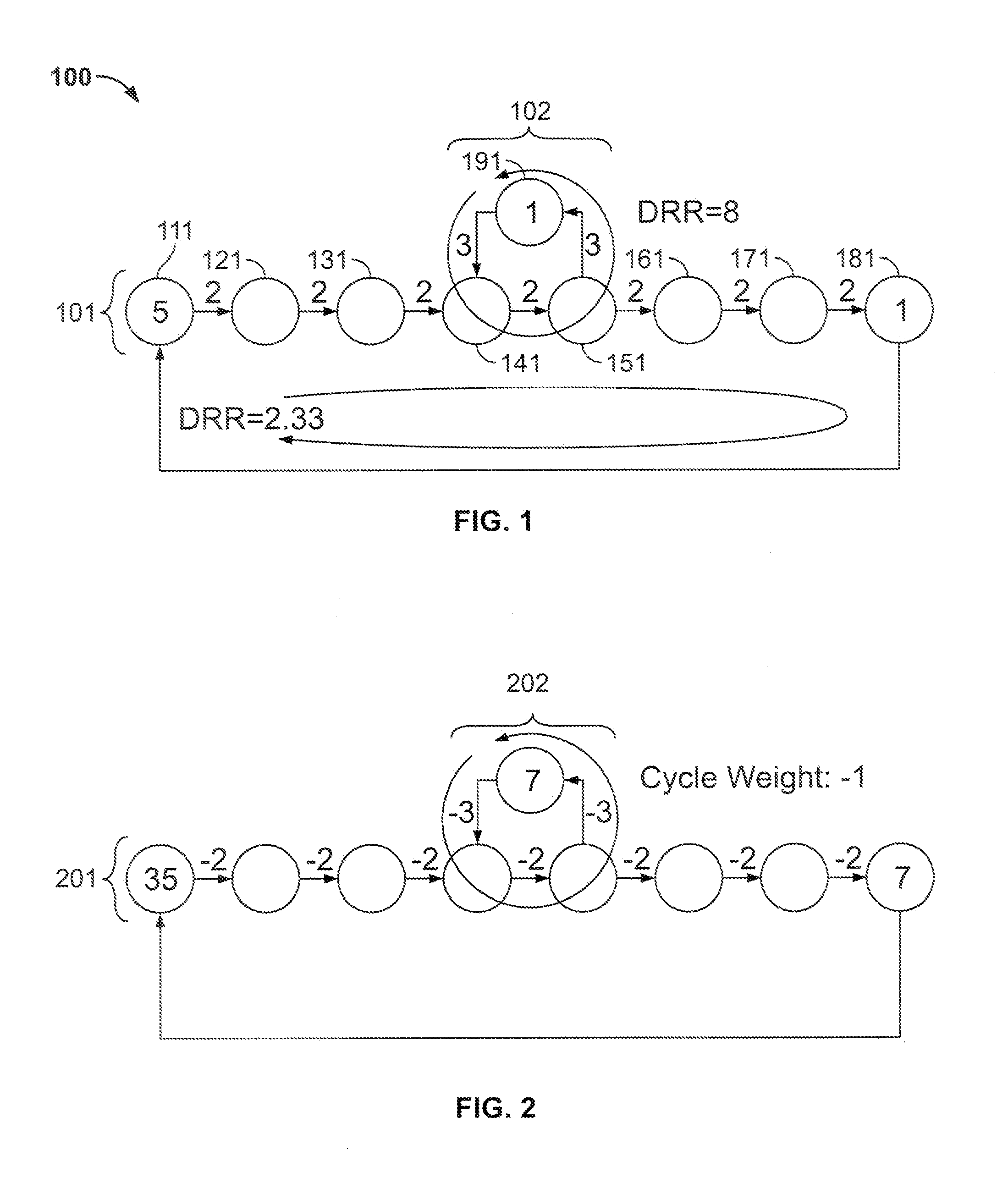

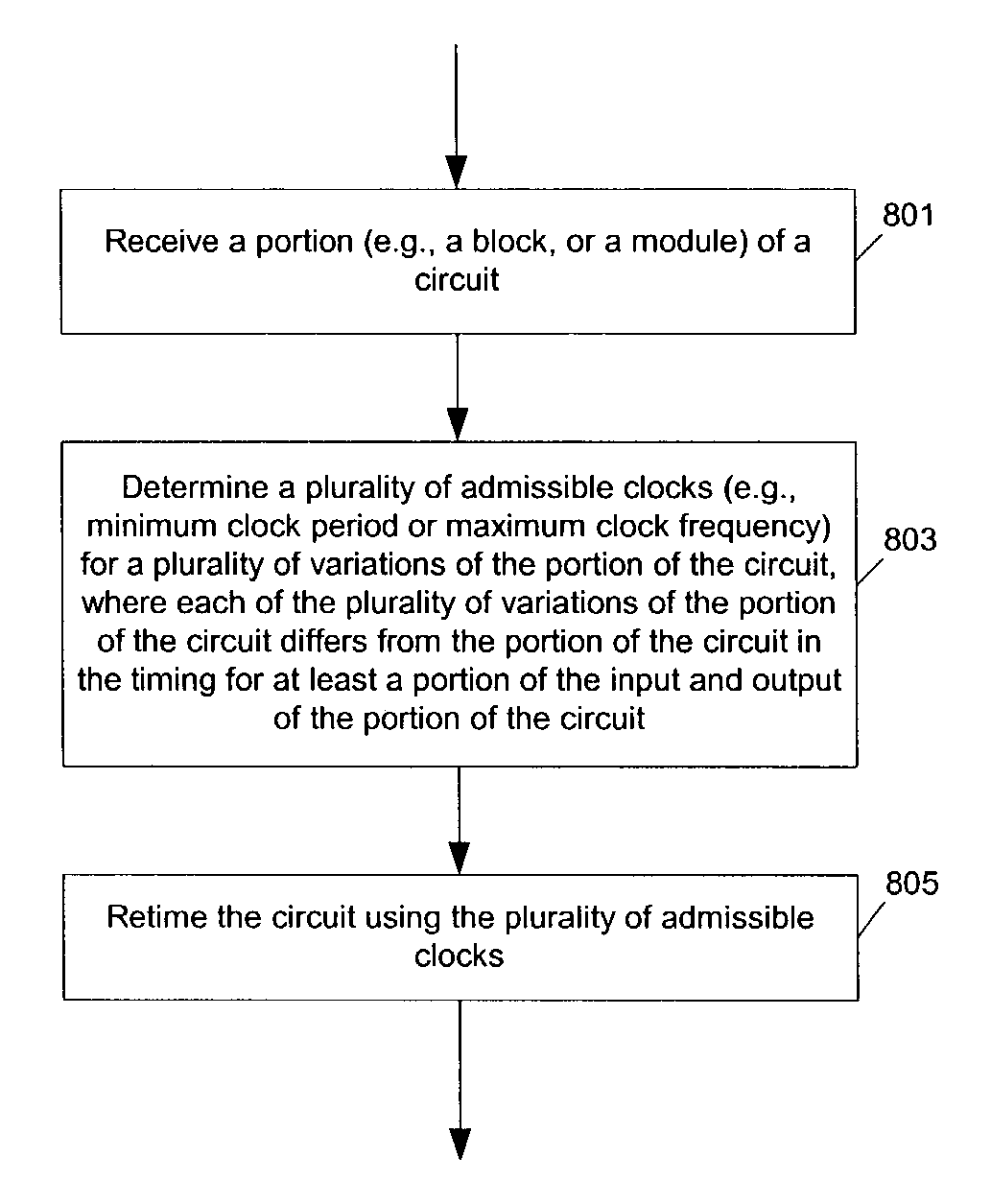

Method and apparatus for circuit design and retiming

ActiveUS7162704B2CAD circuit designSoftware simulation/interpretation/emulationComputer scienceCircuit design

Methods and apparatuses to hierarchically retime a circuit. In at least one embodiment of the present invention, a module of a circuit is designed with a plurality of different latencies to have a plurality of different minimum clock periods (e.g., through retiming at the module level). In one example, the minimum clock periods are determined from detailed timing analyses after the placement and routing for the module; and, in retiming the circuit that contains the module, a data flow graph representation of the module is constructed based on the target clock period of the circuit and the correlation between the latencies and the minimum clock periods. In at least one embodiment of the present invention, hierarchical retiming is performed in which portions of the circuit is retimed to generate results (e.g., for different latencies), which are selectively used for the retiming of the entire circuit based on the target clock period.

Owner:SYNOPSYS INC

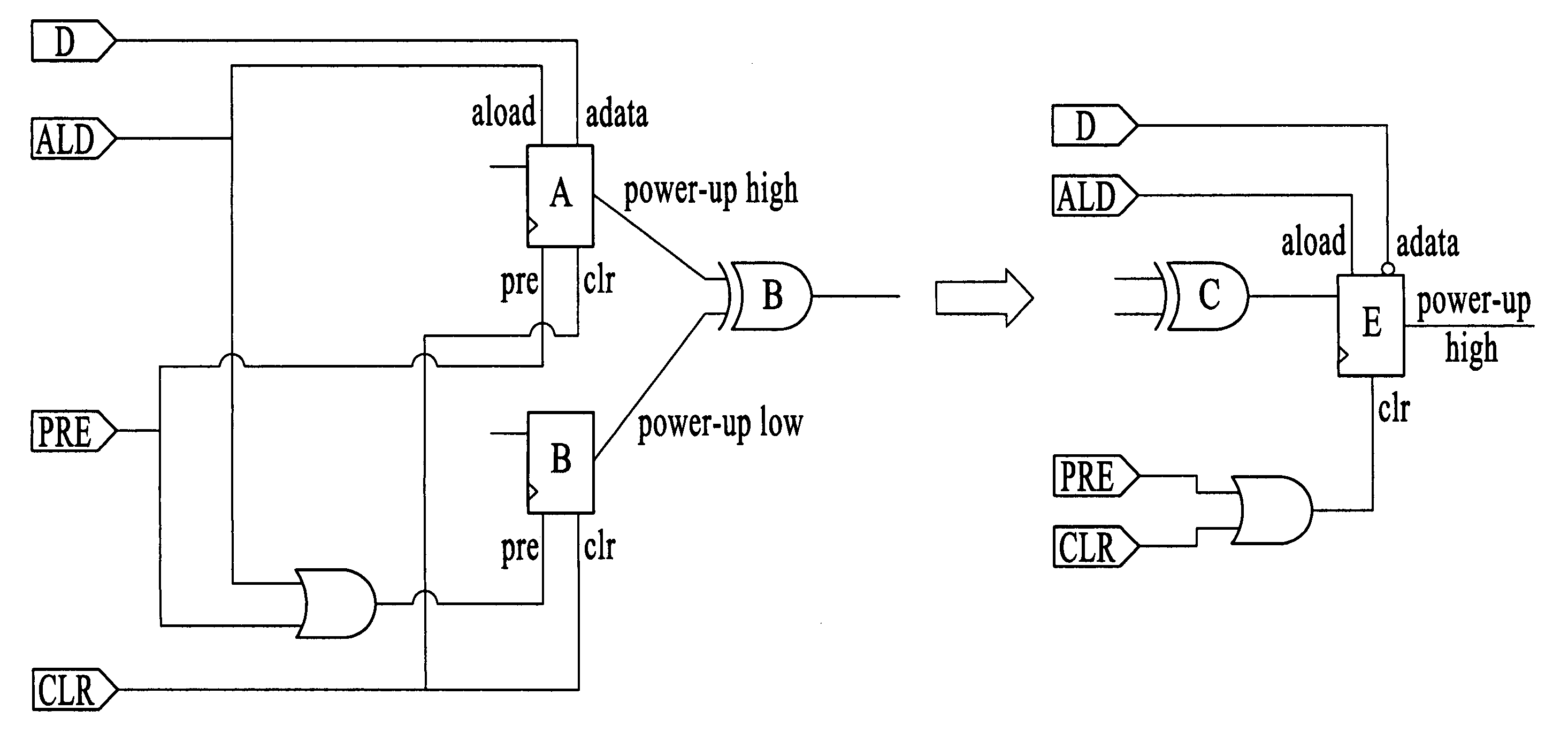

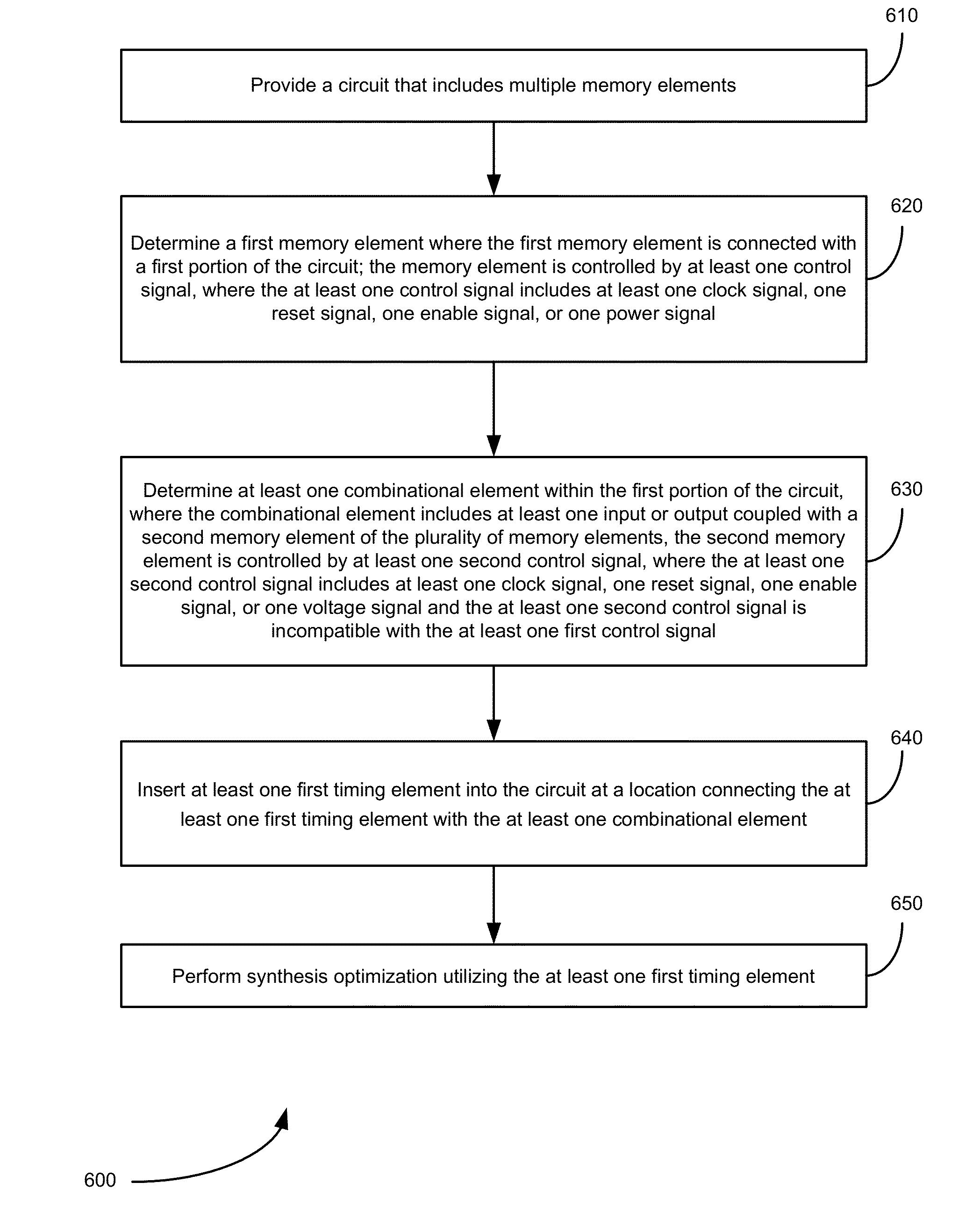

Boundary buffers to model register incompatibility during pre-retiming optimization

ActiveUS8423939B1Improve featuresRetardation valueComputer aided designSoftware simulation/interpretation/emulationControl signalComputer science

Methods, systems, and machine-readable storage medium for logic synthesis that adjust a timing model of a circuit are provided. A first memory element from multiple memory elements of the circuit may be determined, where the first memory element is connected with a first portion of the circuit and is controlled by at least one first control signal. A combinational element within the first portion of the circuit may be determined. The combinational element may include at least one input or output coupled with a second memory element. The second memory element may be controlled by at least one second control signal. The second control signal may be incompatible with the first control signal. A first timing element may be inserted into the circuit at a location connecting the first timing element with the combinational element. A synthesis optimization may be performed utilizing the at least one first timing element.

Owner:CADENCE DESIGN SYST INC

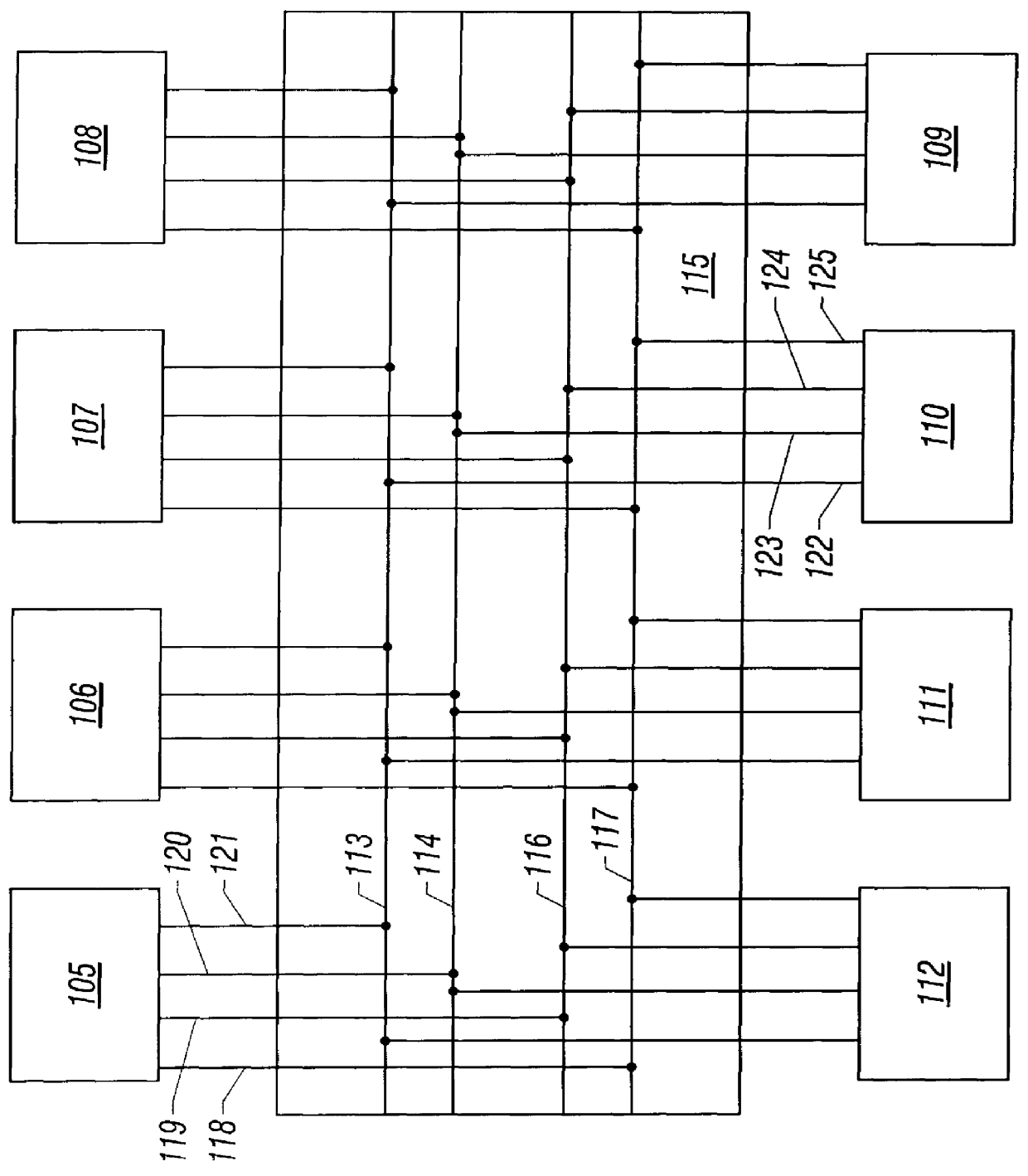

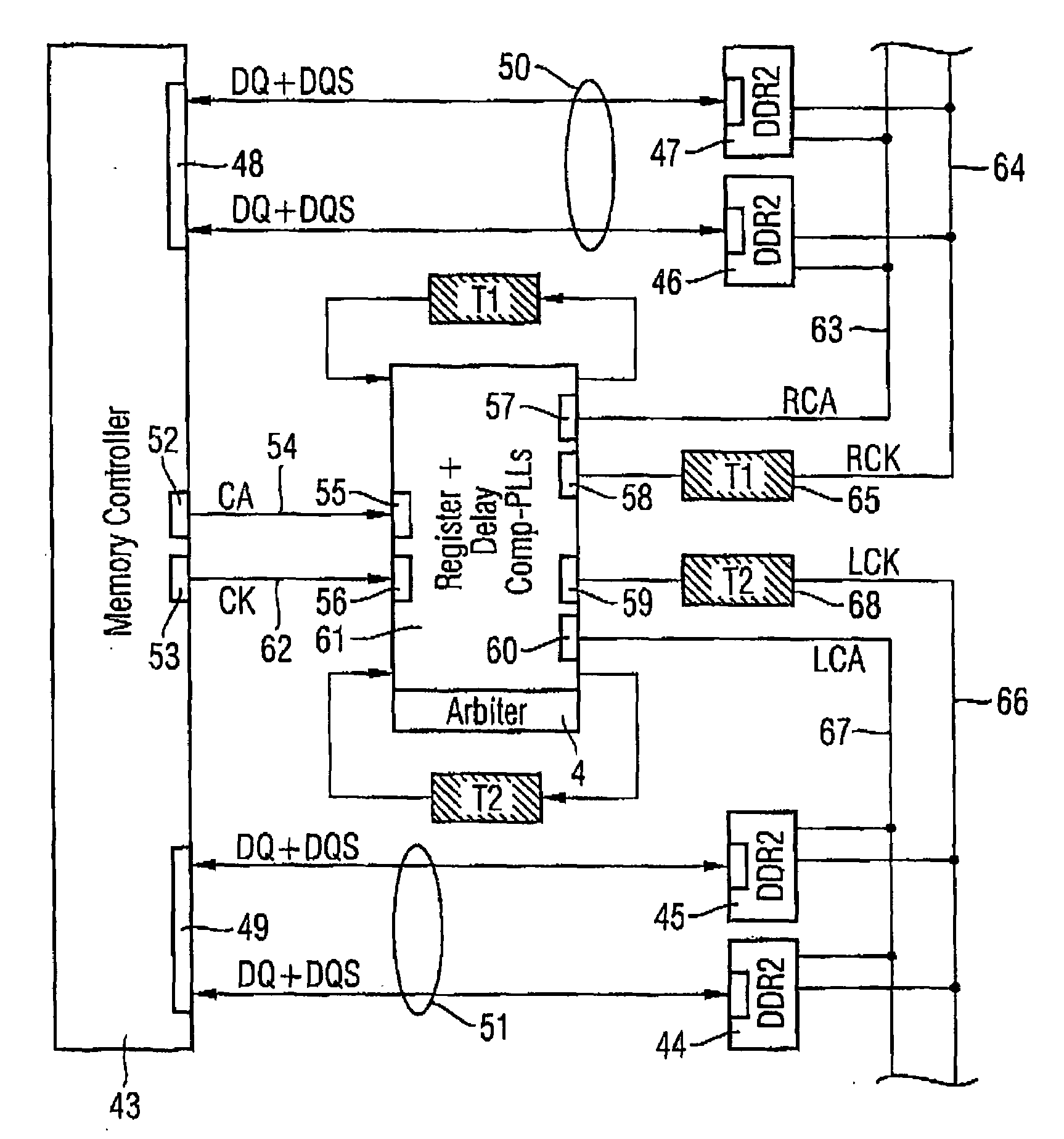

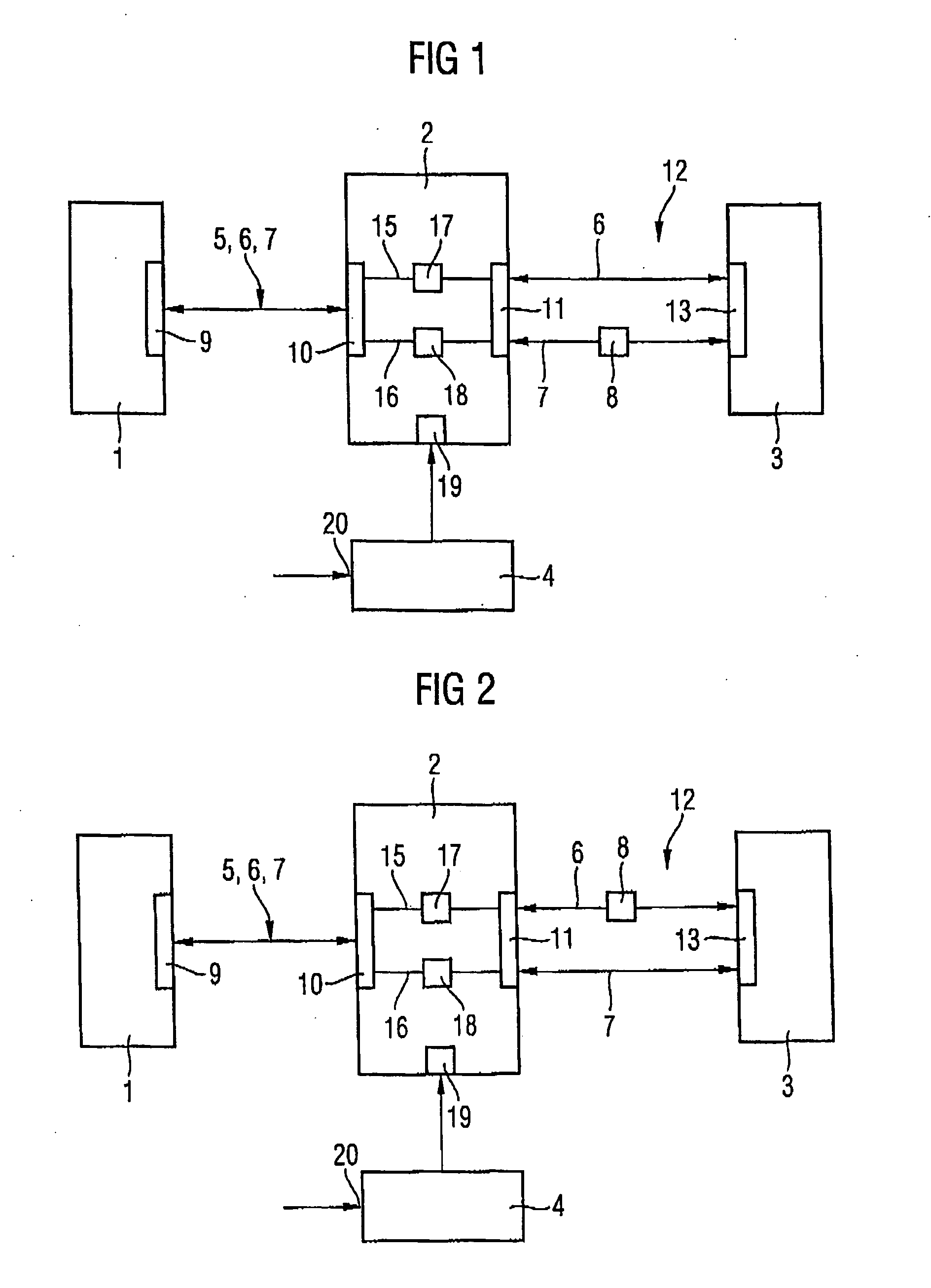

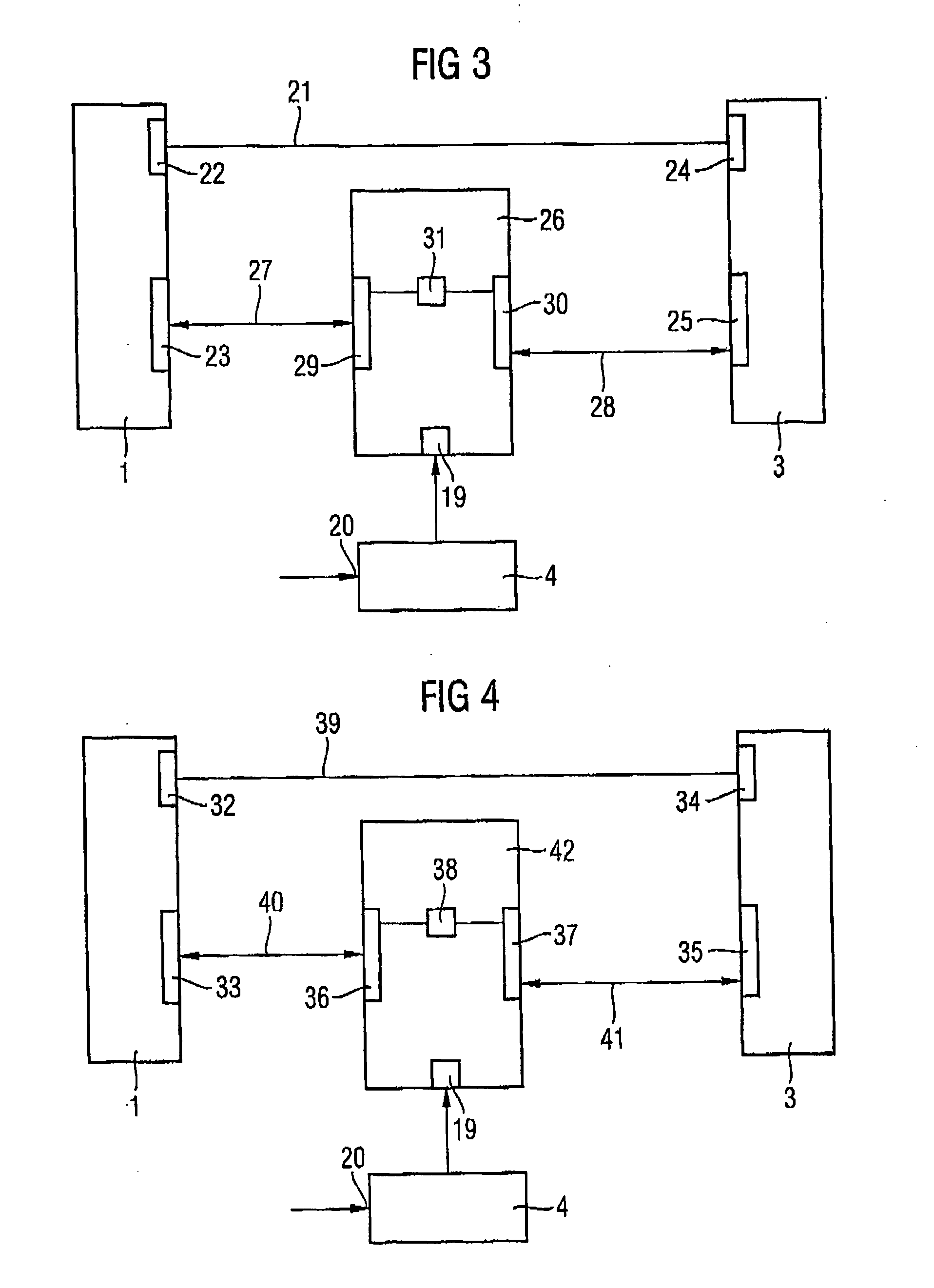

Memory system with a retiming circuit and a method of exchanging data and timing signals between a memory controller and a memory device

The present invention refers to a memory system with a controller and a memory device with a communication channel with a data path and a timing path coupling the controller with the memory device. The communication channel has different propagation times for the data path and the timing path exchanging a information signal and a timing signal between the controller and the memory device. The timing signals are used for determining the value of the information signal, and a retiming circuit that is connected with the communication channel compensates, depending on a compensation signal on an input, the delay between the data path and the timing path for exchanging a information signal and a timing signal between the controller and the memory device.

Owner:INFINEON TECH AG

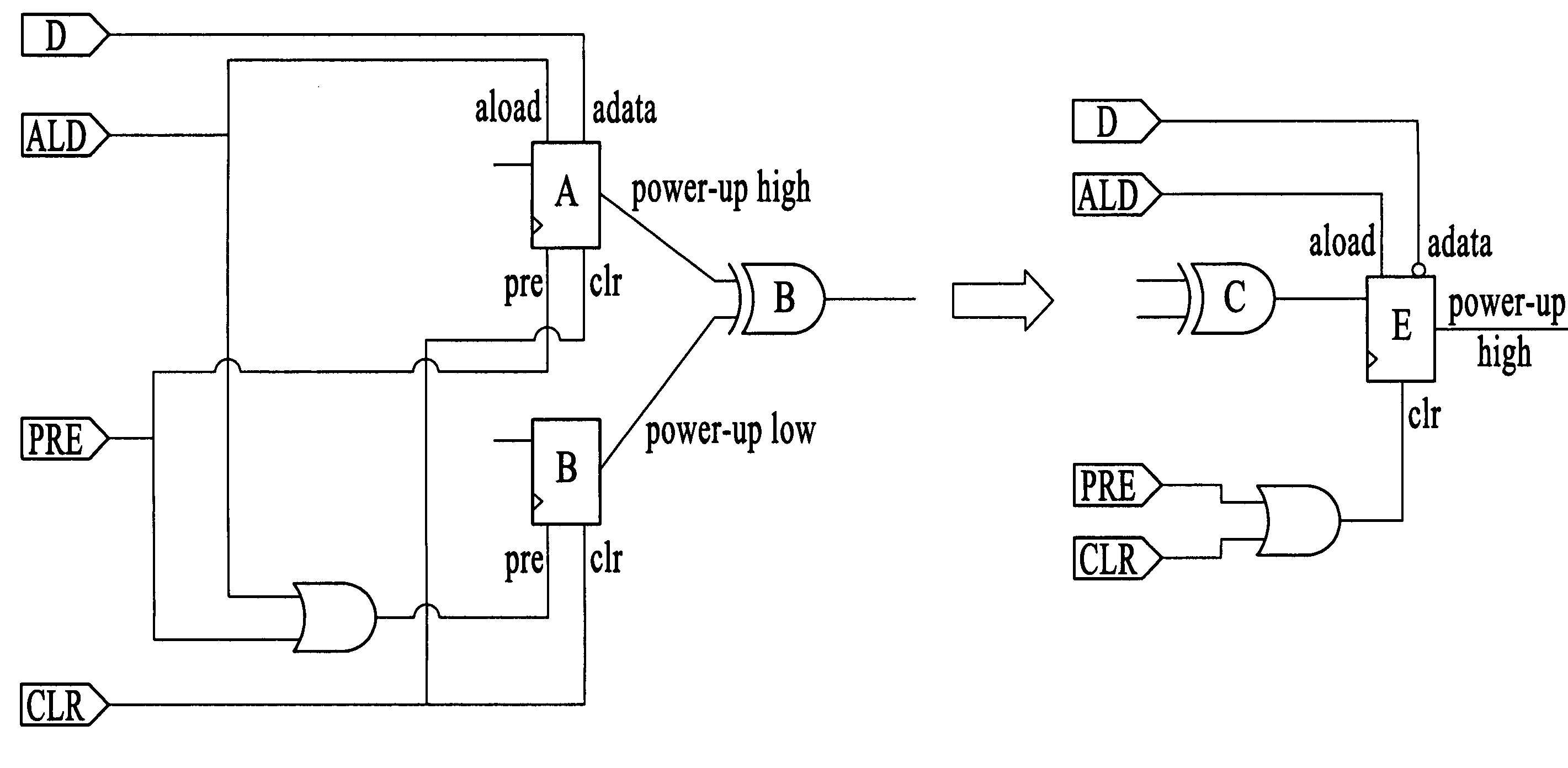

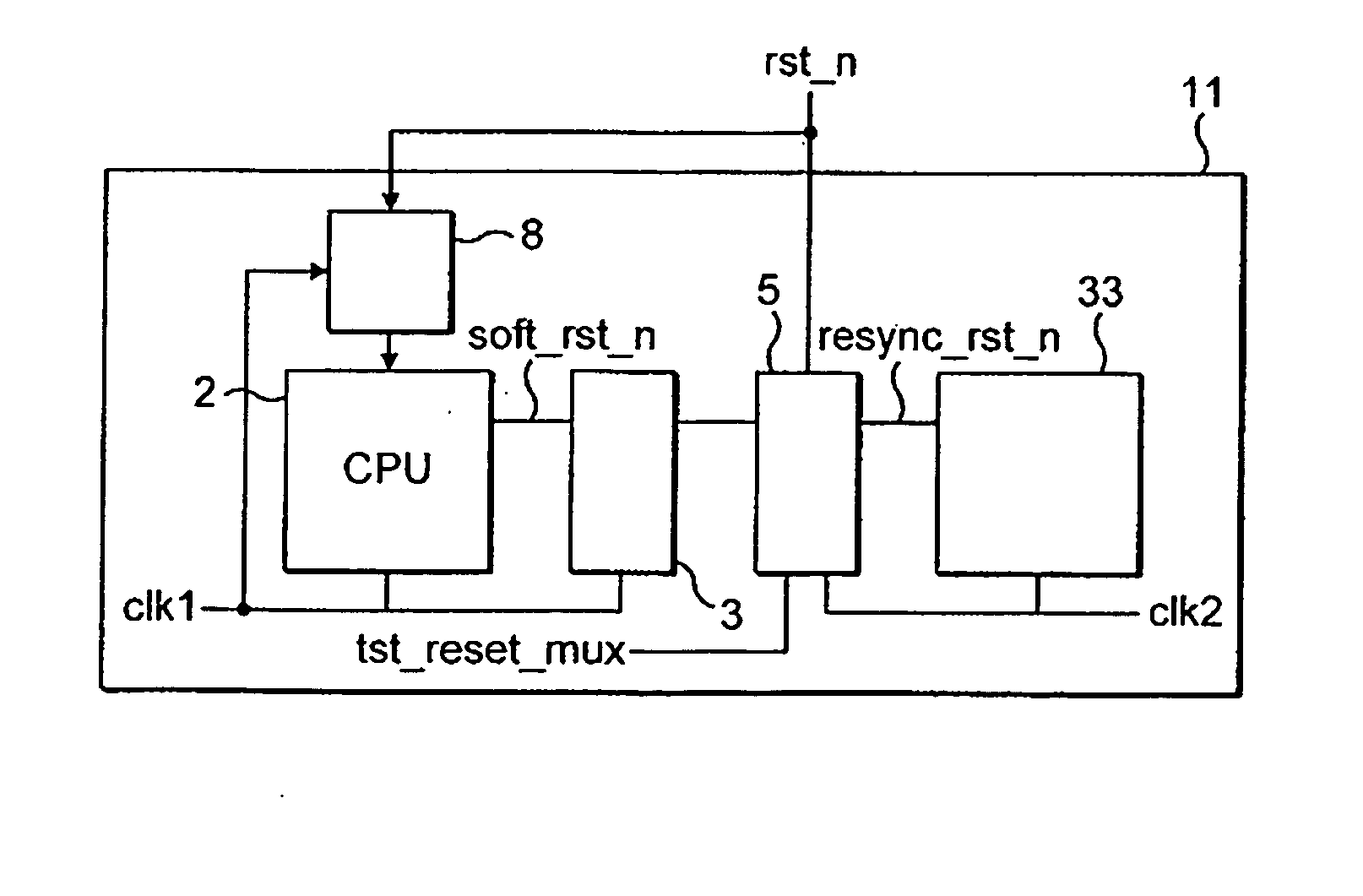

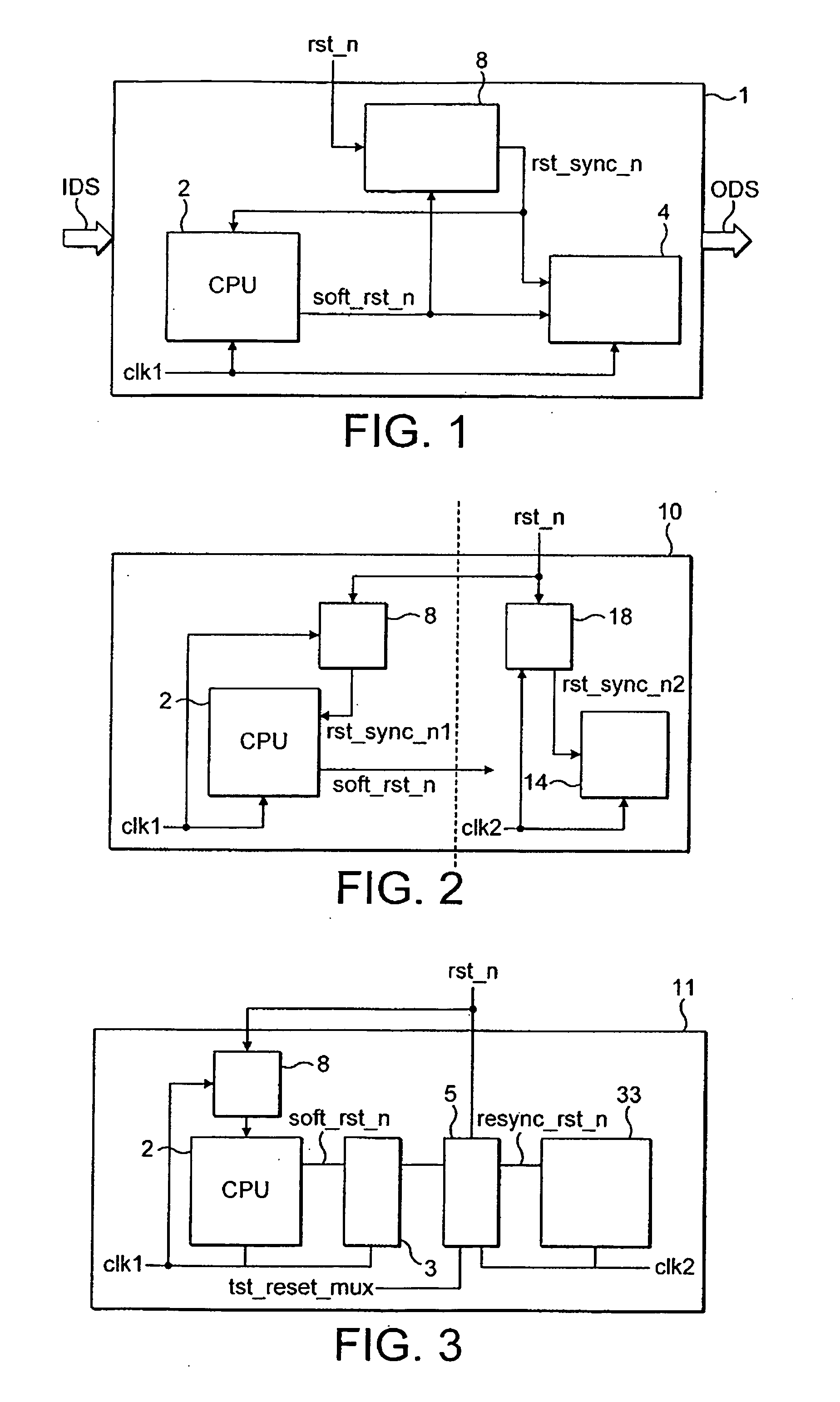

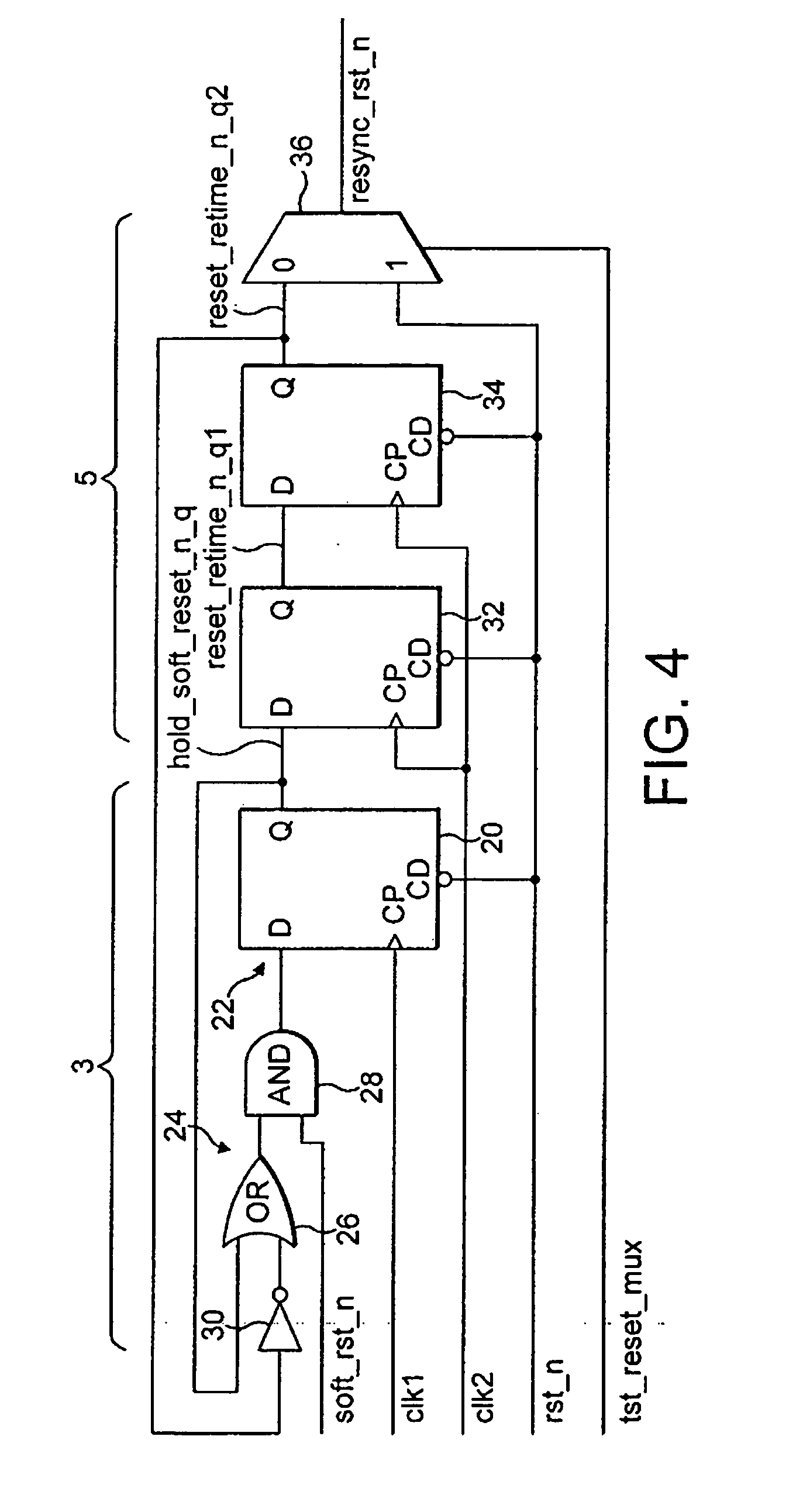

Reset in a system-on-chip circuit

ActiveUS20060036888A1Pulse automatic controlError detection/correctionIntegrated circuitElectronic equipment

An electronic device having first circuitry operating in a first clock environment and second circuitry operating in a second clock environment, the first circuitry being arranged to generate a soft reset signal for resetting the second circuitry, the integrated circuit further including: a soft reset hold circuit clocked in the first clock environment connected to receive the soft reset signal and to generate an output reset signal in an asserted state; and a synchronizer clocked in the second clock environment connected to receive the output reset signal and to generate a retimed reset signal in an asserted state after a predetermined period, wherein the retimed reset signal is fed back to the soft reset hold circuit to cause the output reset signal to adopt a deasserted state at the end of said predetermined period.

Owner:STMICROELECTRONICS (RES & DEV) LTD

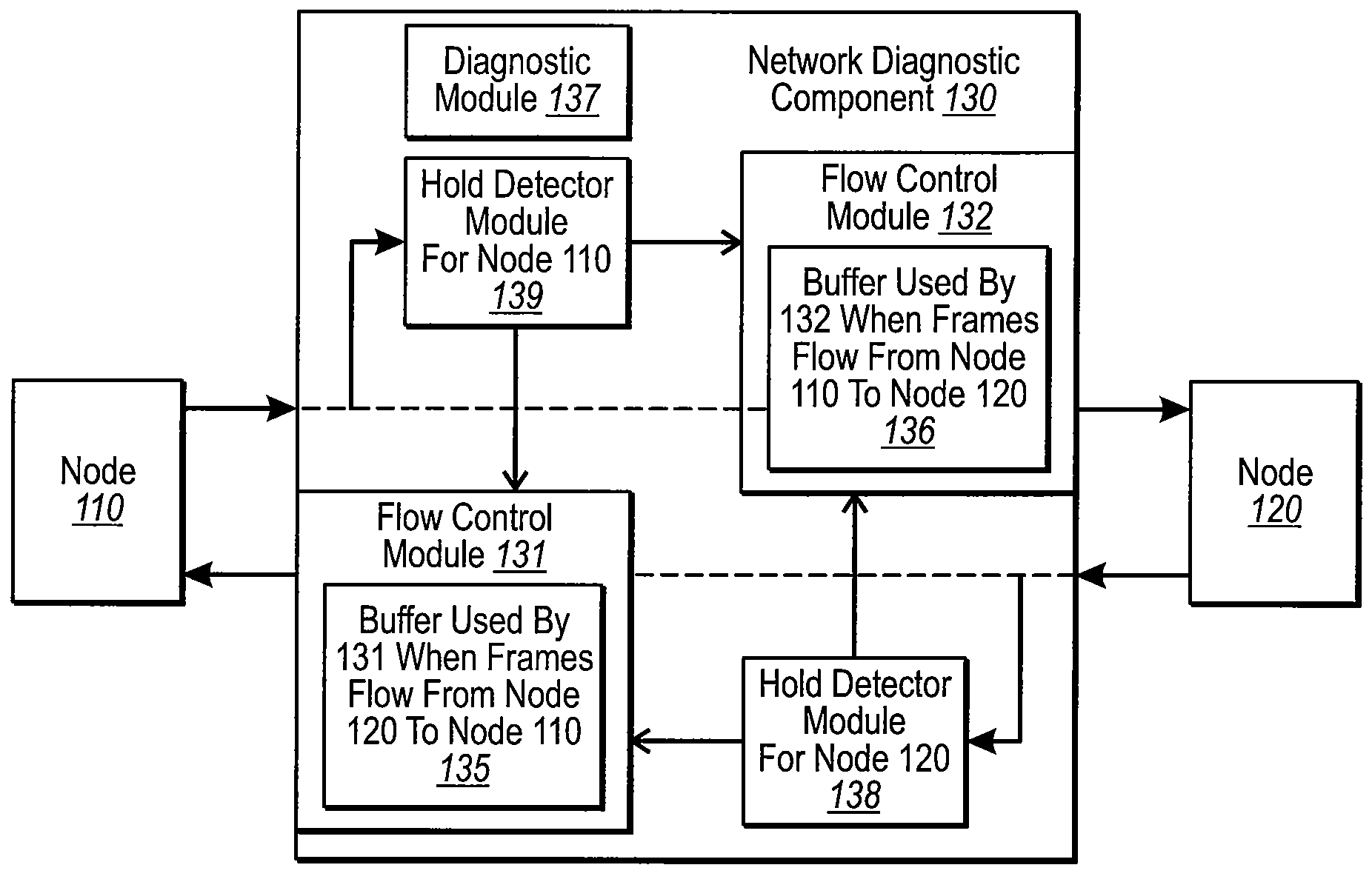

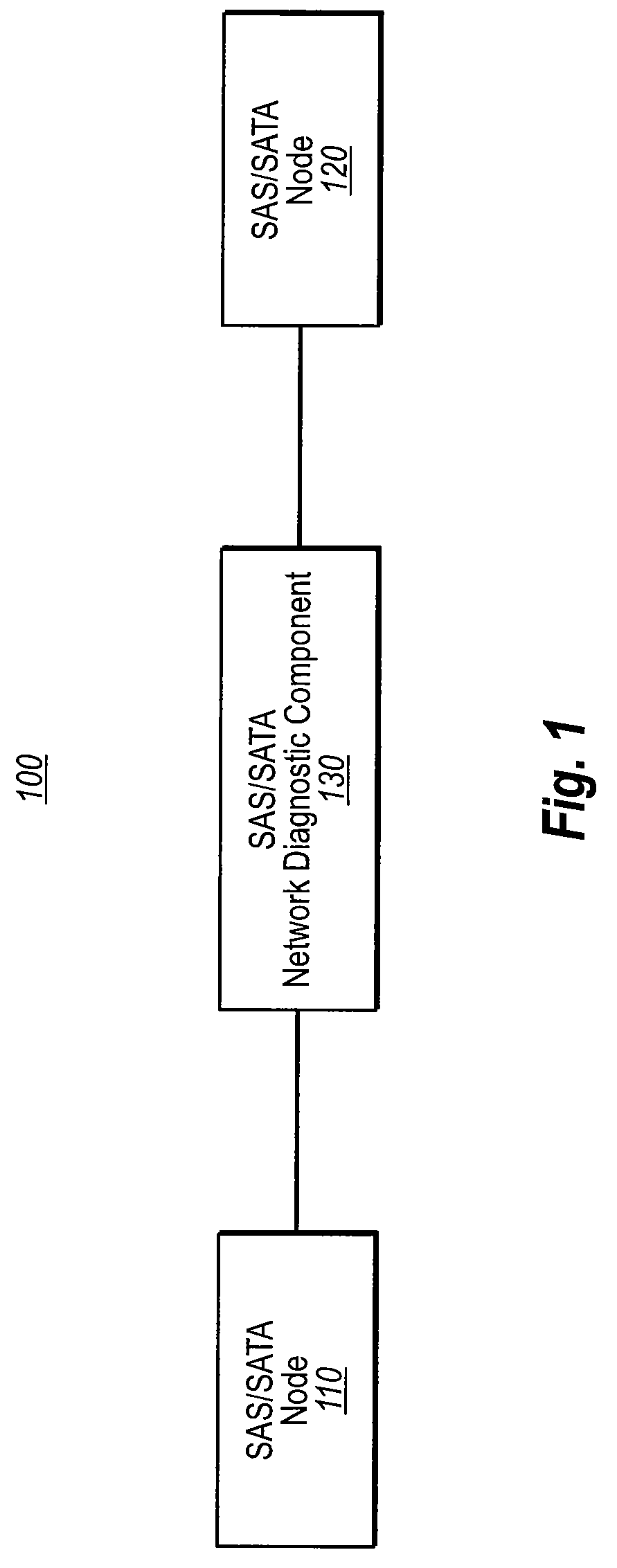

Flow control methodology for digital retiming devices

A network diagnostic device or component such as a network analyzer or a jammer that is placed in-line between two nodes in a network to perform a flow control operation transparently without the requirement of a separate link layer implementation. The network diagnostic device may include a diagnostic module configured to perform network analyzer operations, a memory a first flow control module a second flow control module. In some embodiments, when performing the flow control operation, various modules and / or components may cause the network diagnostic device to enter a first pass-through mode and to then enter into a first flow control handshaking mode from the first pass-through mode. The various modules and / or components may also cause the network diagnostic device to enter a second pass-through mode from the first flow control handshaking mode and to then enter into a second flow control handshaking mode from the first pass-through mode.

Owner:VIAVI SOLUTIONS INC

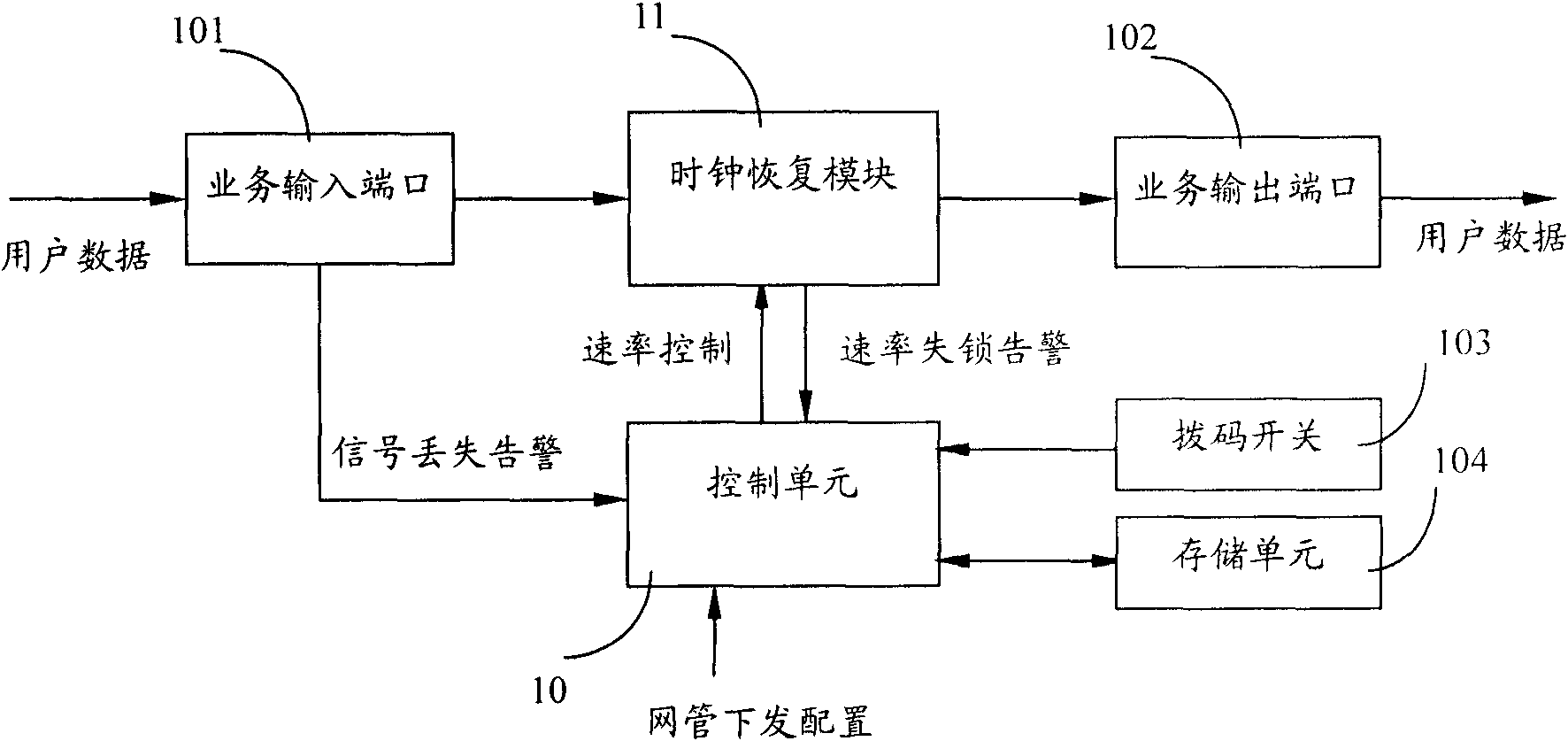

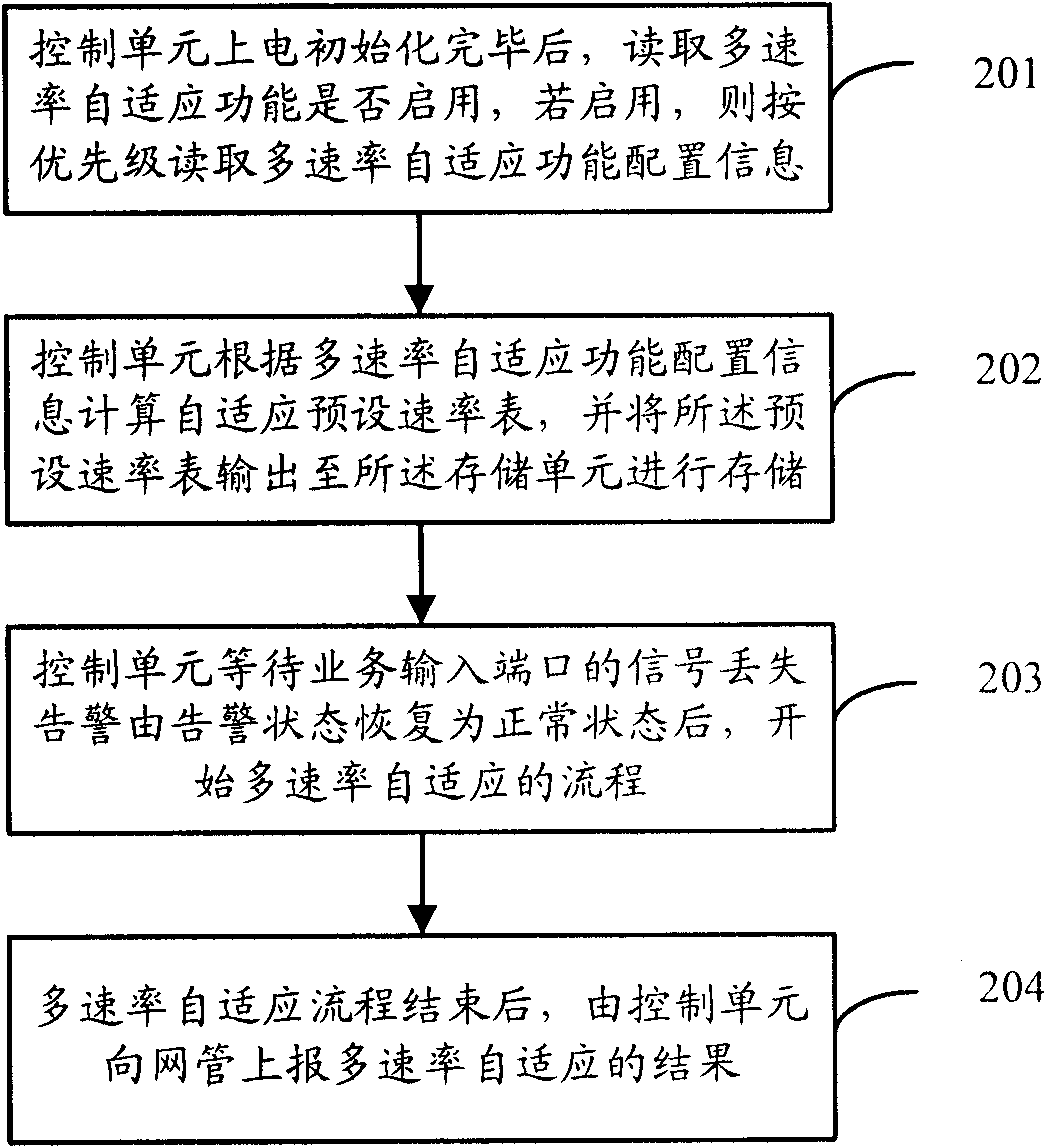

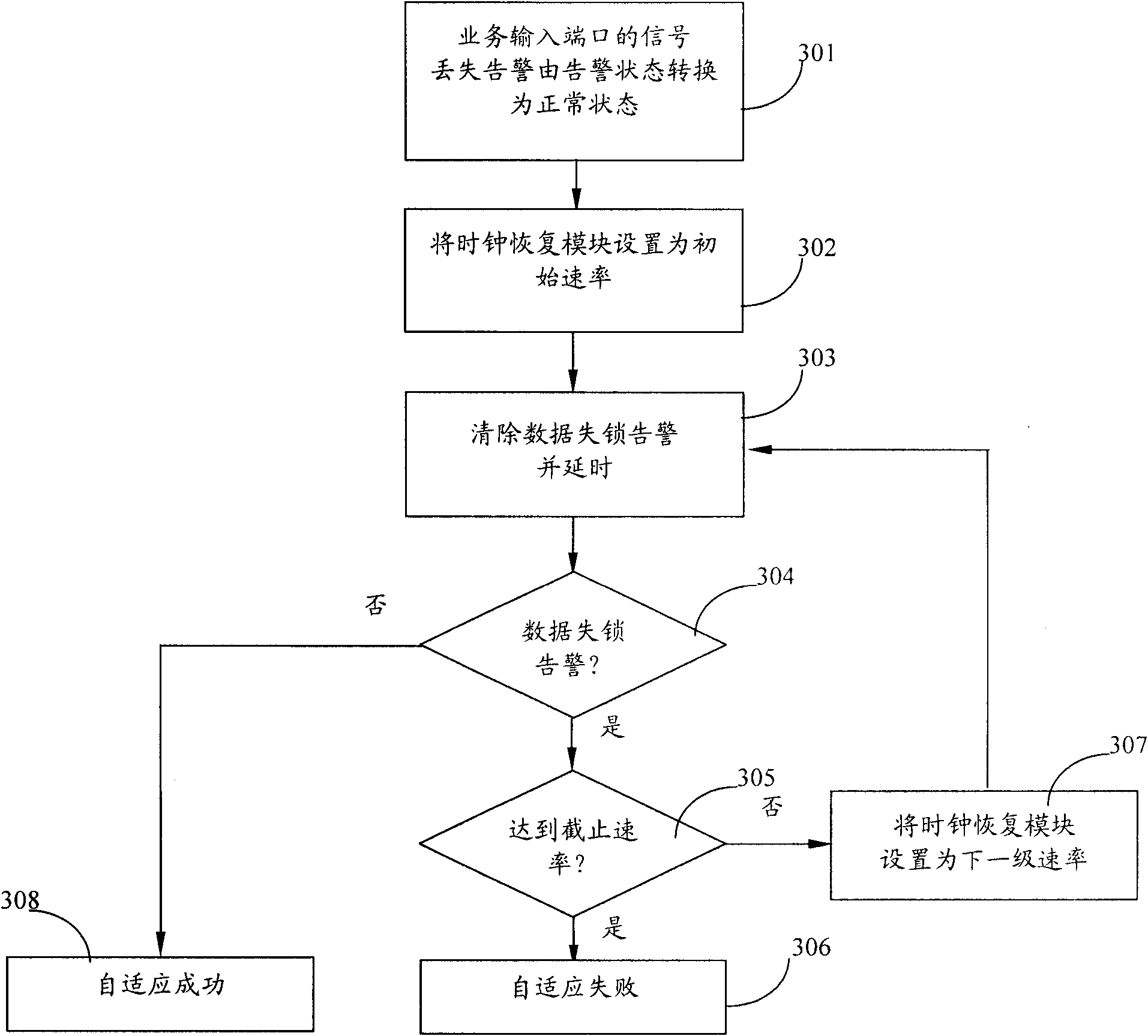

Method for carrying out self adaptation in optical network according to rate and signal transmission device

InactiveCN101800603AAvoid configurationReduce hardware costsFibre transmissionClock recoverySelf adaptive

The invention discloses a signal transmission device in an optical network, which comprises a business input port, a business output port, a control unit, a clock recovery module and a storing unit. A self-adaptation adjusting mechanism is started under the condition that the rate of user data received by the business input port is different from the current set rate; and the set rate is automatically adjusted to be the same with the actual rate of the user data, and the retiming, reshaping and re-amplification processing is carried out on the user data. In addition, the reshaping and re-amplification processing is carried out on the user data under the condition of self-adaptation adjusting failure. The invention also discloses a method for carrying out self adaptation in an optical network according to the rate. The scheme can carry out self adaptation specific to different rates and reduce the hardware cost of equipment and the labor and management cost.

Owner:RAISECOM TECH