Patents

Literature

739 results about "SerDes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

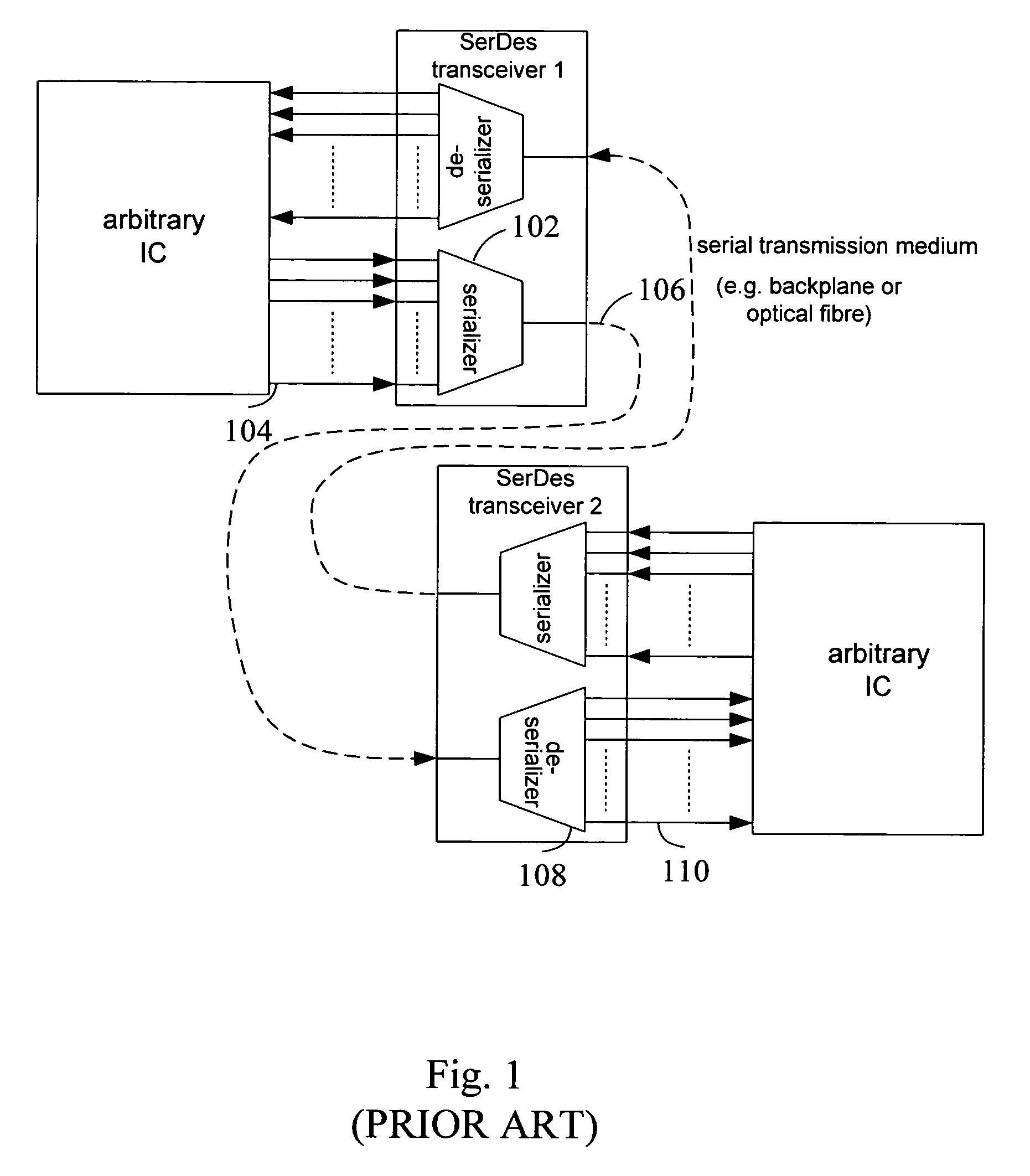

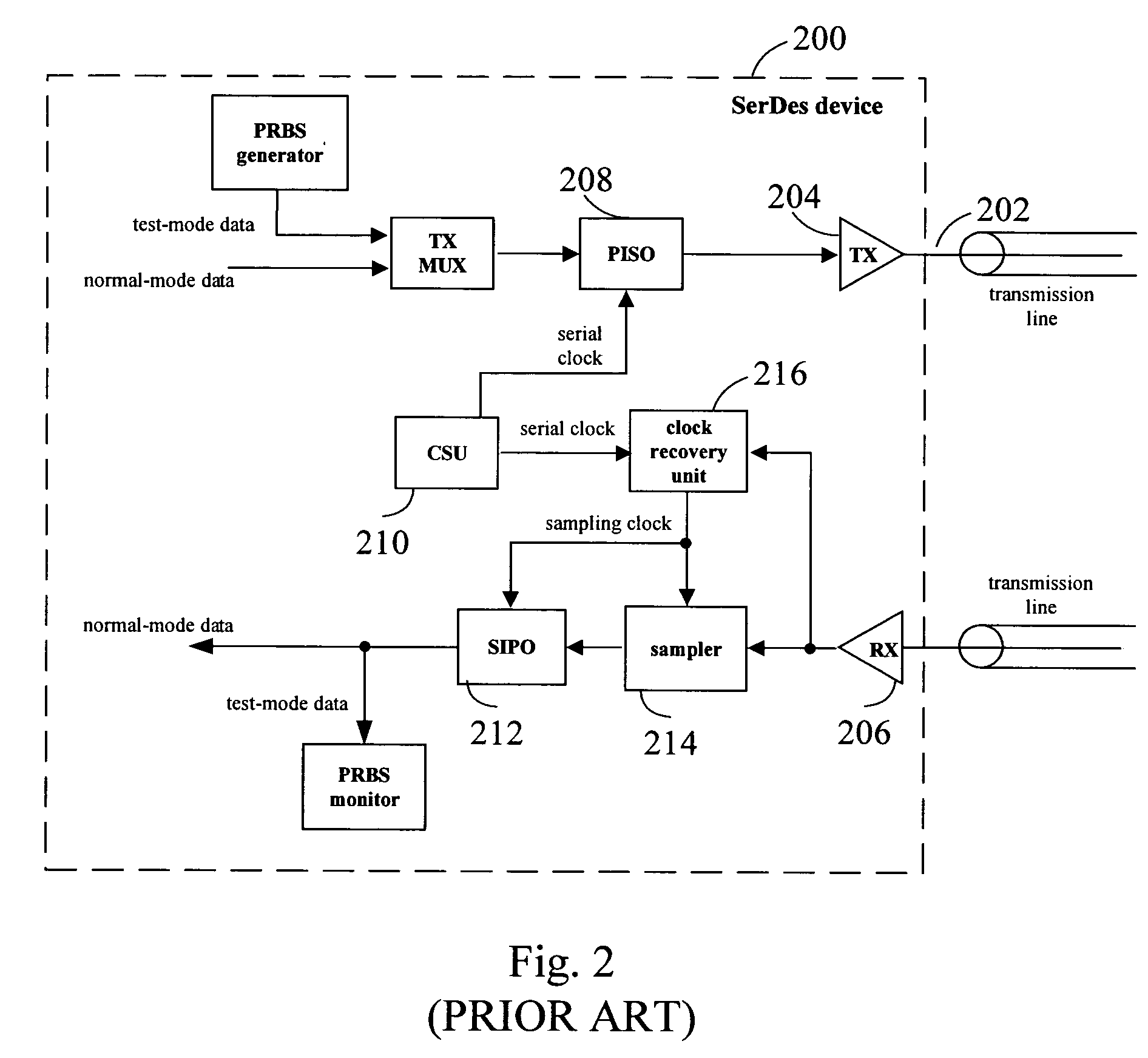

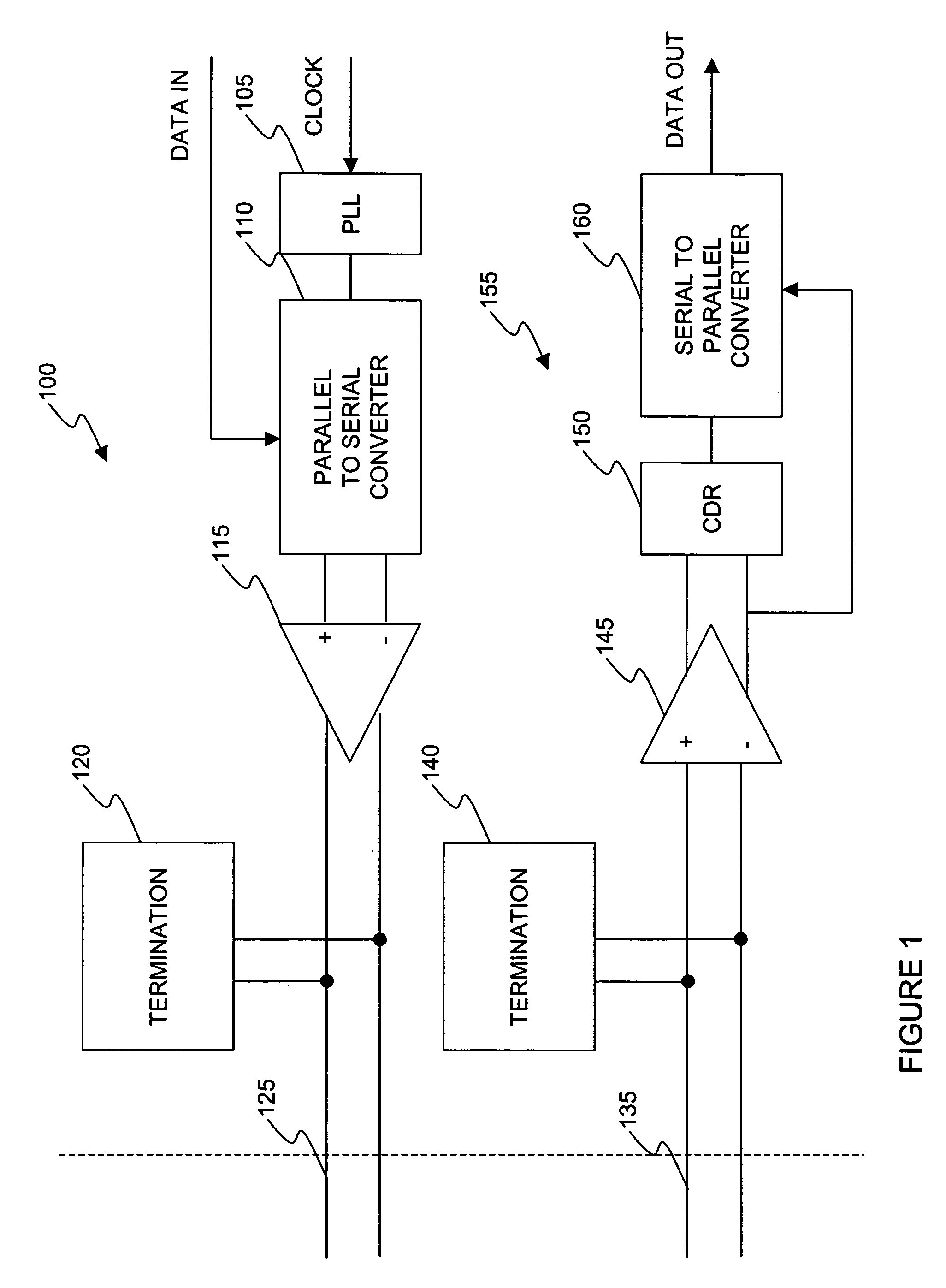

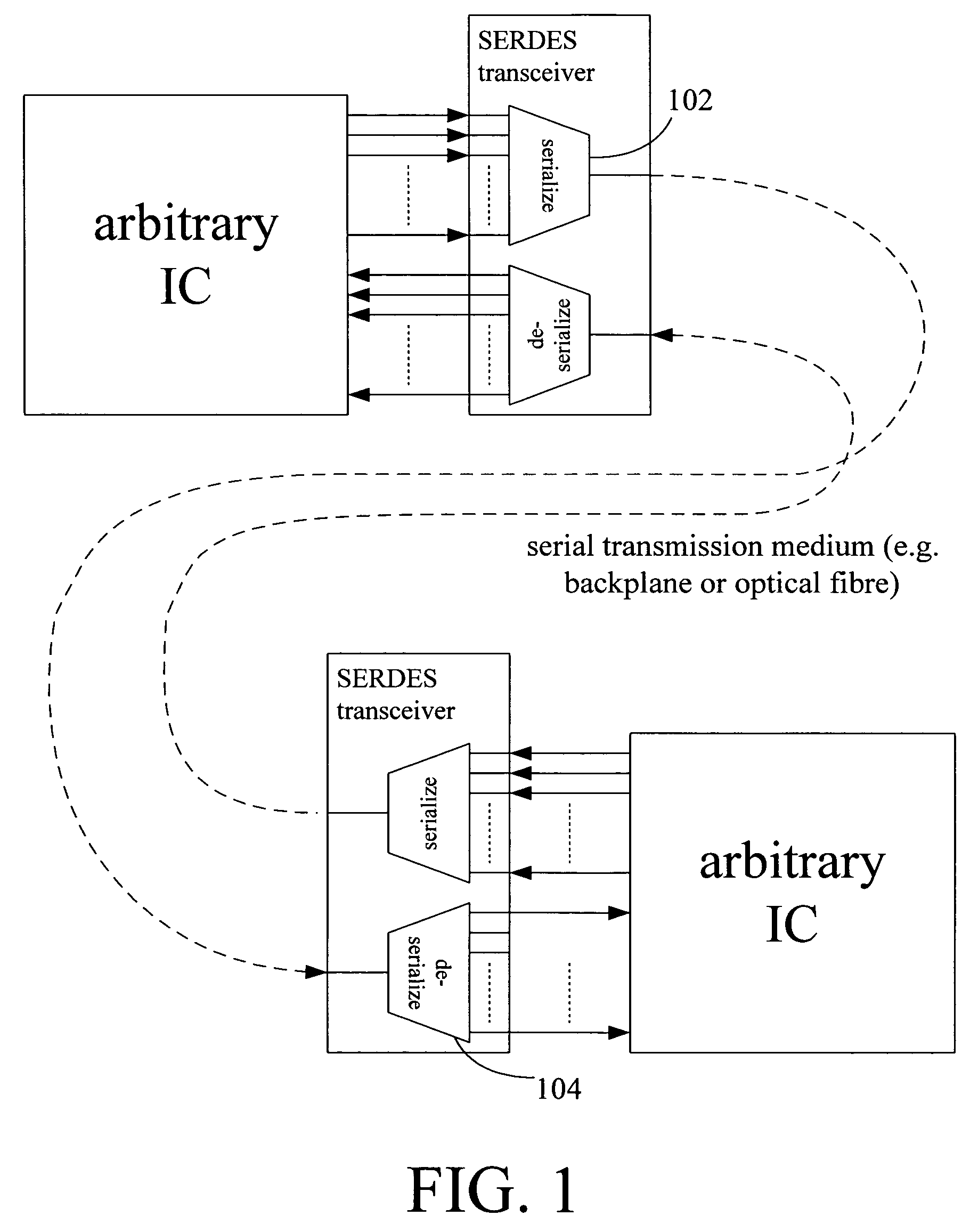

A Serializer/Deserializer (SerDes pronounced sir-deez or sir-dez) is a pair of functional blocks commonly used in high speed communications to compensate for limited input/output. These blocks convert data between serial data and parallel interfaces in each direction. The term "SerDes" generically refers to interfaces used in various technologies and applications. The primary use of a SerDes is to provide data transmission over a single line or a differential pair in order to minimize the number of I/O pins and interconnects.

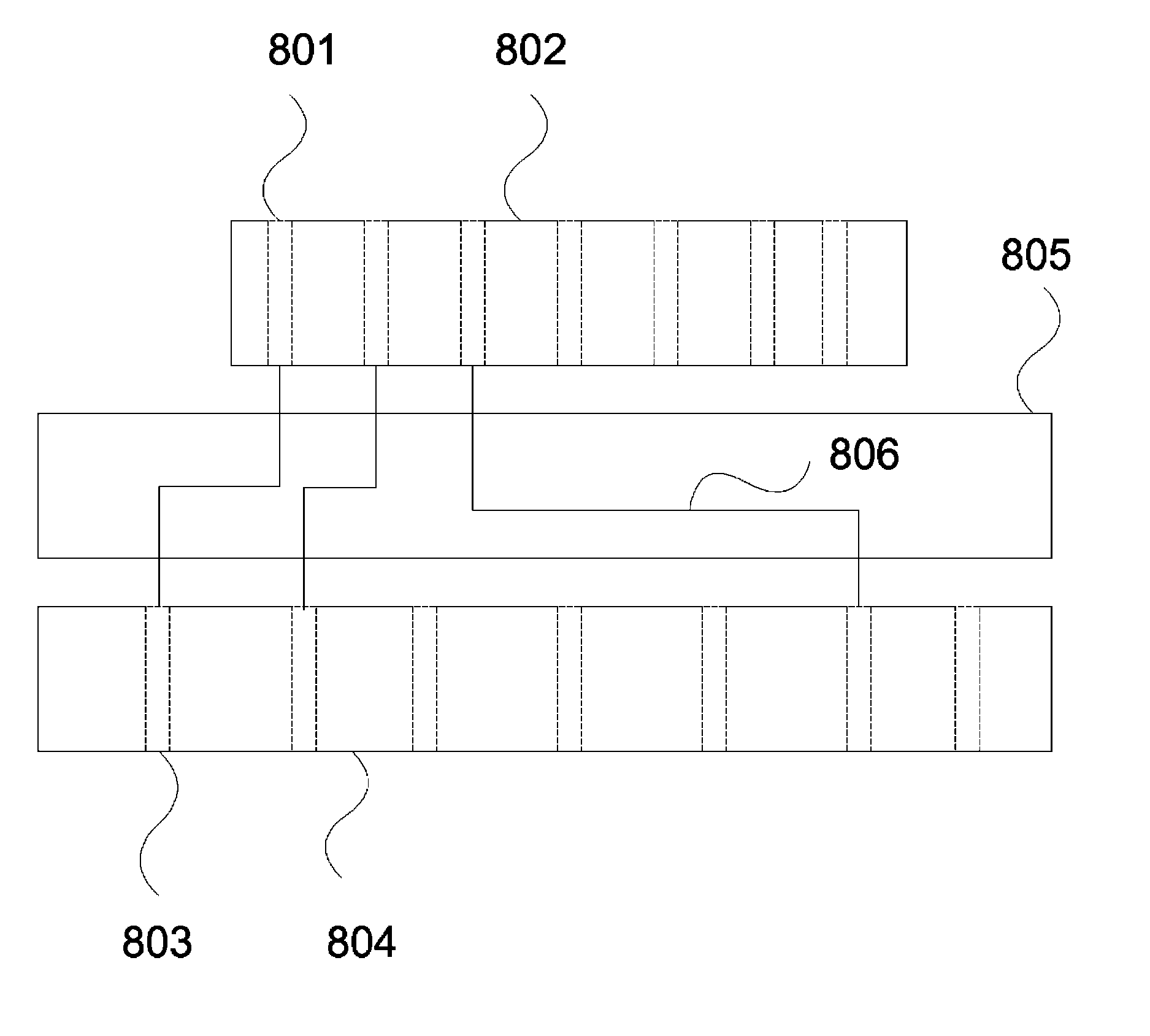

Stacking integrated circuits containing serializer and deserializer blocks using through silicon via

ActiveUS8014166B2Efficiently routedReduce and eliminate and capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

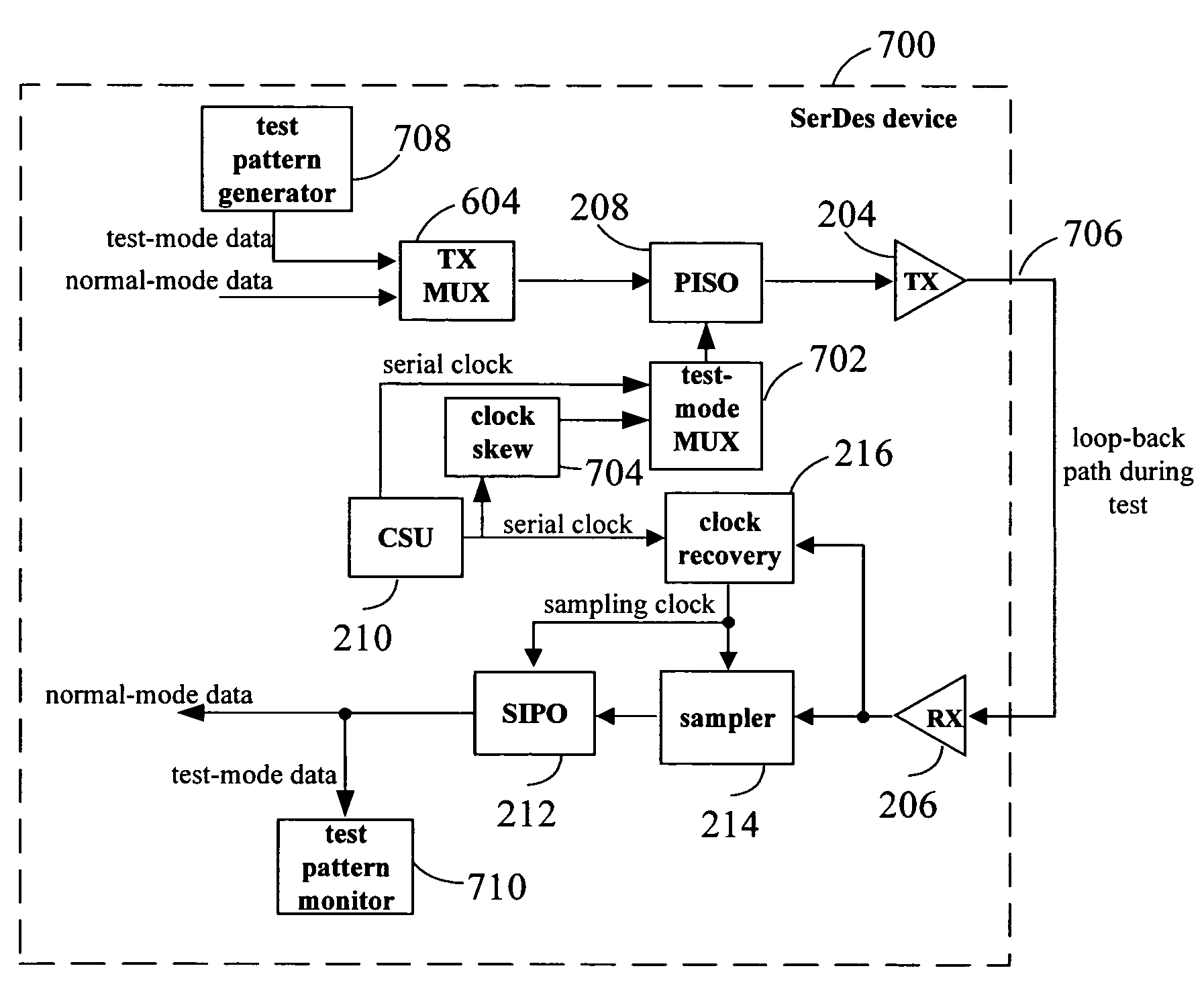

Systems and methods for a built in test circuit for asynchronous testing of high-speed transceivers

ActiveUS7363563B1Maintain performanceCost prohibitiveError preventionPulse automatic controlBuilt-in self-testSerializer

Methods and apparatus provide a transceiver, such as a serializer / deserializer device (SerDes), with enhanced built-in self test (BIST). A built-in self test circuit is provided that decouples a clock signal used for receiving data from a clock signal used in transmitting data. This permits data tracking circuitry of a receiver to be efficiently tested with a relatively simple loop back test.

Owner:MICROSEMI STORAGE SOLUTIONS

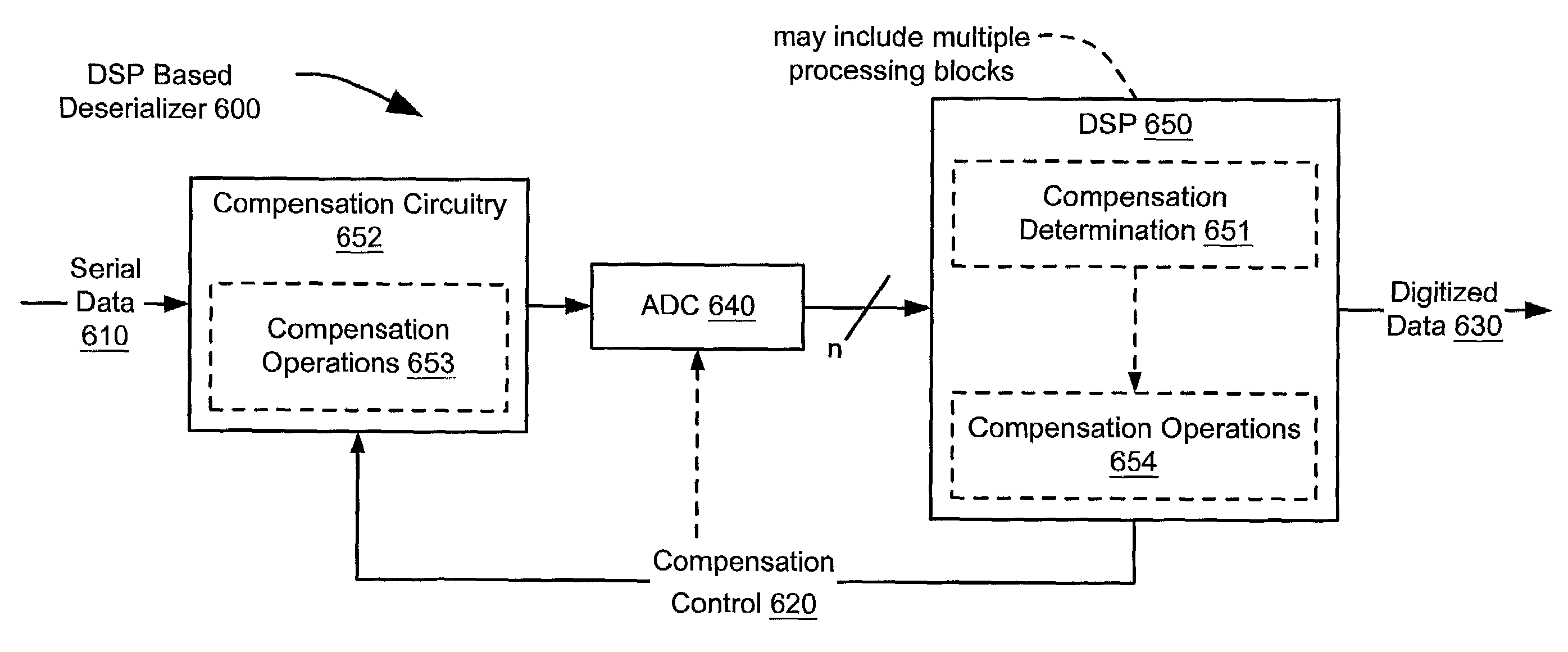

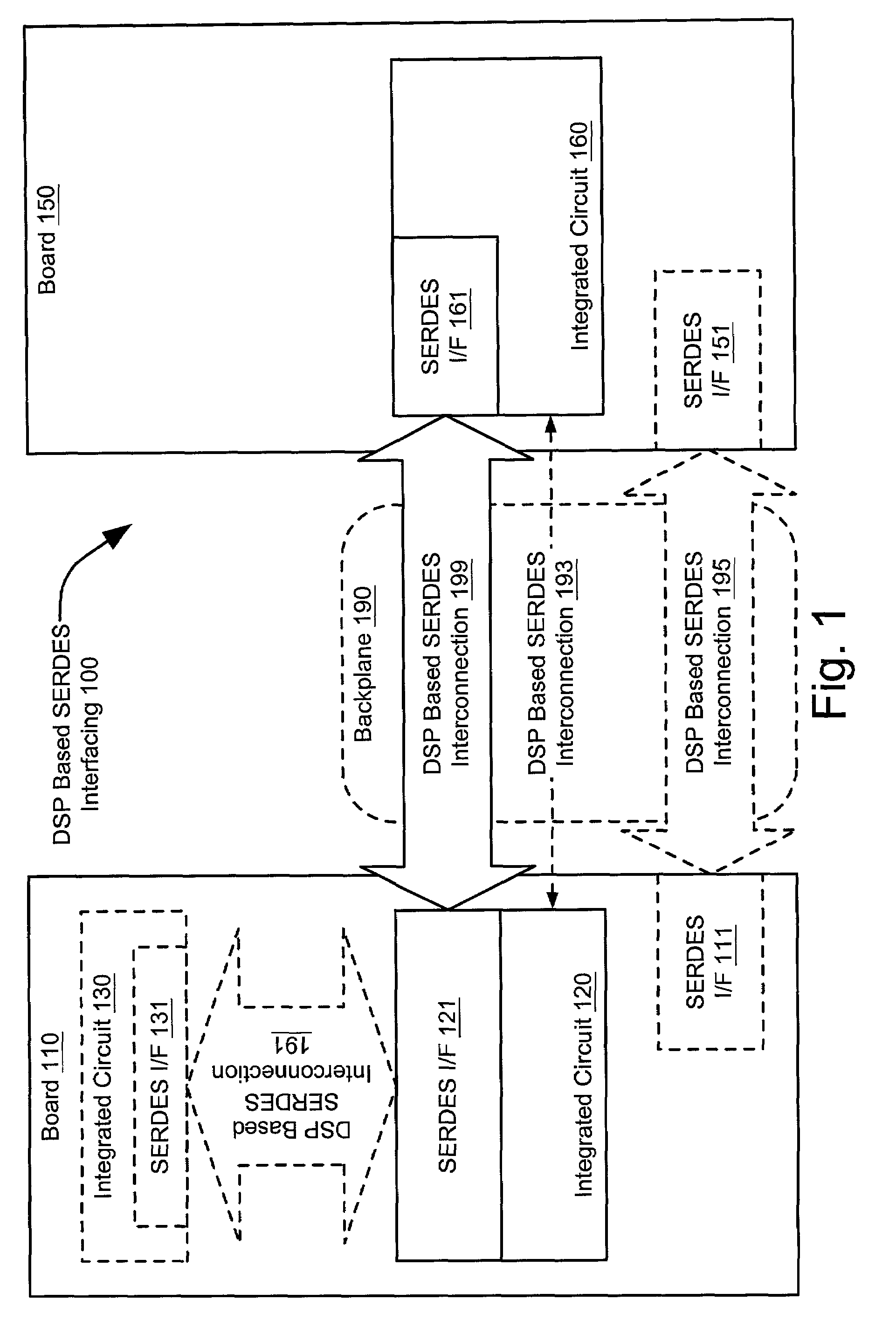

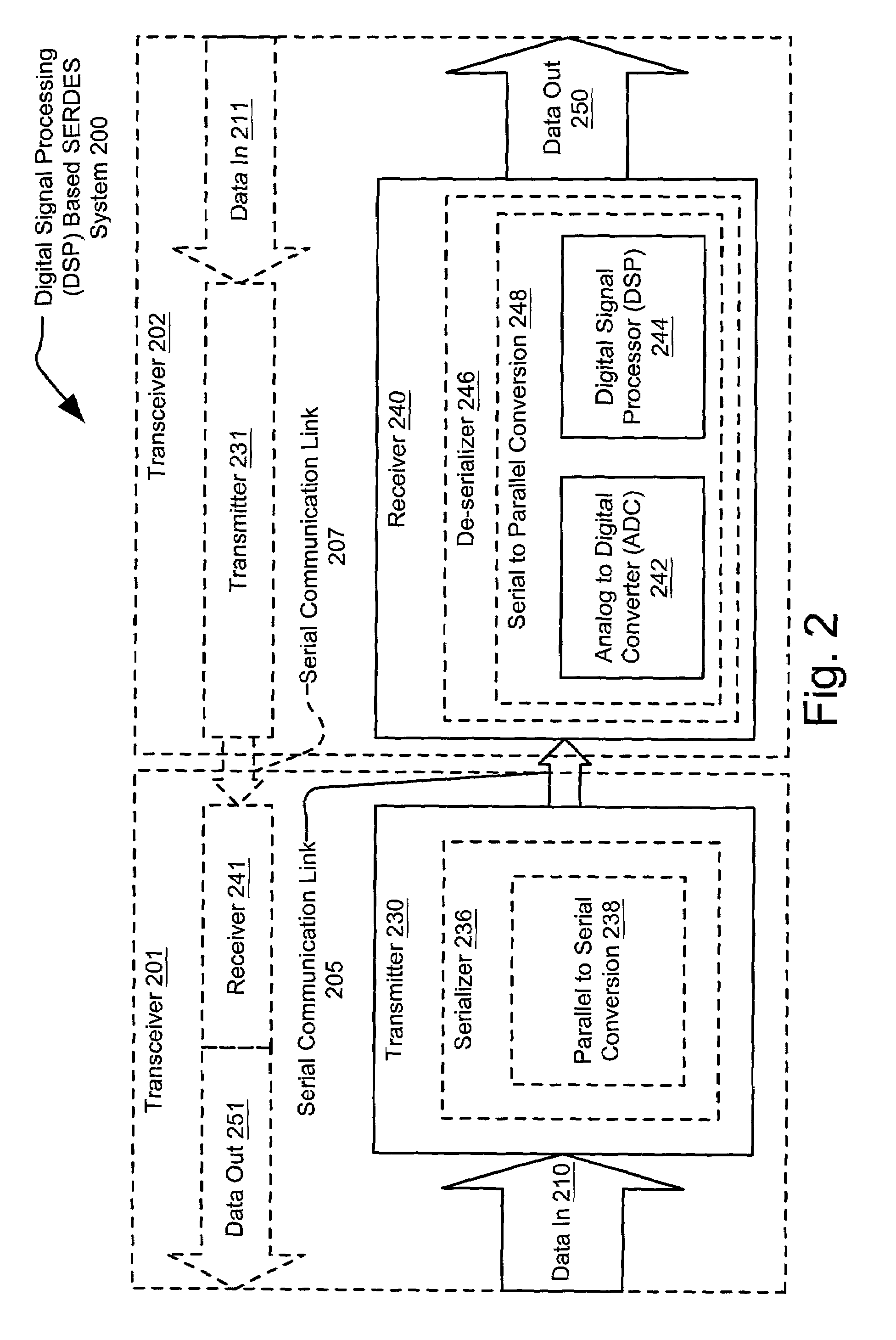

Digital signal processing based de-serializer

ActiveUS7336729B2Lower performance requirementsSolve problemsElectric signal transmission systemsAmplitude-modulated carrier systemsDigital signal processingSerialization

A DSP based SERDES performs compensation operations to support high speed de-serialization. A receiver section of the DSP based SERDES includes one or more ADCs and DSPs. The ADC operates to sample (modulated) analog serial data and to produce digitized serial data (digital representation of the modulated analog serial data). The DSP communicatively couples to the ADC and receives the digitized serial data. Based upon the known characteristics of the digitized serial data and the digitized serial data itself, the DSP determines compensation operations to be performed upon the serial data to compensate for inadequacies of the receiver and / or channel response. These compensation operations may be (1) performed on the analog serial data before digitization by the ADC; (2) applied to the ADC to modify the operation of the ADC; and / or (3) performed on the digitized serial data by the DSP or another device.

Owner:AVAGO TECH INT SALES PTE LTD

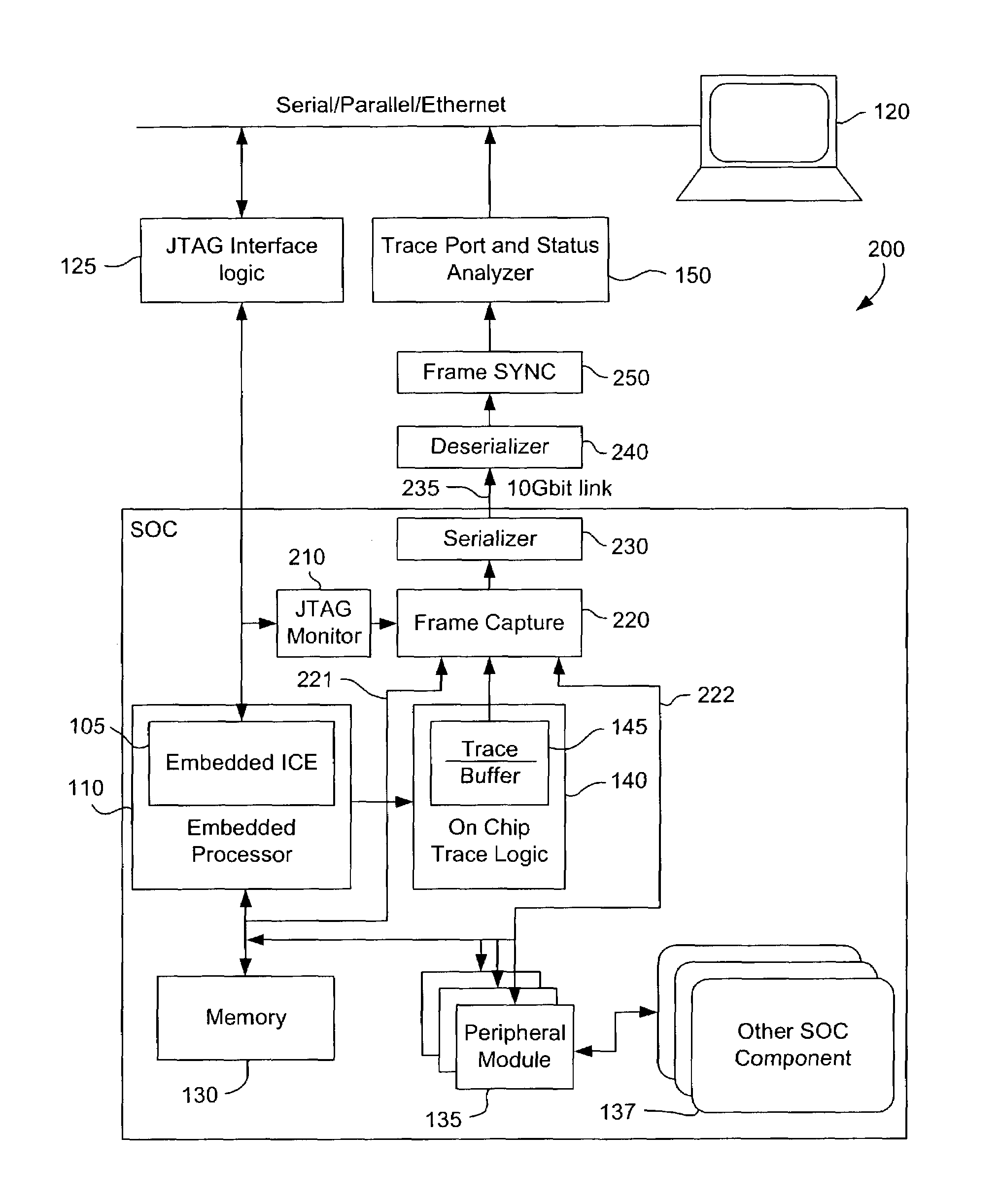

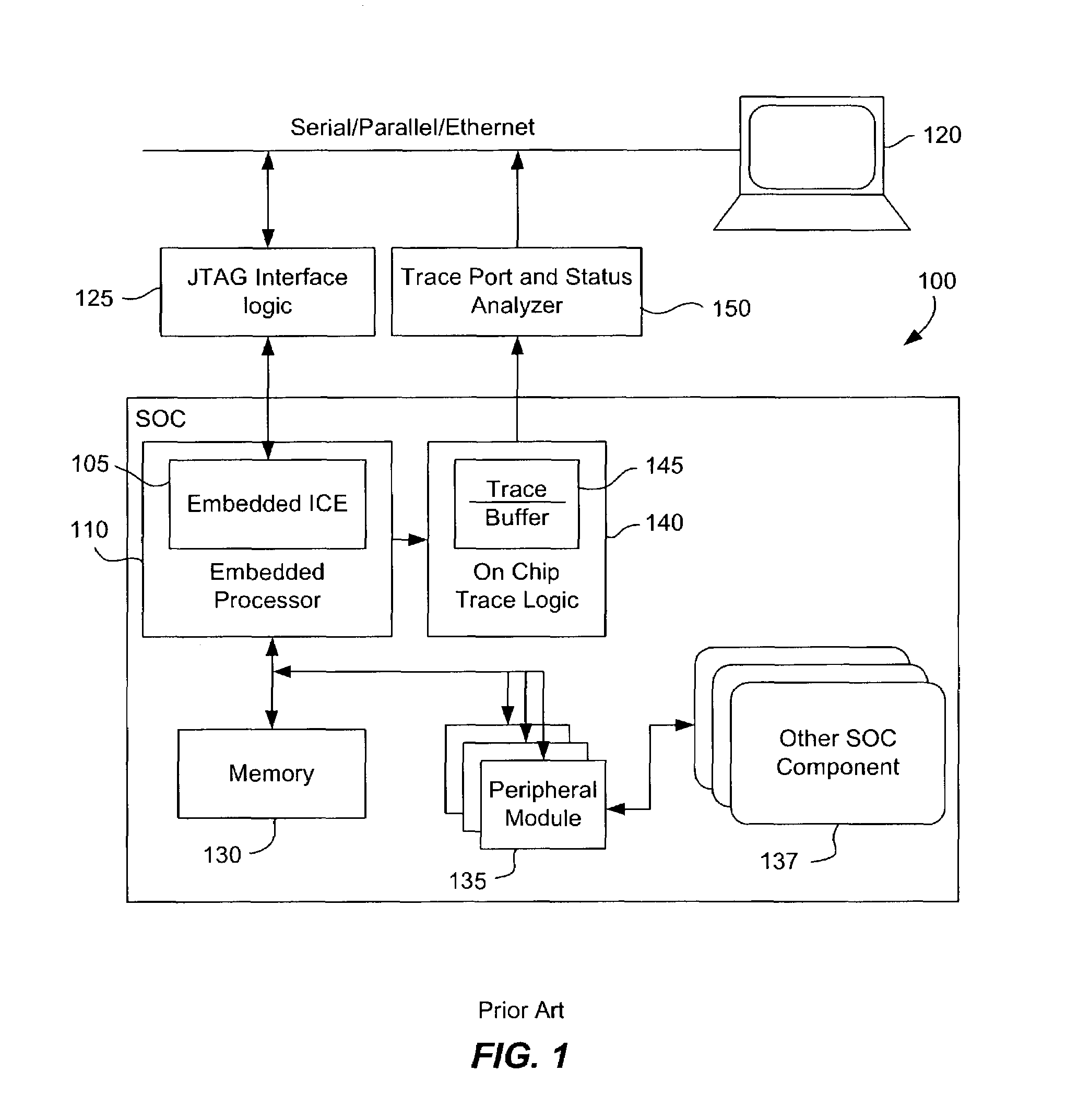

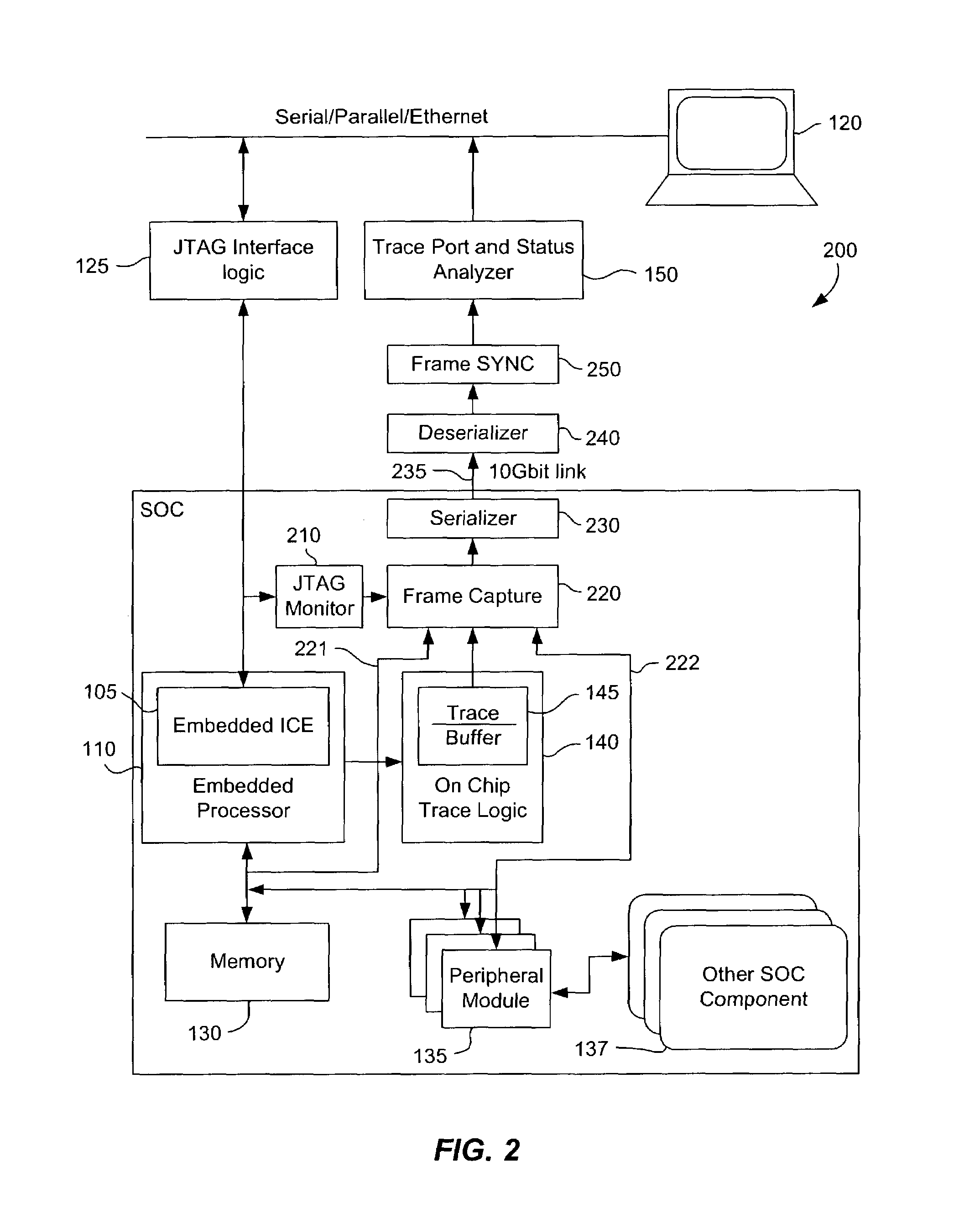

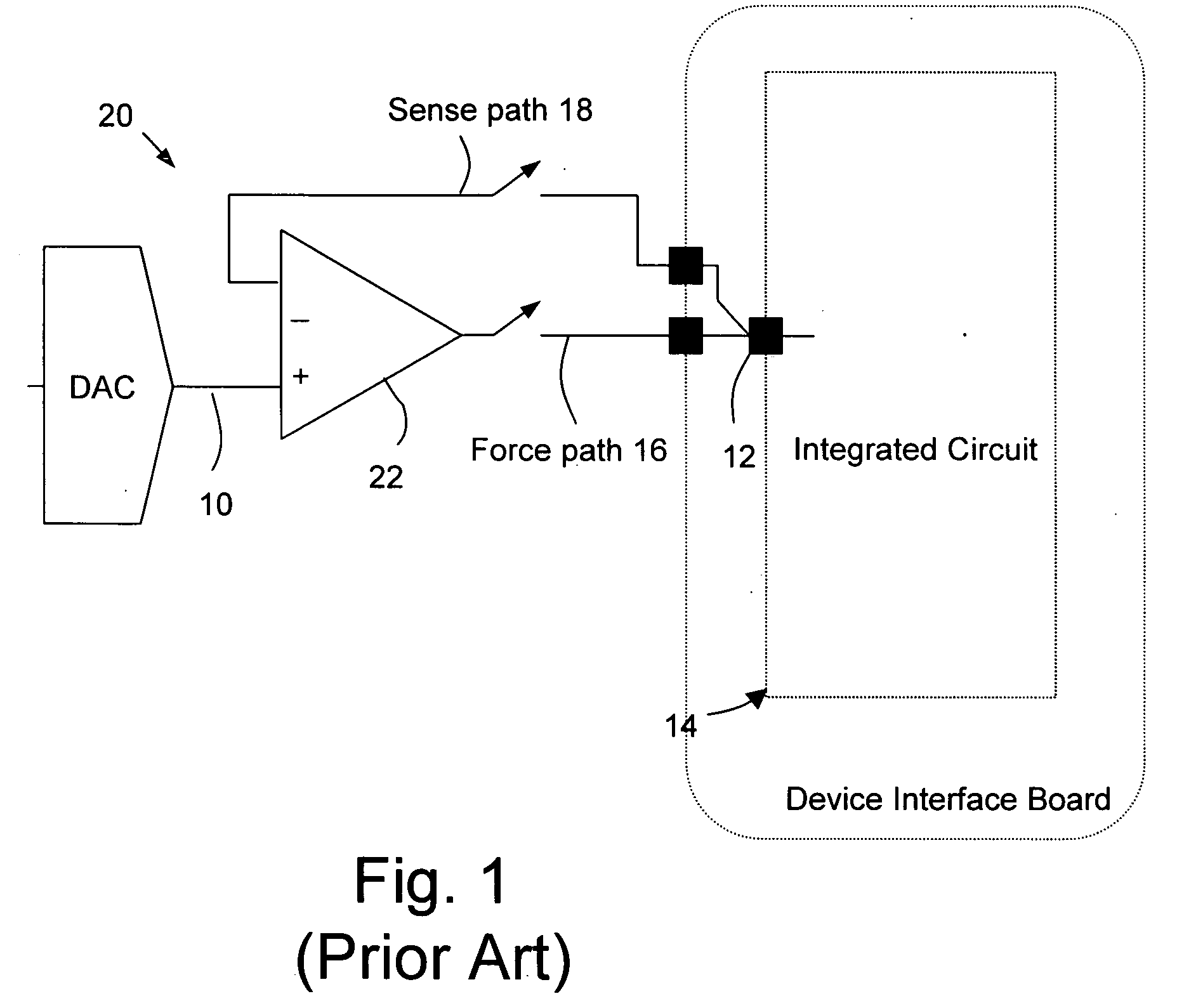

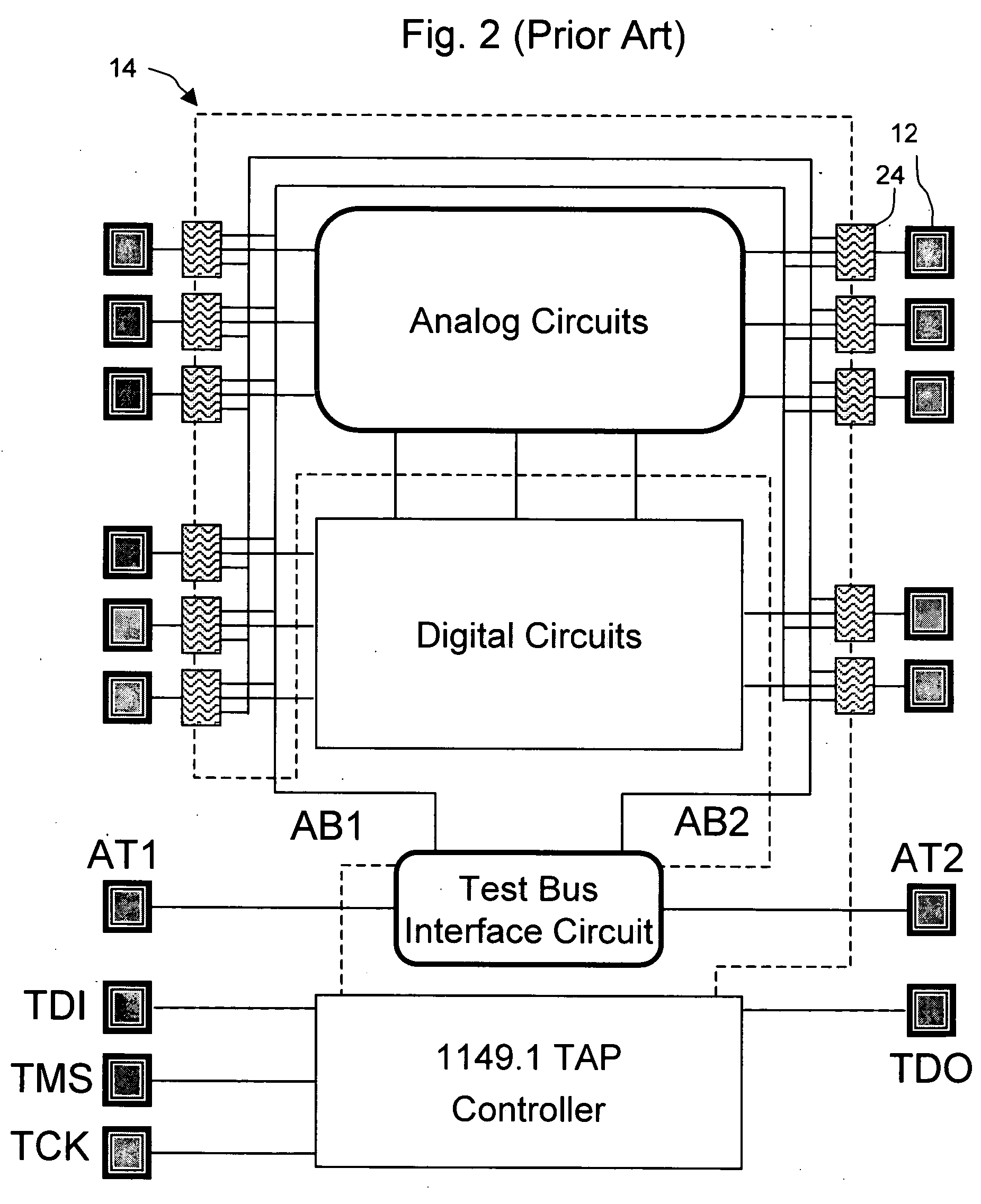

Apparatus and method for testing and debugging an integrated circuit

An integrated circuit which utilizes a serial trace output interface instead of the known parallel trace output interface for transferring test data from the integrated circuit, thereby reducing the number of pins needed for outputting test data. Specifically, a preferred embodiment of the present invention uses a serializer / deserializer (SERDES) interface which captures output testing data in frames, serializes the framed data, and outputs the serialized data on at least one pin. The output serialized data is deserialized, and the deserialized data is synchronized in order to find the frame boundaries. The synchronized frames are then unpacked to retrieve the original testing data. Another preferred embodiment of the present invention uses a bi-directional SERDES both for inputting testing and debugging instructions and data from the analysis software and for outputting testing and debugging results and data to the analysis software.

Owner:MARVELL ASIA PTE LTD

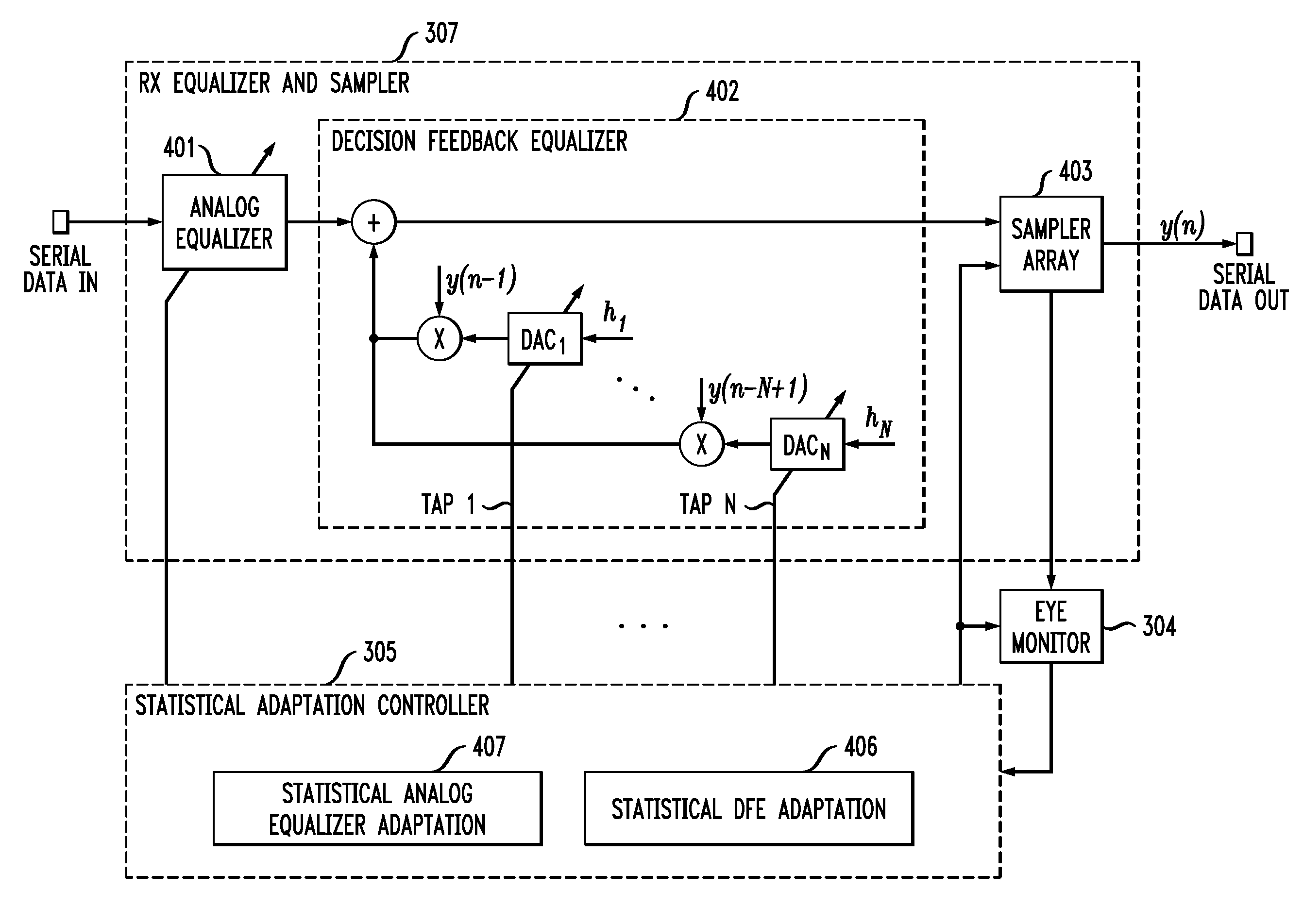

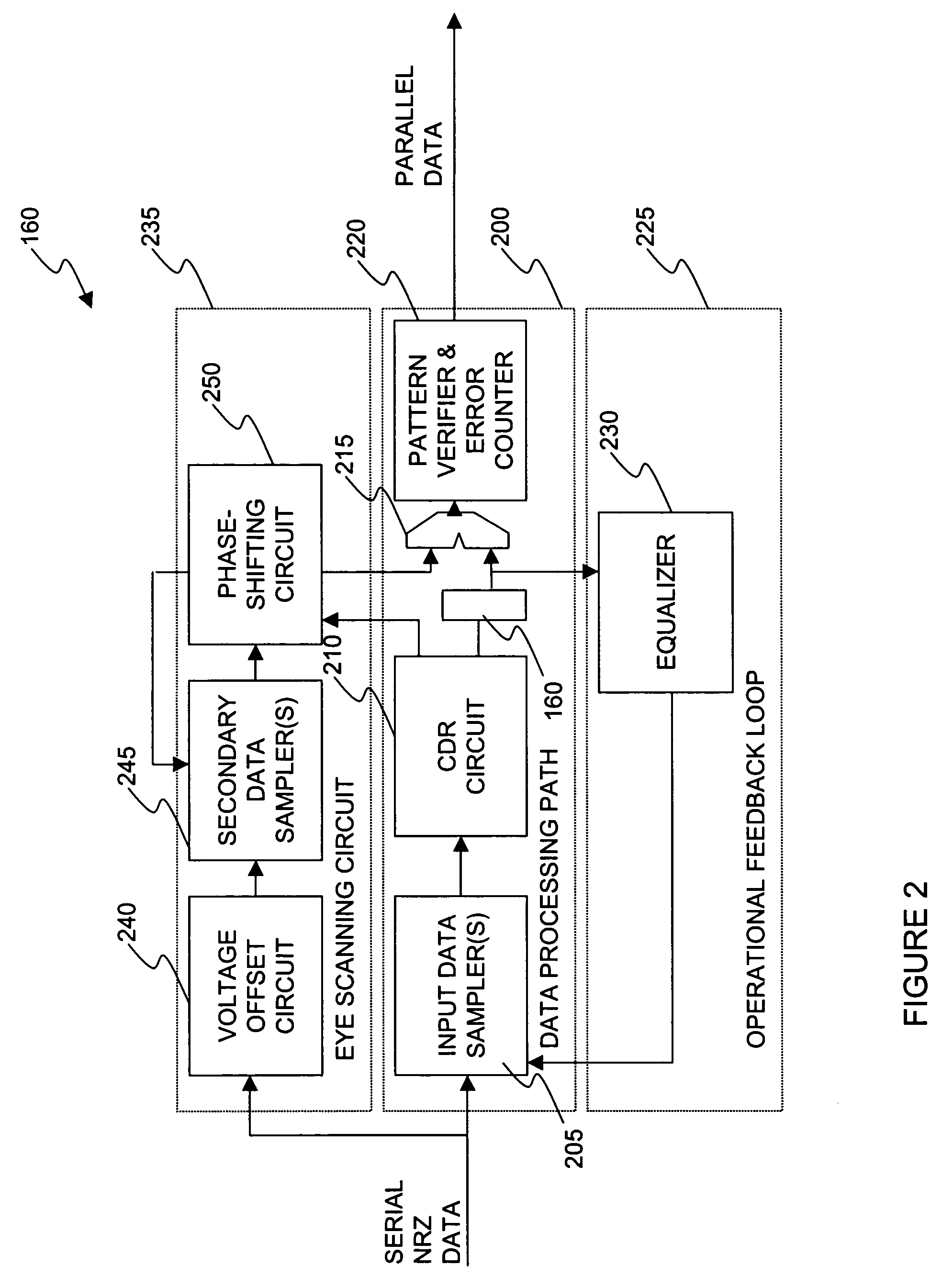

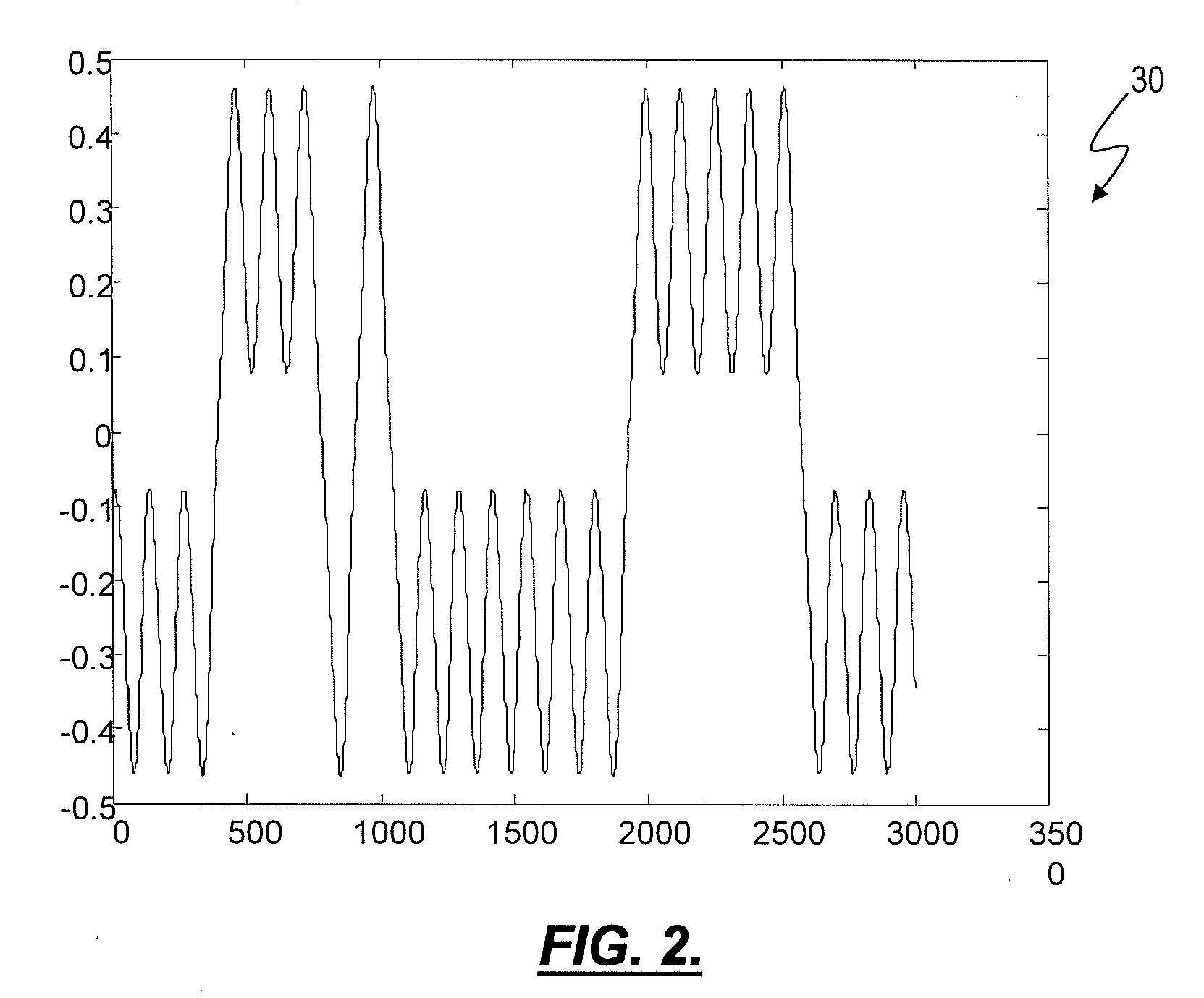

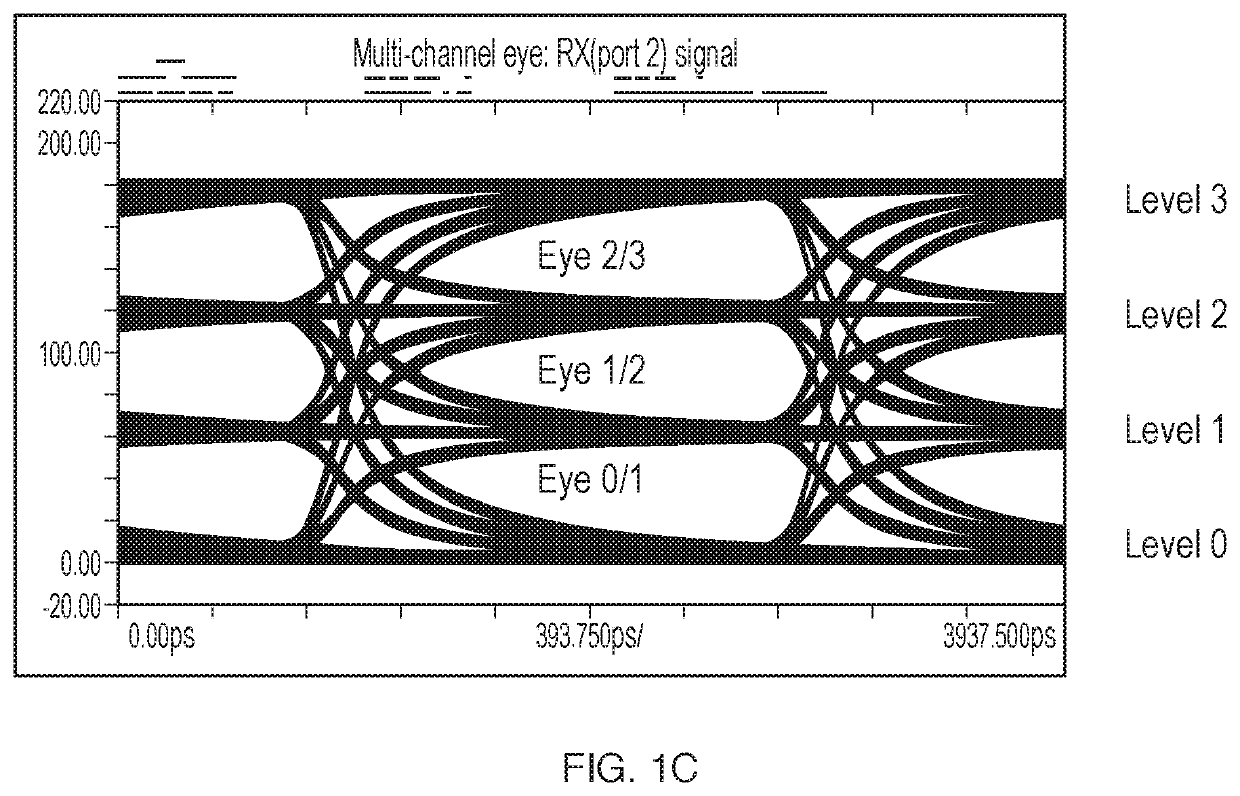

Real-Time Eye Monitor for Statistical Filter Parameter Calibration

In described embodiments, filter parameters for a filter applied to a signal in, for example, a Serializer / De-serializer (SerDes) receiver and / or transmitter are generated based on real-time monitoring of a data eye. The real-time eye monitor monitors data eye characteristics of the signal present in a data path, the data path applying the filter to the signal. The eye monitor generates eye statistics from the monitored data eye characteristics and an adaptive controller generates a set of parameters for the filter of the data path for statistical calibration of the data eye, wherein the eye monitor continuously monitors the data eye and the adaptive controller continuously generates the set of parameters based on the eye statistics.

Owner:LSI CORPORATION

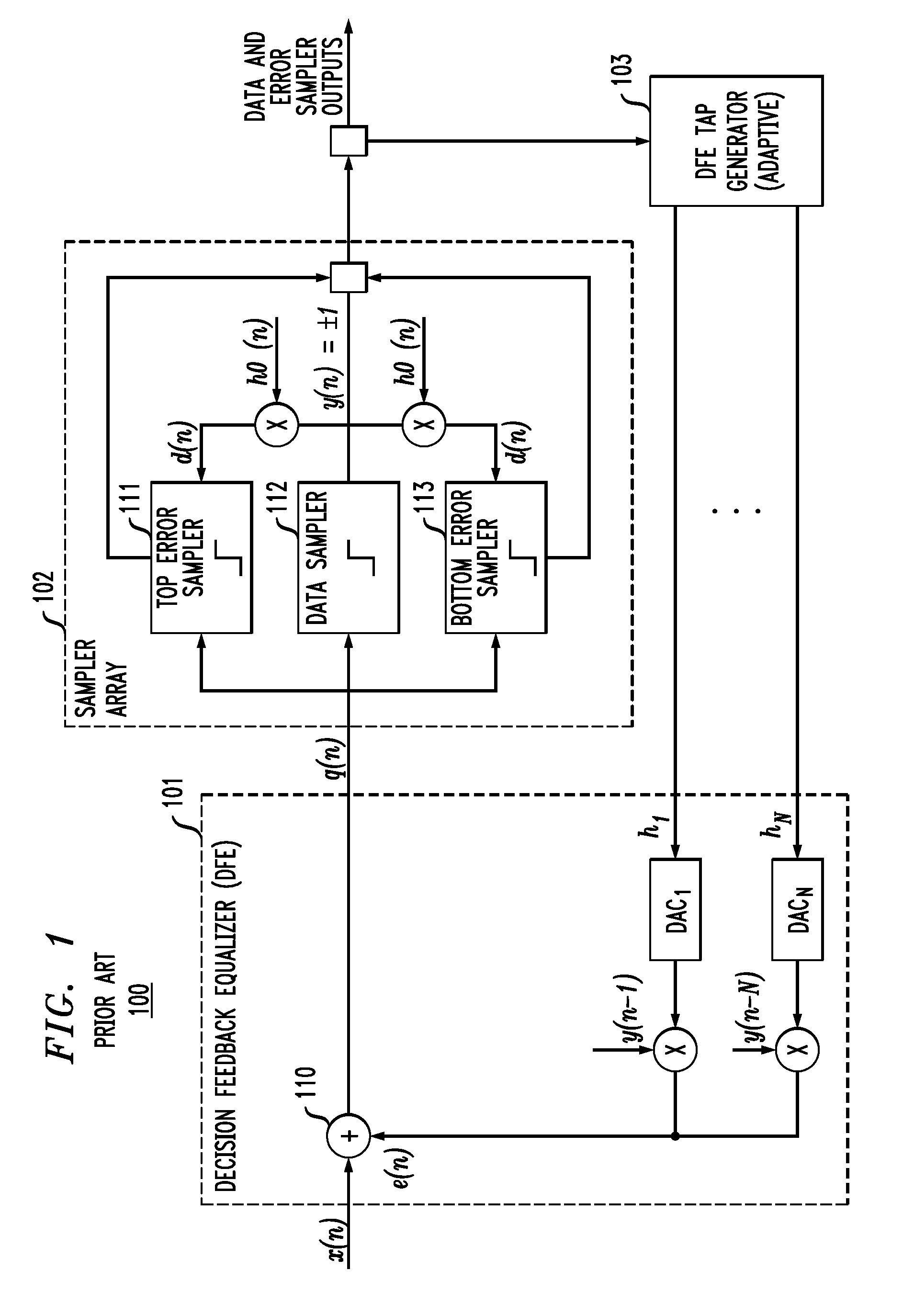

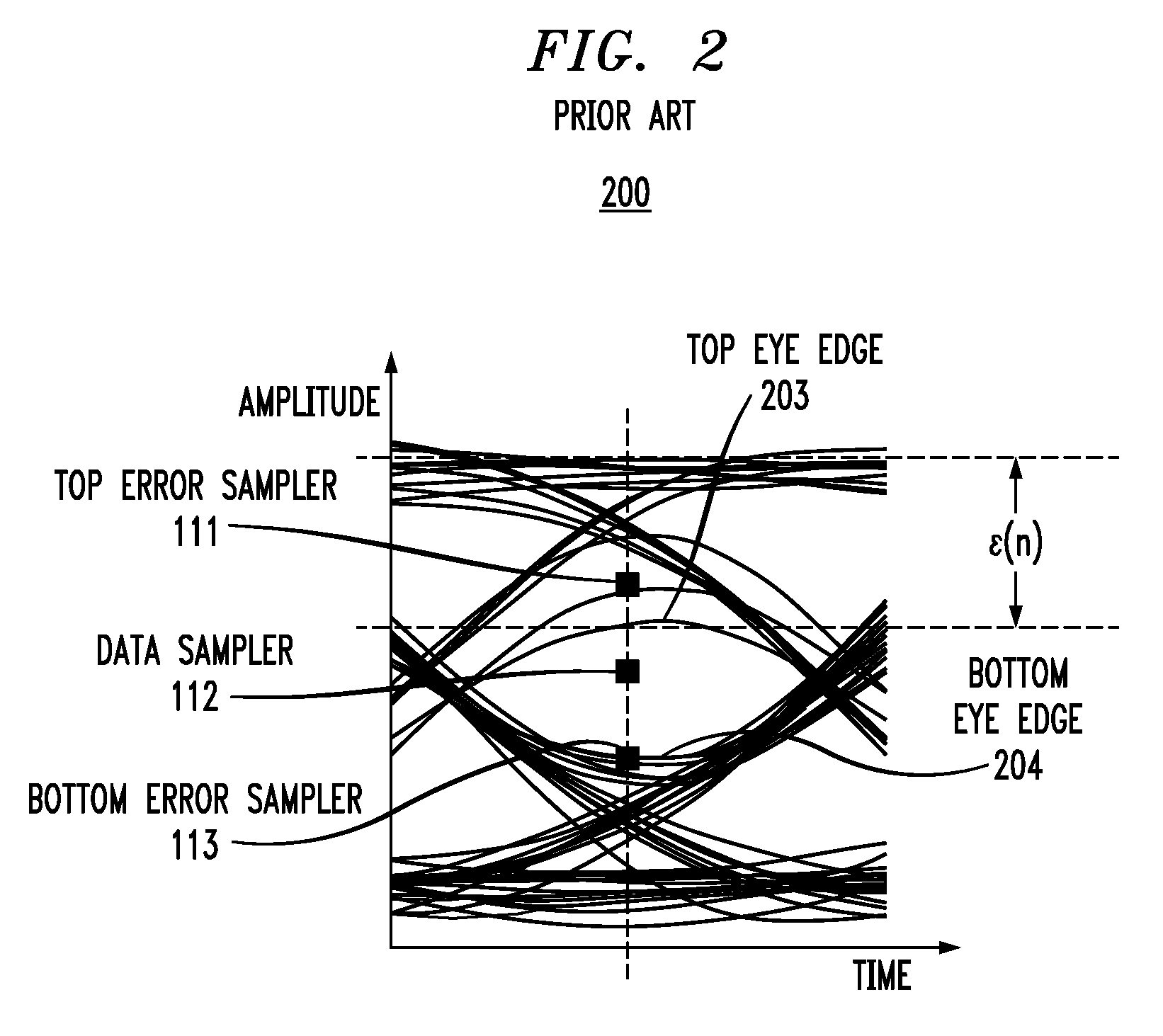

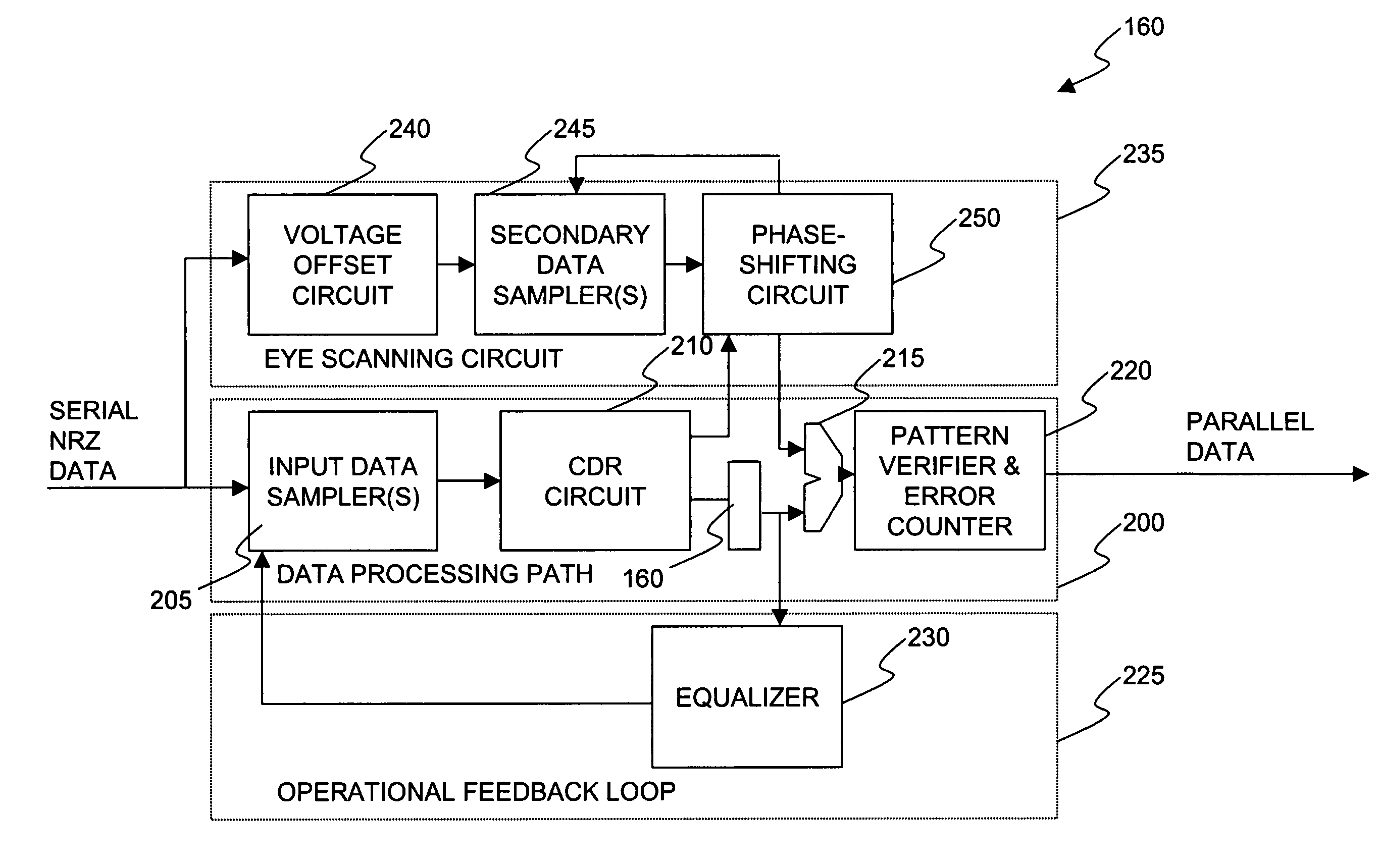

Circuit and method for evaluating the performance of an adaptive decision feedback equalizer-based serializer deserializer and serdes incorporating the same

A circuit and method for evaluating serializer deserializer (SERDES) performance that is particularly advantageous when the SERDES has a decision feedback equalizer (DFE). In one embodiment, the circuit has a data processing path and an operational feedback loop coupled to said data processing path and containing an equalizer, perhaps a DFE. In that embodiment, the circuit includes an eye scanning circuit coupled to said data processing path but separate from said equalizer and configured to measure at least one dimension of an eye relative to which said equalizer is configured for operation without substantially affecting said operation.

Owner:TEXAS INSTR INC

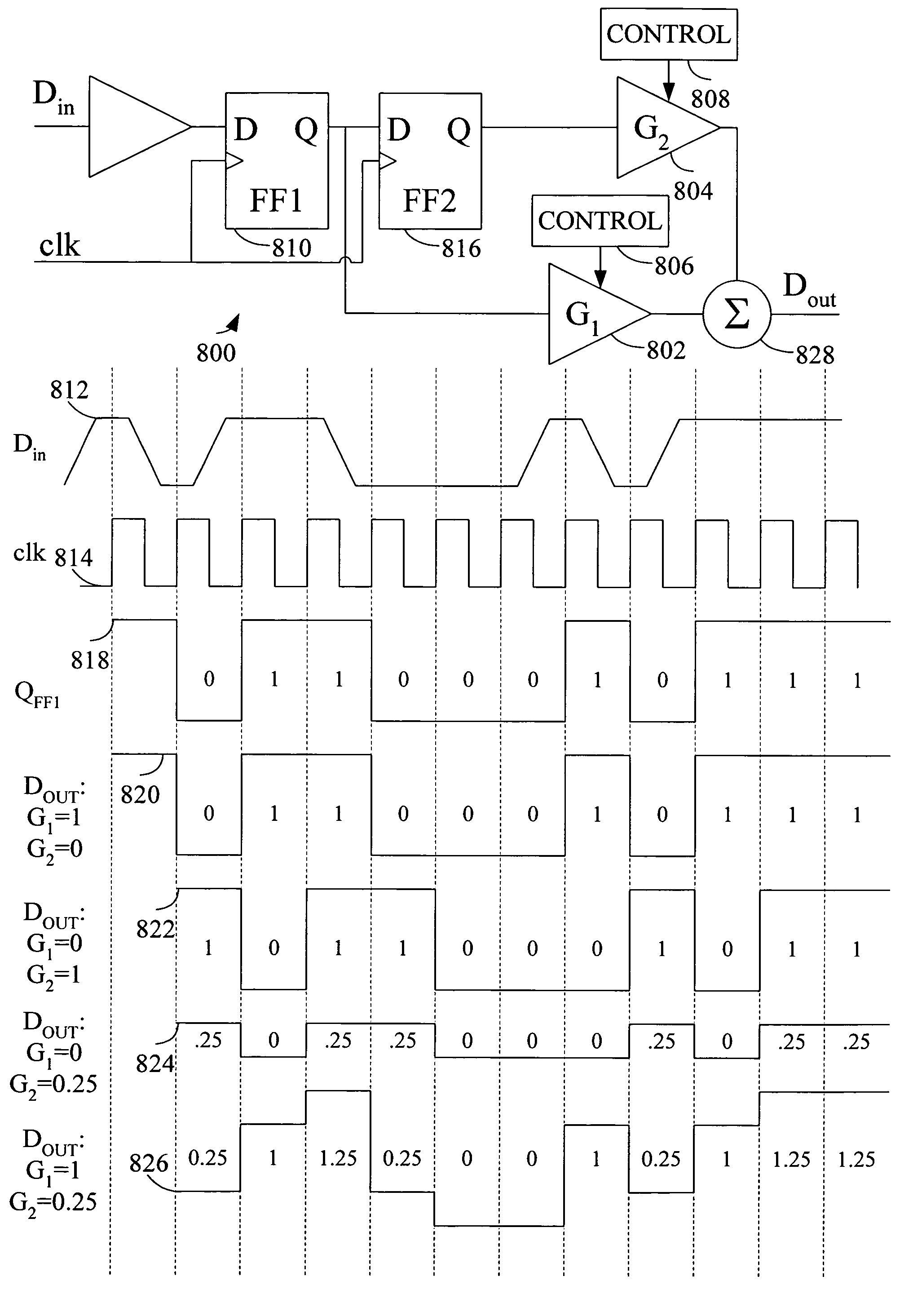

Built in self test (BIST) for high-speed serial transceivers

InactiveUS7756197B1Advantageously highly scaleableIncrease data rateCorrect operation testingTransmission monitoringFinite impulse responseTransceiver

A relatively high-speed serial data transmitter incorporates built in self test (BIST). The BIST circuit advantageously provides tests modes to obviate the need to build expensive test equipment for high-speed serial data devices, such as a serializer / deserializer (SerDes) or other transceivers. Multiple data paths in a finite impulse response (FIR) filter of transmitter of the SerDes or a transceiver can be independently tested. The transmitter output can also be selectively degraded to test a receiver of a transceiver. An attenuated output signal can be provided to test receiver sensitivity. A low-pass filter can be invoked to emulate a backplane, while a loopback circuit can provide the emulated backplane attenuation to the receiver to permit testing of the equalization circuitry of a receiver without requiring the presence of an actual backplane for testing.

Owner:MICROSEMI STORAGE SOLUTIONS

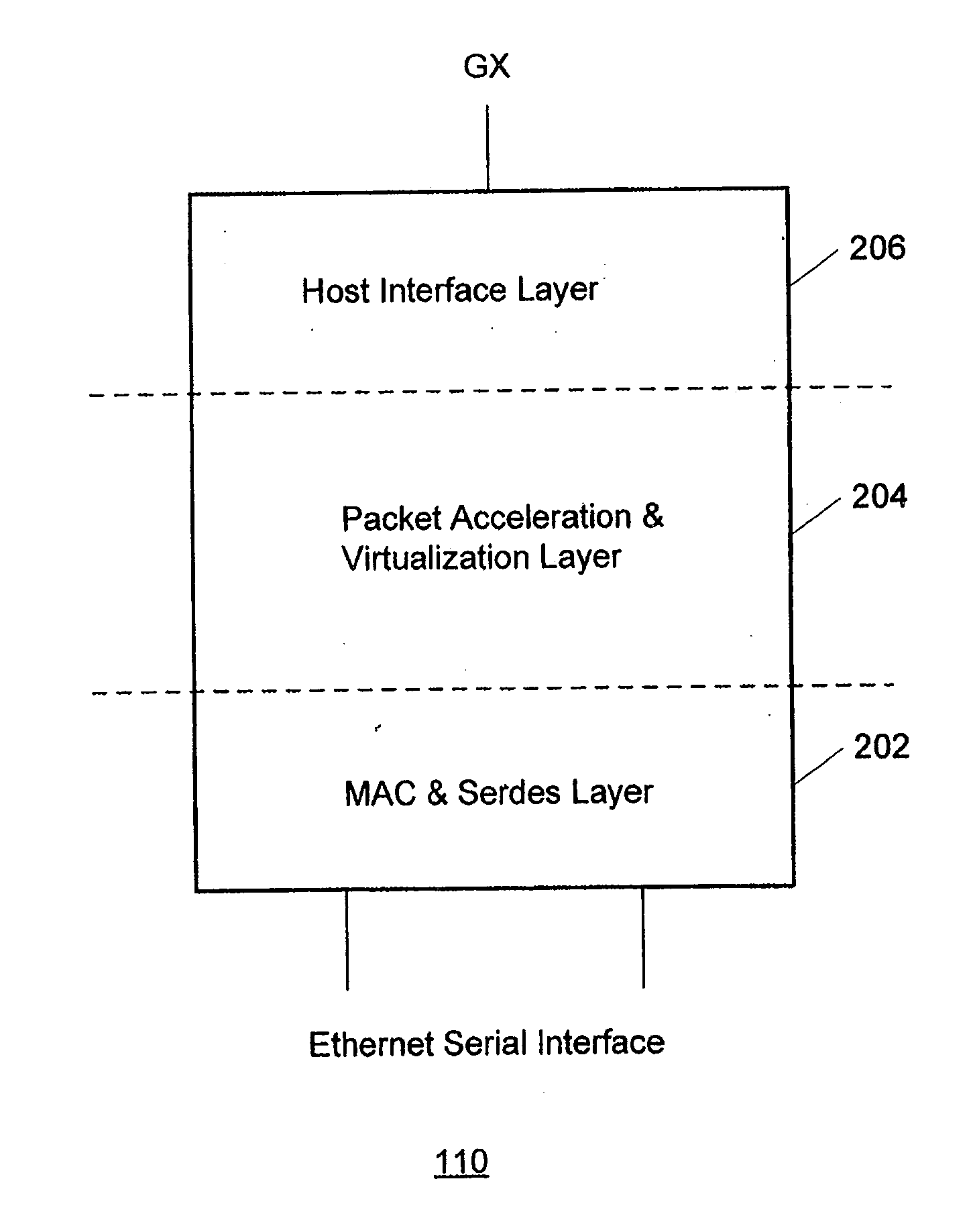

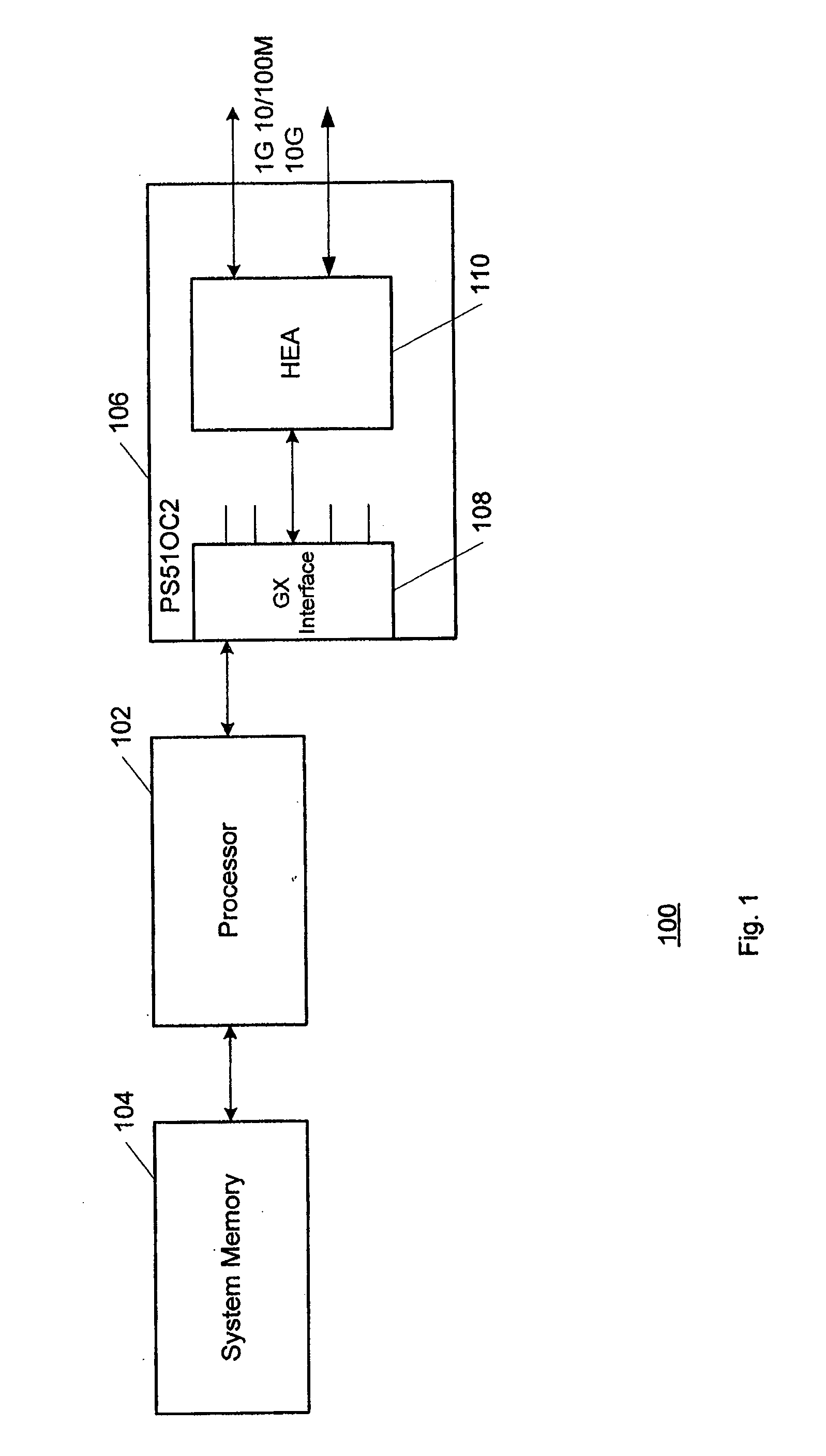

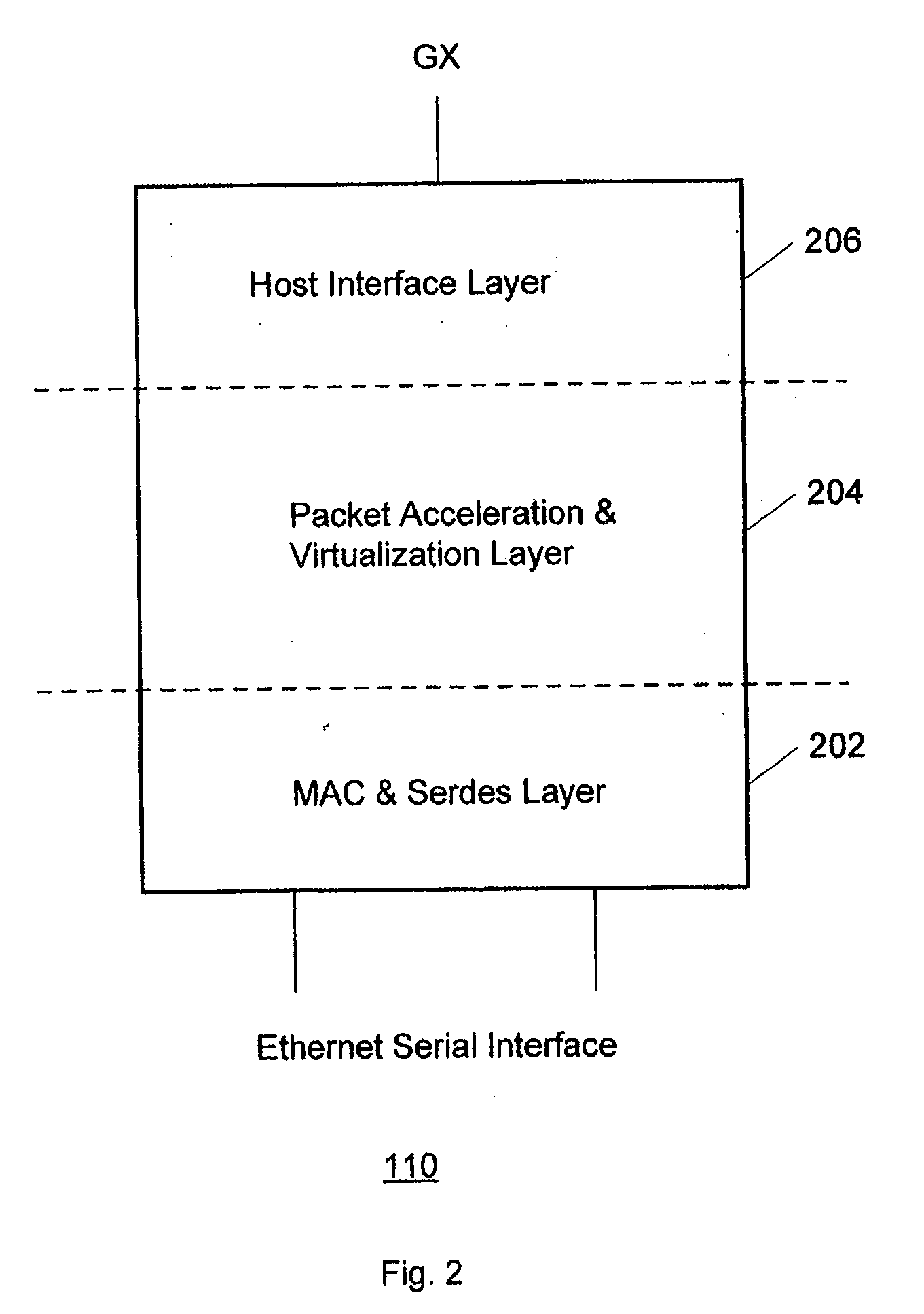

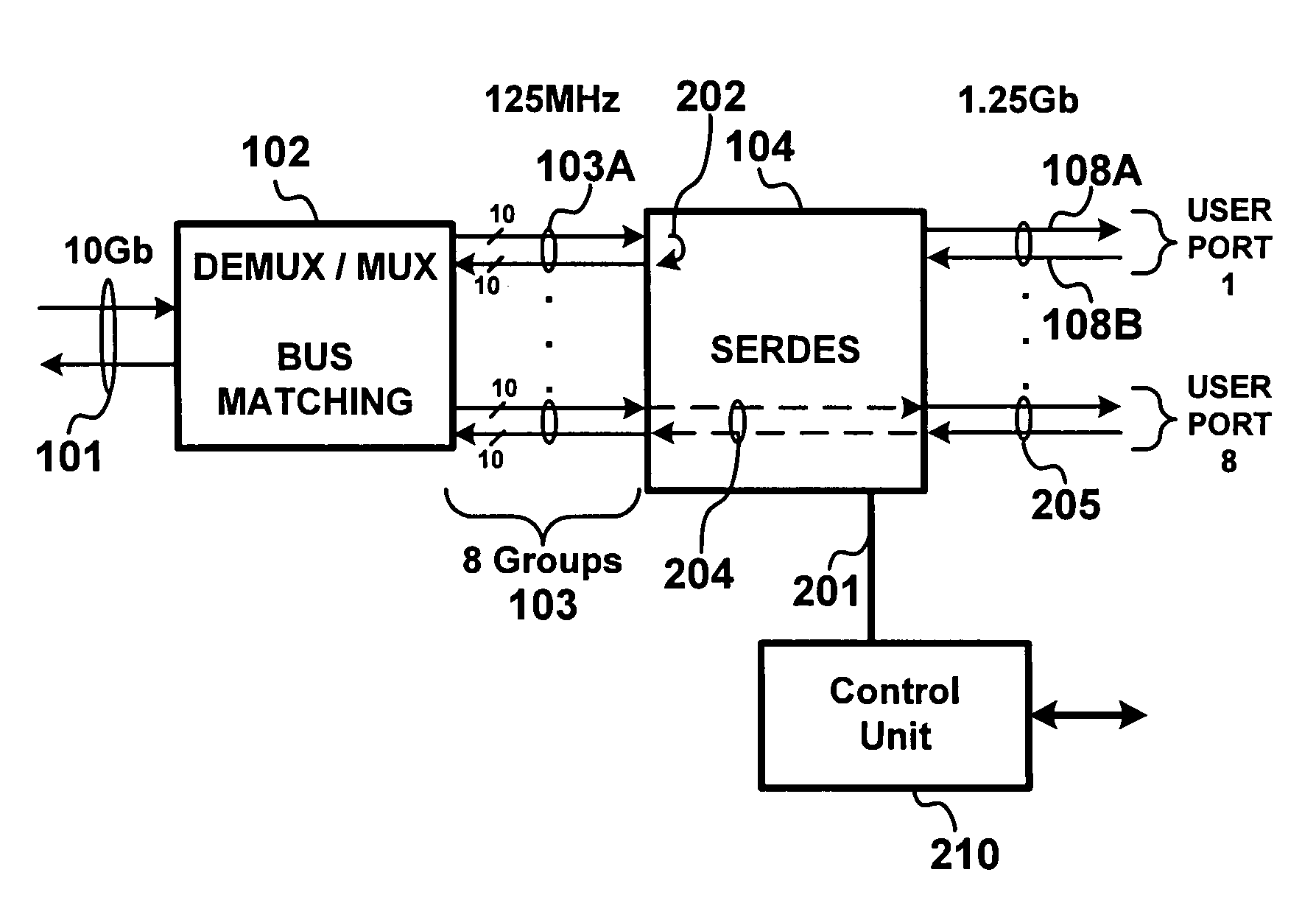

Configurable ports for a host ethernet adapter

A system and method in accordance with the present invention allows for an adapter to be utilized in a server environment that can accommodate both a 10 G and a 1 G source utilizing the same pins. This is accomplished through the use of a high speed serializer / deserializer (high speed serdes) which can accommodate both data sources. The high speed serdes allows for the use of a relatively low reference clock speed on the NIC to provide the proper clocking of the data sources and also allows for different modes to be set to accommodate the different data sources. Finally the system allows for the adapter to use the same pins for multiple data sources.

Owner:INT BUSINESS MASCH CORP

Forward error correction encoding for multiple link transmission capatible with 64b/66b scrambling

InactiveUS20080109707A1Reduce overheadCorrection errorError detection/correctionCode conversionHamming codeHigh bandwidth

Owner:IBM CORP

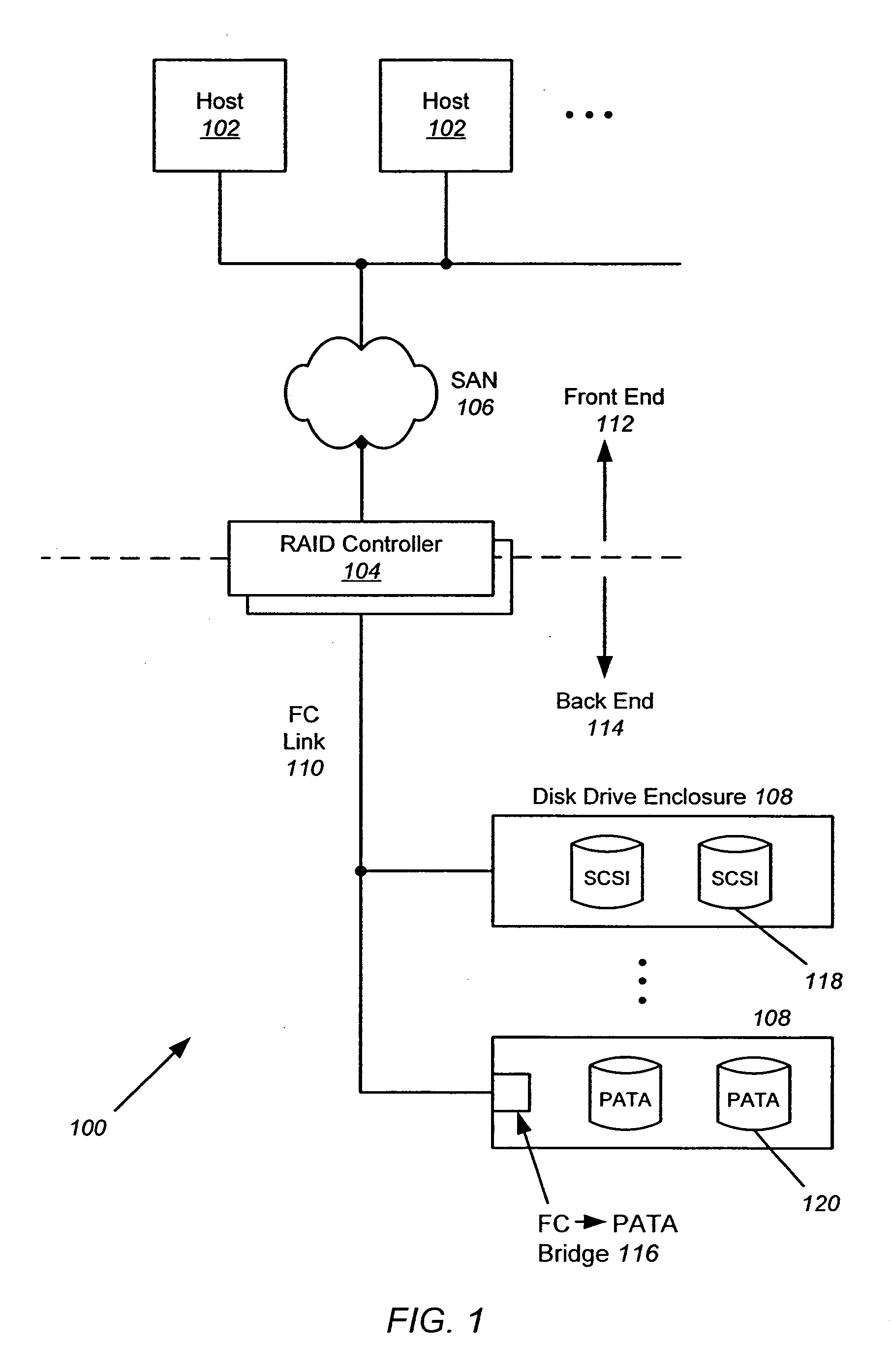

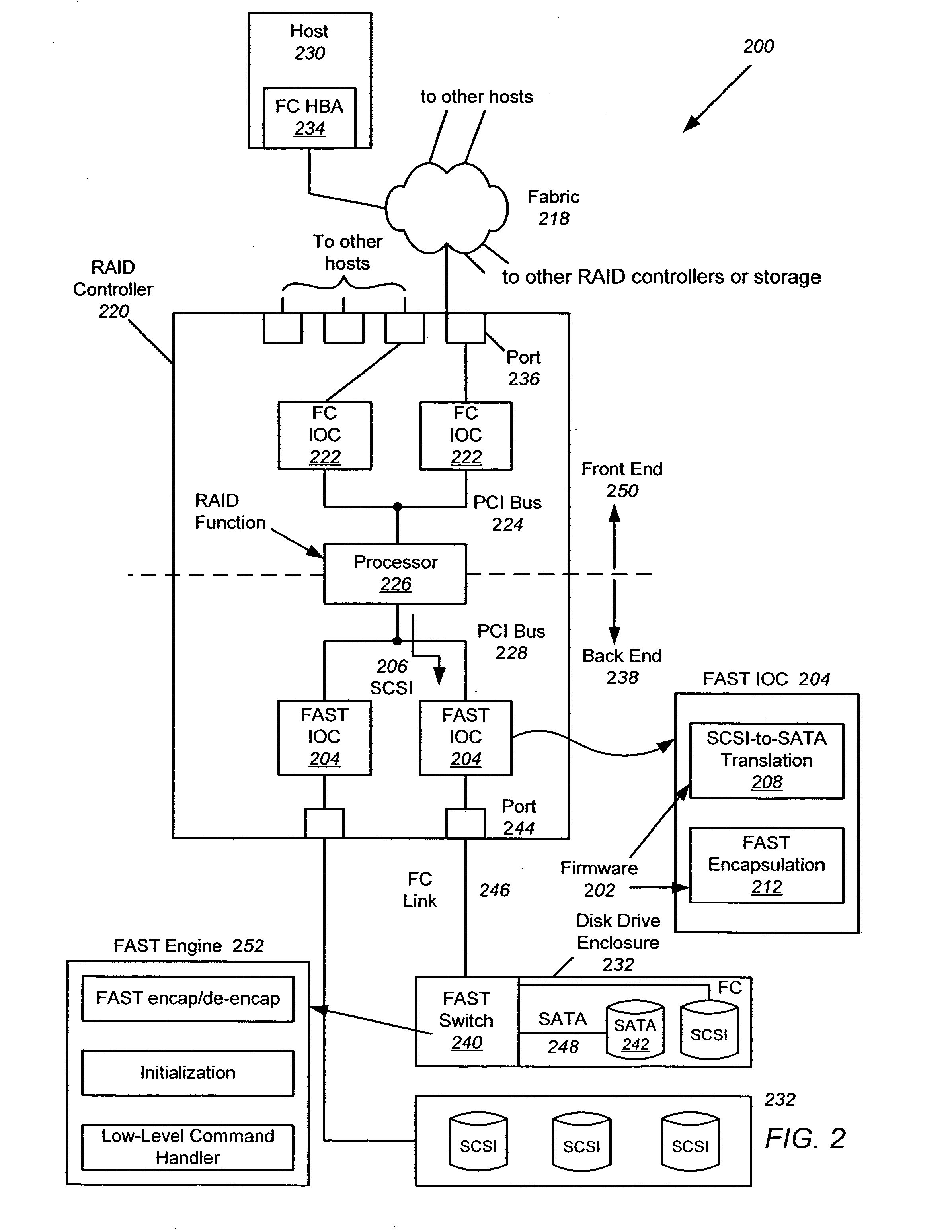

Method and apparatus for auto-protocol discrimination between fibre channel, SAS and SATA devices

InactiveUS20070223517A1No wasteQuick serviceError preventionFrequency-division multiplex detailsAutonegotiationData rate

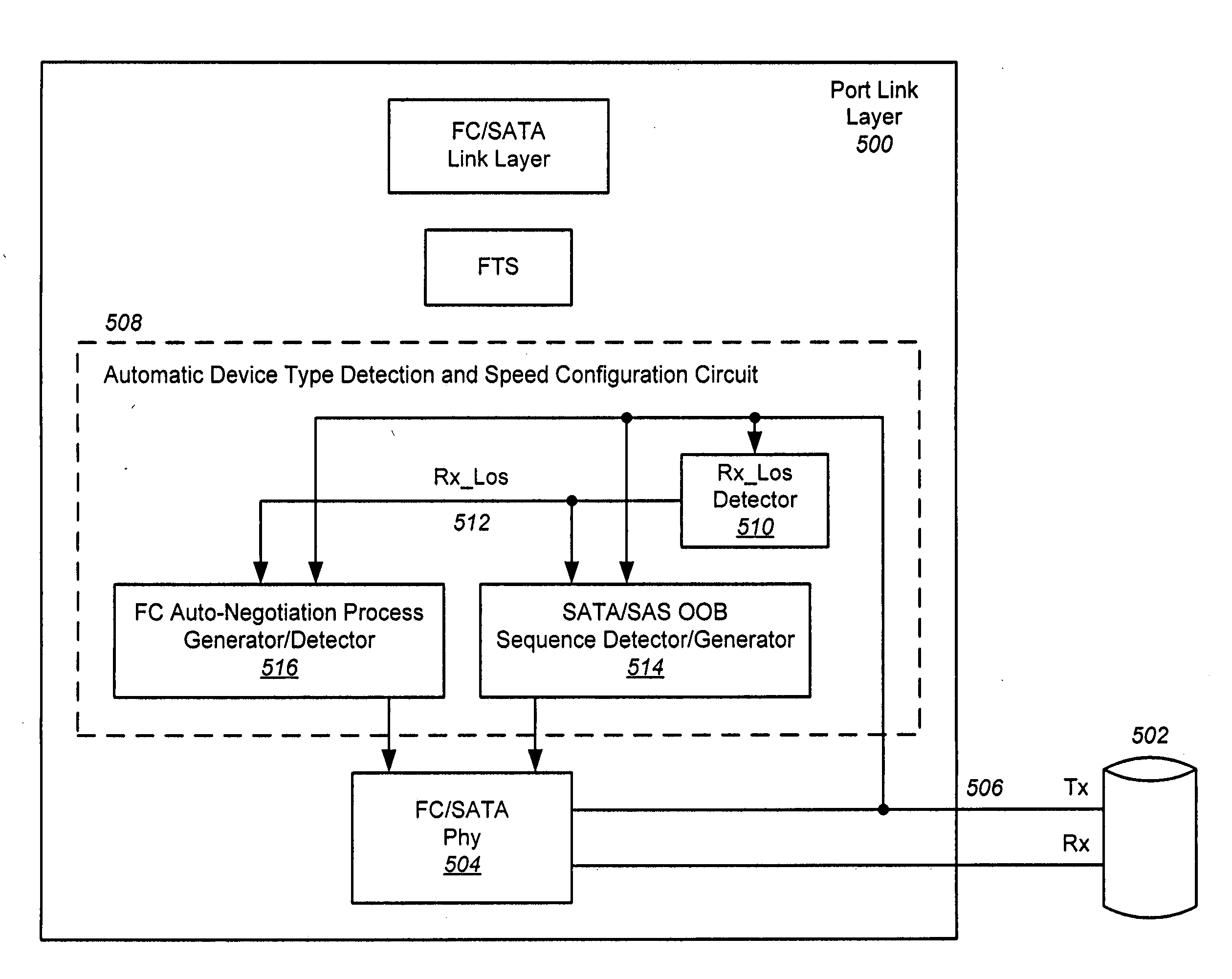

Auto-discrimination between FC and SATA devices upon insertion of a device into a port of a FAST-compatible switch is disclosed. Without user intervention, the port is able to determine the type of device attached, set the appropriate data rate in the Phy or SERDES and, in the case of FC or SATA drives, start the disk insertion process into the active switch zones. The SERDES is first initialized to FC speeds, and the receive path is searched for a receive signal. Upon detecting a receive signal, the detection circuitry then checks to see if a valid SATA Out Of Band (OOB) sequence is received. If a valid SATA OOB sequence is received, the SERDES is configured for SATA speeds and analog settings. If a valid SATA OOB sequence is not received, and instead a FC auto-negotiation process runs to completion, the SERDES remains at FC speeds.

Owner:AVAGO TECH INT SALES PTE LTD

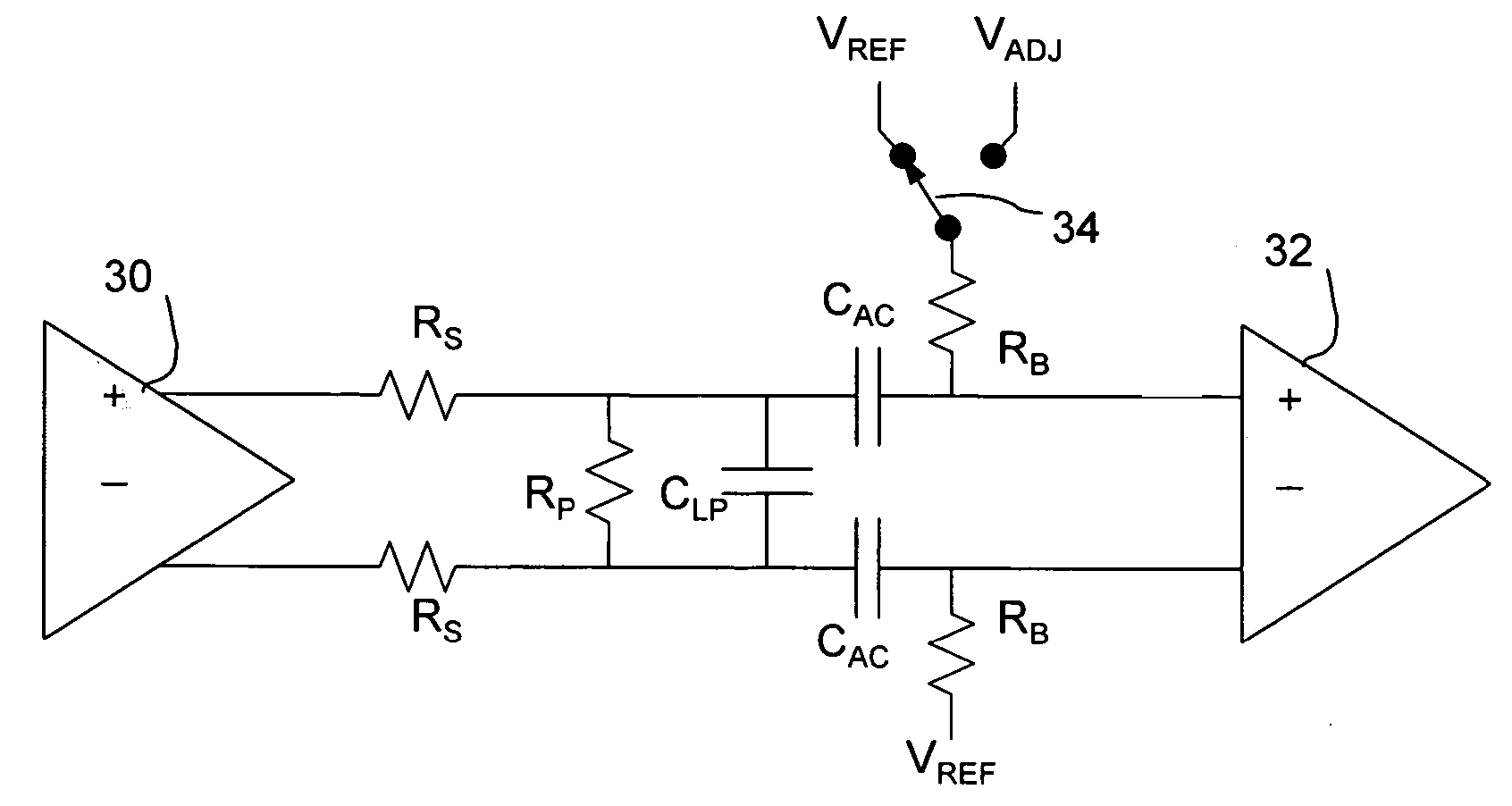

Circuit and method for testing high speed data circuits

InactiveUS20040123197A1Digital circuit testingError detection/correctionCapacitanceDigital transition

A circuit and method are described in which a DC voltage or current is connected to a high frequency, AC-coupled signal path between a transmitter and a receiver, and the bit error rate of the data transmission is tested while applying an altered bias voltage to the received signal. The bias voltage can be connected via a resistor, inductor or transistors. The transmitted signal is attenuated resistively, and a load capacitance is applied whose value causes digital transition times to exceed one unit interval. An intended application is testing of an integrated circuit, serializer / deserializer (serdes) operating above 1 GHz.

Owner:MENTOR GRAPHICS CORP

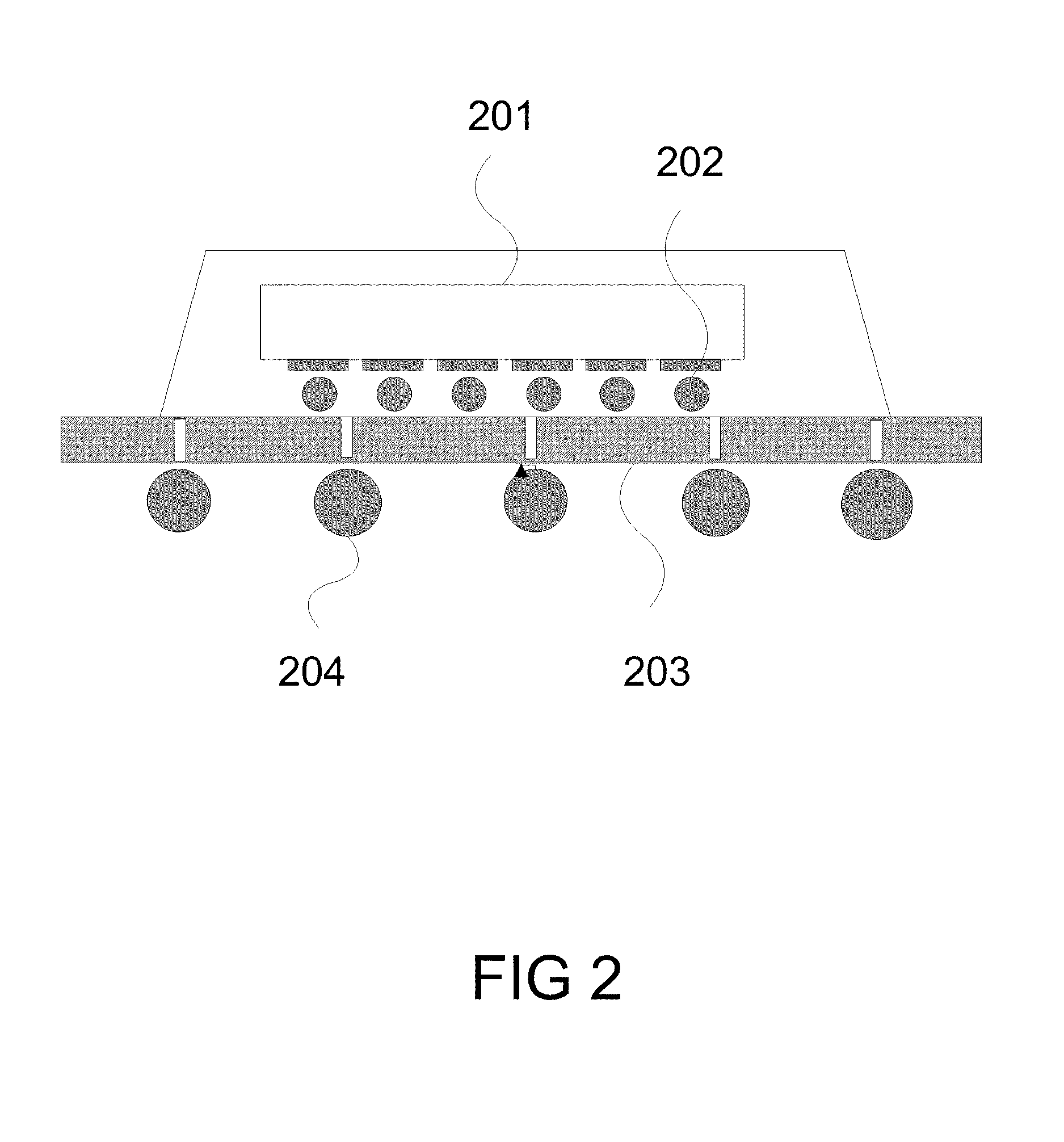

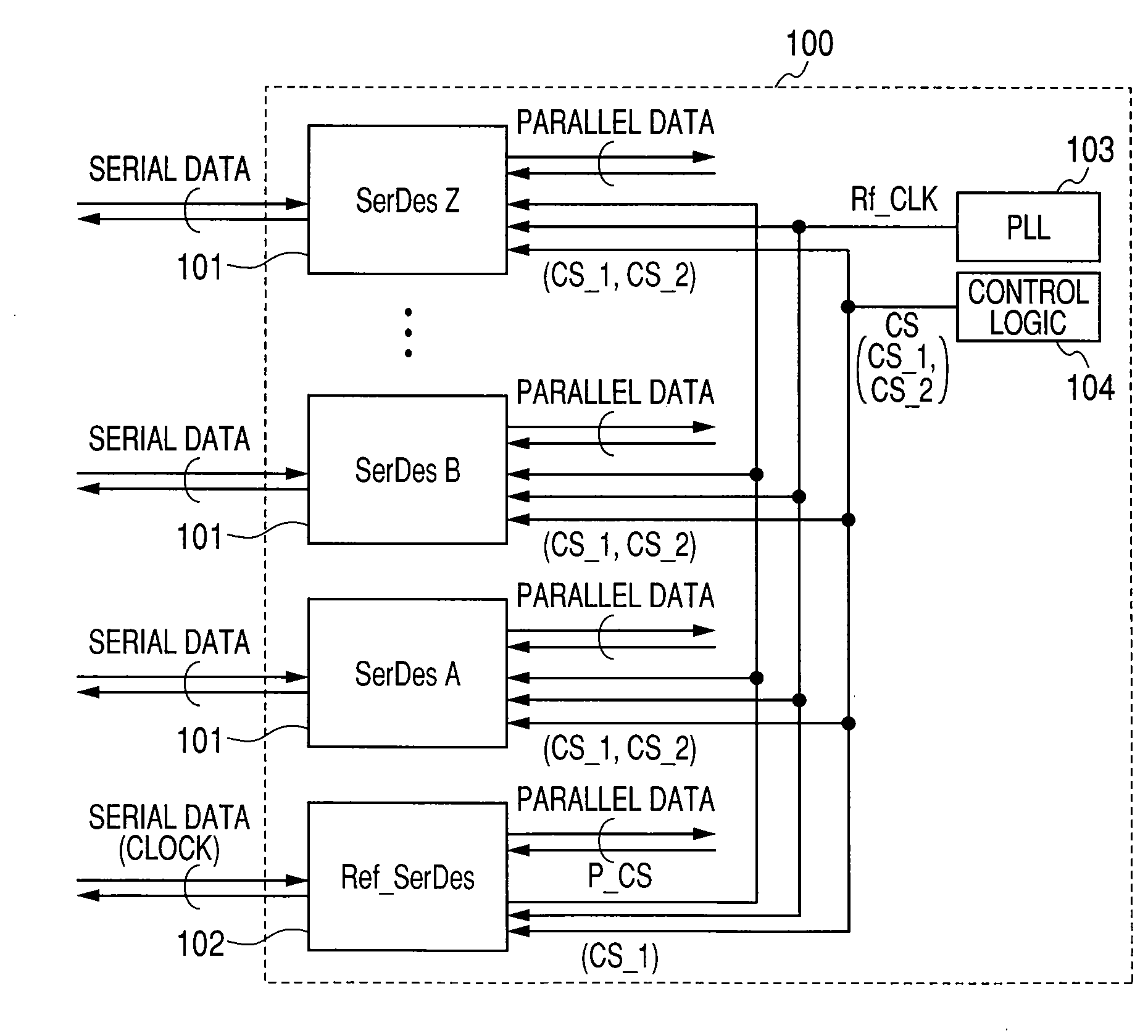

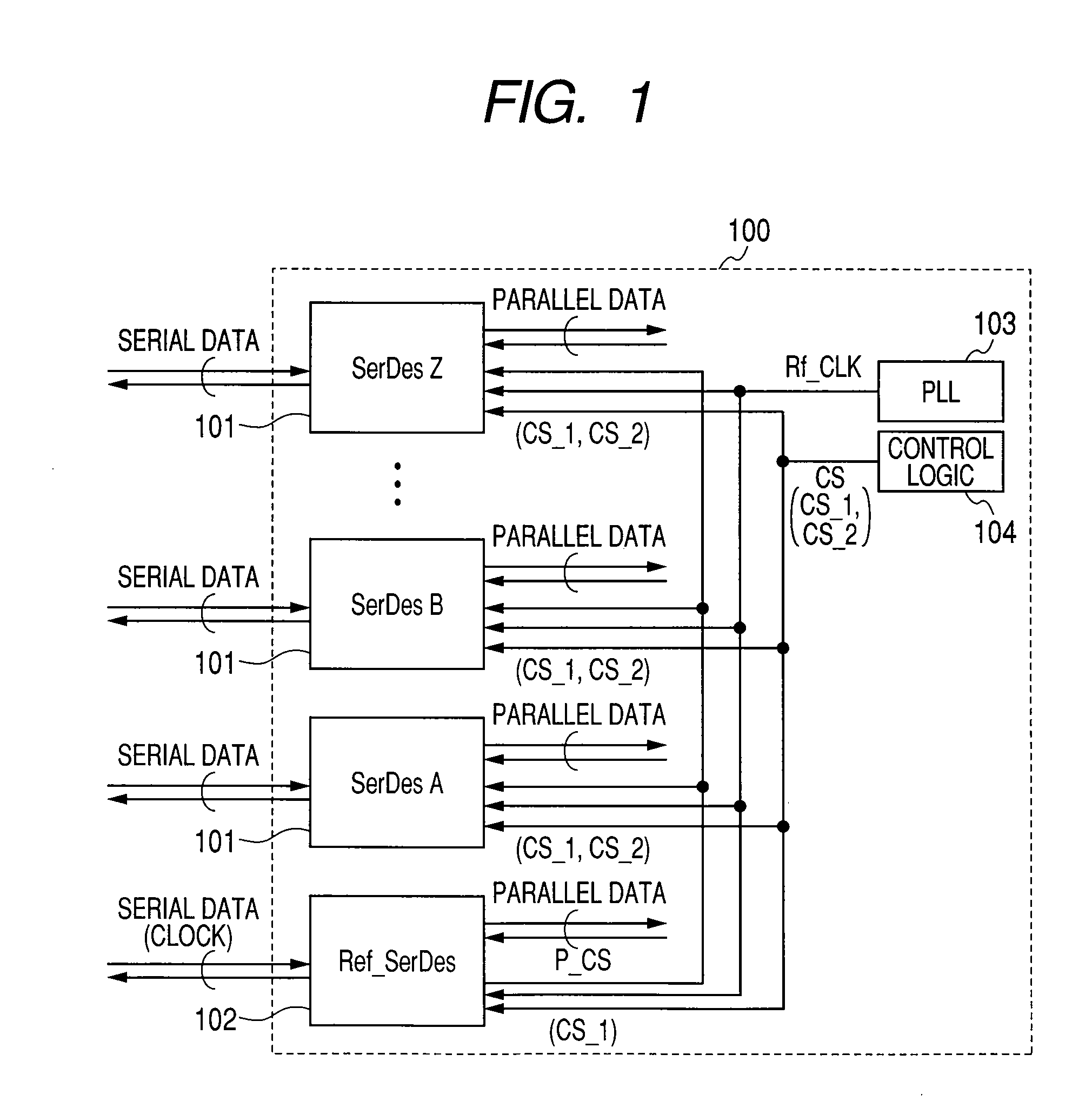

Semiconductor system

InactiveUS20090080584A1Eliminate the effects ofSmooth transferParallel/series conversionSynchronisation information channelsPhase controlComputer science

A semiconductor system has a SerDes circuit for receiving serial data, and a reference SerDes circuit for receiving clock signals running in parallel. The SerDes circuit performs serial to parallel conversion of the serial data captured by the recovery clock whose phase is controlled by utilizing the phase control signal P_CS generated by the reference SerDes circuit.

Owner:HITACHI LTD

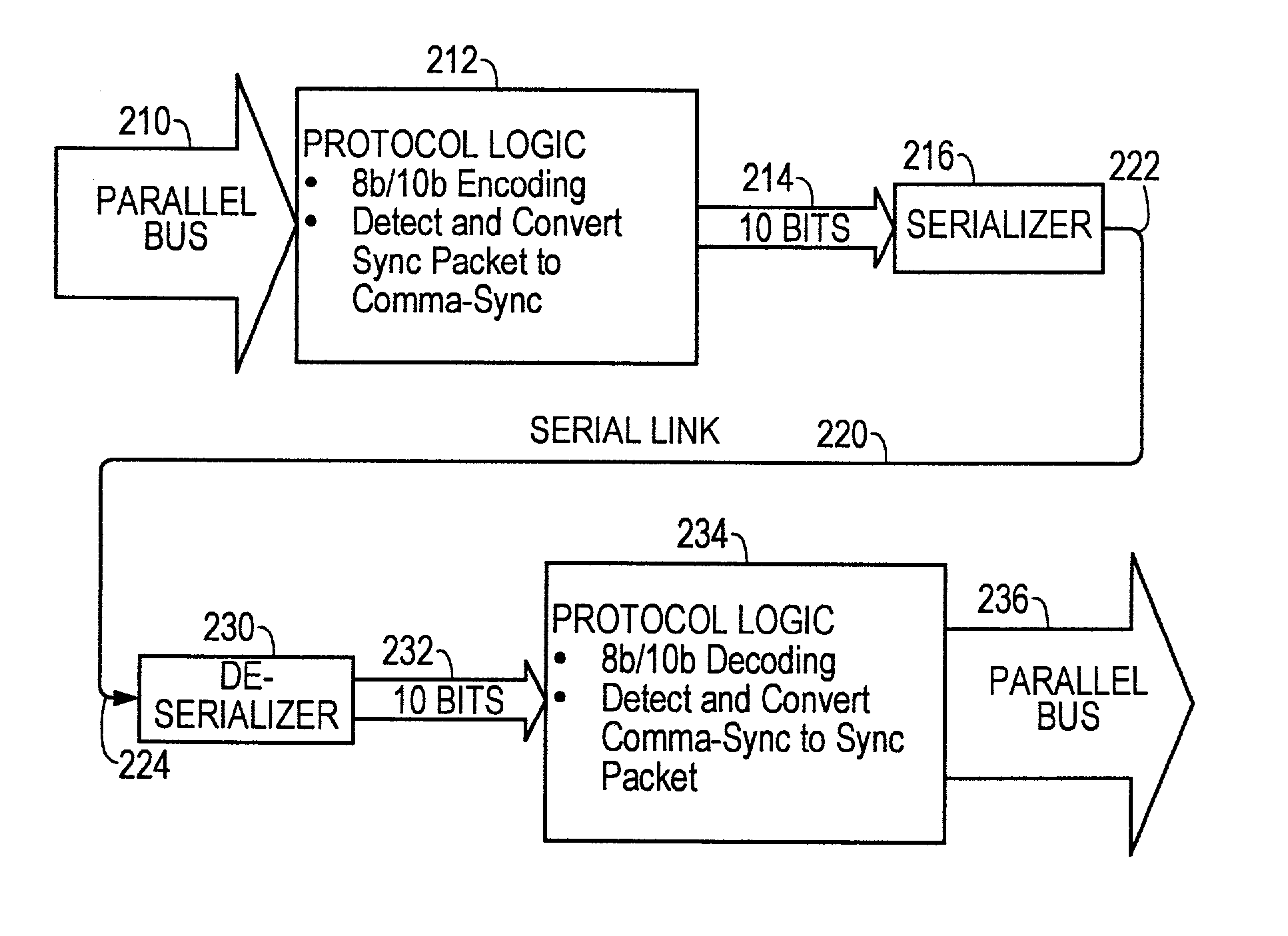

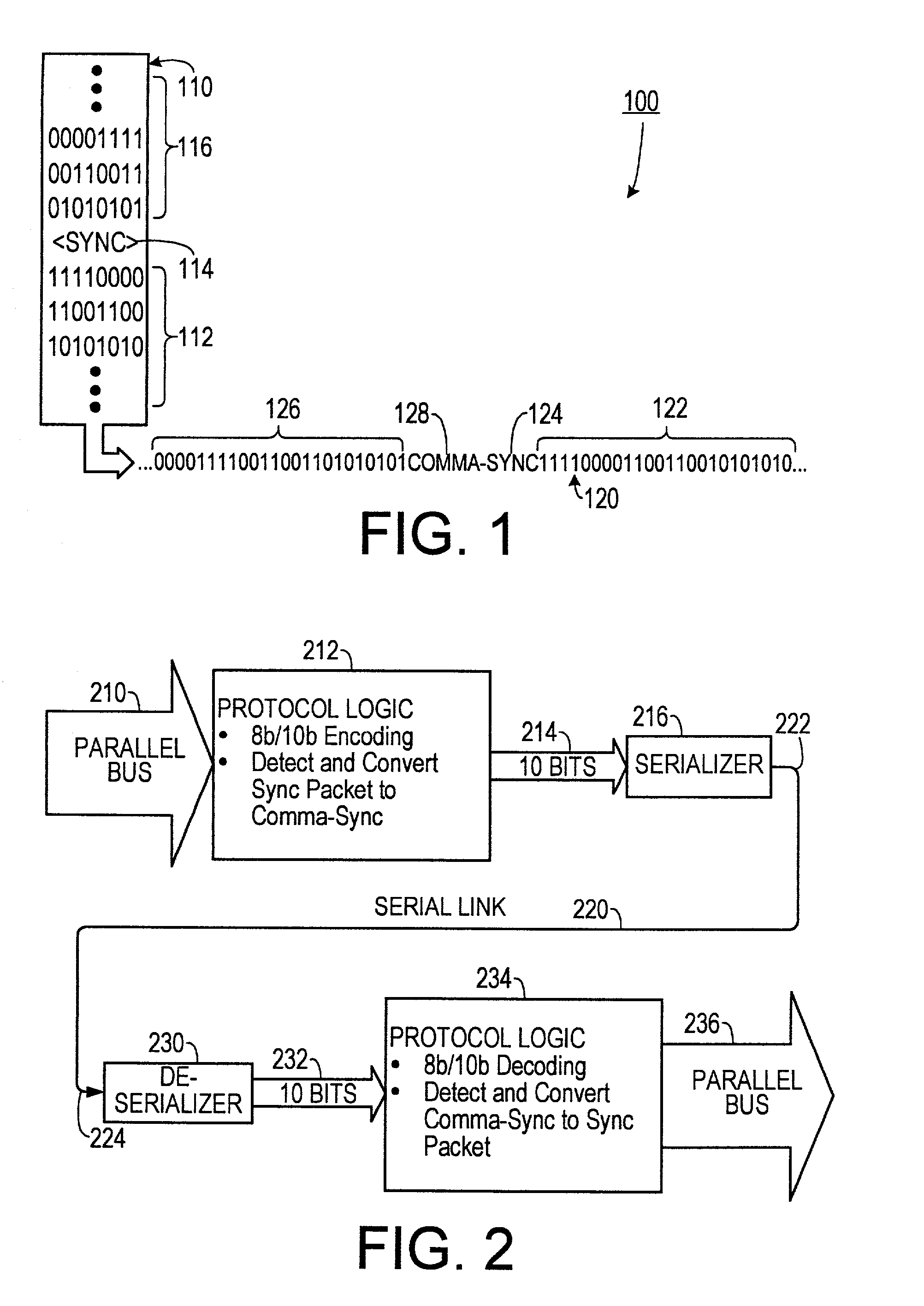

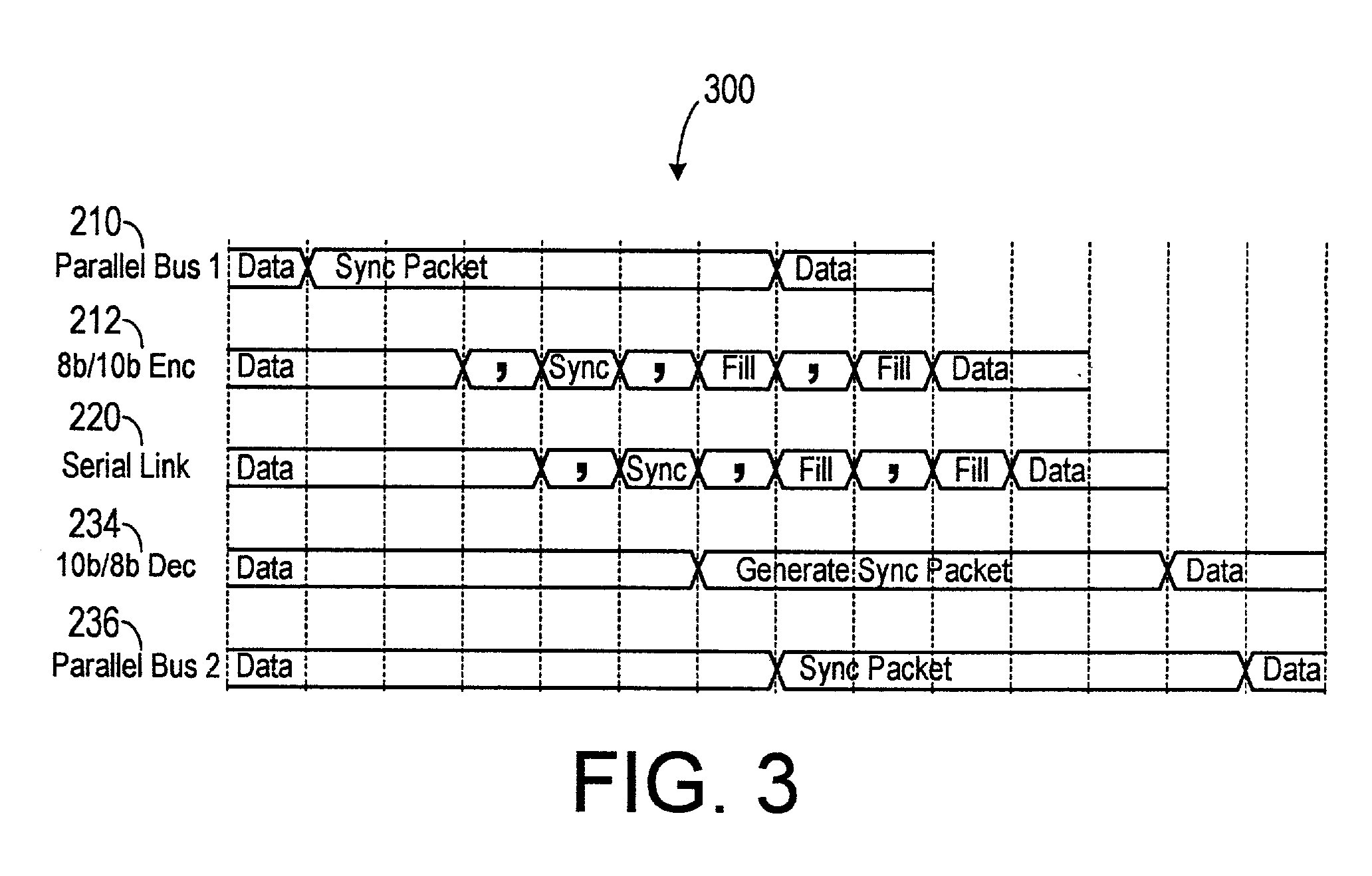

Modification of bus protocol packet for serial data synchronization

ActiveUS7065101B2Multiplex system selection arrangementsTime-division multiplexData transmissionData channel

An apparatus for enabling transmission of parallel data from a first parallel bus to a second parallel bus via a serial data channel includes a first logic element that generates a synchronization character used in a serial data transmission protocol upon detection of a parallel synchronization packet. A serializer converts data from the first logic element into a serial data stream. A de-serializer converts the serial data stream into a plurality of parallel data packets. A second logic element detects the synchronization character and converts the synchronization character into a parallel synchronization packet.

Owner:TWITTER INC

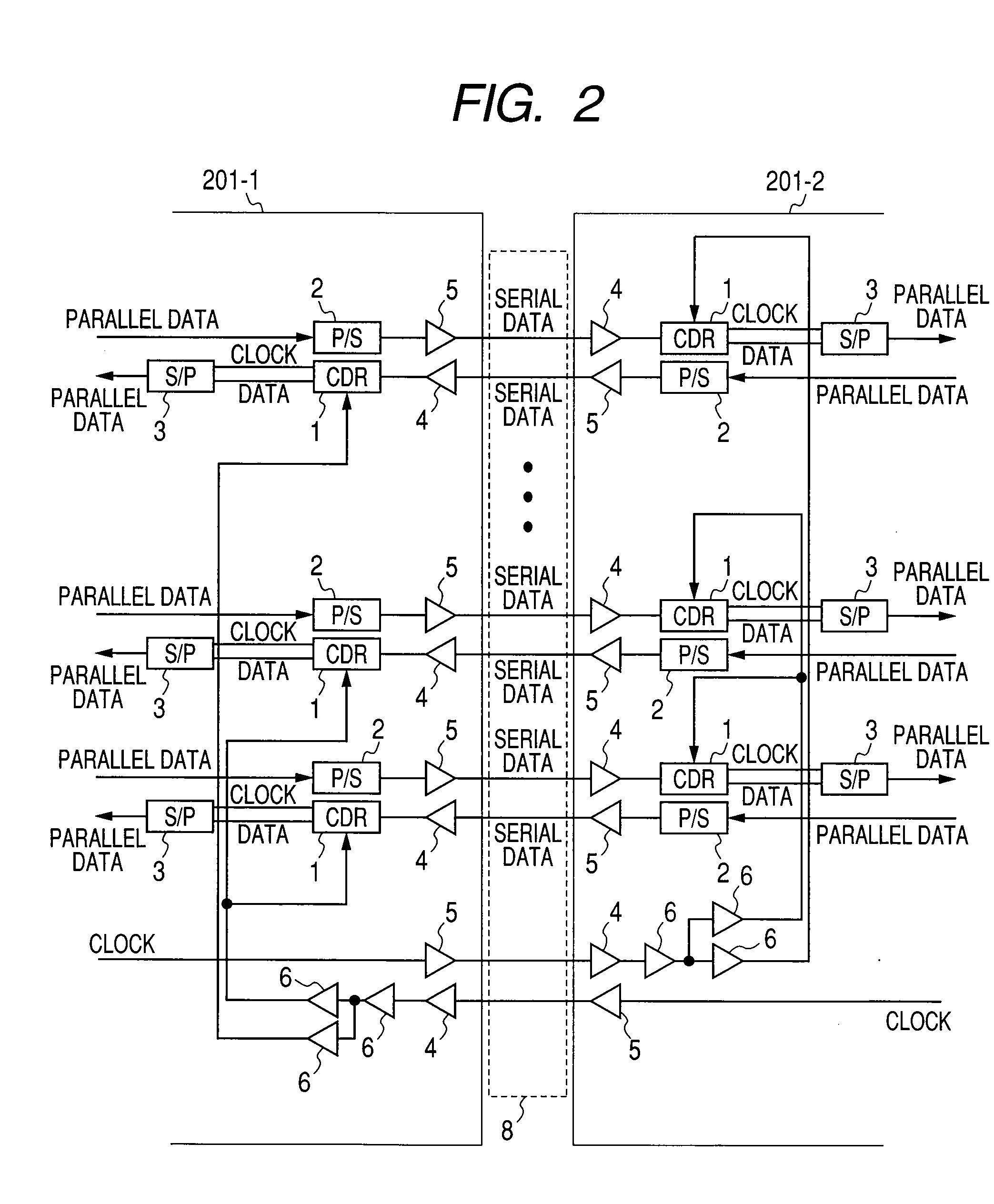

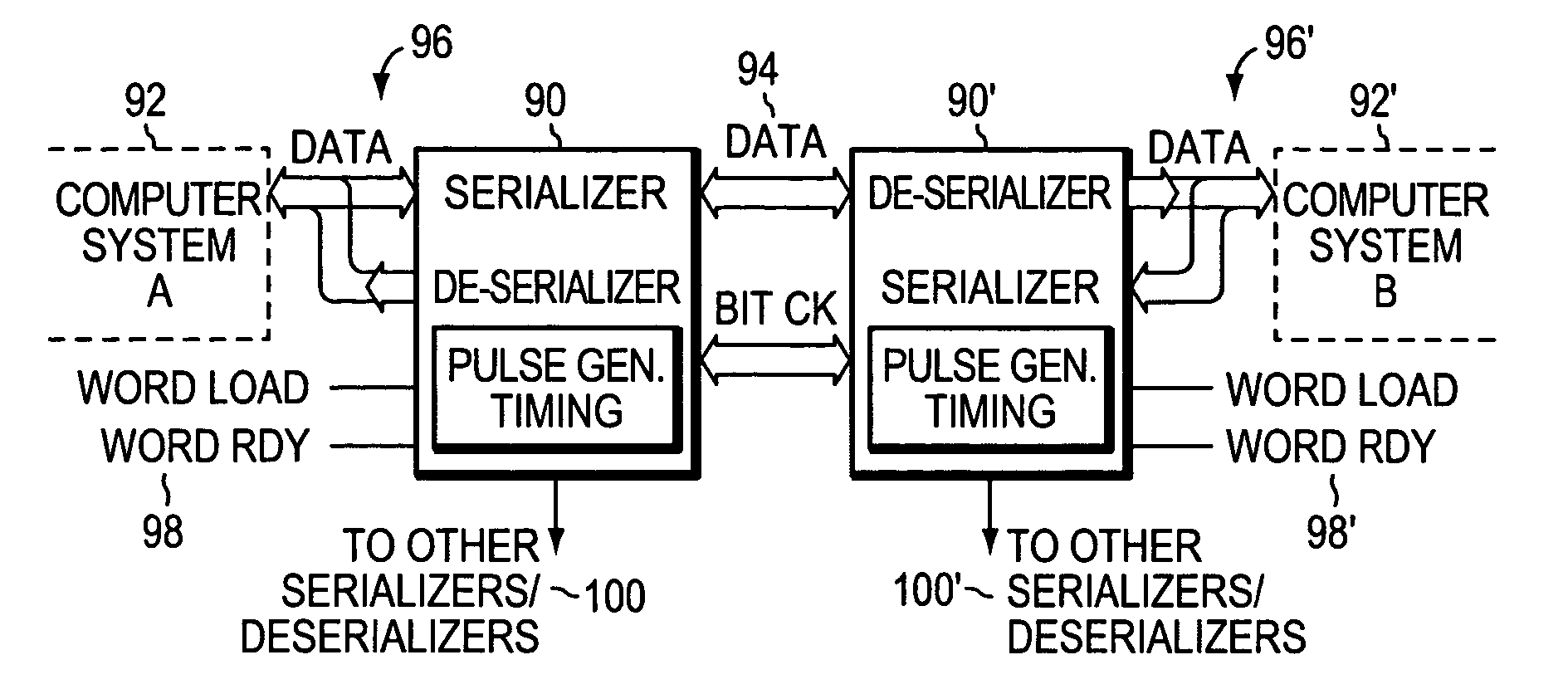

Sending and/or receiving serial data with bit timing and parallel data conversion

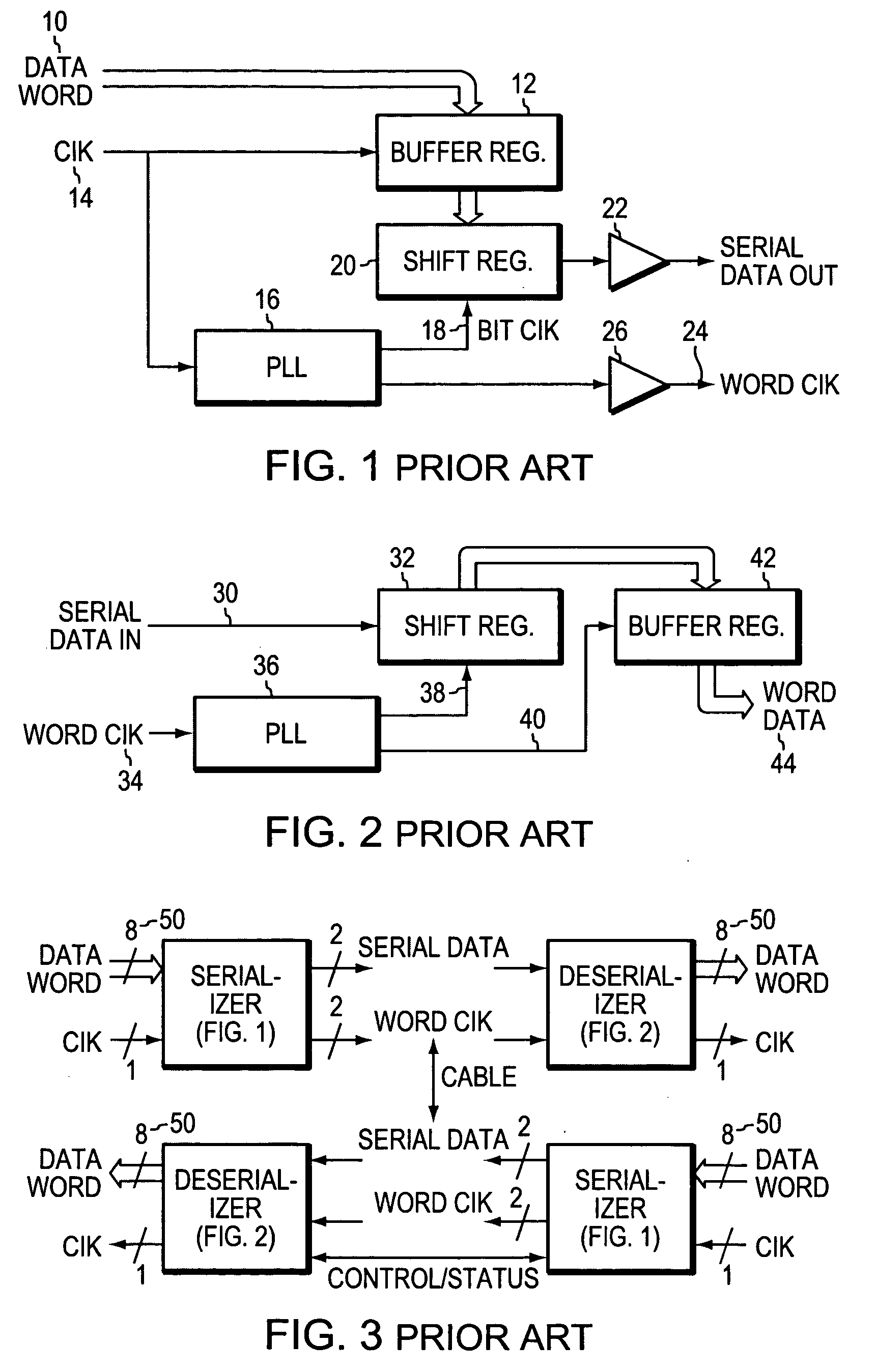

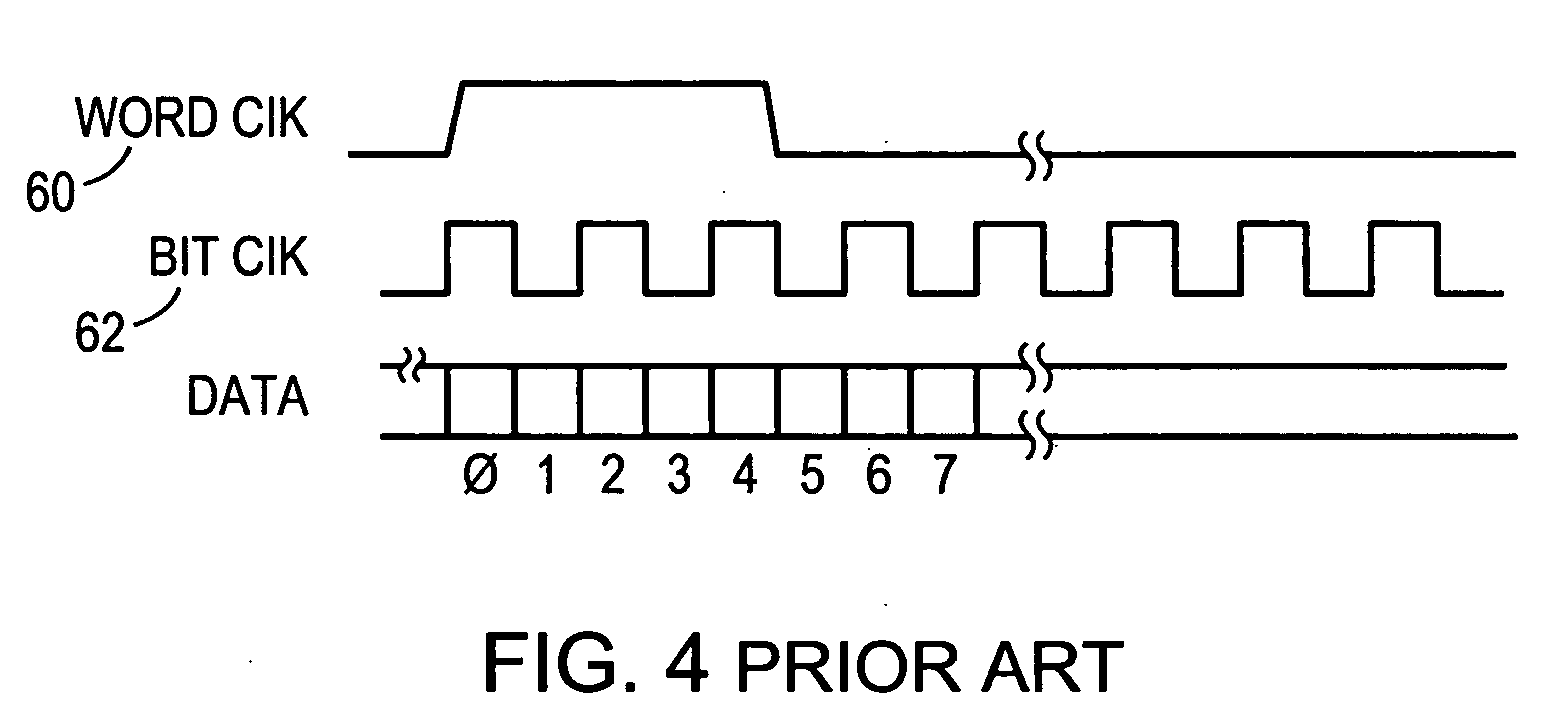

A serializer and a deserializer are disclosed and shown operating singly or as a pair. The invention operates independently from any outside system reference clock. The inventive system provides an internal bit clock that serializes the data when sending and de-serializes the data when receiving. A bit clock or pulse travels with the data word bits to define when a bit is stable. The system uses word boundary bits operating with a bit clock to distinguish different data words, as described in the parent application. The system operates either synchronously or asynchronously with the base computer or other such digital system, including I / O devices. The invention finds use where new data to be sent is strobed into the serializer, but also where a change in the data bit content itself will cause the changed data to be loaded into the serializer and sent bit by bit. The system operates where new data is strobed or loaded by the serializer (not the base computer system) when the last data word has been sent. In this case a signal is generated when the last word has been sent in the serializer that causes new data to be loaded for sending. Half duplex and full duplex configurations as disclosed. Similar, corresponding operations occur at the deserializer.

Owner:SEMICON COMPONENTS IND LLC

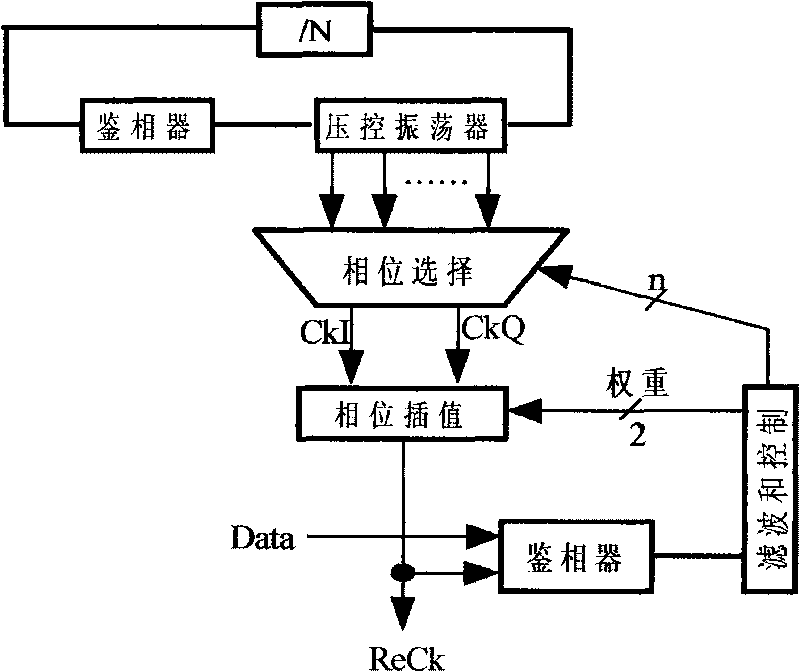

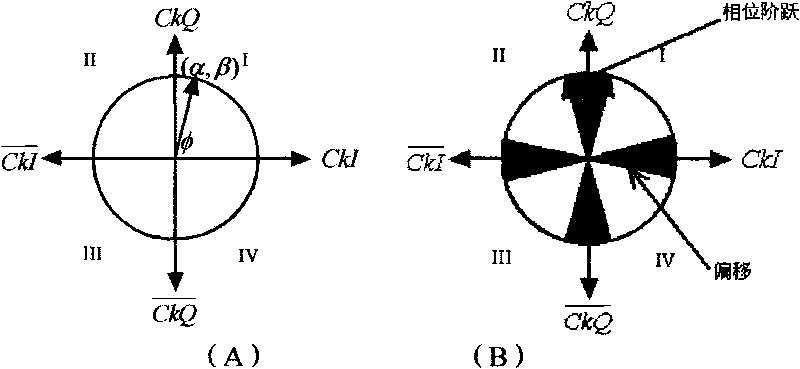

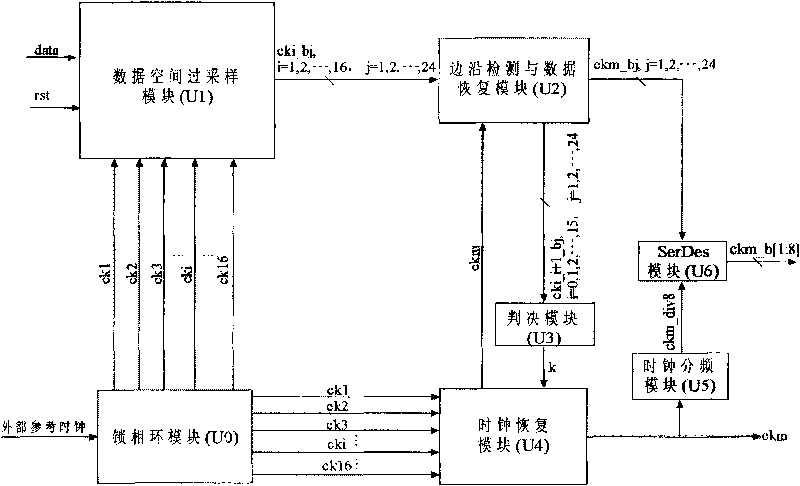

Clock data recovery and serial-parallel conversion circuit based on over sampling

InactiveCN101753288AMeet the precision requirementsWork reliablyPulse automatic controlSynchronising arrangement24-bitTransceiver

A clock data recovery and a serial-parallel conversion circuit based on over sampling for the receiver of a high speed serial transceiver comprise PLL module, a data space over sampling module, an edge detection and data recovery module, a judgment module, clock recovery module, a clock frequency-division module and a SerDes module. The data space over sampling module adopts the 16-phase equal-interval clock outputted by the PLL module to continuously sample the 24 bit data of 3 bytes, stores the sampled data in 16 groups of registers, and each group includes 24 registers. The corresponding bits of adjacent two groups of registers carry out OR operation to finish the edge detection, the detection results are added together in grouping mode, the fastest sampling clock corresponding to the group of data with the maximum distance value can be used as the recovery clock, the data sampled through the sampling clock can be used as recovery data, the sampling clock is performed with 8-fractional frequency to synchronize the bytes of the recovery data so as to finish the clock data recovery and serial-parallel conversion. The invention has clear structure, higher performance and reliable operation.

Owner:XIAN UNIV OF POSTS & TELECOMM

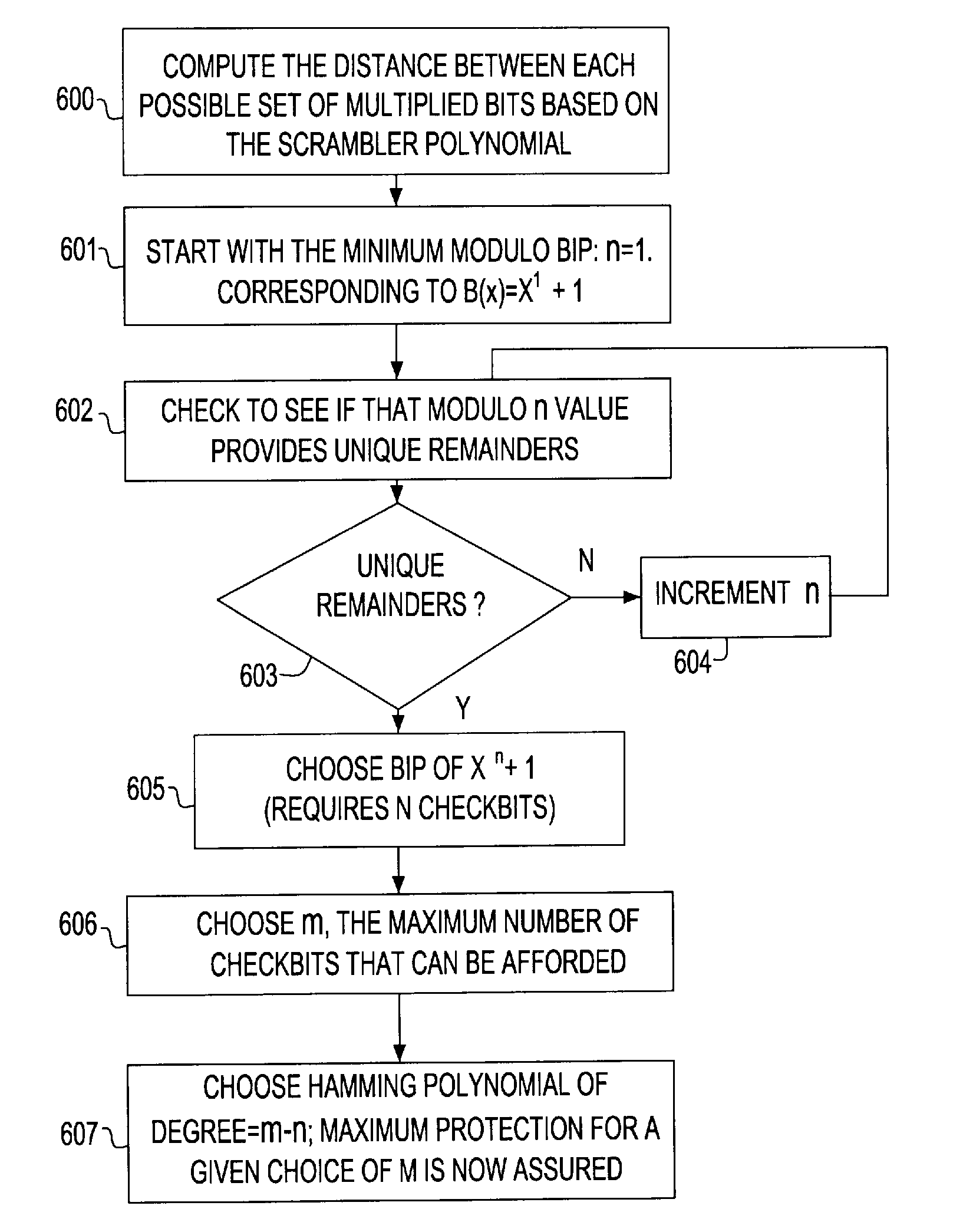

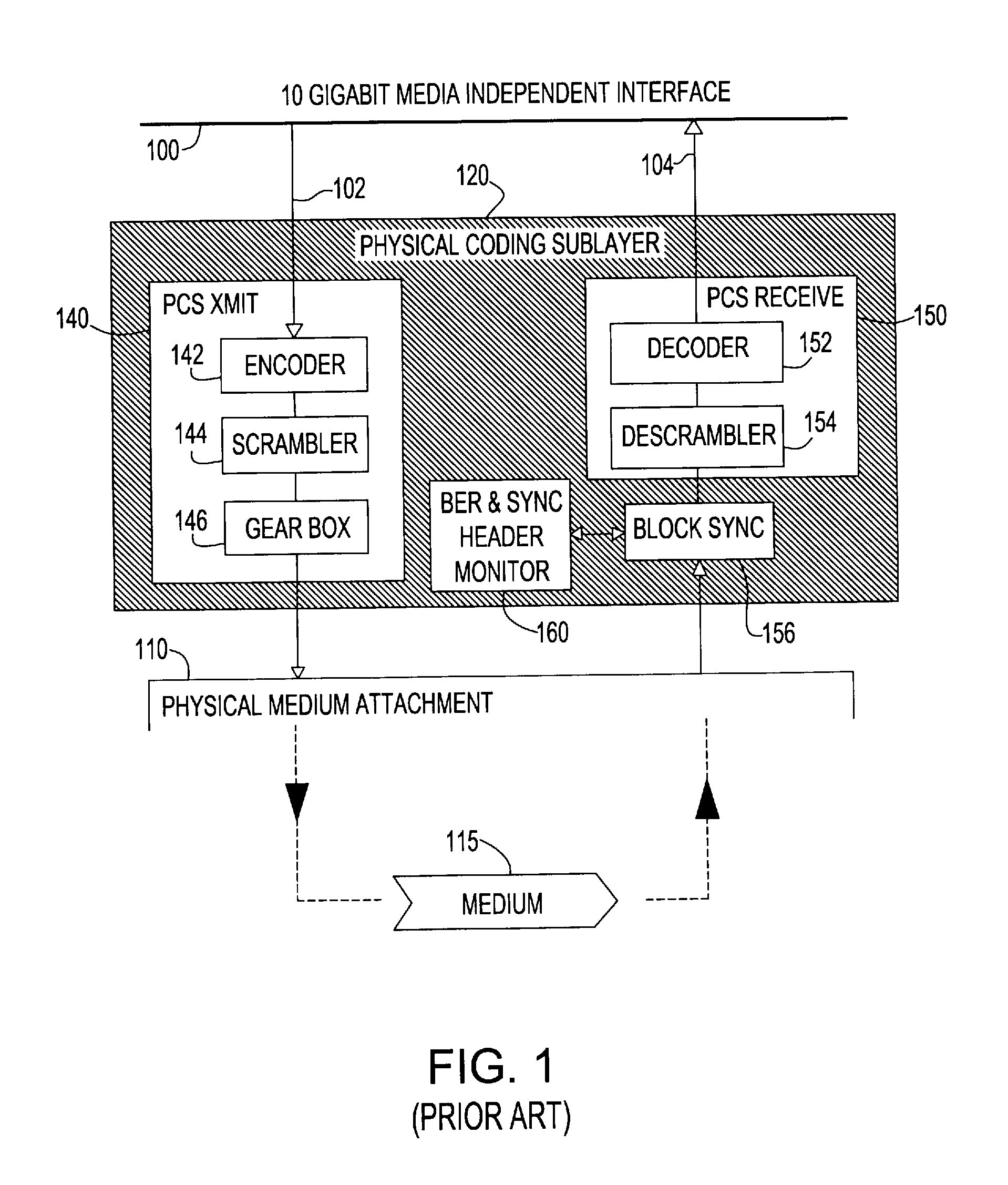

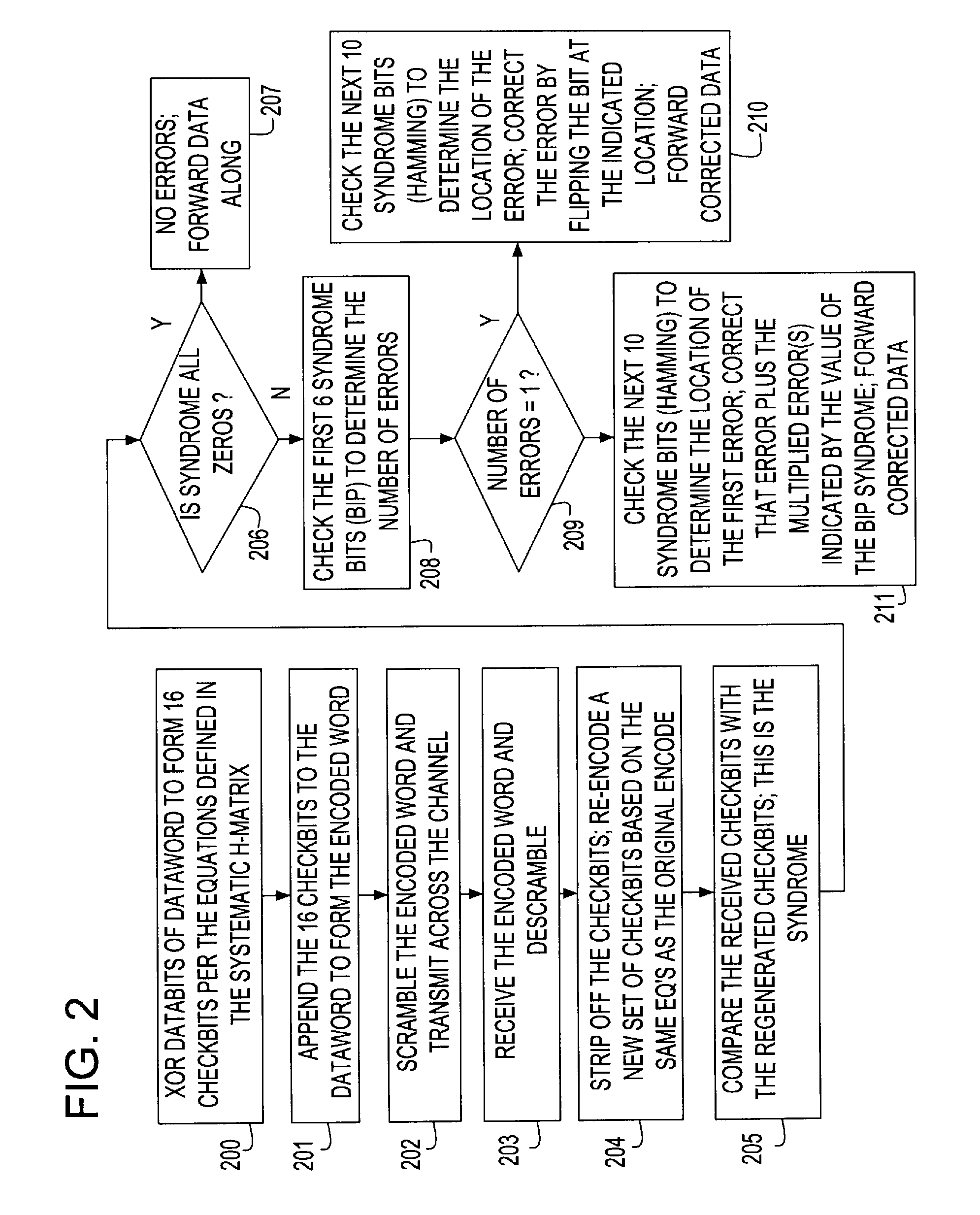

Forward error correction encoding for multiple link transmission compatible with 64B/66B scrambling

InactiveUS7996747B2Reduce overheadEasy to correctError detection/correctionCode conversionHamming codeHigh bandwidth

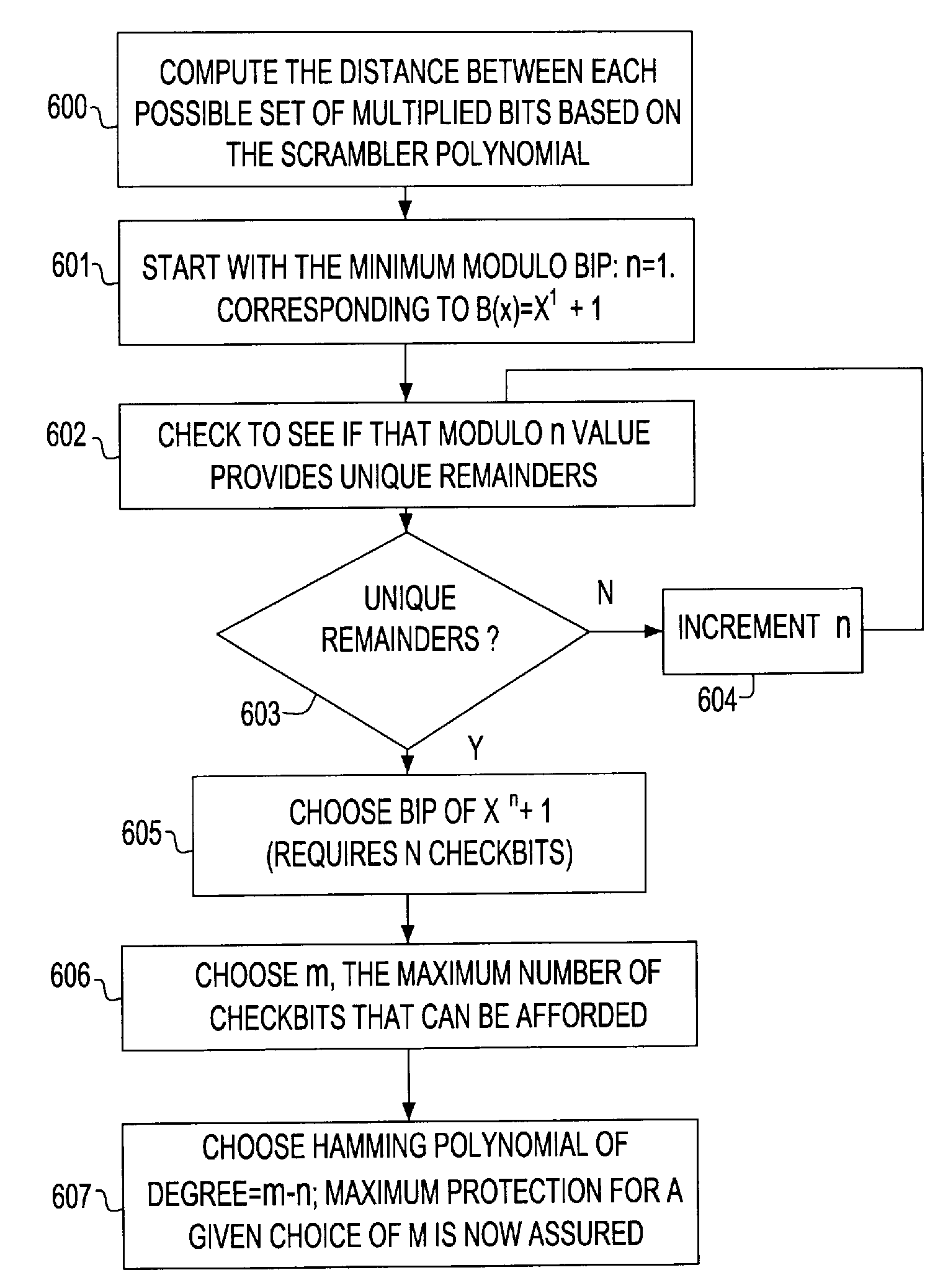

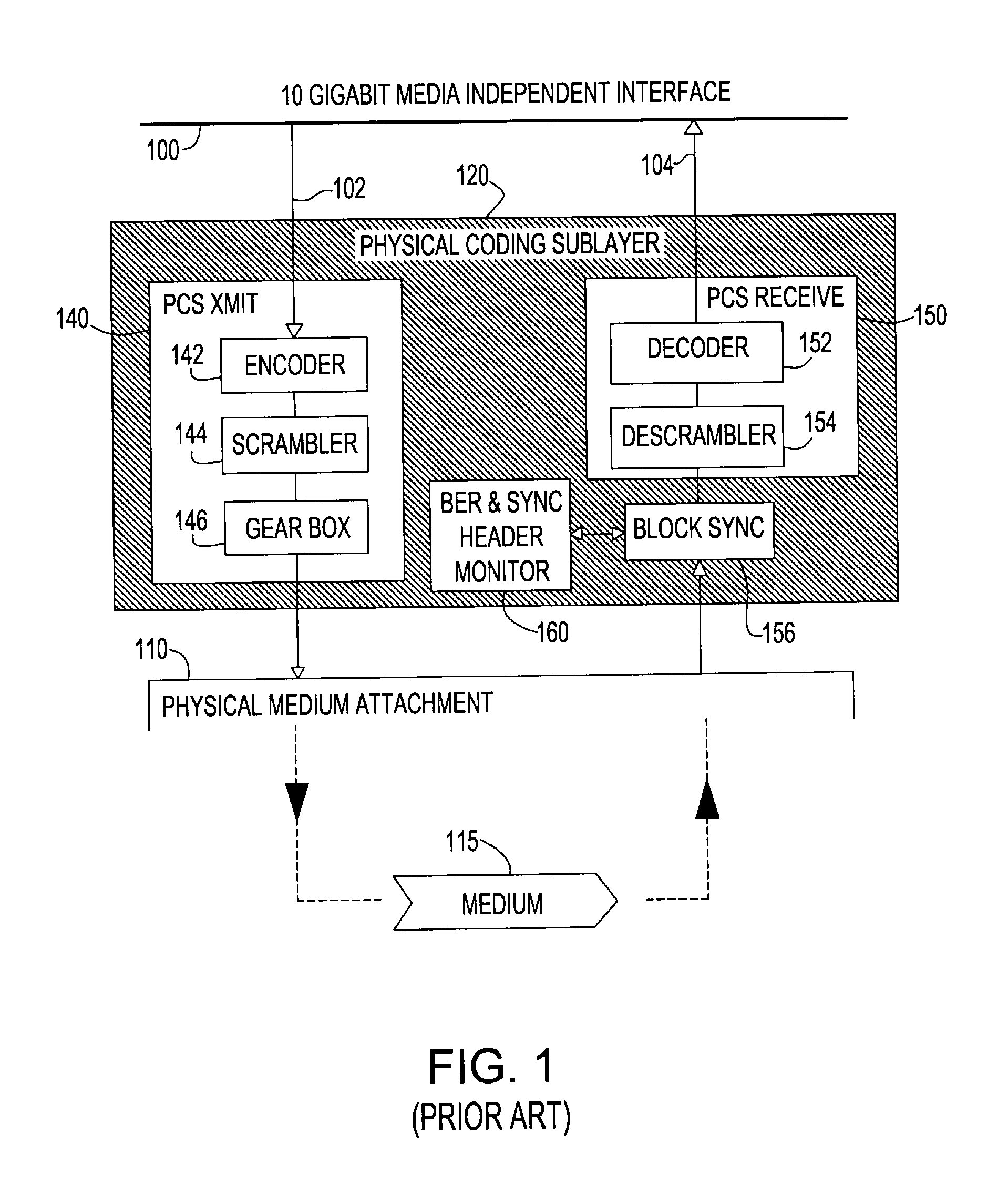

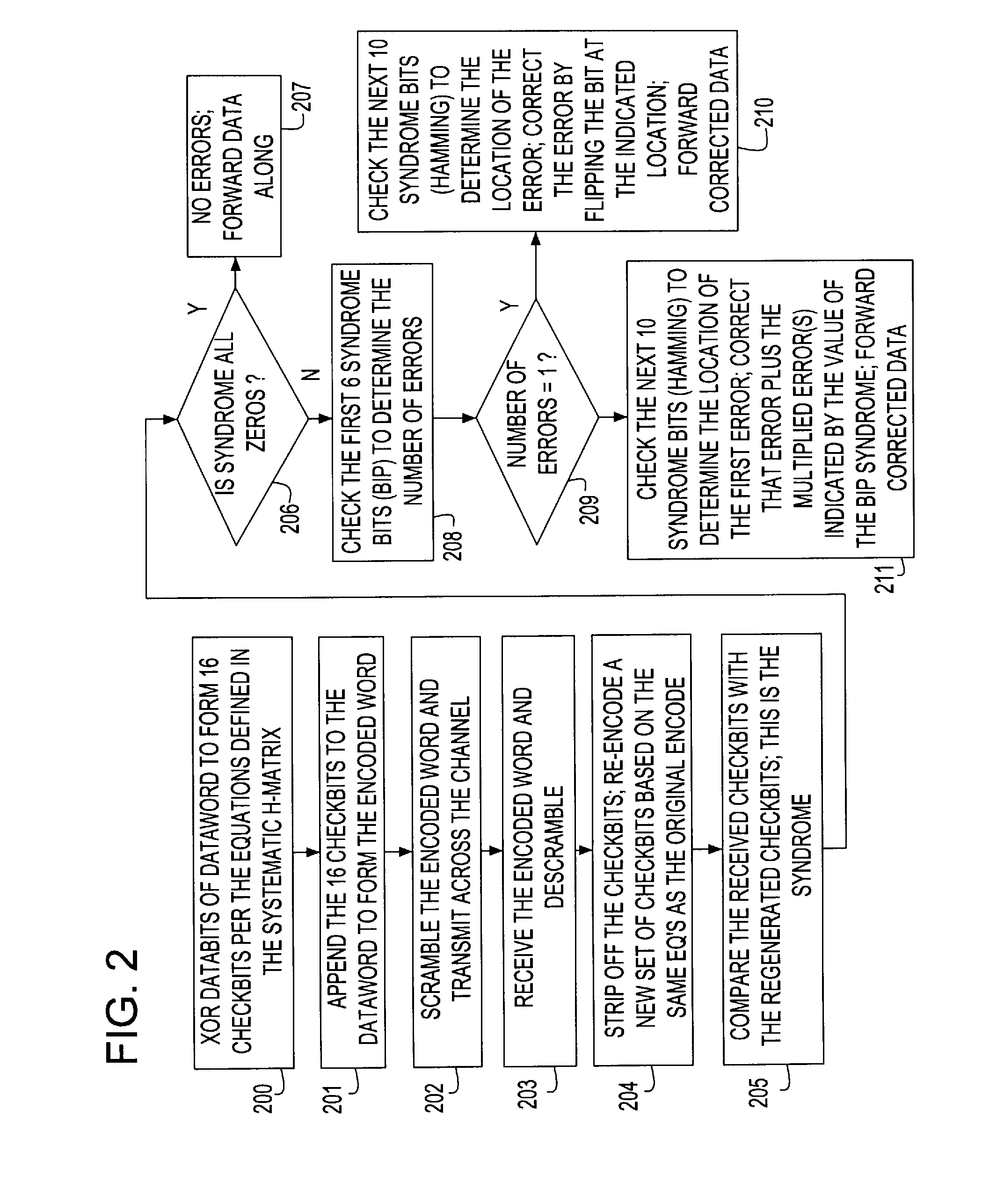

A Forward Error Correction (FEC) code compatible with the self-synchronized scrambler used by the 64B / 66B encoding standard for transmission on Serializer / Deserializer (SerDes) communications channel links. The FEC code allows encoding and decoding to occur before and after scrambling, respectively, so as to preserve the properties of the scrambling operation on the transmitted signal. The code allows the correction of any single transmission error in spite of the multiplication by three of all transmission errors due to the 64B / 66B scrambling process. A Hamming code is combined with a Bit Interleaved Parity code of degree n (BIP-n). These two codes provide for protection both for an error anywhere in the maximum length of the packet as well as for an error replicated two or three times by the descrambling process. All single bit errors, whether multiplied or not, have unique syndromes and are therefore easily correctable. In addition, the packet can be transported across multiple serial links for higher bandwidth applications without a degradation of the code efficiency. The Hamming code can be generated from any irreducible polynomial, such as H(x)=x10+x3+1. The BIP code is chosen to be of degree 6 to fit with 64B / 66B scrambling polynomial and is represented by B(x)=x6+1.

Owner:INT BUSINESS MASCH CORP

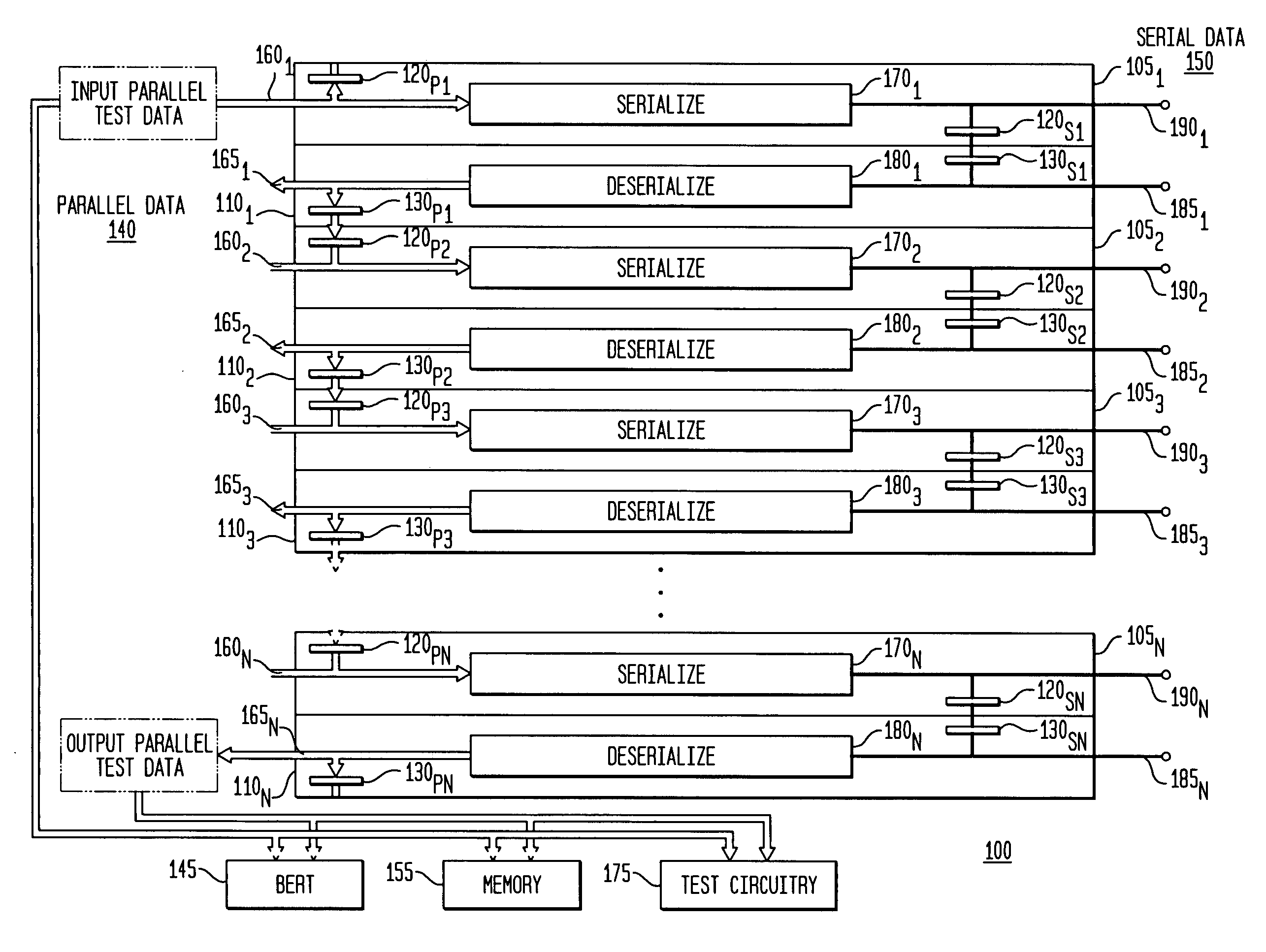

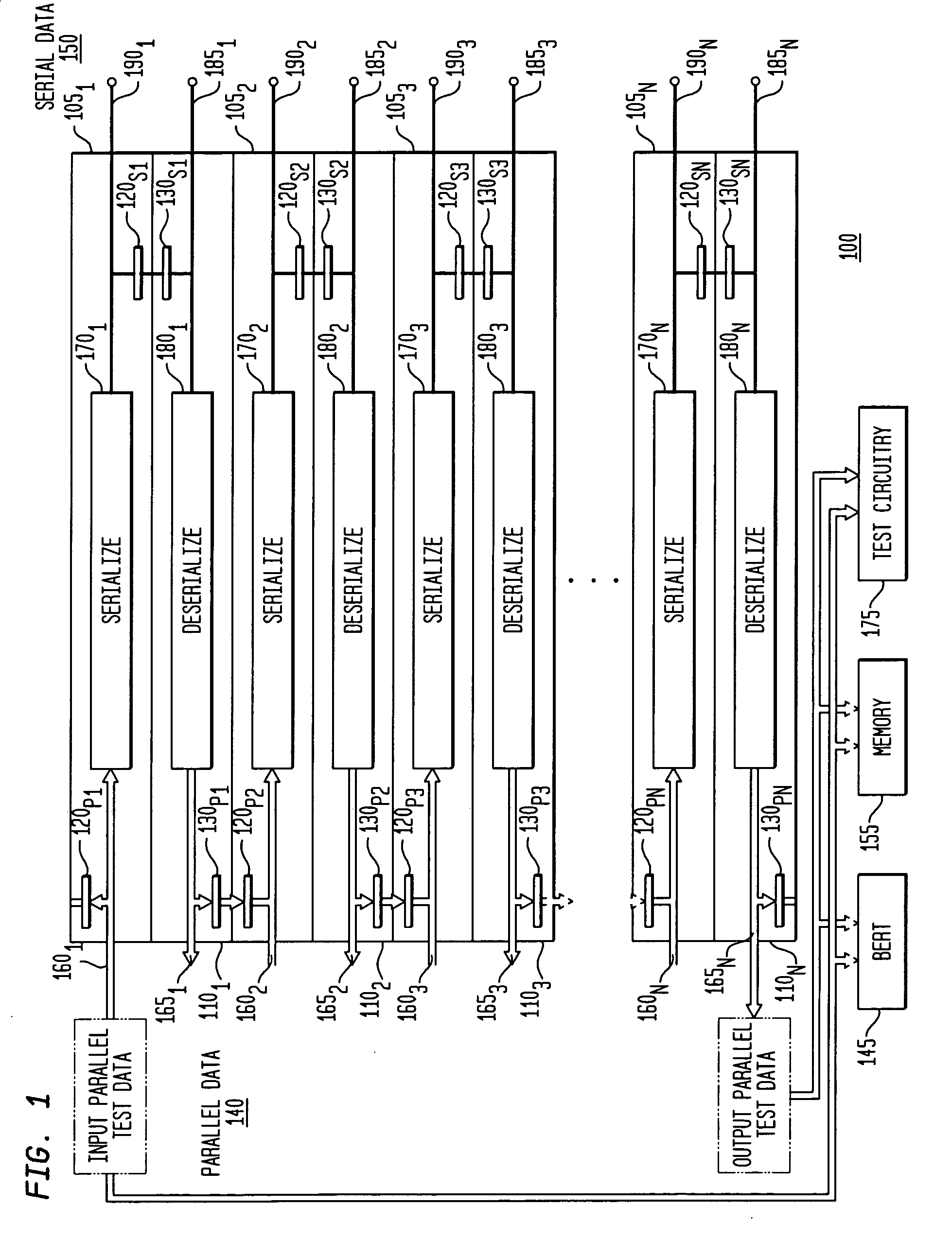

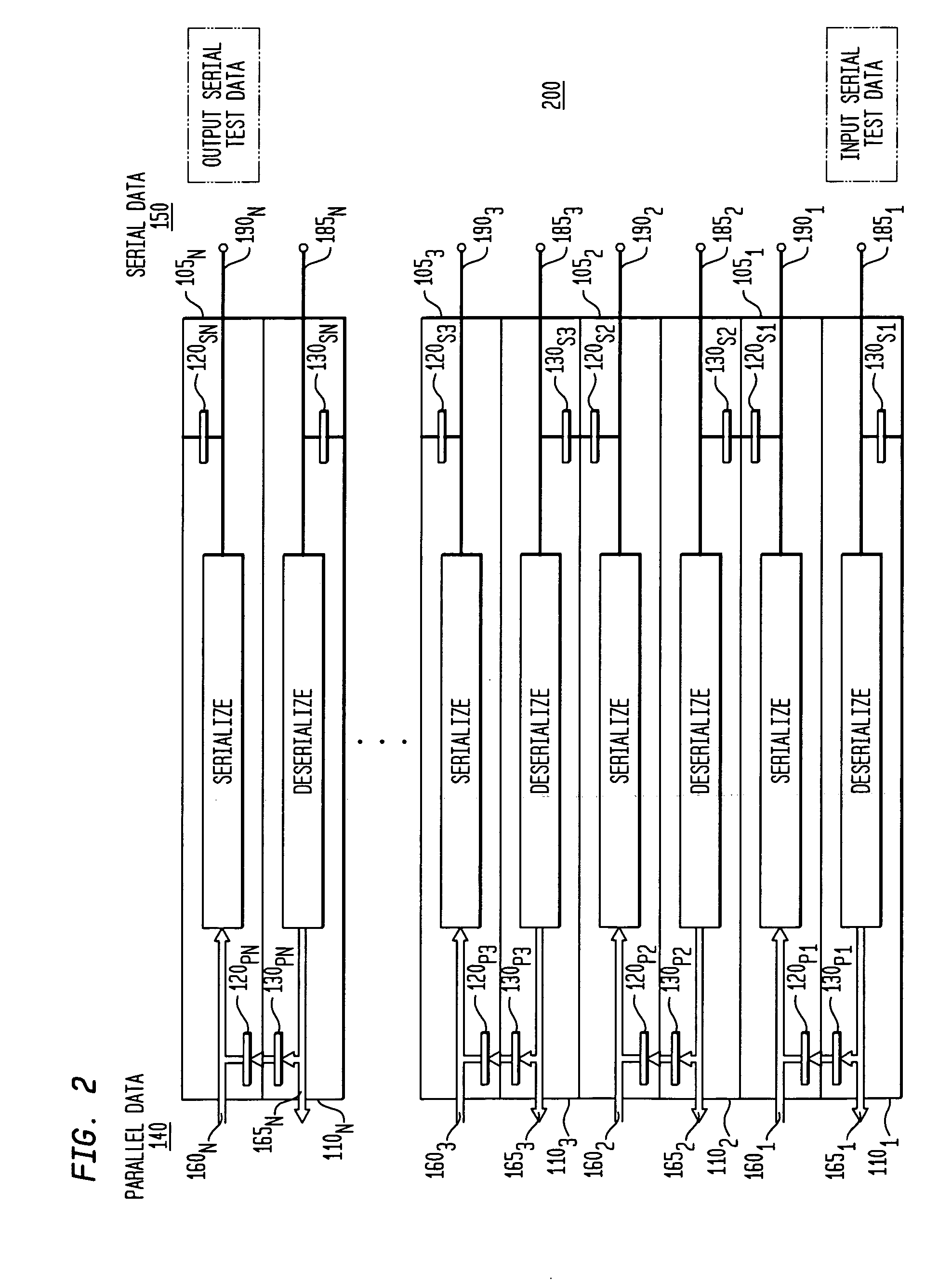

Serializer deserializer (SERDES) testing

ActiveUS20060176943A1Easily and efficiently testingElectrical testingTime-division multiplexSerializerData conversion

The various embodiments of the invention provide an apparatus, system and method of testing a serializer and deserializer data communication apparatus (SERDES). The serializer and deserializer data communication apparatus has a plurality of serialize data communication channels adapted to convert parallel data to serial data and a plurality of deserialize data communication channels adapted to convert serial data to parallel data. An exemplary method provides for coupling an output of a serialize data communication channel and an input of a deserialize data communication channel to provide a serial data loop-back connection and coupling an output of a deserialize data communication channel and an input of a serialize data communication channel to provide a parallel data loop-back connection. Input test data is provided to a first serialize or deserialize data communication channel, and is successively serialized and deserialized through each corresponding serialize data communication channel and deserialize data communication channel to provide output test data. The output test data and the input test data are then compared, with SERDES devices having acceptable or unacceptable bit error rates respectively designated as passed or failed.

Owner:AVAGO TECH INT SALES PTE LTD

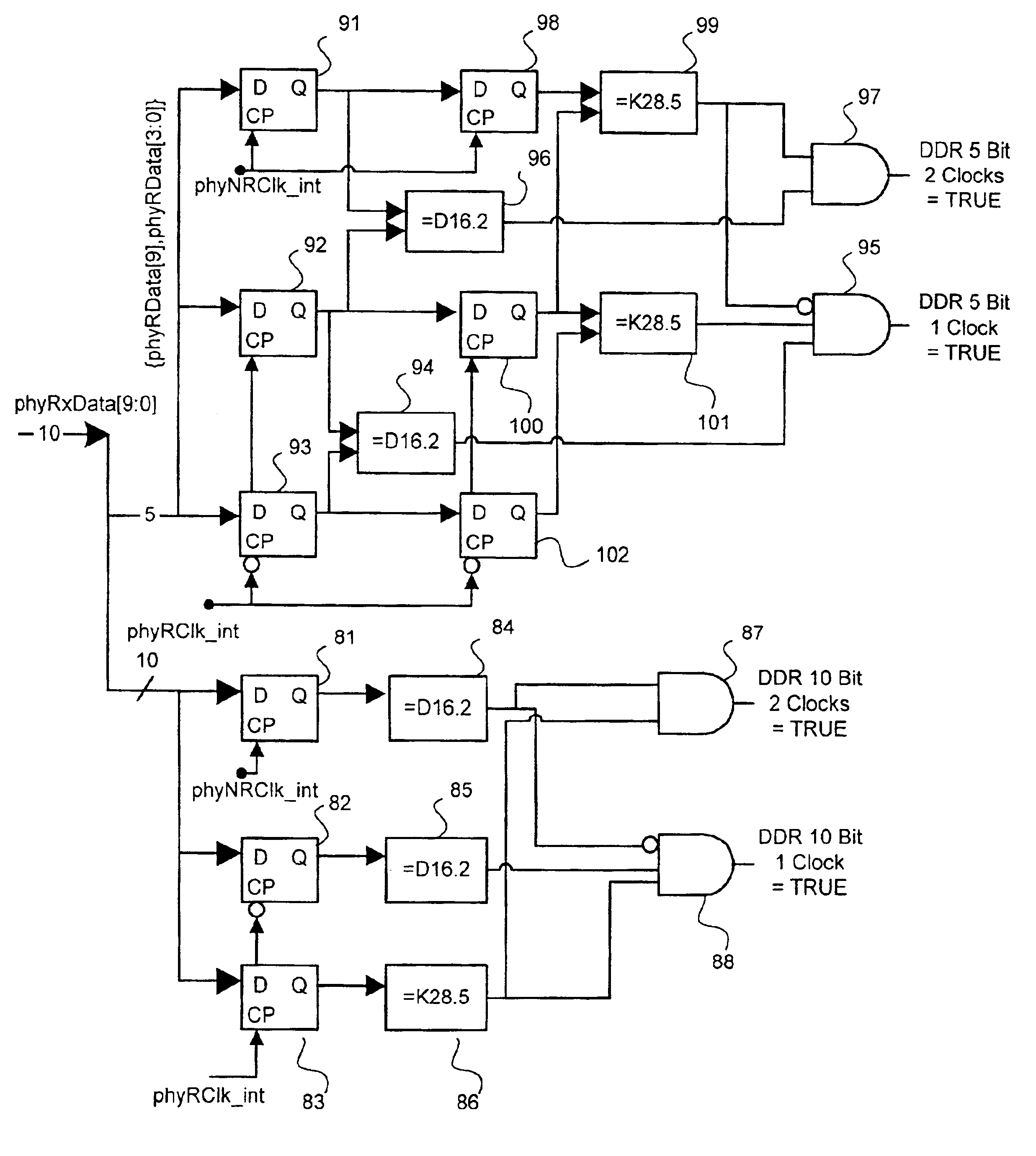

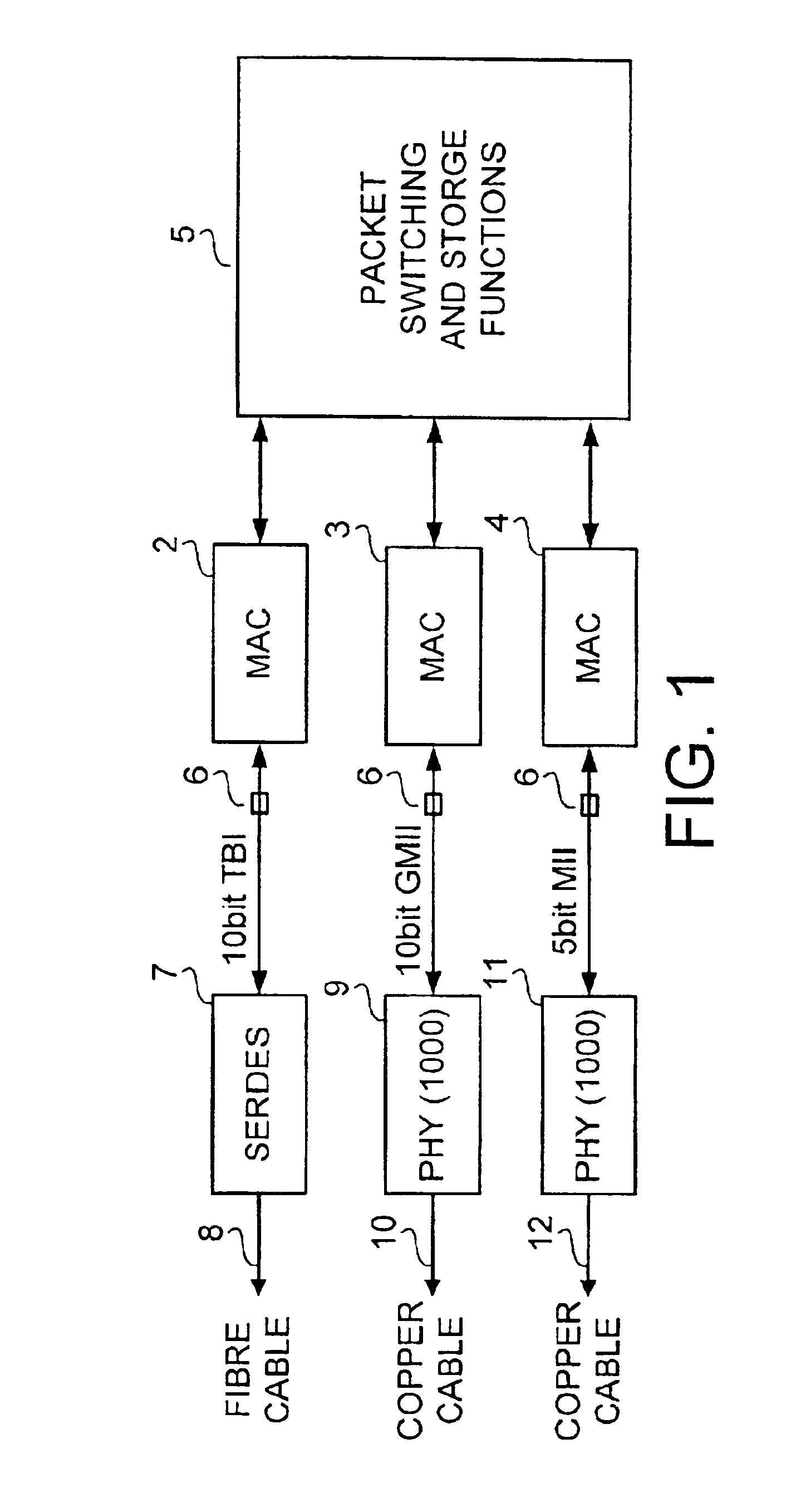

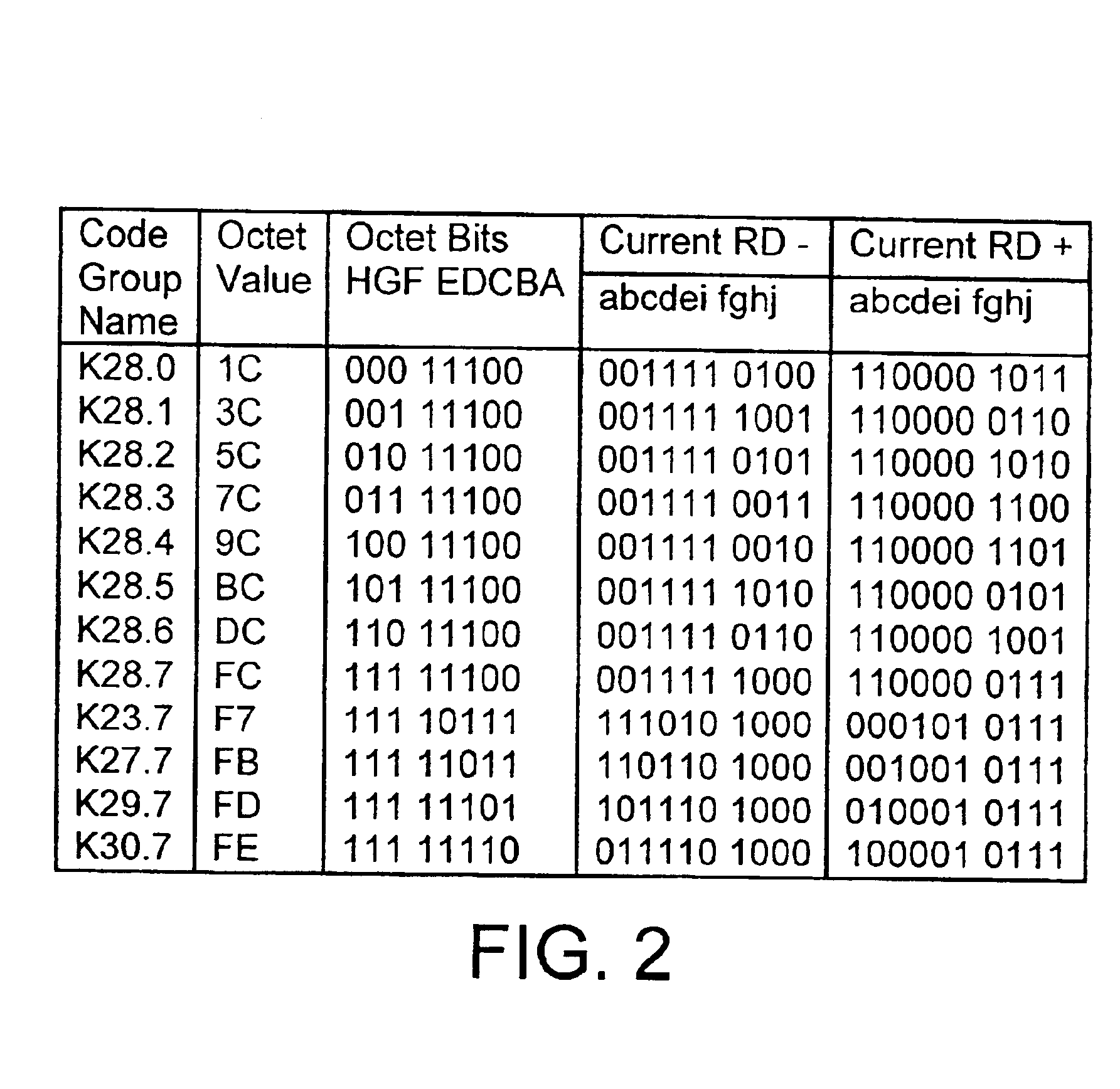

Automatic detector of media interface protocol type

ActiveUS6868088B2Time-division multiplexData switching by path configurationInterface protocolComputer science

A detector for determining which interface protocol is in use by a serialiser / deserialiser, and comprising detecting channels composed of clocked delays and bit comparators for detecting the presence of idle signals coded according to either ten-bit or five-bit protocols using either one or two clocks.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

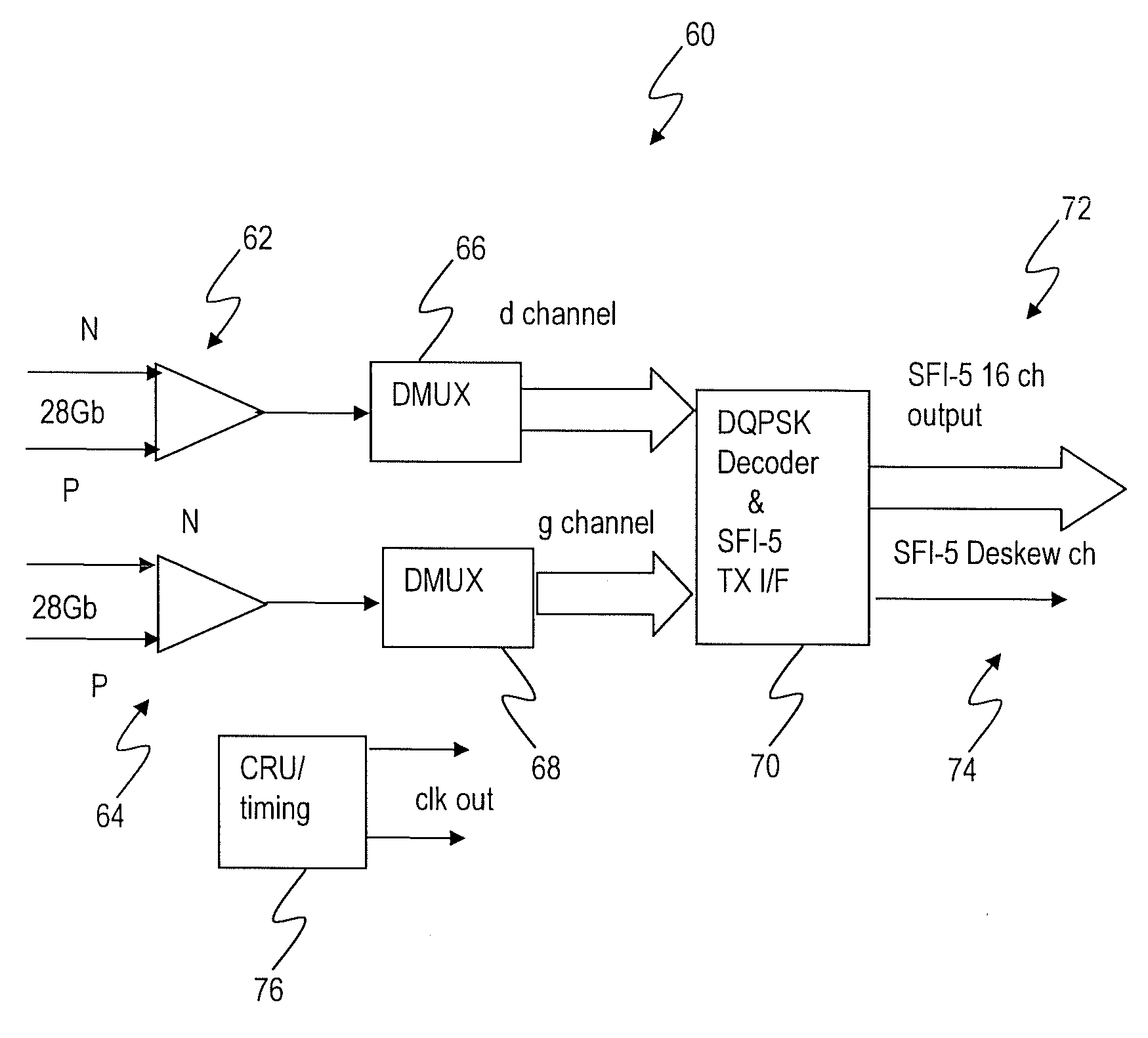

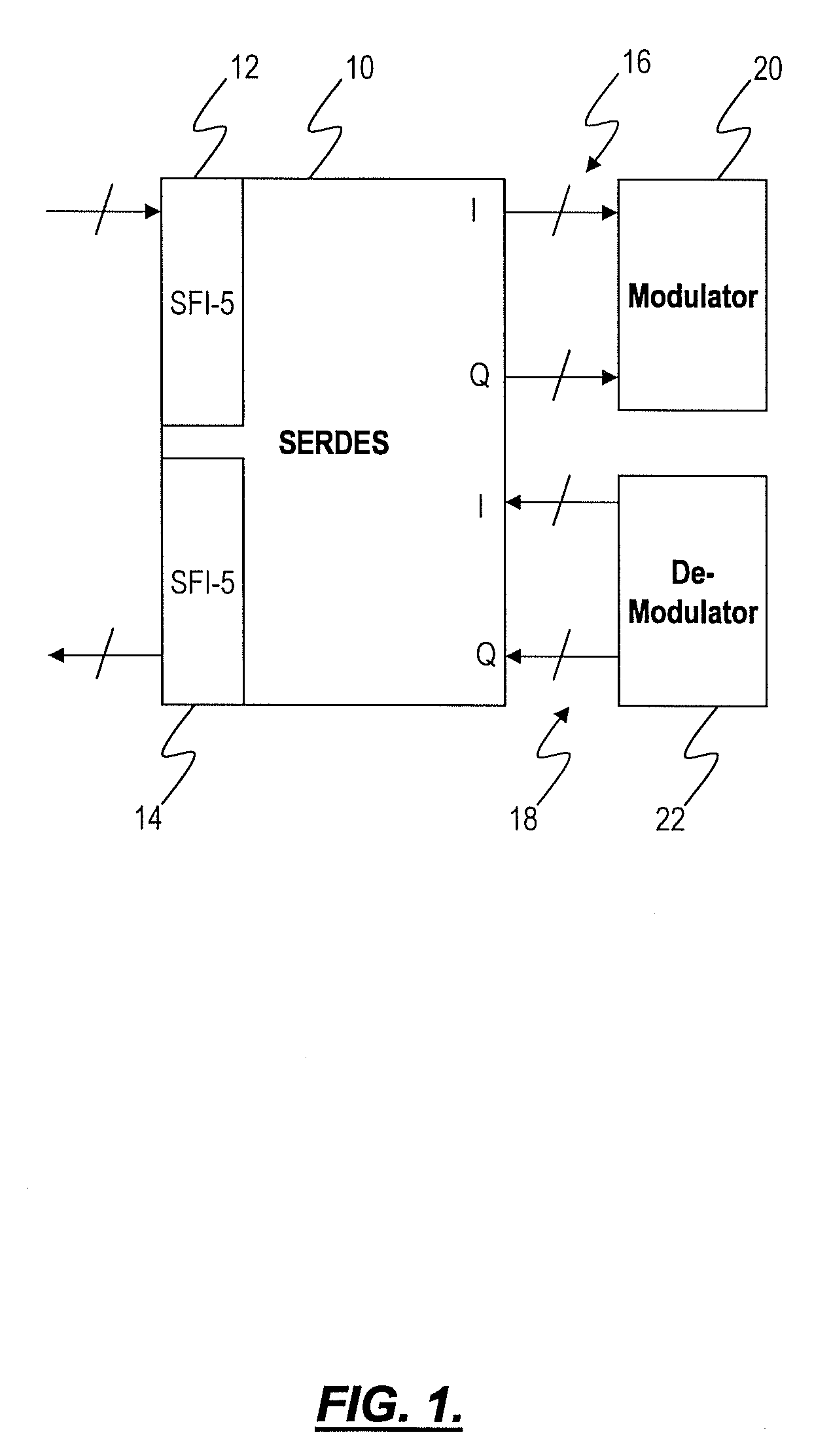

Serializer-deserializer circuit with multi-format and multi-data rate capability

The present invention provides a serializer / deserializer (SERDES) circuit that can cover both client- and network-side interfaces for high-speed data rates. The present invention leverages commonality between the client and network (also known as line) side, and accommodates differences in a flexible manner. In one exemplary embodiment, the present invention provides a four-channel implementation to meet the requirement of both interfaces. The SERDES circuit can be capable of supporting both 40 Gb / s and 56 Gb / s data rates, can include an integrated DQPSK pre-coder and I / Q input / output signals, and can support RZ clock recovery. Additionally, the SERDES circuit can include differential coding support, electronic pre-emphasis, receiver-side electronic dispersion compensation, and the like.

Owner:CIENA

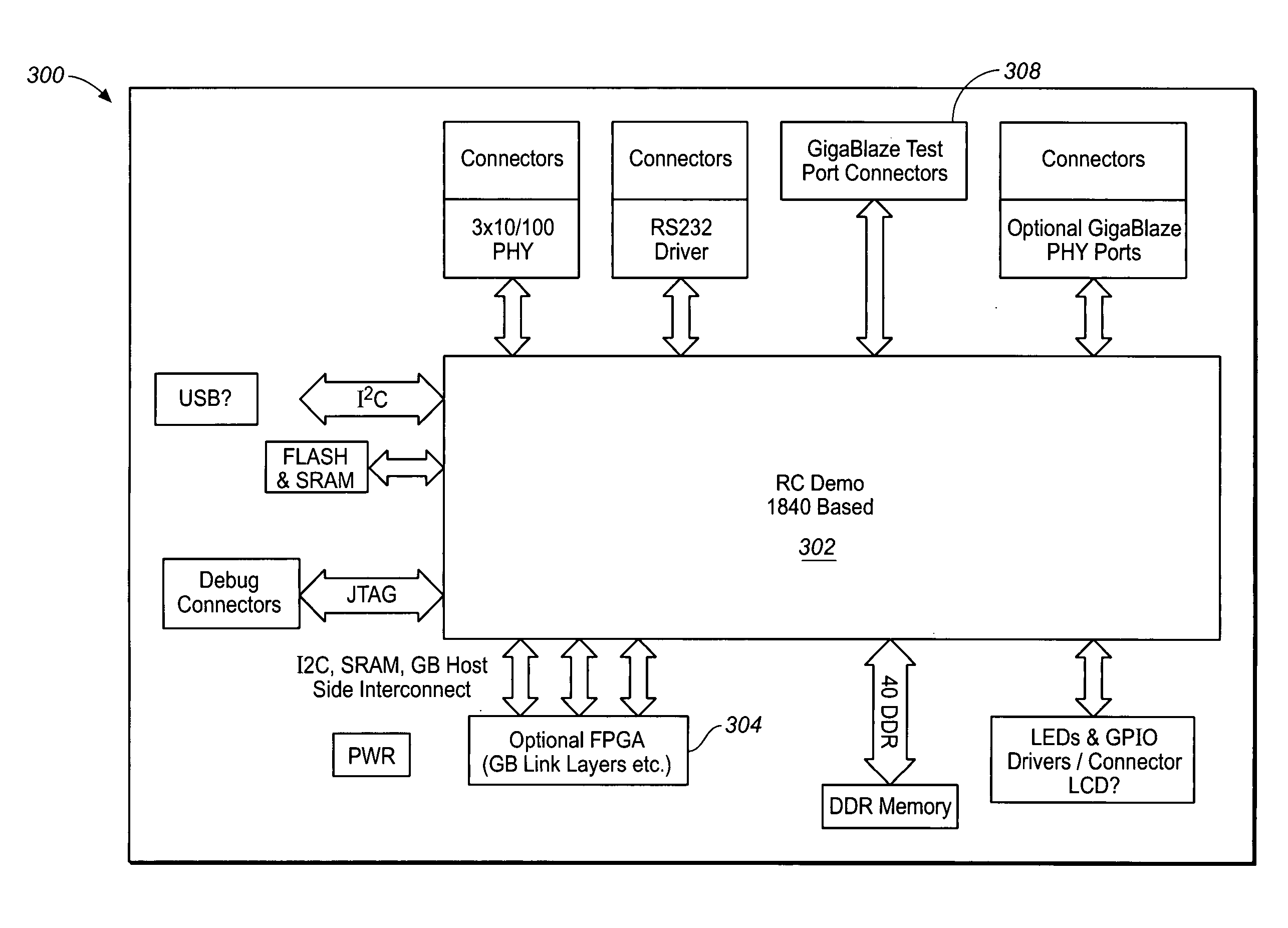

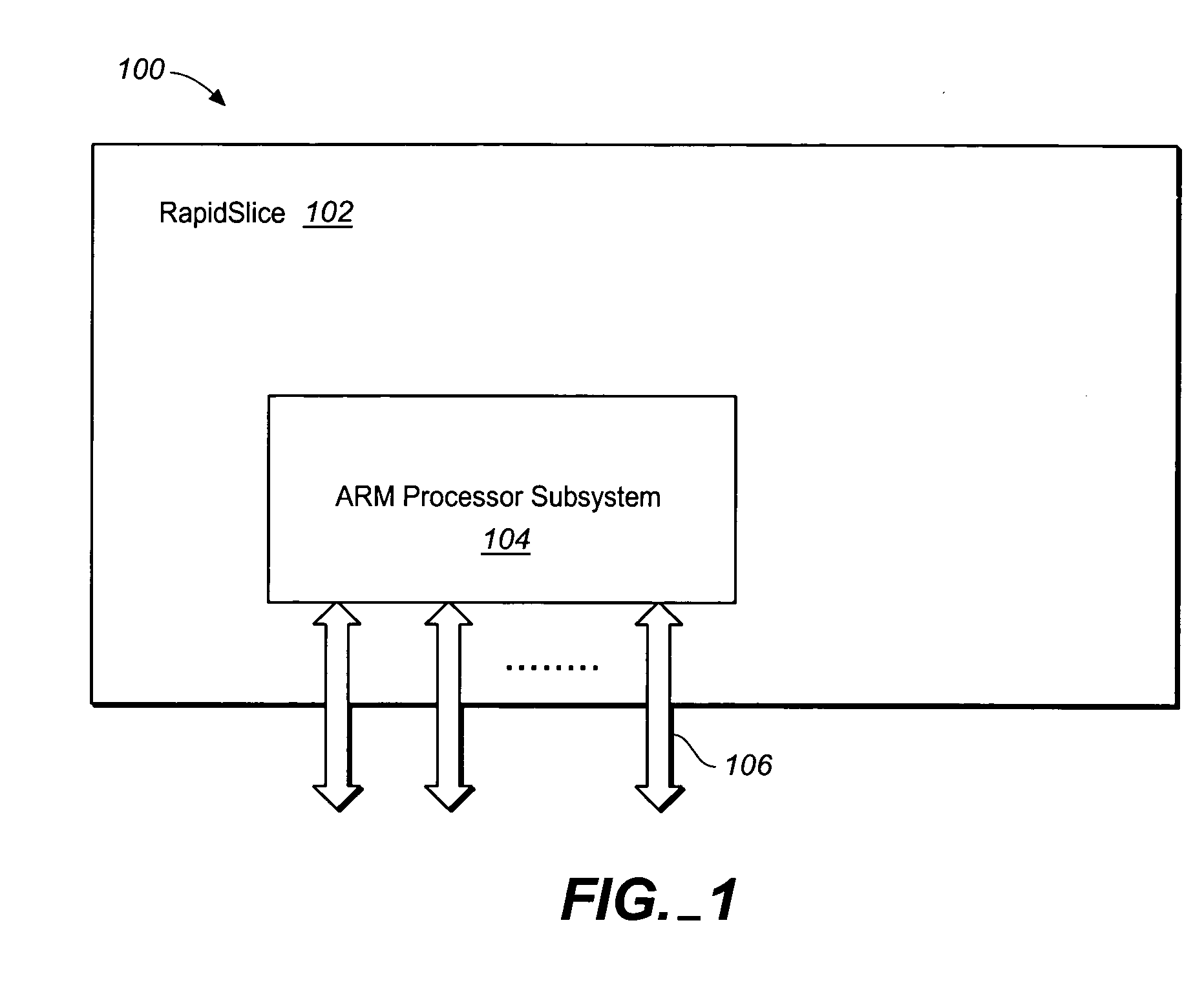

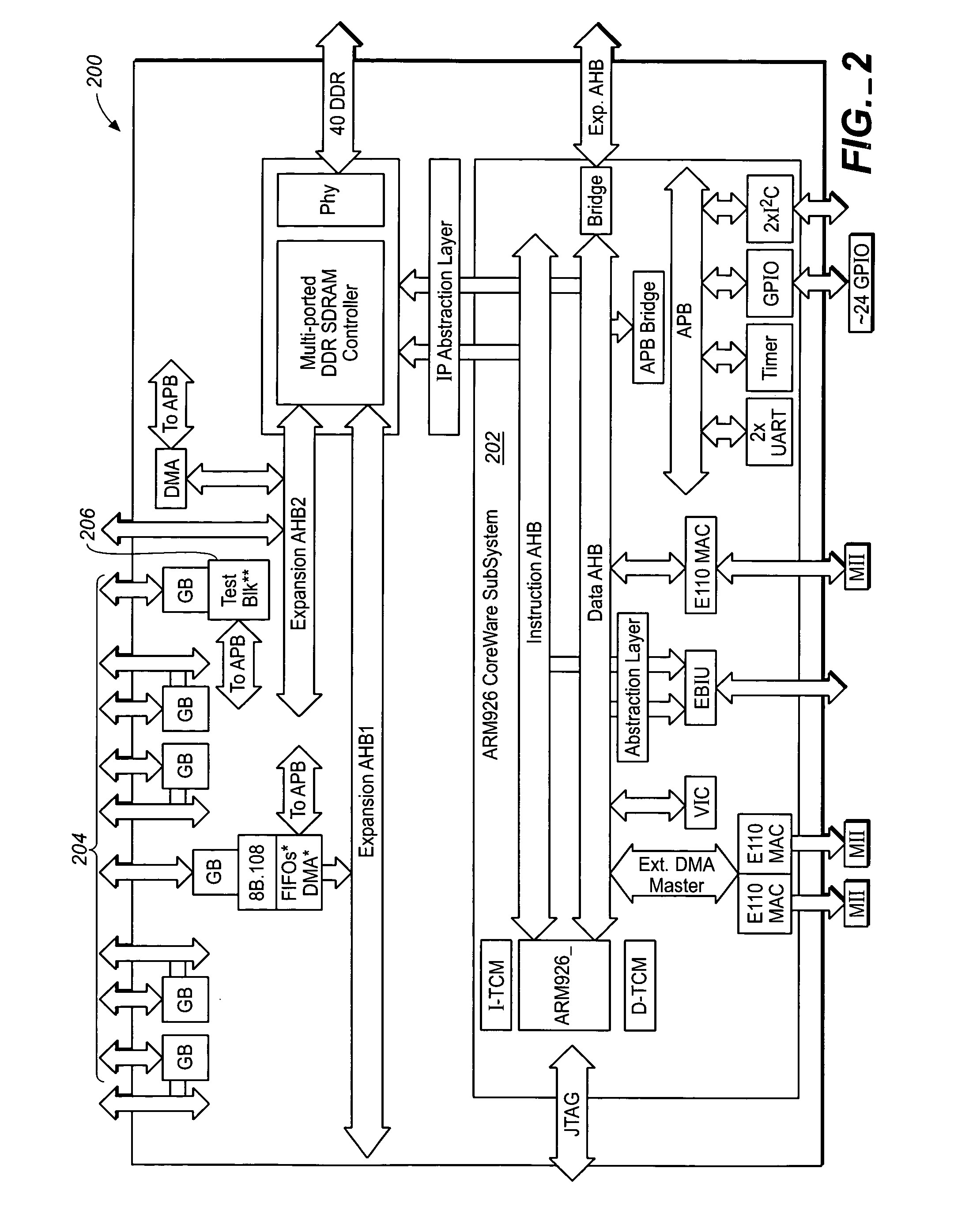

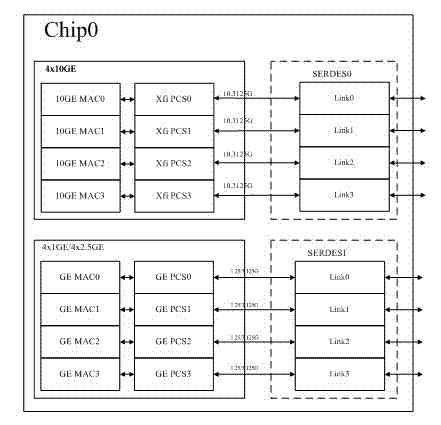

Customizable development and demonstration platform for structured ASICs

ActiveUS20050183042A1Less expenseCAD circuit designSpecial data processing applicationsXAUIFibre Channel

The present invention is directed to a customizable development and demonstration platform for structured ASICs. In an exemplary aspect of the present invention, the present platform may include a structured ASIC which is built on a slice and which may be flexible enough for a number of possible application developments. This flexibility may be achieved by incorporating a programmable processor in the structured ASIC and by defining interfaces and the use of an external FPGA in the present platform. The structured ASIC may include a complete ARM processor subsystem and a plurality of high speed SERDES ports. The processor subsystem may include a bus interface to the external FPGA, allowing custom gate development and test in the FPGA, prior to incorporating it into the customer product. Through the SERDES ports, the test block may be used to show the electrical characteristics of the SERDES IP. In addition, some SERDES ports may be driven from a link layer realized in the FPGA. This may allow the same chip and board to implement SATA (serial advanced technology attachment), GigE, XAUI, XGXS, Fibre Channel, and the like by changing the programming of the FPGA on the board.

Owner:BELL SEMICON LLC

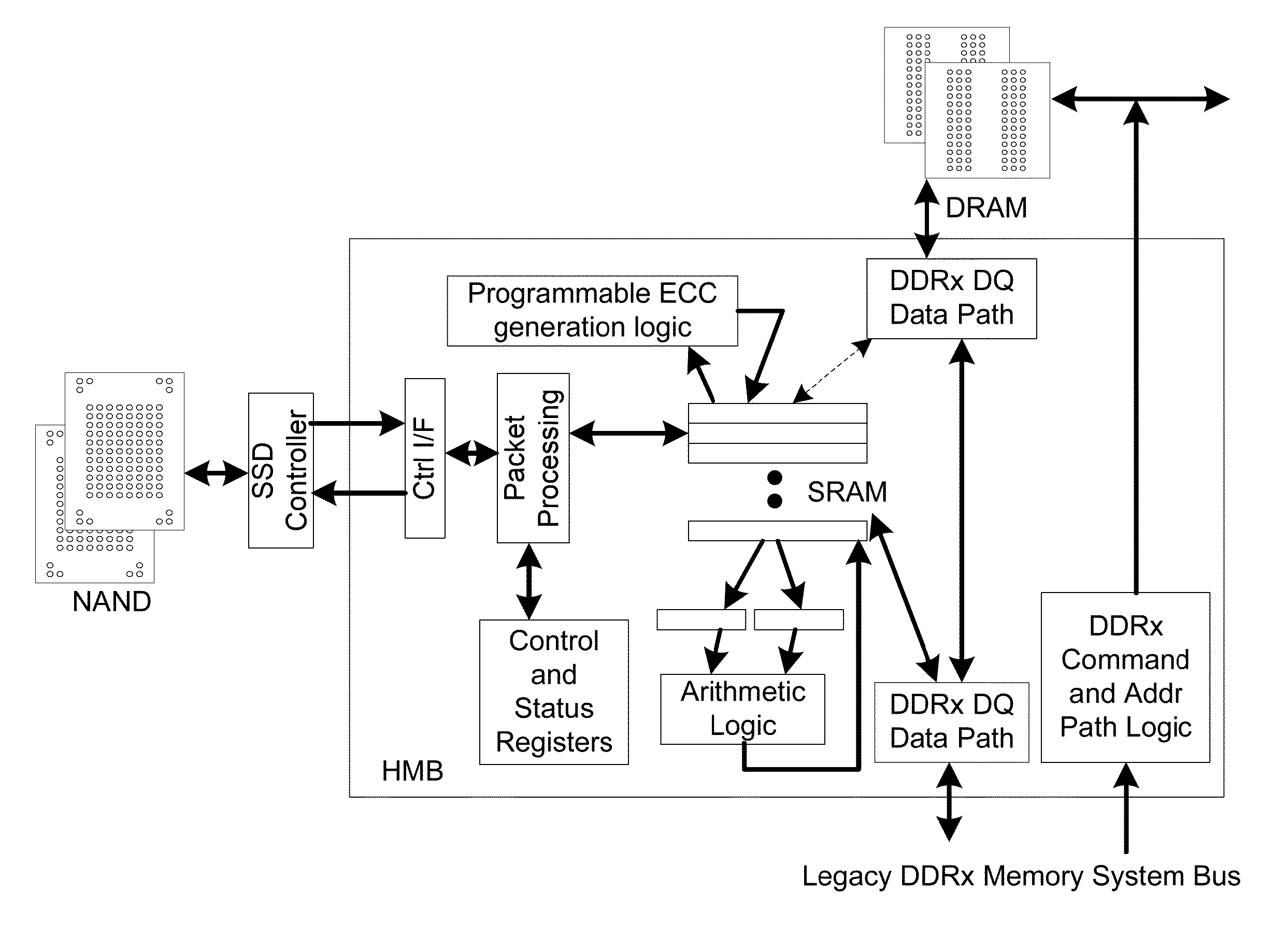

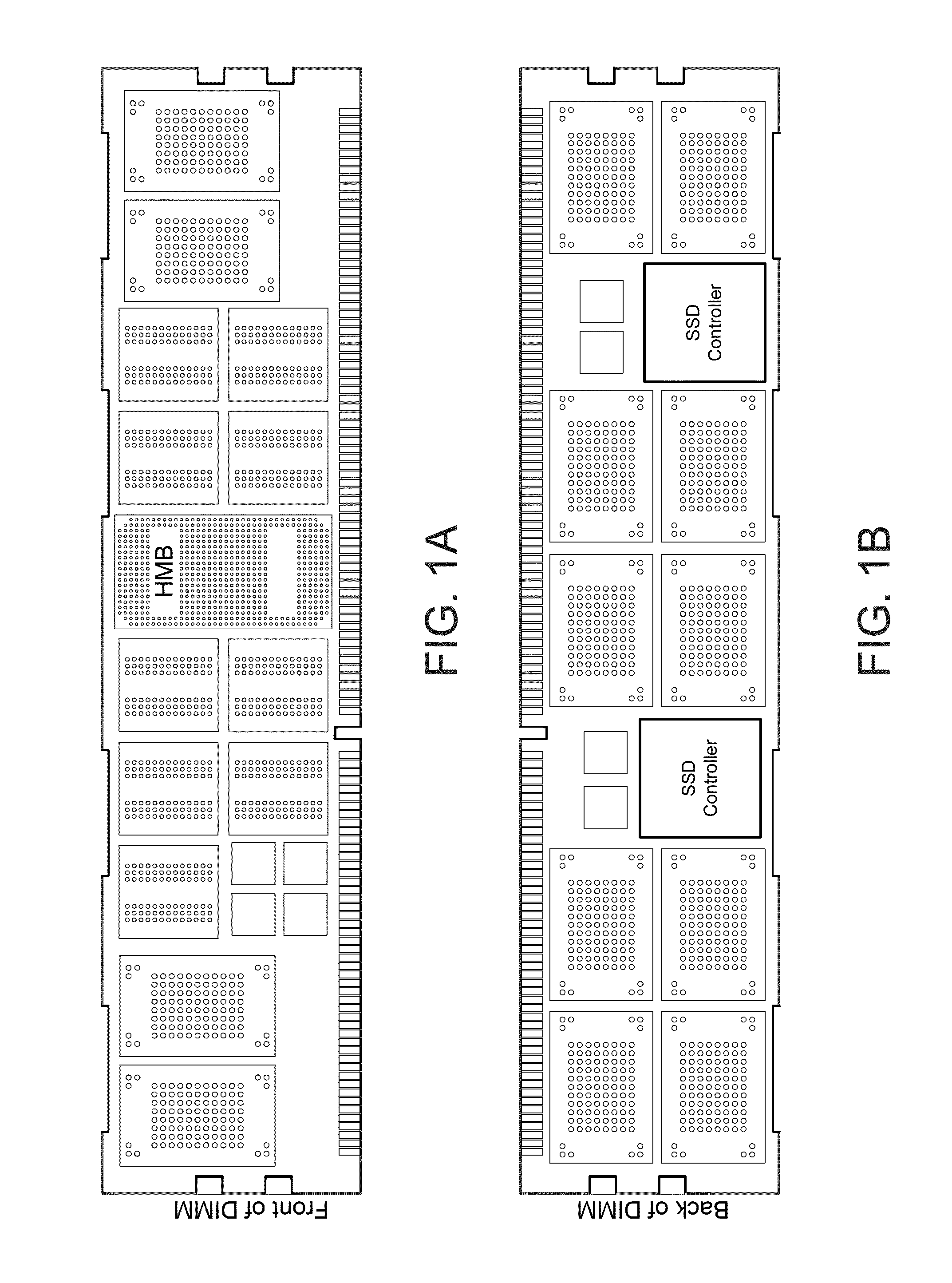

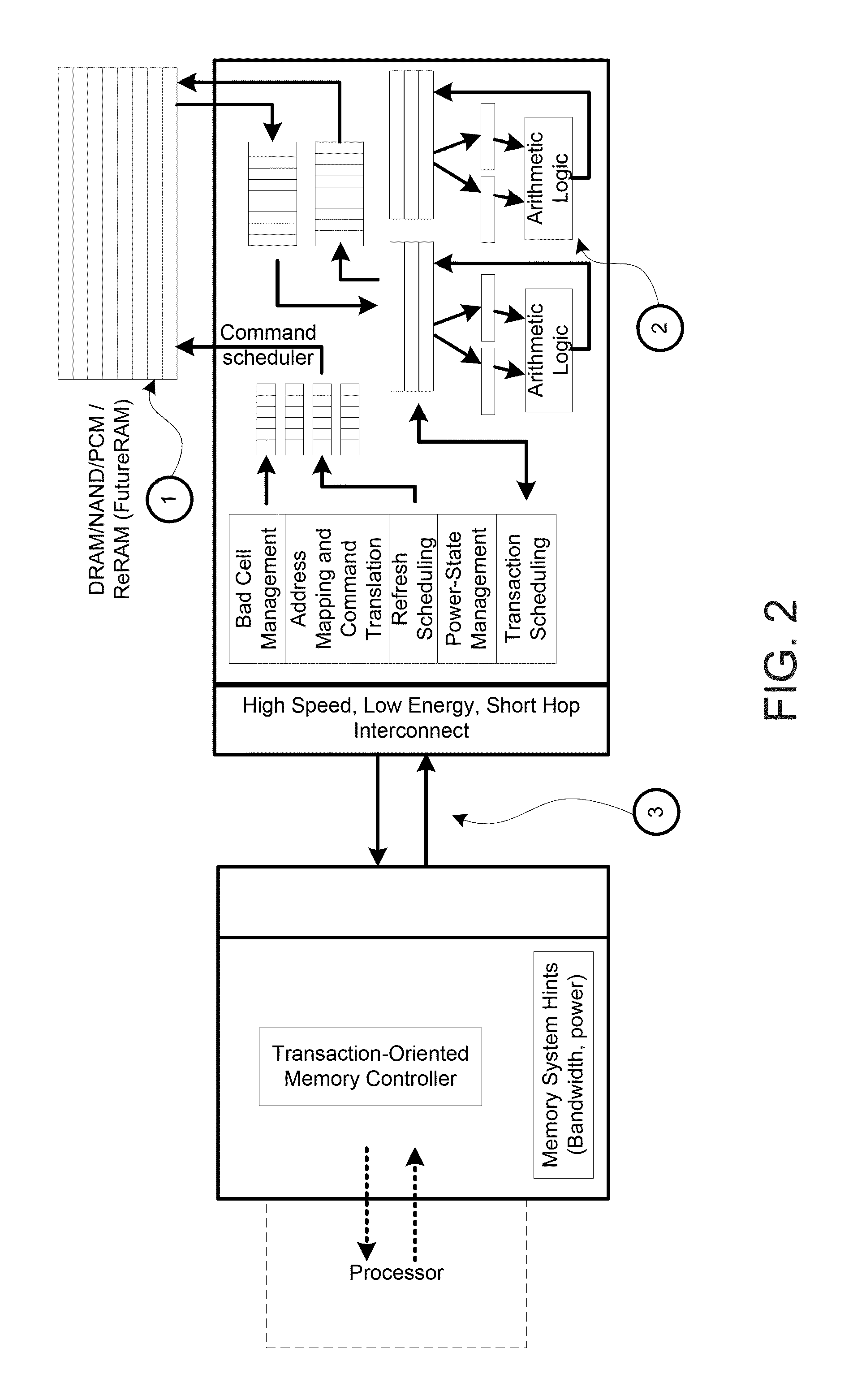

Memory centric computing

A hybrid memory system. This system can include a processor coupled to a hybrid memory buffer (HMB) that is coupled to a plurality of DRAM and a plurality of Flash memory modules. The HMB module can include a Memory Storage Controller (MSC) module and a Near-Memory-Processing (NMP) module coupled by a SerDes (Serializer / Deserializer) interface. This system can utilize a hybrid (mixed-memory type) memory system architecture suitable for supporting low-latency DRAM devices and low-cost NAND flash devices within the same memory sub-system for an industry-standard computer system.

Owner:RAMBUS INC

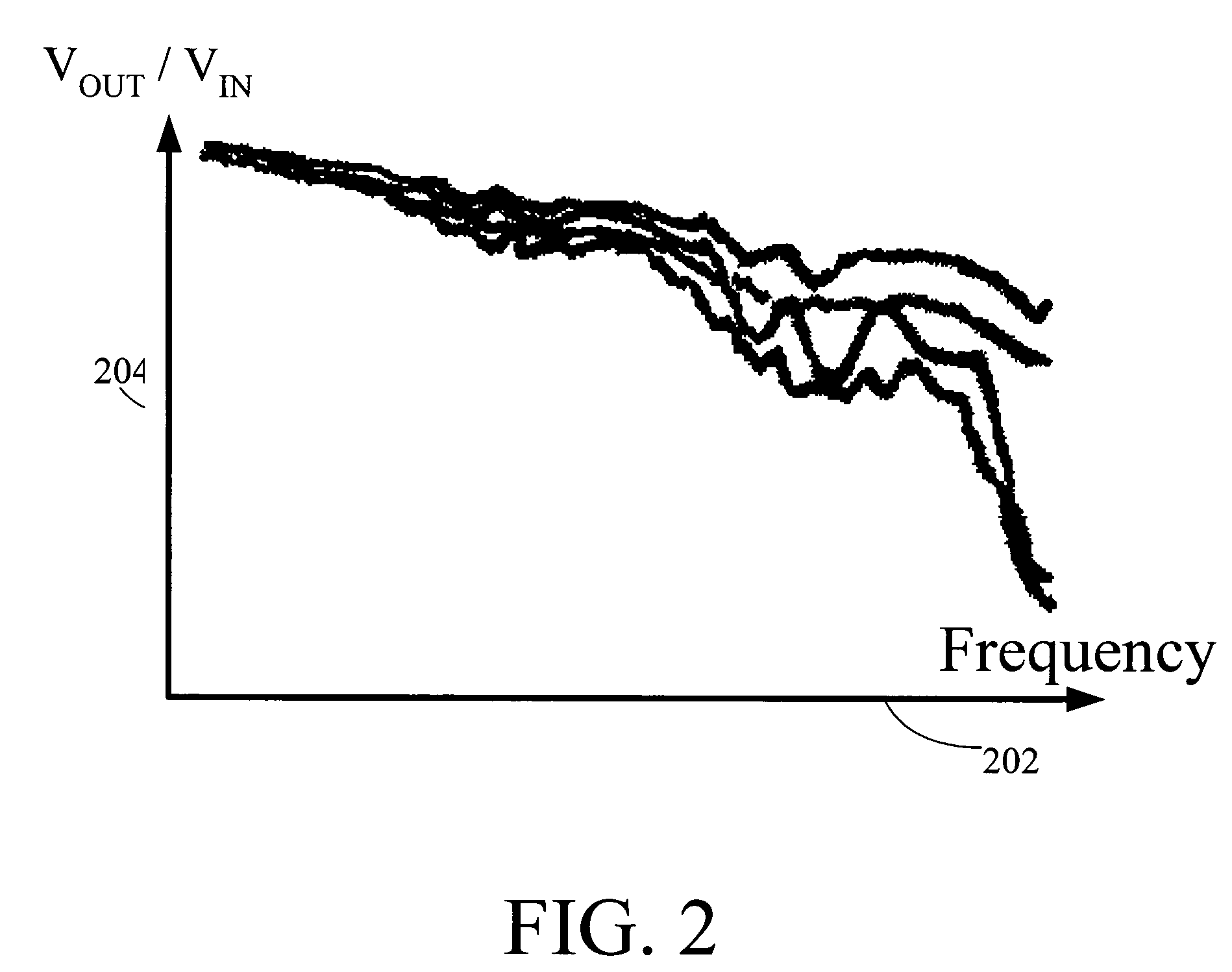

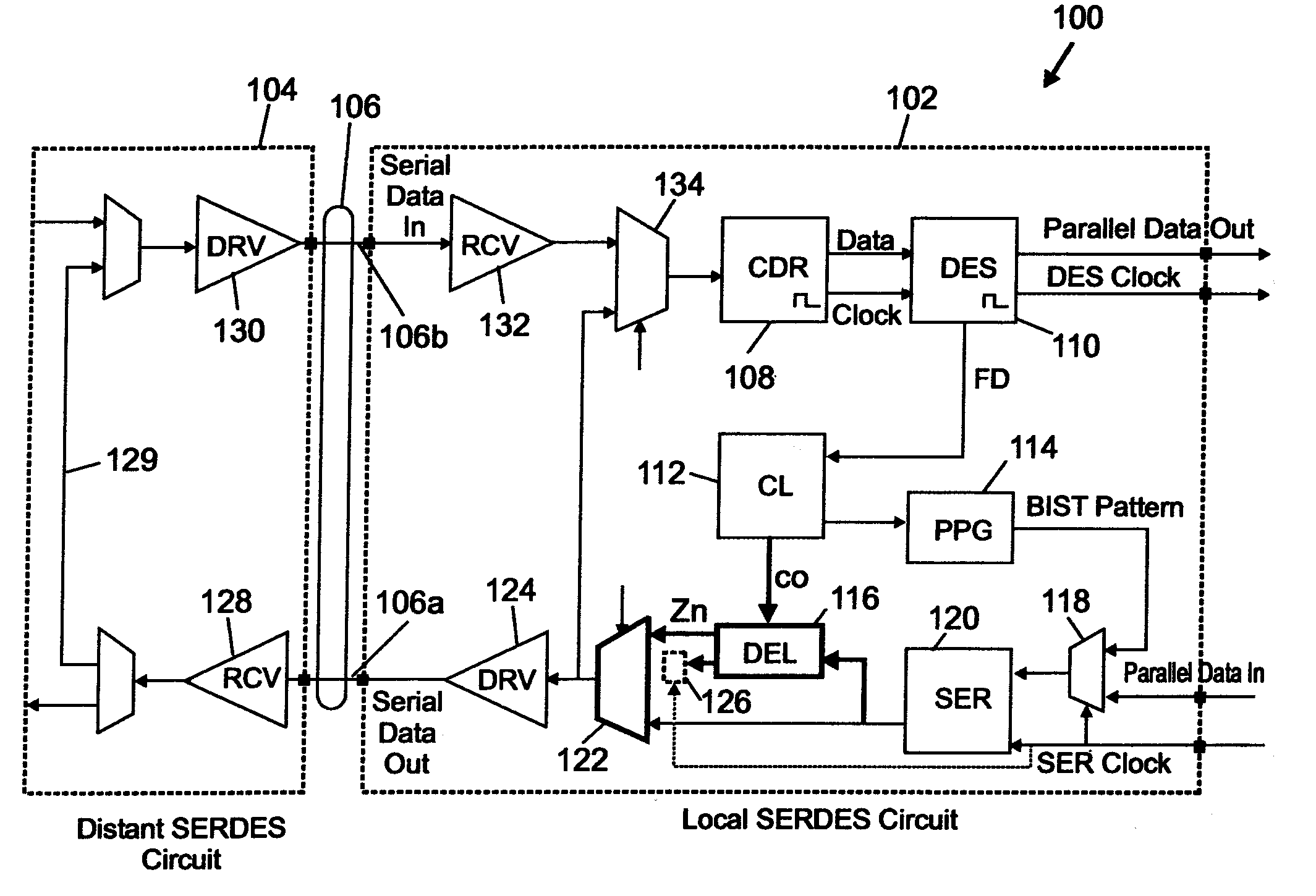

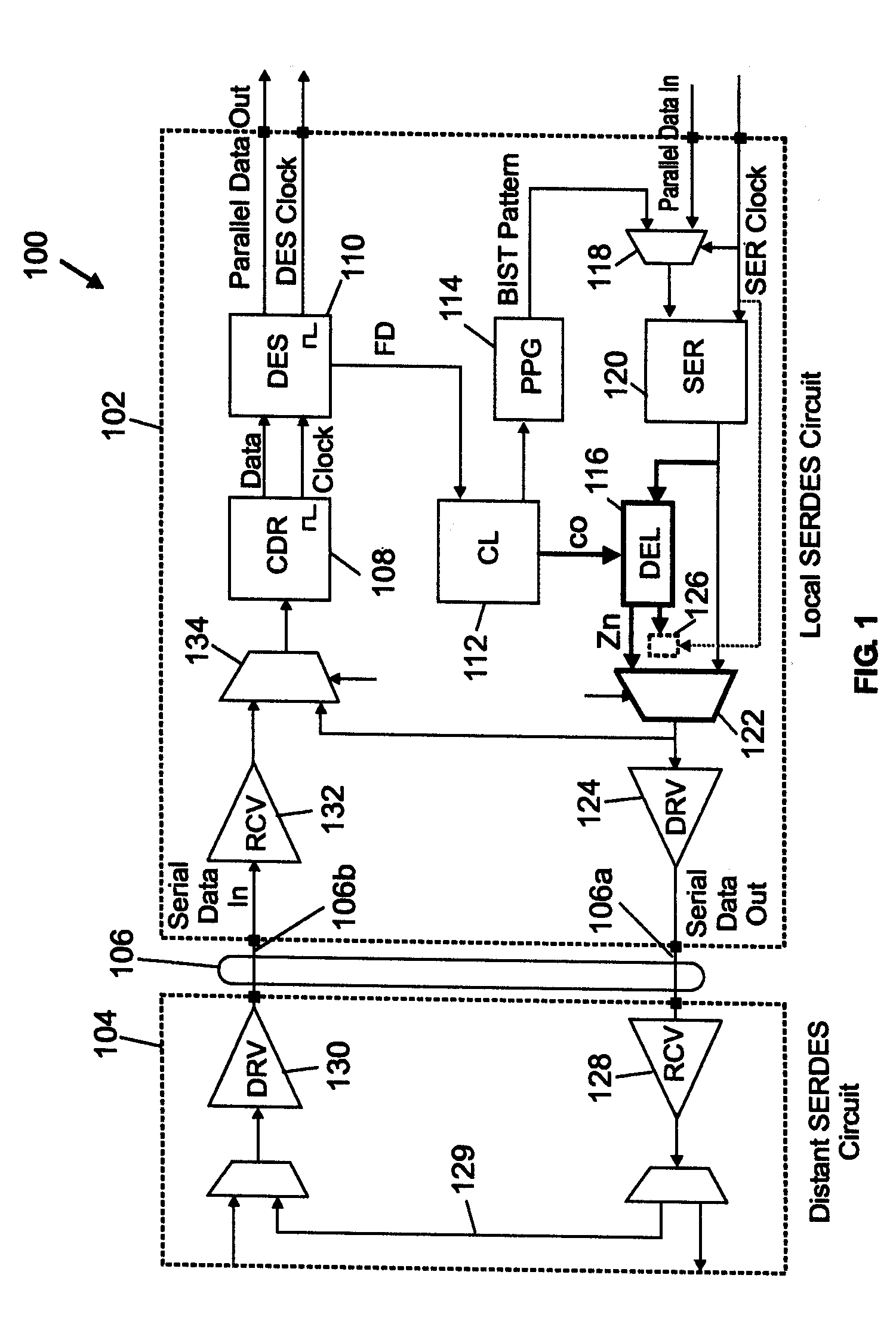

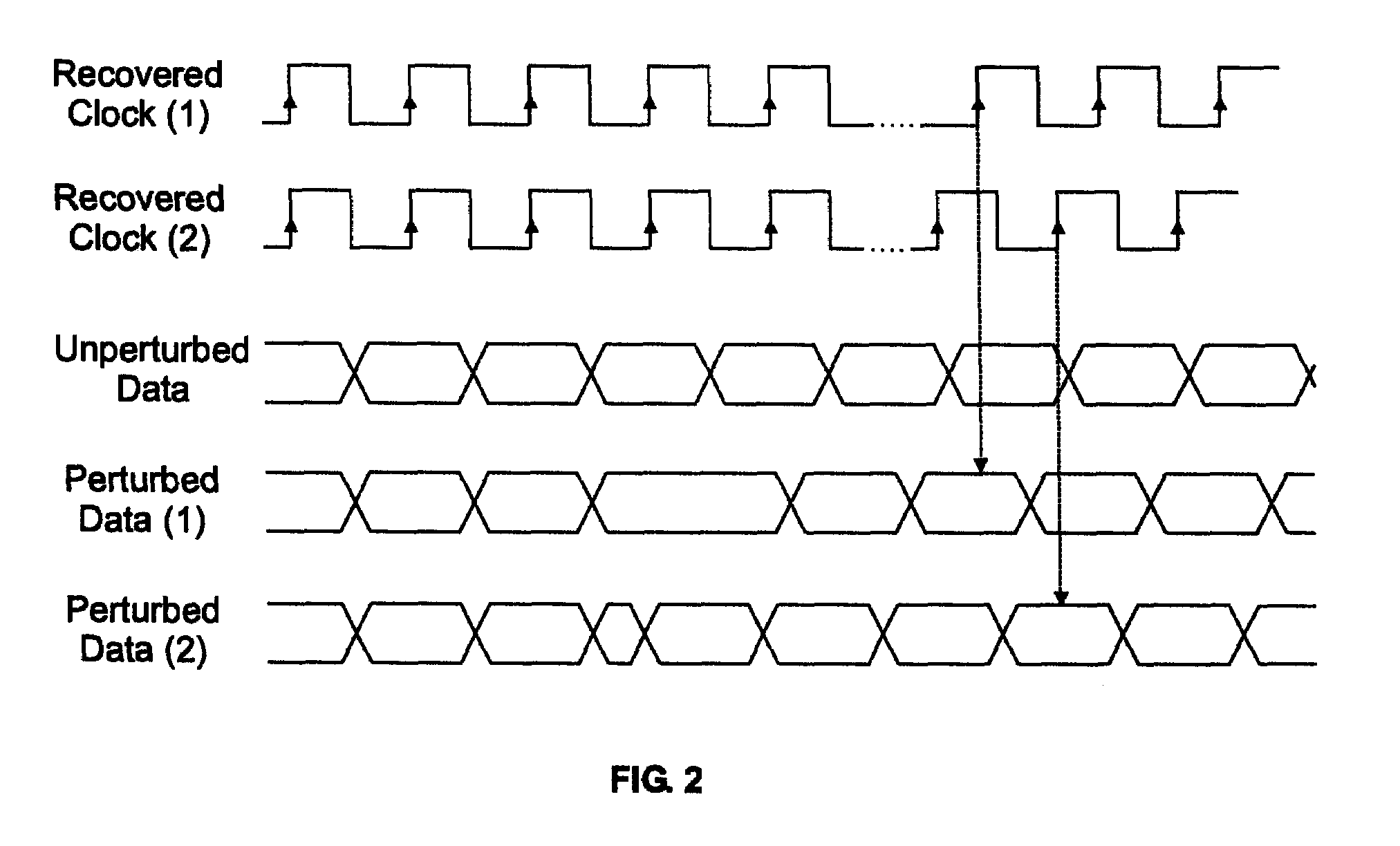

Serializer/deserializer circuit for jitter sensitivity characterization

InactiveUS7251764B2Easily and in situ characterizeParallel/series conversionDigital circuit testingData streamComputer science

Disclosed herein is an improved serializer / deserializer (SERDES) circuit (102) having built-in self-test capabilities that is configured to perform an in-situ jitter sensitivity characterization of the clock and data recovery (CDR) circuit (108). To that end, a delay perturbation is added to the serial data stream at the serializer (120) output, typically using a variable delay (DEL) line (116). Then, the perturbed serial data stream is looped back to the CDR circuit. A dedicated circuit in the control logic (112) coupled to the DEL line and the deserializer circuit (110) analyzes the recovered data to characterize the sensitivity of the CDR circuit to the jitter frequency. By continuously modifying the output delay of said serial data stream, i.e. the amplitude and the frequency of the perturbation, one can generate a perturbed serial data stream, very close to the real jittered data.

Owner:INT BUSINESS MASCH CORP

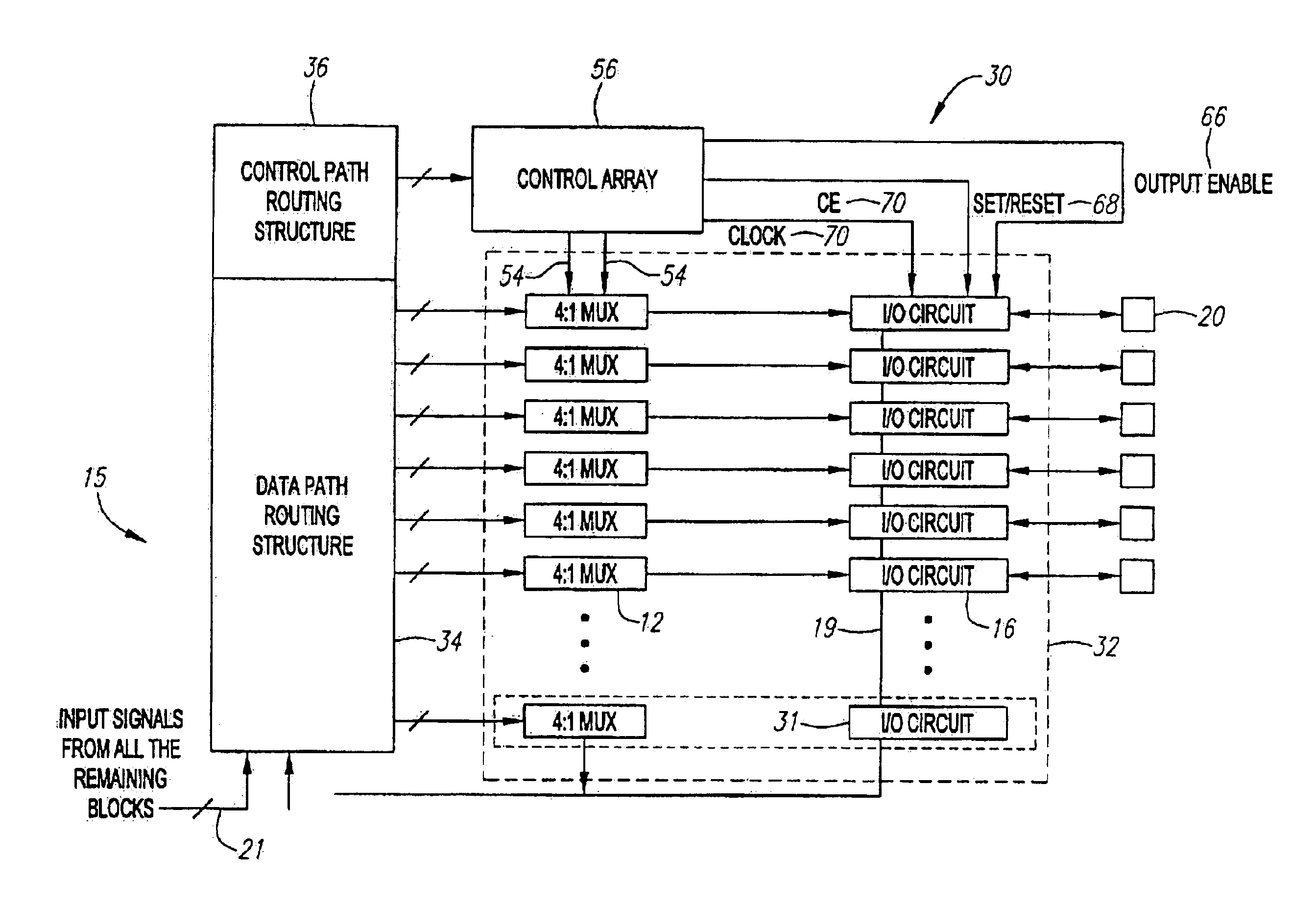

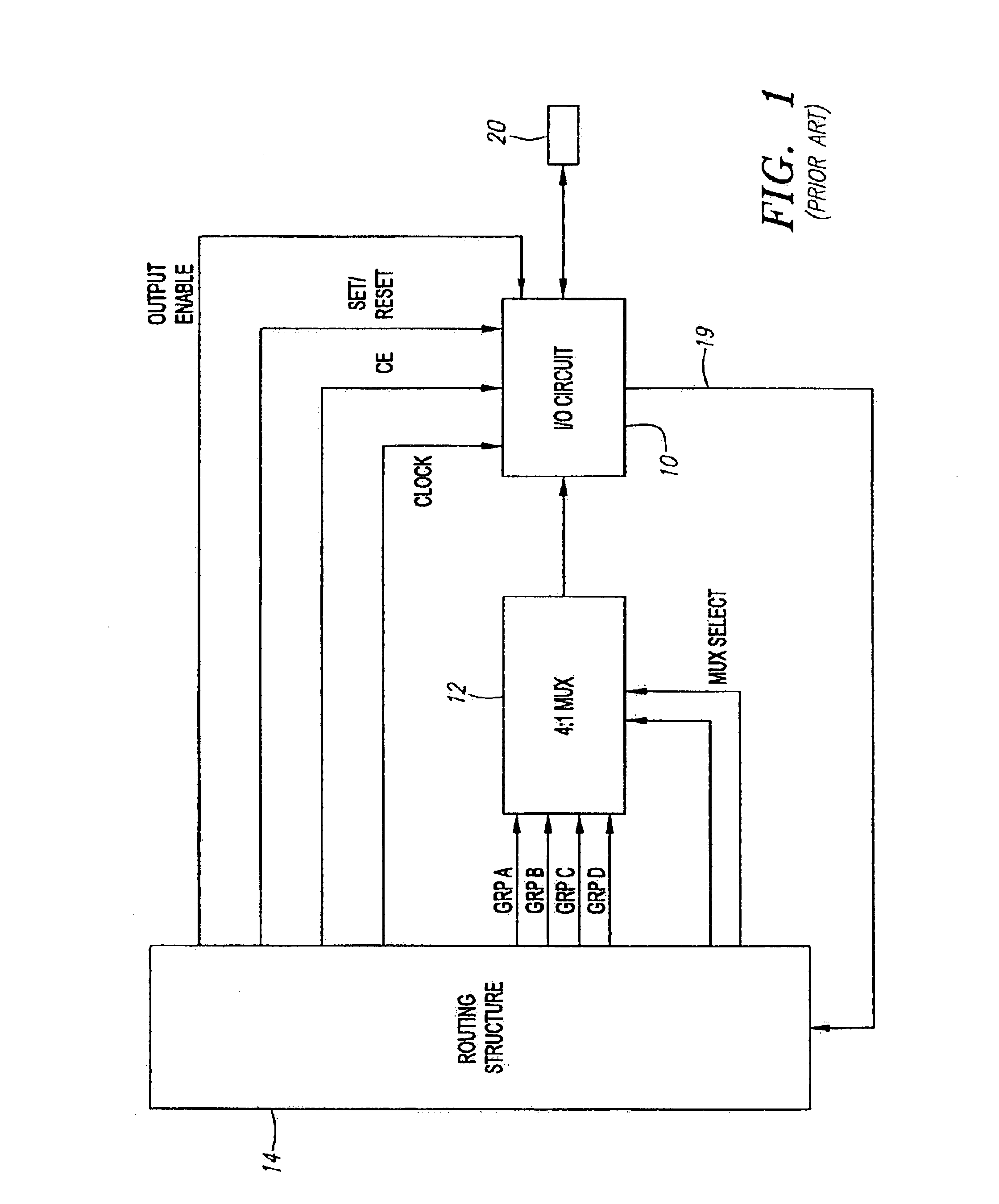

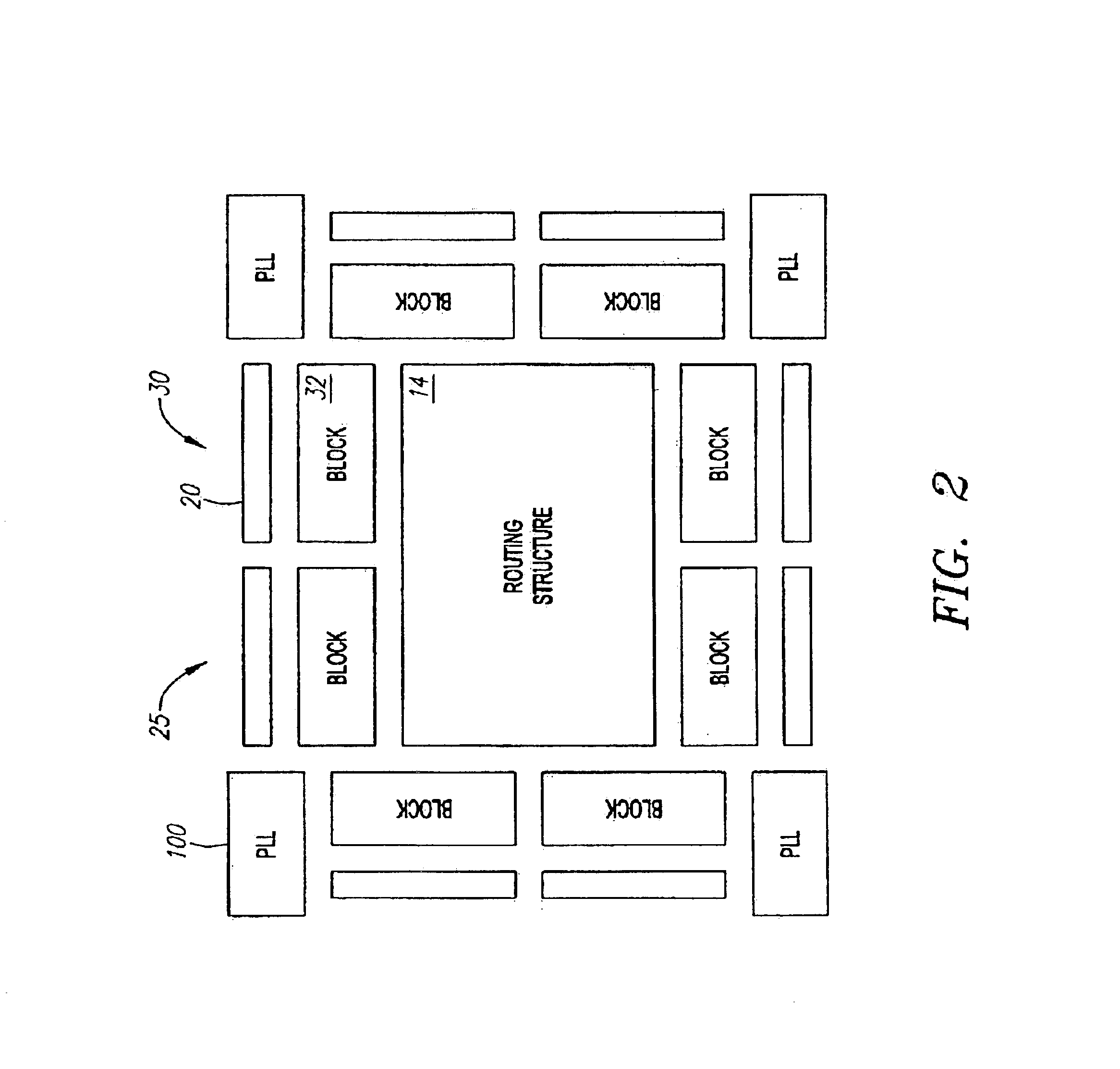

High speed interface for a programmable interconnect circuit

InactiveUS6861868B1Solid-state devicesSemiconductor/solid-state device manufacturingComputer scienceSemiconductor device

A programmable semiconductor device comprising a plurality of I / O circuits arranged into blocks includes a routing structure for each block, wherein each routing structure may programmably route signals between its block's I / O circuits and the I / O circuits within the remaining blocks. Each I / O circuit associates with a pin such that each block has a set of pins. A SERDES and a FIFO buffer associate with each block. Each block's SERDES couples between the block's I / O circuits and the block's set of pins. Each FIFO buffer couples between the SERDES and its block's I / O circuits.

Owner:LATTICE SEMICON CORP

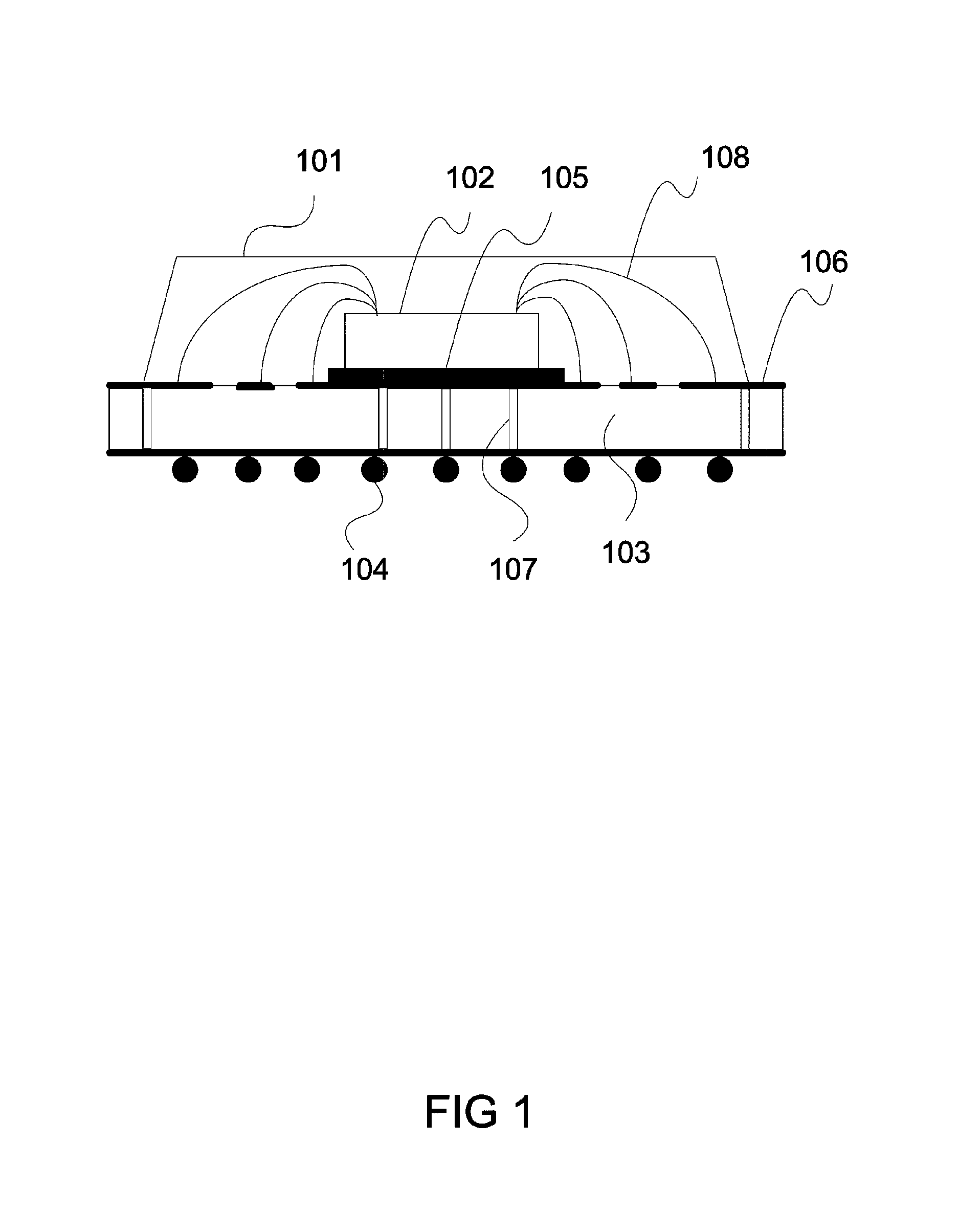

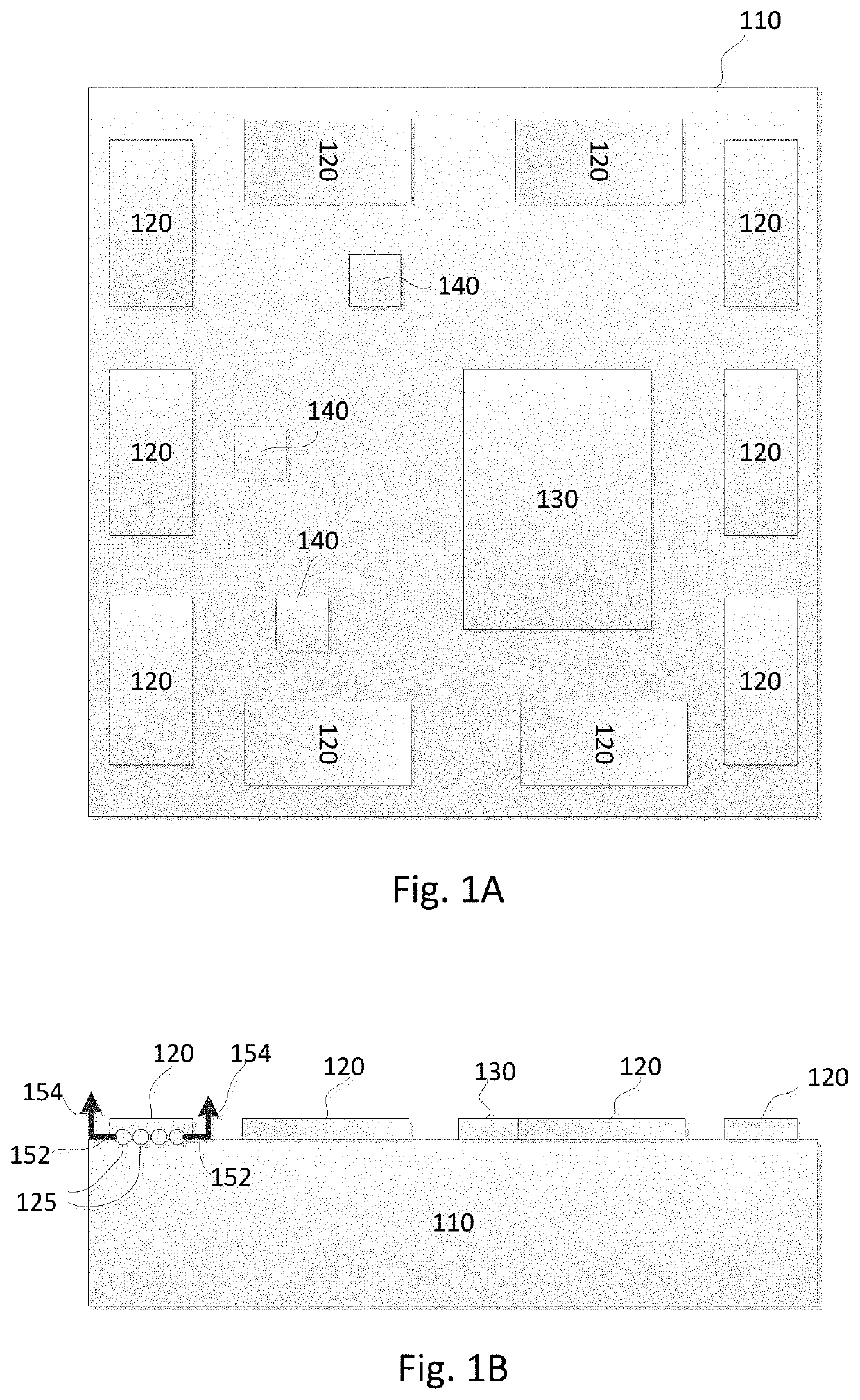

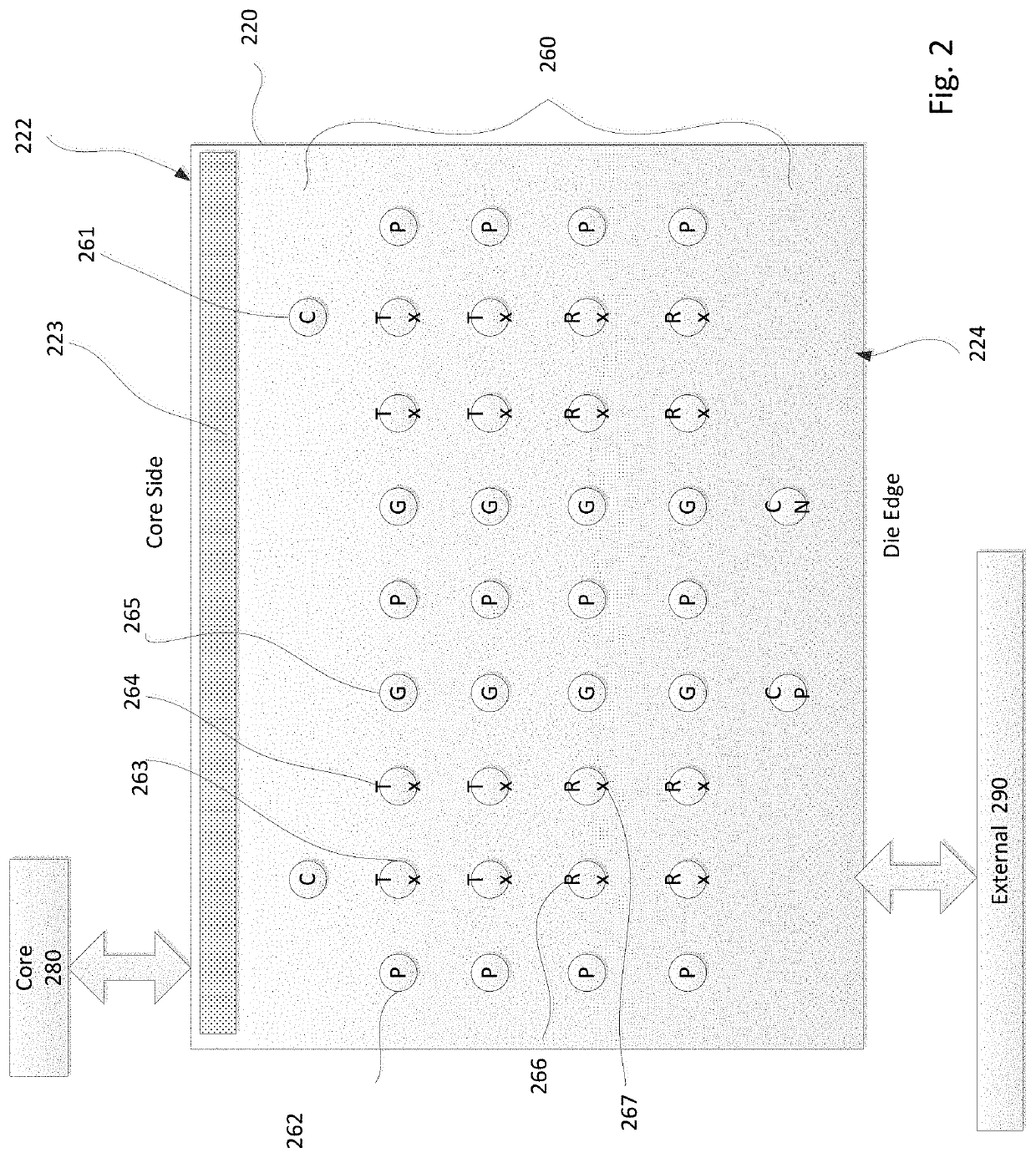

Hard IP blocks with physically bidirectional passageways

ActiveUS10923413B2Not to adversely impact transmitted signalSemiconductor/solid-state device detailsSolid-state devicesCapacitanceComputer architecture

Hard IP blocks, such as SerDes chips, are designed with keepout zones beneath the surface interconnects, the keepout zones being spaces within the chip where there is no circuitry. Connections can be formed between surface interconnects on an under surface of the SerDes chip that faces the host die, and surface interconnects on an upper surface of the SerDes chip that interfaces without external devices. Accordingly, redistribution layers routing around an outer periphery of the SerDes chip are no longer needed, and the resistive capacitive load remains low so as not to adversely impact transmitted signals.

Owner:XCELSIS CORP

Data transfer protocol for 6.25 GBPs Serializer/Deserializer (SERDES)

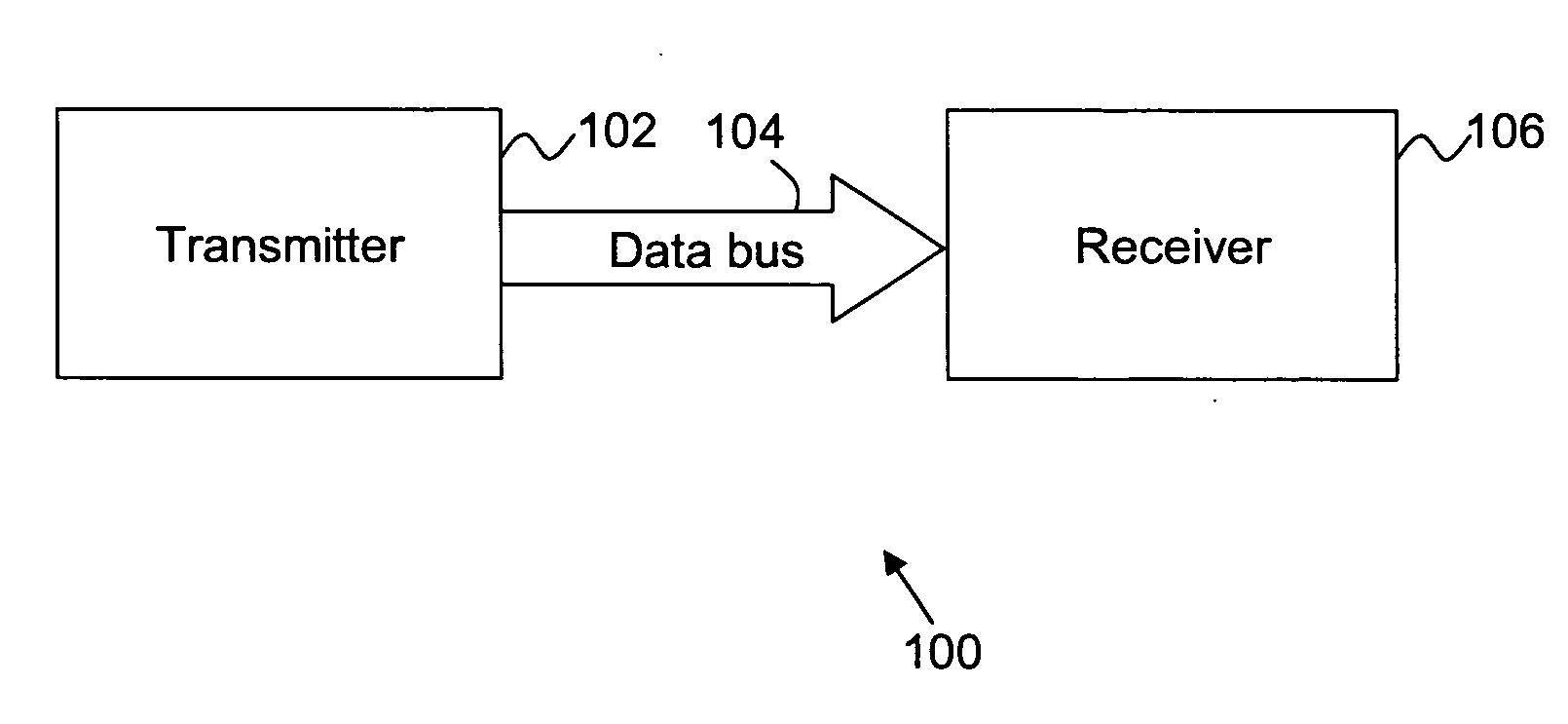

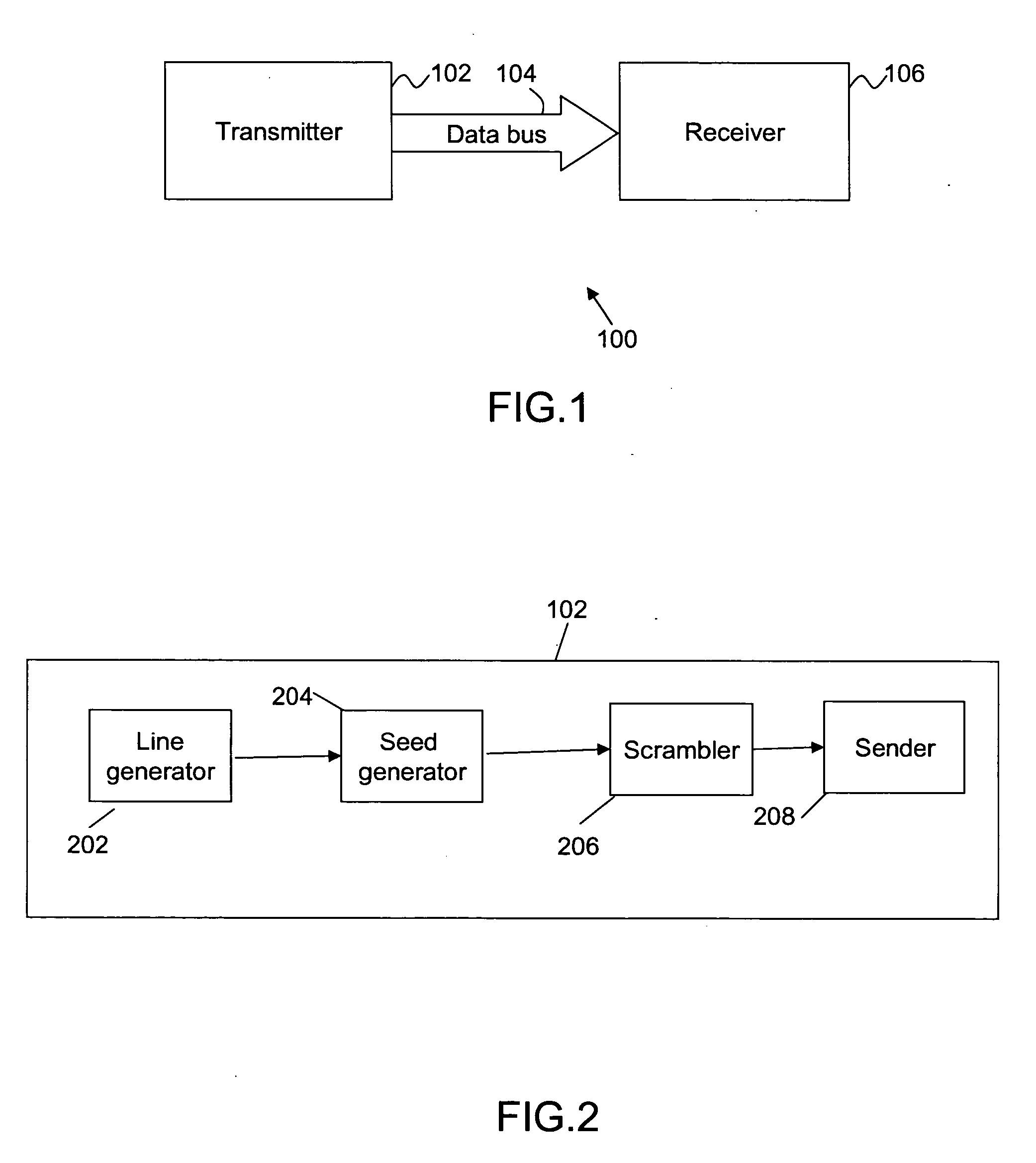

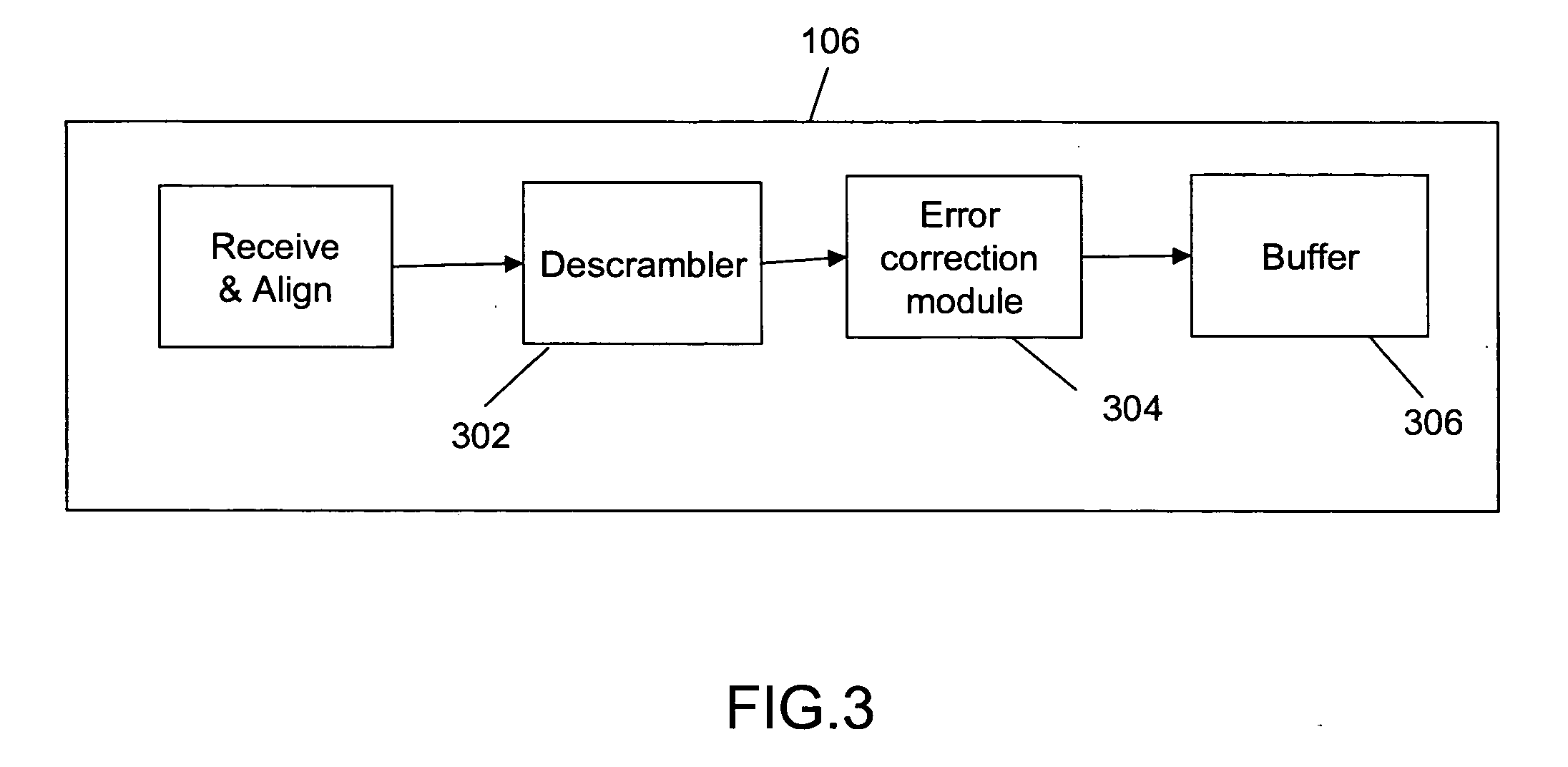

A method and a system for communicating data packets over a data bus is provided. The method includes sending one or more delimiter lines, a delimiter line comprising ‘N’ number of characters, the characters being sent for clock recovery; scrambling the data packets; sending the scrambled data packets after the delimiter line; sending at least one intra-packet within the data packets, the intra-packet being a packet within packets, the intra-packet including ‘control’ information; sending one or more delimiter lines after sending the scrambled data packets; and descrambling them.

Owner:CISCO TECH INC

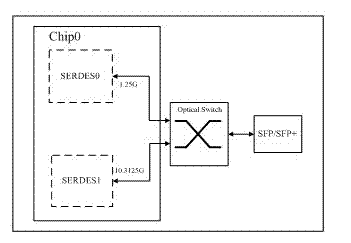

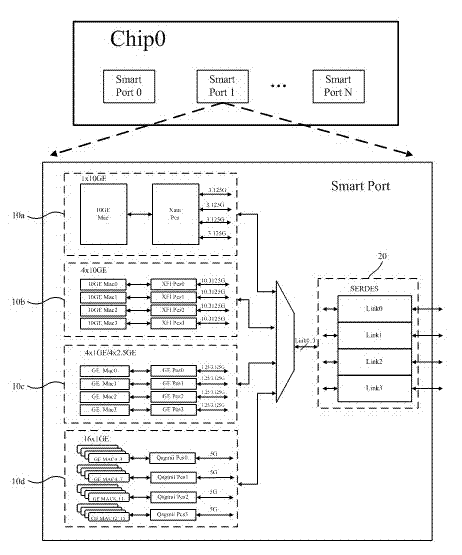

Ethernet port architecture supporting multiple transmission modes

The invention provides an Ethernet port architecture supporting multiple transmission modes. The Ethernet port architecture at least comprises a first scene module which corresponds to a first transmission mode and comprises a first Mac module and a first Pcs module which are connected with each other, a second scene module which corresponds to a second transmission mode and comprises a second Mac module and a second Pcs module which are connected with each other, and a serdes module which is at least connected with the first Pcs module and the second Pcs module, wherein the first scene module and the second scene module multiplex the serdes module and correspondingly switch the first transmission mode and the second transmission mode according to configuration. By the Ethernet port architecture, the single architecture can support multiple transmission modes; the chip cost is relatively low; and the Ethernet port architecture is flexibly applied.

Owner:SUZHOU CENTEC COMM CO LTD

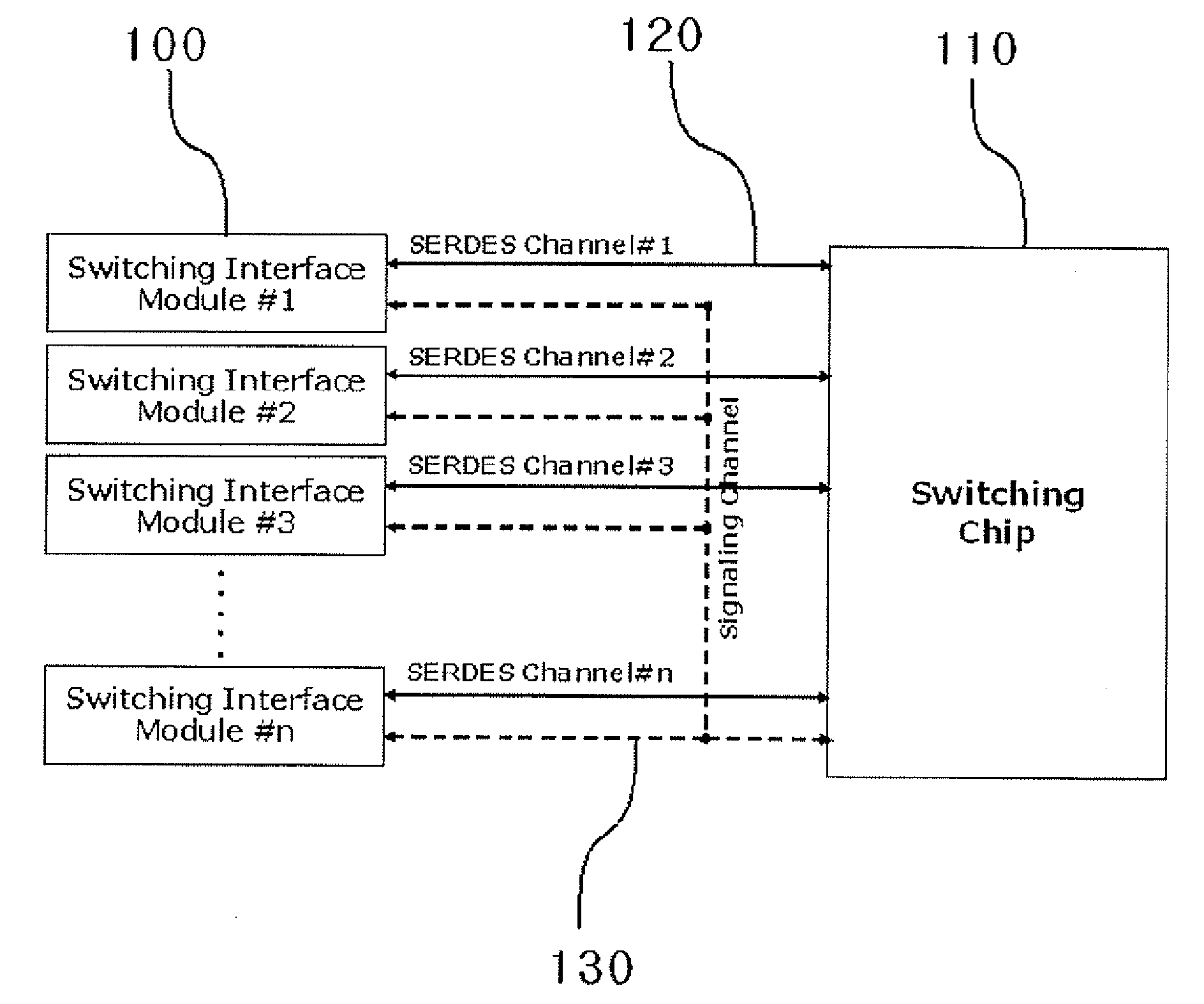

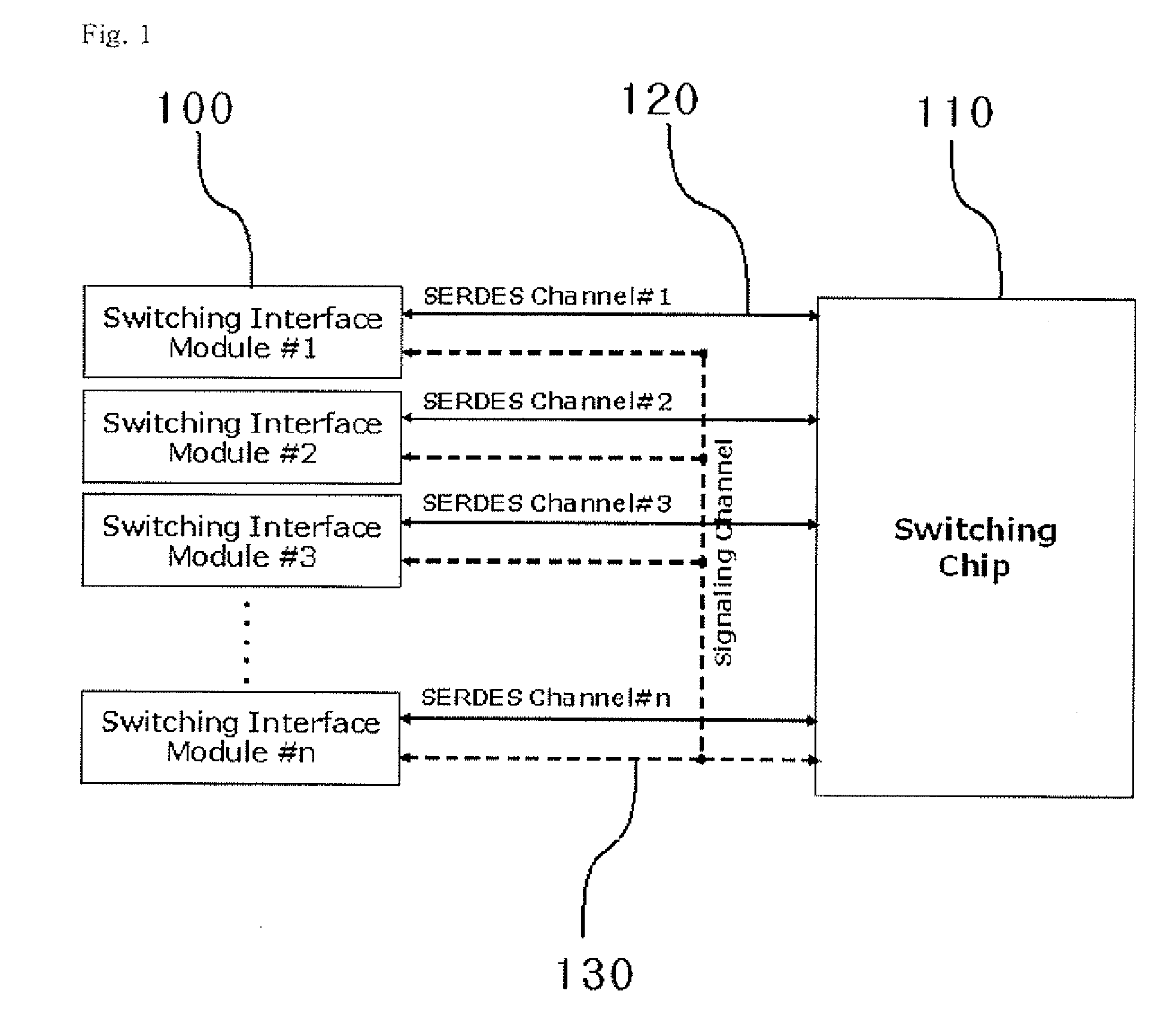

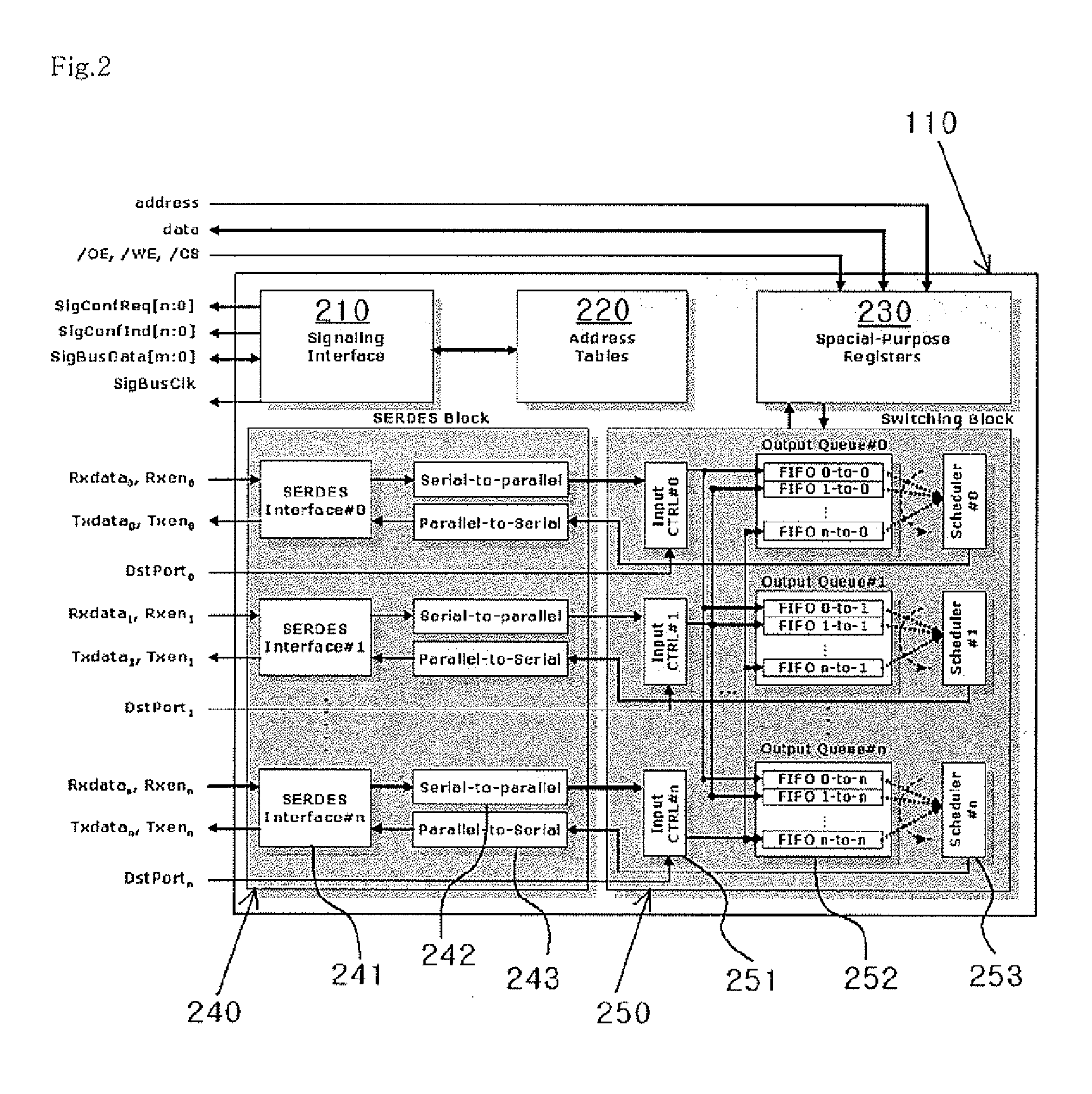

System for switching variable-length data packets of heterogeneous network and method for the same

InactiveUS20070147386A1Easy to modifyData switching by path configurationNetwork connectionsHeterogeneous networkSerialization

The present invention relates to a system for switching variable-length data packets of a heterogeneous network and a method for the same; and, more particularly, to a switching of variable-length data packets of a heterogeneous network through a serial communication between switching chips to switch the packets with a switching interface module having a network value representing a type of a specific network and a port number of a port which is connected to itself. The present invention has a technical characteristic in comprising a system for data switching variable-length packets of heterogeneous network, comprising: at least two switching interface modules connected to at least two networks respectively to transceive packets; a switching chip for receiving the packets from a first switching interface module among said at least two switching interface modules and for switching the received packets to a second switching interface module among said at least two switching interface modules; a SERDES (serialization and deserialization) channel for transmitting the packets between the switching interface module and the switching chip; and a signaling channel for transmitting a port number between the switching interface module and the switching chip.

Owner:KOREA ELECTRONICS TECH INST

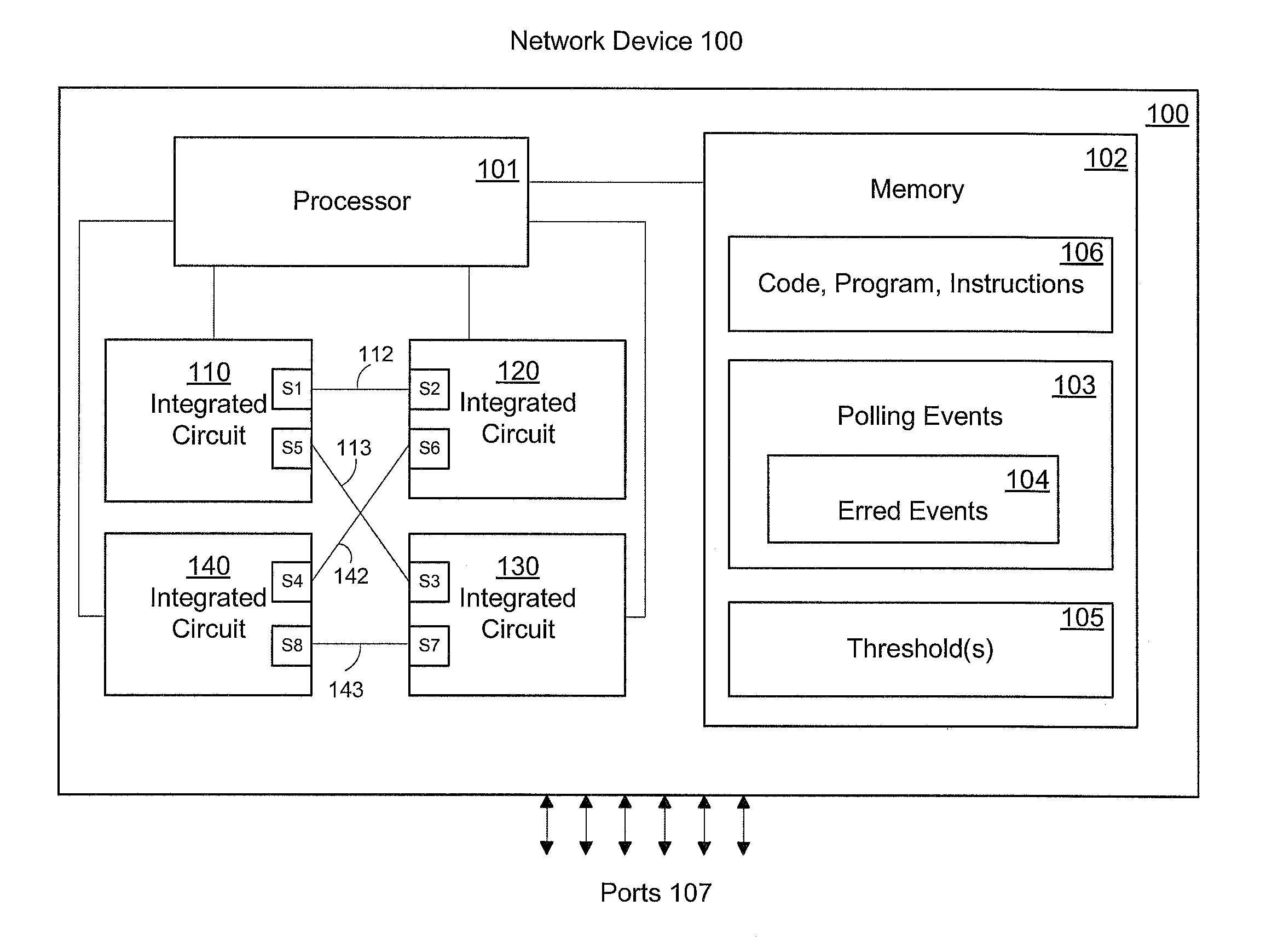

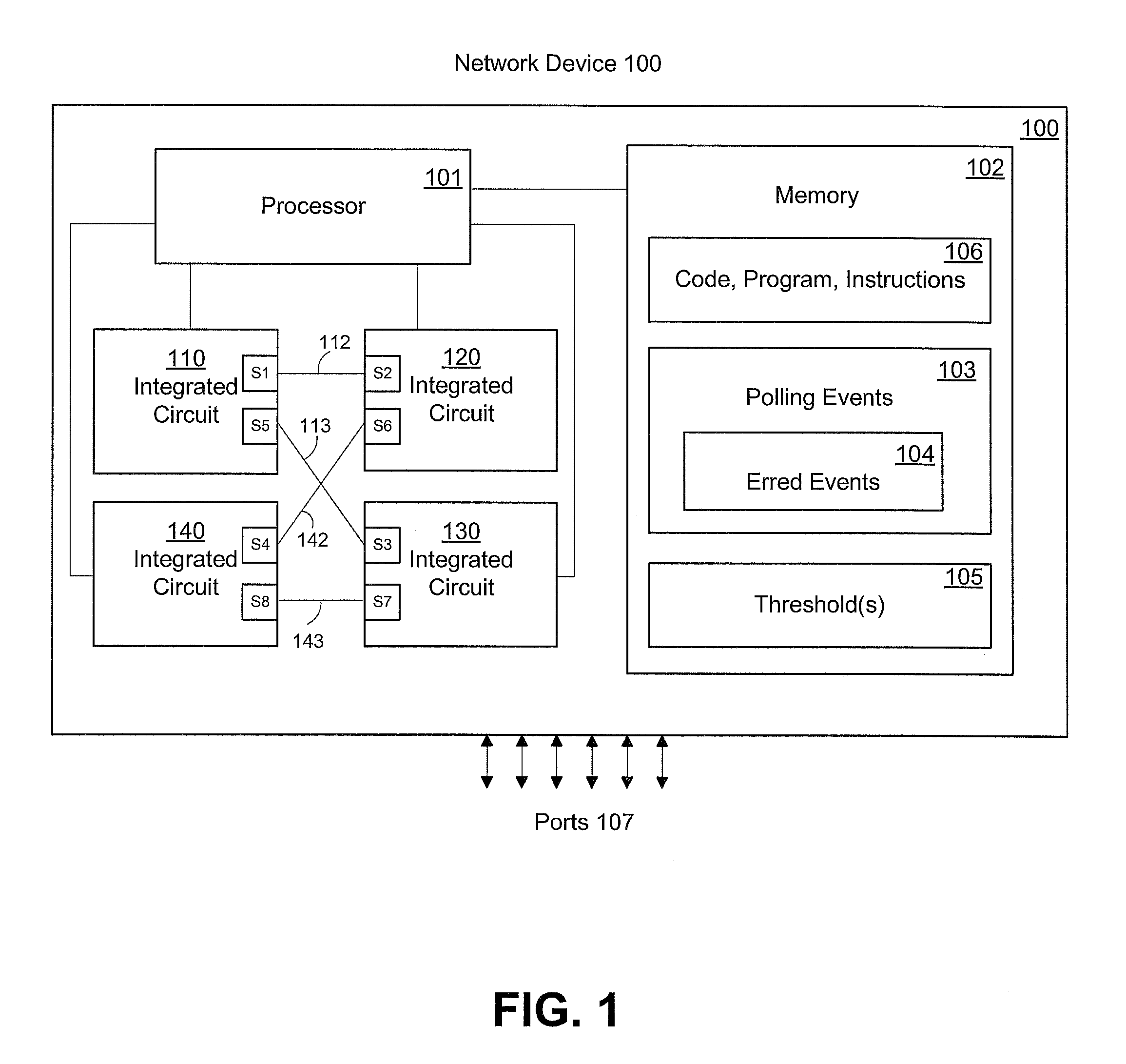

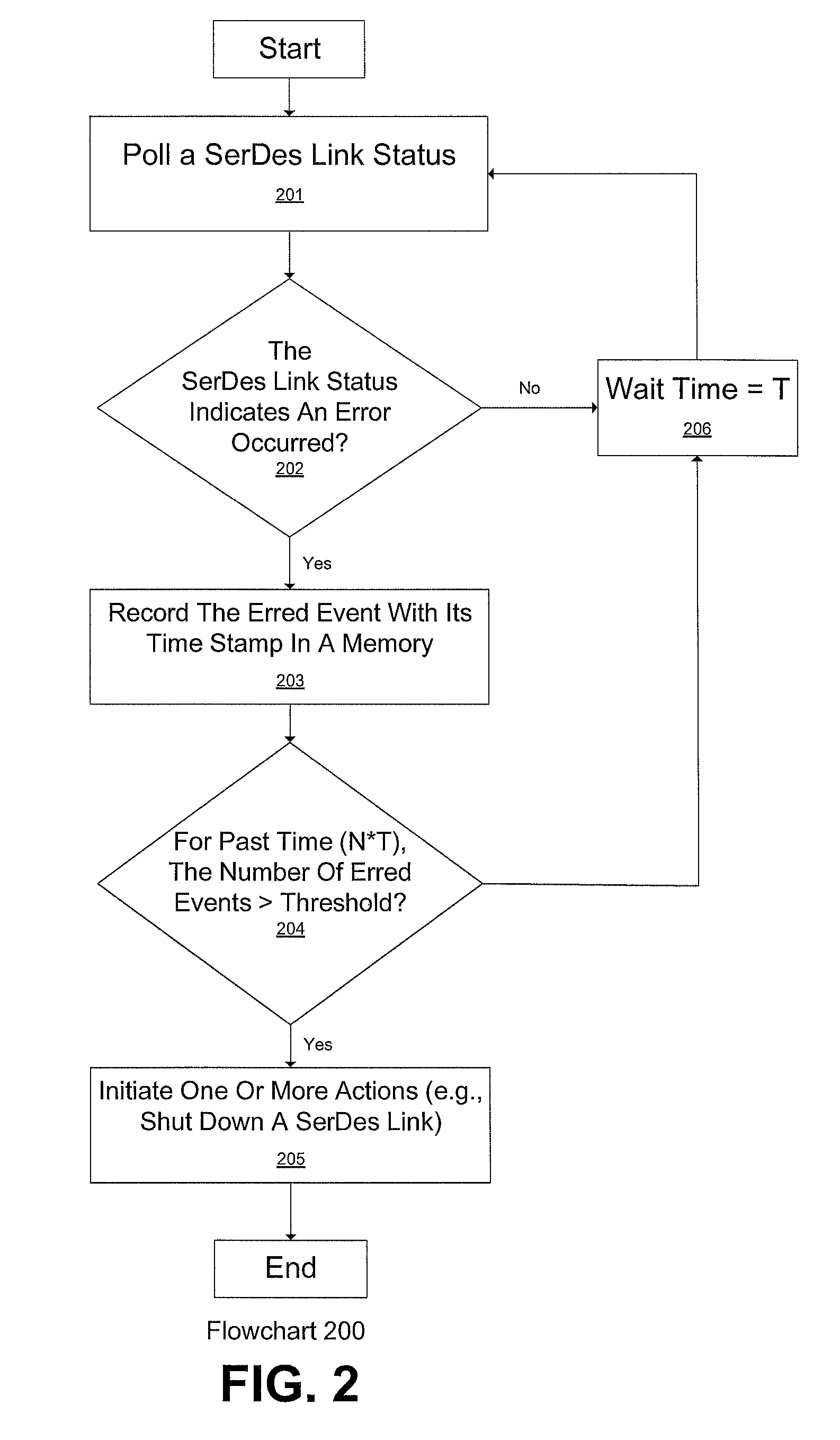

Serdes link error management

Techniques for dynamically measuring and monitoring error rate in Serializer / Deserializer (SerDes) links In one set of embodiments, a method includes polling a SerDes link status of a SerDes link at a predetermined rate. The method also includes storing a predetermined polling results in a memory, determining a number of polling results indicating one or more errors occurred in said SerDes link, determining an action to be taken if said number of polling results exceed a threshold.

Owner:BROCADE COMMUNICATIONS SYSTEMS

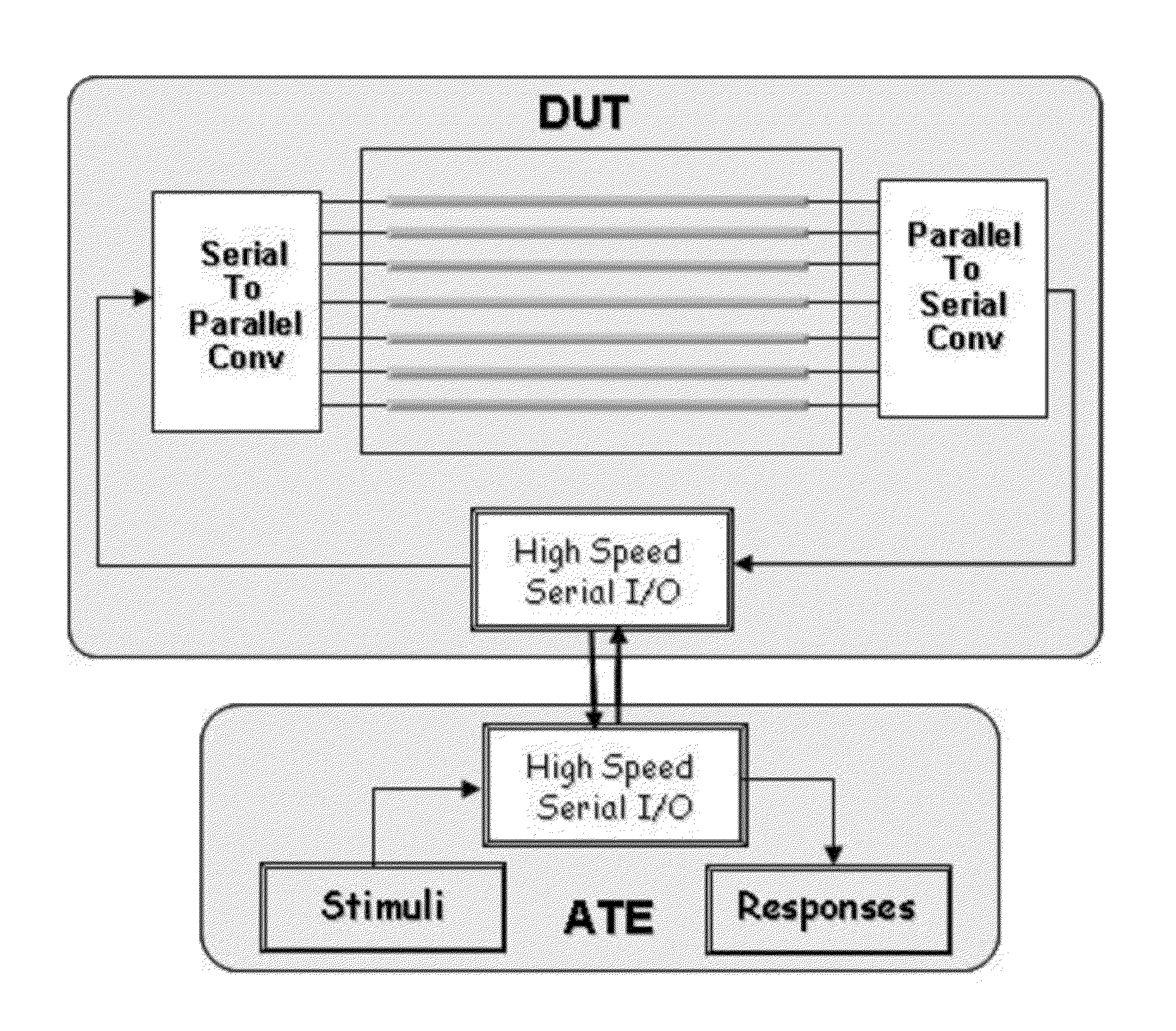

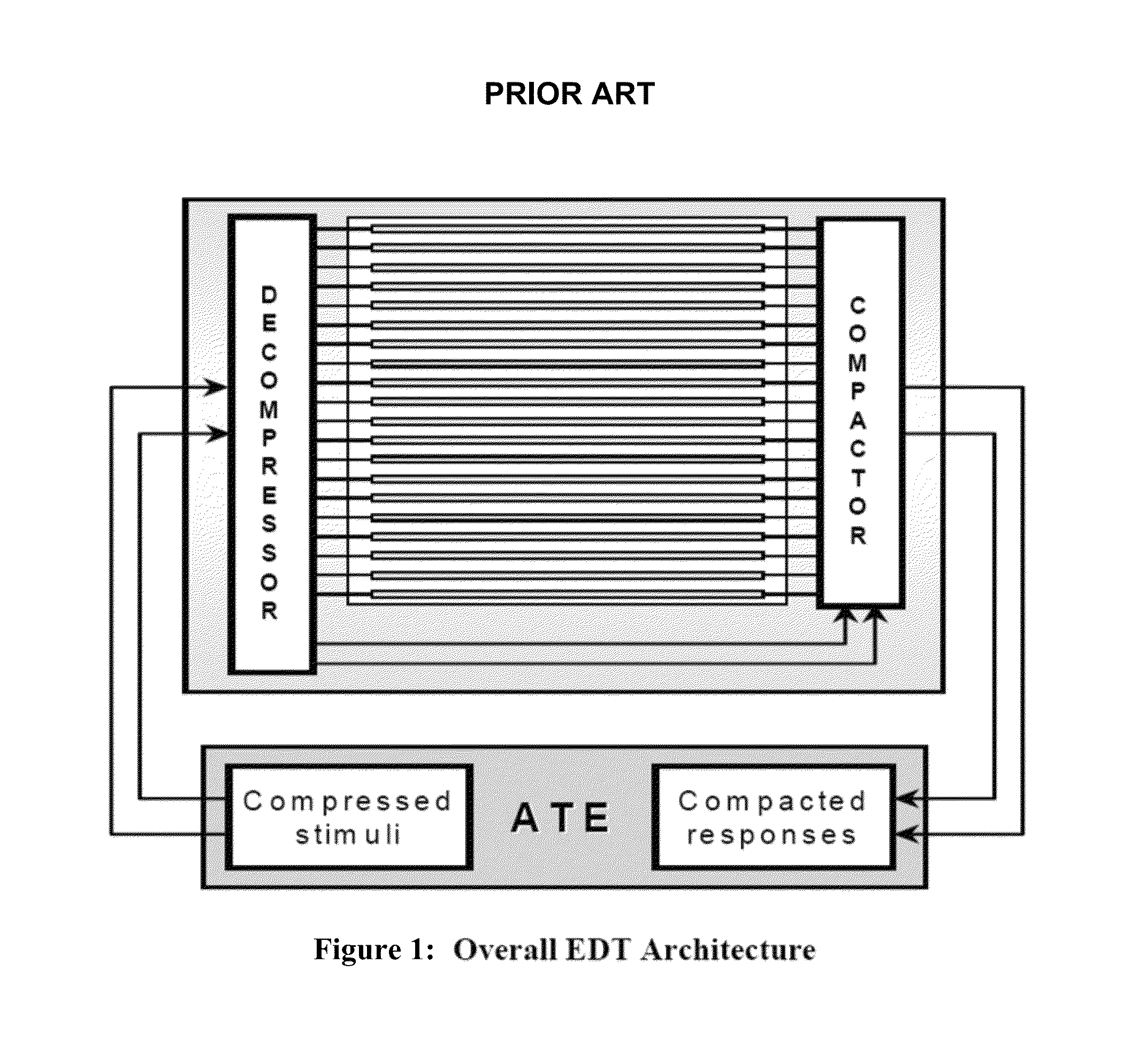

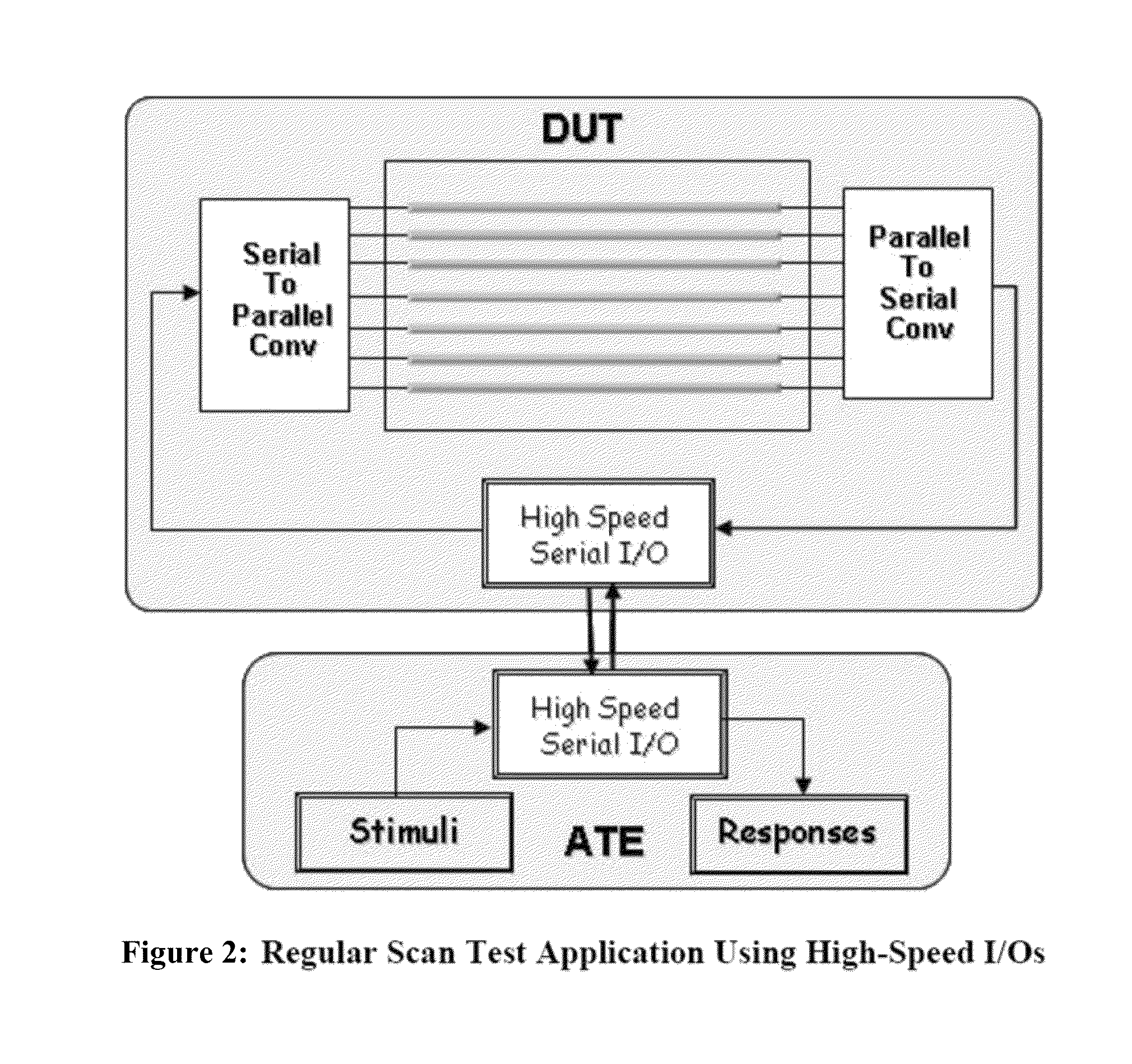

Scan test application through high-speed serial input/outputs

ActiveUS8726112B2Reduce test data volumeMinimize timeElectronic circuit testingData compressionAsynchronous operation

Methods and devices for using high-speed serial links for scan testing are disclosed. The methods can work with any scheme of scan data compression or with uncompressed scan testing. The protocol and hardware to support high speed data transfer reside on both the tester and the device under test. Control data may be transferred along with scan data or be partially generated on chip. Clock signals for testing may be generated on chip as well. In various implementations, the SerDes (Serializer / Deserializer) may be shared with other applications. The Aurora Protocol may be used to transport industry standard protocols. To compensate for effects of asynchronous operation of a conventional high-speed serial link, buffers may be used. The high-speed serial interface may use a data conversion block to drive test cores.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Reconfigurable ADD/DROP, multiplexer/demultiplexer using a transceiver with loop-back function

ActiveUS7161964B2Operation moreSimple and cost-effectiveWavelength-division multiplex systemsTime-division multiplexTransceiverMultiplexer

A reconfigurable ADD / DROP multiplexer / demultiplexer apparatus is implemented by connecting a multiplexer / demultiplexer apparatus to a serializer / deserializer (SERDES) apparatus having a loop-back capability. By selectively activating the loop-back functionality of the SERDES apparatus the combination can be made to function as a reconfigurable ADD / DROP multiplexer / demultiplexer apparatus.

Owner:LUCENT TECH INC