Patents

Literature

1090results about "Parallel/series conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

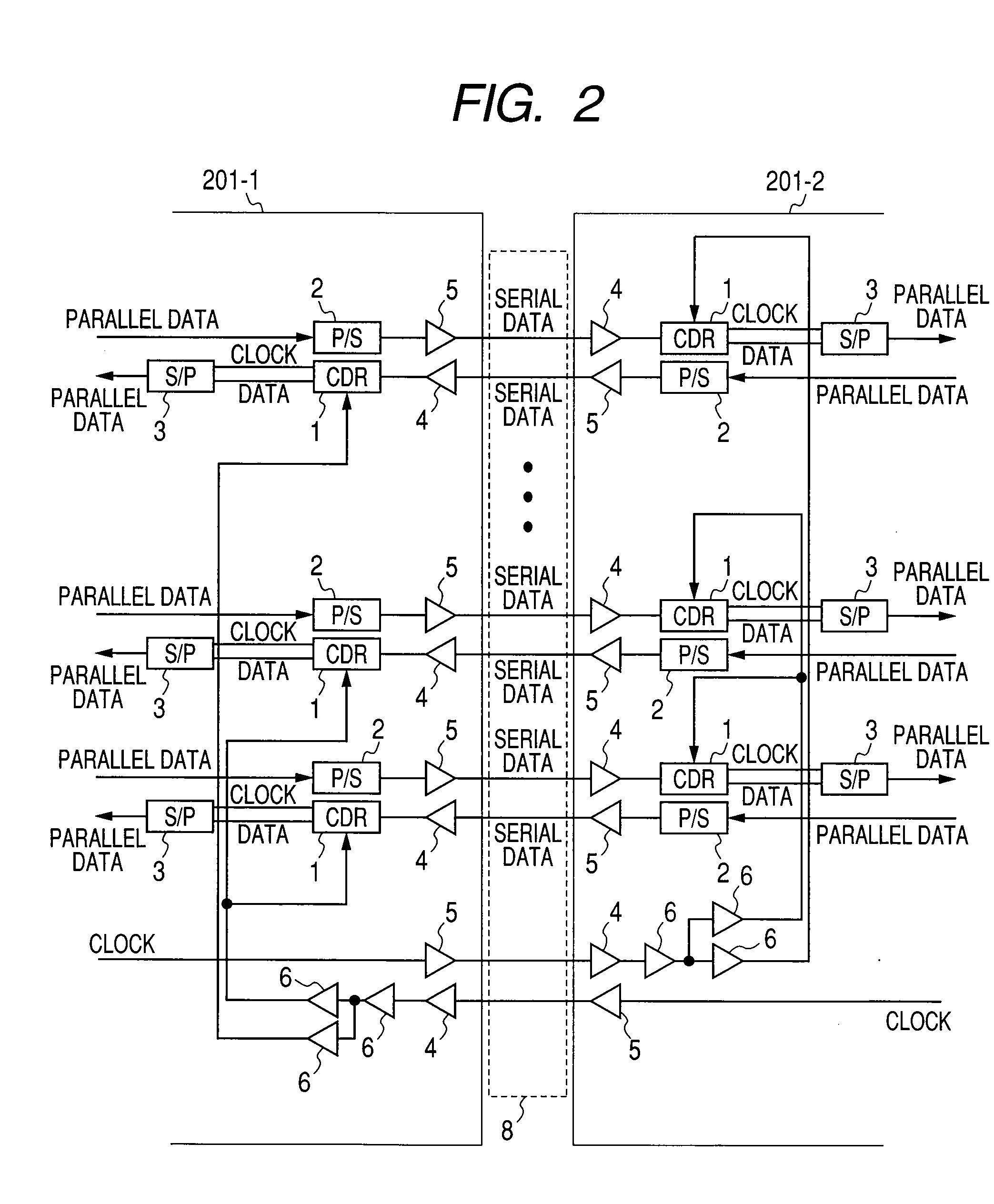

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS20050286643A1Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

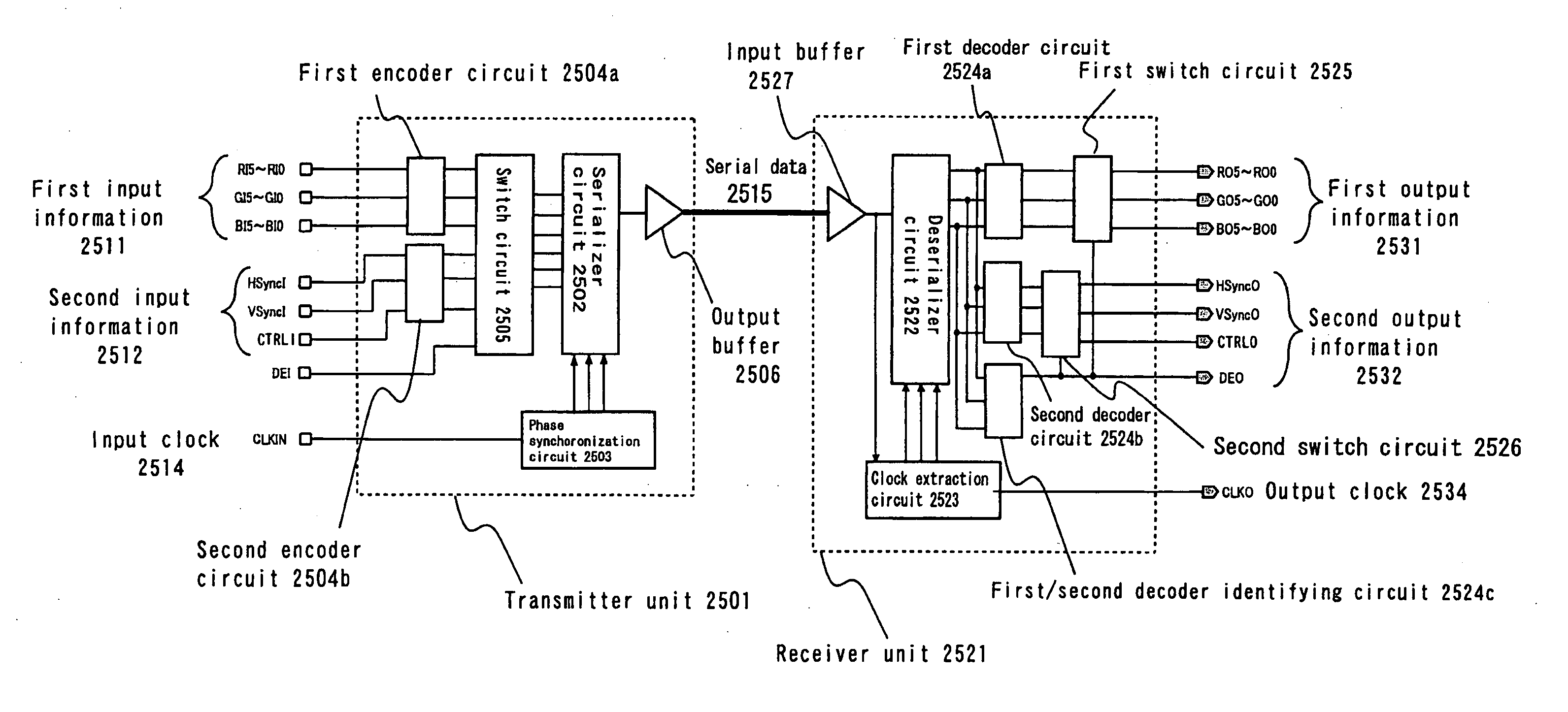

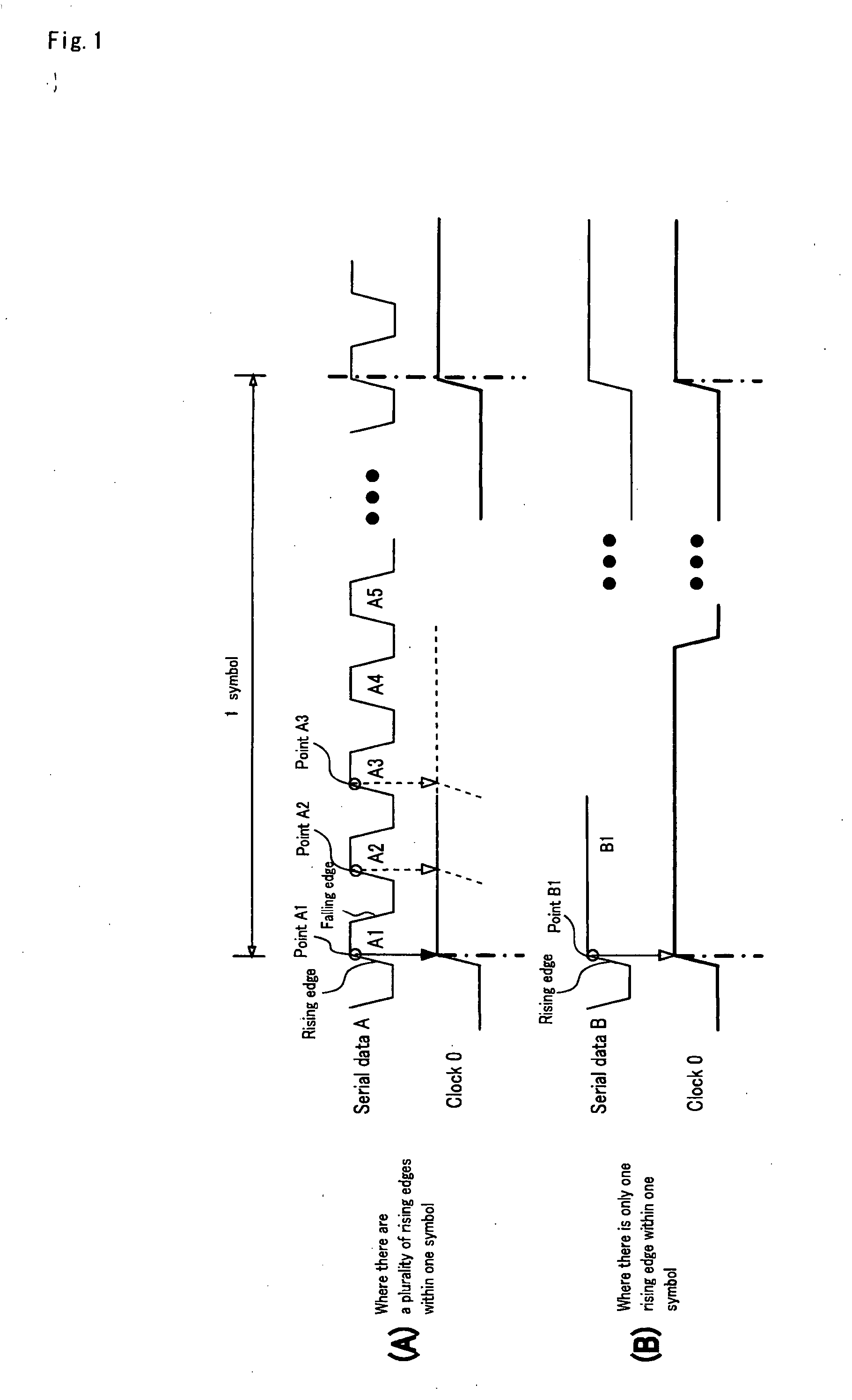

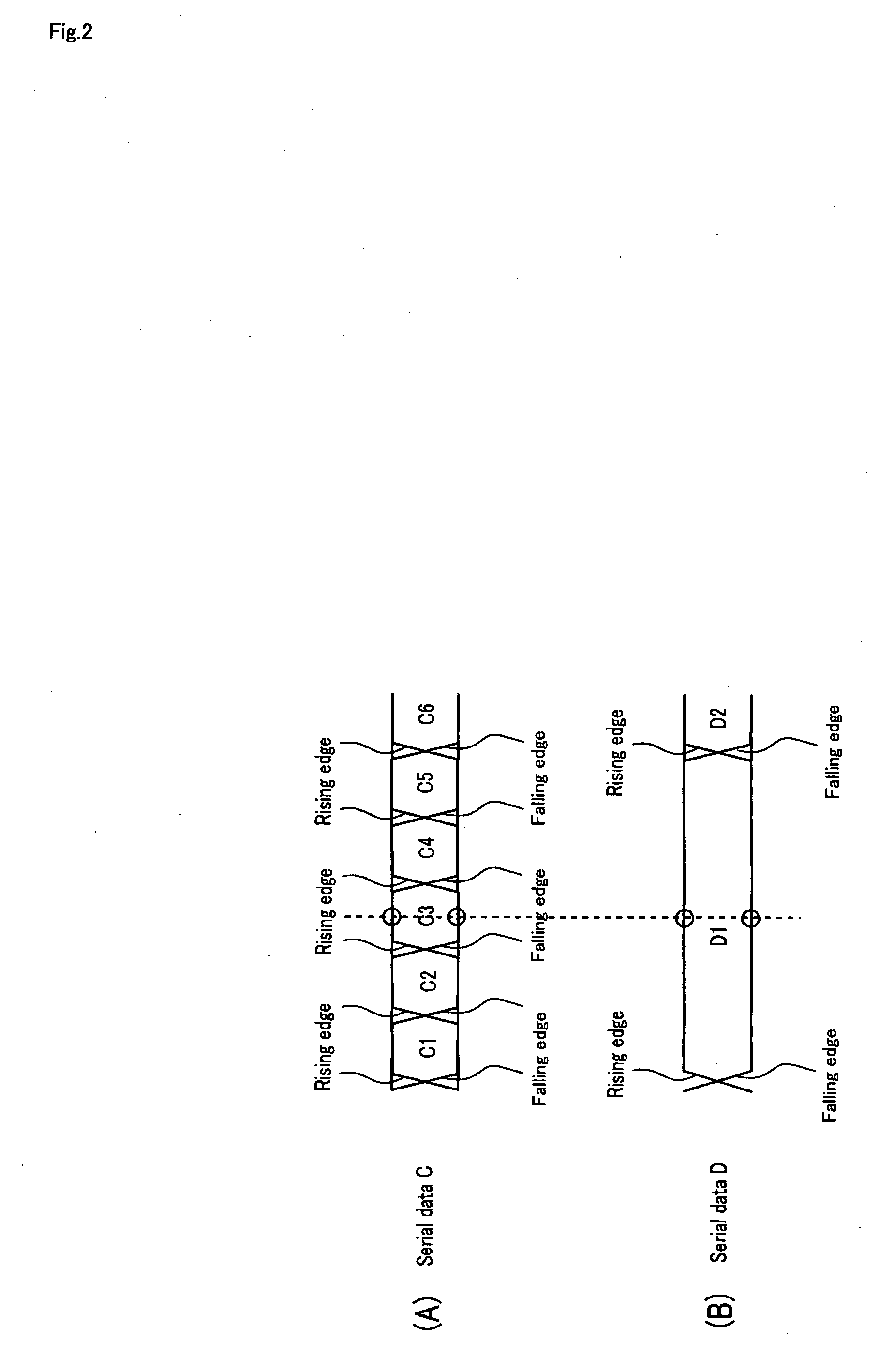

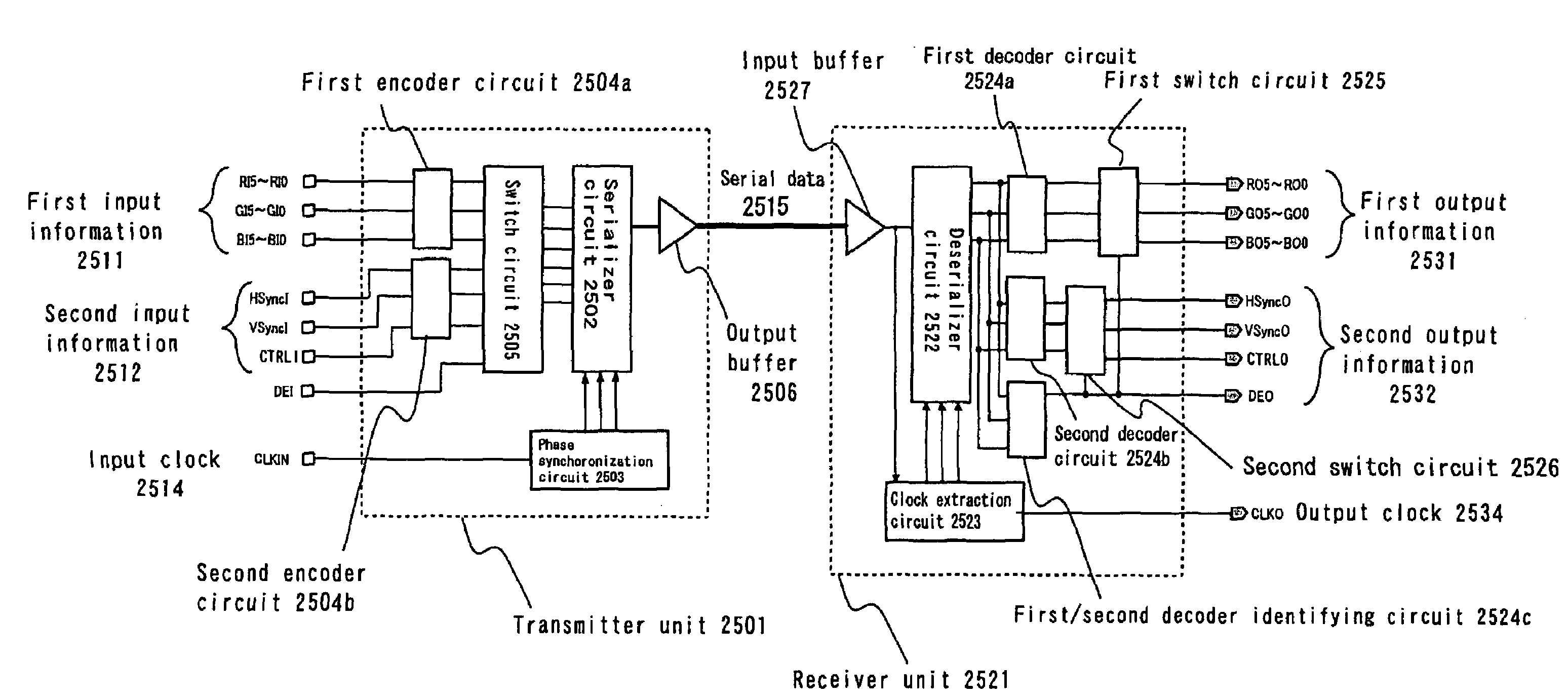

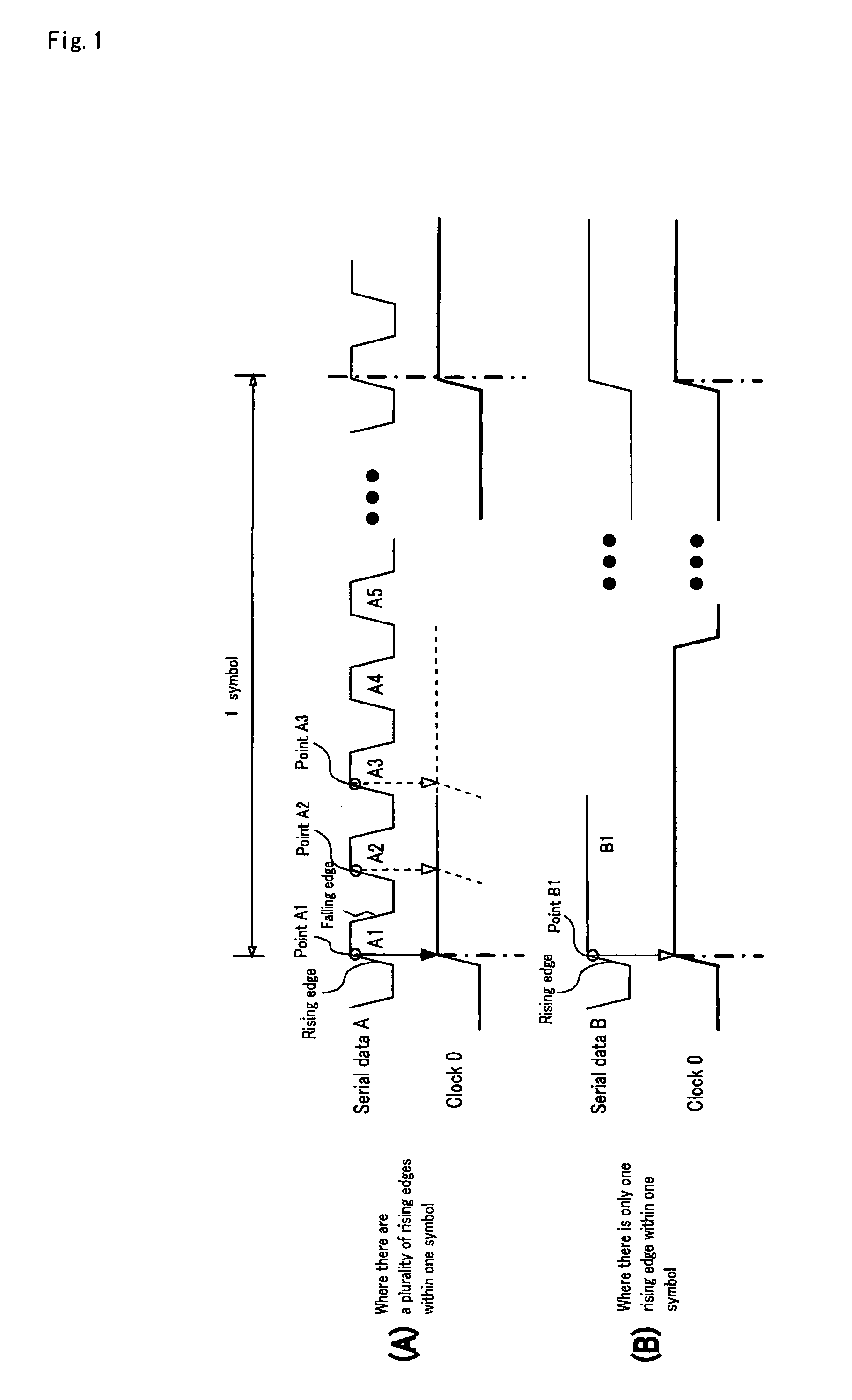

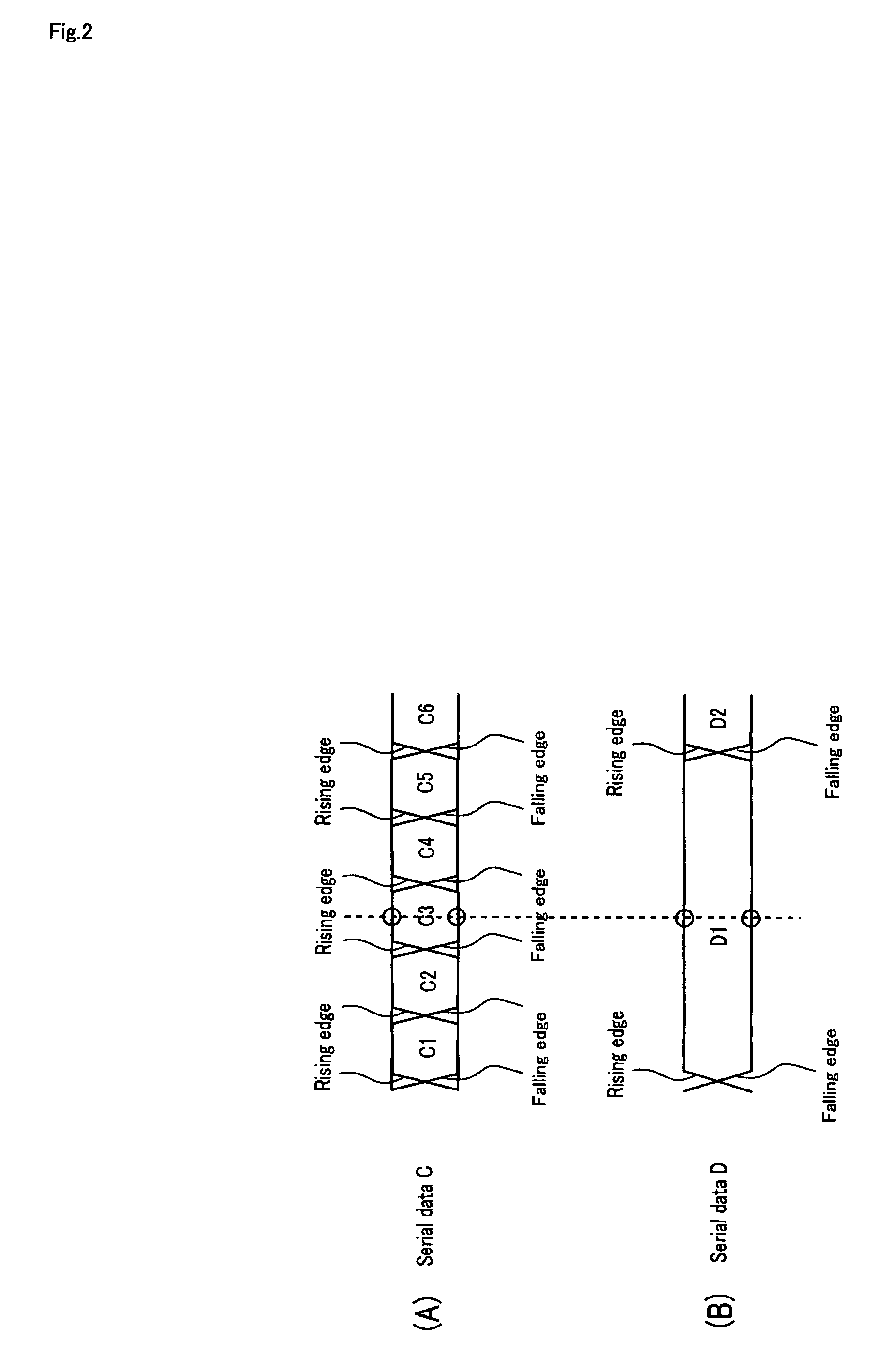

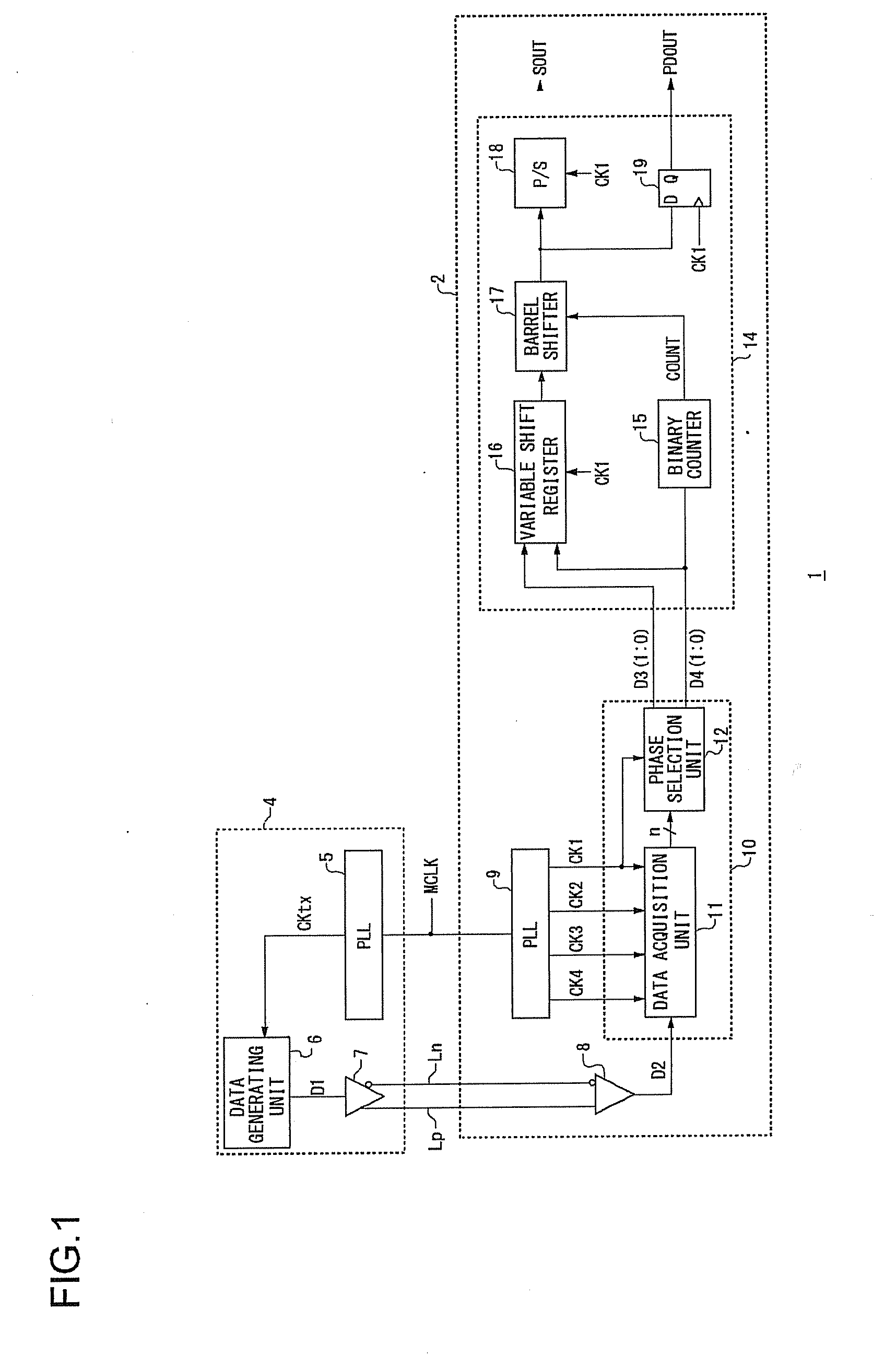

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation. [Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

ActiveUS7535957B2Reduce errorsData transmission is stableTelevision system detailsFrequency/rate-modulated pulse demodulationDigital dataPhase locked loop circuit

[Problems] To realize a reliable and stable transfer of digital data that does not require a reference clock and a handshake operation.[Means for Solving the Problem] The present invention provides a digital data transfer method for alternately and periodically transferring first information and second information respectively in a first period and in a second period, wherein: an amount of information of the first information per unit time in the first period is greater than an amount of information of the second information per unit time in the second period; and the second information in the first period is transferred as pulse-width-modulated serial data.

Owner:THINE ELECTRONICS

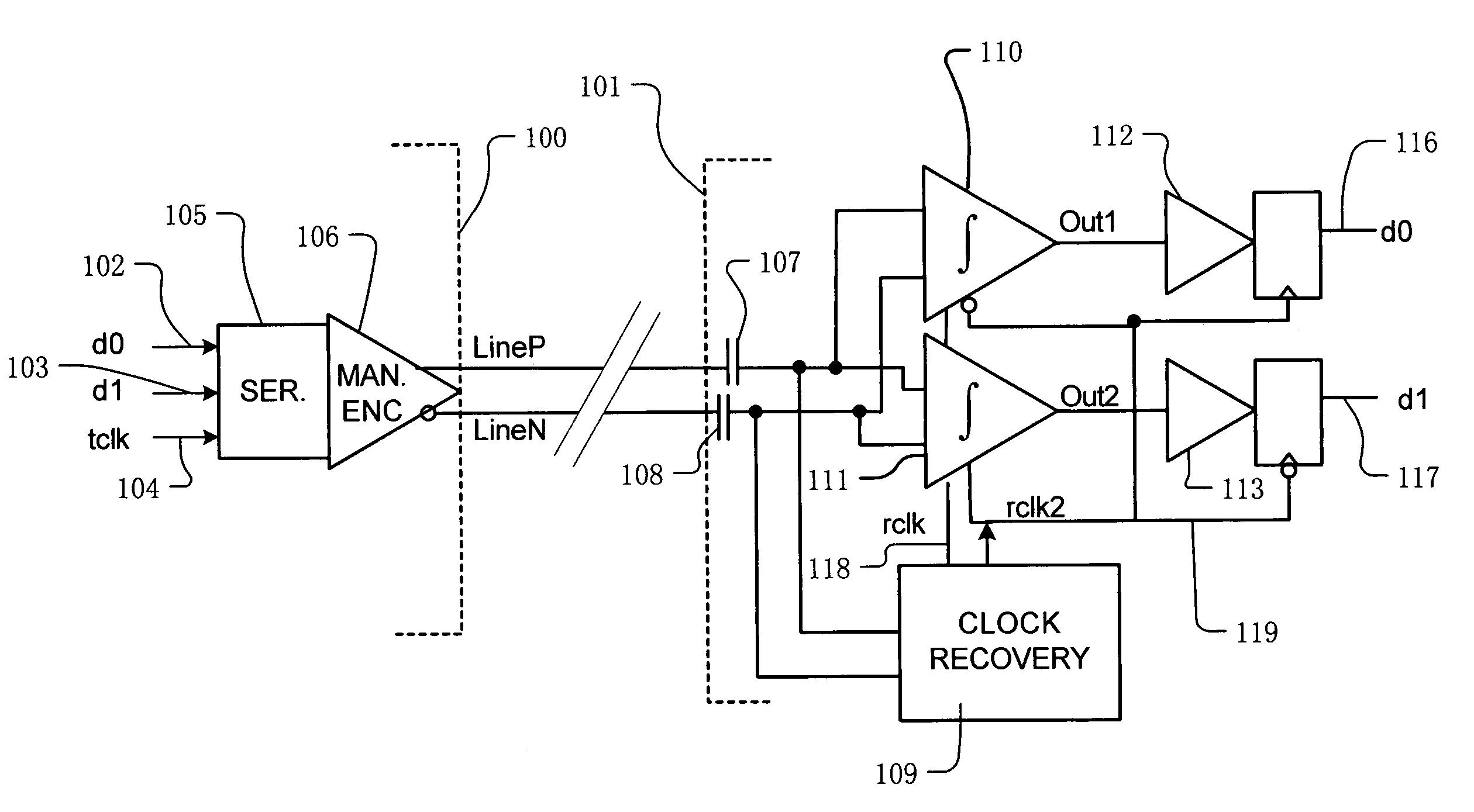

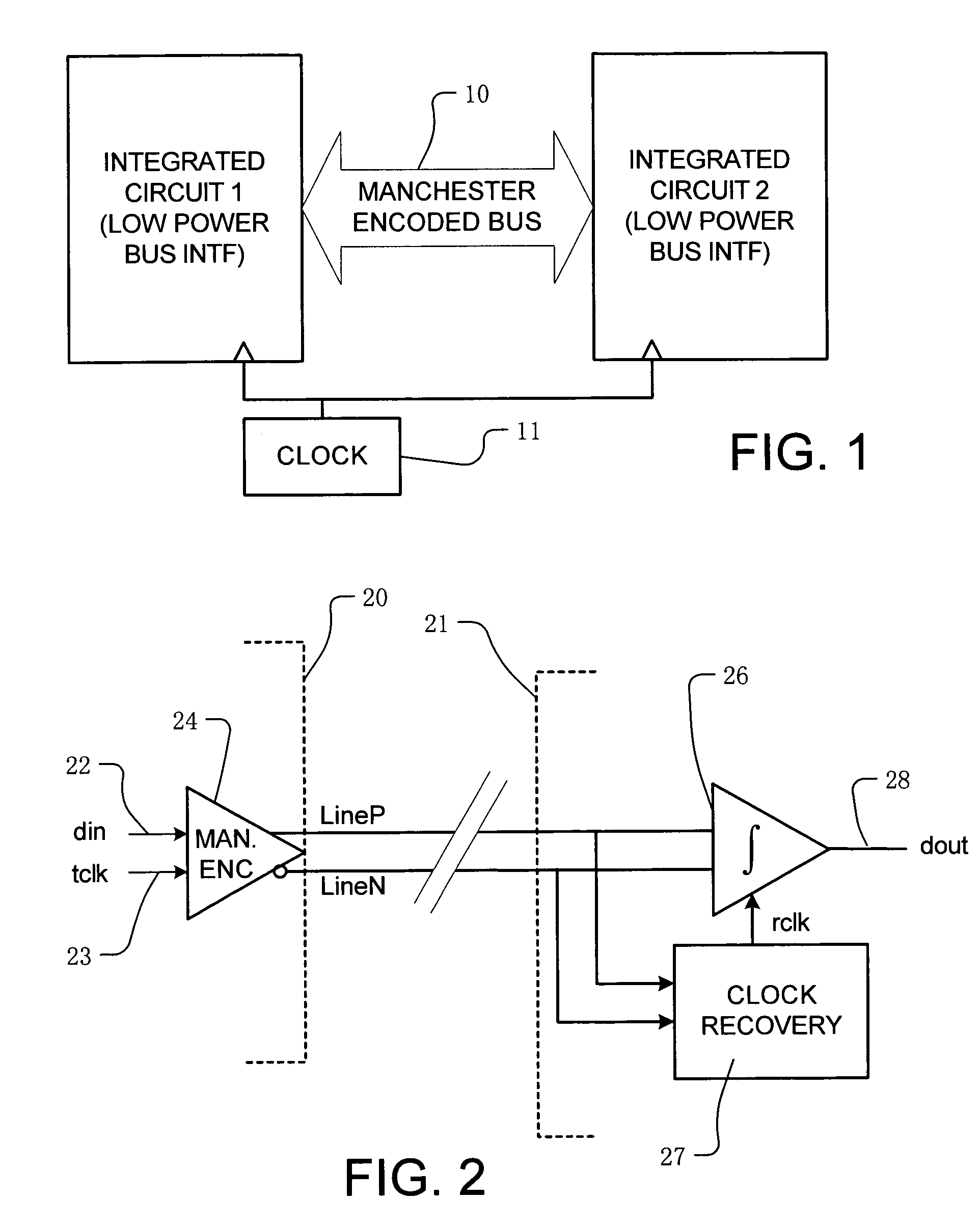

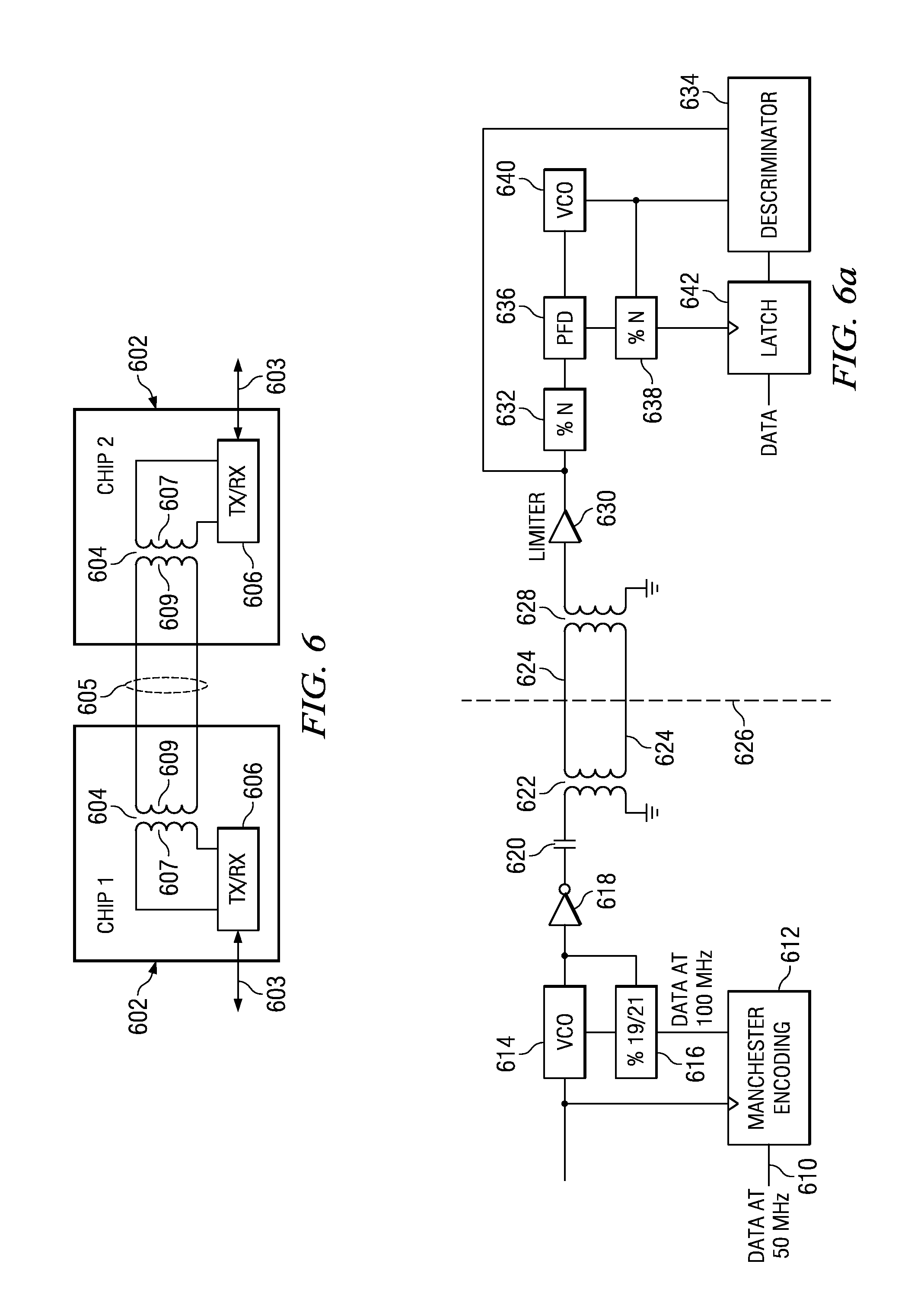

Communication system with low power, DC-balanced serial link

ActiveUS7199728B2Analogue/digital conversionElectric signal transmission systemsManchester codeData stream

A data communication system comprises a transmission line between first and second integrated circuits. An encoder on the first integrated circuit encodes an input data stream to produce a sequence of codewords, wherein codewords in the sequence are members of a set of codewords representing data in the input data stream, and the members of the set are substantially DC balanced, such as a Manchester encoded symbol set. An integrating circuit on the second integrated circuit integrates codewords by integrating for a first interval with a positive polarity within a particular symbol cell, and integrating for a second interval with a negative polarity within the particular symbol cell, to produce output representing the codewords. A sense circuit produces an output data stream.

Owner:RAMBUS INC

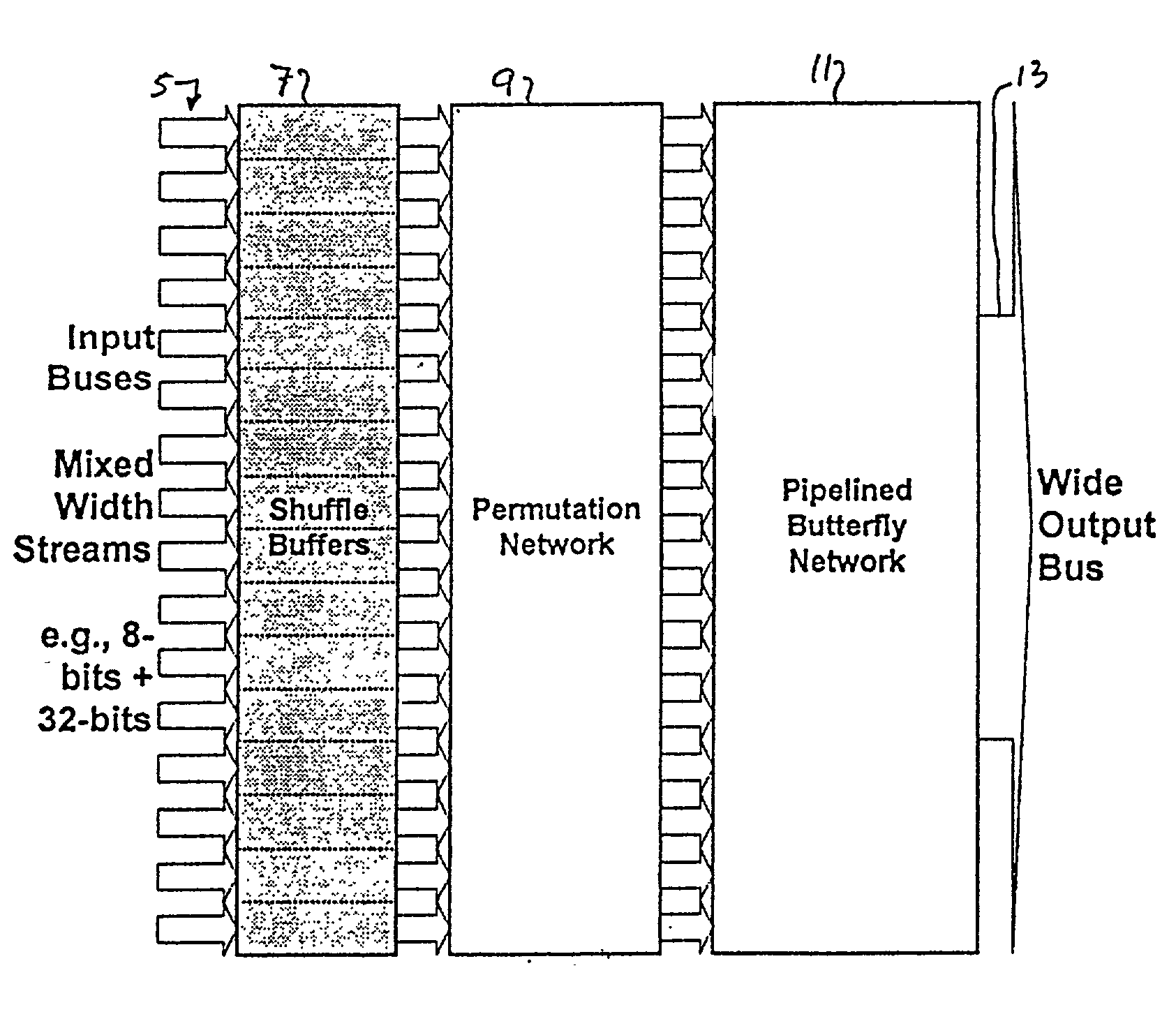

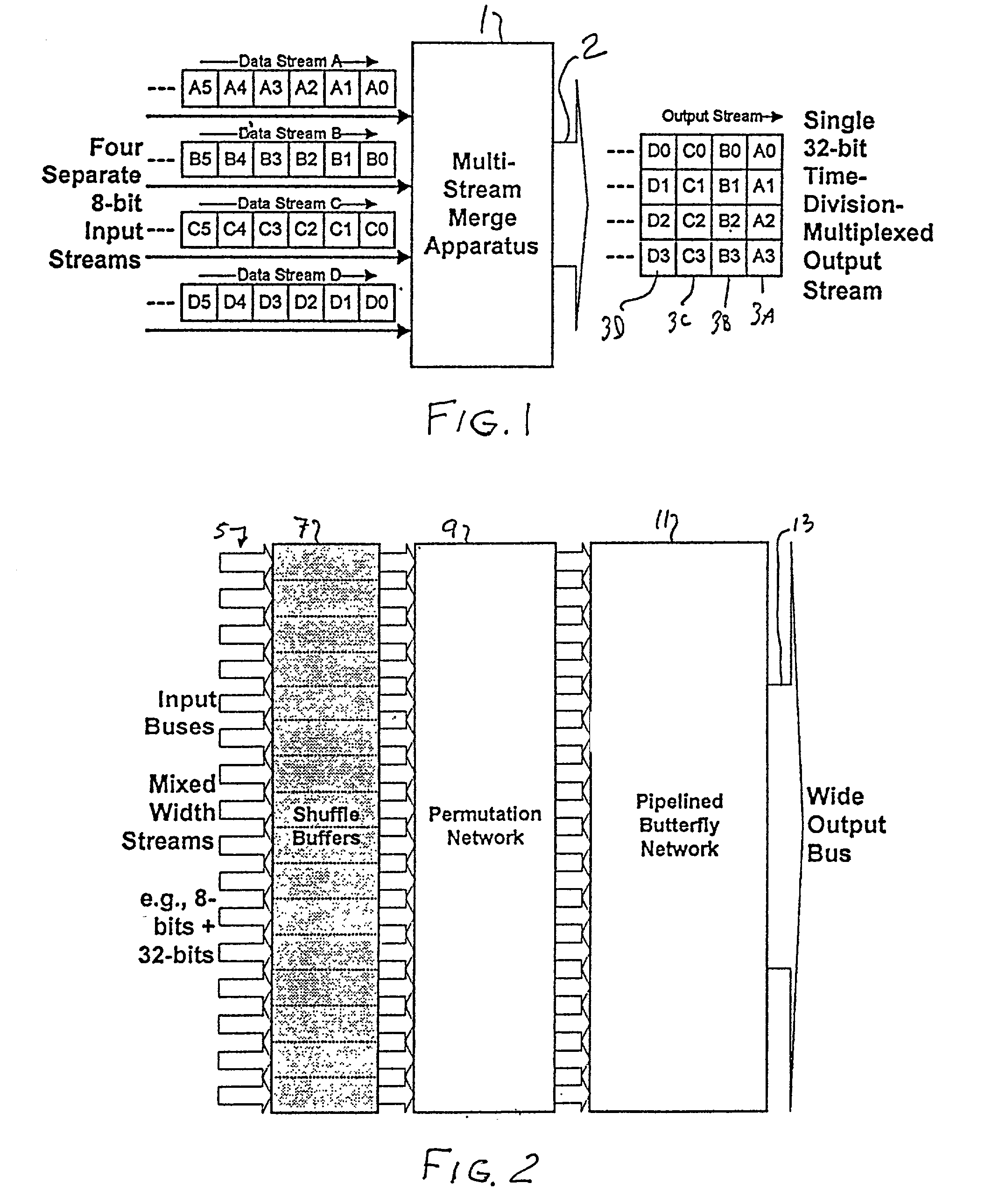

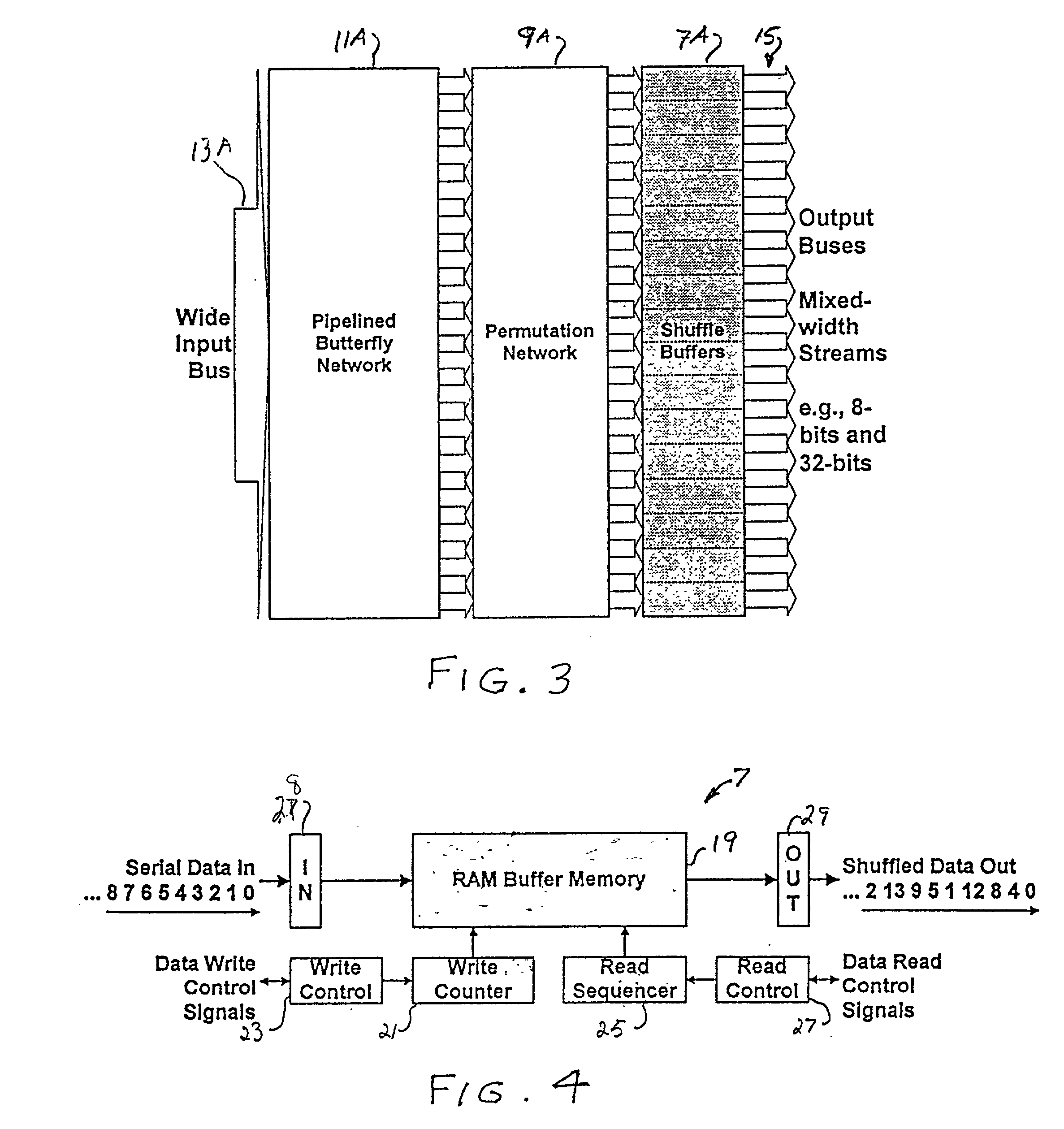

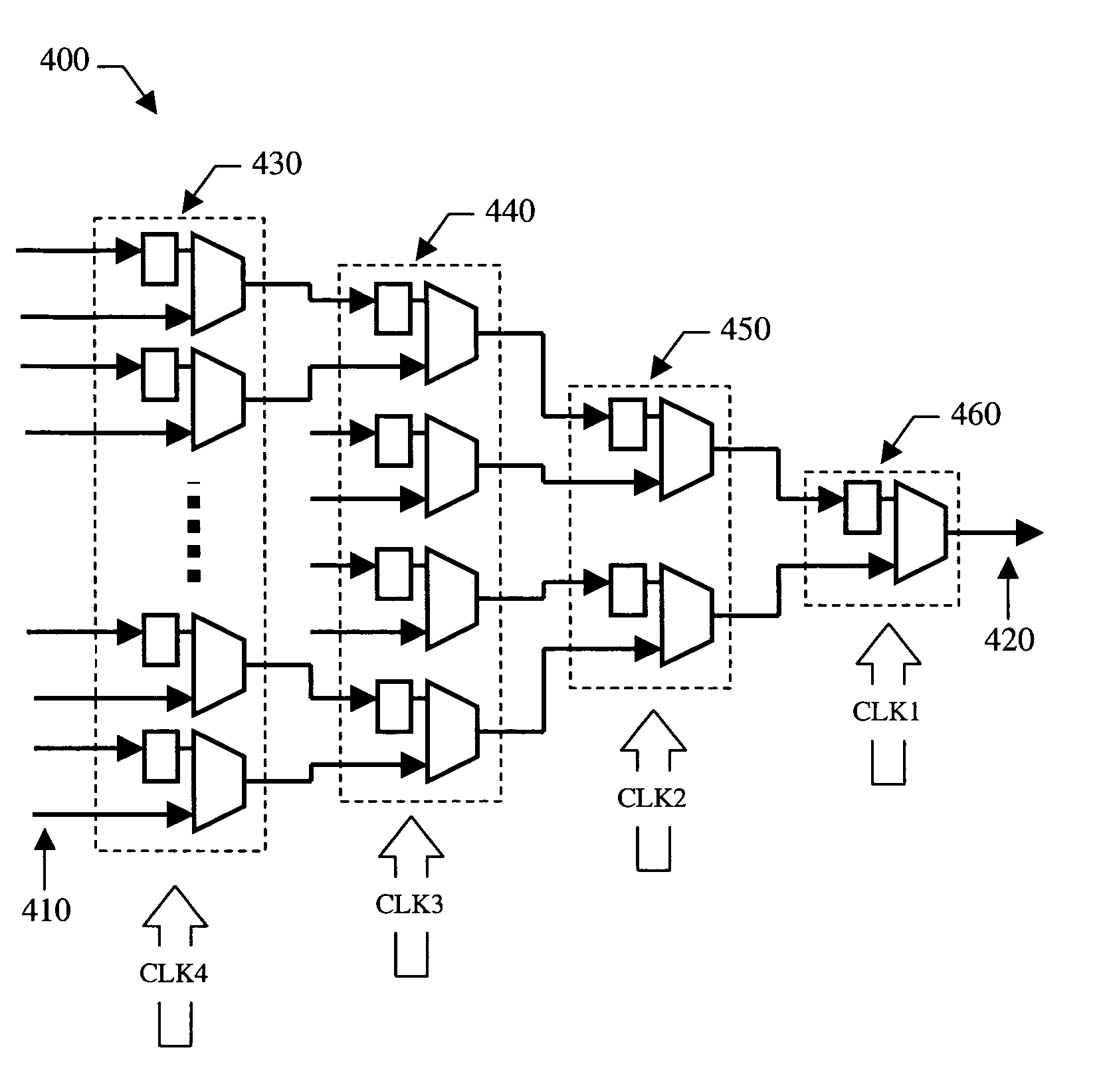

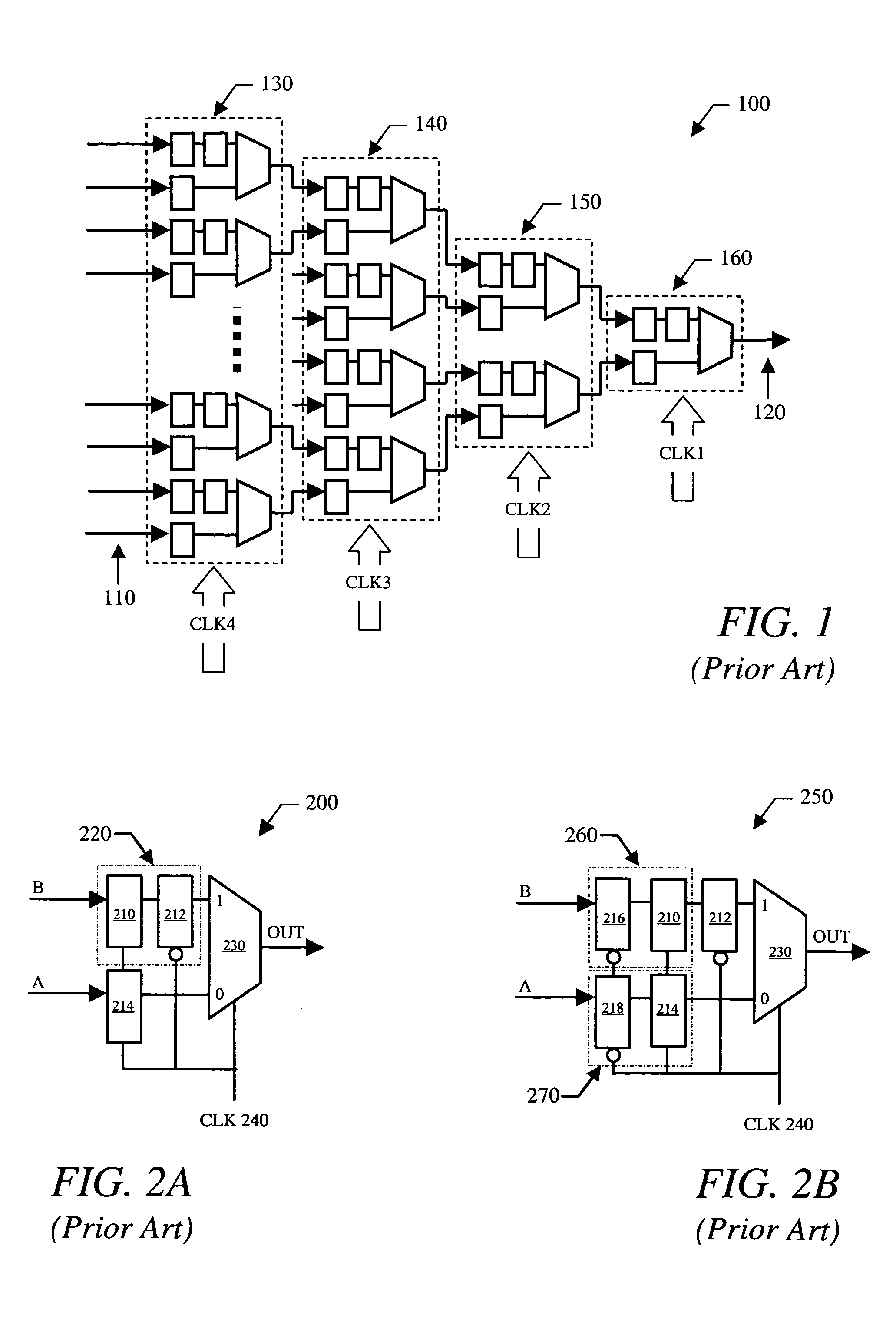

Multi-stream merge network for data width conversion and multiplexing

InactiveUS20030002474A1Less complexParallel/series conversionTime-division multiplexMultiplexingData stream

The present invention relates to a merging network for multiple data streams comprising a pipelined butterfly network. The pipelined butterfly network comprises an input network for receiving a plurality of data streams of mutually constant widths, each data stream having logically related data bits carried on contiguous signal lines, a butterfly network containing suitably interconnected register and multiplexer means for rearranging the received data streams into a time-multiplexed constant-width output data stream, the output data stream having a width equal to or greater than the sum of the widths of the input data streams, and an output network for providing the output data stream interleaved to an output bus.

Owner:PMC-SIERRA

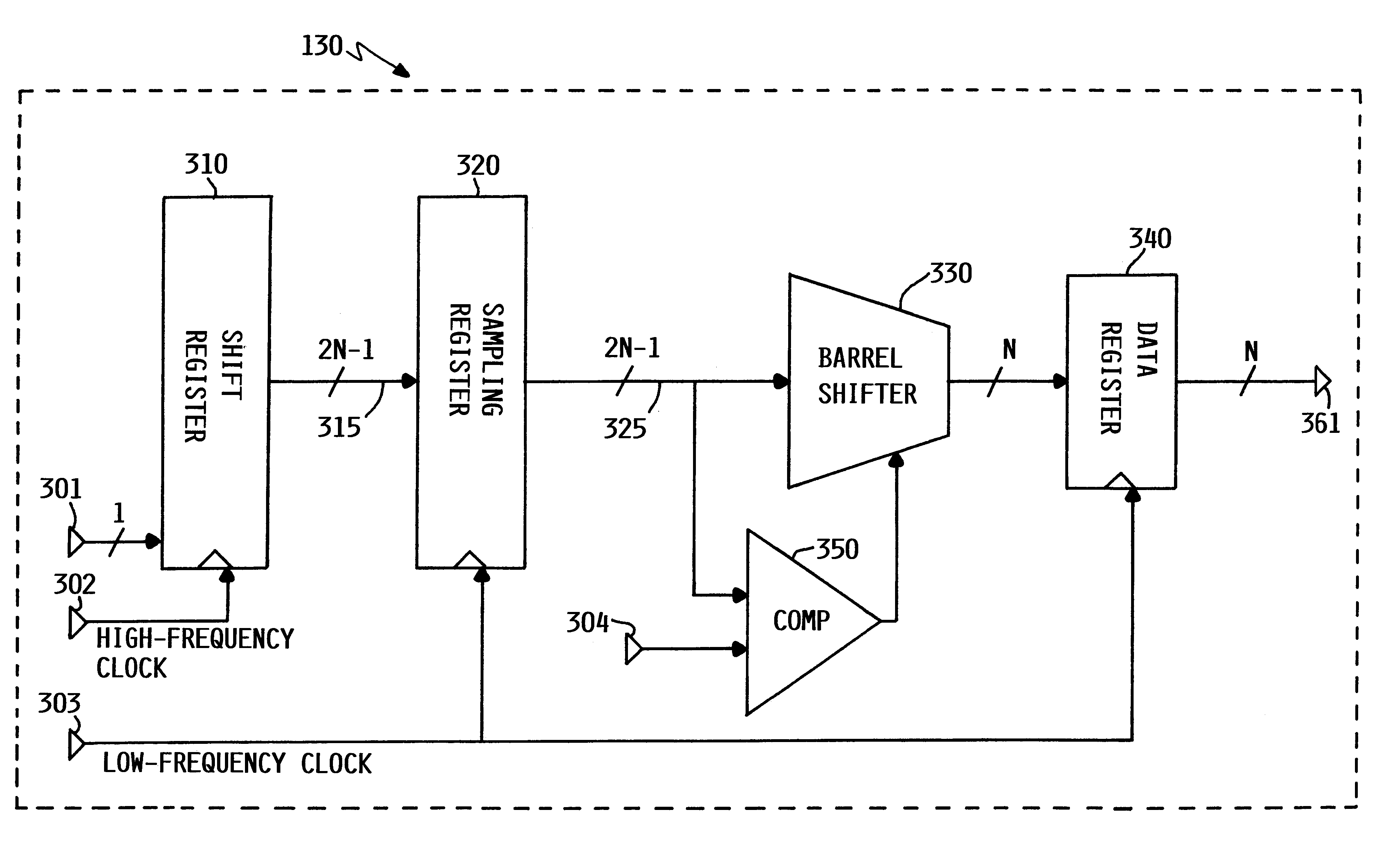

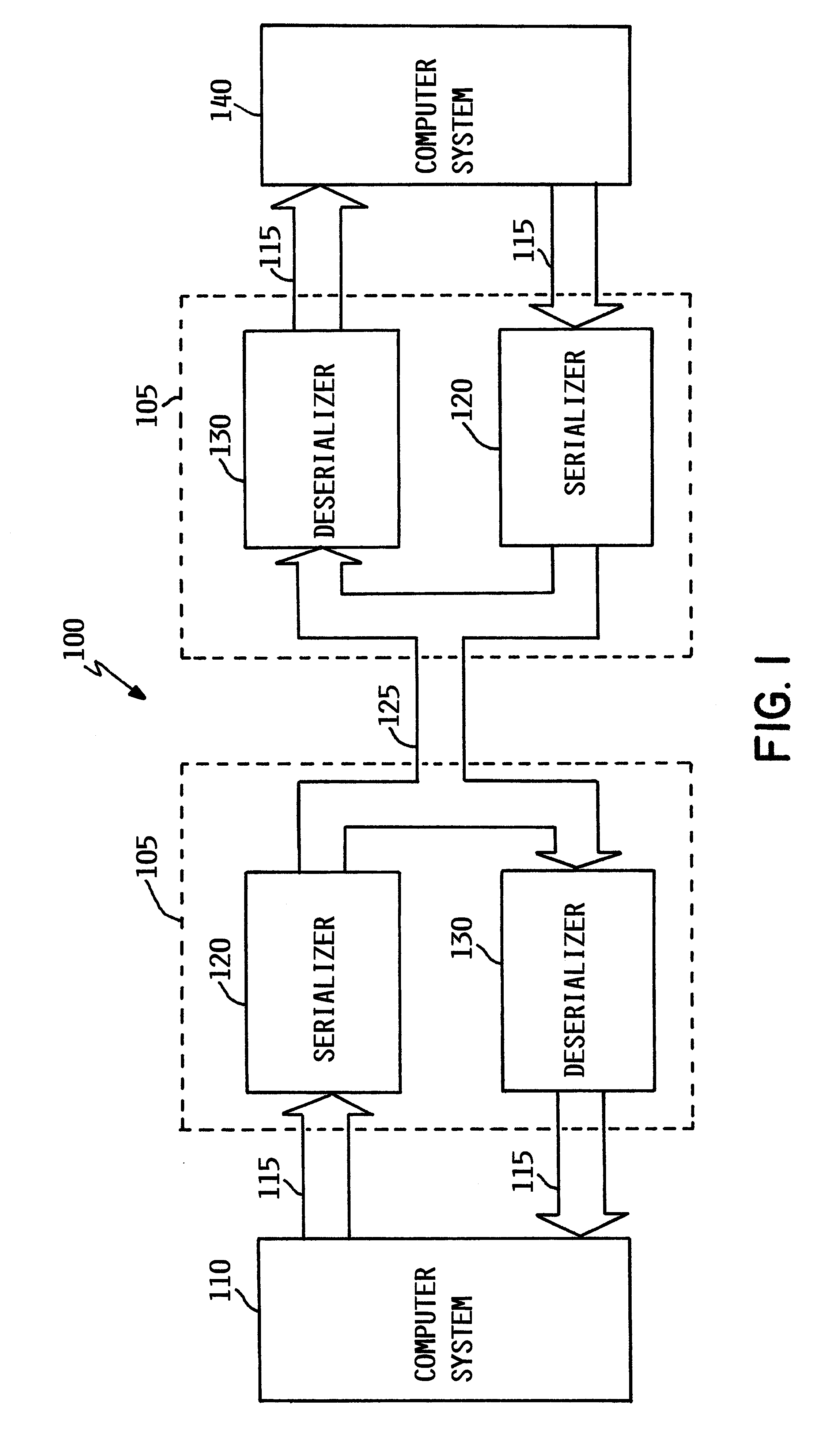

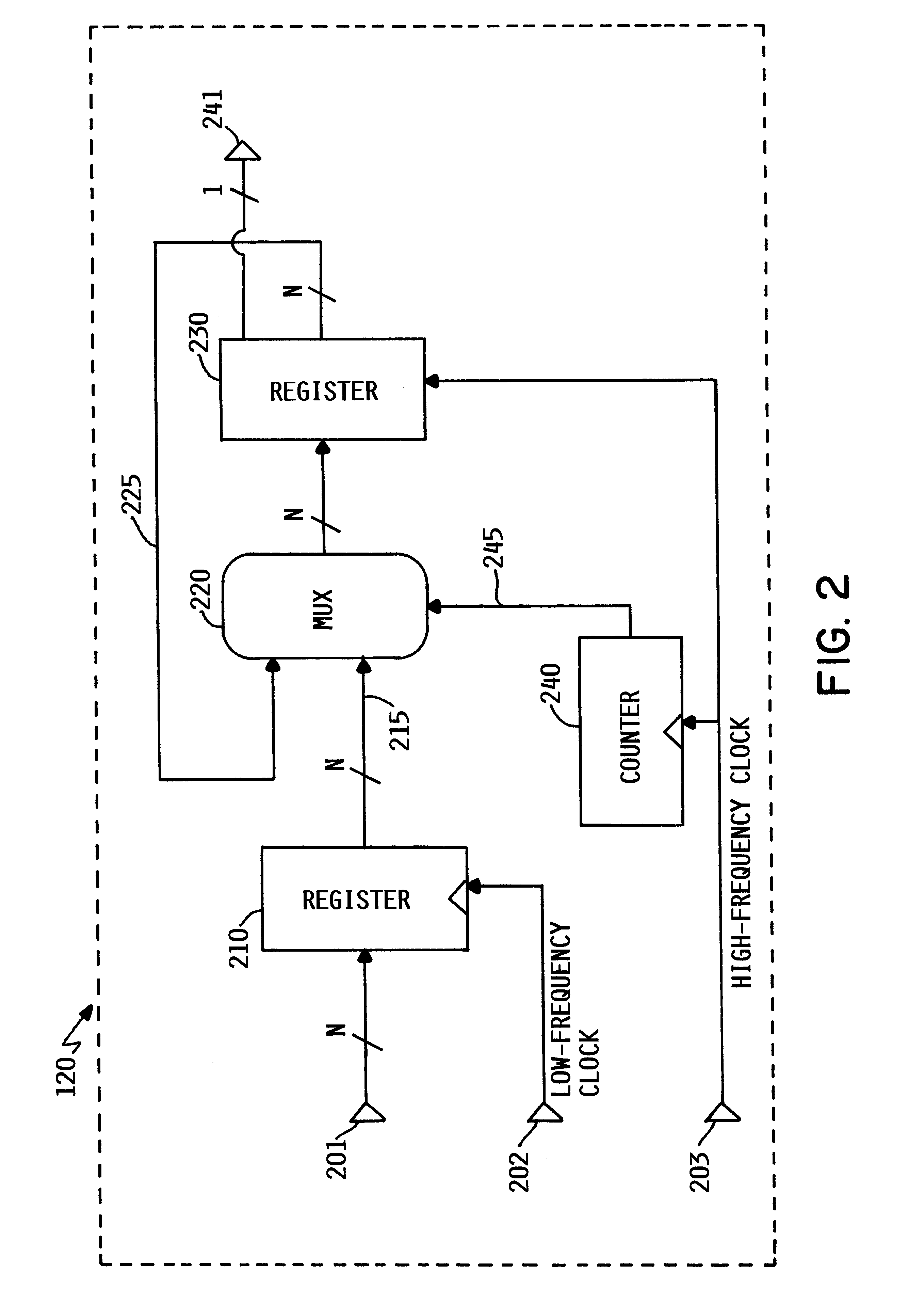

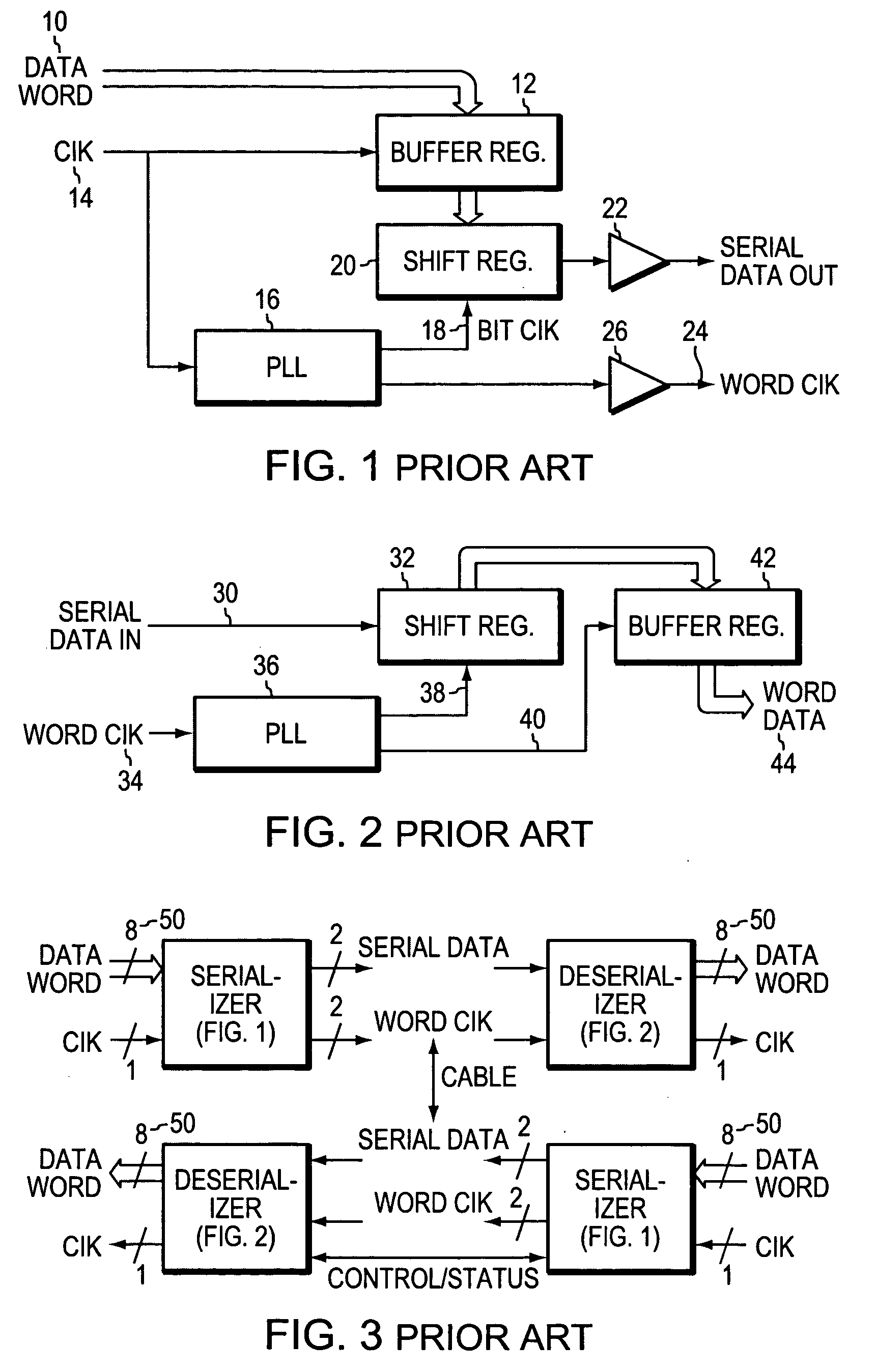

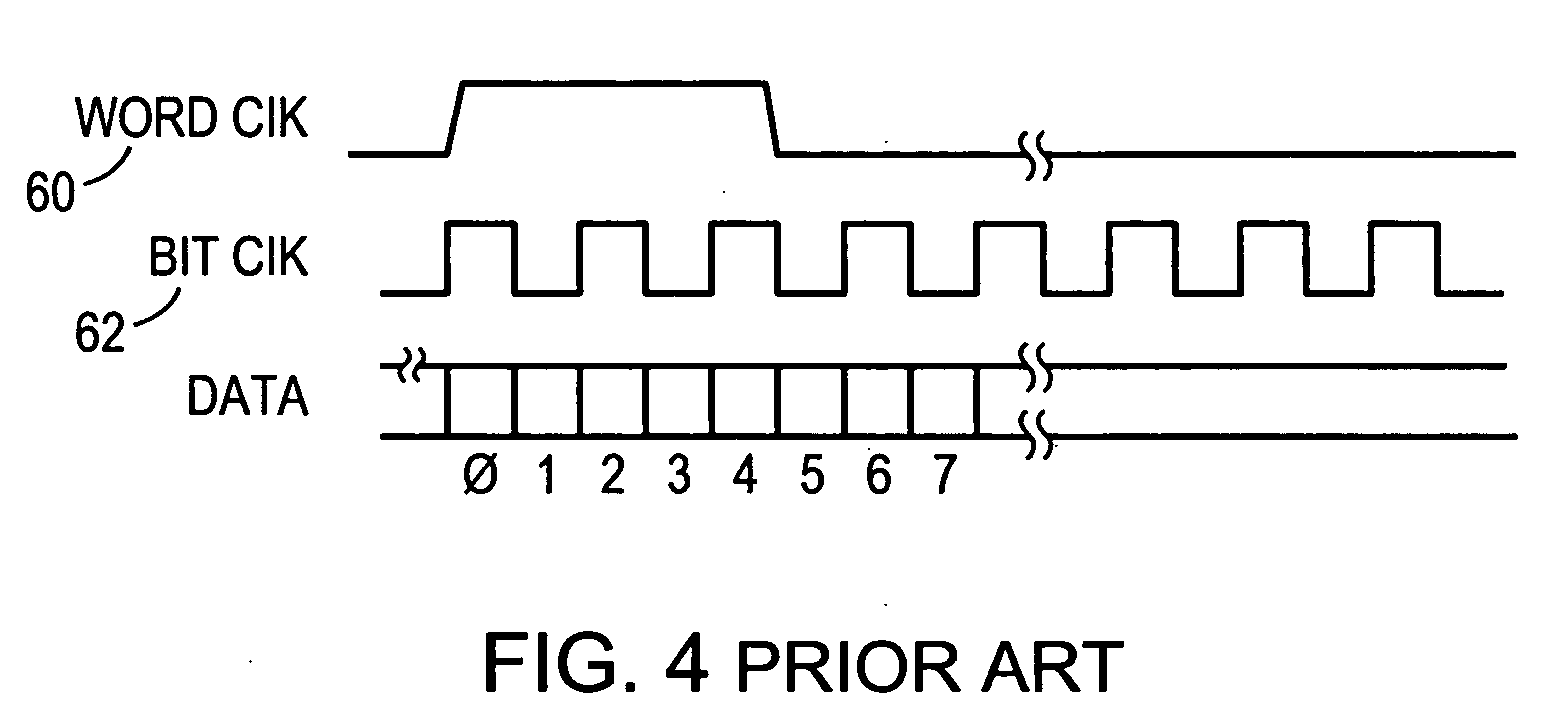

Apparatus and method for optimized self-synchronizing serializer/deserializer/framer

InactiveUS6459393B1Negatively impact design timeNegatively integrated circuit clock loadingParallel/series conversionViruses/bacteriophagesSerial transferTelecommunications link

An apparatus and method for improving the communication capabilities of computer systems is disclosed. The most preferred embodiments of the present invention use a series of data buffers and data registers to process an incoming high speed data signal. By using the buffers and registers, the incoming signal can be reformatted and manipulated at a much lower frequency than the original transmission frequency. The deserializer of the present invention also samples a greater portion of the incoming data signal than usual to further increase reliability. These various features of the invention provide for a more stable and reliable communication link and will also provide a less expensive solution for serialization / deserialization. The present invention includes a serializer that receives parallel data input from a computer and serializes the data for transmission over a high-speed serial communication link. On the receiving end, the present invention provides a deserializer that can quickly and efficiently transform the serial data back into parallel form for use within the computer system on the receiving end. By utilizing two related clock signals, one clock signal being an integer multiple of the other, a self-synchronizing serializer / deserializer can be created. In addition, by increasing the size of the data sample on the receiving end, the comparisons necessary to retrieve a parallel signal from a serial transmission can occur at a much lower frequency than the frequency of the serial transmission. In the most preferred embodiment, the invention is provided as a integrated solution manufactured on a Peripheral Component Interconnect (PCI) card, thereby allowing the present invention to be easy installed into existing computer systems.

Owner:MEDIATEK INC

Universal serializer/deserializer

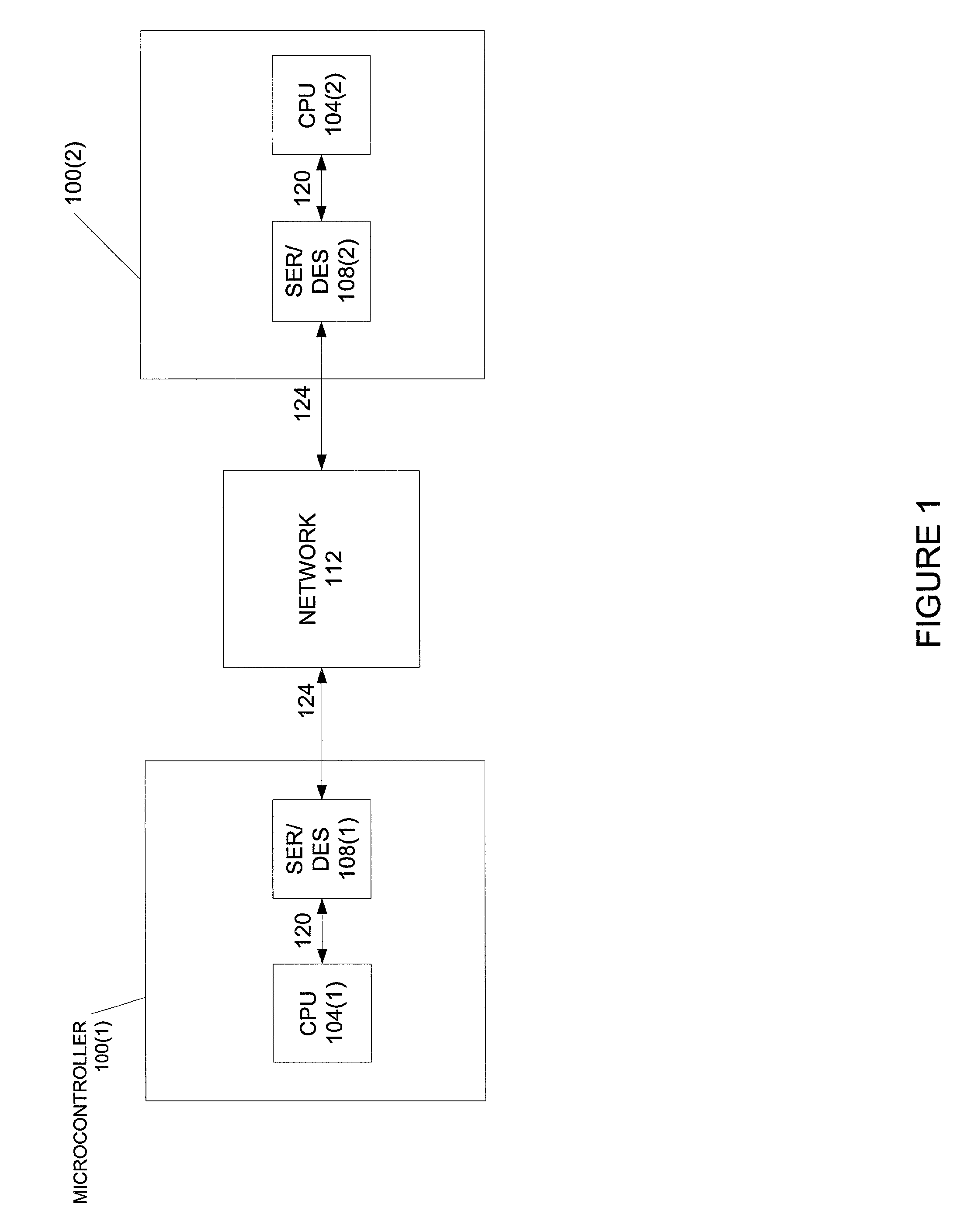

InactiveUS7010612B1Parallel/series conversionTime-division multiplexNetwork Communication ProtocolsComputer module

A universal serializer / deserializer (“ser / des”) is disclosed that provides hardware implemented modules of those functions determined to be most applicable to a communications protocol. Functionality that is determined to be more unique for a given protocol is implemented in software. Accordingly, a universal ser / des is provided that is able to be used for a plurality of different protocols now known, and configured to communicate with protocols that may be developed in the future.

Owner:MAYFIELD XI +8

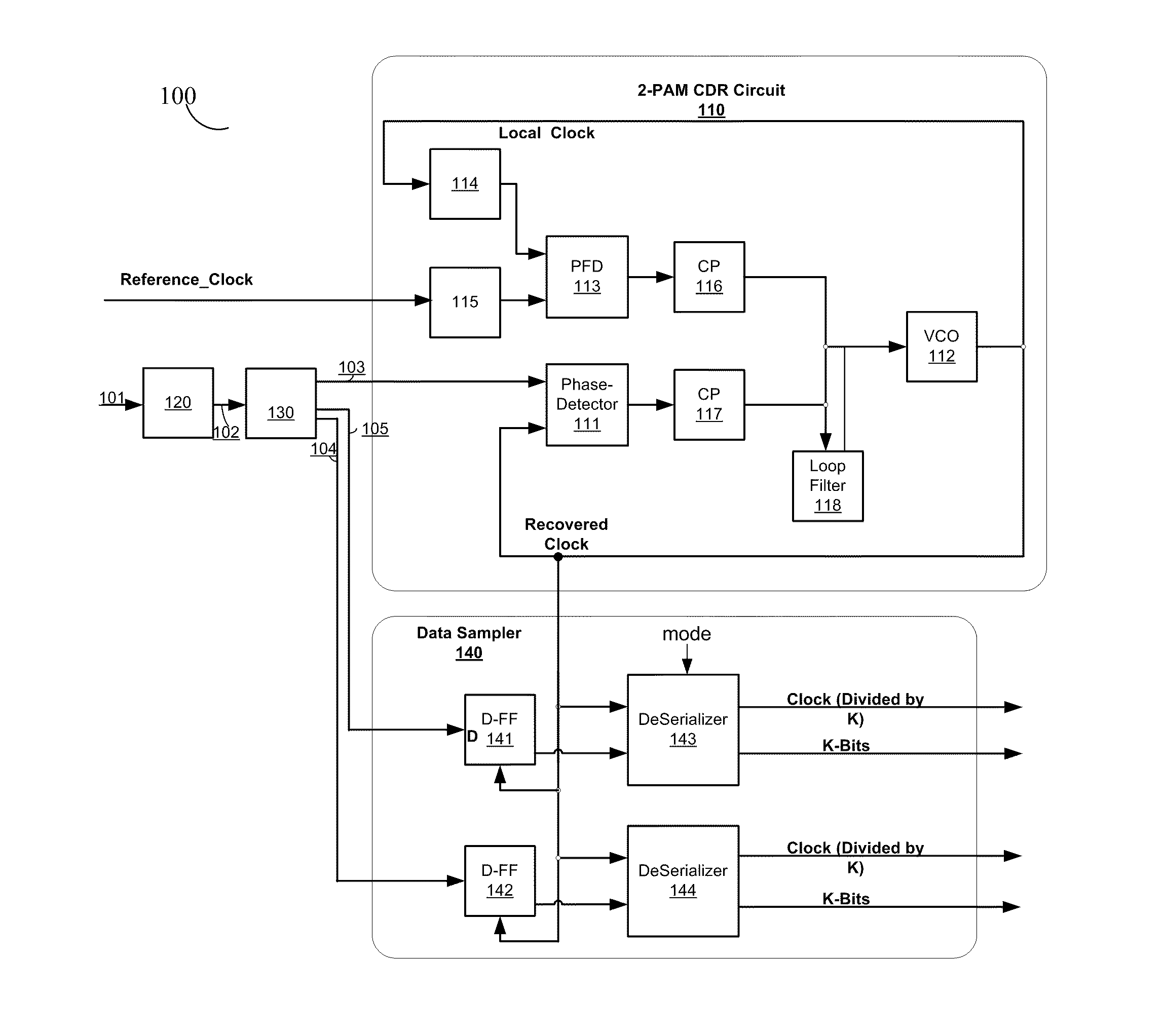

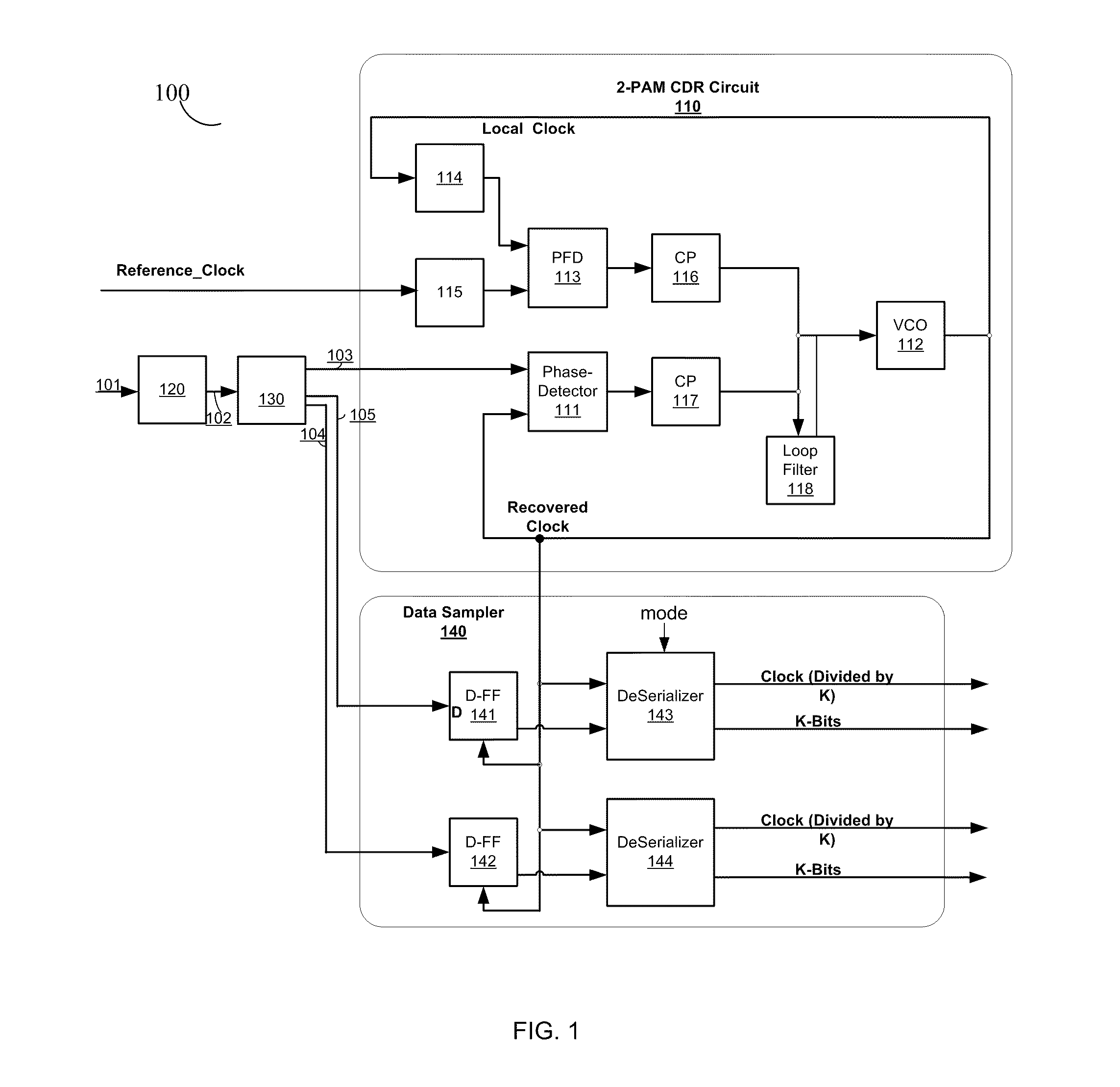

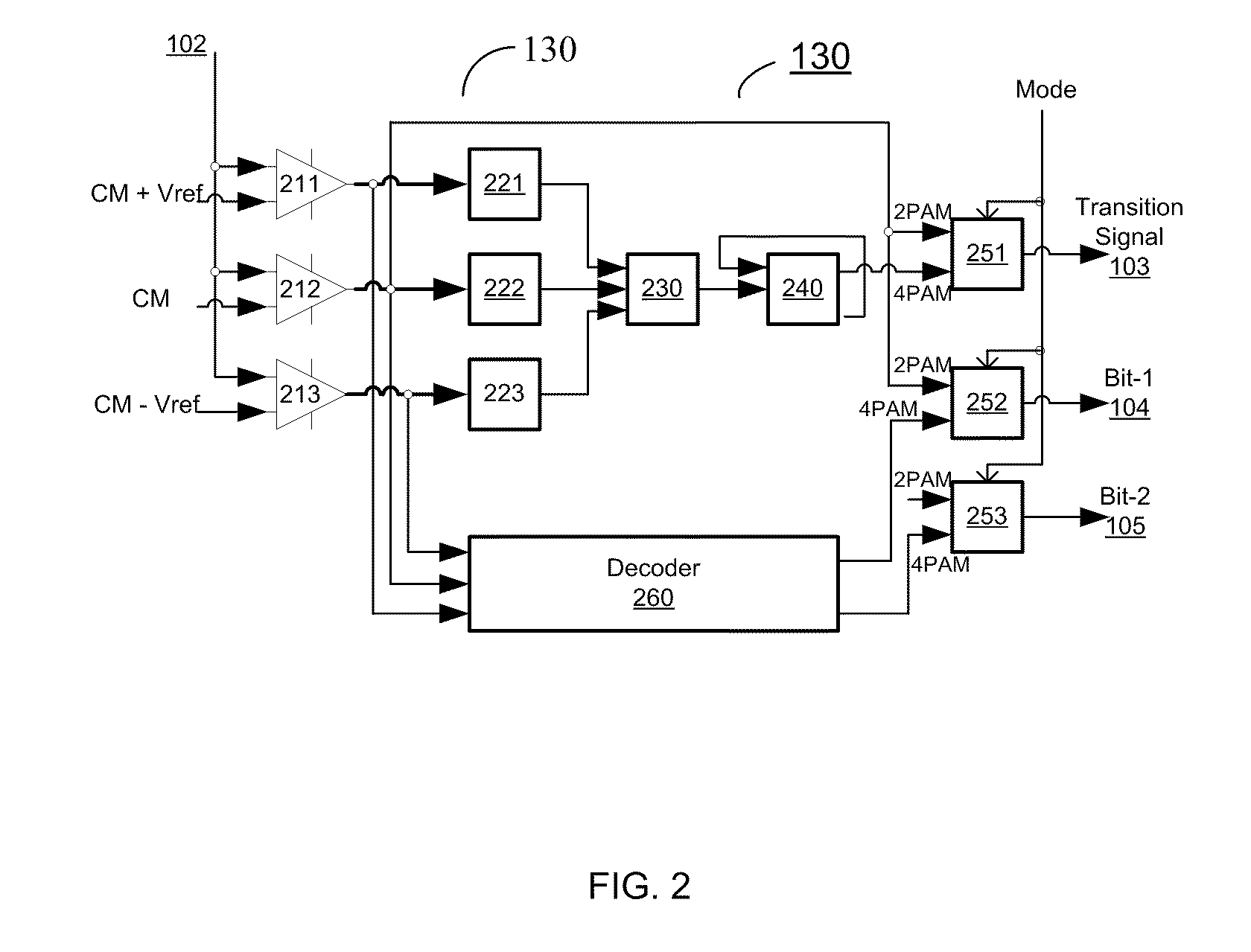

Apparatus and method thereof for clock and data recovery of n-PAM encoded signals using a conventional 2-PAM CDR circuit

An interface circuit for enabling clock and data recovery (CDR) of N-level pulse amplitude modulation (N-PAM) modulated data streams using a 2-PAM CDR circuit. The circuit comprises a number of N−1 comparators for comparing an input data stream to N−1 configurable thresholds, the input data stream is N-PAM modulated and the N−1 configurable thresholds are N−1 different voltage levels; a number of N−1 of edge detectors respectively connected to the N−1 comparators for detecting transitions from one logic value to another logic value, N is a discrete number greater than two; and a determination unit for determining if the detected transitions is any one of a major transition and a minor transition and asserting a transition signal if only a major transition or a minor transition has occurred, the transition signal is fed into a 2-PAM CDR circuit and utilized for recovering a clock signal of the input data stream.

Owner:CADENCE DESIGN SYST INC

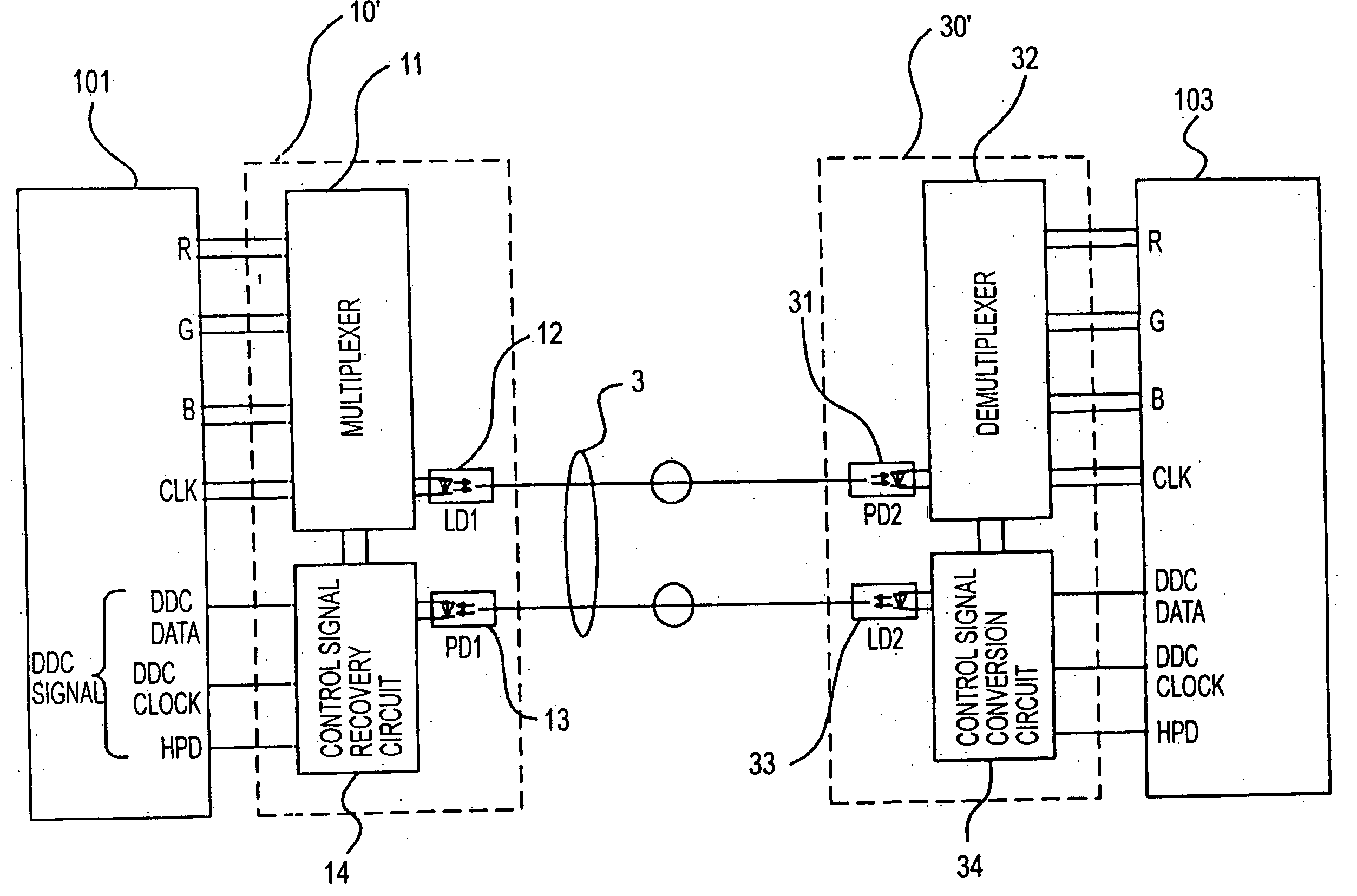

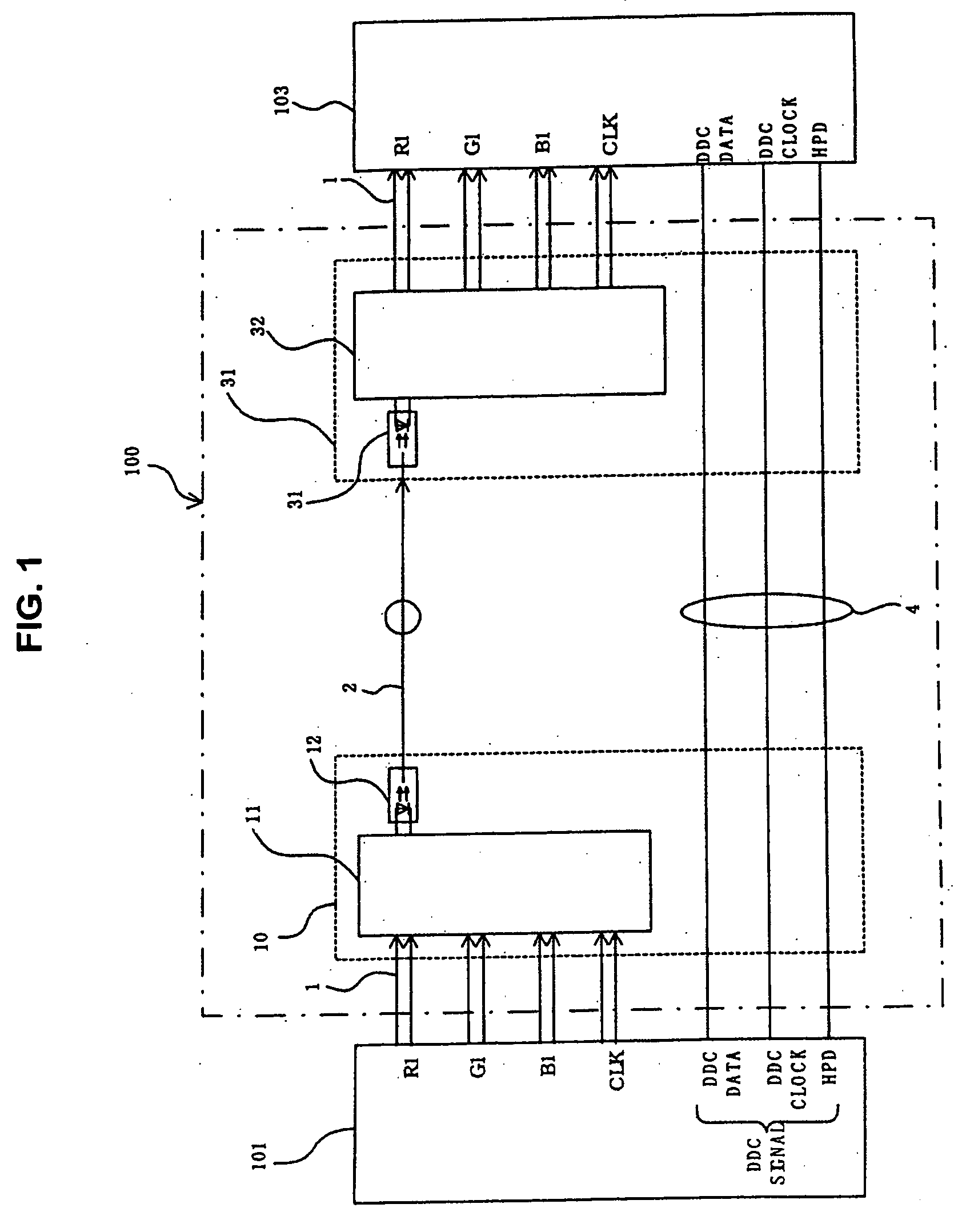

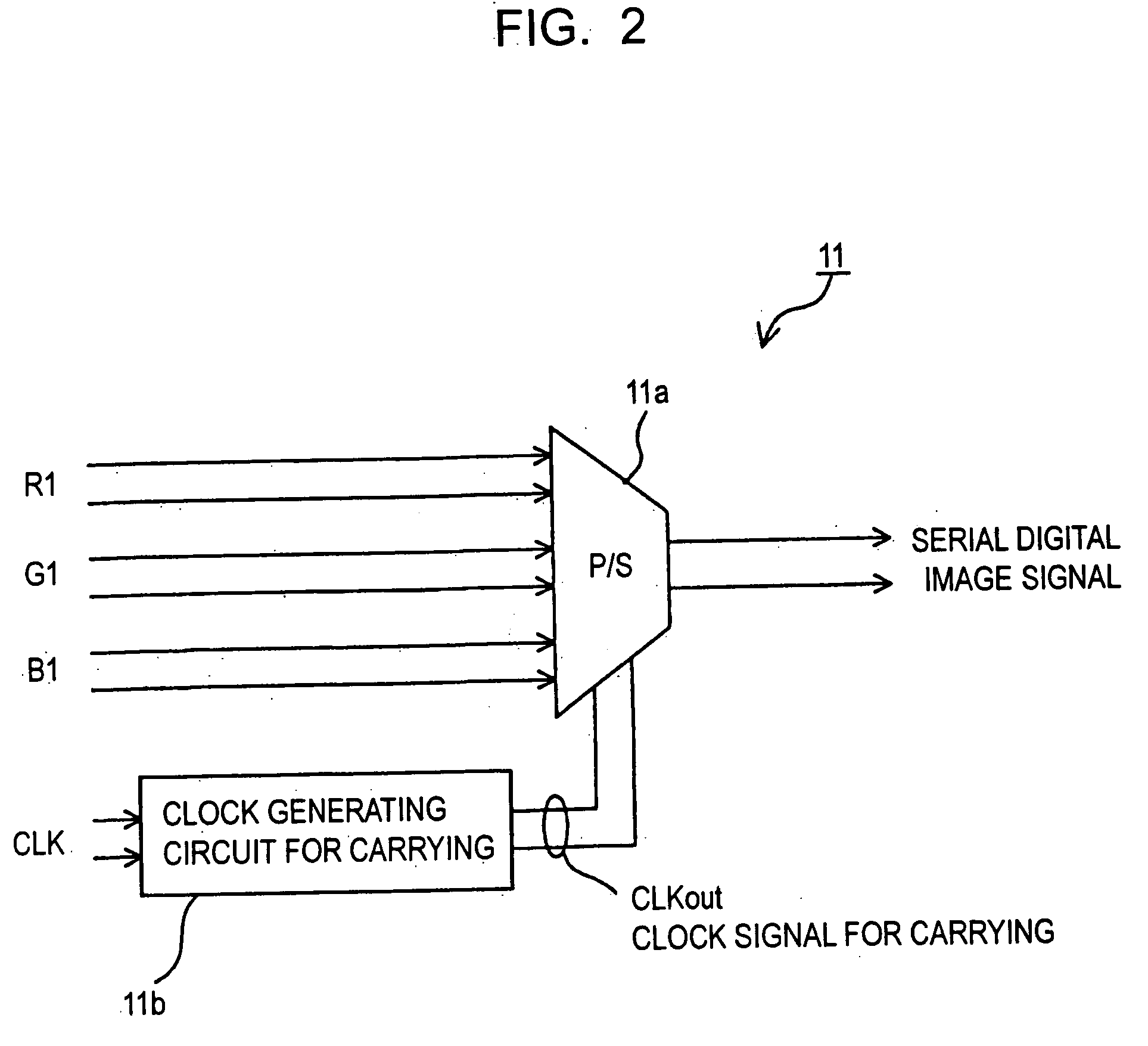

Method for transmitting digital image signal, digital image transmitting device, digital image sending device and digital image receiver

InactiveUS20050063707A1Quality improvementIncrease costTelevision system detailsTelevision system scanning detailsMultiplexerSignal on

A multiplexer of a transmission section generates a clock signal by multiplying a reference clock signal of a digital image signal by a predetermined number ‘K’. A parallel digital image signal is converted into a serial digital signal on the basis of the clock signal, and the serial digital signal is converted into an optical signal in an optical transmission section for transmitting. A demultiplexer extracts a reception clock signal from a serial digital reception signal which is converted into an electric signal in an optical reception section of a reception section, the serial digital reception signal is converted into a parallel signal and a signal corresponding to the parallel digital image signal on the basis of the reception clock signal, and a clock signal corresponding to the reference clock signal is recovered by multiplying the reception clock signal by ‘1 / K’.

Owner:SEIKO EPSON CORP

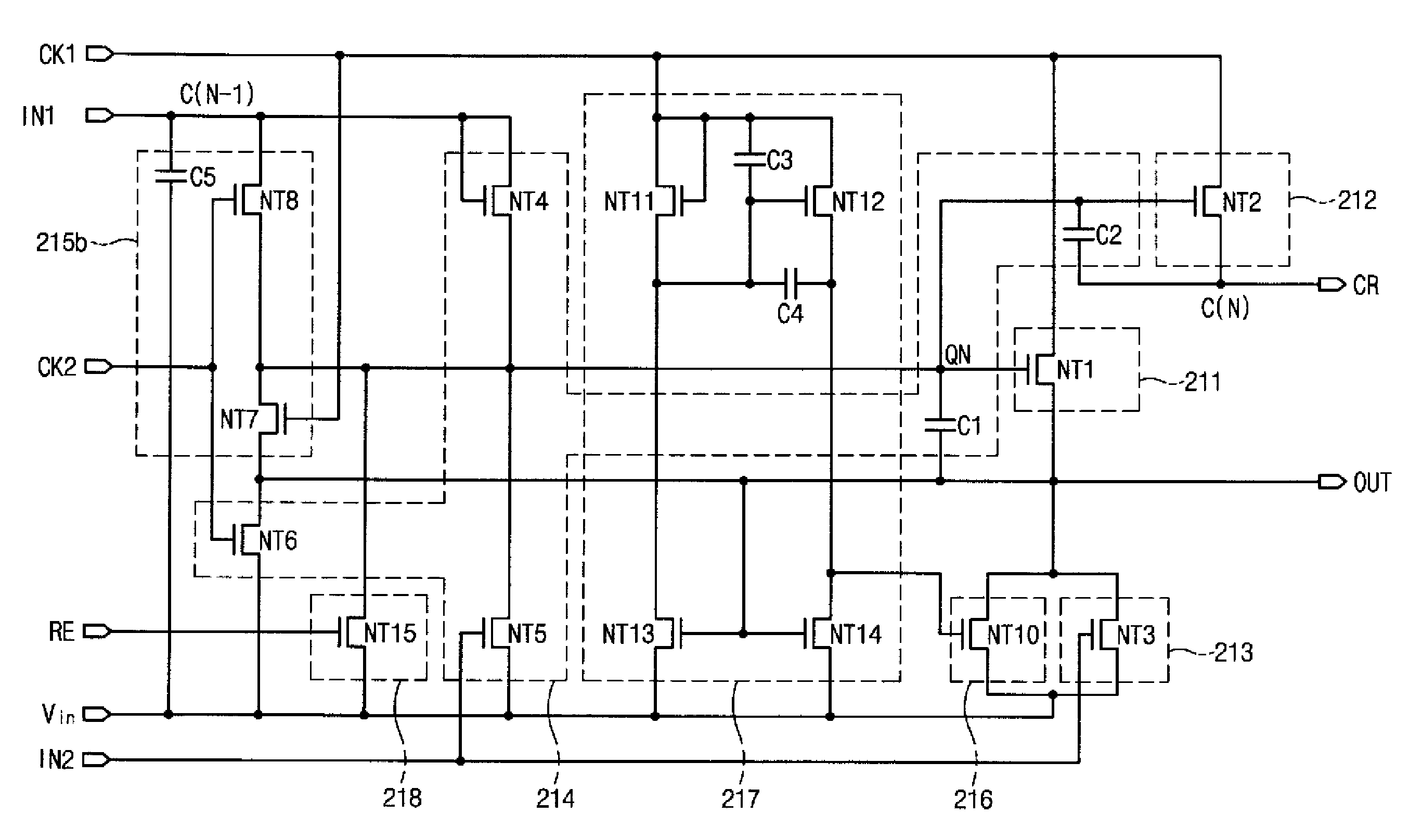

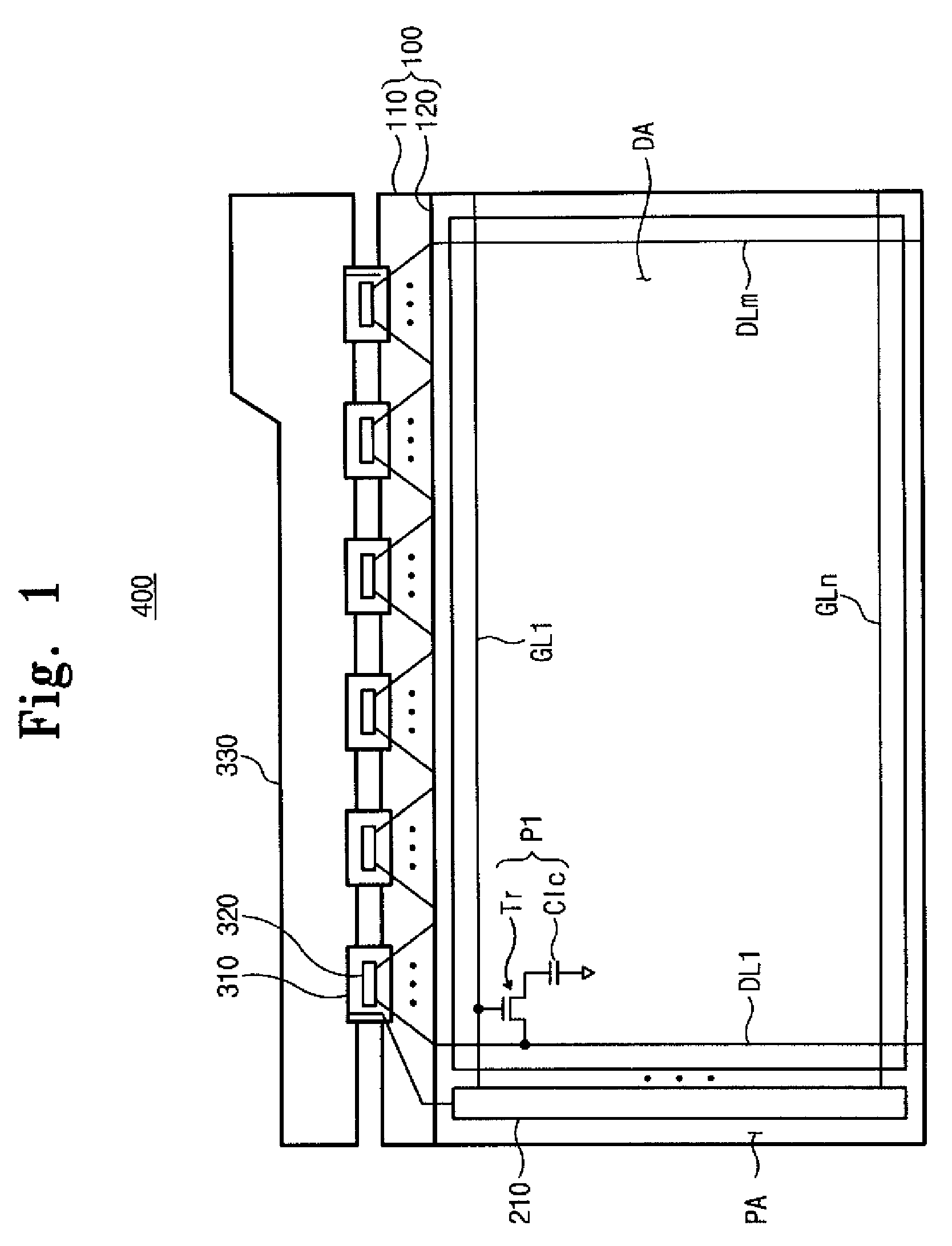

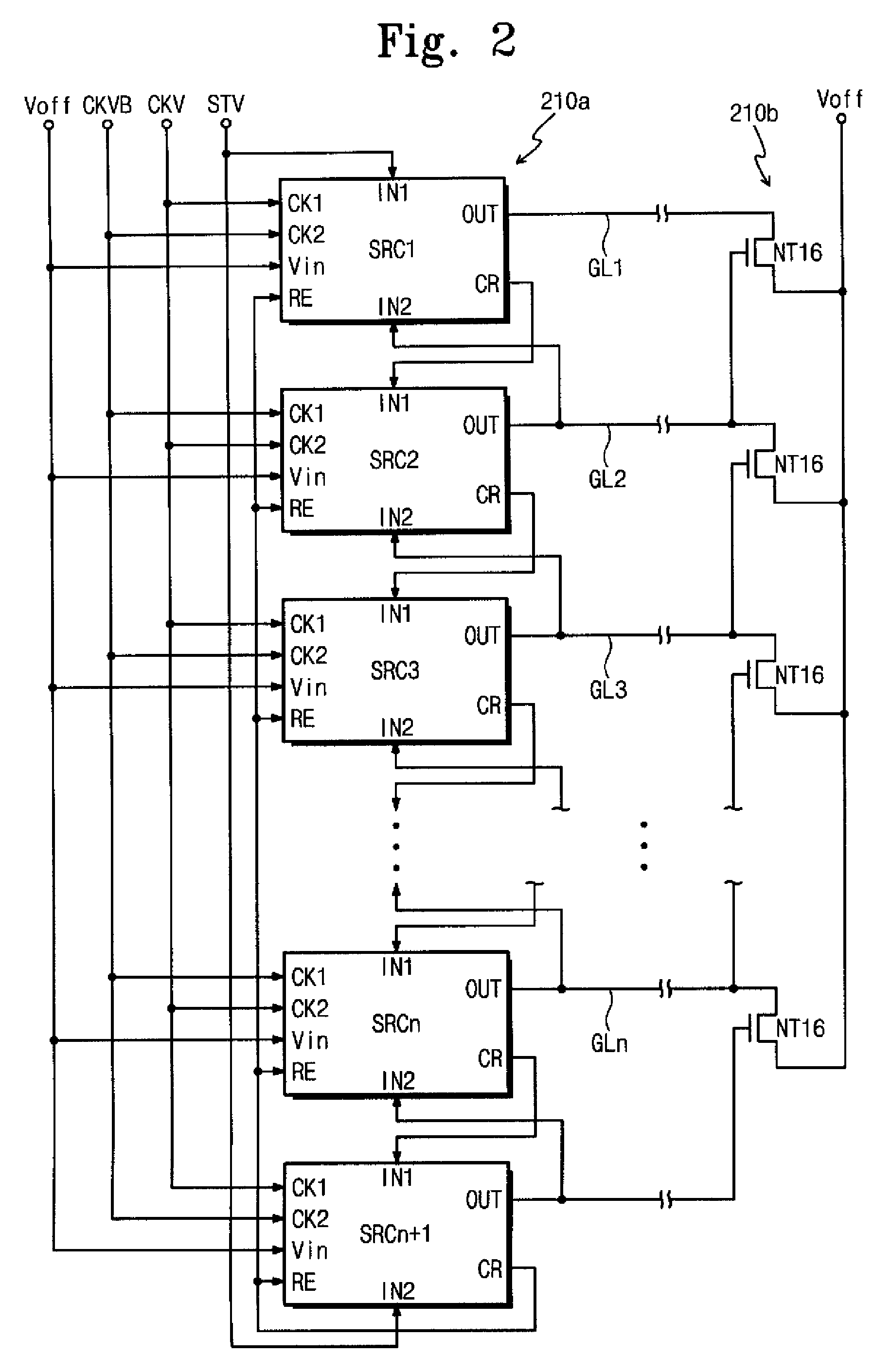

Gate driving circuit and display apparatus having the same

InactiveUS20080048712A1Improve reliabilityFew malfunctionReliability increasing modificationsParallel/series conversionEngineeringDriving circuit

In a gate driving circuit and a display apparatus having the same, a ripple preventing part is connected to a pull-up part and a control terminal (Q-node) to reset the Q-node. The ripple preventing part includes a first ripple preventing device that resets the Q-node during a high period of the first clock within a (n−1)H period, and a second ripple preventing device that resets the Q-node during a high period of a second clock within the (n−1)H period. A back-flow preventing device is connected between a previous carry node and the second ripple preventing device to prevent an electric charge of the Q-node from flowing back to the previous carry node.

Owner:SAMSUNG DISPLAY CO LTD

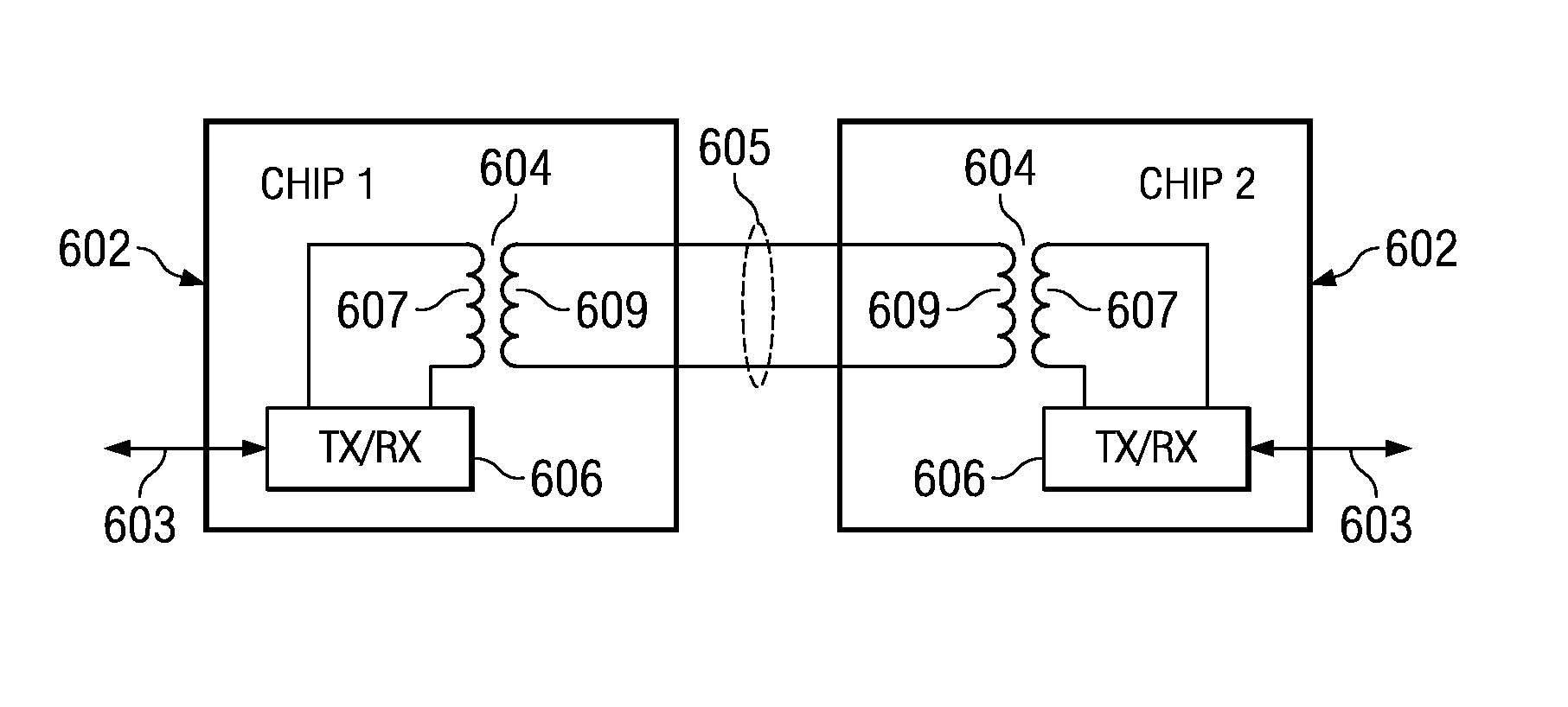

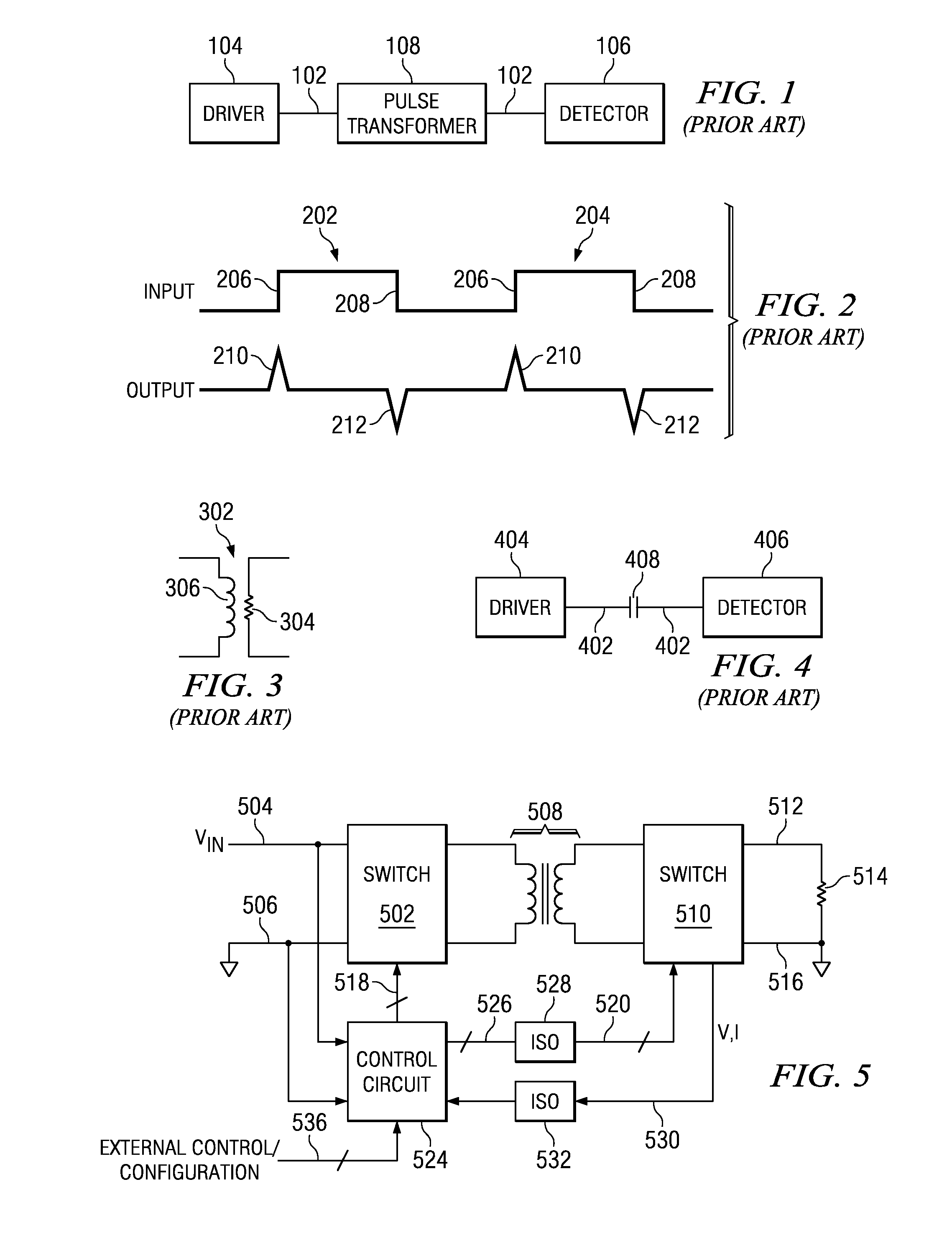

Bidirectional multiplexed RF isolator

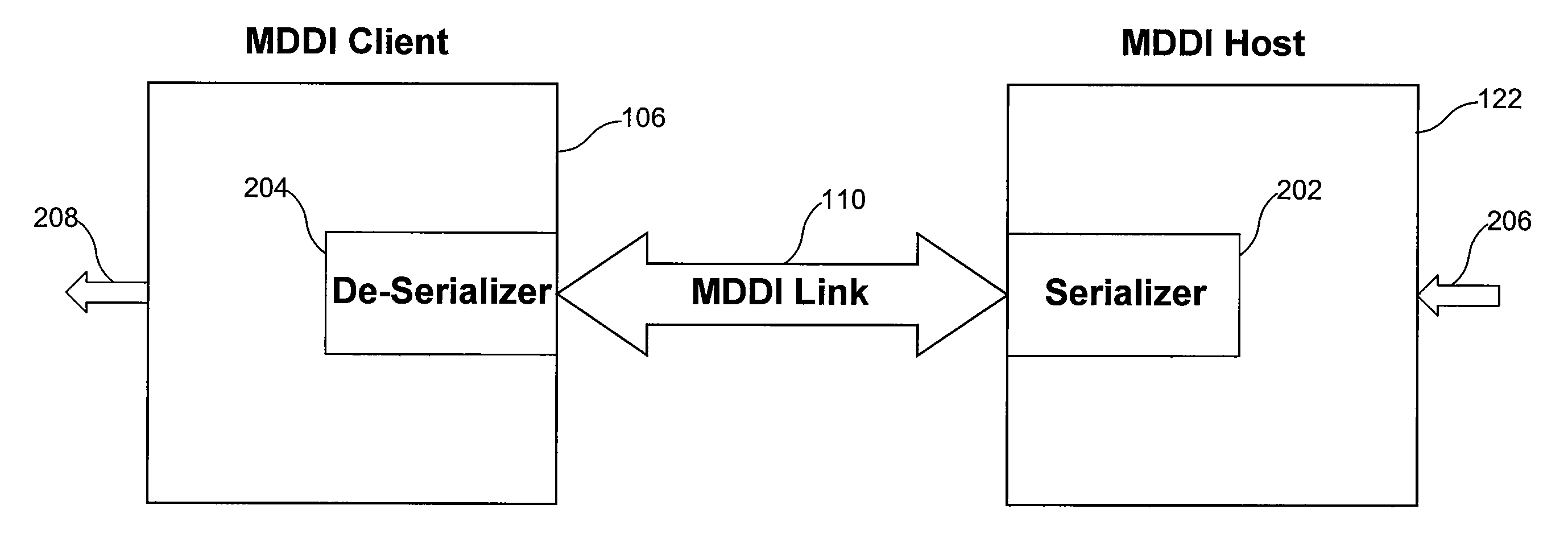

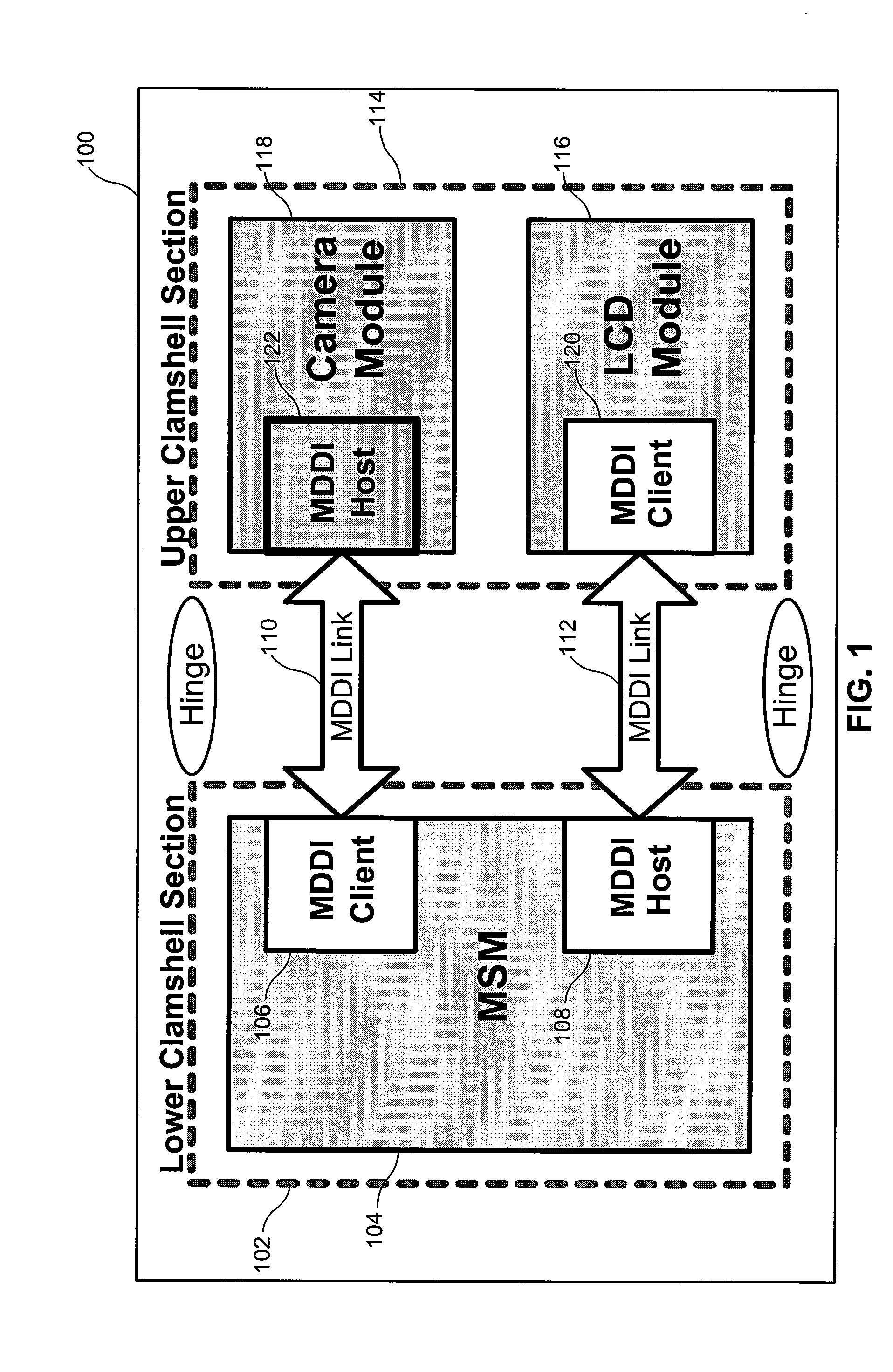

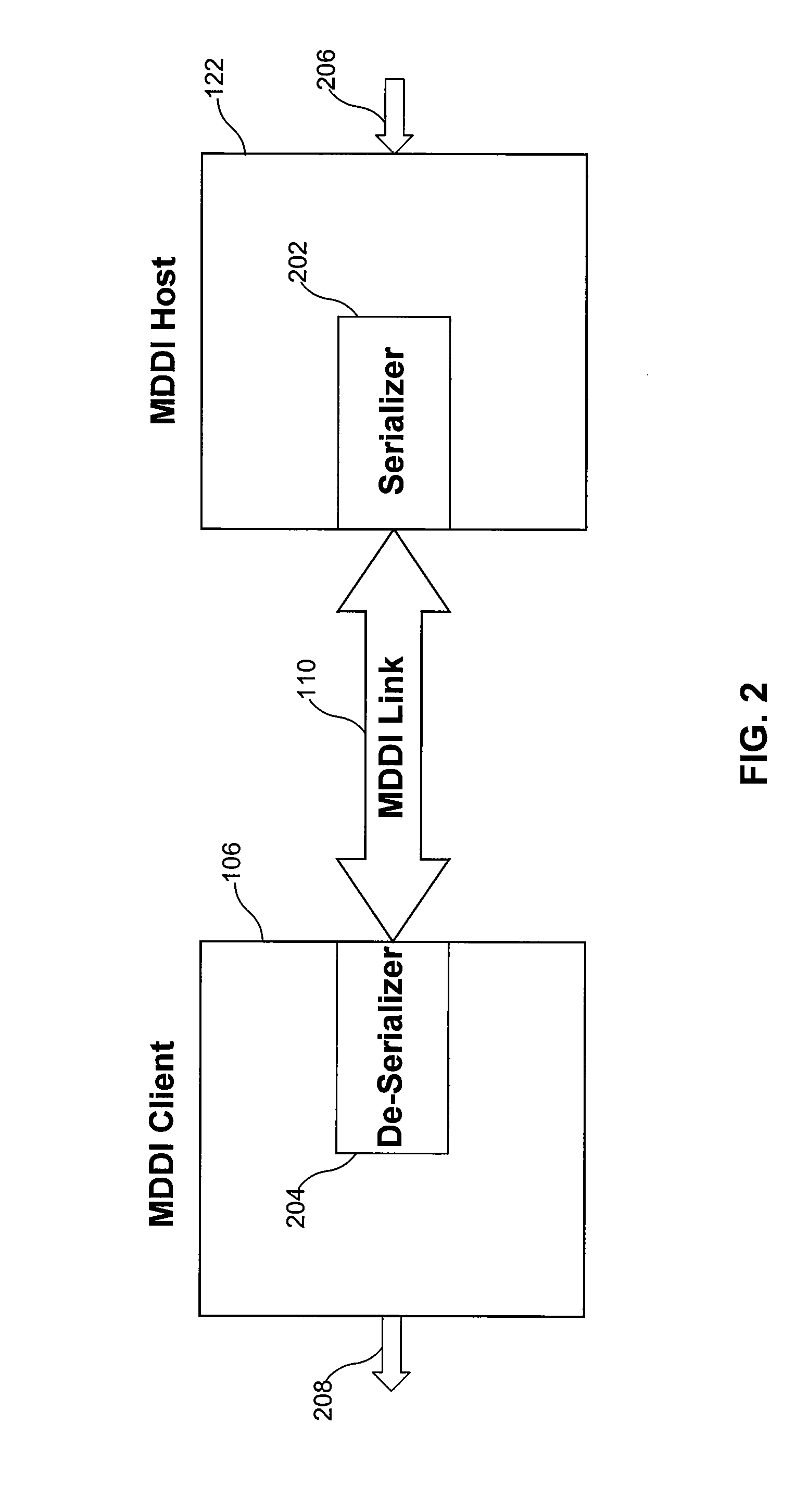

ActiveUS20080267301A1Parallel/series conversionPower distribution line transmissionDigital dataSingle chip

An integrated circuit single chip isolator provides bidirectional data transfer for a plurality of communications channels. A first and second dies are located on a first and second sides of a voltage isolation barrier in the chip and have a first and second plurality of digital data input / output pins associated therewith. First circuitry located on the first die on a first side of the voltage isolation barrier and third circuitry located on the second die on a second side of the voltage isolation barrier serializes a plurality of parallel digital data inputs from the associated plurality of digital data input / output pins onto a one link across the voltage isolation barrier and transmits synchronization clock signals associated with the plurality of digital data inputs over a another link across the voltage isolation barrier. Second circuitry located on the second die on a second side of the voltage isolation barrier and fourth circuitry located on the first die on a first side of the voltage isolation barrier de-serializes the first plurality of digital data inputs from the first link onto the second plurality of digital data input / output pins and receives the first synchronization clock signal associated with the plurality of digital data inputs on the second link. Switches associated with each of the plurality of input / output pins between transmit and receive circuitry.

Owner:SKYWORKS SOLUTIONS INC

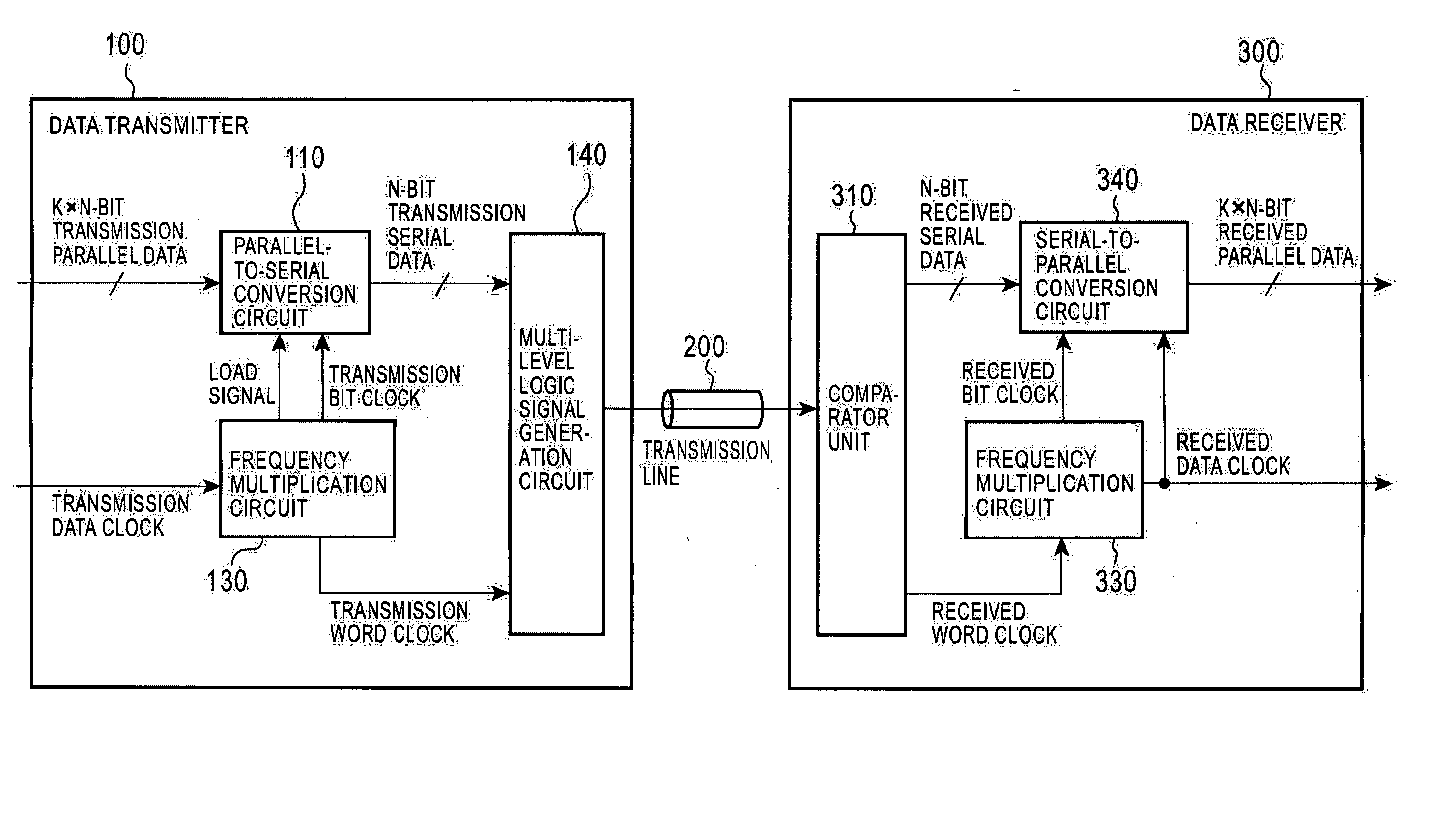

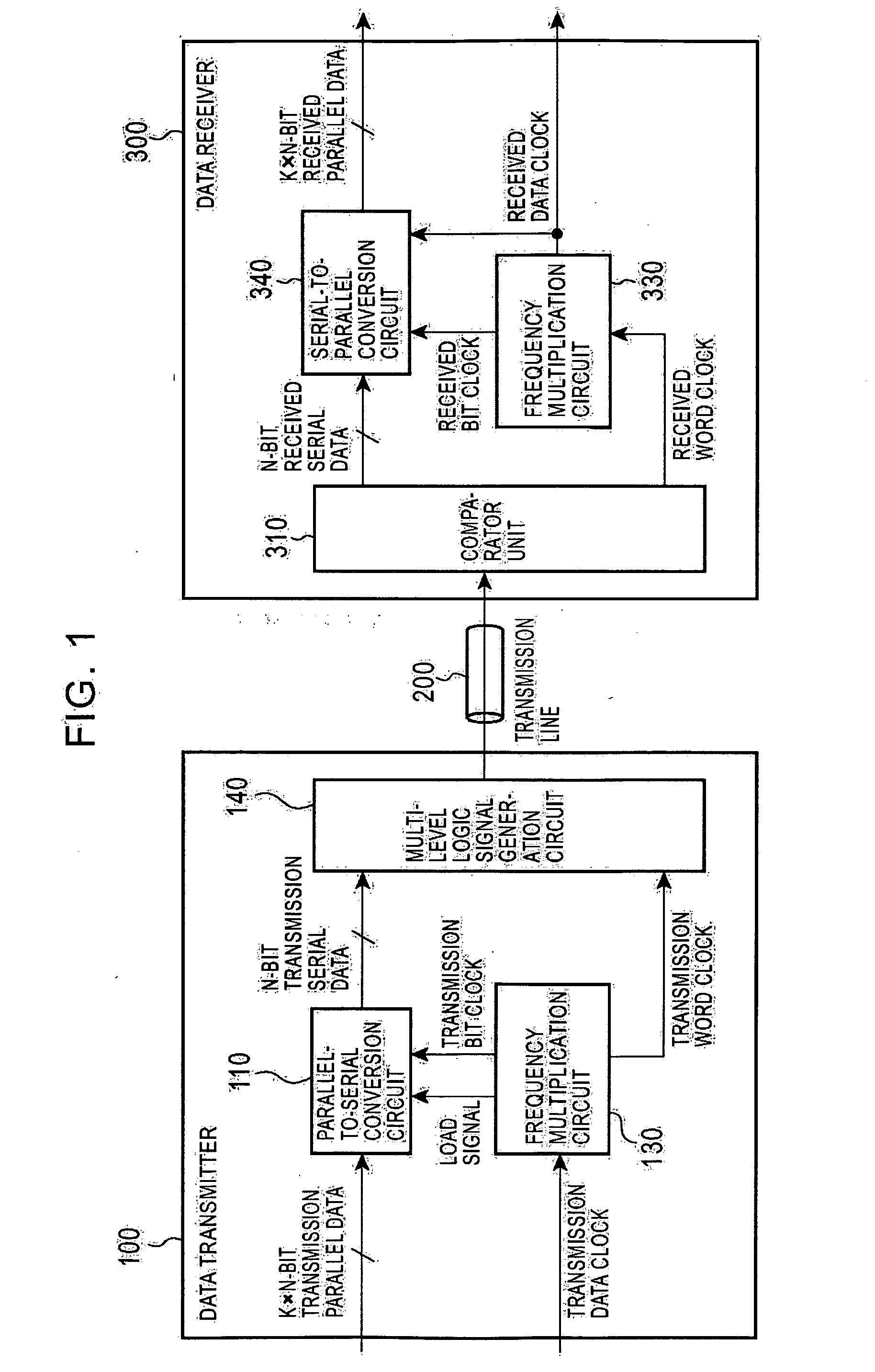

Data transfer system and method, data transmitter, data receiver, data transmission method, and data reception method

ActiveUS20050147178A1Simple structureReduce componentsParallel/series conversionLogic circuits characterised by logic functionTransfer systemWord clock

The present invention provides a data transfer system including a data transmitter and a data receiver. The data transmitter converts a plurality of bits of transmission parallel data into serial data and generates a multi-level logic signal representing a plurality of bits of information in one symbol, the information being obtained by combining the serial data with a word clock as one-bit information. The word clock indicates a word delimiter in the serial data. The data receiver receives the transmitted multi-level logic signal, extracts the serial data and the word clock from the signal, and reproduces the parallel data based on the extracted word clock. In the data transfer system, a multi-bit digital signal can be transmitted as one signal including a word clock. Thus, components and mounting space to be allocated to transfer can be reduced.

Owner:SONY CORP

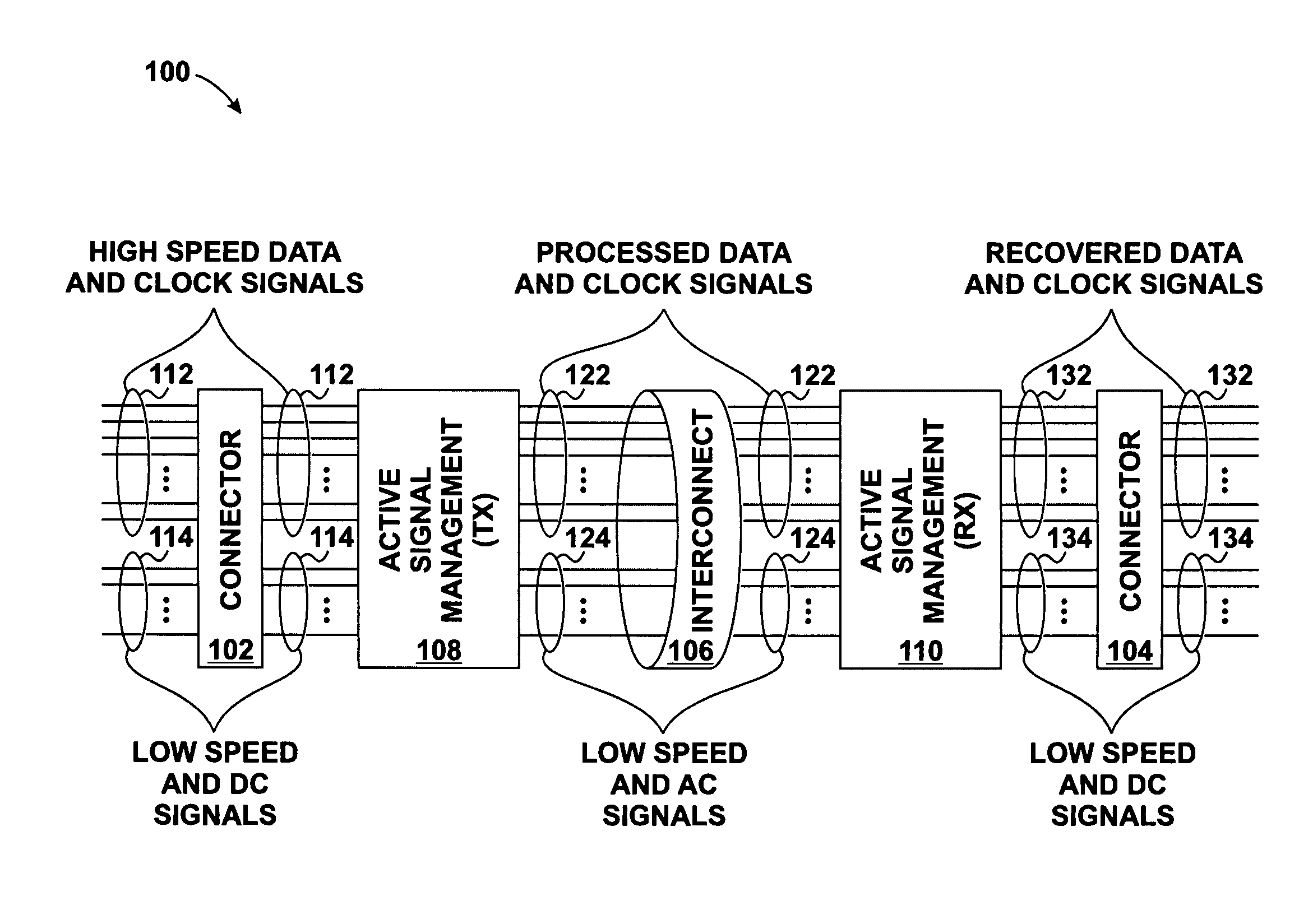

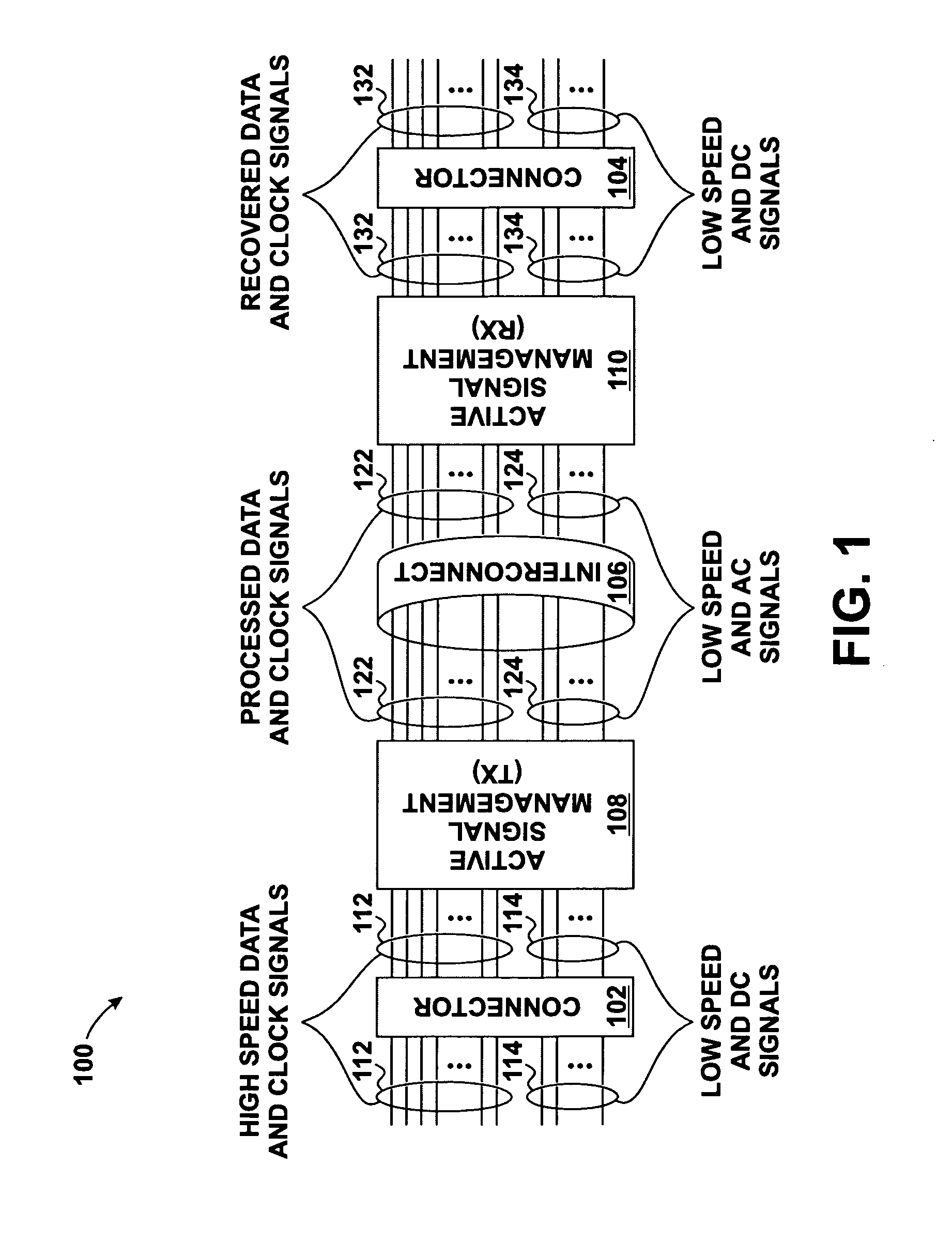

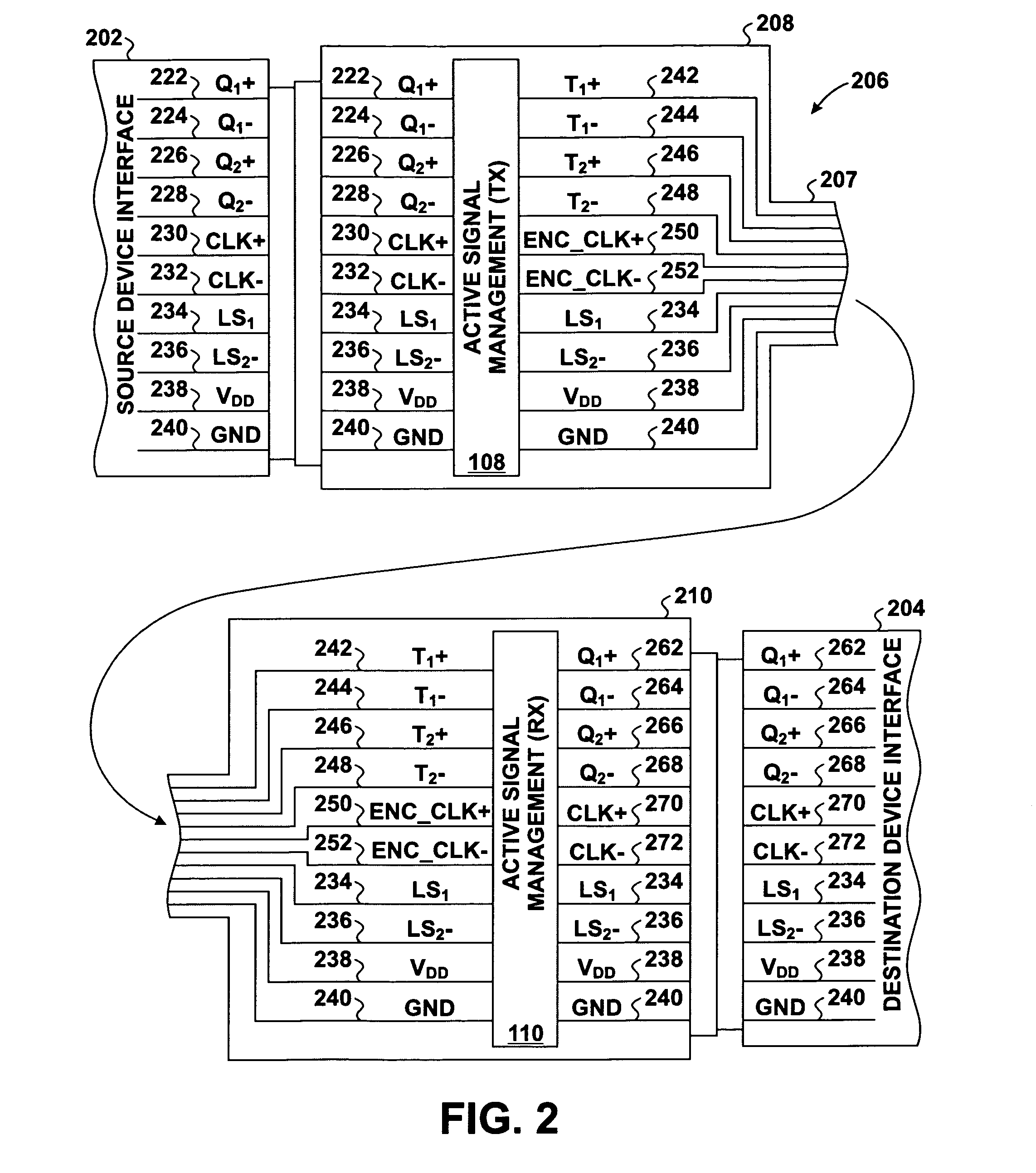

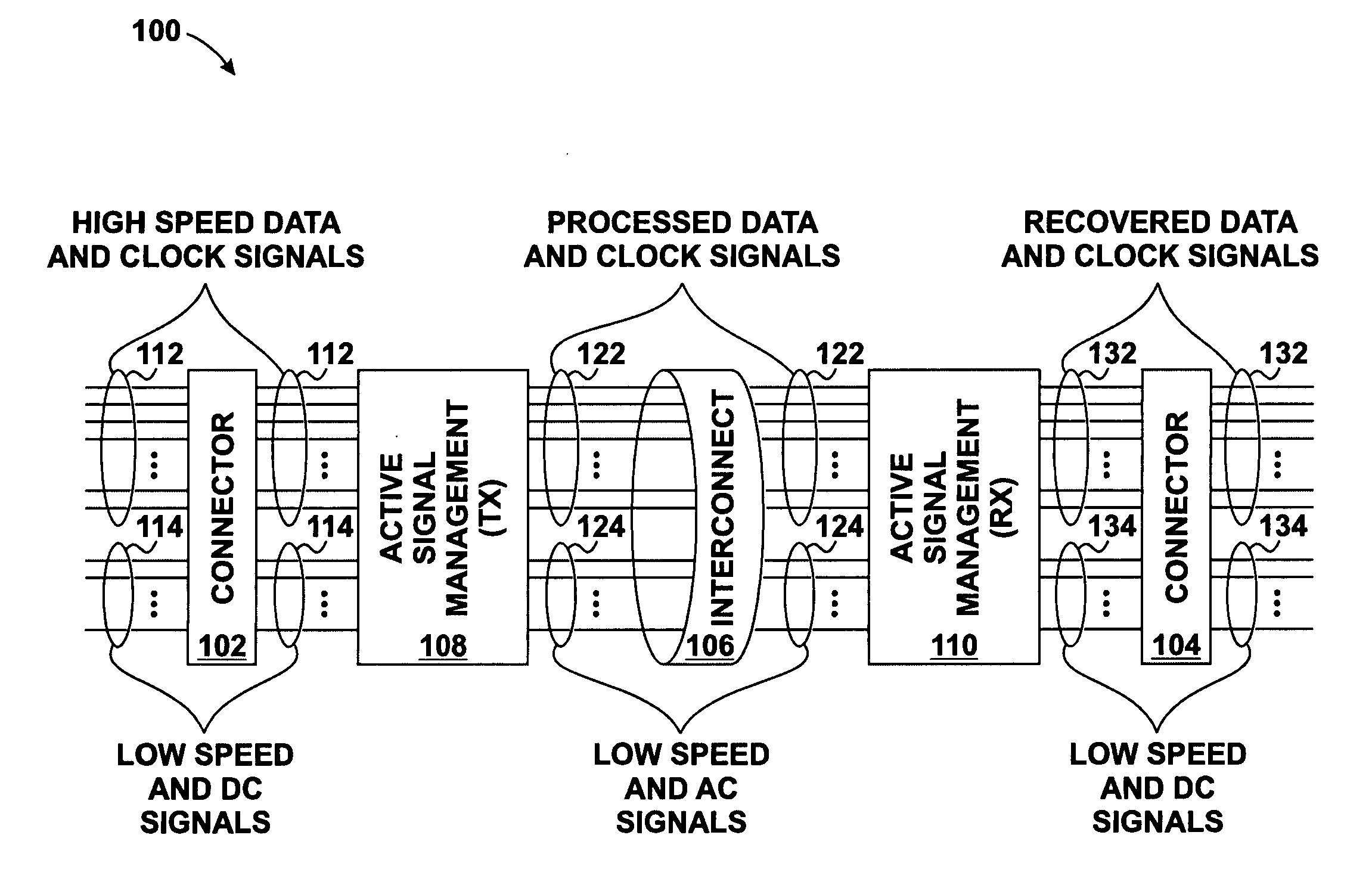

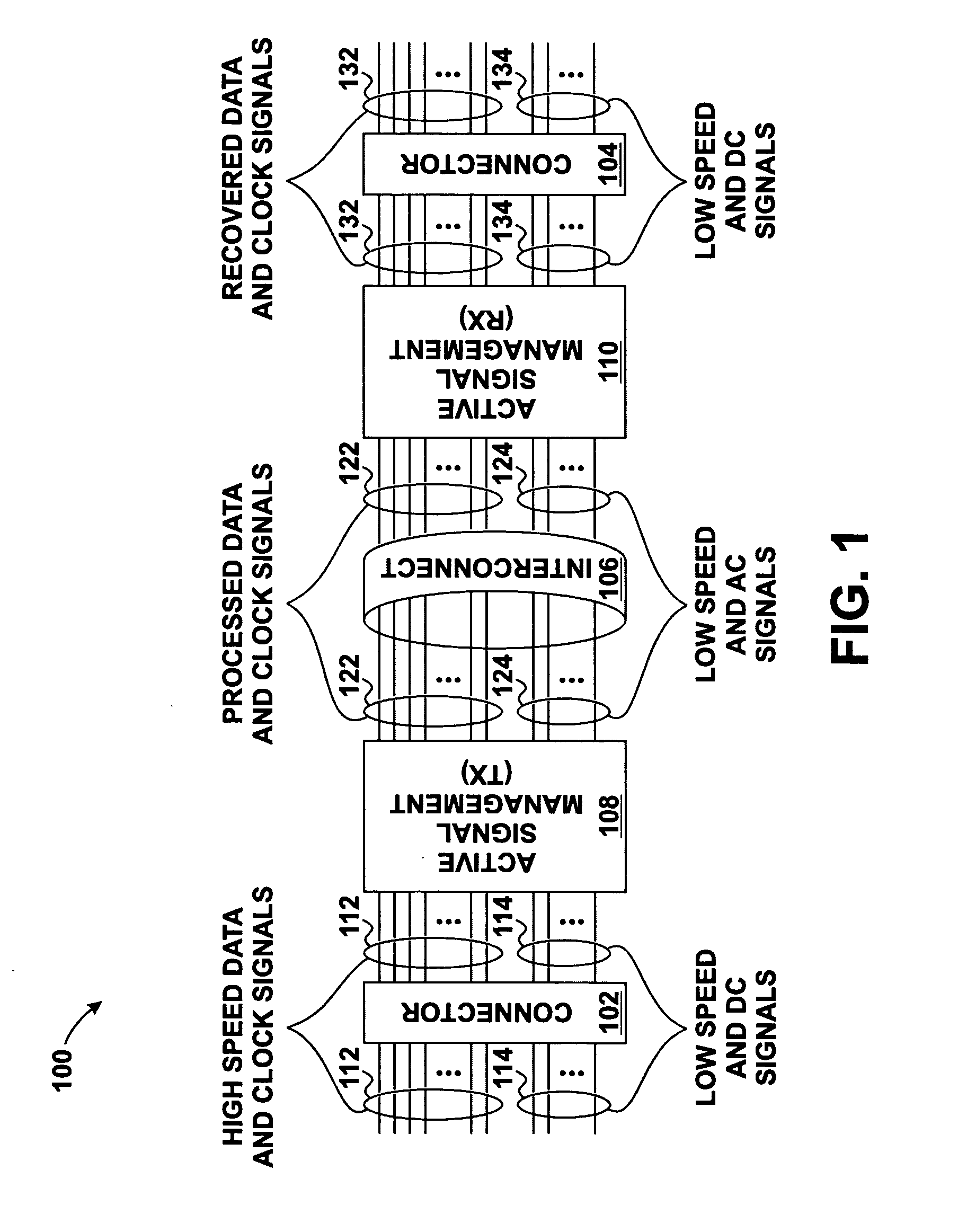

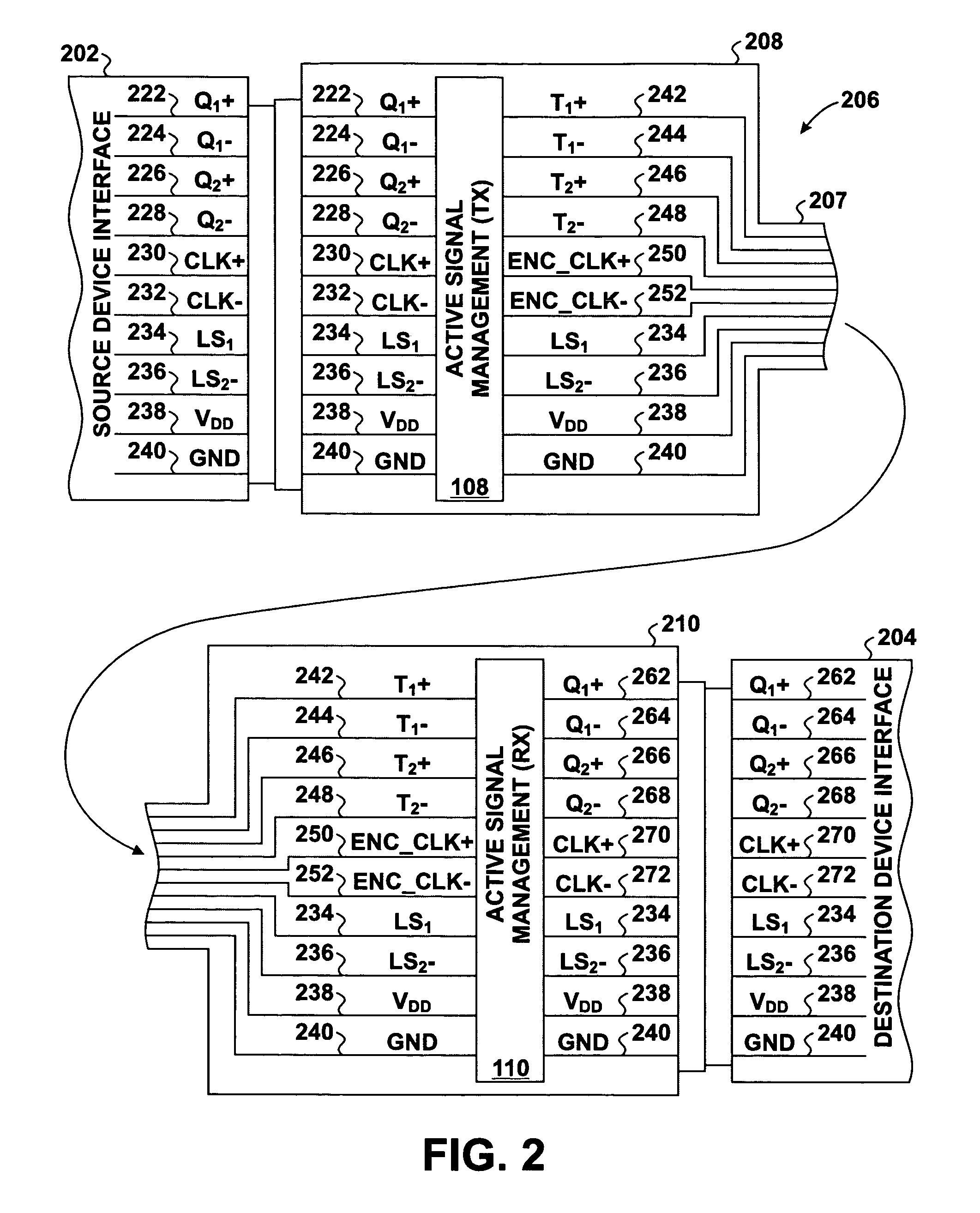

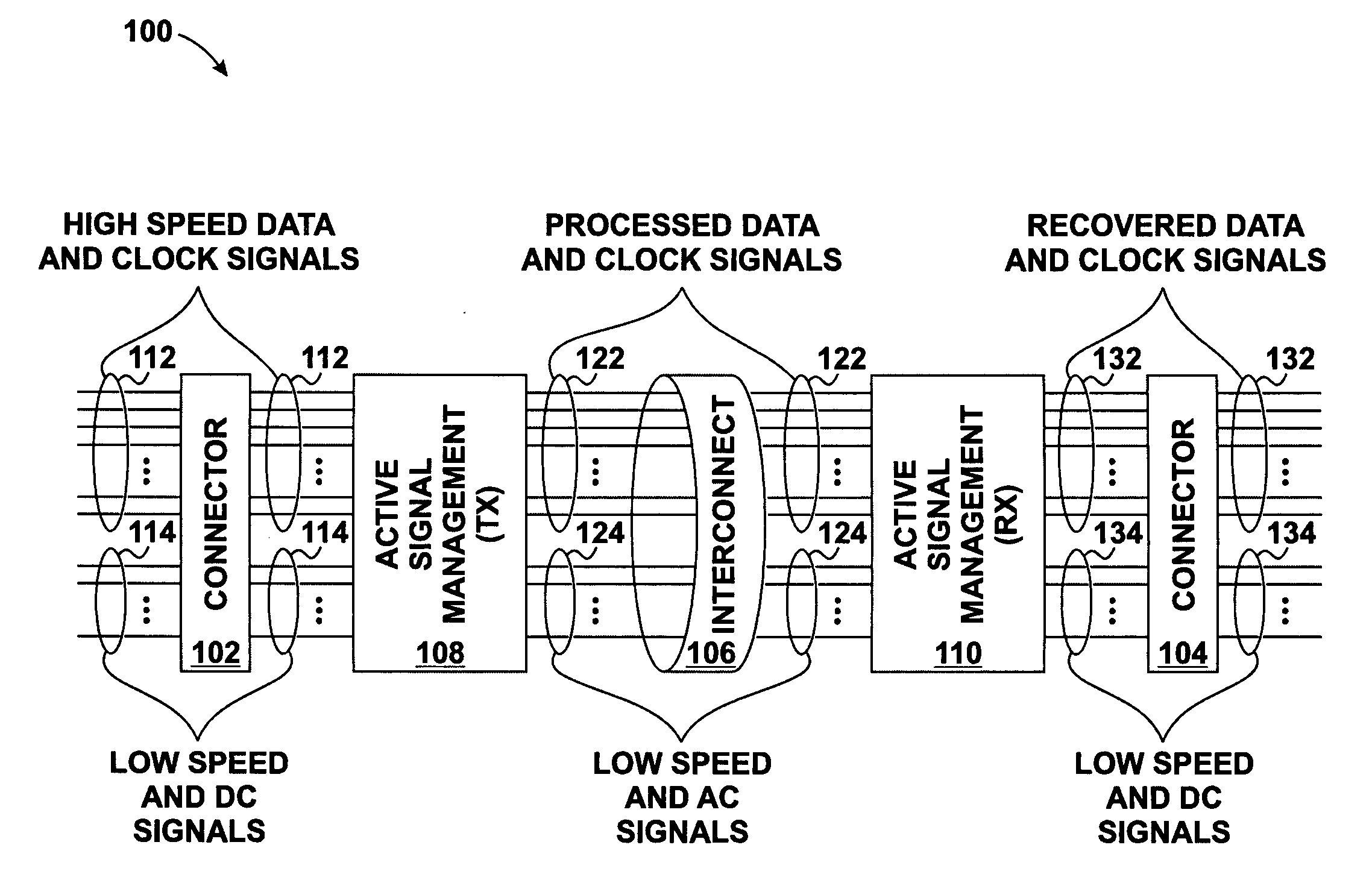

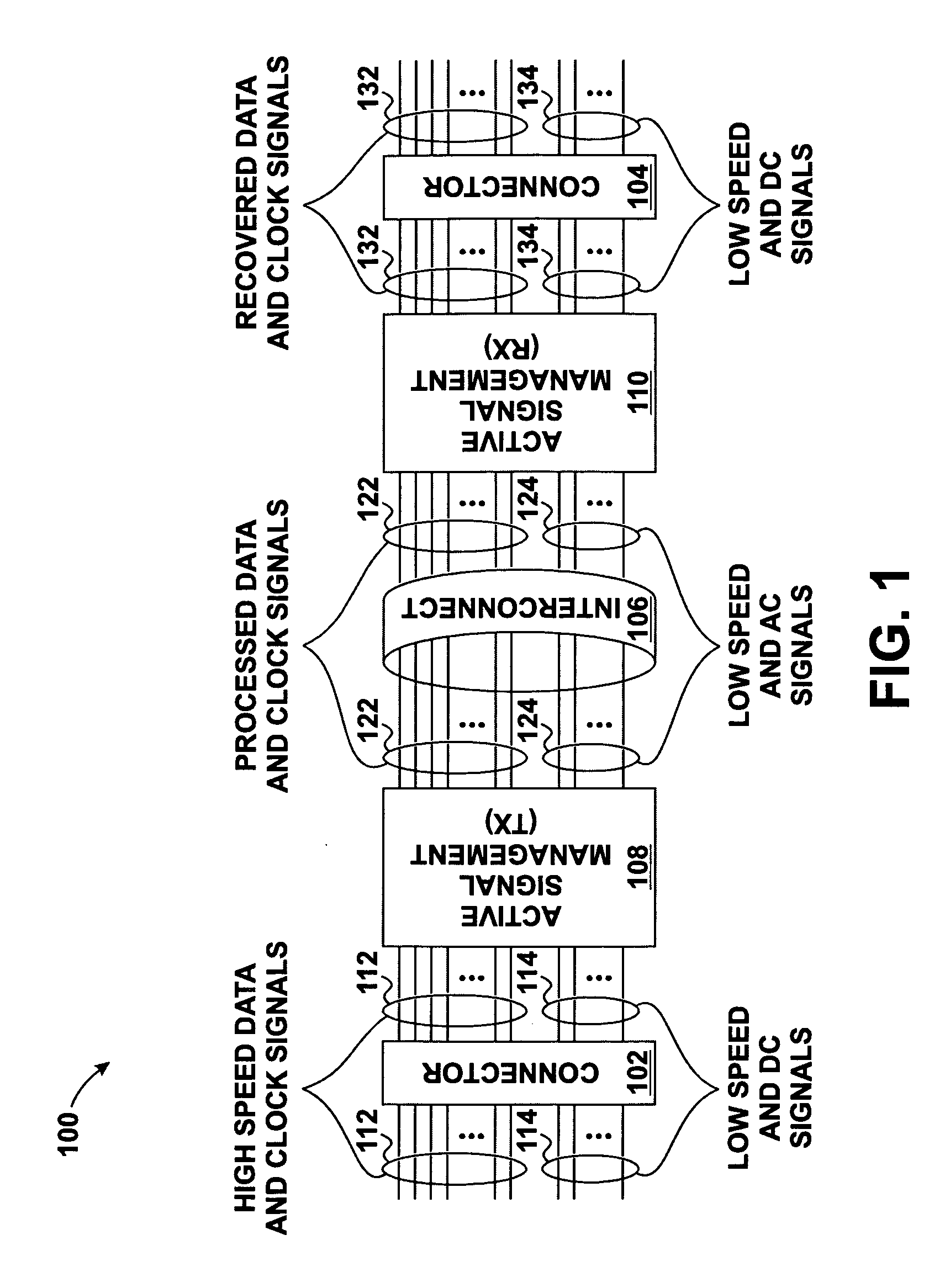

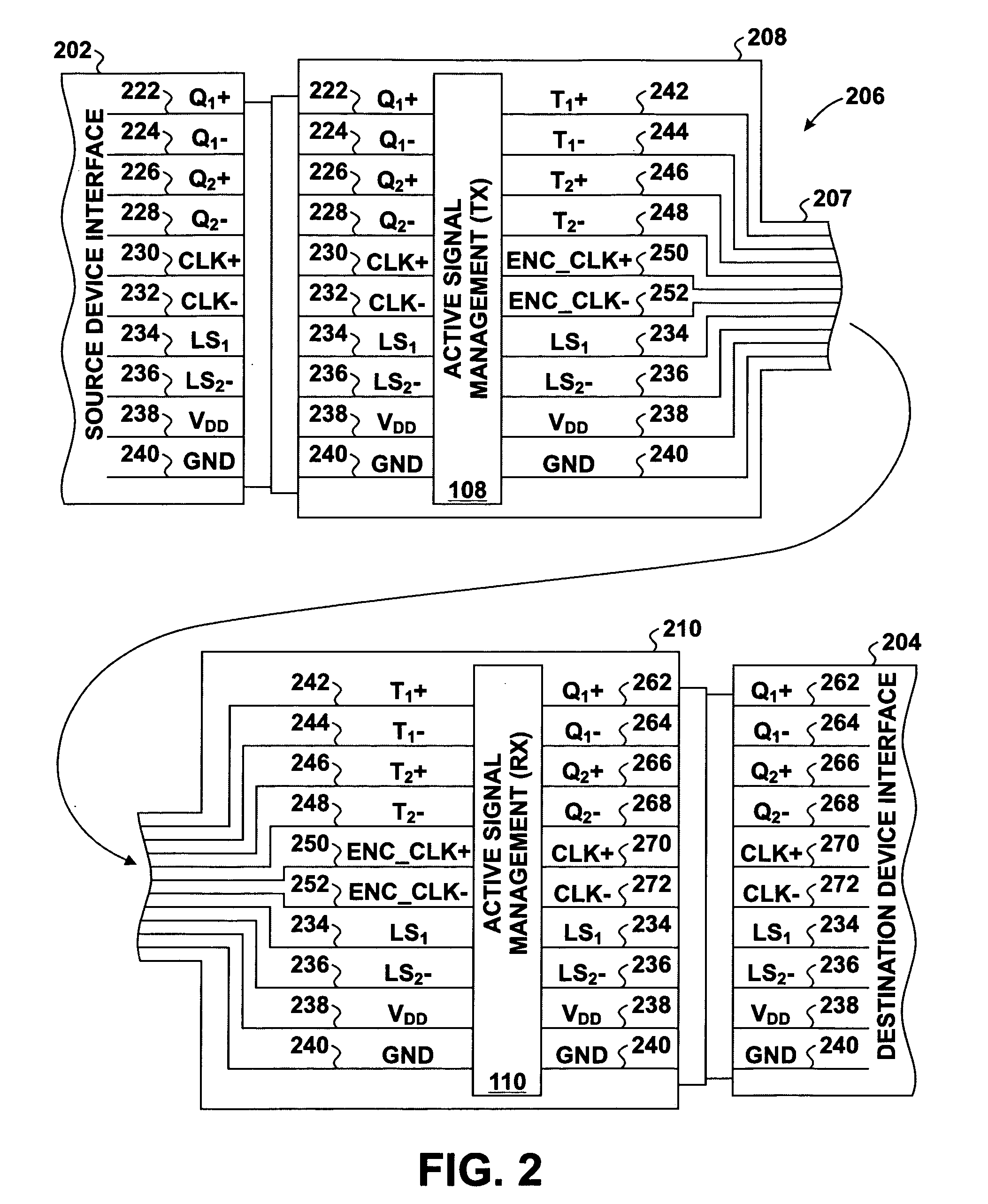

Skew management in cables and other interconnects

InactiveUS20070206643A1Channel dividing arrangementsParallel/series conversionManagement processEngineering

Transmit-side active signal management circuitry applies one or more active signal management processes to a digital signal at a transmit side of an interconnect. At the receive side of the interconnect, receive-side active signal management circuitry applies one or more corresponding active signal management processes, as appropriate, to the received digital signal to recover the information represented by the original digital signal. The interconnect can include a cable used to transmit the signals between a source device and a destination device, whereby one or both of the transmit-side active signal management circuitry and the receive-side active signal management circuitry is implemented at a corresponding cable receptacle of the cable. Alternately, one or both of the transmit-side active signal management circuitry and the receive-side active signal management circuitry can be implemented at a cable adaptor, thereby permitting the use of a passive cable interconnect to transmit the signal.

Owner:XEMI

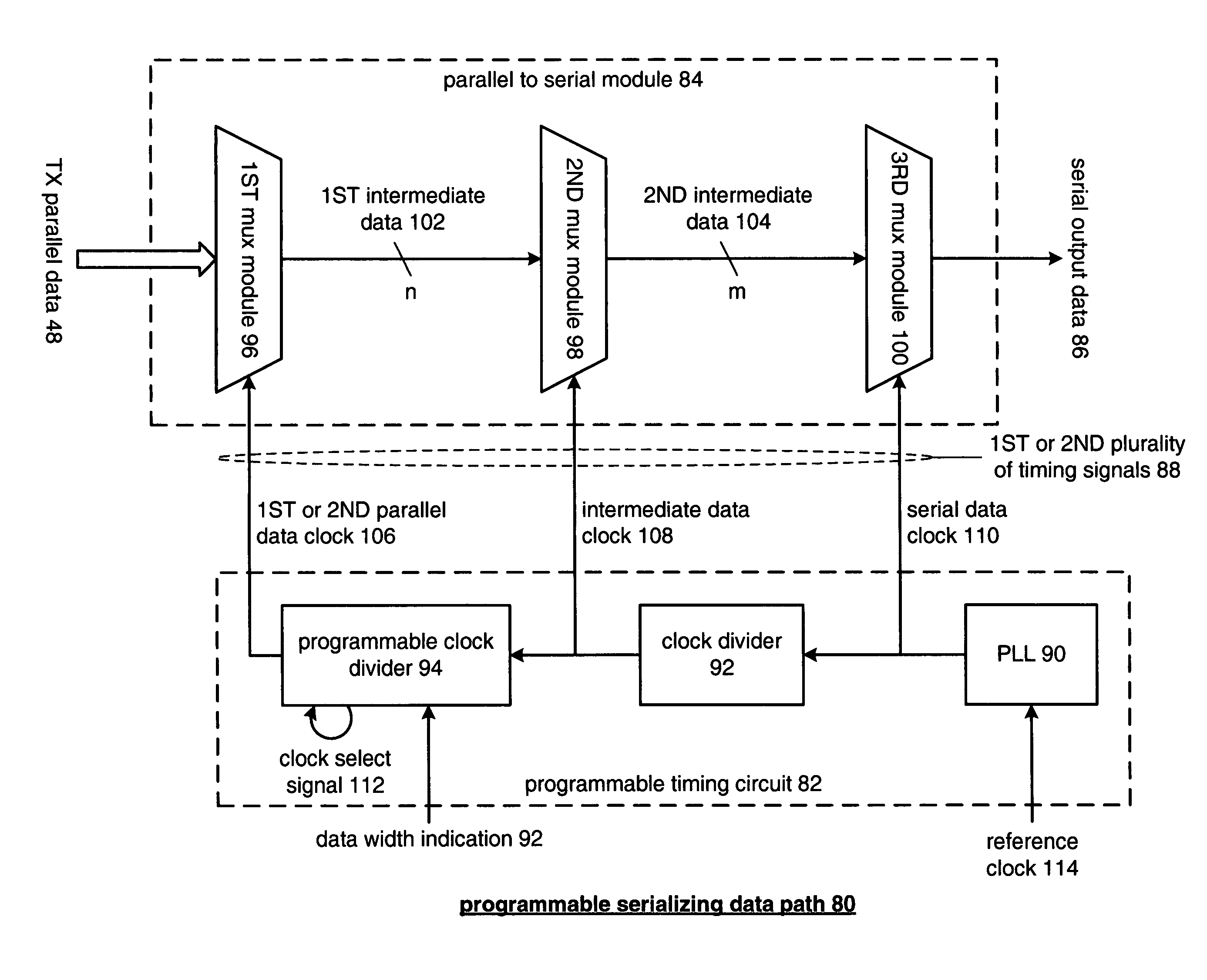

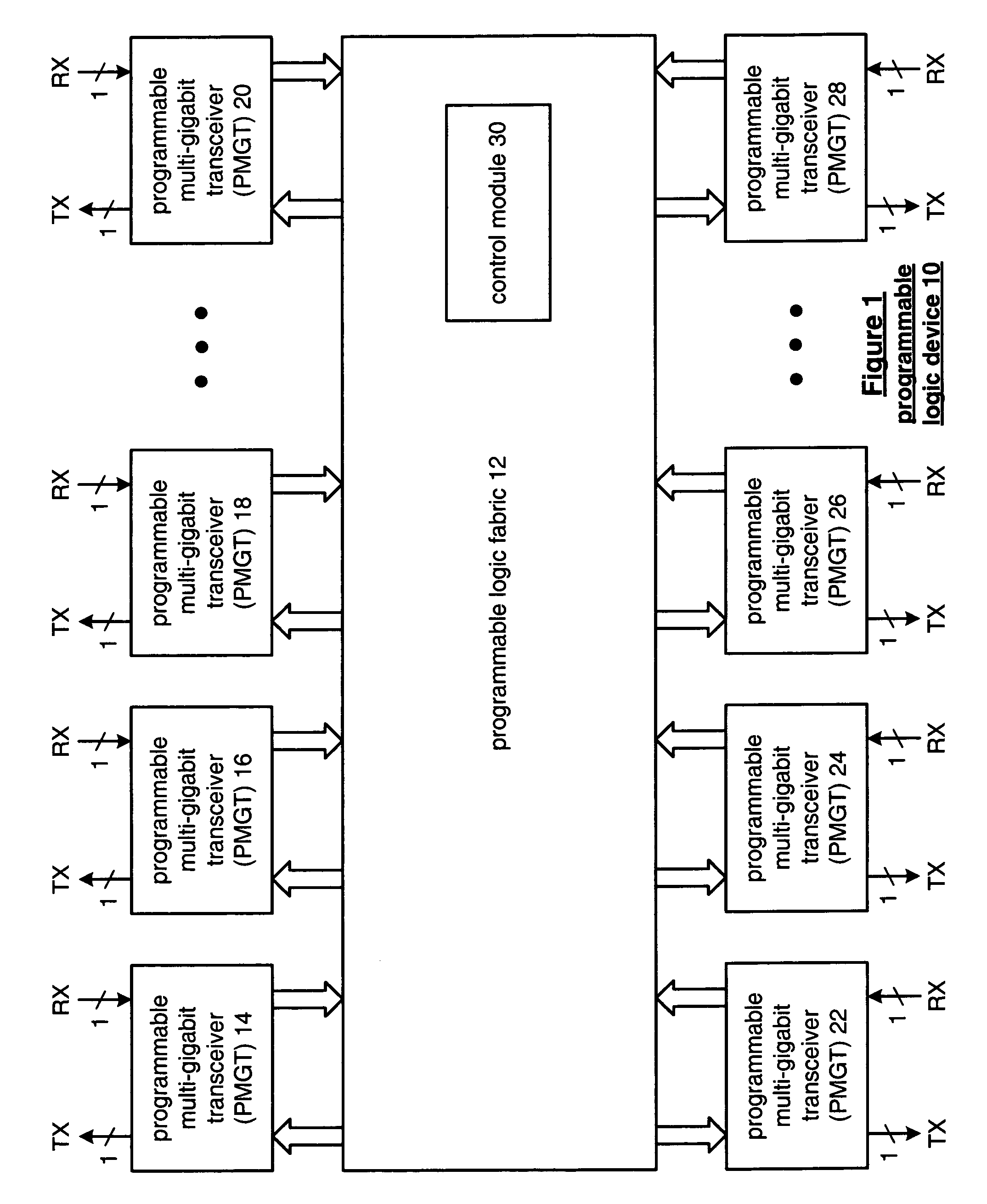

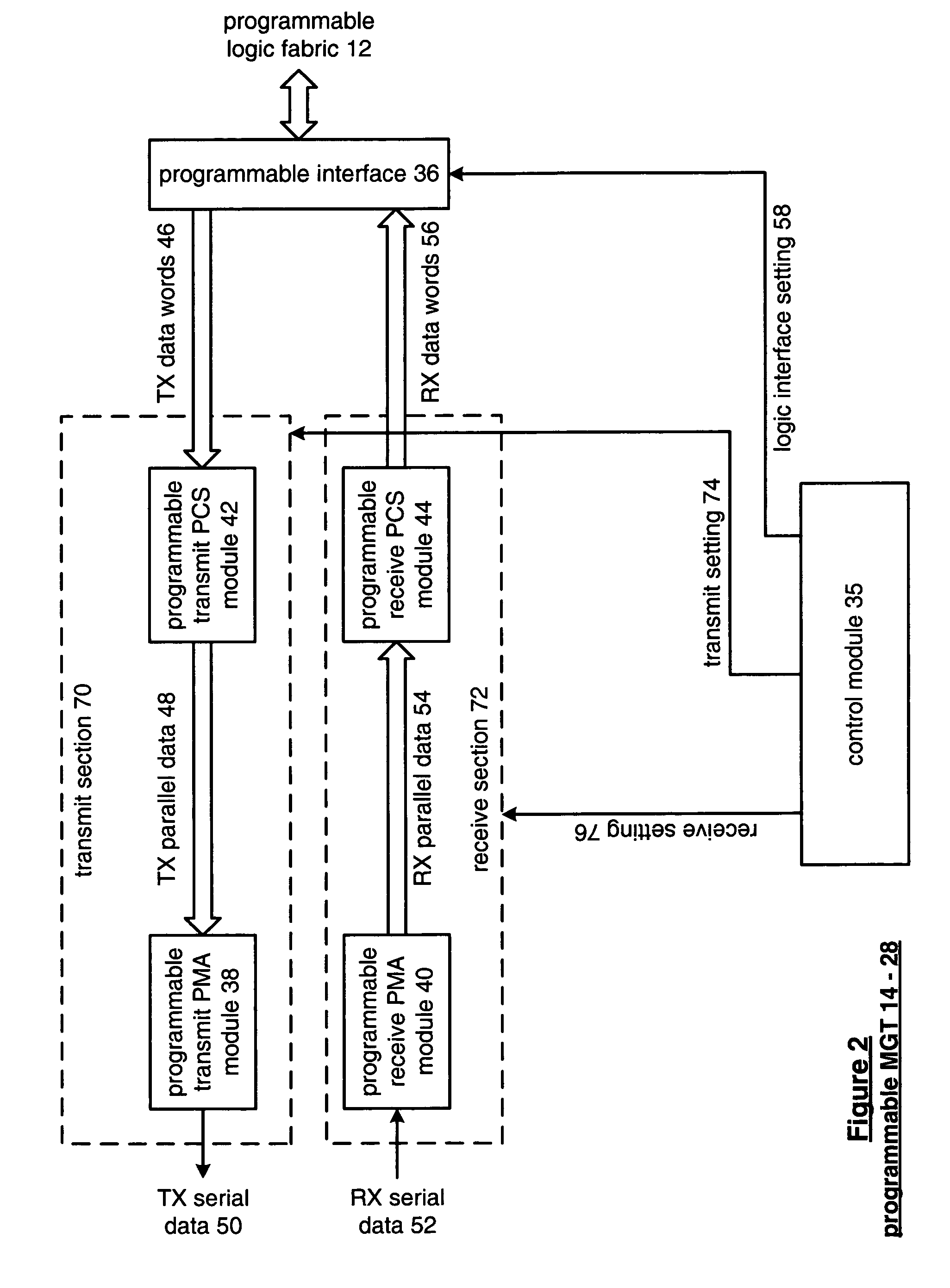

Programmable serializing data path

ActiveUS7015838B1Convenient to accommodateParallel/series conversionElectric digital data processingSerial moduleComputer module

A programmable serial data path includes a programmable timing circuit and a parallel to serial module. The programmable timing circuit is operably coupled to generate a first plurality of timing signals when width of parallel input data is of a first multiple and to generate a second plurality of timing signals when the width of the parallel input data is of a second multiple. The parallel to serial module is operably coupled to convert the parallel input data into serial output data based on the first or second plurality of timing signals.

Owner:XILINX INC

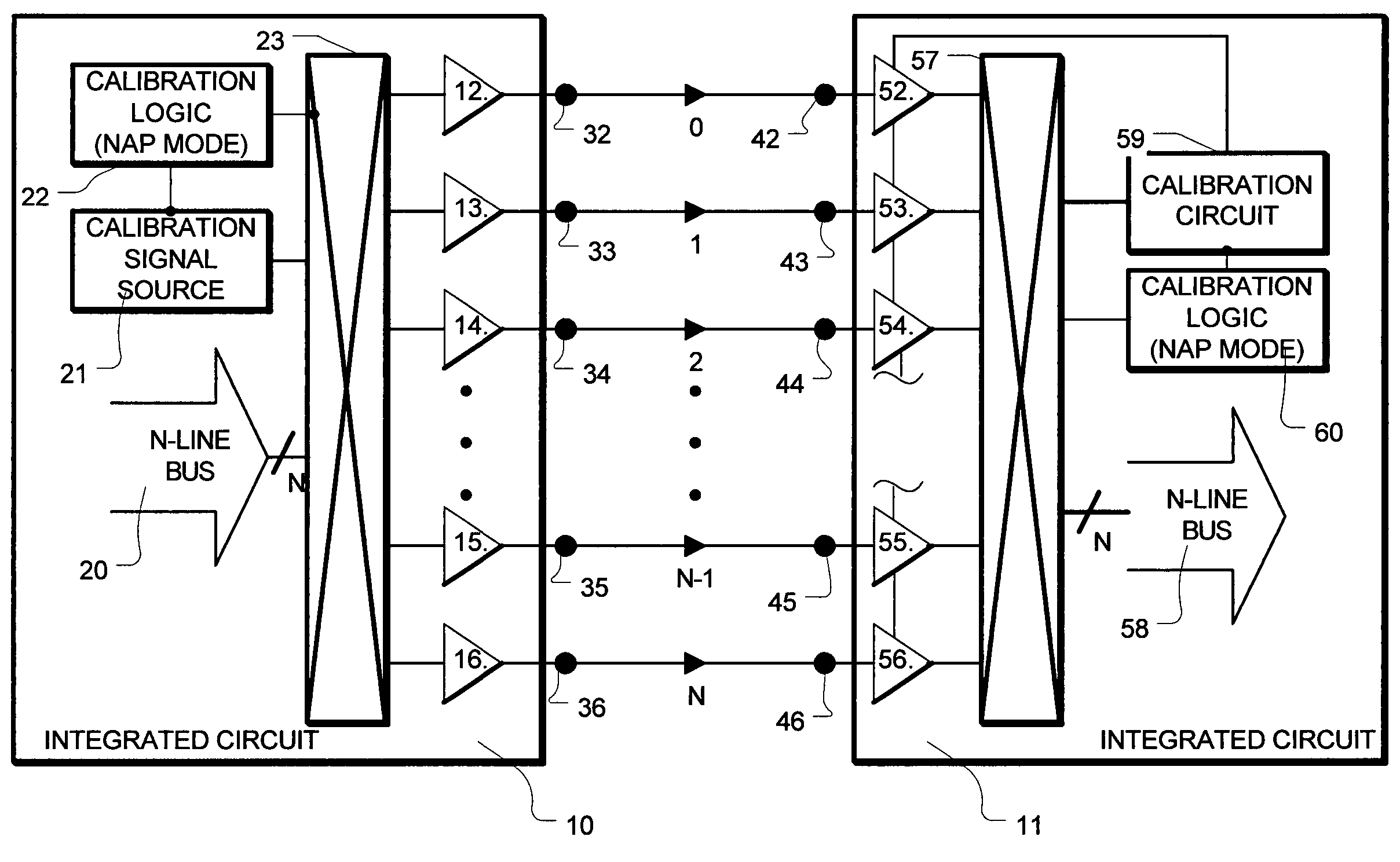

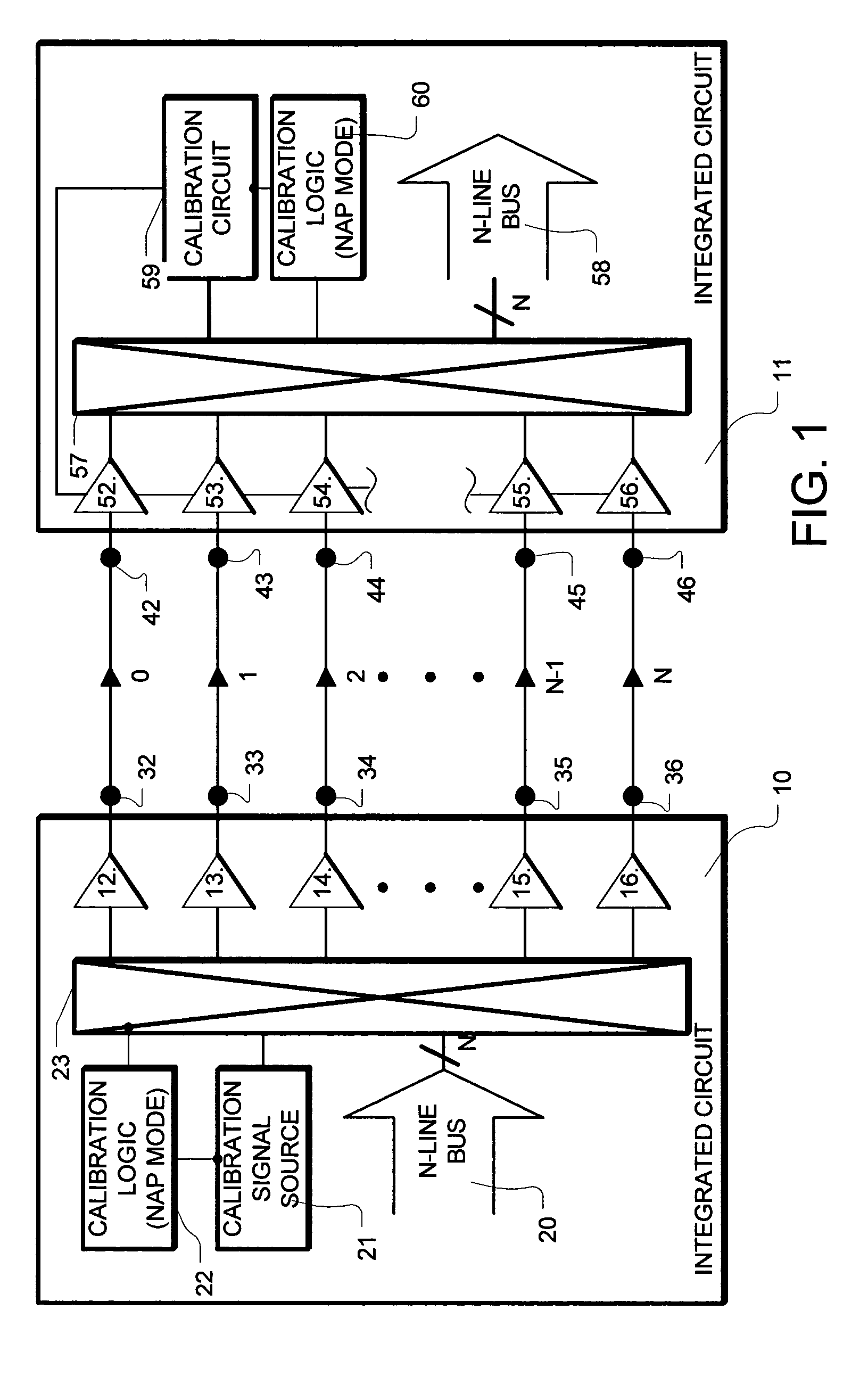

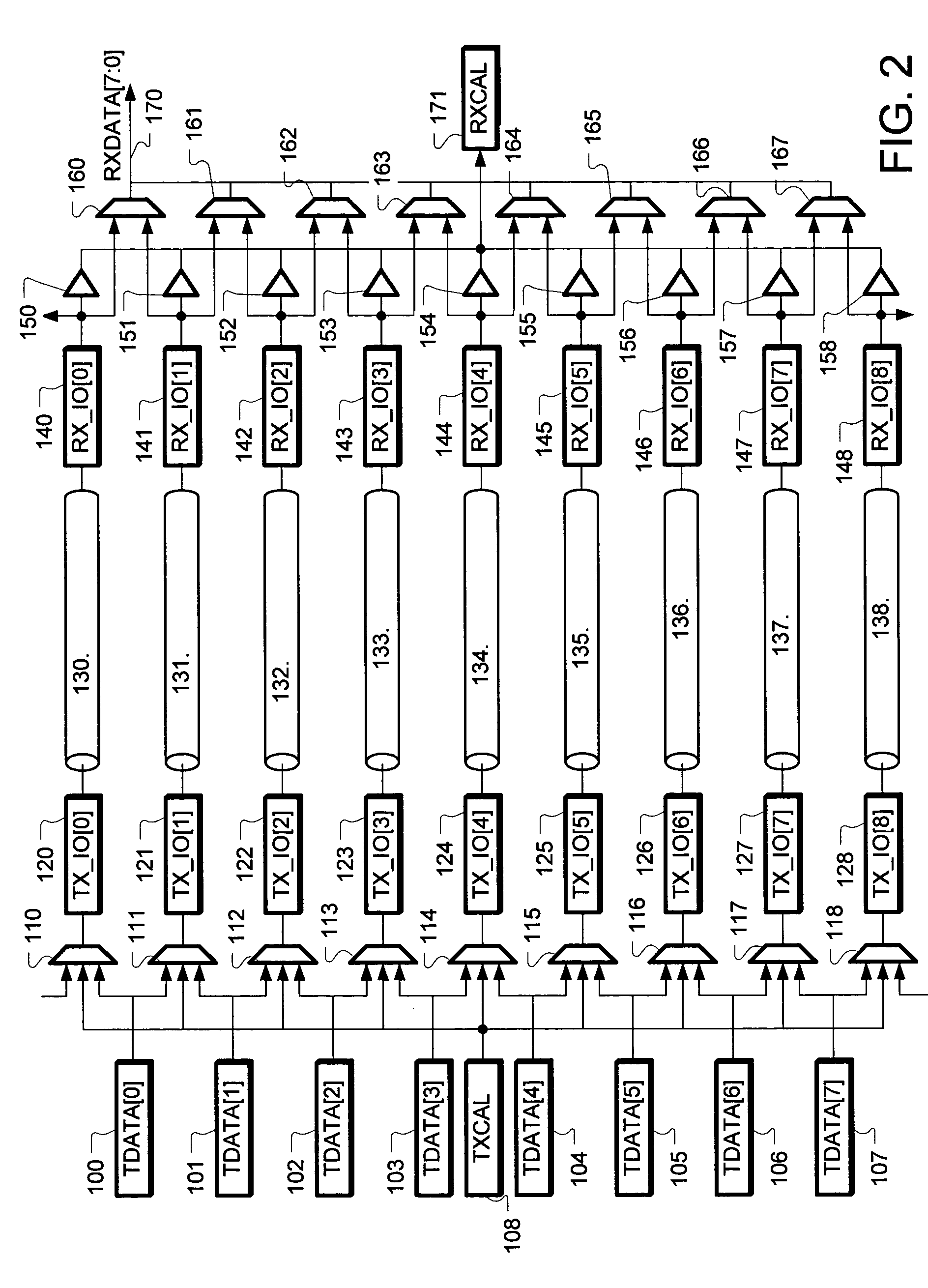

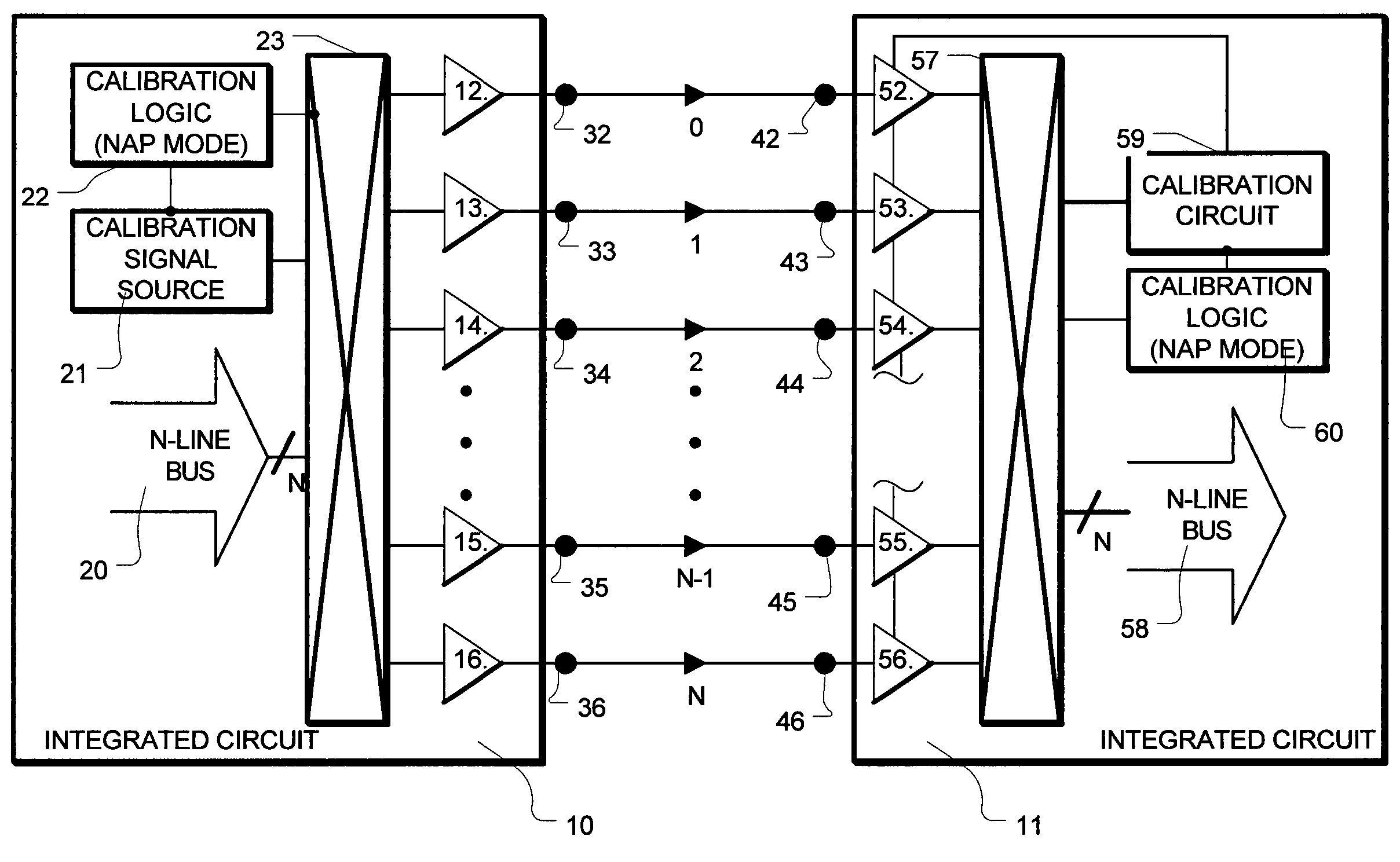

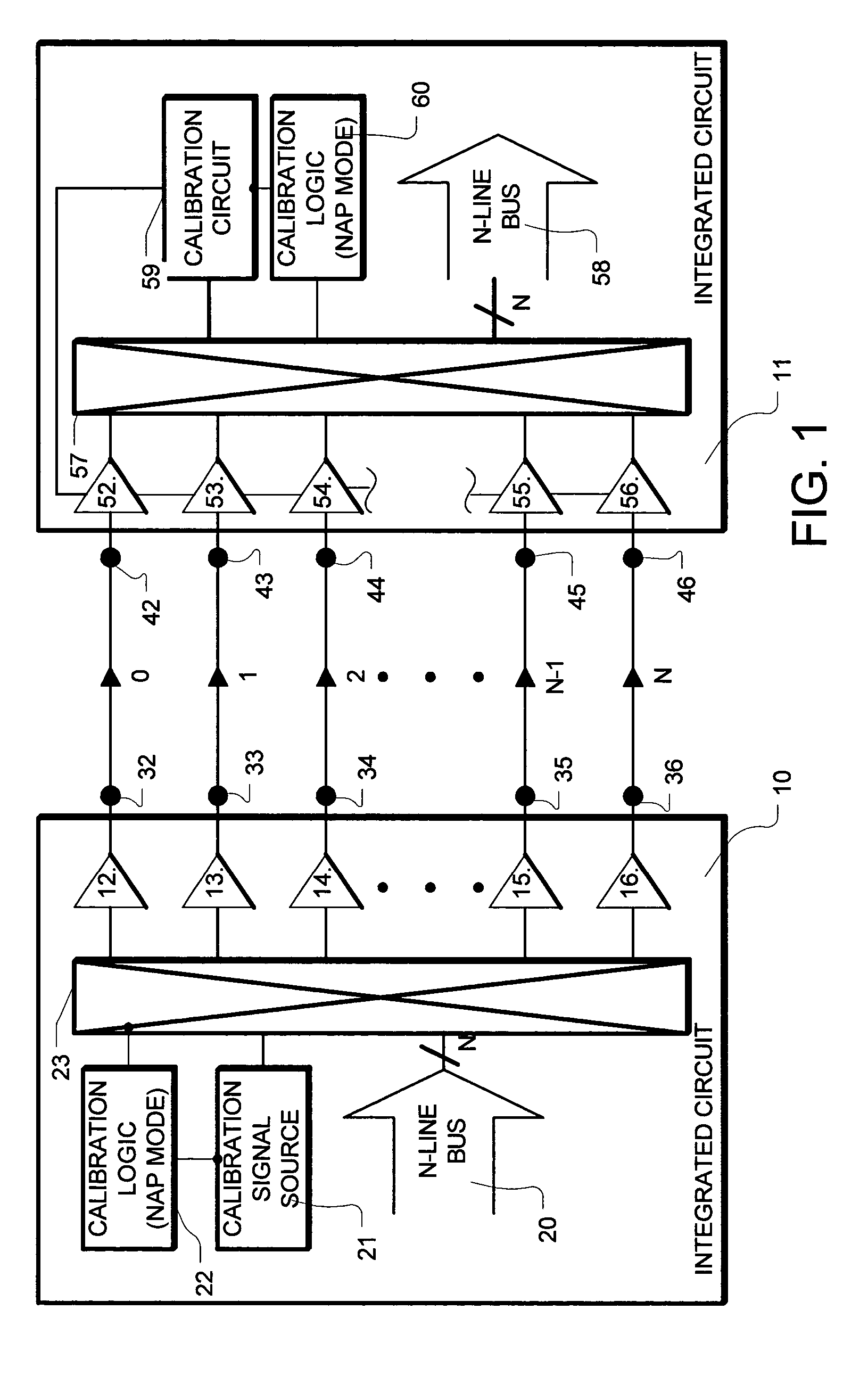

Periodic interface calibration for high speed communication

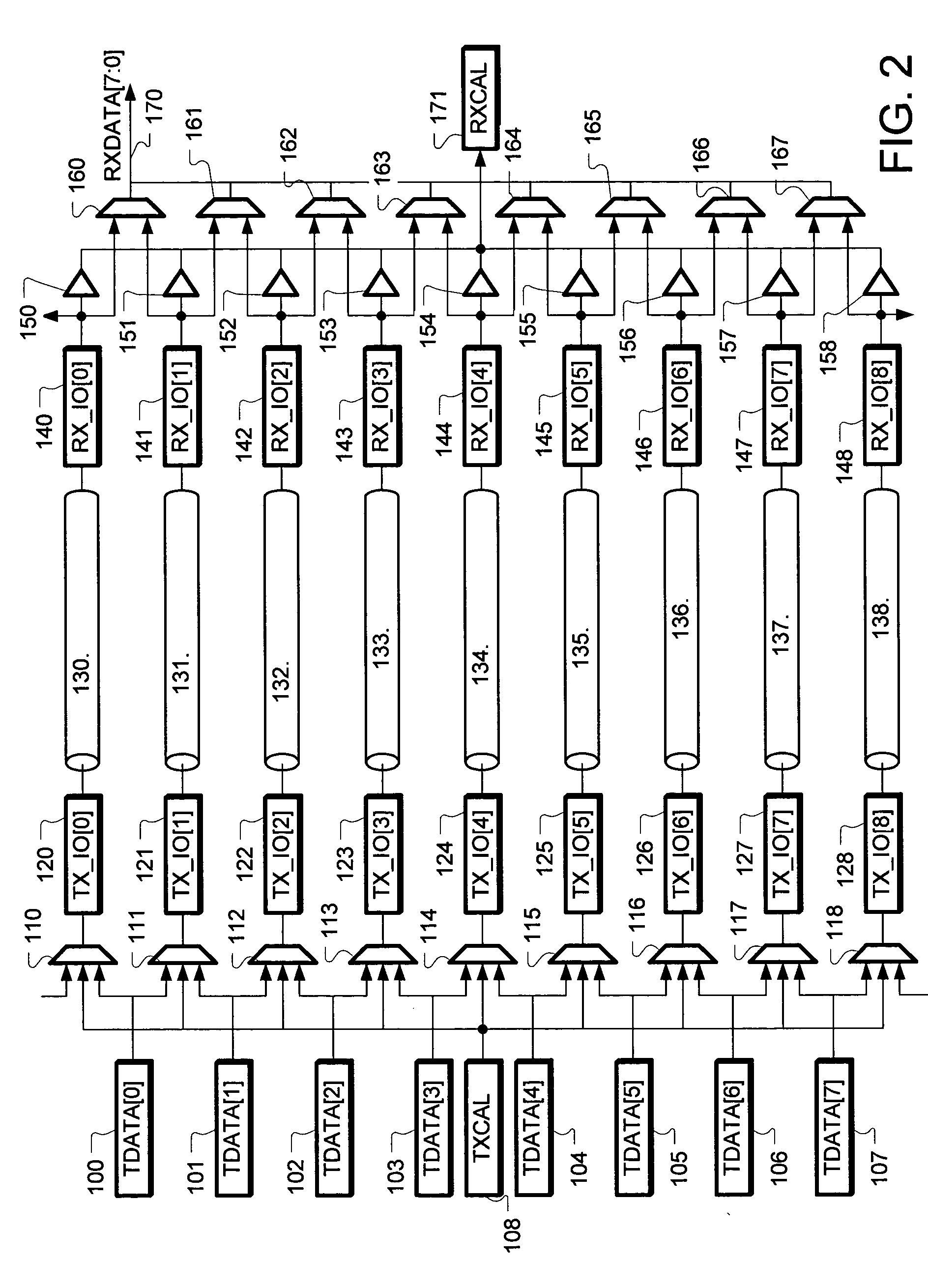

InactiveUS7072355B2Channel dividing arrangementsParallel/series conversionCommunication interfaceEngineering

A high-speed communication interface manages a parallel bus having N bus lines. N+1 communication lines are established. A maintenance operation is performed on one of the N+1 communication lines, while N of the N+1 communication lines is available for data from the N line bus. The communication line on which the maintenance operation is performed, is changed after the operation is complete, so that all of the N+1 communication lines are periodically maintained, without interfering with communications on N of the N+1 communication lines.

Owner:RAMBUS INC

Periodic interface calibration for high speed communication

InactiveUS20050041683A1Continuous operationChannel dividing arrangementsParallel/series conversionCommunication interfaceEngineering

A high-speed communication interface manages a parallel bus having N bus lines. N+1 communication lines are established. A maintenance operation is performed on one of the N+1 communication lines, while N of the N+1 communication lines is available for data from the N line bus. The communication line on which the maintenance operation is performed, is changed after the operation is complete, so that all of the N+1 communication lines are periodically maintained, without interfering with communications on N of the N+1 communication lines.

Owner:RAMBUS INC

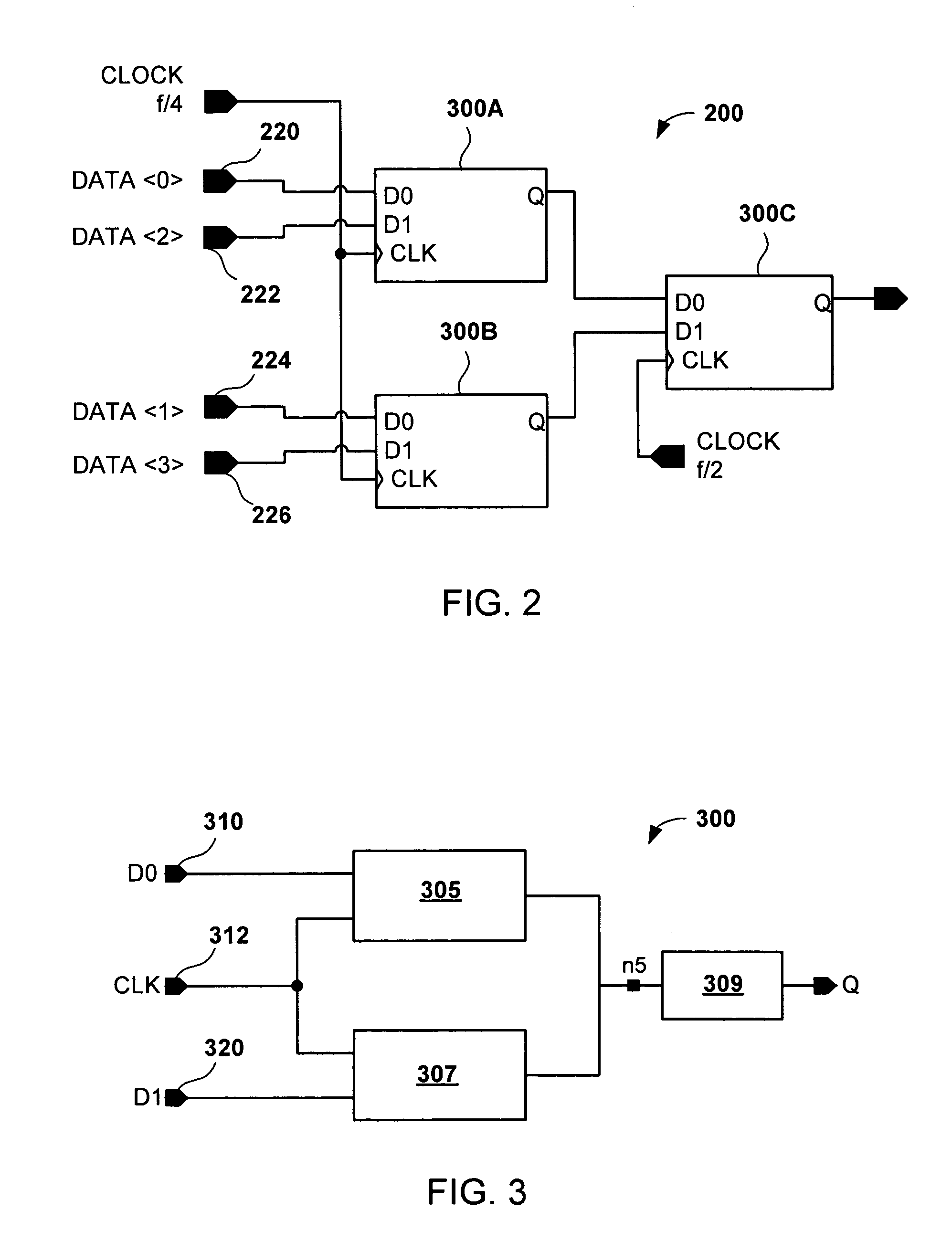

Low output skew double data rate serial encoder

ActiveUS20080036631A1Reduce complexitySmall sizeParallel/series conversionDouble data rateMultiplexer

A Double Data Rate (DDR) serial encoder is provided. In one aspect, the DDR serial encoder includes a non-glitchless multiplexer and digital logic for ensuring a glitch-free encoder output. By using a non-glitchless multiplexer, the size and complexity of the encoder is significantly reduced. In another aspect, the DDR serial encoder has a single layer of logic between the final register stage and the encoder output and a reduced number of paths from the final register stage to the encoder output, thereby resulting in reduced output skew and increased link rate.

Owner:QUALCOMM INC

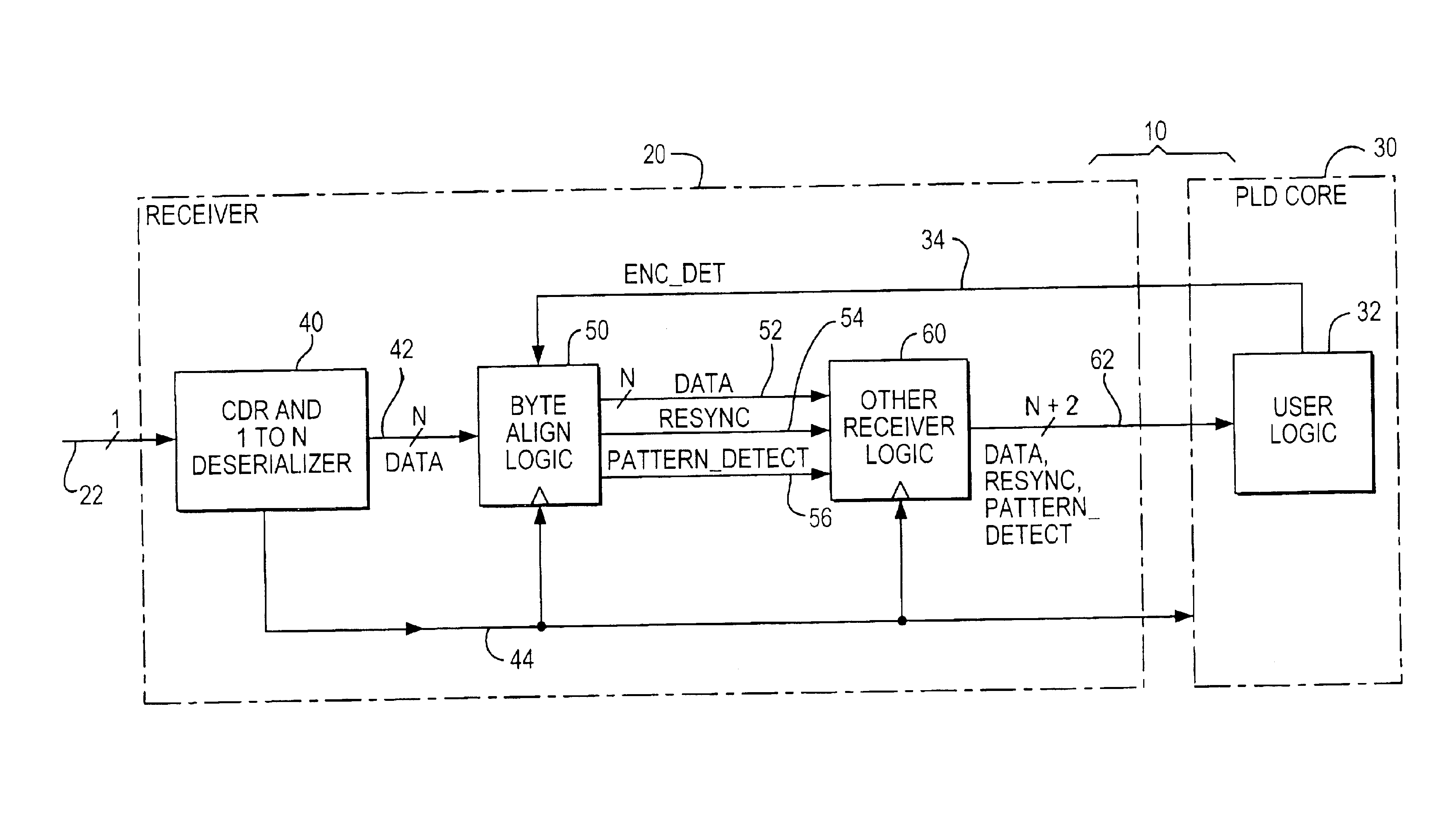

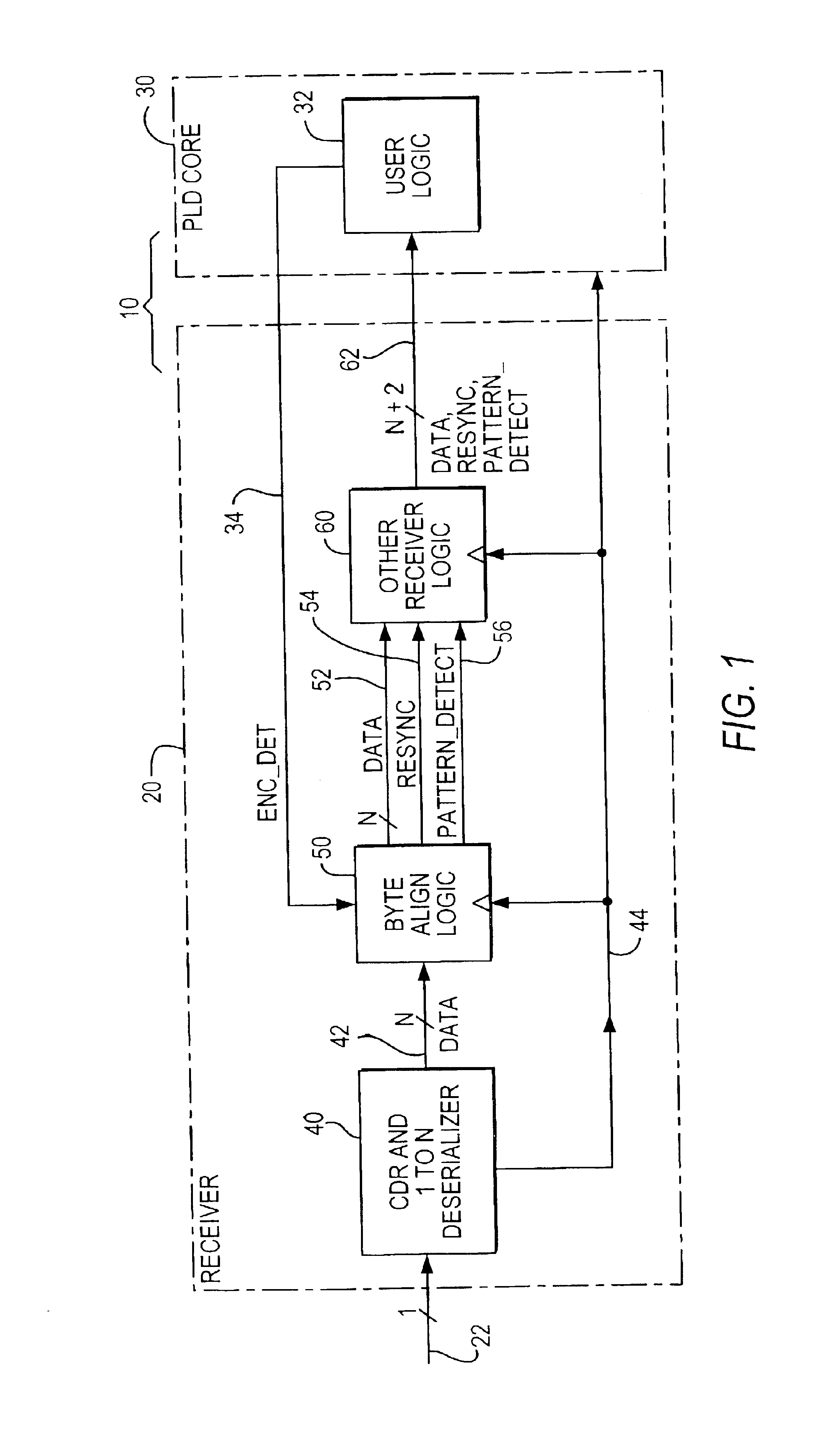

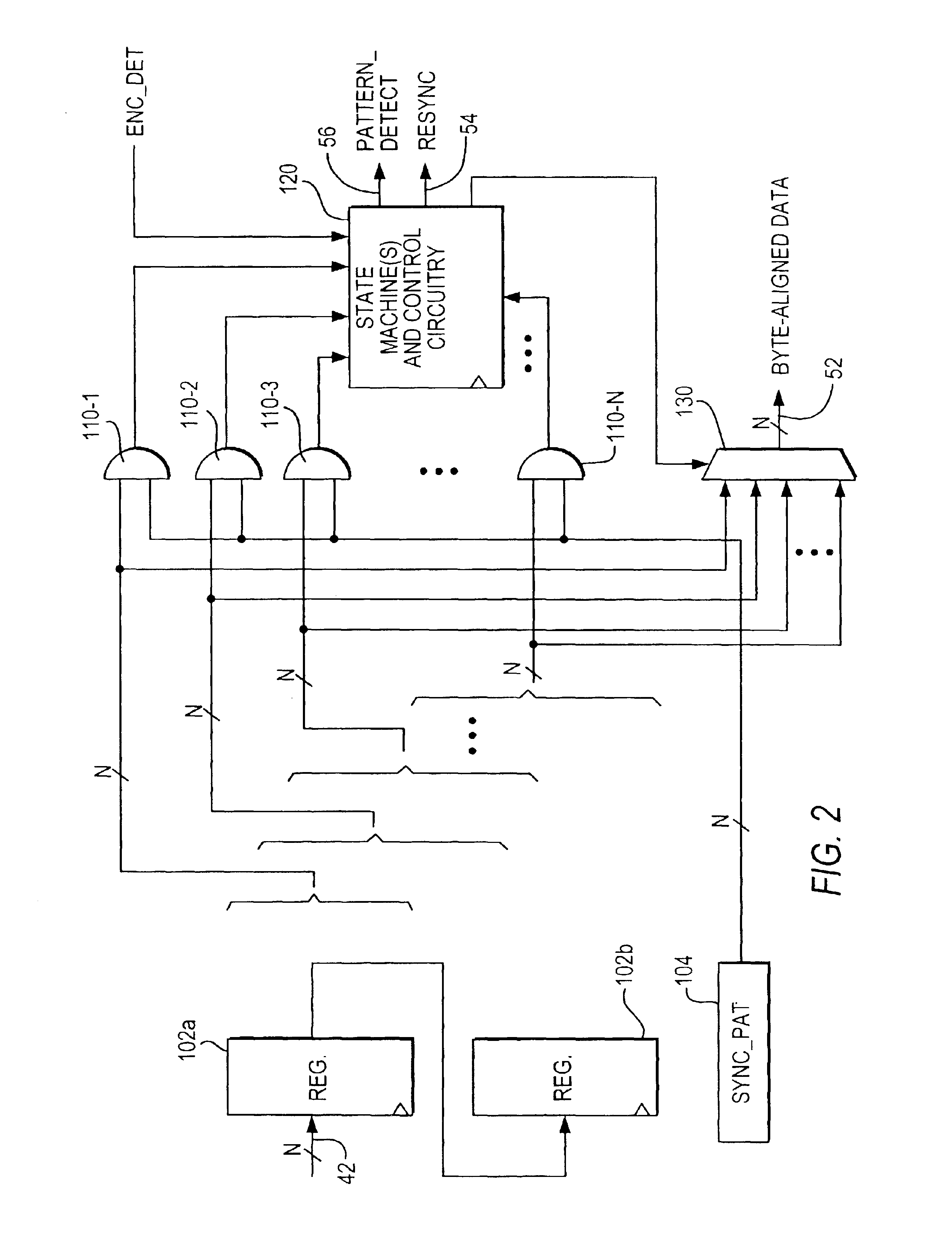

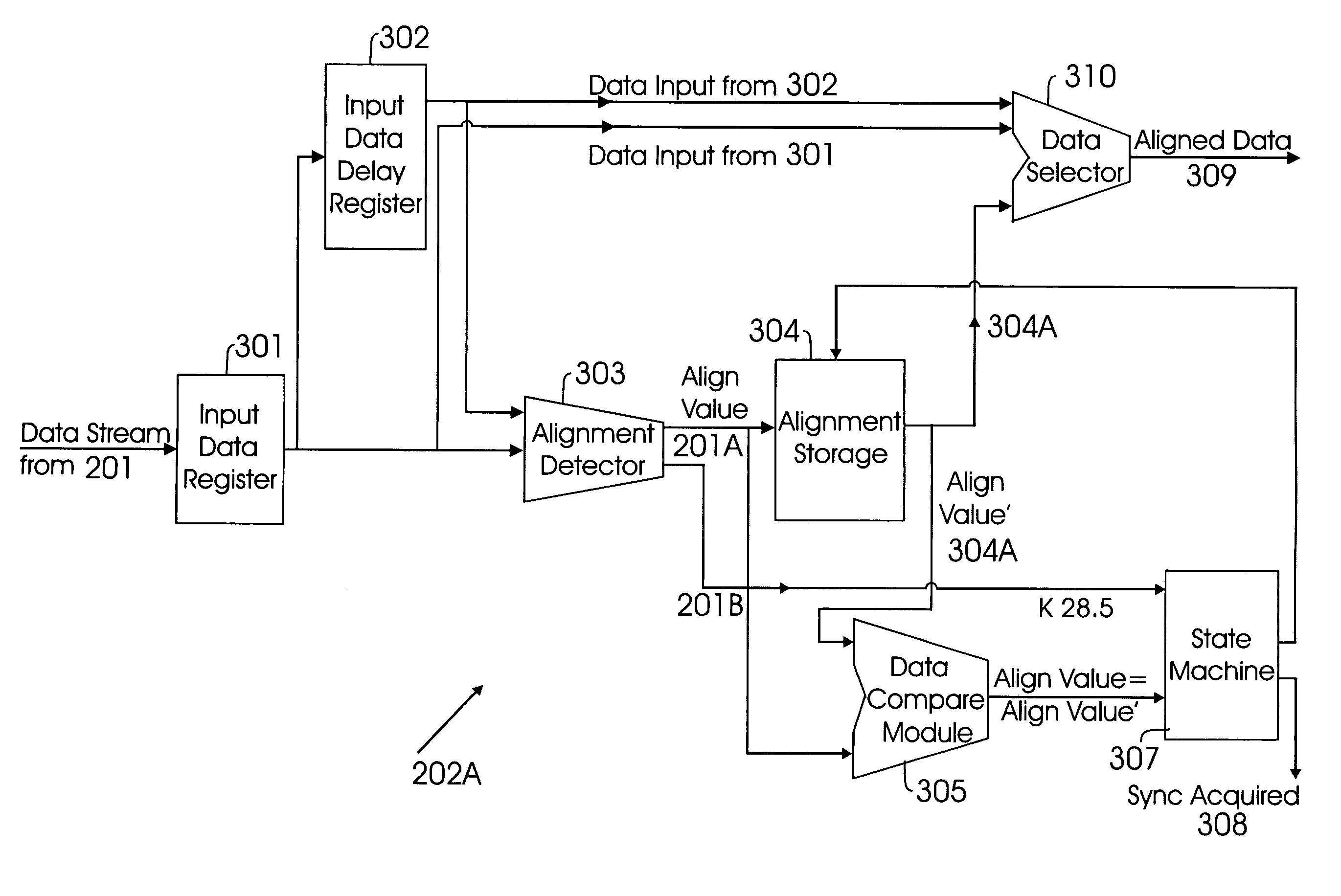

Byte alignment circuitry

Circuitry for locating the boundaries between bytes in a data stream is only selectively enabled to find a possible new byte alignment by a control signal. After the byte alignment circuitry has found a byte alignment, it outputs byte-aligned data and a first status signal indicating the presence of such data. If the byte alignment circuitry subsequently detects information that suggests a possible need for a new or changed byte alignment, it outputs a second status signal to that effect. However, the byte alignment circuitry does not actually attempt to change its byte alignment until enabled to do so by the control signal. Programmable logic circuitry or other utilization circuitry is typically provided to receive the outputs of the byte alignment circuitry and to selectively provide the control signal.

Owner:ALTERA CORP

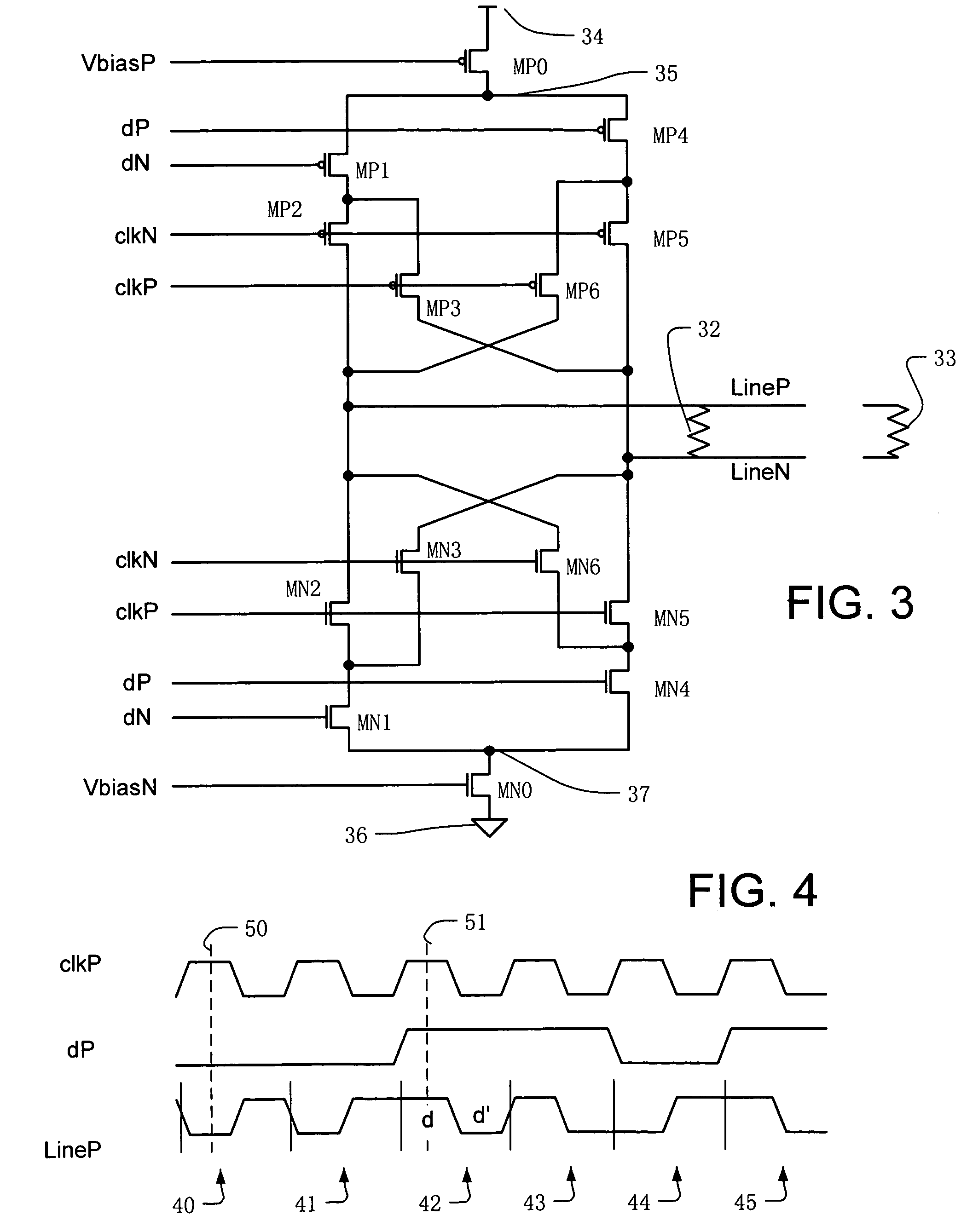

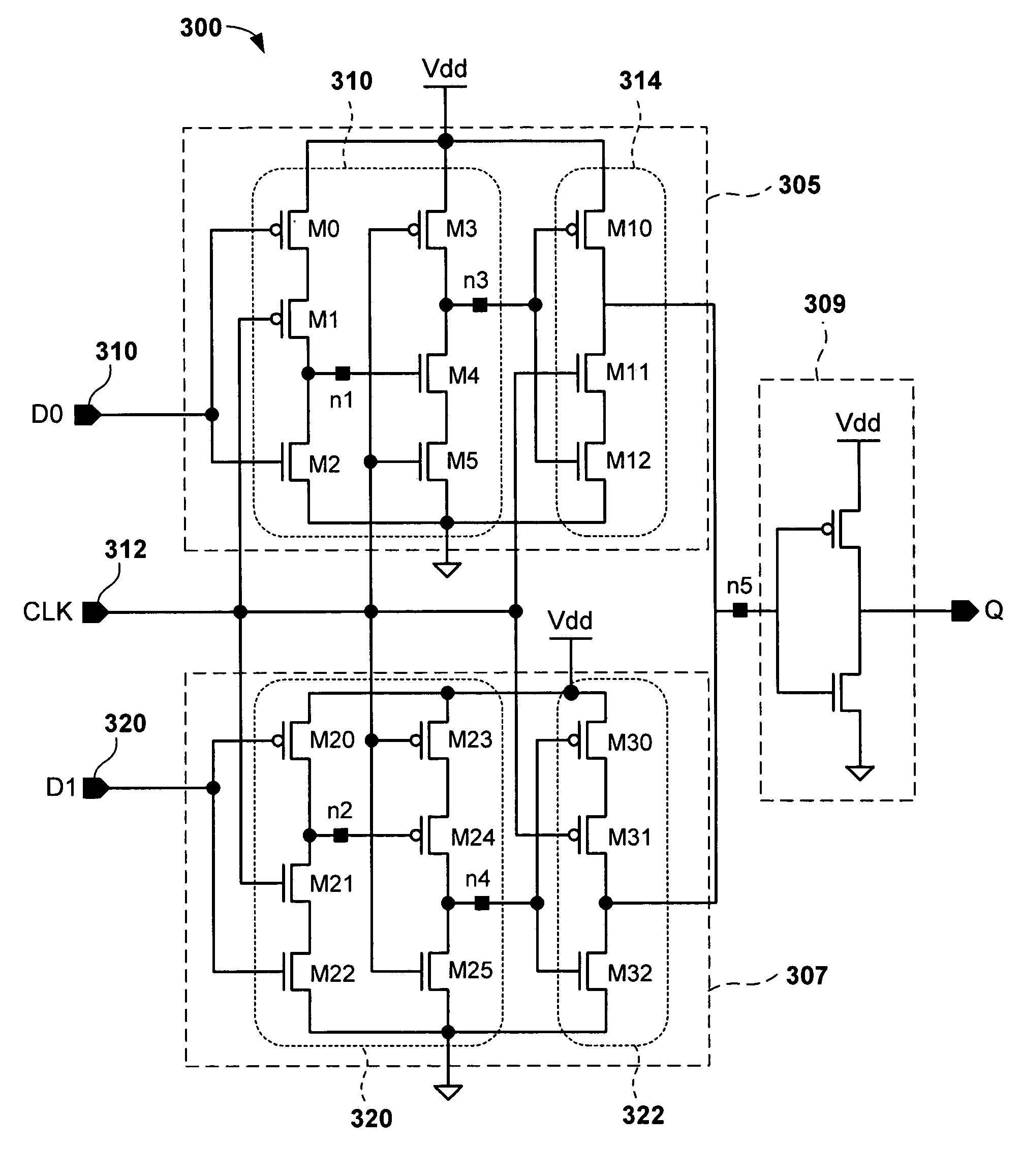

Dual-edge triggered multiplexer flip-flop and method

A dual edge multiplexing flip-flop comprises a first circuit block having a first data input, a first clock signal input, a supply voltage input, and a ground connection; a second circuit block having a second data input, a second clock signal input, a supply voltage input, and a ground connection. Each circuit block is coupled to a common output node. When a common clock signal is input into the clock signal inputs, each circuit block outputs a floating voltage during one half of each clock cycle and a voltage indicative of a corresponding data input signal during the other half of each clock cycle.

Owner:SEIKO EPSON CORP

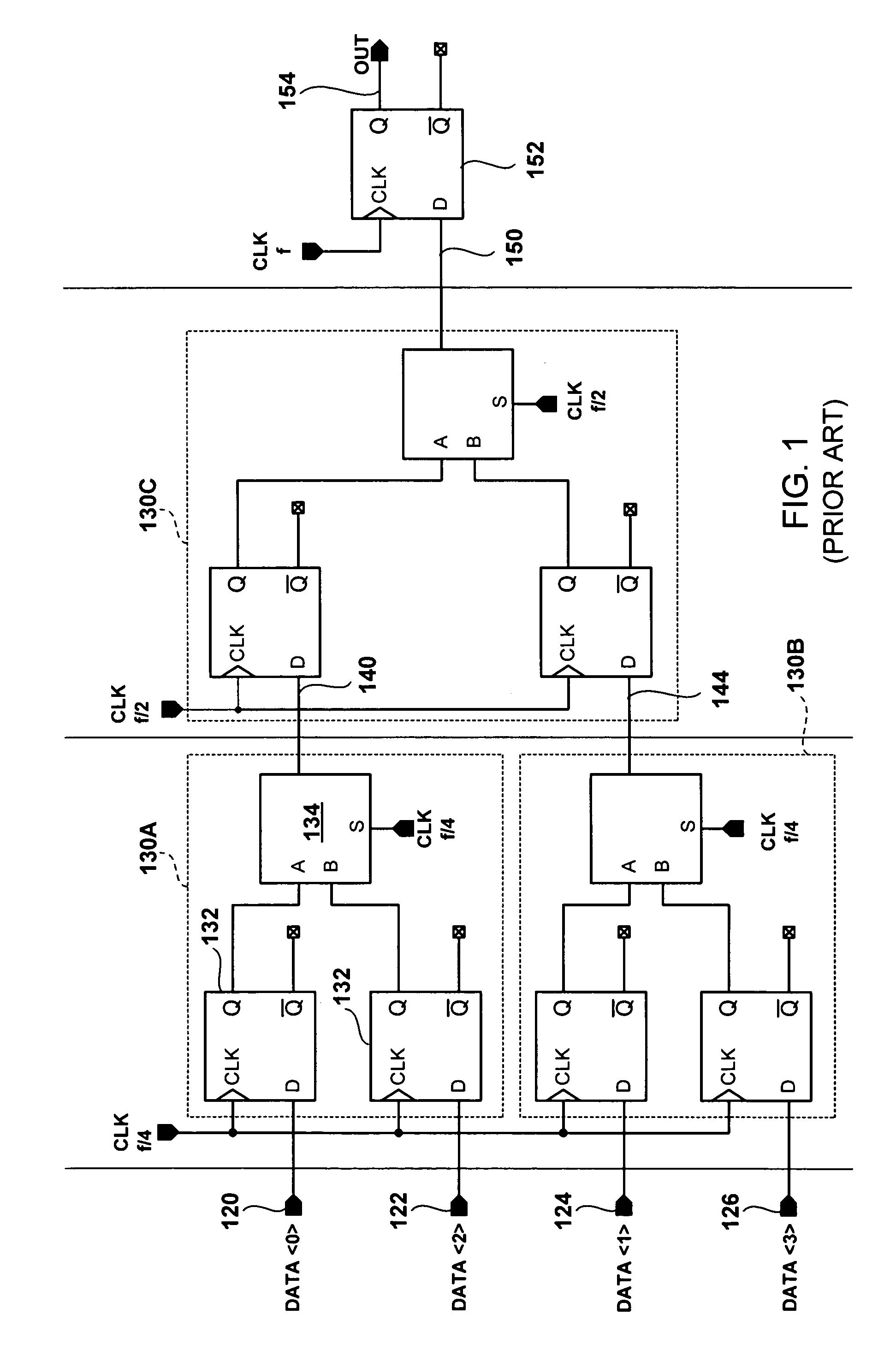

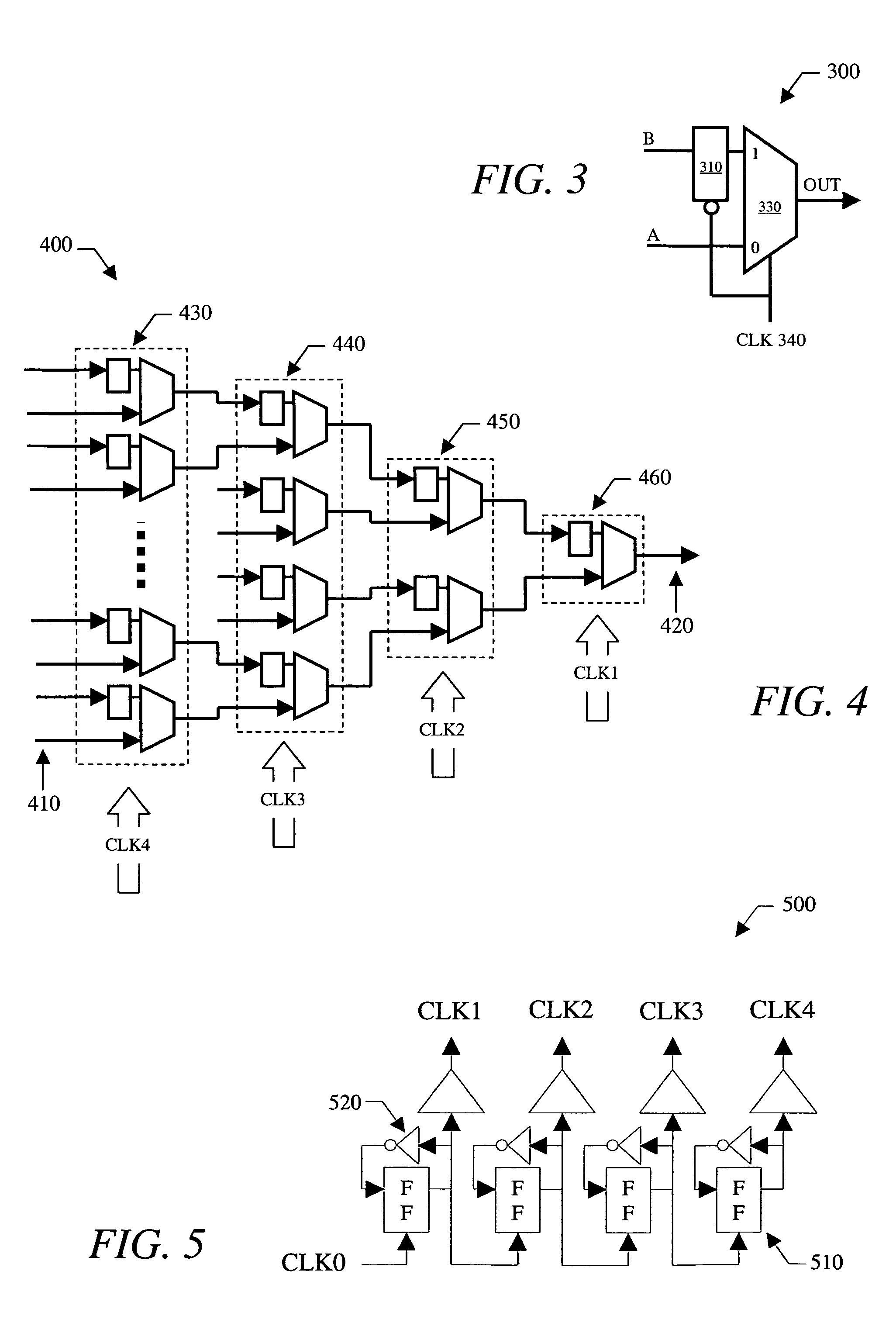

Low power serializer circuit and method

InactiveUS7006021B1Avoid operation failureReduce power consumptionParallel/series conversionComputations using pulse rate multipliers/dividersMultiplexingTransceiver

A serializer within, for example, a transceiver is provided having multiple stages of pipelined multiplexing cells. Each multiplexing cell may be substantially the same and each comprises no more than one latch. In some embodiments, each multiplexing cell includes a multiplexer comprising a pair of inputs and a single latch, which is coupled to one input of the multiplexer. No latches are coupled to the other input of the multiplexer. The serializer generally includes a plurality of stages. Each successive stage includes one-half the number of multiplexing cells included in the previous stage, and each successive stage is clocked by a clocking signal that transitions at twice the frequency of the previous stage clock signal.

Owner:RPX CORP

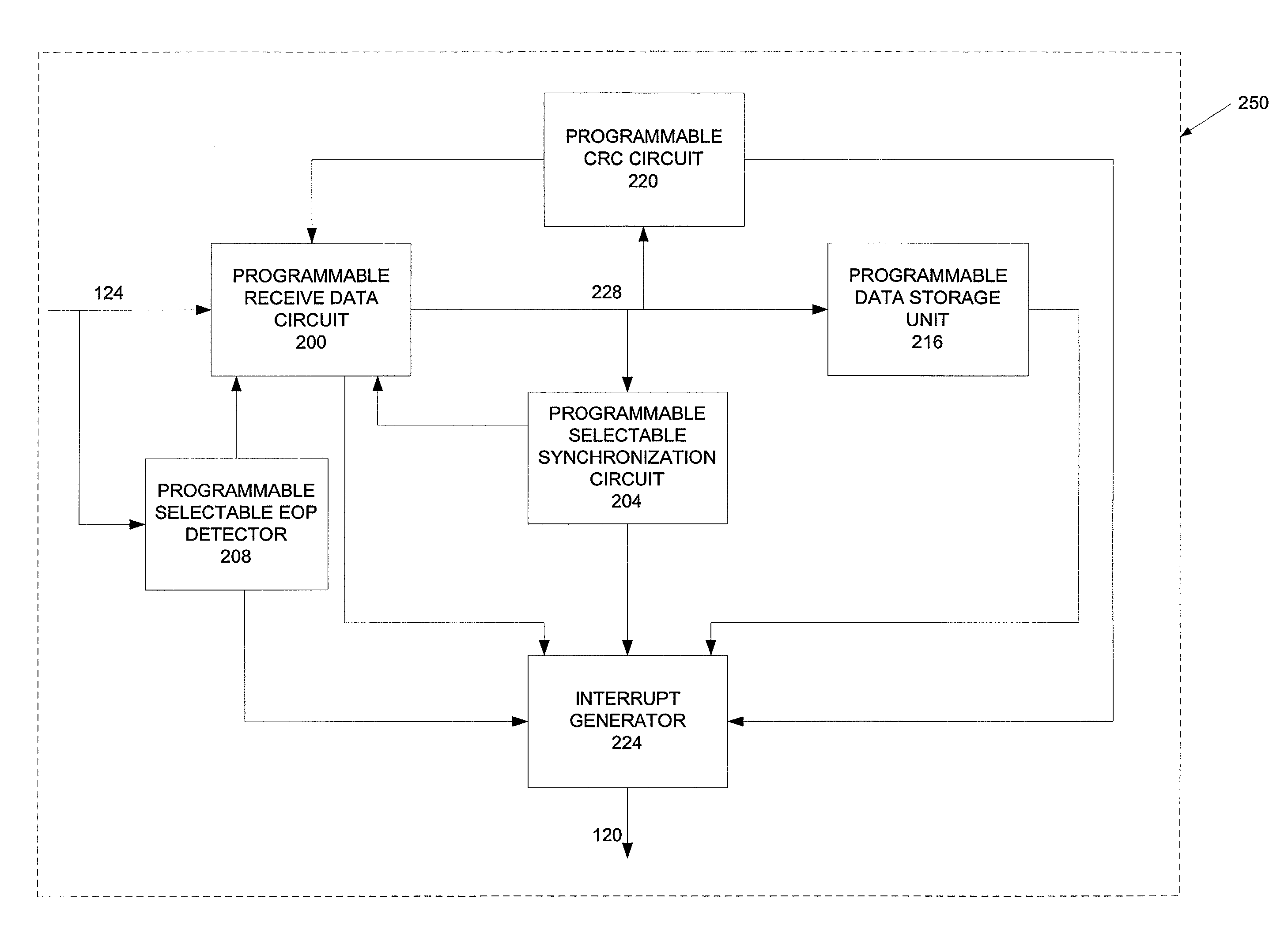

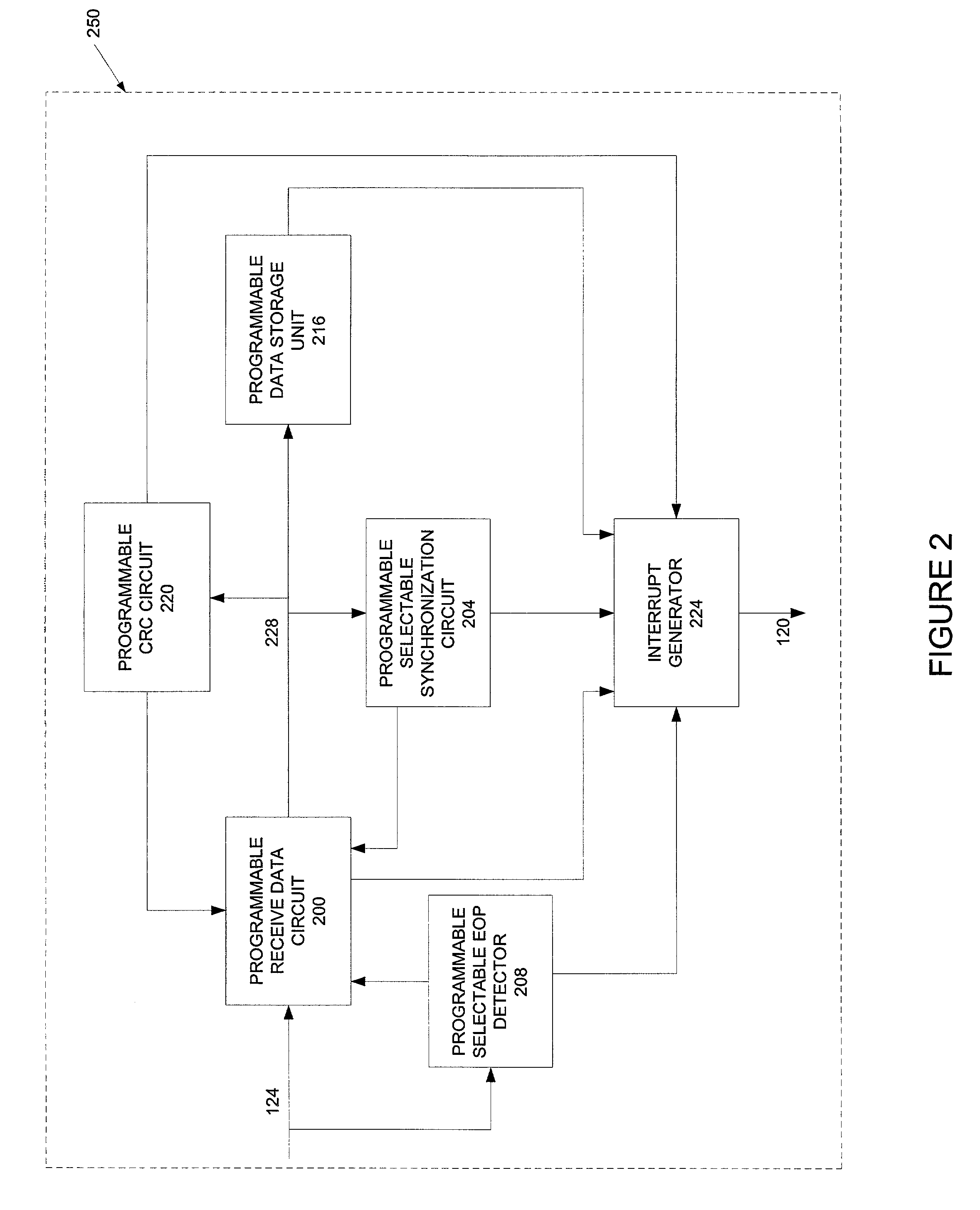

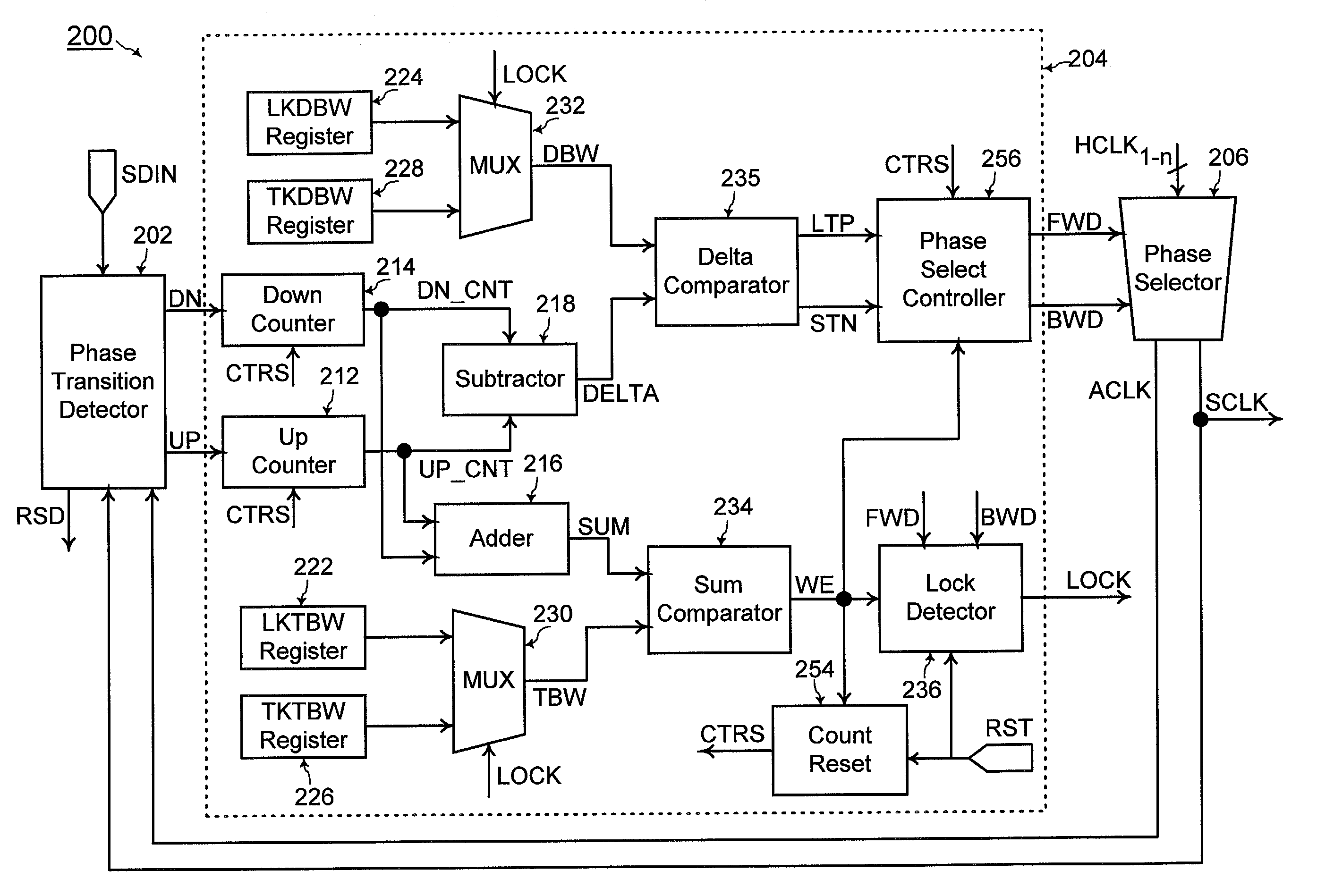

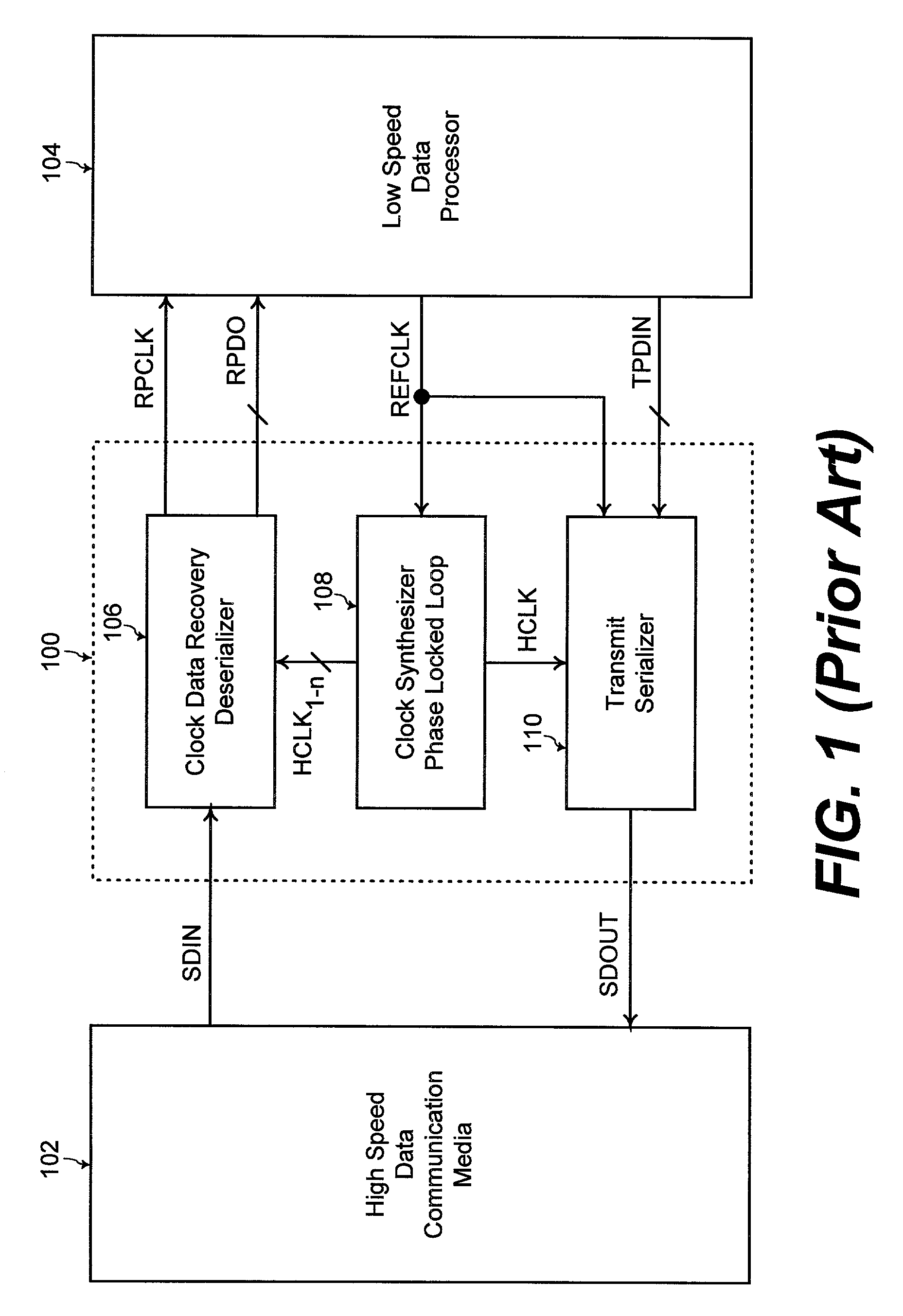

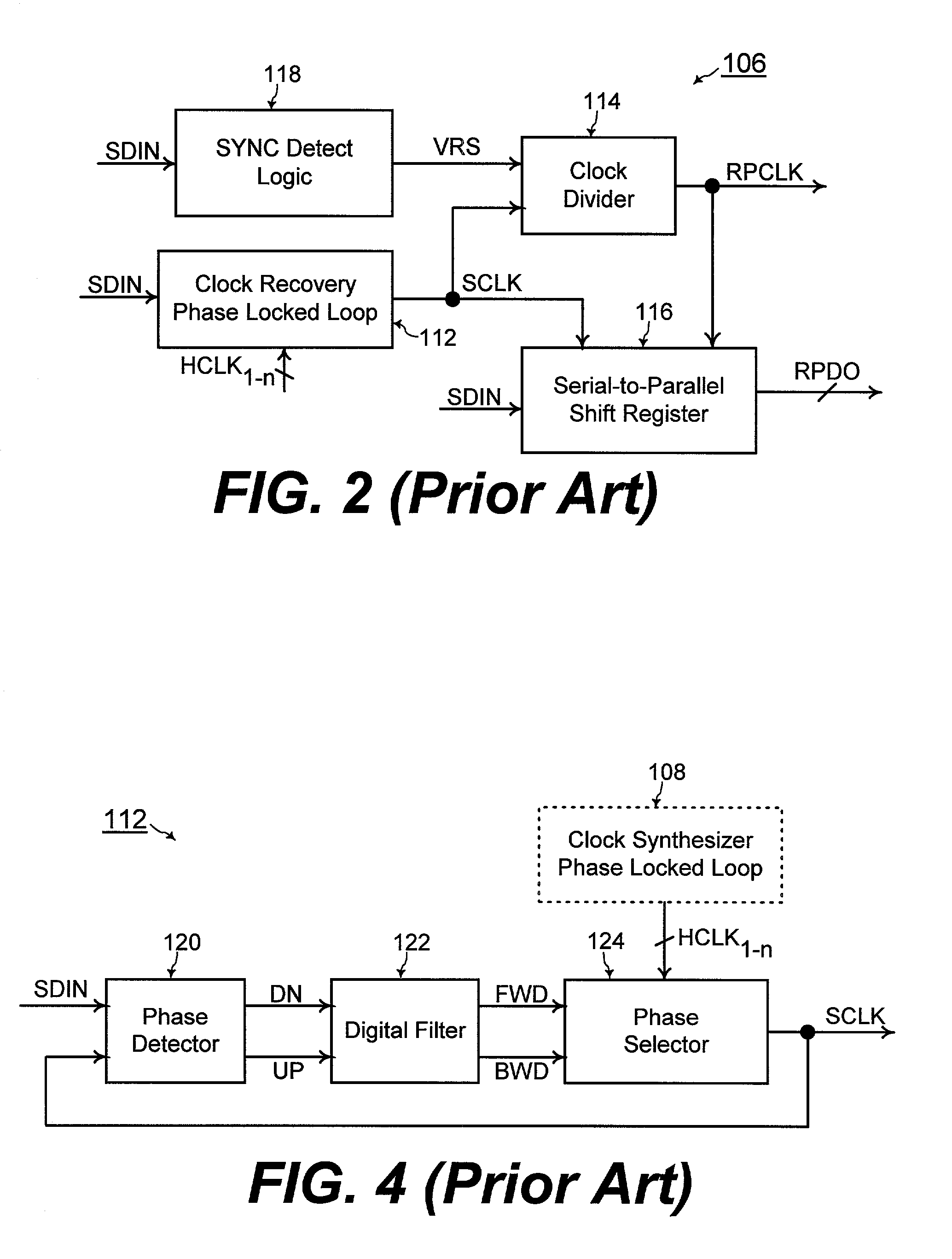

Clock data recovery deserializer with programmable SYNC detect logic

In a CDR (clock data recovery) deserializer, a clock divider receives a recovered clock signal (SCLK) and generates a divided clock signal (RPCLK). The frequency of the divided clock signal is lowered with each cycle of the divided clock signal being generated for each count of cycles of the recovered clock signal up to a predetermined ratio number. A serial-to-parallel shift register shifts in recovered serial data bits with each cycle of the recovered clock signal and outputs the predetermined ratio number of the shifted recovered serial data bits at a predetermined transition of every cycle of the divided clock signal. A SYNC (synchronization) detect logic asserts a VRS (diVider ReSet) signal coupled to the clock divider for controlling the clock divider to generate the predetermined transition for a cycle of the divided clock signal when the VRS signal is asserted. The SYNC detect logic includes a plurality of reloadable register portions for storing a plurality of synchronization bit patterns for a plurality of communications protocol. Each of a plurality of bit pattern comparators inputs an intermediate parallel data output (IPDO) from the shift register with each cycle of the recovered clock signal and compares for every cycle of the recovered clock signal the shifted recovered serial data bits to each of the synchronization bit patterns. A multiplexer selects one of the outputs of the bit pattern comparators as the VRS signal depending on the communications protocol of the recovered serial data bits.

Owner:LATTICE SEMICON CORP

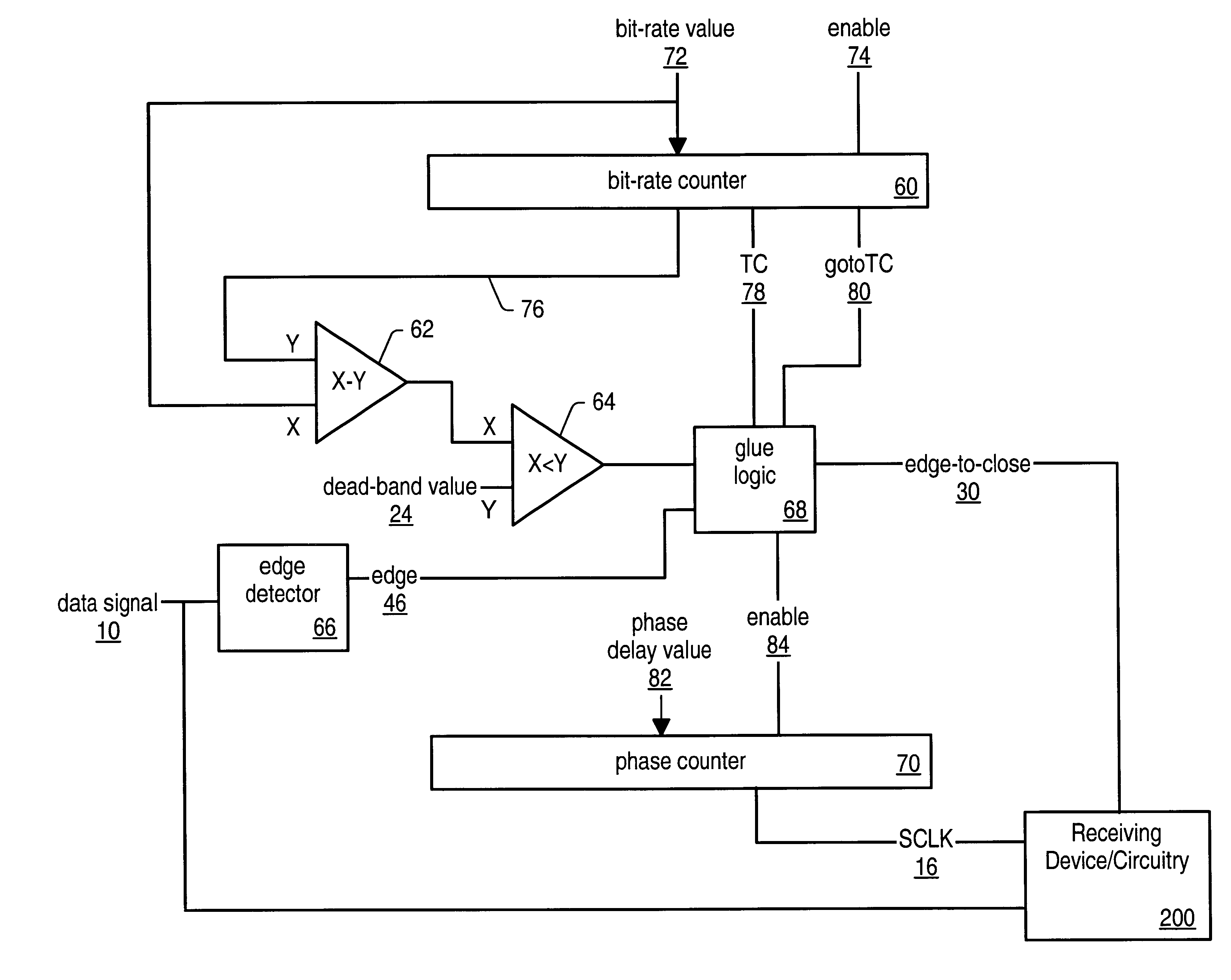

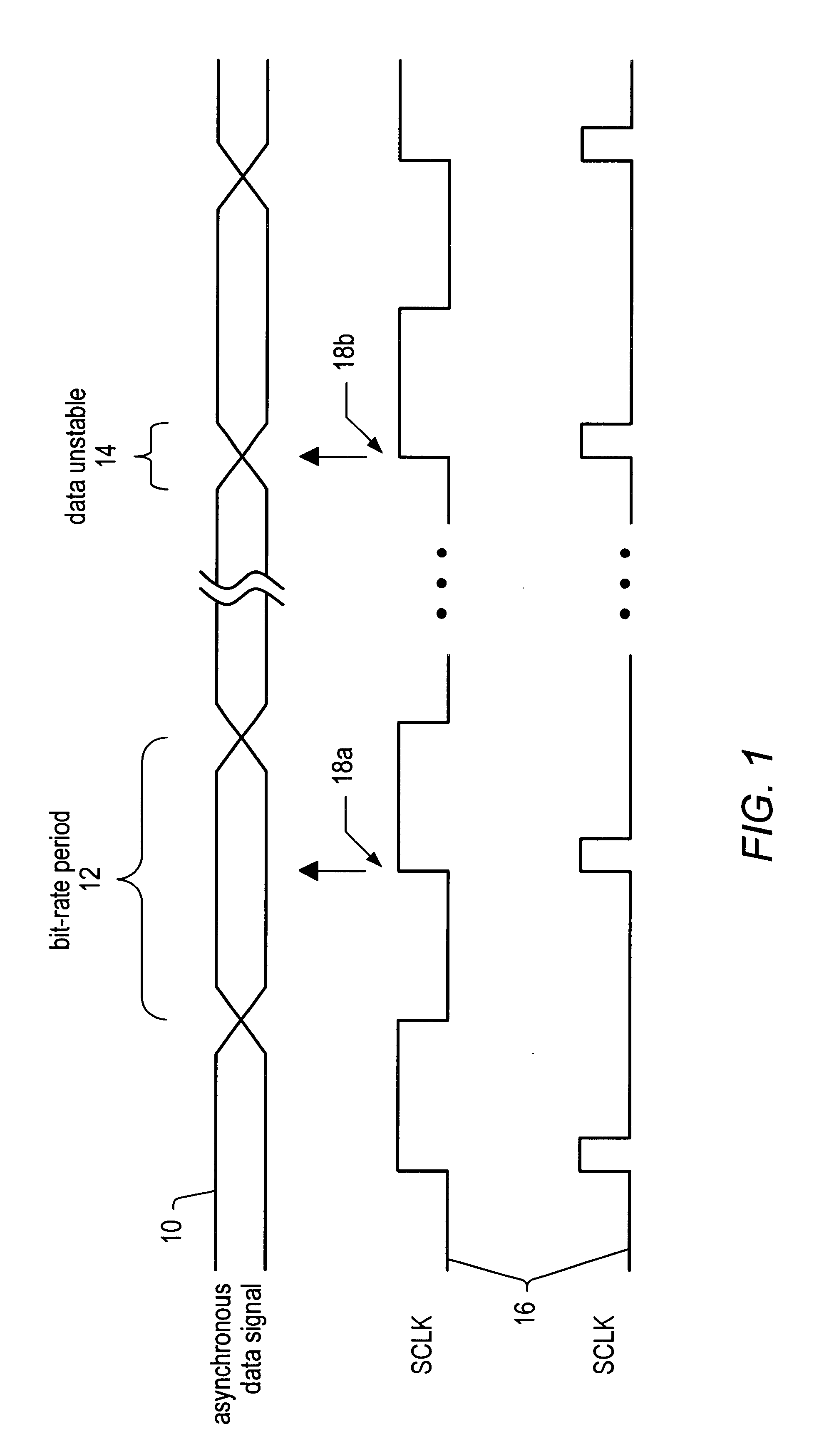

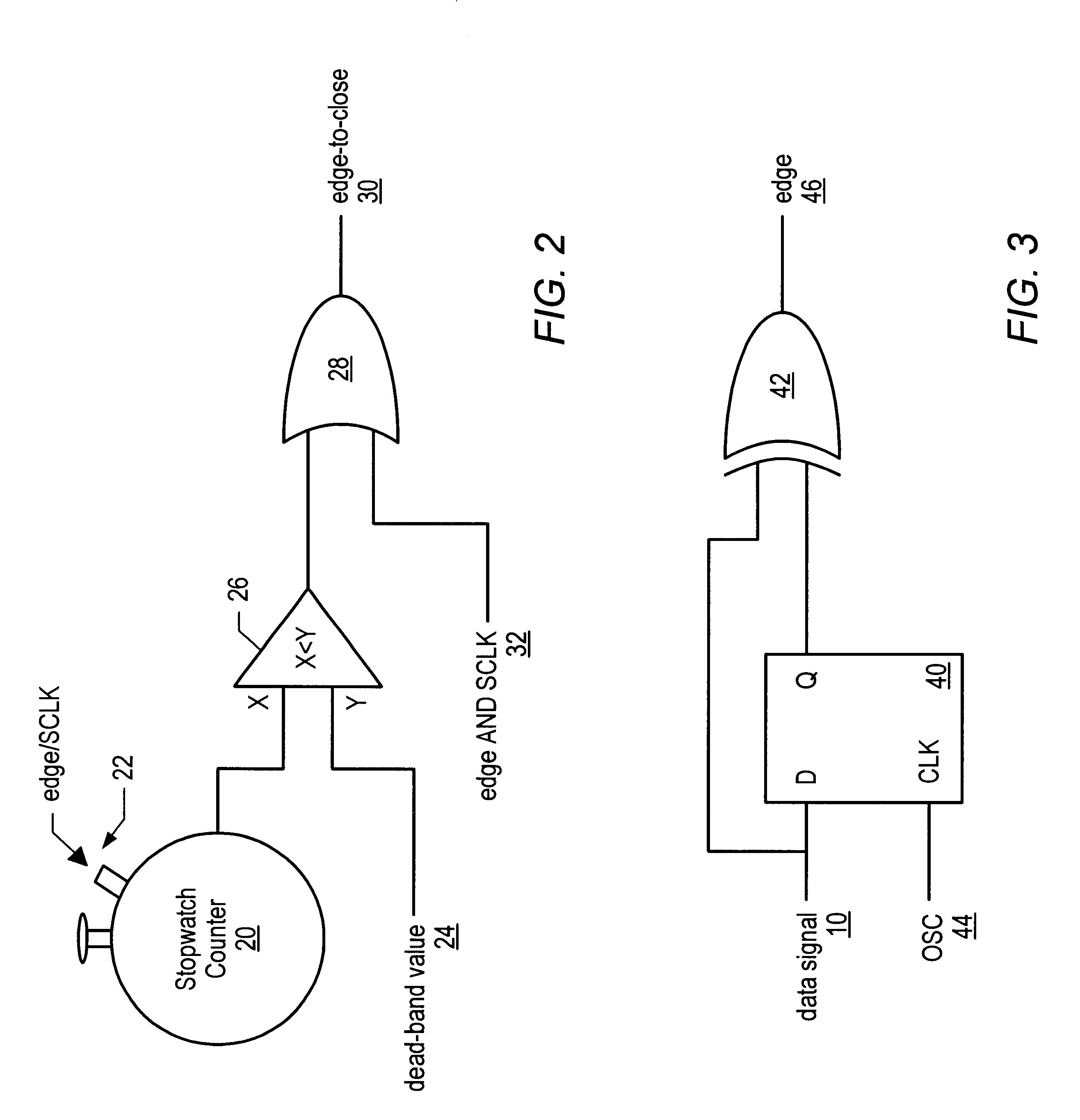

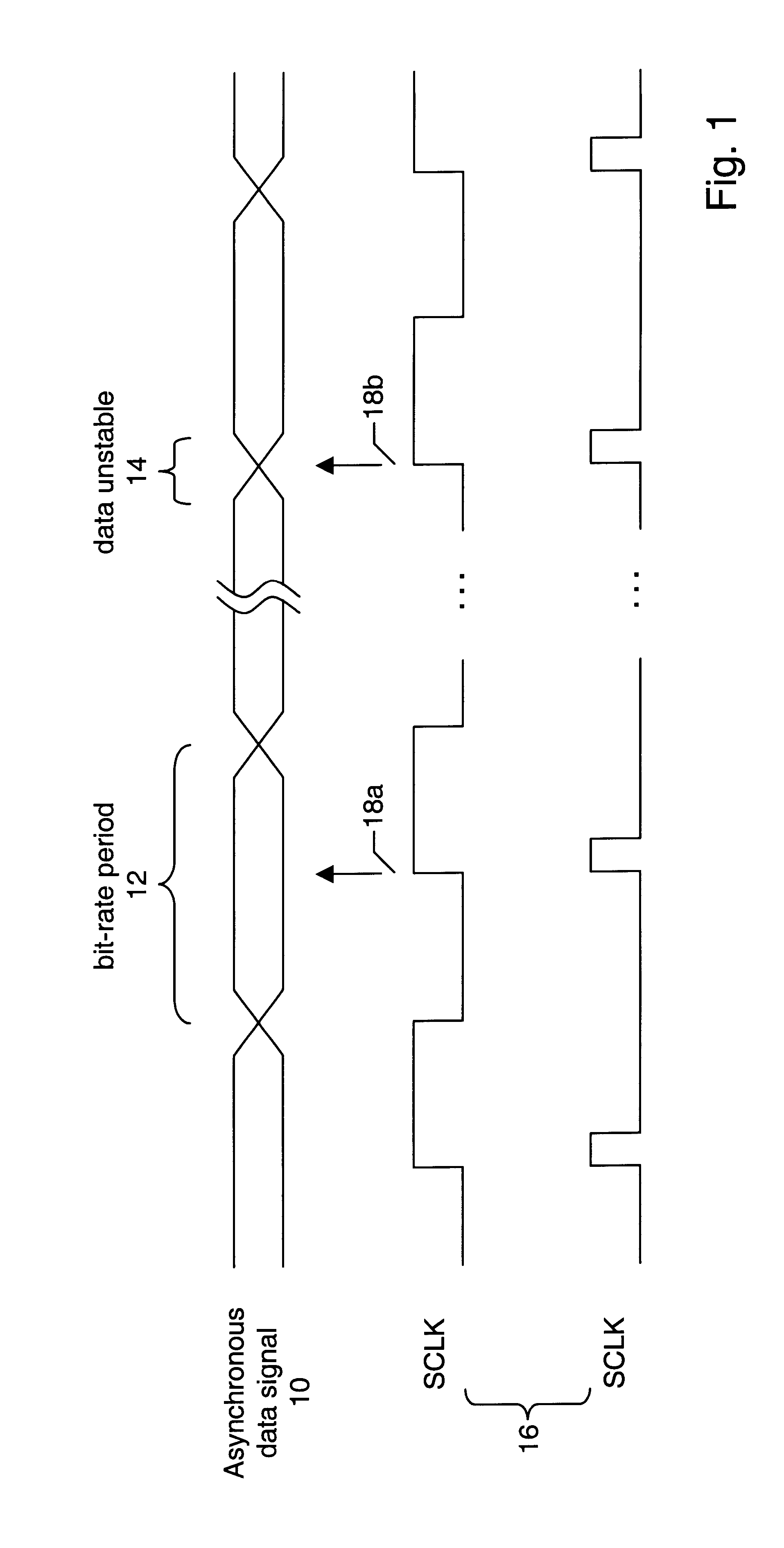

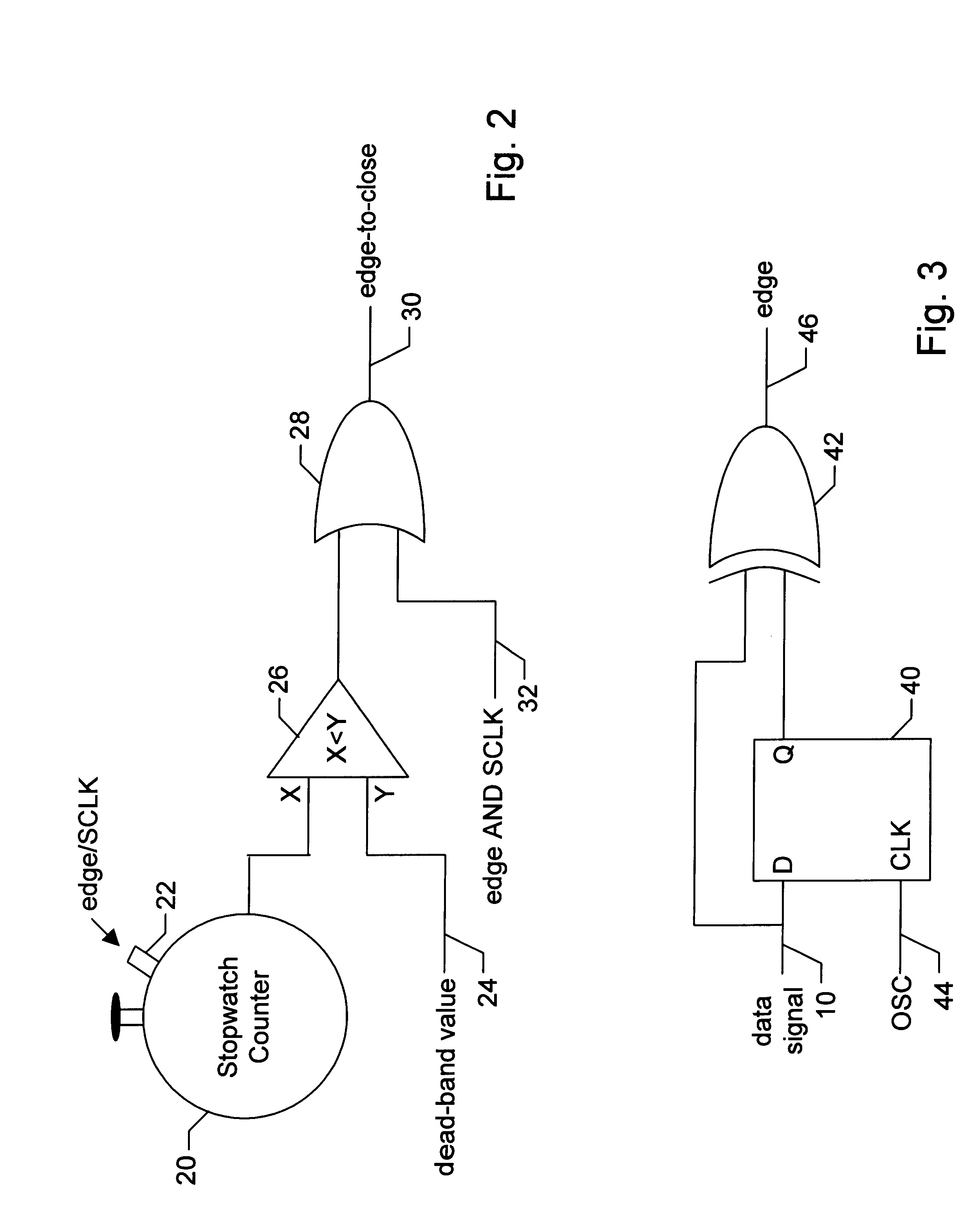

Clock synchronization for asynchronous data transmission

An apparatus for receiving an asynchronous data signal may include a clock generator that generates a clock signal having a frequency approximately equal to the bit rate of the asynchronous data signal. An edge detector may detect transitions of the asynchronous data signal. A dead-band detector may detect when a transition of the clock signal used to sample the data signal occurs within a predetermined amount of time of a transition of the asynchronous data signal so that data sampled on that transition of the clock signal may be invalid. The phase of the clock signal may be adjusted if the transition of the clock signal occurs within this predetermined amount of time. The clock generator may include two programmable counters, one which may be programmed with a bit-rate value so that it generates a signal approximately matching the bit rate of the asynchronous data signal, and the other programmed with a phase-delay value so that it generates a sample clock signal at a phase delay from the signal generated by the first counter. The phase of the sample clock may be adjusted by restarting the counters in response to a transition on the asynchronous data signal. Data may be supplied to a serial-to-parallel converter including a first shift register configured to shift a data word in serially and output the data word in parallel and a second shift register configured to track when the data word had been completely shifted into the first shift register.

Owner:NATIONAL INSTRUMENTS

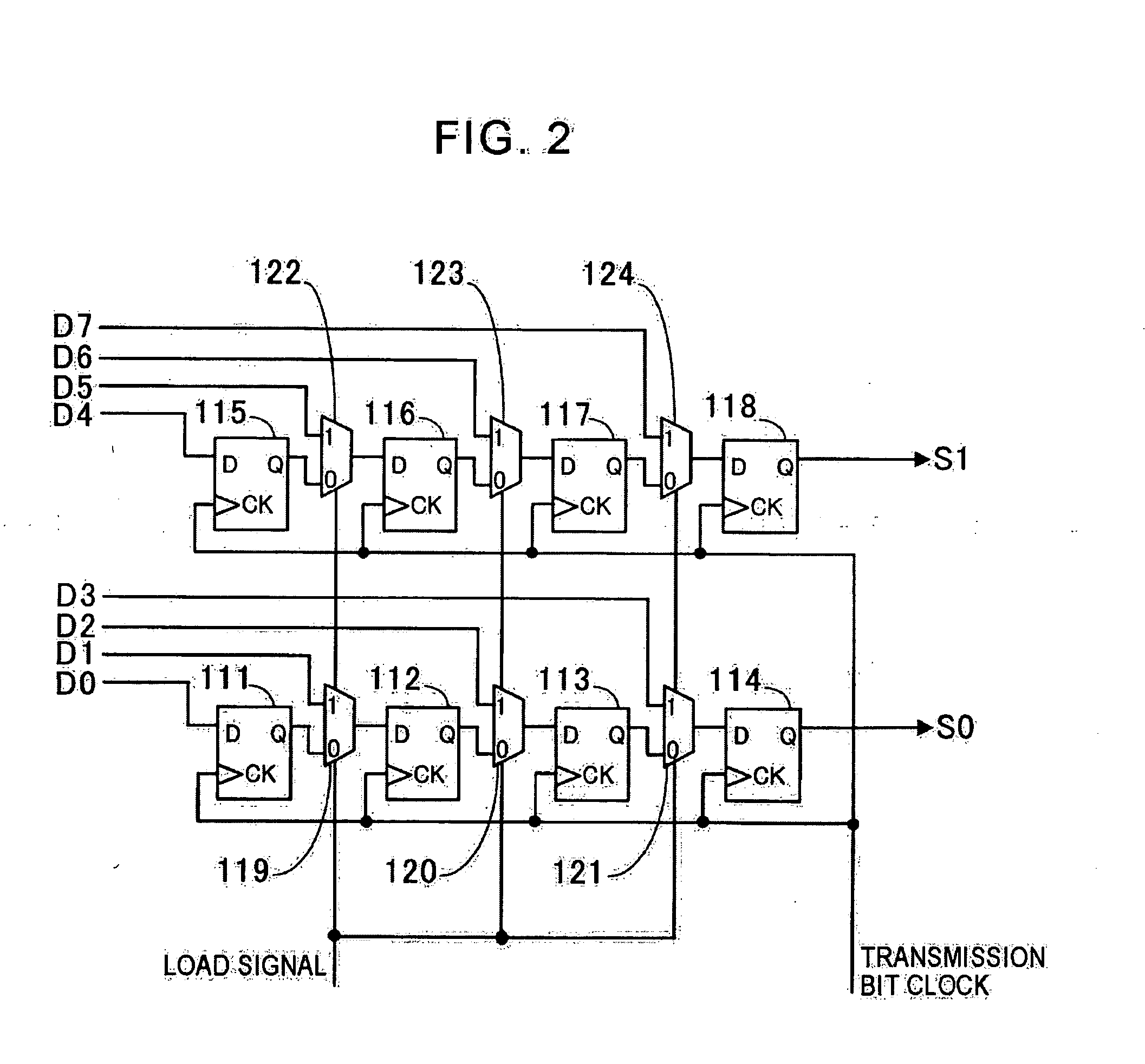

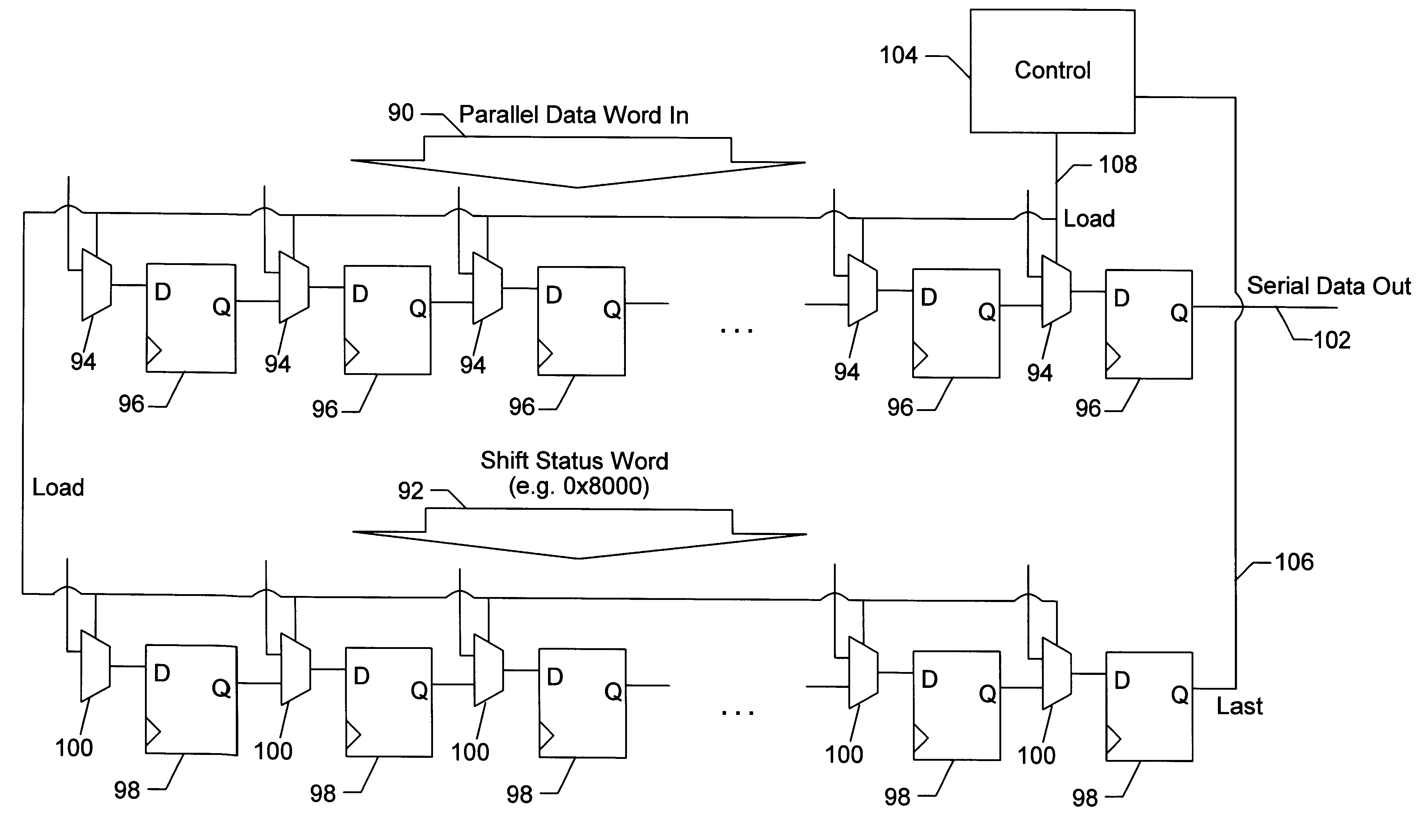

Adjustable serial-to-parallel or parallel-to-serial converter

A clock synchronizer may include two programmable counters, one which may be programmed with a bit-rate value so that it generates a signal approximately matching the bit rate of the asynchronous data signal, and the other programmed with a phase-delay value so that it generates a sample clock signal at a phase delay from the signal generated by the first counter. The phase of the sample clock may be adjusted by restarting the counters in response to a transition on the asynchronous data signal. Data may be supplied to a serial-to-parallel converter including a first shift register configured to shift a data word in serially and output the data word in parallel and a second shift register configured to track when the data word had been completely shifted into the first shift register and to cause the data word to be outputted in parallel from the first shift register so that a new word may be shifted into the first shift register. A status value may be loaded into the second shift register so that when the last bit is converted in the first shift register, the second shift register shifts out a conversion completed indication. The bit length to be converted may be changed by loading a different status value into the second shift register. This same technique may be employed in a parallel-to-serial data converter or in a general data converter that may convert from serial-to-parallel or parallel-to-serial according to a conversion-type signal.

Owner:NATIONAL INSTRUMENTS

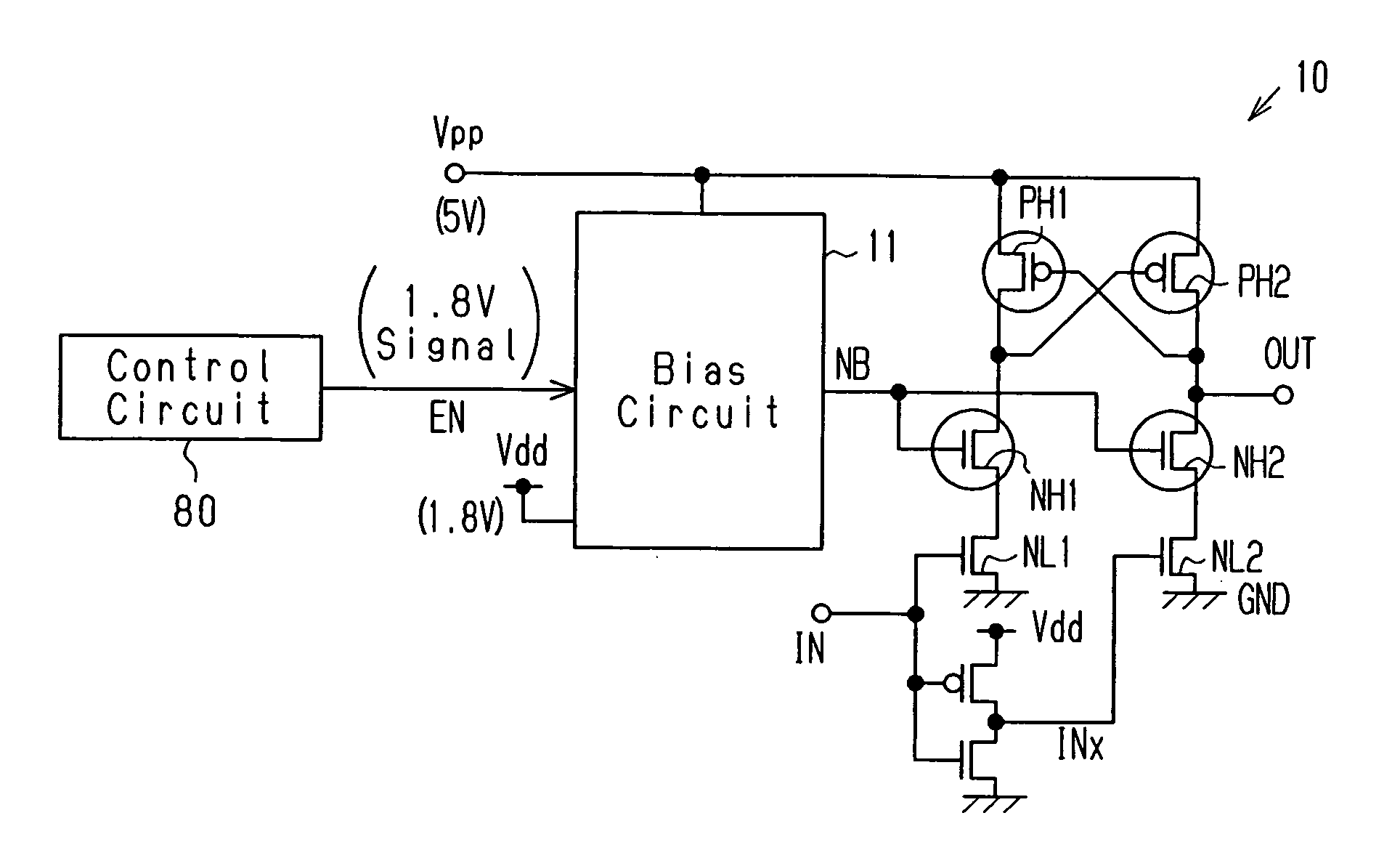

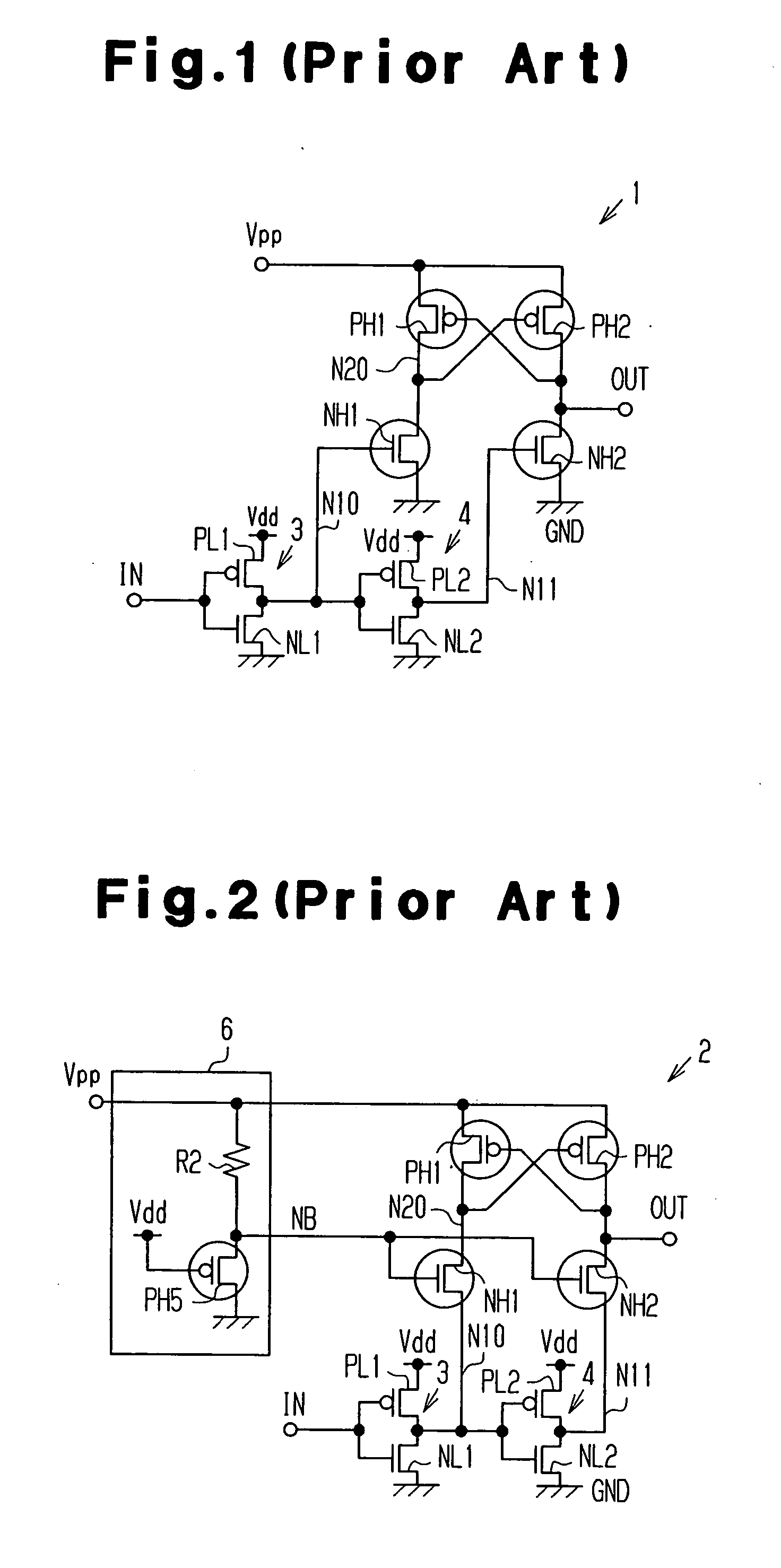

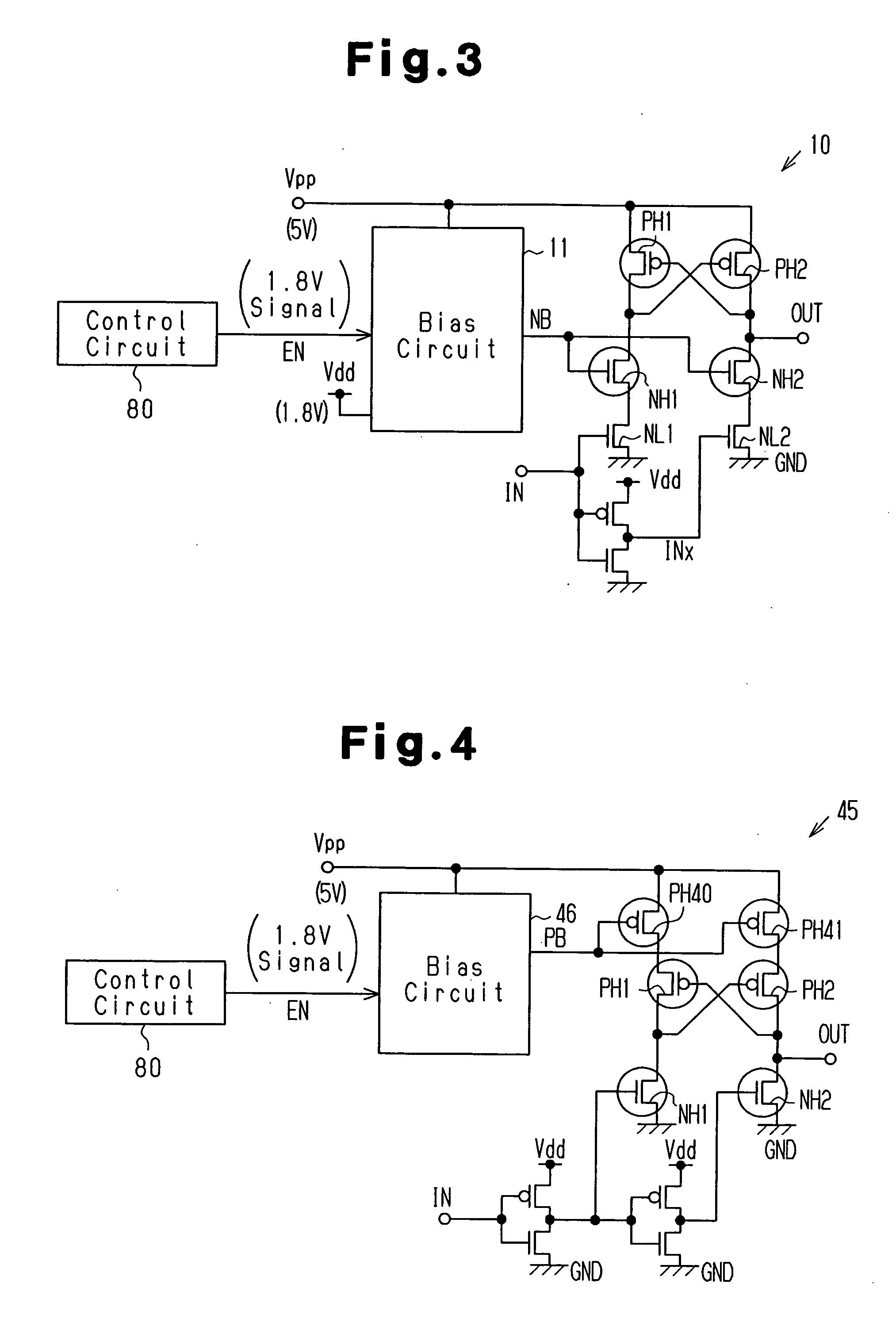

Level conversion circuit

ActiveUS20050237099A1Operation speed blockReduce power supply voltageParallel/series conversionPulse automatic controlControl signalEngineering

A level conversion circuit that prevents the operation speed from decreasing when the power supply voltage decreases while appropriately performing level conversion. The level conversion circuit includes first and second PMOS transistors. A first NMOS transistor is connected to the first PMOS transistor and the second PMOS transistor. A second NMOS transistor is connected to the second PMOS transistor and the first PMOS transistor. A bias circuit, connected to the first and second NMOS transistors, generates a bias potential that is supplied to the first and second NMOS transistors and that is greater than the first voltage by a threshold voltage of the first and second NMOS transistors. The bias circuit further controls current, which determines the bias potential and flows to the bias circuit, in accordance with a control signal having the first voltage.

Owner:CYPRESS SEMICON CORP

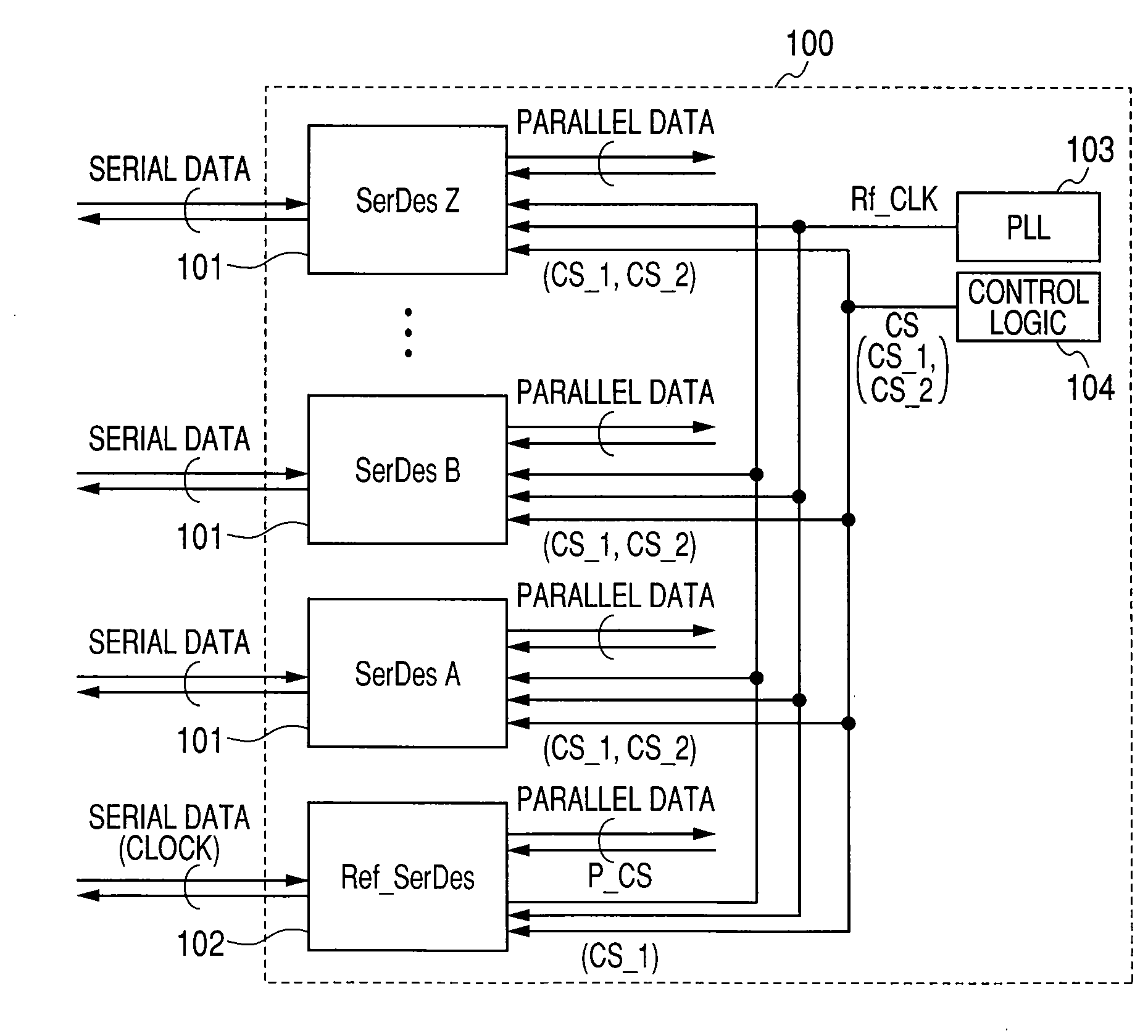

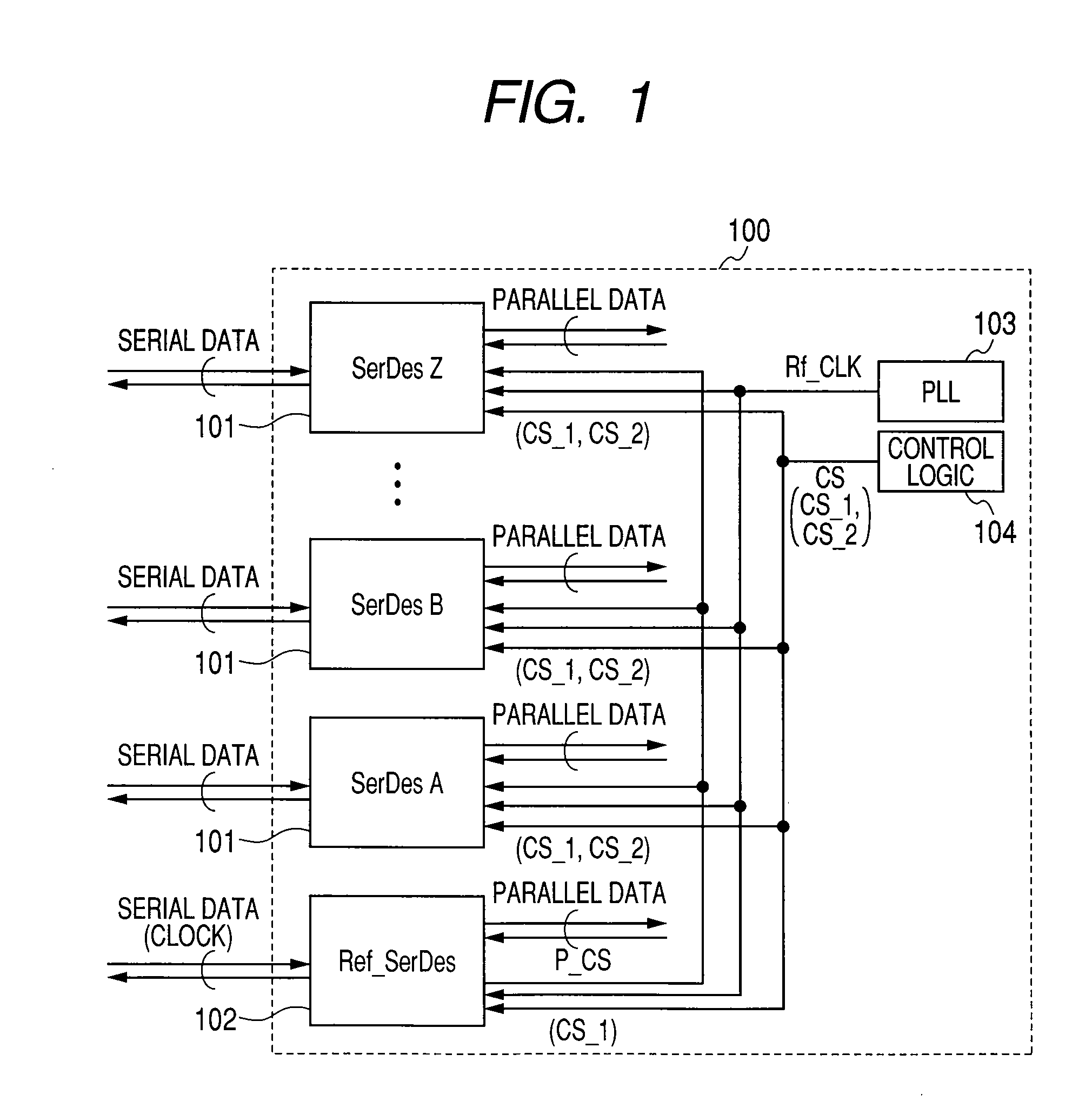

Semiconductor system

InactiveUS20090080584A1Eliminate the effects ofSmooth transferParallel/series conversionSynchronisation information channelsPhase controlComputer science

A semiconductor system has a SerDes circuit for receiving serial data, and a reference SerDes circuit for receiving clock signals running in parallel. The SerDes circuit performs serial to parallel conversion of the serial data captured by the recovery clock whose phase is controlled by utilizing the phase control signal P_CS generated by the reference SerDes circuit.

Owner:HITACHI LTD

Method and apparatus for conversion between quasi differential signaling and true differential signaling

InactiveUS20070103204A1Channel dividing arrangementsParallel/series conversionDifferential signalingManagement process

Transmit-side active signal management circuitry applies one or more active signal management processes to a digital signal at a transmit side of an interconnect. At the receive side of the interconnect, receive-side active signal management circuitry applies one or more corresponding active signal management processes, as appropriate, to the received digital signal to recover the information represented by the original digital signal. The interconnect can include a cable used to transmit the signals between a source device and a destination device, whereby one or both of the transmit-side active signal management circuitry and the receive-side active signal management circuitry is implemented at a corresponding cable receptacle of the cable. Alternately, one or both of the transmit-side active signal management circuitry and the receive-side active signal management circuitry can be implemented at a cable adaptor, thereby permitting the use of a passive cable interconnect to transmit the signal.

Owner:XEMI

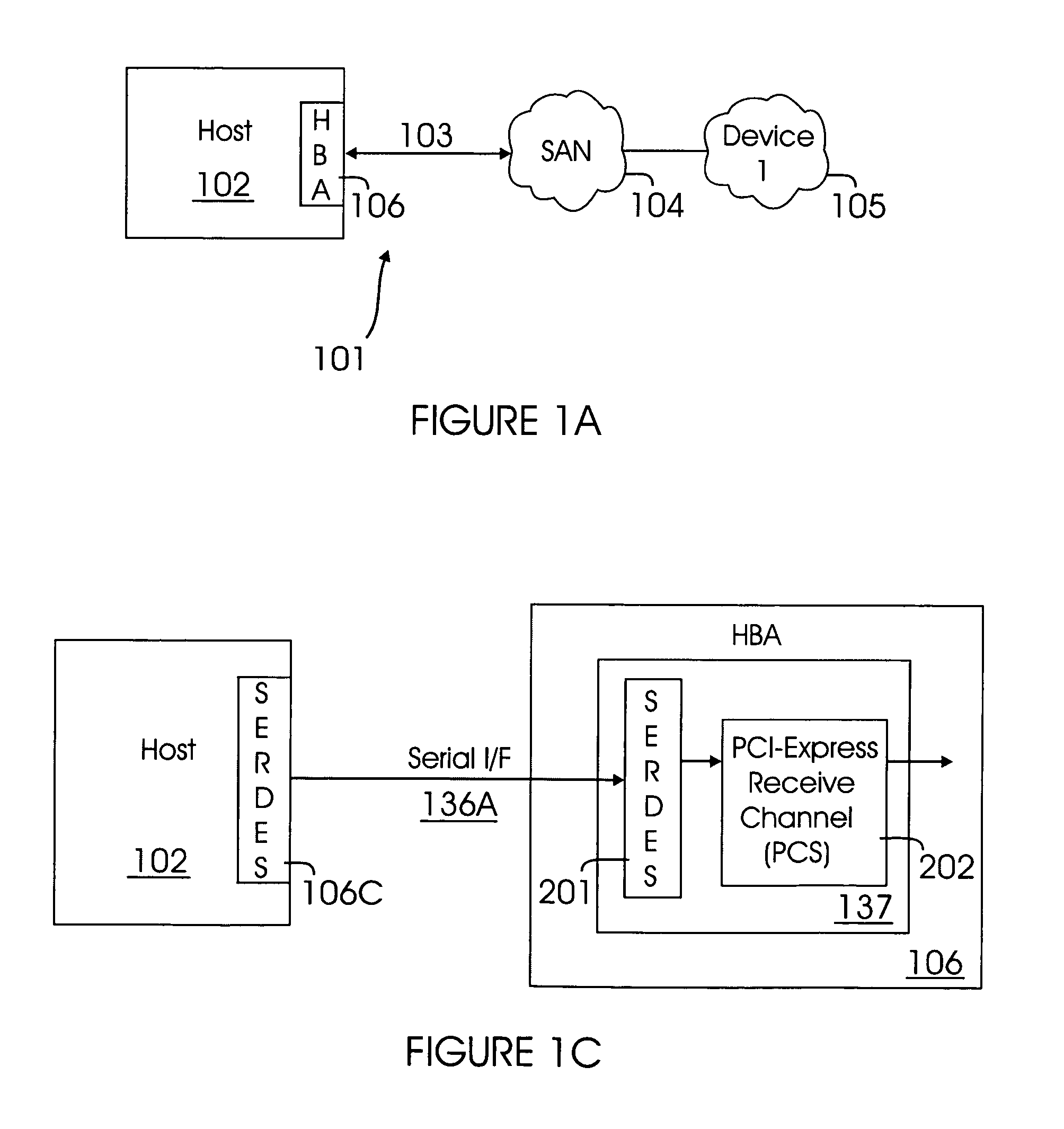

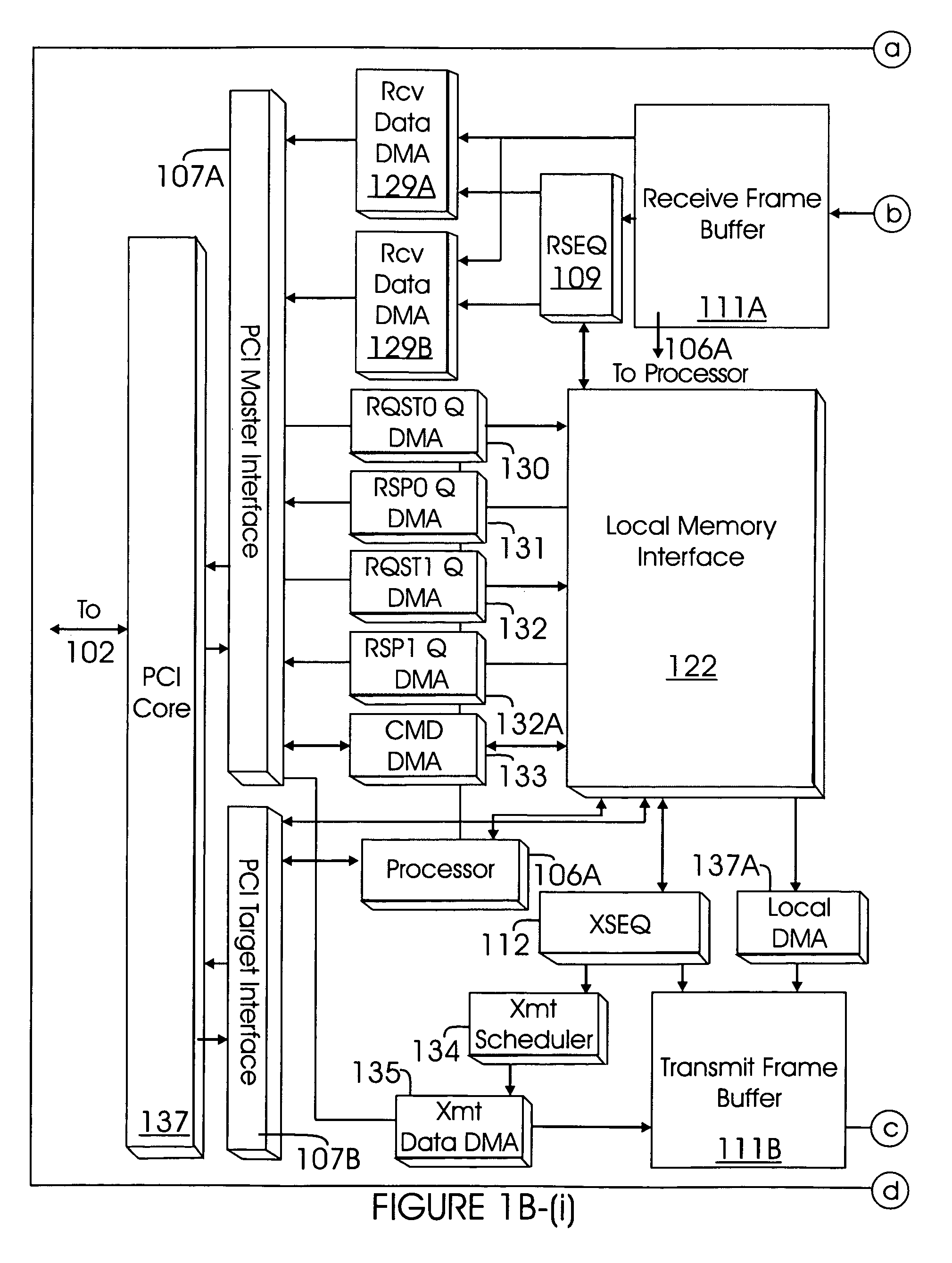

Method and system for synchronizing bit streams for PCI express devices

A PCI Express device is provided. The PCI Express device includes a symbol lock module that includes a state machine for detecting a special character in a serial bit stream received from a serial / de-serializer, wherein the state machine receives a first special character and verifies alignment of the special character by comparing with a previously stored alignment value and the state machine declares a symbol lock if at least more than one special character alignment matches with a same stored alignment value. The special character is a comma sequence. After a symbol lock is declared, the state machine continues to monitor incoming bit stream data and compares each new special character alignment with the previously stored alignment value. During the monitoring if a misaligned special character is detected, then the state machine waits to receive another special character before declaring a loss of synchronization.

Owner:MARVELL ASIA PTE LTD

Encoding and deserialization-serialization for digital signals

InactiveUS20070206641A1Channel dividing arrangementsParallel/series conversionManagement processEngineering

Transmit-side active signal management circuitry applies one or more active signal management processes to a digital signal at a transmit side of an interconnect. At the receive side of the interconnect, receive-side active signal management circuitry applies one or more corresponding active signal management processes, as appropriate, to the received digital signal to recover the information represented by the original digital signal. The interconnect can include a cable used to transmit the signals between a source device and a destination device, whereby one or both of the transmit-side active signal management circuitry and the receive-side active signal management circuitry is implemented at a corresponding cable receptacle of the cable. Alternately, one or both of the transmit-side active signal management circuitry and the receive-side active signal management circuitry can be implemented at a cable adaptor, thereby permitting the use of a passive cable interconnect to transmit the signal.

Owner:XEMI

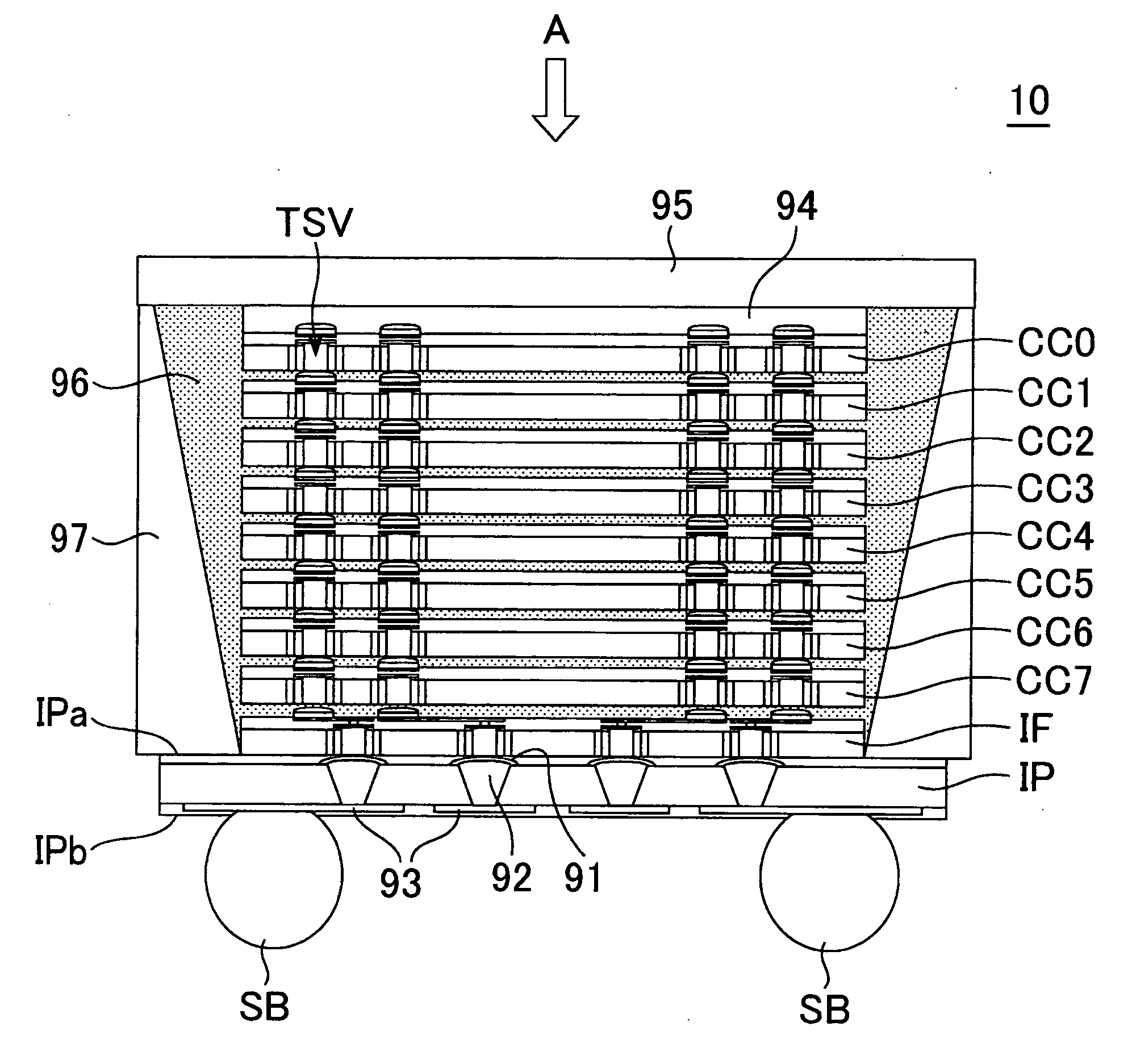

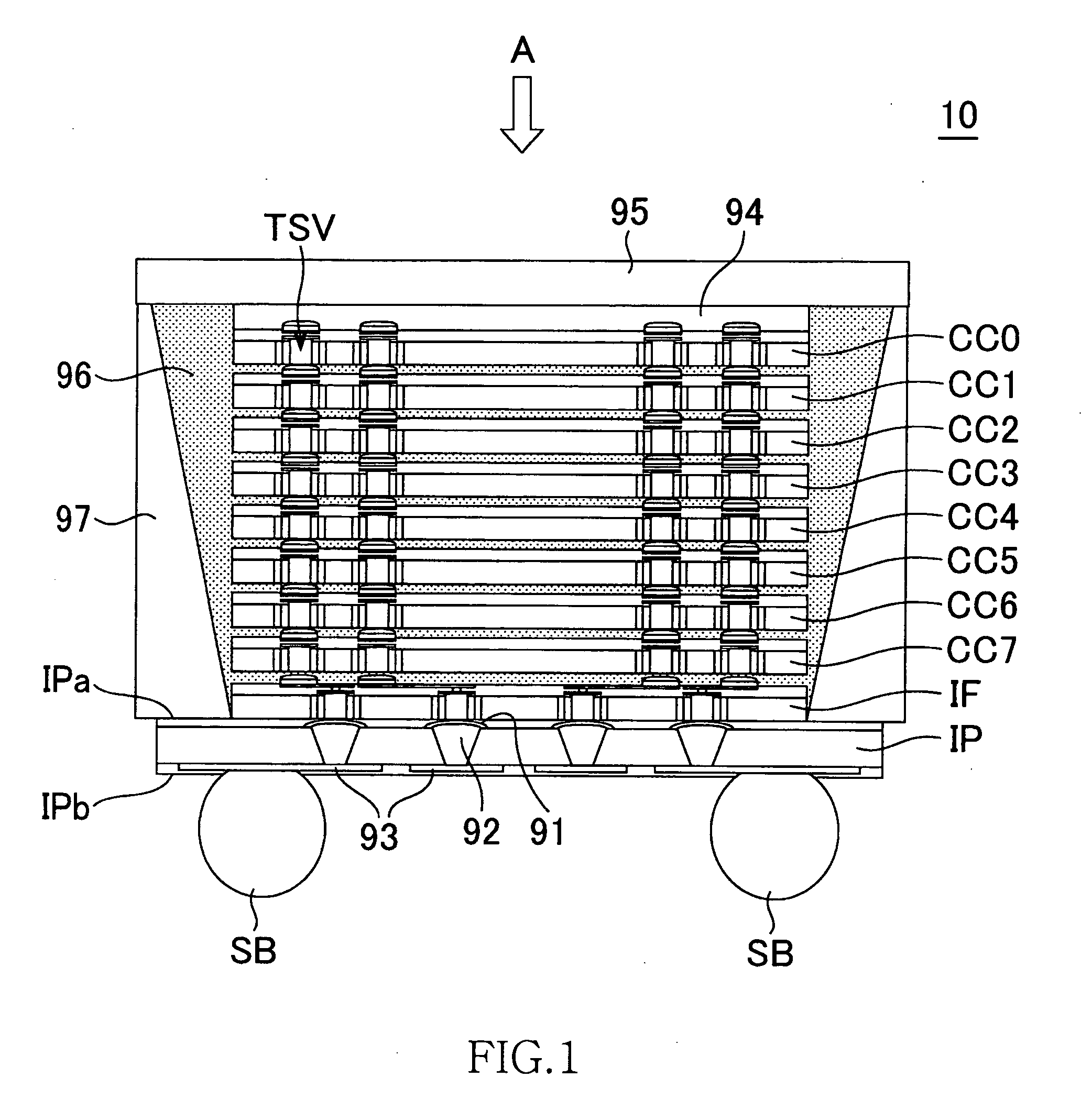

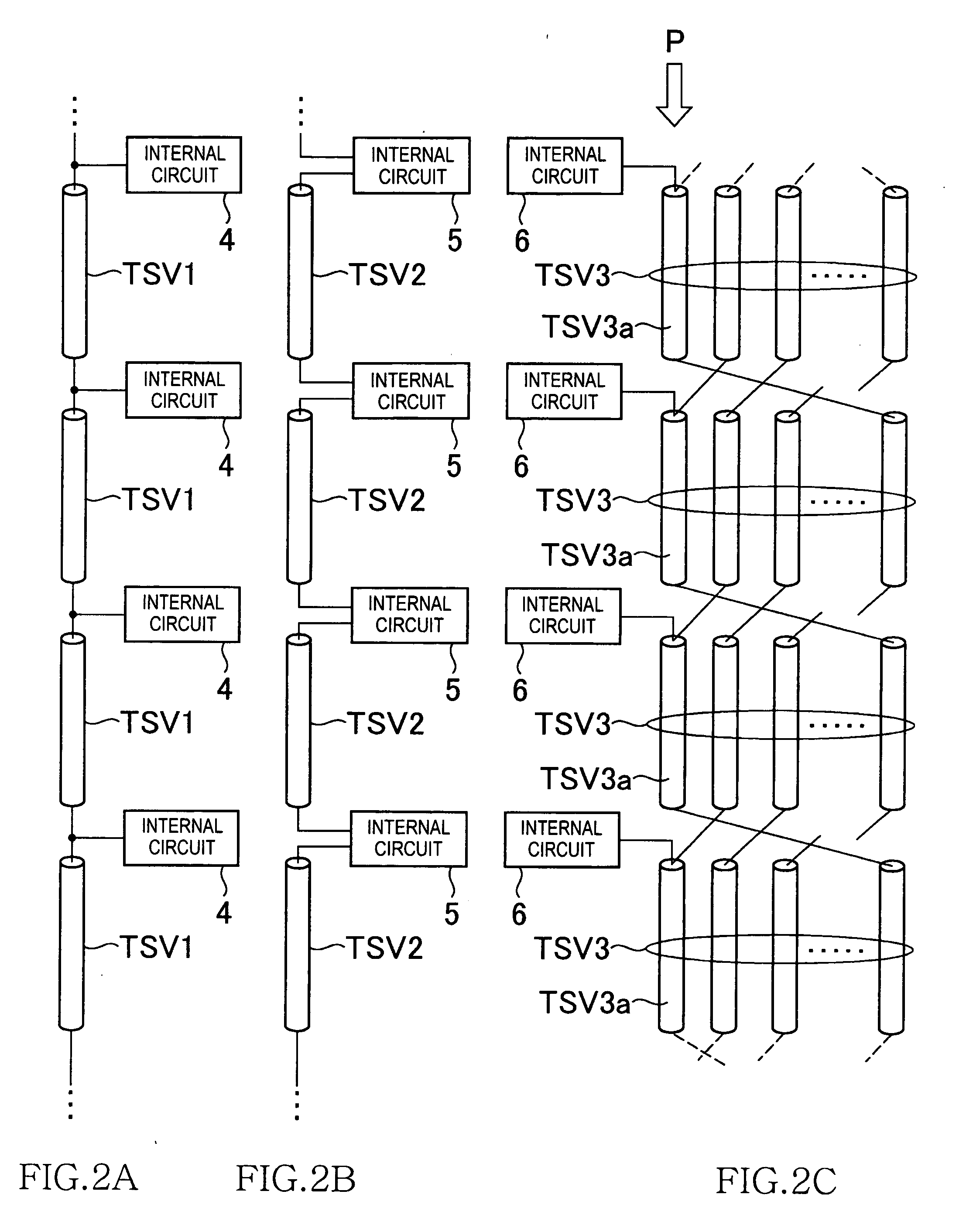

Semiconductor device having plural semiconductor chips laminated to each other

ActiveUS20110057819A1Reduce areaReduce chip areaParallel/series conversionSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor chip

In a stacked semiconductor device in which a plurality of through silicon vias used for data transfer are shared among a plurality of semiconductor chips, a first semiconductor chip included in the semiconductor chips holds through silicon via switching information for specifying a through silicon via among the through silicon vias to be used for data transfer, and transfers the through silicon via switching information to a second semiconductor chip included in the semiconductor chips. According to the present invention, because the through silicon via switching information is transferred from the first semiconductor chip to the second semiconductor chip, a circuit for storing the through silicon via switching information in a nonvolatile manner is not required in the second semiconductor chip. With this arrangement, a chip area of the second semiconductor chip can be reduced.

Owner:LONGITUDE LICENSING LTD

Receiver circuit and receiving method

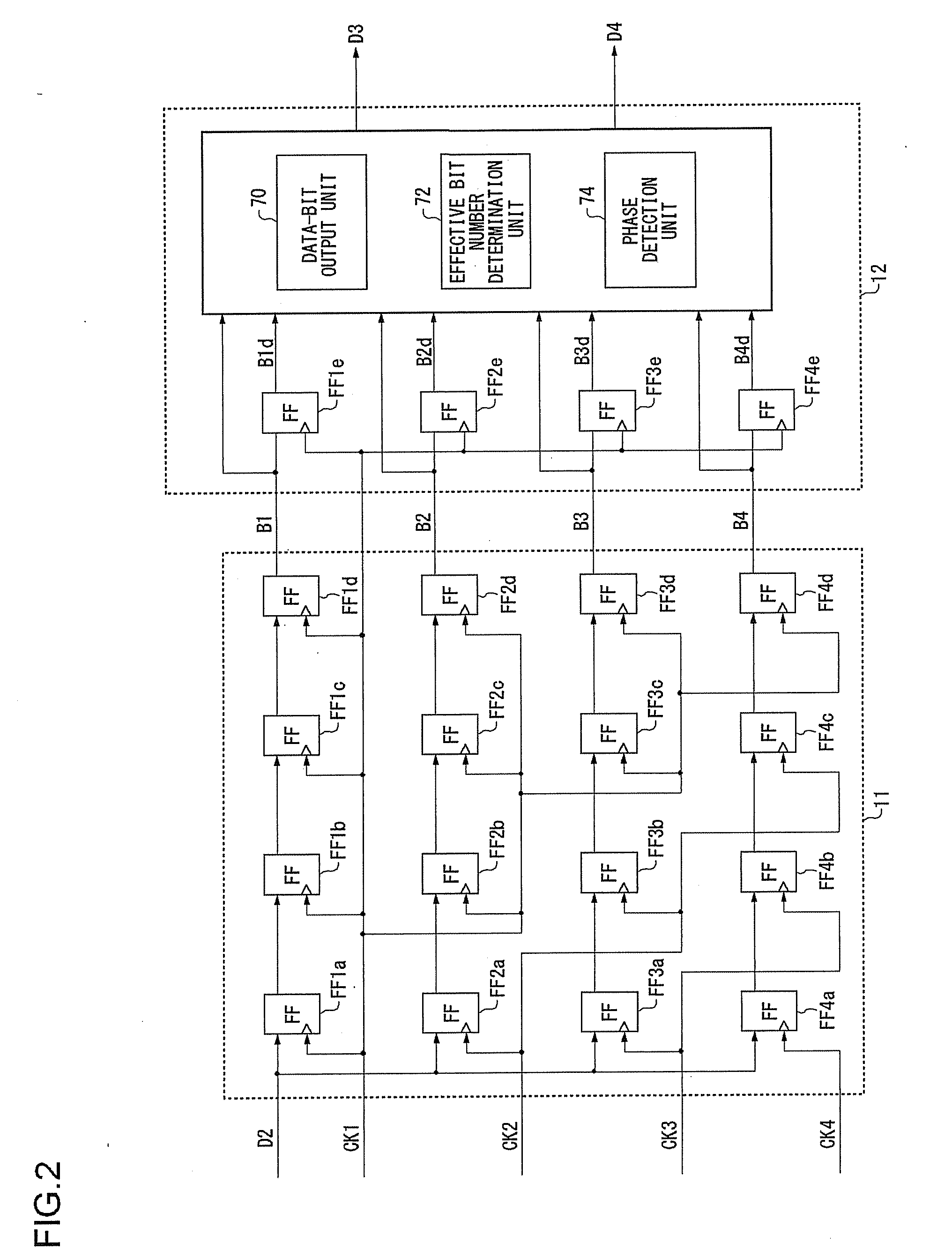

InactiveUS20080159444A1Parallel/series conversionPulse automatic controlPhase shiftedTransition edge

Clock signals are supplied, with a phase shift of 1 / n cycles between adjacent clock signals. A data acquisition unit acquires serial data at a timing of each of the clock signals. A phase detection unit detects the phase of the transition edge of the serial data using n bits of data. An effective bit number determination unit determines the effective bit number, which is the number of bits to be acquired, based upon the phase of the transition edge of the serial data in the current data-bit acquisition step and the phase of the transition edge of the serial data in the previous data-bit acquisition step. A data-bit output unit outputs the effective bit number of the bits of data acquired at a timing of each clock signal having a predetermined phase relation with the transition edge of the serial data.

Owner:ROHM CO LTD

Sending and/or receiving serial data with bit timing and parallel data conversion

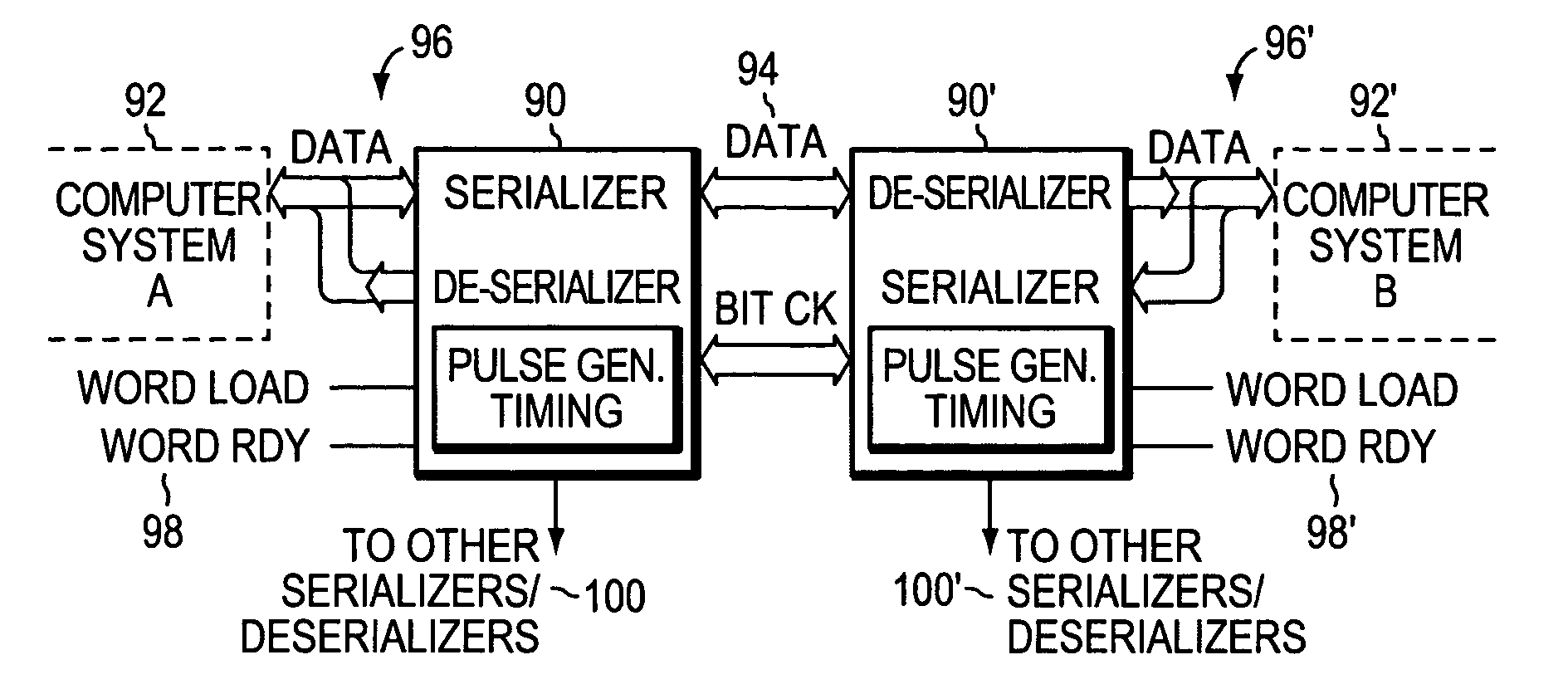

A serializer and a deserializer are disclosed and shown operating singly or as a pair. The invention operates independently from any outside system reference clock. The inventive system provides an internal bit clock that serializes the data when sending and de-serializes the data when receiving. A bit clock or pulse travels with the data word bits to define when a bit is stable. The system uses word boundary bits operating with a bit clock to distinguish different data words, as described in the parent application. The system operates either synchronously or asynchronously with the base computer or other such digital system, including I / O devices. The invention finds use where new data to be sent is strobed into the serializer, but also where a change in the data bit content itself will cause the changed data to be loaded into the serializer and sent bit by bit. The system operates where new data is strobed or loaded by the serializer (not the base computer system) when the last data word has been sent. In this case a signal is generated when the last word has been sent in the serializer that causes new data to be loaded for sending. Half duplex and full duplex configurations as disclosed. Similar, corresponding operations occur at the deserializer.

Owner:SEMICON COMPONENTS IND LLC

Popular searches

Color television details Duration/width modulated pulse demodulation Position-modulated pulse demodulation Pulse duration/width modulation Pulse combined modulation Pulse position modulation Angle demodulation by phase difference detection Pulse frequency/rate modulation Synchronous/start-stop systems Color television with pulse code modulation