Patents

Literature

470 results about "Synchronizer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, a synchronizer is an algorithm that can be used to run a synchronous algorithm on top of an asynchronous processor network, so enabling the asynchronous system to run as a synchronous network.

Agile network protocol for secure communications with assured system availability

InactiveUS6907473B2Prevents denial-of-service attackAvoid attackError detection/correctionMultiple digital computer combinationsSecure communicationPrivate network

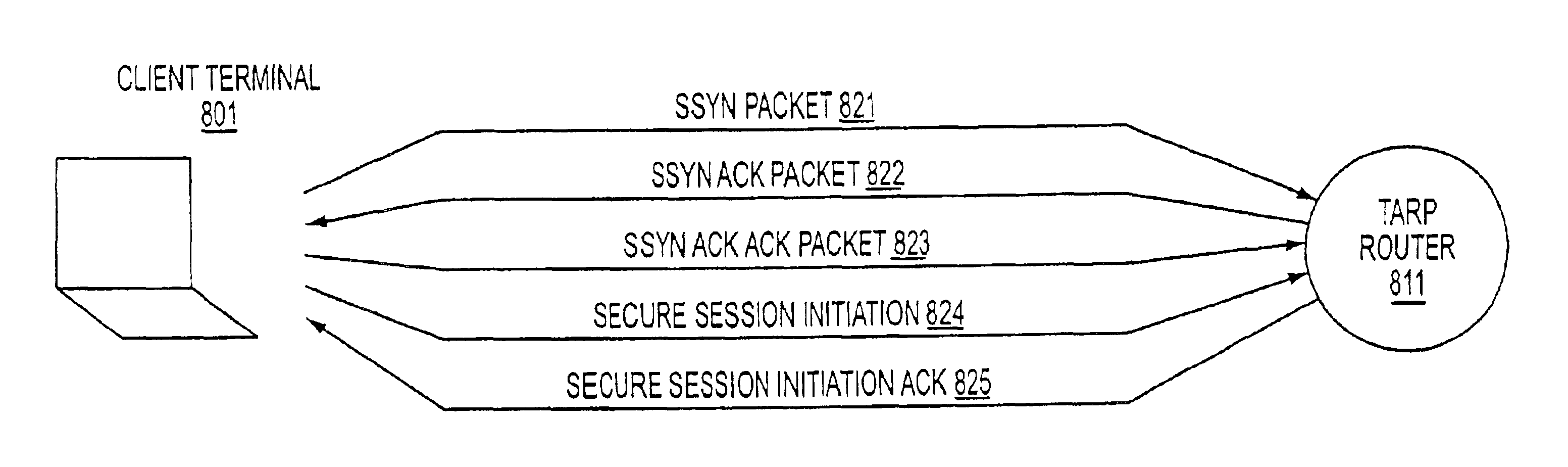

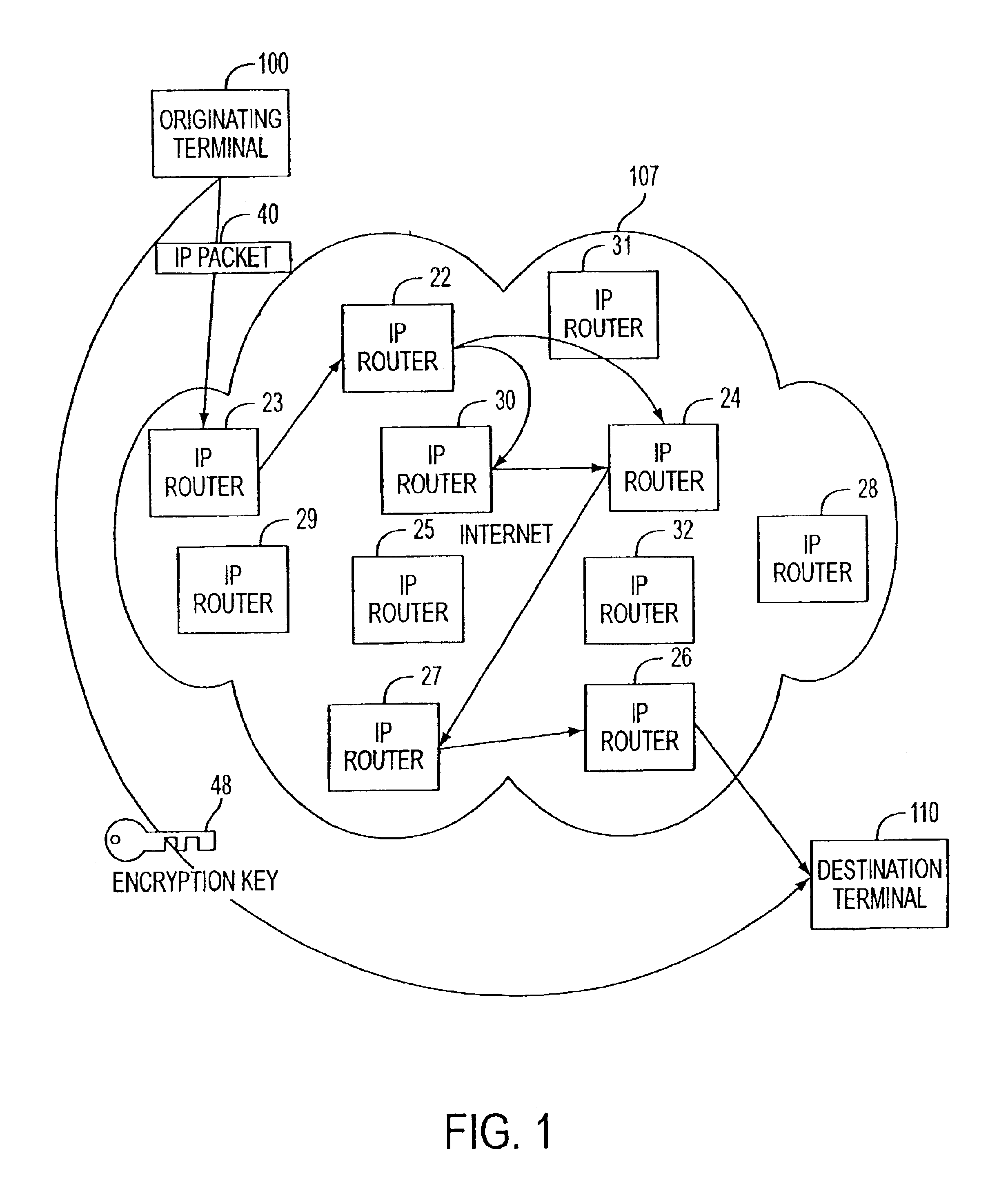

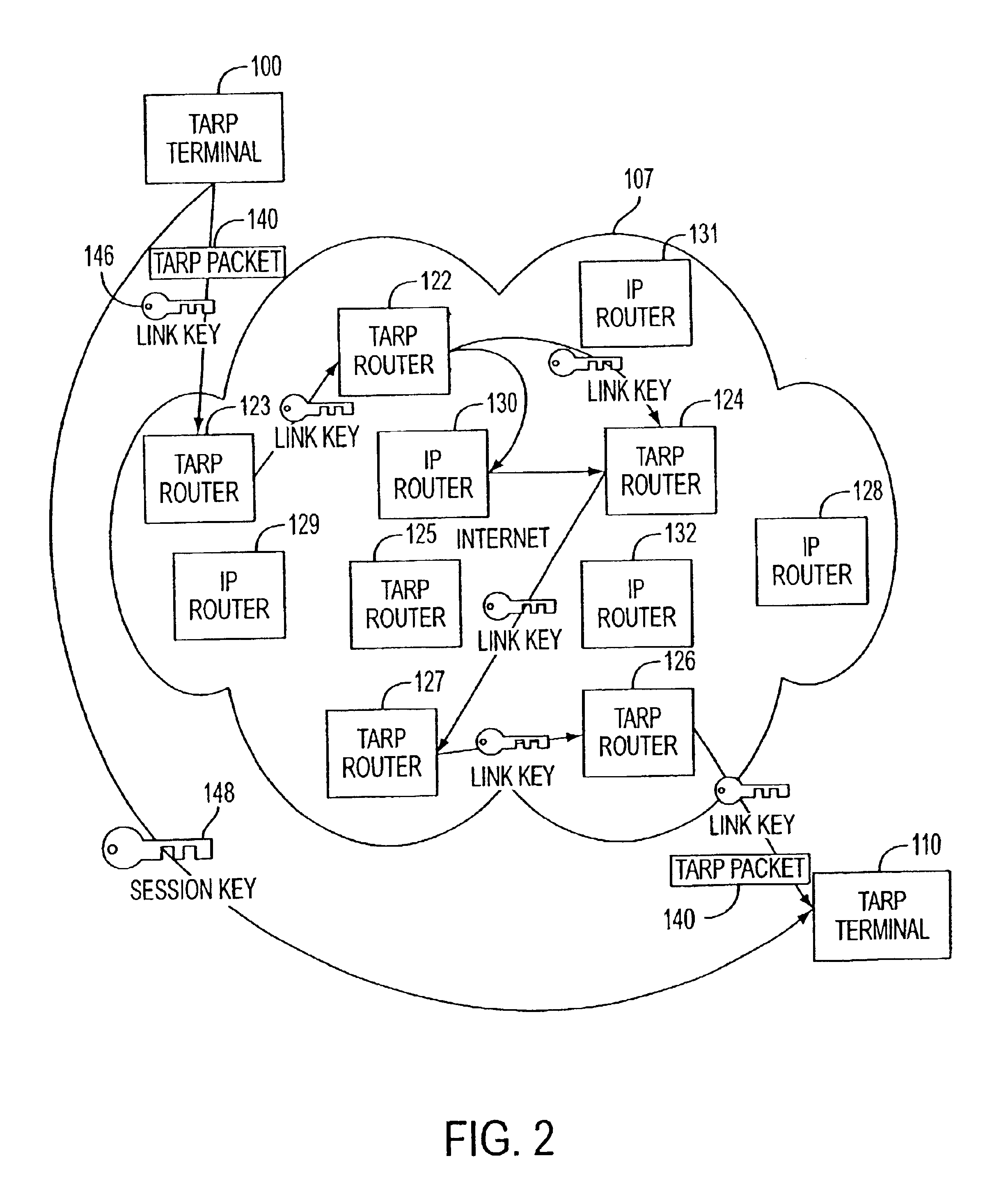

A plurality of computer nodes communicate using seemingly random Internet Protocol source and destination addresses. Data packets matching criteria defined by a moving window of valid addresses are accepted for further processing, while those that do not meet the criteria are quickly rejected. Improvements to the basic design include (1) a load balancer that distributes packets across different transmission paths according to transmission path quality; (2) a DNS proxy server that transparently creates a virtual private network in response to a domain name inquiry; (3) a large-to-small link bandwidth management feature that prevents denial-of-service attacks at system chokepoints; (4) a traffic limiter that regulates incoming packets by limiting the rate at which a transmitter can be synchronized with a receiver; and (5) a signaling synchronizer, that allows a large number of nodes to communicate with a central node by partitioning the communication function between two separate entities.

Owner:VIRNETX

Data package including synchronization data

InactiveUS20020010807A1Digital data information retrievalData processing applicationsNetwork packetData source

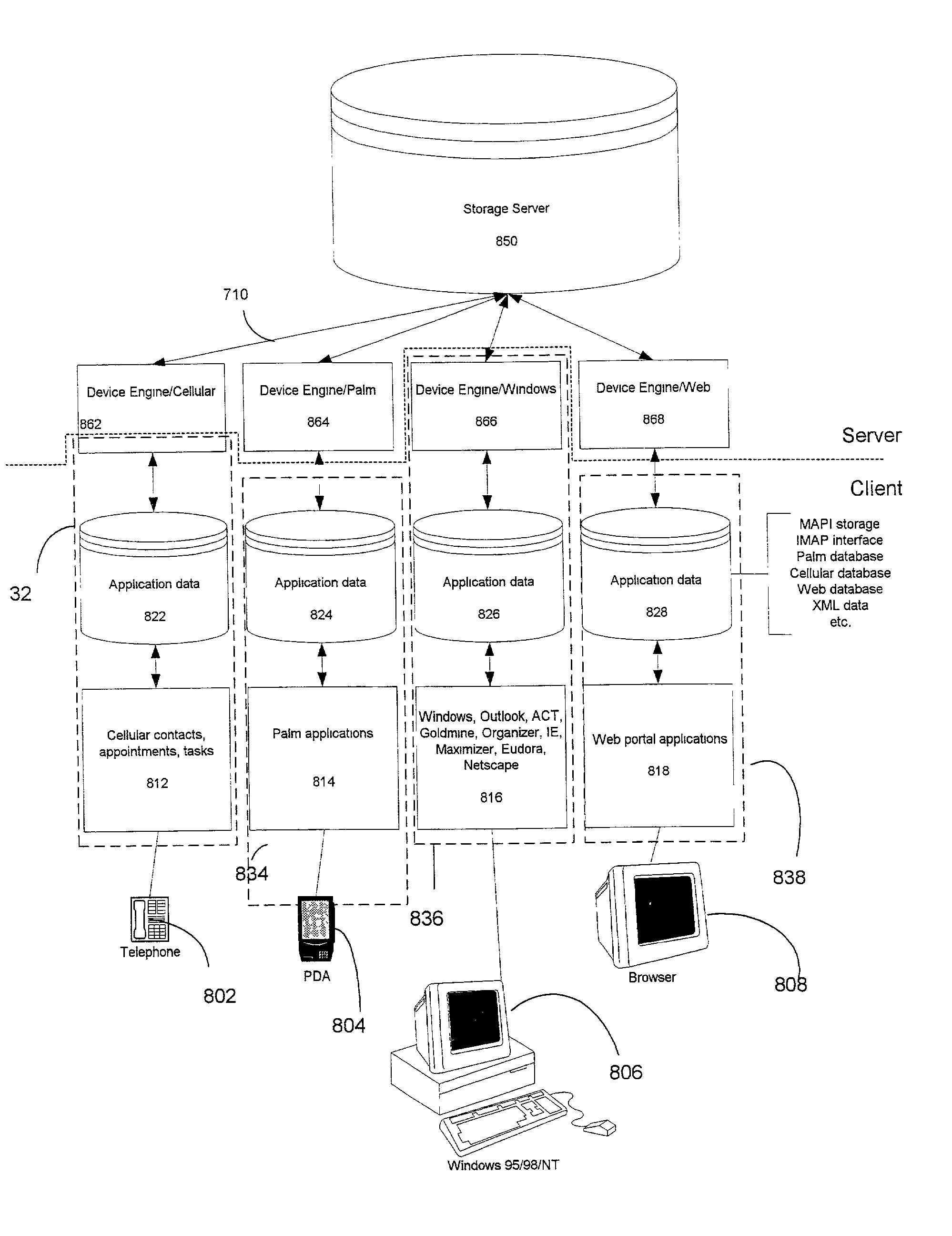

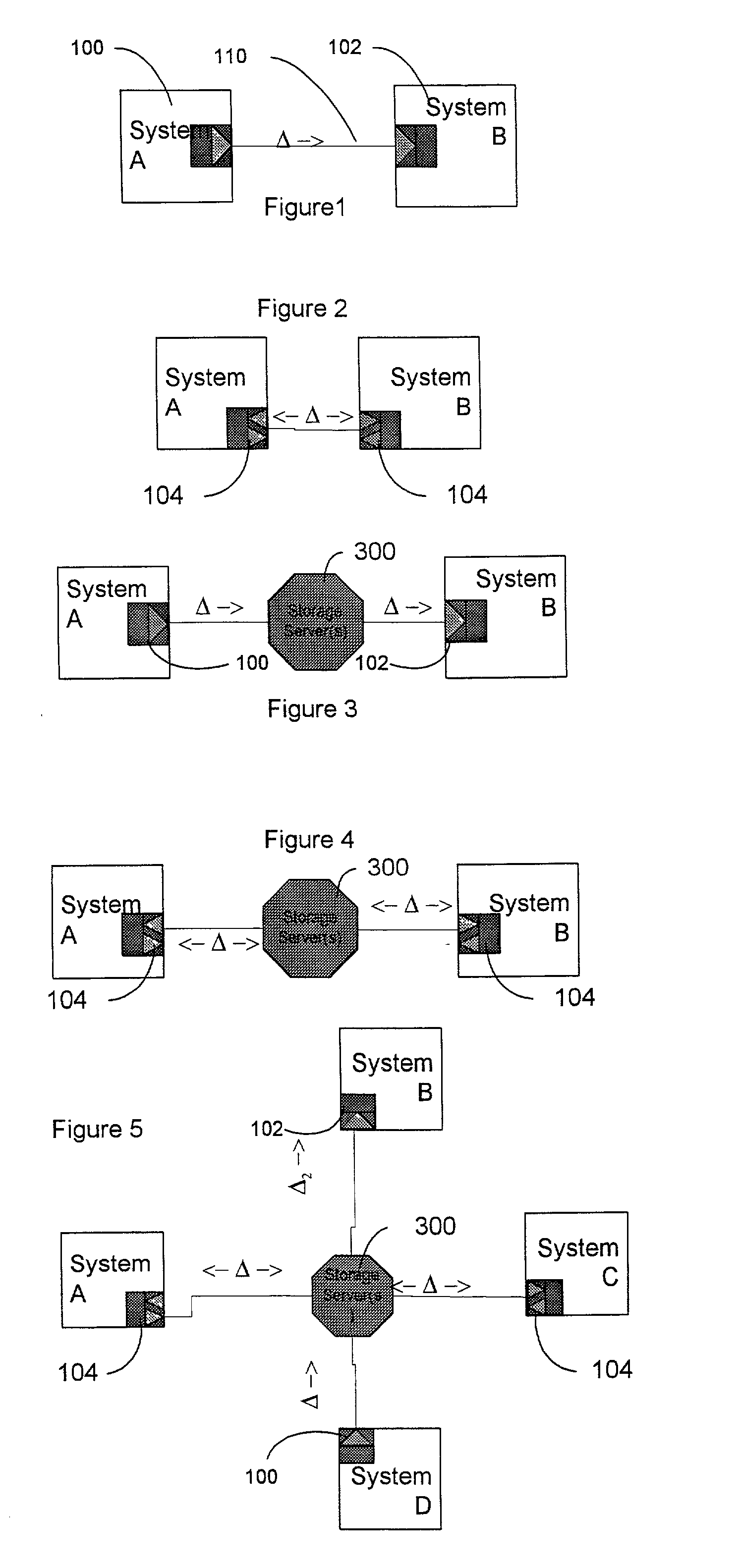

A difference information receiver, a difference information transmitter and a difference information synchronizer which cooperate in a system or device to update data in the device with data received from other systems, or provide data for other systems to use in updating themselves are disclosed. A difference receiver in a device having at least one application data destination having a format includes a difference engine receiving difference information associated with a change to said at least one application data destination; and an application interface, applying said difference information to said at least one data destination. A method for updating data files in a system is also disclosed. The method may include the steps of: receiving difference information for a subset of said data files; and applying said difference information to said subset of said data files. In particular said step of receiving may comprise: receiving a change log detailing changes to data files on another system; and applying said changes to a data store containing data identical to said data files to generate changed data. A difference transmitter comprises an application in a system having a data source in a source format. The application may include an application interface, extracting data from said data source; and a difference engine receiving said data and outputting difference information associated with changes to said data source. A method for updating a data source in a system is also disclosed. The method may include the steps of extracting difference information from at least a subset of said data source; and outputting difference information for at least the subset of said data source. The step of extracting may comprise determining whether changes have been made to the subset of data source in the system; and generating a change log detailing changes to the subset of data source on another system. A difference synchronizer includes an extraction routine for extracting a first set of difference information resulting from changes to the data files; a differencing transmitter for transmitting said first set of difference information to an output; a differencing receiver for receiving a second set of difference information from an input; and a reconstruction routine for applying the second set of difference information to the data files. In a particular embodiment, the invention comprises a device engine including an application object; an application object store; and a delta module.

Owner:SYNCHRONOSS TECH

System, method and article of manufacture for a synchronizer component in a multimedia synchronization framework

InactiveUS7188193B1Special service provision for substationMultiple digital computer combinationsClient-sideBiological activation

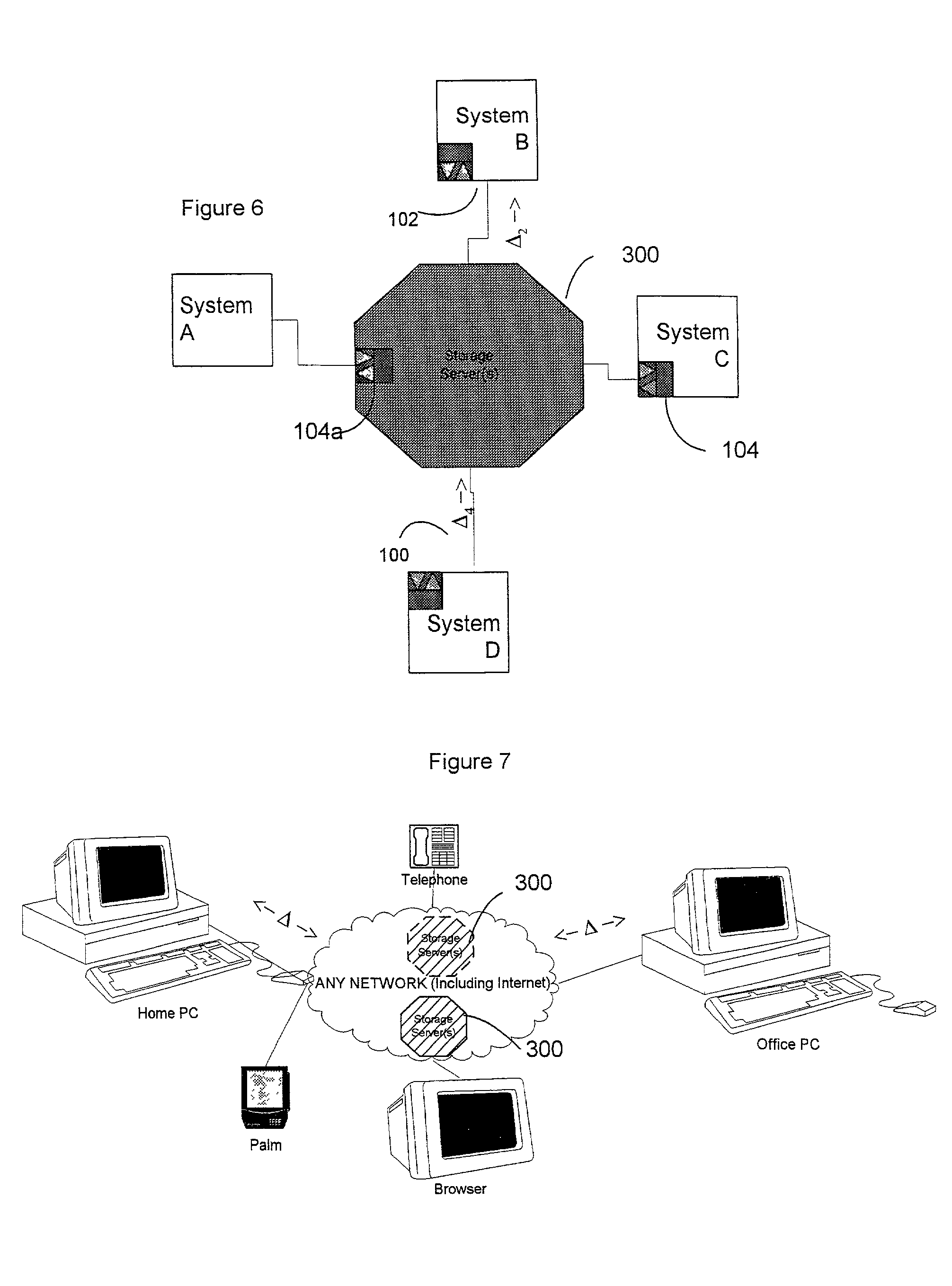

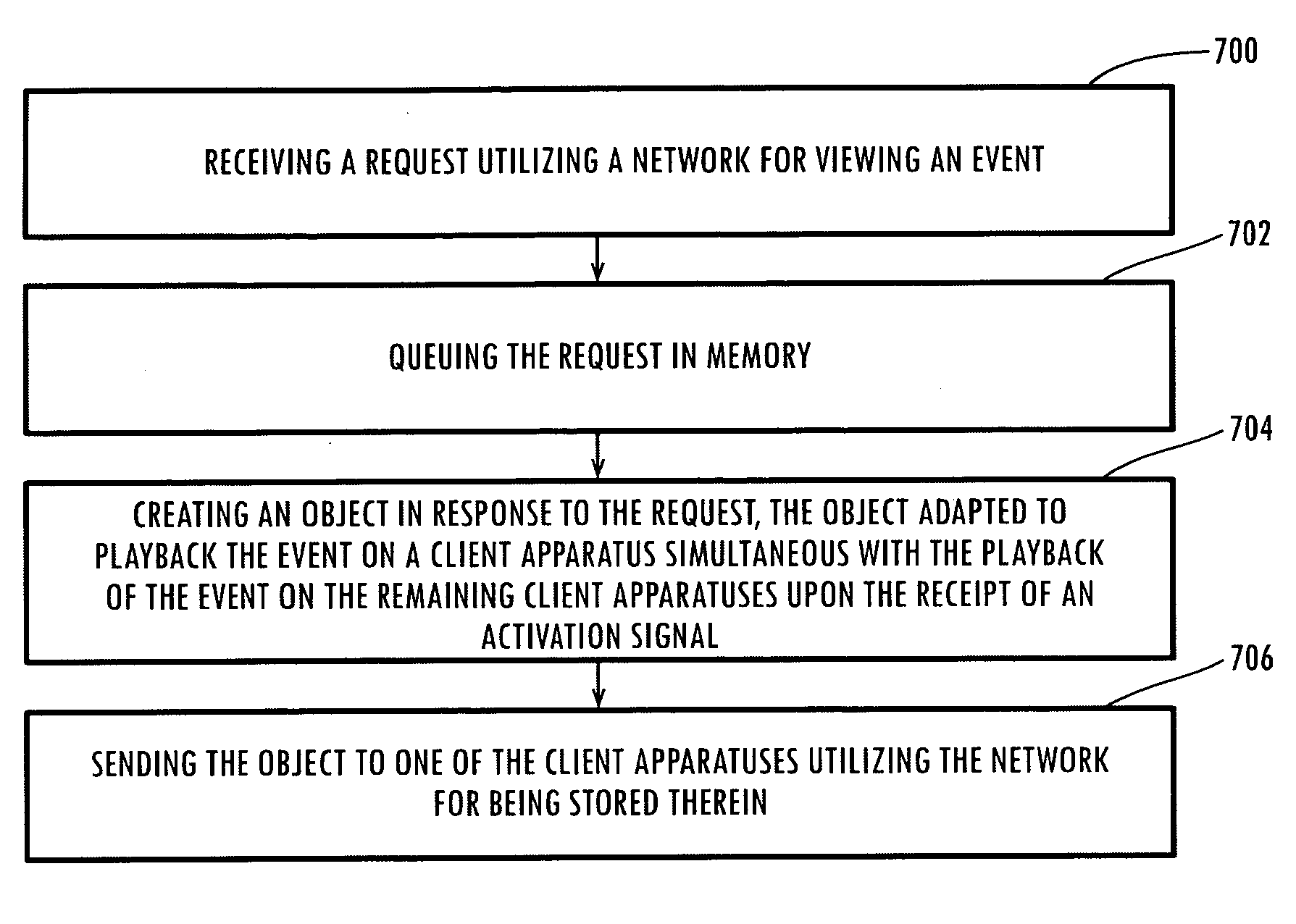

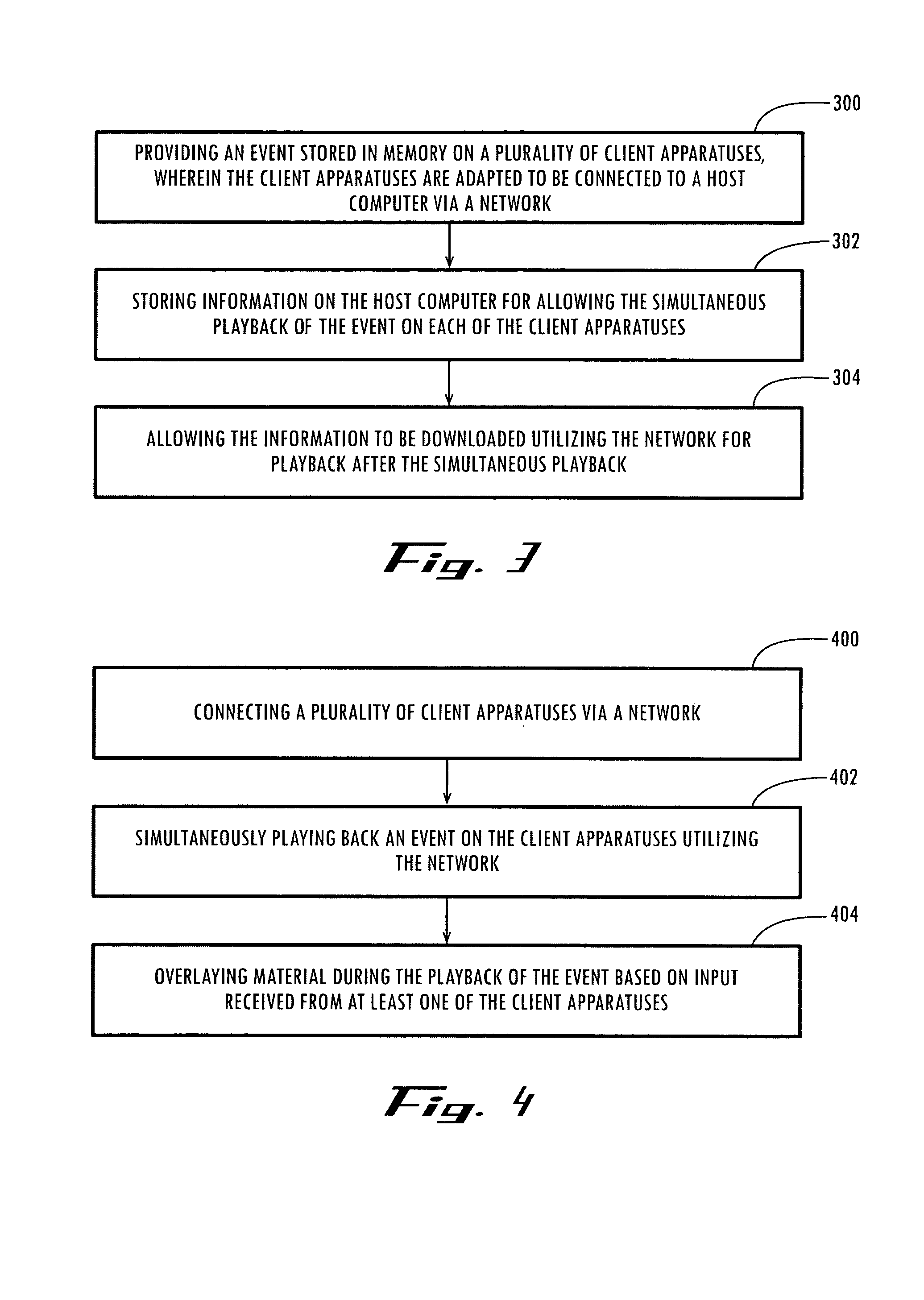

A system, method and article of manufacture are provided for creating a synchronizer object in order to playback an event simultaneously on a plurality of a client apparatuses. First, a request is received utilizing a network for viewing an event. Next, the request is queued in memory. In response to the request, an object is created which is adapted to playback the event on a client apparatus simultaneous with the playback of the event on the remaining client apparatuses upon the receipt of an activation signal. The object is sent to one of the client apparatuses utilizing the network for being stored therein.

Owner:ROVI TECH CORP

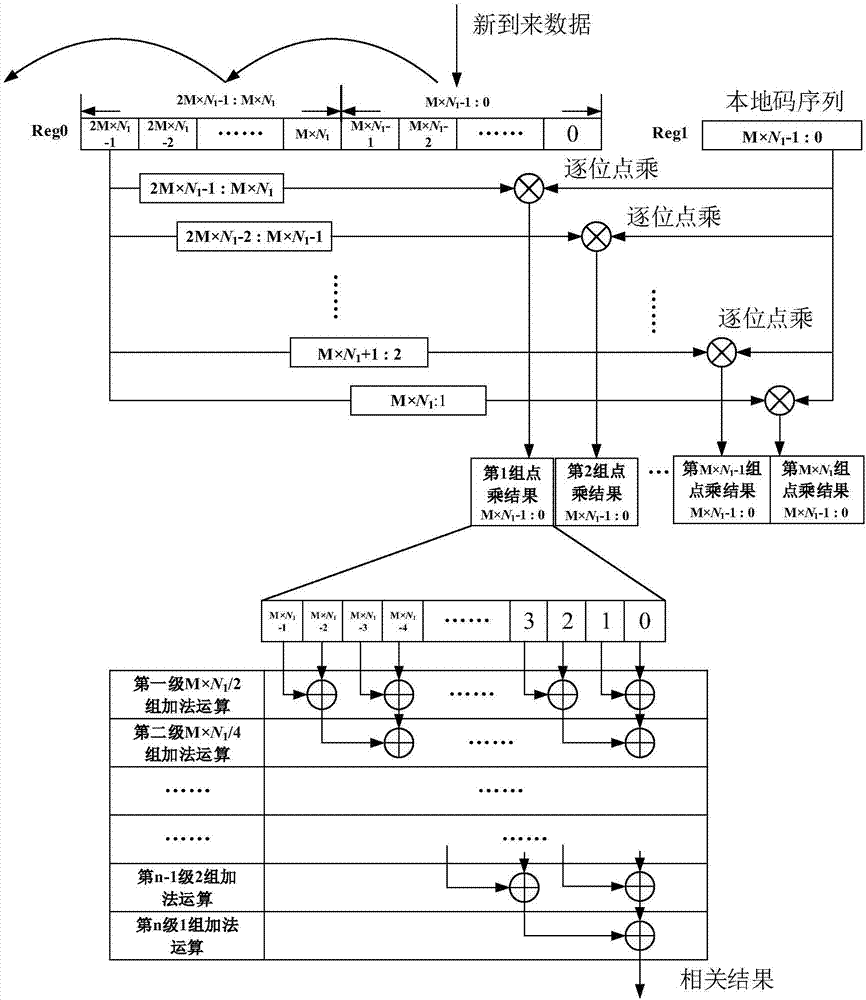

Burst direct sequence spread spectrum system and pseudo code synchronization method of burst direct sequence spread spectrum waveform thereof

InactiveCN107026810ASimple structureQuick captureMulti-frequency code systemsData segmentCarrier frequency offset

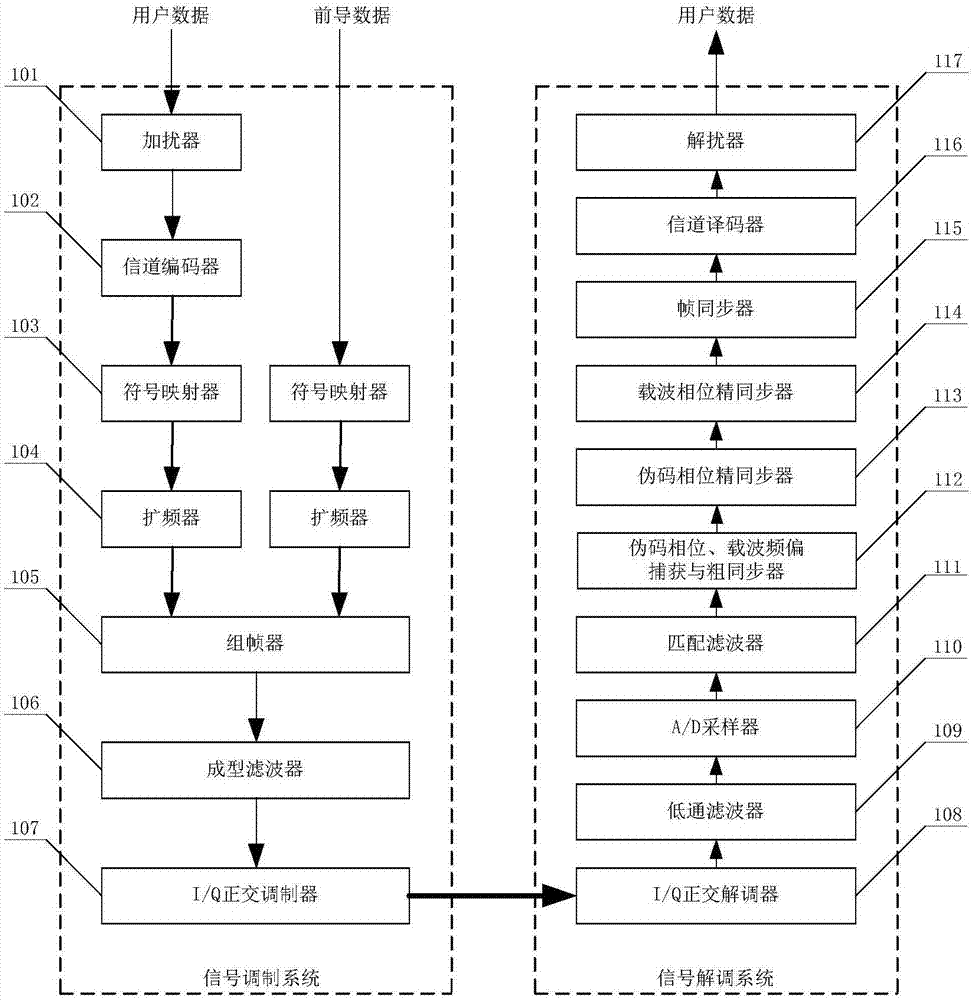

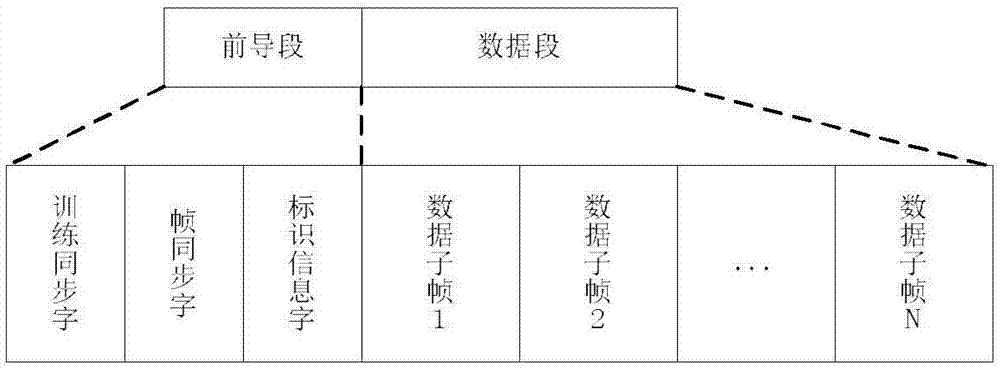

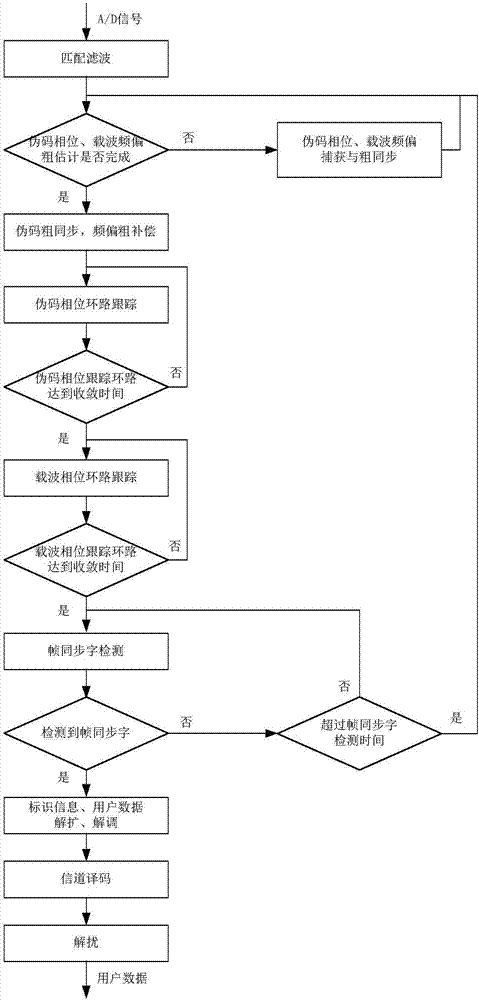

The invention discloses a burst direct sequence spread spectrum system and a pseudo code synchronization method of a burst direct sequence spread spectrum waveform thereof. By adoption of the burst direct sequence spread spectrum system disclosed by the invention, the capturing, tracking and convergence times of a burst direct sequence spread spectrum signal can be greatly shortened, and the frequency offset estimation precision is relatively high. The burst direct sequence spread spectrum system disclosed by the invention is realized by the following technical scheme: in a signal modulation system, a specific segment of lead data is added in front of user data after scrambling and channel encoding are carried out on the user data for accomplishing signal capture and synchronization; and in a signal demodulation system, pseudo code phase capture and carrier frequency offset capture are carried out on a digital baseband signal to accomplish signal capture, coarse pseudo code phase synchronization and coarse frequency offset compensation with a coarse synchronizer, precise signal synchronization of a coarse synchronization signal is separately accomplished by pseudo code phase and carrier phase synchronization loops, identification information and a starting position of a user data segment are determined from a precise synchronization signal by a frame synchronizer, and the user data are restored by channel decoding and descrambling.

Owner:10TH RES INST OF CETC

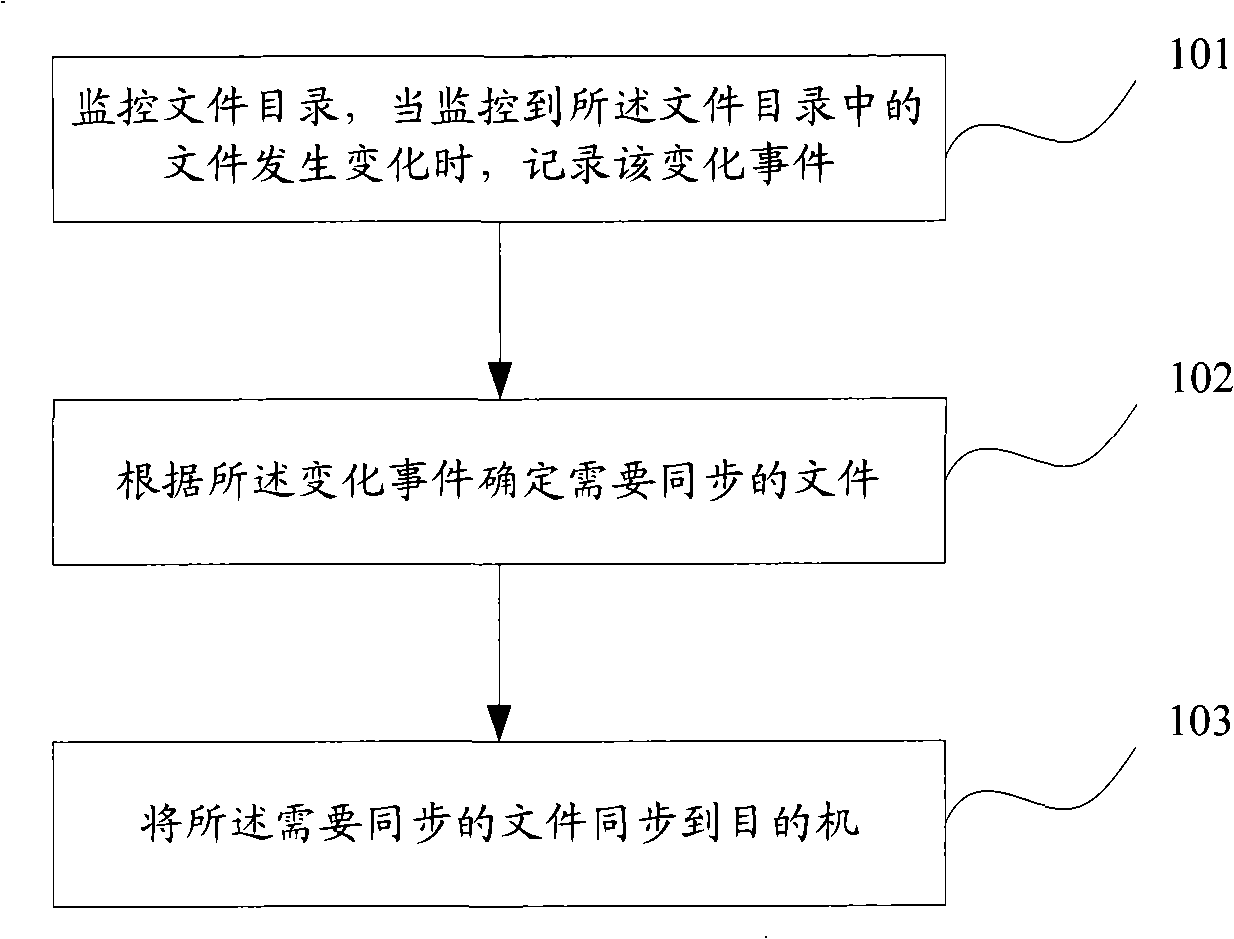

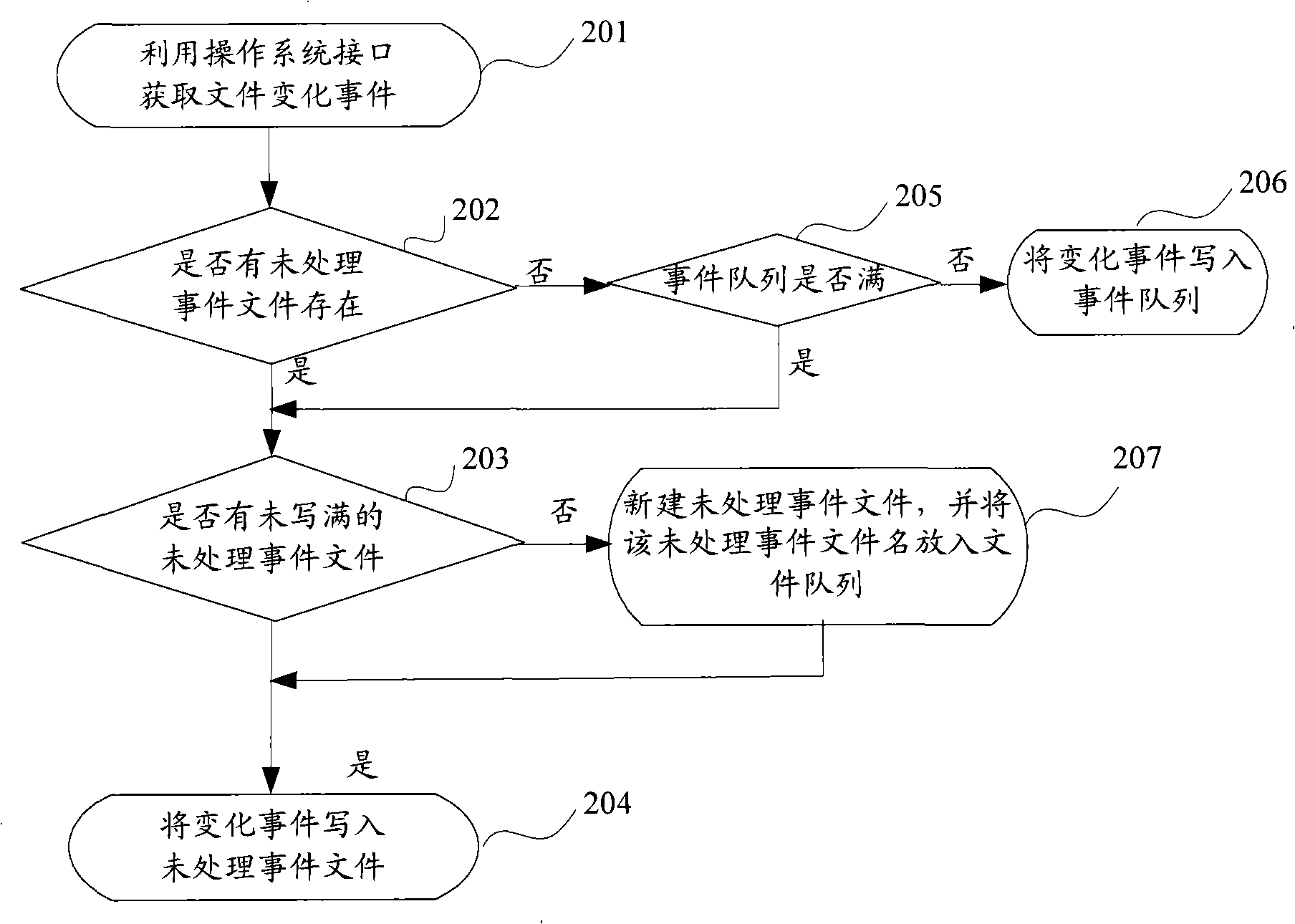

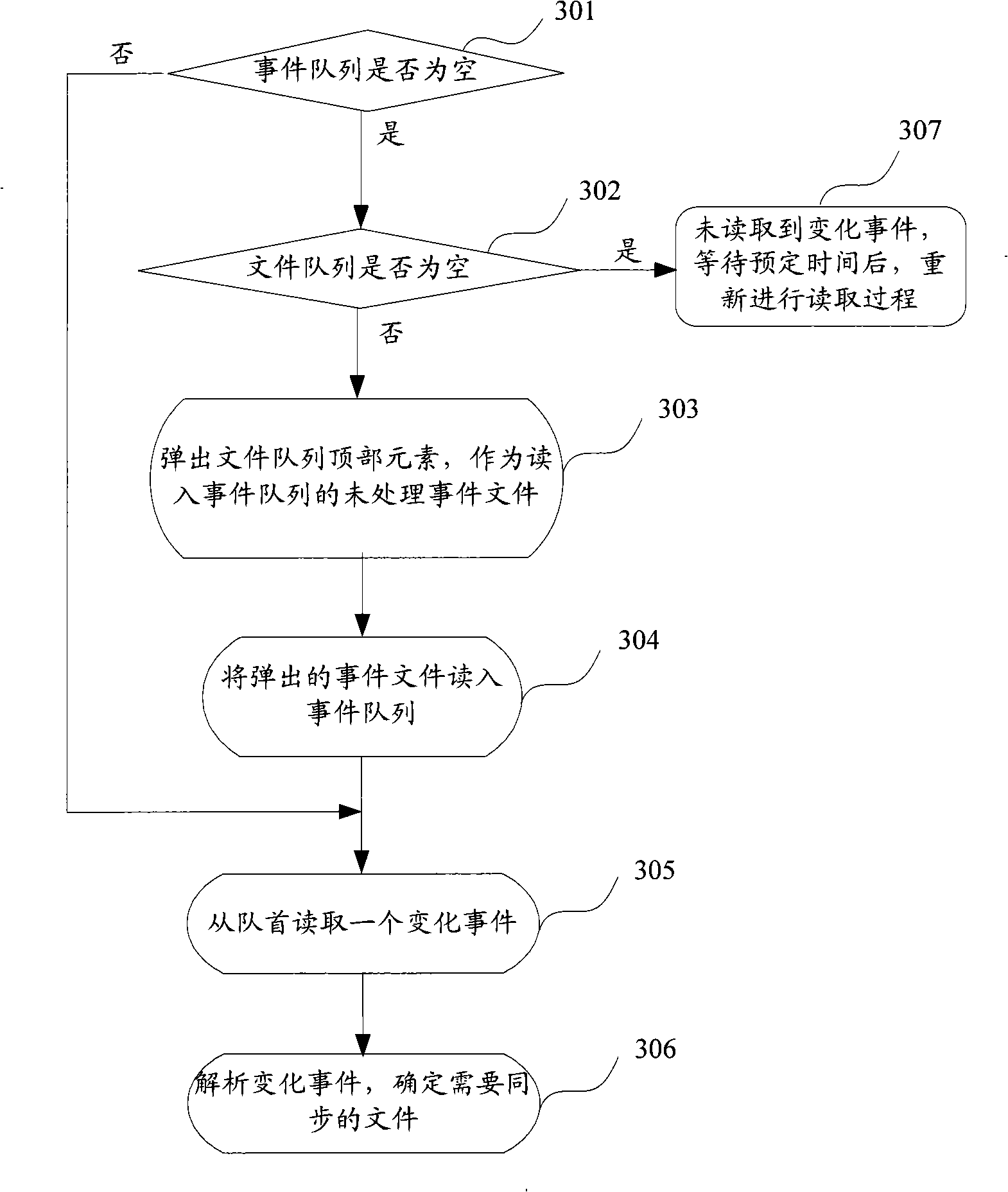

File synchronisation method and device

ActiveCN101281543AGuaranteed real-timeGuaranteed reliabilityDigital data information retrievalSpecial data processing applicationsFile synchronizationDatabase

The invention relates to a data simultaneous technique, discloses a file synchronous method, which comprises: monitoring a file directory, and recording the change event of a change when a file in the file directory changes; determining files to be synchronized; and synchronizing the files to be synchronized to an objective computer. The invention also discloses a file synchronous device, comprising a monitoring unit, a record unit, an analytical unit and a synchronous unit. By using the invention, the real-time performance and reliability of file synchronization can be ensured.

Owner:HUAWEI TECH CO LTD

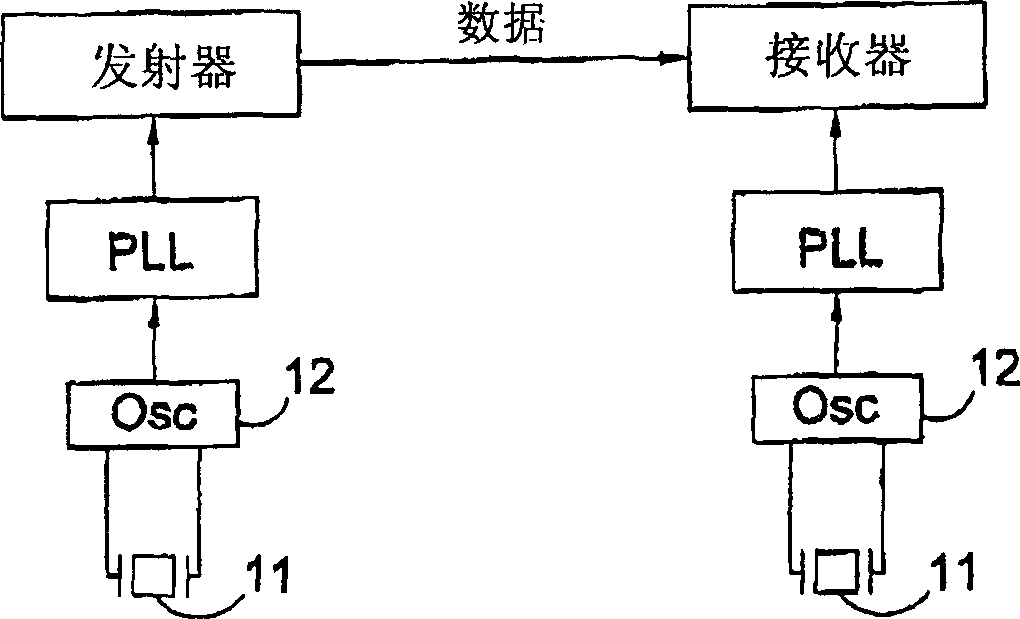

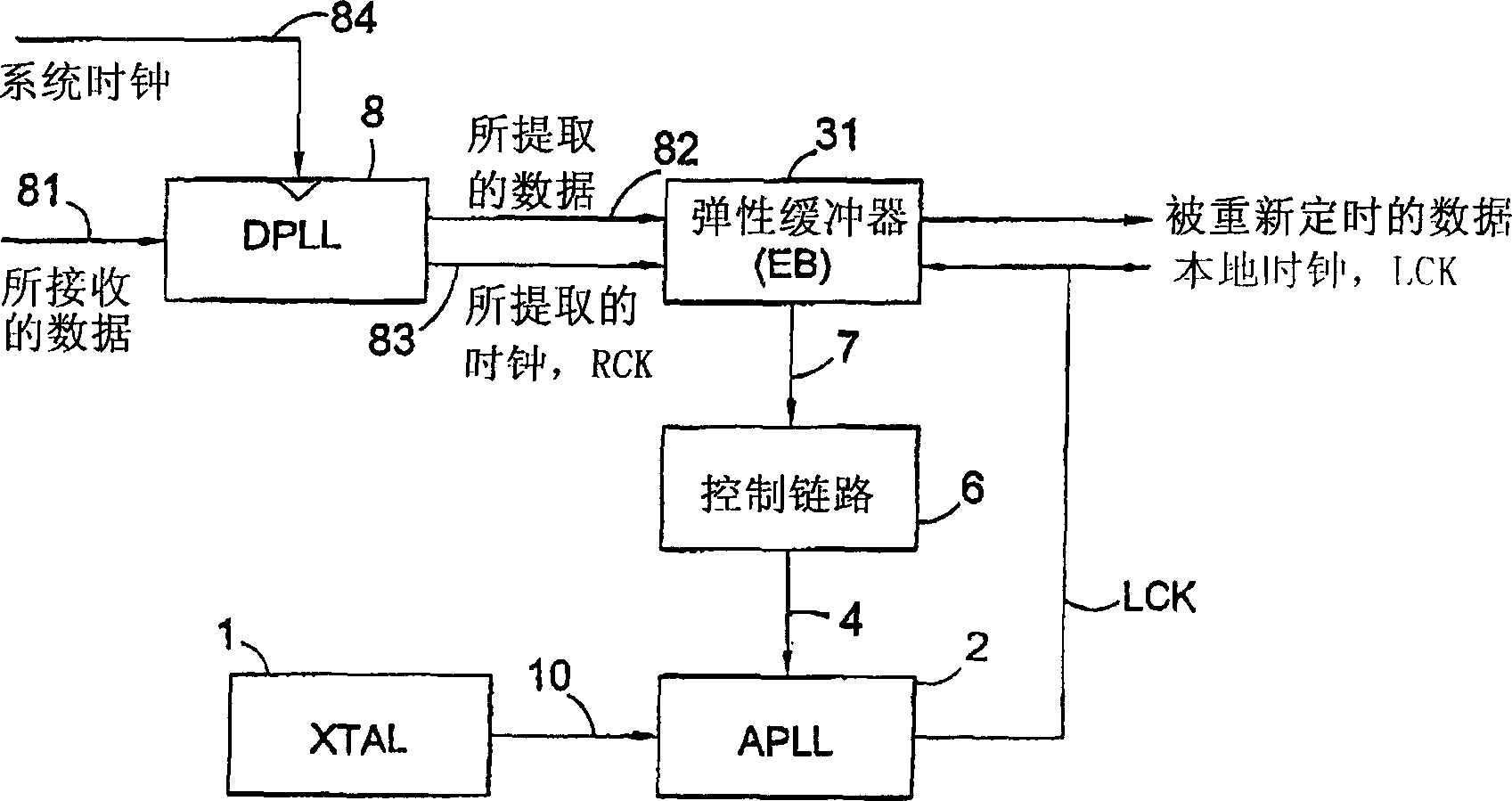

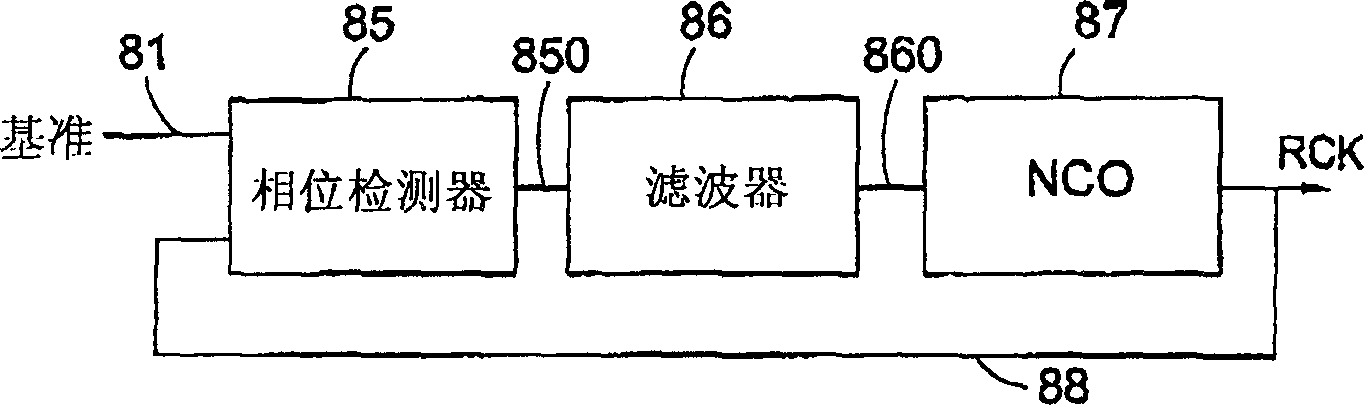

Clock synchronizer and clock and data recovery apparatus and method

A clock synchroniser, and clock and data recovery apparatus incorporating the clock synchroniser, are described, together with corresponding clock synchronisation methods. The clock synchroniser incorporates an elastic buffer. A received clock signal RCK is used to clock data into the buffer, and a locally generated clock LCK is used to clock data out of the buffer. The local clock is synthesised using a PLL, and a fill-level signal from the elastic buffer is used to control to local clock frequency to maintain a desired average quantity of data in the buffer, thereby achieving synchronisation of the received and local clocks. In preferred embodiments the fill-level signal is used to control a variable divider in the feedback path of the PLL, which is supplied with a highly stable reference signal. A synchronised, and low-jitter local clock is thus produced. Preferably, the elastic buffer employs counters of relatively wide word width, and a storage array of much reduced depth, read and write pointers being provided by just a few of the least significant bits of the words.

Owner:CIRRUS LOGIC INT SEMICON

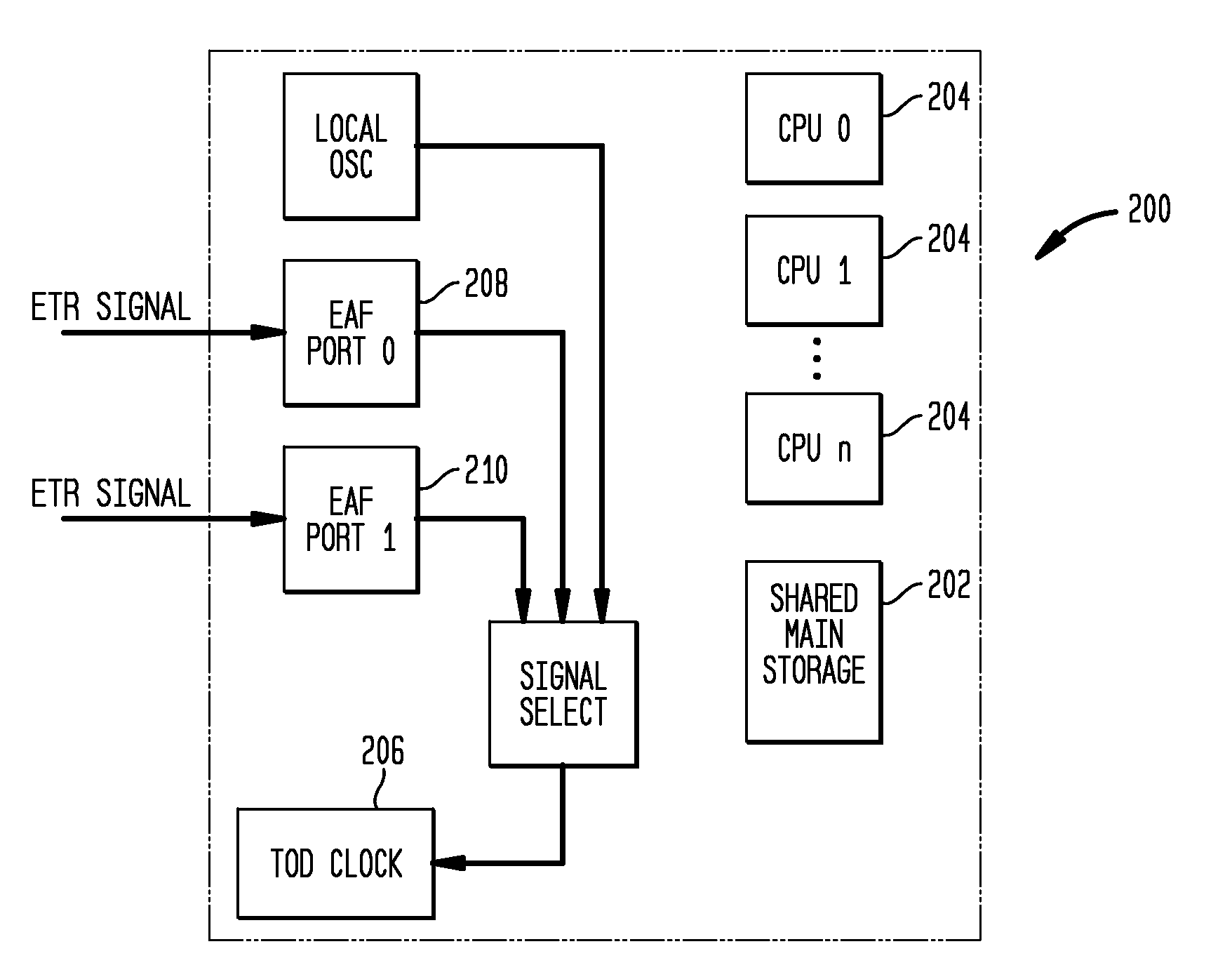

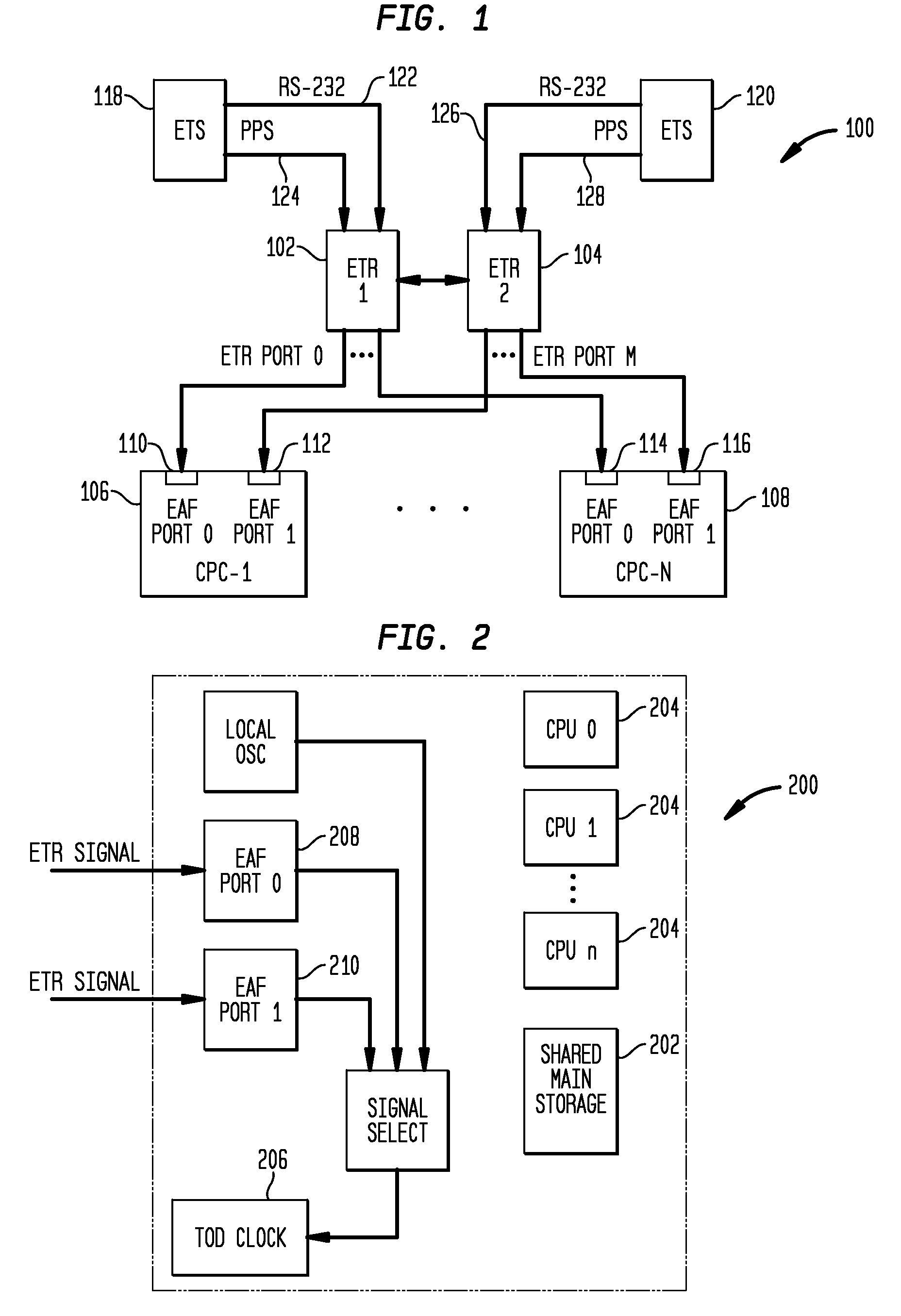

Pulse-per-second attachment for stp

InactiveUS20080072096A1High quality time informationMultiple digital computer combinationsGenerating/distributing signalsSynchronizerTime information

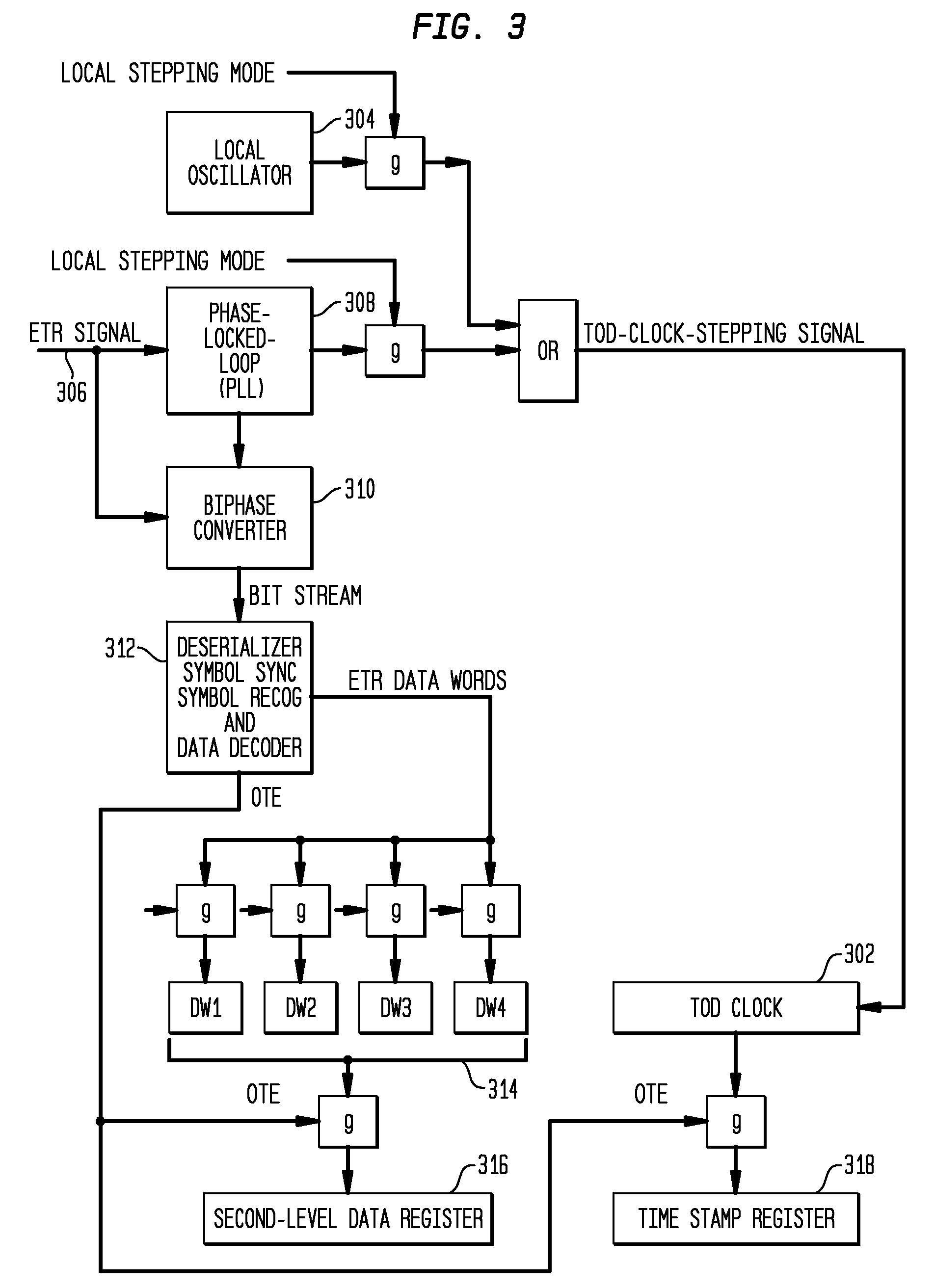

A time synchronization apparatus, method and system are provided. In one aspect, the apparatus comprises at least a time of day clock, a first port operable to receive at least first time information using a first time protocol, a second port operable to receive at least second time information using a second time protocol, a third port operable to receive at least a timing signal, and a time stamp register operable to at least capture current value of the time of day clock upon receipt of the timing signal from the third port or the first time information from the first port or combination thereof

Owner:IBM CORP

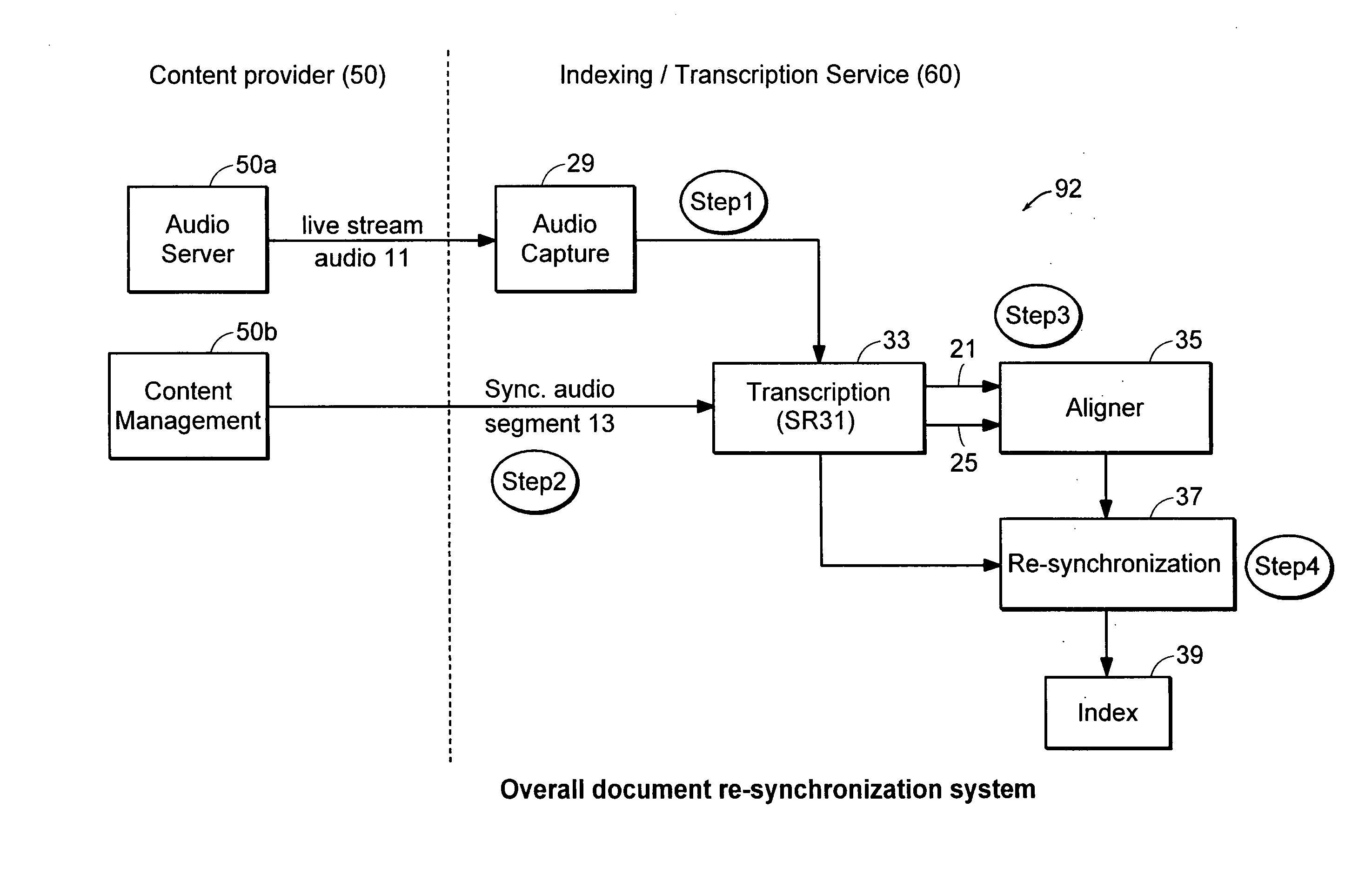

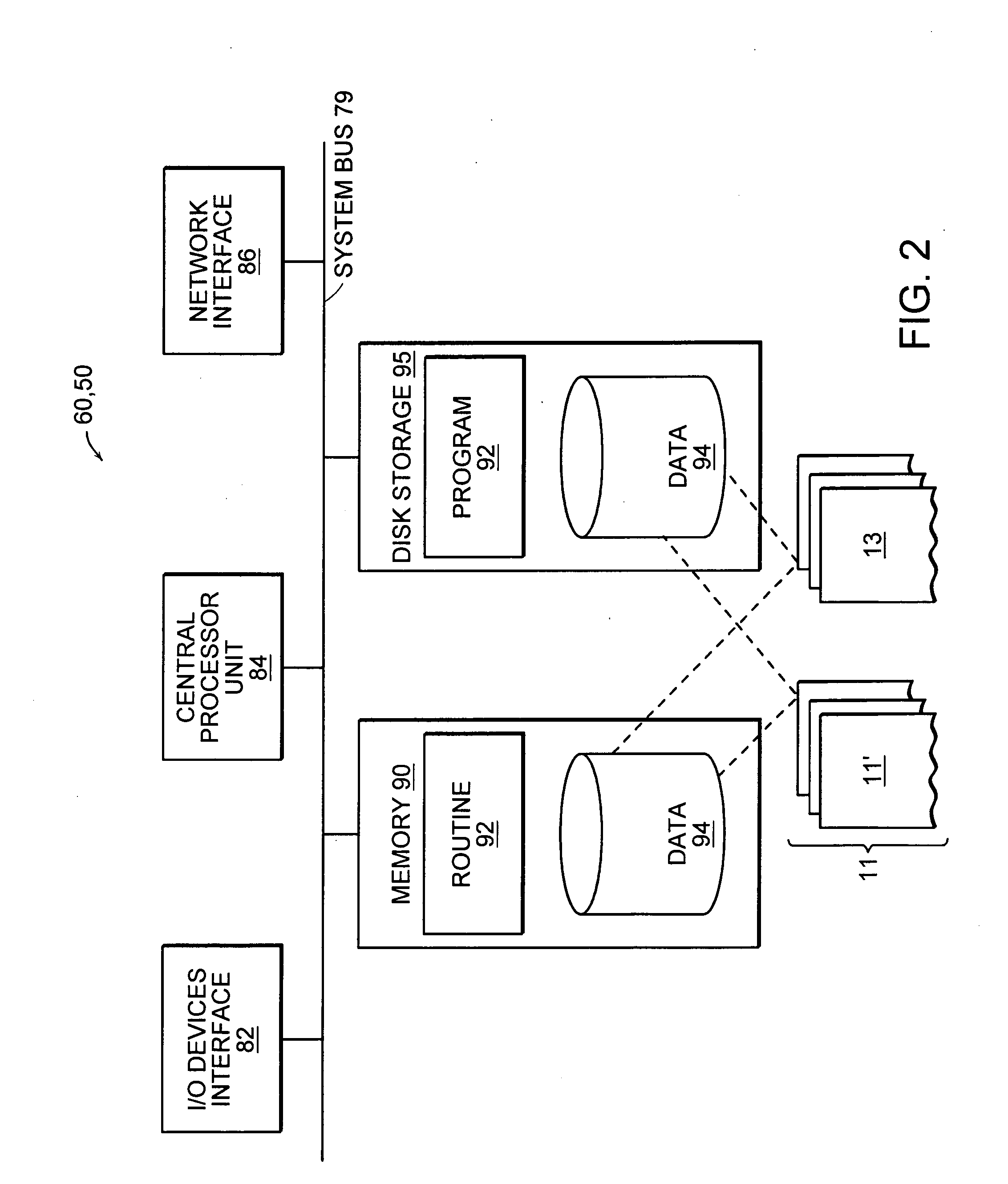

Content-based synchronization method and system for data streams

InactiveUS20060200743A1ElectrocardiographyCarrier indexing/addressing/timing/synchronisingStreaming dataData stream

A computer method and system synchronizes one streaming data signal with another data signal. A subject data signal and working data signal are received. The working data signal has predefined coordinates in a coordinate system (e.g., time origin and unit sampling rate in a time coordinate system for audio). The subject data signal and working data signal are transformed into respective common representations. An alignment process aligns the respective transformed representations by matching the transformed representation of the working data signal to that of the subject signal. A re-synchronizer element transposes the predefined coordinates of the working data signal onto the subject signal in the aligned state of the respective transformed representations. As such, the subject data signal is synchronized to the coordinate system of the working data signal.

Owner:HEWLETT PACKARD DEV CO LP

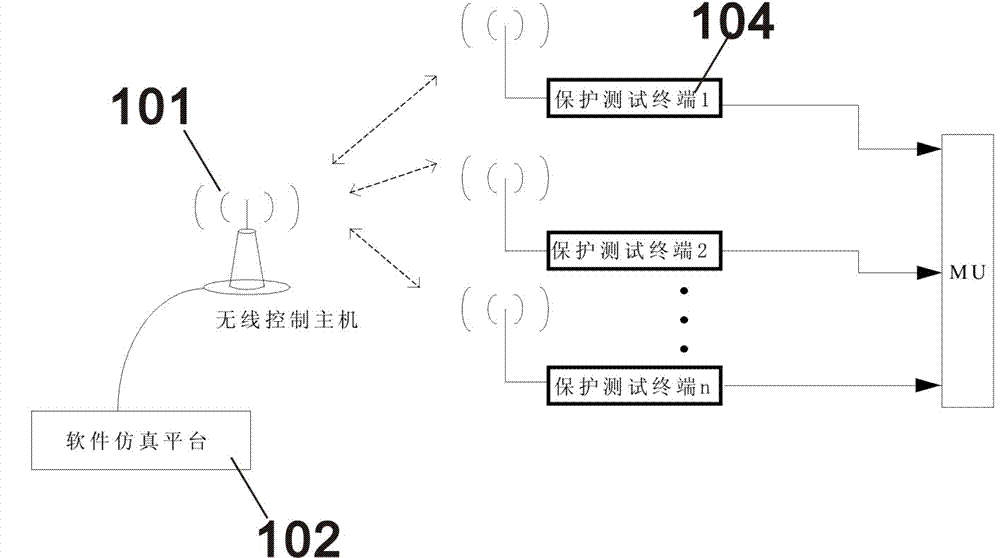

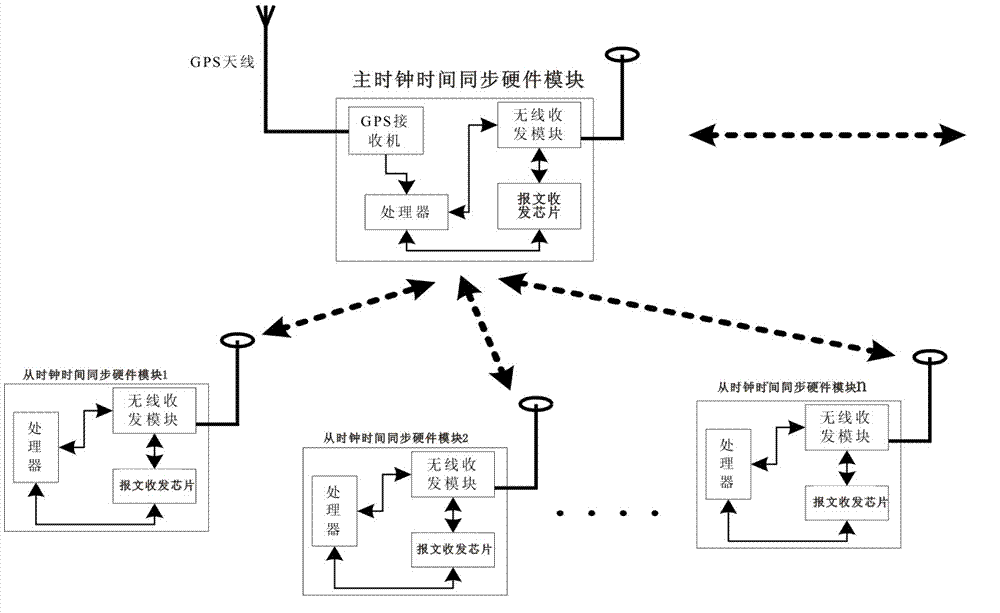

Time synchronizer and time synchronization method applied to protective test equipment of power system

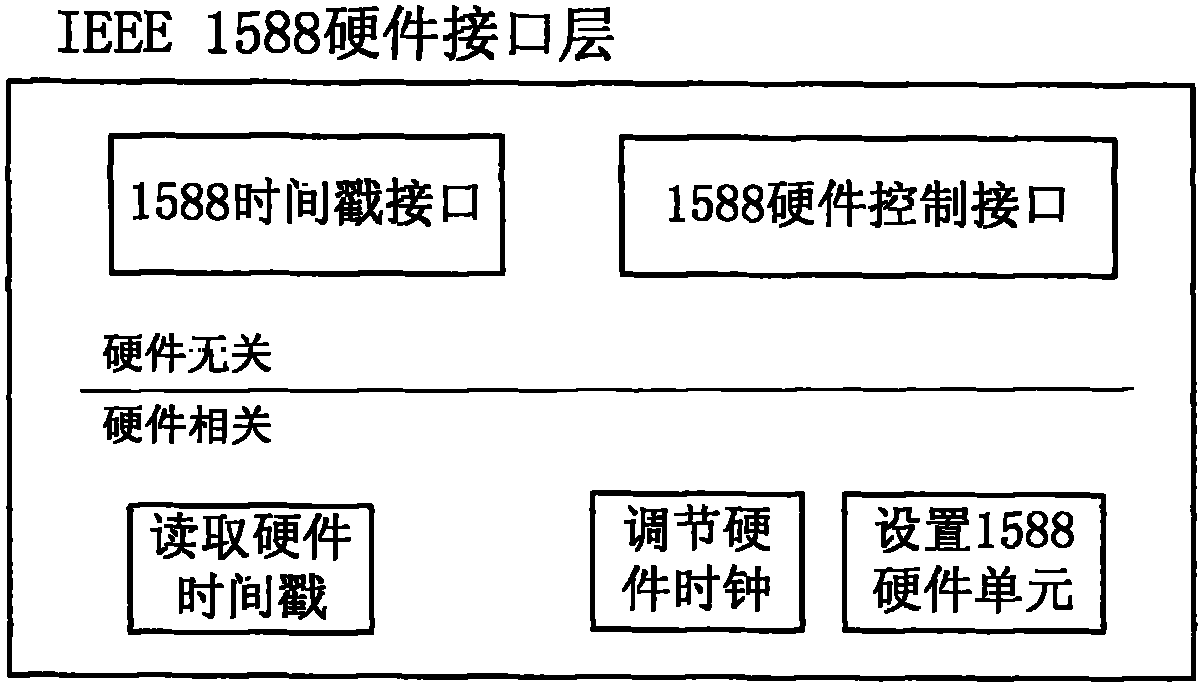

InactiveCN102769908AImprove performanceIncrease flexibilitySynchronisation arrangementHigh level techniquesWireless controlSoftware emulation

The invention discloses a time synchronizer applied to protective test equipment of a power system. The time synchronizer is characterized in that the time synchronizer is provided with a wireless control host machine with a master clock time synchronization hardware module, wherein the wireless control host machine is directly connected with a software simulation platform of an upper computer, and a slave clock time synchronization hardware module is arranged in a protective test terminal. Time synchronization between the master and slave clock time synchronization hardware modules is implemented through a wireless communication application IEEE (Institute of Electrical and Electronic Engineers) 1588 time synchronization protocol. According to the technology provided by the invention, the wireless IEEE1588 time synchronization protocol is applied to a secondary side test protective device of a transformer substation of the power system, so that a network signal of a mutual inductor obtained by simulation is synchronously output in real time, in this way, a signal network output of the power system can be stimulated more authentically so as to test a plurality of secondary side test protective devices of the transformer substation at the same time.

Owner:STATE GRID SICHUAN ELECTRIC POWER CORP ELECTRIC POWER RES INST +1

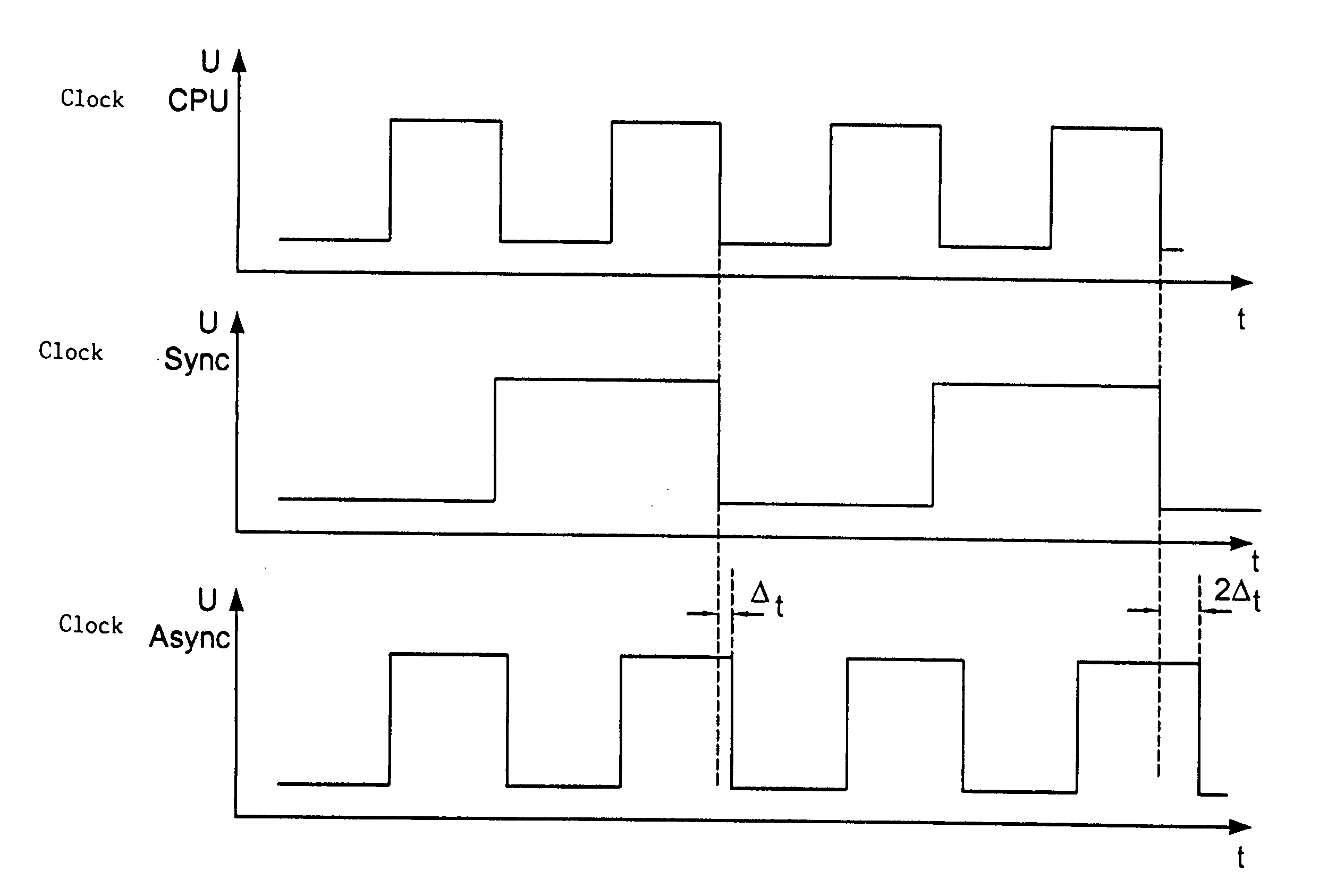

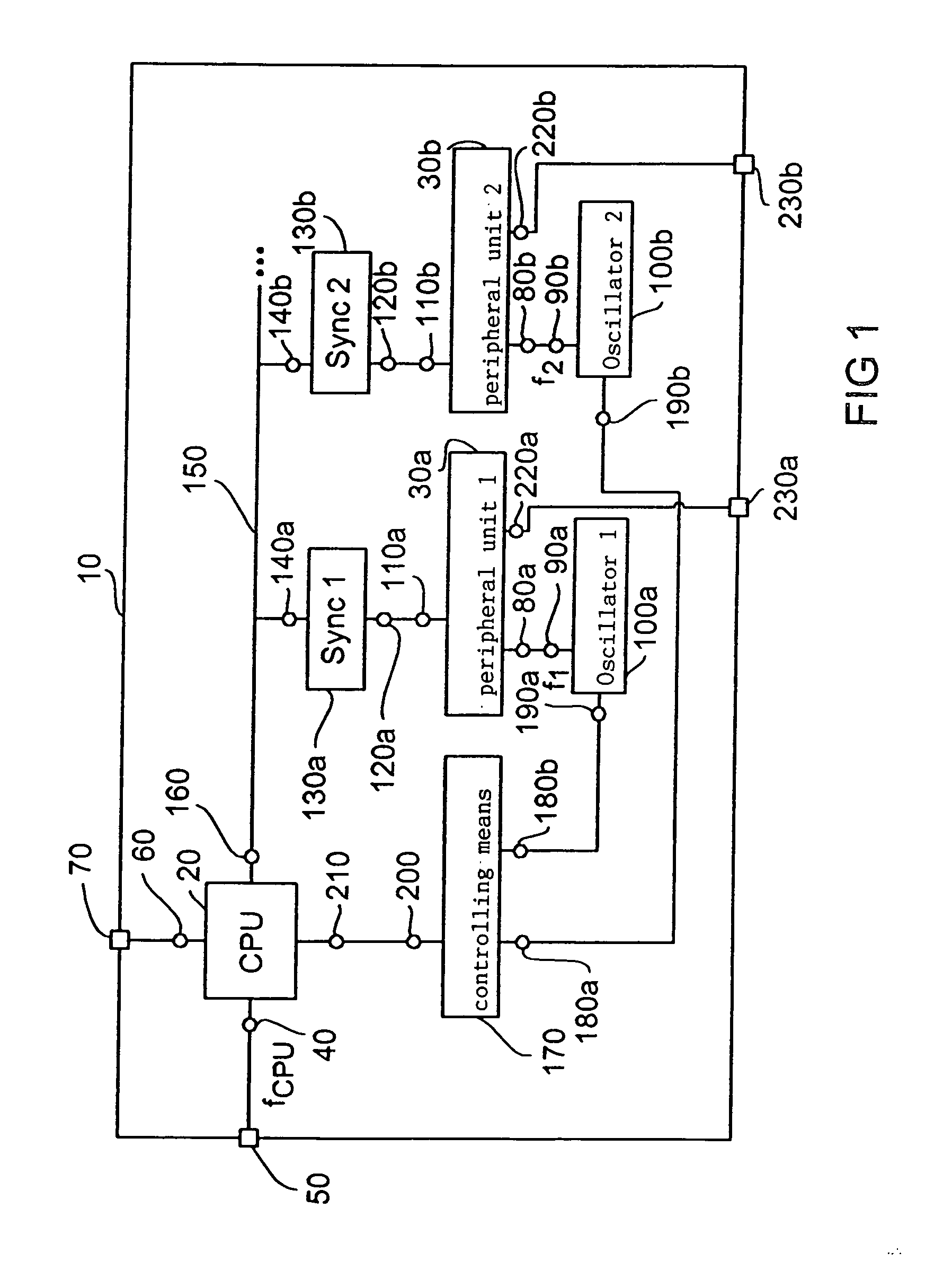

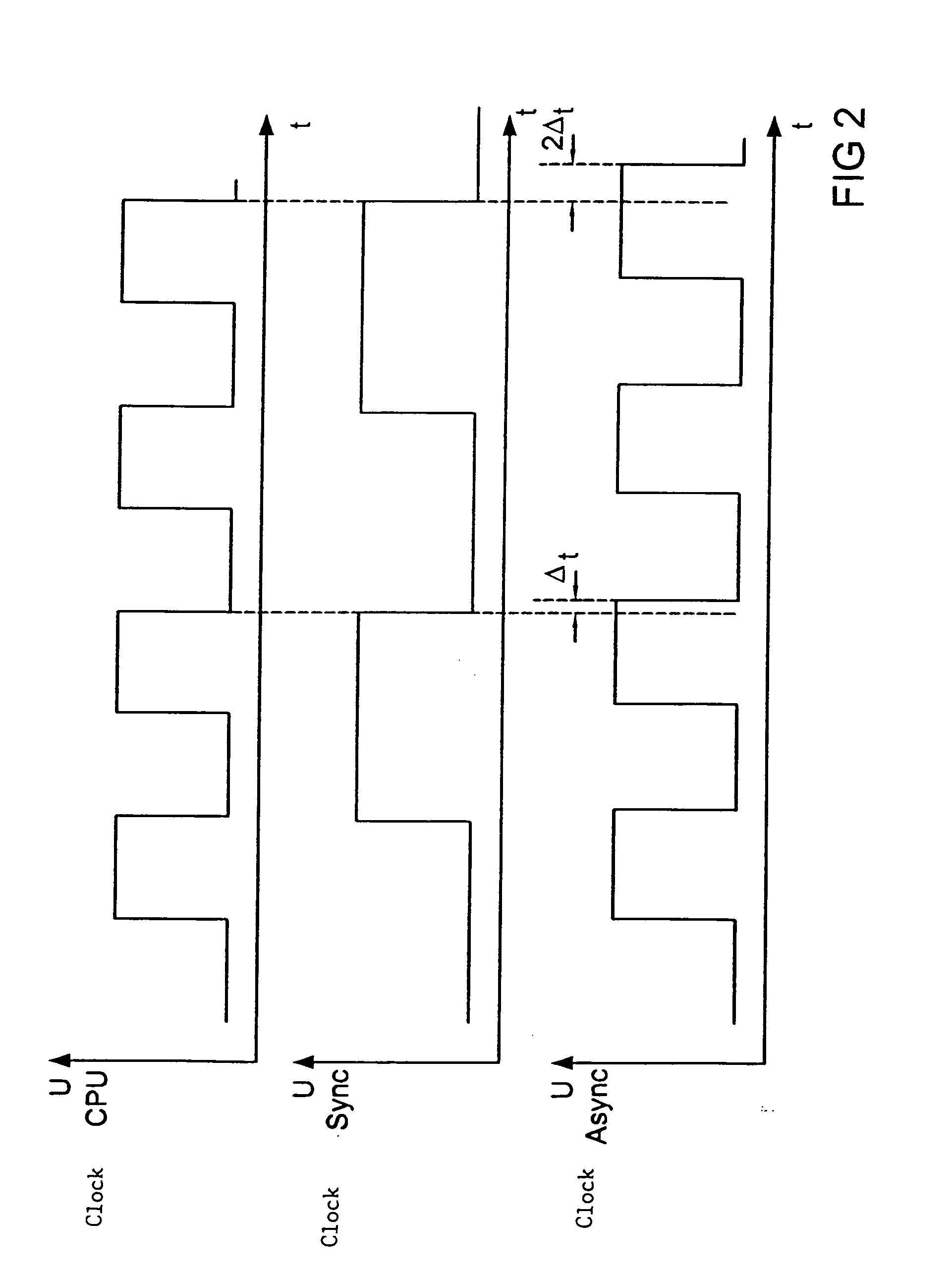

Electronic circuit with asynchronous clocking of peripheral units

InactiveUS20040139363A1Power supply for data processingGenerating/distributing signalsData connectionComputer science

An inventive electronic circuit includes central processing means having a clock connection and a data connection, as well as a peripheral unit having a clock connection and a data connection, the clock connection of the peripheral unit being connected to a signal output of a controllable oscillator or to an external clock input. Synchronization means having a first and a second data connection is connected, the first data connection being connected to the data connection of the peripheral unit. In addition a data bus connects the data connection of the CPU and the second data connection of the synchronization means. The clocking of the peripheral unit asynchronous to the central processing unit yields a more effective operation being better adjustable to certain parameters, such as, for example, the application and the energy of the electronic circuit available.

Owner:INFINEON TECH AG

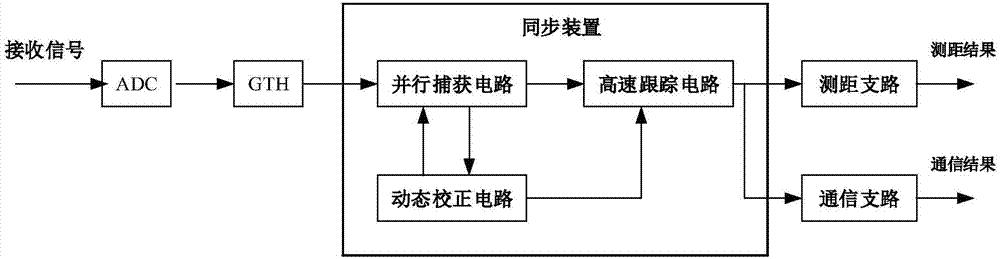

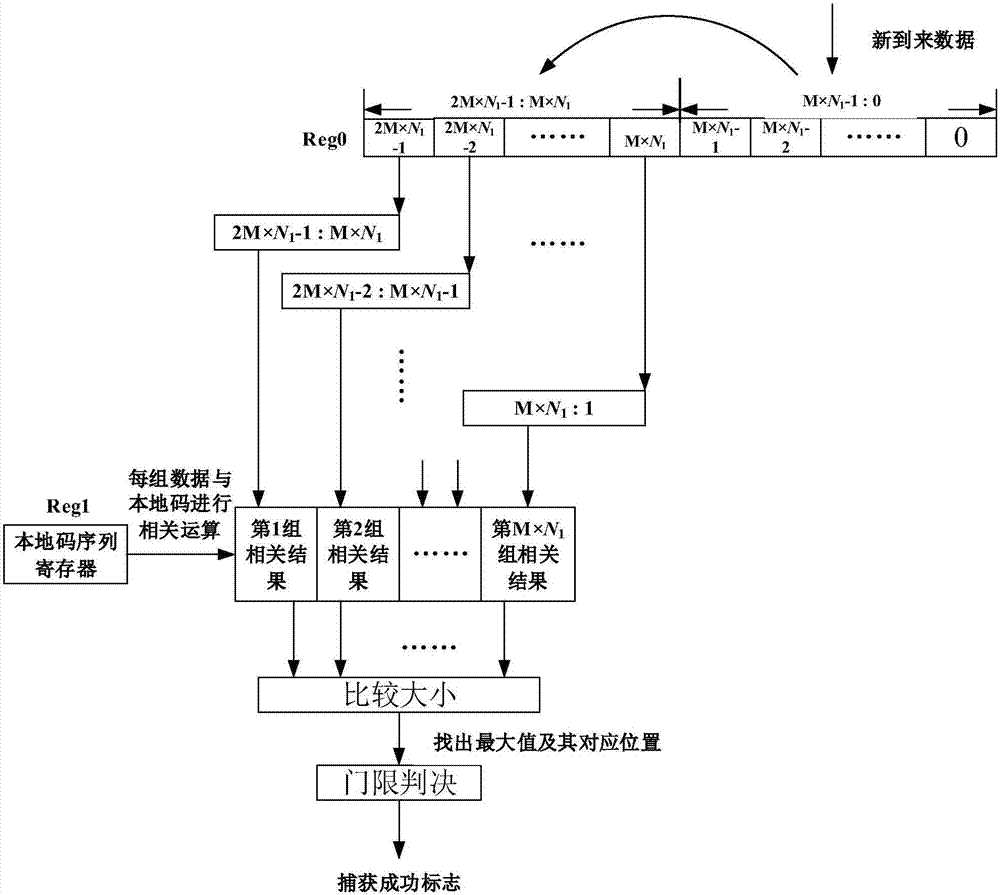

Synchronizer, synchronization method and high-speed receiver by using synchronizer

ActiveCN107425953AReduce processing burdenLow timing requirementsSynchronisation error correctionSynchronisation receiversTransceiverParallel computing

The present invention provides a synchronizer of a laser communication distance measurement integration system, a synchronization method of a laser communication distance measurement integration system and a high-speed receiver by using the synchronizer. The high-speed receiver receives high-speed signals, an analog-digital converter (ADC) is used for sampling of the high-speed signals, the sampling data is sent into a Gigabit transceiver (GTH) to perform serial-parallel conversion, and the high-speed serial data is converted to multi-path parallel data with low rate; the parallel data is sent into the synchronizer for signal synchronization, the parallel data is subjected to steps such as parallel data frame capture, dynamic correction, high-speed phase-locked loop tracking and the like in the synchronizer so as to complete accurate synchronization of the high-speed signals through the receiver; and moreover, on the basis of the accurate synchronization of the signals, and a distance measurement result and communication data can be solved out through the distance measurement branch and the communication branch of the receiver. The clock load is reduced and the complexity of the hardware realization is effectively reduced while ensuring the accurate synchronization of signals and accurate distance measurement and communication result.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

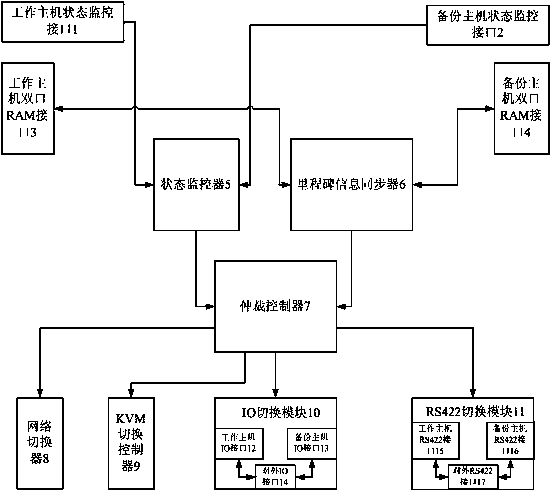

Arbitration device for double computer redundancy hot backup computer

InactiveCN104111881ARealize the arbitration functionMeet the control abilityRedundant hardware error correctionData synchronizationSynchronizer

The invention discloses an arbitration device for a double computer redundancy hot backup computer. The arbitration device for the double computer redundancy hot backup computer comprises an arbitration controller (7), a state control monitor (5) and a network switcher (8), and further comprises a milestone information synchronizer (6), an IO switching module (10), an RS422 switching module (11), a KVM switching controller (9), a work host computer dual port RAM interface (3) and a backup host computer dual port RAM interface. In the initial phase of booting the double computer redundancy hot backup computer, the arbitration device firstly confirms a host computer on duty between a work host computer and a backup host computer, and secondly performs booting synchronization. In the running process after booting the double computer redundancy hot backup computer, the arbitration device firstly performs task synchronization and data synchronization on the work host computer and the backup host computer, and secondly performs switching operation so as to obtain a work shift between the work host computer and the backup host computer. The arbitration device for the double computer redundancy hot backup computer meets the requirements of a display and control platform of a modern naval ship auxiliary device for manipulation ability and timeliness of the double computer redundancy hot backup computer.

Owner:706 INST SECOND RES INST OF CHINAAEROSPACE SCI & IND

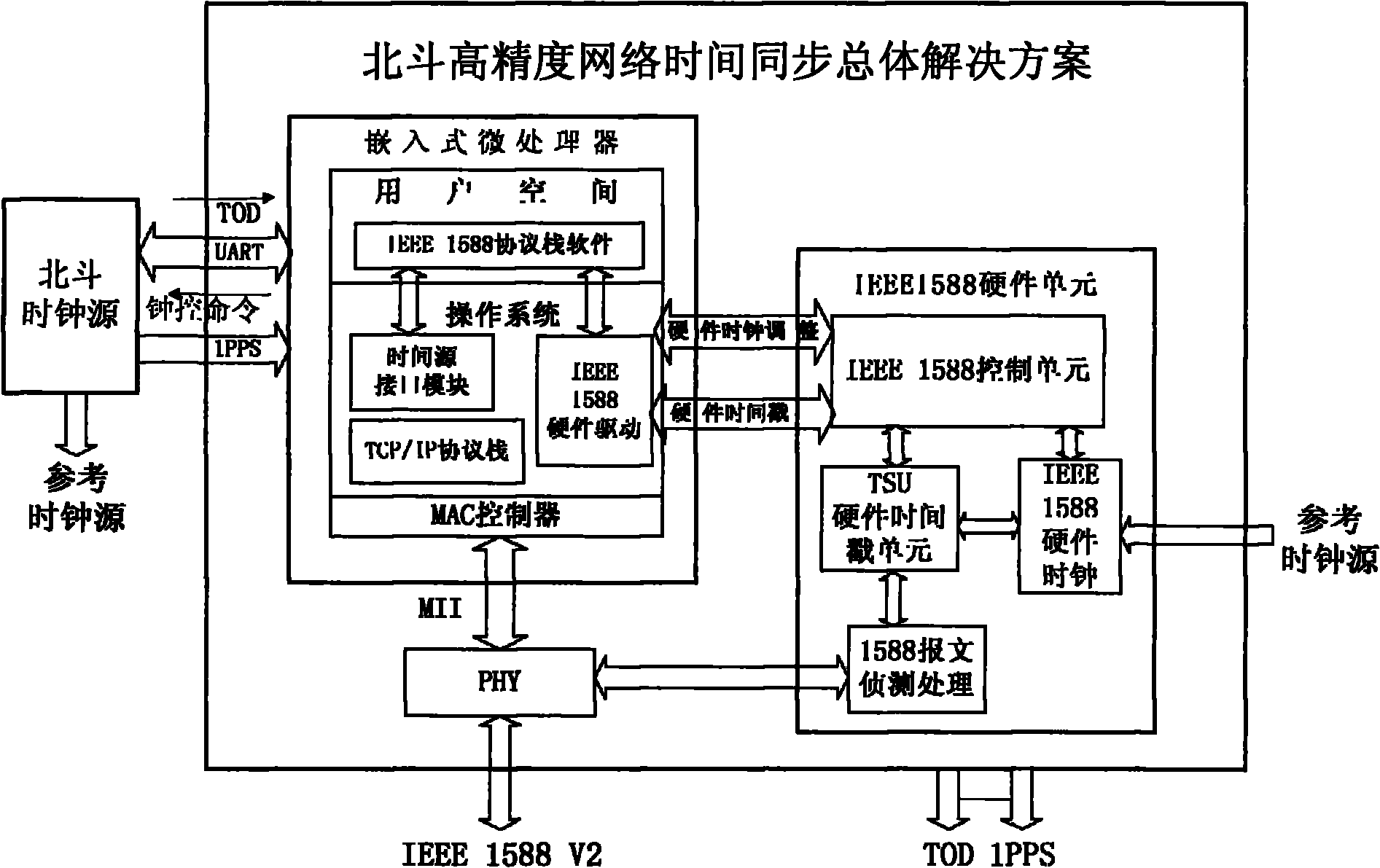

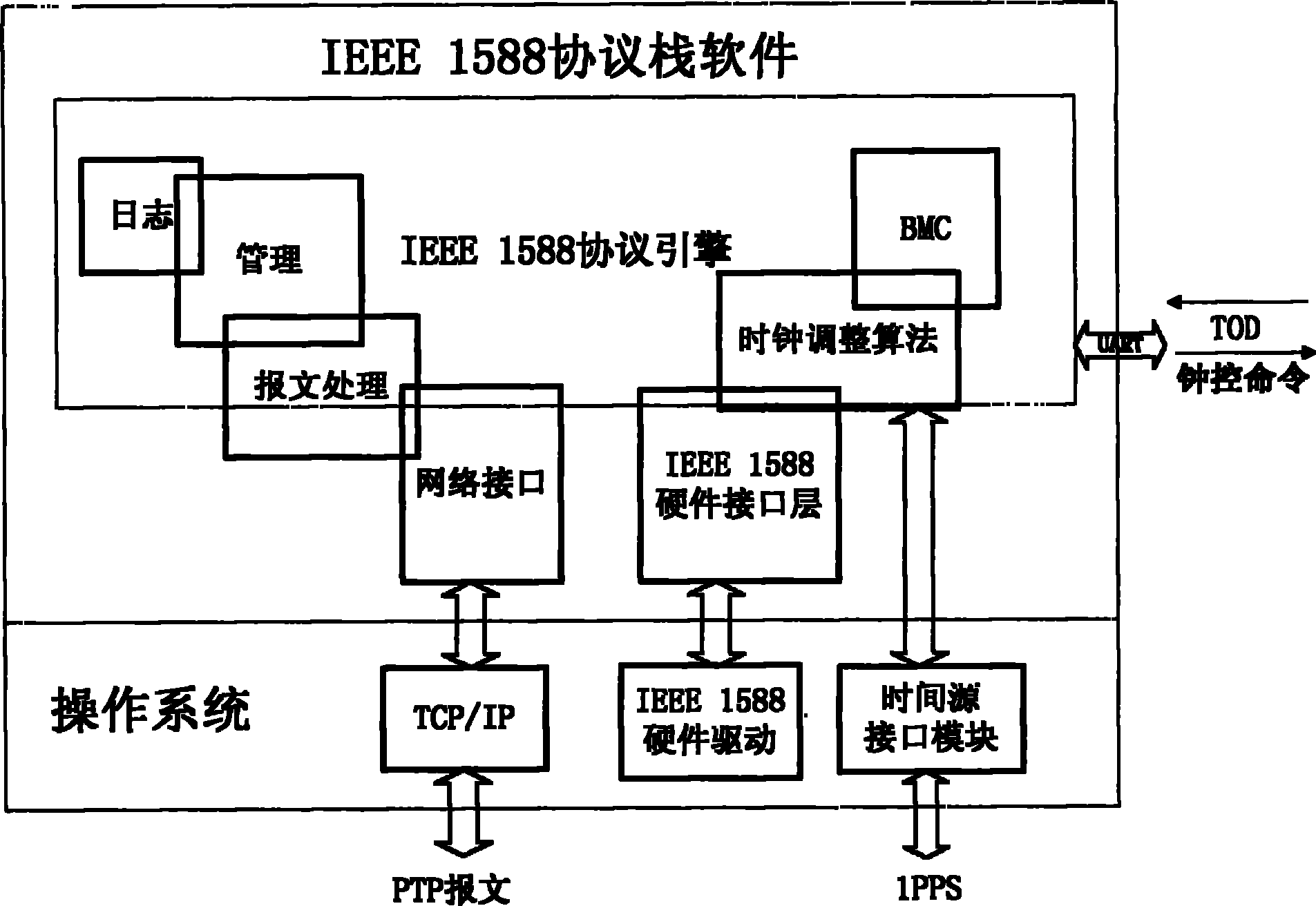

1588 protocol-based beidou time synchronization device and application thereof

ActiveCN102013967AGet rid of dependenceBroad application spacePosition fixationSynchronising arrangementTime informationSoftware system

The invention discloses a 1588 protocol-based beidou time synchronization device. A beidou clock source provides beidou 1PPS / TOD time scale information and a clock signal, and the output clock signal is used as an external reference clock source of an institute of electrical and electronic engineers (IEEE) 1588 hardware unit; an embedded microprocessor receives the 1PPS / TOD time scale information of the beidou clock source, performs clock adjustment on the IEEE1588 hardware unit and reads a time stamp; an IEEE1588 message is transmitted and received, and IEEE1588 network time service is provided; the IEEE1588 hardware unit provides an external reference clock source input interface, generates the IEEE1588 time stamp and the time information of the 1588 hardware clock according to the received external reference clock source, processes the IEEE1588 message and finally restores the IEEE1588 hardware clock to be 1PPS signal to be output; and an IEEE1588 protocol stack software system comprises IEEE1588 protocol stack software, a beidou clock source interface and an IEEE1588 hardware unit driving module.

Owner:郑州威科姆科技股份有限公司

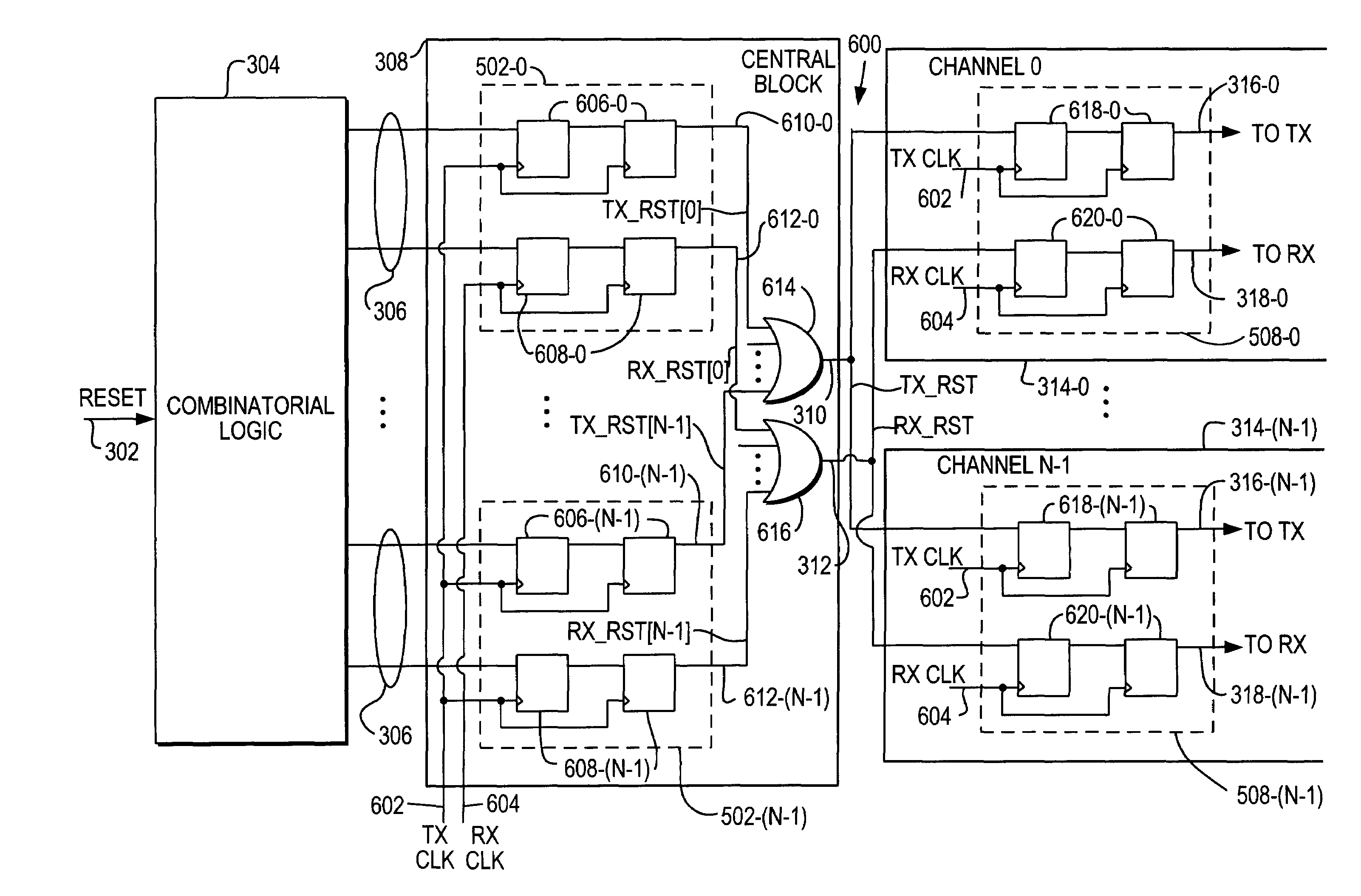

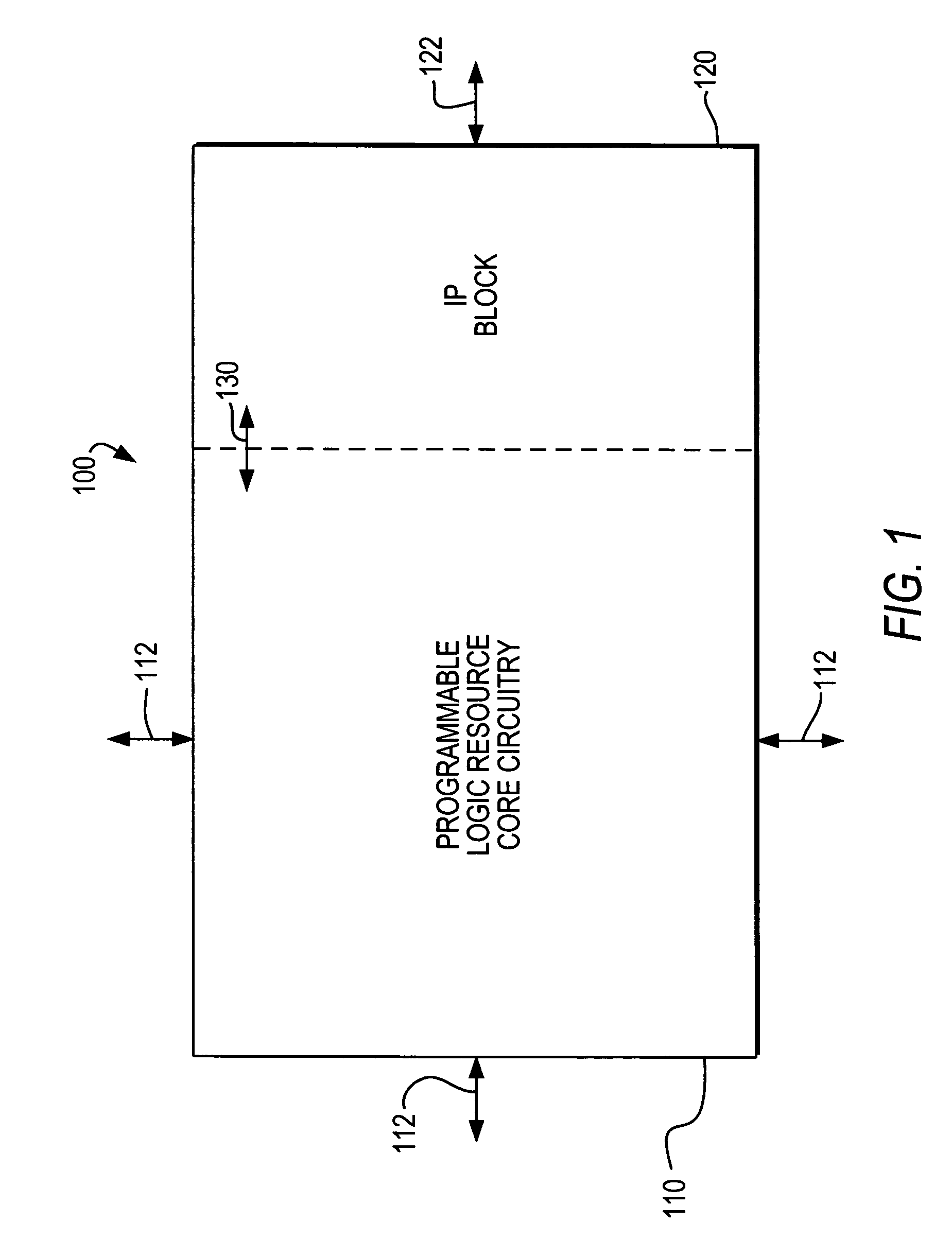

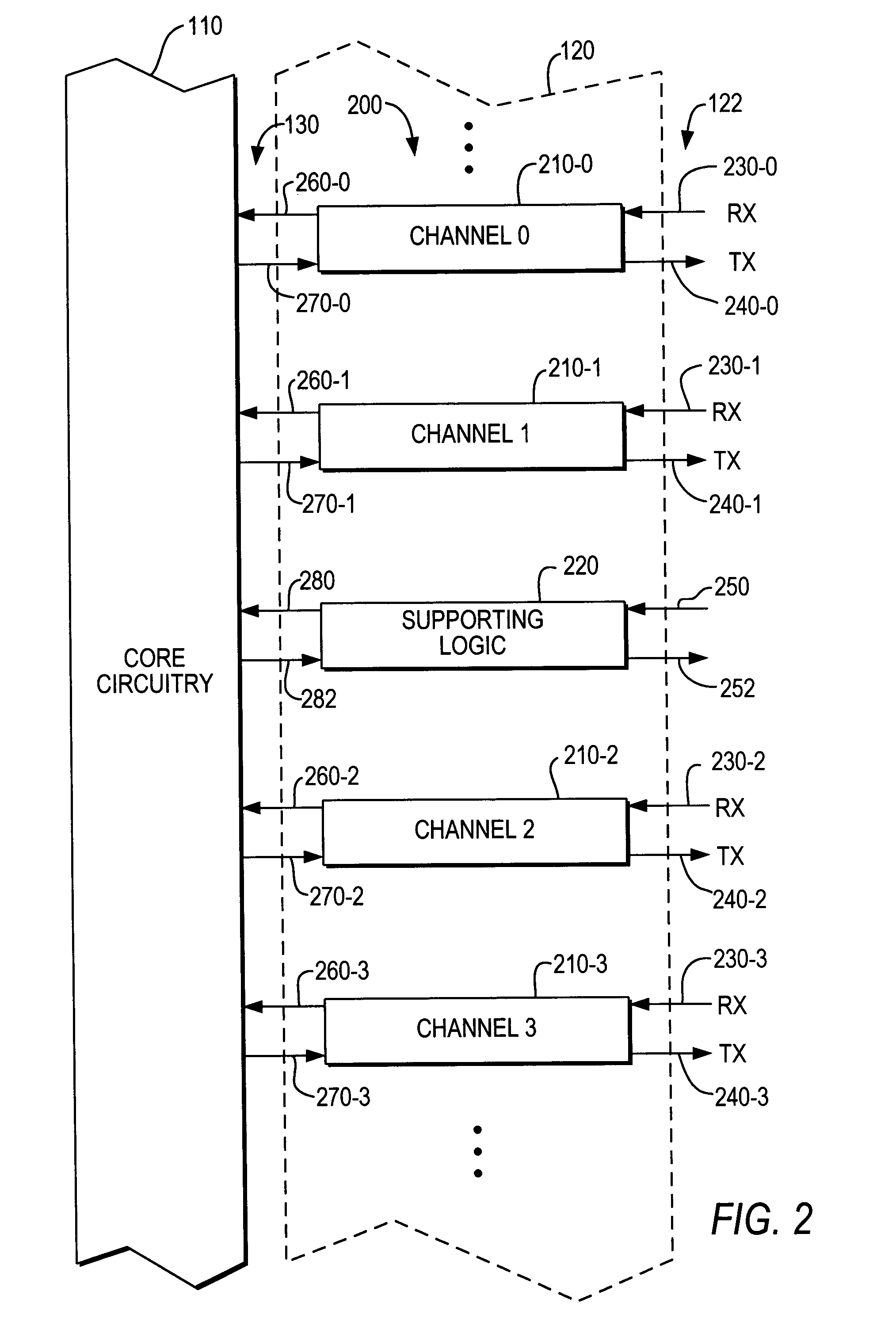

Apparatus and method for reset distribution

InactiveUS7028270B1CAD circuit designSpecial data processing applicationsPropagation delaySignal routing

A skew-tolerant, glitch-free reset distribution apparatus and method are provided in an intellectual property (IP) block that supports a multi-channel input / output protocol. During reset mode, synchronizers are used to create more predictable timing, to pipeline the propagation delay, and to tolerate RC-induced skews of up to a clock period in routing a reset signal to all the channels and within the channels in an IP block. Two control signals, which are available from programmable logic resource core circuitry, are used to control the input of the reset signal into the IP block. Because the control signals are designed to be glitch-free, the reset signal is therefore also glitch-free, thus preventing the IP block from inadvertently transitioning into or out of reset mode.

Owner:ALTERA CORP

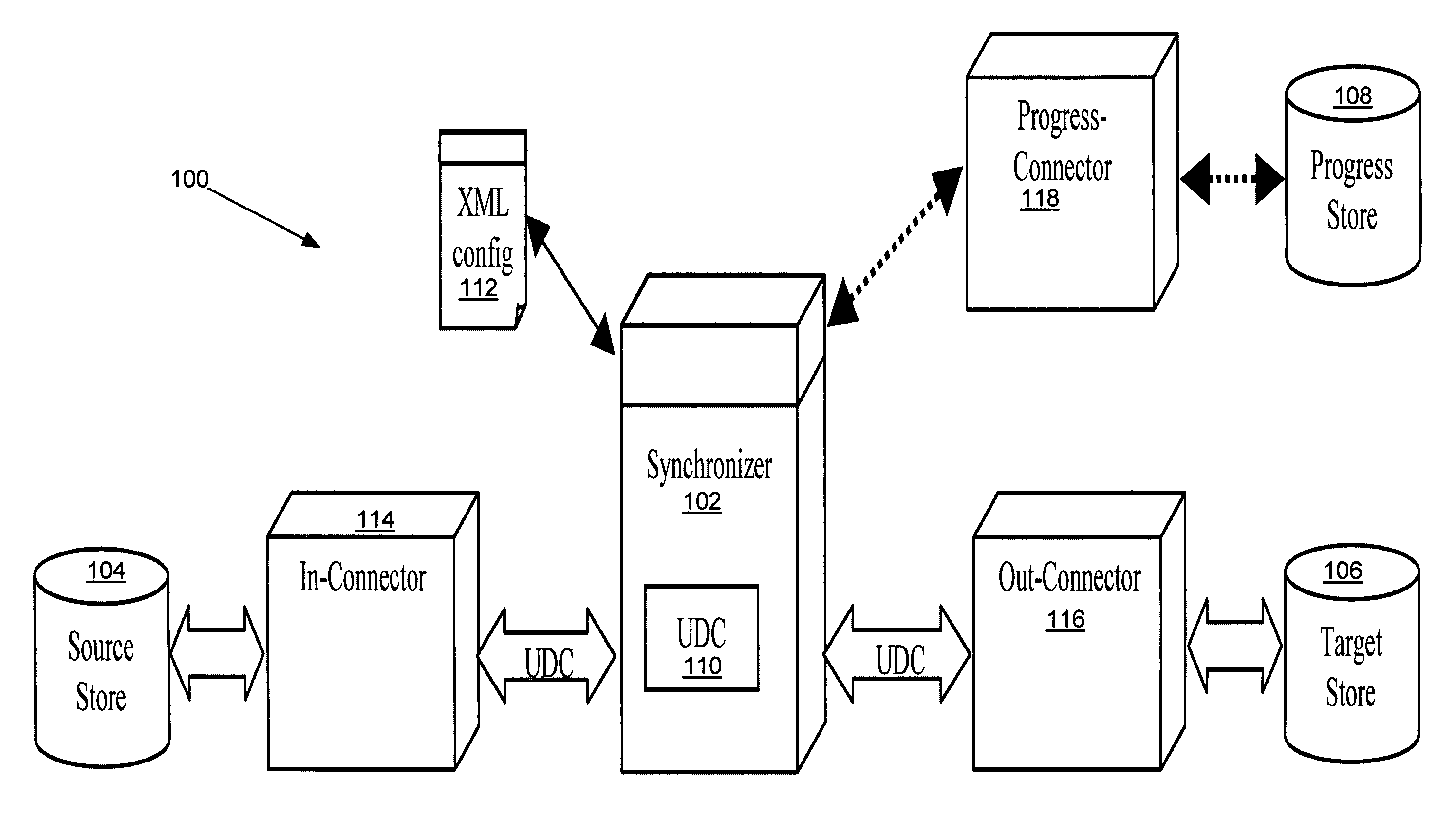

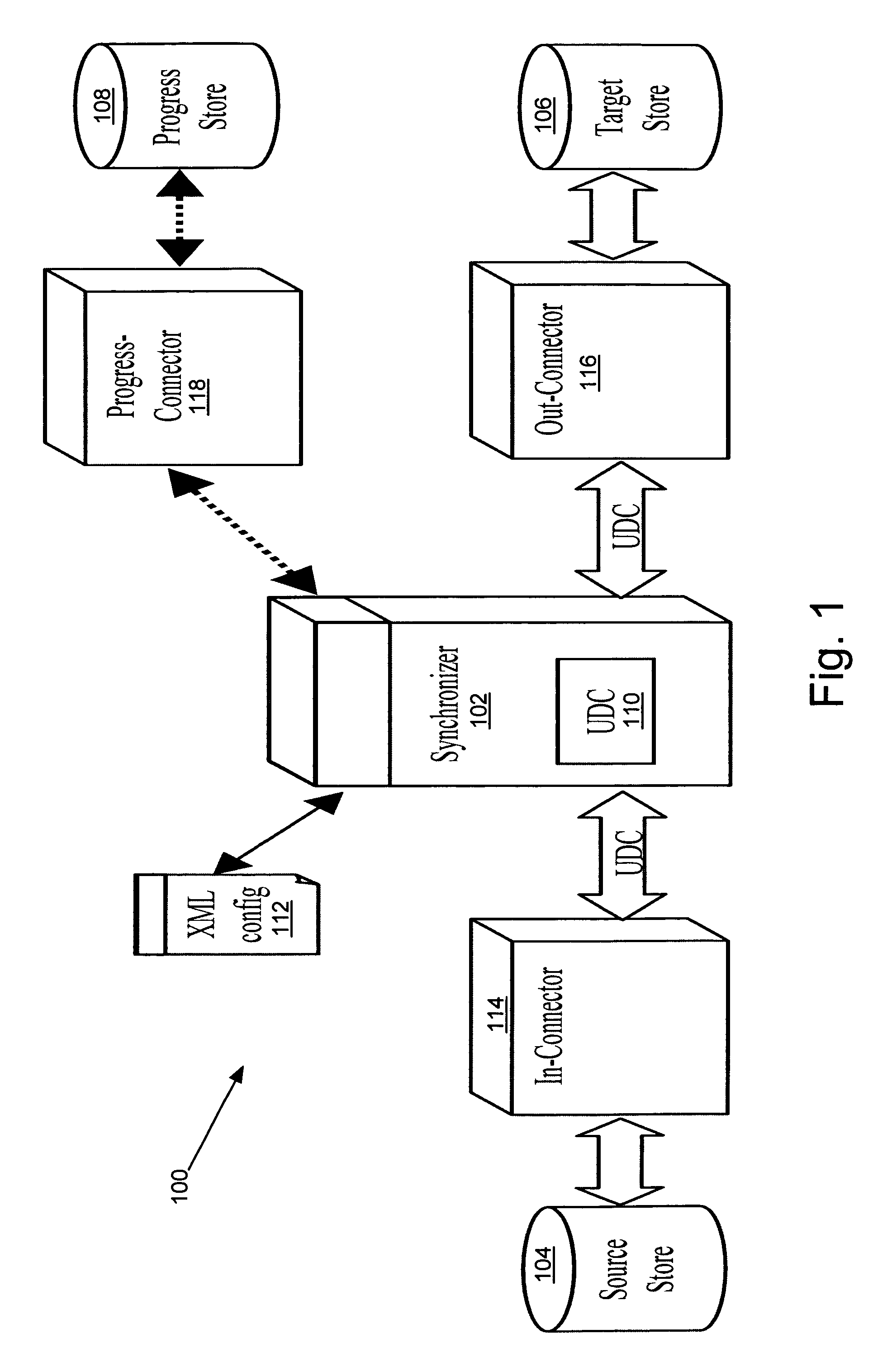

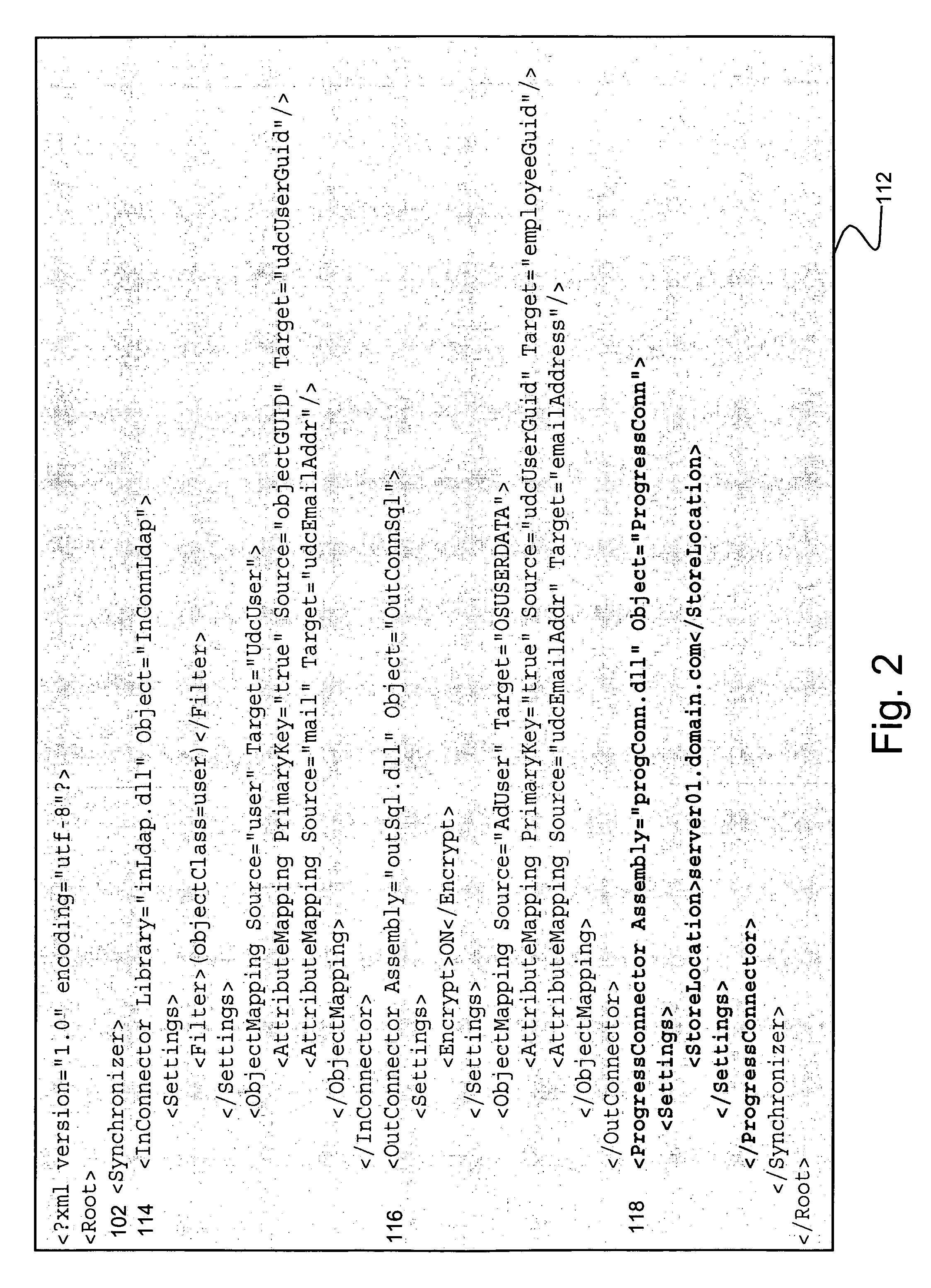

Data synchronizer with failover facility

ActiveUS7693888B2Digital data information retrievalError detection/correctionData synchronizationFailover

A data management system with data stored in multiple disparate formats in synchronized stores, method of synchronizing the data and recovering from synchronization failures and program product therefor. Data changes in one data store are cached in a universal format in an active synchronizer and forwarded to a second store from the universal format cache. Standby synchronizers provide failover handling by identifying synchronization failures and self-selecting a replacement synchronizer to serve as the active synchronizer.

Owner:UNIFY PATENTE GMBH & CO KG

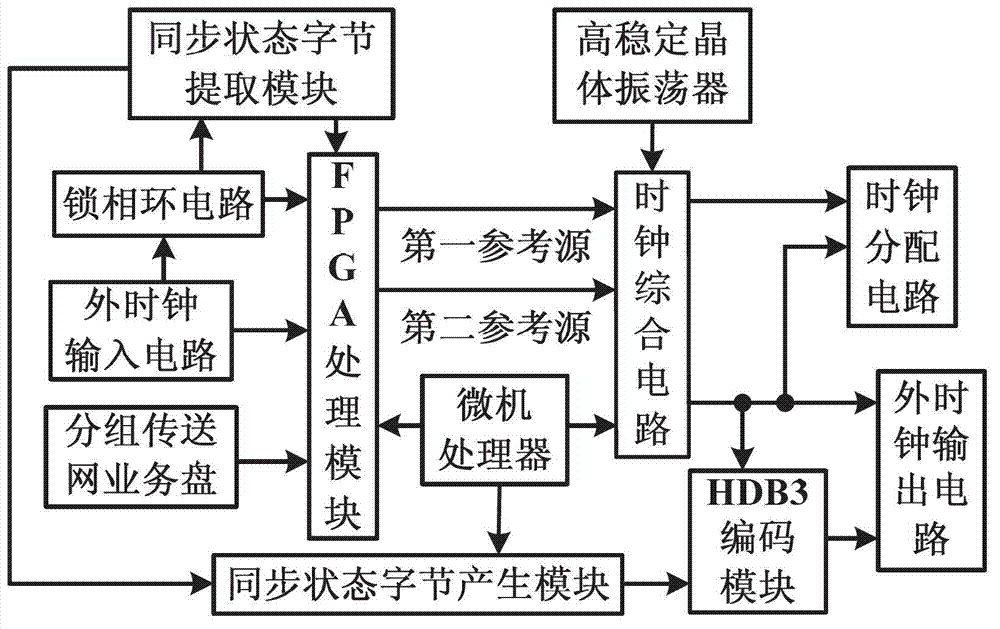

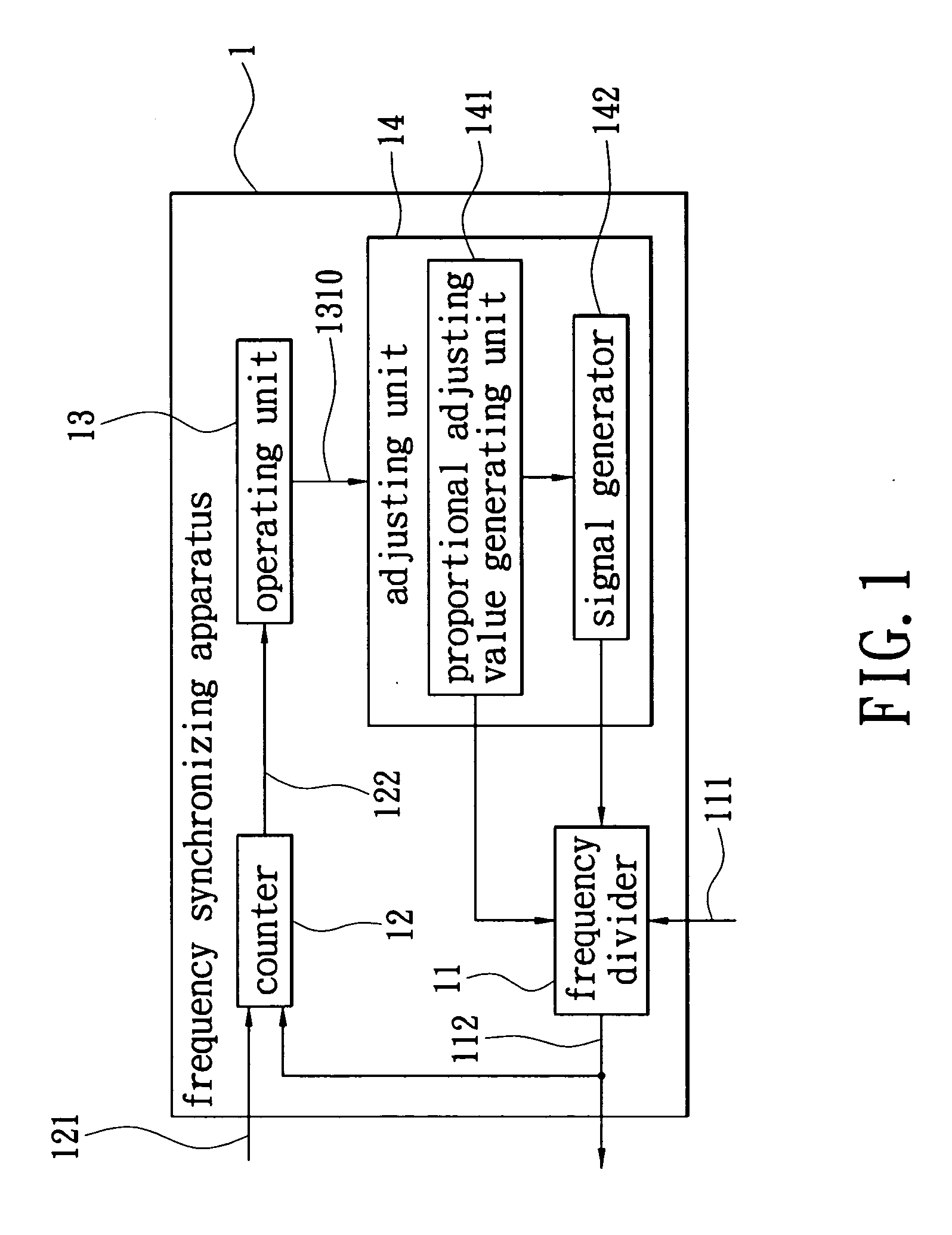

Device and method for synchronizing system frequency in packet transport network

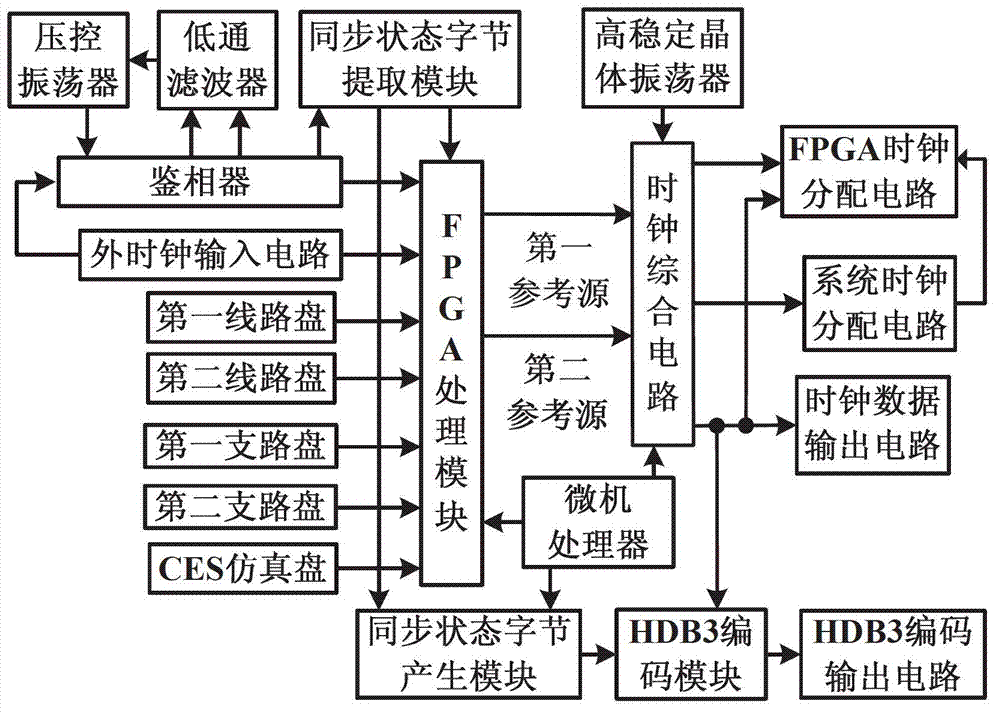

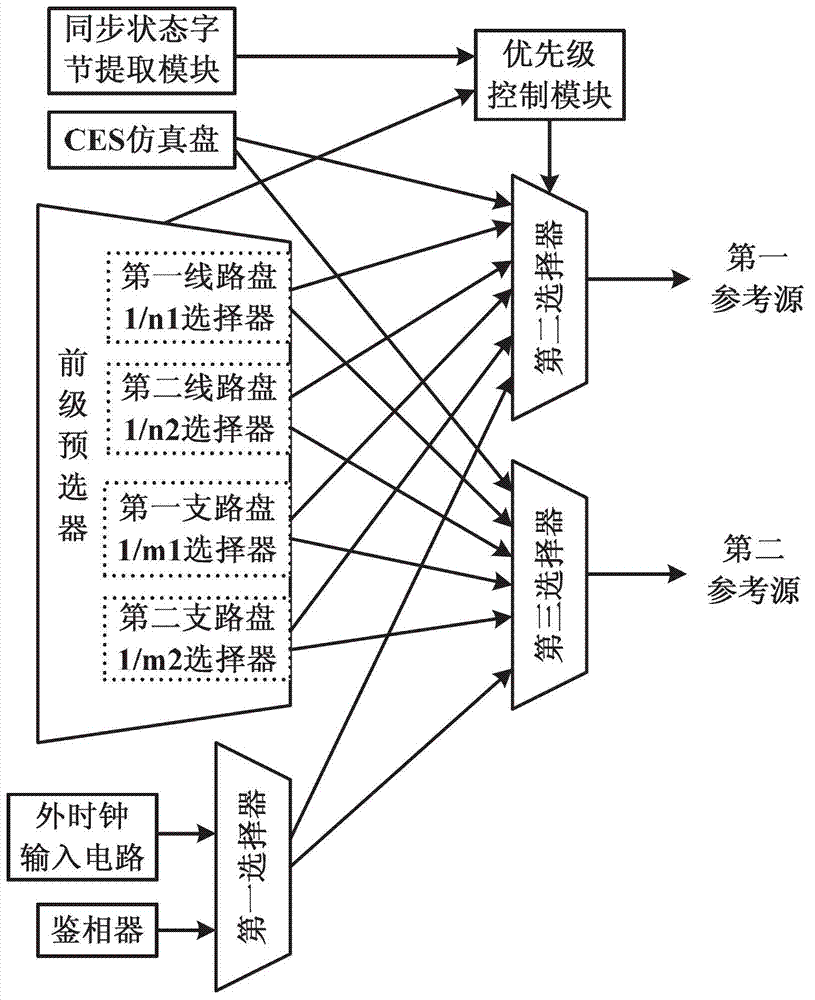

ActiveCN102904706APacket transfer implementationFrequency synchronizationSynchronising arrangementSynchronizerPhase locked loop circuit

The invention discloses a device and a method for synchronizing system frequency in a packet transport network, and relates to a packet transport network in optical communication. The system frequency synchronizing device comprises a microcomputer processor, a field programmable gate array (FPGA) processing module, a clock integrated circuit, a packet transport network service disk, a synchronous state byte extracting module, a synchronous state byte generating module, a phase locked loop circuit, an external clock input circuit, a high stable crystal oscillator, a clock distributing circuit, a HDB3 coding module and an external clock output circuit, wherein the FPGA processing module comprises a preceding stage preselector, a priority level control module, a first selector, a second selector and a third selector. By the device and method, the system frequency in the whole packet transport network can be synchronized rapidly, data business package transmission and smooth transition can be carried out rapidly and hierarchically, and the device is flexible and has high reliability.

Owner:FENGHUO COMM SCI & TECH CO LTD

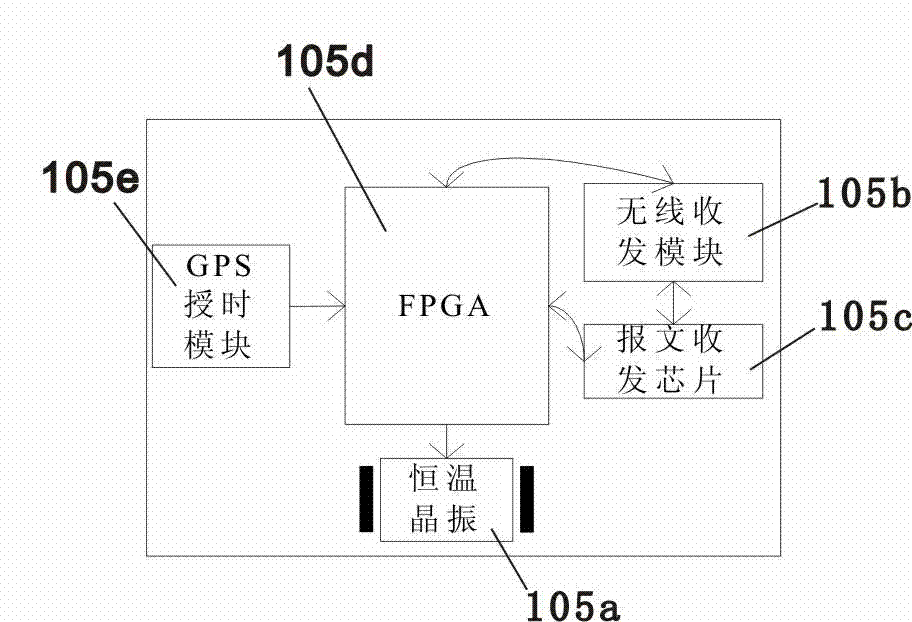

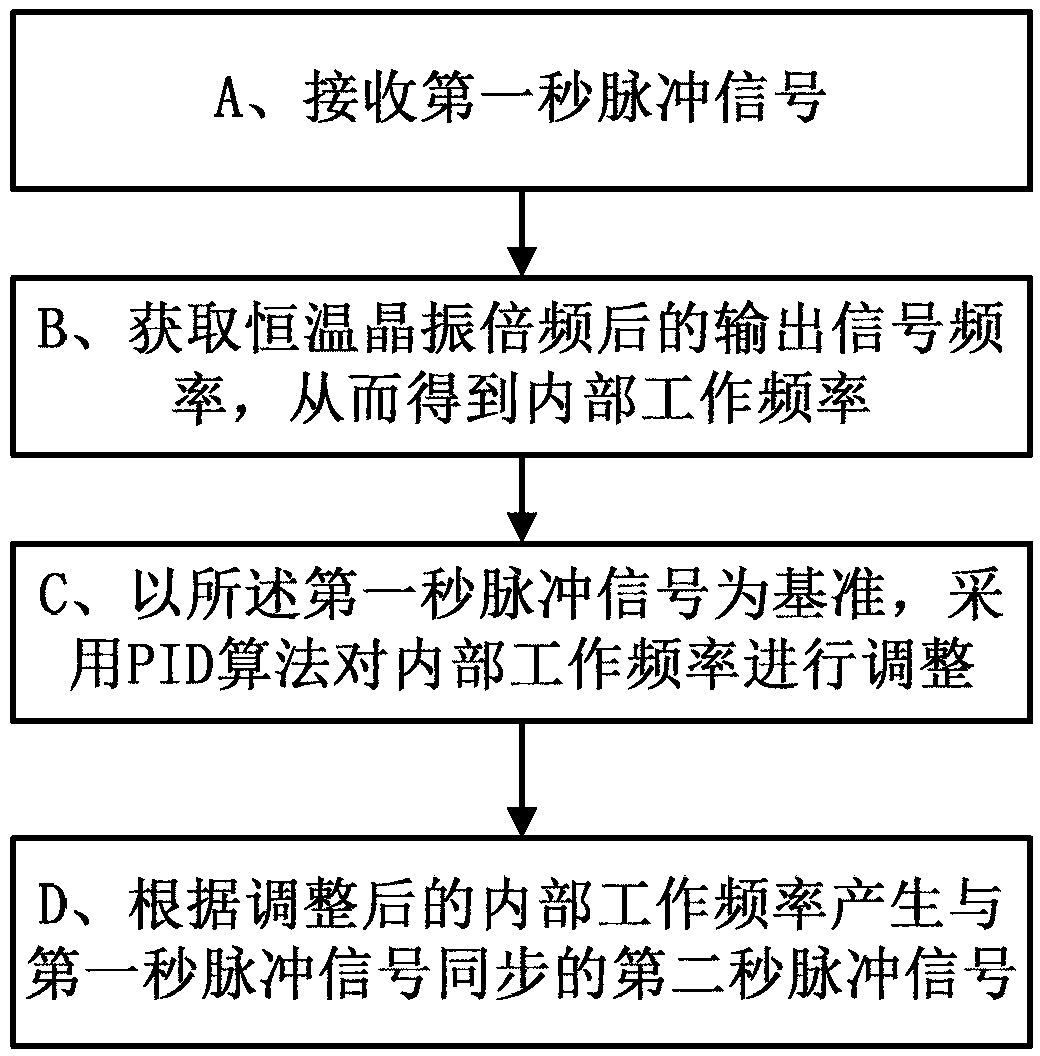

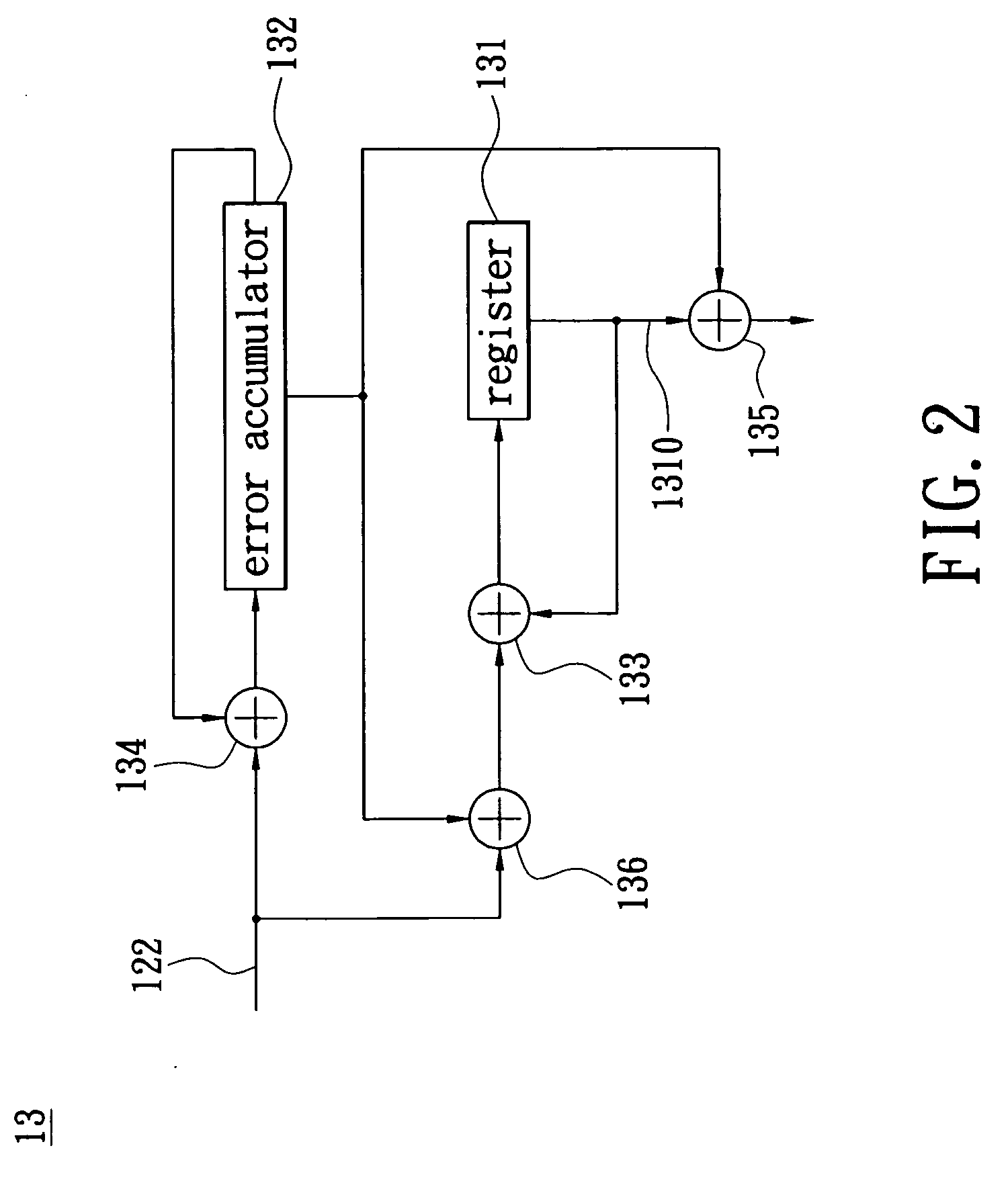

Time-keeping method of time synchronization device

ActiveCN103269262AImprove stabilityImprove synchronicitySynchronising arrangementSynchronizerProportion integration differentiation

The invention discloses a time-keeping method of a time synchronization device. The method comprises the following steps: A, receiving a first pulse per second signal; B, acquiring output signal frequency doubled by a constant-temperature crystal oscillator so as to obtain internal working frequency; C, taking the first pulse per second signal as a base, and adopting a PID (Proportion Integration Differentiation) algorithm to adjust the internal working frequency; and D, generating a second pulse per second signal synchronous to the first pulse per second signal according to the adjusted internal working frequency. According to the time-keeping method of the time synchronization device, the PID algorithm is introduced, a PID strategy is applied to adjust the internal working frequency, the second pulse per second signal is generated according to the adjusted internal working frequency and has the advantages of good stability and high synchronism, the implementation procedure of the second pulse per second signal is simple, and high-accurate time keeping can be implemented with lower cost. The invention relates to the time-keeping method of the time synchronization device, which can be widely applied to the technical field of communication.

Owner:LIUZHOU DADI TELECOMM EQUIP +1

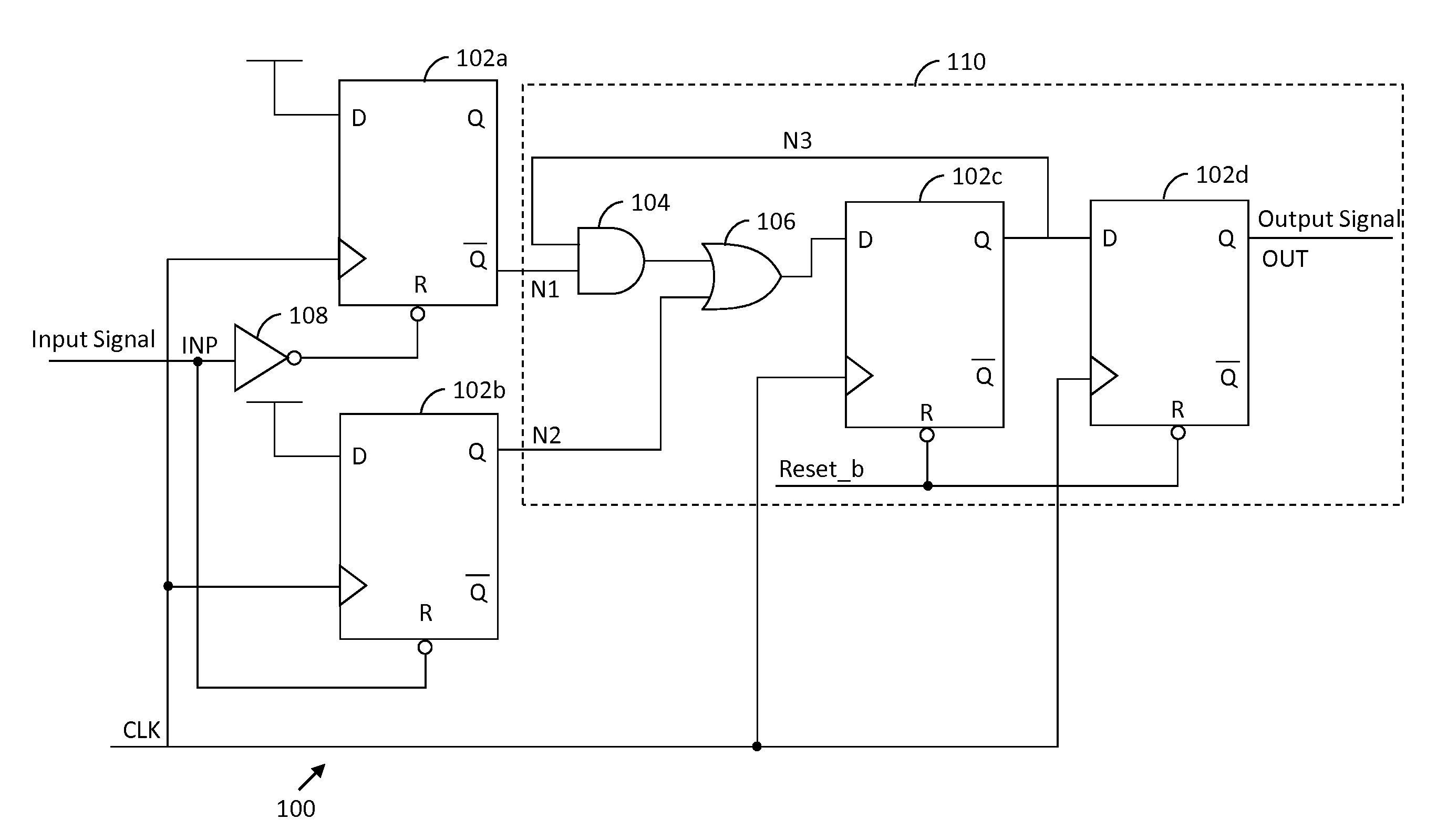

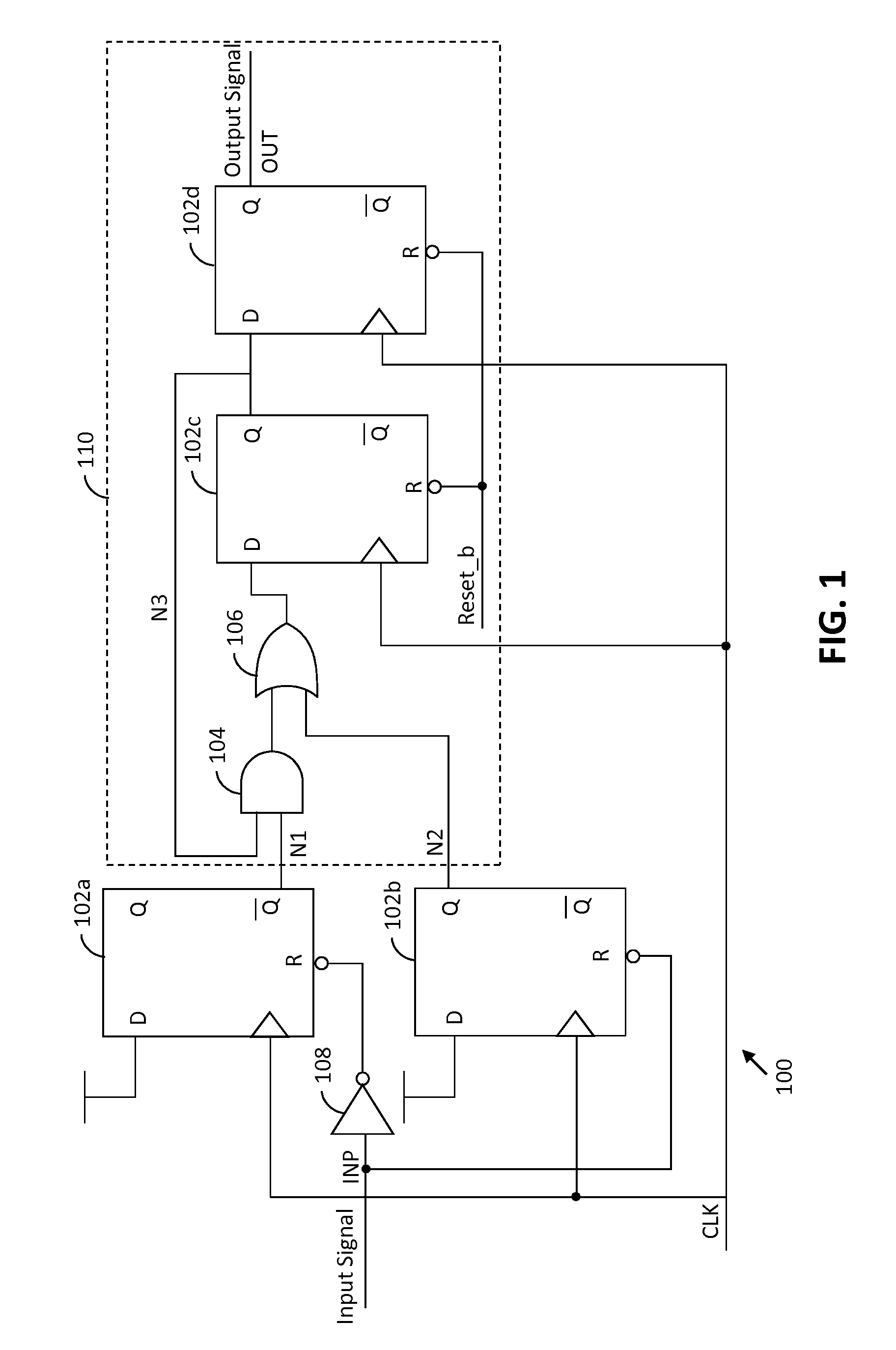

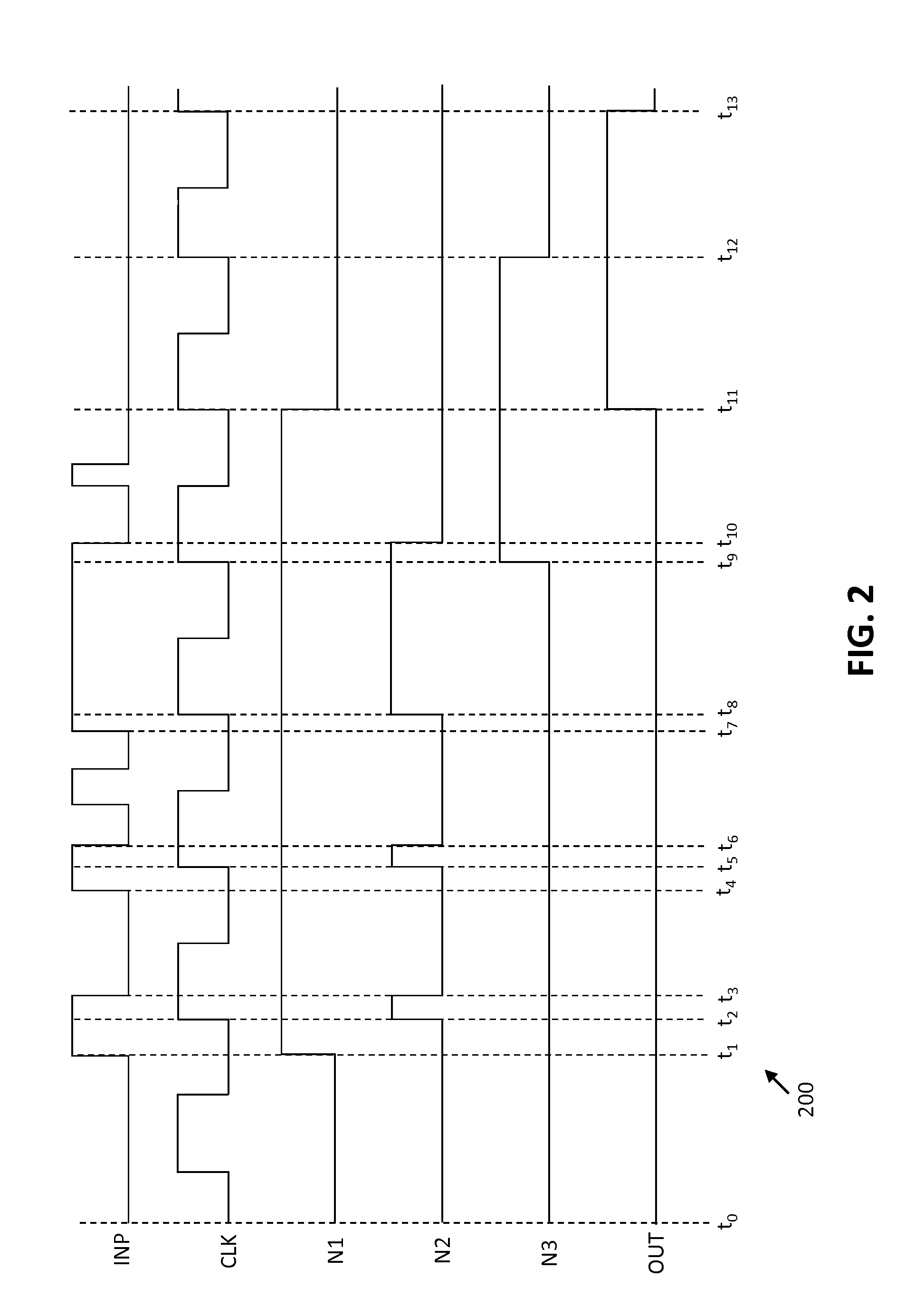

Digital glitch filter

InactiveUS20130038359A1Low costAvoid spreadingPulse automatic controlPulse manipulationGlitchClock signal

A digital glitch filter for filtering glitches in an input signal includes first and second flip-flops and a synchronizer. The synchronizer includes third and fourth flip-flops. A glitch prone input signal is provided to the first and second flip-flops. Additionally, an input clock signal is provided to the first and second flip-flops and the synchronizer. A glitch occurring in the input signal toggles the first and second flip-flops between transmitting and non-transmitting states and first and second intermediate signals are generated. The synchronizer synchronizes the first and second intermediate signals with the input clock signal to generate a filtered output signal.

Owner:NXP USA INC

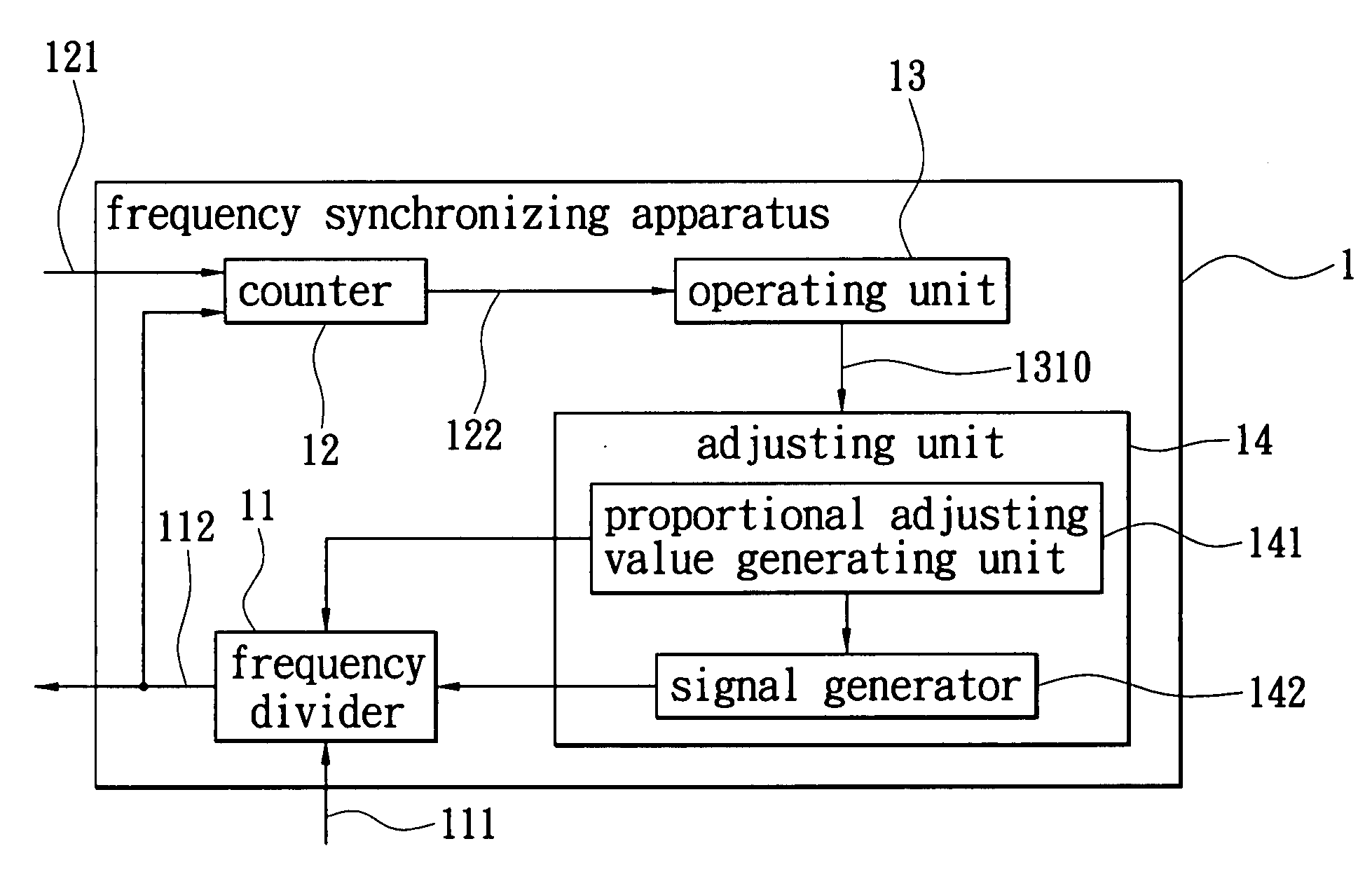

USB frequency synchronizing apparatus and method of synchronizing frequencies

ActiveUS20090116603A1Fix instabilityTransmission control/equlisationPulse automatic controlReference intervalsComputer science

A universal series bus (USB) frequency synchronous apparatus using a start of frame (SOF) signal generated by a master device to mark a reference interval is disclosed. The frequency synchronizing apparatus includes a frequency divider, a counter unit with a default pulse number, an arithmetic unit, and an adjusting unit. The frequency divider divides a high frequency signal by a variable frequency factor to generate a lock frequency signal. The counter is used to detect a pulse number of the lock frequency signal at a reference interval and obtain a pulse difference between the default pulse number and the detected pulse number of the lock frequency signal.

Owner:HOLTEK SEMICON

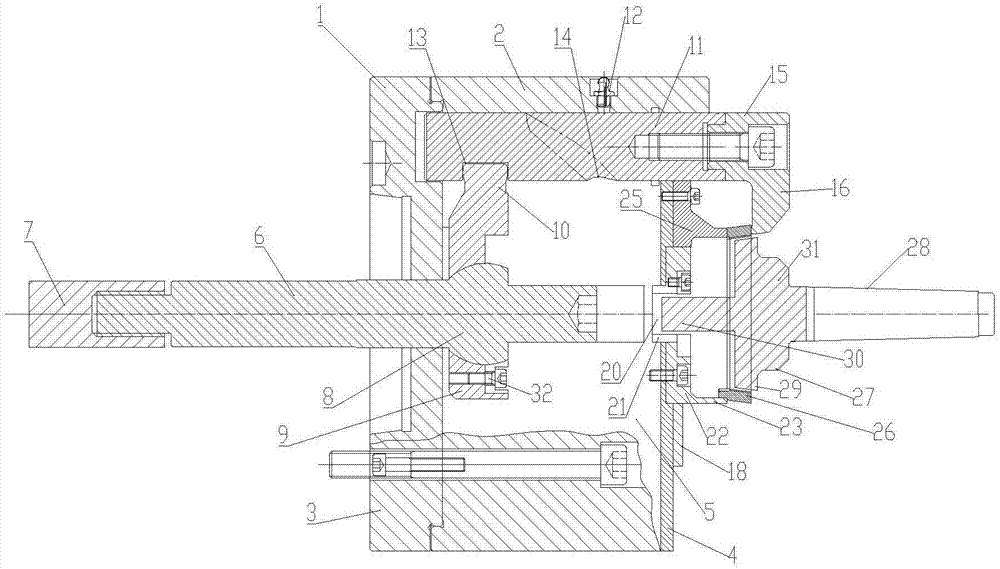

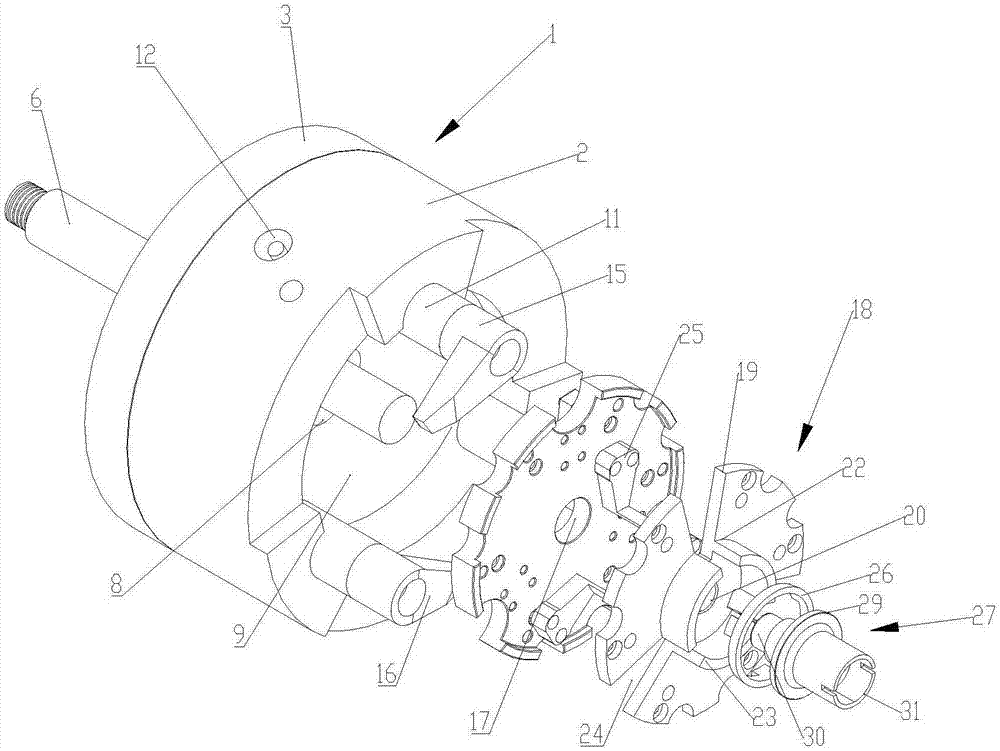

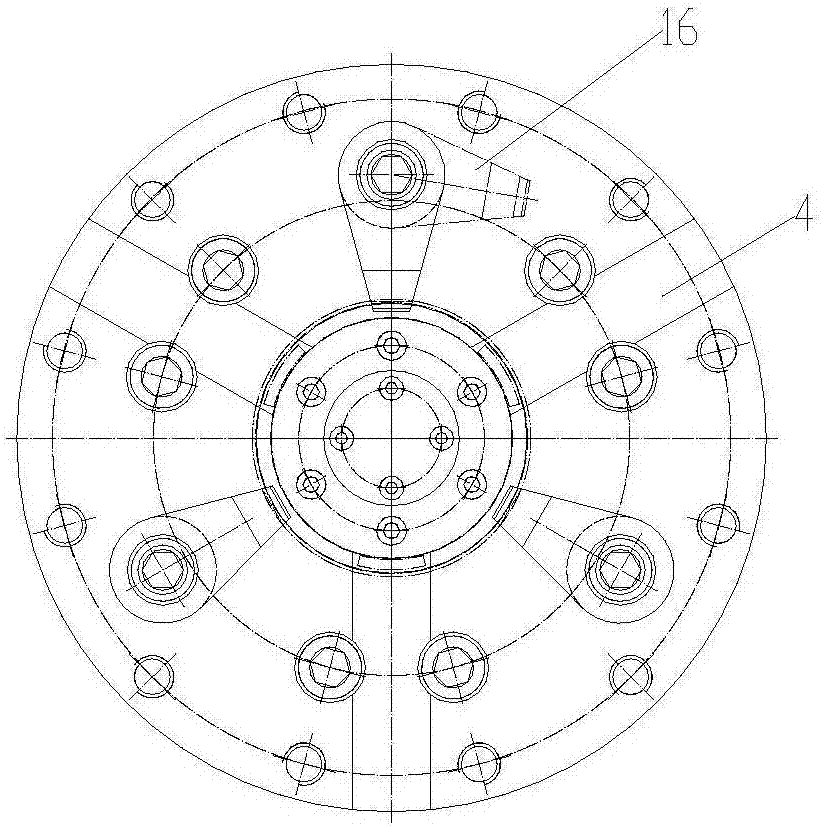

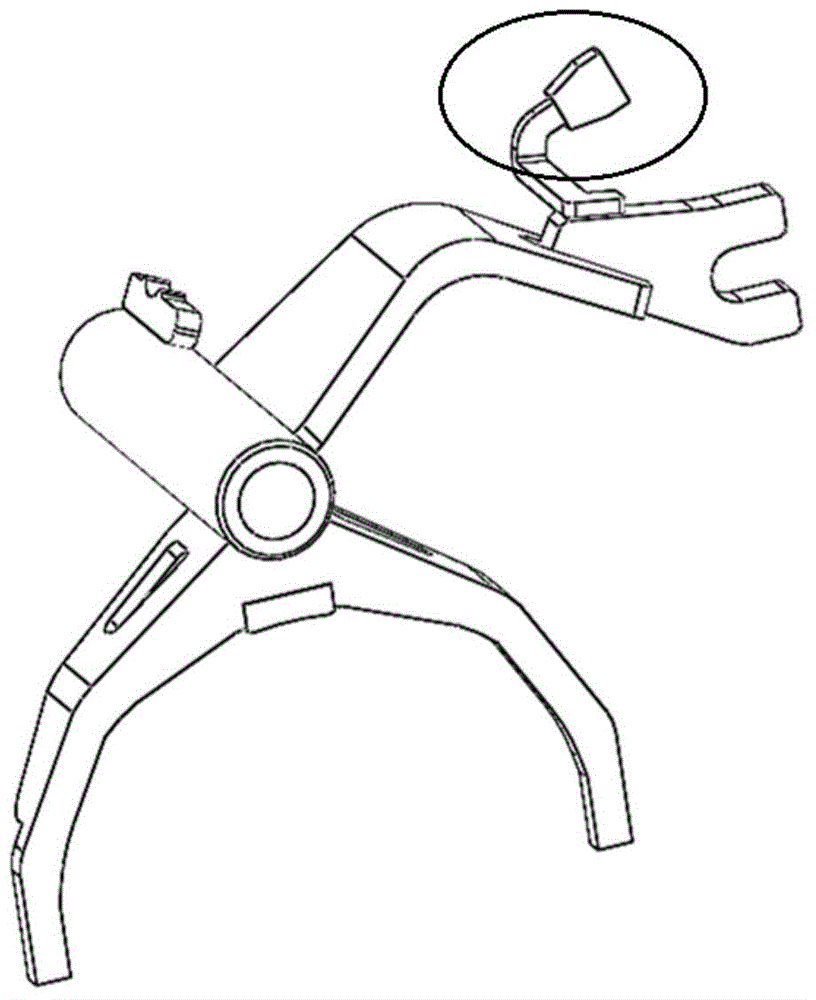

Synchronizer gear ring inner ring machining composite clamp

PendingCN107336040AEasy loadingGuaranteed coaxiality stabilityPositioning apparatusMetal-working holdersSynchronizerLinkage (mechanical)

Owner:WUHAN KYOWA SYNCHRONIZER RING

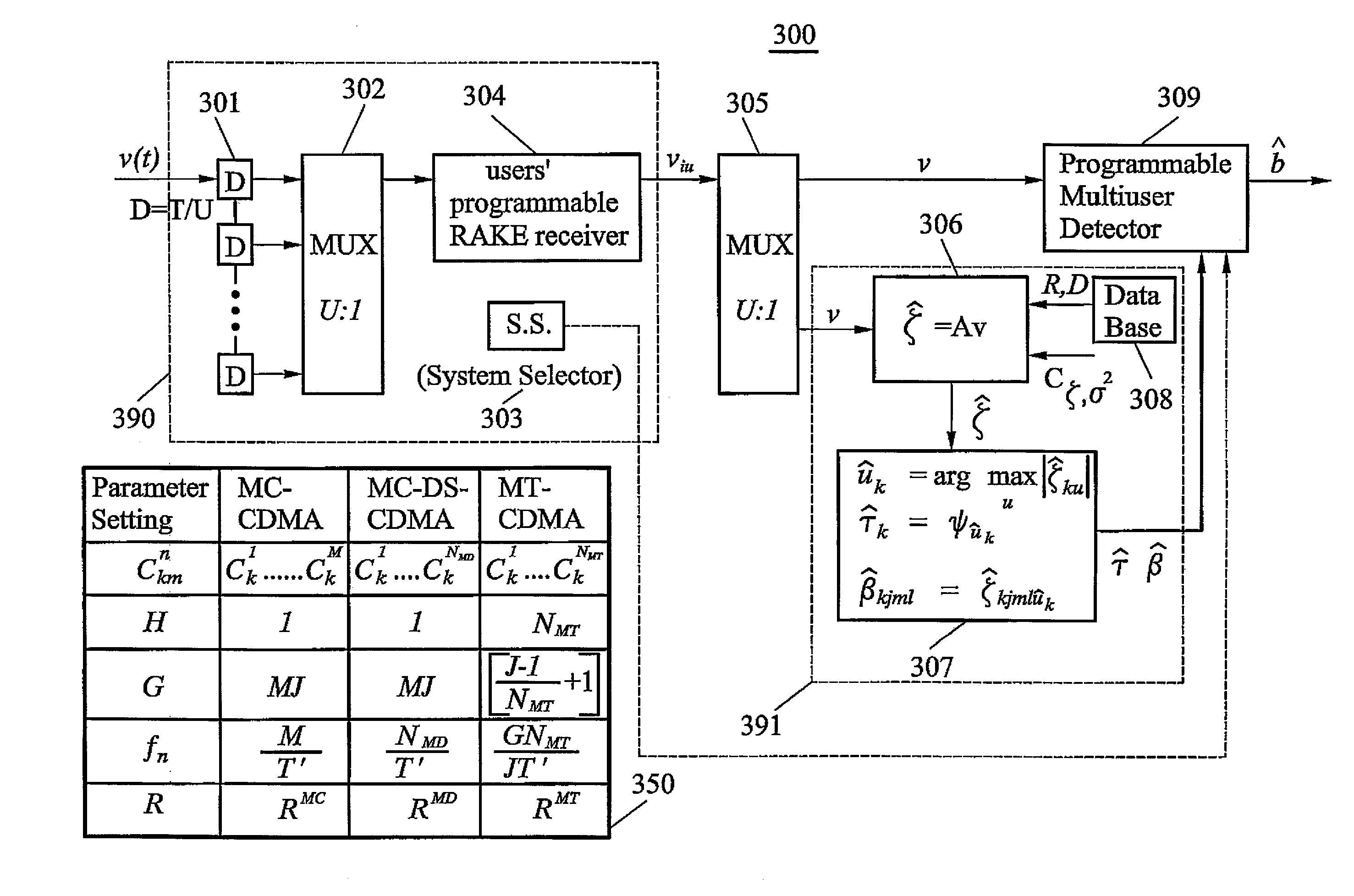

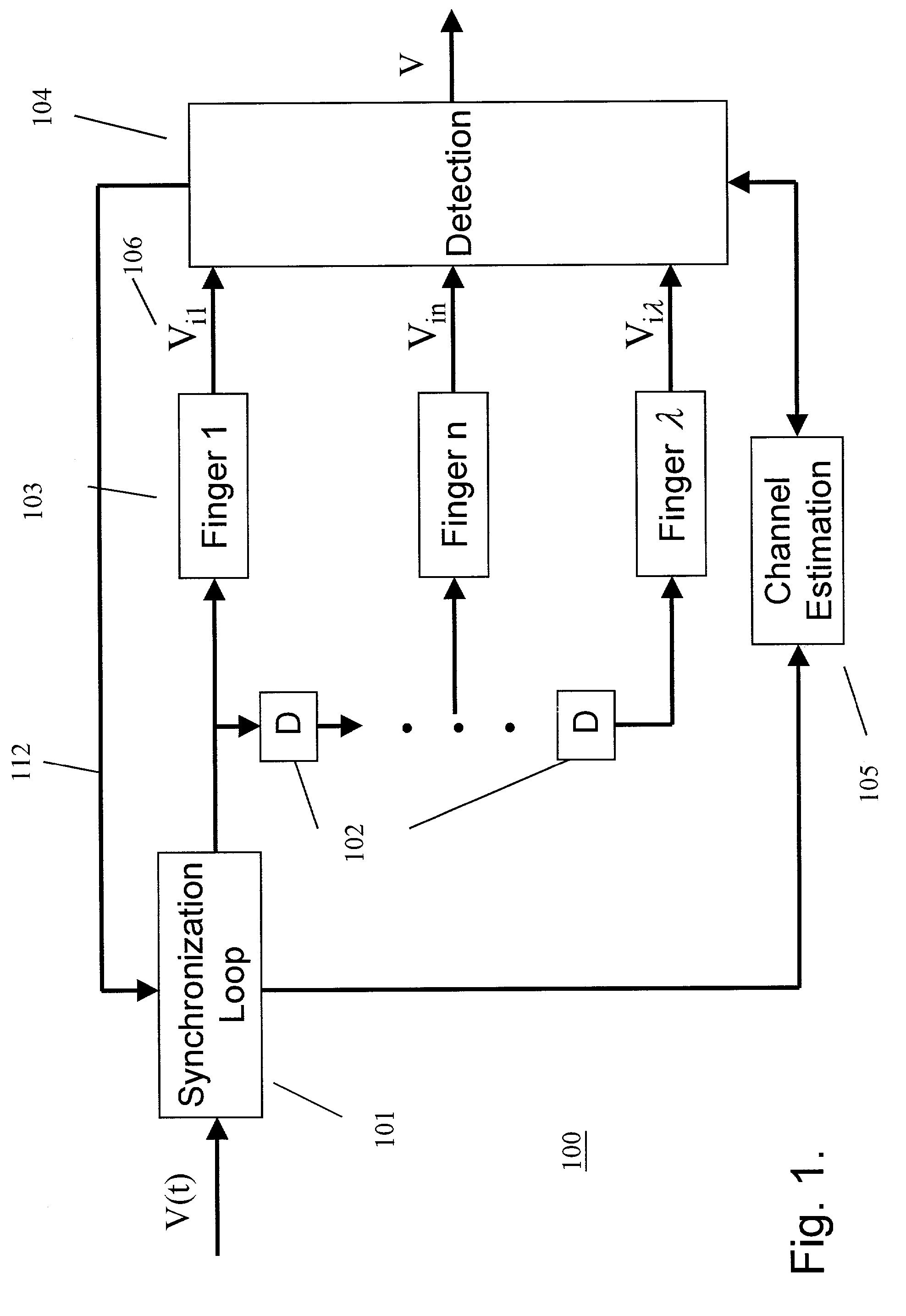

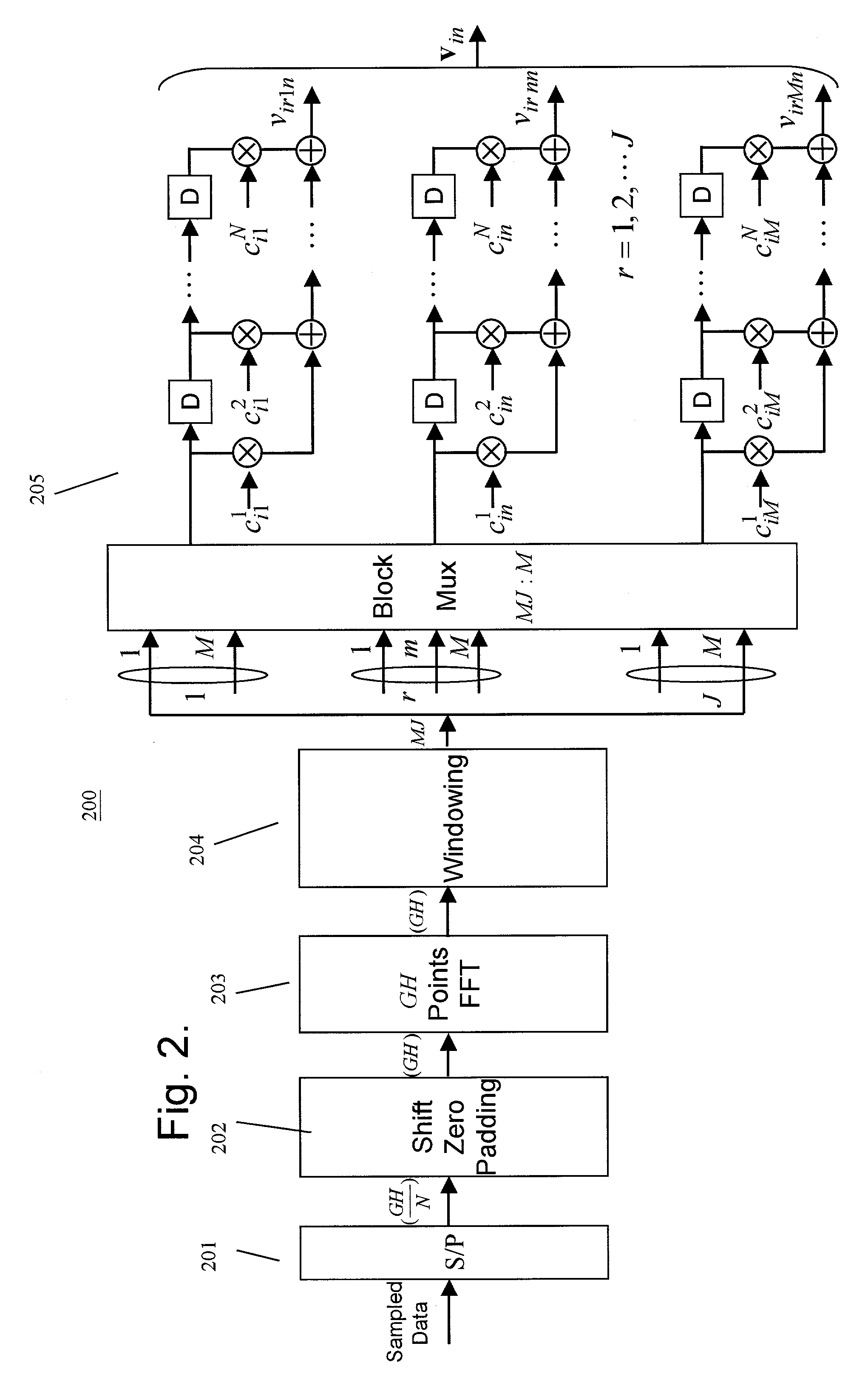

System and method for synchronizing multiuser signals for OFDM CDMA

InactiveUS7161927B2Reduce in quantityEfficient reductionRadio transmissionMulti-frequency code systemsCdma systemsFft fast fourier transform

A system and a method for deriving transmitted signals from multiple users for an OFDM-CDMA communication system are described herein. An optimum synchronizer for use in an OFDM-CDMA system is also provided. In one aspect, the system and method incorporate a programmable structure for different OFDM-CDMA systems (e.g., MC-CDMA, MC-DS-CDMA, and MT-CDMA) that can be efficiently implemented. The programmable structure is based on the linear minimum mean square error (LMMSE) or best linear unbiased estimator (BLUE) techniques. In addition, an efficient algorithm for reducing computations of fast Fourier transform (FFT) is presented.

Owner:MEDIATEK INC

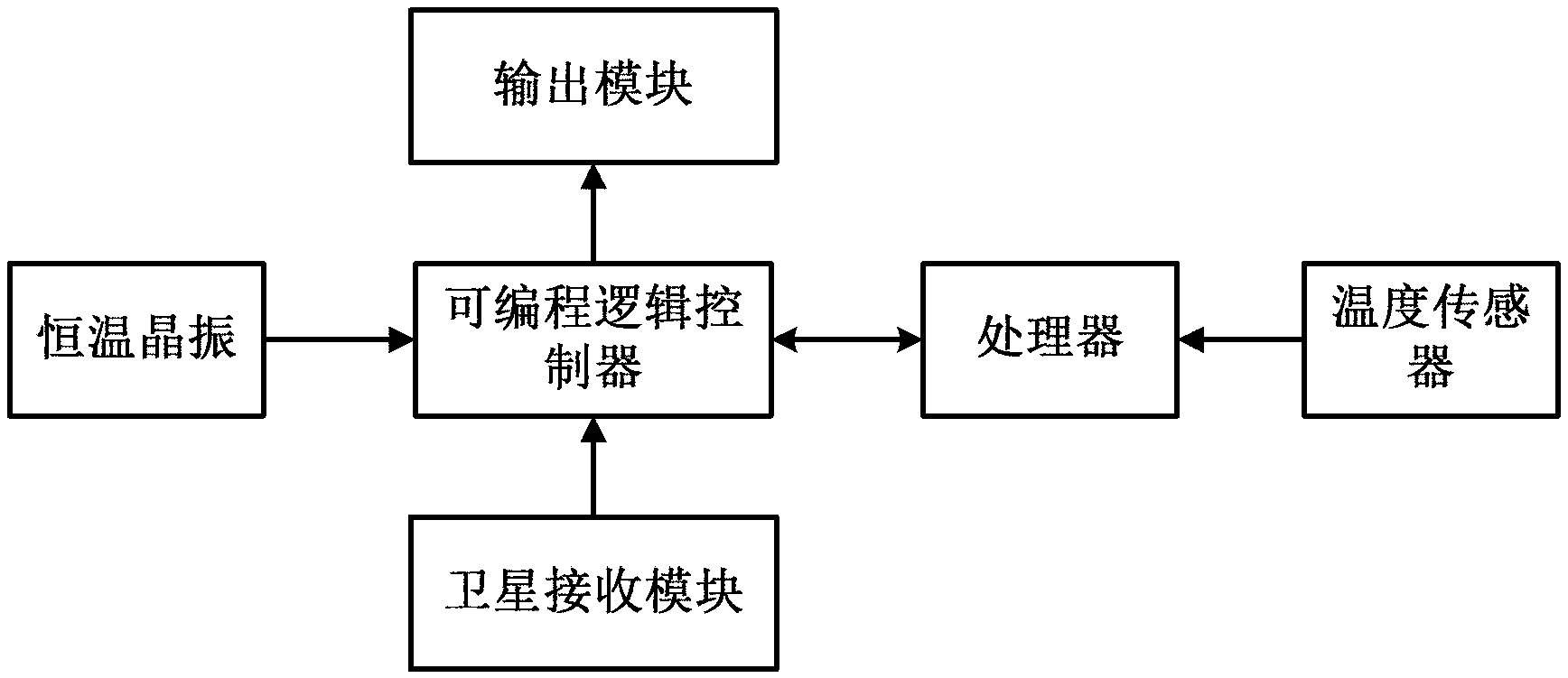

Dynamic high-precision time synchronization device and synchronization method thereof

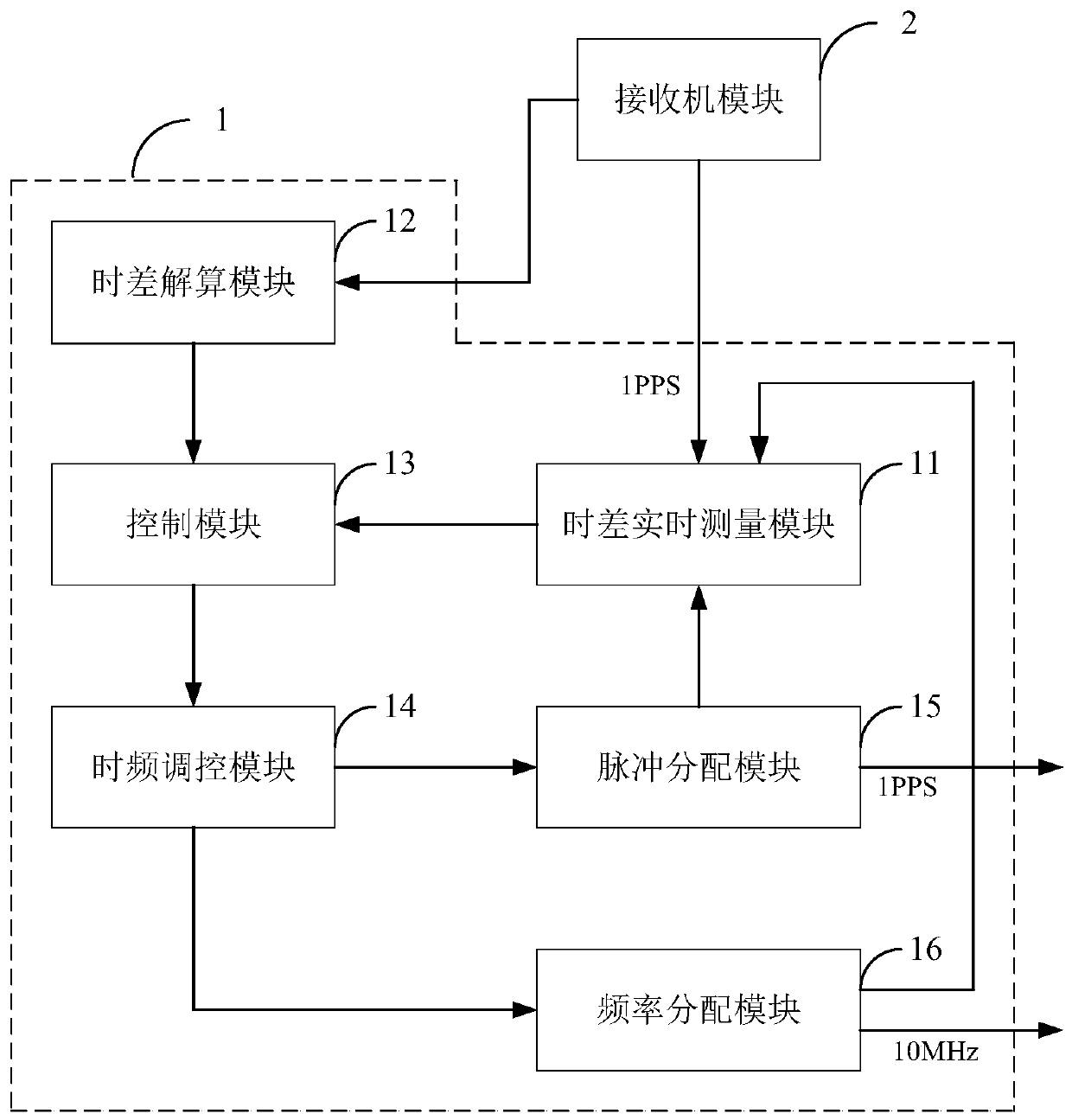

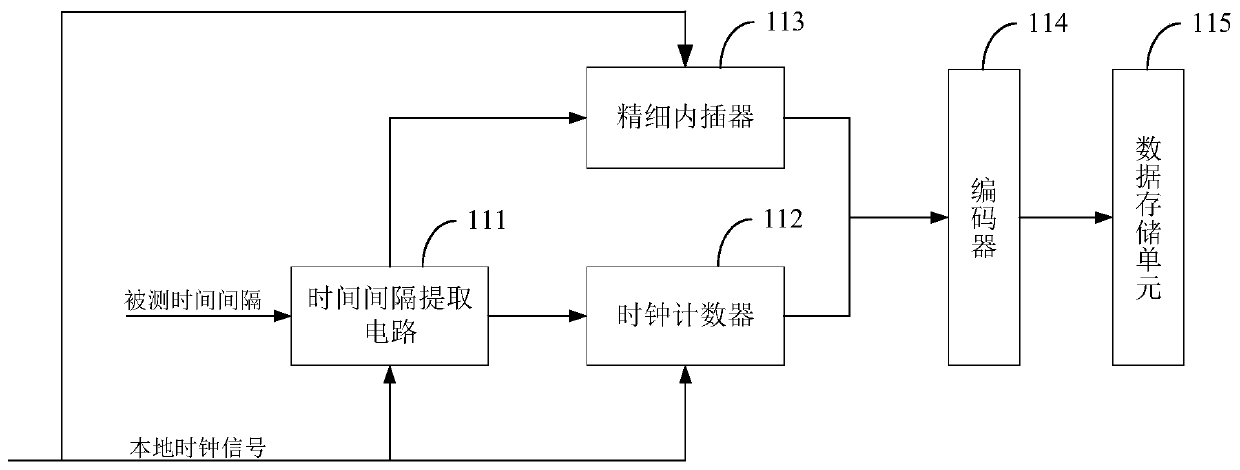

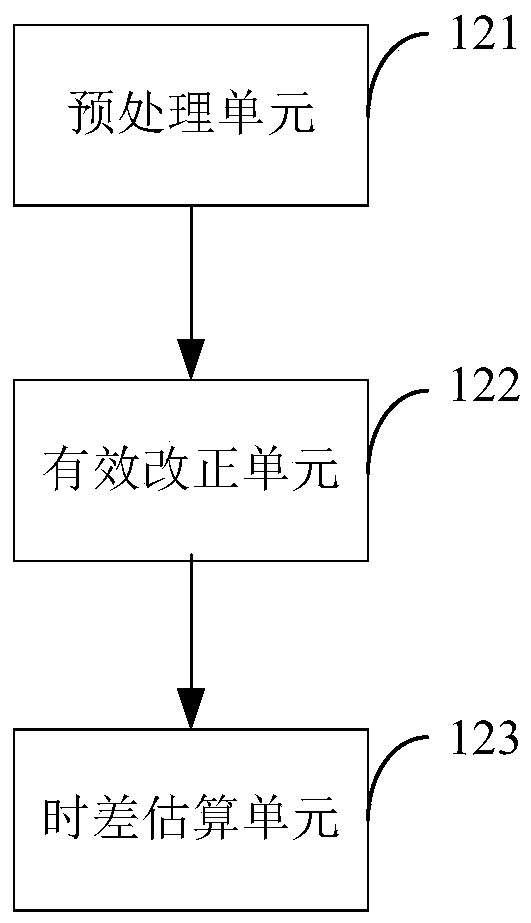

ActiveCN111447032AHigh precision time synchronizationSynchronize Dynamic TimeTime-division multiplexSynchronizerNavigation system

The invention belongs to the technical field of time frequency, and discloses a dynamic high-precision time synchronization device and a synchronization method thereof. The time synchronization devicecomprises a time difference real-time measurement module, a time difference calculation module, a time frequency regulation and control module, a frequency distribution module, a pulse distribution module and a control module. The time difference real-time measurement module accurately measures the time difference between the local time and the reference time in real time; the time difference calculation module realizes precise time tracing of the navigation system through a real-time time difference calculation technology; the core control module is used for calculating time difference datain real time according to the real-time measurement time difference and obtaining a time error and a frequency deviation of the time synchronization device; the time-frequency regulation and control module is used for precisely regulating the phase of a time signal and the frequency of a frequency signal output by the time synchronization device to realize real-time dynamic time synchronization, and finally, the frequency distribution module and the pulse distribution module are used for providing a high-precision time signal pulse per second and a high-precision frequency signal for externalequipment.

Owner:INNOVATION ACAD FOR PRECISION MEASUREMENT SCI & TECH CAS

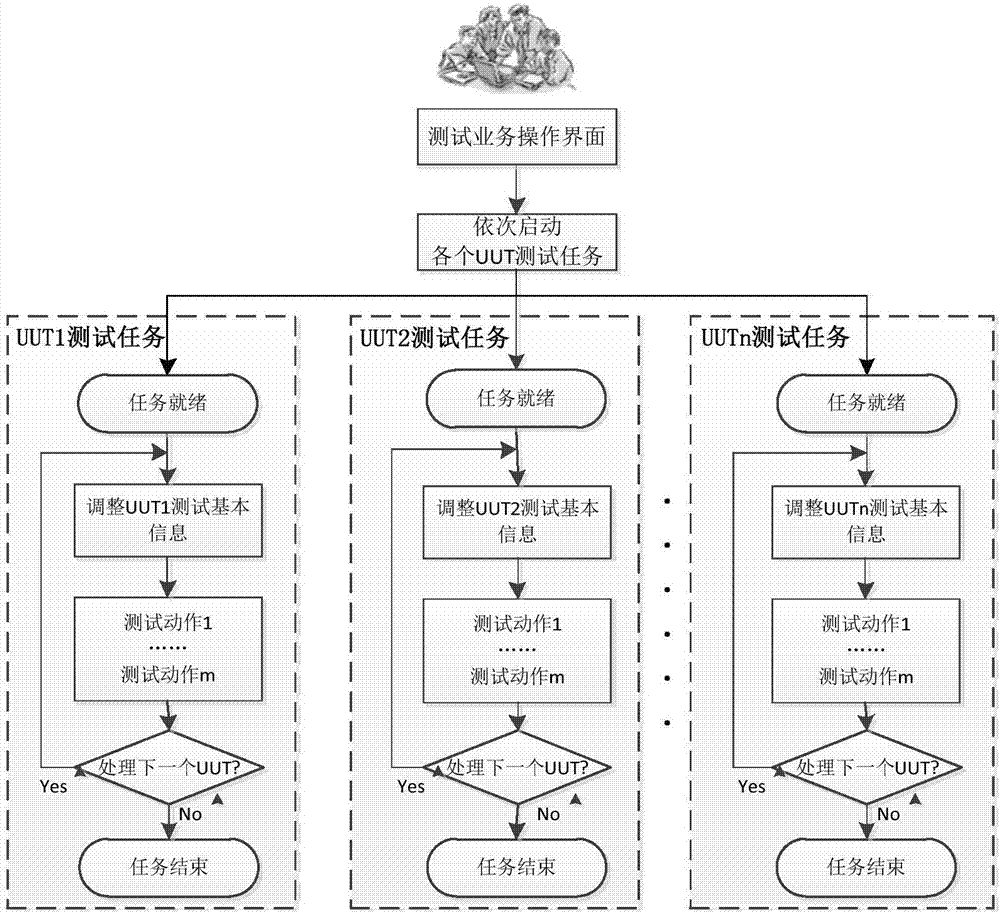

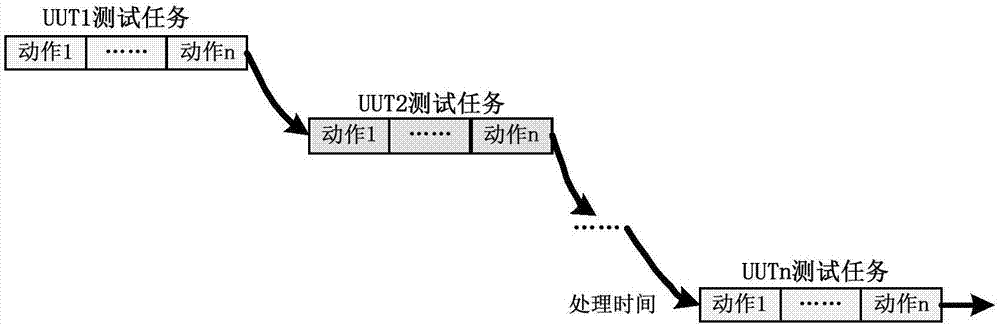

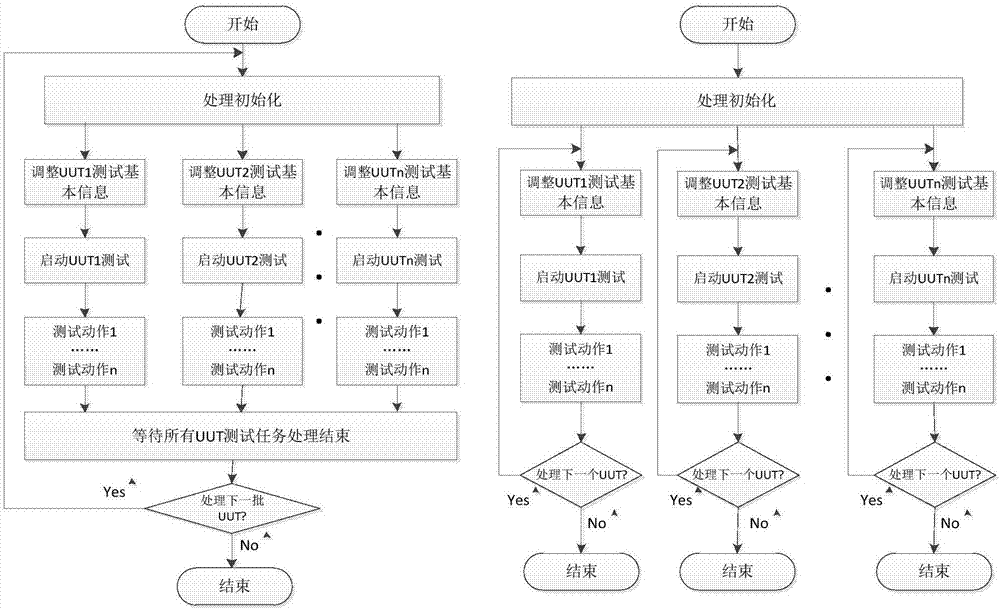

Method of synchronous trigger execution of parallel test tasks

ActiveCN107239331AResolution timeSolve the problem affected by the number of UUT parallel testsProgram initiation/switchingParallel computingTest measurement

The invention discloses a method of synchronous trigger execution of parallel test tasks, and belongs to the technical field of test and measurement. The method of synchronous trigger execution of parallel test task establishes a control mechanism of a test process for the test tasks of various units under test (Unit Under Test, UUT) based on a synchronizer trigger, utilizes the property parameter setting of the synchronizer trigger and a function call to complete the pre-adjustment and setting of control options of the test process, when a user starts the UUT test tasks through an operating interface of the test tasks, all registered application programs of the UUT test tasks can be executed immediately. The method of synchronous trigger execution of parallel test tasks has the advantages that the delay of the execution time of the UUT test tasks is stable and settable and the UUT test tasks are not affected by the UUT parallel test number, and is particularly suitable for the demand scenario of synchronous execution of UUT test tasks.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

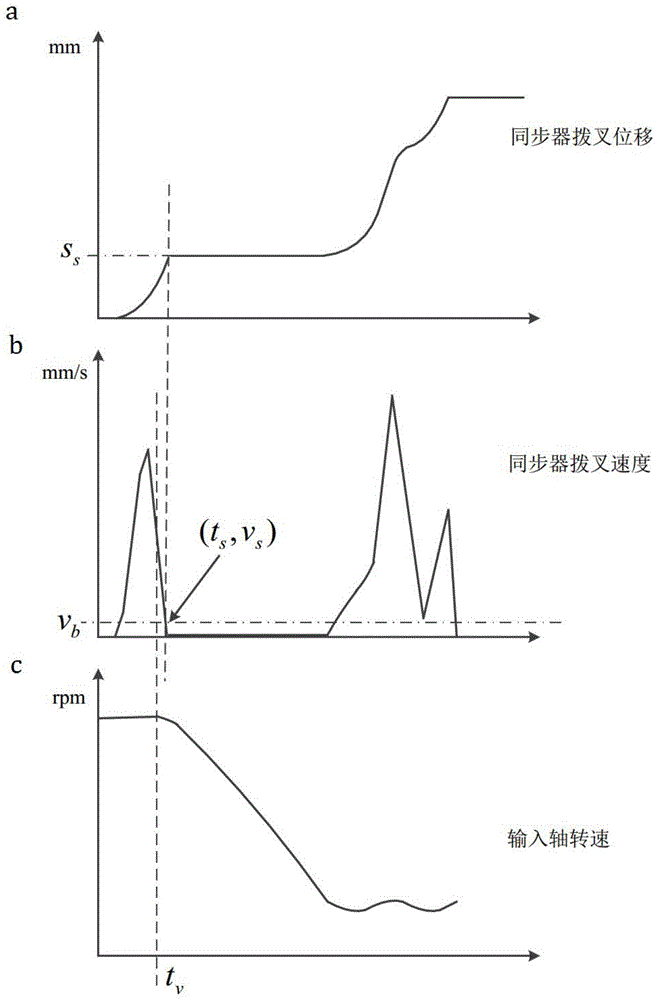

Synchropoint identification method and system of synchronizer

Disclosed is a synchropoint identification method of an automatic double-clutch gear. The synchropoint identification method includes tracking revolving speed of an input shaft and axial speed of a synchronizer fork in real time at the beginning of gear shift synchronizing, tracking the axial speed of the synchronizer fork when the variation of the revolving speed of the input shaft exceeds the threshold, and using the displacement of the synchronizer fork as the updated synchropoint when the variation of the revolving speed is lower than the axial speed threshold. The speed of the synchronizer fork can be used as principal judgment condition and the revolving speed of the input shaft can be used as auxiliary judgment condition, so that impact and collision when a synchronizer coupling and a synchronous ring are locked in place can be avoided, noise and wear can be reduced, service life of synchronizer parts is prolonged, accurate information of synchropoints can be provided for control of a synchronous controller, and control accuracy and performance are improved.

Owner:SHANGHAI AUTOMOBILE GEAR WORKS +1

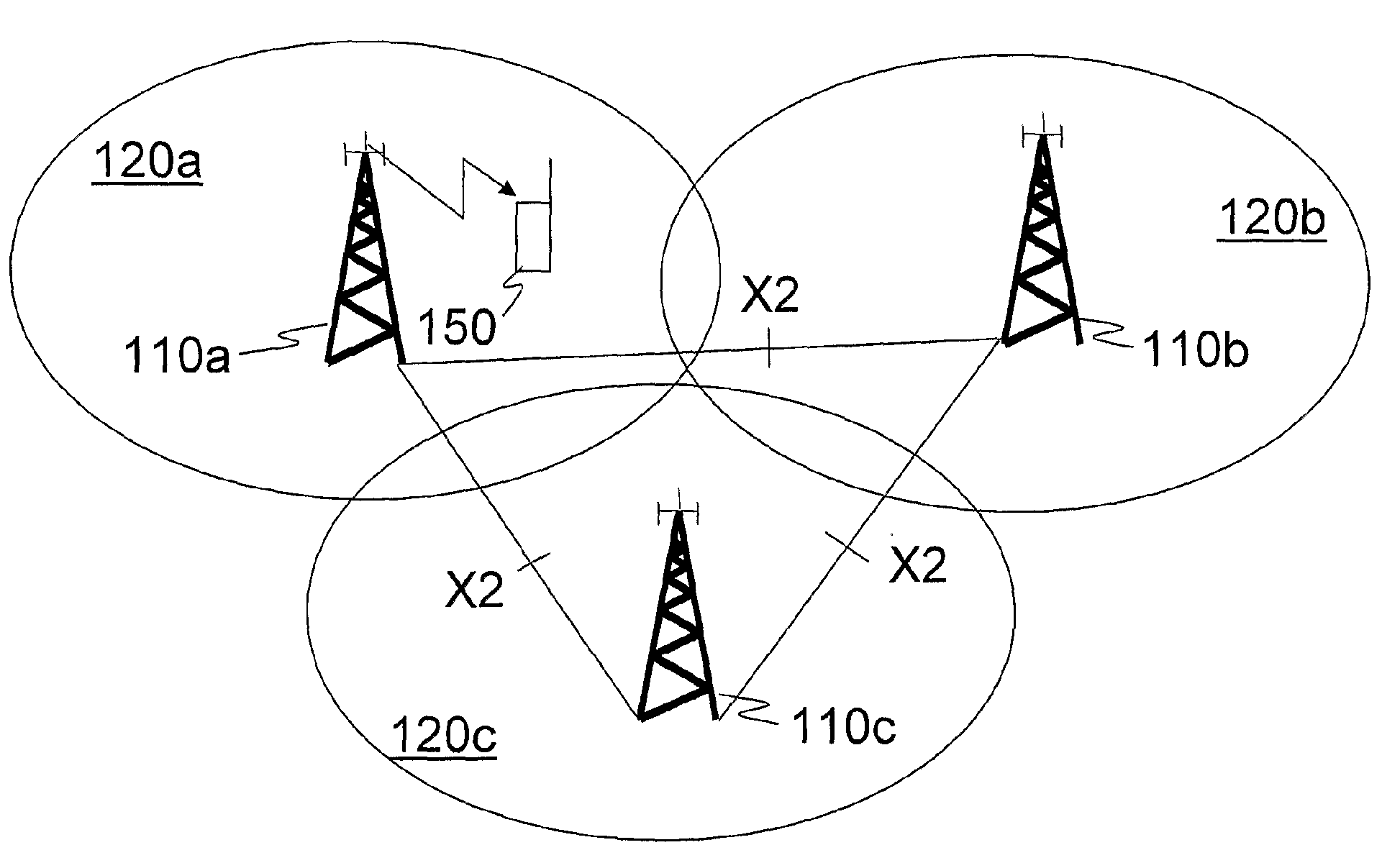

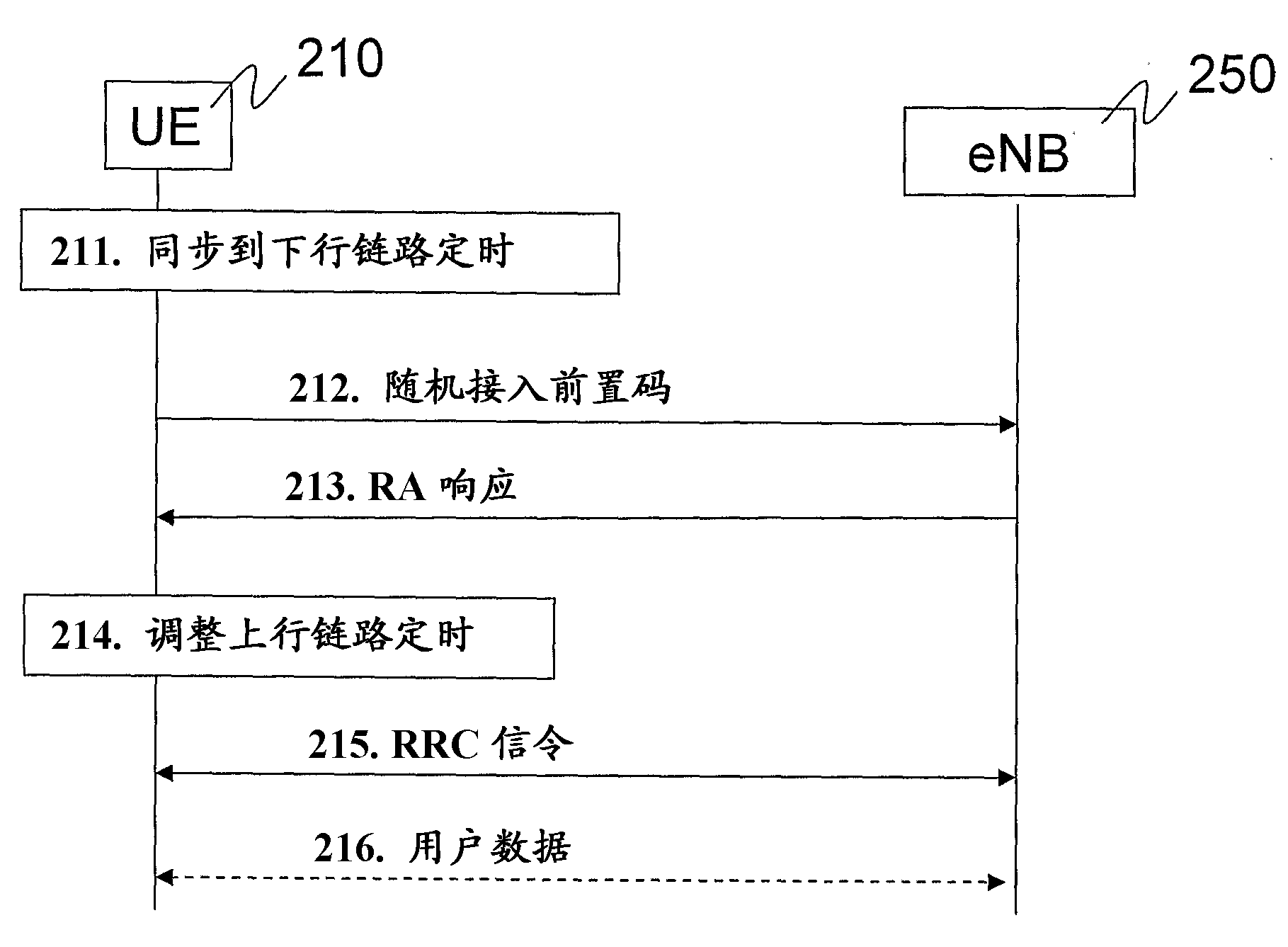

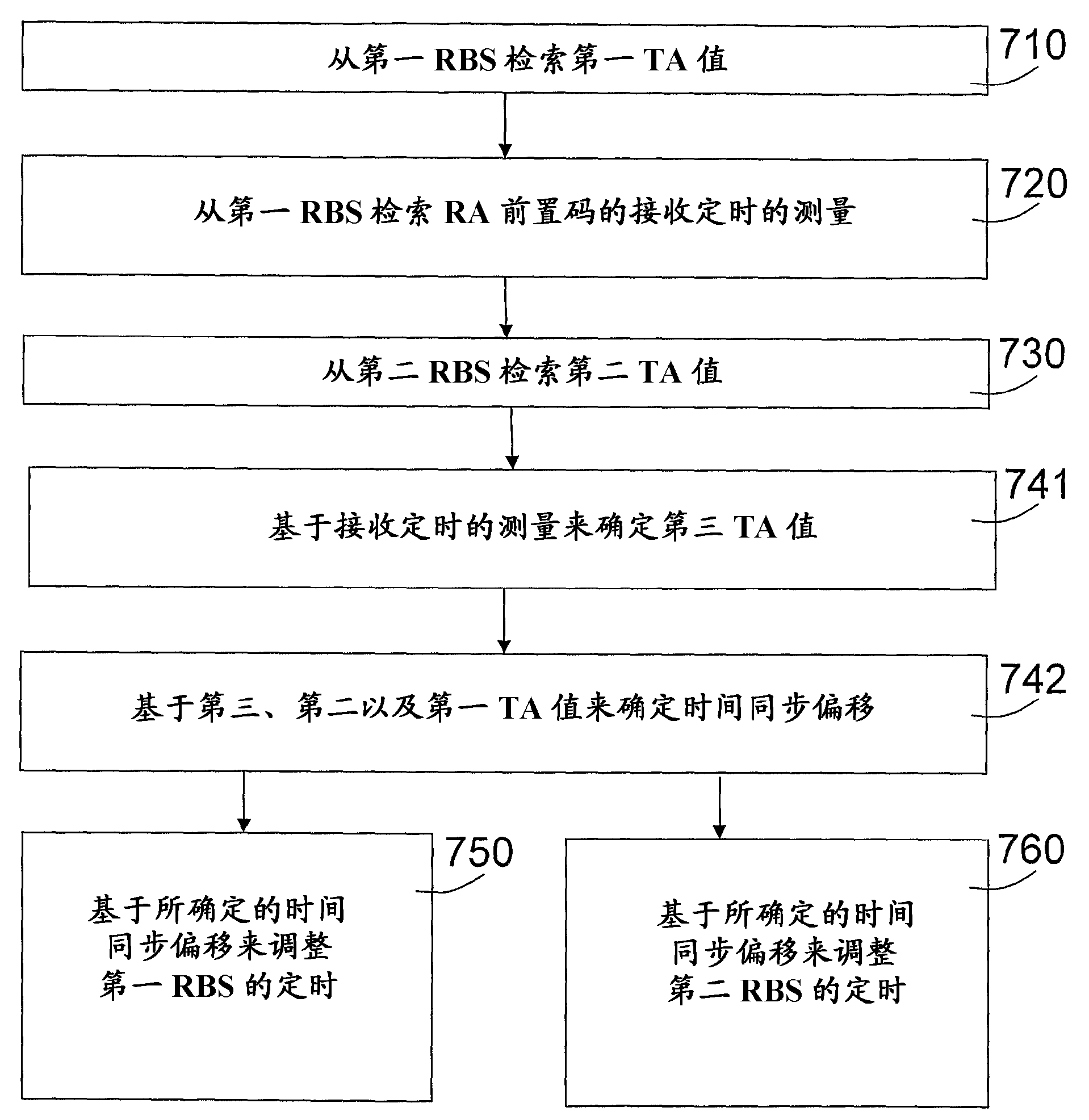

Method and arrangement in a wireless communication system

InactiveCN102948230AExtend service hoursTime synchronizationSynchronisation arrangementSynchronizerCommunications system

The present invention relates to a method and a device for time synchronization of an RBS which has lost its GPS signal. The method in the time synchronization device comprises retrieving from the first radio base station a first timing advance value (710) used by the user equipment to adjust its transmission timing before the handover, and a measurement of a reception timing (720) of a random access preamble. The random access preamble is transmitted from the user equipment to the second radio base station during synchronization. The method also comprises retrieving (730) from the second radio base station a second timing advance value used by the user equipment to adjust its transmission timing after the handover, and determining (740) a time synchronization offset between the first and second radio base station based on the retrieved first timing advance value, the second timing advance value, and the measurement of the reception timing.

Owner:ERICSSON (CHINA) COMMUNICATION COMPANY LTD

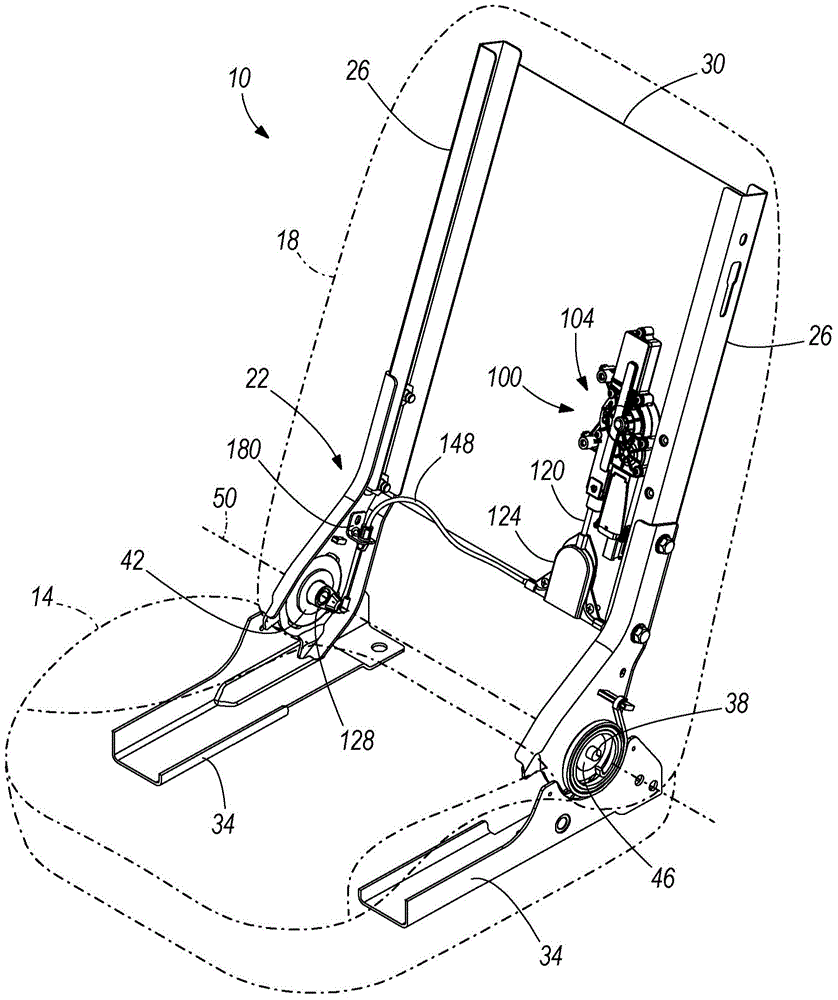

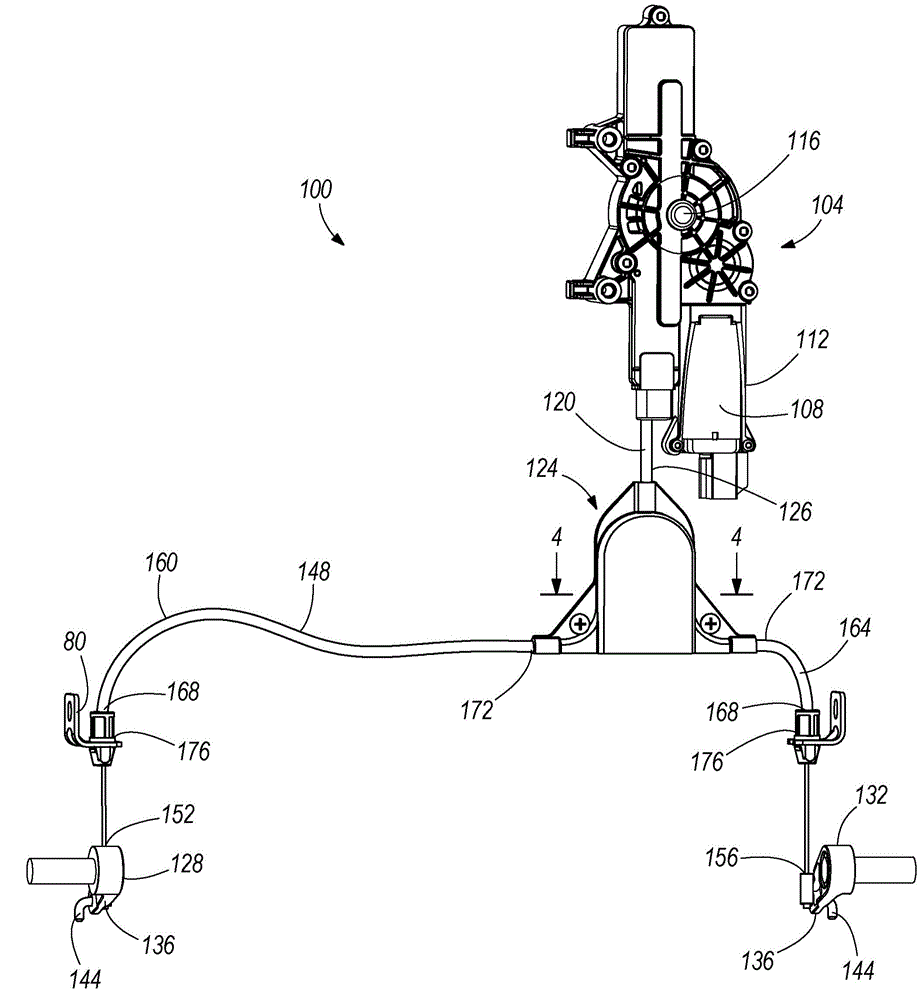

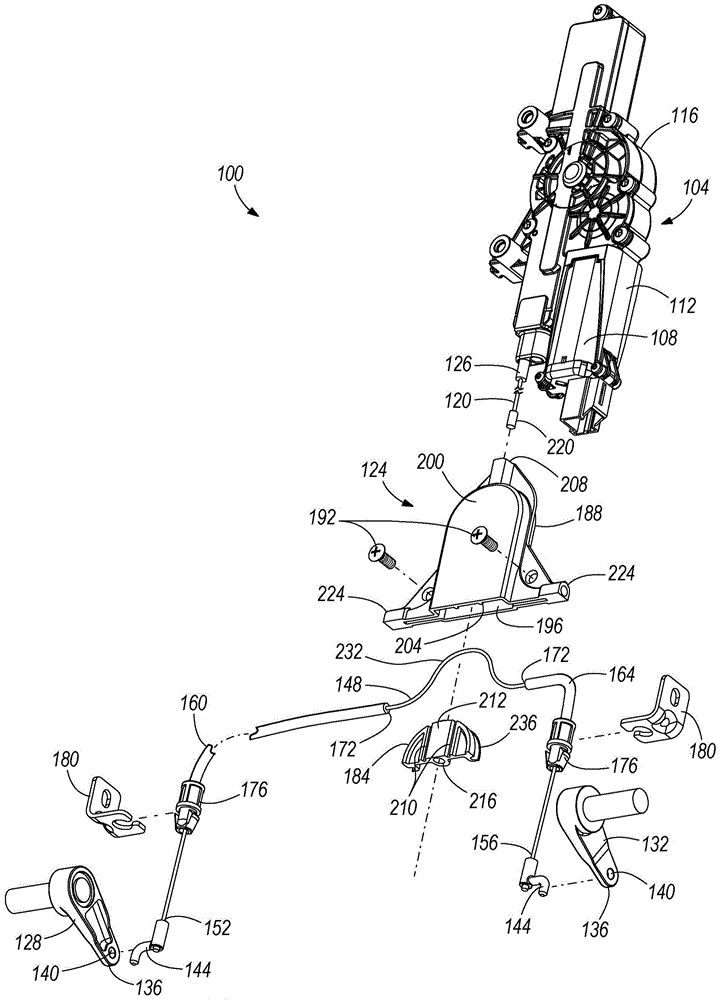

Cable synchronizer system

An actuation system for concurrently actuating a first mechanism and a second mechanism from a first state to a second state includes an actuator and a sliding member operatively engaged with the actuator and movable from a first position to a second position in response to actuation of the actuator. A connecting member has a relaxed state and a taut state. The connecting member includes a first end coupled to the first mechanism, a second end coupled to the second mechanism, and a medial portion cooperative with the sliding member. Movement of the sliding member from the first position to the second position changes the connecting member from the relaxed state to the taut state, whereby the tension is increased in the connecting member.

Owner:LEGGETT & PLATT CANADA

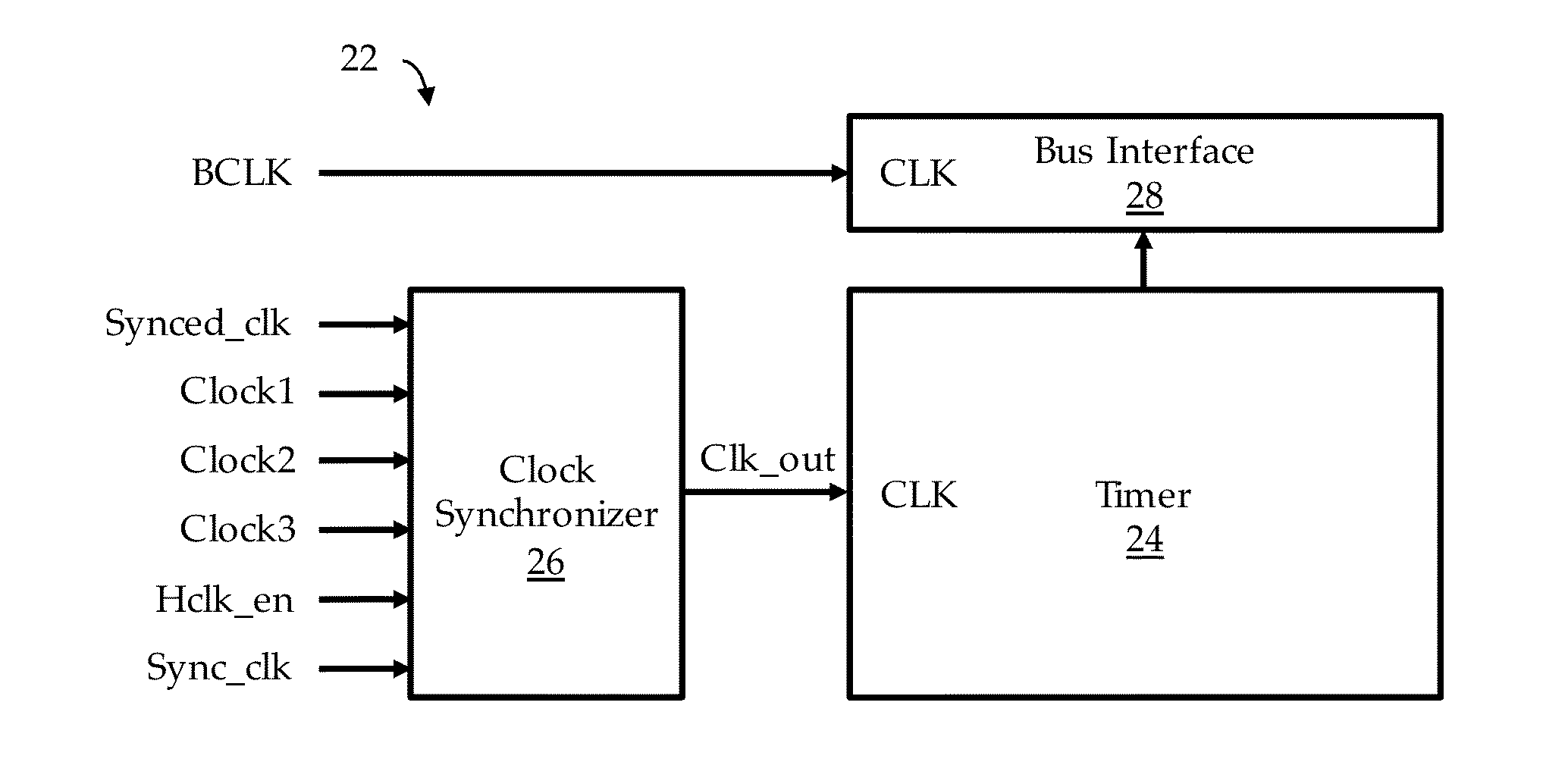

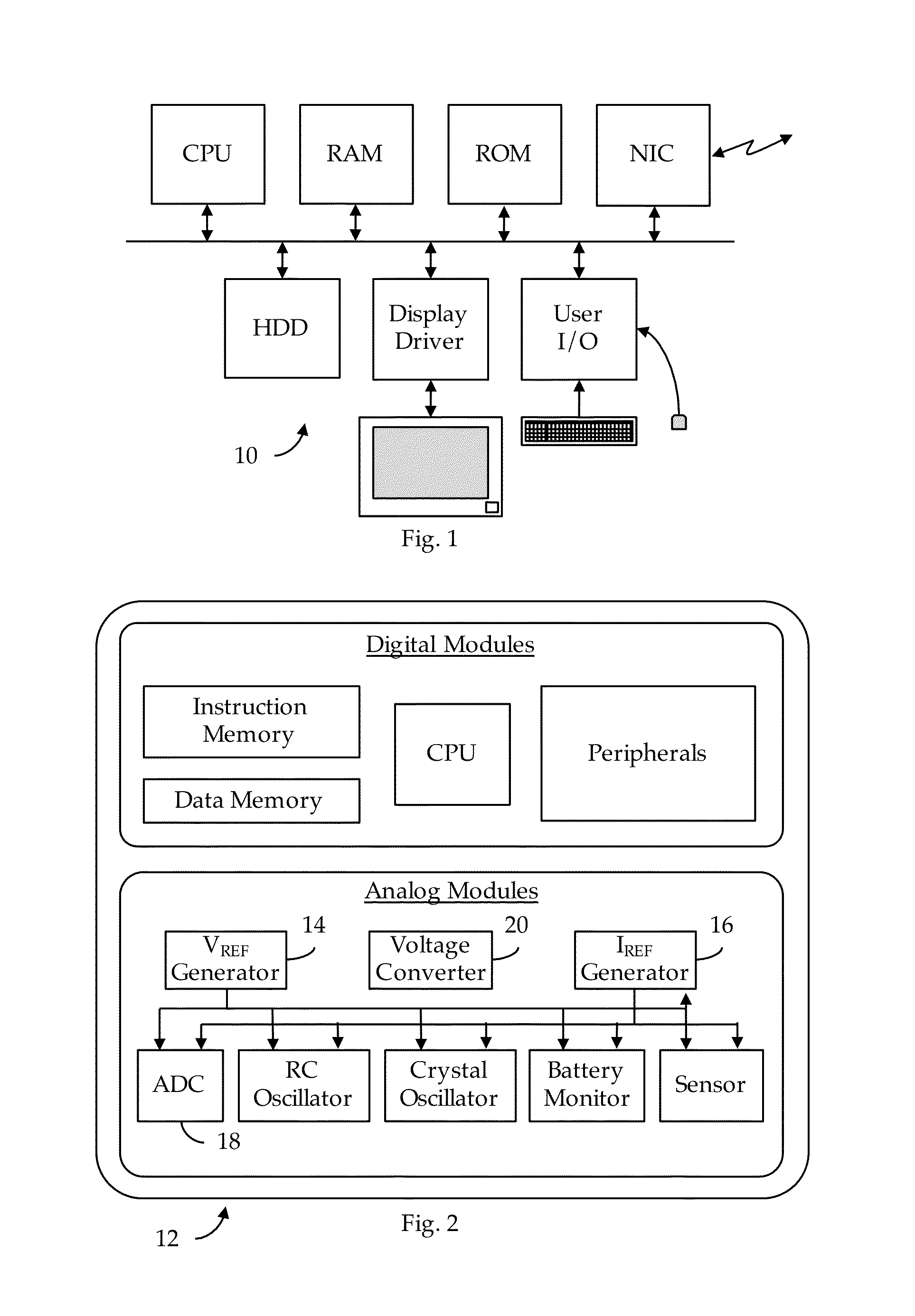

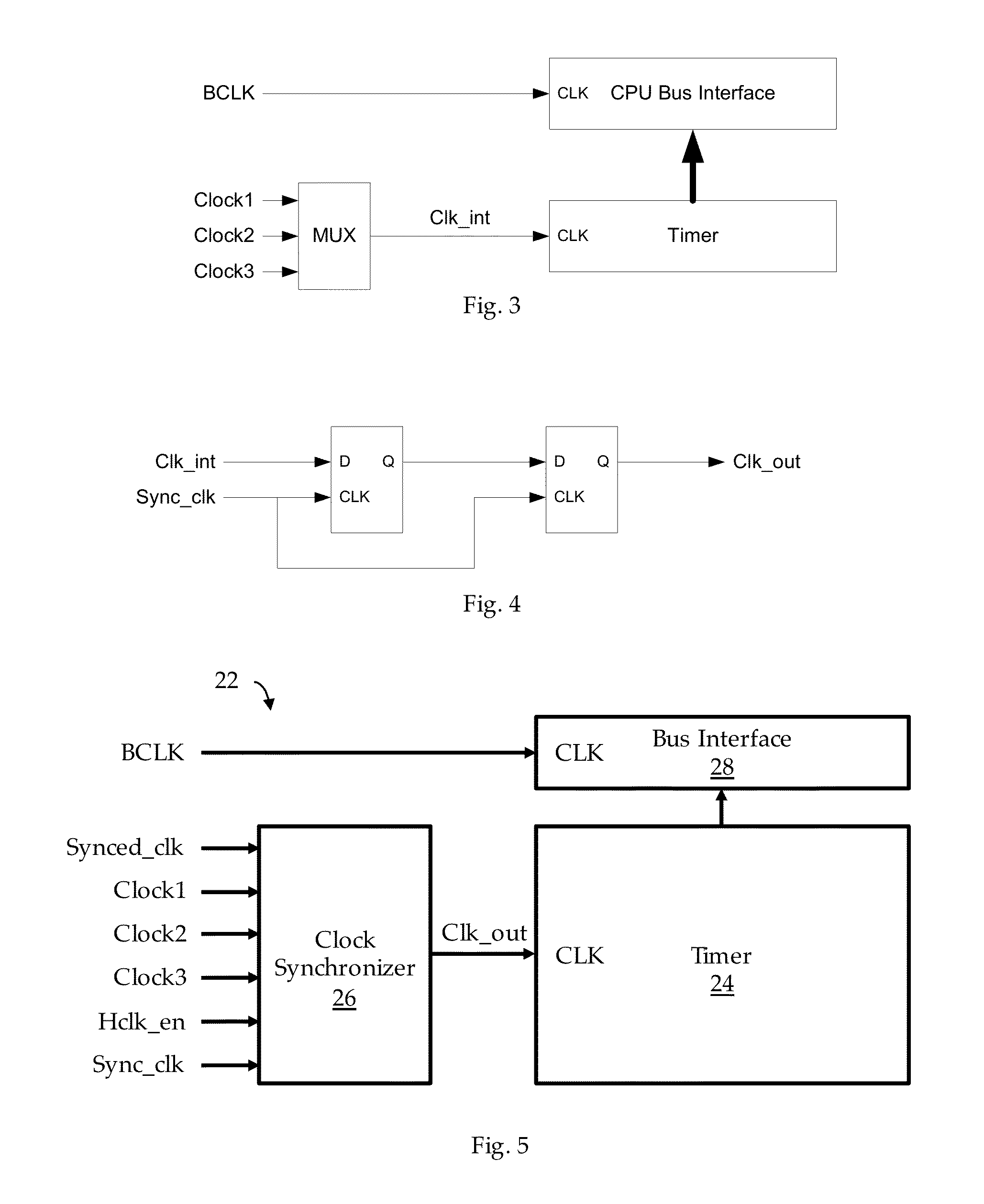

Low Power Asynchronous Counters in a Synchronous System

ActiveUS20160109901A1Efficient power electronics conversionPulse automatic controlClock synchronizationTimer

A clock synchronizer adapted to synchronize reading a Timer that is clocked asynchronously to the system clock.

Owner:AMBIQ MICRO

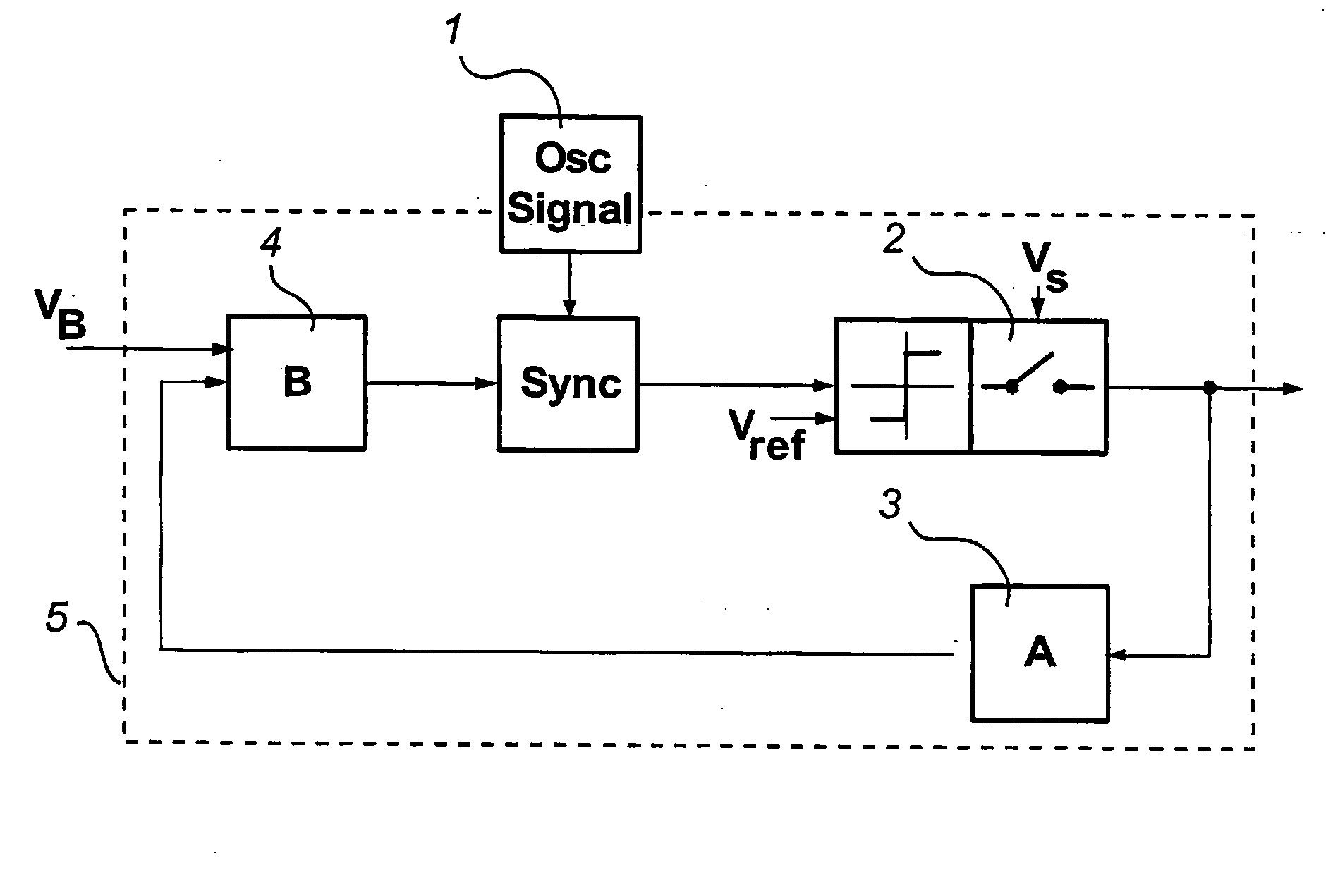

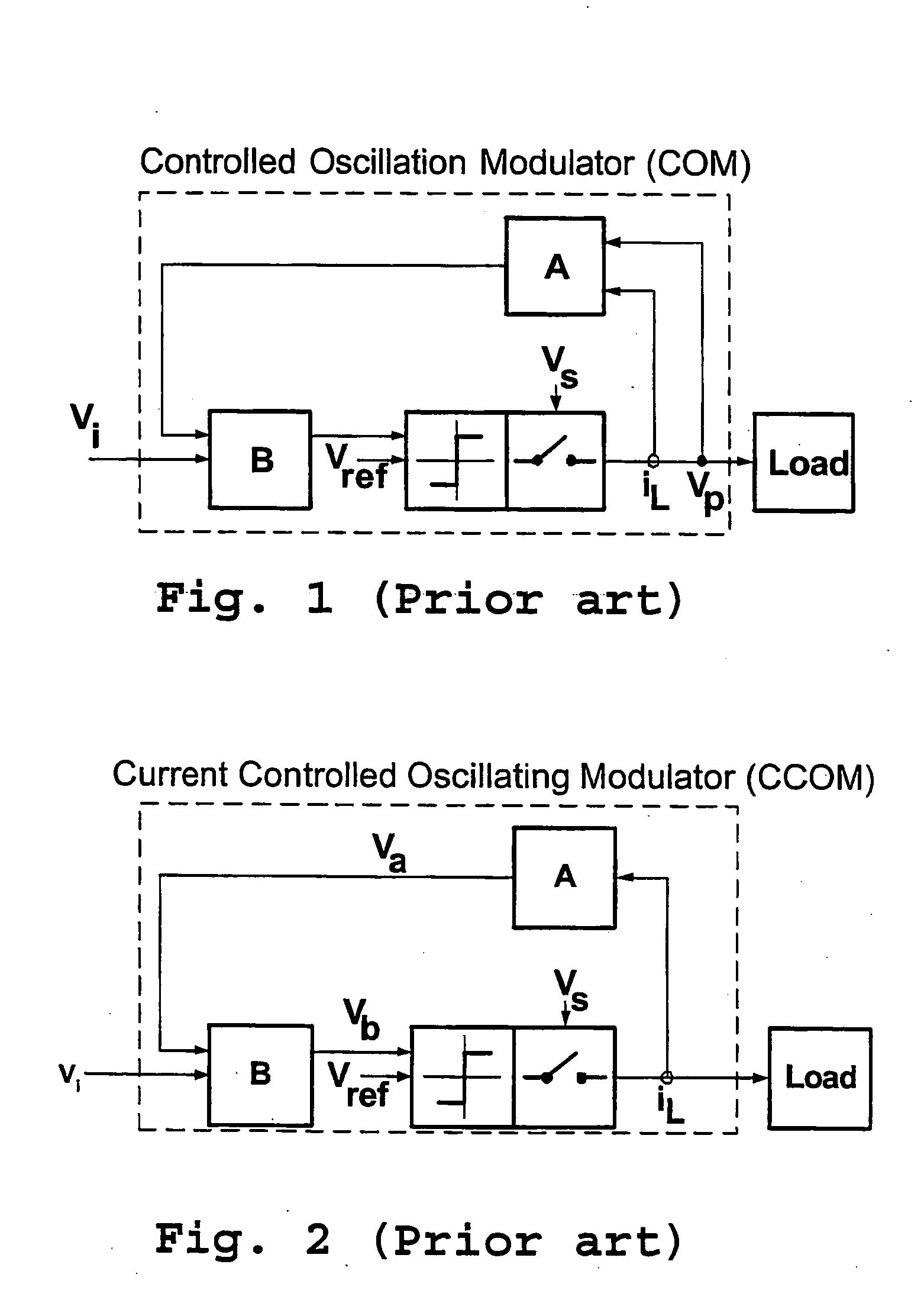

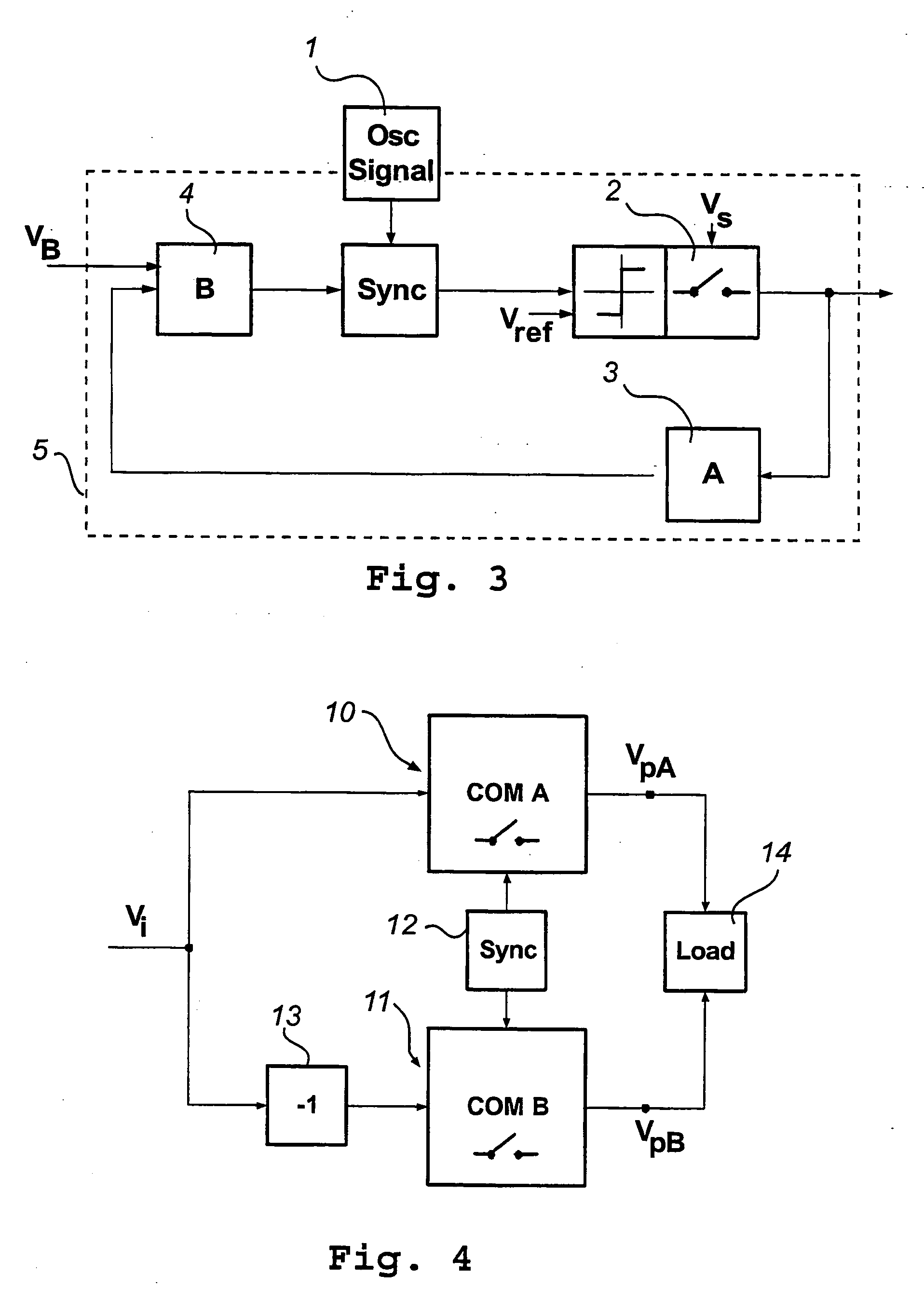

Synchronized controlled oscillation modulator

InactiveUS20050068121A1Easy to adjustOvercome problemsDc-dc conversionPulse modulationSynchronizerSynchronous control

A synchronized controlled oscillation modulator (SCOM), comprising at least one, Controlled Oscillation Modulator (5), and synchronizing means (1, 6) connected to said COM modulator. The modulator can comprise several COM modulators, and the synchronizing means can be arranged between the COM systems, so that the oscillation modulator signal is used as synchronization signal. The invention provides significant advantages in performance, topological simplification, improved robustness, stability and efficiency compared to prior art.

Owner:BANG & OLUFSEN ICEPOWER

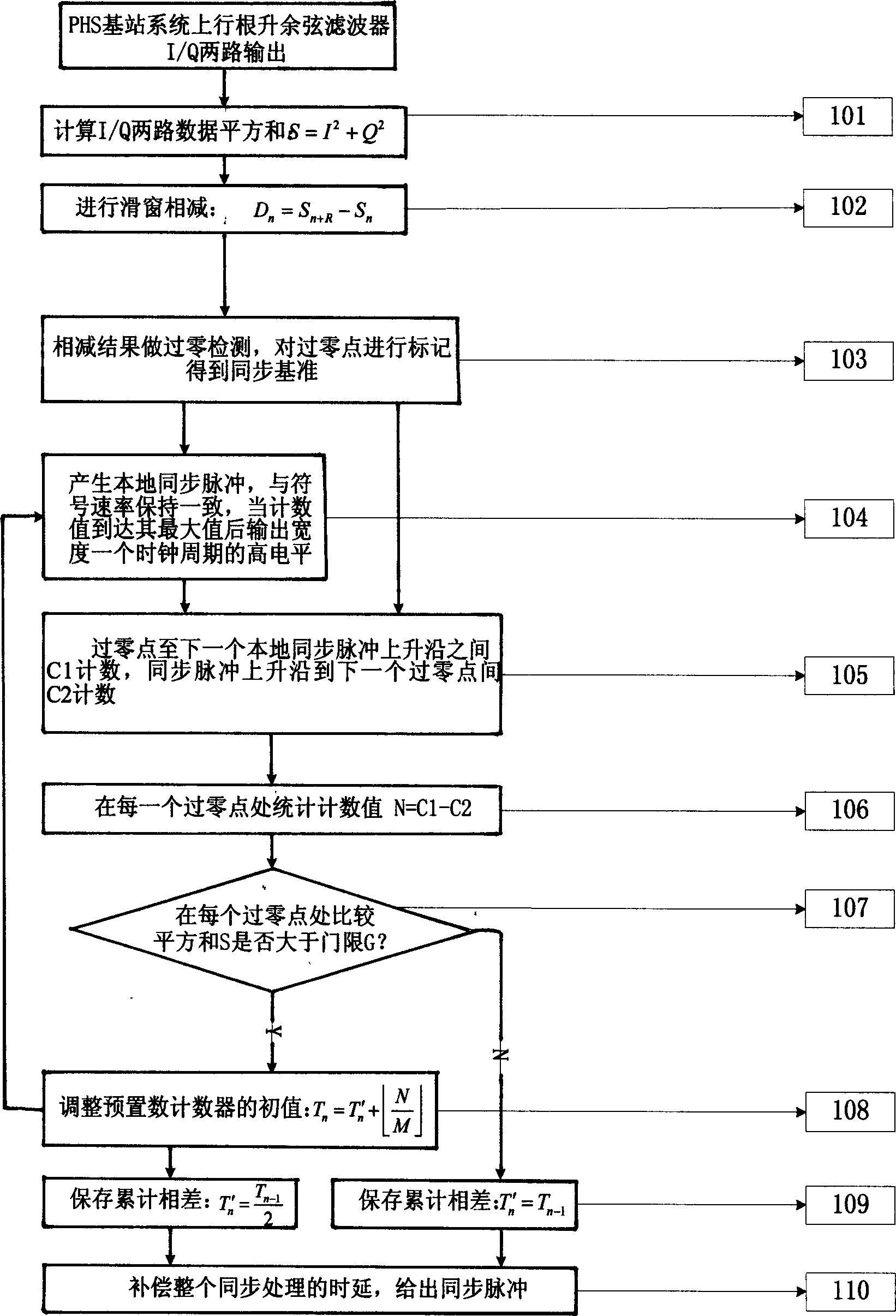

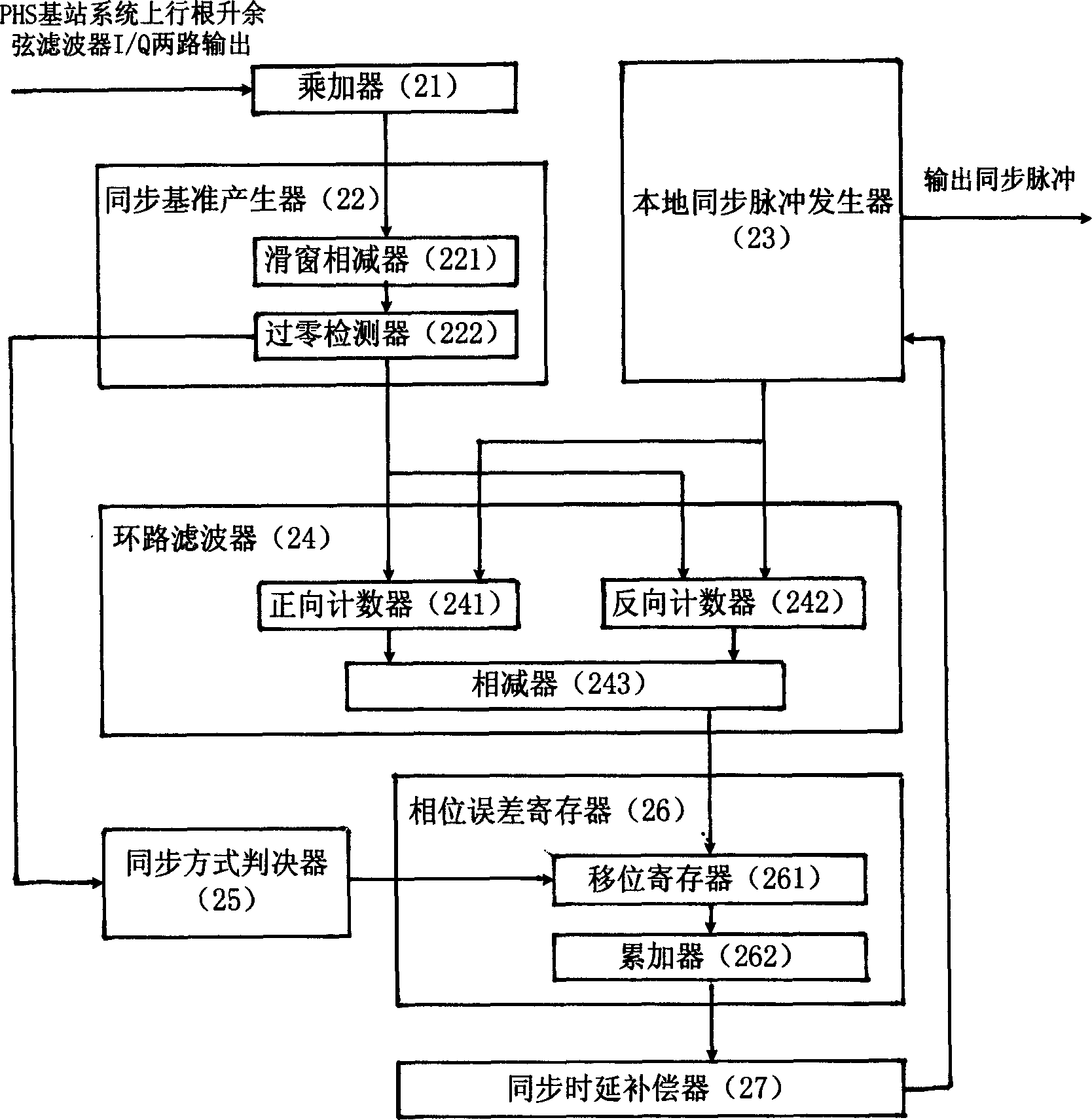

PHS system position synchronous method based on digital lock phase ring and realizing device

InactiveCN1556603ASynchronization base is accurateImprove applicabilitySynchronising arrangementLoop filterData synchronization

The present invention discloses a PHS system position synchronous method based on digital lock phase ring and realizing device, wherein the method comprises steps of recovering synchronous clock by a lock phase ring, synchronizing constant-modulus character of points by using data in system, giving synchronous reference signal by quadratic sum calculation and zero crossing detection, synchronizing bit by using the synchronous reference. The device comprises a multiplier-adder unit, a synchronous reference generator, a local synchronous pulse generator, a digital loop filter, a synchronous mode estimator, a phase error register and a synchronous delay compensator. The method can give accuracy synchronous reference, and has large suitable area and good fault-tolerant capacity.

Owner:ZTE CORP

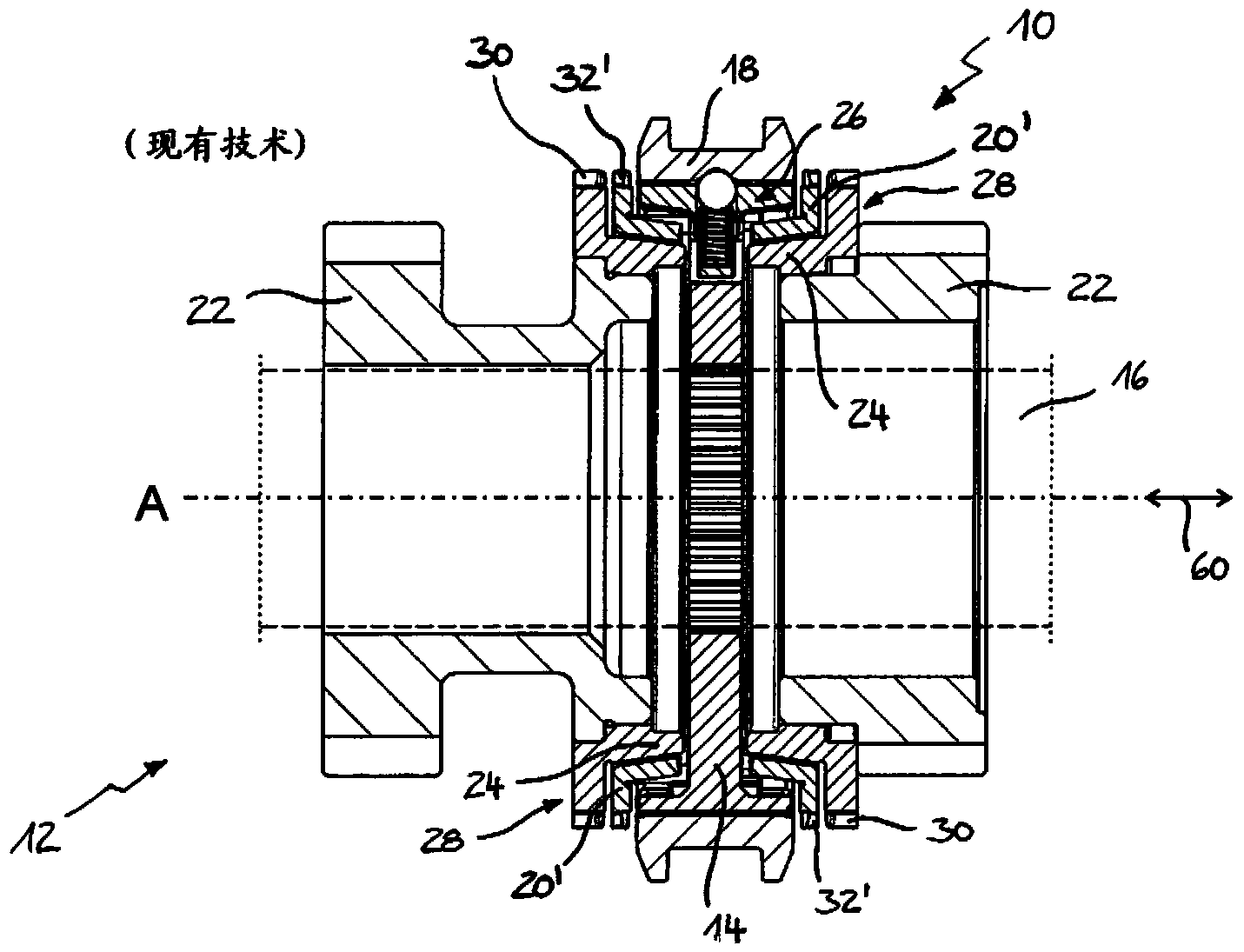

Synchronizer ring for a synchronization unit of a manual transmission and synchronization unit with such a synchronizer ring

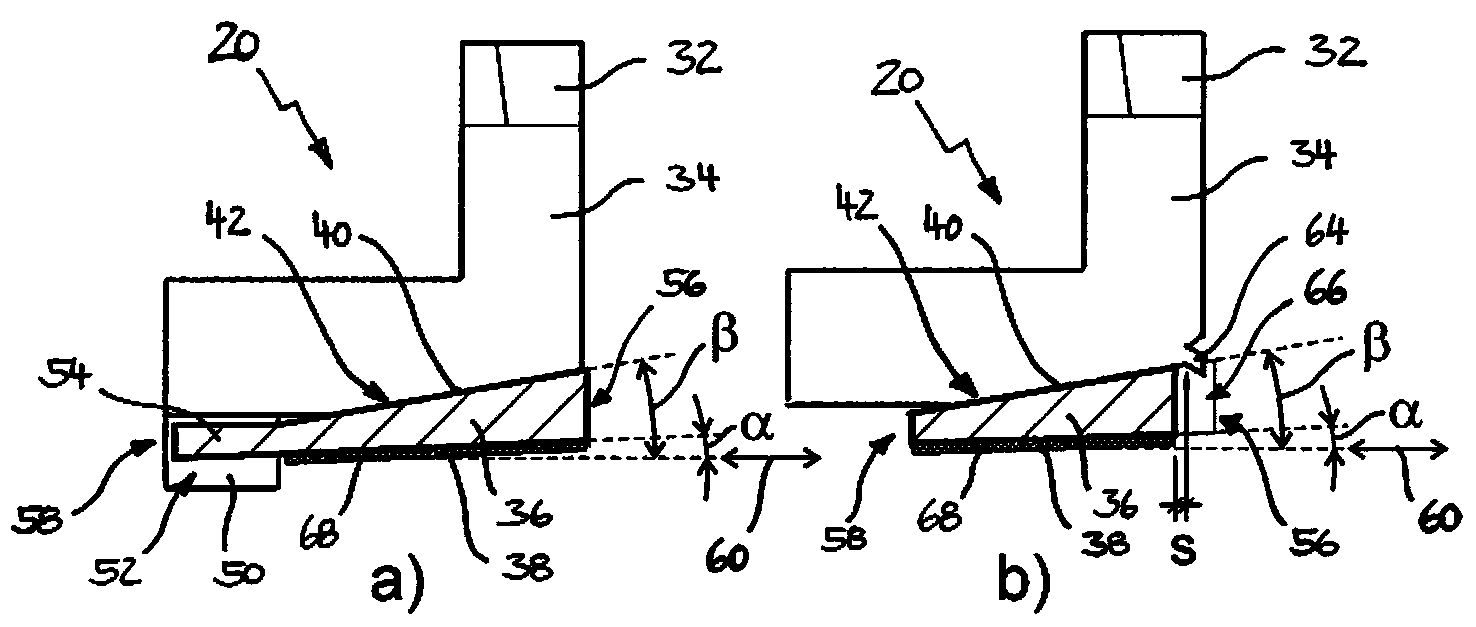

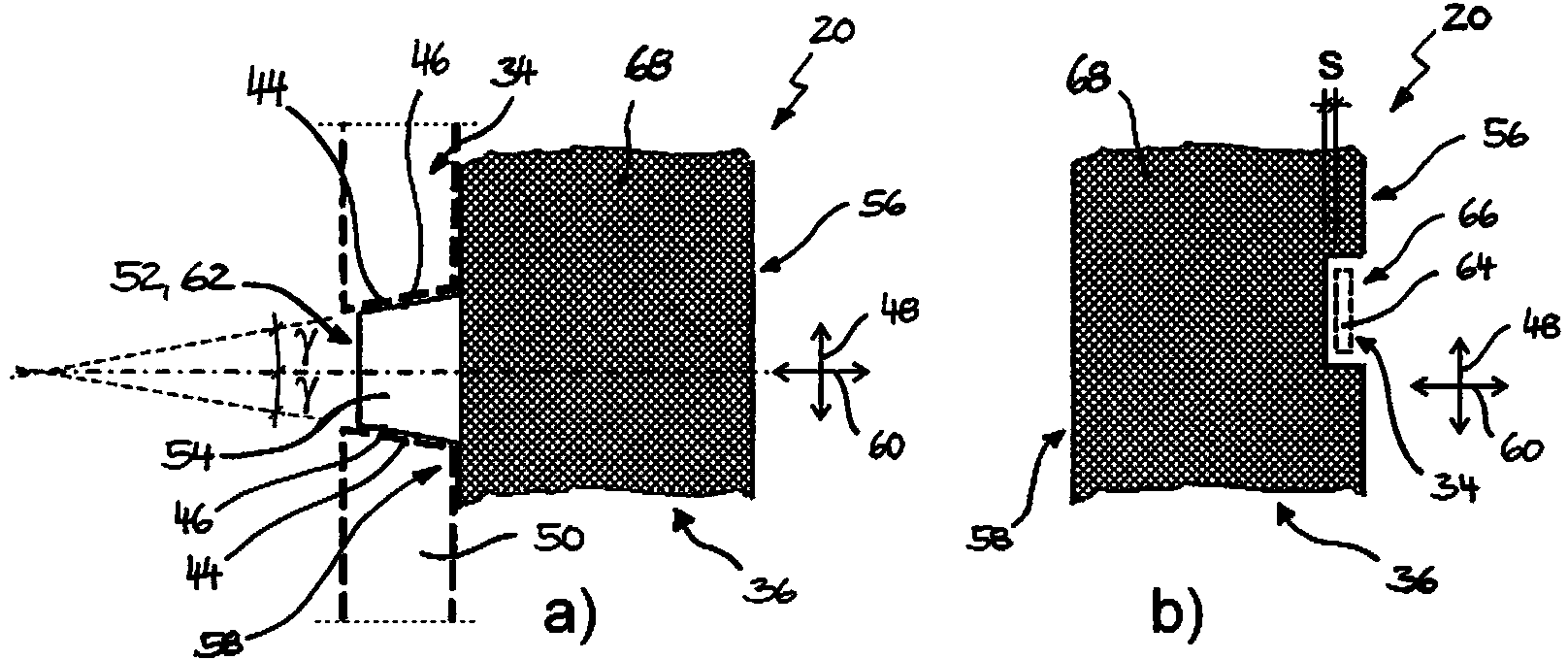

ActiveCN104235221AFriction torque preventsSelf-locking preventionMechanical actuated clutchesGreek letter betaEngineering

The invention relates to a synchronizer ring (20) for a synchronization unit (10) of a gearbox (12), with a locking ring (34) having an annular axis (A) and a locking toothing (32) and a coaxial with the lock ring (34) disposed separate cone ring (36) having a first conical surface (38) having a first cone angle ([alpha]) and a radially opposite second conical surface (40) with a second cone angle ([beta]), wherein the first cone surface (38) in the installed state of the synchronizer ring (20) to a gangradseitigen friction cone (24) of the synchronization unit (10) and the second conical surface (40) at a conical counter surface (42) of the locking ring (34) abuts, wherein the locking ring (34) and the cone ring (36) mutually associated abutment surfaces (44, 46) which couple the locking ring (34) and the cone ring (36) in the circumferential direction (48) , and wherein the stop surfaces (44, 46) of the locking ring (34) and / or of the cone ring (36) relative to the ring axis (A) are at least partially inclined such that the second conical surface (40) and the conical counter surface (42) at a acting between the locking ring (34) and the cone ring (36) are torque loaded axially away from one another.

Owner:HOERBIGER ANTRIEBSTECHN HLDG