PHS system position synchronous method based on digital lock phase ring and realizing device

A digital phase-locked loop and system bit technology, applied in the field of digital communication, can solve the problems of difficult hardware implementation, large influence of synchronization reference, large hardware resource occupation, etc., and achieve the effect of improving the applicable field and fault tolerance performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

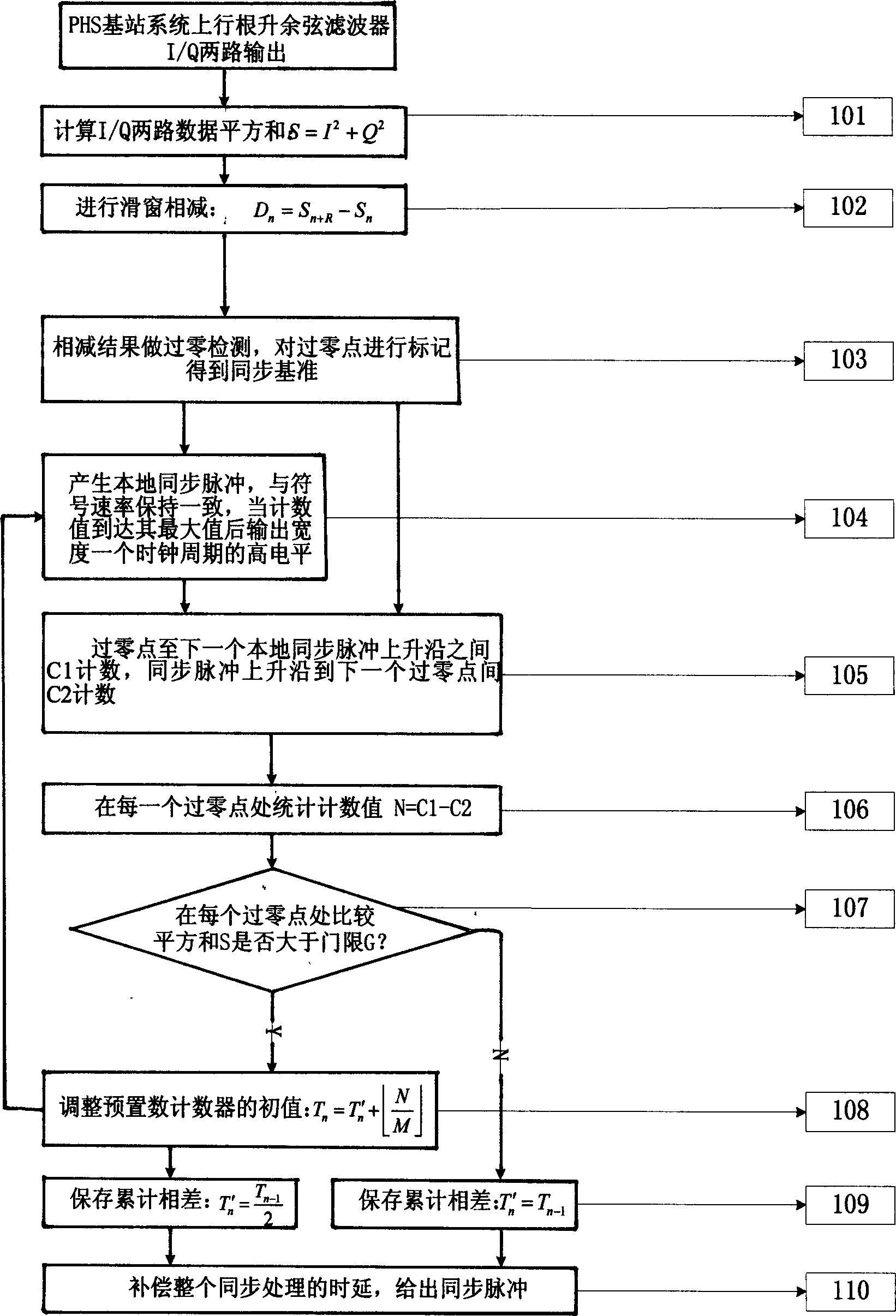

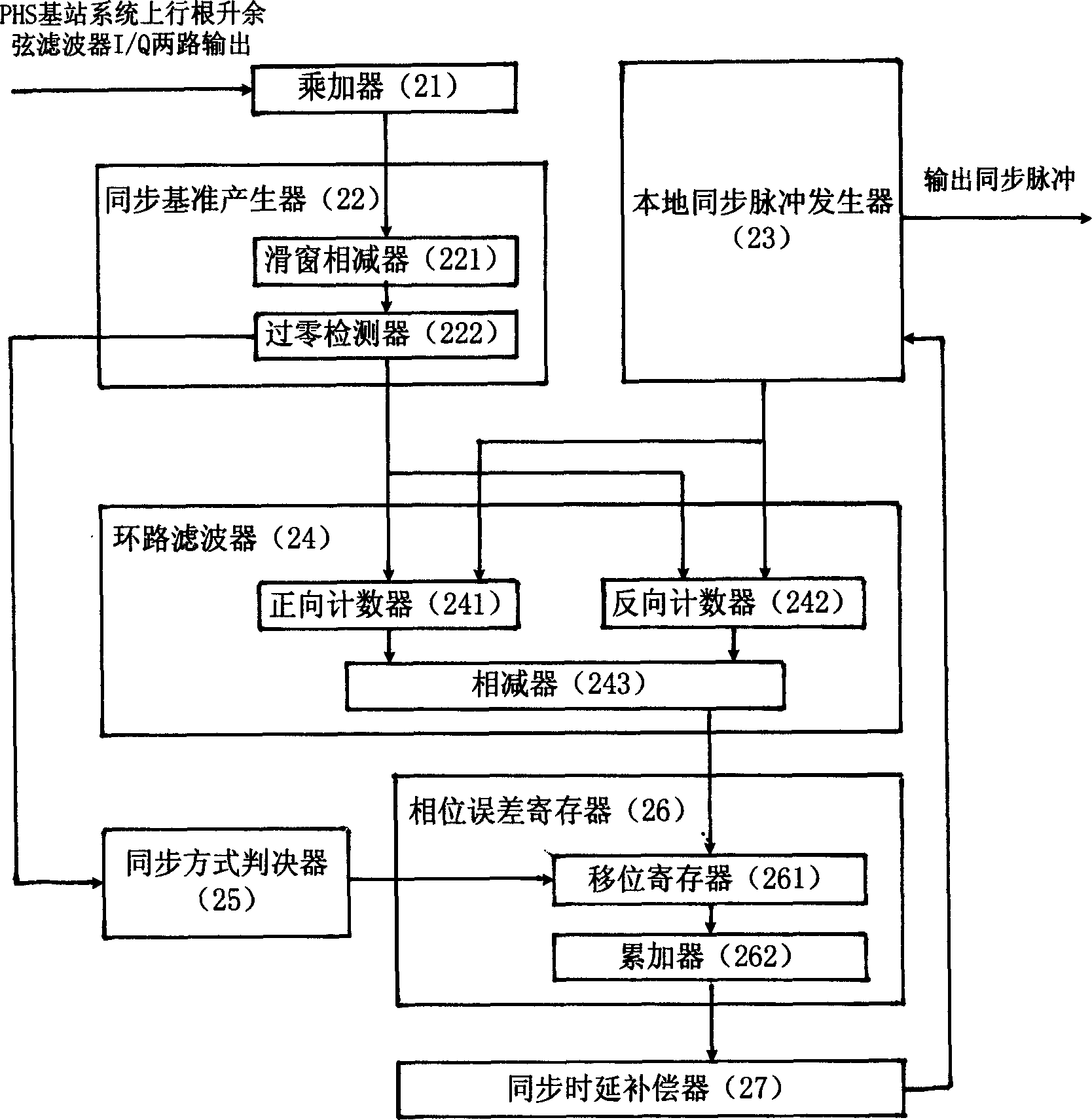

[0035] attached figure 1 It is a flow chart of the method of the present invention. The gist of the present invention is the calculation of zero-crossing points for the synchronization reference and synchronization tracking using a digital phase-locked loop. It includes judging whether the zero-crossing point can be used as a synchronous reference, and controlling the synchronous working state.

[0036] The method described in the present invention can be realized according to the following steps:

[0037] The first step (101), calculate the sum of squares S=I of I / Q two-way PHS base station uplink through shaping filter signal 2 +Q 2 , it is assumed here that the signal rate is R times the symbol rate (that is, R times oversampled data).

[0038] In the second step (102), the obtained square sum signal is subtracted every R sampling points to obtain the signal D n = S n+R -S n .

[0039] The third step (103), for the subtraction result D n After doing zero detection,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More