Patents

Literature

2935 results about "Loop filter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

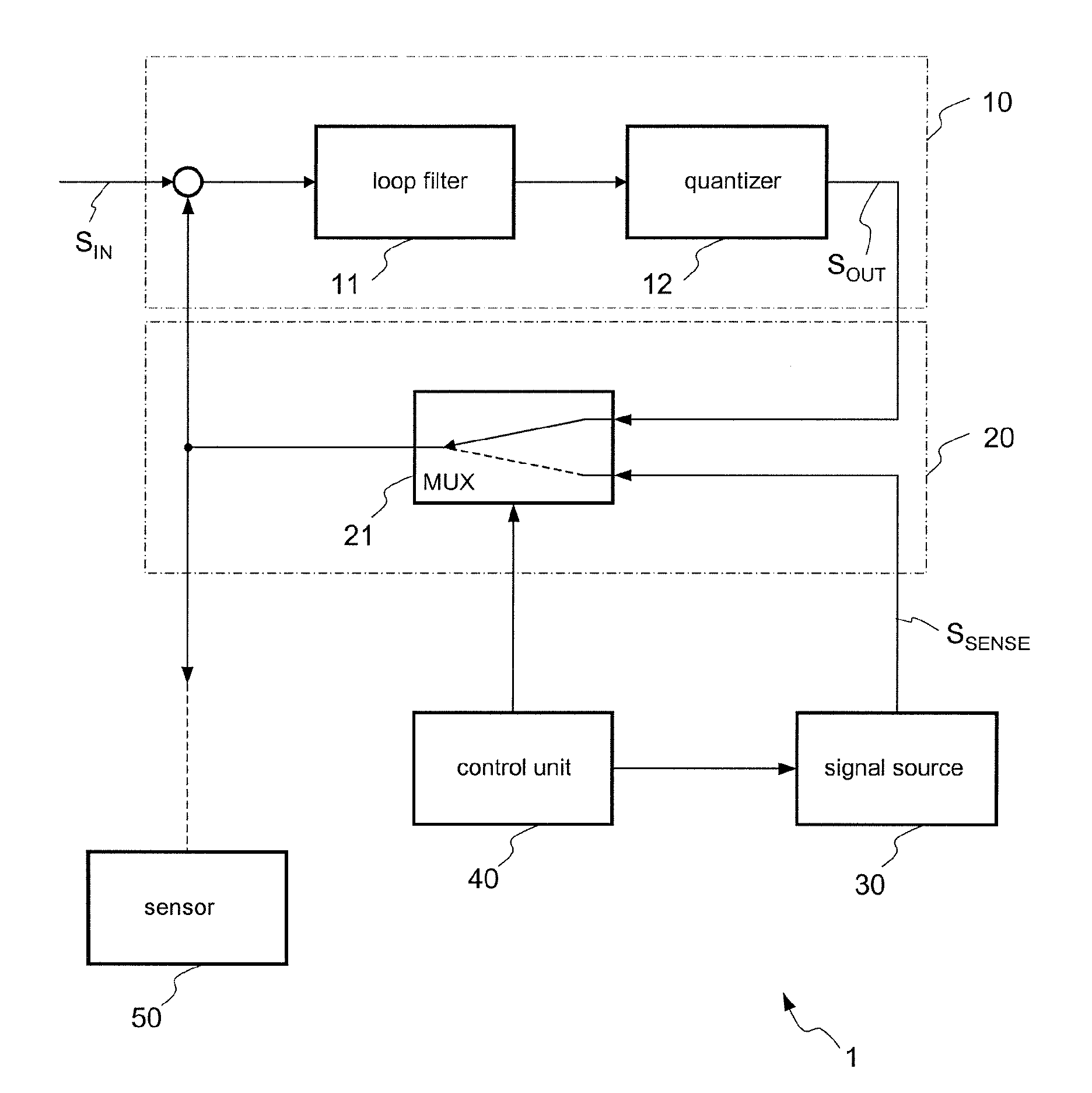

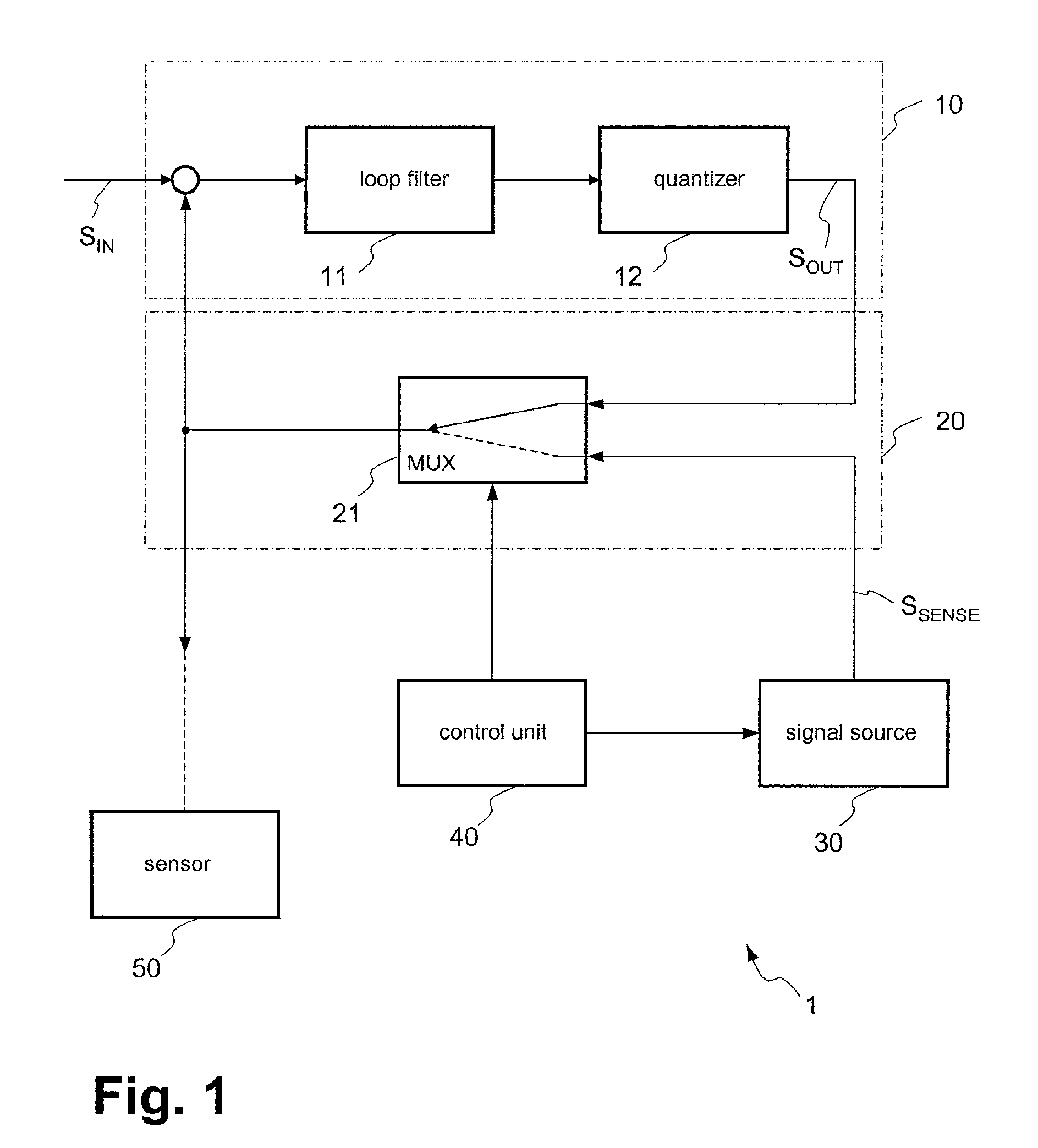

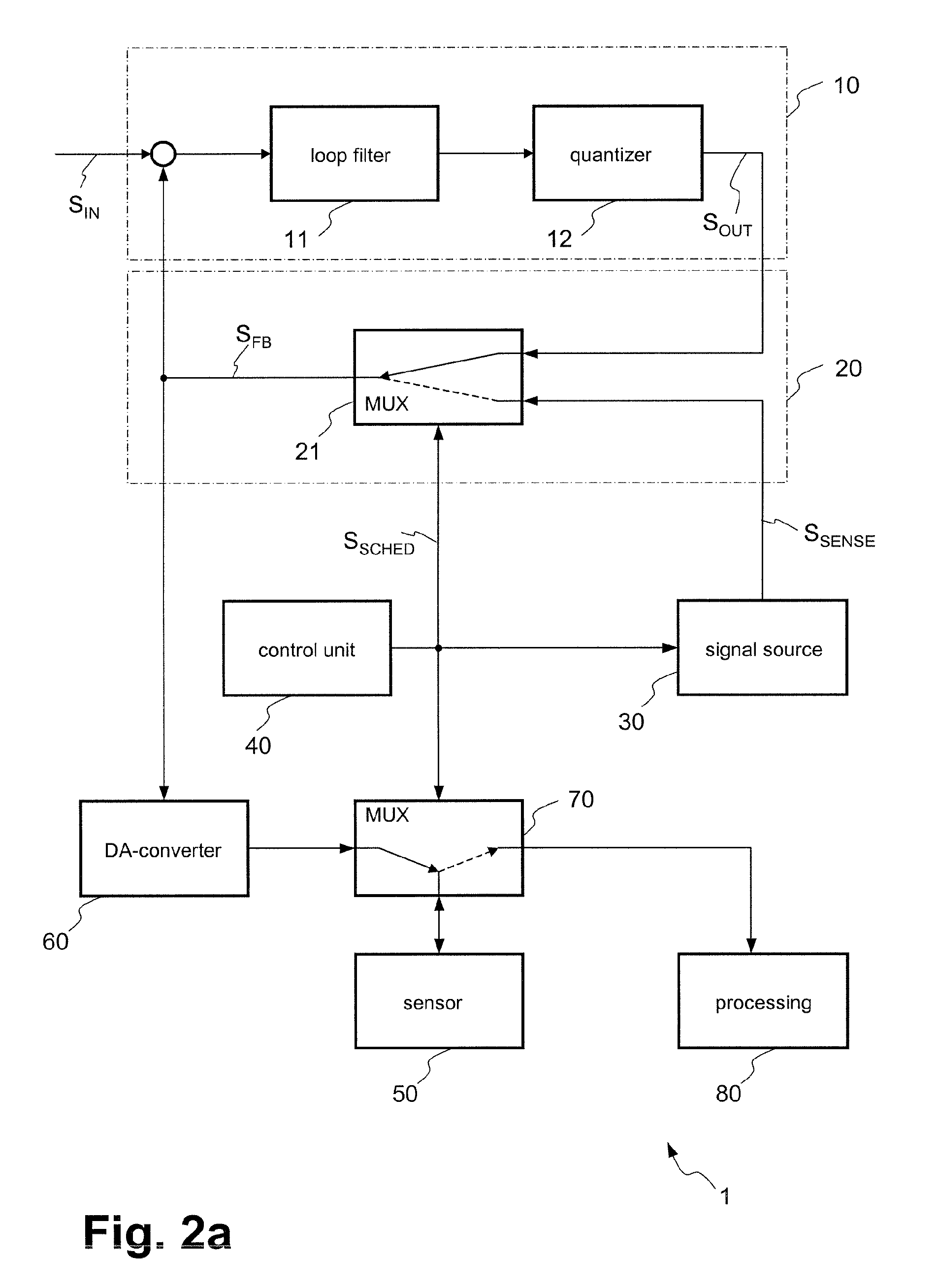

Sigma-delta modulator for operating sensors

InactiveUS7528755B2Electric signal transmission systemsAcceleration measurement using interia forcesLoop filterControl signal

A sigma-delta modulator can be used for actuating a sensor element. The sigma delta modulator includes: a forward branch to which an input signal is fed at an input and which includes a loop filter, a quantizer and an output for providing an output signal. A feedback branch is configured to feed back the output signal of the forward branch at least temporarily to the input of the forward branch. A signal source is configured to generate a readout signal which corresponds to the voltage profile at the sensor element during a measuring process. A control unit is configured to generate a control signal dependent on which either the output signal of the forward branch or the readout signal of the signal source is fed back to the input of the forward branch.

Owner:INFINEON TECH AG

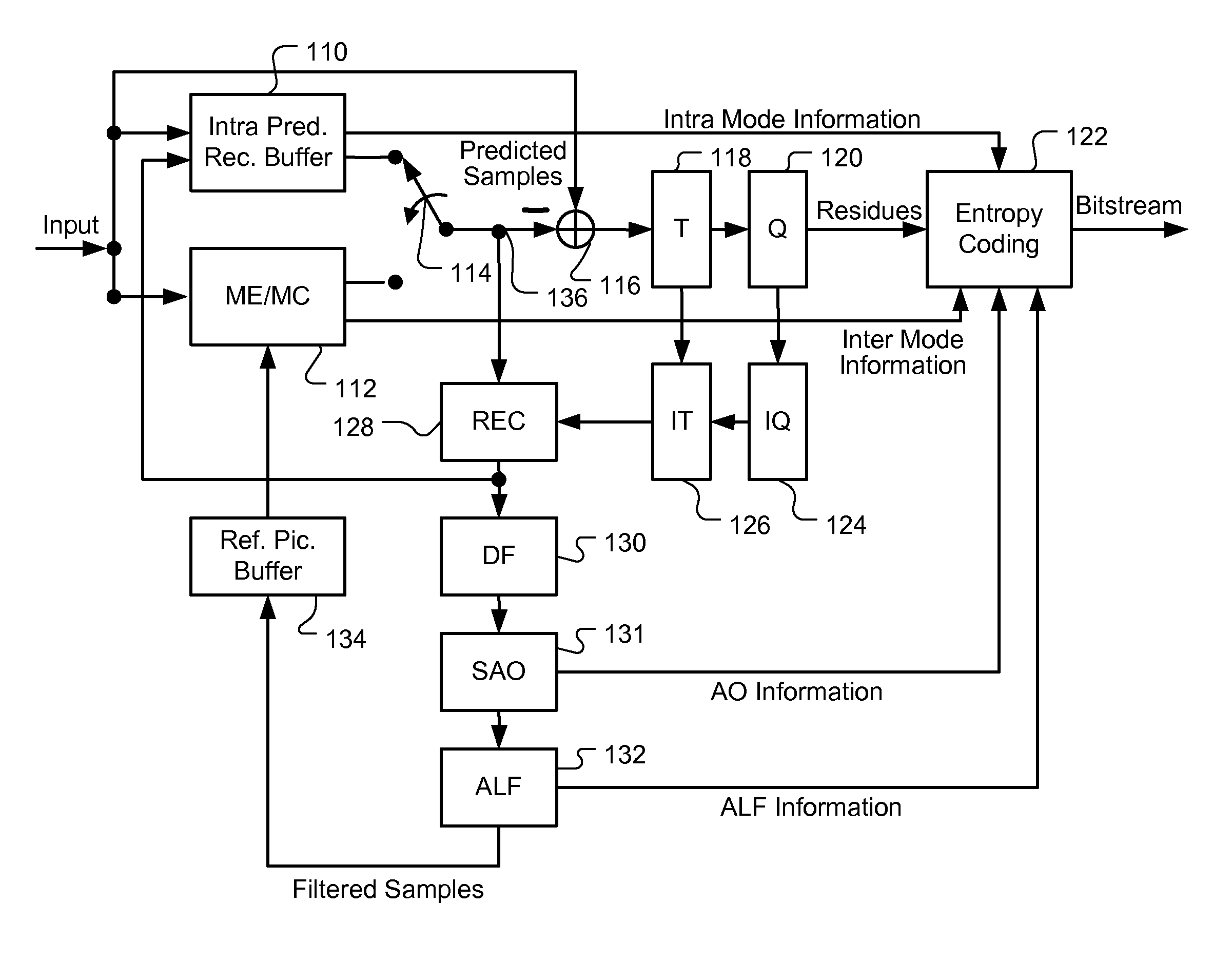

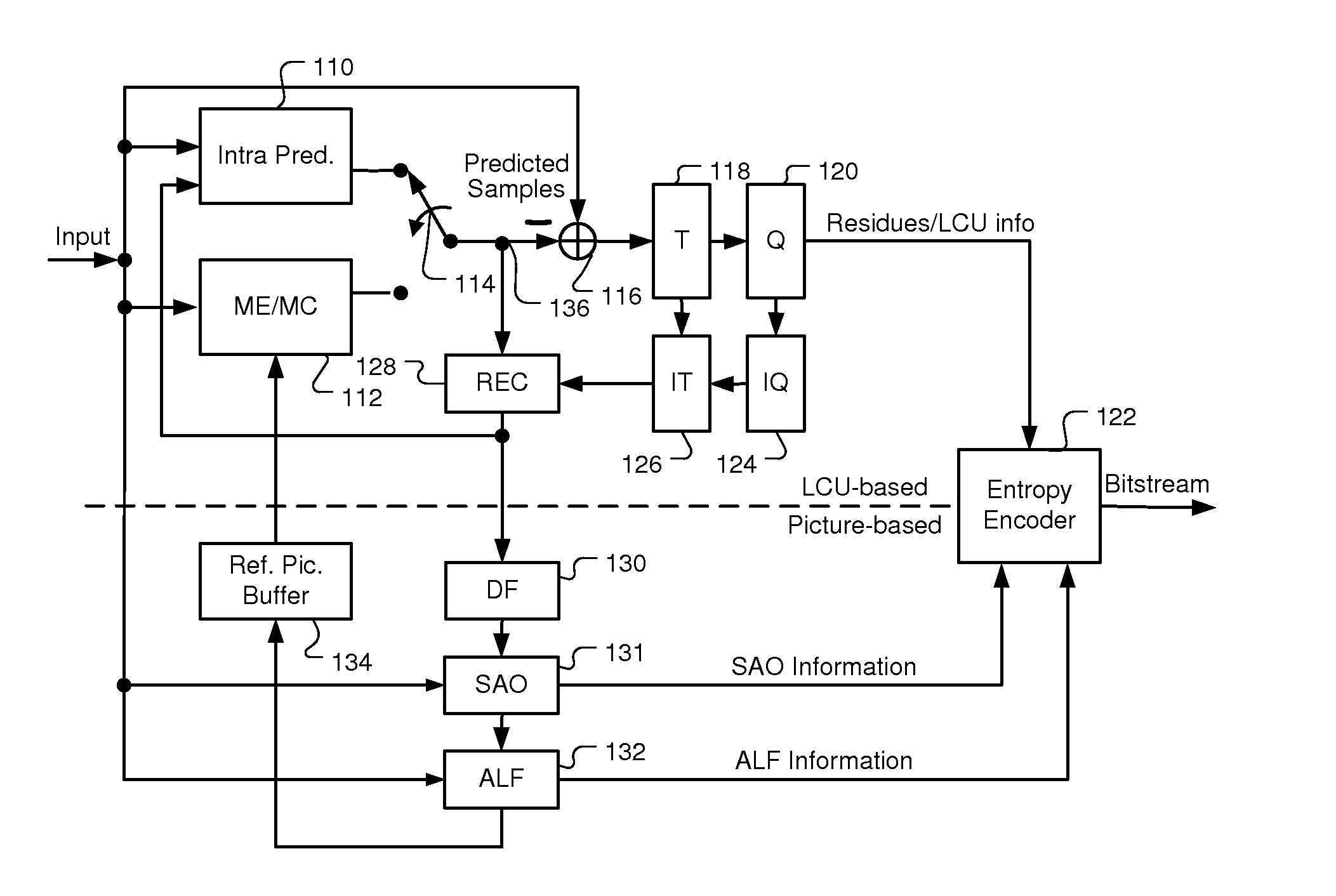

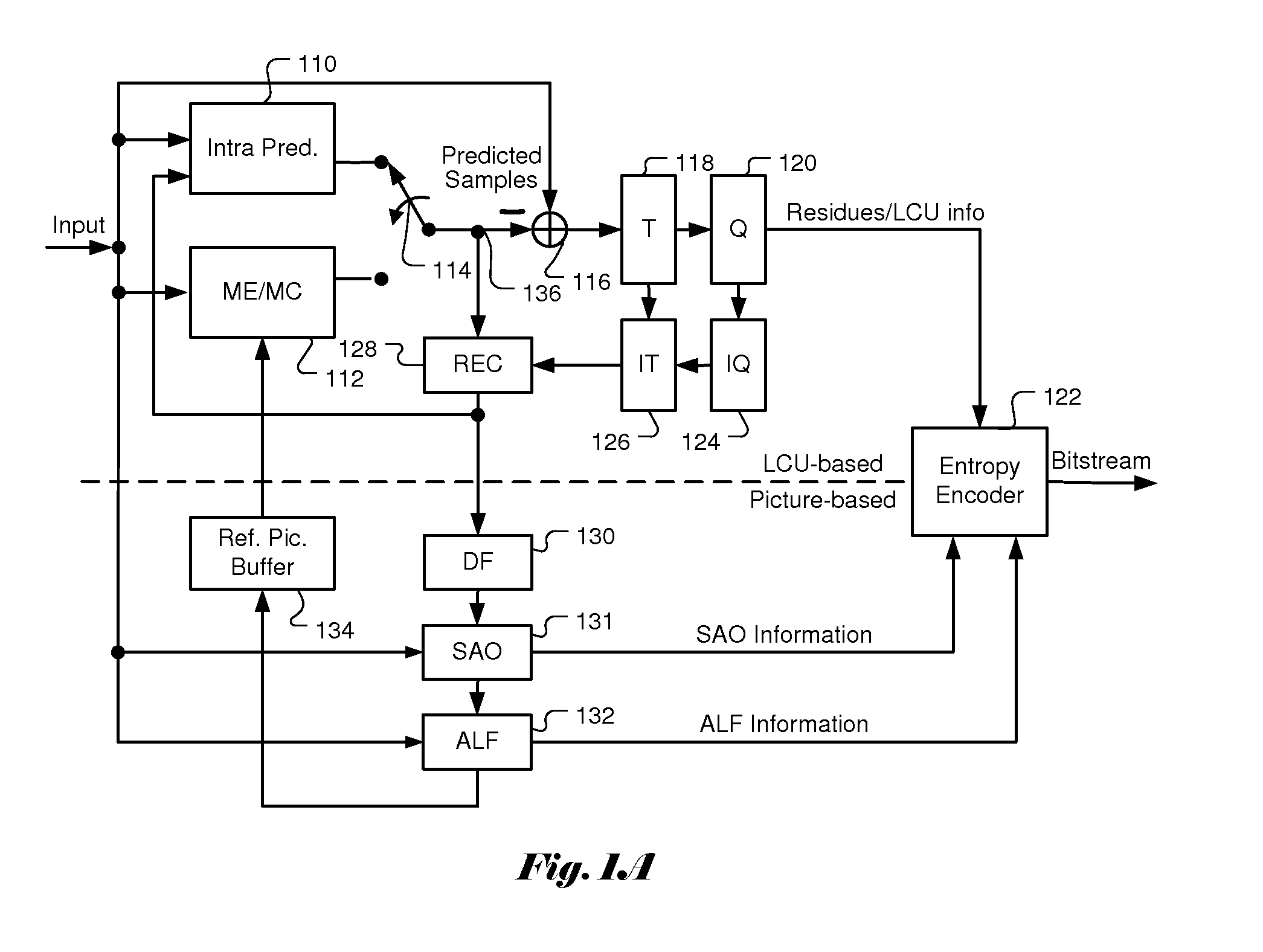

Apparatus and Method of Sample Adaptive Offset for Luma and Chroma Components

InactiveUS20120294353A1Improve coding efficiencyColor television with pulse code modulationColor television with bandwidth reductionComputational scienceLoop filter

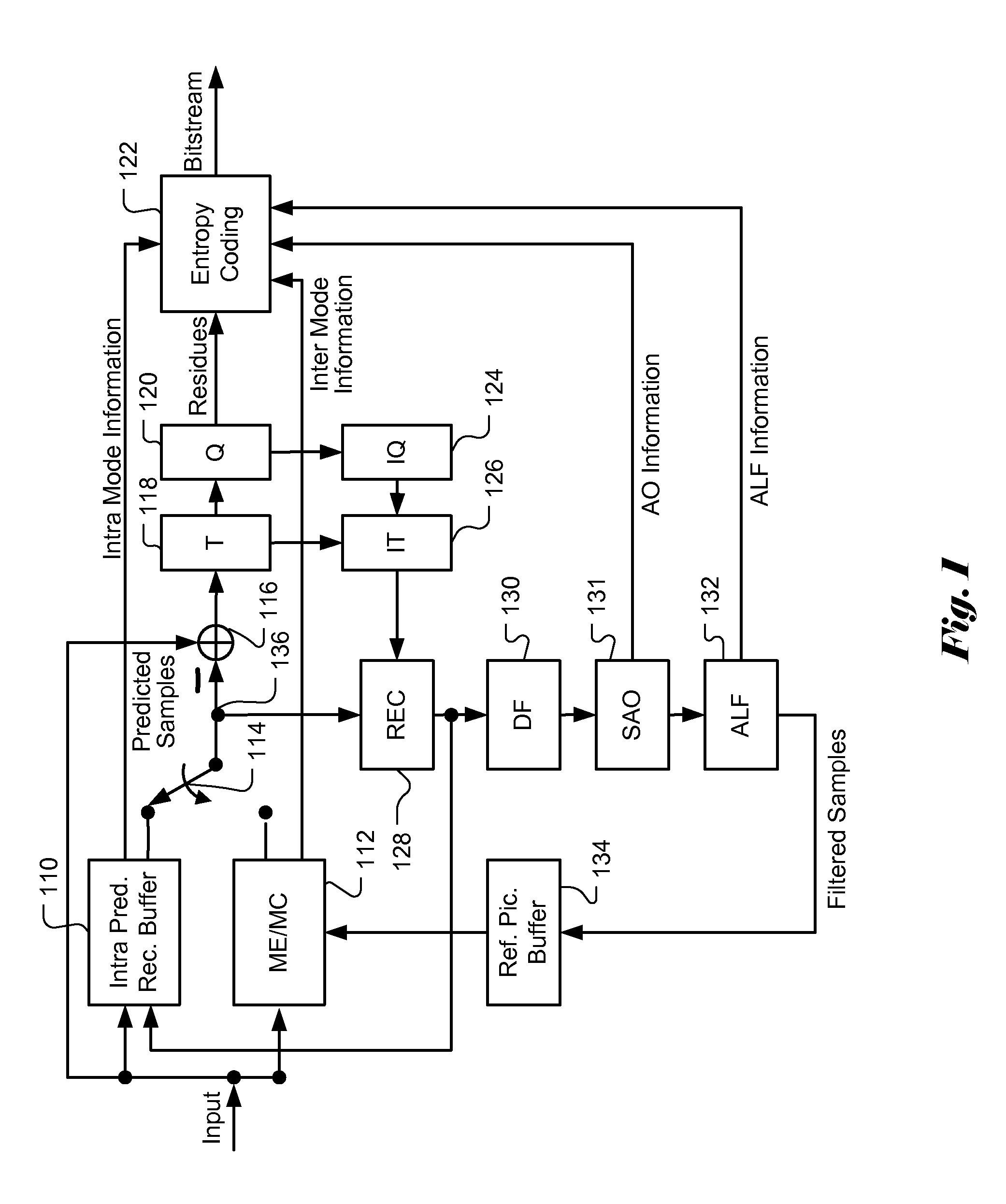

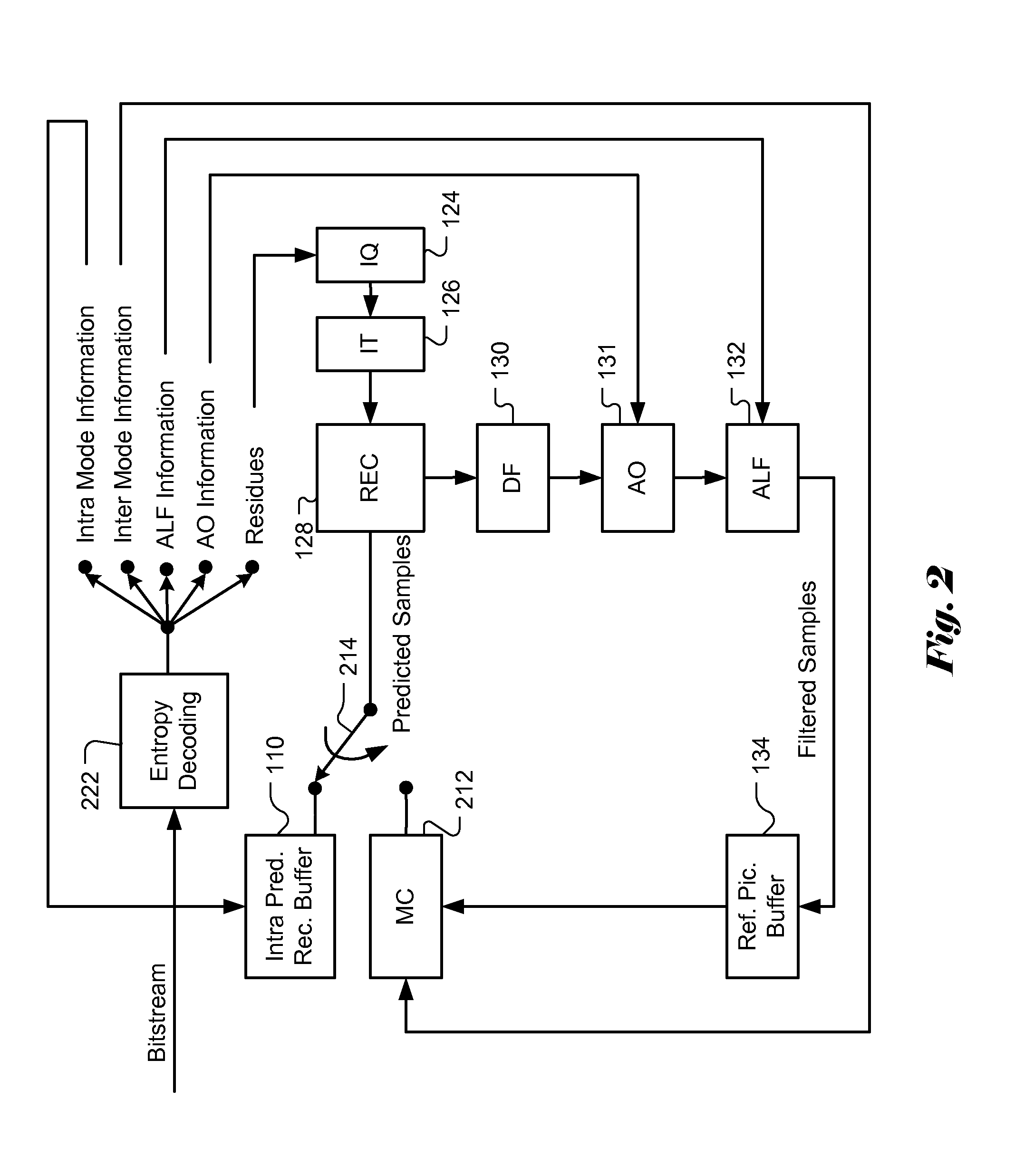

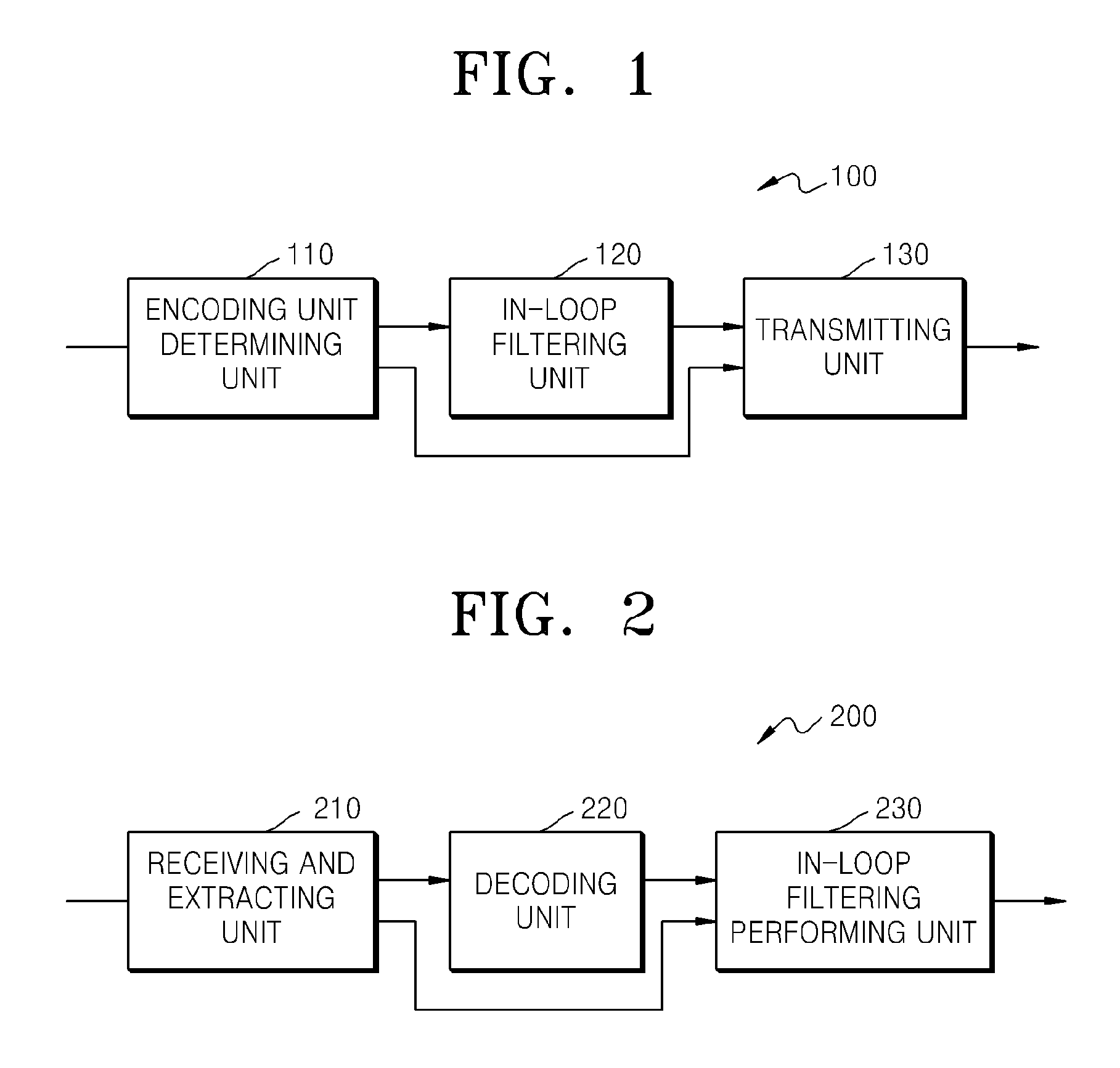

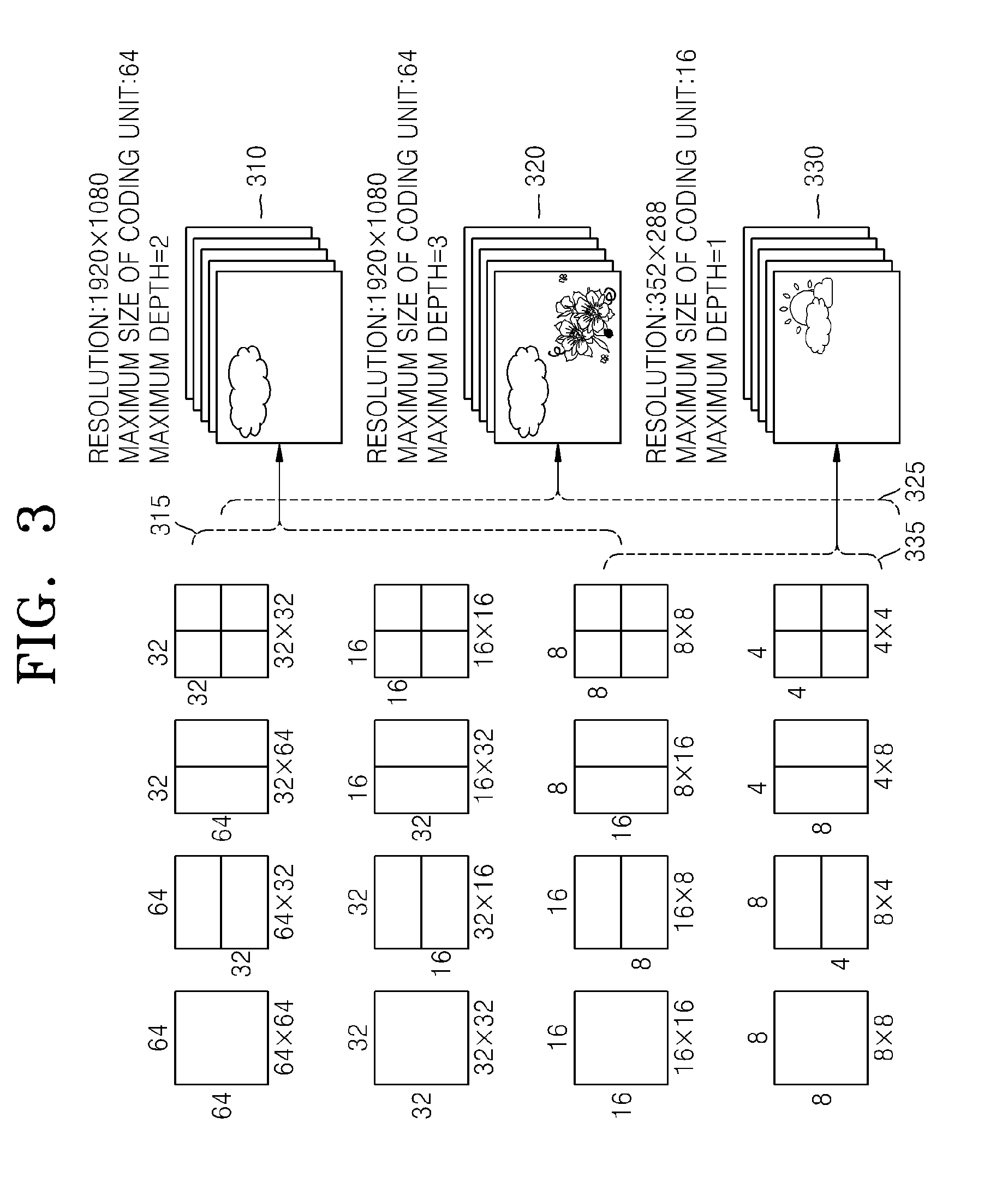

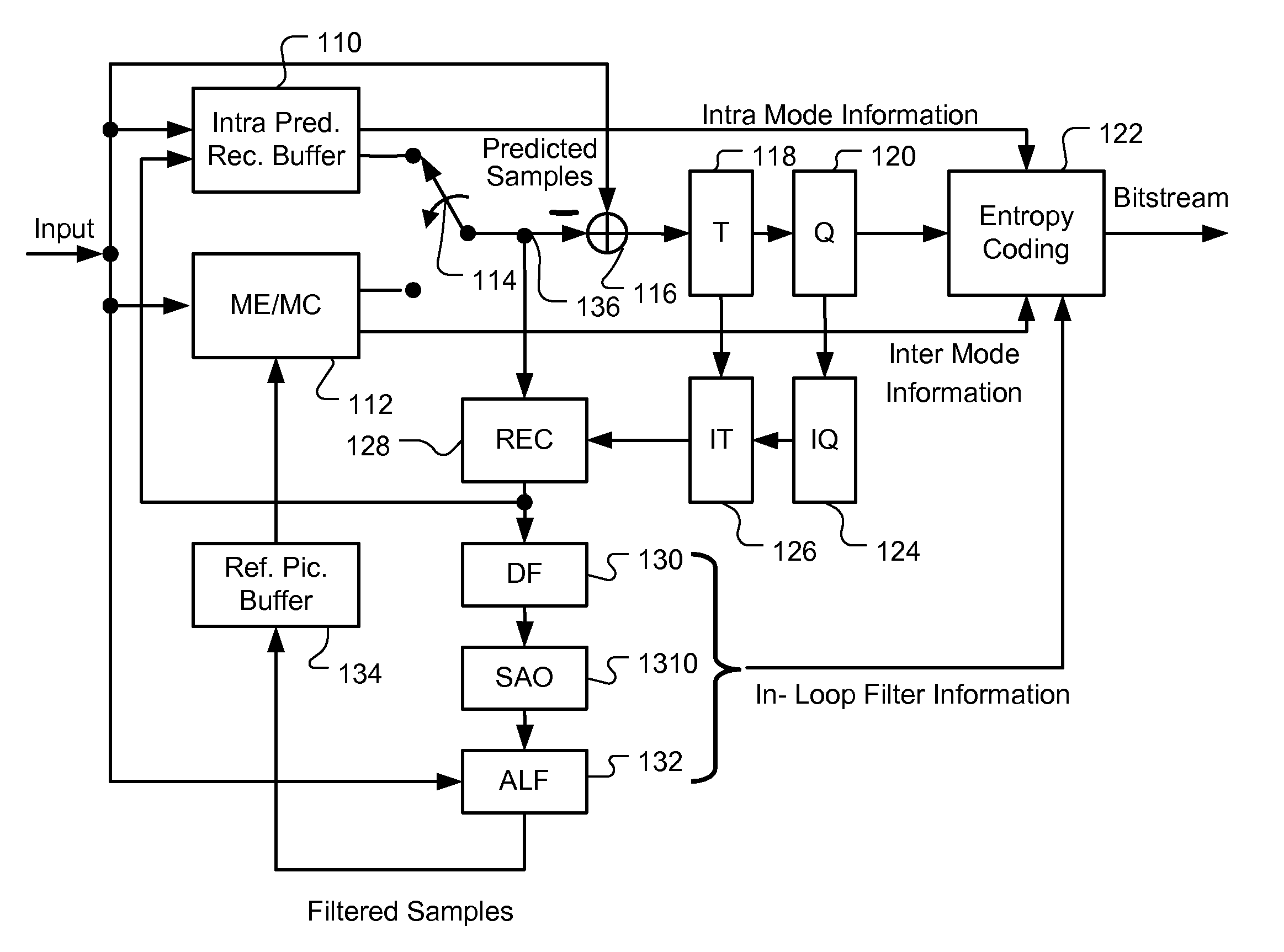

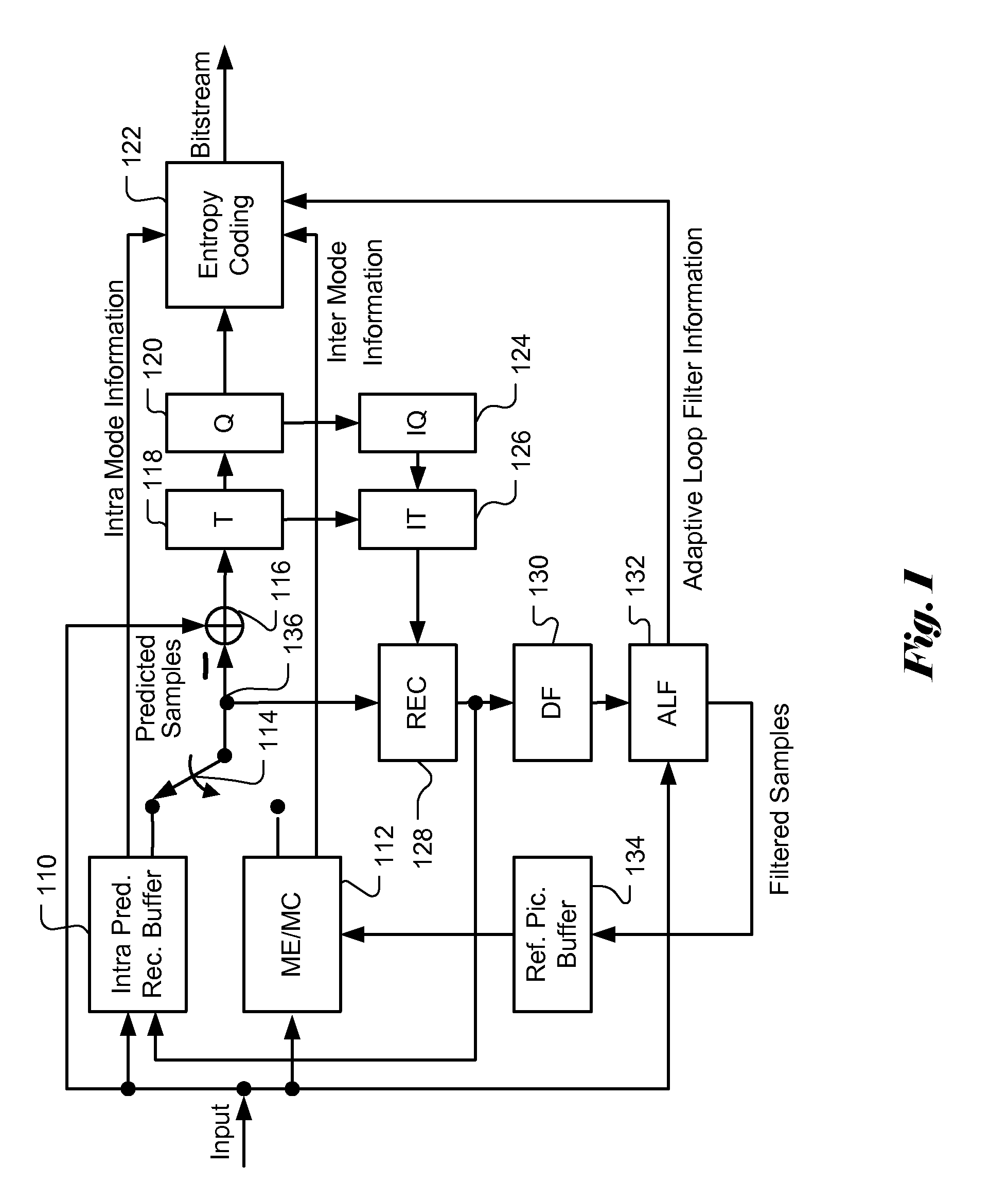

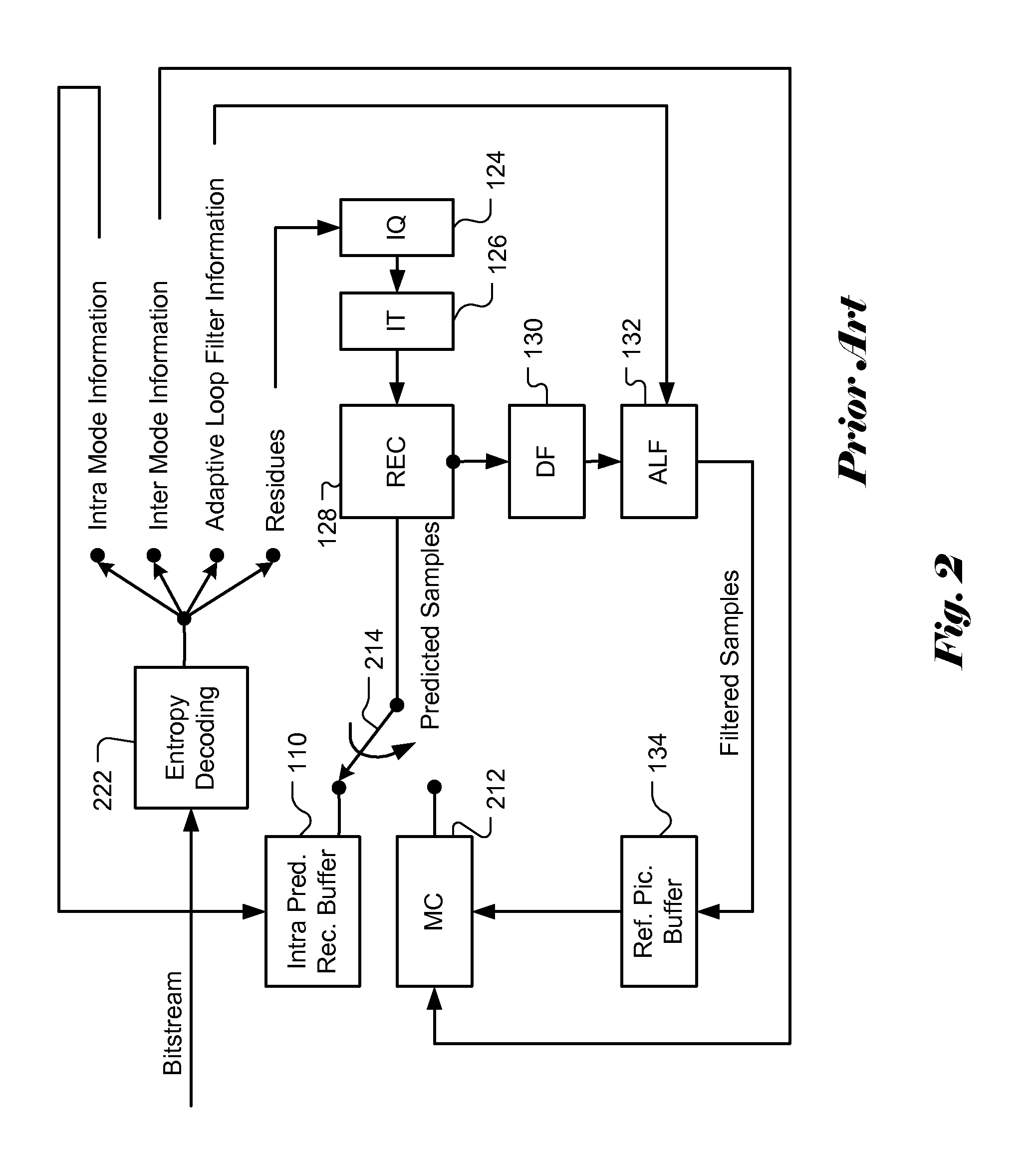

A method and apparatus for processing reconstructed video using in-loop filter in a video coding system are disclosed. The method uses chroma in-loop filter indication to indicate whether chroma components are processed by in-loop filter when the luma in-loop filter indication indicates that in-loop filter processing is applied to the luma component. An additional flag may be used to indicate whether the in-loop filter processing is applied to an entire picture using same in-loop filter information or each block of the picture using individual in-loop filter information. Various embodiments according to the present invention to increase efficiency are disclosed, wherein various aspects of in-loop filter information are taken into consideration for efficient coding such as the property of quadtree-based partition, boundary conditions of a block, in-loop filter information sharing between luma and chroma components, indexing to a set of in-loop filter information, and prediction of in-loop filter information.

Owner:HFI INNOVATION INC

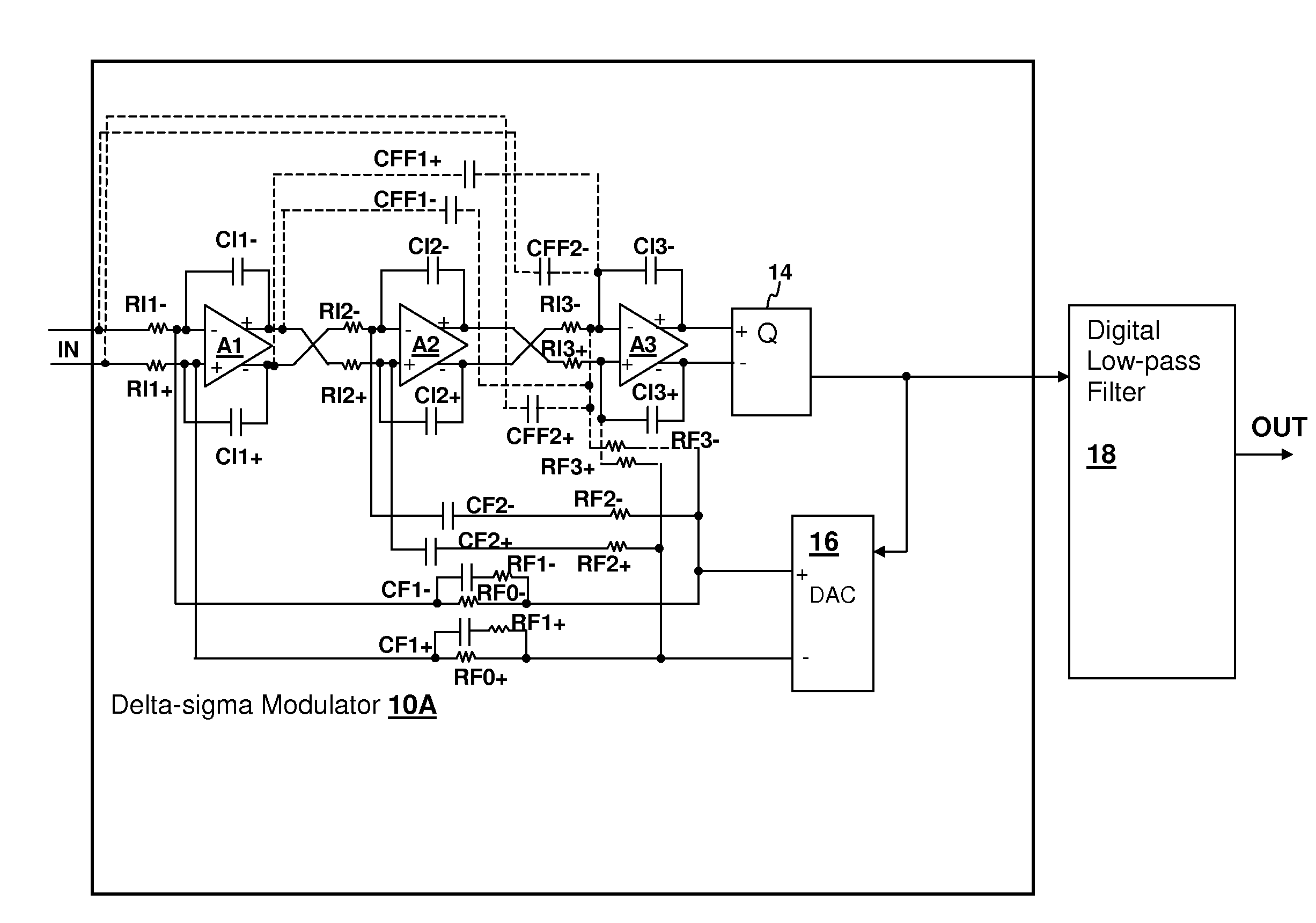

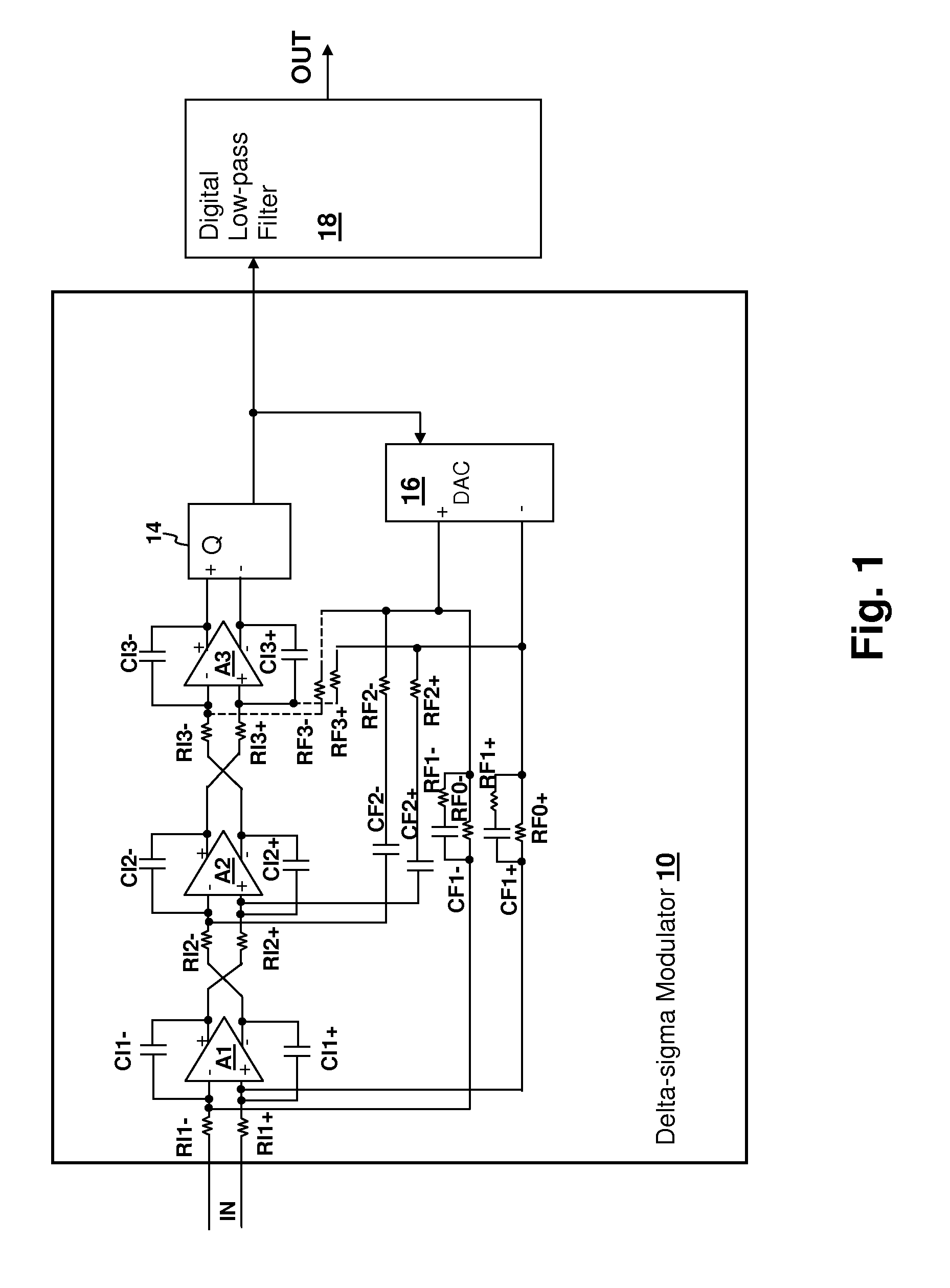

Delta-sigma A/D converter

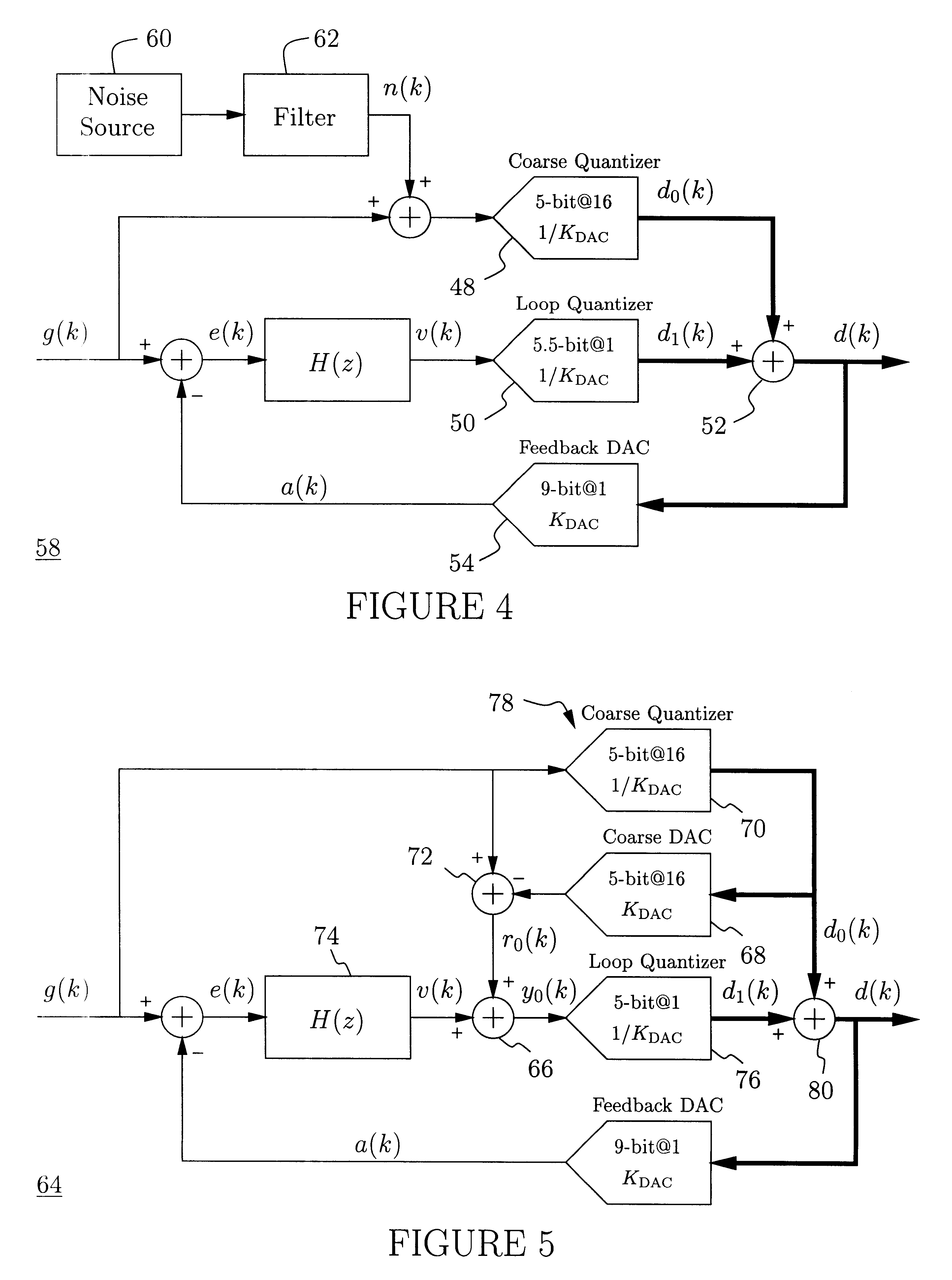

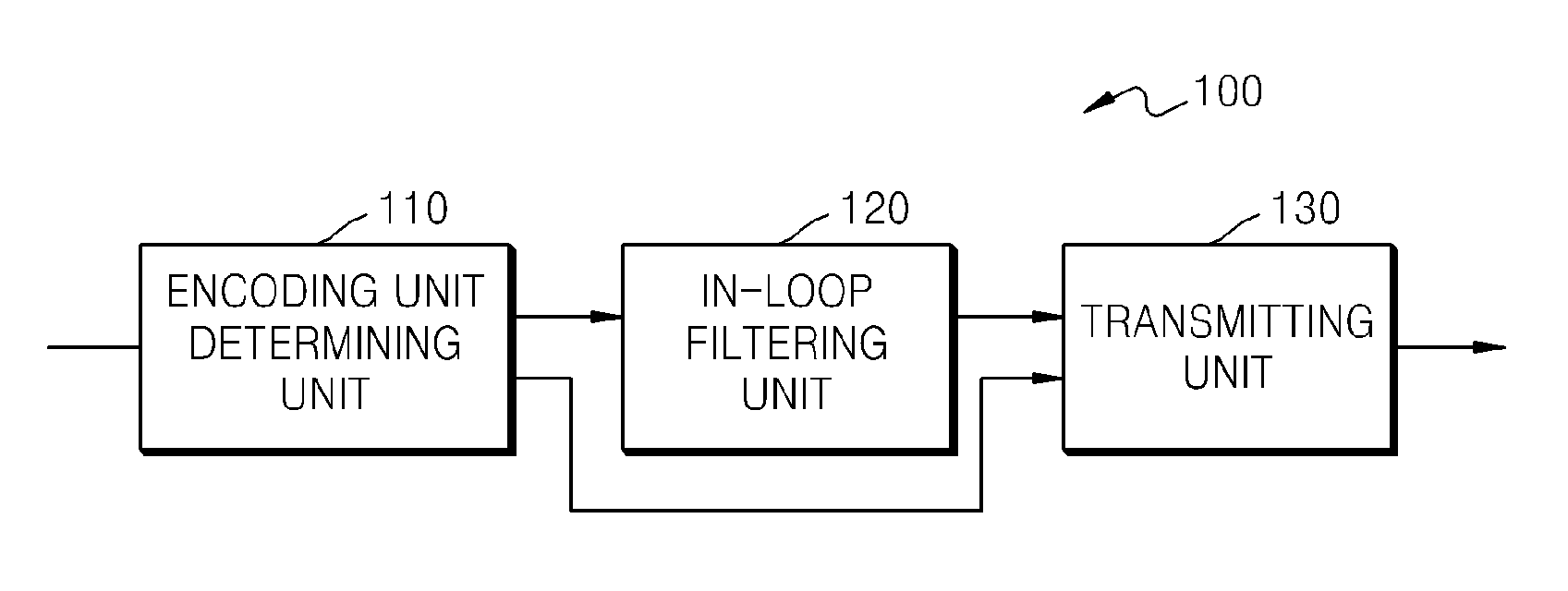

InactiveUS6271782B1Without compromising the modulator's stabilityTo overcome the large delayElectric signal transmission systemsDifferential modulationLoop filterAnalog feedback

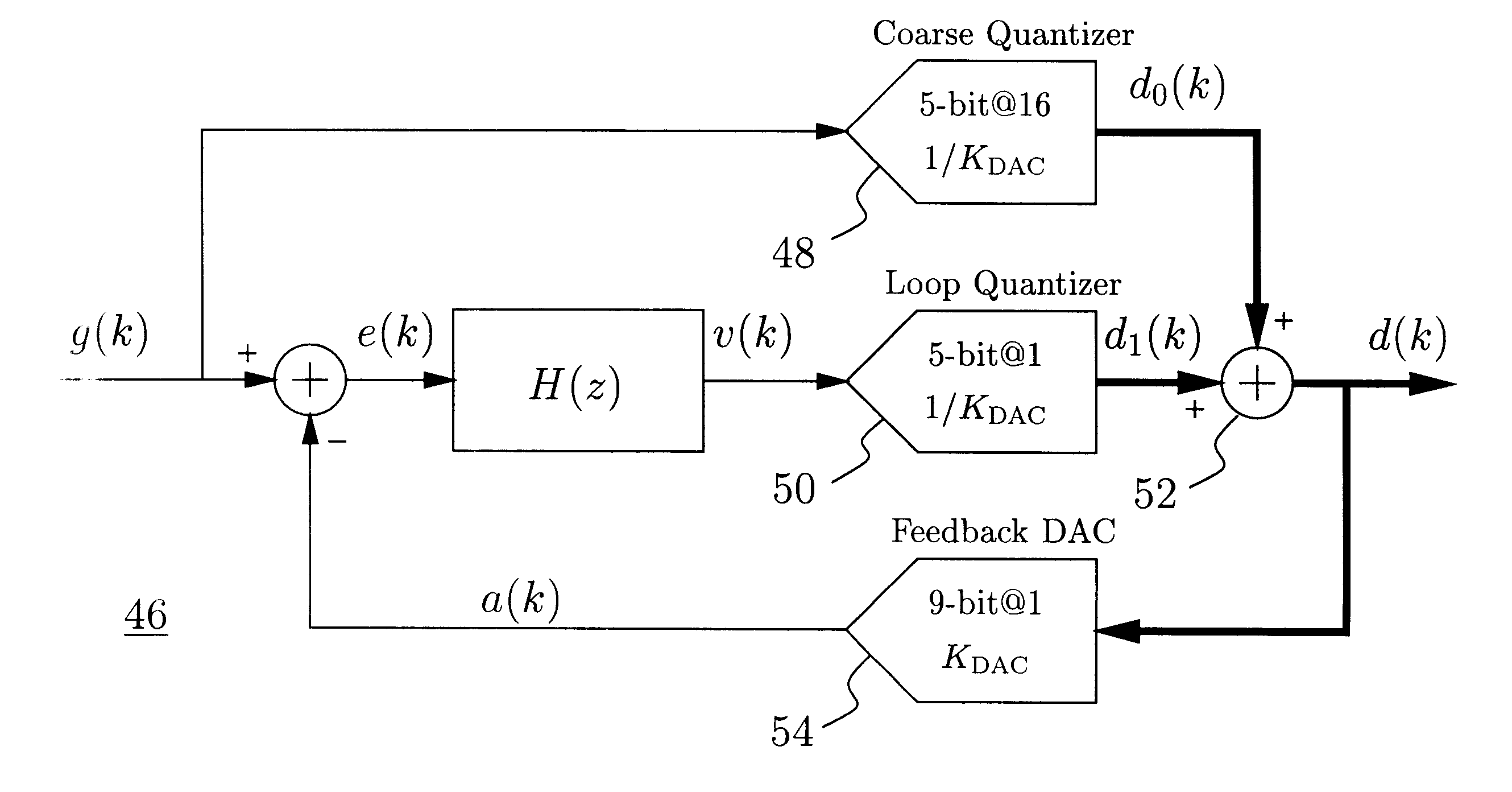

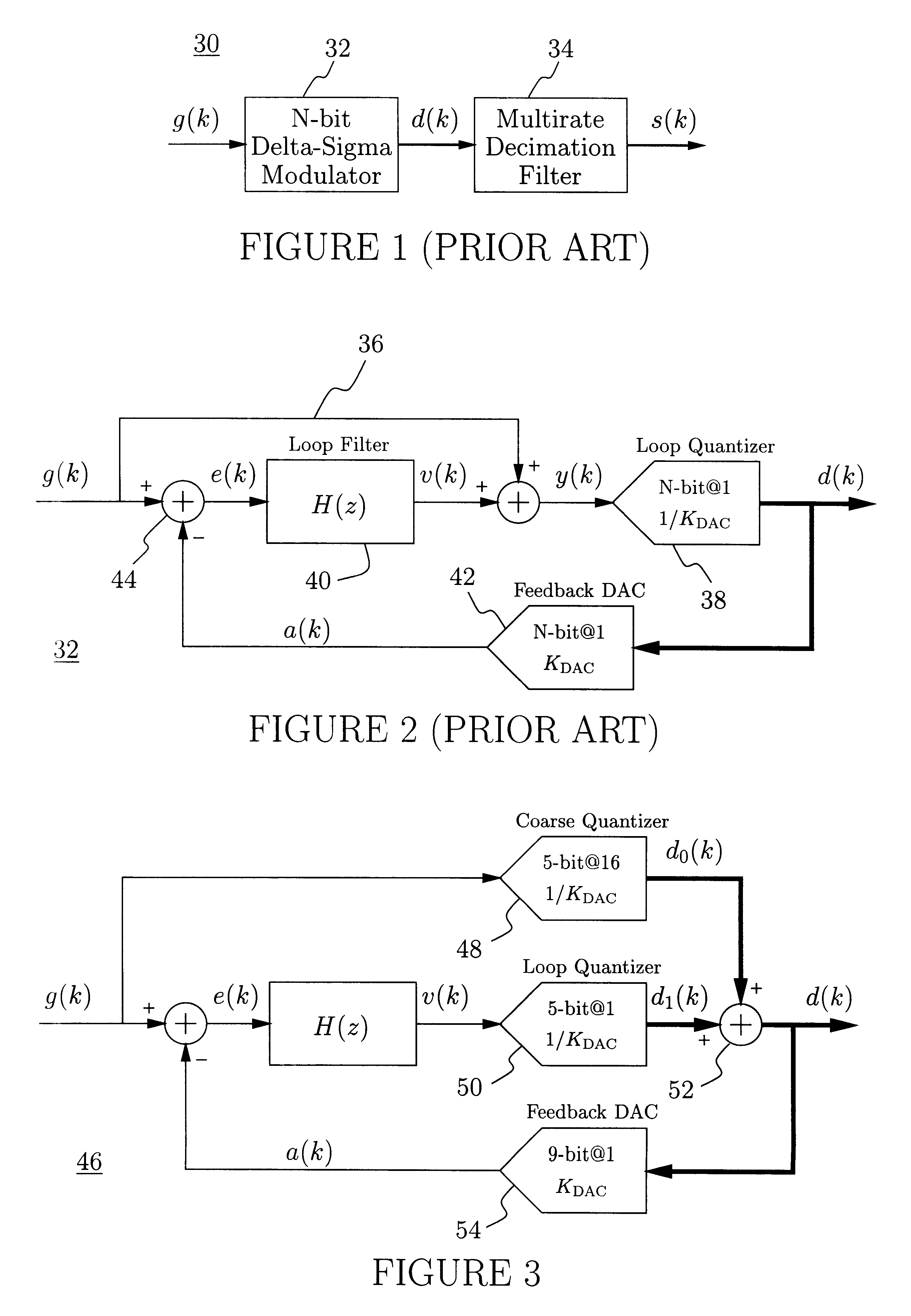

A delta-sigma modulator comprising a first quantizer providing a first digital signal d0(k) representing the input signal g(t); a loop filter with input signal paths; a loop quantizer providing a corrective digital signal d1(k) representing the loop filter's output signal y(t); an array of feedback DACs D / A converting the sum d(k)=df(k)=d0(k)+d1(k) of the first and the corrective digital signals and injecting feedback signals into the loop filter.The loop filter's input node is applied the difference of the input signal g(t) and the global analog feedback signal a3(t). The global feedback signal a3(t) is delayed several clock cycles with respect to the digital output signal d(k). The delay is used to carry out mismatch-shaping and deglitching algorithms in the feedback DACs. The feedback DACs' different delays and gain coefficients are designed such that the modulator is stable. The filter's input signal paths and the compensating DAC are designed such that the gain from the input signal g(t) to the loop quantizer is small, ideally zero. Thus, the loop quantizer's resolving range can be a fraction of the first quantizer's resolving range, whereby the output signal's d(k) resolution can be much higher than the individual resolutions of d0(k) and d1(k).The delta-sigma modulator is well suited for the implementation of high-resolution wide-bandwidth A / D converters. Important applications include digital communication systems.

Owner:ANALOG DEVICES BV

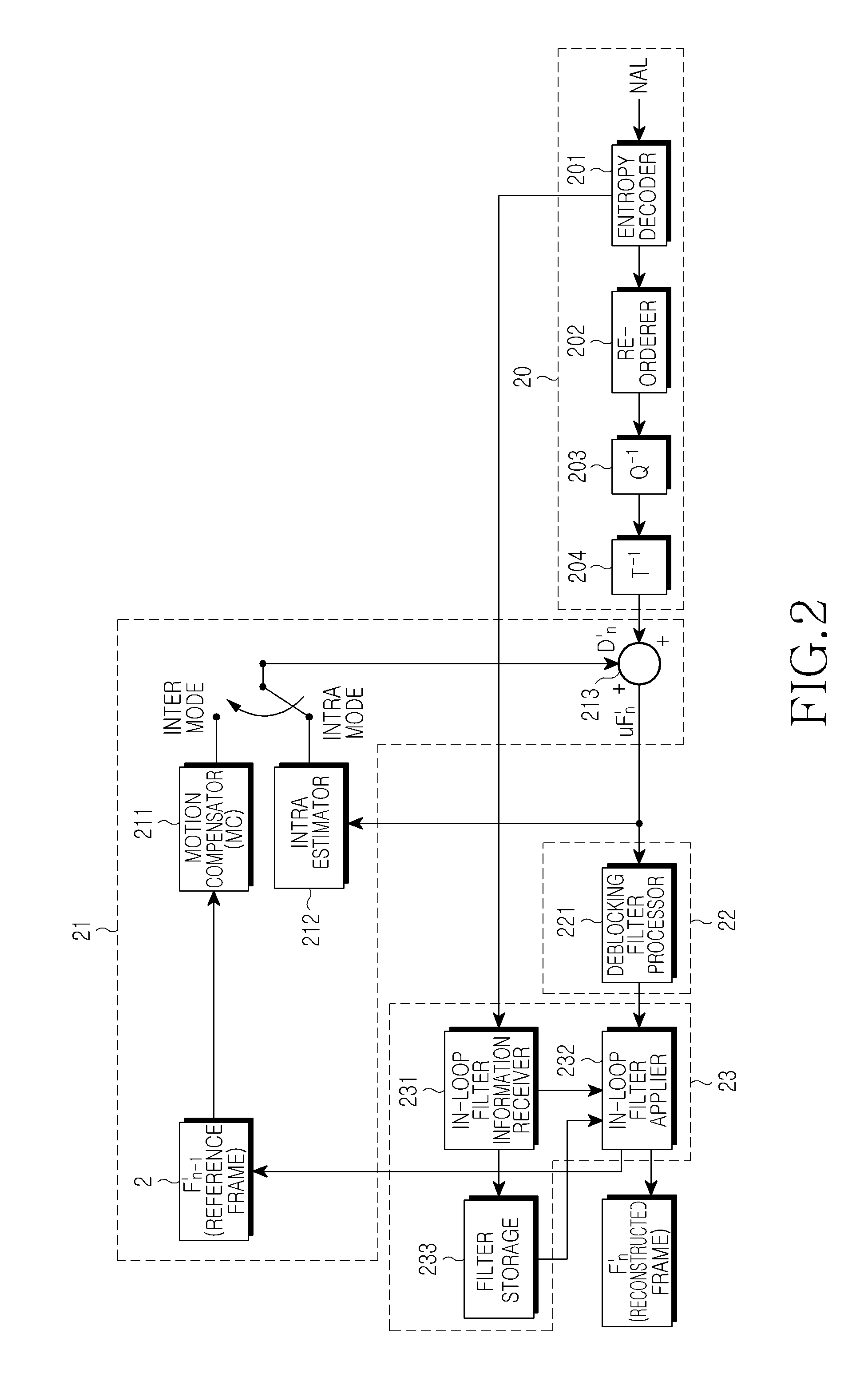

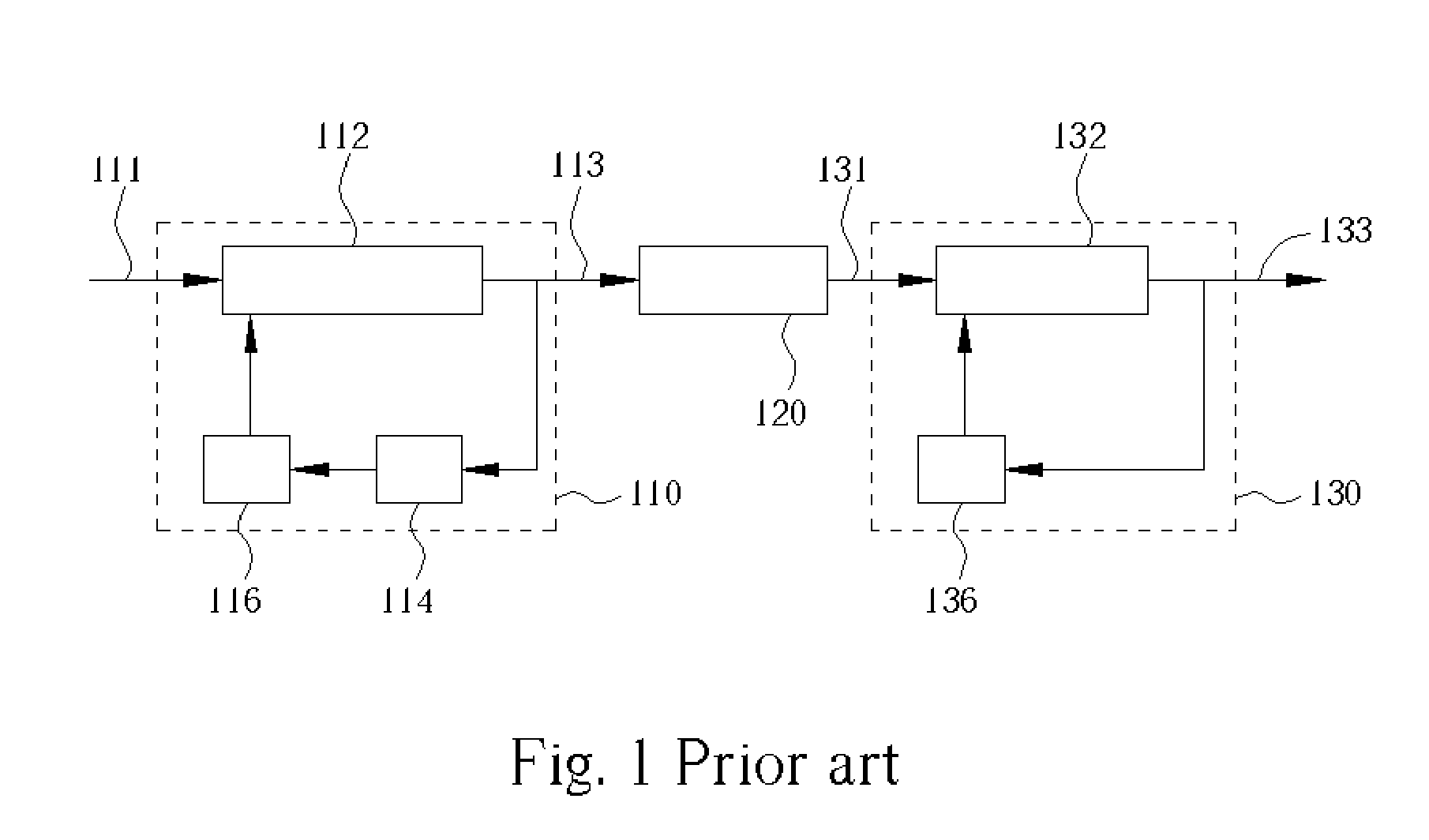

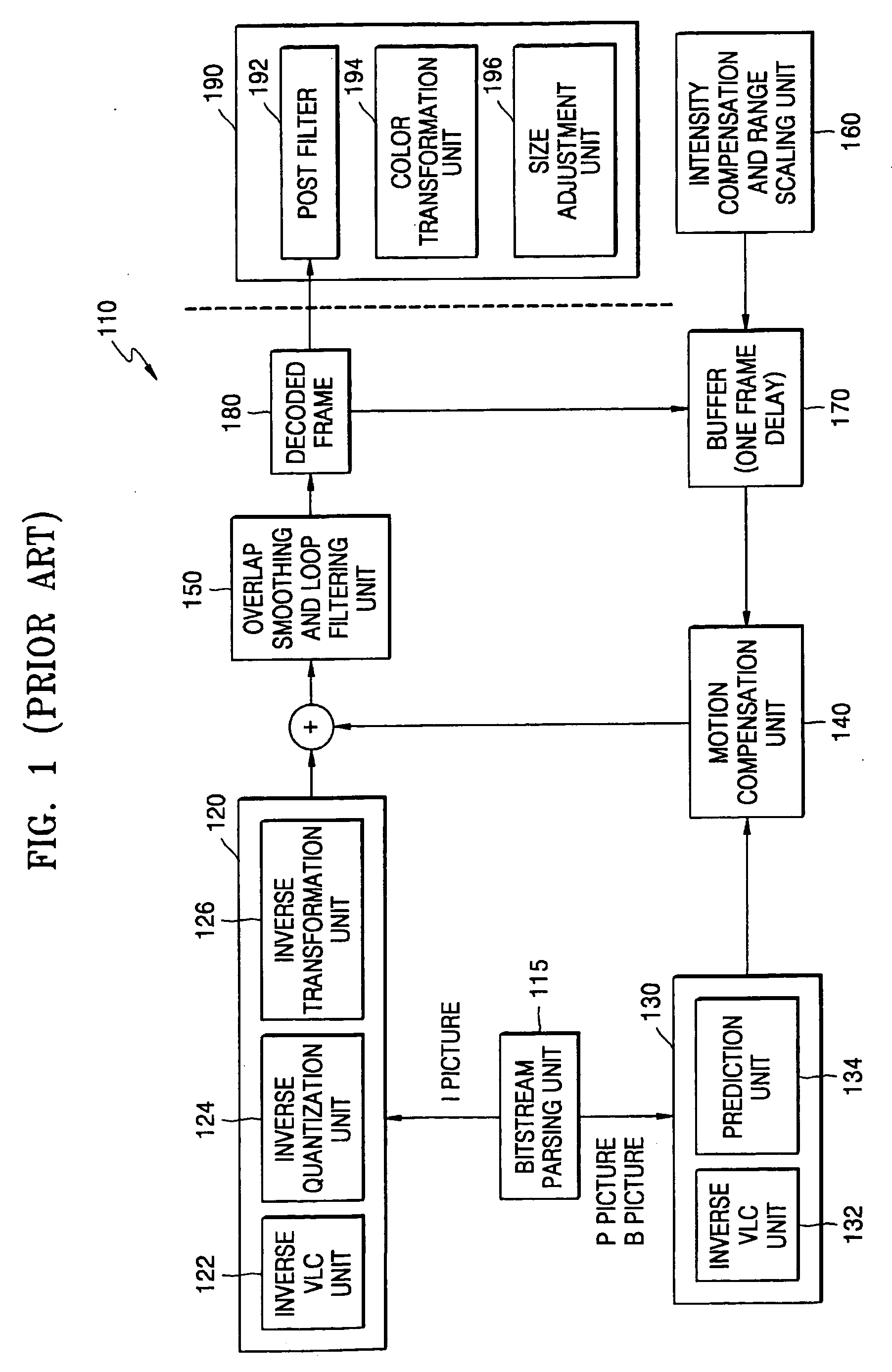

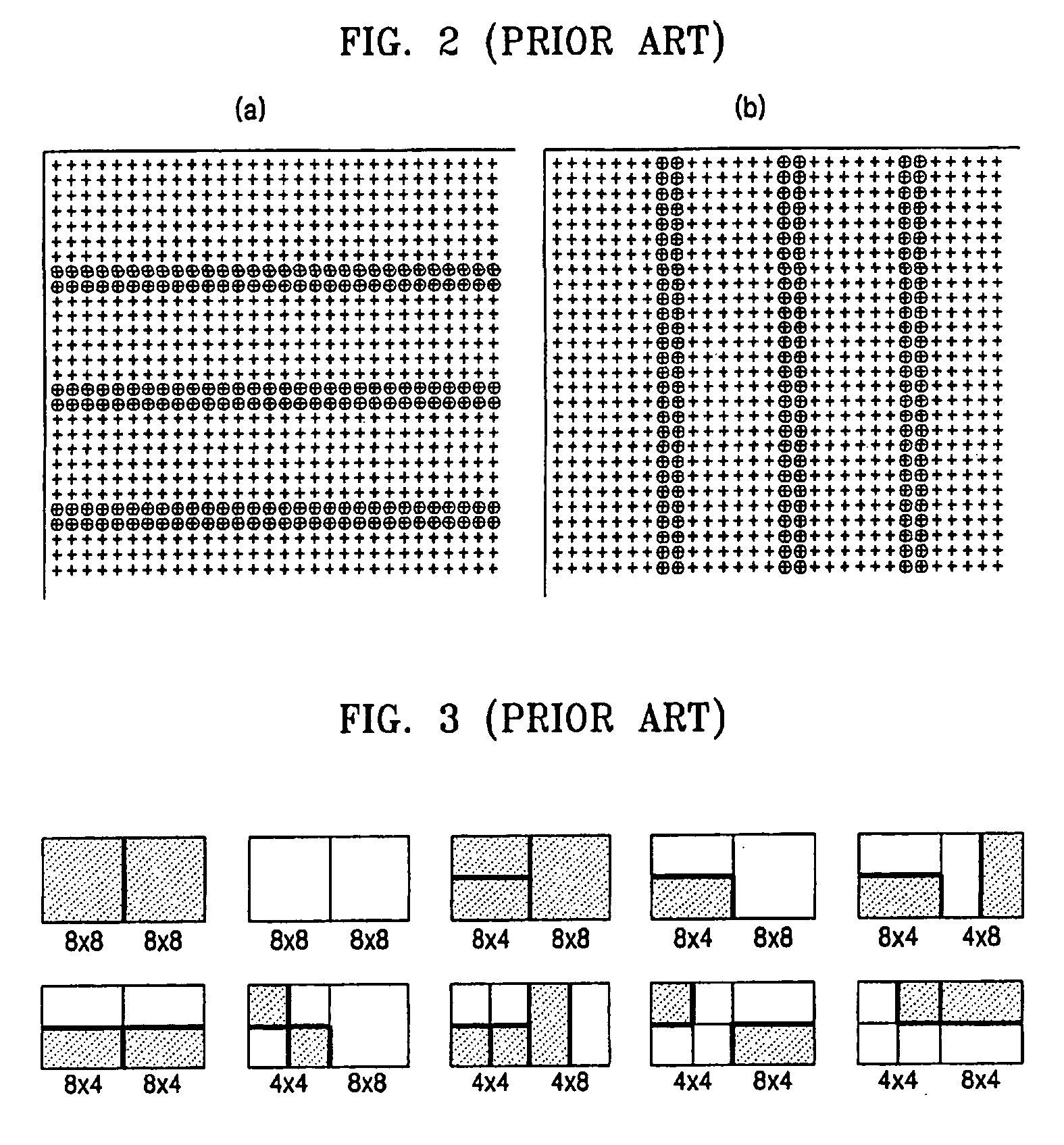

Method and apparatus for encoding video by performing in-loop filtering based on tree-structured data unit, and method and apparatus for decoding video by performing the same

InactiveUS20110243249A1Error minimizationColor television with pulse code modulationPulse modulation television signal transmissionLoop filterComputer architecture

Owner:SAMSUNG ELECTRONICS CO LTD

Method and Apparatus for Slice Common Information Sharing

ActiveUS20120207227A1Color television with pulse code modulationColor television with bandwidth reductionLoop filterInformation sharing

A method and apparatus for sharing information in a video coding system are disclosed. Embodiments according to the present invention use an information sharing flag to determine whether to share in-loop filter information in the picture level. The information sharing flag may be incorporated in the sequence level, the picture level or the slice level to indicate whether information sharing is enabled. Multiple information sharing flags may also be used to adaptively control information sharing. Furthermore, method and apparatus of using multiple Adaptation Parameter Sets (APSs) for information sharing of in-loop filters are disclosed. APS identifiers of in-loop filters may be incorporated in the slice header to allow each of the in-loop filters select respective filter information from the multiple APSs. A flag is incorporated in SPS to indicate whether multiple APS or single APS is used. Various exemplary syntax designs are disclosed to illustrate information sharing.

Owner:HFI INNOVATION INC

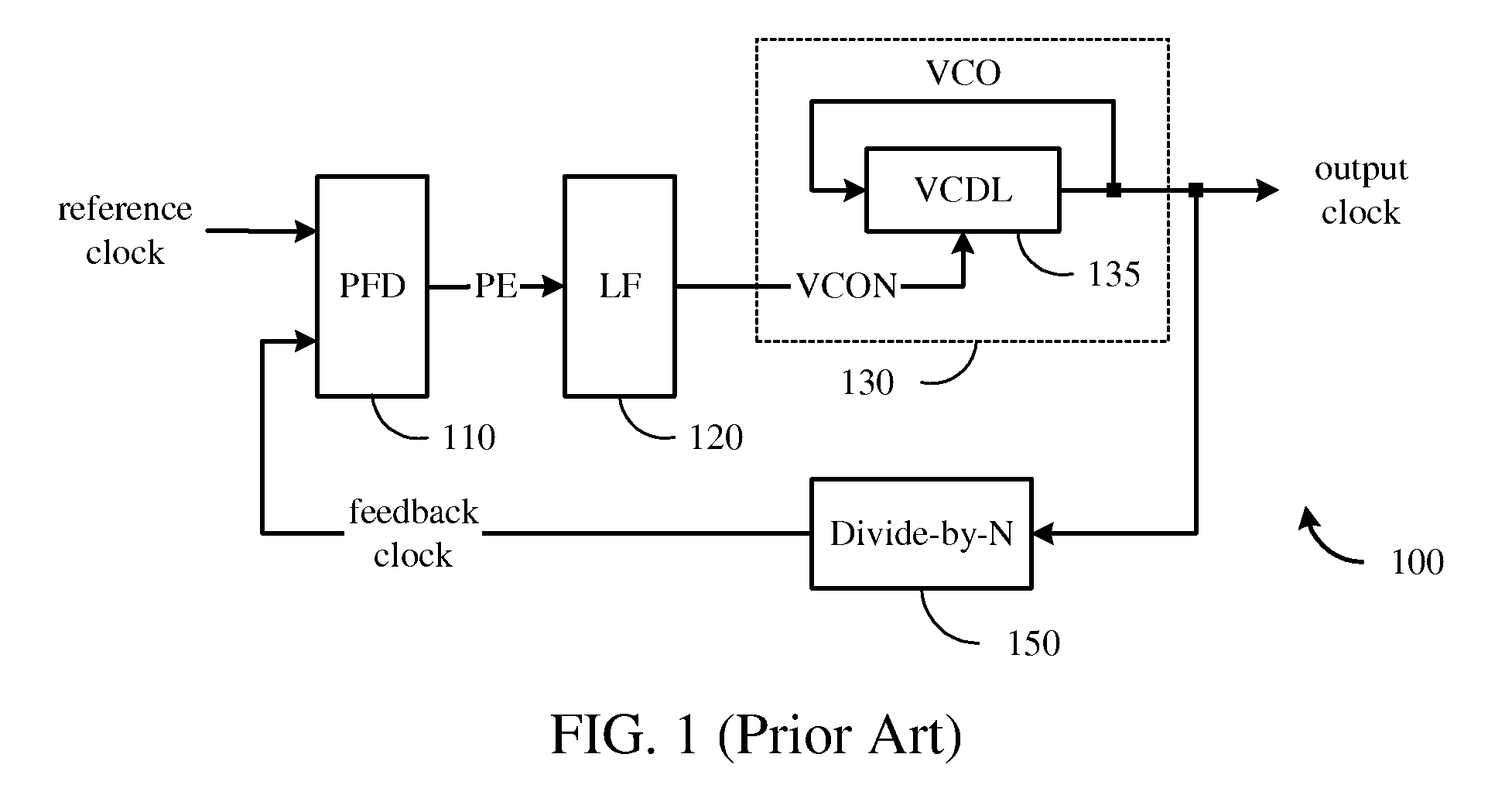

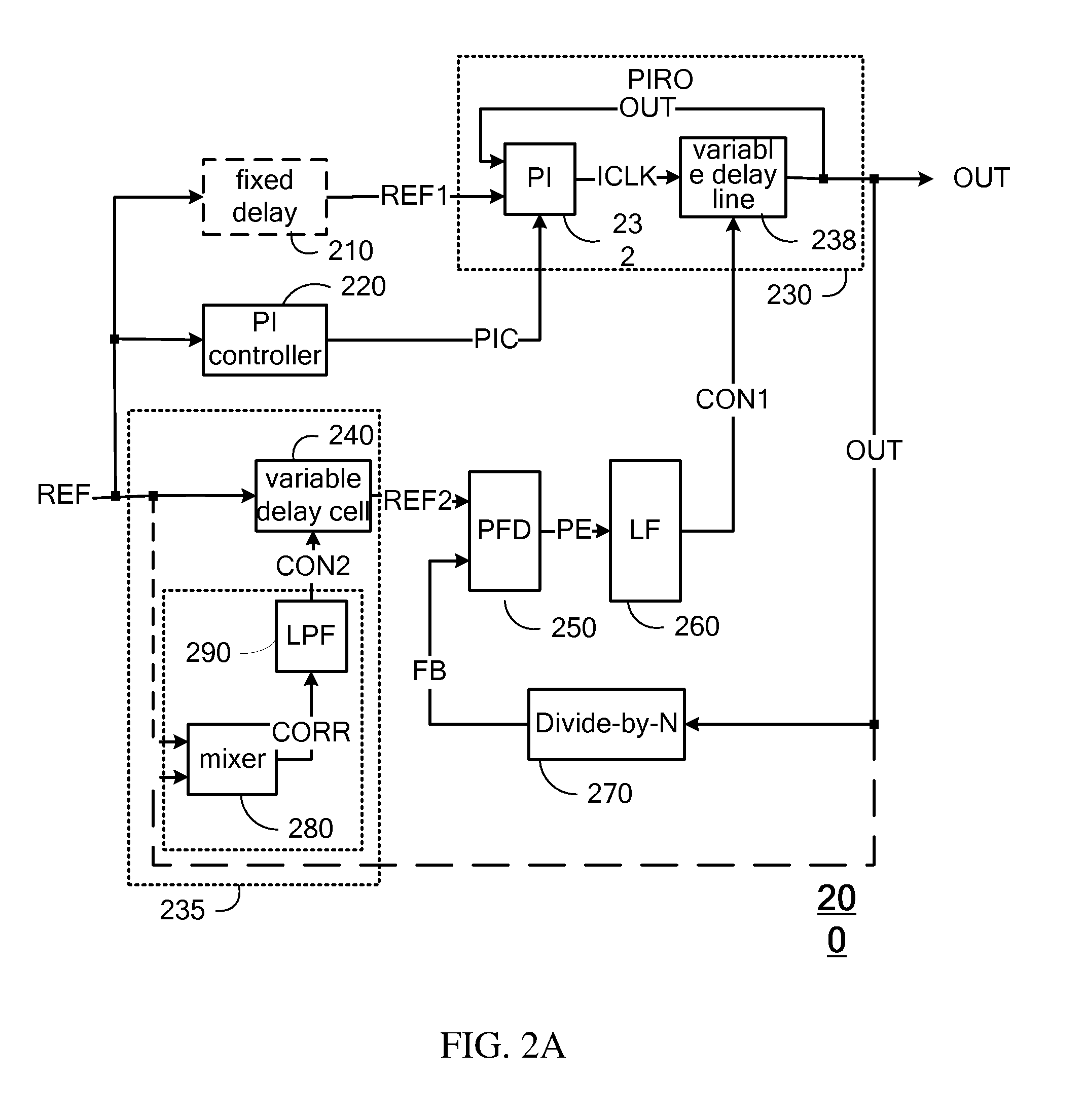

Phase lock loop with phase interpolation by reference clock and method for the same

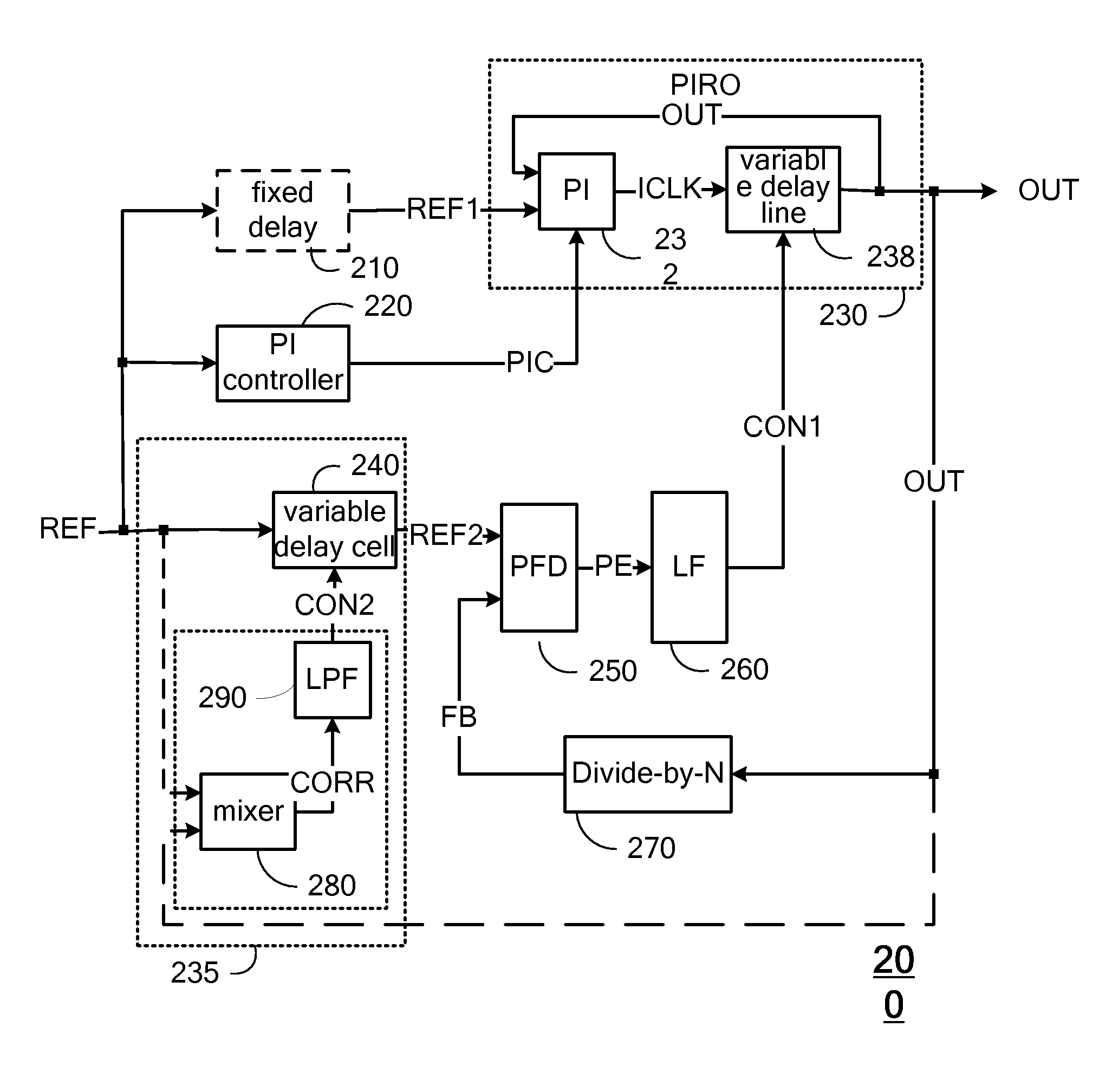

The present invention relates to a PLL that utilizes a phase interpolation by a reference clock. The PLL includes a phase-interpolated controller for generating a phase-interpolation control signal; a phase / frequency detector for detecting a phase difference between a second reference clock and a feedback clock and outputting a phase error signal to represent the phase difference; a loop filter for filtering the phase error signal to generate a first control signal; a phase-interpolated oscillator for generating an output clock under a control by the phase-interpolation control signal and the first control signal; and a divide-by-N circuit for dividing down the output clock by a factor of N to generate the feedback clock, where N is an integer.

Owner:REALTEK SEMICON CORP

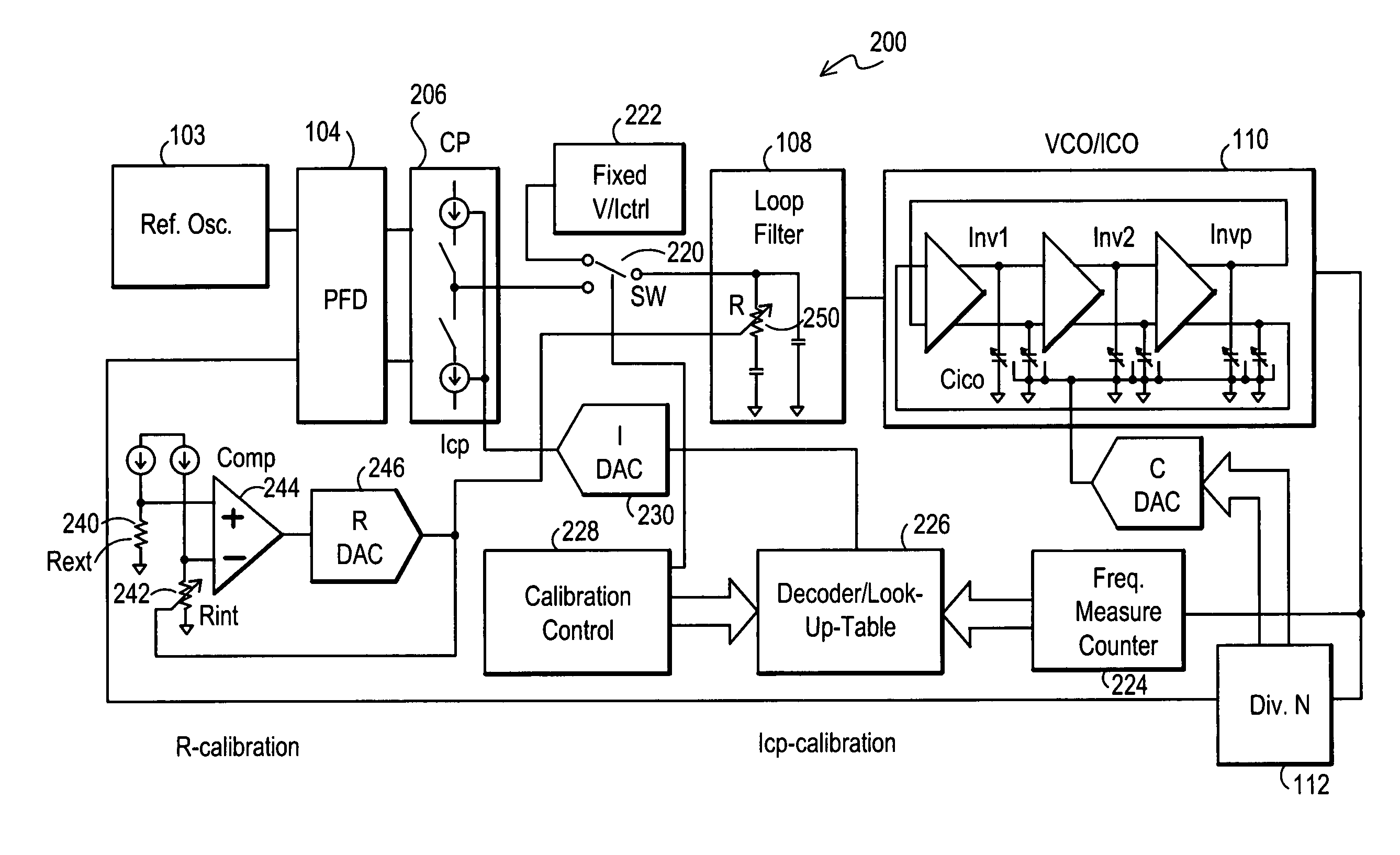

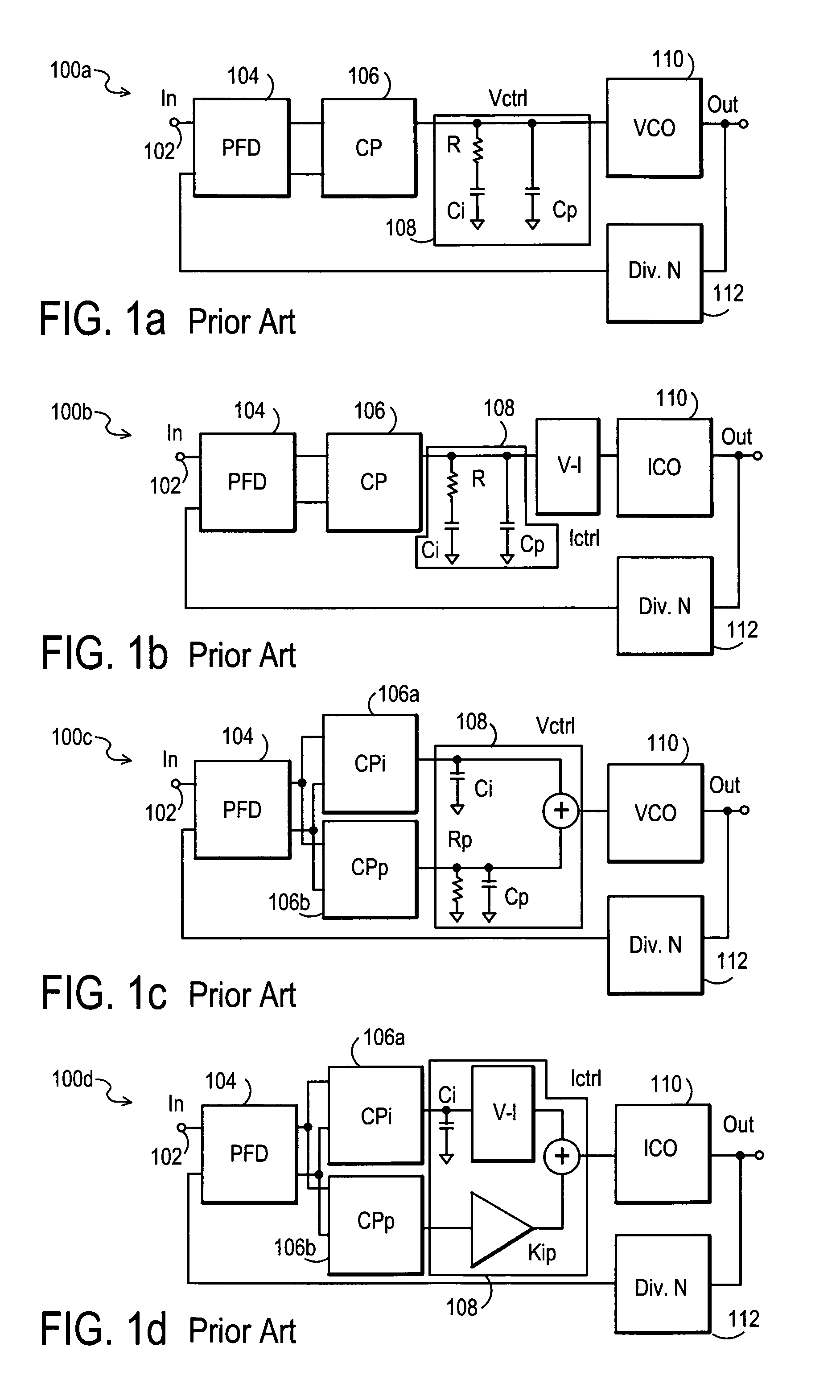

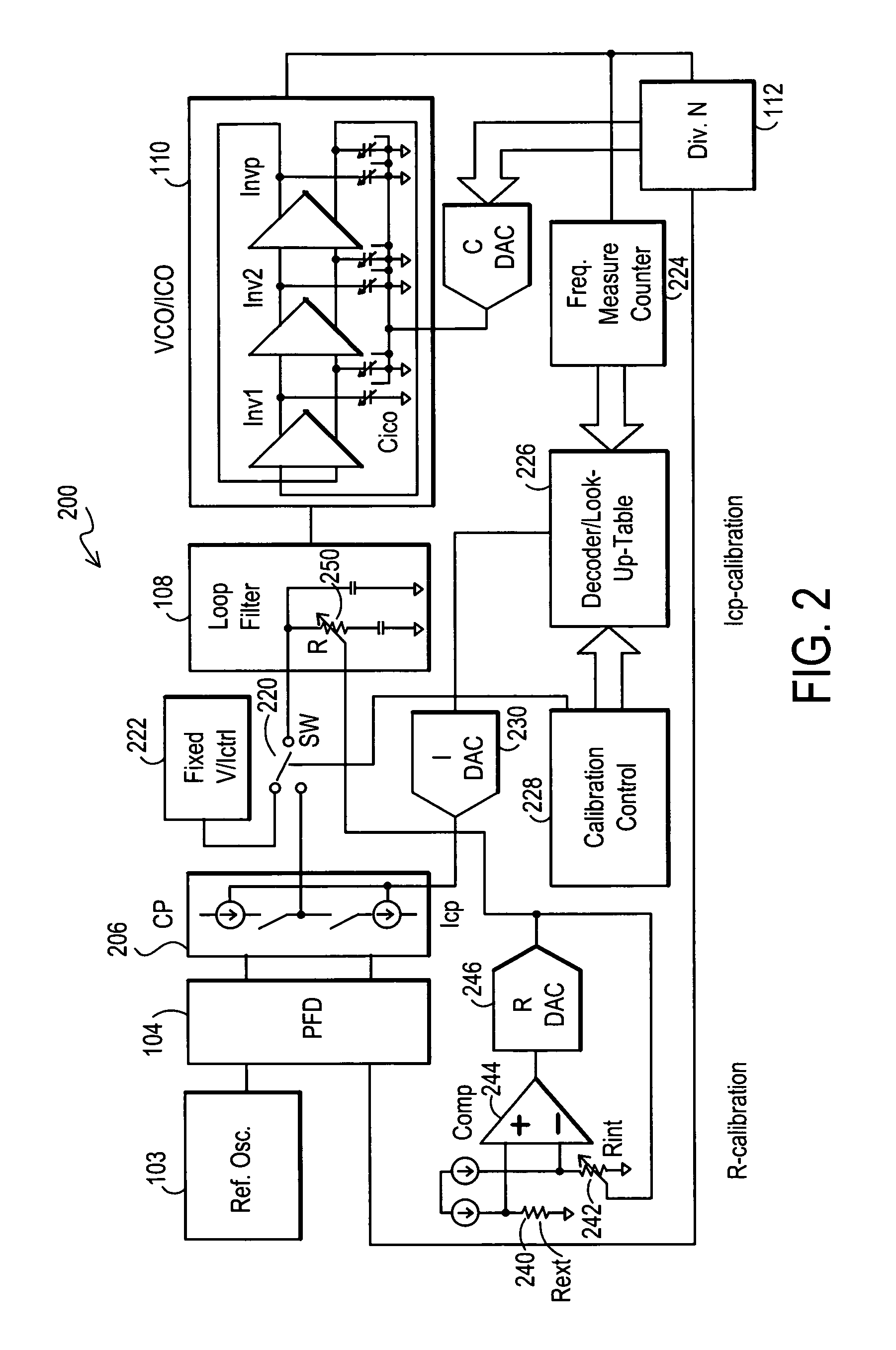

Method and apparatus to achieve a process, temperature and divider modulus independent PLL loop bandwidth and damping factor using open-loop calibration techniques

InactiveUS7095287B2Reduce complexityImprove accuracyPulse automatic controlFrequency analysisDamping factorProportional control

Several open-loop calibration techniques for phase-locked-loop circuits (PLL) that provide a process, temperature and divider modulus independence for the loop bandwidth and damping factor are disclosed. Two categories of open-loop techniques are presented. The first method uses only a single measurement of the output frequency from the oscillator and adjusts a single PLL loop element that performs a simultaneous calibration of both the loop bandwidth and damping factor. The output frequency is measured for a given value of the oscillator control signal and the charge-pump current is adjusted such that it cancels the process variation of the oscillator gain. The second method uses two separate and orthogonal calibration steps, both of them based on the measurement of the output frequency from the oscillator when a known excitation is applied to the open loop signal path. In the first step the loop bandwidth is calibrated by adjusting the charge-pump current based on the measurement of the forward path gain when applying a constant phase shift between the two clocks that go to the phase frequency detector, while the integral path is hold to a constant value. During the second step the damping factor is calibrated by adjusting the value of the integral loop filter capacitor based on the measurement of the oscillator output frequency when excited with a voltage proportional with the integral capacitor value, while the proportional control component is zeroed-out.

Owner:SILICON LAB INC

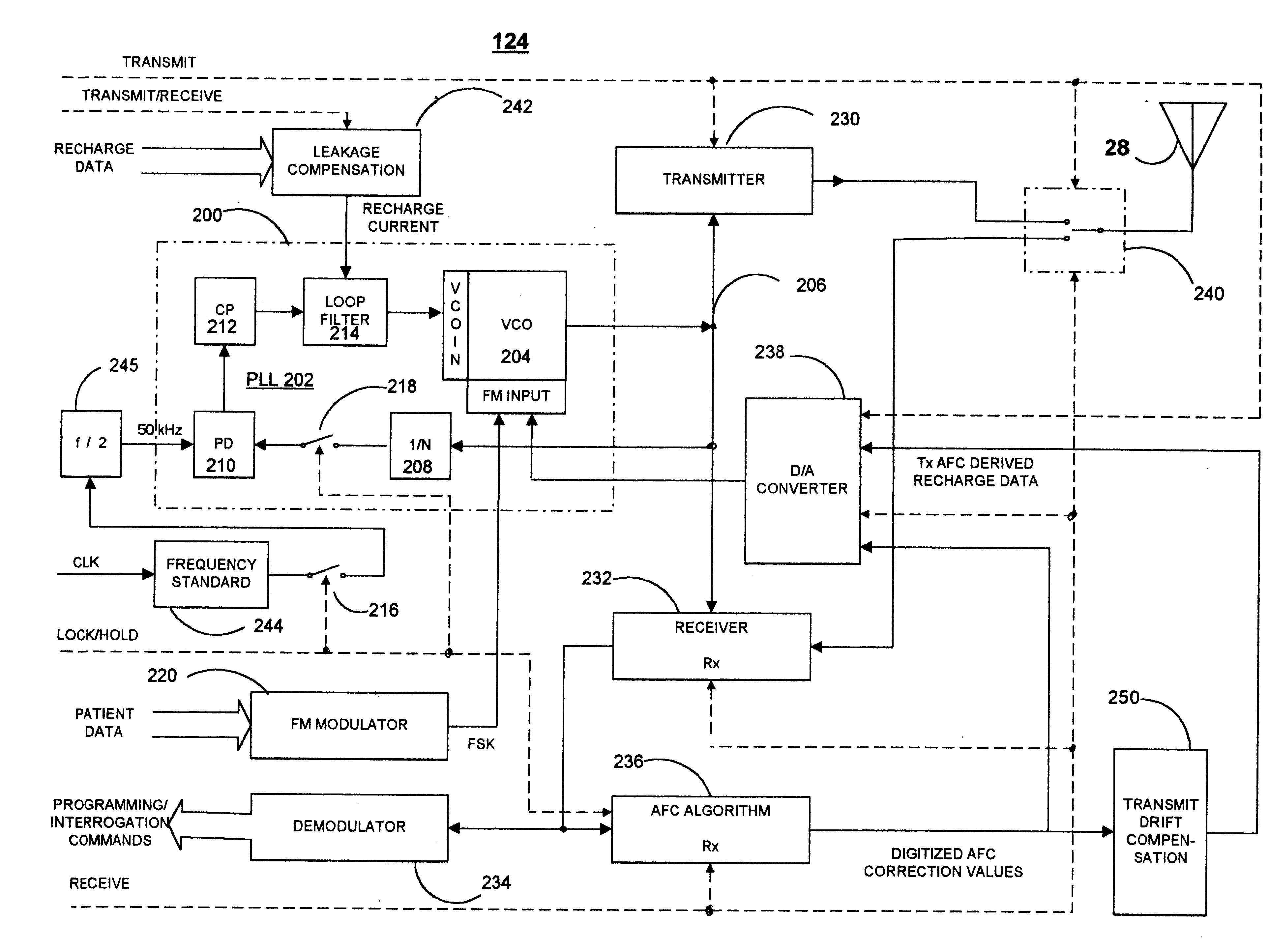

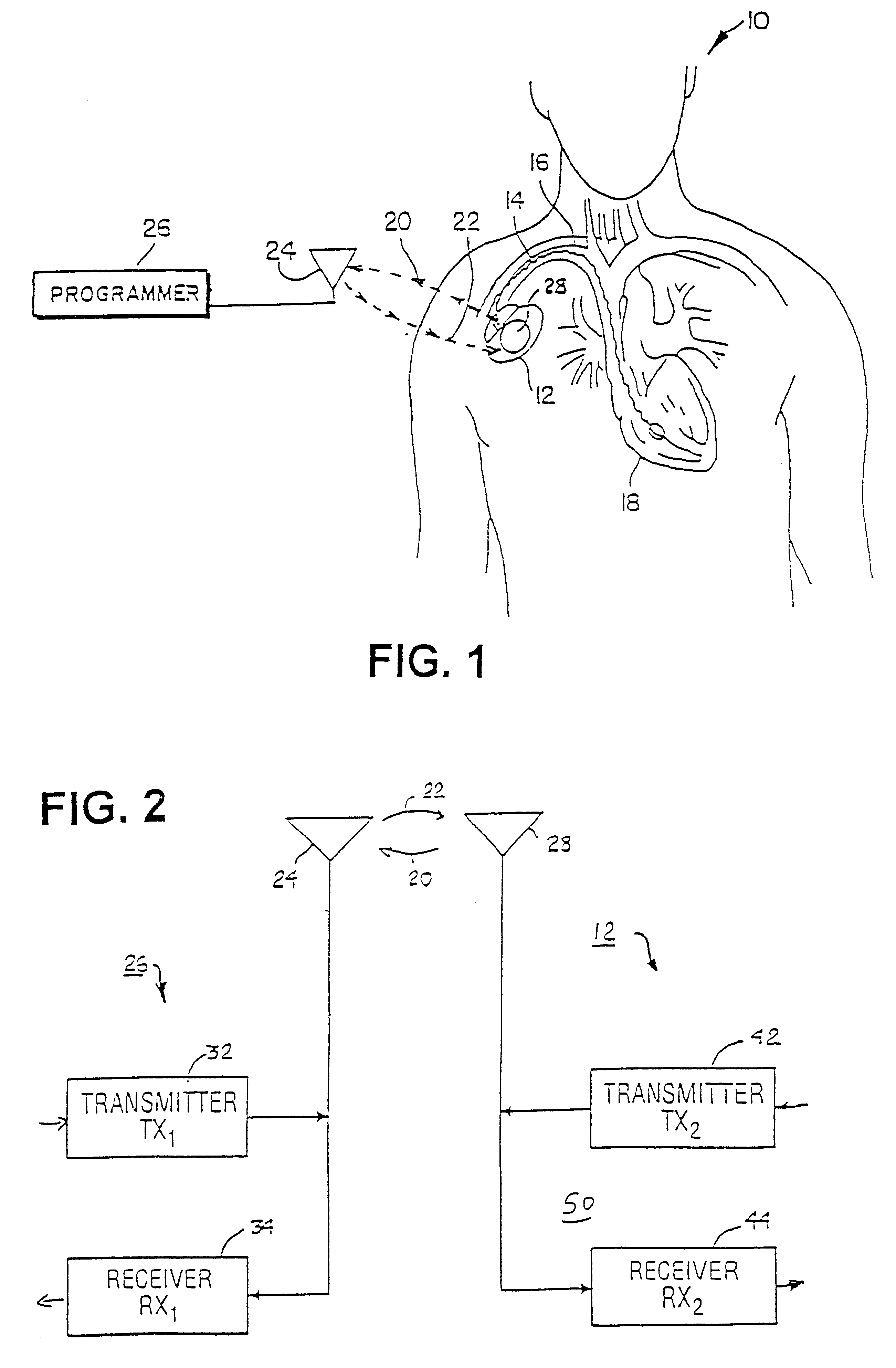

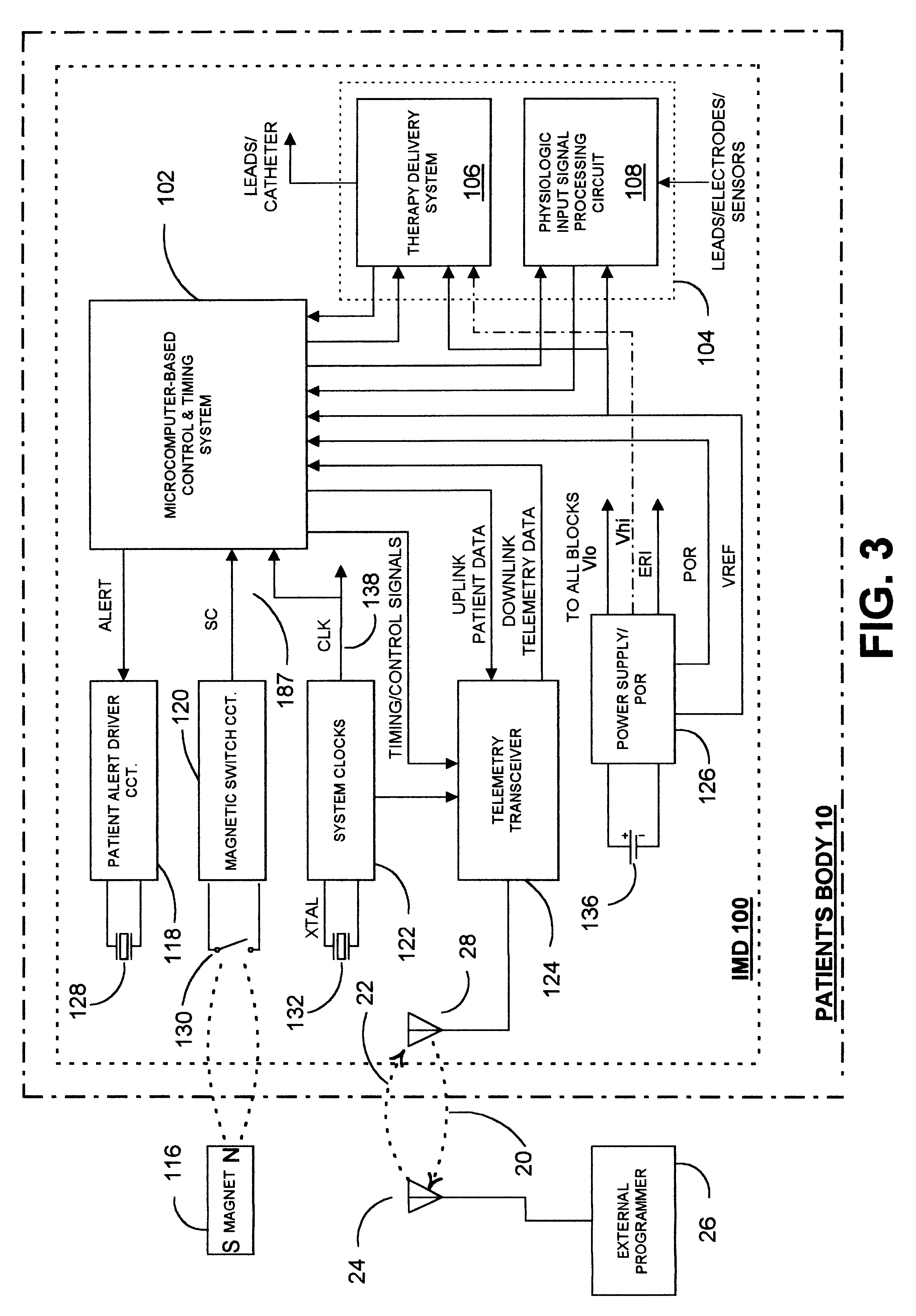

Low energy consumption RF telemetry control for an implantable medical device

In an implantable medical device, a frequency synthesizer employed in the RF transceiver of the IMD operating system functions in a PLL LOCK mode wherein the VCO frequency is governed by the PLL and an energy saving HOLD mode wherein the PLL is not operational and the VCO generated carrier frequency can drift over time. The PLL circuit is powered up and coupled with a control voltage input and the output of the VCO to develop a frequency control voltage stored by a capacitive loop filter during initial LOCK portions of both uplink and downlink telemetry transmission time periods. A frequency modulation (FM) input of the VCO receives data bit modulation voltages that modulates the carrier frequency during uplink transmission of patient data. During the HOLD portion of a downlink telemetry transmission, an AFC algorithm is enabled and derives a frequency correction value from the difference in frequency of the constant received carrier frequency and the drifting VCO generated carrier frequency, and the frequency correction value is applied to the VCO FM input to compensate for loop filter capacitor discharge of the control voltage causing the drift. The AFC algorithm derived frequency correction value is stored in memory and is also applied during the HOLD portion of an uplink telemetry transmission to the VCO FM input to compensate for loop filter capacitor discharge of the control voltage causing the drift. In addition, a recharge current is applied to the capacitive loop filter.

Owner:MEDTRONIC INC

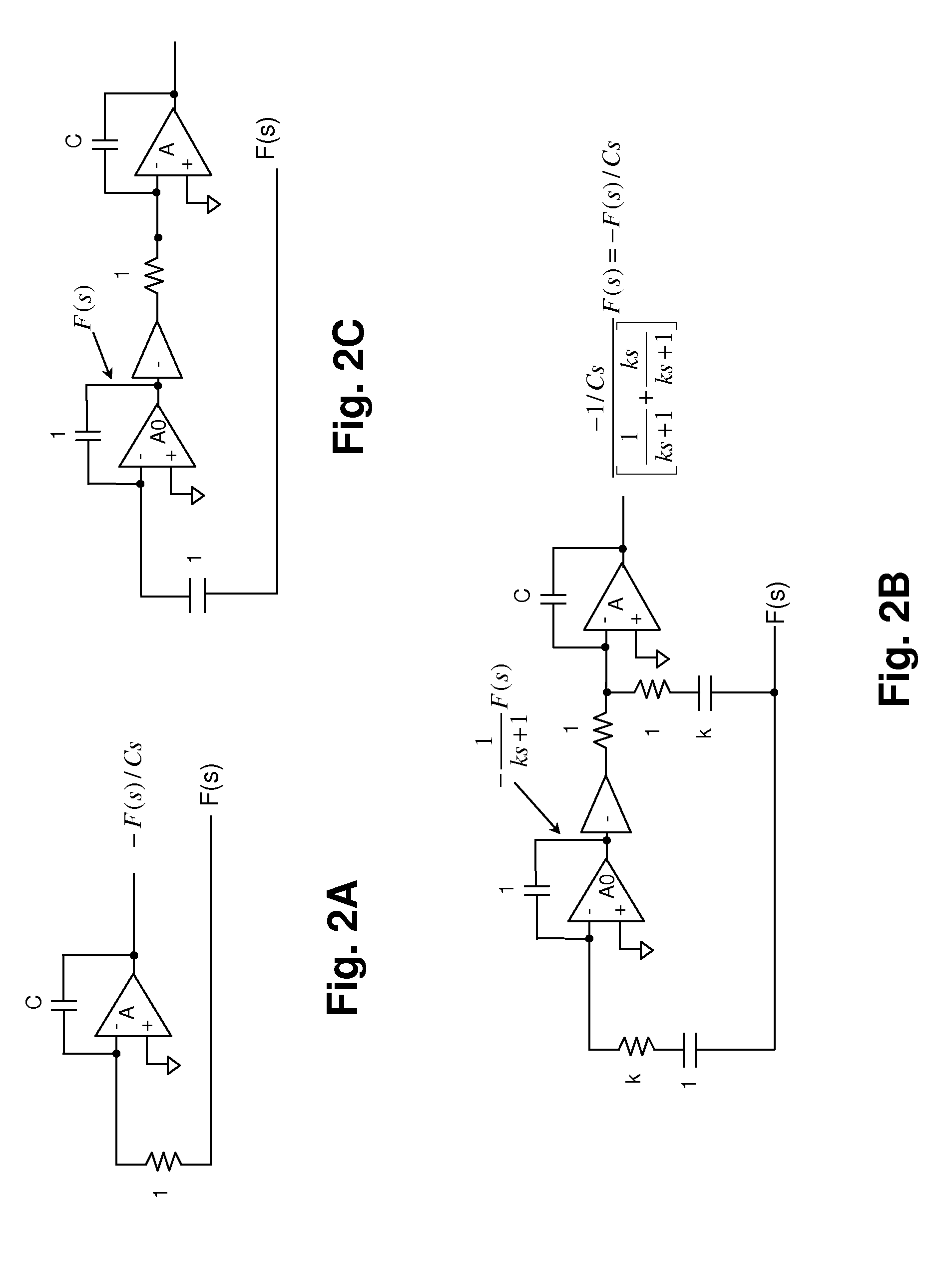

Low-pass filter for a PLL, phase-locked loop and semiconductor integrated circuit

InactiveUS7030688B2Reduce circuit sizeReduce circuit areaPulse automatic controlOscillations generatorsLoop filterBand-pass filter

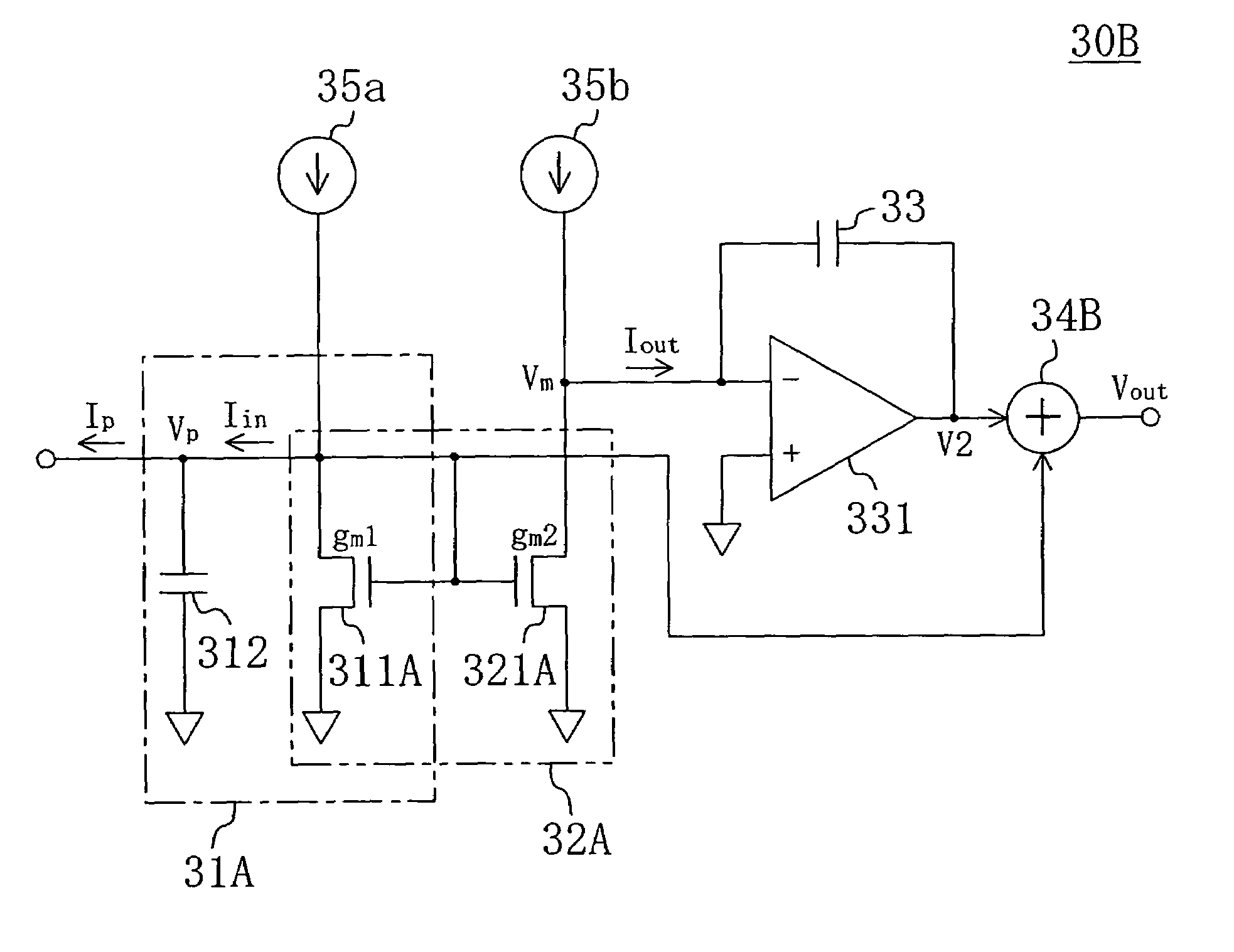

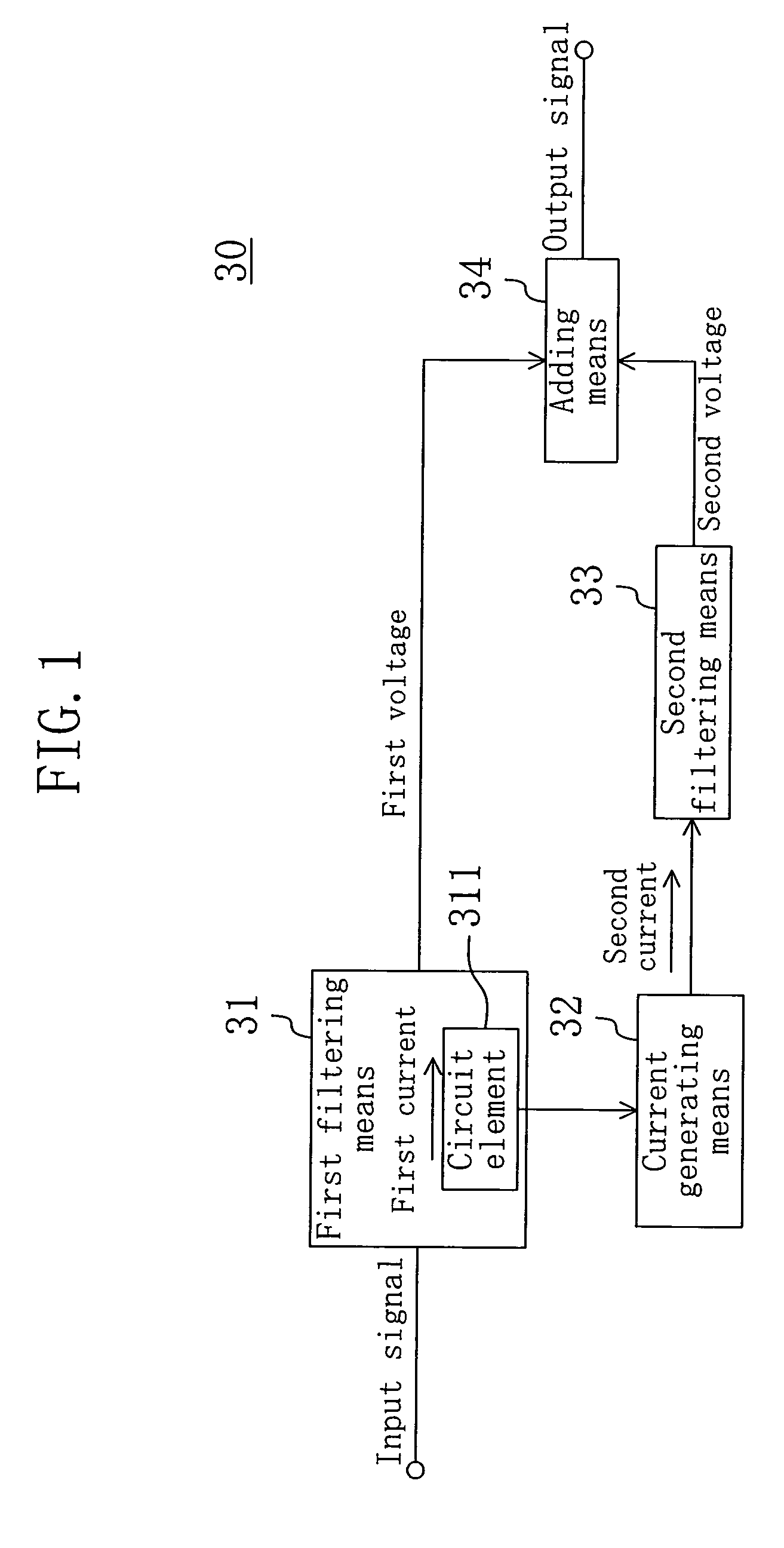

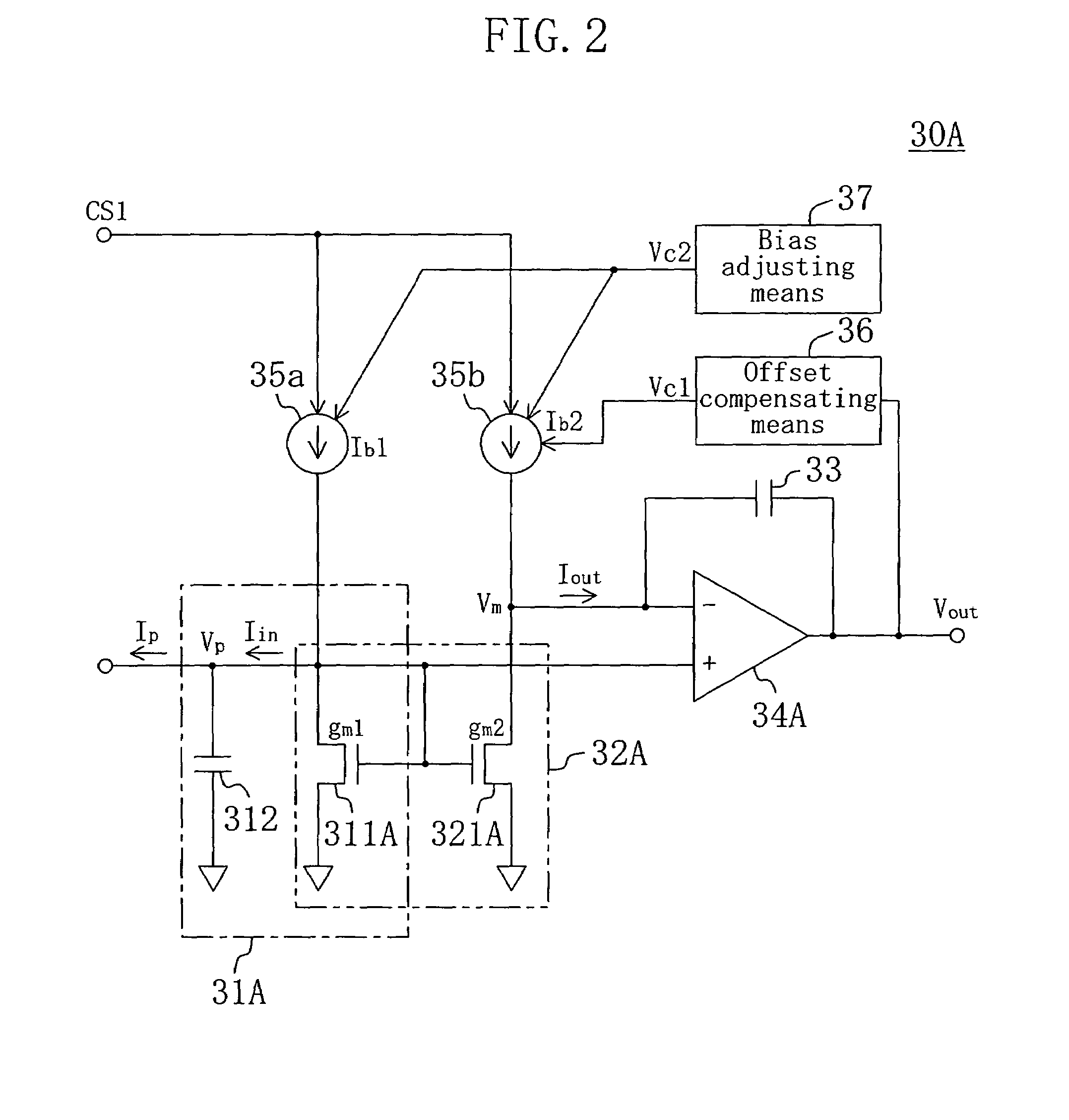

The invention provides a low-pass filter suitably used as a loop filter for a PLL or a DLL that has a filtering characteristic equivalent to that of a conventional one and can be realized in a smaller circuit area. The low-pass filter includes first filtering means (31) for accepting, as an input, an input signal to the low-pass filter and outputting a first voltage; a circuit element (311) included in the first filtering means (31) for allowing a first current to flow in accordance with the first voltage; current generating means (32) for generating a second current at a given rate to the first current; second filtering means (33) for accepting, as an input, the second current and outputting a second voltage; and adding means (34) for adding the first voltage and the second voltage and outputting an output signal of the low-pass filter, in which the second current is set to be smaller than the first current.

Owner:PANASONIC CORP

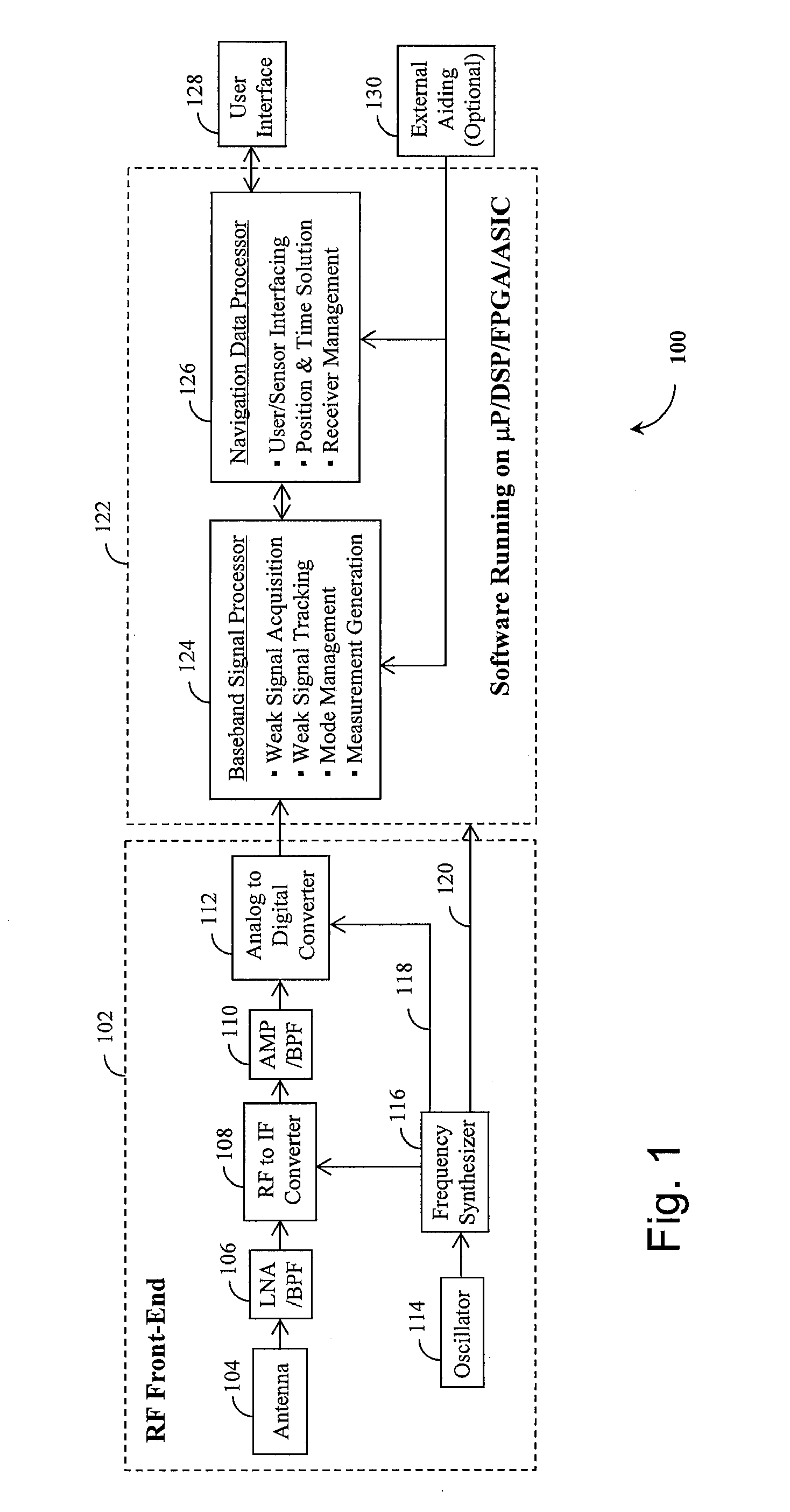

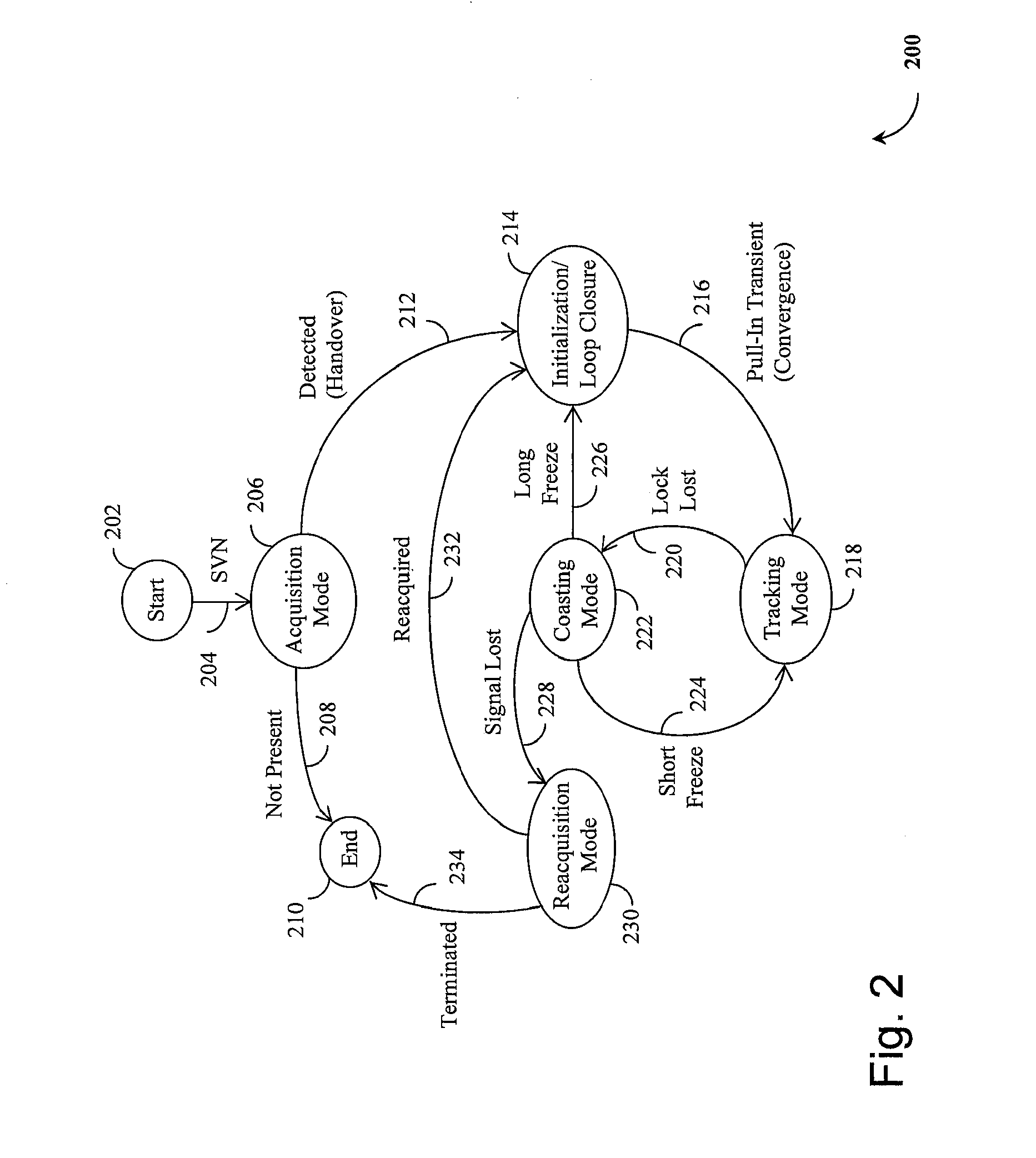

Method and device for tracking weak global navigation satellite system (GNSS) signals

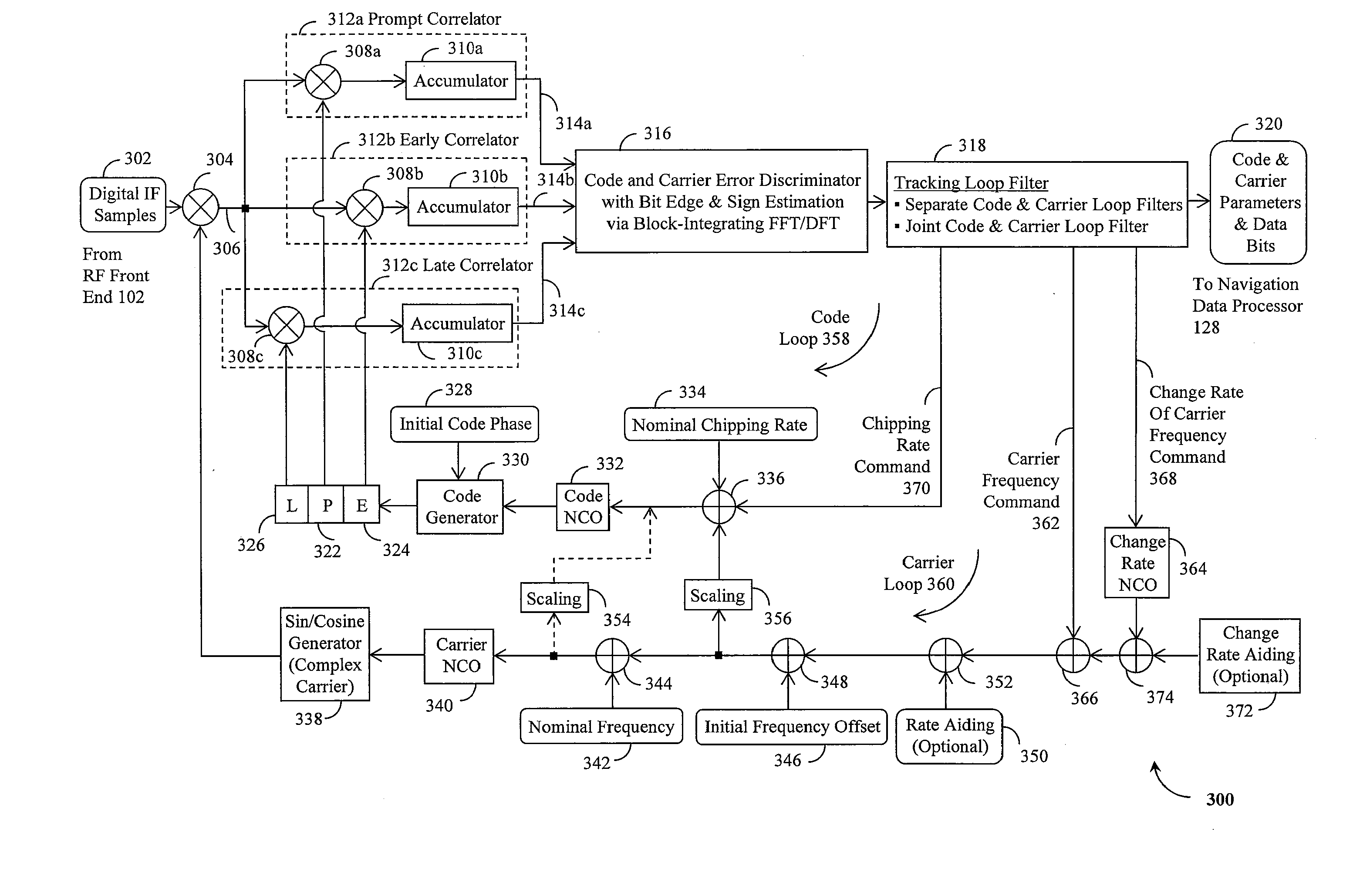

A Global Navigation Satellite System (GNSS) receiver and associated method capable of tracking weak GNSS signals from a plurality of GNSS satellites. In a preferred embodiment, code and carrier tracking loops are initially closed around the code phase, carrier frequency, and data bit edge estimates handed over from an acquisition mode. In subsequent tracking, early, prompt, and late copies of the code replica are correlated with the incoming signal. The prompt correlations are coherently integrated over an extended updating interval for data bit edge and sign estimation as well as for carrier phase and frequency error discrimination whereas the early and late correlations are used for code error discrimination. Code delay and carrier phase and frequency errors are used to update the code and carrier tracking loop filters. Together with data bits, they form observables of a GNSS signal's time and frequency parameters for timing and position fixing.

Owner:CSR TECH HLDG

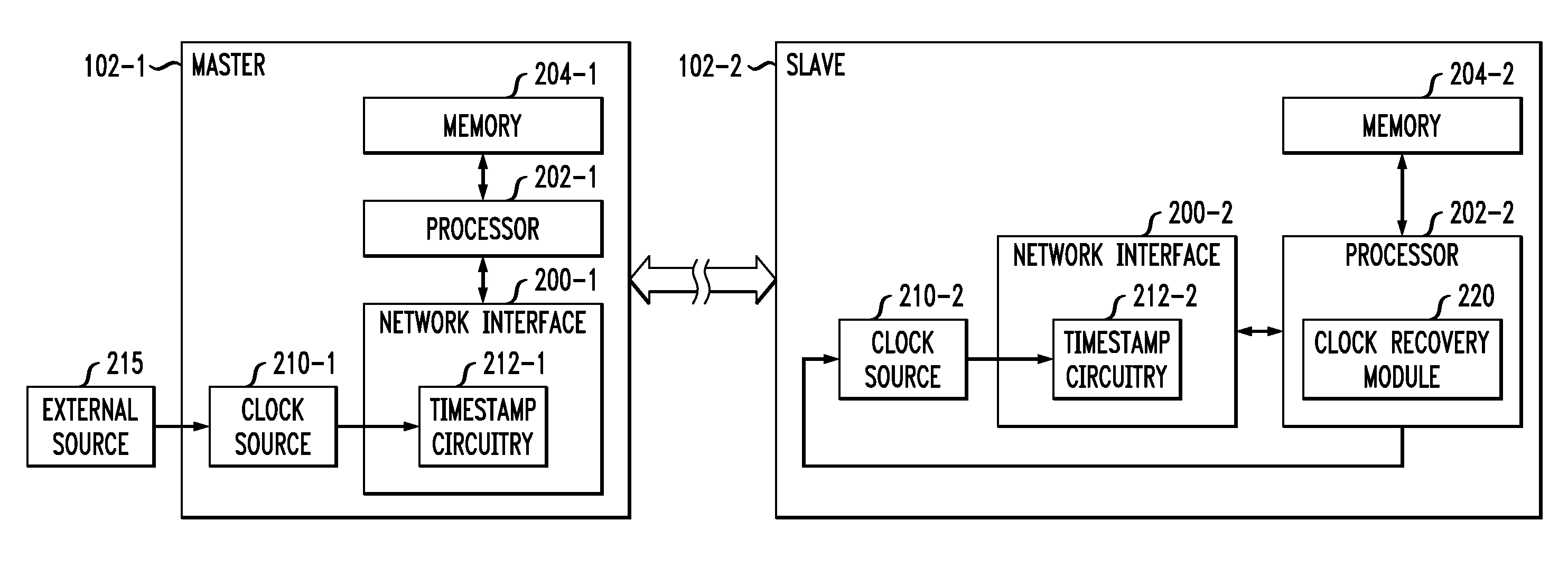

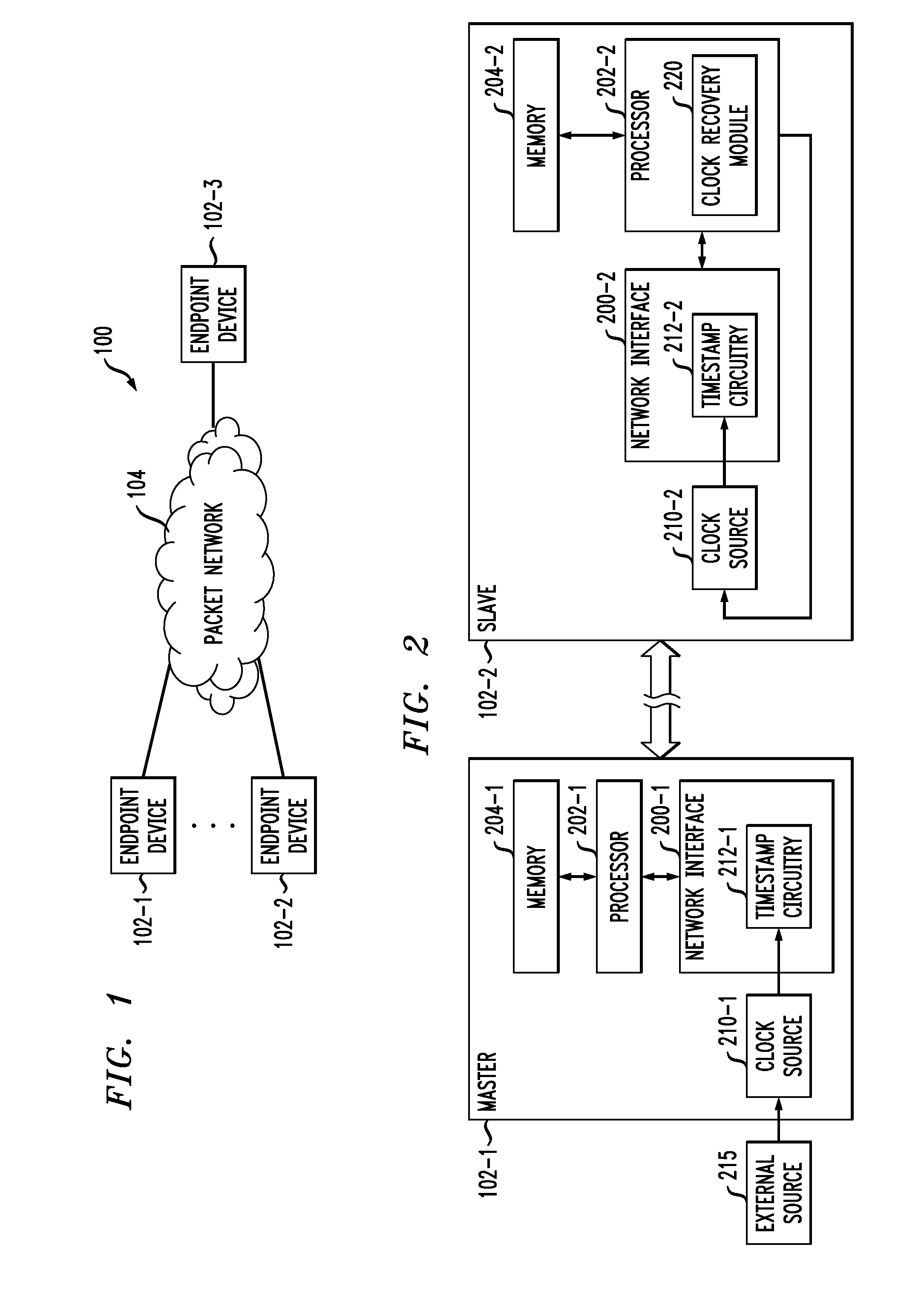

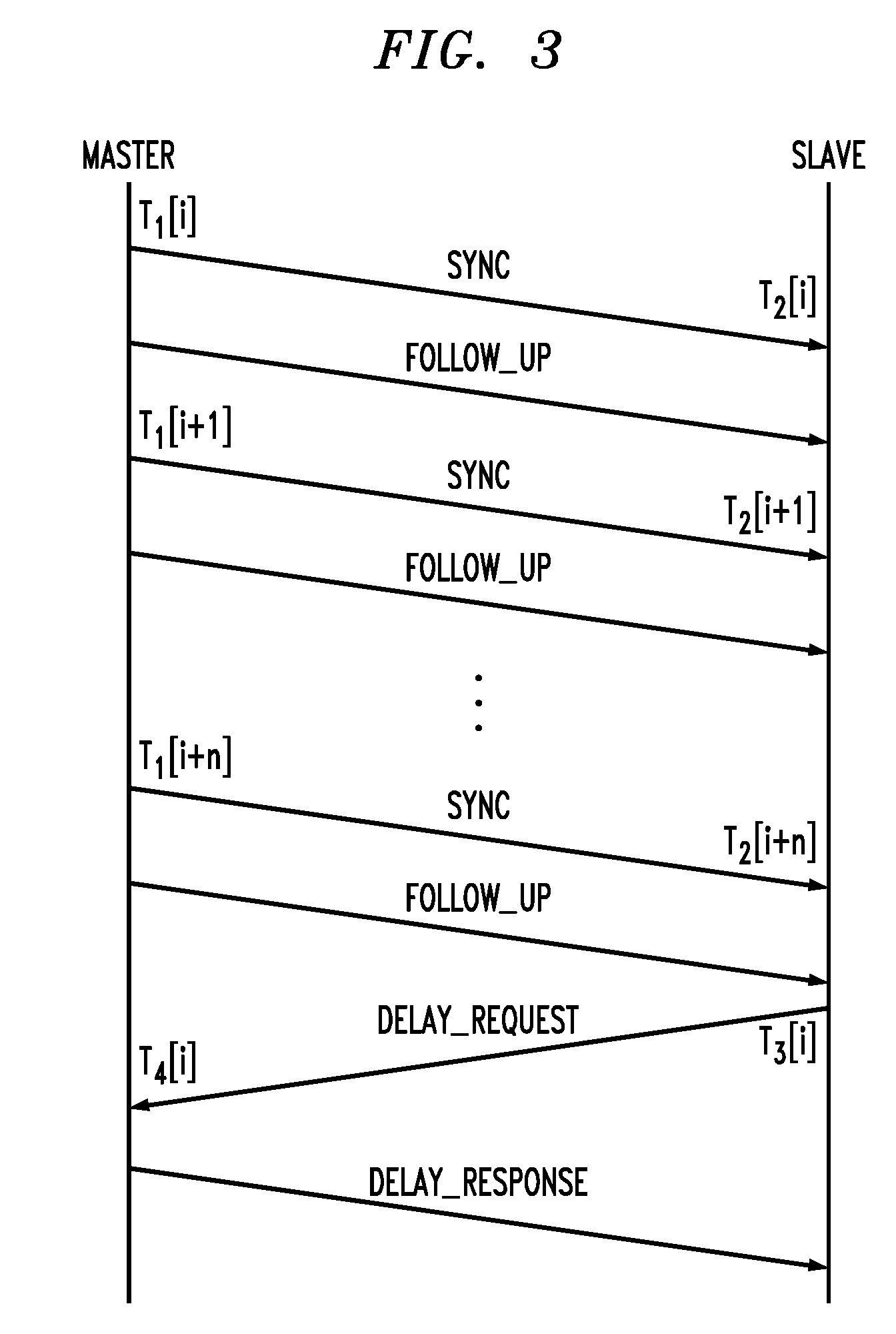

Method, Apparatus and System for Frequency Synchronization Between Devices Communicating over a Packet Network

InactiveUS20100158051A1Simple technologyImprove performancePulse automatic controlTime-division multiplexLoop filterTimestamp

An endpoint or other communication device of a communication system includes a clock recovery module. The communication device is operative as a slave device relative to another communication device that is operative as a master device. The clock recovery module comprises a clock recovery loop configured to control a slave clock frequency of the slave device so as to synchronize the slave clock frequency with a master clock frequency of the master device. The clock recovery loop utilizes a frequency error estimator implemented as a maximum-likelihood estimator with slope fitting based on a sequence of arrival timestamps, and a loop filter implemented as a series combination of an adaptive-bandwidth filter and a proportional-integral controller. The clock recovery module may further comprise a discontinuity detector configured to detect a discontinuity in delays of respective timing messages, and a loop controller operative to place the clock recovery loop in a particular state responsive to detection of the discontinuity.

Owner:PIECE FUTURE PTE LTD

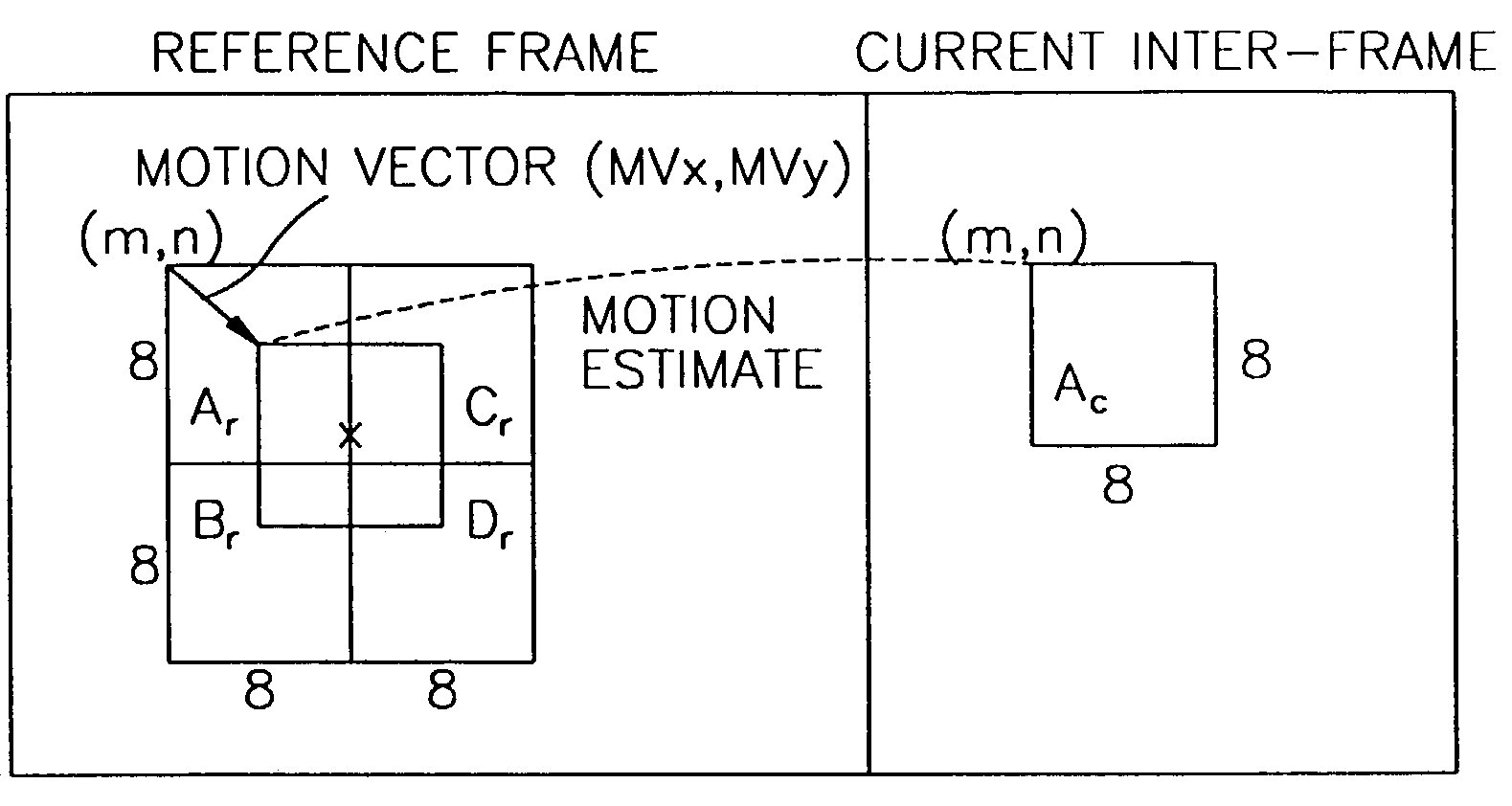

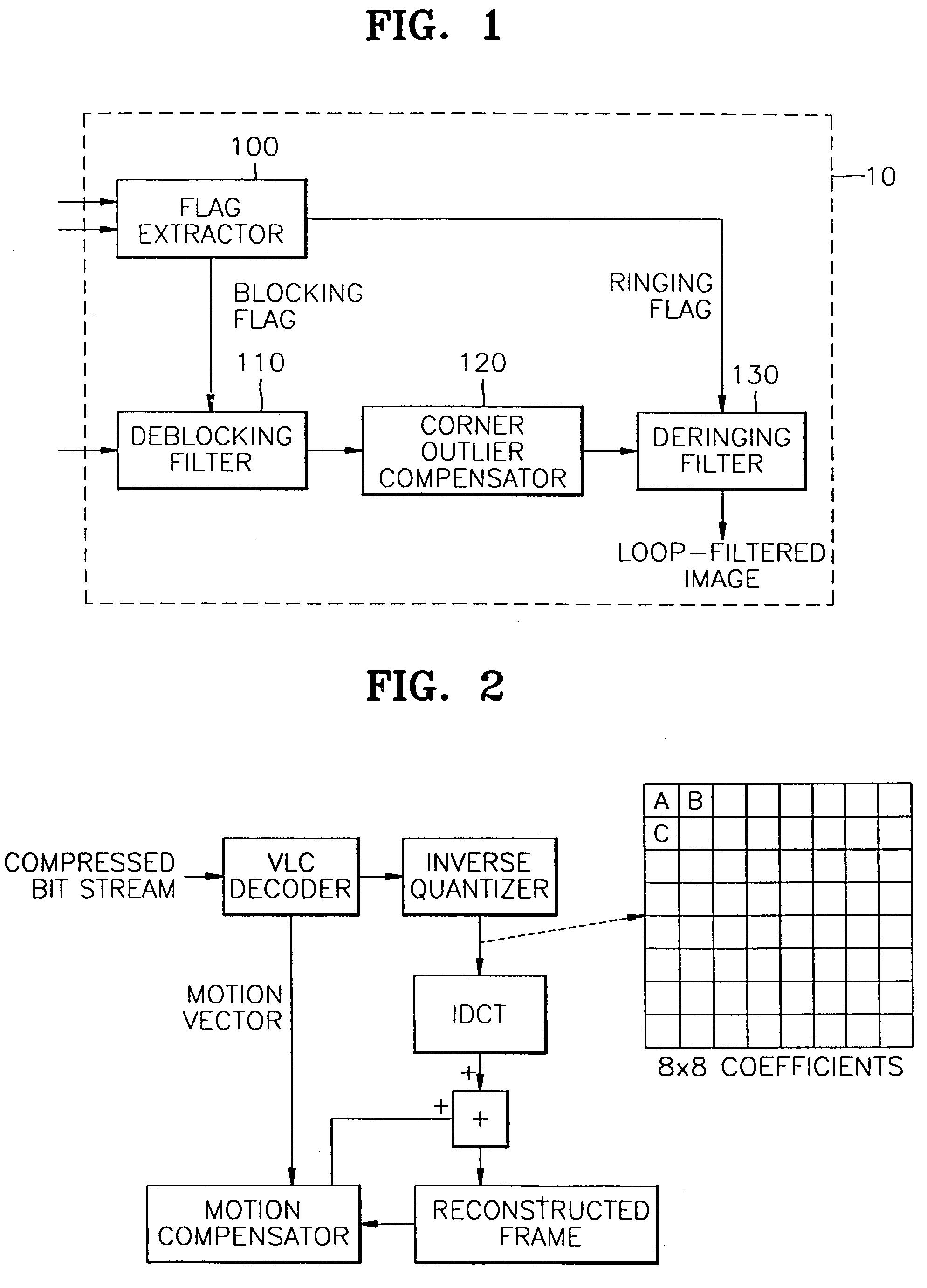

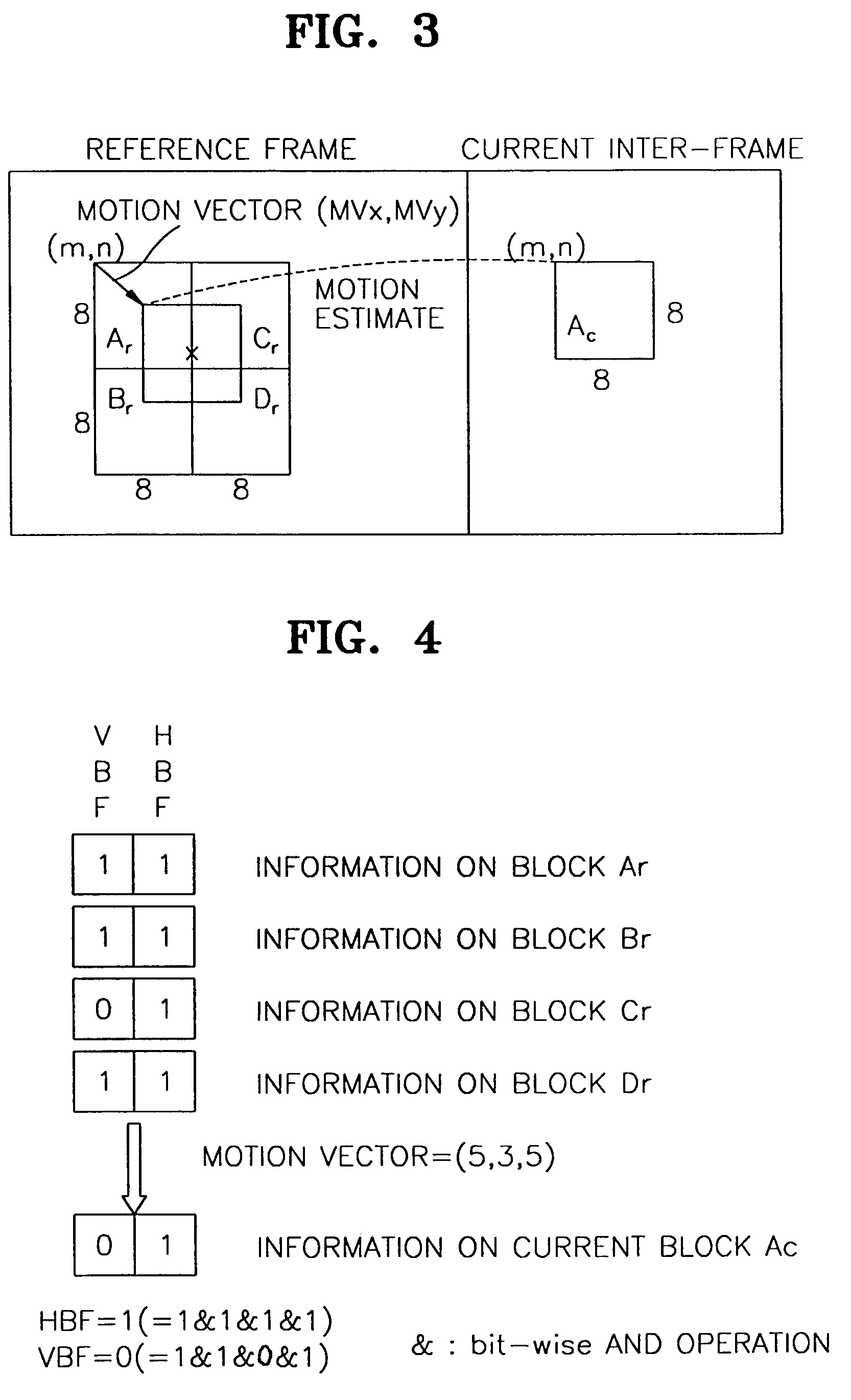

Loop-filtering method for image data and apparatus therefor

InactiveUS7251276B2Reducing quantization effectReduce impactTelevision system detailsImage enhancementLoop filterAdaptive filter

A loop-filtering method for reducing quantization effect generated when an image data is encoded and decoded, and an apparatus therefor. The loop-filtering method includes the steps of extracting a flag indicating whether the image data requires loop-filtering using the distribution of inverse quantized coefficients (IQCs) of an inverse quantized image data and a motion vector indicating the difference between the previous frame and the current frame. The image data corresponding to the flag is then filtered by a predetermined method if the extracted flag indicates a need for the loop-filtering. Using the flags and an adaptive filter reduces the quantization effect and is useful to reduce the amount of computation required for the filtering. Also, the filtering can be performed through parallel processing without multiplication and division, so that the complexity of hardware can be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD +1

De-blocking filter processing apparatus and de-blocking filter processing method

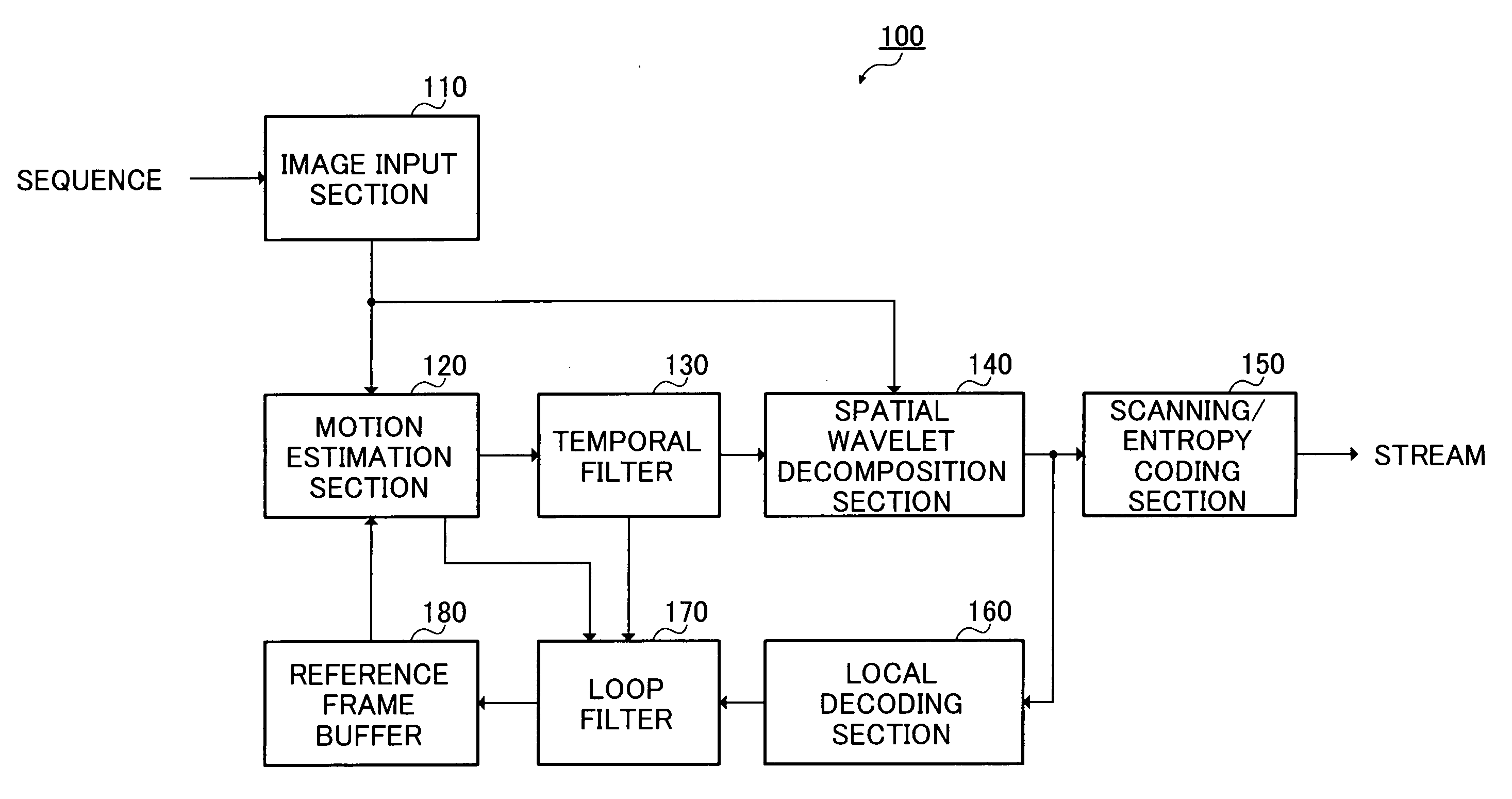

InactiveUS20050078750A1Improve picture qualityColor television with pulse code modulationColor television with bandwidth reductionComputational scienceLoop filter

A de-blocking filter processing apparatus that achieves high picture quality without consuming processing apparatus power unnecessarily. A loop filter 170 used as a de-blocking filter processing apparatus first acquires a variable-size motion estimation block in a frame for which motion estimation processing is performed. Then, de-blocking filter processing is applied adaptively to a frame for which motion estimation processing is performed, in accordance with the acquired motion estimation block. Application of de-blocking filter processing is executed only at a boundary between a particular motion estimation block and a motion estimation block adjacent to that motion estimation block in a frame for which motion estimation processing is performed.

Owner:PANASONIC CORP

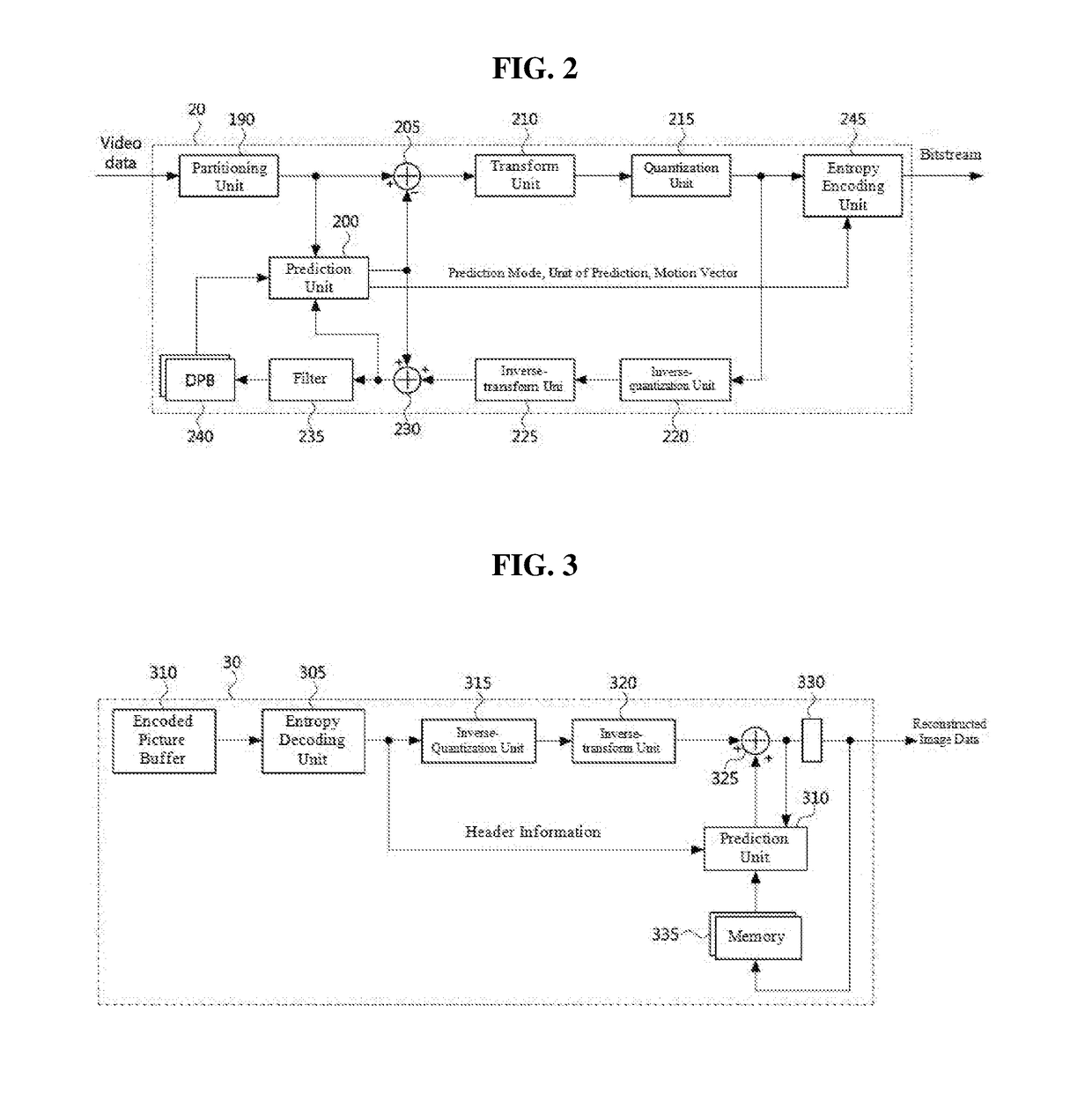

Apparatus and method for in-loop filtering of image data and apparatus for encoding/decoding image data using the same

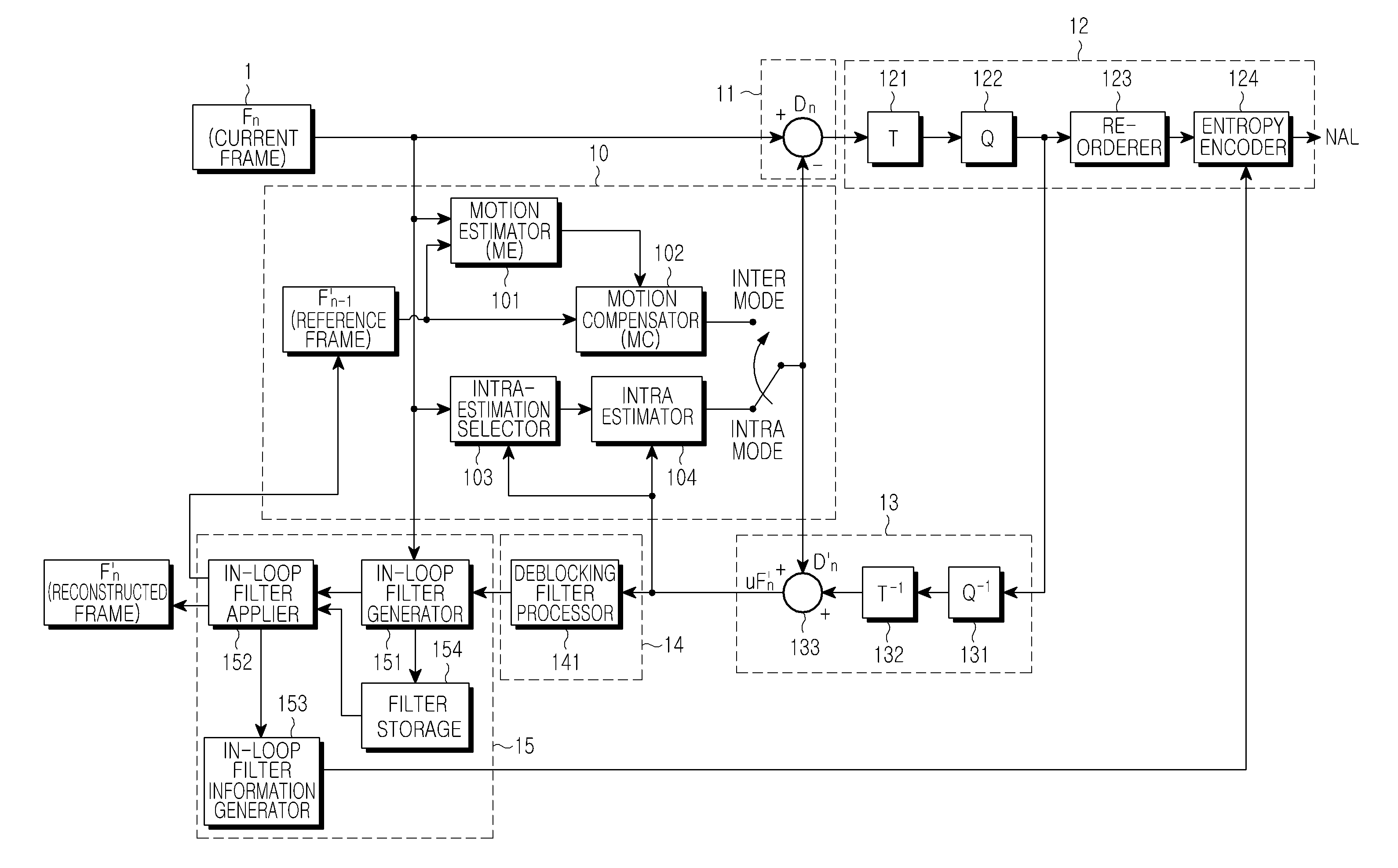

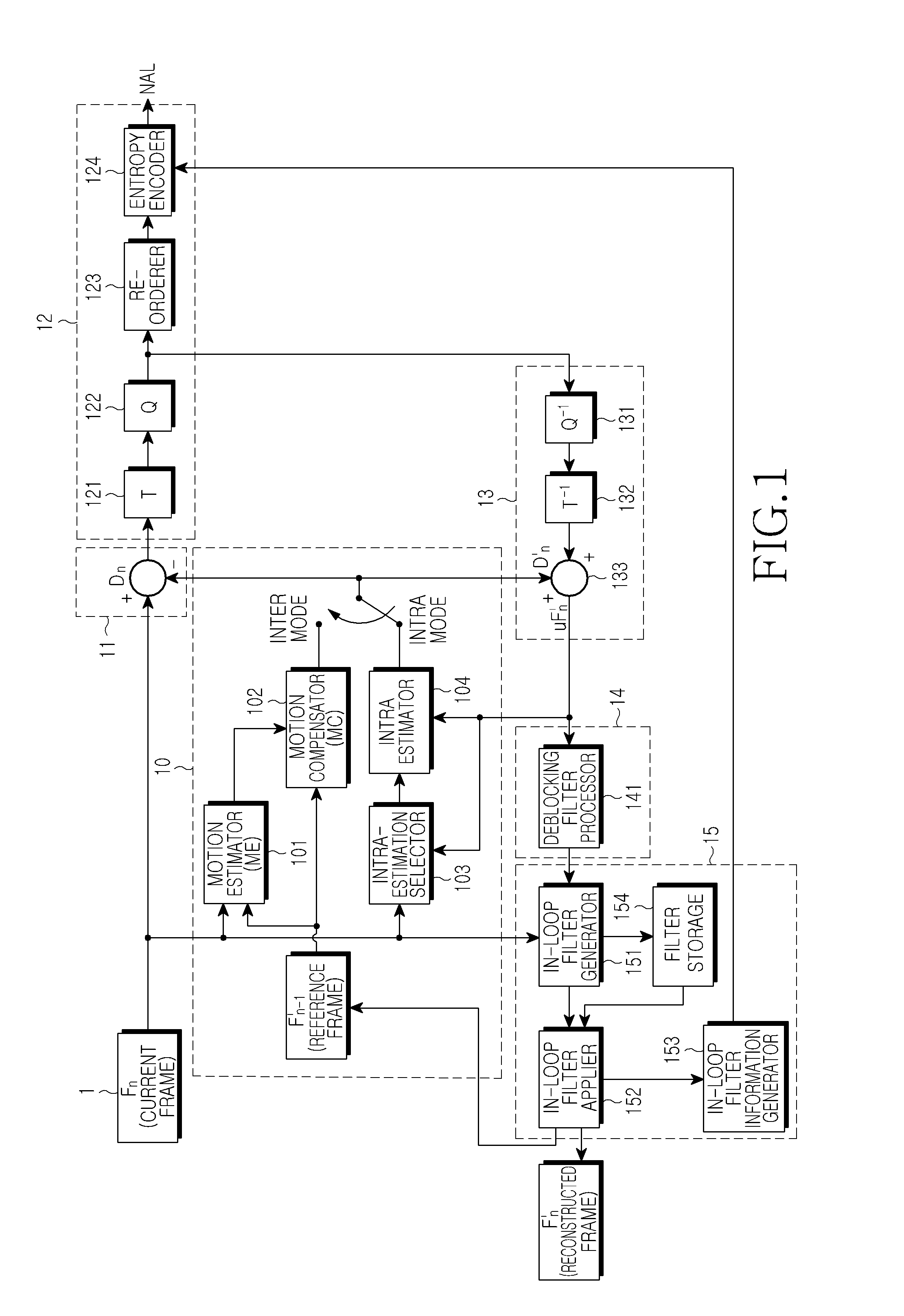

InactiveUS20100329361A1Eliminate errorsColor television with pulse code modulationColor television with bandwidth reductionComputational scienceLoop filter

An in-loop filtering apparatus for eliminating an error of deblocking-filtered image data in an encoder of image data, the apparatus including: an in-loop filter generator which generates in-loop filters using different filter coefficients for a block boundary and a block inside of the deblocking-filtered image; an in-loop filter applier which performs selective filtering on at least one of the block boundary and the block inside using the generated in-loop filters; and an in-loop filter information generator which generates in-loop filter information including at least one of coefficients of the generated in-loop filters, information indicating an area to which in-loop filtering is applied between the block boundary and the block inside, a size of a block to which in-loop filtering is applied, and a flag indicating whether to use an in-loop filter generated for a current frame or an in-loop filter generated for a previous frame.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Method for encoding and decoding image using adaptive deblocking filtering, and apparatus therefor

ActiveUS20180176601A1Improve performanceHigh imaging performanceDigital video signal modificationLoop filterPattern recognition

Disclosed is an encoding / decoding method and apparatus related to adaptive deblocking filtering. There is provided an image decoding method performing adaptive filtering in inter-prediction, the method including: reconstructing, from a bitstream, an image signal including a reference block on which block matching is performed in inter-prediction of a current block to be encoded; obtaining, from the bitstream, a flag indicating whether the reference block exists within a current picture where the current block is positioned; reconstructing the current block by using the reference block; adaptively applying an in-loop filter for the reconstructed current block based on the obtained flag; and storing the current block to which the in-loop filter is or is not applied in a decoded picture buffer (DPB).

Owner:DOLBY LAB LICENSING CORP

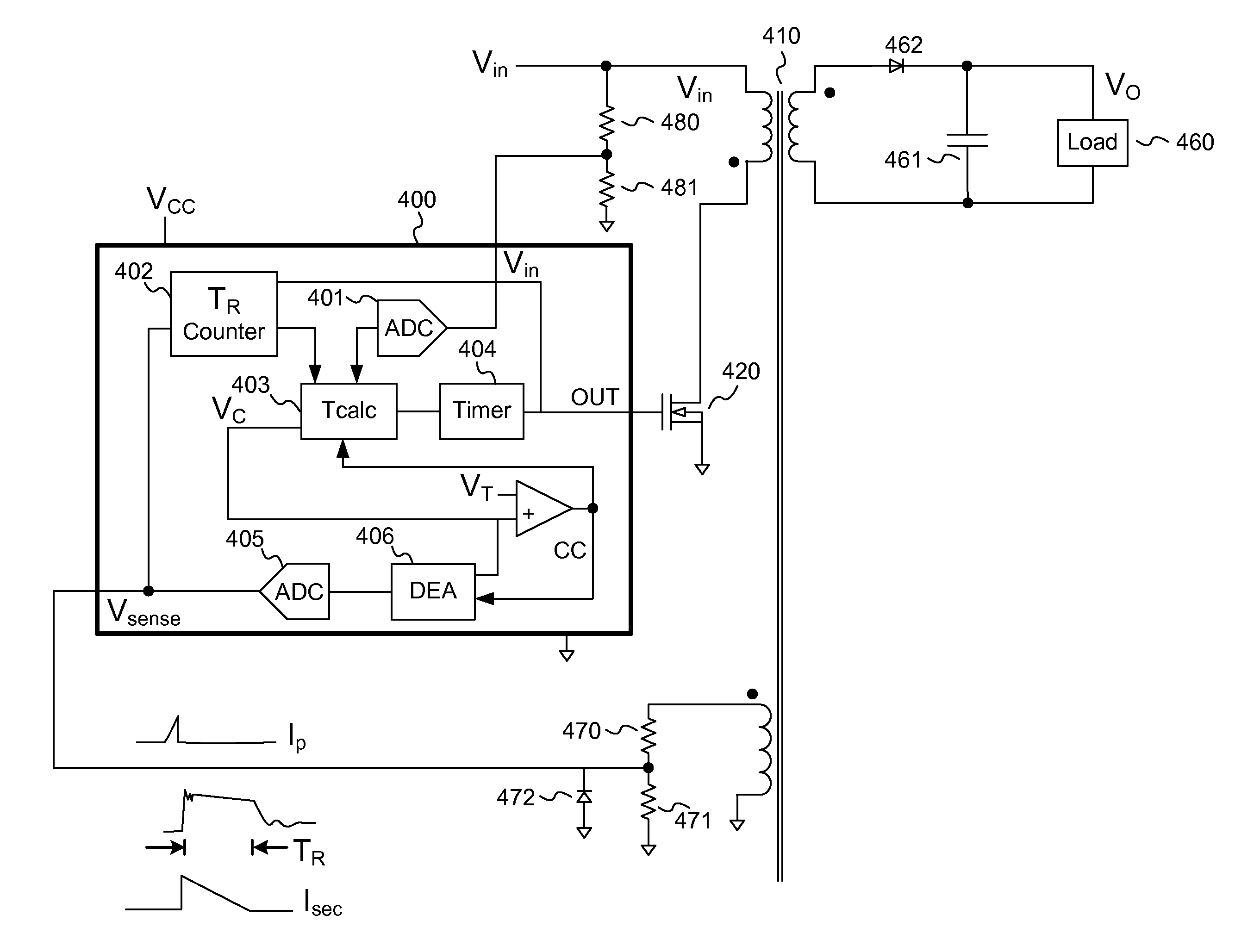

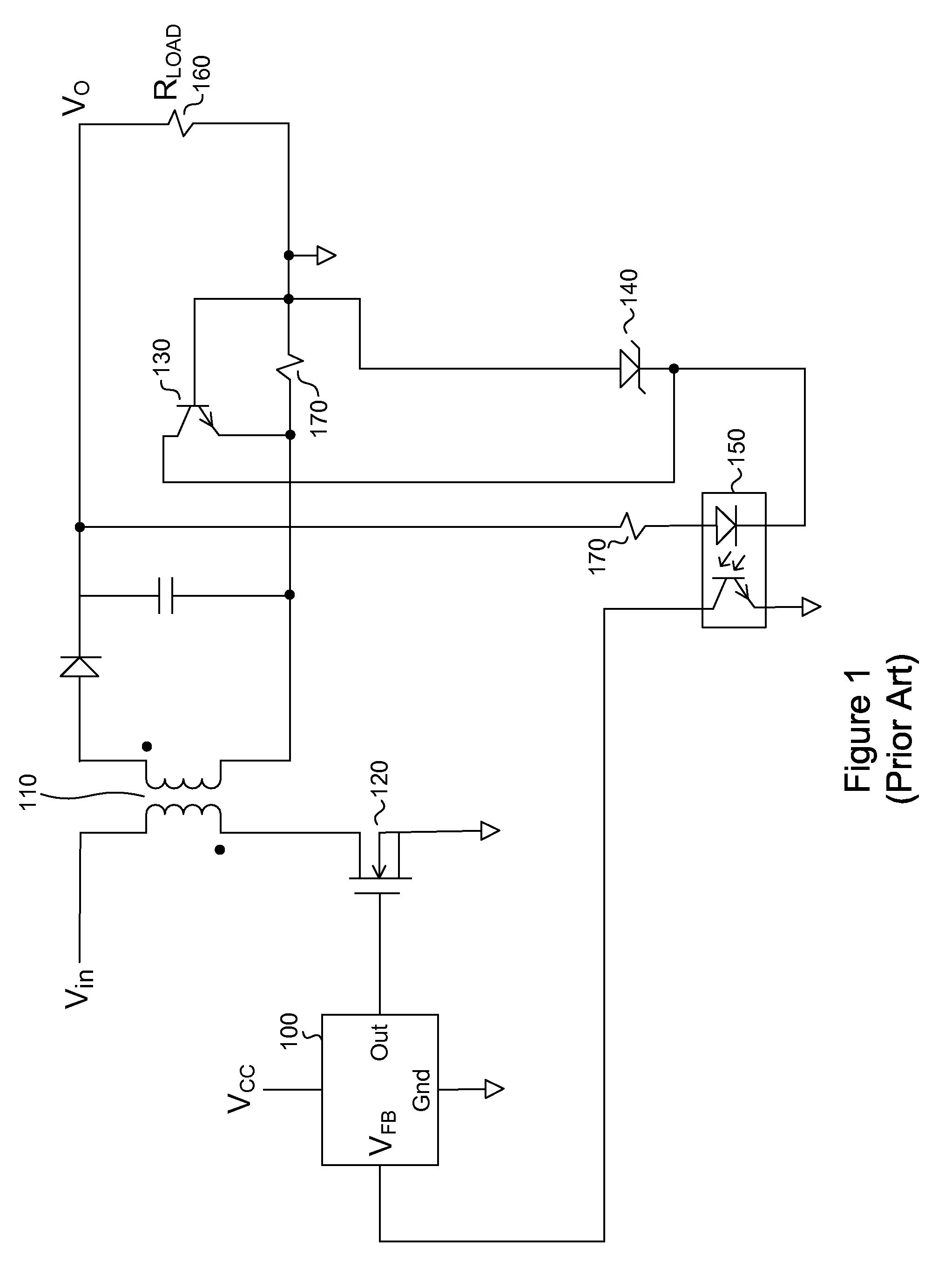

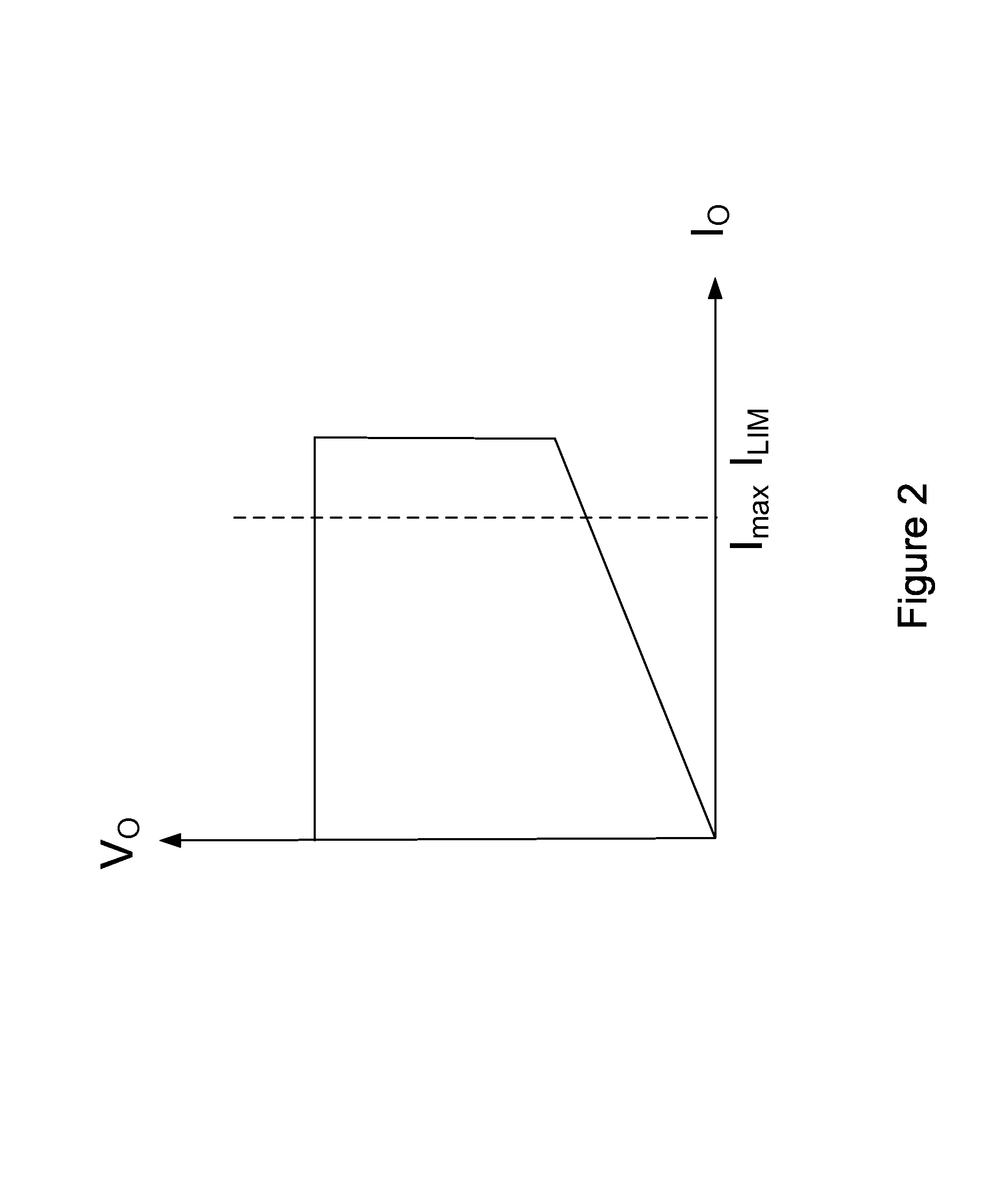

On-time control for constant current mode in a flyback power supply

ActiveUS7505287B1Easy to implementDc-dc conversionElectric variable regulationLoop filterCurrent limiting

The present invention is a system and a method that controls the current limit such that it is maintained within a small range for any acceptable input voltages, e.g., 90 to 264 Volts RMS, causes the output voltage of a PWM controller to drop as the output load increases so as to maintain a constant current output, and does cycle by cycle calculation compensating for the VIN ripple output from the bridge and bulk filter capacitor so that no loop filter is required in the constant current mode.

Owner:DIALOG SEMICONDUCTOR INC

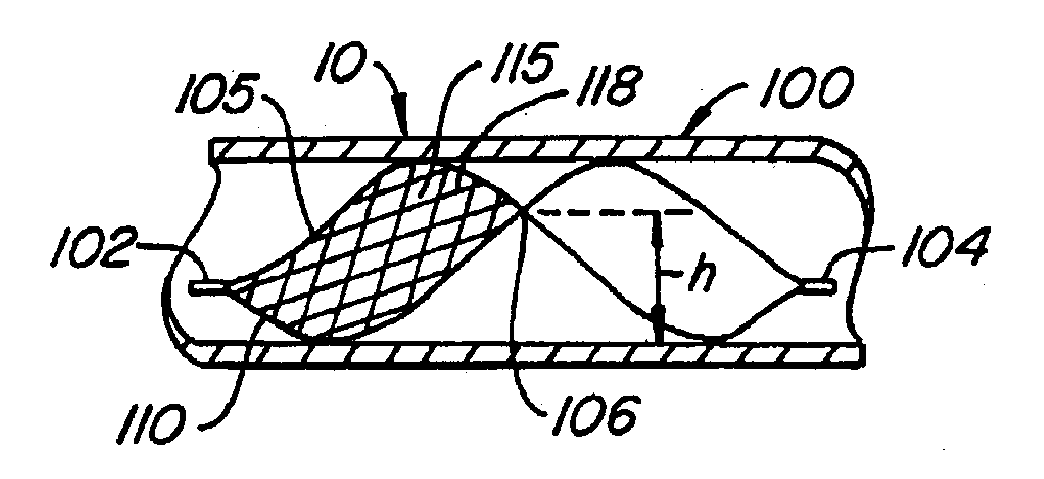

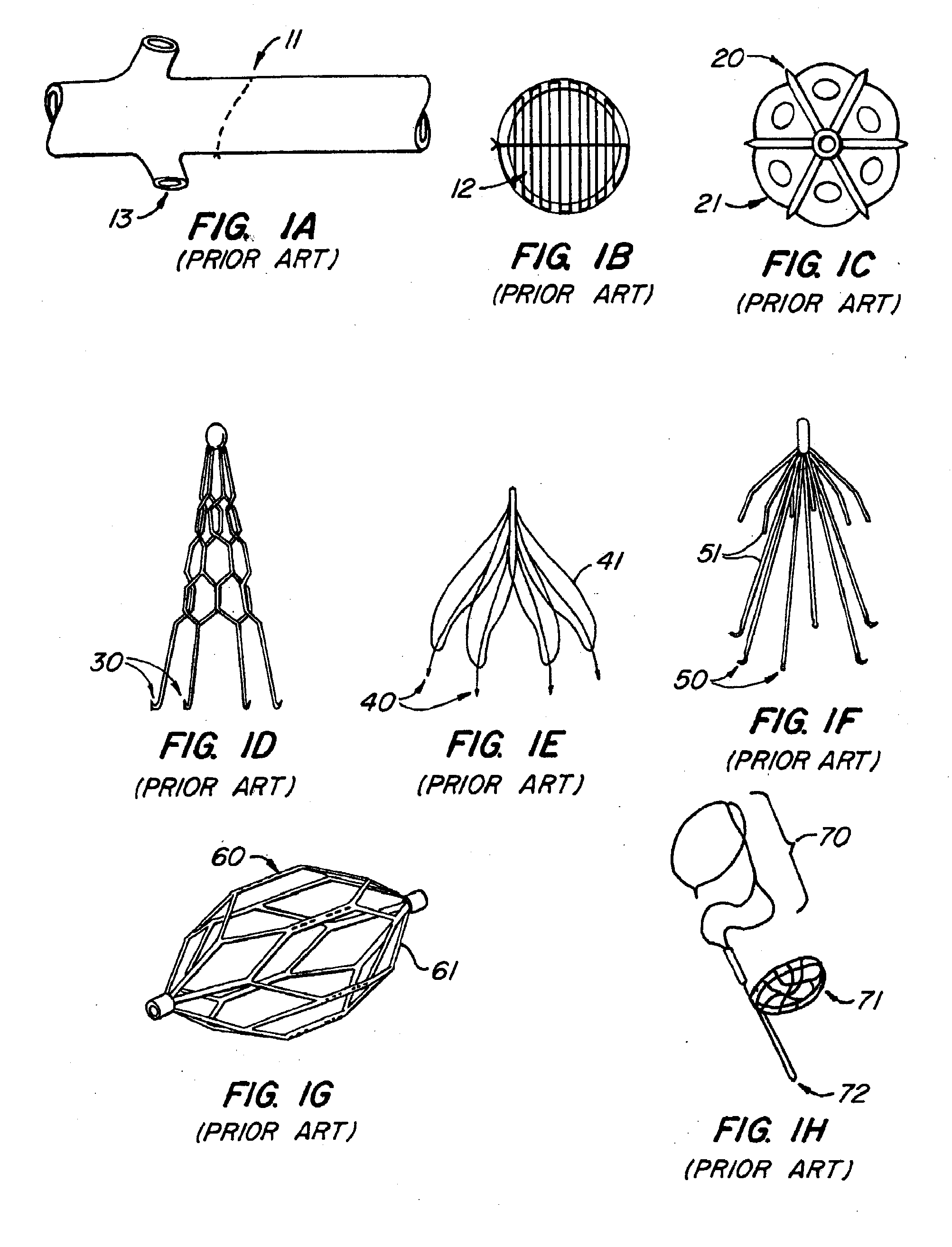

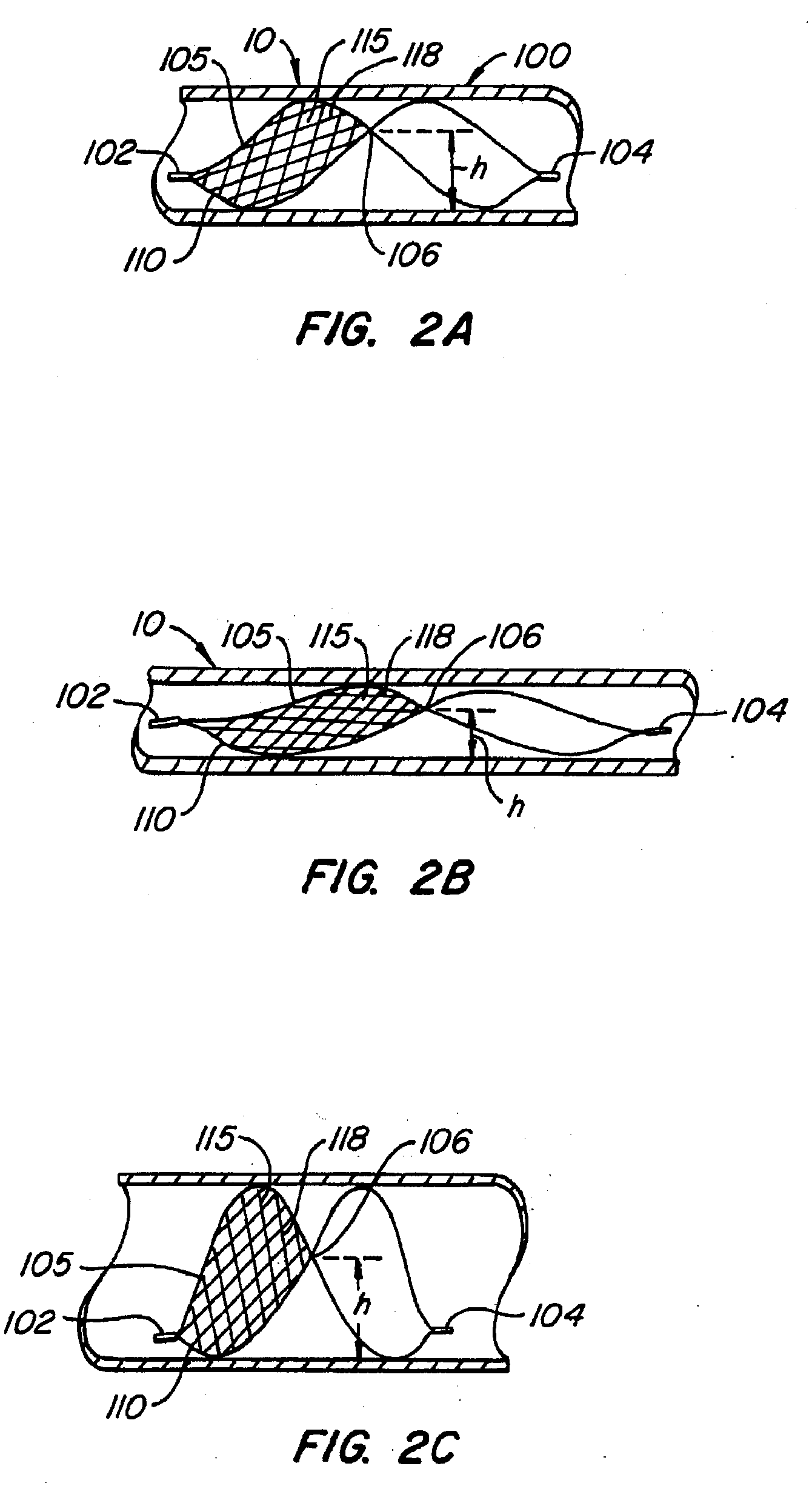

Methods for maintaining a filtering device within a lumen

In one embodiment of the present invention there is provided a method of filtering blood flow in a lumen by positioning an open loop filter support structure within a lumen; maintaining a position of the open loop filter support structure within the lumen using radial force generated by the open loop filter support structure; and filtering blood flow in the lumen using a filter supported by the open loop filter support structure. In one aspect, there is also applying radial force generated by the open loop filter support structure along the axial dimension of the lumen. In another embodiment of the present invention there is provided a method of providing a filter across a lumen flow path by providing a filter support structure having a first end, a crossover section, and a second end; and fixing the position of the filter support structure within the lumen by positioning the first end against a first portion of the lumen and positioning the second end against a second portion of the lumen; and using the filter support structure to provide a filter across the lumen flow path. In one aspect, the ends do not pierce the lumen surface.

Owner:CRUX BIOMEDICAL

Feedback topology delta-sigma modulator having an ac-coupled feedback path

A feedback topology delta-sigma modulator having an AC-coupled feedback path reduces signal level in the loop filter, easing linearity requirements and reduces capacitor size requirements for the filter integration stages. The delta-sigma modulator includes a loop filter having multiple integrator stages, a quantizer, and a feedback network providing at least two feedback paths to corresponding integrators in the loop filter. In one aspect, only one of the feedback paths from the quantizer output is DC coupled, and at least one other of the feedback paths is DC-coupled, which reduces the signal levels in the loop filter integrators. In another aspect, at least one of the feedback paths from the quantizer is AC coupled, providing a similar result. The AC feedback path may be provided through a series-connected resistor and capacitor. The DC feedback path may be provided through a resistor, a switched-capacitor network, or may be a quantizer-controlled current source.

Owner:CIRRUS LOGIC INC

Pair of optically locked semiconductor narrow linewidth external cavity lasers with frequency offset tuning

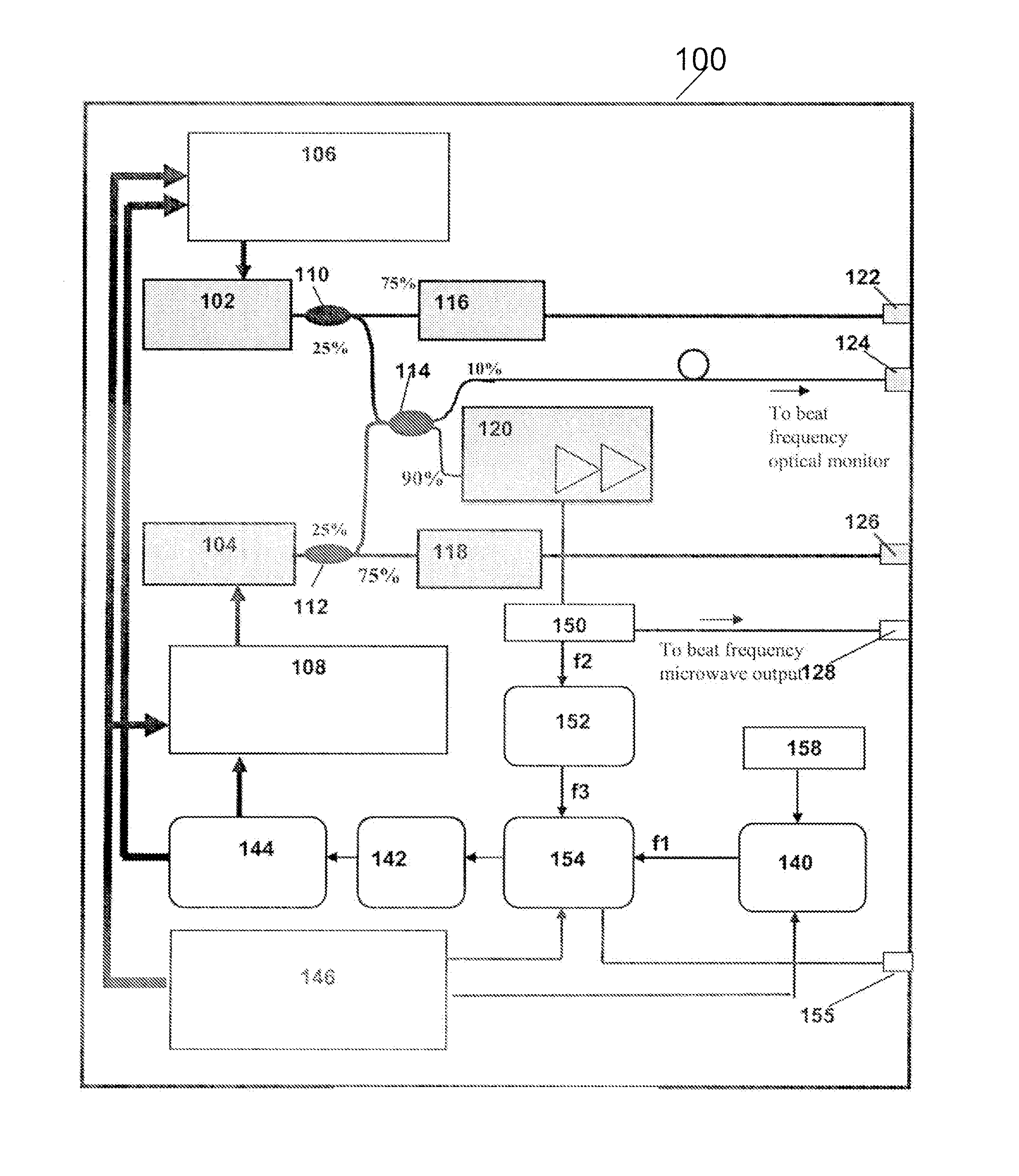

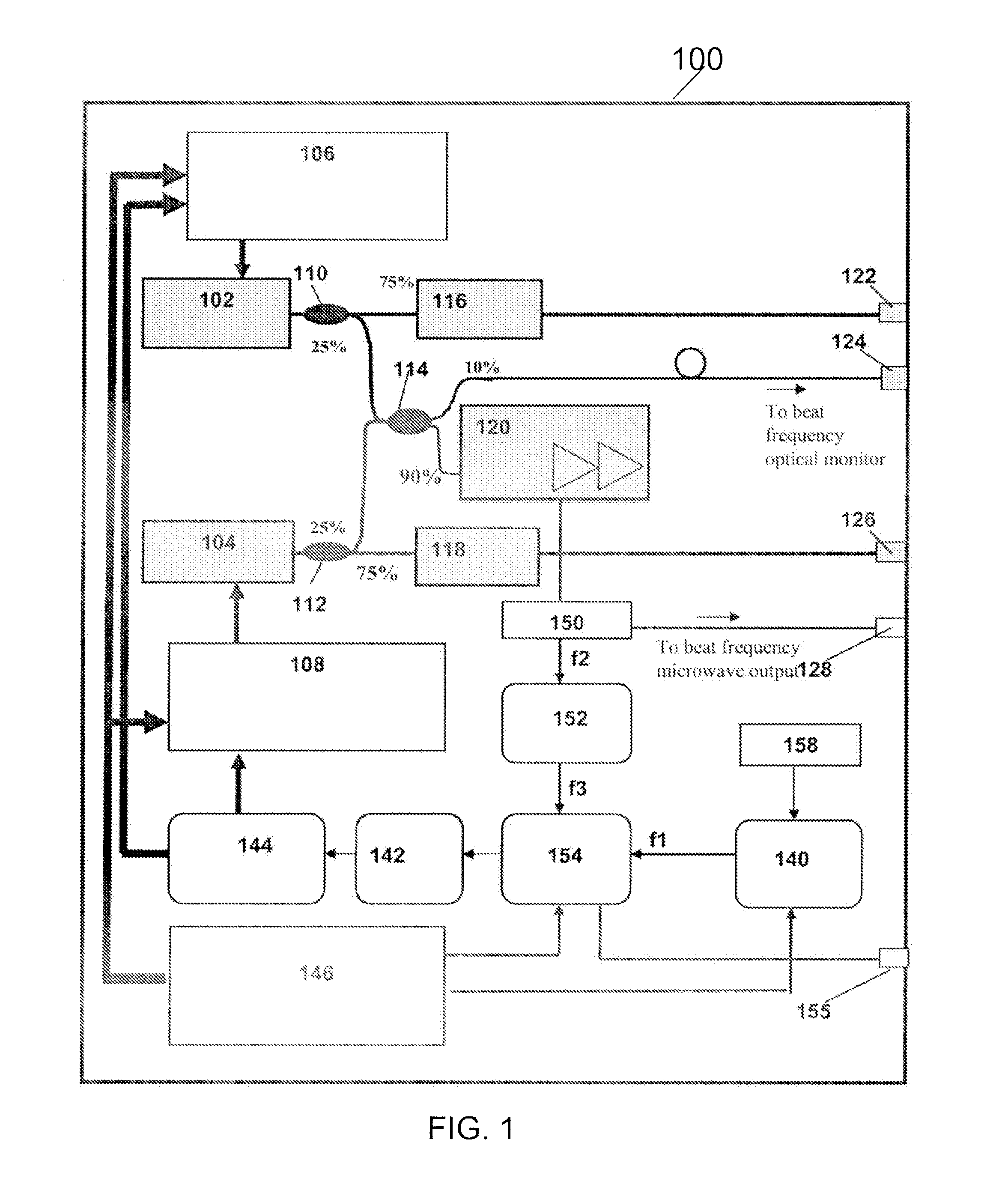

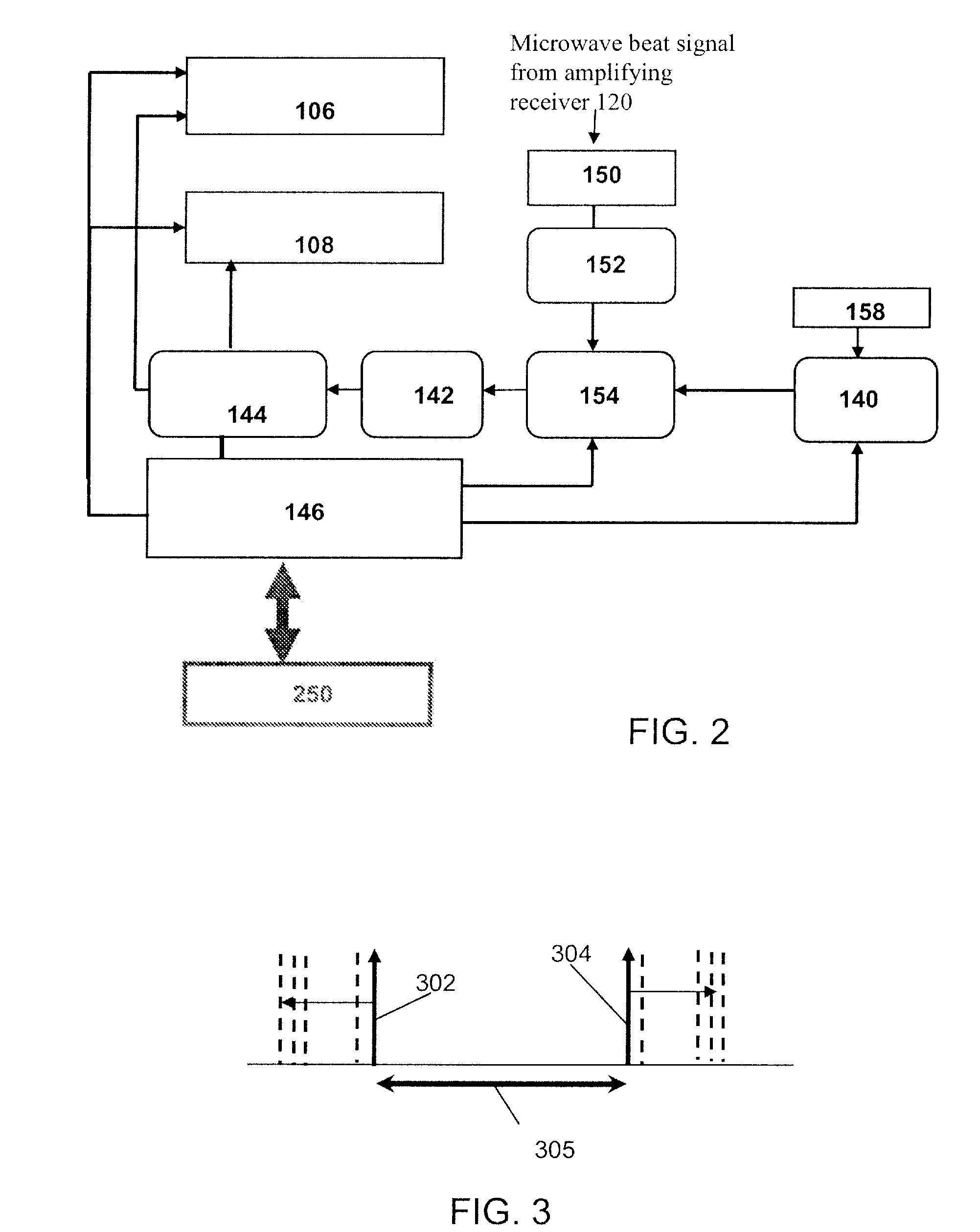

ActiveUS20100303111A1Guaranteed long-term stable operationLess-high frequency noiseLaser detailsLaser optical resonator constructionLoop filterExternal cavity laser

An optical phase lock loop (OPLL) system is disclosed that includes a master external cavity laser (ECL), and a substantially identical slave ECL. The master and slave ECLs are fabricated using a planar semiconductor device with waveguide-integrated planar Bragg gratings (PBG). Both the master and slave ECLs have a narrow linewidth and a low frequency-noise. Each of the ECLs has their own controller-modulator circuits for thermal tuning or electrical tuning via direct modulation. A laser-select-logic (LSL) module receives and processes a filtered phase error signal from a loop filter coupled to an electronic PLL device, and directs the processed phase error signal to one or both of the master and slave controller-modulators according to a logical determination of a required mode of operation of the OPLL system in order to achieve a stable and identical phase performance of the master and the slave ECLs. The required mode of operation is chosen from a locking mode, a prediction mode, a tracking mode, and a searching mode.

Owner:OPTASENSE

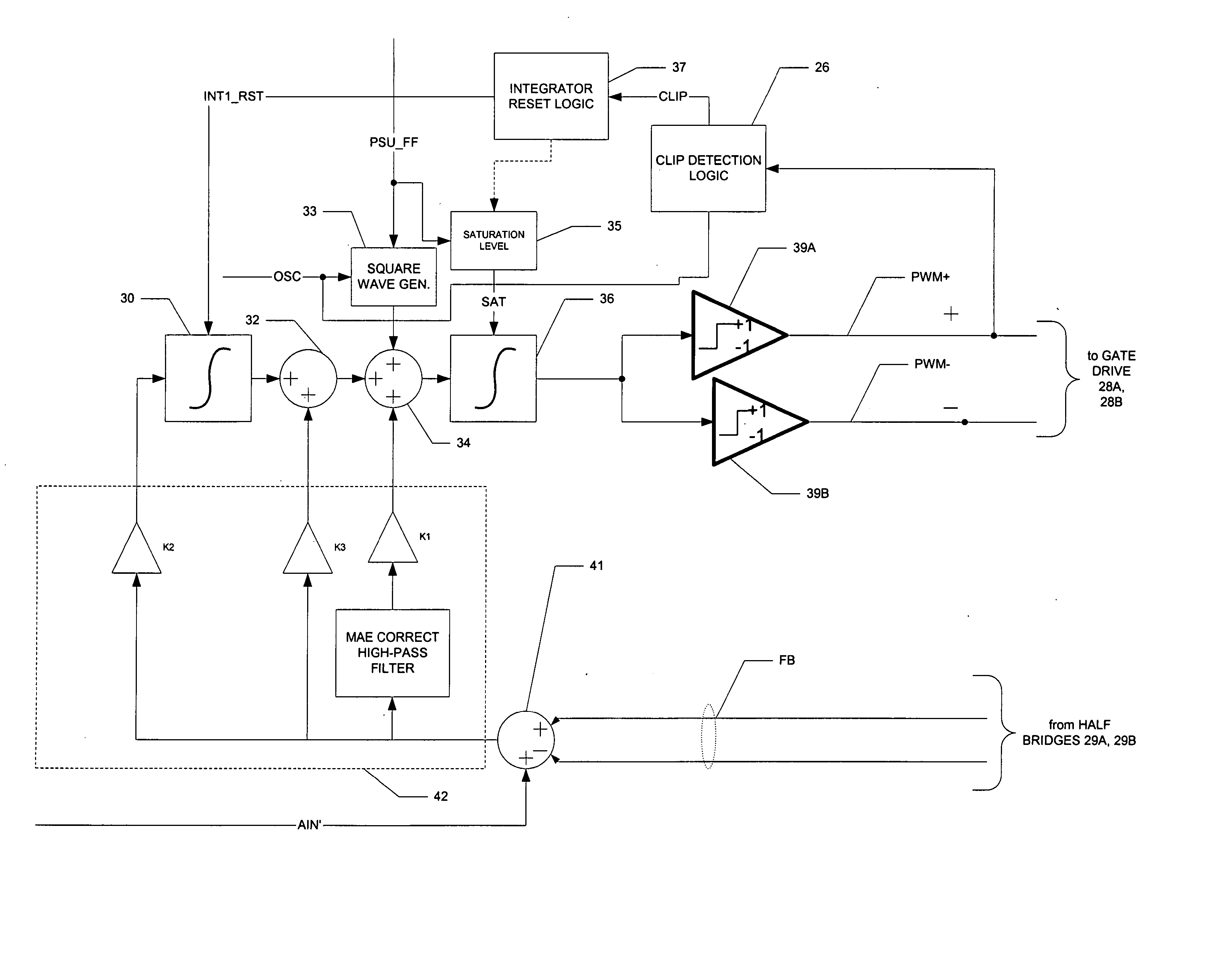

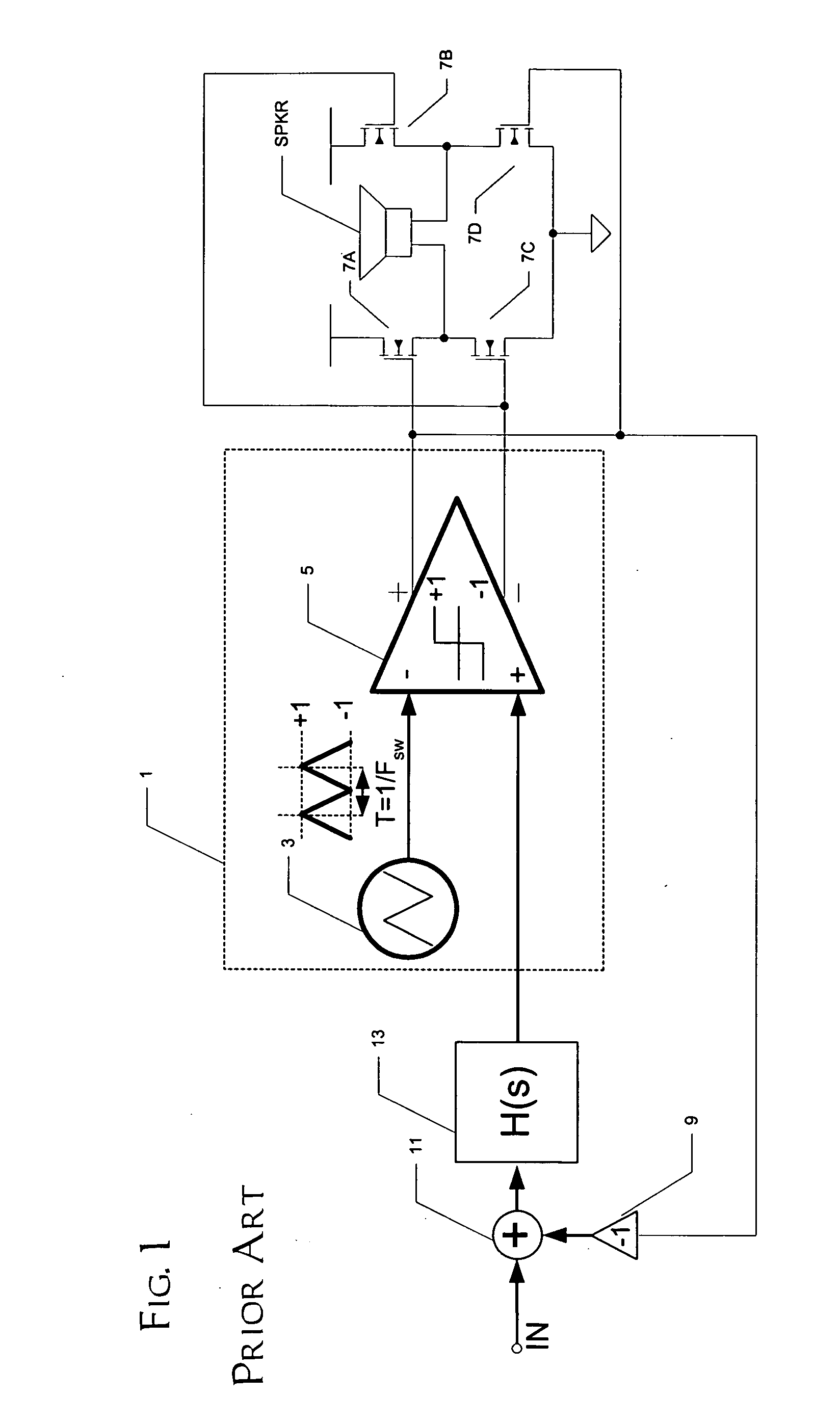

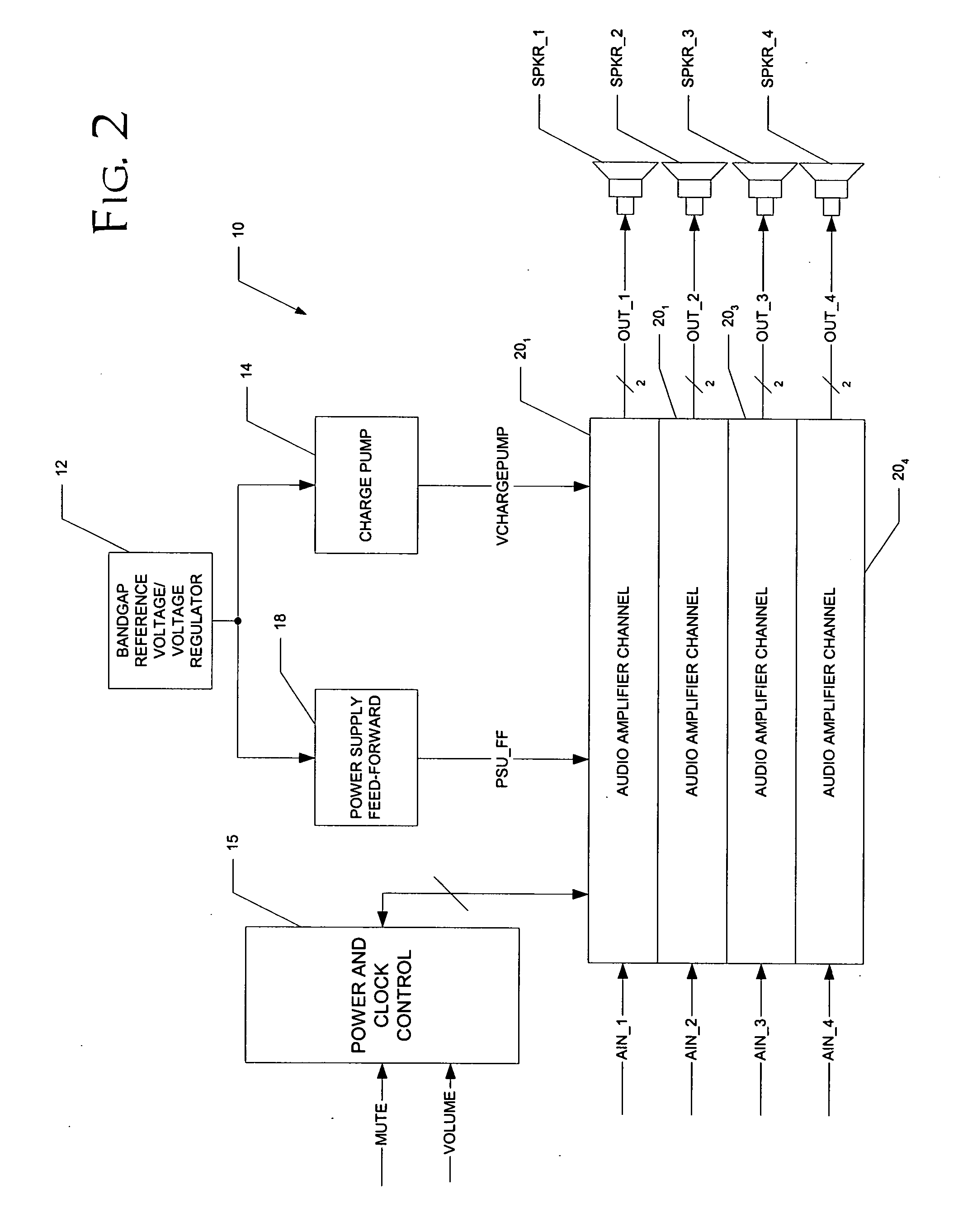

Recovery from clipping events in a class D amplifier

ActiveUS20050083114A1Shorten recovery timeAmplifier combinationsDc amplifiers with modulator-demodulatorLoop filterIntegrator

A class AD audio amplifier system (10) with improved recovery from clipping events is disclosed. The amplifier system (10) includes multiple audio channels (20), each of which can be constructed to include a pulse-width-modulator (PWM) (24). The PWM modulator (24) includes a pair of comparators (39A, 39B; 52+, 52−) that generate complementary PWM output signals based upon the comparison between a filtered difference signal and a reference waveform. Clip detection logic (26) is provided to detect clipping at the output of the channel (20), preferably by detecting successive edges of the reference waveform without an intervening edge of a PWM output signal. In response to detecting clipping, a first integrator (30; 45) is reset to remove residuals and to eliminate the first integrator (30; 45) from the loop filter of the modulator (24). A saturation level circuit (35) applies a clamping voltage, preferably in both clipping and non-clipping situations, to a second integrator (36; 47). As a result, the loop filter is prevented from entering extreme conditions during clipping, which greatly reduces the clipping recovery time.

Owner:TEXAS INSTR INC

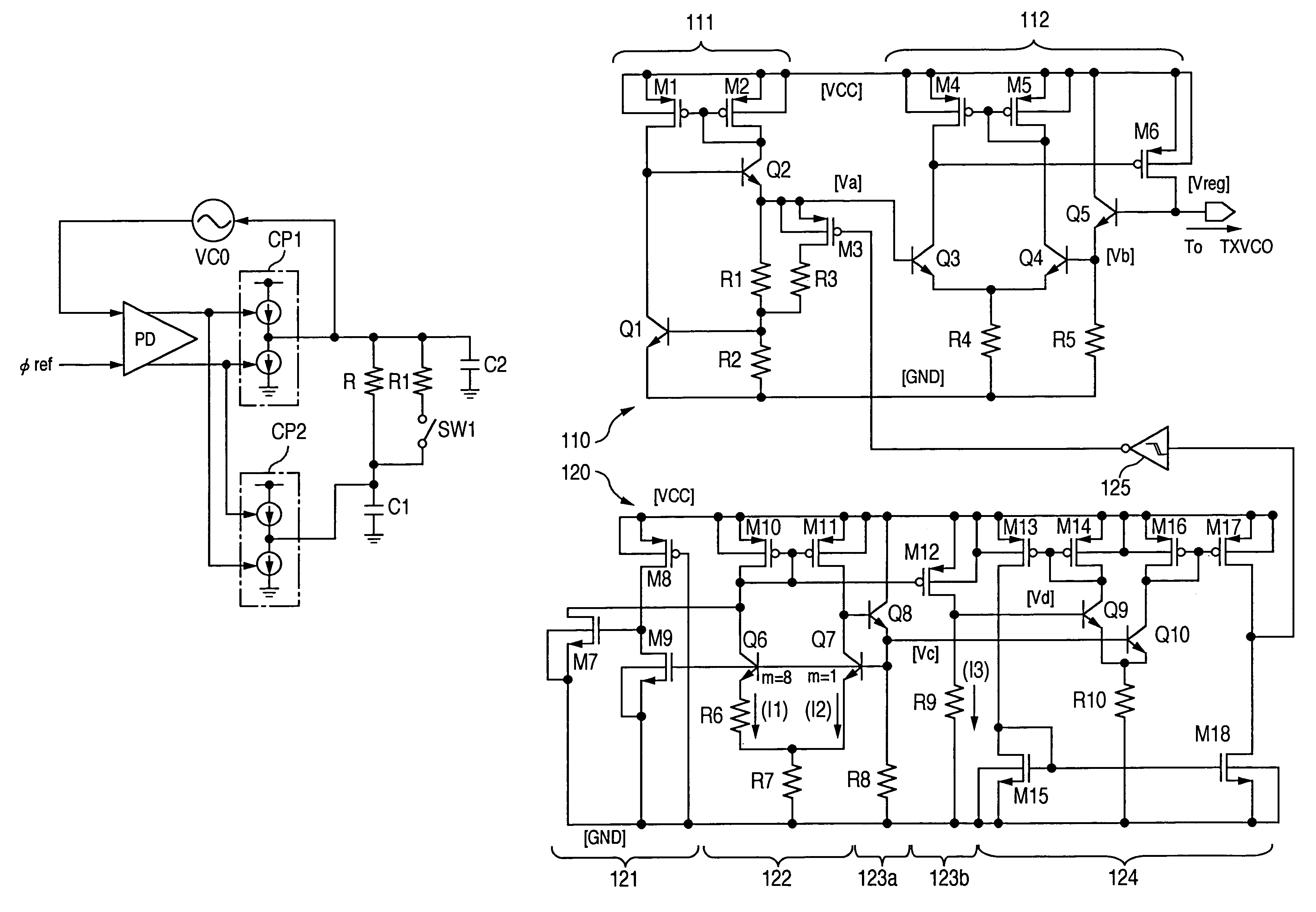

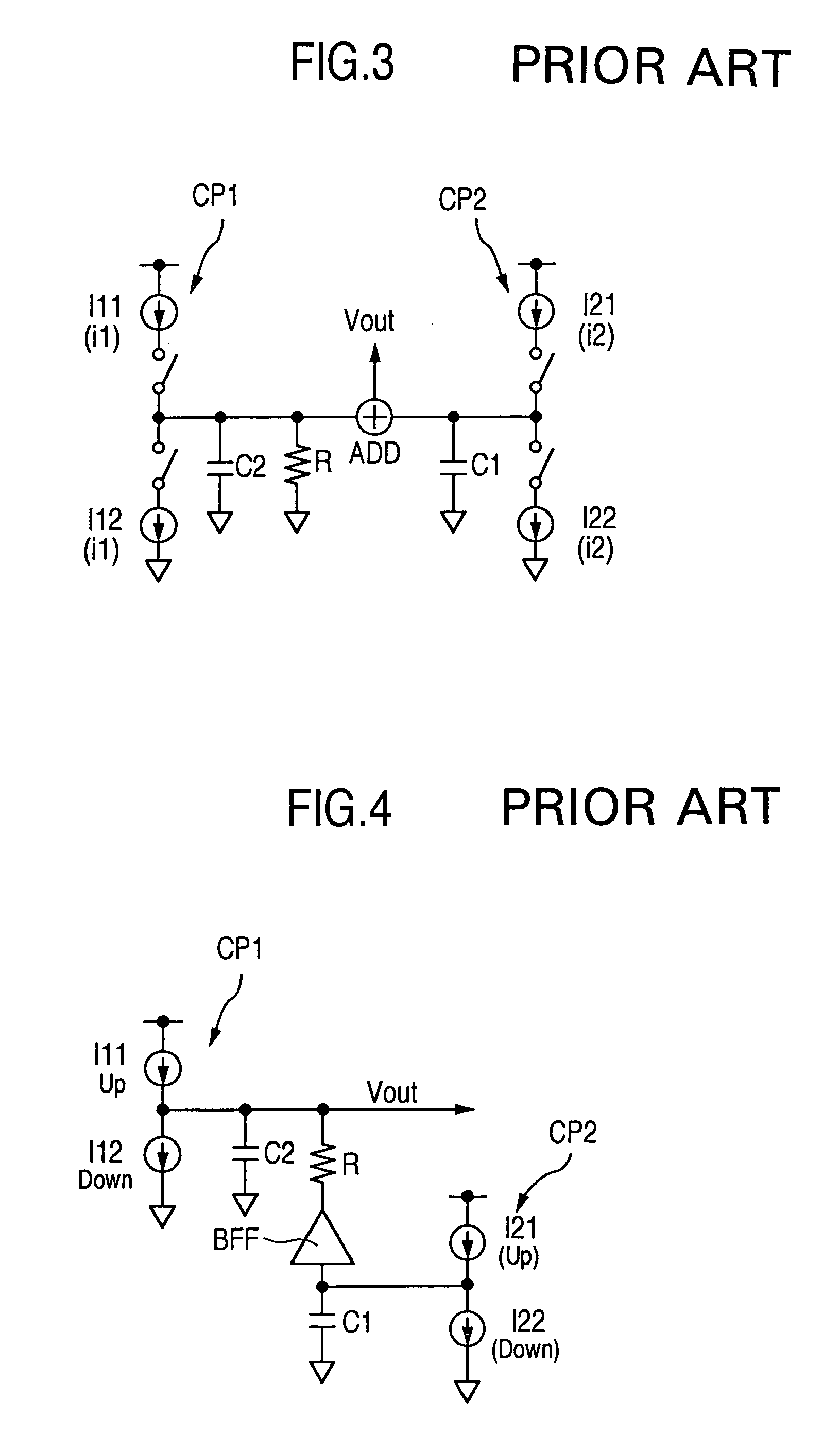

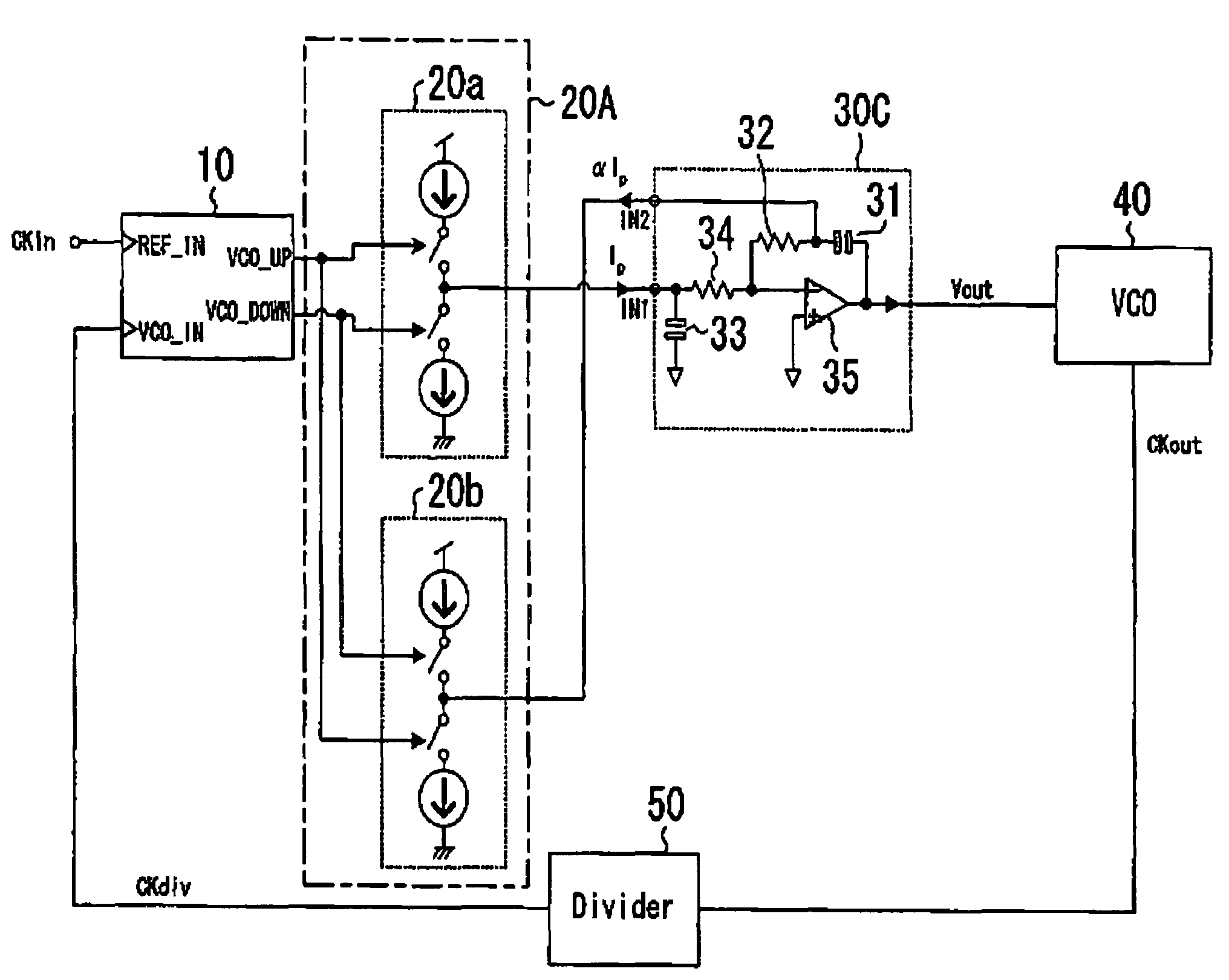

Semiconductor integrated circuit having built-in PLL circuit

InactiveUS7015735B2Reduce capacitanceAvoid excessive temperaturePulse automatic controlAngle demodulation by phase difference detectionCapacitanceCharged current

A semiconductor integrated circuit having a built-in PLL circuit which has two charge pump circuits for charging and discharging capacitive elements of a loop filter in response to signals generated by a phase comparator circuit. One of the two charge pump circuits has current sources which generate current values smaller than those generated by current sources of the other charge pump circuit. The loop filter has a first capacitive element connected to a charge / discharge node, and a second capacitive element connected to the charge / discharge node through a resistive element. The first capacitive element is charged and discharged by the one charge pump circuit, while the second capacitive element is charged and discharged by the other charge pump circuit. A charging current source of the one charge pump circuit operates simultaneously with a discharging current source of the other charge pump circuit, i.e., the charge pump circuits operate in opposite phase.

Owner:RENESAS ELECTRONICS CORP +1

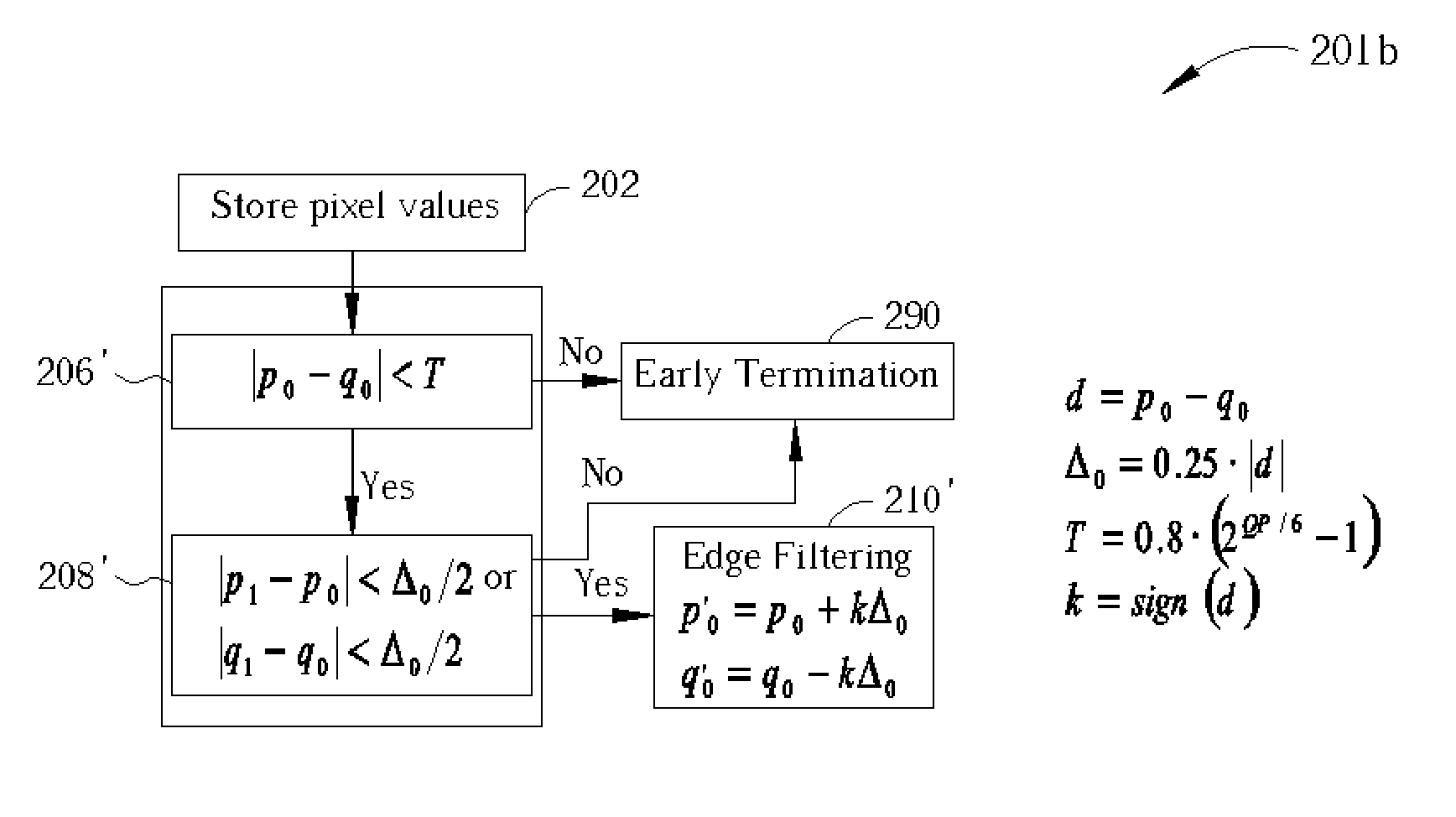

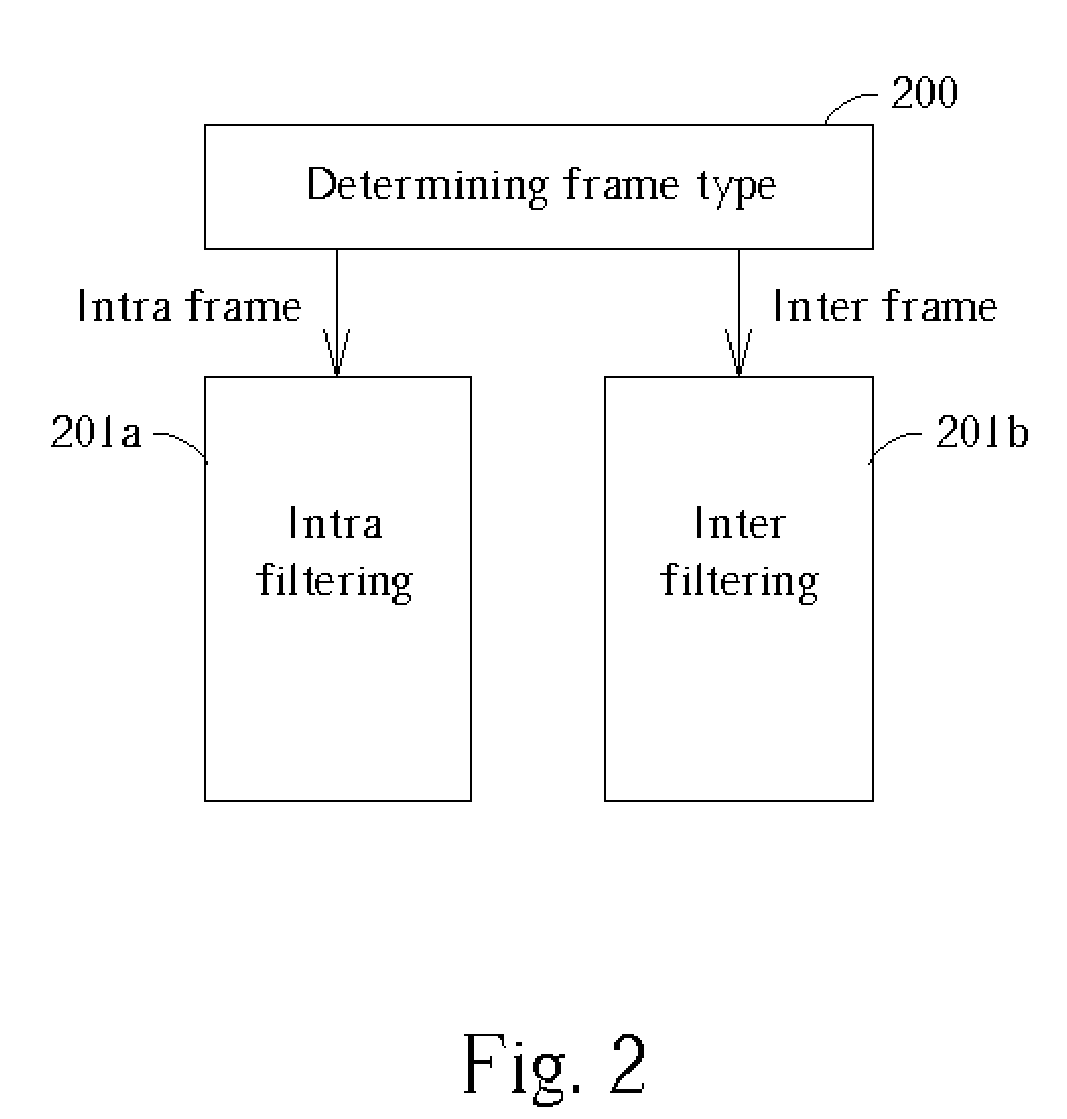

Method and apparatus for removing blocking artifacts of video picture via loop filtering using perceptual thresholds

InactiveUS20050196066A1Improve processing efficiencyRapid determinationCharacter and pattern recognitionDigital video signal modificationLoop filterVideo processing

A video processing method and a related device for processing blocking artifacts between two blocks within a video picture uses loop filtering and compares two boundary edge pixels at both sides of a boundary between two blocks according to at least one perceptual threshold to determine if pixel values of the two boundary edge pixels should be adjusted to decrease the difference corresponding to the pixel values of the two boundary edge pixels.

Owner:ALICORP

Filtering method, apparatus, and medium used in audio-video codec

InactiveUS20060013315A1Efficient executionExpand memoryColor television with pulse code modulationColor television with bandwidth reductionPattern recognitionLoop filter

A filtering method, apparatus, and medium used in an audio-video codec are provided. The filtering method may include determining a predetermined macroblock as a filtering region; expanding the filtering region to further include a portion of a macroblock adjacent to the predetermined macroblock near a boundary between the predetermined macroblock and the macroblock adjacent to the predetermined macroblock; and performing a deblocking filtering operation on the expanded filtering region in a causal manner according to the passage of time. The filtering method, apparatus, and medium can be easily realized using a non-causal loop filter and buffers. The filtering method, apparatus, and medium can efficiently filter blocking artefacts without increasing a required memory bandwidth and causing frame delays.

Owner:SAMSUNG ELECTRONICS CO LTD

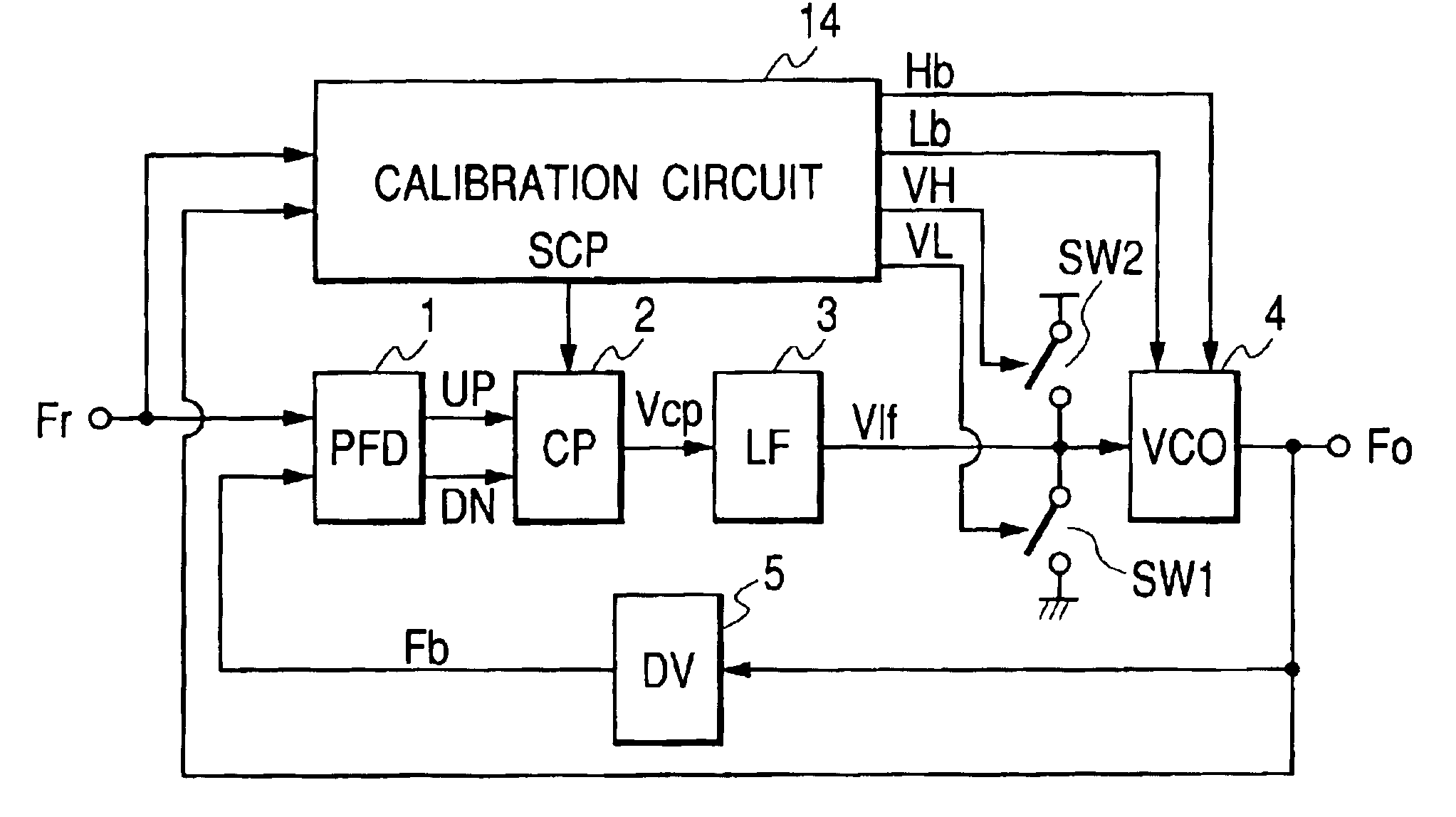

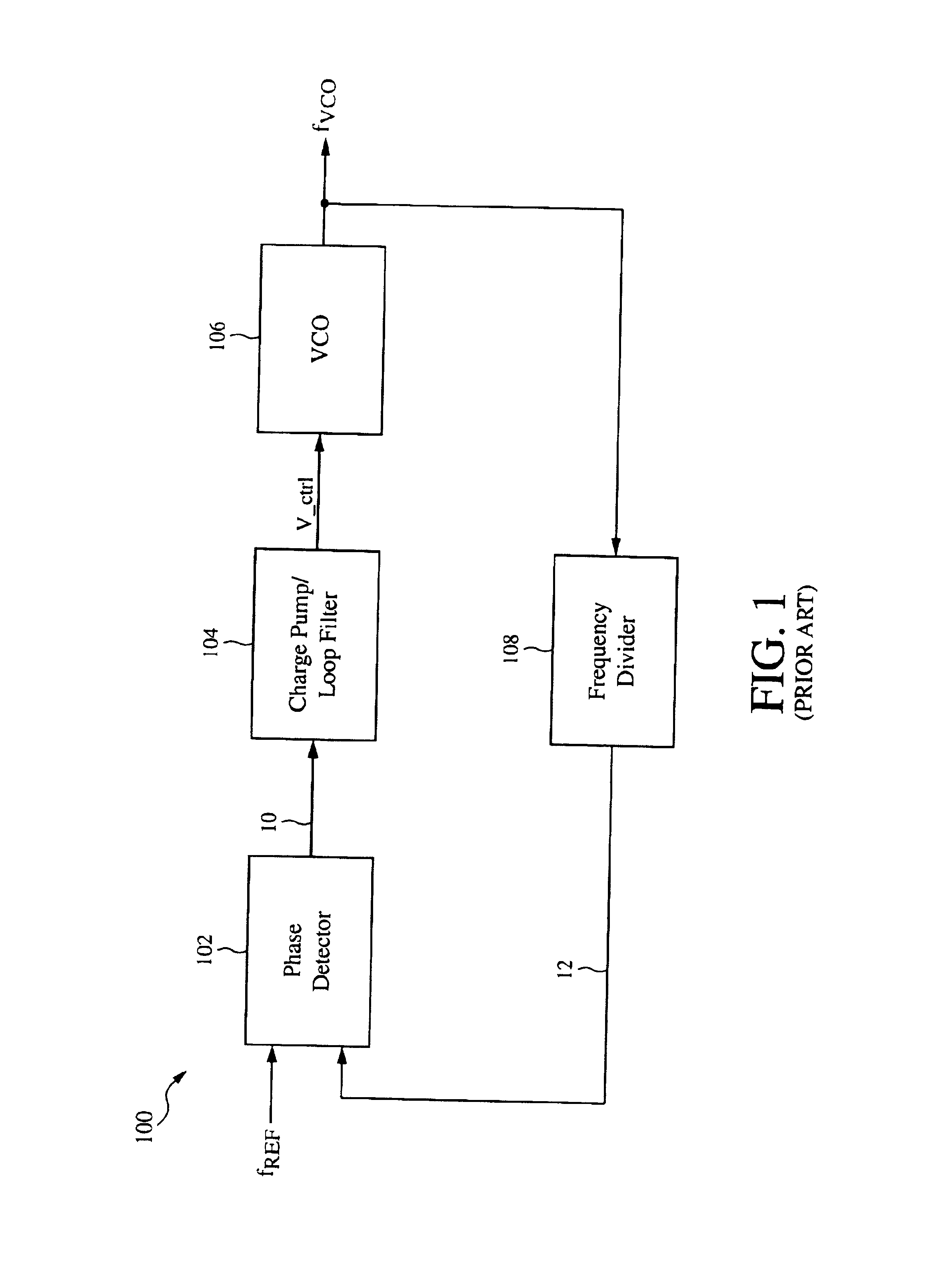

Phase synchronizing circuit

InactiveUS6870411B2Increase speedReduce the oscillation frequencyPulse automatic controlLower limitLoop filter

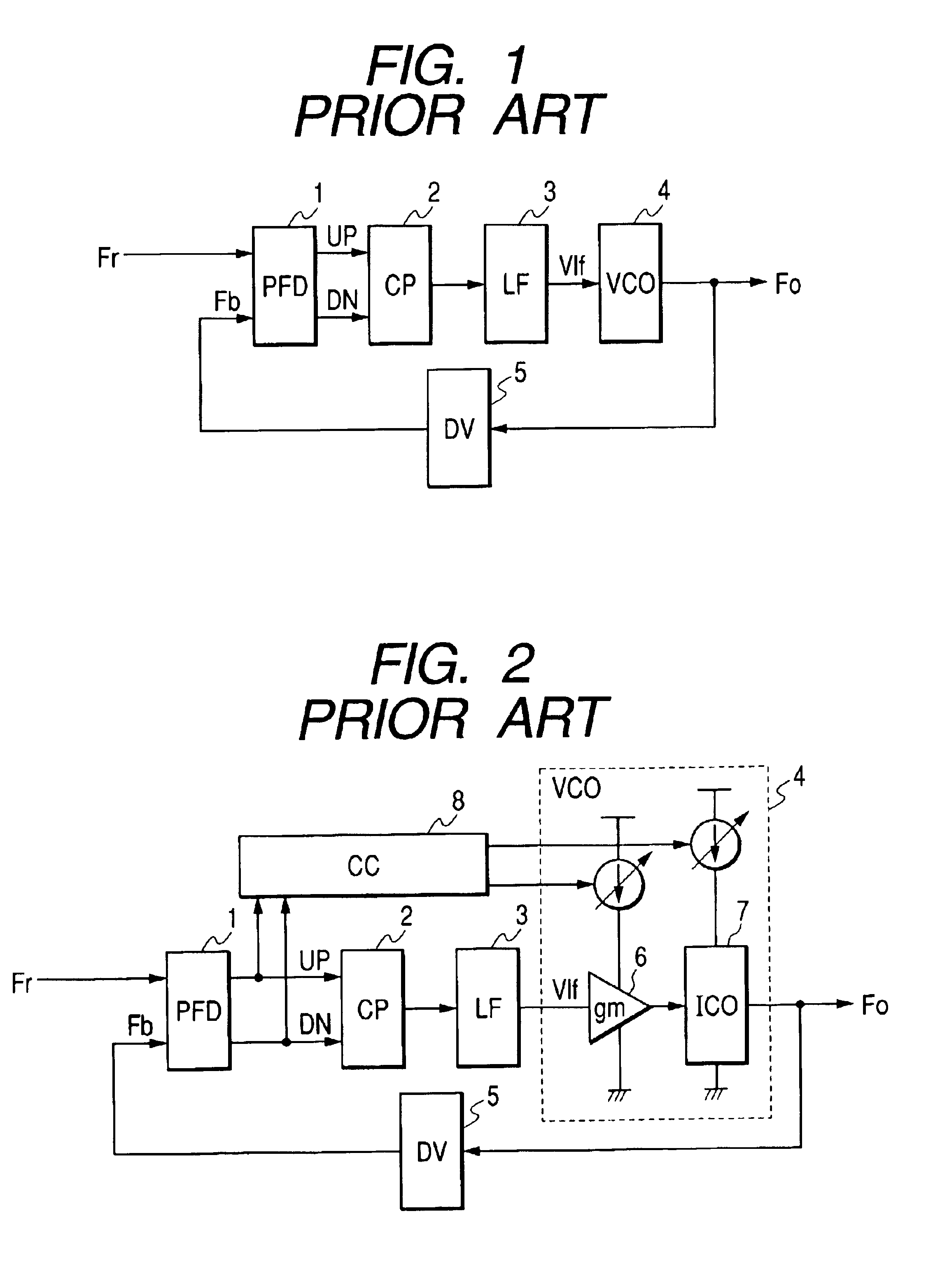

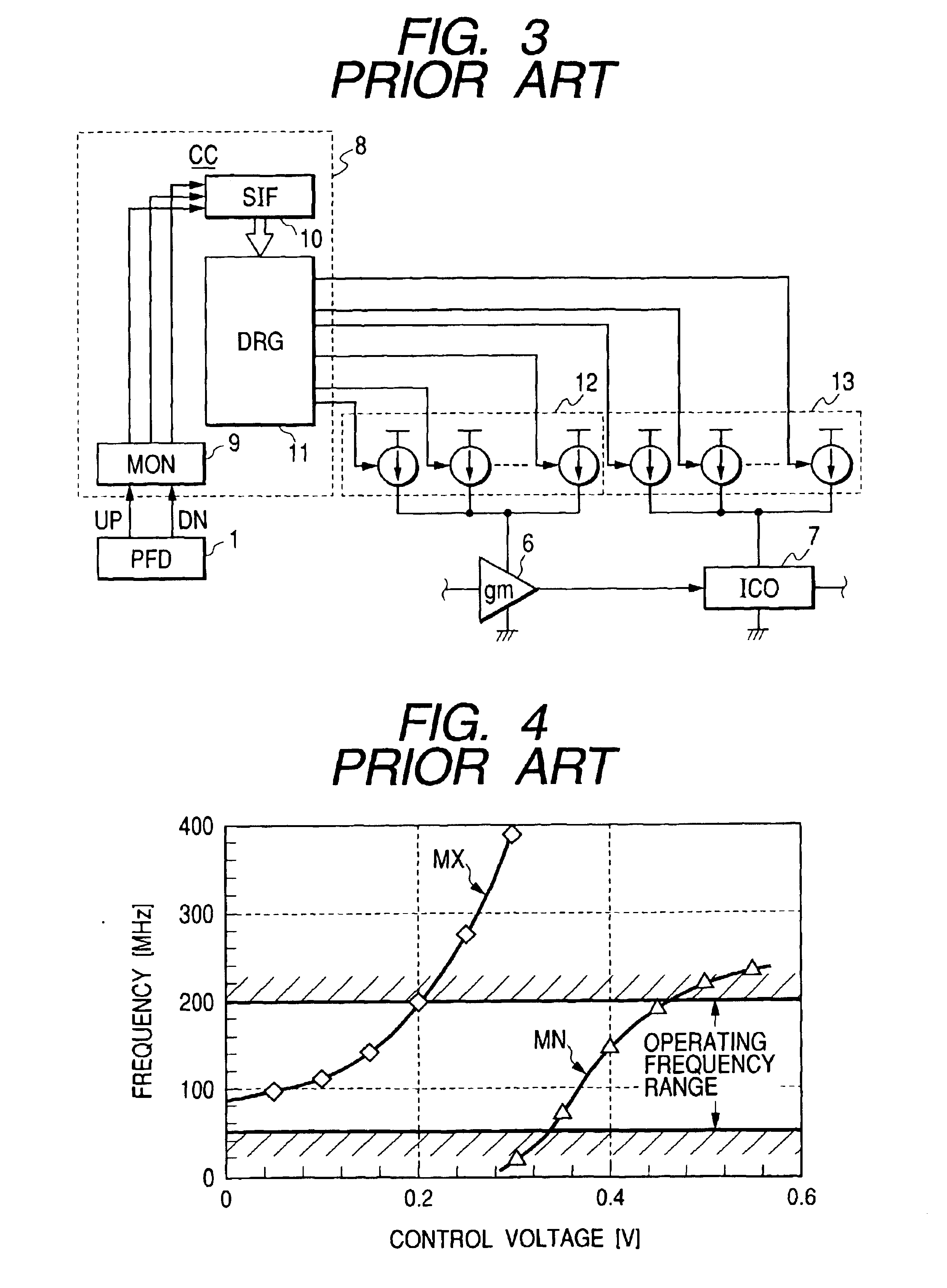

An object of this invention is to provide a phase synchronizing circuit capable of automatically adjusting a VCO such that the VCO satisfies a predetermined frequency range even in a frequency range in which the VCO oscillates by a leak current generated if a low threshold process is applied. The phase synchronizing circuit is composed of a PLL consisting of a phase comparator, a charge pump, a loop filter, a VCO, and a divider, and a calibration circuit for automatically adjusting a frequency range of the VCO. Before a convergence operation is started, a switch is closed in response to a signal Rst of the calibration circuit such that an output of the loop filter is leveled to the ground and the PLL is set to be an open loop. A VCO output Fo is set at an upper limit frequency or a lower limit frequency in response to a Vcal signal, and its frequency is measured by comparing its period with a period of a reference signal Fr, and signals Hb, Lb used for adjusting the frequency of the VCO are updated. The signals Hb, Lb are updated until the VCO satisfies the predetermined frequency range, and subsequently their values are maintained. The switch opens in response to the signal Rst, and the PLL is changed over to a close loop to start phase synchronization.

Owner:RENESAS ELECTRONICS CORP

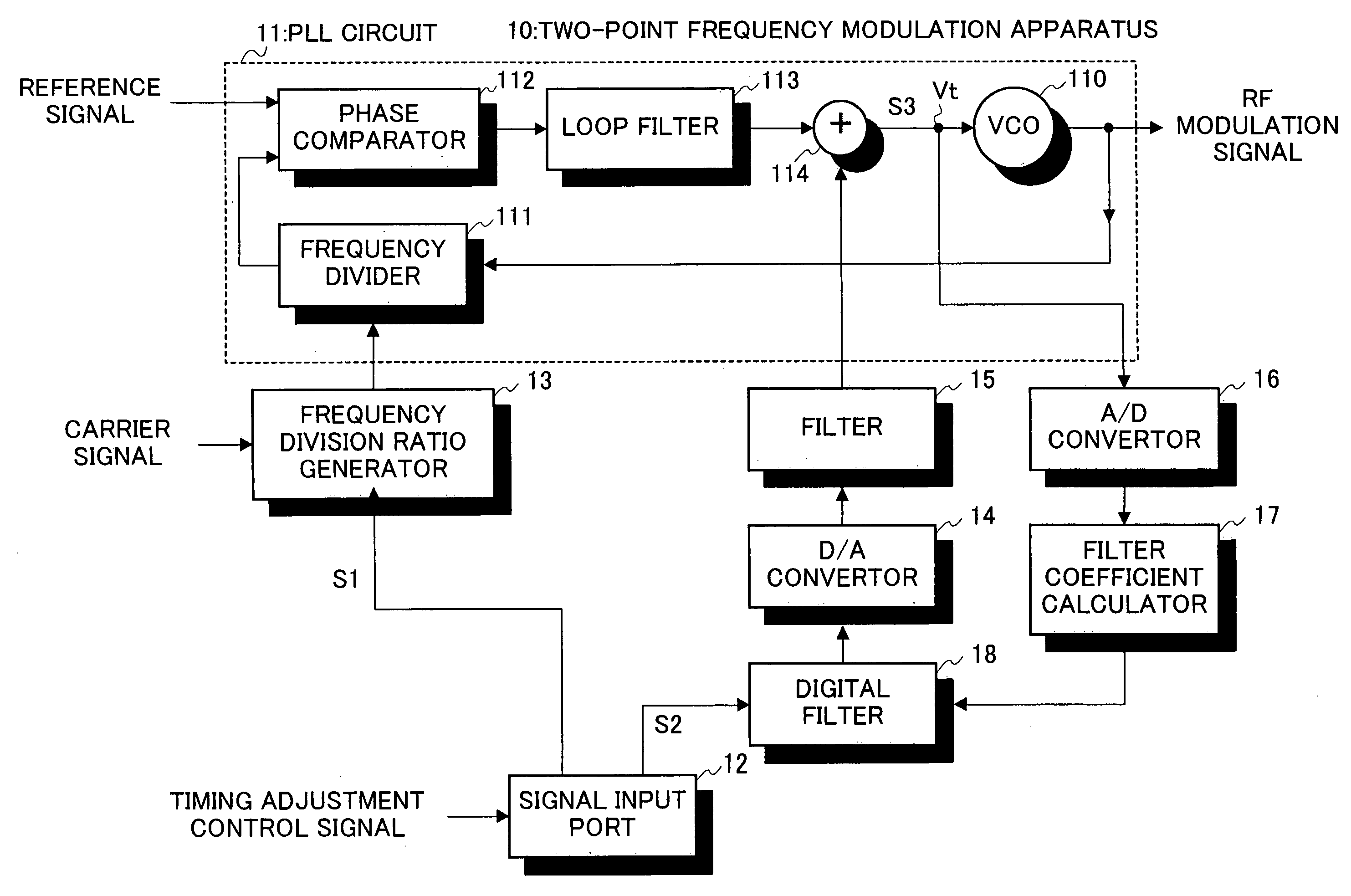

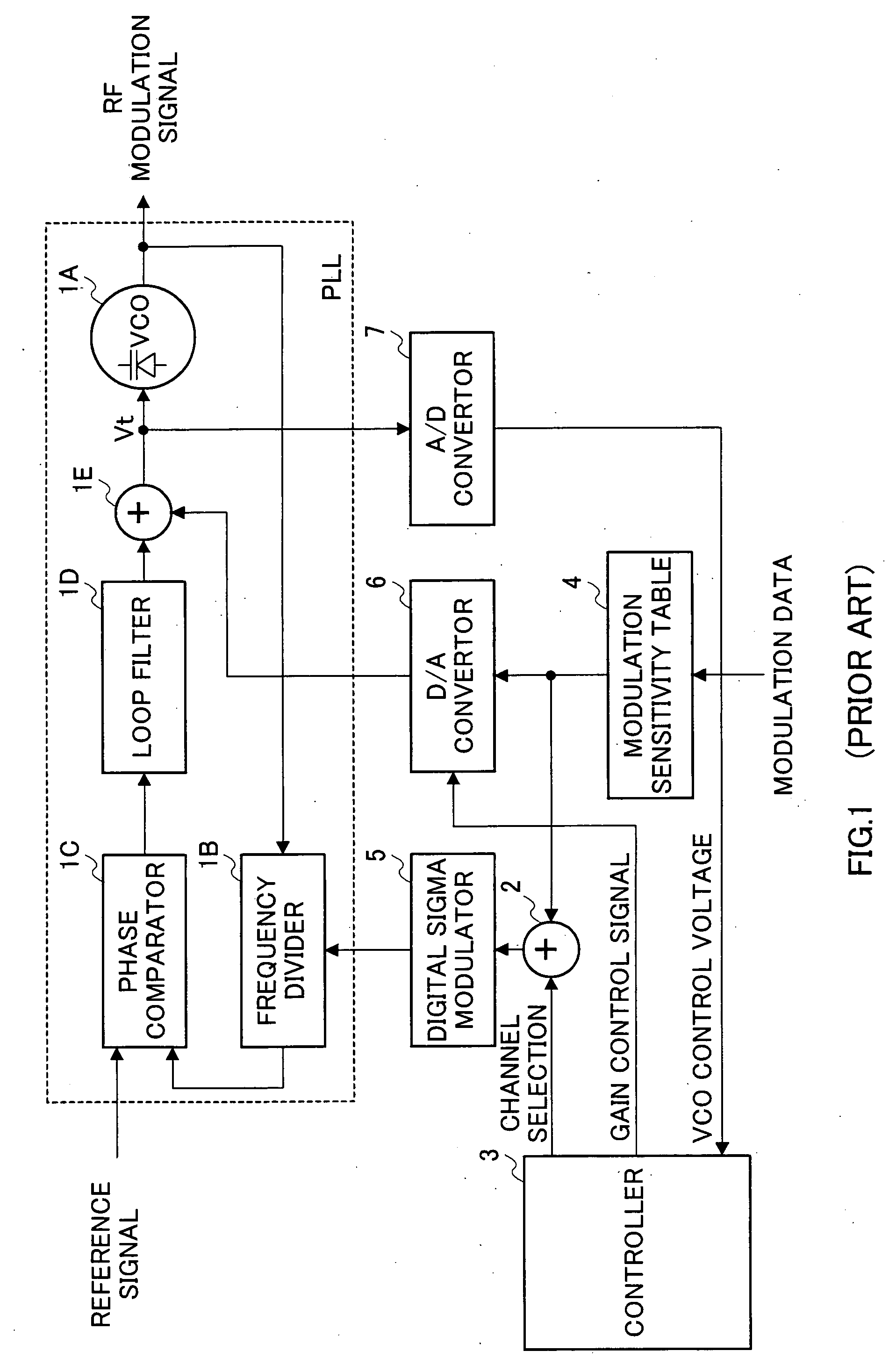

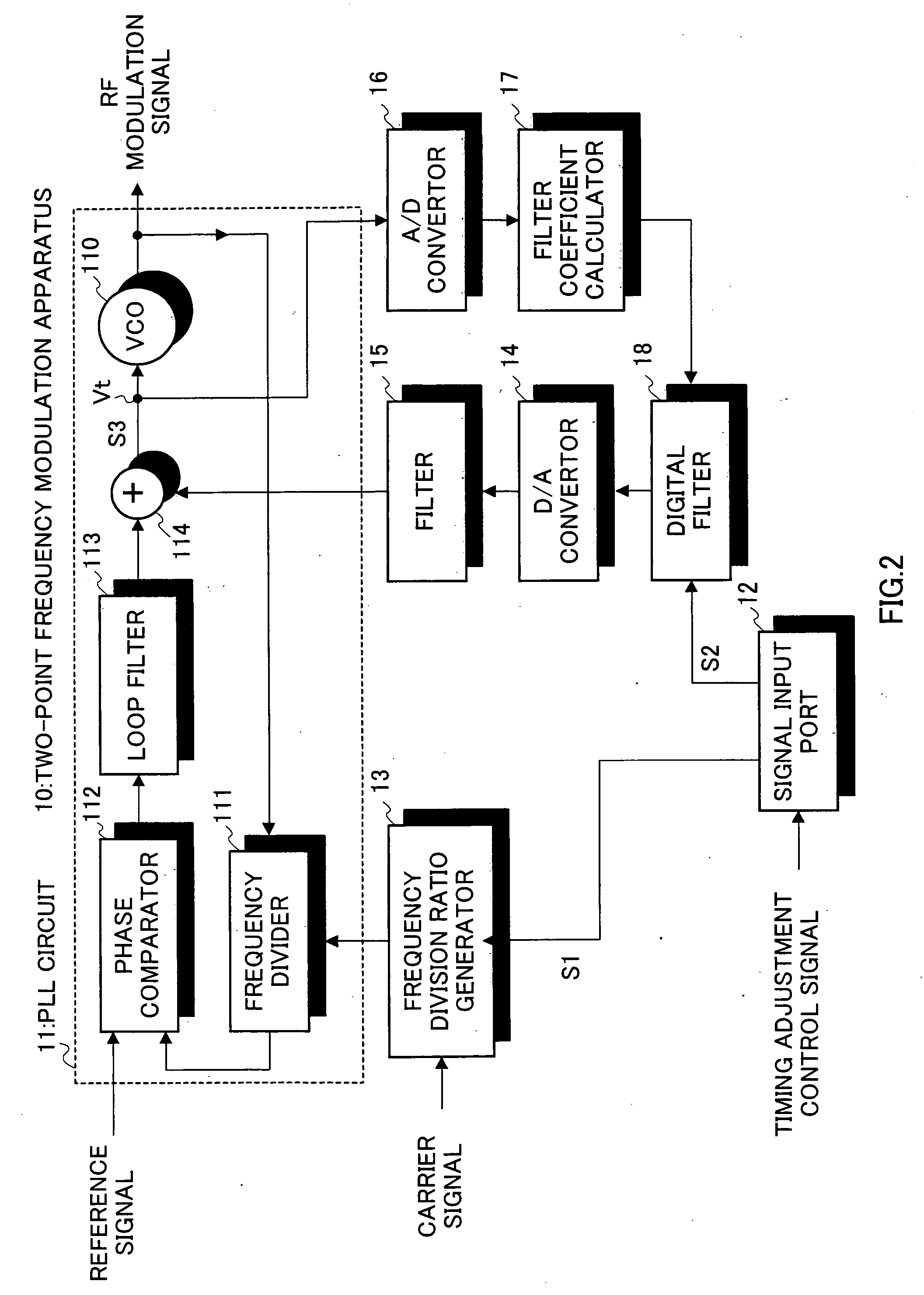

Two-point frequency modulation apparatus, wireless transmitting apparatus, and wireless receiving apparatus

InactiveUS20050232385A1Reduces input timing differenceHigh modulation accuracyPulse automatic controlAngle modulation detailsLoop filterPhase difference

A two-point frequency modulation apparatus is provided that reduces input timing difference and improves modulation accuracy. Two-point frequency modulation apparatus 10 has: PLL circuit 11; frequency division ratio generator 13 that generates the frequency division ratio in frequency divider 111 based on first digital baseband signal S1 and carrier signal; adder 114 that adds second digital baseband signal S2 to the output signal of loop filter 113; a delay index calculator (filter coefficient calculator 17) that calculates the delay index based on the magnitude of change in the amplitude of the output signal of adder 114; and a delay adjuster (digital filter 18) that shifts the phase of one of first digital baseband signal S1 and second digital baseband signal S2 according to the delay index so as to reduce the phase difference.

Owner:PANASONIC CORP

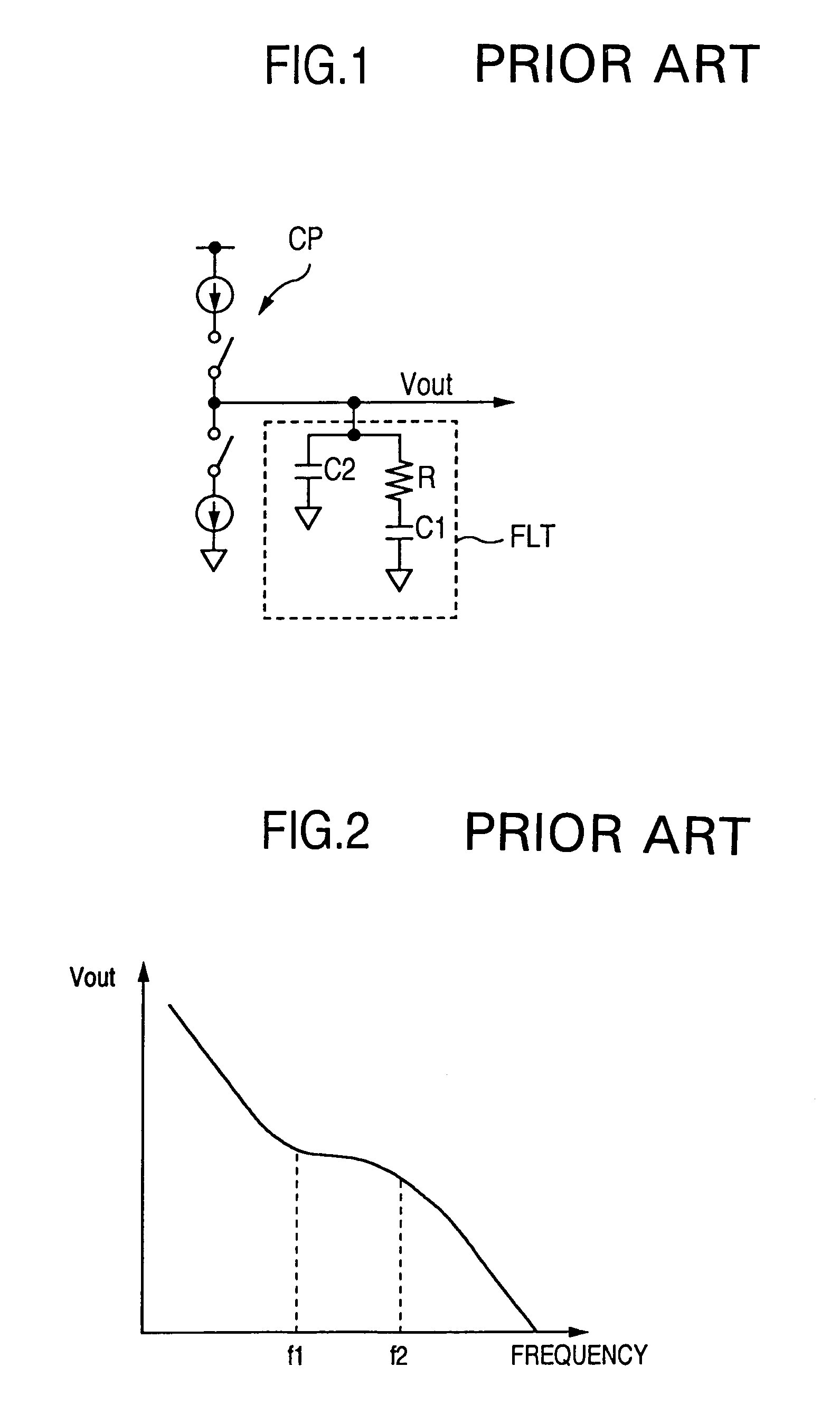

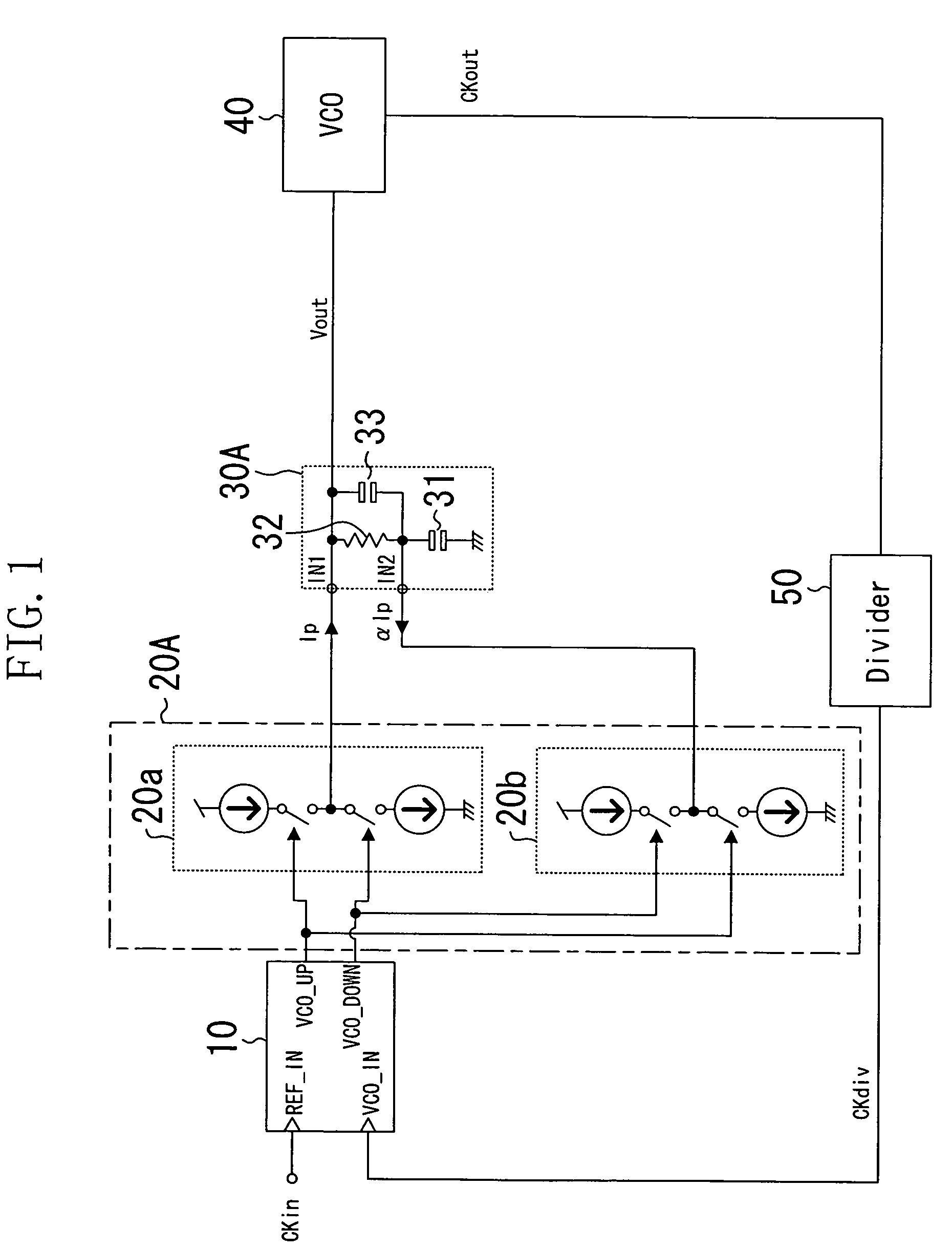

Low-pass filter, feedback system, and semiconductor integrated circuit

InactiveUS7078948B2Reduce circuit areaSmall sizeFluid heatersMultiple-port networksCircuit complexityCapacitance

In a low-pass filter which is preferably used as a loop filter in a PLL or DLL, filter characteristics which are the same as those of a conventional low-pass filter are realized without causing collateral problems, such as an increase in the circuit area, the circuit complexity, or the resistance value, which may be caused due to size reduction of a capacitive element in the conventional low-pass filter. Thus, in a loop filter including a capacitive element and a resistive element which are connected in series, the first input terminal is provided at the side including the resistive element, and the second input terminal is provided at a connection point of the capacitive element and the resistive element. The first input terminal is supplied with the first electric current. On the other hand, the second electric current, which is a part of the first electric current supplied to the first input terminal, is extracted from the second input terminal, so that the electric current flowing into the capacitive element is smaller than the electric current flowing through the resistive element.

Owner:PANASONIC CORP

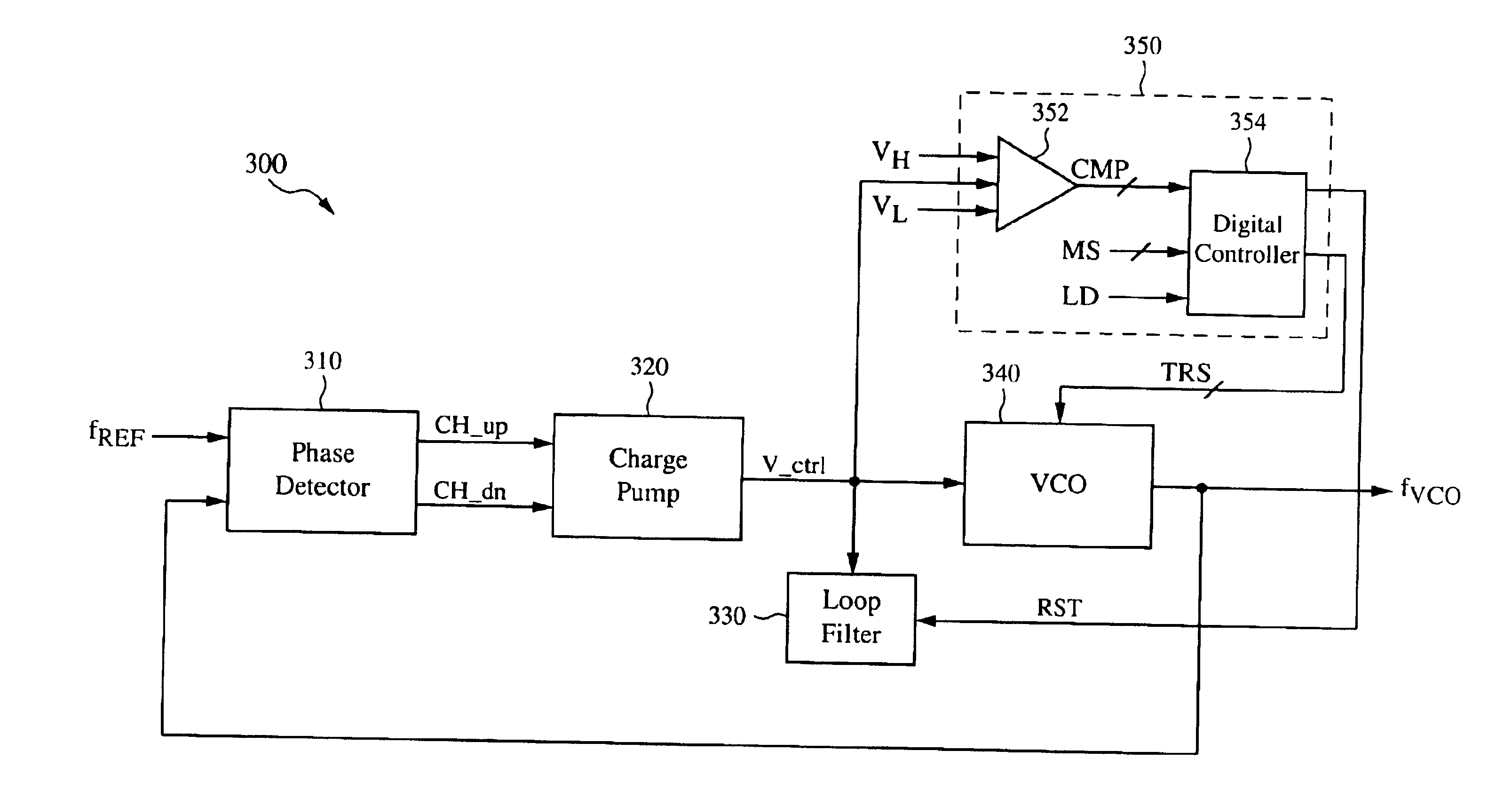

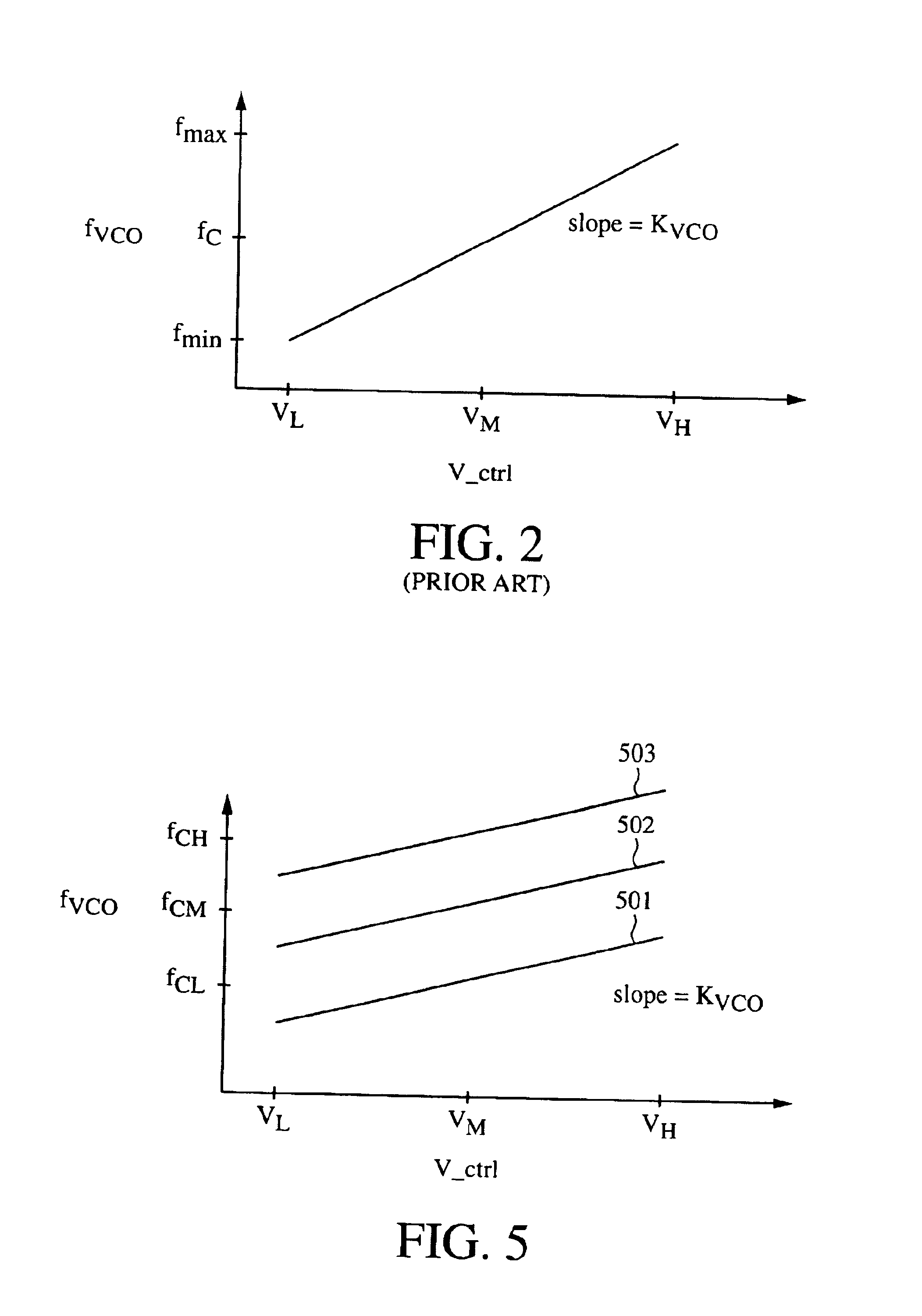

Phase locked loop circuit with self adjusted tuning

A phase-locked loop (PLL) circuit includes a voltage-controlled oscillator (VCO) having a first input to receive a control voltage, one or more second inputs to receive one or more tuning range control signals, and an output to provide an oscillation output signal, a phase detector having inputs to receive the oscillation output signal and a reference signal, a charge pump having an input coupled to the output of the phase detector and having an output to generate the control voltage, a loop filter having an input to receive the control voltage and having a control terminal, and a controller having inputs to receive the control voltage, a high reference voltage, a low reference voltage, and one or more mode signals, and having a first output connected to the control terminal of the loop filter and second outputs to generate the tuning range signals.

Owner:PROMISE TECHNOLOGY

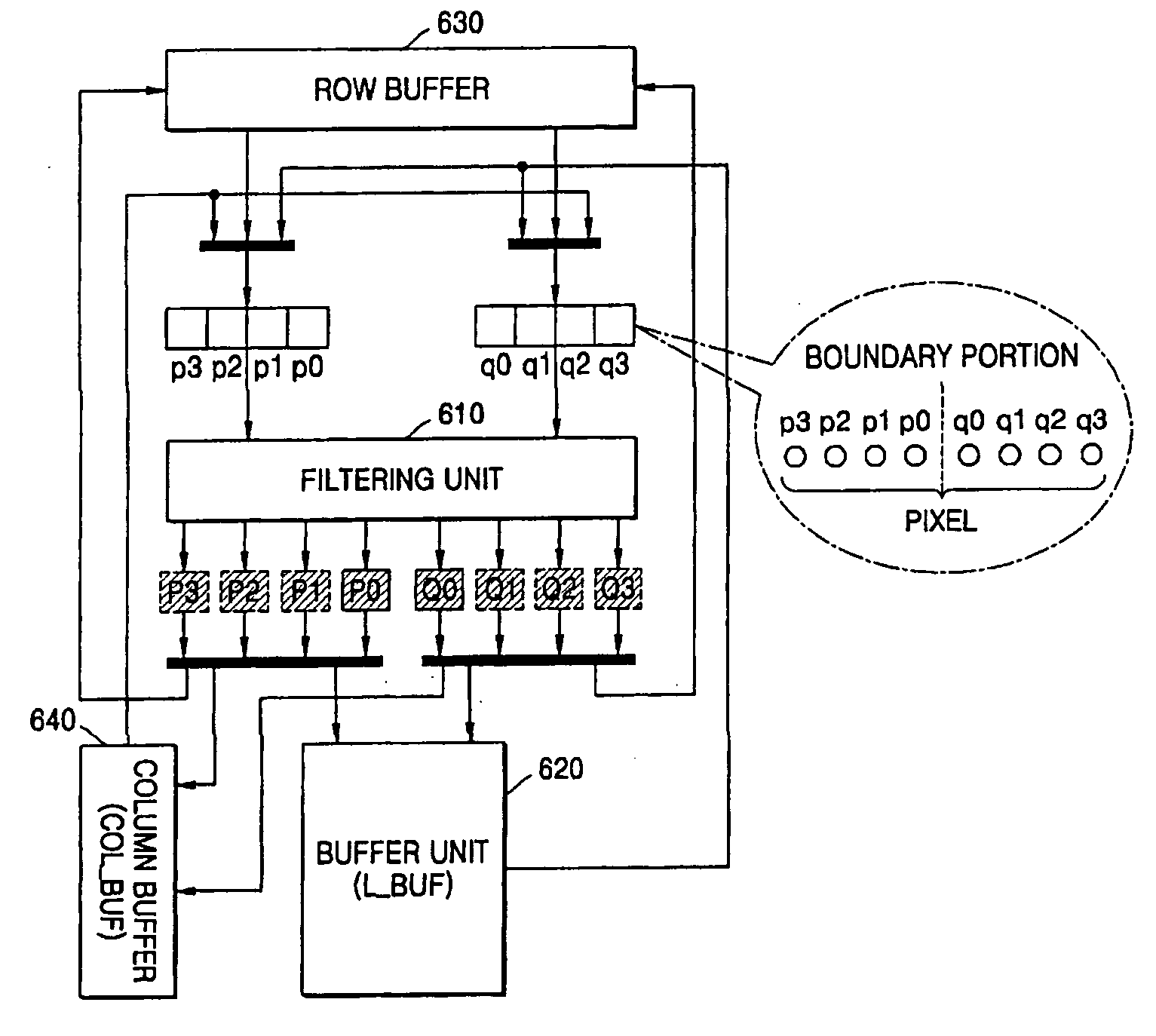

Method and apparatus for reduction of in-loop filter buffer

InactiveUS20130322523A1Color television with pulse code modulationColor television with bandwidth reductionLoop filterComputer graphics (images)

A method and apparatus for in-loop processing of reconstructed video are disclosed. The method and apparatus configure the in-loop processing so that the processing requires no pixel or reduced pixels from other side of a virtual boundary. When the in-loop processing of the to-be-processed pixel requires a pixel from the other side of the virtual boundary, the pixel from the other side of the virtual boundary is replaced by a replacement pixel. The in-loop processing can also be configured to skip the pixel when the processing requires a pixel from other side of the virtual boundary. The in-loop processing can also be configured to change ALF filter shape or filter size when the in-loop processing requires a pixel from other side of the virtual boundary. A filtered output can be combined linearly or nonlinearly with the to-be-processed pixel to generate a final filter output.

Owner:MEDIATEK INC

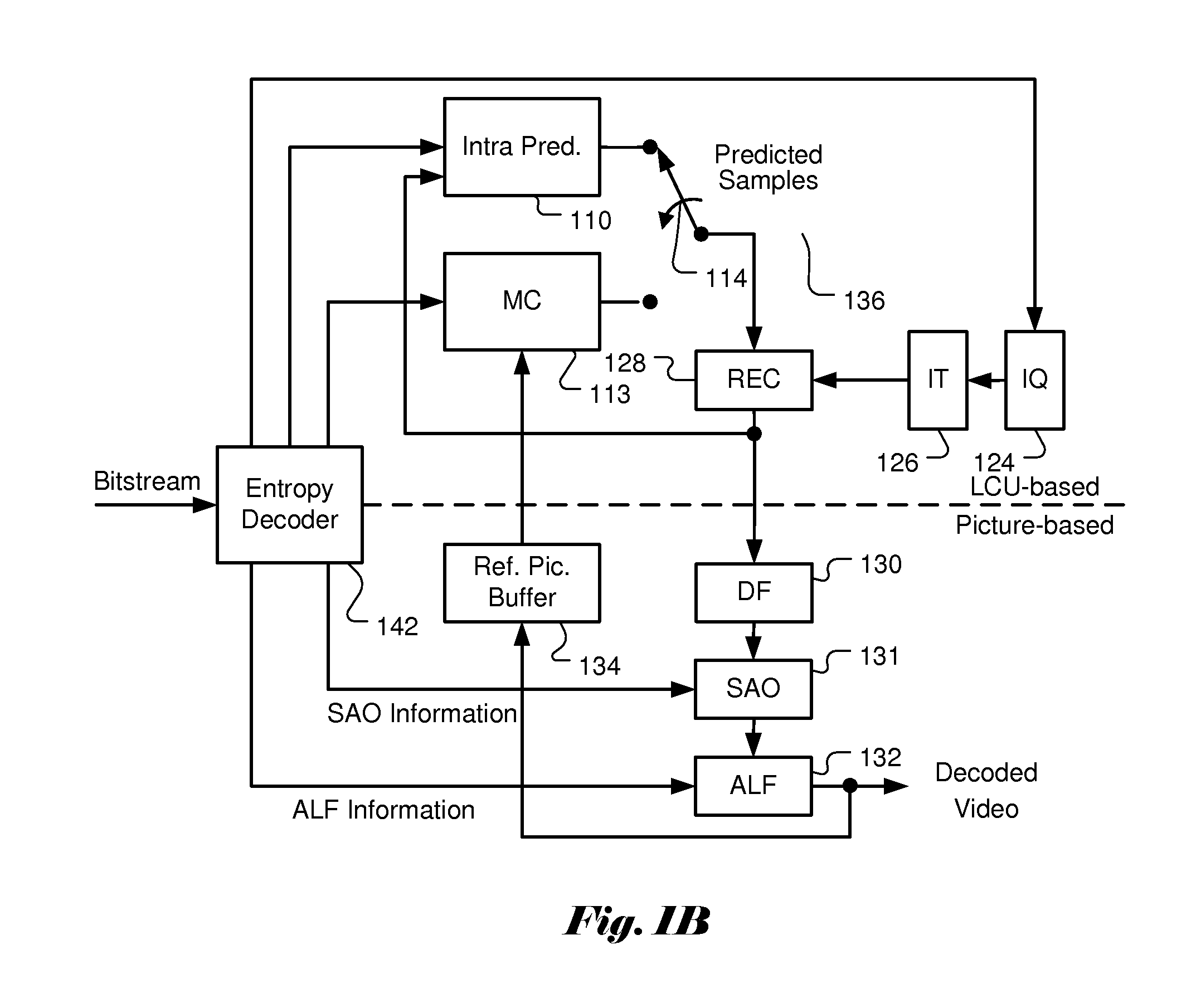

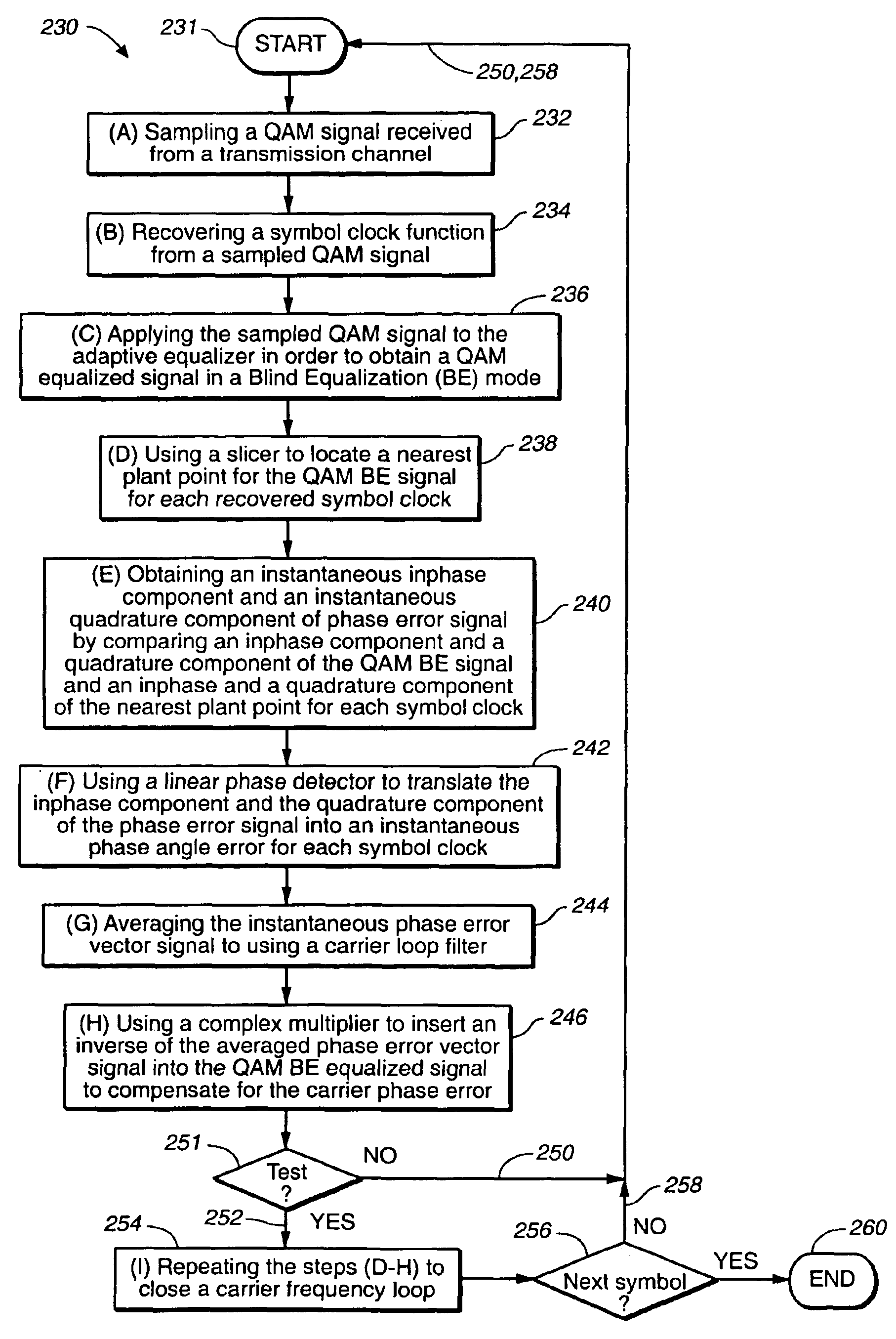

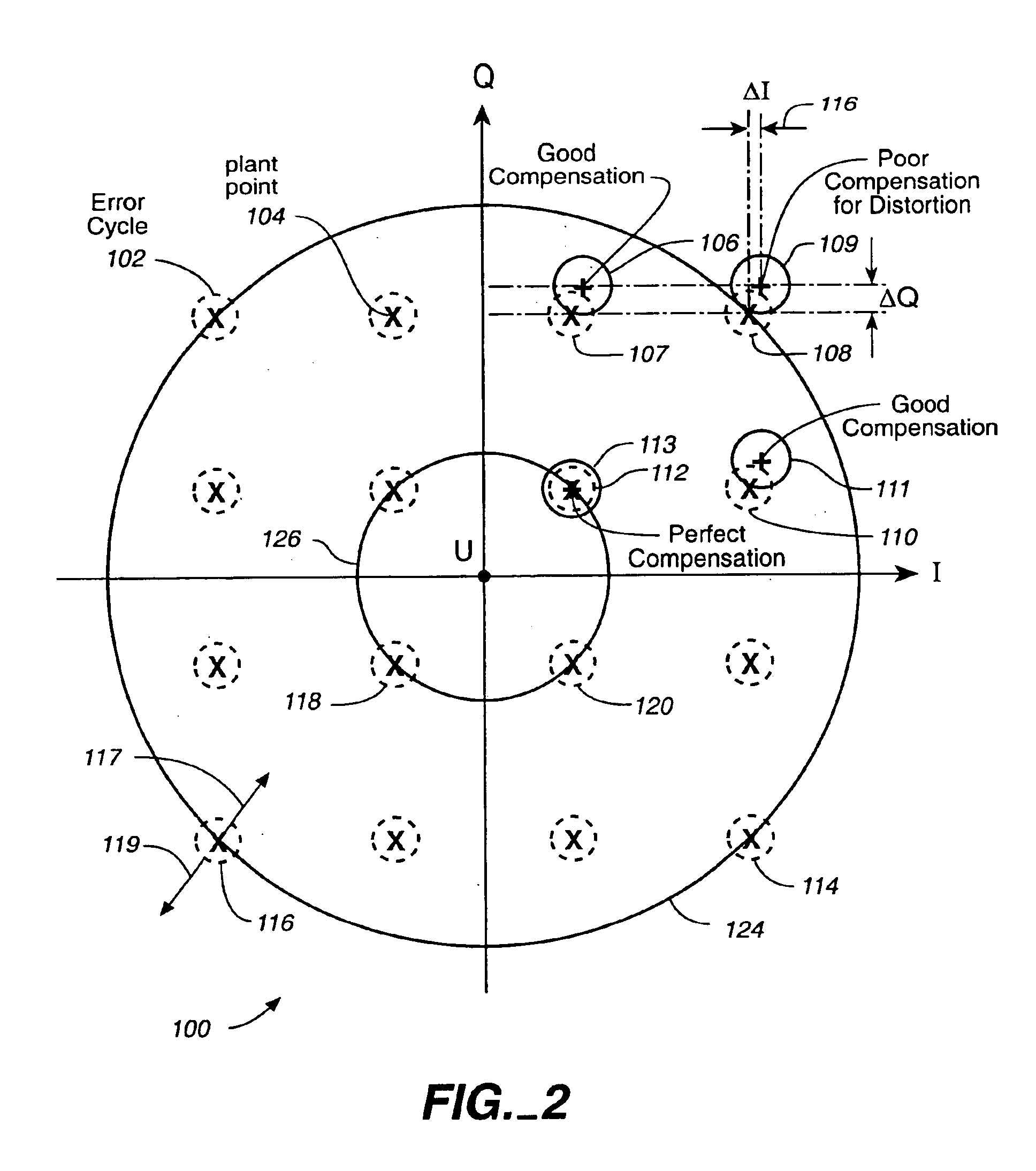

Linear phase robust carrier recovery for QAM modems

InactiveUS6904098B1Large loop bandwidthLower latencyDc level restoring means or bias distort correctionAutomatic frequency control detailsQam modulationBlind equalization

In a QAM demodulator including an adaptive equalizer, a method of carrier tracking comprising the following steps is disclosed: (A) sampling a QAM signal received from a transmission channel; (B) recovering a symbol clock function from the sampled QAM signal; (C) applying the sampled QAM signal to the adaptive equalizer in order to obtain a QAM equalized signal in a Blind Equalization (BE) mode; (D) using a slicer to locate a nearest plant point for the QAM Blind equalized signal for each recovered symbol clock; (E) using a complex conjugate multiplier to obtain an instantaneous inphase component and an instantaneous quadrature component of a phase angle error signal; (F) using a linear phase detector to obtain an instantaneous phase angle error for each symbol clock; (G) averaging the instantaneous phase angle error signal by using a carrier loop filter; (H) using a complex multiplier to insert an inverse of the averaged phase angle error signal into the QAM Blind equalized signal to compensate for the carrier phase angle error; and (I) repeating the steps (D-H) to close a carrier frequency loop.

Owner:REMEC BROADBAND WIRELESS NETWORKS LLC

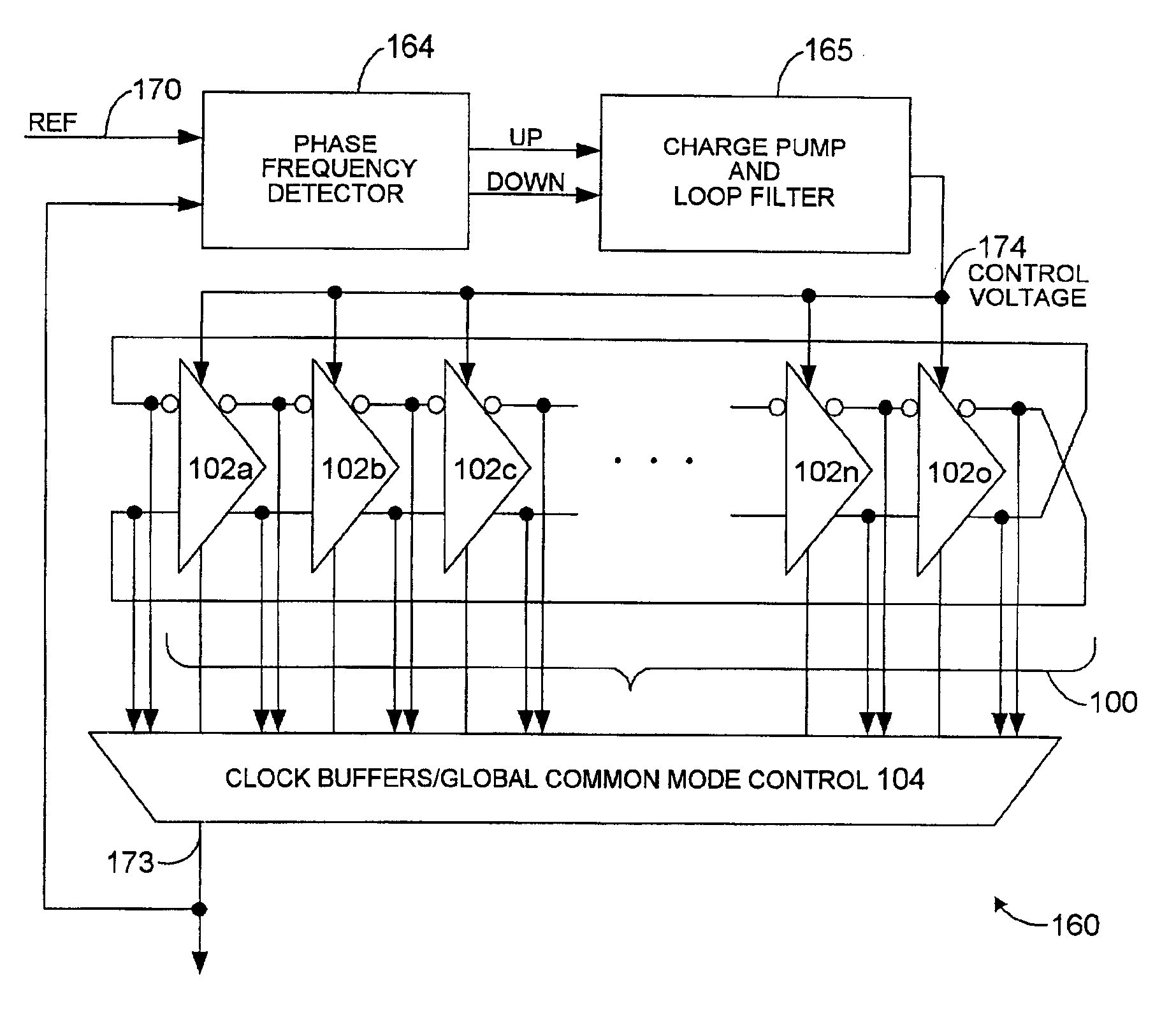

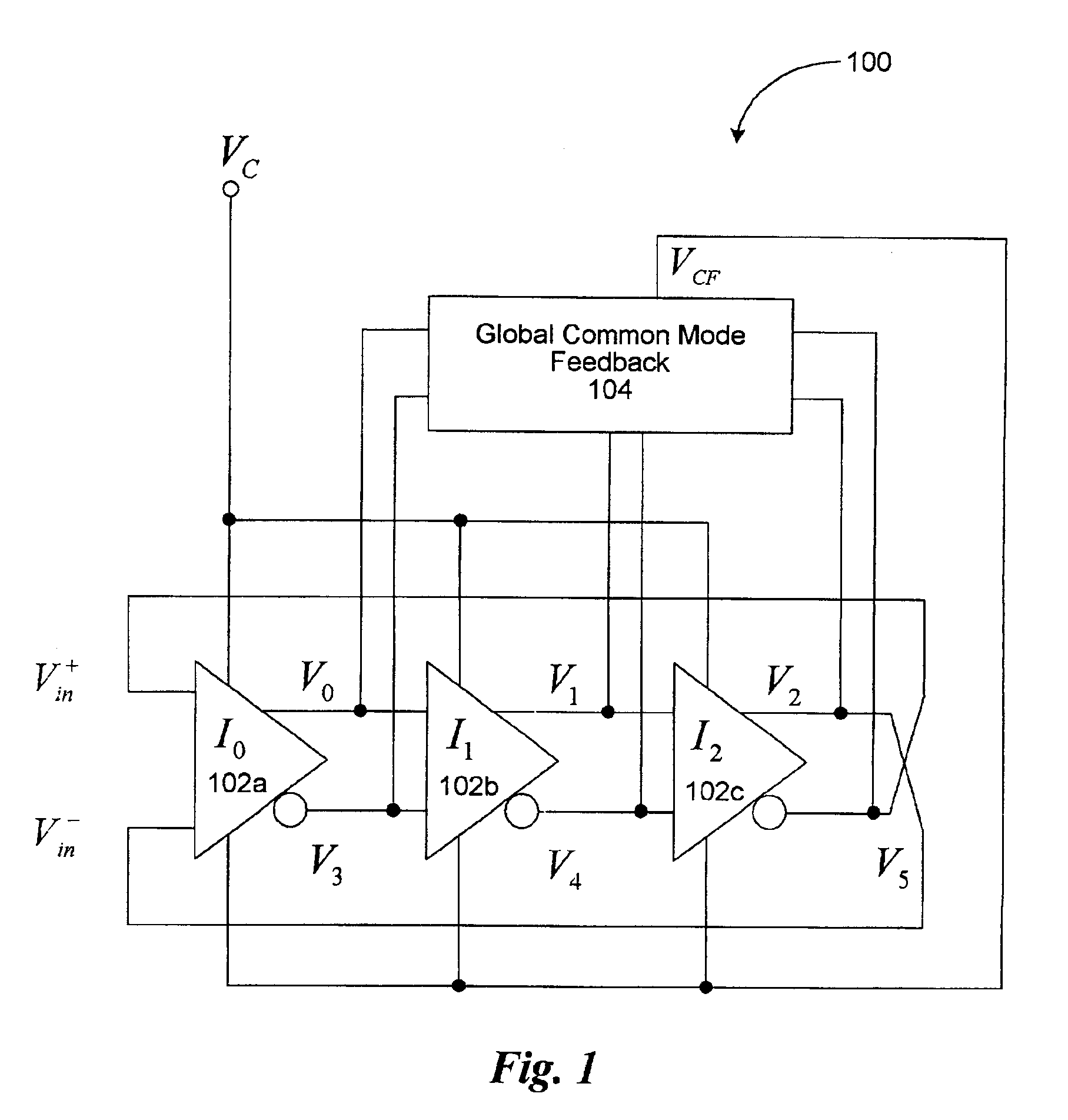

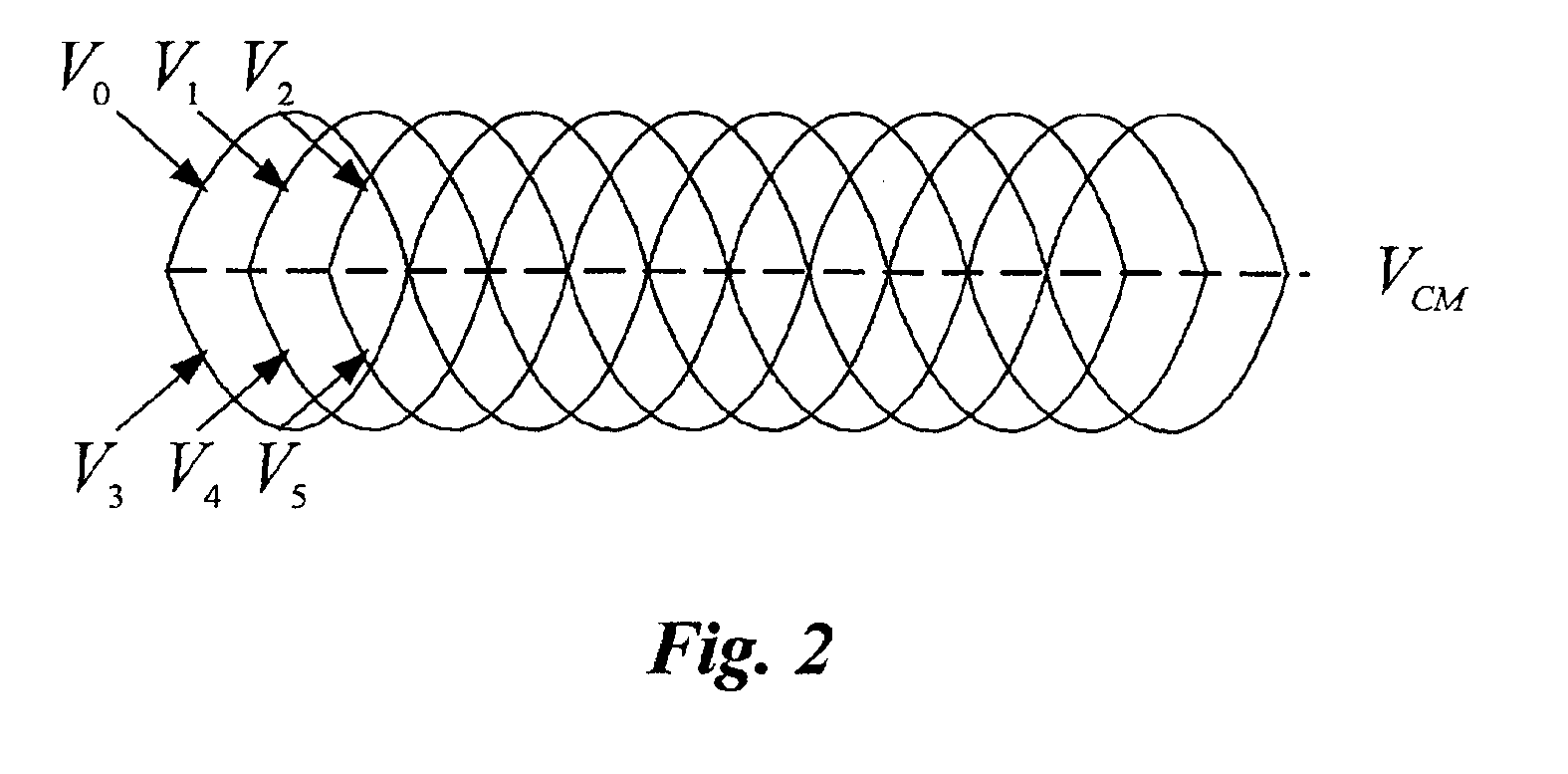

Multi-phase voltage controlled oscillator (VCO) with common mode control

A voltage controlled oscillator ("VCO") circuit capable of generating signals with reduced jitter and / or low-phase noise is provided. One embodiment provides a plurality of cascaded VCO cells, where each VCO cell can include a source coupled differential pair, a bias transistor connected to the differential pair for biasing the differential pair, a resistive load pair connected to the differential pair, and a voltage controlled capacitor pair or varactor pair connected to the differential pair. The varactors provide control over the frequency of the oscillations produced by the VCO circuit in combination with a control voltage. A phase frequency detector combined with a charge pump and loop filter provide the control voltage.

Owner:UNIVERSAL CONNECTIVITY TECH INC