Patents

Literature

862 results about "Greek letter sigma" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Sigma (upper-case Σ, lower-case σ, lower-case in word-final position ς; Greek: σίγμα) is the eighteenth letter of the Greek alphabet.

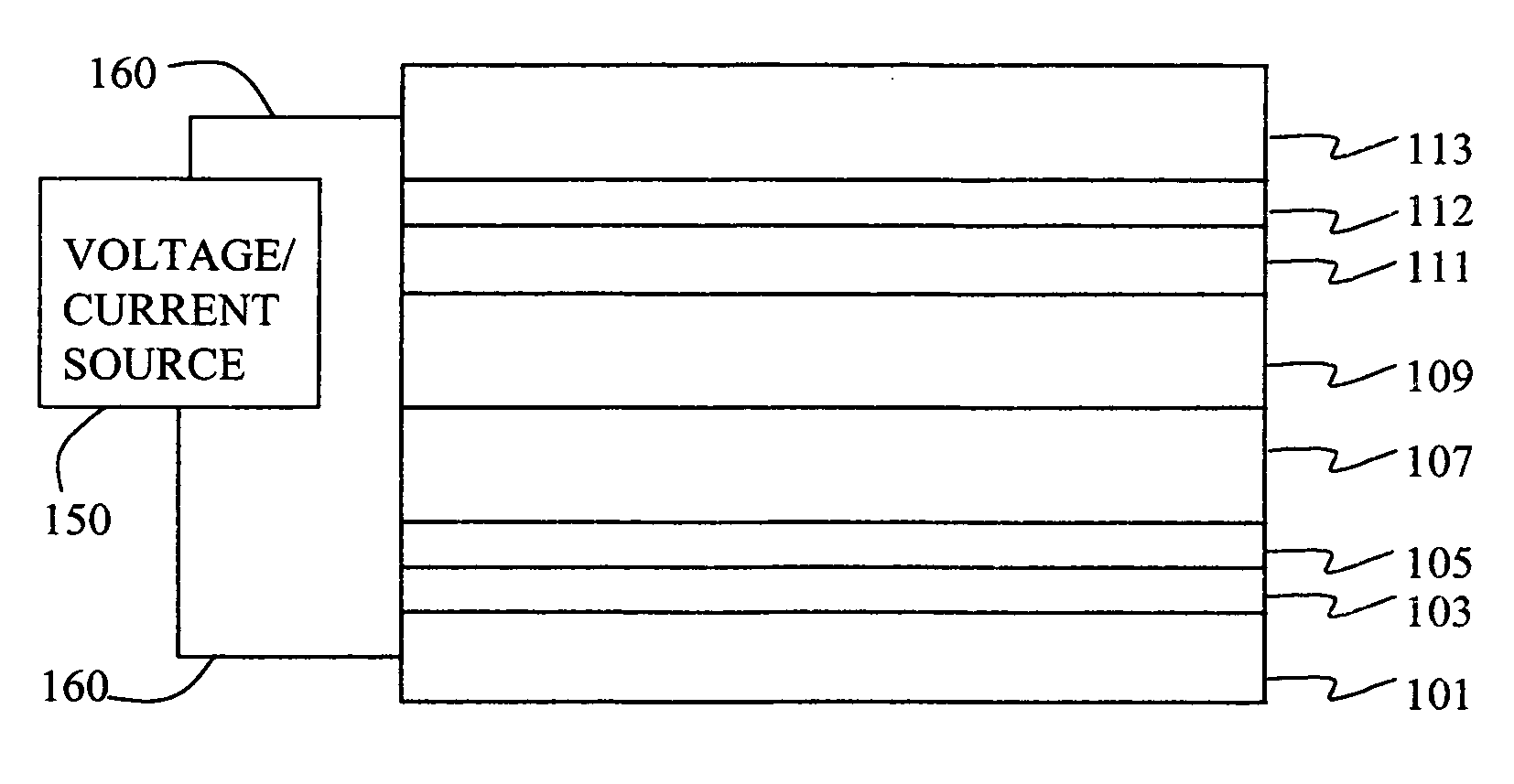

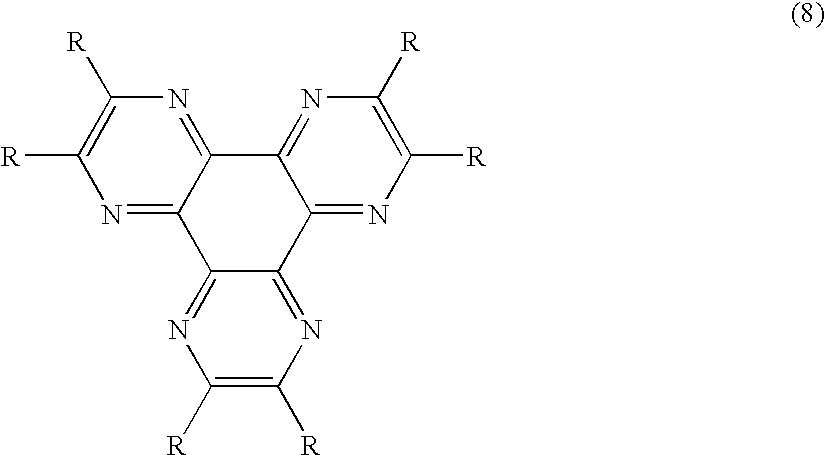

Organic element for low voltage electroluminescent devices

InactiveUS20070092755A1Reduce the driving voltageIncrease brightnessDischarge tube luminescnet screensLamp detailsHydrogenLow voltage

An OLED device comprises a cathode, a light emitting layer and an anode, in that order, and comprises; (i) a further layer located between the cathode and the light emitting layer, containing (a) 10 vol % or more of a carbocyclic fused ring aromatic compound, and (b) at least one salt or complex of a Group IA, IIA, IIIA and IIB element of the Periodic Table, and (ii) an additional layer, located between the anode and the light emitting layer, containing a compound of Formula (8) wherein: each R independently represents hydrogen or an independently selected substituent, at least one R representing an electron-withdrawing substituent having a Hammett's sigma para value of at least 0.3. Such devices exhibit reduce drive voltage while maintaining good luminance.

Owner:EASTMAN KODAK CO

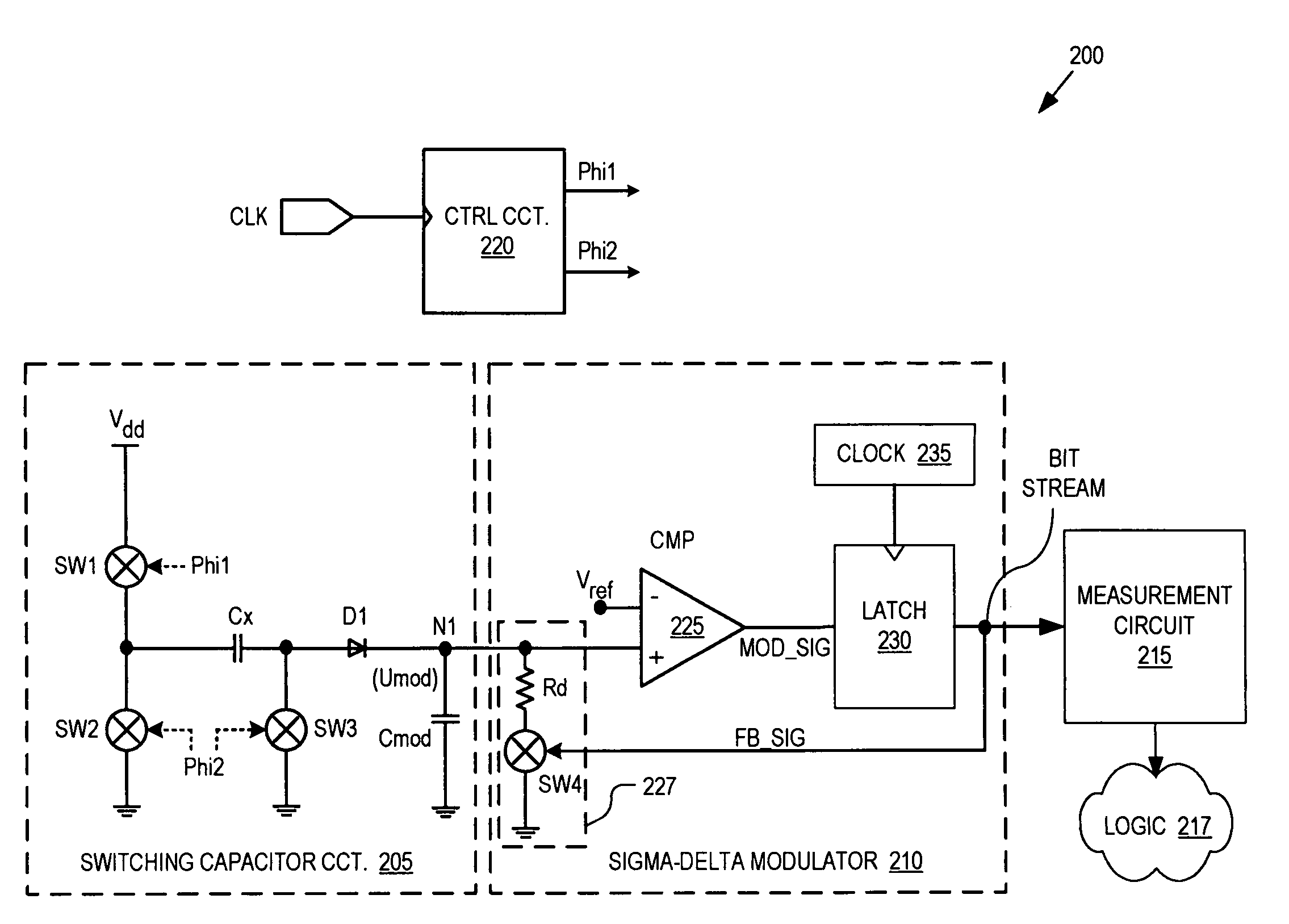

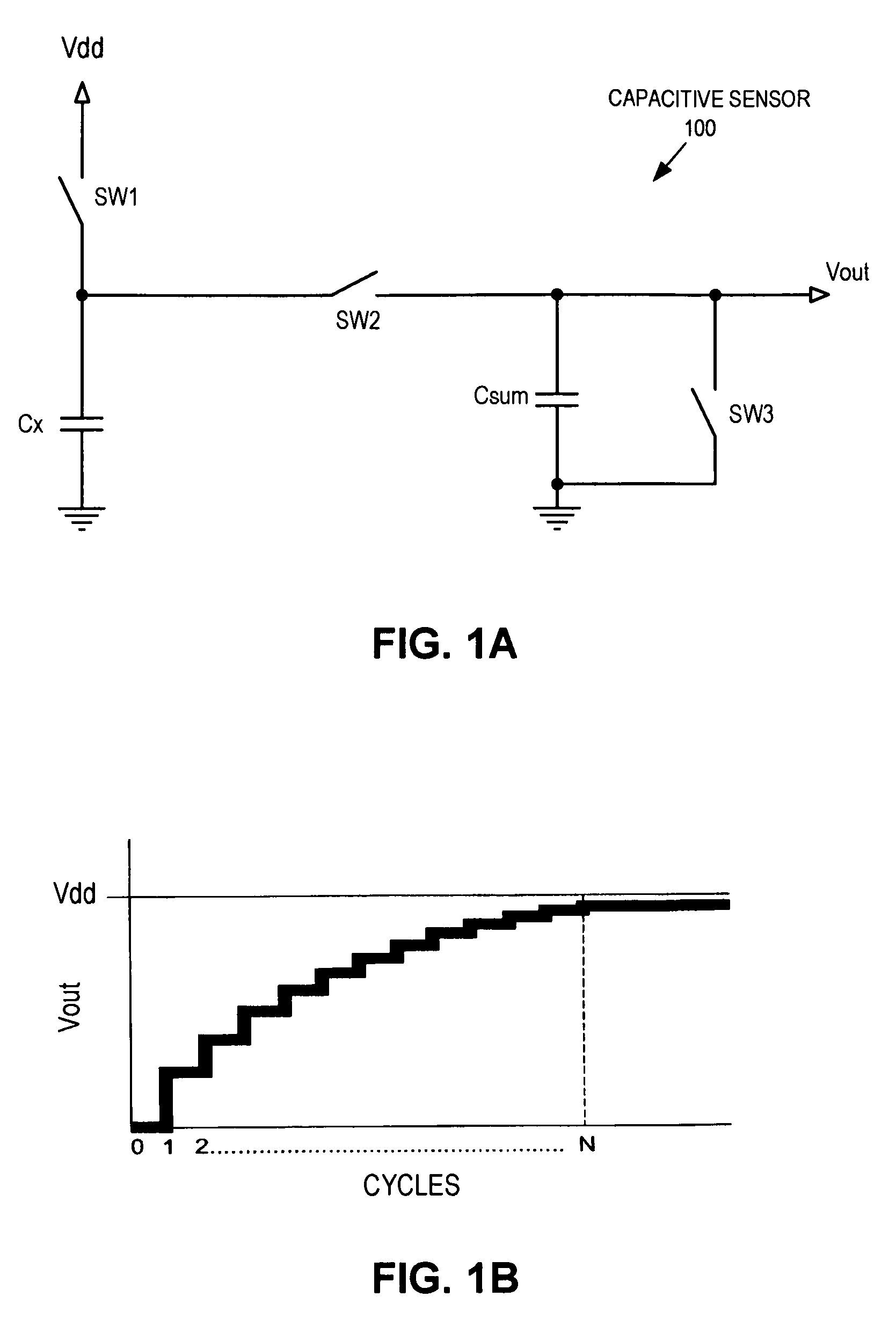

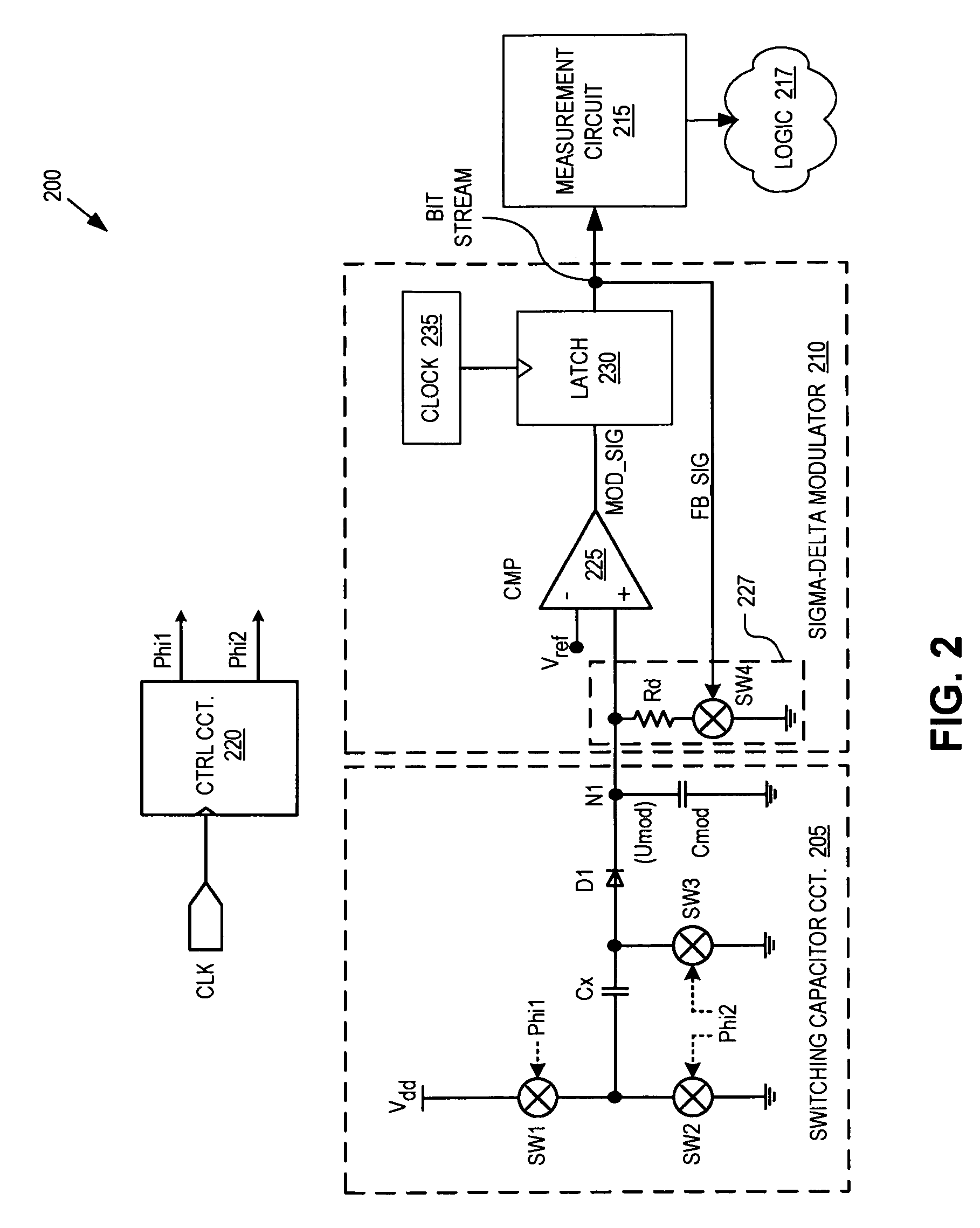

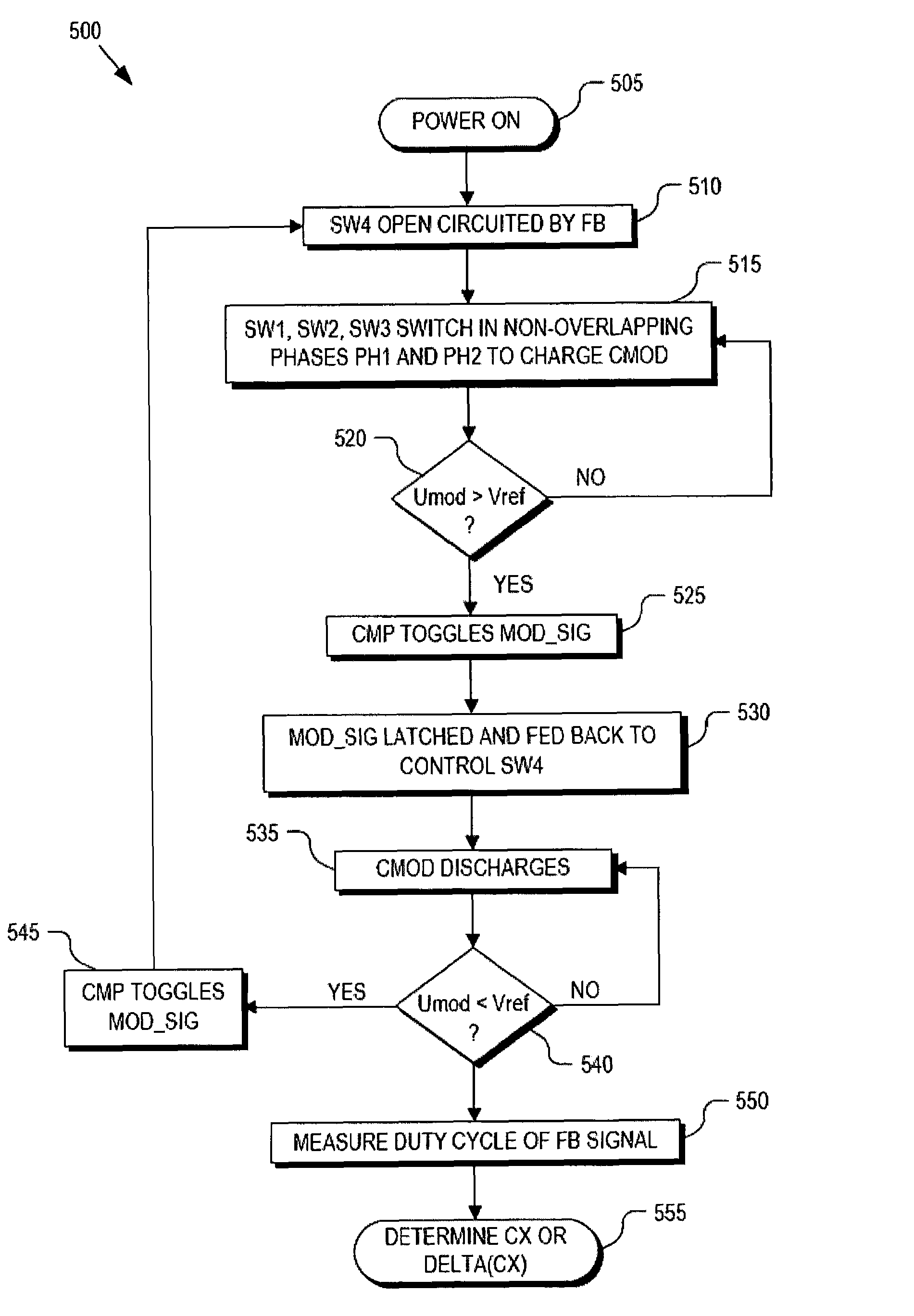

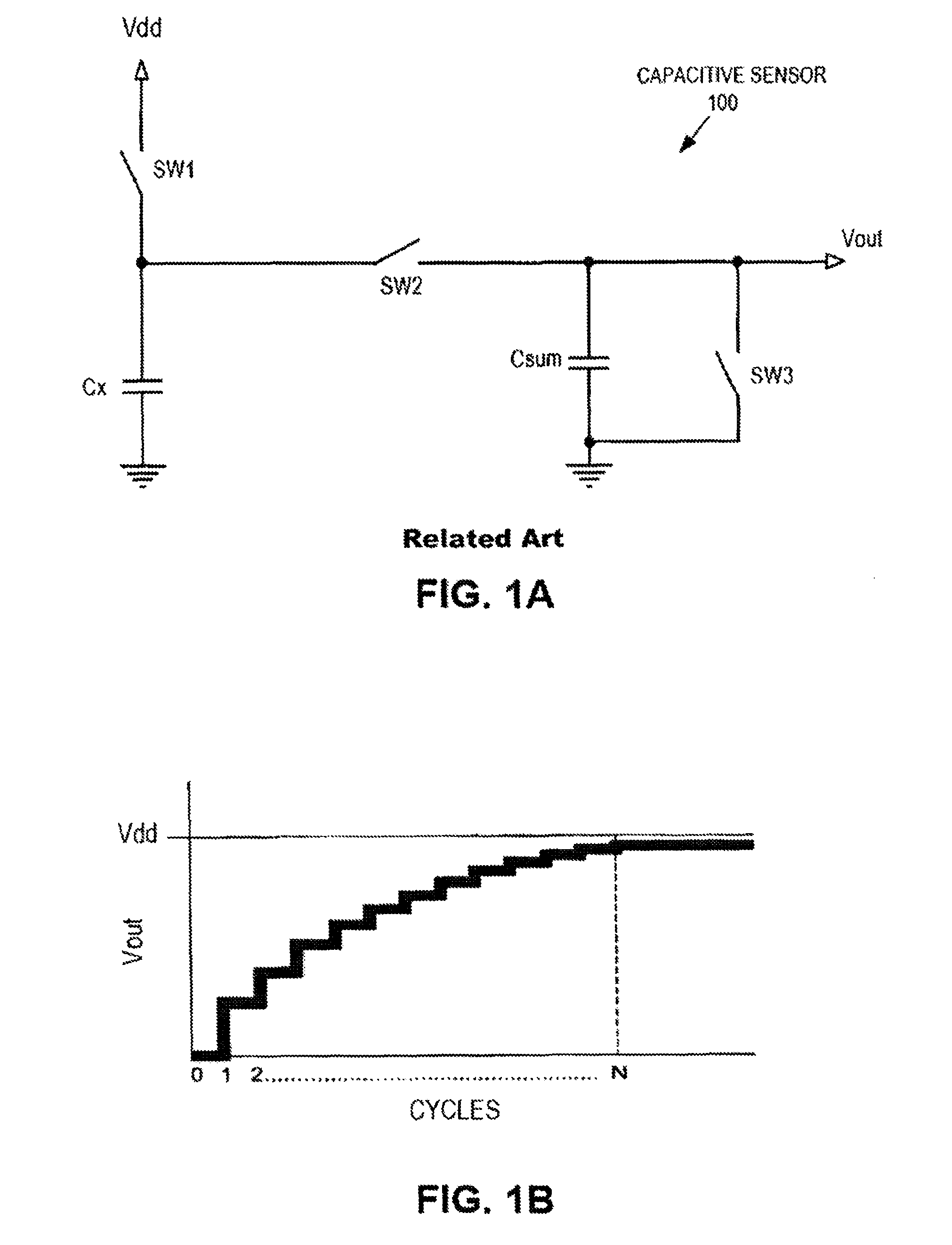

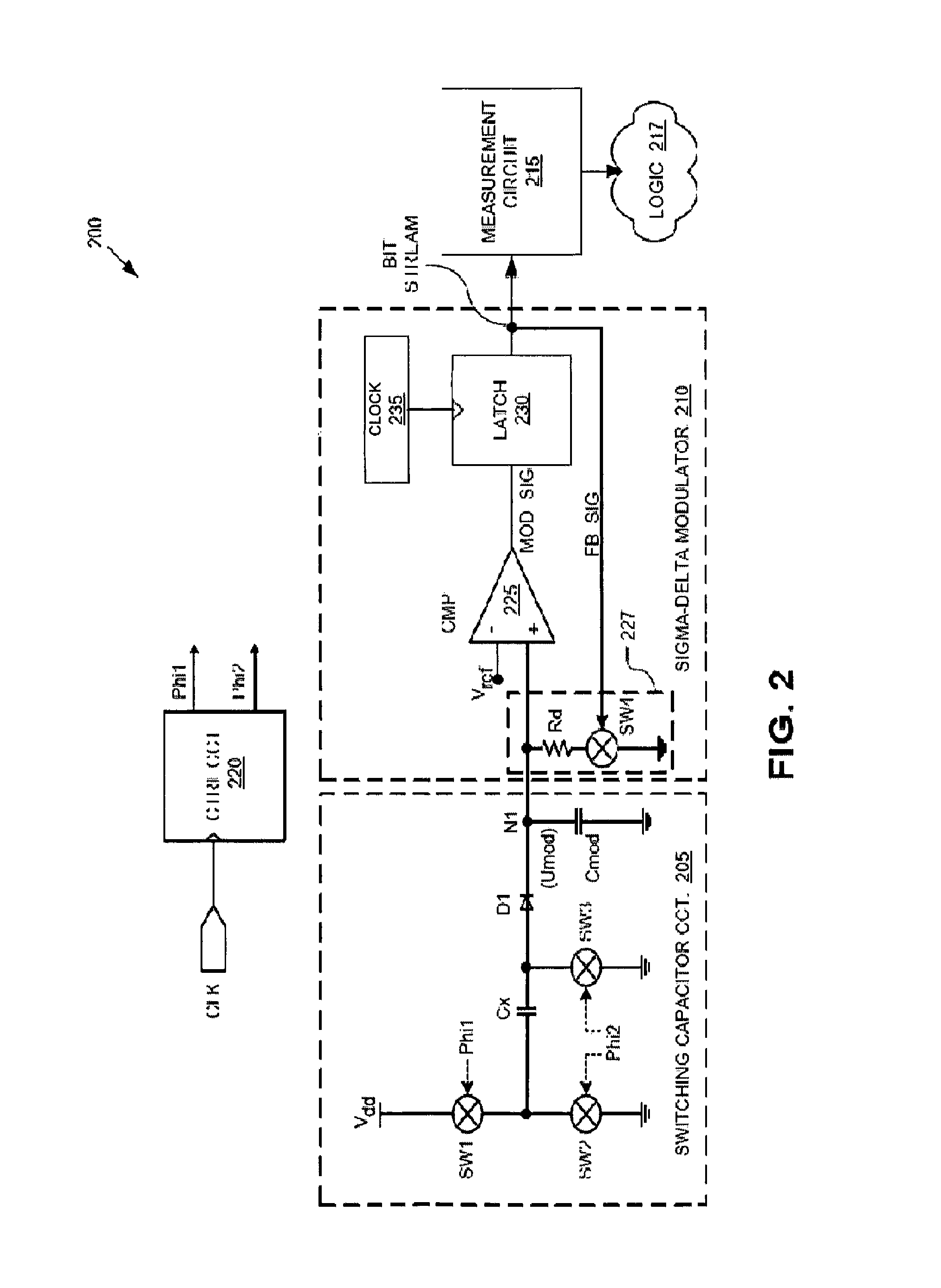

Capacitive field sensor with sigma-delta modulator

A capacitive sensor includes a switching capacitor circuit, a comparator, and a charge dissipation circuit. The switching capacitor circuit reciprocally couples a sensing capacitor in series with a modulation capacitor during a first switching phase and discharges the sensing capacitor during a second switching phase. The comparator is coupled to compare a voltage potential on the modulation capacitor to a reference and to generate a modulation signal in response. The charge dissipation circuit is coupled to the modulation capacitor to selectively discharge the modulation capacitor in response to the modulation signal.

Owner:CYPRESS SEMICON CORP

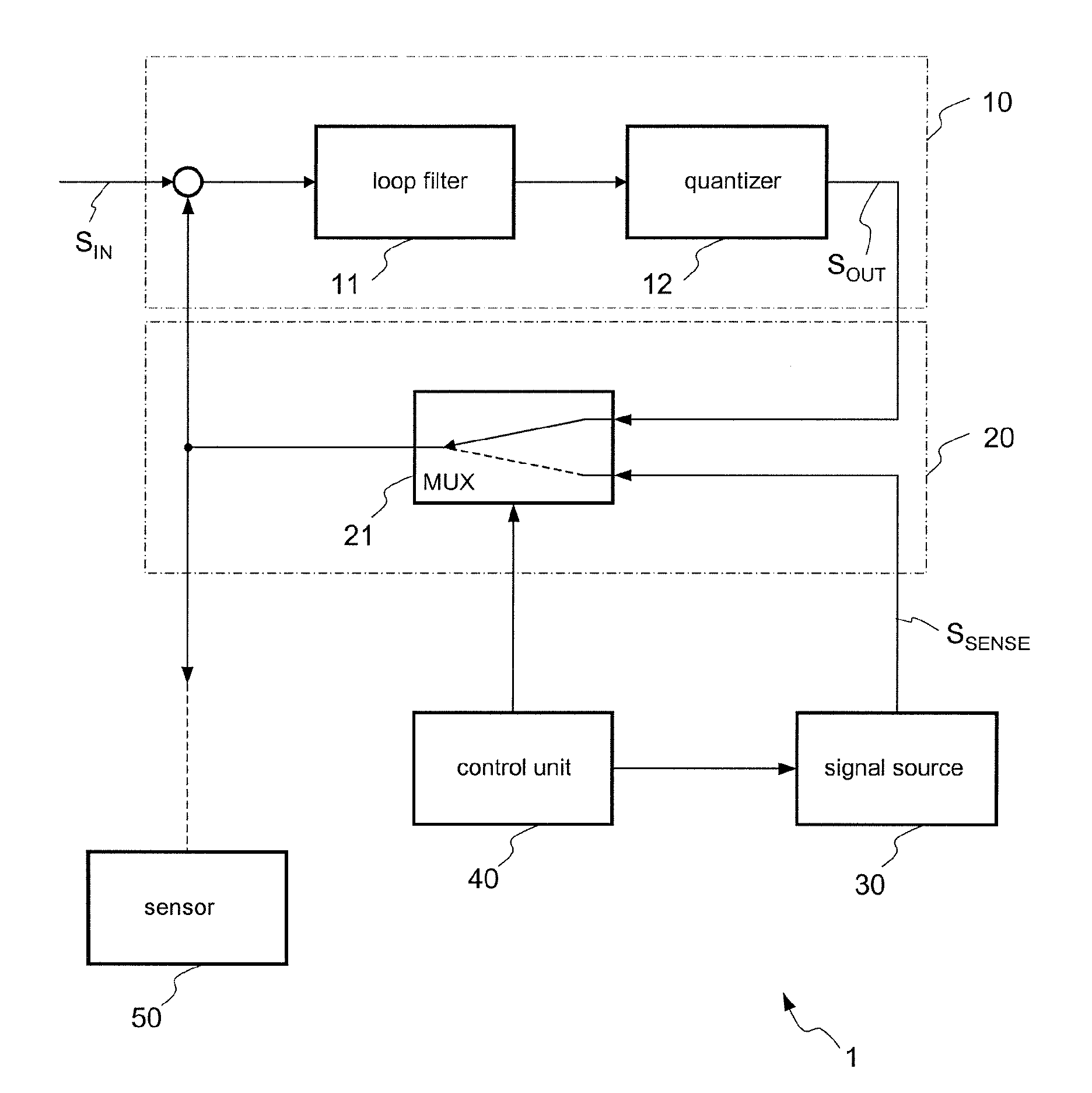

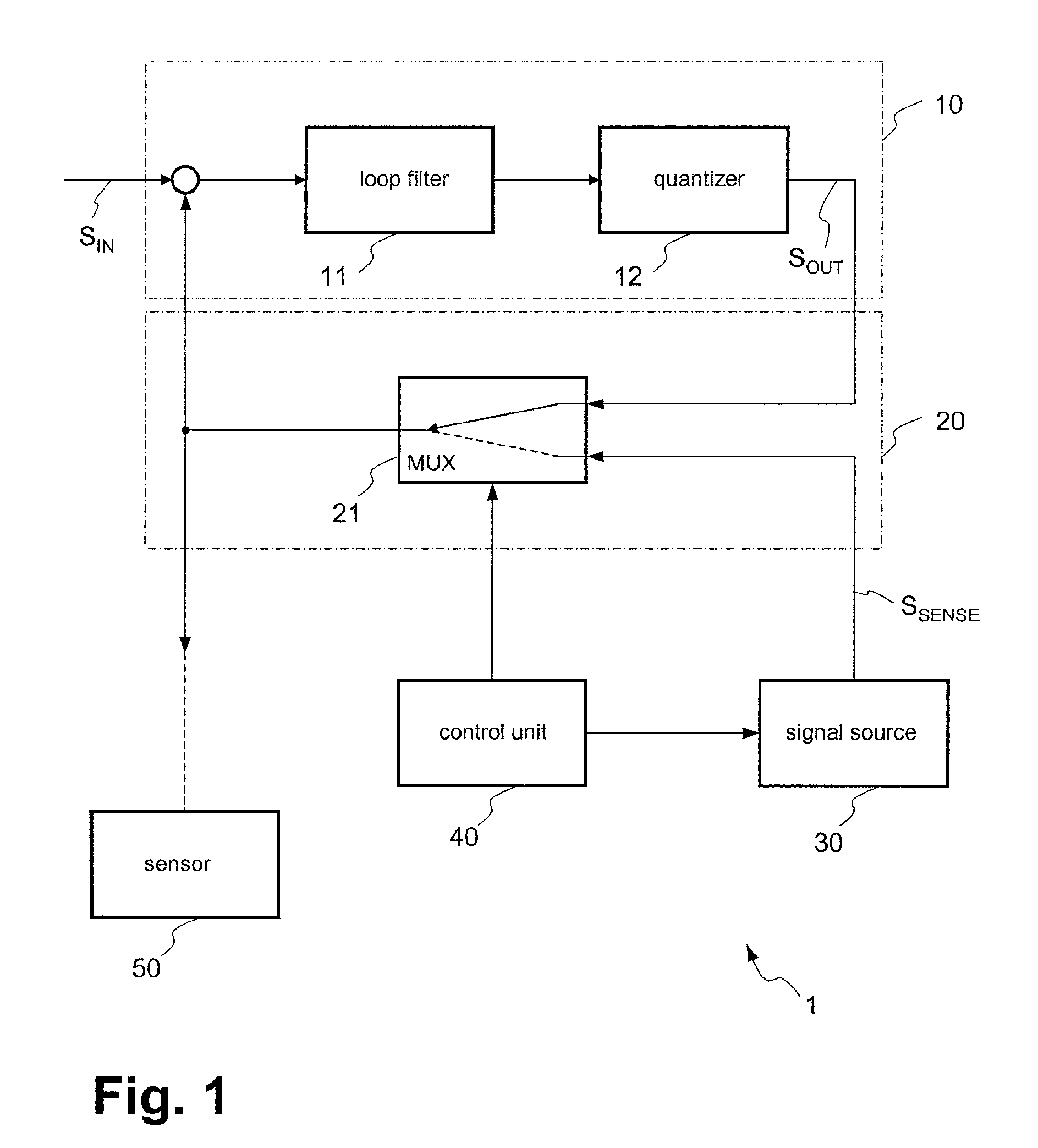

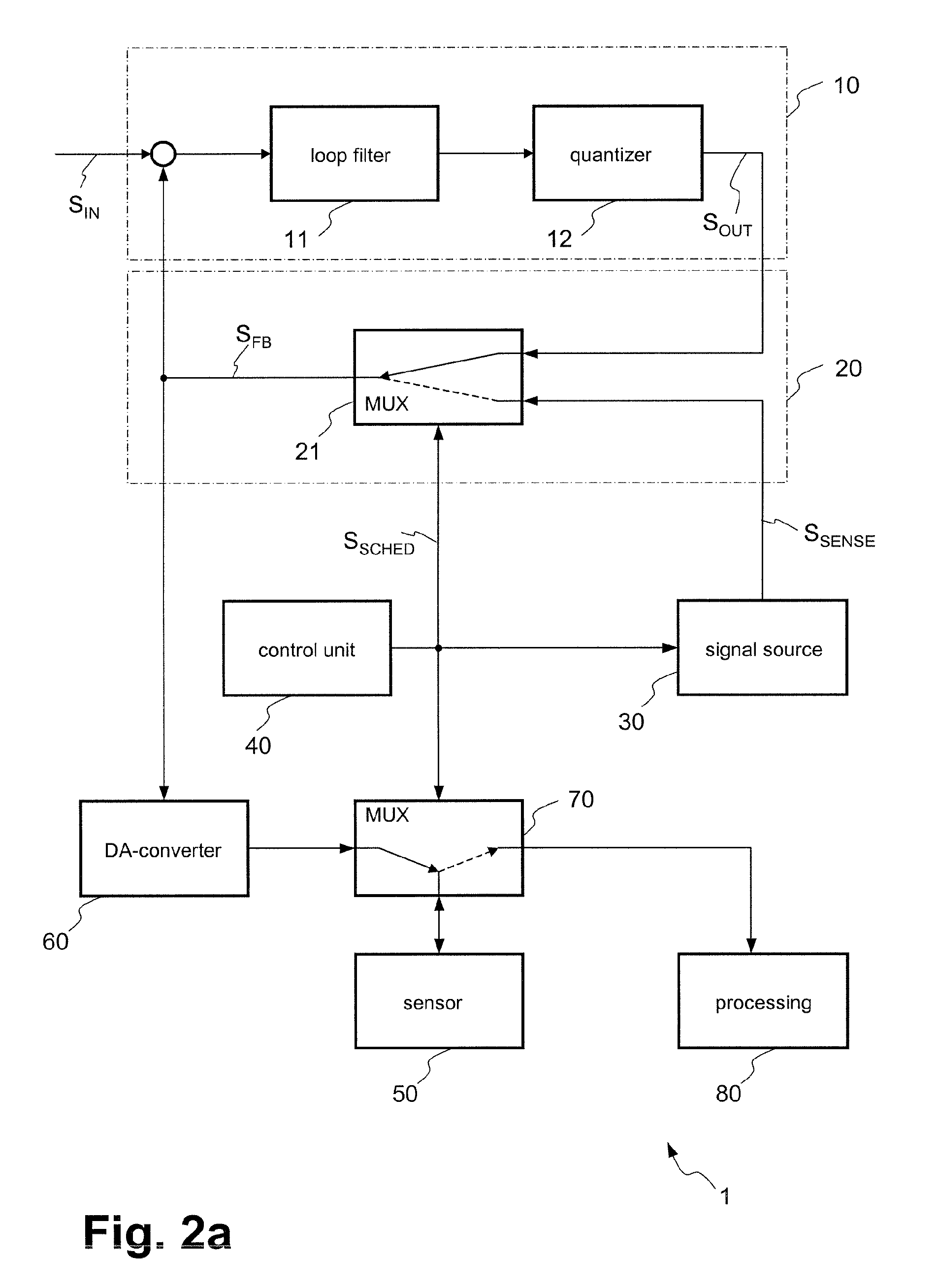

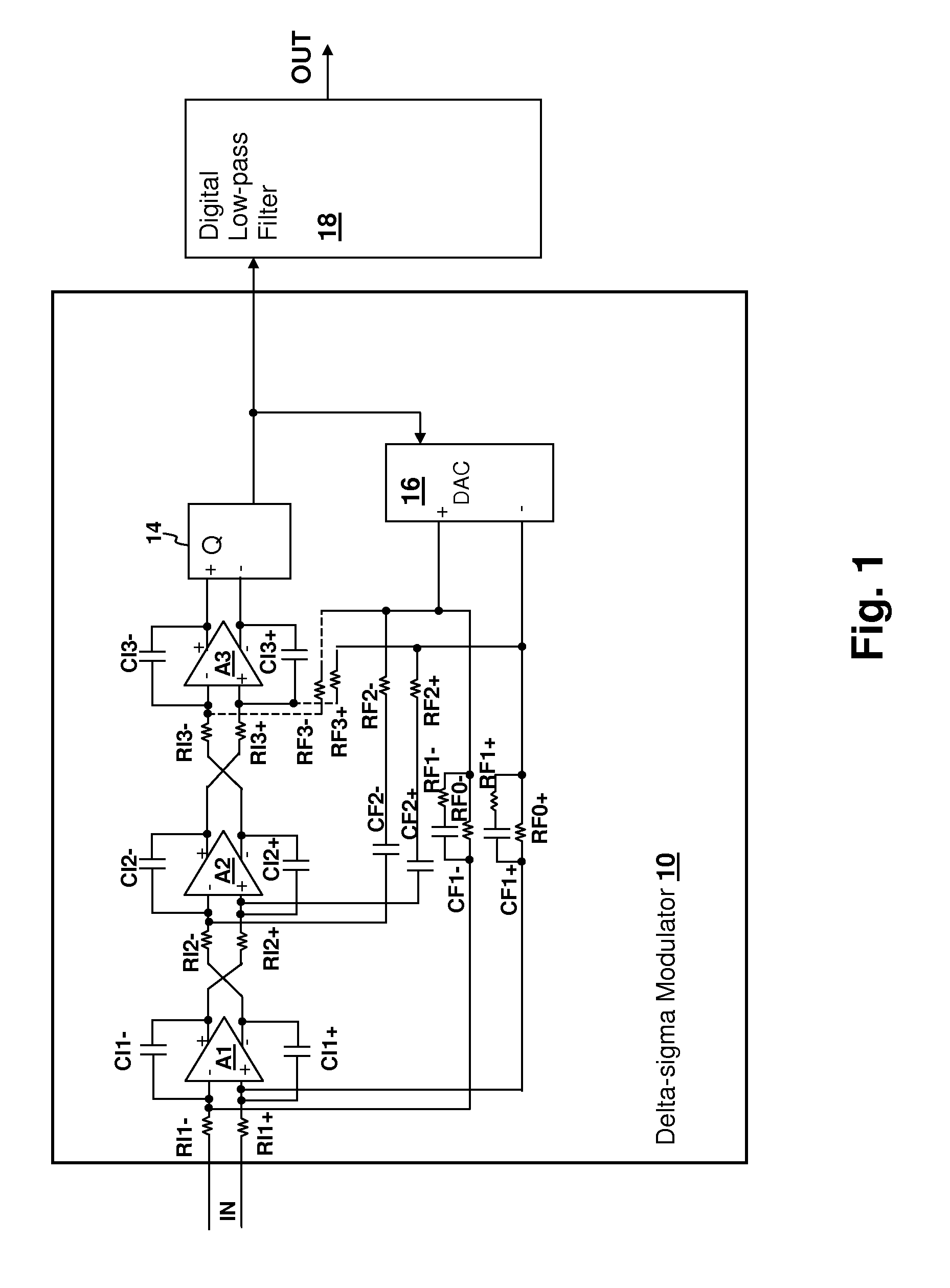

Sigma-delta modulator for operating sensors

InactiveUS7528755B2Electric signal transmission systemsAcceleration measurement using interia forcesLoop filterControl signal

A sigma-delta modulator can be used for actuating a sensor element. The sigma delta modulator includes: a forward branch to which an input signal is fed at an input and which includes a loop filter, a quantizer and an output for providing an output signal. A feedback branch is configured to feed back the output signal of the forward branch at least temporarily to the input of the forward branch. A signal source is configured to generate a readout signal which corresponds to the voltage profile at the sensor element during a measuring process. A control unit is configured to generate a control signal dependent on which either the output signal of the forward branch or the readout signal of the signal source is fed back to the input of the forward branch.

Owner:INFINEON TECH AG

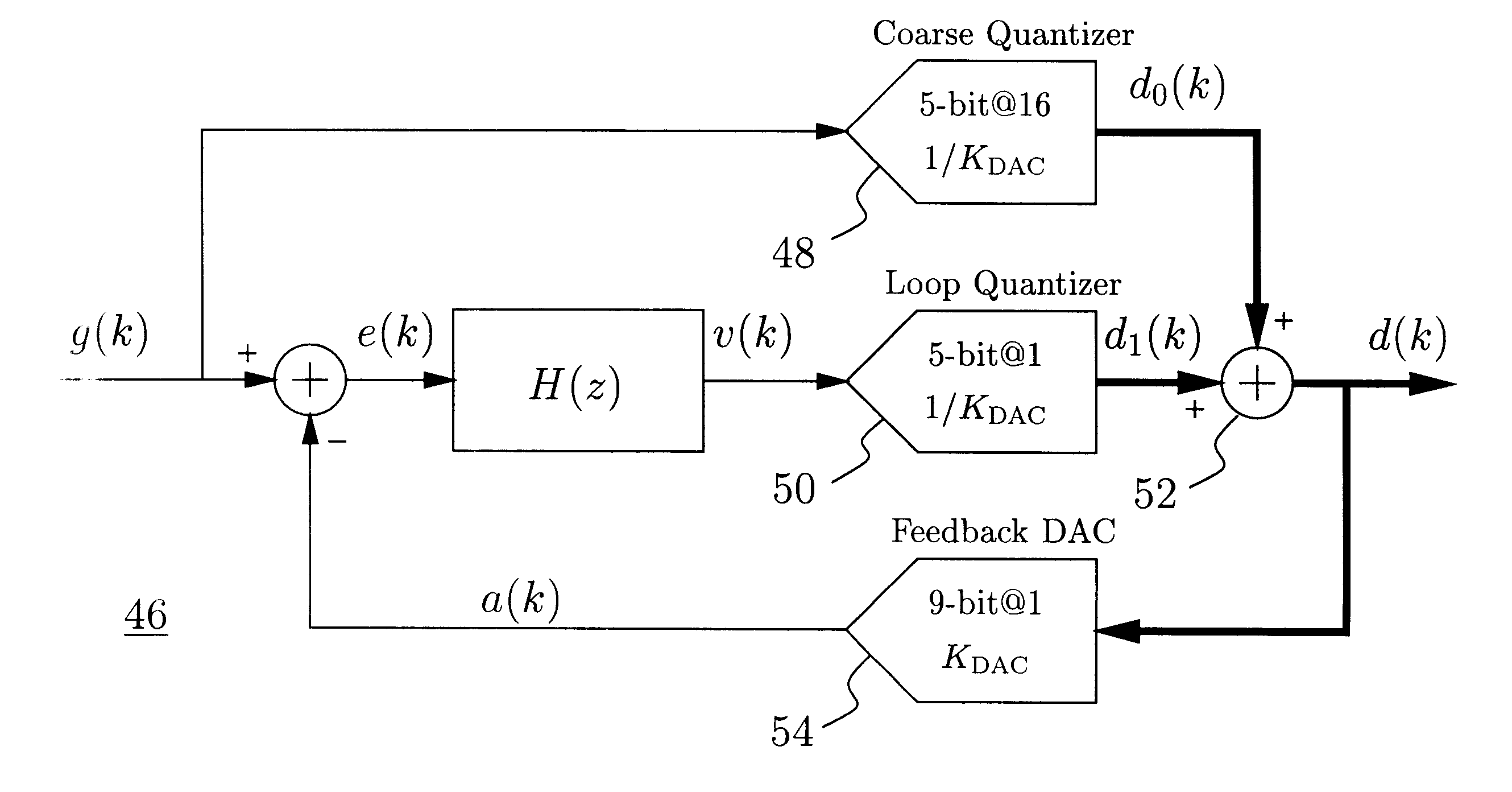

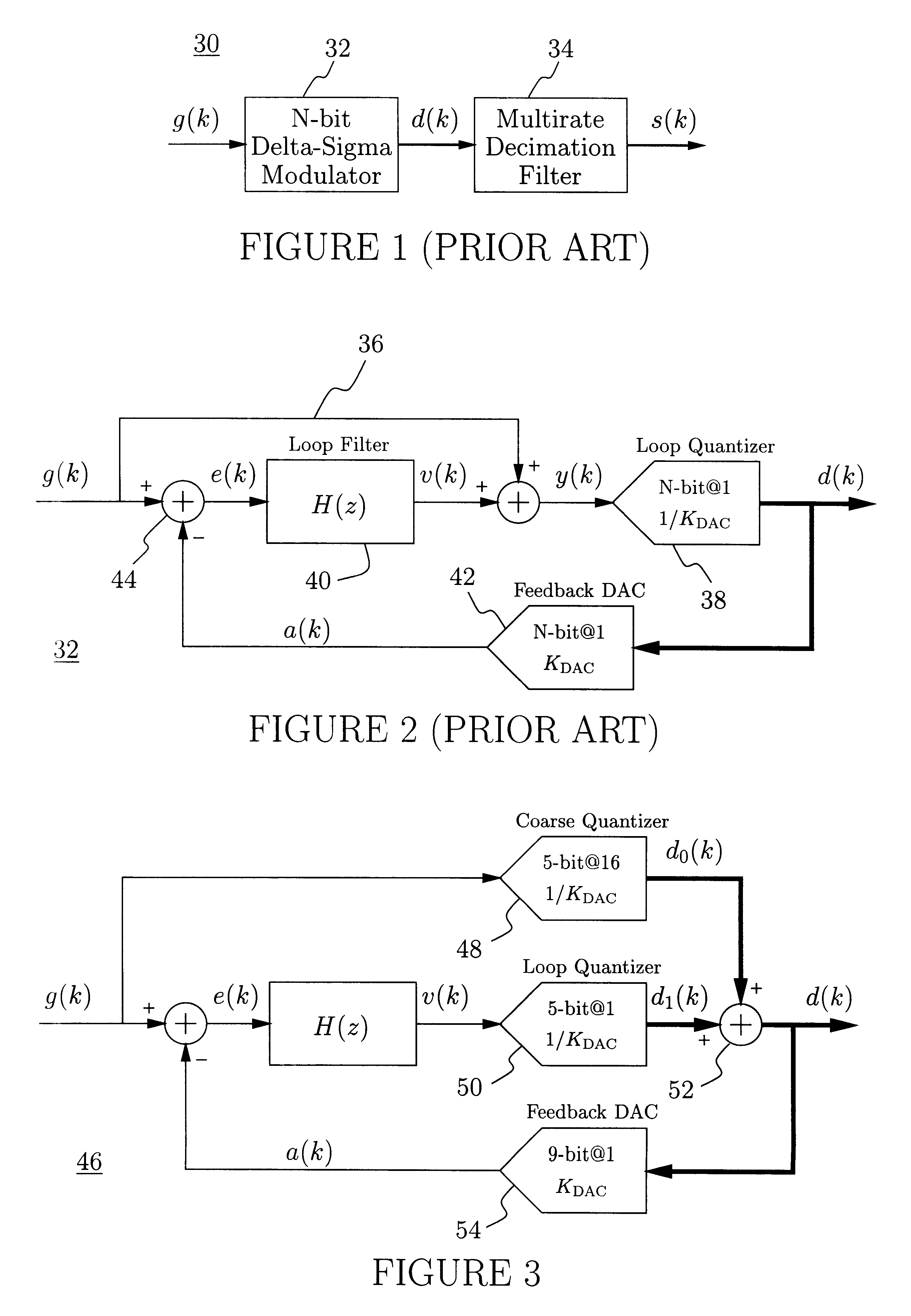

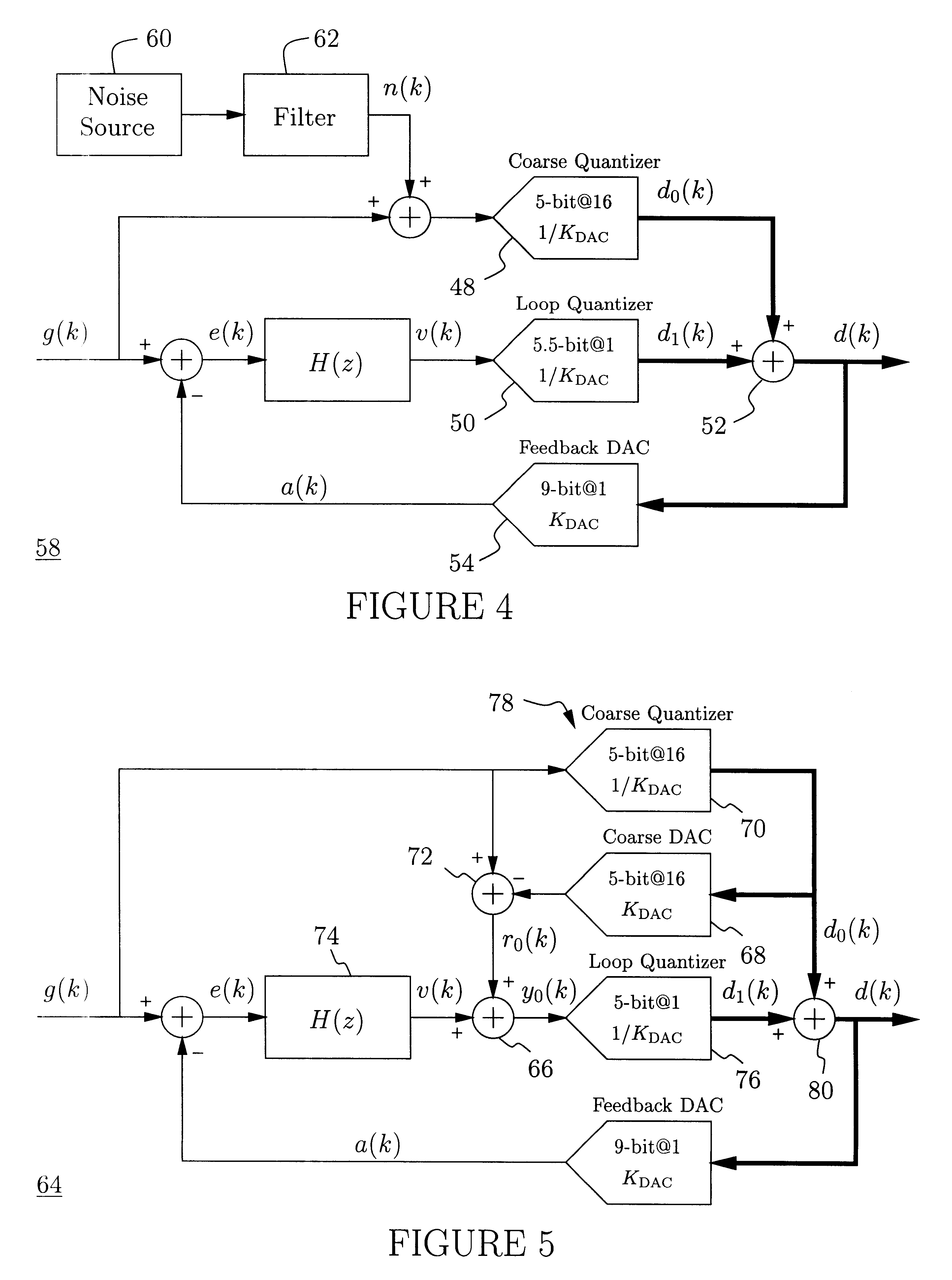

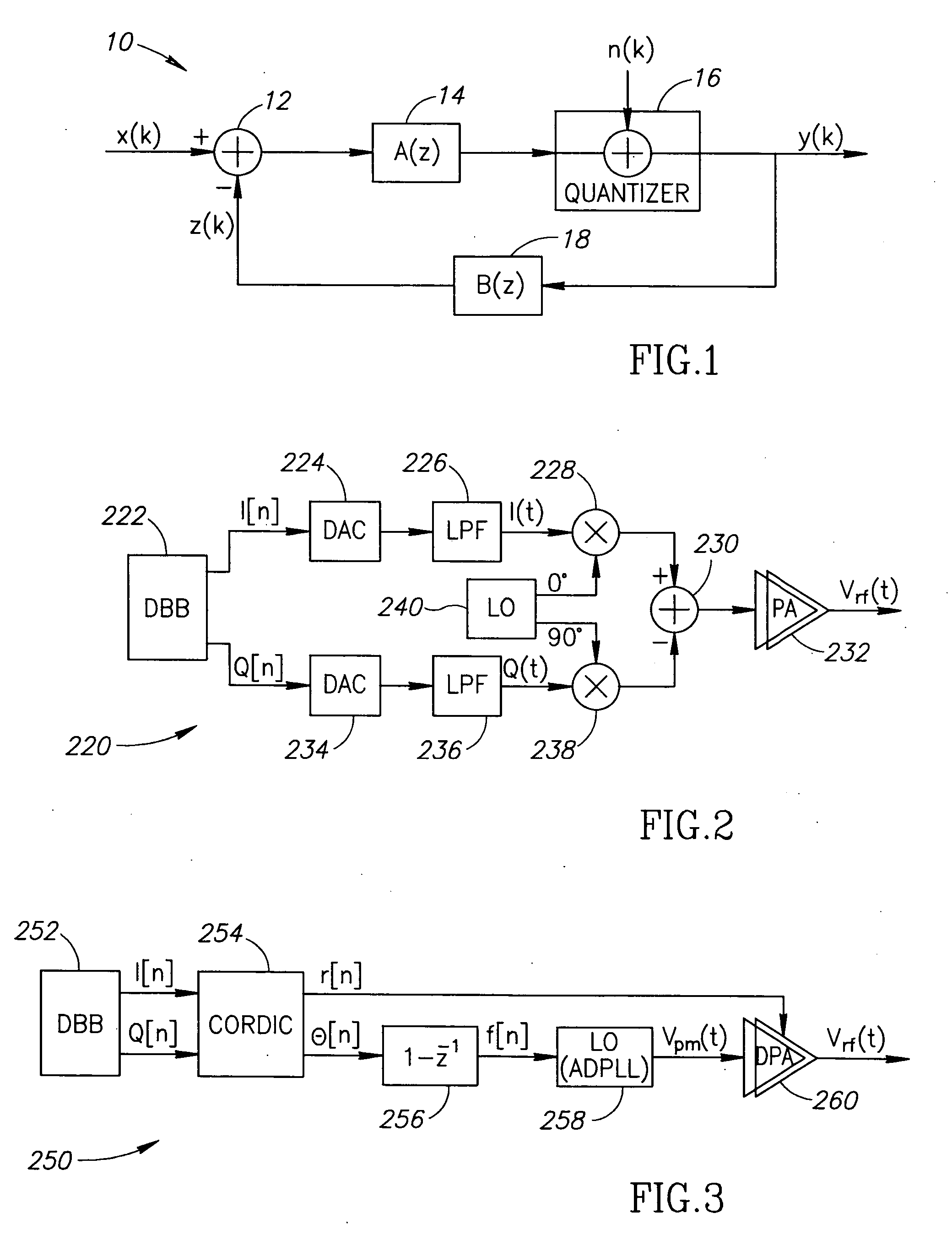

Delta-sigma A/D converter

InactiveUS6271782B1Without compromising the modulator's stabilityTo overcome the large delayElectric signal transmission systemsDifferential modulationLoop filterAnalog feedback

A delta-sigma modulator comprising a first quantizer providing a first digital signal d0(k) representing the input signal g(t); a loop filter with input signal paths; a loop quantizer providing a corrective digital signal d1(k) representing the loop filter's output signal y(t); an array of feedback DACs D / A converting the sum d(k)=df(k)=d0(k)+d1(k) of the first and the corrective digital signals and injecting feedback signals into the loop filter.The loop filter's input node is applied the difference of the input signal g(t) and the global analog feedback signal a3(t). The global feedback signal a3(t) is delayed several clock cycles with respect to the digital output signal d(k). The delay is used to carry out mismatch-shaping and deglitching algorithms in the feedback DACs. The feedback DACs' different delays and gain coefficients are designed such that the modulator is stable. The filter's input signal paths and the compensating DAC are designed such that the gain from the input signal g(t) to the loop quantizer is small, ideally zero. Thus, the loop quantizer's resolving range can be a fraction of the first quantizer's resolving range, whereby the output signal's d(k) resolution can be much higher than the individual resolutions of d0(k) and d1(k).The delta-sigma modulator is well suited for the implementation of high-resolution wide-bandwidth A / D converters. Important applications include digital communication systems.

Owner:ANALOG DEVICES BV

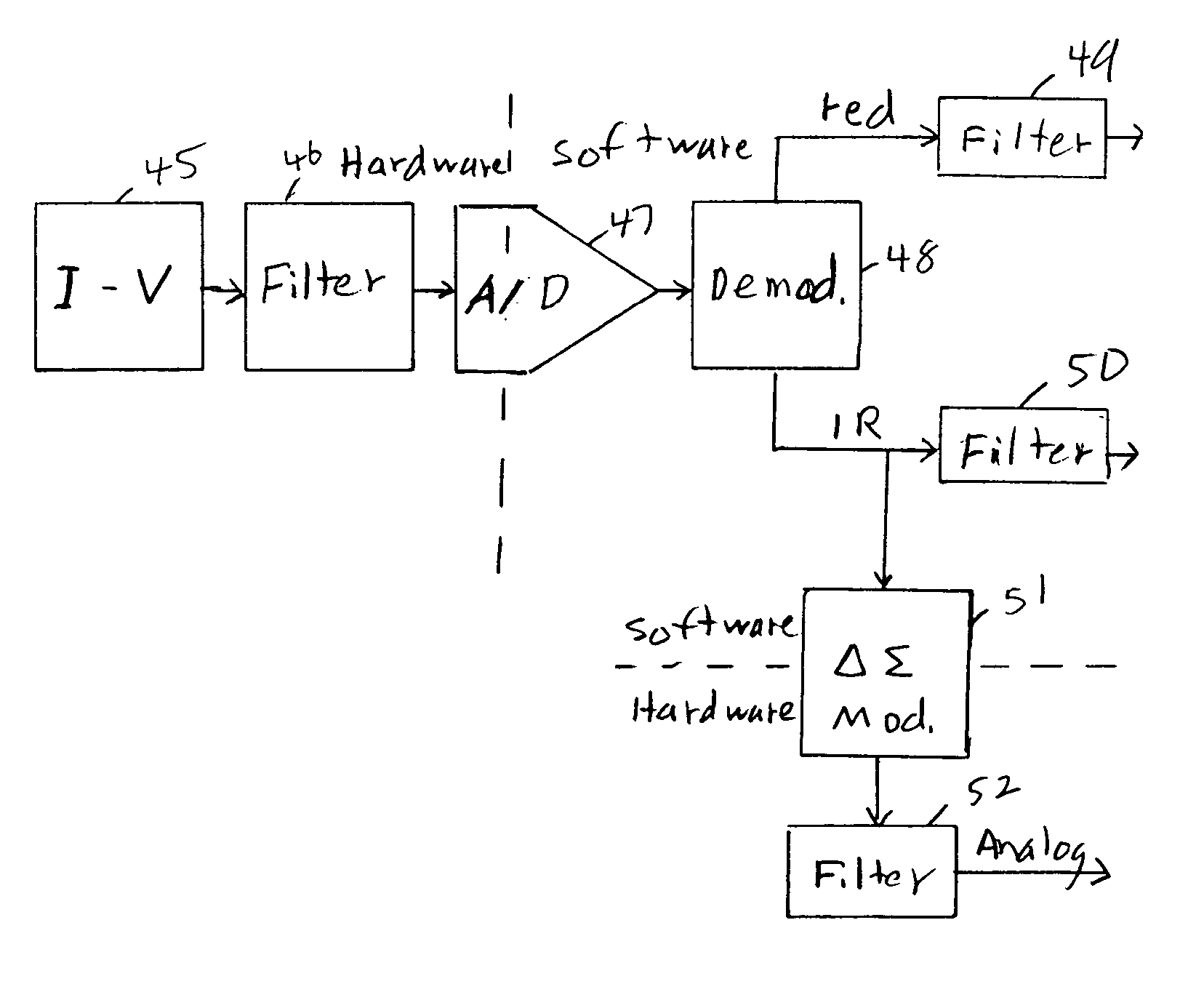

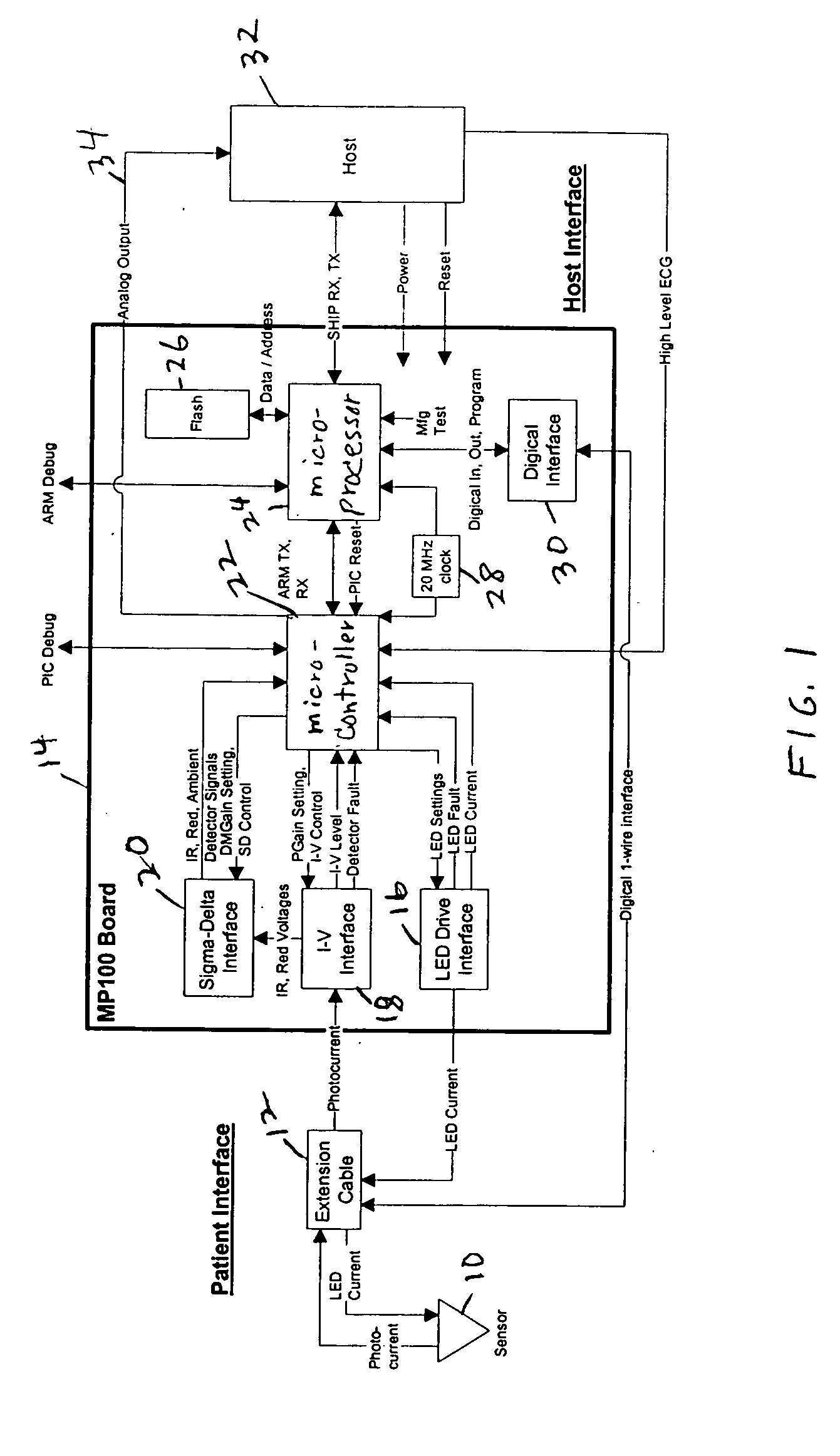

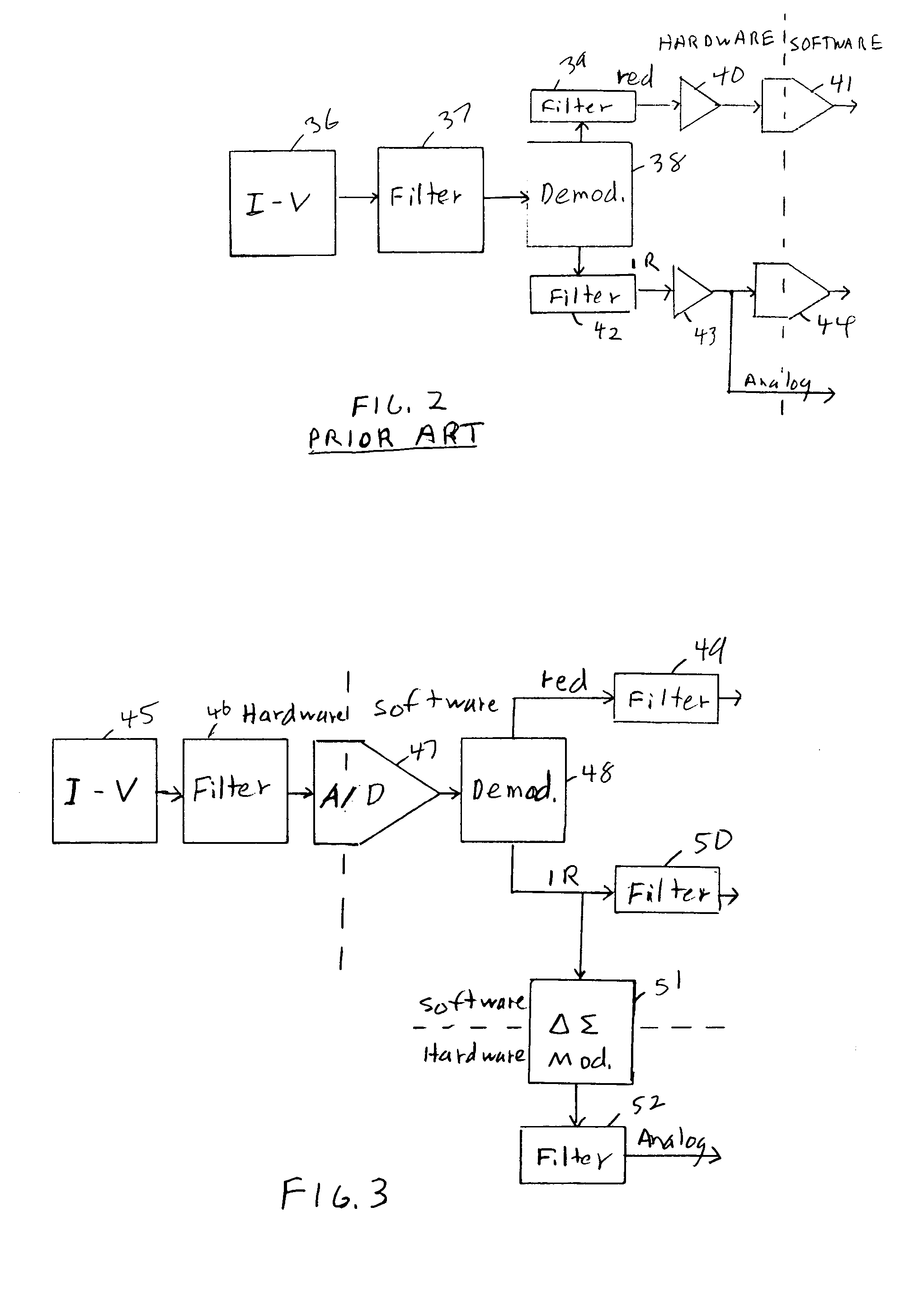

Delta-sigma modulator for outputting analog representation of physiological signal

ActiveUS20050187453A1Quick conversionReduce noiseCatheterDiagnostic recording/measuringWave shapeGreek letter sigma

A method and apparatus for providing a substantially real-time representation of an analog representation of a physiological signal. The waveform signal from the sensor is converted into digital form. A delta-sigma modulator is used as a simple Digital-to-analog Converter (ADC). The output can then be provided through a simple hardware filter to give an analog output signal in nearly real-time, which can be used for other instruments, synchronization, display, etc.

Owner:TYCO HEALTHCARE GRP LP

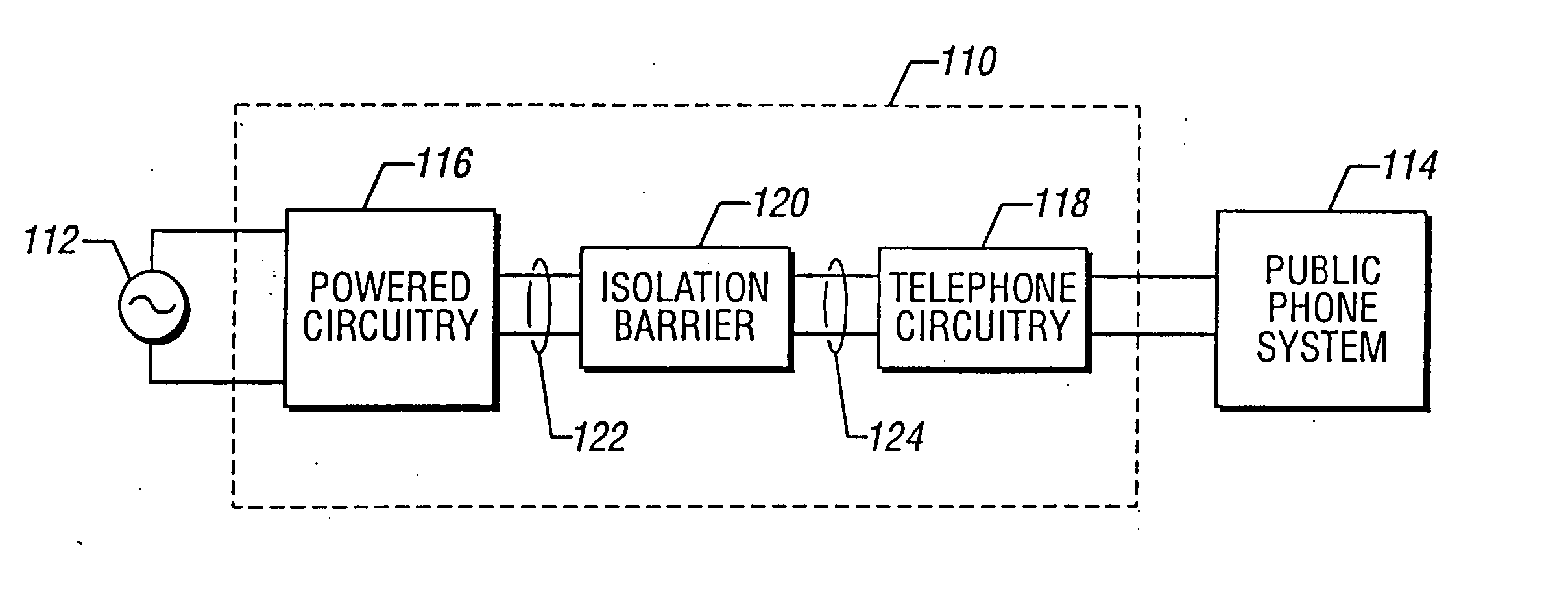

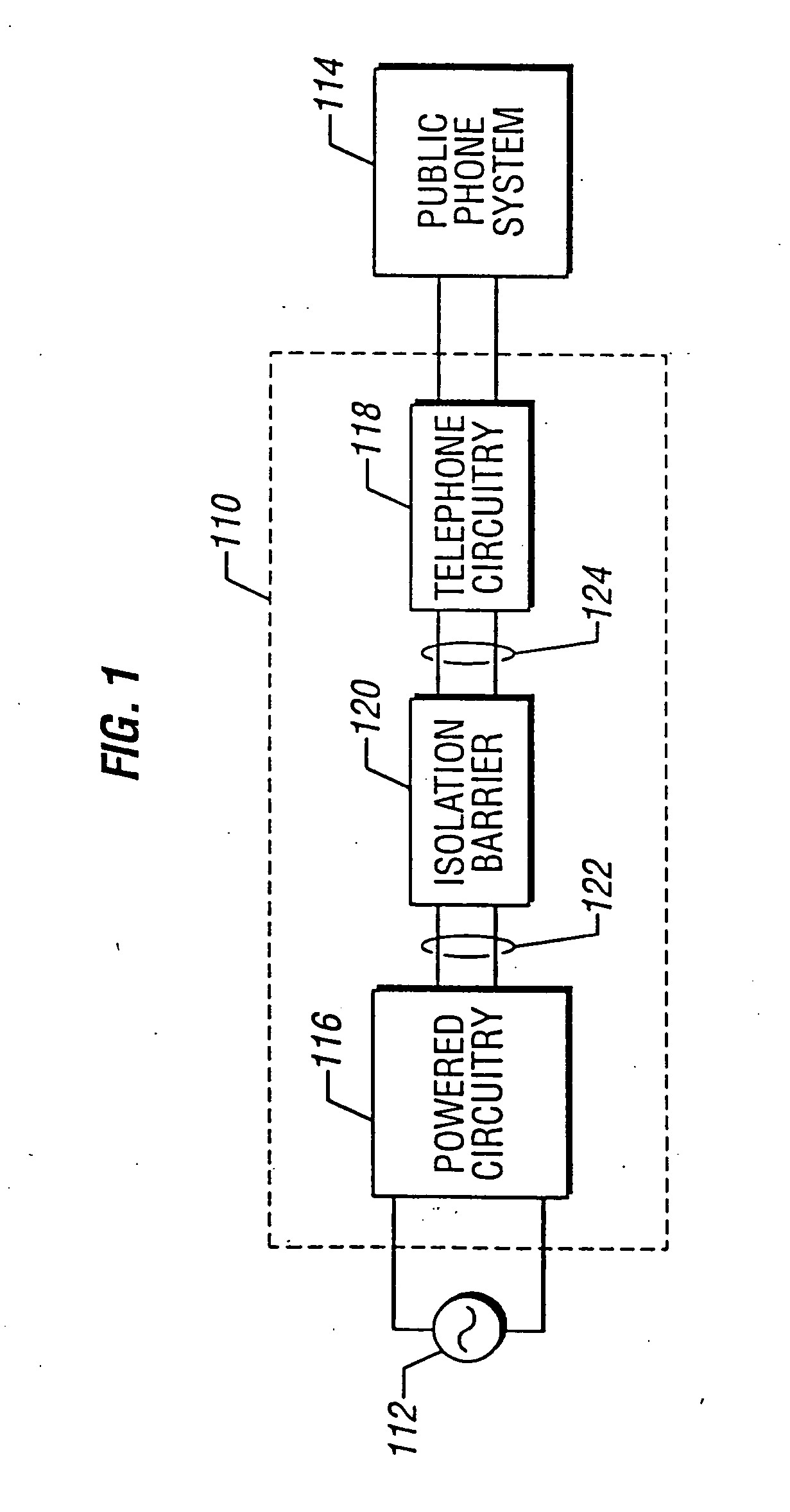

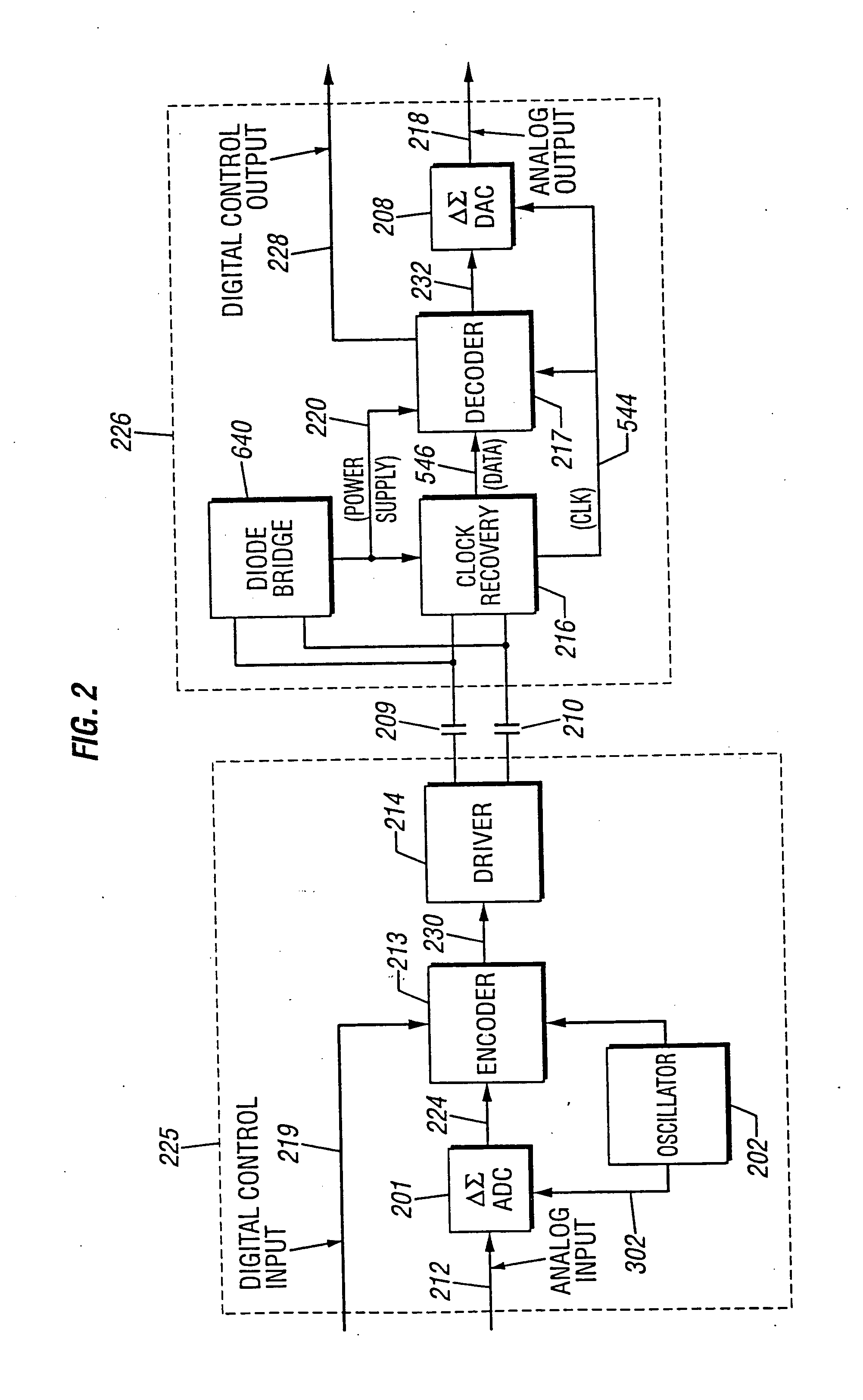

Direct digital access arrangement circuitry and method for connecting DSL circuitry to phone lines

InactiveUS20050036604A1Exact reproductionInterconnection arrangementsDc level restoring means or bias distort correctionCapacitanceDigital data

An isolation system is provided that is suitable for use in telephony, medical instrumentation, industrial process control and other applications. Preferred embodiments of the invention comprise a capacitive isolation barrier across which a digital signal is communicated. The system provides a means of communication across the isolation barrier that is highly immune to amplitude and phase noise interference. Clock recovery circuitry may be employed on one side of the isolation barrier to extract timing information from the digital signal communicated across the barrier, and to filter the effects of phase noise introduced at the barrier. Delta-sigma converters may be disposed on both sides of the isolation barrier to convert signals between analog and digital domains. An isolated power supply may also be provided on the isolated side of the barrier, whereby direct current is generated in response to the digital data received across the isolation barrier. A bidirectional isolation system is provided whereby bidirectional communication of digital signals is accomplished using a single pair of isolation capacitors. In preferred embodiments, the digital data communicated across the barrier consists of digital delta-sigma data signals multiplexed in time with other digital control, signaling and framing information. Finally, the isolation system may include a pulse transformer to accommodate ADSL circuitry, whereby power is transmitted through the pulse transformer.

Owner:SILICON LAB INC

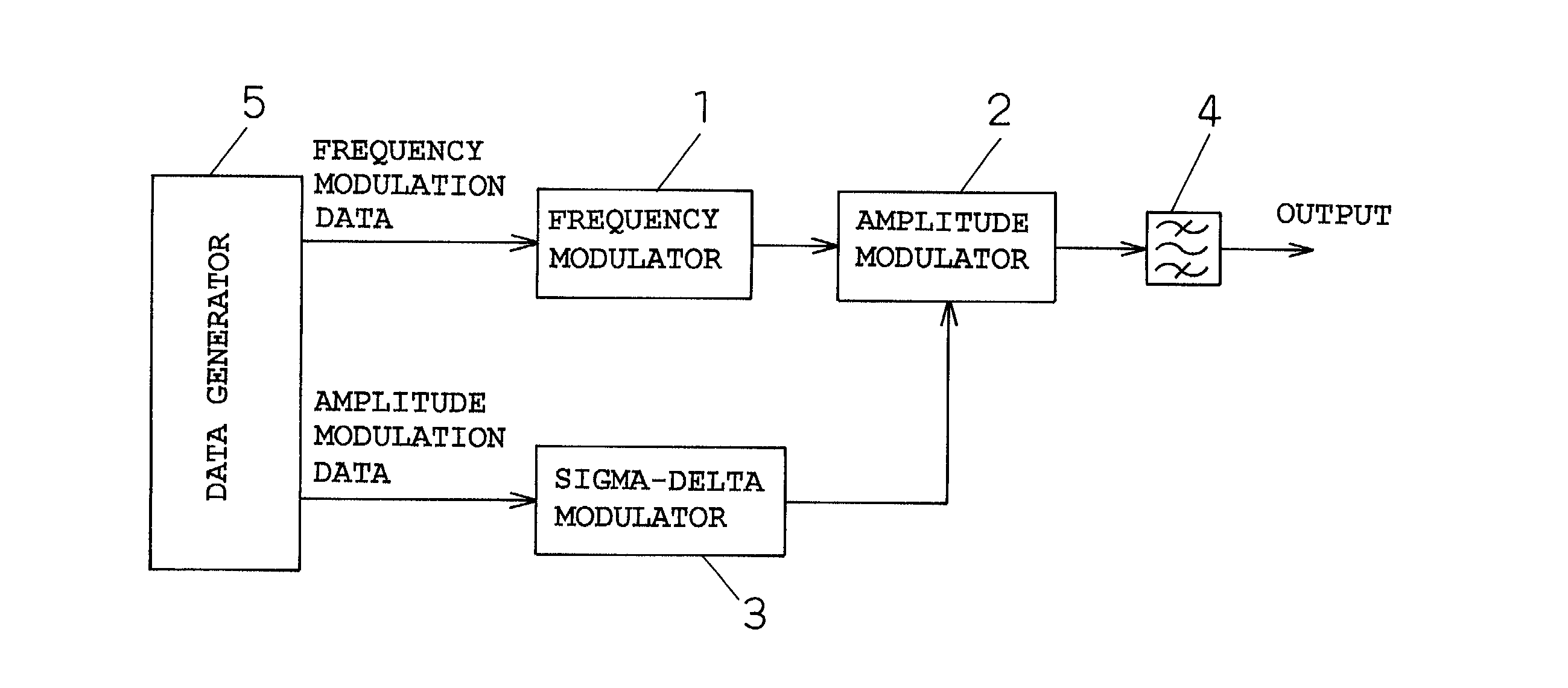

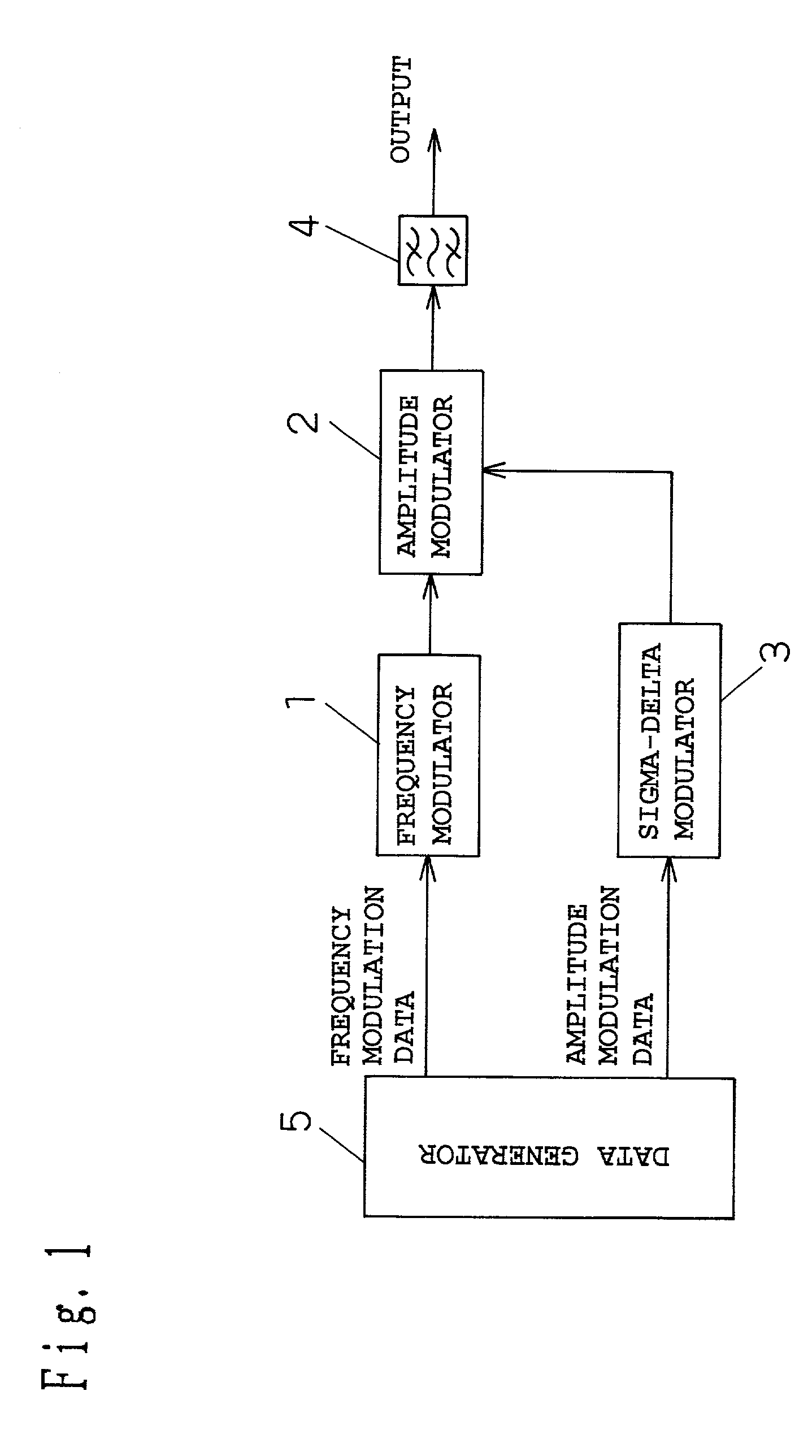

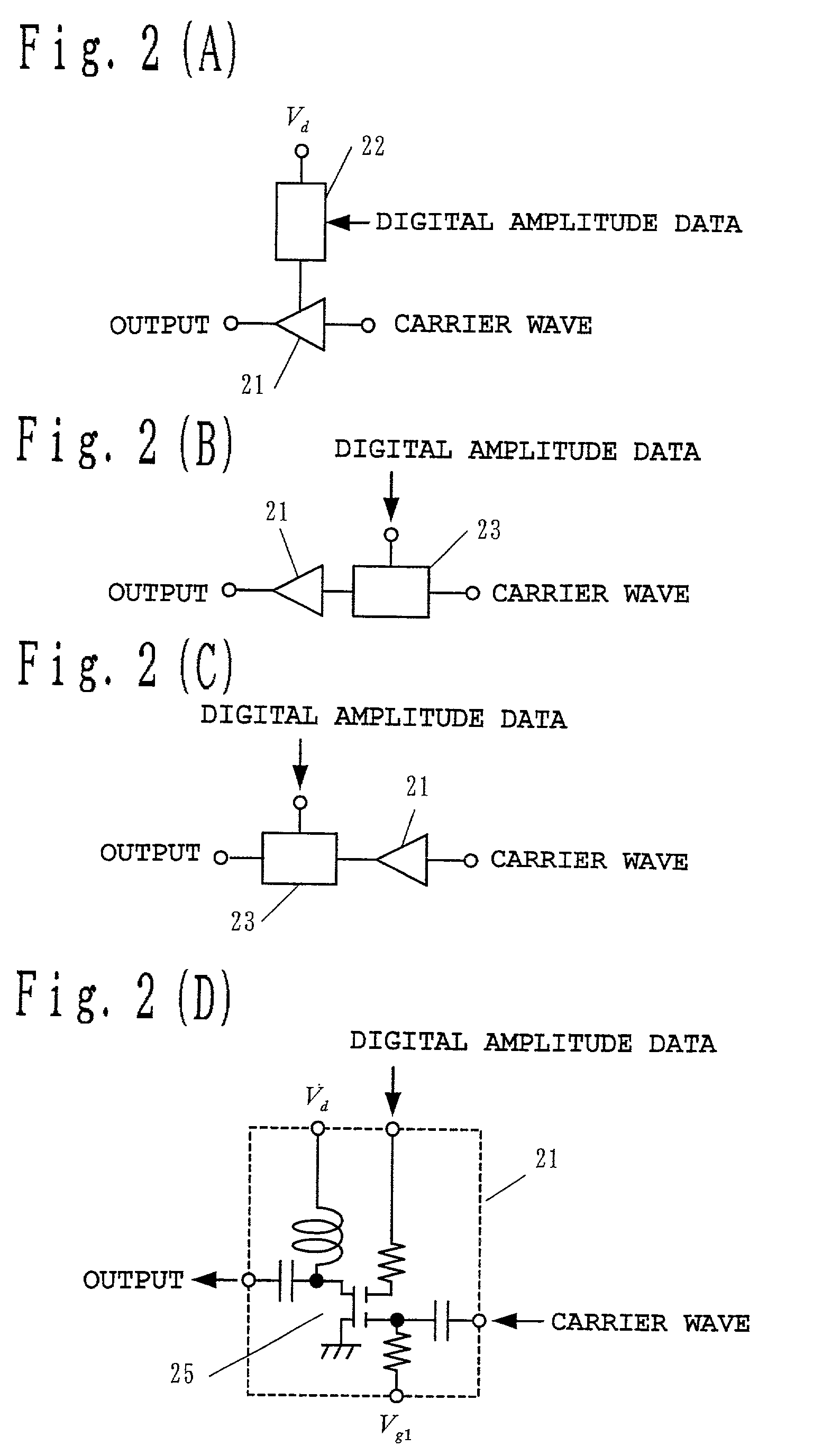

Transmitting circuit apparatus and method

ActiveUS7013090B2Improve linearityHigh transmission output power efficiencyResonant long antennasPower amplifiersCarrier signalGreek letter sigma

A transmitting circuit apparatus hasa frequency modulator that performs frequency modulation of a carrier wave with frequency modulation data and outputs the frequency-modulated carrier wave;a sigma-delta modulator which performs sigma delta modulation of amplitude modulation data; andan amplitude modulator that performs amplitude modulation of the frequency-modulated carrier wave with an output signal of the sigma-delta modulator and outputs the amplitude-modulated carrier wave.

Owner:PANASONIC CORP

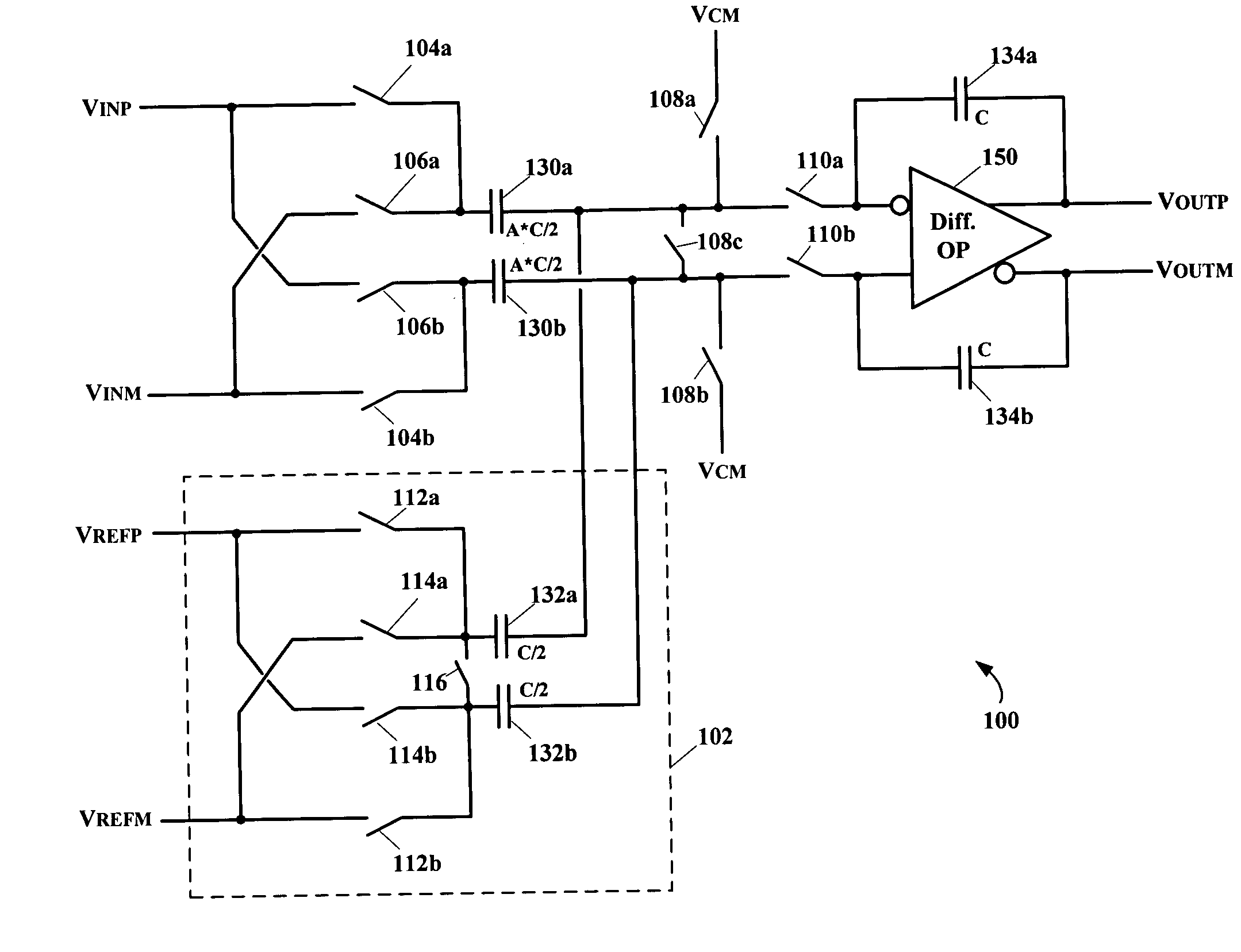

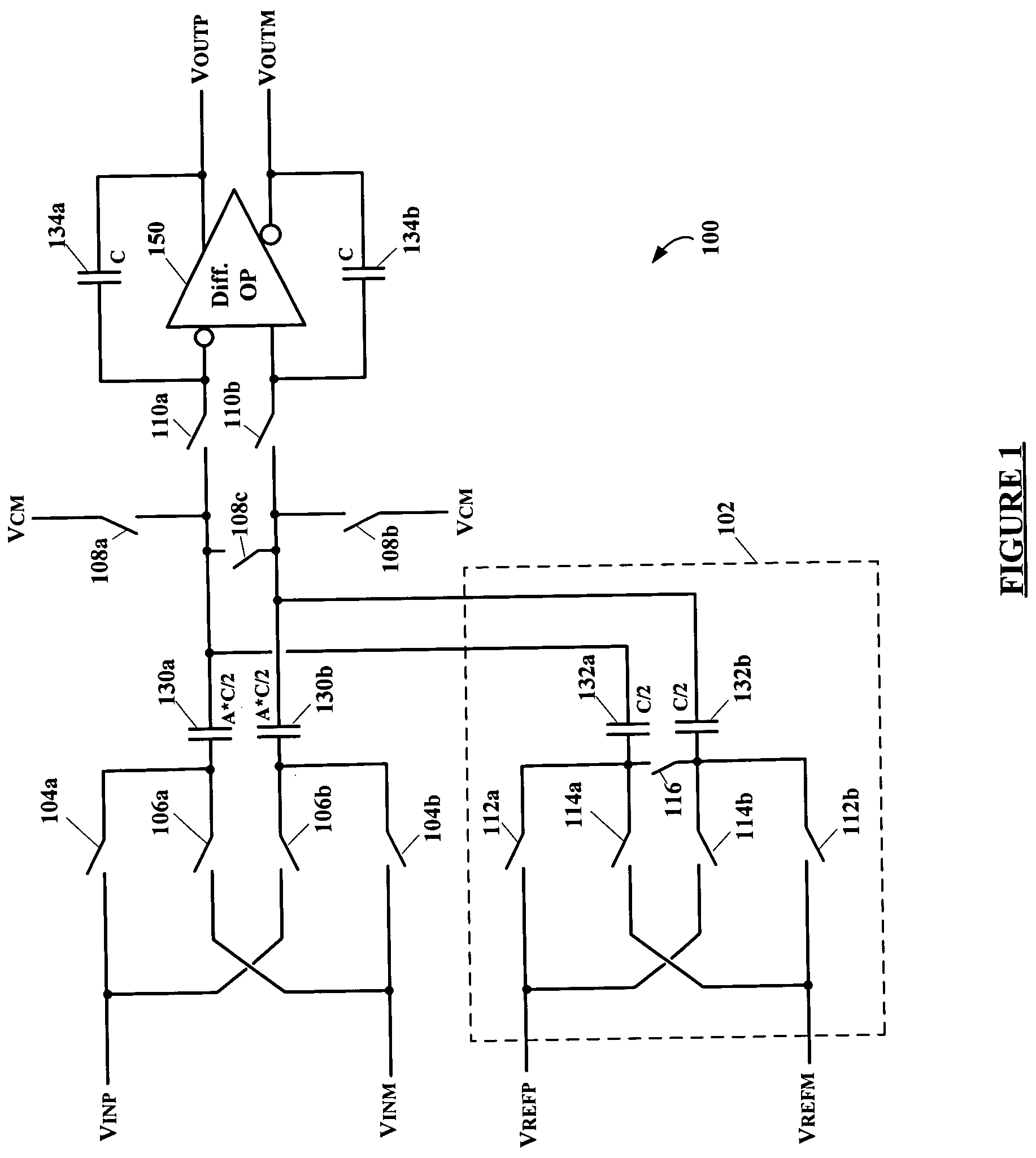

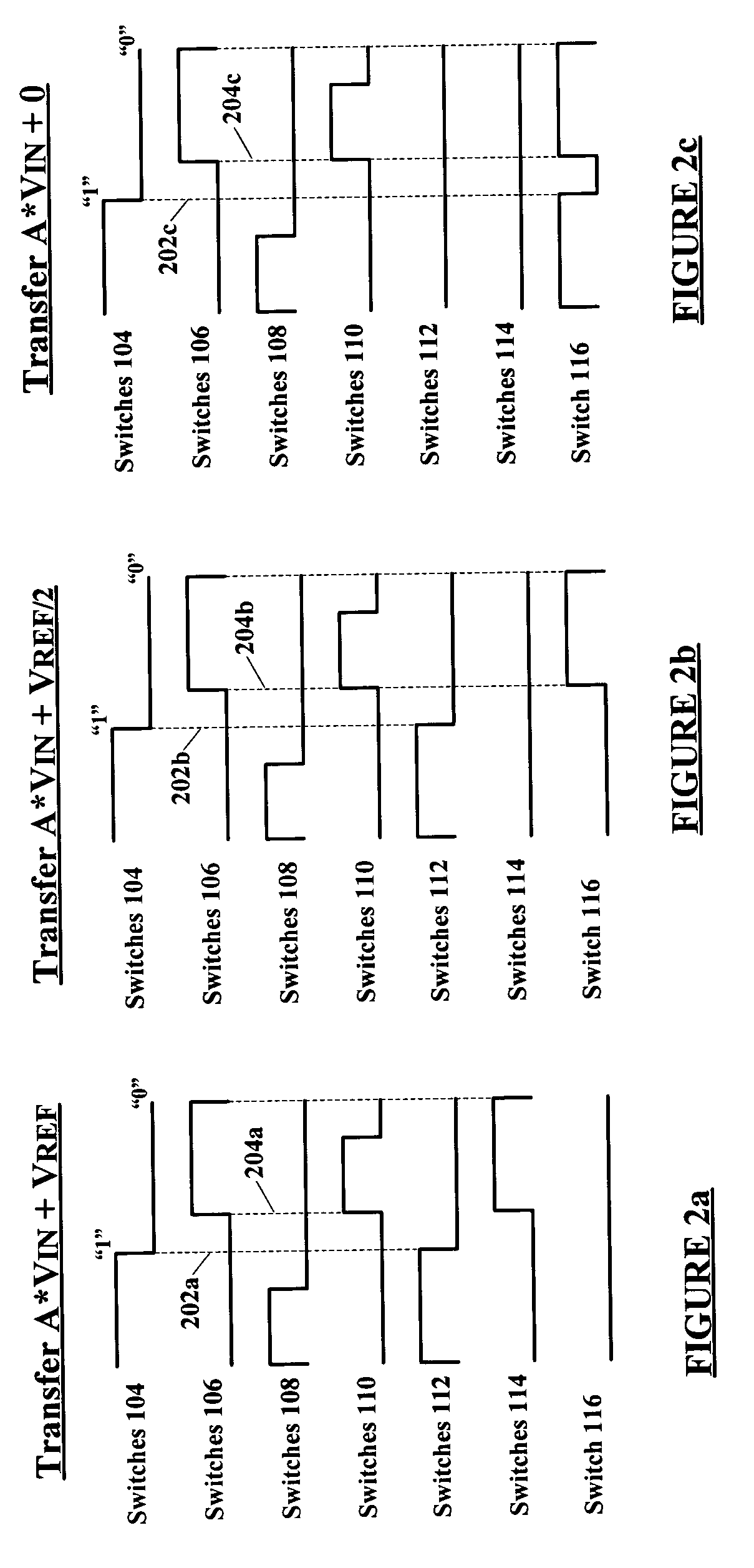

Five-level feed-back digital-to-analog converter for a switched capacitor sigma-delta analog-to-digital converter

ActiveUS7102558B2Improve performanceLow-power consumption of a switched capacitorElectric signal transmission systemsAnalogue conversionVoltage referenceGreek letter sigma

A five-level feed-back digital-to-analog converter (DAC) in a switched capacitor sigma-delta analog-to-digital converter has an improved switching sequence that boosts from two to five the number of quantization levels of the feed-back DAC. Switching sequences are used to obtain five equally distributed charge levels C*VREF, C*VREF / 2, 0, −C*VREF / 2 and −C*VREF. When summed with an input voltage, VIN, the five-level feed-back DAC produces five equally distributed output voltages of A*VIN+VREF, A*VIN+VREF / 2, A*VIN+0, A*VIN−VREF / 2 and A*VIN−VREF, where A is gain, VIN is the input voltage, and VREF is the reference voltage.

Owner:MICROCHIP TECH INC

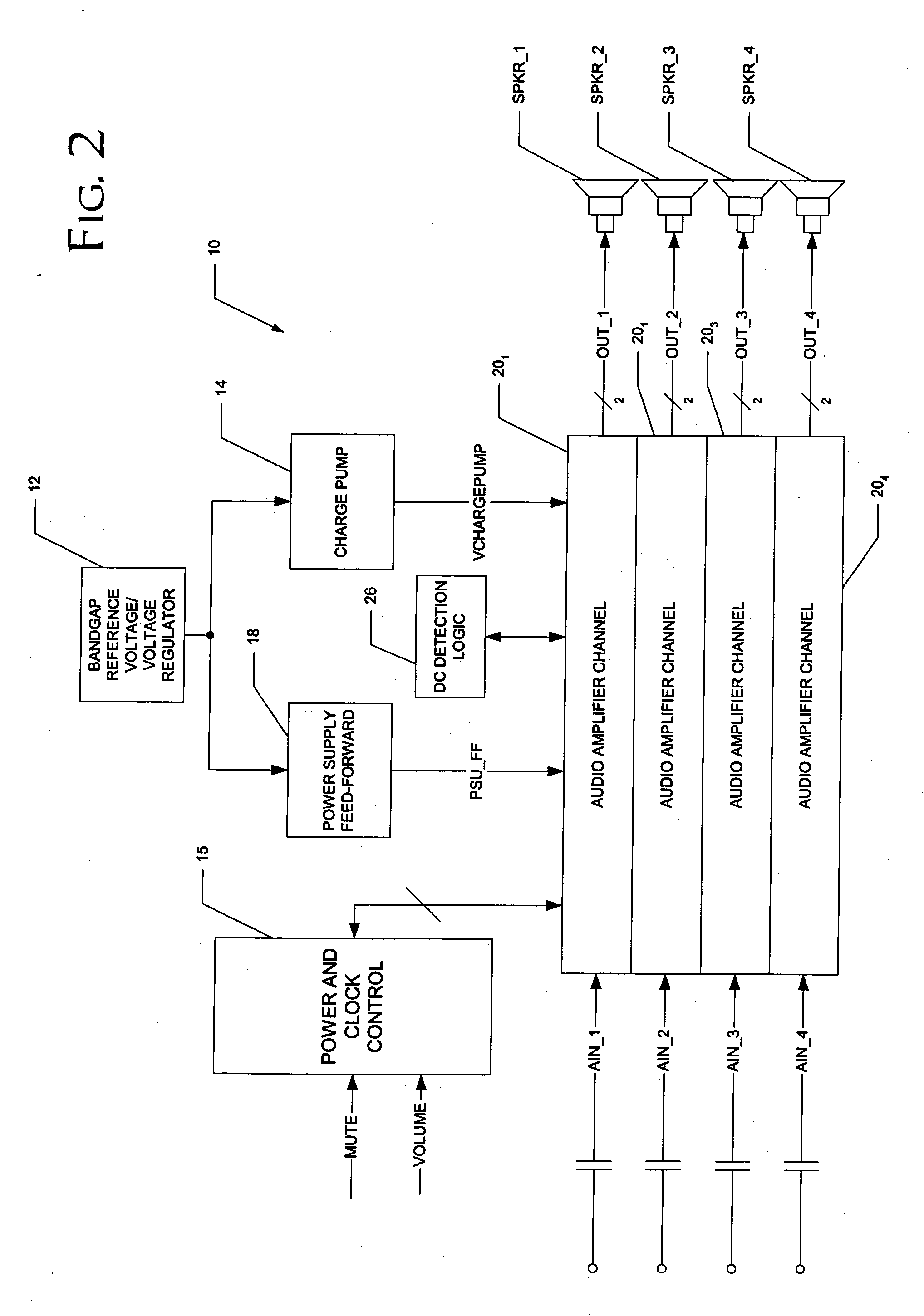

Detection of DC output levels from a class D amplifier

ActiveUS7078964B2Simple analog portionLow cutoff frequencyDuration/width modulated pulse demodulationPulse duration/width modulationUnsafe conditionAudio power amplifier

Owner:TEXAS INSTR INC

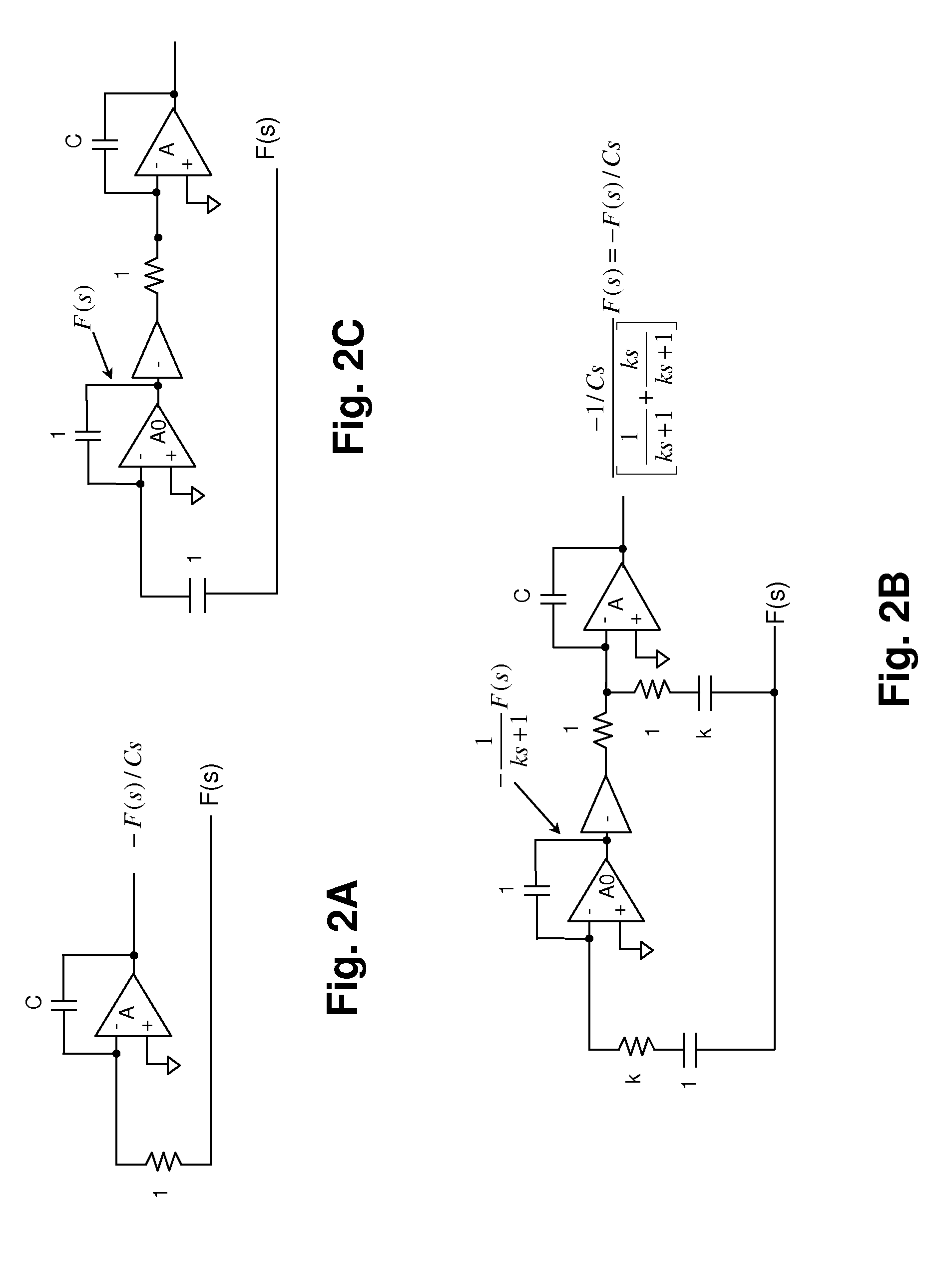

Feedback topology delta-sigma modulator having an ac-coupled feedback path

A feedback topology delta-sigma modulator having an AC-coupled feedback path reduces signal level in the loop filter, easing linearity requirements and reduces capacitor size requirements for the filter integration stages. The delta-sigma modulator includes a loop filter having multiple integrator stages, a quantizer, and a feedback network providing at least two feedback paths to corresponding integrators in the loop filter. In one aspect, only one of the feedback paths from the quantizer output is DC coupled, and at least one other of the feedback paths is DC-coupled, which reduces the signal levels in the loop filter integrators. In another aspect, at least one of the feedback paths from the quantizer is AC coupled, providing a similar result. The AC feedback path may be provided through a series-connected resistor and capacitor. The DC feedback path may be provided through a resistor, a switched-capacitor network, or may be a quantizer-controlled current source.

Owner:CIRRUS LOGIC INC

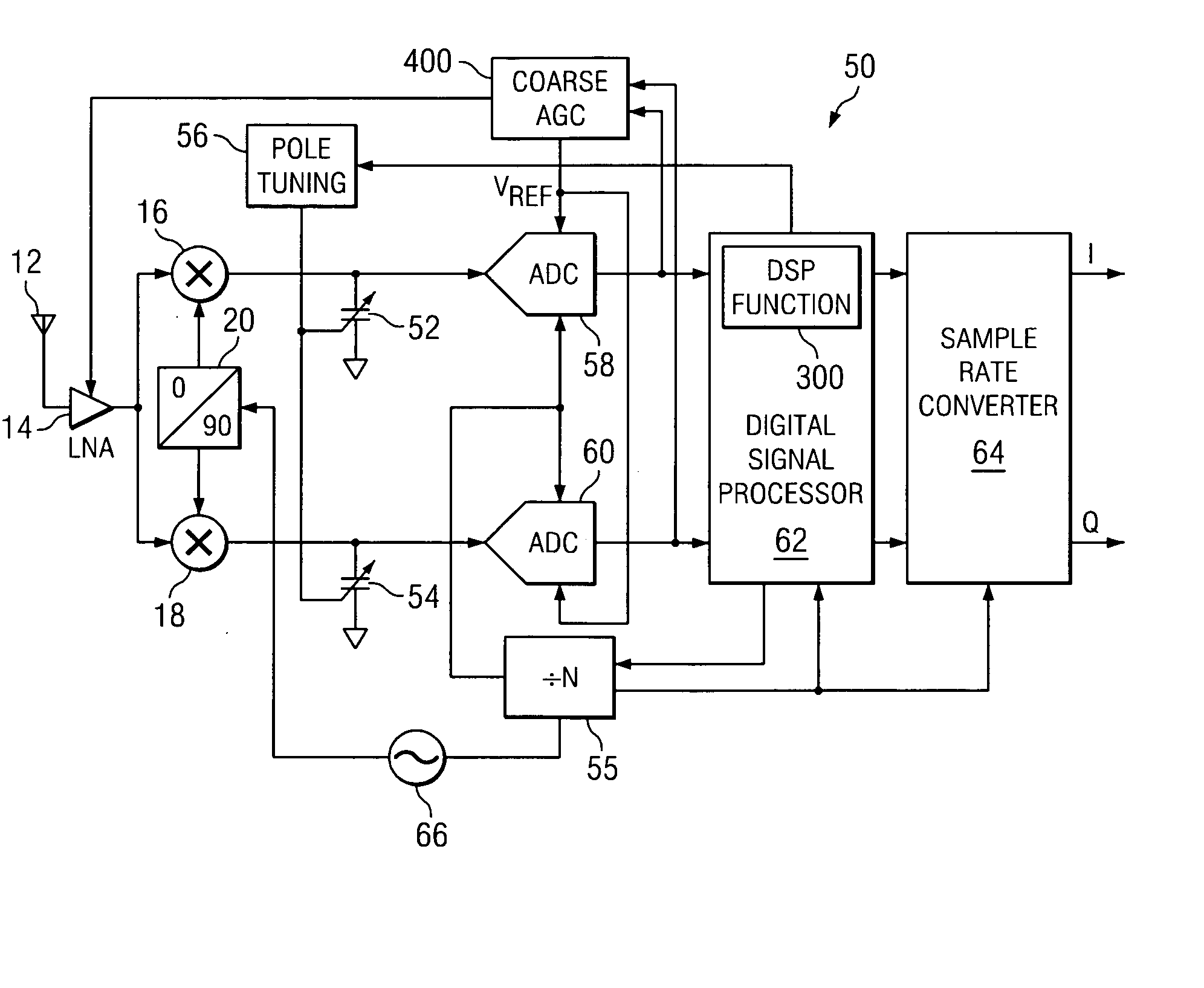

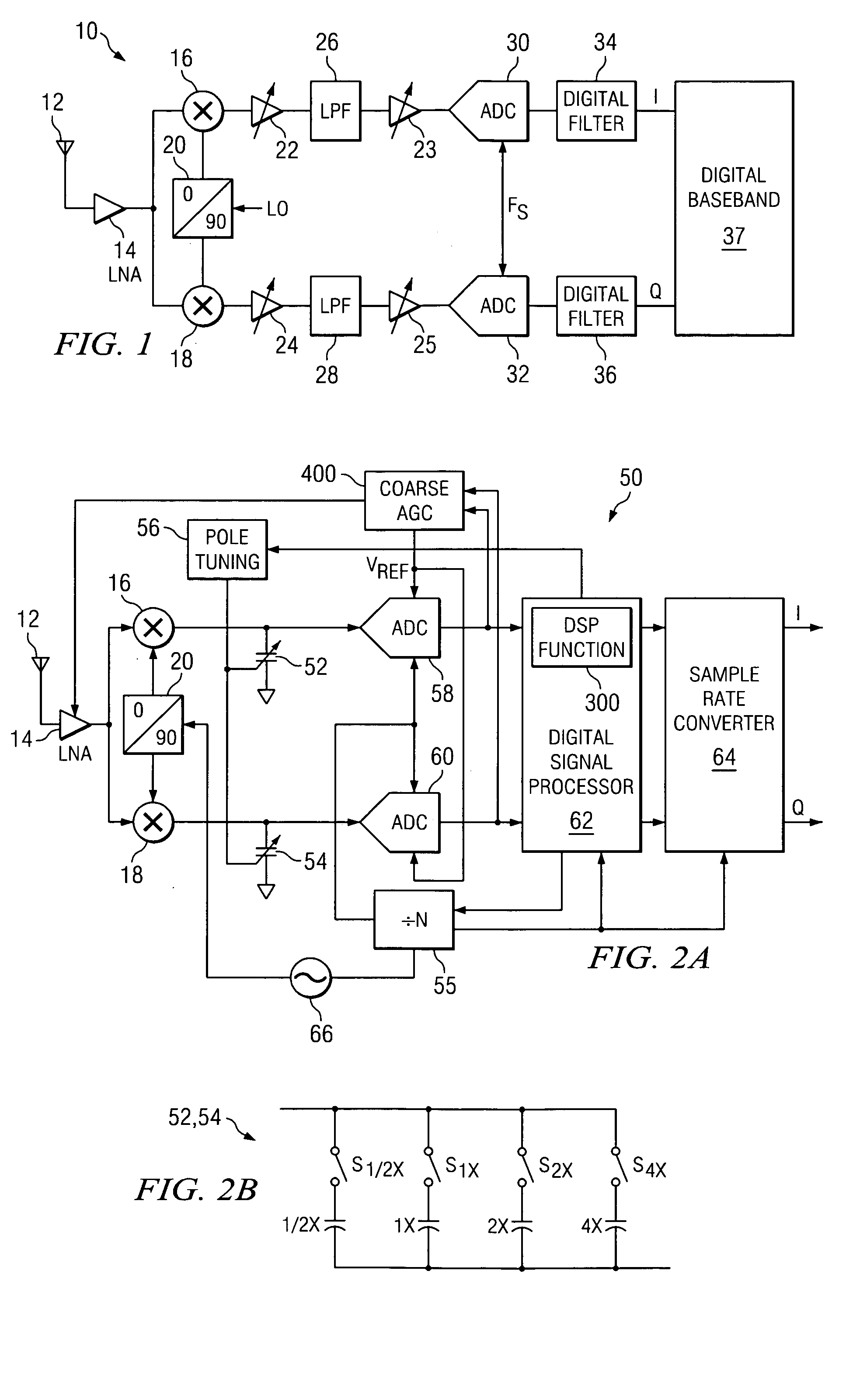

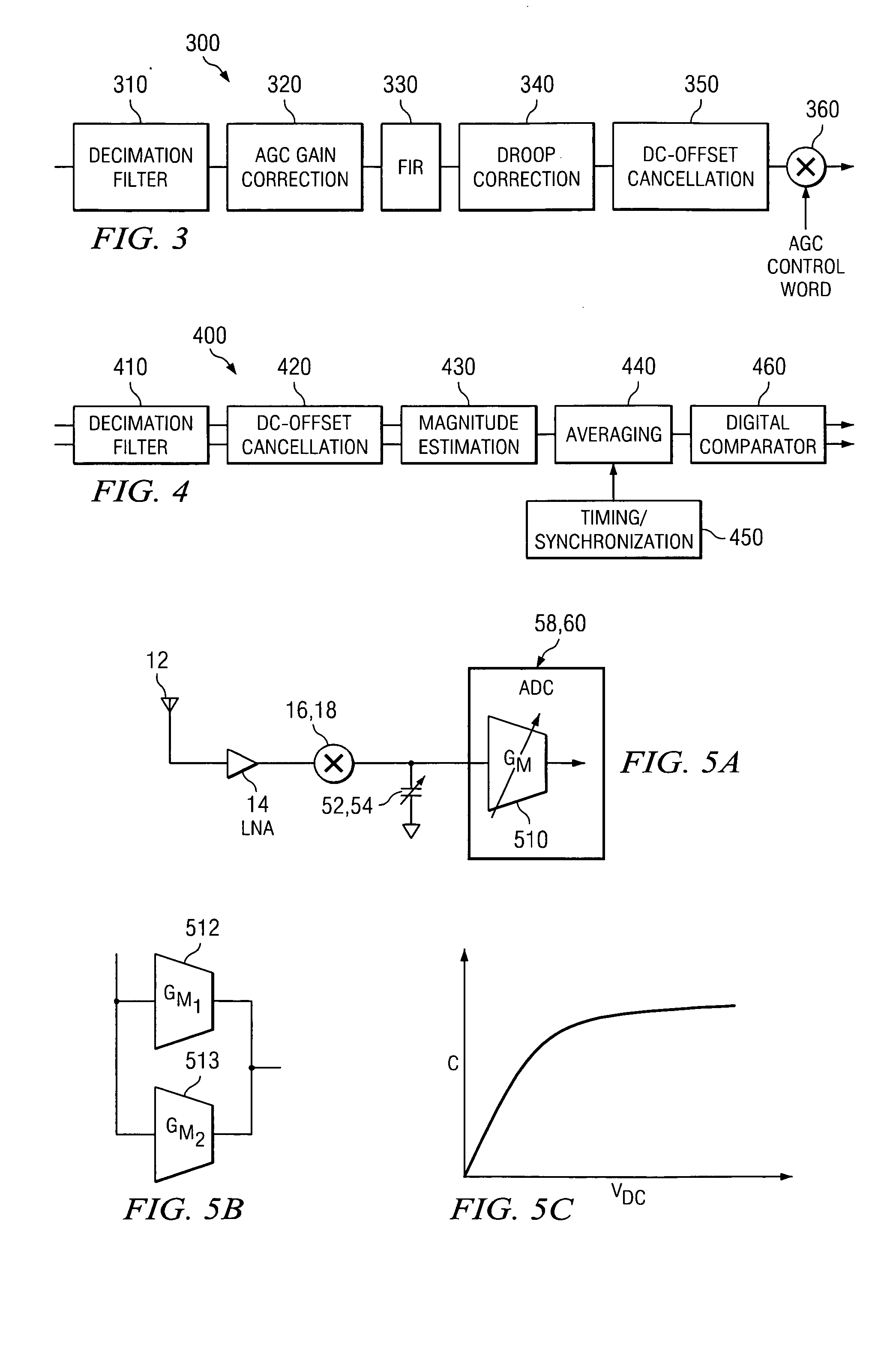

System and method for digital radio receiver

ActiveUS20050070325A1Reduce the sampling frequencySubstation equipmentRadio transmissionCommunications systemDigital radio

A communications system comprising a processor, a variable oscillator, a radio frequency (RF) quadrature demodulator, a variable capacitor, a continuous-time, sigma-delta analog-to-digital converter (ADC), and a frequency divider, all integrated on a single semiconductor chip. The ADC samples the RF quadrature demodulator output. The processor sets the communications system frequency by controlling the oscillator, the frequency divider and the variable capacitor.

Owner:TEXAS INSTR INC

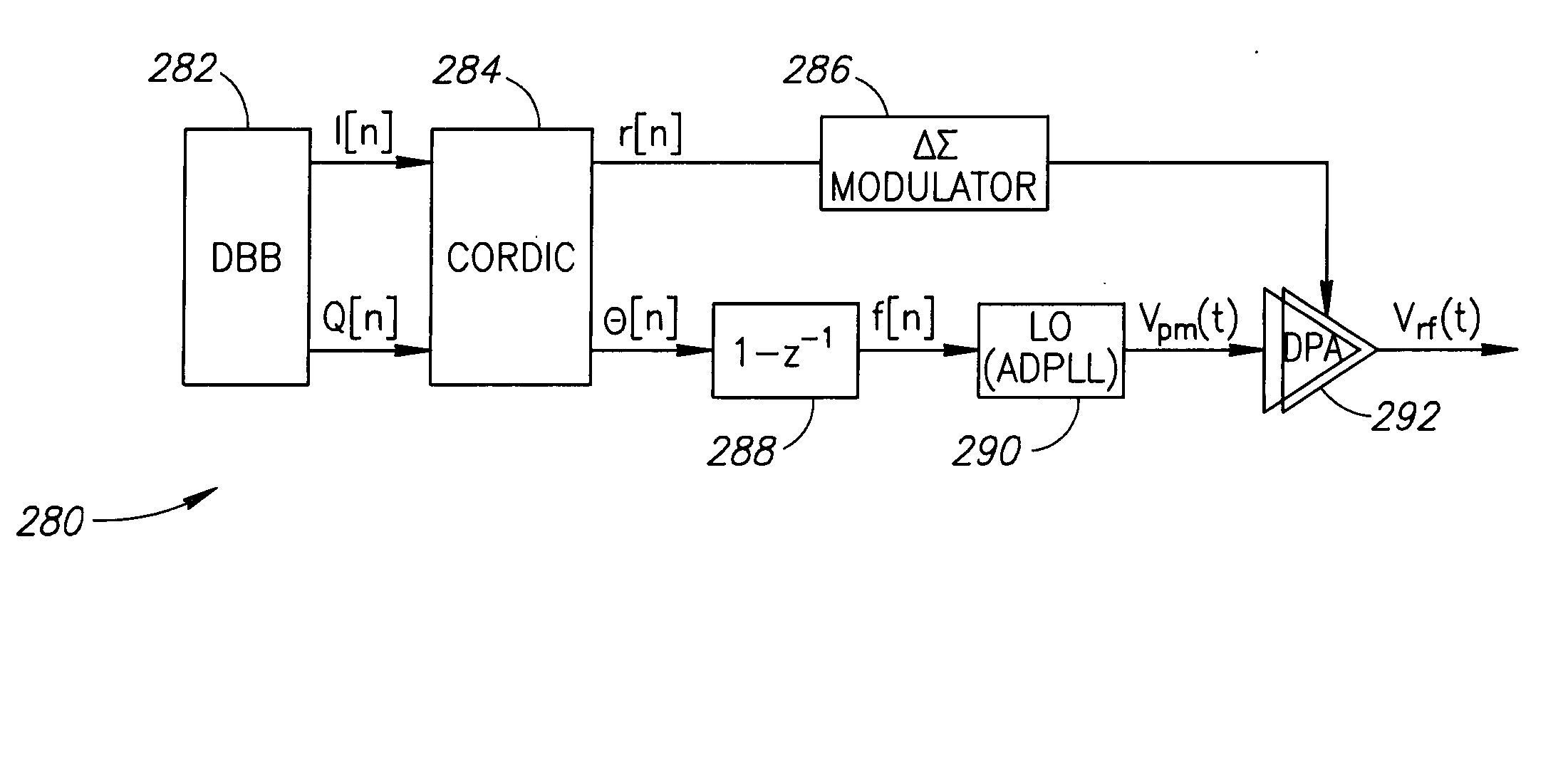

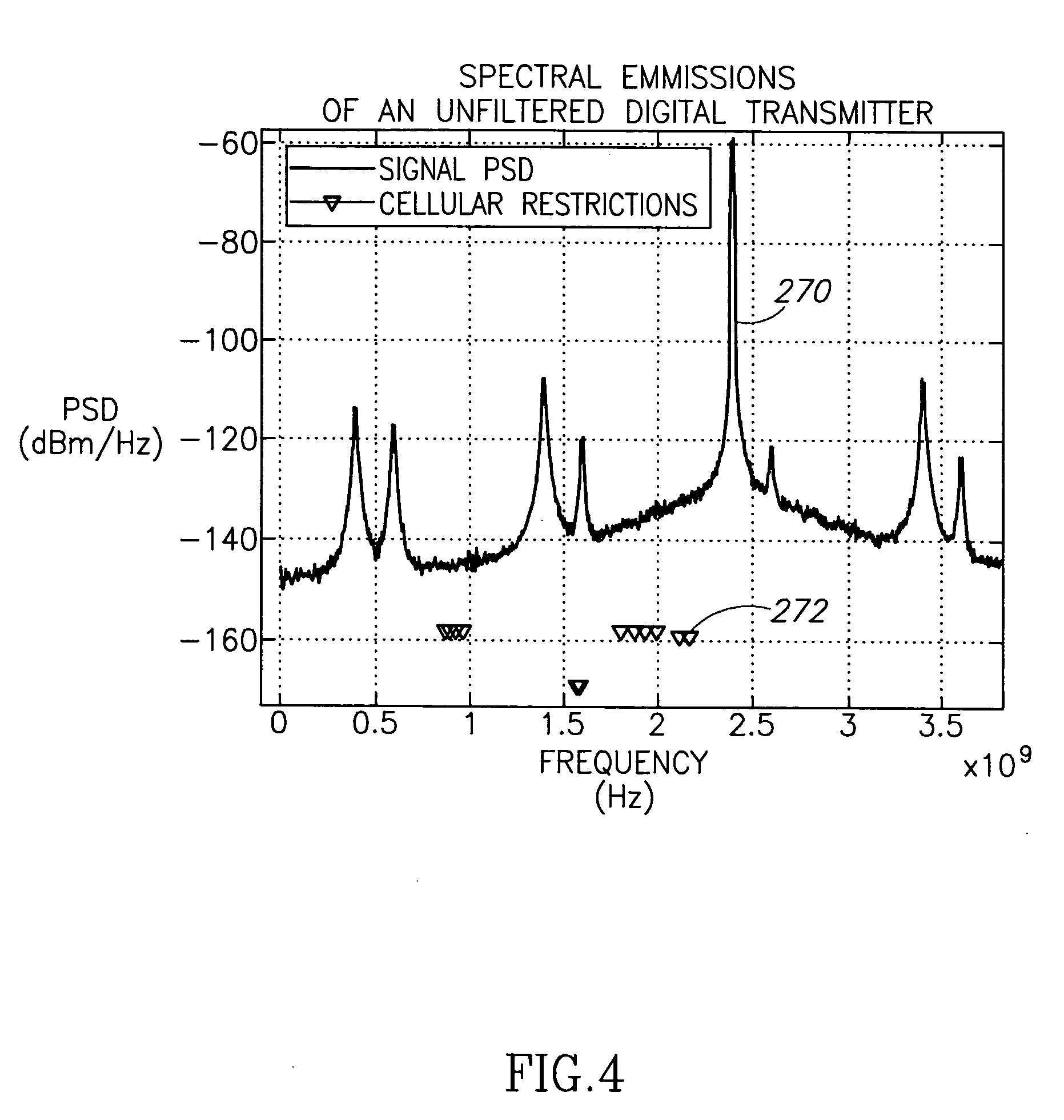

Transmitter for wireless applications incorporation spectral emission shaping sigma delta modulator

ActiveUS20060119493A1Sufficient attenuationDesired noise shapingAnalogue conversionSecret communicationSpectral emissionFrequency spectrum

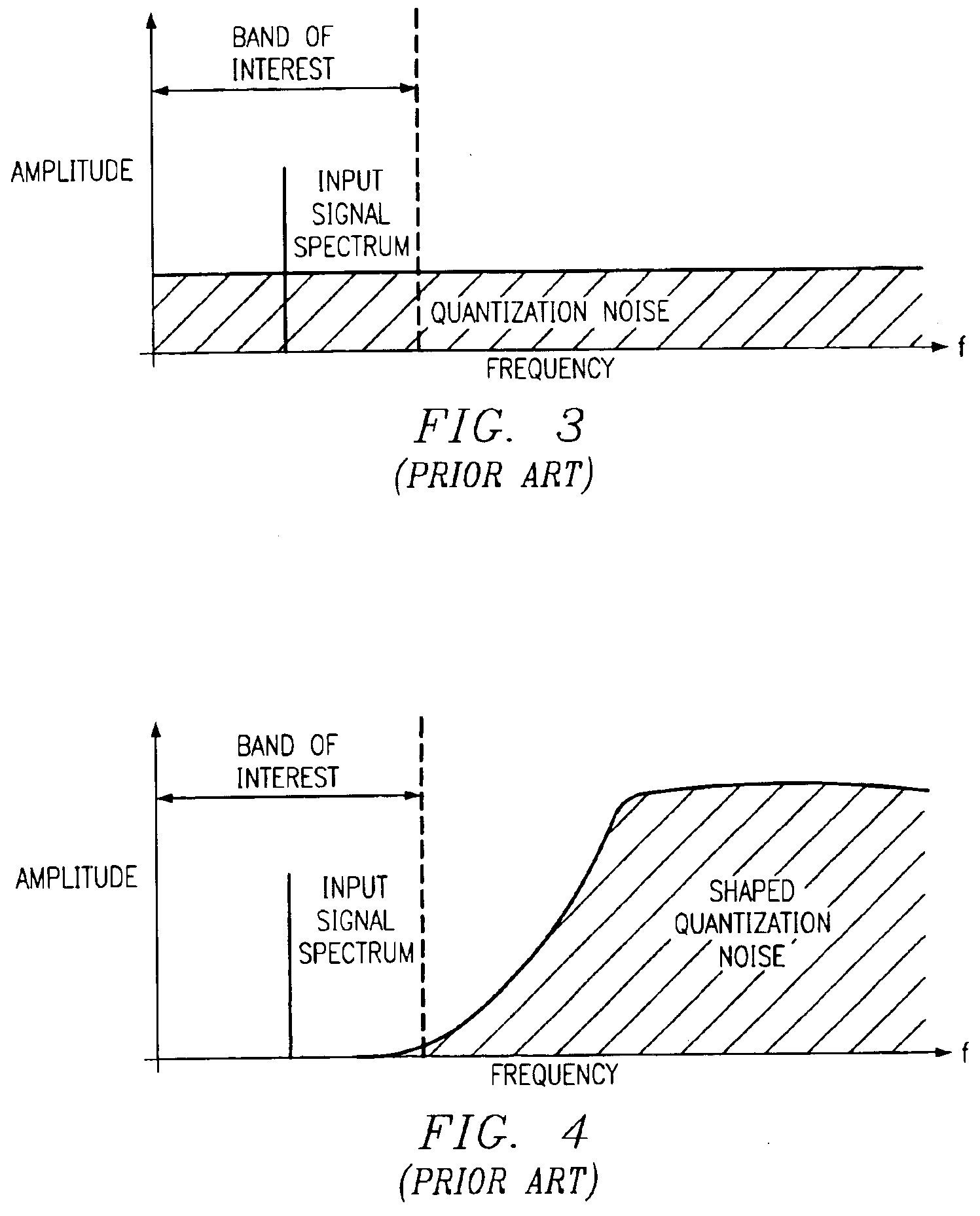

A transmitter employing a sigma delta modulator having a noise transfer function adapted to shift quantization noise outside at least one frequency band of interest. A technique is presented to synthesize the controllers within a single-loop sigma delta modulator such that the noise transfer function can be chosen arbitrarily from a family of functions satisfying certain conditions. Using the novel modulator design technique, polar and Cartesian (i.e. quadrature) transmitter structures are supported. A transmitter employing polar transmit modulation is presented that shapes the spectral emissions of the digitally-controlled power amplifier such that they are significantly and sufficiently attenuated in one or more desired frequency bands. Similarly, a transmitter employing Cartesian transmit modulation is presented that shapes the spectral emissions of a hybrid power amplifier such that they are significantly and sufficiently attenuated in one or more desired frequency bands.

Owner:TEXAS INSTR INC

Sigma Delta Over-Sampling Charge Pump Analog-To-Digital Converter

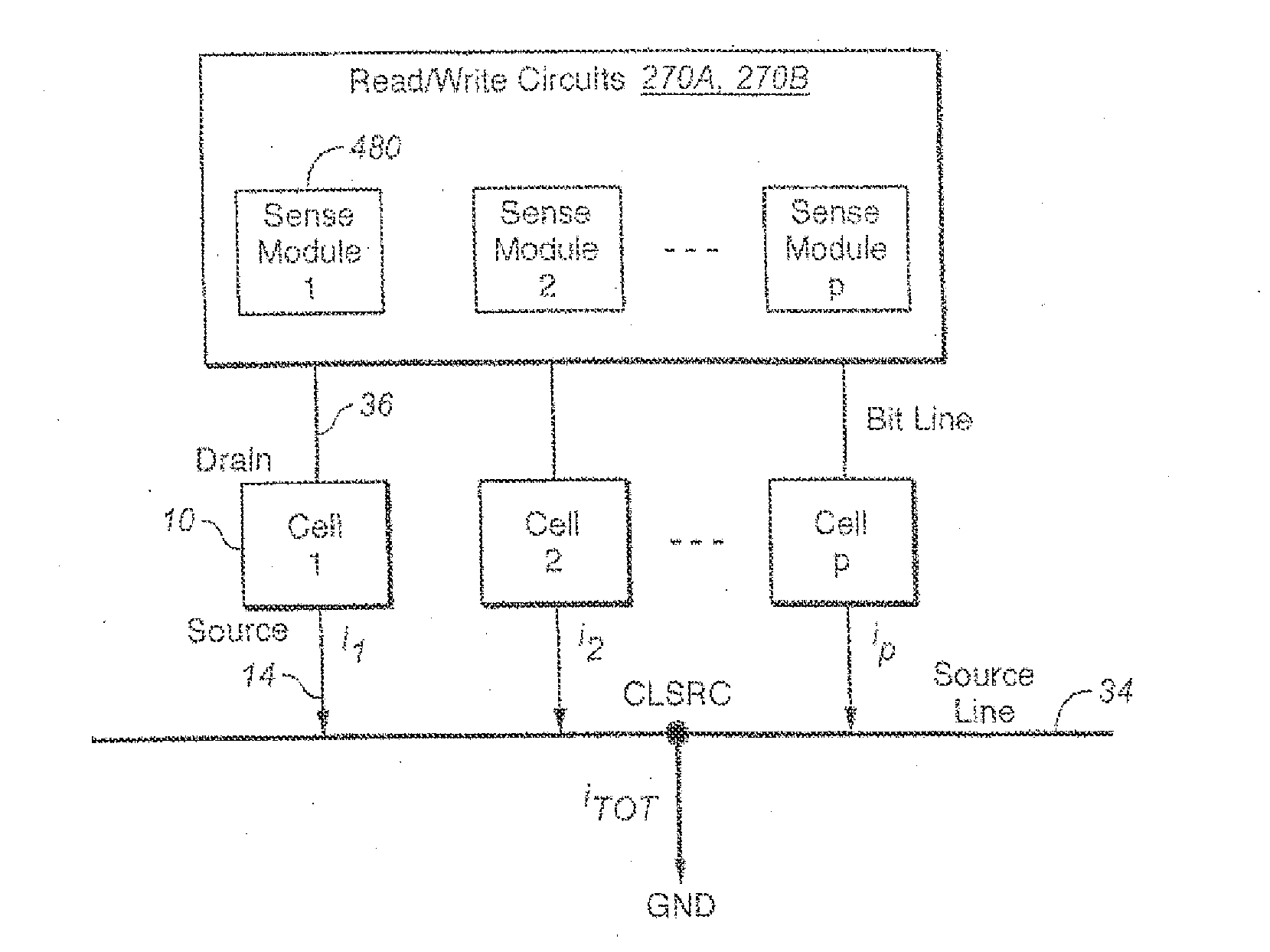

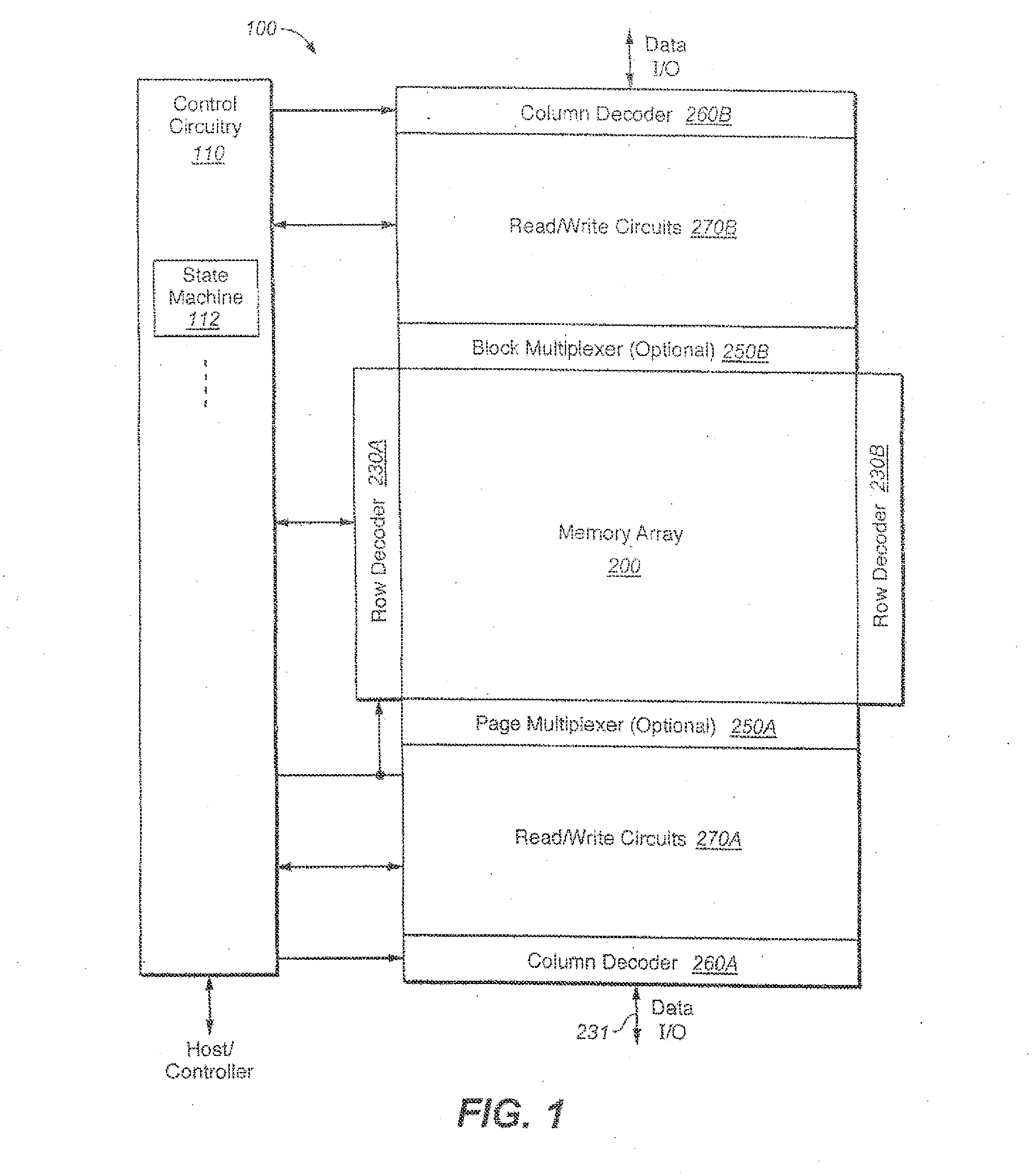

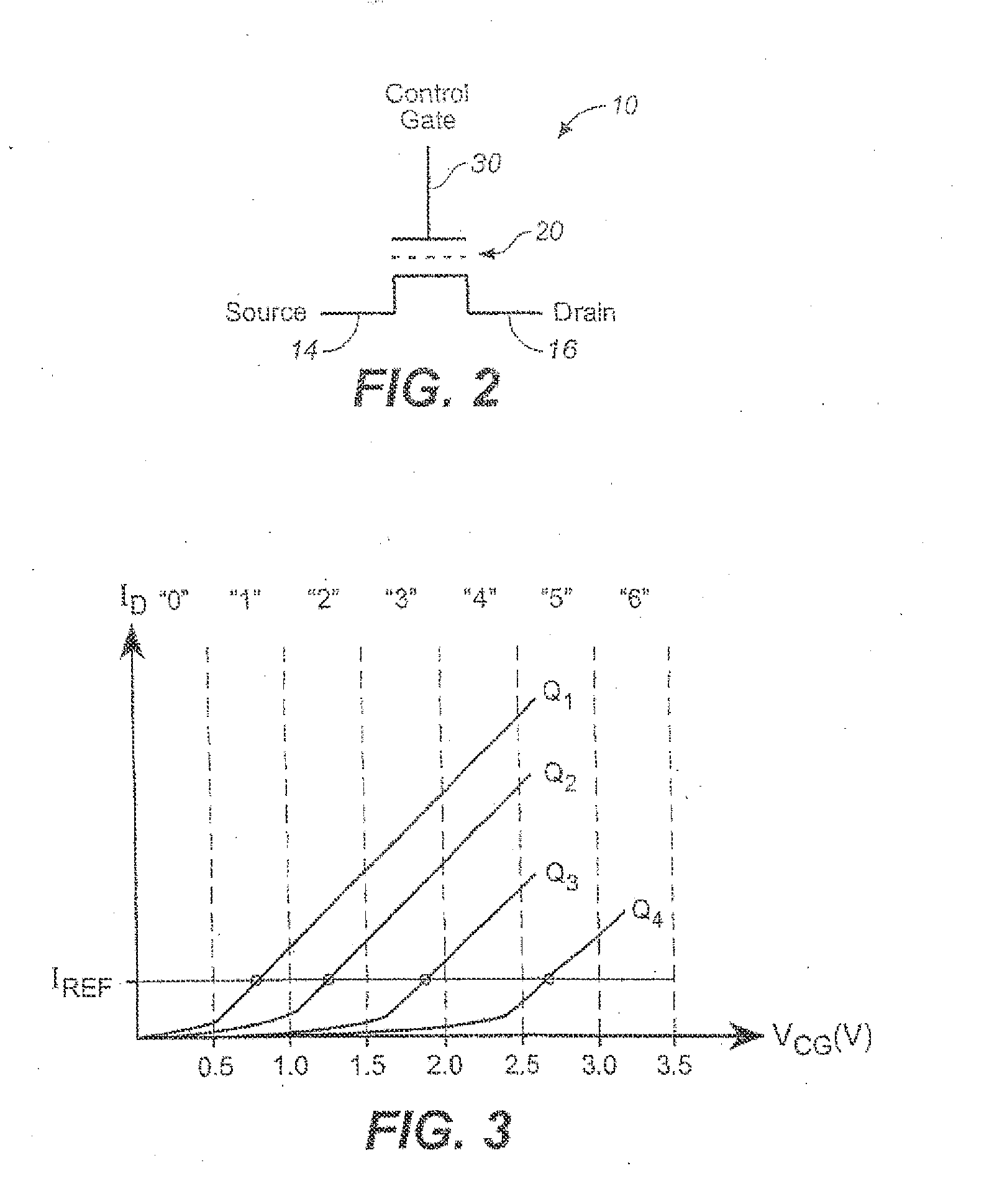

ActiveUS20140085985A1Eliminate low frequency noiseRead-only memoriesApparatus without intermediate ac conversionImage resolutionNoise shaping

Techniques are presented for determining current levels based on the behavior of a charge pump system while driving a load under regulation. While driving the load under regulation, the number of pump clocks during a set interval is counted. This can be compared to a reference that can be obtained, for example, from the numbers of cycles needed to drive a known load current over an interval of the duration. By comparing the counts, the amount of current being drawn by the load can be determined. This technique can be applied to determining leakage from circuit elements, such as word lines in a non-volatile memory. The accuracy and level of resolution can be further increased through use of sigma delta noise shaping.

Owner:SANDISK TECH LLC

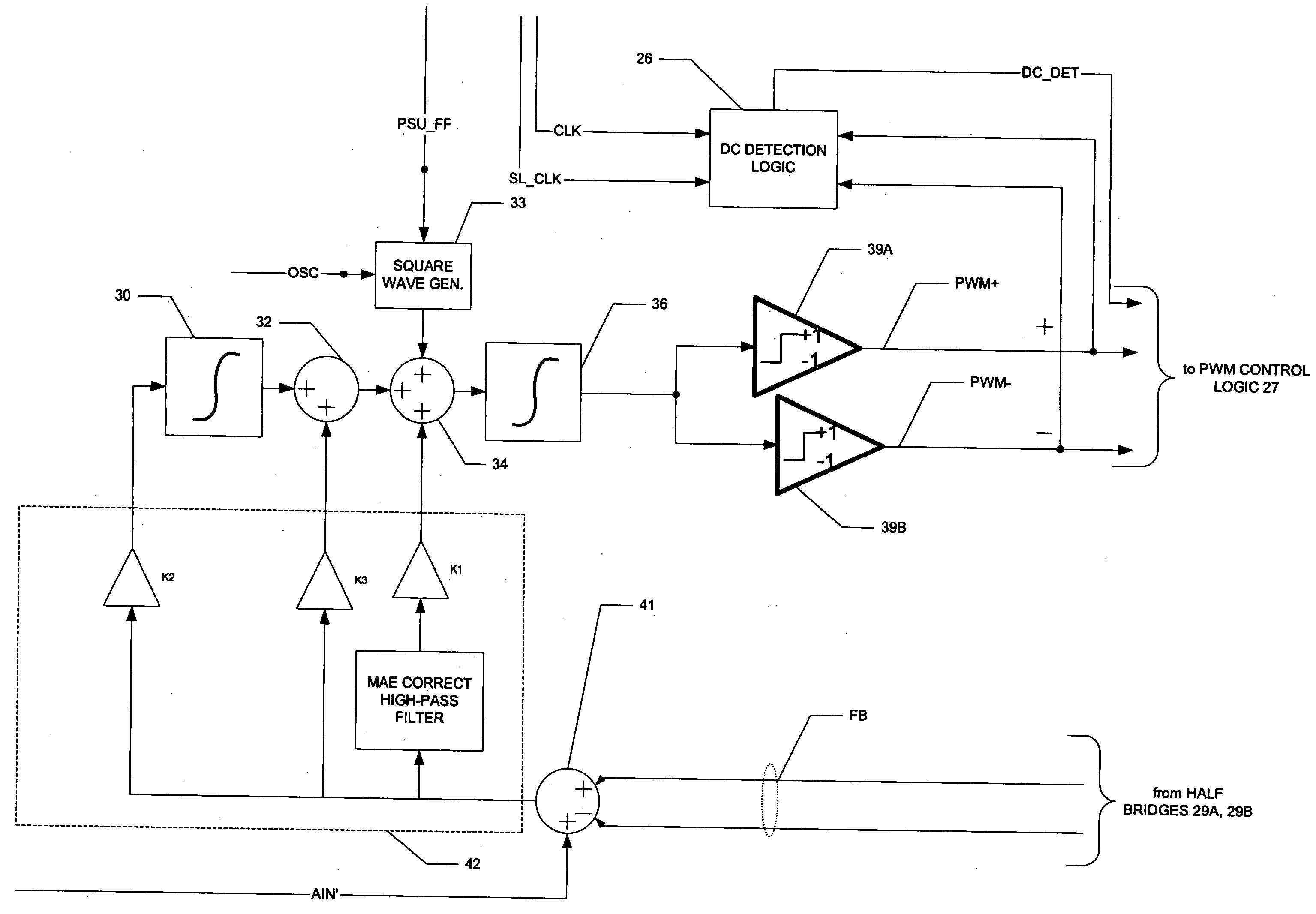

Detection of DC output levels from a class D amplifier

ActiveUS20050083116A1Simple analog portionLow cutoff frequencyDuration/width modulated pulse demodulationPulse duration/width modulationUnsafe conditionAudio power amplifier

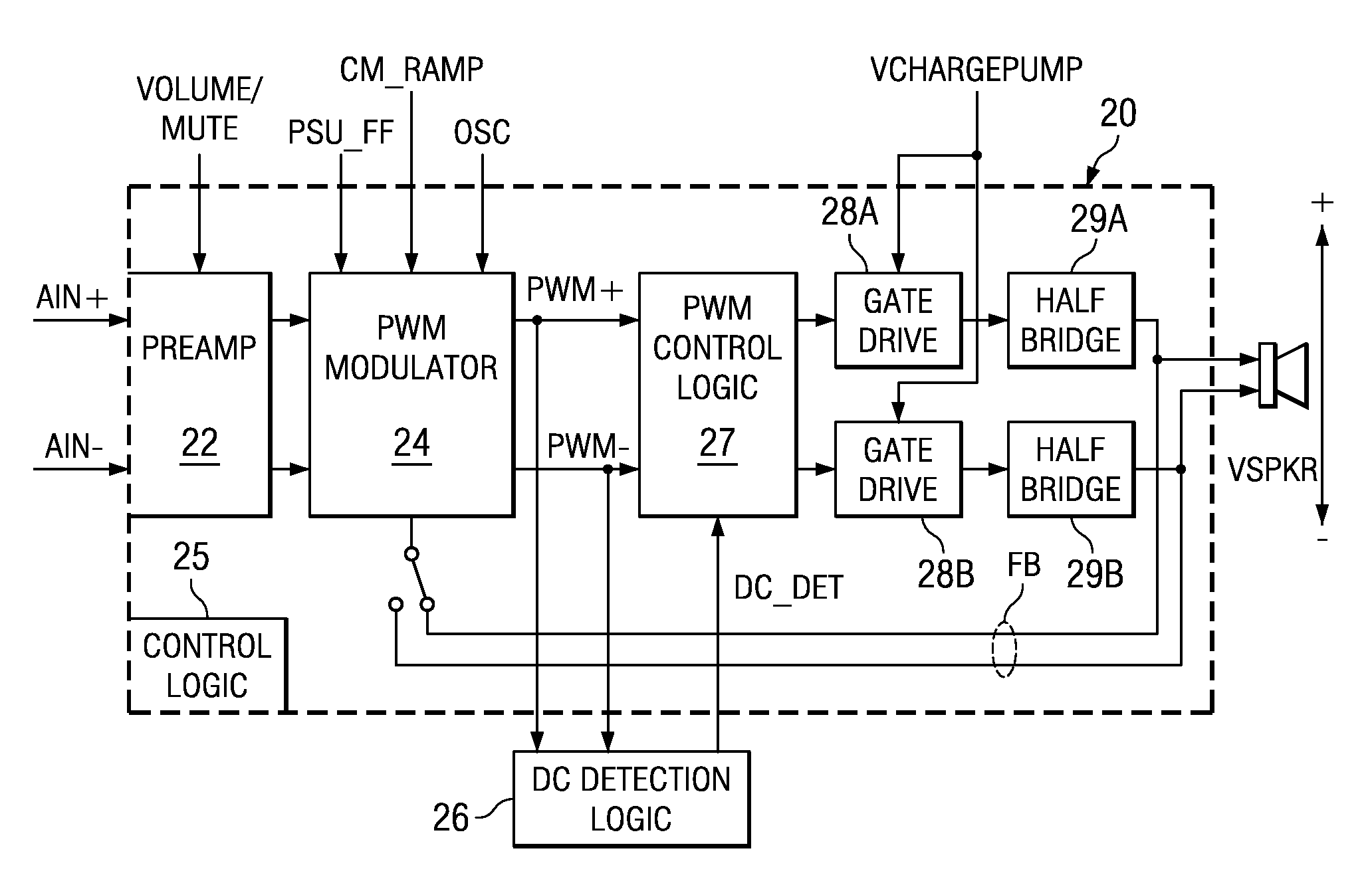

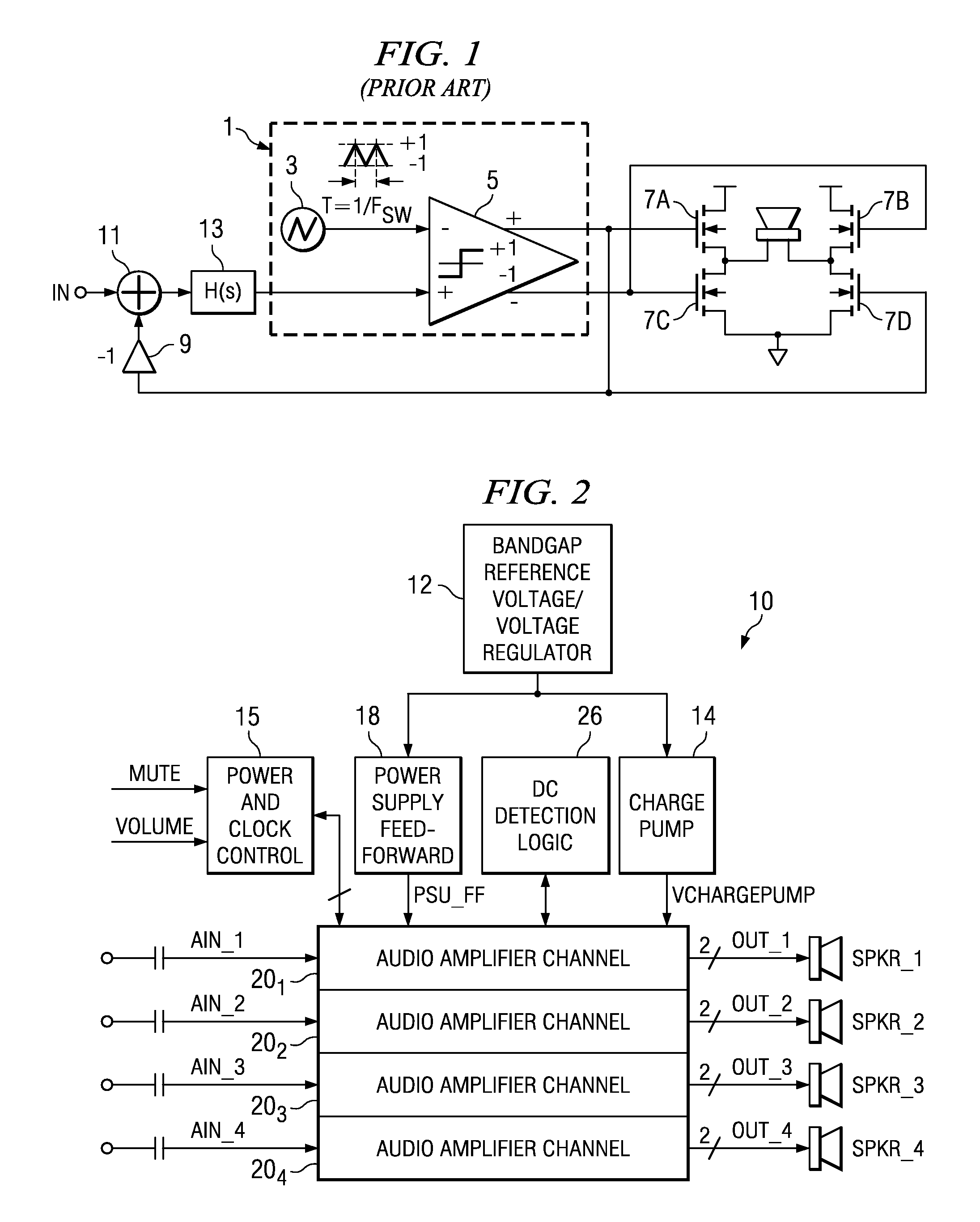

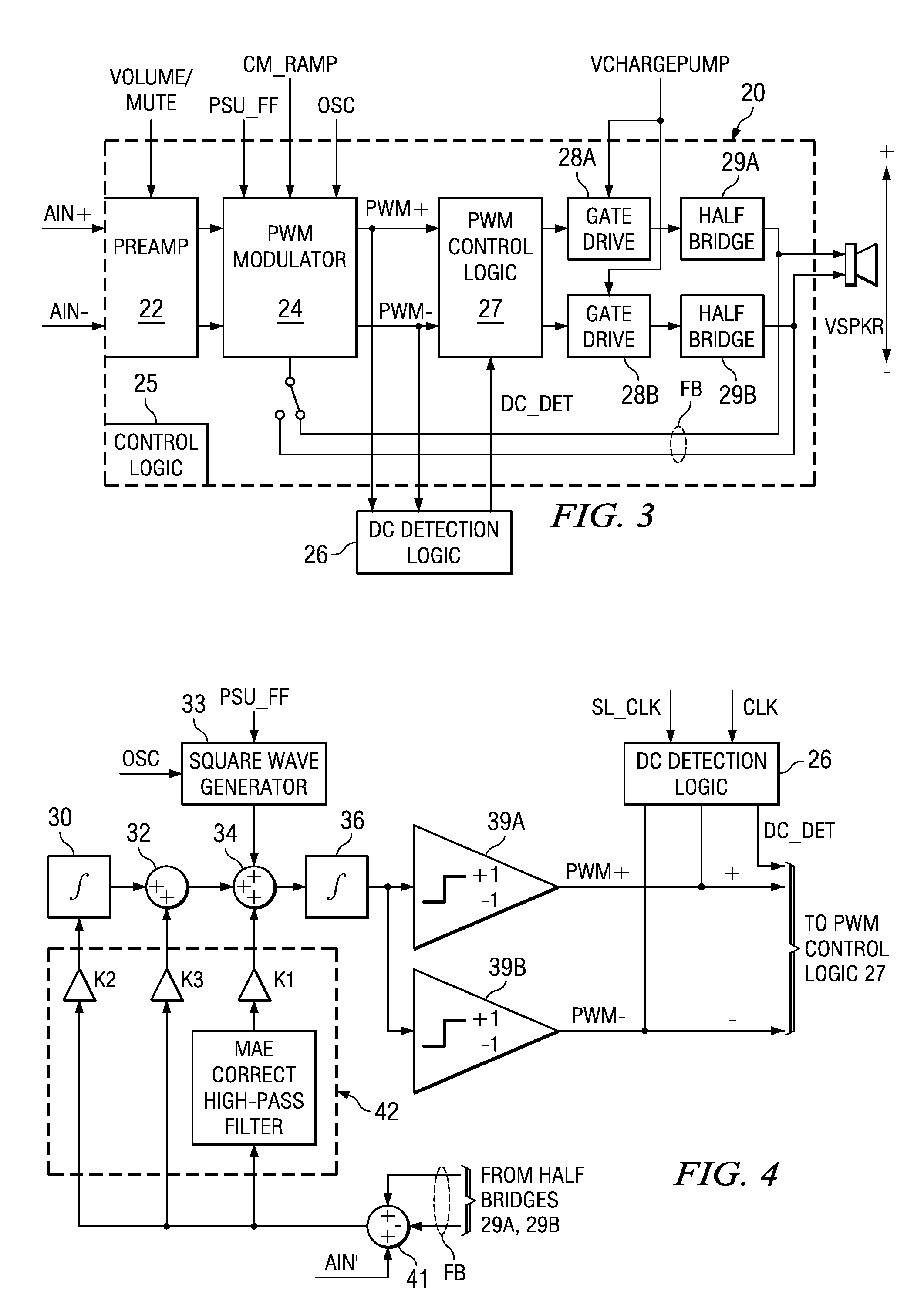

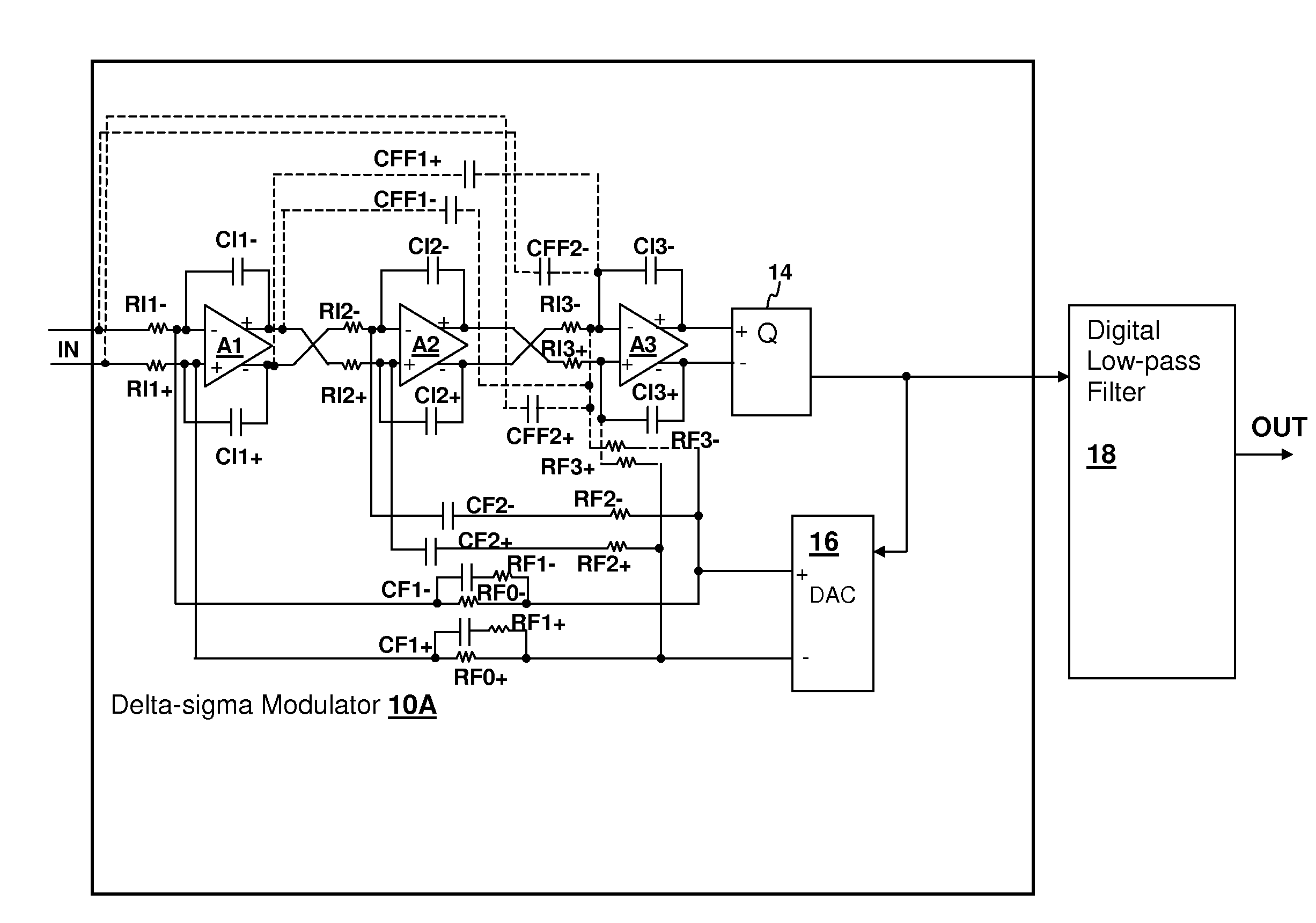

A class AD audio amplifier system (10) with DC output detection logic (26) is disclosed. The amplifier system (10) includes multiple audio channels (20), each of which includes a pulse-width-modulator (PWM) (24). The DC detection logic (26) includes a sigma-delta modulator (60) and a digital low-pass filter (62) that monitors the PWM output signals from the PWM modulators (24). The sigma-delta modulator (60) operates at a first clock frequency, while the low-pass filter (62) operates at a much lower clock frequency, so that AC audio components, PWM harmonics, and sigma-delta quantization error is suppressed from the DC detection. The modulated filtered signal is compared against a threshold level (THRSH) to determine whether the amplitude of a DC component at the PWM output is sufficiently high to constitute a fault. If so, a fault detection signal (DC_DET) is issued, and the PWM modulators (24) are disabled to prevent unsafe conditions in the system (10).

Owner:TEXAS INSTR INC

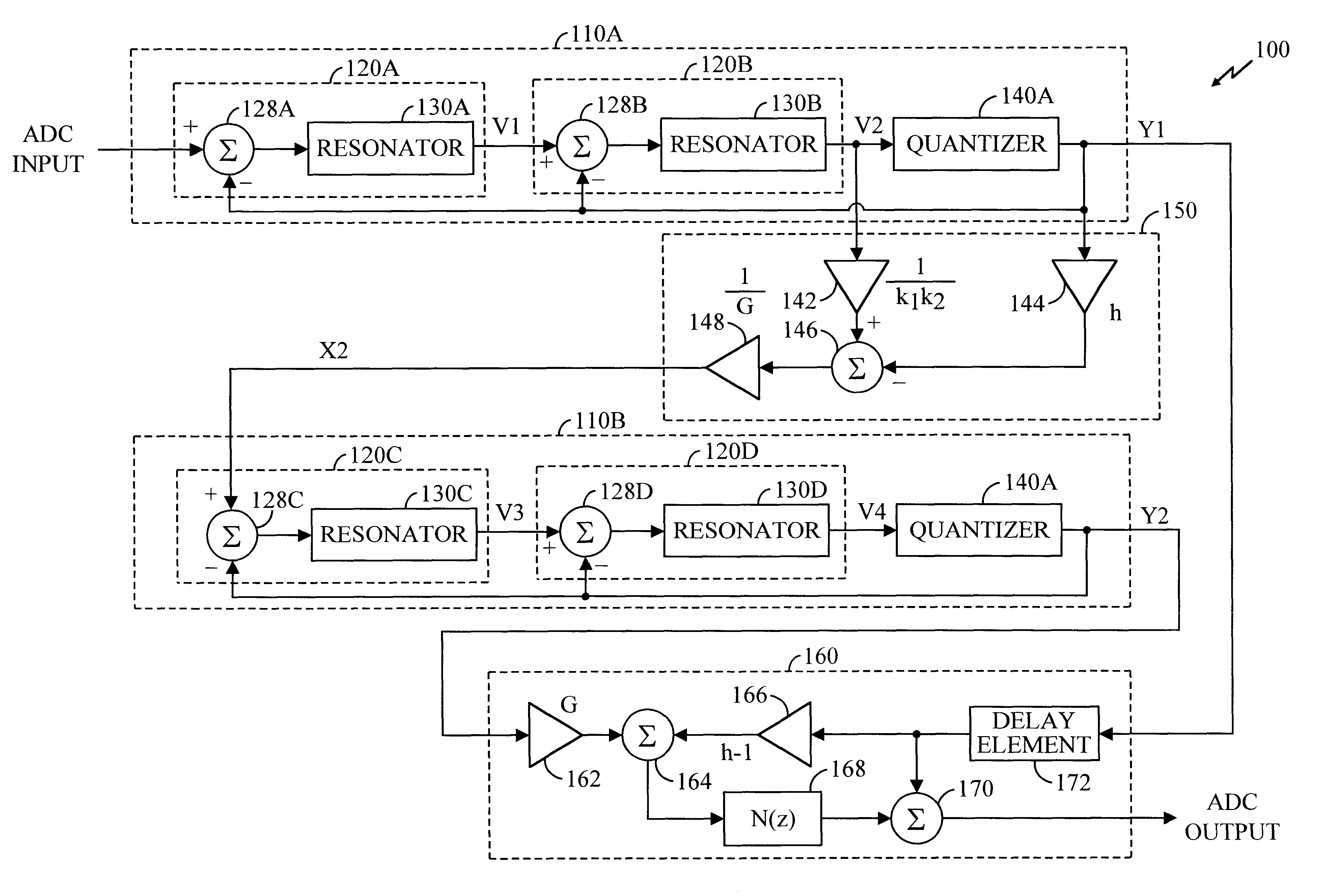

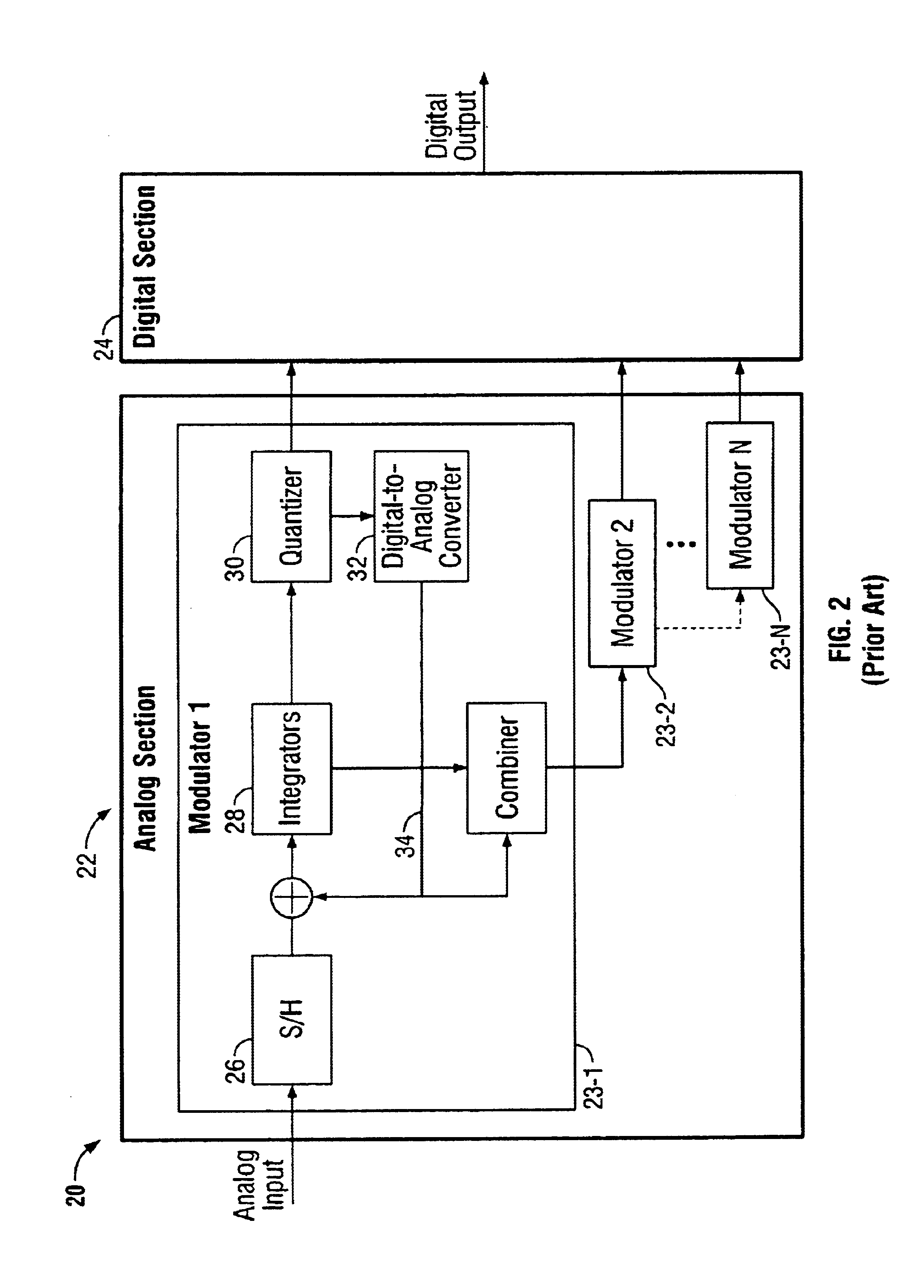

Multi-sampling SIGMA-DELTA analog-to-digital converter

A bandpass SIGMADELTA ADC utilizing either a single-loop or a MASH architecture wherein the resonators are implemented as either a delay cell resonator, a delay cell based resonator, a Forward-Euler resonator, a two-path interleaved resonator, or a four-path interleaved resonator. The resonator can be synthesized with analog circuit techniques such as active-RC, gm-C, MOSFET-C, switched capacitor, or switched current. The switched capacitor or switched current circuits can be designed using single-sampling, double-sampling, or multi-sampling circuits. The non-stringent requirement of a SIGMADELTA ADC using switched capacitor circuits allows the ADC to be implemented in a CMOS process to minimize cost and reduce power consumption. Double-sampling circuits provide improved matching and improved tolerance to sampling clock jitter. In particular, a bandpass MASH 4-4 SIGMADELTA ADC provides a simulated signal-to-noise ratio of 85 dB at an oversampling ratio of 32 for a CDMA application. The bandpass SIGMADELTA ADC can also be used in conjunction with undersampling to provide a frequency downconversion.

Owner:QUALCOMM INC

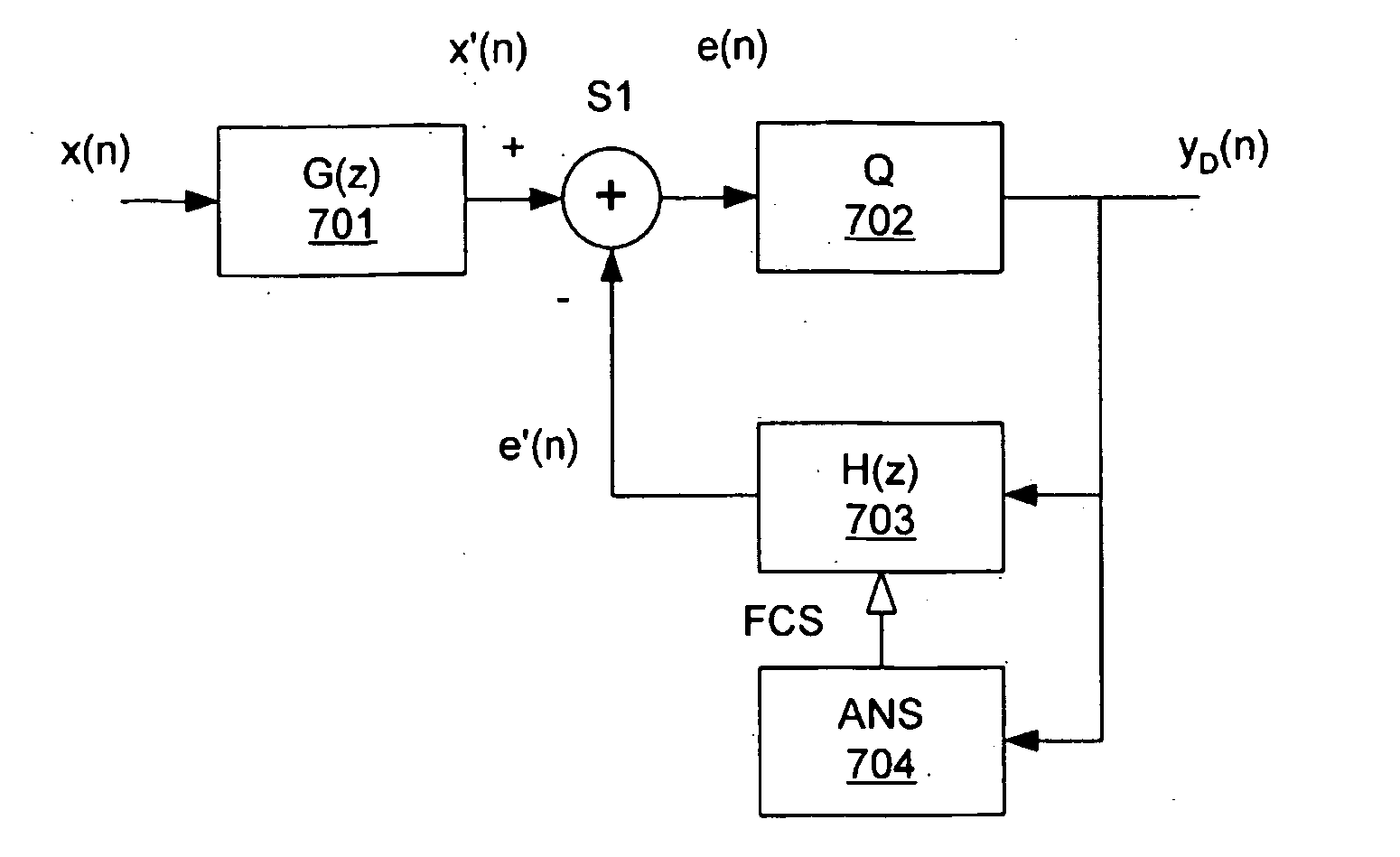

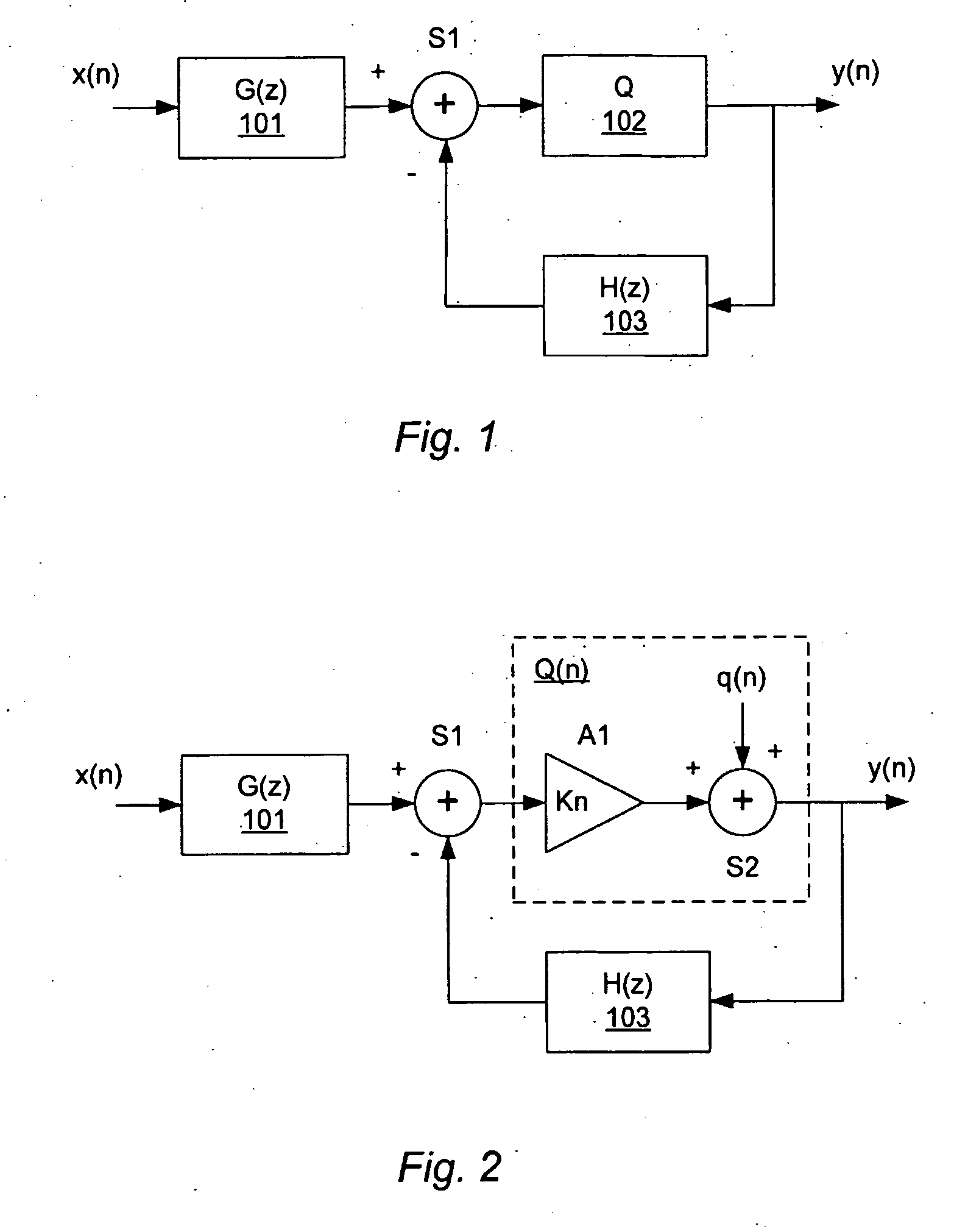

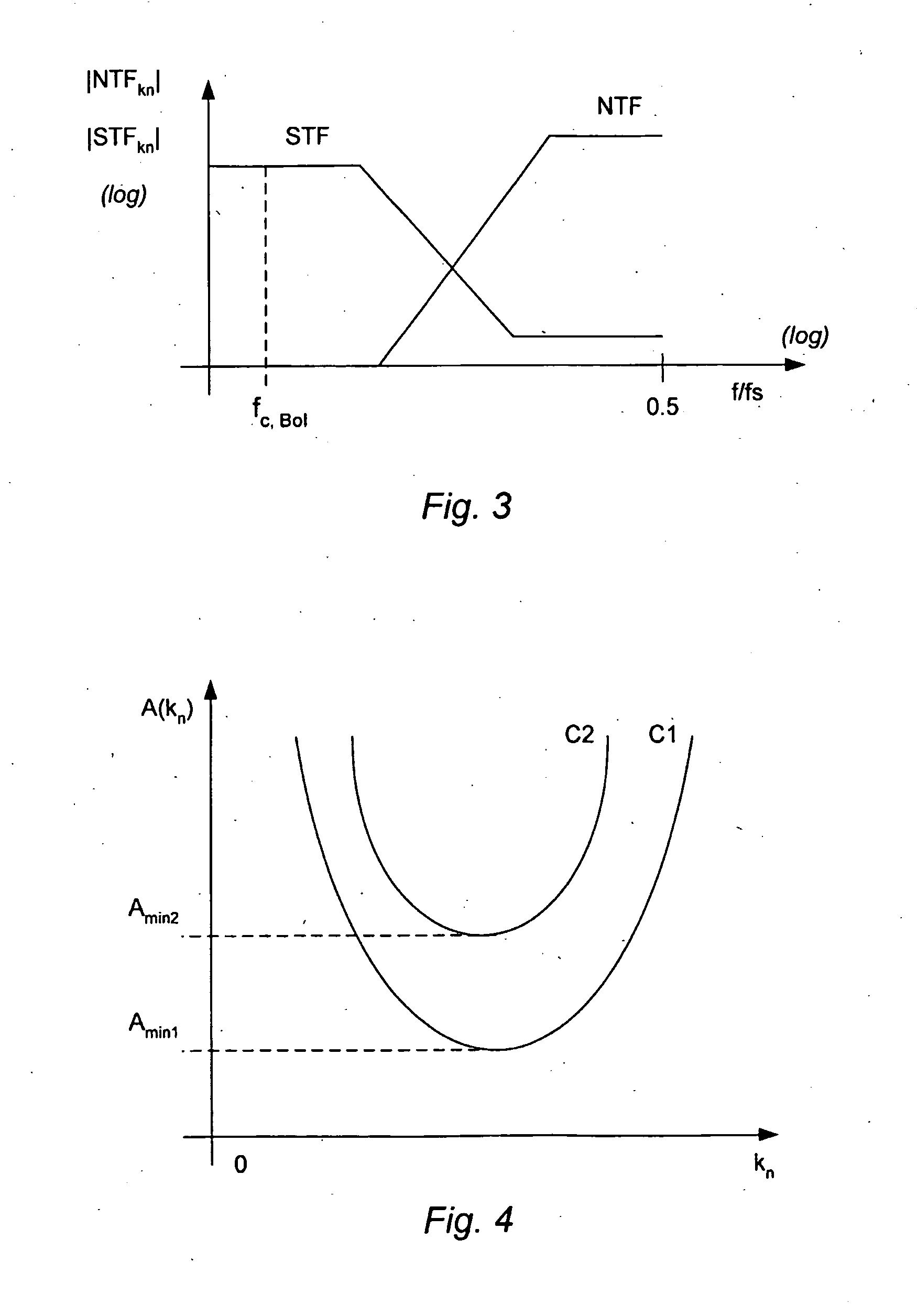

Sigma delta modulator

ActiveUS20090066549A1More freedomStable maintenanceDelta modulationDifferential modulationSignal transfer functionGreek letter sigma

A method of controlling a sigma delta modulator with a loop which establishes a signal transfer function, STF, and a quantization noise transfer function, NTF, of the sigma delta modulator, wherein the sigma delta modulator receives an input signal, x(n), and provides a modulated output signal, y(n) in response to the input signal. The method is characterized in comprising the step of controlling the sigma delta modulator to change the quantization noise transfer function, NTF, in response to a signal feature, A(n), which is correlated with the input signal.

Owner:ANALOG DEVICES INC

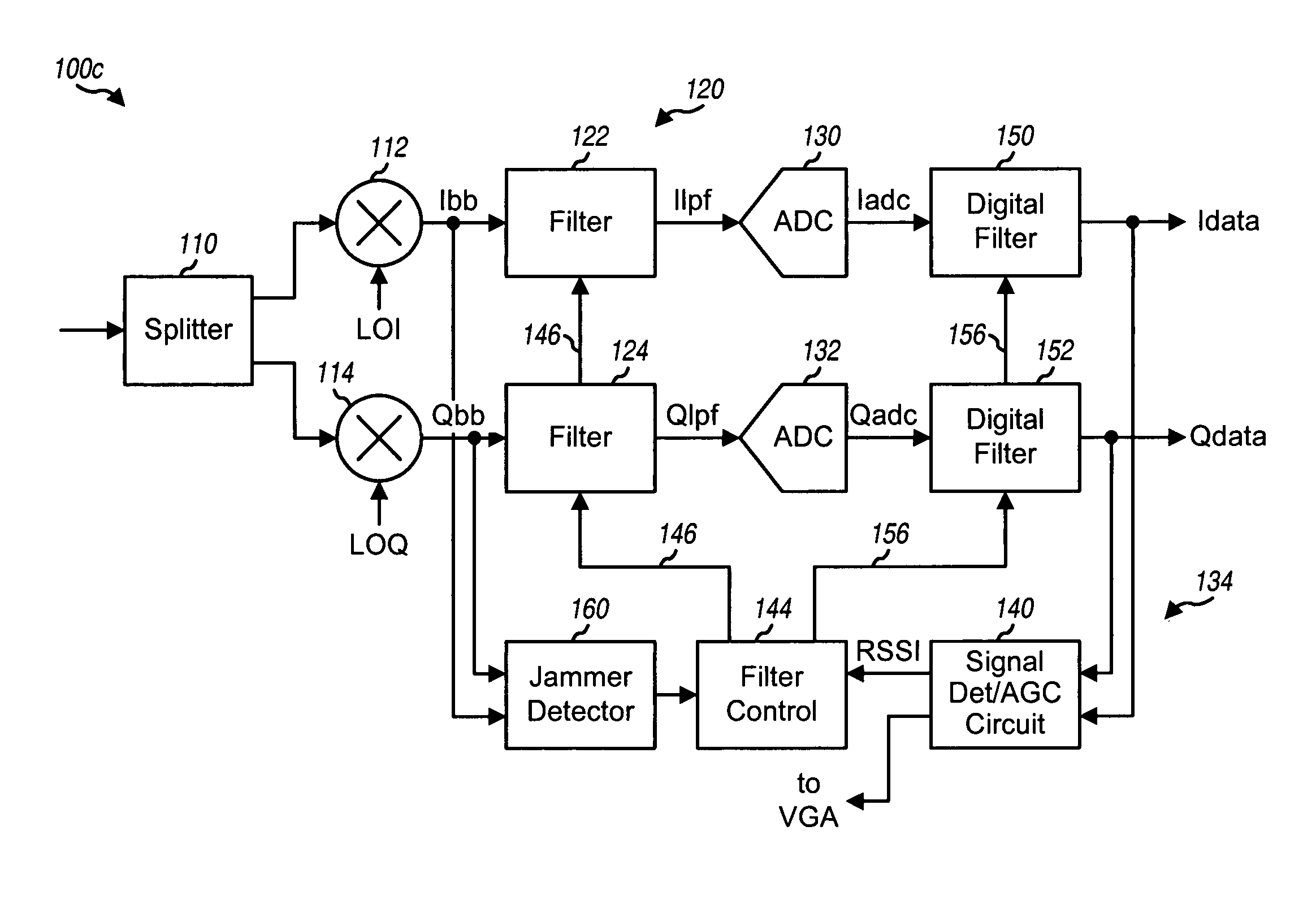

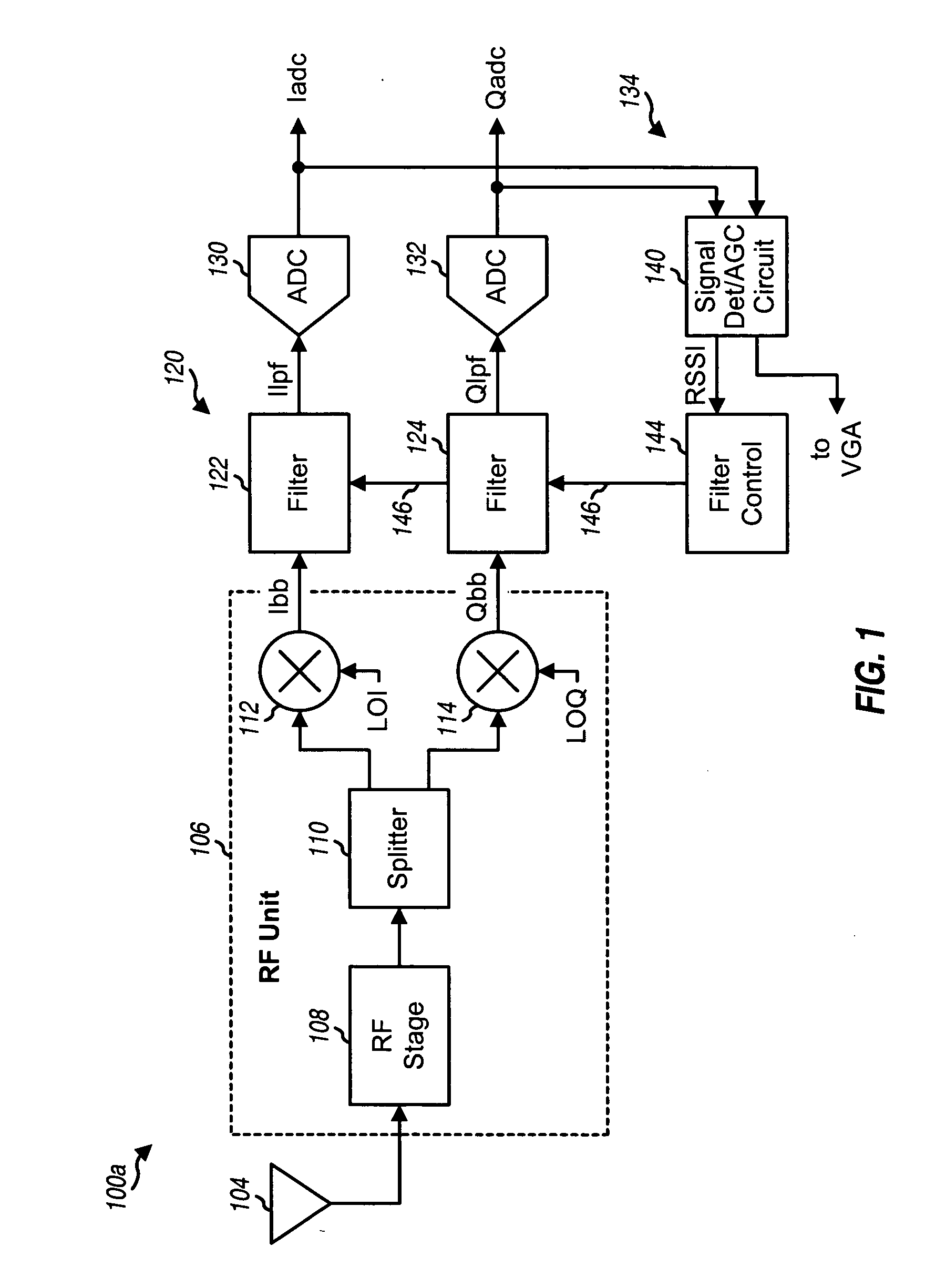

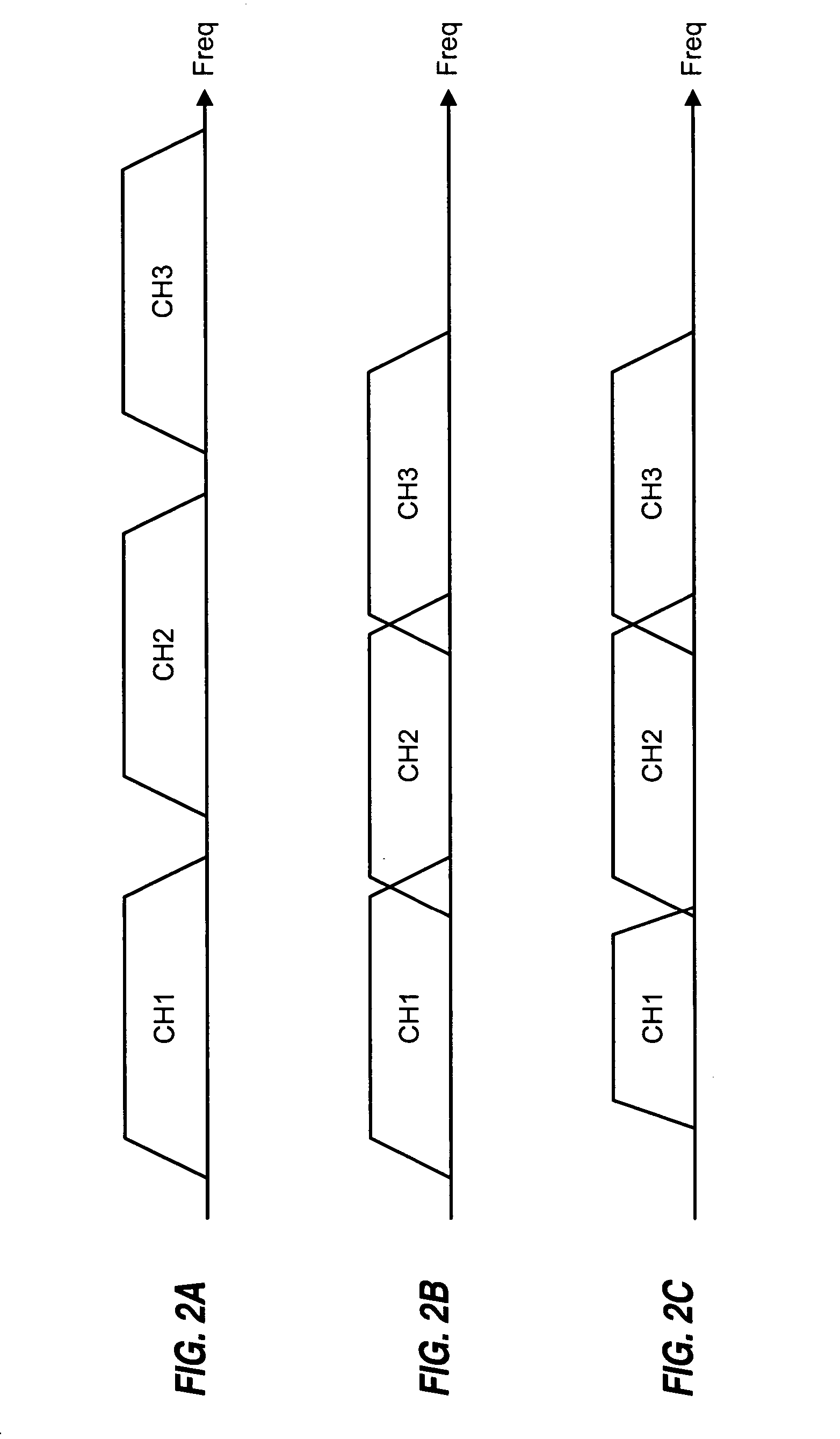

Noise reduction filtering in a wireless communication system

ActiveUS20060109939A1Avoid performanceLower performance requirementsError preventionDigital technique networkControl signalNoise shaping

A technique for noise reduction in a wireless communication system uses controllable bandwidth filters (120) to filter a received signal. In a typical implementation, the filters (120) are used at baseband frequencies. A measurement (RSSI) is indicative of the strength of the received signal. A control circuit (144) generates a control signal (146) to control the bandwidth of the filters (120). If the received signal strength is above a first threshold, a wider bandwidth may be used for the filters (120). If the received signal is below a second threshold, the control circuit (144) generates the control signal (146) to set the filters (120) to a more narrow bandwidth. The system (100) may also be used with digital filters (150, 152) following digitization by analog to digital converters (ADCs) (130, 132). The system (100) is particularly well-suited for operation with noise-shaped ADCs (130, 132), such as Delta-Sigma converters.

Owner:QUALCOMM INC

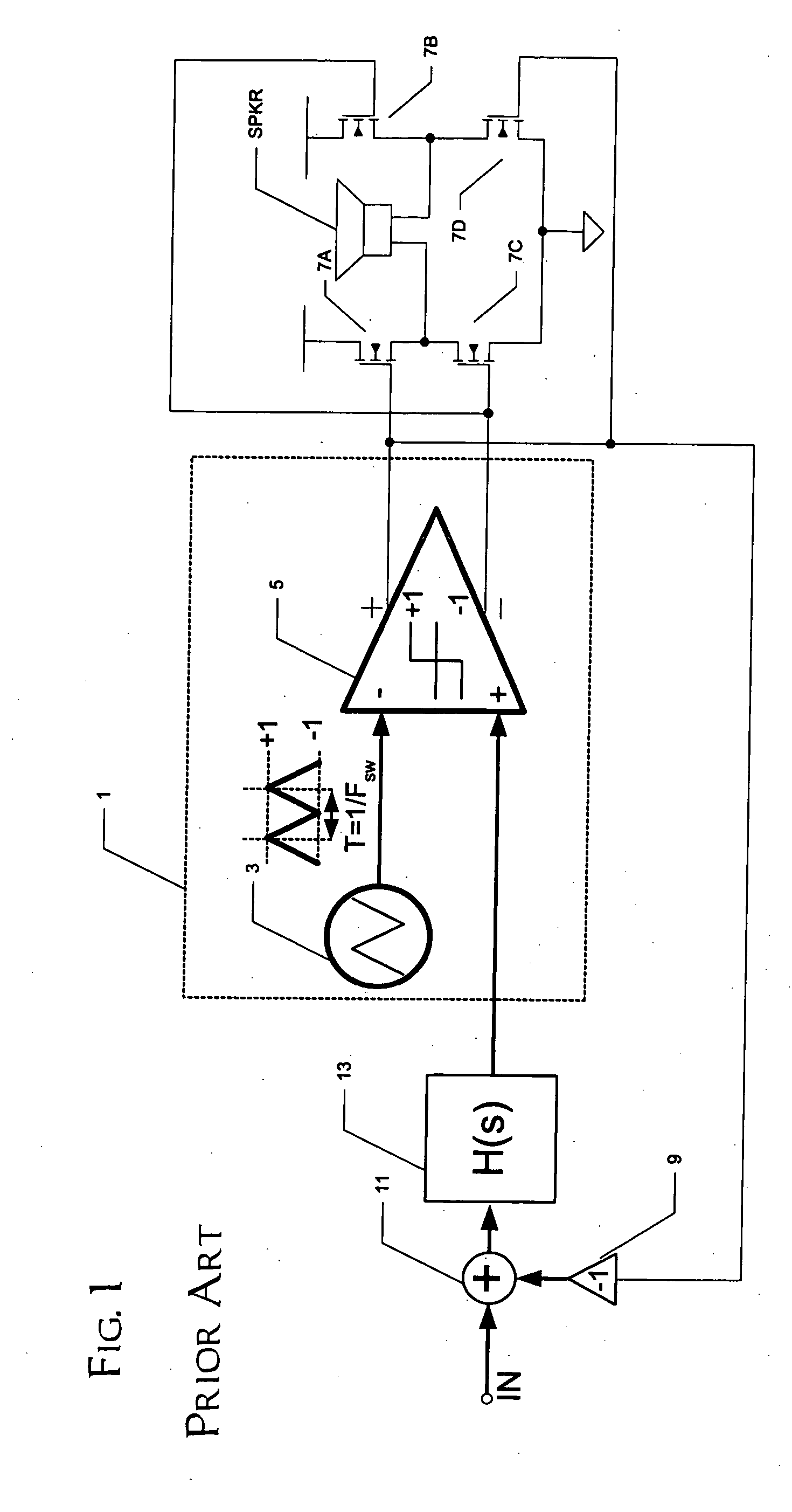

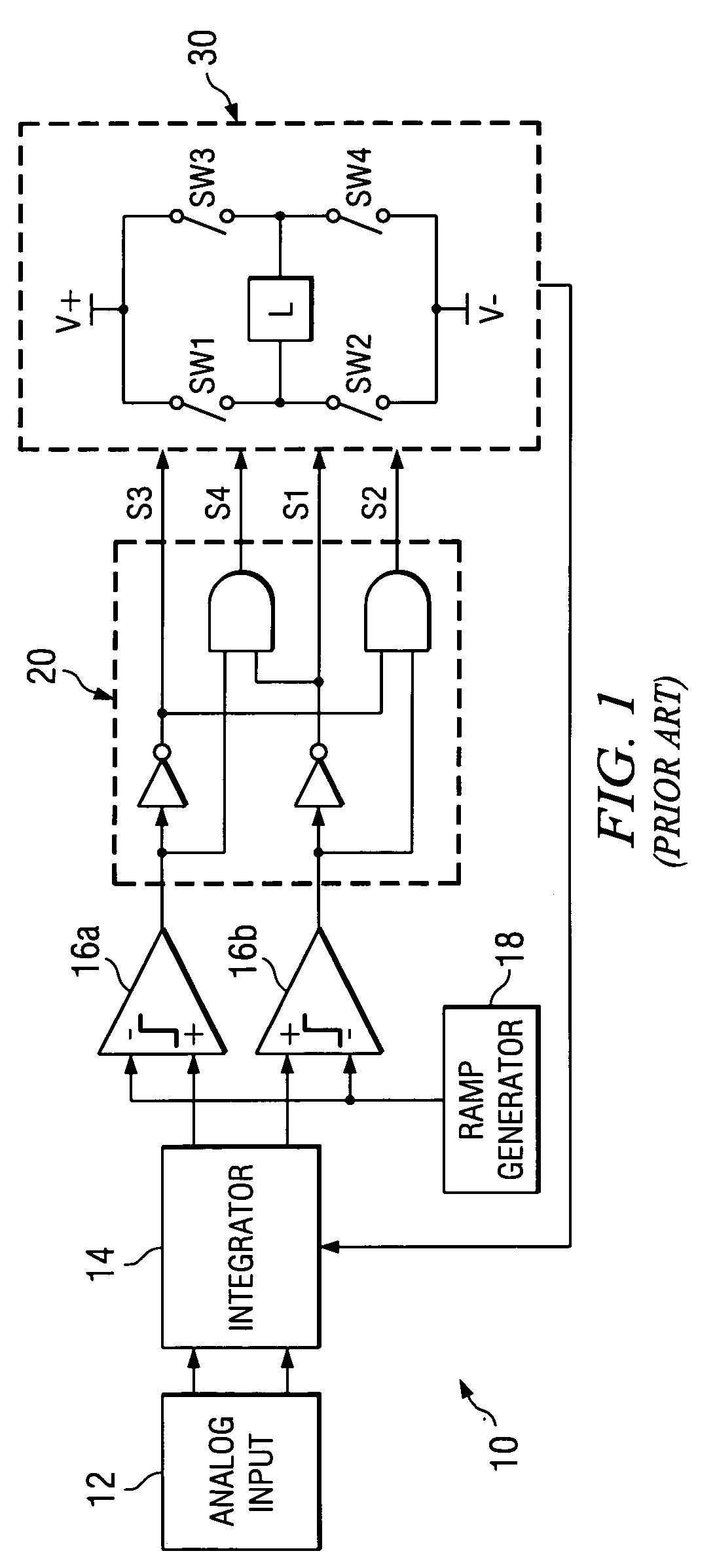

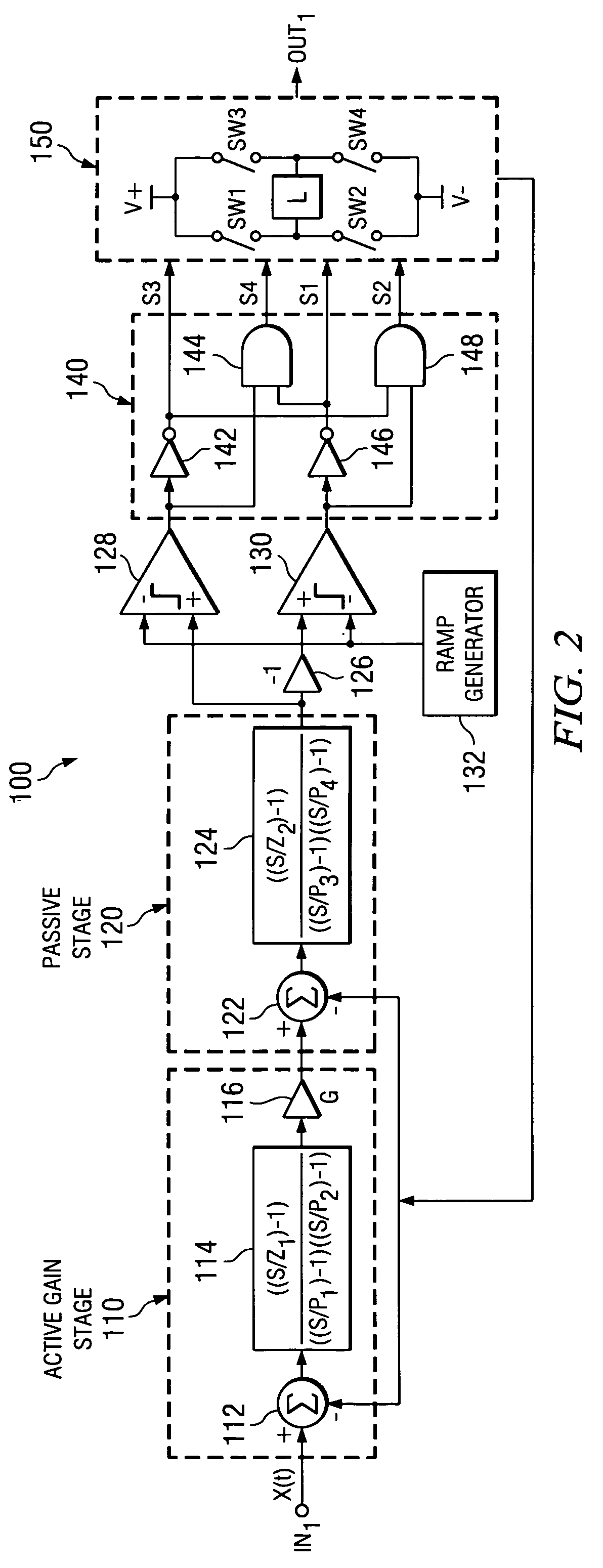

Class-D amplifier having high order loop filtering

InactiveUS20060044057A1High SNDR performanceImprove PSRRNegative-feedback-circuit arrangementsDc amplifiers with modulator-demodulatorLow-pass filterClass-D amplifier

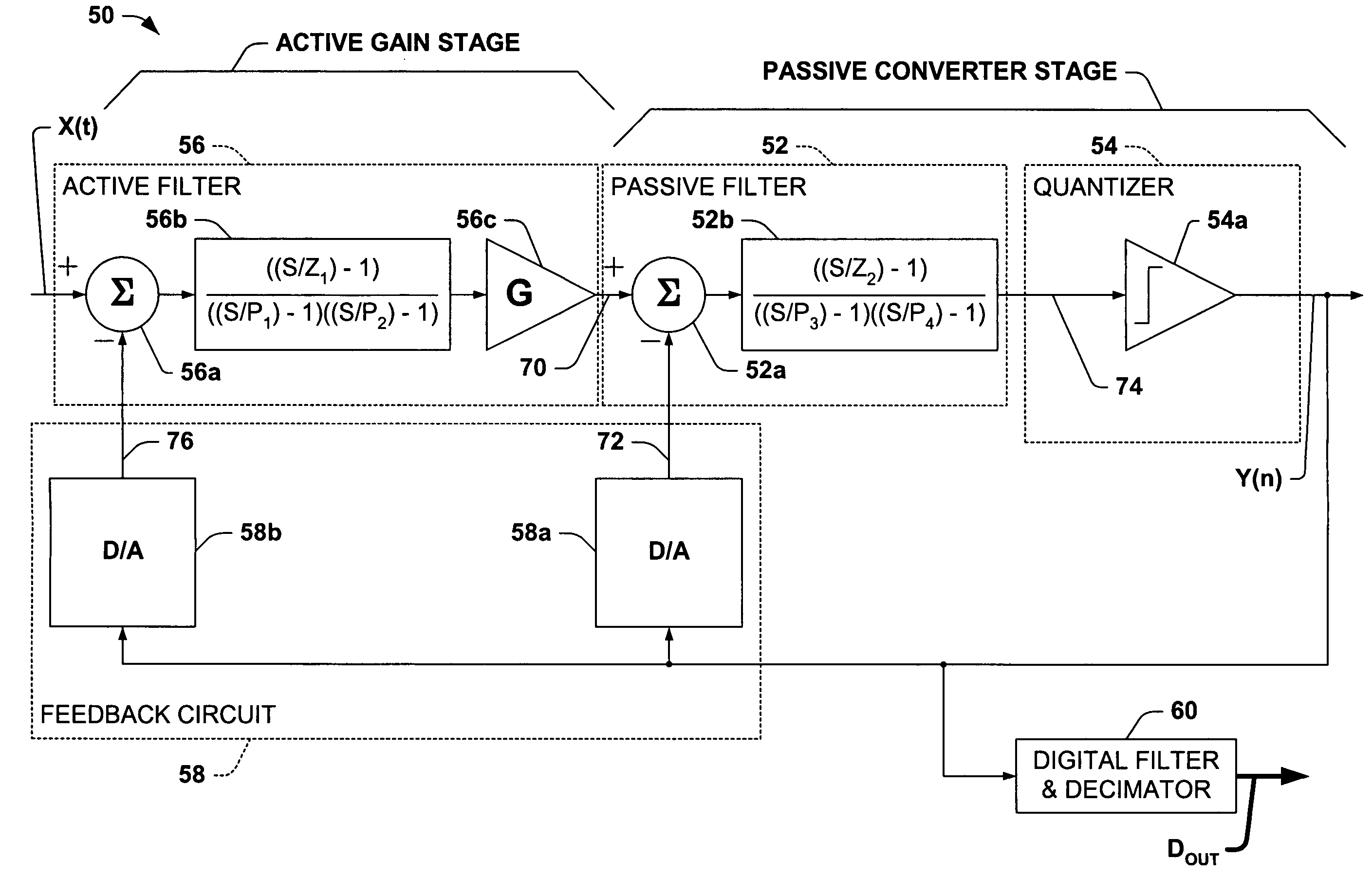

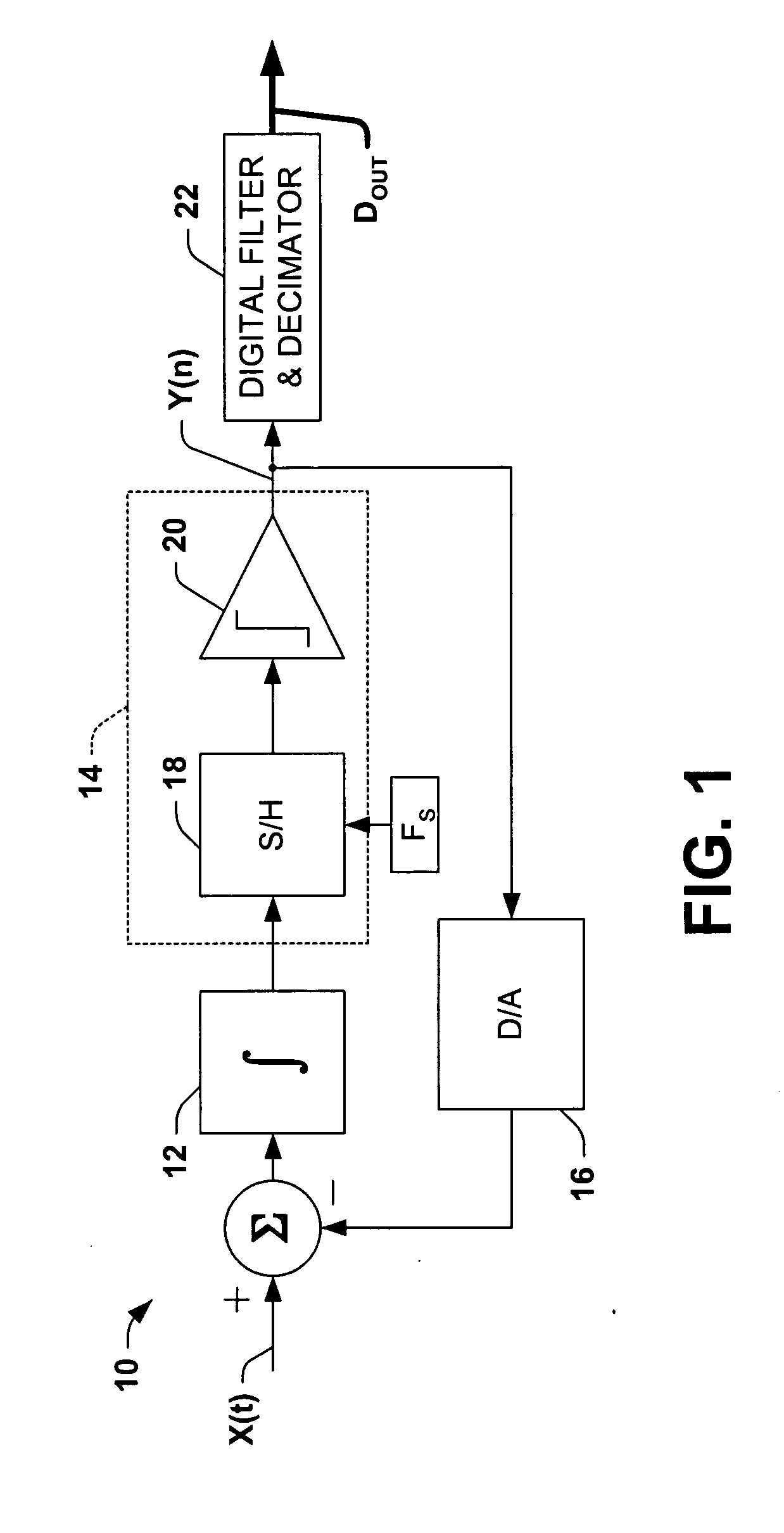

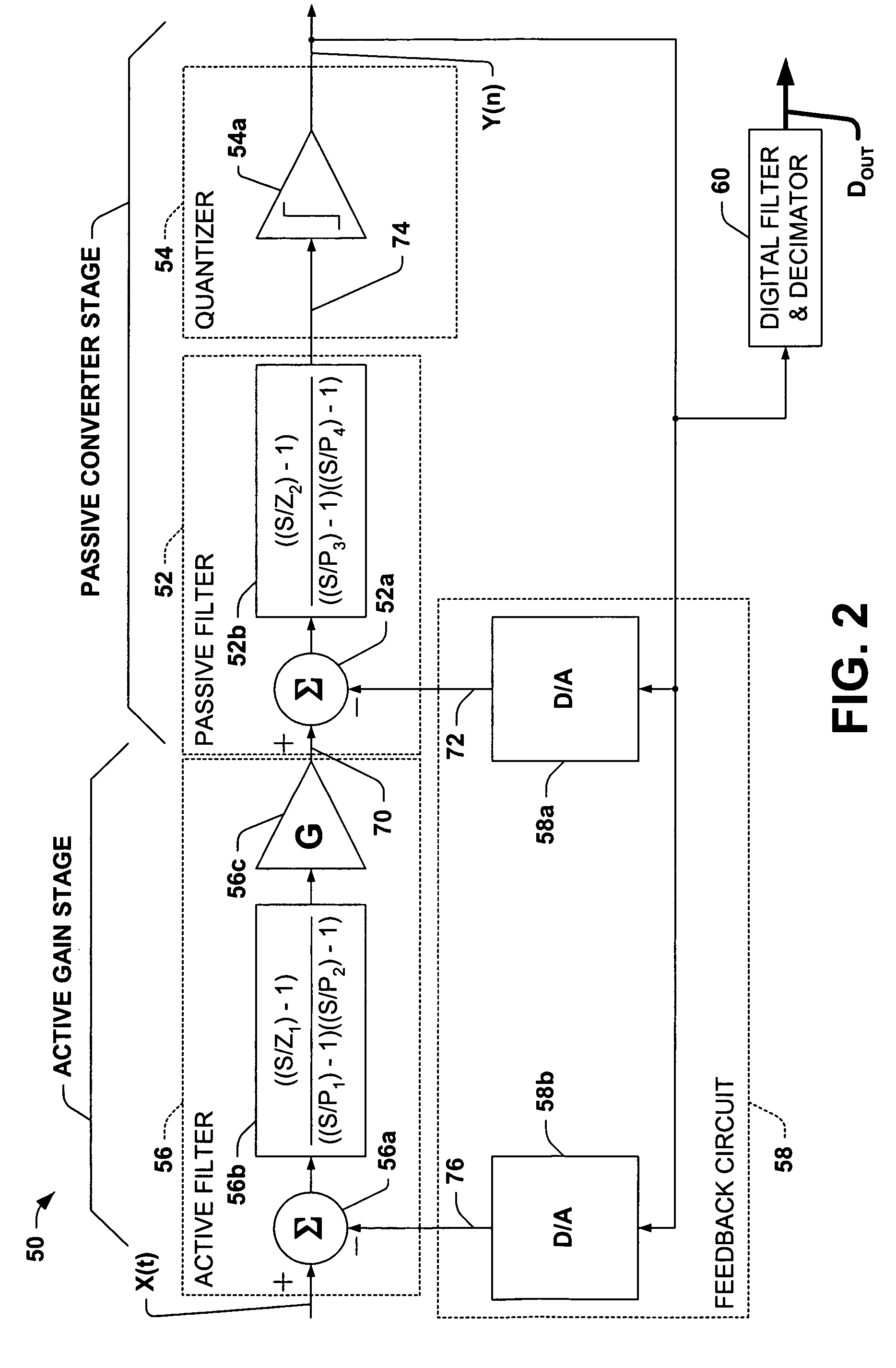

An amplifier having an active and passive gain stage connect to a load for driving a load according to a system analog input. A first embodiment of the amplifier in accordance with the present invention includes a logic network connected between a comparator network and a switching system, wherein the comparator network connects to the passive gain stage. Specifically, the active gain stage may include an active filter connected to receive an analog or digital input and provide a difference between the analog or digital input and the feedback signal relative to the gain factor of a gain unit connected to the active filter. The passive gain stage includes a passive filter. The logic network generates at least one switching signal which controls the switching system that includes at least one switching device to selectively provide power to the load. An output signal from the switching system provides output for the amplifier and is fed back to the active gain stage. In another embodiment, the output is a two-level signal and the passive and active filters are second order low pass filters, where the gain factor is about 25 or more. In yet another embodiment, the gain factor is approximately 250. Moreover, the amplifier may include a digital delta-sigma modulator connected to supply a two level input.

Owner:TEXAS INSTR INC

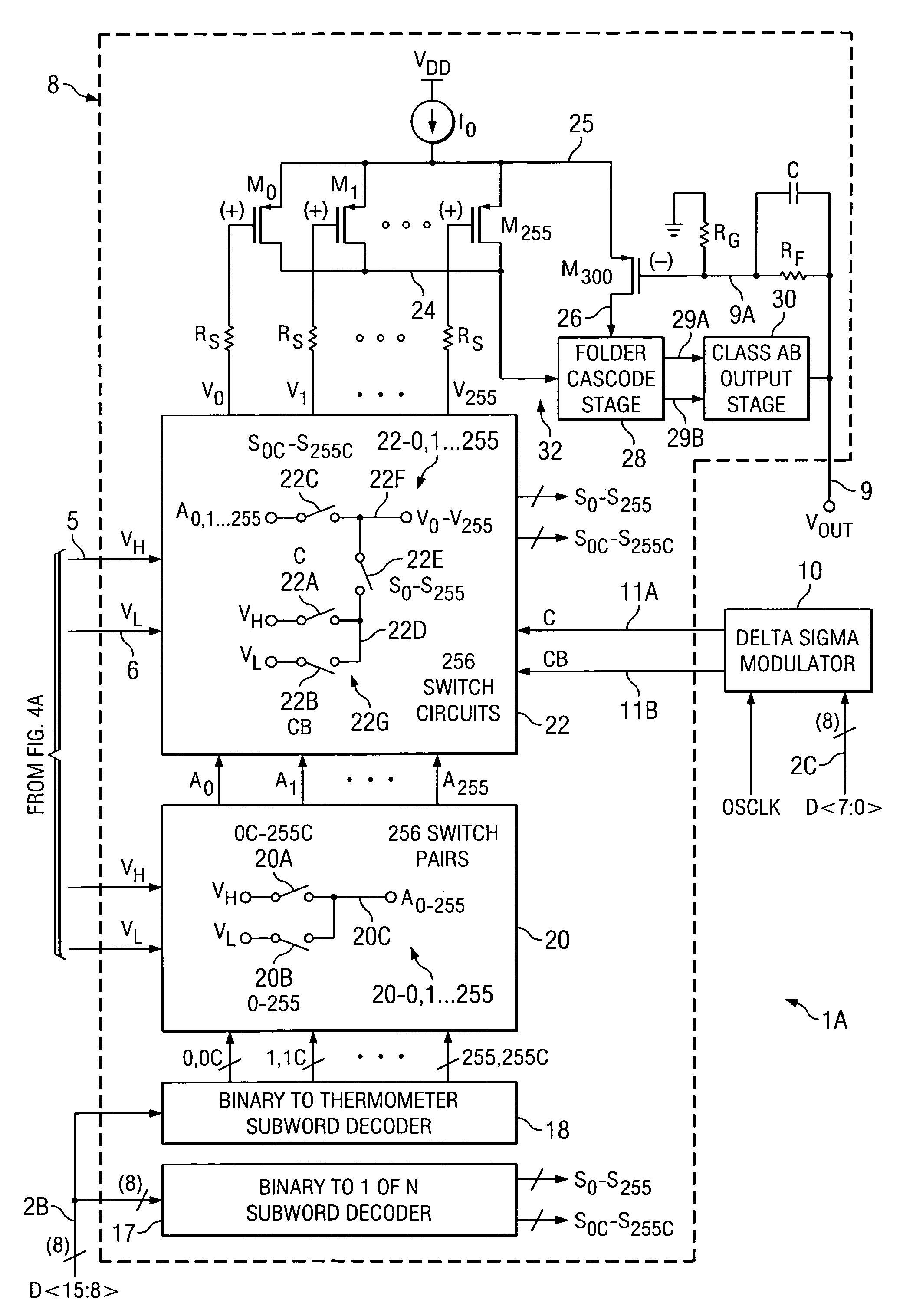

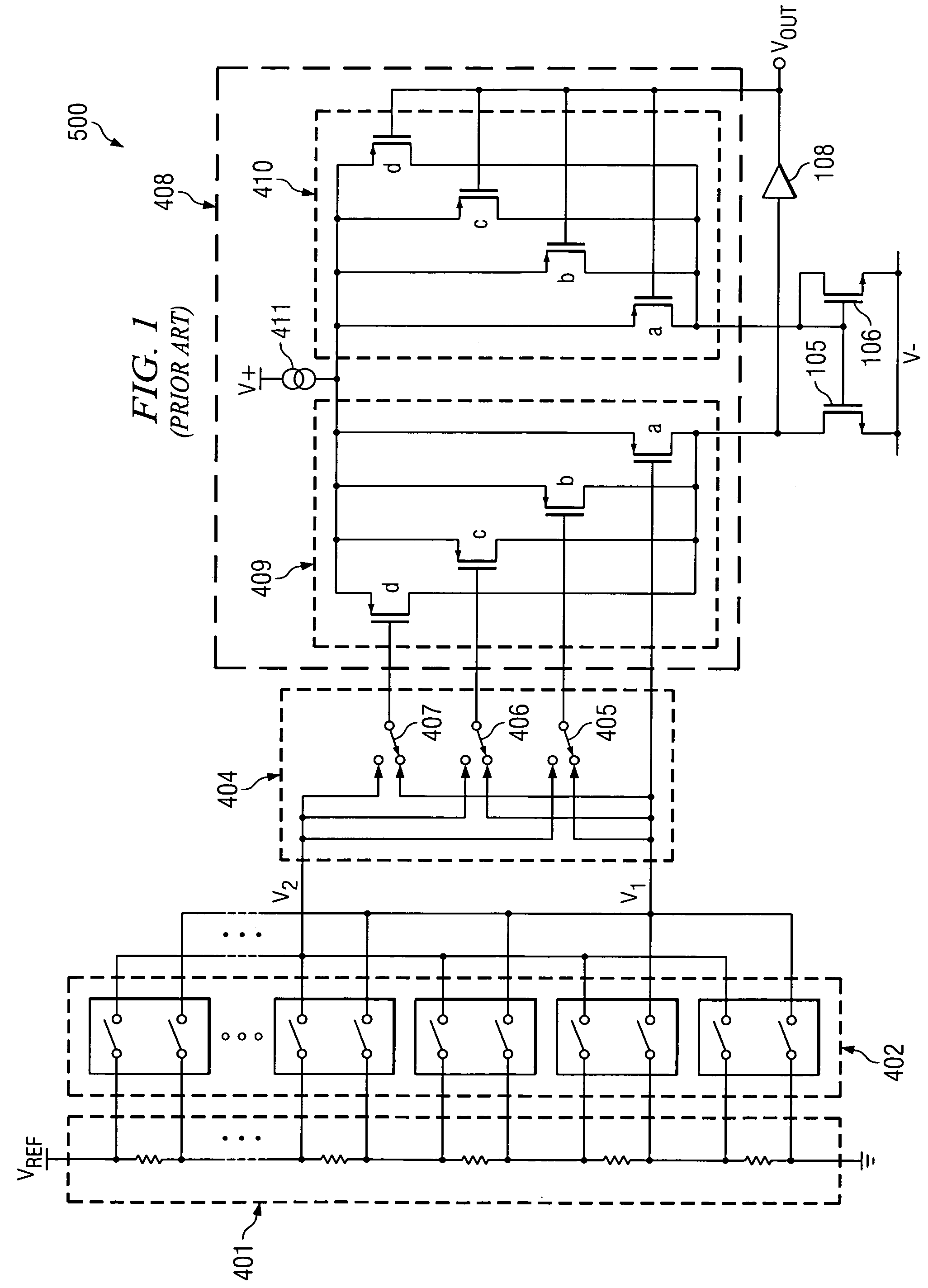

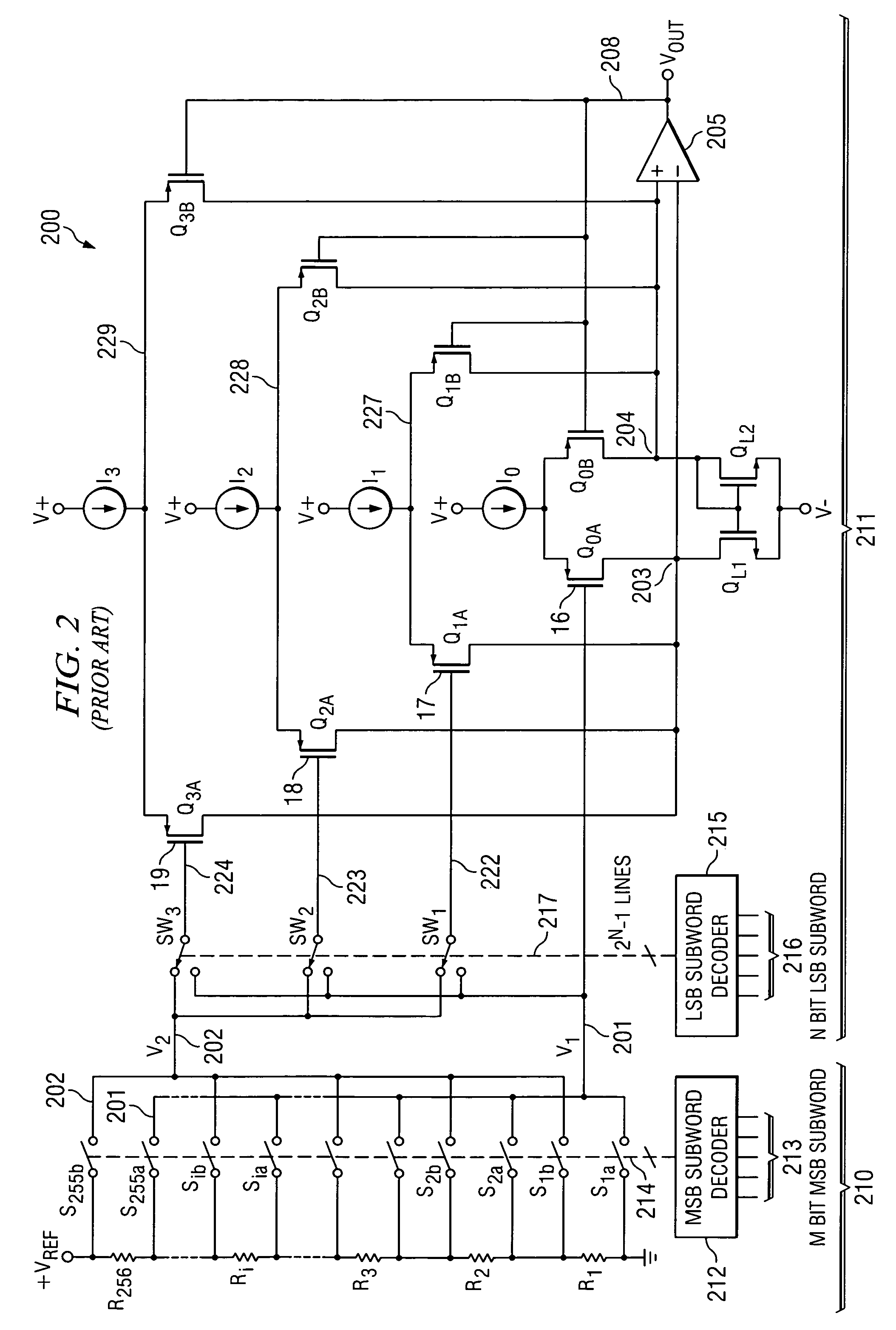

High-speed, high-resolution voltage output digital-to-analog converter and method

ActiveUS7283082B1Increase speedFast output voltageElectric signal transmission systemsAnalogue conversionMultiplexingEngineering

A string DAC having 2M string resistors includes a plurality of switches for selectively coupling, according to the decoding of an M-bit MSB subword, the voltage across a string resistor to an interpolation sub-DAC which interpolates it according to the decoding of an N-bit mid-subword. The voltage across the string resistor is multiplexed, according to the decoding of an N-bit mid-subword, to various inputs of 2N differential transistor pairs of an interpolation amplifier. A P-bit delta sigma modulator produces a delta sigma modulated signal, according to a P-bit LSB subword, to control multiplexing of voltages on the terminals of the string resistor to an input of one of the differential transistor pairs selected by decoding of the N-bit mid-subword to monotonically average a contribution of the selected differential transistor pair to generation of an output voltage representing a word including the M-bit, N-bit, and P-bit subwords.

Owner:TEXAS INSTR INC

Capacitive field sensor with sigma-delta modulator

A capacitive sensor includes a switching capacitor circuit, a comparator, and a charge dissipation circuit. The switching capacitor circuit reciprocally couples a sensing capacitor in series with a modulation capacitor during a first switching phase and discharges the sensing capacitor during a second switching phase. The comparator is coupled to compare a voltage potential on the modulation capacitor to a reference and to generate a modulation signal in response. The charge dissipation circuit is coupled to the modulation capacitor to selectively discharge the modulation capacitor in response to the modulation signal.

Owner:CYPRESS SEMICON CORP

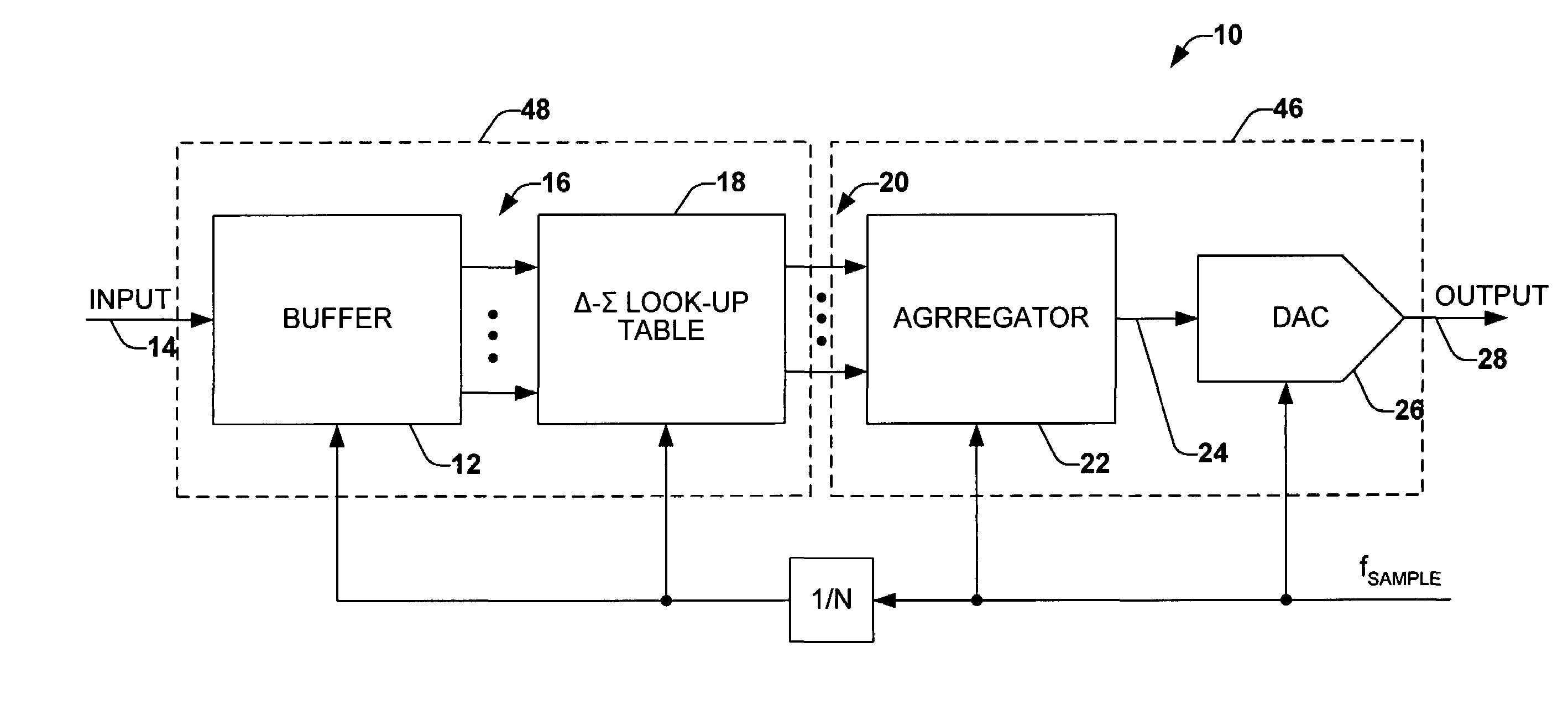

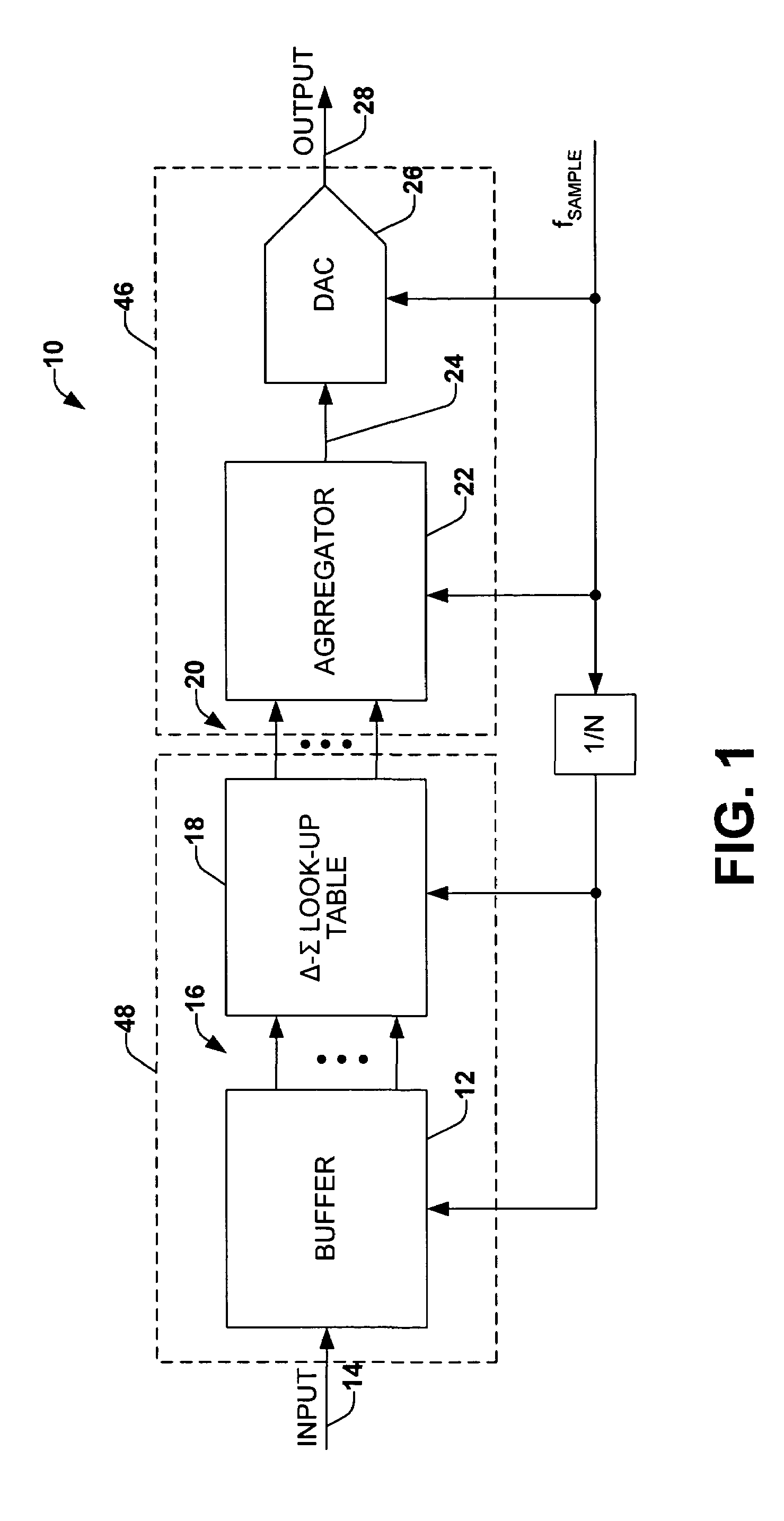

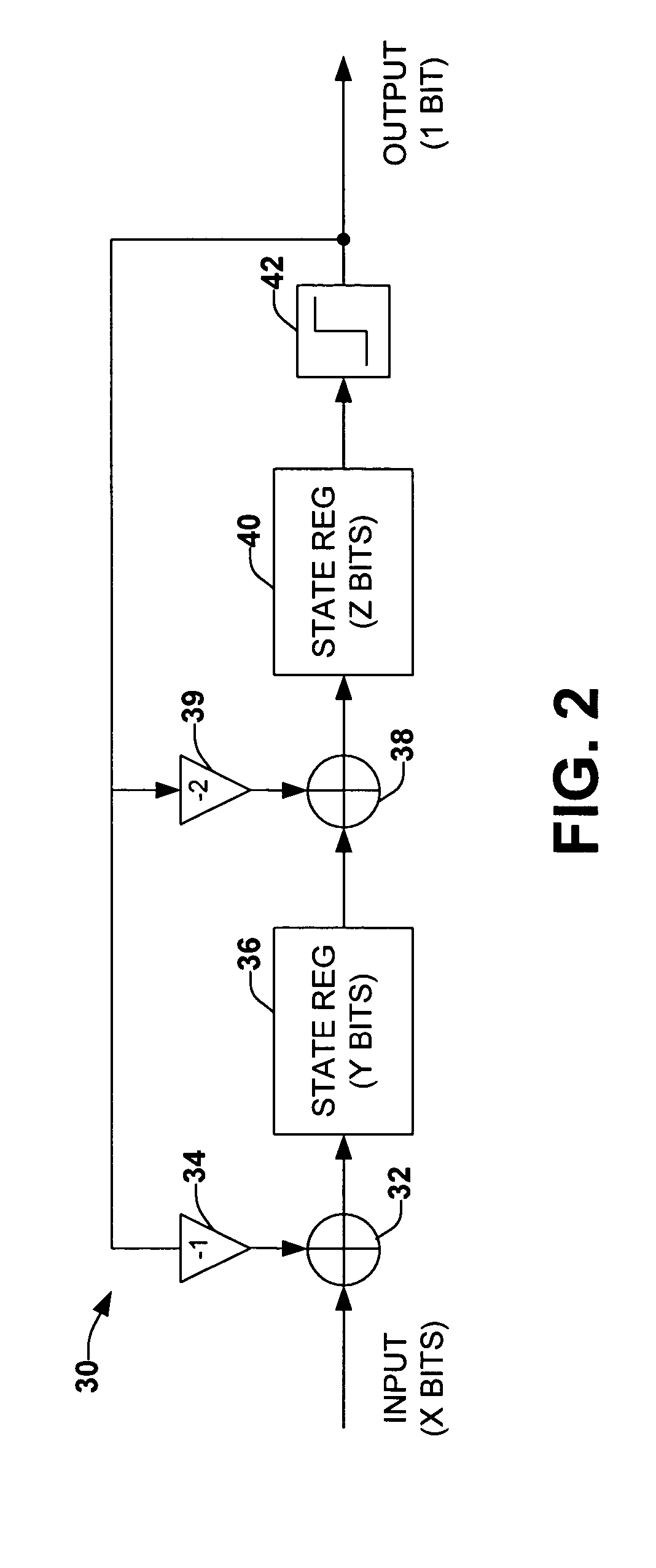

Look-up table delta-sigma conversion

Signal conversion is implemented employing a memory system operating as a look-up table that stores a plurality of sets of output samples associated with each of a plurality of respective input samples. The look-up table thus can generate a corresponding set of output samples in response to a given input sample, thereby emulating desired digital upsampling and delta-sigma modulation. The output samples can be aggregated, such as by multiplexing, to provide an output data stream at a desired sample rate.

Owner:NORTHROP GRUMMAN SYST CORP

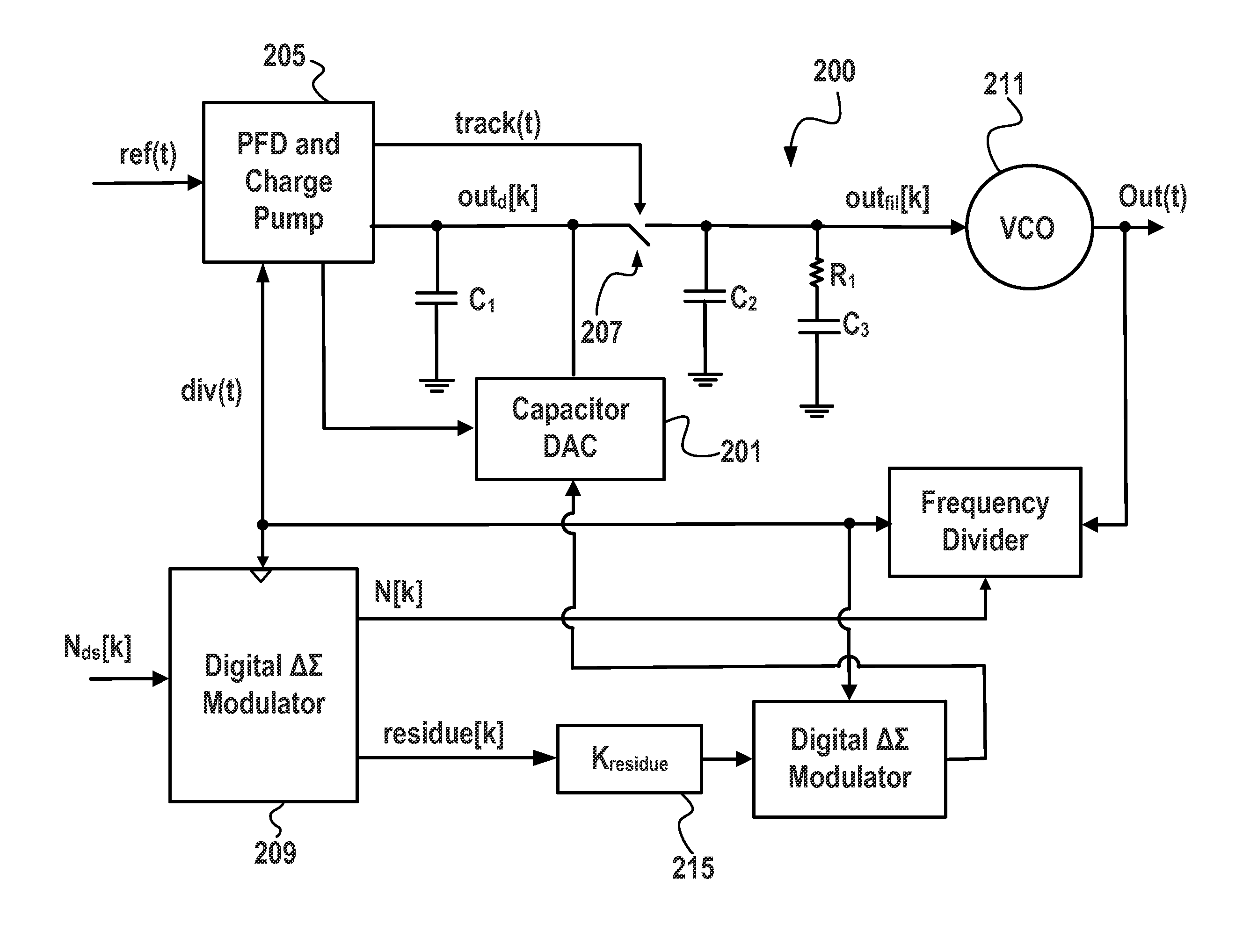

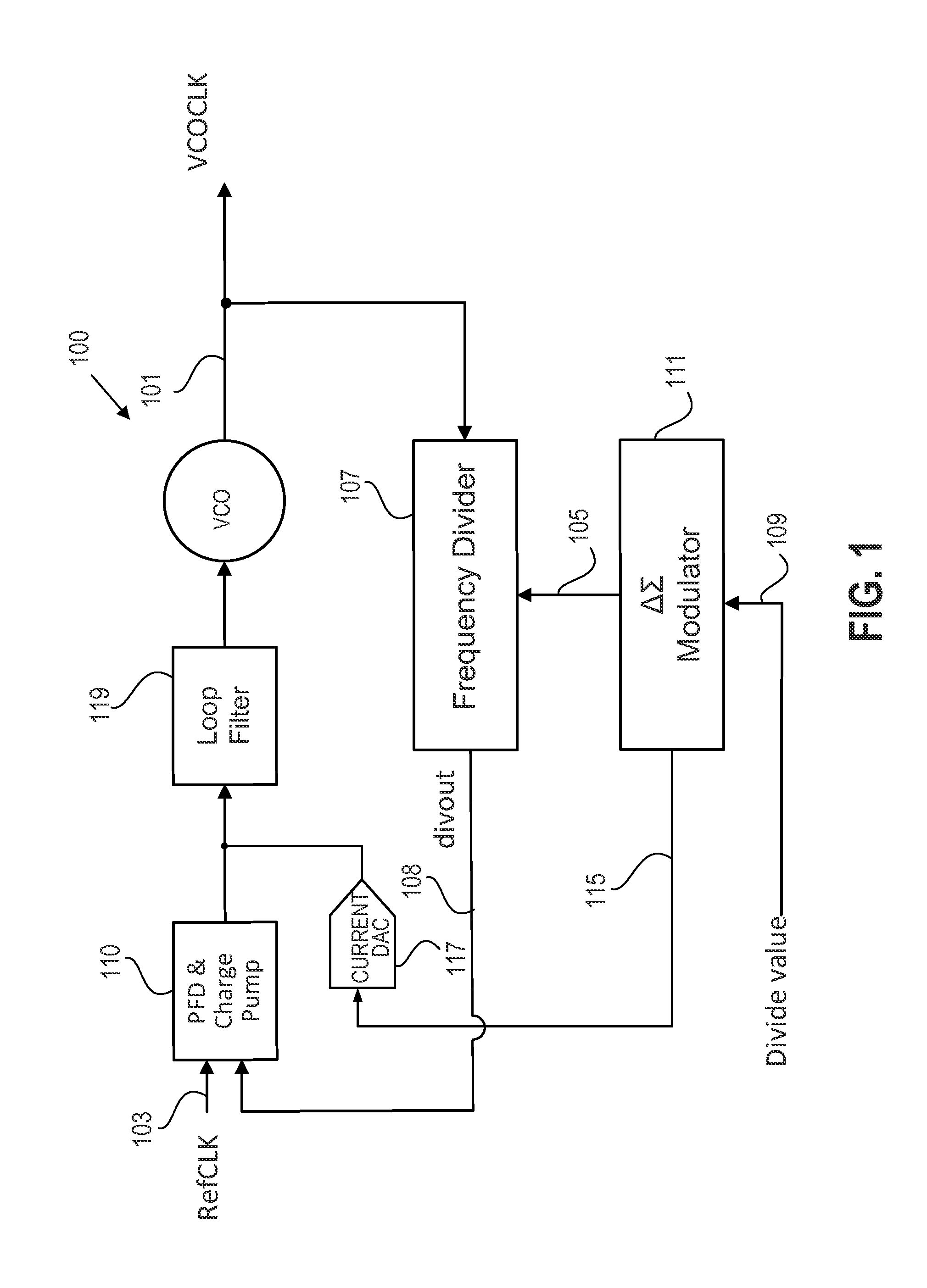

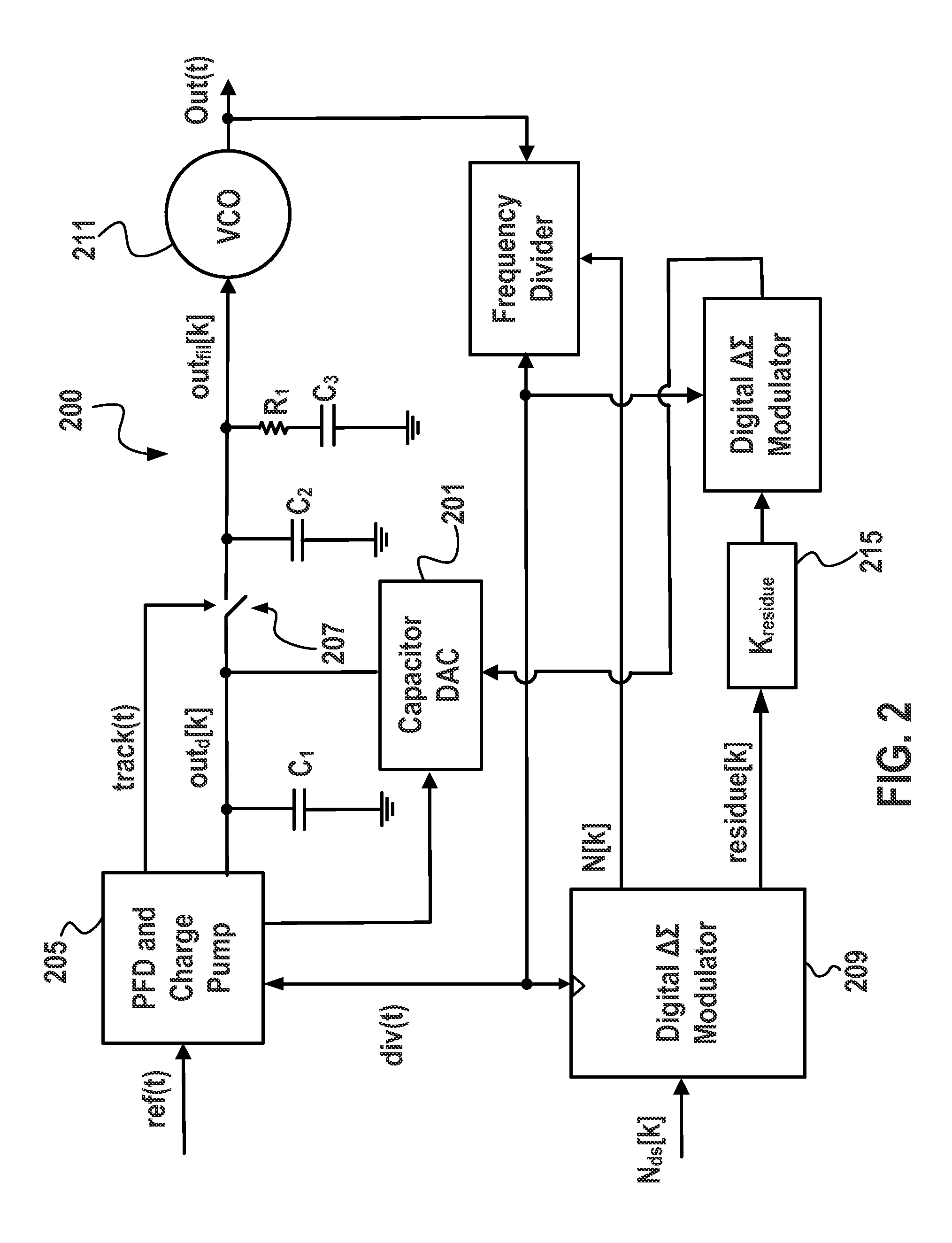

Cancellation of delta-sigma quantization noise within a fractional-n PLL with a nonlinear time-to-digital converter

ActiveUS20150145571A1Reduce quantization noisePulse automatic controlAnalogue conversionEngineeringGreek letter sigma

A fractional-N phase-locked loop (PLL) includes a nonlinear time to digital converter that generates a digital representation of a phase error corresponding to a time difference between a feedback signal of the fractional-N PLL and a reference signal. A nonlinear quantization noise cancellation circuit supplies a correction signal to ensure that the generated digital representation has reduced quantization noise. The correctional signal may be applied in the analog or digital domain.

Owner:SKYWORKS SOLUTIONS INC

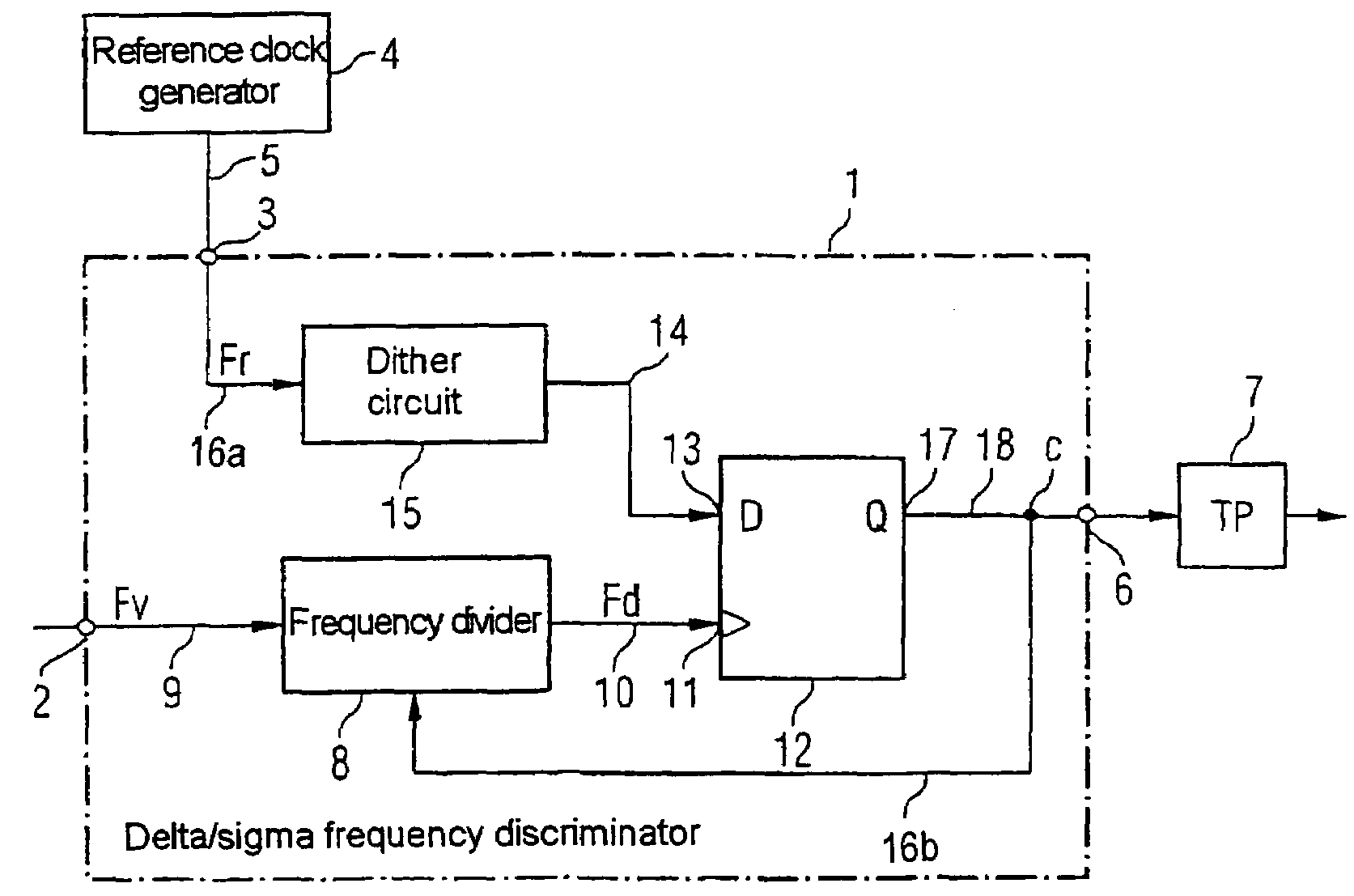

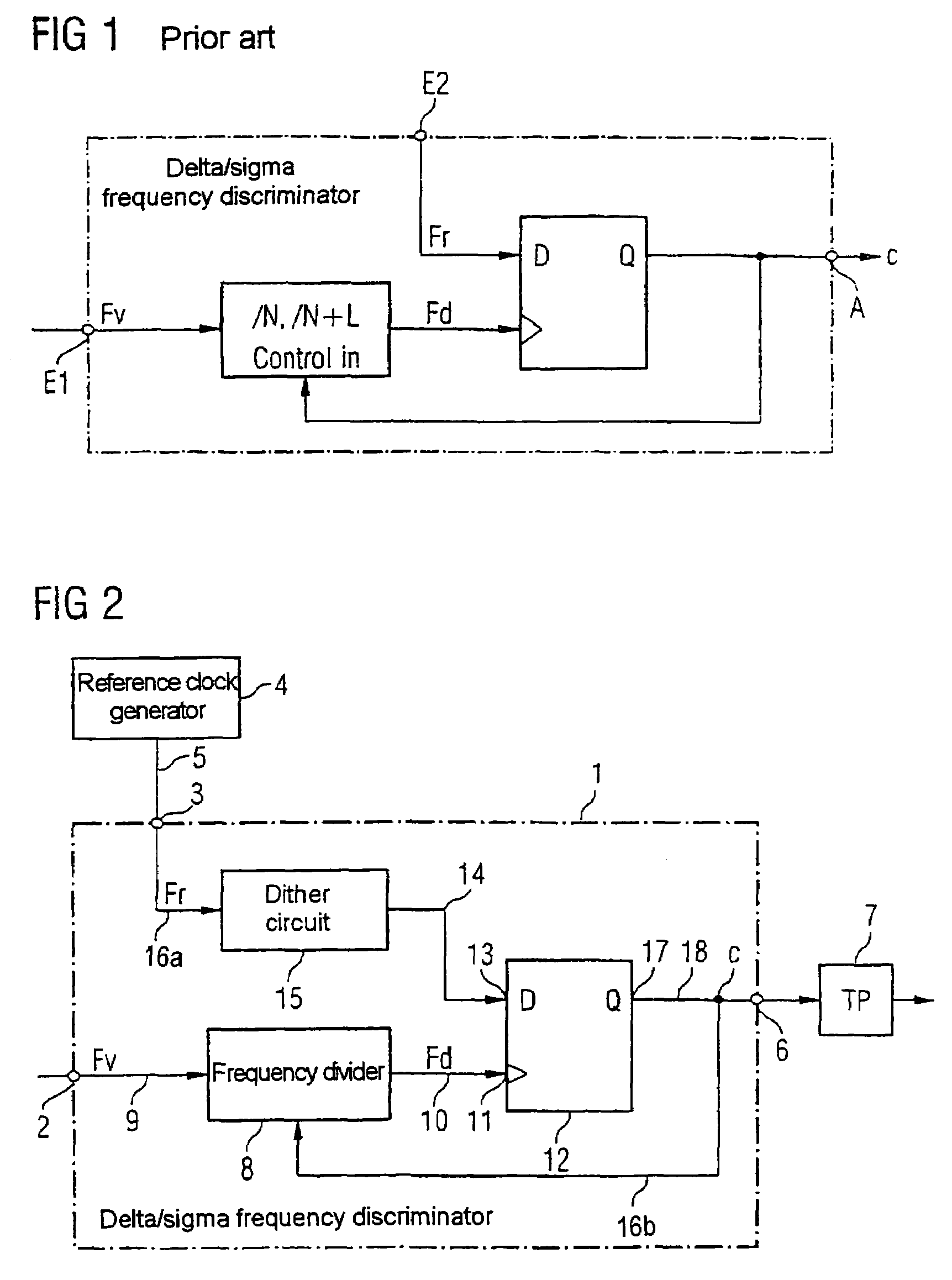

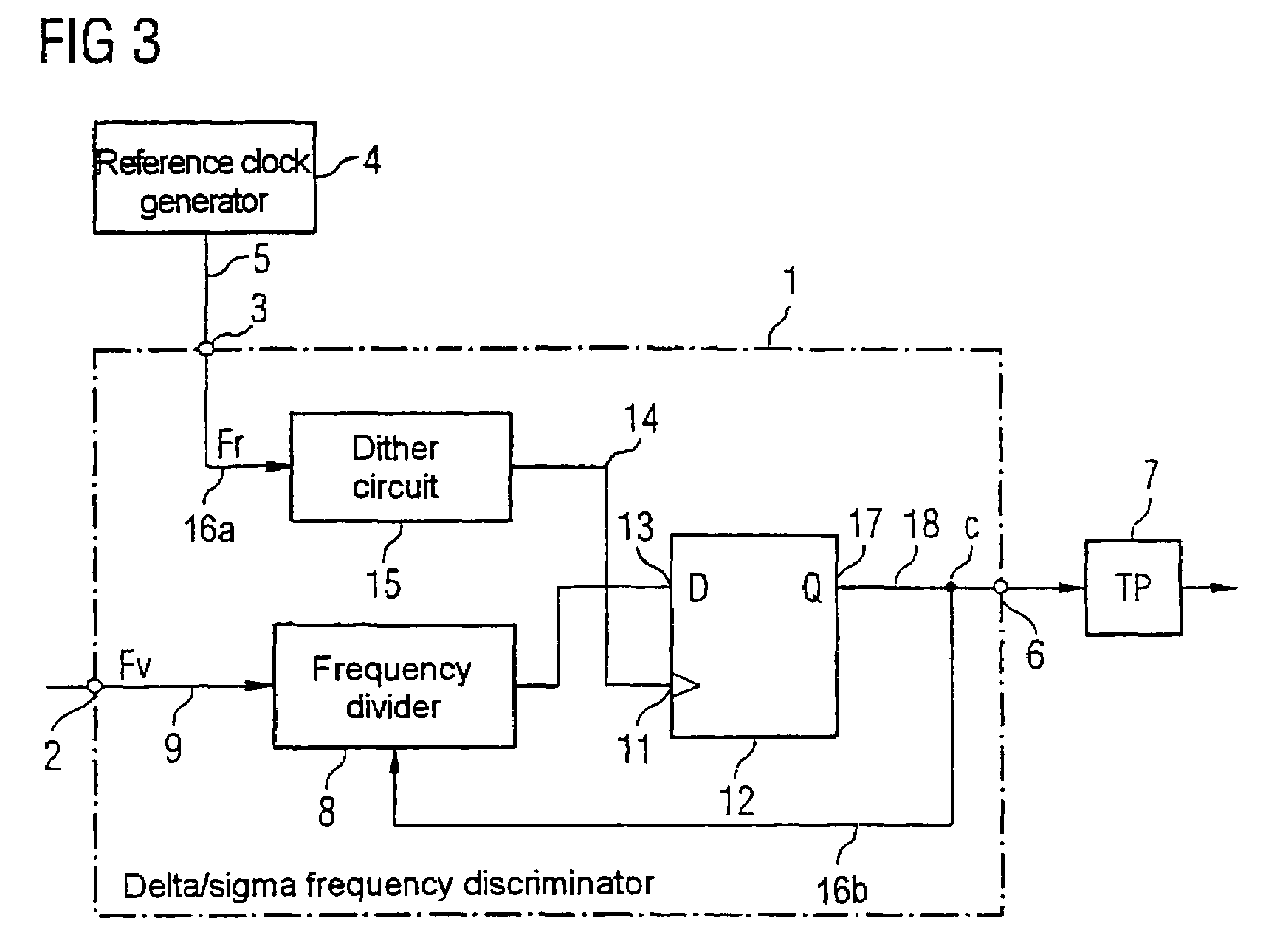

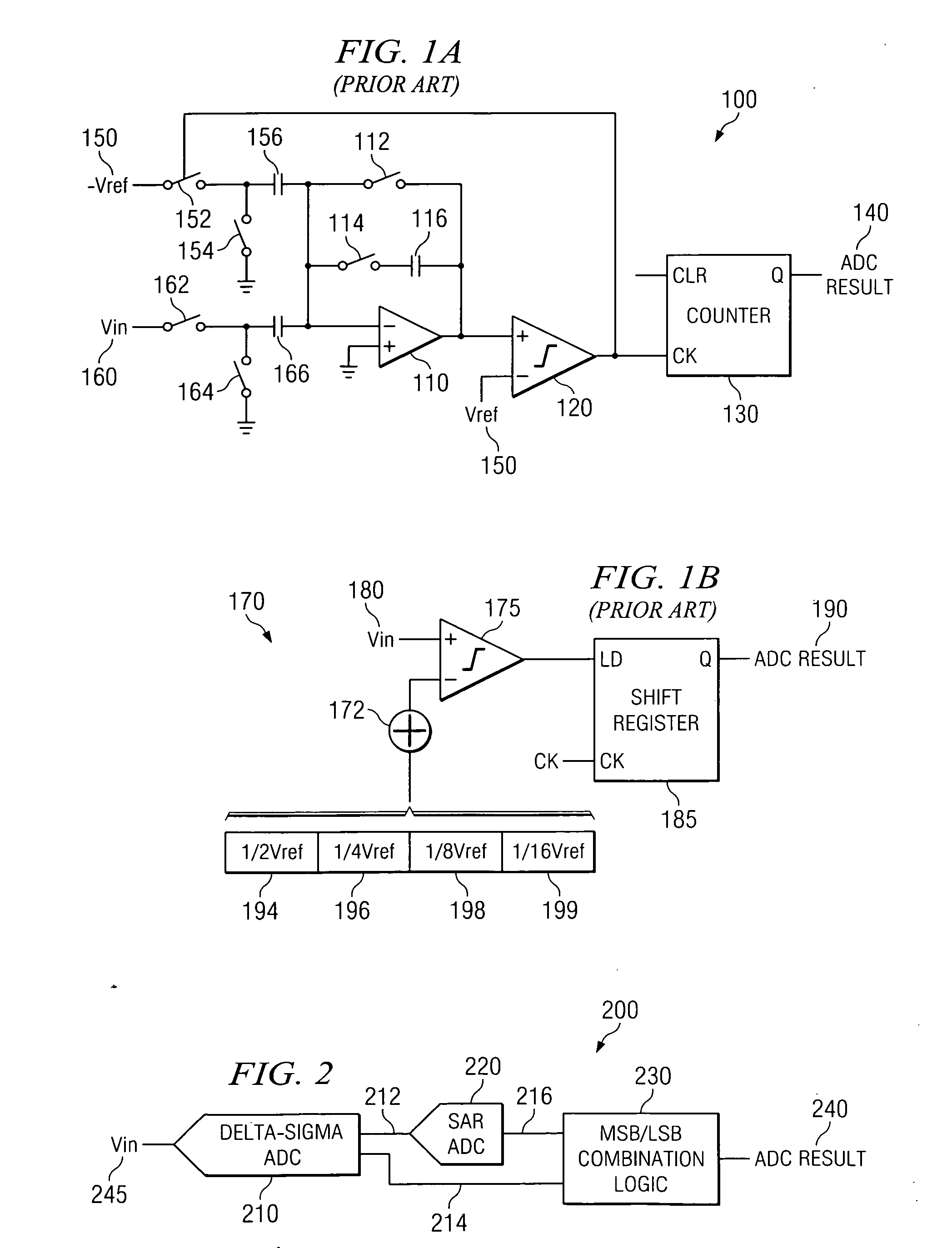

Delta/sigma frequency discriminator

ActiveUS7230458B2Little circuit complexityElectric signal transmission systemsPulse automatic controlDiscriminatorFrequency spectrum

Delta / sigma frequency discriminator (1) for converting a frequency (Fv) of an input signal into a digital output signal (C) comprising a frequency divider (8) which divides the input signal at a frequency dividing ratio which can be switched in dependence on the digital output signal (C), with at least one sampling register (12) which samples the divided input signal by means of a reference clock signal for generating the digital output signal (C), and with a dither circuit (15) which varies the clock period (T) of the reference clock signal so that interfering modulation tones in the signal spectrum of the digital output signal (C) are suppressed.

Owner:INFINEON TECH AG

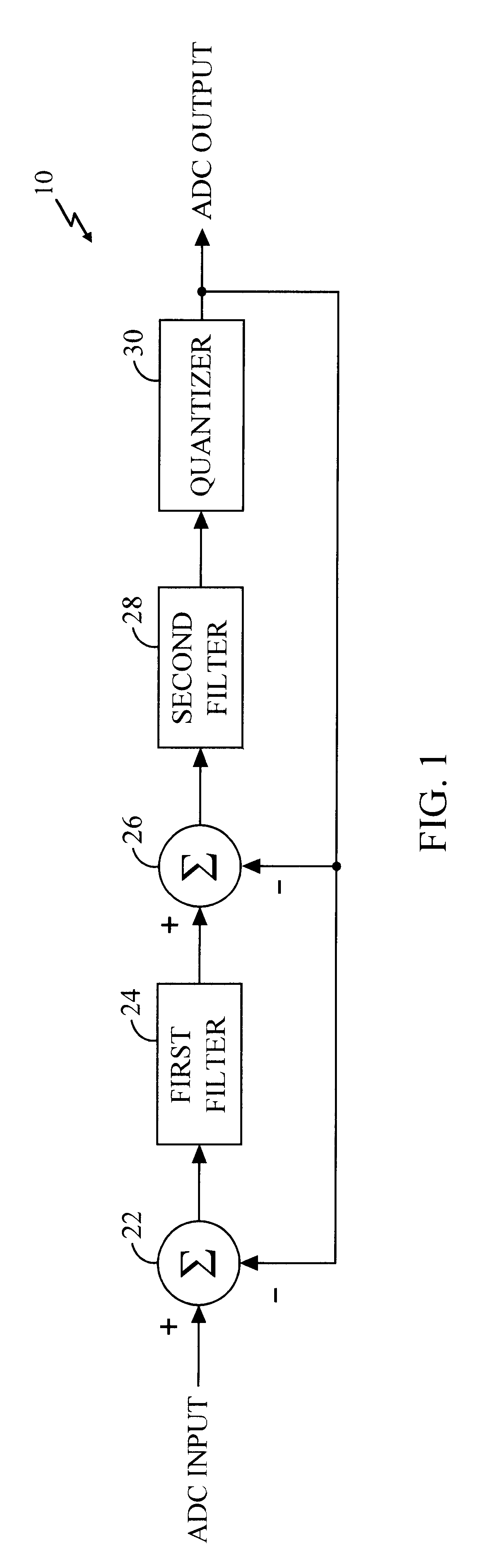

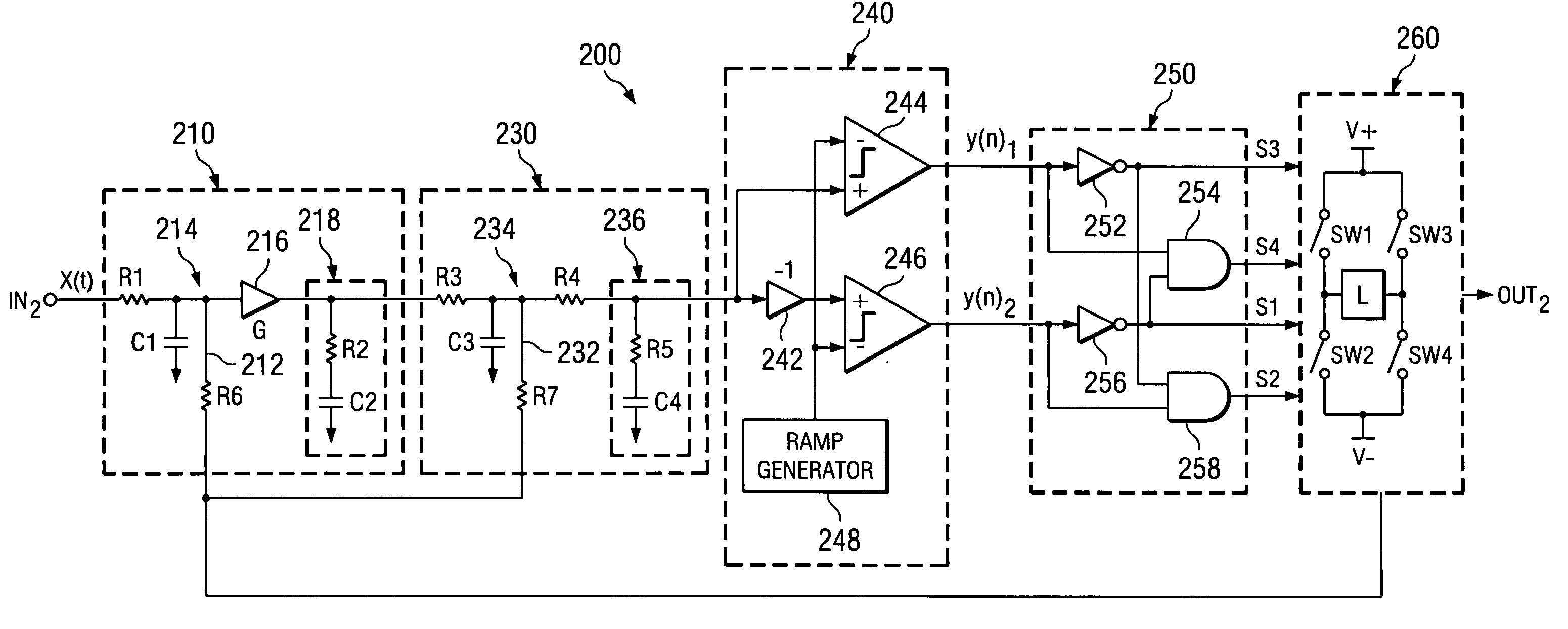

Continuous time fourth order delta sigma analog-to-digital converter

ActiveUS20050116850A1Reduce adverse effectsWell formedDelta modulationA d converterGreek letter sigma

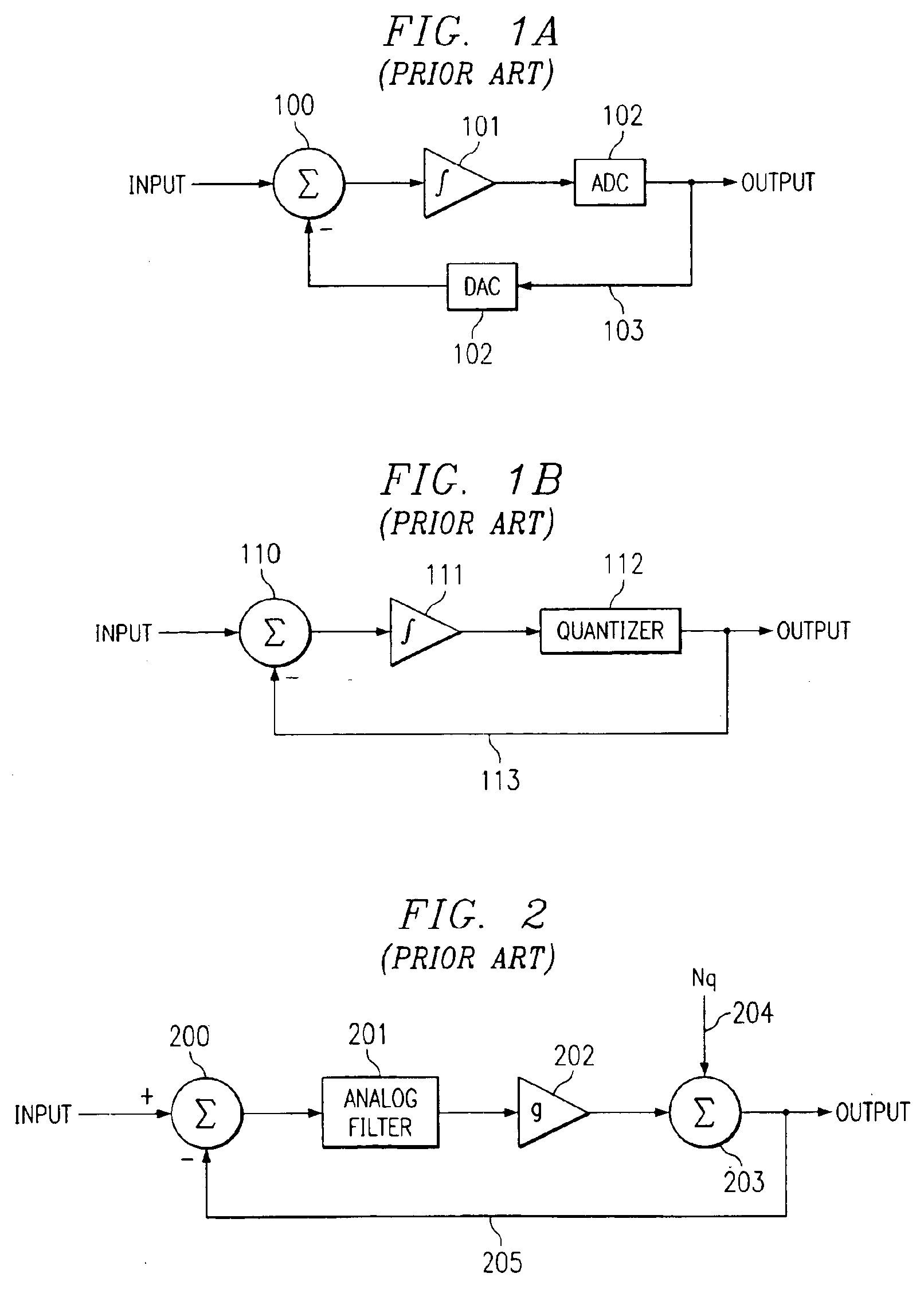

A fourth order delta sigma analog-to-digital converter is presented, comprising a passive delta sigma modulator including a passive filter, a quantizer, and a digital-to-analog converter in a first feedback loop, and an active filter having a large gain factor in a second feedback loop around the passive delta-sigma modulator.

Owner:TEXAS INSTR INC

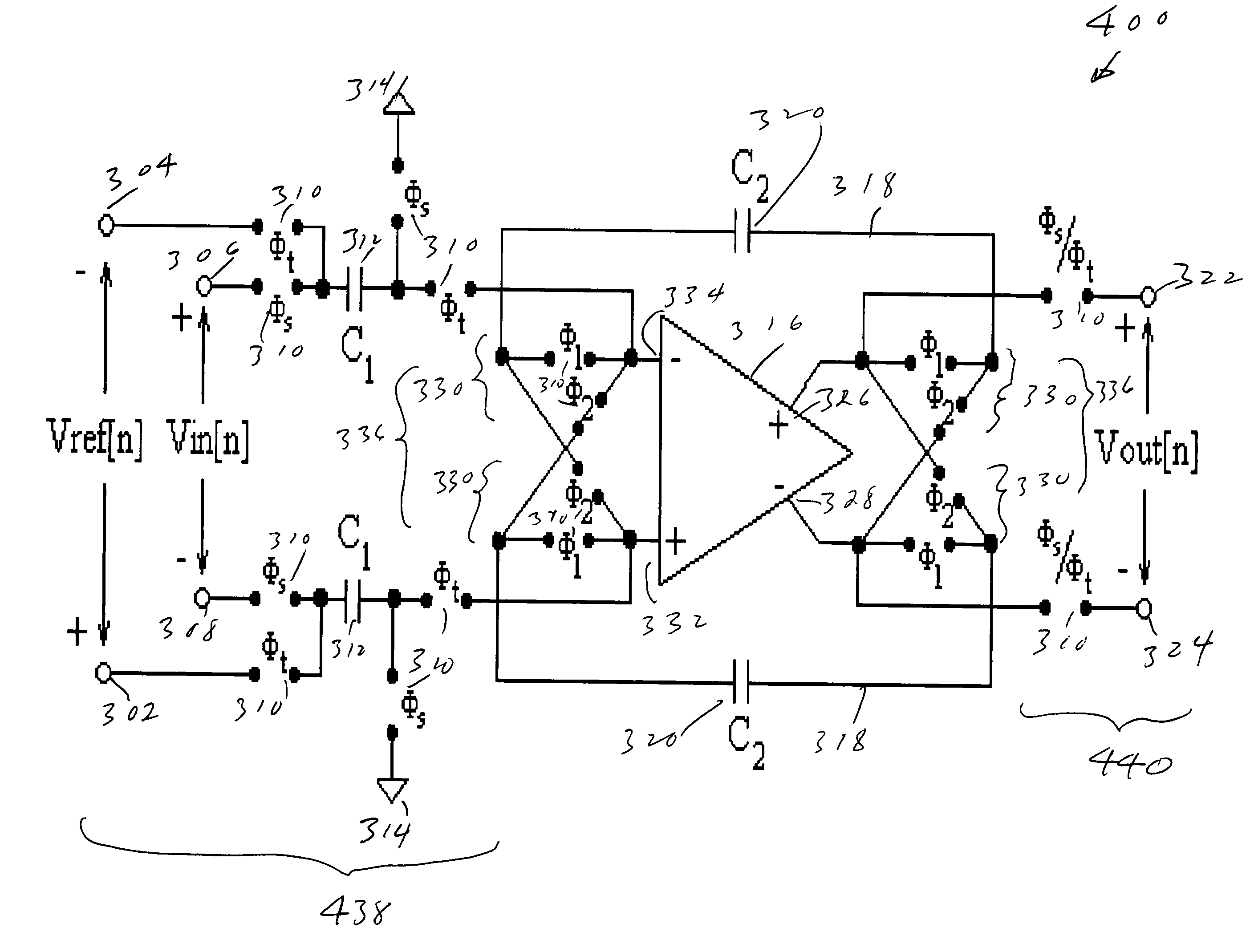

Switched-capacitor high-pass mirrored integrator

InactiveUS7038532B1Improve noise characteristicsComputing operations for integral formationComputing operations for integration/differentiationCapacitanceAudio power amplifier

In a high-pass (mirrored) integrator structure that employs chopper modulation, the input and output of the mirrored integrator are connected to the input and output ports of the operational amplifier, bypassing the chopper stabilization modulators. The mirrored integrator can be used in sigma-delta analog-to-digital converters.

Owner:UNIVERSITY OF ROCHESTER

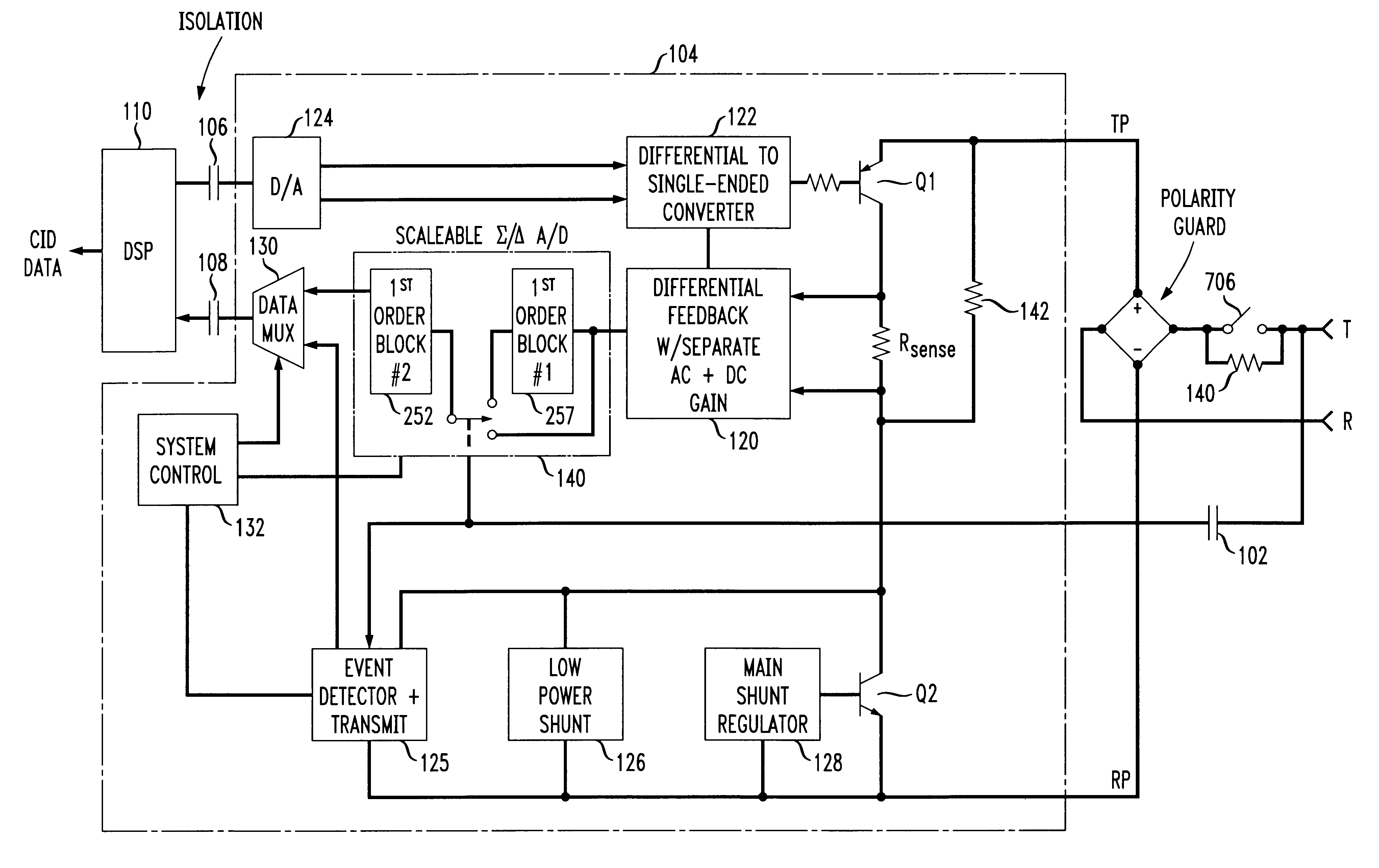

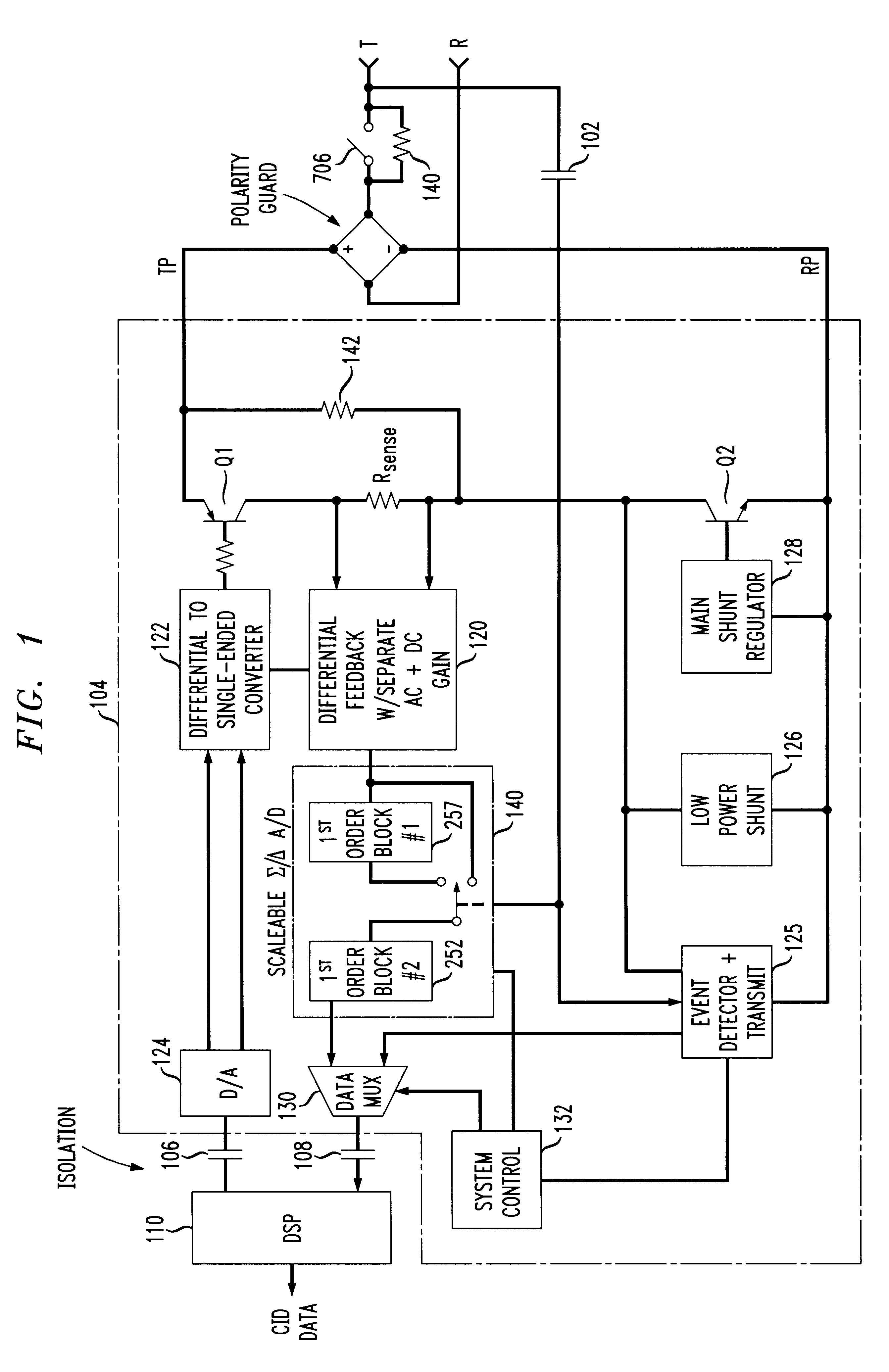

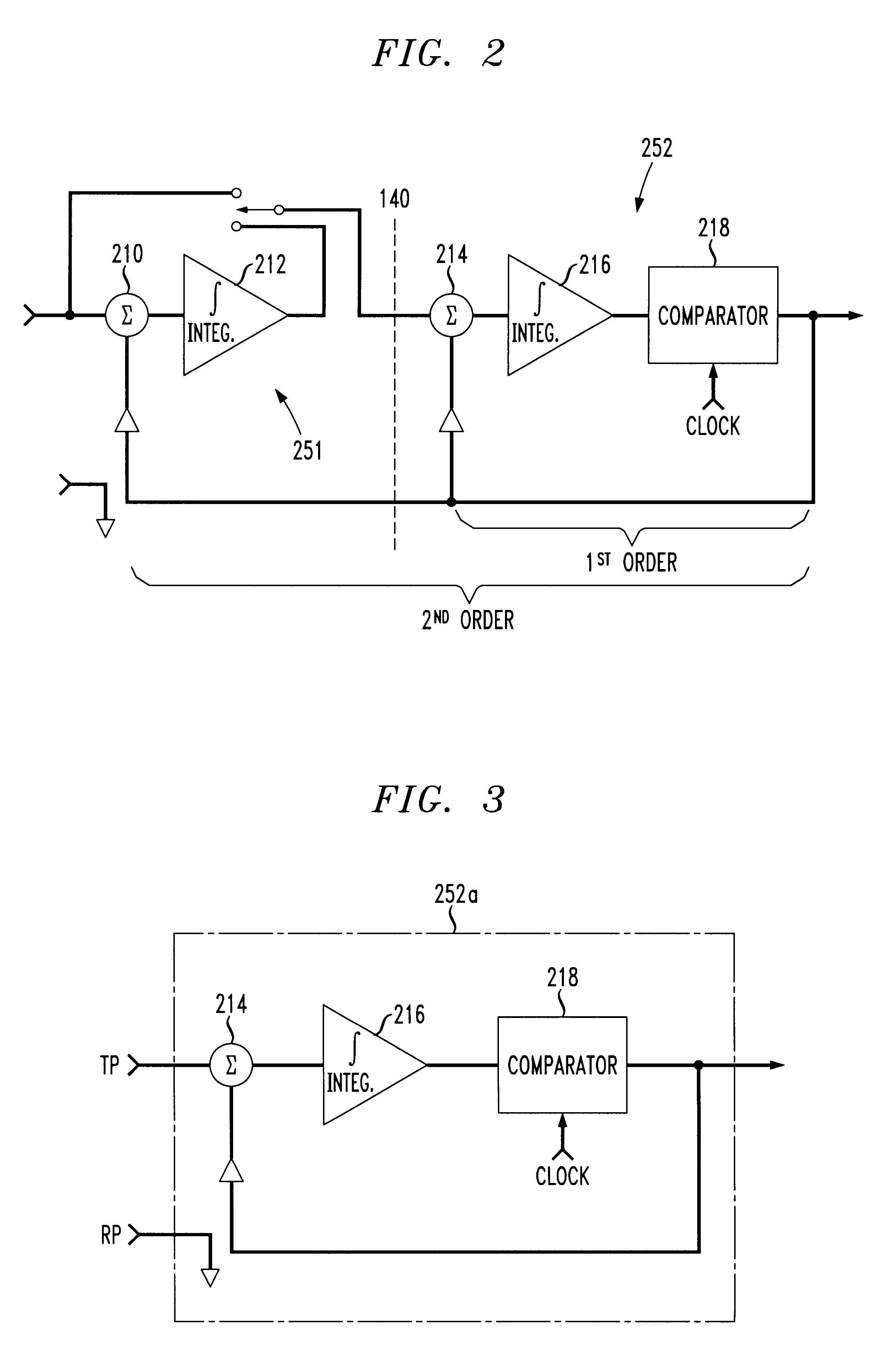

Call related information reception using sigma/delta modulation

InactiveUS6205219B1Interconnection arrangementsUnauthorised/fraudulent call preventionGreek letter sigmaDigitization

A method and apparatus to receive and demodulate call related information, e.g., Caller ID information, in an audio codec placed on the line side and powered by current drawn from the telephone line. The audio codec includes a 1st order SIGMA / DELTA A / D converter to digitize the signal from the telephone line with SIGMA / DELTA modulation. The 1st order SIGMA / DELTA A / D converter may be a scaleable component capable of alternative operation in a 2nd order. The SIGMA / DELTA encoded digitized signal is digitally processed by a DSP including an amplifier module, a digital filter, a limit / slice module, and an FSK decoder to receive and output the call related information. Placement of the audio codec on the line side and the scaleable SIGMA / DELTA A / D converter provides significantly reduced power requirements for the audio codec, thus allowing operation from power derived from the telephone line. In another embodiment, to further reduce power consumption of the audio codec, the 1st order SIGMA / DELTA A / D converter is sampled at a slower rate than is conventional, e.g., by first dividing or otherwise providing a slower sampling clock.

Owner:LUCENT TECH INC +1

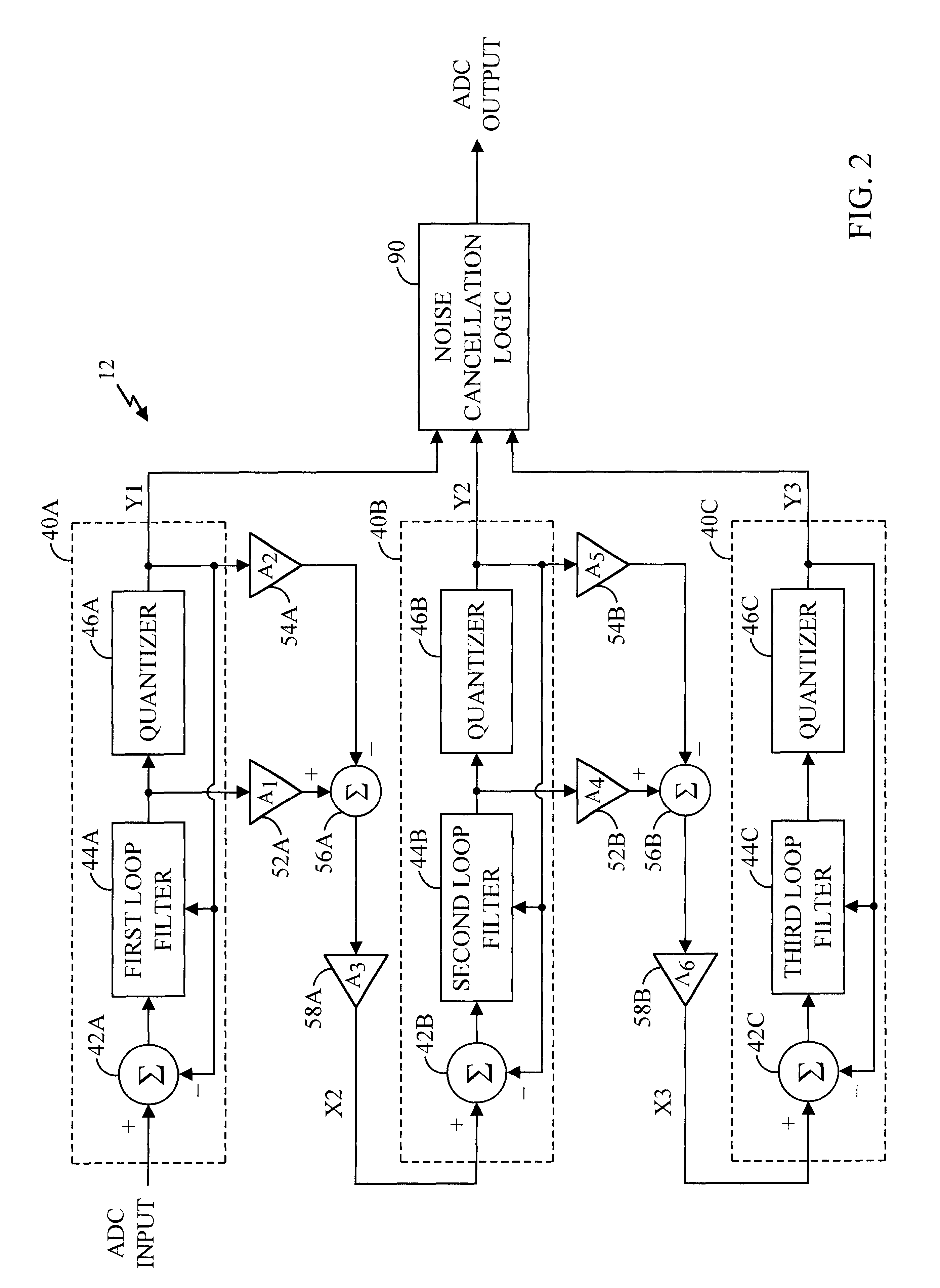

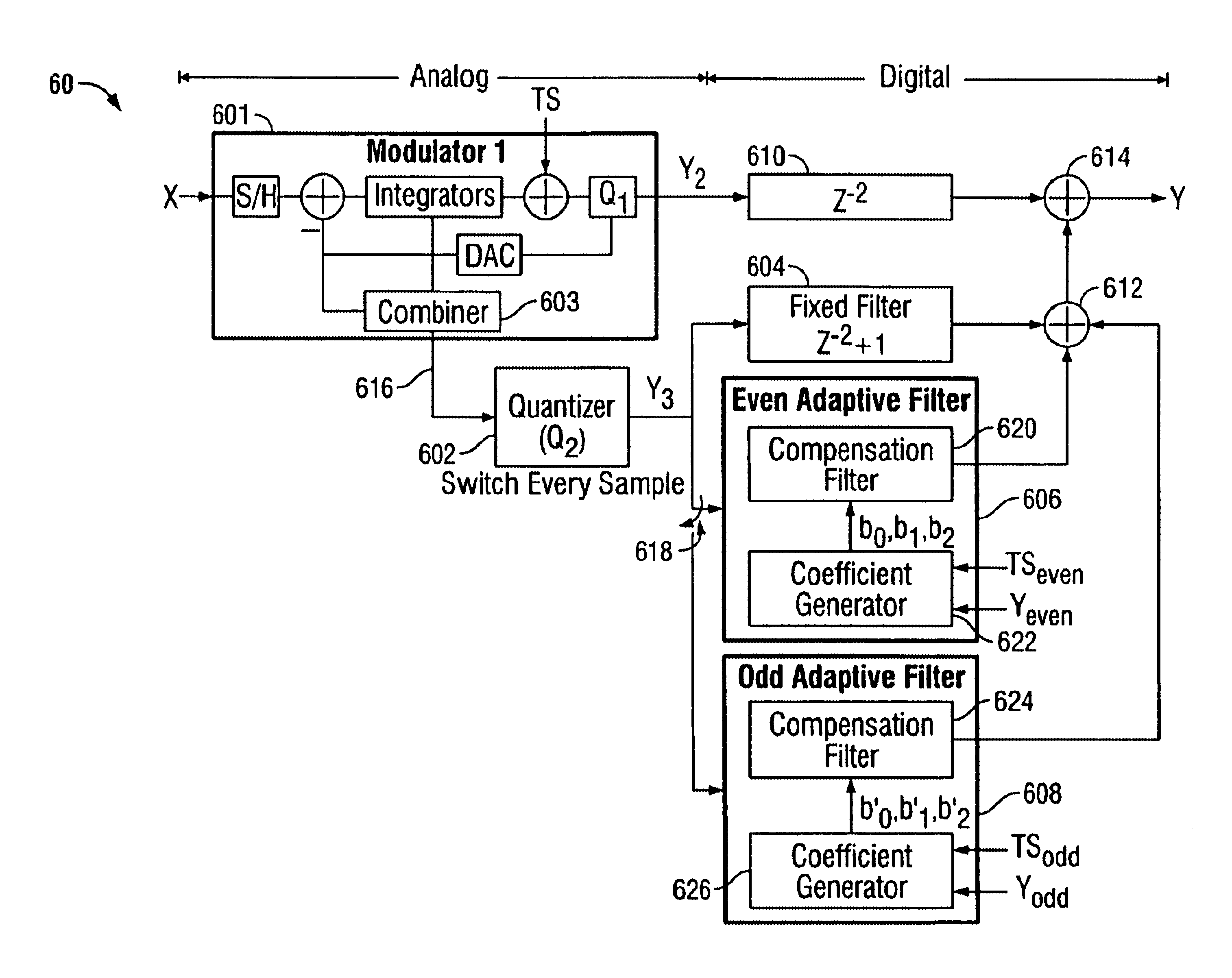

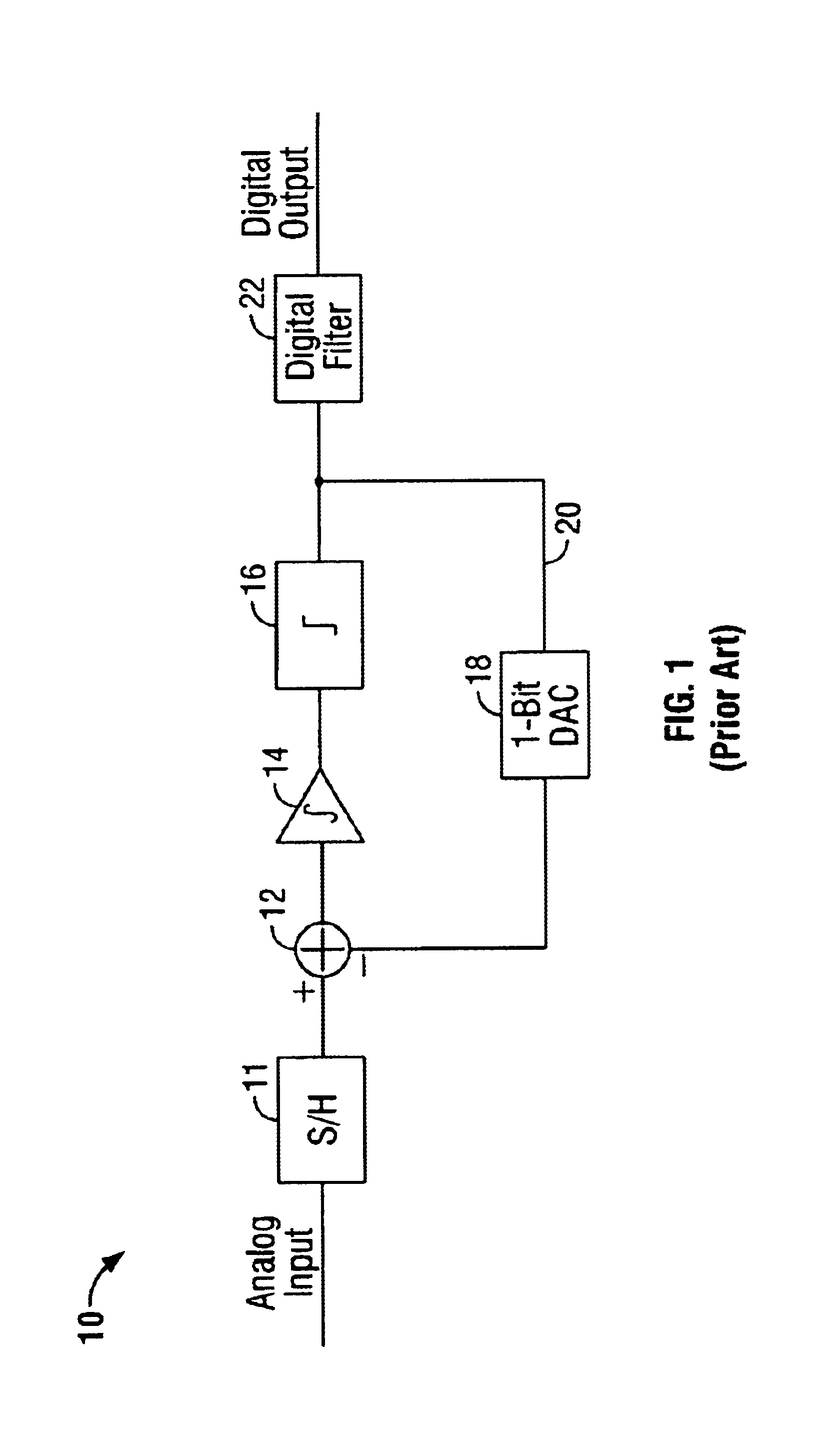

Interleaved digital correction for MASH delta-sigma ADC

InactiveUS6873281B1Improved signal-to-noise ratio performanceAnalogue/digital conversionElectric signal transmission systemsClock rateEngineering

Methods of and apparatuses for optimizing quantization noise cancellation in multi-phase sampled MASH ADCs are disclosed. A test signal is combined with quantization noise produced by a delta-sigma modulator. Two parallel adaptive filters (i.e. even and odd filters) are configured to receive respective even and odd samples of a digital output signal of a MASH ADC analog modulator. Adaptive coefficients for the even adaptive filter are derived from correlation results between the even samples of the test signal and associated even samples of the final digital output signal. Similarly, adaptive coefficients for the odd adaptive filter are derived from correlation results between the odd samples of the test signal and associated odd samples of the final digital output signal. Using the adaptive coefficients, the even and odd adaptive filters are able to independently compensate for analog variations in the two paths. Fixed, slowly varying, and clock rate variations may all be tracked out using the methods and apparatus of the present invention.

Owner:SYNOPSYS INC

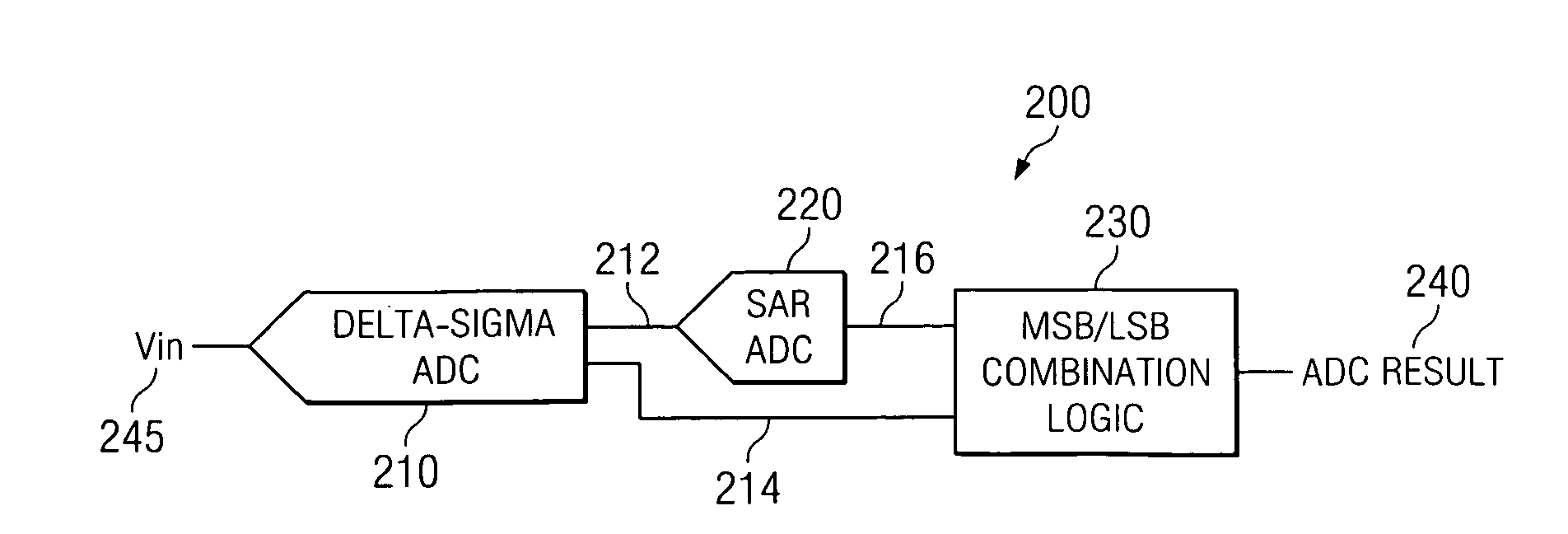

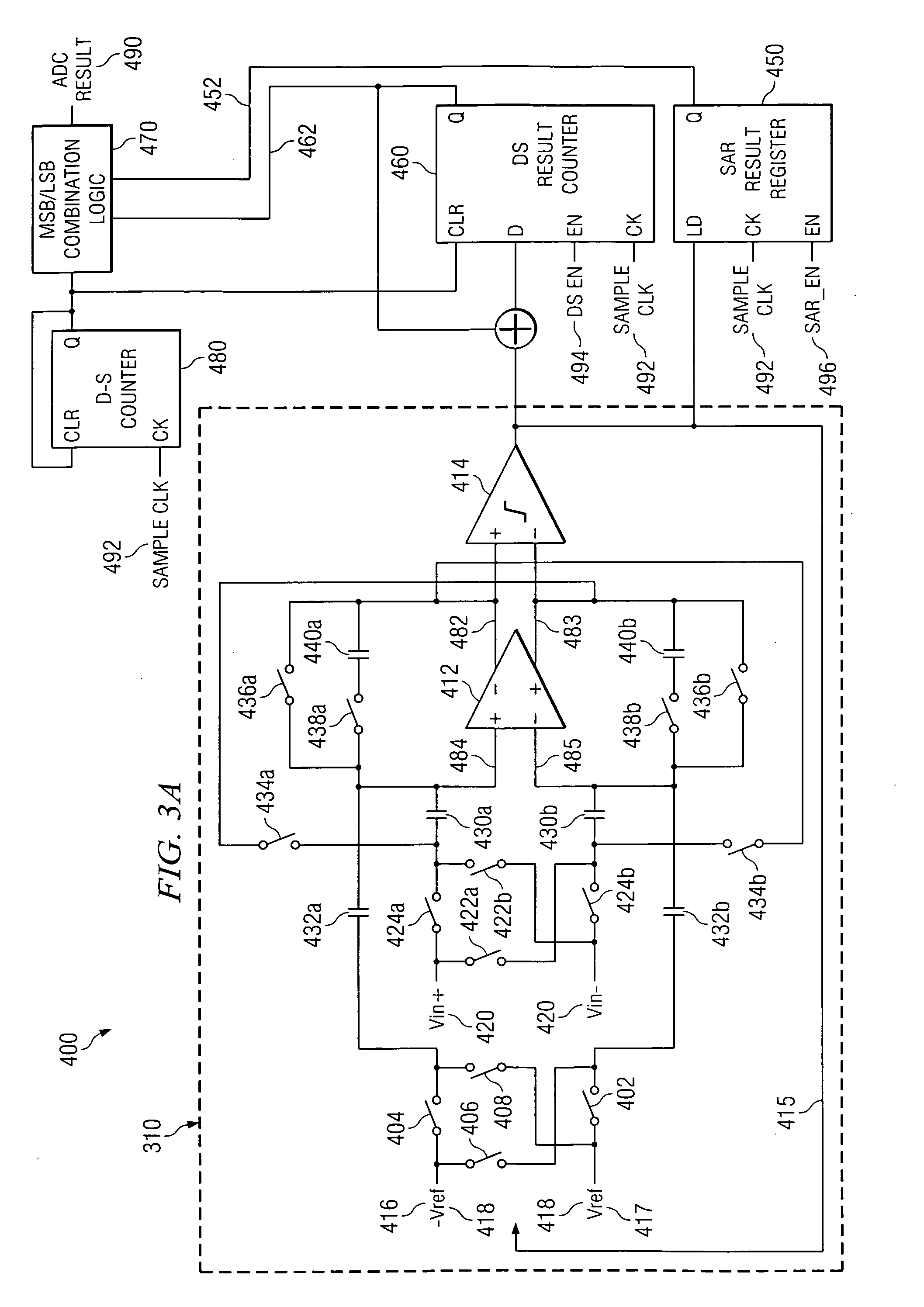

Integrating/SAR ADC and method with low integrator swing and low complexity

ActiveUS20080258959A1Reduce the amount of solutionReduce voltageElectric signal transmission systemsAnalogue conversionIntegratorGreek letter sigma

A reconfigurable circuit (10) includes an integrator (30) having switches (SW1-6) for selectively coupling input capacitors (C0,1,2,3,6,7) and integrating capacitors (C4,5) to terminals of the integrator (30) for operation of a hybrid delta-sigma / SAR ADC (400) so as to create a reference voltage value (Vref) equal to the sum of a first voltage (ΔVbe) and a second voltage (Vbe). A first integration is performed to reduce the integrator output voltage swing. A residue (Vresidue) of the integrator is multiplied by 2. Then the second voltage (Vbe) is integrated in a first direction if a comparator (22) coupled to the integrator changes state or in an opposite direction if the comparator does not change state. The first voltage (ΔVbe) is integrated in a direction that causes the integrator output voltage (Vout) to equal either 2×Vresidue−Vref or 2×Vresidue+Vref.

Owner:TEXAS INSTR INC

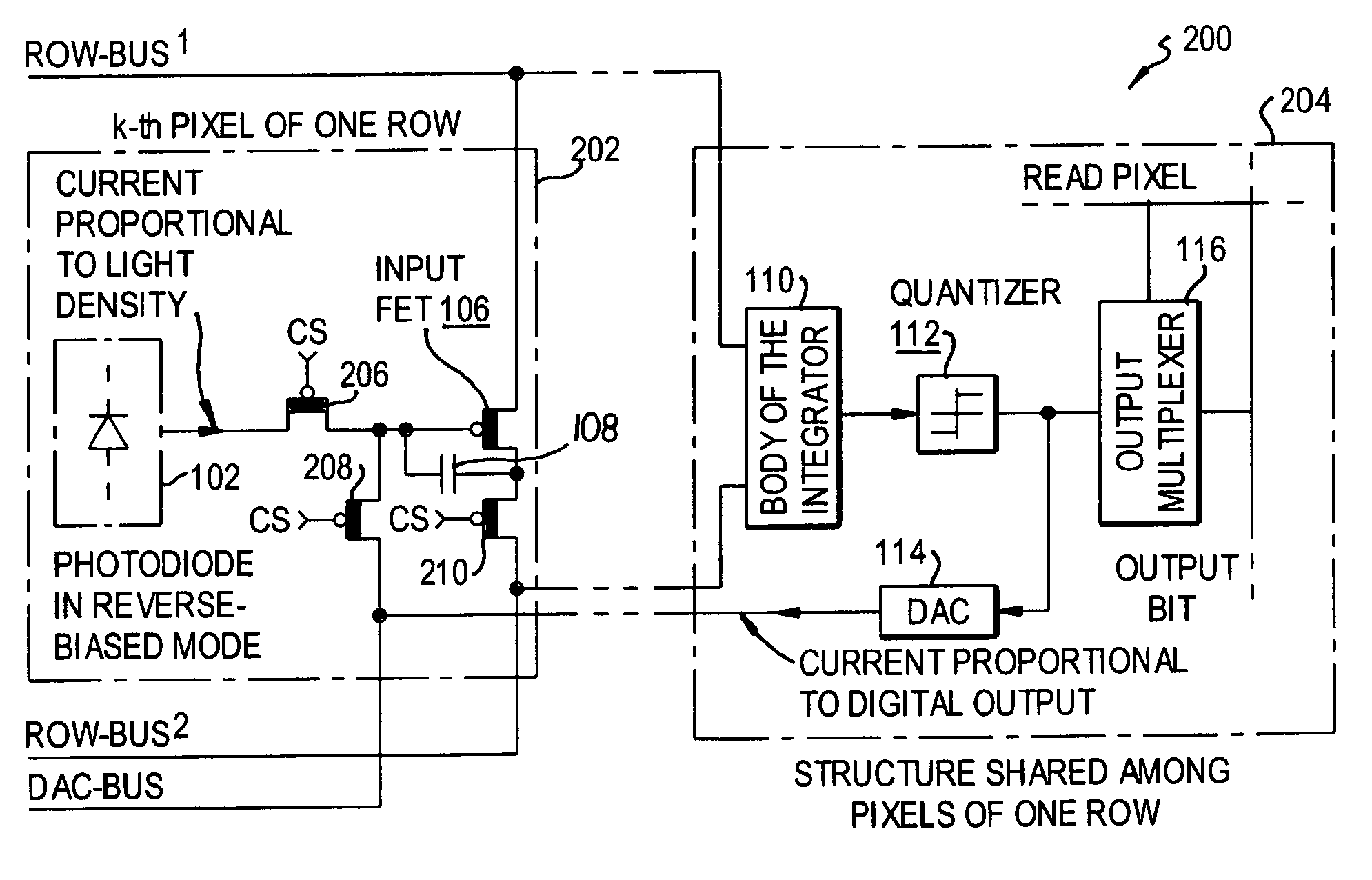

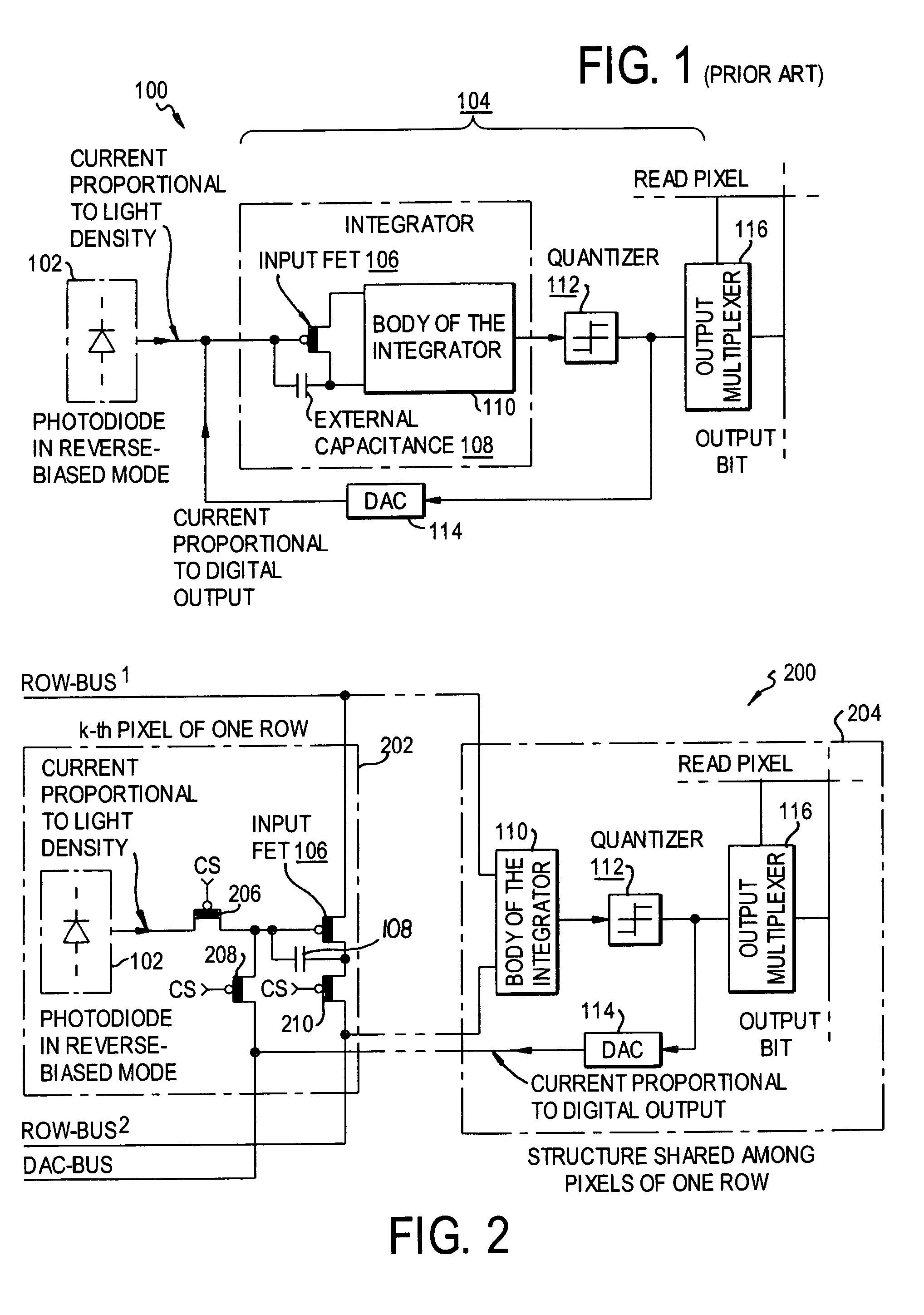

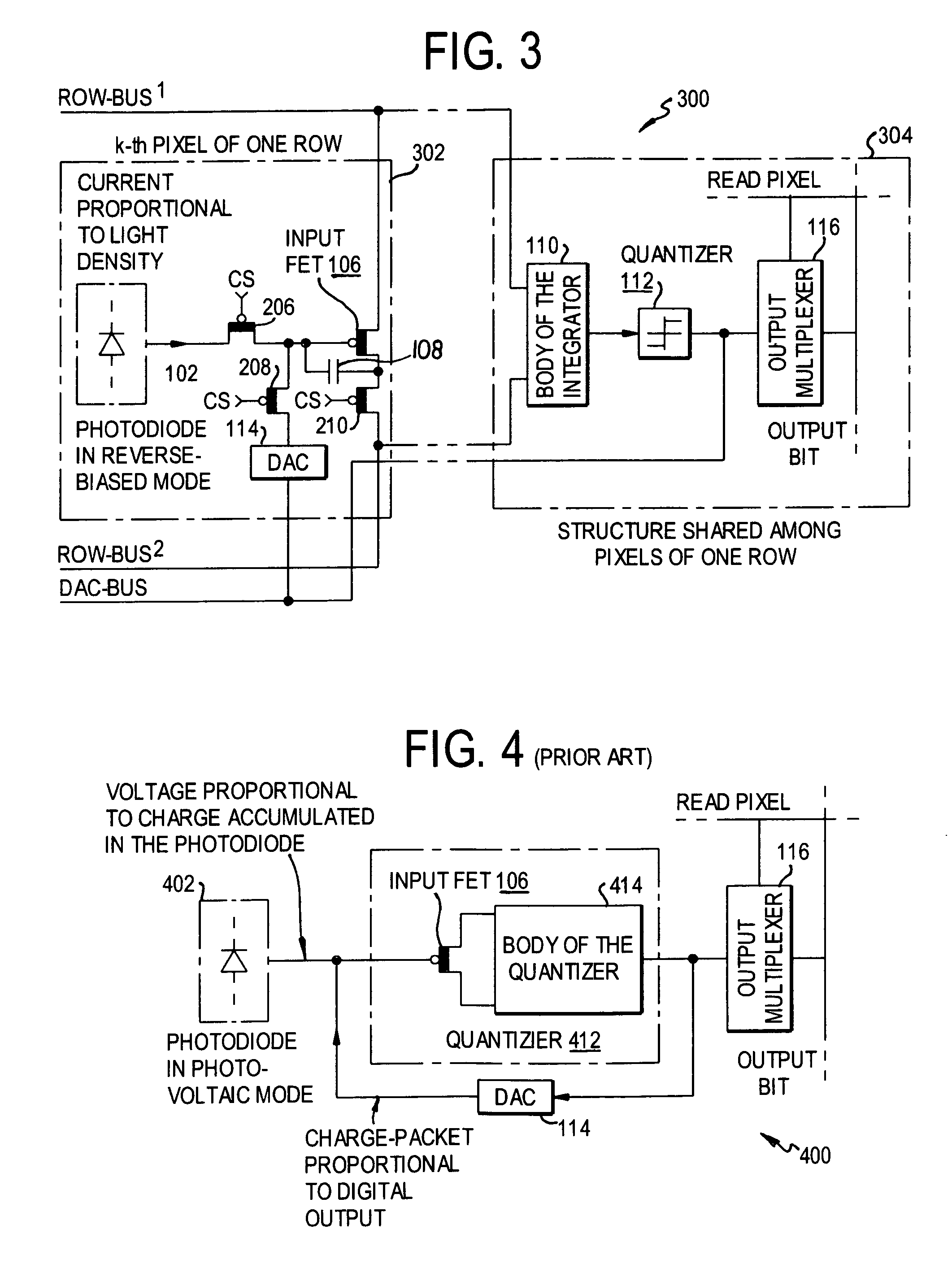

Multiplexed-input-separated sigma-delta analog-to-digital converter design for pixel-level analog-to-digital conversion

InactiveUS7023369B2Improve linearityReduce power consumptionTelevision system detailsElectric signal transmission systemsMultiplexingIntegrator

An image-sensing element has an array of photodiodes or other photodetecting elements and performs sigma-delta analog-to-digital conversion on the outputs of the photodetecting elements. The sigma-delta analog-to-digital converters have components divided between pixel-level and row-level structures, with each row-level structure connected to its pixel-level structures to define a multiplexed-input-separated sigma-delta analog-to-digital converter. The converter can include an integrator or can rely on an integration effect of the photodetecting element. The feedback required for sigma-delta analog-to-digital conversion can involve digital-to-analog converters located at each row-level structure or at each pixel-level structure.

Owner:UNIVERSITY OF ROCHESTER

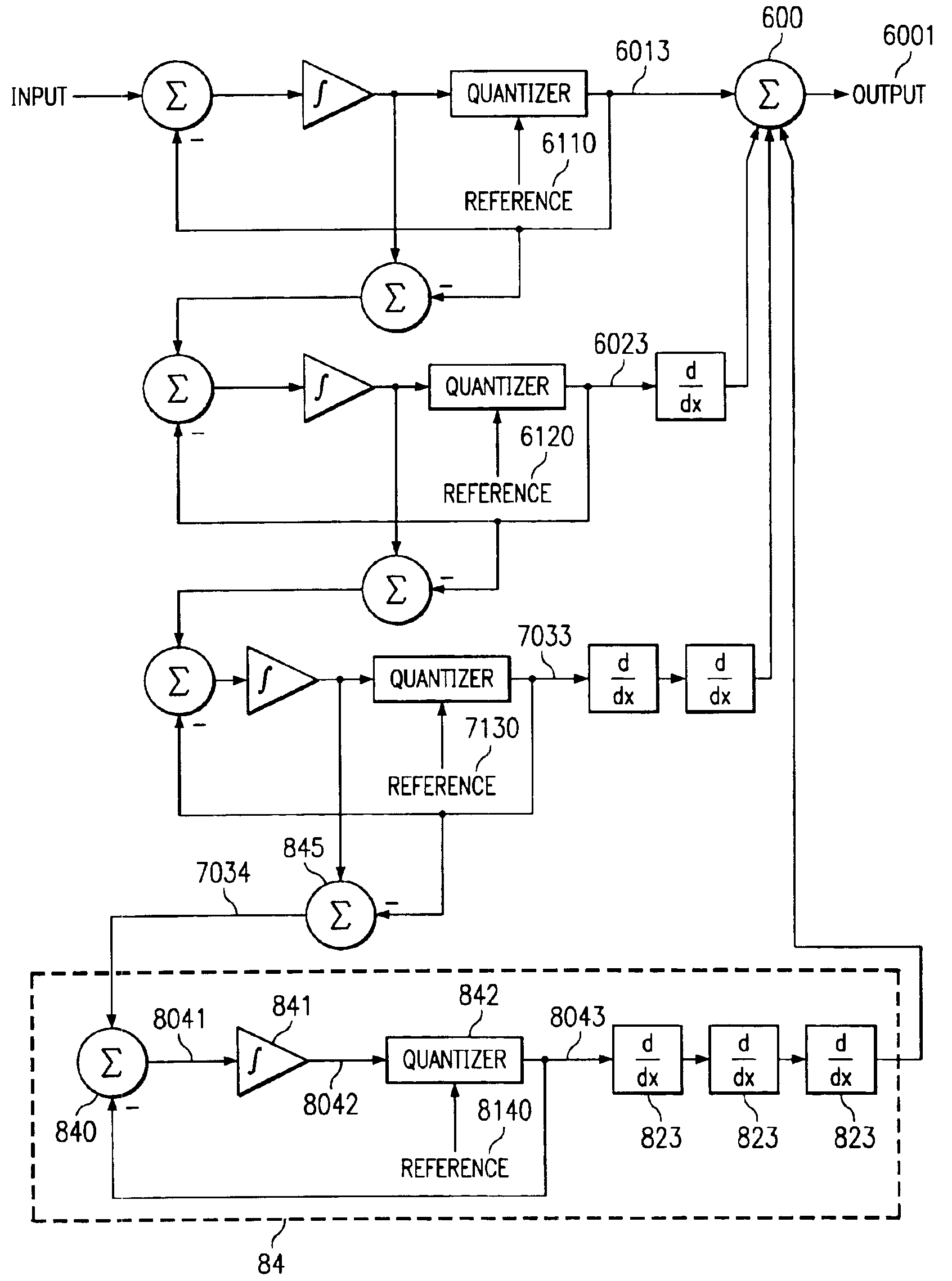

Delta-sigma modulator system and method

InactiveUS6920182B2Improved noise suppressionImproved noise noise shapingPulse automatic controlDelta modulationGreek letter sigmaEngineering

The invention discloses a system and method for improving the out-of-band noise response of a multi-order delta-sigma modulator. The system and method includes programmable delta-sigma modulators which may be programmed to vary the reference signals at each modulator stage subsequent to the first stage relative to the reference signal of the first modulator stage. The resulting signal output will then typically exhibit the enhanced noise suppression characteristics of a dithered signal without the added circuitry and power required of a dithering apparatus.

Owner:CSR TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com