Patents

Literature

667 results about "Voltage swing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

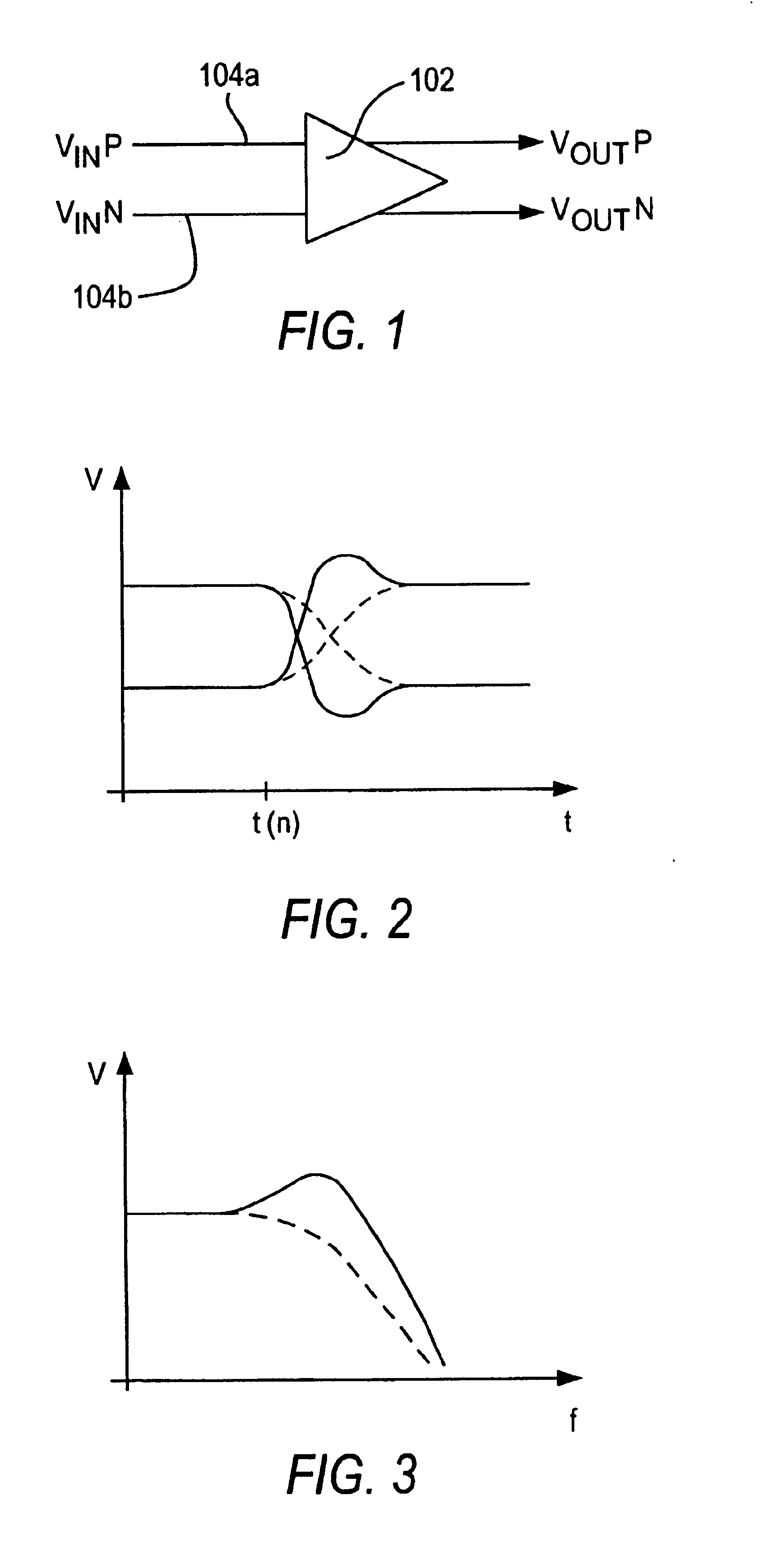

The voltage swing is a term that describes how much the output of an OpAmp can swing around its equilibrium state. It is also measure of how close the output of an OpAmp can move to either one the supply rails. If the output can move the same amount to higher and lower voltages the swing is said to be symmetrical.

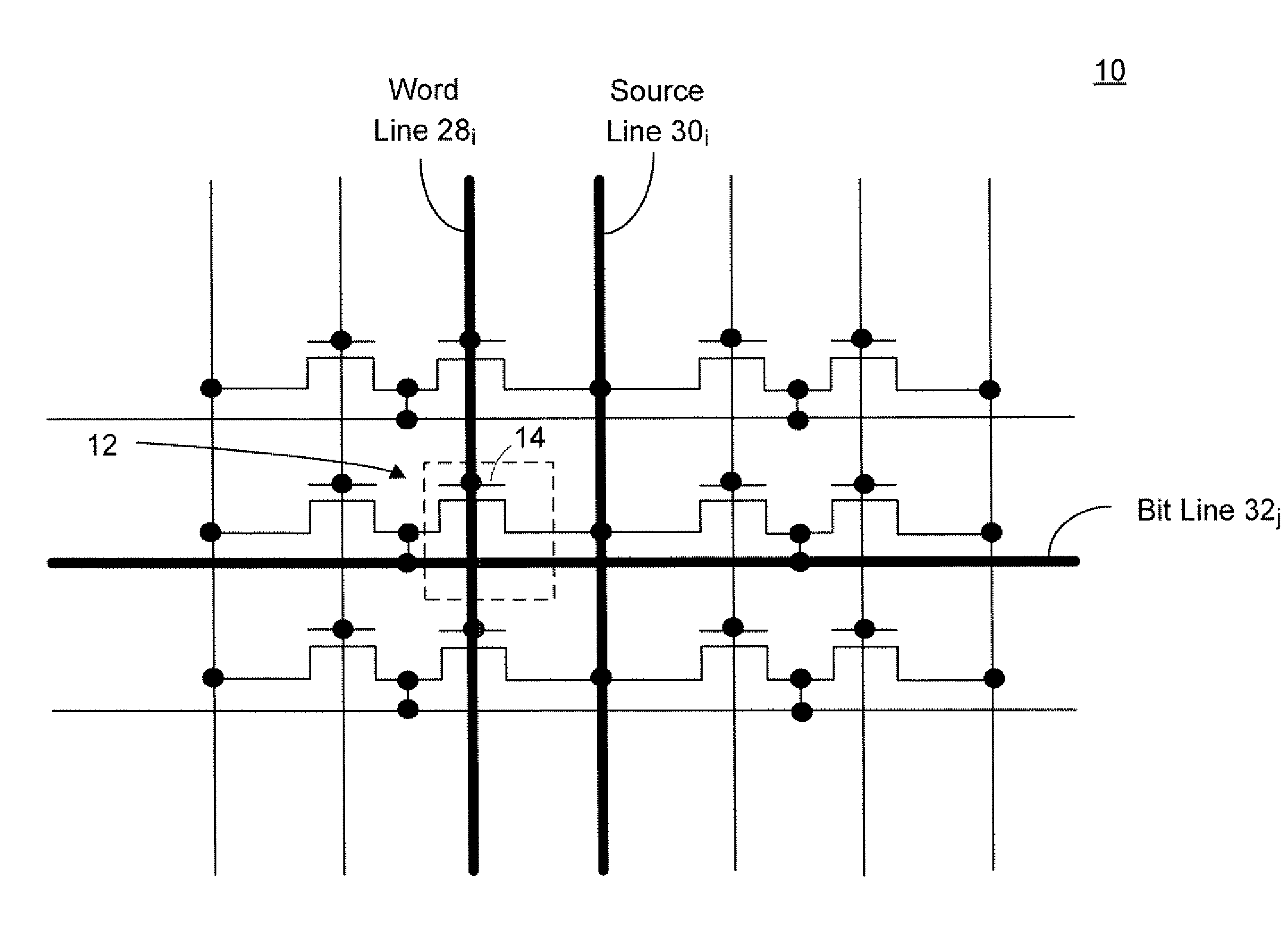

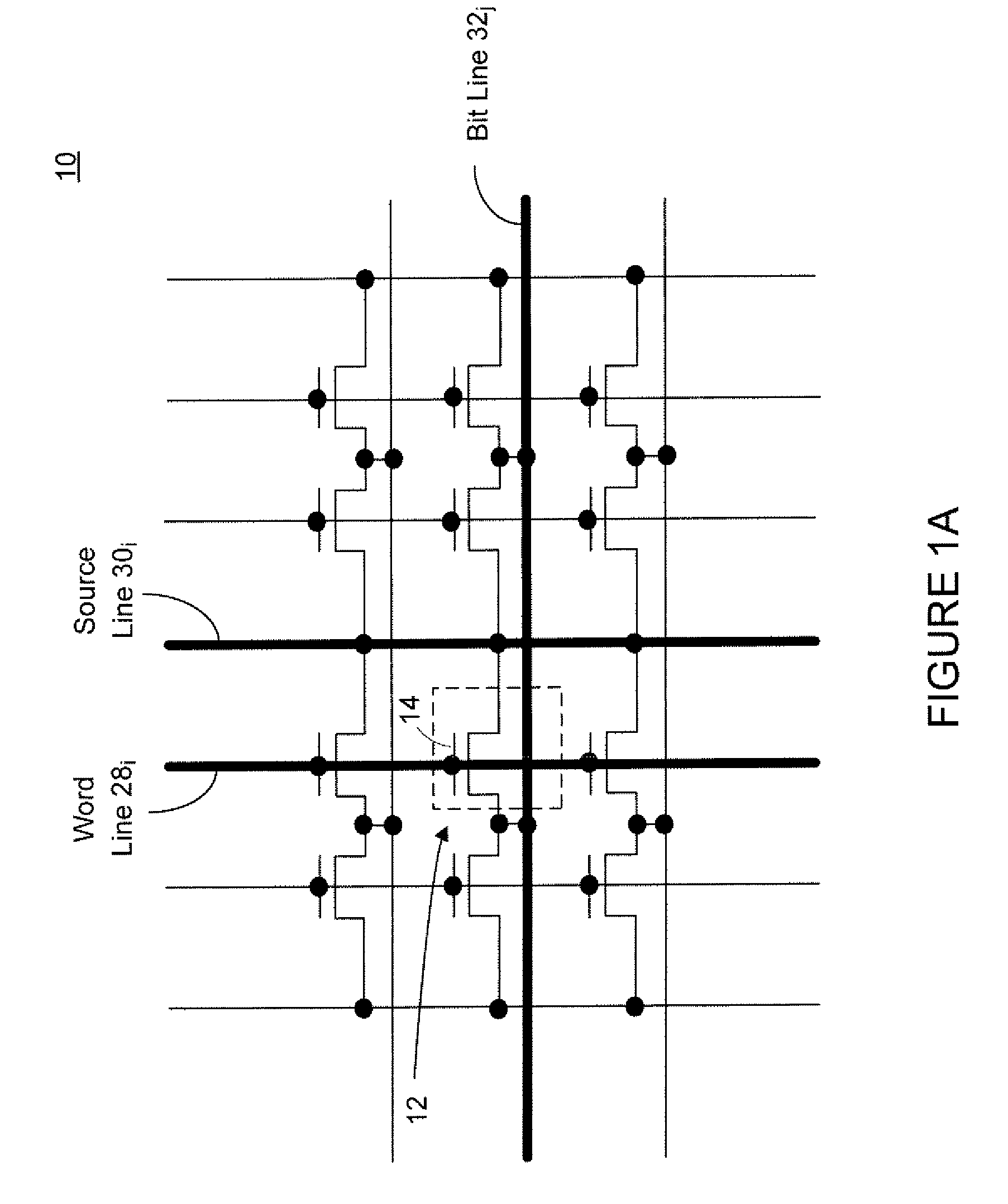

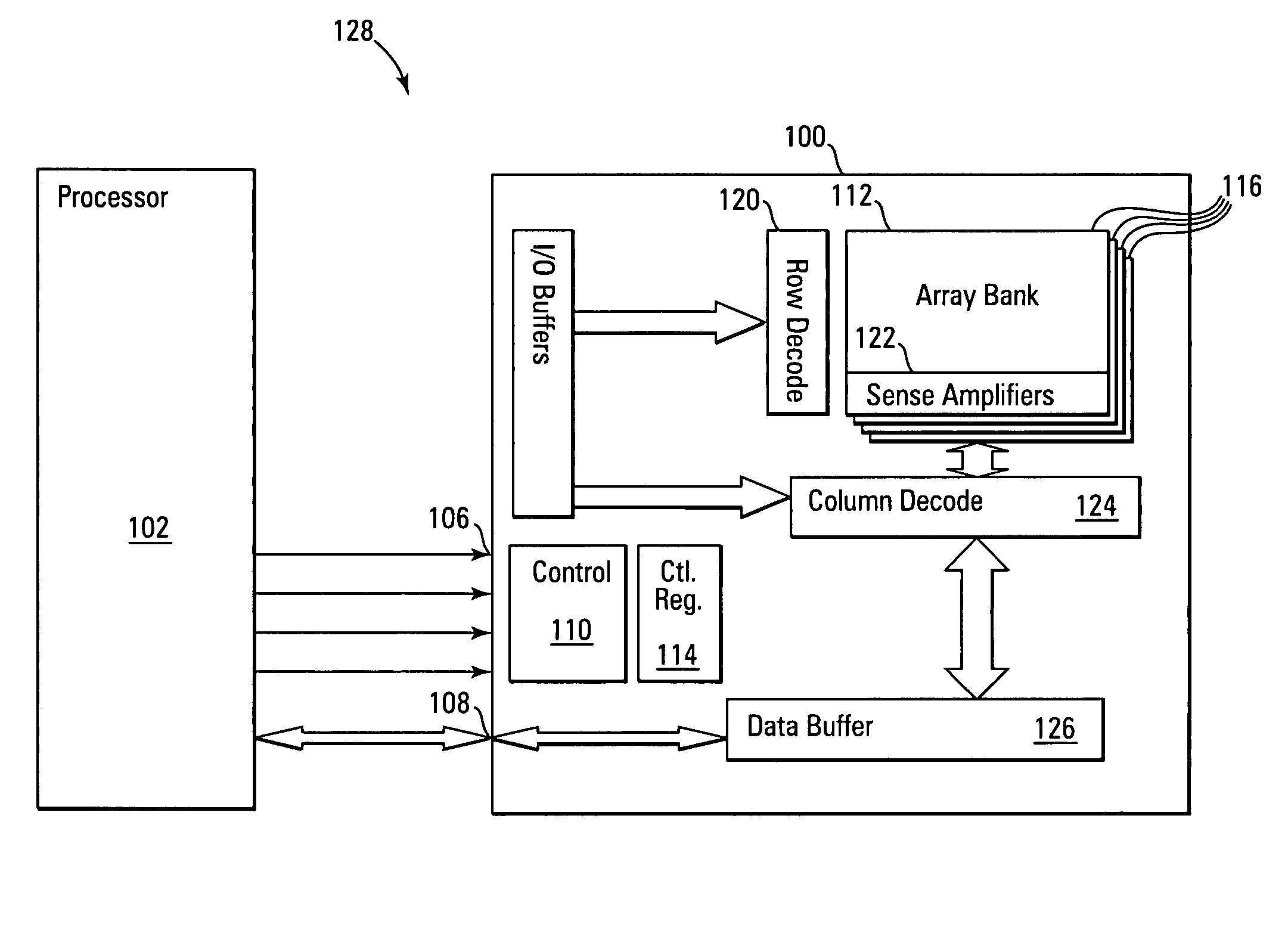

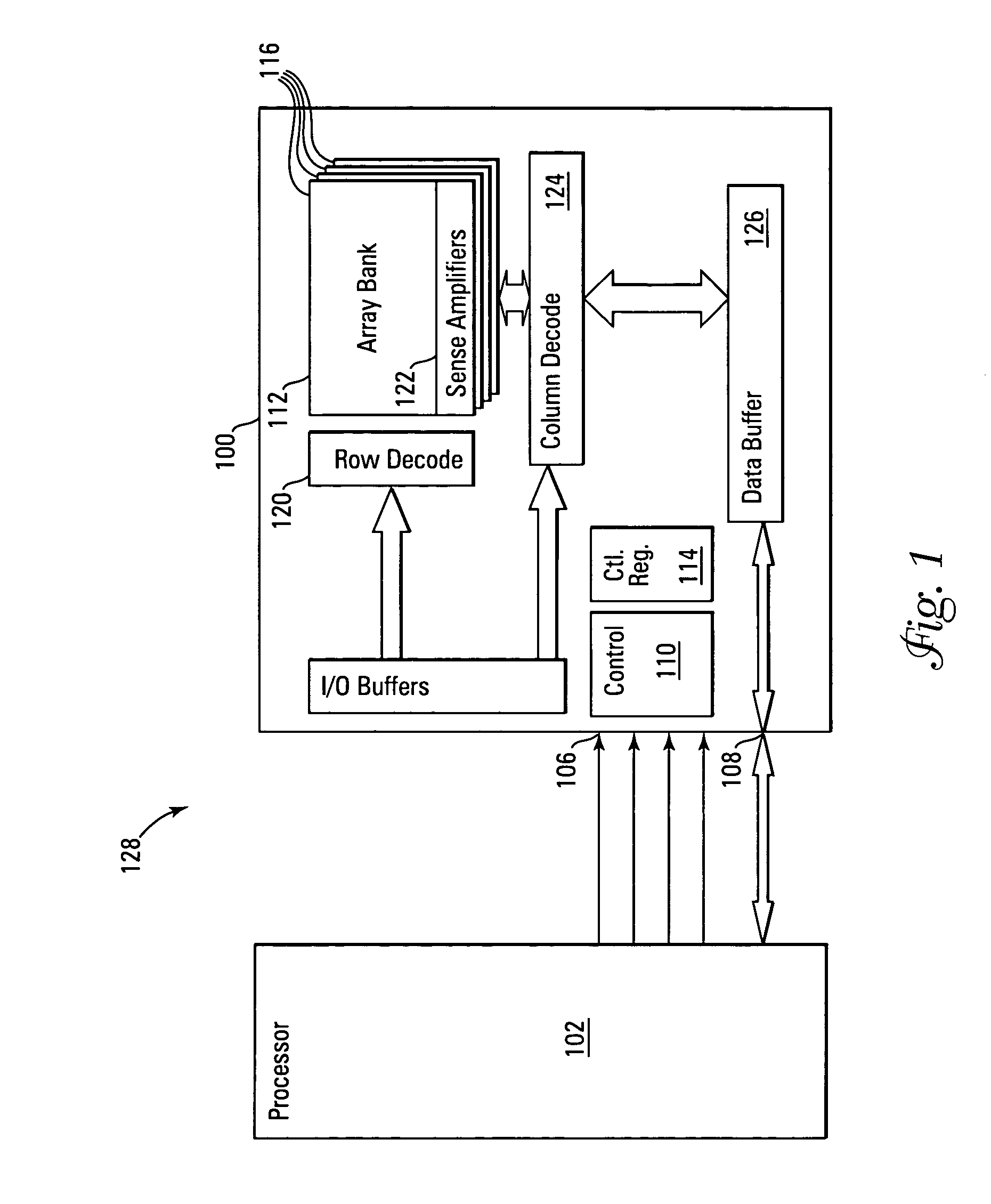

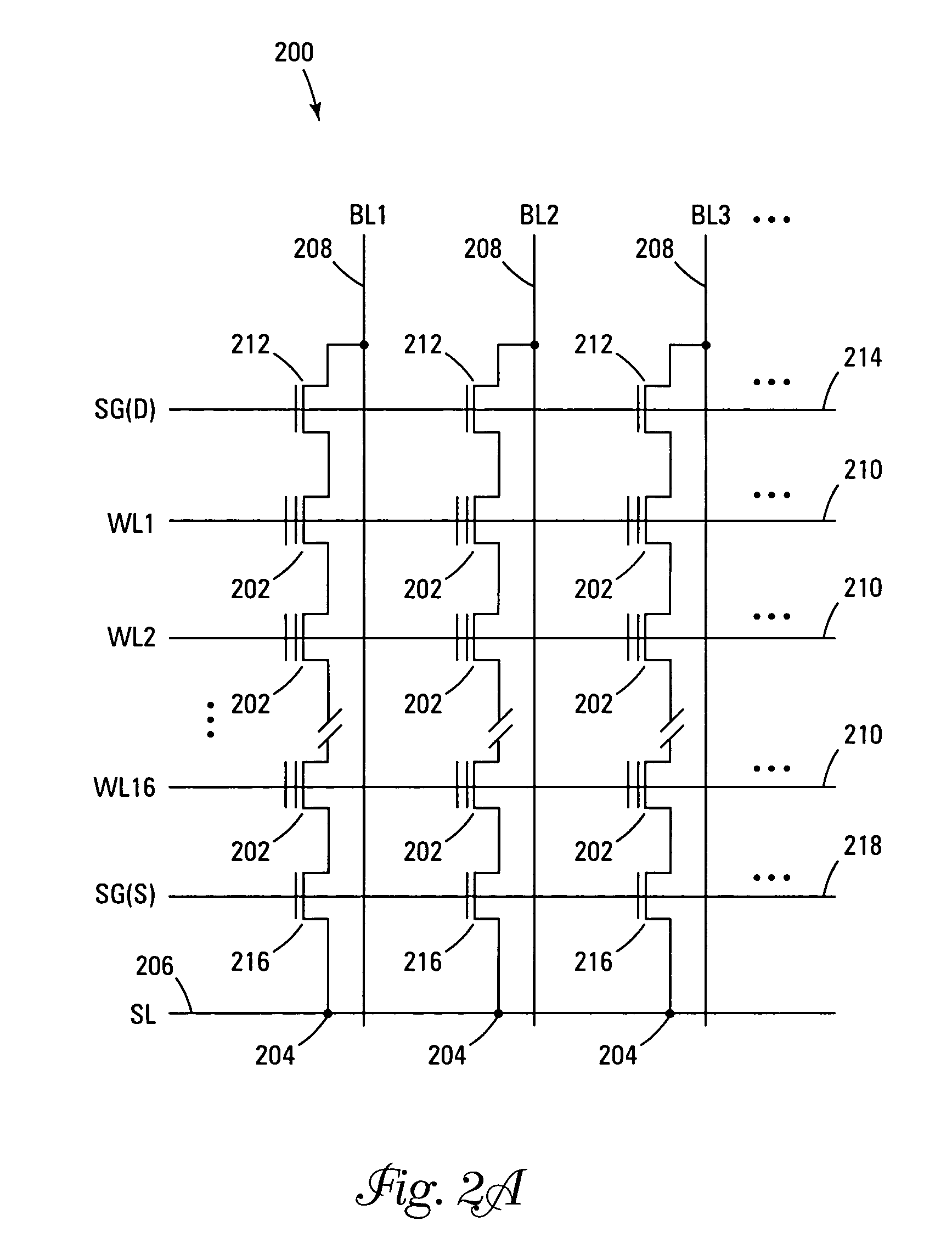

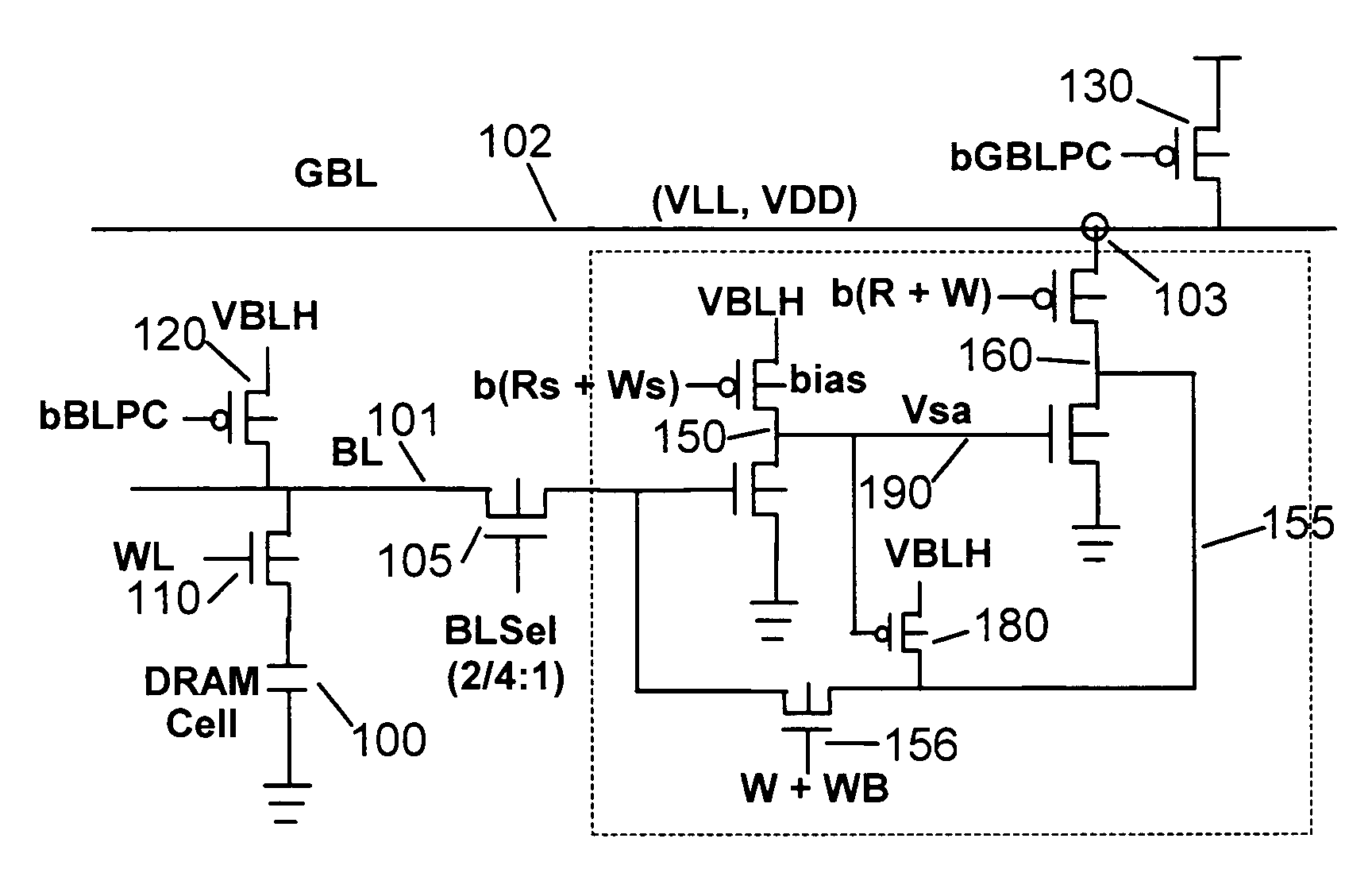

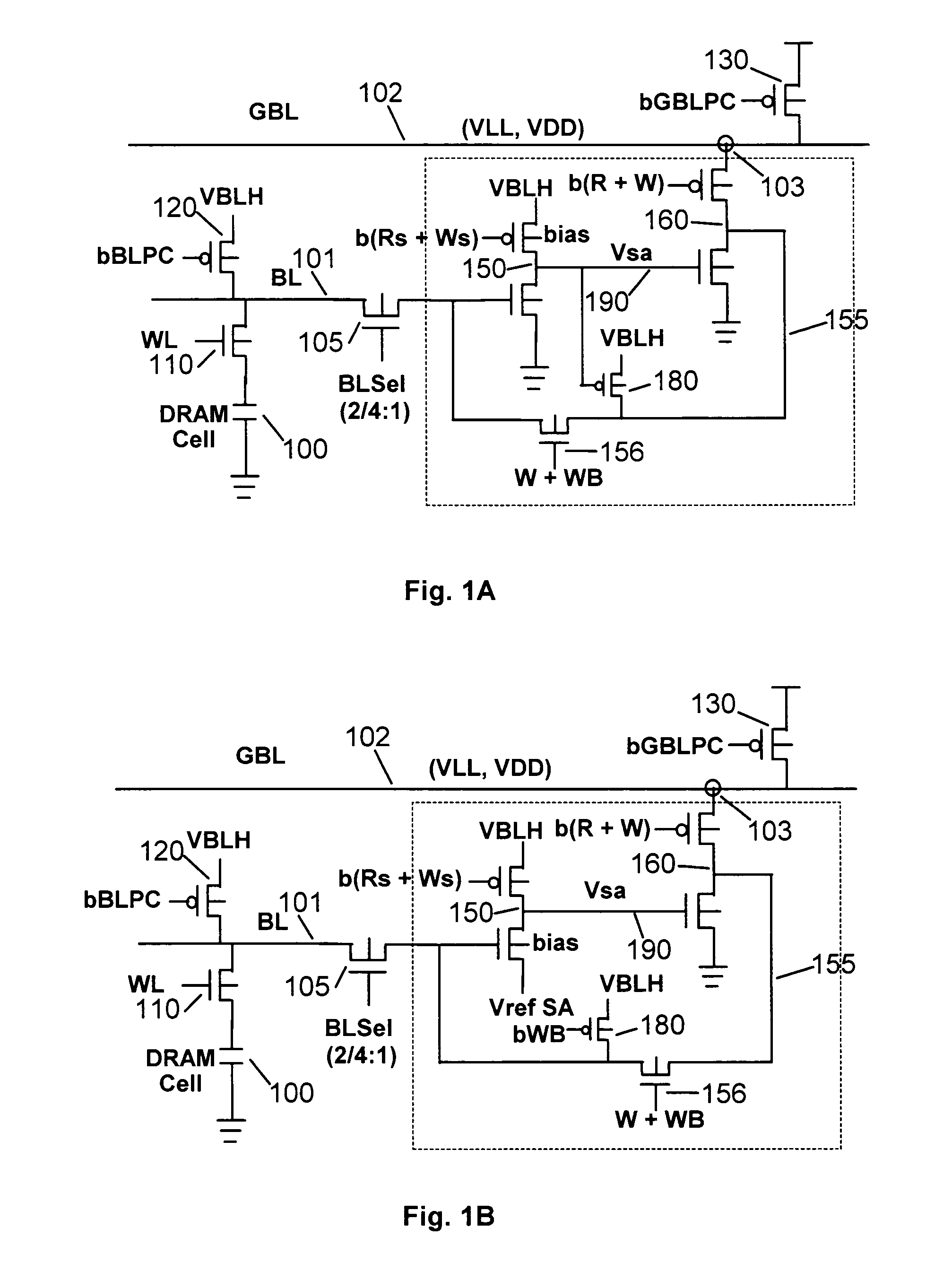

Techniques for reducing a voltage swing

Techniques for reducing a voltage swing are disclosed. In one particular exemplary embodiment, the techniques may be realized as an apparatus for reducing a voltage swing comprising: a plurality of dynamic random access memory cells arranged in arrays of rows and columns, each dynamic random access memory cell including one or more memory transistors. The one or more memory transistors of the apparatus for reducing a voltage swing may comprise: a first region coupled to a source line, a second region coupled to a bit line, a first body region disposed between the first region and the second region, wherein the first body region may be electrically floating, and a first gate coupled to a word line spaced apart from, and capacitively coupled to, the first body region. The apparatus for reducing a voltage swing may also comprise a first voltage supply coupled to the source line configured to supply a first voltage and a second voltage to the source line, wherein a difference between the first voltage and the second voltage may be less than 3.5V.

Owner:MICRON TECH INC

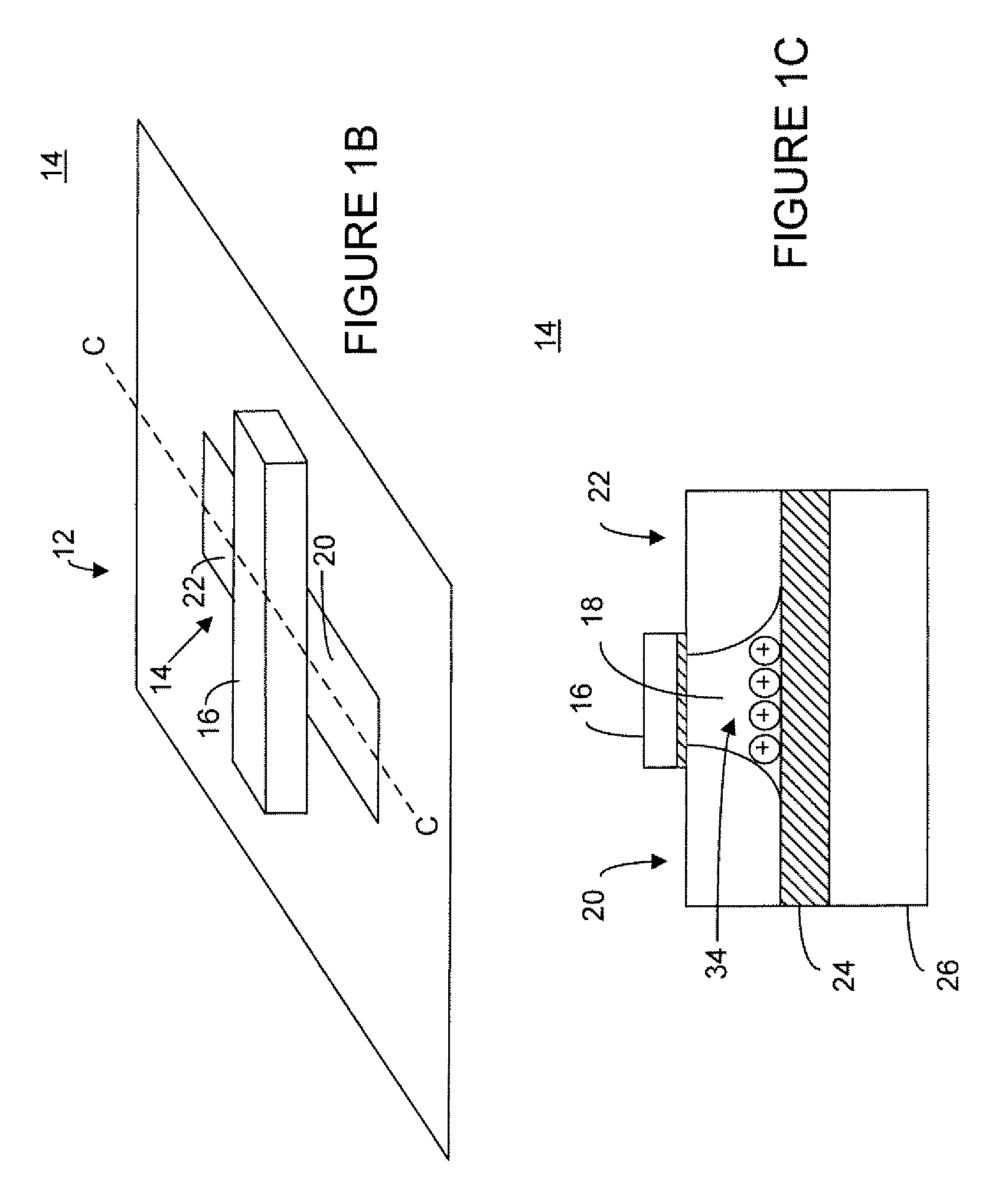

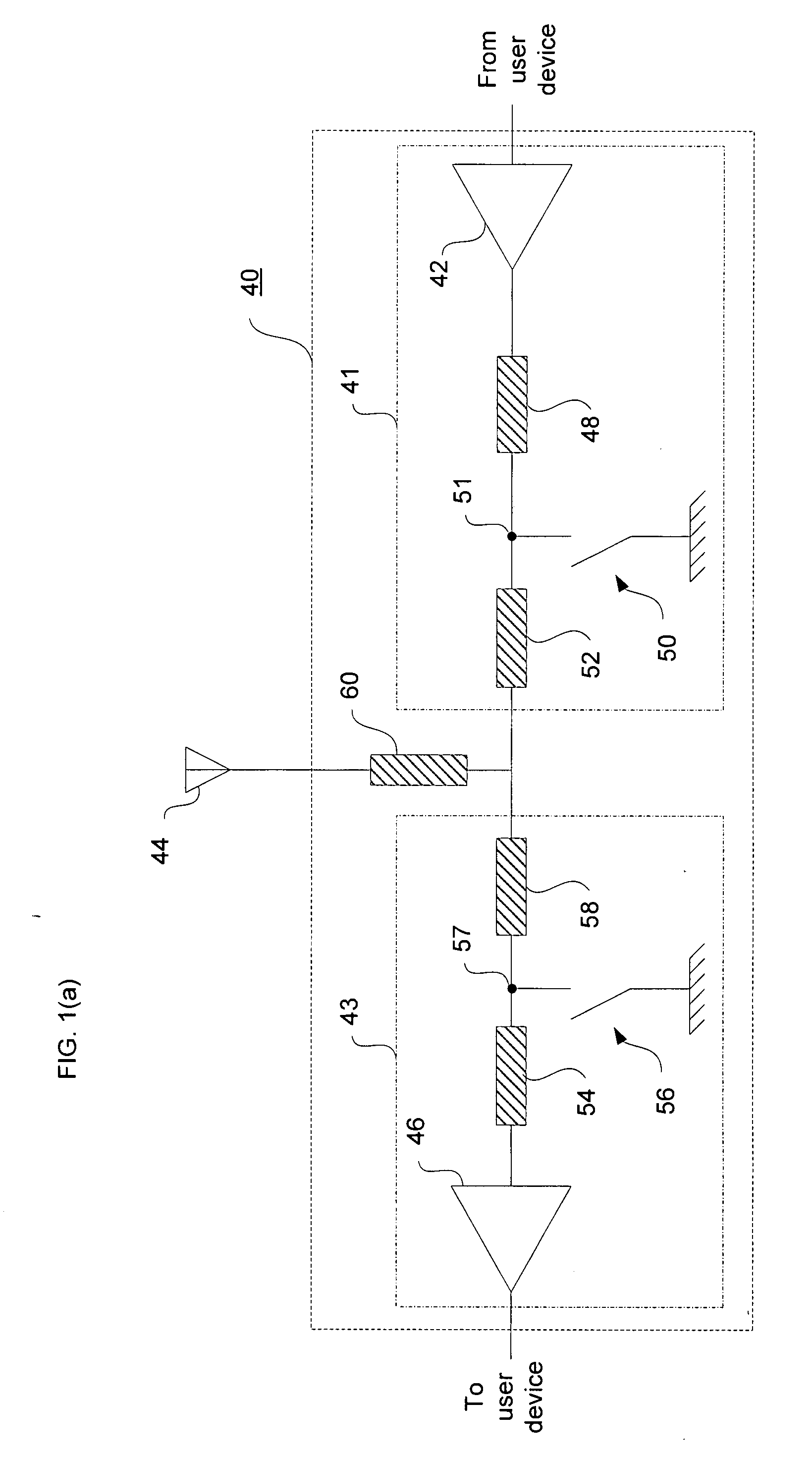

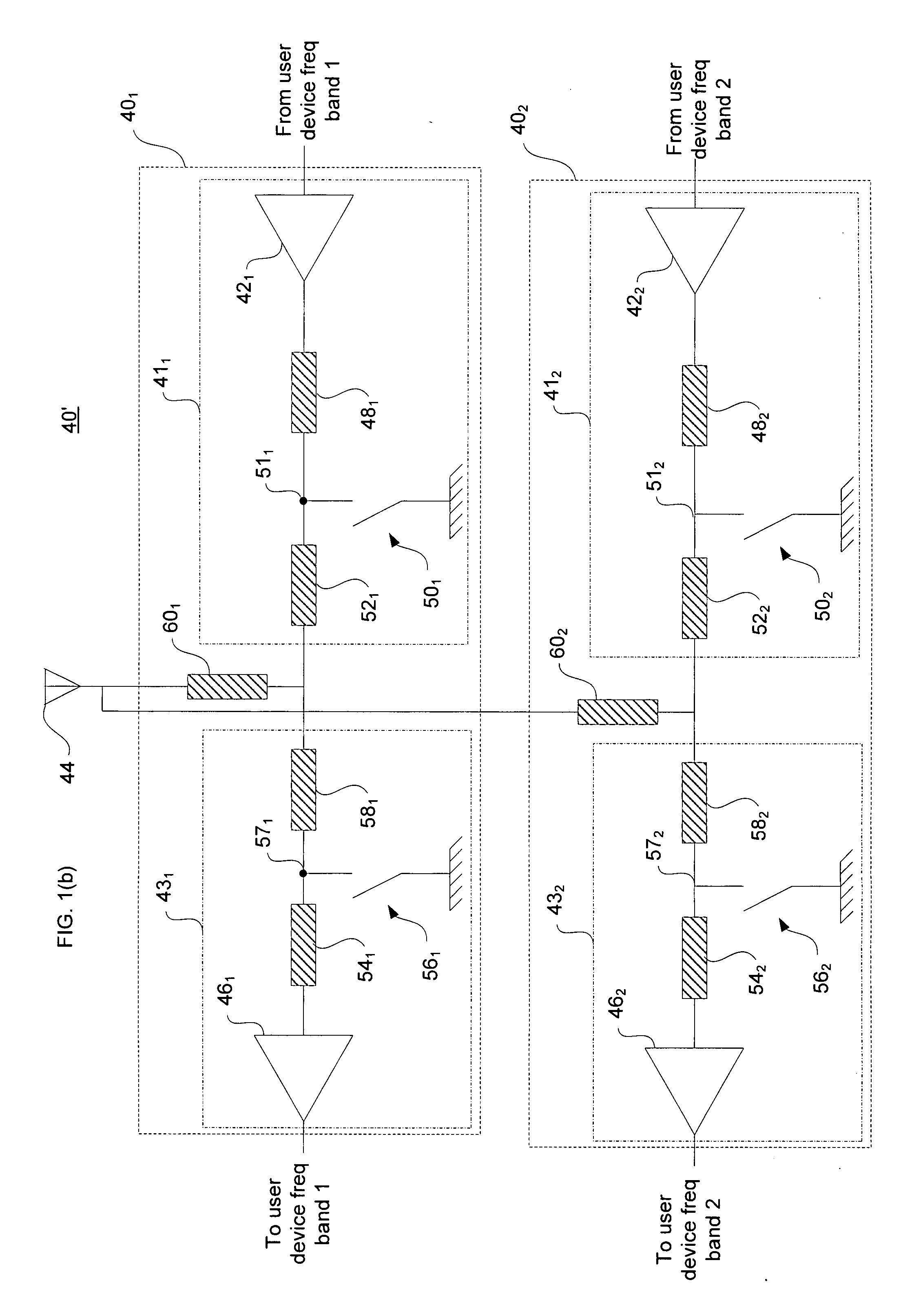

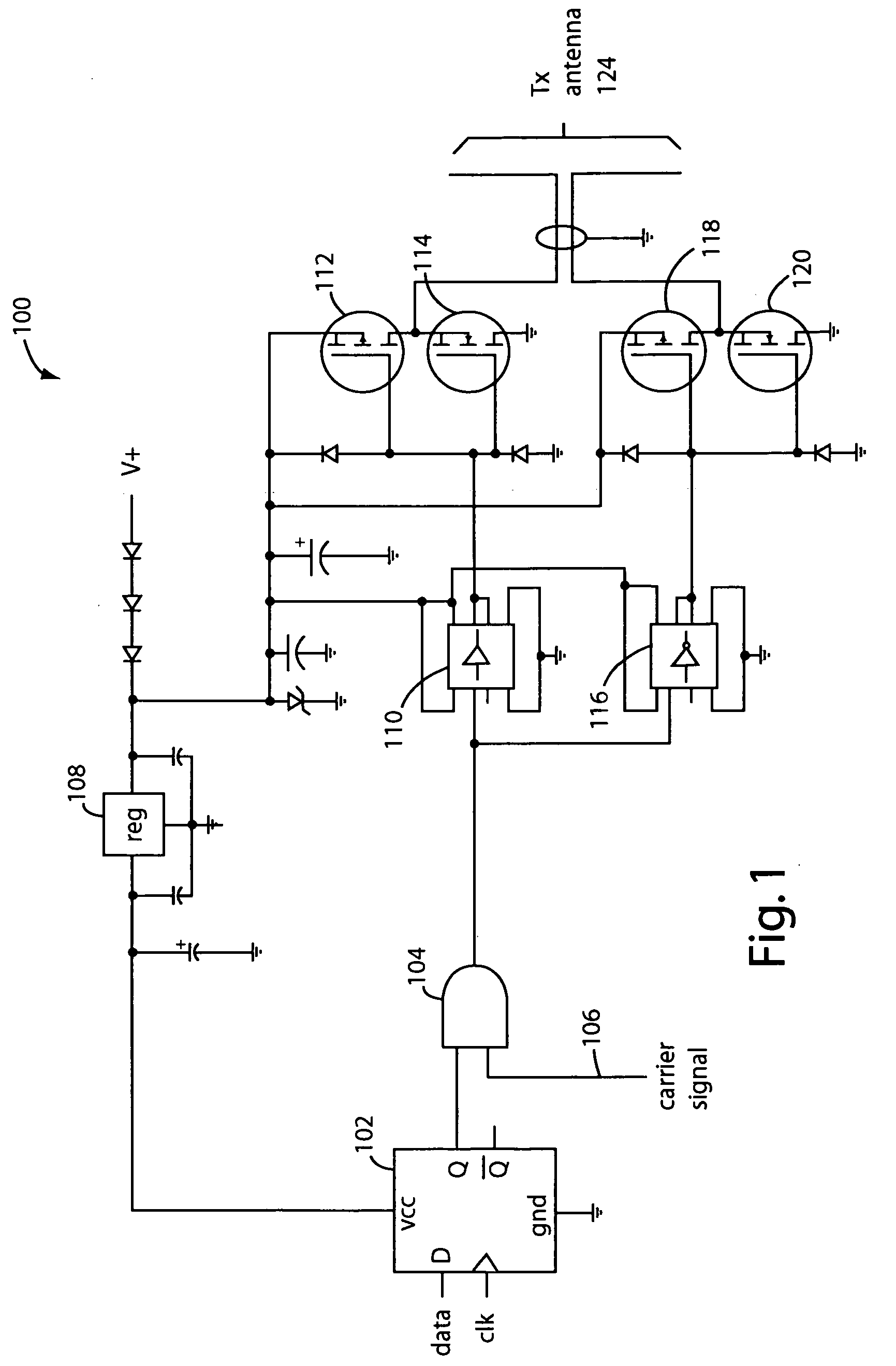

RF transceiver switching system

The present invention relates to transceiver systems and methods which employ shunt switches during transmit and receive operating modes. The shunt switches may be configured with various reactive networks to achieve high or low impedance states at power amplifiers or low noise amplifiers in order to reflect or transmit power along a given path. The shunt switches are designed for protection against excessive voltage swings that would otherwise damage components in the transceiver switching circuit. The switching circuits may be implemented in a single chip architecture, which results in manufacturing efficiencies, lower cost and higher reliability circuits. Single or multi band devices may also be employed.

Owner:RESONANCE SEMICON CORP

NAND flash depletion cell structure

InactiveUS20060044872A1Scale upIncrease supplyRead-only memoriesDigital storageCapacitanceRC time constant

NAND architecture Flash memory strings, memory arrays, and memory devices are described that utilize depletion mode floating gate memory cells. Depletion mode floating gate memory cells allow for increased cell current through lower channel rdS resistance and decreased “narrow width” effect, allowing for increased scaling of NAND memory cell strings. In addition, the required voltages for reading and programming operations are reduced, allowing the use of more efficient, lower voltage charge pumps and a reduction circuit element feature sizes and layouts. Cell inhibit of unselected cells is also increased, reducing the likelihood of cell disturb in the memory array. Operation speed is improved by increasing read current of the selected NAND string and by increasing the ability to overcome the RC time constants of circuit lines and capacitances through lowered voltage swings and increased current supplies.

Owner:MICRON TECH INC

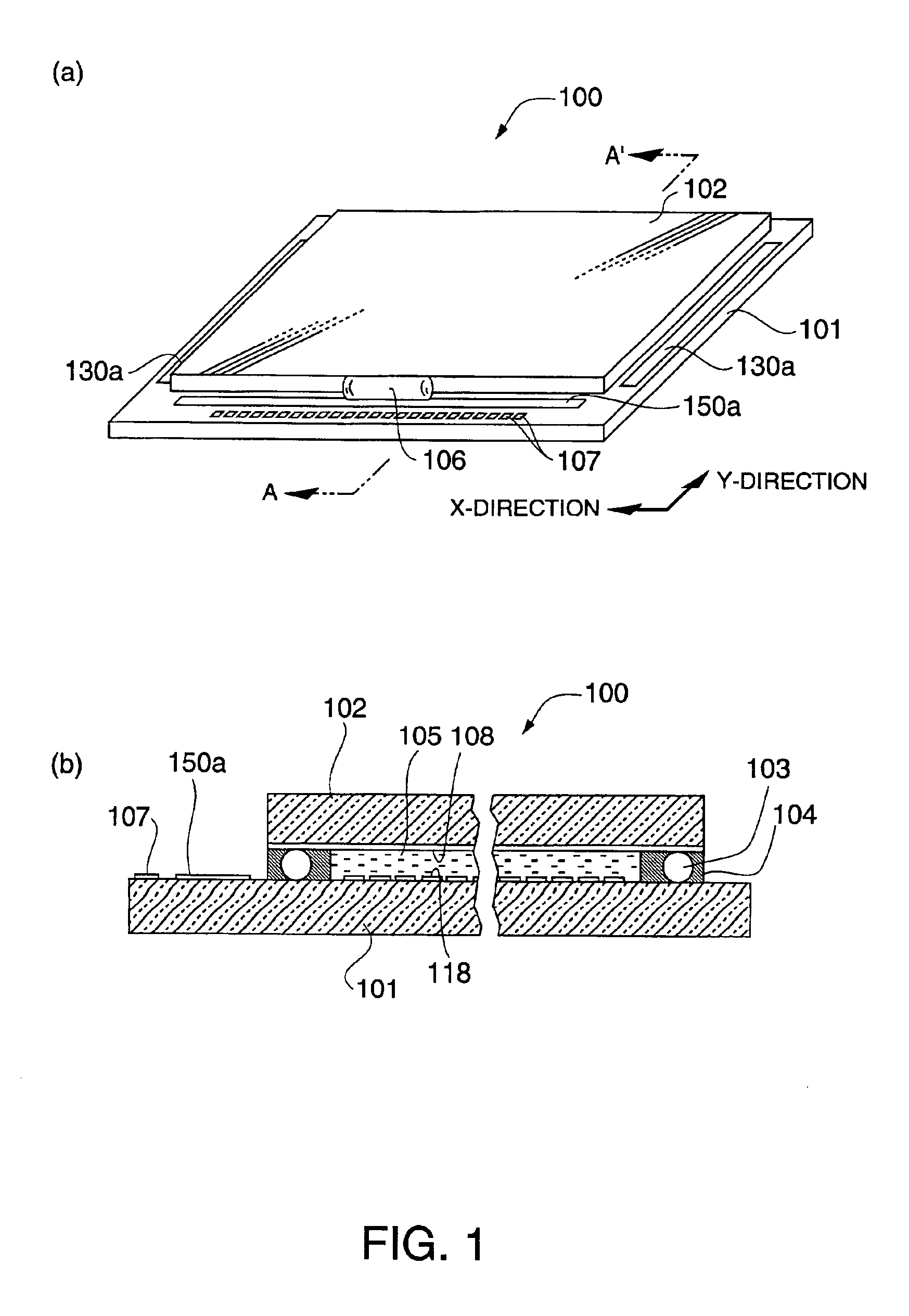

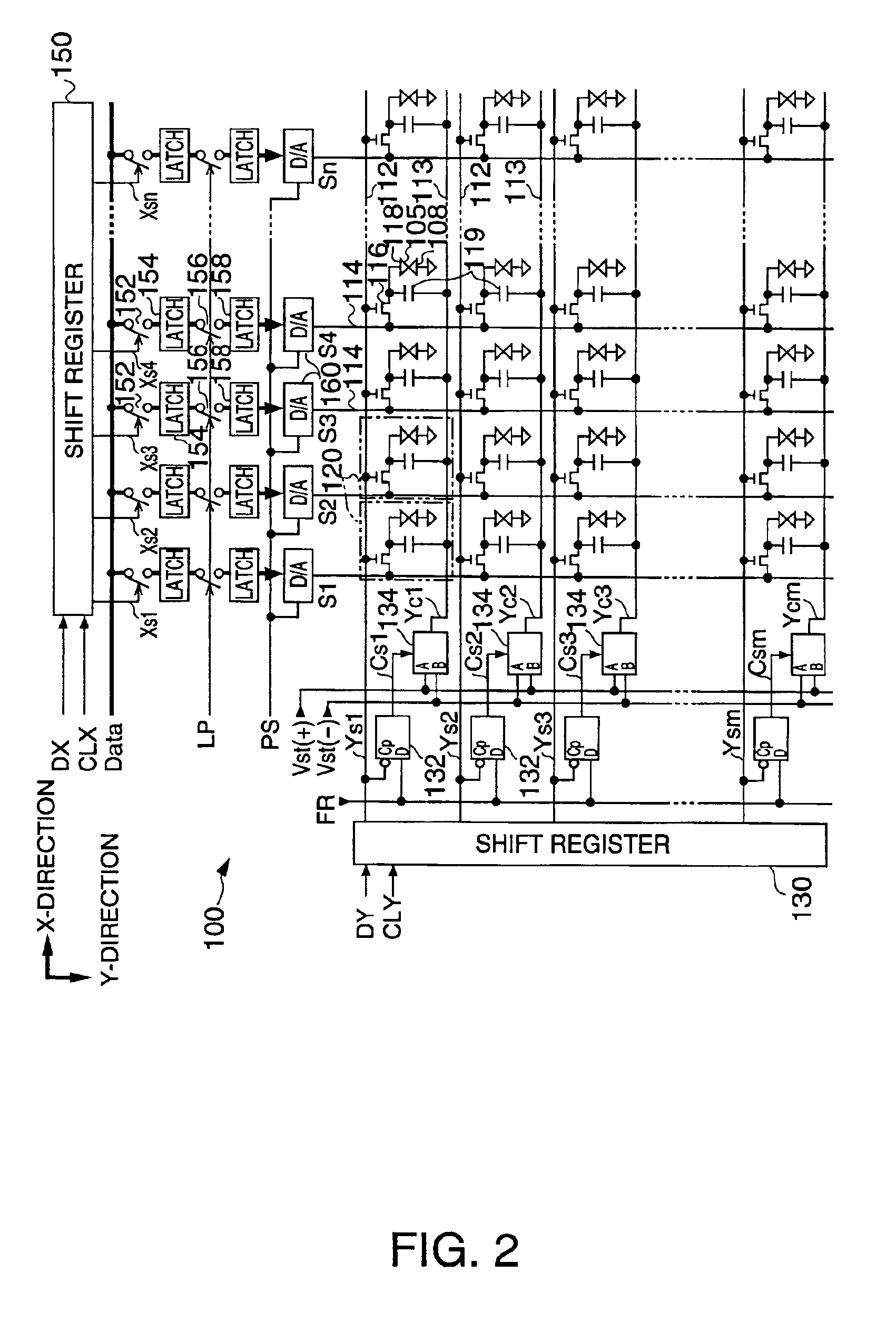

Liquid crystal display device, driving circuit, driving method, and electronic devices

InactiveUS6897845B2Integrated reductionMiniaturizationCathode-ray tube indicatorsNon-linear opticsLiquid-crystal displayCapacitor voltage

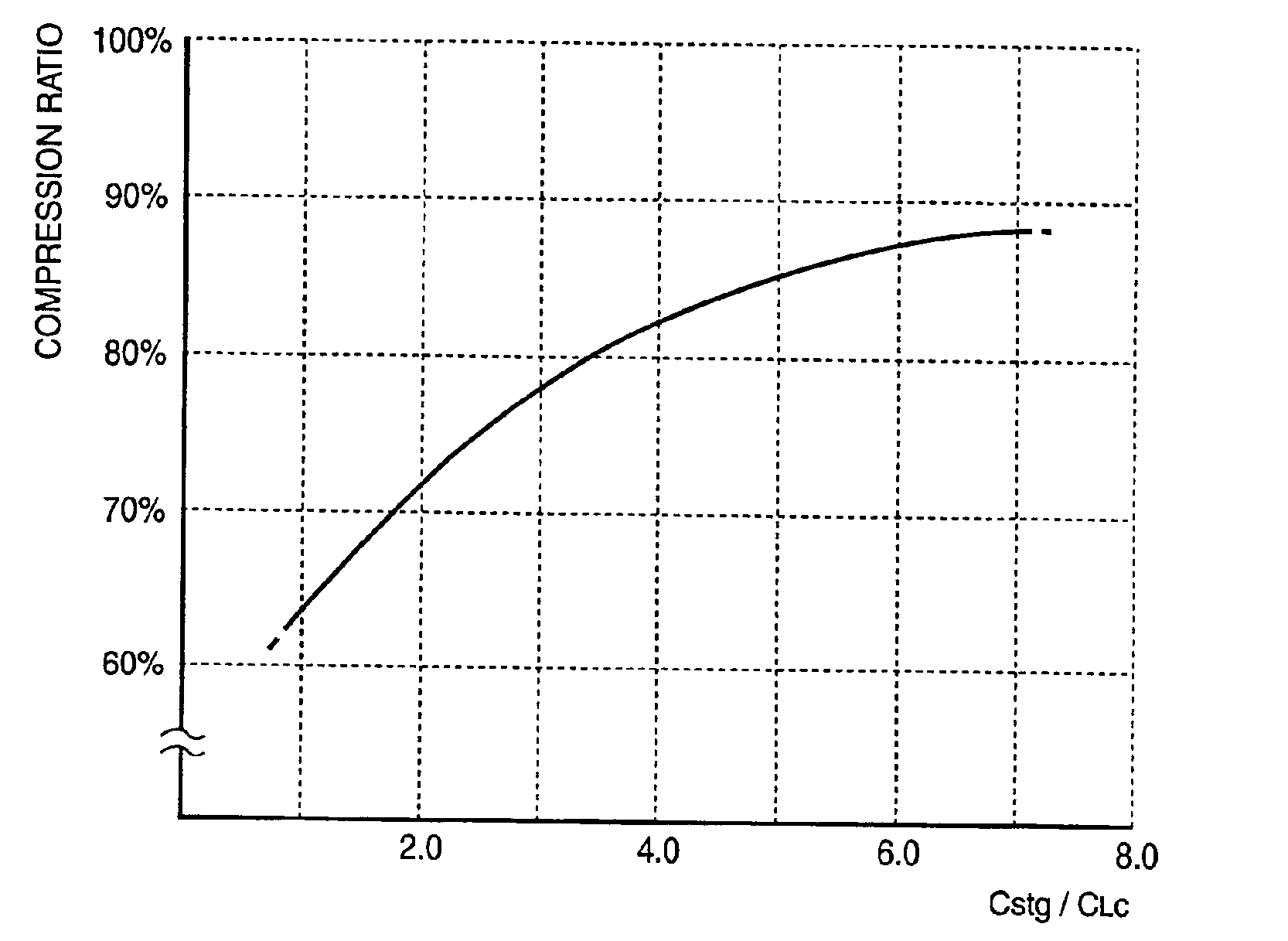

The voltage swing of a data signal, which is supplied to a data line, is maintained to be small, thereby reducing the power consumption. When a scanning signal supplied to a scanning line is set to an on-voltage, a data signal with a voltage, depending on the density and depending on the writing polarity, is applied to a data line. In this case, a TFT is turned on. Thus, a liquid crystal capacitor and storage capacitor store the charge corresponding to the voltage of the data signal. Then, the scanning signal is set to an off-voltage to turn the TFT off, and the voltage of the other terminal of the storage capacitor is raised from the low-level of capacitor voltage to the high-level, and the charge corresponding to the raised voltage amount is redistributed to the liquid crystal capacitor. Thus, the effective voltage value applied to the liquid crystal capacitor can correspond to the voltage swing of the data signal or more.

Owner:BOE TECH GRP CO LTD

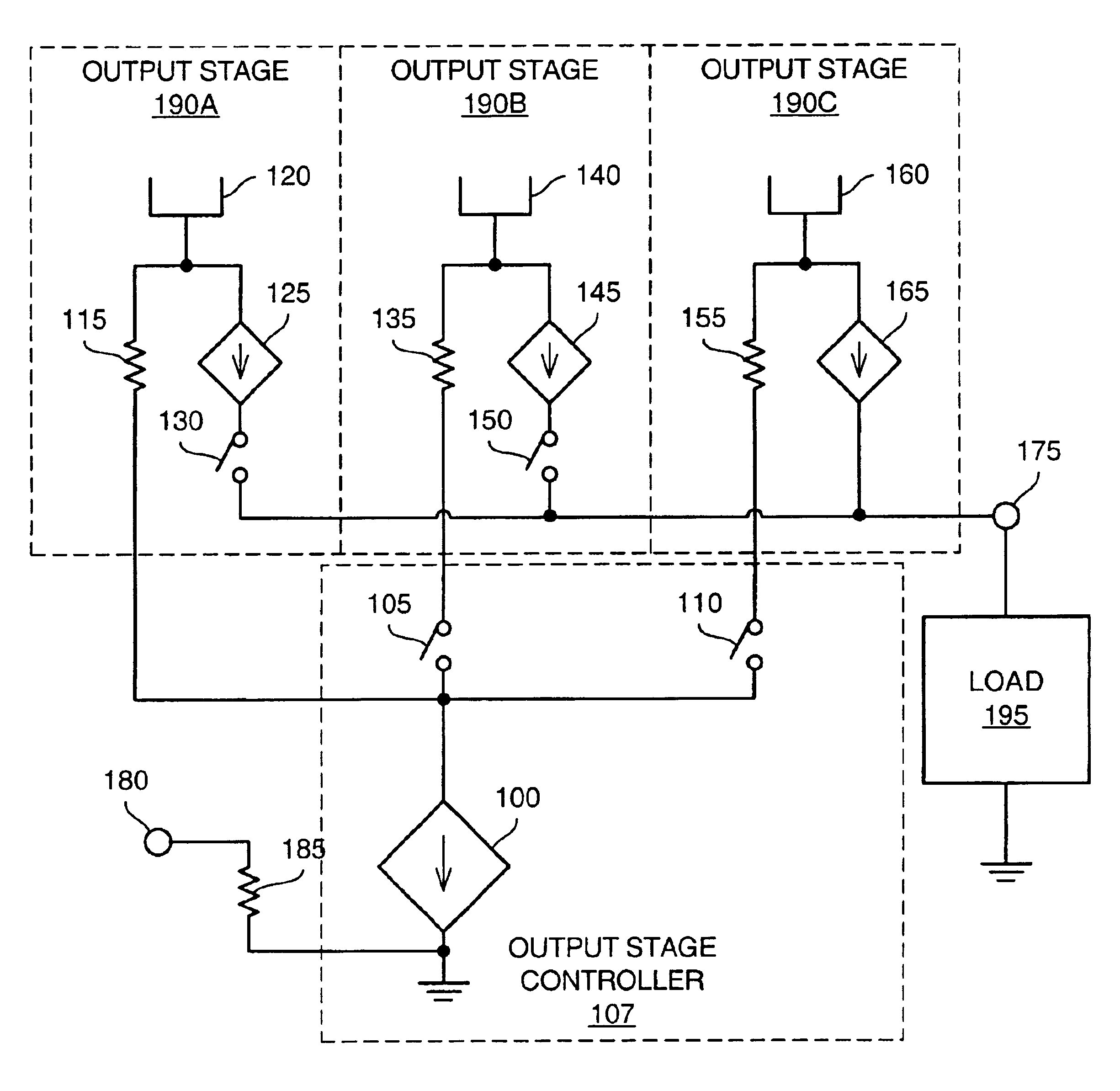

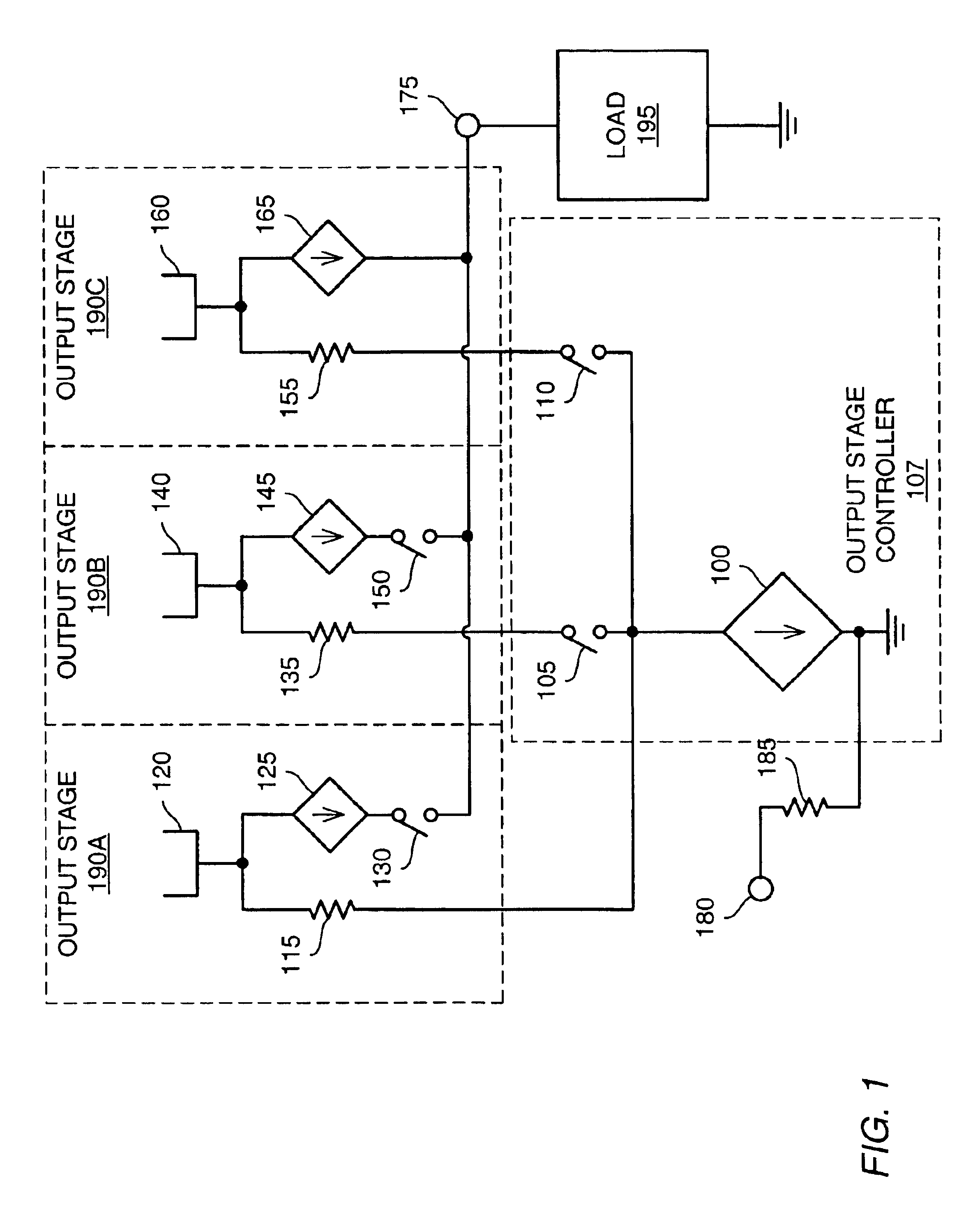

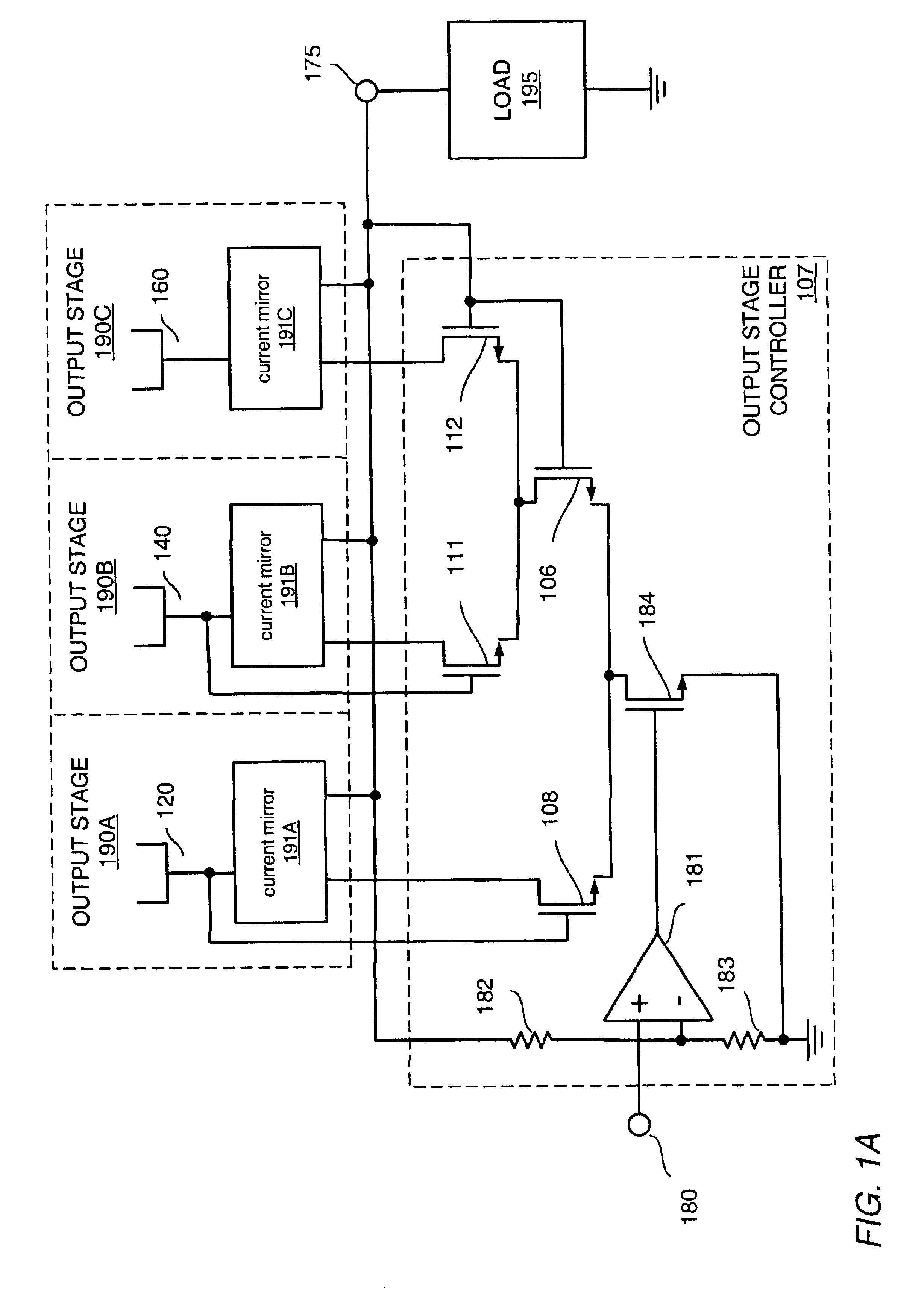

Efficient class-G amplifier with wide output voltage swing

InactiveUS6838942B1Reduce noiseImprove efficiencyGated amplifiersPower amplifiersCMOSAudio power amplifier

Various embodiments of methods and apparatus for an amplifier with wide output voltage swing are disclosed. The amplifier may include multiple output stages, each associated with a distinct supply voltage. Each output stage may contribute current to the output of the amplifier over a range of amplifier output voltages and these ranges may overlap. Each output stage may contribute current until the amplifier output voltage reaches the supply voltage associated with that output stage. The amplifier output may be as great as the largest supply voltage minus a drop equal to Rdson for an output transistor multiplied by the output current. In a CMOS implementation, this voltage drop may be approximately 0.15V. When the amplifier output voltage is close to the supply voltage associated with an output stage, both that output stage and the output stage associated with the next highest supply voltage may contribute to the amplifier output.

Owner:MICROCHIP TECH INC

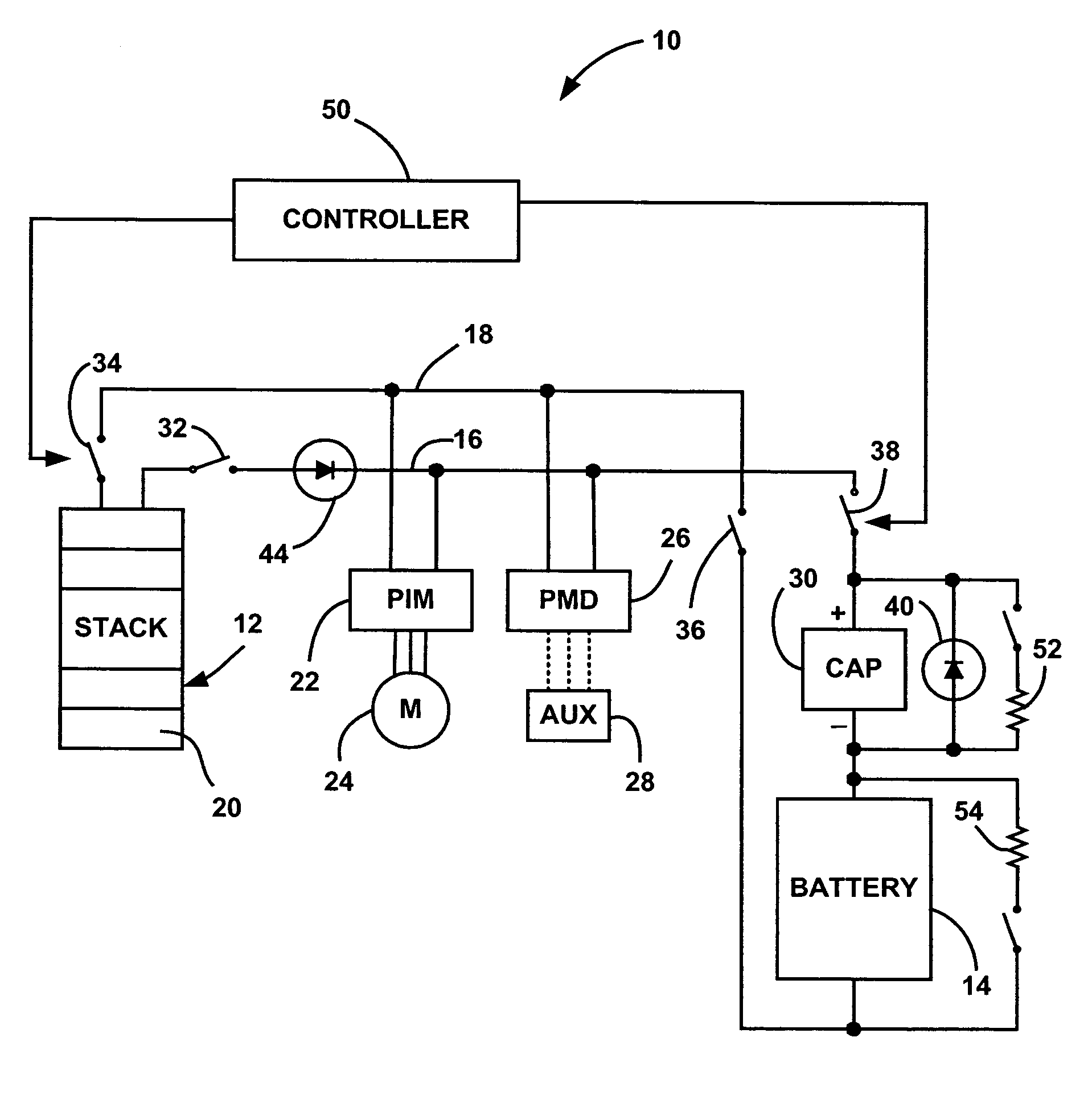

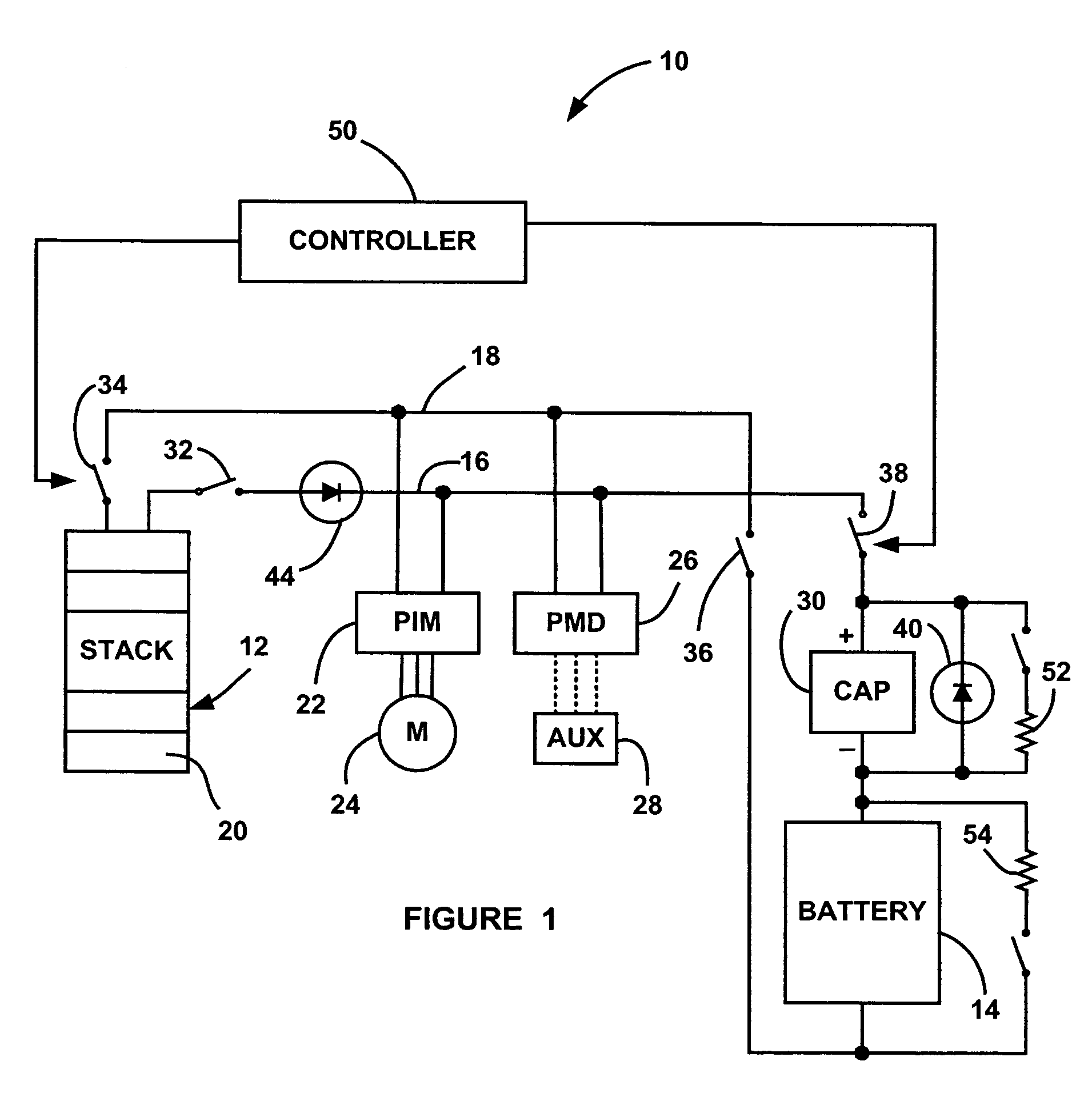

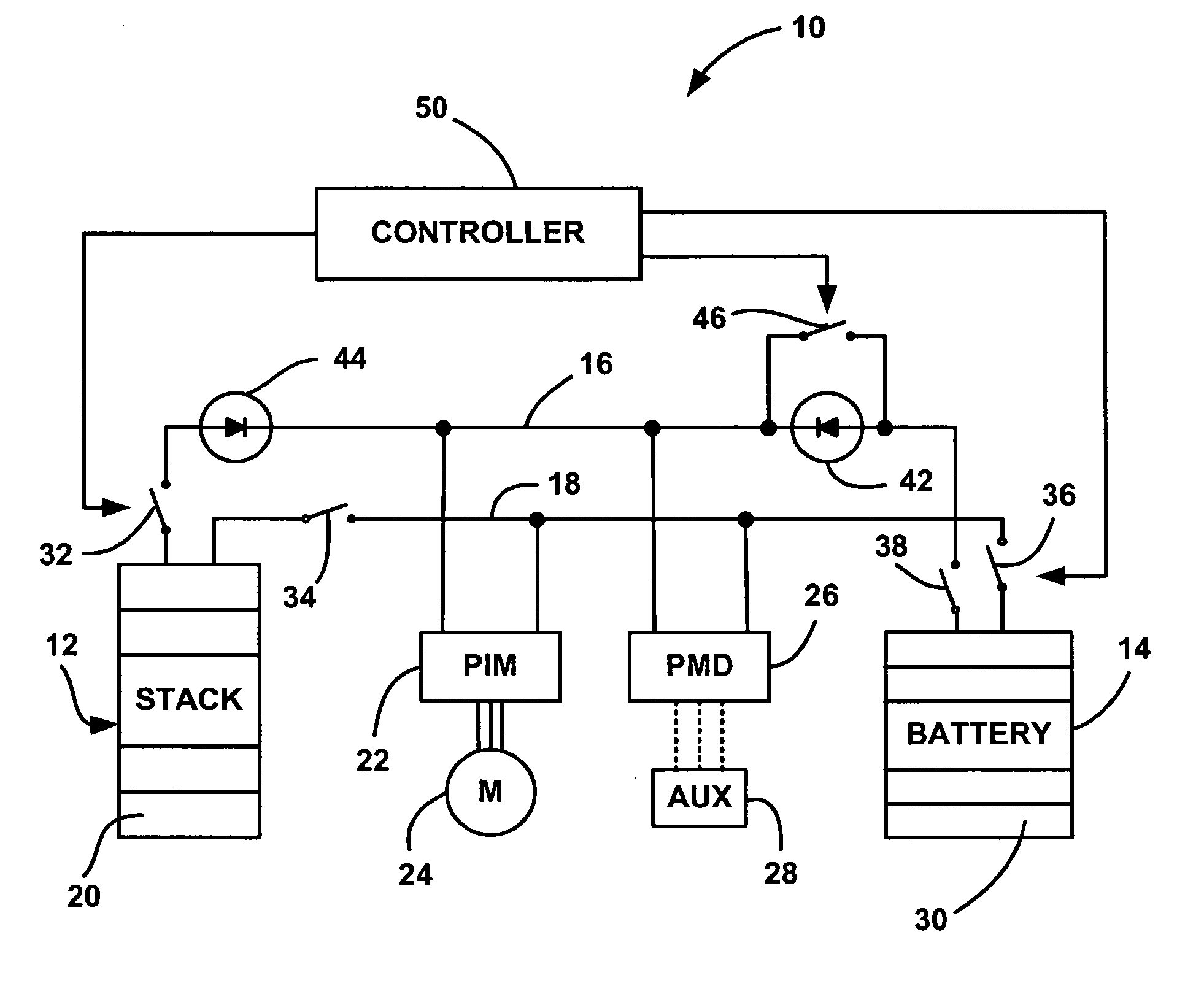

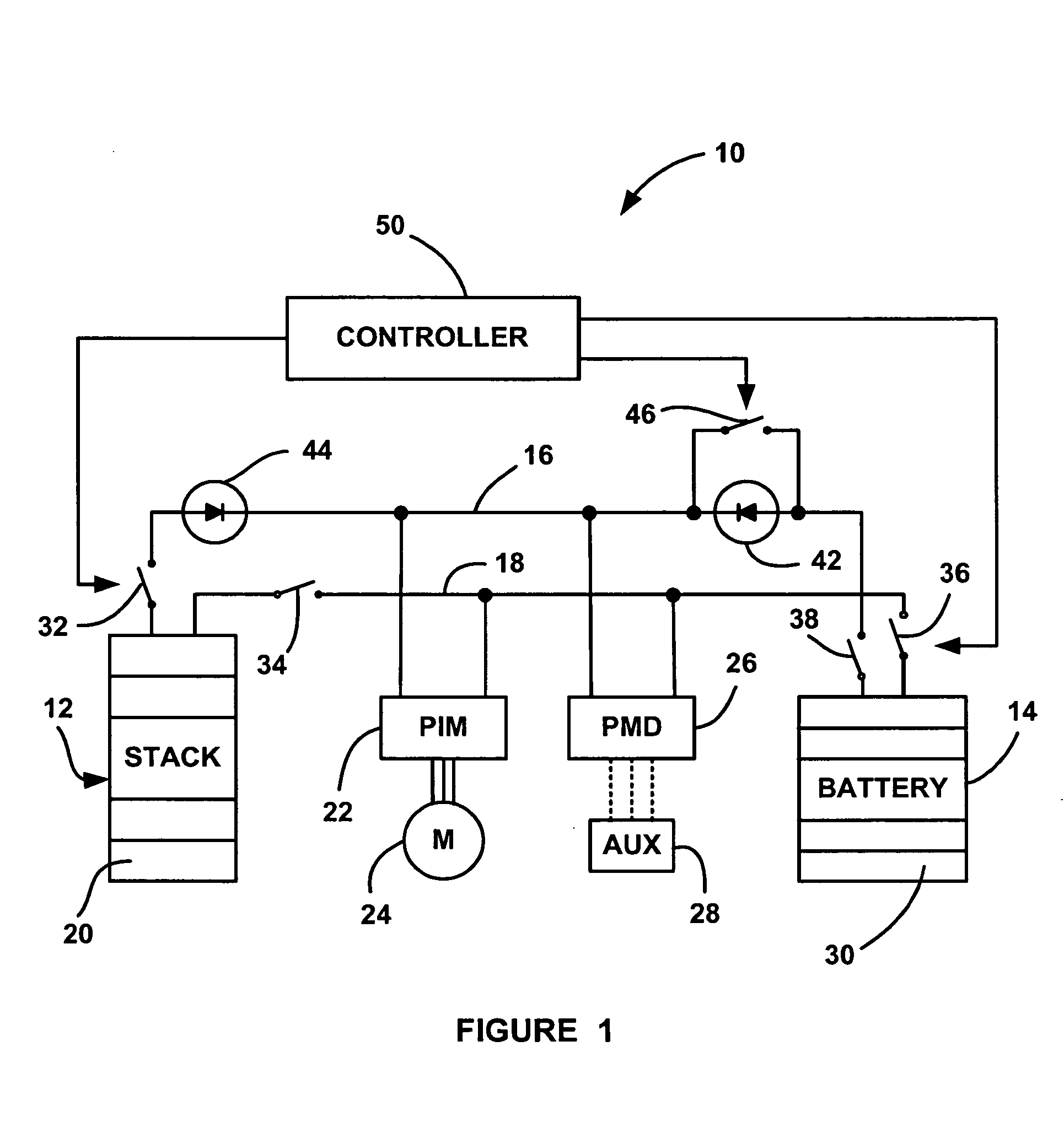

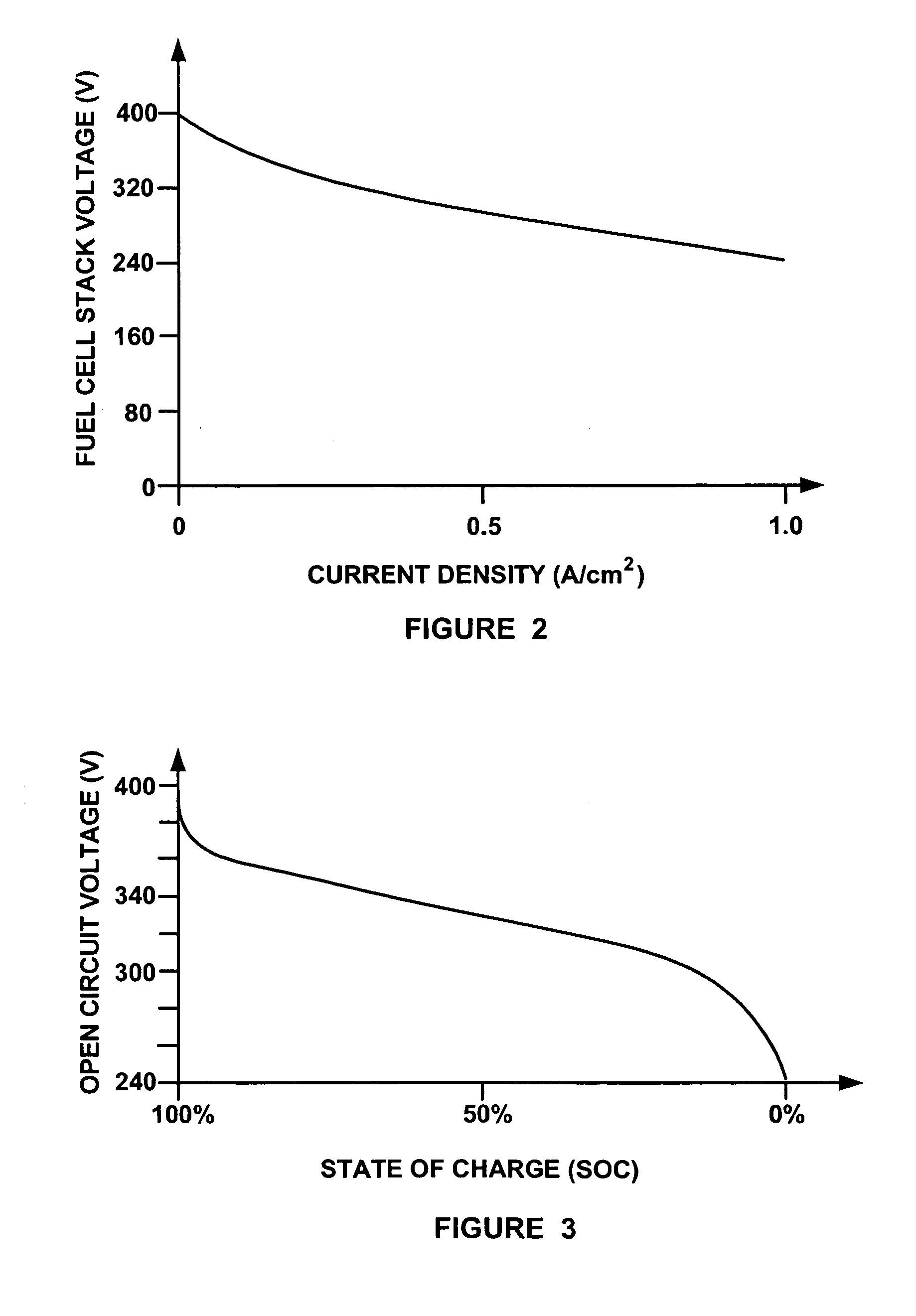

Hybrid fuel cell system with battery capacitor energy storage system

A fuel cell system that employs a super capacitor and battery electrically coupled in series with each other and in parallel with a fuel cell stack on a power bus line. As the voltage on the power bus line changes over the operating requirements of the system, the super capacitor is charged and discharged over a relatively large voltage swing, such as an 85% SOC swing. The super capacitor equalizes or voltage matches the voltage variation on the power bus line as set by the stack voltage to the voltage of the battery. Therefore, the battery, while providing the majority of the energy and power during charge and discharge, has a relatively small defined SOC swing, which acts to maintain the battery life. The system can also include a diode electrically coupled in parallel with the super capacitor that provides reverse voltage protection and electrical power by-pass.

Owner:GM GLOBAL TECH OPERATIONS LLC

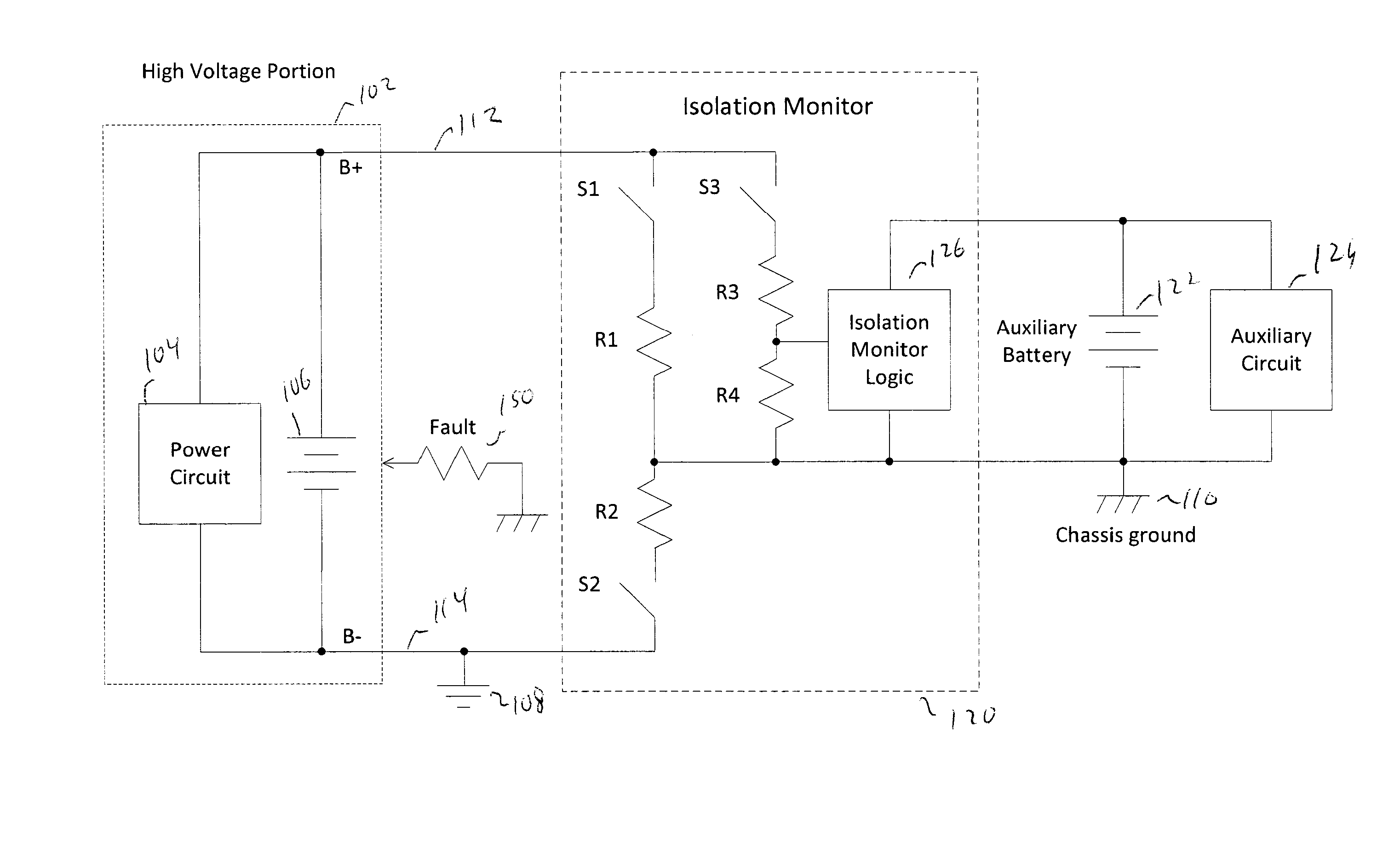

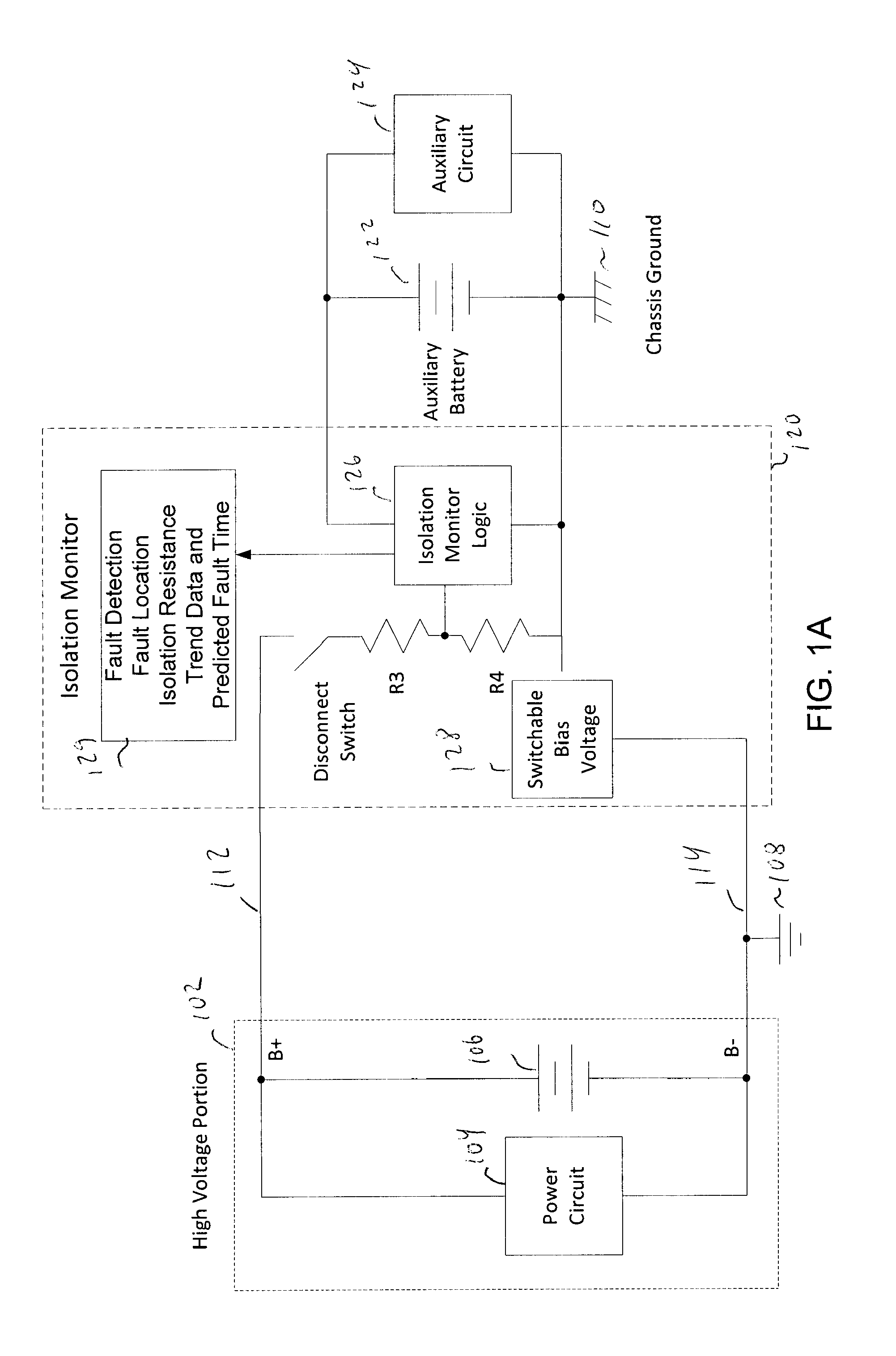

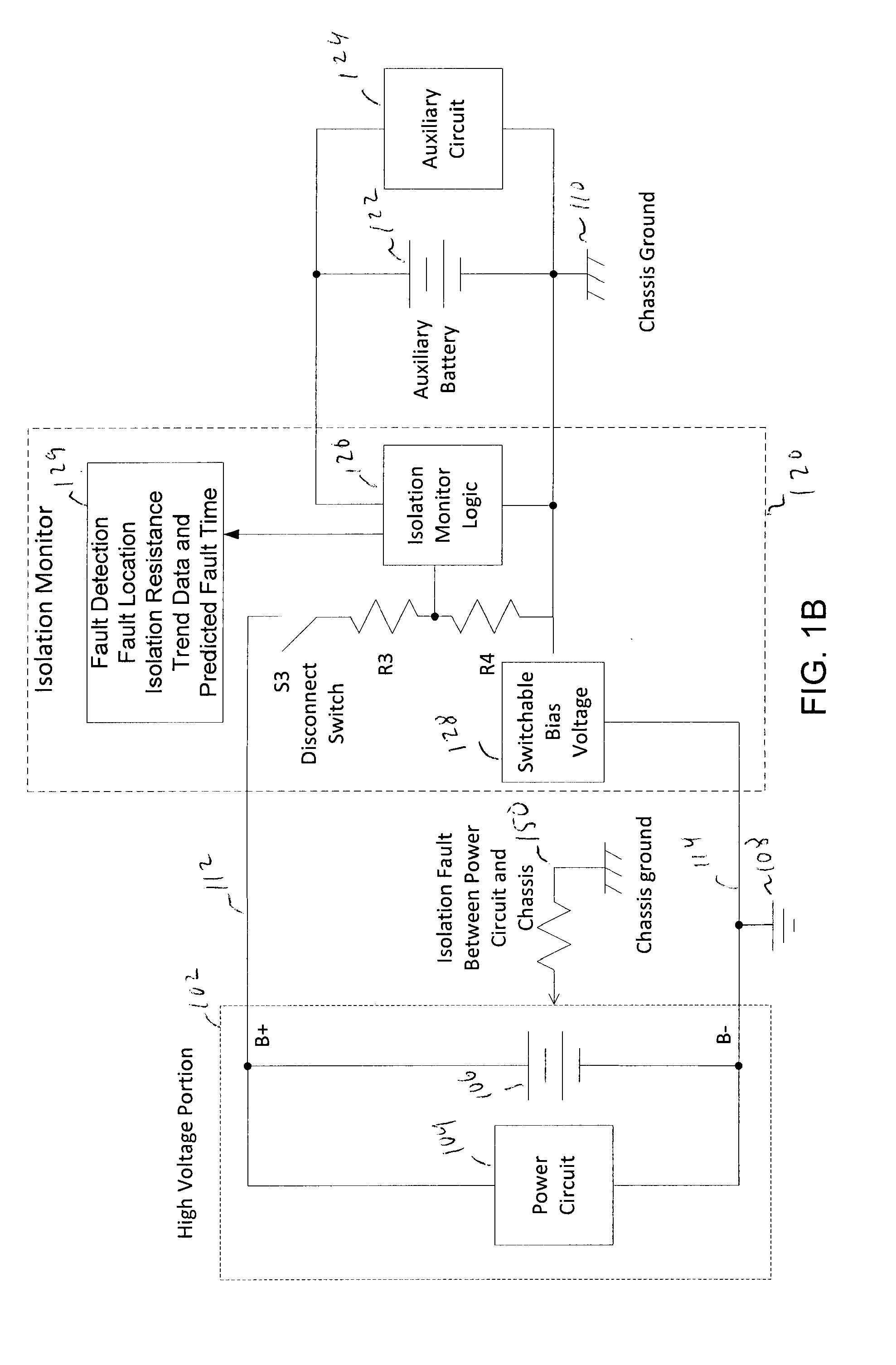

Isolation monitor

ActiveUS20130300430A1Electric devicesOperating modesElectrical resistance and conductanceEngineering

An isolation monitor is disclosed in which a switchable bias voltage is imposed on a chassis ground. An isolation voltage is measured when a bias voltage is applied. When there are no electrical faults, the isolation voltage swings up and down to known values. When a fault occurs, the isolation voltage will not to swing to the known values, and thus the isolation resistance can be measured and alarm generated if the isolation resistance falls below a threshold value.

Owner:CURTIS INSTRUMENTS INC

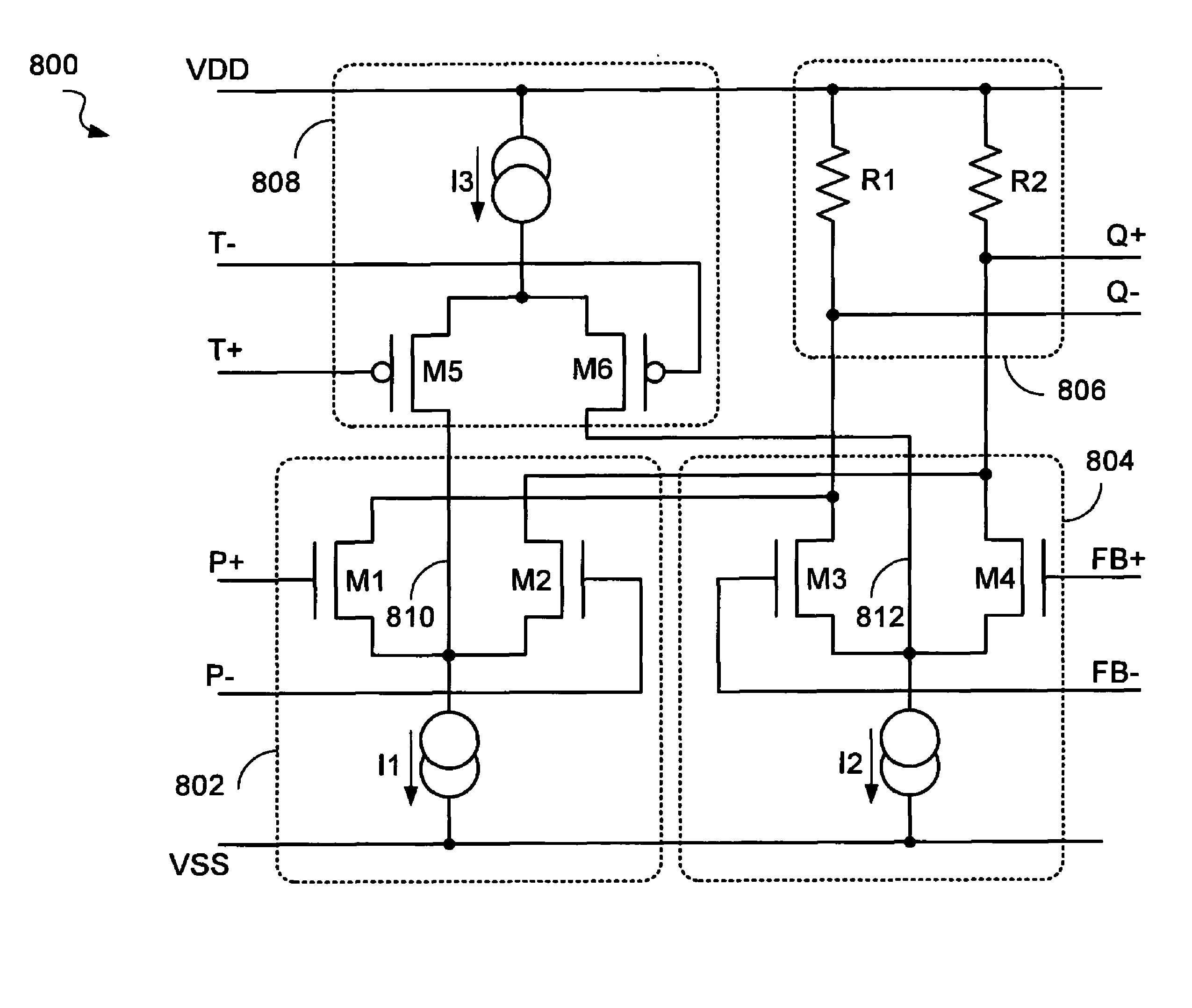

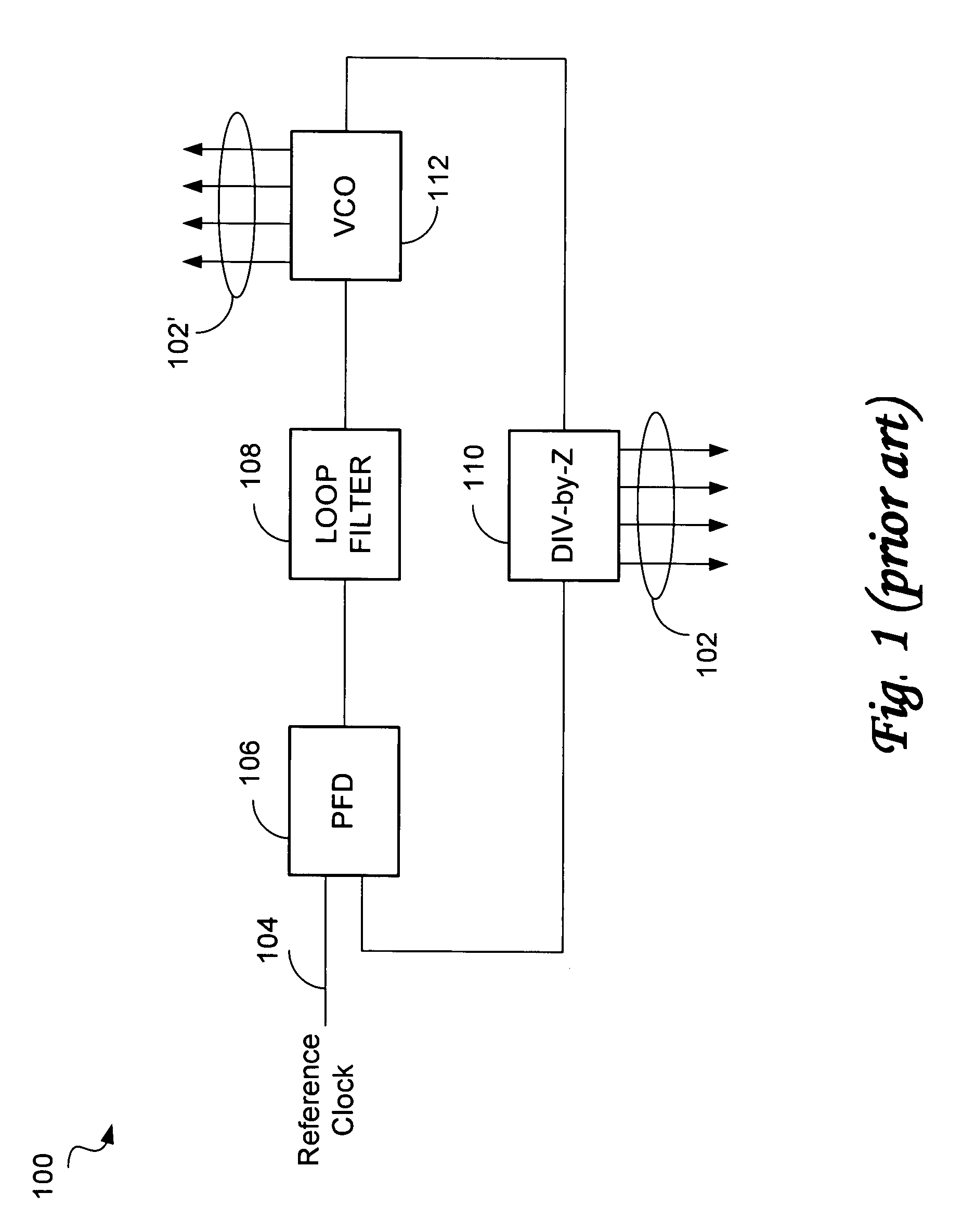

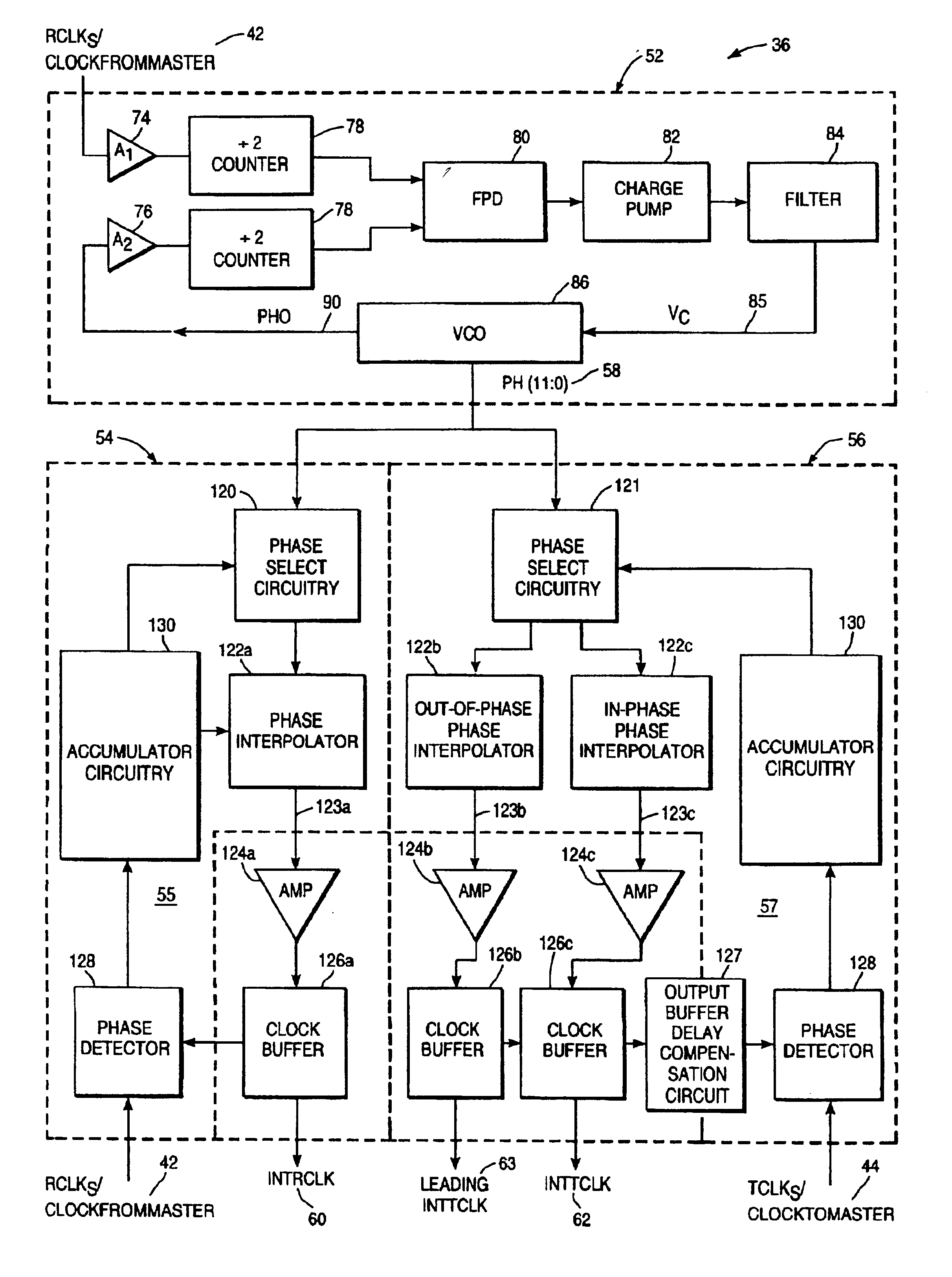

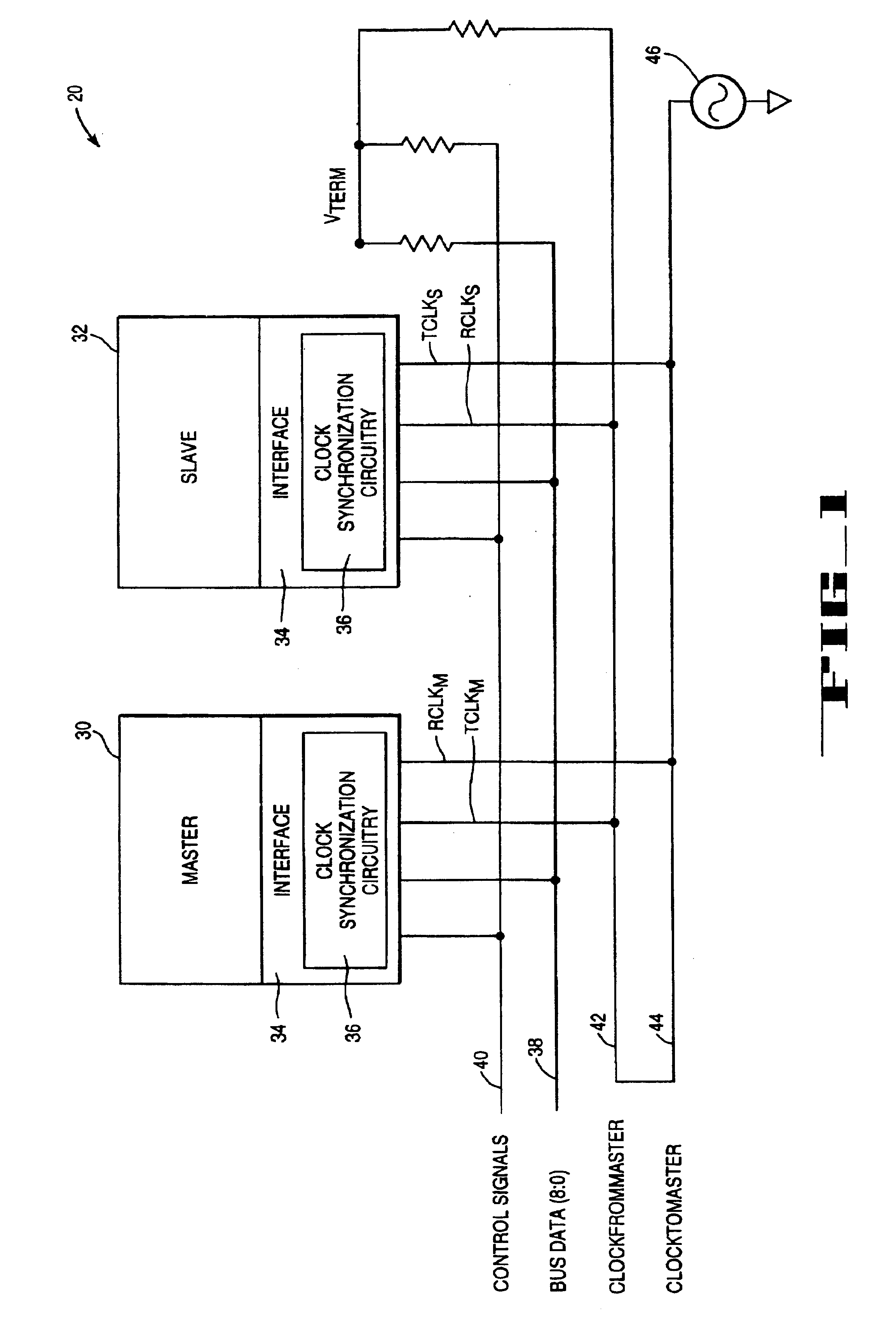

Voltage Controlled Oscillator (VCO) with a wide tuning range and substantially constant voltage swing over the tuning range

A wide tuning range and constant swing VCO is described that is based on a multipass Ring Oscillator enhanced with feed-backward connections. This VCO is designed to overcome tuning range limitations of prior-art “feed-forward” ring oscillators. The Feedback multipass Ring Oscillator of the invention provides decreasing frequency when tuned by increasing the feedback, thus covering a much wider tuning range irrespective of the speed limit of the technology while at the same time providing almost constant amplitude.

Owner:RAMBUS INC

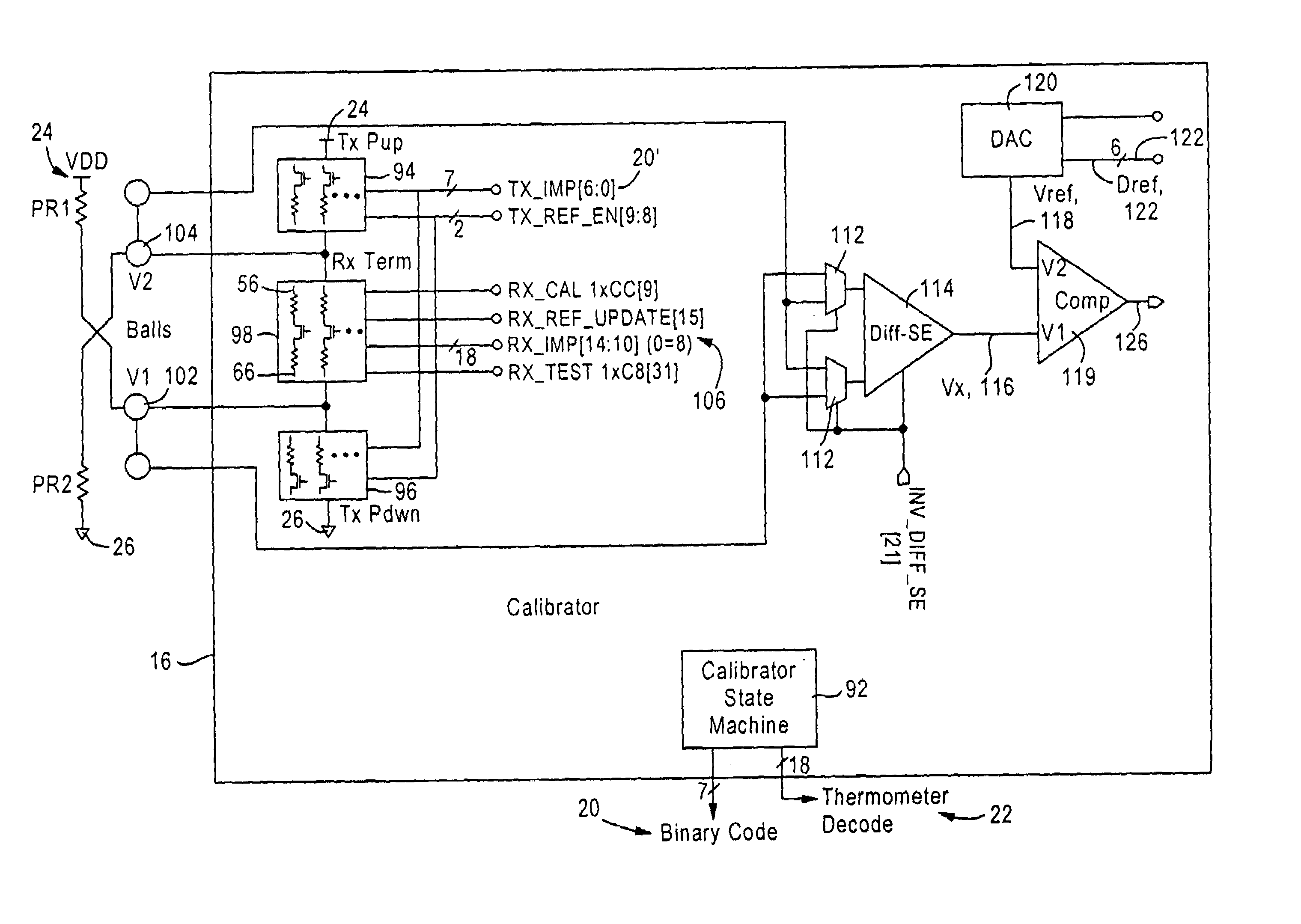

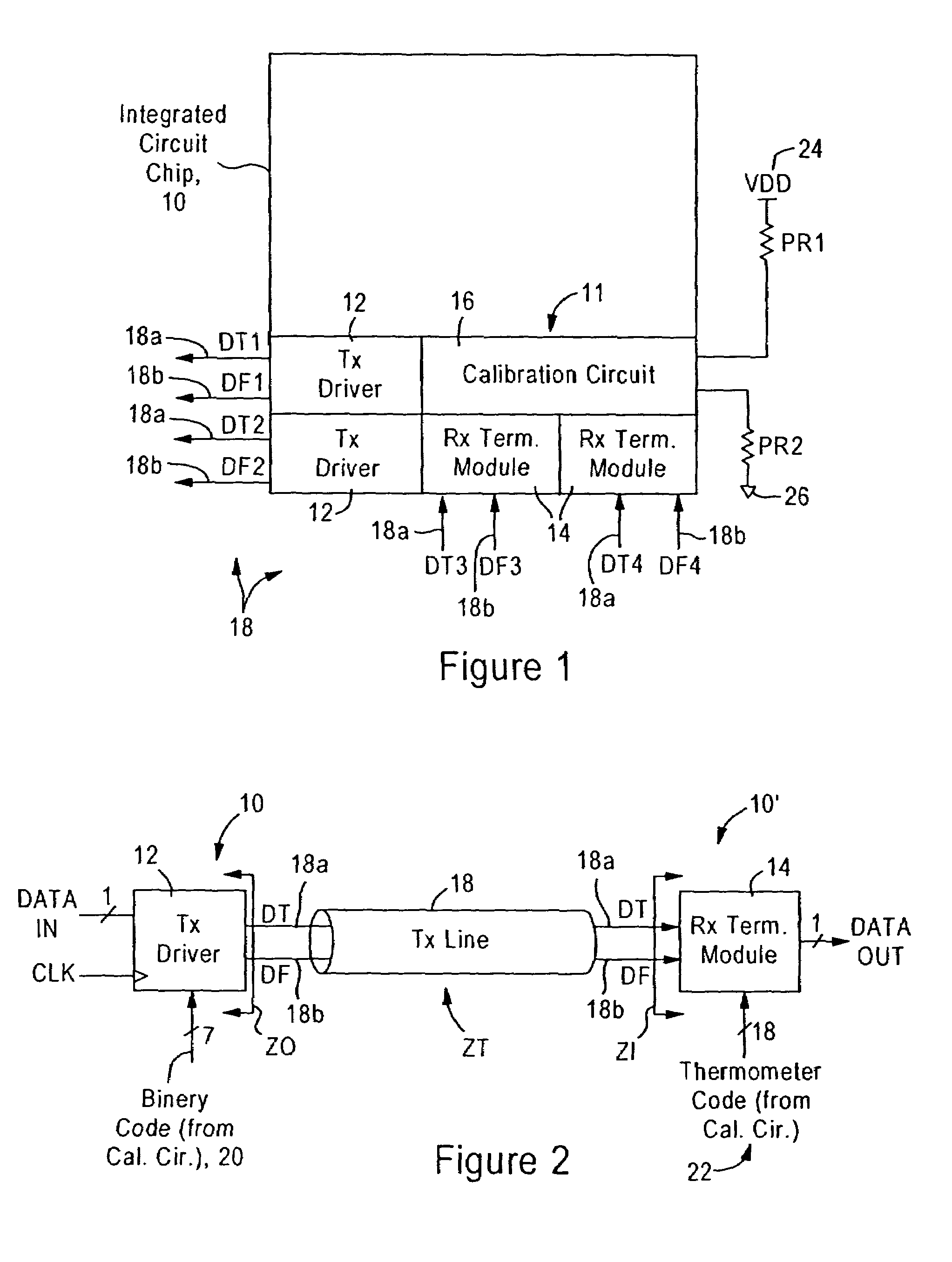

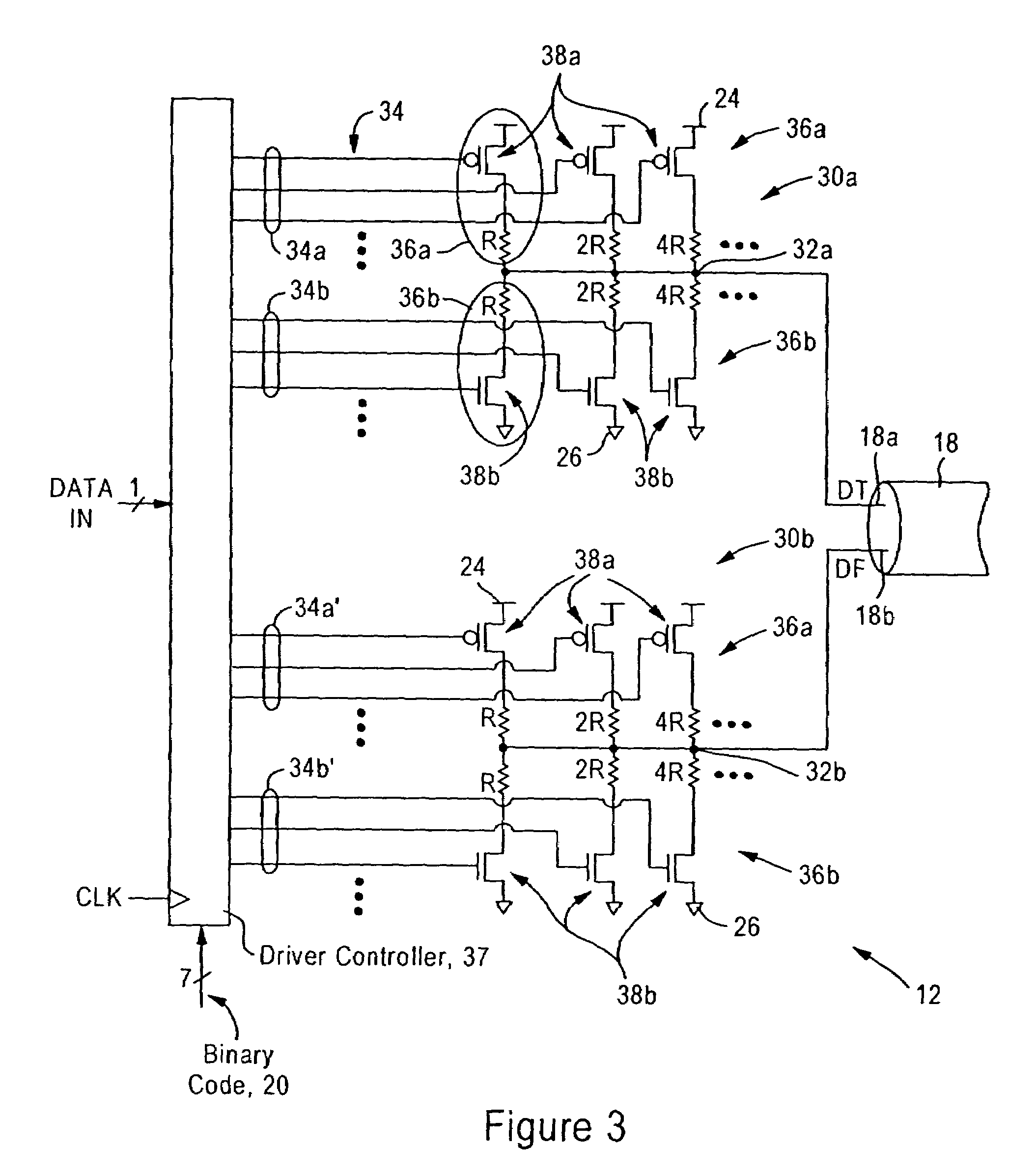

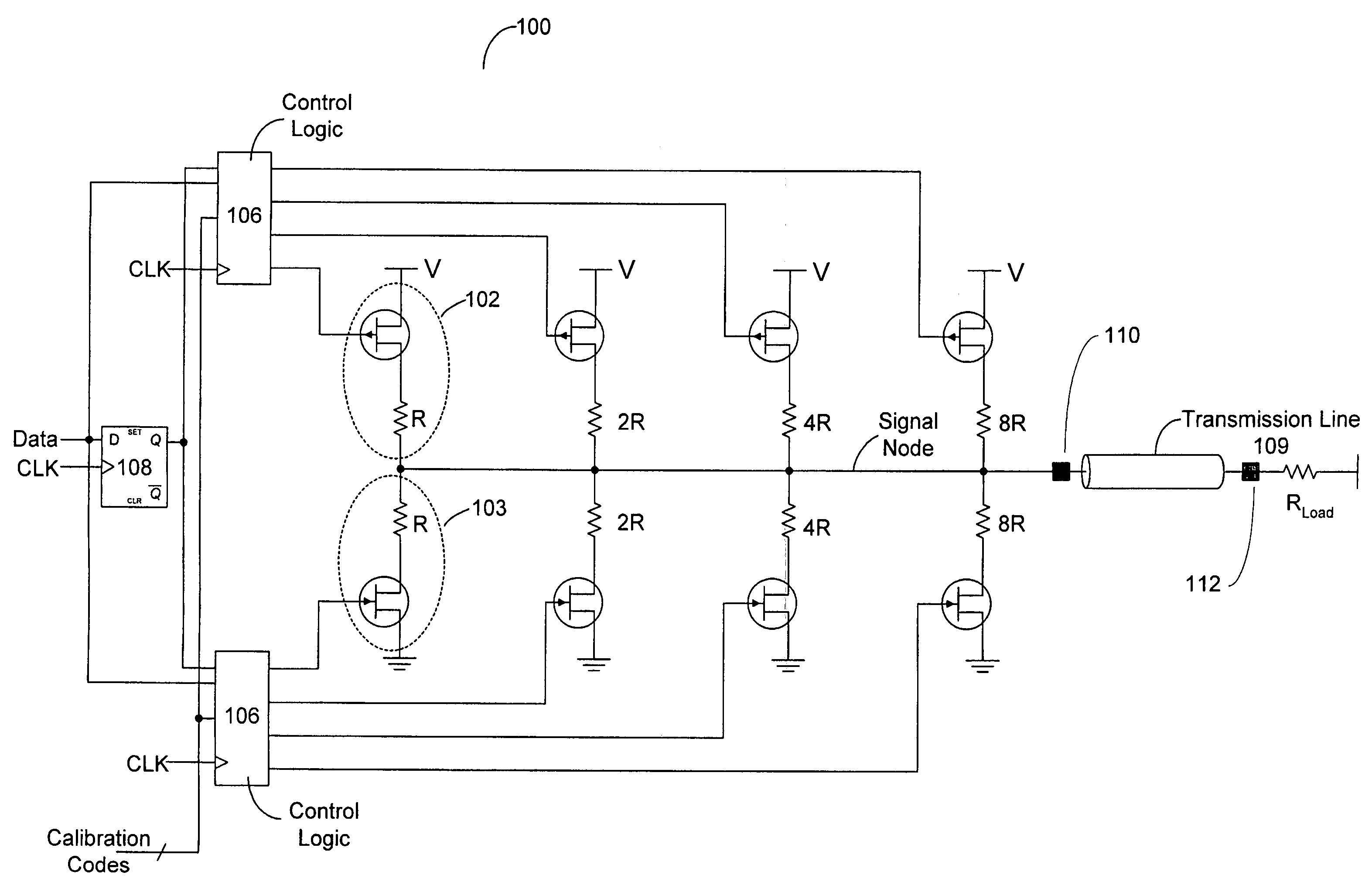

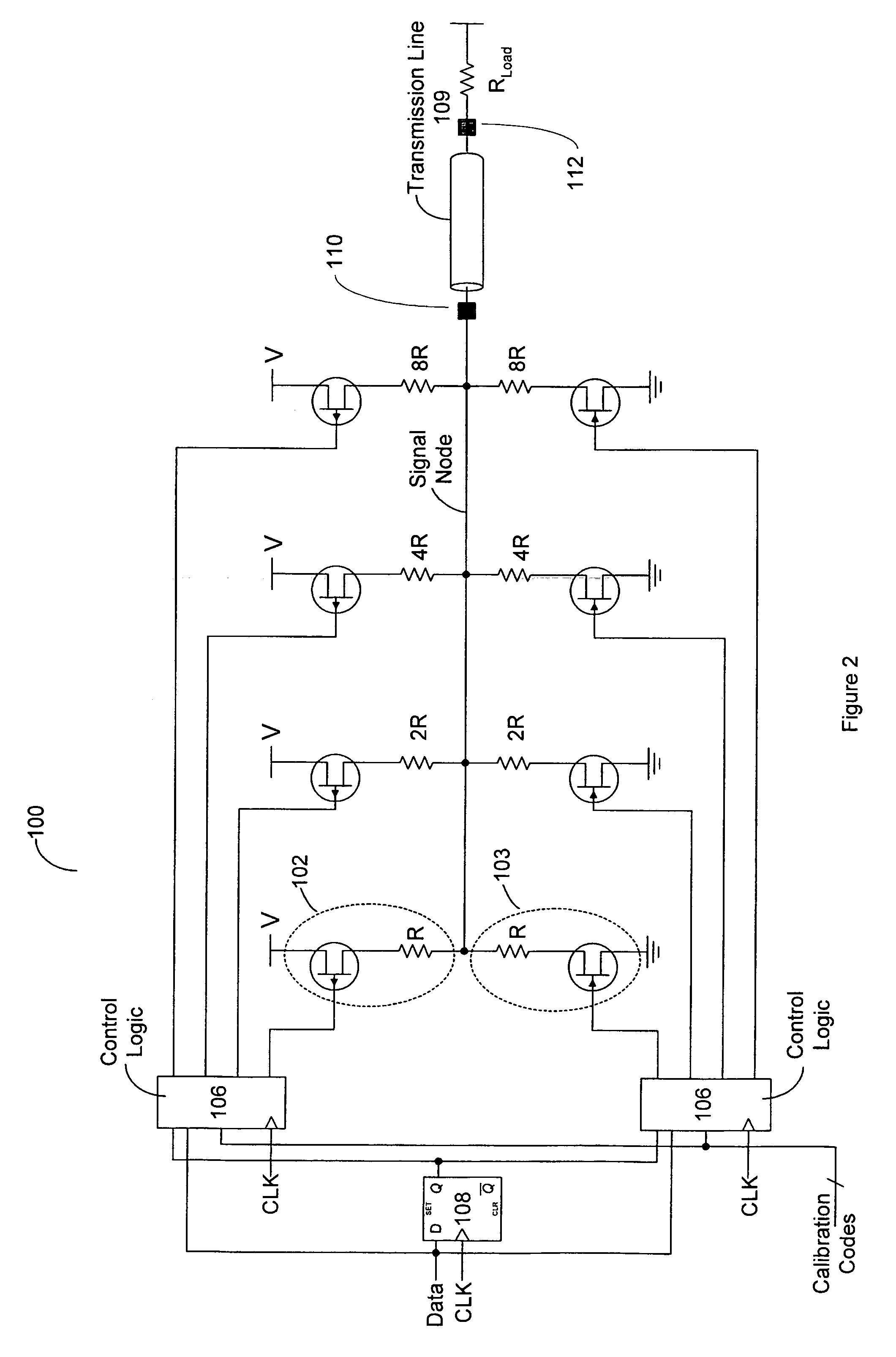

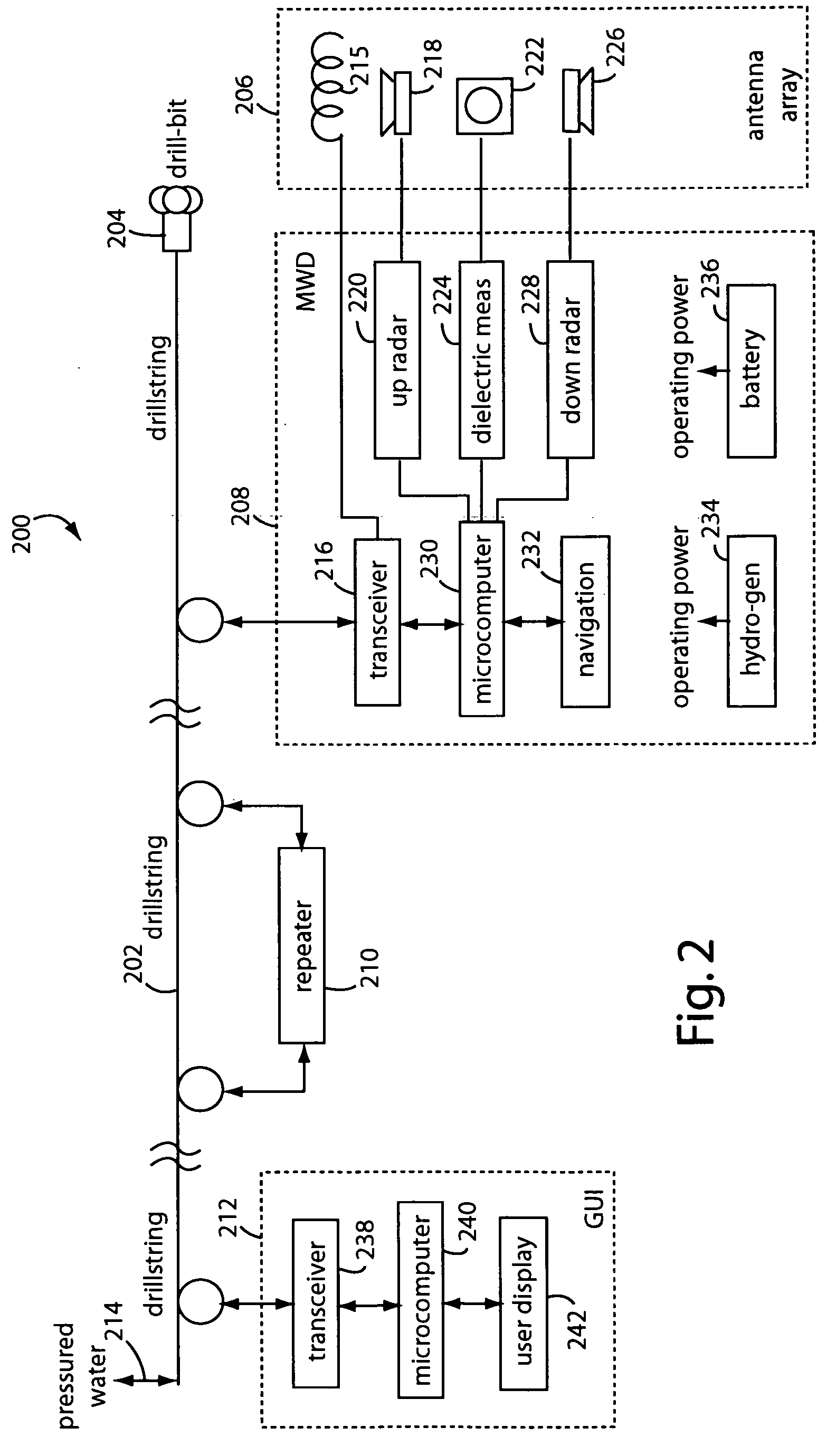

Voltage mode transceiver having programmable voltage swing and external reference-based calibration

ActiveUS7135884B1Reduce input capacitanceImprove the level ofInput/output impedence modificationReliability increasing modificationsExternal referenceInput impedance

An integrated device includes a voltage mode transmit driver for matching an output impedance to an output transmission line based on a binary code, an input termination module configured for matching an input impedance to an input transmission line based on an input impedance calibration value using thermometer-based decoding. The voltage mode transmit driver includes, for each differential output signal, a resistor network circuit having pull-up circuits and pull-down circuits for changing the voltage on the differential output signal, and having binary weighted resistance values relative to each other. The input termination module includes pull-up circuits and pull-down circuits having inverse hyperbolic resistance values relative to each other, and using thermometer-based decoding to ensure a linear change in input impedance during transitions in the input impedance calibration value. A calibration circuit generates the binary code and the input impedance calibration value based on replicas of the pull-up and pull-down circuits.

Owner:MEDIATEK INC

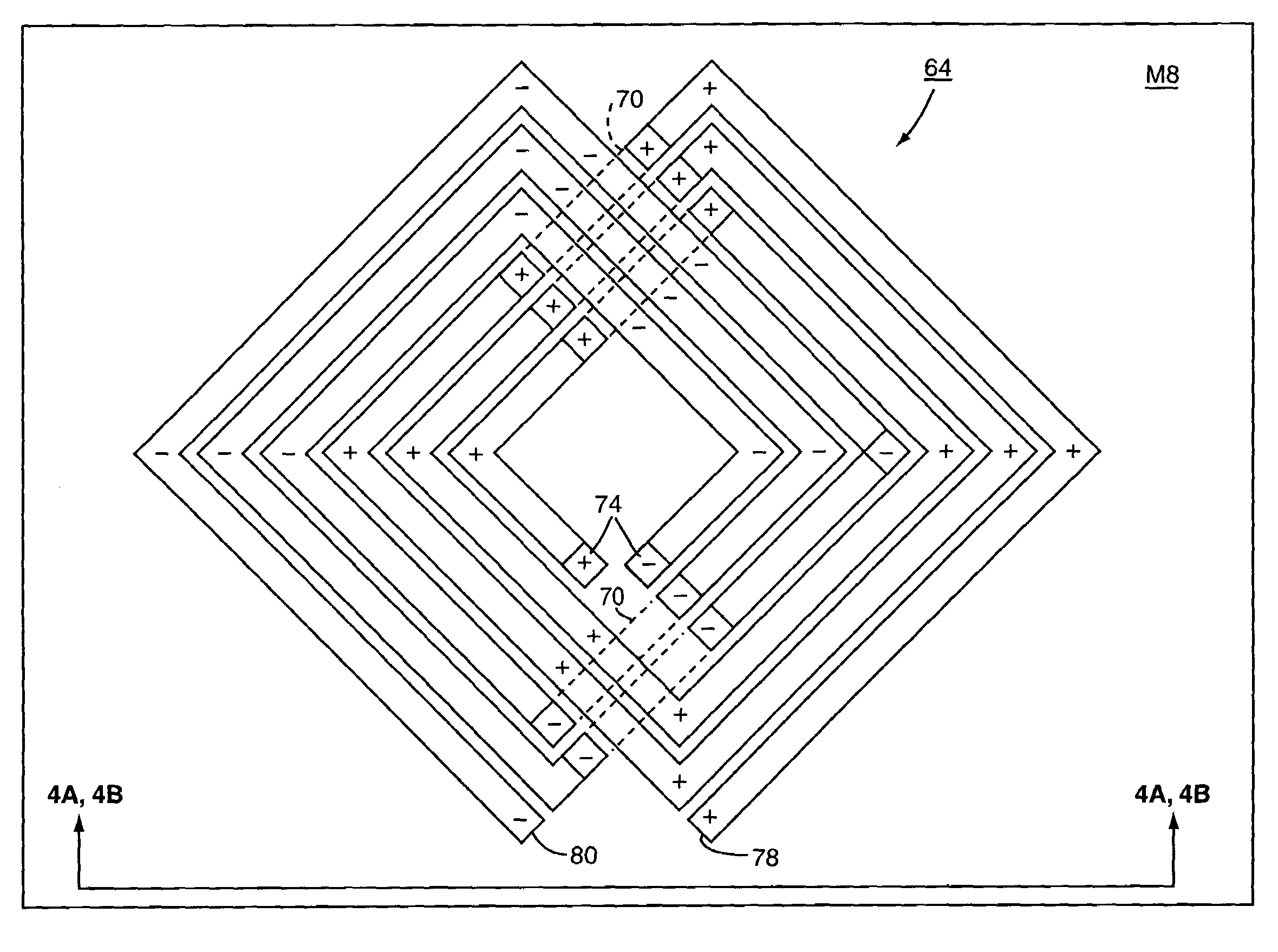

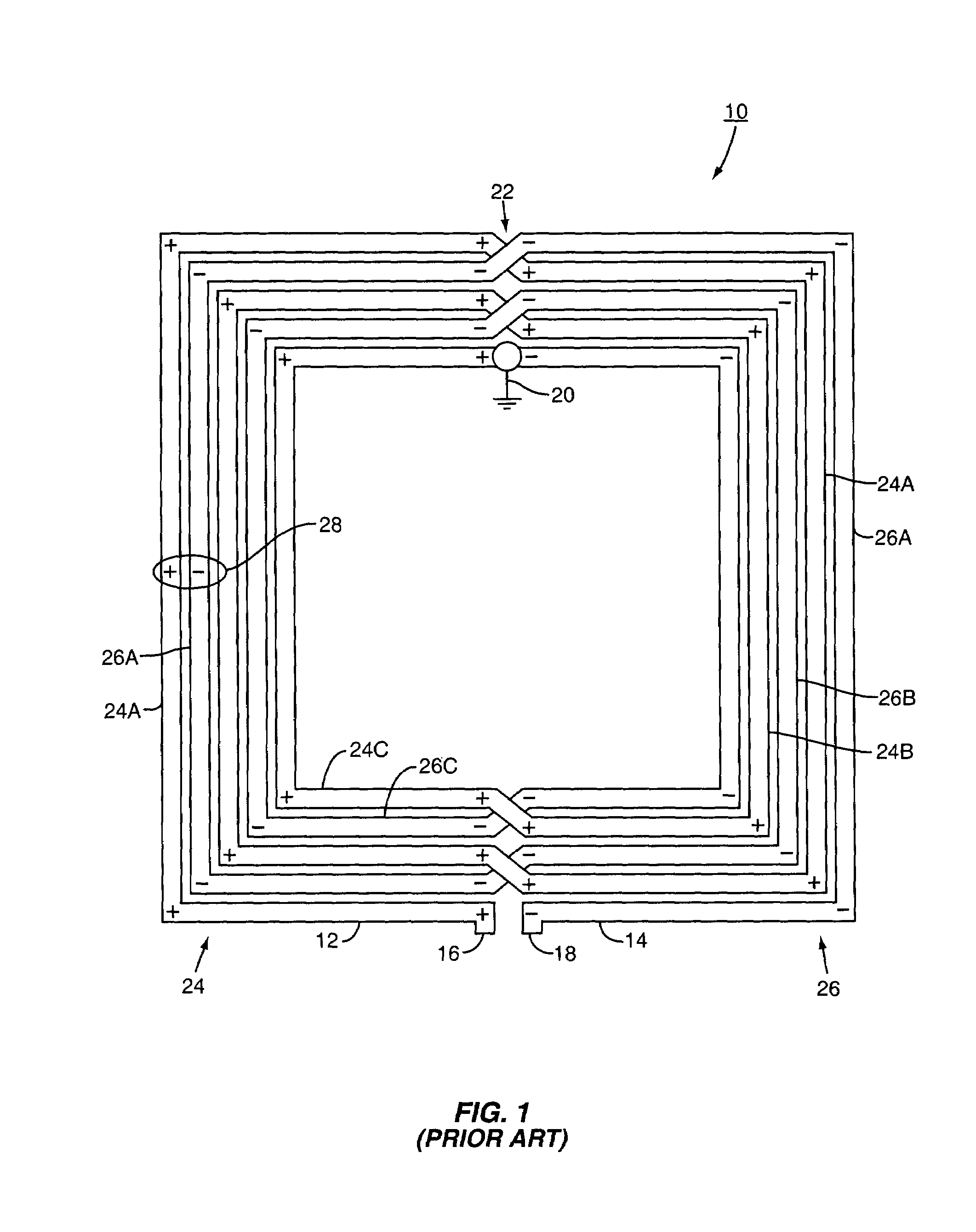

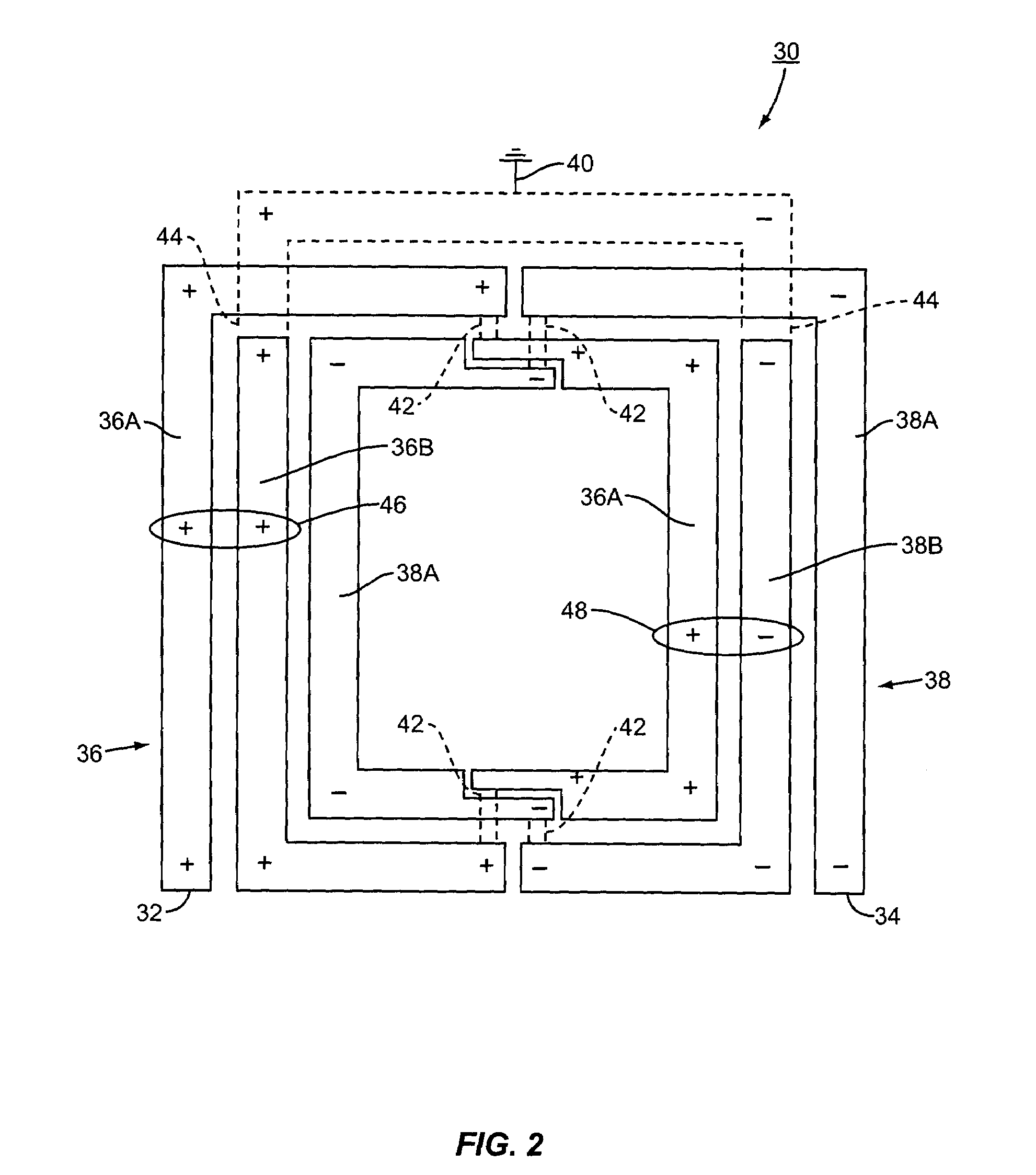

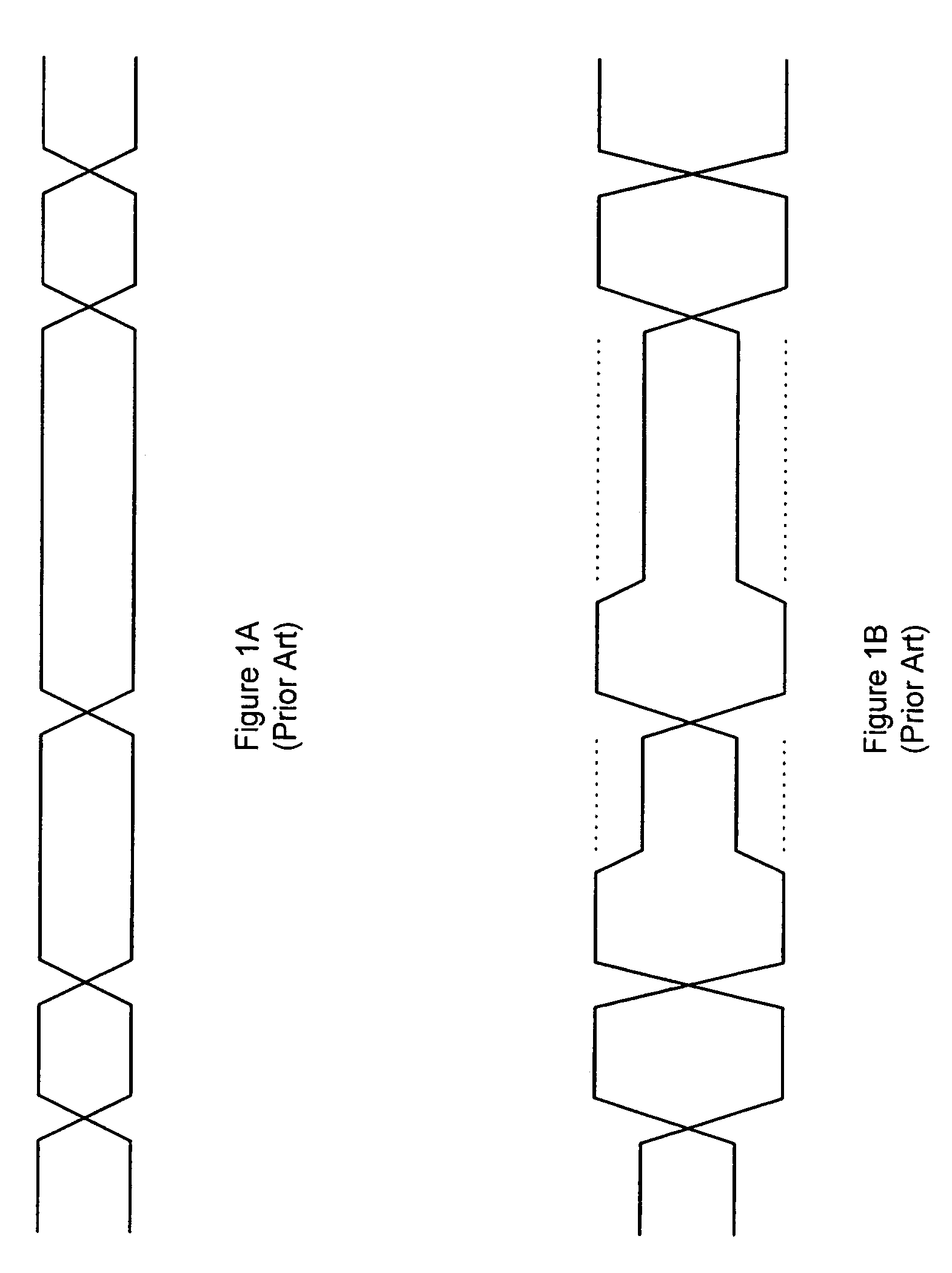

Differential inductor design for high self-resonance frequency

ActiveUS6972658B1Low effective capacitanceRaise the self-resonant frequencySemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

A differential inductor is formed from branch coils that are staggered with respect to one another rather than concentrically coiled within one another. Each coil is formed from conductive strips. The conductive strips with the largest voltage swings thereon are shielded from one another by conductive strips with lower voltage swings thereon. This shielding allows the effective capacitance of the differential inductor to be lowered, which in turn raises the range of frequencies at which the differential inductor can operate.

Owner:QORVO US INC

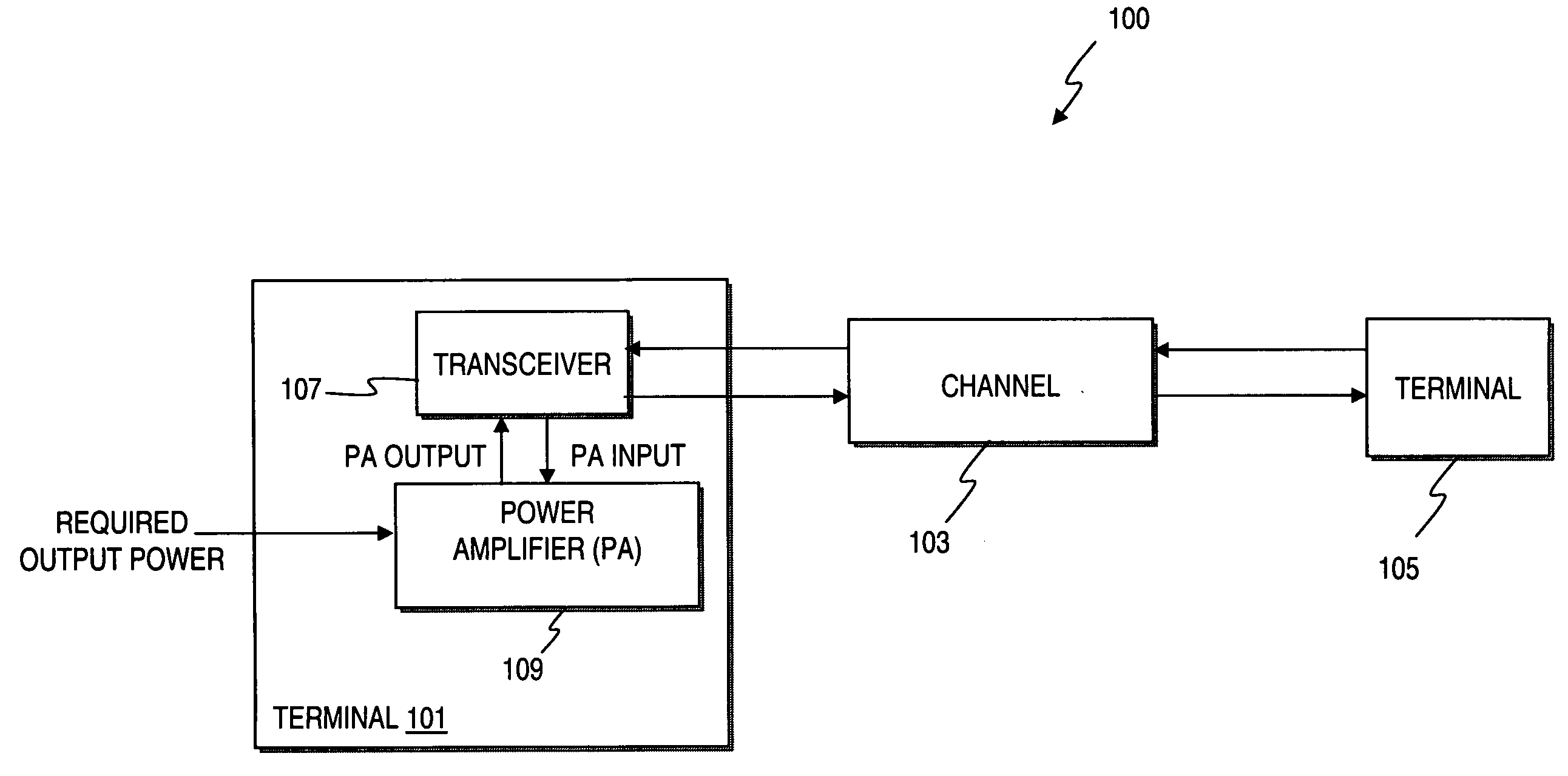

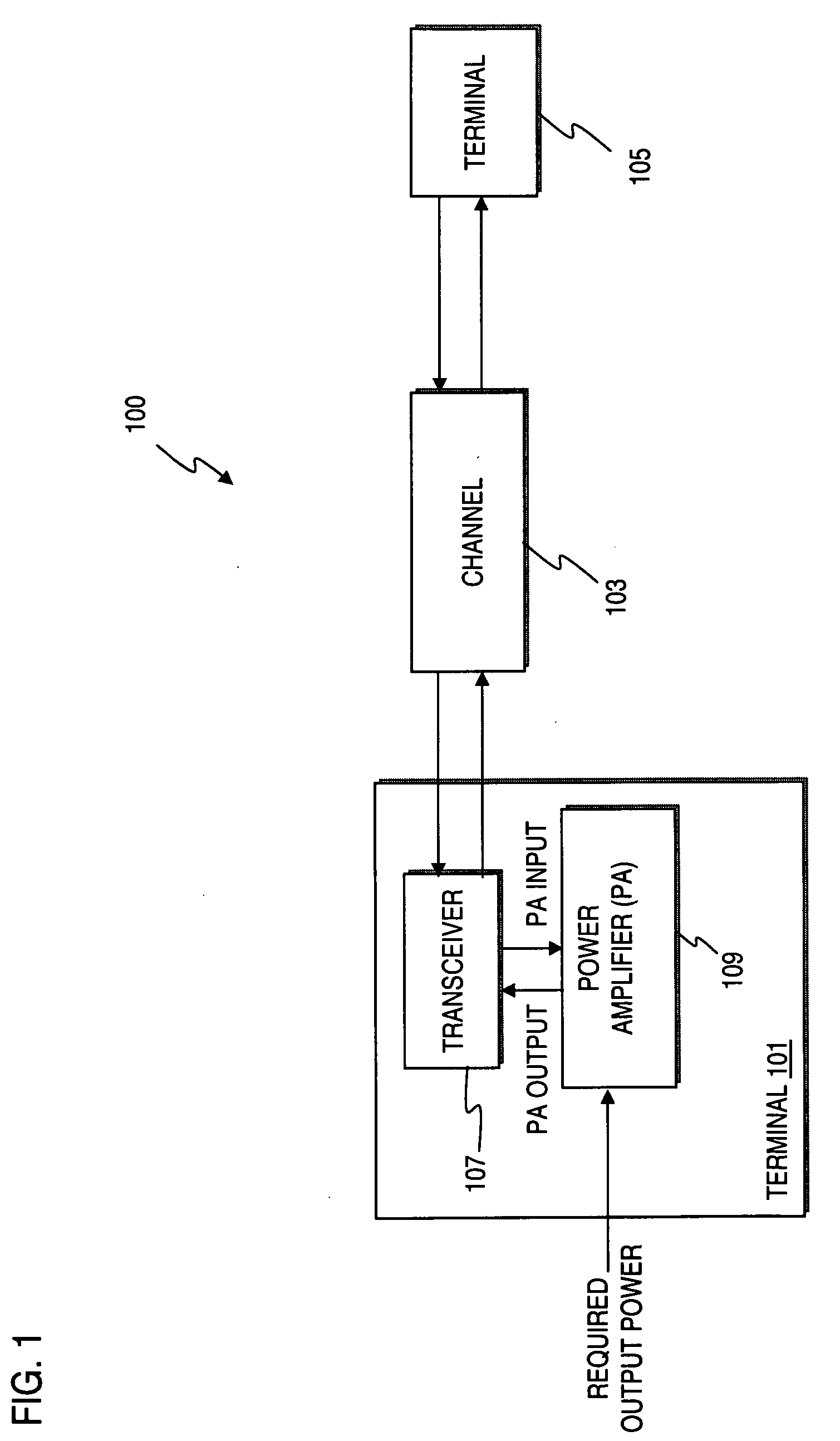

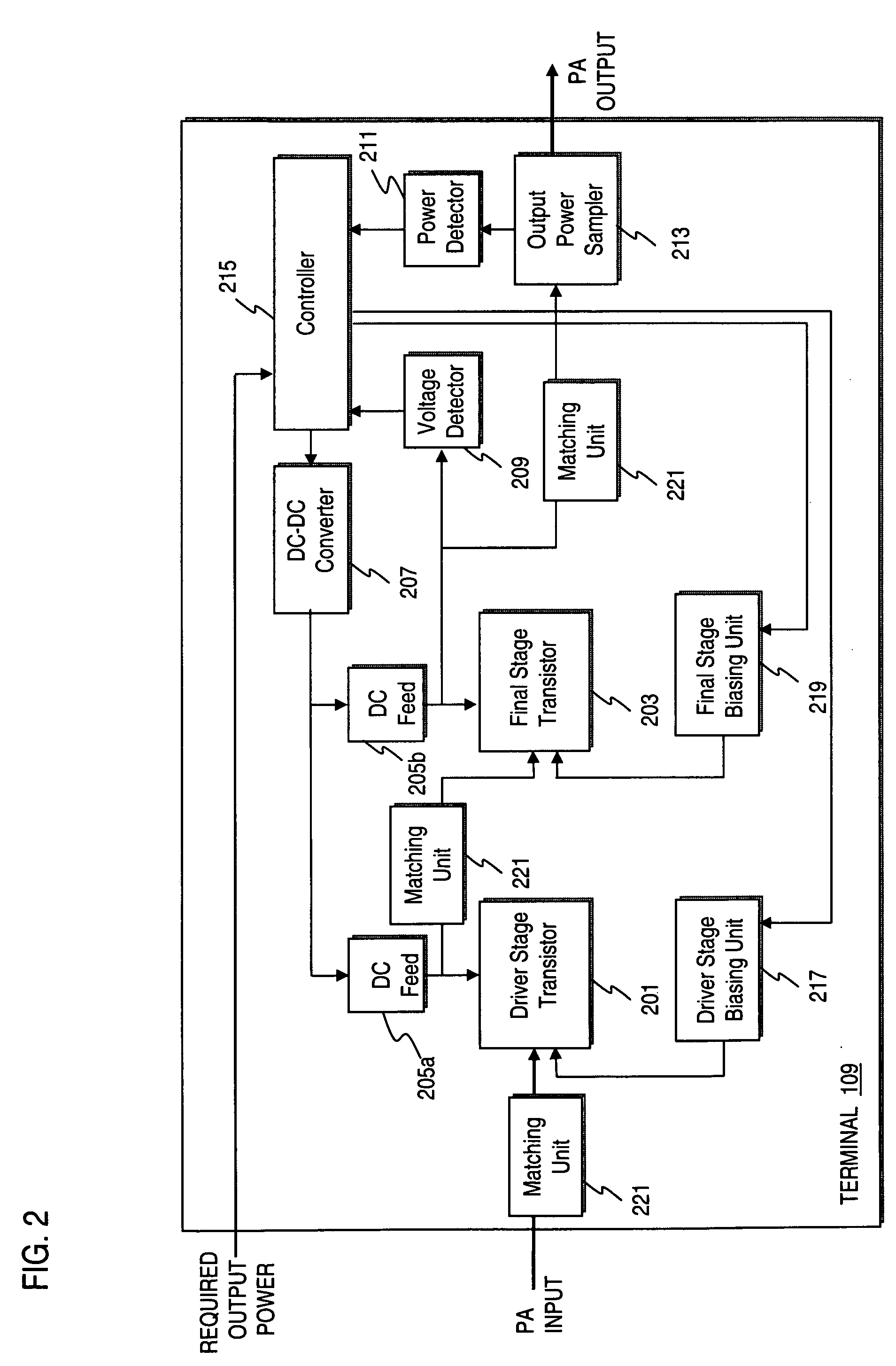

Method and apparatus for providing adaptive supply voltage control of a power amplifier

InactiveUS20080003962A1Readily apparentGain controlPower amplifiersAudio power amplifierPower detector

An approach is provided for adaptive supply voltage control of a power amplifier. A voltage detector detects a voltage swing, and a power detector detects power. A controller is coupled to the voltage detector and the power detector. The controller receives a signal specifying a required output power and determines, using the detected voltage swing and the detected power, a supply rail voltage corresponding to the required output power at a particular loading condition. A converter applies the determined supply rail voltage for generating the required output power.

Owner:NOKIA CORP

Apparatus and method for producing dummy data and output clock generator using same

InactiveUS7464282B1Improve performanceAvoid failurePulse automatic controlDigital storageDummy dataDatapath

An apparatus and method for producing dummy data is based on timing paths co-located with the address / data paths of the memory. An output clock generator uses the dummy data. The technique for producing dummy data is particularly important for memory systems in which the output of memory cells do not normally provide large voltage swings, making them less practical for self timing approaches to dummy data generation.

Owner:T RAM ASSIGNMENT FOR THE BENEFIT OF CREDITORS LLC +1

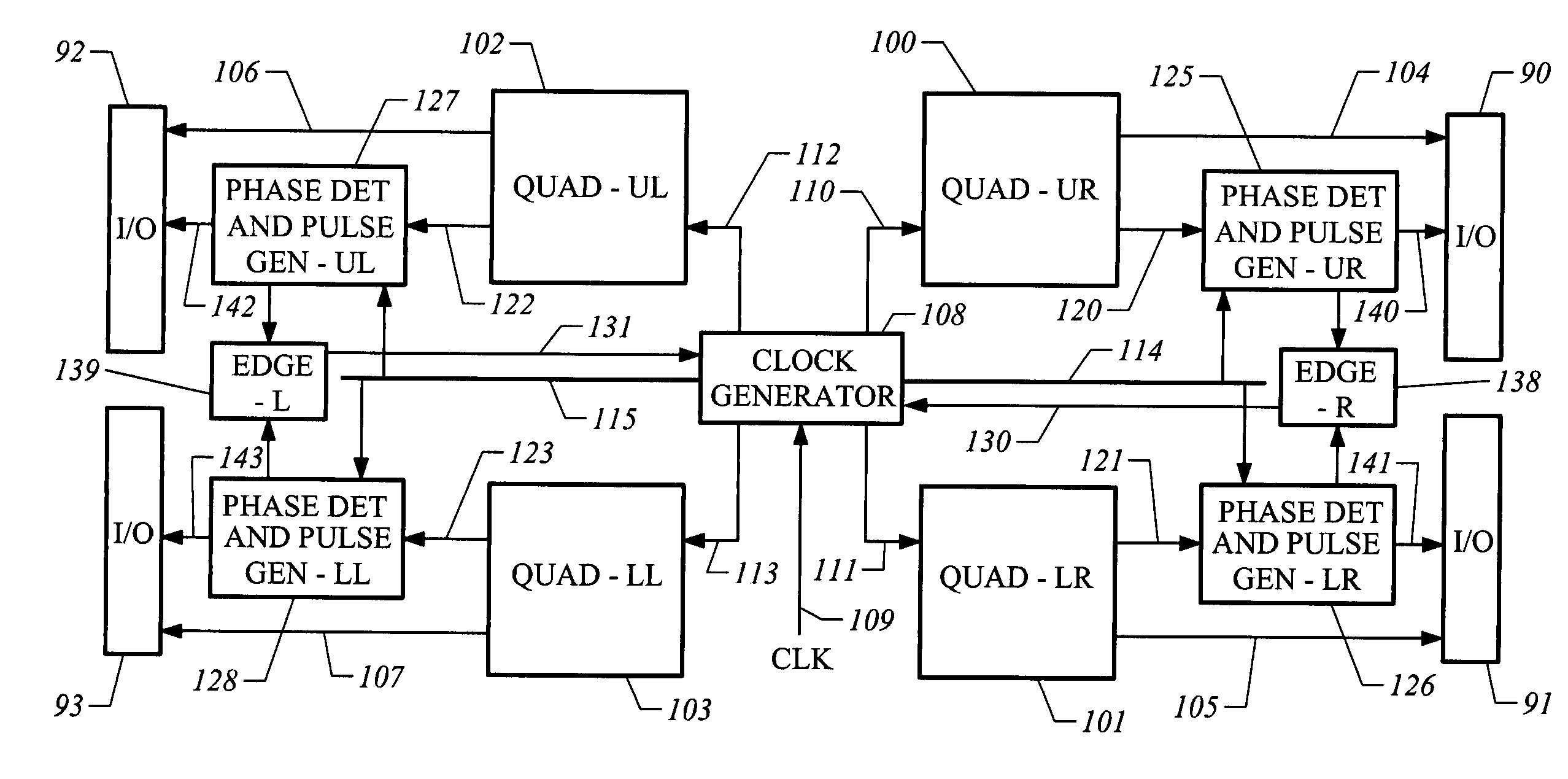

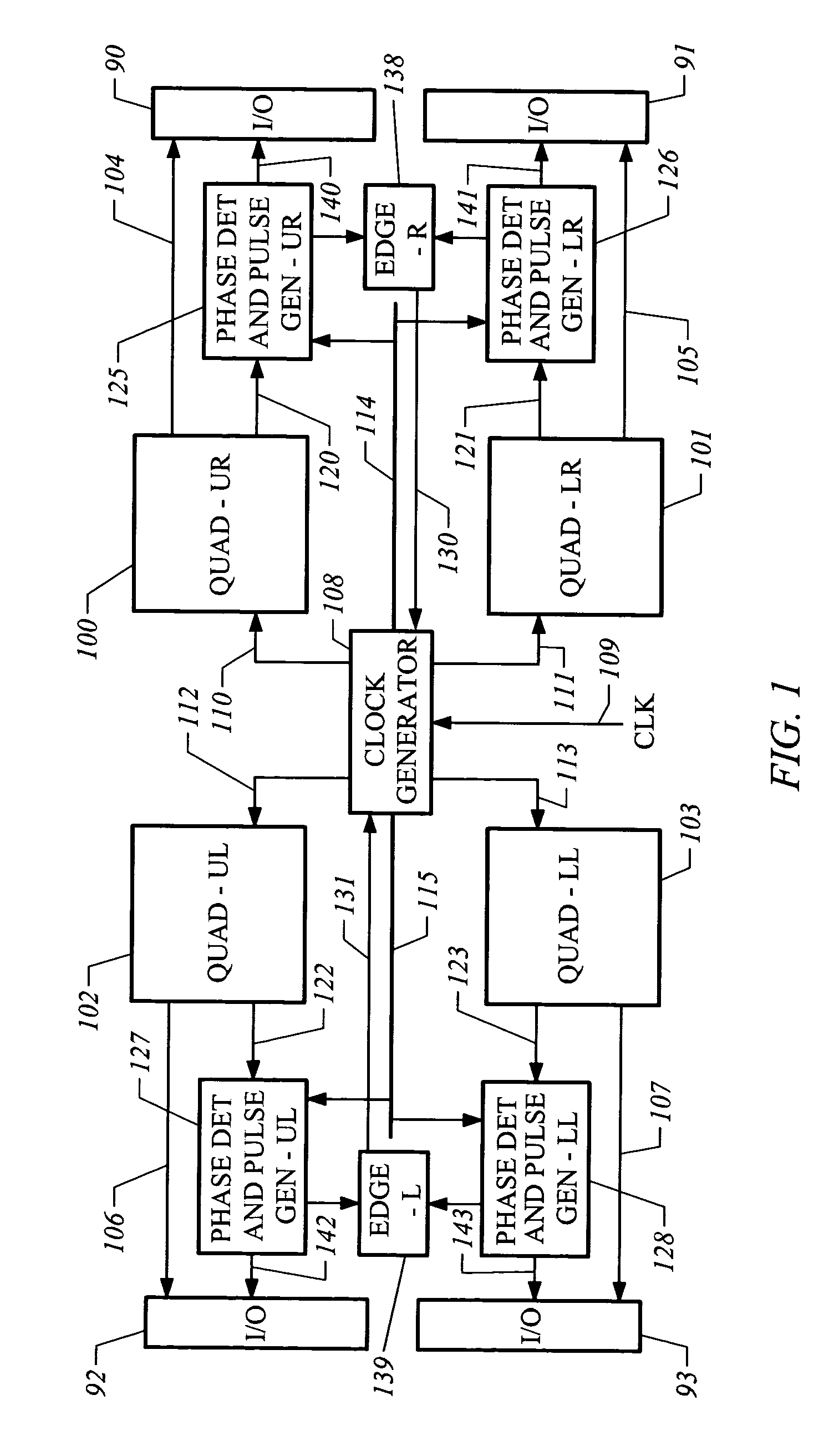

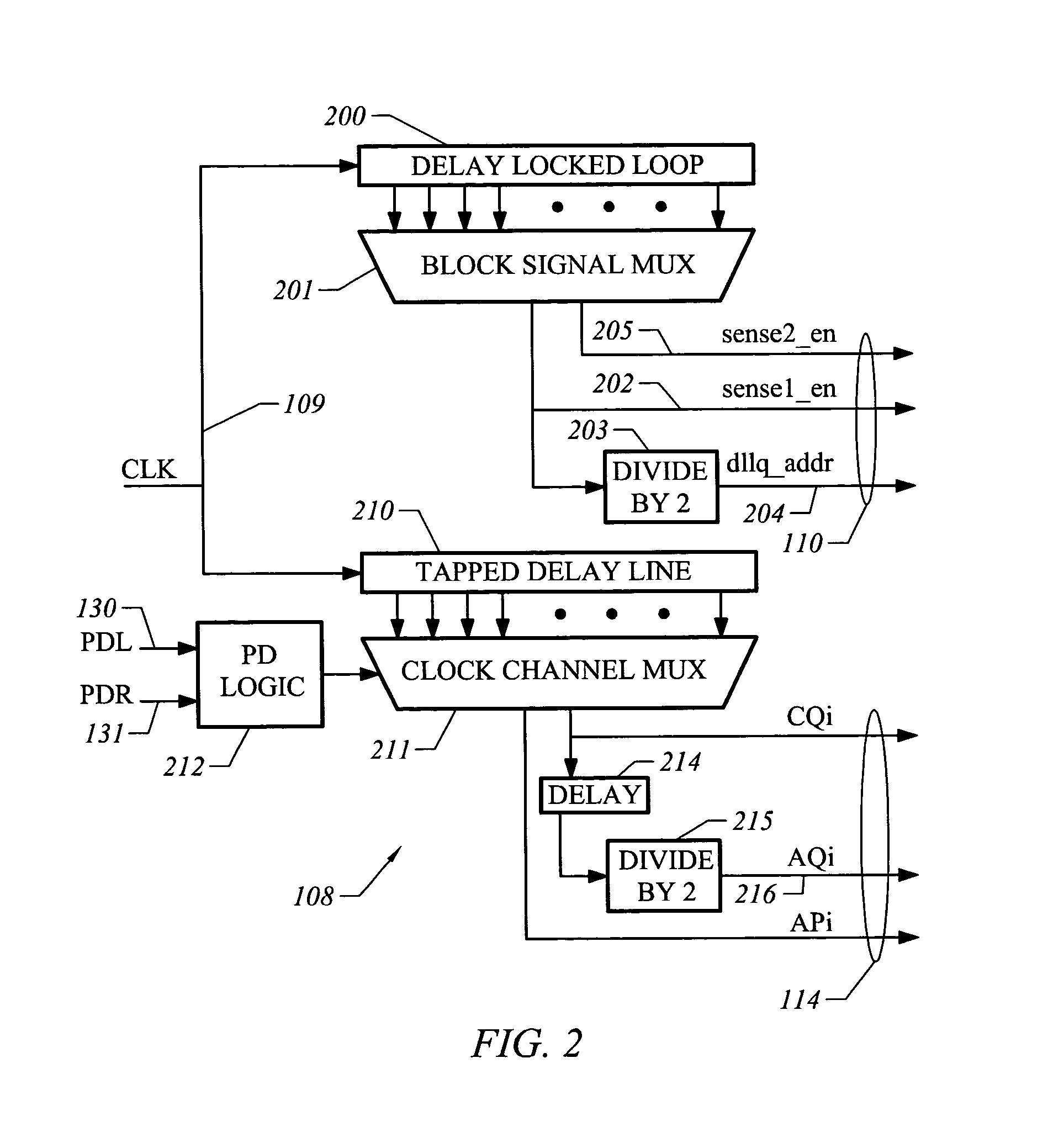

Single cycle read/write/writeback pipeline, full-wordline I/O DRAM architecture with enhanced write and single ended sensing

InactiveUS7099216B2Reduce active powerReduce noise couplingDigital storageComputer architectureAudio power amplifier

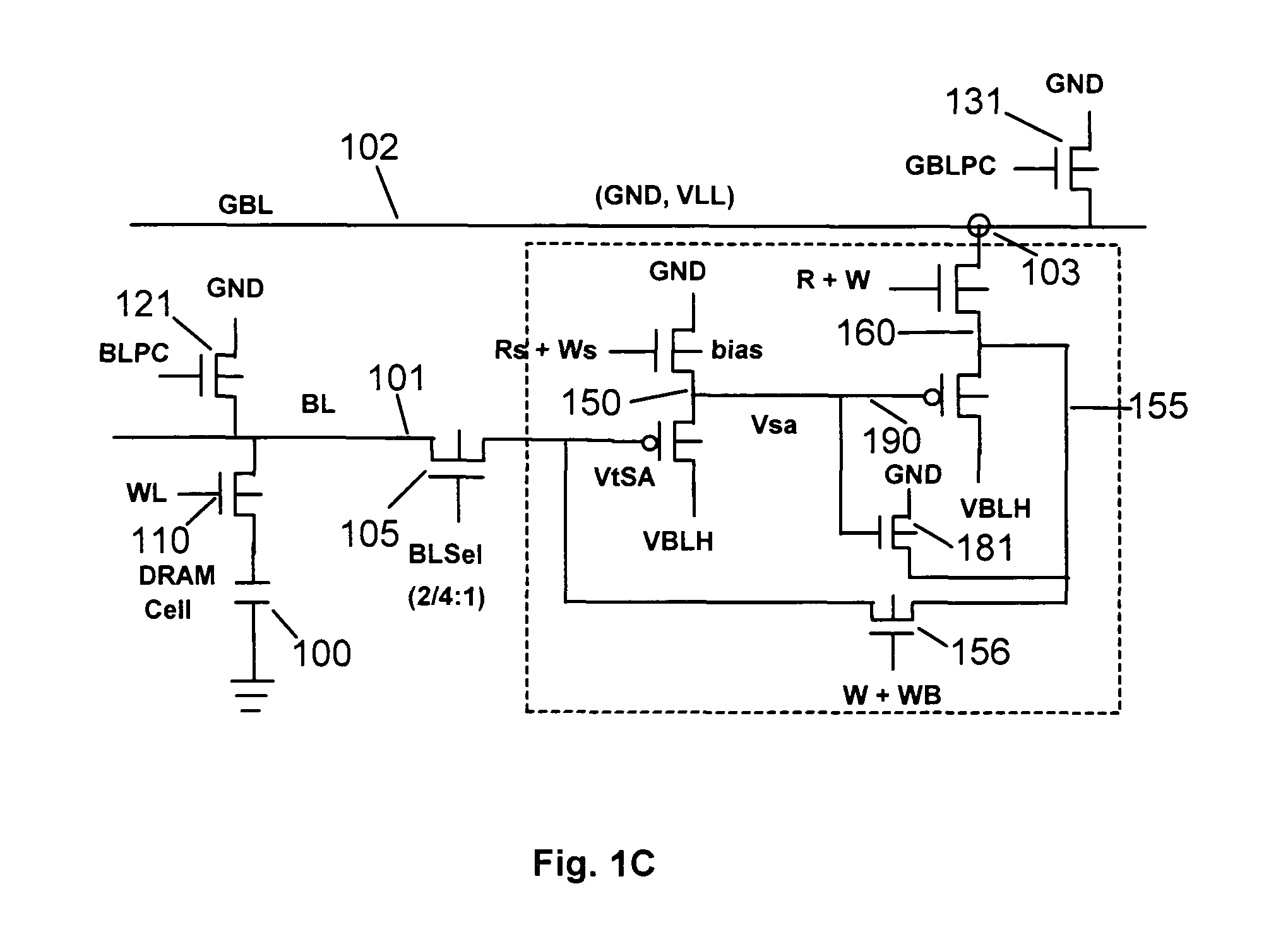

A DRAM is disclosed which includes a single ended bitline structure, a single ended global bitline structure, primary sense amplifiers with data storage and data write-back capability and with capability to decouple from the global bitlines, a full-wordline I / O structure where essentially all memory cell that belong to the same wordline are being operated on, and a pipelined architecture. The DRAM further includes a small voltage swing design. The primary sense amplifiers can include more than one amplification stages. Such a DRAM is suitable for applications in conjunction with processors as an embedded DRAM.

Owner:GLOBALFOUNDRIES INC

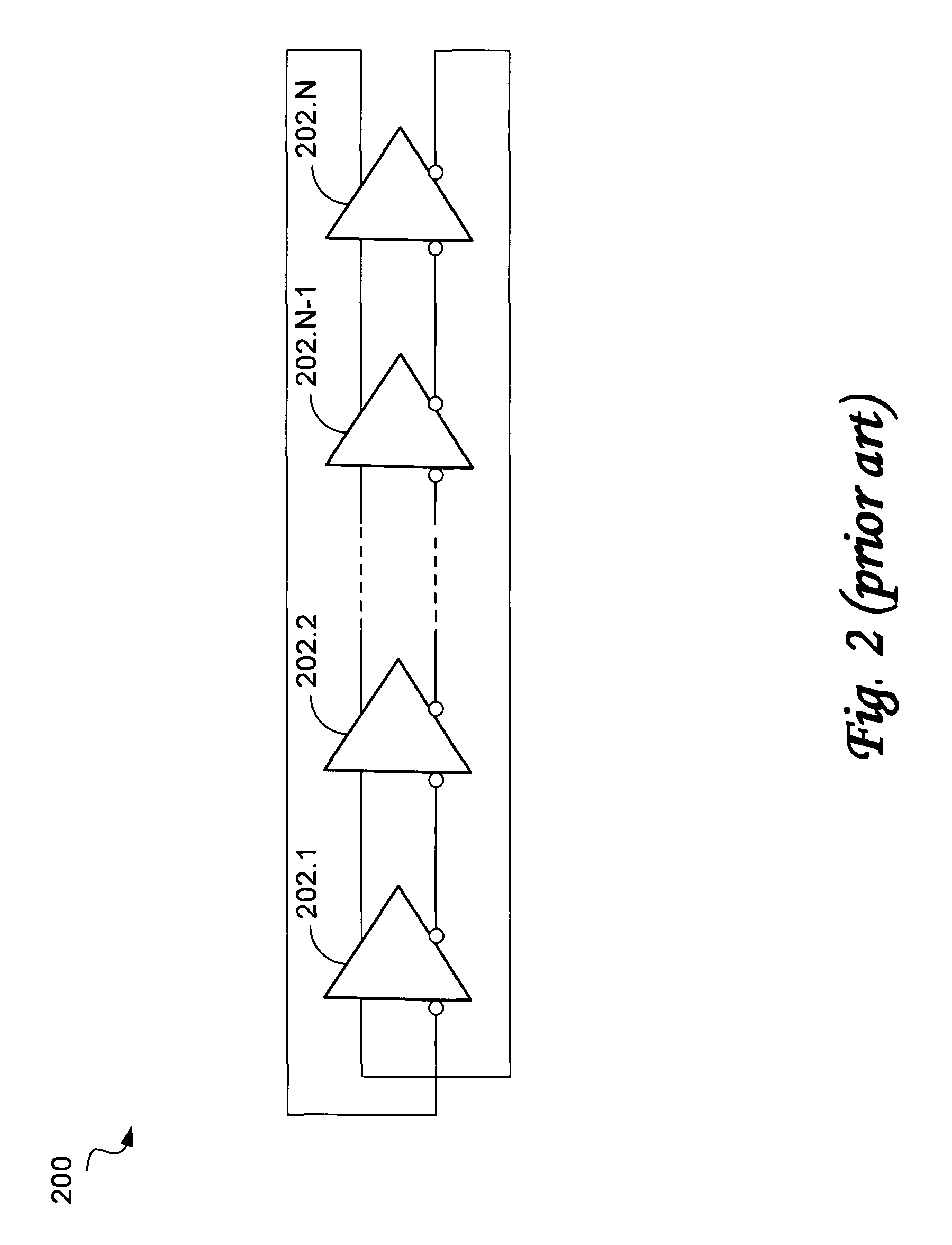

Delay stage circuitry for a ring oscillator

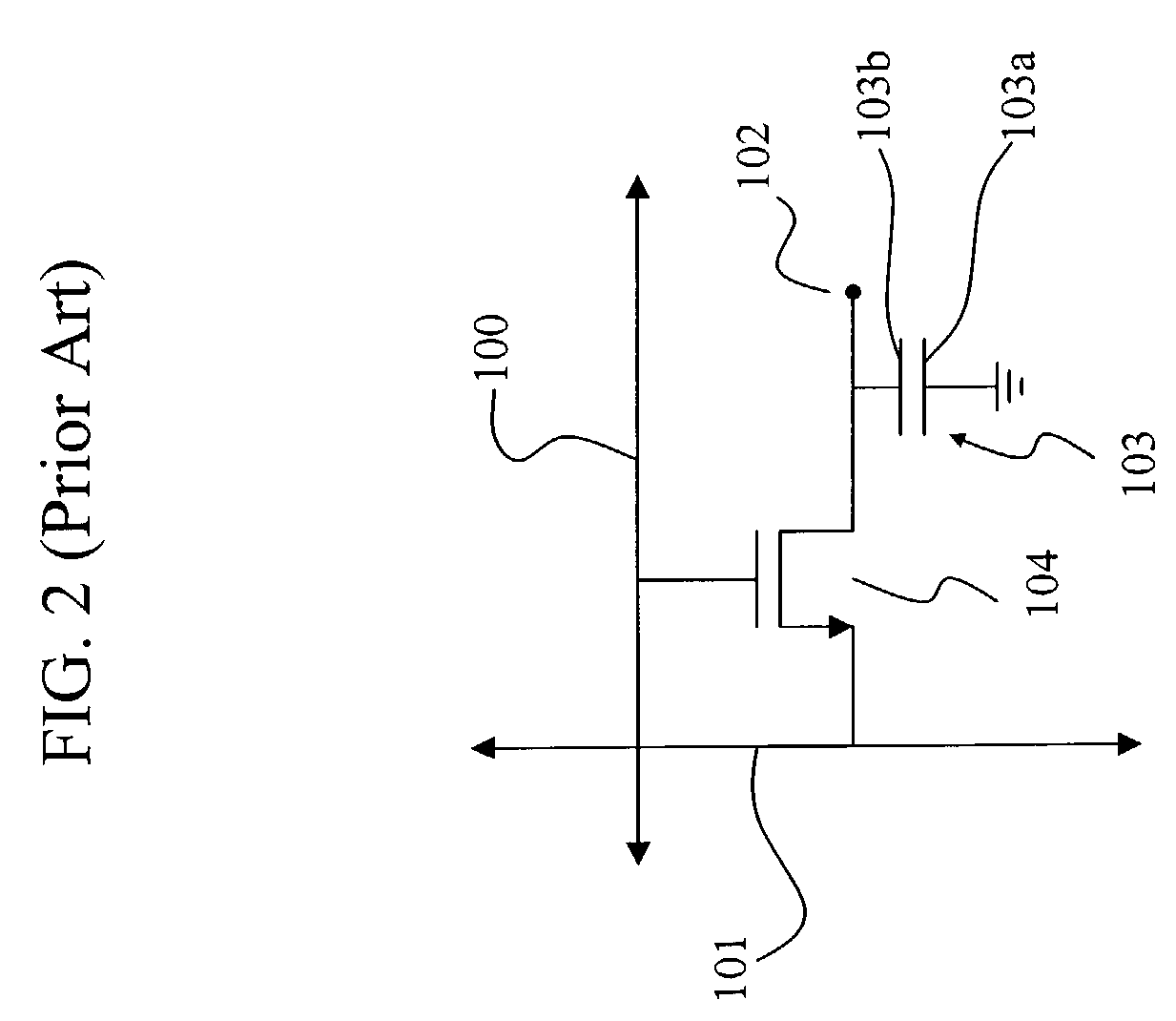

InactiveUSRE38482E1Easy to optimizePulse automatic controlTime-division multiplexEngineeringVoltage clamp

A ring oscillator includes an even-numbered plurality of ring coupled delay stages. Each delay stage includes a differential amplifier, a voltage clamping circuit, and a current source. The differential amplifier receives first and second input signals from a preceding delay stage. The differential amplifier provides a first output signal and a complementary second output signal at first and second nodes, respectively. The voltage clamping circuit is coupled between the first and second nodes to limit a peak-to-peak voltage swing of each of the first and second output signals. The current source is coupled to the differential amplifier and varies a bias current in accordance with a delay bias voltage.

Owner:RAMBUS INC

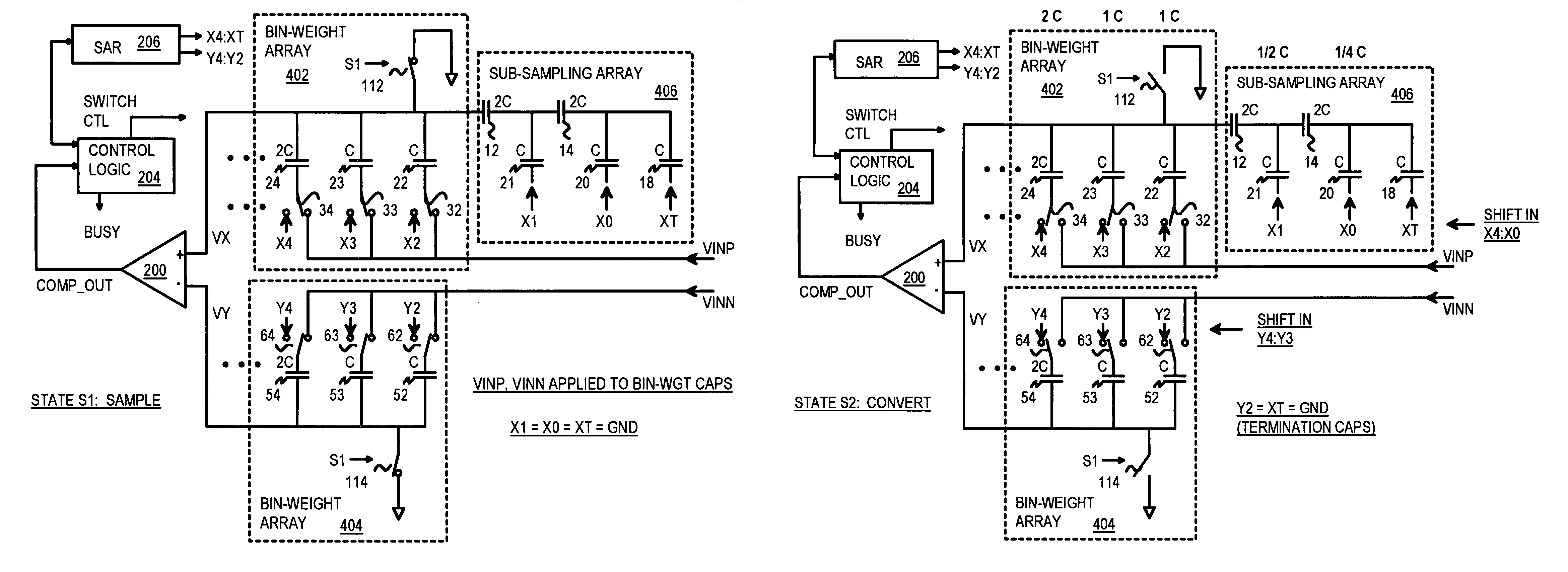

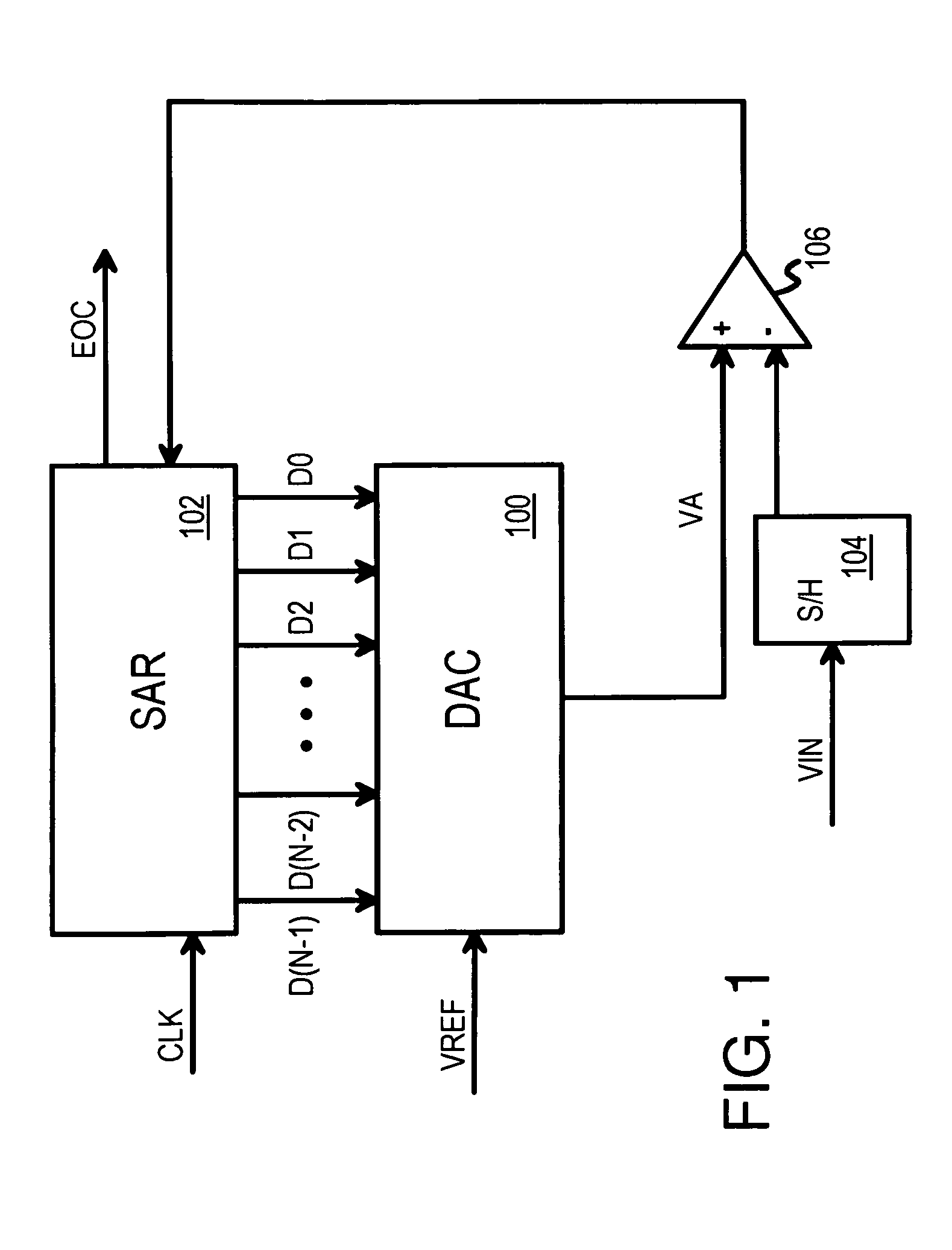

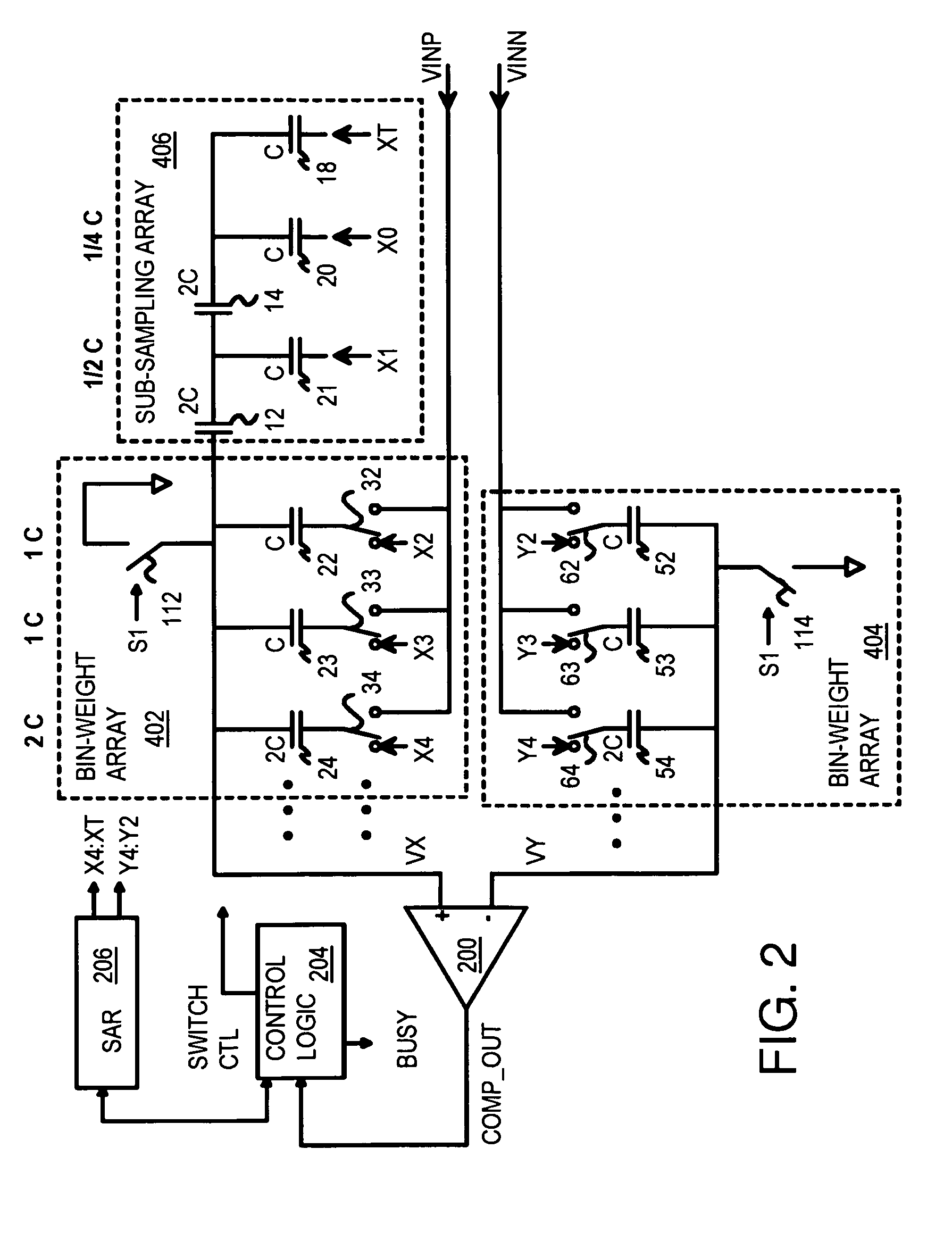

Hybrid analog-to-digital converter (ADC) with binary-weighted-capacitor sampling array and a sub-sampling charge-redistributing array for sub-voltage generation

InactiveUS7812757B1Electric signal transmission systemsAnalogue-digital convertersCapacitanceCoupling

A hybrid Analog-to-Digital Converter (ADC) has a binary-weighted capacitor array and a sub-voltage capacitor array that are coupled together by a coupling capacitor. The sub-voltage capacitor array uses a minimum capacitor size that matches the minimum capacitor size of the binary-weighted capacitor array. The coupling capacitor is double the minimum size and reduces a voltage effect on a charge sharing line by half. Second coupling capacitors in the sub-voltage capacitor array each reduce the voltage effect by half, so that first, second, and third sub-voltage capacitors in the sub-voltage capacitor array produce ½, ¼, and ⅛ voltage swings using the minimum size capacitance. Only MSB capacitors in the binary-weighted capacitor array sample the analog input voltage. During conversion, MSB's from a Successive-Approximation-Register (SAR) are applied to binary-weighted capacitors while LSB's are applied to sub-voltage capacitors. The total capacitance is reduced by applying the LSB's only to the sub-voltage capacitor array.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Transmit based equalization using a voltage mode driver

A driver circuit. In one embodiment, the driver circuit includes a plurality of pull-up circuits and a plurality of pull-down circuits. The driver circuit also includes control logic that is coupled to activate / deactivate the pull-up and pull-down circuits. The driver circuit may perform emphasized signal transmissions having a voltage swing of a first magnitude or de-emphasized signal transmissions having a voltage swing of a second magnitude, wherein the first magnitude is greater than the second magnitude. The control logic is further configured to activate and / or deactivate pull-up and / or pull-down circuits such that the driver circuit output impedance in the emphasized mode is substantially equal to the output impedance in the de-emphasized mode.

Owner:ADVANCED MICRO DEVICES INC

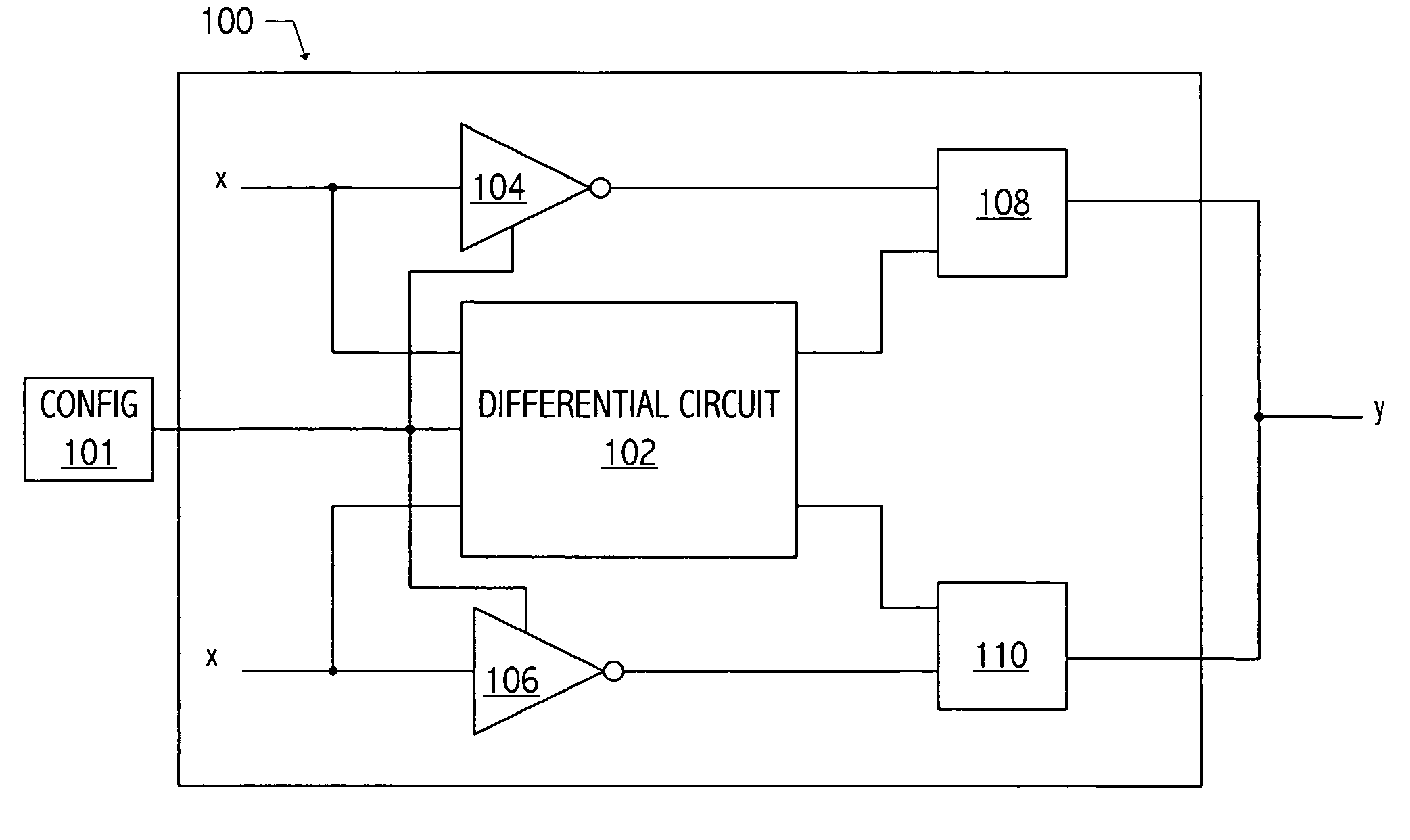

Multiple signal format output buffer

ActiveUS20050285629A1Reduce duplicationReduce needLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsSnubberIntegrated circuit

An output buffer circuit drives multiple signal formats. The output buffer circuit reduces duplication of output bond pads on an integrated circuit die. The output buffer circuit reduces a need for including conversion buffers on system boards. A single integrated circuit including the output buffer circuit may meet a variety of applications. The output buffer achieves these results with a programmable output voltage swing and a programmable output common mode voltage. In some embodiments of the present invention, an integrated circuit includes at least one single-ended buffer and at least one differential circuit coupled to a pair of outputs. One of the single-ended buffer and the differential circuit is selectively enabled to provide a signal to the outputs.

Owner:SKYWORKS SOLUTIONS INC

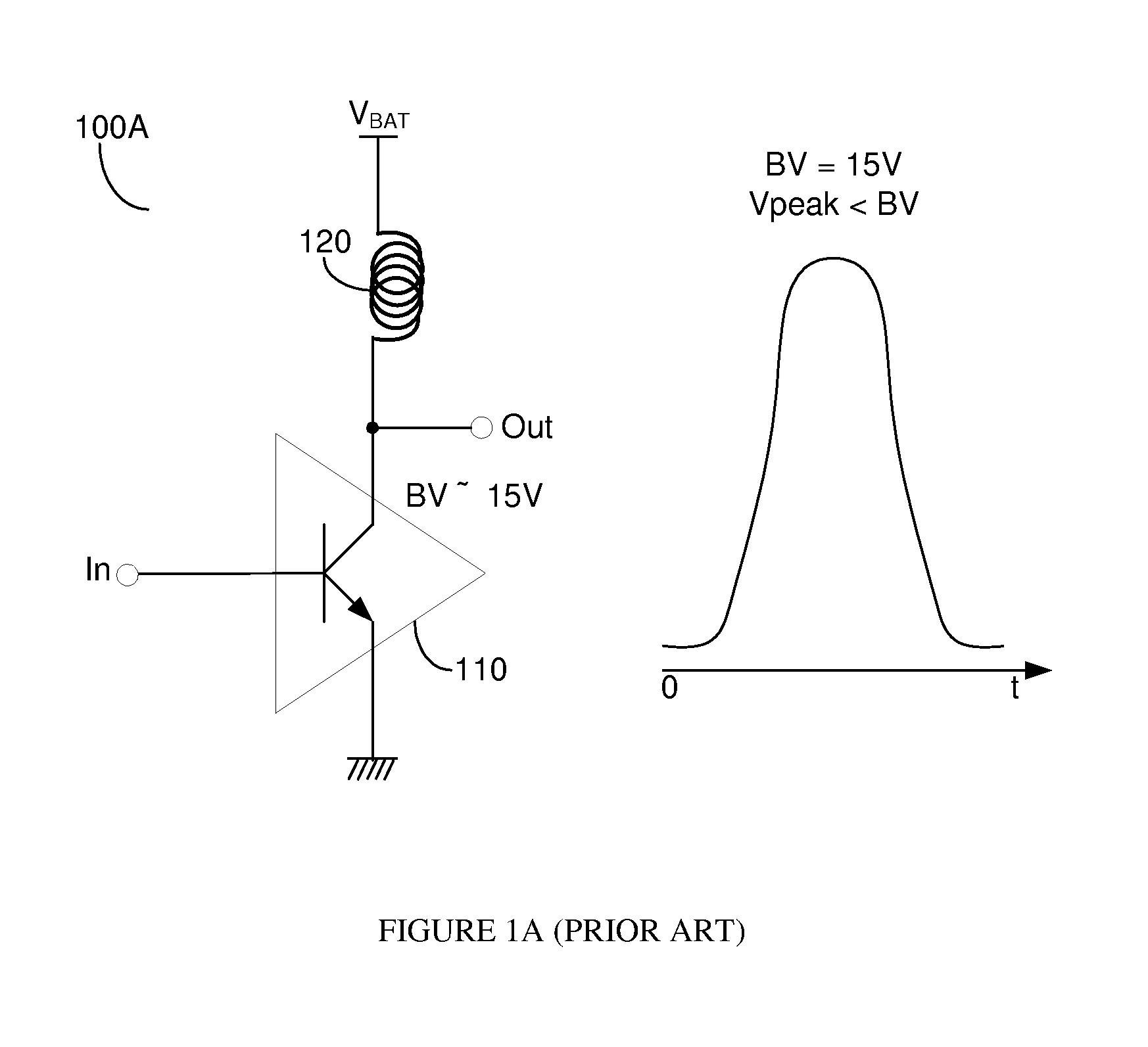

Output Stage of a Power Amplifier Having a Switched-Bulk Biasing and Adaptive Biasing

ActiveUS20120139643A1High frequency amplifiersAmplifier modifications to reduce detrimental impedenceAudio power amplifierSelf adaptive

A power amplifier (PA) using switched-bulk biasing to minimize the risk of output stage snapback effect is disclosed. An adaptive biasing of the output stage prevents device breakdown while accommodating large voltage swings. These protection techniques can be applied to all types of cascode configurations of a PA, including single-ended, differential, quadrature, segmented and any combination thereto.

Owner:QORVO INT PTE LTD

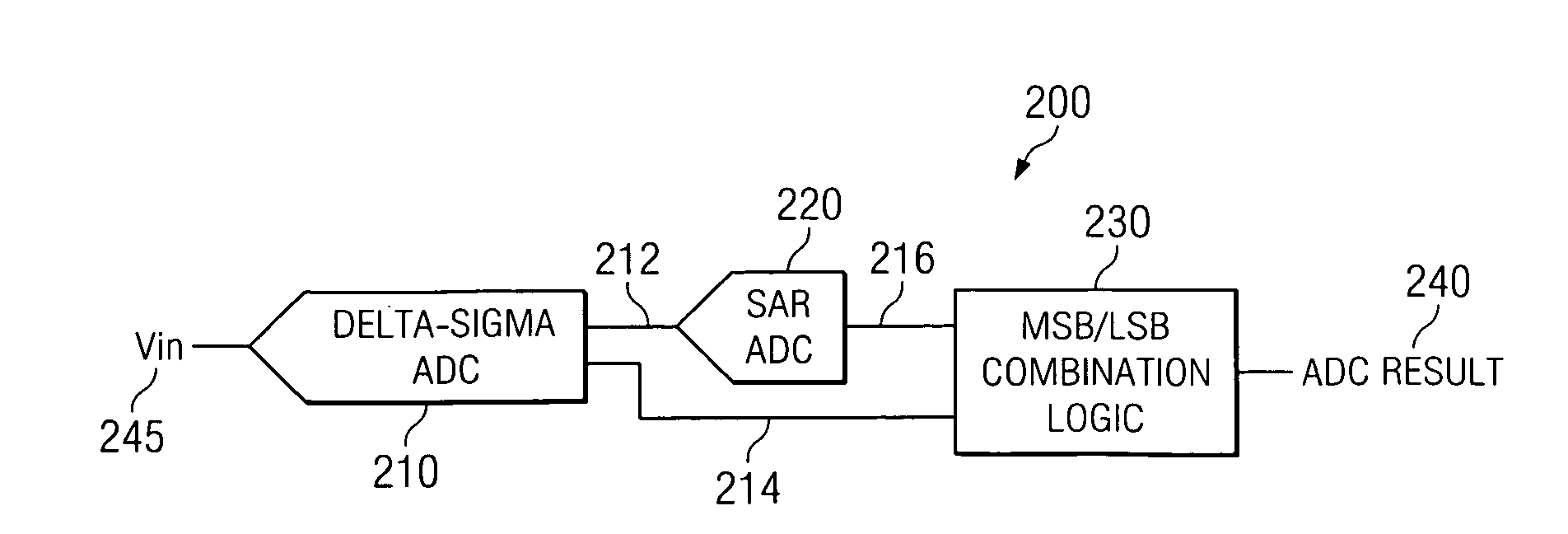

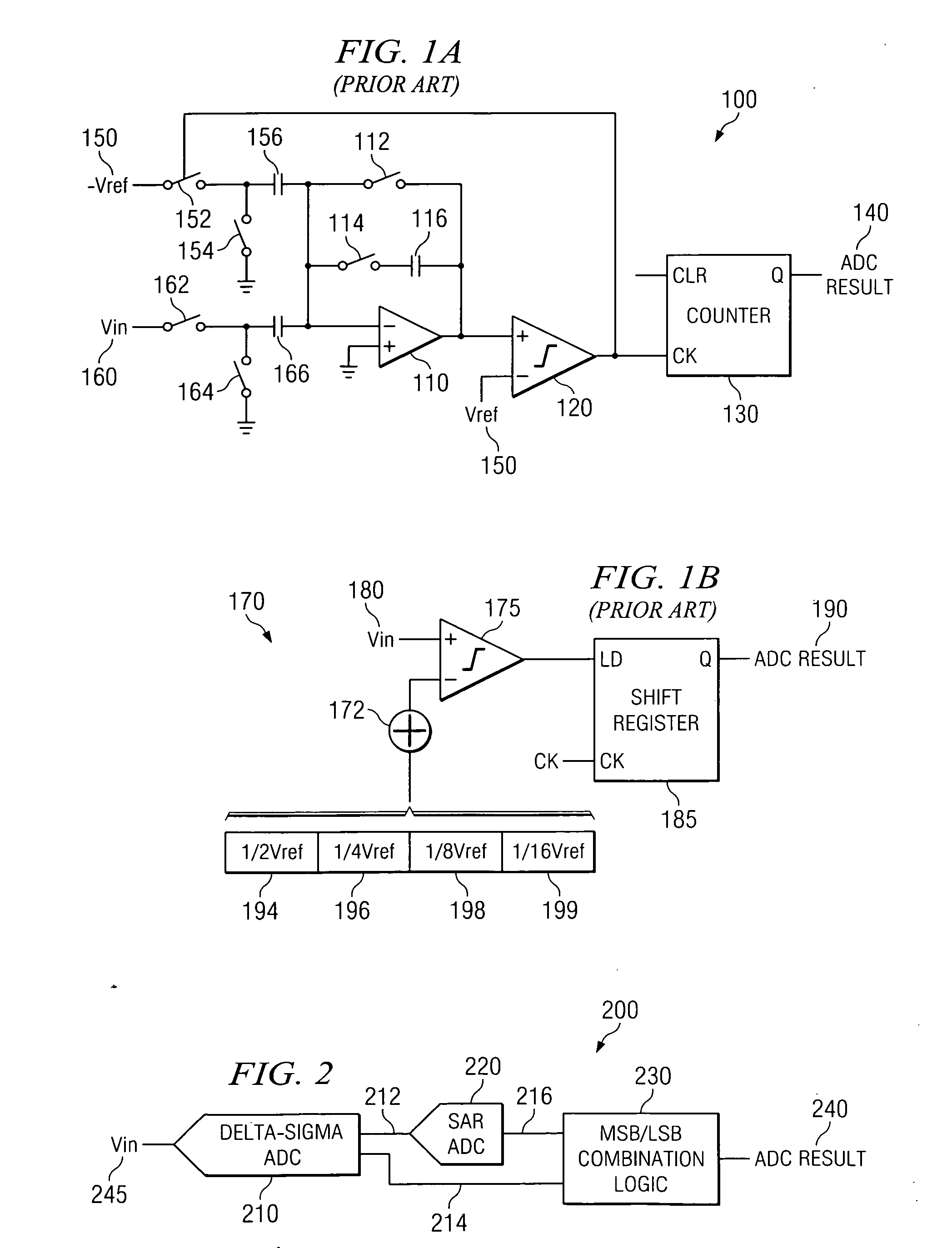

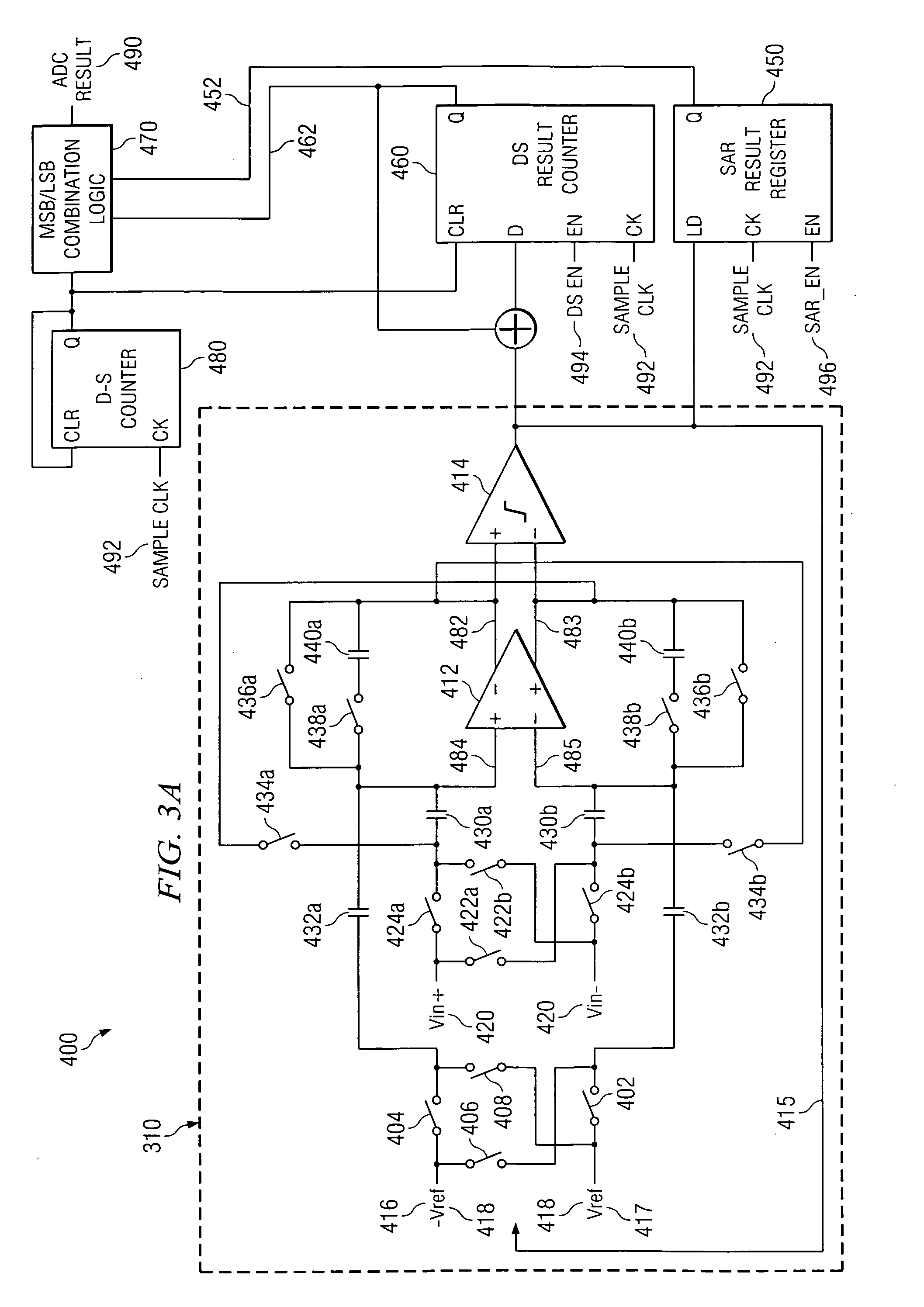

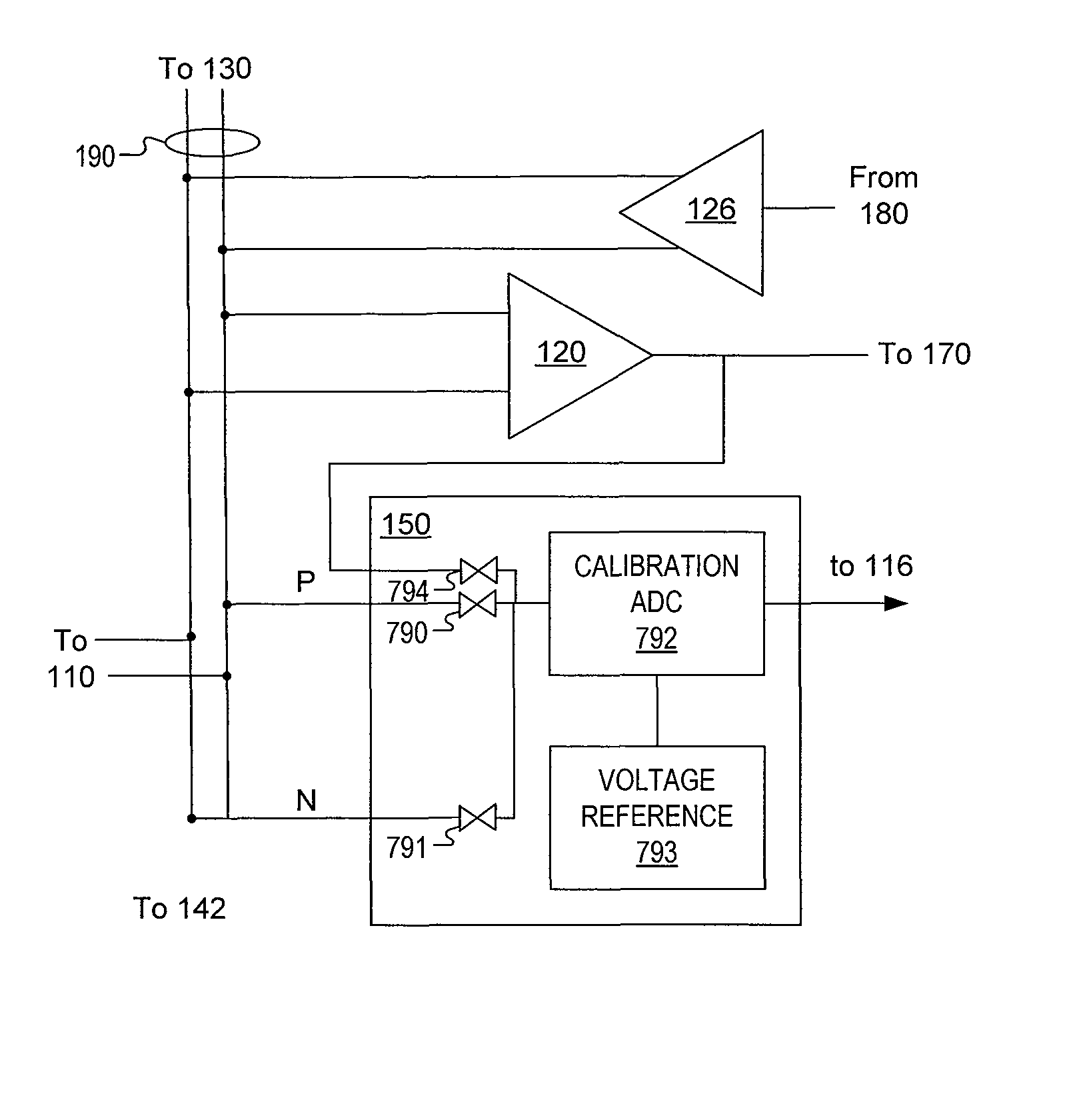

Integrating/SAR ADC and method with low integrator swing and low complexity

ActiveUS20080258959A1Reduce the amount of solutionReduce voltageElectric signal transmission systemsAnalogue conversionIntegratorGreek letter sigma

A reconfigurable circuit (10) includes an integrator (30) having switches (SW1-6) for selectively coupling input capacitors (C0,1,2,3,6,7) and integrating capacitors (C4,5) to terminals of the integrator (30) for operation of a hybrid delta-sigma / SAR ADC (400) so as to create a reference voltage value (Vref) equal to the sum of a first voltage (ΔVbe) and a second voltage (Vbe). A first integration is performed to reduce the integrator output voltage swing. A residue (Vresidue) of the integrator is multiplied by 2. Then the second voltage (Vbe) is integrated in a first direction if a comparator (22) coupled to the integrator changes state or in an opposite direction if the comparator does not change state. The first voltage (ΔVbe) is integrated in a direction that causes the integrator output voltage (Vout) to equal either 2×Vresidue−Vref or 2×Vresidue+Vref.

Owner:TEXAS INSTR INC

DC/DC-less coupling of matched batteries to fuel cells

ActiveUS20060238033A1Eliminate needDc network circuit arrangementsBatteries circuit arrangementsBattery state of chargeEngineering

A fuel cell system that employs a matched battery that matches the battery voltage to a fuel cell power bus voltage so as to eliminate the need for a DC / DC converter. The internal characteristics and parameters of the matched battery allow it to operate over the large load dependent voltage swing of the fuel cell, and prevent the battery state of charge from going below a damaging value. The battery type, number of battery cells and the battery internal impedance are selected to provide the desired matching. In one embodiment, the battery is a lithium ion battery. The system also includes a diode electrically coupled to the power bus line and a by-pass switch electrically coupled to the power bus line in parallel with the diode. The by-pass switch is selectively opened or closed to allow the fuel cell stack to recharge the battery and prevent the battery from being overcharged.

Owner:GM GLOBAL TECH OPERATIONS LLC

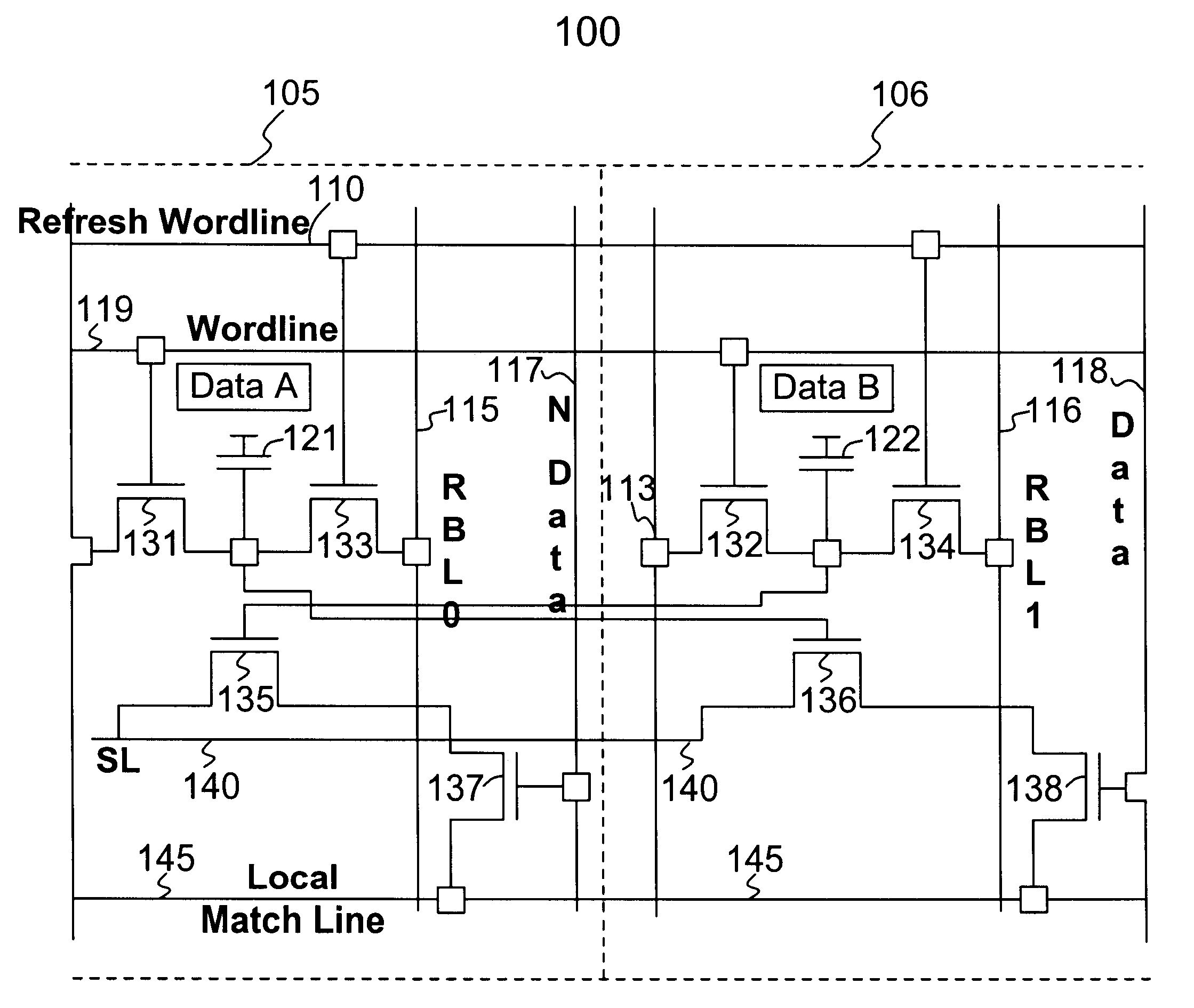

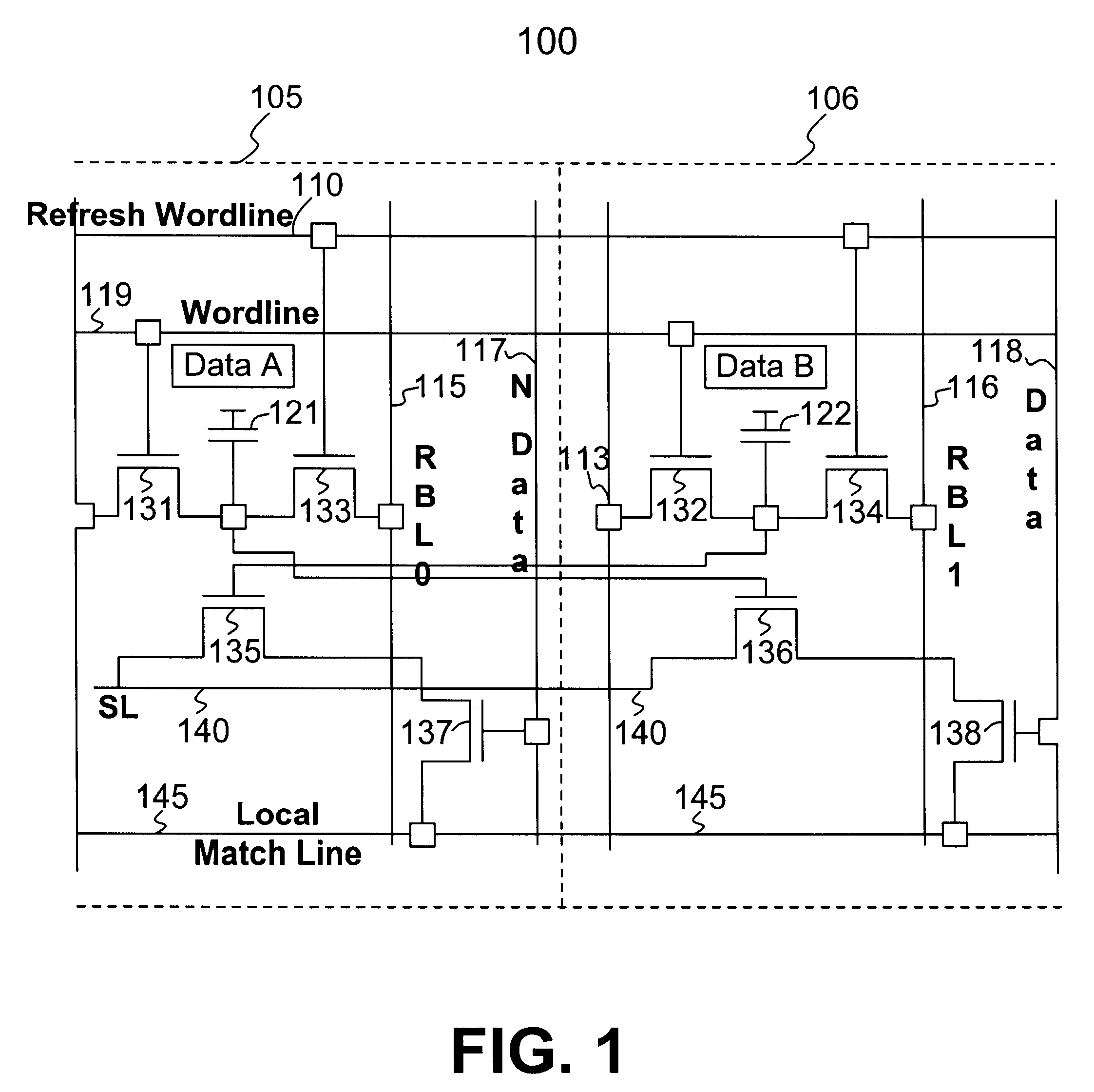

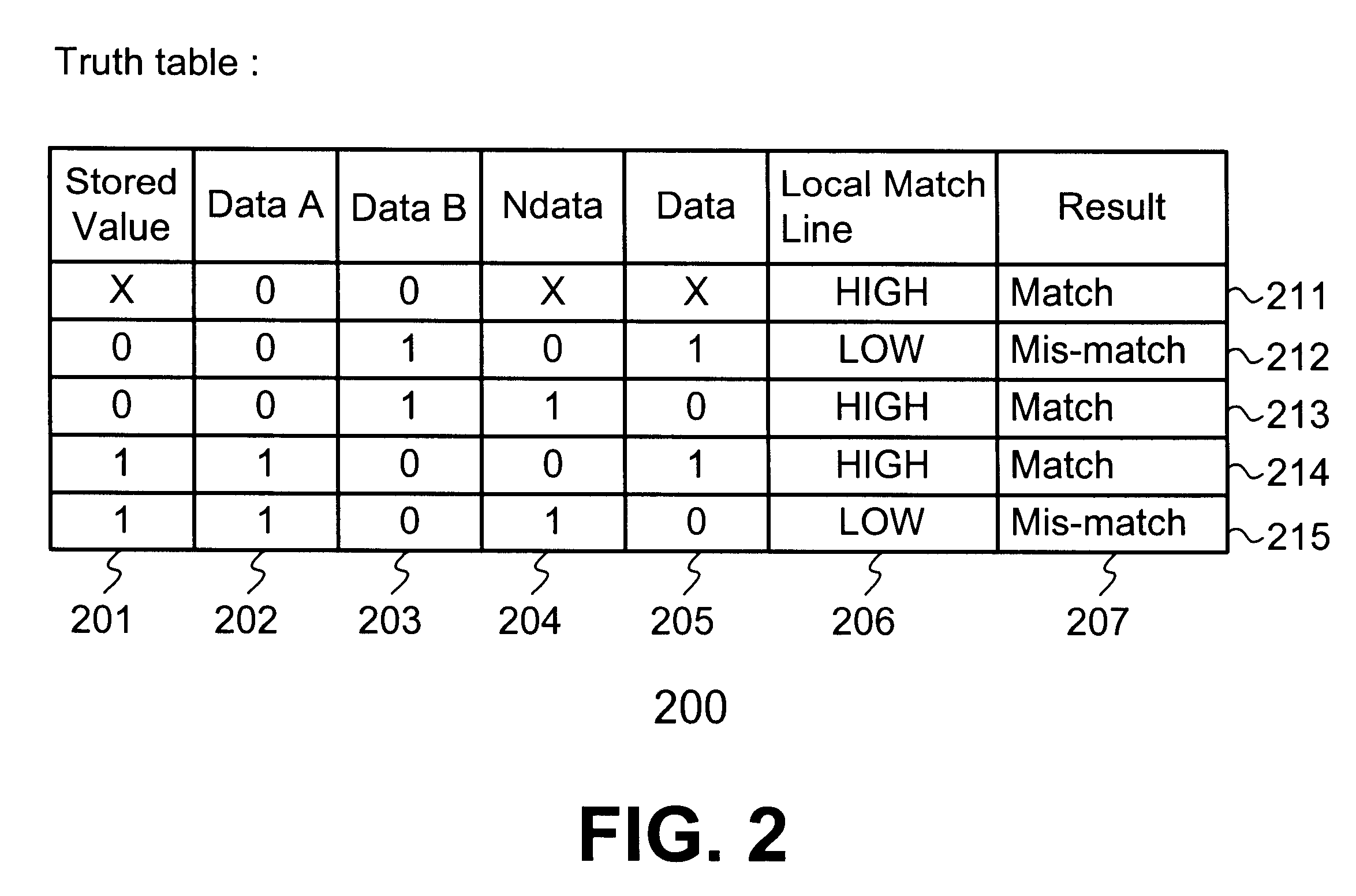

DRAM based refresh-free ternary CAM

A ternary state content addressable memory (CAM) cell that includes two DRAM cells. In addition to a port for controlling and transmitting data to the CAM, another port is exclusively used for refreshing the DRAM cells. A refresh word line is coupled to the two DRAM cells for performing DRAW cell refresh. A refresh bit line is coupled to the first of the two DRAM cells for refreshing this first DRAM cell. A refresh bit line is coupled to the second of the two DRAM cells for refreshing this second DRAM cell. Problematic power consumption and voltage swing found in a conventional CAM are overcome in the CAM. A swing line (SL) is coupled to said first and second DRAM cells and a local match line (LML) of said CAM cell, said SL having an adjustable voltage level for changing voltage swing in said LML to regulate trade-off between power consumption and speed of said CAM cell.

Owner:ATEL VENTURE FUND LLC

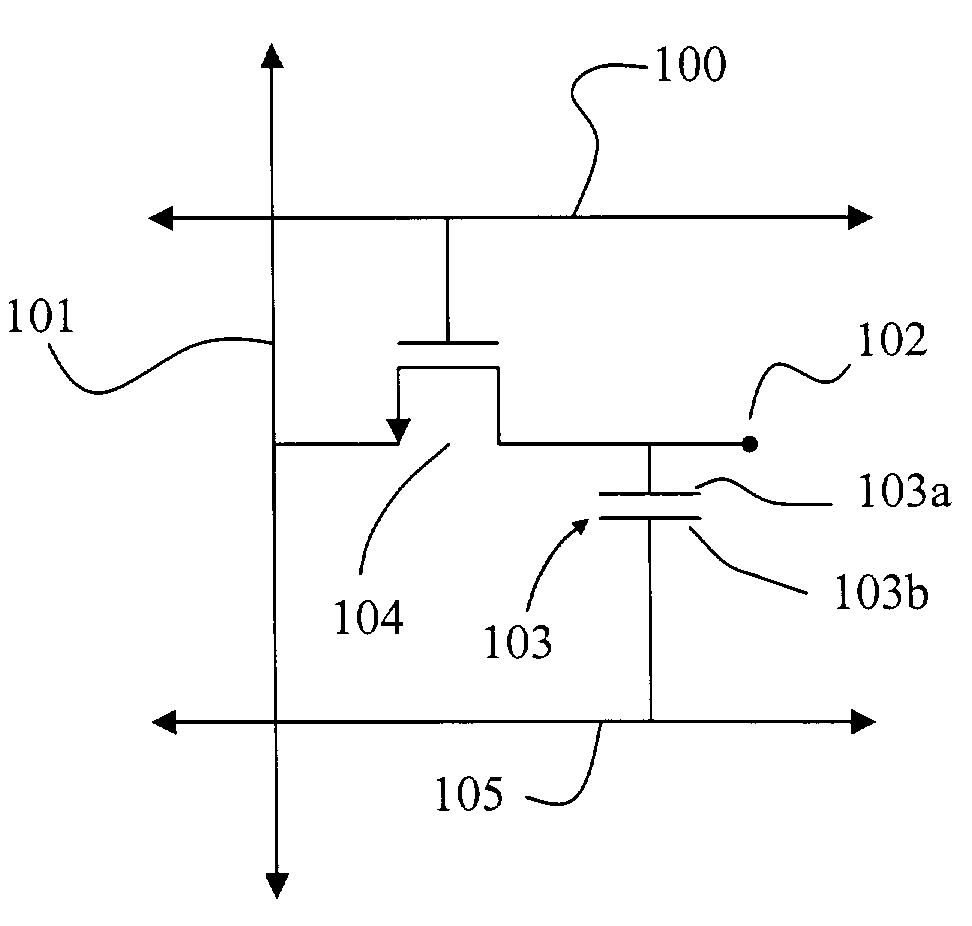

Spatial light modulator with charge-pump pixel cell

ActiveUS7012592B2Output voltage swing (Reduce areaSemiconductor/solid-state device manufacturingCathode-ray tube indicatorsSpatial light modulatorEngineering

A voltage storage cell circuit includes an access transistor and a storage capacitor, wherein the source of said access transistor is connected to a bitline, the gate of said access transistor is connected to a wordline, and wherein the drain of said access transistor is connected to a first plate of said storage capacitor forming a storage node, and wherein the second plate of said storage capacitor is connected to a pump signal. This arrangement allows for a novel pixel circuit design with area requirements comparable to that of a 1T1C DRAM-like pixel cell, but with the advantage of an output voltage swing of the full range allowed by the breakdown voltage of the pass transistor. A spatial light modulator such as a micromirror array can comprise such a voltage storage cell.

Owner:TEXAS INSTR INC +1

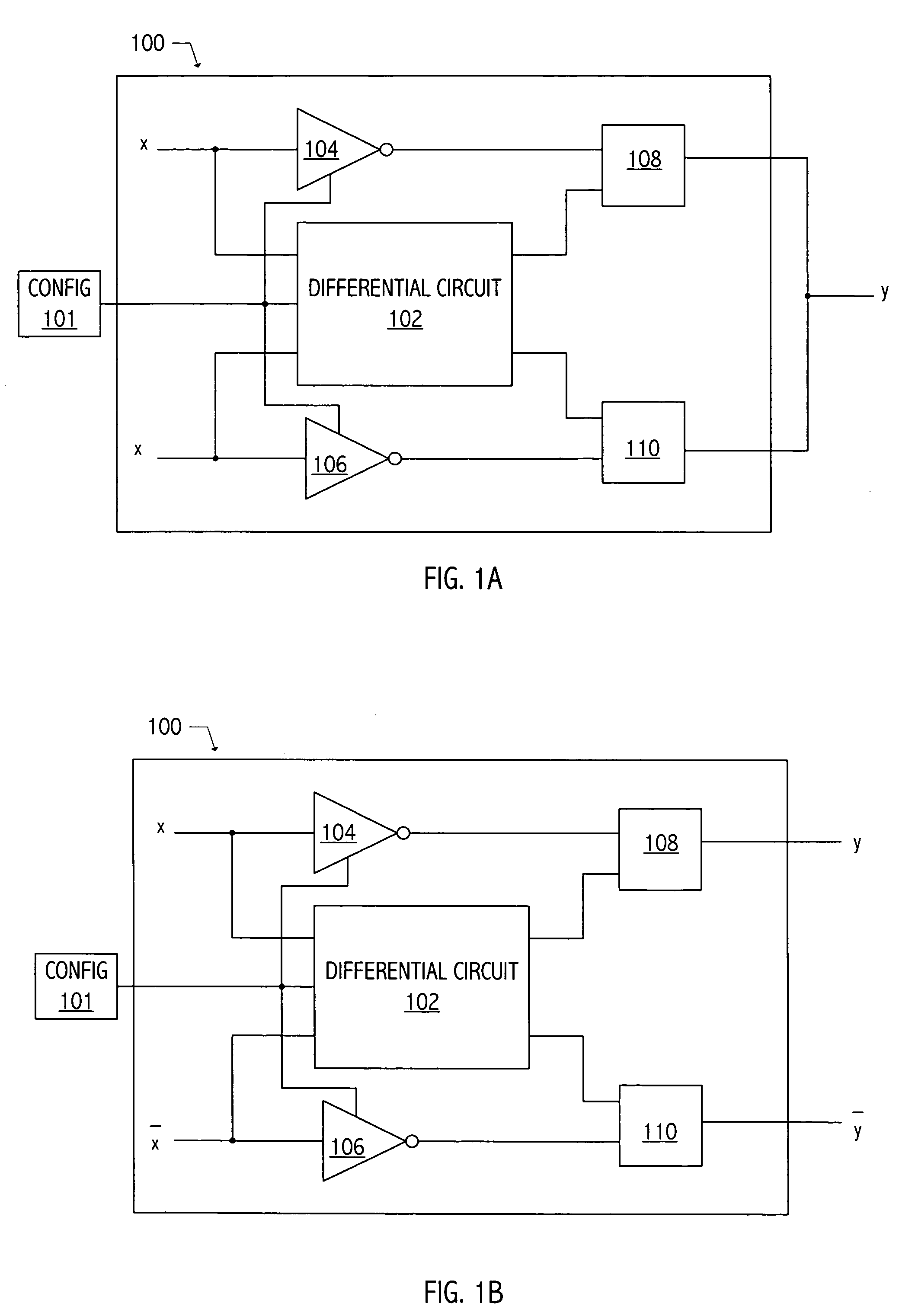

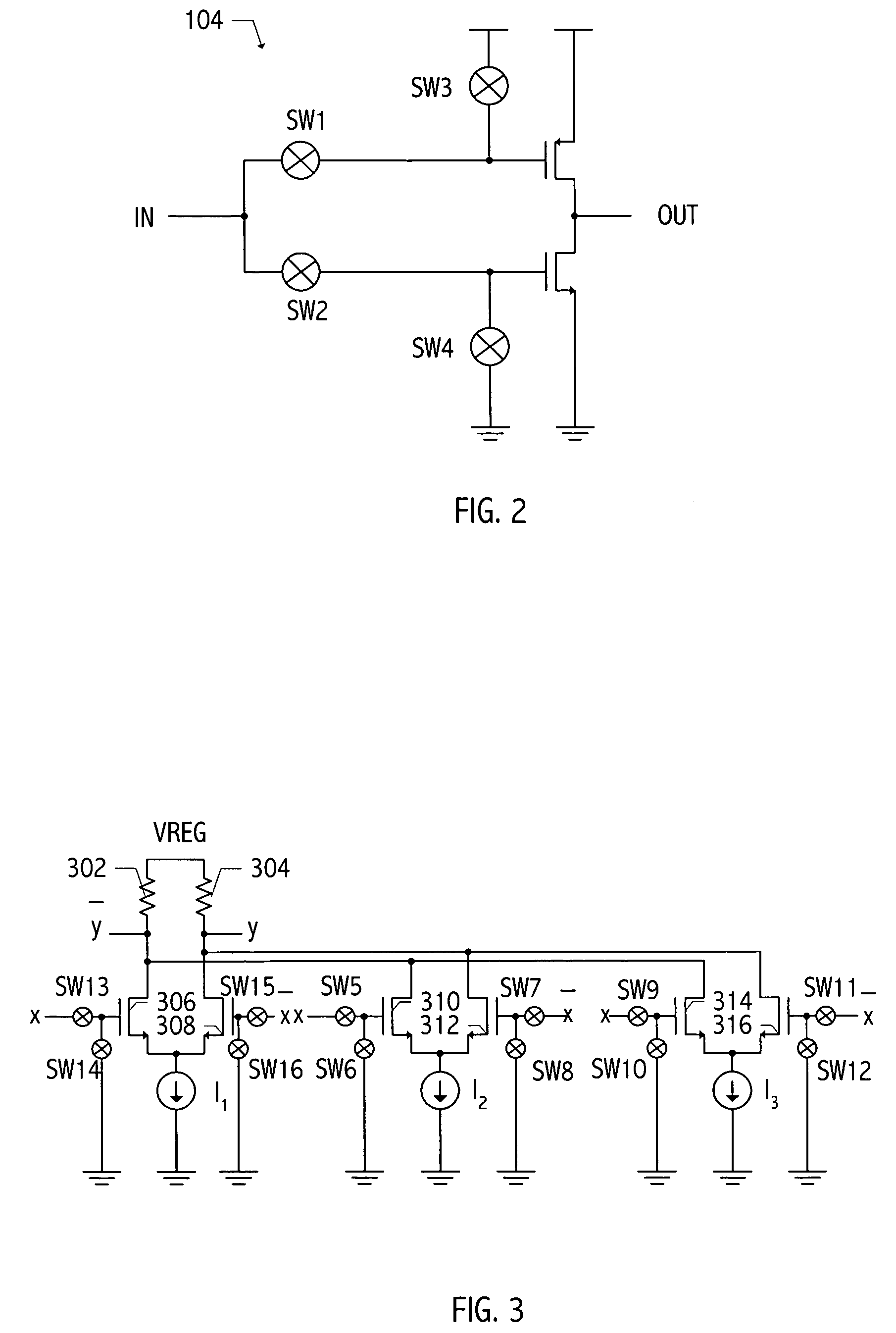

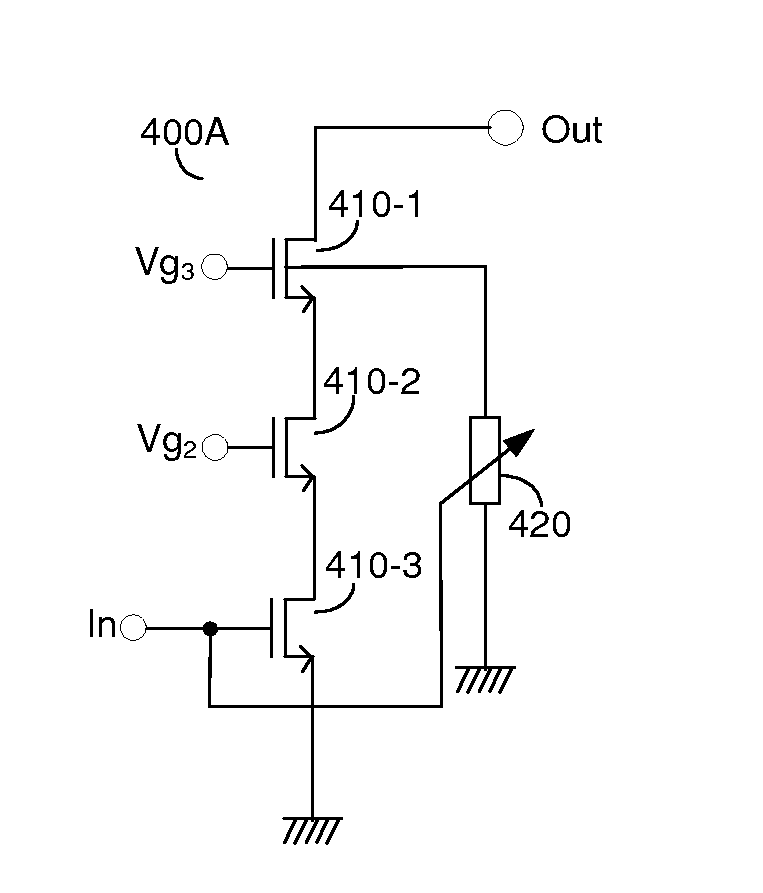

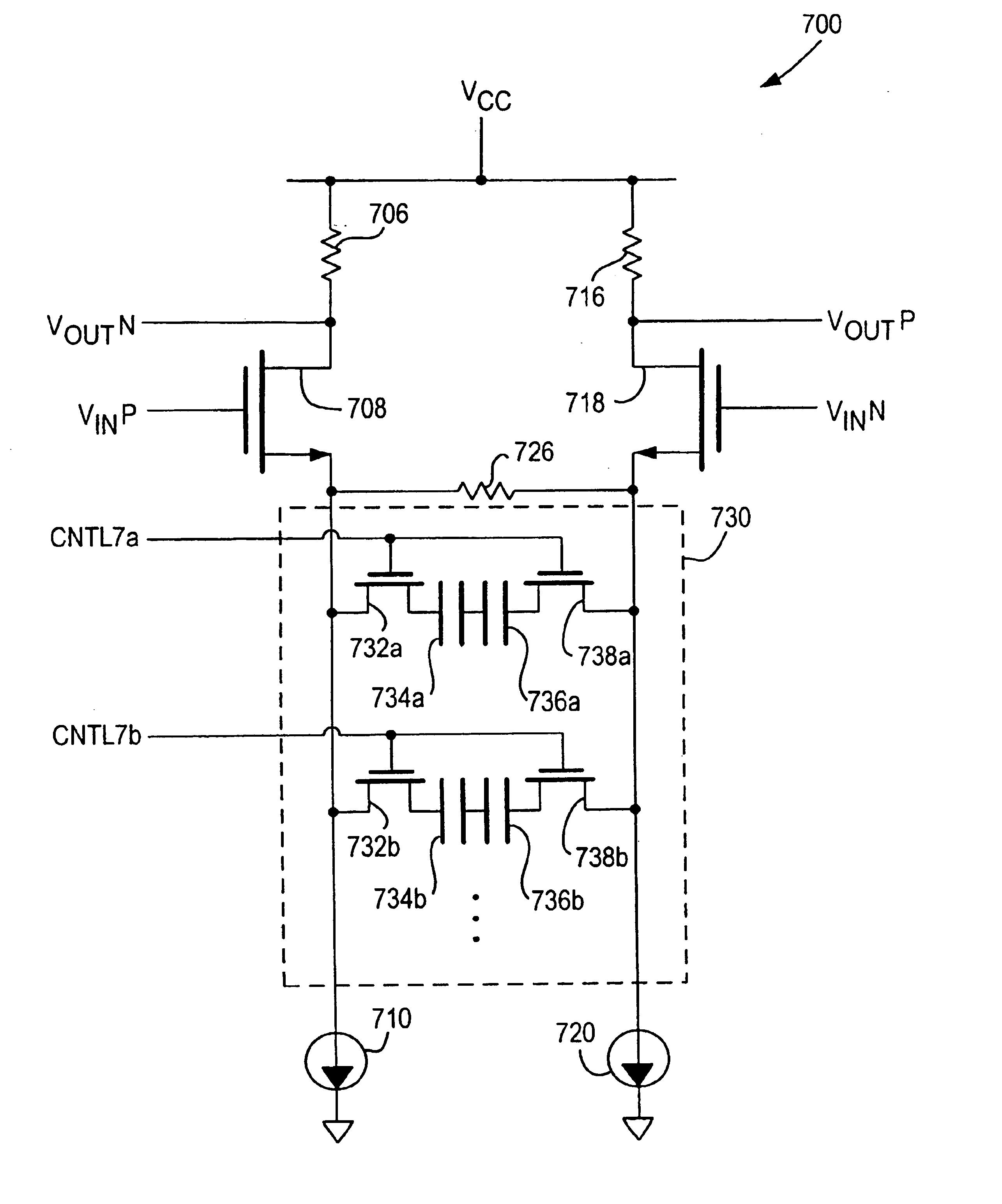

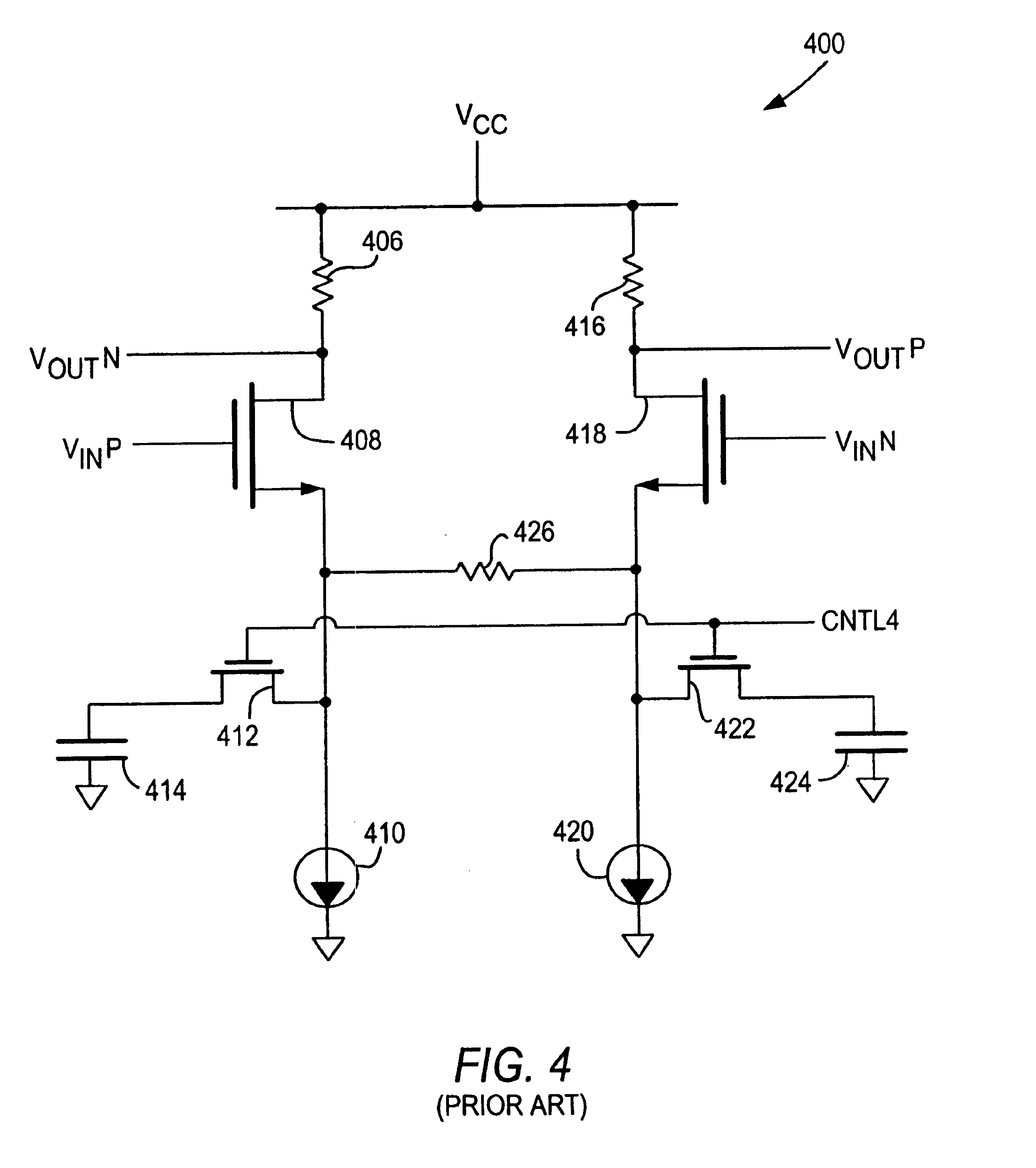

Programmable differential capacitors for equalization circuits

InactiveUS6870404B1Improve circuit performanceCommon noise rejectionMultiple input and output pulse circuitsElectric pulse generatorCapacitanceDifferential signaling

Programmable differential capacitance is implemented in equalization circuits. The programmable differential capacitance improves the common mode rejection ratio of circuits processing differential signals of various frequencies and voltage swings. Multiple capacitance devices provide the programmable capacitance, which provides an equalization circuit with different, selectable (i.e., programmable) values of capacitance for boosting the transition speed and strength of differential signals processed by the equalization circuit.

Owner:ALTERA CORP

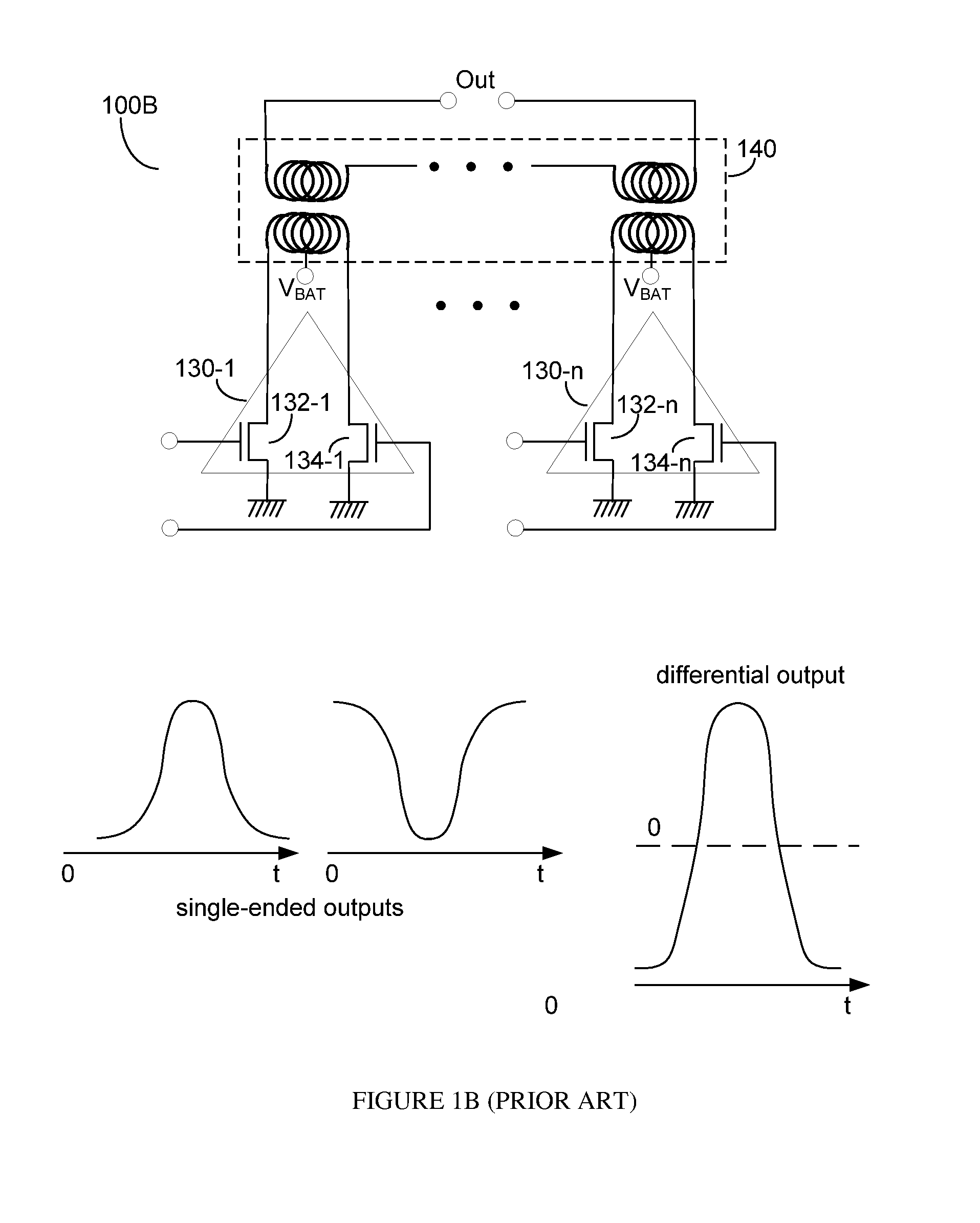

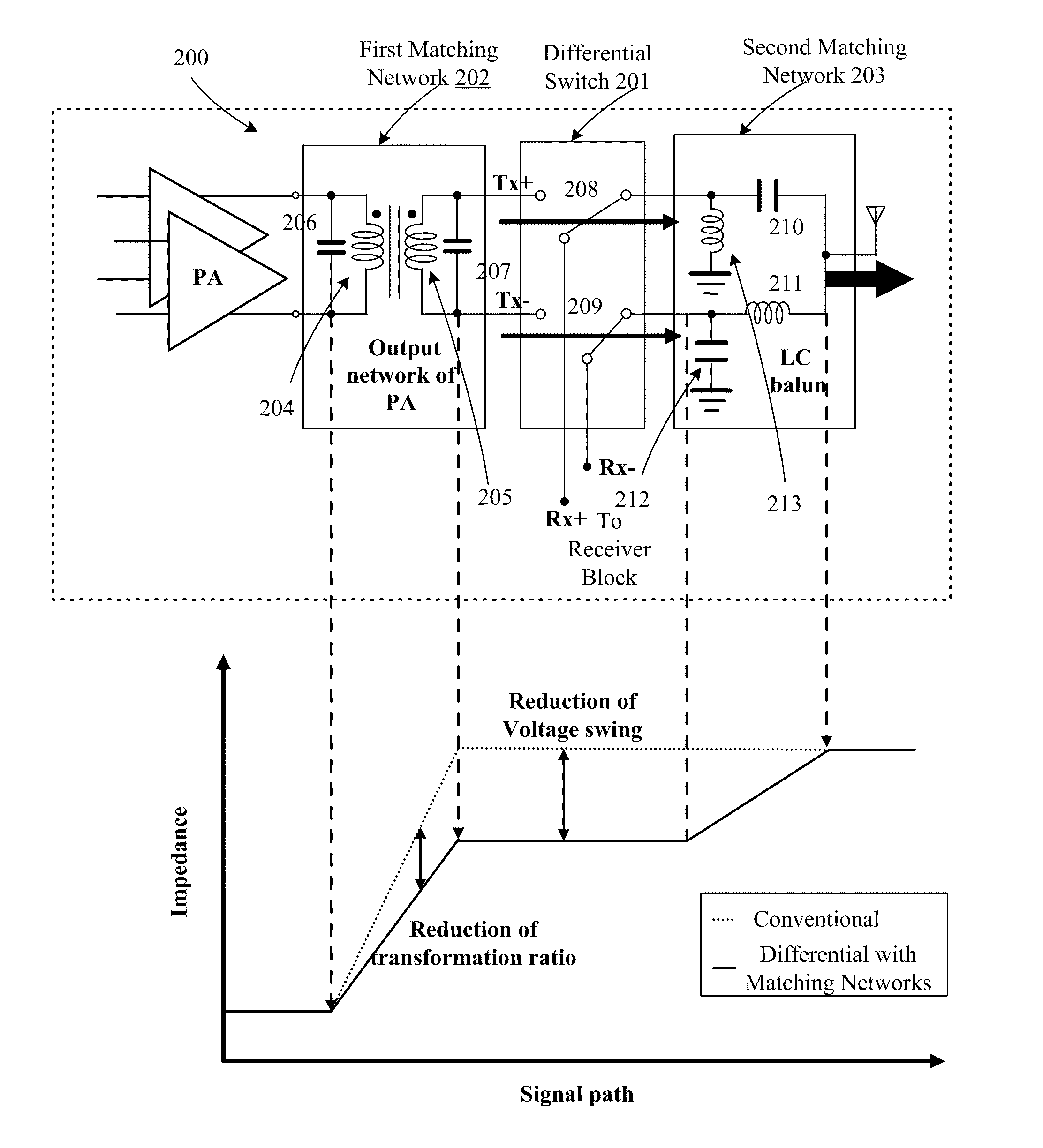

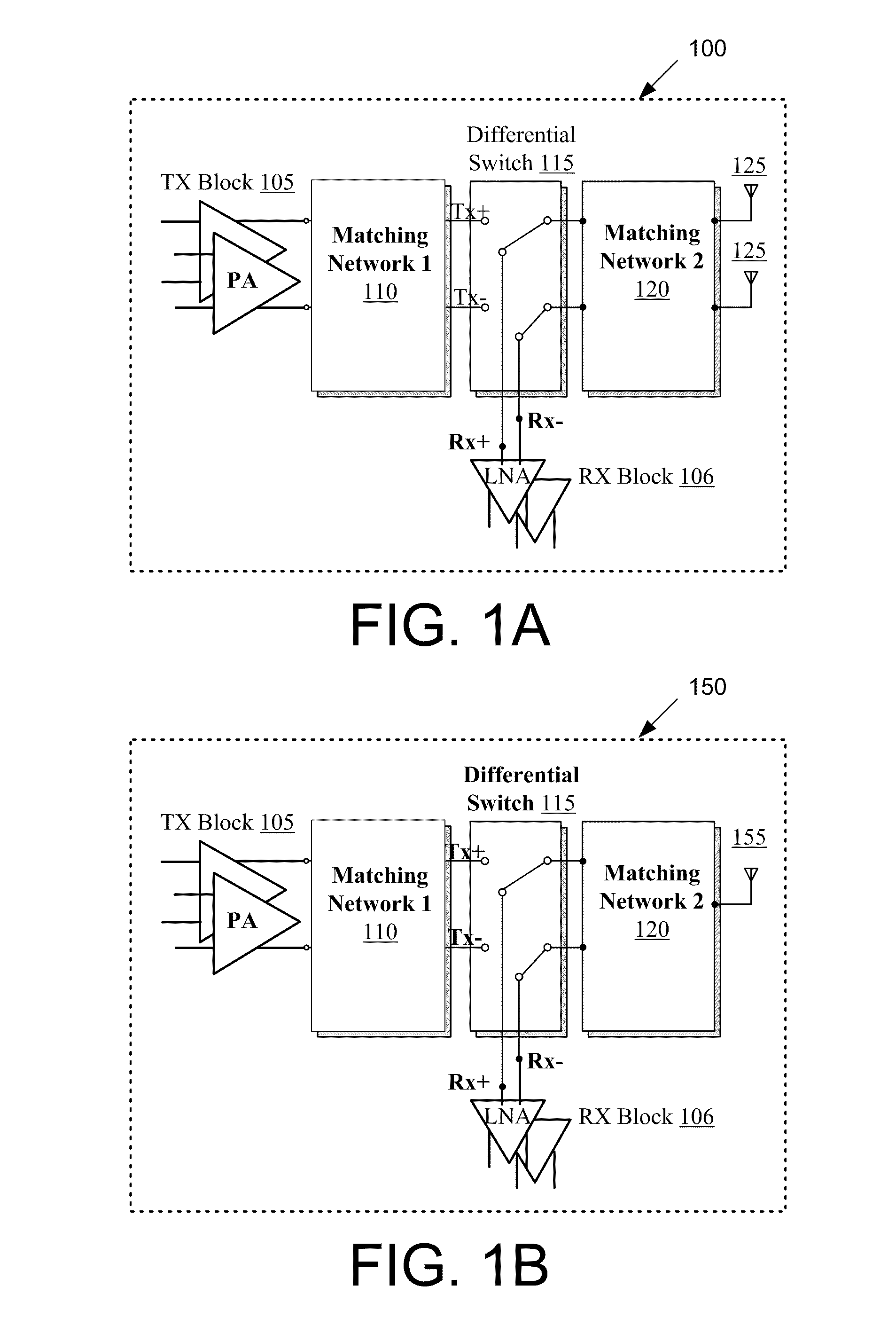

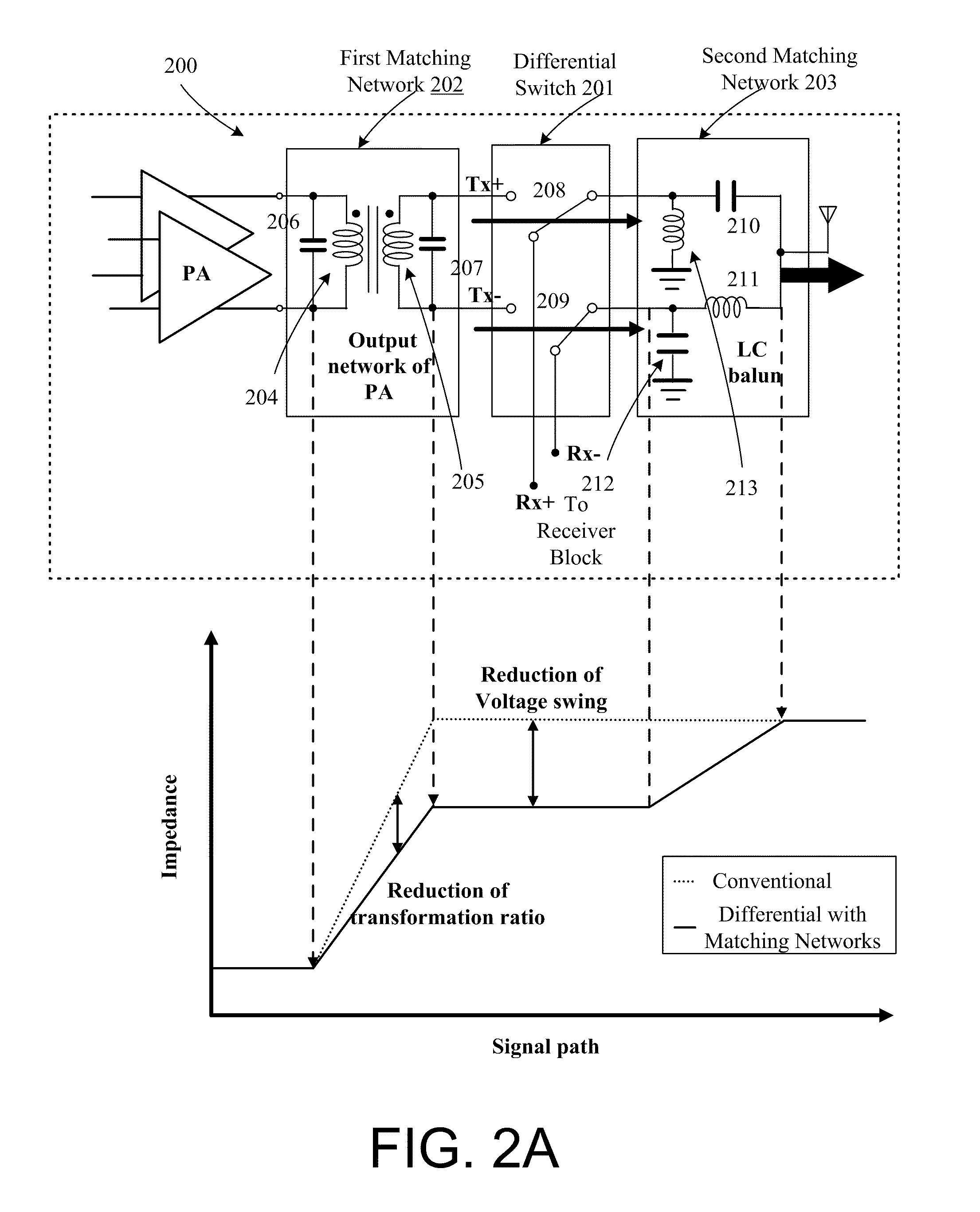

Systems and methods for complementary metal-oxide-semiconductor (CMOS) differential antenna switches using multi-section impedance transformations

ActiveUS20110273355A1Improving impedanceReduced switch operating impedanceAntennas earthing switches associationTransmissionCMOSAudio power amplifier

Example embodiments of the invention are directed to CMOS differential antenna switches with multi-section impedance transformation. The differential architecture can provide relief from large voltage swings of the power amplifiers by distributing the voltage stress over the receiver switch with two of the identical or substantially similar single-ended switches. In order to reduce the voltage stress further, multi-section impedance transformations can be used. Degraded insertion loss due to the impedance transformation technique can be compensated by selecting an optimal impedance for the antenna switch operation. Accordingly, the use of the multi-section impedance transformations with the differential antenna switch architecture enables high power handling capability for the antenna switch with acceptable efficiency for the transmitter module.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

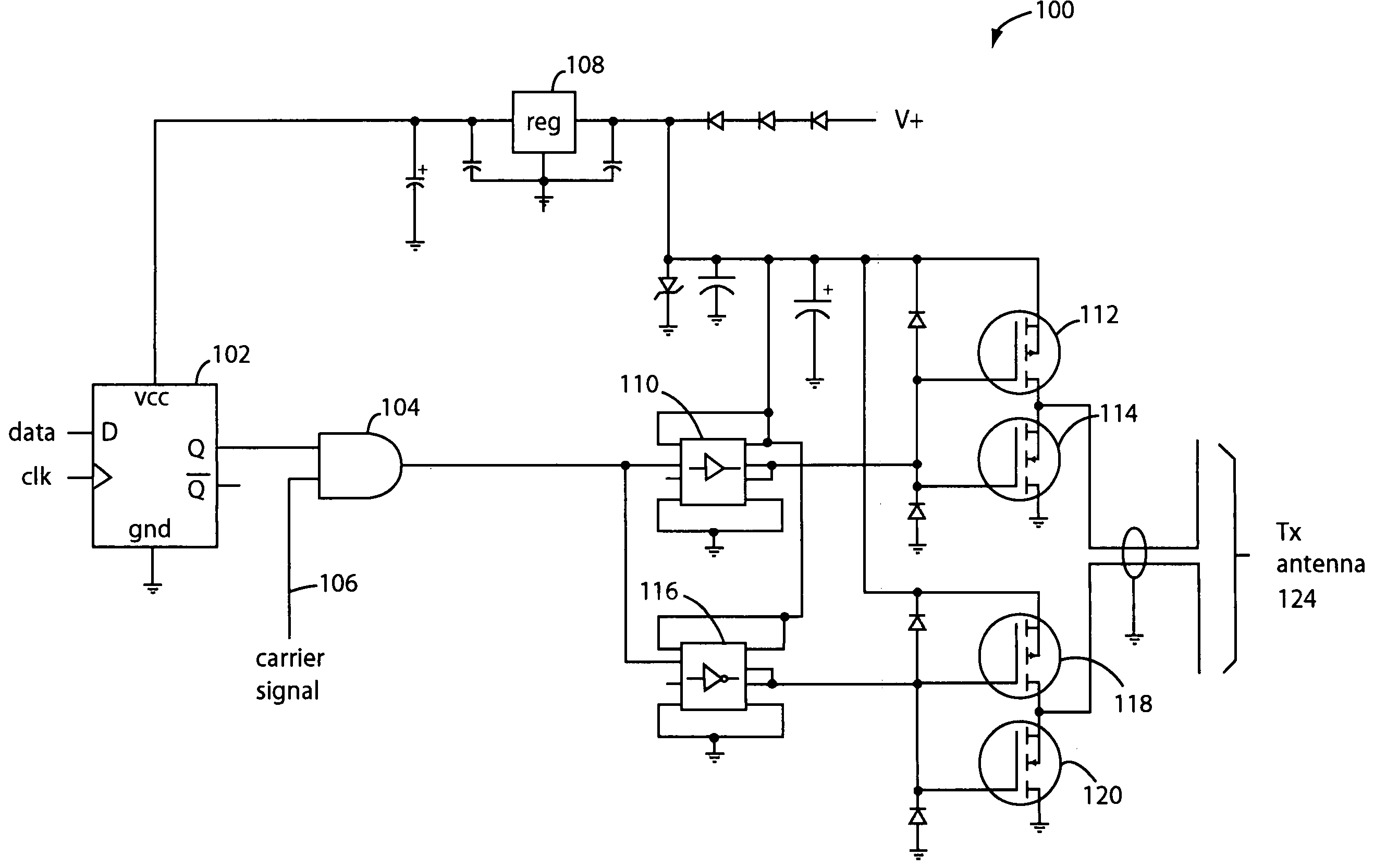

Class-L power-output amplifier

InactiveUS20050159117A1Efficient operation of batteryIncrease powerResonant long antennasGain controlAudio power amplifierEngineering

A radio power output amplifier comprises a balanced radio power output that differentially drives a dipole antenna or other balanced load. One half of the differential power output drives one side of the antenna from ground to the maximum positive rail, while the other half of the differential power output drives the opposite side of the antenna from the maximum positive rail to ground. The result is a voltage swing across the antenna that is twice that which would occur if a single ended output was driving an unbalanced load. Since the power output is the square of the voltage divided by the load impedance, the result is four times the power output.

Owner:BAUSOV IGOR +1

Differential serial interface for supporting a plurality of differential serial interface standards

ActiveUS8638838B1Reliability increasing modificationsModulated-carrier systemsVoltage swingTransceiver

An apparatus for communicating data. In one embodiment, the apparatus comprises a differential serial interface that supports a plurality of differential serial interface standards and a rail-to-rail common mode range, the differential serial interface comprising a silicon integration of a transceiver comprising (i) a transmitter module coupled to a differential interface and (ii) a receiver module coupled to the differential interface via a common mode isolation circuit, wherein the transceiver is direction-selectable; a variable termination resistance circuit, coupled to the differential interface, for providing adjustable termination for the transmitter module and the receiver module; a frequency-based load detector for detecting connection to a remote receiver; and a calibration circuit for calibrating termination impedance, voltage swing, at least one of pre-emphasis levels or de-emphasis levels, at least one of transmitter eye or receiver eye, and return loss of the differential serial interface to support the plurality of differential serial interface standards.

Owner:TERADICI CORP

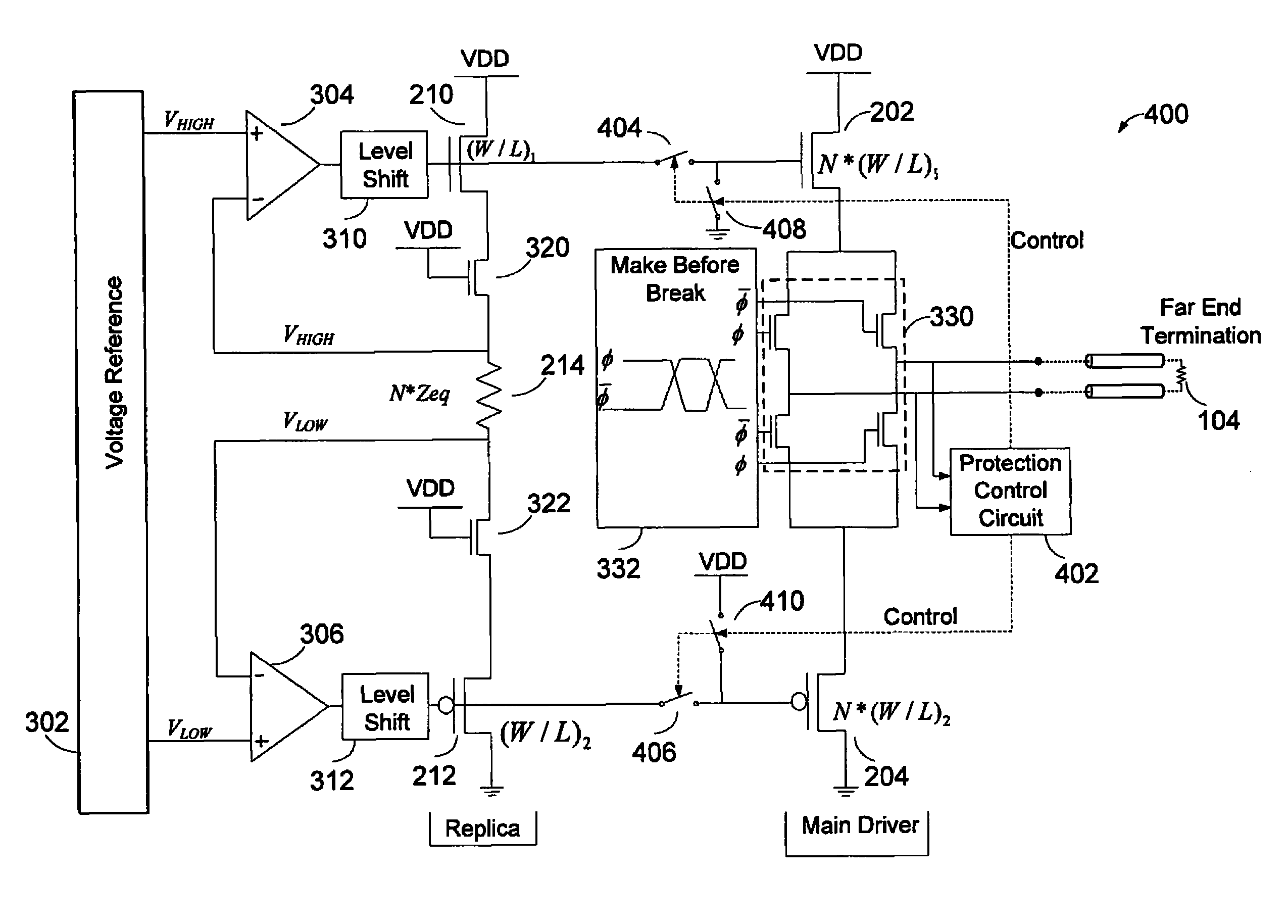

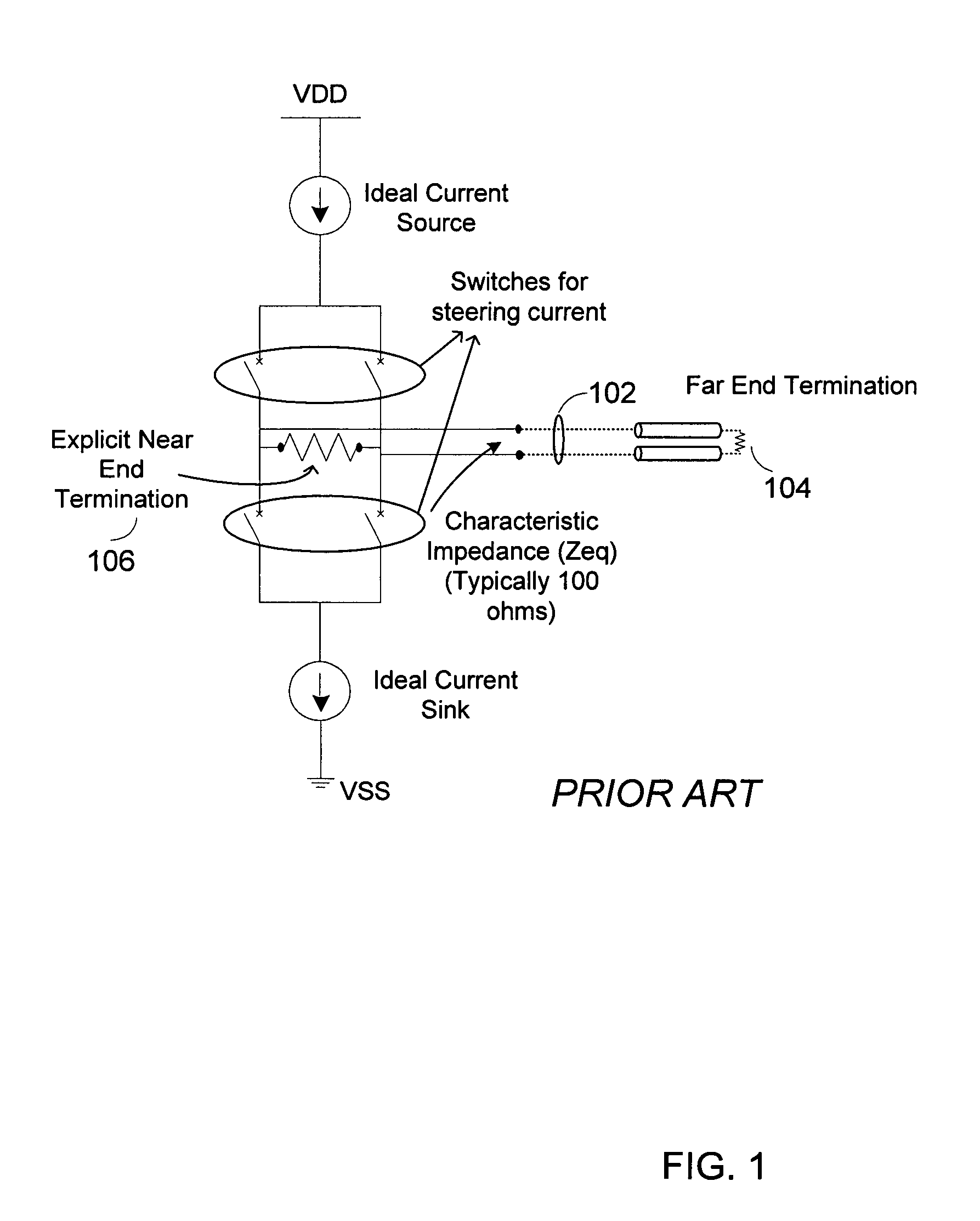

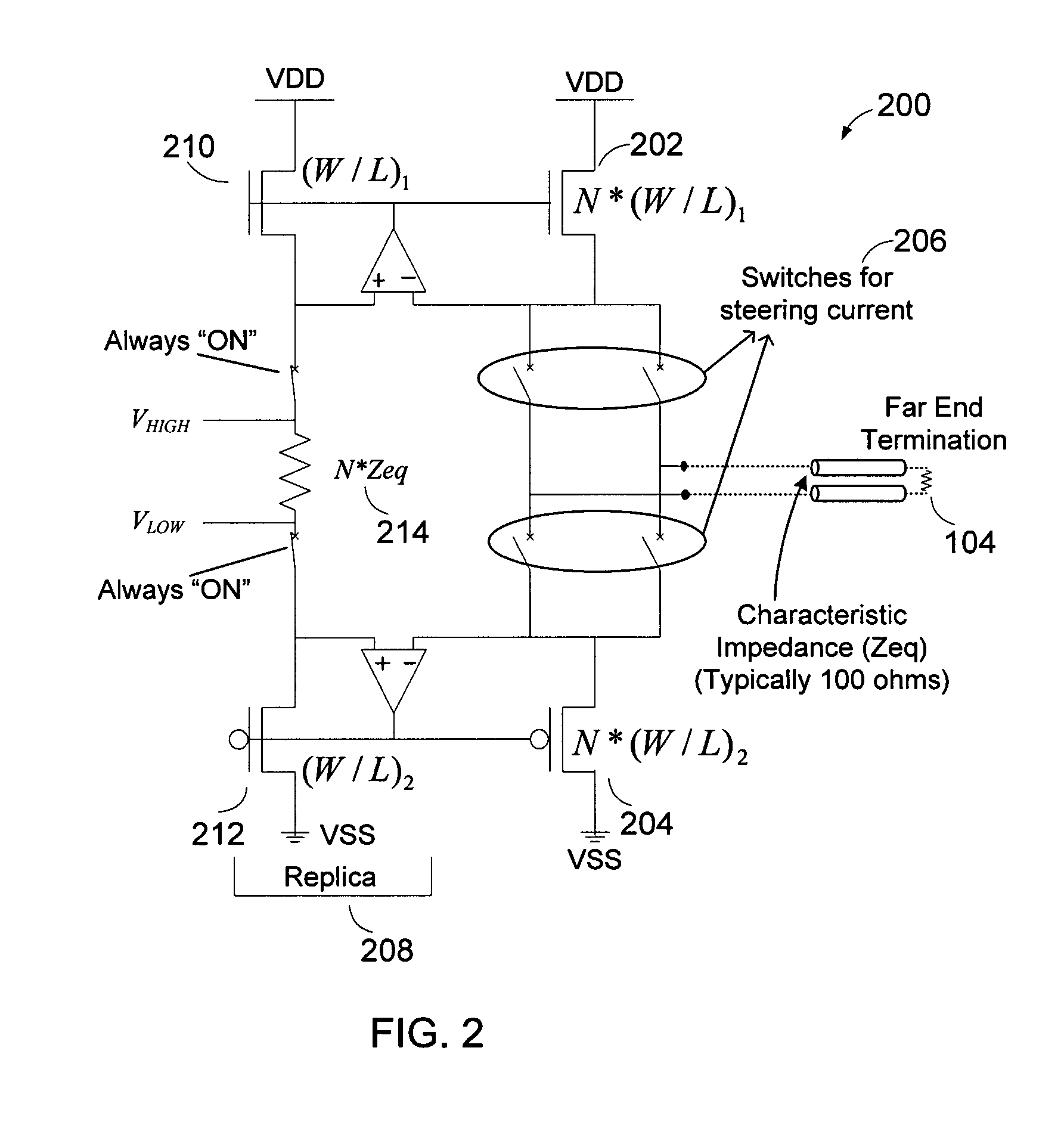

Hot-pluggable differential signaling driver

ActiveUS7898295B1Improve efficiencyReduction in power-off leakage current currentReliability increasing modificationsElectronic switchingDifferential signalingEngineering

Apparatus and methods provide low voltage differential signaling (LVDS) driver with replica circuit biasing and protection for hot plugging. The replica biasing is non-intrusive in nature, and can control the voltage swing tightly over parametric variations. The absence of an explicit near-end driver termination improves efficiency, while replica biasing controls output voltage swing levels. Hot-pluggable compatibility is achieved by a reduction in power-off leakage current and short circuit current protection.

Owner:MICROSEMI STORAGE SOLUTIONS

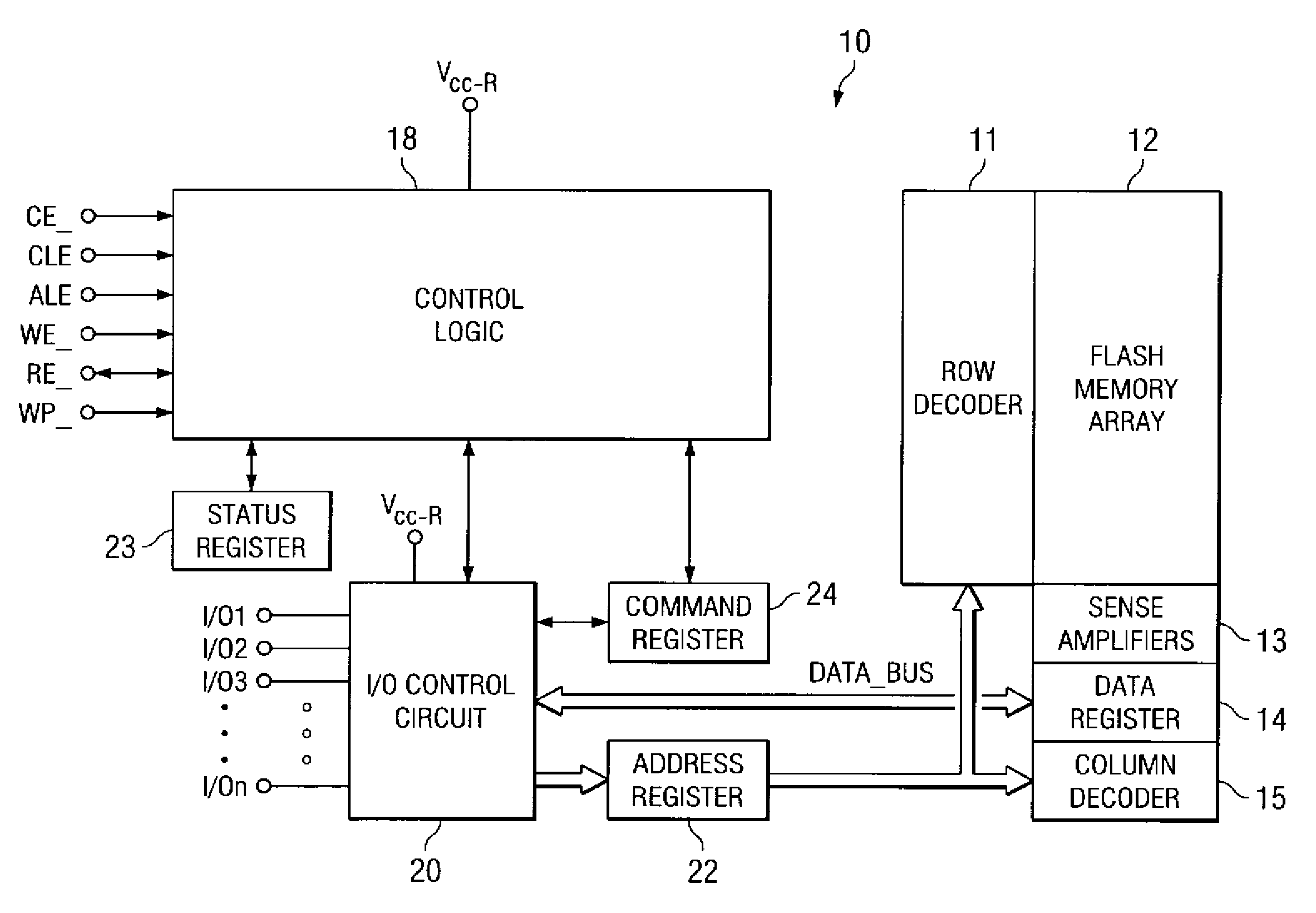

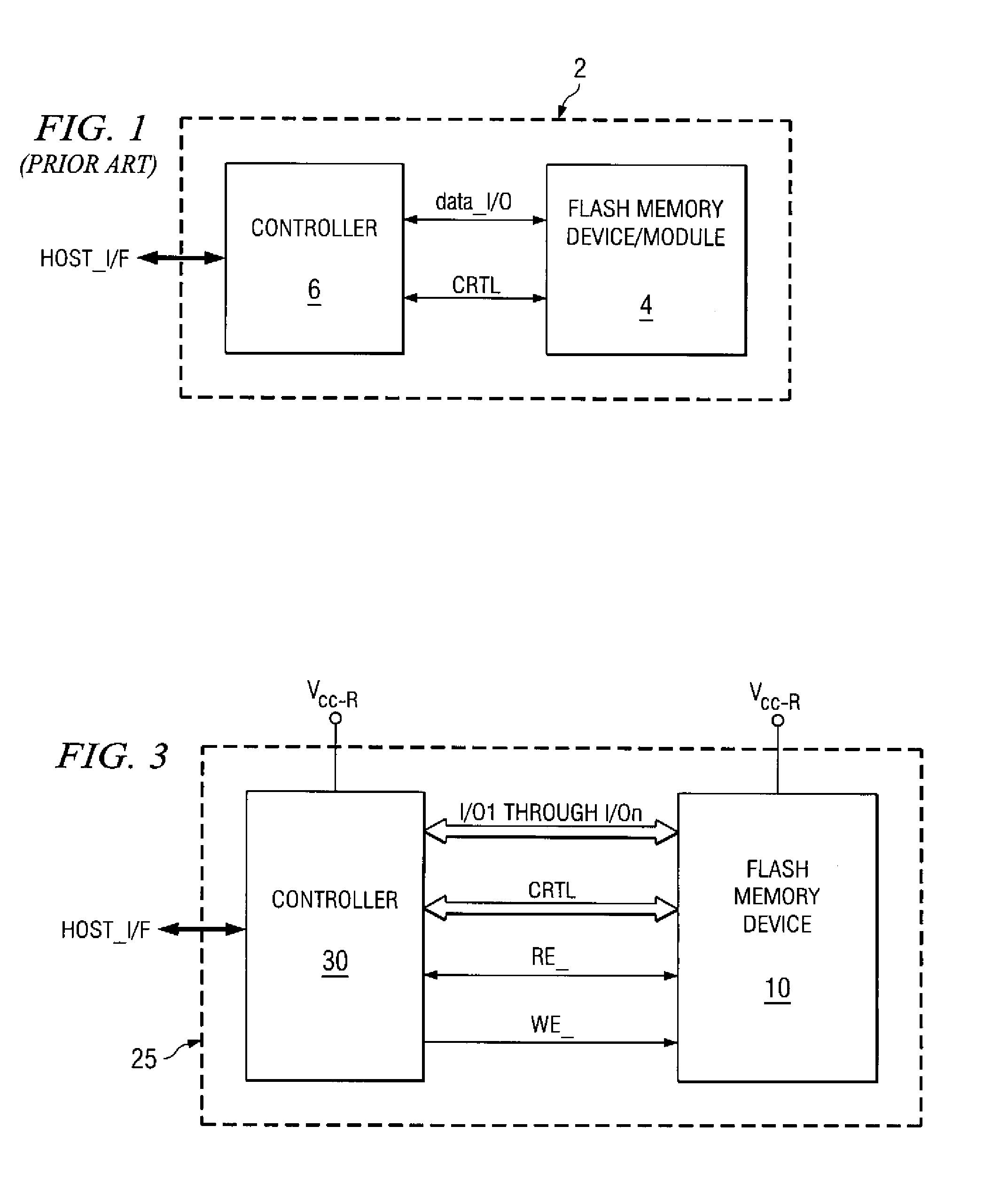

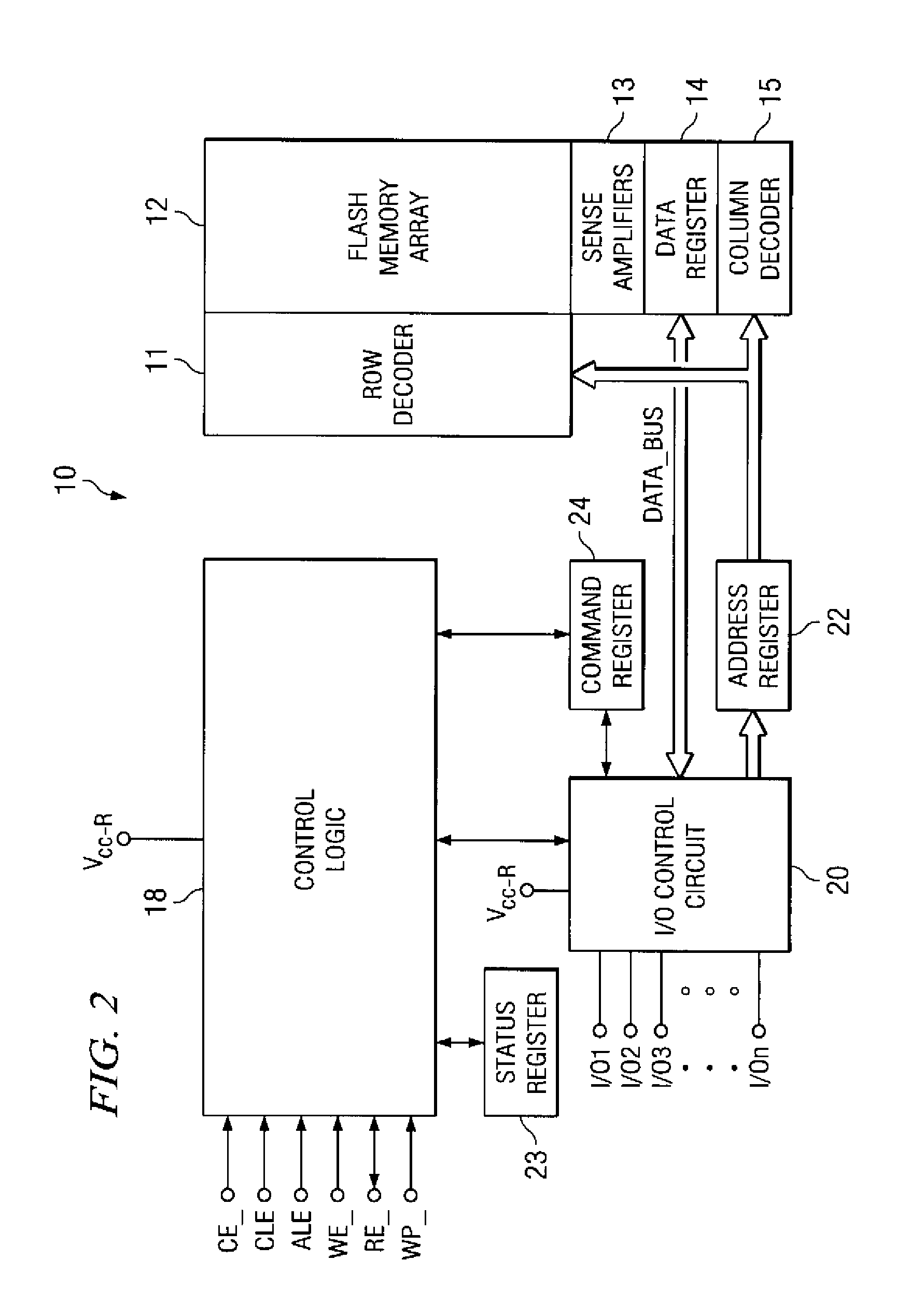

High-performance flash memory data transfer

ActiveUS7366029B2Minimize data transferMinimize data skewRead-only memoriesDigital storageControl signalNormal mode

A flash memory system including a flash memory device and a controller, operable according to an advanced data transfer mode is disclosed. The flash memory device is operable both in a “legacy” mode, in which read data is presented by the memory synchronously with each cycle of a read data strobe from the controller, and in which input data is latched by the memory synchronously with each cycle of a write data strobe from the controller. In the advanced mode, which can be initiated by the controller forwarding an initiation command to the memory, the flash memory itself sources the read data strobe at a higher frequency, for example at twice the frequency, of that available in the normal mode. In the advanced mode, the input data is presented by the controller synchronously with a higher frequency write data strobe than is available in the normal mode. The voltage swing of the data and control signals is reduced from conventional standards, to reduce power consumption.

Owner:SANDISK TECH LLC

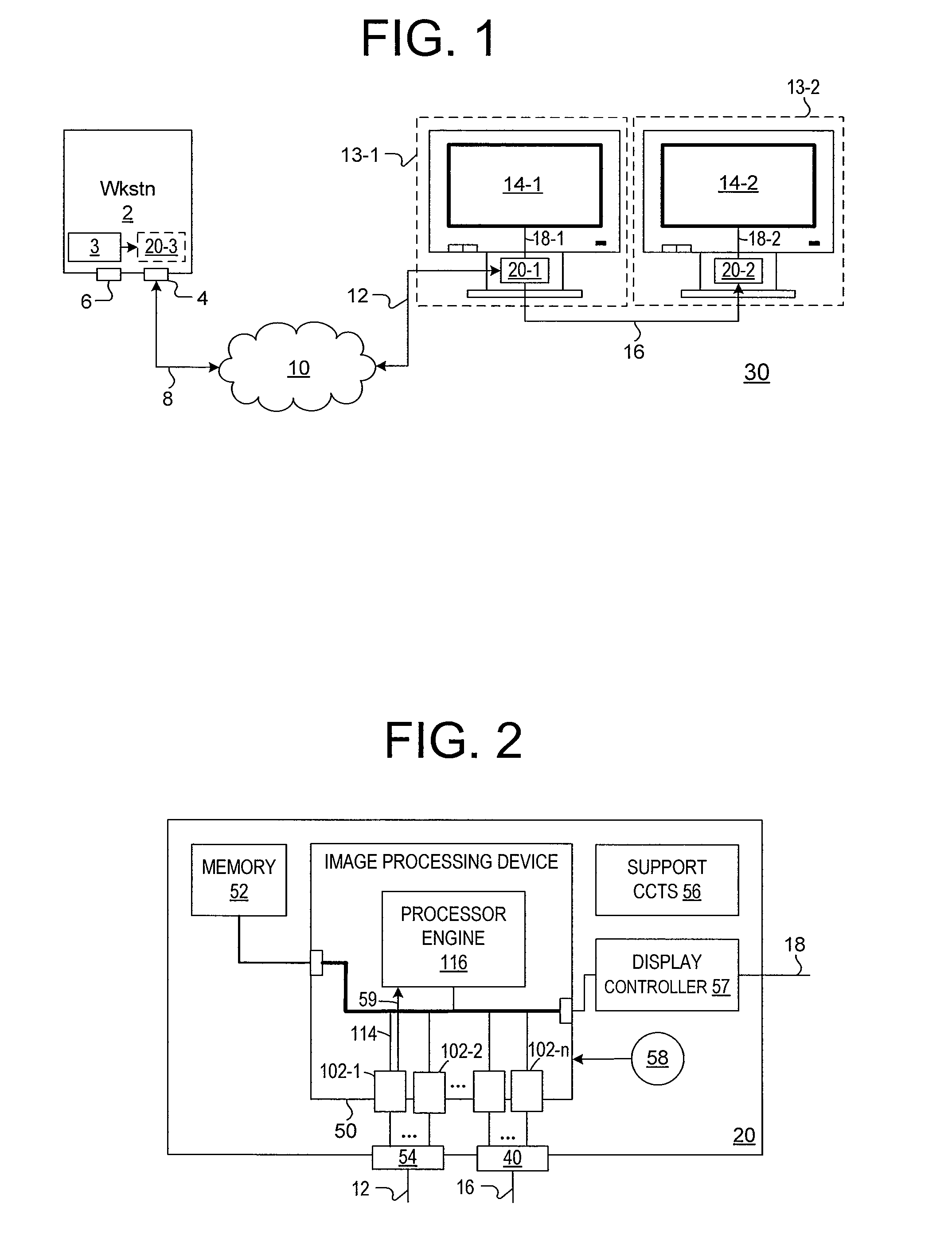

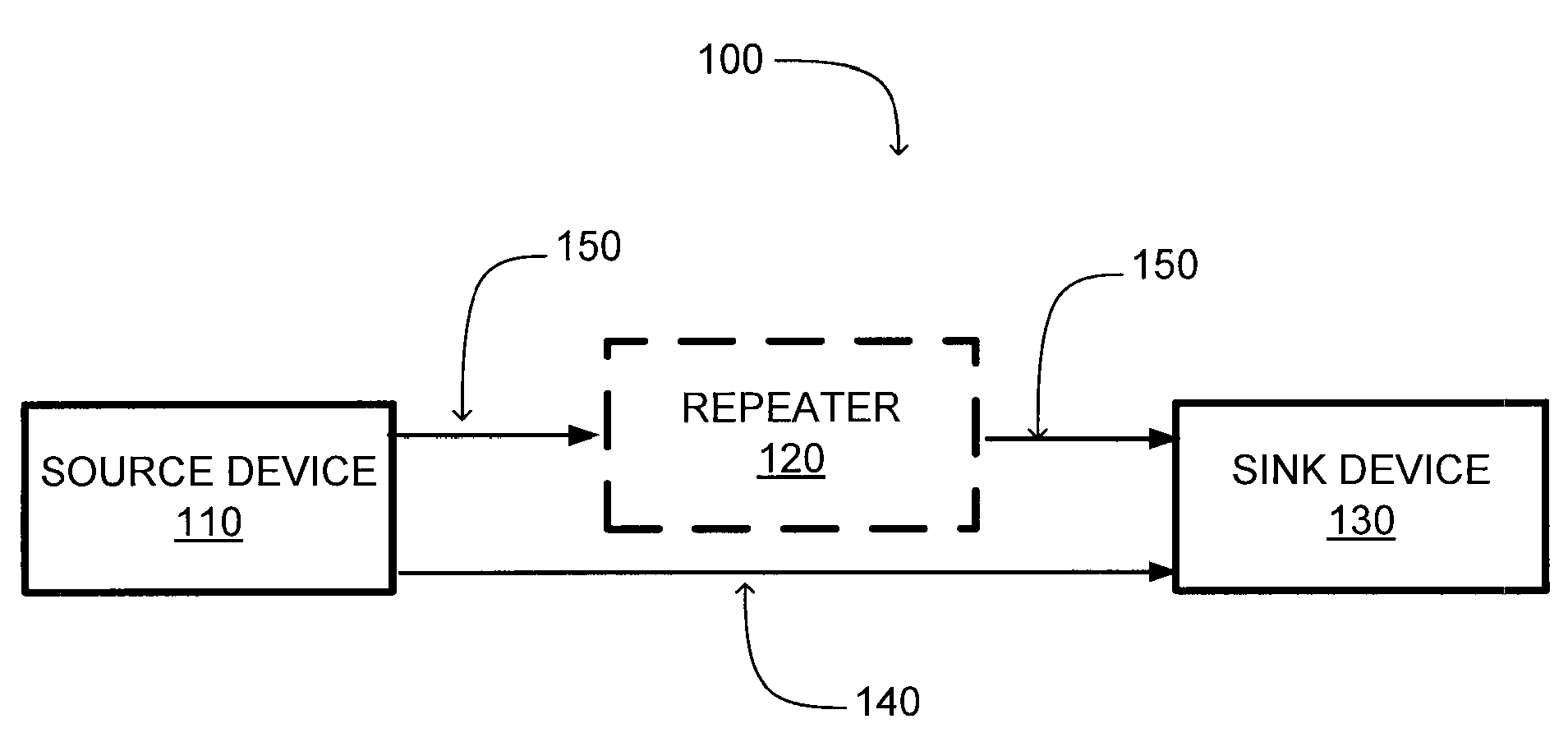

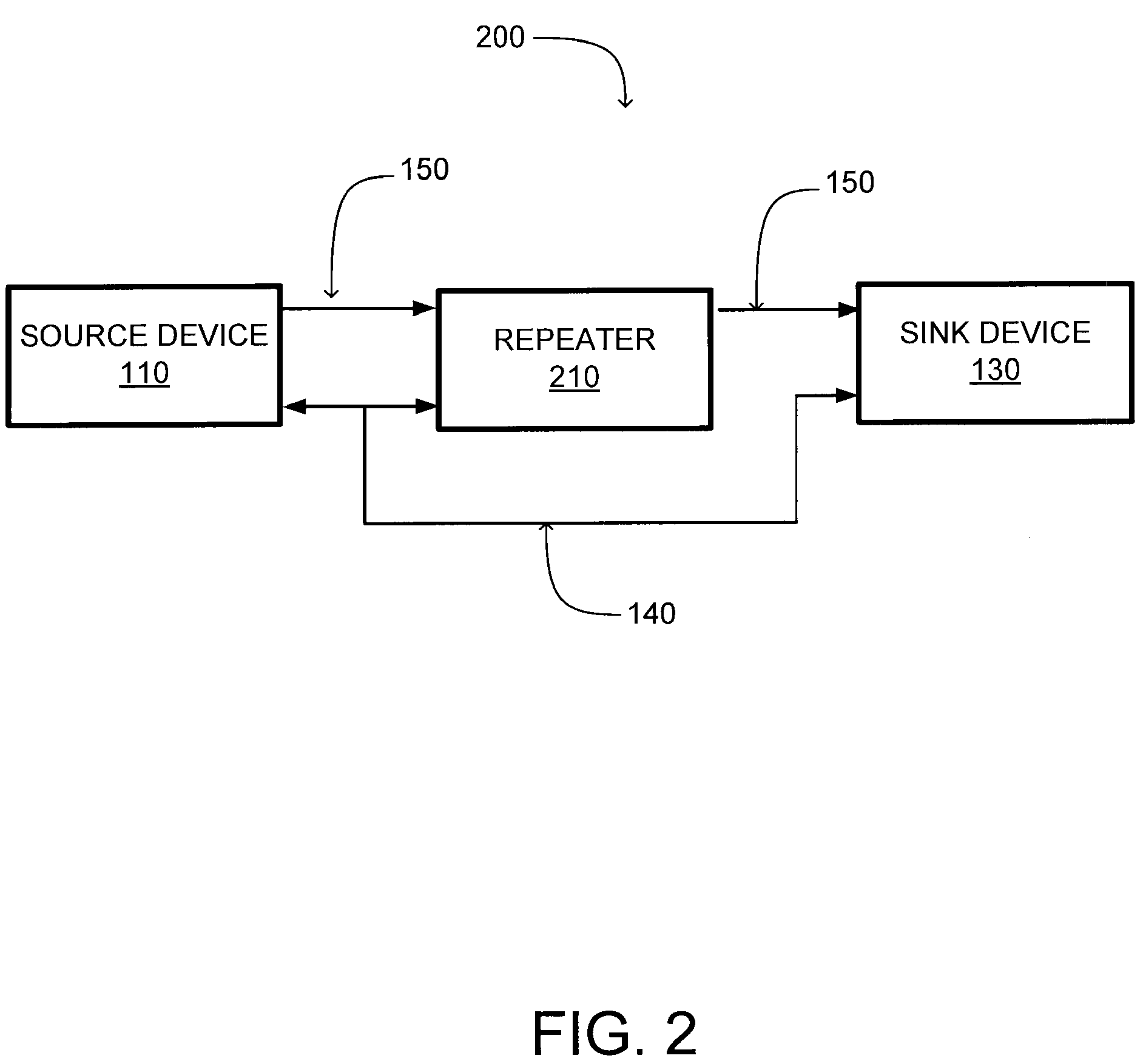

Link training scheme for displayport source repeaters

ActiveUS20090279473A1Exact copyFacilitate transmissionFrequency-division multiplex detailsTime-division multiplexVoltage swingData transmission

A system and a method for configuring communication between a source device and a sink device using captured configuration data are described. The source device communicates with a repeater, which modifies received data to facilitate transmission to the sink device, using a communication channel. The communication channel transmits video and / or audio data from the source device to the sink device. An auxiliary communication channel is used to communicate configuration data between the source device and sink device to optimize transmission and receipt of data through the communication channel. The repeater is coupled to the auxiliary communication channel and passively captures configuration data from the auxiliary communication channel. The repeater uses a subset of the captured configuration data (e.g., data rate, voltage swing, pre-emphasis, etc.) to modify how the repeater transmits data to the sink device using the communication channel.

Owner:PARADE TECH

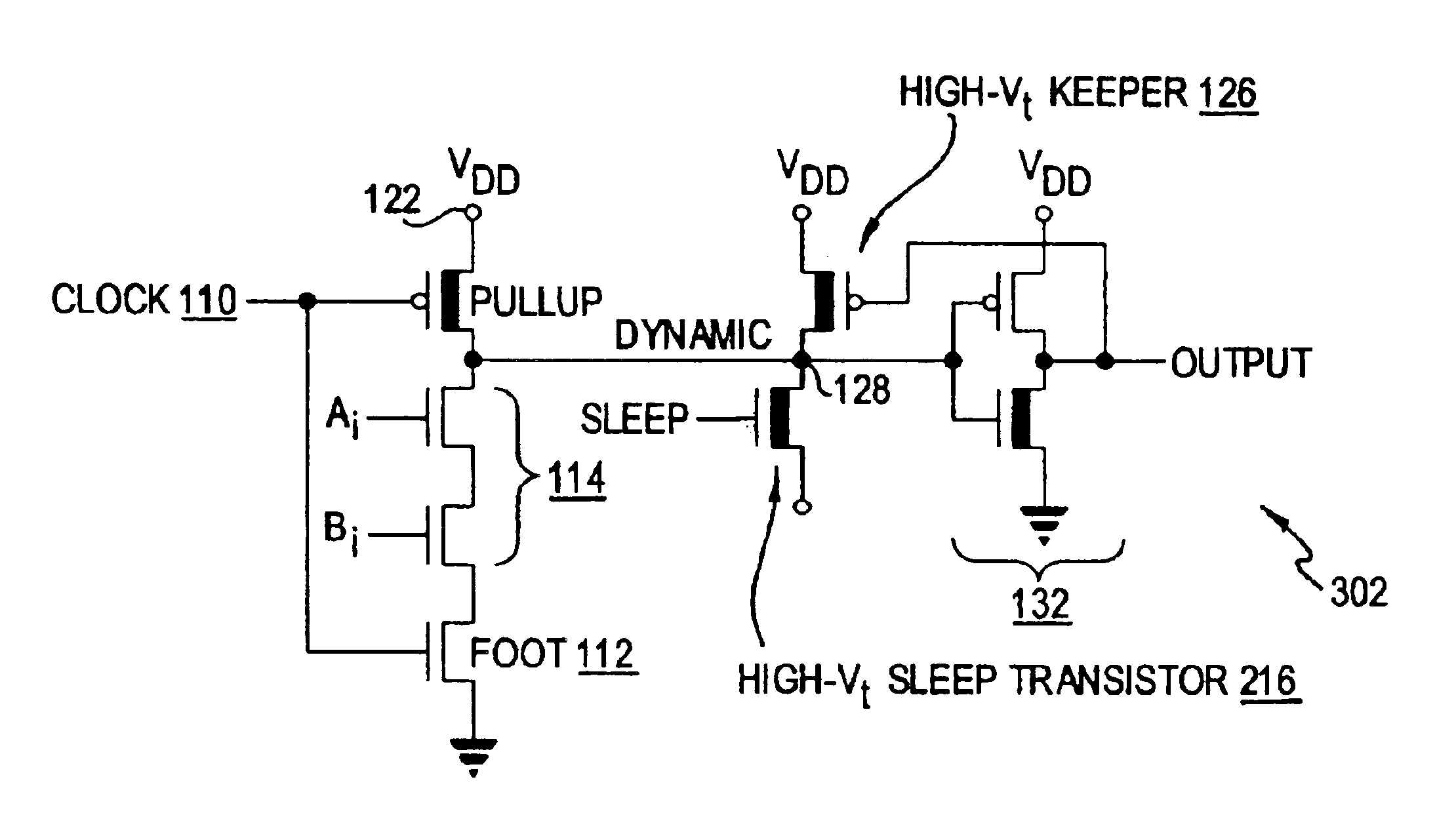

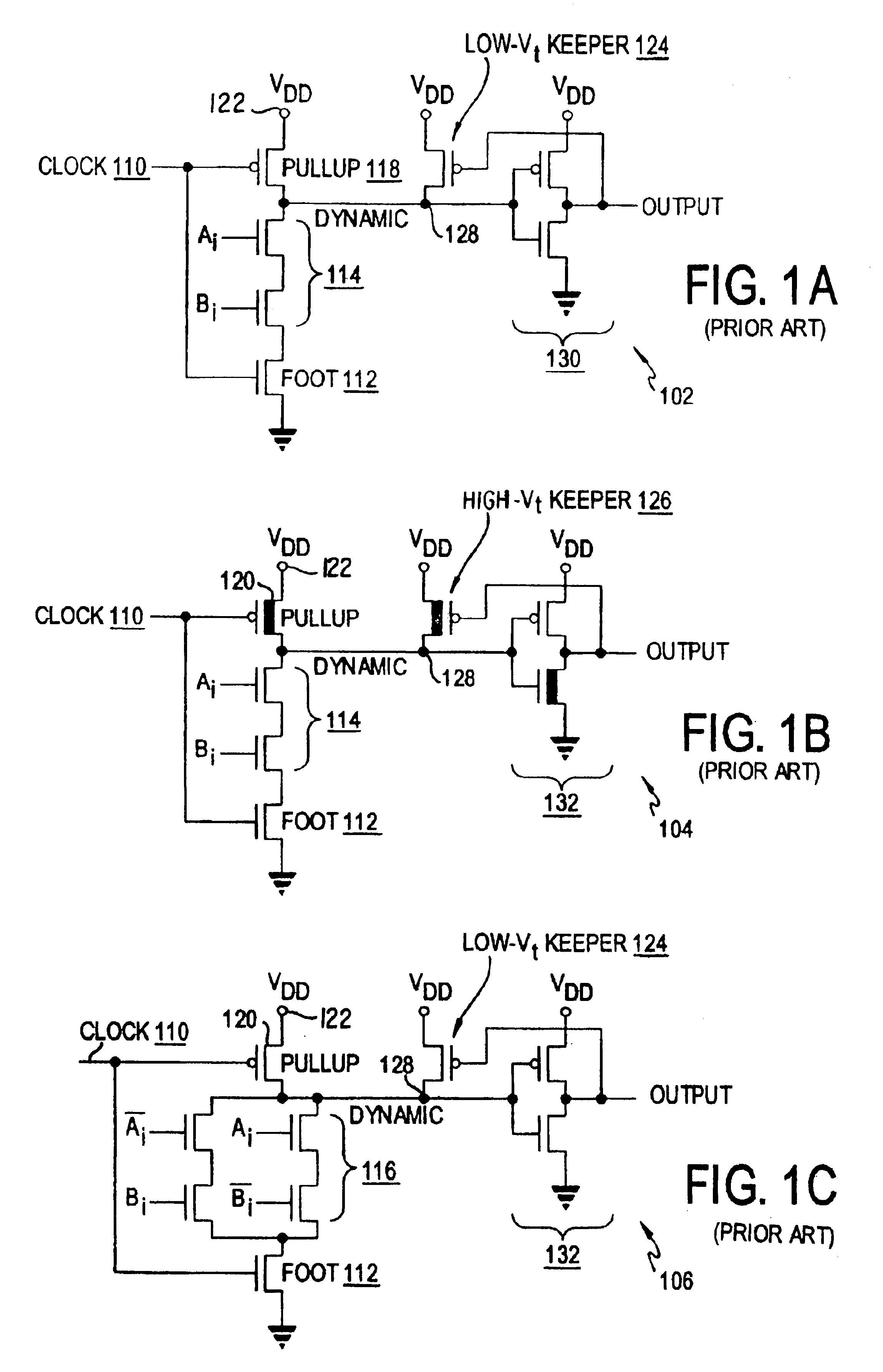

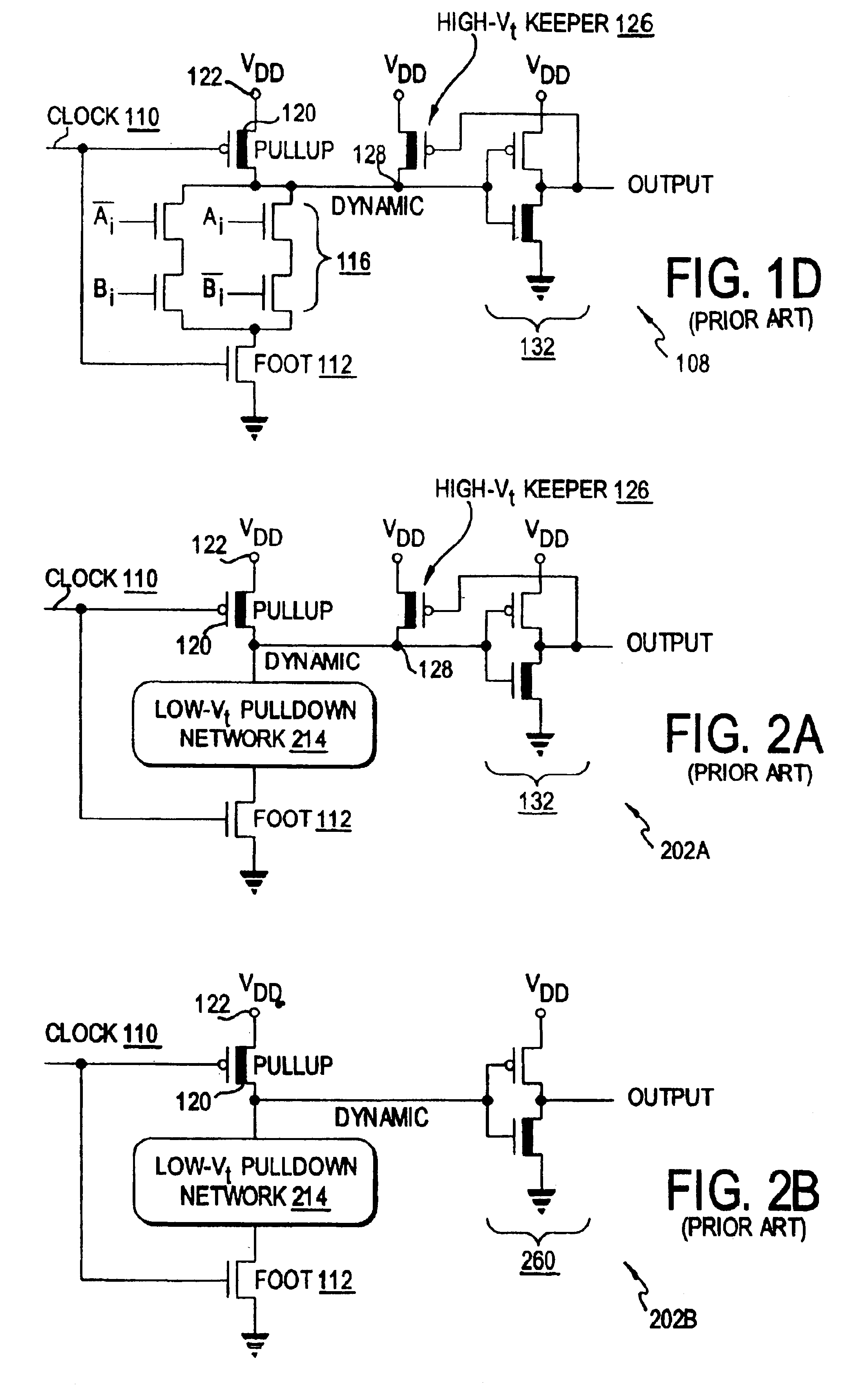

Dual threshold voltage and low swing domino logic circuits

InactiveUS6900666B2Lowering standby leakage energyReducing leakage energyPower reduction in field effect transistorsPower reduction by control/clock signalDomino logicGate voltage

A domino logic circuit is configured to reduce power consumption. In a first embodiment, a sleep switch grounds the dynamic node during sleep mode. In a second embodiment, a low-swing circuit at the output reduces the output and keeper transistor gate voltage swings. A third embodiment combines those two techniques.

Owner:UNIVERSITY OF ROCHESTER