Patents

Literature

75 results about "Snapback" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

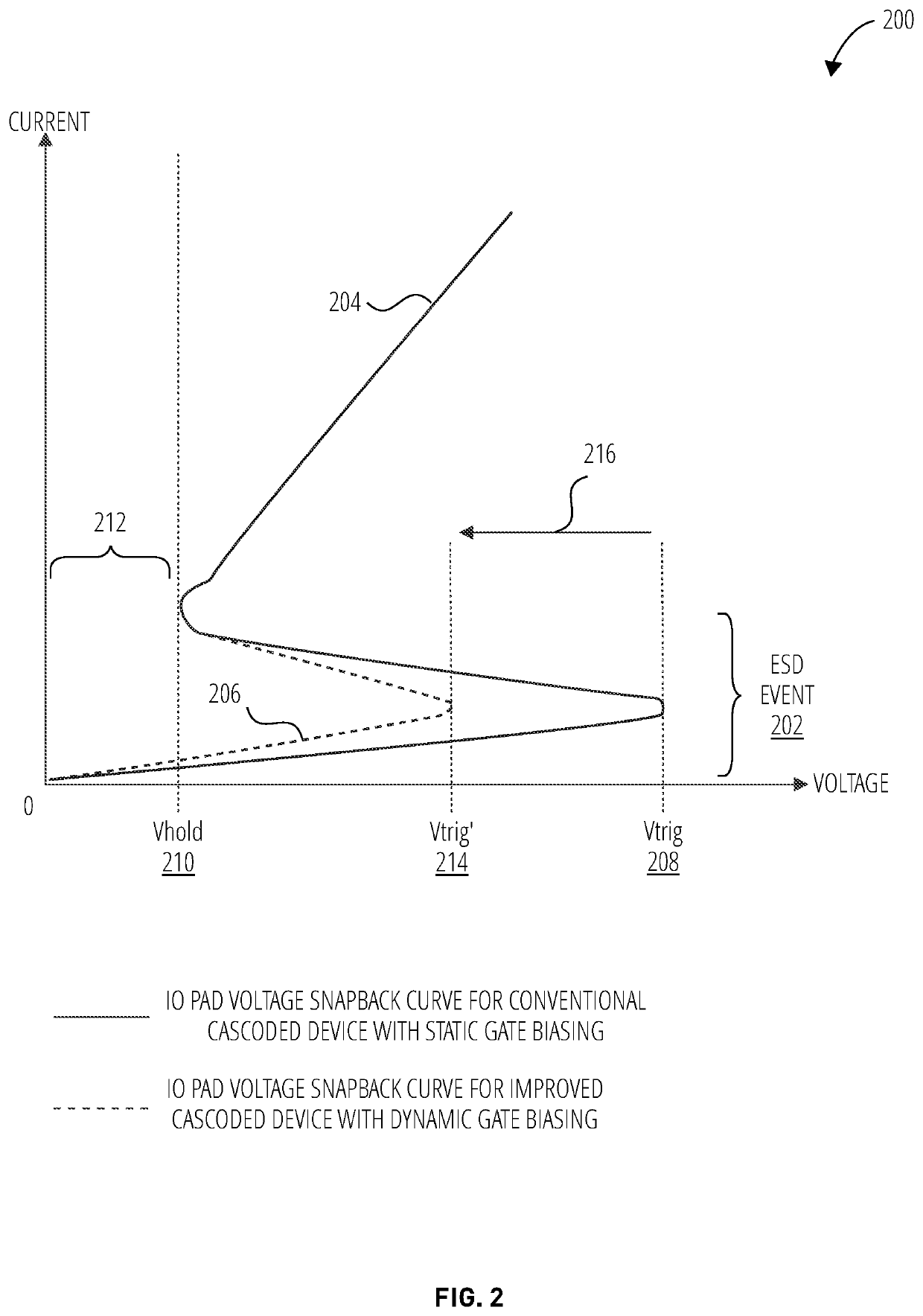

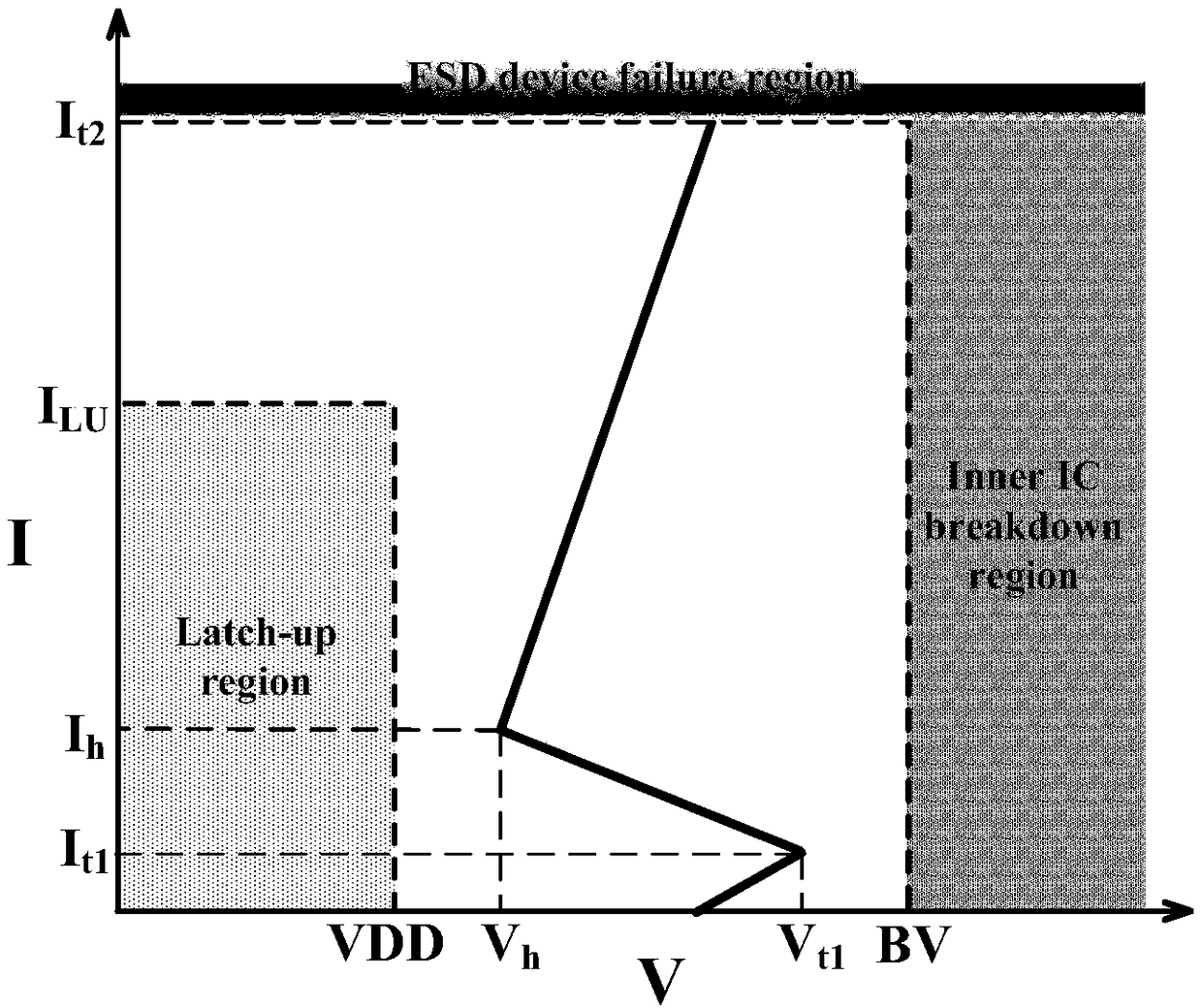

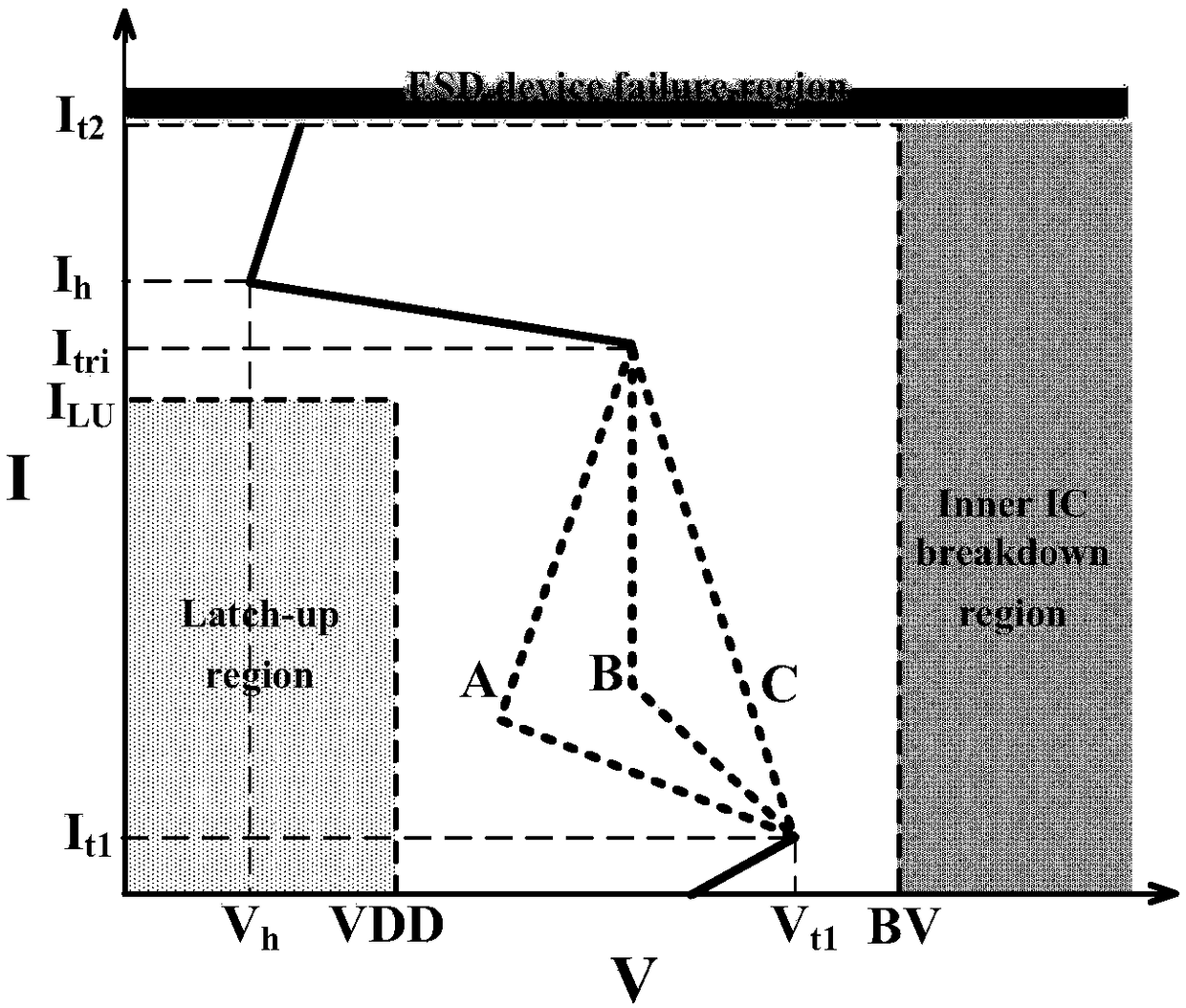

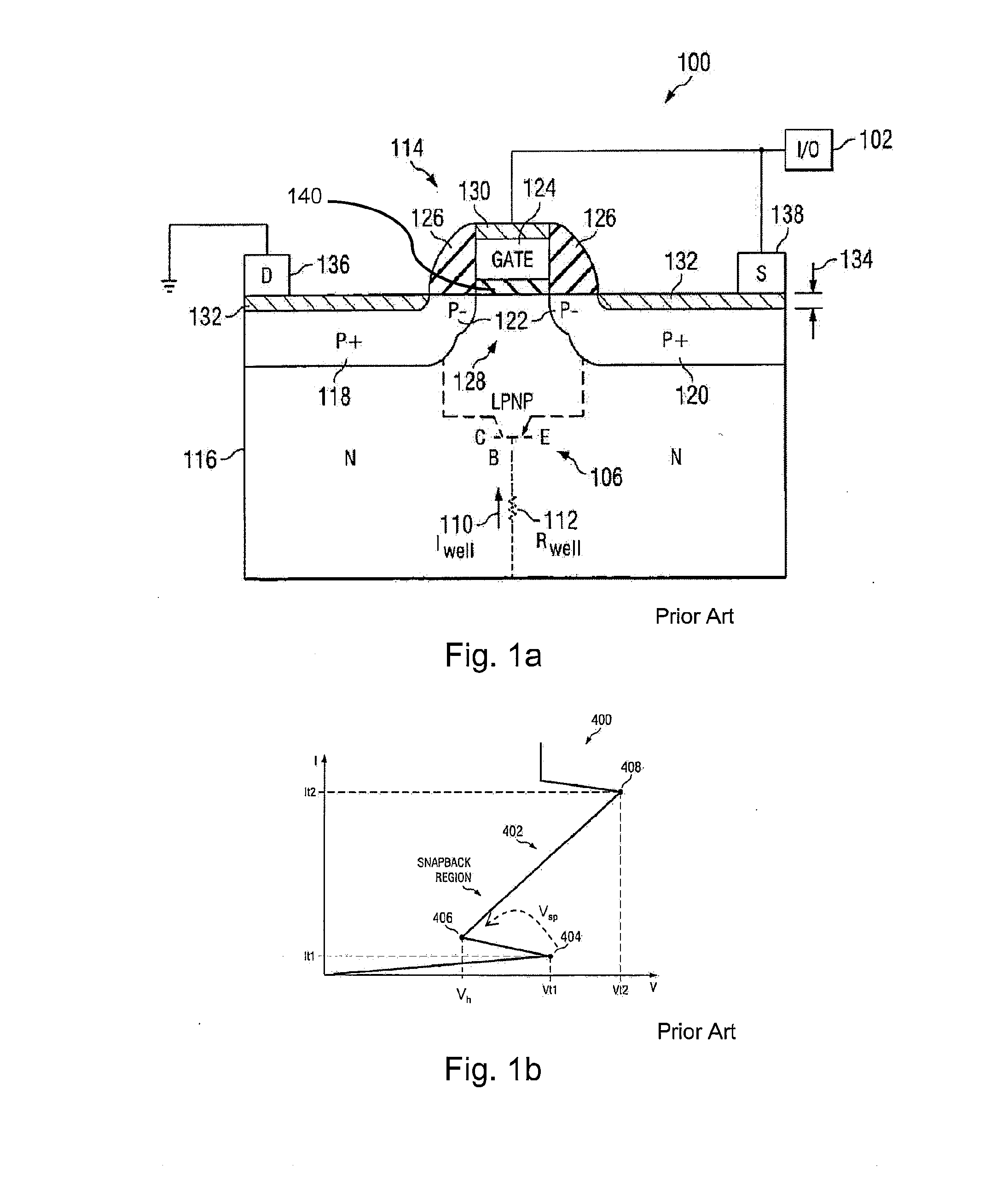

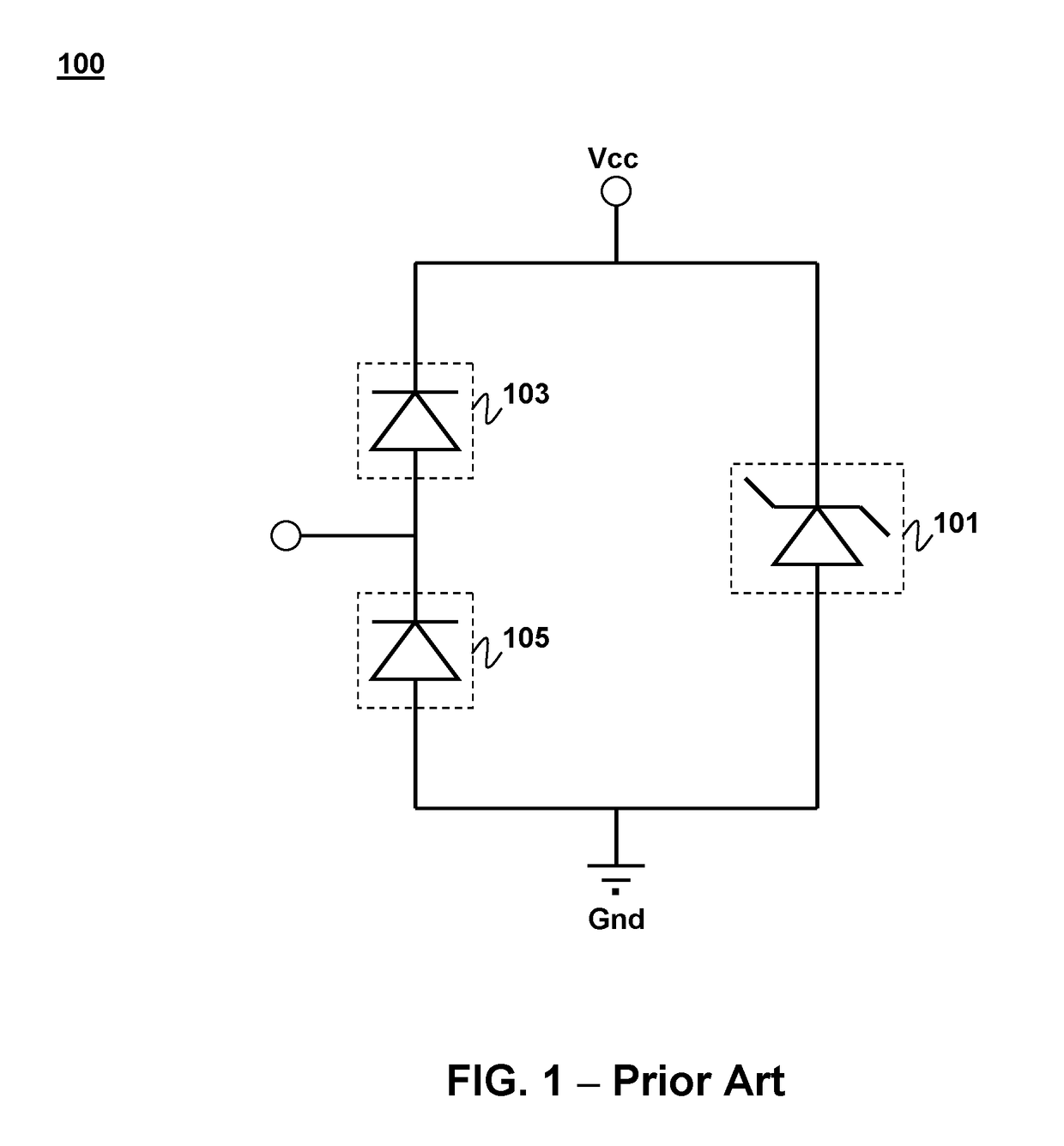

Snapback is a mechanism in a bipolar transistor in which avalanche breakdown or impact ionization provides a sufficient base current to turn on the transistor. It is used intentionally in the design of certain ESD protection devices integrated onto semiconductor chips. It can also be a parasitic failure mechanism when activated inadvertently, outwardly appearing much like latchup in that the chip seems to suddenly blow up when a high voltage is applied.

Semiconductor device

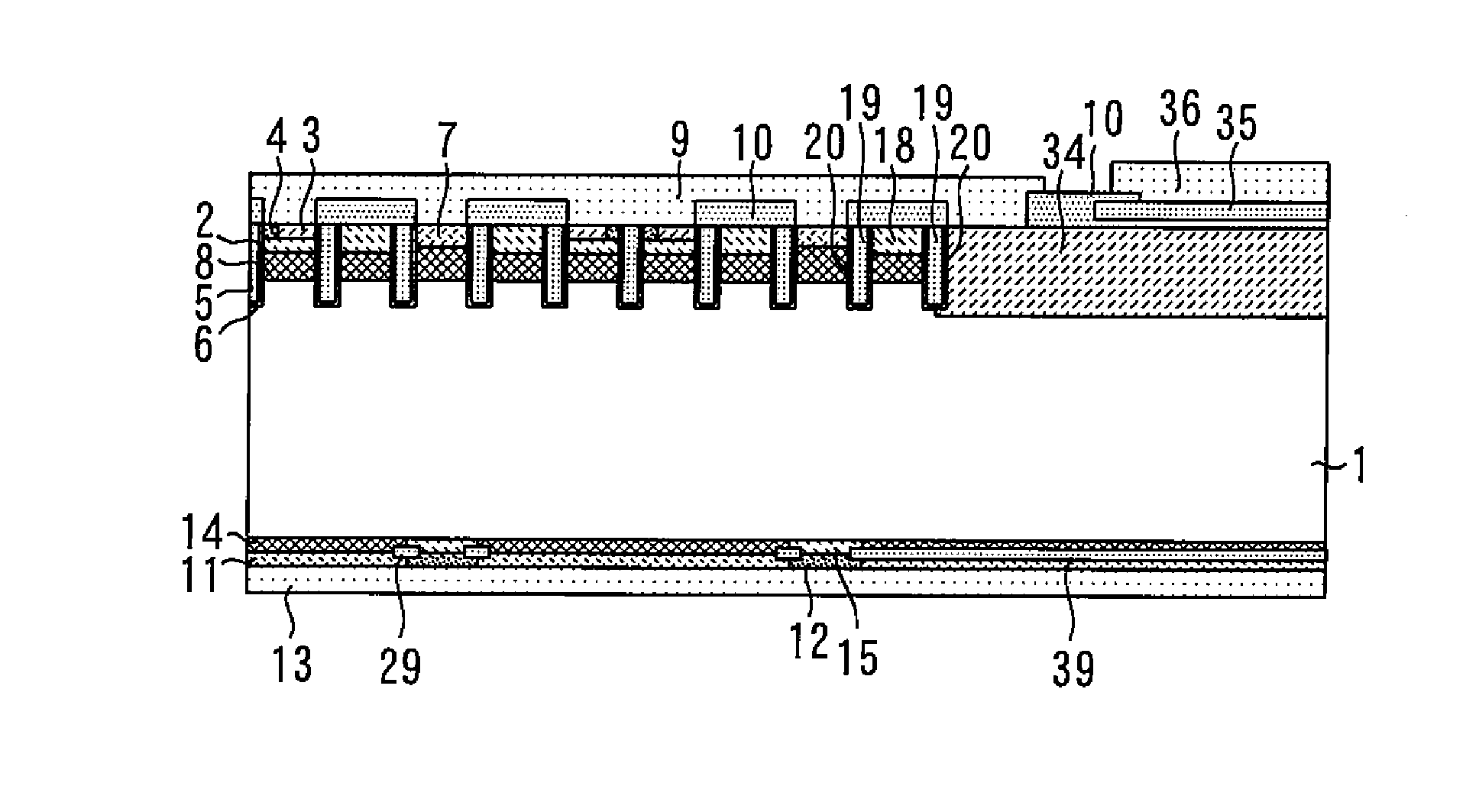

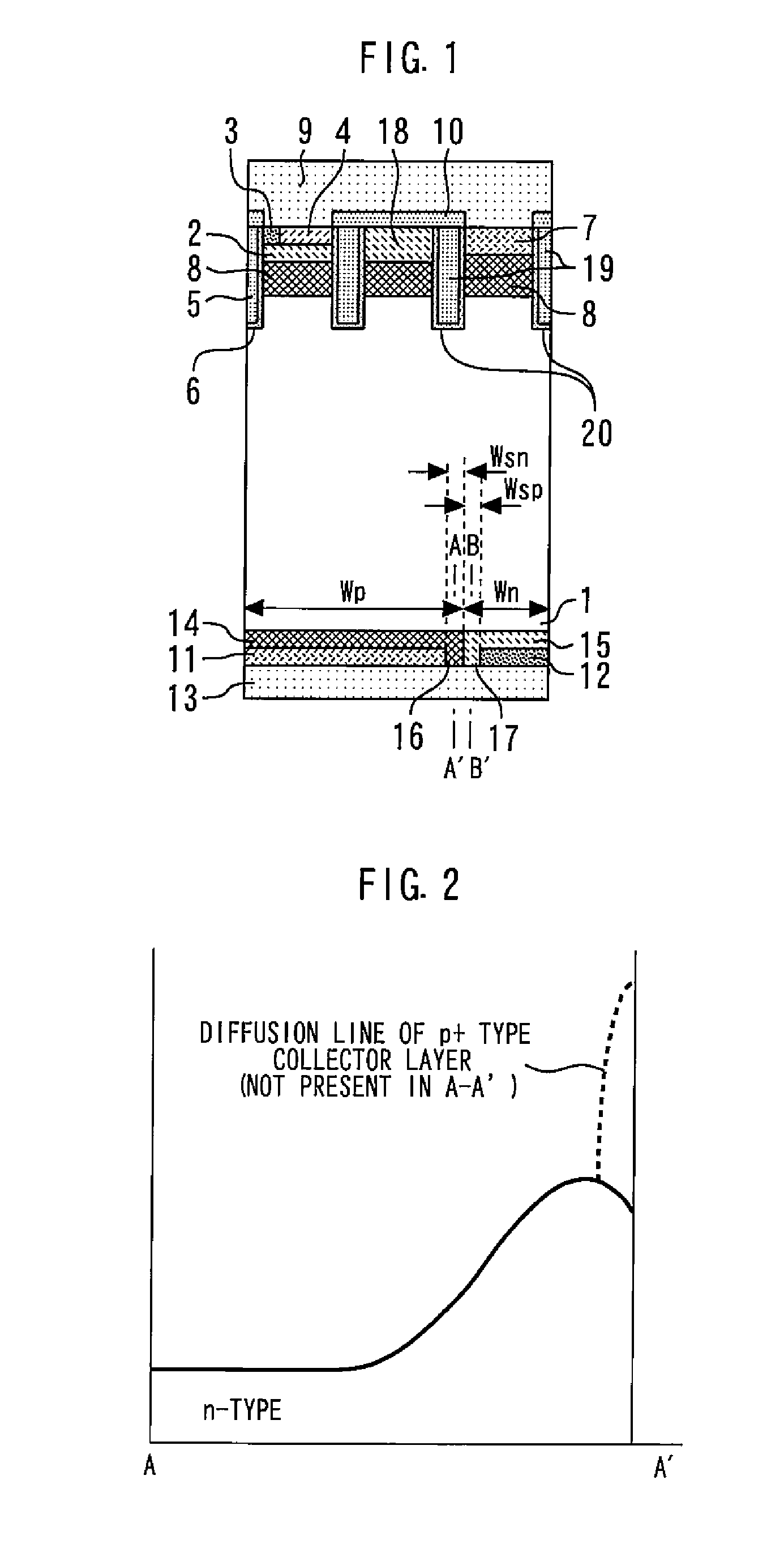

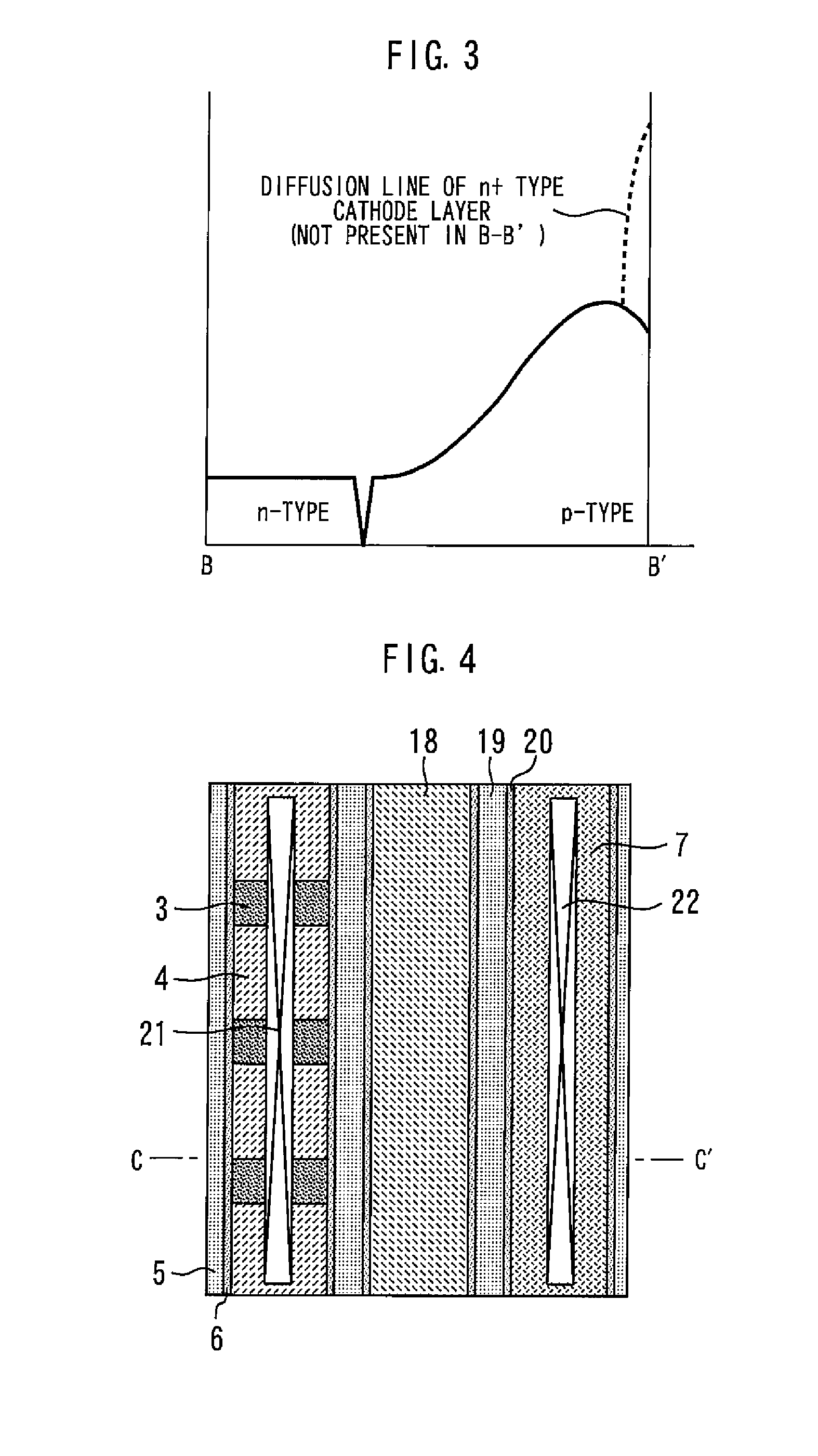

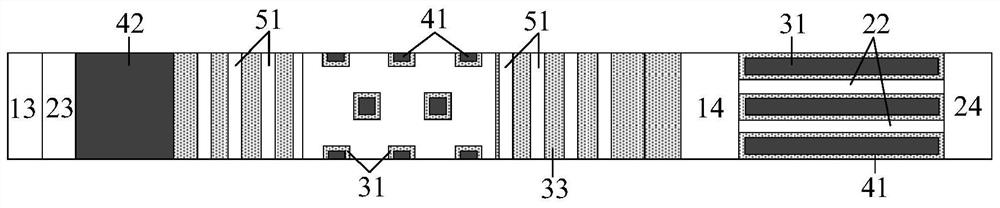

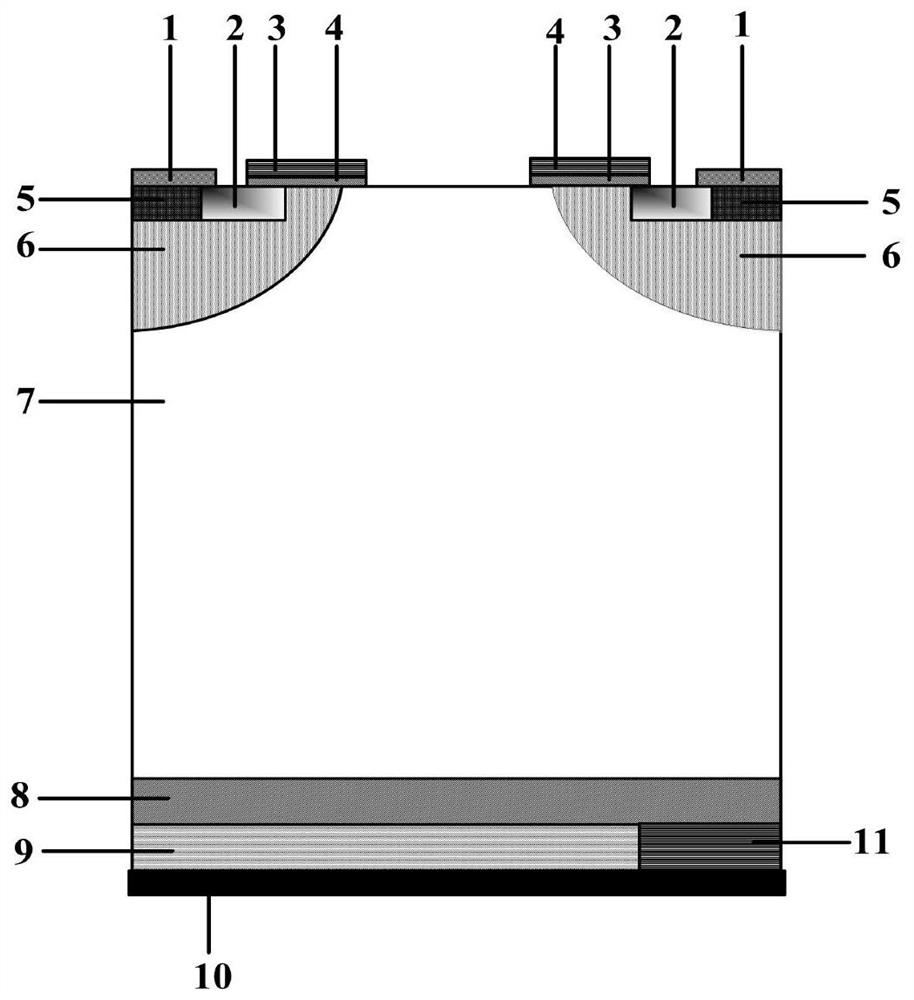

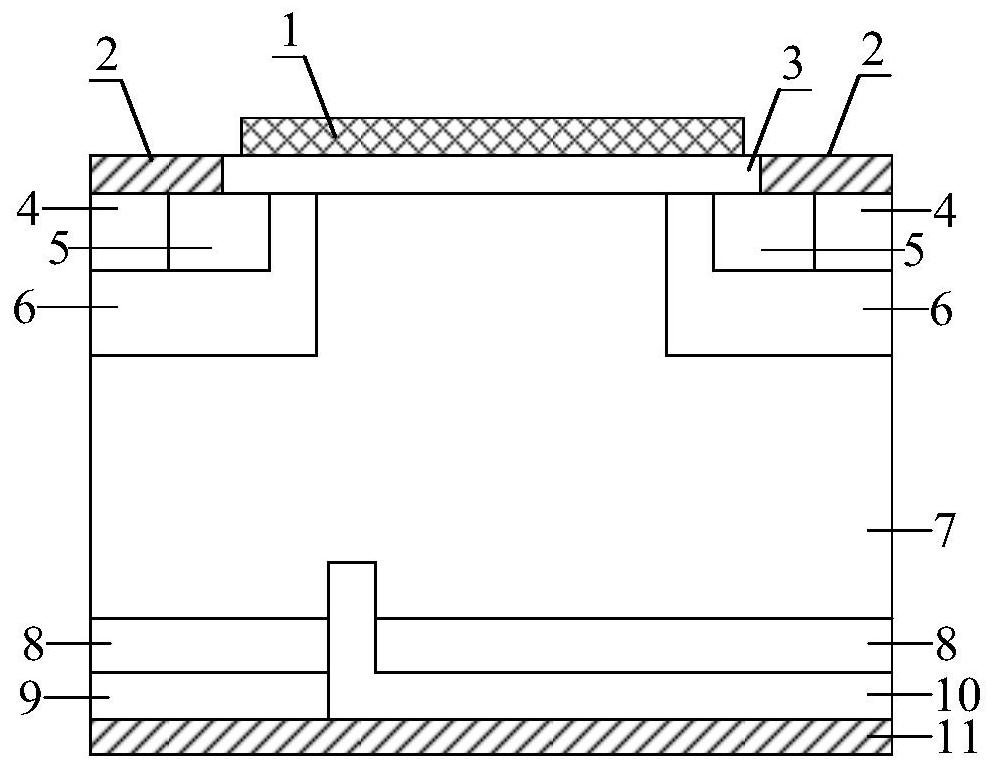

In the reverse-conducting IGBT according to the present invention, an n-type buffer layer surrounds a p-type collector layer. A p-type separation layer surrounds an n-type cathode layer. The n-type buffer layer separates the p-type collector layer and the p-type separation layer from each other. The p-type separation layer separates the n-type cathode layer and the n-type buffer layer from each other. Therefore, the present invention makes it possible to reduce snapback.

Owner:MITSUBISHI ELECTRIC CORP

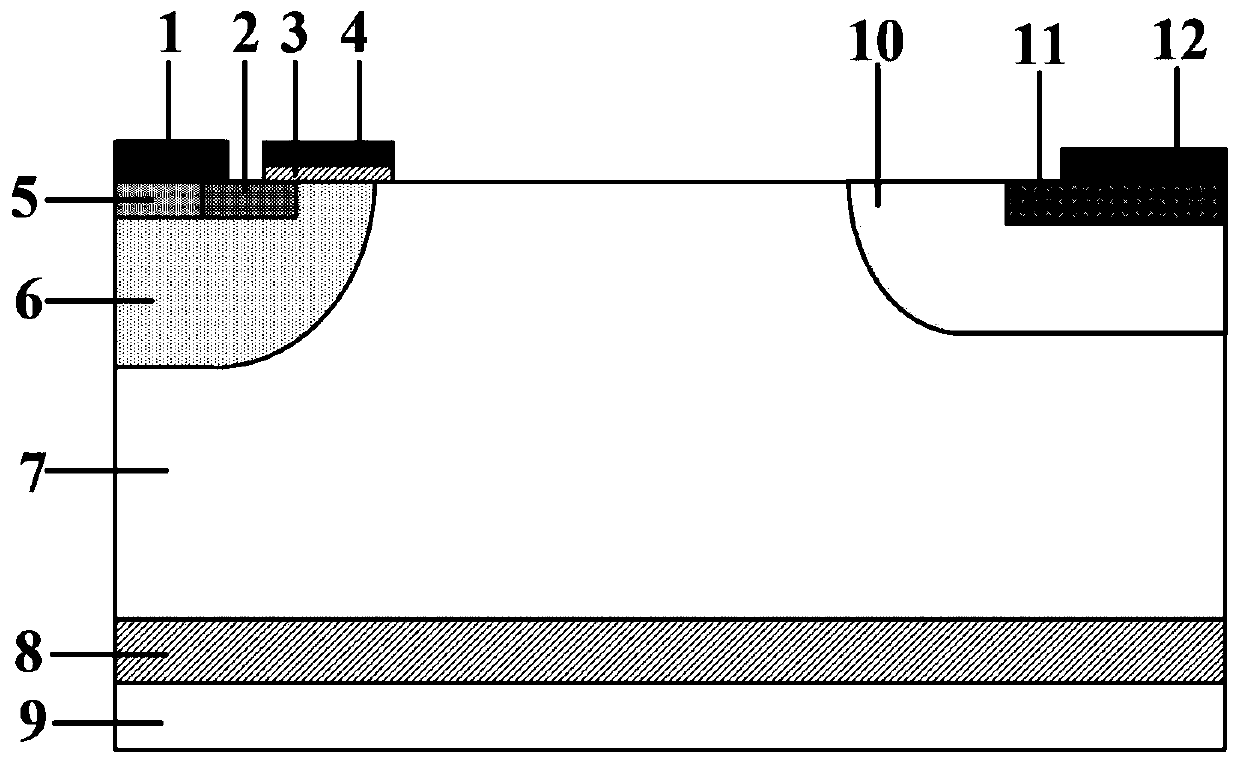

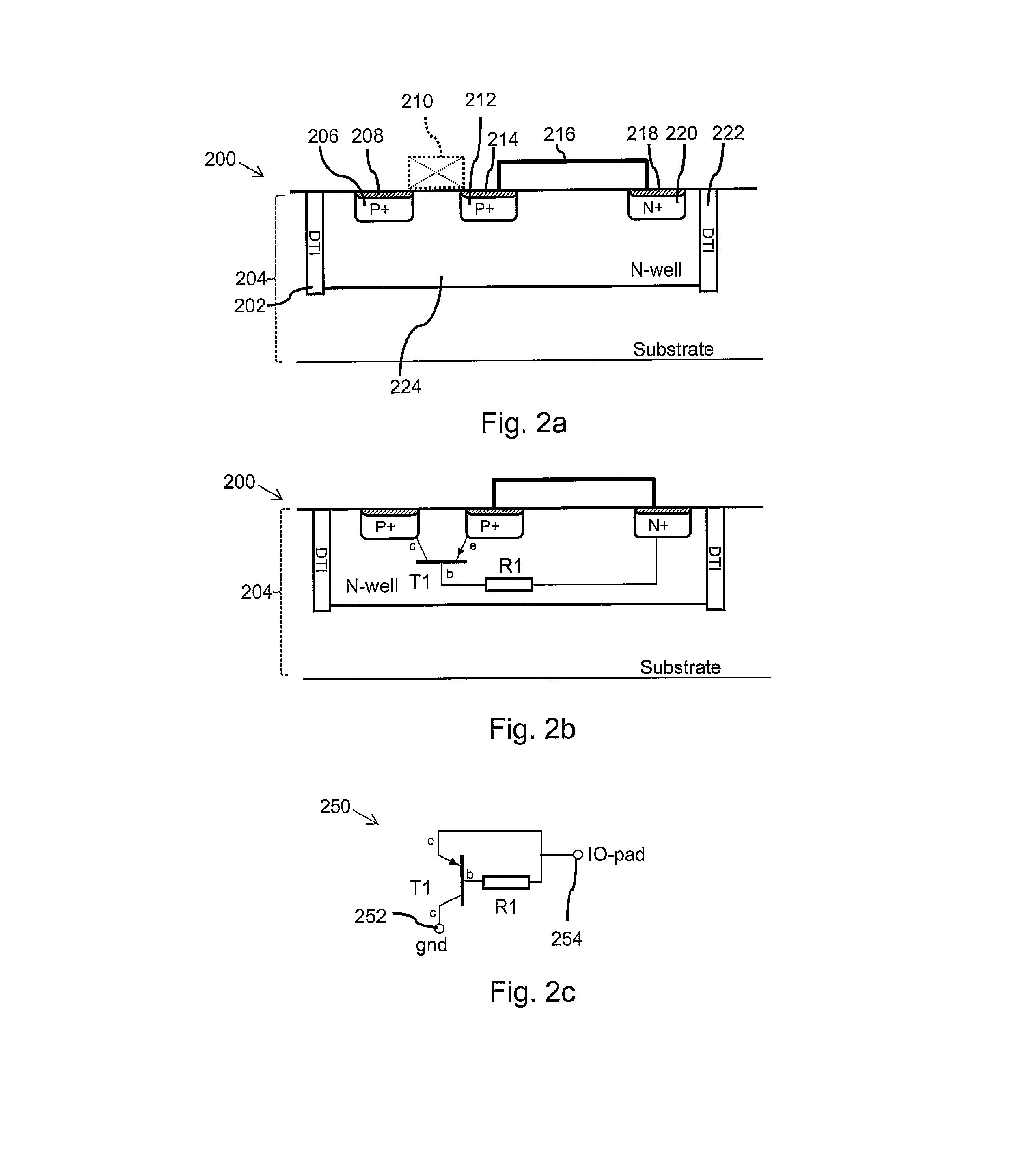

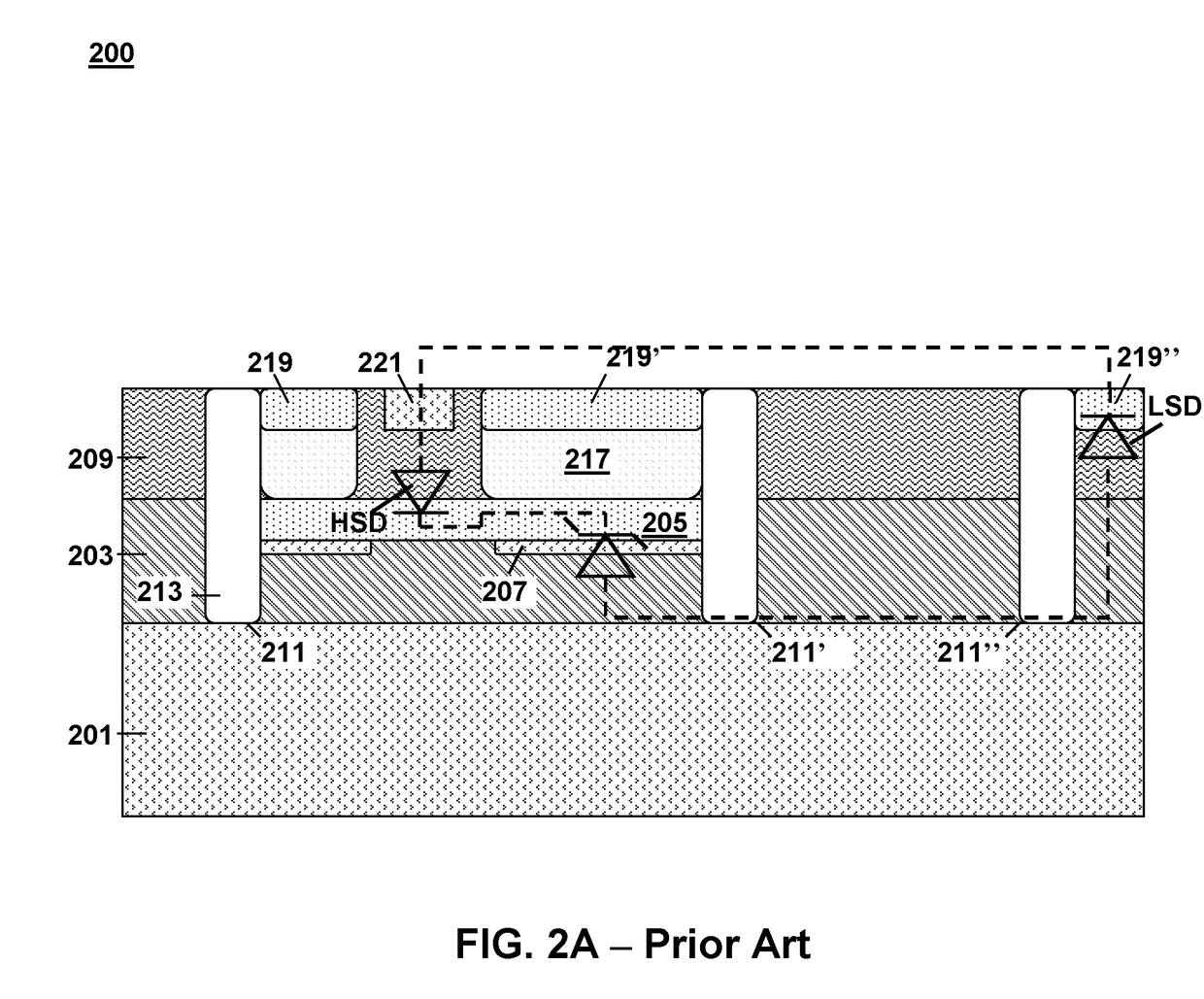

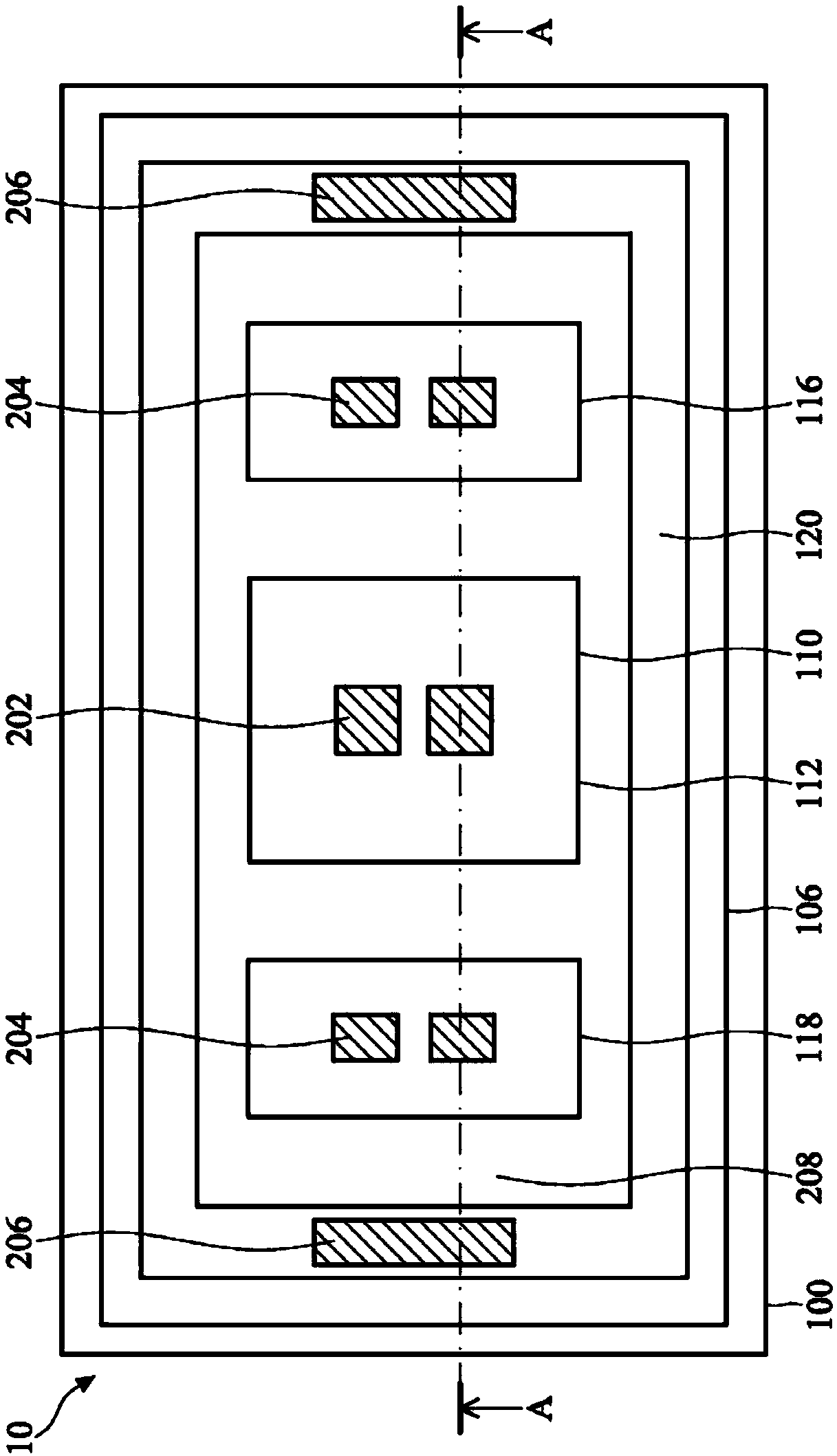

Low Voltage NPN with Low Trigger Voltage and High Snap Back Voltage for ESD Protection

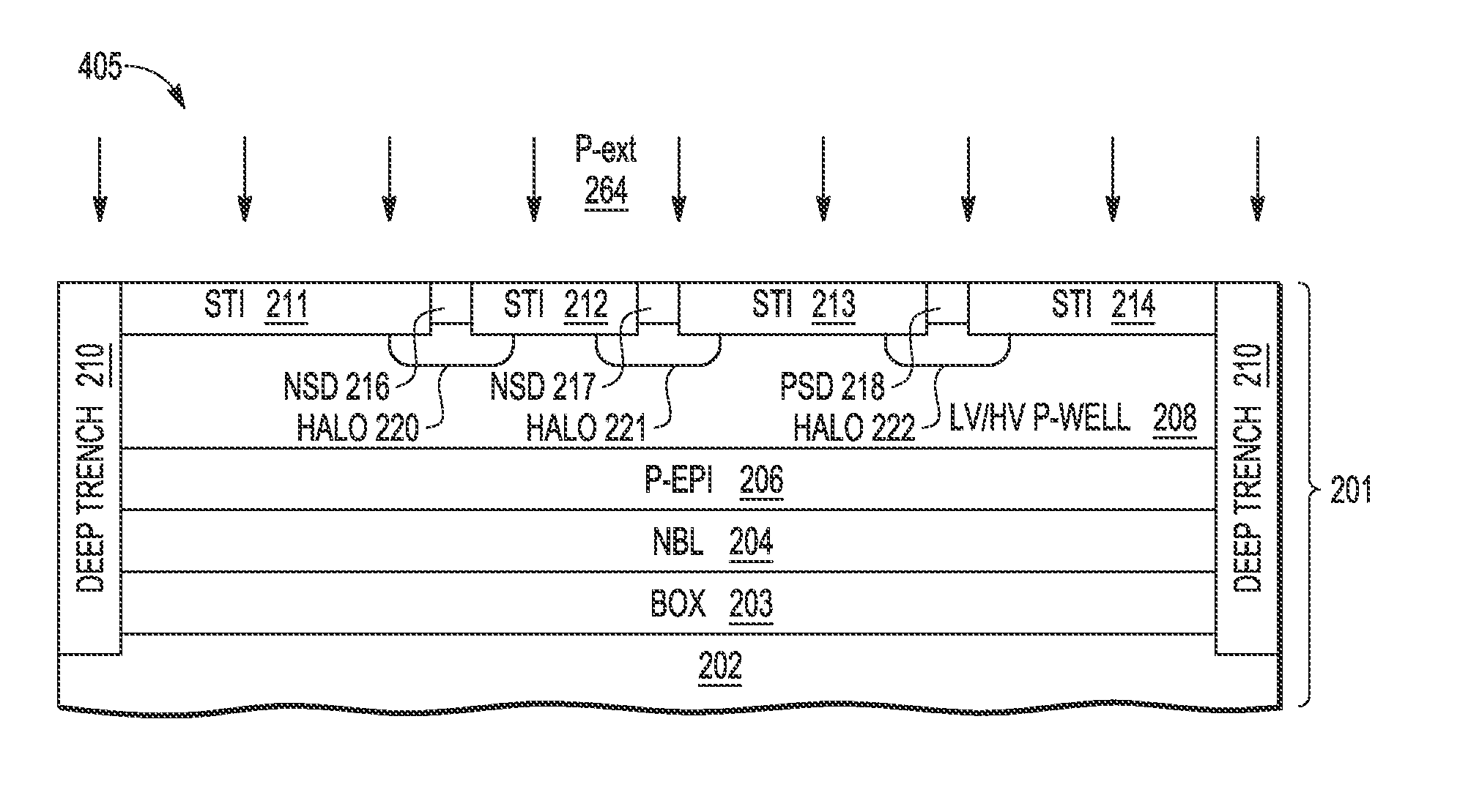

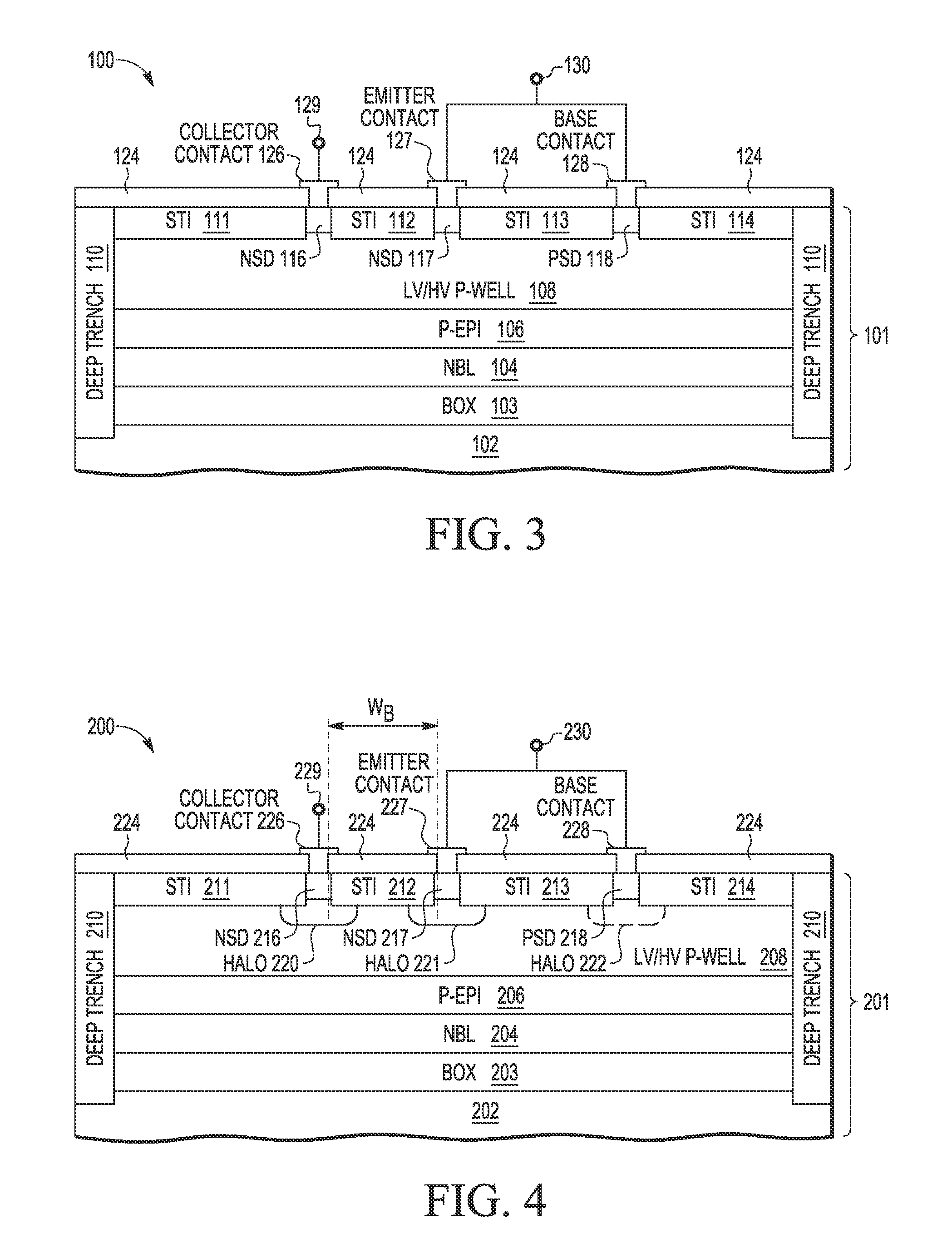

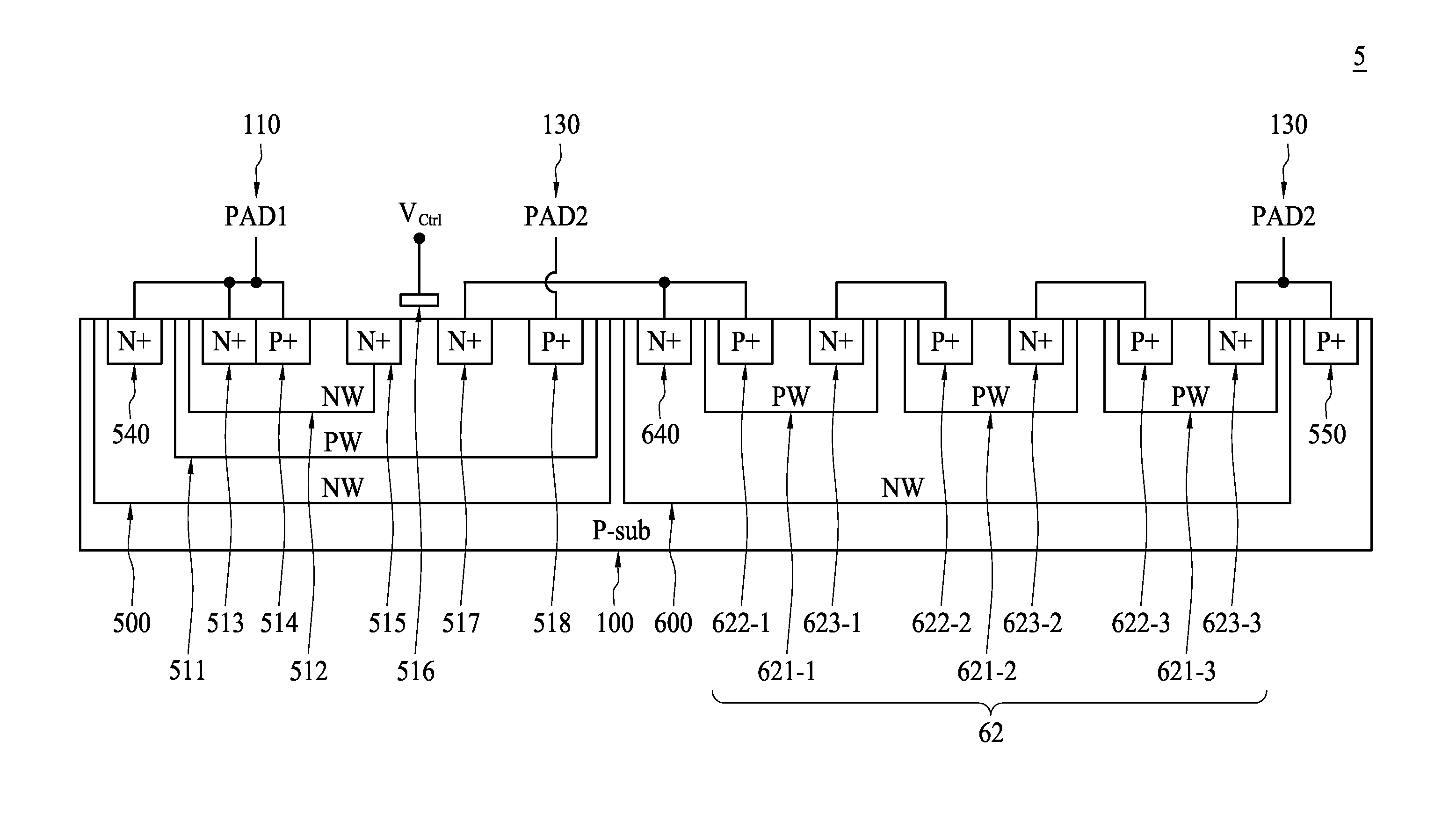

An area-efficient, low voltage ESD protection device (200) is provided for protecting low voltage pins (229, 230) against ESD events by using one or more stacked low voltage NPN bipolar junction transistors, each formed in a p-type material with an N+ collector region (216) and P+ base region (218) formed on opposite sides of an N+ emitter region (217) with separate halo extension regions (220-222) formed around at least the collector and emitter regions to improve the second trigger or breakdown current (It2) and set the snapback voltage (Vsb) and triggering voltage (Vt1) at the desired level.

Owner:NXP USA INC

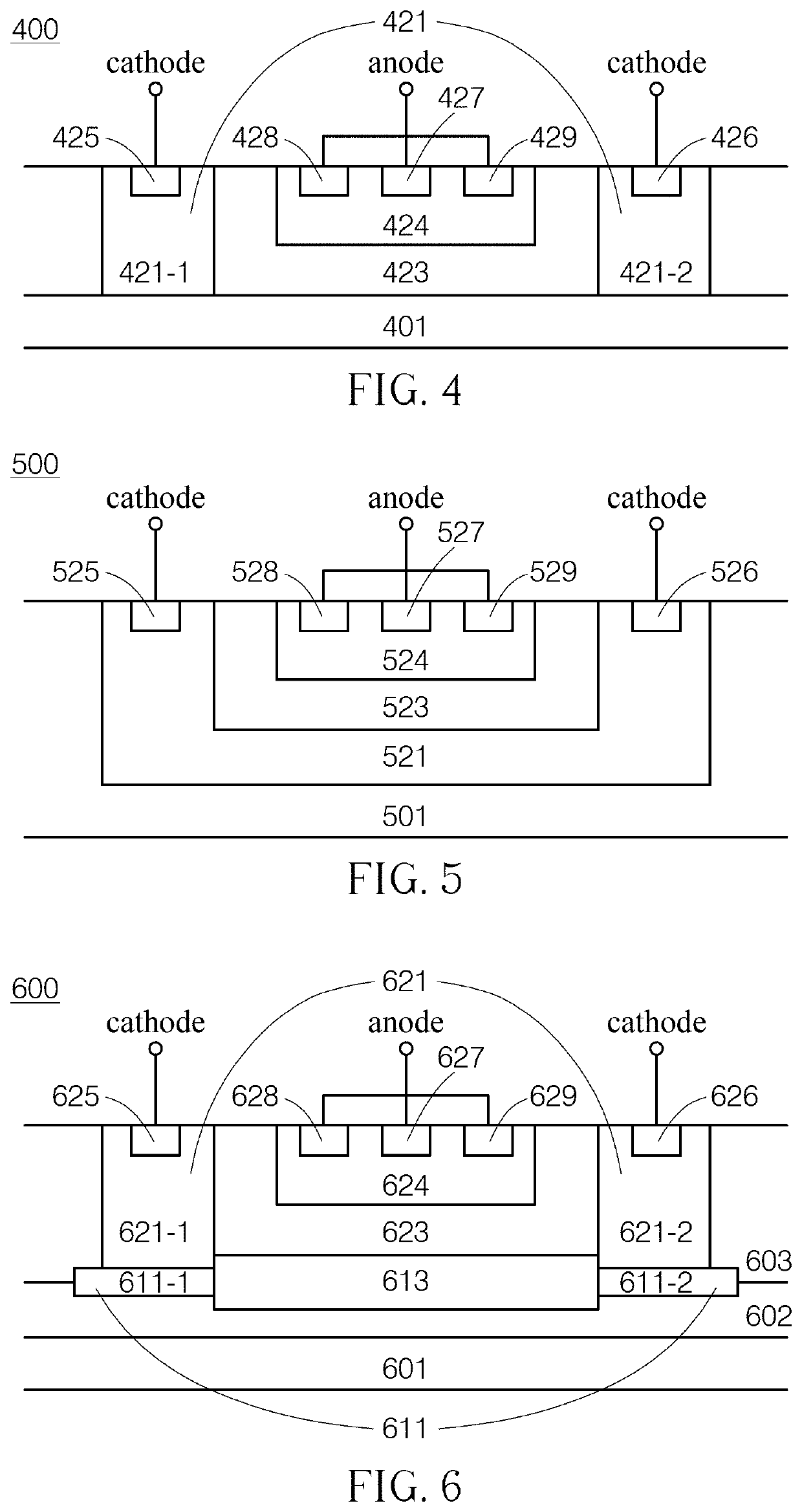

ESD protection circuit

ActiveUS20140197450A1Save layout area andDissipating an ESD currentTransistorSemiconductor/solid-state device detailsHemt circuitsEngineering

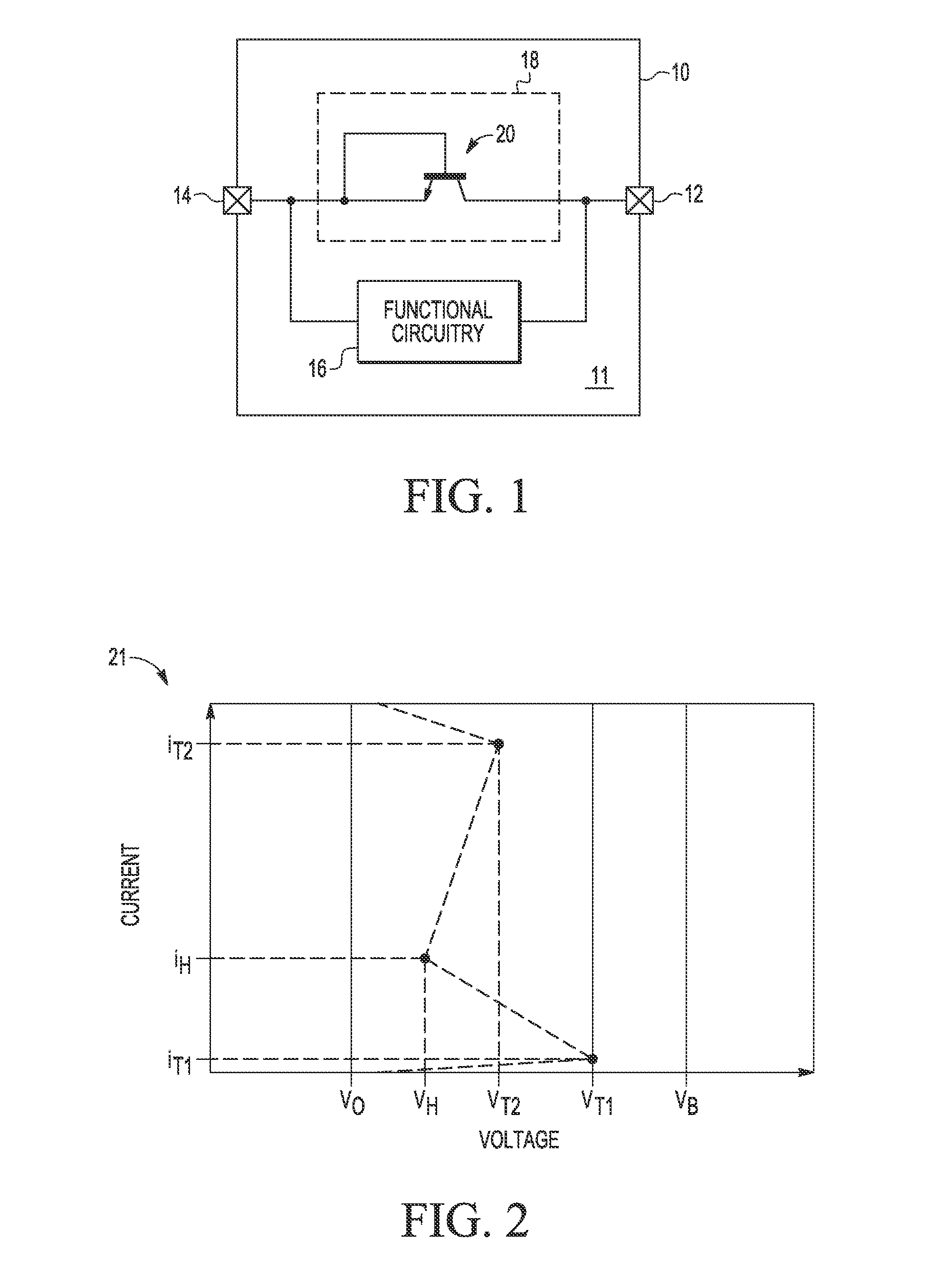

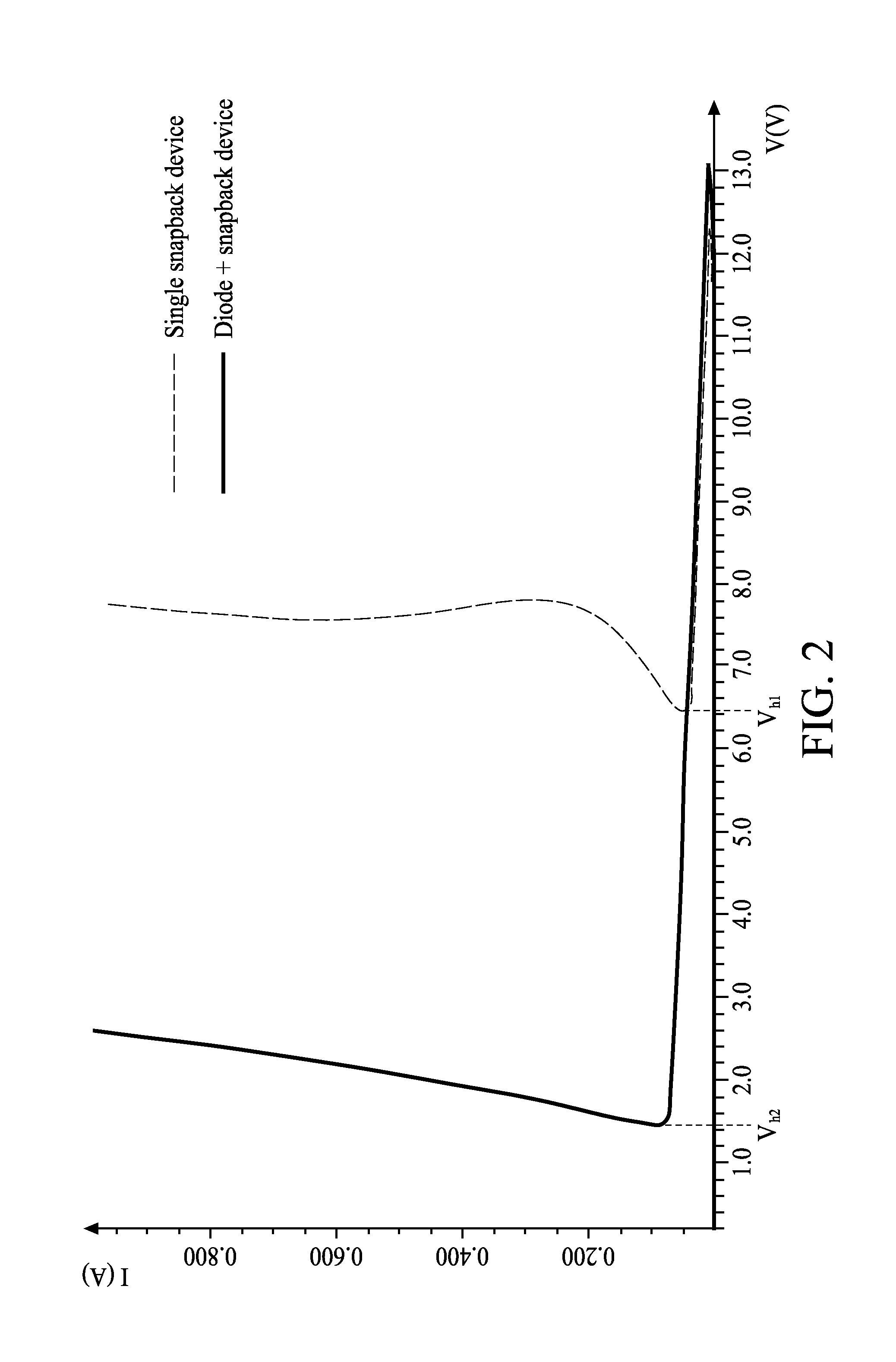

An electrostatic discharge (ESD) protection circuit is coupled between first and second pads to protect an internal circuit therebetween. Under a normal operating condition, a voltage on the first pad is higher than that on the second pad. The ESD protection circuit includes a substrate of a first conductivity type; first well of a second conductivity type in the substrate, wherein the first well is coupled to the first pad; a snapback device housed in the first well; and a diode string in the substrate, connected in series with the snapback device and separated from the first well, wherein the serially connected diode string and snapback device is connected between the first pad and the second pad. With the isolation from the first well, the holding voltage of the ESD protection circuit can be tuned by adjusting the number of diodes in the diode string without using a guard ring.

Owner:MACRONIX INT CO LTD

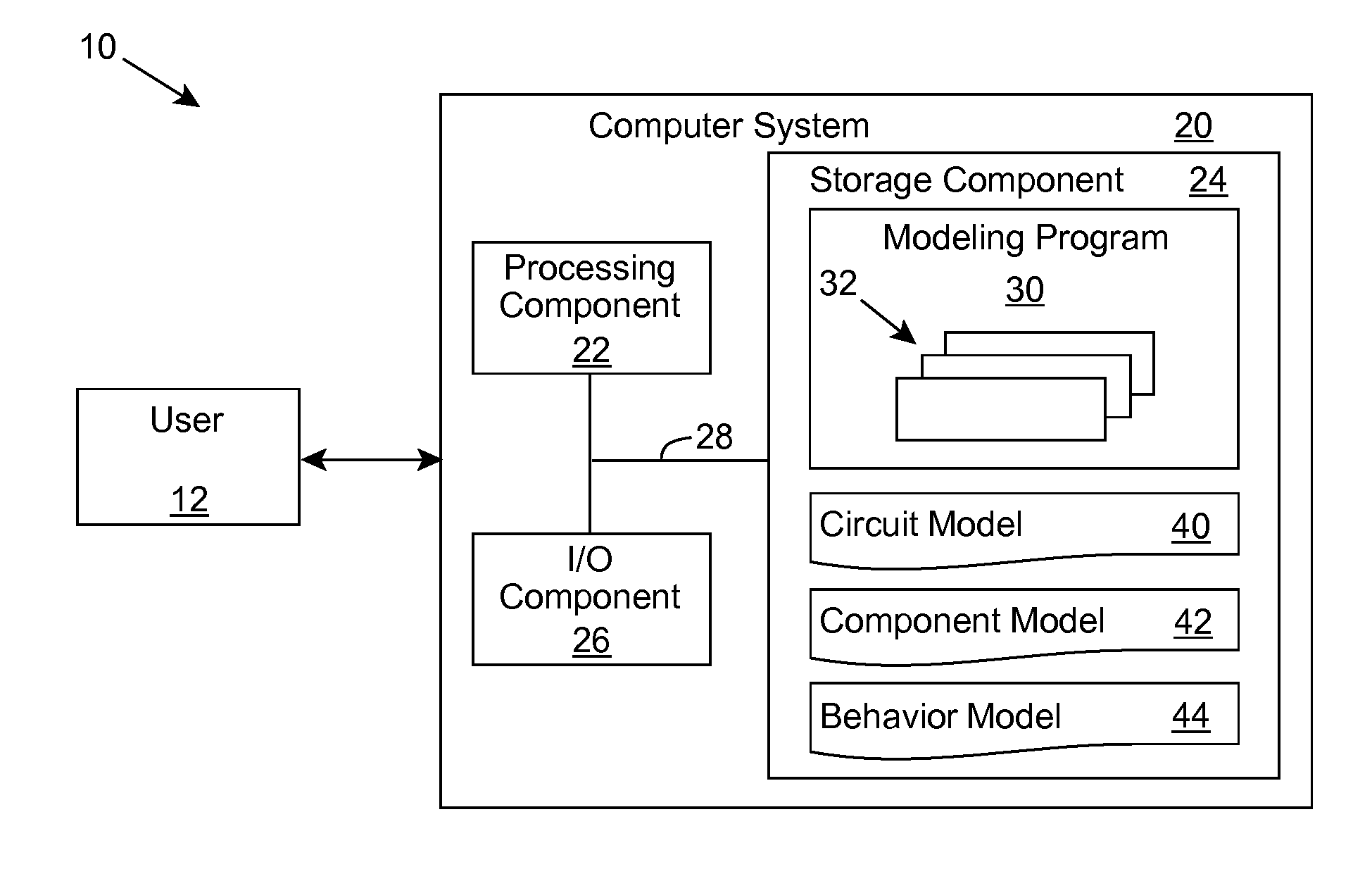

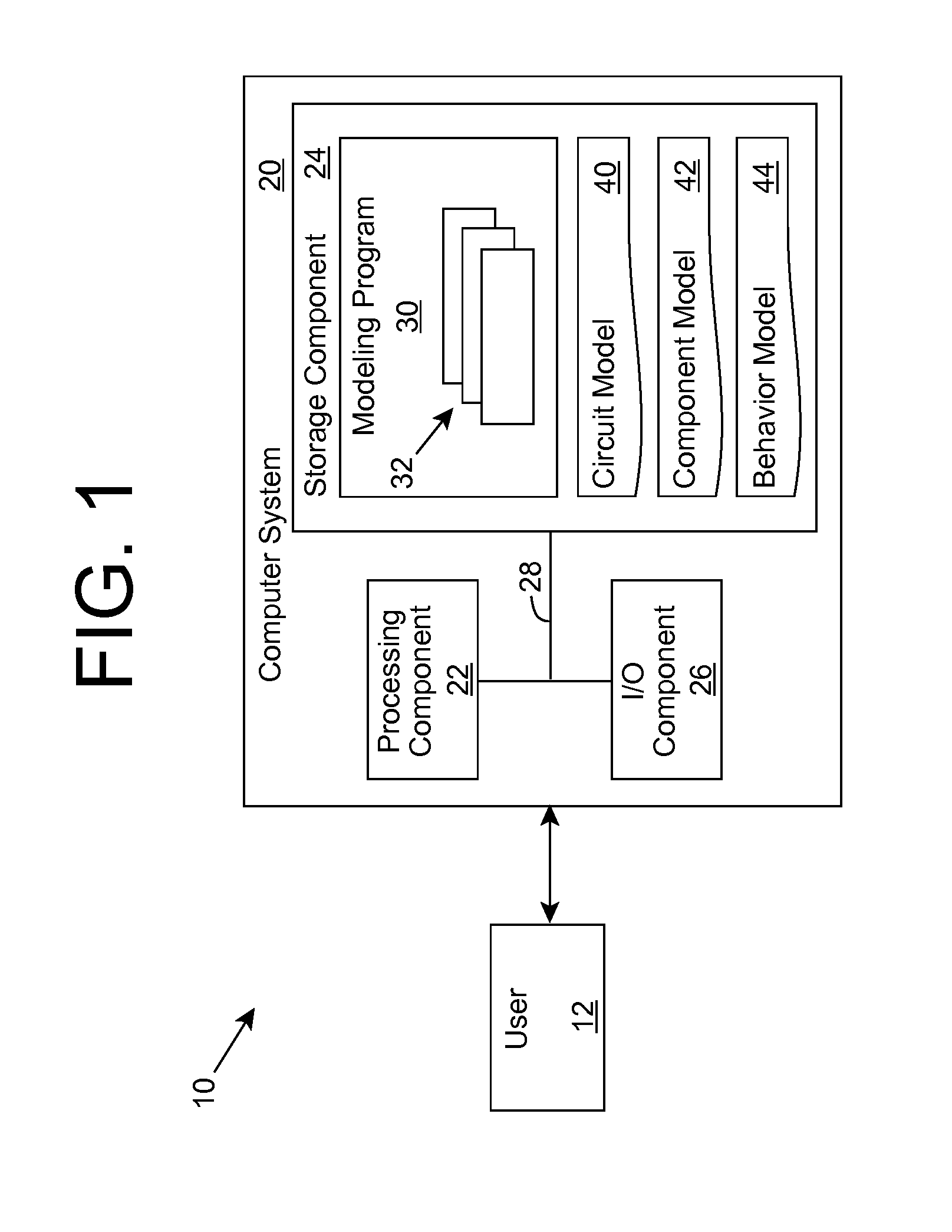

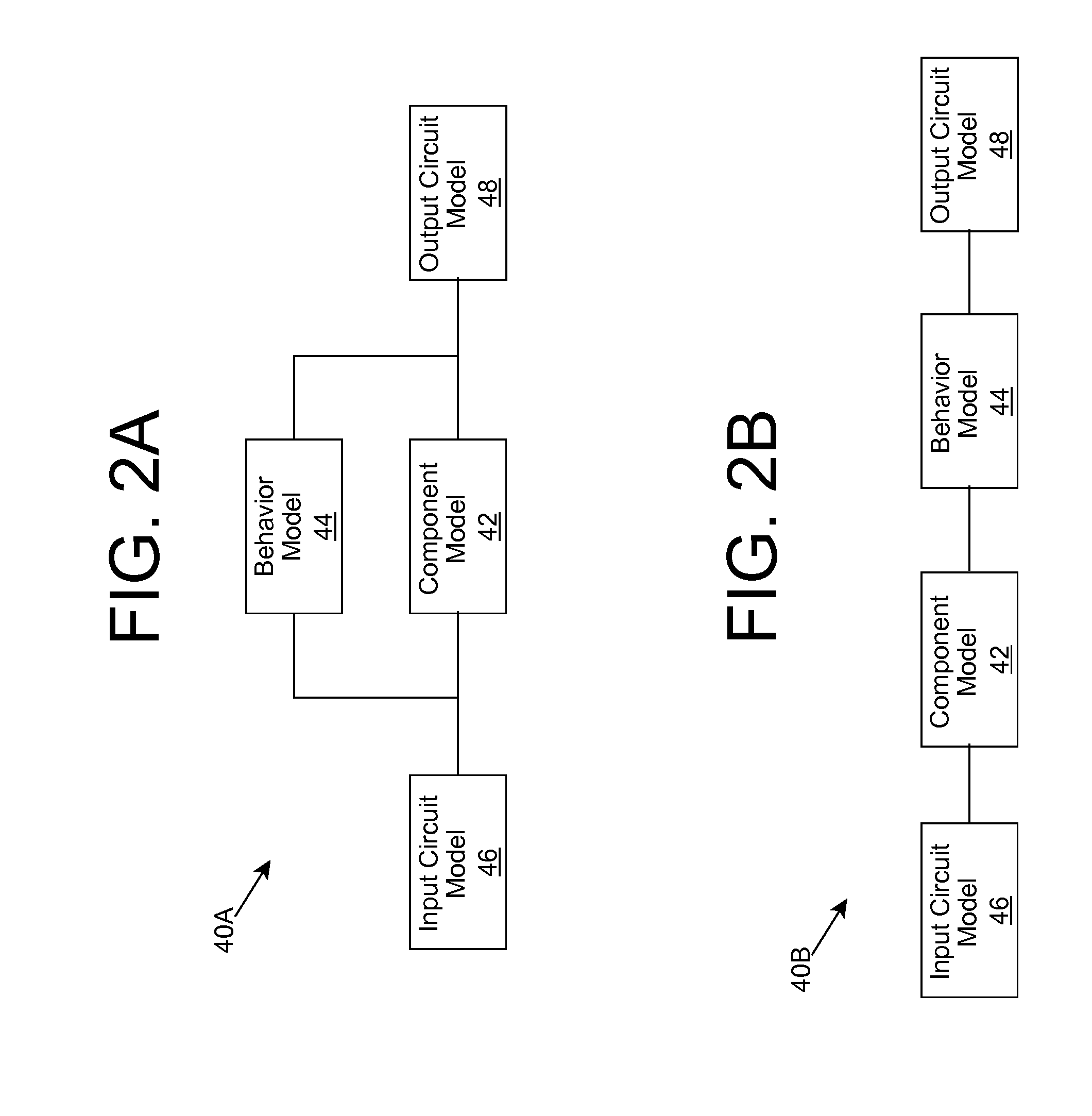

Component behavior modeling using separate behavior model

A behavior model is provided, which is configured to simulate one aspect of the behavior of a component apart from the component model for the component. The behavior model can be included in a circuit model used to simulate operation of a circuit. The circuit model can include a component model for a component and a corresponding behavior model, which is located in parallel or series with the component model. The component model and behavior model can collectively simulate all of the behavior of the component within the circuit. In an embodiment, the behavior model simulates snapback behavior exhibited by the component.

Owner:GLOBALFOUNDRIES INC

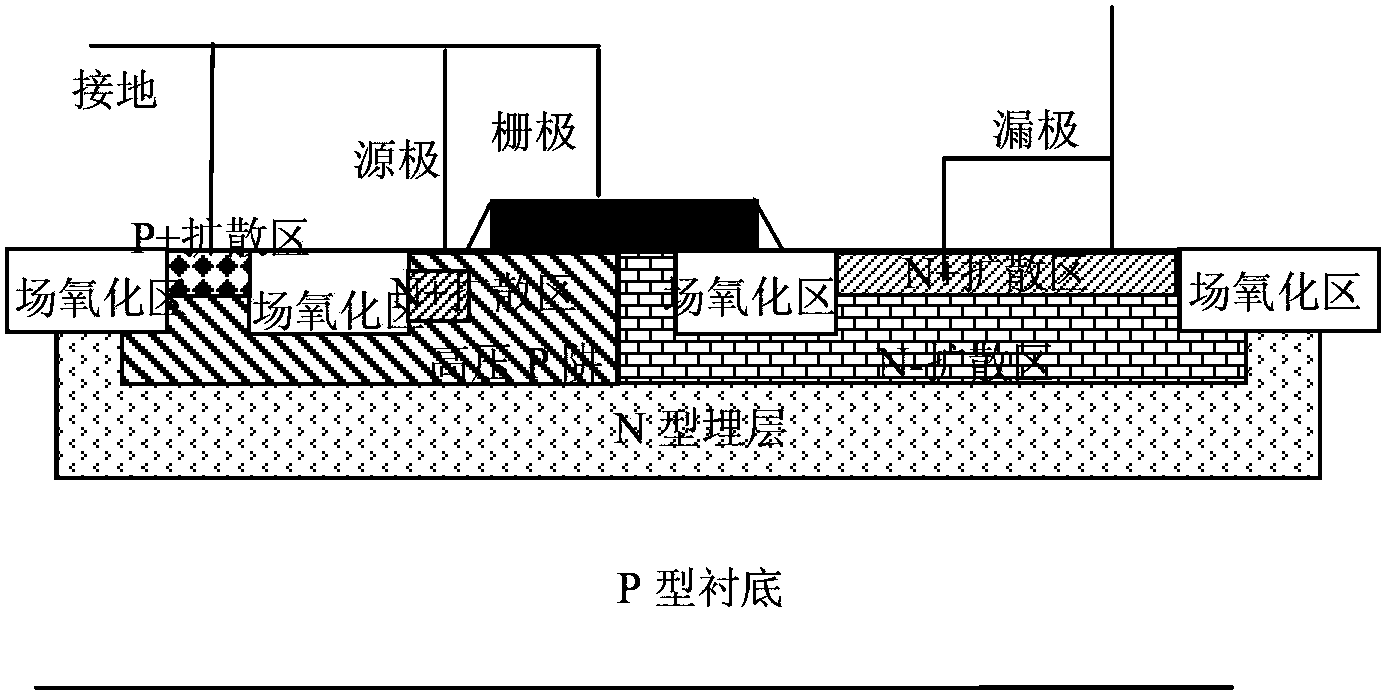

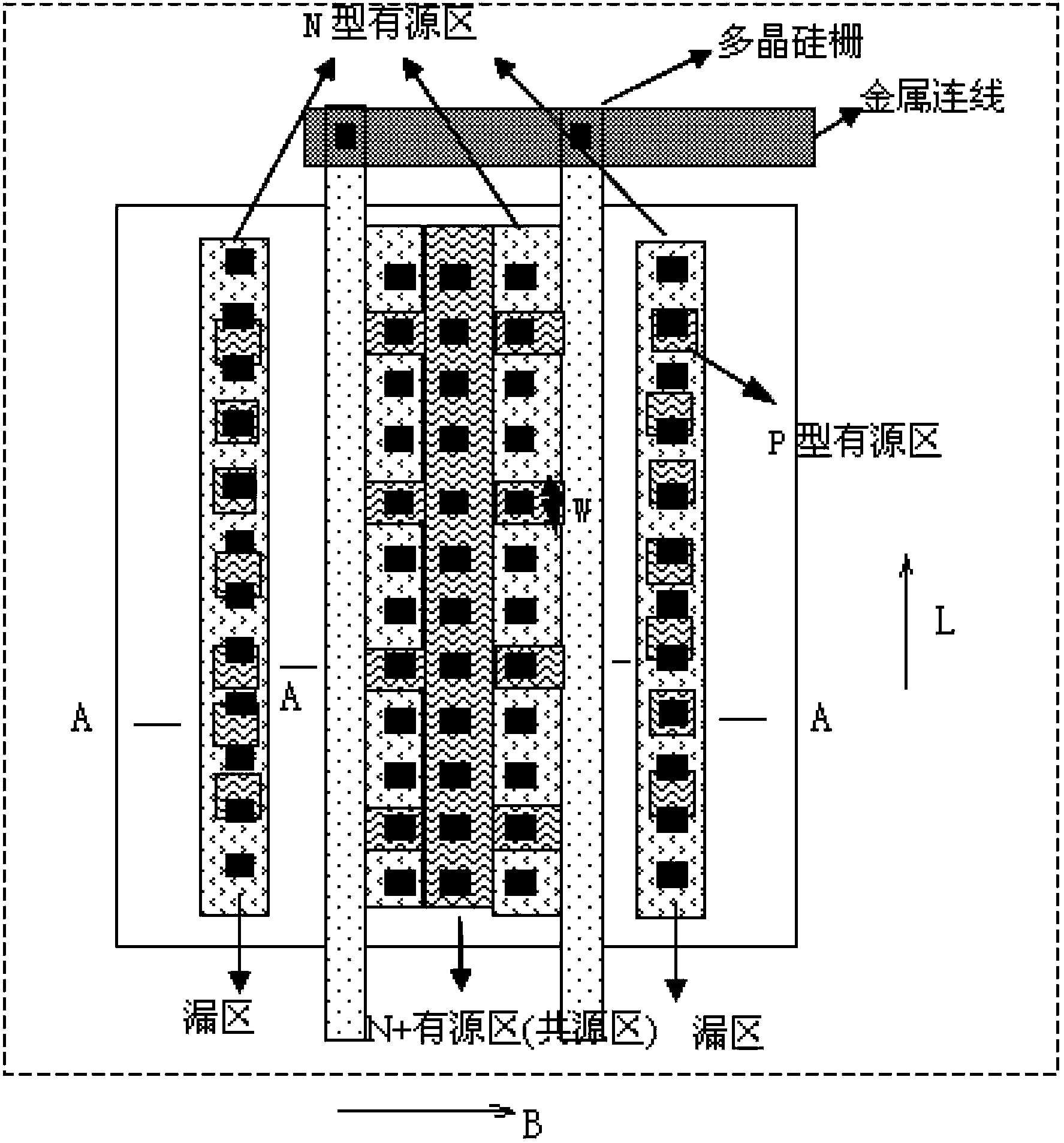

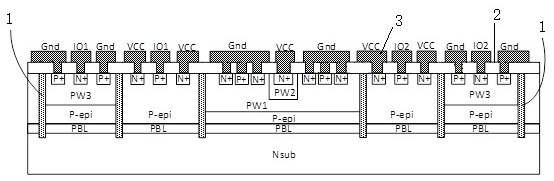

High-voltage NLDMOS (N-type laterally diffused metal oxide semiconductor) structure for electrostatic protection

The invention discloses a high-voltage NLDMOS (N-type laterally diffused metal oxide semiconductor) structure for electrostatic protection. The high-voltage NLDMOS structure comprises an NLDMOS formed in an N-type buried layer above a silicon substrate. The NLDMOS is arranged to be a multi-finger structure. A source region between two drain regions is a joint source region. N-type active regions and P-type active regions are arranged at intervals along the length direction in active regions of the drain regions. The P-type active regions are inserted into the joint source region and embedded in the N-type active regions. The N-type active regions in the source region are separated respectively by the P-type active regions. The P-type active regions and the N-type active regions are arranged at intervals along the length direction. All drain electrodes are connected to an ESD (electro-static discharge) access end. All source electrodes are connected to the ground. All grid electrodes are connected to a signal end. By changing the width of a diffused region P+, close to the grid electrodes, on the source region, the high-voltage NLDMOS structure can effectively adjust trigger current and snapback voltage. By the high-voltage NLDMOS structure applied to high-voltage electrostatic protection, locking-resisting capability of an LDMOS (laterally diffused metal oxide semiconductor) can be effectively improved, and electrostatic protection capability of the LDMOS can be ensured not to be affected.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

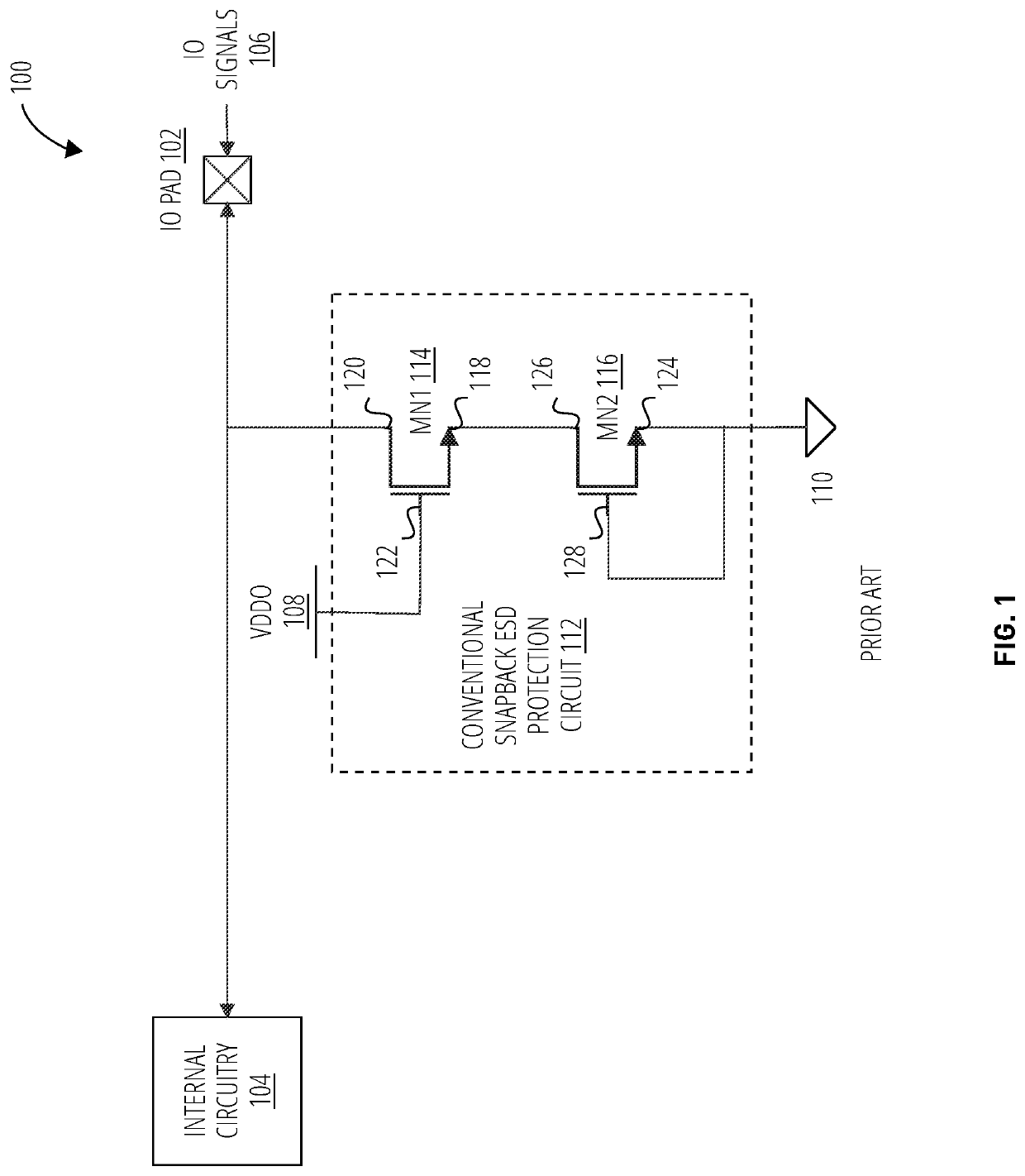

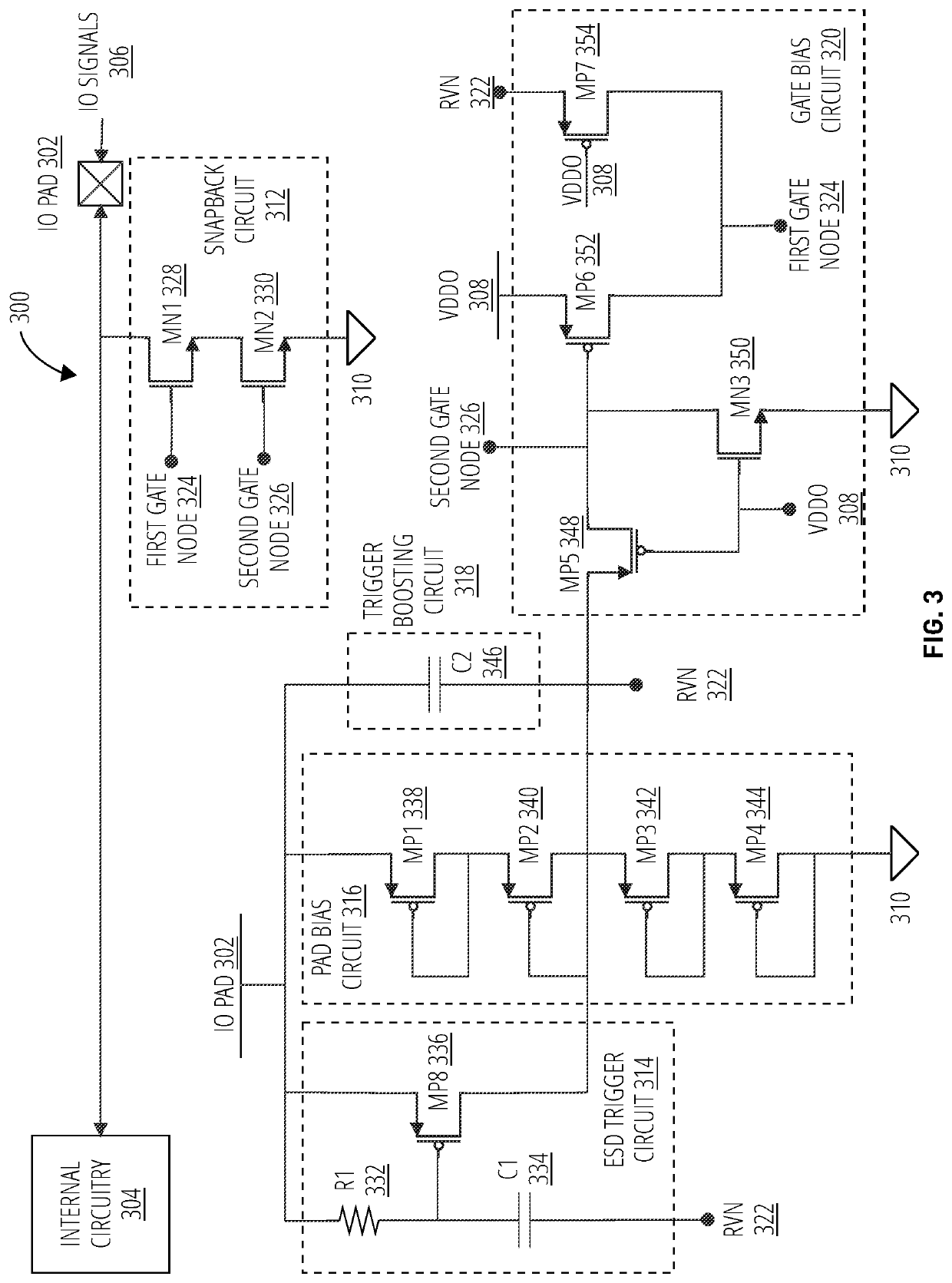

Snapback electrostatic discharge protection for electronic circuits

Snapback ESD protection circuits that include an Input / Output pad, a ground source, a first and a second NMOS transistor, and trigger circuit, pad bias circuit, and gate bias circuit. The first transistor drain connects to the pad. The second transistor drain connects to the first transistor source. The second transistor source connects to ground. The trigger circuit connects to the pad and a reference voltage to detect an ESD event at the pad. The pad bias circuit connects to the pad, the trigger circuit, ground, and the reference voltage to manage a voltage level for the reference voltage. The gate bias circuit connects to the reference voltage, a supply voltage, ground, and the gates of the first and second transistor to dynamically control the voltage of each gate of the first and a second NMOS transistor.

Owner:WESTERN DIGITAL TECH INC

SOI lateral insulated gate bipolar transistor

ActiveCN111969049AIncrease saturation currentLower forward voltage dropSemiconductor devicesEngineeringElectrode Contact

The invention provides an SOI transverse insulated gate bipolar transistor, which is characterized in that a first dielectric oxide layer and a floating field plate polycrystalline silicon electrode form a longitudinal floating field plate which is distributed in a whole second conduction type drift region to form a longitudinal floating field plate array; and a longitudinal field plate connectedwith the collector contact electrode is formed in the collector region by the same process, and a second conductive type well region is inserted in parallel to form an anode resistance structure. Whenthe transistor is in an on state, an accumulation layer can be formed on the surface of the longitudinal floating field plate, and the saturation current of the device is improved. The longitudinal field plate introduced into the well region of the second conductive type can accurately control the size of the anode resistance, eliminates the impact on the output characteristics of the device fromthe snapback phenomenon, and improves the stability of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

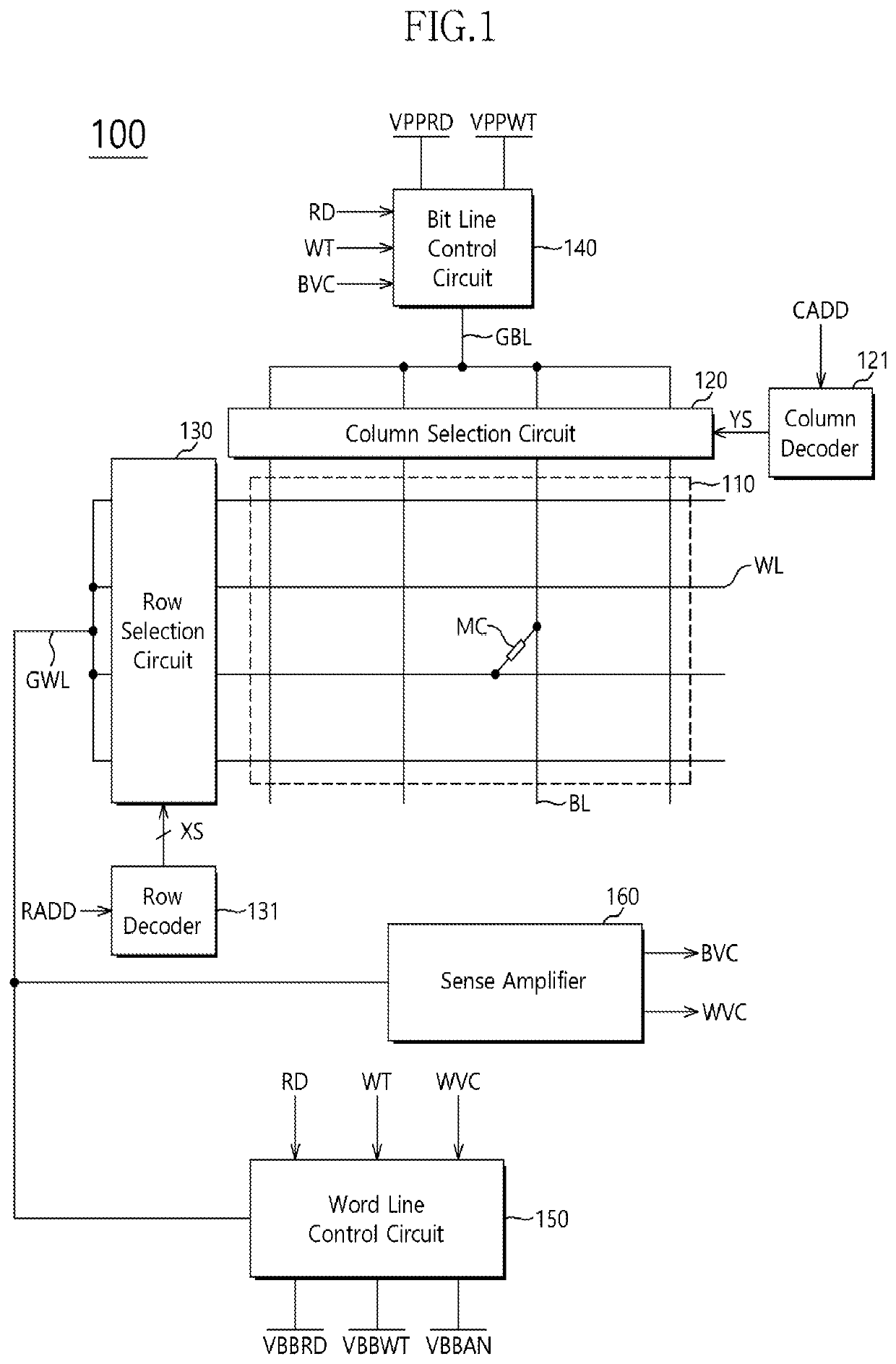

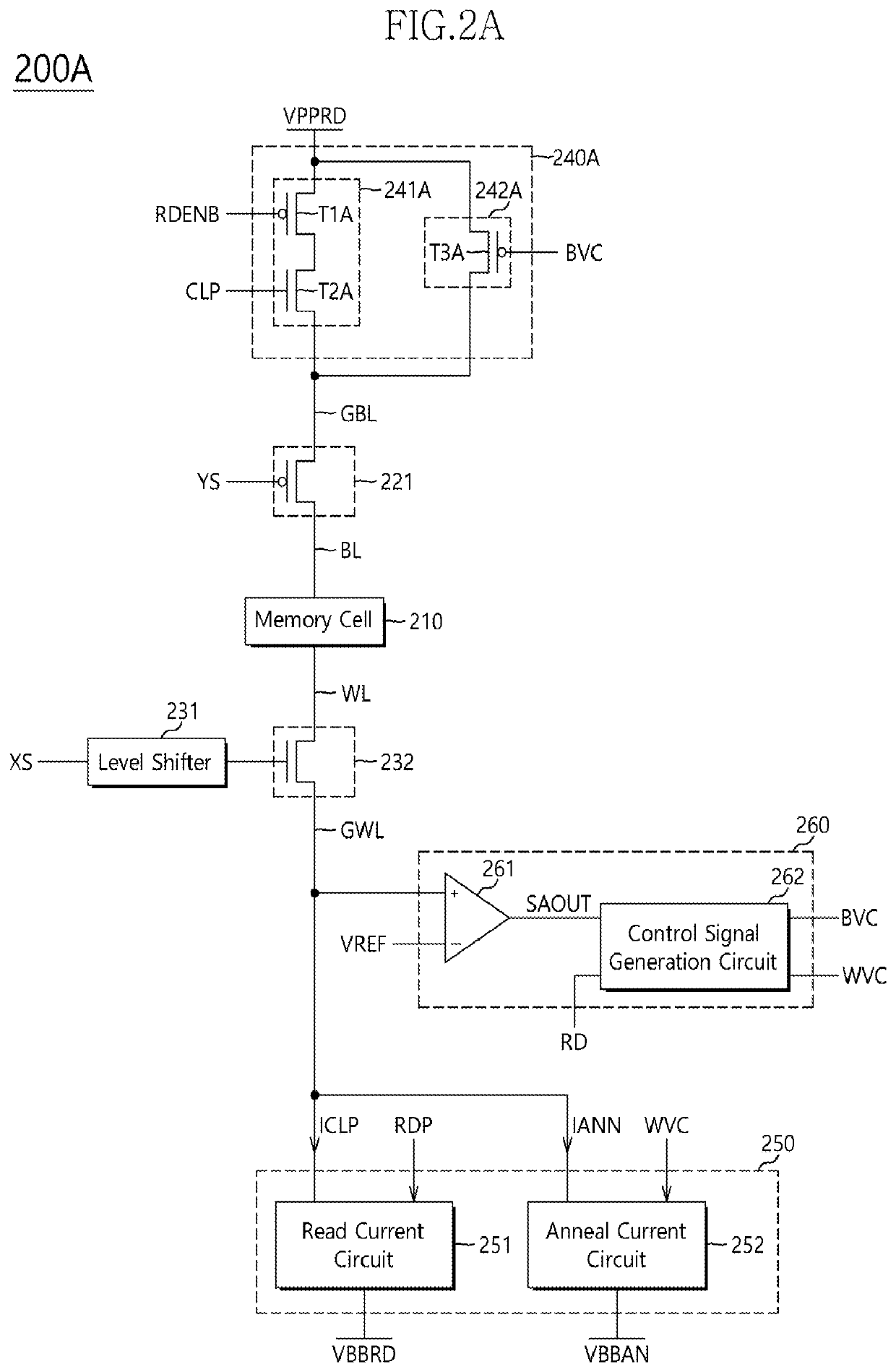

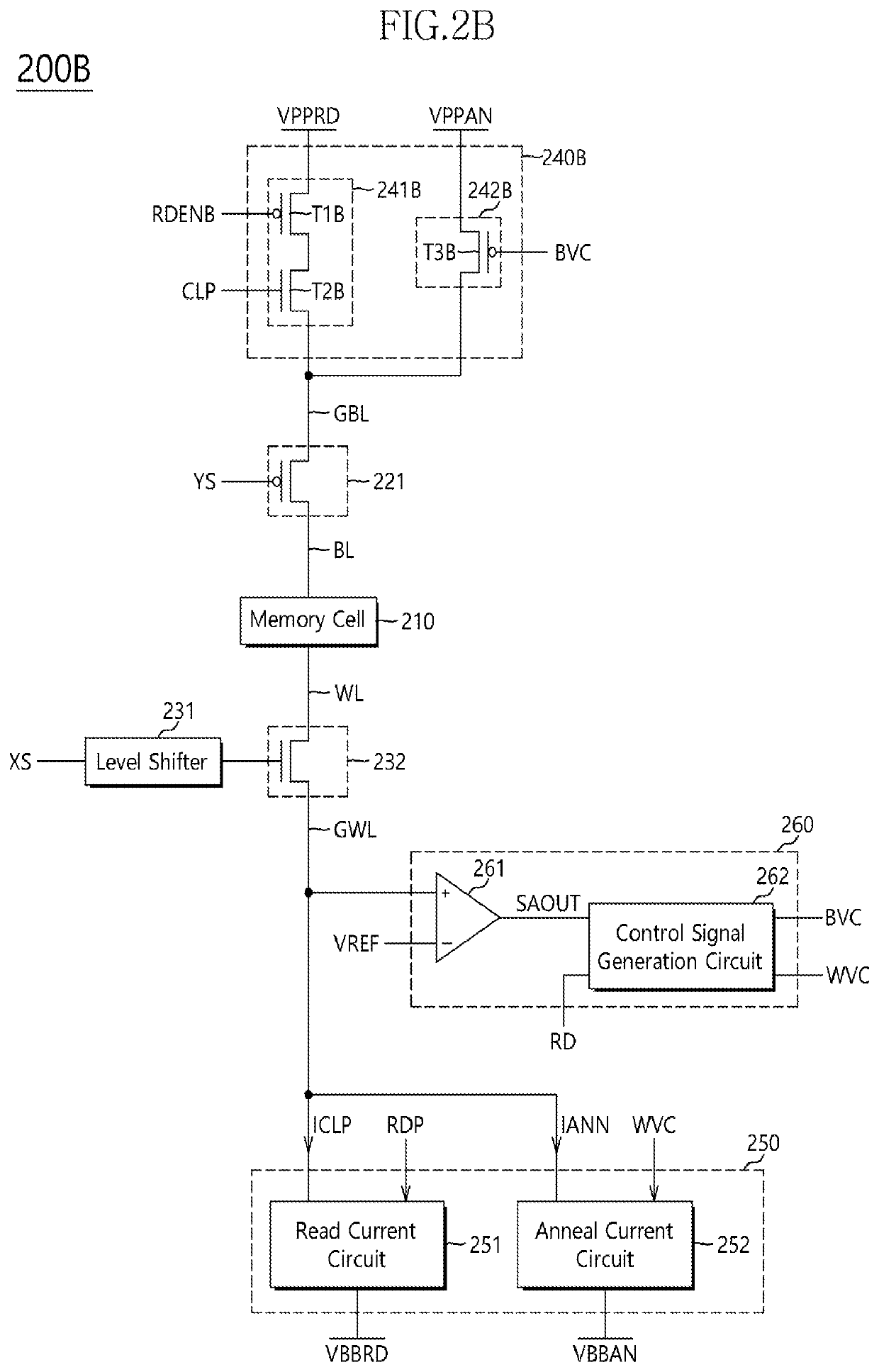

Nonvolatile memory apparatus for mitigating read disturbance and system using the same

A nonvolatile memory apparatus may include a memory cell, a bit line control circuit, and a word line control circuit. The memory cell may be coupled between a global bit line and a global word line. During a read operation, the bit line control circuit may provide a first high voltage to the global bit line and provide a second high voltage to the global bit line when snapback of the memory cell occurs. During the read operation, the word line control circuit may provide a second read supply voltage to the global word line and provide an anneal supply voltage to the global word line when snapback of the memory cell occurs.

Owner:SK HYNIX INC

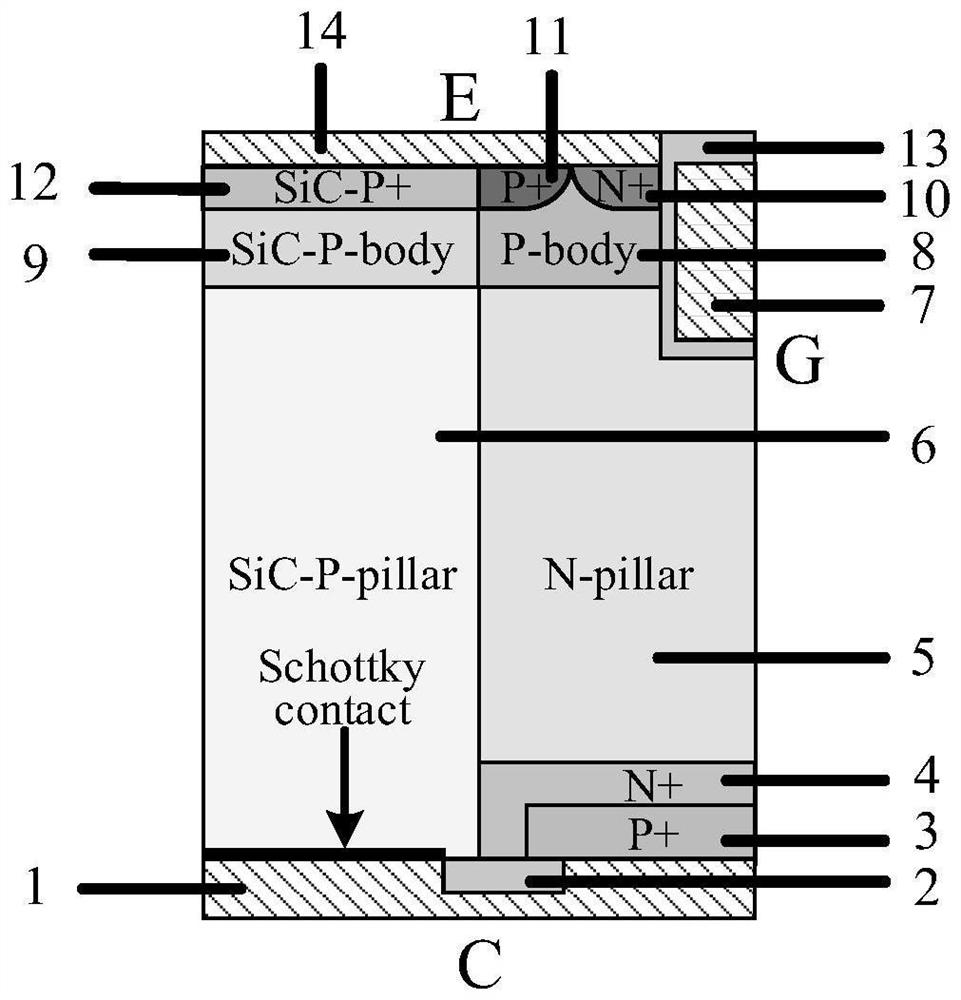

Super-junction reverse conducting IGBT (Insulated Gate Bipolar Translator) with heterojunction

ActiveCN114256331AEliminate the snapback phenomenonReduce reverse recovery chargeEfficient power electronics conversionSemiconductor devicesCarbide siliconHeterojunction

The invention belongs to the technical field of power semiconductors, and particularly relates to a super-junction reverse conducting IGBT (Insulated Gate Bipolar Translator) with a heterojunction. The cell structure of the heterojunction super-junction reverse conducting IGBT comprises a collector electrode structure, a voltage-withstanding layer structure, a grid electrode structure and an emitting electrode structure, compared with a traditional structure, the collector electrode structure is firstly improved, an insulating medium is arranged in the middle of collector electrode metal, a collector electrode region is completely arranged below an N drift region, and the voltage-withstanding layer structure is arranged in the middle of the N drift region; meanwhile, a P drift region on the other side and a P well and a P contact region on the drift region are all made of silicon carbide, so that the snapback phenomenon of a traditional super-junction reverse conducting IGBT during forward conduction is eliminated, and reverse recovery charges can be effectively reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

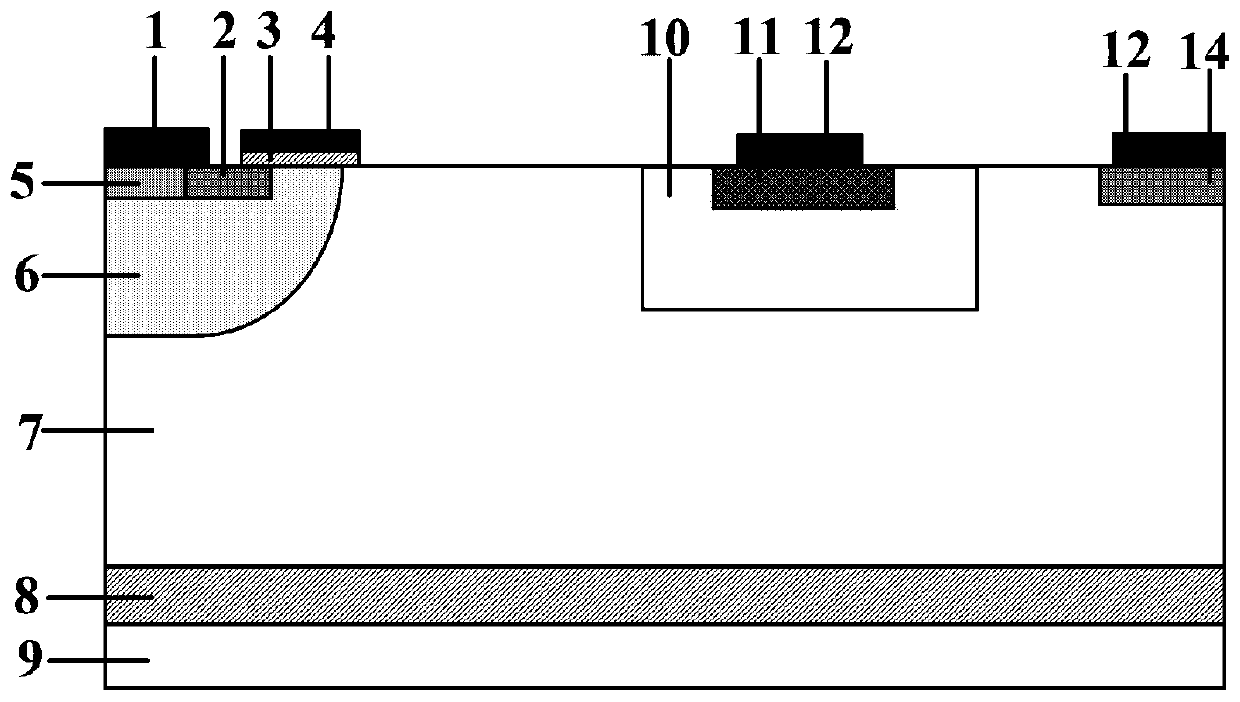

Bi-directional ESD protection device

ActiveCN109103182AImprove robustnessAvoid latch-upSolid-state devicesSemiconductor devicesCurrent distributionMetal anode

A bi-directional ESD protection device comprises a P-type substrate, an N-type epitaxial layer, an NTOP layer, a first PWELL zone, a first N + contact region, a first P + contact region, a first NTOPlayer, a second PWELL region, a second N + contact region, a second P + contact region and a second NTOP layer; the first N + contact region and the first P + contact region form a metal anode by metal short-circuiting, the second N + contact region and the second P+ contact region form a metal cathode by metal short-circuiting. As the NTOP layer is introduced above the N-type epitaxial layer to change the current distribution, the IV curve of the device presents the characteristic of multiple snapbacks, and the robustness of the device under the ESD pulse current is improved; to avoid devicelatch-up, the sustain current can be adjusted by adjusting the spacing between the NTOP layer and the first PWELL region and the second PWELL region.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

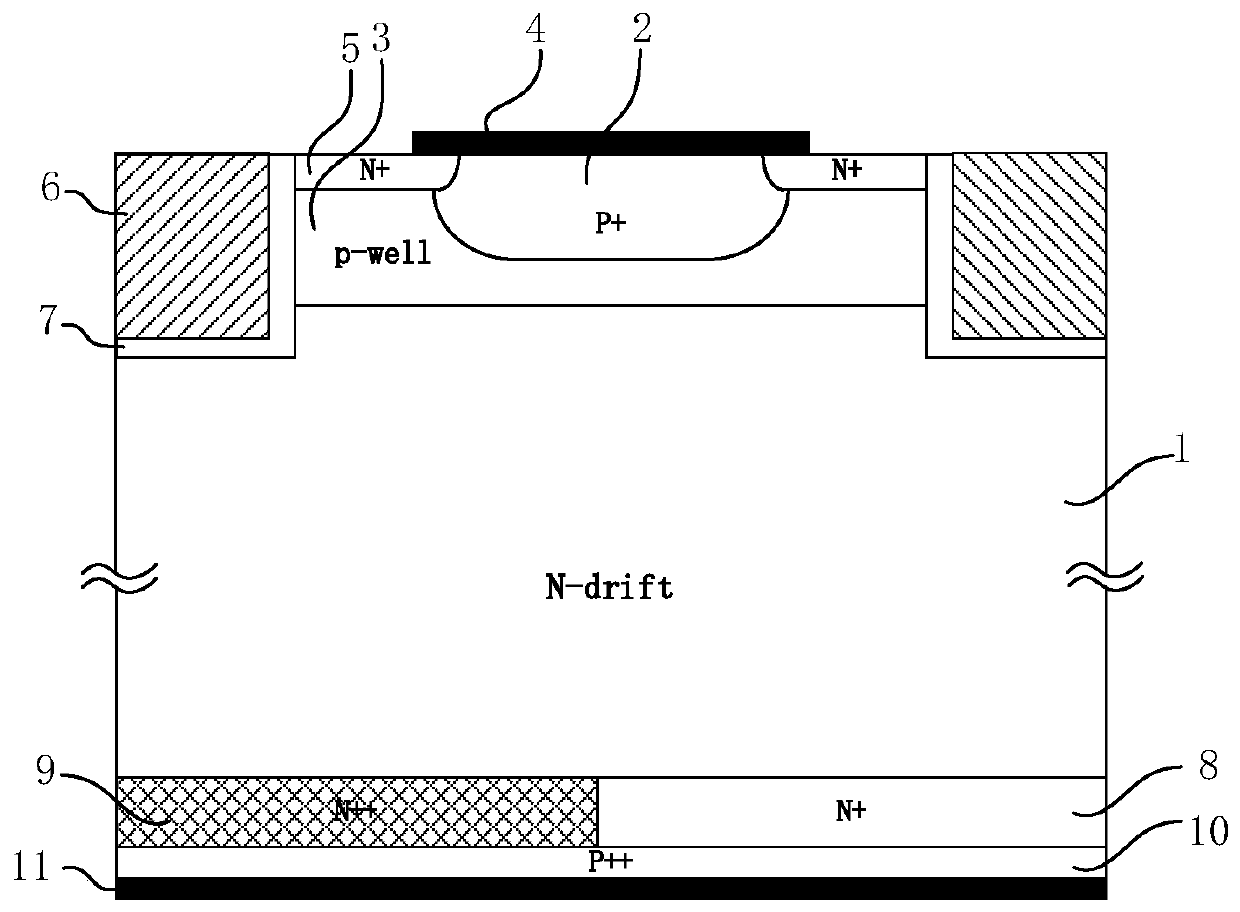

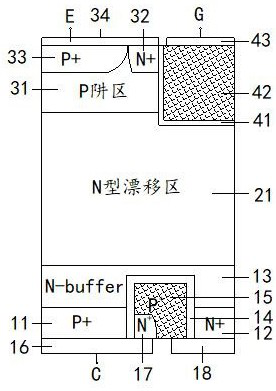

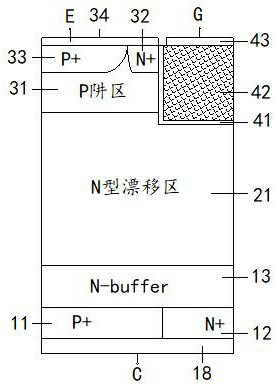

Reverse conducting IGBT without Snapback effect and manufacturing method thereof

ActiveCN110400834AThe snapback phenomenon will not occurLow costSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

The present invention relates to semiconductor technology, and more particularly to a reverse conducting IGBT without a Snapback effect and a manufacturing method thereof. The main scheme of the invention is that: the collector structure at the back surface of an IGBT is improved, the reverse blocking voltage of the device is reduced as much as possible by optimizing the doping concentration and the thickness of a P++ collector region and an N++ layer, and the reverse conduction is achieved by adopting the avalanche breakdown effect and the tunnel breakdown effect in the reverse blocking mode.Compared to a conventional reverse-conducting IGBT, since there is no an N+ short-circuit region, and there is no transition from an MOSFET conduction mode to an IGBT conduction mode during forward conduction, the snapback phenomenon cannot occur when the forward conducting of the new reverse-conducting IGBT provided by the invention is performed. Since the threshold voltage of the reverse conducting of the novel reverse conducting IGBT proposed by the present invention is larger than that of the conventional reverse conducting IGBT, the reverse conducting IGBT is suitable for a case that theforward conducting time is mostly occupied such as a quasi-resonant circuit and the reverse conducting time is short. Besides, the novel reverse conducting IGBT provide in the invention has the advantages such as the small forward voltage drop and good soft recovery characteristics.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

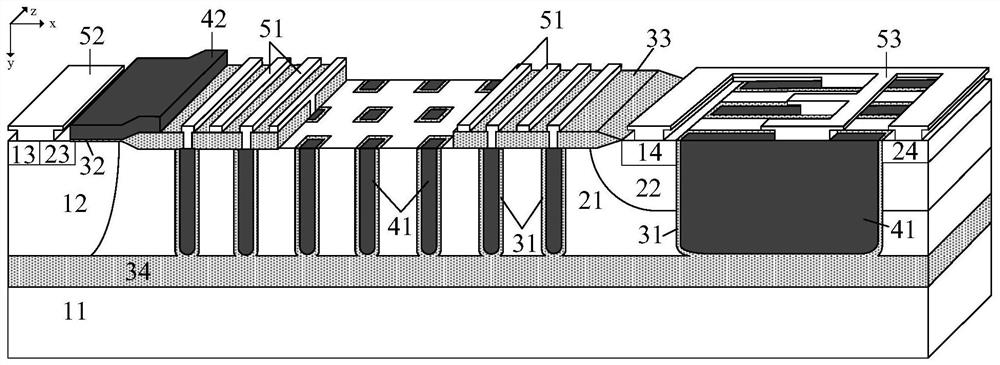

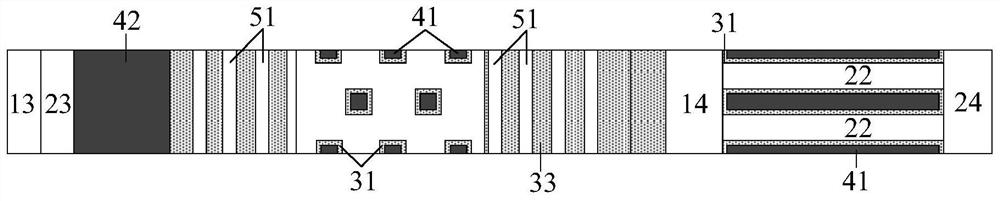

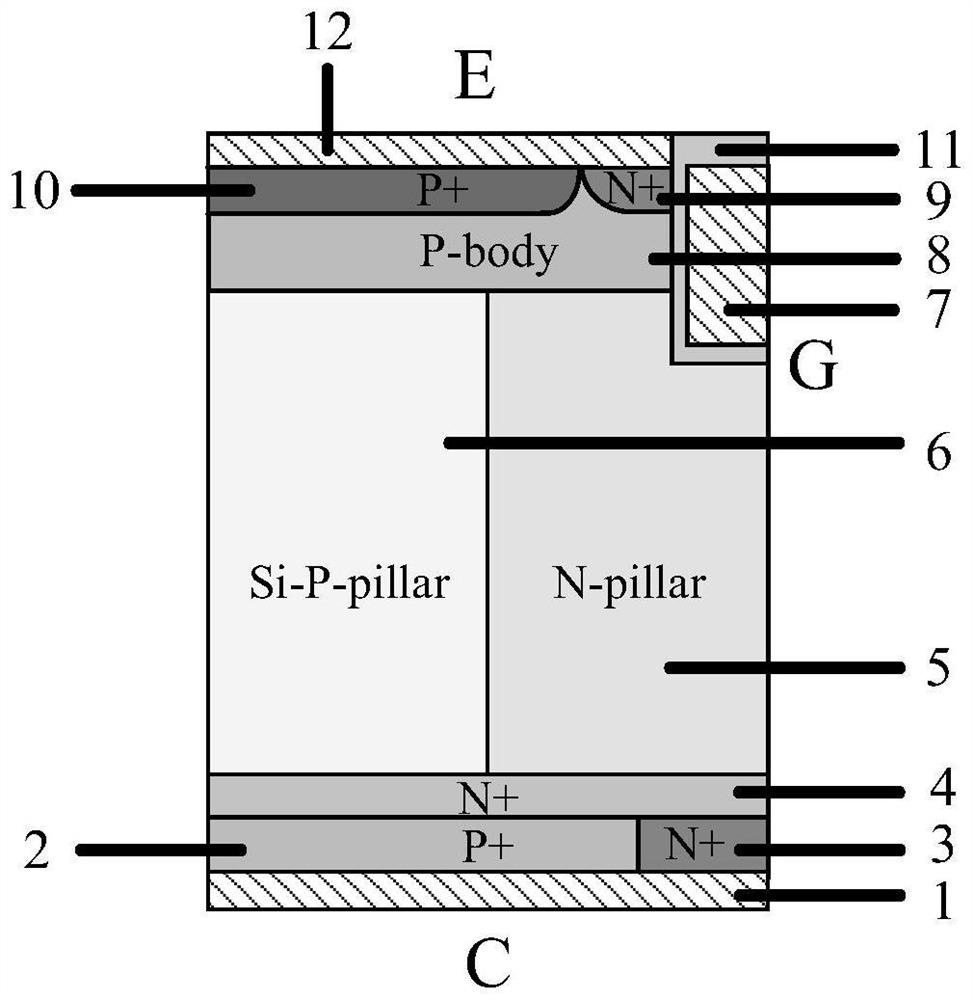

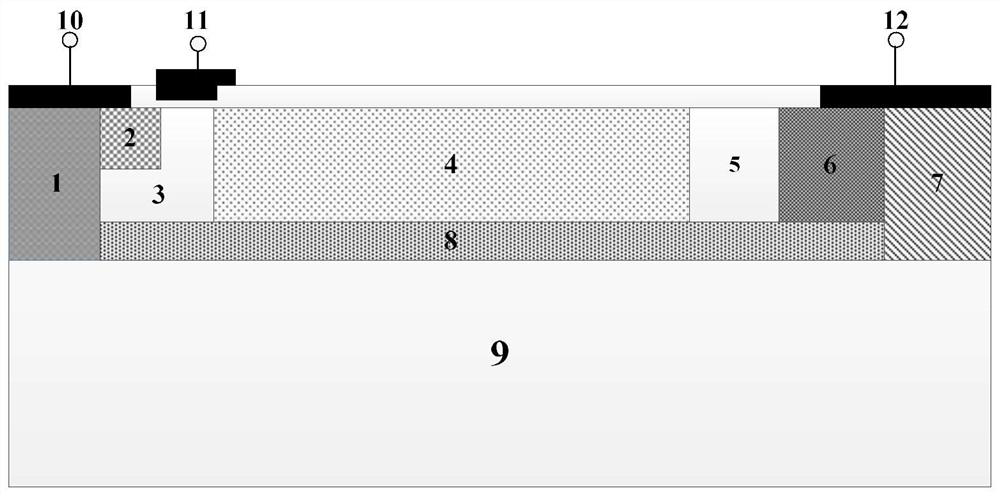

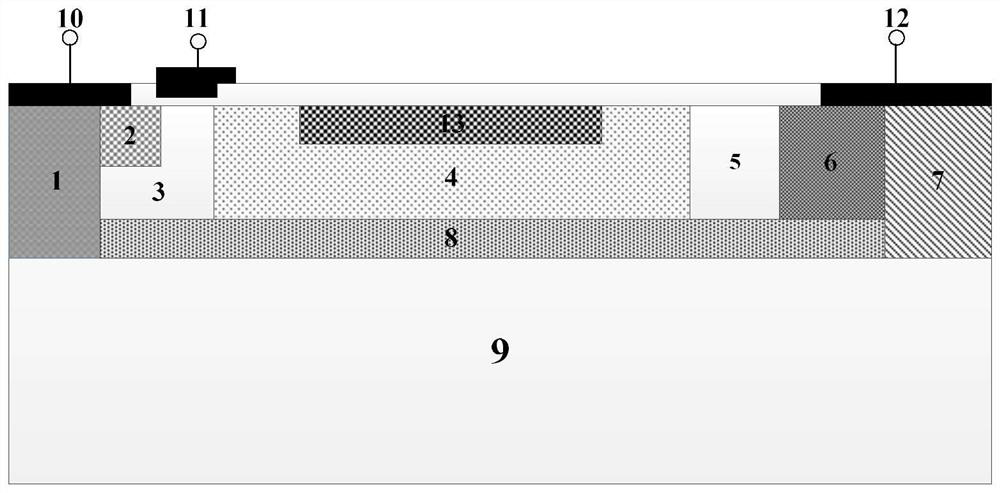

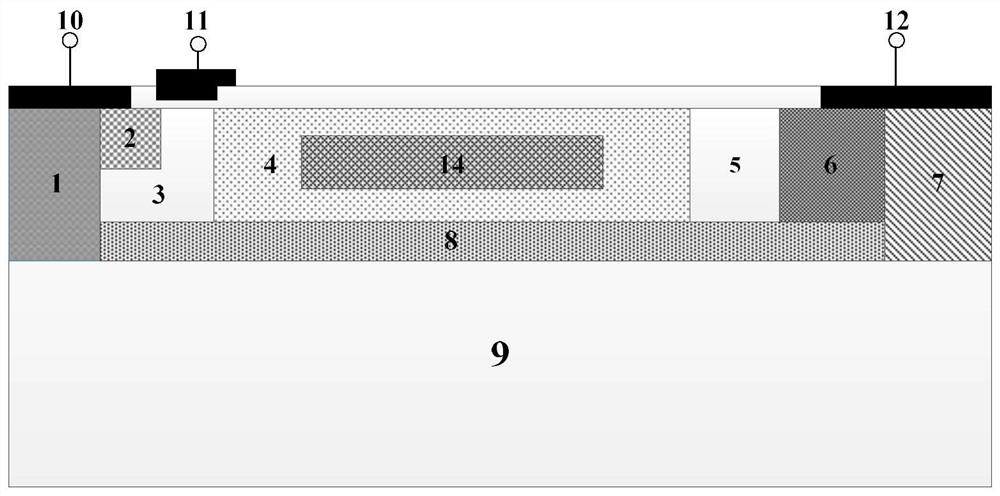

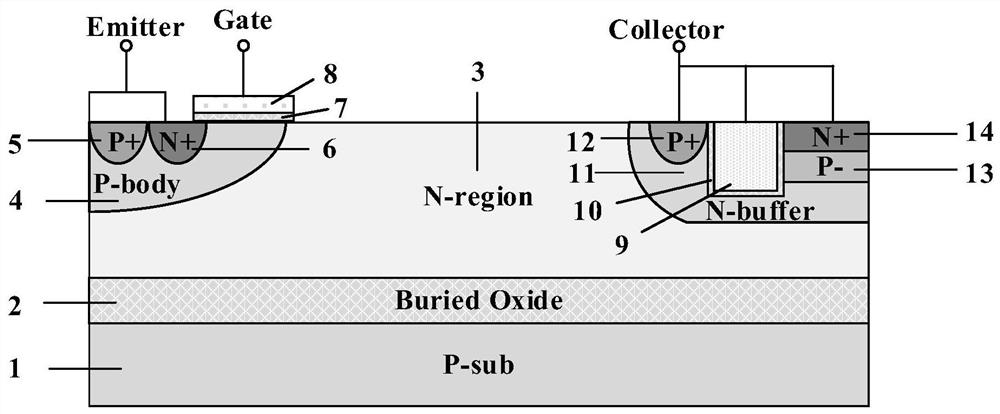

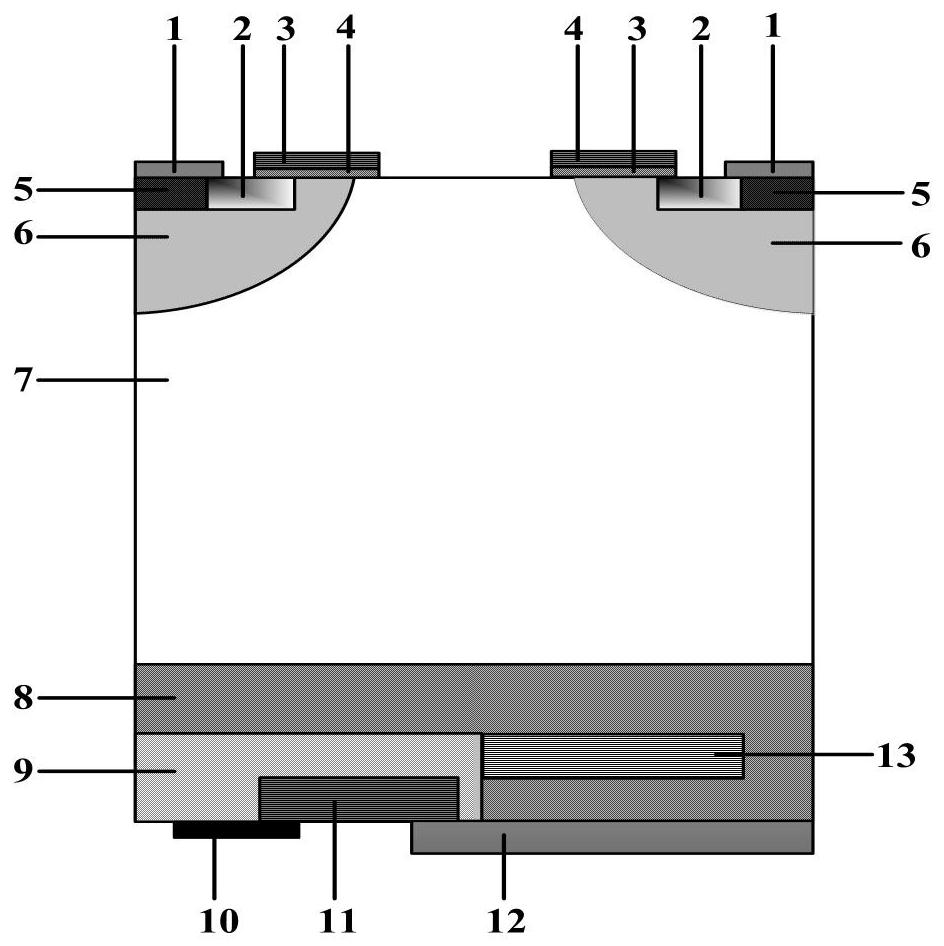

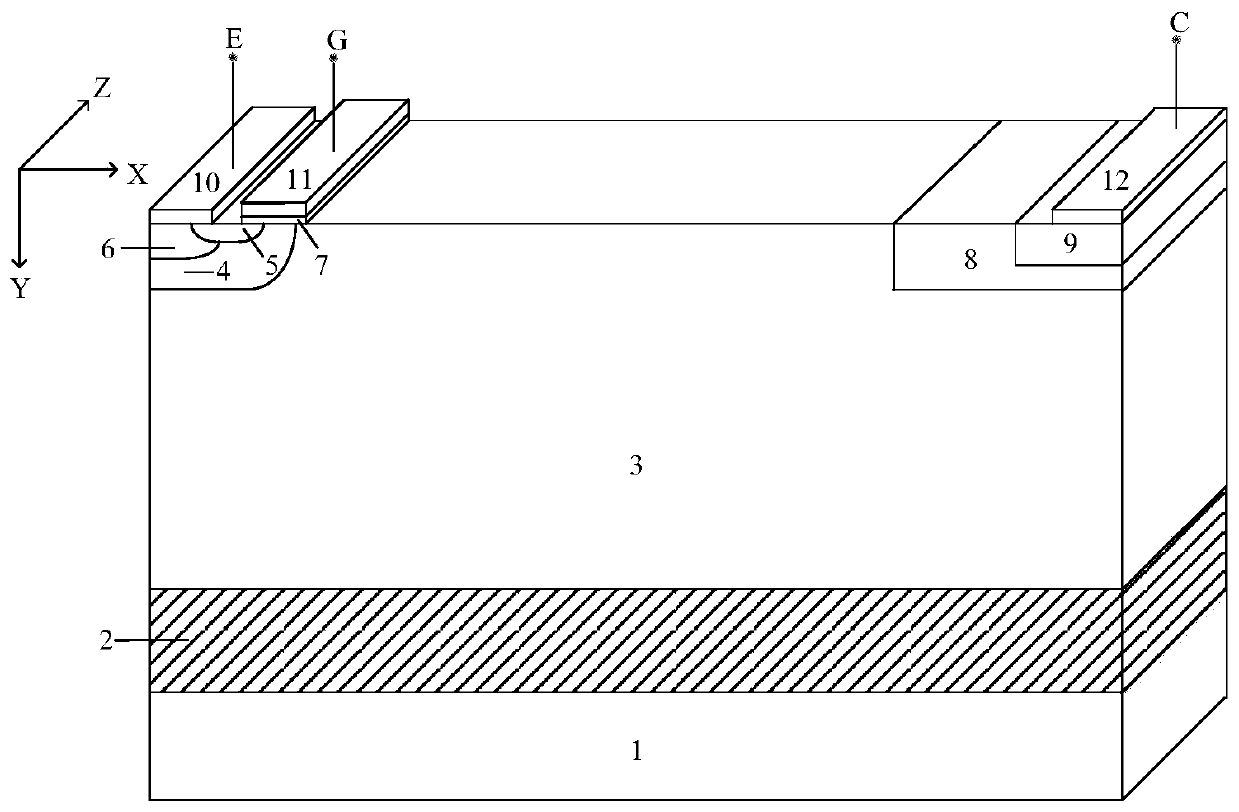

RC-LIGBT device with substrate integrated with anti-parallel fly-wheel diode

ActiveCN113782592AReduce conduction voltage dropAchieve integrationEfficient power electronics conversionSemiconductor devicesEngineeringSemiconductor

The invention relates to an RC-LIGBT device with a substrate integrated with an anti-parallel fly-wheel diode, and belongs to the technical field of power semiconductors. The device comprises an IGBT conductive region formed by a P + emitter, an N + electron emitter, a P-body, an N-type drift region, a buffer layer and a P-type collector electrode, and a PIN freewheeling diode conductive region formed by the P + emitter, a P-type substrate and an N-type collector electrode, wherein during positive conduction, the IGBT conductive region works, no negative resistance effect exists, and the conduction voltage is reduced, and during reverse conduction, the PIN freewheeling diode conductive region works, and a hole current path is provided to realize integration of the diode. According to the invention, the negative resistance Snapback effect of a traditional RC-LIGBT is eliminated while the turn-off loss can be greatly reduced.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

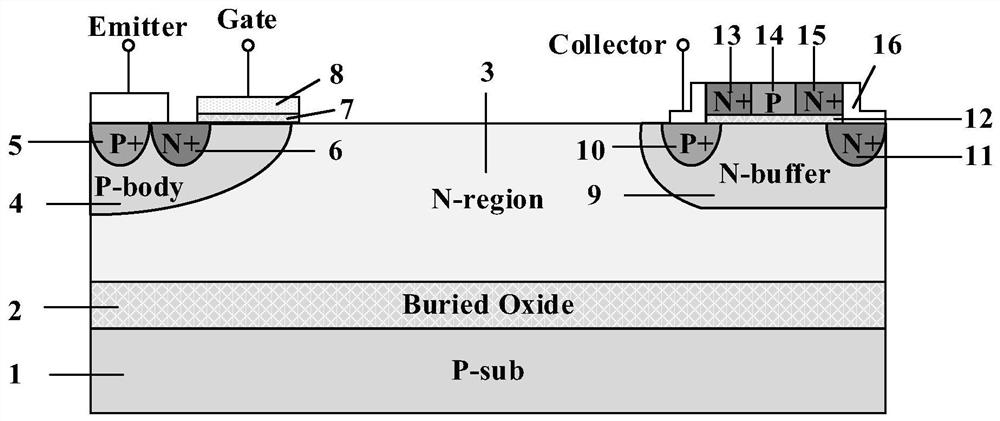

LIGBT device with integrated NMOS transistor

ActiveCN112687681ADoes not occupy an areaReduced turn-off lossEfficient power electronics conversionSolid-state devicesReverse recoveryConductive materials

The invention belongs to the technical field of power semiconductors, and relates to an LIGBT device with an integrated NMOS transistor. The device is mainly characterized in that an N+ collector region is introduced near a P+ collector region, an NMOS transistor is integrated above the collector region, the MOS transistor is isolated from the collector region below through a layer of an insulating medium, one end of the MOS transistor is in P+ short connection with a collector electrode, and the other end of the MOS transistor is in N+ short connection with the collector electrode through a conductive material. When the new device is in reverse conduction, the integrated NMOS transistor provides a path for current, so the new device has better reverse recovery characteristics. During forward conduction, threshold voltage is increased by increasing the concentration of a P-type channel region in the integrated NMOS transistor, and the punch-through of the MOS transistor is prevented, so the snapback effect can be effectively inhibited. When the device is turned off, the integrated NMOS transistor provides a path for electron extraction, so the new device has shorter turn-off time and lower turn-off loss. The LIGBT device provided by the invention has the advantages that a reverse conduction function can be achieved and the turn-off loss is lower compared with a traditional LIGBT device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

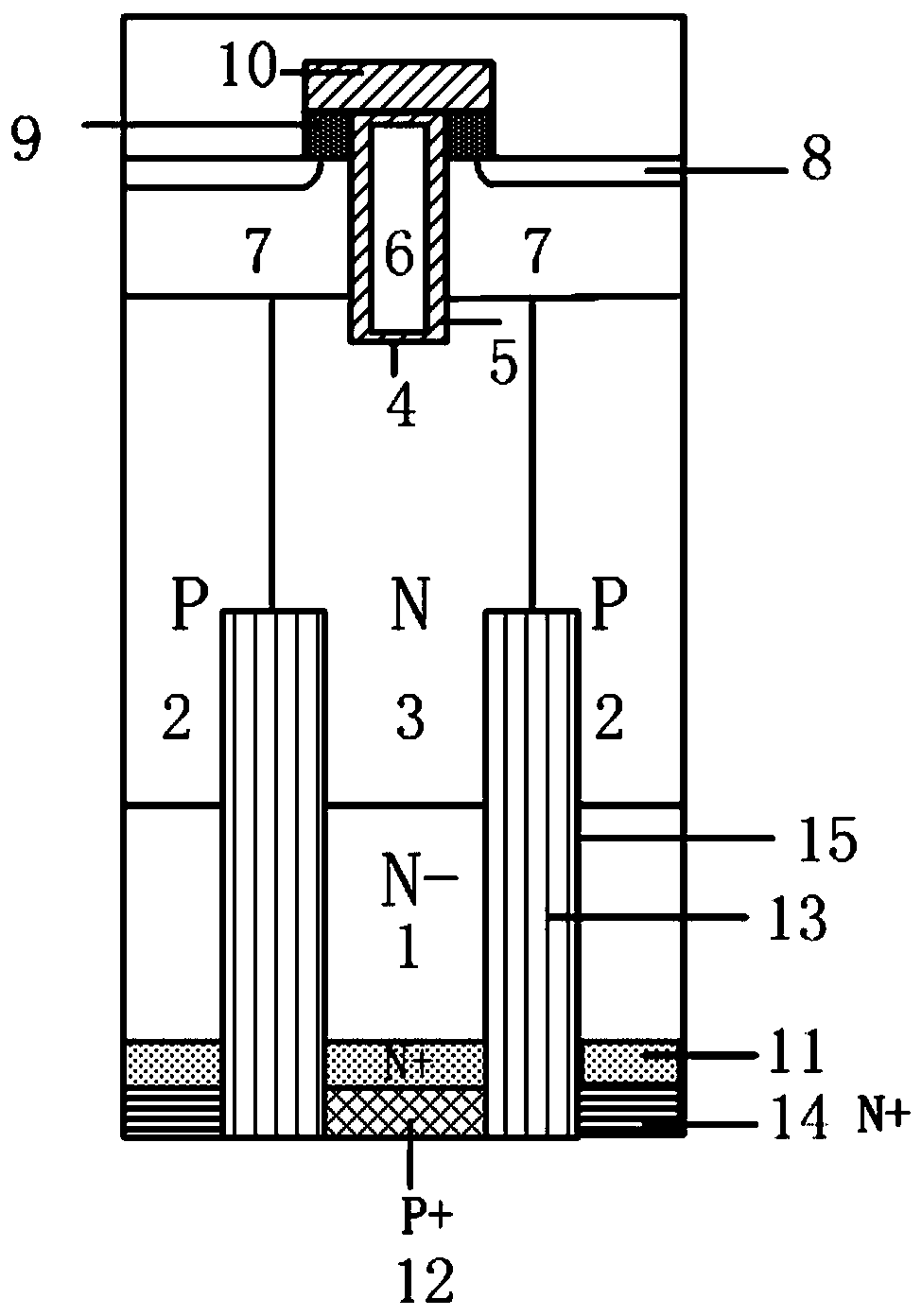

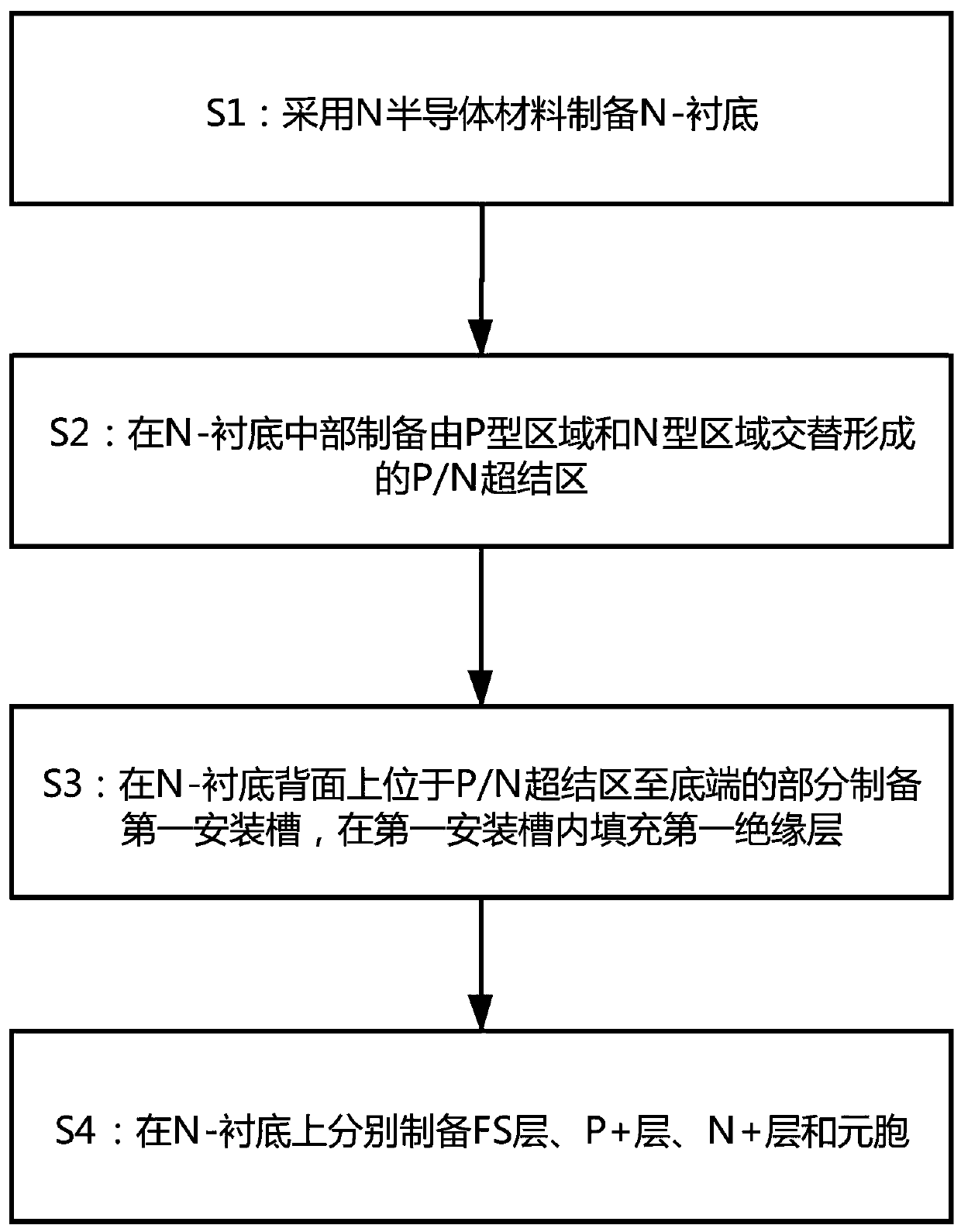

IGBT device structure and preparation method thereof

InactiveCN111584624AGuaranteed withstand voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

The invention provides an IGBT device structure and a preparation method thereof, which belong to the technical field of semiconductor power devices and process manufacturing. The IGBT device structure comprises an N-substrate, a super junction region, cells, an FS layer, a P + layer, an N + layer and a filling layer. According to the invention, the N-substrate, the super junction region, the cells, the FS layer, the P + layer and the N + layer can guarantee the withstand voltage of the device; a first mounting groove is formed in the N-substrate; the first mounting groove is filled with a first insulating layer; the first insulating layer is made of a high-K insulating material, so that when the device is turned on, the hole carrier density in the FS layer is improved, the IGBT region andthe MOSFET region are effectively isolated; and the on-resistance of the device is effectively reduced, and the snapback phenomenon when the device is turned on is inhibited.

Owner:潘克学

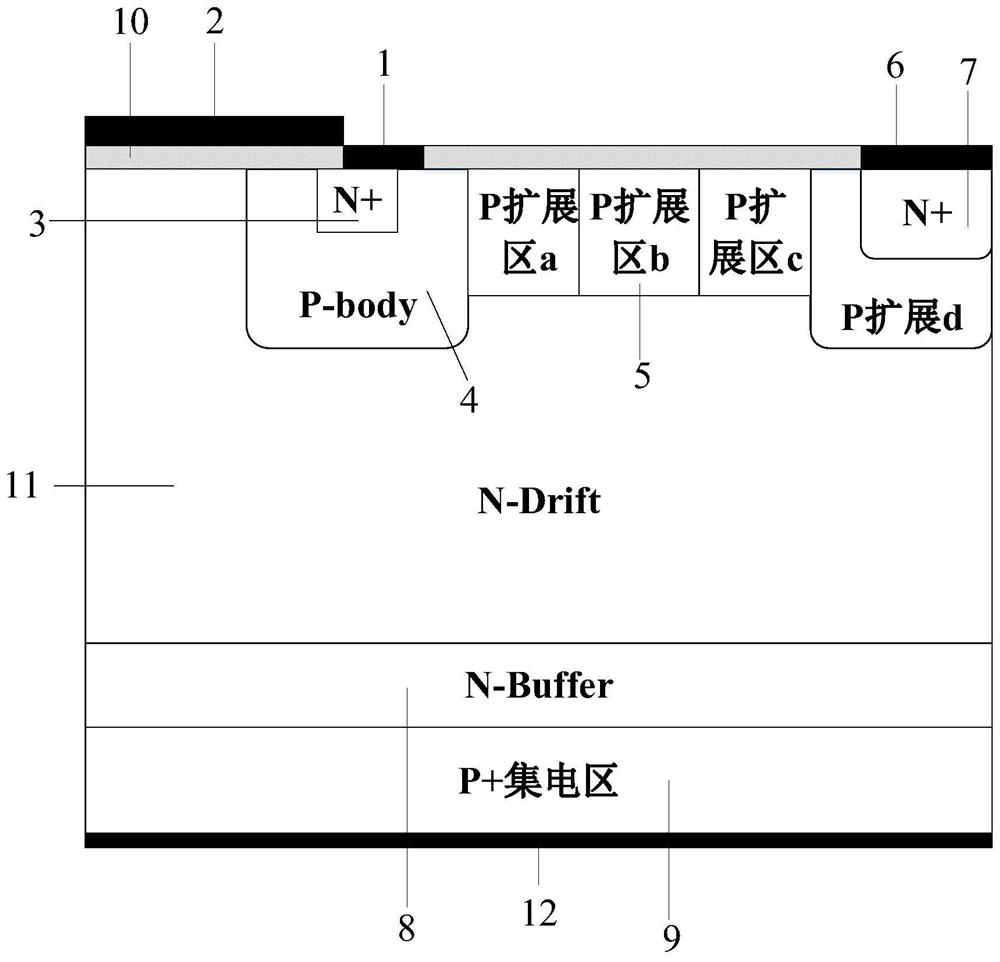

SA-LIGBT device with longitudinally separated anode

ActiveCN111326576AExtended flow pathImprove short circuit resistanceSemiconductor devicesEngineeringMaterials science

The invention relates to an SALIGBT device with a longitudinally separated anode structure, and belongs to the field of semiconductor power devices. According to the invention, the N+ anode and the P+anode of a traditional SA-LIGBT are separated, the N+ anode is arranged in the device, and the flow path of electrons in a unipolar conductive mode is prolonged by increasing the longitudinal depth of the N+ anode; a P-type floating layer below the N+ anode can increase the anode distribution resistance of the device, and the snapback effect is completely eliminated by adjusting the longitudinaldepth of the N+ anode and the doping concentration of the P-type floating layer. According to the invention, the longitudinal length of the device is utilized to reduce the chip area; the forward conduction voltage drop of the LIGBT with the new structure is 0.91V during forward conduction, which is reduced by 6.2% and 24% respectively compared with a separated anode short circuit type LIGBT and aconventional anode short circuit type LIGBT; and when the LIGBT is turned off, the N+ anode can rapidly extract electrons in a drift region, and the turn-off time of the N+ anode is 370ns and is reduced by 82% and 23% compared with a traditional LIGBT and a dielectric isolation type LIGBT.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

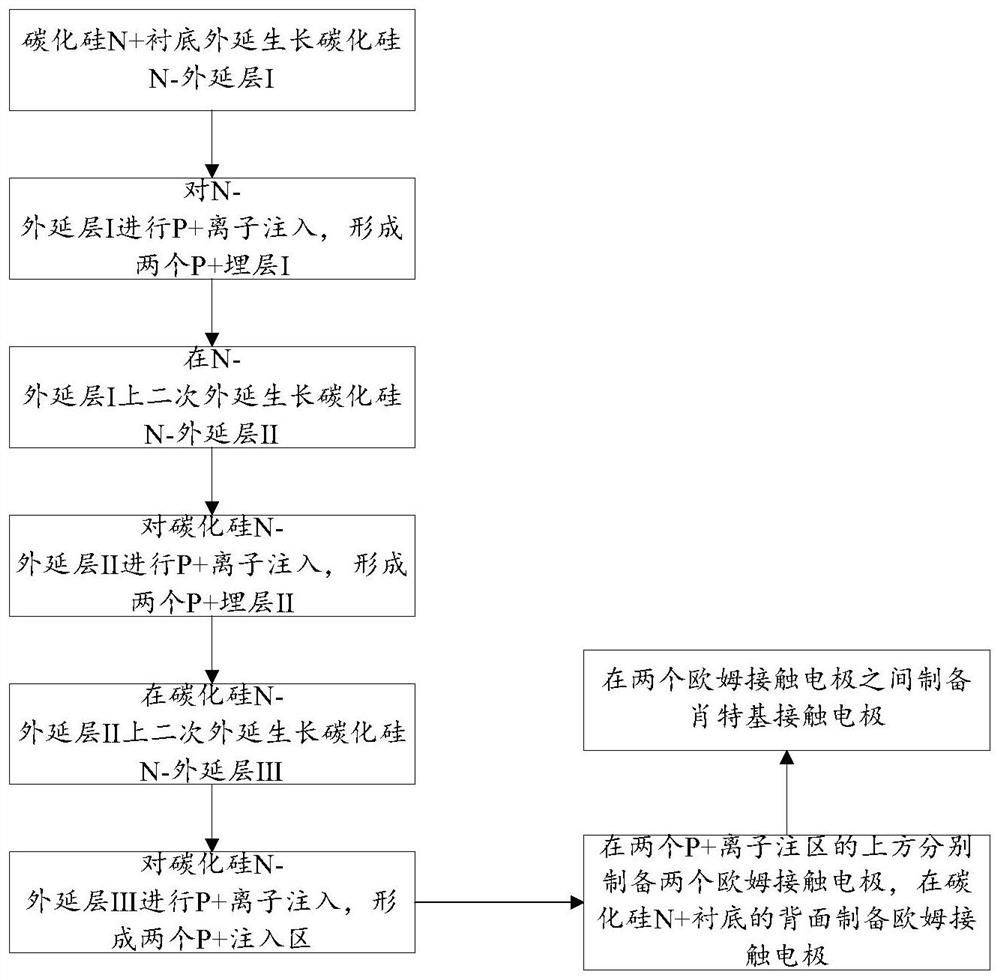

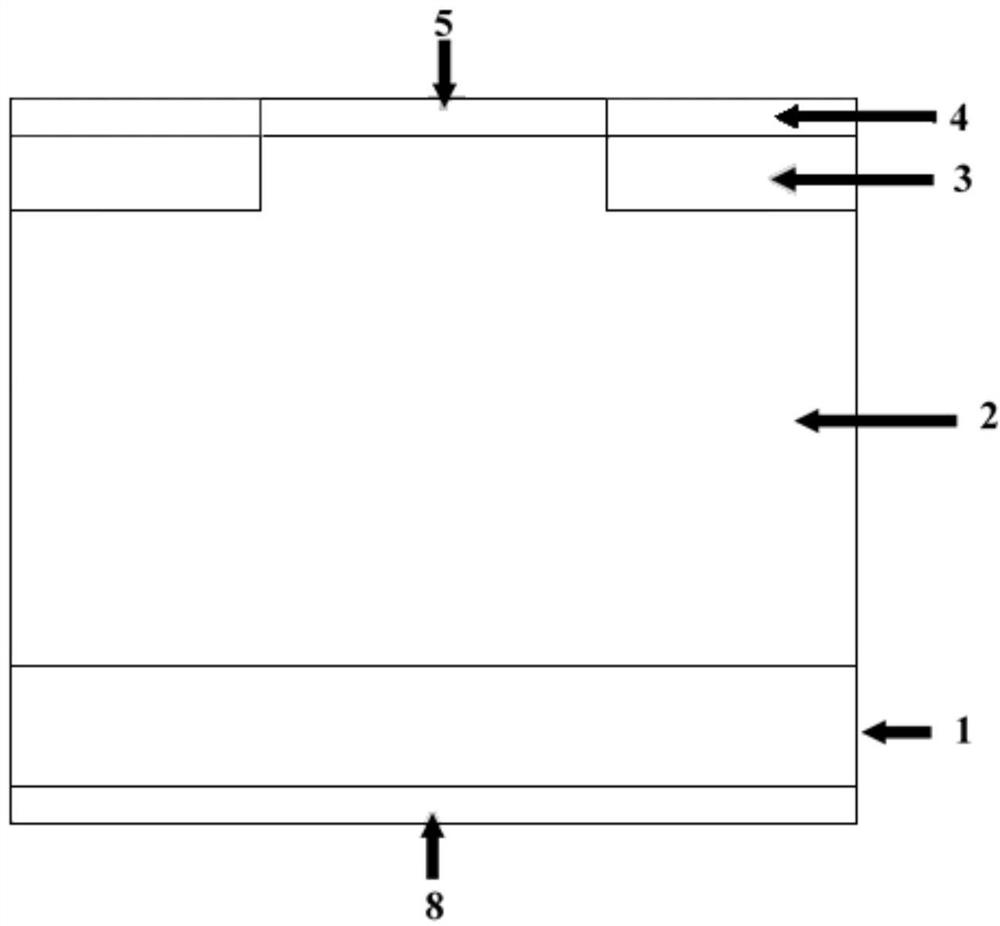

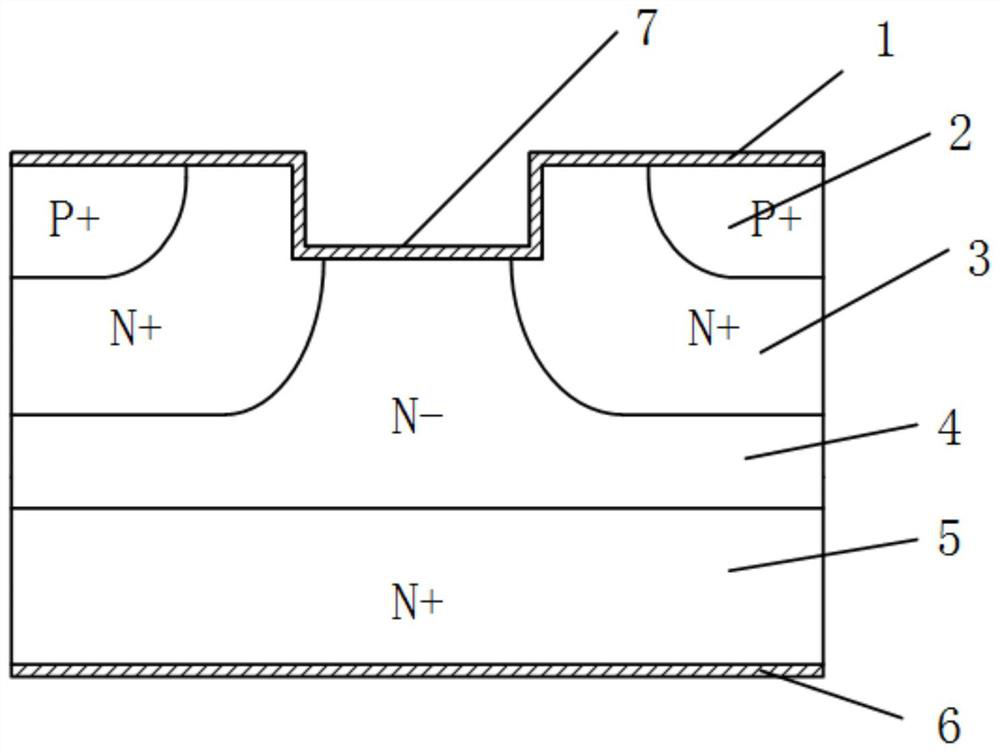

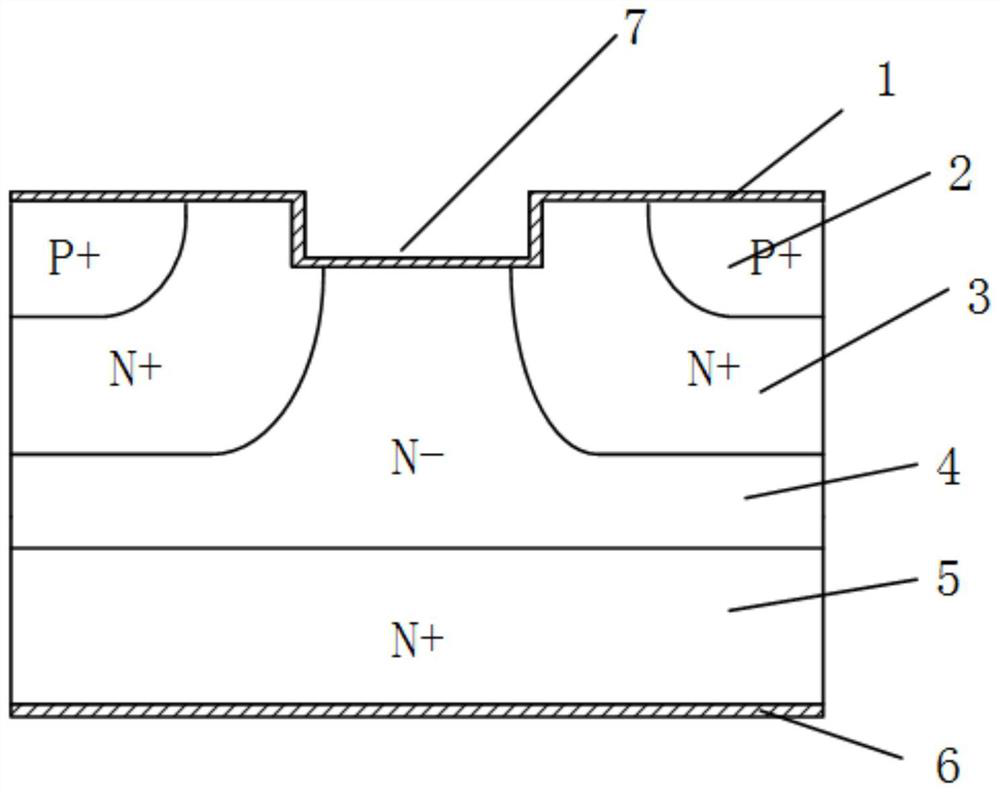

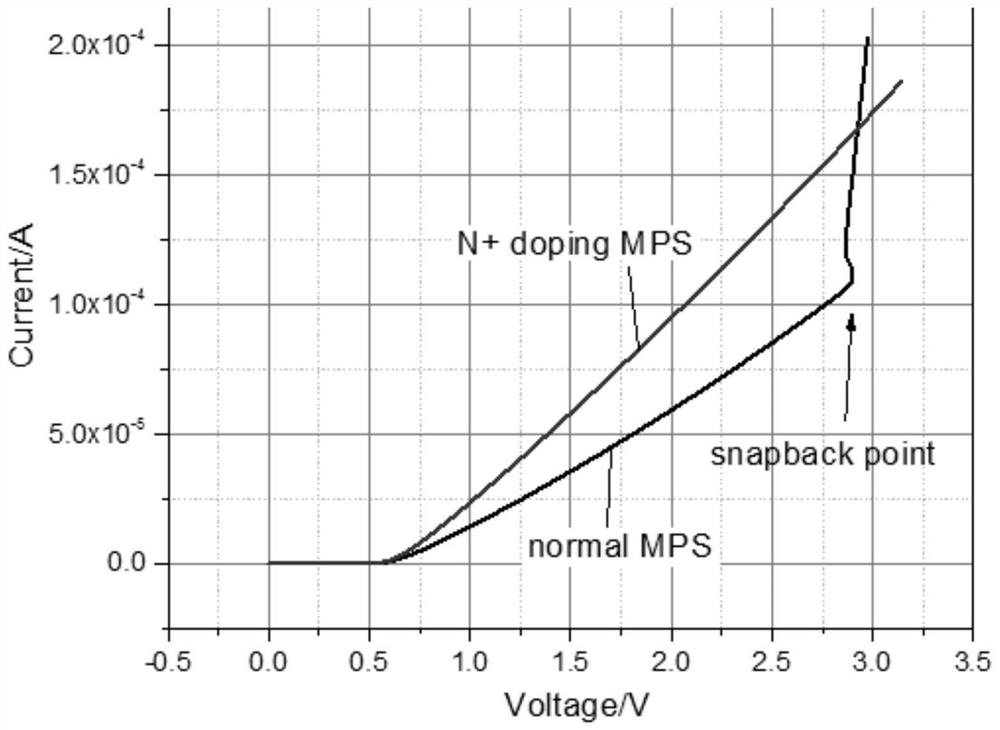

Silicon carbide MPS diode with buried layer structure and preparation method thereof

PendingCN114267718AEliminate the snapback phenomenonLower breakover voltageSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactElectrical polarity

The silicon carbide MPS diode comprises a cathode ohmic contact electrode, a silicon carbide N + substrate and a silicon carbide N-epitaxial layer which are laminated from bottom to top, two P + injection regions are formed at the top of the silicon carbide N-epitaxial layer, the two P + injection regions are respectively contacted with the tops of the two P + buried layers I through the two P + buried layers II, and the widths of the P + injection regions and the P + buried layers I are greater than those of the P + buried layers II; two ohmic contact electrodes are arranged at the tops of the two P + injection regions, and a Schottky contact electrode is arranged between the two ohmic contact electrodes. The P + injection region and the P + buried layer I are connected through the narrow P + buried layer II, the proportion of PN junctions is increased in the epitaxial layer, and the snapback phenomenon during forward conduction of the MPS diode is eliminated; and meanwhile, the breakover voltage of the MPS diode from a unipolar working state to a bipolar working state is reduced, so that the diode enters the bipolar working state under a relatively low forward current, the high-current working temperature of the diode is reduced, and higher surge current resistance is achieved.

Owner:安徽长飞先进半导体有限公司

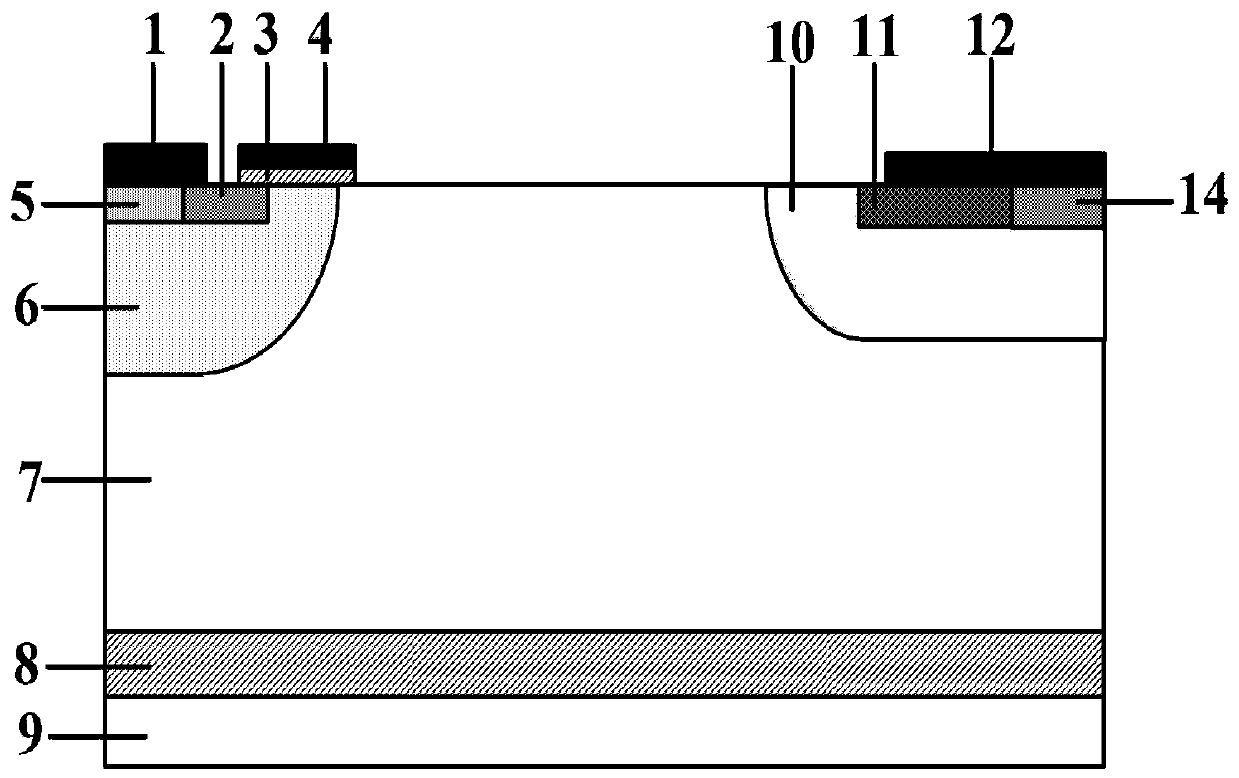

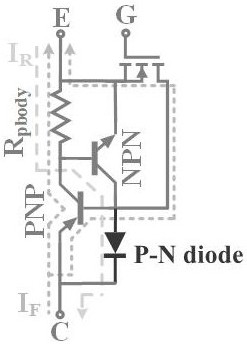

ESD protection device with low trigger voltage

ActiveUS20210066284A1Lower the trigger voltageImprove abilitiesTransistorSolid-state devicesSilicon-controlled rectifierEngineering physics

The present invention provides an ESD protection device with the mechanism of punch through to achieve low trigger voltage. At the same time, the structure of ESD protection device includes parasitic NPN and parasitic PNP. Parasitic NPN and parasitic PNP will form a silicon controlled rectifier (SCR) device with snapback behavior to increase the protection capability of ESD protection device.

Owner:CHANG WEN TSUNG

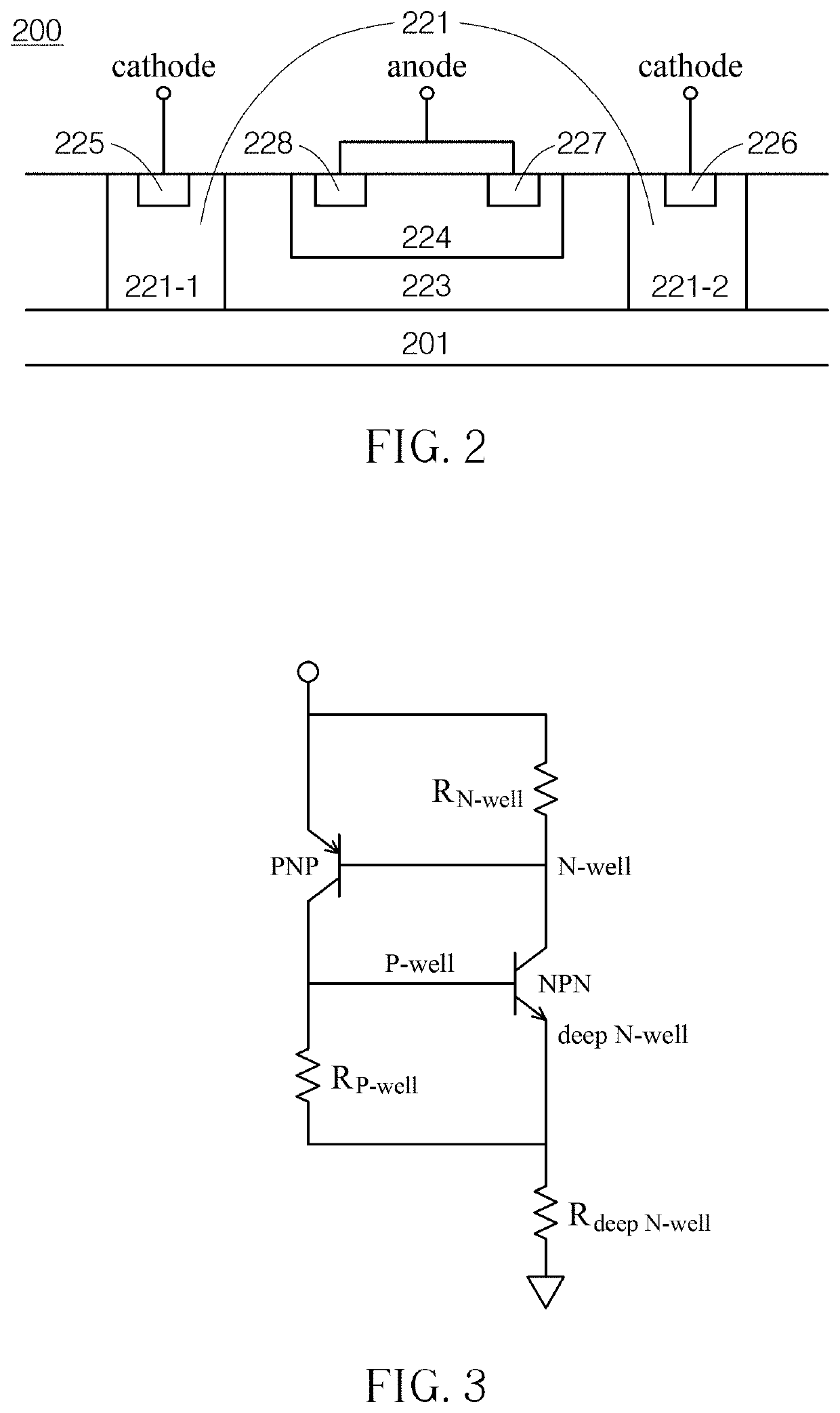

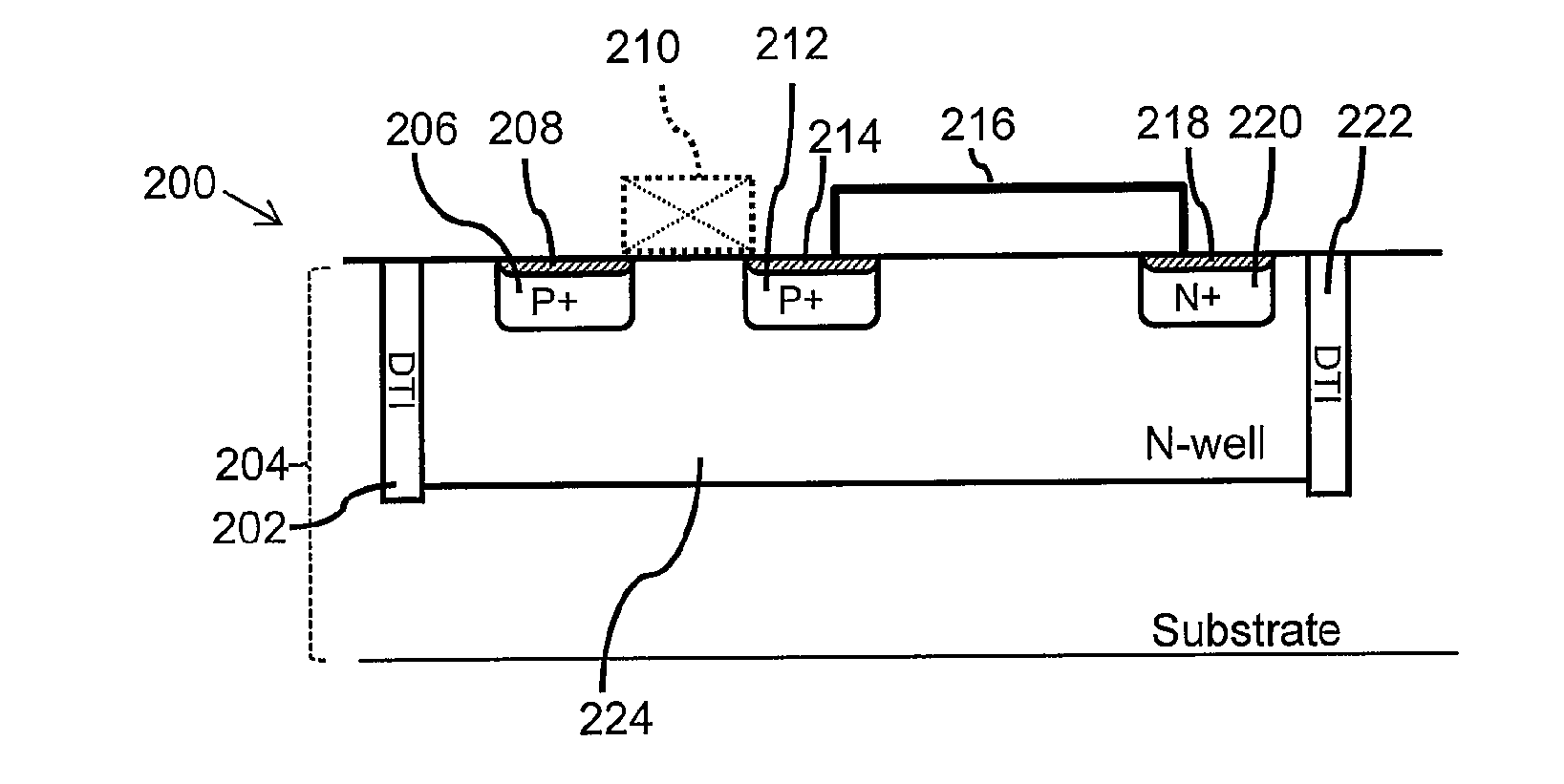

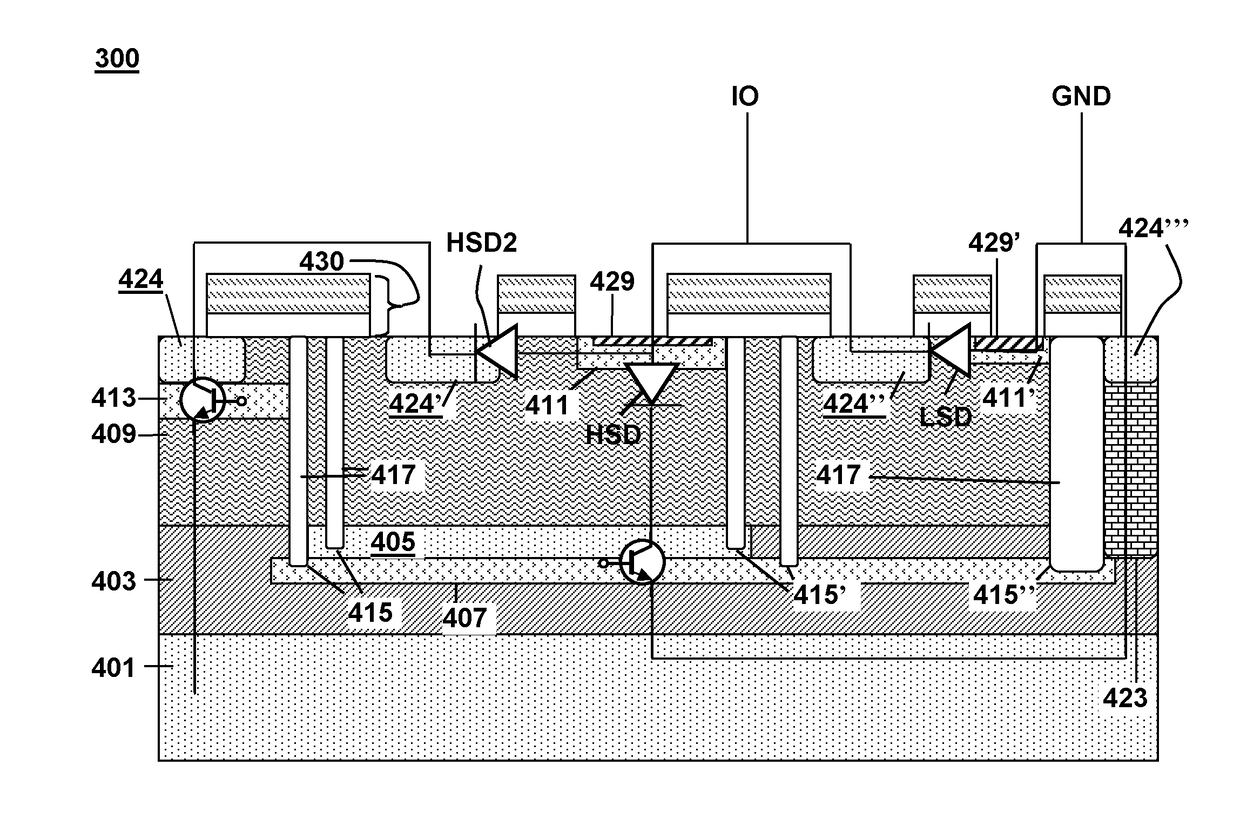

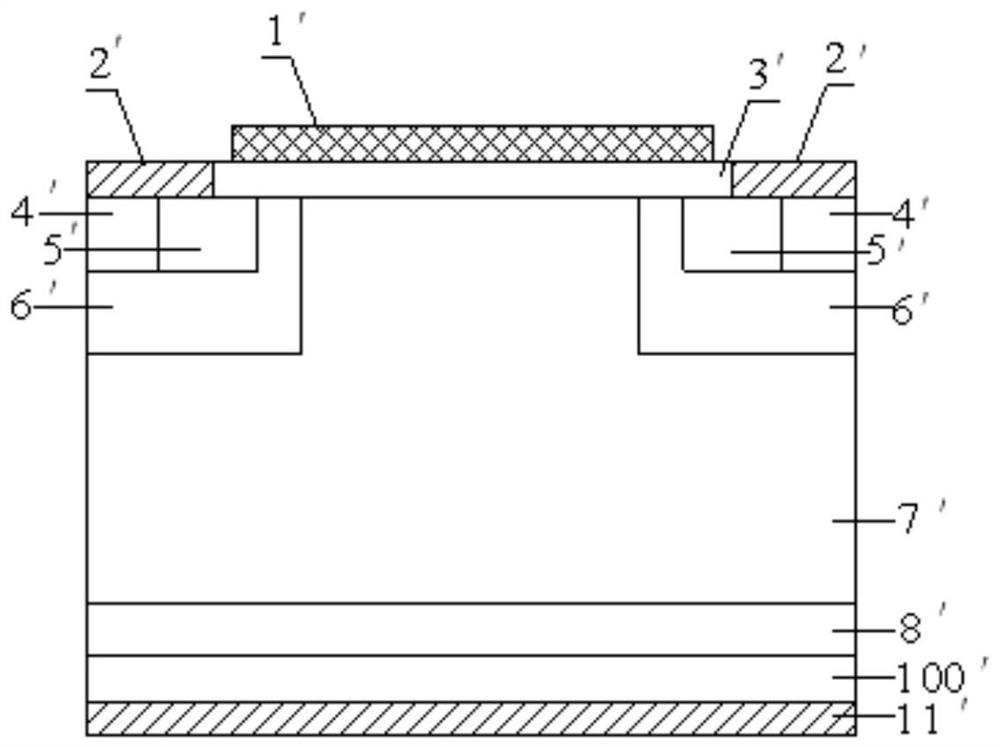

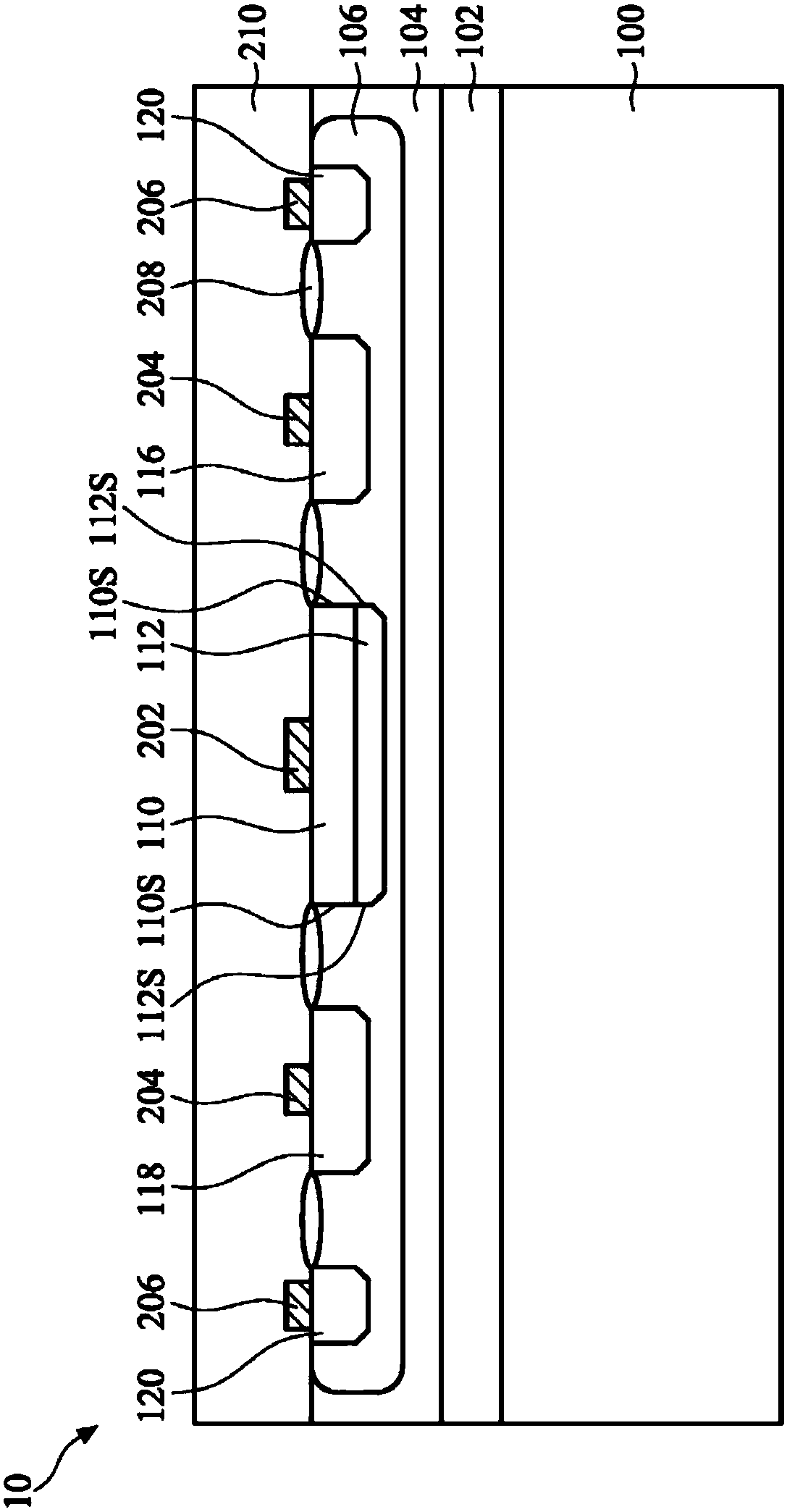

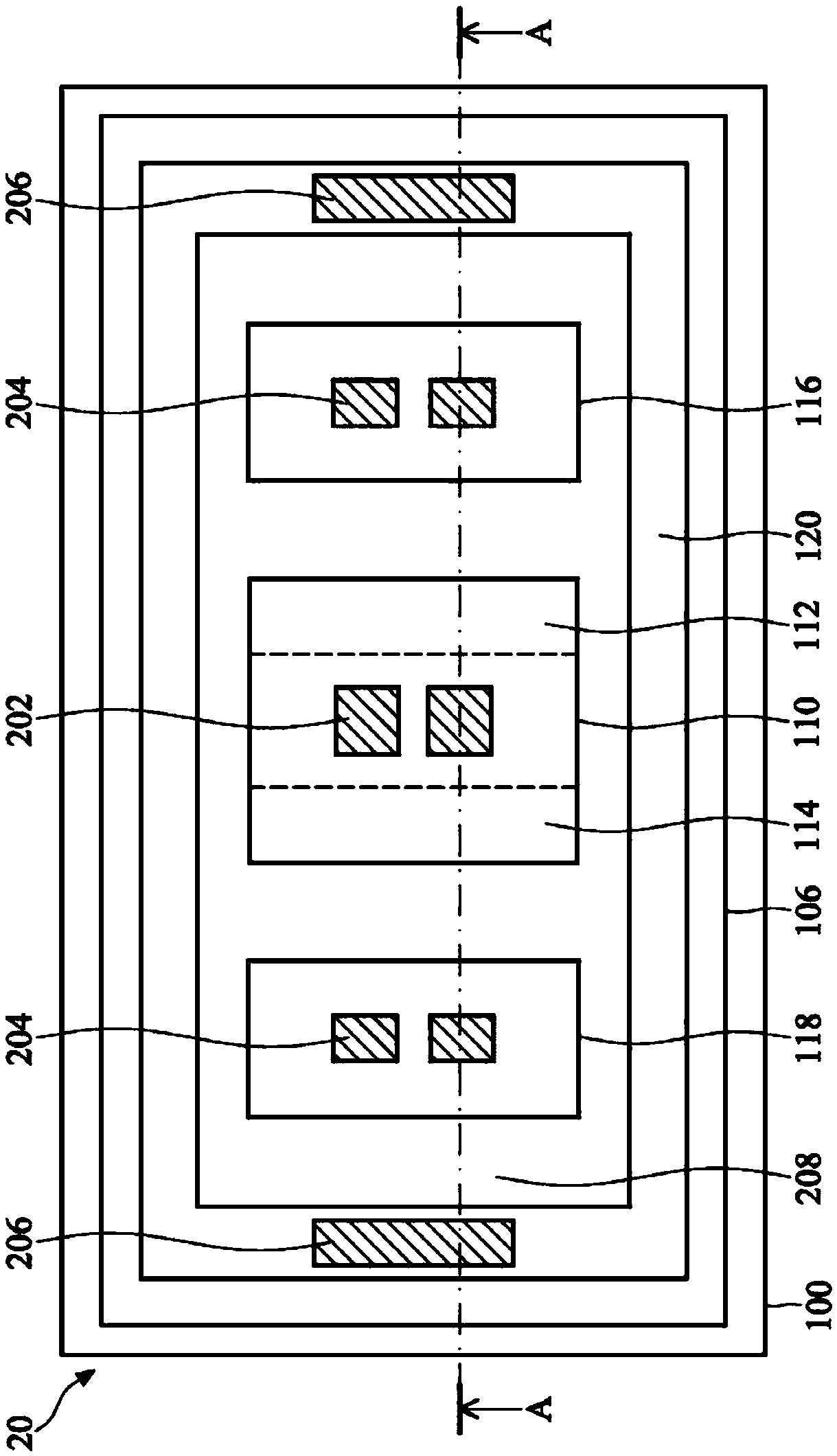

Semiconductor device comprising an ESD protection device, an ESD protection circuitry, an integrated circuit and a method of manufacturing a semiconductor device

A semiconductor device includes an ESD protection device. In a N-well, two P+ doped regions form a collector and emitter of a parasitic transistor of the ESD protection device. The N-well area between the P+ doped regions, forms a base of the parasitic transistor. At some distance away from the P+ doped regions an N+ doped region is provided. The N-well in between the N+ doped region and base of the transistor forms a parasitic resistor of the ESD protection device. The N+ doped region and the emitter of the transistor are coupled to each other via an electrical connection. The ESD protection device has a limited snapback behaviour and has a well-tunable trigger voltage.

Owner:NXP USA INC

Snapback transient voltage suppressor

InactiveCN113257806ALower breakdown voltageLower the trigger voltageTransistorSolid-state devicesTransient voltage suppressorDielectric layer

The invention discloses a snapback transient voltage suppressor, and belongs to the field of semiconductor protection devices. The suppressor comprises: an epitaxial layer formed on a substrate; a plurality of preset regions formed in the epitaxial layer and isolated by an isolation structures, wherein the first preset region and the fifth preset region comprise a first P+ region, a first N+ region and a second P+ region, the second preset region and the fourth preset region comprise a second N+ region, a third P+ region and a third N+ region, and the third preset region comprises a first P-type well region, a second P-type well region, a fourth N+ region formed in the second P-type well region, and two fourth P+ regions and two fifth N+ regions formed in the first P-type well region; a dielectric layer formed on the upper surface of the epitaxial layer, wherein the dielectric layer comprises metal holes corresponding to the P+ regions and the N+ regions; and a plurality of metal layers formed in each of the metal holes. The suppressor has the beneficial effects that the breakdown voltage and the trigger voltage are lower, the protection response is faster, the on resistance and the clamping voltage are smaller, and the protection capability for a post-stage integrated circuit is stronger.

Owner:SHANGHAI CHANGYUAN WAYON MICROELECTRONICS

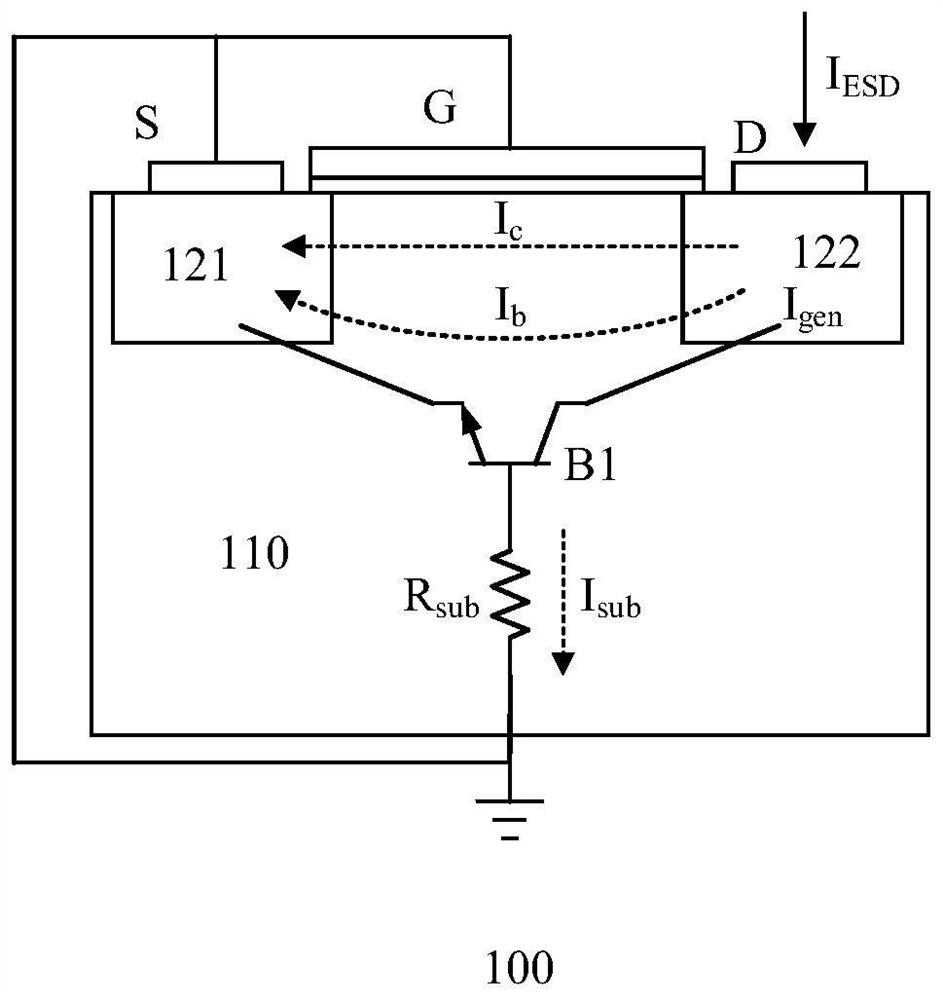

Semiconductor device modeling method

ActiveCN111737937AImprove applicabilityHigh speedComputer aided designSpecial data processing applicationsIonization currentDevice material

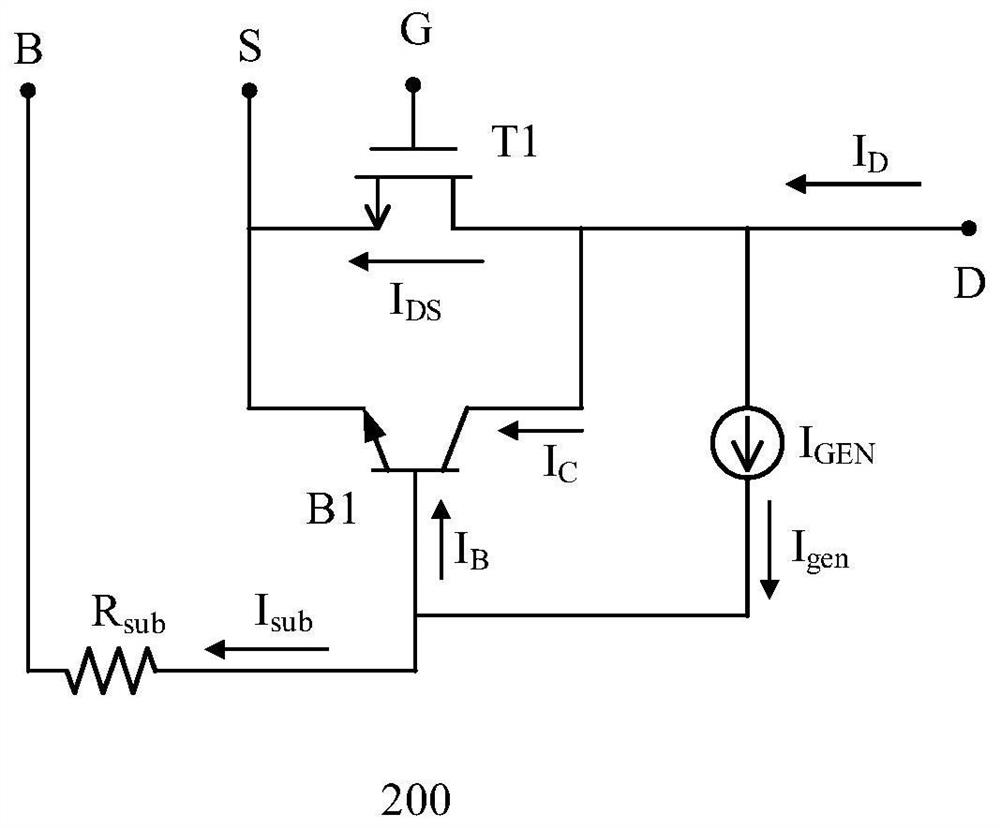

The invention discloses a semiconductor device modeling method which comprises the steps that a native transistor model and a parasitic transistor model are established, and a substrate of the nativetransistor model is connected to a base electrode of the parasitic transistor model and grounded through a substrate resistor; the drain electrode of the native transistor model and the collector electrode of the parasitic transistor are connected to the drain end of the semiconductor device through a drain end resistor; the source of the native transistor model and the emitter of the parasitic transistor are both connected to the source of the semiconductor device. According to the semiconductor device modeling method, a native transistor model and a parasitic transistor model respectively comprise a collision ionization current formula; by setting two collision ionization current formulas, the rise of the substrate voltage can be ensured, the starting of a parasitic transistor model is ensured, the analogue simulation of a snapback phenomenon is ensured, the parameter acquisition of the ESD device is ensured, the model is simple, the convergence is good, and the simulation speed is high.

Owner:JOULWATT TECH INC LTD

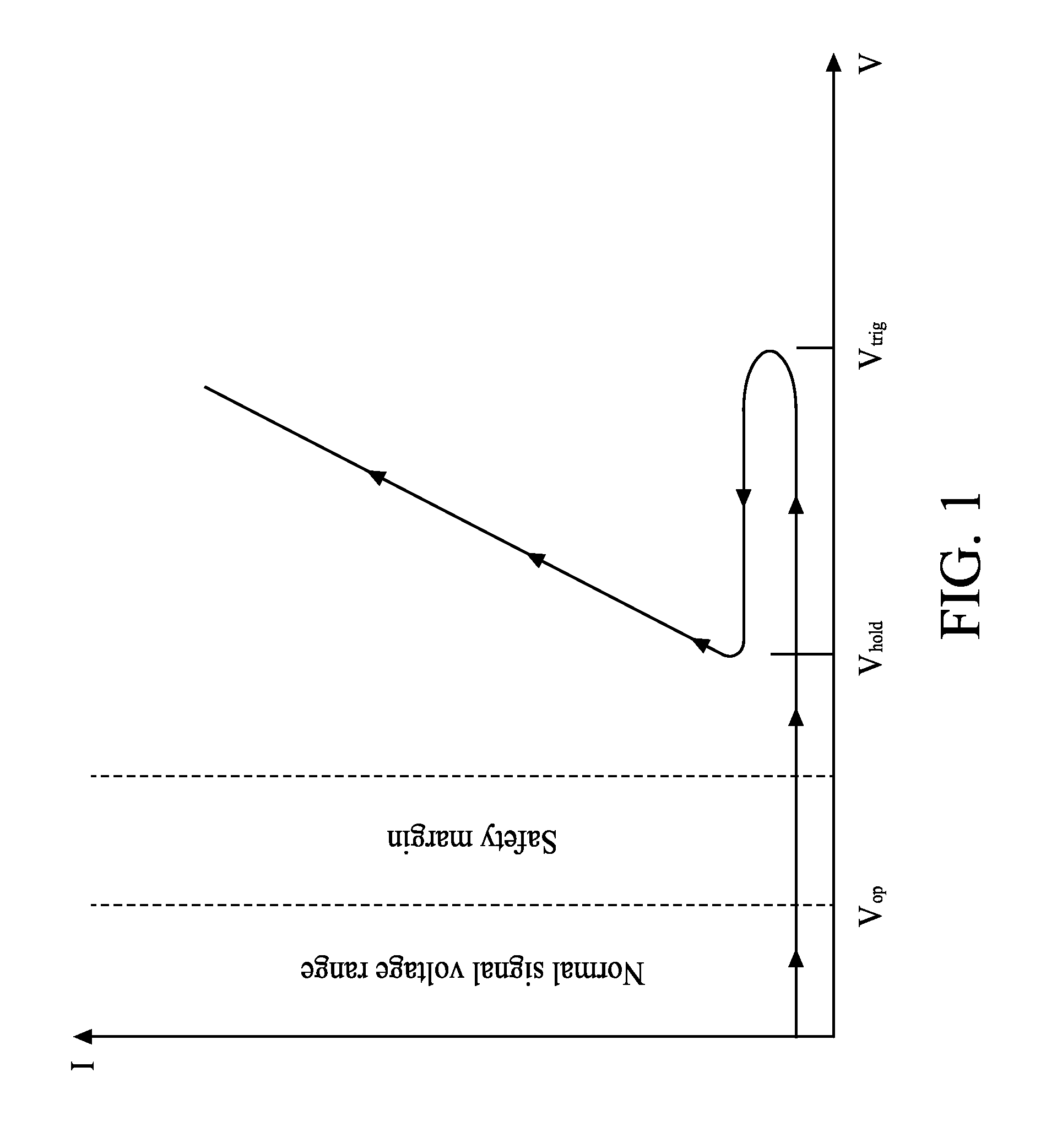

Transient voltage suppressor (TVS) with reduced breakdown voltage

ActiveUS20170179107A1Reduce capacitanceThyristorSolid-state devicesCapacitanceTransient voltage suppressor

A low capacitance transient voltage suppressor with snapback control and a reduced voltage punch-through breakdown mode includes an n+ type substrate, a first epitaxial layer on the substrate, a buried layer formed within the first epitaxial layer, a second epitaxial layer on the first epitaxial layer, and an implant layer formed within the first epitaxial layer below the buried layer. The implant layer extends beyond the buried layer. A set of source regions is formed within a top surface of the second epitaxial layer. Implant regions are formed in the second epitaxial layer, with a first implant region located below the first source region.

Owner:ALPHA & OMEGA SEMICON INC

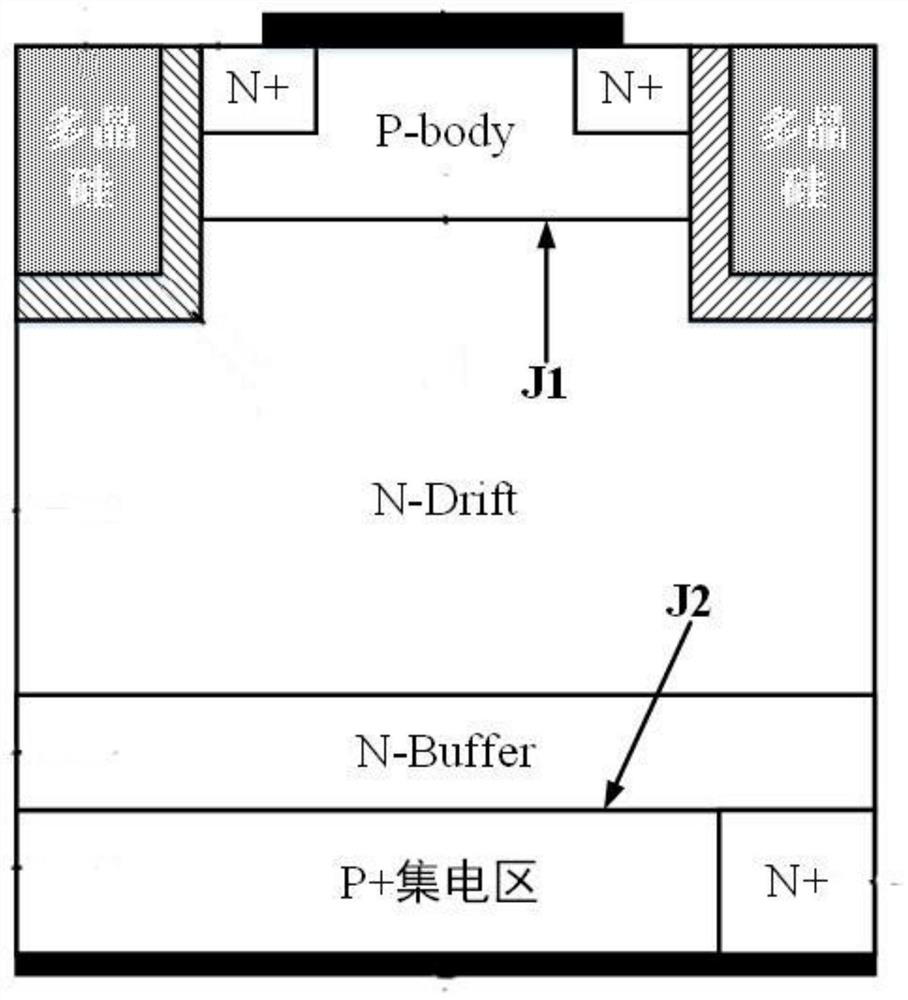

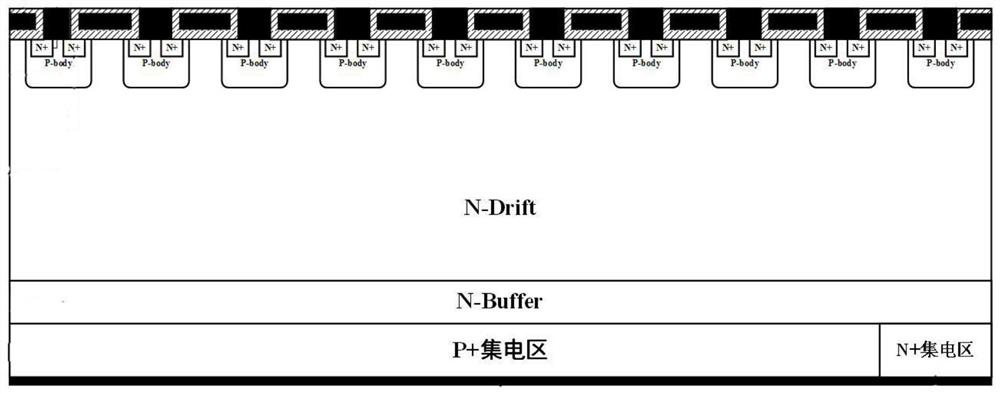

RC-IGBT device with collector polysilicon electronic channel

ActiveCN112466935AControl short circuit resistanceEliminate the snapback effectEfficient power electronics conversionSemiconductor devicesHigh concentrationBlocking layer

The invention relates to an RC-IGBT device with a collector polysilicon electronic channel, and belongs to the technical field of semiconductors. The device has the following three characteristics: (1) a P collector region of a traditional RC-IGBT is divided into two sections, namely a high-concentration P + hole region and a low-concentration P-type electron blocking layer; and (2) an N + collector is arranged in the high-concentration P + hole region. And (3) an N-type polycrystalline silicon layer is introducedto the bottom of the collector. During forward conduction, the short-circuit resistance RCS of the collector can be changed by adjusting the doping of the polycrystalline silicon layer and the P-type electron blocking layer, so that the snapback effect is completely eliminated; during turn-off, the polycrystalline silicon layer can rapidly extract electrons, so that the turn-off loss is effectively reduced; and simulation results show that compared with a TRC RC-IGBT, the device completely eliminates the snapback effect during forward conduction, and the turn-off loss Eoff of the device is reduced by 59% when the forward conduction voltage drop is 2.8 V.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

rc-igbt device and its preparation method

ActiveCN108649068BIncrease potential differenceInhibit the Snapback effectSemiconductor/solid-state device manufacturingSemiconductor devicesElectron holePotential difference

The invention provides an RC-IGBT device and a preparation method thereof. The RC-IGBT device includes a first collector region with a first conductivity type and a second collector region with a second conductivity type, the first collector region has a first end extending through the field stop region, for connecting the field The cut-off region is separated into a first cut-off region and a second cut-off region, the first collector region is arranged in contact with the first cut-off region except for the first end, and the second collector region is arranged in contact with the second cut-off region. Due to the isolation effect of the first end of the first collector region on the field stop region, electrons or holes need to climb through the first end, which increases the carrier movement path, thereby increasing the RC-IGBT device in the field. The potential difference above the first collector region at the initial stage of conduction makes the PN junction easier to open, and the device is easier to switch from unipolar conduction to bipolar conduction, thereby suppressing the Snapback effect generated by the RC‑IGBT device at the initial stage of conduction .

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

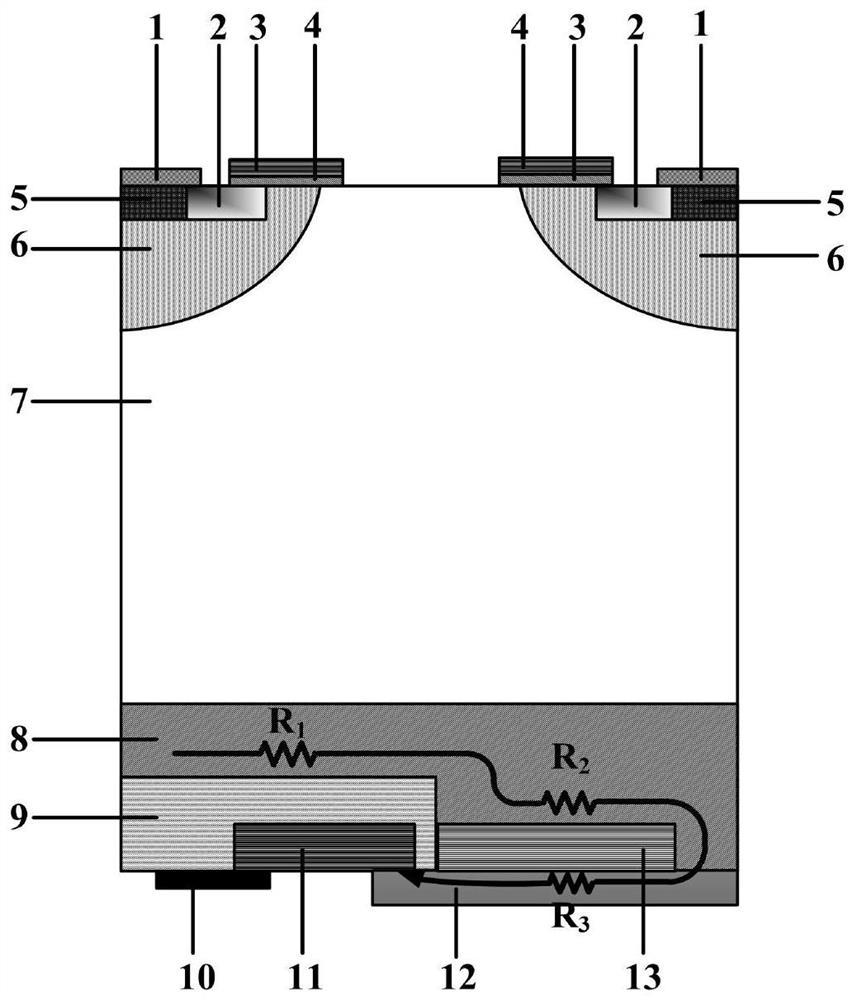

An rc-igbt device based on junction termination

ActiveCN109192773BFreewheeling capabilityEliminate the Snapback phenomenonSemiconductor devicesMOSFETEngineering physics

The invention discloses an RC-IGBT device based on a junction terminal. Based on a traditional RC-IGBT device structure, a junction terminal extension area (5) is arranged in the junction termination area, and an N+ type collector area is arranged in the junction termination extension area. (7), connect the bottom P-type collector with the N-type collector of the junction terminal area with an interconnection line. ) The PN junction formed by ) is reverse-biased, so that the device directly works in the IGBT mode and does not work in the MOSFET mode, so there will be no Snapback phenomenon during the conduction process; in the freewheeling diode mode, the P-type base (4), The P-type junction terminal extension area (5) and the N+ type collector area (7) form a PN diode, and when the voltage drop exceeds the turn-on voltage of the PN diode, the device is turned on and can conduct current. Therefore, the RC-IGBT based on the junction terminal provided by the present invention completely eliminates the Snapback phenomenon in the forward conduction process of the traditional RC-IGBT.

Owner:希力微电子(深圳)股份有限公司

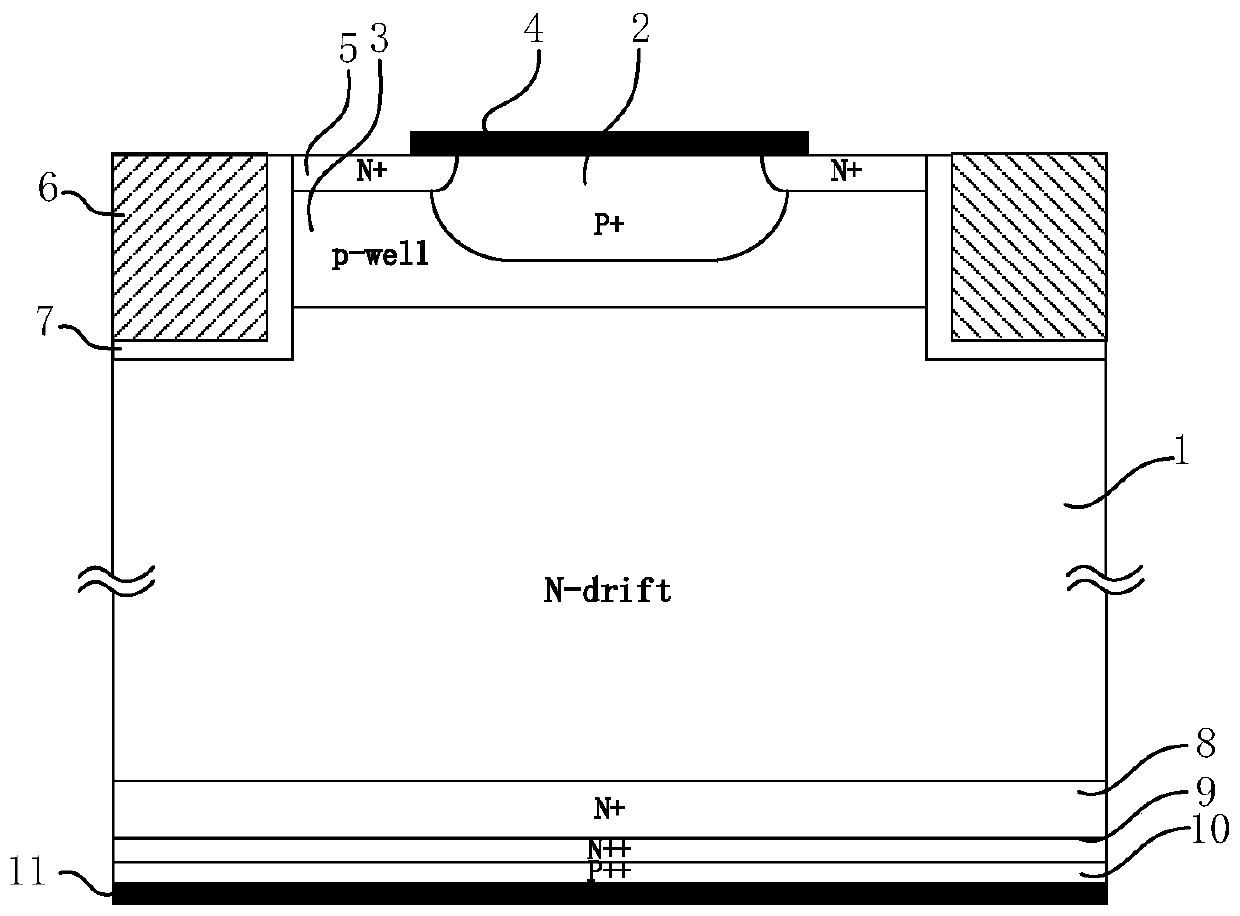

Reverse conducting IGBT (Insulated Gate Bipolar Translator) capable of eliminating voltage turn-back phenomenon

PendingCN114792724AUniform currentEliminate the snapback phenomenonSolid-state devicesSemiconductor devicesEngineeringConductive materials

The invention discloses a reverse conducting IGBT (Insulated Gate Bipolar Translator) capable of eliminating a voltage turn-back phenomenon, which comprises a semi-cellular structure, and the semi-cellular structure comprises a collector electrode structure, a voltage-withstanding layer structure, an emitter electrode structure and a grid electrode structure, the collector structure is located at one end of the voltage-withstanding layer structure, and the emitter structure and the gate structure are located at two sides of the other end of the voltage-withstanding layer structure; wherein the collector structure comprises a P + collector region, an N + collector region, an N-type buffer layer, a P + conductive material, collector metal, an N-type conductive material and floating metal; one side of the N-type buffer layer is connected to the voltage withstanding layer structure, one side of the P + collector region and one side of the N + collector region are connected to the other side of the N-type buffer layer, a gap is formed between the P + collector region and the N + collector region, and collector metal is arranged on the other side of the P + collector region; on the basis of a conventional reverse conducting IGBT structure, the snapback phenomenon is eliminated by optimizing and improving the collector electrode structure, and the reverse conducting current is more uniform.

Owner:成都智达和创信息科技有限公司

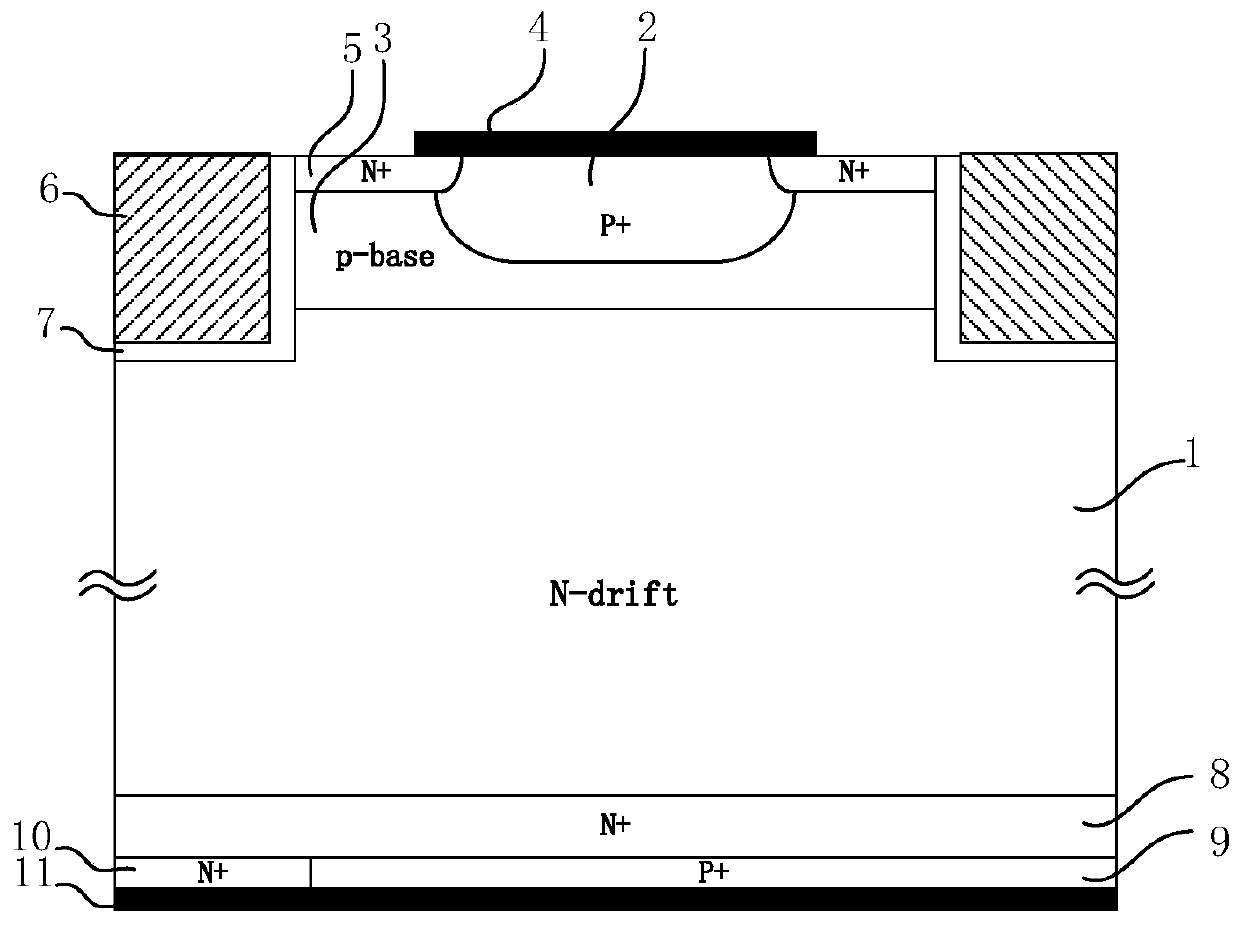

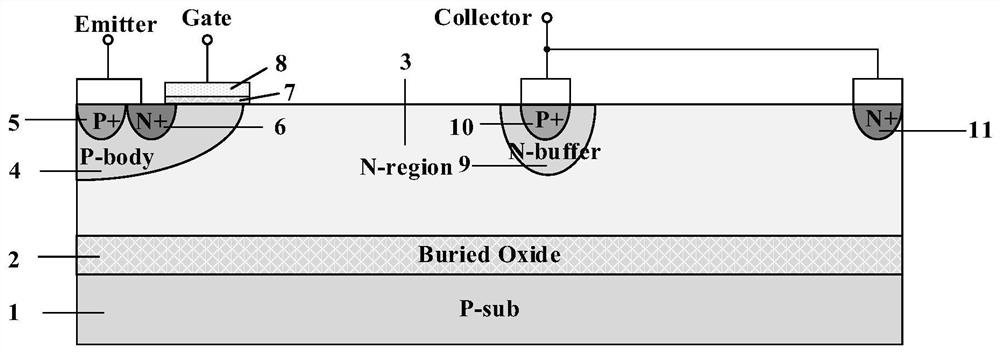

Lateral power device with mixed conduction mode and method of making same

ActiveCN107808899BHas a mixed conduction modeImprove breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingDielectricLDMOS

The invention provides a lateral power device with a mixed conduction mode and a preparation method thereof, comprising a P-type substrate, a buried oxide layer, an N-type drift region, a P-type base region, an N-type buffer region, an N-type source region, a P-type Contact region, P-type collector region, emitter, collector, gate dielectric layer, gate electrode, N-type drift region surface has N-type strips and P-type strips, N-type strips and P-type strips are perpendicular to the device drift region surface The channel length direction is arranged alternately, and there is a P-type RESURF layer in the drift region under the N-type strip and P-type strip; there is a dielectric groove structure between the N-type strip, P-type strip, and P-type RESURF layer and the N-type buffer zone; The concentration of N-type strips and P-type strips is greater than the concentration of N-type drift regions; the depth of the dielectric groove structure is not less than the depth of N-type strips, P-type strips and P-type collector regions; the invention realizes surface SJ-LDMOS and LIGBT The mixed conduction can obtain lower turn-on voltage drop, higher withstand voltage, faster switching speed, lower turn-off loss, and eliminate the snapback effect, greatly improving device performance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

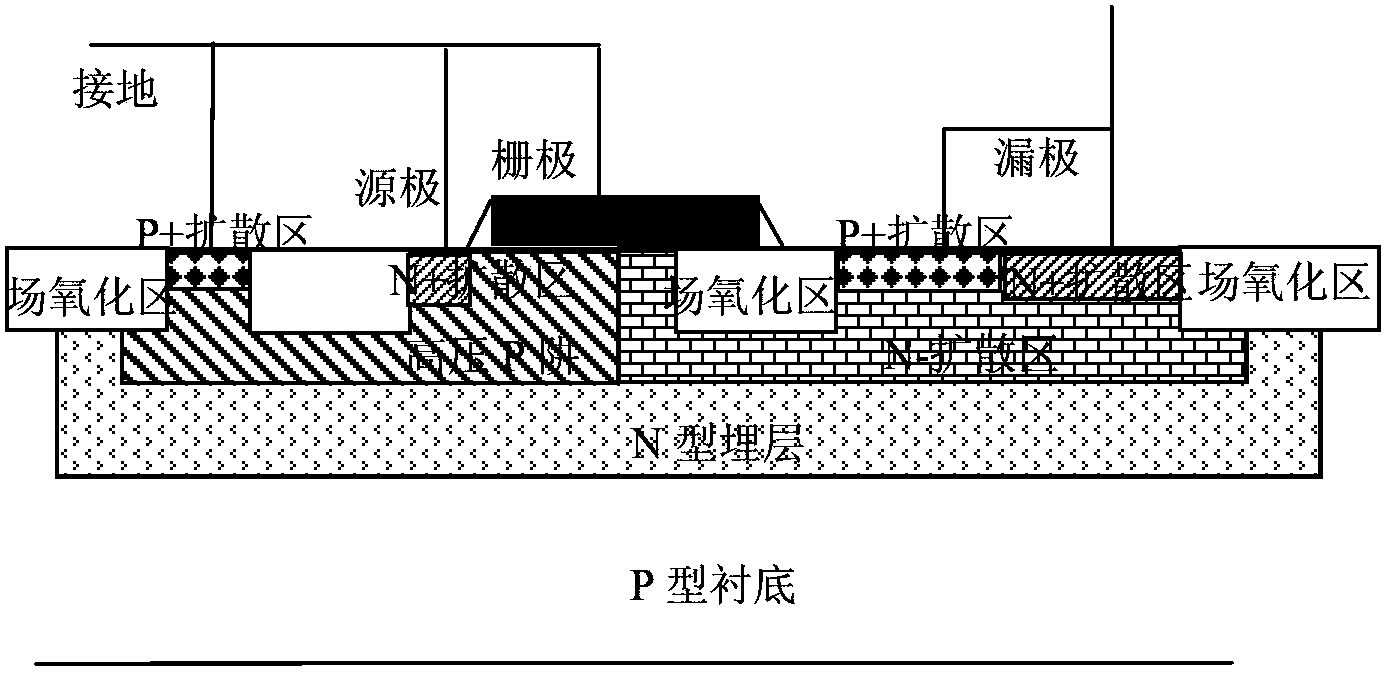

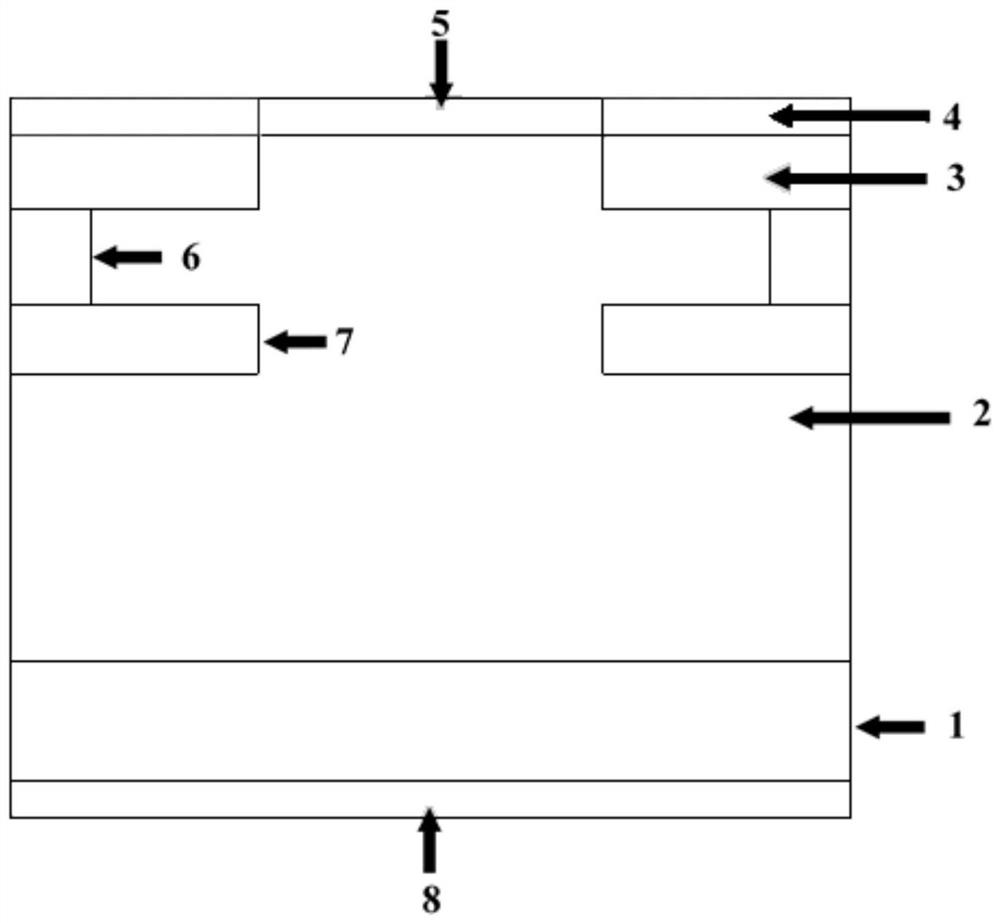

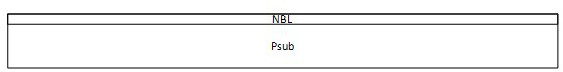

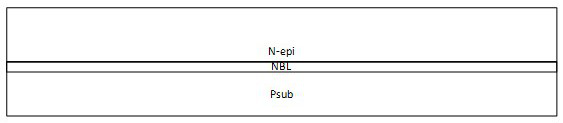

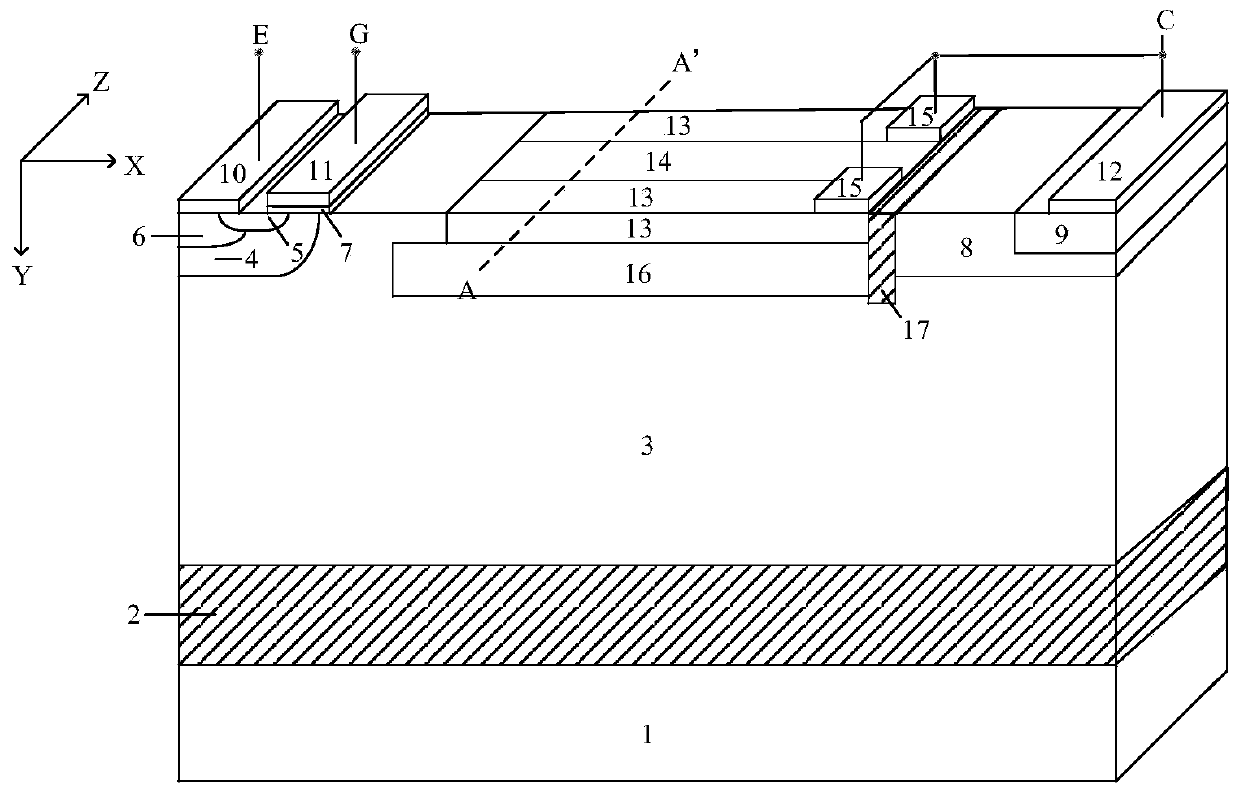

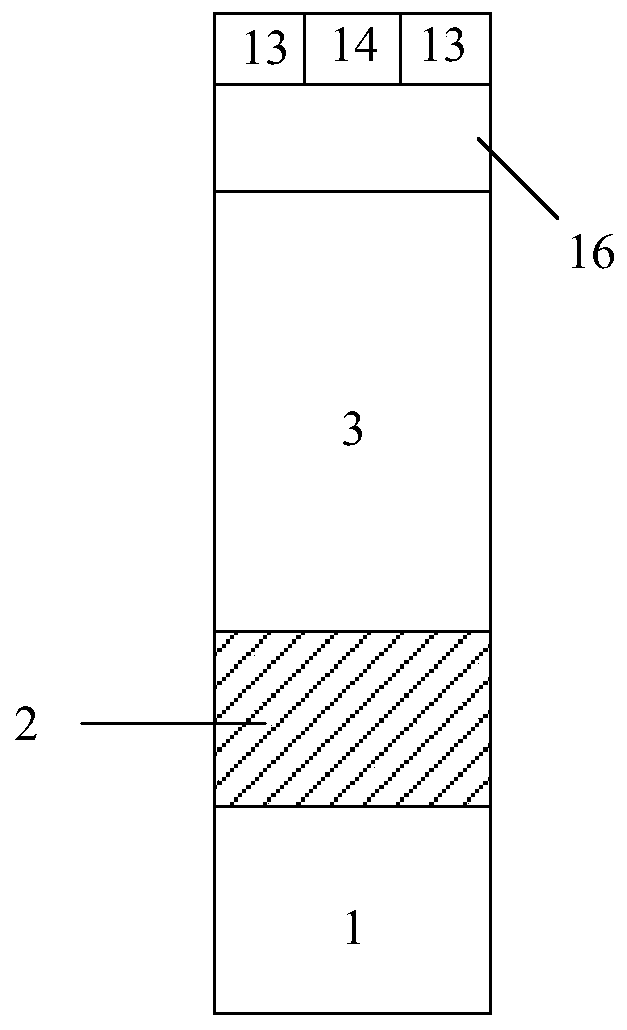

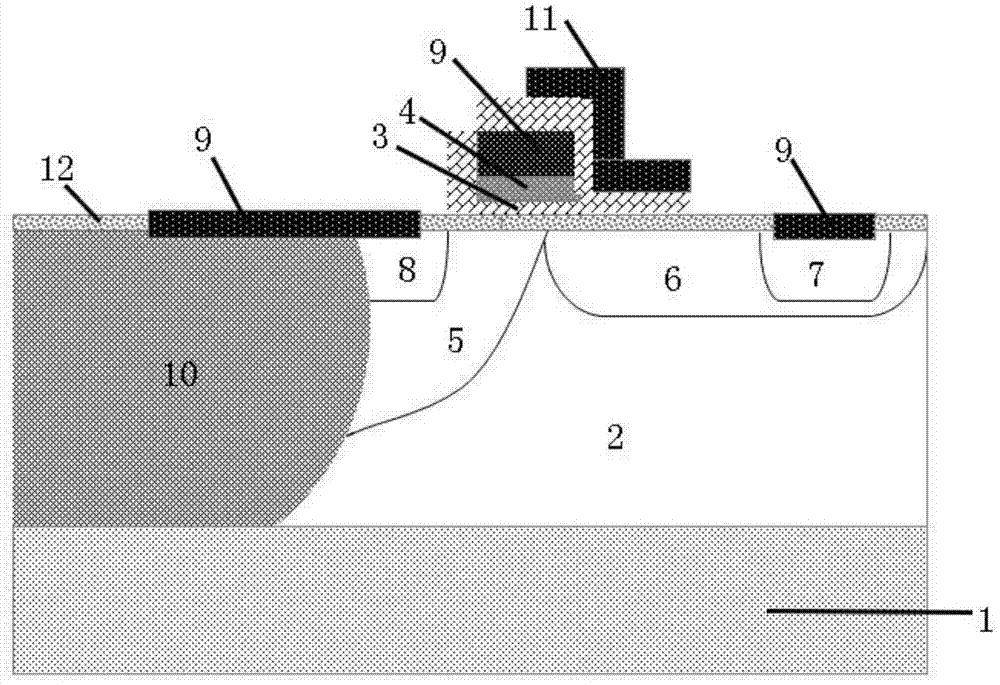

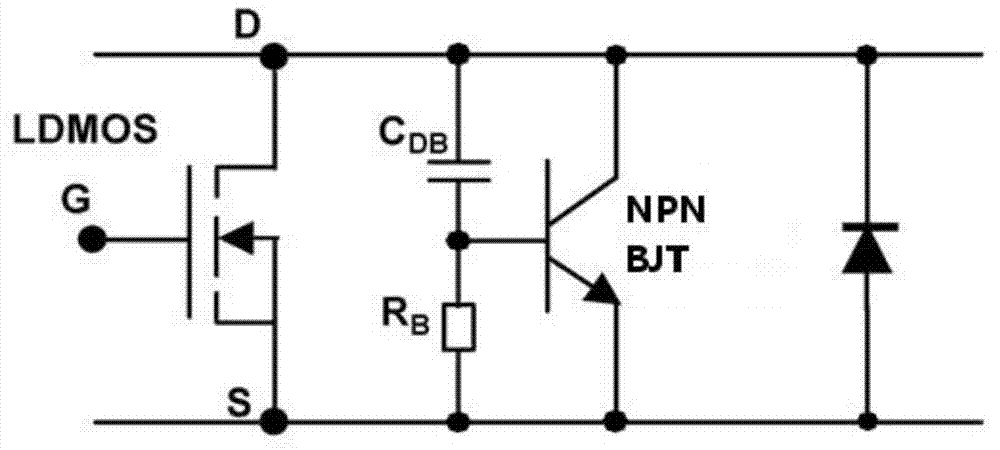

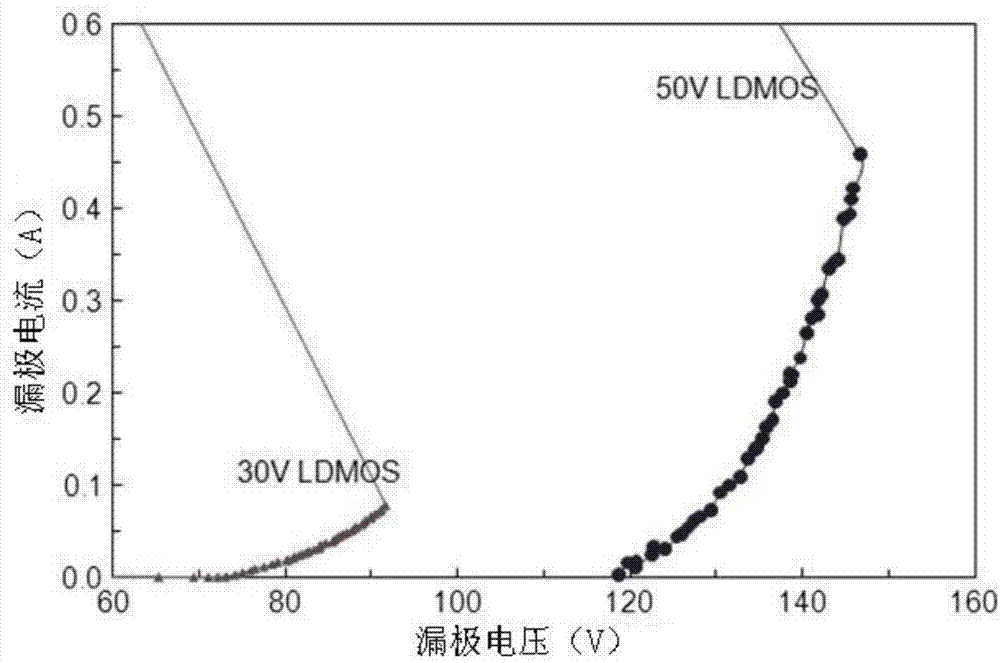

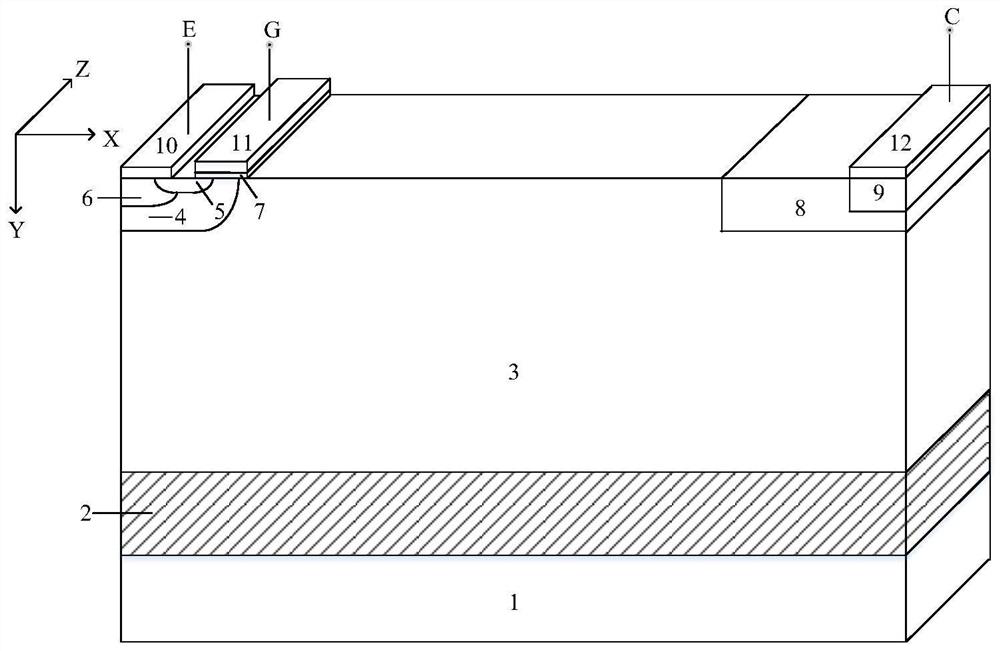

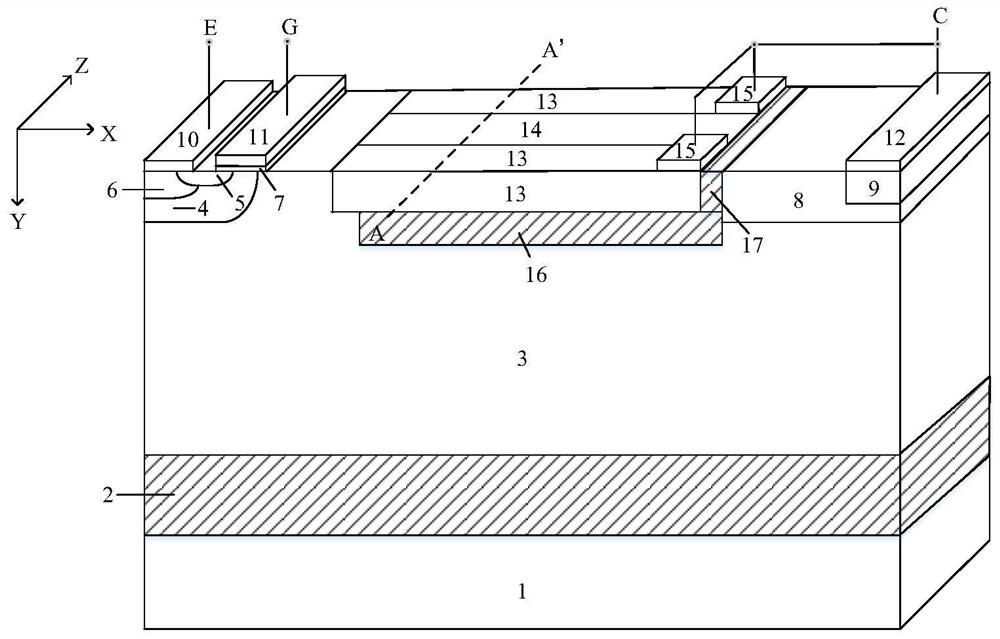

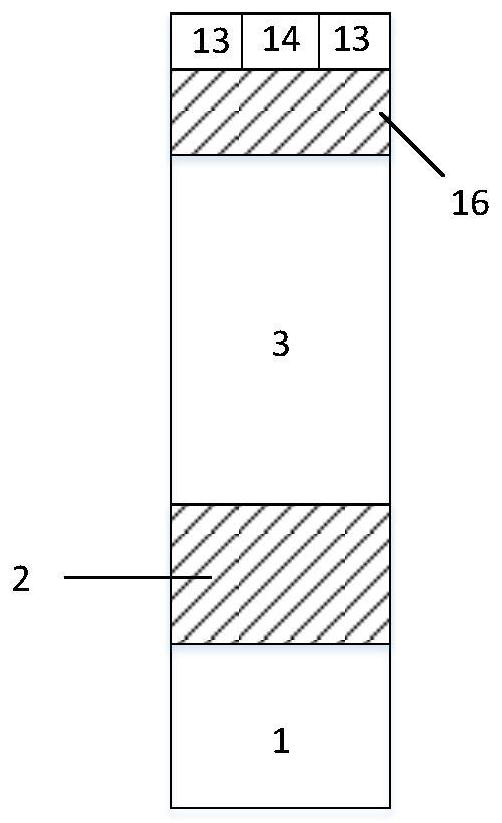

rfldmos device and manufacturing method

ActiveCN103035727BImprove transconductanceLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEngineering

A radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) device is disclosed which additionally includes a lightly-doped P-type buried layer under a P-type channel region and a moderately-dope P-type buried layer in the lightly-doped P-type buried layer. The two buried layers result in a lower base resistance for an equivalent parasitic NPN transistor, thereby impeding the occurrence of snapback in the device. Additionally, an equivalent reverse-biased diode formed between the channel region and the buried layers is capable of clamping the drain-source voltage of the device and sinking redundant currents to a substrate thereof. Furthermore, the design of a gate oxide layer of the RF LDMOS device to have a greater thickness at a proximal end to a drain region can help to reduce the hot-carrier effect, and having a smaller thickness at a proximal end to the source region can improve the transconductance of the RF LDMOS device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Lateral power device with mixed conduction mode and method of making same

ActiveCN107785414BHas a mixed conduction modeImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricLDMOS

The invention provides a lateral power device with a mixed conduction mode and a preparation method thereof, comprising a P-type substrate, a buried oxide layer, an N-type drift region, a P-type base region, an N-type buffer region, an N-type source region, a P-type Contact region, P-type collector region, emitter, collector, gate dielectric layer, gate electrode, N-type drift region surface has N-type strips and P-type strips, N-type strips and P-type strips are perpendicular to the device drift region surface The channel length direction is arranged alternately, and there is a dielectric buried layer in the drift region under the N-type strip and the P-type strip; there is a dielectric groove structure between the N-type strip, the P-type strip, the dielectric buried layer and the N-type buffer zone; the N-type strip and the P-type strip. The concentration of the P-type strip is greater than the concentration of the N-type drift region; the invention realizes the mixed conduction of the surface SJ-LDMOS and LIGBT, and can obtain lower conduction voltage drop, higher withstand voltage, faster switching speed, and more Low turn-off loss, and eliminate the snapback effect, greatly improving device performance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

SiC MPS diode device and preparation method thereof

ActiveCN111799336ASuppression of rapid return of pressure dropImprove injection efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropMaterials science

The invention belonging to the technical field of microelectronics discloses a SiC MPS diode device and a preparation method thereof.The device comprises a cathode, an N + substrate, an N-epitaxial layer, P + injection regions and an anode which are sequentially arranged from bottom to top, and is characterized in that a trench structure is arranged between the two P + injection regions, N + injection regions are arranged between the two sides of the trench structure and the P + injection regions respectively, and the P + injection regions are surrounded by the N + injection regions to form awell structure. The SiC MPS diode device provided by the invention is provided with the trench structure; according to the SiC MPS diode device integrated with the trench structure, the internal potentials of the PiN structure and the Schottky structure can be promoted to be more uniform when the device is in forward conduction to be close to the potential distribution in the PiN body, so that thephenomenon of rapid return of voltage drop of the device is effectively inhibited; N + injection is additionally carried out on the original PiN diode on the basis of the trench type SiC MPS diode, and the purposes of improving the injection efficiency of the PiN transistor and improving the surge capacity of the device are achieved.

Owner:XIDIAN UNIV

Transient voltage suppression device

ActiveCN109817616ASolid-state devicesSemiconductor/solid-state device manufacturingPhysical chemistrySemiconductor

Embodiments of the present invention provide a transient voltage suppression device. The transient voltage suppression device includes a substrate, a first semiconductor layer of a first conductivitytype disposed on the substrate, a second semiconductor layer of a second conductivity type disposed on the first semiconductor layer, and a first well and a second well of the first conductivity typedisposed in the second semiconductor layer. The second well is disposed adjacent to the first well but separated from each other. The transient voltage suppression device further includes a first heavily doped region disposed between the first well and the second well and extending into the second conductivity type of the first well and the second well, a second heavily doped region of the first conductivity type disposed in the first well under the first heavily doped region, and a third heavily doped region of the first conductivity type disposed in the second well under the first heavily doped region. The transient voltage suppression device can reduce the snapback voltage of the transient voltage suppression device and further increase the secondary breakdown current.

Owner:NUVOTON