Patents

Literature

170results about How to "Lower forward voltage drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

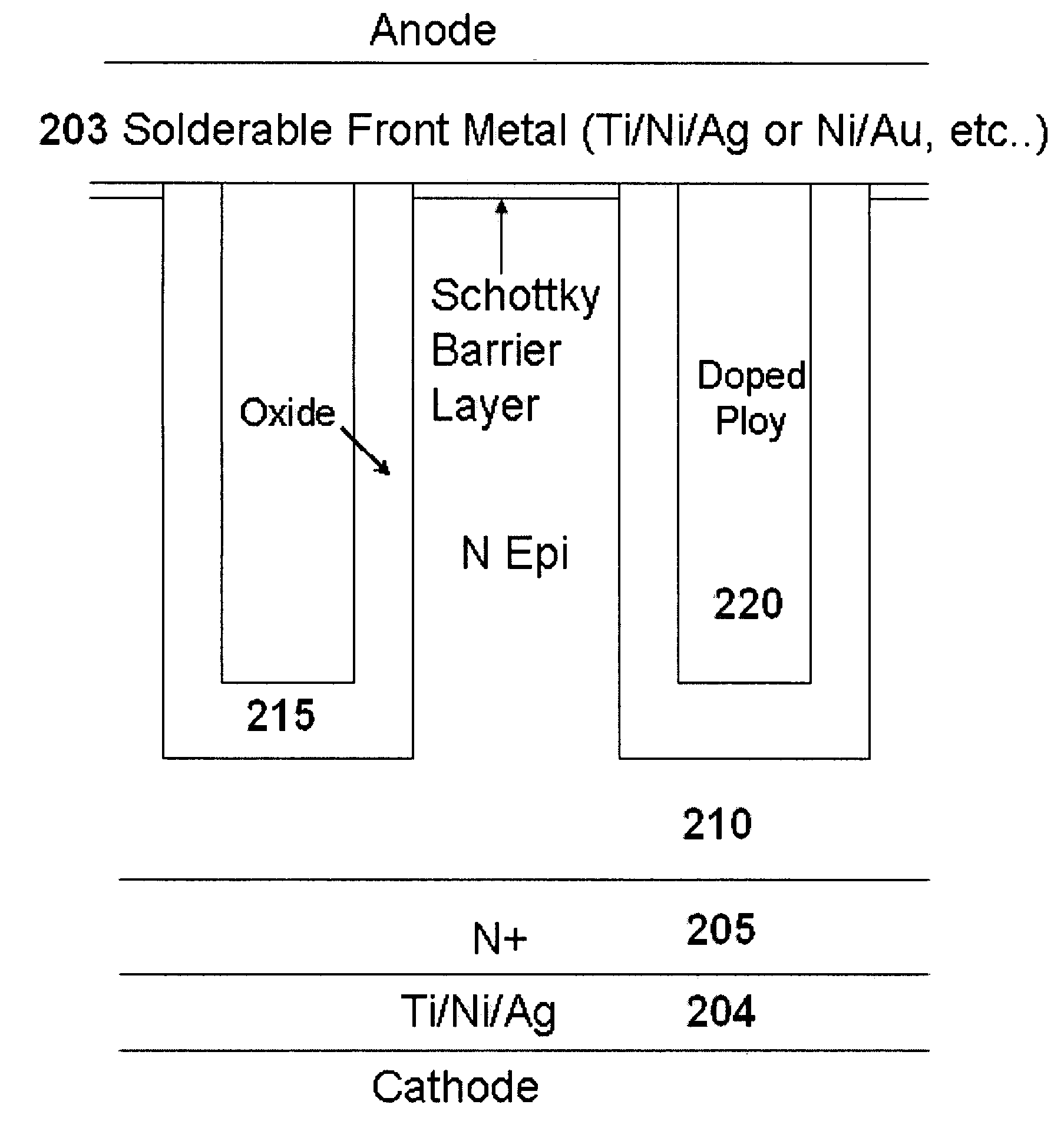

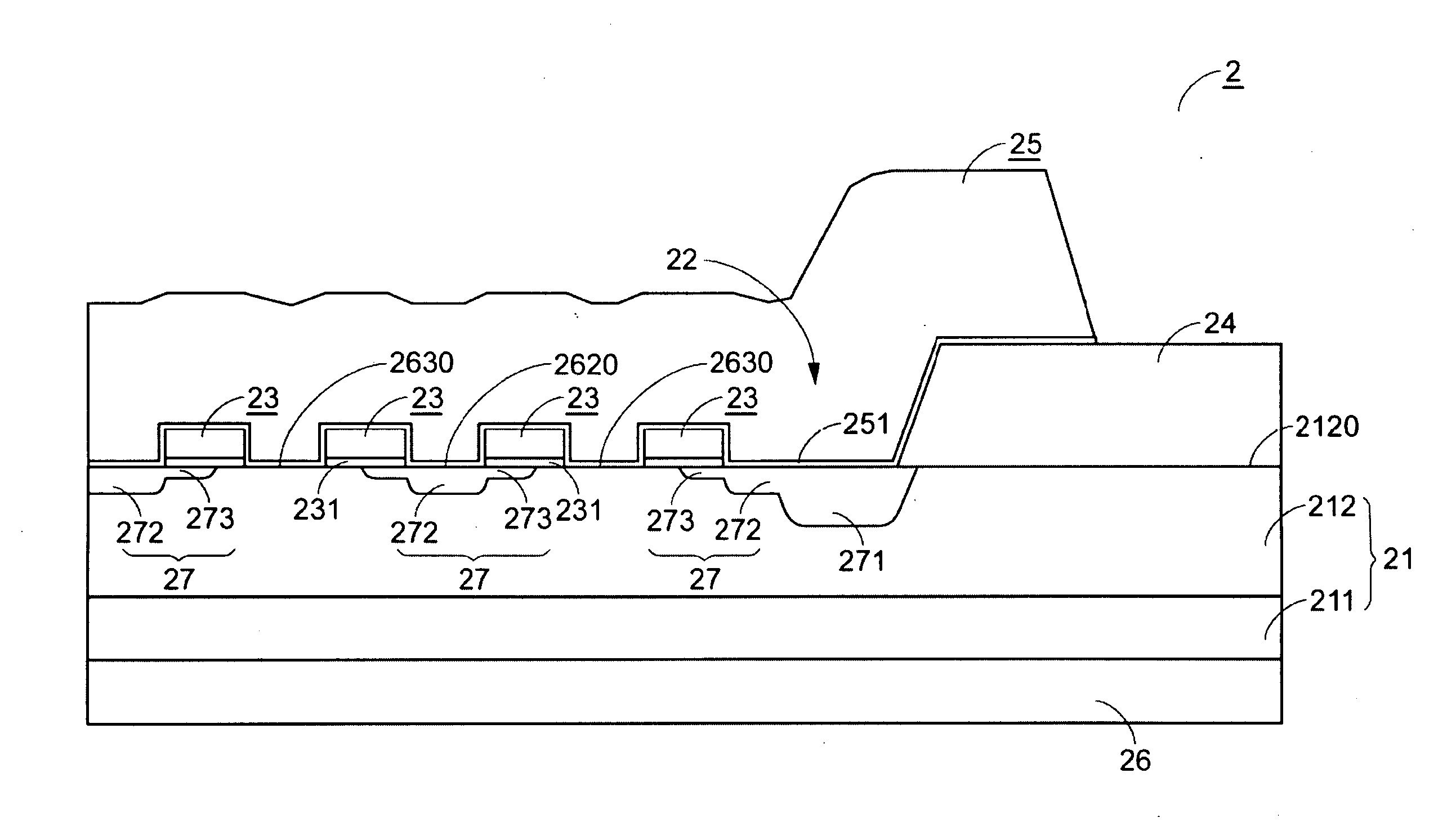

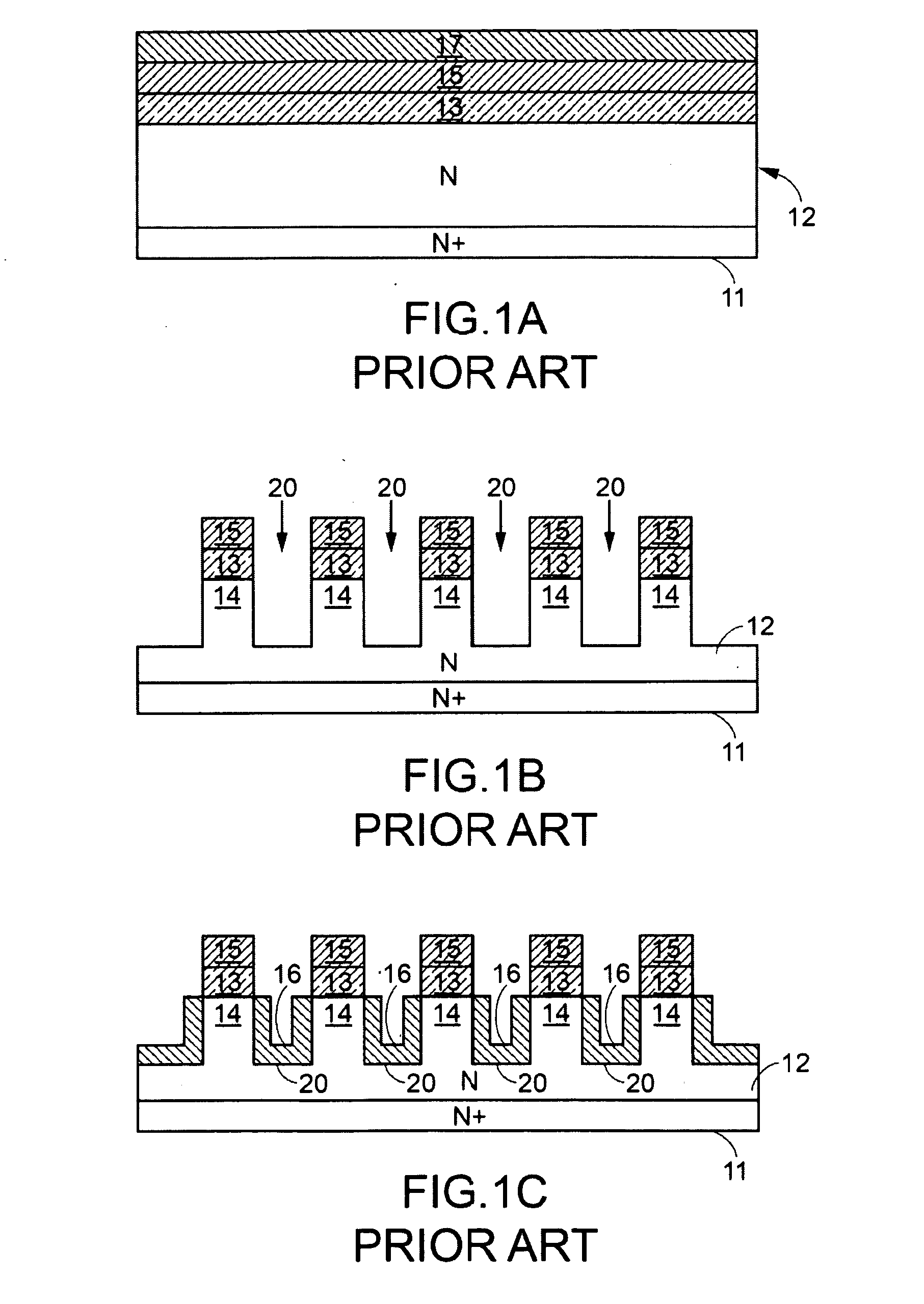

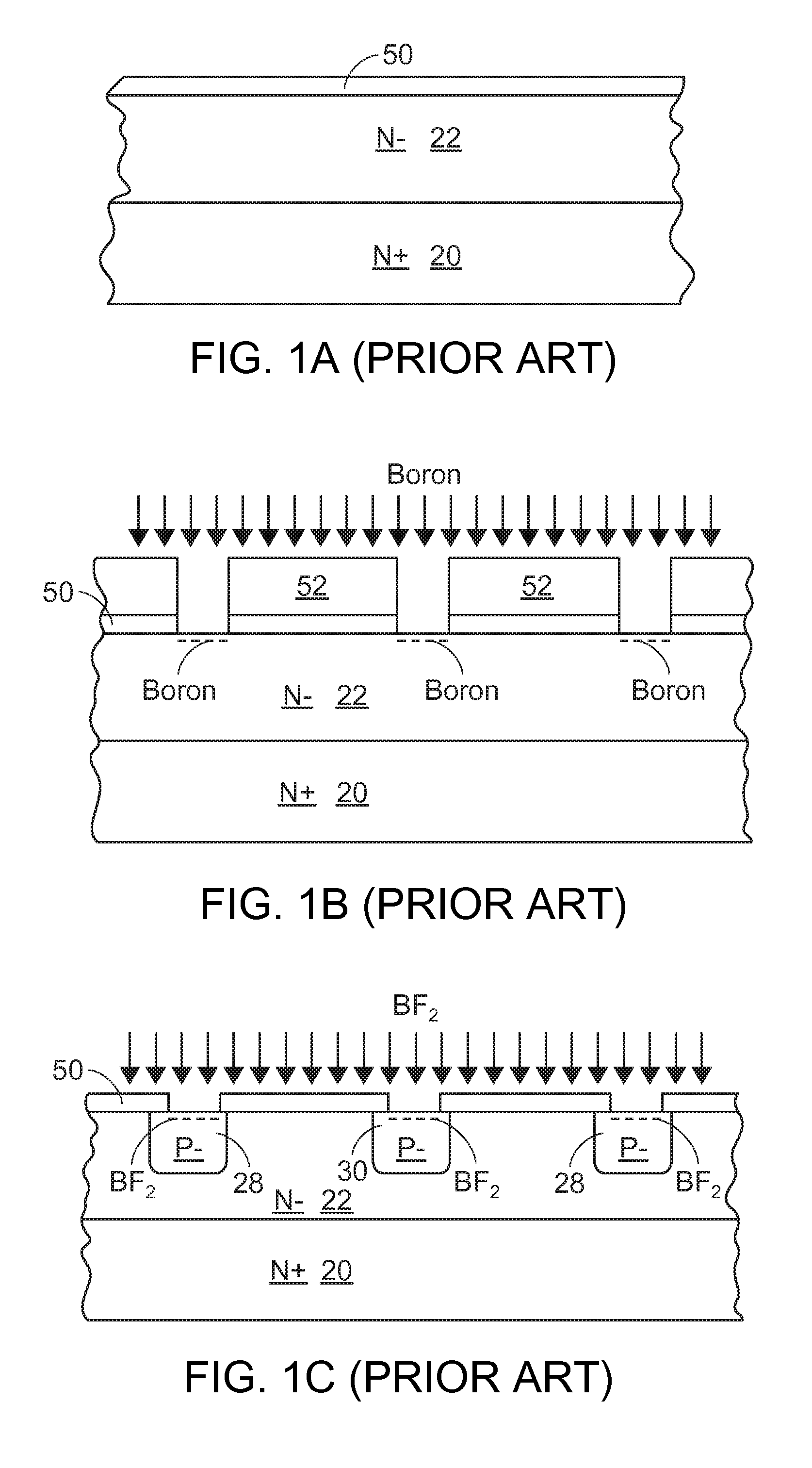

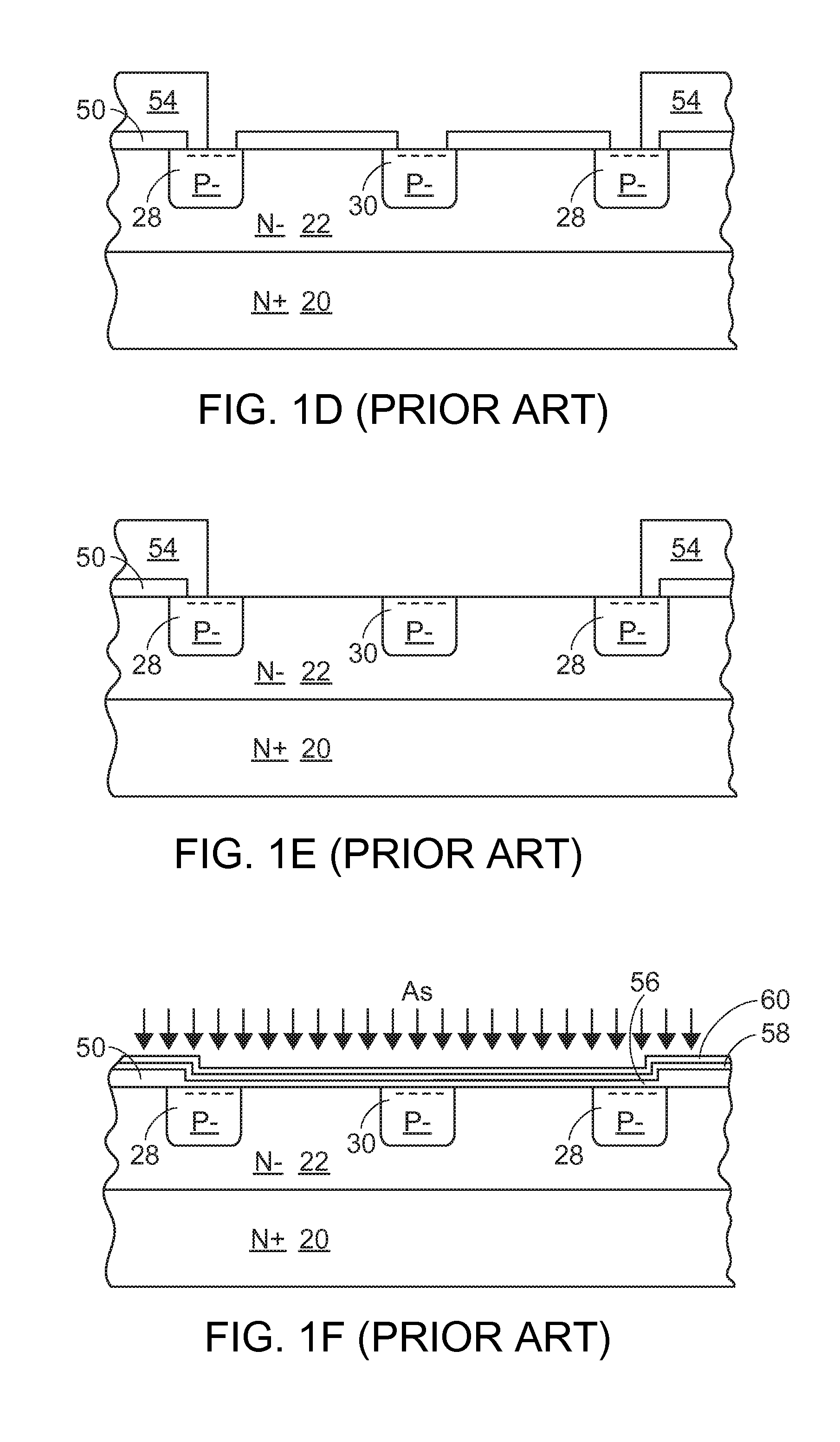

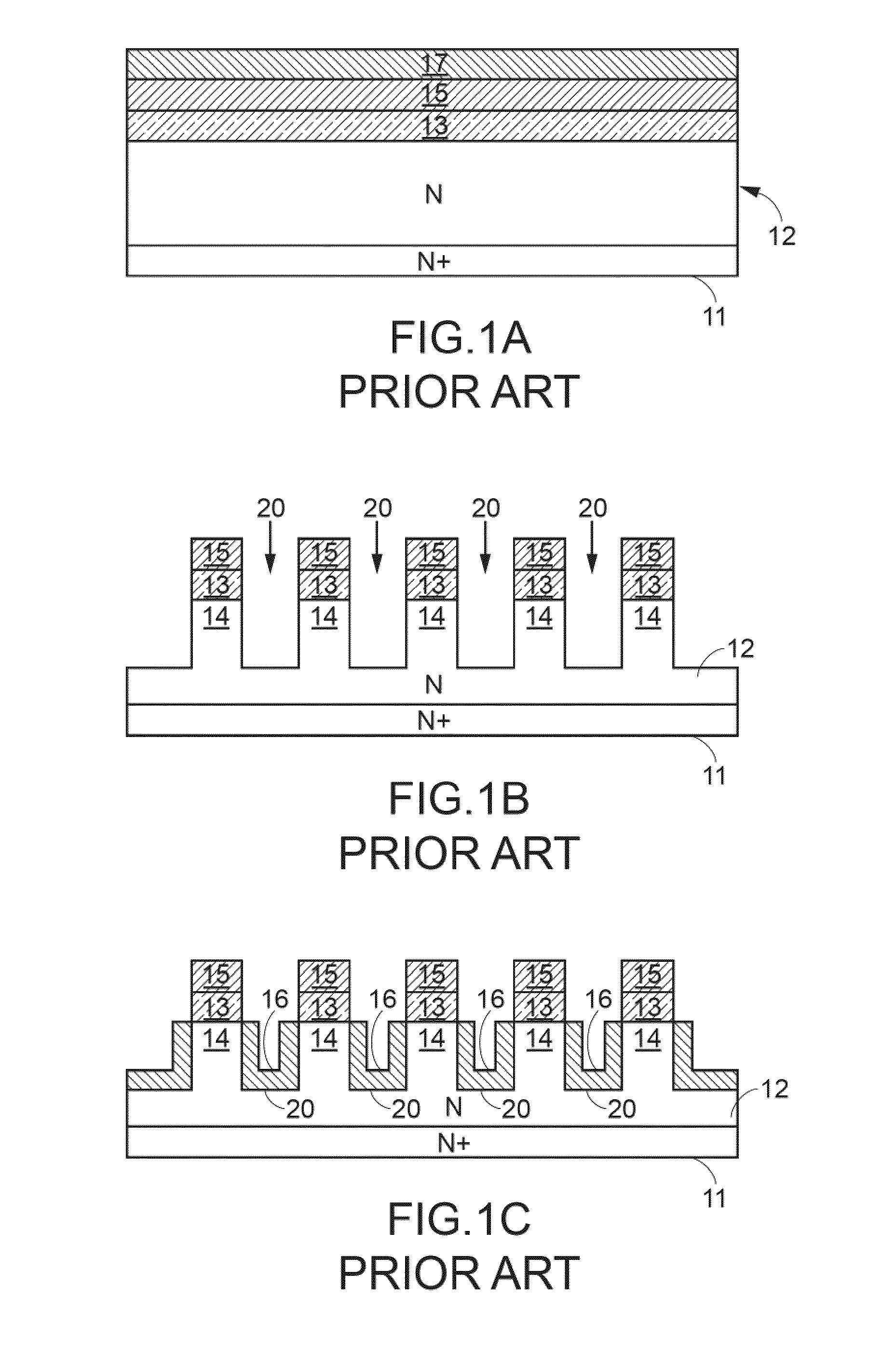

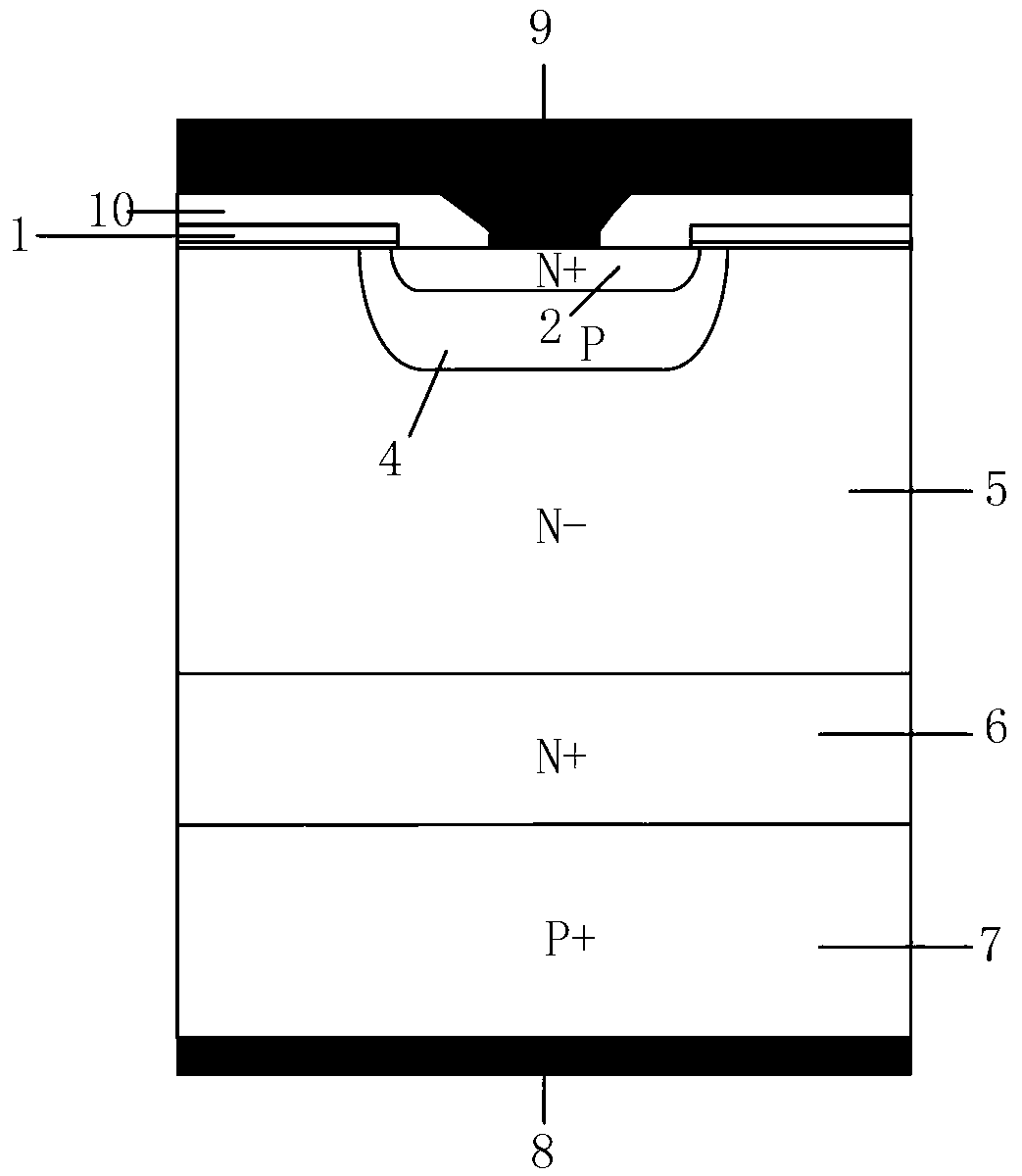

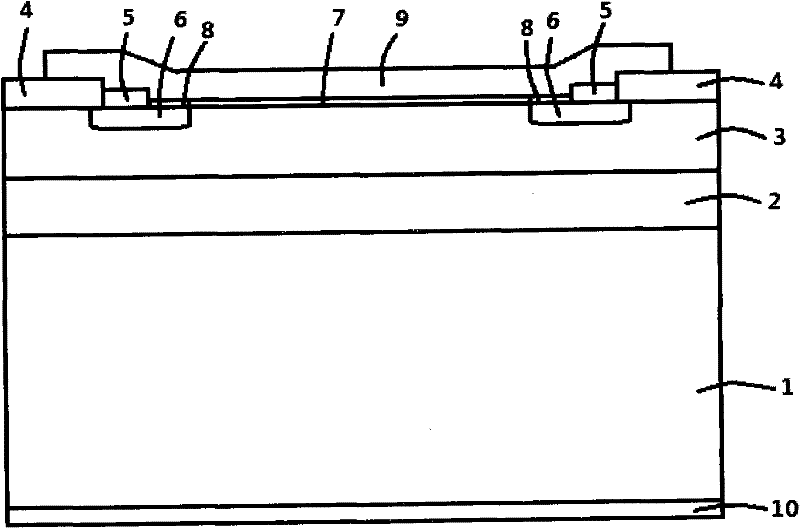

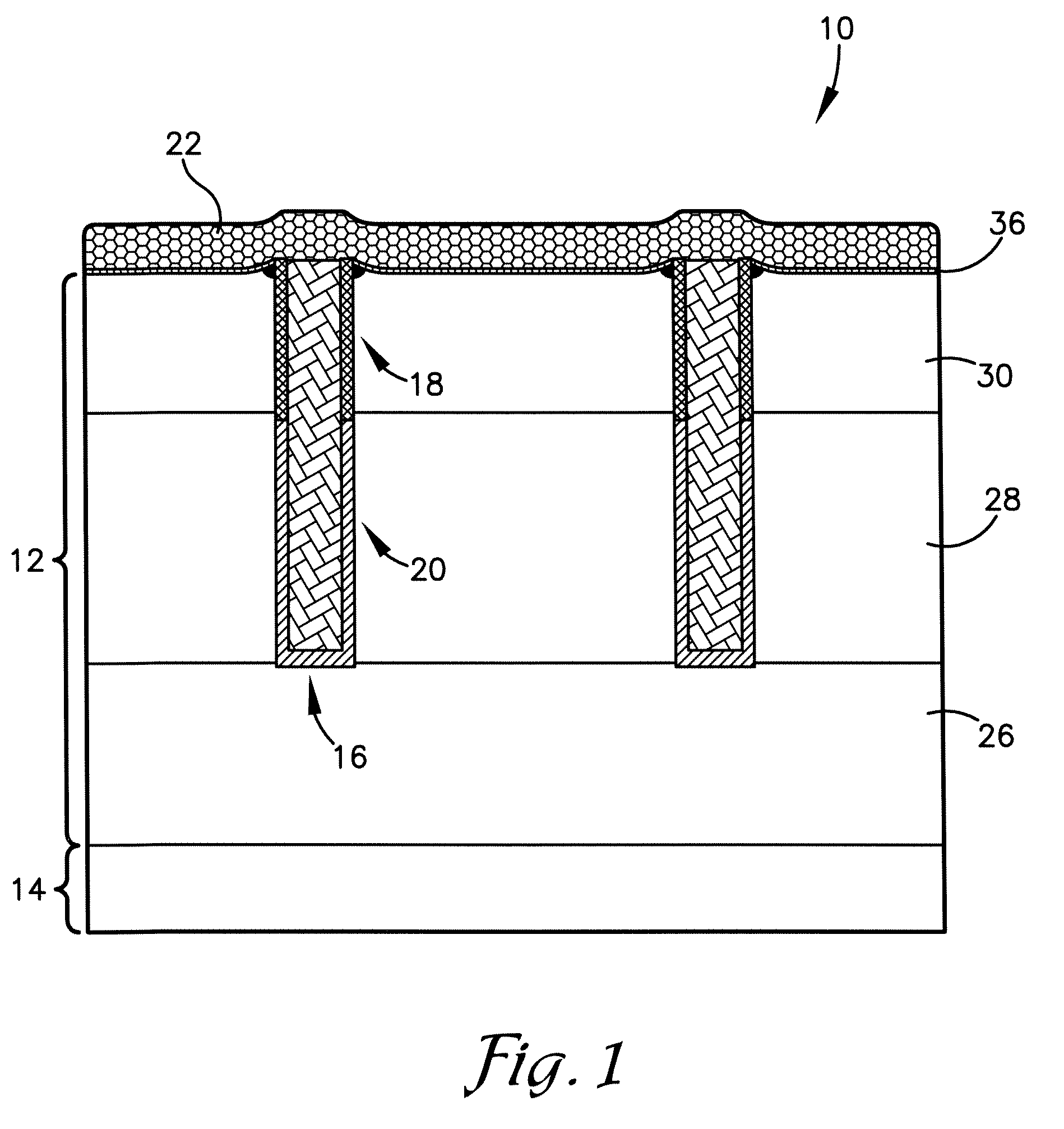

Trench schottky with multiple epi structure

InactiveUS20090309181A1Reduce doping concentrationIncrease the doping concentrationSemiconductor devicesDopantSchottky barrier

A trench Schottky barrier rectifier includes an cathode electrode at a face of a semiconductor substrate and an multiple epitaxial structure in drift region which in combination provide high blocking voltage capability with low reverse-biased leakage current and low forward voltage. The multiple structure of the drift region contains a concentration of first conductivity dopants therein which comprises two or three different uniform value from a Schottky rectifying junction formed between the anode electrode and the drift region. The thickness of the insulating region (e.g., SiO2) in the MOS-filled trenches is greater than 1000 Å to simultaneously inhibit field crowing and increase the breakdown voltage of the device. The multiple epi structure is preferably formed by epitaxial growth from the cathode region and doped in-situ.

Owner:FORCE MOS TECH CO LTD

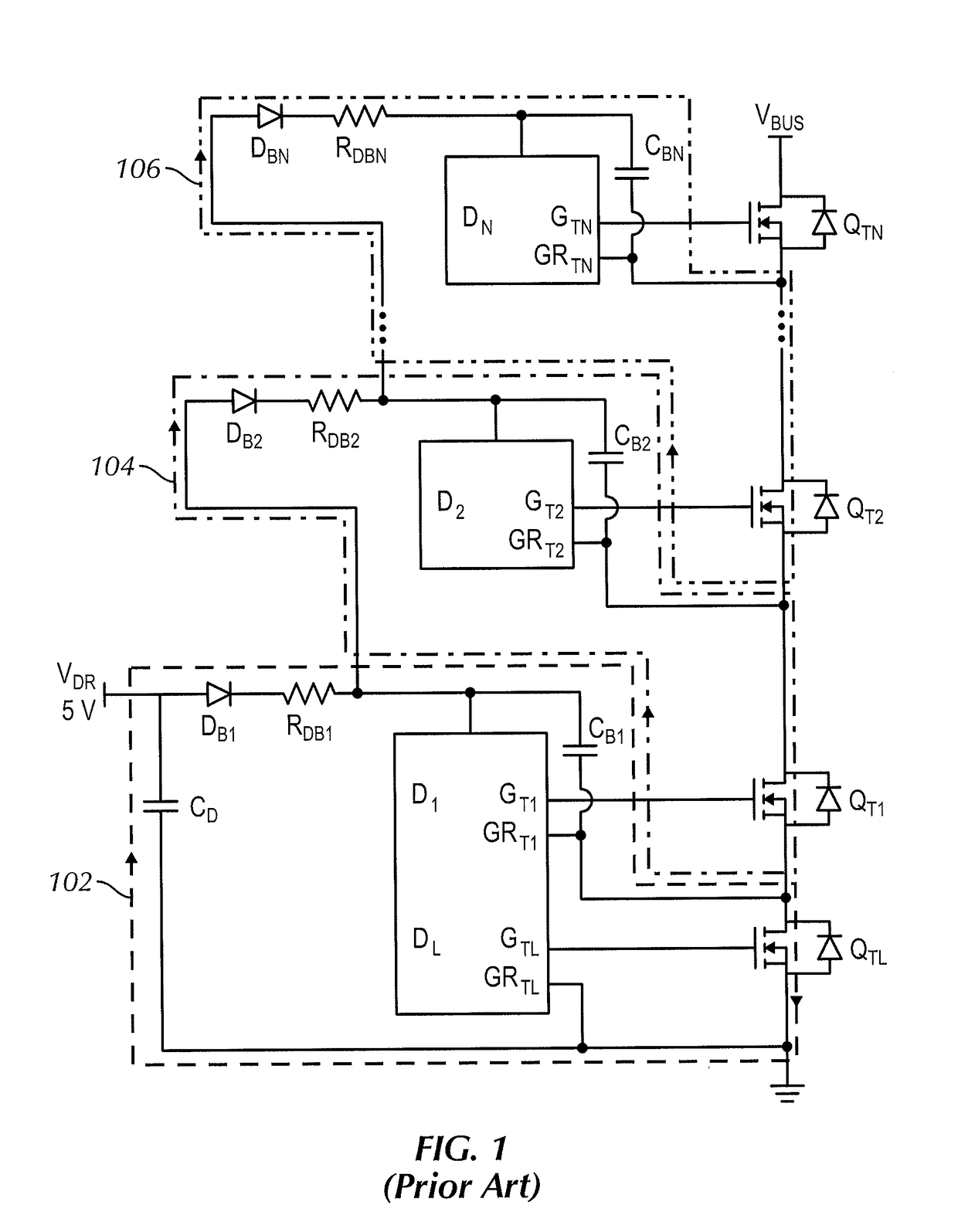

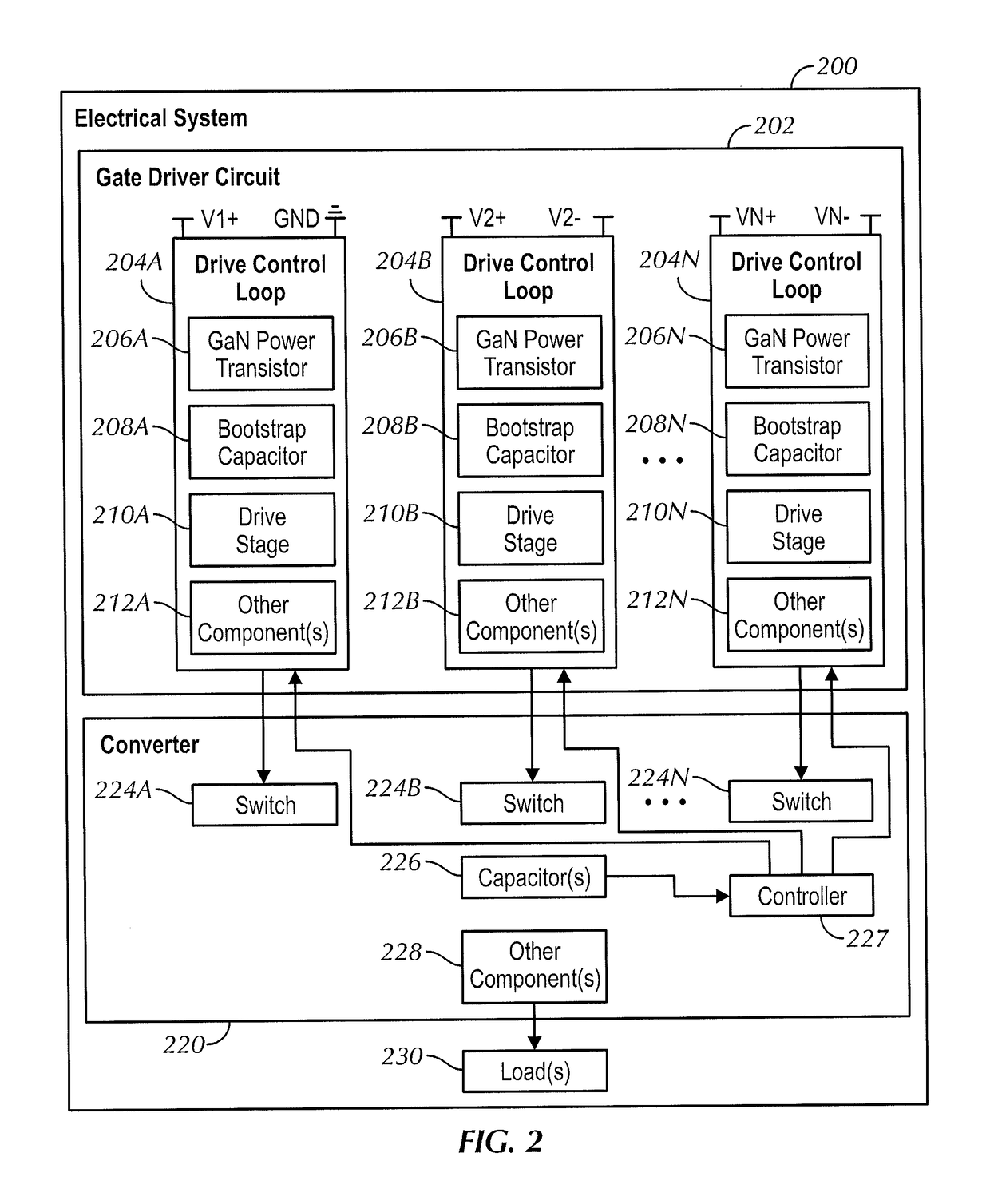

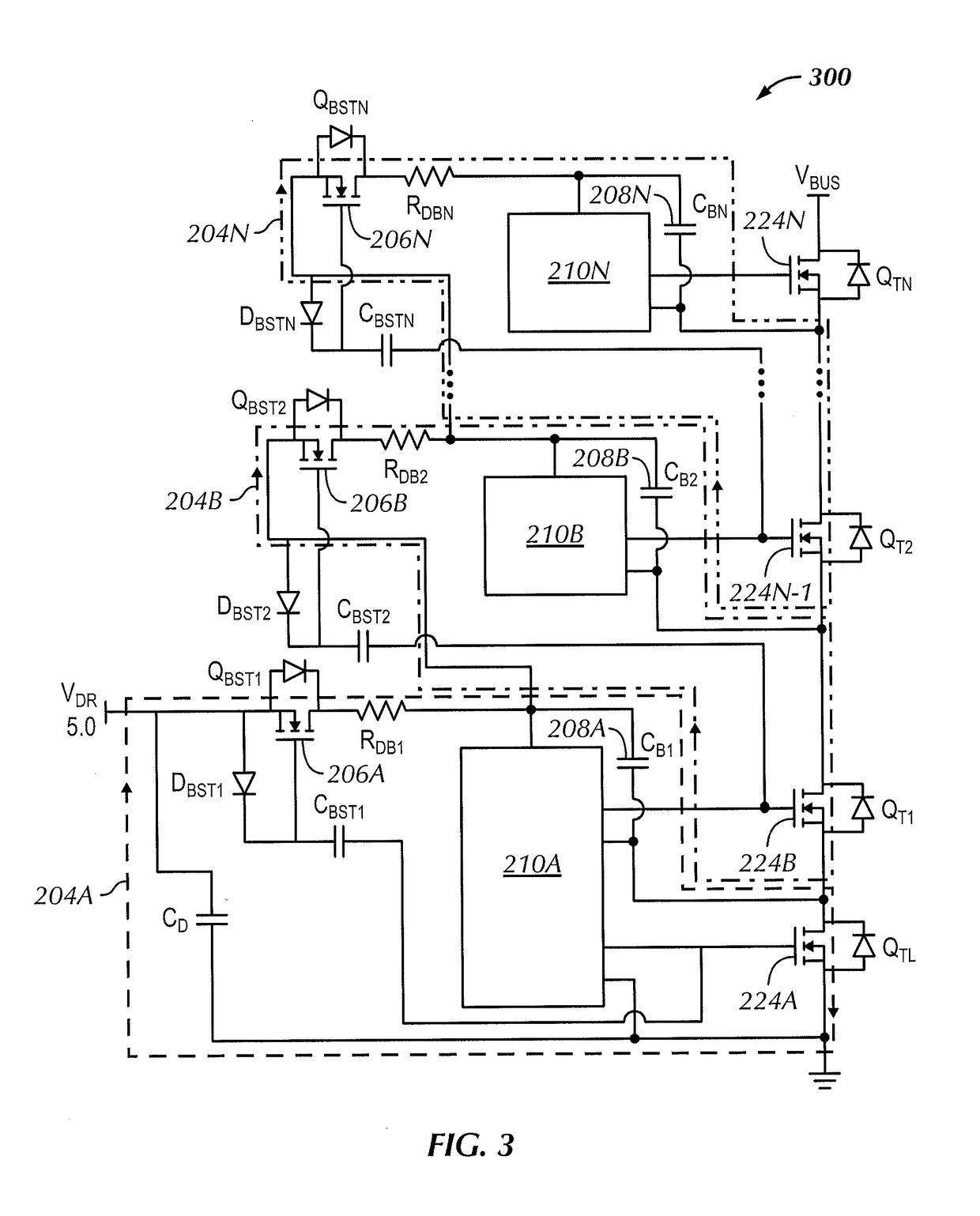

Low voltage drop cascaded synchronous bootstrap supply circuit

ActiveUS20190028094A1Reduce voltage dropLower forward voltage dropTransistorEfficient power electronics conversionCapacitanceLow voltage

A cascaded synchronous bootstrap supply circuit with reduced voltage drop between the cascaded bootstrap capacitors by replacing bootstrap diodes with gallium nitride (GaN) transistors. GaN transistors have a much lower forward voltage drop than diodes, thus providing a cascaded gate driver bootstrap supply circuit with a reduced drop in bootstrap capacitor voltage, which is particularly important as the number of levels increases.

Owner:EFFICIENT POWER CONVERSION CORP

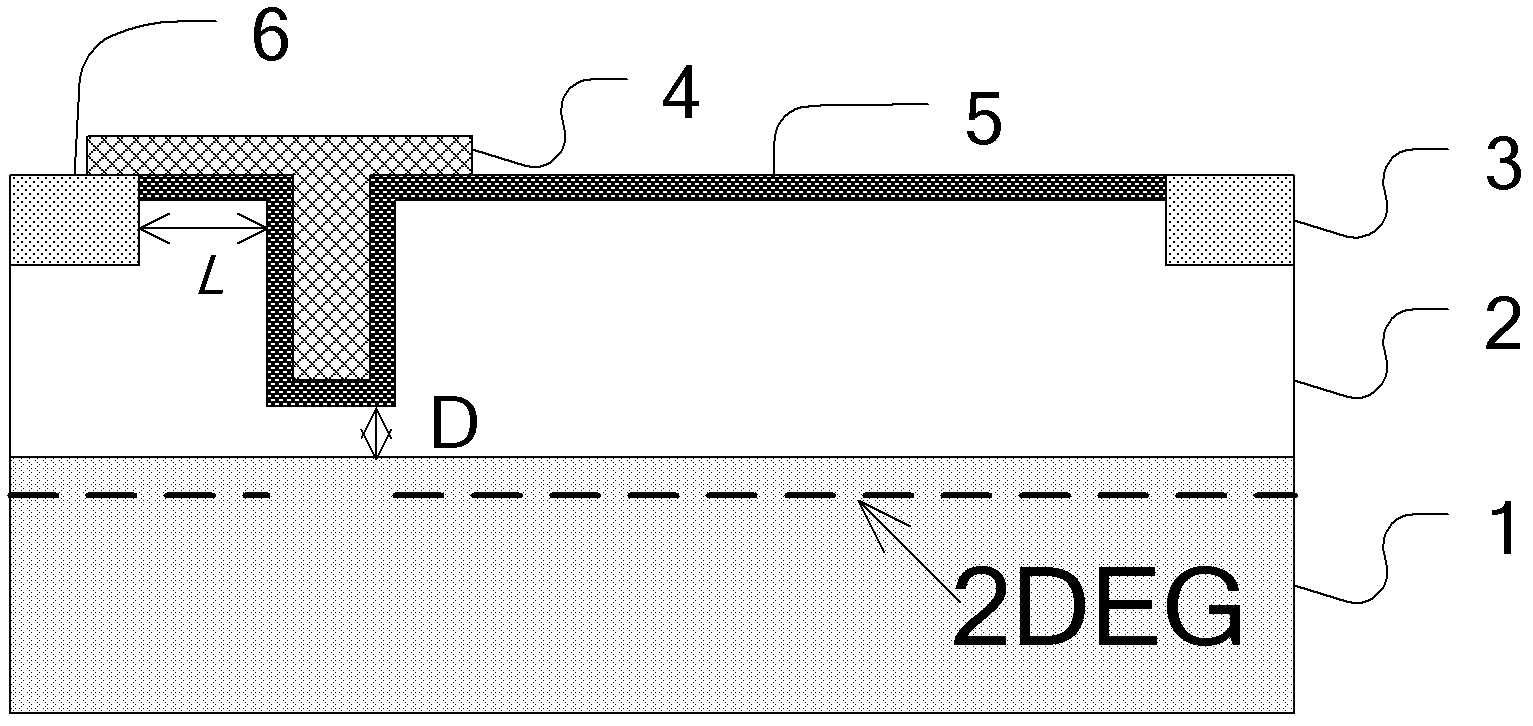

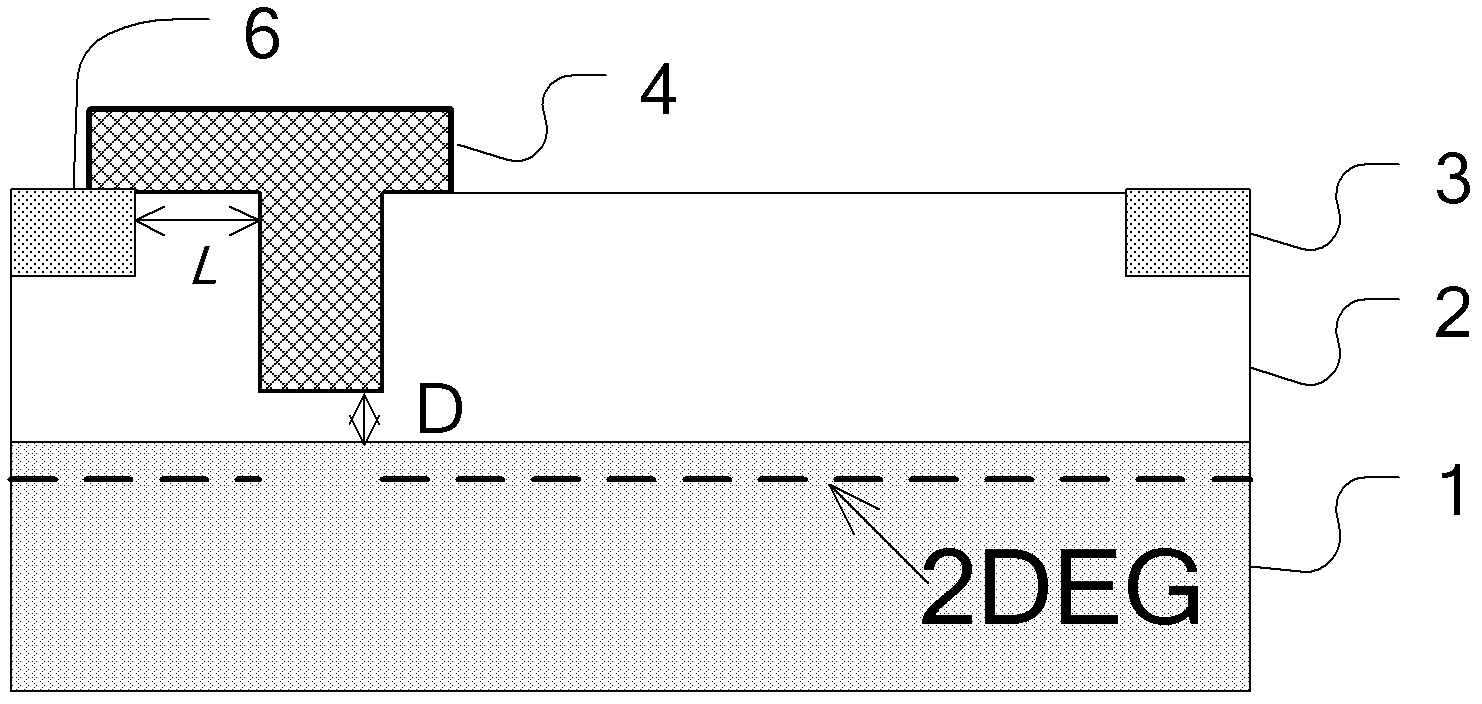

Normally-off field-controlled channel gan heterojunction diode

InactiveCN102280494AImplement field control featuresEfficient use ofSemiconductor devicesControl channelPositive power

A normally-off type field-controlled channel GaN heterojunction diode belongs to the technical field of semiconductor devices. The invention adopts the technology of combining insulating layer-groove, modulation doping and groove-modulation doping to change the conductive channel structure of the existing GaN heterojunction diode, and convert the original normally-on spontaneously polarized GaN heterojunction The junction conductive channel is changed into a normally-off field-controlled conductive channel combining spontaneous polarization and piezoelectric polarization in the present invention, which realizes the field-controlled characteristics of the GaN heterojunction diode conductive channel and reduces the forward conduction resistance and enhanced reverse cut-off capability. The invention has lower forward conduction resistance and power consumption, stronger reverse cut-off ability, and is compatible with AlGaN / GaN HEMT power switching device technology, which is beneficial to the application of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

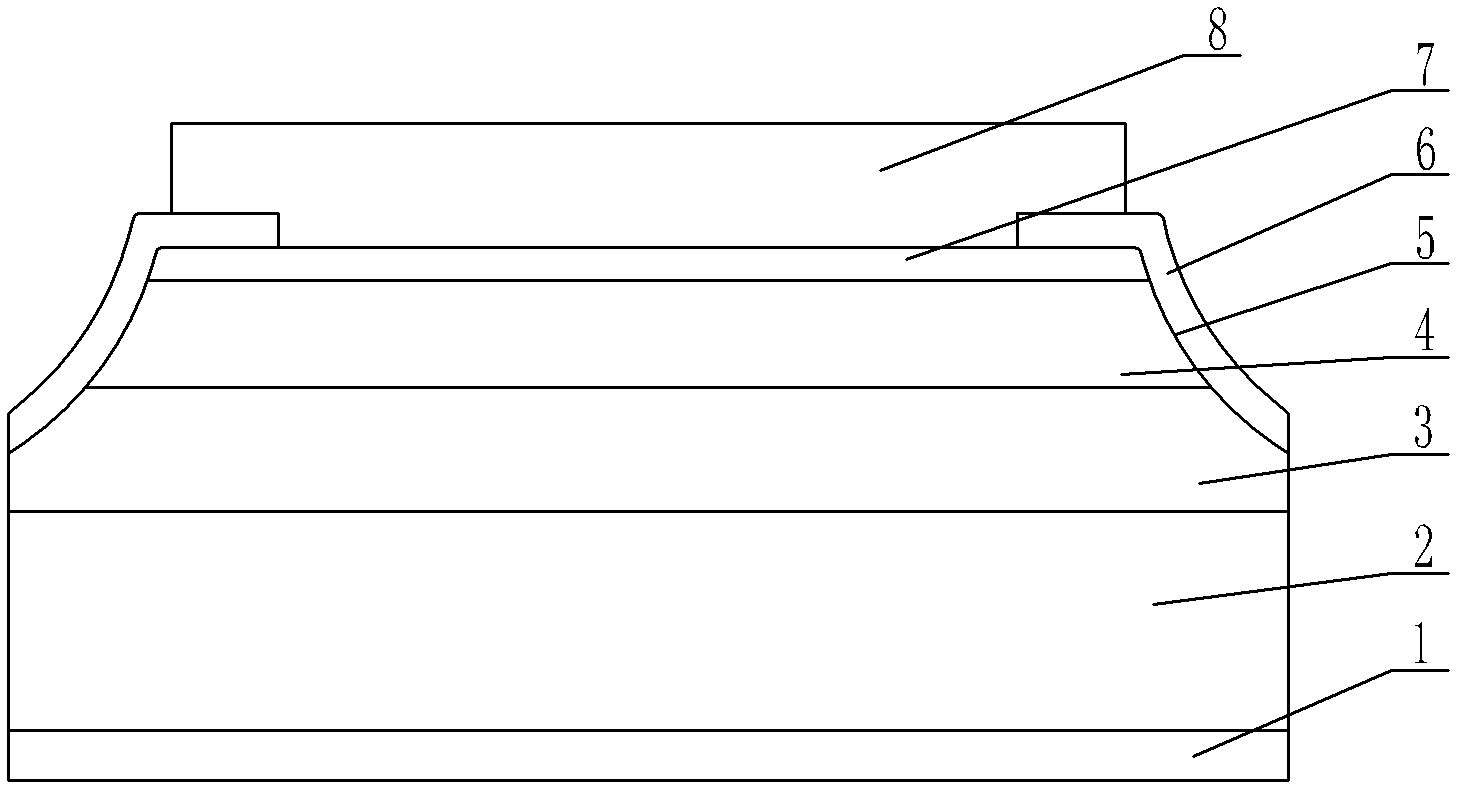

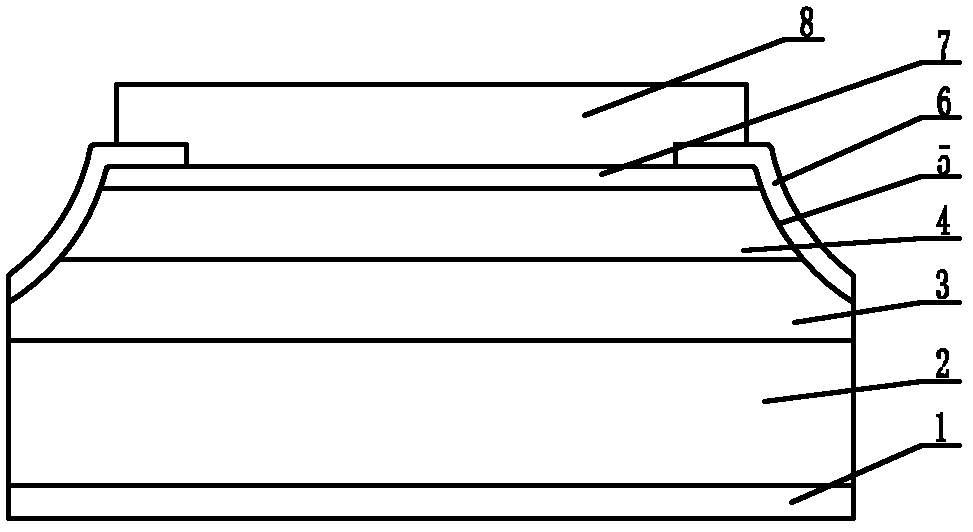

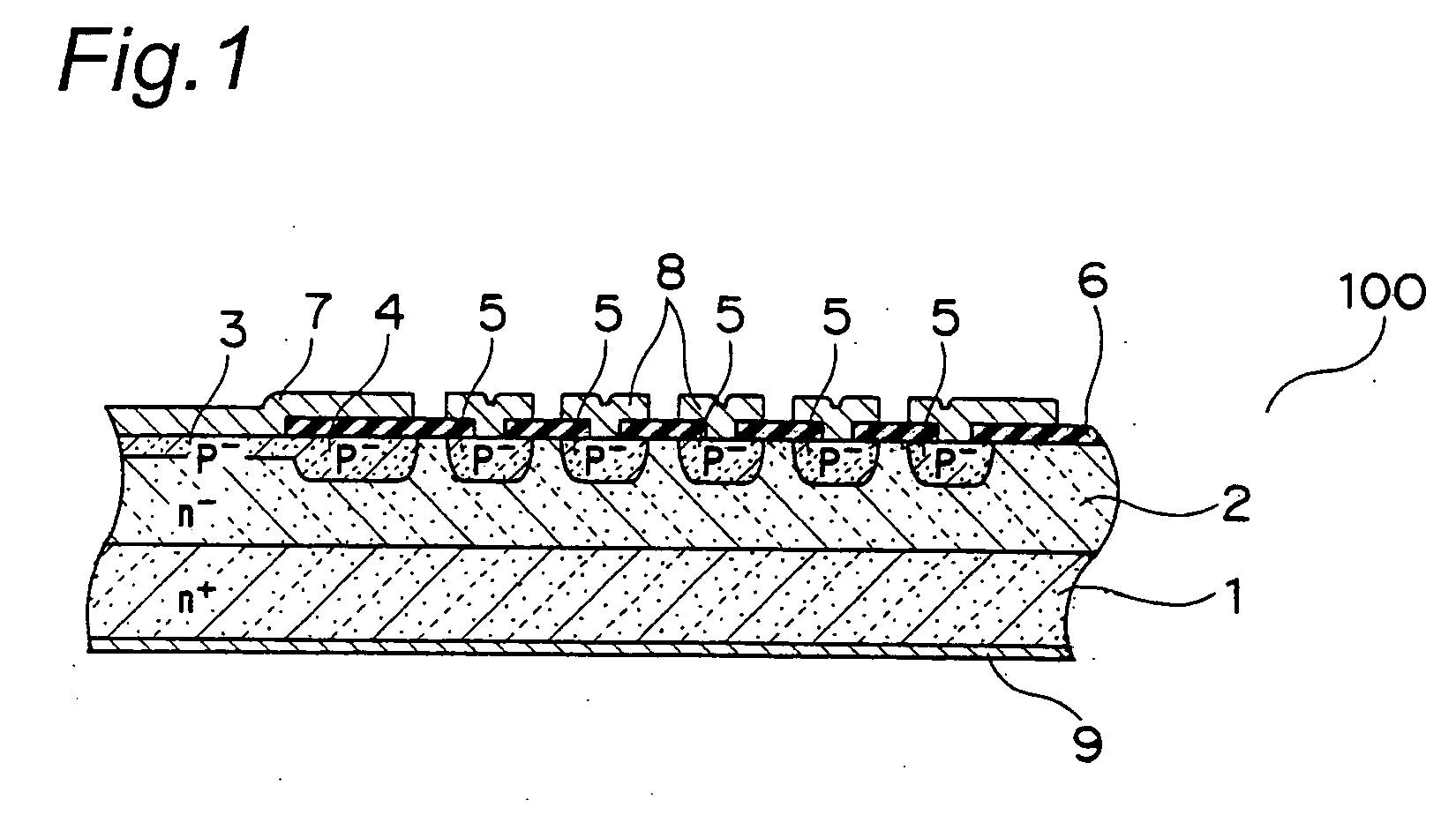

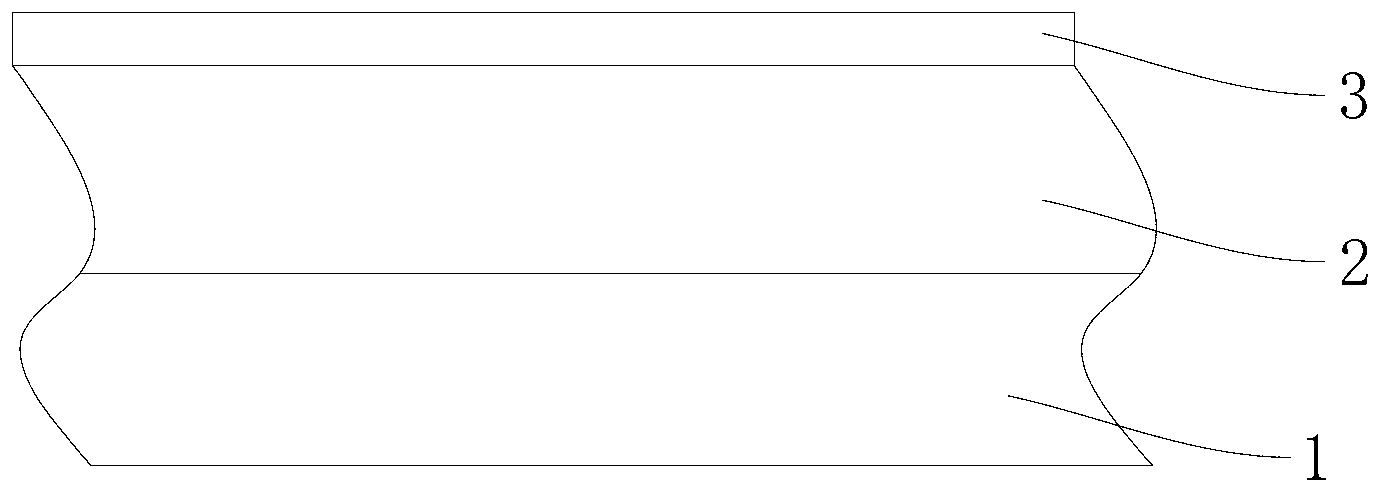

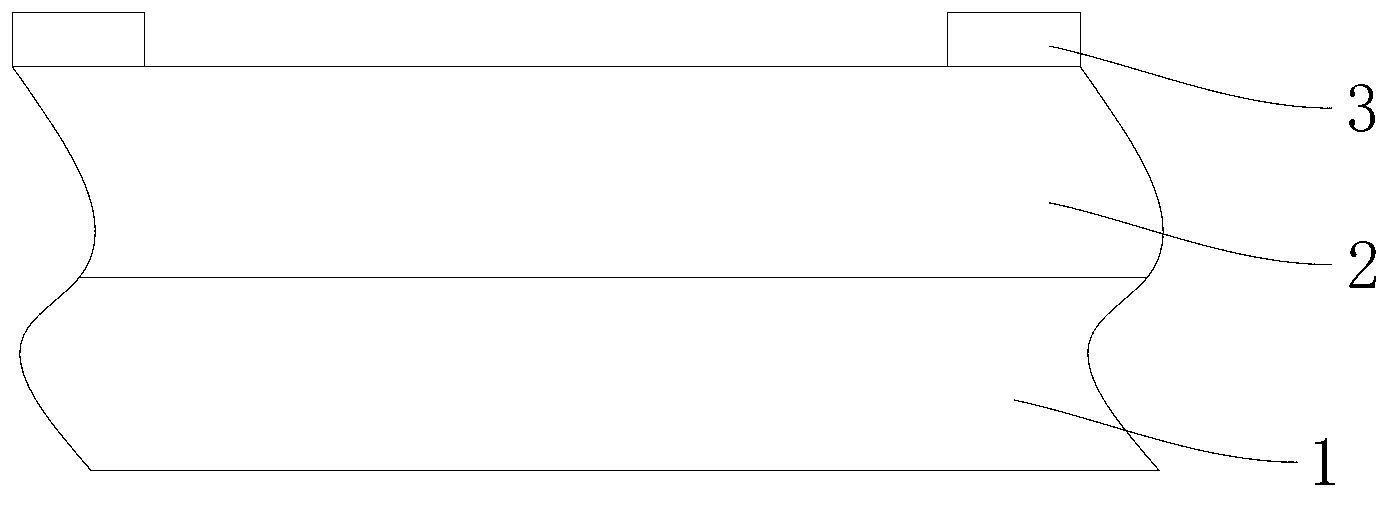

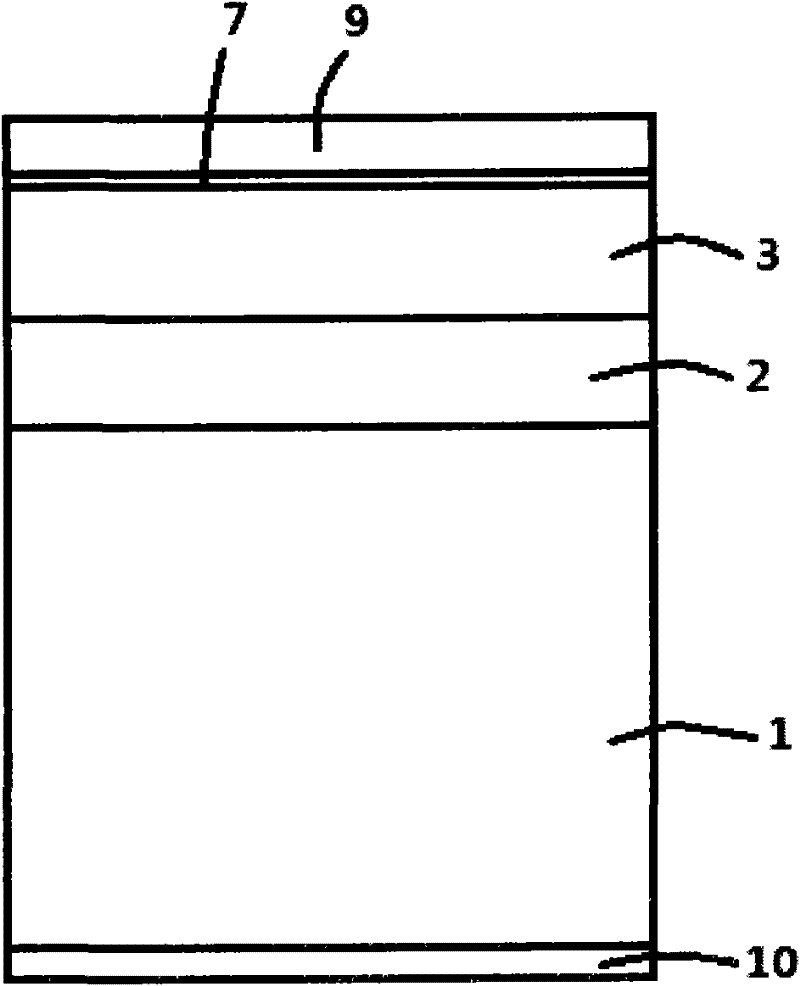

Fast recovery epitaxial diode and preparation method thereof

InactiveCN102496572AGood ohmic contactPrevent extensionSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropSilicon chip

The invention relates to a fast recovery epitaxial diode comprising a metal cathode layer, an N + substrate silicon chip, a first epitaxial layer, a second epitaxial layer, a third epitaxial layer, wherein the above-mentioned parts are successively connected. A mesa silicon groove penetrates the third epitaxial layer and is extended into the second epitaxial layer; a glass passivation layer that is arranged inside the mesa silicon groove and is provided with a window is extended to the top surface of the third epitaxial layer; and a metal anode layer that is arranged at the upper portion of the glass passivation layer passes through the window that is arranged on the glass passivation layer and then is connected with the third epitaxial layer. According to the invention, an epitaxial technology is used to accurately control impurity concentration and thickness of all the epitaxial layers; and a mesa channeling technology and a glass passiviation technology are utilized to manufacture a terminal structure, thereby substantially reducing a technology flow. Besides, the fast recovery epitaxial diode has good consistency and repeatability; high quality characteristics including low forward direction voltage drop, super speediness, and soft recovery characteristic and the like of the fast recovery epitaxial diode can be easily realized.

Owner:MACMIC SCIENCE & TECHNOLOGY CO LTD

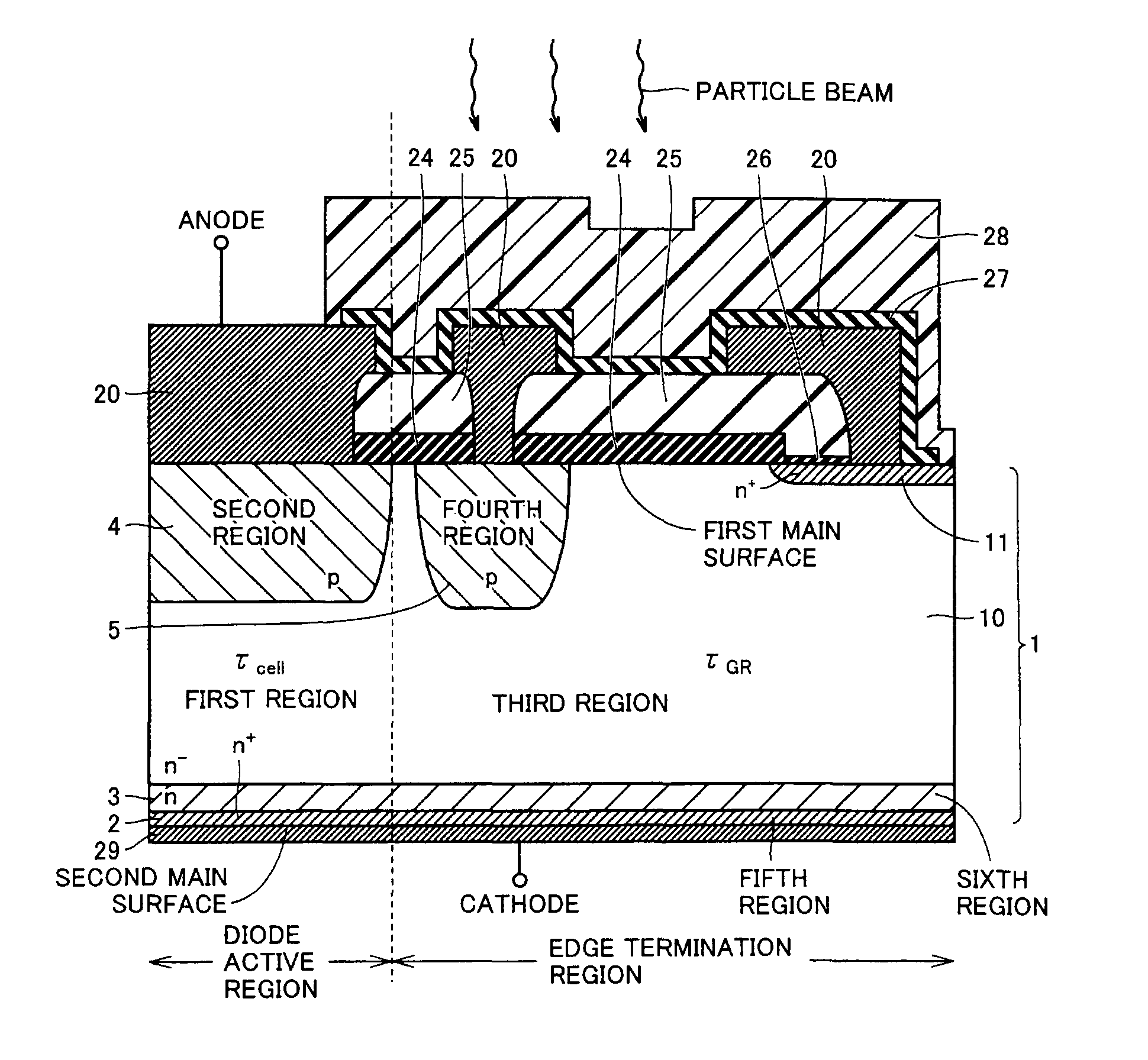

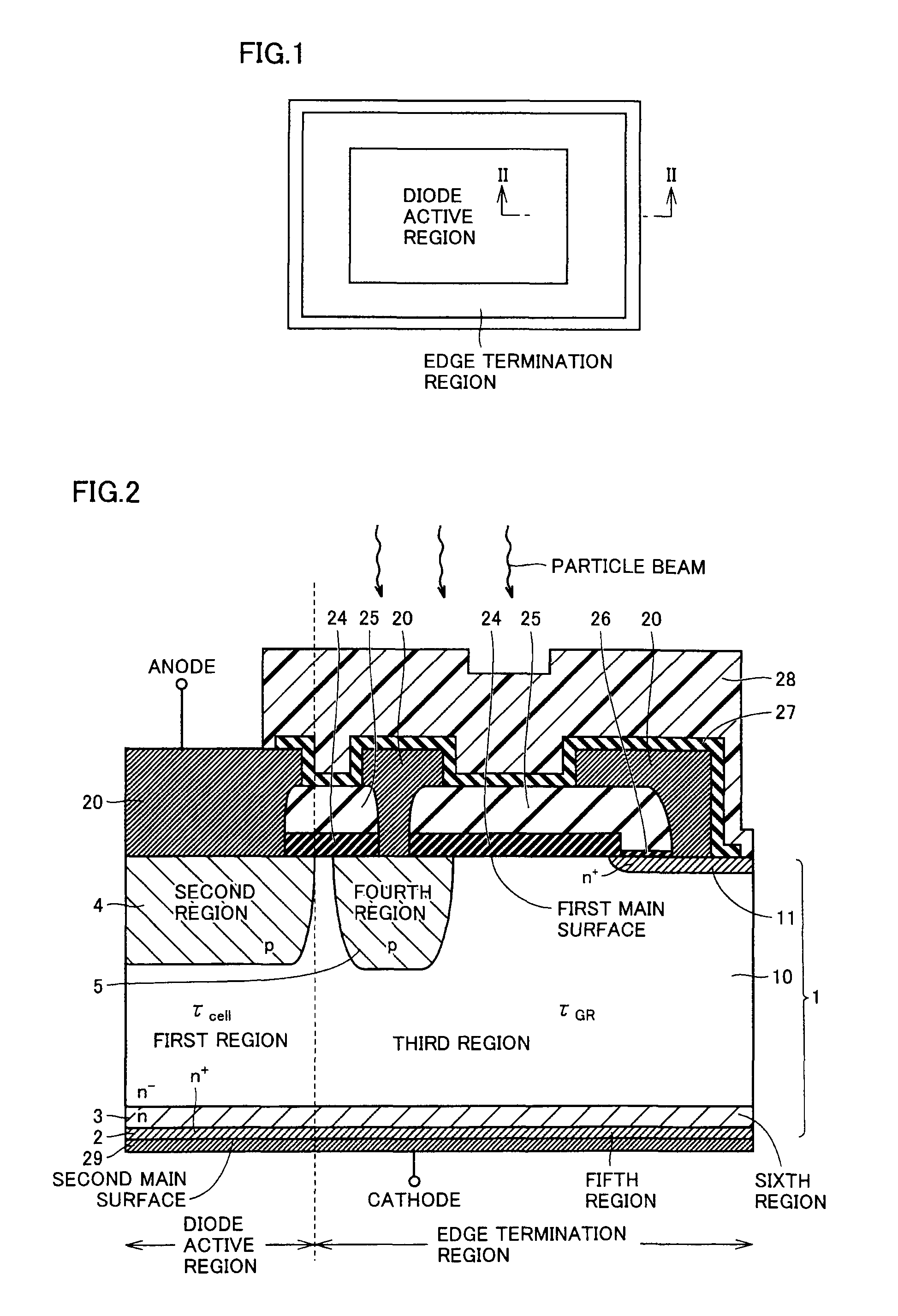

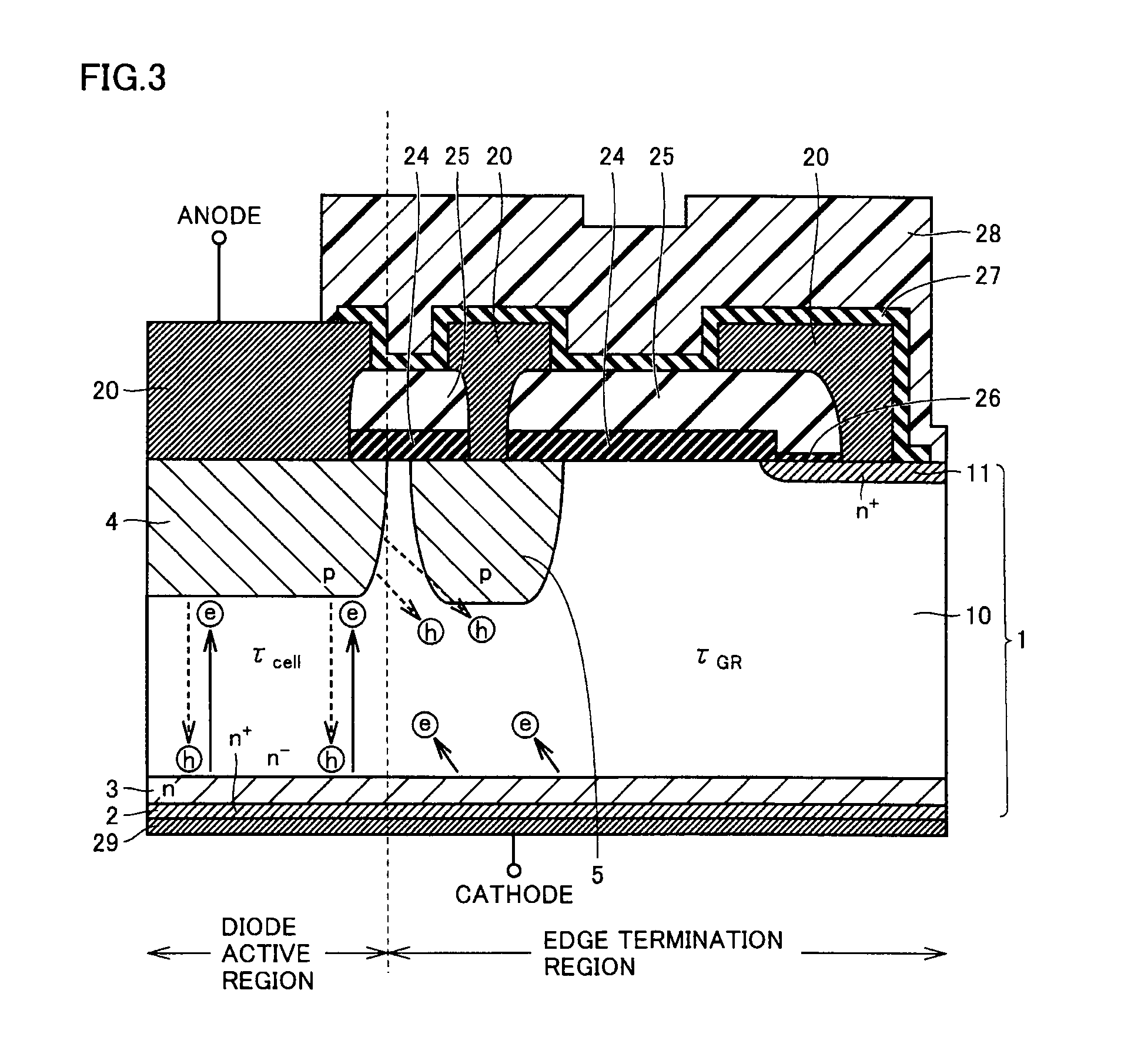

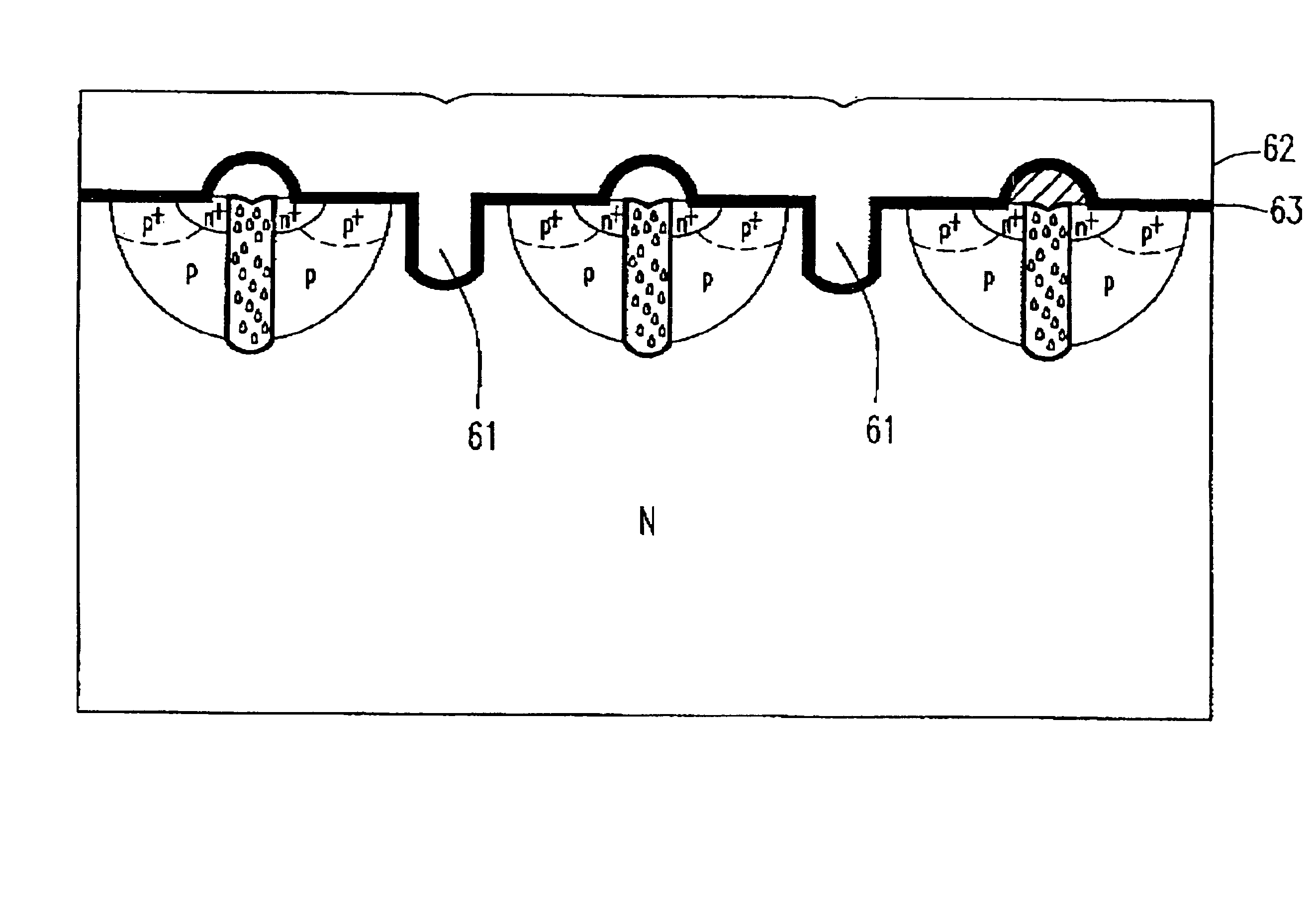

Semiconductor device

ActiveUS8686469B2Increase in current densityImprove breakdown voltageTransistorSemiconductor/solid-state device detailsCharge carrierCrystallographic defect

A semiconductor device includes a semiconductor substrate having a diode active region and an edge termination region adjacent to each other, a first region of a first conductivity type in the diode active region, a second region of a second conductivity type, a third region of the first conductivity type in the edge termination region, and a fourth region of the second conductivity type. The first region and the third region share a drift region of the first conductivity type. The first region and the third region share a fifth region of the first conductivity type. The drift region in the third region is greater in number of crystal defects per unit volume than the drift region in the first region in order that the drift region in the third region is shorter in carrier lifetime than the drift region in the first region.

Owner:MITSUBISHI ELECTRIC CORP

Low forward voltage drop schottky barrier diode and manufacturing method therefor

InactiveUS6921957B2Lower forward voltage dropImprove efficiencyTransistorSolid-state devicesSchottky barrierForward voltage

A new low forward voltage drop Schottky barrier diode and its manufacturing method are provided. The method includes steps of providing a substrate, forming plural trenches on the substrate, and forming a metal layer on the substrate having plural trenches thereon to form a barrier metal layer between the substrate and the surface metal layer for forming the Schottky barrier diode.

Owner:ONIZUKA ELECTRONICS

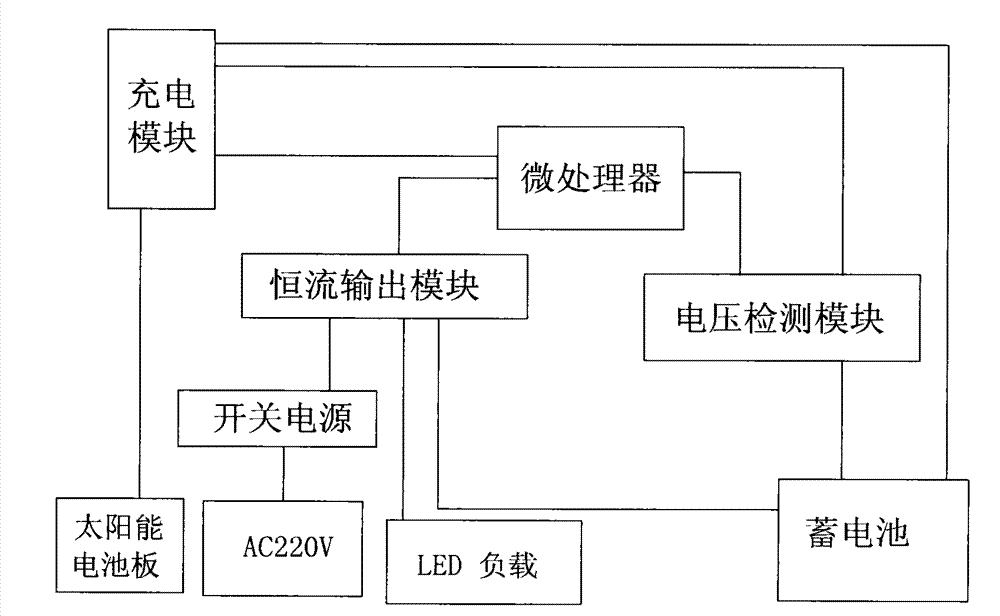

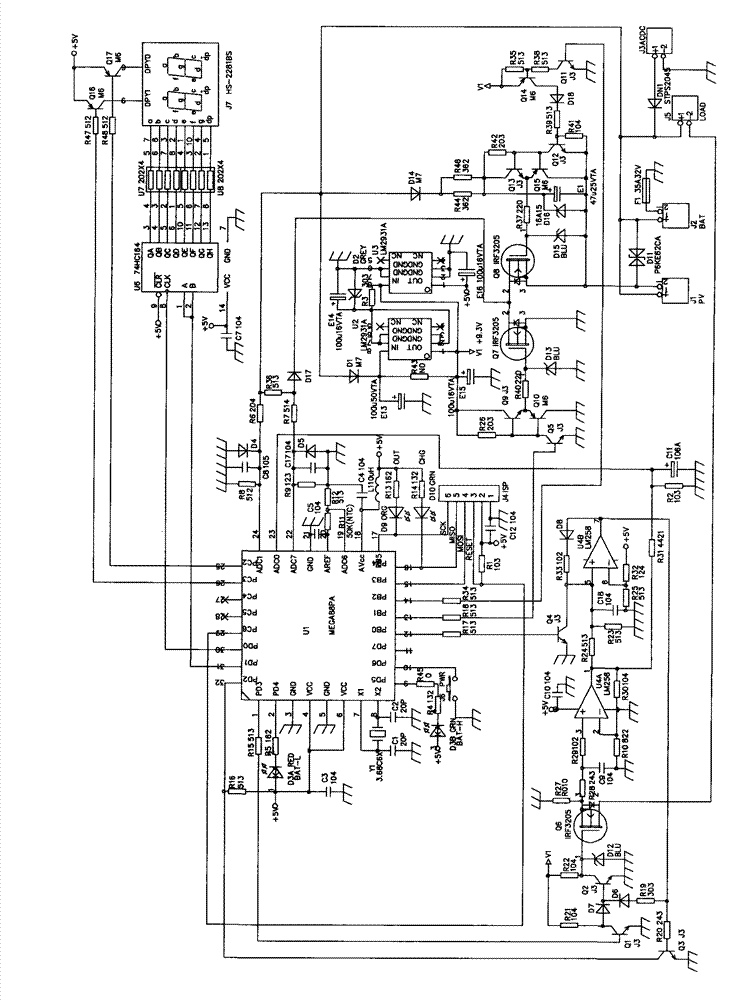

Mains complementation controller for solar street lamp and control method of controller

ActiveCN103209522AIngenious structural designReasonable structural designElectric light circuit arrangementEnergy saving control techniquesAutomatic controlSolar street light

The invention discloses a mains complementation controller for a solar street lamp. The controller comprises a solar cell panel, a charging module, a microprocessor, a constant-current output module, a switching power supply, a voltage detection module and a battery. The invention also discloses a control method of the controller. The controller is skillful and reasonable in structural design, when the electric quantity stored in the battery by the solar energy is insufficient, the controller is switched to a mains supply automatically in a seamless mode, the effect that the solar energy is used preferentially and the mains supply serves as a supplement can be effectively achieved, and charging and discharging can be controlled automatically according to different working parameters and states, so that the charging and the discharging are kept at the optimal states, the utilization efficiency of the solar energy is improved, the energy resources are effectively saved, the whole process is automatic, and the intelligent degree is high. The control method is simple in step, easy to implement, capable of supplying electricity by the battery and achieving seamless switching to the mains supply, effectively guaranteeing the sufficient utilization of solar energy resources, greatly prolonging the service life of the battery and reducing the maintenance cost and beneficial to popularization and application.

Owner:SICHUAN TAIYI NEW ENERGY DEV

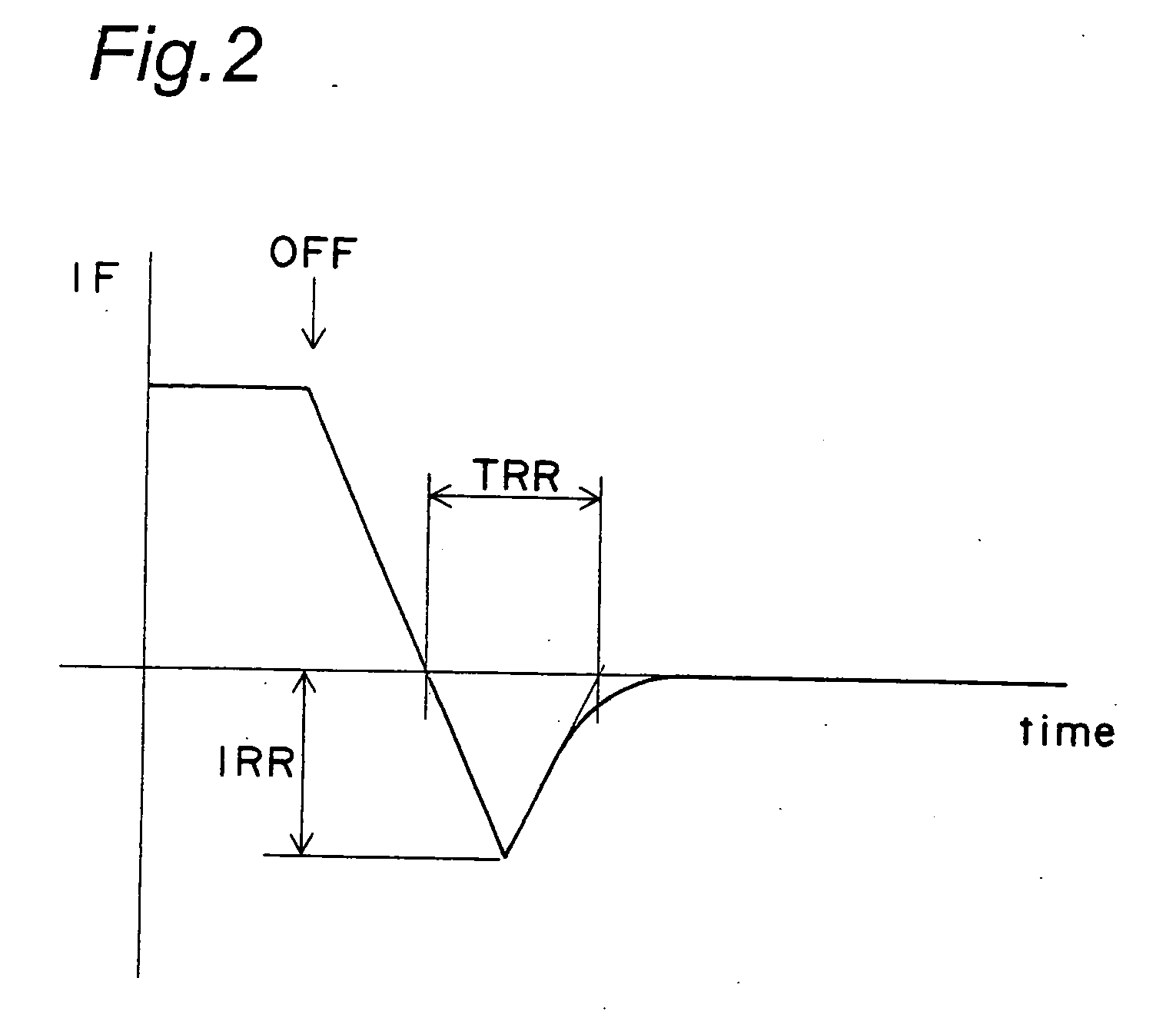

Mos p-n junction schottky diode device and method for manufacturing the same

ActiveUS20090261428A1Improve performanceReduce leakage currentSemiconductor/solid-state device manufacturingDiodeOhmic contactReverse recovery

A MOS P-N junction Schottky diode device includes a substrate having a first conductivity type, a field oxide structure defining a trench structure, a gate structure formed in the trench structure and a doped region having a second conductivity type adjacent to the gate structure in the substrate. An ohmic contact and a Schottky contact are formed at different sides of the gate structure. The method for manufacturing such diode device includes several ion-implanting steps to form several doped sub-regions with different implantation depths to constitute the doped regions. The formed MOS P-N junction Schottky diode device has low forward voltage drop, low reverse leakage current, fast reverse recovery time and high reverse voltage tolerance.

Owner:PFC DEVICE HLDG

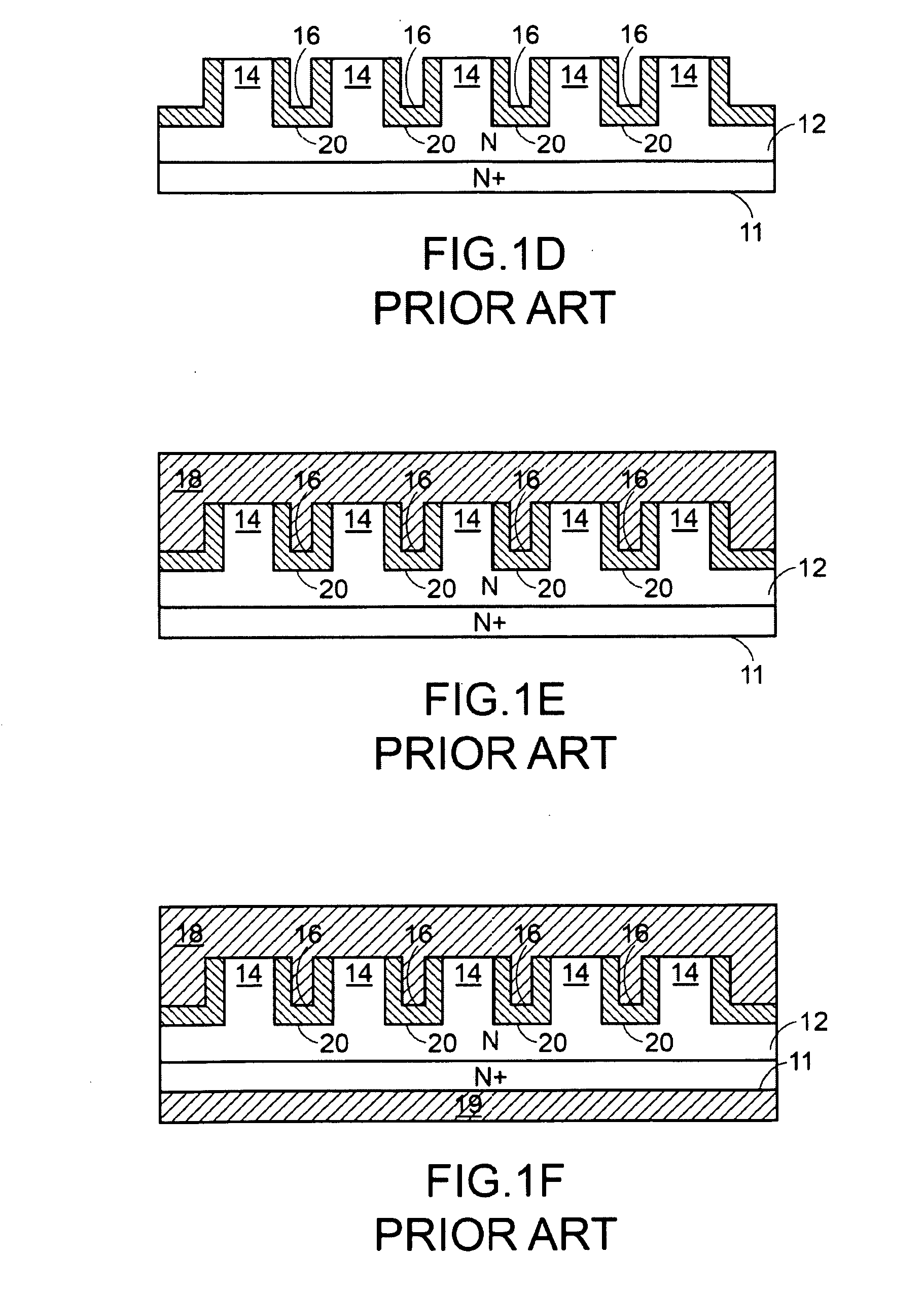

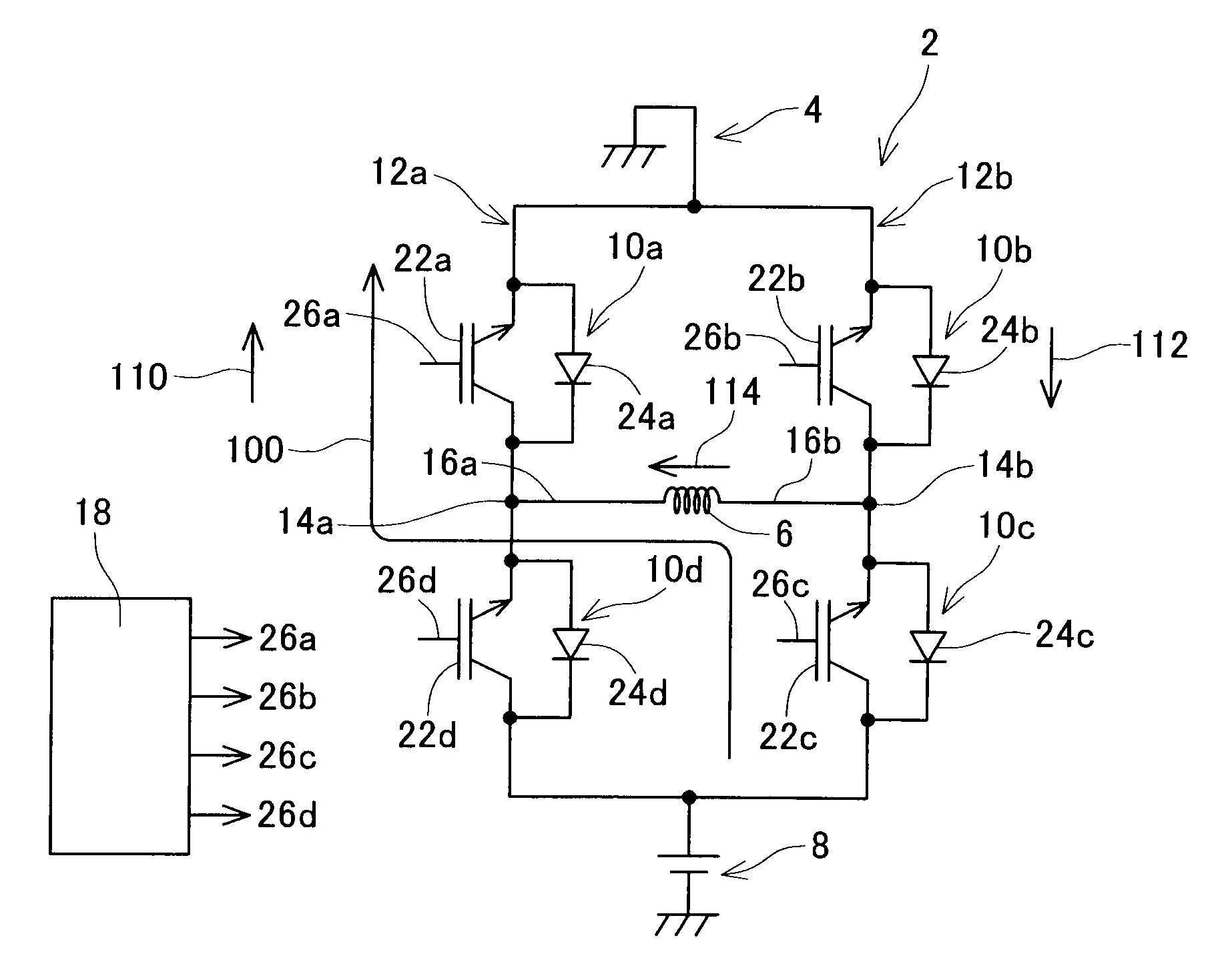

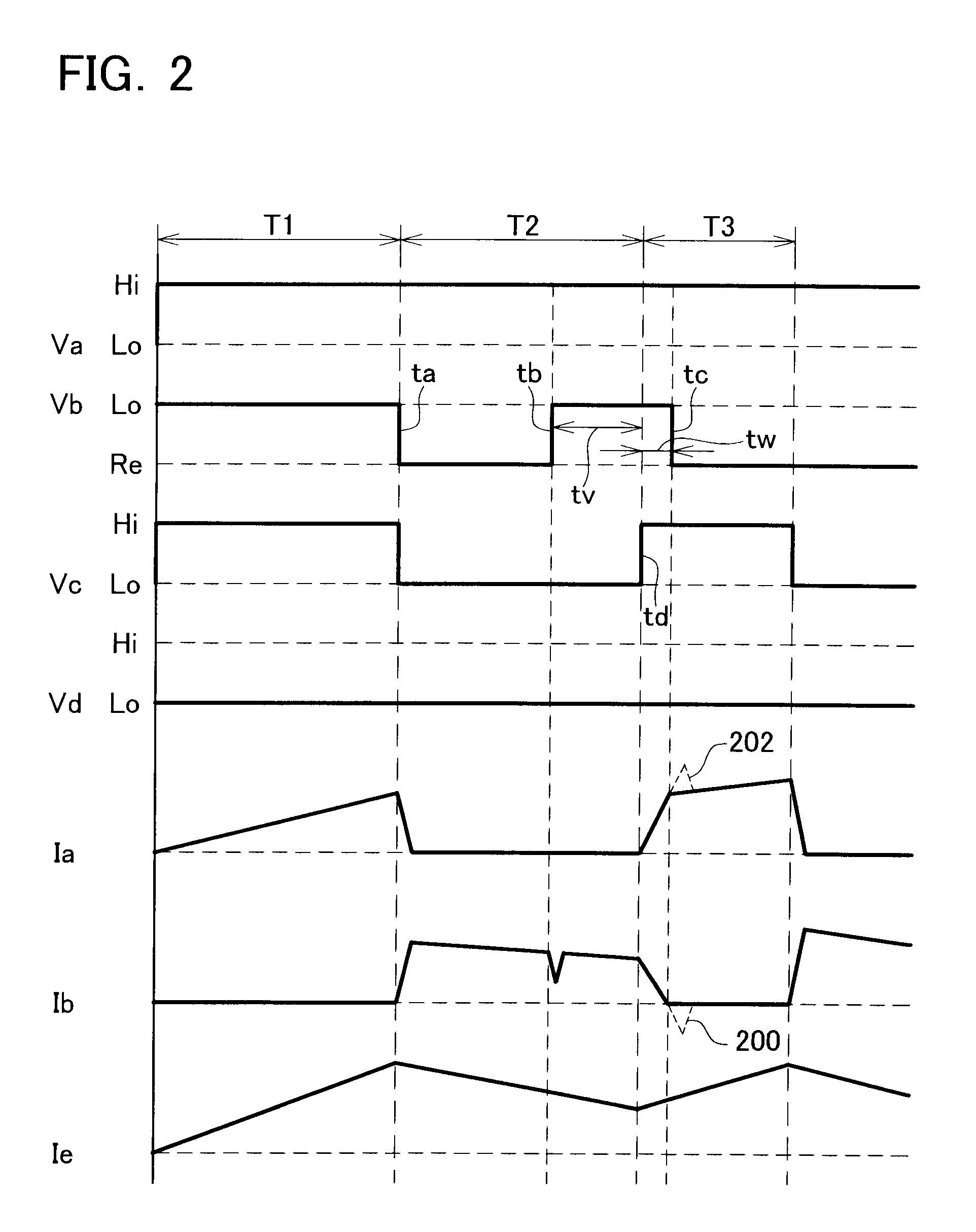

Power supply device and method for driving the same

ActiveUS20100283514A1Lower forward voltage dropGain is not constantAc-dc conversionElectronic switchingBody contactEngineering

In a reverse conducting semiconductor device, which forms a composition circuit, a positive voltage that is higher than a positive voltage of a collector electrode may be applied to an emitter electrode. In this case, in a region of the reverse conducting semiconductor device in which a return diode is formed, a body contact region functions as an anode, a drift contact region functions as a cathode, and current flows from the anode to the cathode. When a voltage having a lower electric potential than the collector electrode is applied to the trench gate electrode at that time, p-type carriers are generated within the cathode and a quantity of carriers increases within the return diode. As a result, a forward voltage drop of the return diode lowers, and constant loss of electric power can be reduced. Electric power loss can be reduced in a power supply device that uses such a composition circuit in which a switching element and the return diode are connected in reverse parallel.

Owner:DENSO CORP

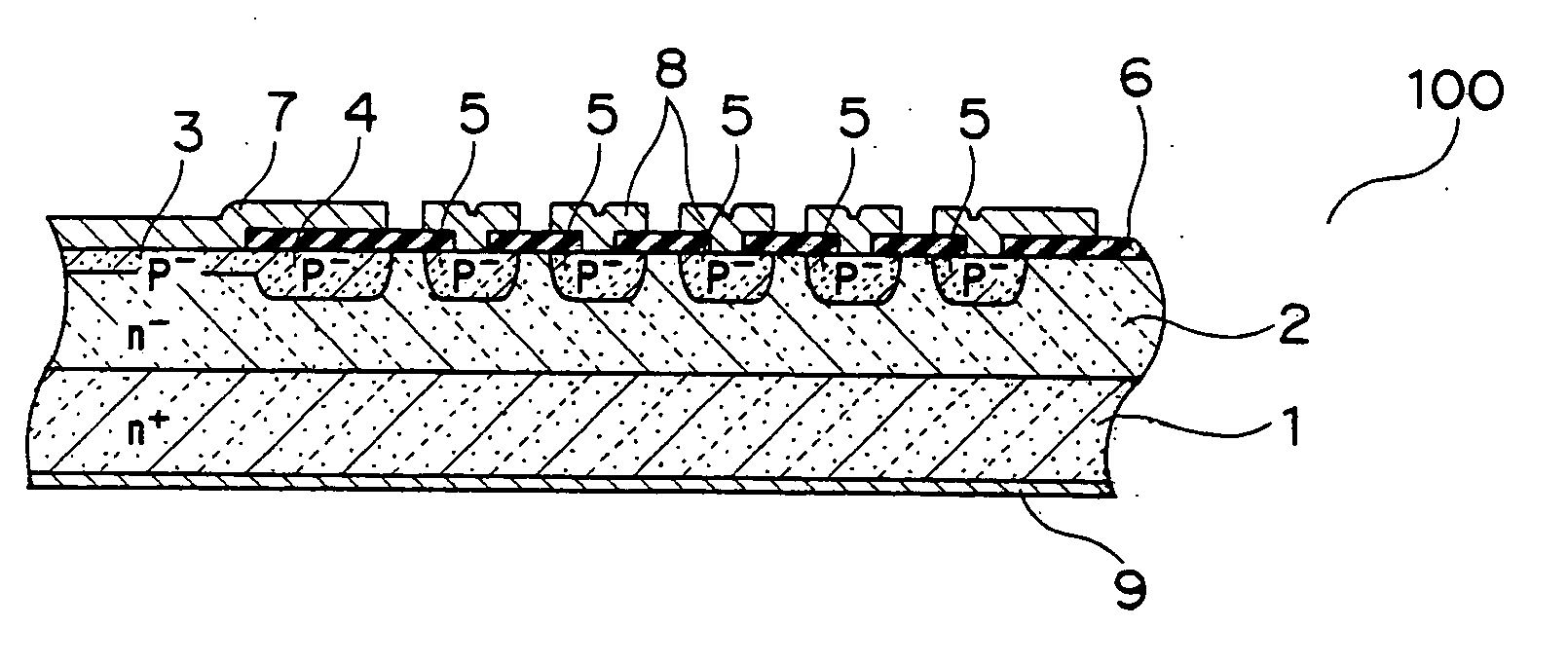

Semiconductor device

ActiveUS20060170075A1Increasing forward voltage dropAvoid recoveryTransistorScaffold connectionsSemiconductorImpurity

A semiconductor device, including: a semiconductor substrate of the first conductivity type having a first surface and a second surface; a base region of the second conductivity type formed on the first surface of the semiconductor substrate; a guard ring region of the second conductivity type formed around the base region, and having the second type impurity of which concentration is lower than that of the base region; a first electrode formed on the base region; and a second electrode formed on the second surface of the semiconductor substrate, further including a base peripheral region formed around the base region and being connected to the base region, wherein the base peripheral region is deeper than the base region and has the substantially constant depth, and the concentration of the second conductivity type impurity included in the base peripheral region is lower than that included in the base region.

Owner:MITSUBISHI ELECTRIC CORP

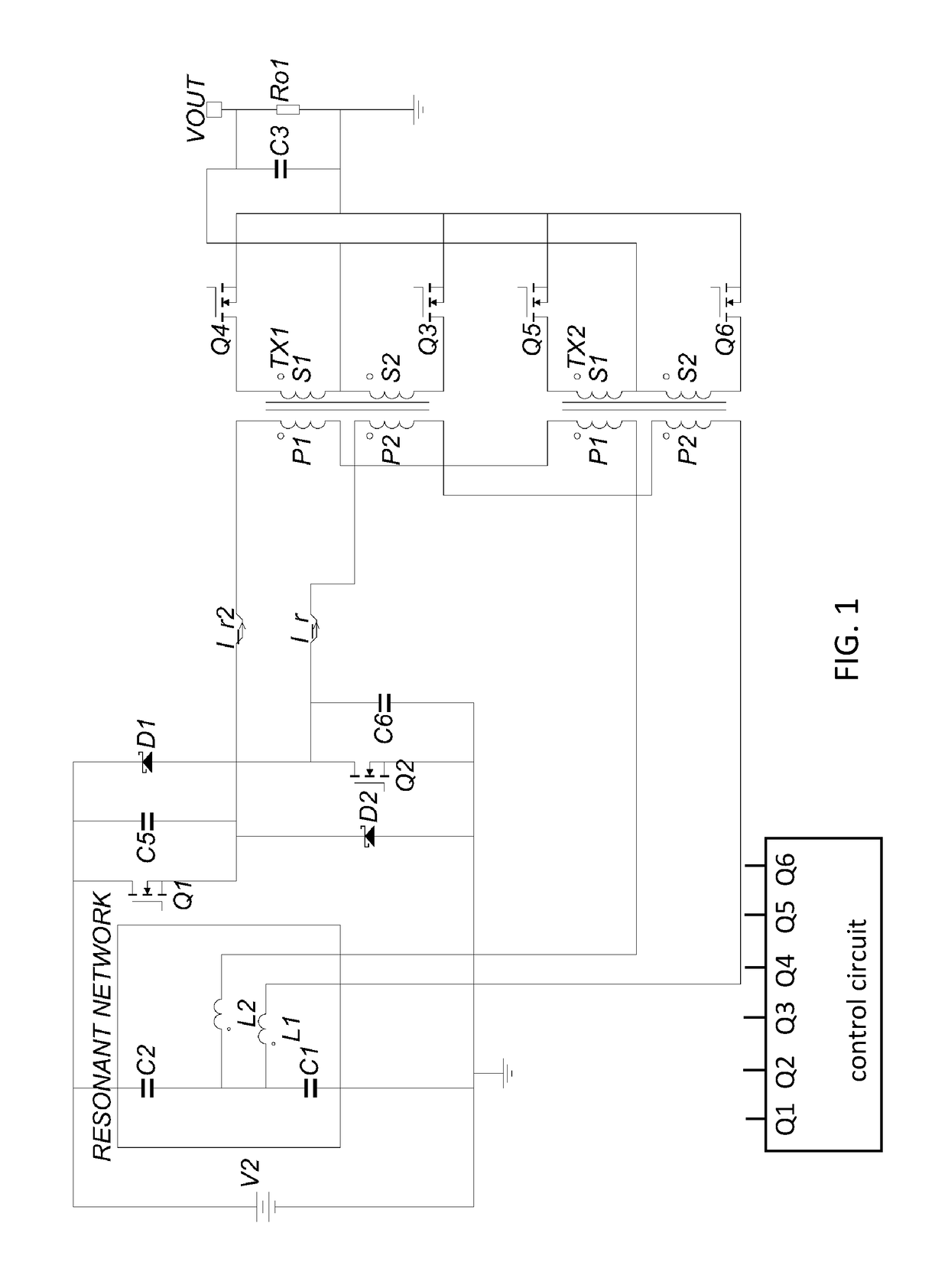

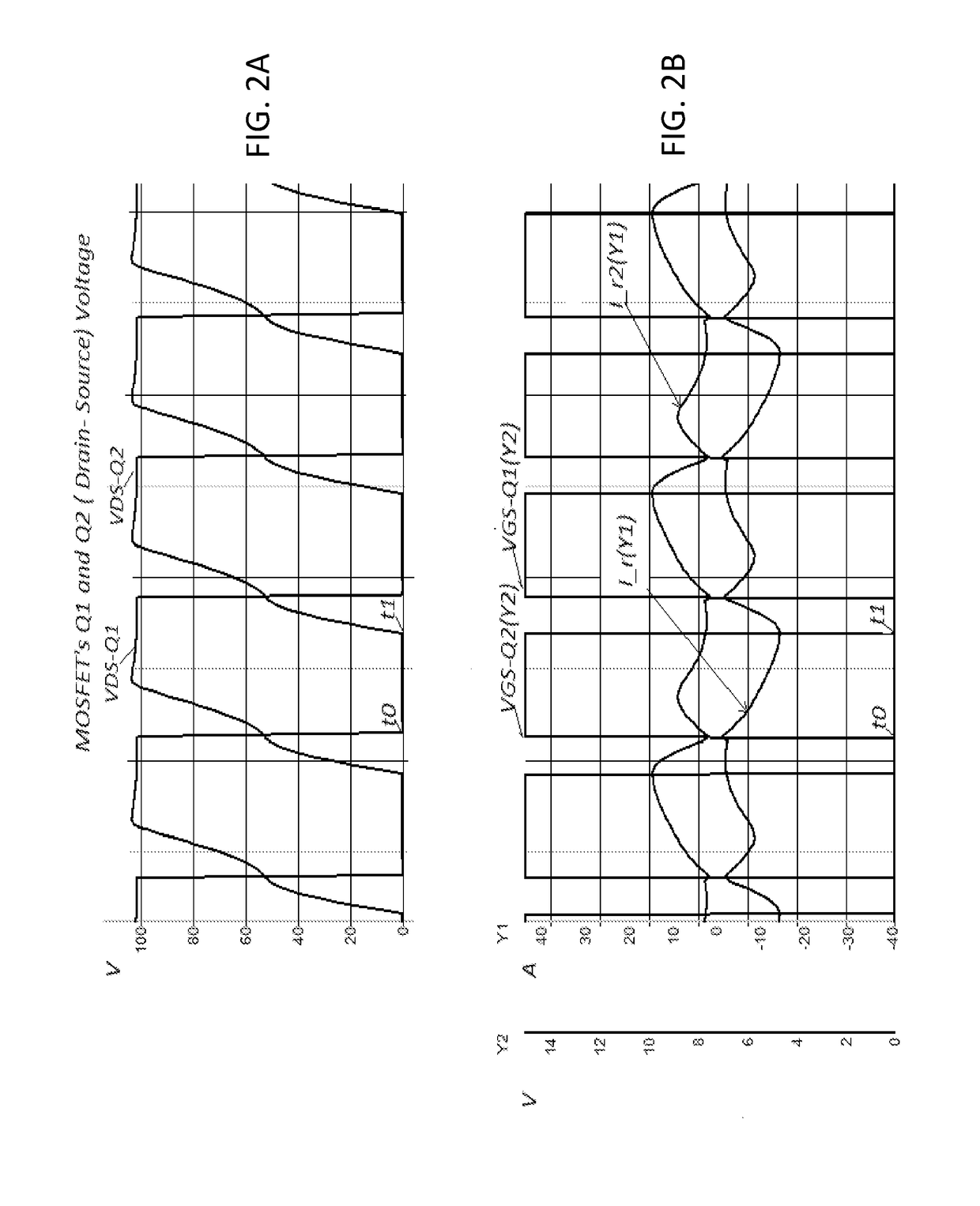

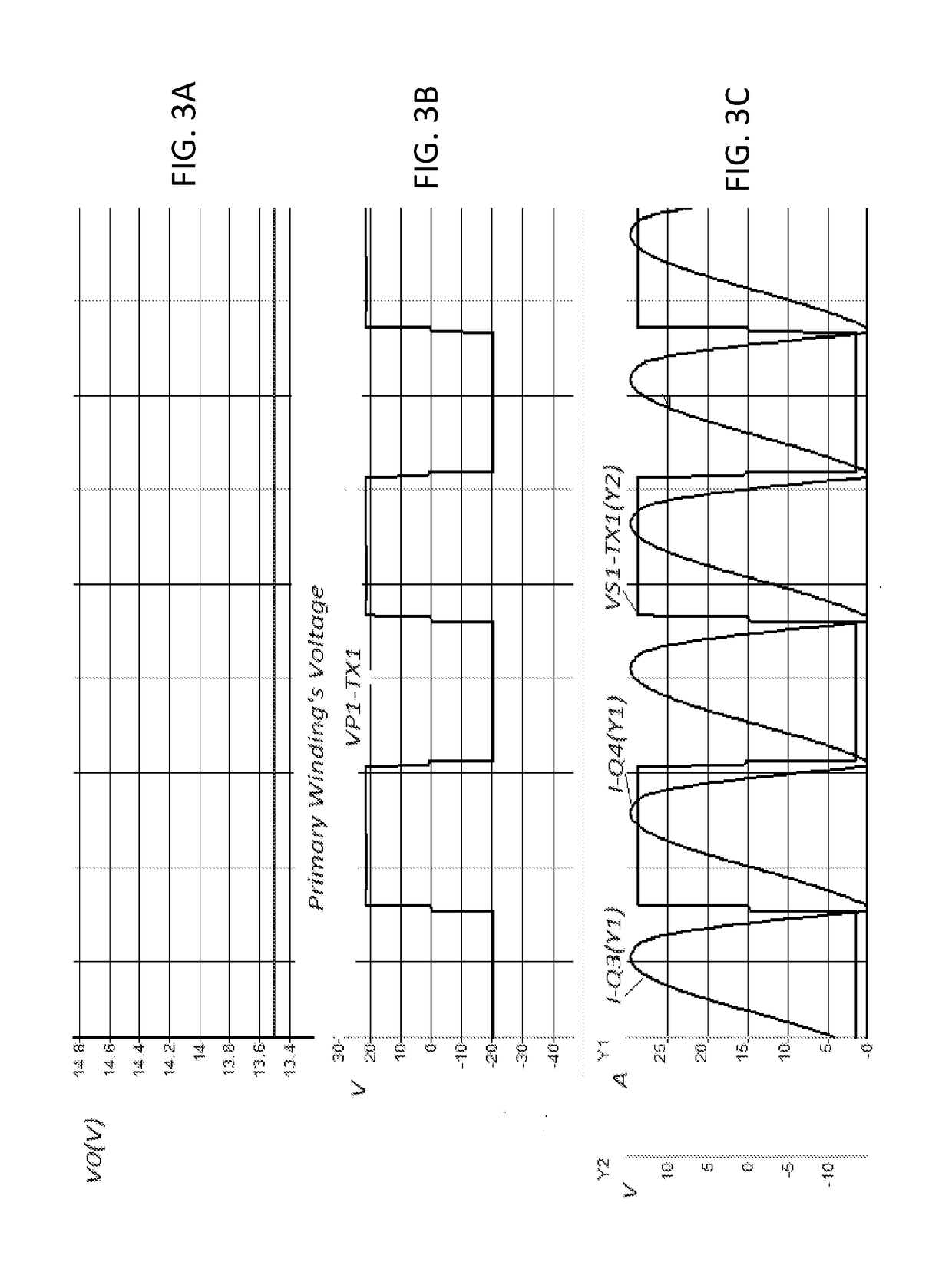

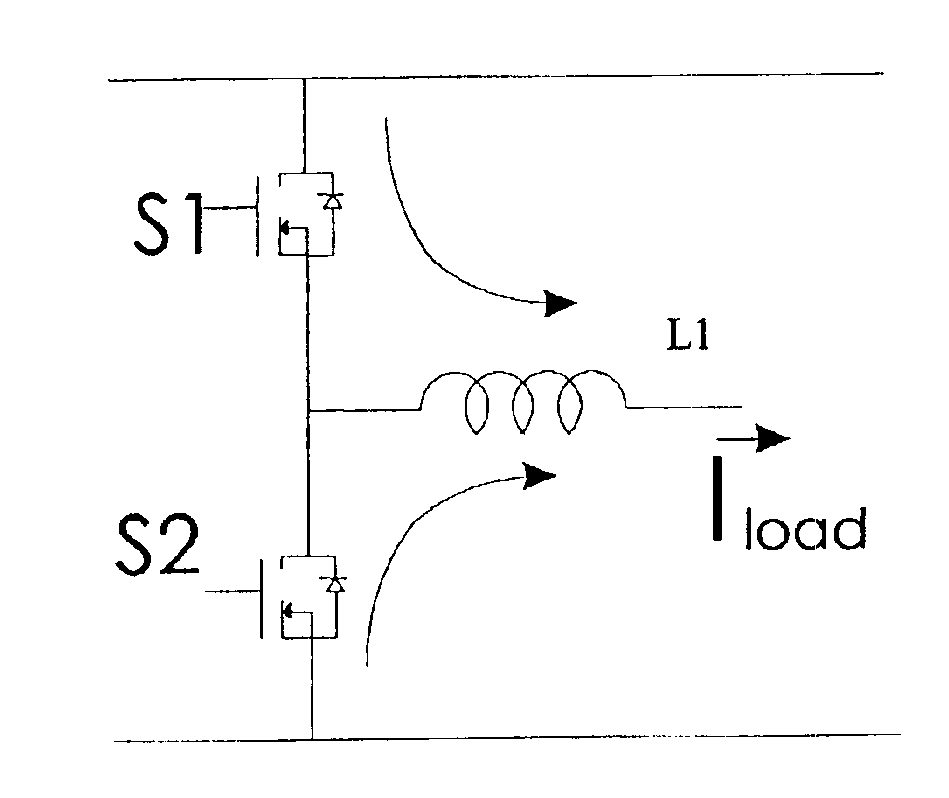

Multi-transformer llc resonant converter circuit

ActiveUS20180351469A1Reduce conduction lossSmall sizeEfficient power electronics conversionAc-dc conversionPower flowLlc converter

An LLC converter includes a resonant circuit connected to a DC input voltage, a switching circuit connected to the DC input voltage, transformers each including primary windings and secondary windings, and synchronous rectifiers each connected to one secondary winding and to ground. The primary windings of the transformers include a first primary winding and a second primary winding. The first primary windings of the transformers are connected in series, and the second primary windings of each of the plurality of transformers are connected in series. The series-connected first primary windings and the series-connected second primary windings are directly connected in parallel with the resonant circuit. A first current from a first switch flows into the series-connected first primary windings, and a second current from a second switch flows into the series-connected second primary windings. Currents from each of the secondary windings are equal or substantially equal.

Owner:MURATA MFG CO LTD

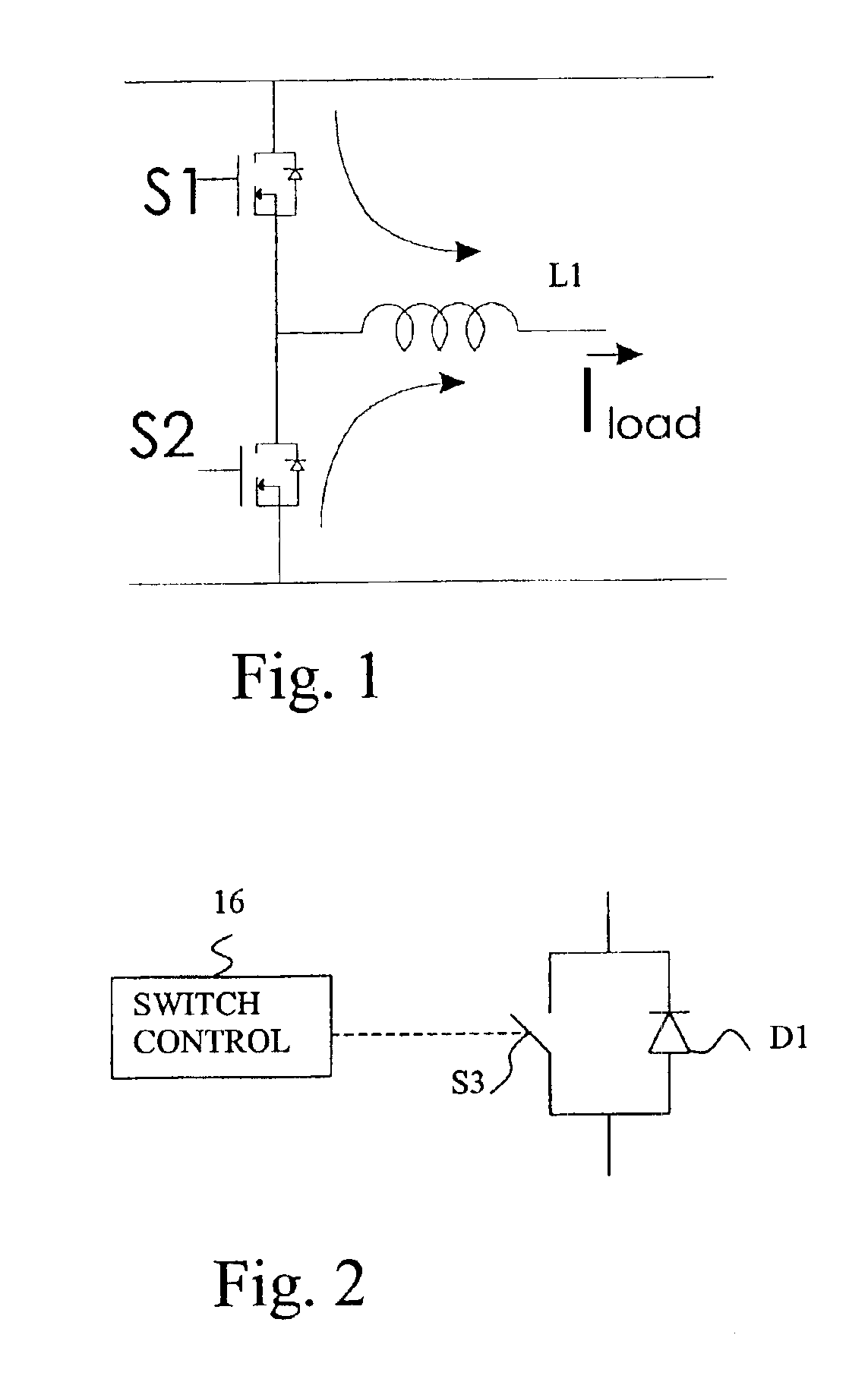

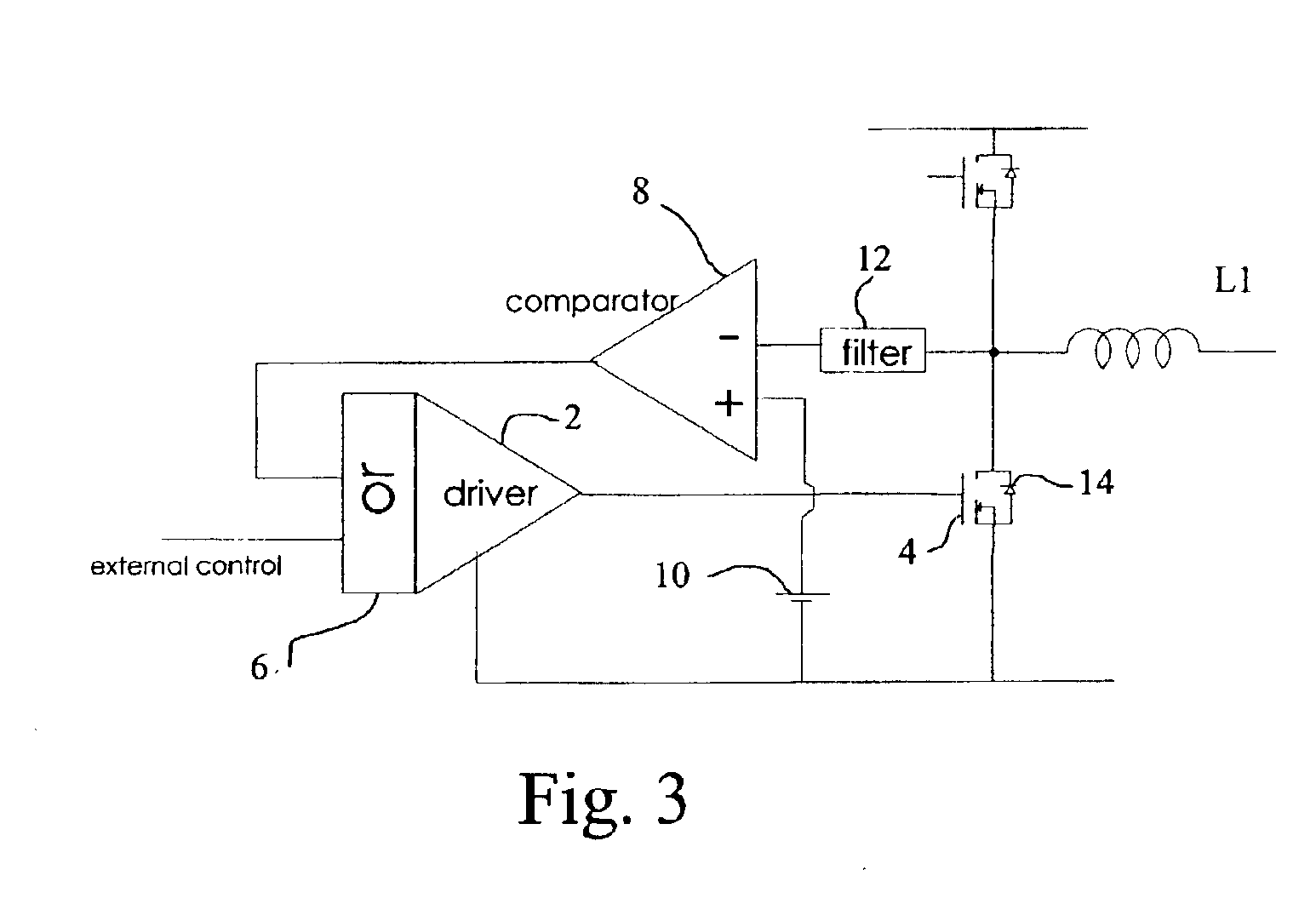

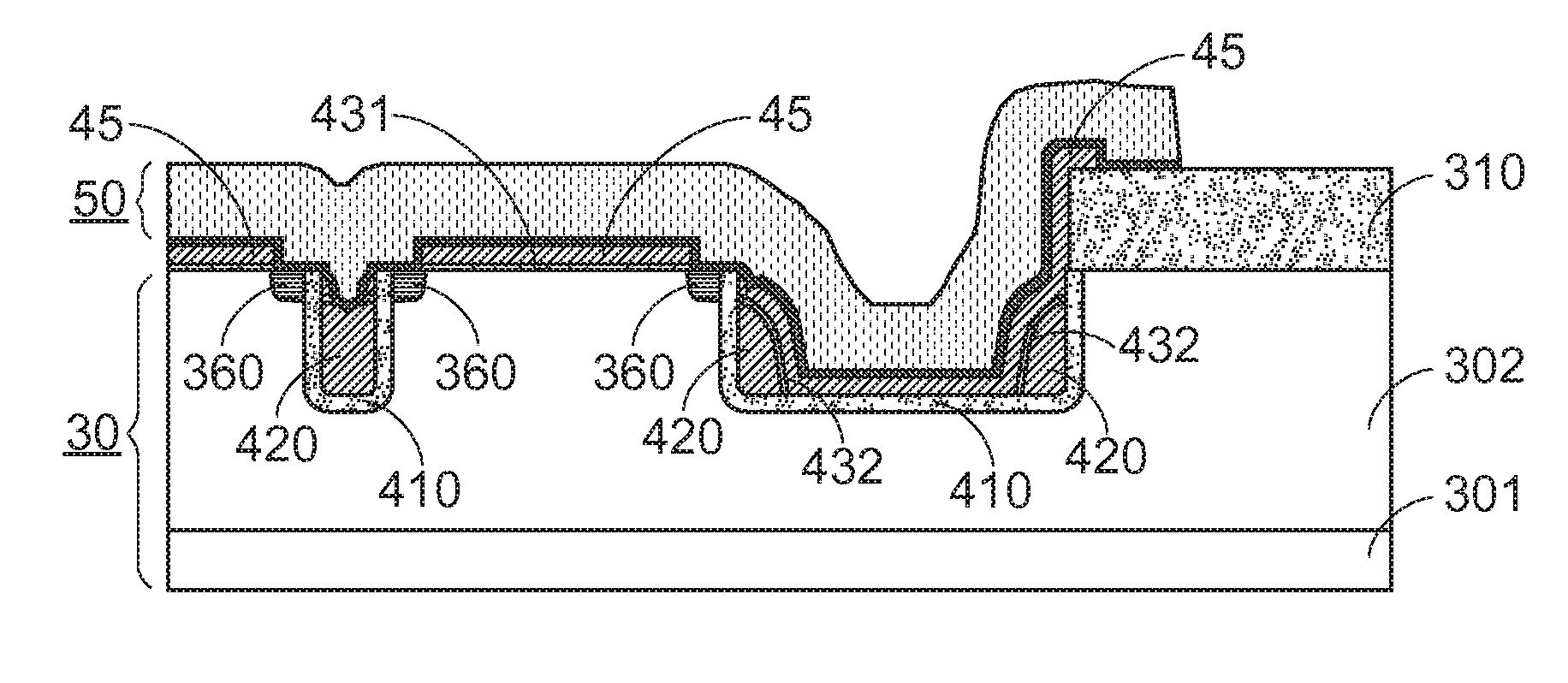

Synchronous rectification for low voltage motor drive

InactiveUS6956359B2Lower forward voltage dropImprove operationEfficient power electronics conversionAc-dc conversionMotor driveLow voltage

An inductive load driven by power MOSFETs, such as in a low voltage motor drive, using synchronous rectification to reduce the voltage drop across a body diode of a power MOSFET. A comparative feed back circuit measures voltage across the power MOSFET to determine when the body diode is conducting, and turns the MOSFET ON during conductive cycles, and OFF to block reverse current. The obtained synchronous rectification function is highly sensitive to current flow, while using a very small number of parts in a configuration that has less complexity.

Owner:INTERNATIONAL RECTIFIER COEP

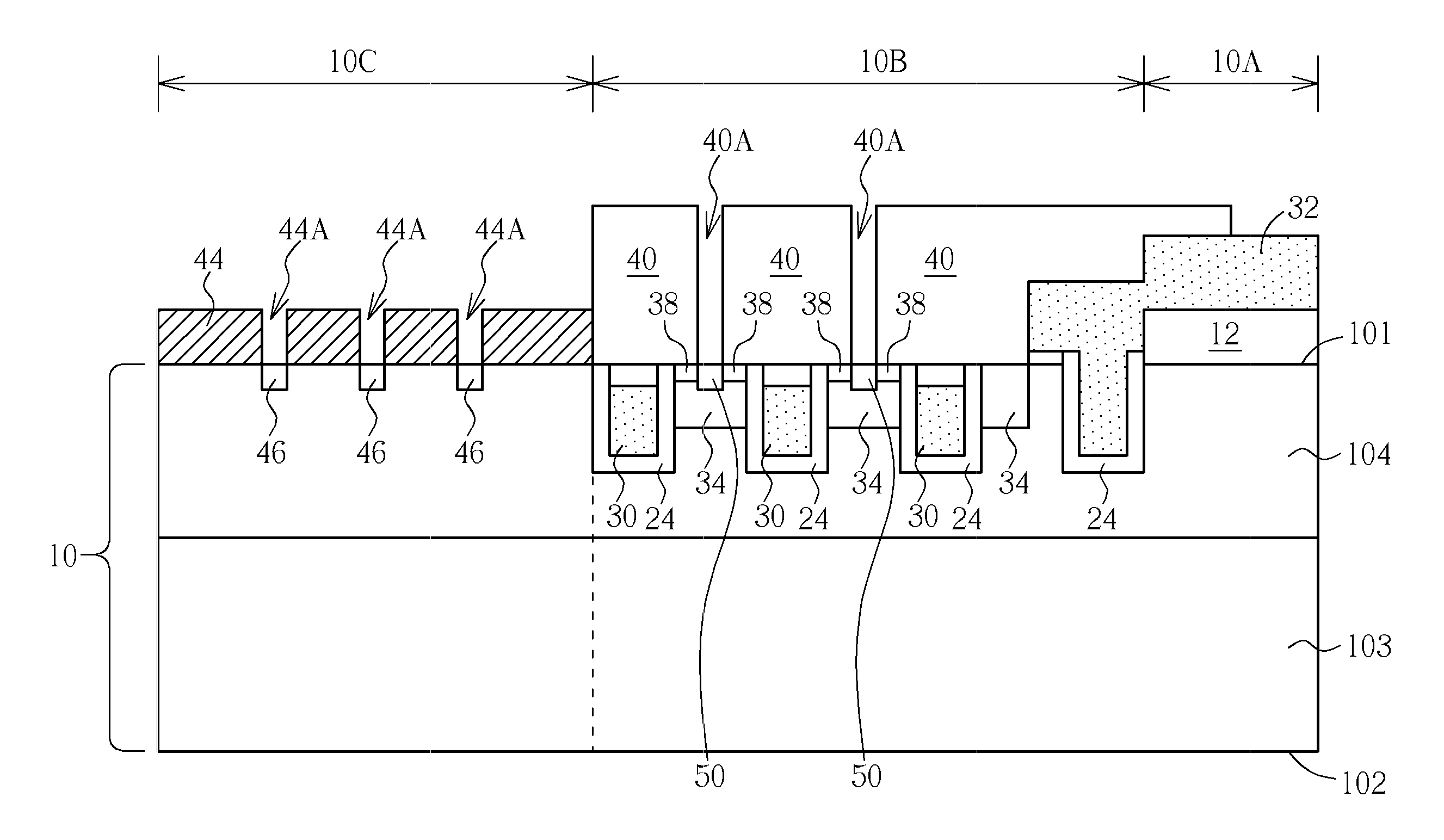

Trench isolation mos p-n junction diode device and method for manufacturing the same

ActiveUS20120049287A1Simplify namingShorter reverse recovery timeTransistorSolid-state devicesReverse recoveryEngineering

A trench isolation metal-oxide-semiconductor (MOS) P-N junction diode device and a manufacturing method thereof are provided. The trench isolation MOS P-N junction diode device is a combination of an N-channel MOS structure and a lateral P-N junction diode, wherein a polysilicon-filled trench oxide layer is buried in the P-type structure to replace the majority of the P-type structure. As a consequence, the trench isolation MOS P-N junction diode device of the present invention has the benefits of the Schottky diode and the P-N junction diode. That is, the trench isolation MOS P-N junction diode device has rapid switching speed, low forward voltage drop, low reverse leakage current and short reverse recovery time.

Owner:PFC DEVICE HLDG

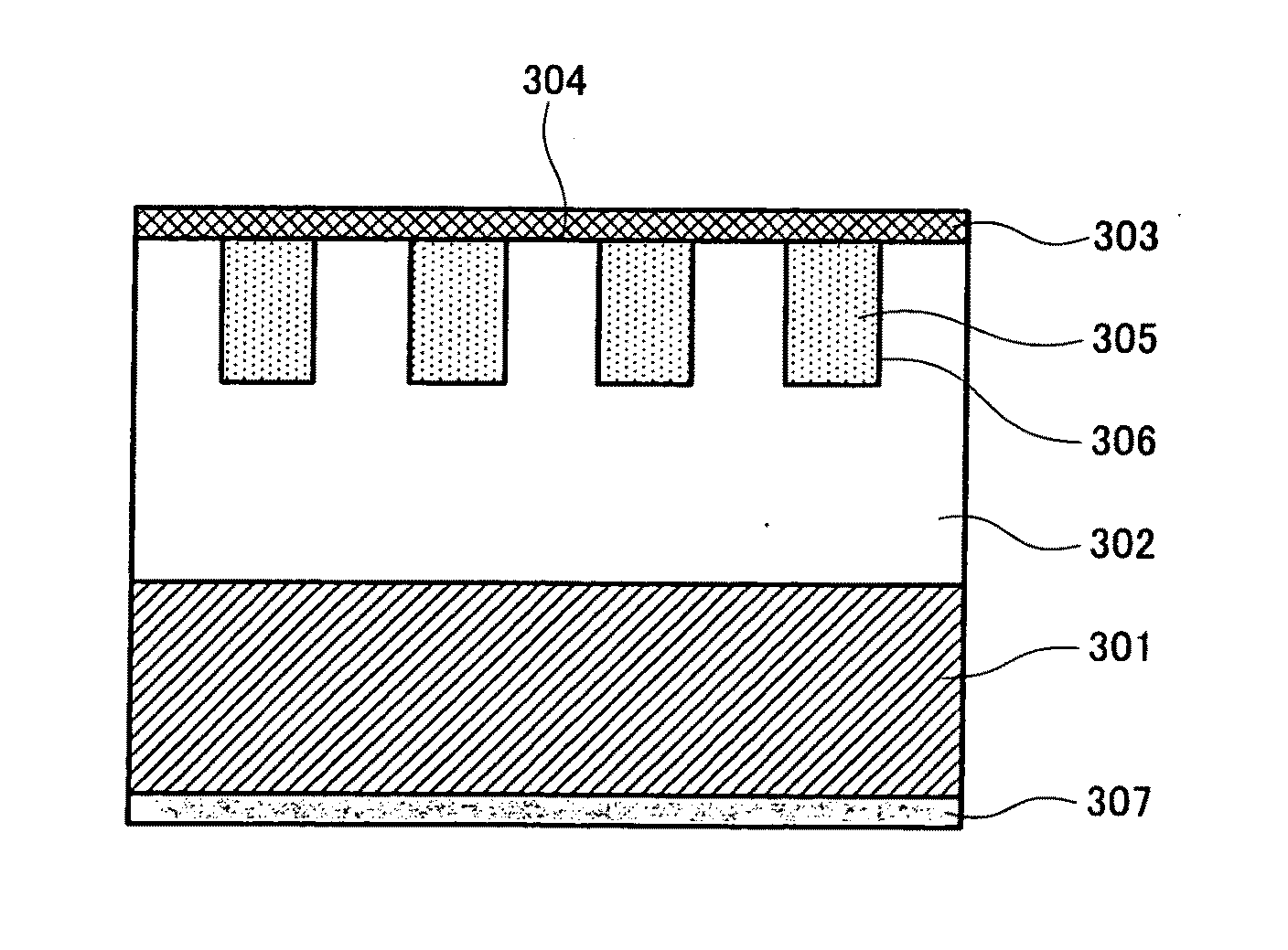

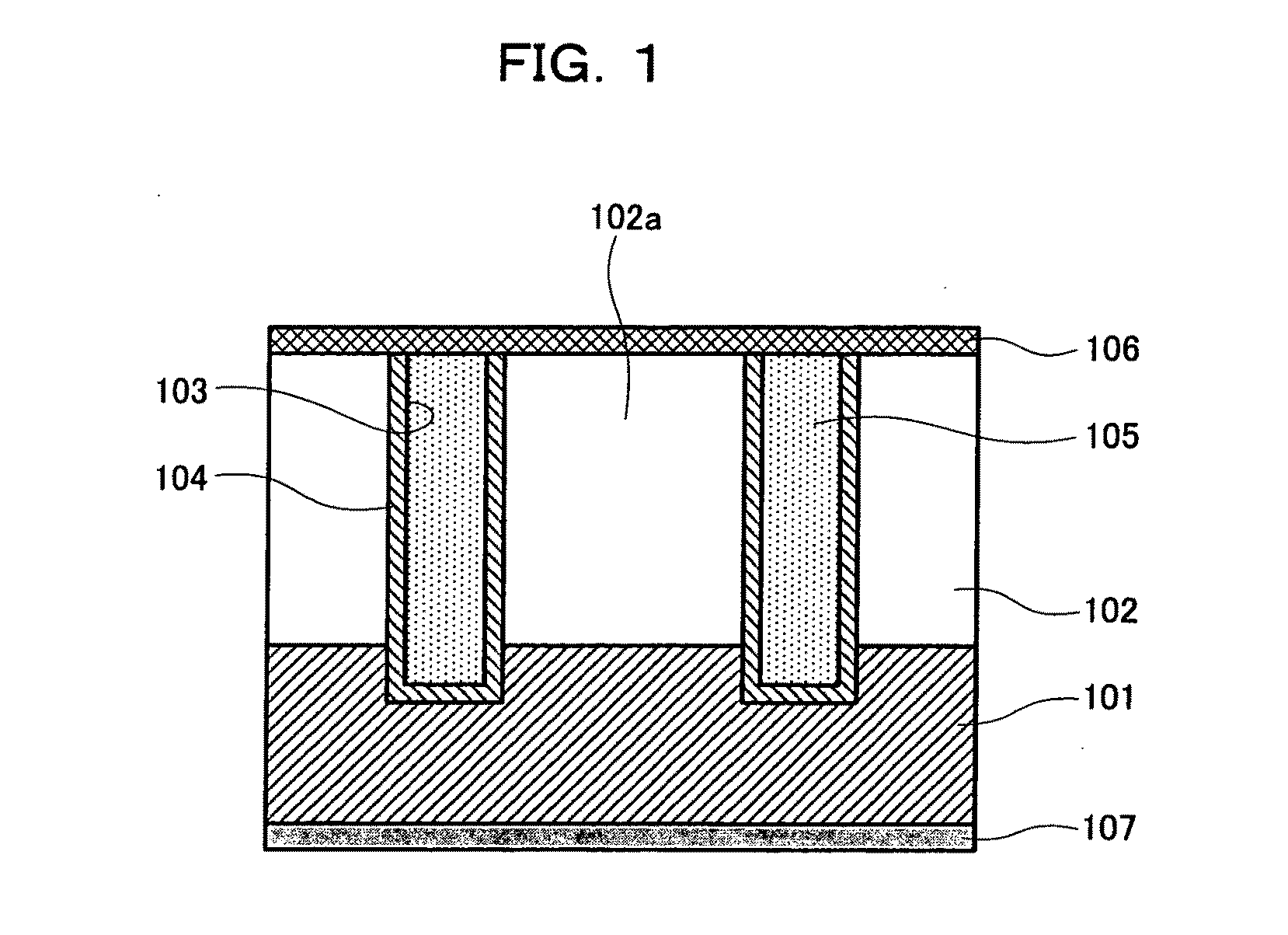

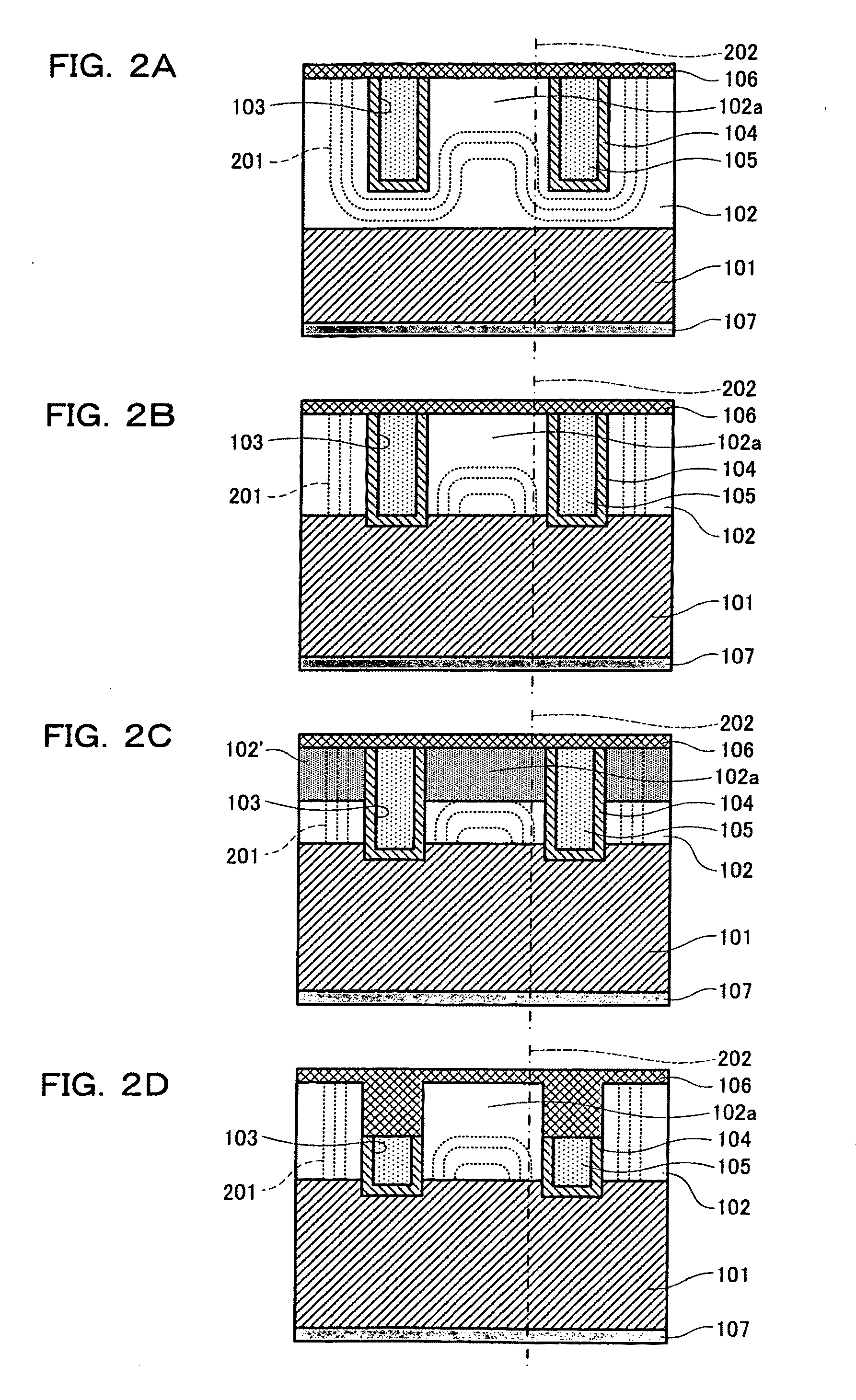

Schottky barrier semiconductor device

InactiveUS20110227187A1Prevent voltageIncreased stopping voltageSemiconductor devicesSchottky barrierEngineering

The present invention provides a Schottky barrier semiconductor device having a semiconductor substrate 101, a low-concentration semiconductor layer 102, trenches 103 formed in the low-concentration semiconductor layer 102 and extending to the semiconductor substrate 101, and a mesa portion 102a formed between the trenches 103. This provides a high durability against a surge or transient voltage.

Owner:PANASONIC CORP

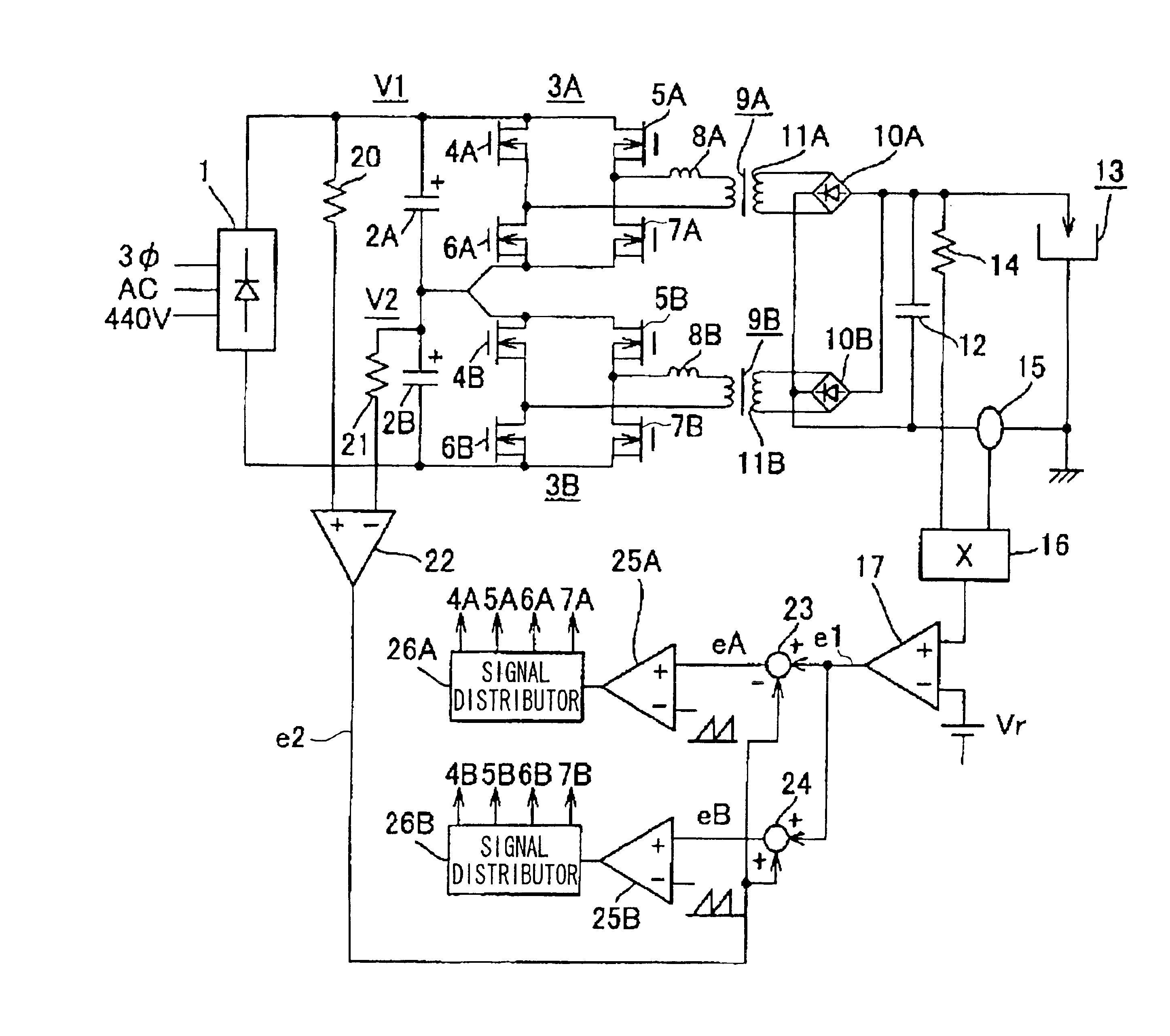

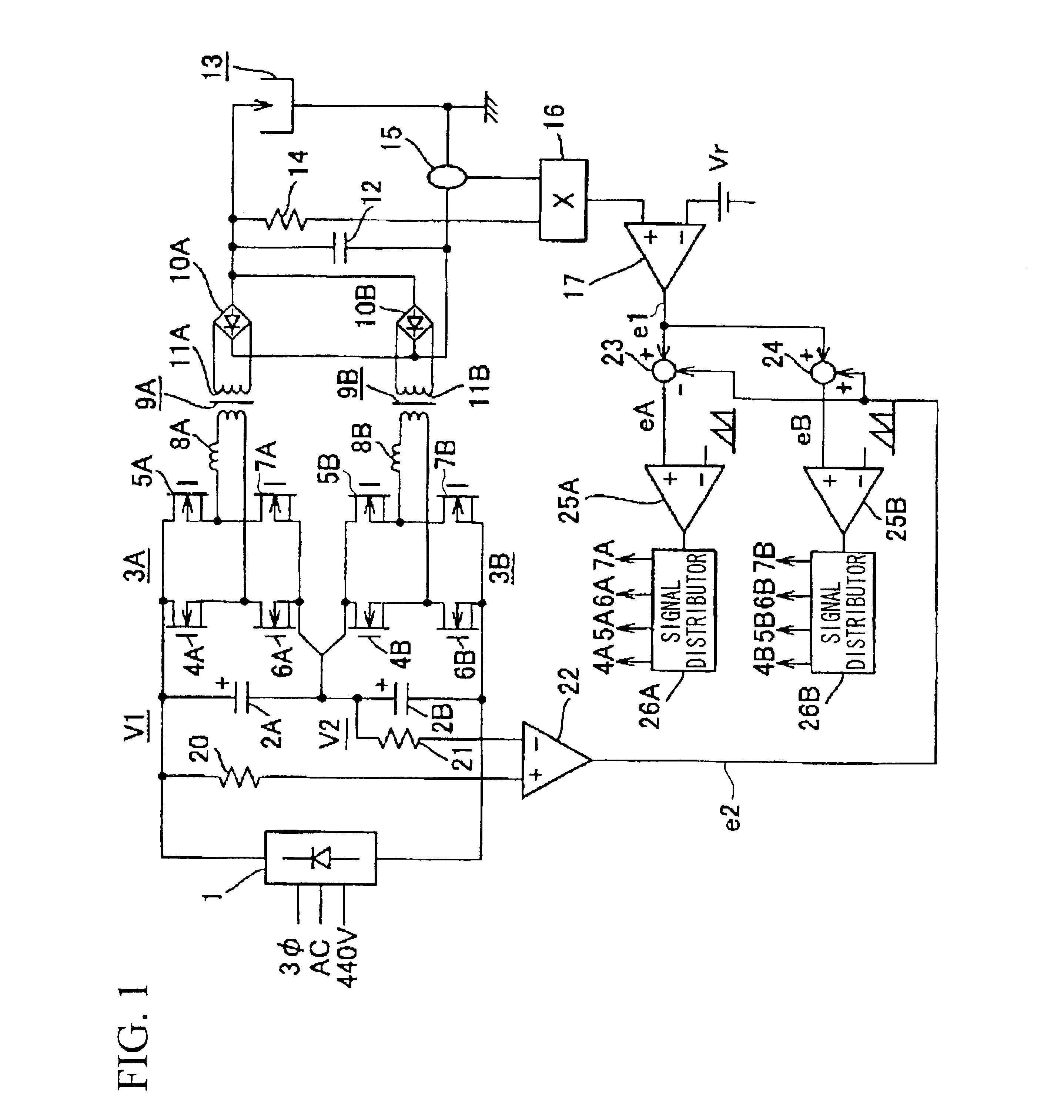

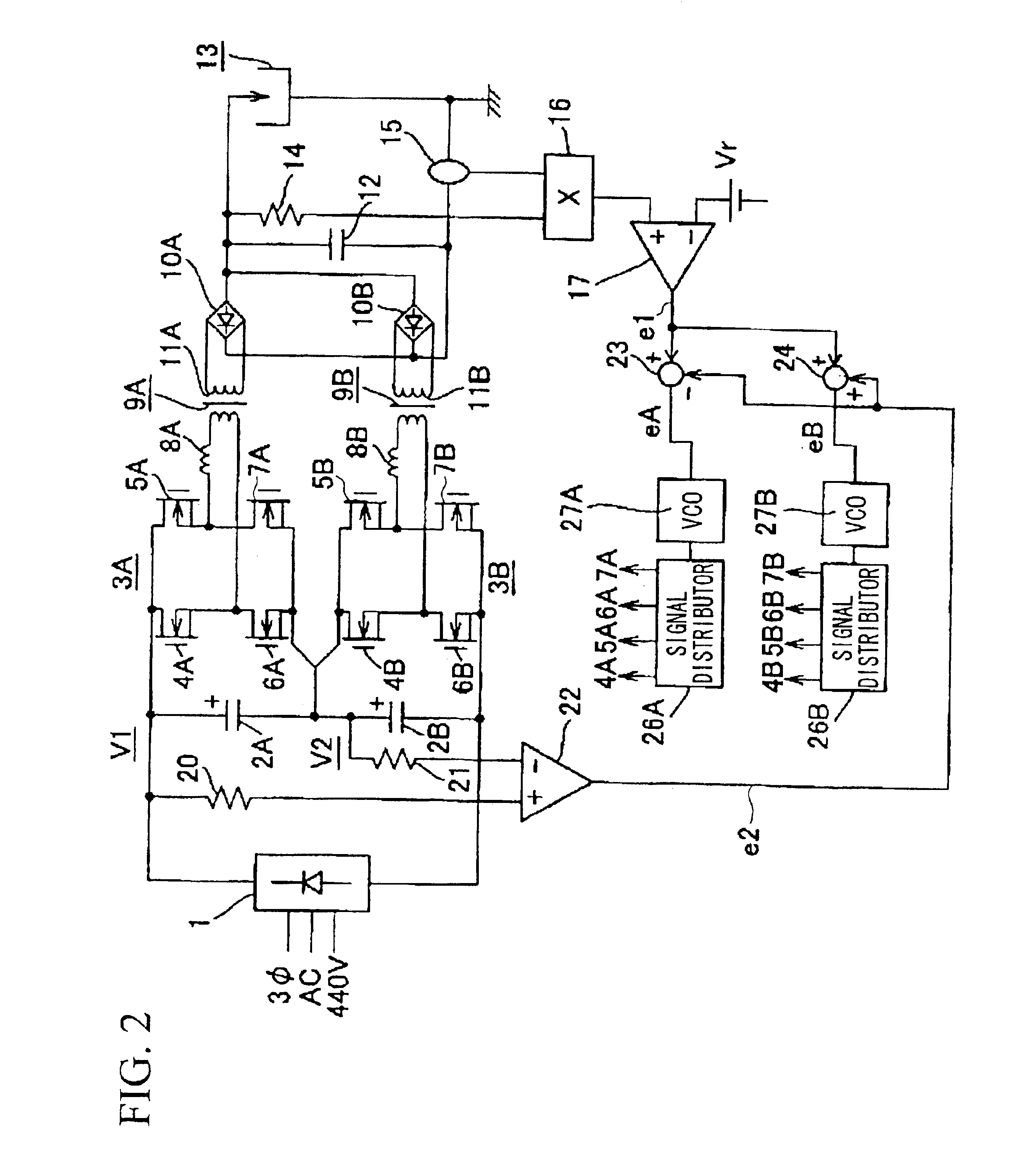

Power conversion device

InactiveUS6914794B2Reduce withstand voltageHigh frequencyApparatus with intermediate ac conversionElectric variable regulationControl signalEngineering

A low cost power conversion device operating at a high frequency with high efficiency is realized by using semiconductor switching devices such as FETs being inexpensive and having low withstand voltages and low forward voltage drops. A second error signal obtained by comparing the voltages across two input capacitors connected between both ends of a DC input power supply is subtracted / added from / to a first error signal obtained from a voltage corresponding to a combined DC output of rectifying circuits and the voltage corresponding to a predetermined reference power. Based on the resultant signals, the voltage of a control signal supplied to an inverter circuit in which the voltage across an input capacitor is higher is increased, while the voltage of a control signal supplied to another inverter circuit in which the voltage across another input capacitor is lower is decreased, thereby balancing the voltages across the input capacitors.

Owner:ORIGIN CO LTD

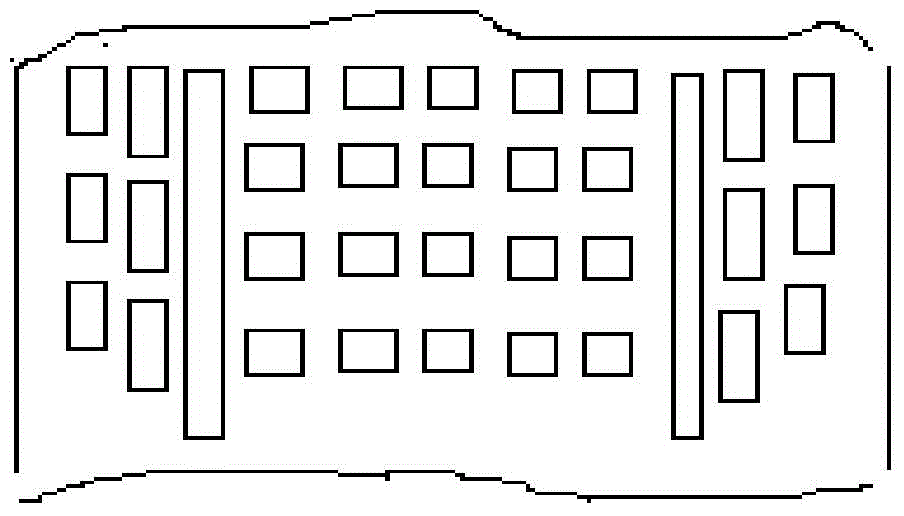

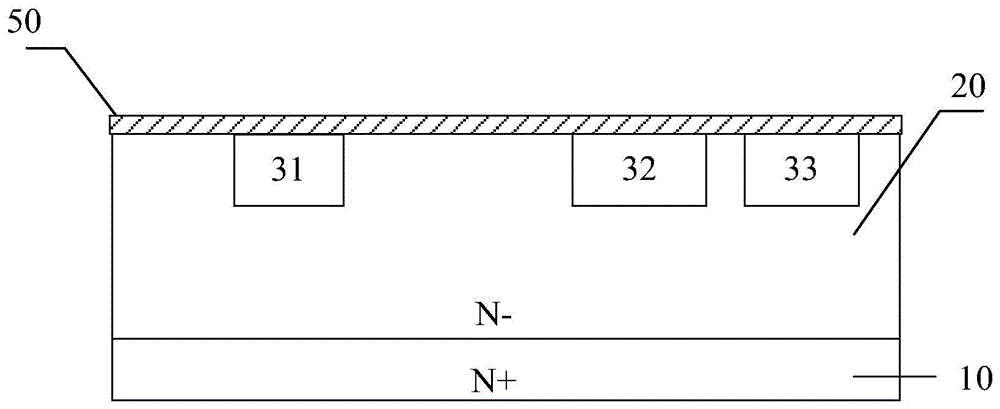

Low-cost TMBS device structure and manufacturing method

InactiveCN110047944AIncrease the expansion areaIncrease the areaSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierCondensed matter physics

The invention relates to a low-cost TMBS device structure and a manufacturing method, and belongs to the technical field of integrated circuit or discrete device manufacturing. The low-cost TMBS device structure comprises a heavily doped silicon substrate, wherein a lightly doped silicon epitaxial layer is arranged on the heavily doped silicon substrate; a silicon groove array is arranged on the lightly doped silicon epitaxial layer; a SiO2 layer is arranged on the inner side wall of the silicon groove array; the silicon groove array is filled with a heavily doped Poly; a Schottky barrier metal layer is arranged on the silicon groove array; and an electrode metal layer is arranged on the Schottky barrier metal layer. The silicon groove array comprises a primitive cell trench unit, a primitive cell large trench, an extension trench and a cut-off trench, Schottky barrier metal layers are arranged on the upper surfaces of the primitive cell trench unit and the primitive cell large trench,and a SiO2 layer and a Schottky barrier metal layer are arranged on the lightly doped silicon epitaxial layer between the primitive cell large trench and the extension trench. According to the invention, the process steps are reduced, the terminal structure is optimized, the terminal electric field distribution is more uniform, and the breakdown voltage is improved; and the forward voltage drop of the device is reduced.

Owner:江苏新顺微电子股份有限公司

Method for forming semiconductor device

InactiveUS20100216290A1Reduced power dissipationExtra cost of be saveSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDopant

A method for forming semiconductor device, which simultaneously forms a trench MOS transistor device, and an embedded schottky barrier diode (SBD) device in a semiconductor substrate. The embedded SBD device has lower forward voltage drop, which reduces power dissipation. In addition, the voltage bearing ability may be modified easily by virtue of altering the dopant concentration or the width of the voltage bearing dopant region, or the thickness of epitaxial silicon layer. Furthermore, extra cost of purchasing SBD diode may be saved.

Owner:ANPEC ELECTRONICS CORPORATION

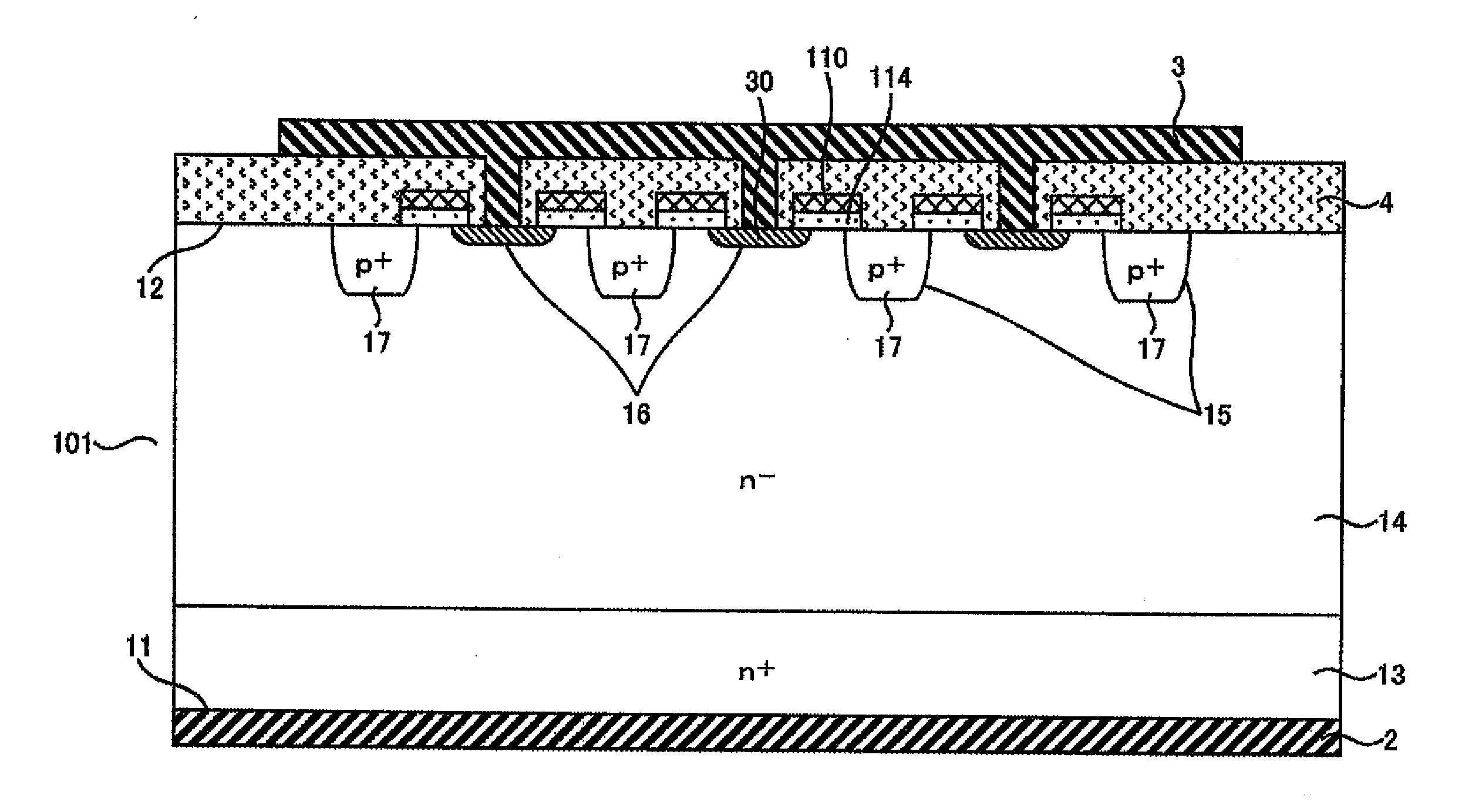

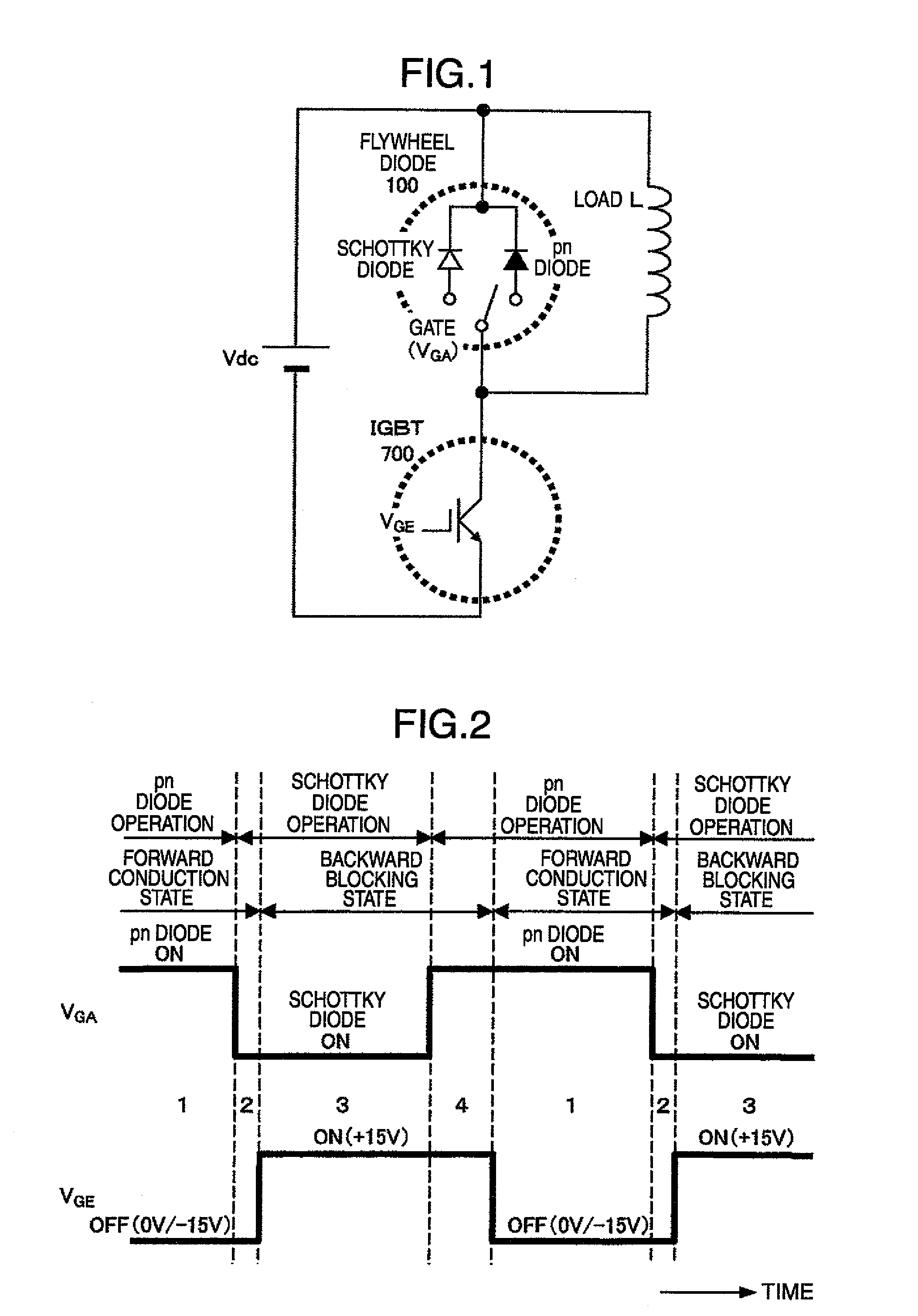

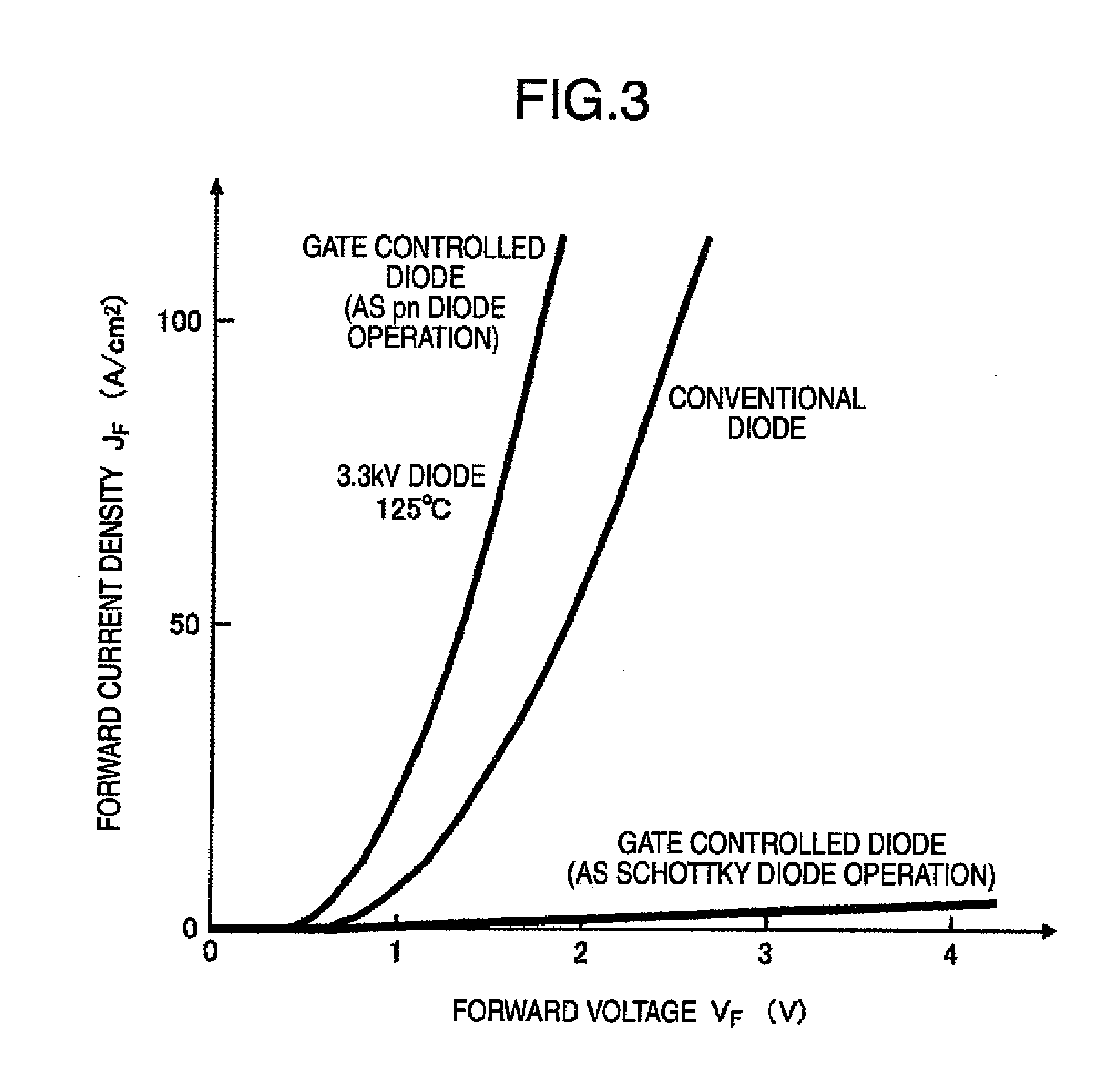

Semiconductor device and power converter using it

ActiveUS20110073905A1Lower forward voltage dropTotal current dropTransistorSolid-state devicesFlyback diodeSchottky diode

A semiconductor device and a power converter using it wherein a switching power device and a flywheel diode are connected in series, the flywheel diode includes a region having a Schottky junction to operate as a Schottky diode and a region having a pn junction to operate as a pn diode and control operation is performed such that when current flows forwardly through the flywheel diode, the pn diode operates and when the flywheel diode recovers backwardly, the Schottky diode operates mainly.

Owner:HITACHI LTD

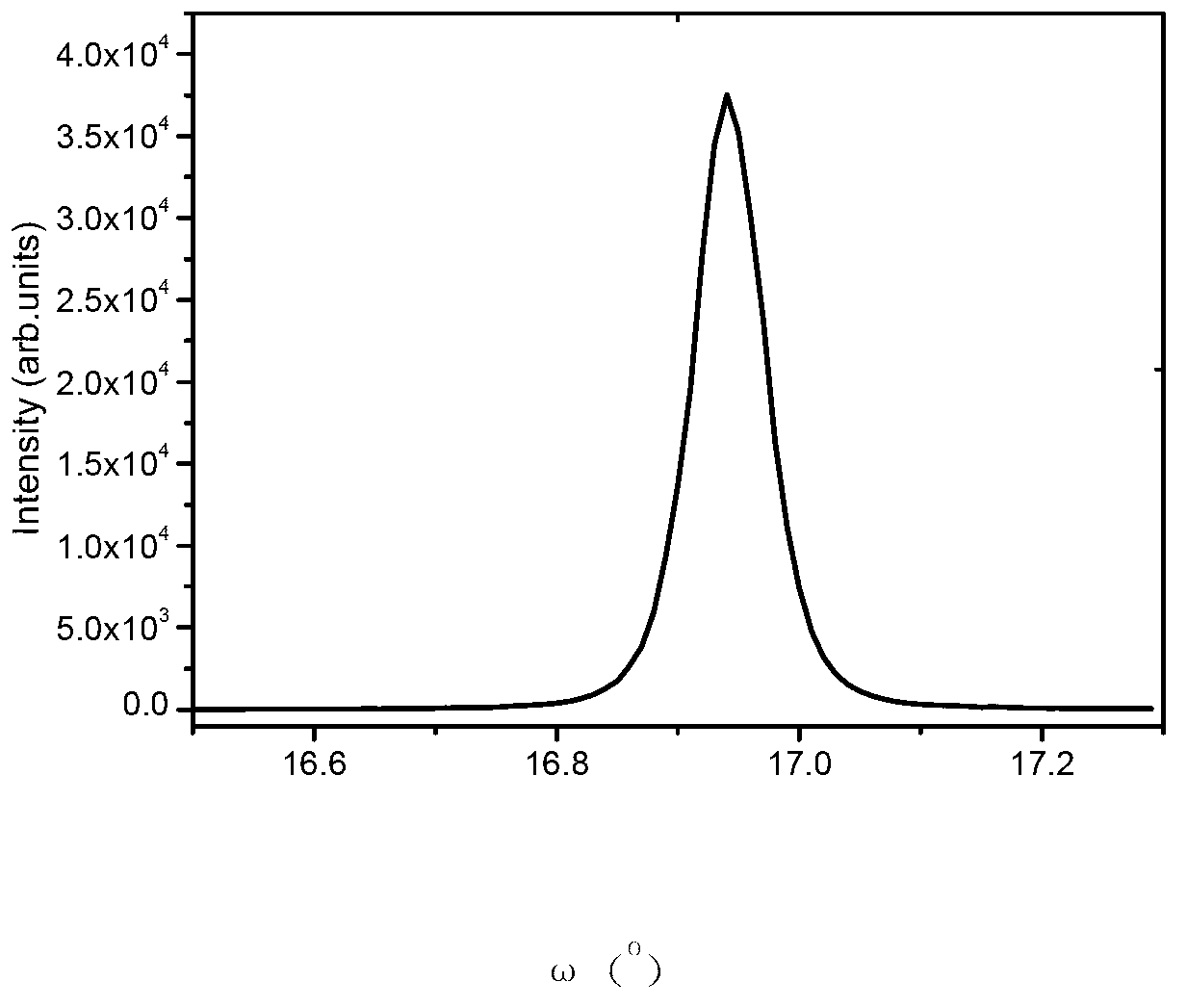

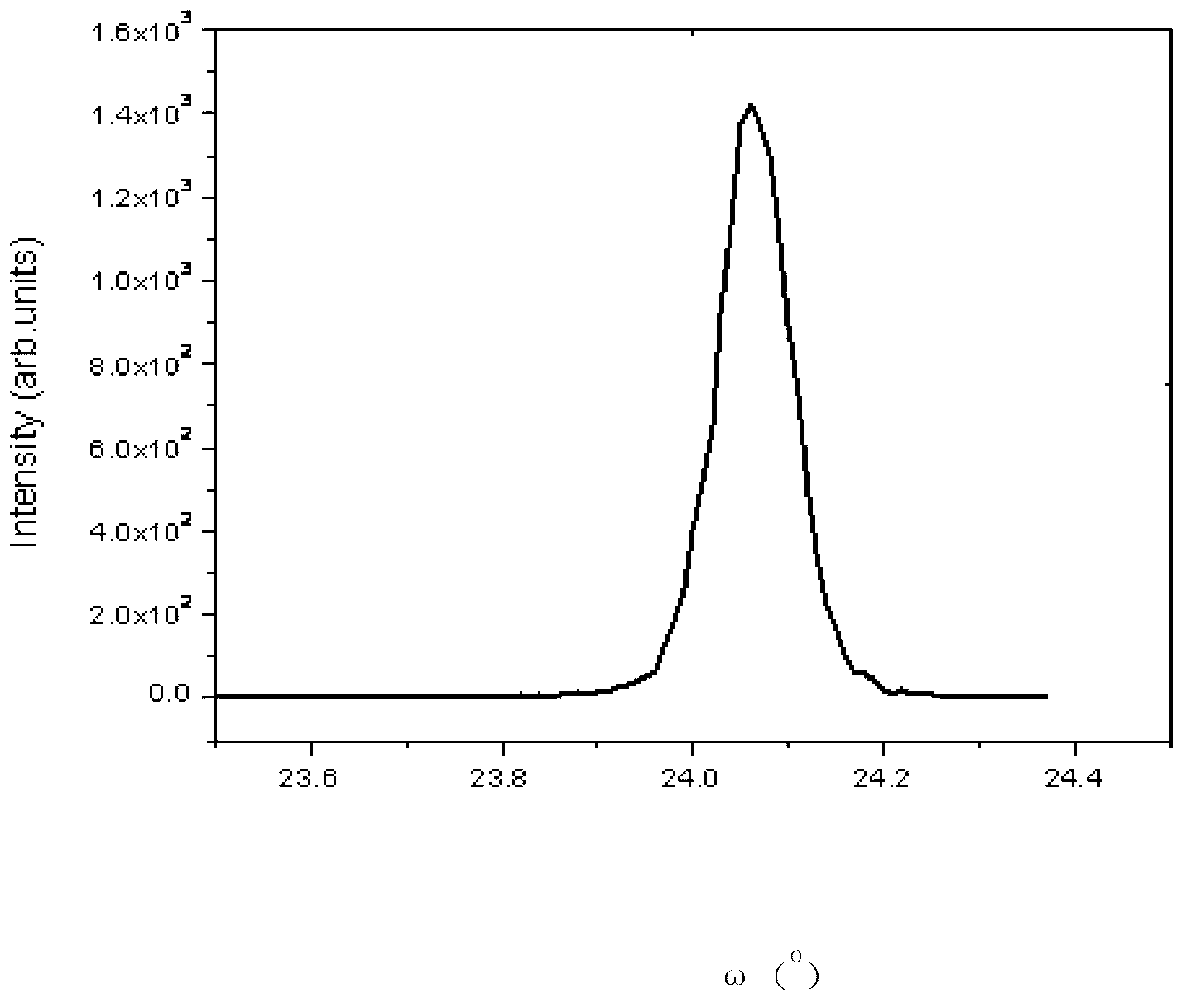

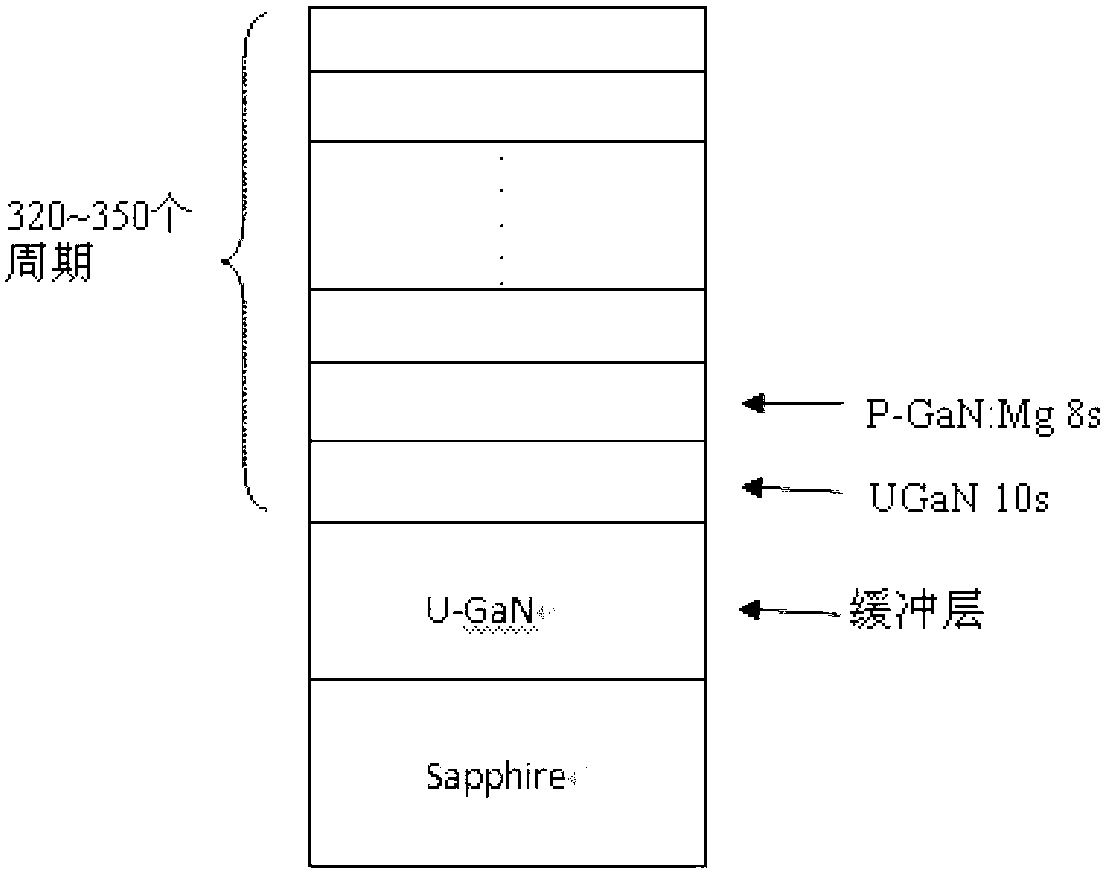

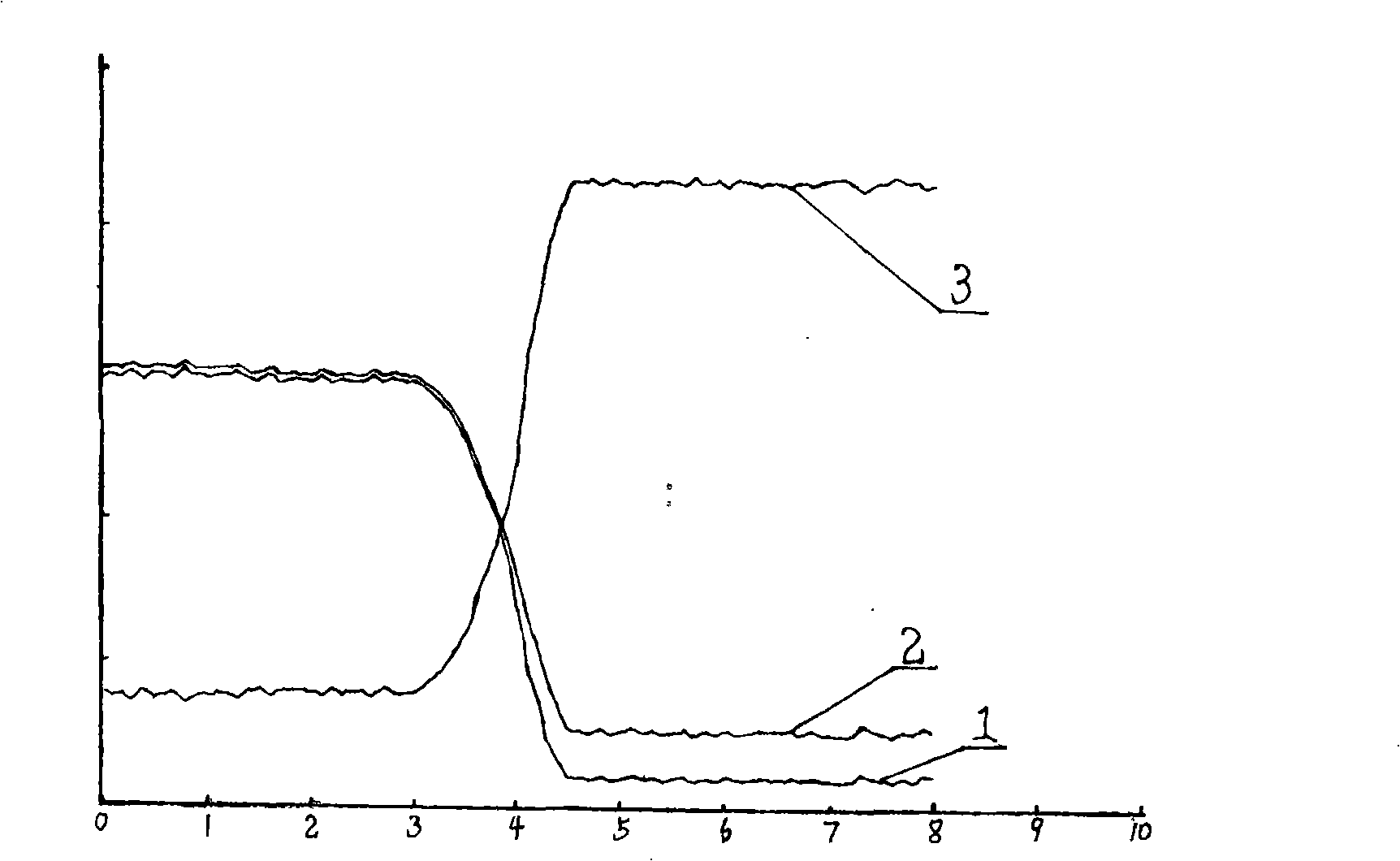

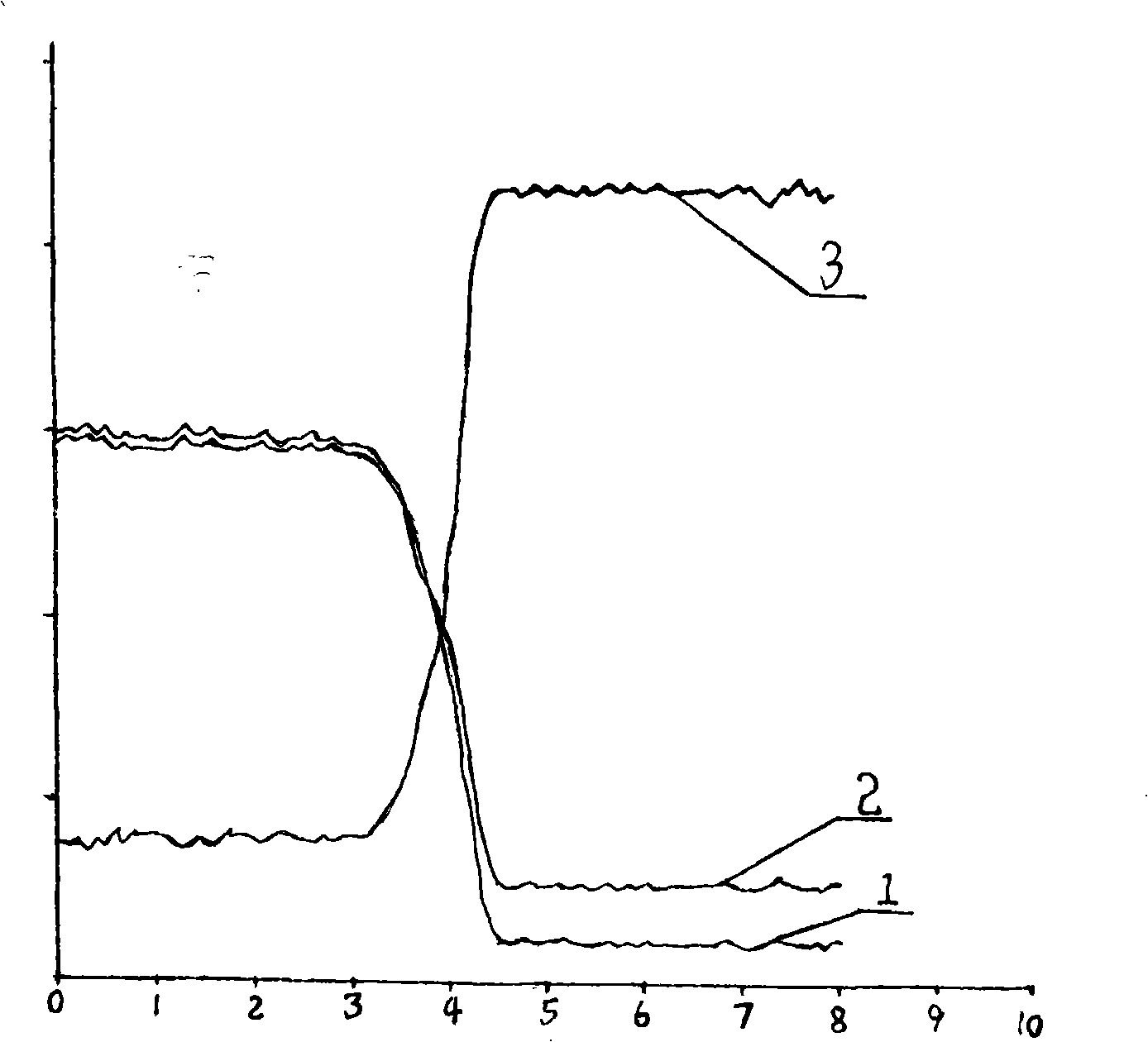

Method for controlling growth of P-type GaN low-flow dopant

InactiveCN103215642AHigh activation rateQuality improvementPolycrystalline material growthFrom chemically reactive gasesDopantSemiconductor materials

The invention relates to a method for controlling the growth of a P-type GaN low-rate dopant, and belongs to the field of preparation of semiconductor materials. According to the method, a low-temperature core-forming layer, an unintentionally doped GaN layer and then a p-type GaN layer are sequentially grown upwards on a substrate with Cp2Mg as the p-type dopant, the non-doped GaN layer is grown for 10 seconds before the growth of the p-type GaN layer, then a CP2Mg source is inlet and grown for 8 seconds, and the growth is repeated for 320-350 periods with the 18 seconds as the single period; and the flow of the CP2Mg is controlled in the range of 35-50 sccm, and the growth temperature is 920-980 DEG C. Based on the method, the Mg atom intermingling efficiency is increased, the self-compensation effect of the Mg atom is restrained, the hole concentration is improved, the crystal quality is improved, and therefore the high-performance p-type GaN material is obtained; and the method provides beneficial assistance for reducing the forward voltage drop of a GaN-based LED (light-emitting device) and prolonging the service life.

Owner:BEIJING UNIV OF TECH

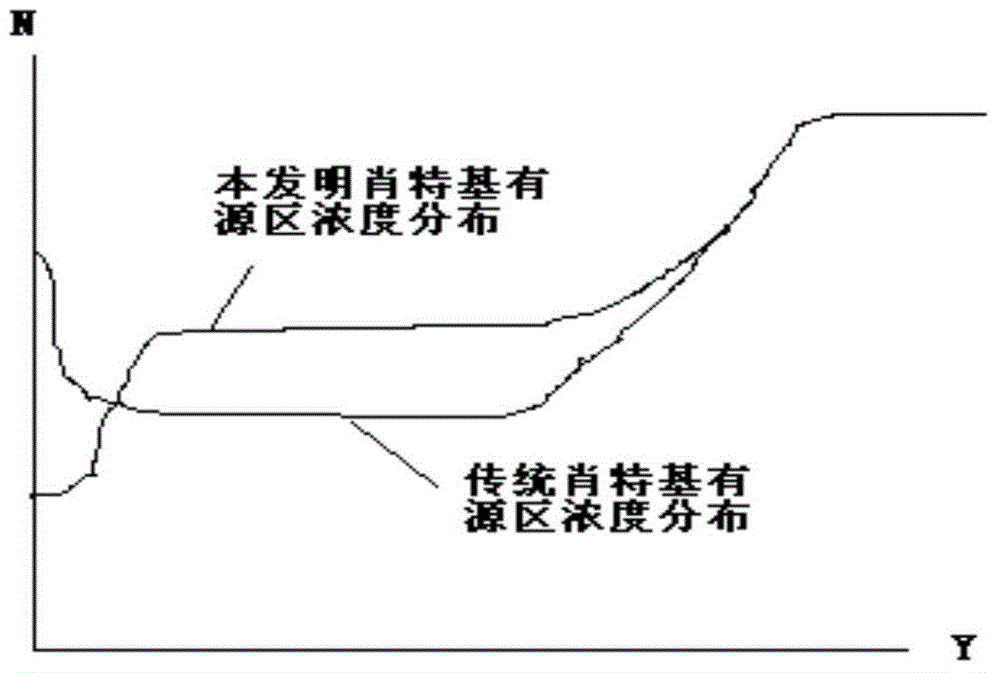

Extension method of material for low forward voltage drop Schottky diode

ActiveCN101295638AControl and optimize heating timeLower forward voltage dropSemiconductor/solid-state device manufacturingPositive pressurePressure reduction

The invention discloses an extension method for a material used for a lower positive pressure reduction schottky diode. The invention controls and optimizes the temperature rising time of each step by adjusting the program of temperature rising and the careful cooperation of hydrogen flux to lead the impurities of a wafer from an underlay to be expanded outwards during a heat treatment process and finally lead the transition area of a silicon epitaxial wafer to reach the range of 1.2 to 1.3 micron by expelling the air by hydrogen. The resistance rate uniformity in the wafer is less than 3 percent by adopting the method of the invention, thereby leading the transition area of the wafer to be controlled between 1.0 and 1.3 micron and leading the resistance rate uniformity in a furnace to be less than 5 percent; besides, the repetitiveness and the reproducibility of the resistance rate and the thickness between furnaces are good; the repetitiveness in the furnace and the transition area of the wafer is good; the uniformity and the consistency of the positive pressure reduction and negative pressure reduction of the schottky diode manufactured by the material are good.

Owner:HEBEI POSHING ELECTRONICS TECH

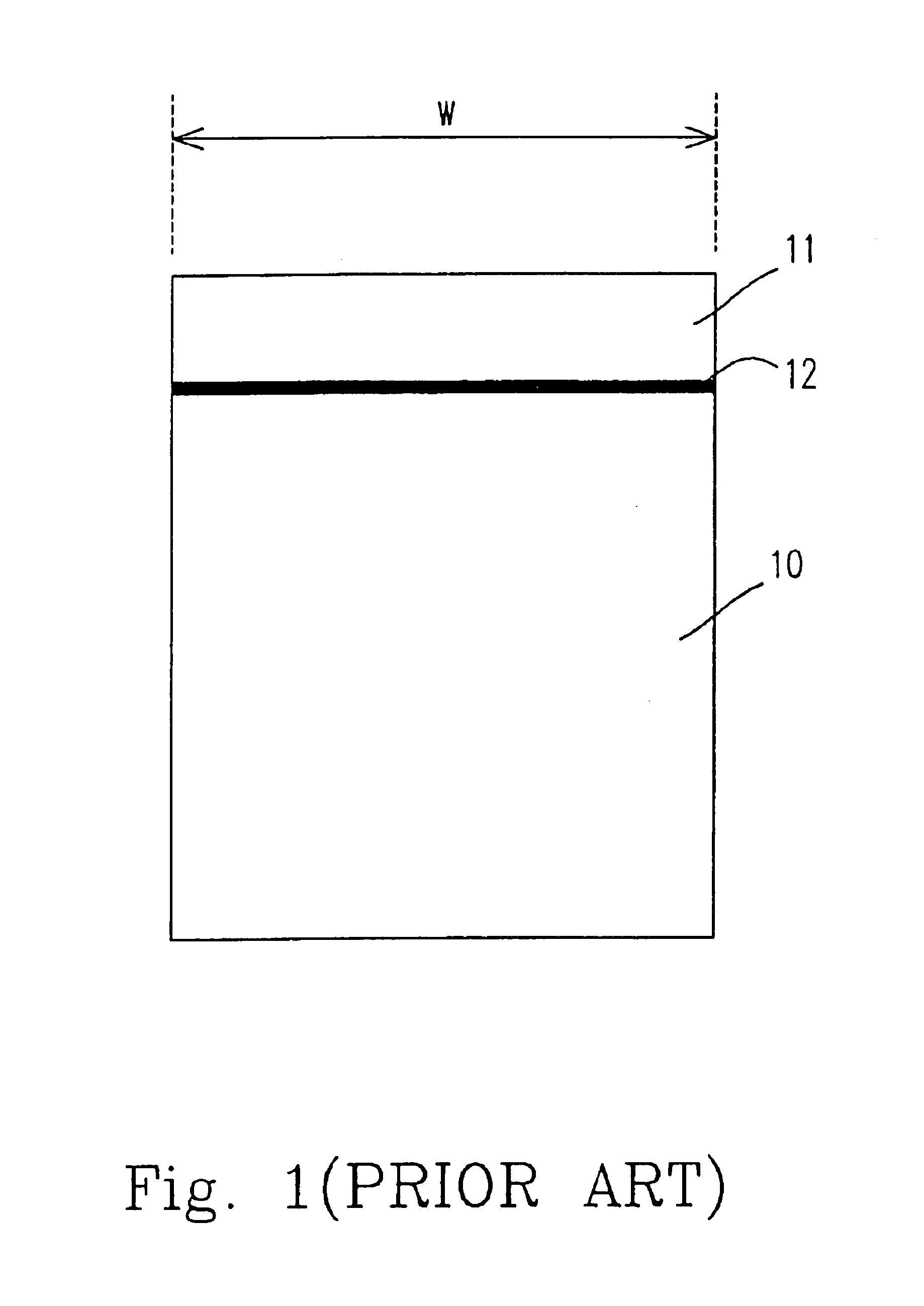

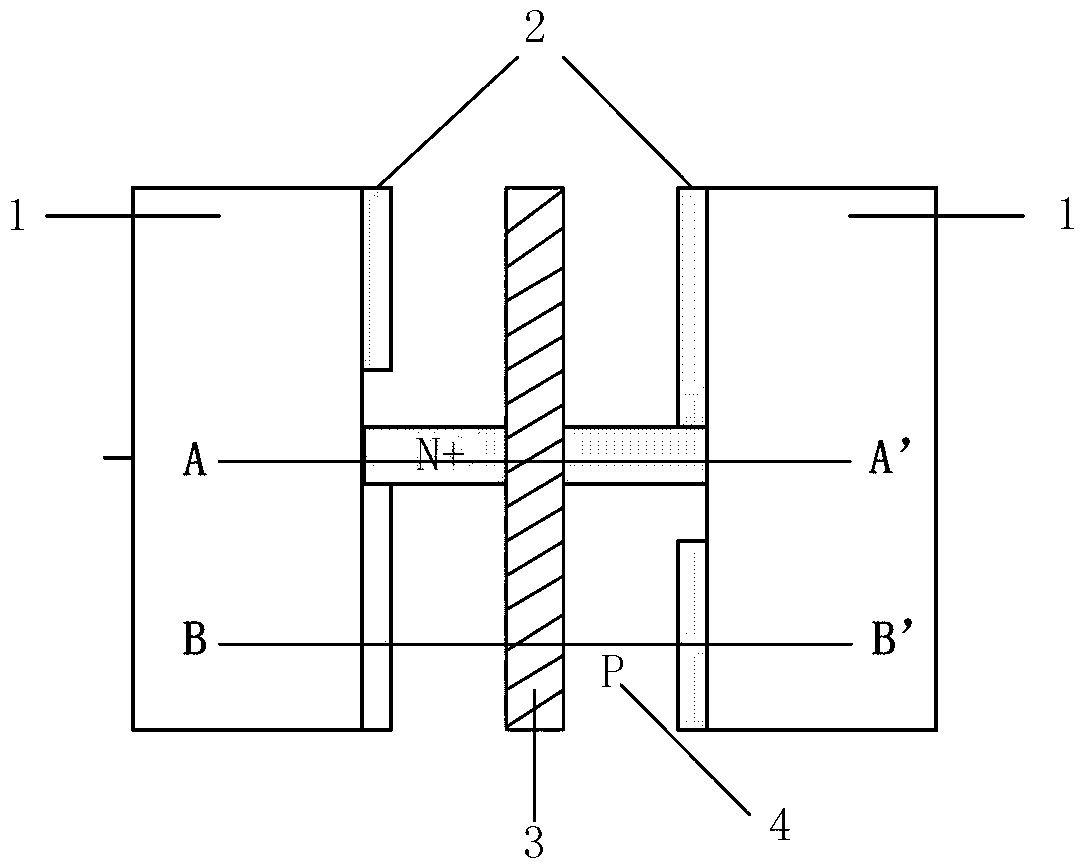

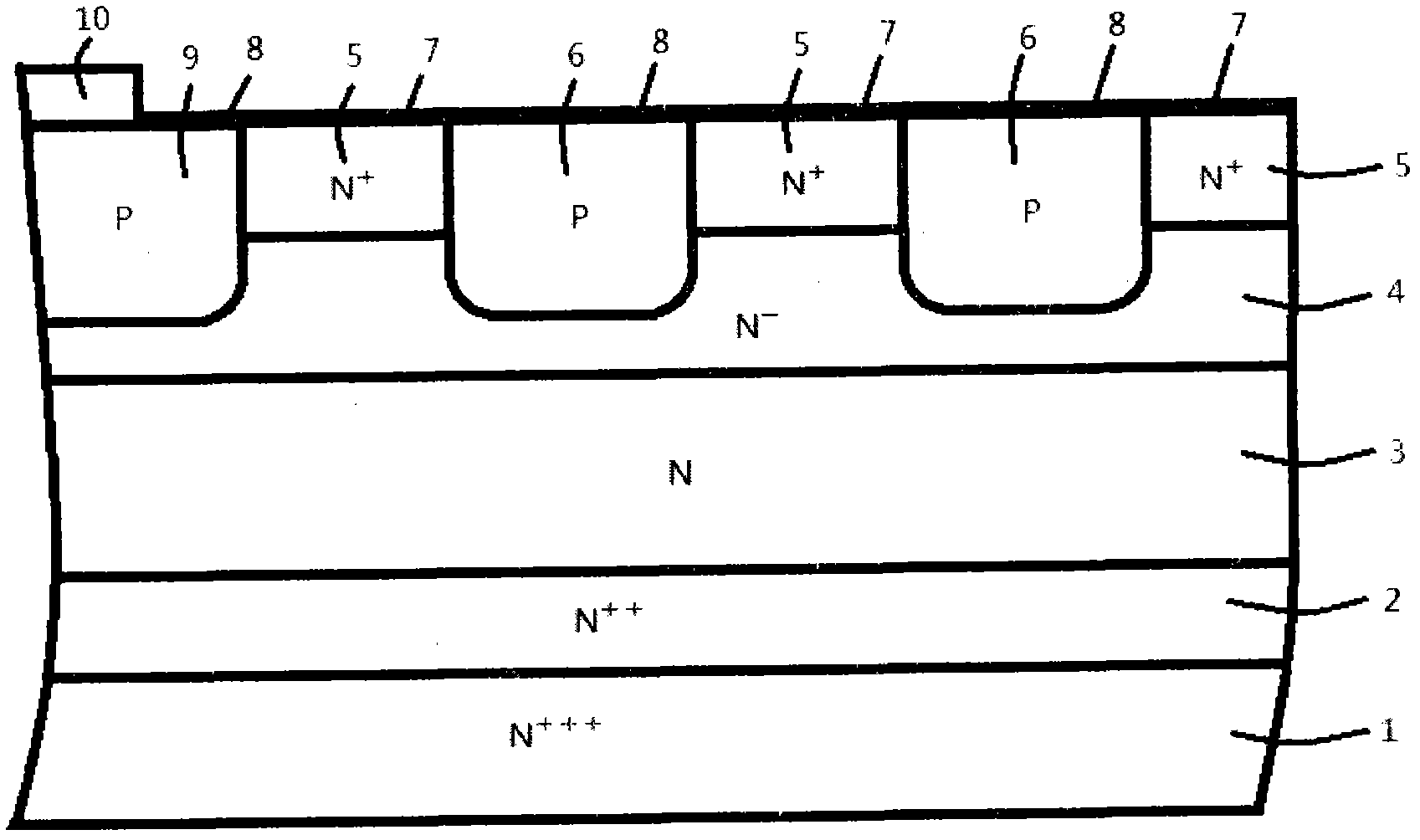

Mos p-n junction diode device and method for manufacturing the same

ActiveUS20090261427A1Improve performanceReduce leakage currentSemiconductor/solid-state device manufacturingDiodeResistReverse recovery

A MOS P-N junction diode device includes a substrate having a first conductivity type, a field oxide structure defining a trench structure, a gate structure formed in the trench structure and a doped region having a second conductivity type adjacent to the gate structure in the substrate. The method for manufacturing such diode device includes several ion-implanting steps. After the gate structure is formed by isotropic etching using a patterned photo-resist layer as a mask, an ion-implanting step is performed using the patterned photo-resist layer as a mask to form a deeper doped sub-region. Then, another ion-implanting step is performed using the gate structure as a mask to form a shallower doped sub-region between the gate structure and the deeper doped sub-region. The formed MOS P-N junction diode device has low forward voltage drop, low reverse leakage current, fast reverse recovery time and high reverse voltage tolerance.

Owner:PFC DEVICE

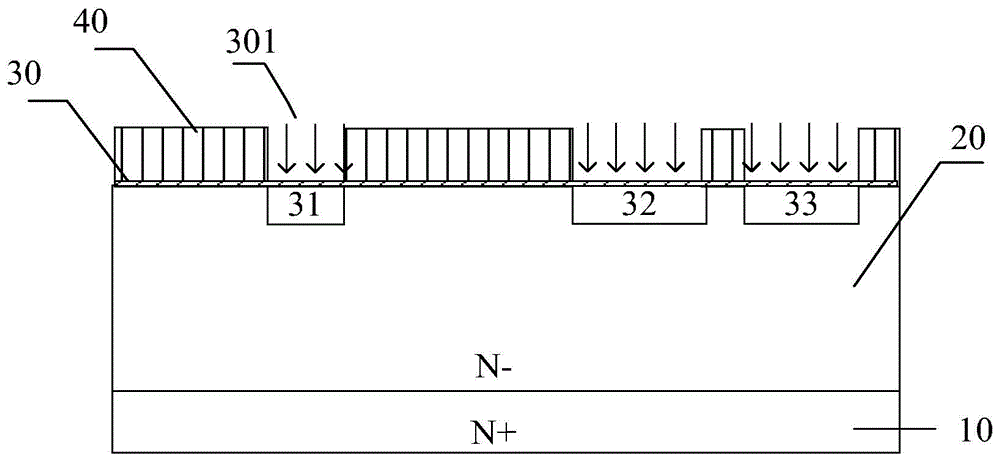

MOS super barrier rectifier device and manufacturing method thereof

InactiveCN103325839AGuaranteed depthLow costSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringImpurity

The invention discloses an MOS super barrier rectifier device which is provided with a groove, a second conduction type injection region wraps the groove, the structure can replace a protecting ring structure, a primary photomask is removed compared with the prior art, the depth of the second conduction type injection region is guaranteed, and good pressure proof functions are performed. In addition, the invention further discloses a manufacturing method. According to the method, after the groove is formed, the second conduction type injection region is injected and formed by carrying out heat treatment on activator impurities, the photomask needed when a protecting ring is formed and the processes of long-time trap pushing are removed, cost is saved, the damage, caused by injection by using macro-energy, to the surfaces of devices is avoided, transverse diffusion distance of micro-energy injection region is small, and the control over the length of a channel region and the distance between adjacent second conduction type injection regions is better.

Owner:ZHANGJIAGANG CASS SEMICON

Insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance

InactiveCN103258848AImprove short circuit performanceImproves latch-up resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCompensation effectEngineering

The invention discloses an insulated gate bipolar transistor (IGBT) device with positive temperature coefficient emitter ballast resistance (EBR), and belongs to the technical field of power semiconductor devices. In a conventional IGBT device of an EBR structure, the EBR is composed of a strip-shaped N<+> emitter region strip, the resistance value of the EBR generally represents a negative-temperature coefficient, namely, the higher the temperature is, the smaller the resistance value is, saturation current of the IGBT is increased, and the short-circuit capacity of the IGBT device with the positive temperature coefficient EBR will be remarkably reduced in high-temperature environments. According to the IGBT device with the positive temperature coefficient EBR, deep energy level acceptor impurities, including In or Ti or Co or Ni, are doped into the N<+> emitter region, holes produced after ionization of the deep energy level acceptor impurities have a certain compensation effect on N-type impurities, positive temperature coefficient EBR is achieved, thus the resistance value of the EBR is increased along with rise of the temperature of the IGBT device, and the short circuit capacity and latch resistant capacity of the IGBT are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Low-electric-leakage and low-forward-voltage-drop Schottky diode structure and manufacturing method of low-electric-leakage and low-forward-voltage-drop Schottky diode structure

InactiveCN104134703AEasy to prepareEasy to operateSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierEngineering

The invention mainly aims at providing a low-electric-leakage and low-forward-voltage-drop Schottky diode structure and a manufacturing method of the low-electric-leakage and low-forward-voltage-drop Schottky diode structure. The manufacturing method is characterized in that a terminal is protected with the junction termination extension technology, neutralization modulation is carried out on Schottky main junction depletion regions at the same time, injections of the two terms are carried out at the same time, the breakdown voltage is improved, the good low-electric-leakage effect can be achieved, and the process manufacturing procedure is simple. After the low-electric-leakage and low-forward-voltage-drop Schottky diode structure and the manufacturing method are applied, a low-electrical-resistivity epitaxial wafer can be adopted for manufacturing a Schottky diode, the forward voltage drop is effectively reduced, the high-voltage effect is achieved, and the low-electric-leakage and low-forward-voltage-drop effect is improved. By means of the low-electric-leakage and low-forward-voltage-drop Schottky diode structure and the manufacturing method, the efficient Schottky barrier diode can be obtained; compared with a traditional diode structure, the application scope of the diode is wide.

Owner:SHANGHAI ANWEI ELECTRONICS

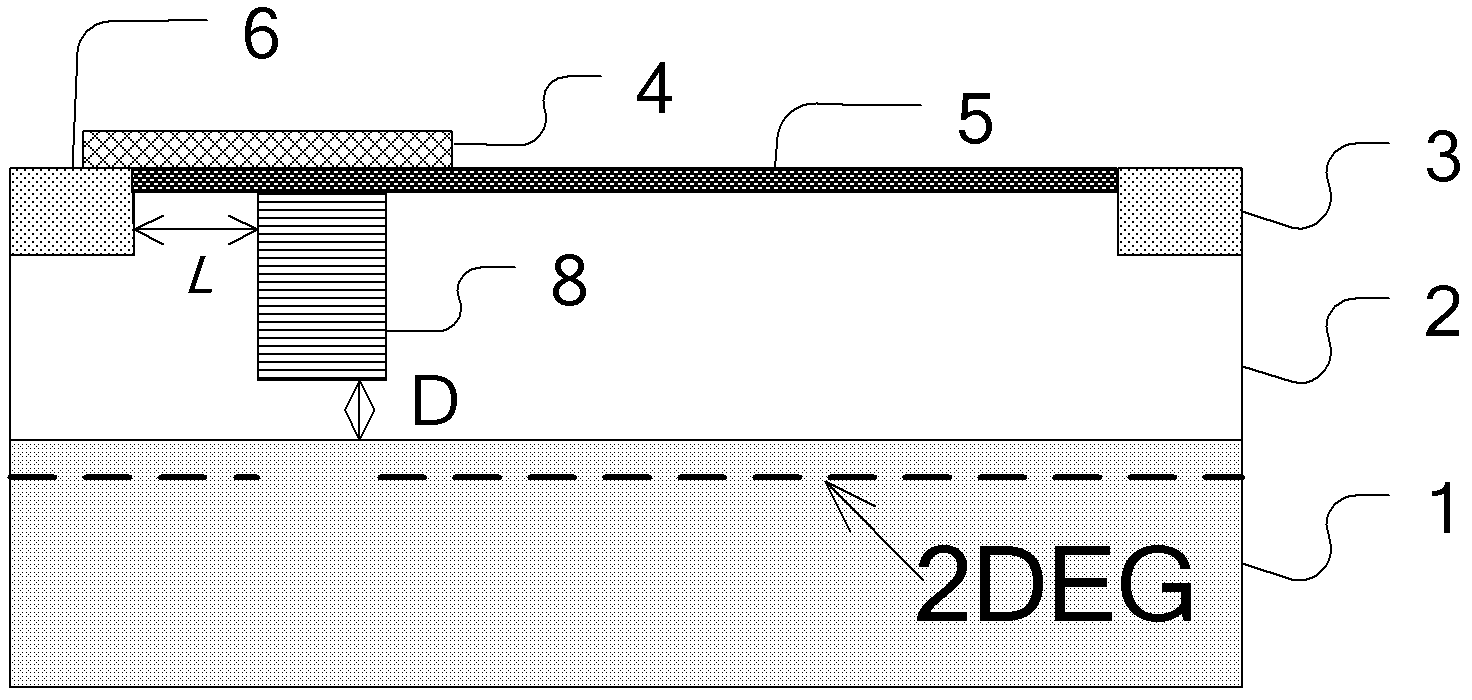

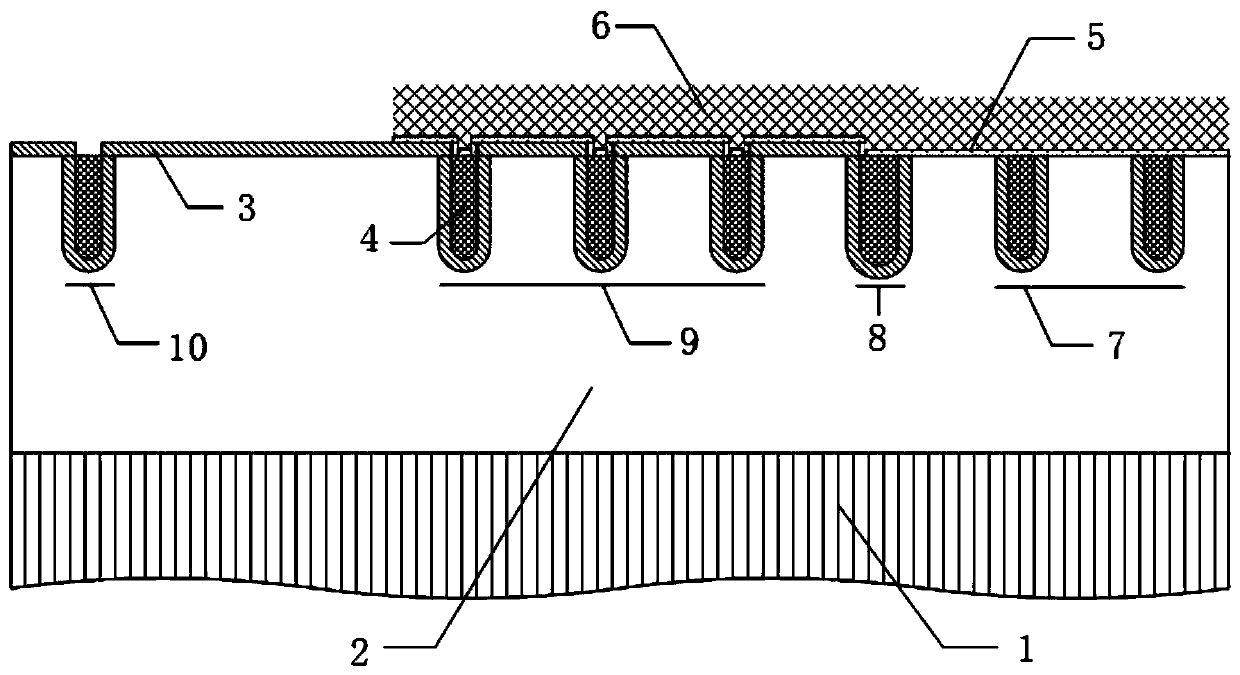

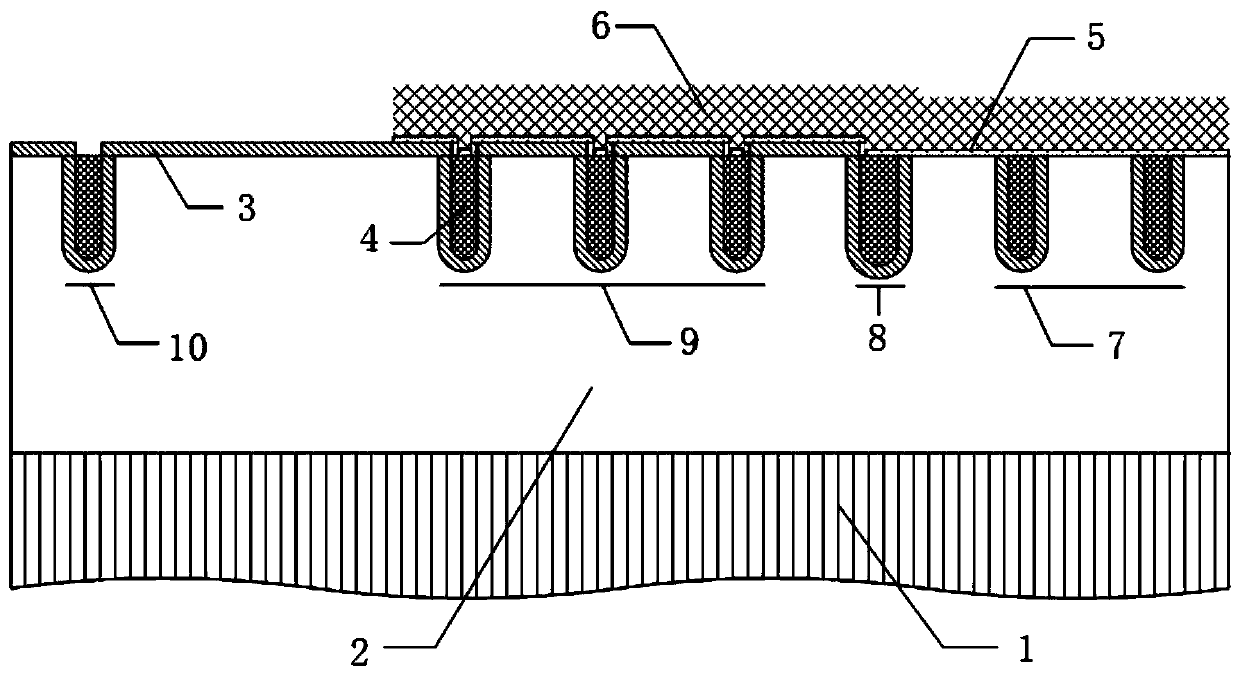

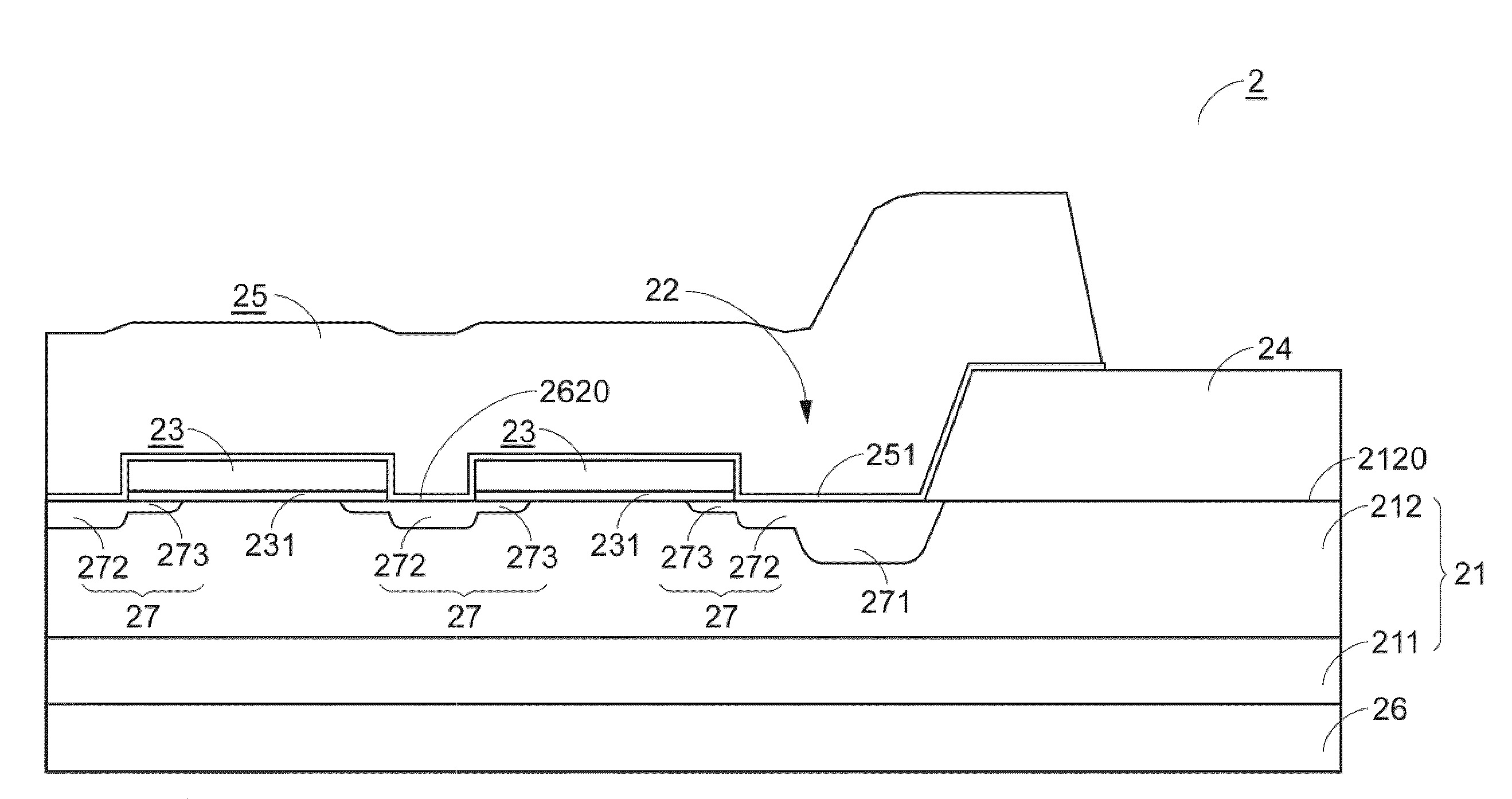

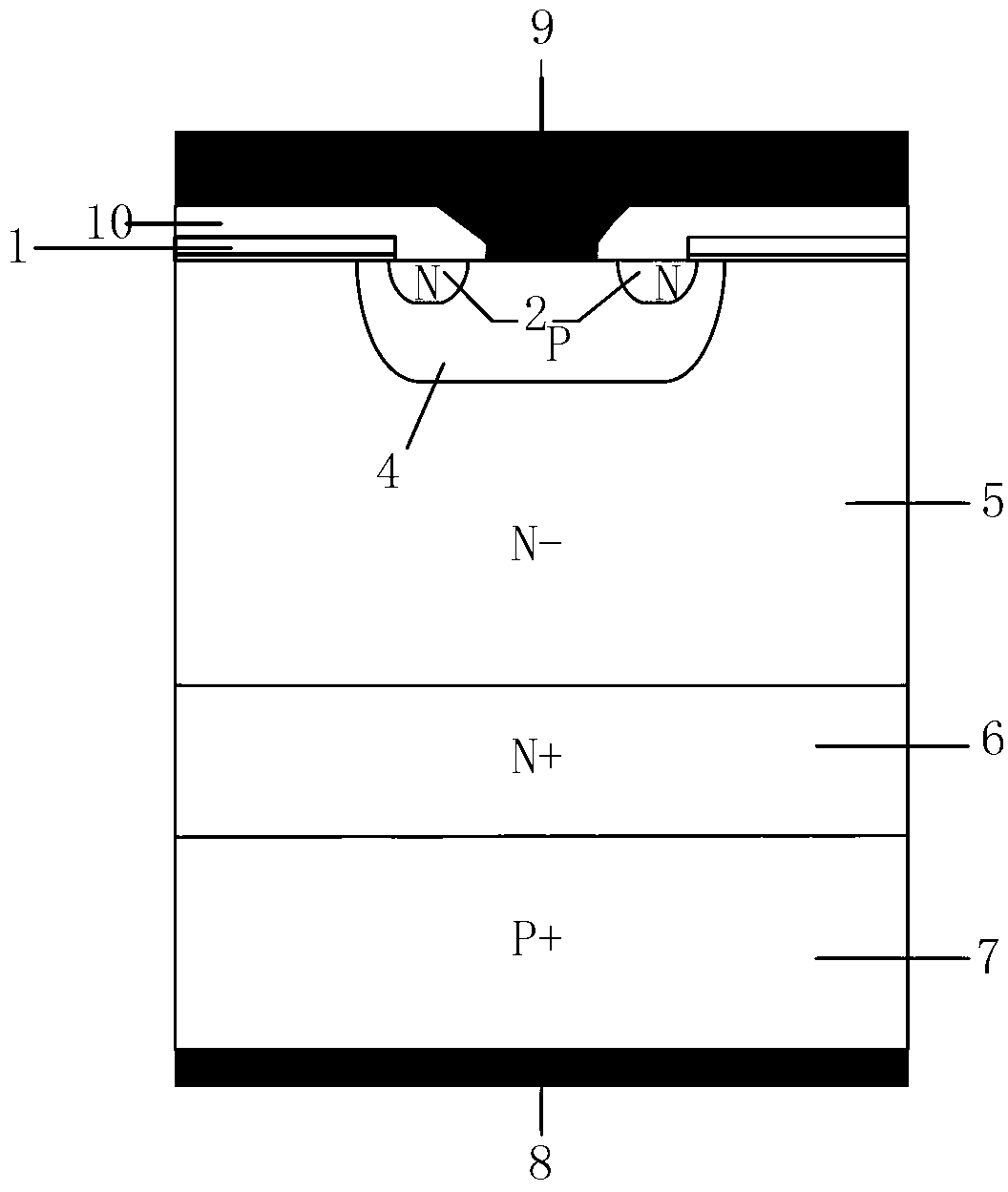

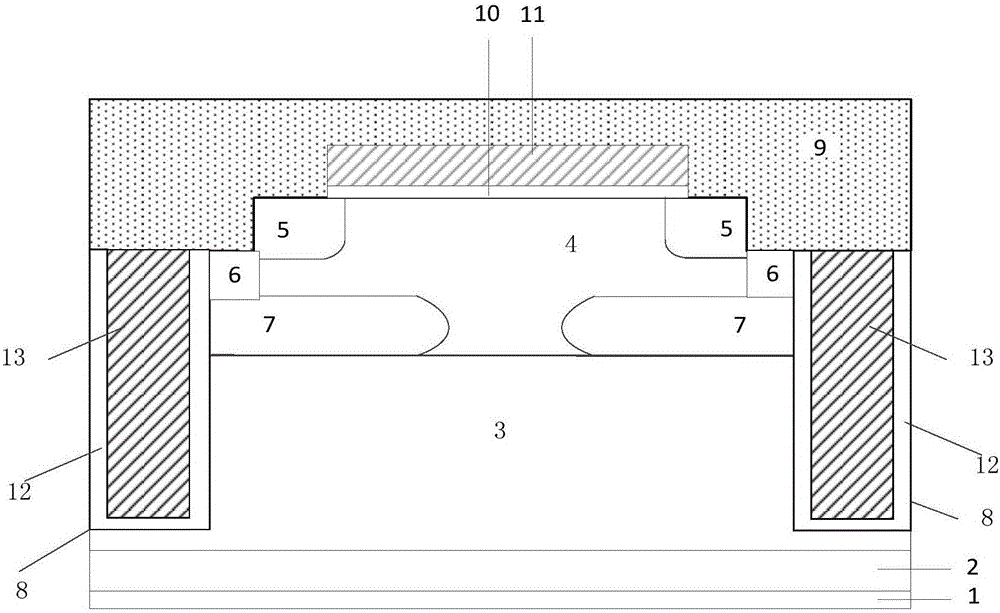

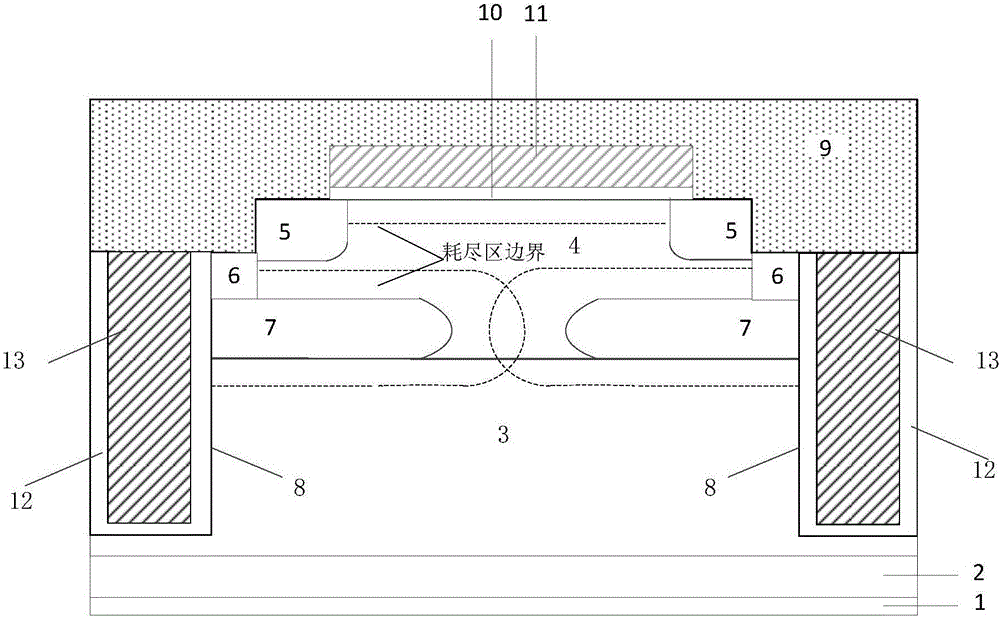

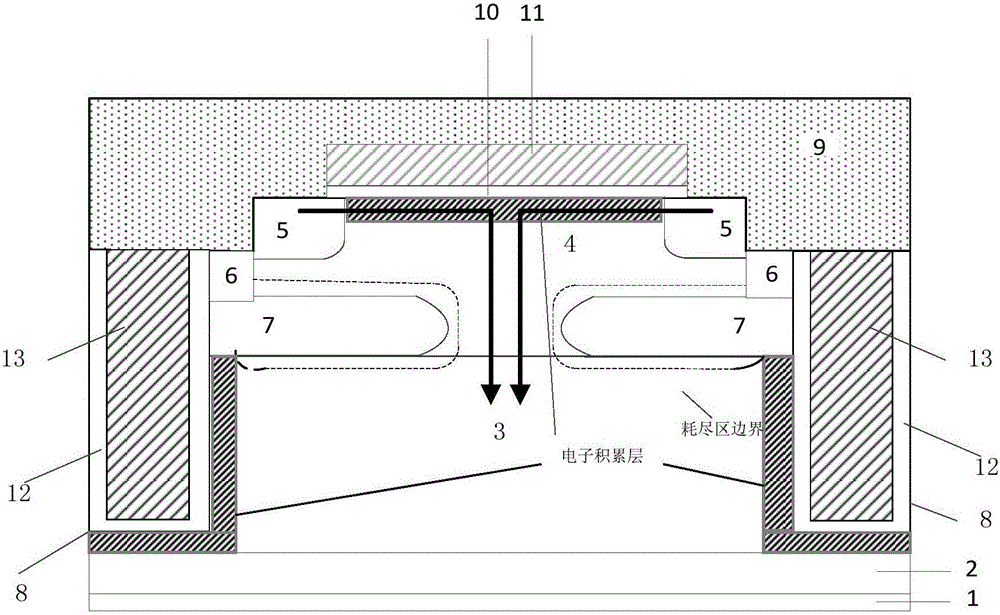

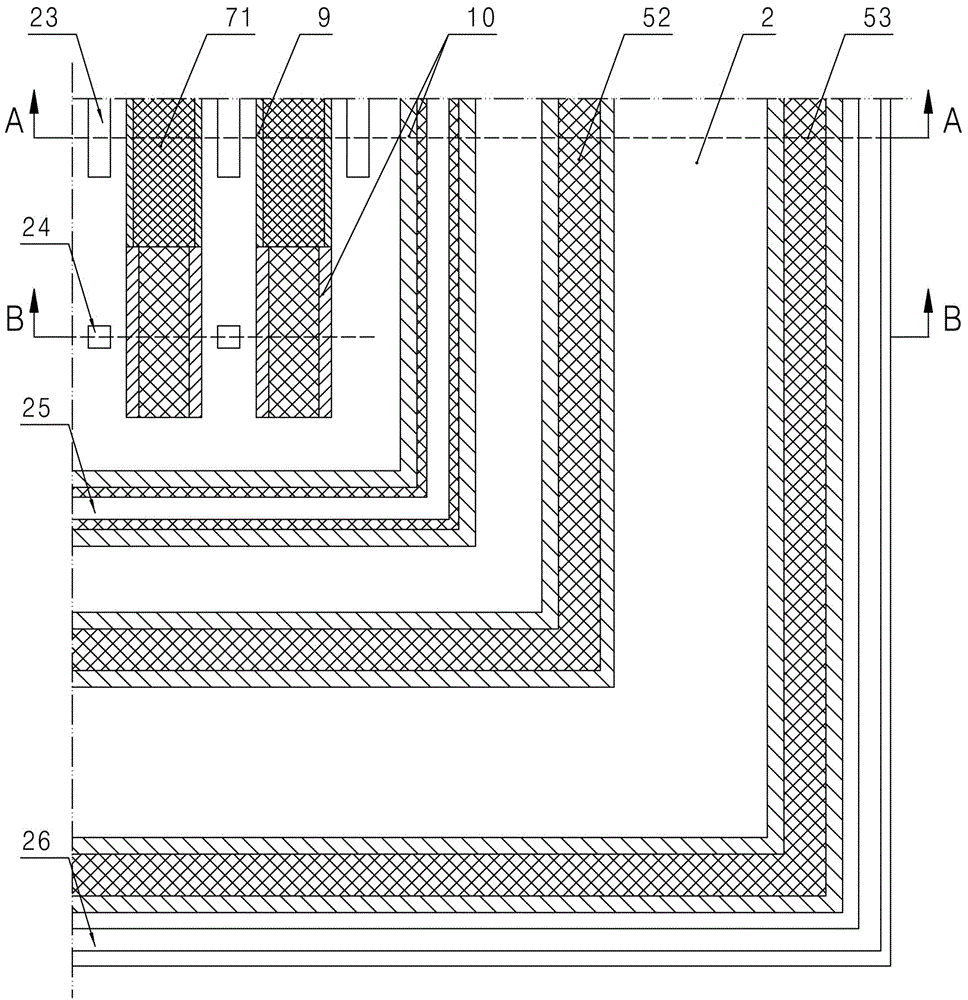

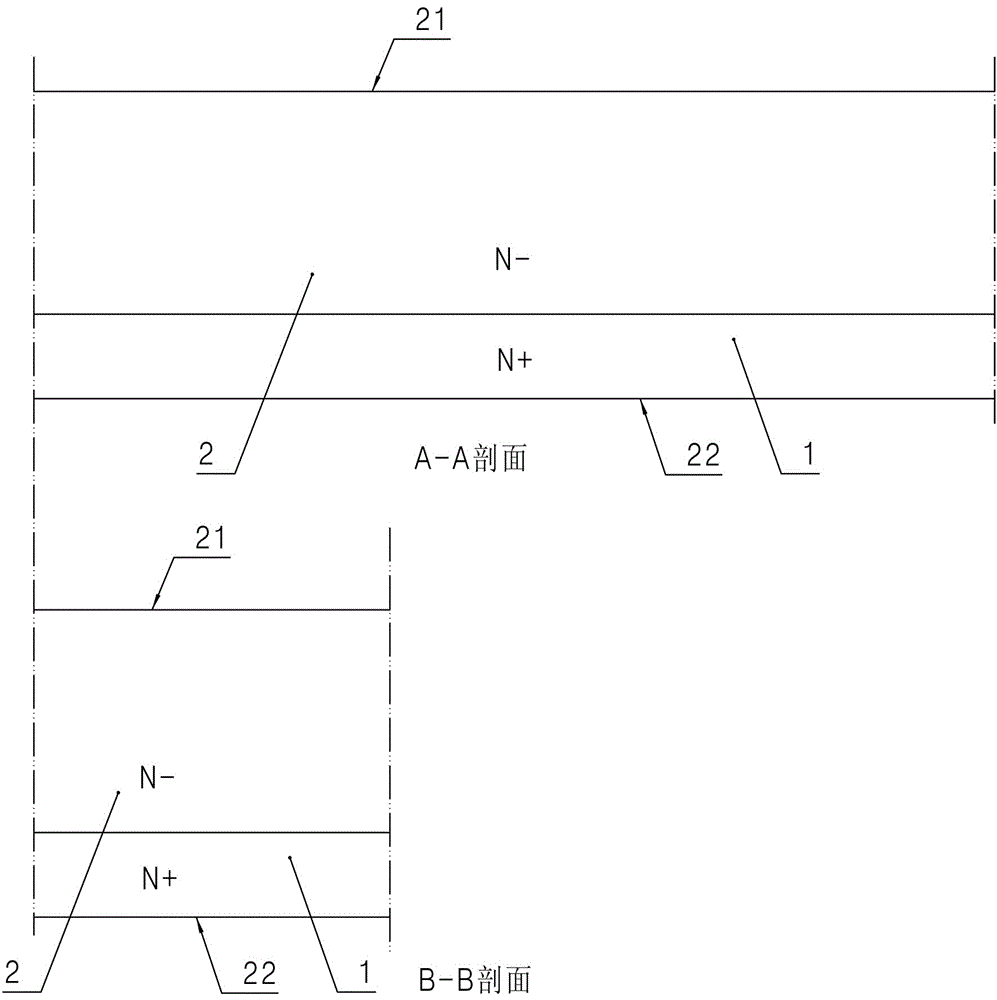

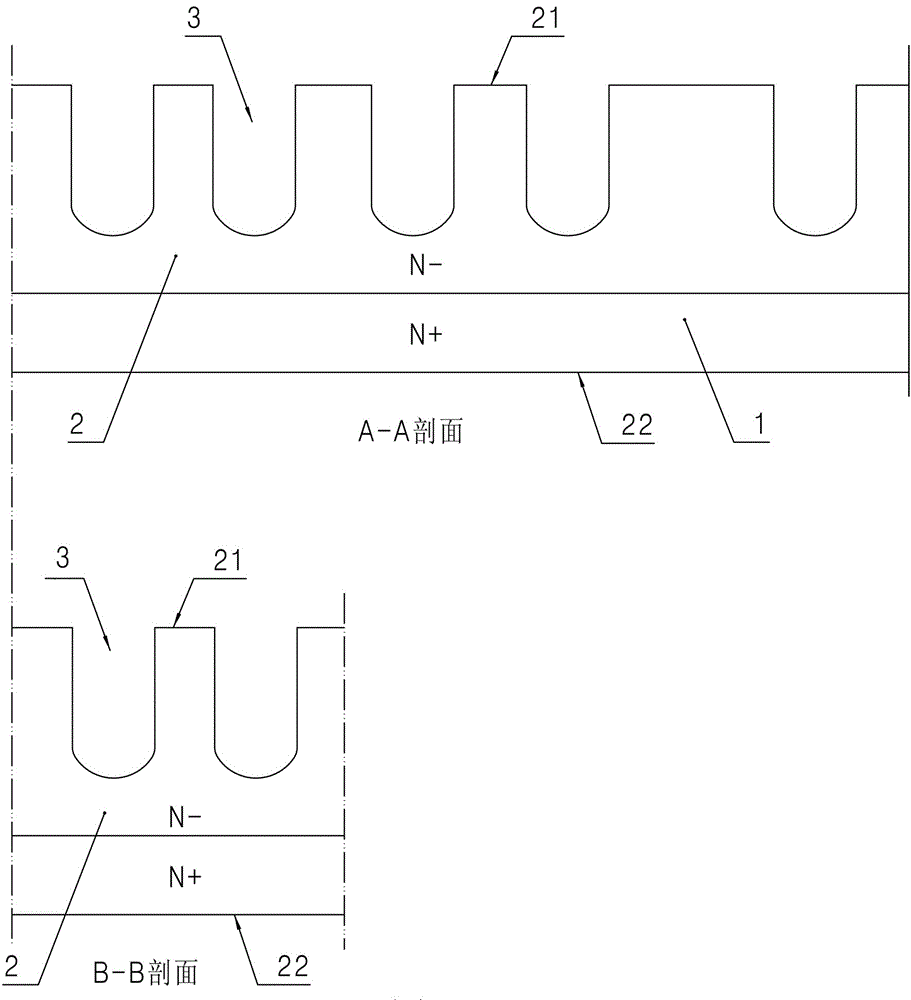

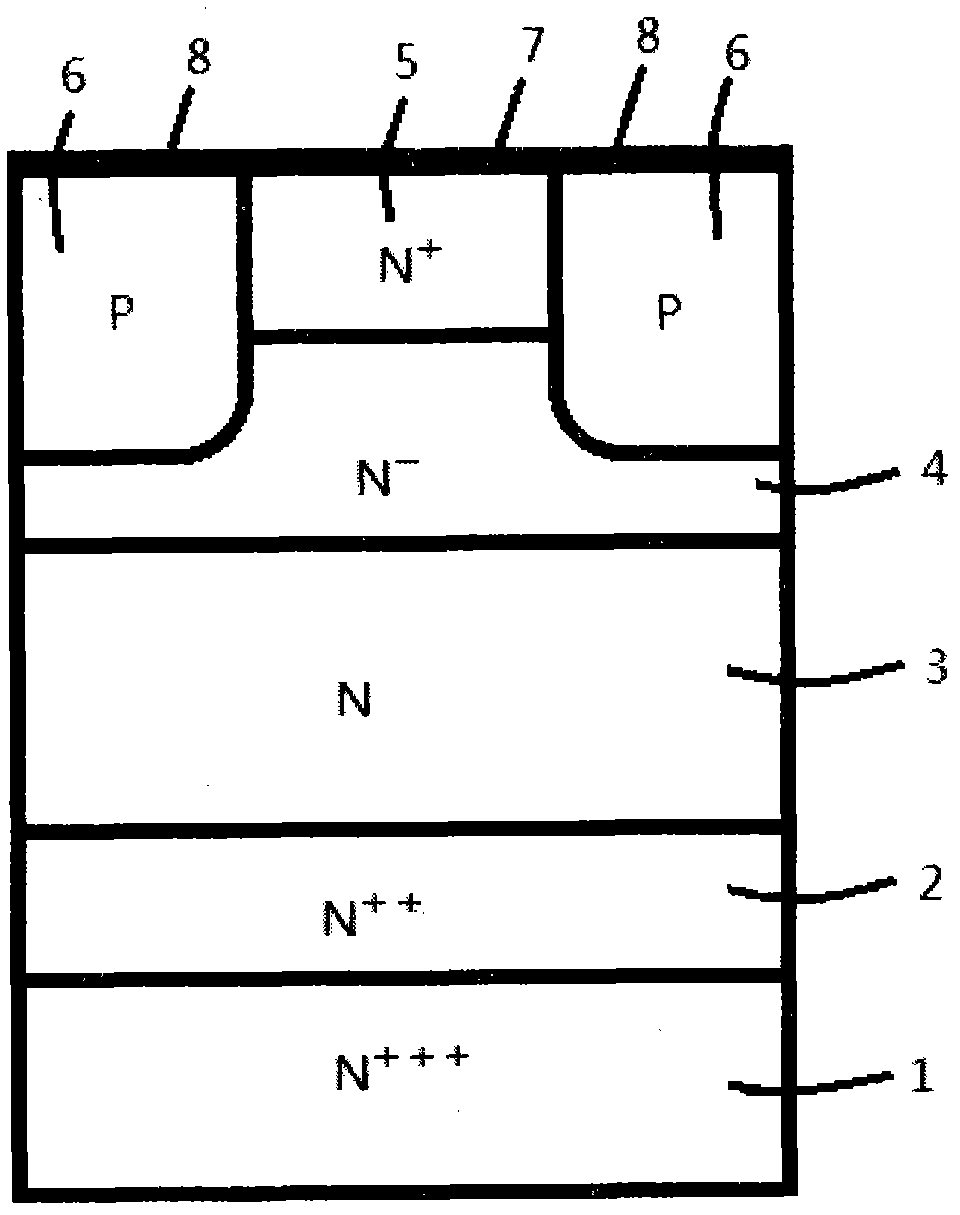

Metal oxide semiconductor diode with accumulation layer

The invention relates to semiconductor technologies, in particular to a metal oxide semiconductor diode with an accumulation layer.The metal oxide semiconductor diode has the advantages that the metal oxide semiconductor diode is provided with a surface electron accumulation layer structure and a junction field effect transistor structure and accordingly can have low start voltages; the in-vivo electron accumulation layer can be formed on an N-type semiconductor surface which is in contact with a groove 8 after the metal oxide semiconductor diode is forwardly conducted, and the metal oxide semiconductor diode is provided with an N-type region 3 with high doping concentration and accordingly can have low forward voltage drop; transverse electric fields are formed between the N-type region 3 and doped polycrystalline silicon 13 when the metal oxide semiconductor diode is reversely blocked, accordingly, exhaust lines are expanded towards the N-type region 3 in an in-vivo, electric fields of a drift region are distributed in a rectangular manner, and the reverse blocking voltages of the metal oxide semiconductor diode can be increased; the metal oxide semiconductor diode is novel in structure, is high in withstand voltage and low in conduction voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

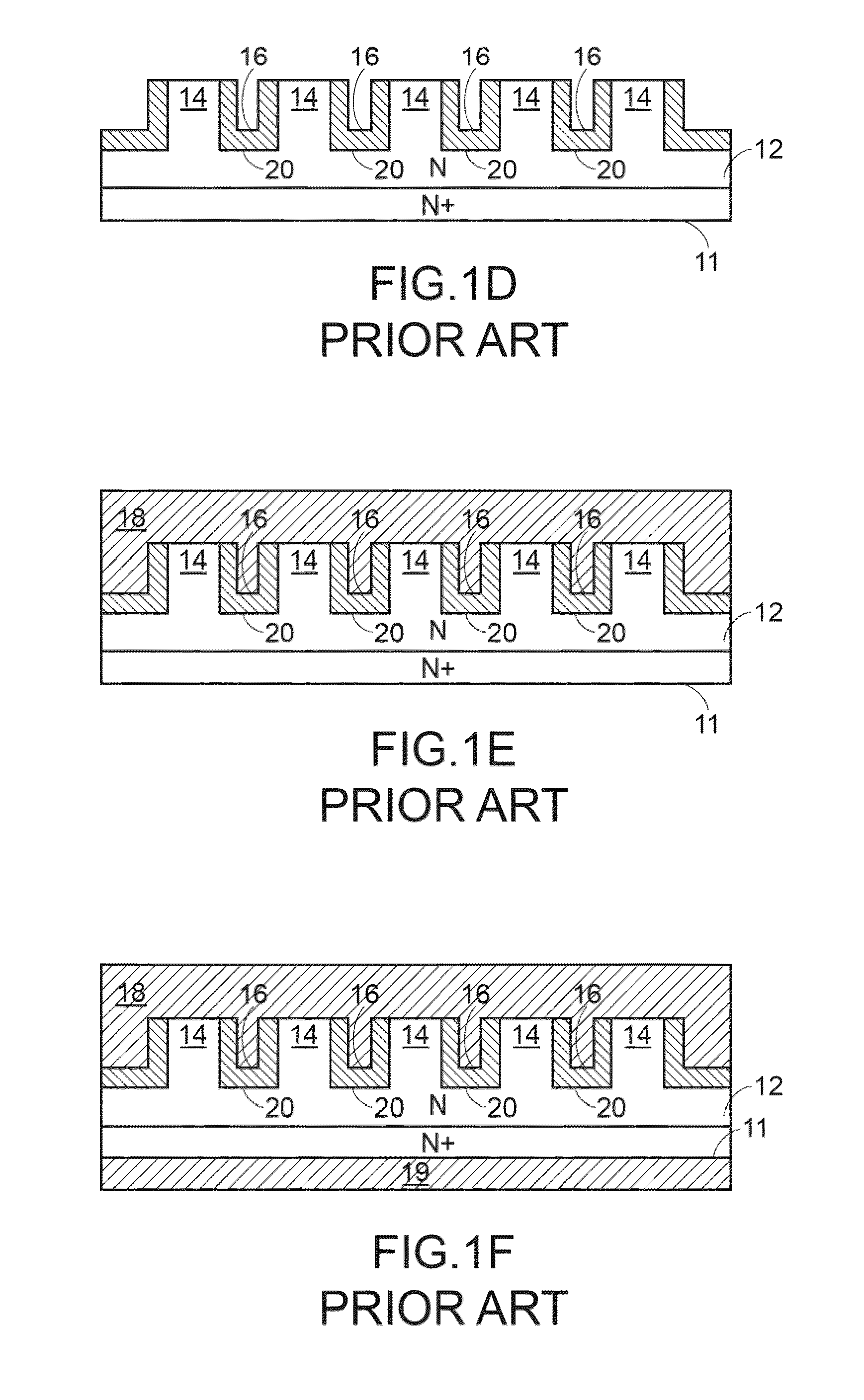

Semiconductor power device with ultralow power consumption and preparation method

InactiveCN105895671ALow costSave 3 photolithography stepsSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryEngineering

The invention discloses a semiconductor power device with ultralow power consumption, wherein the quantity of photo-etching layers is small, and reverse recovery time is short. The device comprises a semiconductor baseplate, wherein a cellular area and a terminal protection area are disposed on the semiconductor base plate; and cells are disposed in the cellular area. The structure of the cellular area comprises a cellular groove, wherein upper conductive polycrystalline silicon layers and lower conductive polycrystalline silicon layers are disposed in the cellular groove; two sides of the upper conductive polycrystalline silicon layers are symmetrically disposed at extension parts which are located on two sides of the lower conductive polycrystalline silicon layers so as to form a cap-shaped structure. At least two voltage partition rings and at least one stop ring are disposed in the terminal protection area. The conductive polycrystalline silicon layer close to a voltage partition groove of the cellular area is electrically connected to a source electrode of the device; the rest conductive polycrystalline silicon layers in the voltage partition groove are suspended; and a Schottky diode is disposed in a transition area which is located between the cellular area and the terminal protection area. The invention also discloses a method which can be used for manufacture of the semiconductor power device with the ultralow power consumption.

Owner:ZHANGJIAGANG CASS SEMICON

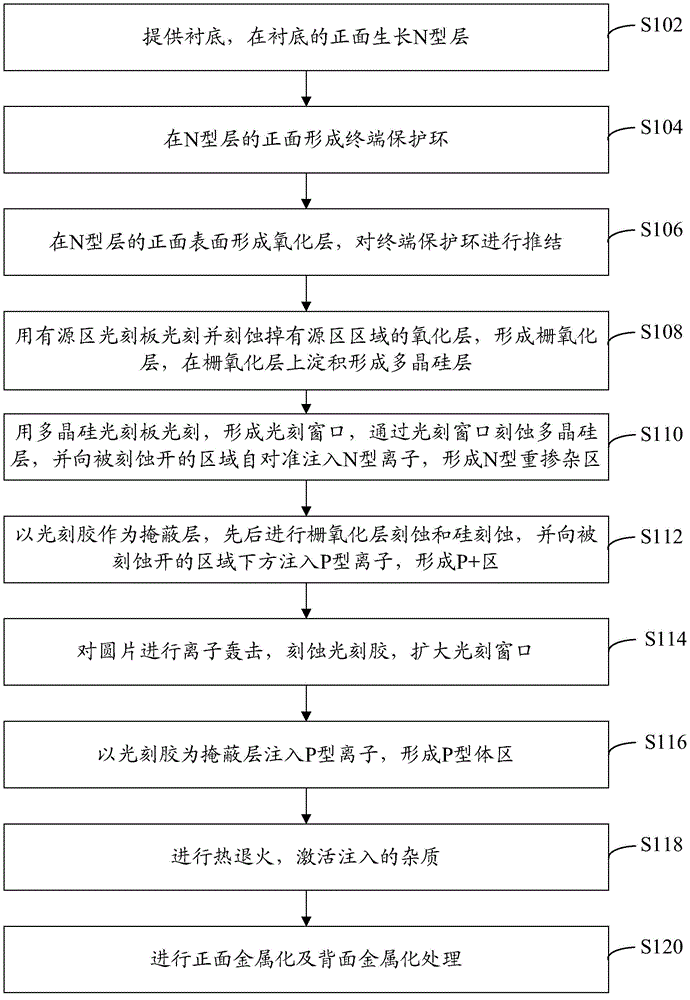

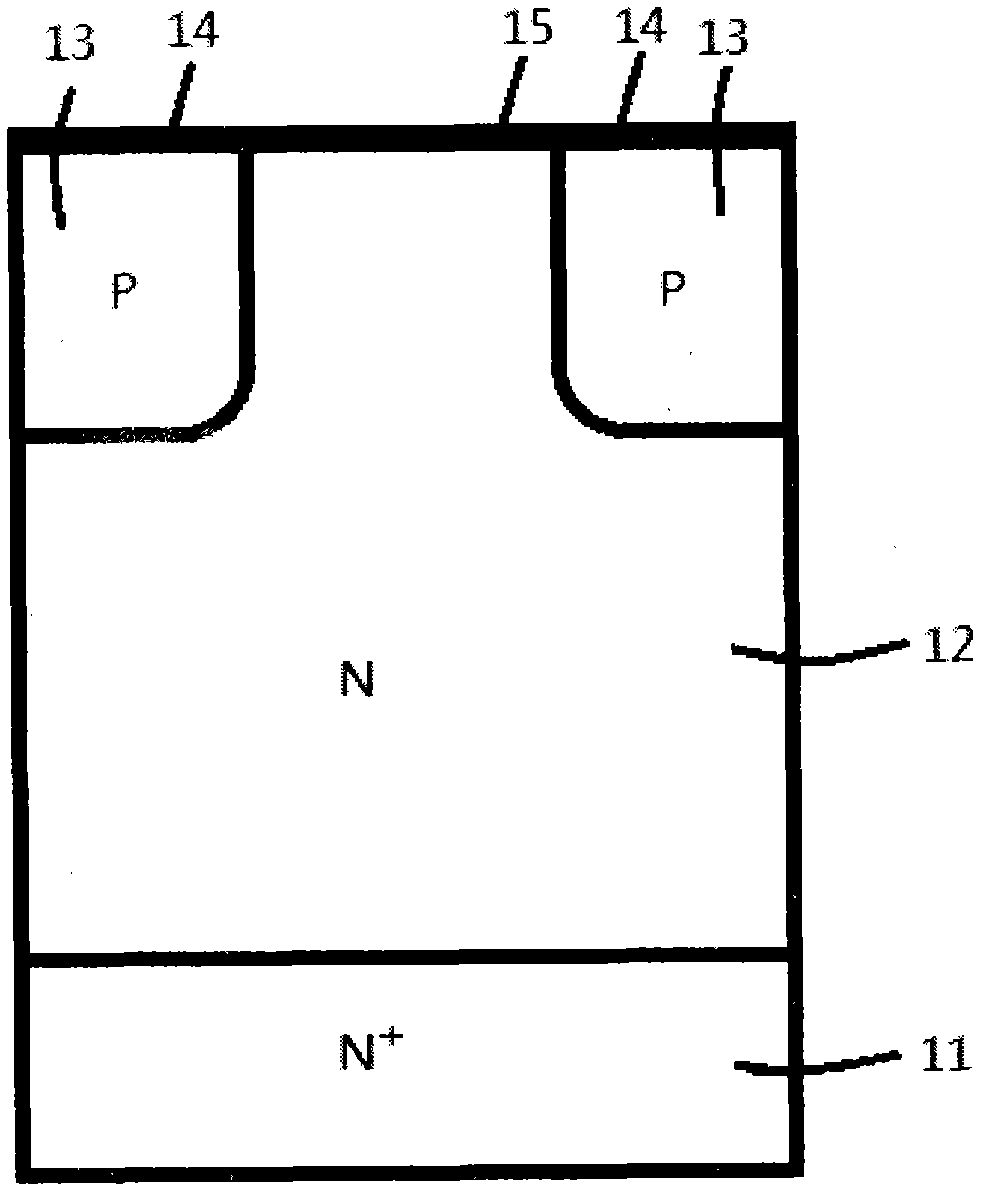

Preparation method of power diode

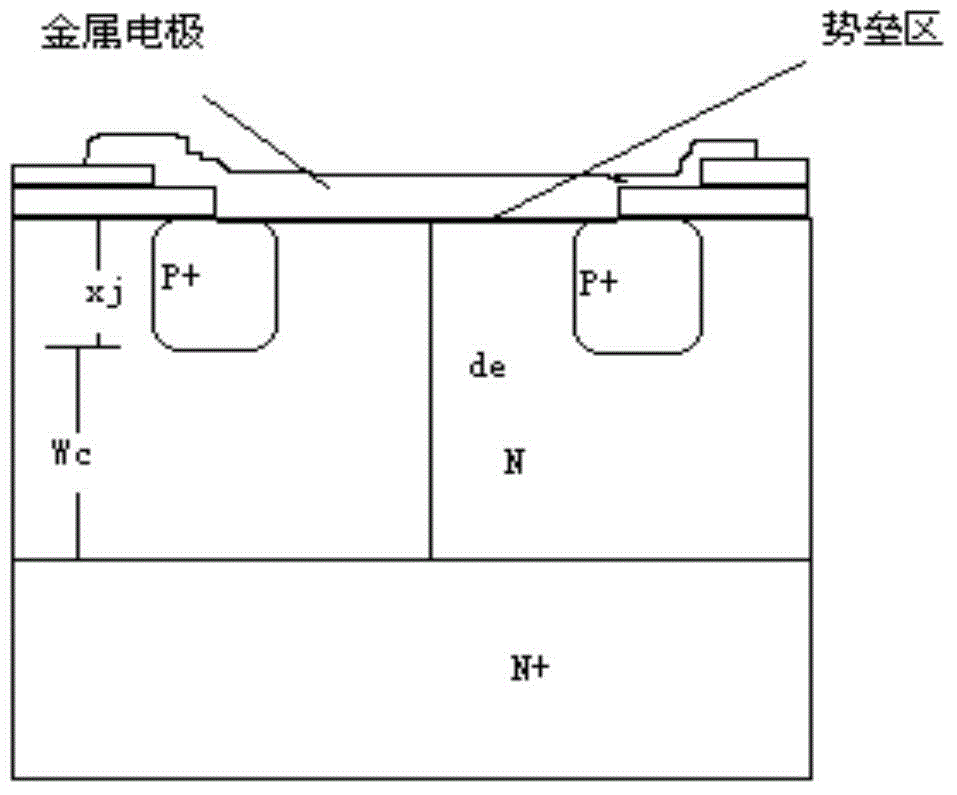

ActiveCN104576361AReduce reverse leakage currentLower forward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionIon

The invention provides a preparation method of a power diode. The preparation method comprises the following steps: providing a substrate and growing an N type layer; forming a terminal protection ring; forming an oxide layer, and performing knot guiding on the terminal protection ring; forming a gate oxide layer, and depositing a polycrystalline silicon layer on the gate oxide layer; forming an N type heavily doped region; forming a P+ region; performing ion bombardment on a wafer, etching photoresist, and enlarging the photo-etched window; forming a P type body region; performing thermal annealing to activate the injected impurities; performing front metallization and back metallization. According to the preparation method of the power diode, the photo-etched window is enlarged by the ion bombardment to the photoresist which is used as a masking layer when being injected to form the P type body region; the ion bombardment time can be adjusted to control the feature size of the polycrystalline silicon photoresist, so as to adjust the length of the P type body region, namely the length of an MOS channel, and optimize the relation between the reverse leakage current and the forward voltage drop of the device.

Owner:CSMC TECH FAB2 CO LTD

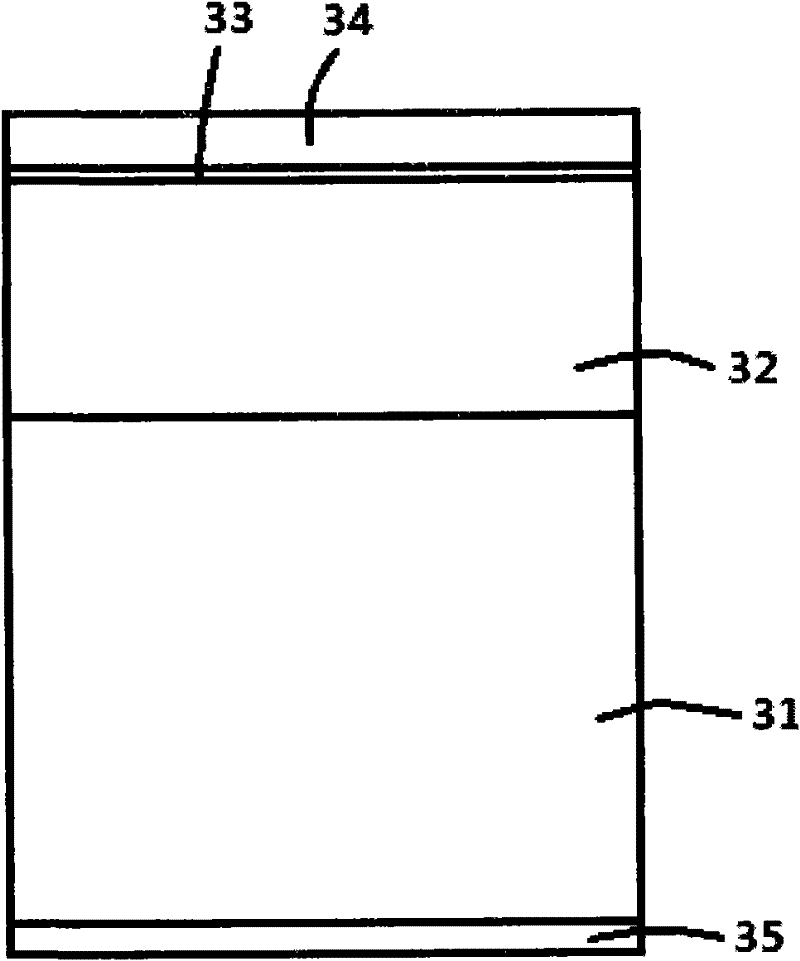

Junction barrier schottky having low forward voltage drop

InactiveCN102376777AElectrical parameter characteristic optimizationLower forward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierSemiconductor materials

The invention discloses a novel junction barrier schottky device which comprises a substrate layer, a buffering layer, a drifting layer, a light doping layer, a plurality of restraining areas, a heavy doping layer and a schottky barrier layer, wherein the restraining areas which are separated from each other are located in the light doping layer and the heavy doping layer. When a reverse bias is applied to a semiconductor device, a large-area exhausting region is spread and formed in a semiconductor material of the light doping layer. The invention also provides a manufacturing method for the semiconductor device. The semiconductor device provided by the invention has a low forward voltage drop and a high device-switching speed. Electrical parameter characteristics of the semiconductor device are further optimized.

Owner:上海芯石微电子有限公司

Schottky diode and manufacturing method thereof

InactiveCN102456748AElectrical parameter characteristic optimizationLower forward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierEngineering

The invention discloses a novel schottky diode device. The device comprises a substrate layer, a gradual doping buffer layer, a drifting layer and a schottky barrier layer. The invention also provides a manufacturing method of a schottky diode. A semiconductor device provided by the invention has low forward voltage drop, and the electrical parameter characteristic of the device is further optimized.

Owner:上海芯石微电子有限公司

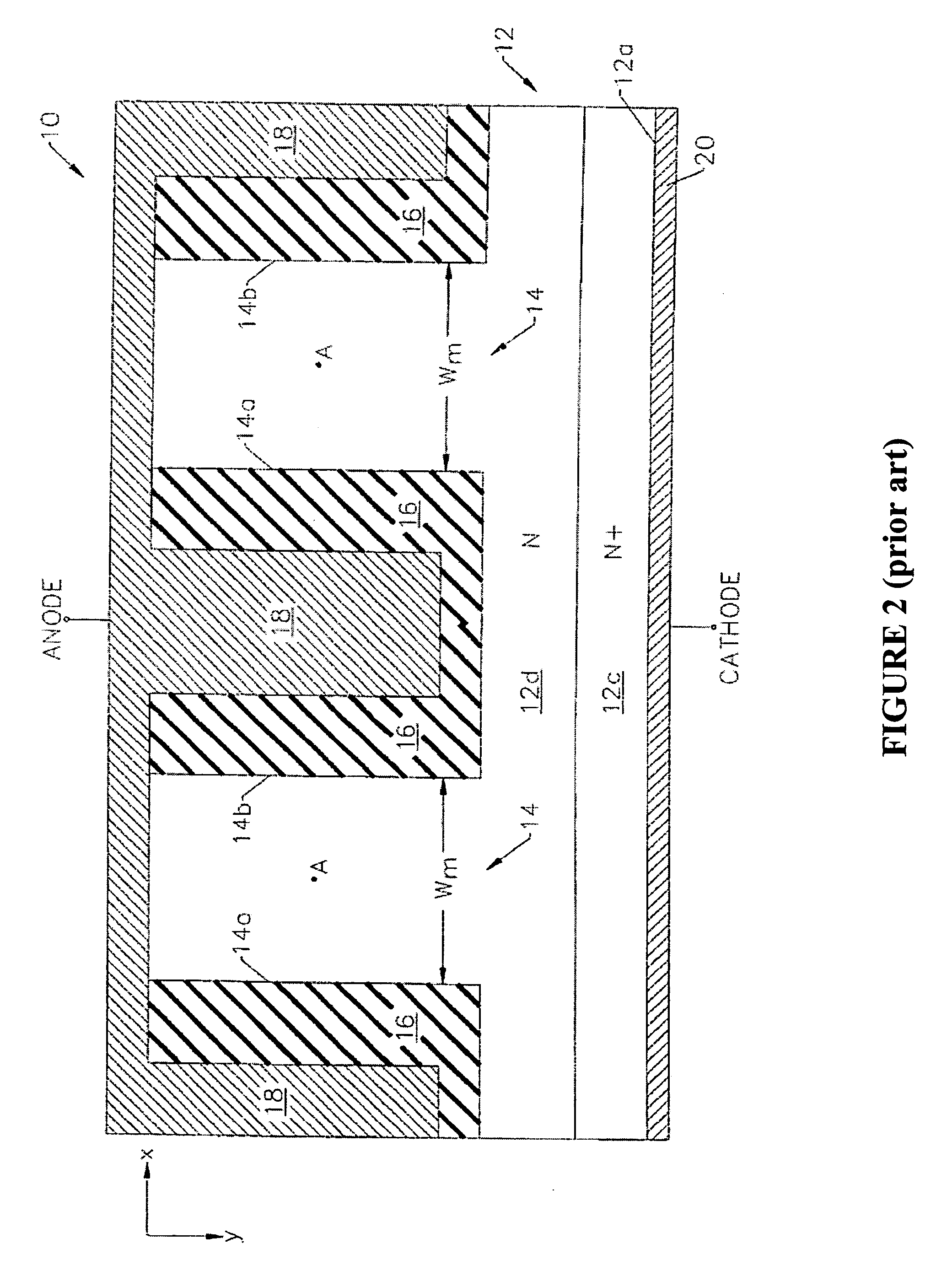

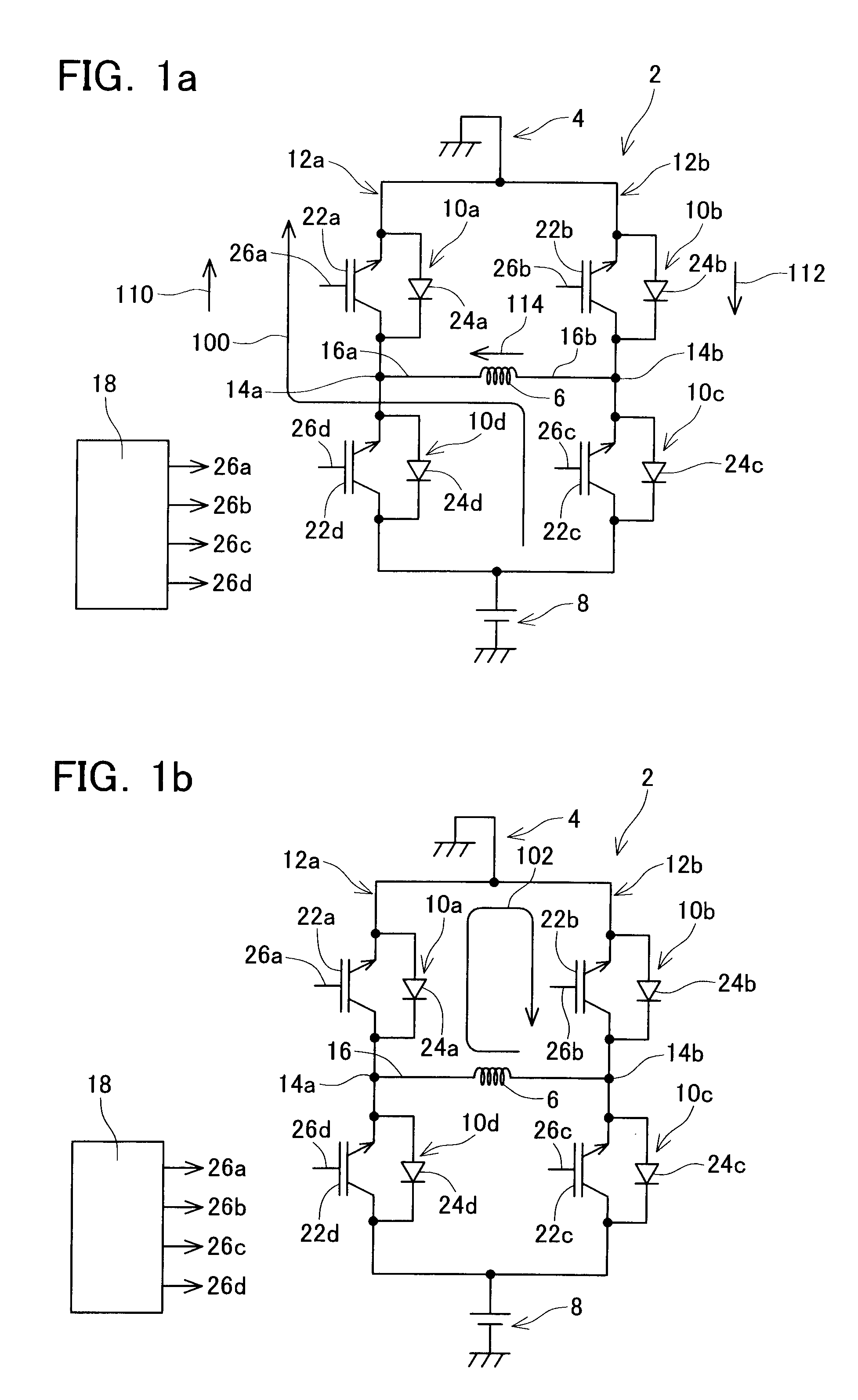

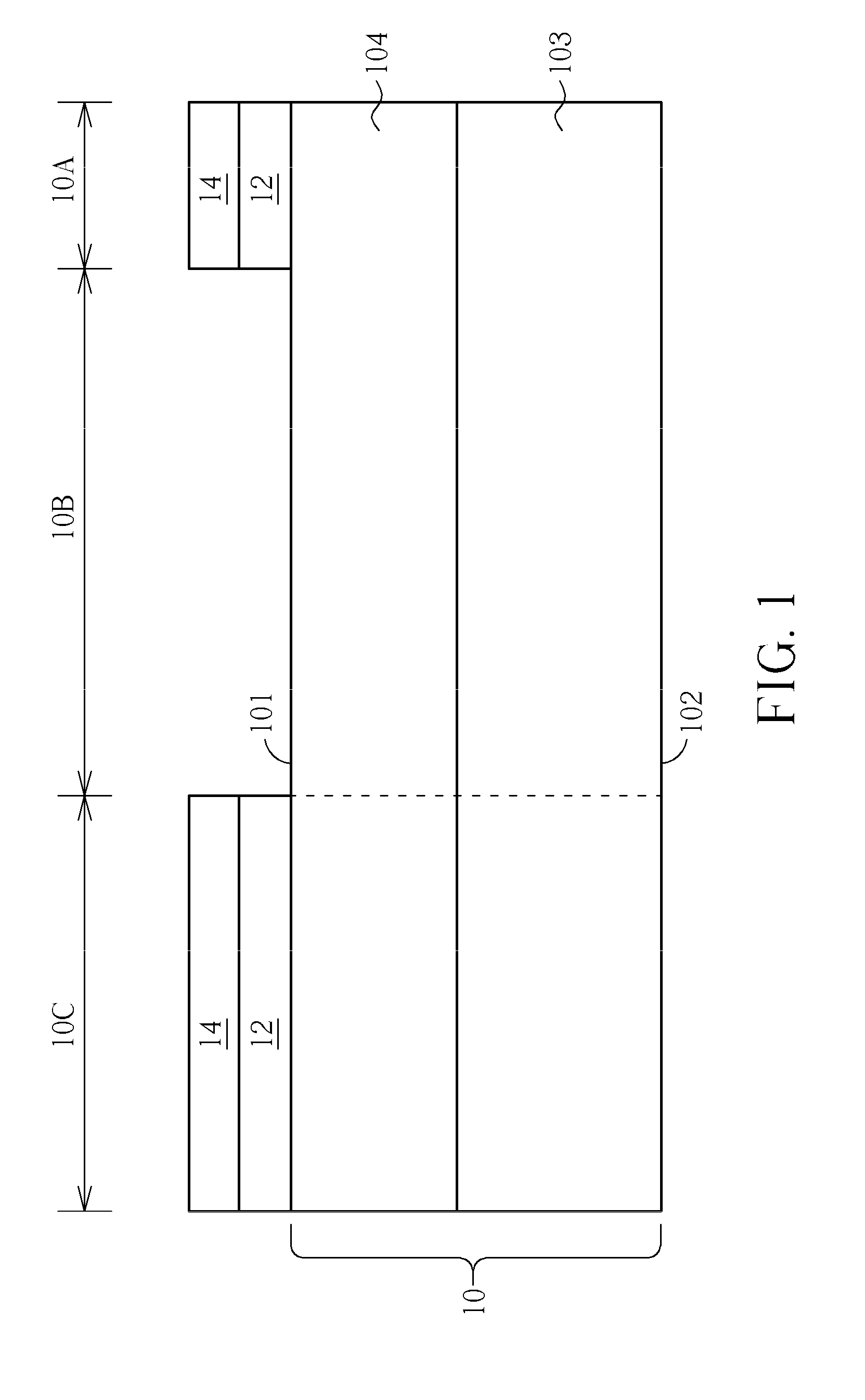

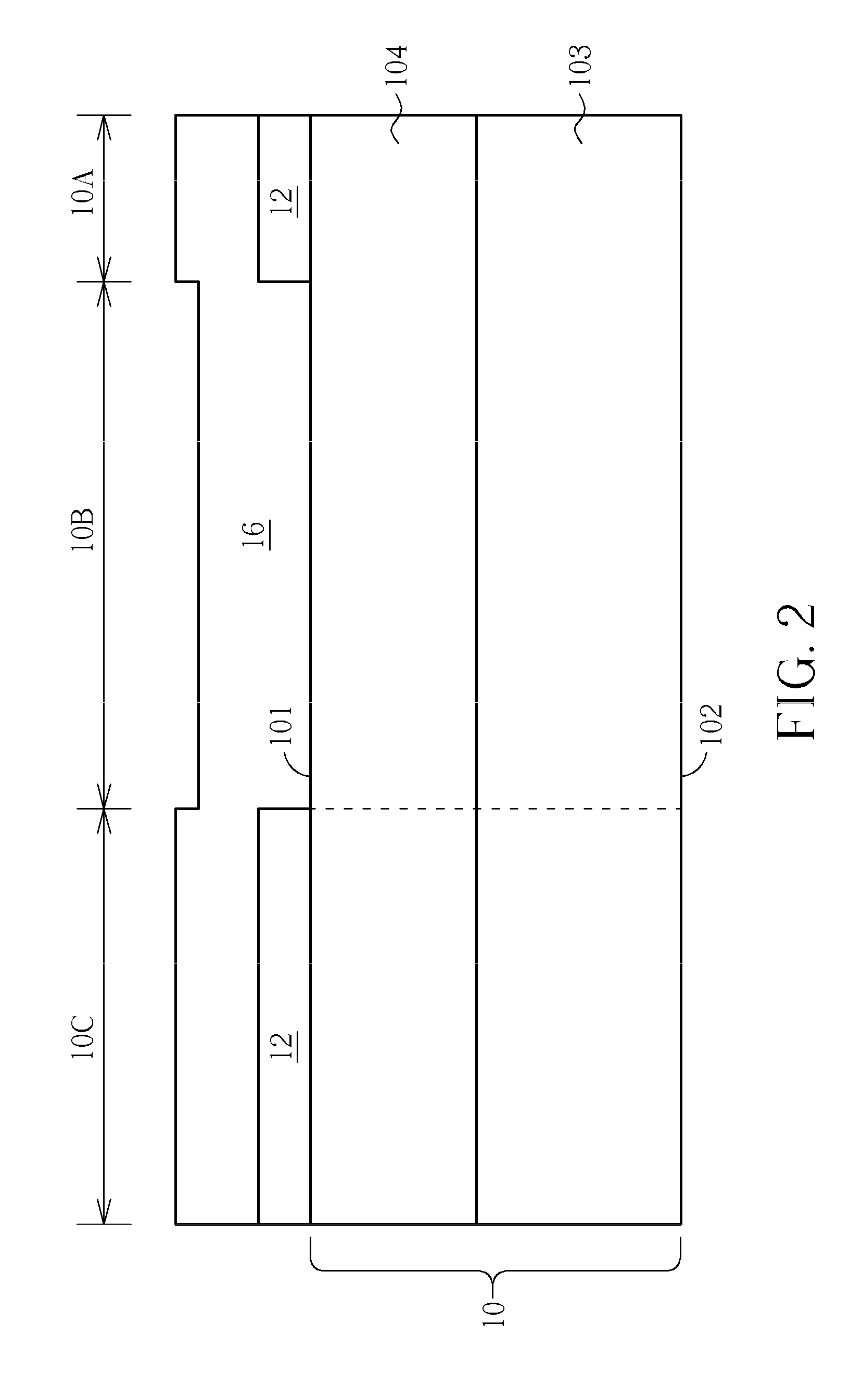

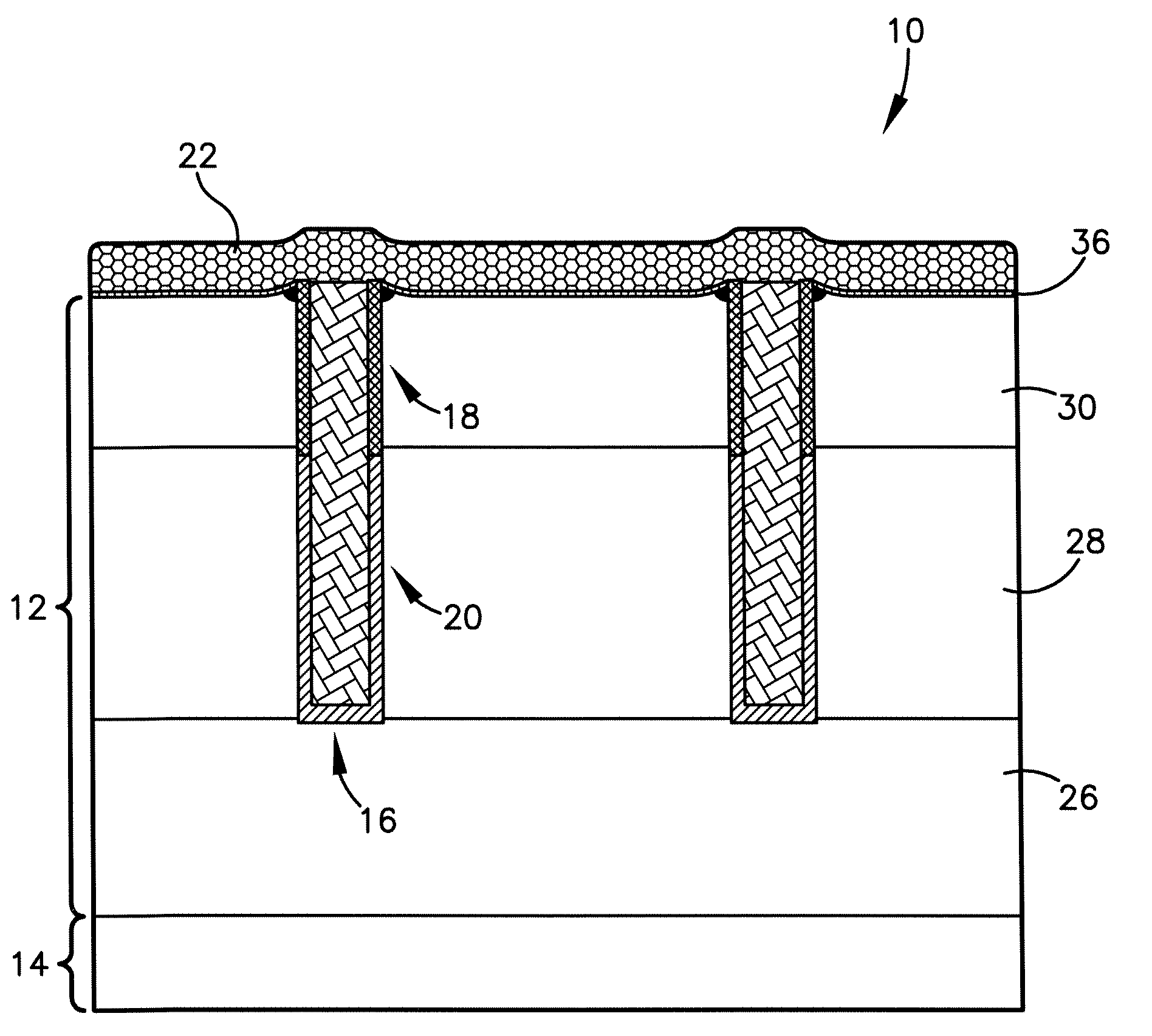

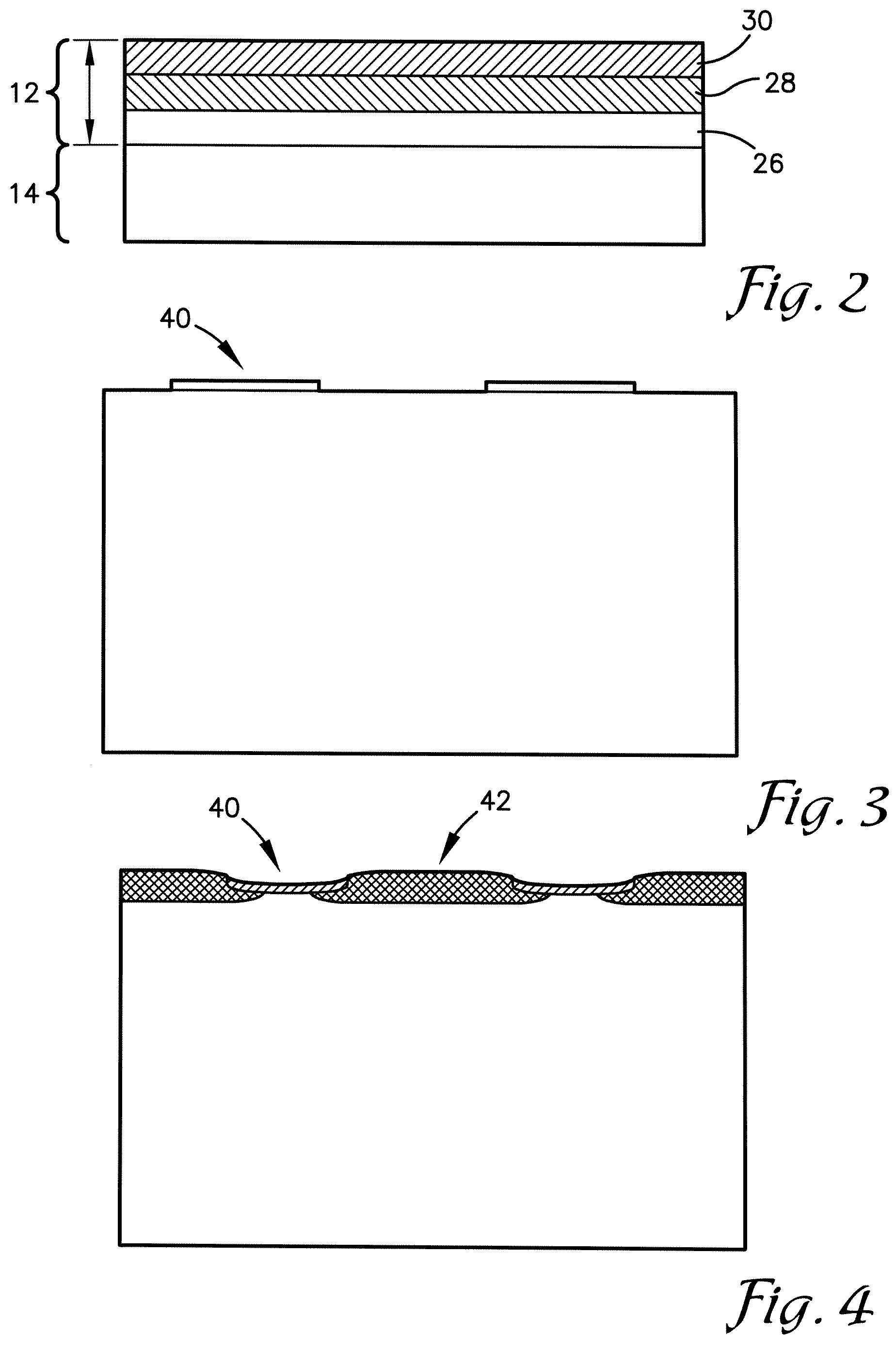

High-efficiency Schottky rectifier and method of manufacturing same

ActiveUS7709864B2Fast switching speedLower forward voltage dropTransistorSemiconductor/solid-state device manufacturingSchottky barrierPower circuits

A rectifier device (10) comprising a multi-layer epitaxial film (12) and a rectifier and a transistor manufactured in the film (12), wherein the transistor is oriented vertically relative to the plane of the rectifier. The rectifier and transistor are separated by a transition zone of inverted bias. The rectifier is a Schottky barrier rectifier, and the transistor is a JFET. More specifically, the device (1) comprises the film (12), a trench (16), a first region (18) associated with an upper portion of the trench (16), and second region (20) associated with a lower portion. The interface between the p+ material of the second region (20) and the n material of the film (12) creates a p+ / n junction. The device (10) has use in high frequency, low-loss power circuit applications in which high switching speed and low forward voltage drop are desirable.

Owner:DIODES INC