Patents

Literature

657results about How to "Reduce voltage drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

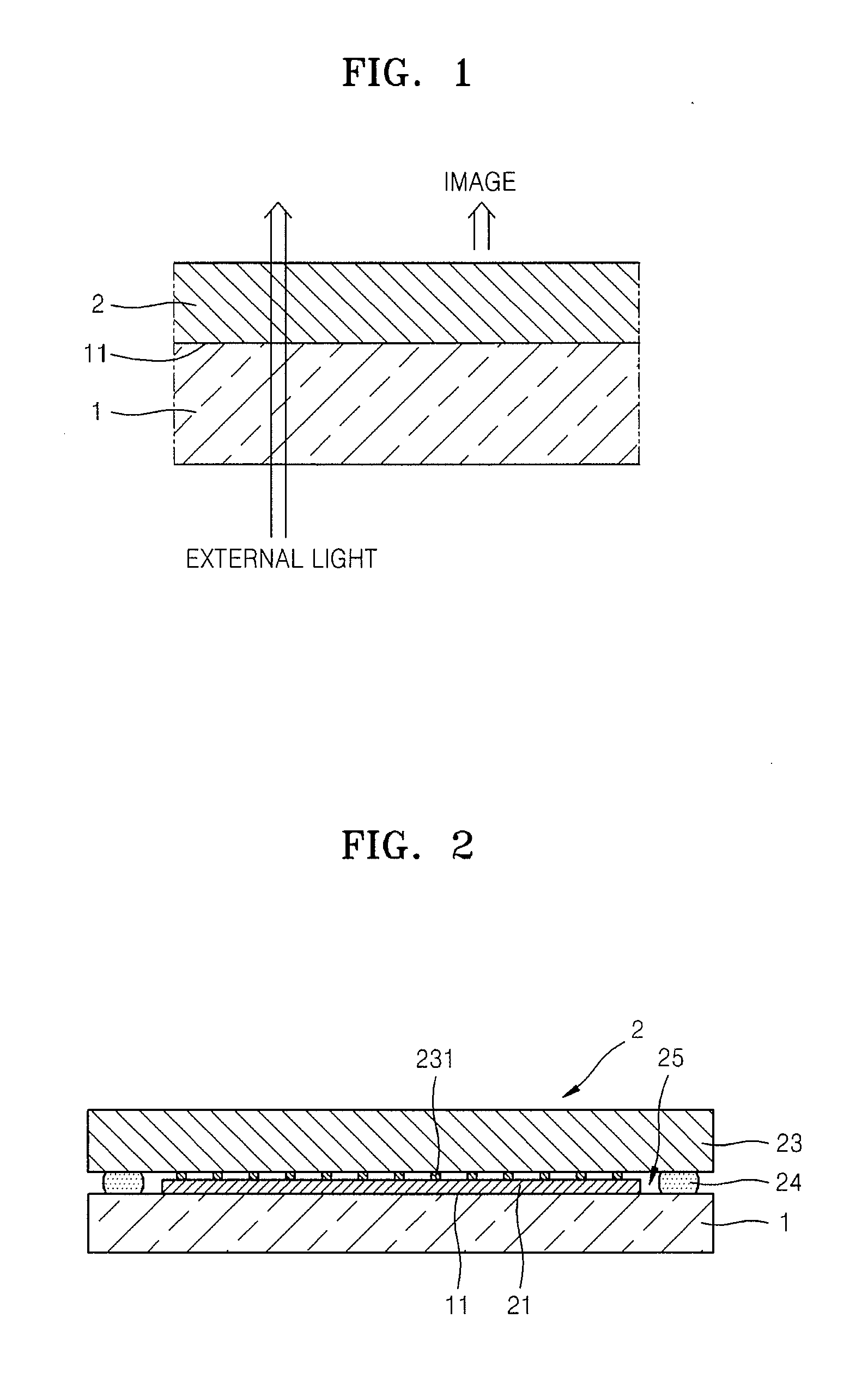

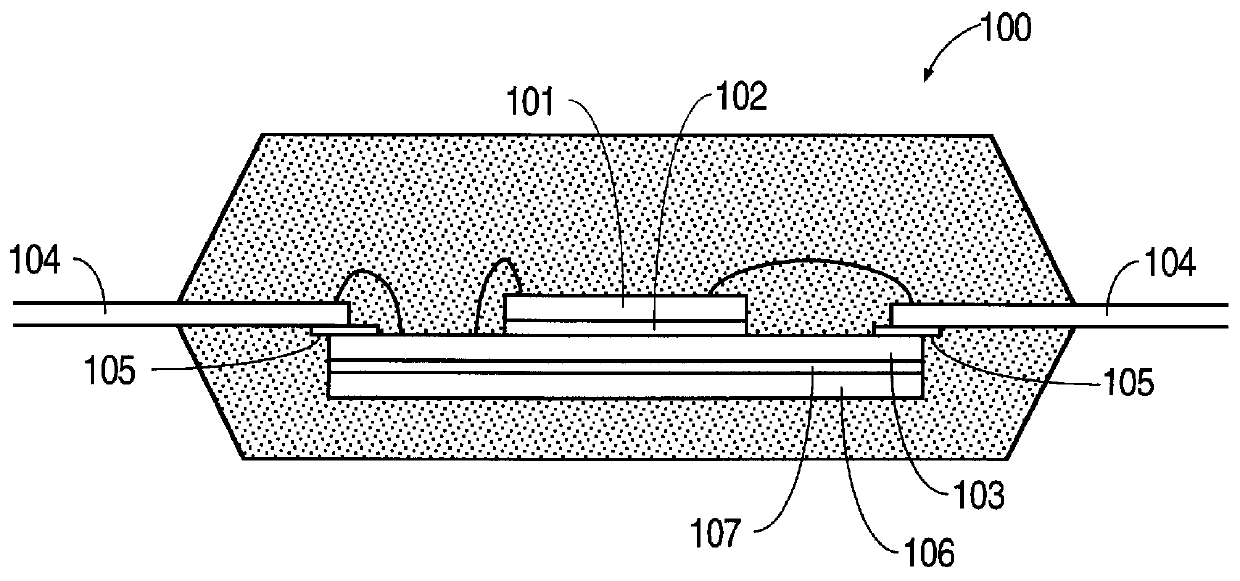

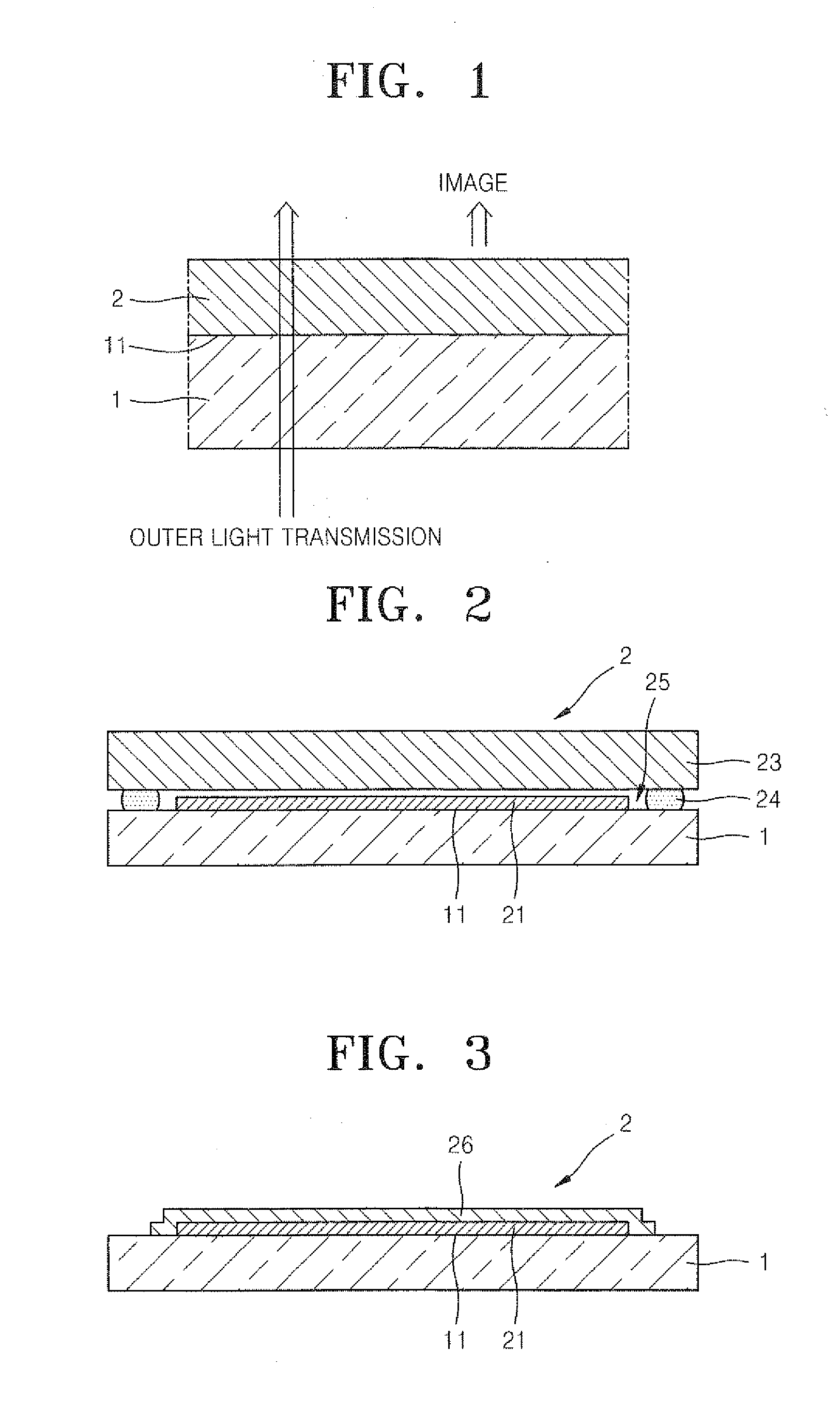

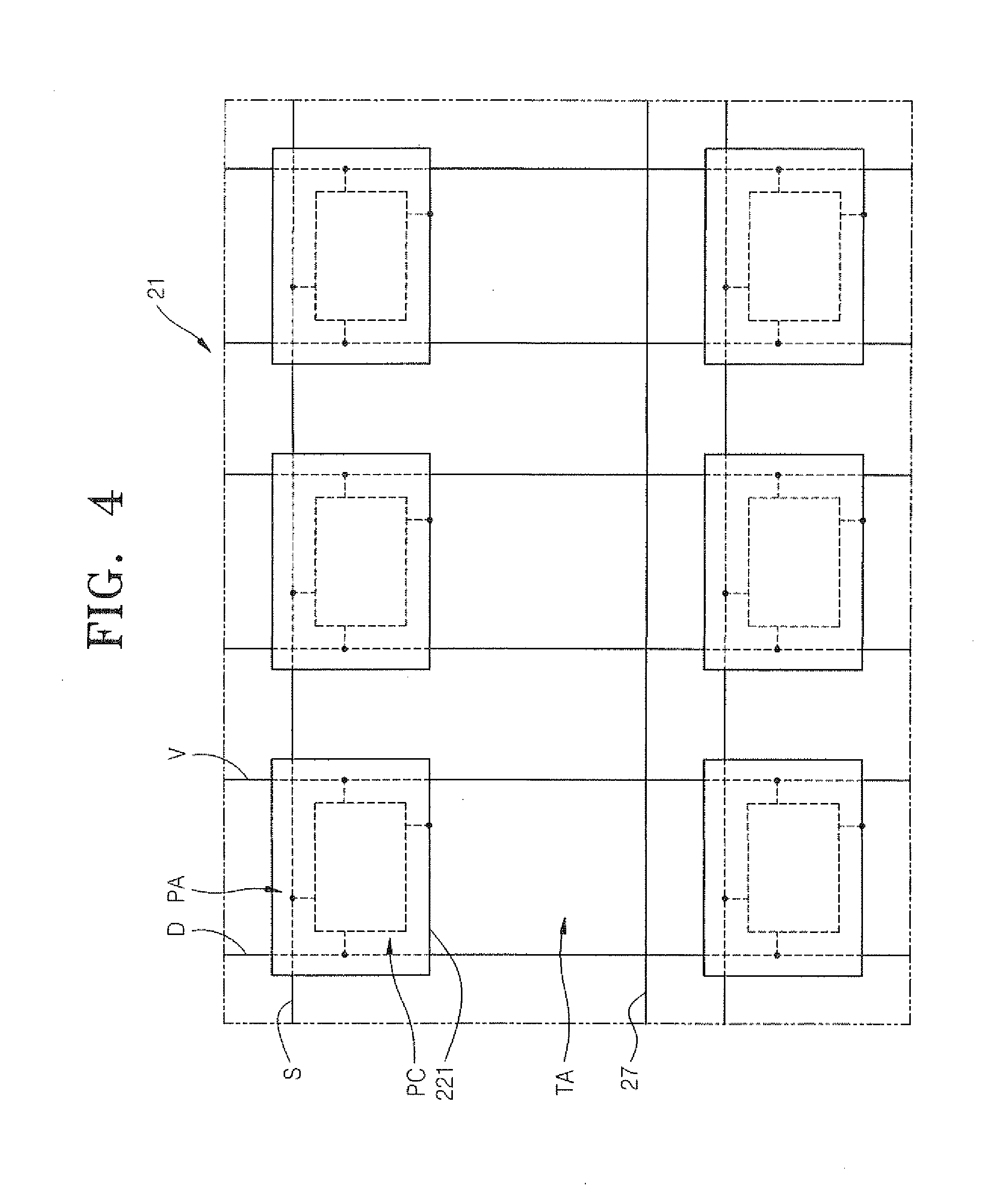

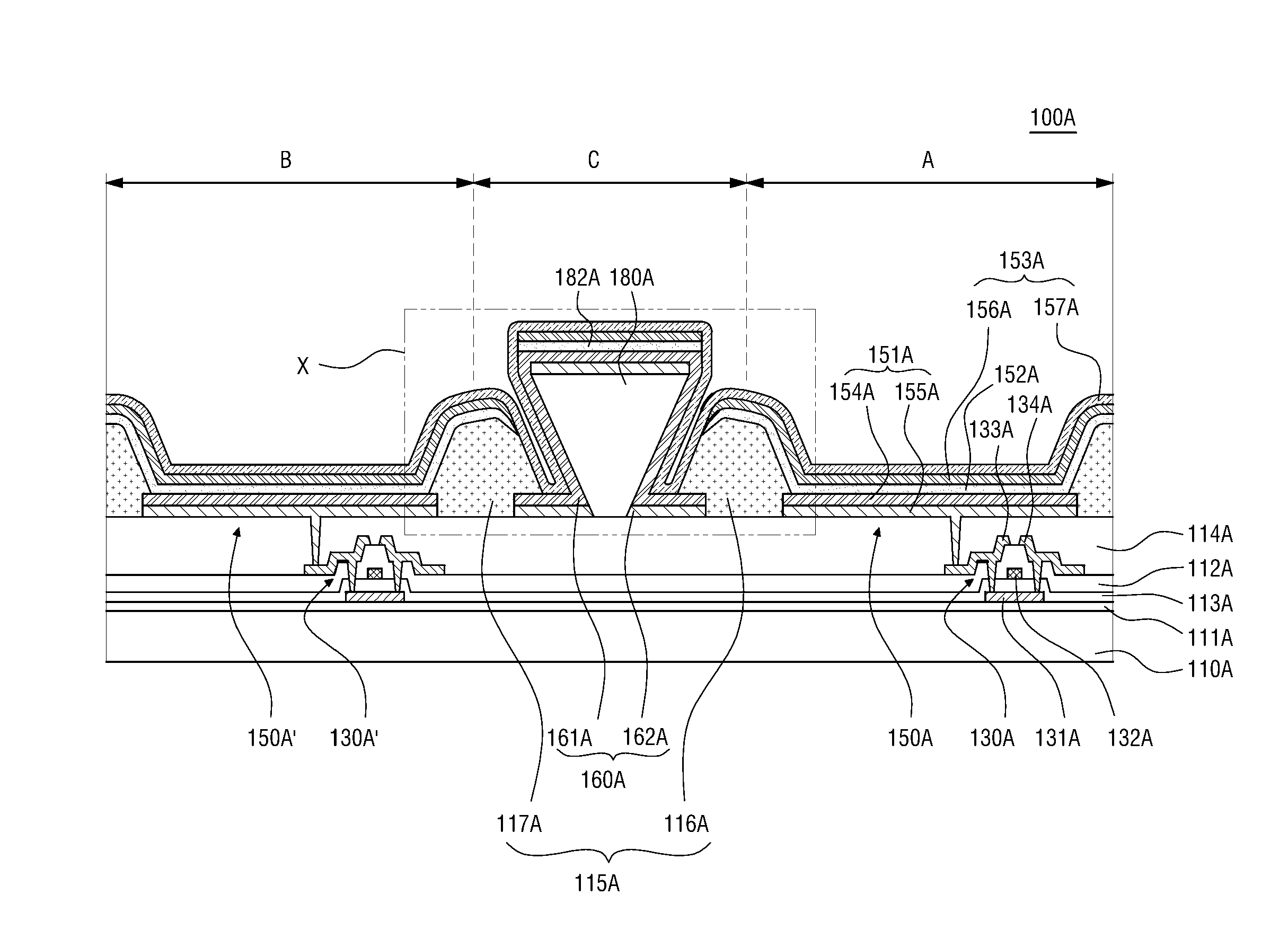

Organic light-emitting display device

ActiveUS20120001184A1Prevents and reduces distortion of imagePreventing and reducing light transmittingSolid-state devicesSemiconductor/solid-state device manufacturingTransmittanceDisplay device

A transparent organic light-emitting display device has an improved transmittance and a reduced voltage drop in an opposite electrode. The organic light-emitting display device includes: a first substrate having a transmitting region and a plurality of pixel regions separated from each other by the transmitting region interposed between the pixel regions; a plurality of pixel electrodes being located at the pixel regions, respectively; an opposite electrode facing the pixel electrodes and being at the transmitting region and the pixel regions; a second substrate facing the opposite electrode and being bonded to the first substrate; a first conductive unit being between the second substrate and the opposite electrode, opposite ends of the first conductive unit contacting the second substrate and the opposite electrode, respectively; and a second conductive unit facing the first conductive unit and contacting the opposite electrode that is between the first conductive unit and the second conductive unit.

Owner:SAMSUNG DISPLAY CO LTD

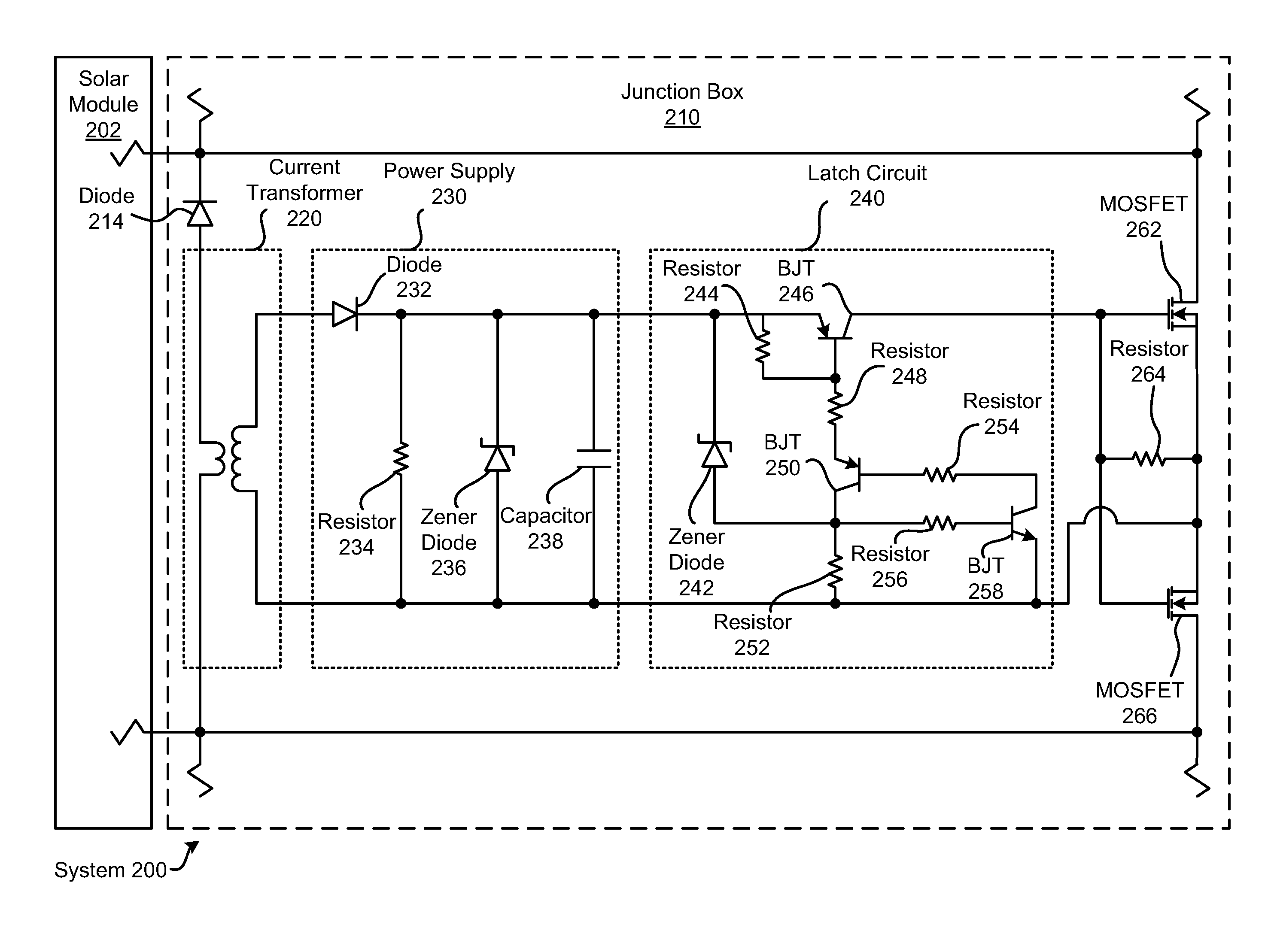

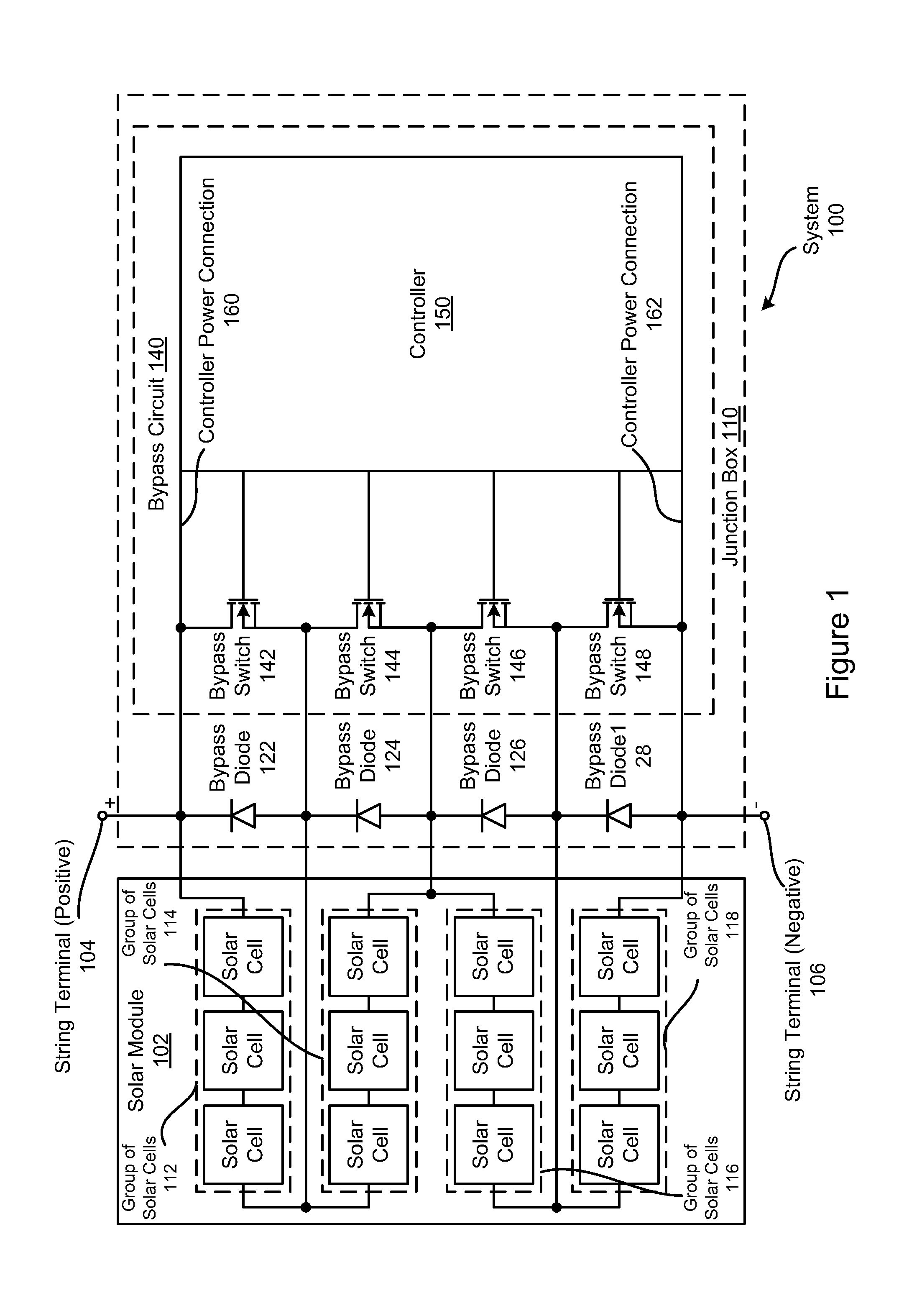

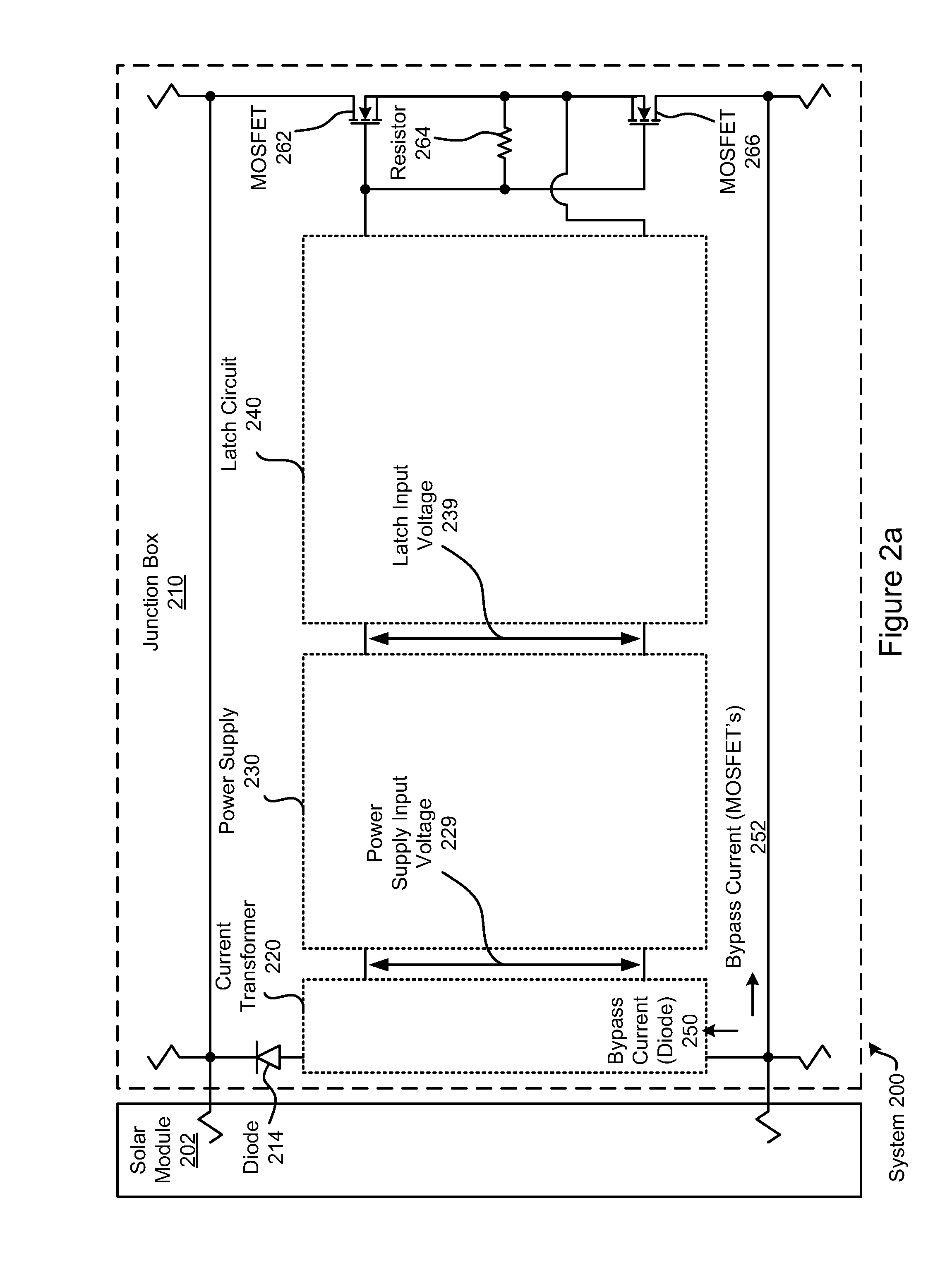

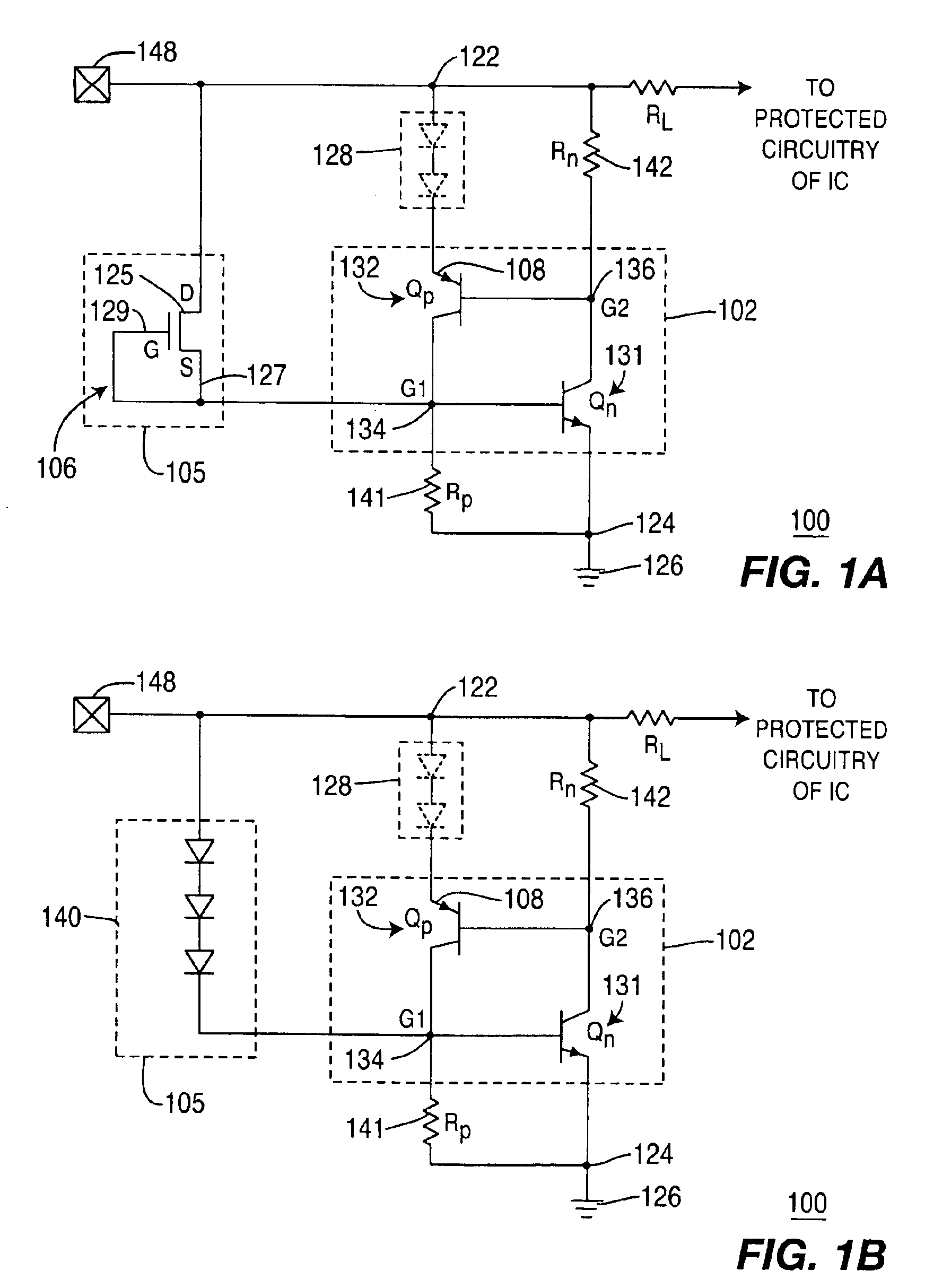

Systems and Methods to Provide Enhanced Diode Bypass Paths

ActiveUS20120199172A1Effectively allowReduce voltage dropBatteries circuit arrangementsPV power plantsMOSFETEngineering

Systems and methods are herein disclosed for efficiently allowing current to bypass a group of solar cells having one or more malfunctioning or shaded solar cells without overwhelming a bypass diode. This can be done using a switch (e.g., a MOSFET) connected in parallel with the bypass diode. By turning the switch on and off, a majority of the bypass current can be routed through the switch, which is configured to handle larger currents than the bypass diode is designed for, leaving only a minority of the current to pass through the bypass diode.

Owner:NEWLIGHT CAPITAL LLC

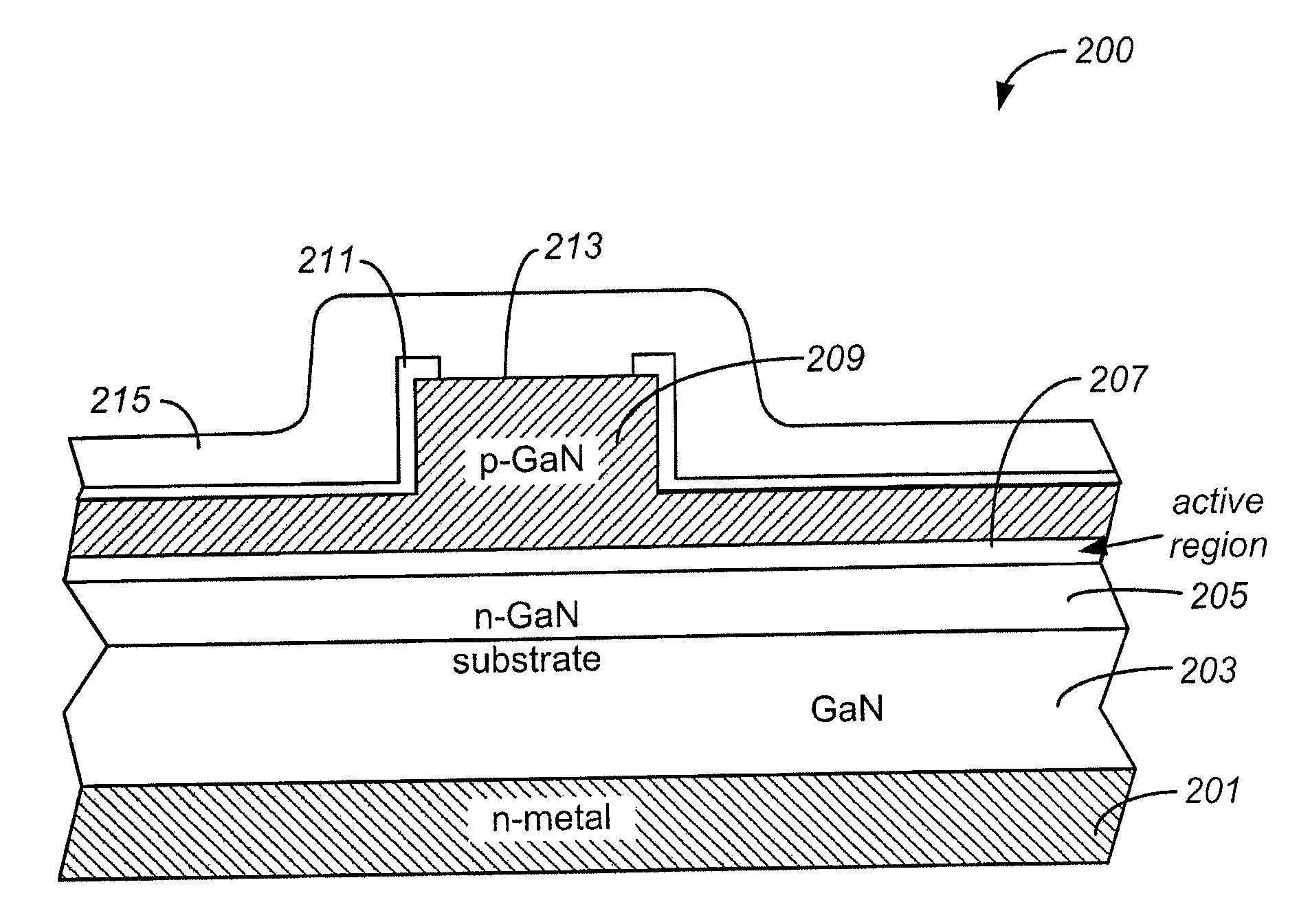

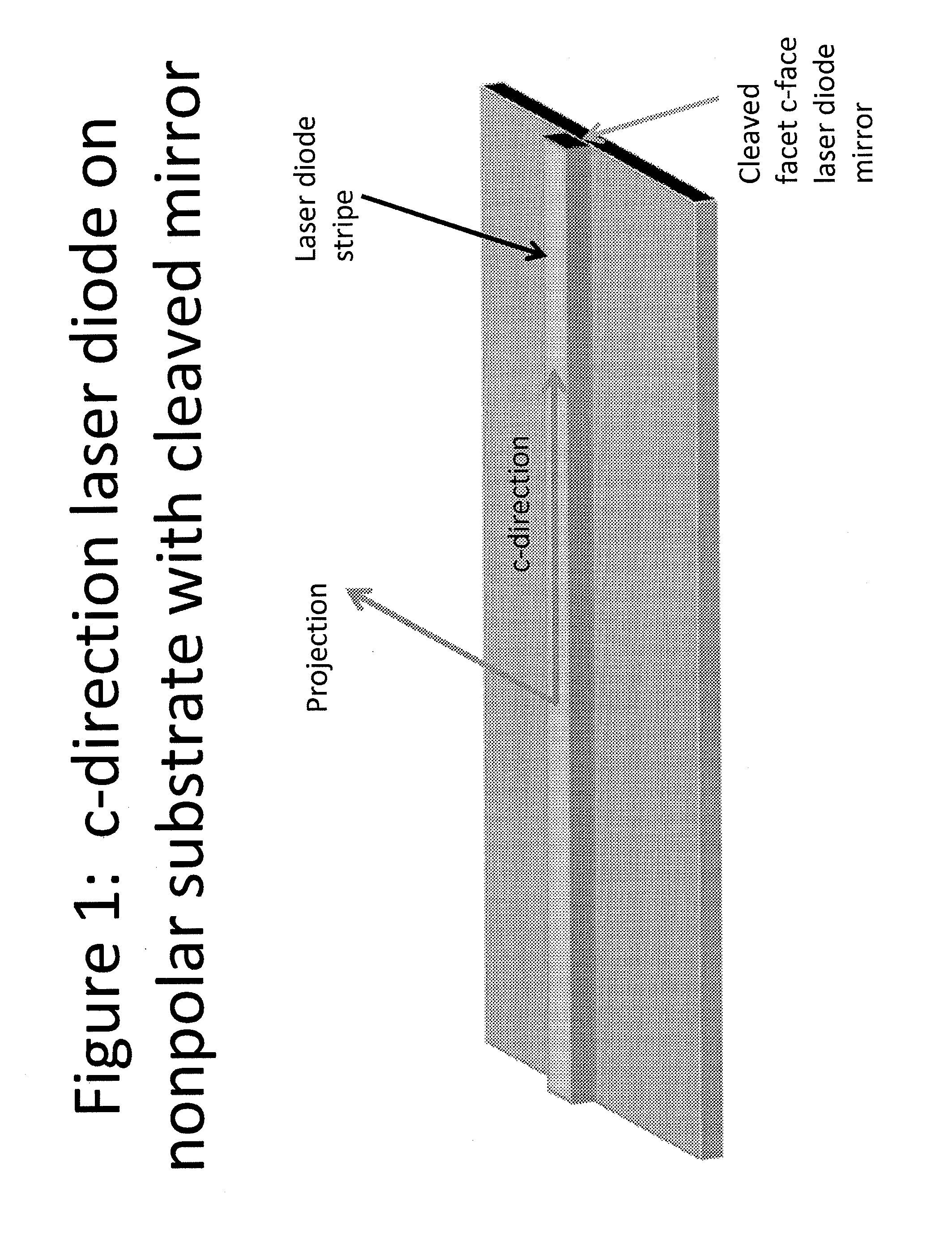

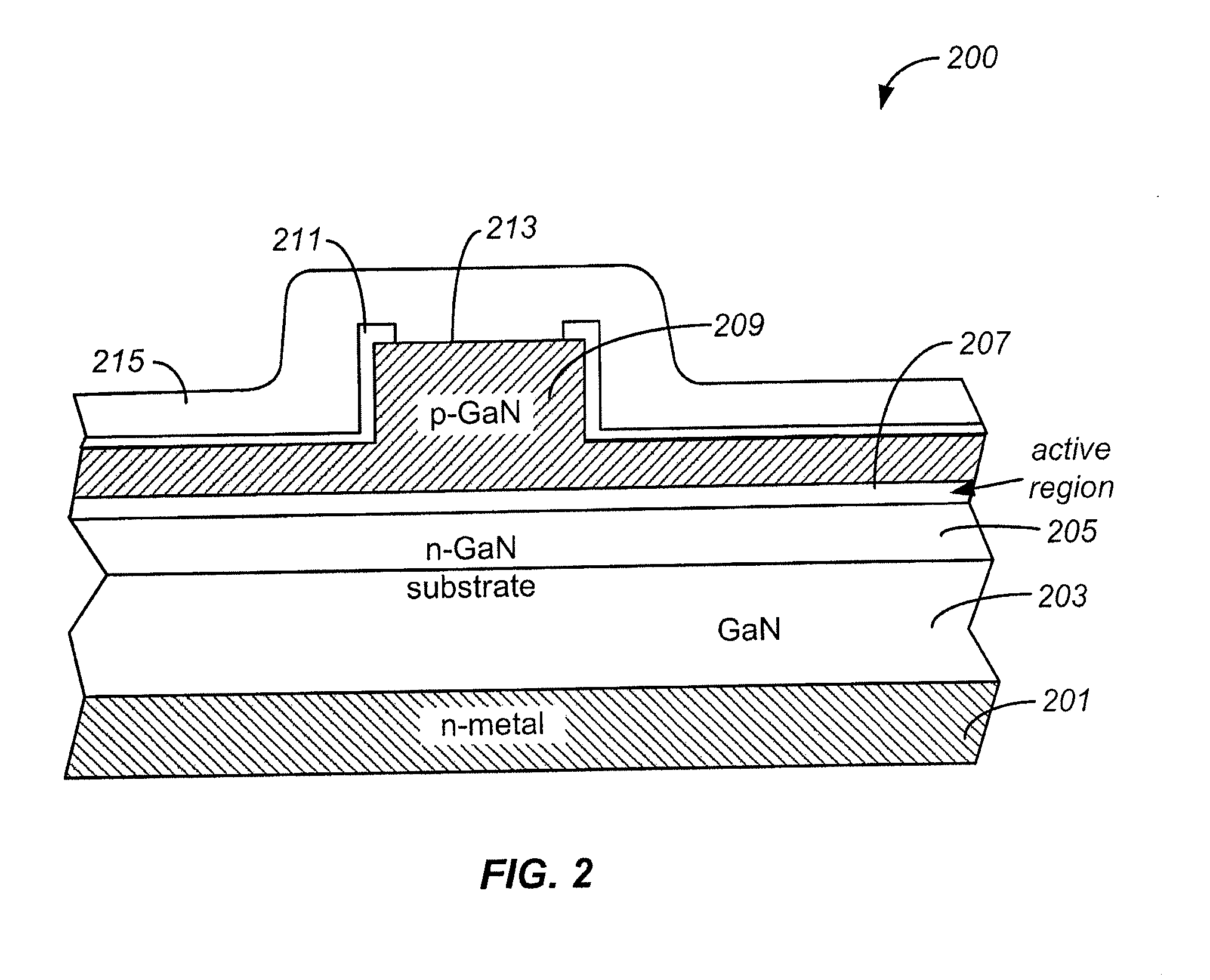

Method of Fabricating Optical Devices Using Laser Treatment of Contact Regions of Gallium and Nitrogen Containing Material

ActiveUS20120104359A1Improve device performanceSmooth connectionSolid-state devicesSemiconductor/solid-state device manufacturingNitrogenGallium

Owner:KYOCERA SLD LASER INC

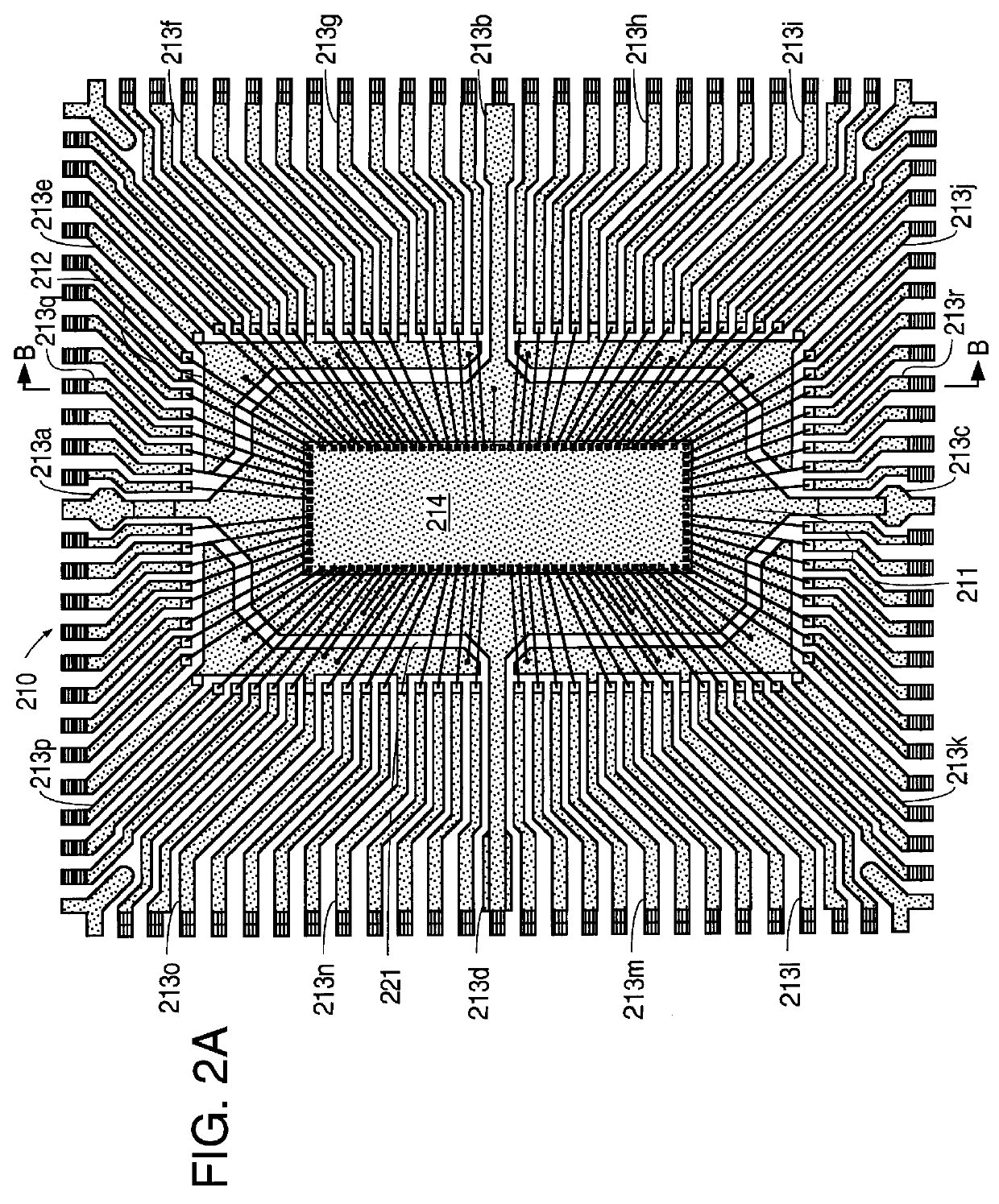

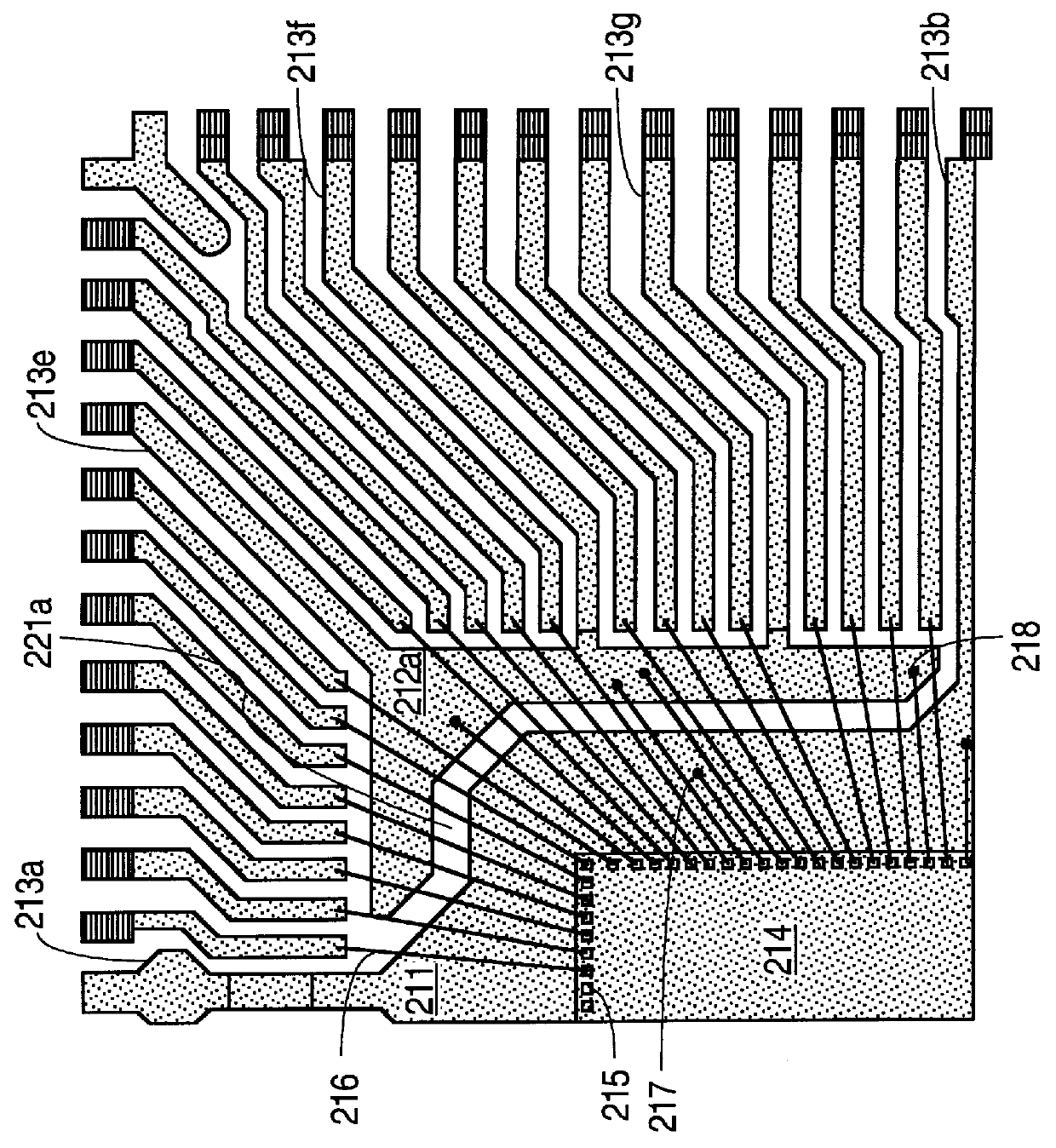

Leadframe with power and ground planes

InactiveUSRE36907E1Reduced effective inductanceReduce crosstalkSemiconductor/solid-state device detailsSolid-state devicesVoltage sourceLead frame

A leadframe for use in an integrated circuit package is described. The leadframe comprises a plurality of electrically conductive leads, a die attach pad, and an electrically conductive ring or rings formed generally around the circumference of the die attach pad and between the die attach pad and leads. In one embodiment, at least one of the leads is formed integrally with each ring. The die attach pad may also be formed integrally with one or more leads. In another embodiment, the ring or rings are formed so that they are electrically isolated from the die attach pad, and the die attach pad, leads, and ring or rings are all formed in substantially the same plane. In some embodiments, the ring or rings are broken into electrically isolated sections. Each of the ring sections (and die attach pad, if appropriate) may be electrically connected to a voltage source outside the integrated circuit package (e.g., a power supply or ground). The leadframe is formed from a single sheet of material by, for instance, stamping or etching. The leadframe may be used in either ceramic or plastic packages. The leadframe reduces switching noise and crosstalk, allows more flexibility in placement of power and / or ground bond pads on the die, and allows provision of ground and power planes in an integrated circuit package that is thinner than previous integrated circuit packages containing both ground and power planes.

Owner:INTEGRATED DEVICE TECH INC

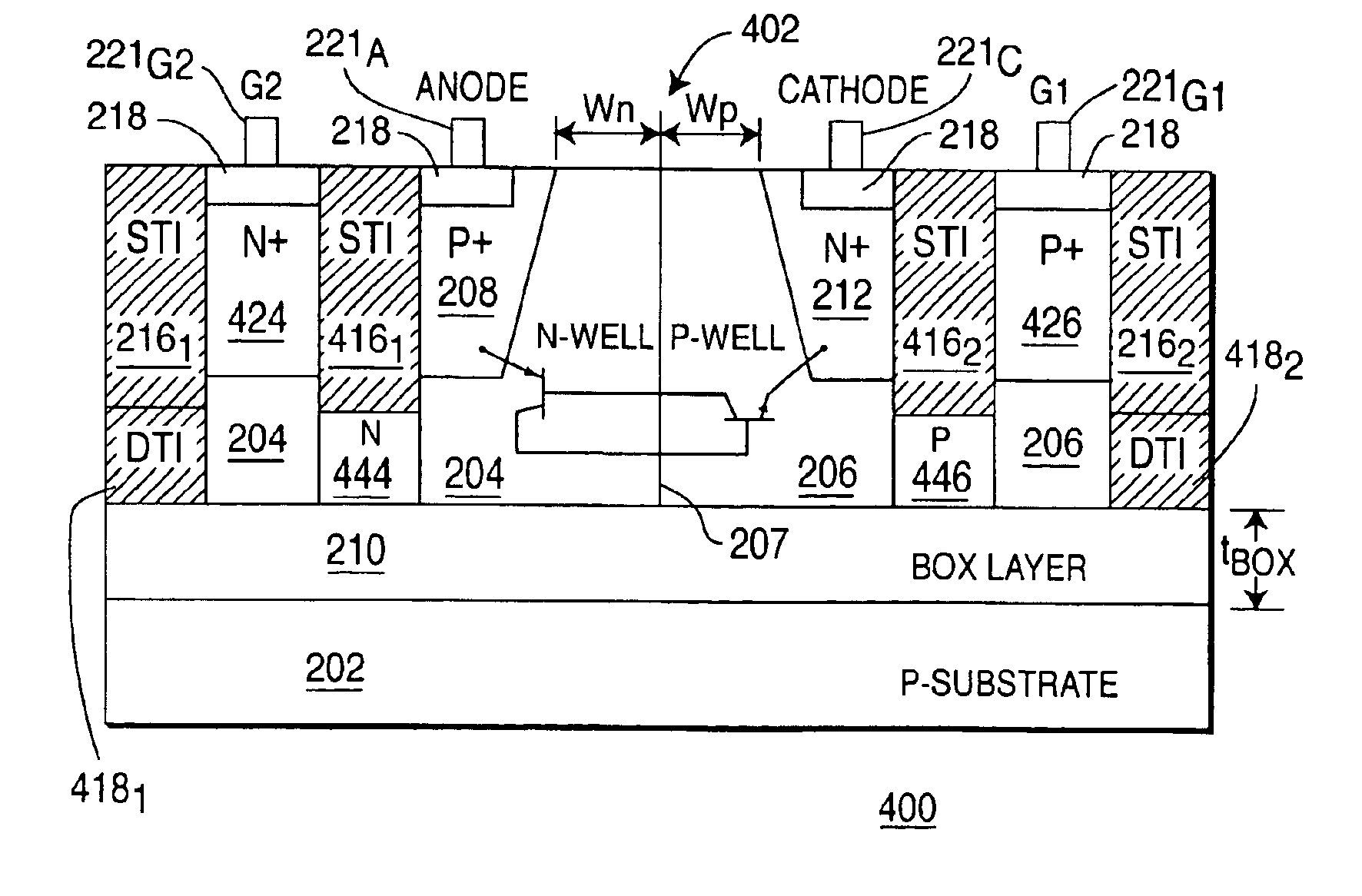

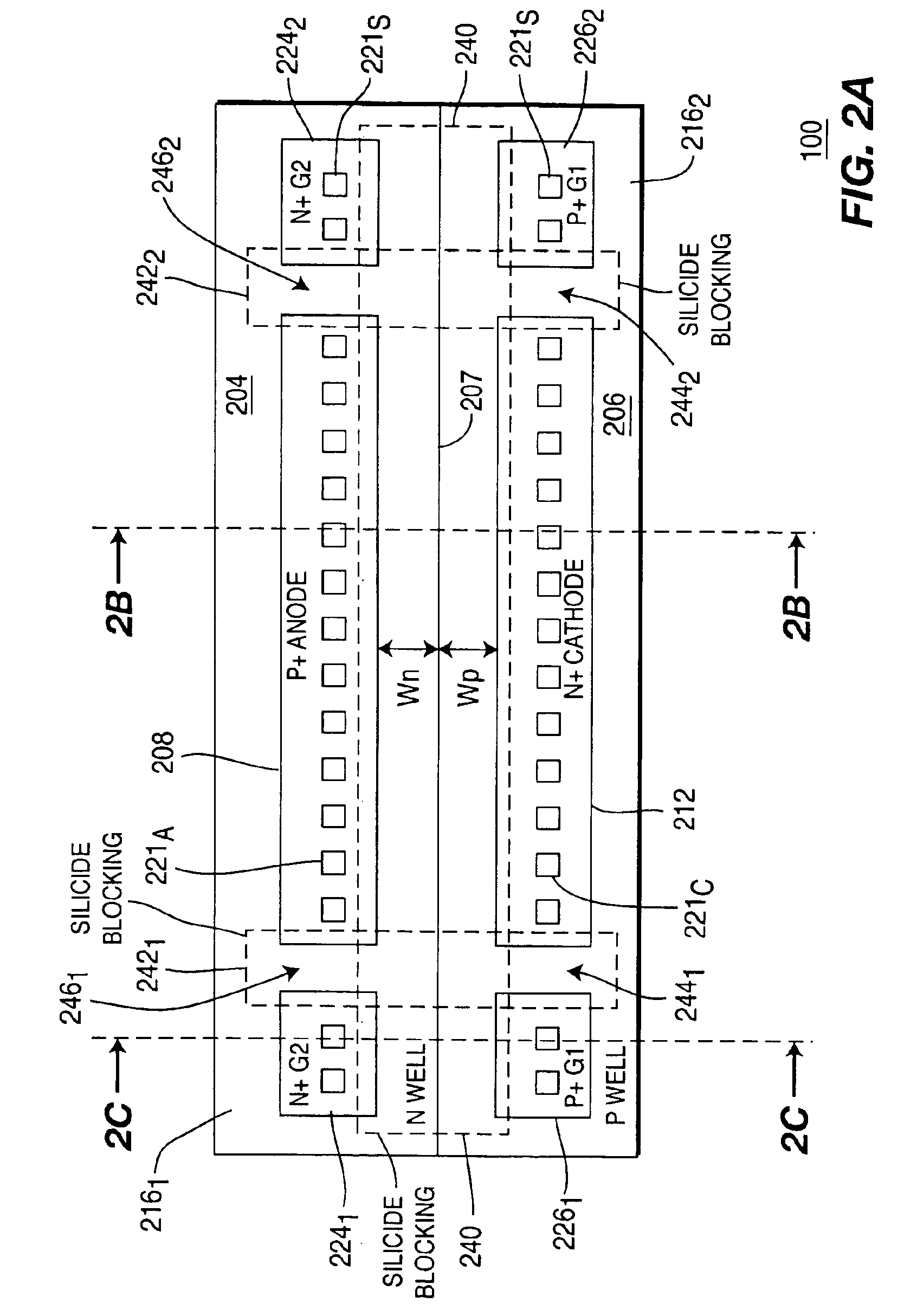

Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies

ActiveUS6909149B2Low triggeringLow holding voltageTransistorThyristorSilicon-controlled rectifierLow voltage

A silicon-on-insulator (SOI) electrostatic discharge (ESD) protection device that can protect very sensitive thin gate oxides by limiting the power dissipation during the ESD event, which is best achieved by reducing the voltage drop across the active (protection) device during an ESD event. In one embodiment, the invention provides very low triggering and holding voltages. Furthermore, the SOI protection device of the present invention has low impedance and low power dissipation characteristics that reduce voltage build-up, and accordingly, enable designers to fabricate more area efficient protection device

Owner:SOFICS BVBA

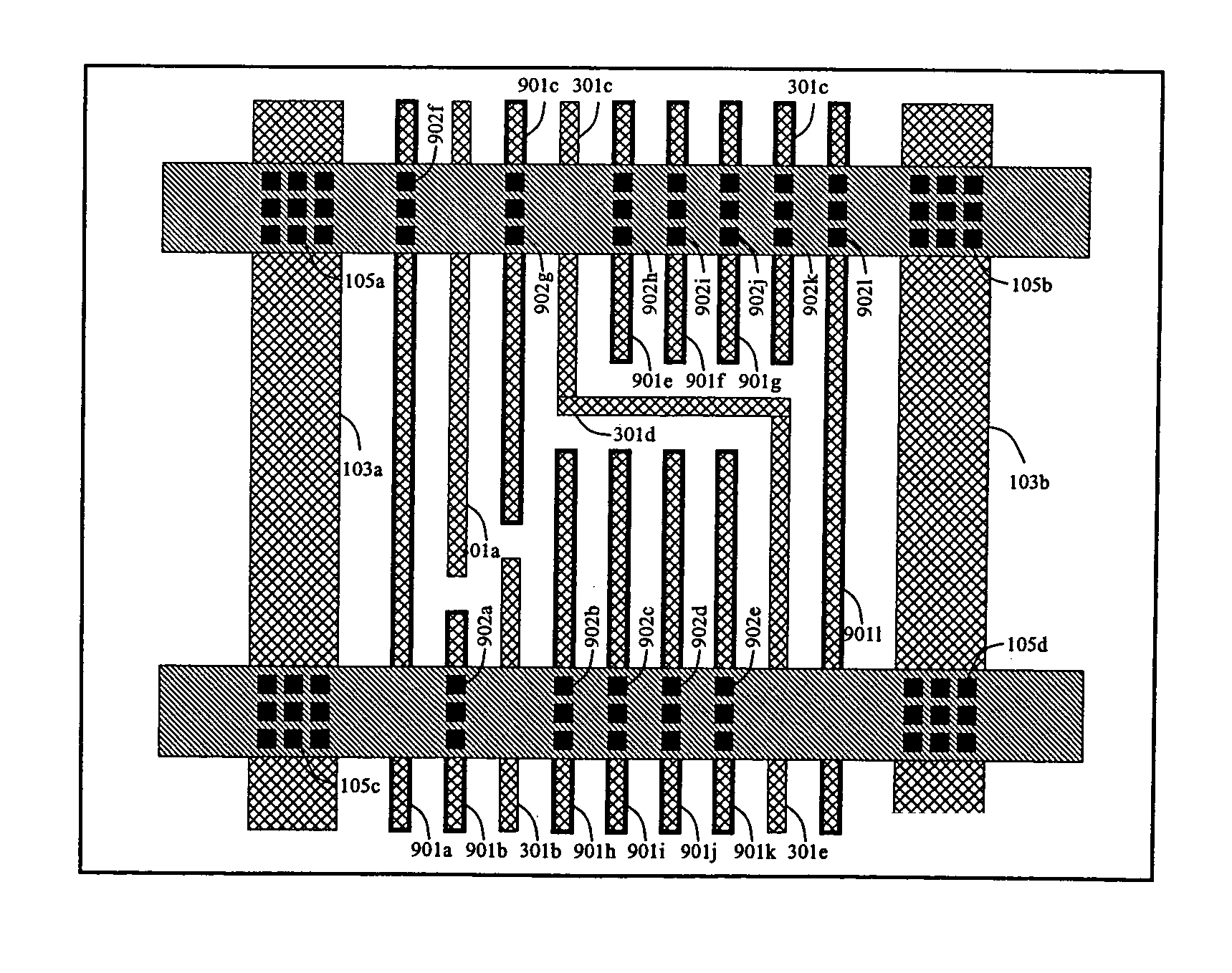

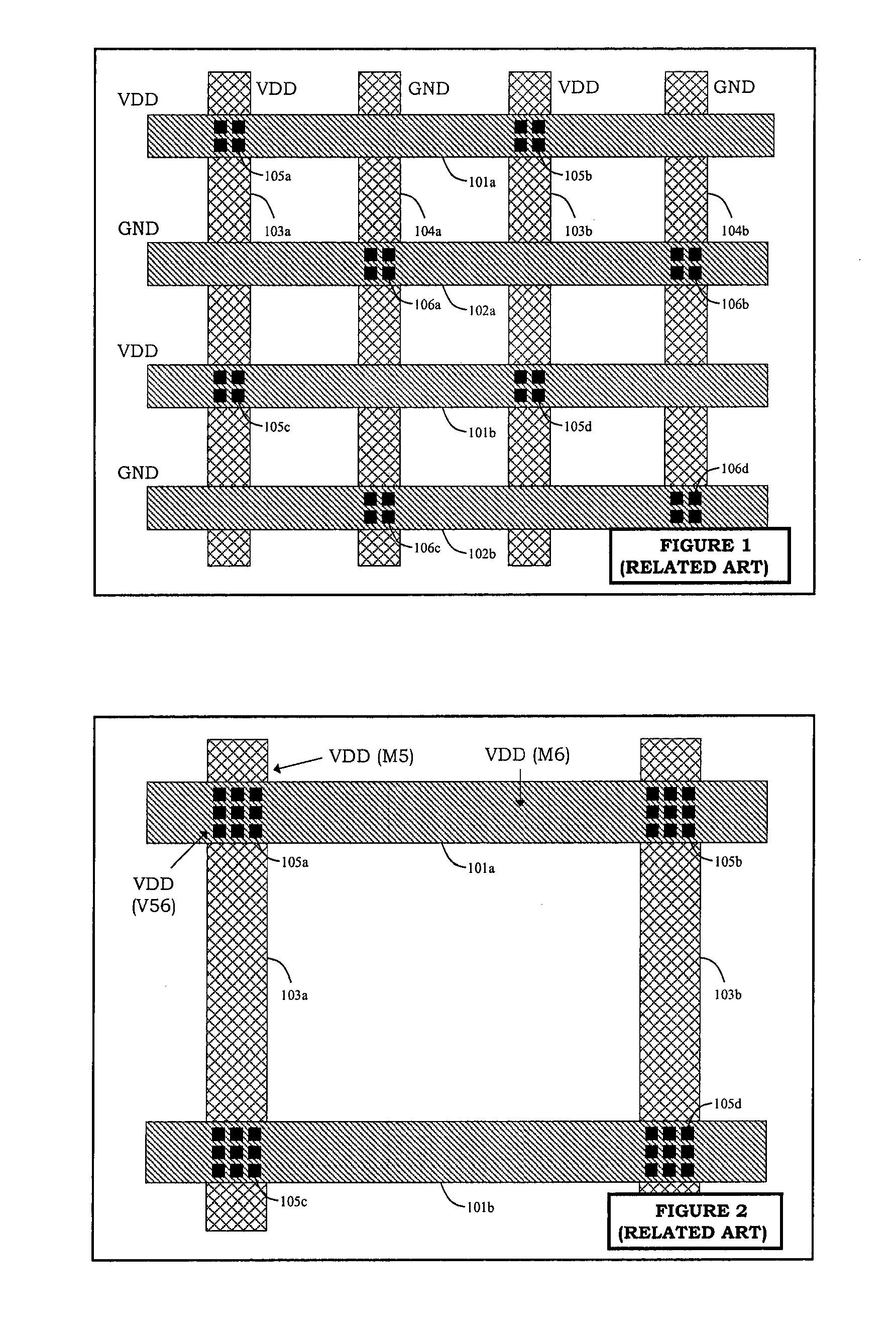

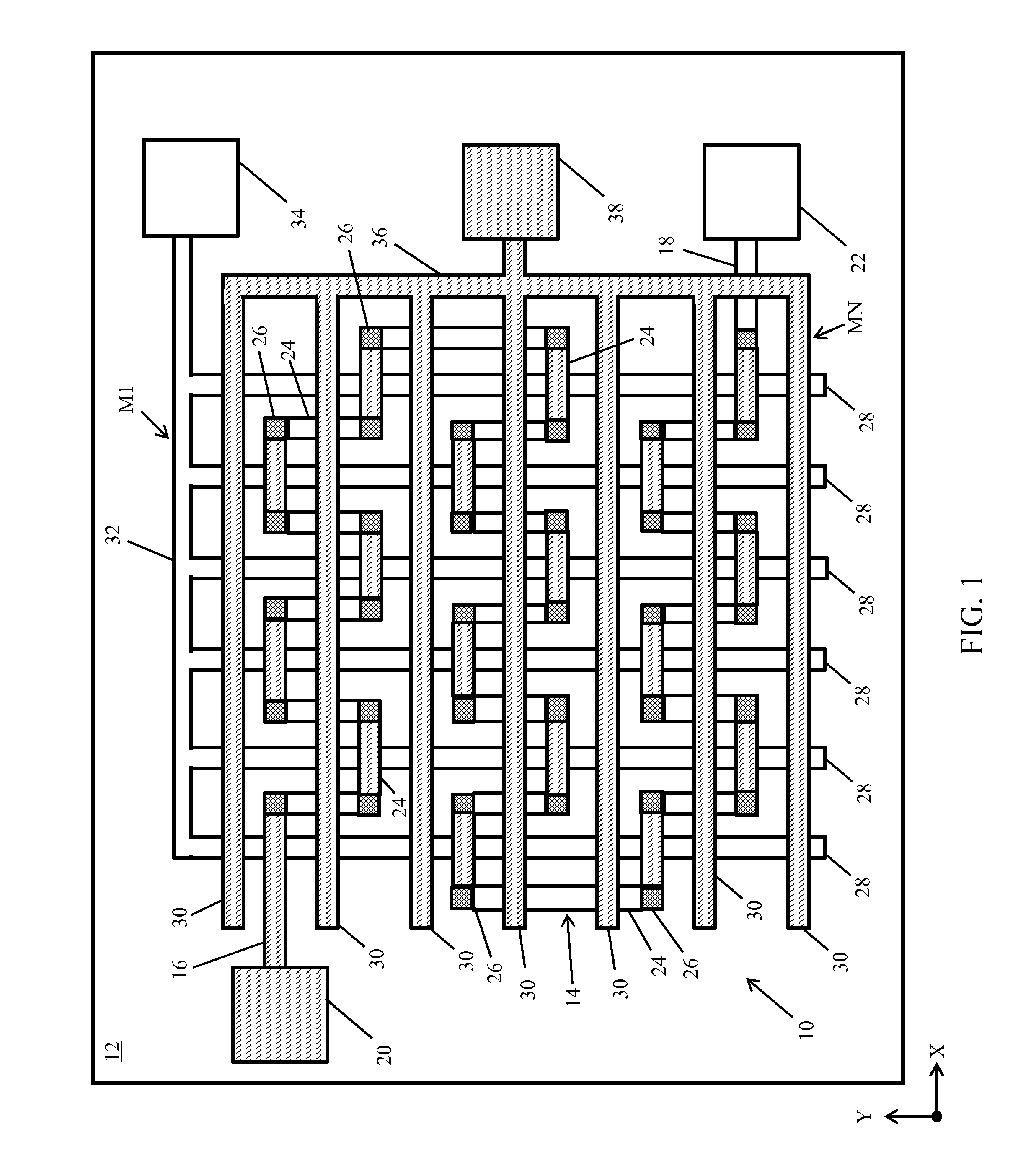

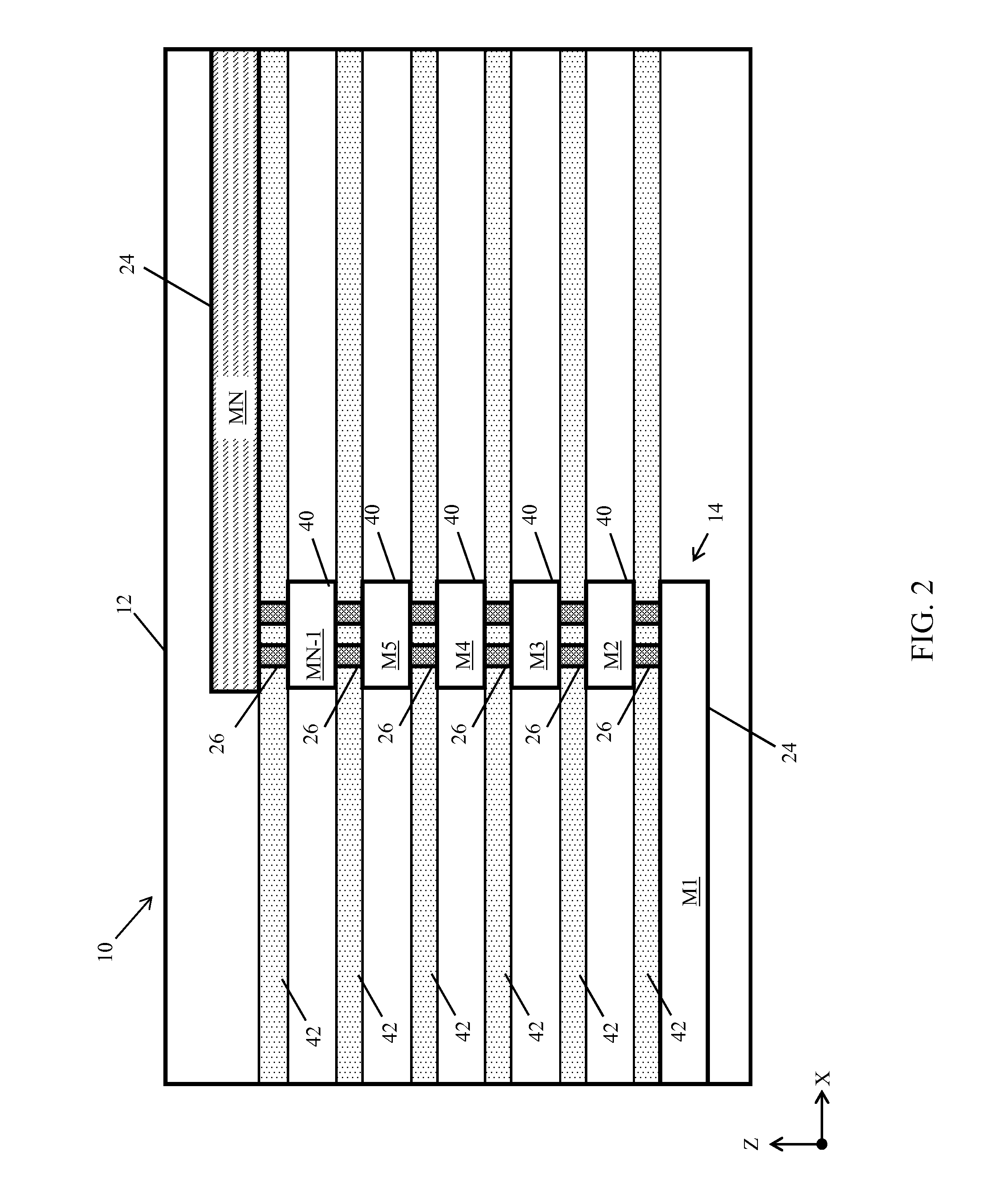

Redundantly tied metal fill for IR-drop and layout density optimization

ActiveUS7240314B1Reduce voltage dropAvoid volume increaseSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceVoltage drop

An integrated circuit and a method for using metal fill geometries to reduce the voltage drop in power meshes. Metal fill geometries are connected to the power mesh using vias or wires at multiple locations. Metal fill geometries are connected to other floating metal fill geometries using vias or wires at multiple locations. The circuit design introduces maximum redundancy between metal fill geometries and power mesh geometries, but partial redundancy between metal fill geometries and metal fill geometries. In particular, the redundancy in connectivity between metal fill geometries and metal fill geometries is kept minimal to reduce the number of geometries introduced. The high redundancy between metal fill geometries and power mesh geometries and the partial redundancy among metal fill geometries result in a smaller IR-drop by reducing the effective resistance on a power mesh. Hence, the invention use redundancy carefully and advantageously to achieve simultaneous metal density and IR-drop optimization without introducing excessive number of metal fill geometries.

Owner:SYNOPSYS INC

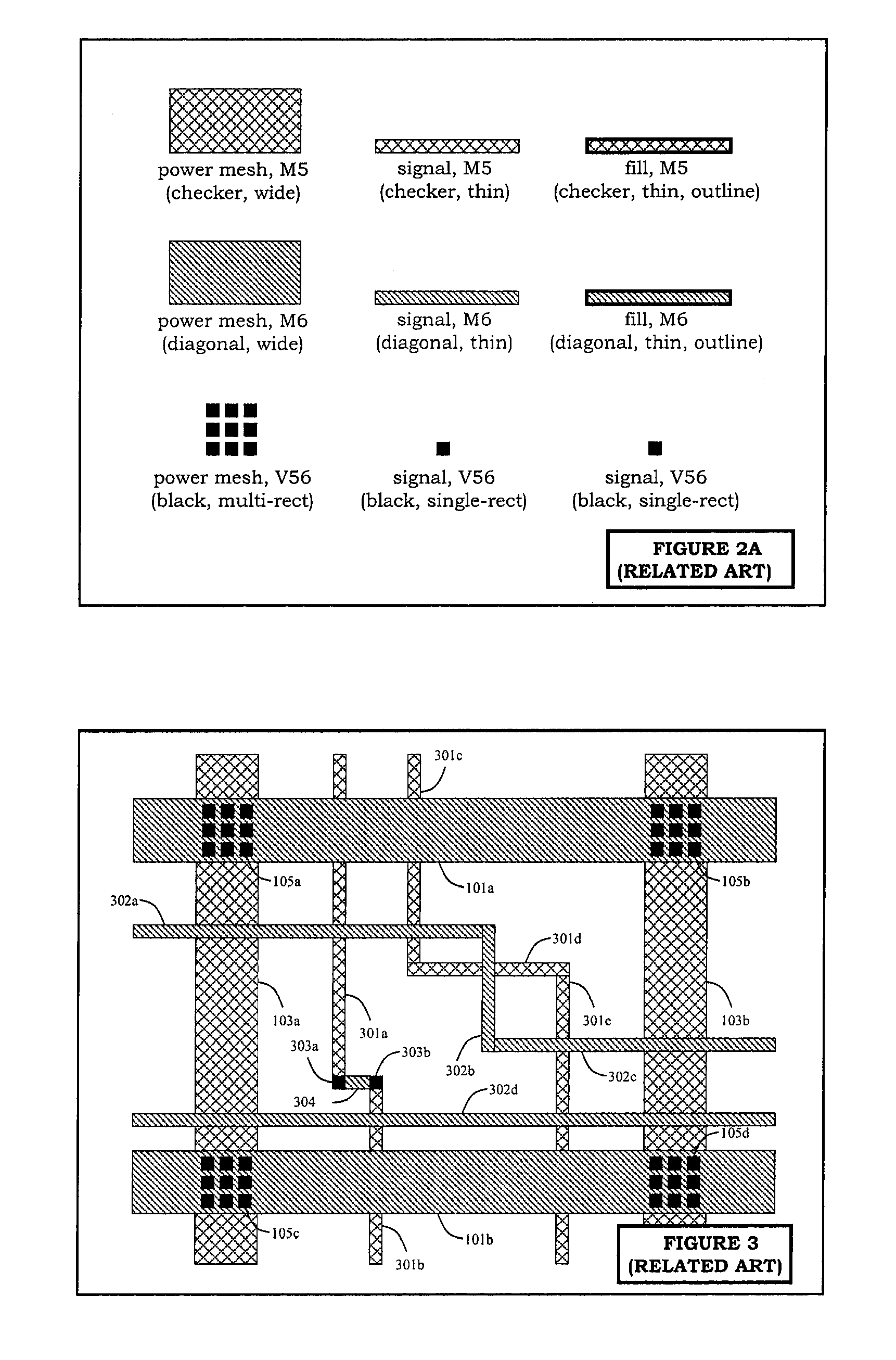

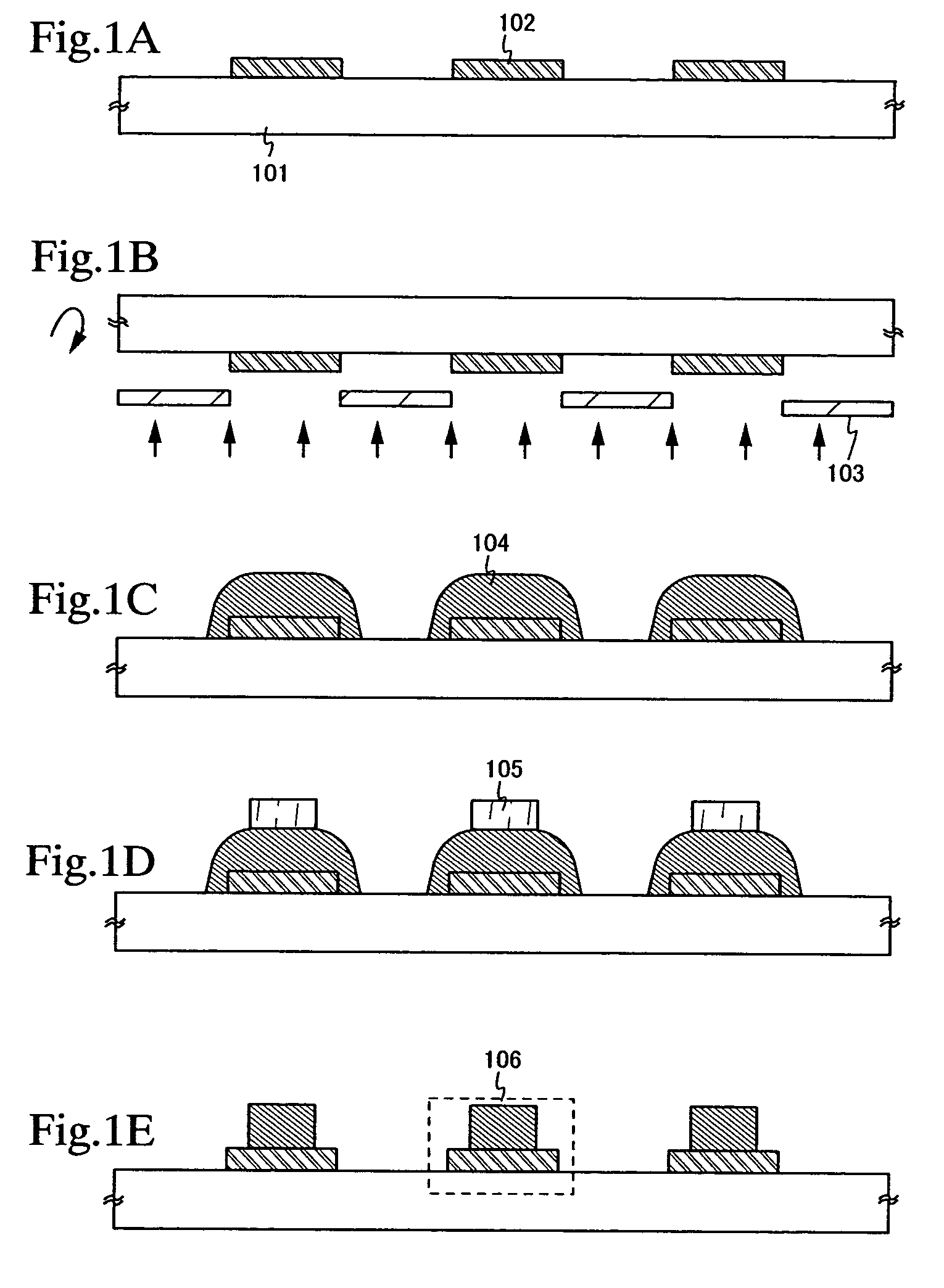

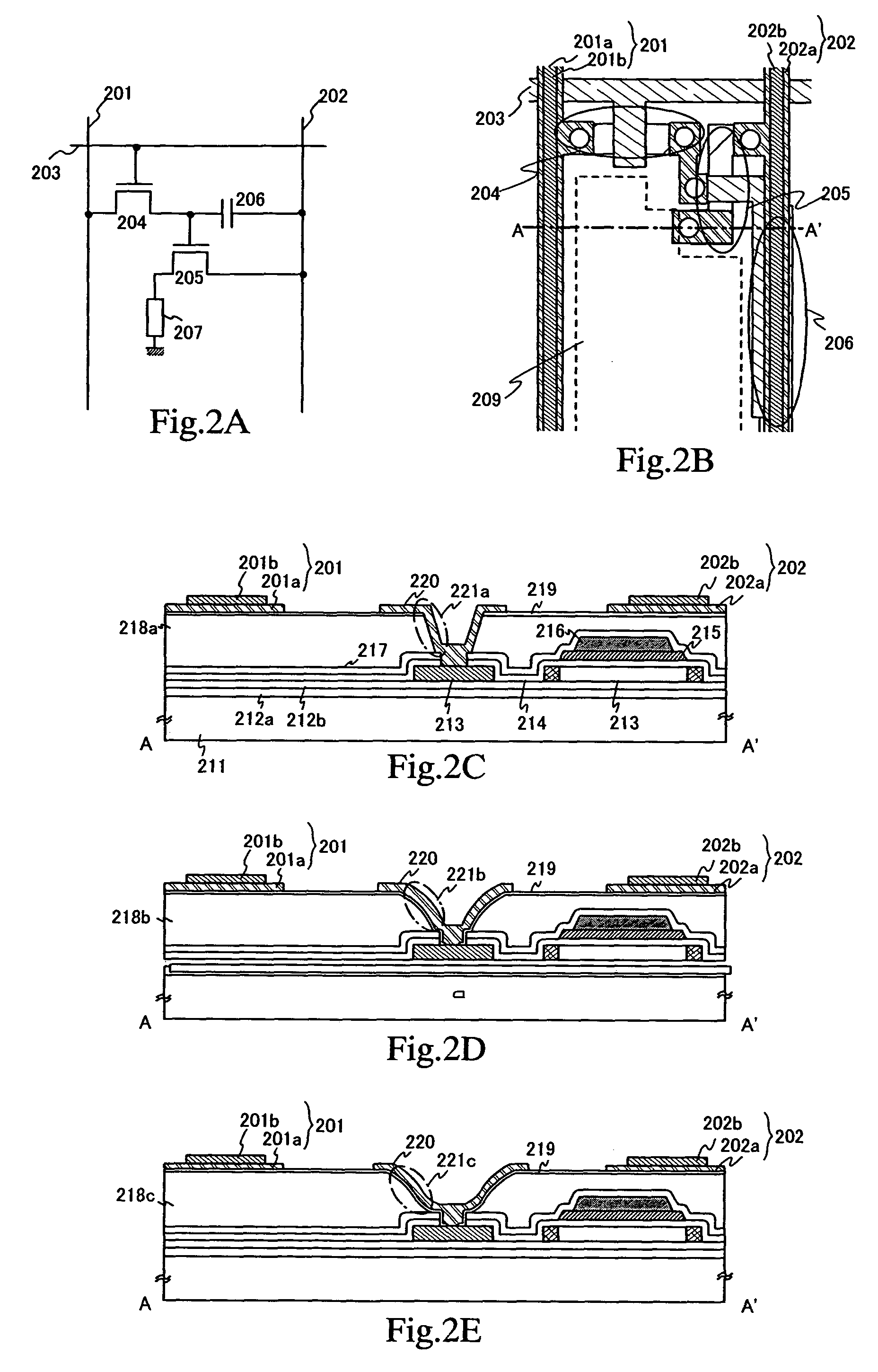

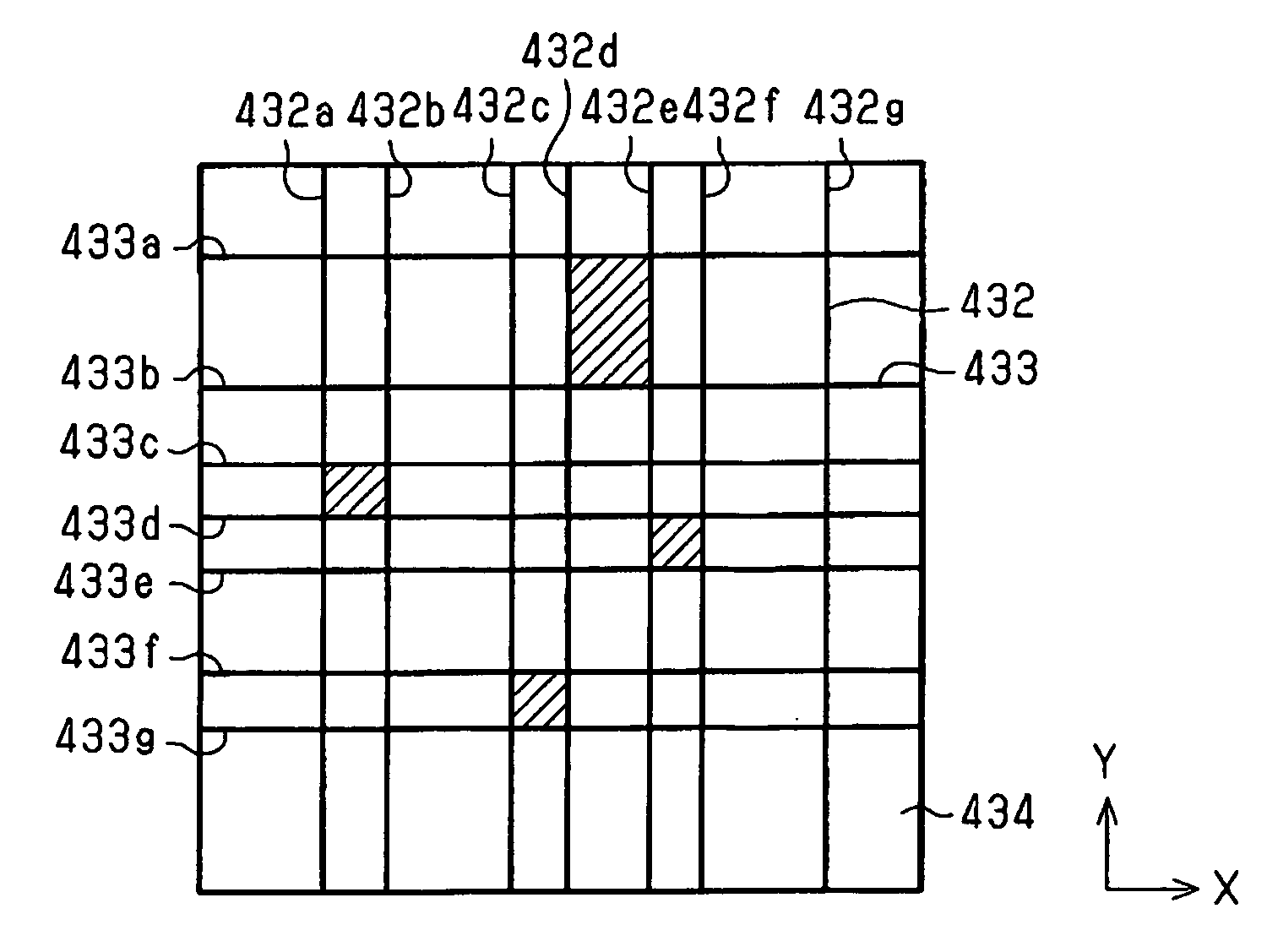

Electrooptic device, method for producing the same, and electronic apparatus

ActiveUS20060158095A1Reduce variationImprove reliabilityDischarge tube luminescnet screensElectroluminescent light sourcesElectro-opticsElectronic equipment

An electrooptic device includes a first substrate and a second substrate. The first substrate includes an electrooptic element in which an electrooptic substance is interposed between a first electrode and a second electrode, the electrooptic element being disposed on a surface of the first substrate that opposes the second substrate; an electronic element for driving the electrooptic element; and a power supply wire for supplying power to at least one of the electrooptic element and the electronic element. The second substrate includes a second auxiliary wire for supplying auxiliary power to at least one of the electrooptic element and the electronic element, the second auxiliary wire being disposed on a surface of the second substrate that opposes the first substrate, the second auxiliary wire having a planar shape that corresponds with a non-opening region of the electrooptic element.

Owner:ELEMENT CAPITAL COMMERCIAL CO PTE LTD

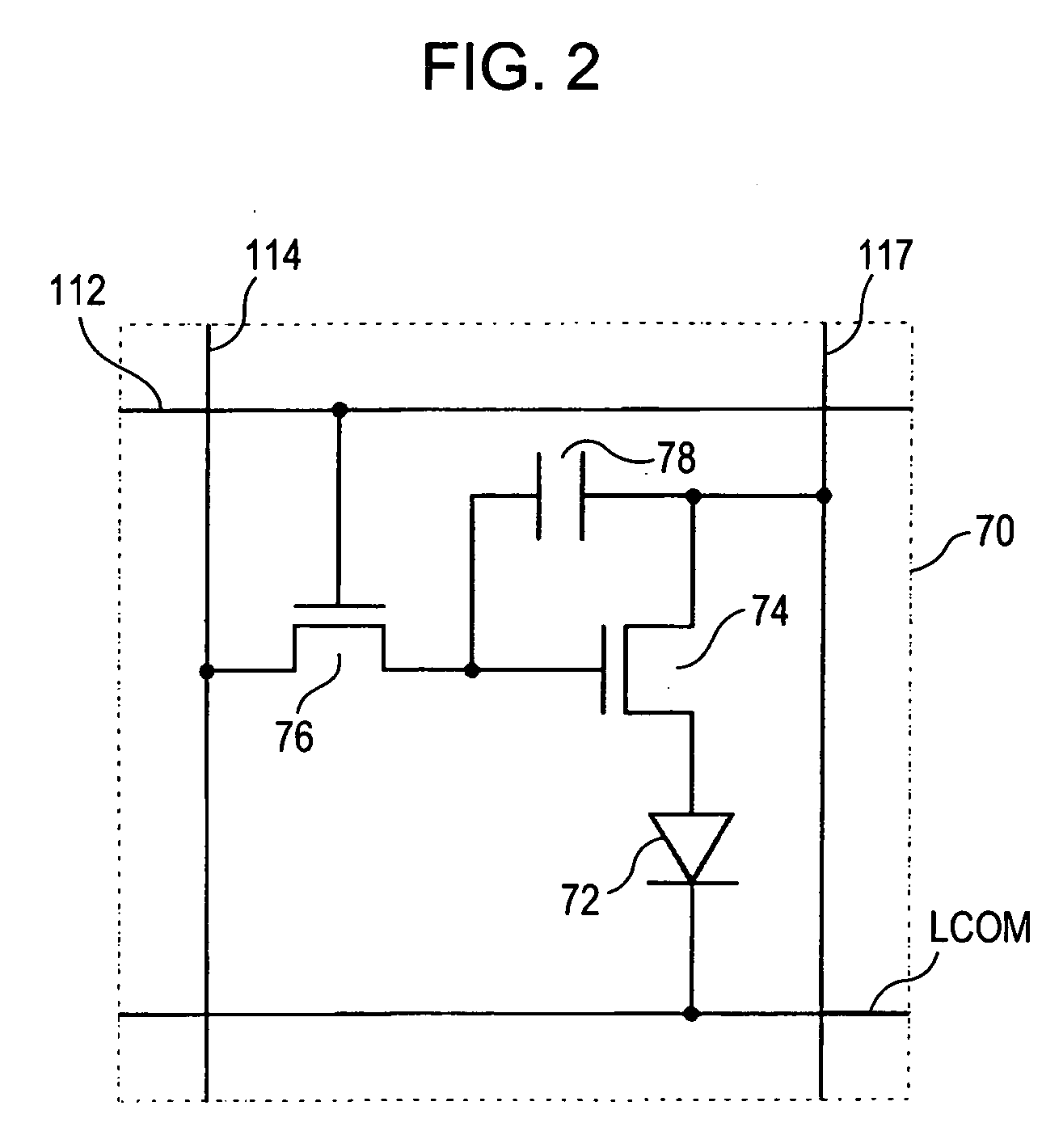

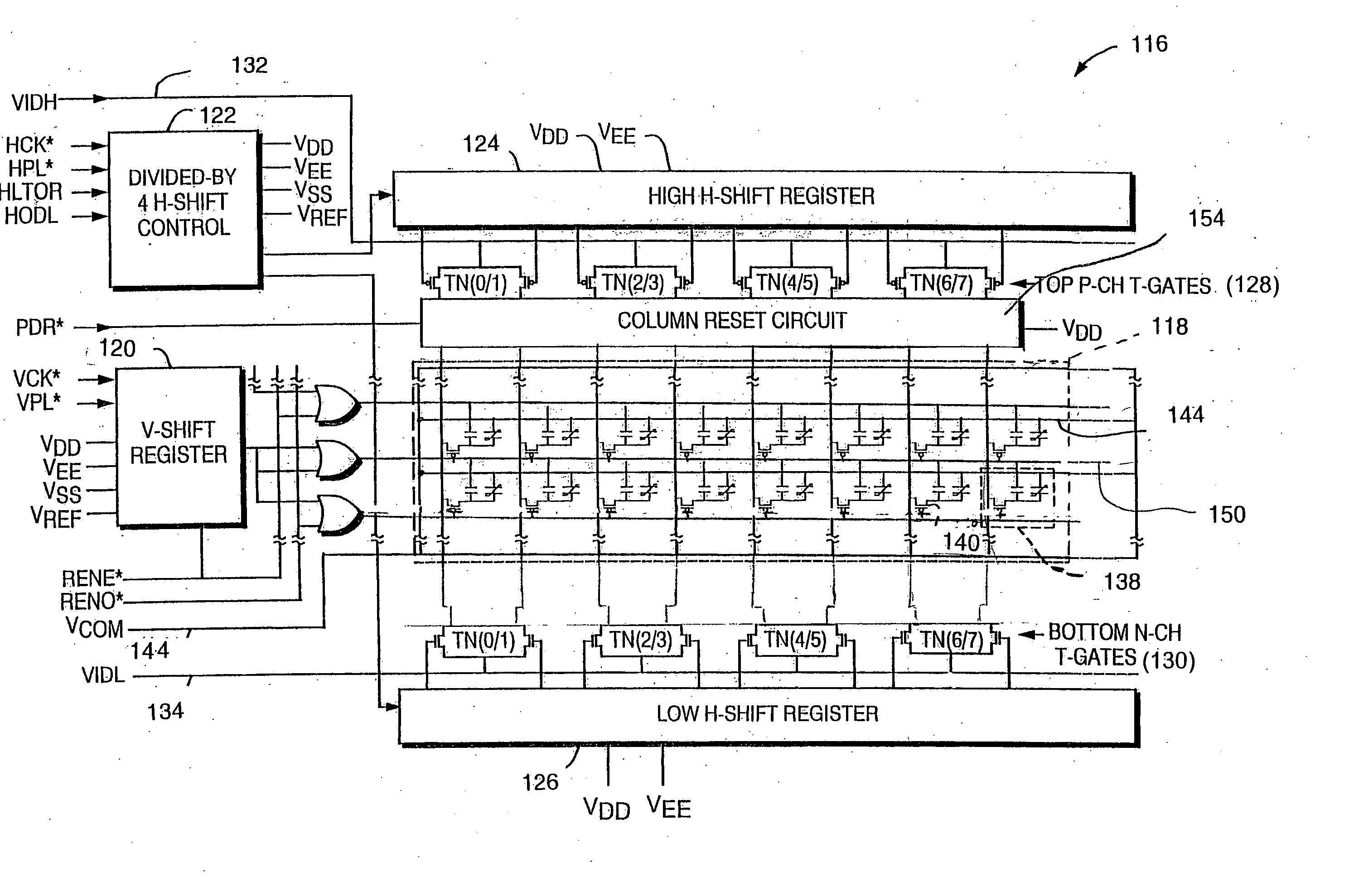

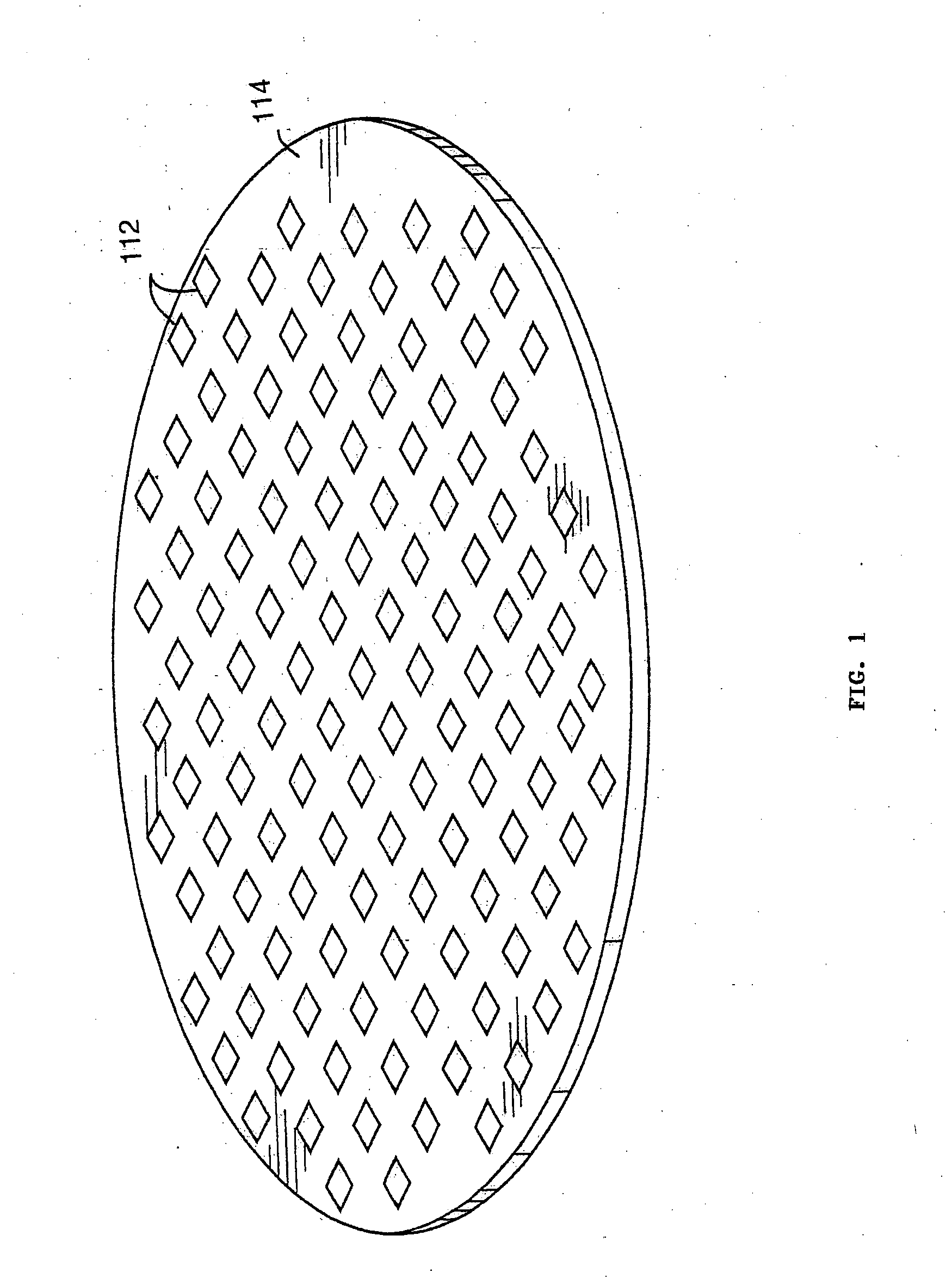

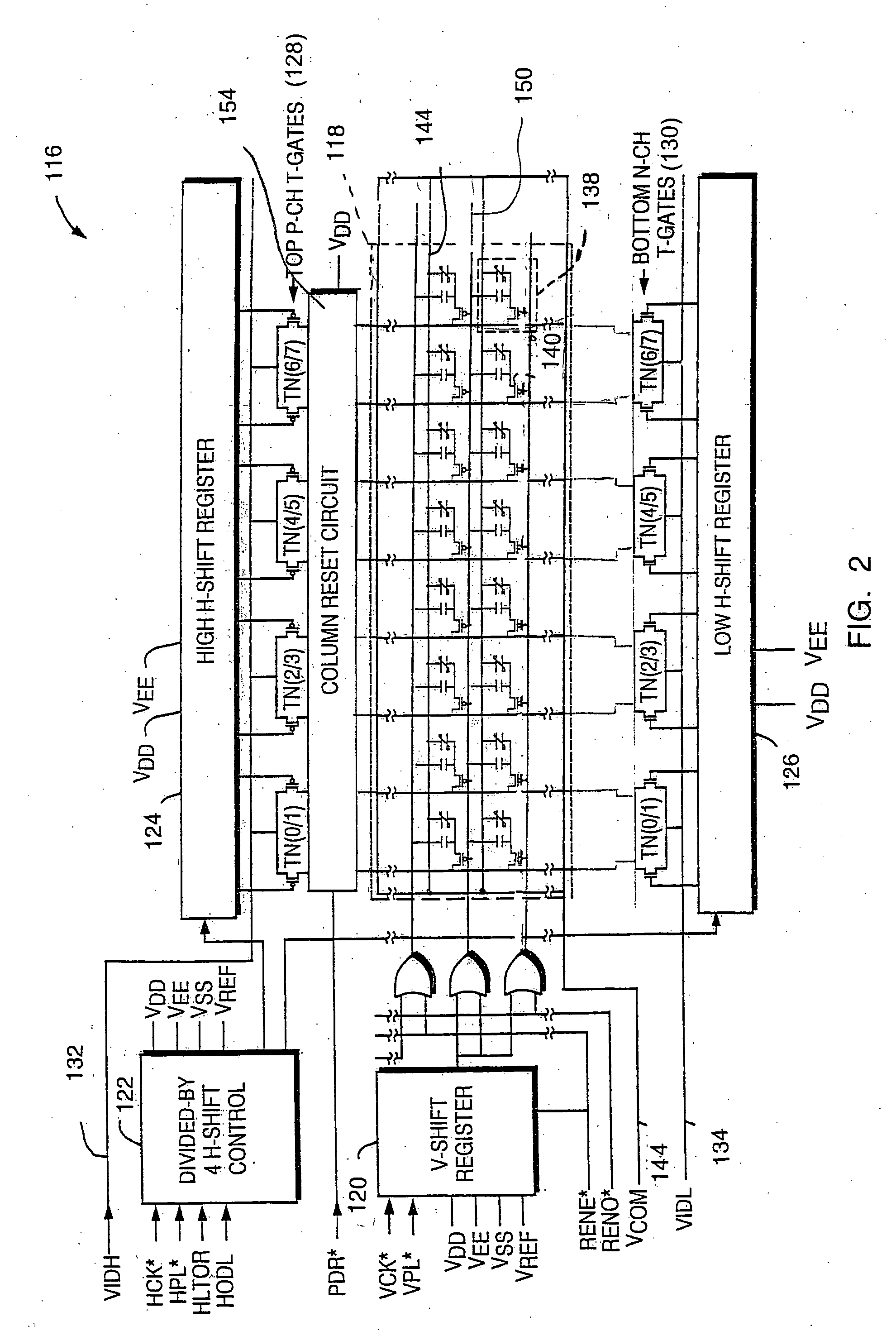

Portable microdisplay system

InactiveUS20070018919A1High voltageReduce voltage dropTelevision system detailsCathode-ray tube indicatorsHead-up displayLiquid-crystal display

An active matrix color crystal display has an active matrix circuit, a counterelectrode panel and an interposed layer of liquid crystal. The active matrix display is located in a portable microdisplay system. The image is written to the the display therein causing the liquid crystal to move to a specific image position. A light source is flashed to illuminate the display. The pixel electrodes are set to a specific value to cause the liquid crystal to move towards a desired position. The process of writing, flashing, and setting the electrode intensity value to reorient the liquid crystal to produce an image is repeated. Portable system can include a digital camera, cellular telephone, camcorder, heads up display, instant print camera, pager,

Owner:ZAVRACKY MATTHEW +12

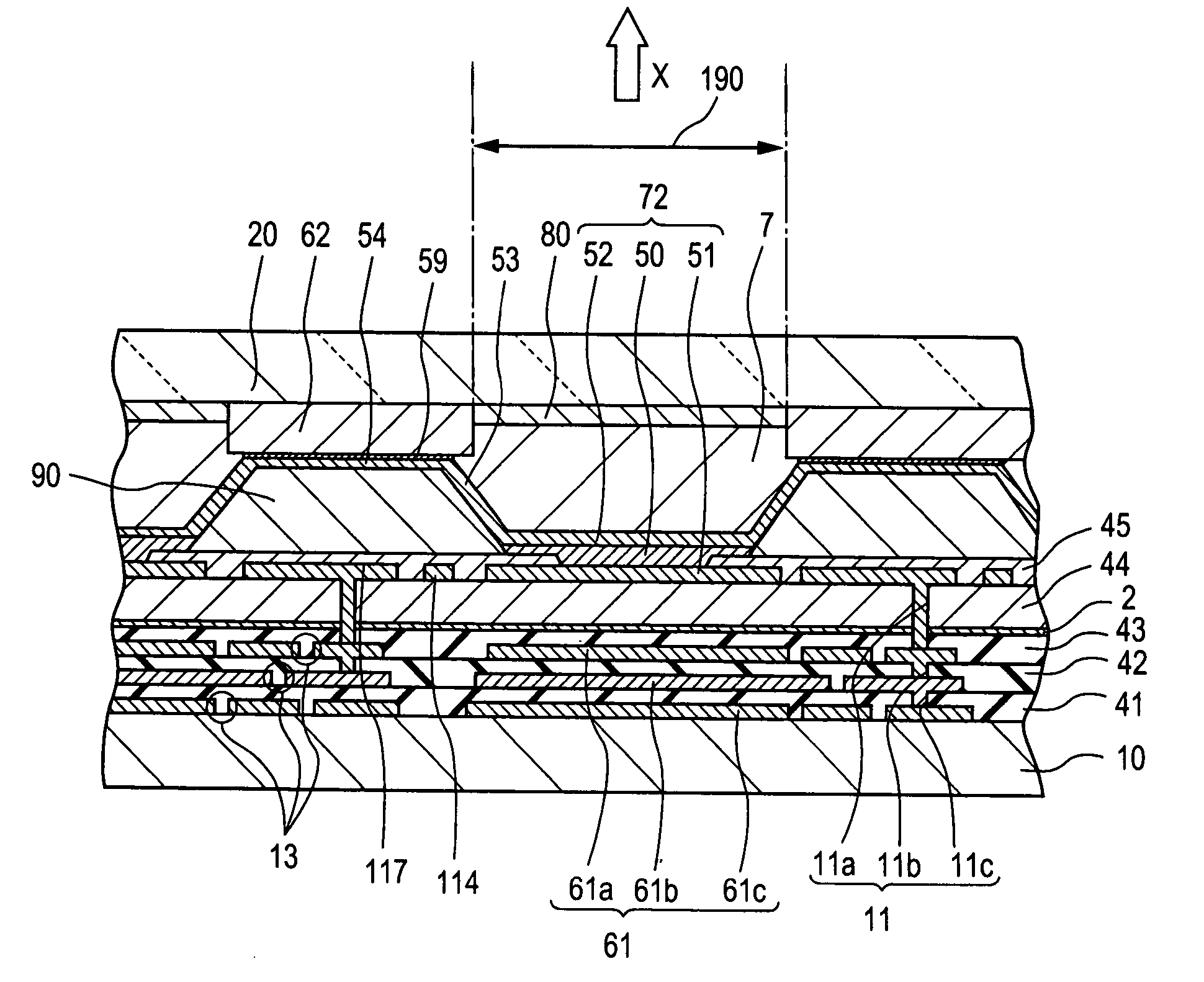

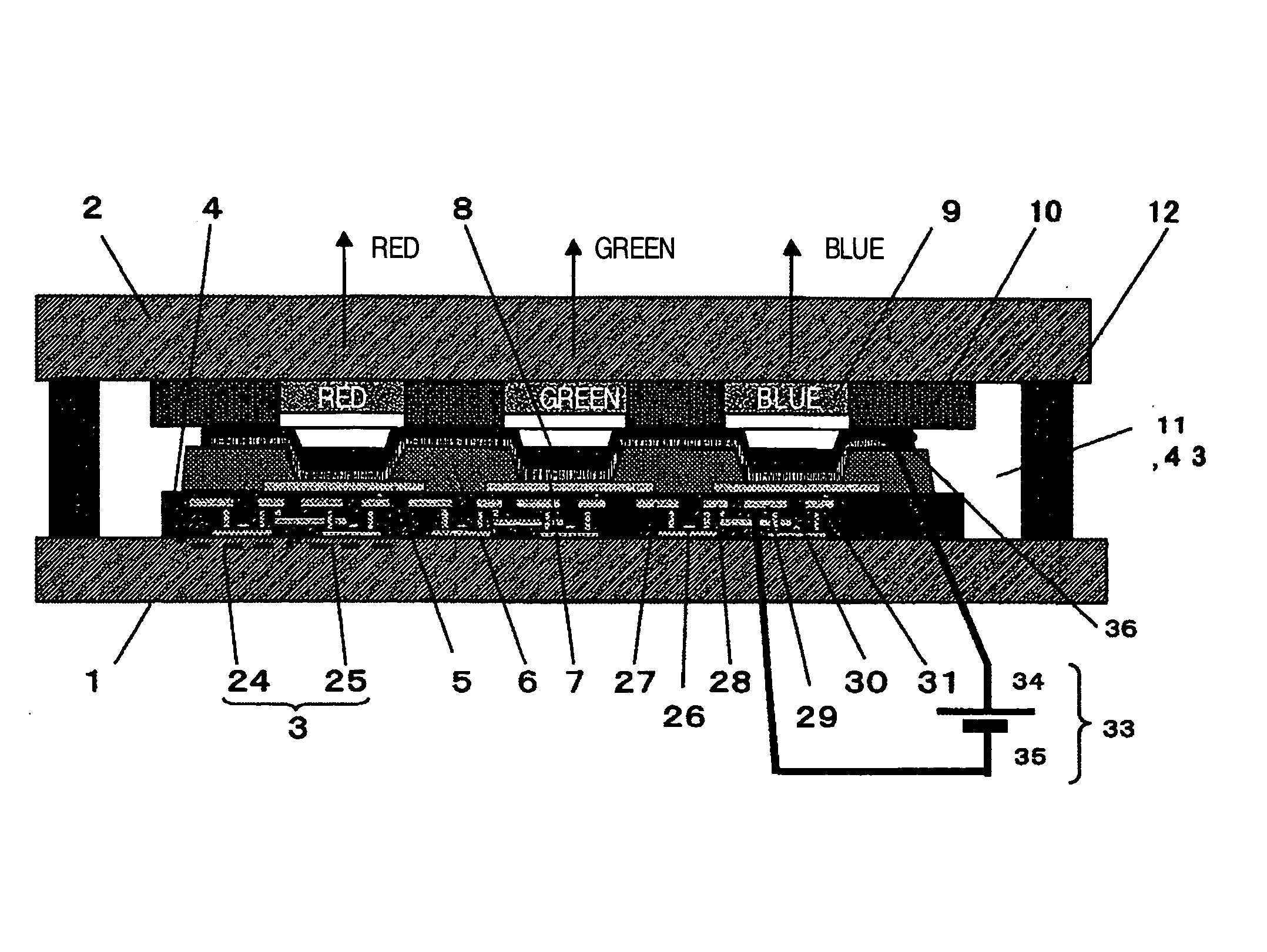

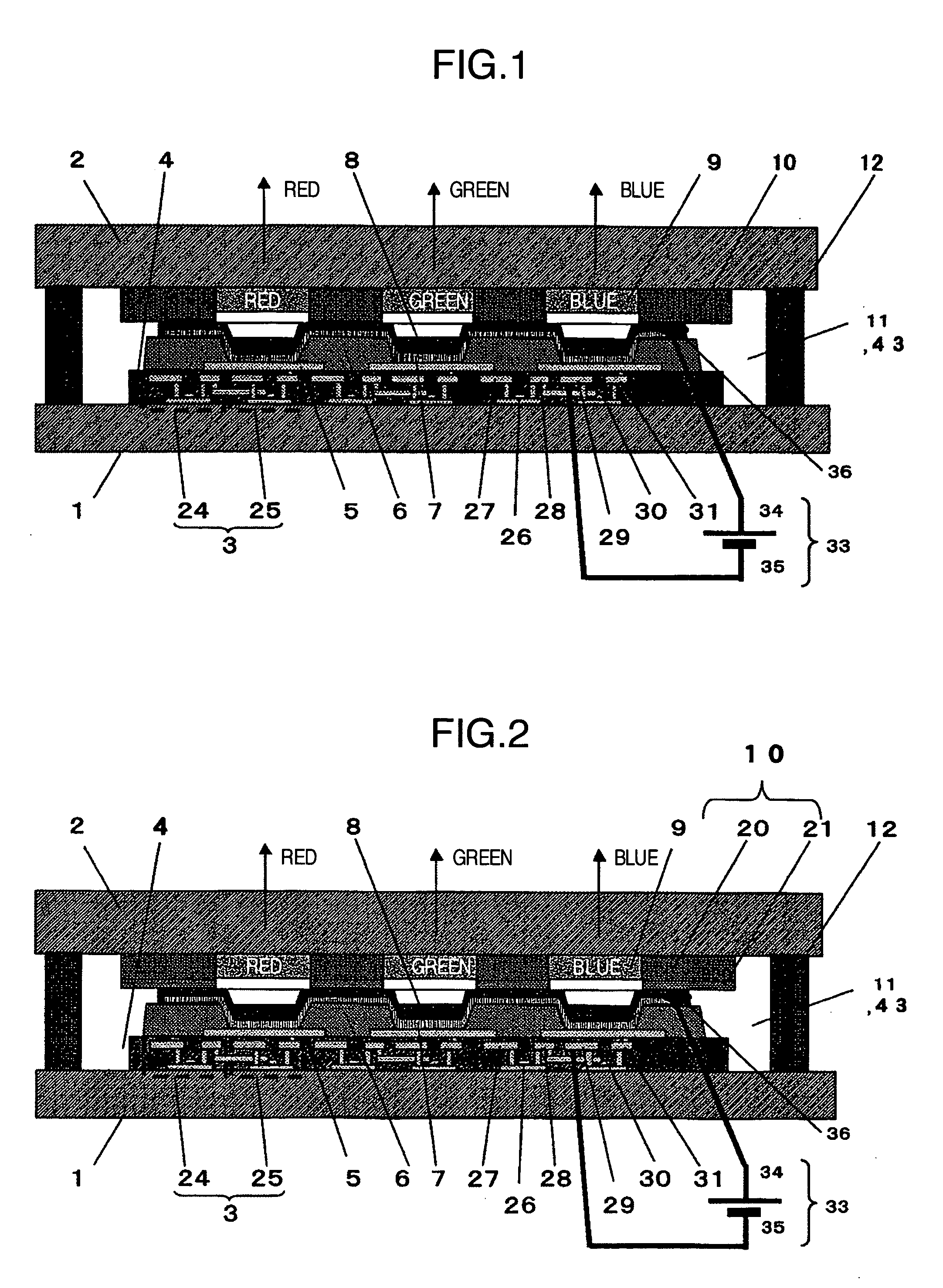

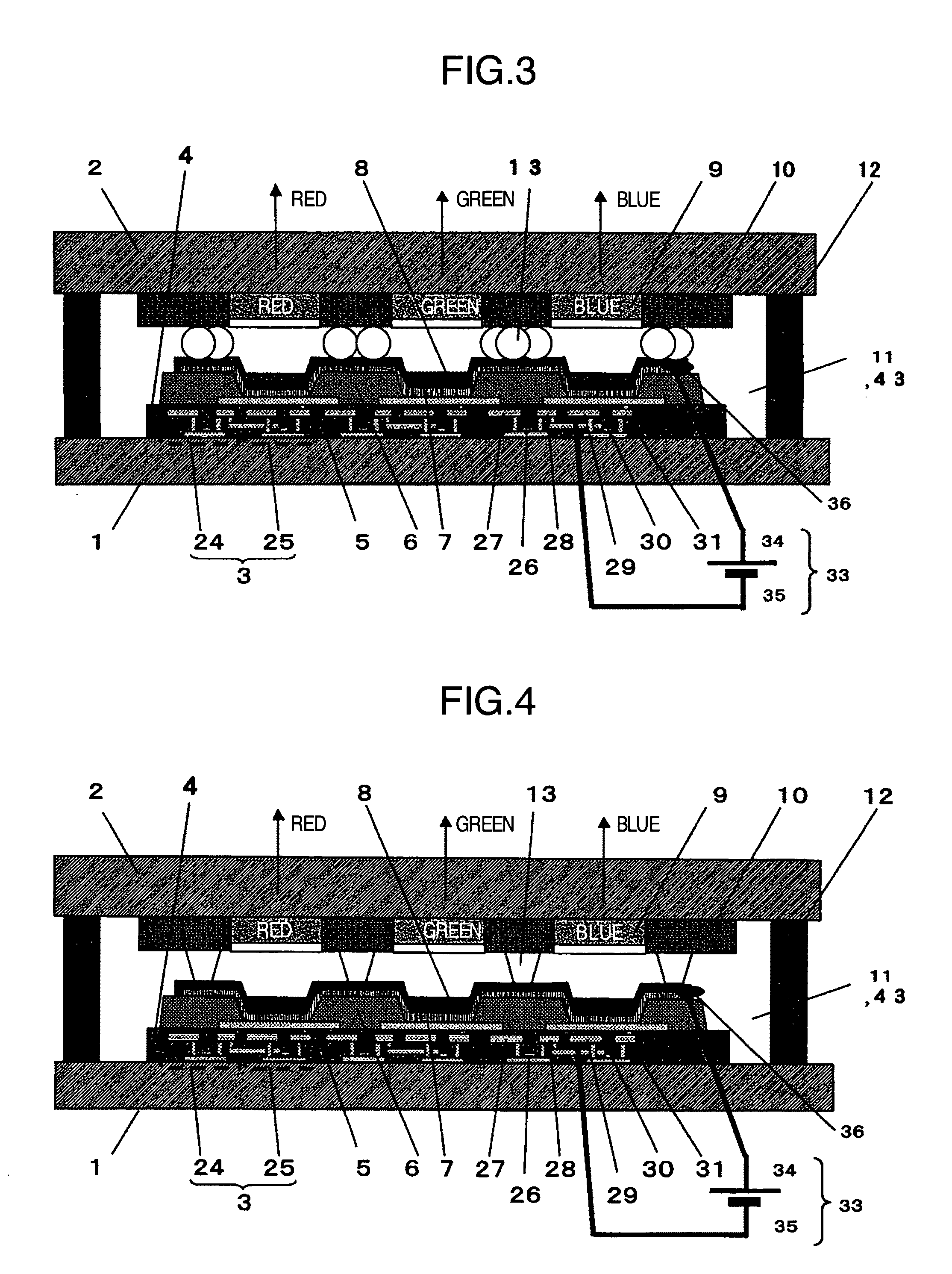

Organic electroluminescence display apparatus

ActiveUS20050212413A1Reduce voltage dropAvoid distributingDischarge tube luminescnet screensElectroluminescent light sourcesVoltage dropOptoelectronics

The organic electroluminescence display apparatus of the present invention comprises a first and second substrates, the former being coated with banks for separating pixels, a lower electrode, organic light-emitting layer and upper electrode of a transparent material in this order, and the latter being coated with a color filter and electroconductive shadow pattern, wherein the organic light-emitting layer surrounded by the banks for separating pixels faces the color filter, and the first and second substrates face each other in such a way that the upper electrode over the banks for separating pixels is electrically connected to the electroconductive shadow pattern. This structure connects at least one of the upper electrode and electroconductive shadow pattern to a power supply point, to control ununiform emitted light brightness which may result from voltage drop at the upper transparent electrode. Moreover, the organic light-emitting layer can be formed without a vapor deposition mask having a precise aperture pattern, to efficiently produce the organic EL display apparatus.

Owner:SAMSUNG DISPLAY CO LTD +1

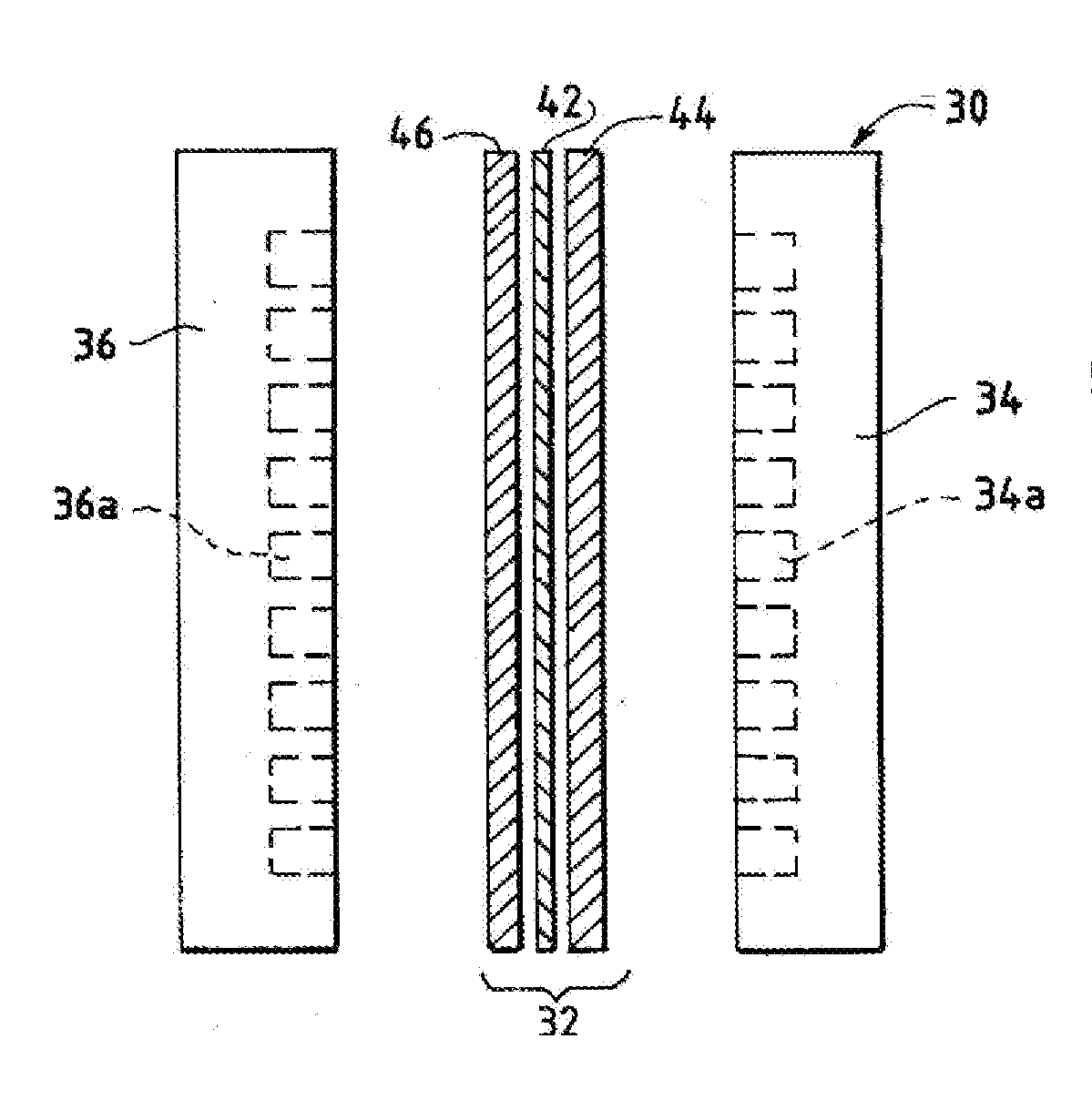

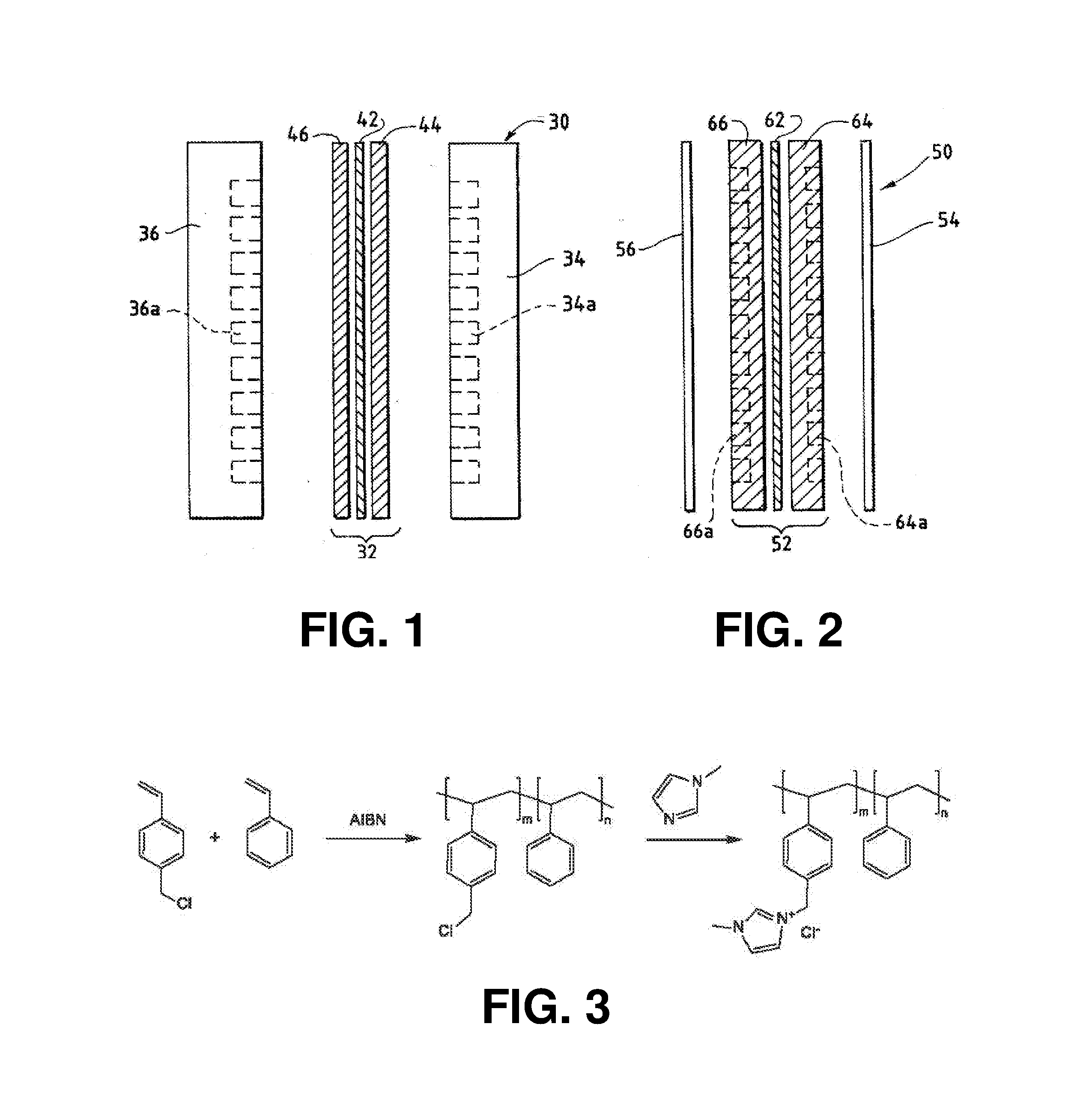

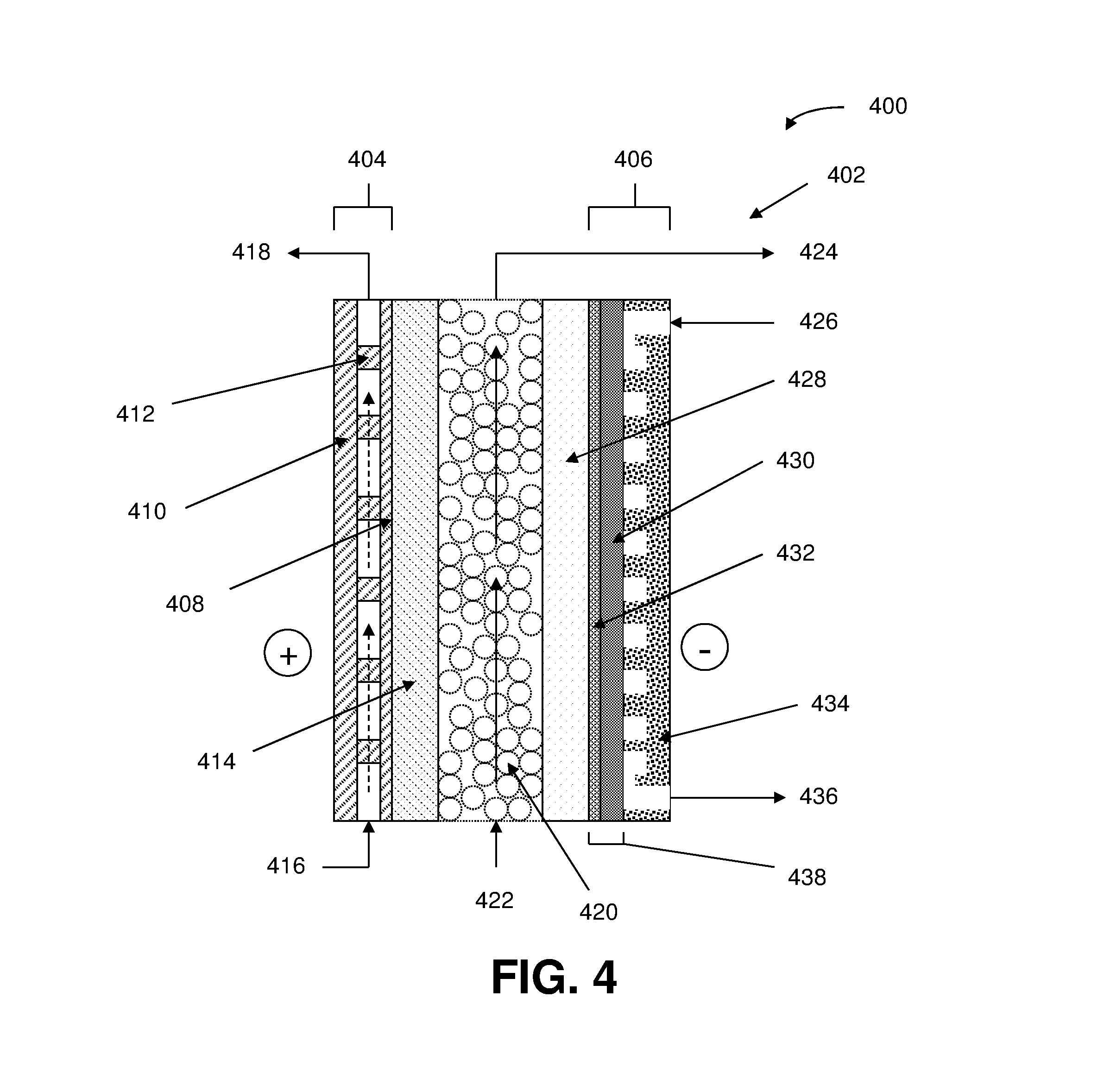

Method And System For Electrochemical Production Of Formic Acid From Carbon Dioxide

An electrochemical device converts carbon dioxide to a formic acid reaction product. The device includes an anode and a cathode, each comprising a quantity of catalyst. The anode and cathode each have reactant introduced thereto. Two membranes, a cation exchange polymer electrolyte membrane and an anion exchange polymer electrolyte membrane, are interposed between the anode and the cathode, forming a central flow compartment where a carbon dioxide reduction product, such as formic acid, can be recovered. At least a portion of the cathode catalyst is directly exposed to gaseous carbon dioxide during electrolysis. The average current density at the membrane is at least 20 mA / cm2, measured as the area of the cathode gas diffusion layer that is covered by catalyst, and formate ion selectivity is at least 50% at a cell potential difference of 3.0 V. In some embodiments, at least one polymer electrolyte membrane comprises a polymer in which a constituent monomer is (p-vinylbenzyl)-R, where R is selected from the group consisting of imidazoliums, pyridiniums and phosphoniums. In some embodiments, the polymer electrolyte membrane is a Helper Membrane comprising a polymer containing an imidazolium ligand, a pyridinium ligand, or a phosphonium ligand.

Owner:DIOXIDE MATERIALS

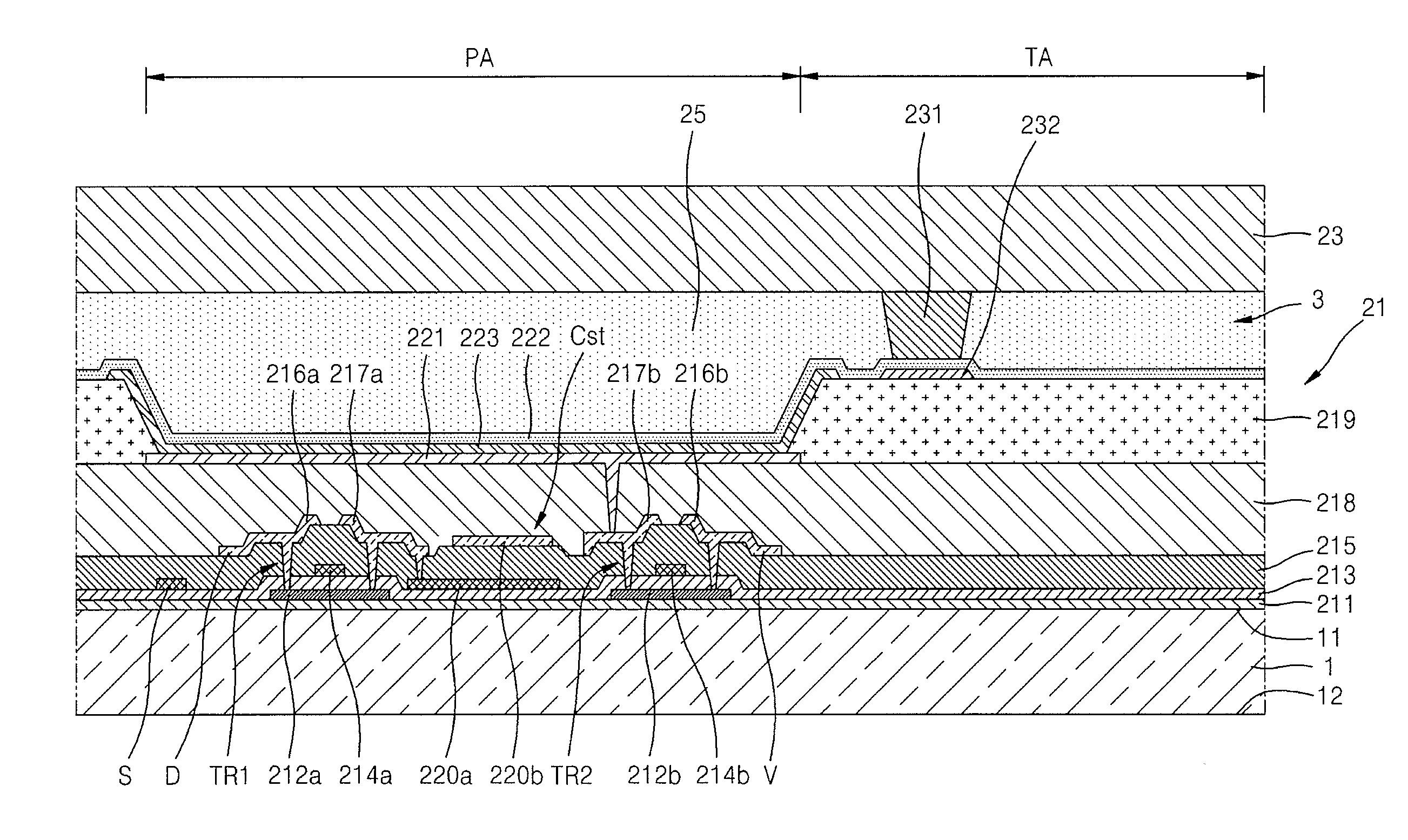

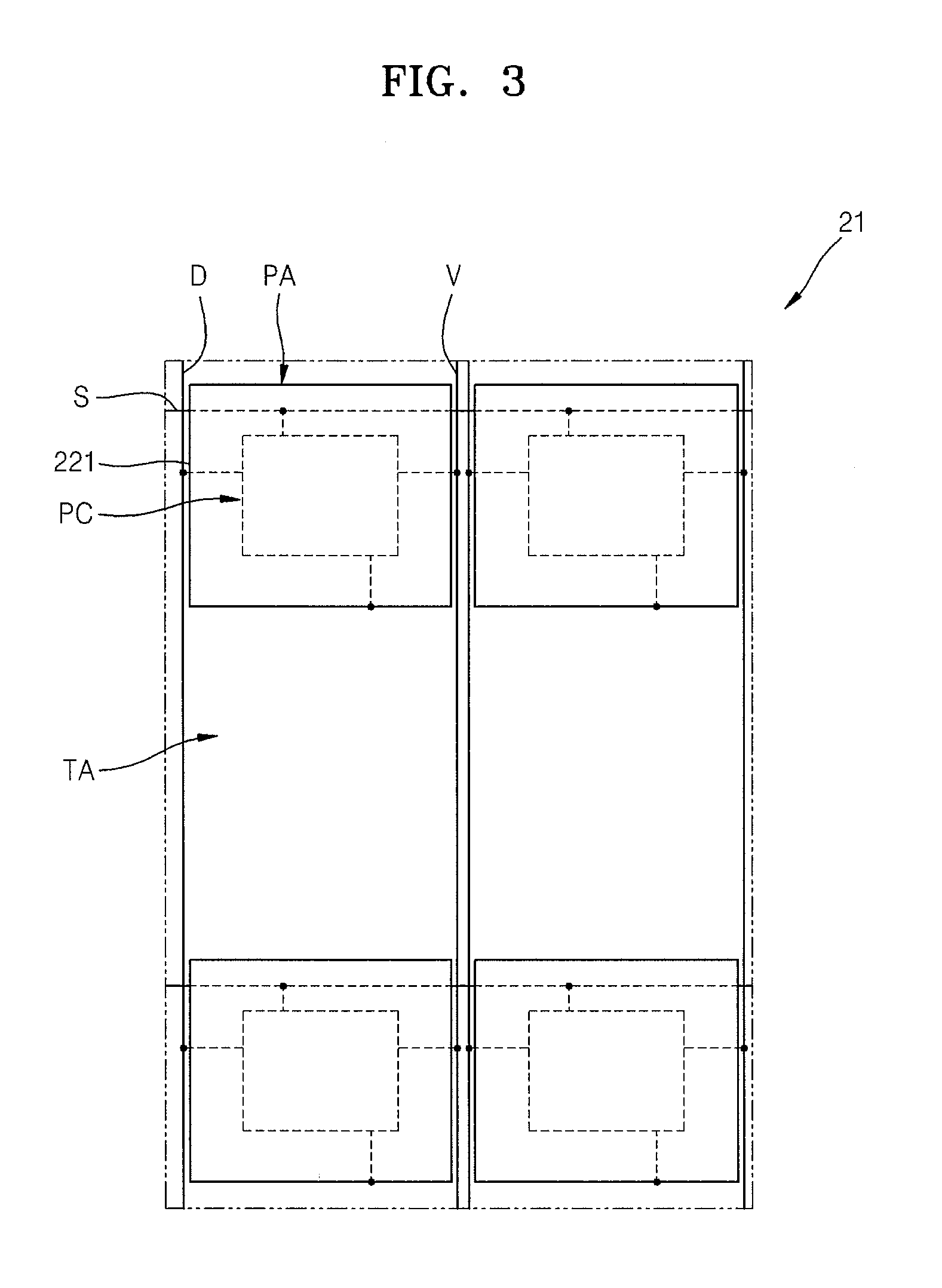

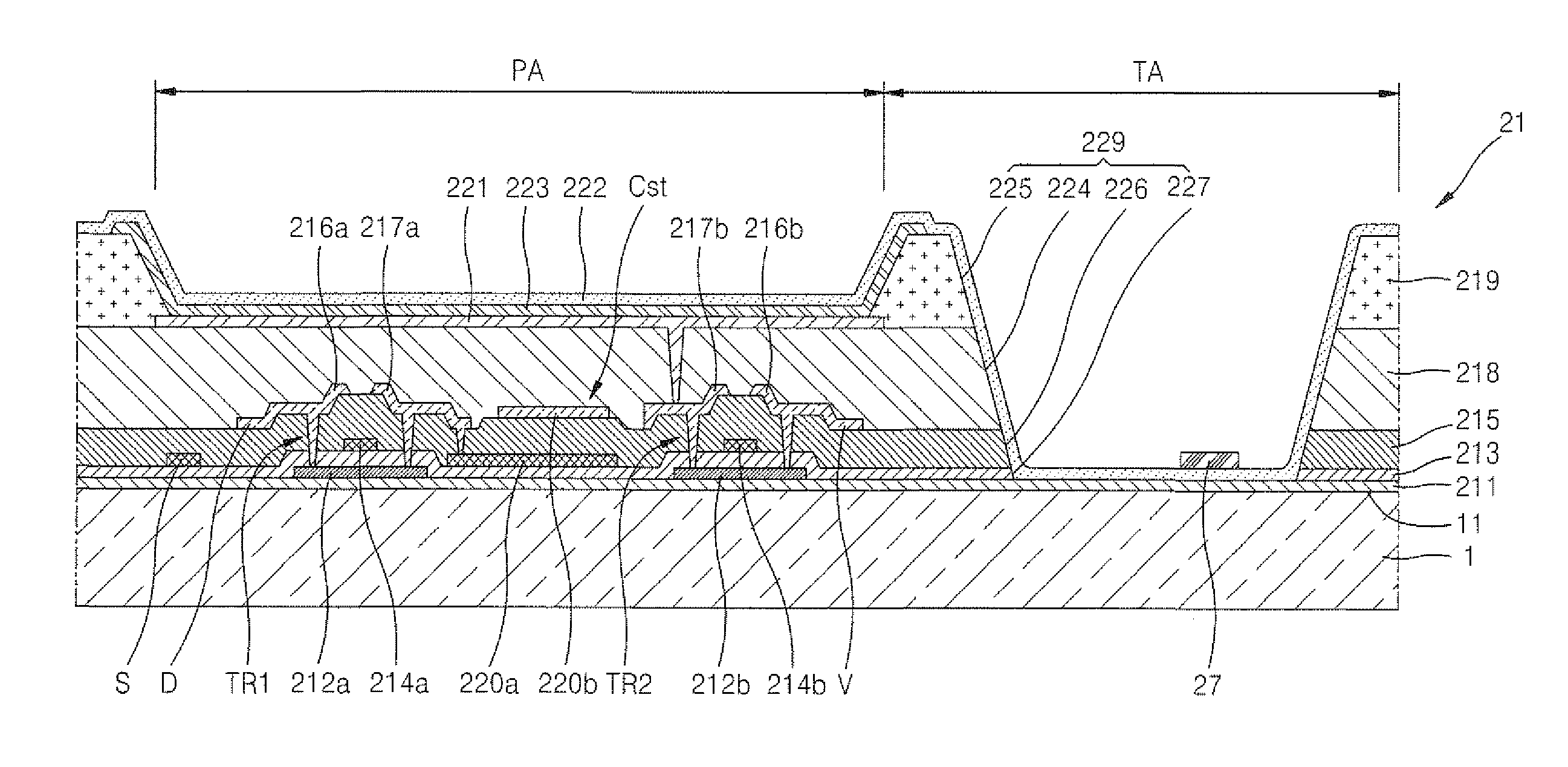

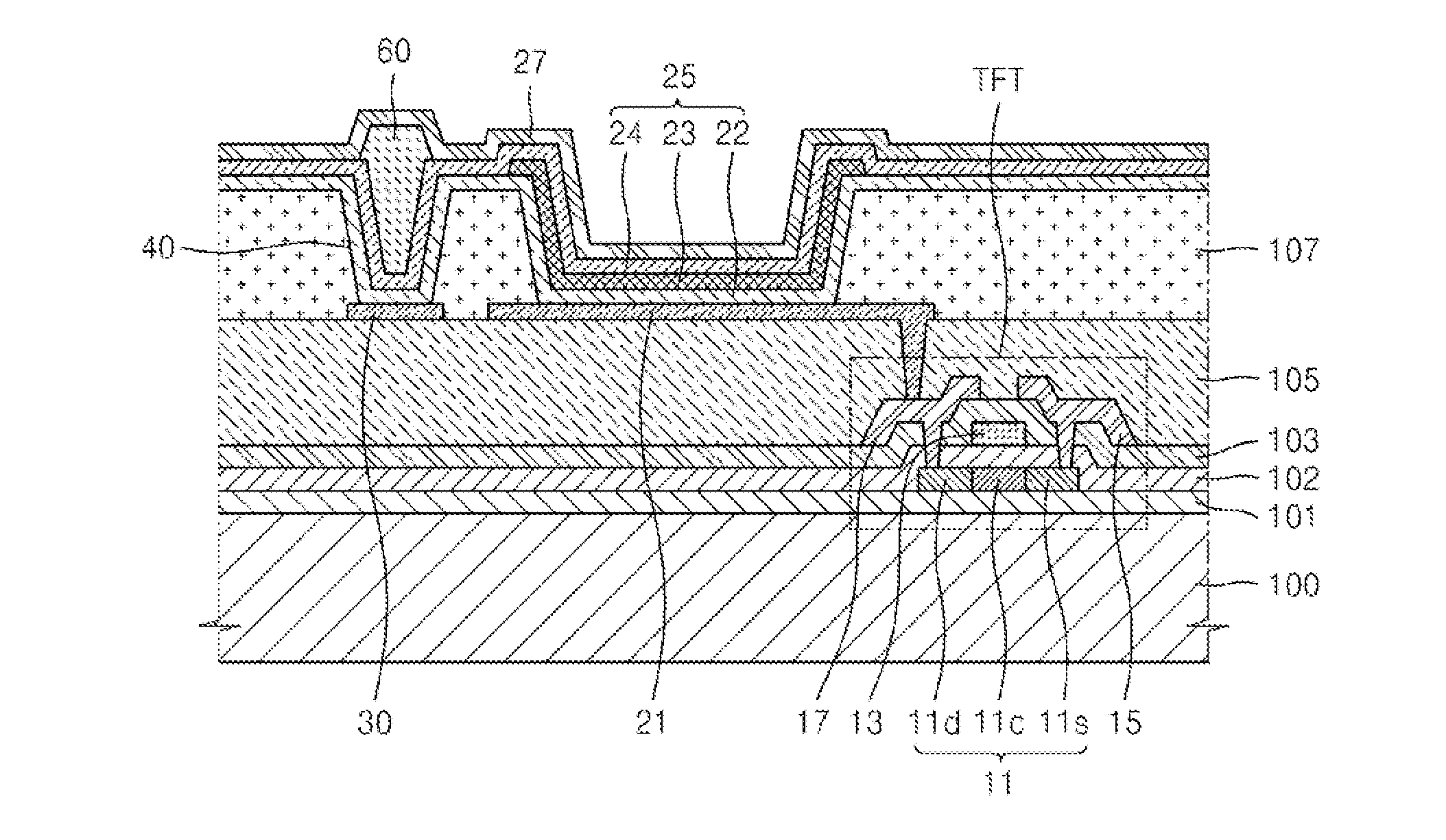

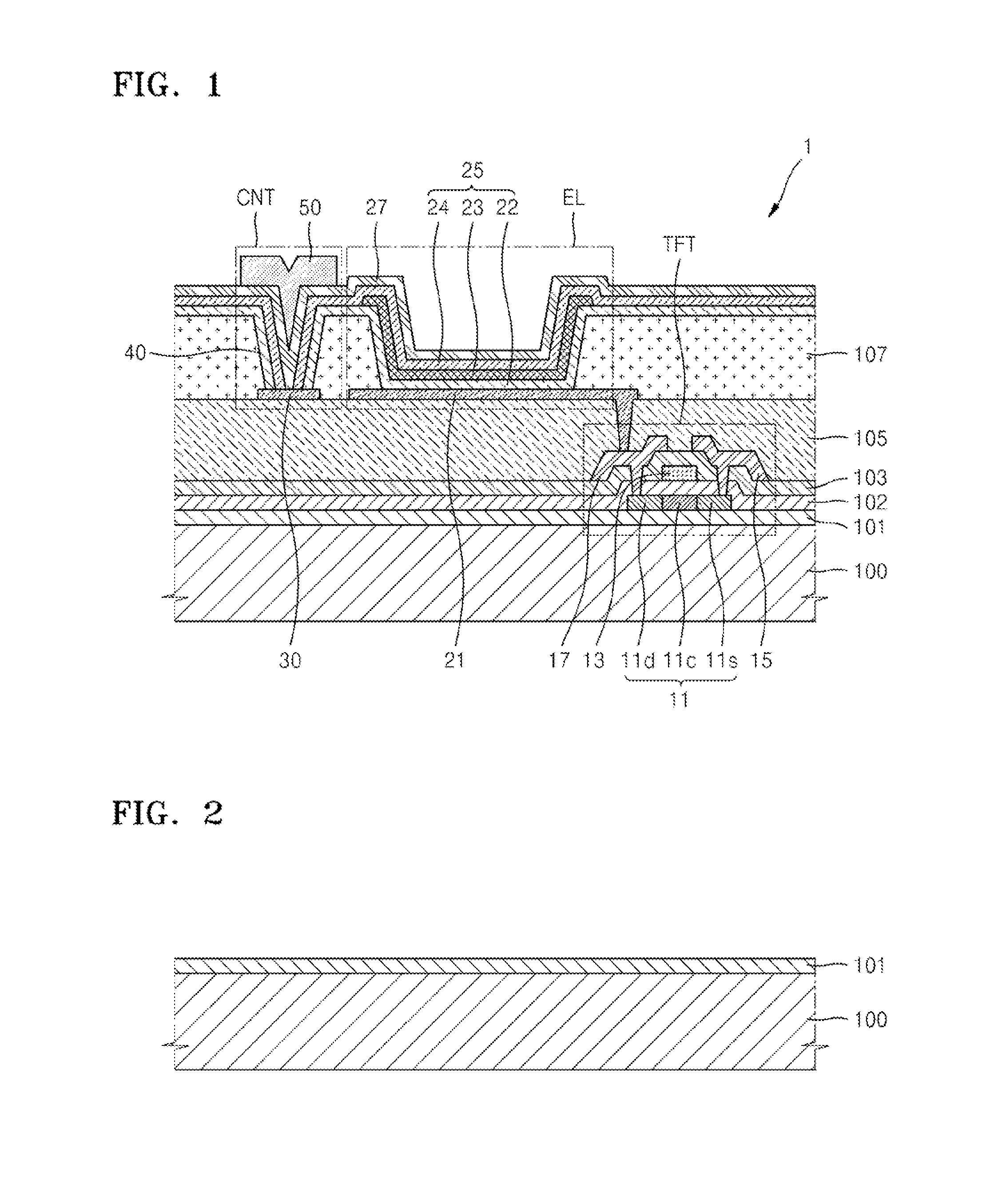

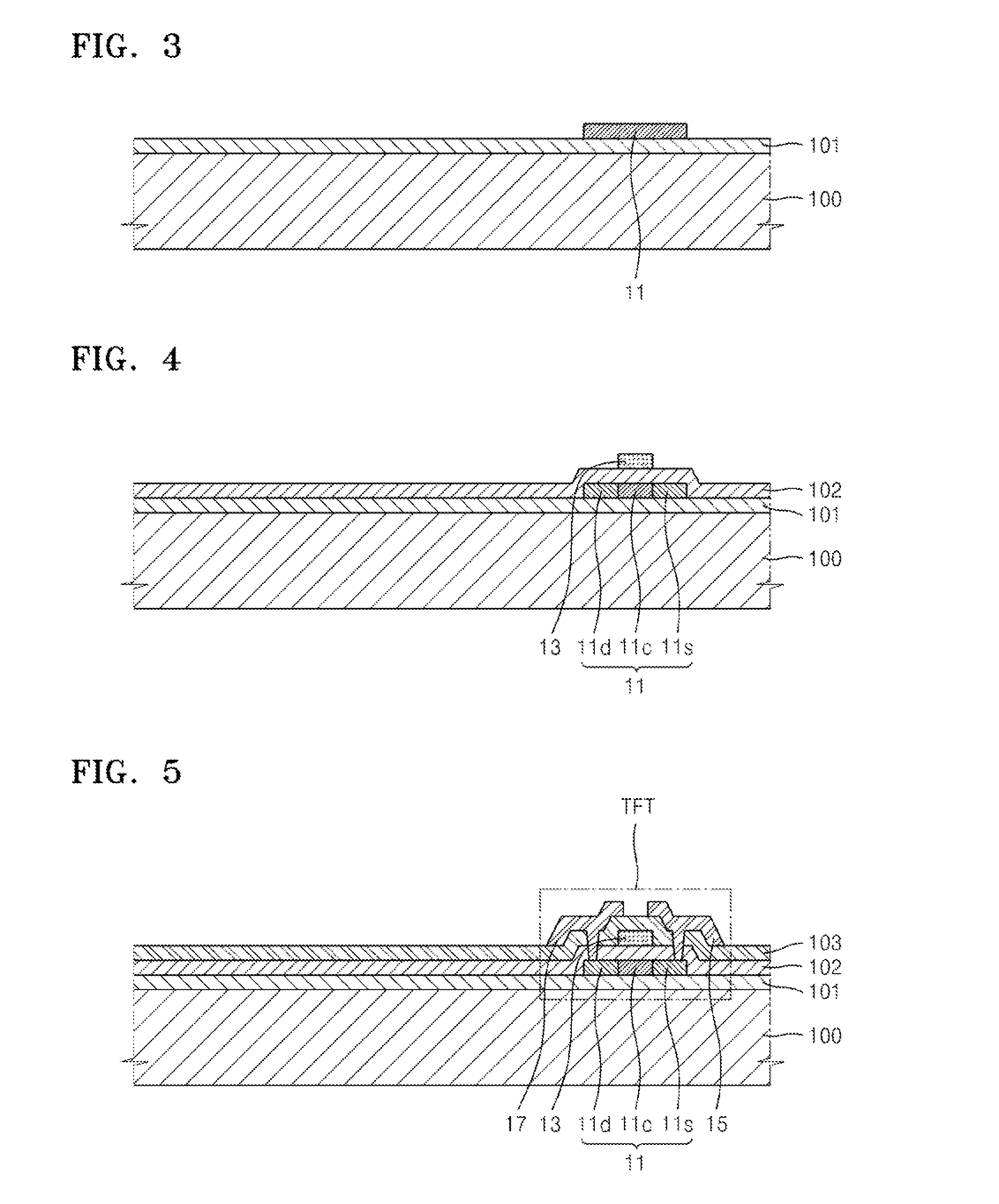

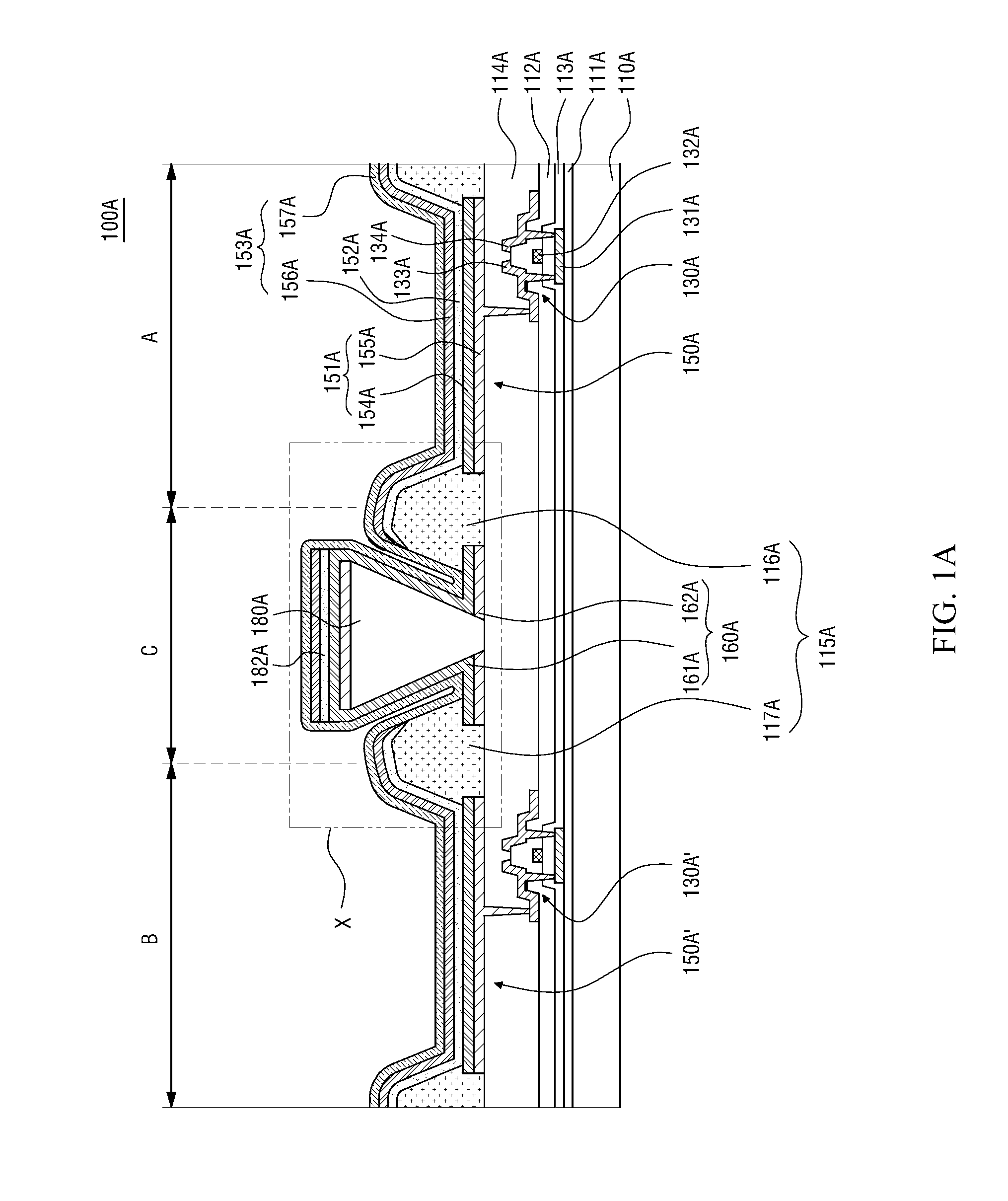

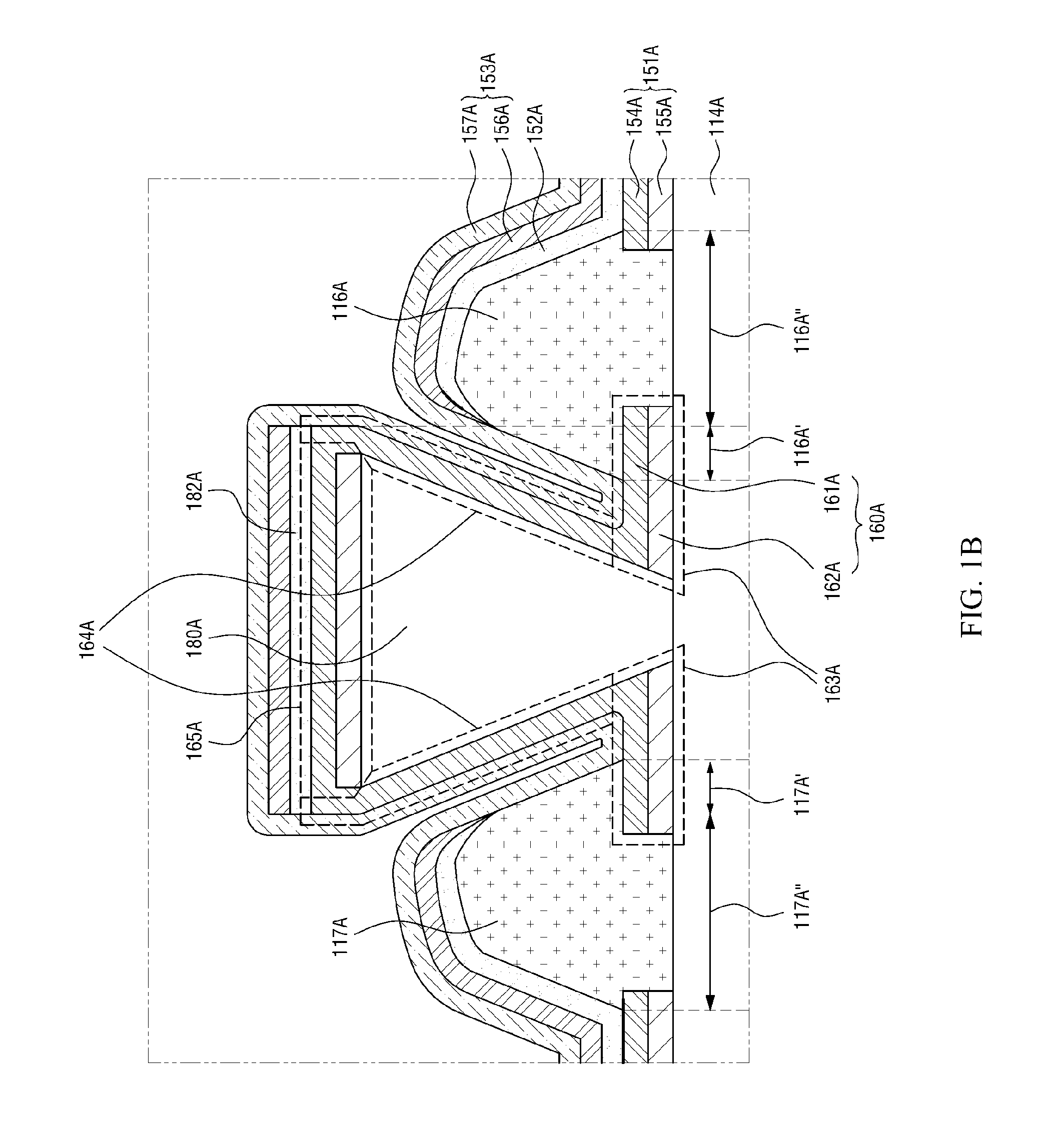

Organic Light-Emitting Display Device

ActiveUS20110204369A1High light transmittanceReduce voltage dropElectroluminescent light sourcesSolid-state devicesTransmittanceDisplay device

An organic light-emitting display device which is transparent by improving a transmittance in transmitting regions and which reduces a voltage drop in an opposite electrode comprises: a substrate having a transmitting region and pixel regions separated from each other by the transmitting region; thin film transistors positioned on the substrate and disposed in the pixel regions, respectively; a passivation layer covering the thin film transistors, formed in the transmitting region and the pixel regions, and having a first opening formed in a location corresponding to at least a portion of the transmitting region; pixel electrodes formed on the passivation layer so as to be electrically connected to the thin film transistors, respectively, located in the pixel regions, and disposed so as to overlap and cover the thin film transistors, respectively; an opposite electrode facing the pixel electrodes, formed so as to be able to transmit light, and located in the transmitting region and the pixel regions; an organic emission layer interposed between the pixel electrodes and the opposite electrode so as to emit light; and a conduction unit formed of a conductive material, disposed so as to overlap with the first opening, and contacting the opposite electrode.

Owner:SAMSUNG DISPLAY CO LTD

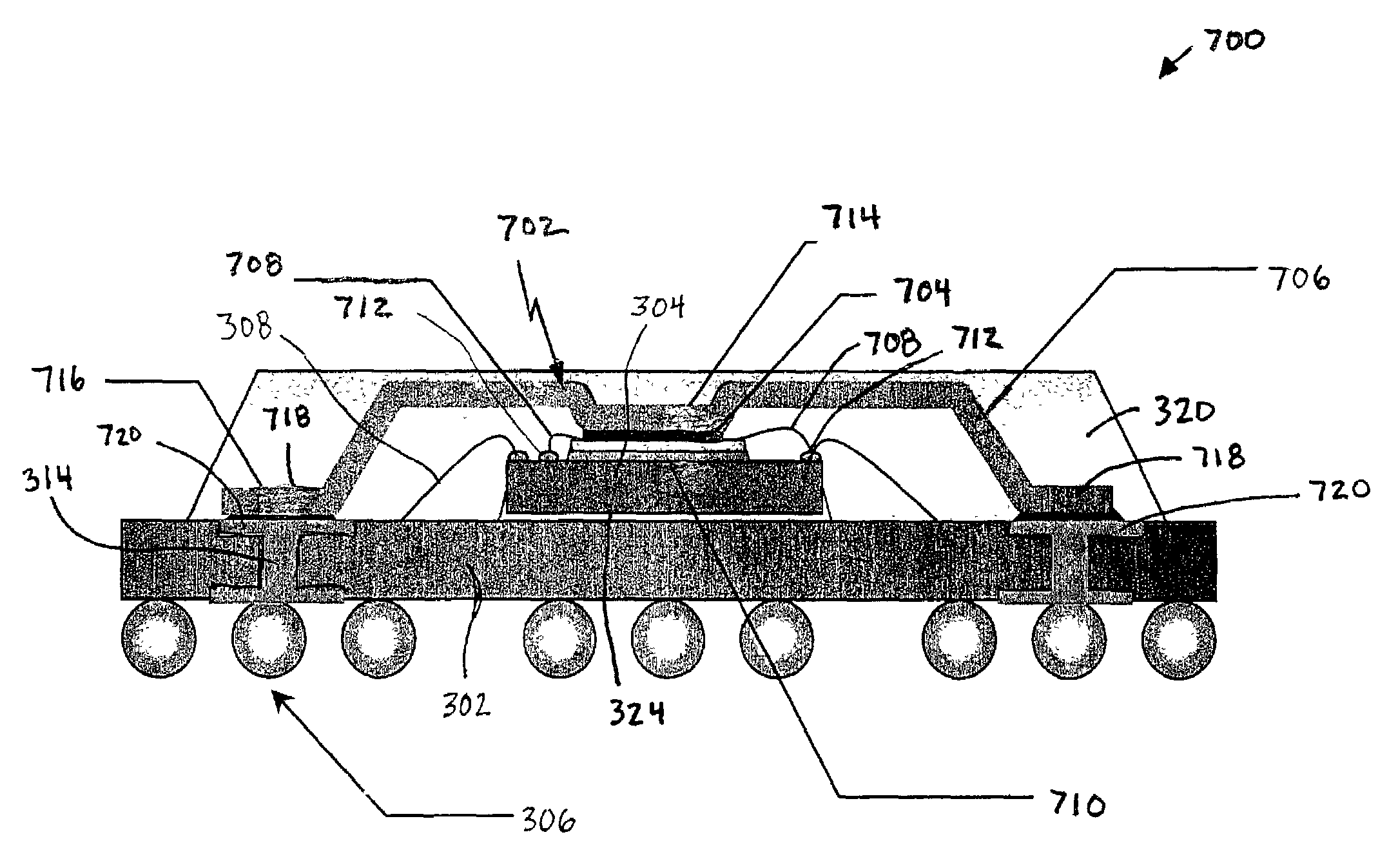

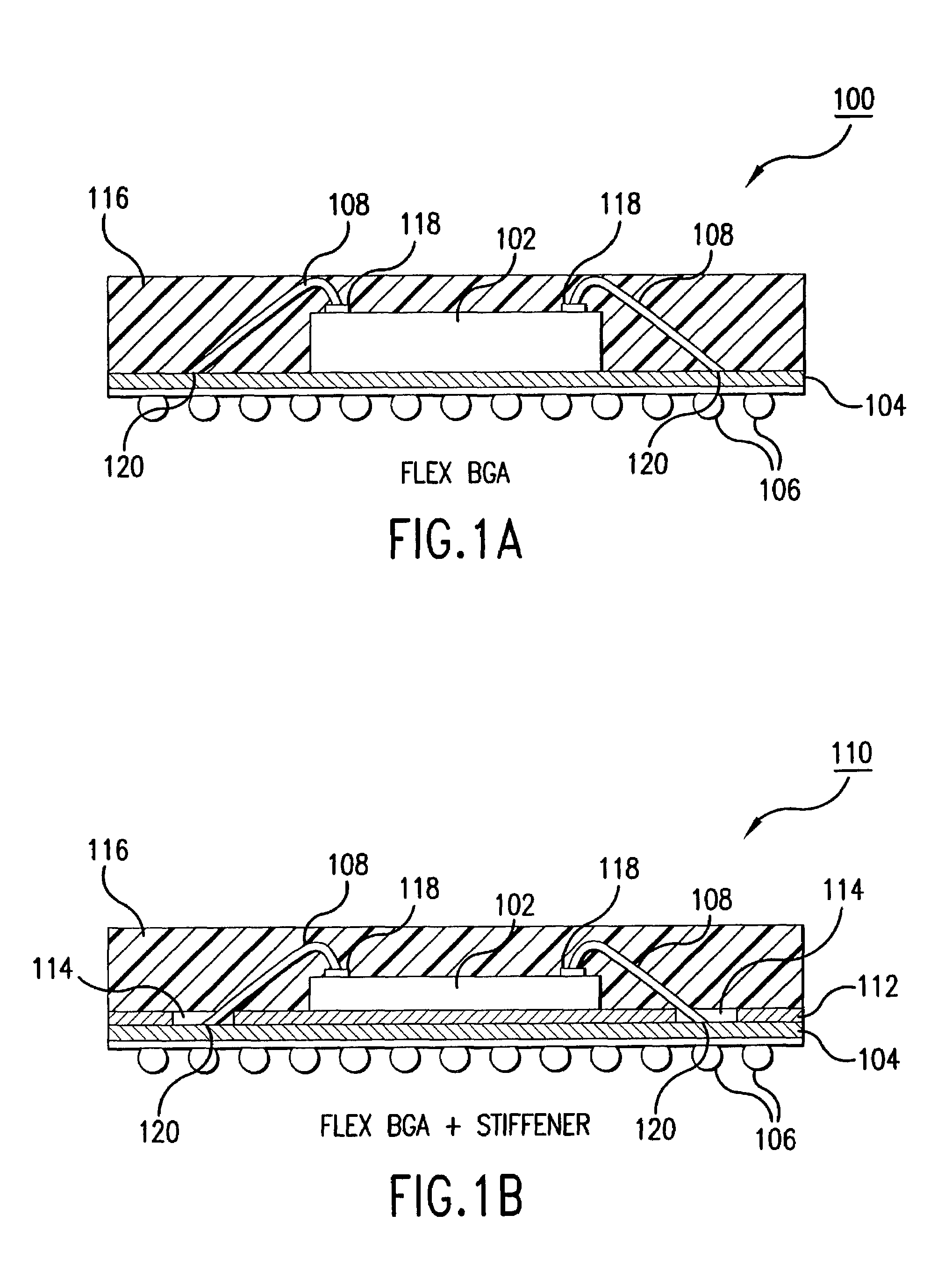

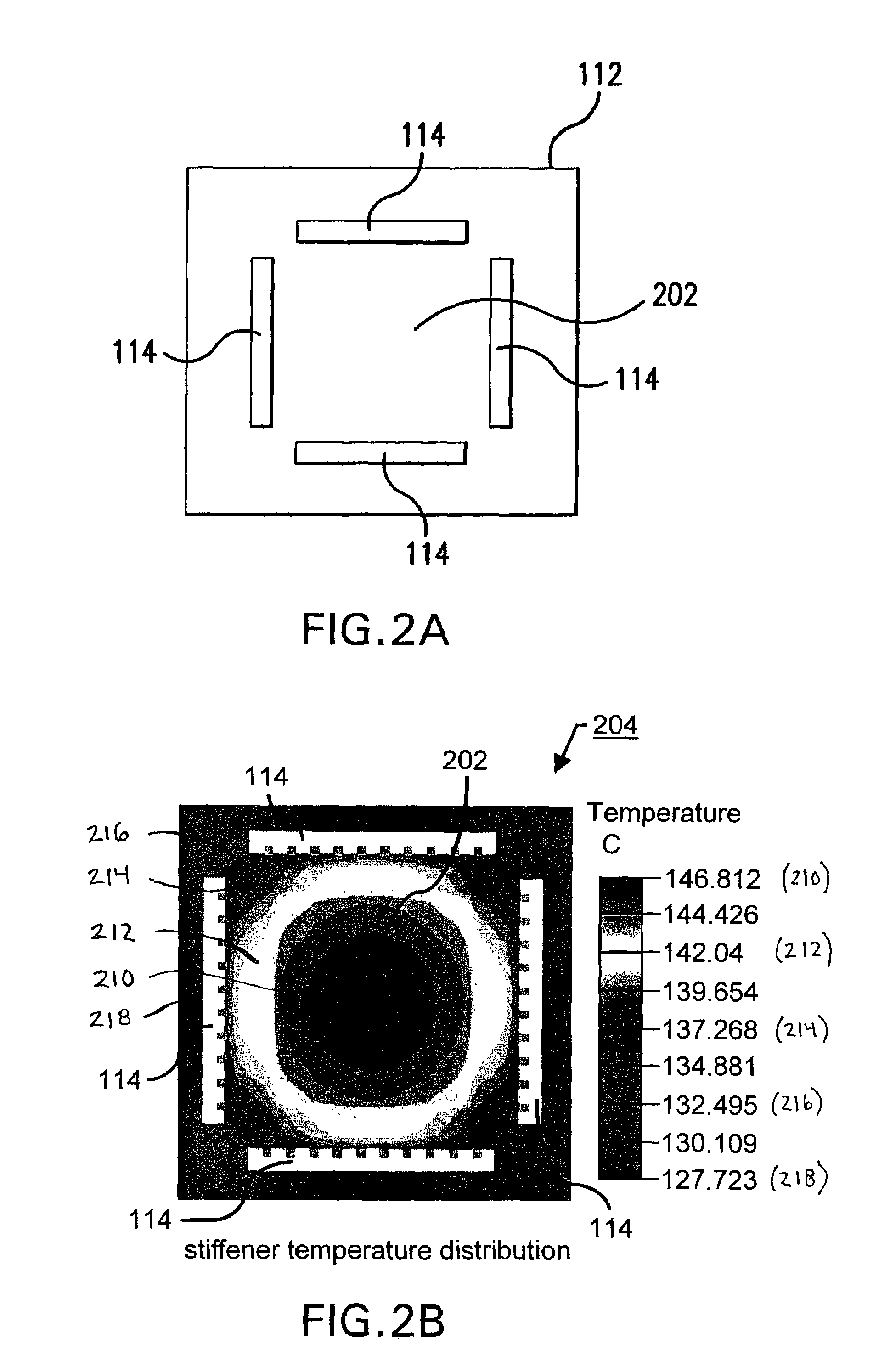

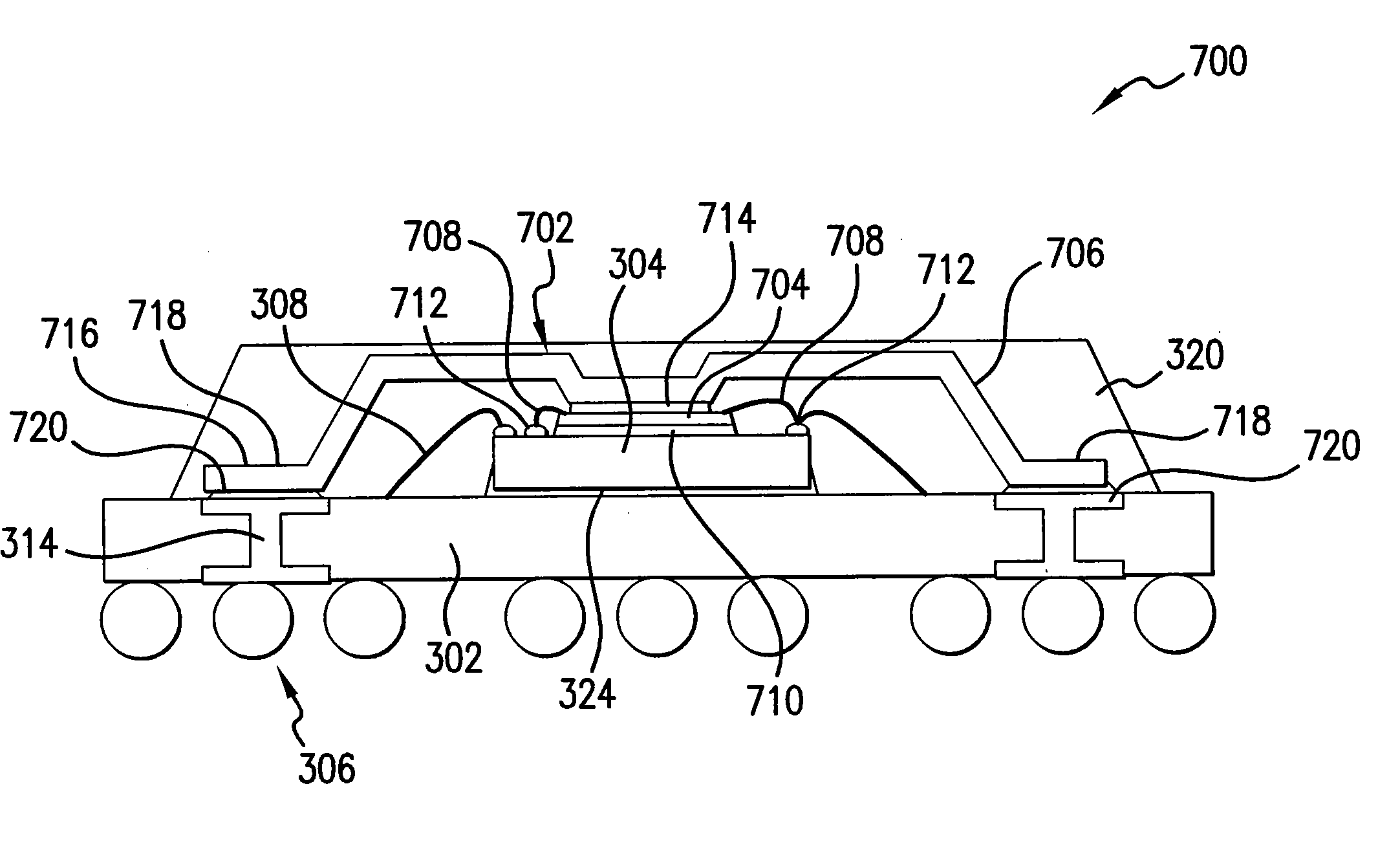

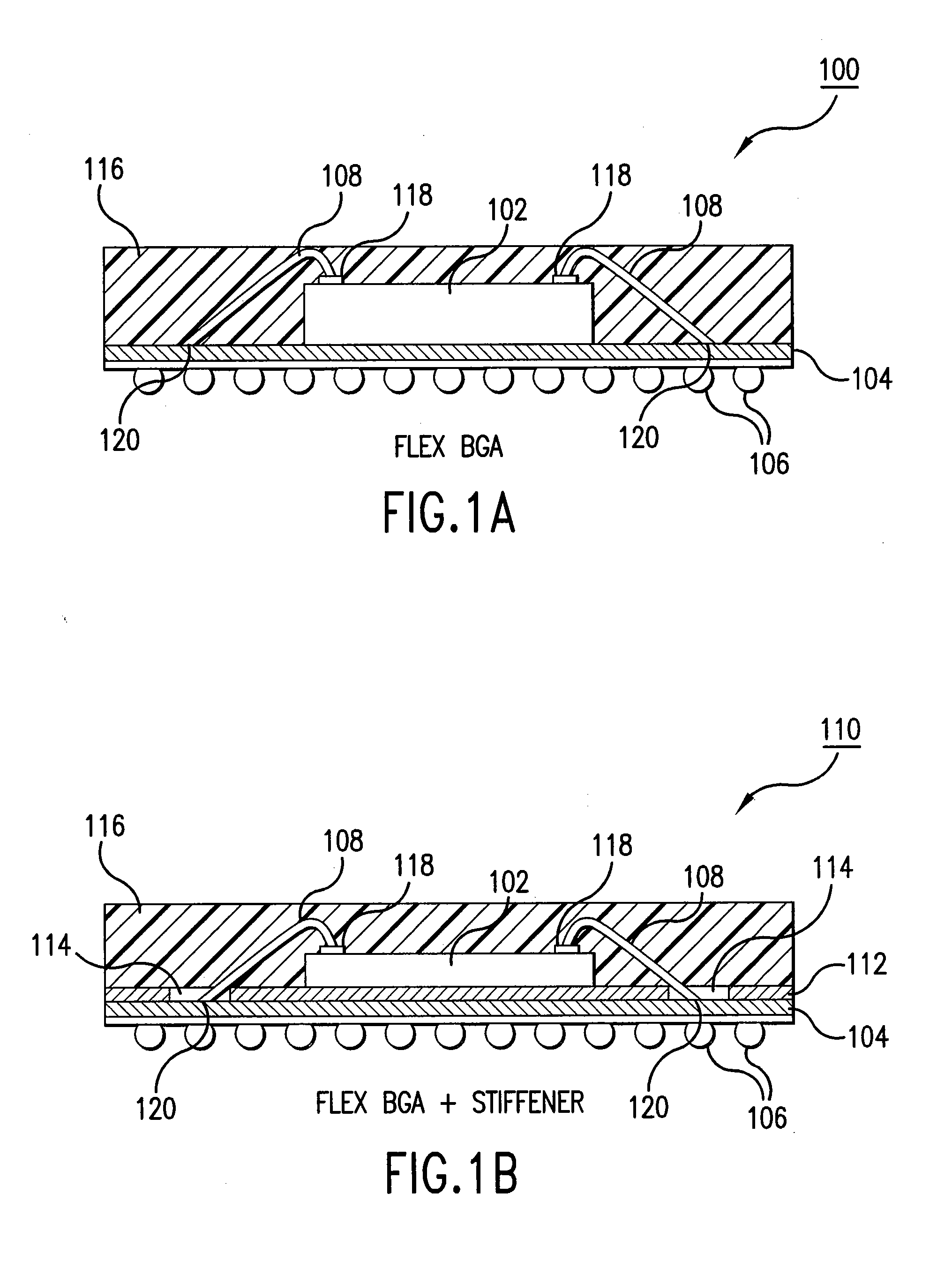

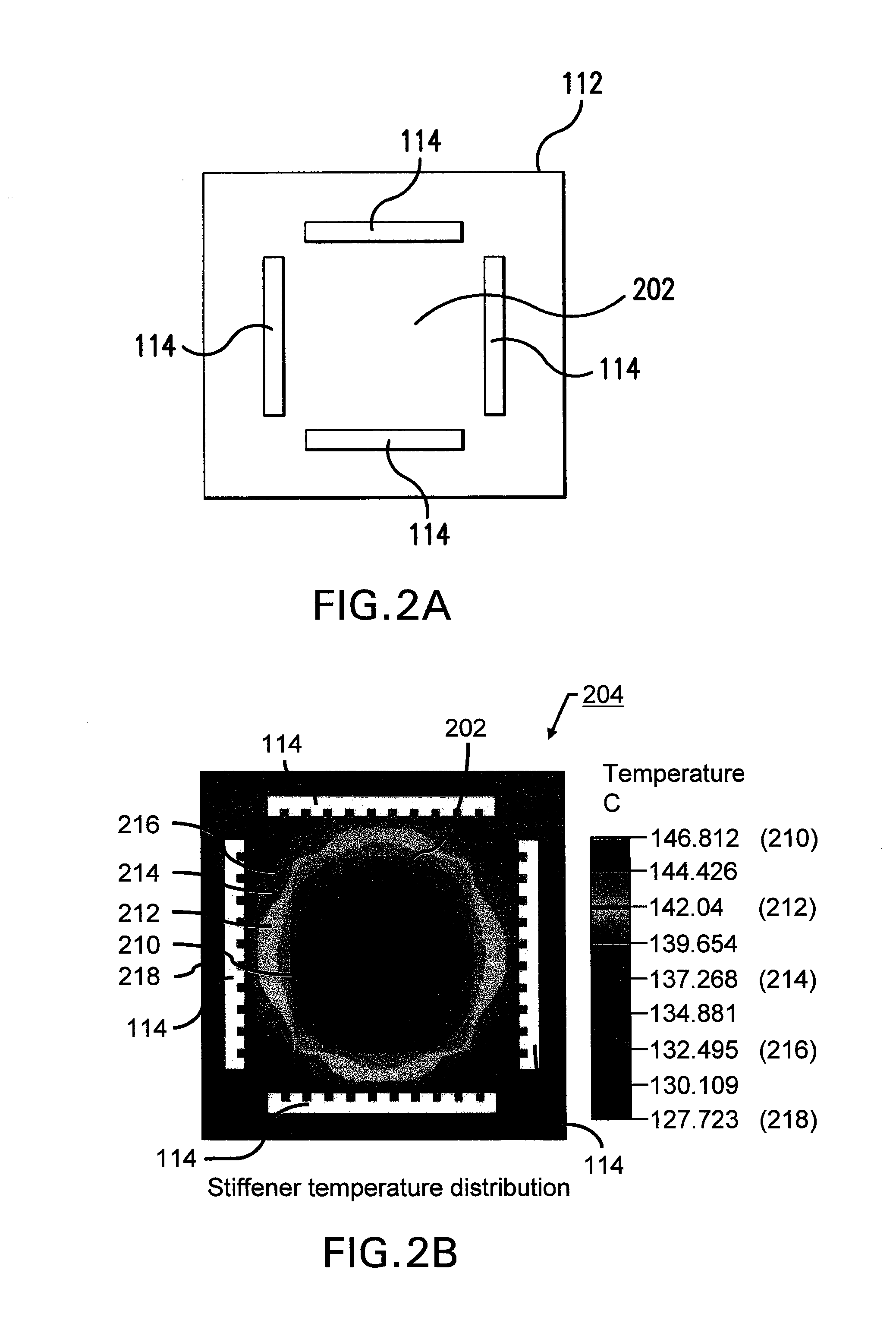

Low voltage drop and high thermal performance ball grid array package

InactiveUS7196415B2Fast heat conductionEnhanced thermal and electrical connectionSemiconductor/solid-state device detailsSolid-state devicesContact padLow voltage

Owner:AVAGO TECH INT SALES PTE LTD

Low Voltage Drop and High Thermal Performance Ball Grid Array Package

InactiveUS20070108598A1Fast heat conductionEnhanced thermal and electrical connectionSemiconductor/solid-state device detailsSolid-state devicesContact padLow voltage

An apparatus and method for a low voltage drop and thermally enhanced integrated circuit (IC) package are described. A substantially planar substrate having a plurality of contact pads on a first surface is electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate. An IC die having a first surface is mounted to the first surface of the substrate. The IC die has a plurality of I / O pads electrically connected to the plurality of contact pads on the first surface of the substrate. A heat sink assembly is coupled to a second surface of the IC die and to a first contact pad on the first surface of the substrate to provide a thermal path from the IC die to the first surface of the substrate. The heat sink assembly can also provide an electrical path from the IC die to the first surface of the substrate. The heat sink assembly may have one or two heat sink elements to provide thermal and / or electrical connectivity between the IC die and the substrate.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Integrated circuit (IC) test structure with monitor chain and test wires

ActiveUS9435852B1Reduce voltage dropSemiconductor/solid-state device testing/measurementElectronic circuit testingElectricityEngineering

Aspects of the present disclosure provide an integrated circuit (IC) test structure. An IC structure according to the present disclosure can include: a monitor chain having a first end electrically connected to a second end through a plurality of metal wires each positioned within one of a first metal level and a second metal level, wherein the first metal level is vertically separated from the second metal level; a first test wire positioned within the first metal level and extending in a first direction, wherein the first test wire is electrically insulated from the monitor chain; and a second test wire positioned within the second metal level and extending in a second direction, wherein the second test wire is electrically insulated from the monitor chain and the first test wire, and wherein the first direction is different from the second direction.

Owner:GLOBALFOUNDRIES US INC

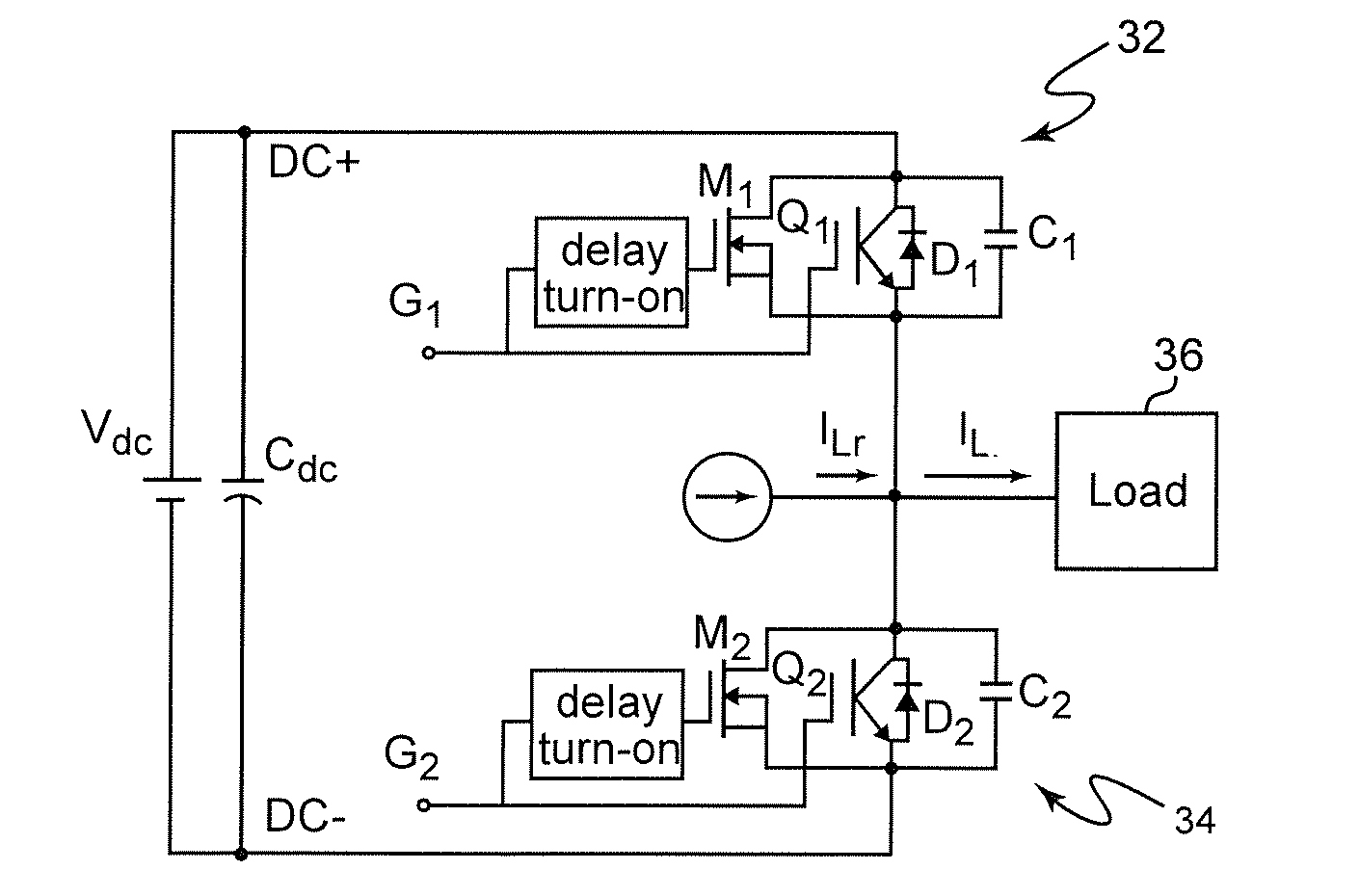

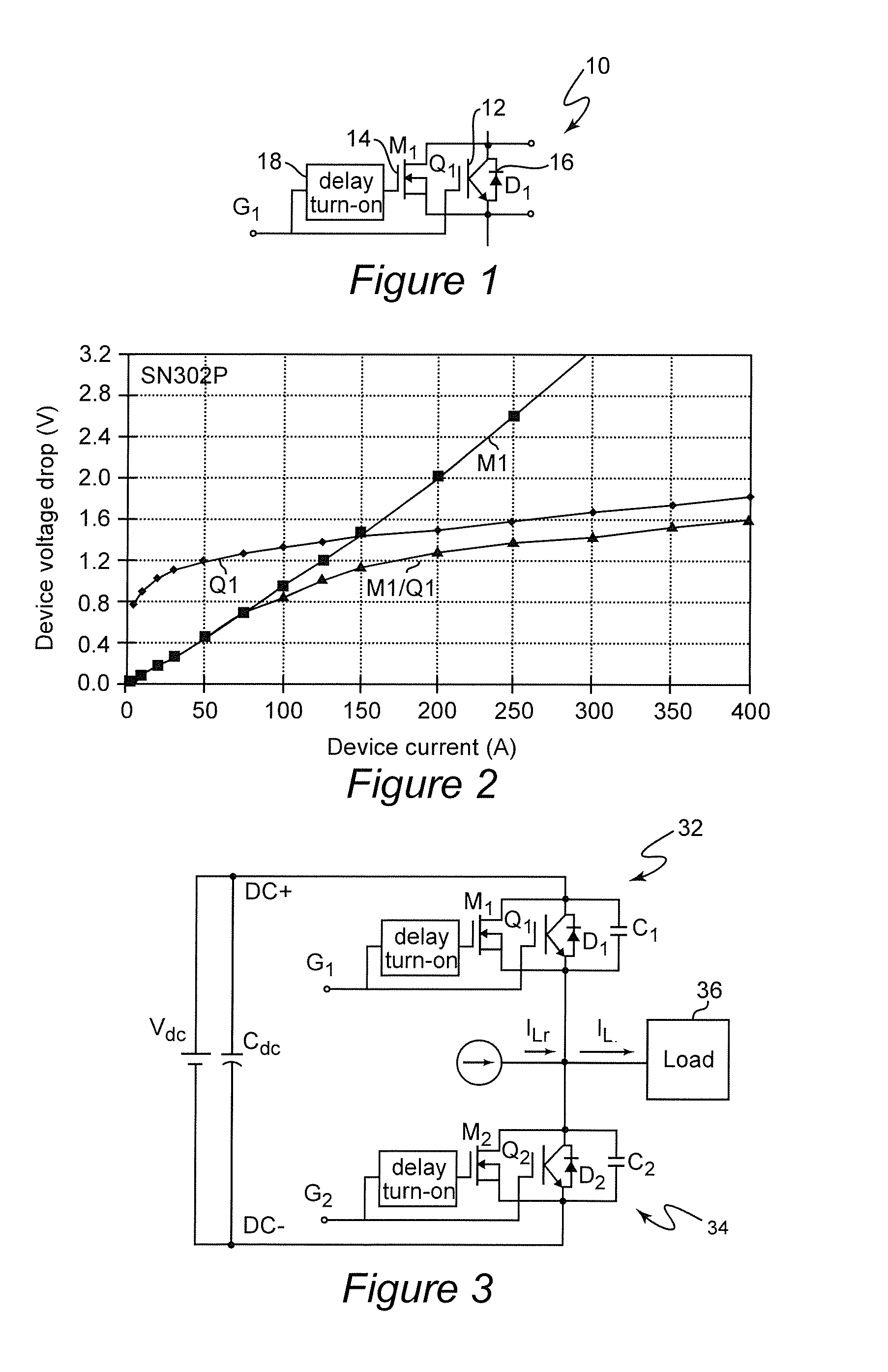

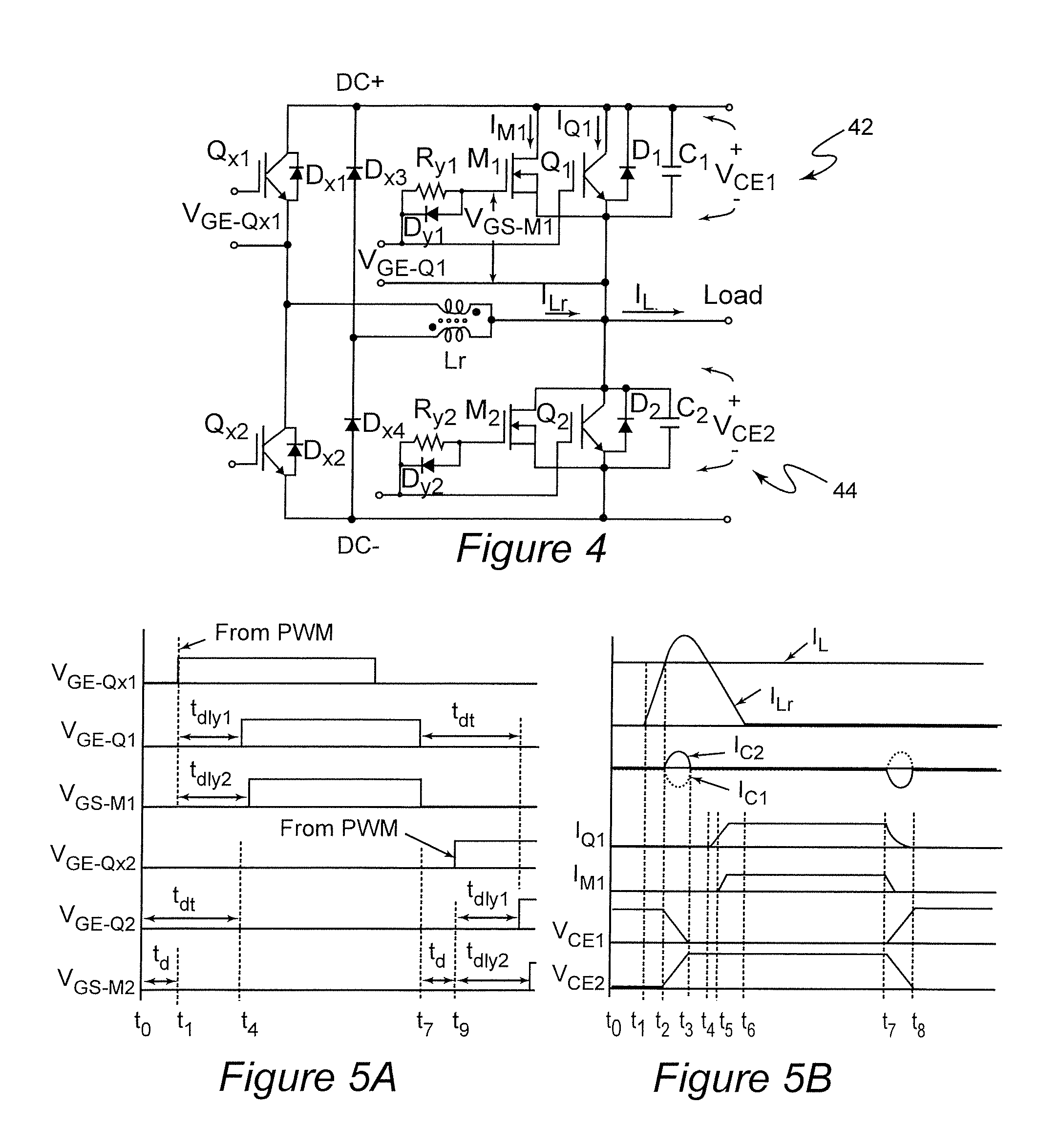

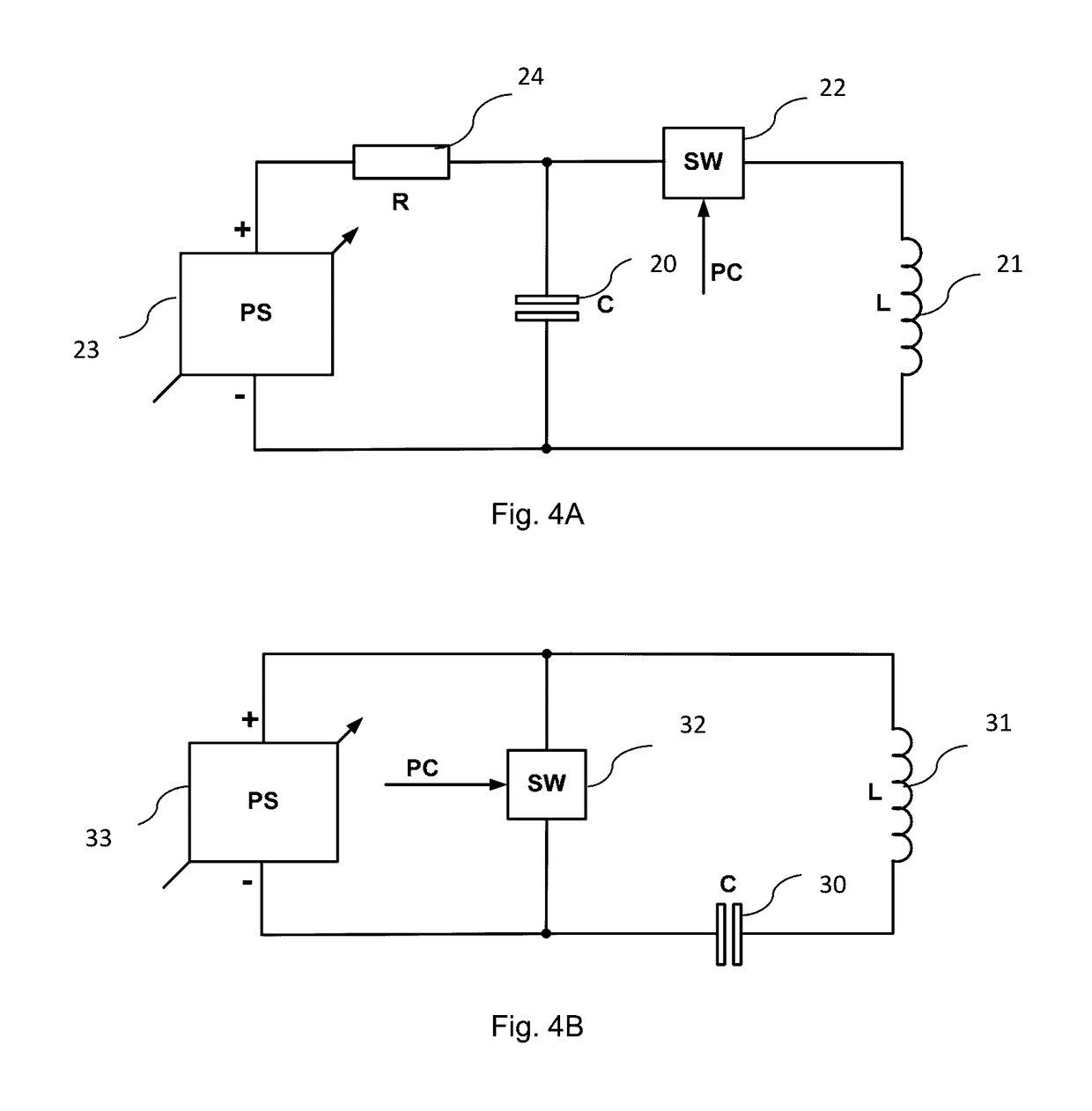

Hybrid switch for resonant power converters

ActiveUS20120057387A1Reduce conduction lossConstant voltage dropEfficient power electronics conversionAc-dc conversionResonant power convertersVoltage drop

A hybrid switch comprising two semiconductor switches connected in parallel but having different voltage drop characteristics as a function of current facilitates attainment of zero voltage switching and reduces conduction losses to complement reduction of switching losses achieved through zero voltage switching in power converters such as high-current inverters.

Owner:VIRGINIA TECH INTPROP INC

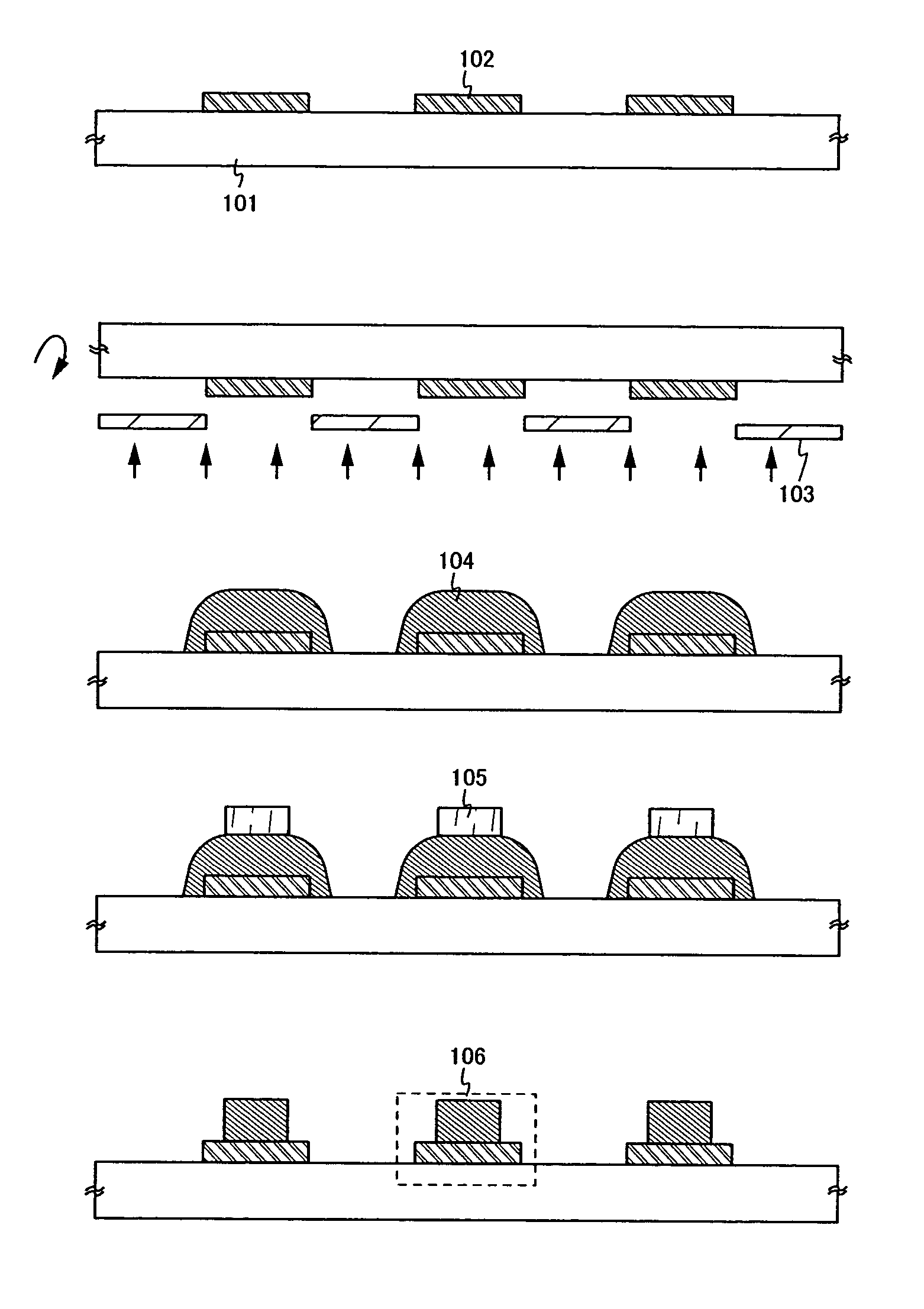

Manufacturing method of semiconductor device

InactiveUS7094684B2Reduce wire resistanceReduce signalingSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceImaging quality

It is an object of the present invention to suppress an influence of voltage drop due to wiring resistance to make an image quality of a display device uniform. In addition, it is also an object of the present invention to suppress delay due to a wiring for electrically connecting a driving circuit portion to an input / output terminal to improve an operation speed in the driving circuit portion.In the present invention, a wiring including copper for realizing lowered wiring resistance, subjected to microfabrication, is used as a wiring used for a semiconductor device and a barrier conductive film for preventing diffusion of copper is provided for a TFT as a part of the wiring including copper to form the wiring including copper without diffusion of copper into a semiconductor layer of the TFT. The wiring including copper is a wiring including a laminate film of at least a conductive film containing copper as its main component, subjected to microfabricaiton, and the barrier conductive film.

Owner:SEMICON ENERGY LAB CO LTD

Organic light emitting display apparatus and method of manufacturing the same

ActiveUS20140346459A1Reduce voltage dropElectroluminescent light sourcesSolid-state devicesAuxiliary electrodeOptoelectronics

An organic light emitting display apparatus includes pixel electrodes formed on a substrate for respective pixels. Auxiliary electrodes are formed on at least parts of the periphery of the pixel electrodes. A first organic function layer is formed on the substrate and covers the pixel electrodes and the auxiliary electrodes. An emissive layer is formed on the first organic function layer for the respective pixels. A second organic function layer is formed on the substrate and covers the emissive layer. A cathode electrode is formed on the entire substrate and faces the pixel electrodes and covers the second organic function layer. Secondary cathode electrodes are formed, on at least parts of the auxiliary electrodes, in contact with the cathode electrode through a contact hole.

Owner:SAMSUNG DISPLAY CO LTD

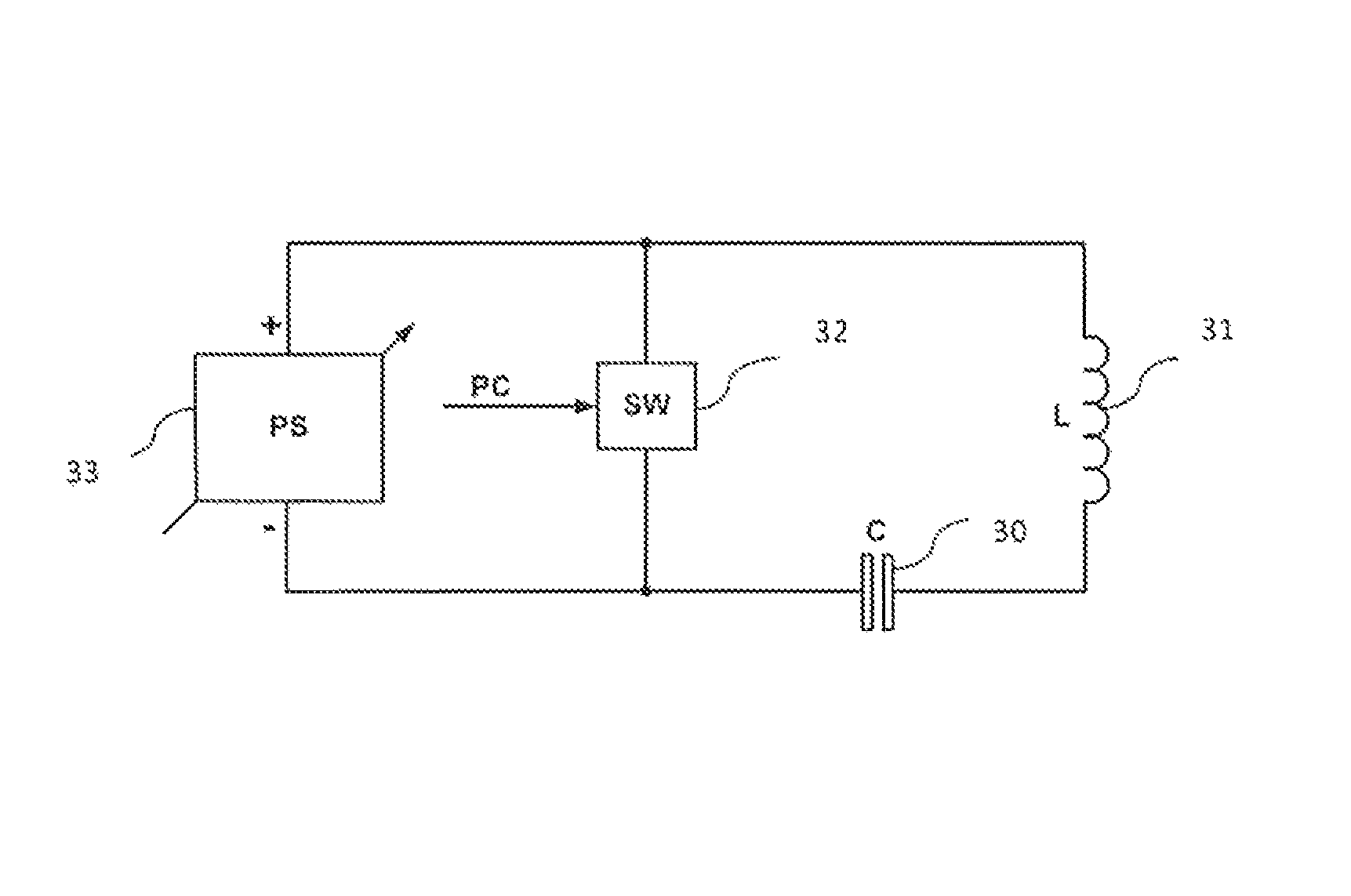

Magnetic stimulation methods and devices for therapeutic treatments

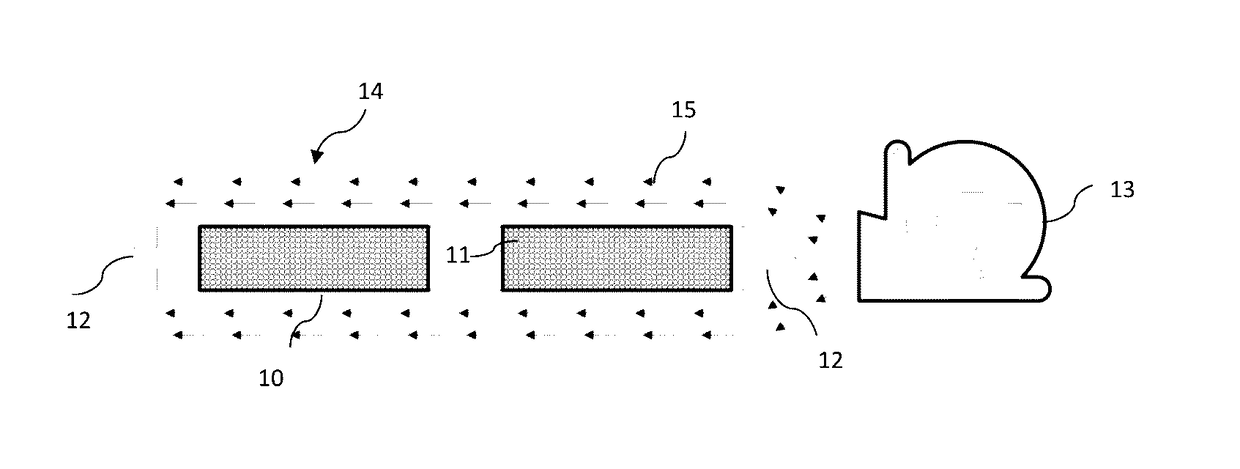

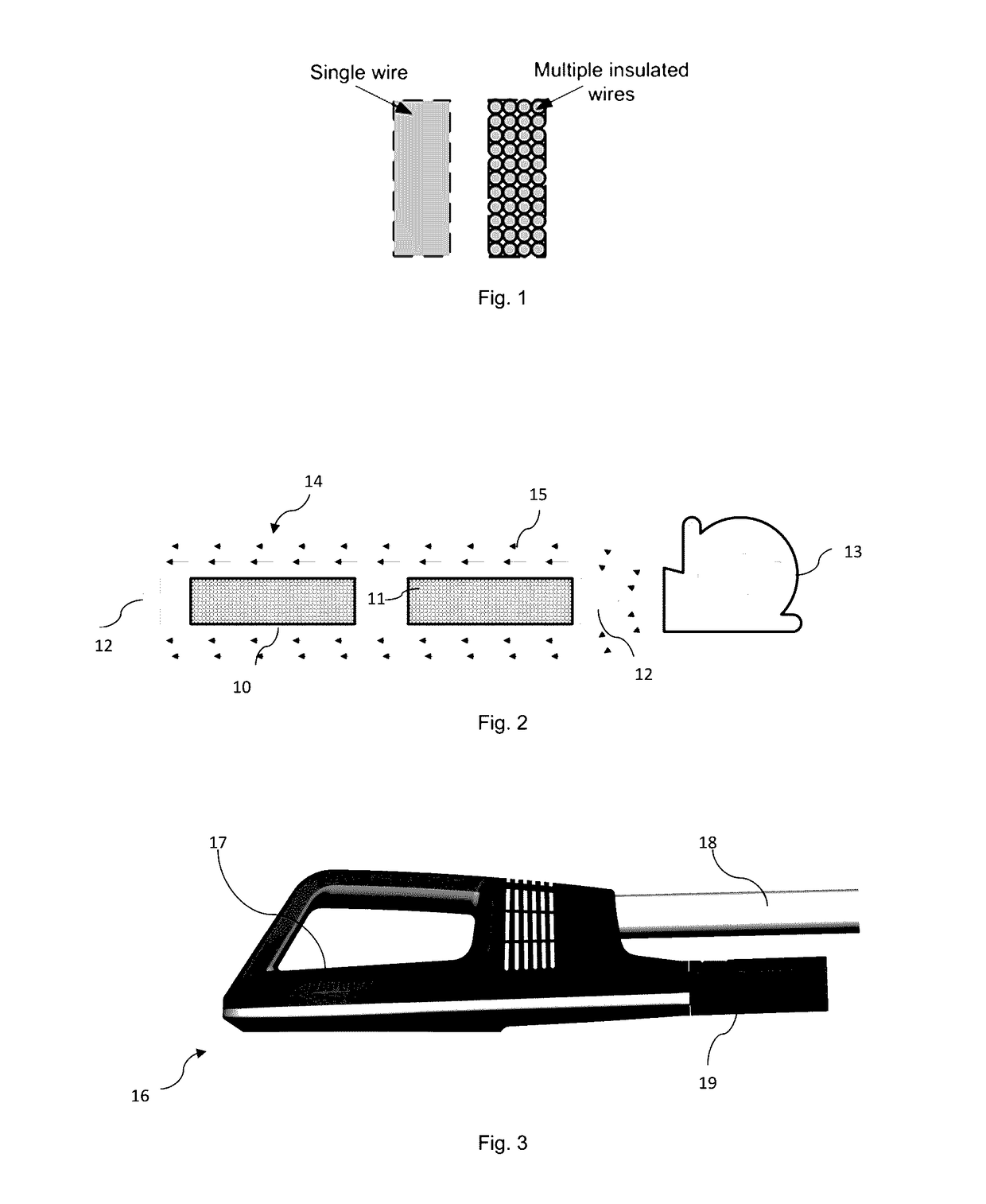

ActiveUS9586057B2Improve effectivenessReduce self-heatingElectrotherapyMagnetotherapy using coils/electromagnetsPhysical Therapy ModalityTherapeutic treatment

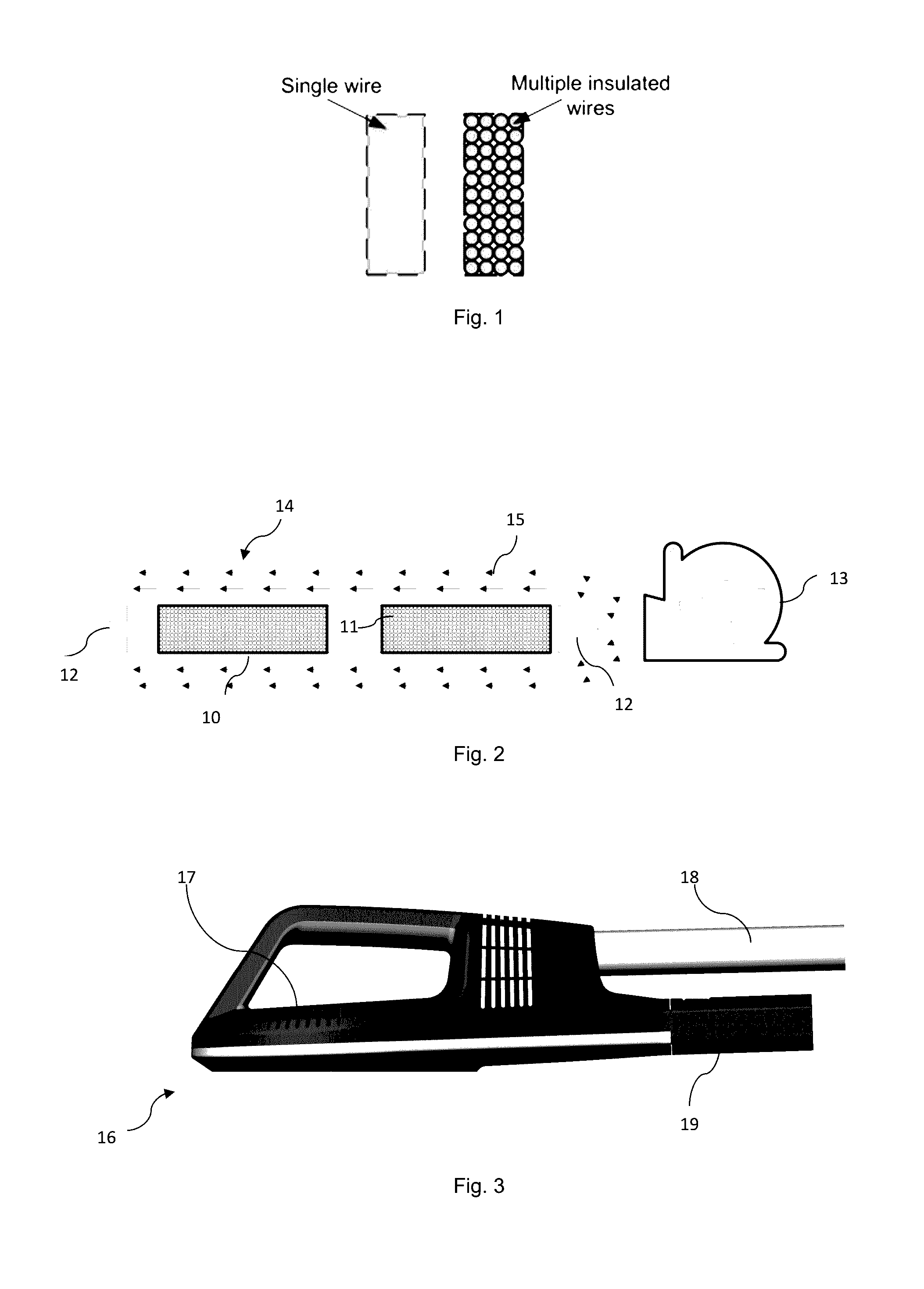

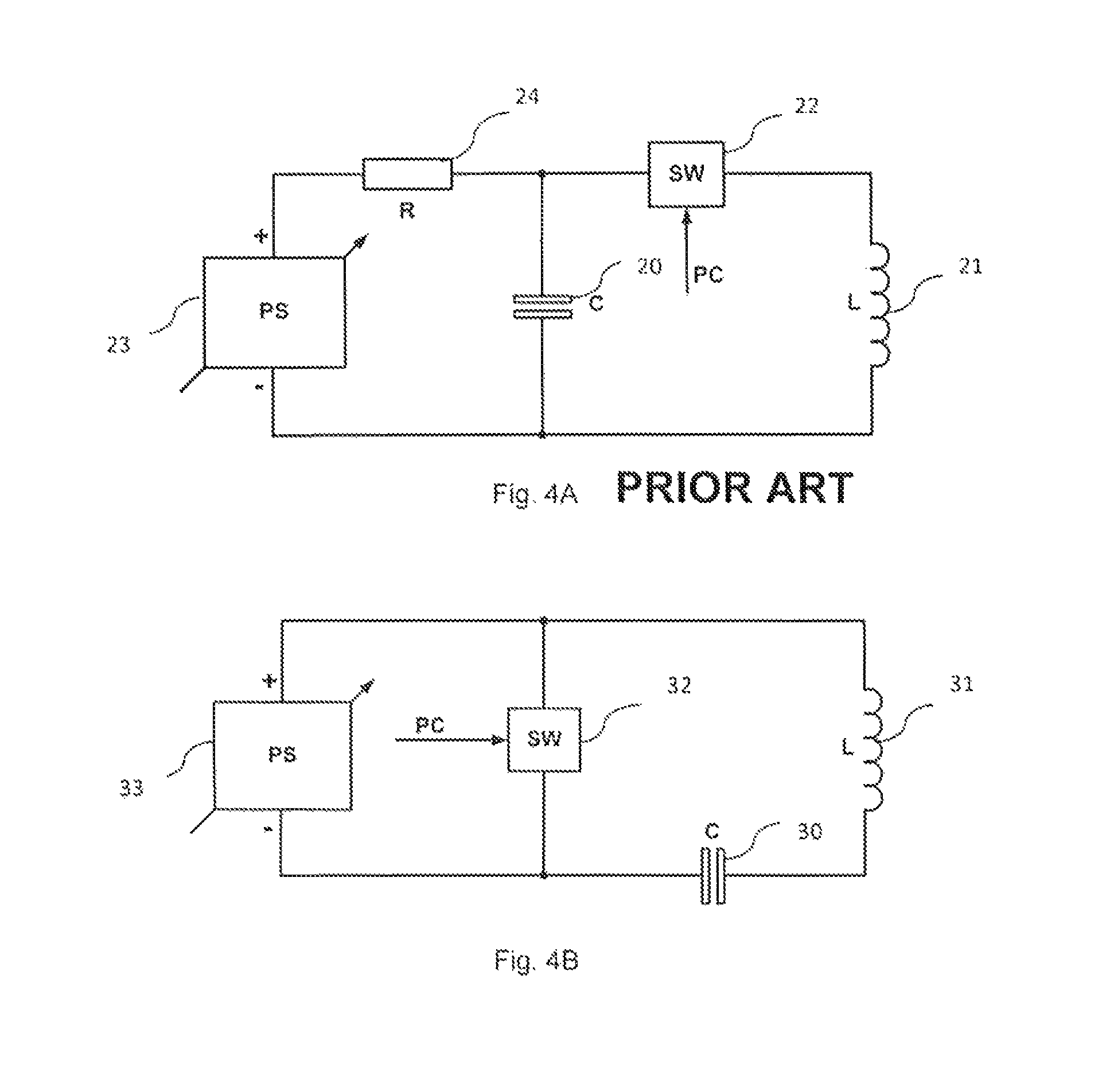

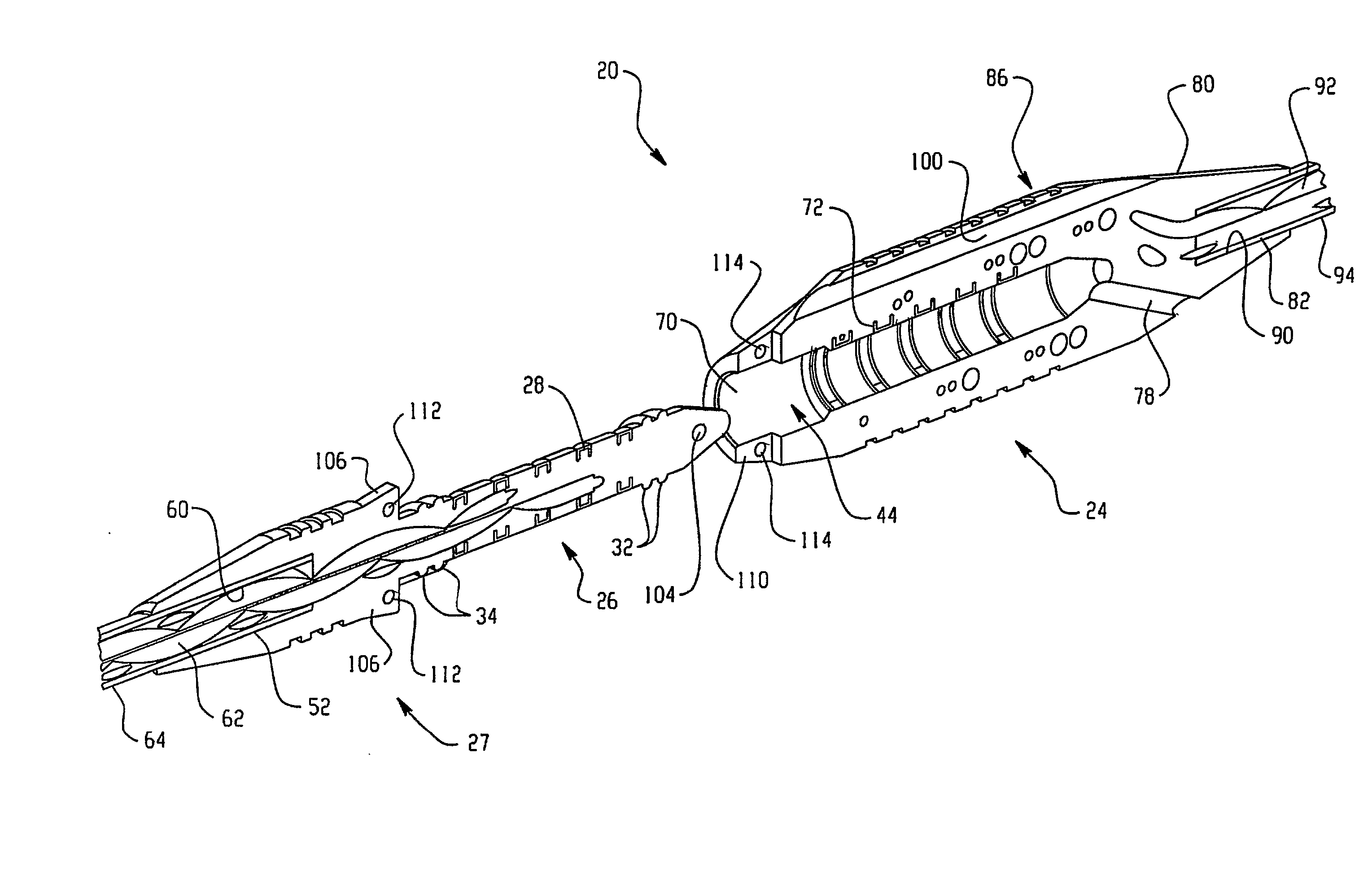

Methods and devices producing time varying magnetic field have therapeutic uses. The device contains a coil made of insulated wires, an energy storage device, an energy source and a switch. The coil is flexibly attached in a case. The device has at least one blower for cooling the coil. The methods and devices can be used in for example in physiotherapy, neuropsychiatric therapy, aesthetic therapy, urology or urogynecology.

Owner:BTL MEDICAL SOLUTIONS AS

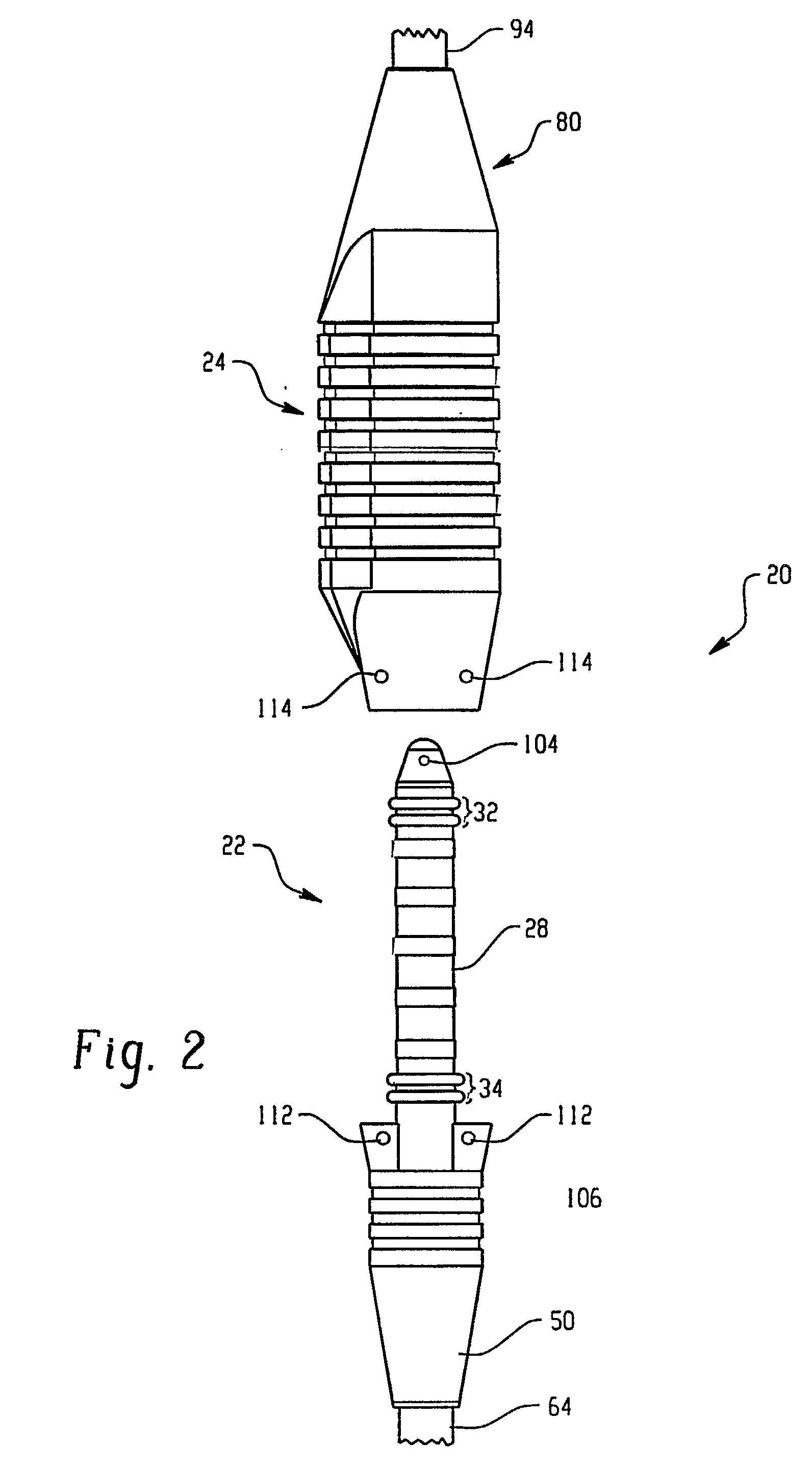

Flexible connector for implantable wiring harness

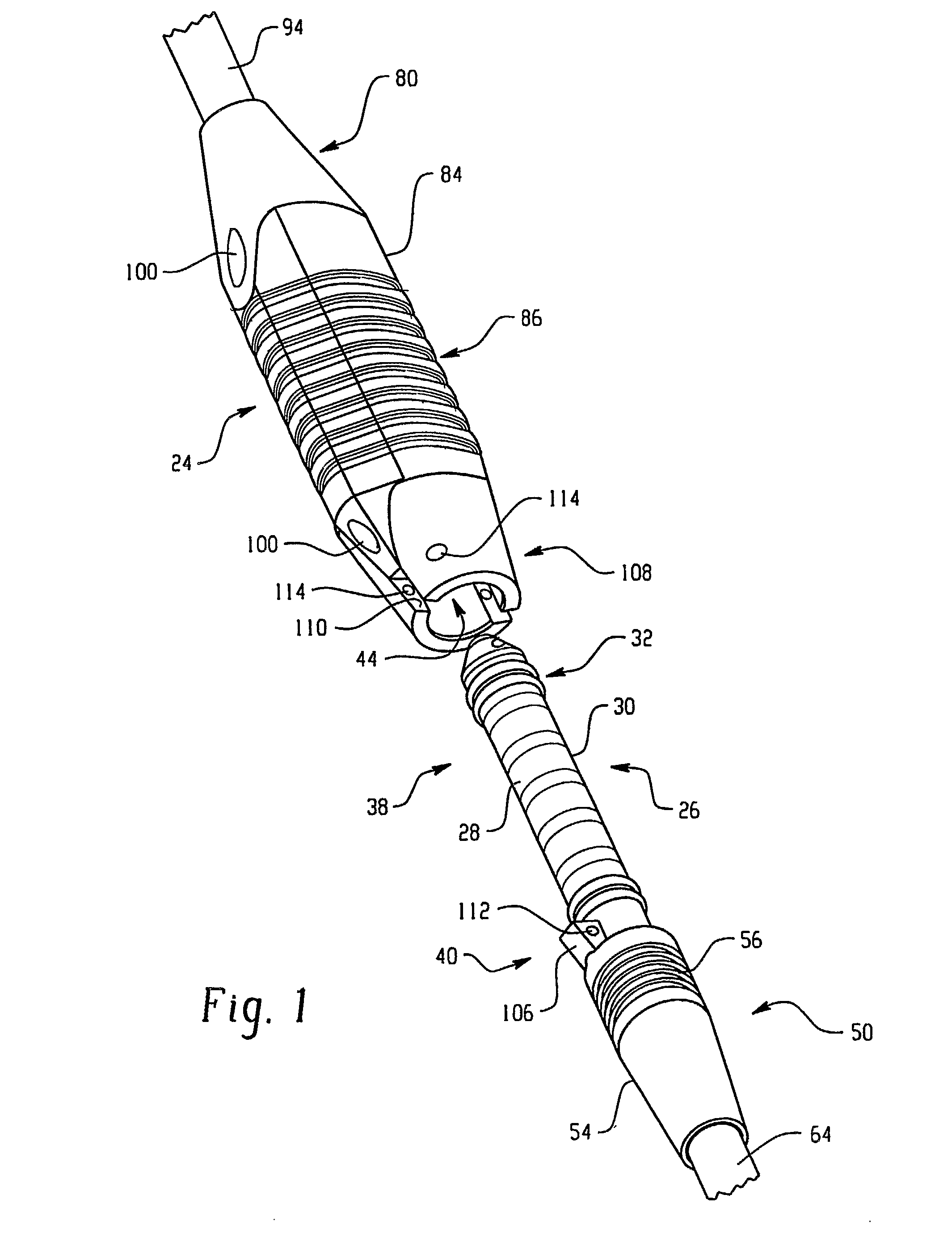

ActiveUS20080009198A1Relieve pressureMaximize quality of lifeCoupling device detailsTwo-part coupling devicesVoltage dropElectrical connection

The present invention is directed to a linear connector assembly comprising a plug connector (22) and a receptacle connector (24). The plug connector (22) includes an elongated member (26), and an electrical contact (72) disposed about a portion of the elongated member. The receptacle connector (24) includes a wall defining a cavity (44) dimensioned to sealingly receive the elongated member, and an electrical contact having a surface disposed in the wall for electrical connection with the plug contact. The electrical contacts of the plug connector (22) and the receptacle connector (24) have spherical surface portions whereby a spherical interlace between the electrical contacts is formed upon make-up and reduces voltage drops between the contacts.

Owner:PMI IND INC

Battery charging and discharging by using a bi-directional transistor

ActiveUS7528582B1Reduce voltage dropSufficient voltageCircuit monitoring/indicationIndicating/monitoring circuitsCharge currentCurrent limiting

Owner:MICROSEMI CORP

Magnetic stimulation methods and devices for therapeutic treatments

ActiveUS9636519B2Improve effectivenessReduce self-heatingMagnetotherapy using coils/electromagnetsSurgical instrument detailsPhysical Therapy ModalityEngineering

Methods and devices producing time varying magnetic field have therapeutic uses. The device contains a coil made of insulated wires, an energy storage device, an energy source and a switch. The coil is flexibly attached in a case. The device has at least one blower for cooling the coil. The methods and devices can be used in for example in physiotherapy, neuropsychiatric therapy, aesthetic therapy, urology or urogynecology.

Owner:BTL MEDICAL SOLUTIONS AS

Organic light emitting display device and method for manufacturing the same

ActiveUS20140183501A1Reduce voltage dropOptimizationSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

Provided are an organic light emitting display device and a method for manufacturing the same. The organic light emitting display device comprises at least a first pixel area and a second pixel area. A partition is disposed between the first pixel area and the second pixel area. An auxiliary electrode is disposed between the first pixel area and the second pixel area and over the partition. Additionally, a first conductive element is disposed over the first pixel area, the second pixel area, and the auxiliary electrode and the first conductive element is electrically connected to the auxiliary electrode.

Owner:LG DISPLAY CO LTD

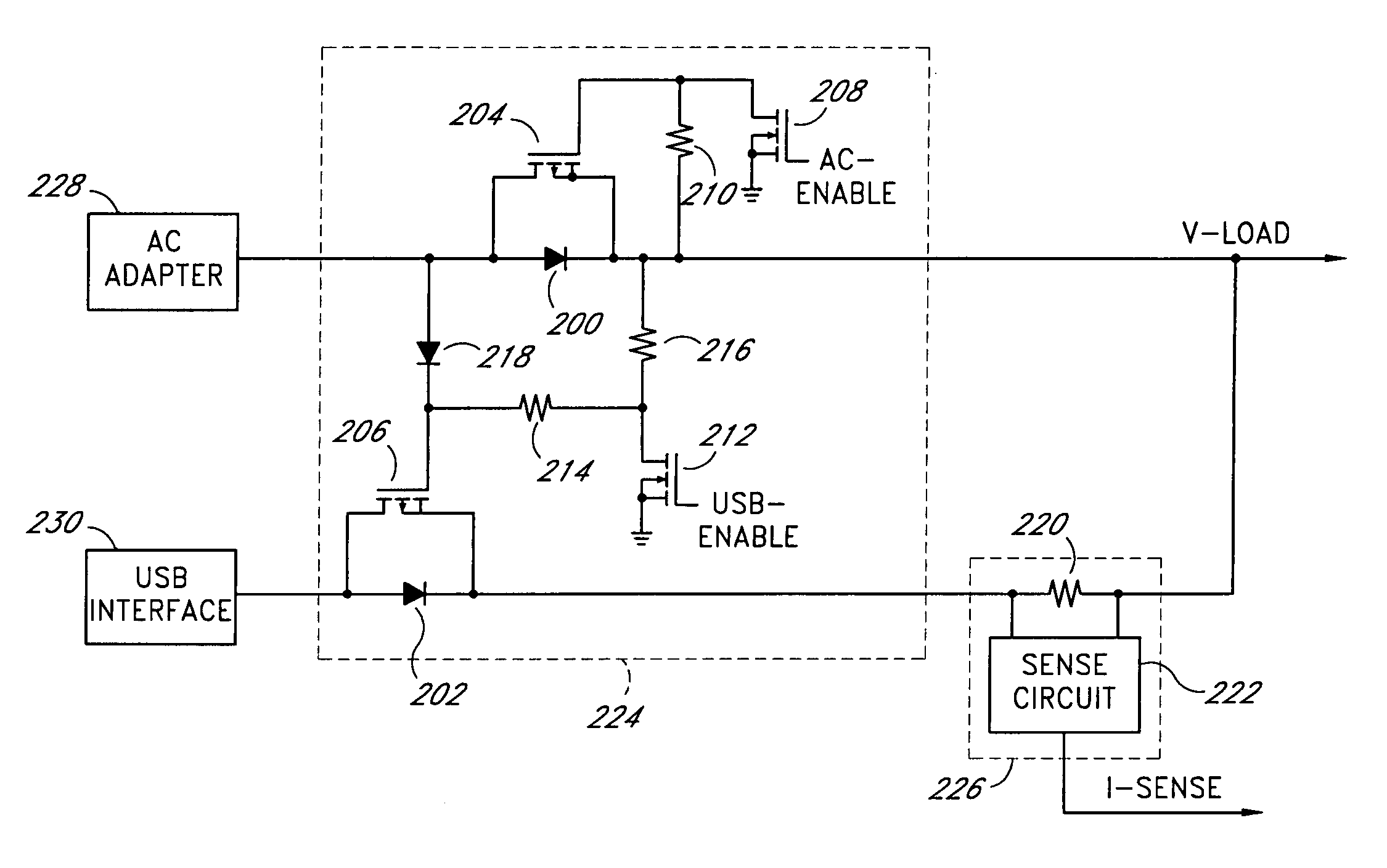

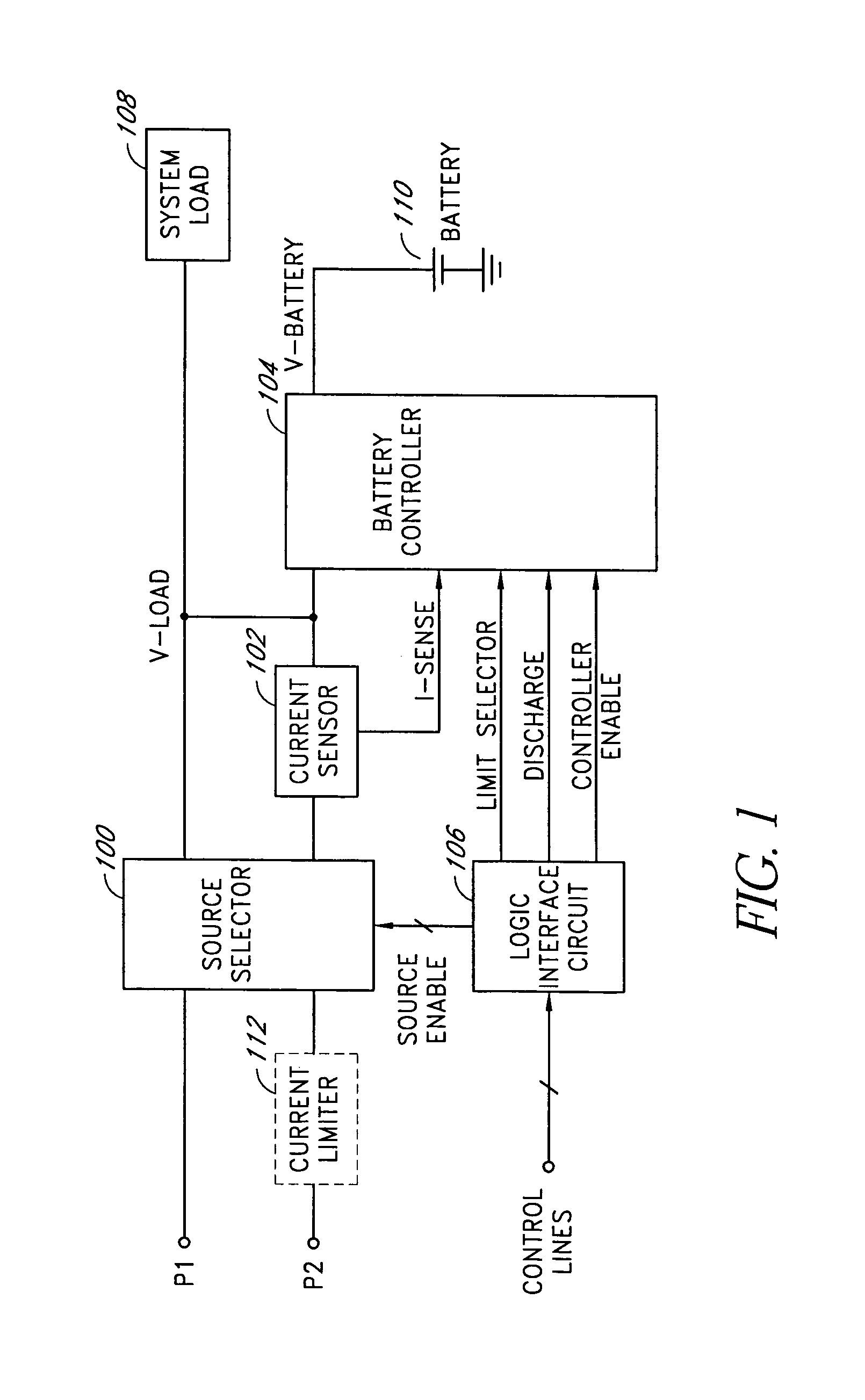

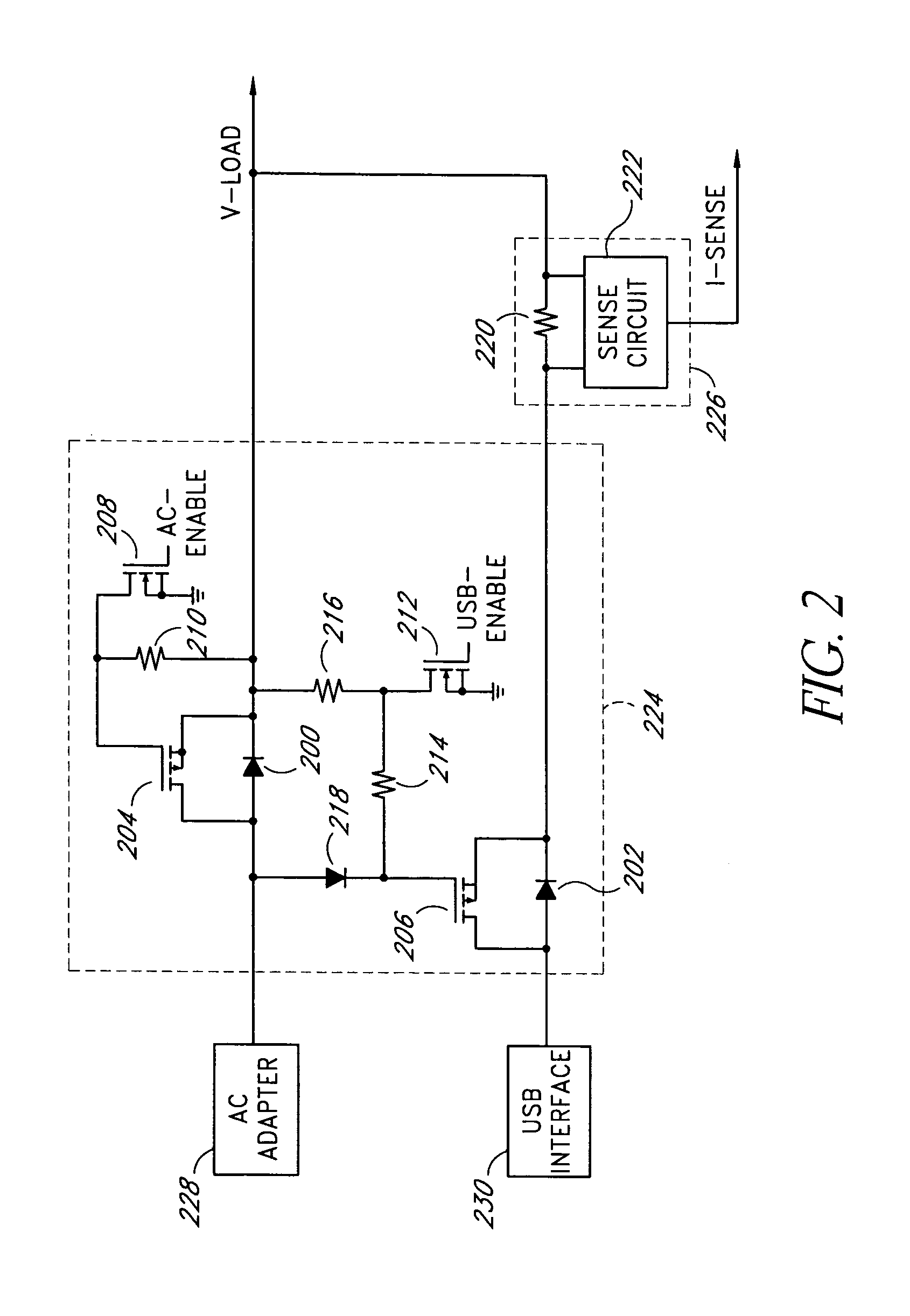

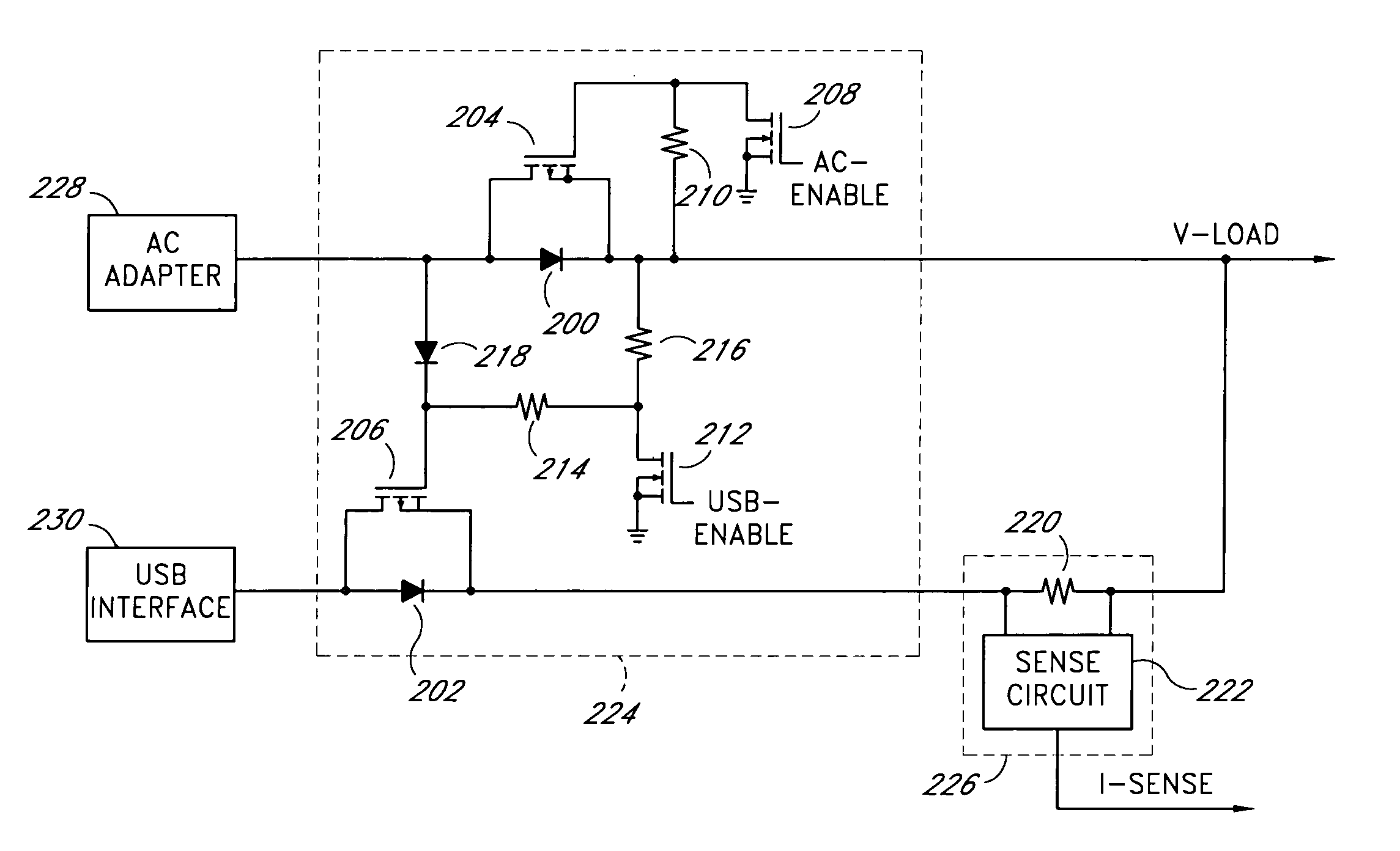

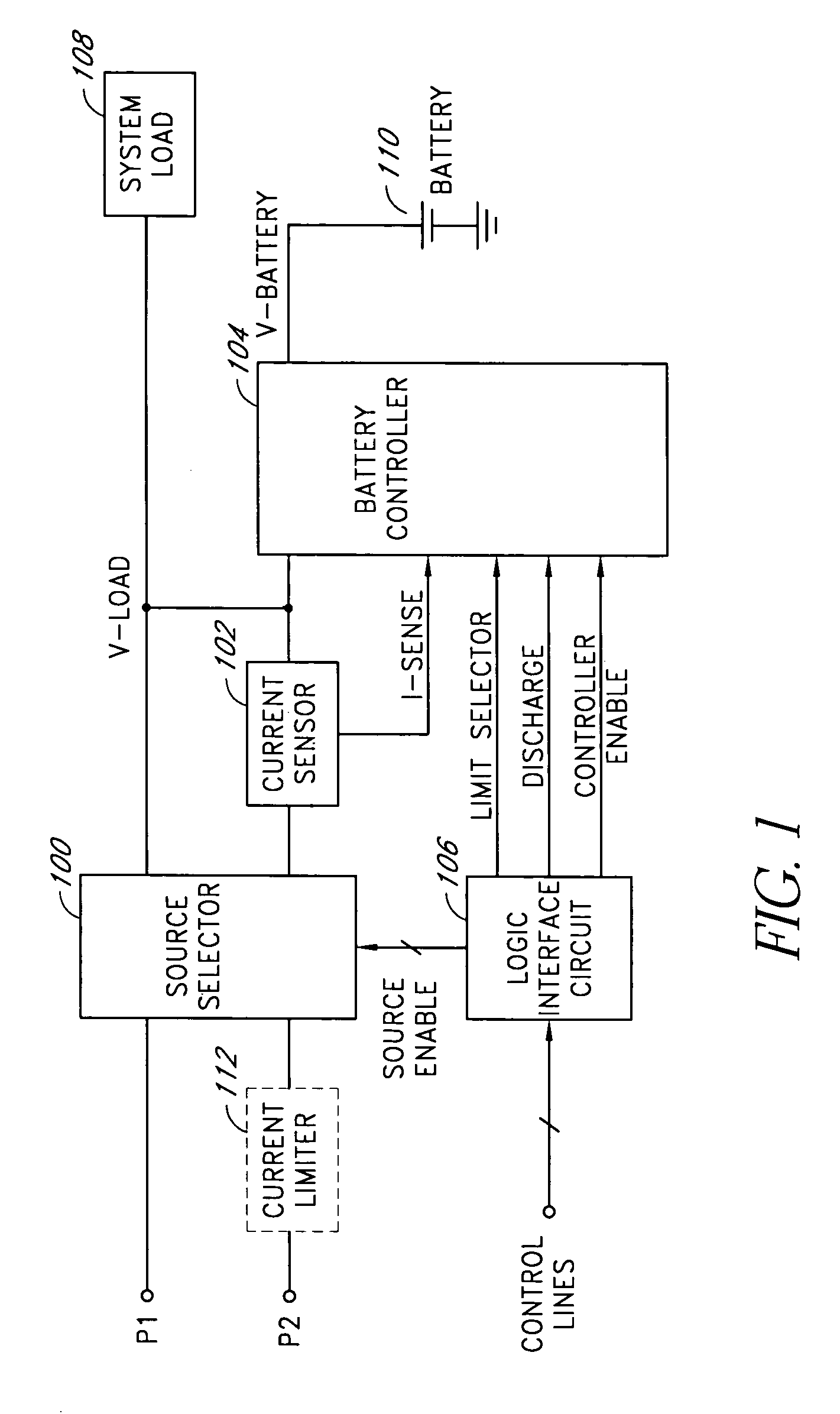

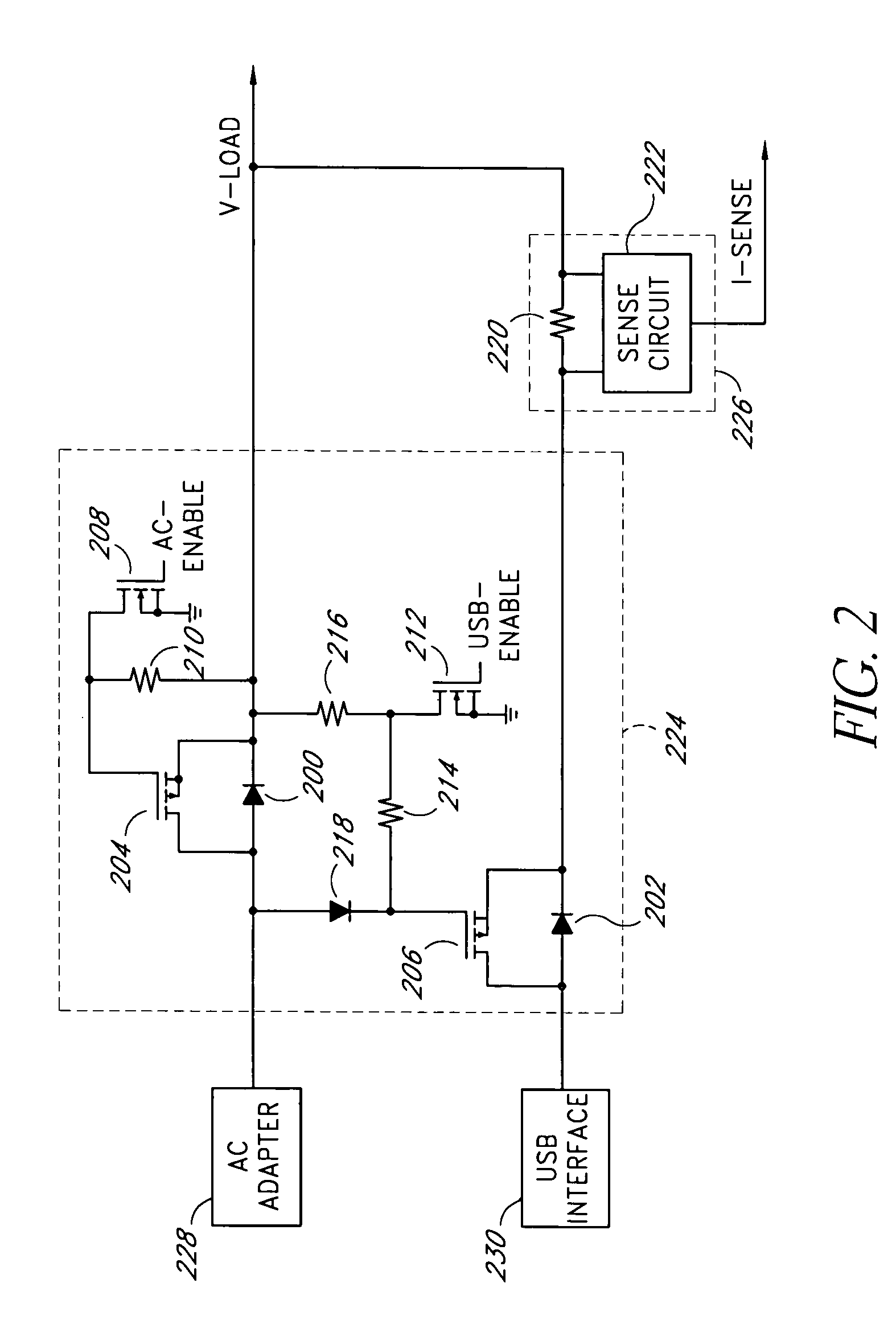

Linearly regulated battery charger

ActiveUS7525291B1Reduce voltage dropSufficient voltageCircuit monitoring/indicationIndicating/monitoring circuitsCurrent limitingCharge current

A battery charger for an electronic device receives current limited power from an external power source, such as a Universal Serial Bus power interface. The battery charger can linearly regulate a charging current to an internal battery and limit the charging current so as not to demand current in excess of what the external power source can provide. A bi-directional pass element coupled between a system power terminal and the internal battery controls the charging current and effectively isolates the internal battery from a system load during charging of the battery while providing a low impedance path from the internal battery to the system load during discharging of the battery.

Owner:IP GEM GRP LLC

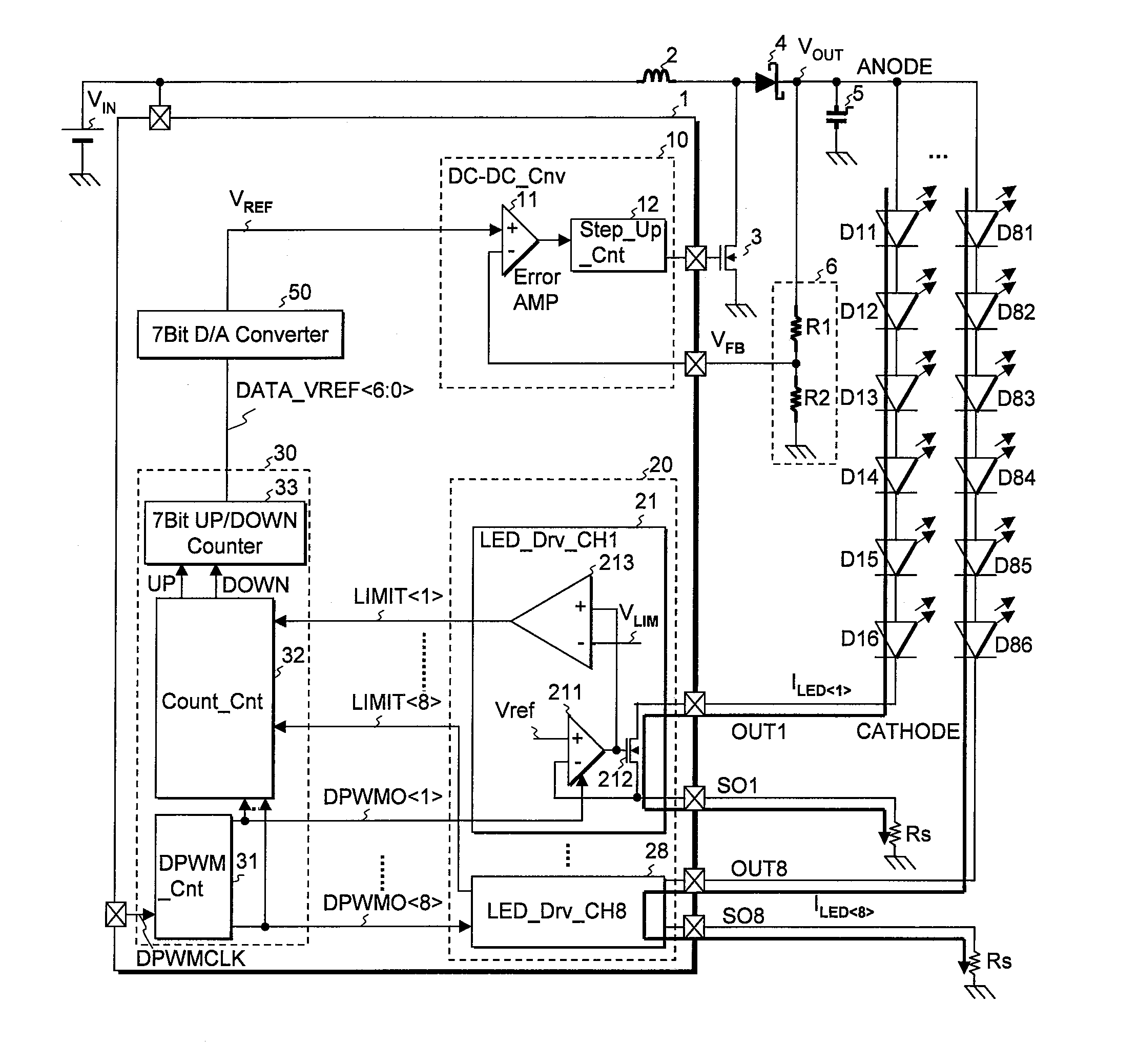

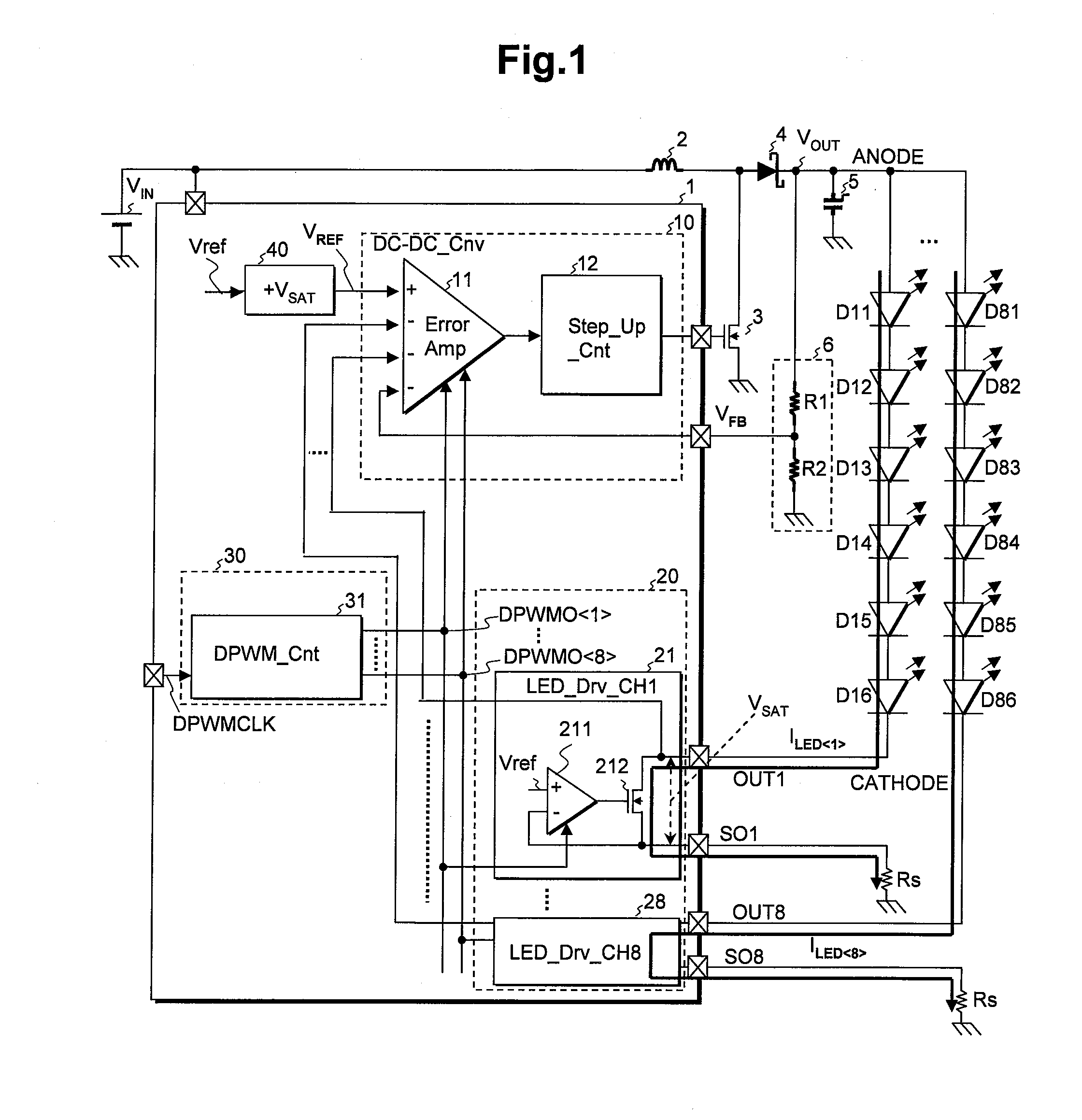

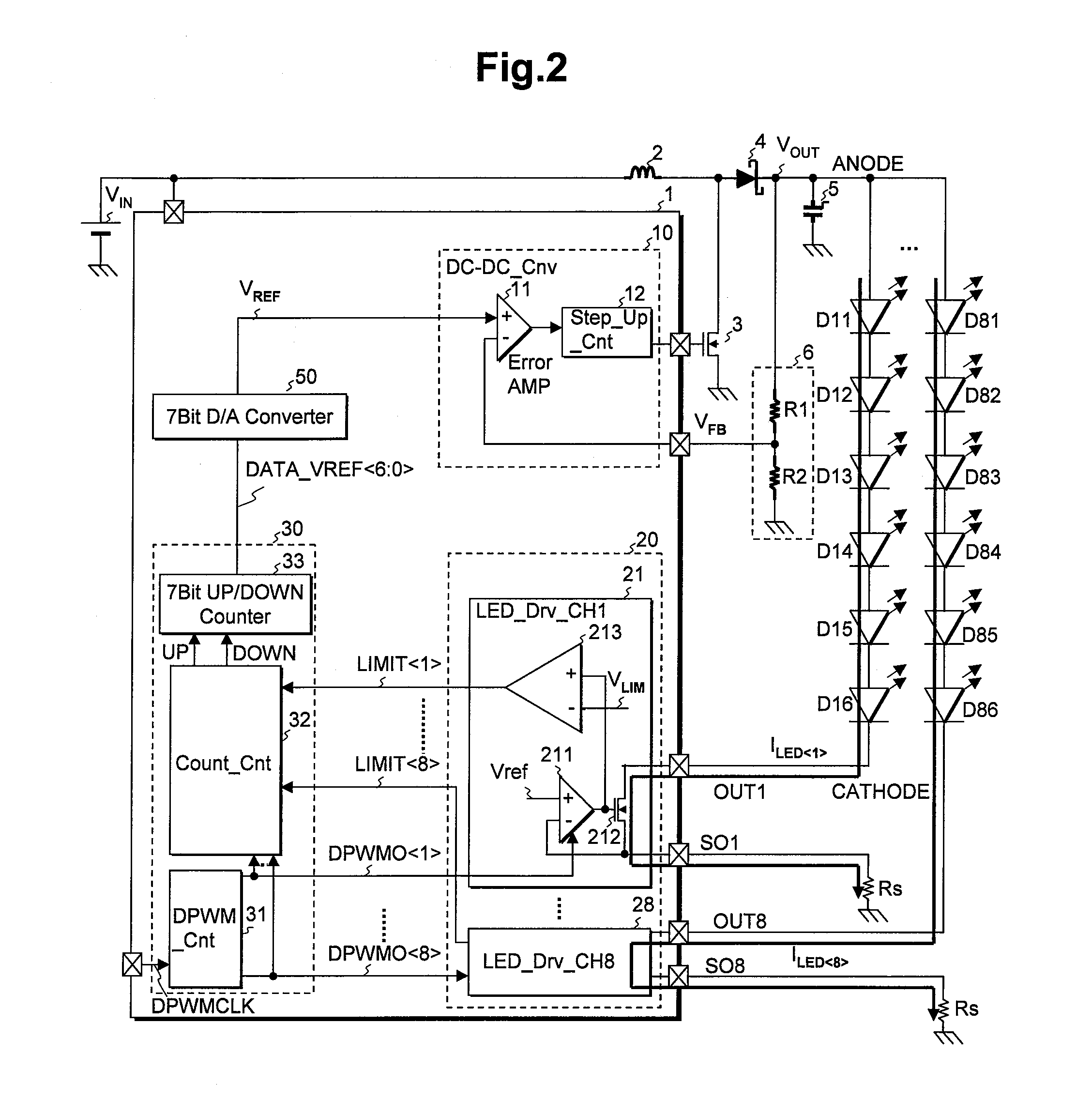

Semiconductor integrated circuit and operation method thereof

ActiveUS20120133291A1Reduce voltage dropIncrease the output voltageElectrical apparatusElectroluminescent light sourcesDigital dataDriving current

A DC-DC converter supplies an output voltage to a plurality of channels of a light emitting device array in common. A current driver has a plurality of driver units which drive the channels. Each of the driver units includes a drive transistor and a detector which detects an abnormality of a drive current. A logic unit generates digital data in response to a plurality of detection signals and supplies the same to a D / A converter. An analog reference voltage of the D / A converter is supplied to the DC-DC converter. The logic unit executes a calibration operation which determines digital data for setting the minimum output DC voltage at the normal operation of all the channels by sequential updating of the digital data.

Owner:RENESAS ELECTRONICS CORP

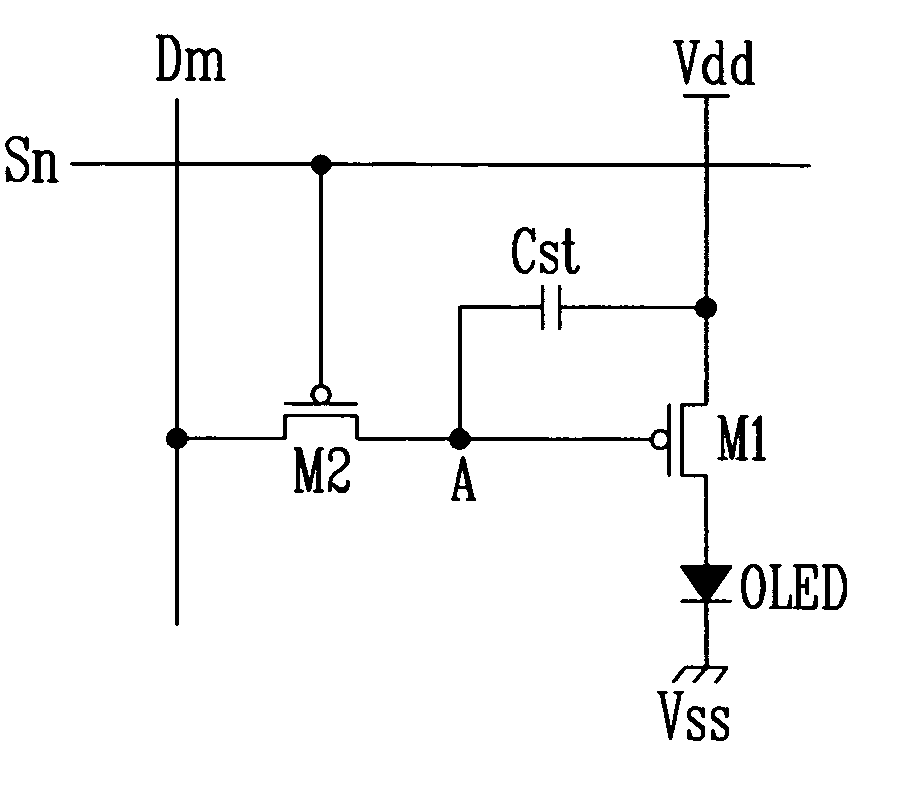

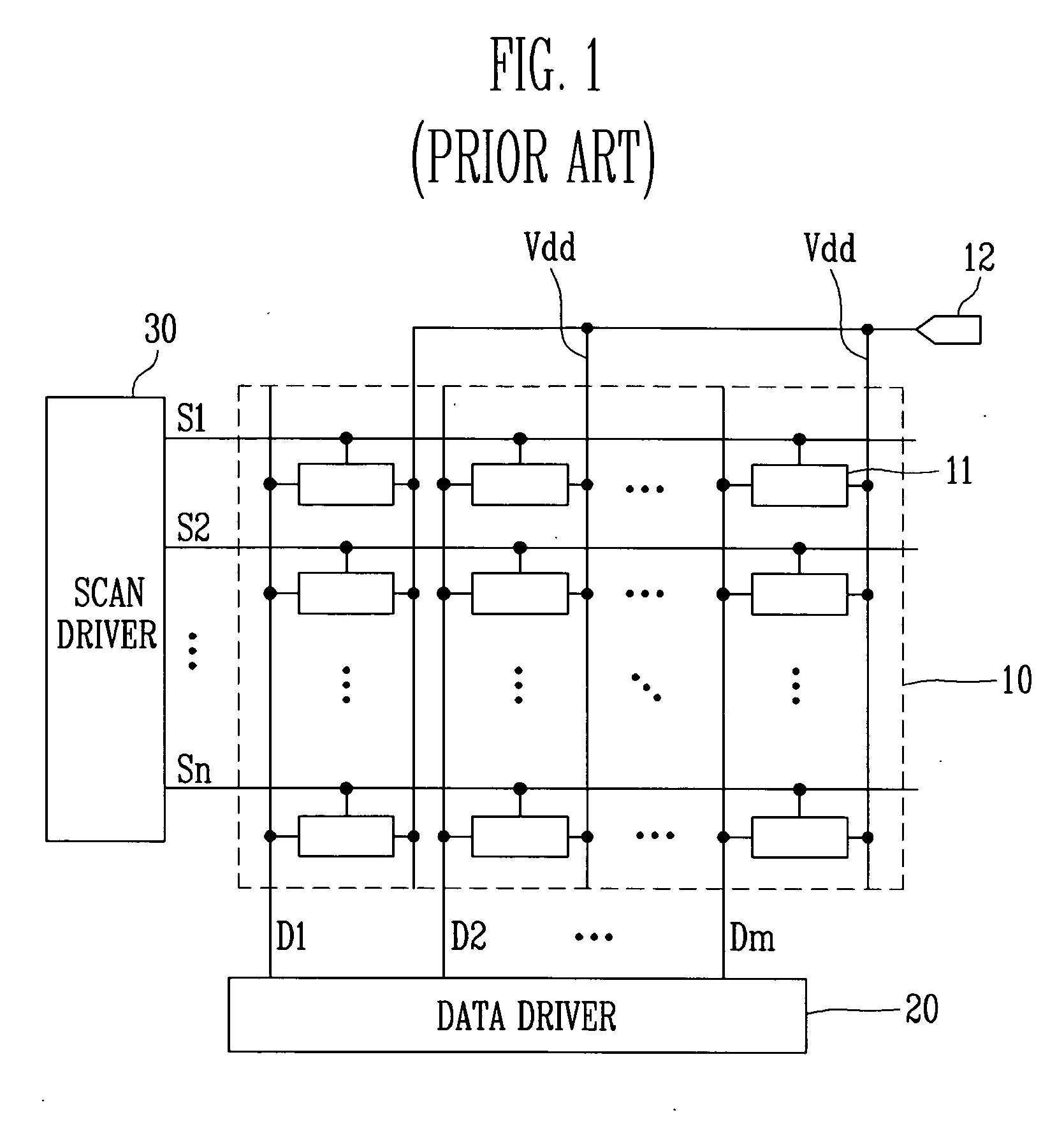

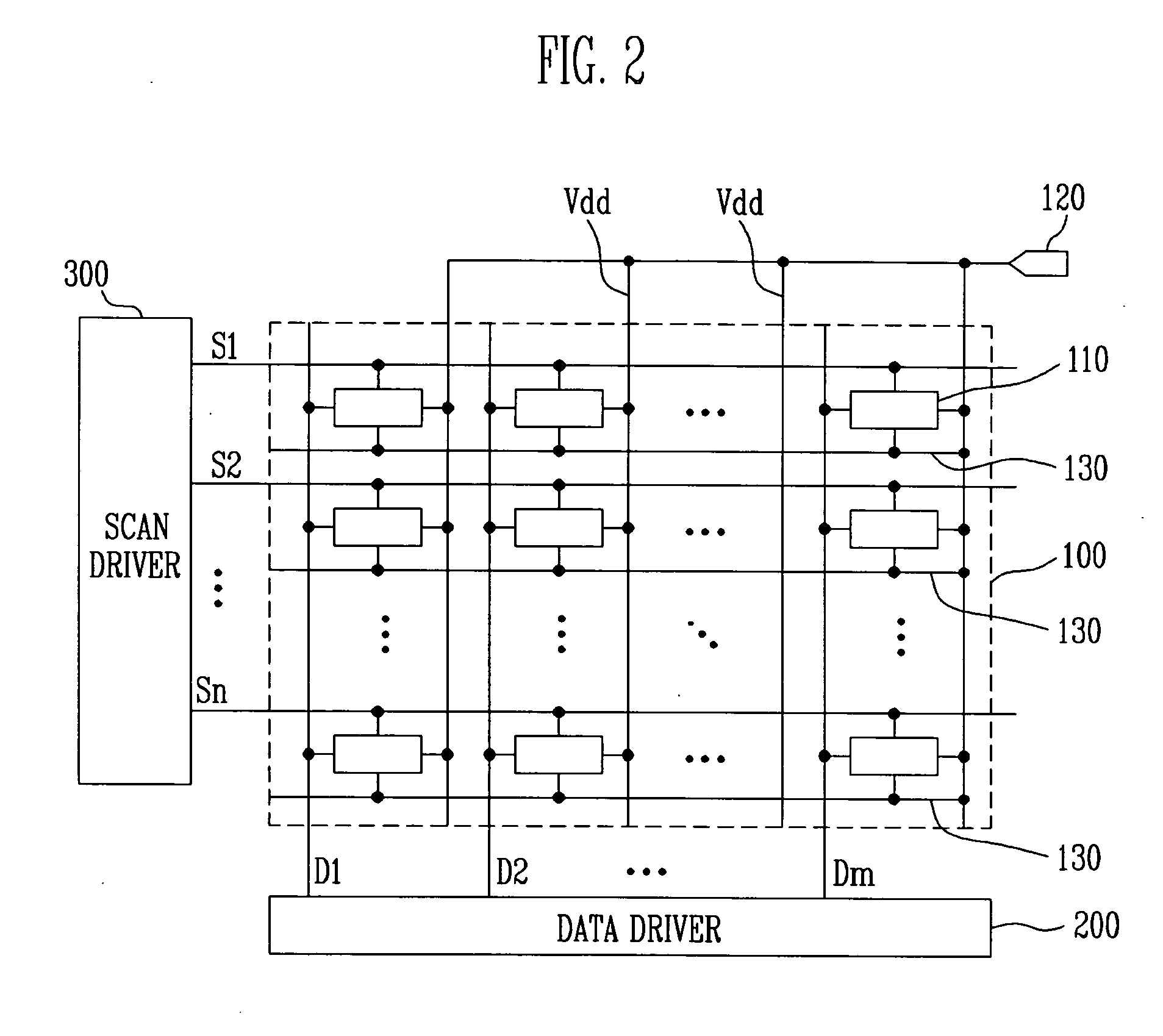

Organic light emitting display and method of fabricating the same

InactiveUS20060132055A1Reduce voltage dropVoltage levels of the pixel power sources uniformStatic indicating devicesElectroluminescent light sourcesElectricityEngineering

An organic light emitting display includes pixel power source lines electrically connected with each other by metal lines to make the voltage levels of the pixel power sources uniform and reduce the voltage drops of the pixel driving power sources.

Owner:SAMSUNG MOBILE DISPLAY CO LTD

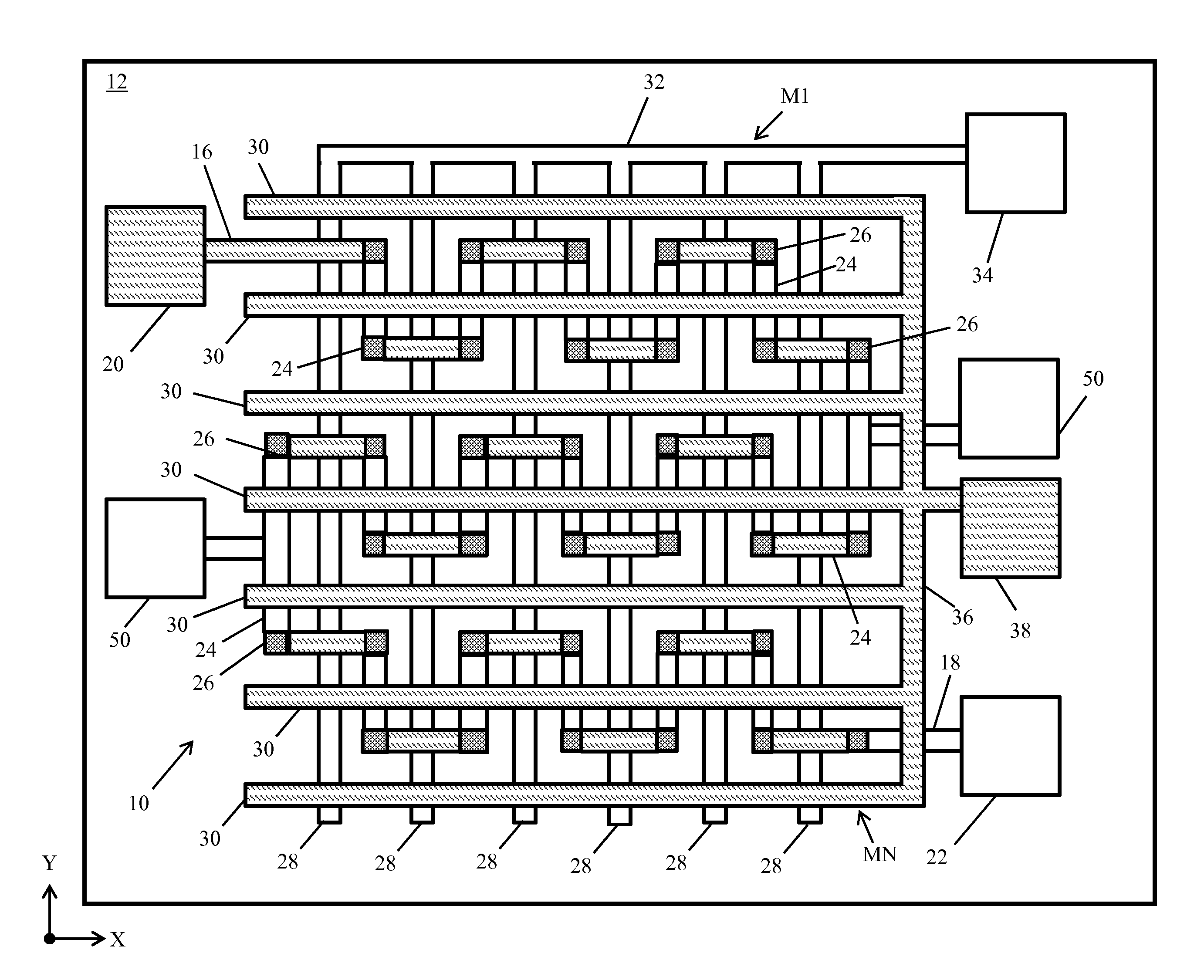

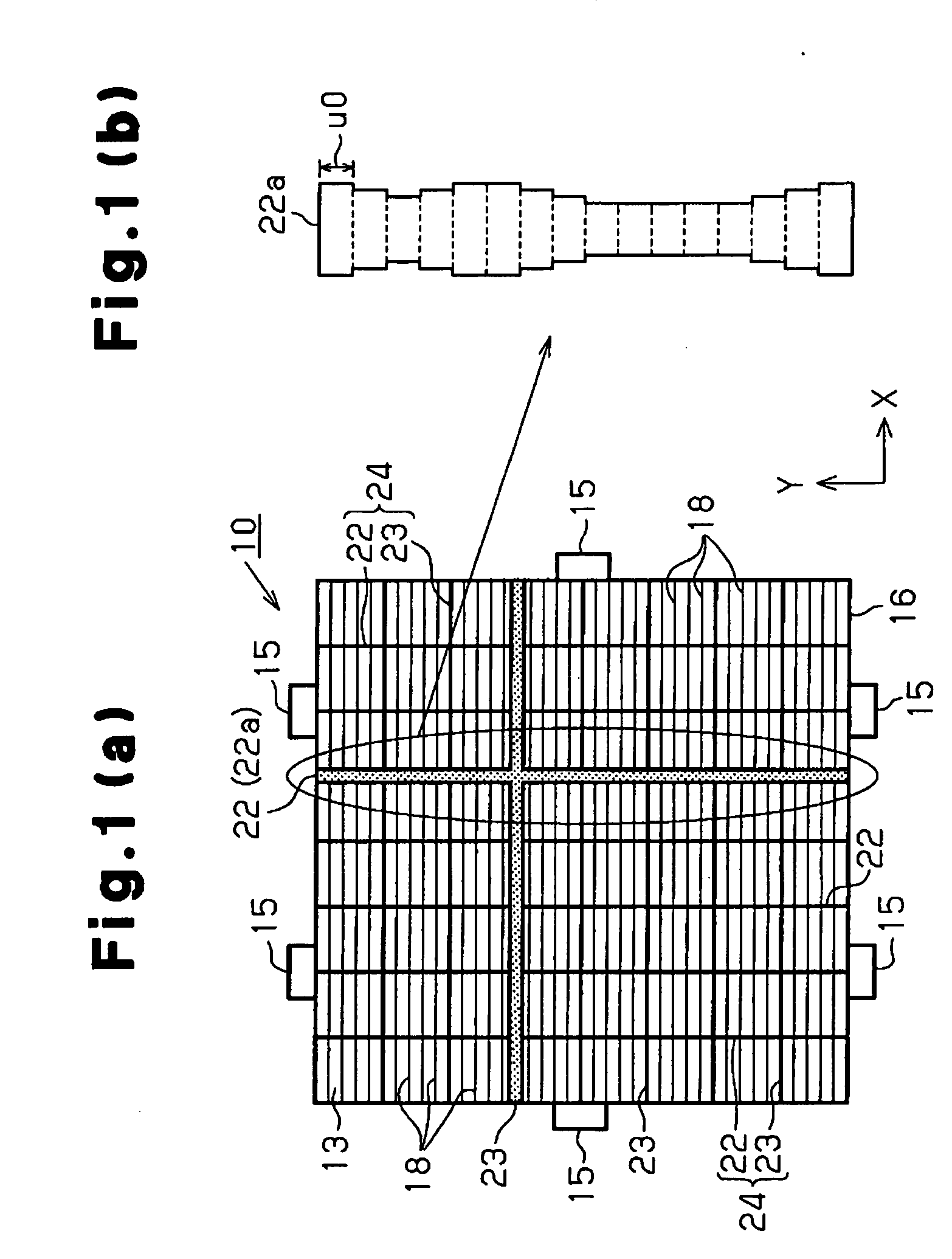

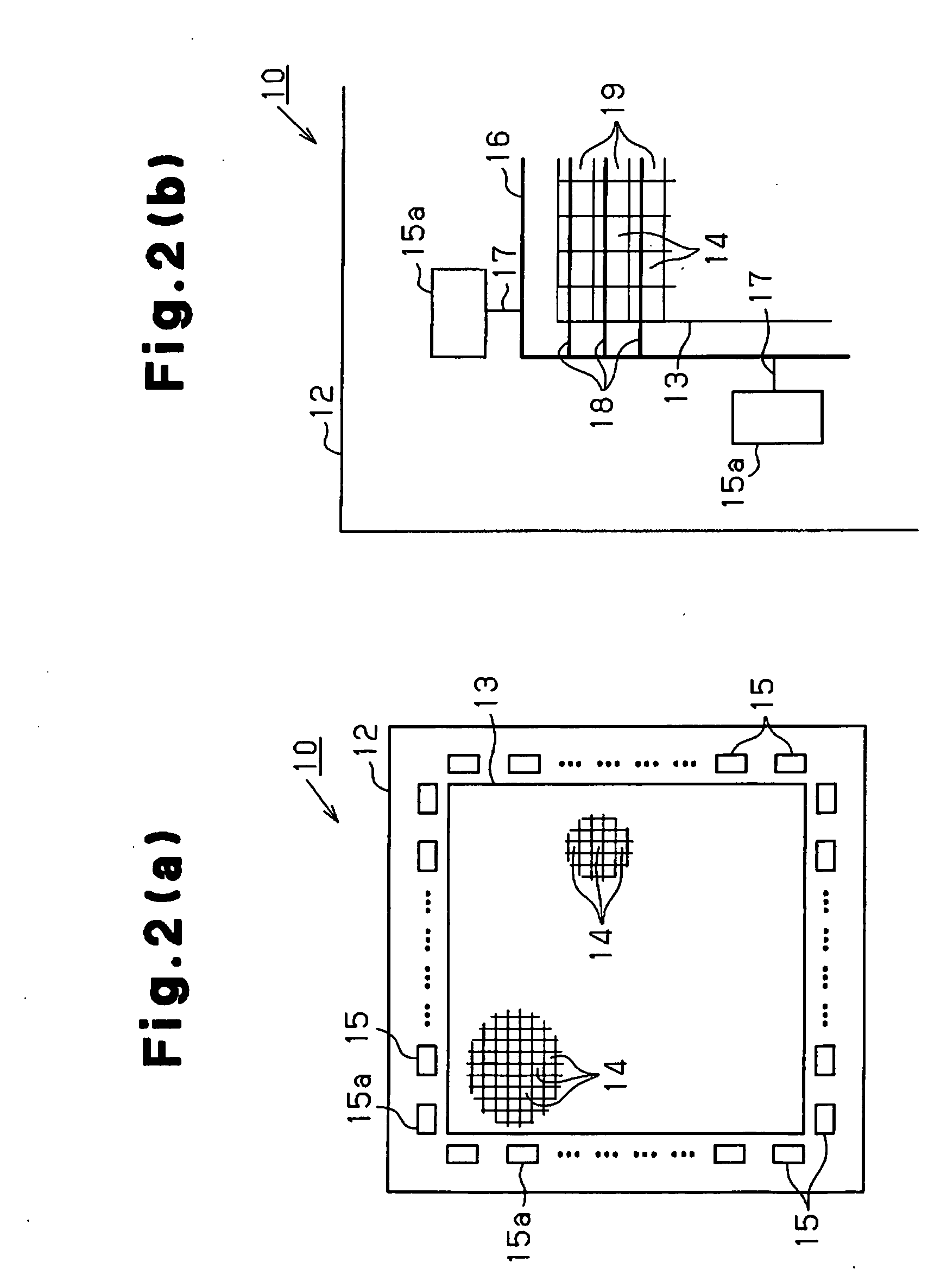

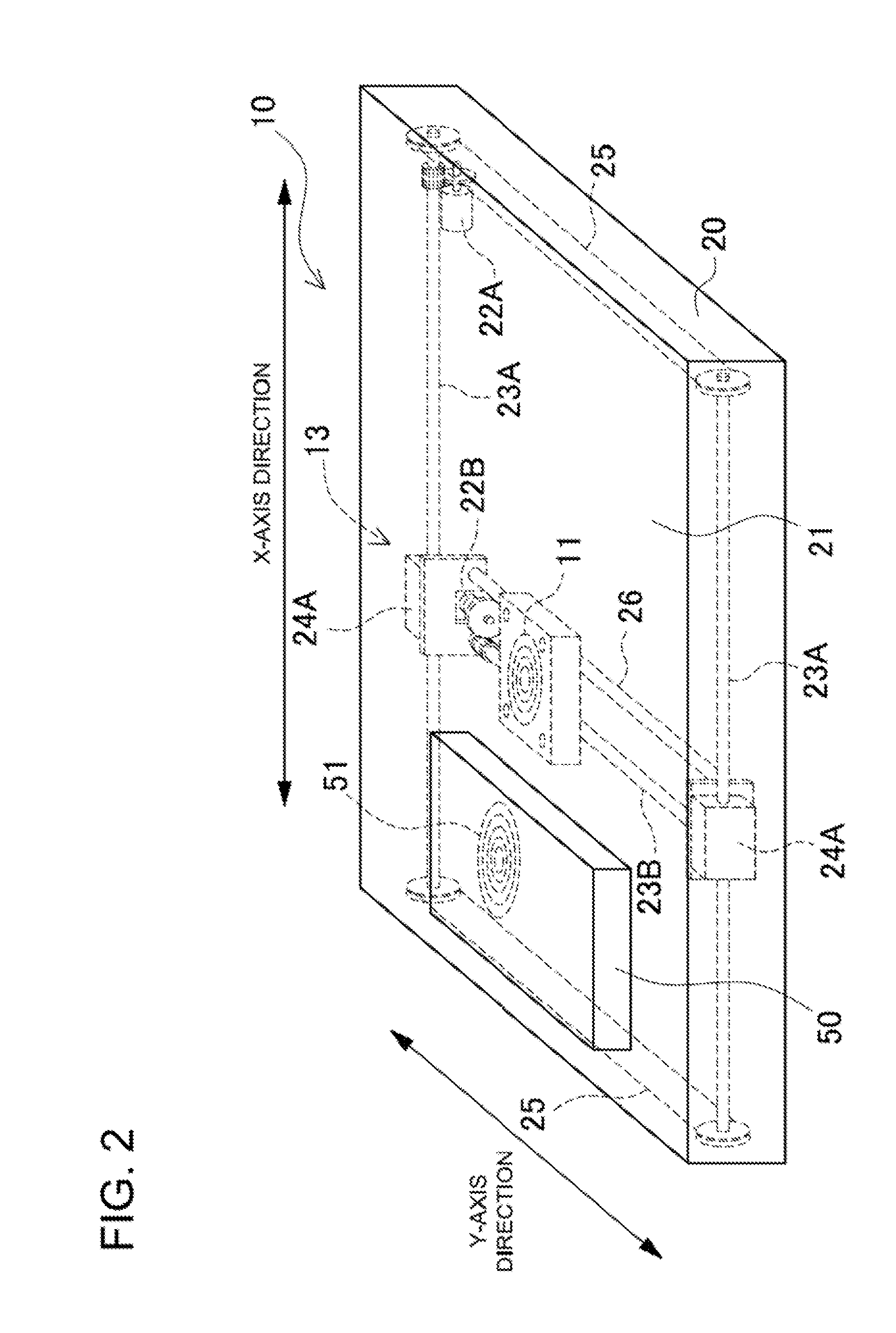

Semiconductor integrated circuit device and its power supply wiring method

InactiveUS20060239102A1Improve stabilityReduce voltage dropSemiconductor/solid-state device detailsSolid-state devicesBasic power supplySemiconductor

The present invention discloses a power supply wiring method for stabilizing operation of a semiconductor integrated circuit device. A power supply mesh 24, which is arranged on an upper layer of a basic power supply wires 18 for supplying power to a logic circuit portion 13, includes vertical reinforcing power supply wires 22 and lateral reinforcing power supply wires 23. The widths of the vertical reinforcing power supply wires and lateral reinforcing power supply wires are optimized to mitigate IR drop or excessive current density in each division unit u0.

Owner:SANYO ELECTRIC CO LTD

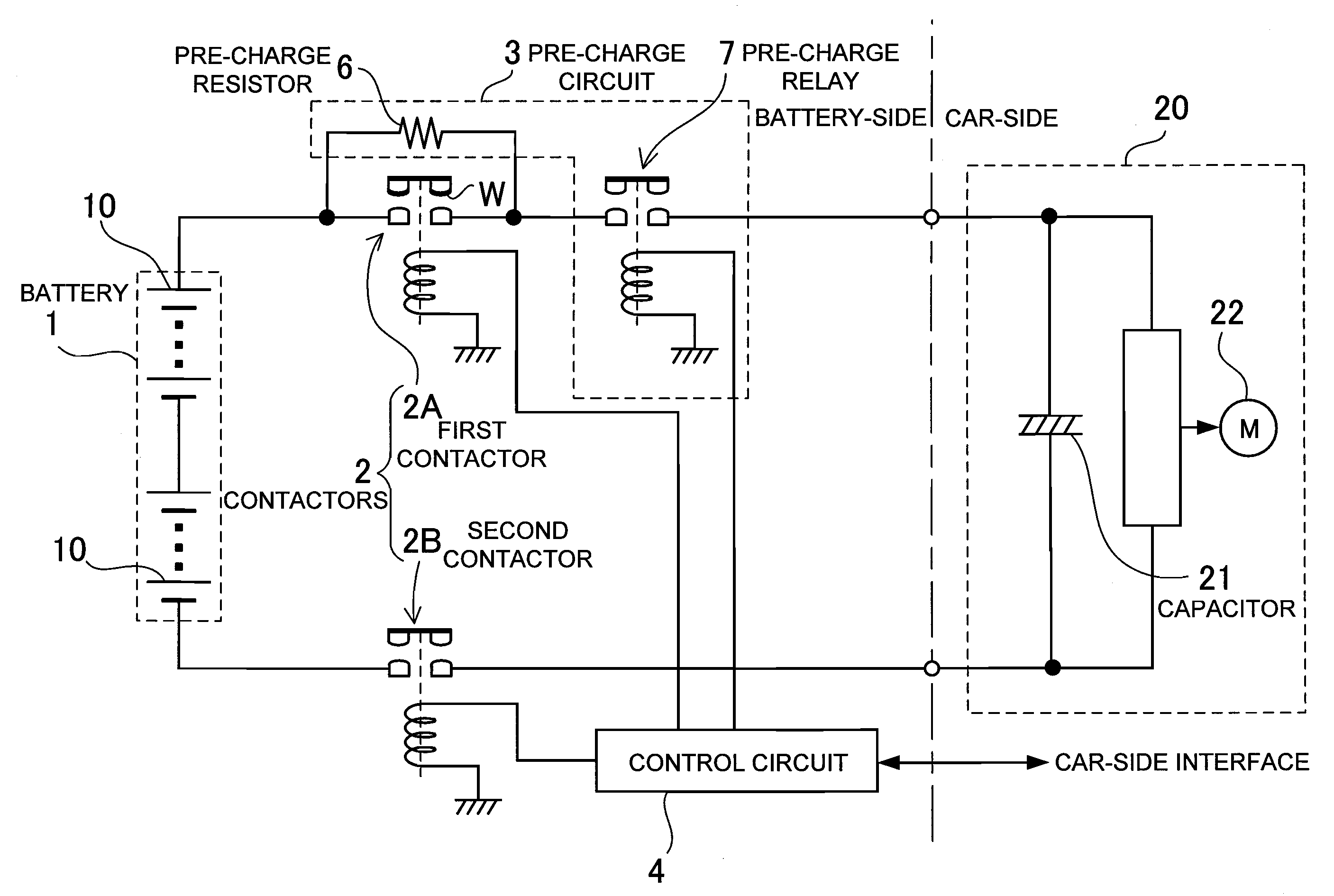

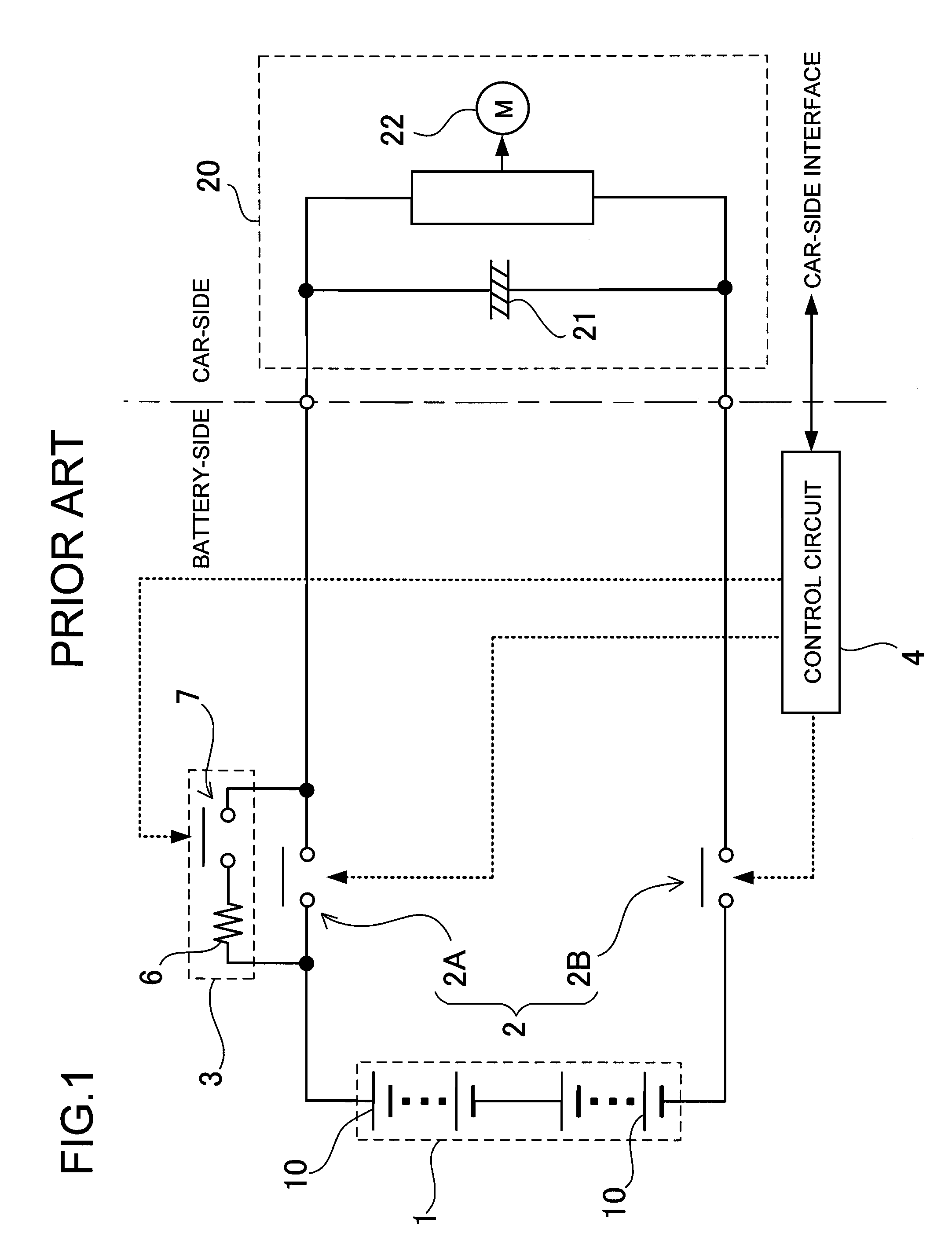

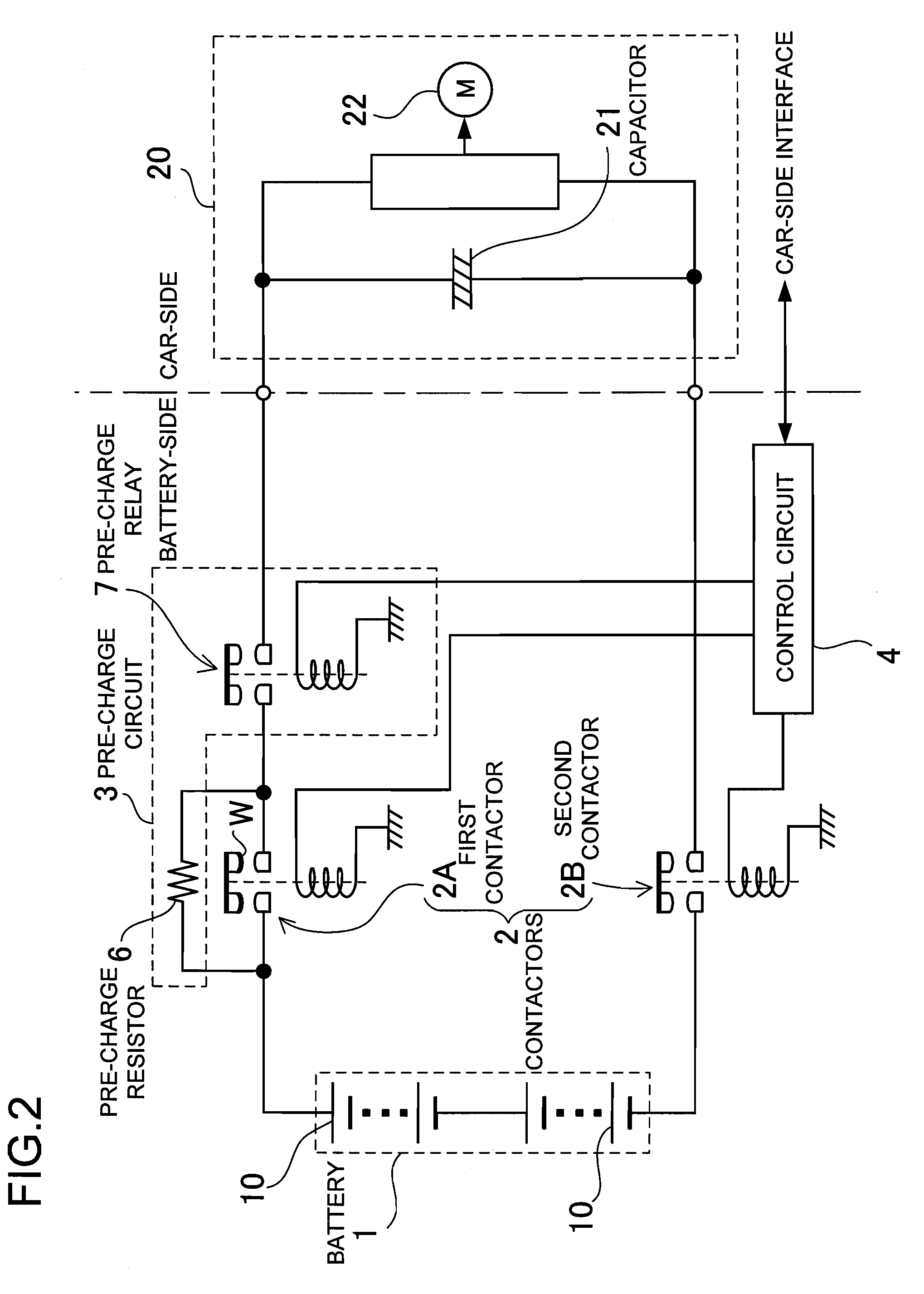

Car power source apparatus

InactiveUS20090212627A1Reliable cut-offLong lastingElectric devicesElectric powerPre-chargeControl circuit

The car power source apparatus is provided with contactors 2 connected to the output-side of the battery 1; a pre-charge circuit 3 made up of a series connected pre-charge resistor 6 and a pre-charge relay 7, which is connected with a contactor 2 to supply auxiliary charge to a capacitor 21 connected to the car-side of the battery 1; and a control circuit 4 to control the contactors 2 and pre-charge relay 7.The pre-charge resistor 6 is connected in parallel with a contactor 2, and the pre-charge relay 7 is connected in series with that contactor 2. The control circuit 4 switches the pre-charge relay 7 ON to pre-charge the car-side capacitor 21, and then switches the contactor 2 ON to connect the battery 1 to the car-side.

Owner:SANYO ELECTRIC CO LTD

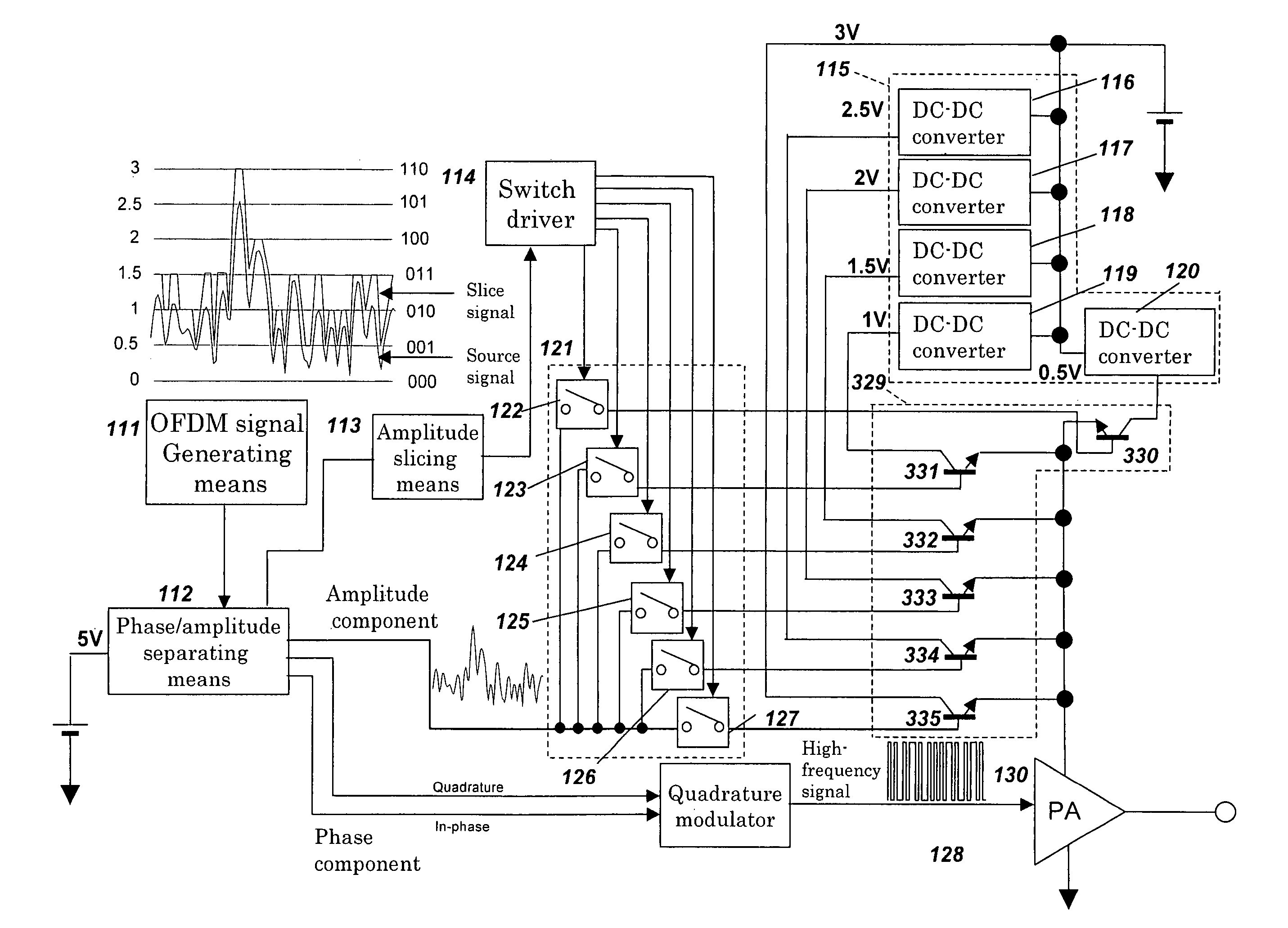

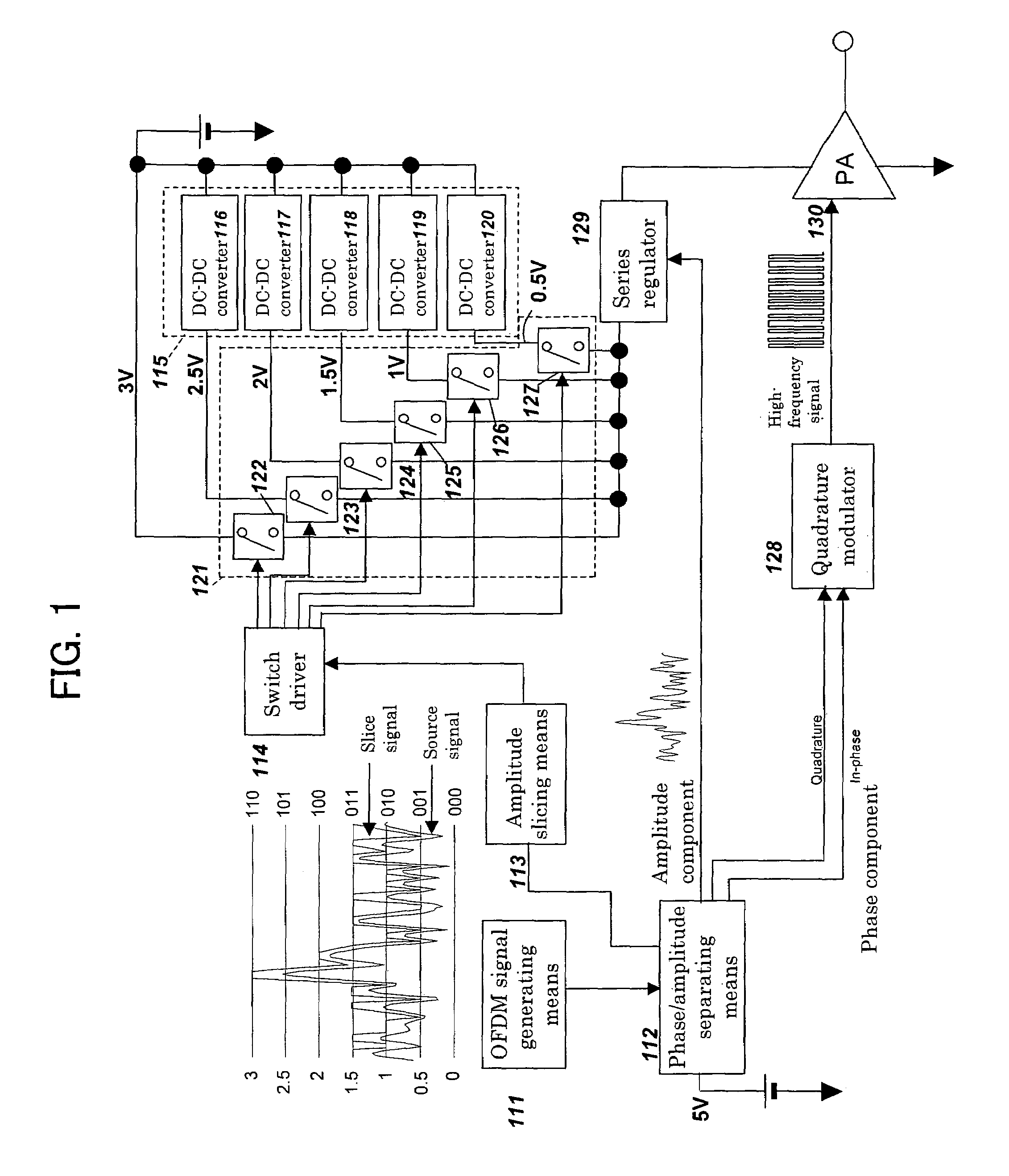

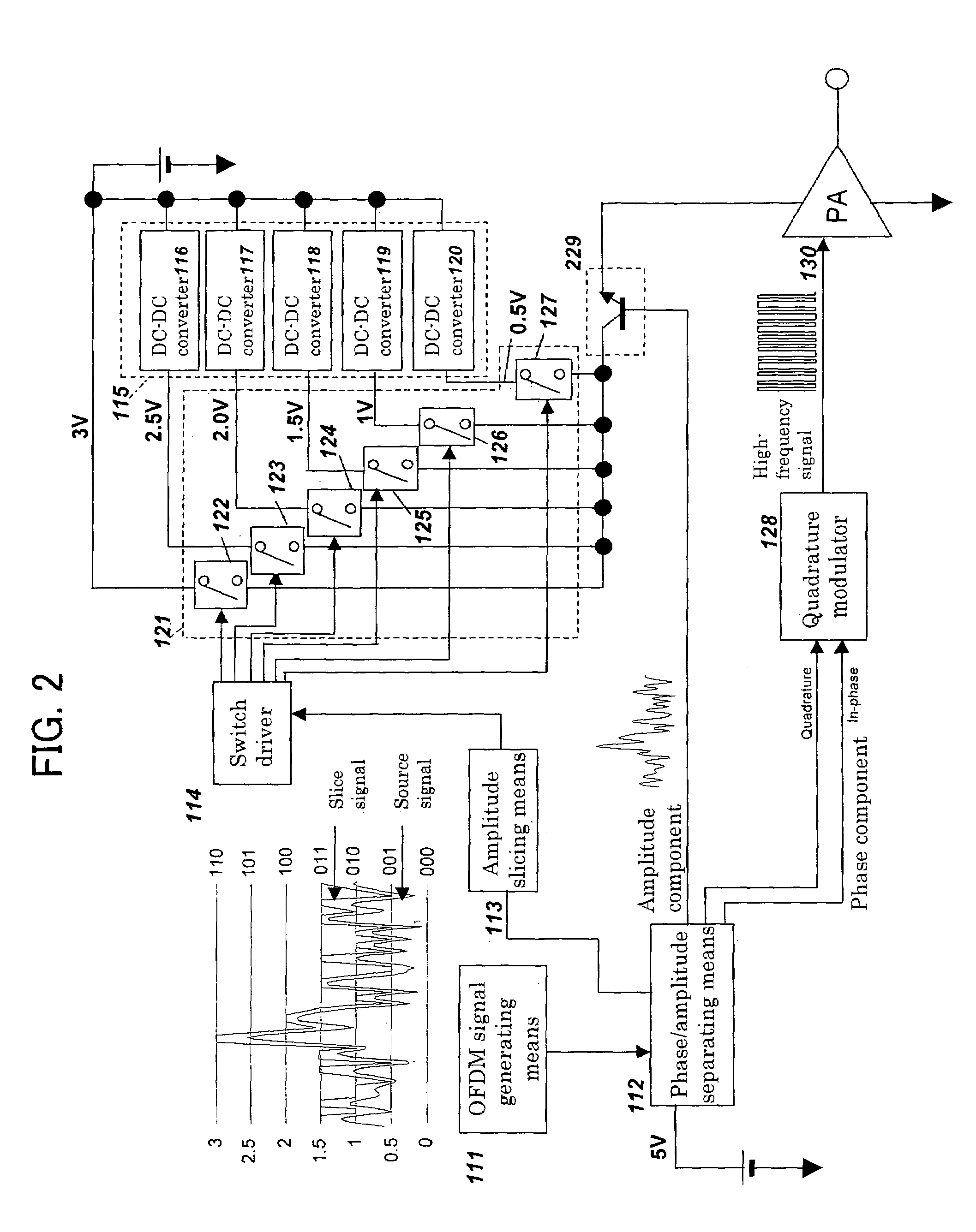

Transmitter

InactiveUS7116946B2Without lowering efficiencyReduce voltage dropResonant long antennasPower amplifiersHigh frequency powerAudio power amplifier

The present invention provides a transmitter conforming to the EER method in a wide frequency band at high efficiency. For this purpose, the amplitude component of a modulated signal is input to the power supply terminal of a high-frequency power amplifier 130, the I and Q quadrature signals thereof are input to the high-frequency input terminal of the high-frequency power amplifier 130, and the original modulated signal is obtained from the output of the high-frequency power amplifier 130. A collector voltage is supplied from DC—DC converter group 615 having output voltages being different sequentially to an emitter follower 729 via a switch group 621. One of the outputs of the DC—DC converters 616 to 620 is selected depending on the level of the amplitude component as the collector voltage and supplied to the emitter follower, whereby the difference between the emitter voltage of he emitter follower 729 and the collector voltage of the emitter follower 729 is made smaller and the efficiency of the emitter follower 729 is raised; furthermore, the power supply voltage of the high-frequency power amplifier 130 is voltage-converted by the emitter follower 729, whereby operation in a wide frequency band is made possible.

Owner:PANASONIC CORP

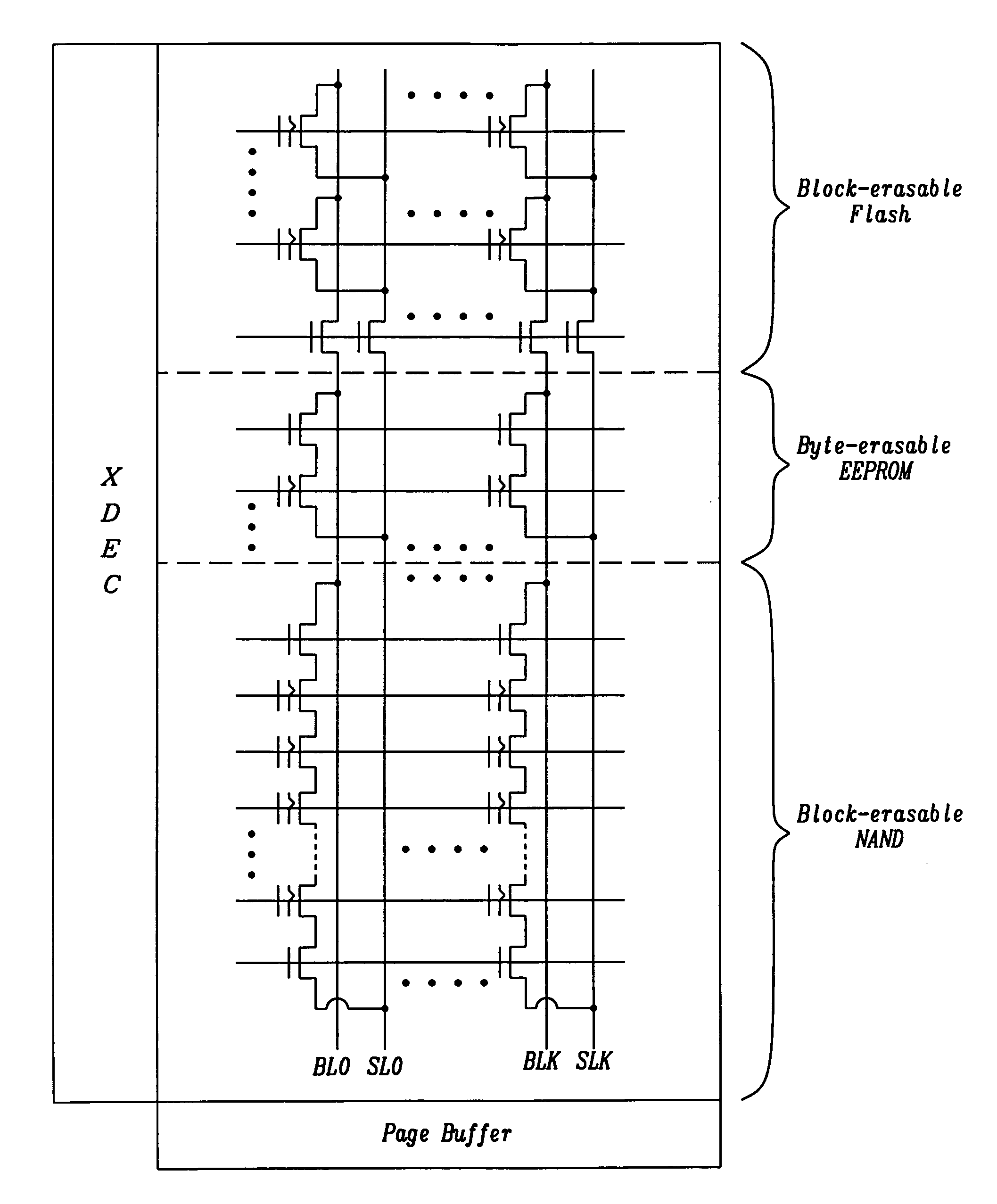

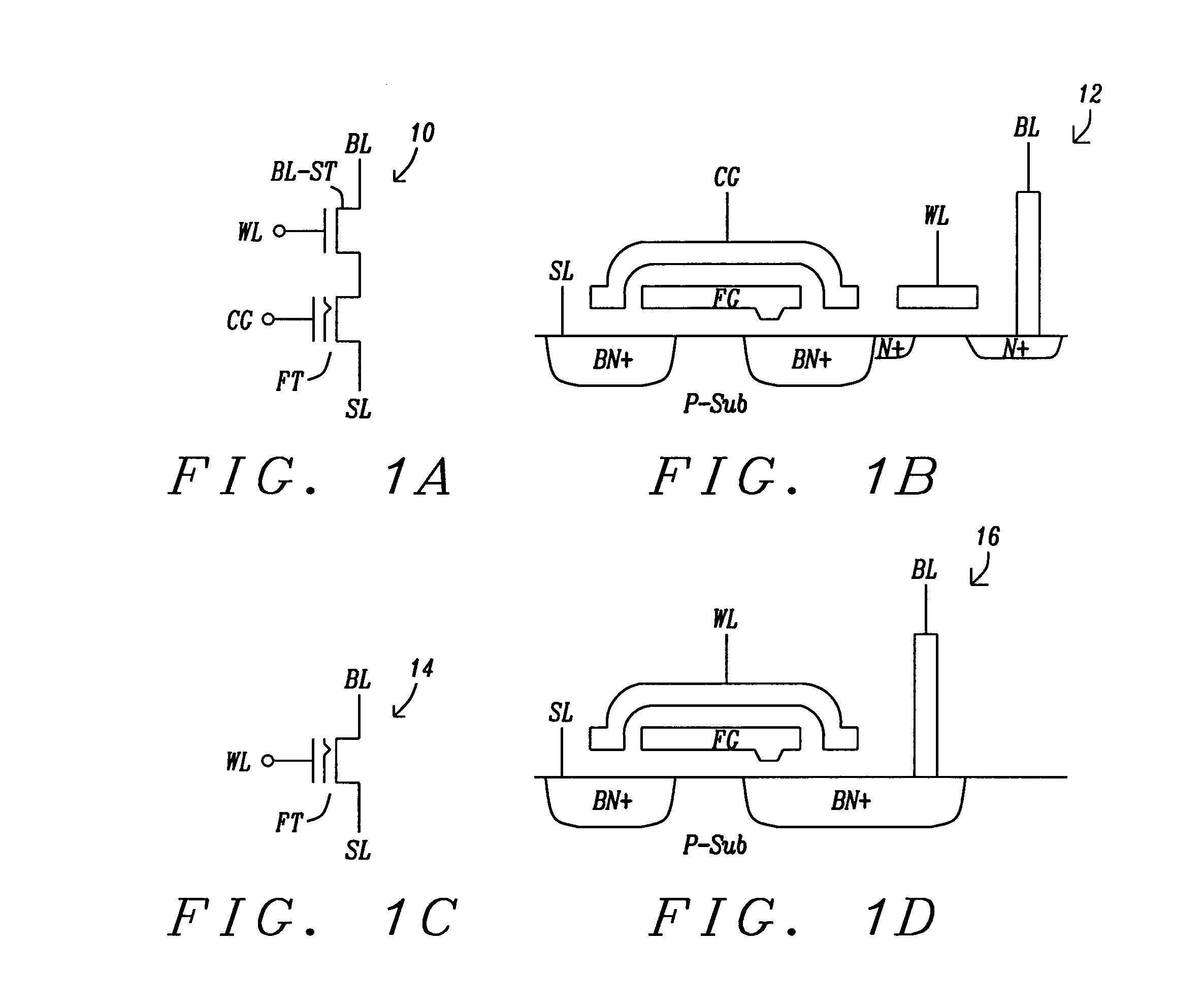

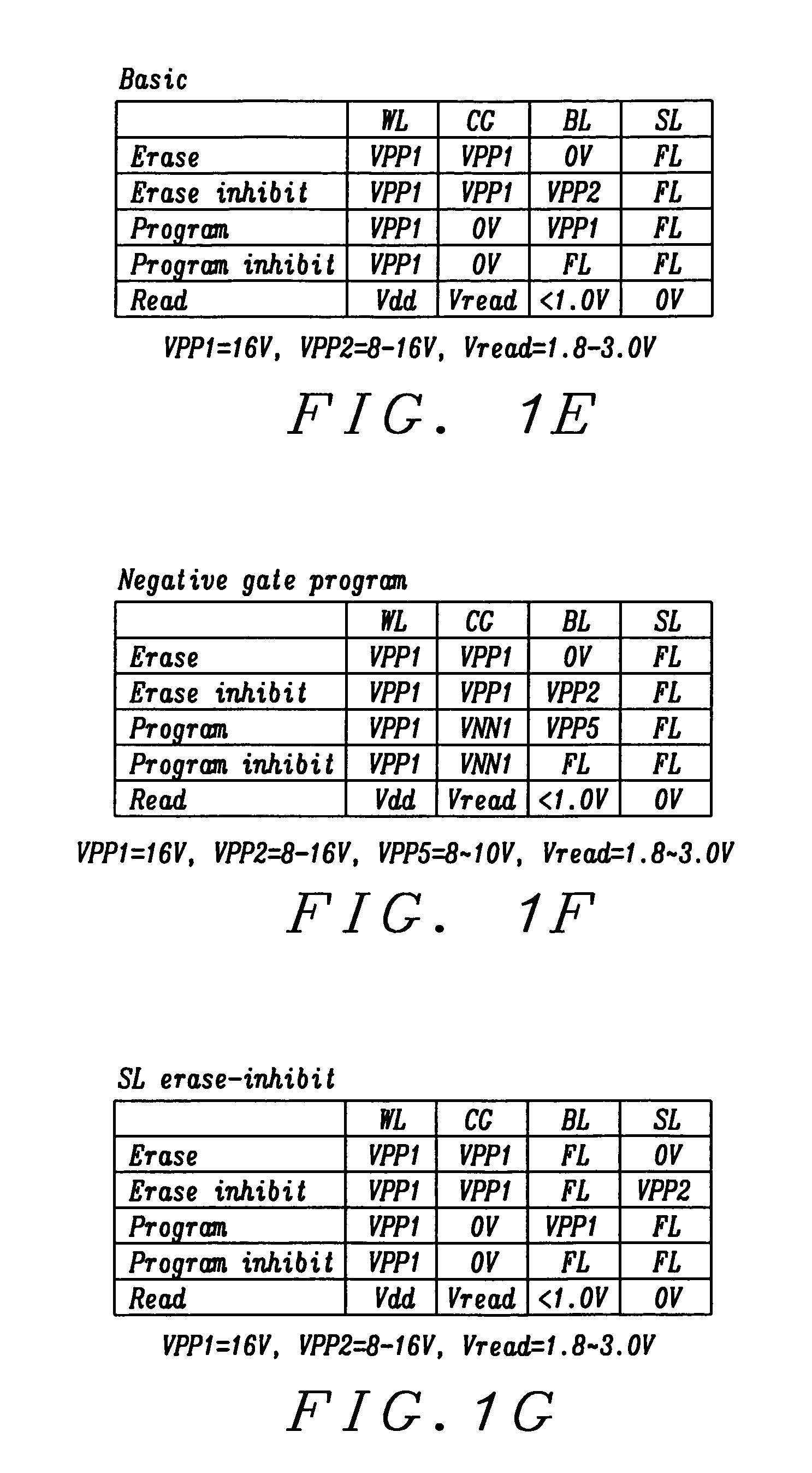

Most compact flotox-based combo NVM design without sacrificing EEPROM endurance cycles for 1-die data and code storage

InactiveUS20120063223A1Increase data rateReduce layout areaRead-only memoriesDigital storageByteComputer science

Disclosed is a low-cost hybrid storage solution that allows Code like sector-alterable NOR and Data like block-alterable NAND and byte-alterable EEPROM being integrated on a same die. The disclosed combo NVM design of the present invention is a truly Data-oriented NVM design that allows 2T-EEPROM to integrate both 0.5T-NAND and 1T-NOR without sacrificing any EEPROM's byte-write performance in the same die. The invention provides several new embodiment sets of preferable bias conditions of Program, Program-Inhibit, Erase and Erase-Inhibit for operating bit-write, byte-write, sector-write and page-write for several preferable Flotox-based EEPROM, NOR and NAND or combo NVM arrays that include types of shared SL, 8-pair BLs and SLS, with or without GBL, normally Erased Vt and Programmed Vt, or the reversed Erased-Vt or Programmed-Vt, etc. Further disclosed is a flexible X-decoder design to allow the flexible selection of pages to be erased to save erase time. Also disclosed is using on-chip negative voltage for FT's gate along with the less positive HV applied to FTs' channel region for same write performance but with the benefits of channel length reduction in cell and less BVDS electric requirement in peripheral devices for more scalable manufacturing process.

Owner:APLUS FLASH TECH

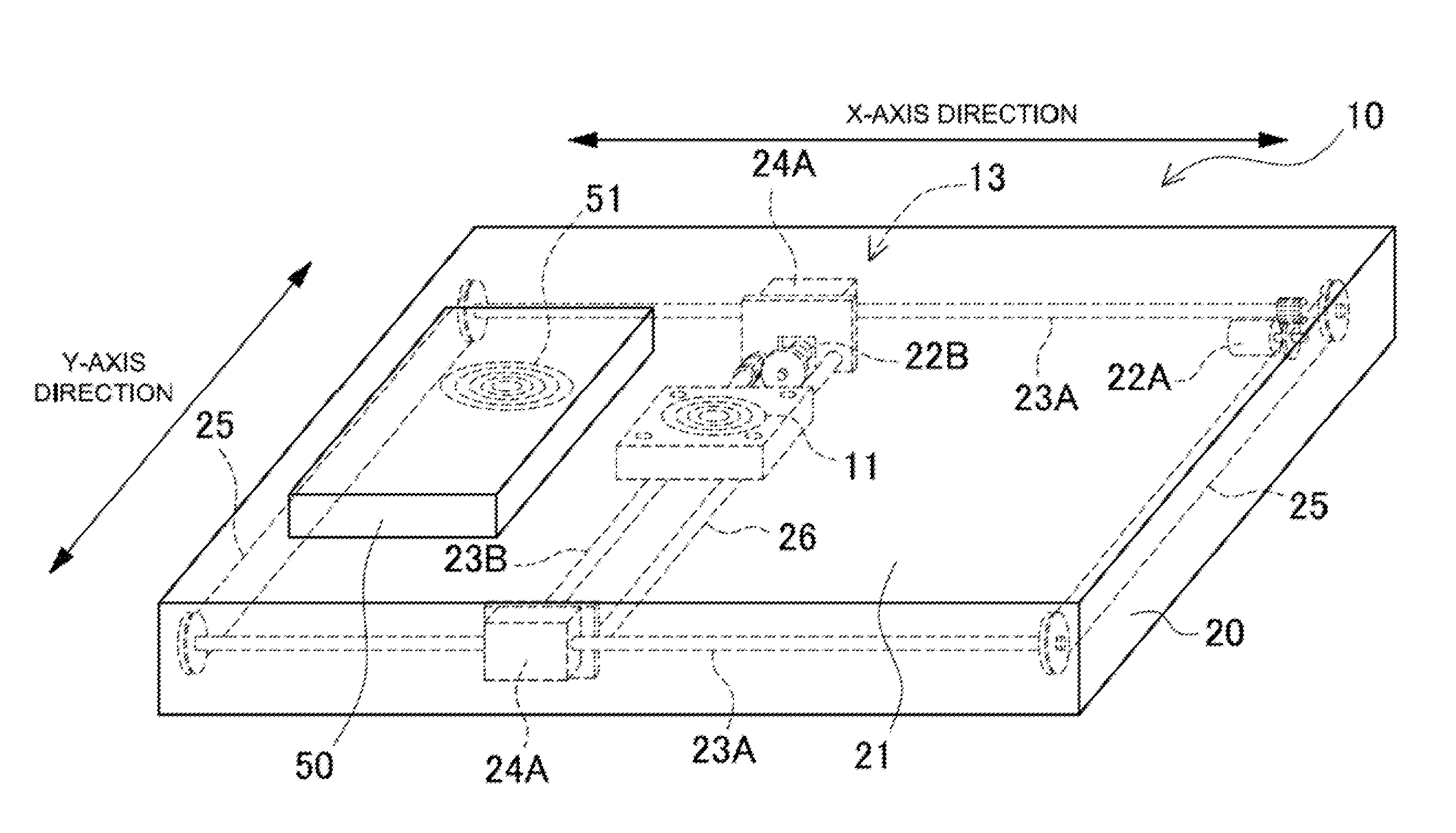

Device housing a battery and charging pad

InactiveUS20110128714A1Reduces rectifying circuit element ON-resistanceReduce voltage dropElectric powerBattery overcharge protectionElectric power transmissionControl circuit

A charging pad 10 is provided with a power supply coil 11, and a device housing a battery 50 containing an induction coil 51. A device housing a battery 50 is provided with a rectifying circuit 53 that rectifies AC power induced in the induction coil 51, a charging circuit 54 that charges the internal battery 52 with output from the rectifying circuit 53, a shorting circuit 56 that short circuits the terminals of the induction coil 51, and a control circuit 57 that controls the shorting circuit 56 ON when a charging abnormality is detected. If the control circuit 57 detects a charging abnormality during power transmission from the charging pad 10 power supply coil 11 to the device housing a battery 50 induction coil 51, it controls the shorting circuit 56 ON to cut-off the supply of power from the induction coil 51 to the rectifying circuit 53.

Owner:SANYO ELECTRIC CO LTD