Patents

Literature

31results about How to "Avoid volume increase" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

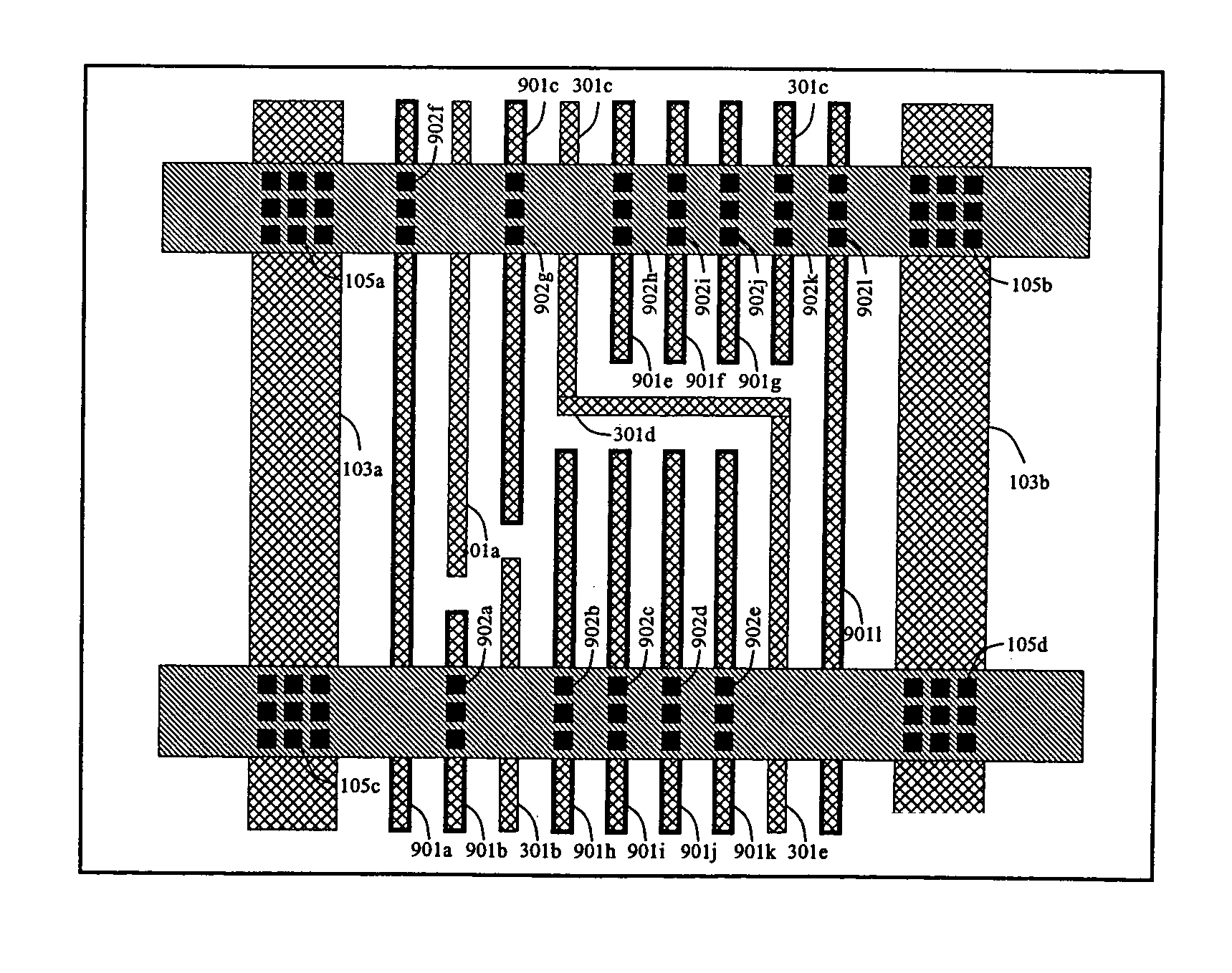

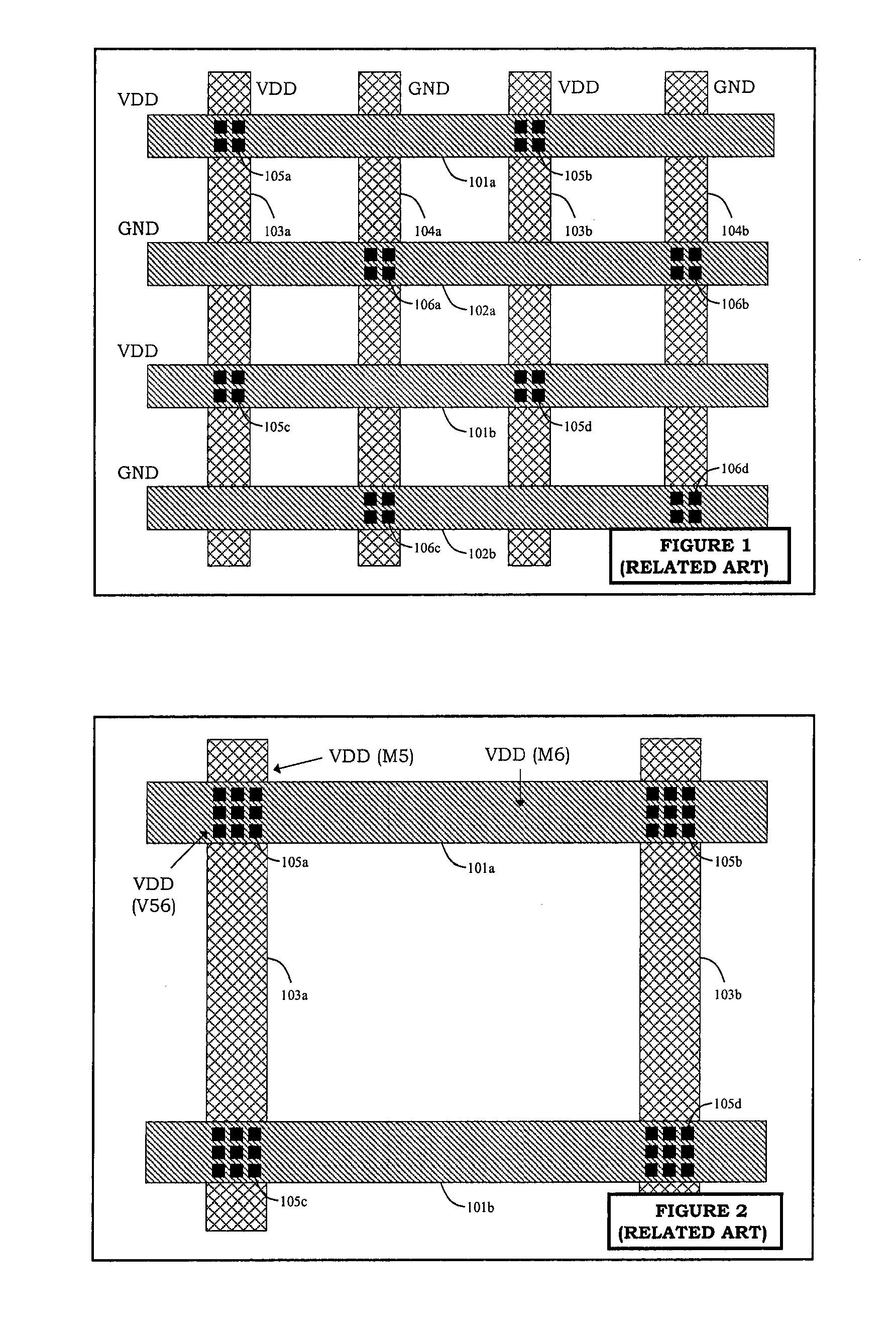

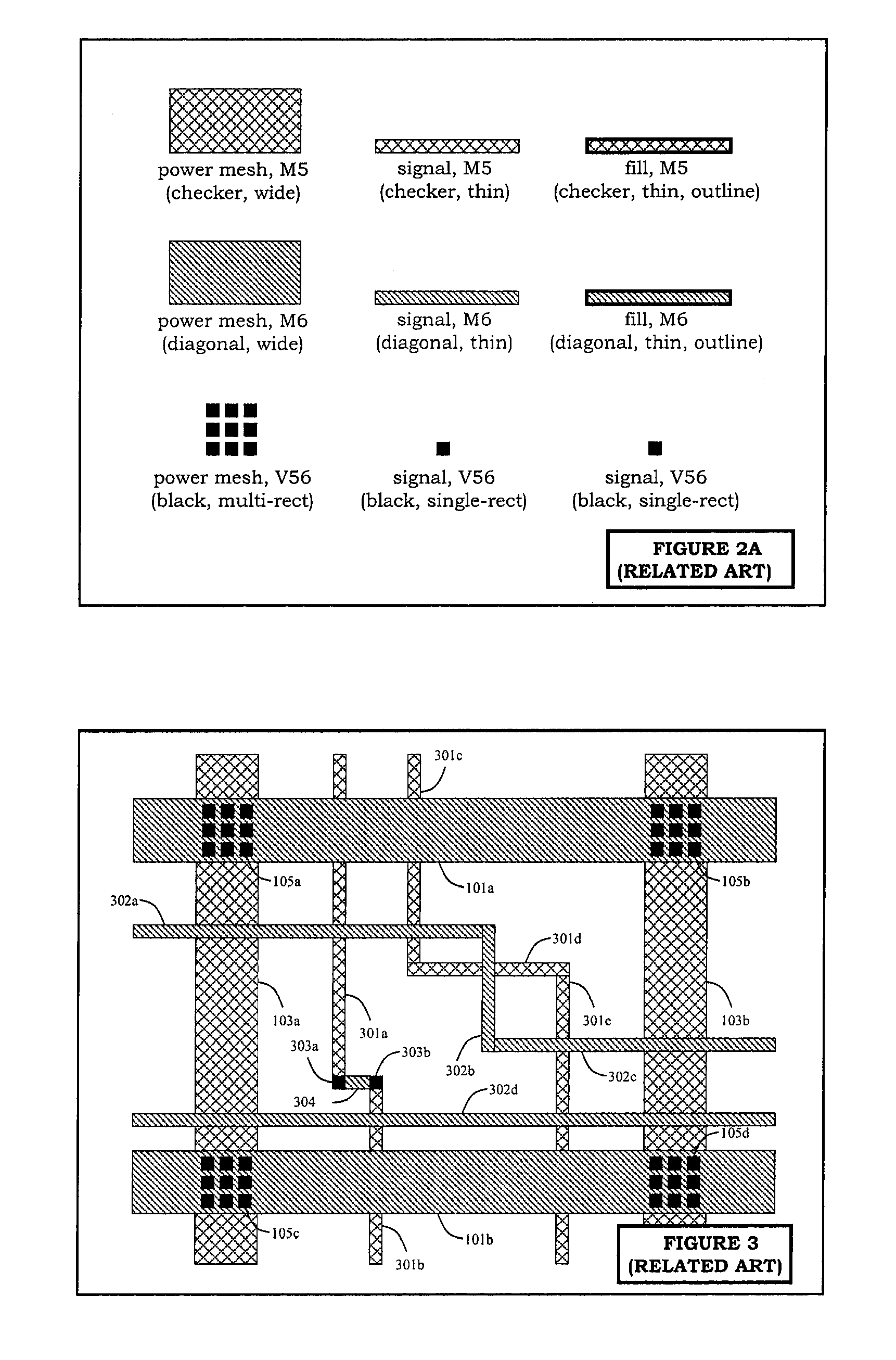

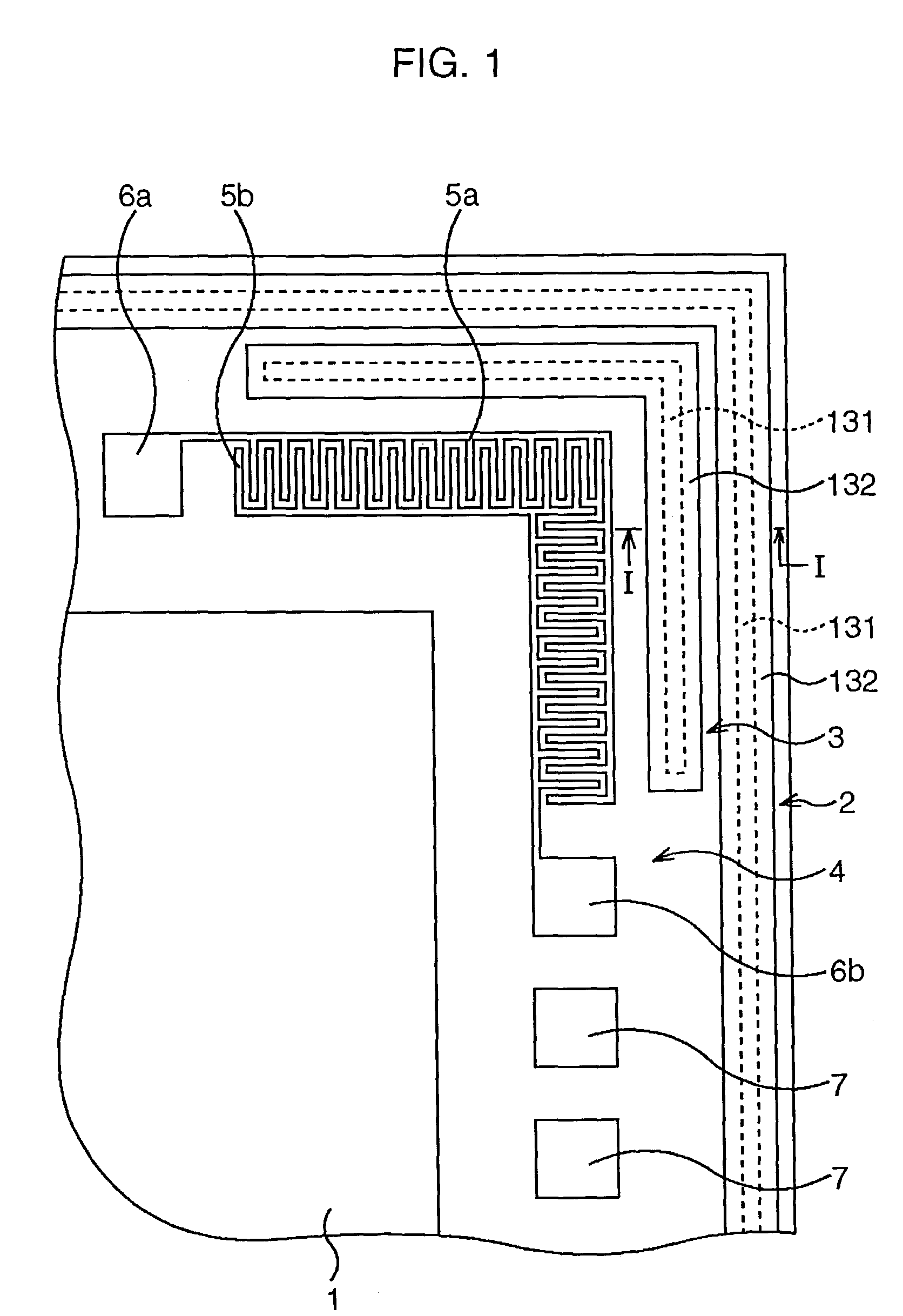

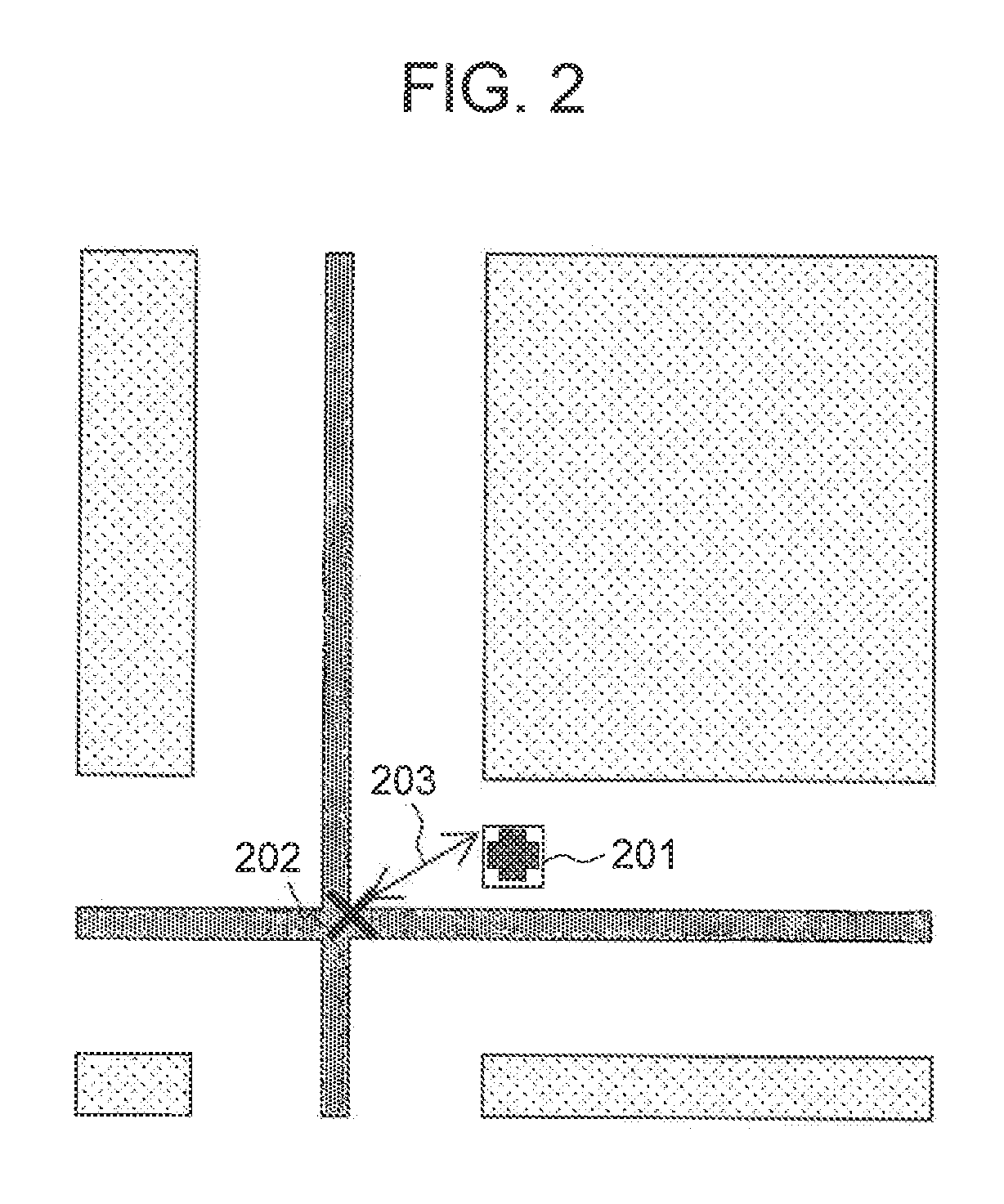

Redundantly tied metal fill for IR-drop and layout density optimization

ActiveUS7240314B1Reduce voltage dropAvoid volume increaseSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceVoltage drop

An integrated circuit and a method for using metal fill geometries to reduce the voltage drop in power meshes. Metal fill geometries are connected to the power mesh using vias or wires at multiple locations. Metal fill geometries are connected to other floating metal fill geometries using vias or wires at multiple locations. The circuit design introduces maximum redundancy between metal fill geometries and power mesh geometries, but partial redundancy between metal fill geometries and metal fill geometries. In particular, the redundancy in connectivity between metal fill geometries and metal fill geometries is kept minimal to reduce the number of geometries introduced. The high redundancy between metal fill geometries and power mesh geometries and the partial redundancy among metal fill geometries result in a smaller IR-drop by reducing the effective resistance on a power mesh. Hence, the invention use redundancy carefully and advantageously to achieve simultaneous metal density and IR-drop optimization without introducing excessive number of metal fill geometries.

Owner:SYNOPSYS INC

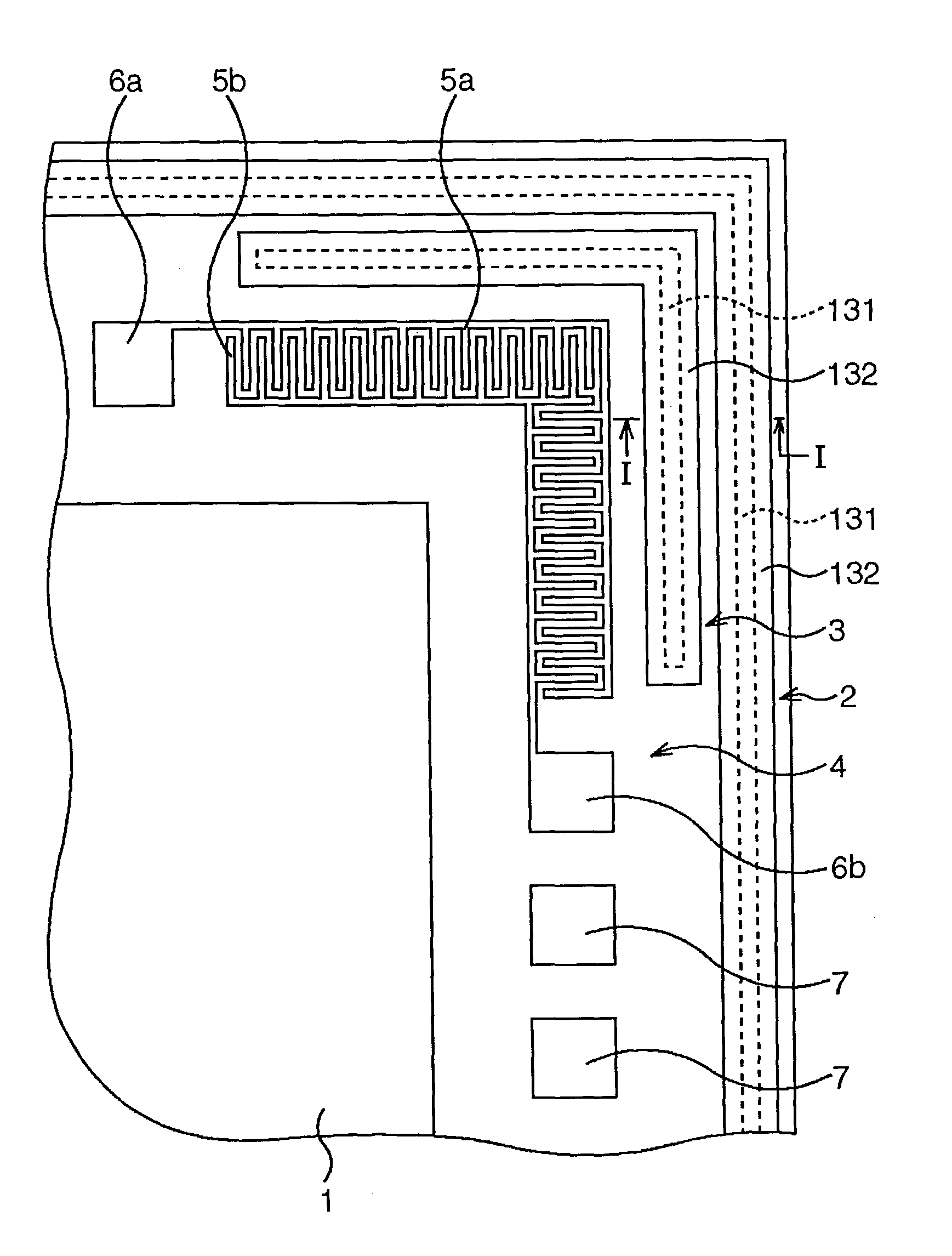

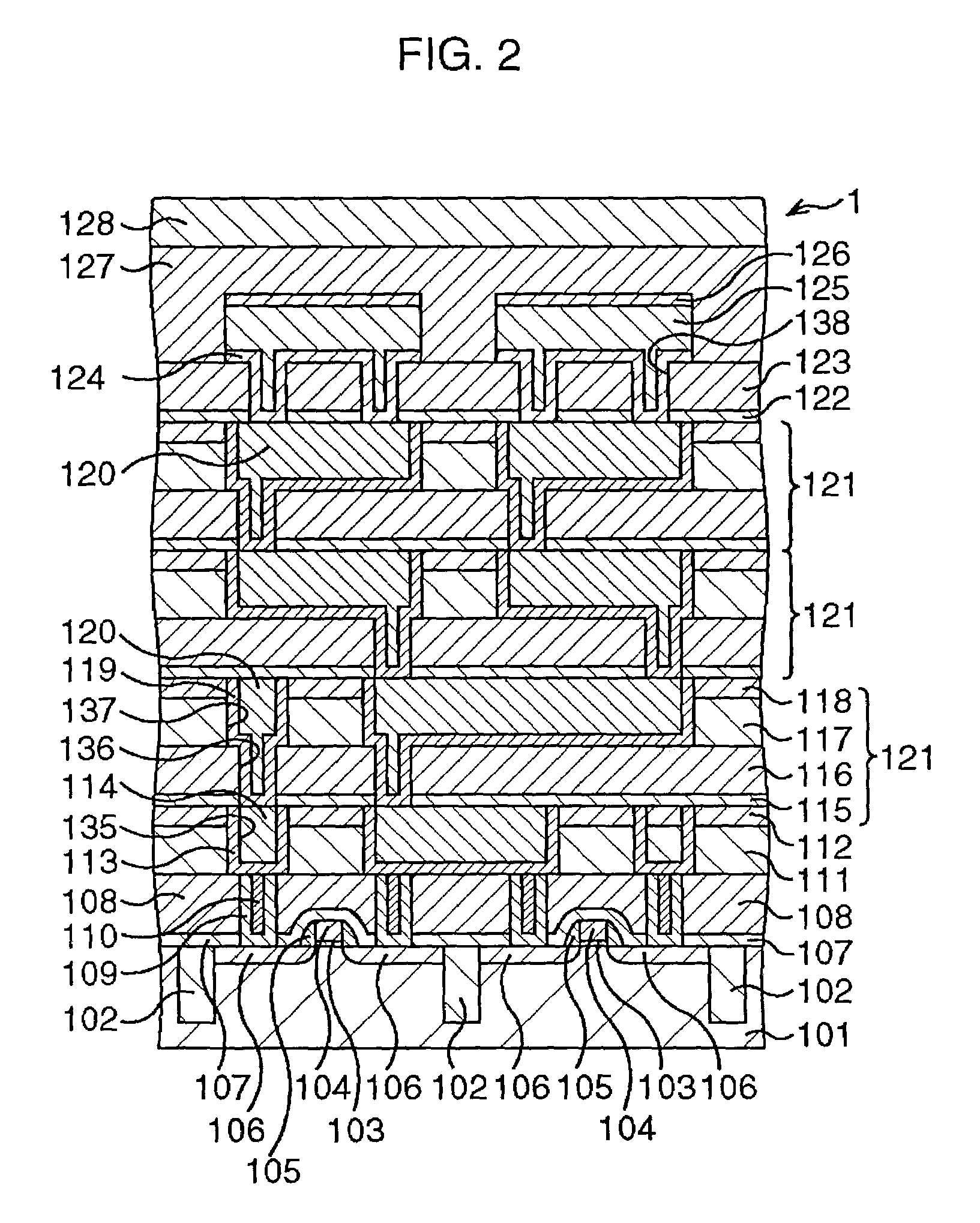

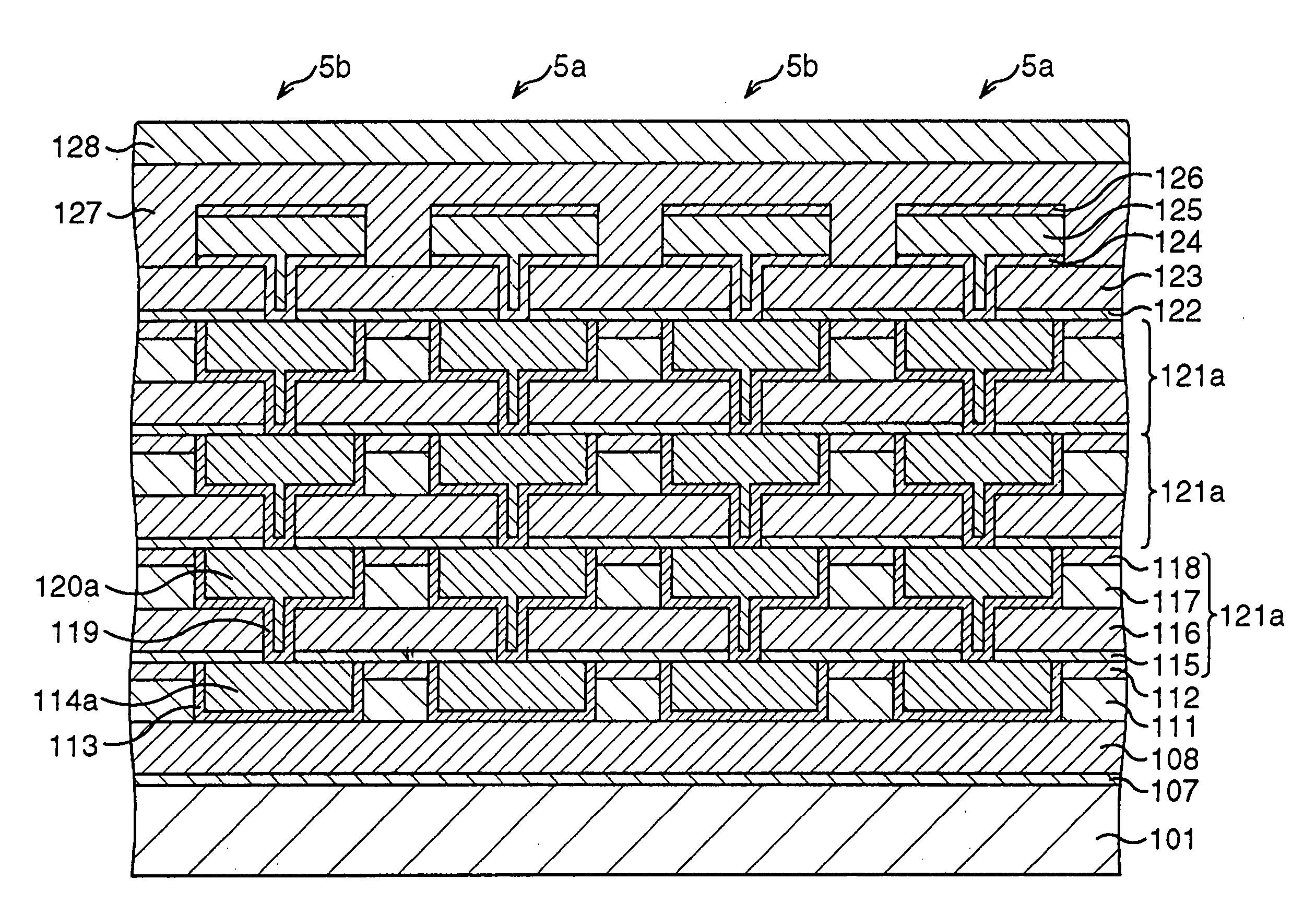

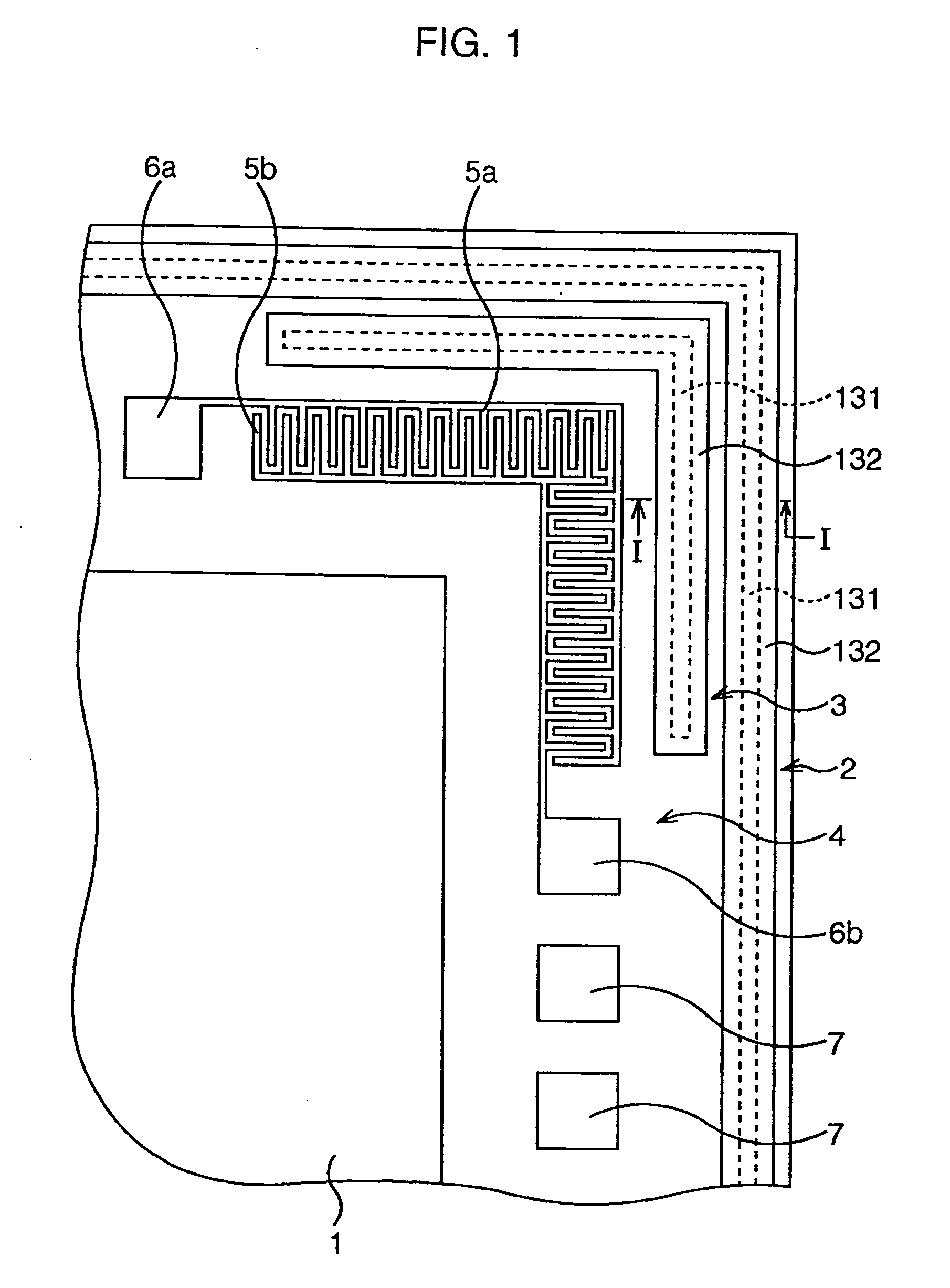

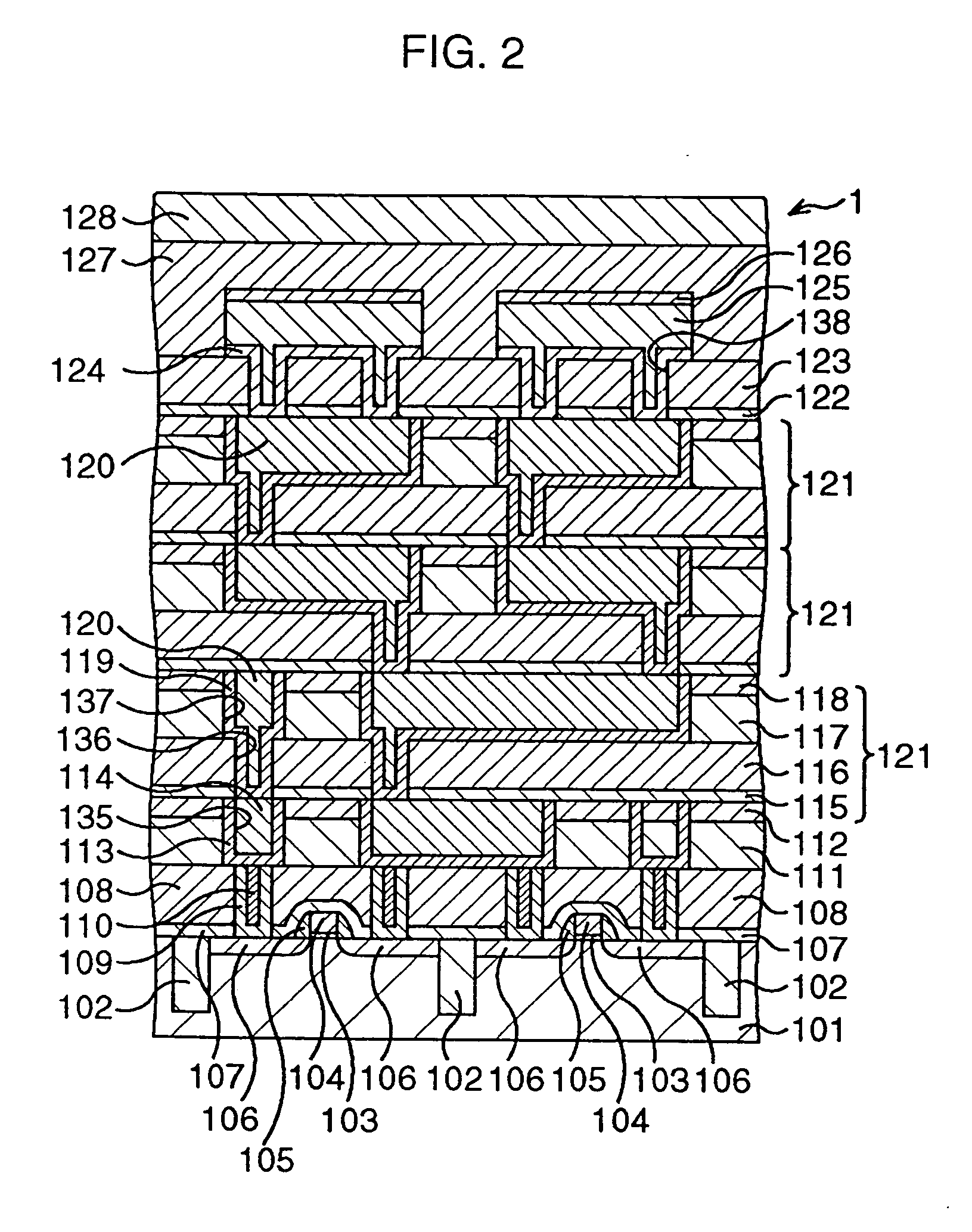

Semiconductor device, method of manufacturing the same, and phase shift mask

InactiveUS7129565B2Increase the areaImprove moisture resistanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringMoisture resistance

A main wall part is provided so as to surround an integrated circuit part. A sub-wall part which is in “L” shape is provided between each corner of the main wall part and the integrated circuit part. Therefore, even if the stress is concentrated due to heat treatment or the like, the stress is dispersed to the main wall part and the sub-wall part, and hence peeling between layers and a crack are unlikely to occur, as compared with the conventional art. Further, even if the crack and the like occur at the corner, moisture from the outside hardly reaches the integrated circuit part when the main wall part and the sub-wall part are coupled to each other. For this reason, it is possible to ensure an extremely high moisture resistance.

Owner:FUJITSU SEMICON LTD

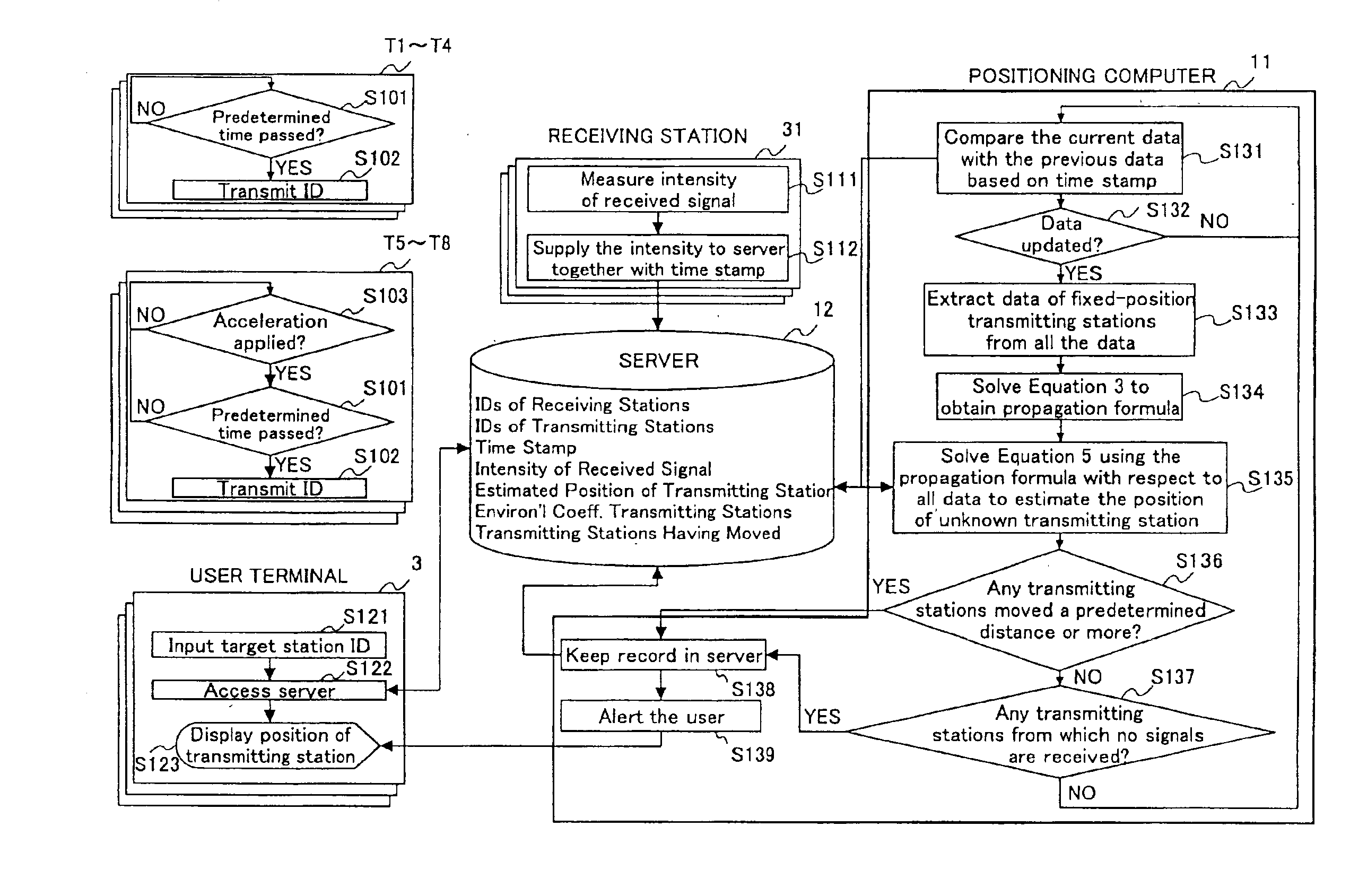

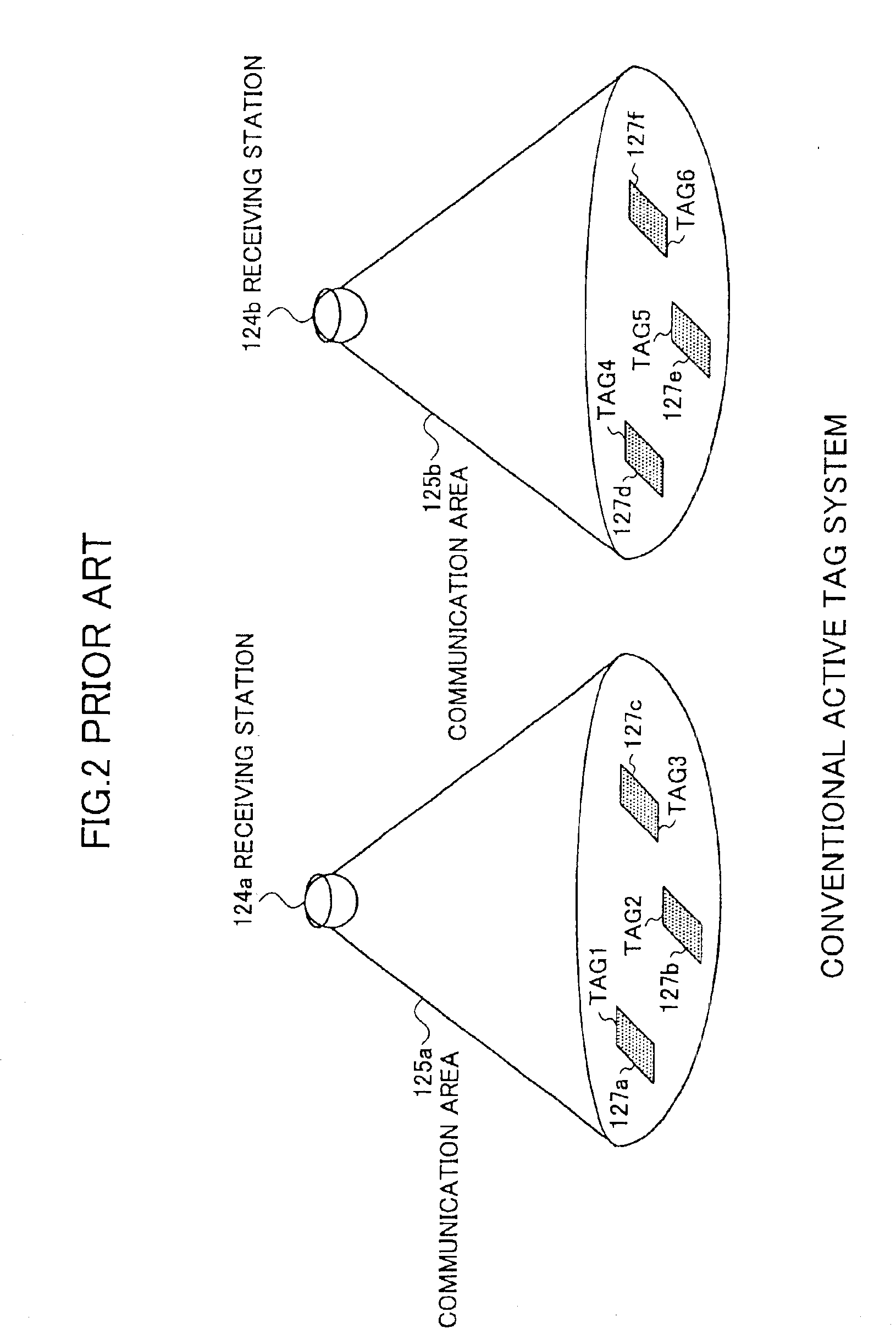

Locating system and method for determining positions of objects

A locating system for determining a position of an object comprises a transmitting station that transmits a first ID signal containing a first identifier of this transmitting station; a receiving station that receives the first ID signal, measures the intensity of the first ID signal, and extracts the first identifier; a data management unit that stores and manages the intensity in association with the first identifier, the intensity and the identifier being supplied from the receiving station; and a positioning computer that estimates the position of the transmitting station using a first correcting formula defining a relation between the intensity and the distance, based on the data stored in the data management unit.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

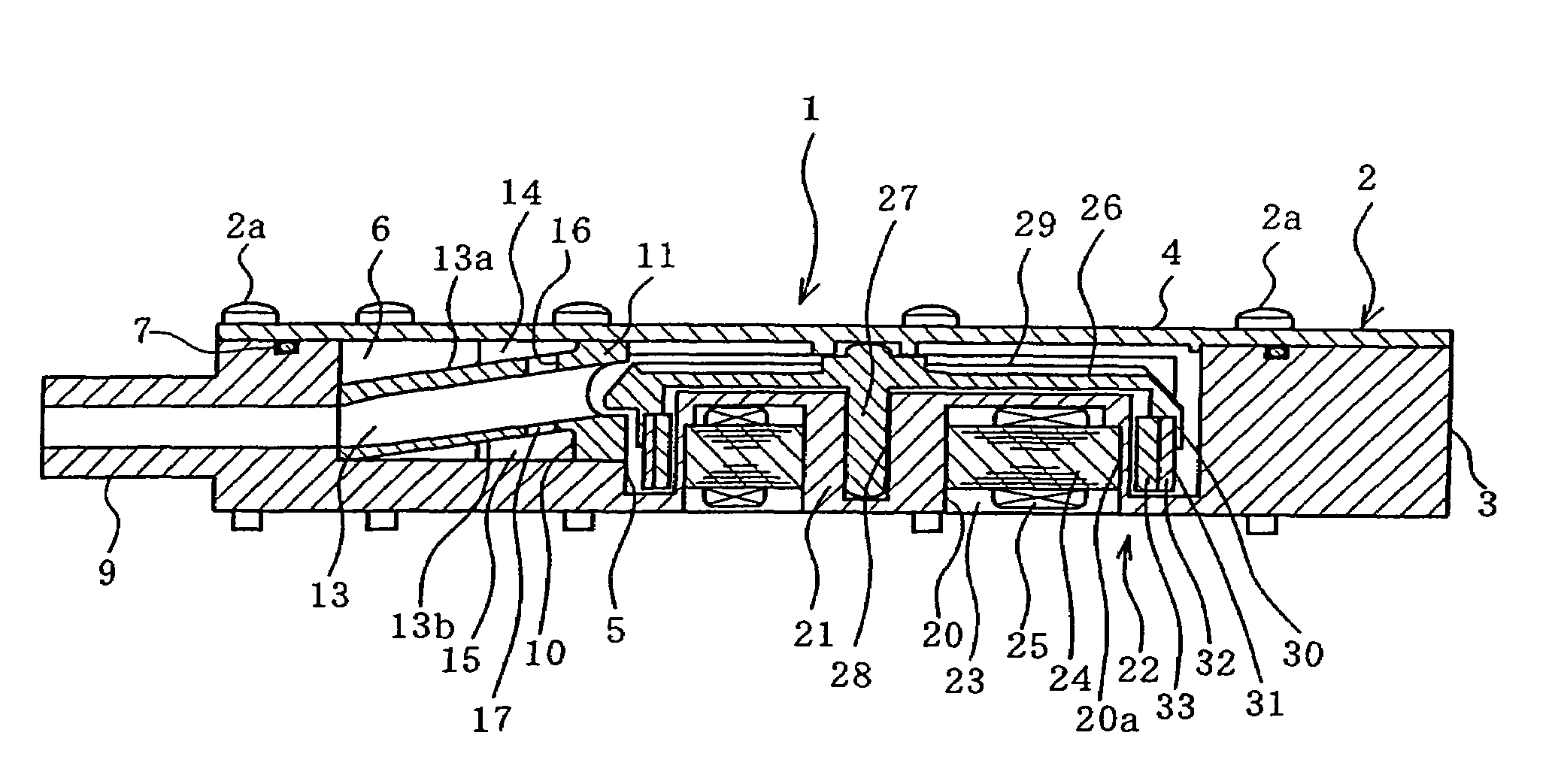

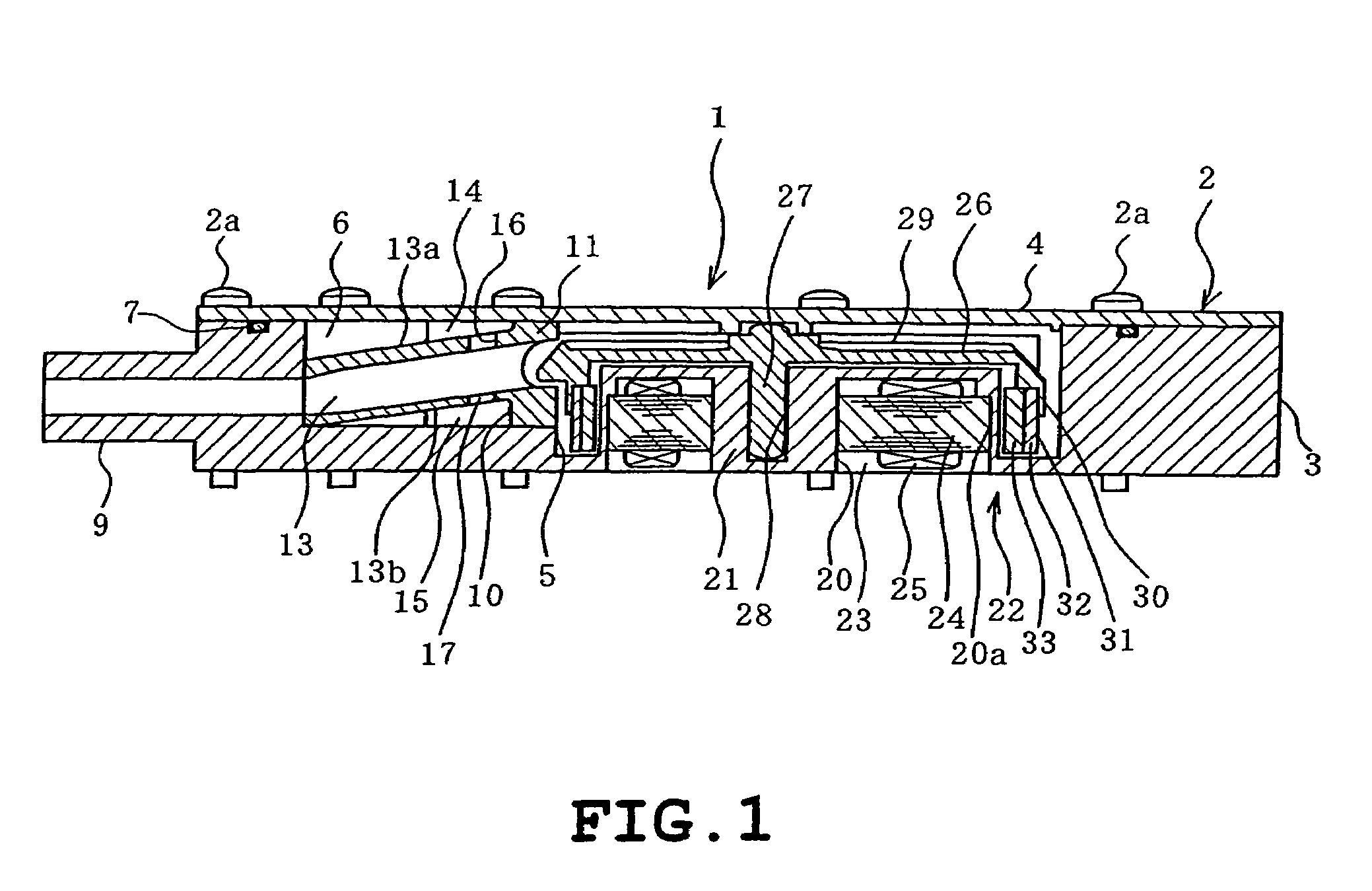

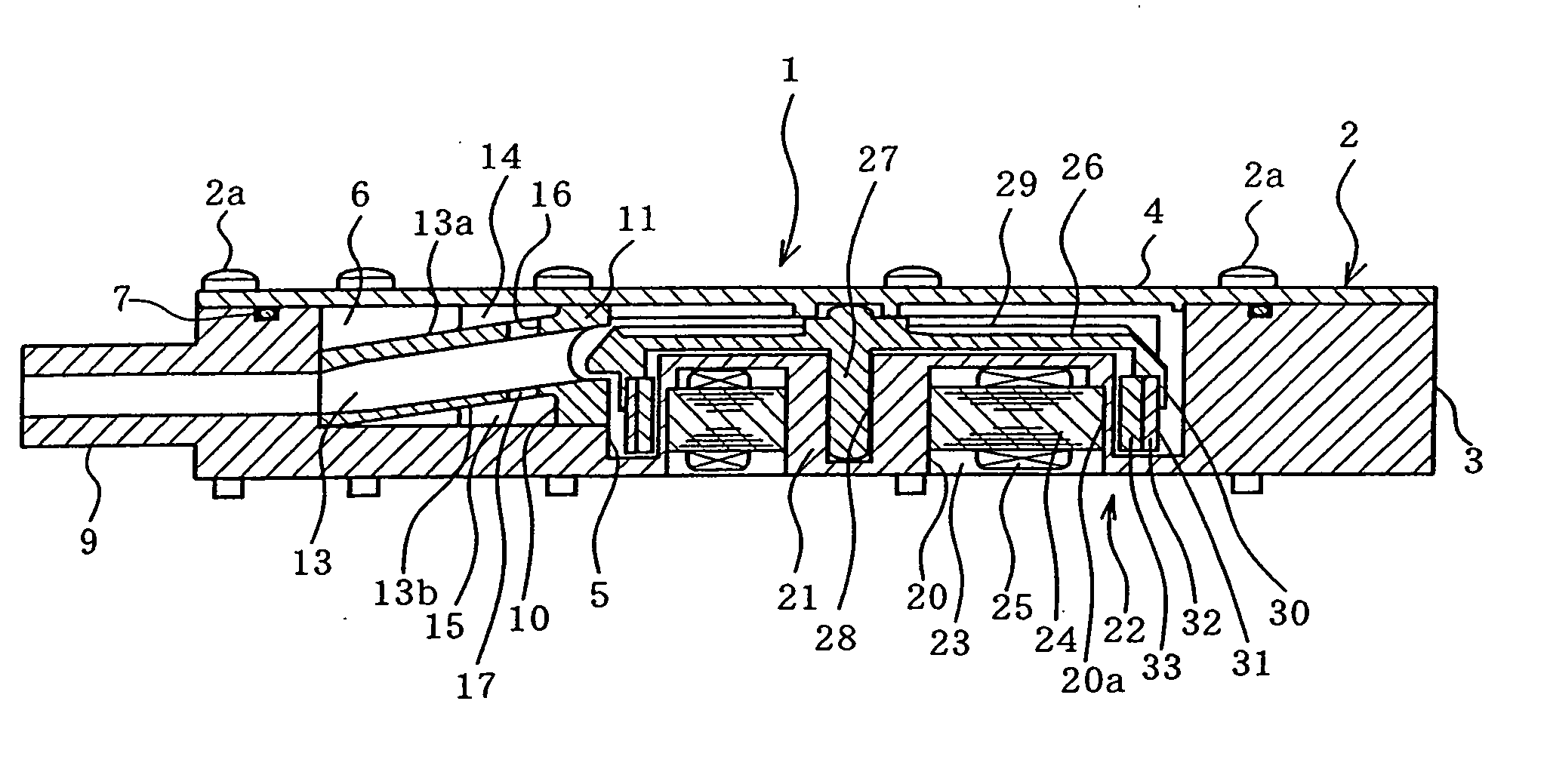

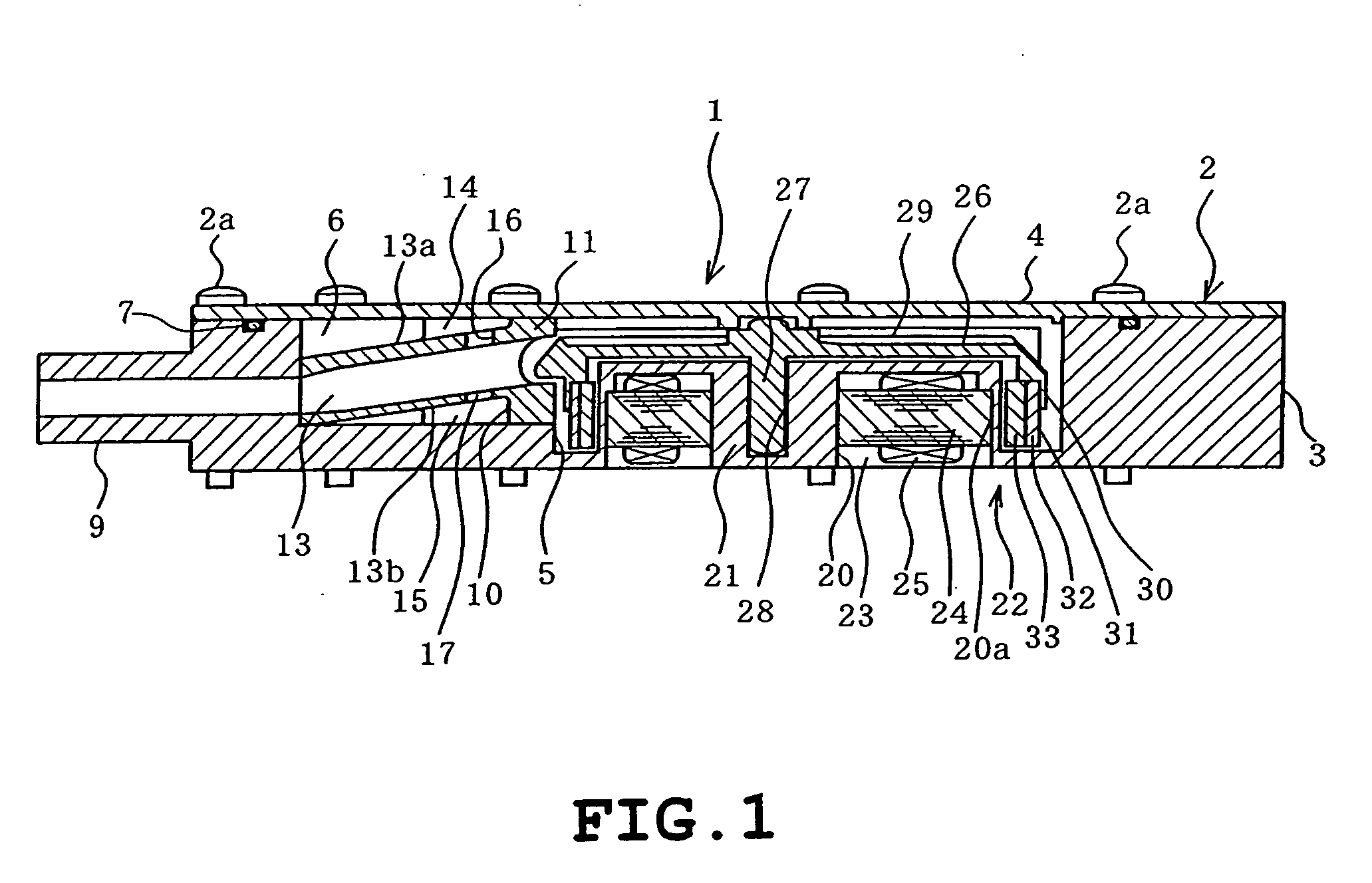

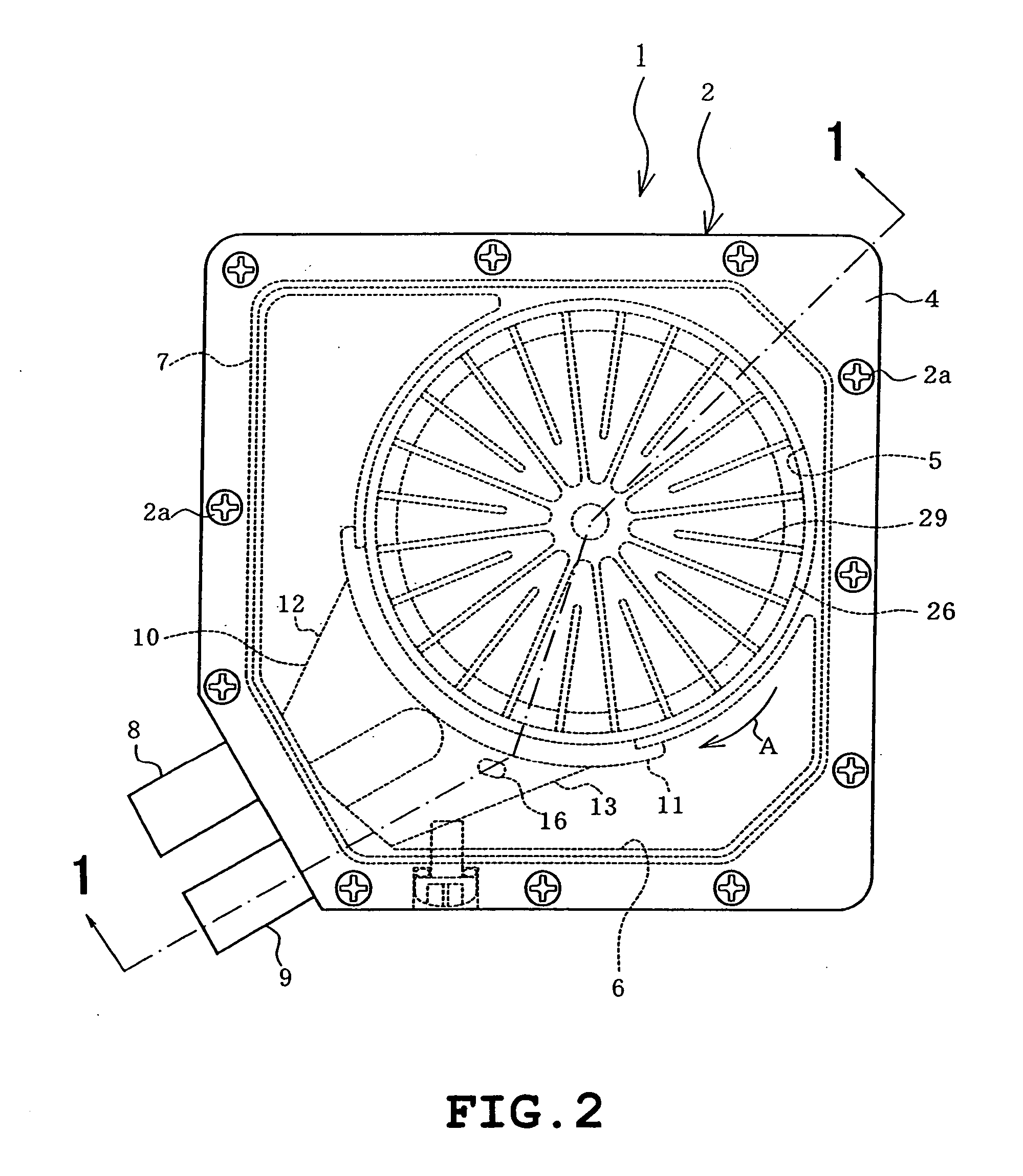

Fluid pump, cooling system and electrical appliance

InactiveUS7371056B2Avoid volume increaseEliminate needCircumferential flow pumpsTransverse flow pumpsPump chamberEngineering

A fluid pump includes a case including a pump chamber, a reserve tank for storing spare liquid and located in the case but outside the pump chamber and formed so that a space independent of the pump chamber is defined by the reserve tank, a fluid path forming member arranged inside the reserve tank and including a discharge path communicating between a discharge port and the pump chamber, and a communication hole which is formed in a side of the fluid path forming member so as to assume such a position that the communication hole faces an inside of the reserve tank so that the hole communicates between the discharge path and the inside of the reserve tank, the communication hole being sized so that air in the pump chamber is allowed to flow through the hole into the reserve tank.

Owner:KK TOSHIBA

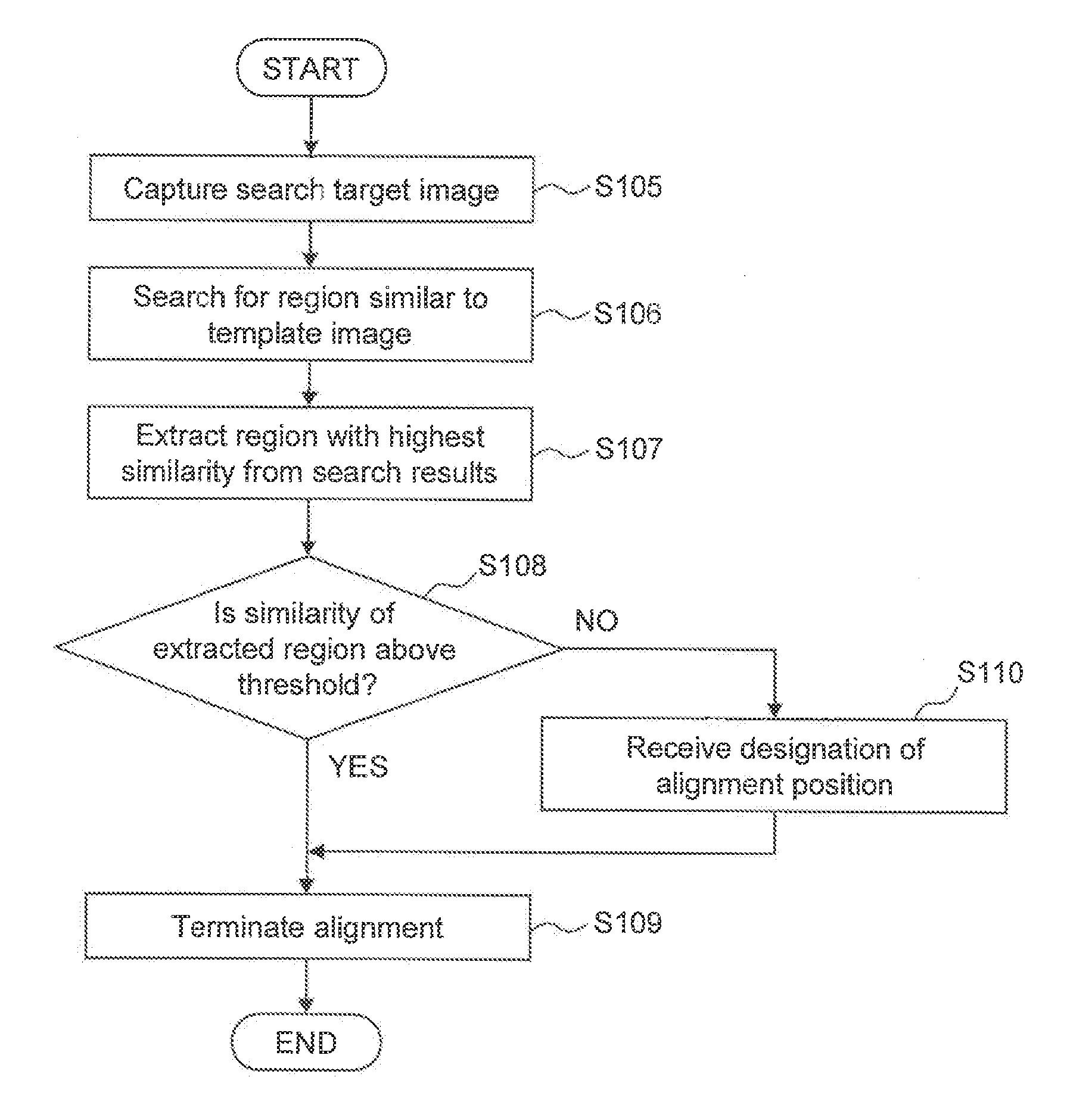

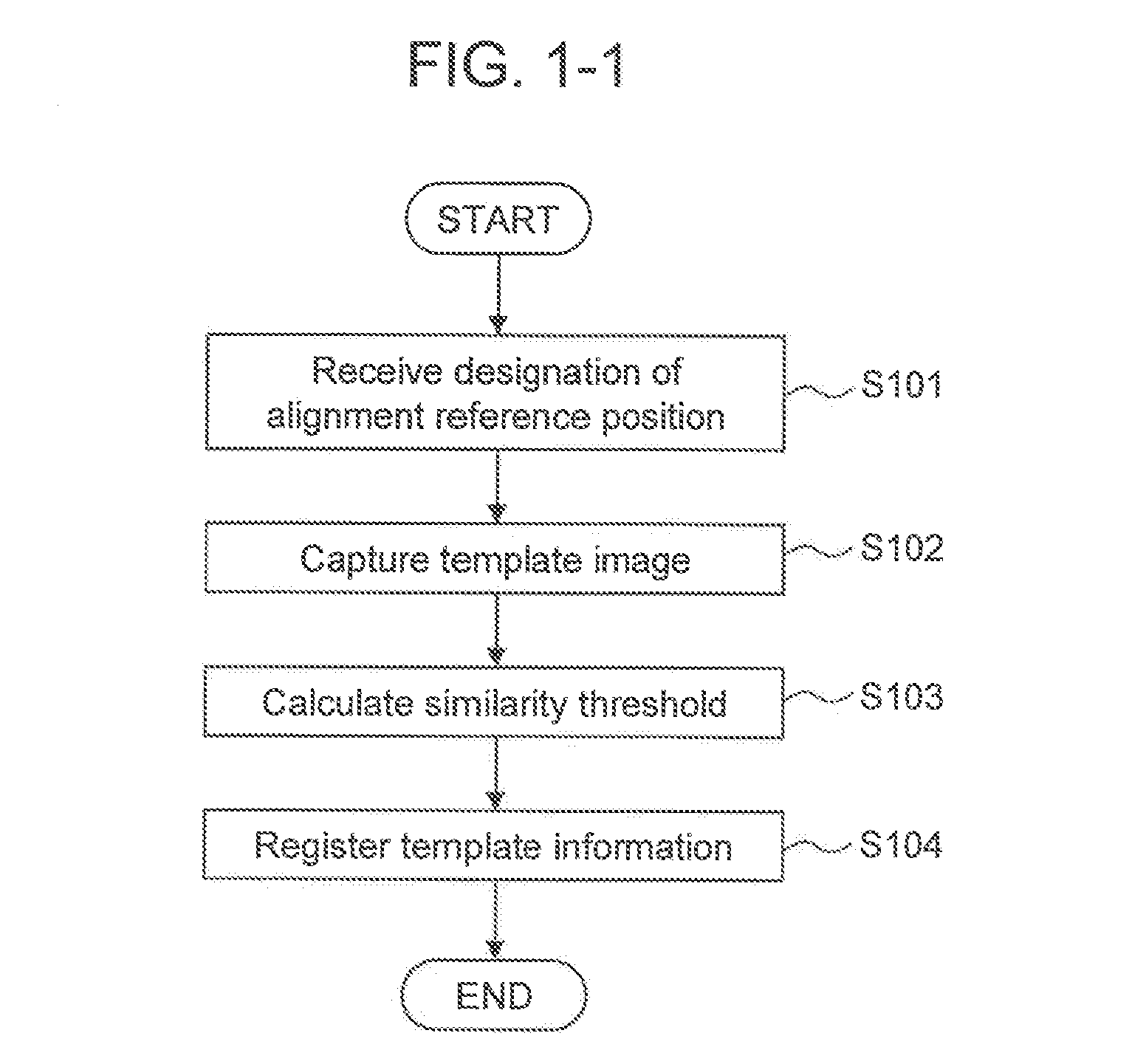

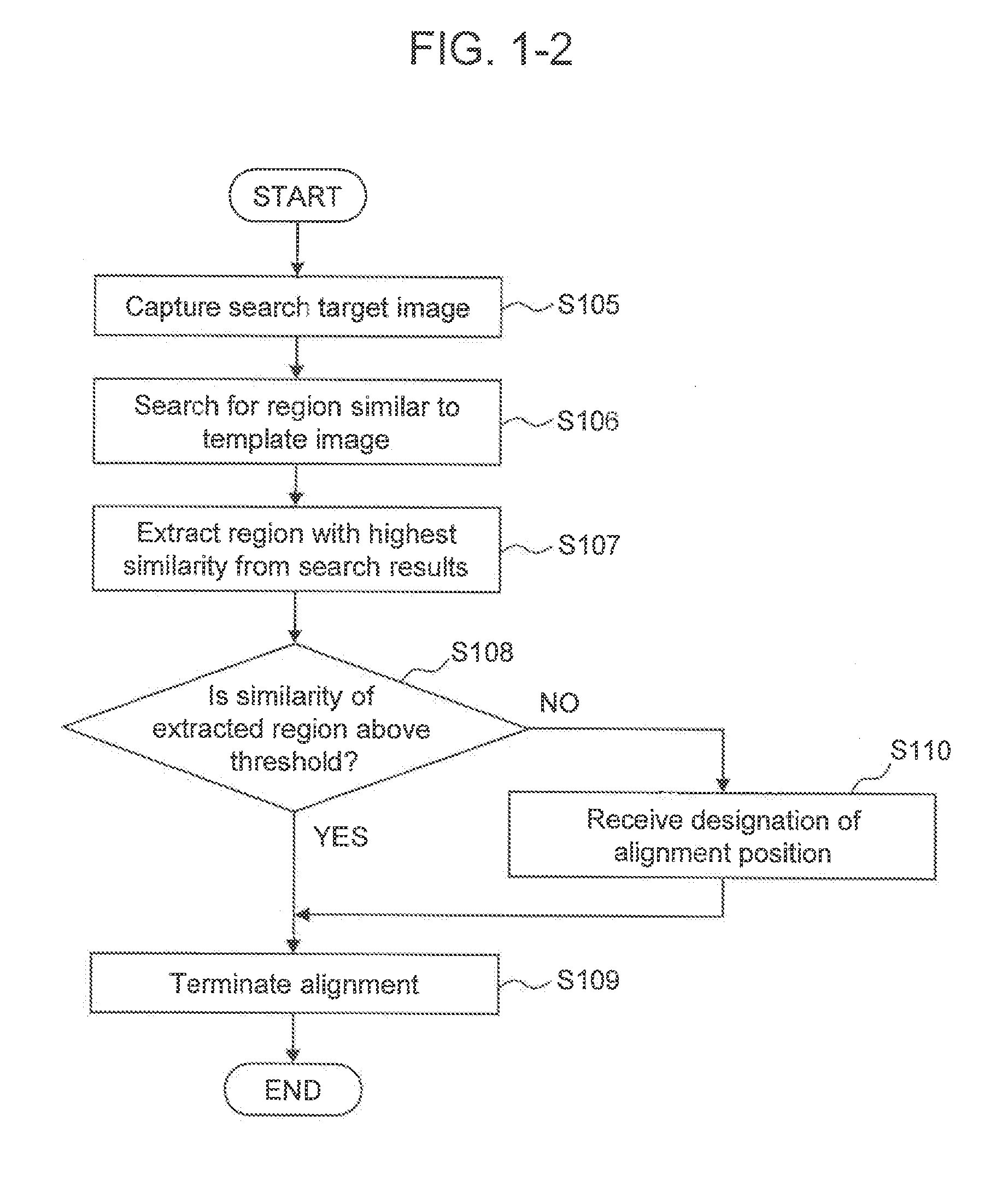

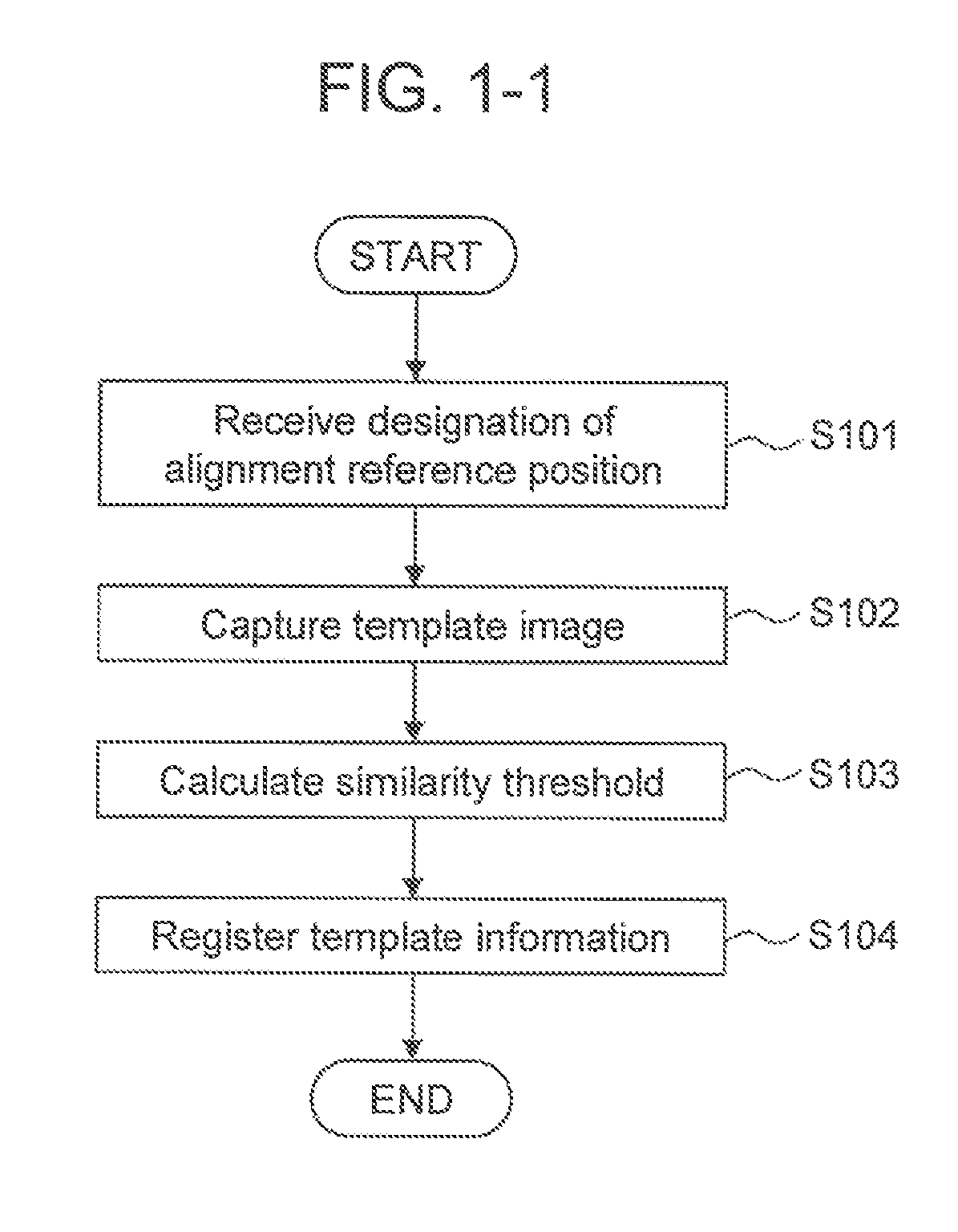

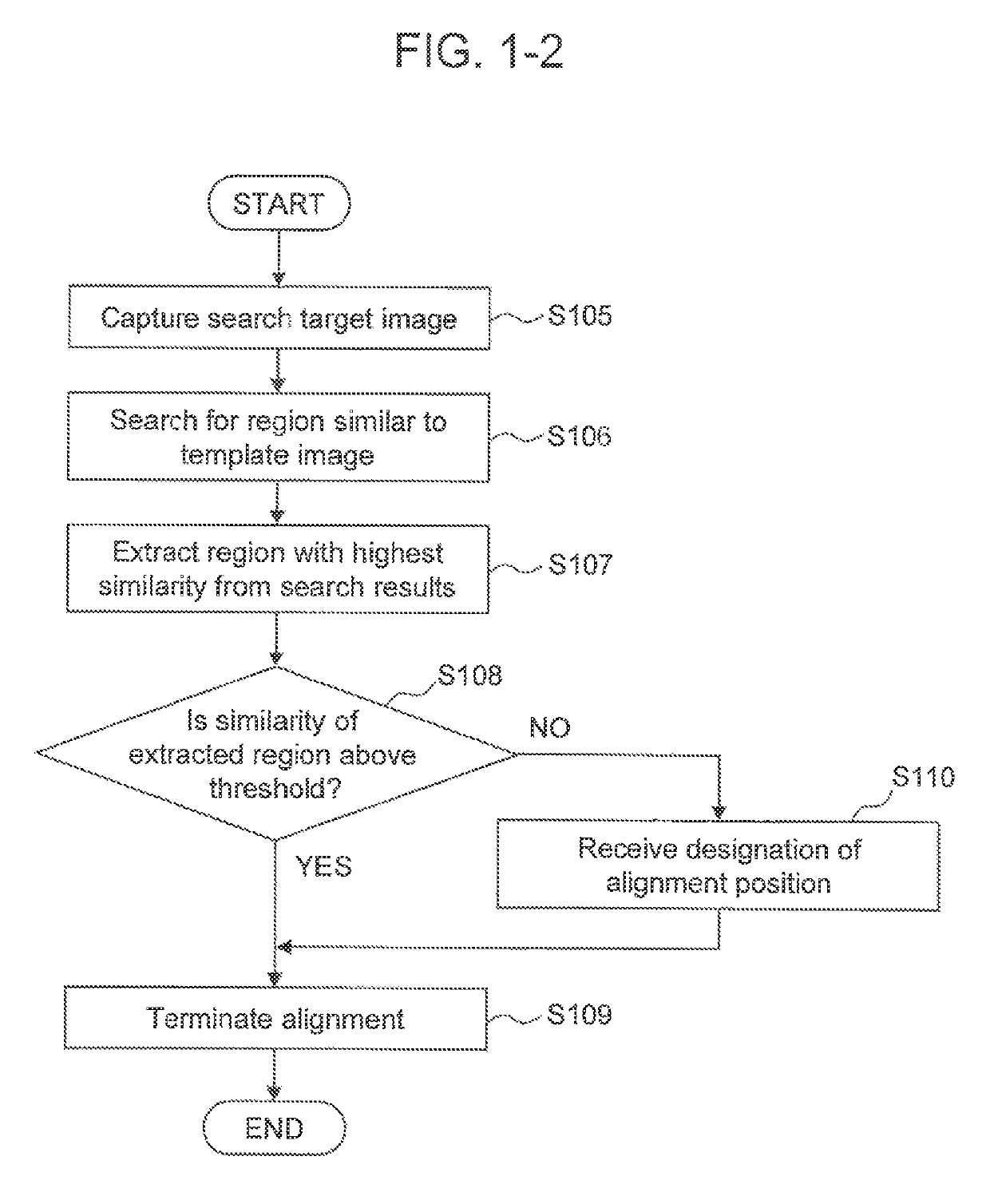

Pattern matching method and apparatus

ActiveUS20130278748A1Suppress failureReduce the numberImage enhancementImage analysisPattern recognitionPattern matching

When the degree of matching between patterns decreases due to a pattern fluctuation or an appearance fluctuation that has occurred during manufacturing steps, a heavy work burden would be placed on an operator. A data processing unit of a pattern matching apparatus calculates a threshold for determination of matching between a first template image and a partial region of a search target image obtained by capturing an image of the surface of a sample, on the basis of a result of evaluation of a similarity between the search target image and a second template image, the second template image having been captured in a wider range than the first template image.

Owner:HITACHI HIGH-TECH CORP

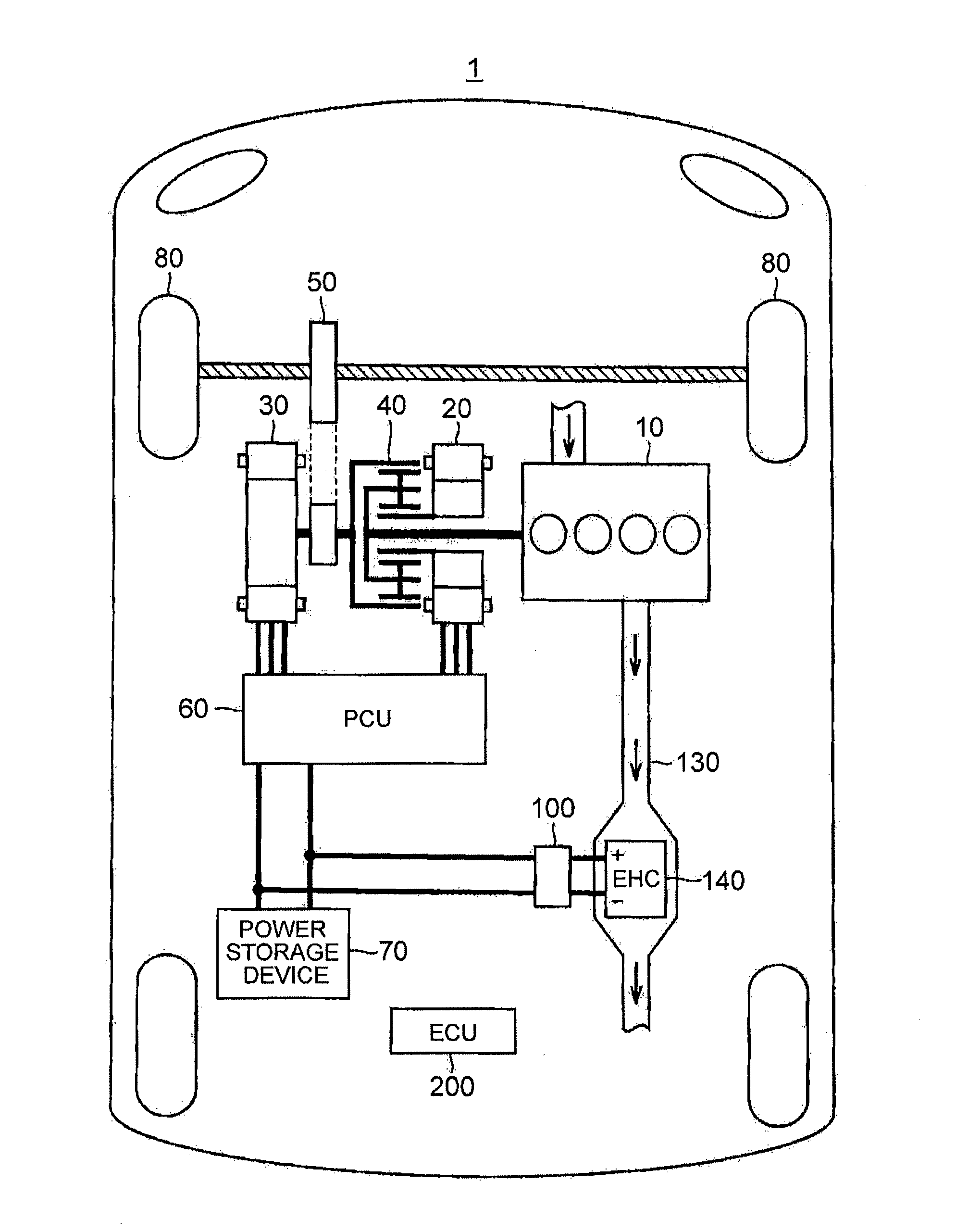

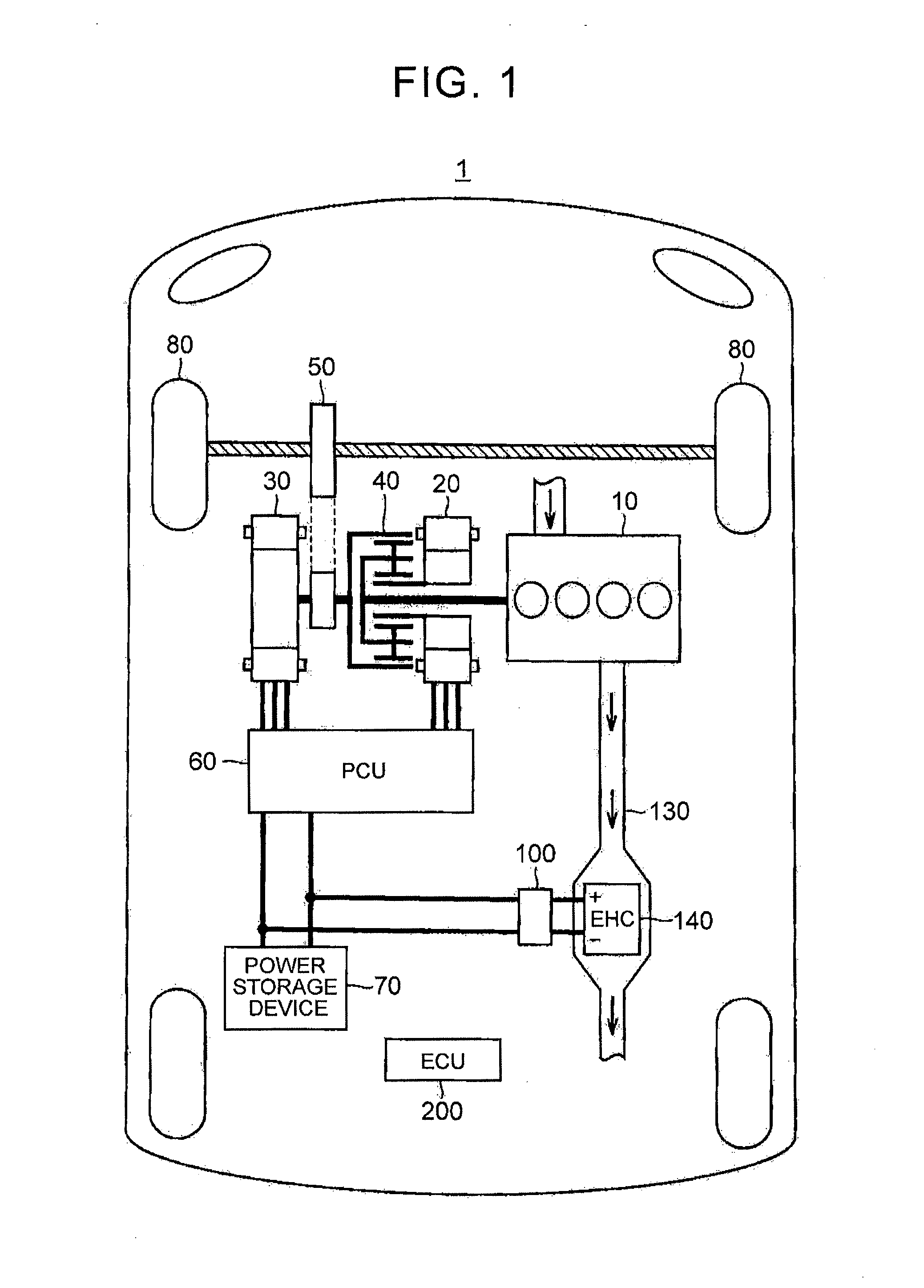

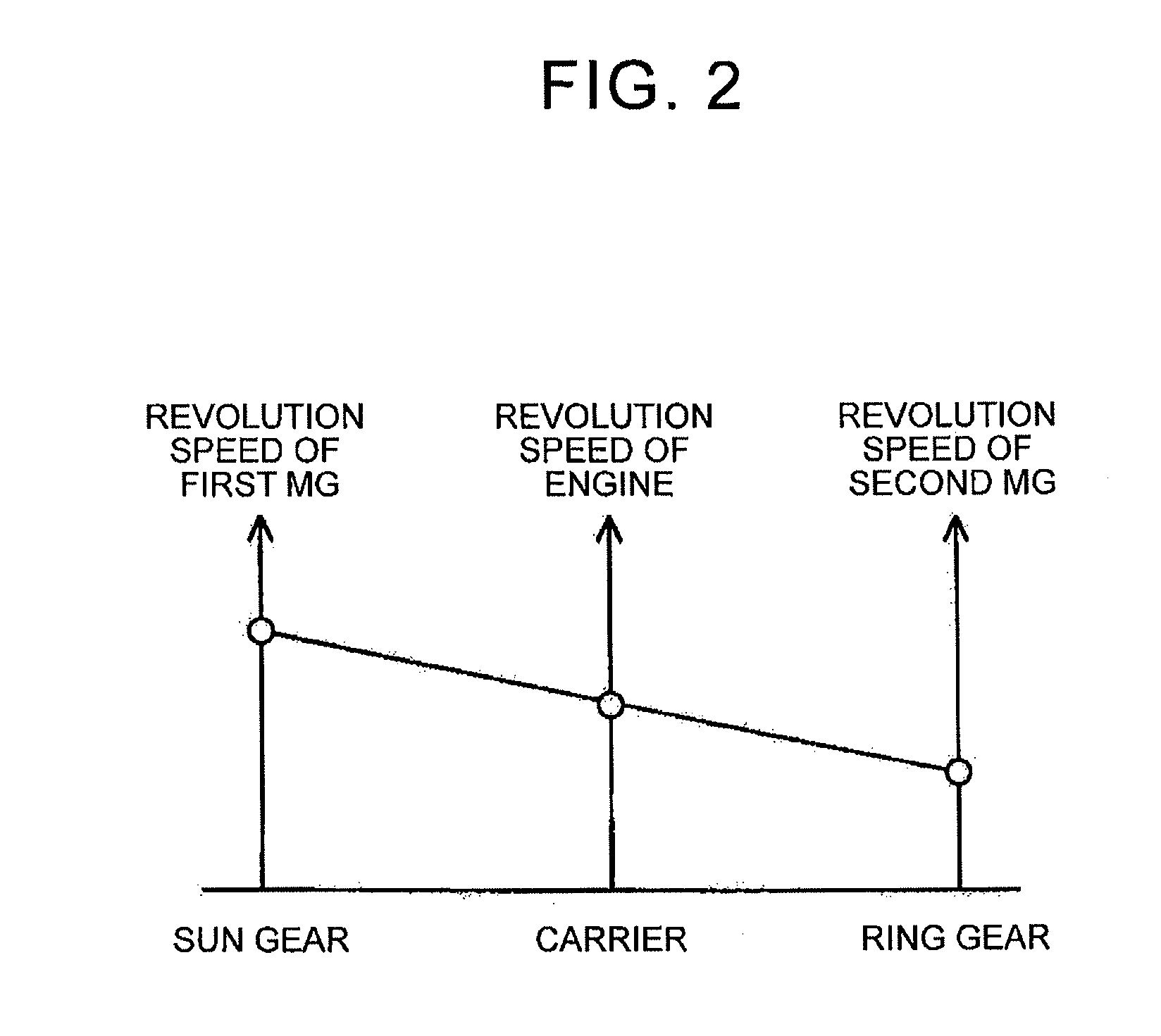

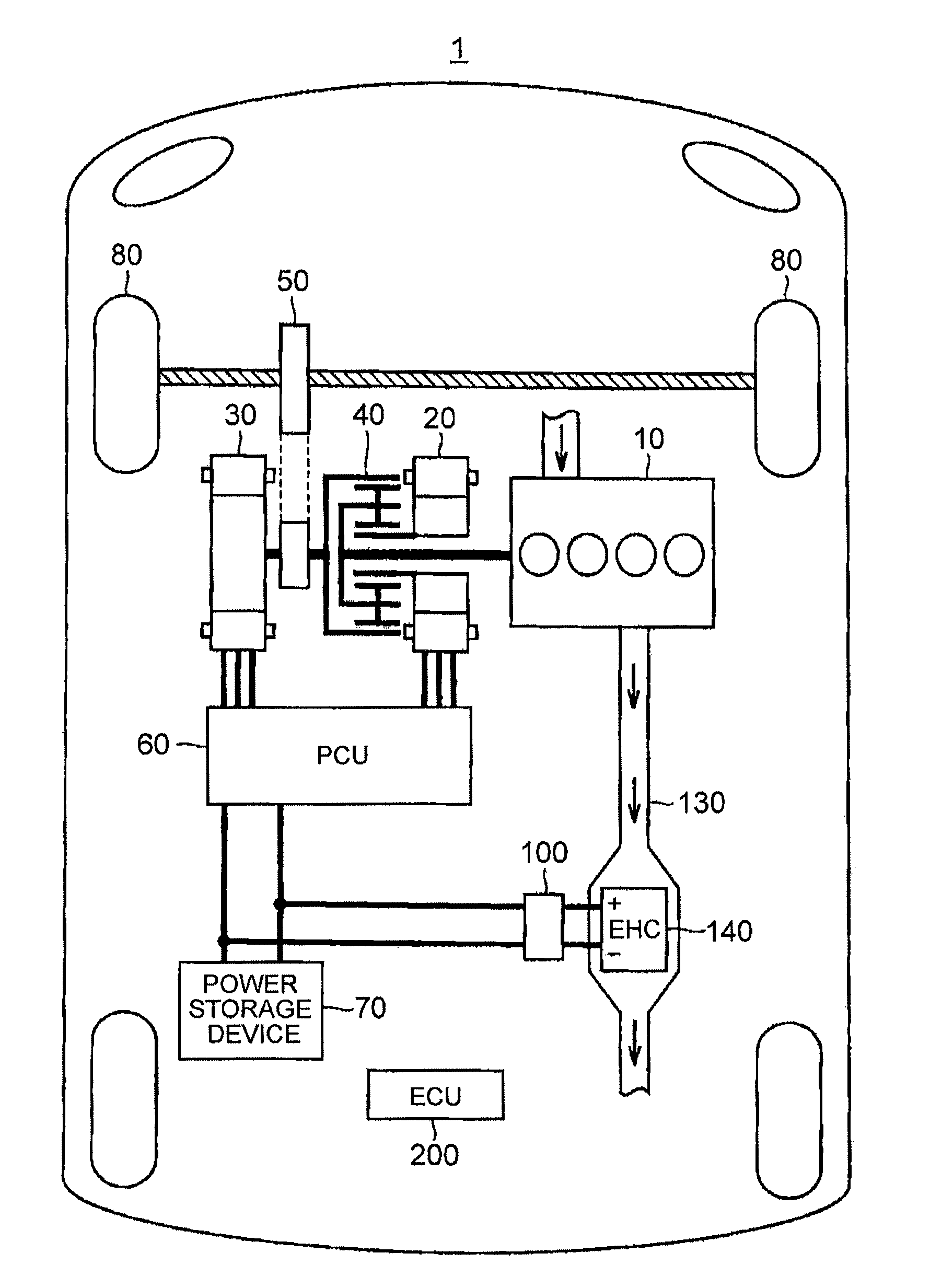

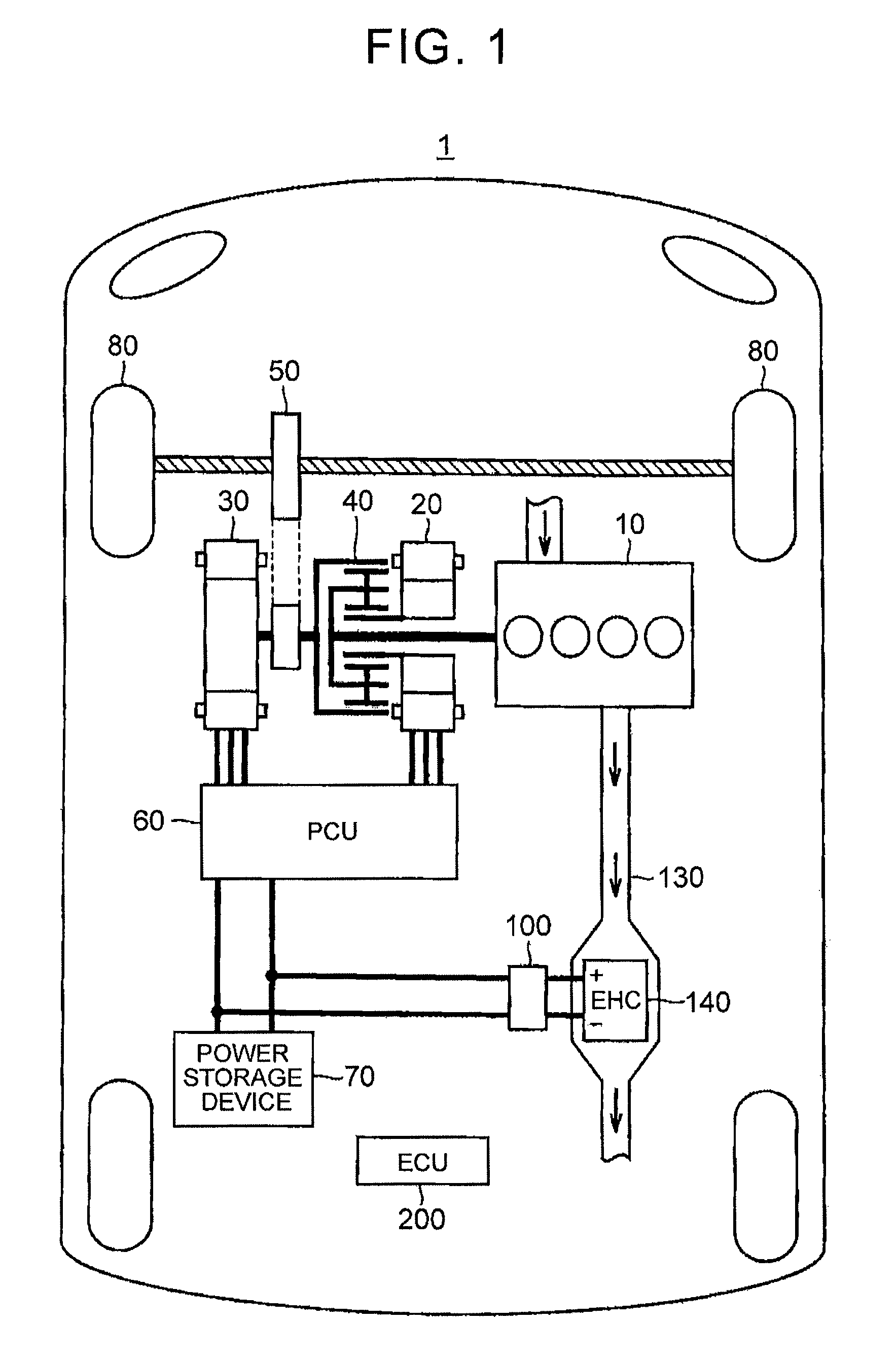

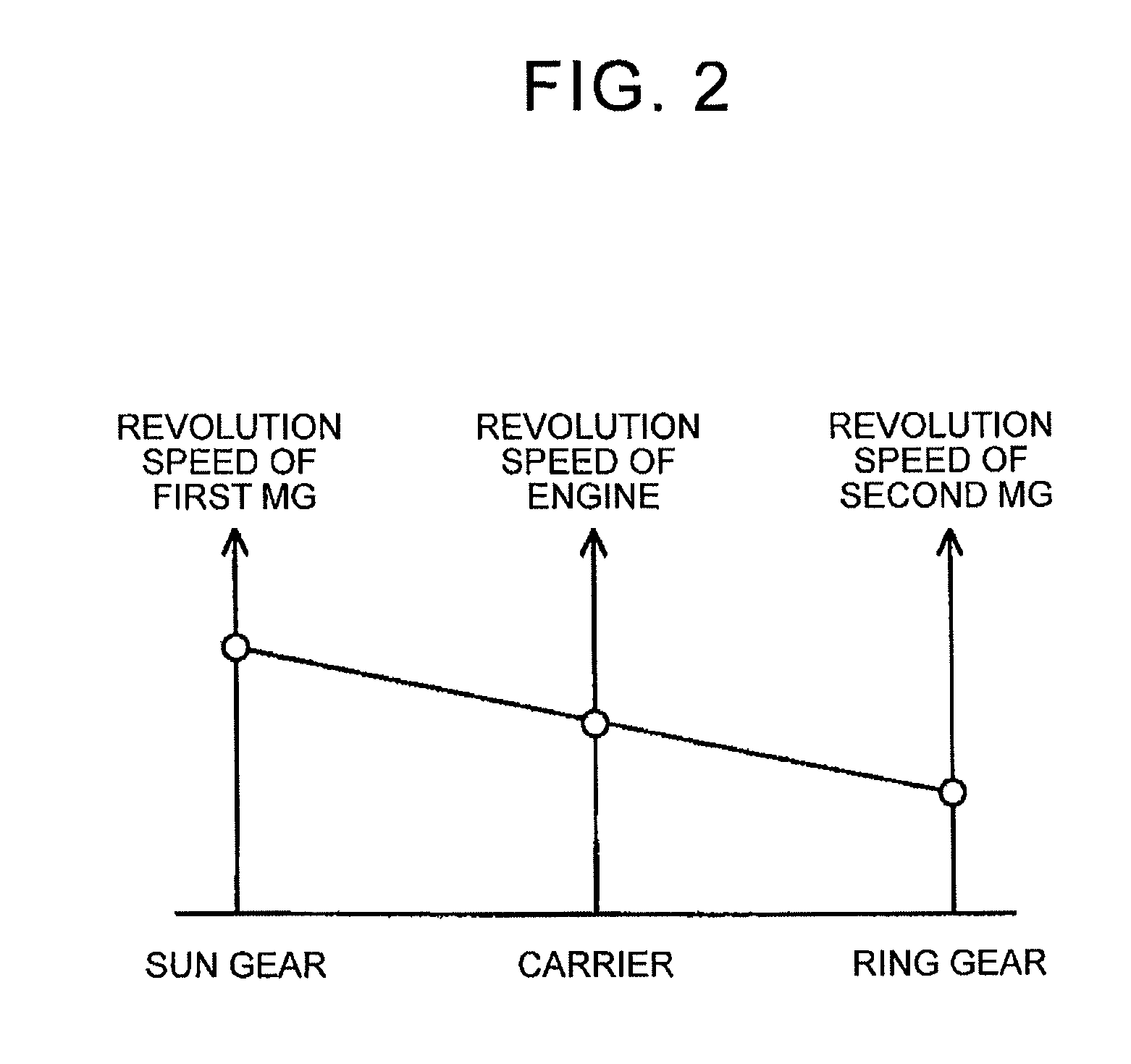

Hybrid vehicle

InactiveUS20140109556A1Insulation resistance is reducedIncrease the number ofHybrid vehiclesExhaust apparatusElectricityElectrical resistance and conductance

A hybrid vehicle equipped with an internal combustion engine and a motor-generator for running the vehicle, includes: a power storage device to be supplied to the motor-generator; a current leakage detection circuit detecting a decrease in insulation resistance, the current leakage detection circuit being electrically connected to a negative electrode of the power storage device; an electrical heated catalyst device; and a power supply device that converts electric power from the power storage device into energization power of the electrical heated catalyst device by a power conversion path passing through an insulating mechanism. The power supply device includes a switching device. The switching device is opened when the electrical heated catalyst device is energized, and is closed when the decrease in insulation resistance of the electrical heated catalyst device is detected.

Owner:TOYOTA JIDOSHA KK

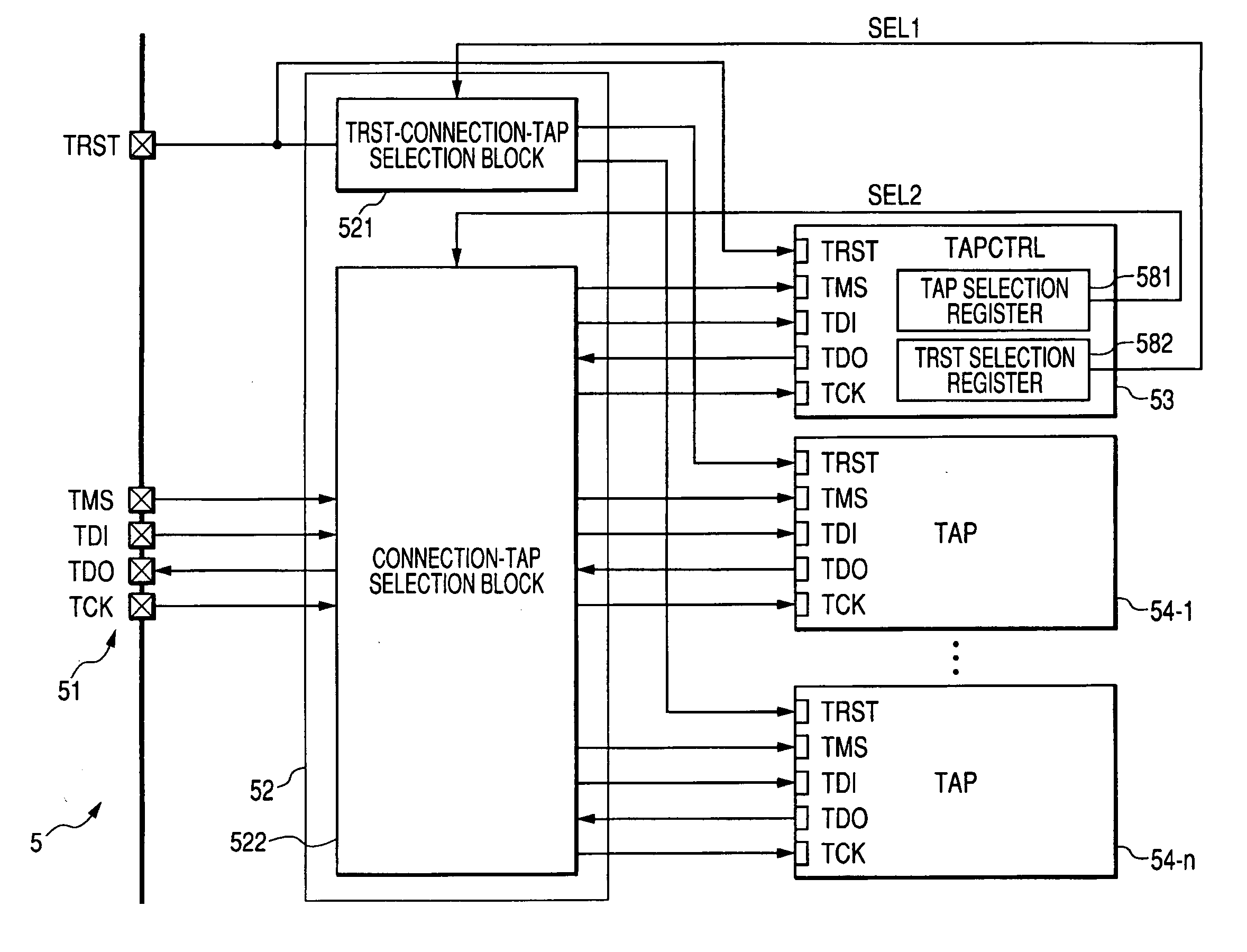

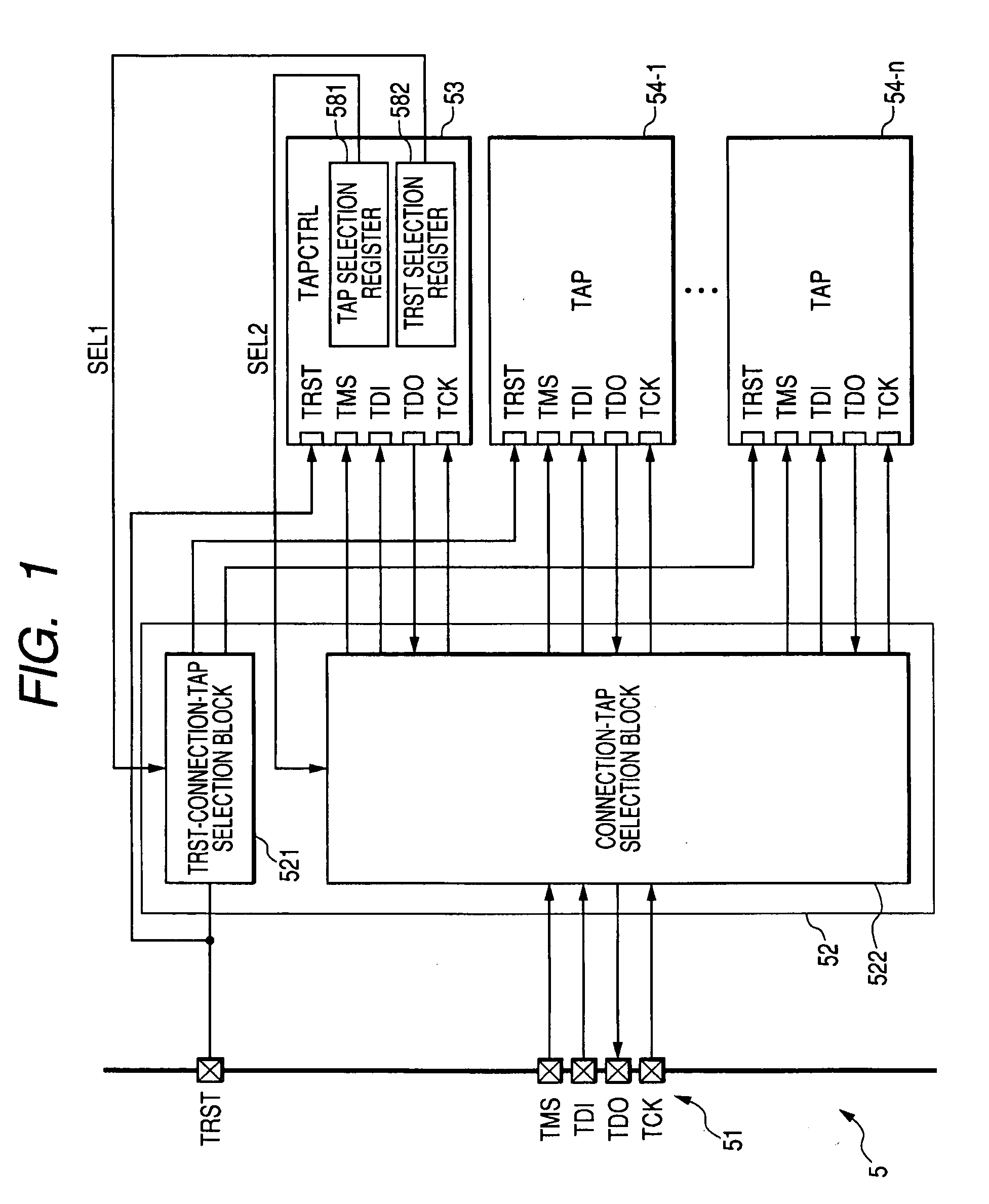

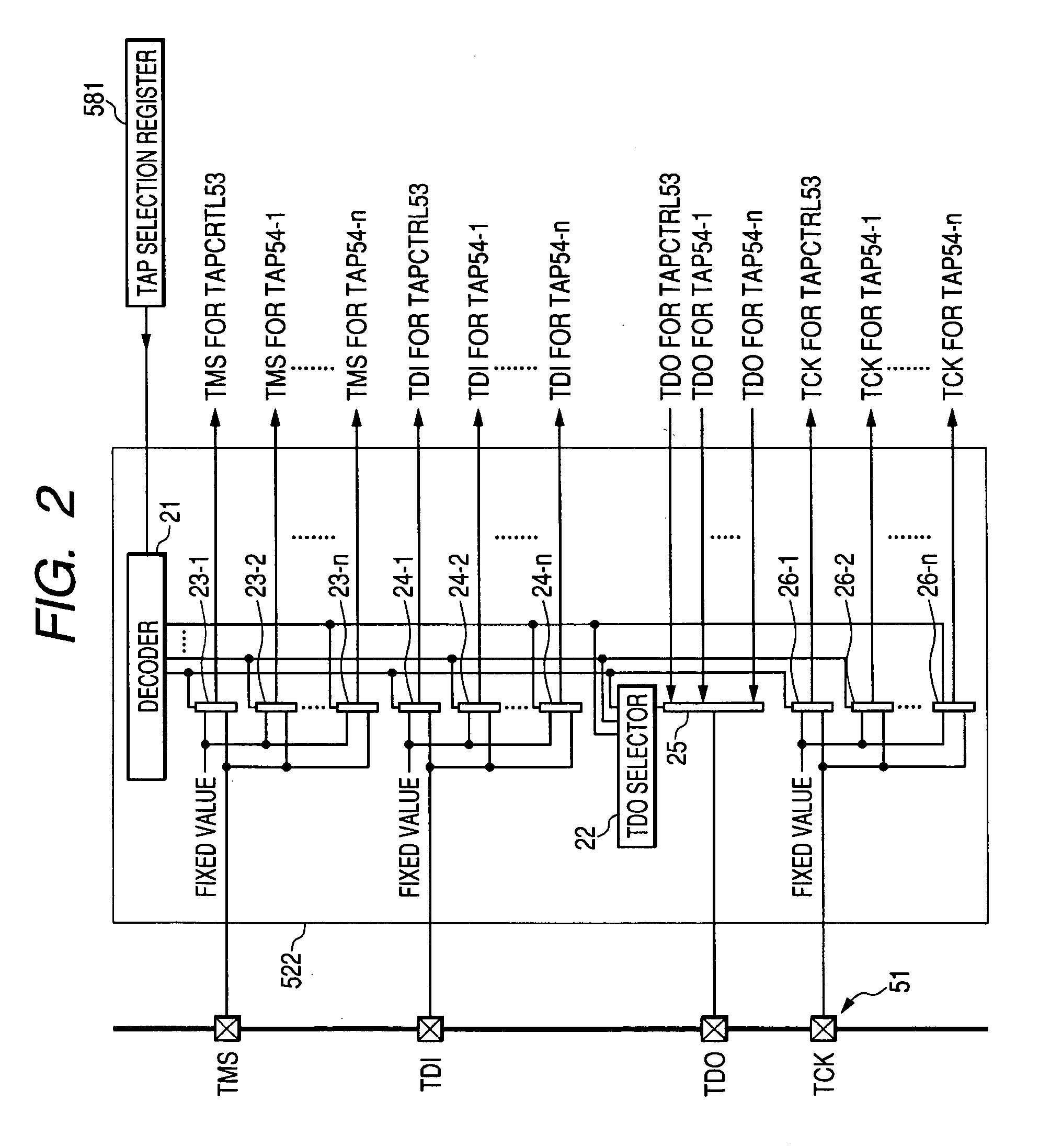

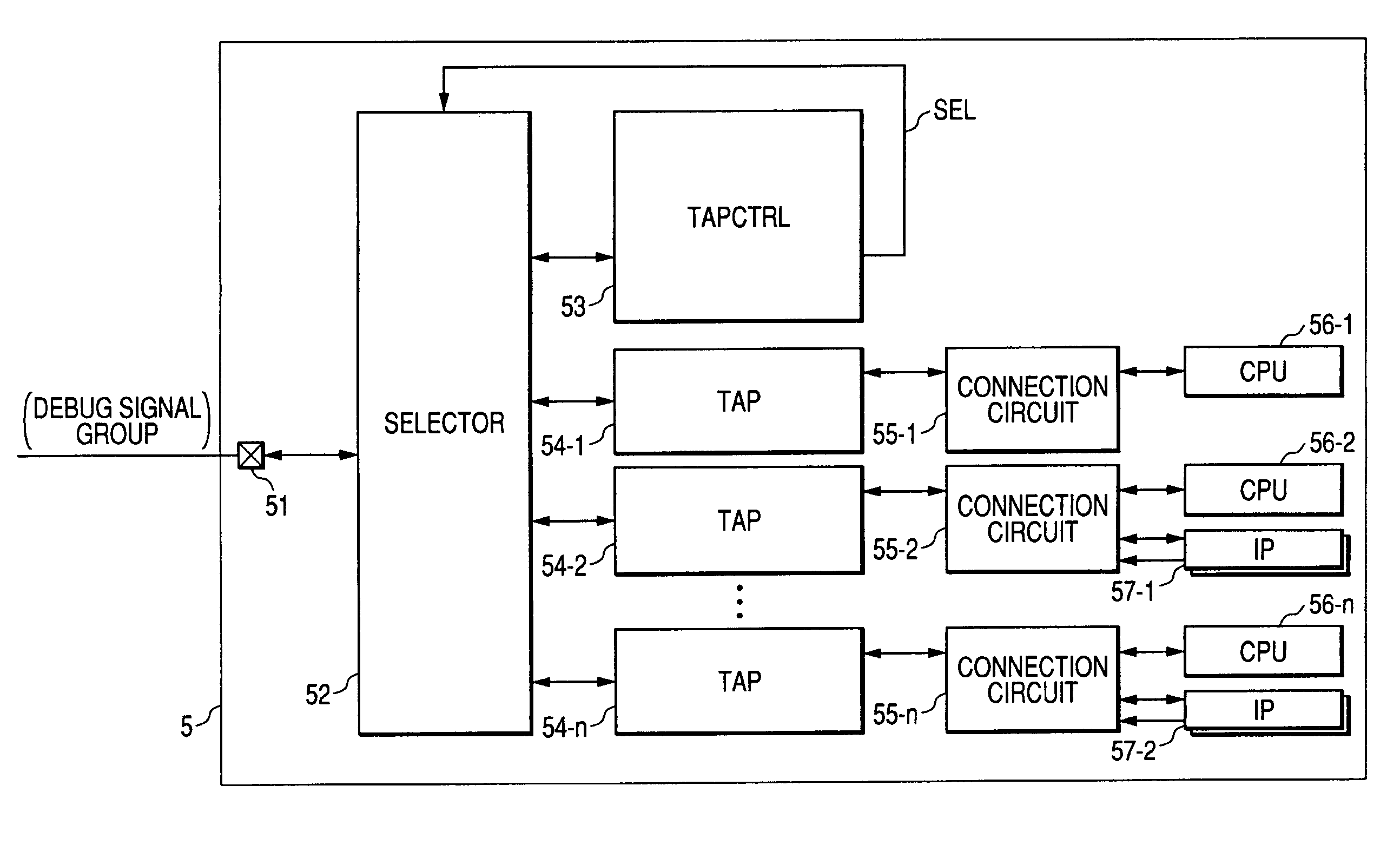

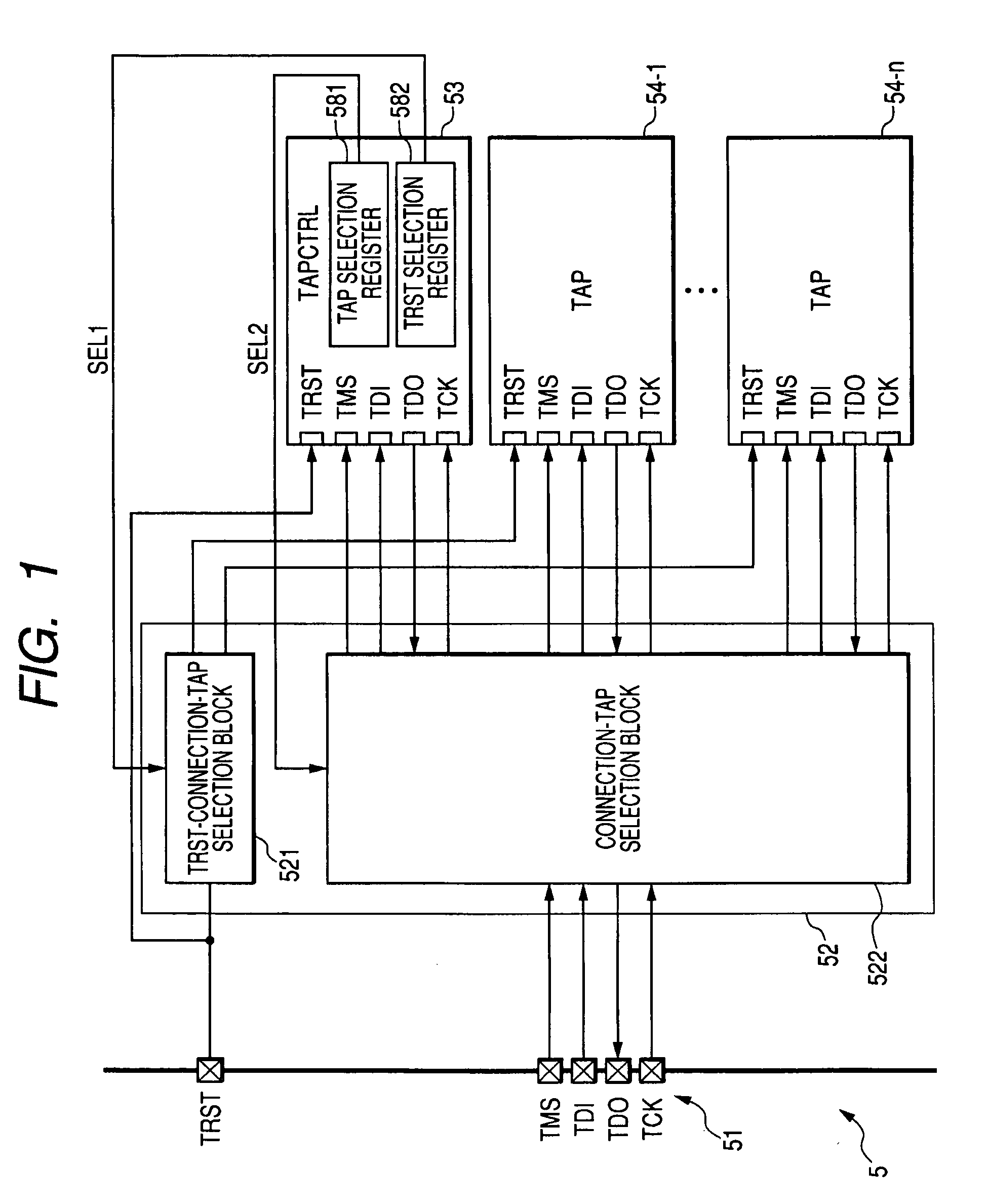

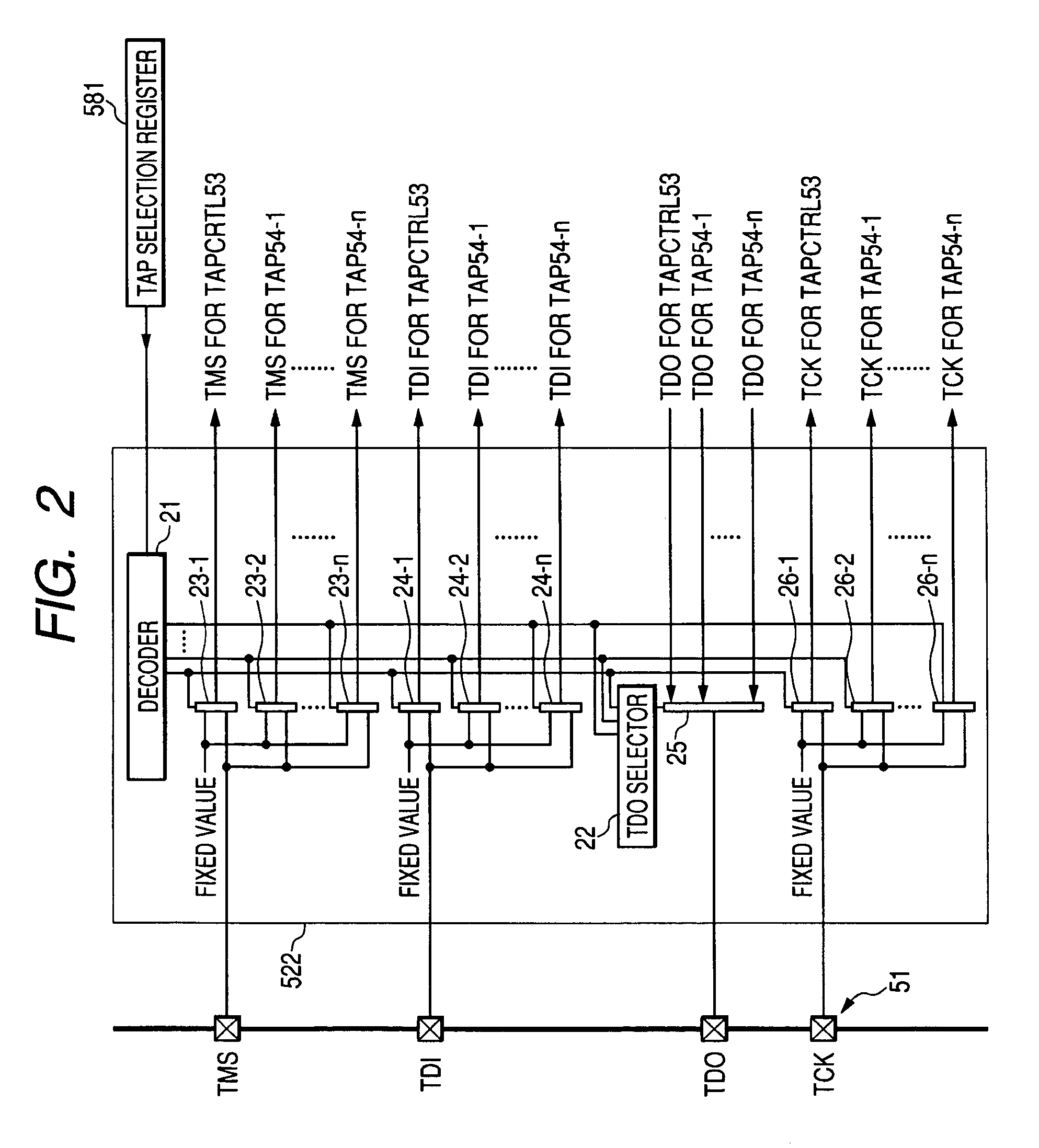

Semiconductor integrated circuit device

ActiveUS20070226558A1Increase the number ofEasy to debugElectronic circuit testingEngineeringJoint Test Action Group

The present invention is directed to facilitate debugging in a semiconductor integrated circuit device including a plurality of microprocessors. A semiconductor integrated circuit device includes: a plurality of processors; a plurality of debug interfaces enabling debugging of the corresponding processors; a plurality of common terminals shared by the plurality of debug interfaces; a selection circuit capable of selectively connecting the plurality of debug interfaces to the common terminals; and a controller capable of controlling selecting operation in the selection circuit in accordance with a predetermined instruction. A first selector capable of selectively connecting the plurality of debug interfaces to a TRST terminal in the terminal group conformed with the JTAG specifications, and a second selector capable of selectively connecting the plurality of debug interfaces to terminals other than the TRST terminal are provided. With the configuration, even in the case where the number of processors increases, the invention can flexibly address the increase.

Owner:RENESAS ELECTRONICS CORP

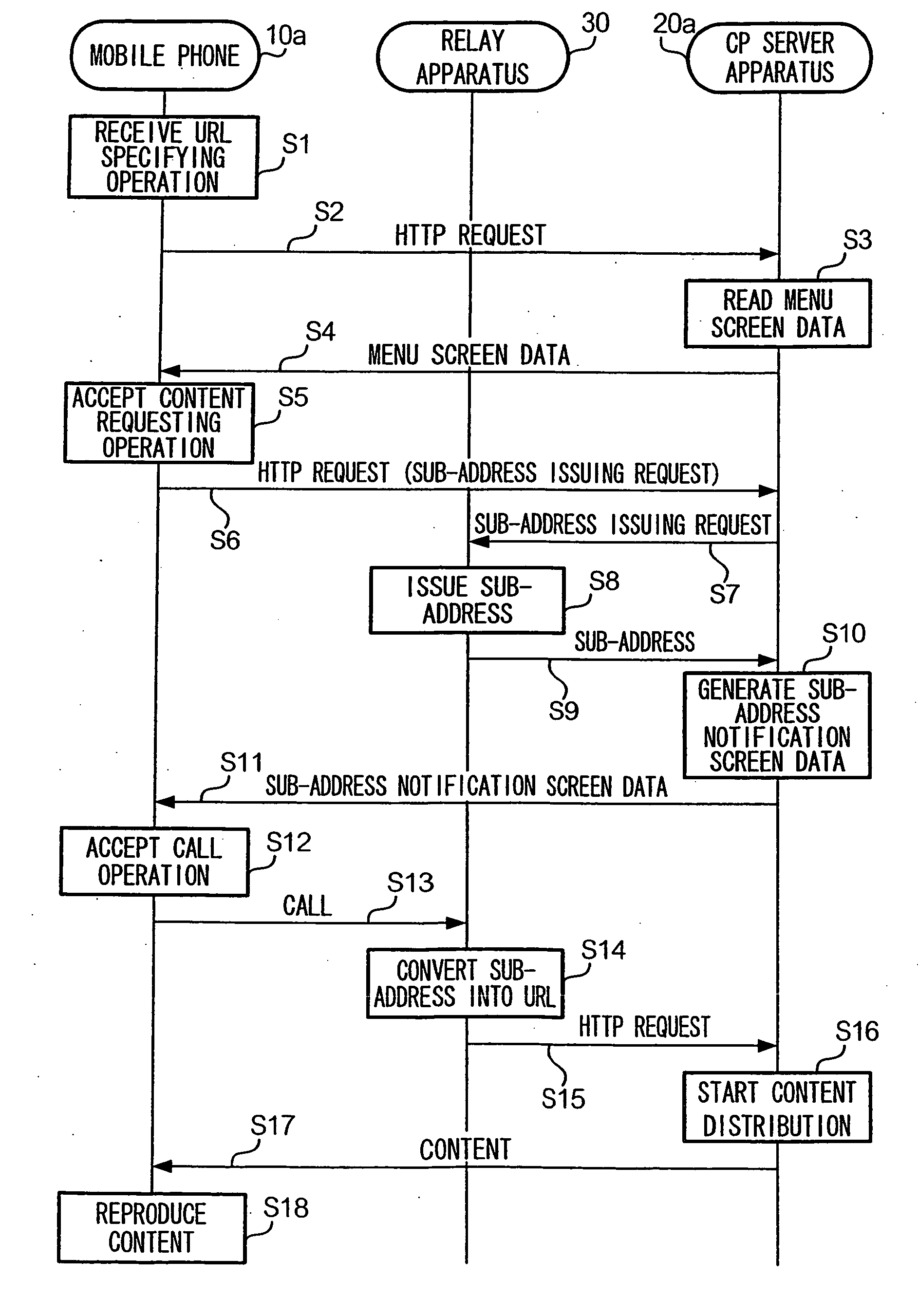

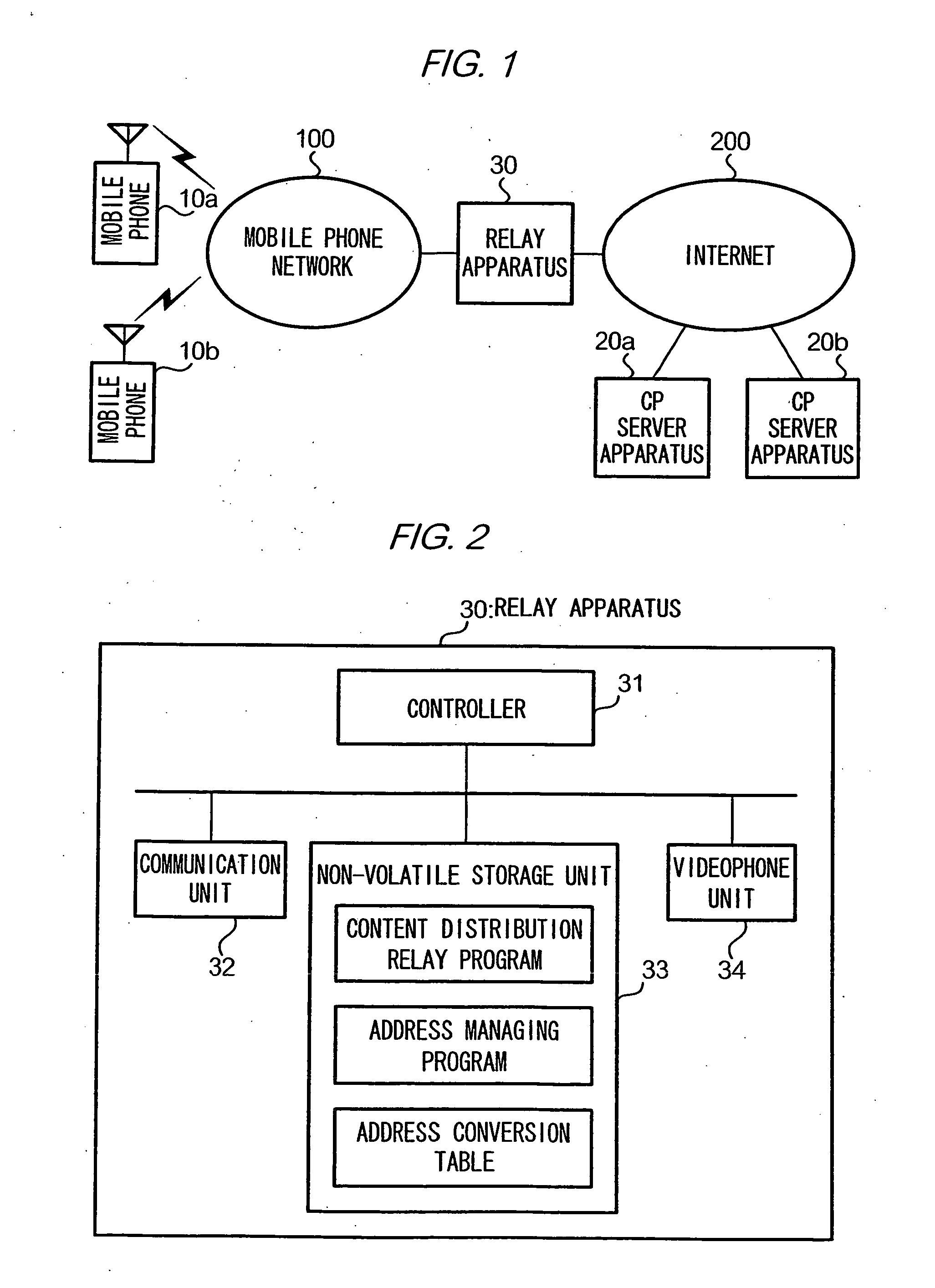

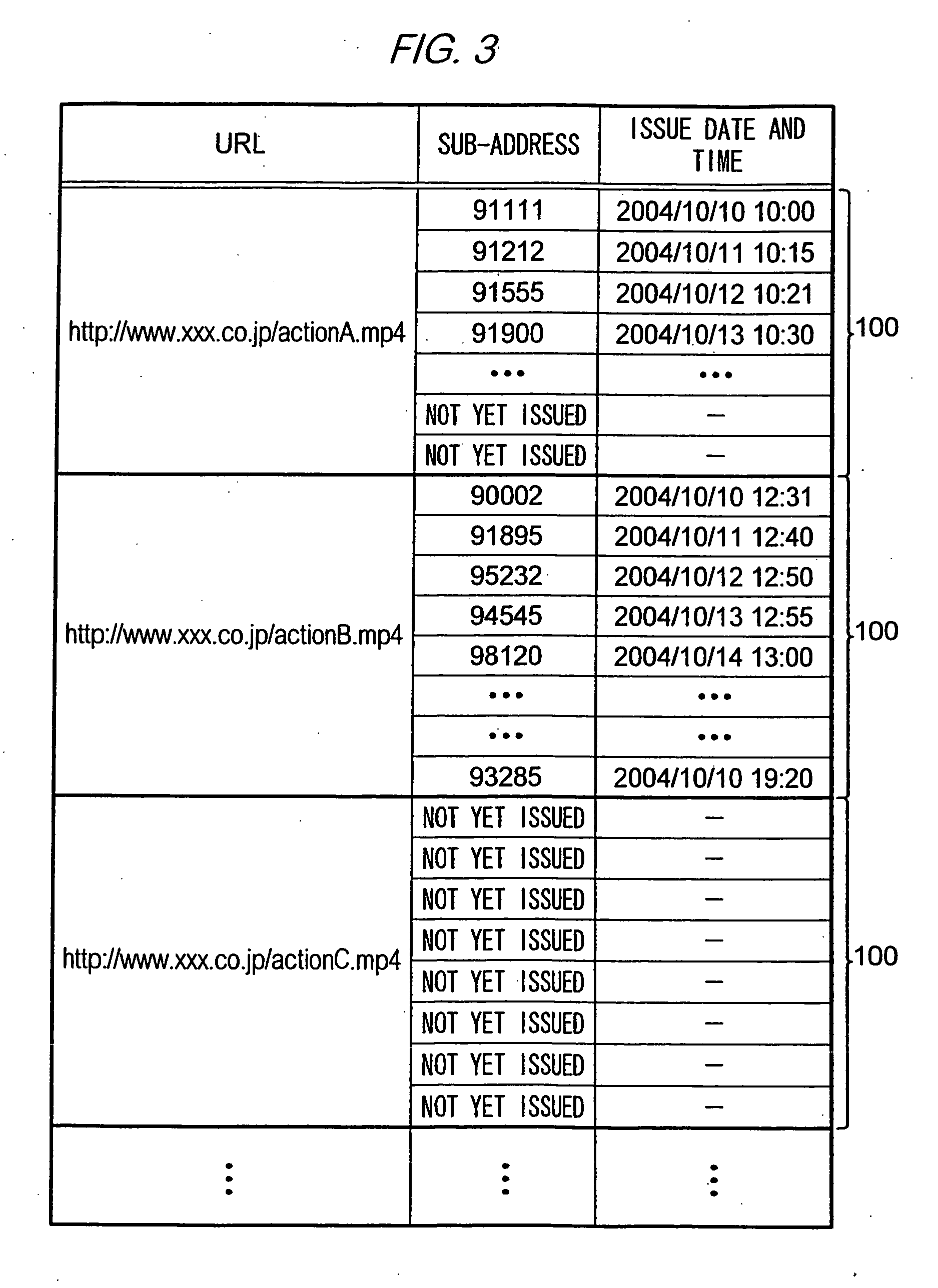

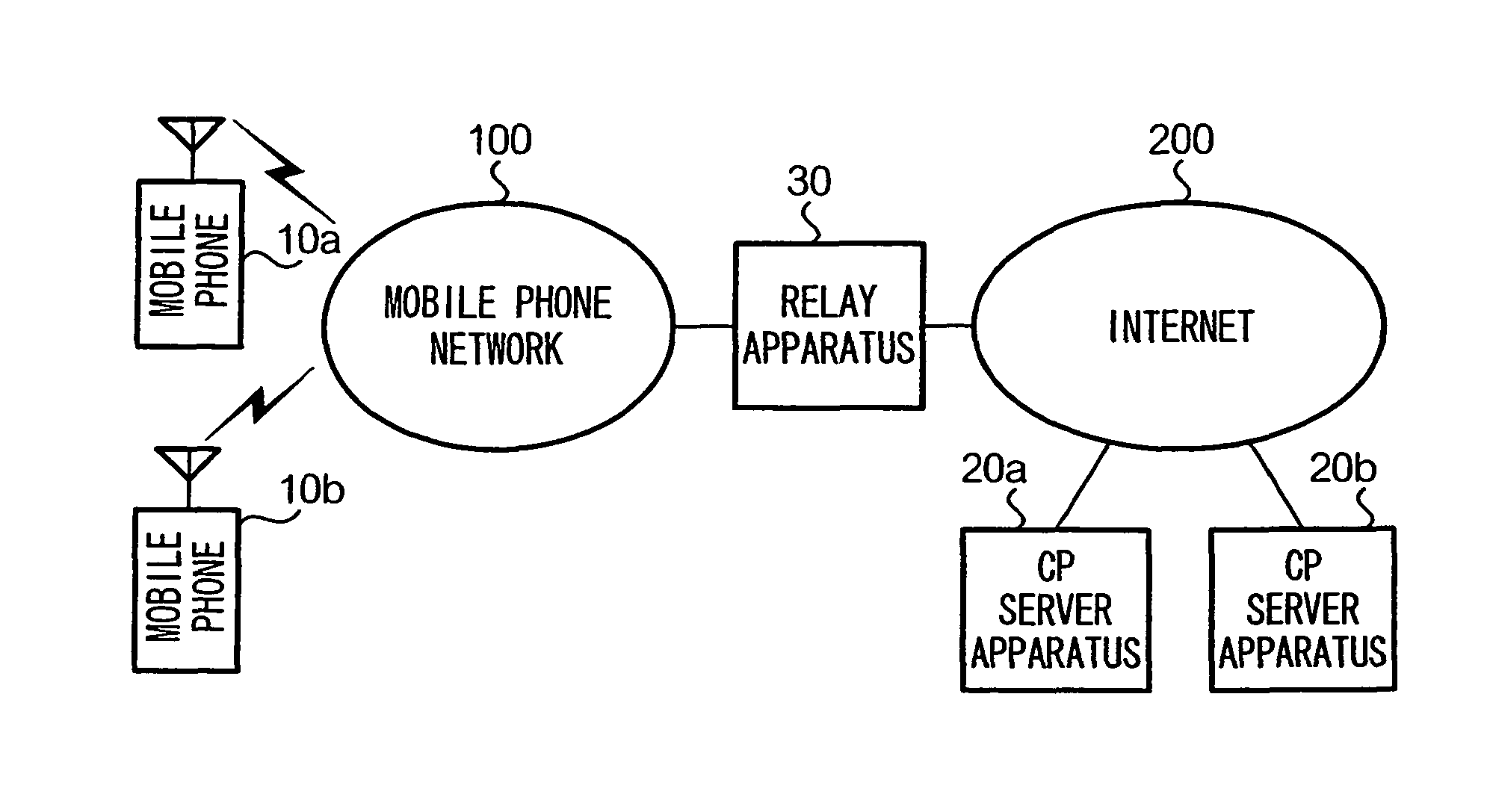

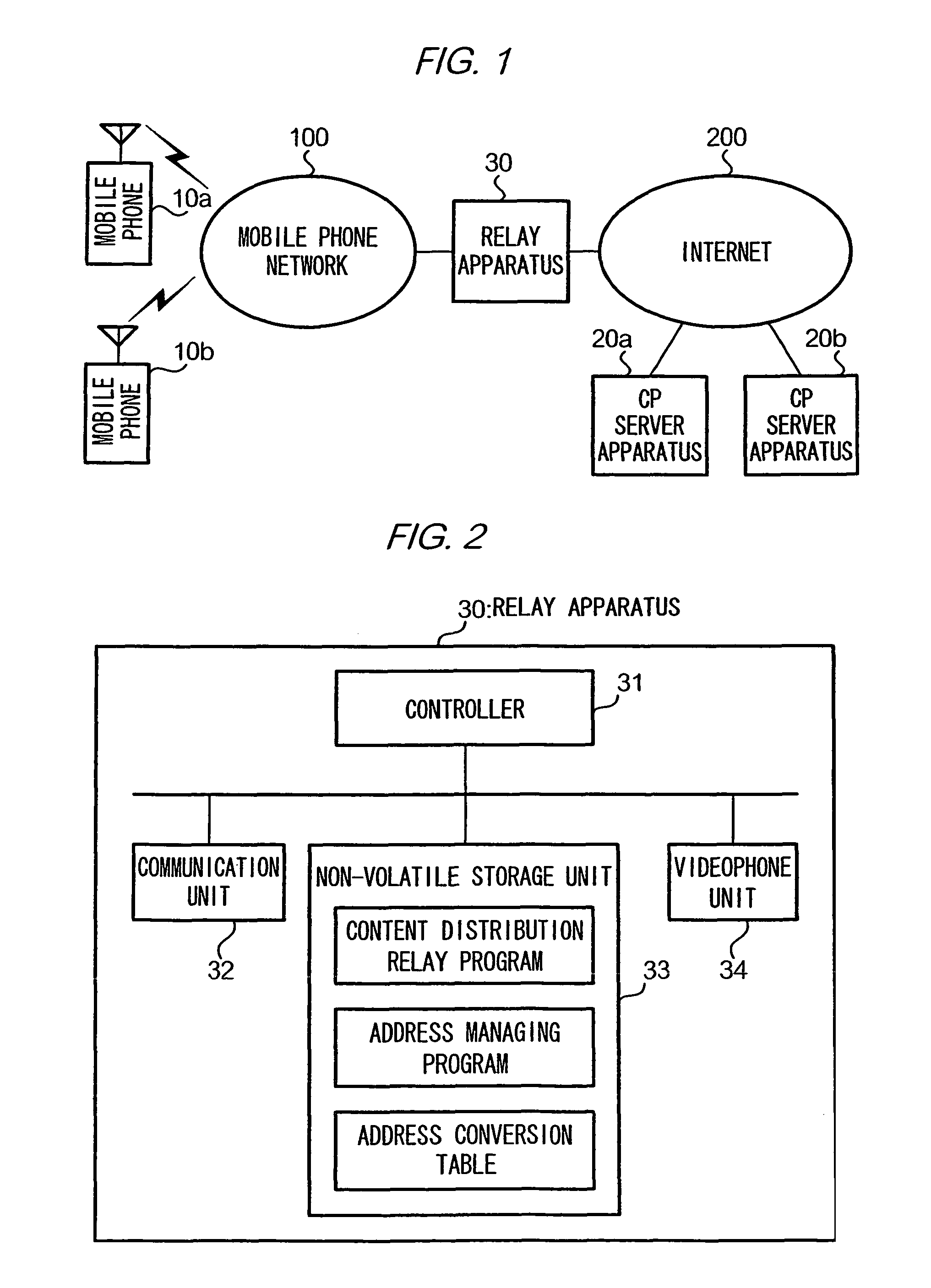

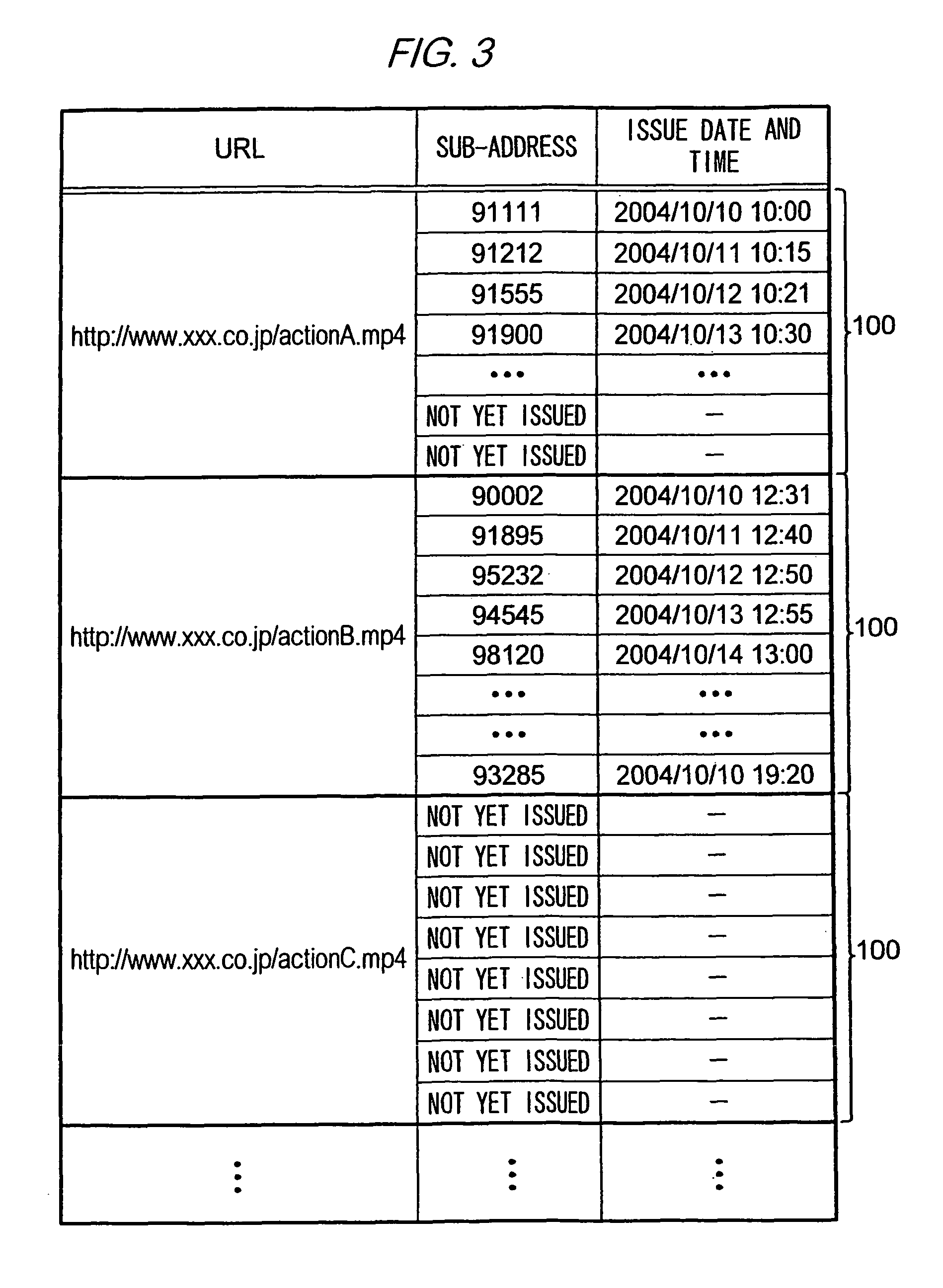

Content distribution method and relay apparatus

InactiveUS20060248168A1Avoid volume increaseIncrease in of of complicationFrequency-division multiplex detailsRepeater/relay circuitsComputer hardwareContent distribution

A relay apparatus 30 issues a new sub-address at a timing when mobile phones (10a, 10b) requested content from a CP server apparatuses (20a, 20b), that is, at a timing when a sub-address is required. The content specified by this sub-address is distributed from the CP server apparatuses via the relay apparatus (30) to the mobile phones. In system of the present invention it is possible to utilize the same sub-address many times for different content items. It is therefore possible to avoid increasing the number of digits of the sub-address as well as the complexity of the sub-address structure, in a case where the types of content or the number of content items increases.

Owner:NTT DOCOMO INC

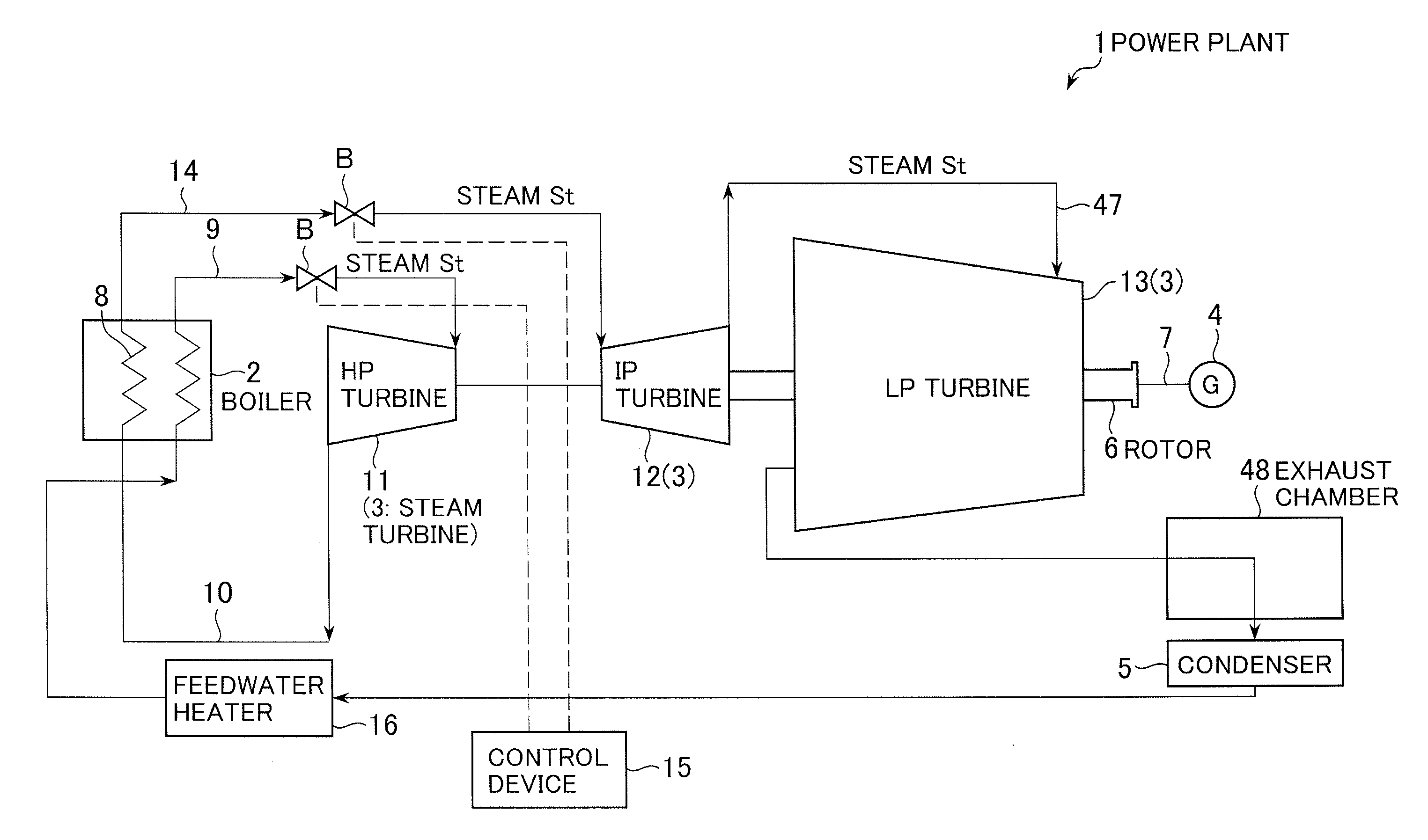

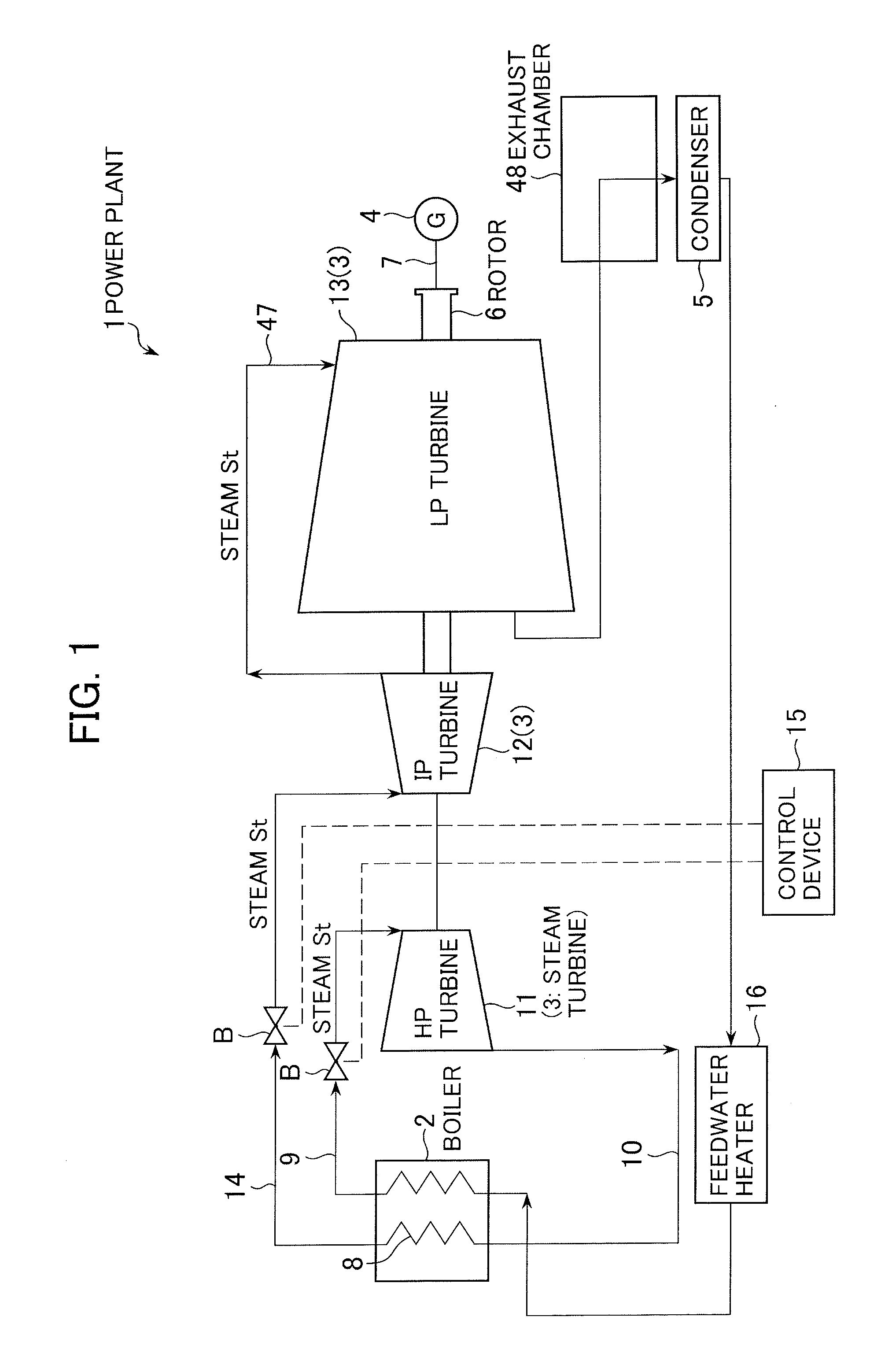

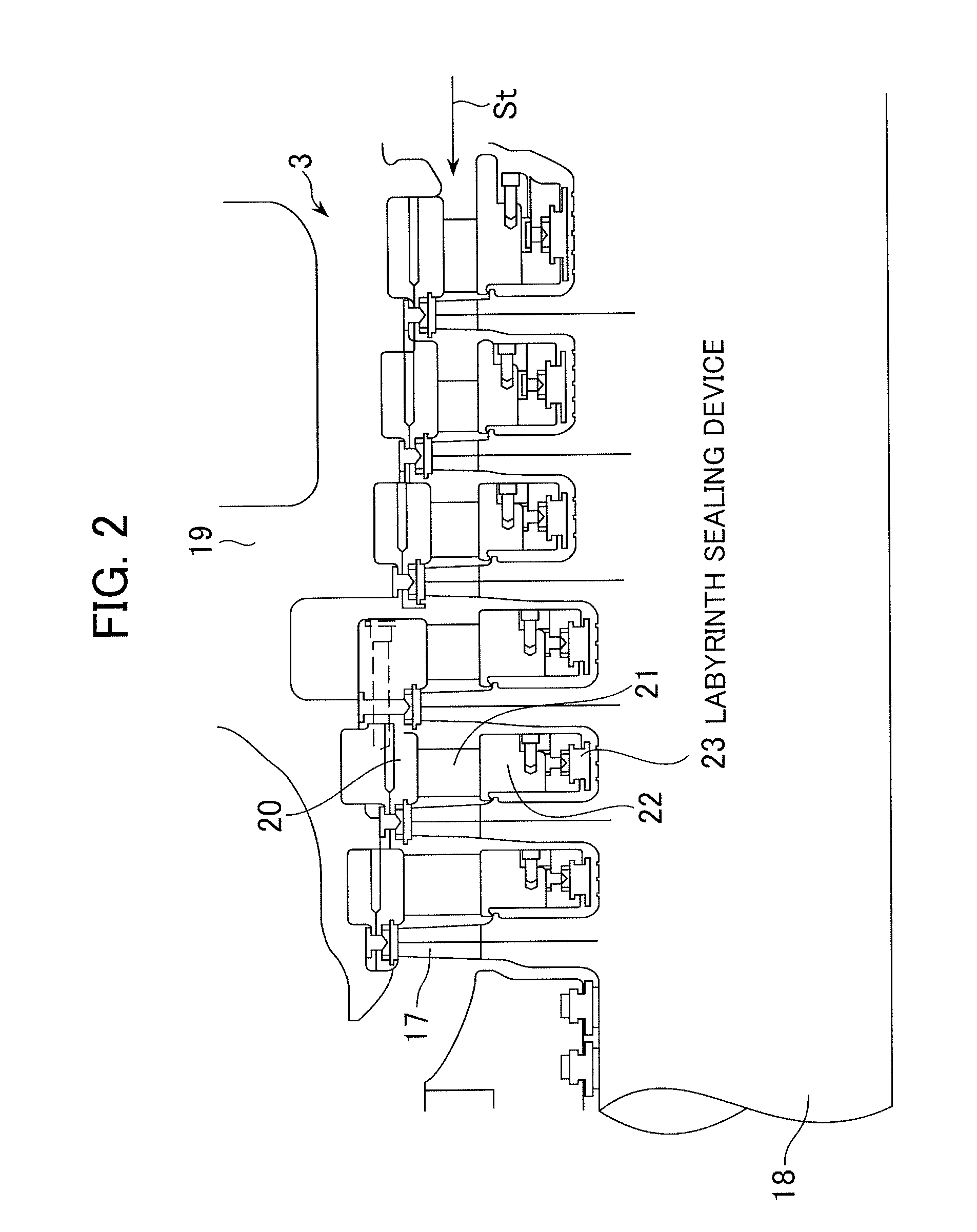

Sealing Device for Steam Turbines and Method for Controlling Sealing Device

InactiveUS20120014778A1Avoid volume increaseImprove sealingEngine sealsPump componentsSteam pressureEngineering

Subject: To provide a sealing structure, and control method therefor, which improve sealing performance between a rotating region and a fixed region, prevent fins from being damaged, and prevent increases in the amount of steam leakage from any clearances newly formed by further abrasion of an abradable material.Solution: The sealing structure in which free-cutting spacers 28 on a sealing base plate 25 and sealing fins 24 on a rotor 18 are opposed to each other is provided, in the sealing structure of which the sealing base plate 25 is disposed so as to be movable in an axial direction of the rotor 18. When a steam turbine 3 increases in load, a pressure head 30 moves in an axial steam-pressure loading direction of the rotor 18 and the sealing base plate 25 connected to the pressure head 30 moves in the axial steam-pressure loading direction. Since the free-cutting spacers 28 at positions opposed to those of the sealing fins 24 existing after the movement of the sealing base plate are maintained in a non-contact state, clearances between the sealing fins 24 and the free-cutting spacers 28 are dimensionally minimized.

Owner:MITSUBISHI HITACHIPOWER SYST LTD

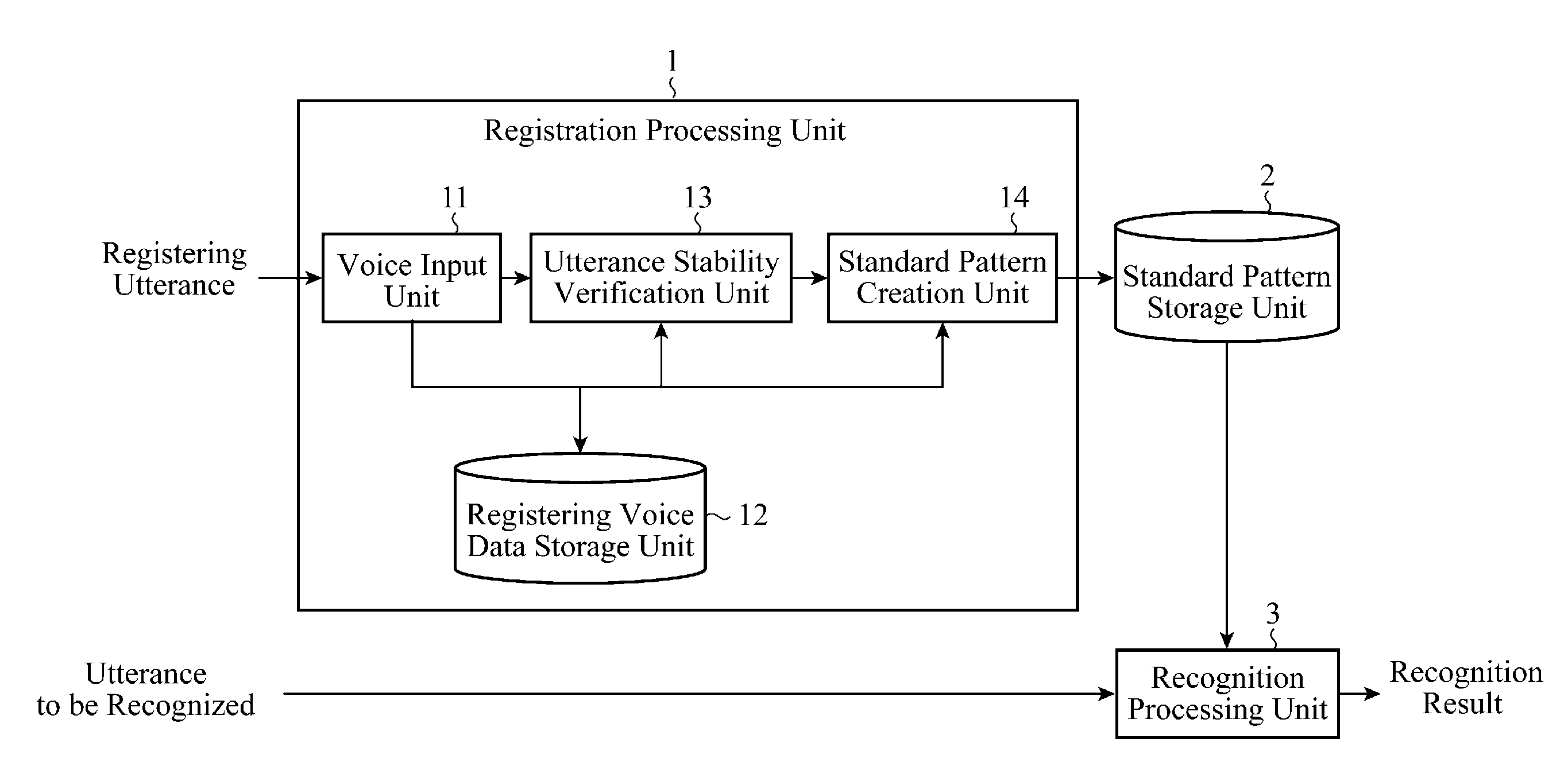

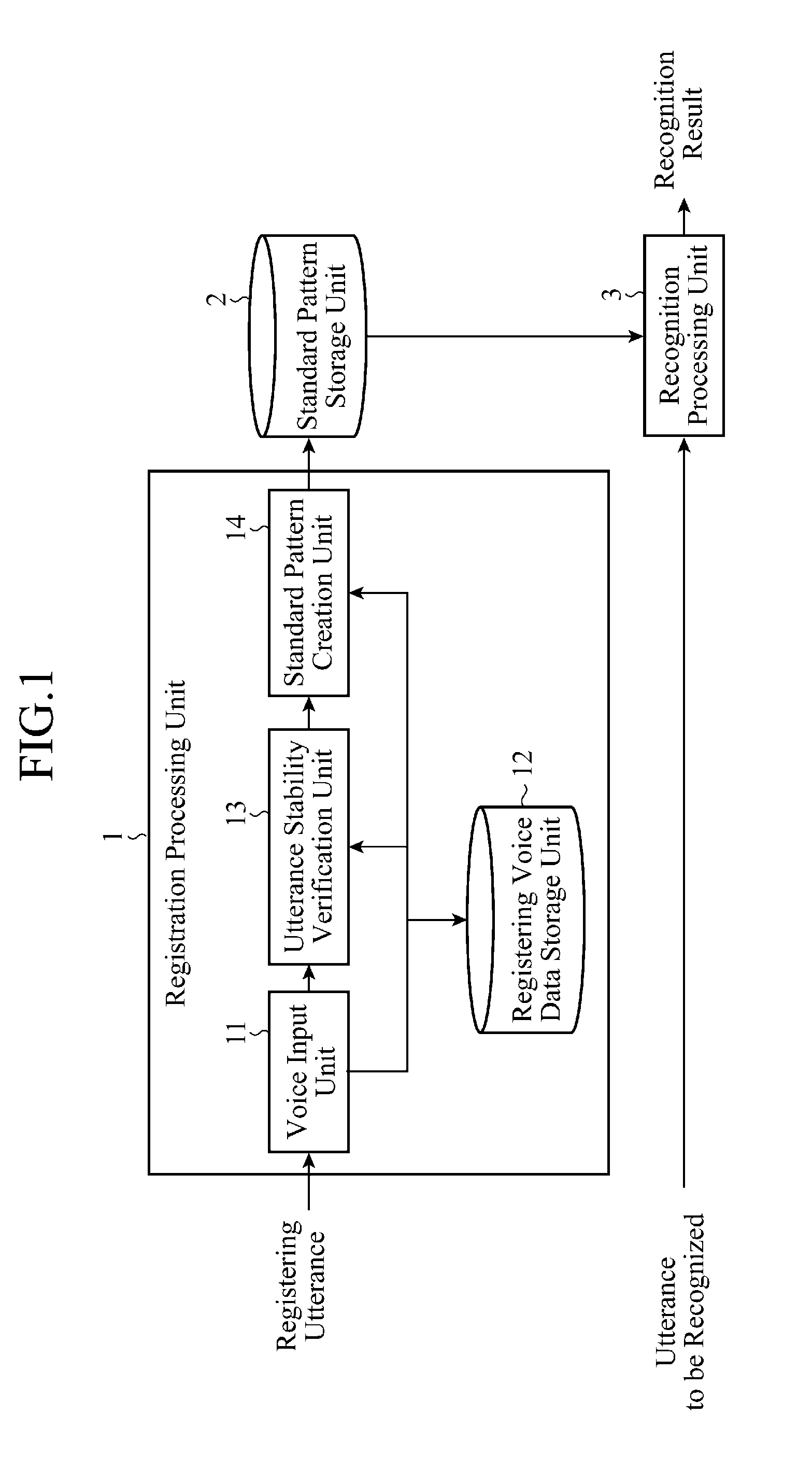

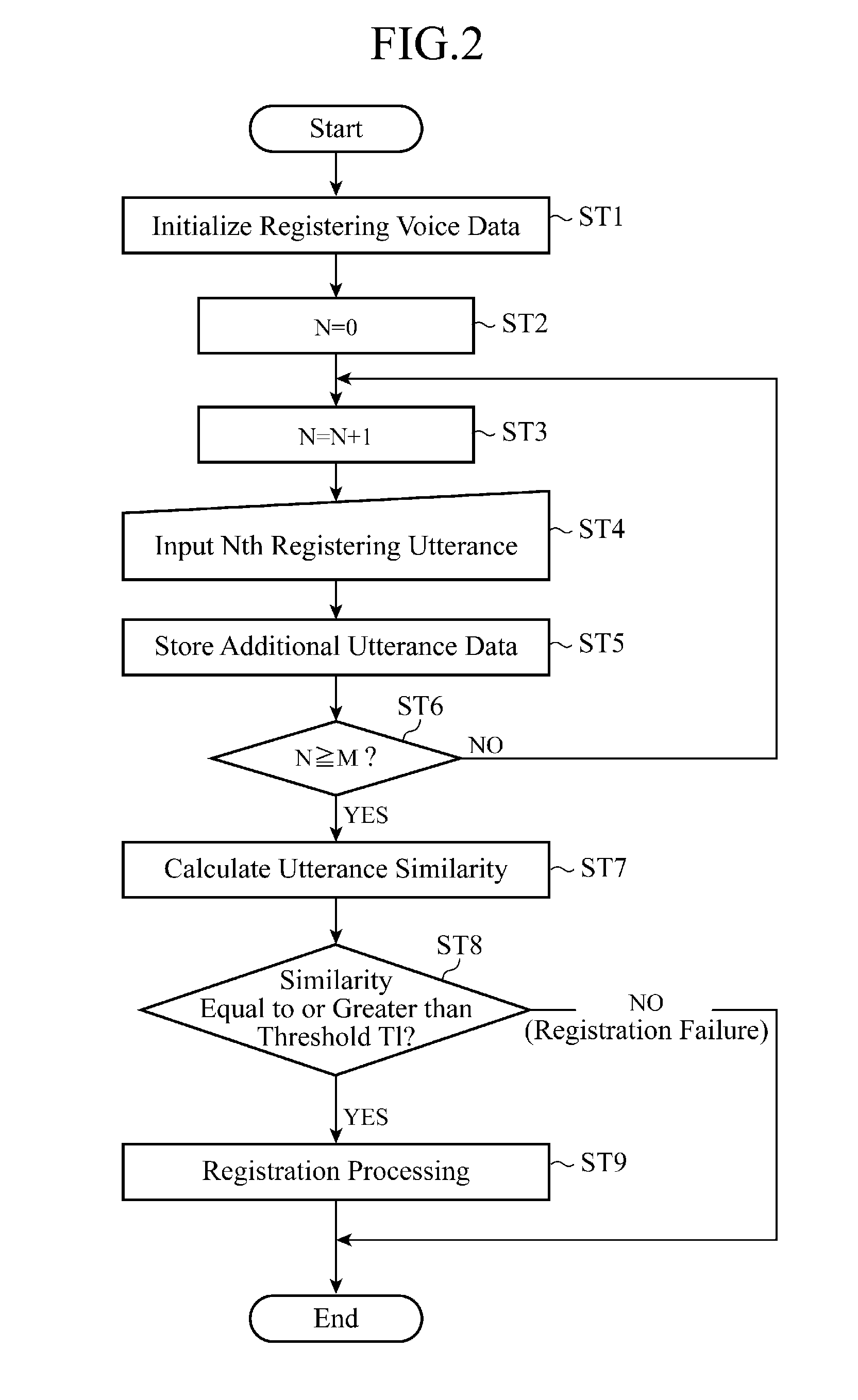

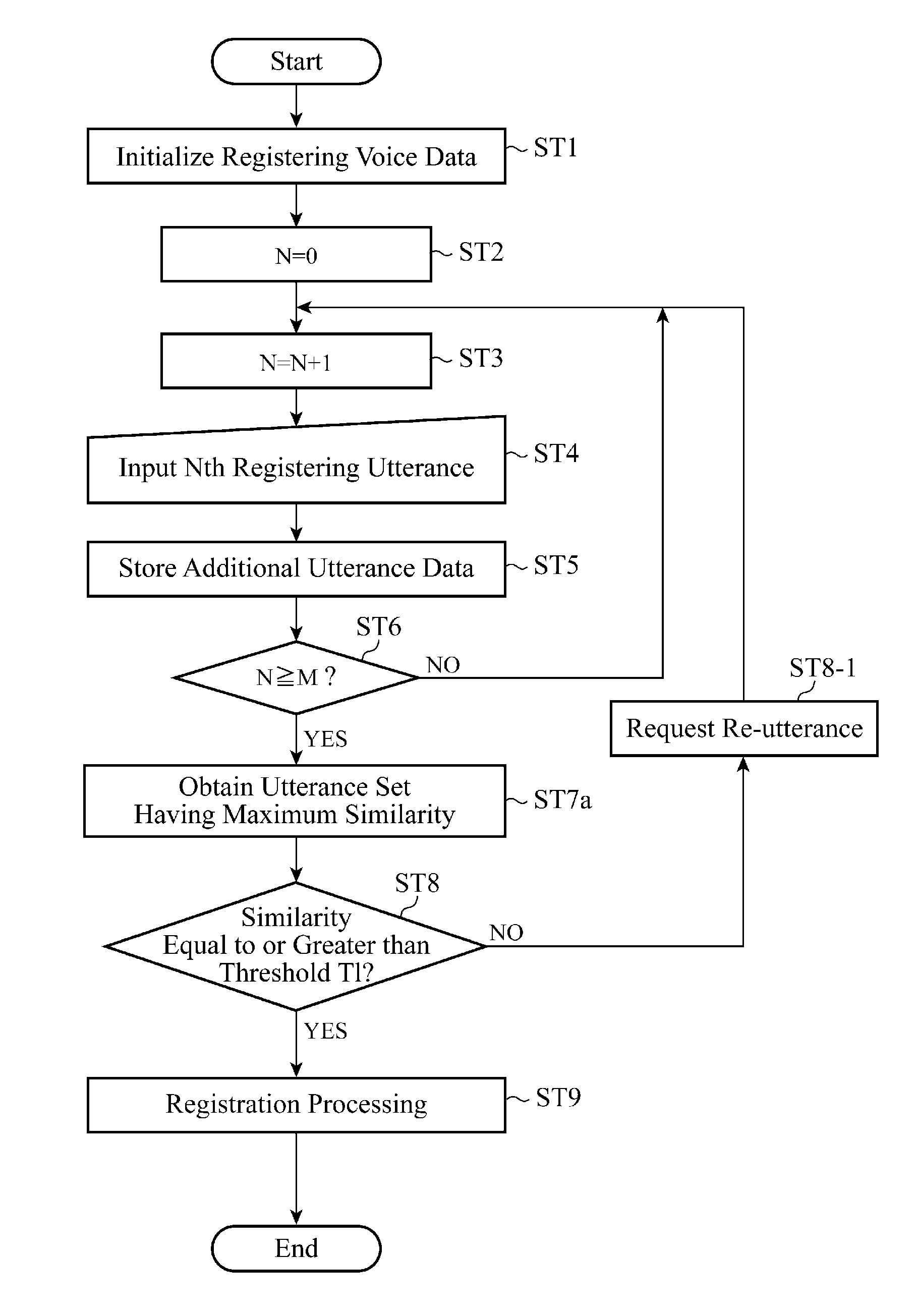

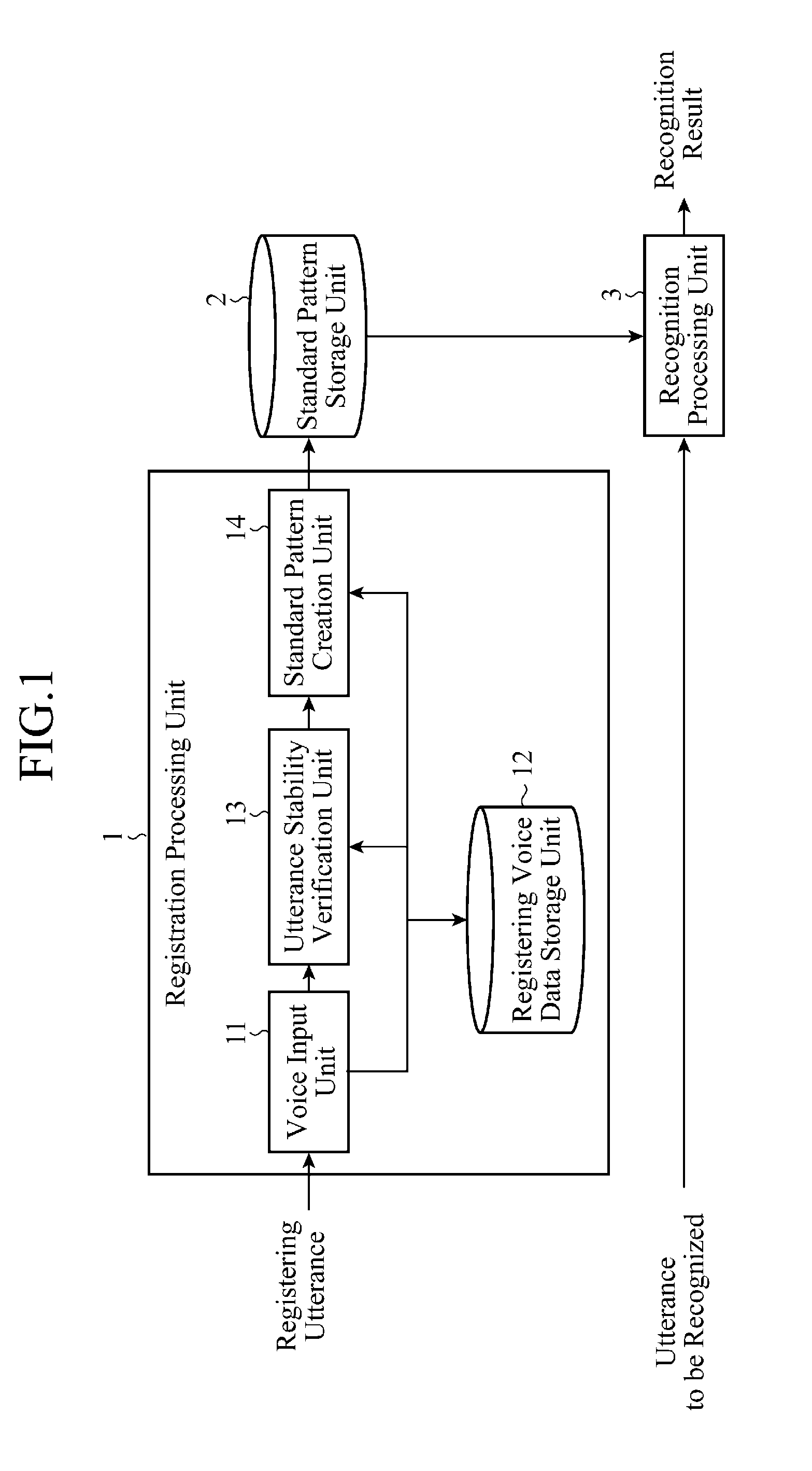

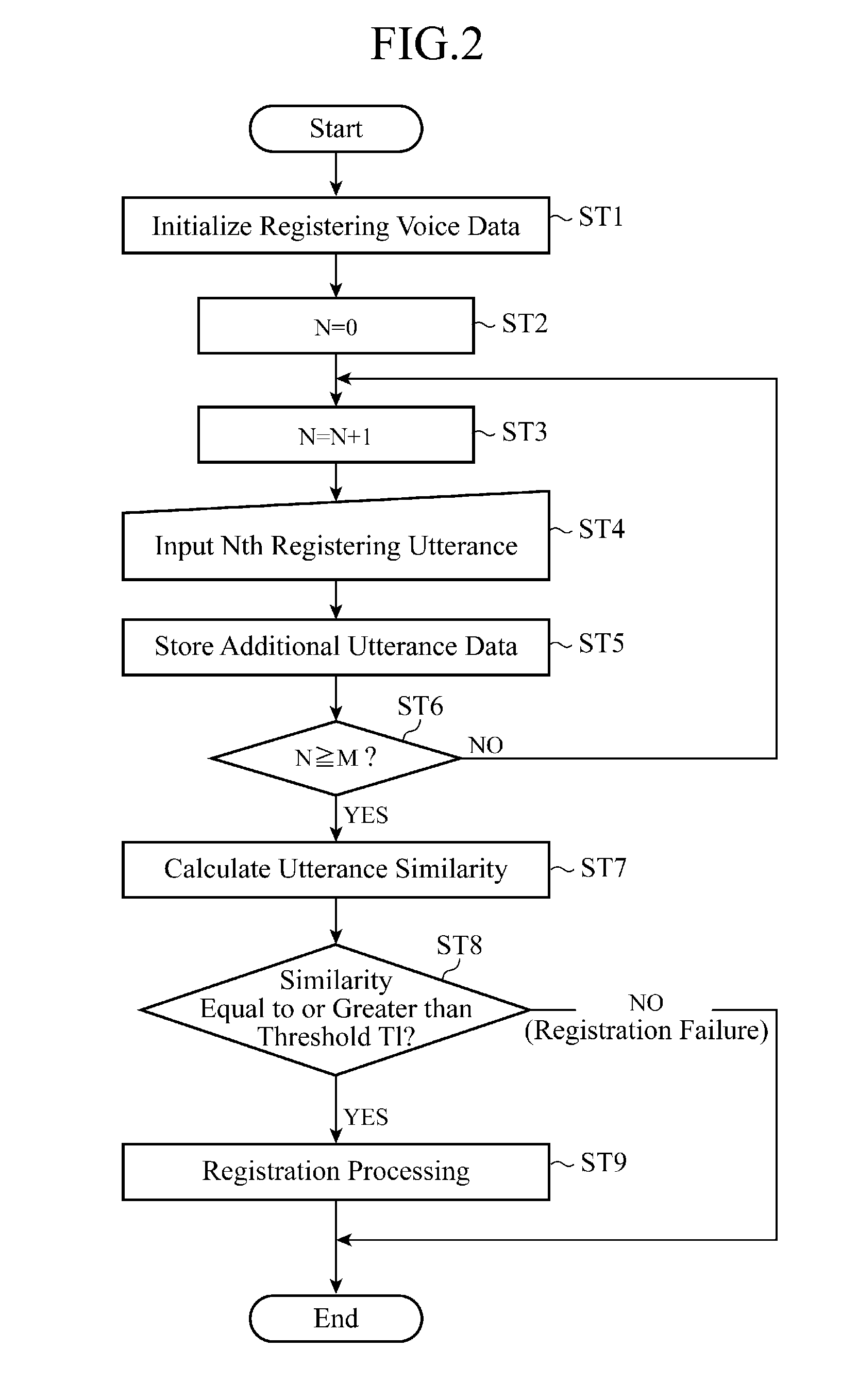

Voice recognition system

ActiveUS20110276331A1Easy to identifyImprove convenienceSpeech recognitionSpeech identificationSpeech input

A voice recognition system includes: a voice input unit 11 for inputting a voice uttered a plurality of times; a registering voice data storage unit 12 for storing voice data uttered the plurality of times and input into the voice input unit 11; an utterance stability verification unit 13 for determining a similarity between the voice data uttered the plurality of times that are read from the registering voice data storage unit 12, and determining that registration of the voice data is acceptable when the similarity is greater than a threshold Tl; and a standard pattern creation unit 14 for creating a standard pattern by using the voice data where the utterance stability verification unit 13 determines that registration is acceptable.

Owner:MITSUBISHI ELECTRIC CORP

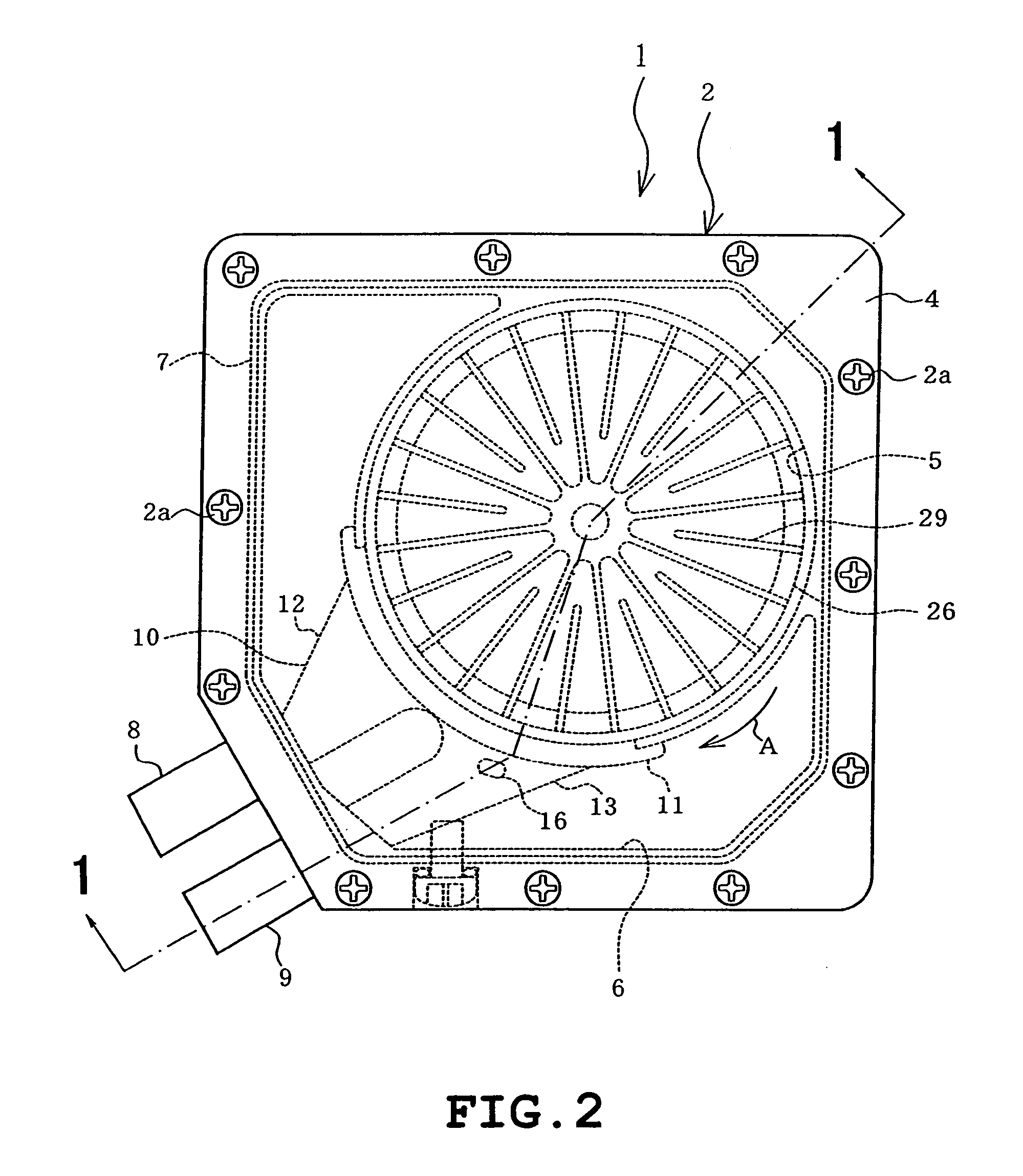

Fluid pump, cooling system and electrical appliance

InactiveUS20050249609A1Eliminate needAvoid volume increaseCircumferential flow pumpsTransverse flow pumpsImpellerPump chamber

A fluid pump for circulating the cooling liquid to cool the heat-generating part is disclosed. The fluid pump includes a case including a pump chamber for storing a liquid, a suction port and a discharge port provided on the case so as to communicate with the pump chamber, an impeller having pump vanes and rotatably placed in the pump chamber, which suctions a liquid into the pump chamber via the suction port and discharges the liquid out of the pump chamber via the discharge port by rotation, a motor for driving the impeller, installed in the case and having a stator and a rotor to which the impeller is integrally attached for rotating together, a reserve tank for storing spare liquid located and formed in the case but outside the pump chamber, a fluid path forming member arranged inside the reserve tank, including a discharge path communicating between the discharge port and the pump chamber, and a communication hole formed in the fluid path forming member so as to communicate between the discharge path and inside of the reserve tank.

Owner:KK TOSHIBA

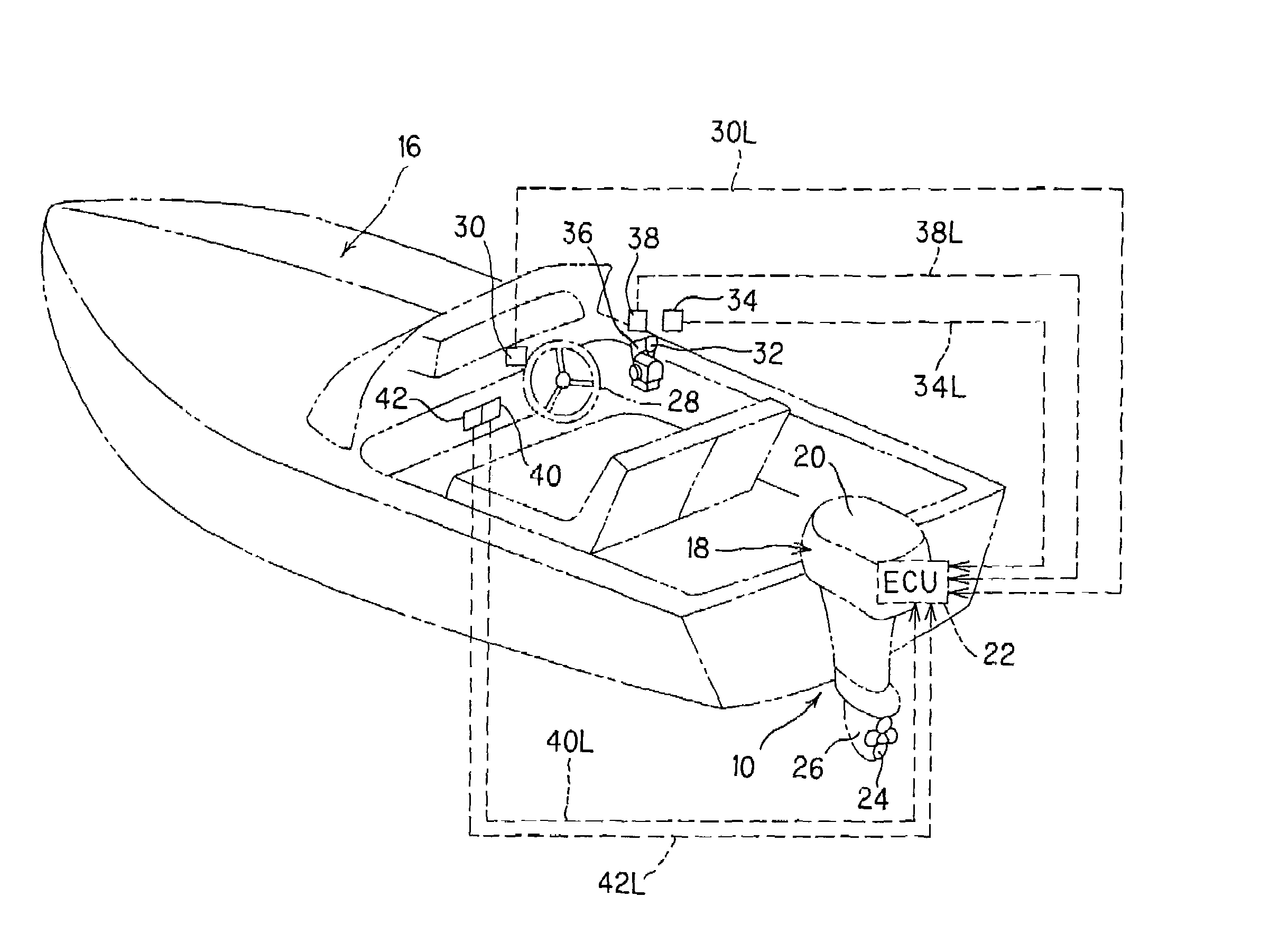

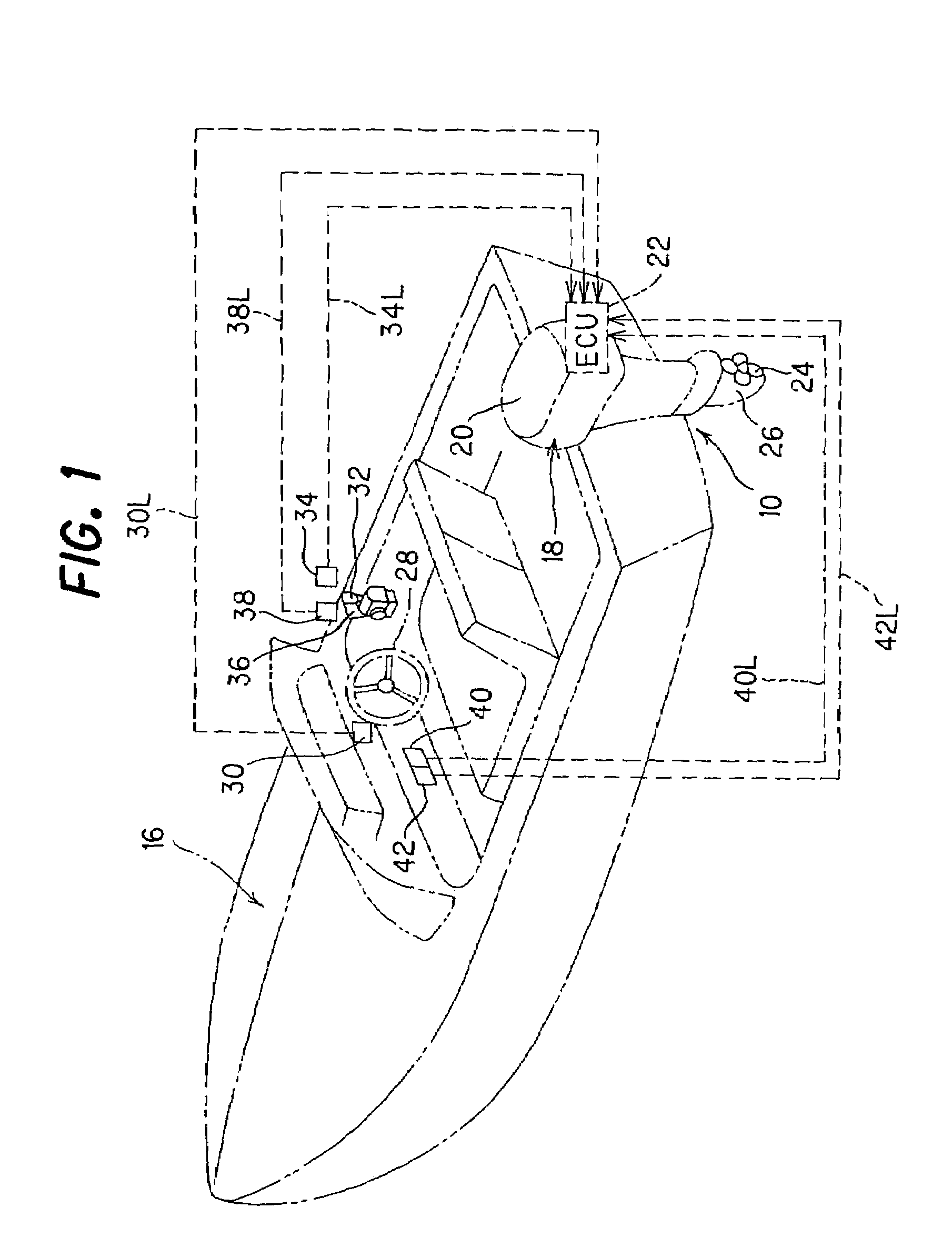

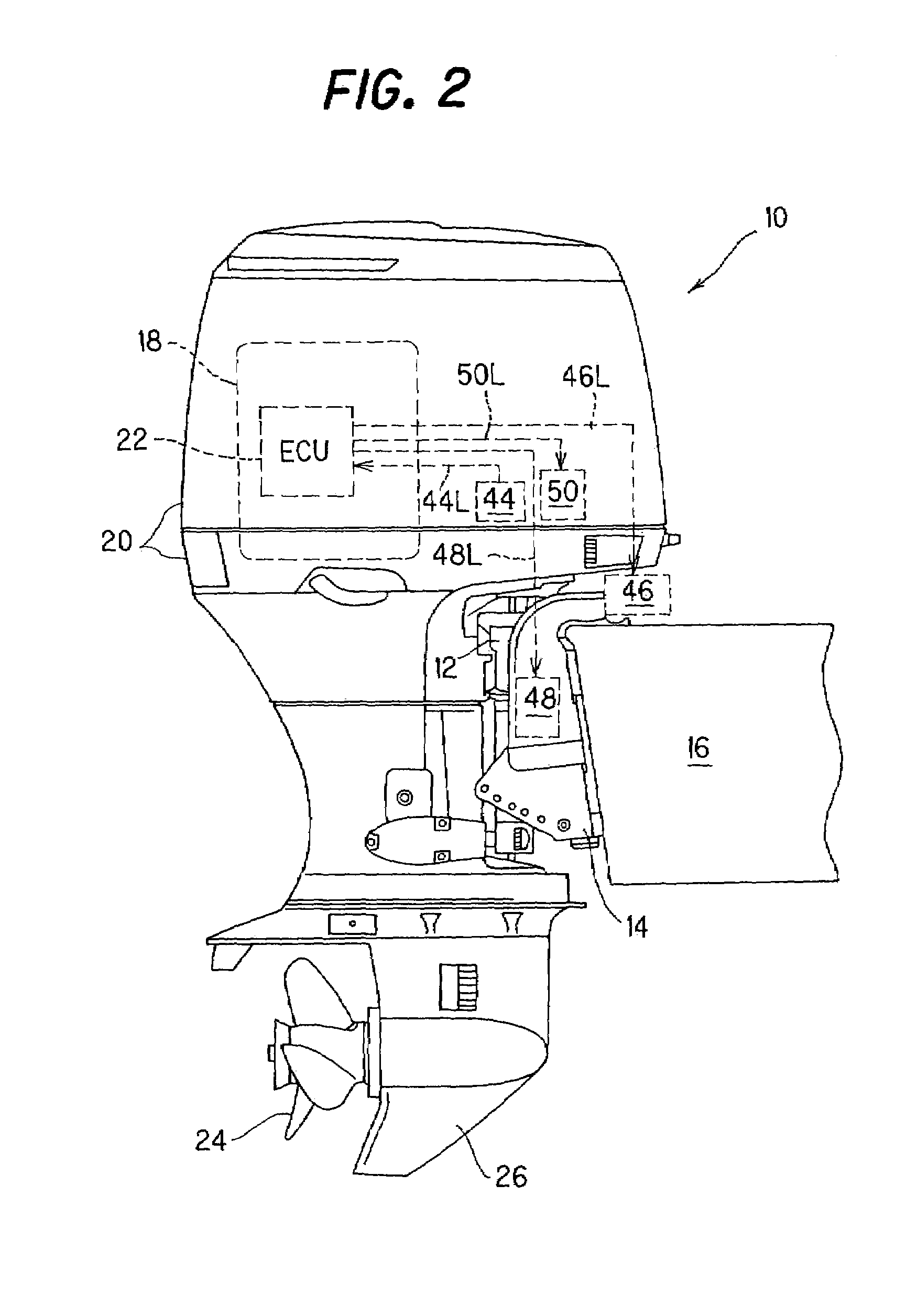

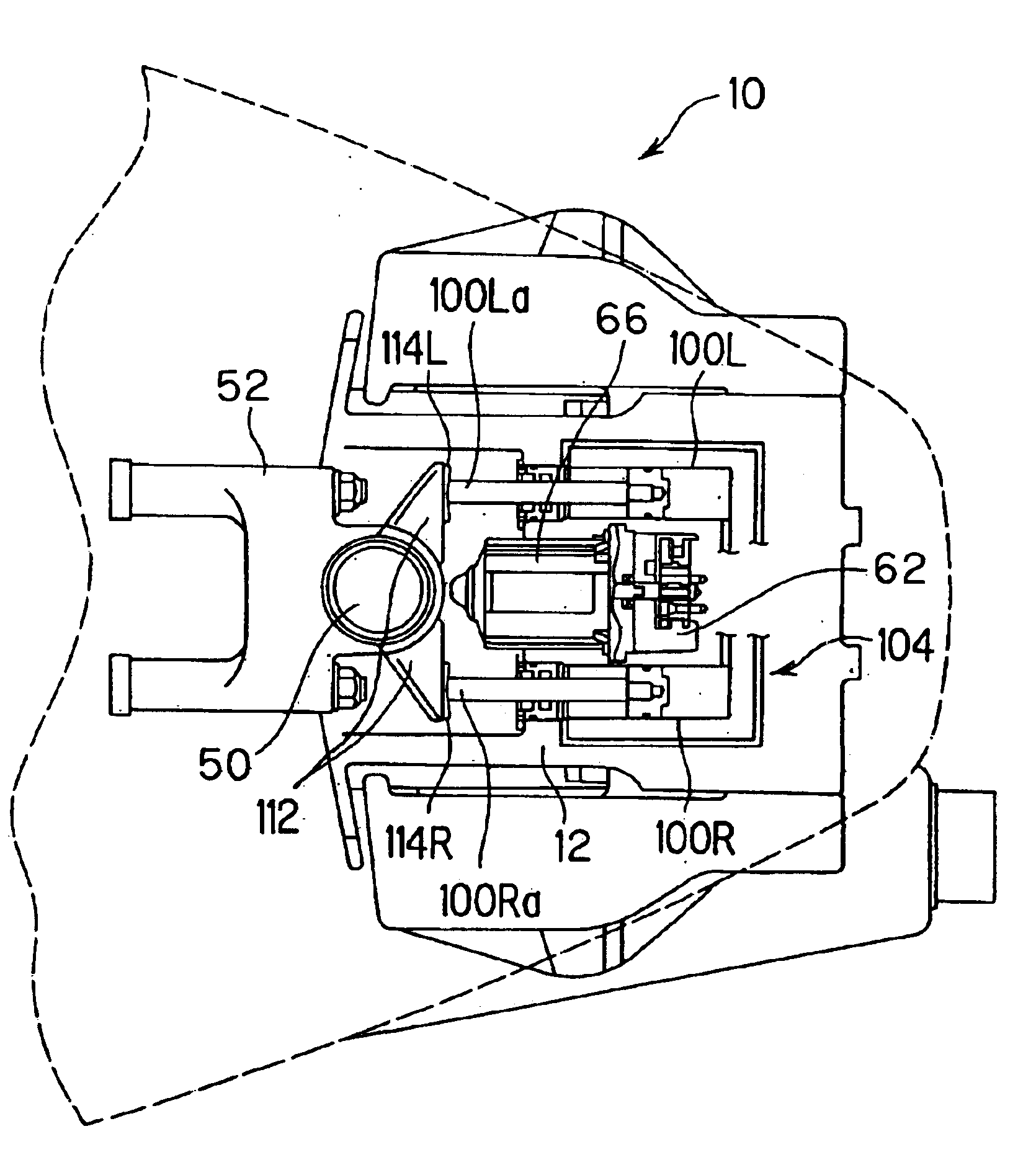

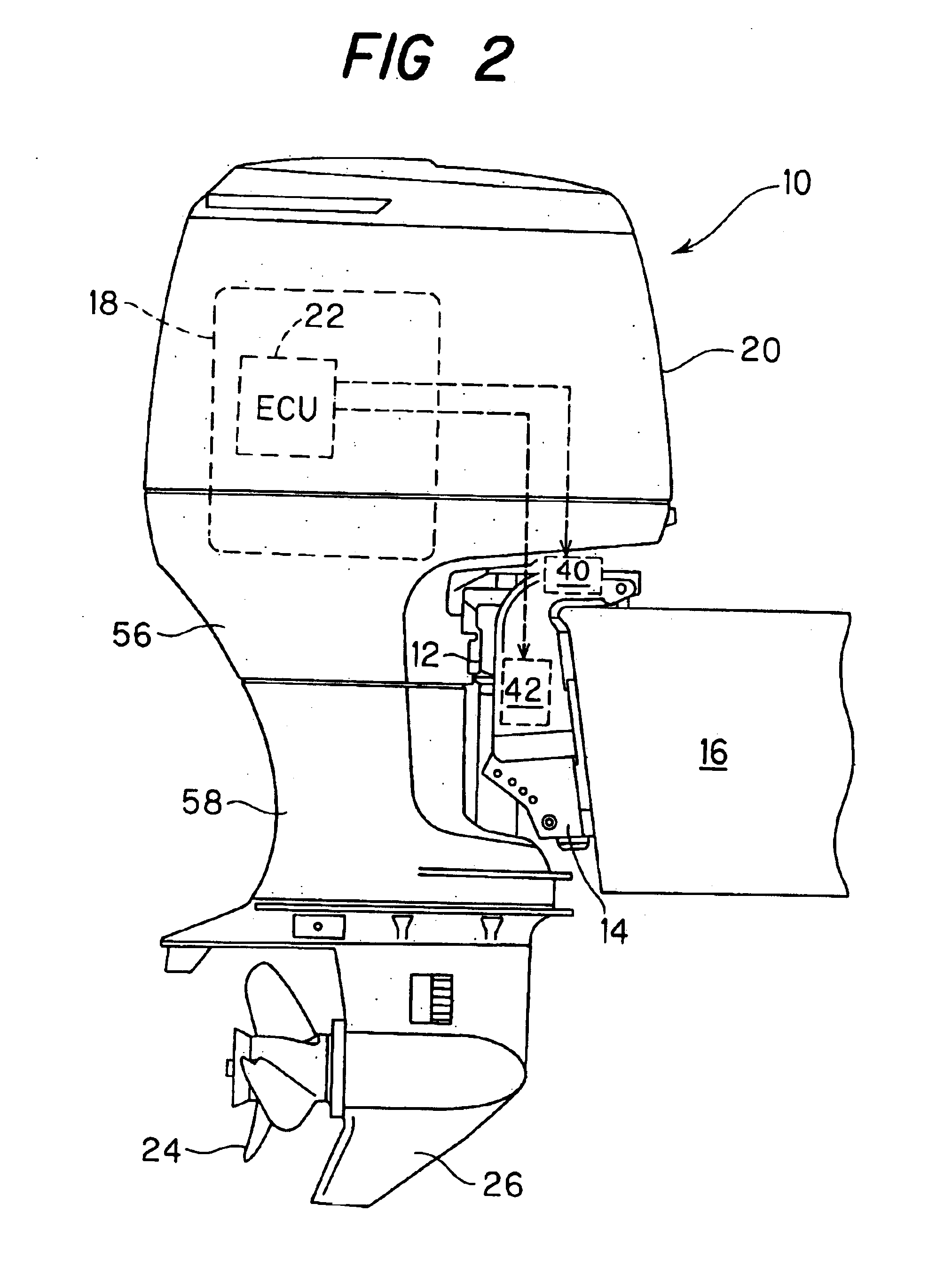

Outboard motor shift mechanism

InactiveUS7140932B2Operation feeling can be improvedReduce the numberPropulsion power plantsOutboard propulsion unitsPropellerEngineering

In a shift mechanism for an outboard motor mounted on a stem of a boat and having an internal combustion engine at its upper portion and a propeller at its lower portion that is powered by the engine to propel the boat, having an electric motor installed in the outboard motor, a shift rod rotatably connected to the electric motor, a shifter clutch connected to the shift rod, the shifter clutch being movable by the shift rod from a neutral position to engage with at least one of a forward gear and a reverse gear, and a controller controlling the electric motor to rotate the shift rod such that the shifter clutch engages with the forward gear or the reverse gear, corresponding to an inputted shift instruction made by the operator, there is provided a shock mitigator mitigating shock generated during the shift. The shock mitigator comprises projections formed on the clutch and the forward / reverse gear. Alternatively, the electric motor and its reduction-gear mechanism are accommodated in a case to be located above the shift rod. Further, there is provided an emergency gear that allows the shift rod to be rotated manually to effect shift.

Owner:HONDA MOTOR CO LTD

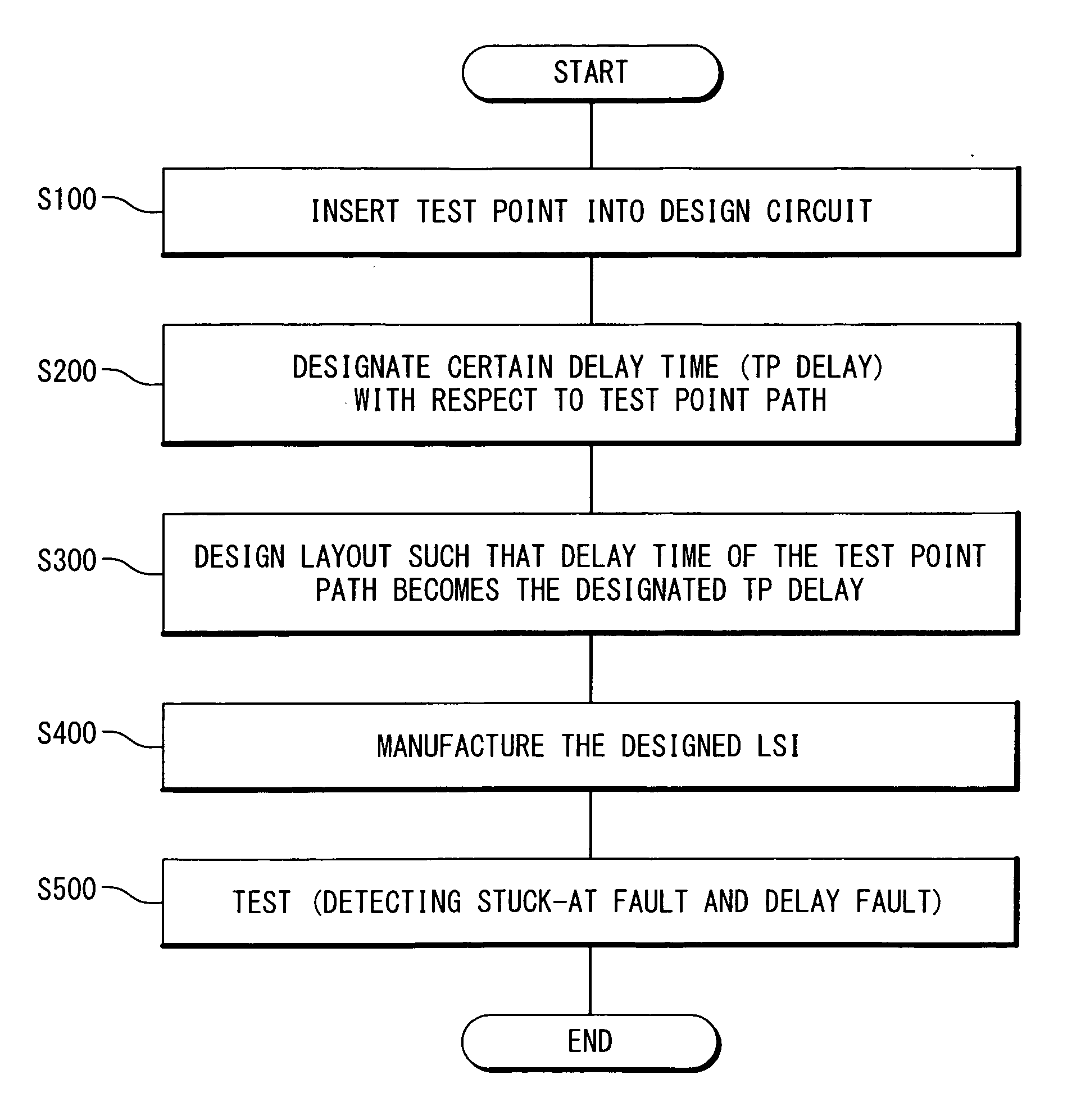

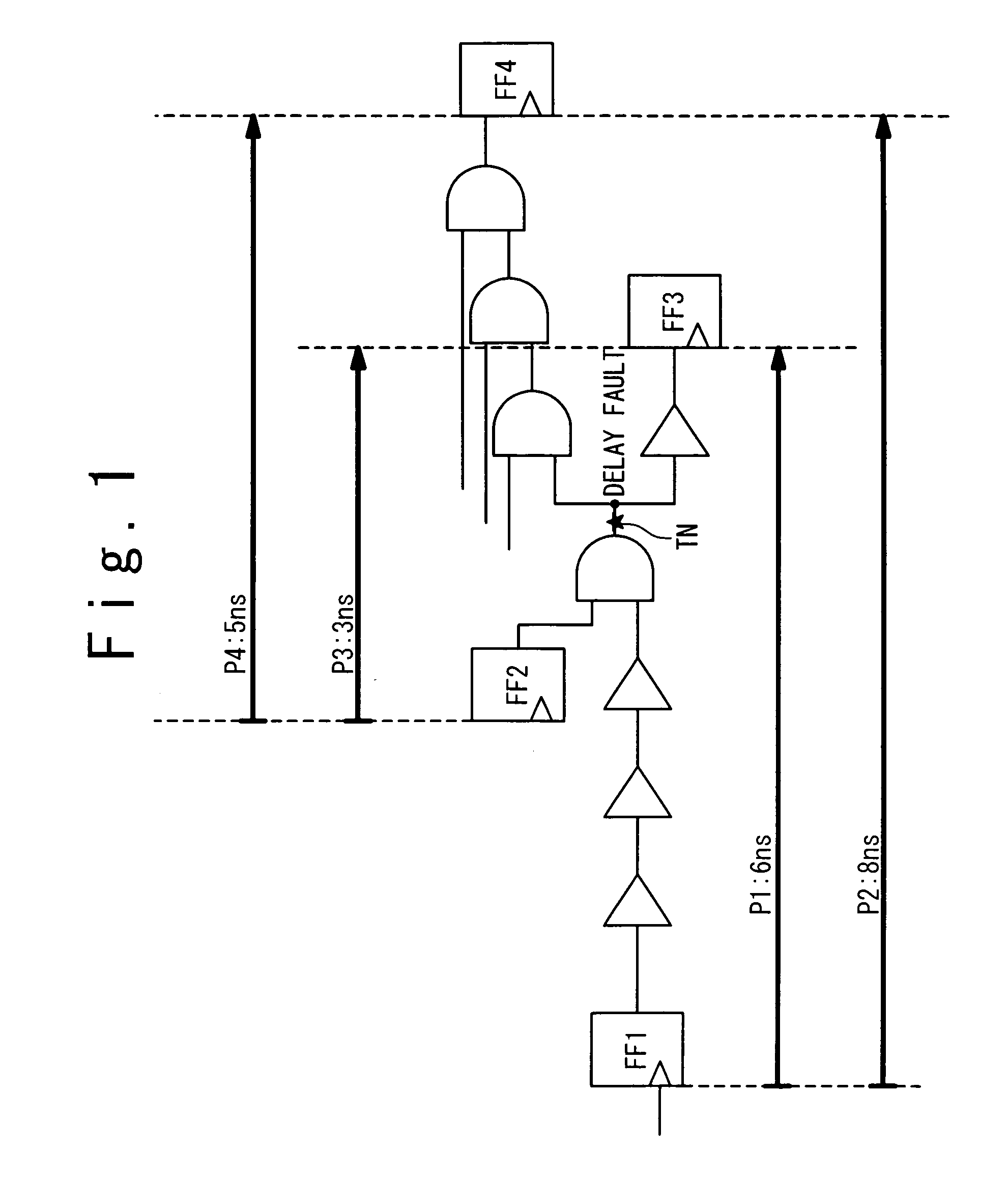

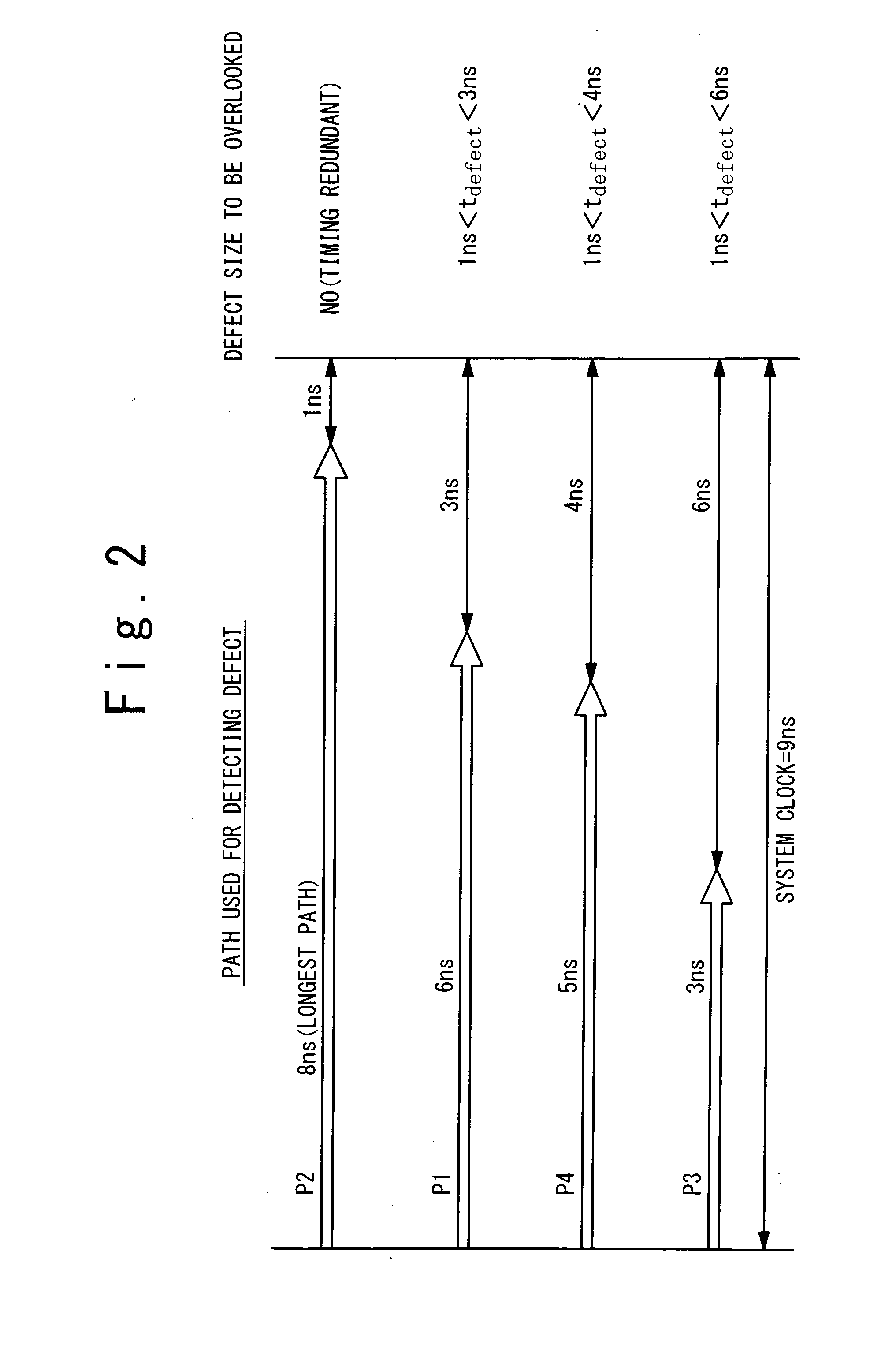

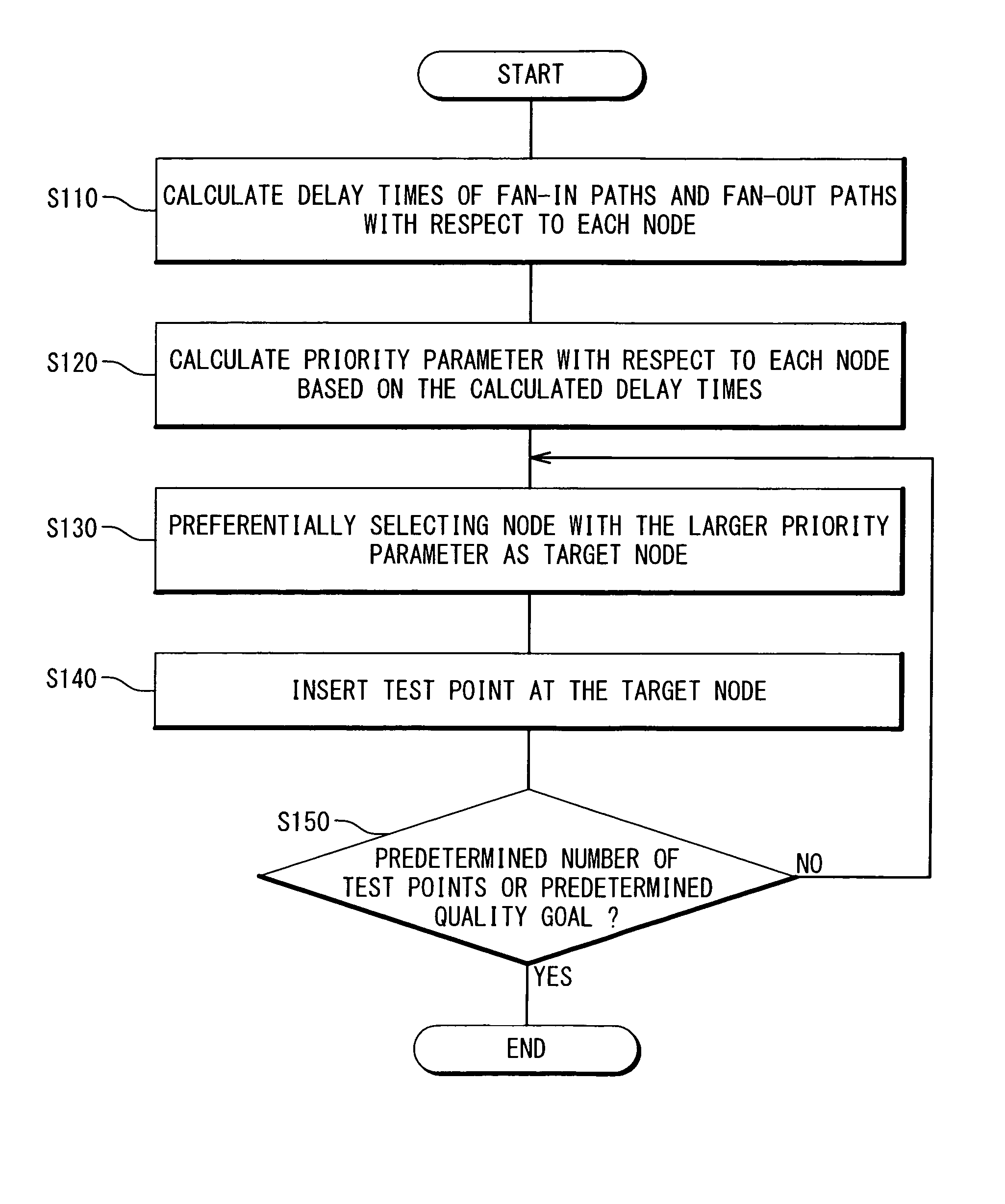

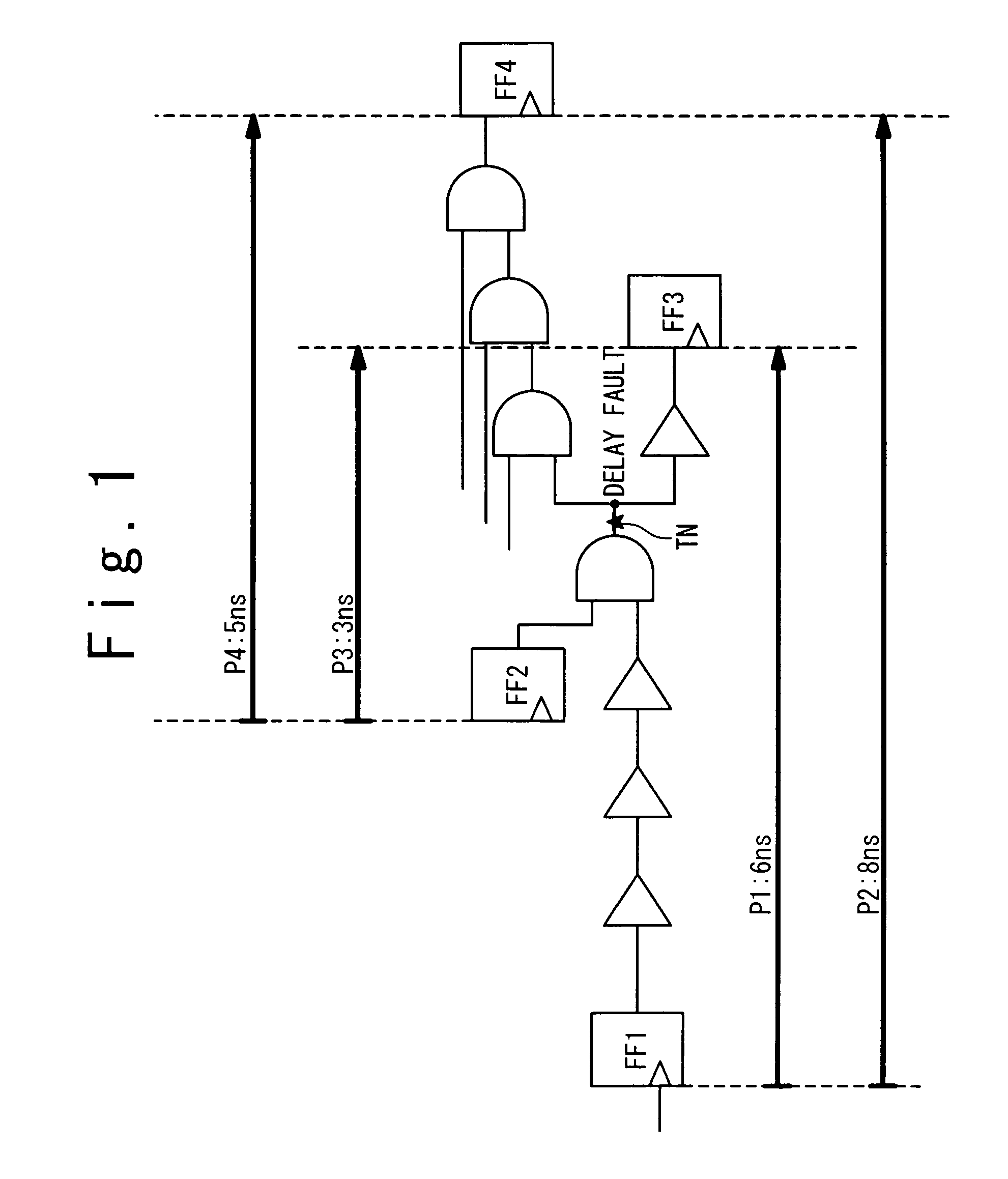

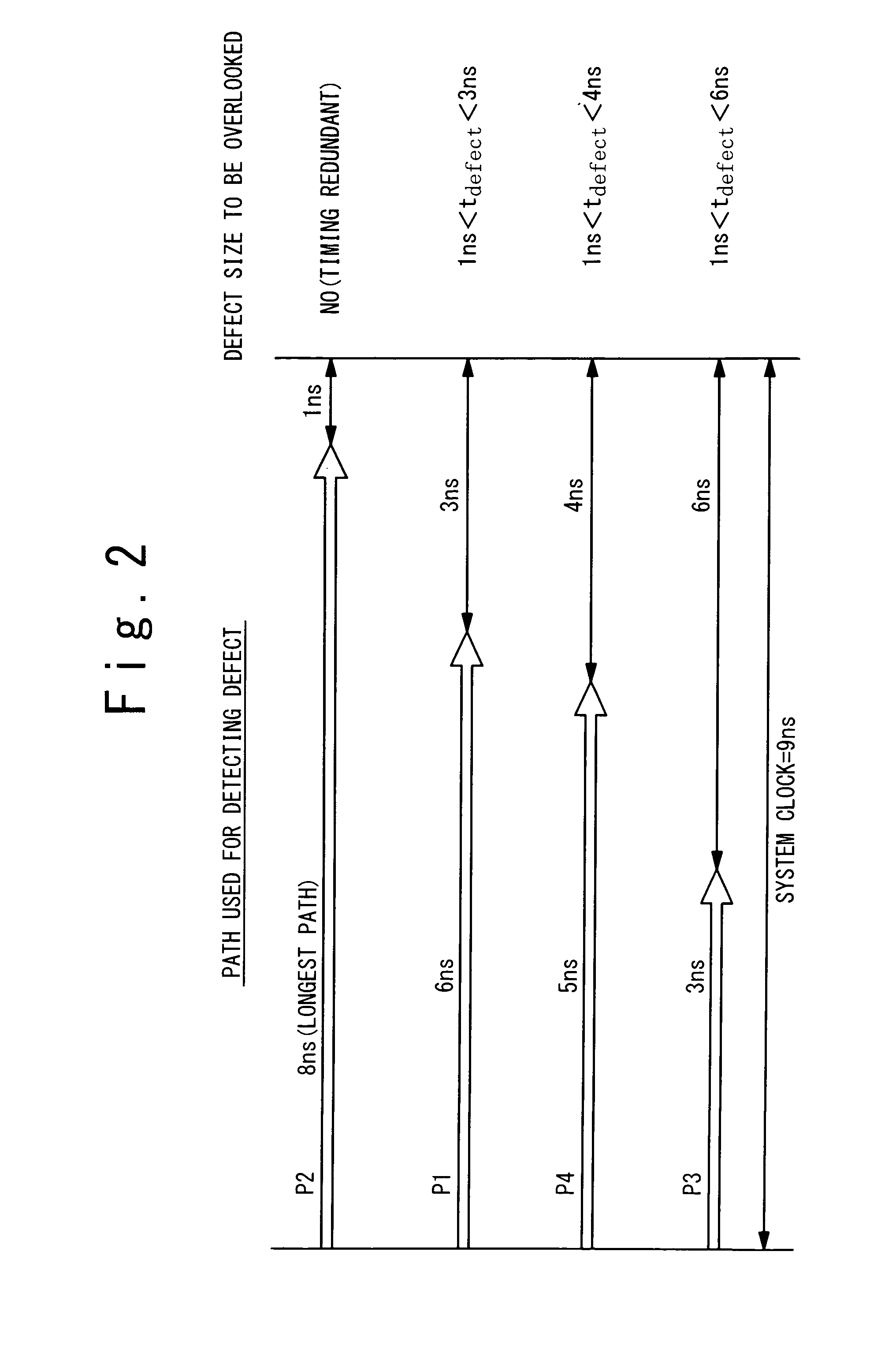

Semiconductor integrated circuit and method of designing thereof based on TPI

InactiveUS20080295050A1To overcome the large delayReduce in quantityElectrical testingSoftware simulation/interpretation/emulationDelayed timeDesign methods

A method of designing a semiconductor integrated circuit based on the TPI technique, comprising: (A) selecting a target node from a plurality of nodes included in a design circuit; (B) inserting a test point at the target node; (C) designating a delay time with respect to a test point path that is a path connected to the test point; and (D) laying out the design circuit such that a delay time of the test point path becomes the designated delay time. The (A) selecting includes: (A1) calculating delay times of fan-in paths and fan-out paths with respect to each of the plurality of nodes; and (A2) selecting the target node from the plurality of nodes based on the calculated delay times.

Owner:RENESAS ELECTRONICS CORP

Voice recognition system for registration of stable utterances

ActiveUS8977547B2Easy to identifyImprove convenienceAutomatic call-answering/message-recording/conversation-recordingSpeech recognitionSpeech identificationSpeech input

A voice recognition system includes: a voice input unit 11 for inputting a voice uttered a plurality of times; a registering voice data storage unit 12 for storing voice data uttered the plurality of times and input into the voice input unit 11; an utterance stability verification unit 13 for determining a similarity between the voice data uttered the plurality of times that are read from the registering voice data storage unit 12, and determining that registration of the voice data is acceptable when the similarity is greater than a threshold Tl; and a standard pattern creation unit 14 for creating a standard pattern by using the voice data where the utterance stability verification unit 13 determines that registration is acceptable.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor integrated circuit and method of designing thereof based on TPI

InactiveUS8056036B2To overcome the large delayReduce in quantityElectrical testingSoftware simulation/interpretation/emulationDelayed timeDesign methods

A method of designing a semiconductor integrated circuit based on the TPI technique, comprising: (A) selecting a target node from a plurality of nodes included in a design circuit; (B) inserting a test point at the target node; (C) designating a delay time with respect to a test point path that is a path connected to the test point; and (D) laying out the design circuit such that a delay time of the test point path becomes the designated delay time. The (A) selecting includes: (A1) calculating delay times of fan-in paths and fan-out paths with respect to each of the plurality of nodes; and (A2) selecting the target node from the plurality of nodes based on the calculated delay times.

Owner:RENESAS ELECTRONICS CORP

Hybrid vehicle

InactiveUS9169764B2Reduce resistanceAvoid volume increaseExhaust apparatusMachines/enginesElectrical resistance and conductanceElectricity

Owner:TOYOTA JIDOSHA KK

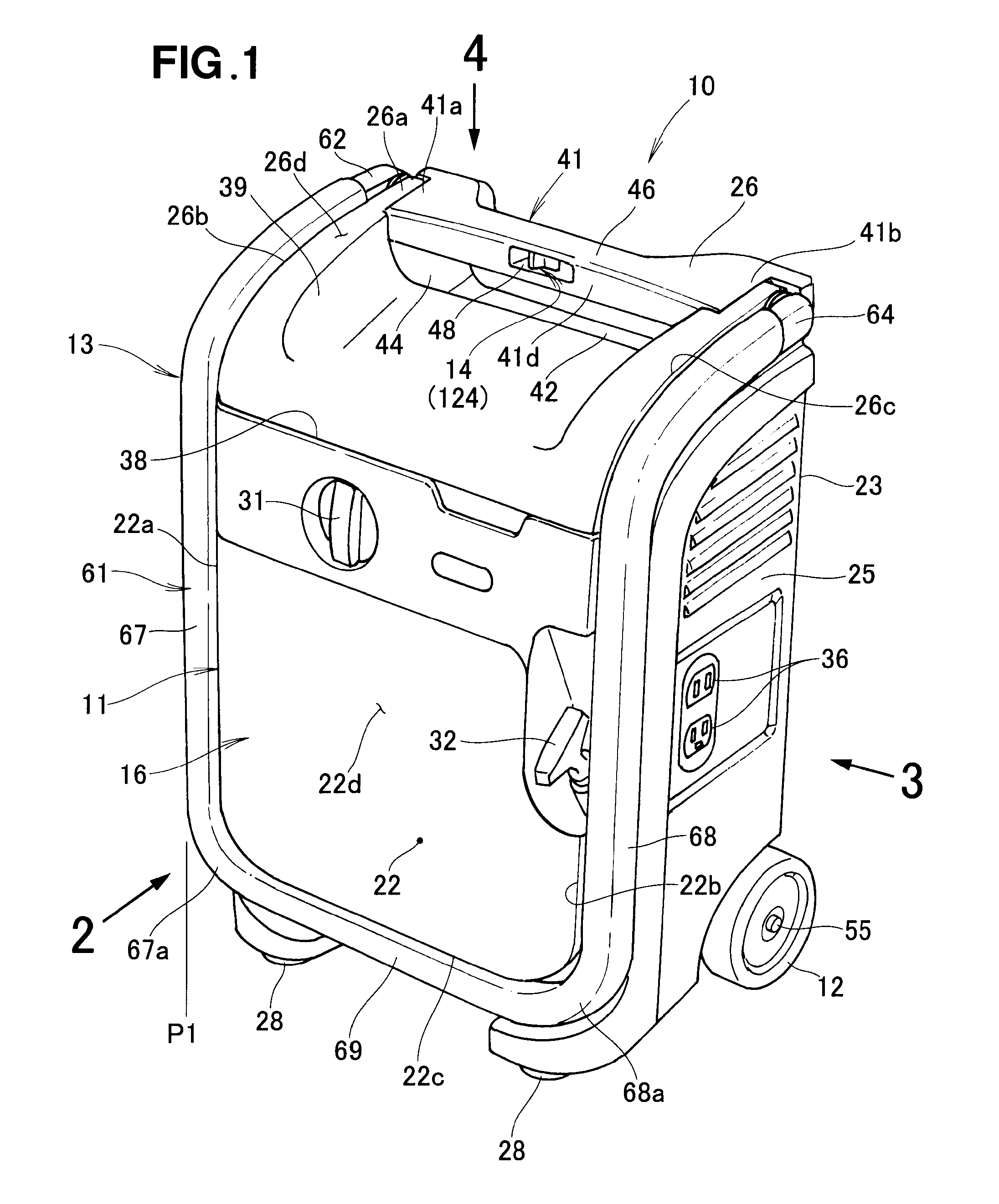

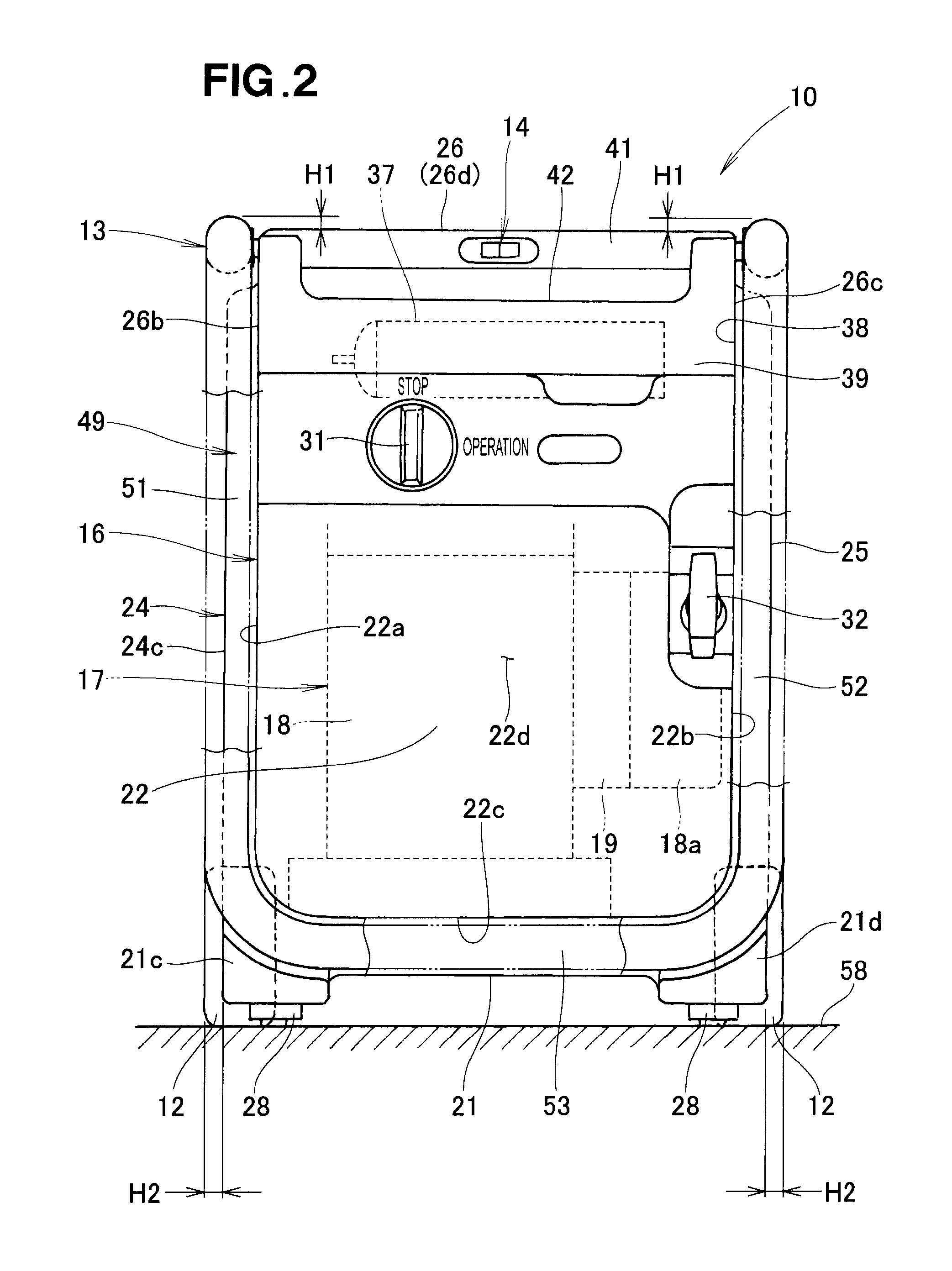

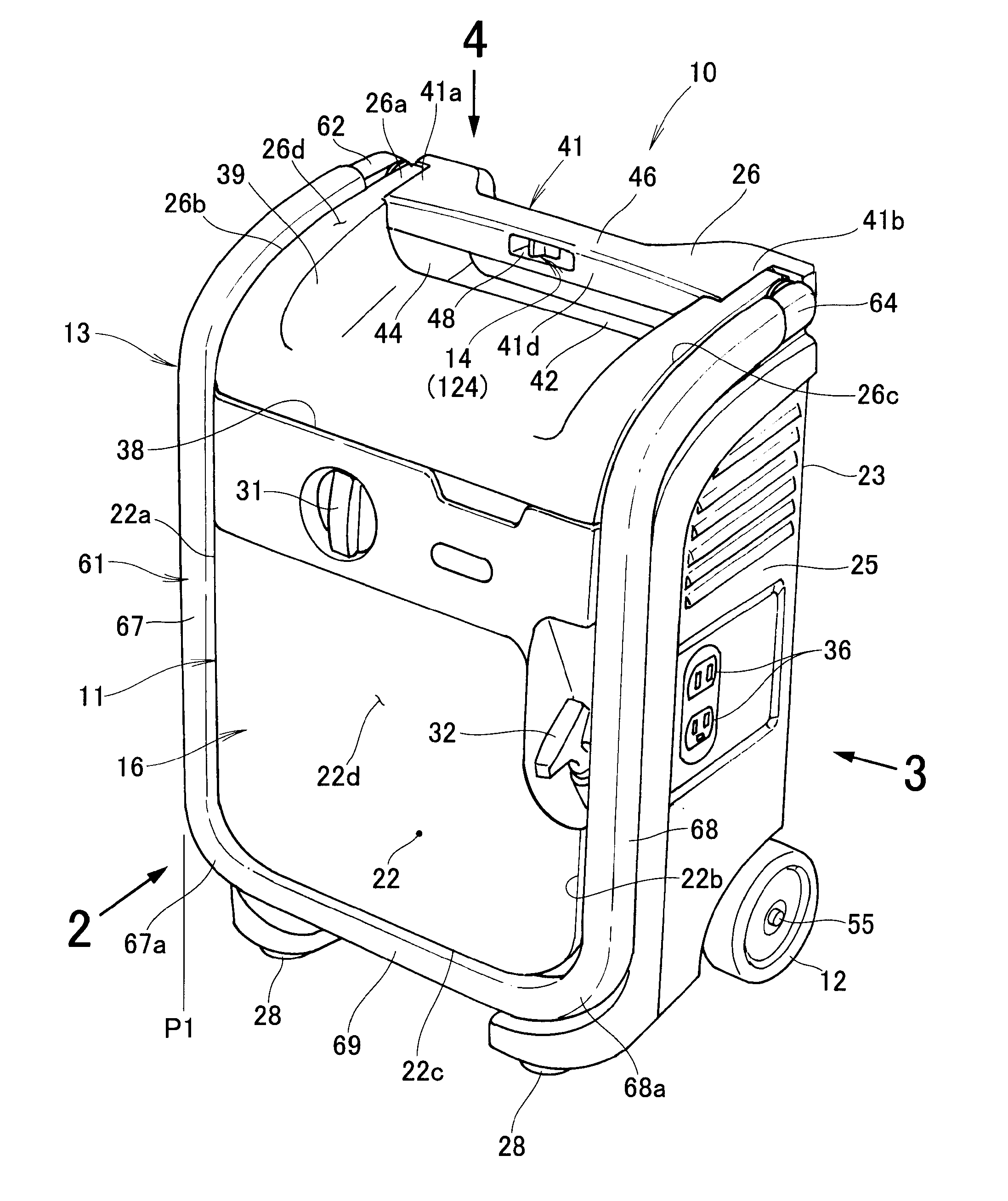

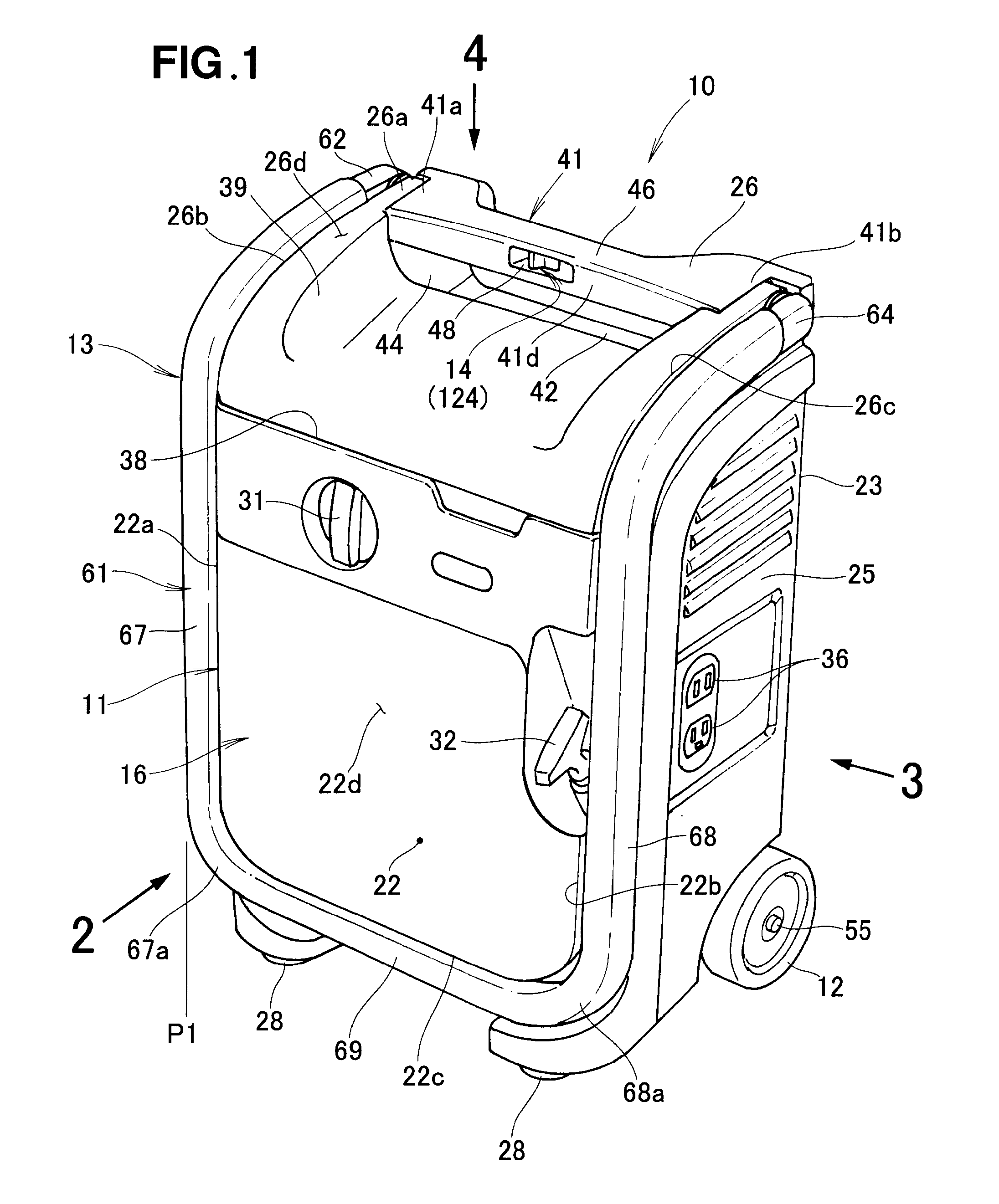

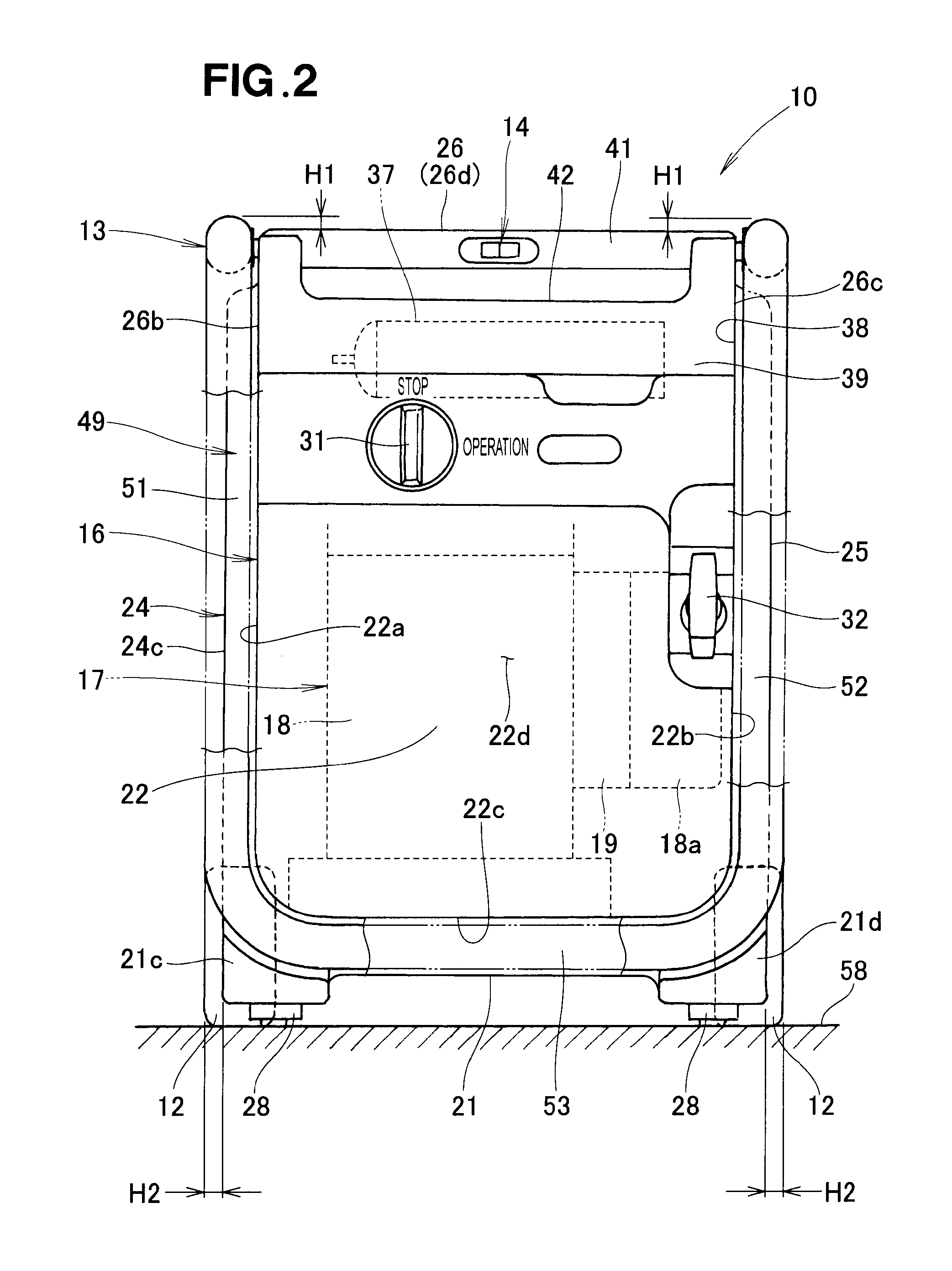

Working machine

ActiveUS8302976B2Reliably protect to-be-protected membersReduce the numberWash-standsUnderstructuresEngineeringMechanical engineering

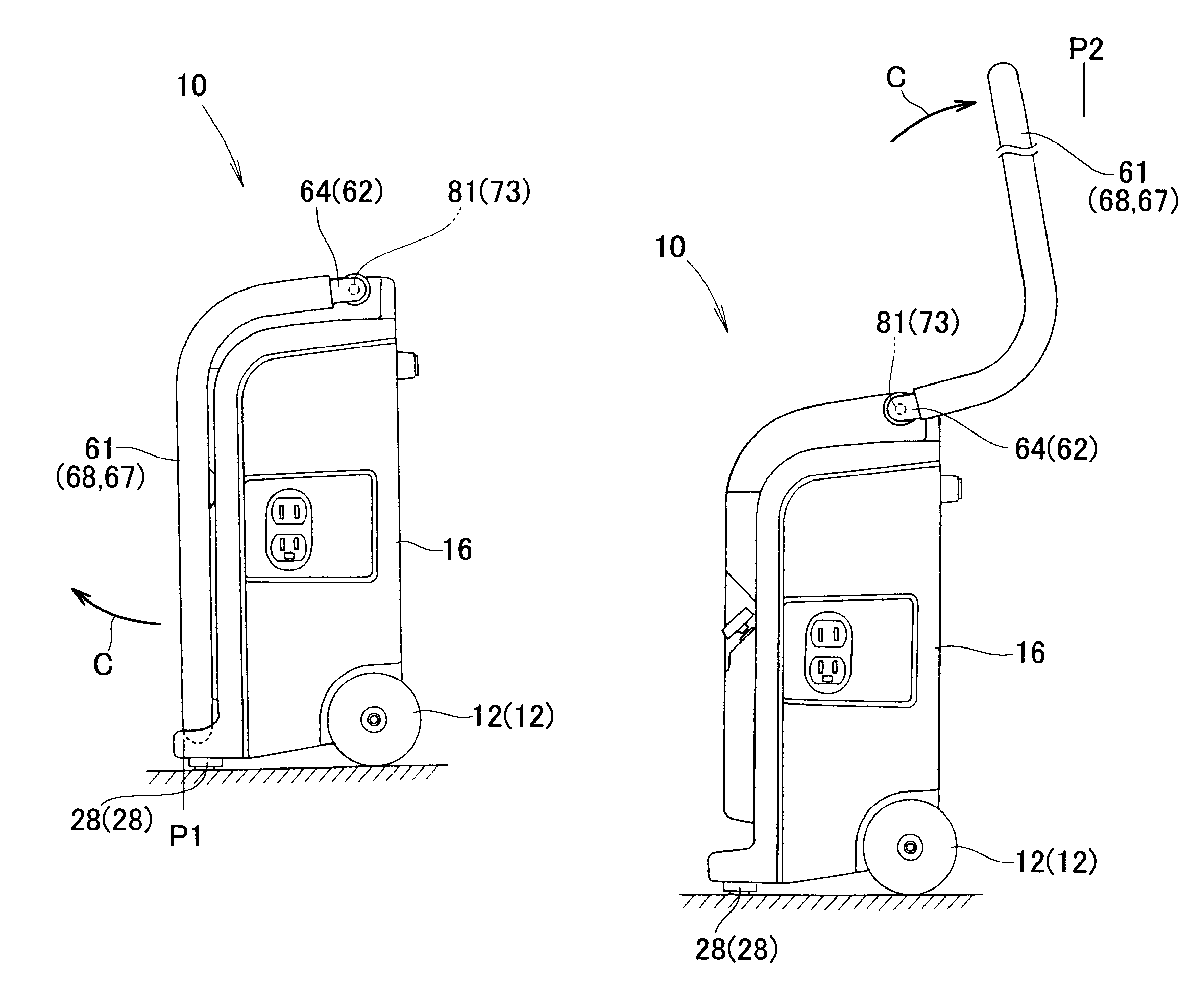

In a working machine, a towing handle is mounted on a top section of a machine body in such a manner that the handle is pivotable between a stored position and a deployed position, and the machine body is towable with the handle in the deployed position. The handle in the stored position extends along outer peripheral portions of the top section and a predetermined wall section of the machine, and the wall section has an upper end region that extends in a machine-towing direction to connect to the top section and has to-be-protected member provided thereon. The handle in the stored position projects outwardly beyond the top section and the wall section.

Owner:HONDA MOTOR CO LTD

Working machine

ActiveUS20110057401A1Reliably protect to-be-protected membersReduce the numberWash-standsUnderstructuresEngineeringMechanical engineering

In a working machine, a towing handle is mounted on a top section of a machine body in such a manner that the handle is pivotable between a stored position and a deployed position, and the machine body is towable with the handle in the deployed position. The handle in the stored position extends along outer peripheral portions of the top section and a predetermined wall section of the machine, and the wall section has an upper end region that extends in a machine-towing direction to connect to the top section and has to-be-protected member provided thereon. The handle in the stored position projects outwardly beyond the top section and the wall section.

Owner:HONDA MOTOR CO LTD

Test access control for plural processors of an integrated circuit

ActiveUS7743278B2Easy to debugIncrease the number ofElectronic circuit testingError detection/correctionEngineeringControl selection

The present invention is directed to facilitate debugging in a semiconductor integrated circuit device including a plurality of microprocessors. A semiconductor integrated circuit device includes: a plurality of processors; a plurality of debug interfaces enabling debugging of the corresponding processors; a plurality of common terminals shared by the plurality of debug interfaces; a selection circuit capable of selectively connecting the plurality of debug interfaces to the common terminals; and a controller capable of controlling selecting operation in the selection circuit in accordance with a predetermined instruction. A first selector capable of selectively connecting the plurality of debug interfaces to a TRST terminal in the terminal group conformed with the JTAG specifications, and a second selector capable of selectively connecting the plurality of debug interfaces to terminals other than the TRST terminal are provided. With the configuration, even in the case where the number of processors increases, the invention can flexibly address the increase.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device, method of manufacturing the same, and phase shift mask

InactiveUS20060194124A1Reduce chip areaSecure high moisture resistanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMoisture resistanceEngineering

A main wall part is provided so as to surround an integrated circuit part. A sub-wall part which is in “L” shape is provided between each corner of the main wall part and the integrated circuit part. Therefore, even if the stress is concentrated due to heat treatment or the like, the stress is dispersed to the main wall part and the sub-wall part, and hence peeling between layers and a crack are unlikely to occur, as compared with the conventional art. Further, even if the crack and the like occur at the corner, moisture from the outside hardly reaches the integrated circuit part when the main wall part and the sub-wall part are coupled to each other. For this reason, it is possible to ensure an extremely high moisture resistance.

Owner:FUJITSU SEMICON LTD

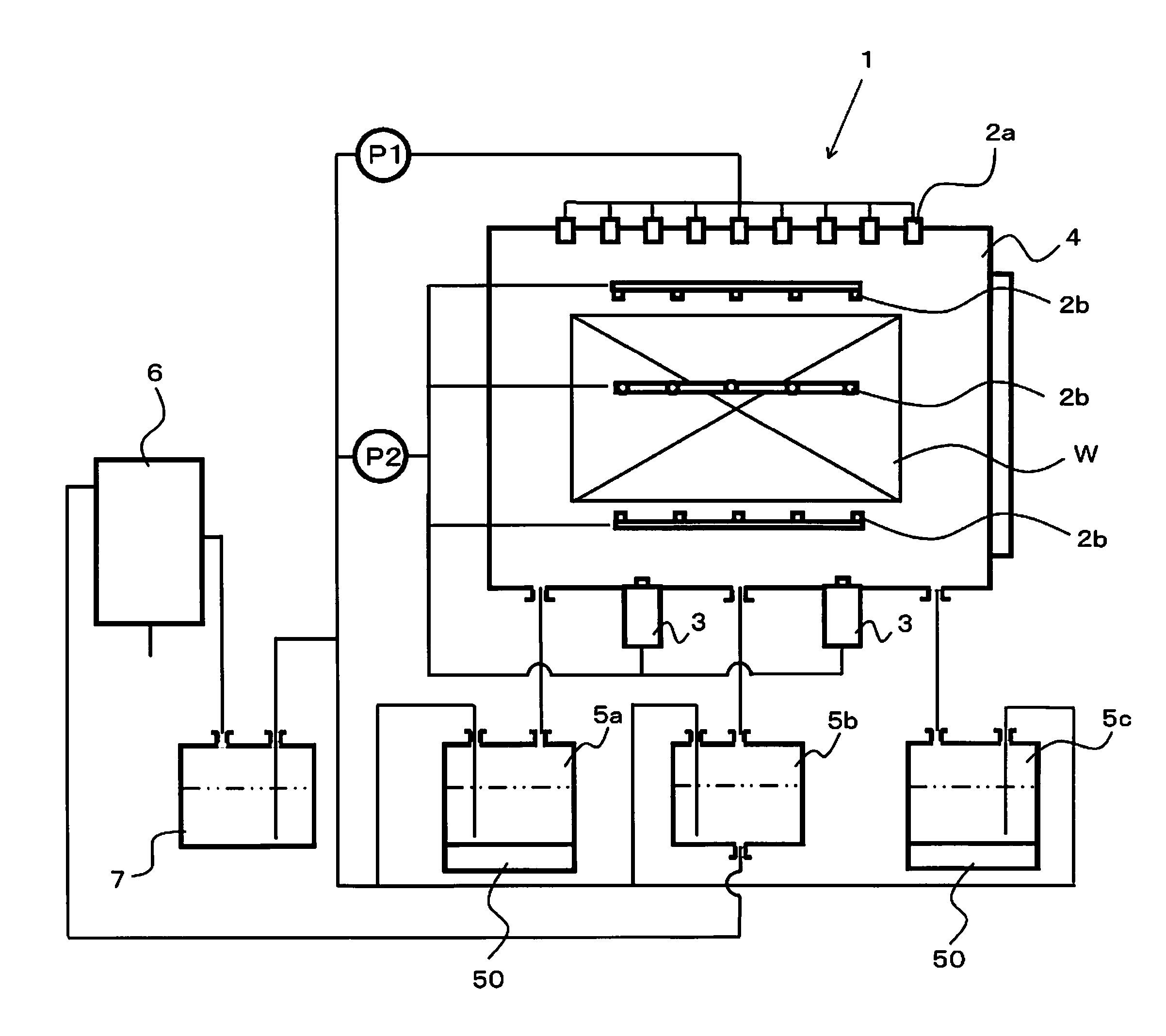

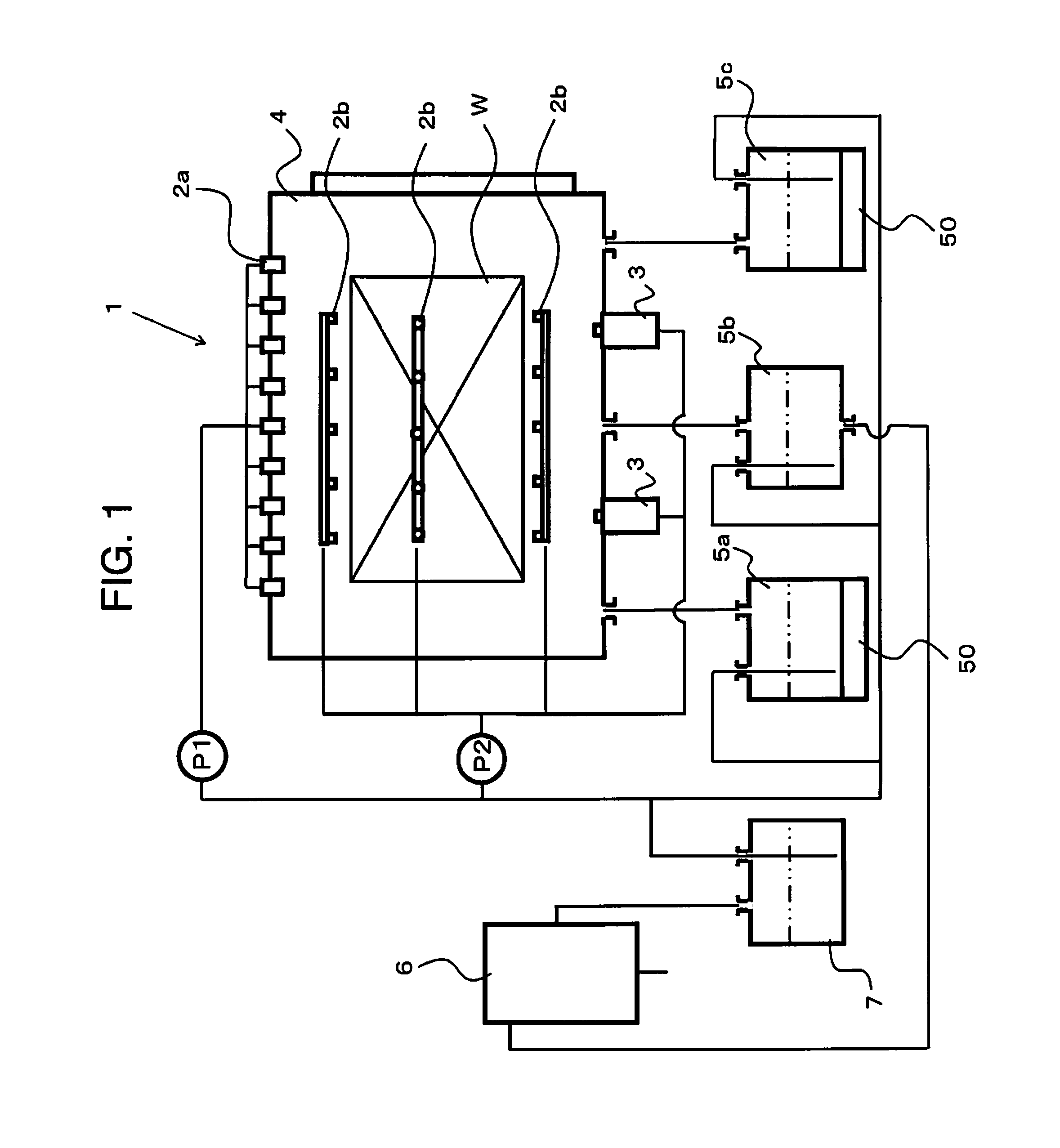

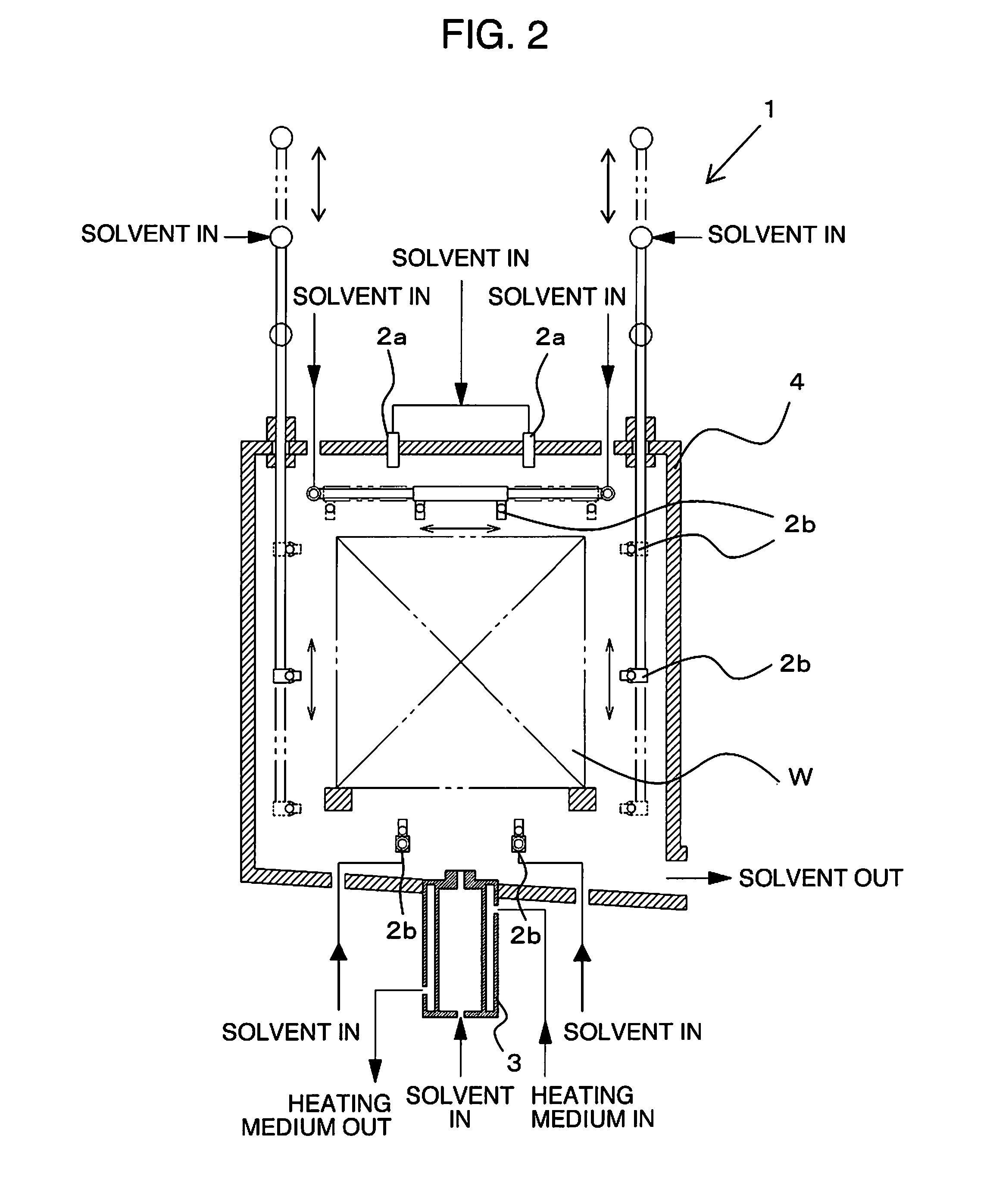

Vacuum degreasing and cleaning apparatus and vacuum degreasing and cleaning method

InactiveUS20120312335A1Improve introduction efficiencyImprove removal efficiencyCleaning using liquidsEngineeringCleaning methods

There is provided a vacuum degreasing and cleaning apparatus, including a cleaning chamber having an injector and a sprayer that eject a solvent to an object to be cleaned, a plurality of storage tanks that store the solvent, a distiller that distills the solvent in the storage tank, and a replenisher tank that stores the solvent distilled by the distiller, wherein a heating means is provided in the inside of the sprayer in a nesting way. There is also provided a vacuum degreasing and cleaning method using the aforementioned vacuum degreasing and cleaning apparatus, wherein the solvent is pressurized and supplied to the inside of the sprayer, heated to a temperature not lower than a saturation temperature in the cleaning chamber under a reduced pressure, and thereafter sprayed in the cleaning chamber under the reduced pressure.

Owner:NACHI-FUJIKOSHI

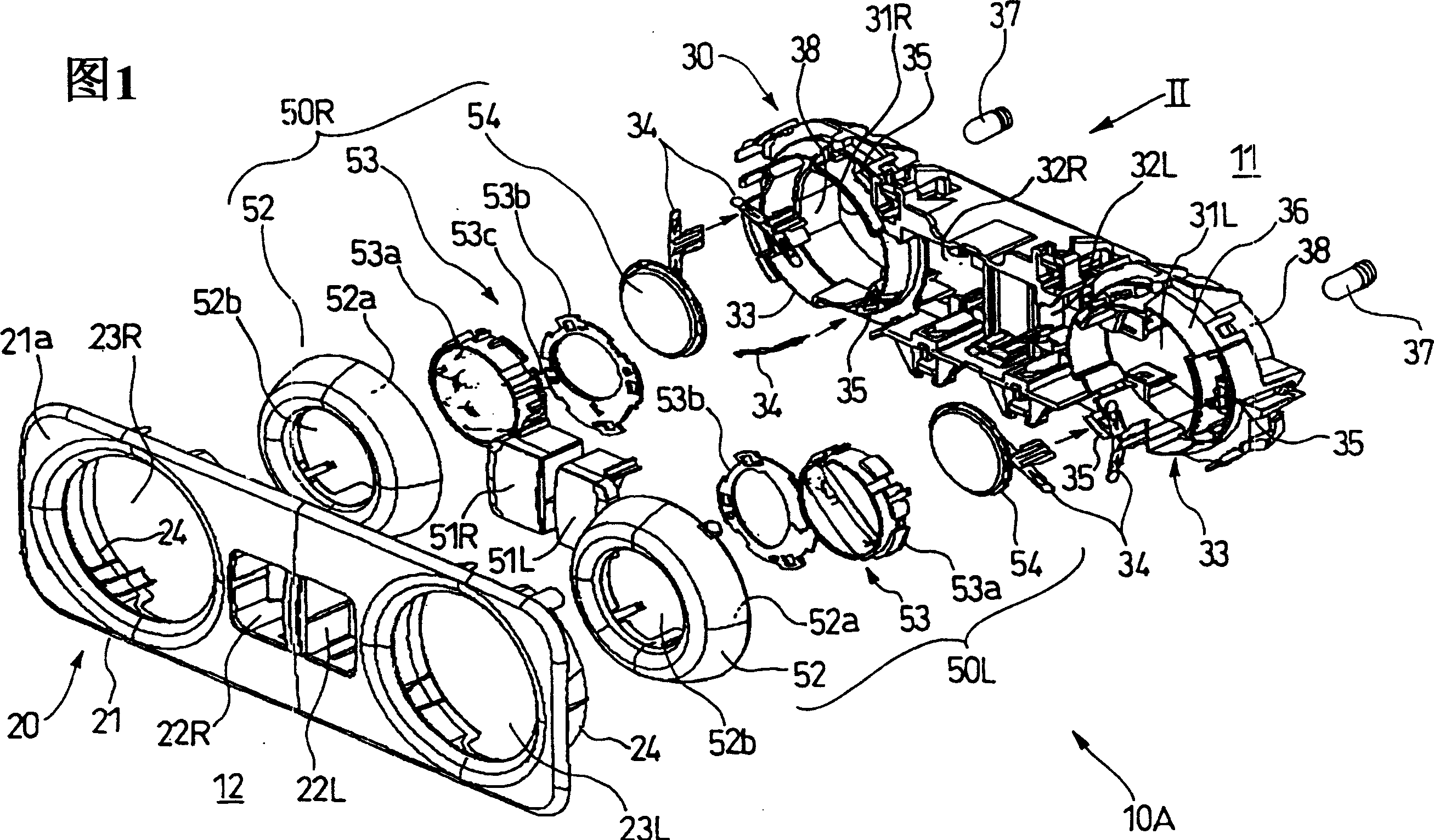

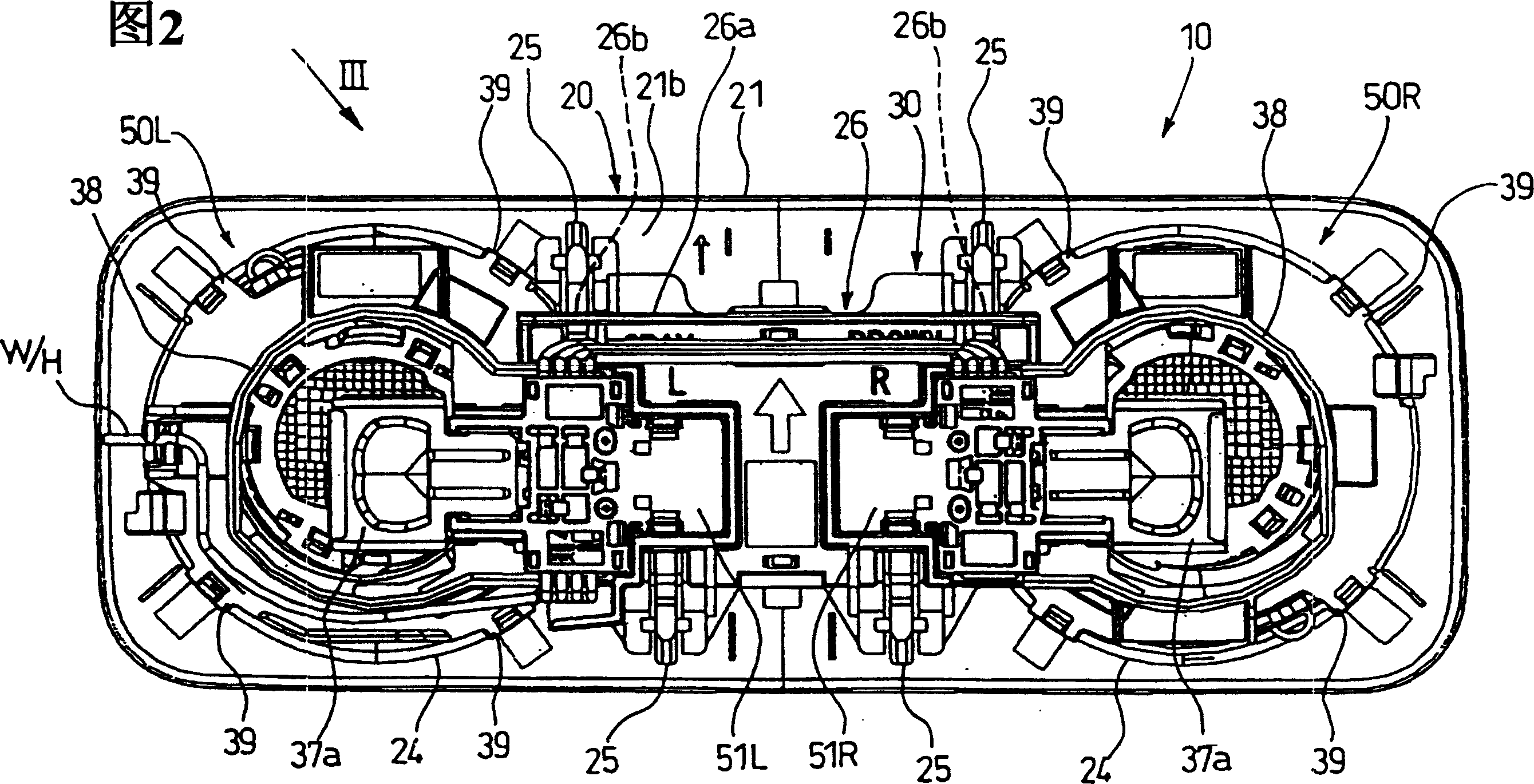

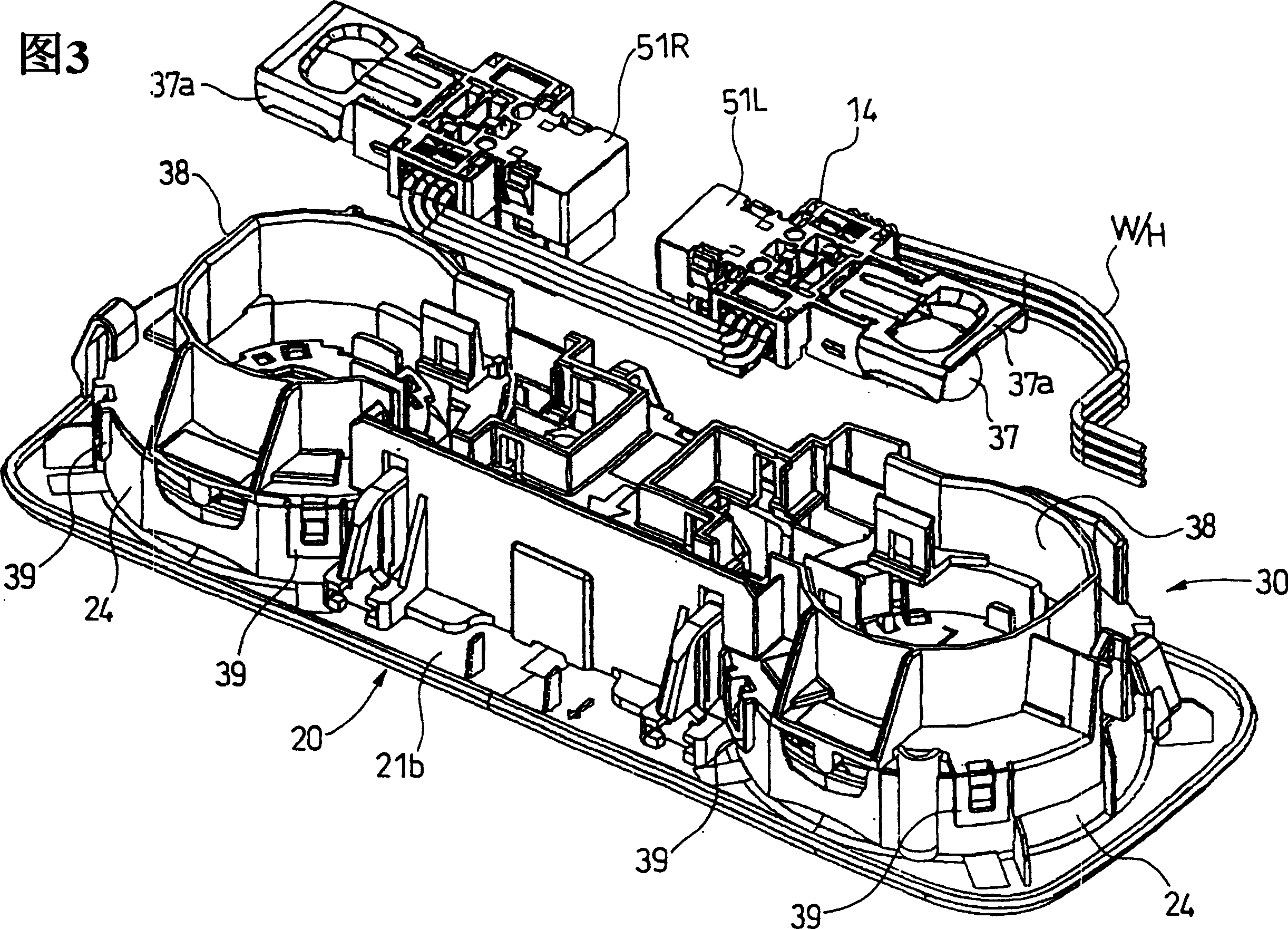

Internal illuminating lamp

ActiveCN1609505ASmooth rotationEasy to fixLighting support devicesSpotlightingMechanical engineeringTransmitted light

A bezel member ( 52 ) to which a lens ( 54 ) which transmits light from a light source ( 37 ) is supported on a main body ( 30 ) to be fixed to a vehicle body ( 11 ). A spherical surface ( 52 a) is formed on one of the main body ( 30 ) or a bezel member ( 52 ), and sliding members ( 34 ) for being pressed against the spherical surface ( 52 a) are formed on the other one of them, so that the bezel member ( 52 ) can be rotated with respect to a supporting member ( 33 ) of the main body ( 30 ) and fixed to a given position. Since a metal plate is used as the sliding members ( 34 ) in this interior illumination lamp ( 10 ), a problem such that the light source cannot be fixed to the desired direction due to abrasion or change of properties of the felt sliding member as in the related art due to the temperature or deterioration with age can be solved. Also, in comparison with the case in which the spring or the like is employed, increase in cost due to increase in the number of parts can be avoided.

Owner:YAZAKI CORP

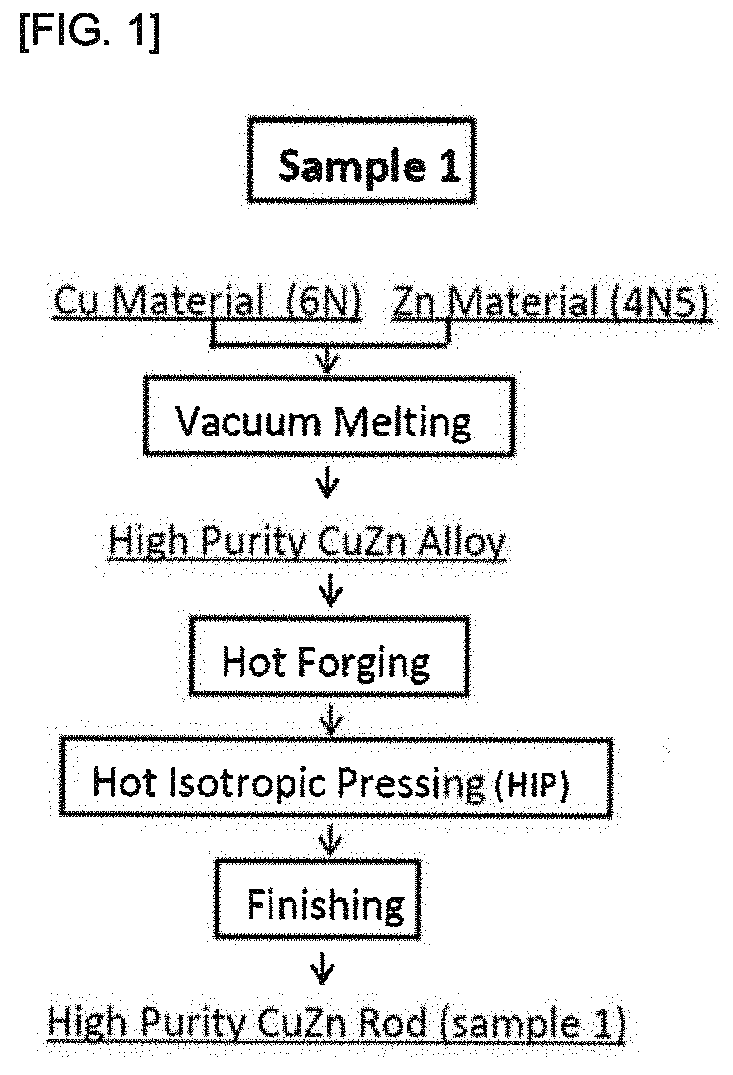

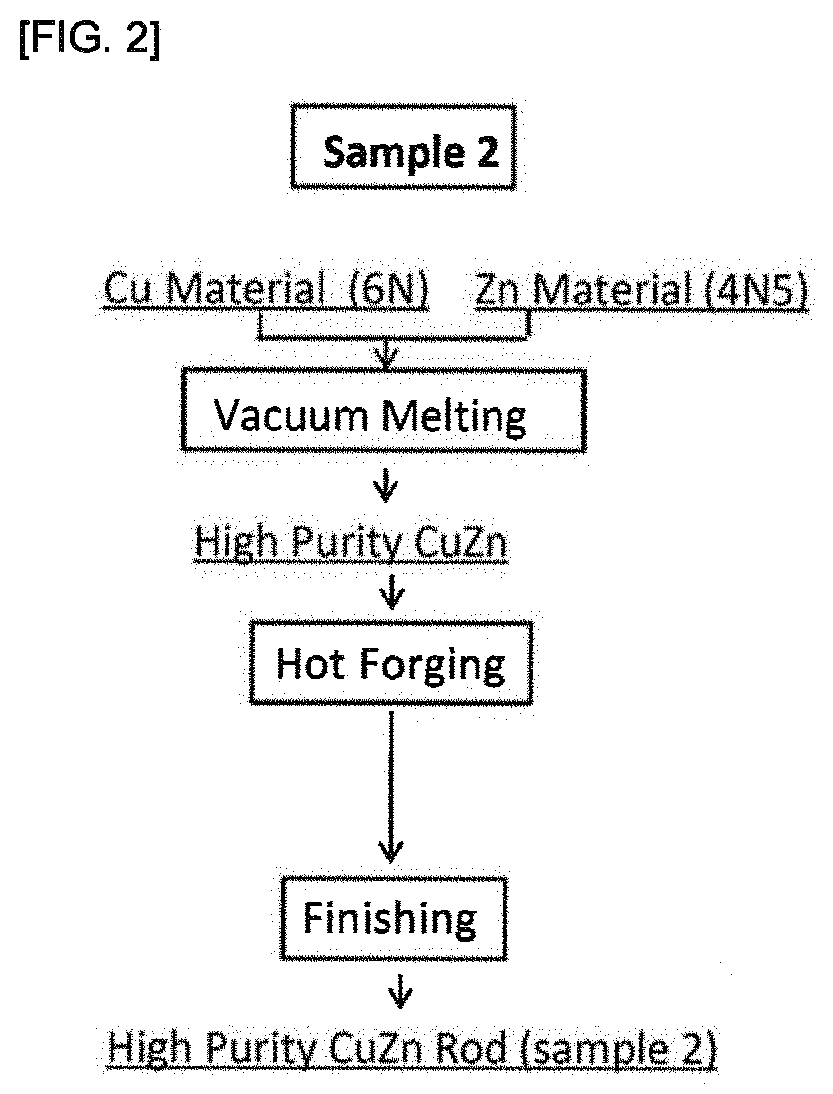

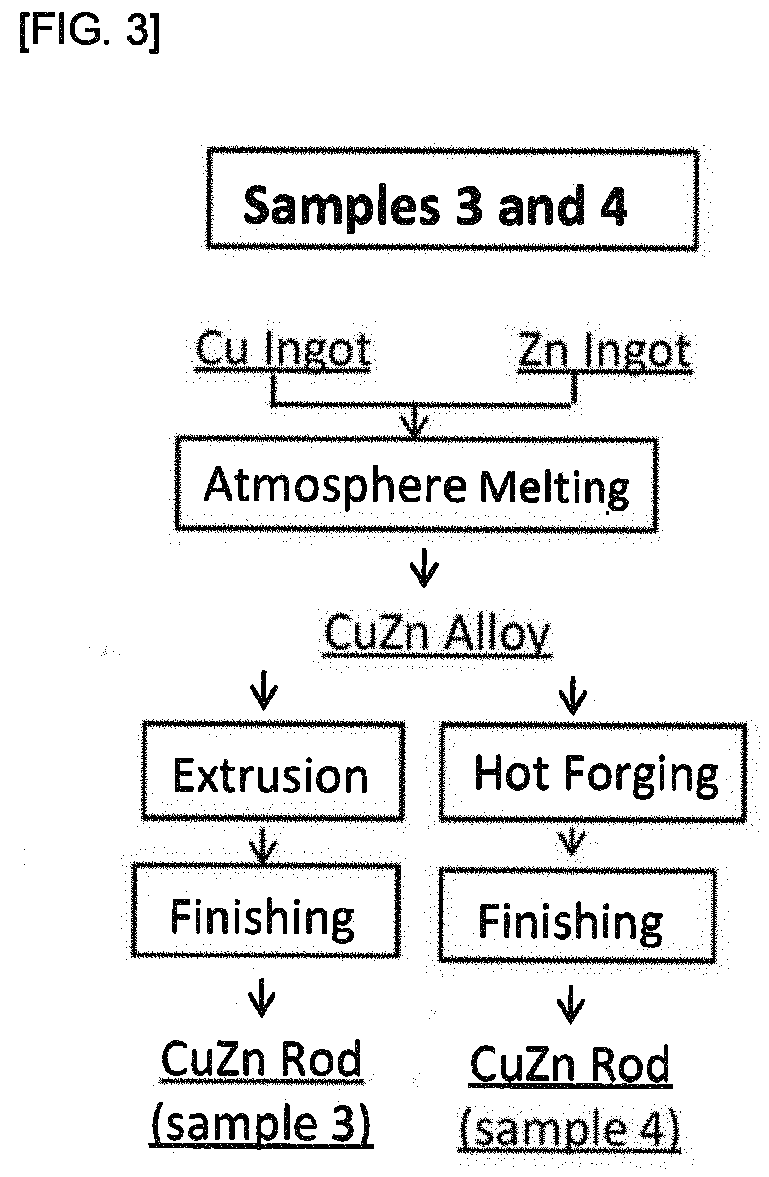

CORROSION RESISTANT CuZn ALLOY

PendingUS20210317550A1Increase the number ofSuitable for useLaser detailsCell electrodesMicroscopic observationZinc alloys

The present invention provides a corrosion-resistant CuZn alloy, the alloy having a Zn content of from 15 to 55% by mass, the balance being Cu and inevitable impurities, wherein a total content of Zn and Cu is 99.995% by mass or more, and wherein a number of pores is 1 / cm2 or less based on optical microscopic observation.

Owner:JX NIPPON MINING& METALS CORP

Content distribution method and relay apparatus

InactiveUS7848274B2Avoid volume increaseIncrease in of of complicationFrequency-division multiplex detailsRepeater/relay circuitsContent distributionComputer hardware

A relay apparatus 30 issues a new sub-address at a timing when mobile phones (10a, 10b) requested content from a CP server apparatuses (20a, 20b), that is, at a timing when a sub-address is required. The content specified by this sub-address is distributed from the CP server apparatuses via the relay apparatus (30) to the mobile phones. In system of the present invention it is possible to utilize the same sub-address many times for different content items. It is therefore possible to avoid increasing the number of digits of the sub-address as well as the complexity of the sub-address structure, in a case where the types of content or the number of content items increases.

Owner:NTT DOCOMO INC

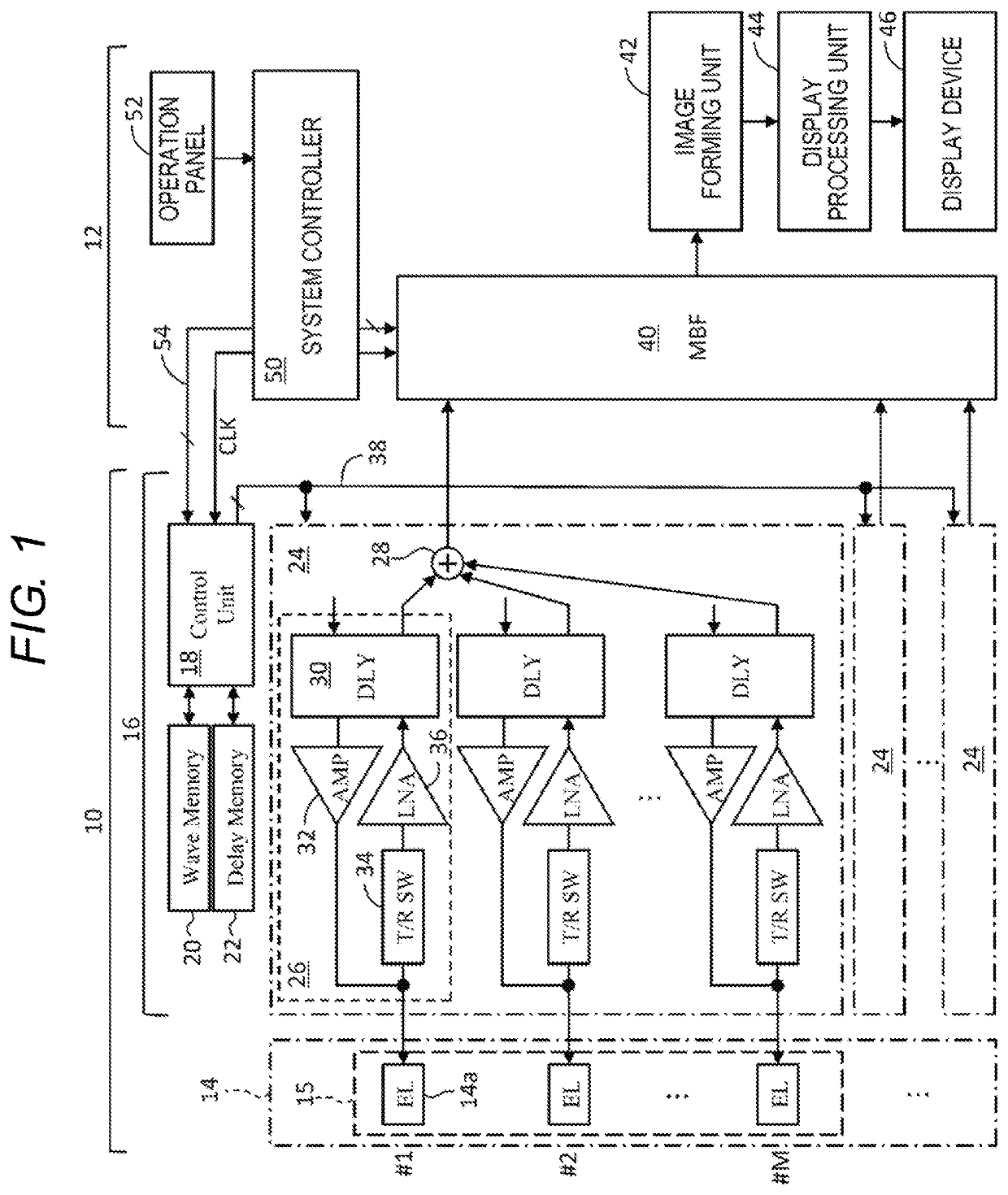

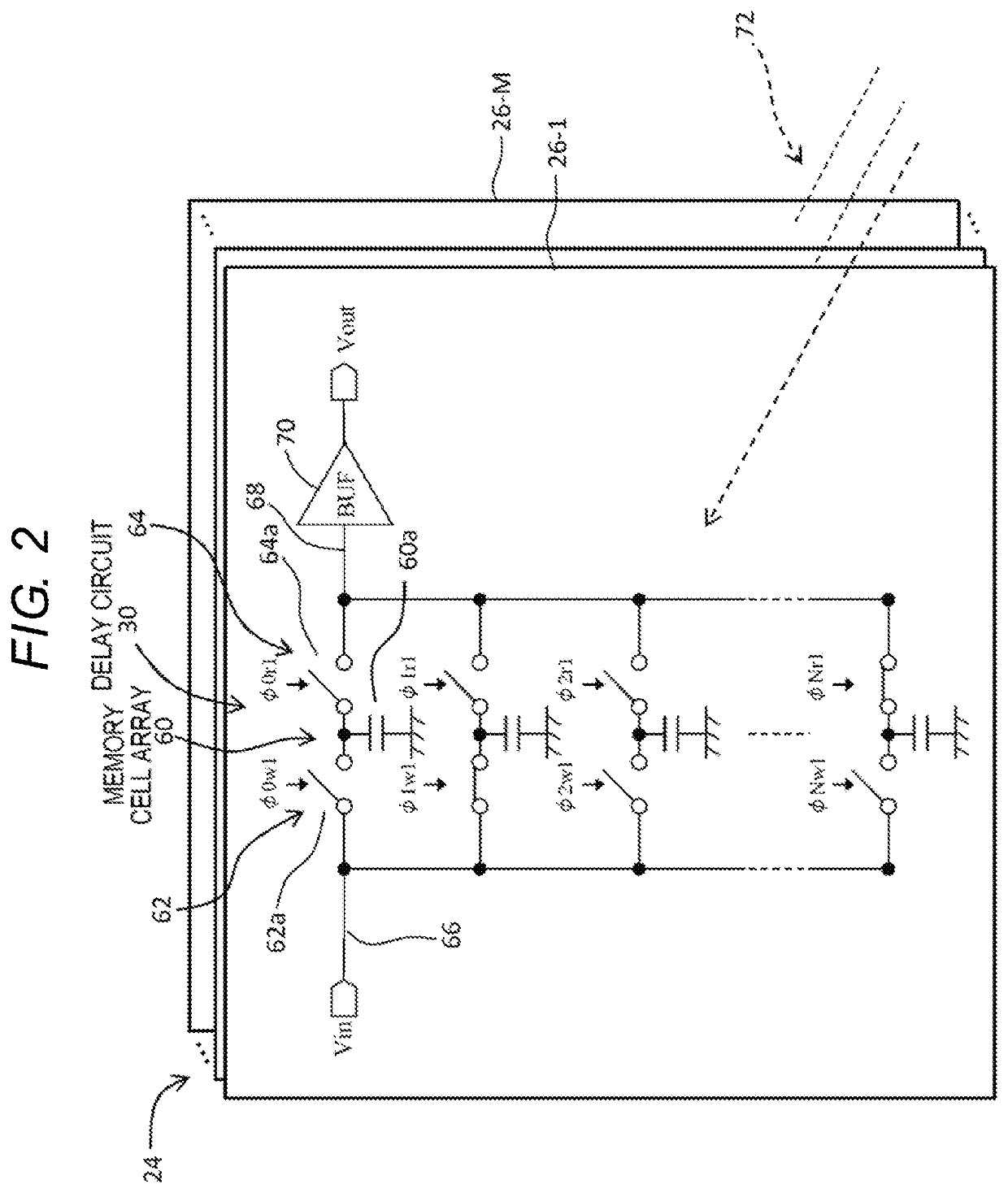

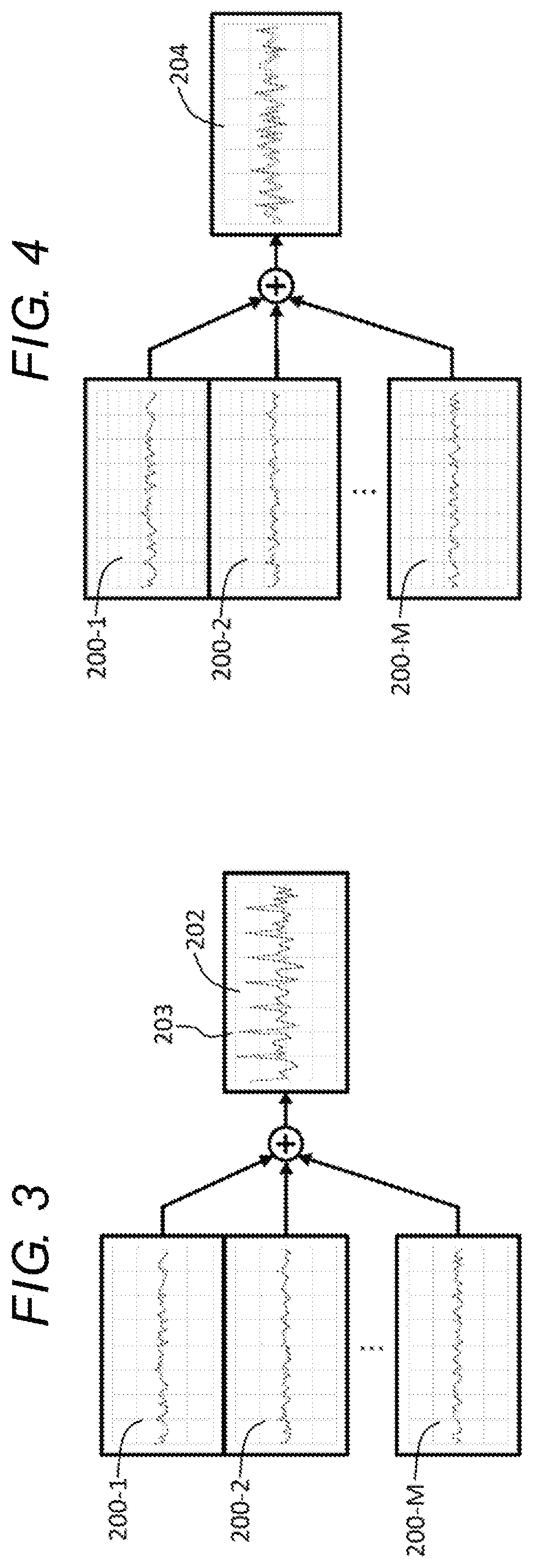

Ultrasonic Diagnosis Device and Electronic Circuit

InactiveUS20200022682A1Increase the number ofReduce noiseOrgan movement/changes detectionCatheterMemory cellControl cell

An electronic circuit in an ultrasonic probe includes a plurality of sub beamformers and a control unit. Each sub beamformer includes M delay circuits and an adding circuit. Each delay circuit includes a memory cell array which is formed of N memory cells. Conditions of cyclic operations of the M memory cell arrays (for example, timings of start triggers) are made irregular, such that use starting stage numbers in the M memory cell arrays are different.

Owner:FUJIFILM HEALTHCARE CORP

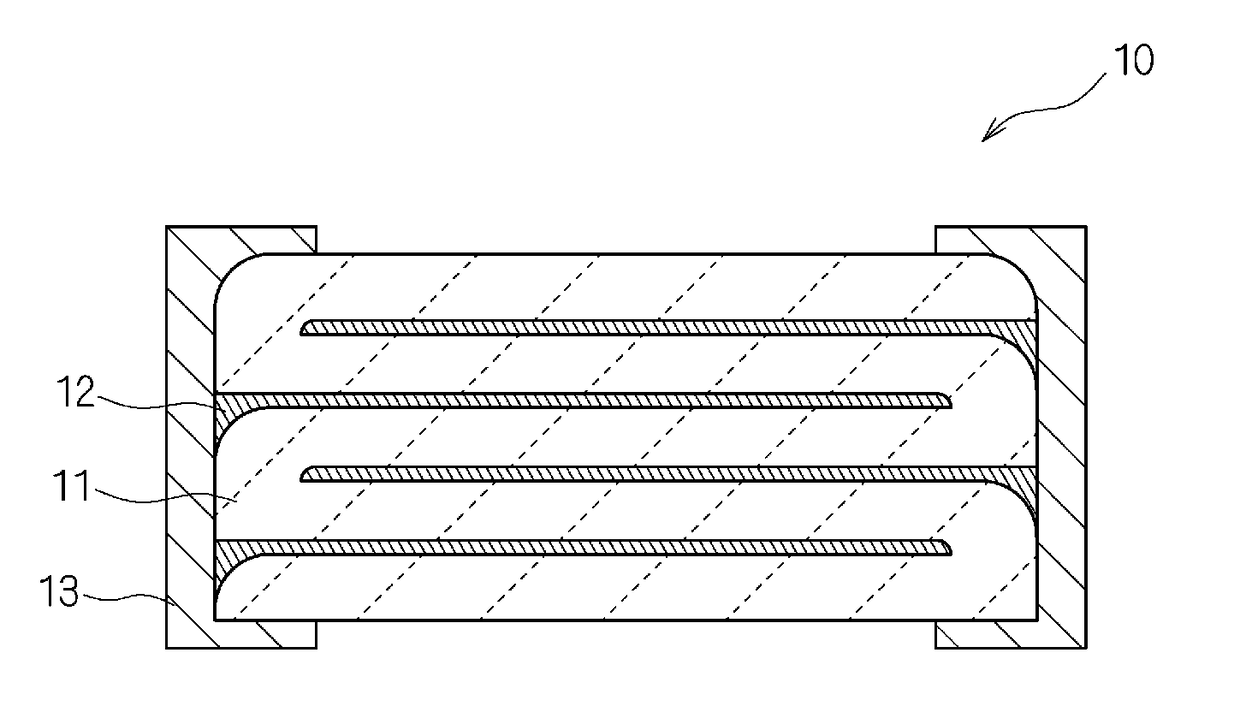

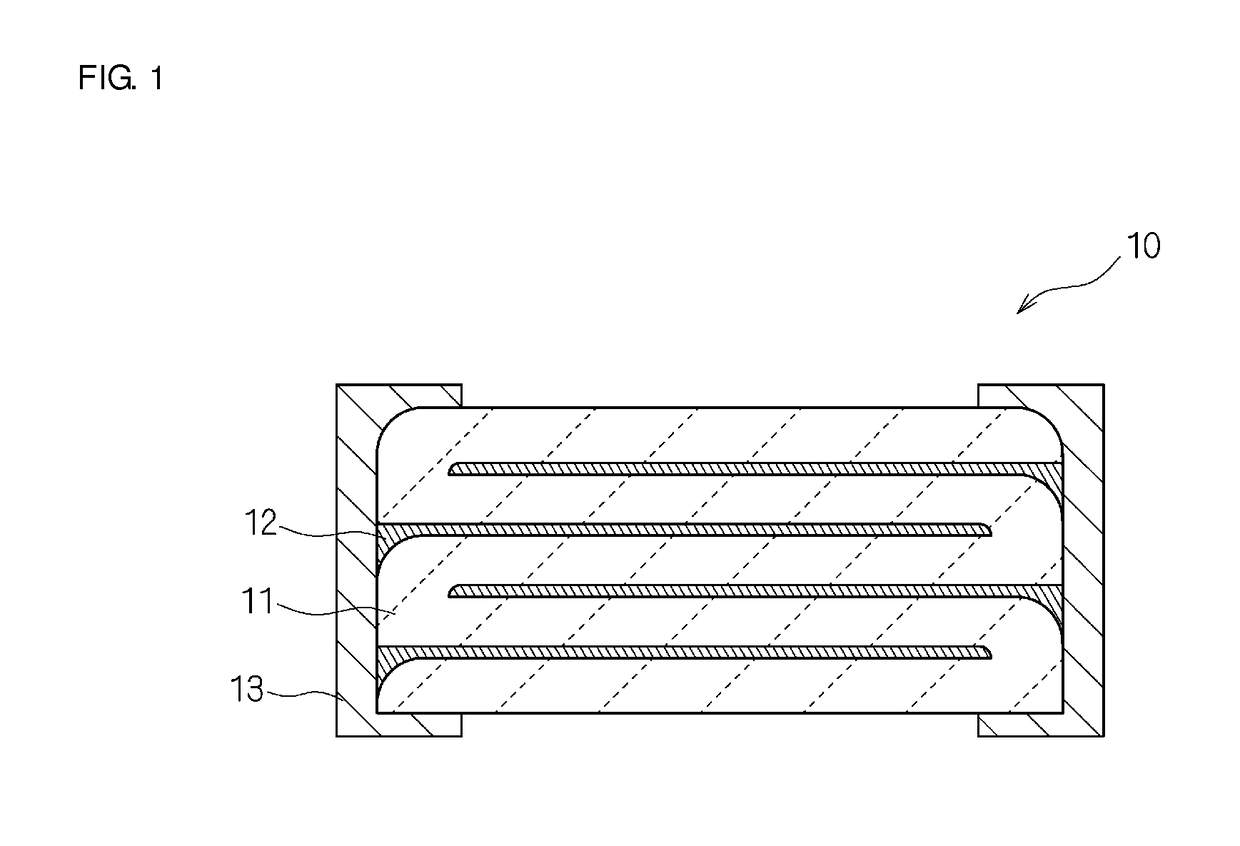

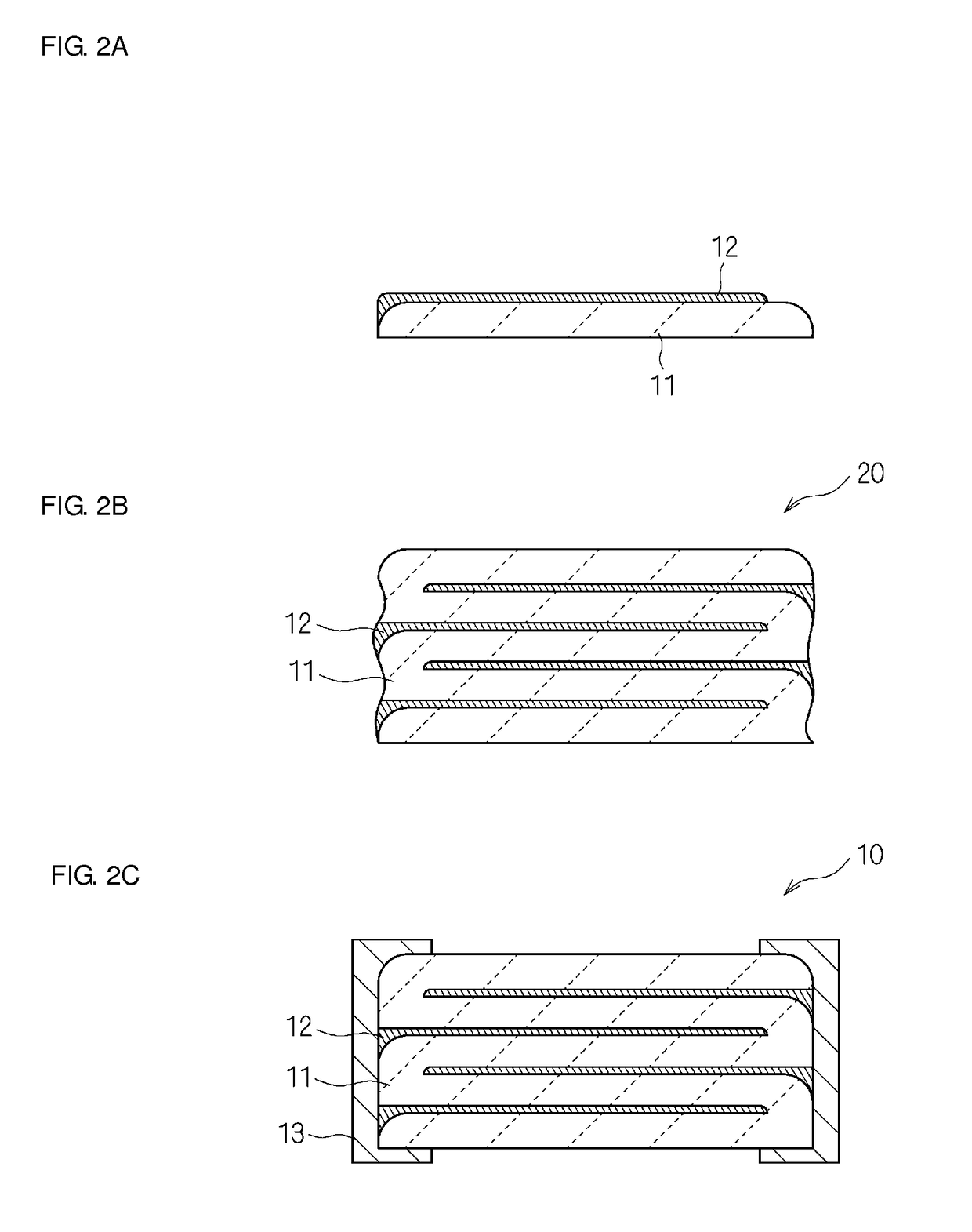

Multilayer ceramic electronic component and method for manufacturing multilayer ceramic electronic component

ActiveUS9905364B2Avoid volume increaseIncrease volumeFixed capacitor electrodesFixed capacitor dielectricMetallurgyElectronic component

A multilayer ceramic electronic component includes a multilayer body including ceramic layers and inner electrode layers, the inner electrode layers being disposed on interfaces between the ceramic layers, and an outer electrode on an external surface of the multilayer body and electrically connected to first end portions of the inner electrode layers exposed to the external surface of the multilayer body. Each of the ceramic layers includes a thin portion with a continuously reducing thickness near the first end portion. Each inner electrode layer includes a thick portion near a connection with the outer electrode, the thick portion having a thickness continuously increasing toward the connection on a first side in accordance with a shape of the thin portion in the ceramic layer. A distance between a second end portion in the inner electrode layer not joined to the outer electrode, and the thick portion adjacent to the second end portion is equal to or longer than an interlayer distance between the inner electrode layers.

Owner:MURATA MFG CO LTD

Pattern matching method and apparatus

ActiveUS10318805B2Avoid failureSuppress caseImage enhancementImage analysisPattern recognitionPattern matching

When the degree of matching between patterns decreases due to a pattern fluctuation or an appearance fluctuation that has occurred during manufacturing steps, a heavy work burden would be placed on an operator. A data processing unit of a pattern matching apparatus calculates a threshold for determination of matching between a first template image and a partial region of a search target image obtained by capturing an image of the surface of a sample, on the basis of a result of evaluation of a similarity between the search target image and a second template image, the second template image having been captured in a wider range than the first template image.

Owner:HITACHI HIGH-TECH CORP

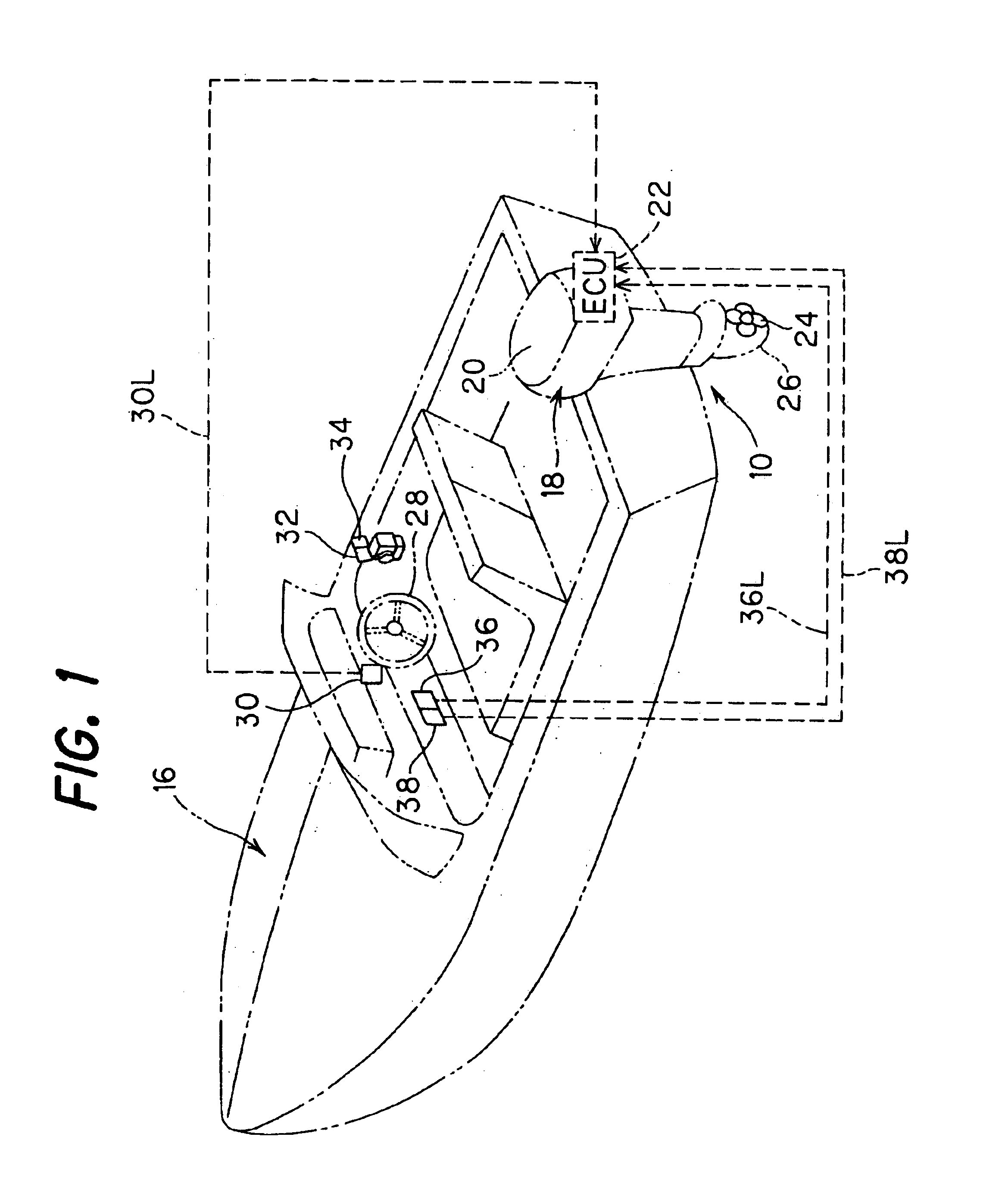

Outboard motor steering system

InactiveUS6926568B2Increase in of weightSteering feeling can be improvedPropulsion power plantsOutboard propulsion unitsExternal combustion enginePropeller

An outboard motor steering system for an outboard motor mounted on a stern of a boat and having an internal combustion engine at its upper portion and a propeller with a rudder at its lower portion that is powered by the engine to propel and steer the boat, having a swivel shaft connected to the propeller to turn the propeller relative to the boat and housed in a swivel case, a hydraulic actuator such as a double-acting cylinder connected to the swivel shaft to rotate the swivel shaft, a hydraulic pressure supplier connected to the hydraulic actuator to supply hydraulic pressure, and a controller that controls supply of the hydraulic pressure to the hydraulic actuator in response to a steering signal inputted by an operator such that the outboard motor is steered relative to the boat. In the system, the hydraulic actuator and the hydraulic pressure supplier are housed in the swivel case. The system is thus simply configured to avoid increase in number of components and weight, and does not cause a problem regarding space utilization and operation efficiency, while improving steering feel.

Owner:HONDA MOTOR CO LTD

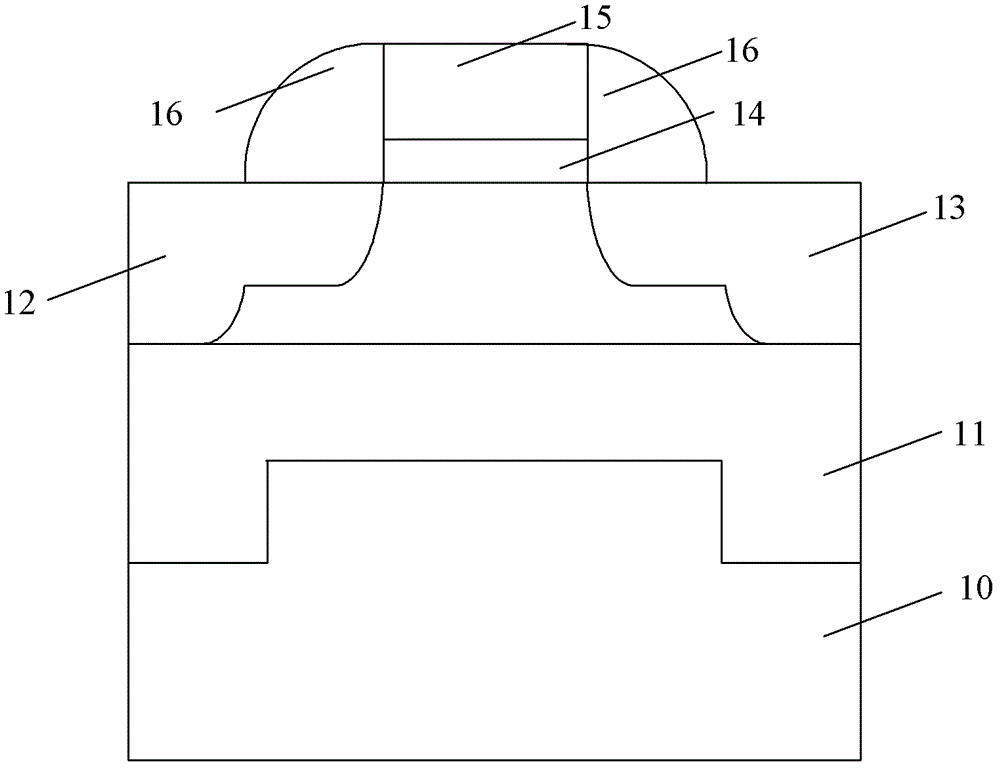

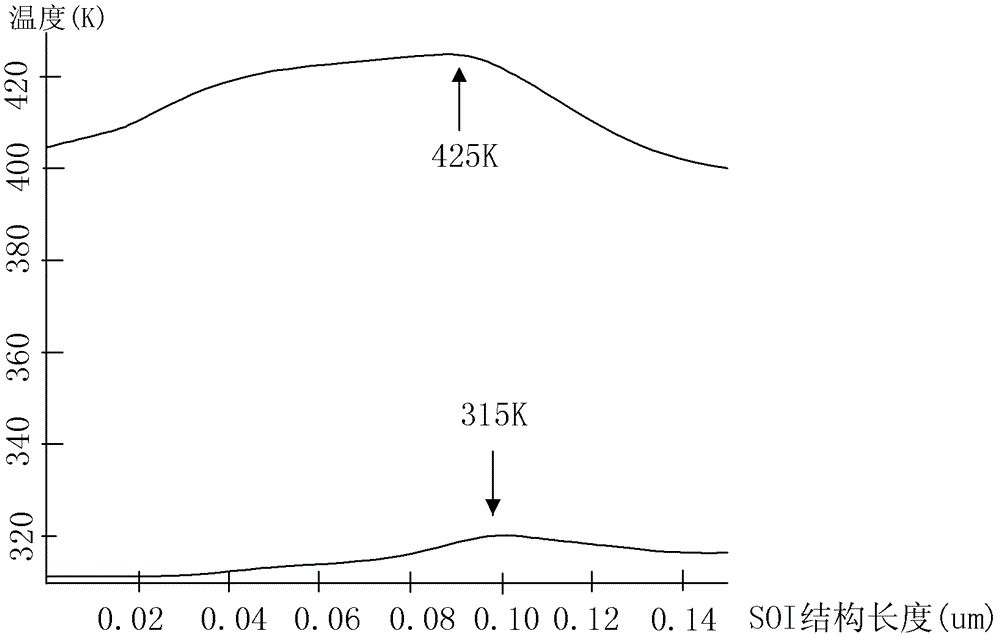

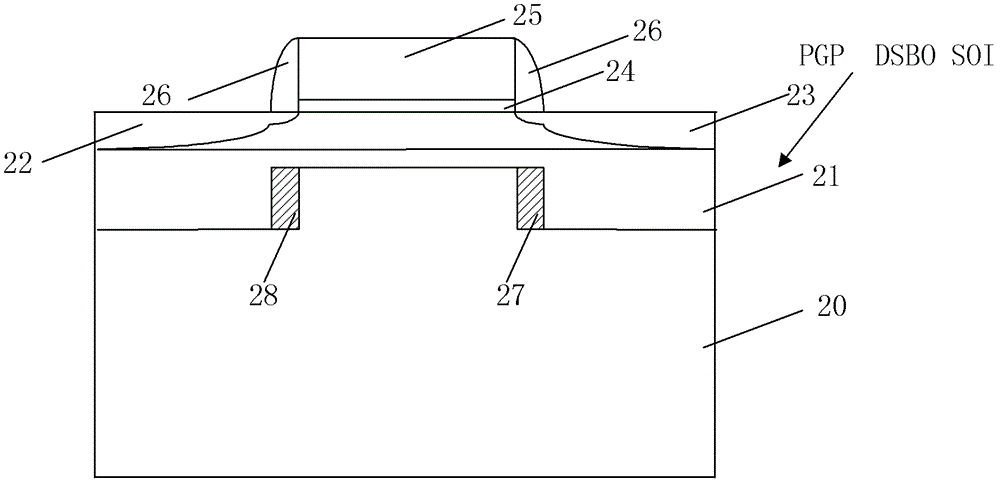

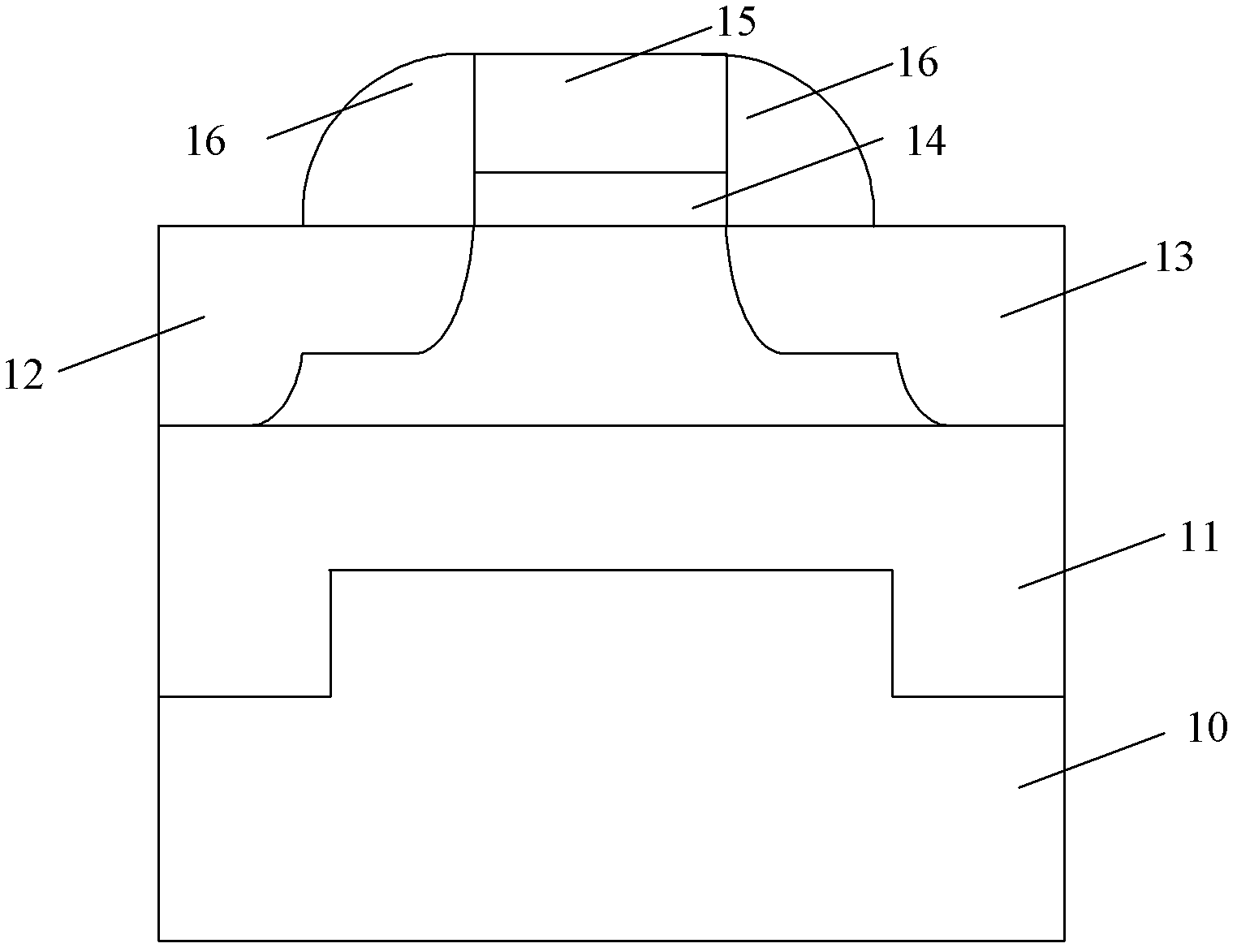

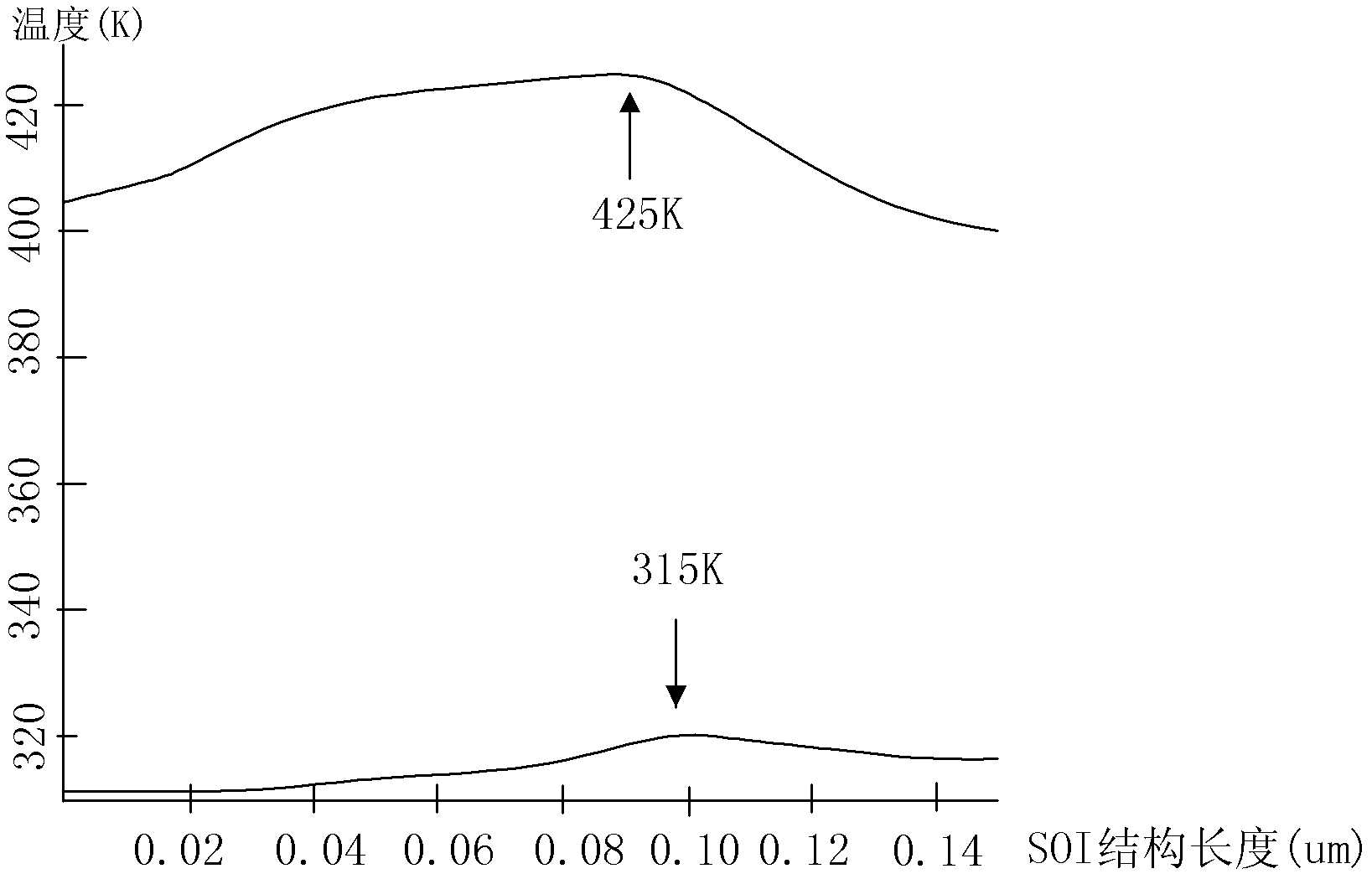

Silicon-on-insulator (SOI) structures with step-type buried oxide layers

ActiveCN102354678BAvoid volume increaseLower threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerEngineering

The invention provides two types of silicon-on-insulator (SOI) structures with step-type buried oxide layers. The first type of SOI structure comprises a P-type semiconductor substrate, a gate insulation layer formed above a P-type channel, a grid electrode formed above the gate insulation layer and a side wall which covers the grid electrode and the side edge of the gate insulation layer, wherein an N-type source region, an N-type drain region, the step-type buried oxide layers positioned in the N-type source region and the N-type drain region and below the P-type channel are formed on the semiconductor substrate; the thicknesses of the buried oxide layers positioned in the N-type source region and the N-type drain region are respectively greater than that of the buried oxide layer positioned below the P-type channel; and a P-type element heavily doped region is arranged in the P-type semiconductor substrate below the corresponding thinner buried oxide layer below the side wall adjacent to one side of the N-type drain region. Different from the first type of SOI structure, the second type of SOI structure is characterized in that the top of the substrate is provided with the N-type doped region, and the source region and the drain region are P-type. By utilizing the technical scheme of the invention, the short channel effect of the existing SOI structures can be solved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

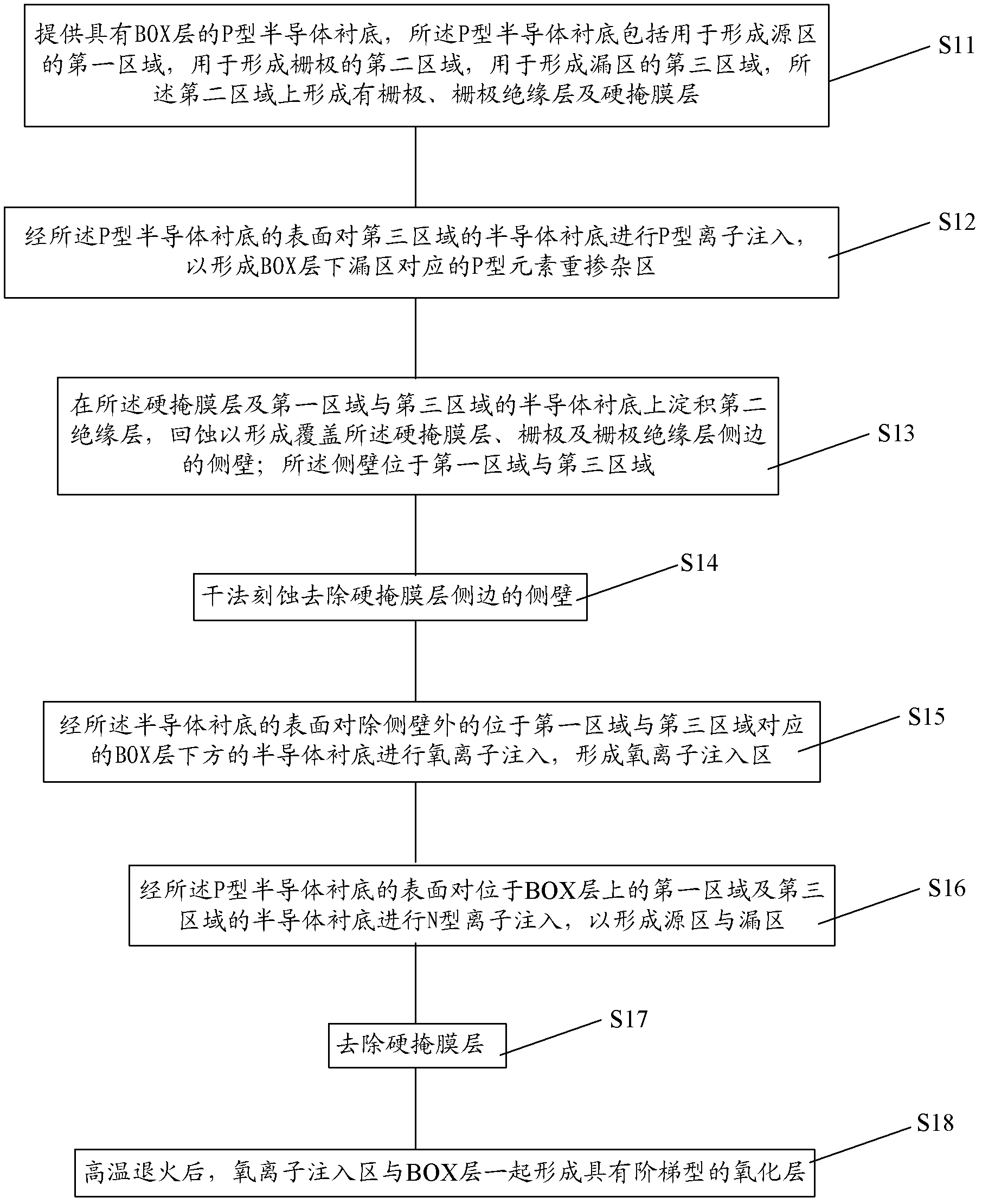

Manufacturing method for silicon-on-insulator (SOI) structure provided with stepped oxidization buried layer

ActiveCN102339784BLower threshold voltageImprove performanceSemiconductor/solid-state device manufacturingOxygen ionsSilicon on insulator

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP