Manufacturing method for silicon-on-insulator (SOI) structure provided with stepped oxidization buried layer

A fabrication method and technology of buried oxide layer, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as short channels, and achieve the effects of reducing leakage current, reducing leakage current, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

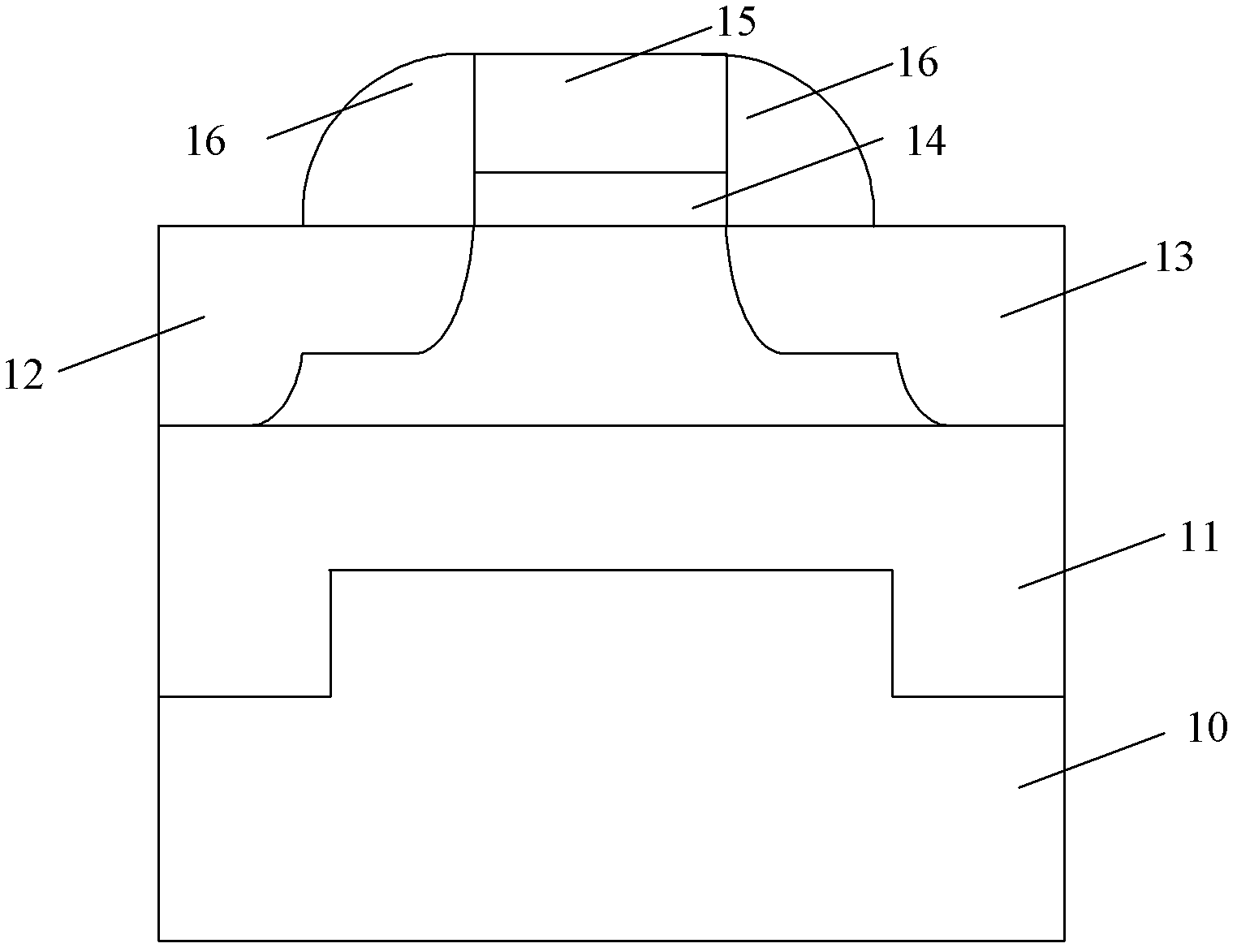

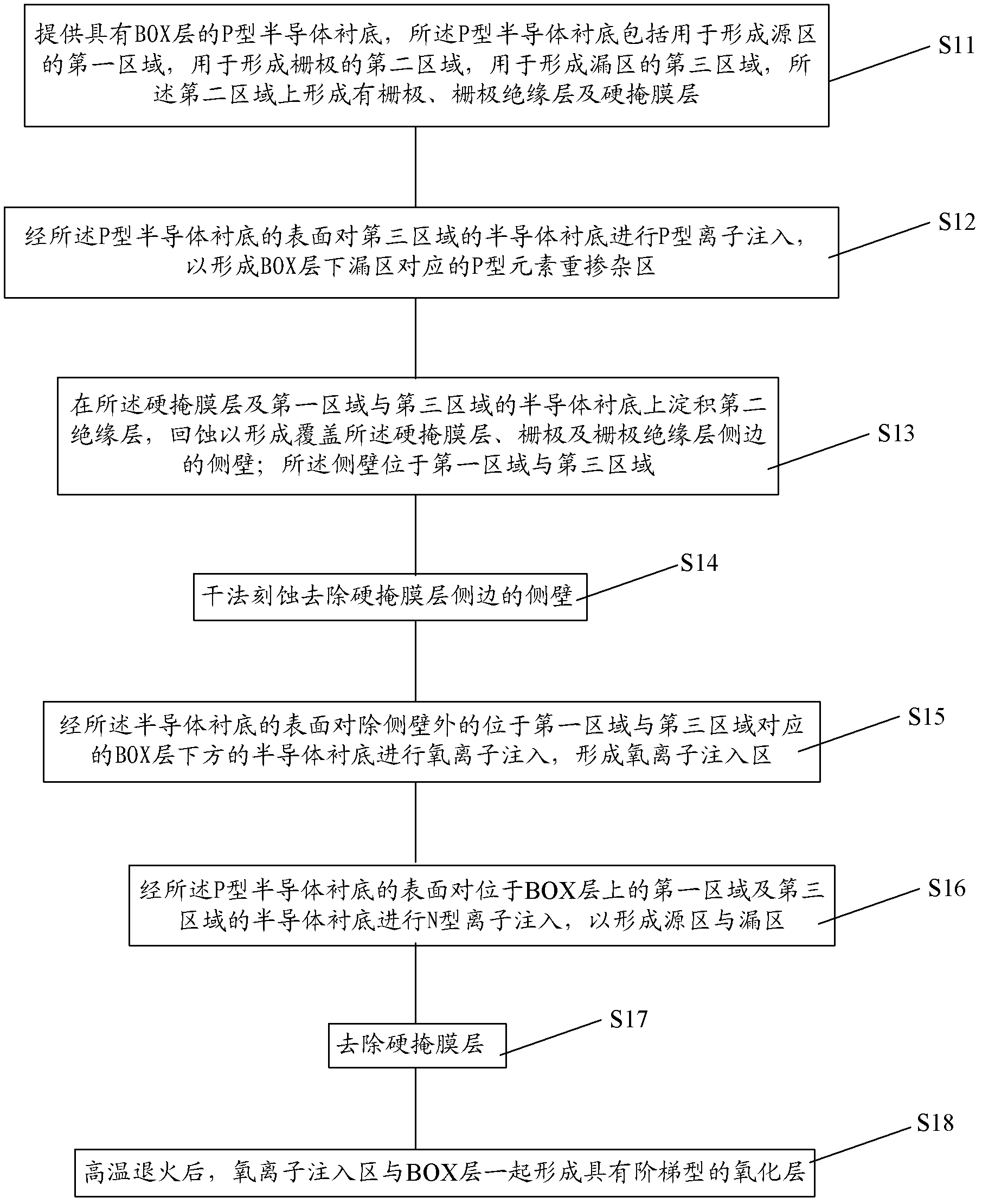

[0076] The present invention provides two methods for manufacturing SOI structures with stepped oxide buried layers. The first method is as follows: image 3 shown. The following combination Figure 4-Figure 17 This method will be specifically described.

[0077] Step S11 is executed to provide a P-type semiconductor substrate having a BOX layer, the P-type semiconductor substrate comprising a first region for forming a source region, a second region for forming a gate, and a first region for forming a drain region. The third region, a gate, a gate insulating layer and a hard mask layer are formed on the second region.

[0078] In the specific implementation process of this step, the following steps S111-S114 are included.

[0079] Step S111, providing a P-type semiconductor substrate 20 with a structure such as Figure 4 As shown, the semiconductor substrate 20 includes a first region (not marked) for forming a source region, a second region (not marked) for forming a gat...

no. 2 example

[0110] If the SOI structure provided by the first embodiment is called NMOS, the difference from the first embodiment is that the SOI structure provided by the second embodiment is PMOS. It can be understood that, regardless of NMOS or PMOS, the P-type element heavily doped region They are all regions with the lowest potential. Therefore, setting a P-type element heavily doped region in the PMOS SOI structure can also prevent the electric field lines drawn from the drain region in the existing DSBO SOI structure from partially terminating in the source region, and thus As a result, the height of the barrier at the end of the source region is reduced, which in turn leads to the problem that electrons in the source region easily cross the barrier and enter the drain region, which increases the threshold voltage of the SOI structure, reduces the leakage current when the SOI structure is in the off state, and improves the Performance of SOI structure devices.

[0111] The second m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More