Patents

Literature

2136 results about "Silicon on insulator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

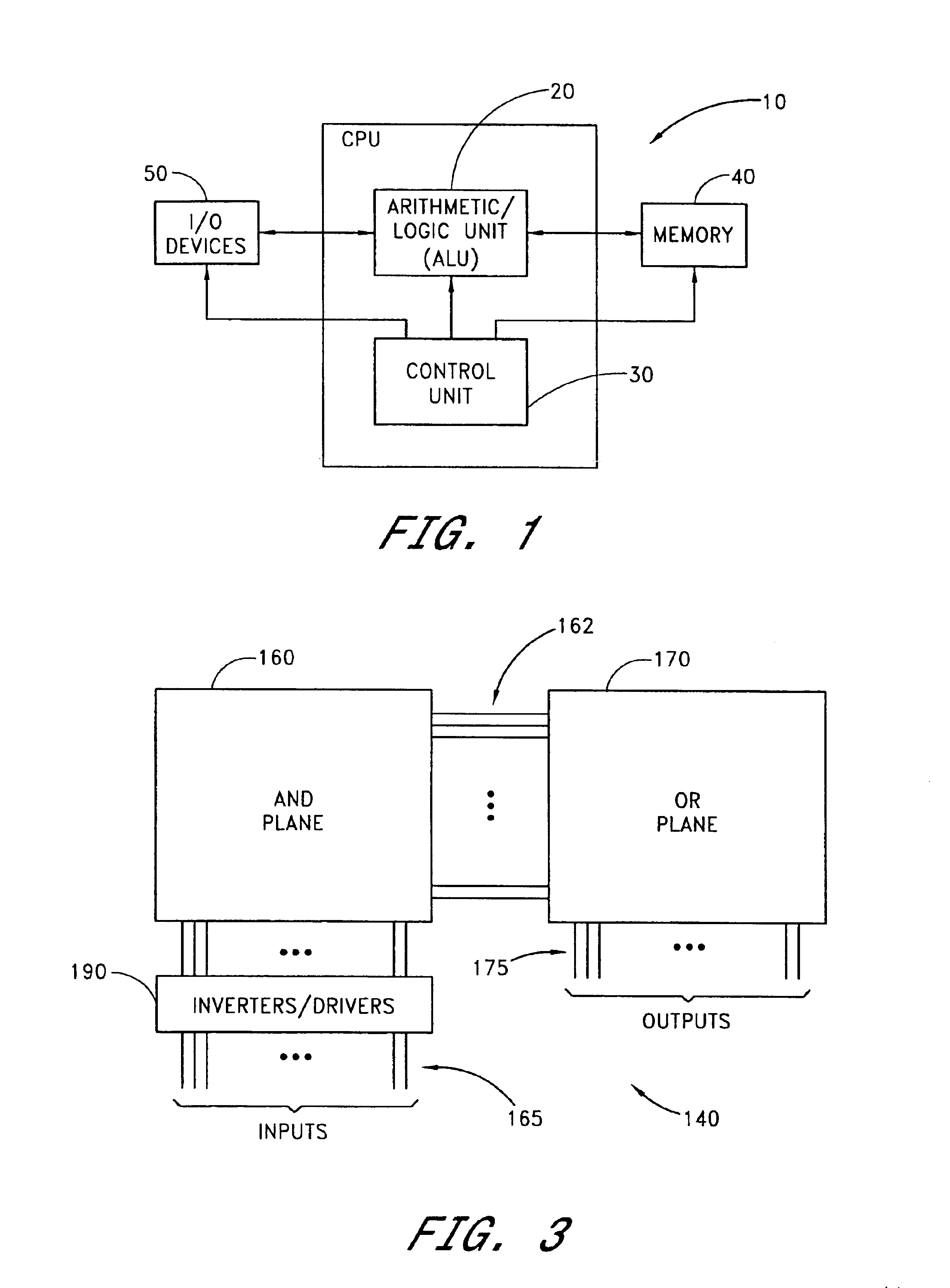

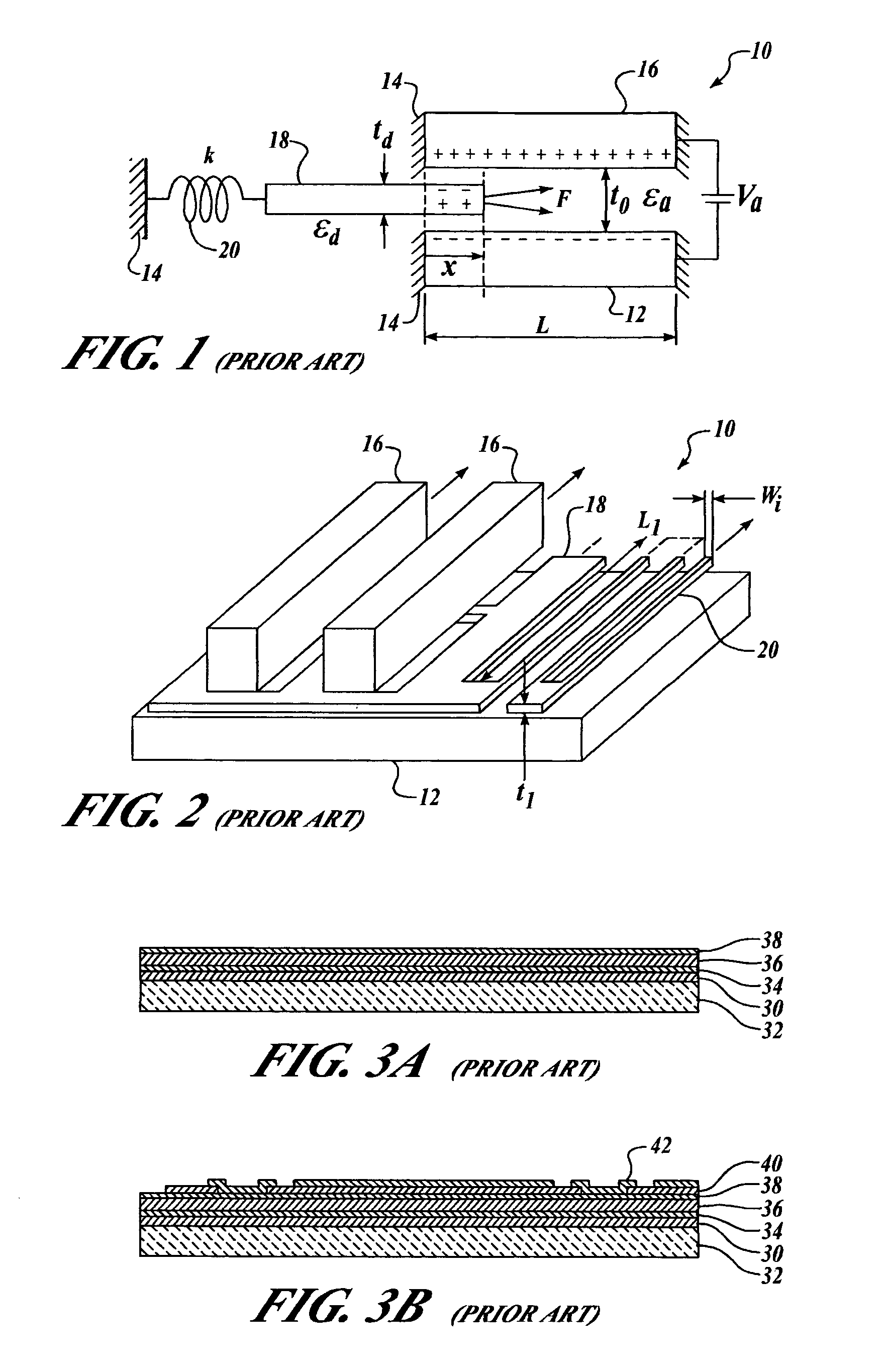

In semiconductor manufacturing, silicon on insulator (SOI) technology is fabrication of silicon semiconductor devices in a layered silicon–insulator–silicon substrate, to reduce parasitic capacitance within the device, thereby improving performance. SOI-based devices differ from conventional silicon-built devices in that the silicon junction is above an electrical insulator, typically silicon dioxide or sapphire (these types of devices are called silicon on sapphire, or SOS). The choice of insulator depends largely on intended application, with sapphire being used for high-performance radio frequency (RF) and radiation-sensitive applications, and silicon dioxide for diminished short-channel effects in other microelectronics devices. The insulating layer and topmost silicon layer also vary widely with application.

Three-dimensional integrated semiconductor devices

InactiveUS6943067B2Semiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

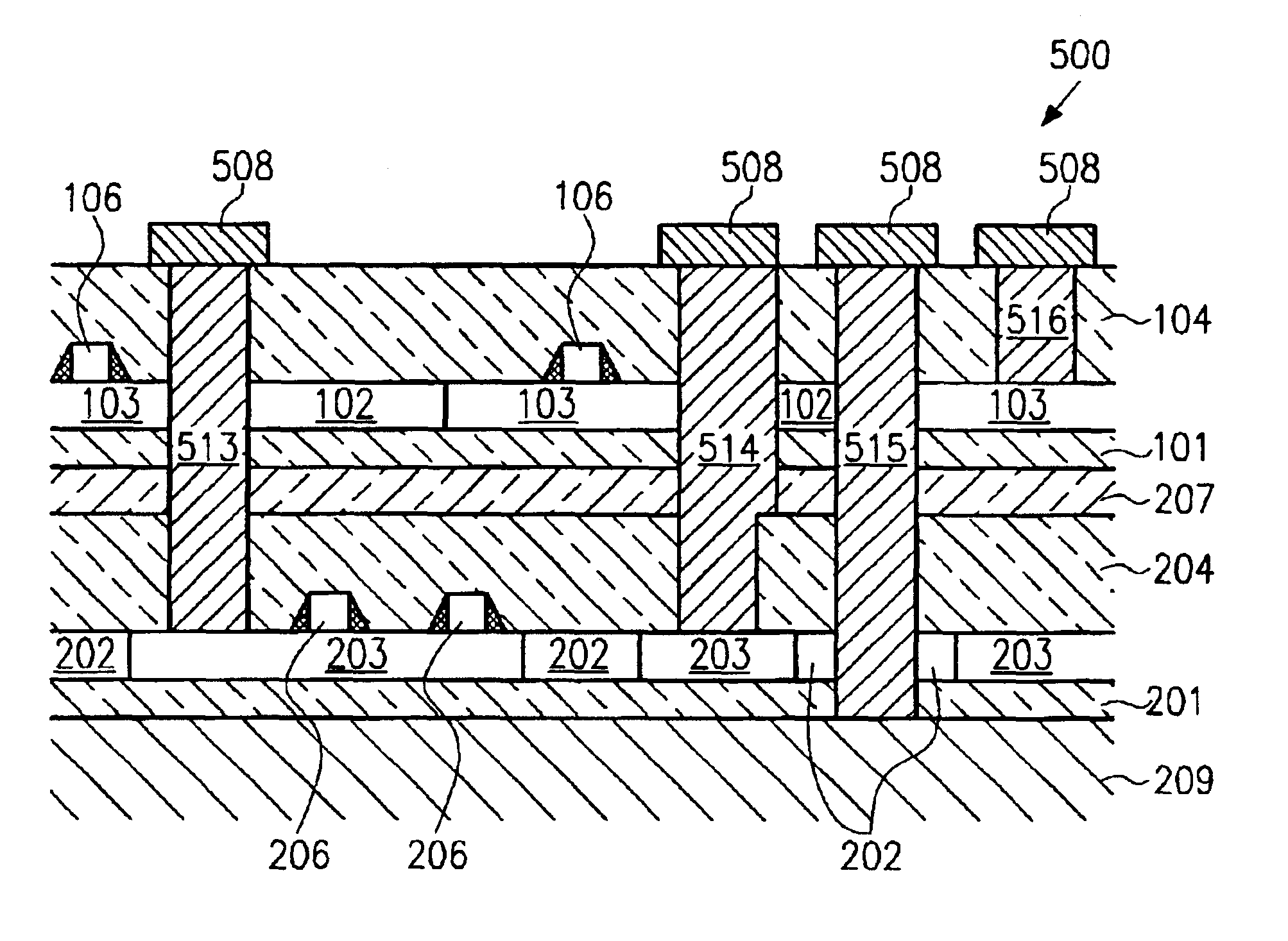

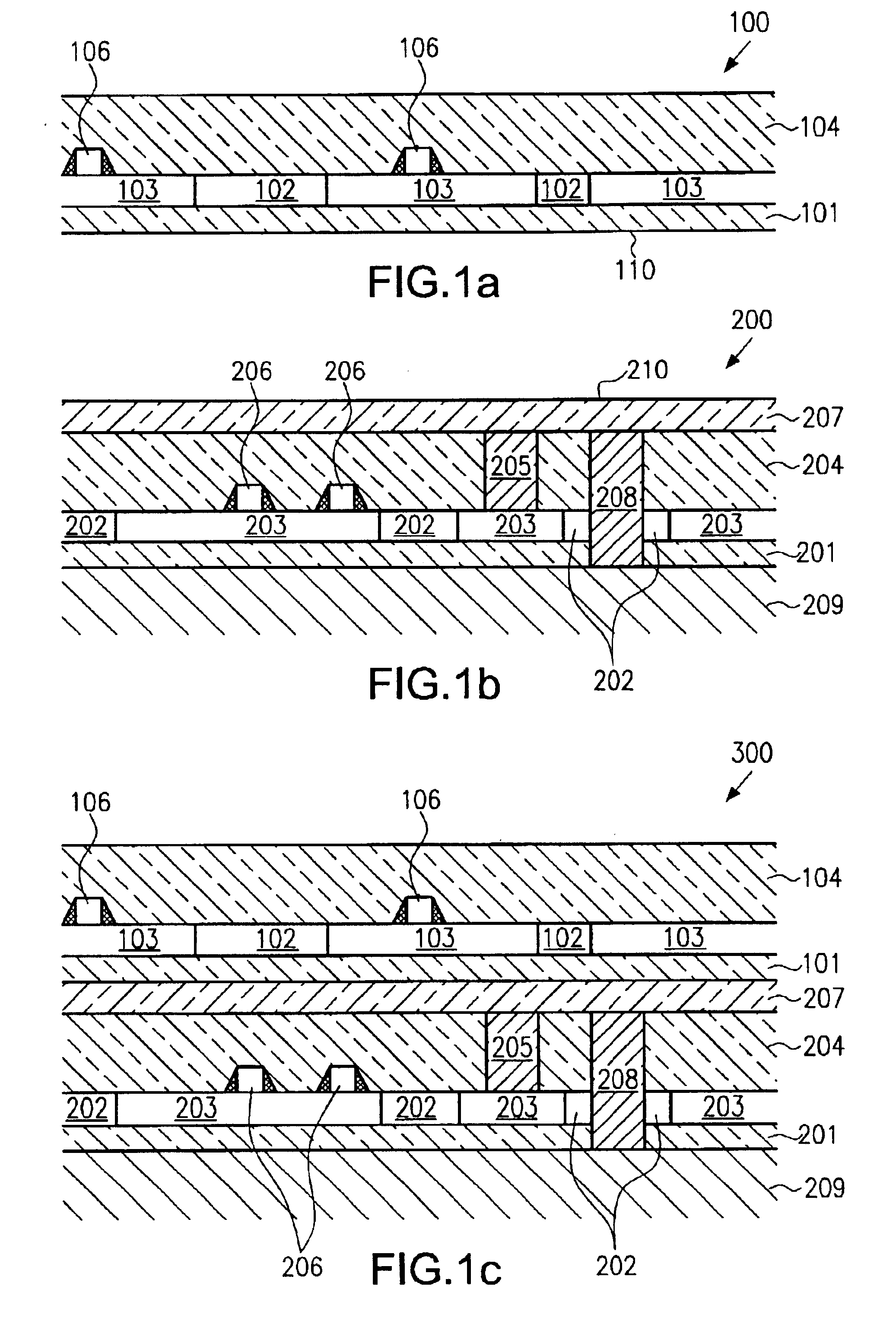

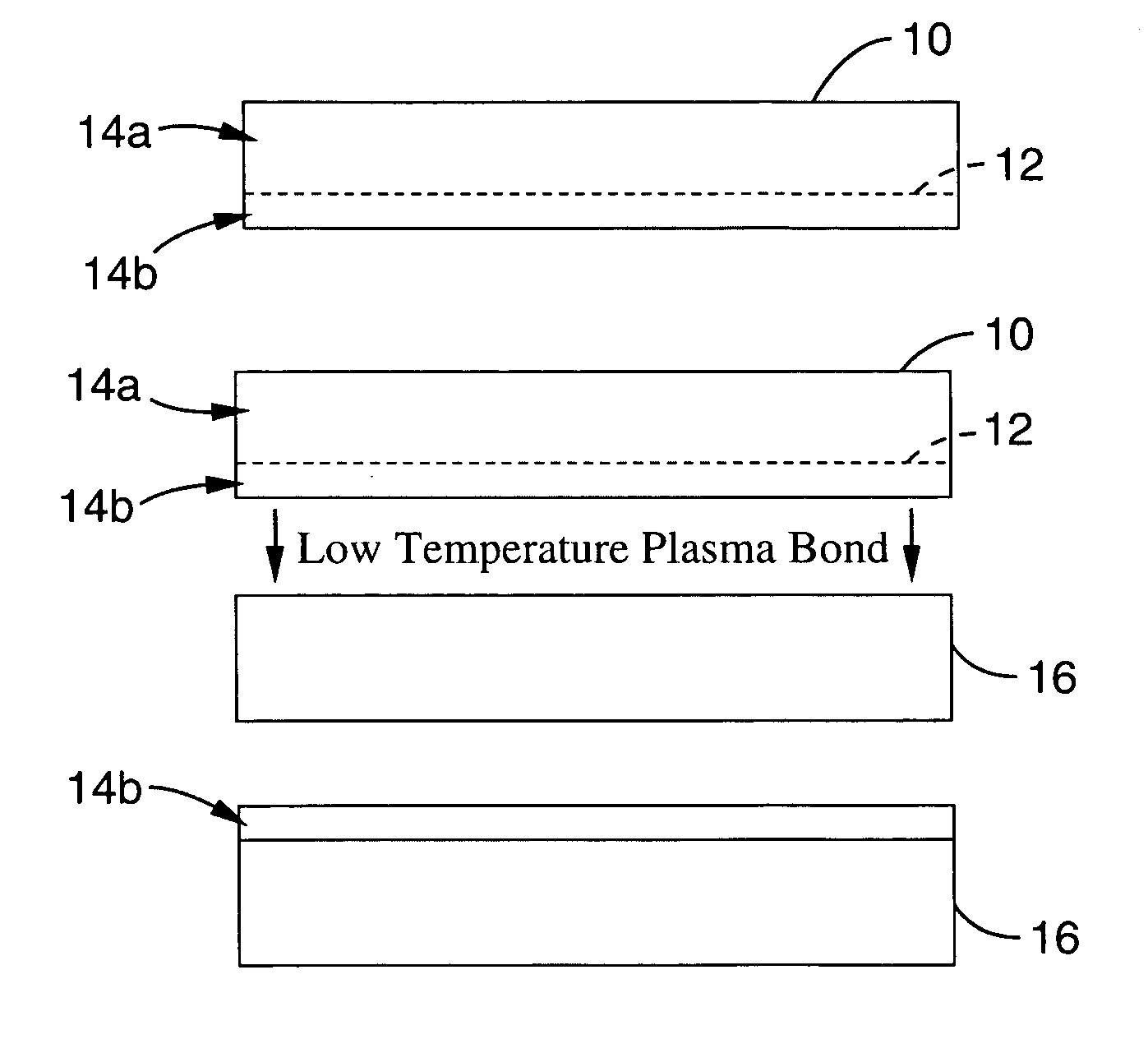

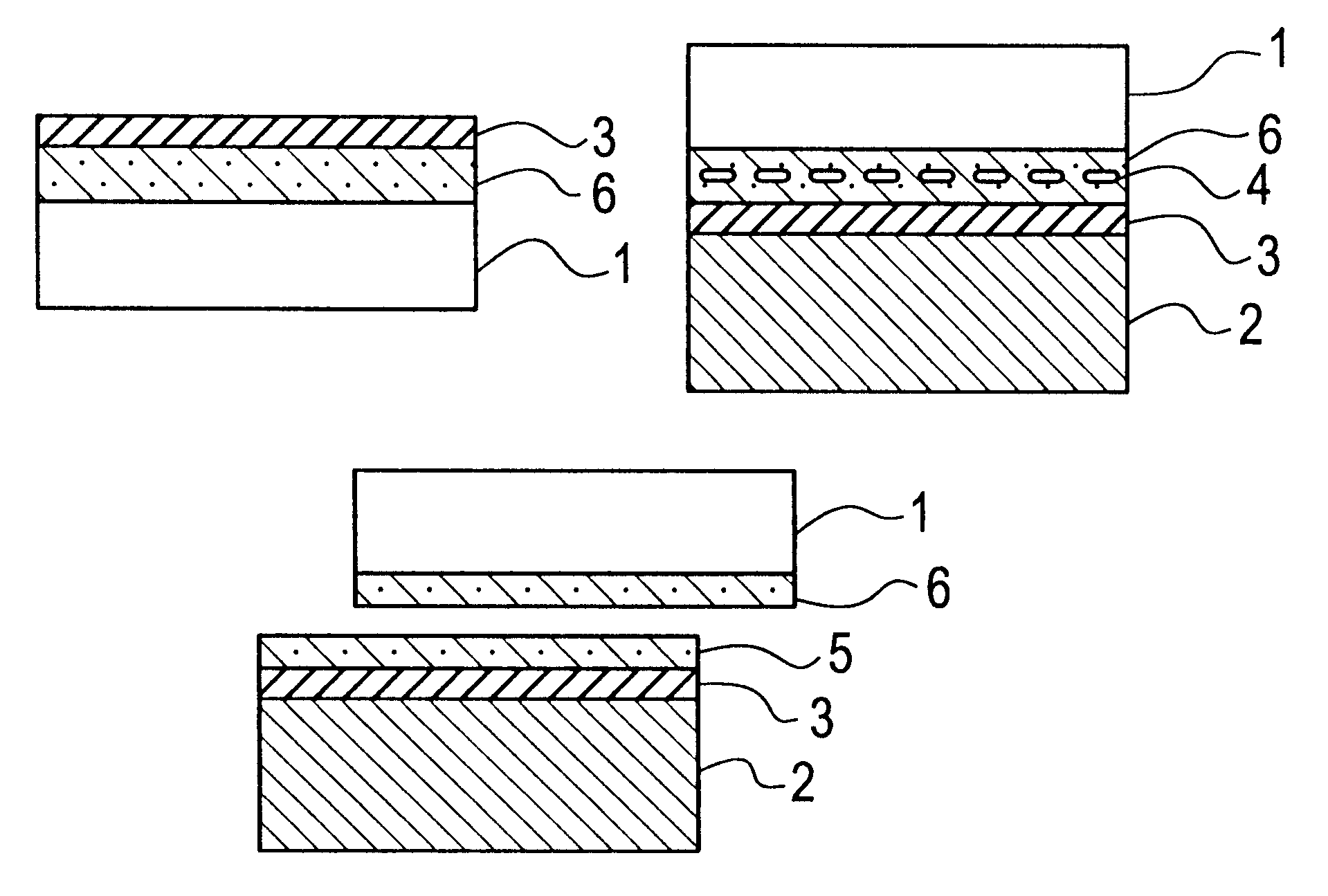

The present invention describes a process for three-dimensional integration of semiconductor devices and a resulting device. The process combines low temperature wafer bonding methods with backside / substrate contact processing methods, preferably with silicon on insulator devices. The present invention utilizes, in an inventive fashion, low temperature bonding processes used for bonded silicon on insulator (SOI) wafer technology. This low temperature bonding technology is adopted for stacking several silicon layers on top of each other and building active transistors and other circuit elements in each one. The back-side / substrate contact processing methods allow the interconnection of the bonded SOI layers.

Owner:ADVANCED MICRO DEVICES INC

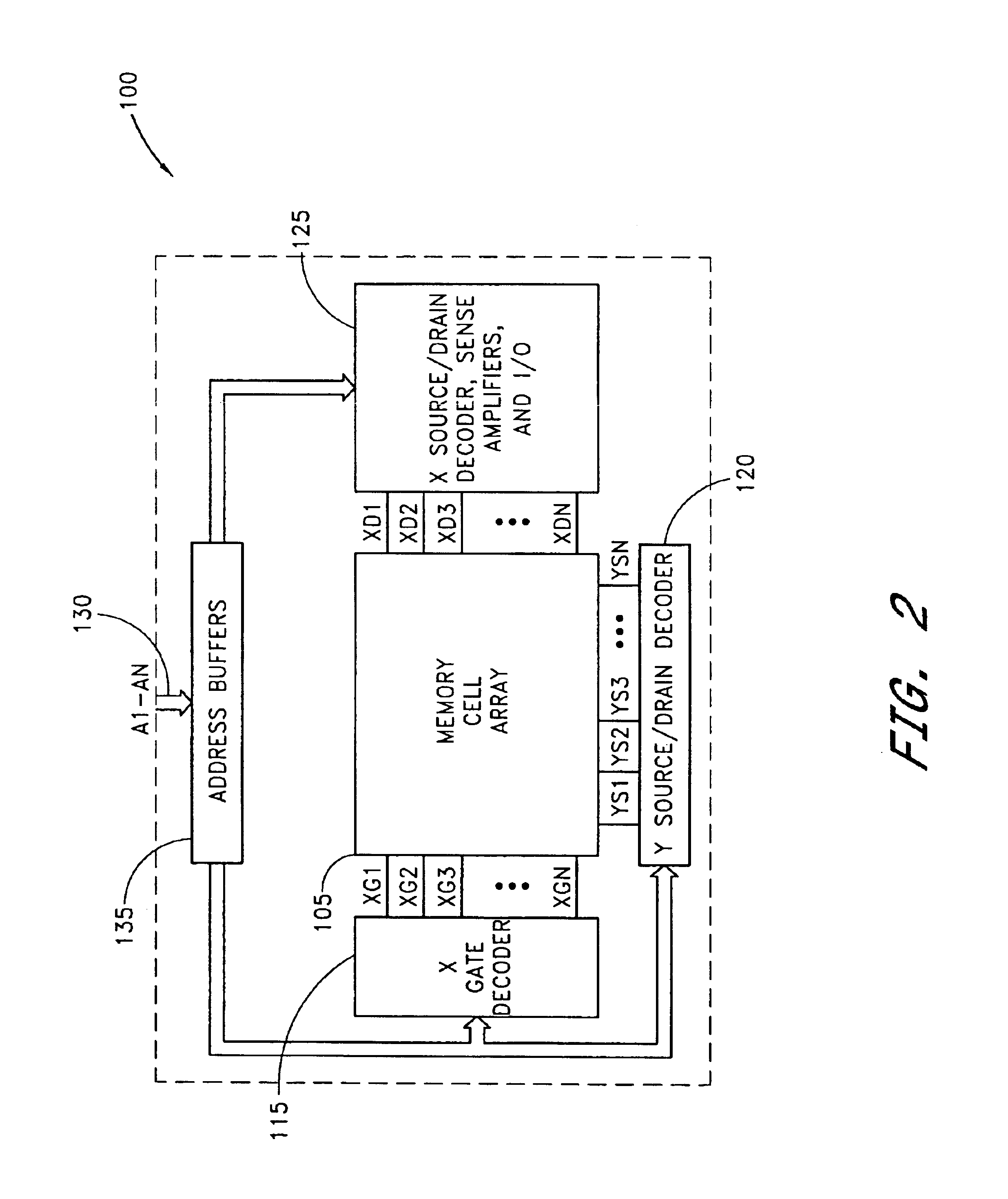

Nonvolatile memory on SOI and compound semiconductor substrates and method of fabrication

A nonvolatile memory array is provided. The array includes an array of nonvolatile memory devices, at least one driver circuit, and a substrate. The at least one driver circuit is not located in a bulk monocrystalline silicon substrate. The at least one driver circuit may be located in a silicon on insulator substrate or in a compound semiconductor substrate.

Owner:SANDISK TECH LLC

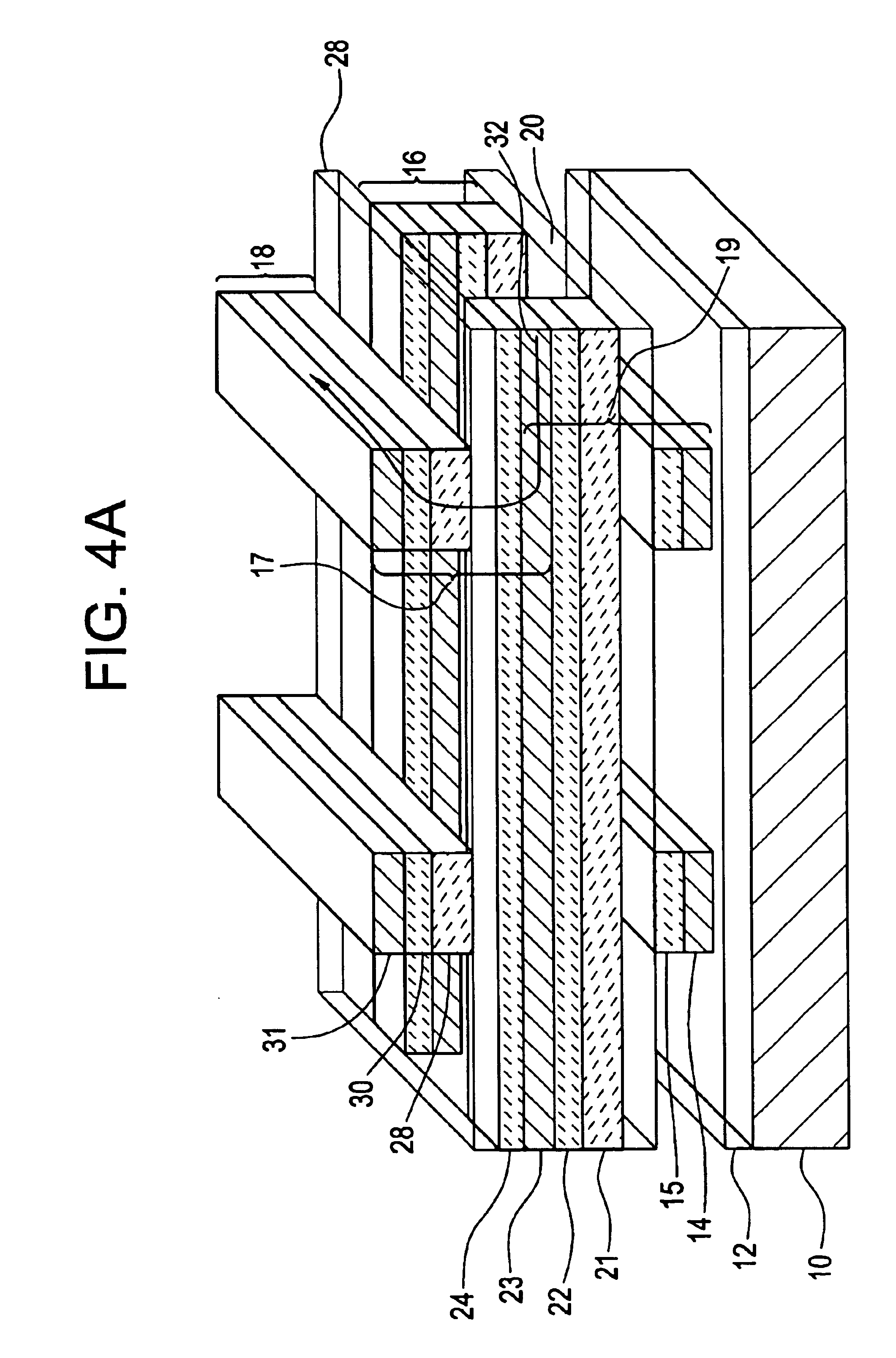

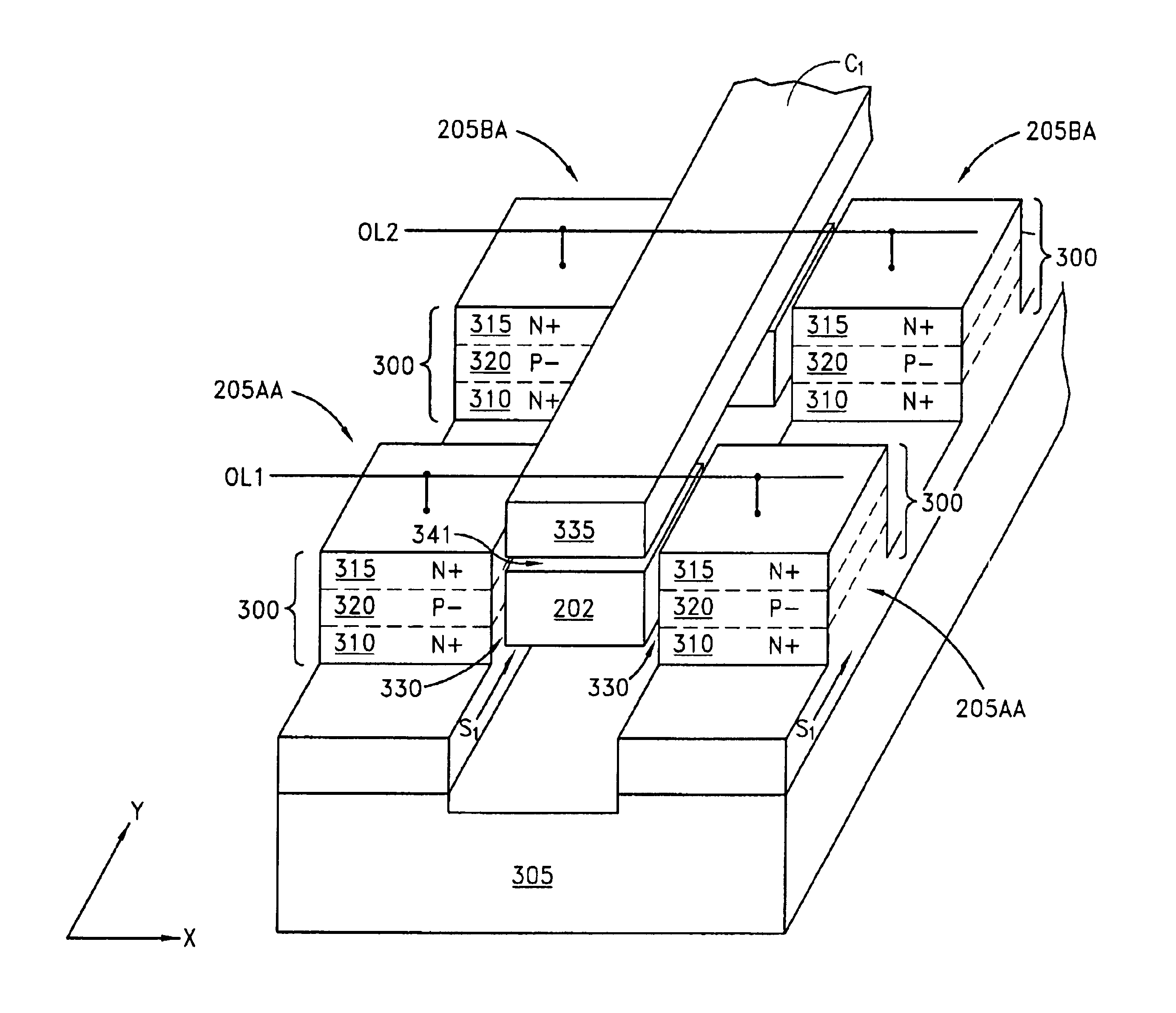

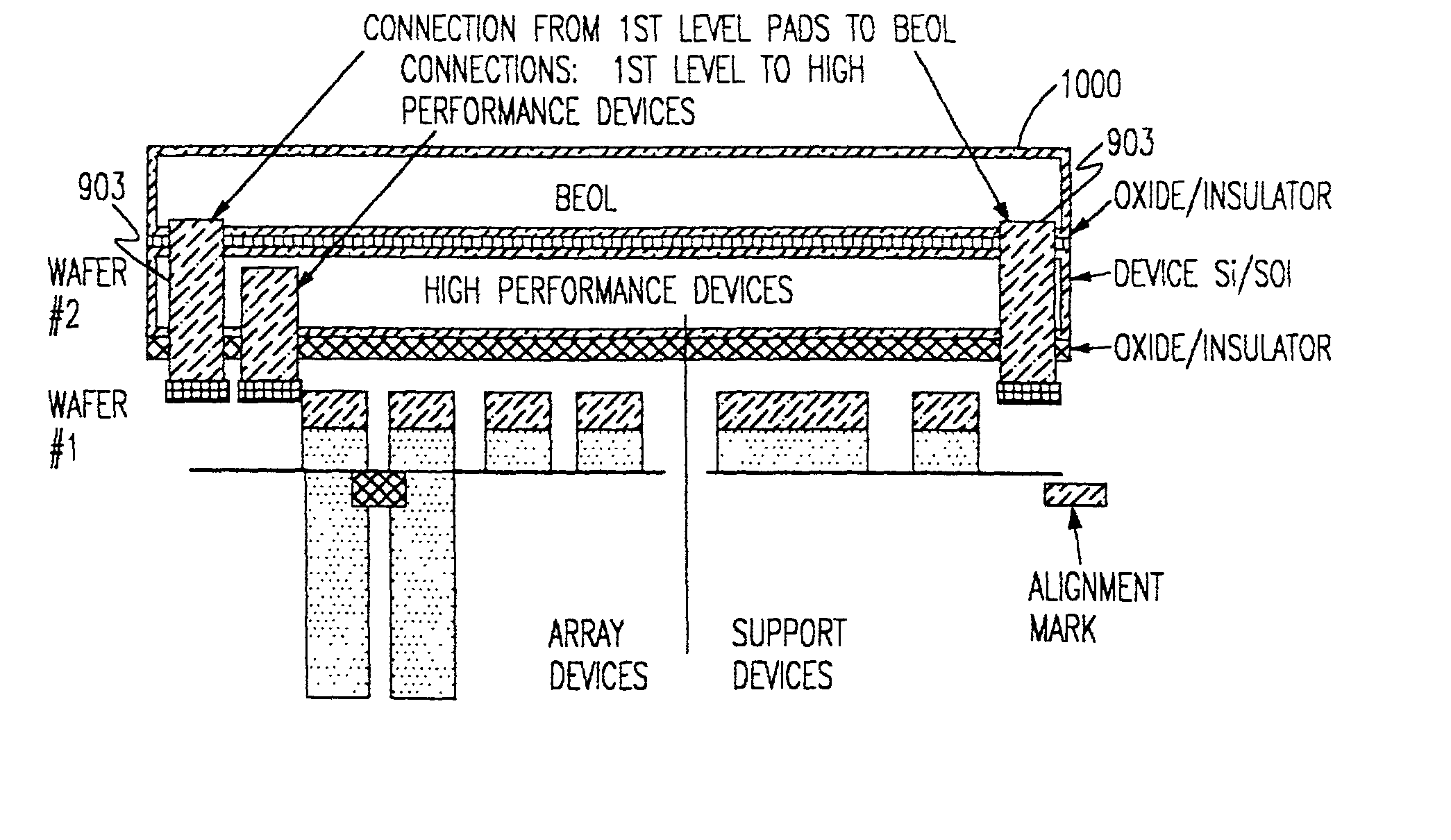

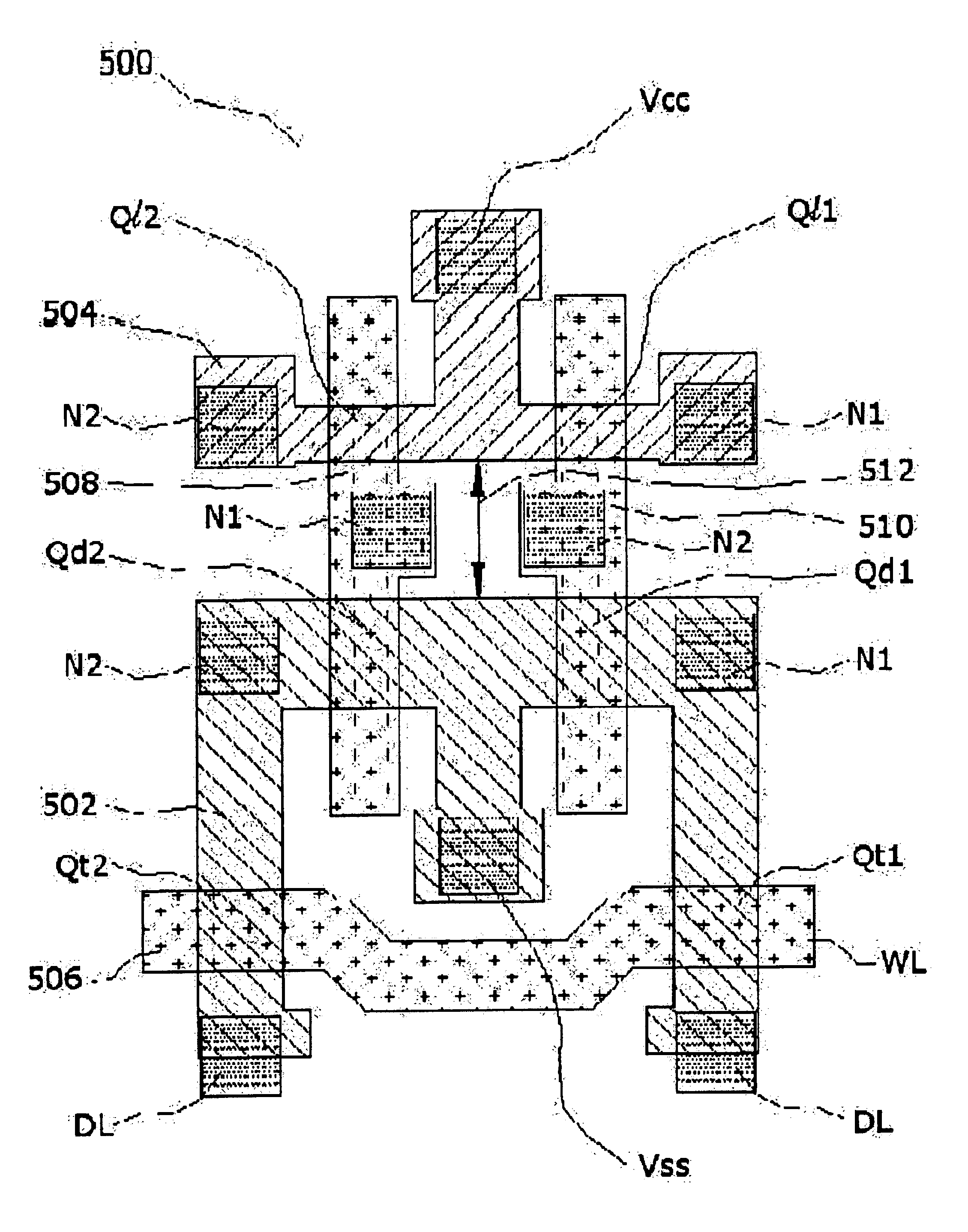

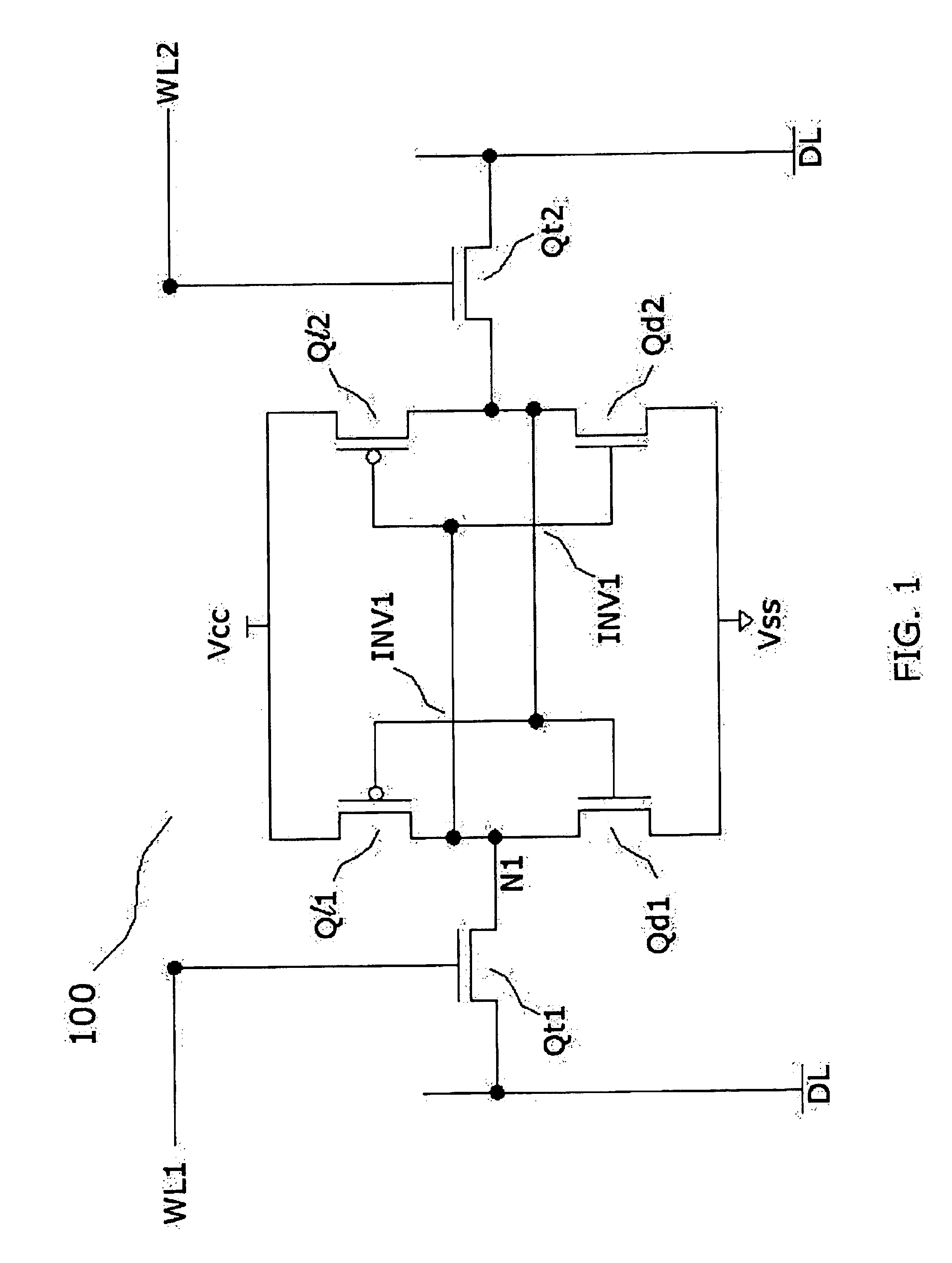

SOI stacked DRAM logic

A composite, layered, integrated circuit formed by bonding of insulator layers on wafers provides for combination of otherwise incompatible technologies such as trench capacitor DRAM arrays and high performance, low power, low voltage silicon on insulator (SOI) switching transistors and short signal propagation paths between devices formed on respective wafer layers of a chip. In preferred embodiments, an SOI wafer is formed by hydrophilic bonding of a wafer over an integrated circuit device and then cleaving a layer of the second wafer away using implanted hydrogen and low temperature heat treatment. Further wafers of various structures and compositions may be bonded thereover and connections between circuit elements and connection pads in respective wafers made using short vias that provide fast signal propagation as well as providing more numerous connections than can be provided on chip edges.

Owner:INT BUSINESS MASCH CORP

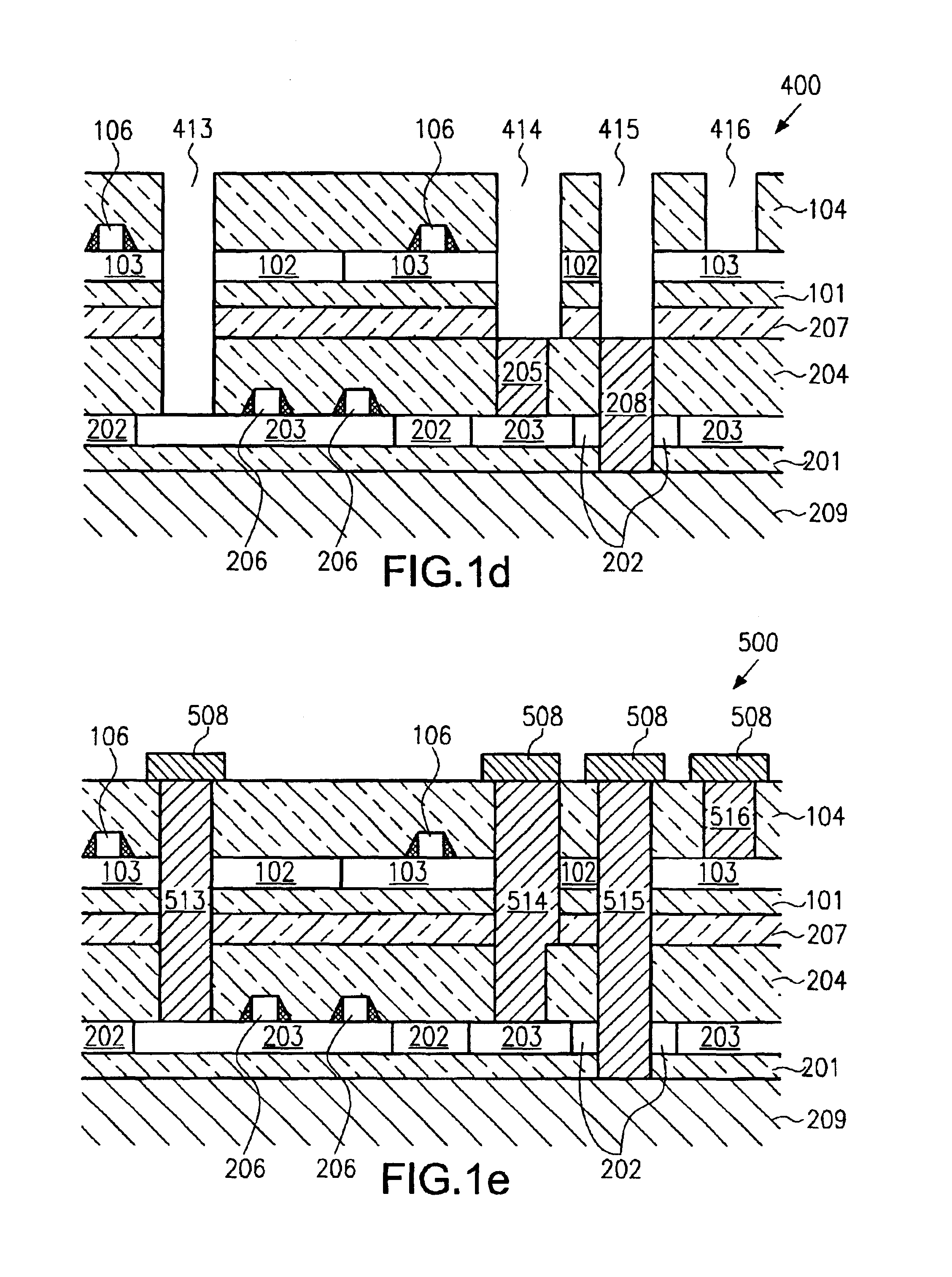

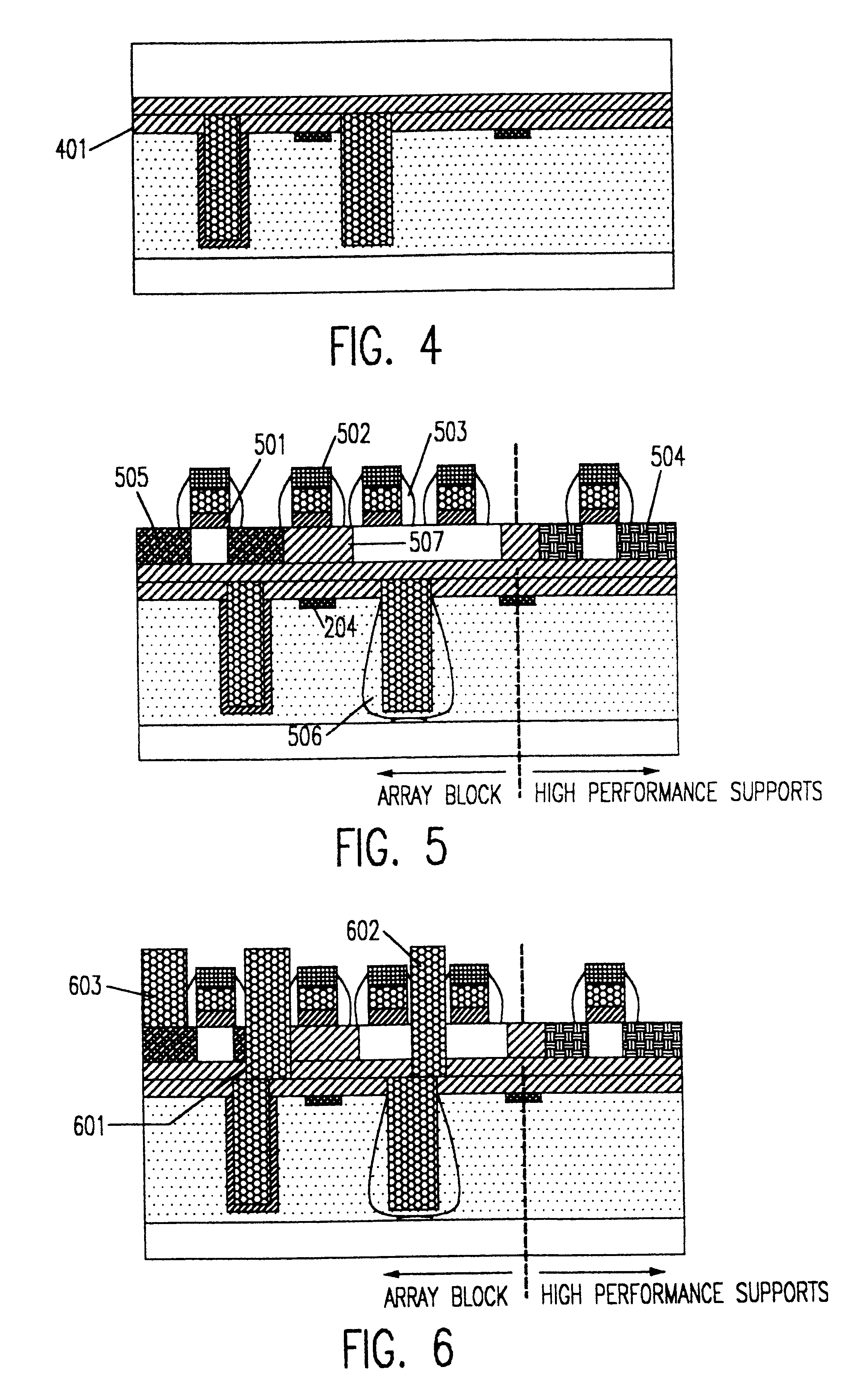

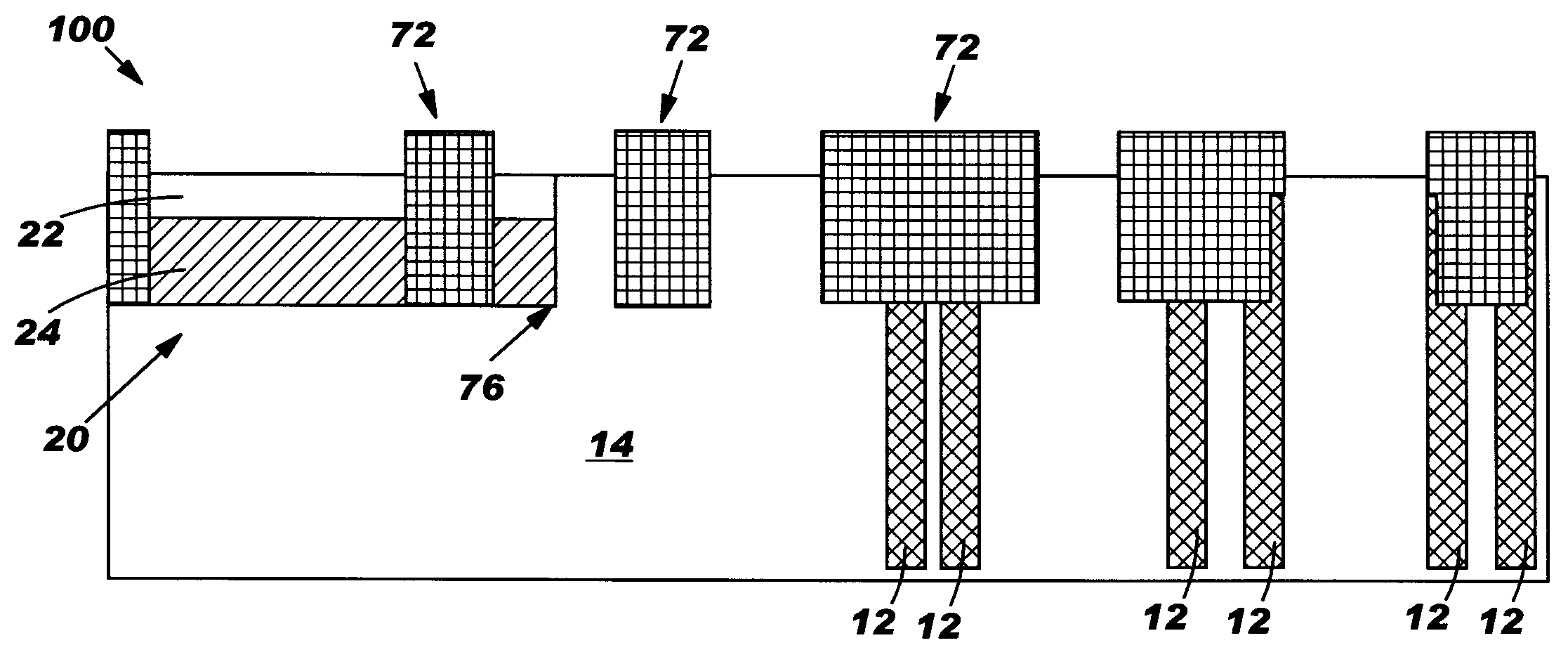

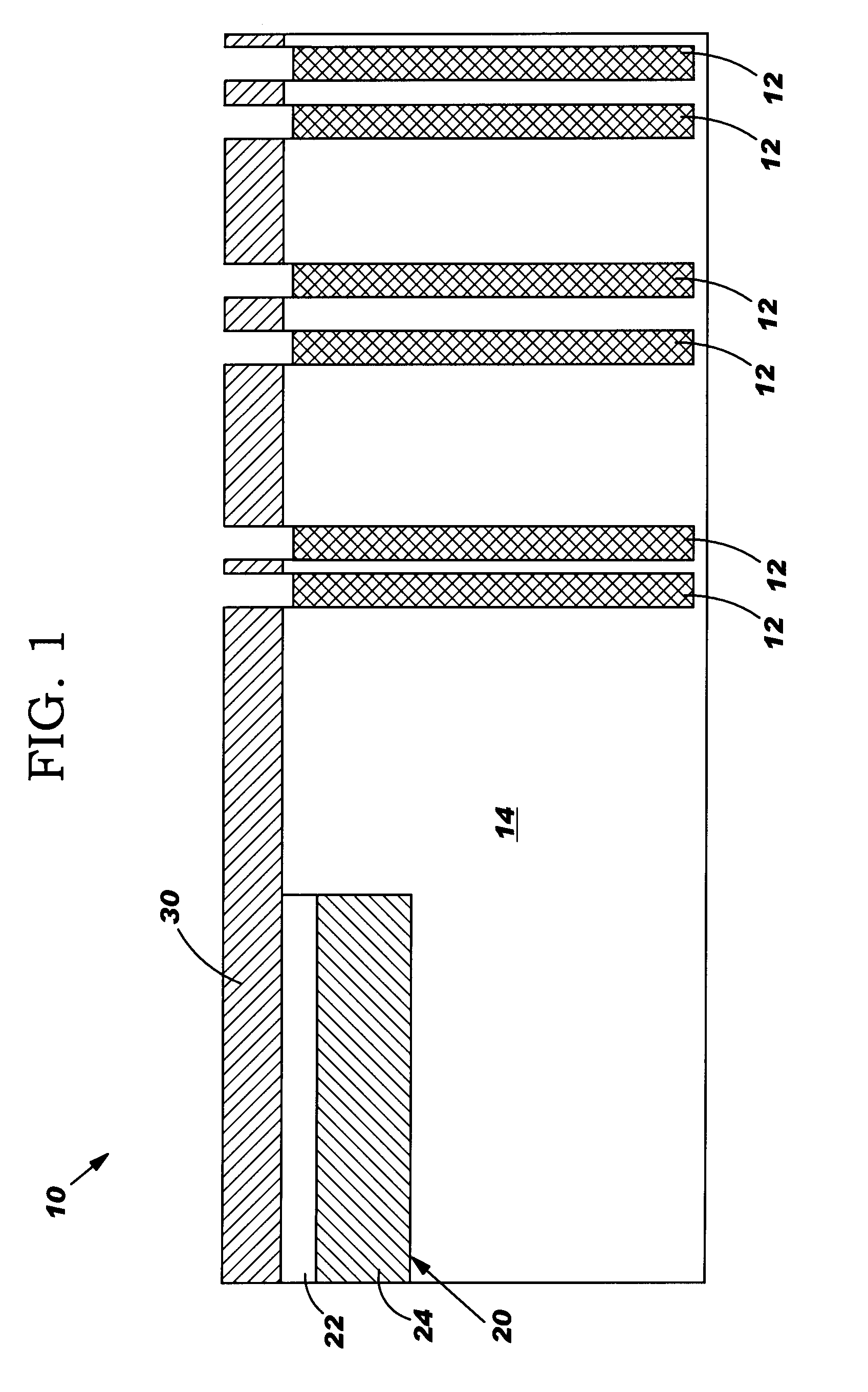

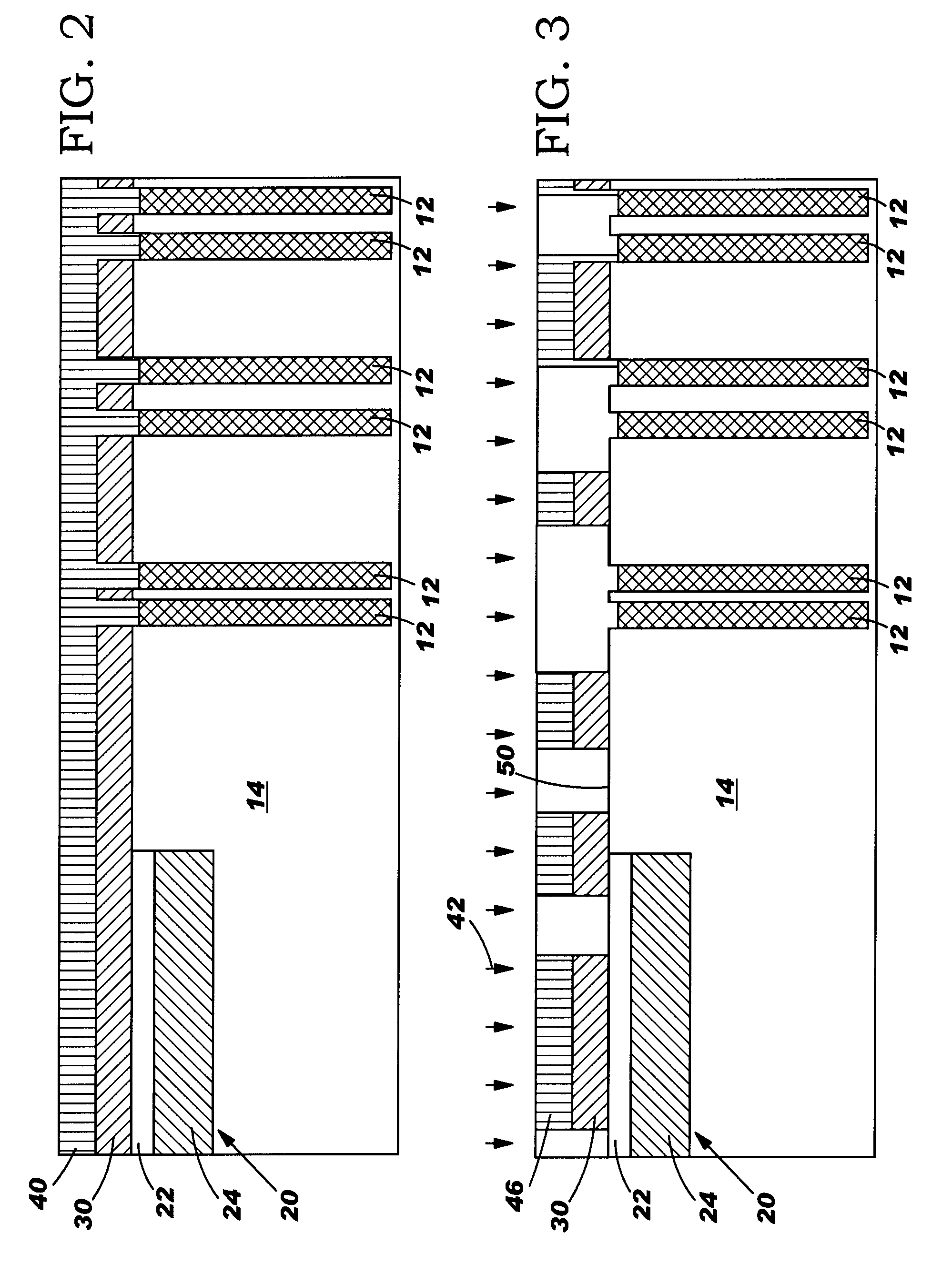

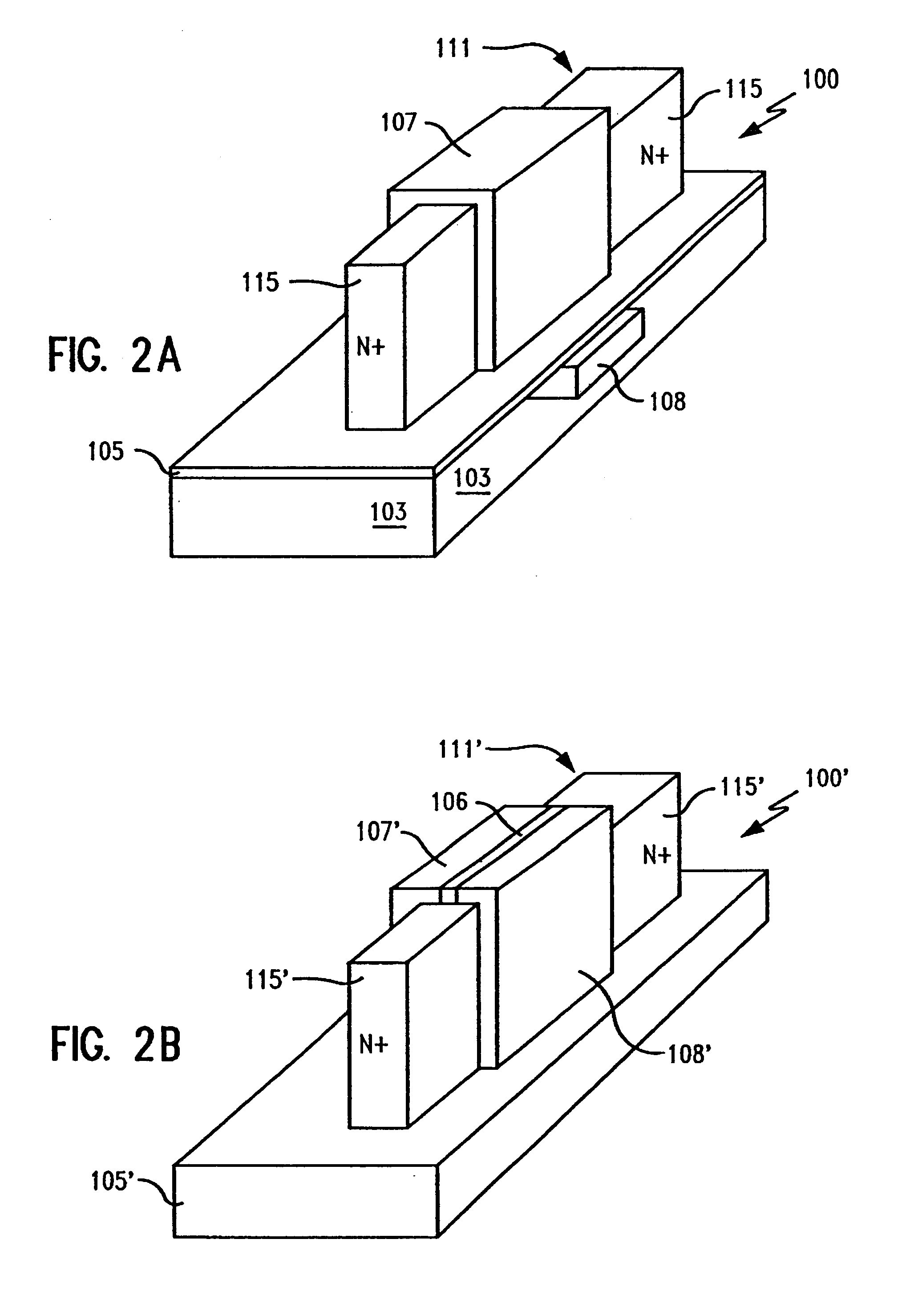

Floating gate transistor with horizontal gate layers stacked next to vertical body

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F<2 >is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

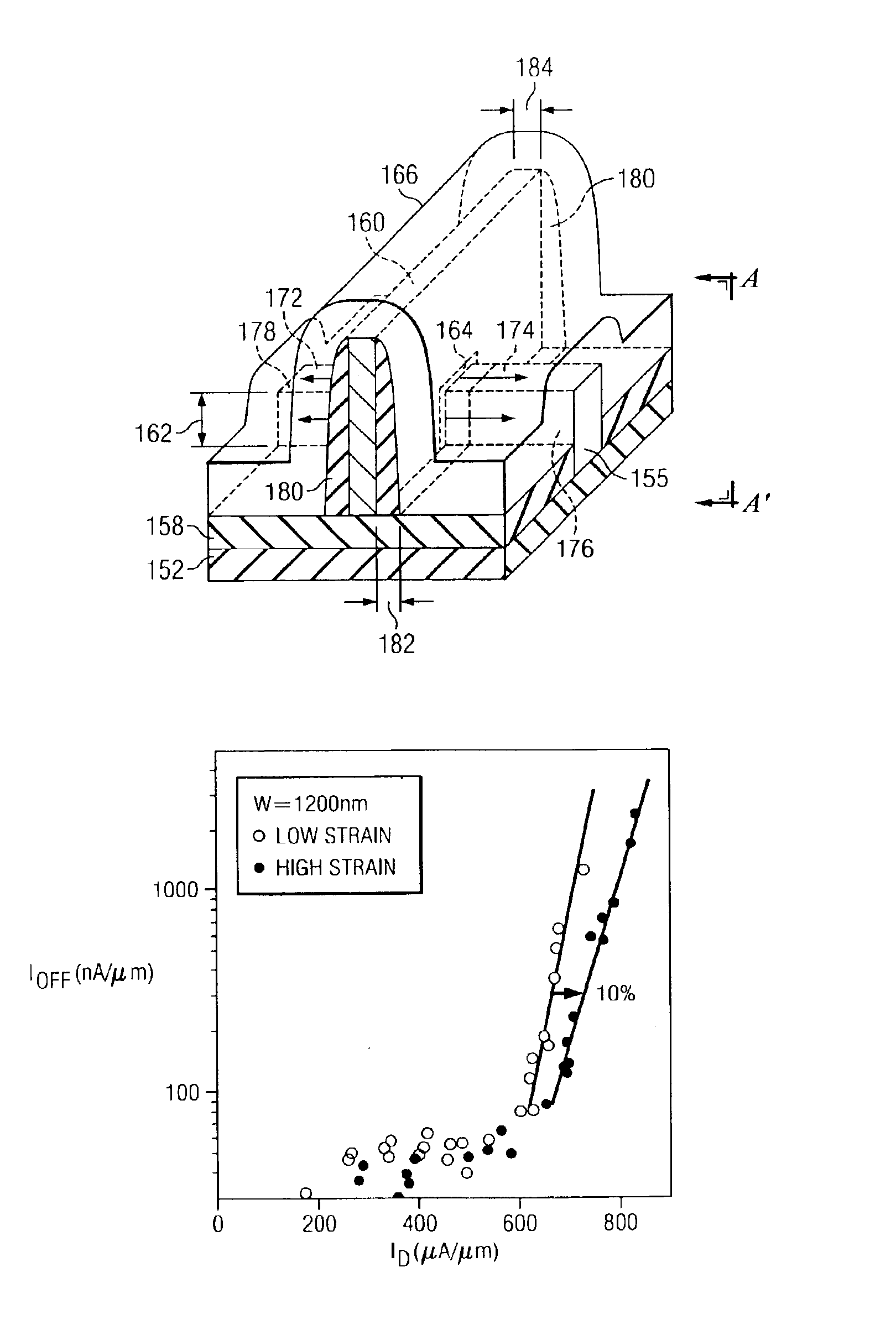

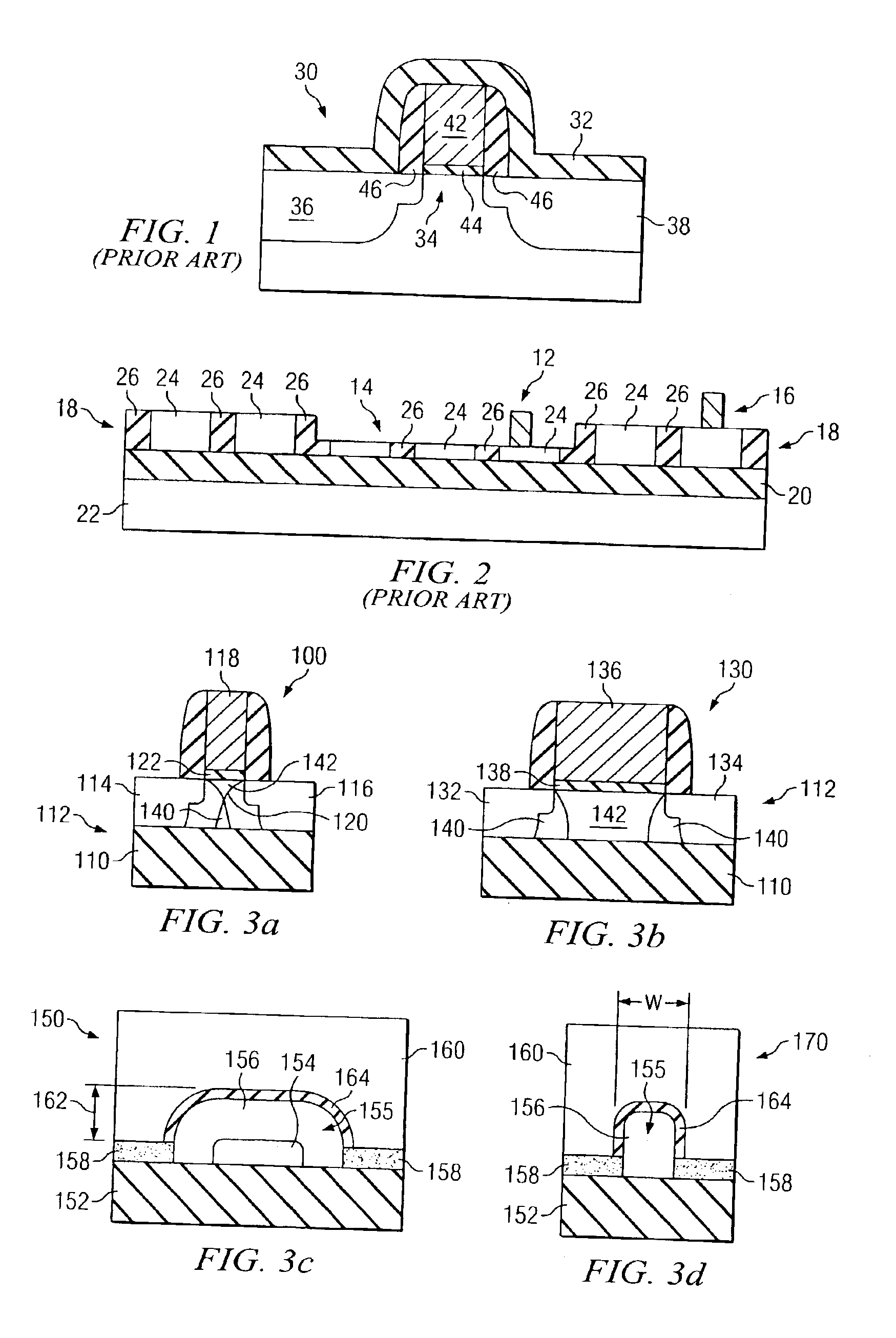

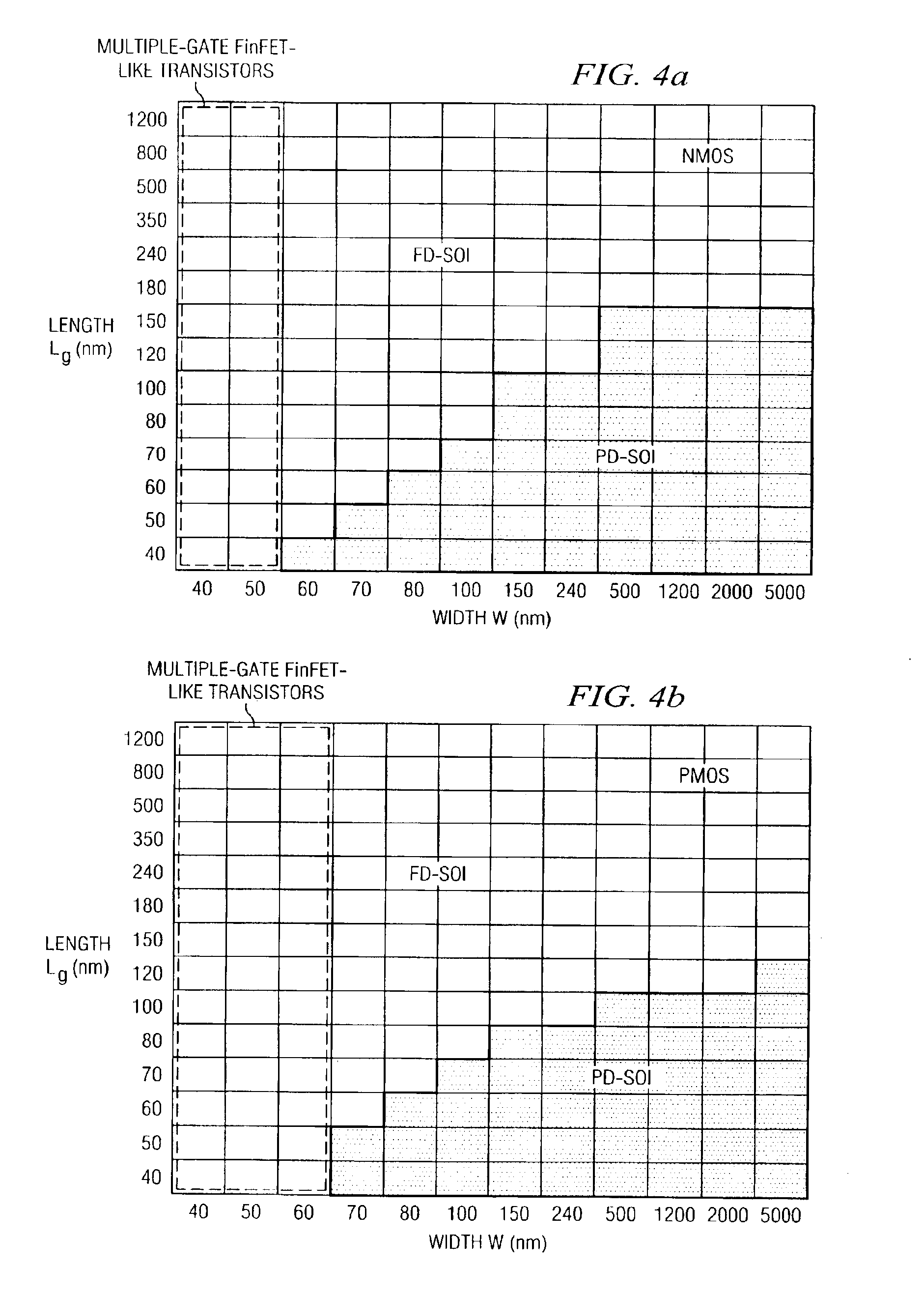

Semiconductor-on-insulator chip incorporating strained-channel partially-depleted, fully-depleted, and multiple-gate transistors

InactiveUS6867433B2Good effectSuppression of floating body effectTransistorSolid-state devicesMOSFETSemiconductor chip

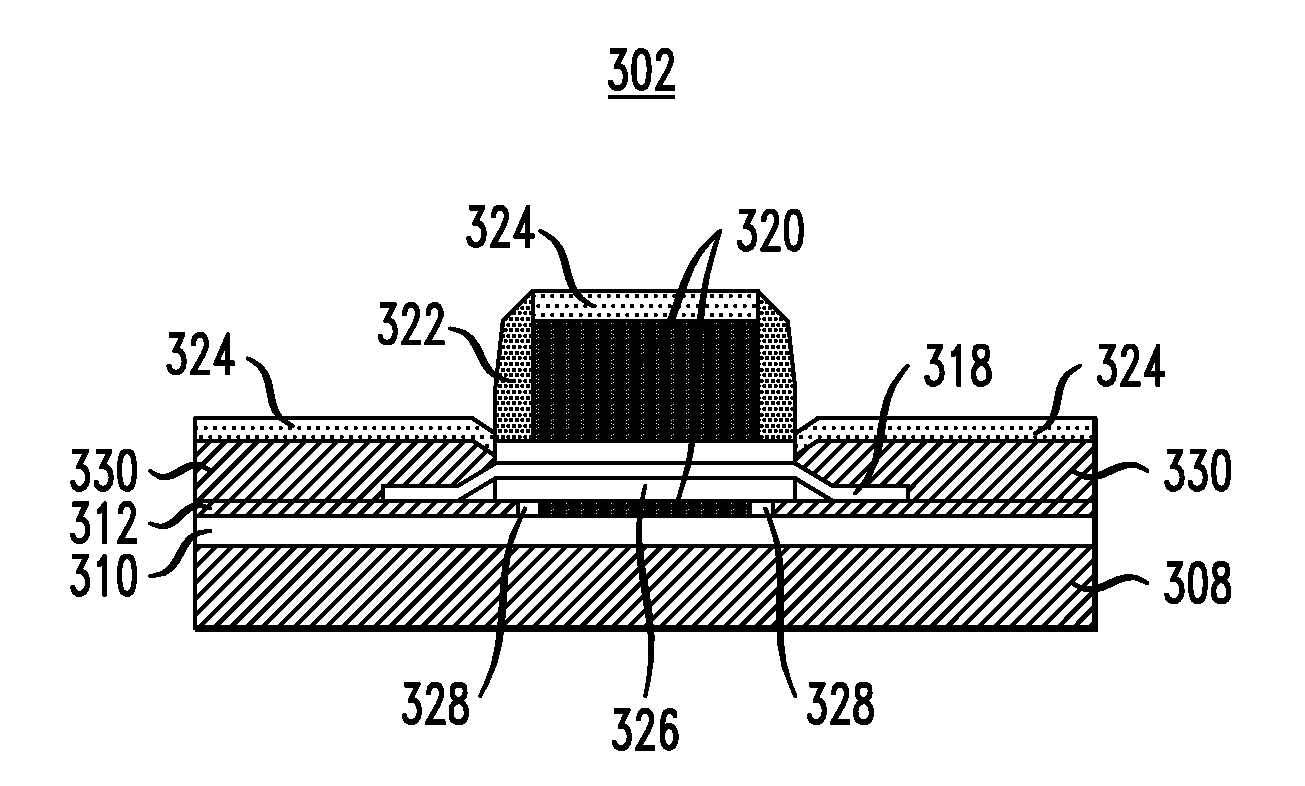

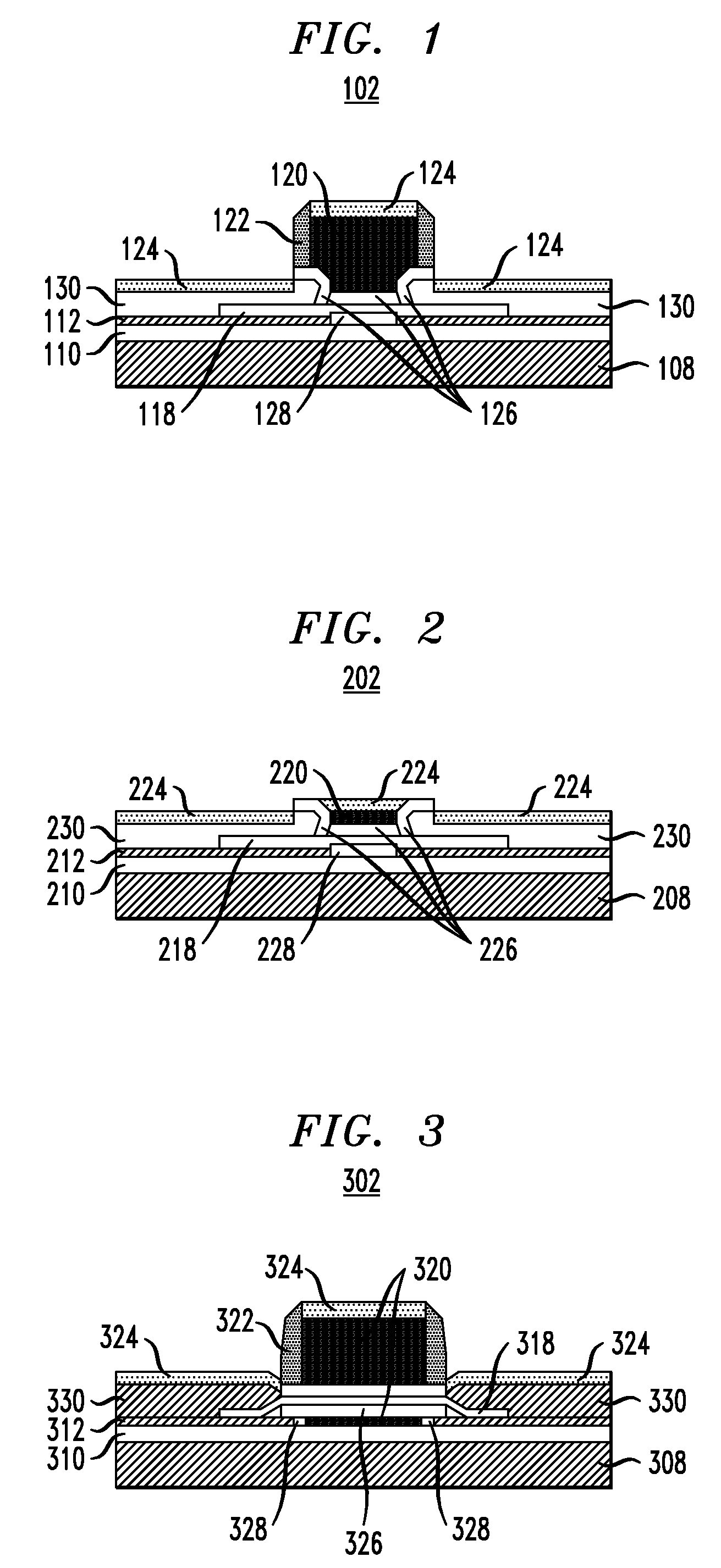

In accordance with a preferred embodiment of the present invention, a silicon-on-insulator (SOI) chip includes a silicon layer of a predetermined thickness overlying an insulator layer. A multiple-gate fully-depleted SOI MOSFET including a strained channel region is formed on a first portion of the silicon layer. A planar SOI MOSFET including a strained channel region formed on another portion of the silicon layer. For example, the planar SOI MOSFET can be a planar fully-depleted SOI (FD-SOI) MOSFET or the planar SOI MOSFET can be a planar partially-depleted SOI (PD-SOI) MOSFET.

Owner:TAIWAN SEMICON MFG CO LTD

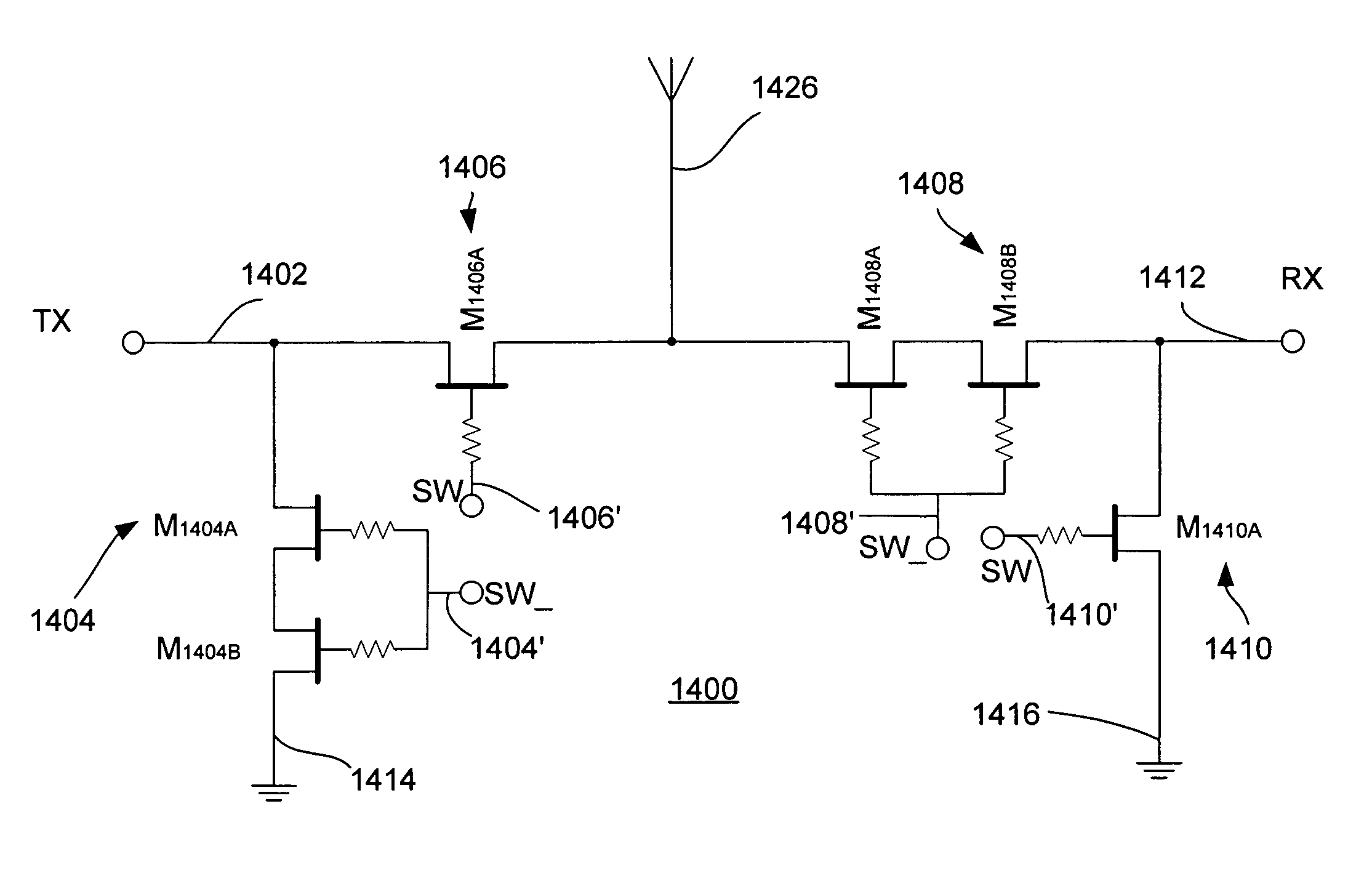

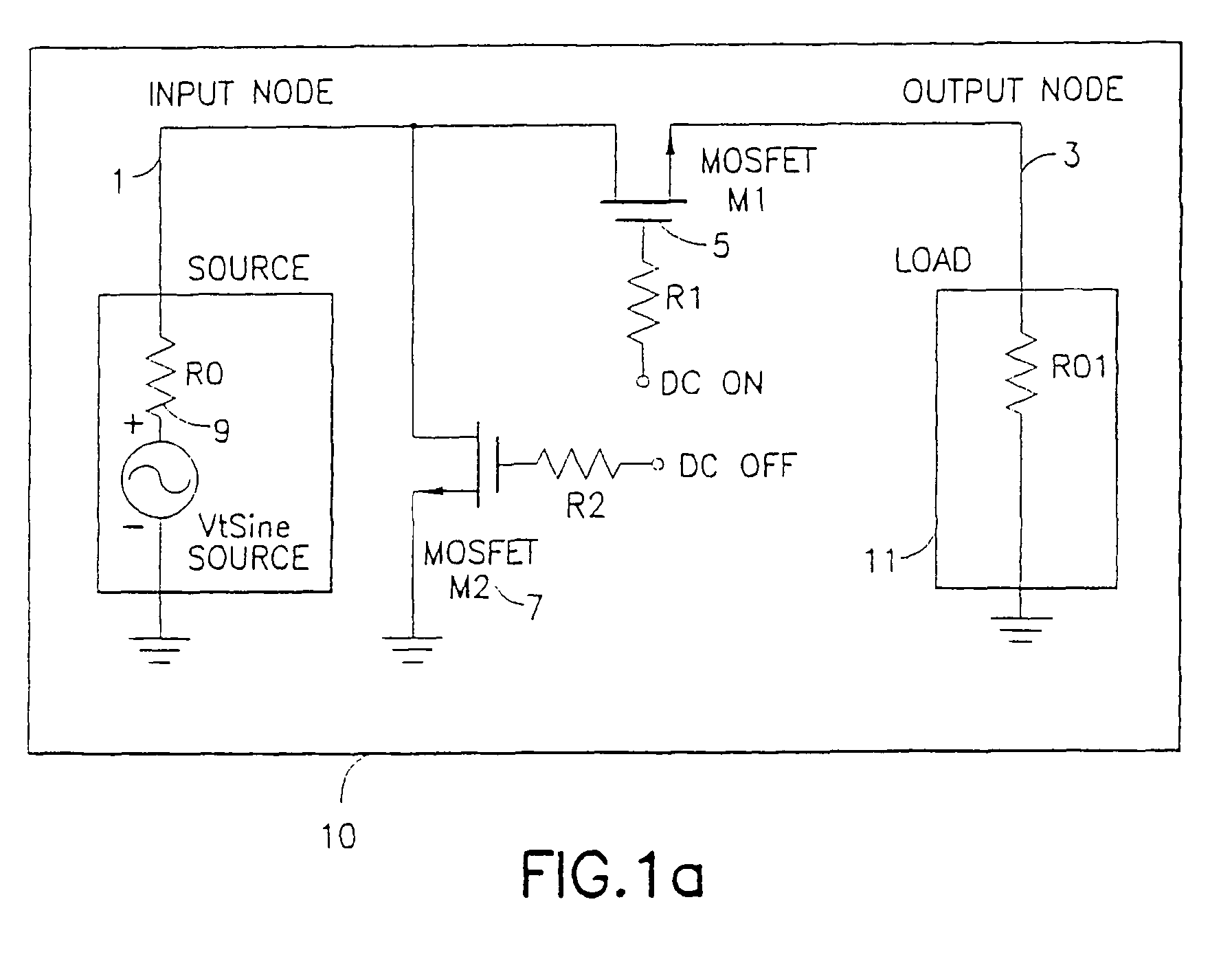

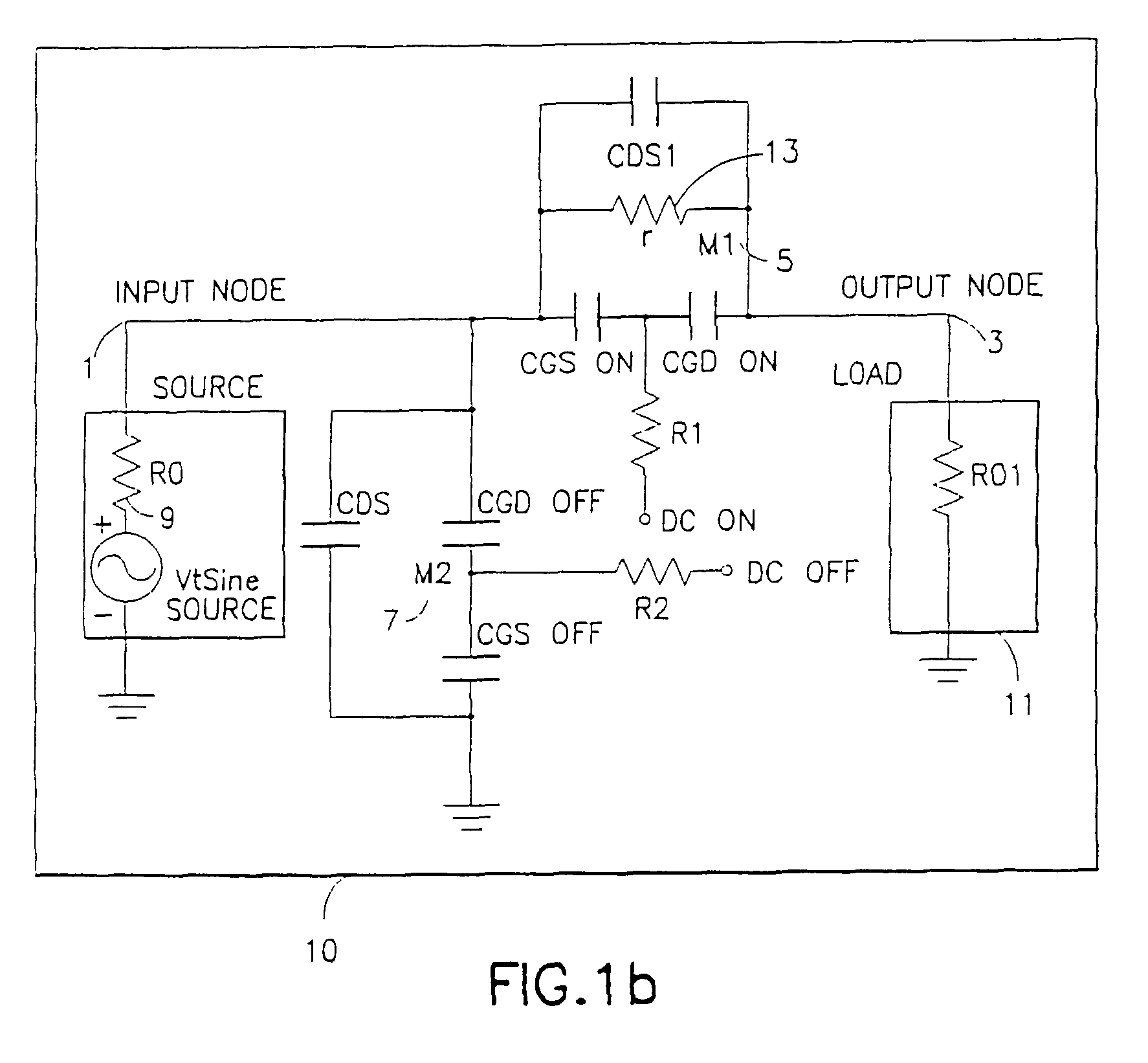

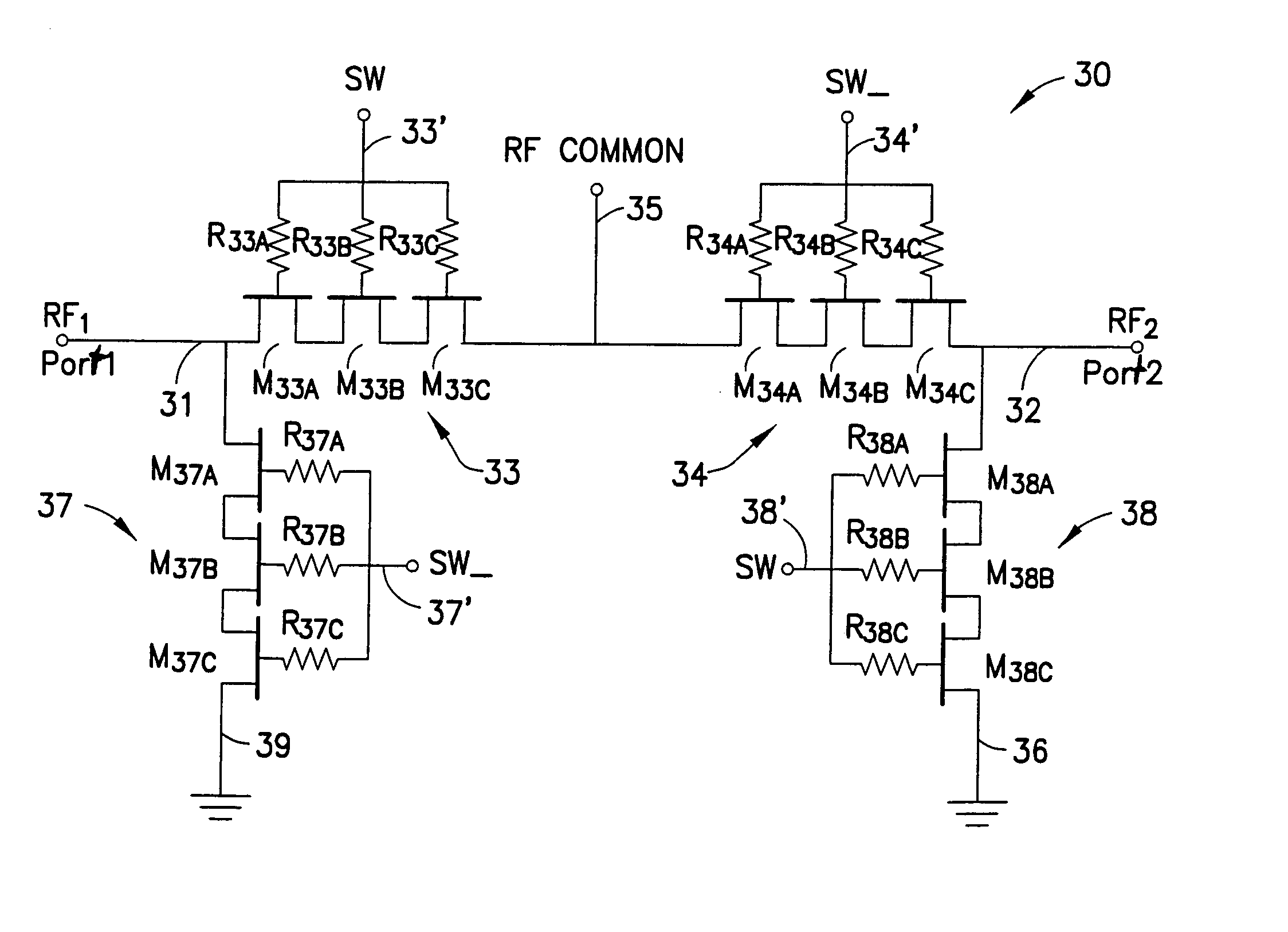

Symmetrically and asymmetrically stacked transistor group RF switch

A silicon-on-insulator (SOI) RF switch adapted for improved power handling capability using a reduced number of transistors is described. In one embodiment, an RF switch includes pairs of switching and shunting stacked transistor groupings to selectively couple RF signals between a plurality of input / output nodes and a common RF node. The switching and shunting stacked transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. In one embodiment, the transistor groupings are “symmetrically” stacked in the RF switch (i.e., the transistor groupings all comprise an identical number of transistors). In another embodiment, the transistor groupings are “asymmetrically” stacked in the RF switch (i.e., at least one transistor grouping comprises a number of transistors that is unequal to the number of transistors comprising at least one other transistor grouping). The stacked configuration of the transistor groupings enable the RF switch to withstand RF signals of varying and increased power levels. The asymmetrically stacked transistor grouping RF switch facilitates area-efficient implementation of the RF switch in an integrated circuit. Maximum input and output signal power levels can be withstood using a reduced number of stacked transistors.

Owner:PSEMI CORP

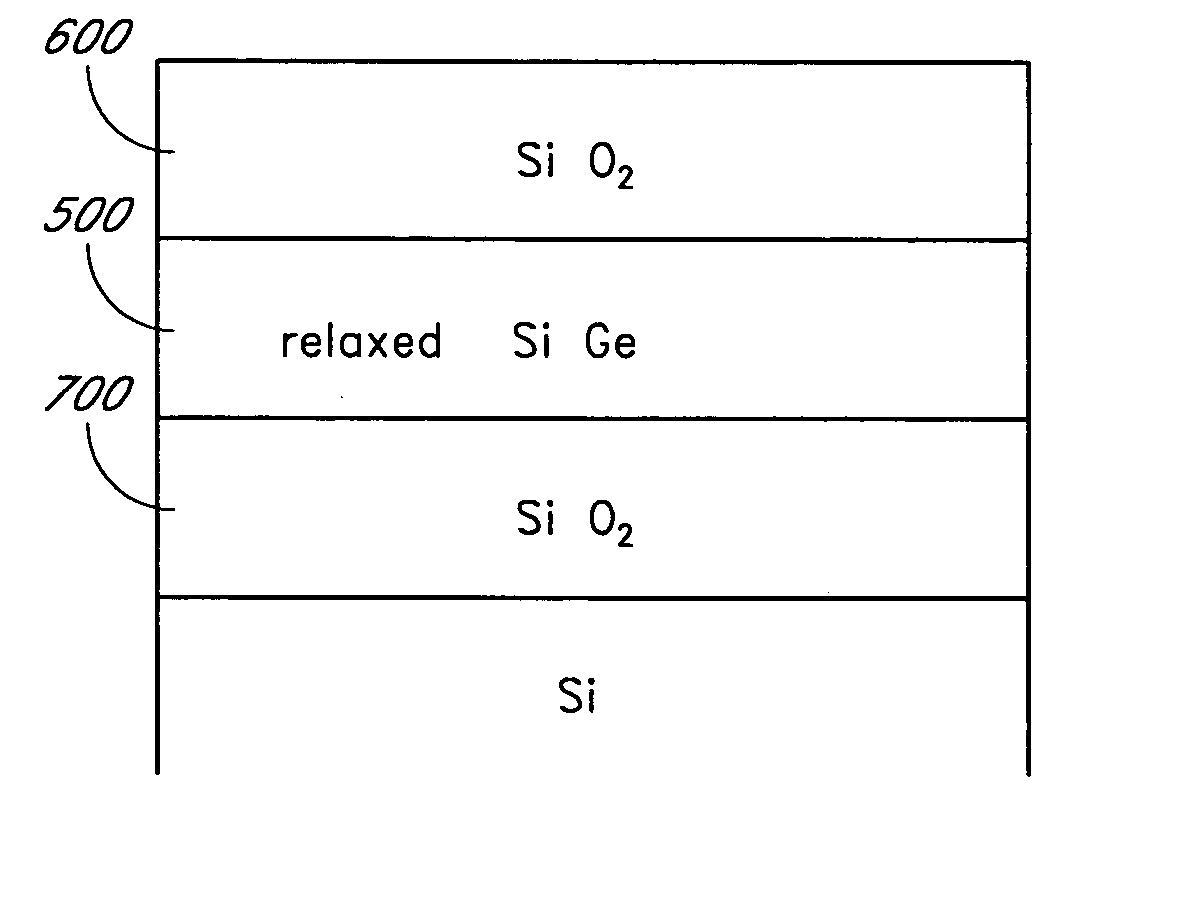

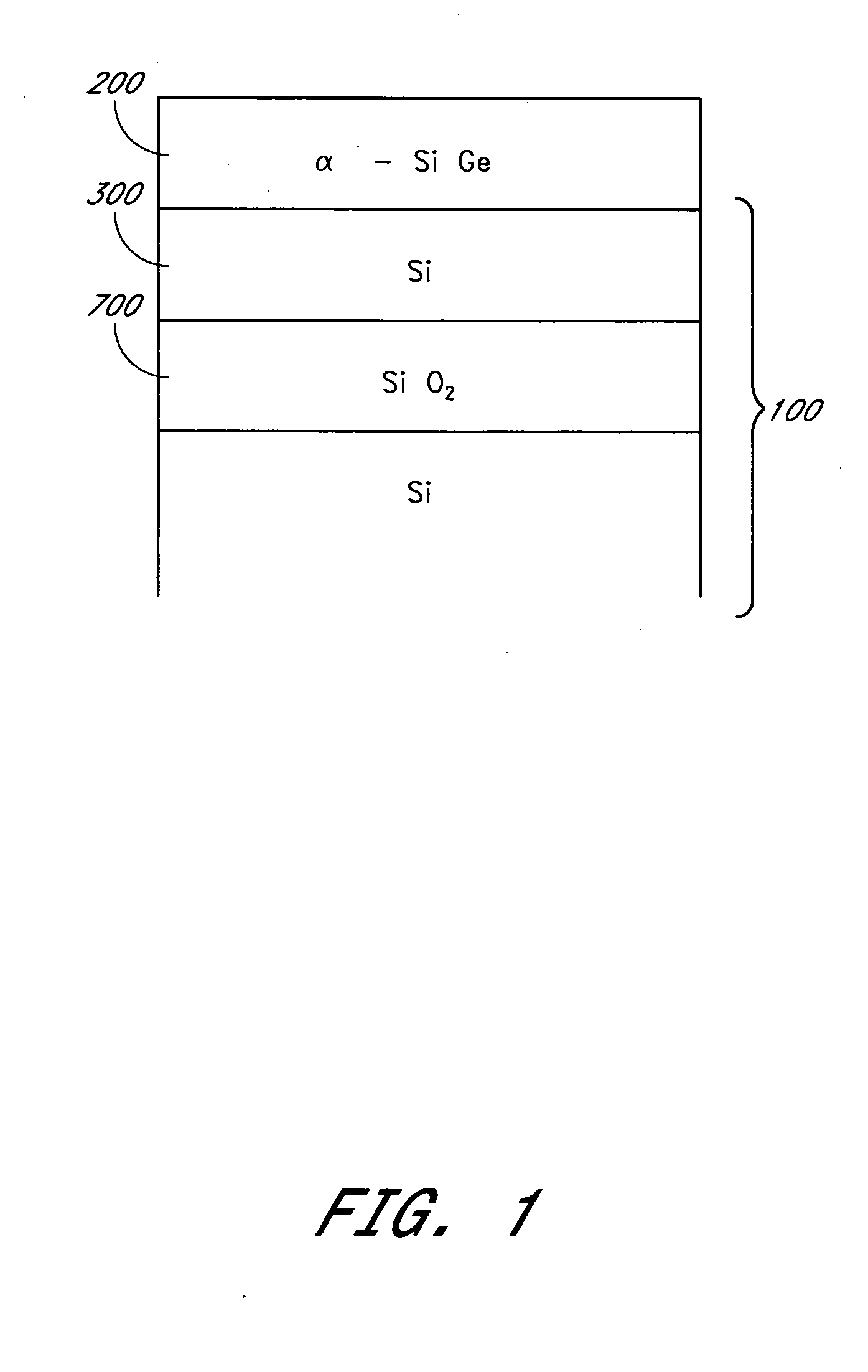

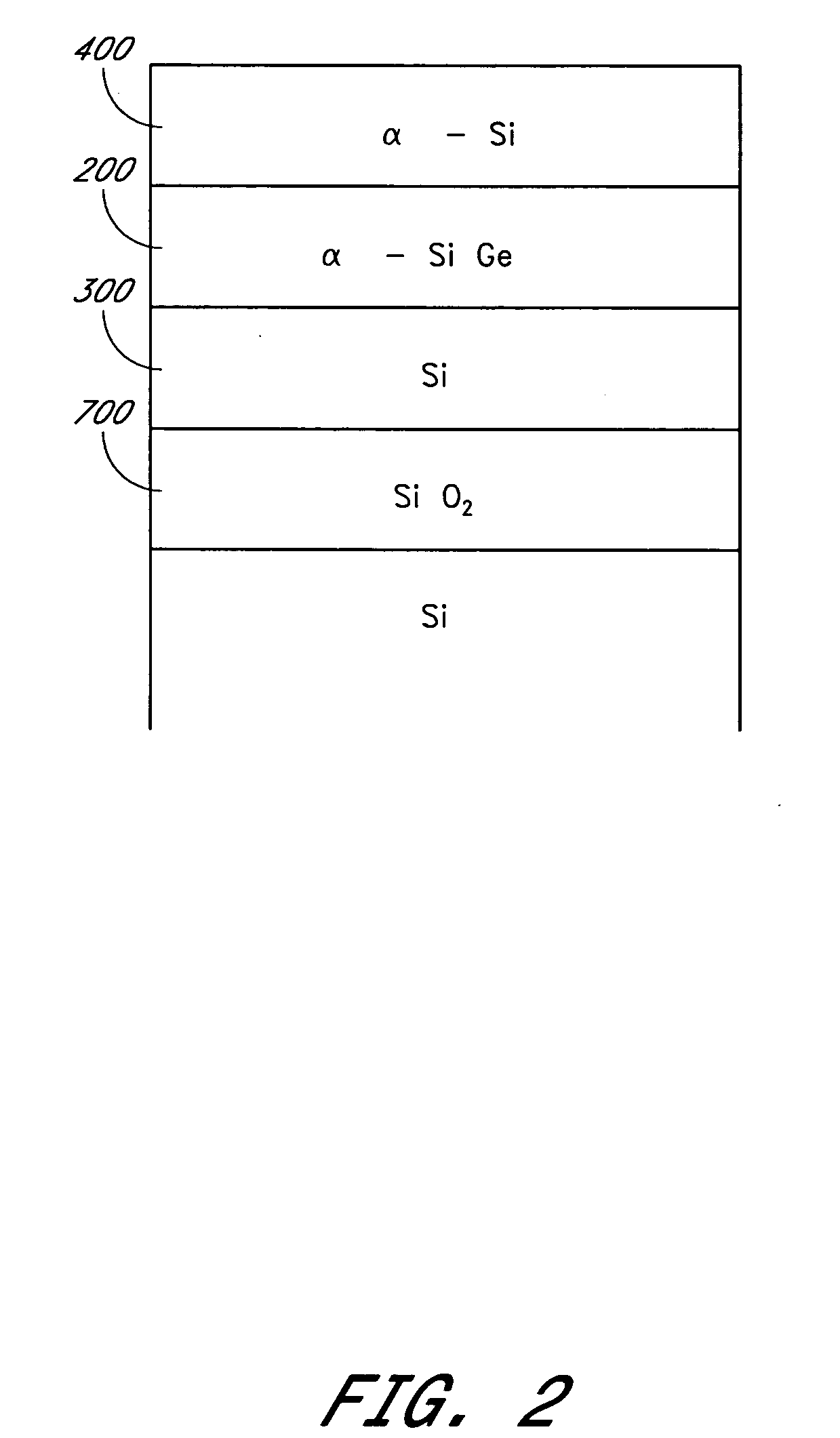

Deposition of silicon germanium on silicon-on-insulator structures and bulk substrates

Methods are provided for producing SiGe-on-insulator structures and for forming strain-relaxed SiGe layers on silicon while minimizing defects. Amorphous SiGe layers are deposited by CVD from trisilane and GeH4. The amorphous SiGe layers are recrystallized over silicon by melt or solid phase epitaxy (SPE) processes. The melt processes preferably also cause diffusion of germanium to dilute the overall germanium content and essentially consume the silicon overlying the insulator. The SPE process can be conducted with or without diffusion of germanium into the underlying silicon, and so is applicable to SOI as well as conventional semiconductor substrates.

Owner:ASM IP HLDG BV

Fully depleted soi device for reducing parasitic back gate capacitance

ActiveUS20180097076A1Semiconductor/solid-state device detailsSolid-state devicesCapacitanceGate dielectric

A method is presented for forming a semiconductor structure. The method includes forming a bilayer buried insulator over a substrate, forming an extremely thin silicon-on-insulator (ETSOI) over the bilayer buried insulator, forming a dummy gate, and forming a source / drain next to the dummy gate, the source / drain defining a raised source / drain region. The method further includes depositing a dielectric material over the raised source / drain regions, removing the dummy gate to define a recess, implanting a species within a first layer of the bilayer buried insulator, and depositing a gate dielectric and a conducting material within the recess. The method further includes removing the substrate, etching the implanted portion of the first layer of the bilayer buried insulator to expose a surface of a second layer of the bilayer buried insulator, and forming a back gate over the exposed second layer, the back gate self-aligned to the ETSOI channel.

Owner:IBM CORP

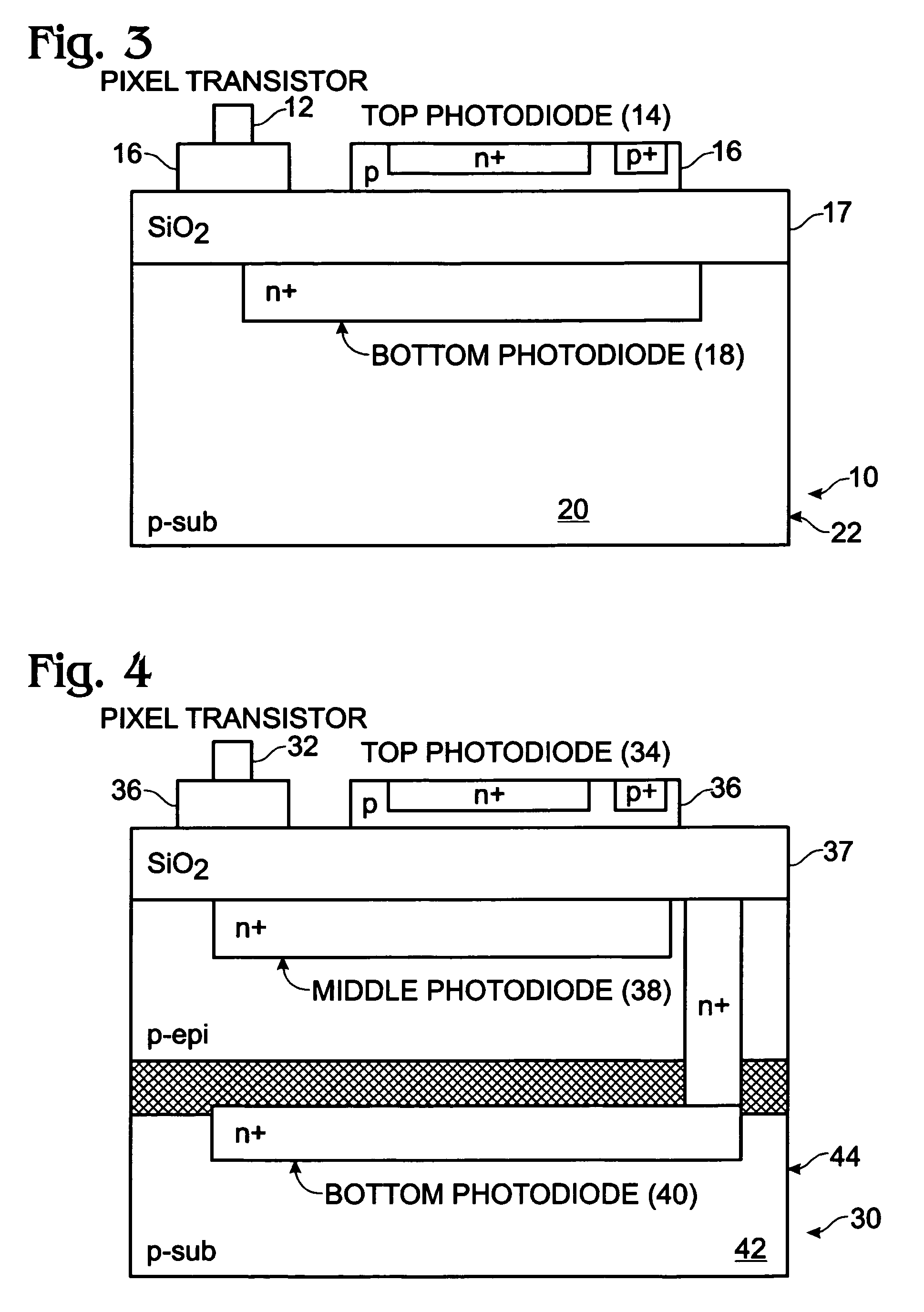

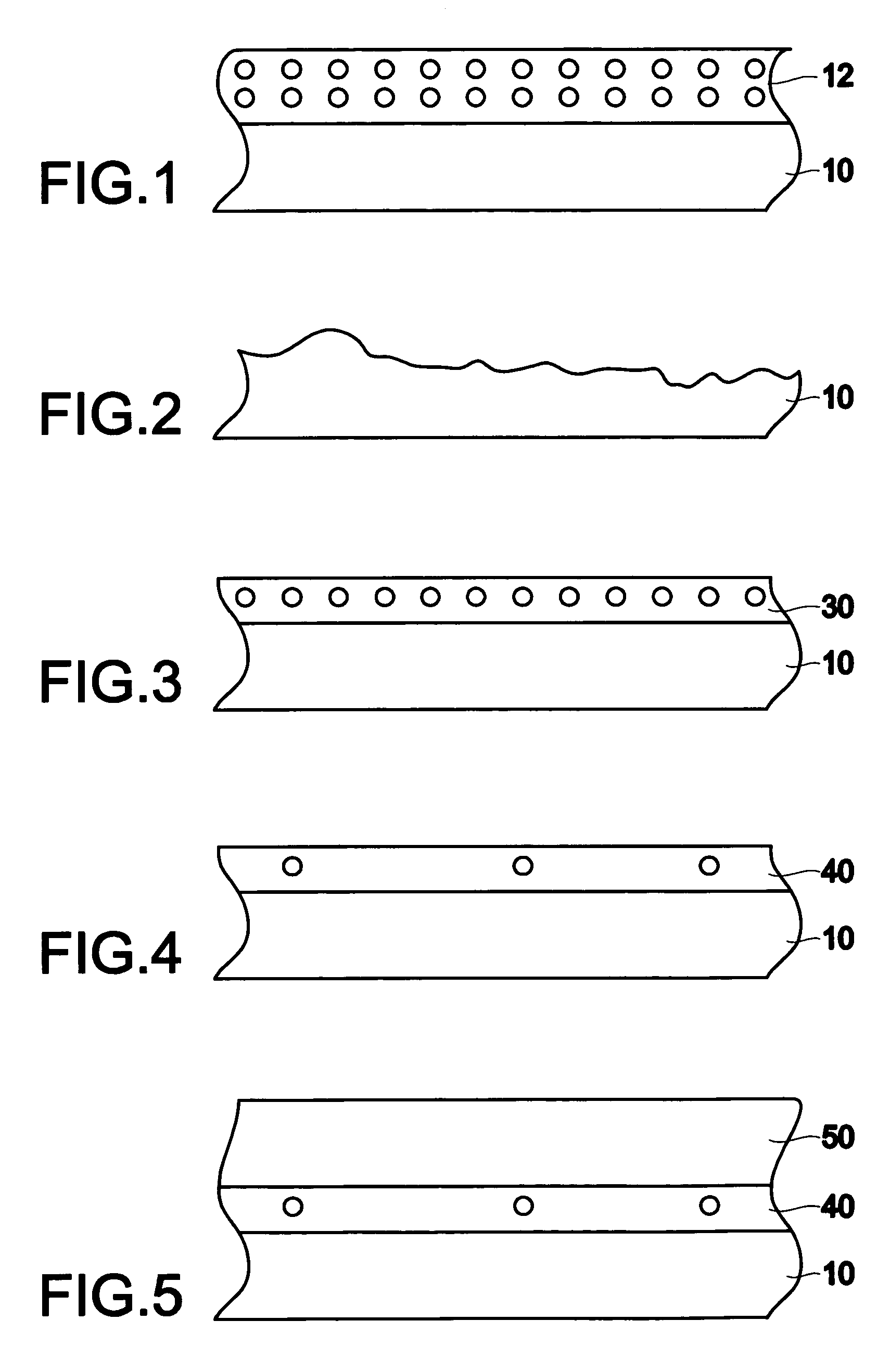

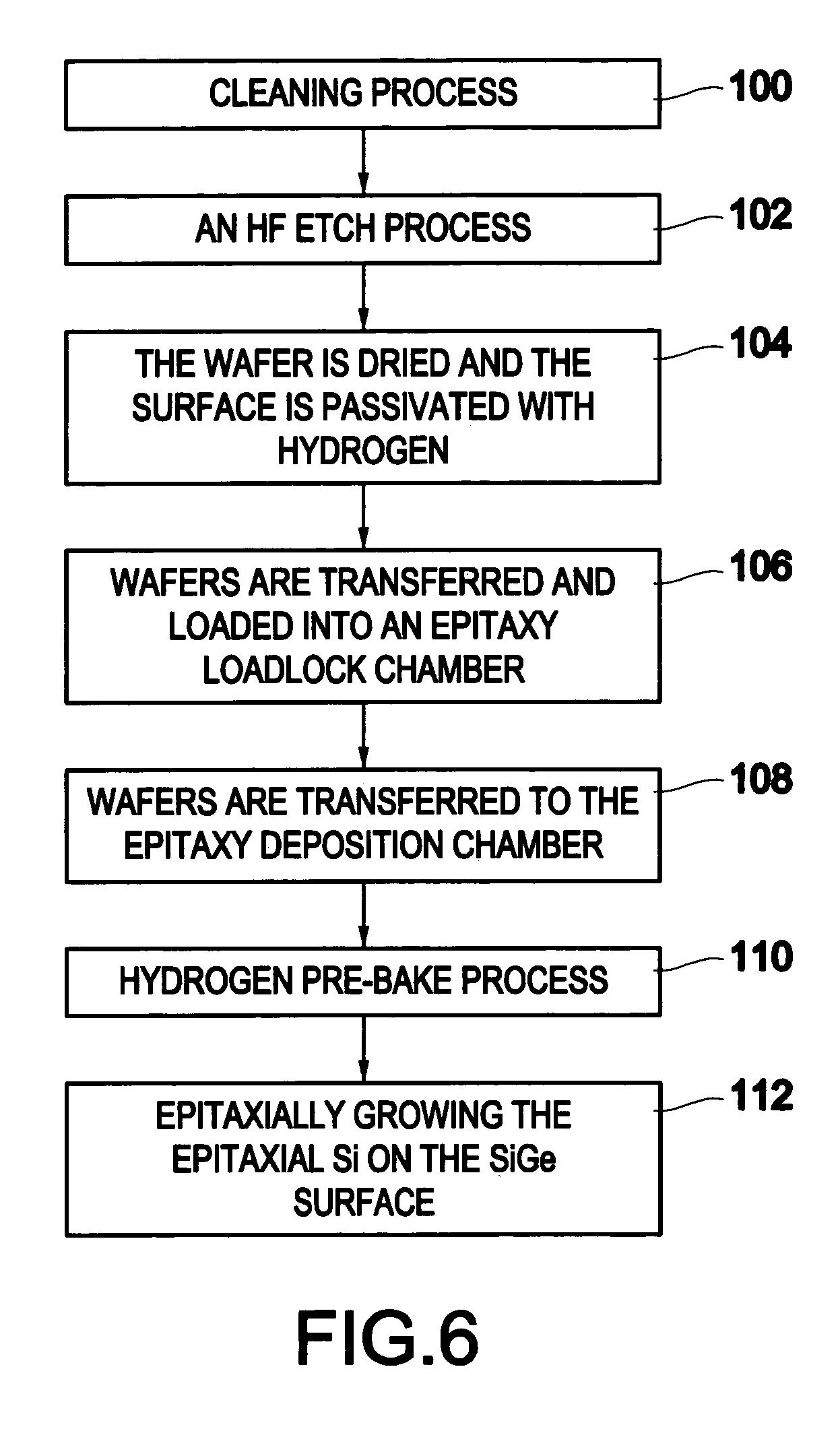

Method of preventing surface roughening during hydrogen pre-bake of SiGe substrates using chlorine containing gases

InactiveUS20050148162A1Prevent surfaceAvoid creatingPolycrystalline material growthSemiconductor/solid-state device manufacturingPartial oxidationSilicon on insulator

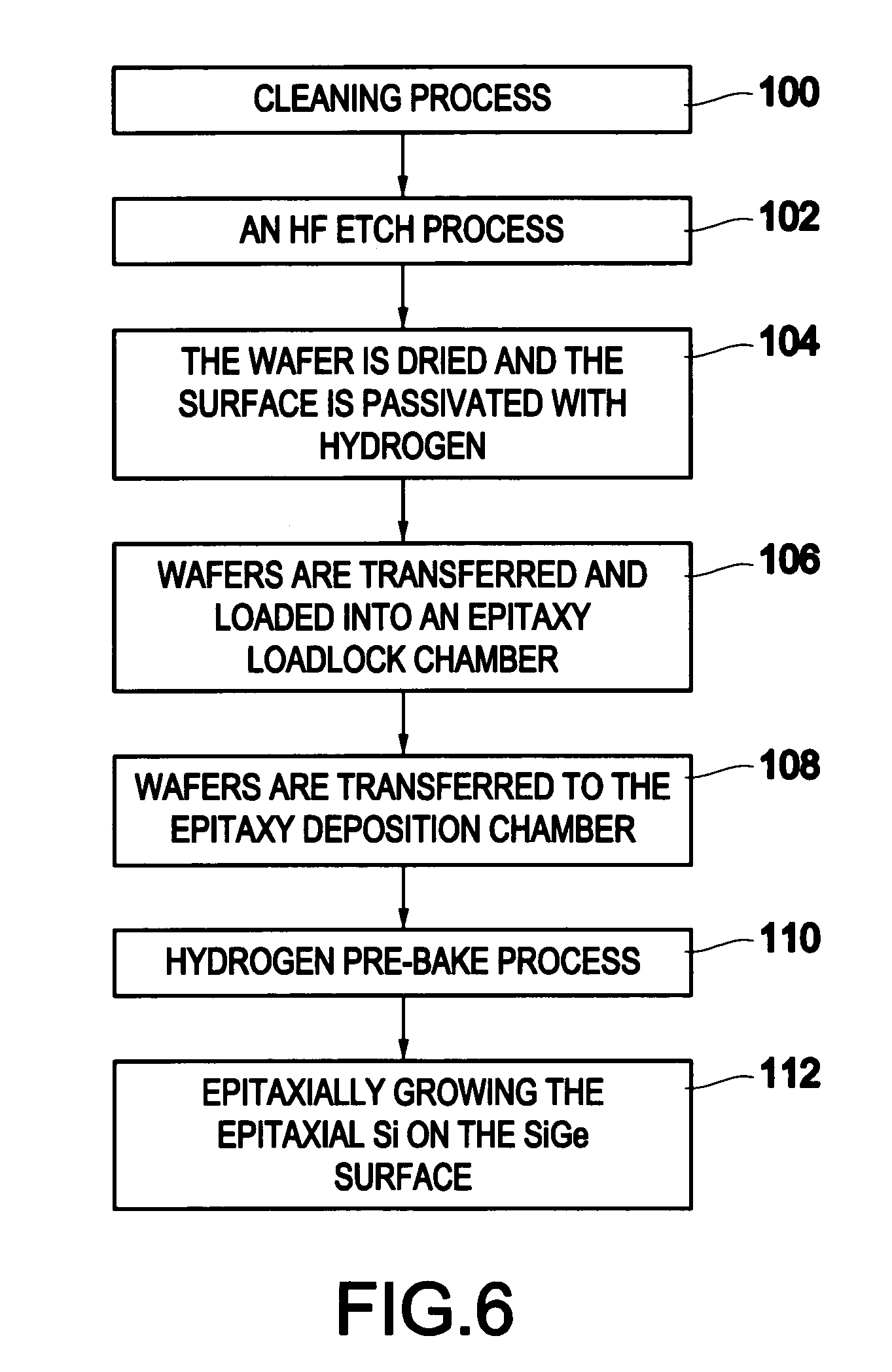

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves only a sub-monolayer of oxygen (typically 1×1013-1×1015 / cm2 of oxygen) at the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process in a chlorine containing environment which heats the silicon germanium, strained silicon, or thin silicon-on-insulator surface sufficiently to remove the remaining oxygen from the surface. By introducing a small amount of chlorine containing gases, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:IBM CORP

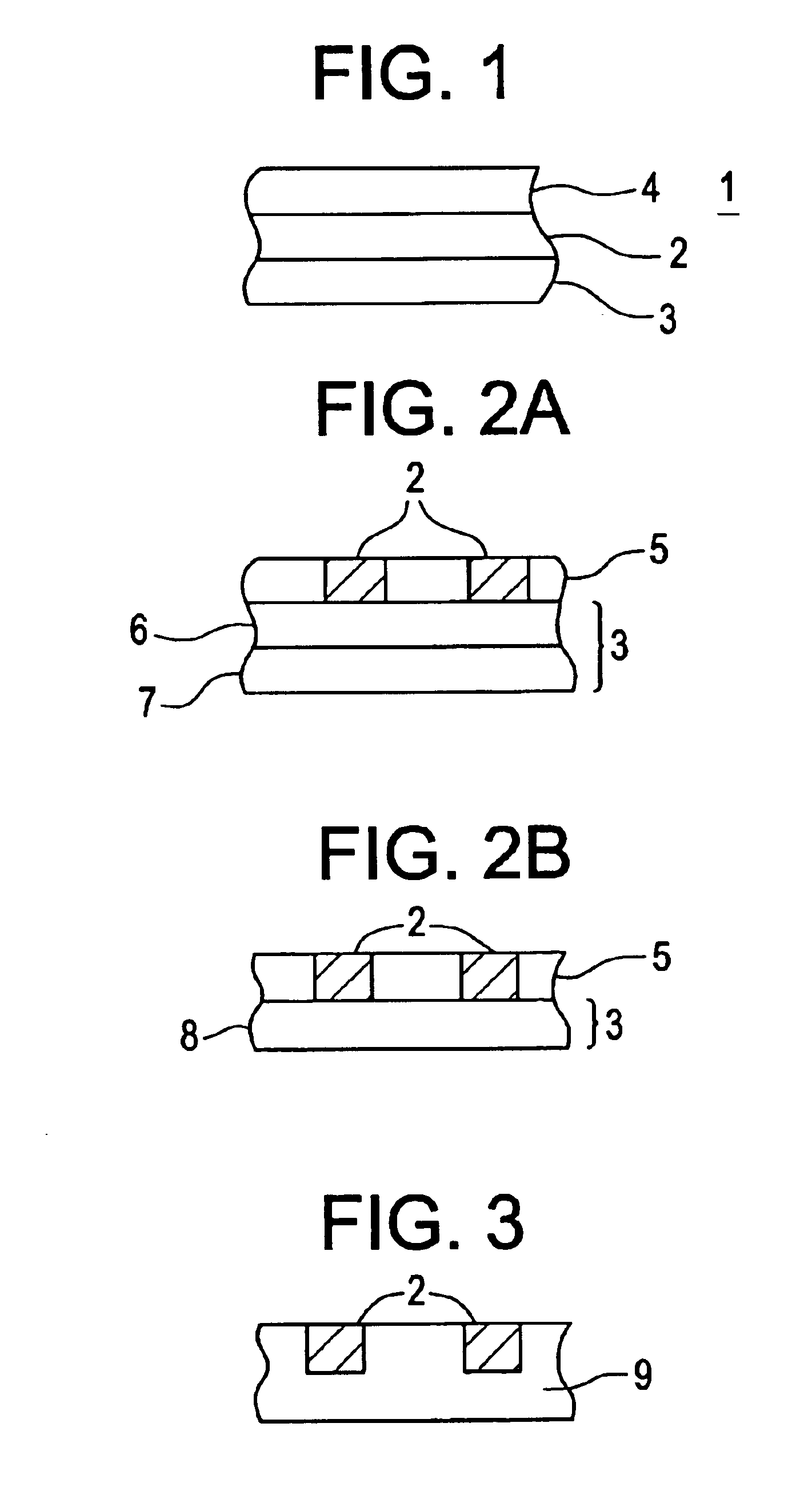

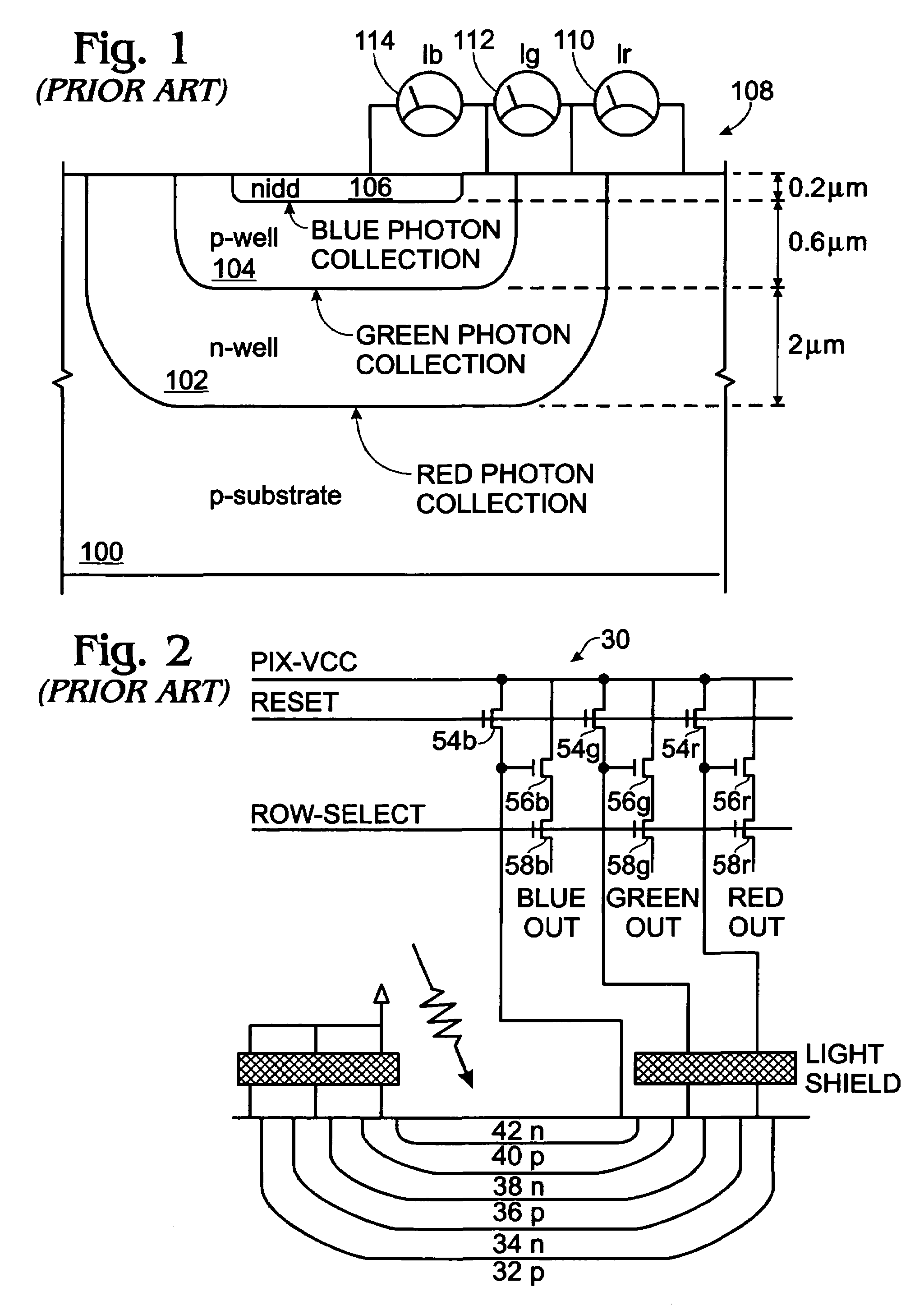

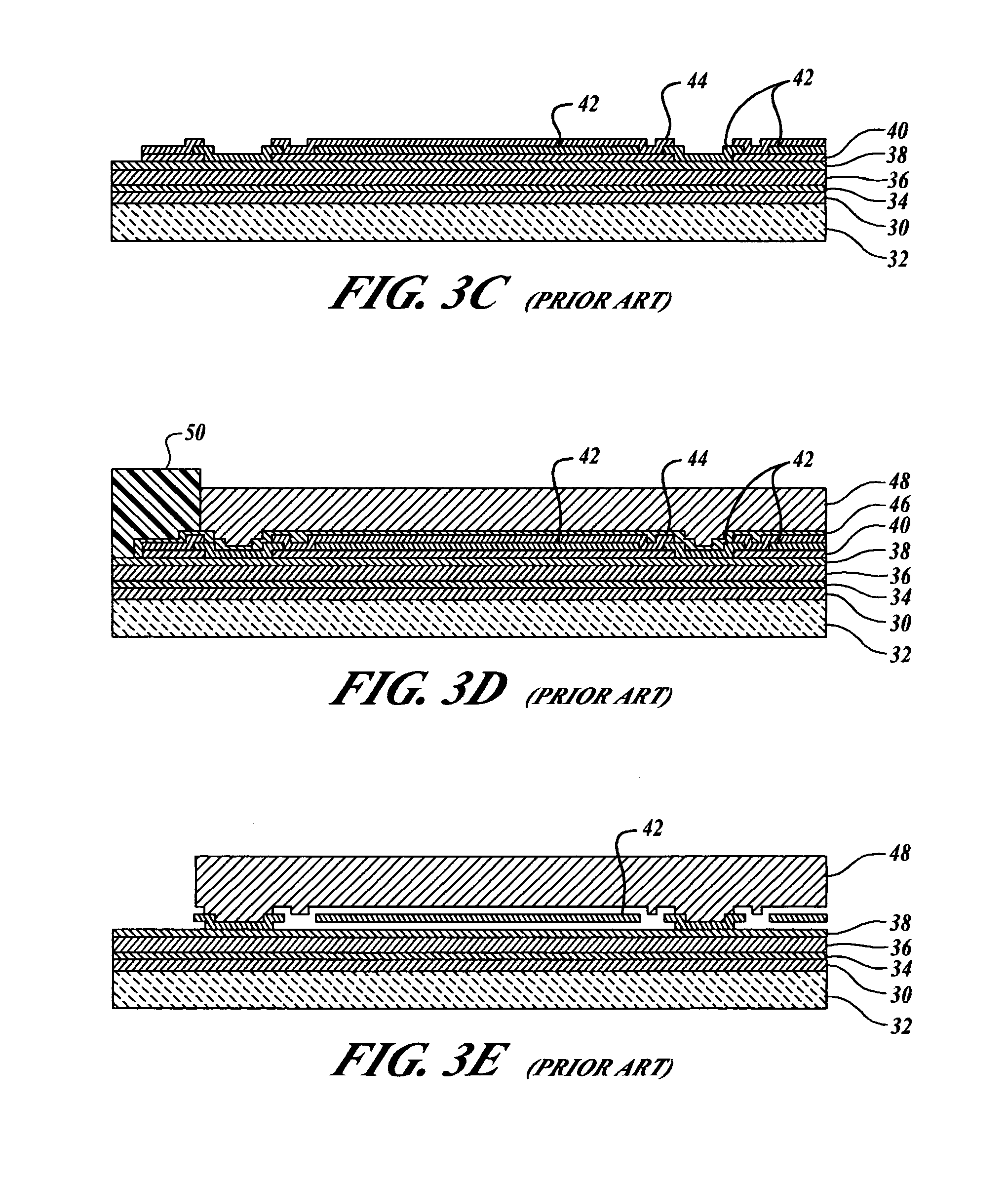

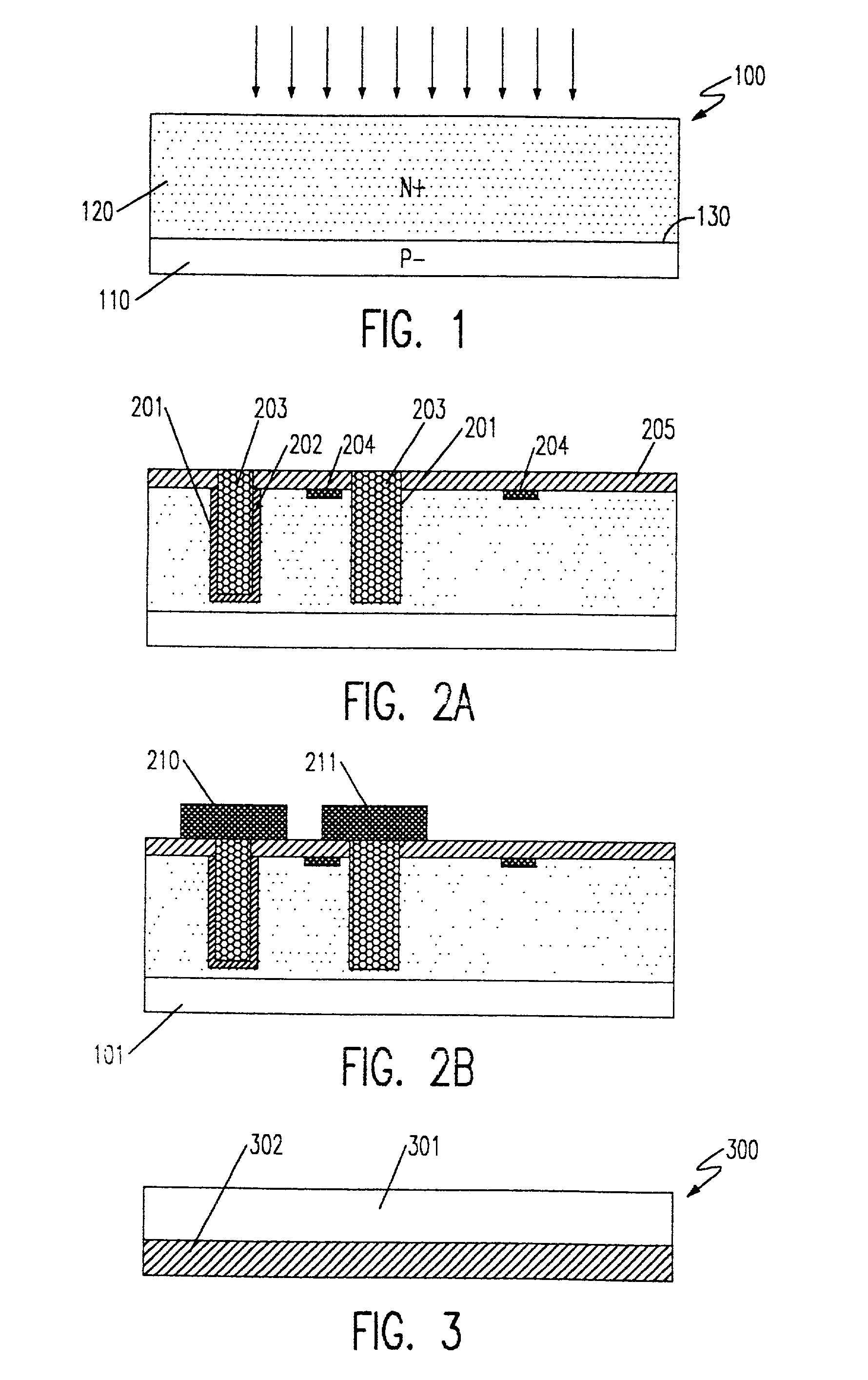

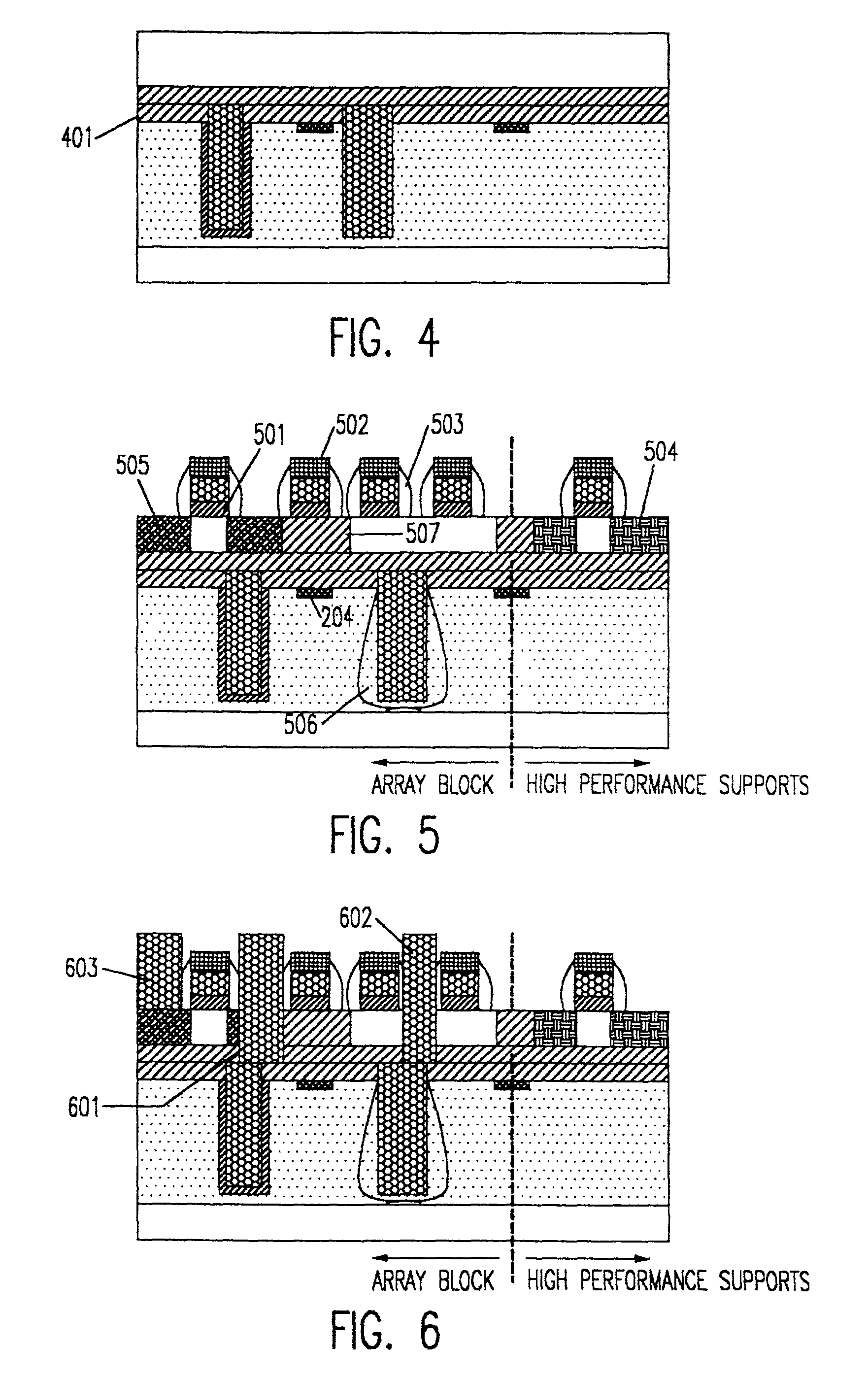

Real-time CMOS imager having stacked photodiodes fabricated on SOI wafer

InactiveUS7419844B2Solid-state devicesSemiconductor/solid-state device manufacturingElectrical connectionLength wave

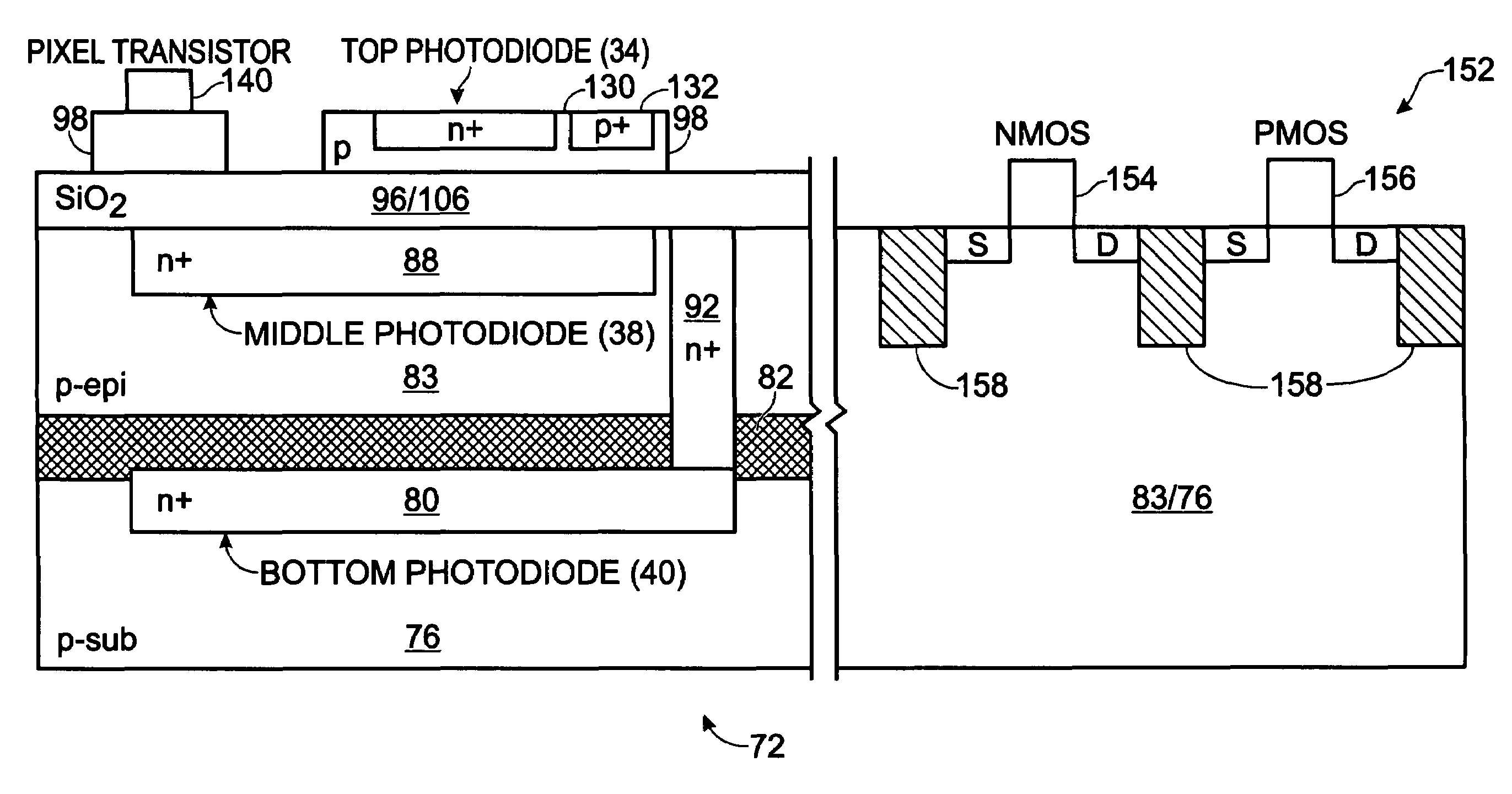

A CMOS active pixel sensor includes a silicon-on-insulator substrate having a silicon substrate with an insulator layer formed thereon and a top silicon layer formed on the insulator layer. A stacked pixel sensor cell includes a bottom photodiode fabricated on the silicon substrate, for sensing light of a longest wavelength; a middle photodiode fabricated on the silicon substrate, for sensing light of a medium wavelength, which is stacked above the bottom photodiode; and a top photodiode fabricated on the top silicon layer, for sensing light of a shorter wavelength, which is stacked above the middle and bottom photodiodes. Pixel transistor sets are fabricated on the top silicon layer and are associated with each pixel sensor cell by electrical connections which extend between each of the photodiodes and respective pixel transistor(s). CMOS control circuitry is fabricated adjacent to an array of active pixel sensor cells and electrically connected thereto.

Owner:SHARP KK

Method of preventing surface roughening during hydrogen prebake of SiGe substrates

InactiveUS6958286B2Polycrystalline material growthSemiconductor/solid-state device manufacturingRough surfaceHydrofluoric acid

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves a first amount of oxygen (typically 1×1013−1×1015 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process which heats the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface sufficiently to remove additional oxygen from the surface and leave a second amount of oxygen, less than the first amount, on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The heating process leaves an amount of at least 5×1012 / cm2 of oxygen (typically, between approximately 1×1013 / cm2 and approximately 5×1013 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. By leaving a small amount of oxygen on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:INT BUSINESS MASCH CORP

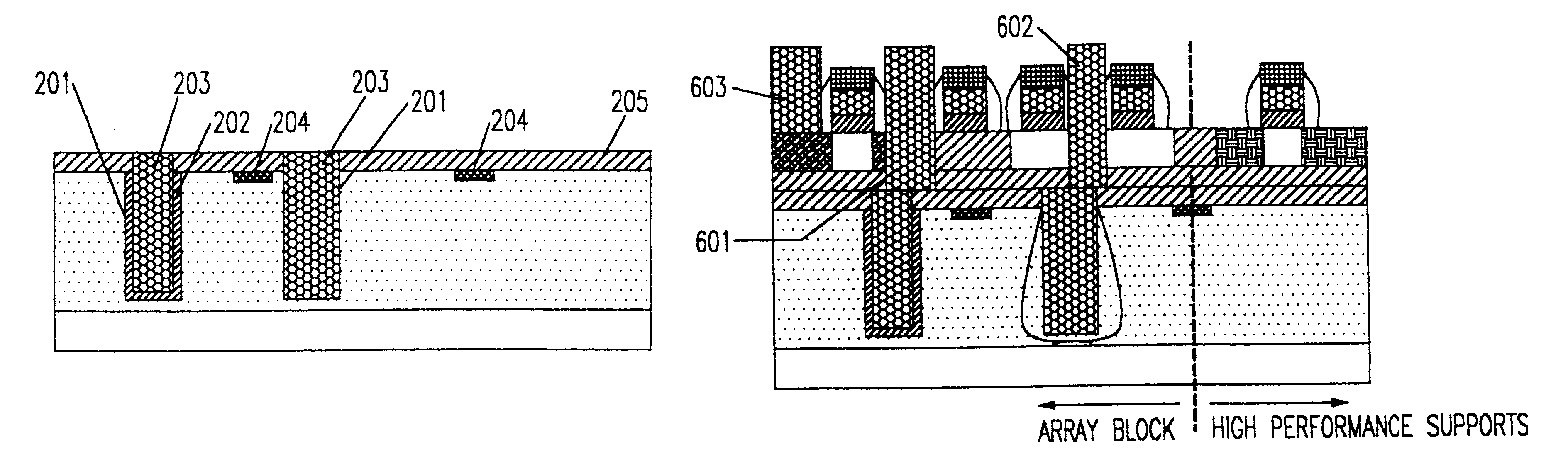

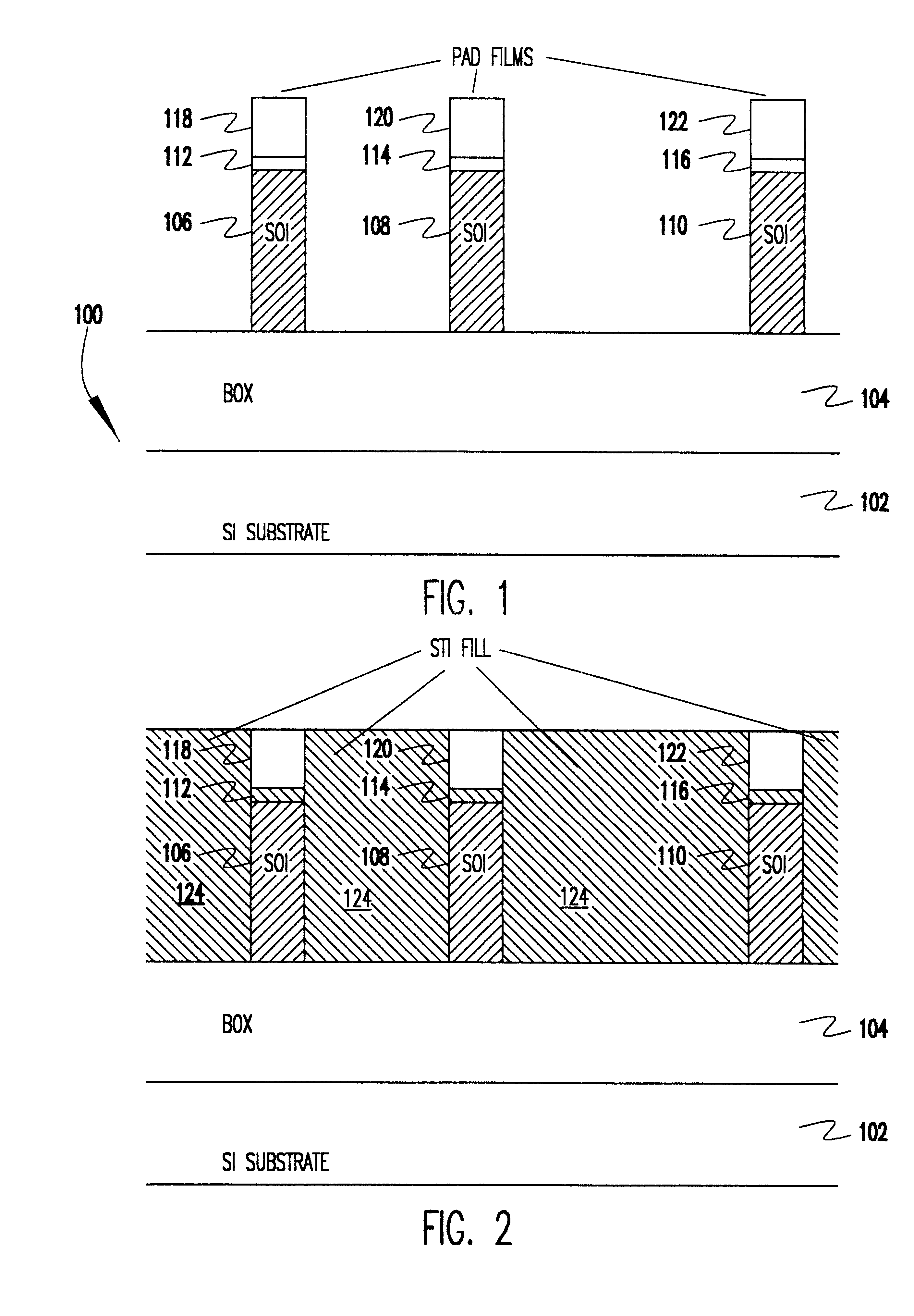

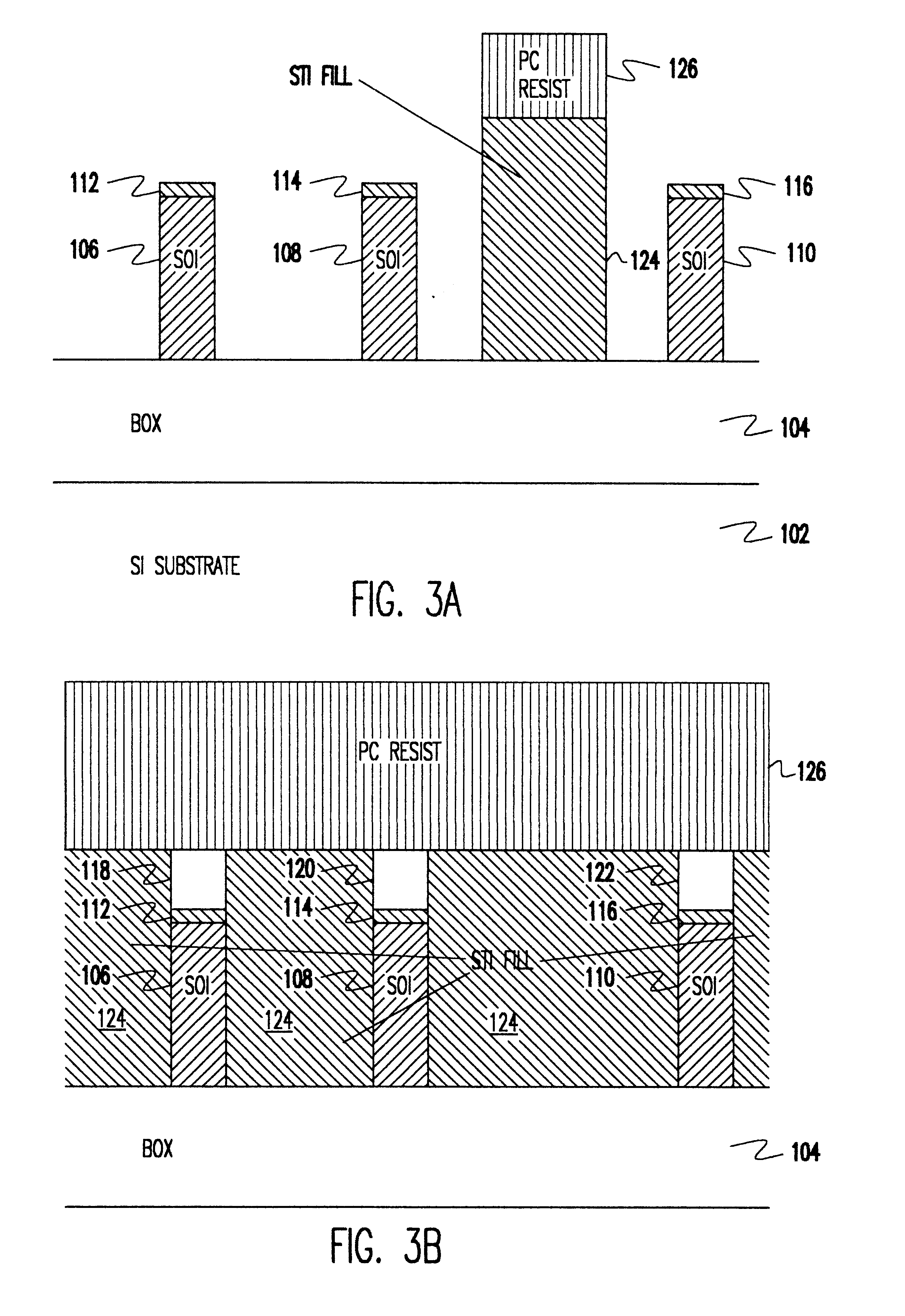

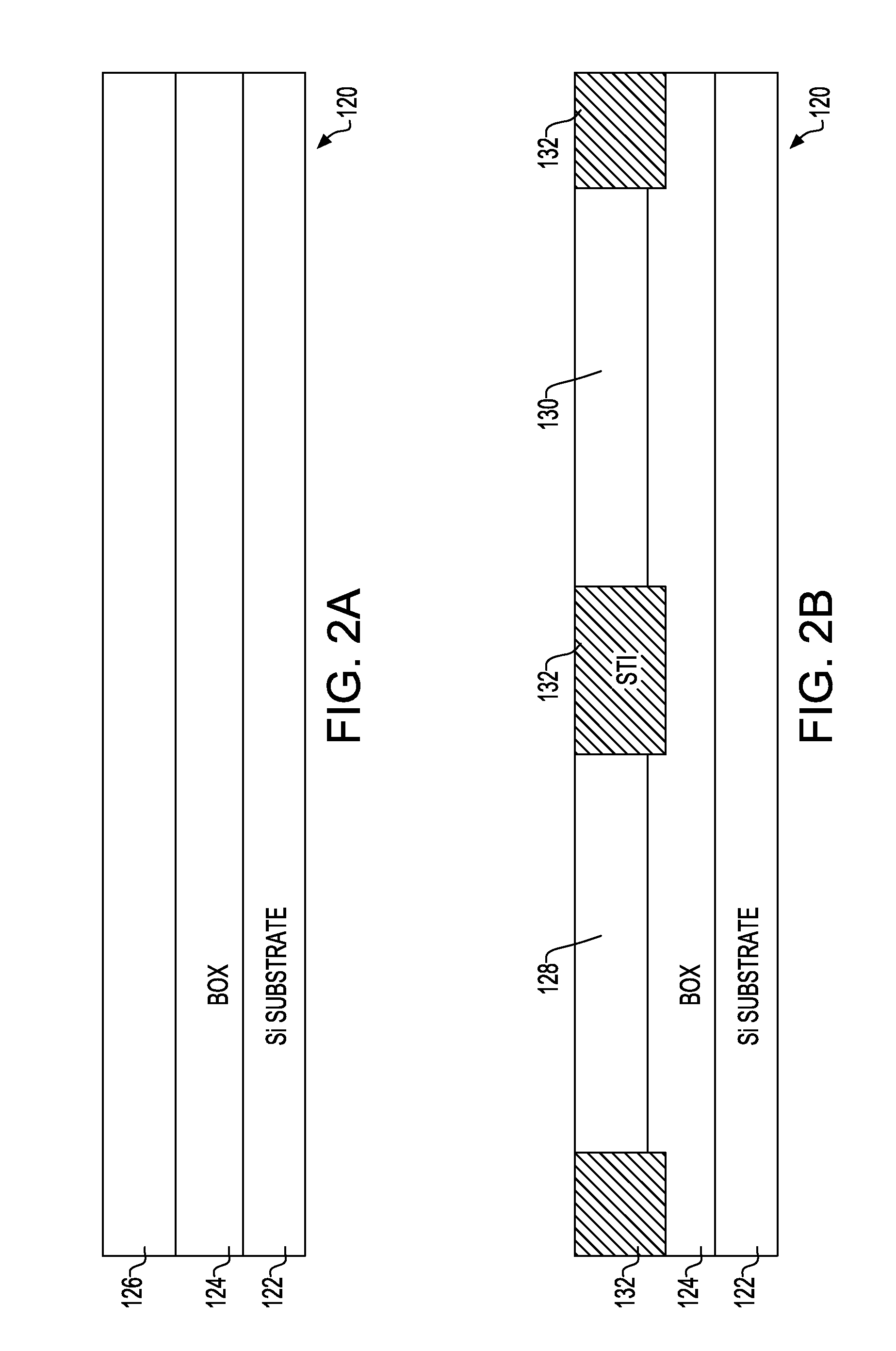

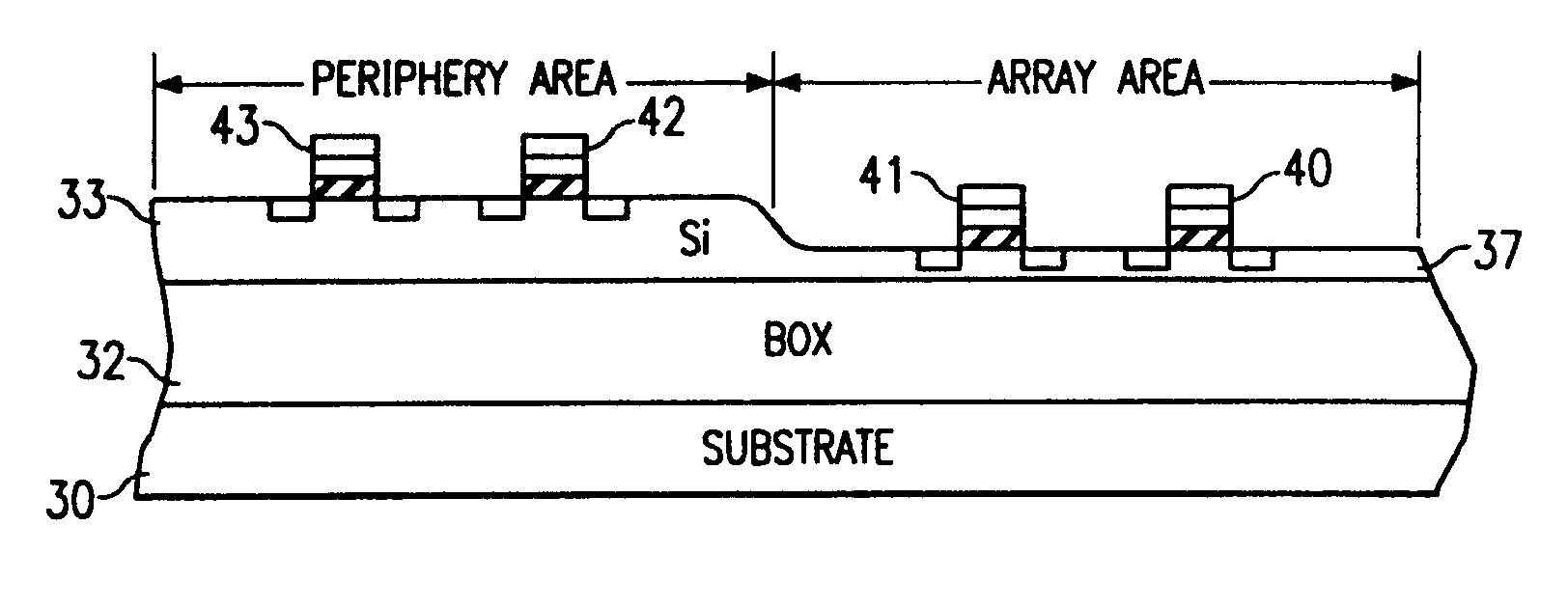

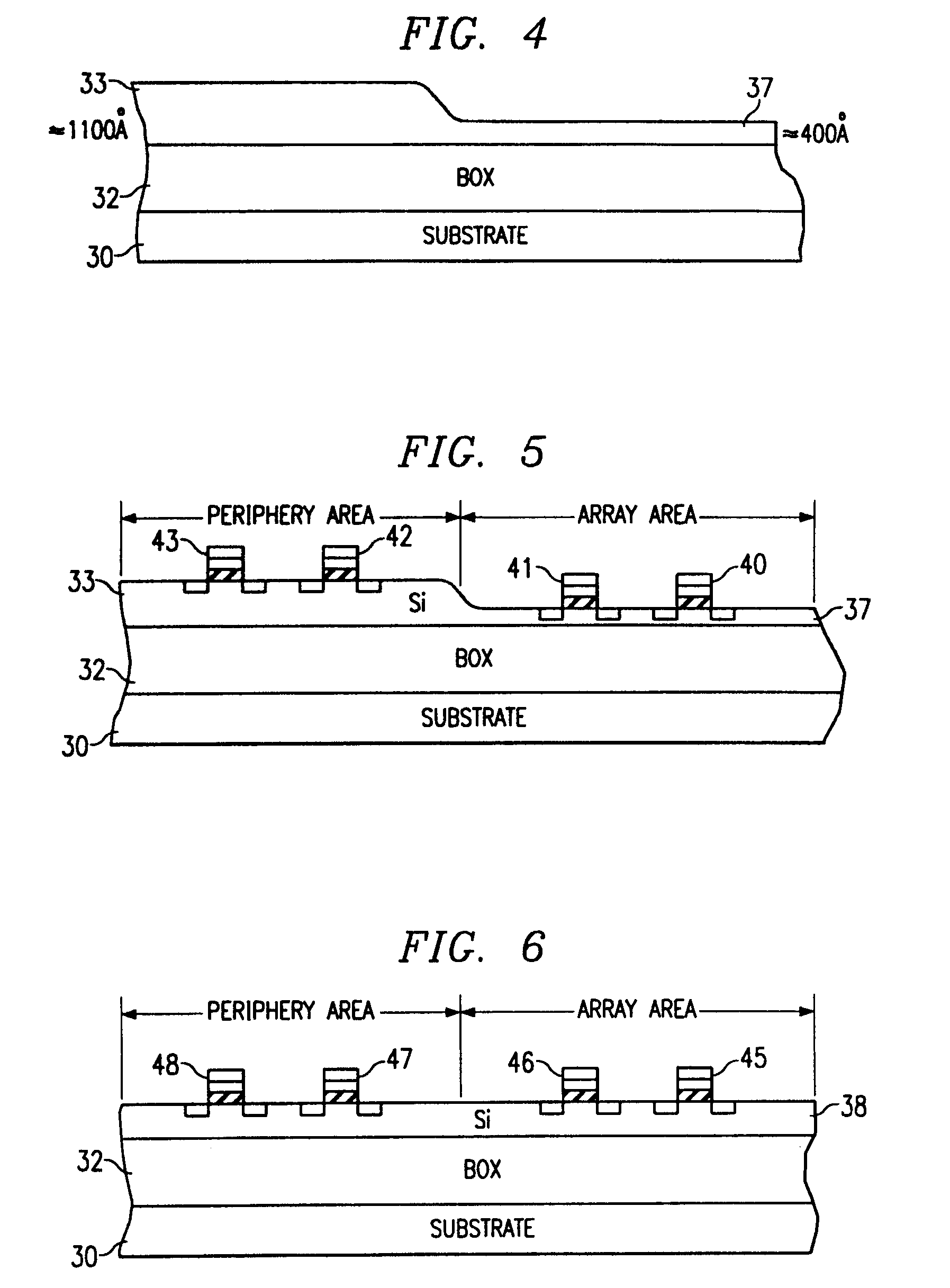

STI formation in semiconductor device including SOI and bulk silicon regions

InactiveUS7118986B2Simple processProblem for CMP processTransistorDecorative surface effectsSemiconductorSilicon on insulator

Methods for forming or etching silicon trench isolation (STI) in a silicon-on-insulator (SOI) region and a bulk silicon region, and a semiconductor device so formed, are disclosed. The STI can be etched simultaneously in the SOI and bulk silicon regions by etching to an uppermost silicon layer using an STI mask, conducting a timed etch that etches to a desired depth in the bulk silicon region and stops on a buried insulator of the SOI region, and etching through the buried insulator of the SOI region. The buried insulator etch for this process can be done with little complexity as part of a hardmask removal step. Further, by choosing the same depth for both the bulk and SOI regions, problems with a subsequent CMP process are avoided. The invention also cleans up the boundary between the SOI and bulk regions where silicon nitride residuals may exist.

Owner:GLOBALFOUNDRIES INC

Double planar gated SOI MOSFET structure

A double gated silicon-on-insulator (SOI) MOSFET is fabricated by using a mandrel shallow trench isolation formation process, followed by a damascene gate. The double gated MOSFET features narrow diffusion lines defined sublithographically or lithographically and shrunk, damascene process defined by an STI-like mandrel process. The double gated SOI MOSFET increases current drive per layout width and provides low out conductance.

Owner:GLOBALFOUNDRIES INC

Method of manufacturing vibrating micromechanical structures

A method for fabrication of single crystal silicon micromechanical resonators using a two-wafer process, including either a Silicon-on-insulator (SOI) or insulating base and resonator wafers, wherein resonator anchors, a capacitive air gap, isolation trenches, and alignment marks are micromachined in an active layer of the base wafer; the active layer of the resonator wafer is bonded directly to the active layer of the base wafer; the handle and dielectric layers of the resonator wafer are removed; viewing windows are opened in the active layer of the resonator wafer; masking the single crystal silicon semiconductor material active layer of the resonator wafer with photoresist material; a single crystal silicon resonator is machined in the active layer of the resonator wafer using silicon dry etch micromachining technology; and the photoresist material is subsequently dry stripped.

Owner:HONEYWELL INT INC

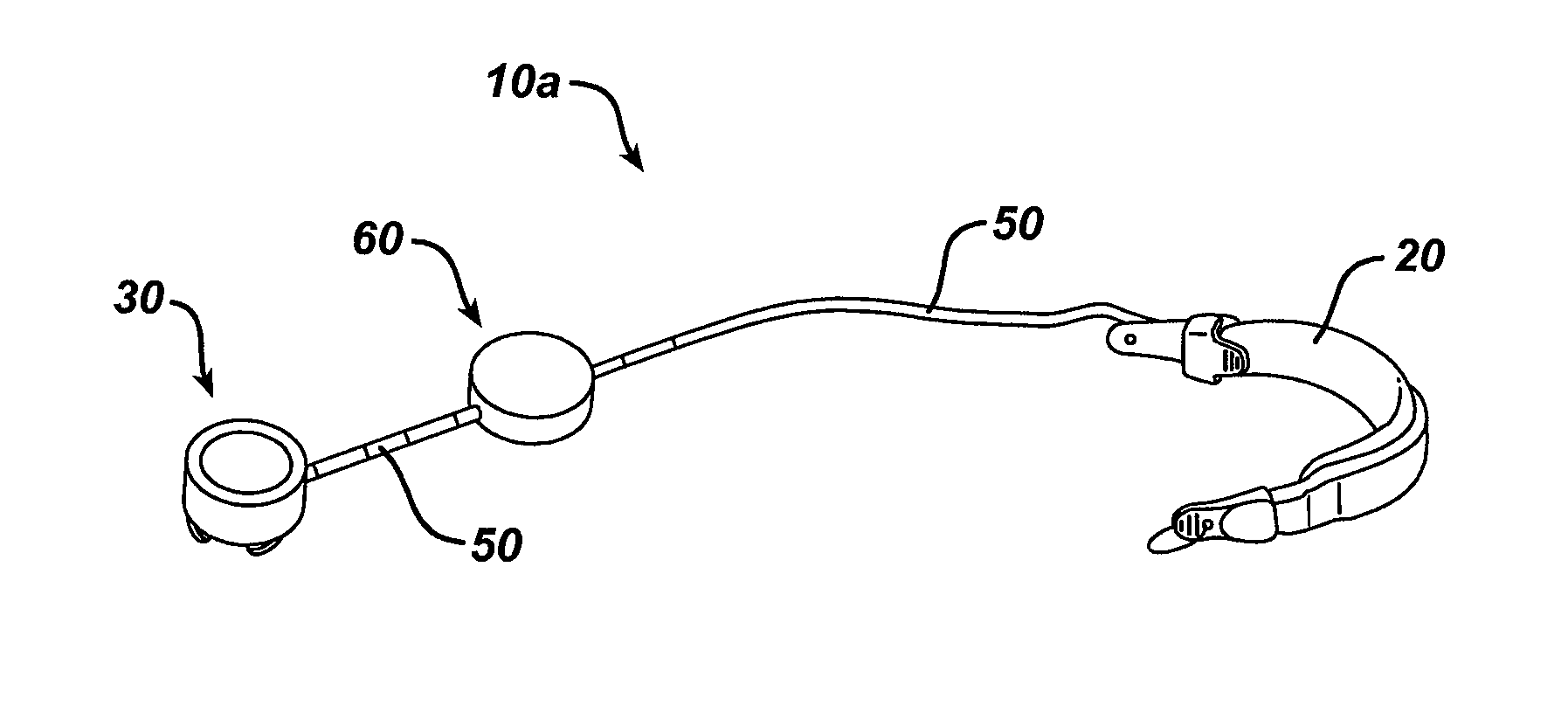

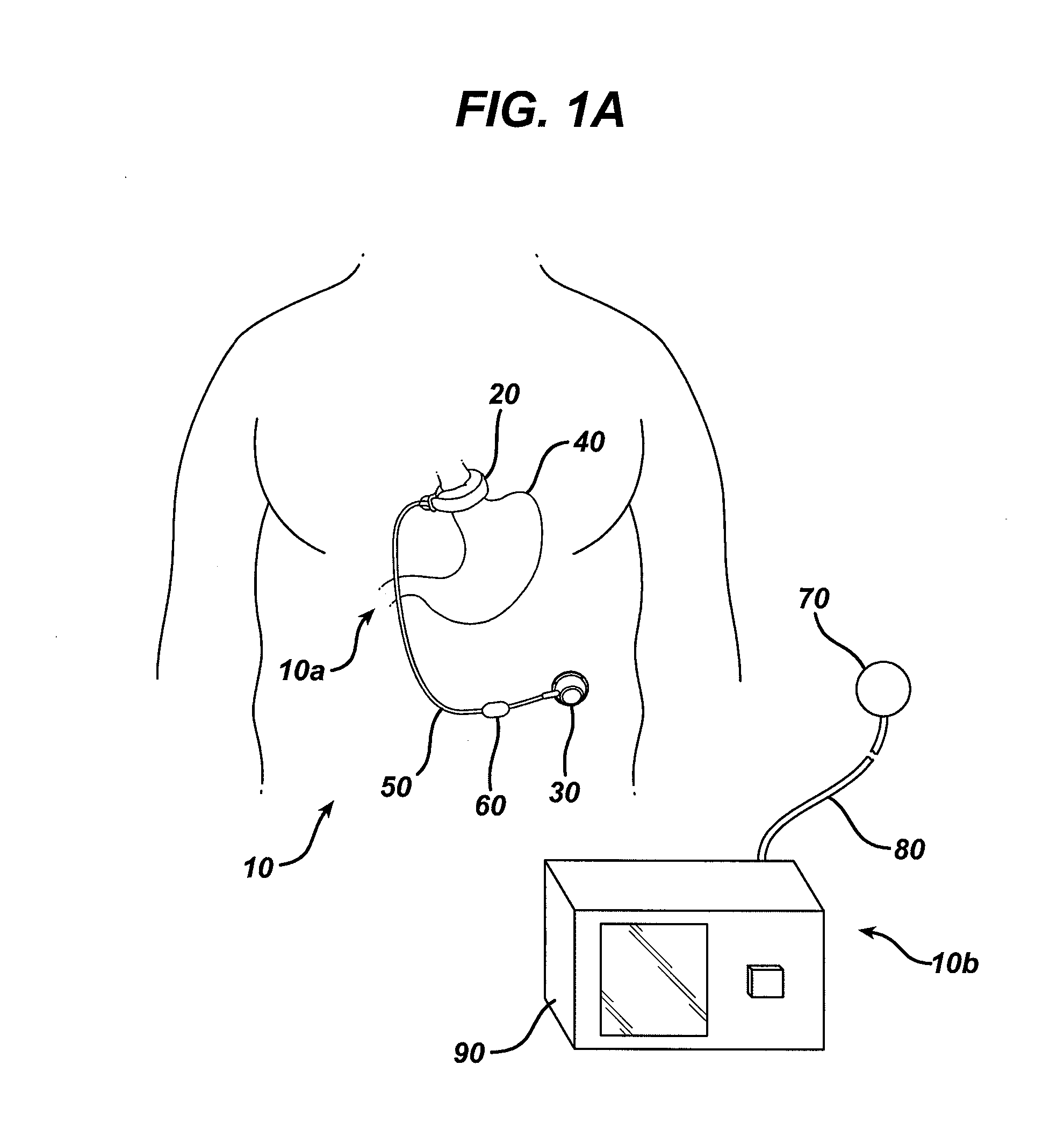

System and method of sterilizing an implantable medical device

An implantable system having internal circuitry configured to withstand a pre-determined amount of sterilization radiation is provided. In general, the system includes an internal control module in electrical communication with an implantable medical device. The internal control module can include a circuit board configured to withstand radiation and / or any number of integrated circuits (e.g., application specific integrated circuits) wherein the circuits or at least some portion thereof are fabricated so as to withstand some amount of radiation. For example, some portion of the circuitry can be fabricated utilizing radiation compliant material(s), silicon-on-insulator technology, and / or gallium arsenide technology. Additionally, the circuitry can include various components which are inherently resistant to such radiation (e.g., components fabricated utilizing magnetic field based technology, surface acoustical wave devices, etc.). A method of sterilizing an implantable medical device via radiation is also provided.

Owner:ETHICON ENDO SURGERY INC

SOI stacked dram logic

A composite, layered, integrated circuit formed by bonding of insulator layers on wafers provides for combination of otherwise incompatible technologies such as trench capacitor DRAM arrays and high performance, low power, low voltage silicon on insulator (SOI) switching transistors and short signal propagation paths between devices formed on respective wafer layers of a chip. In preferred embodiments, an SOI wafer is formed by hydrophilic bonding of a wafer over an integrated circuit device and then cleaving a layer of the second wafer away using implanted hydrogen and low temperature heat treatment. Further wafers of various structures and compositions may be bonded thereover and connections between circuit elements and connection pads in respective wafers made using short vias that provide fast signal propagation as well as providing more numerous connections than can be provided on chip edges.

Owner:IBM CORP

Smooth thin film layers produced by low temperature hydrogen ion cut

A method for producing wafer splitting from ion implantation into silicon after low temperature direct bonding with surface roughness that is ˜1 nm (RMS). This result is an order of magnitude smoother than the previous work (˜10 nm RMS). The key improvement in this work is the use of a low temperature bond resulting in a strong bond before the material is cut. The smooth as-split surfaces produced using a low temperature bond are very important for creation of very thin (<50 nm) silicon-on-insulator (SOI), three-dimensional bonded structures and nanostructures that are split after processing.

Owner:EPIR TECH INC

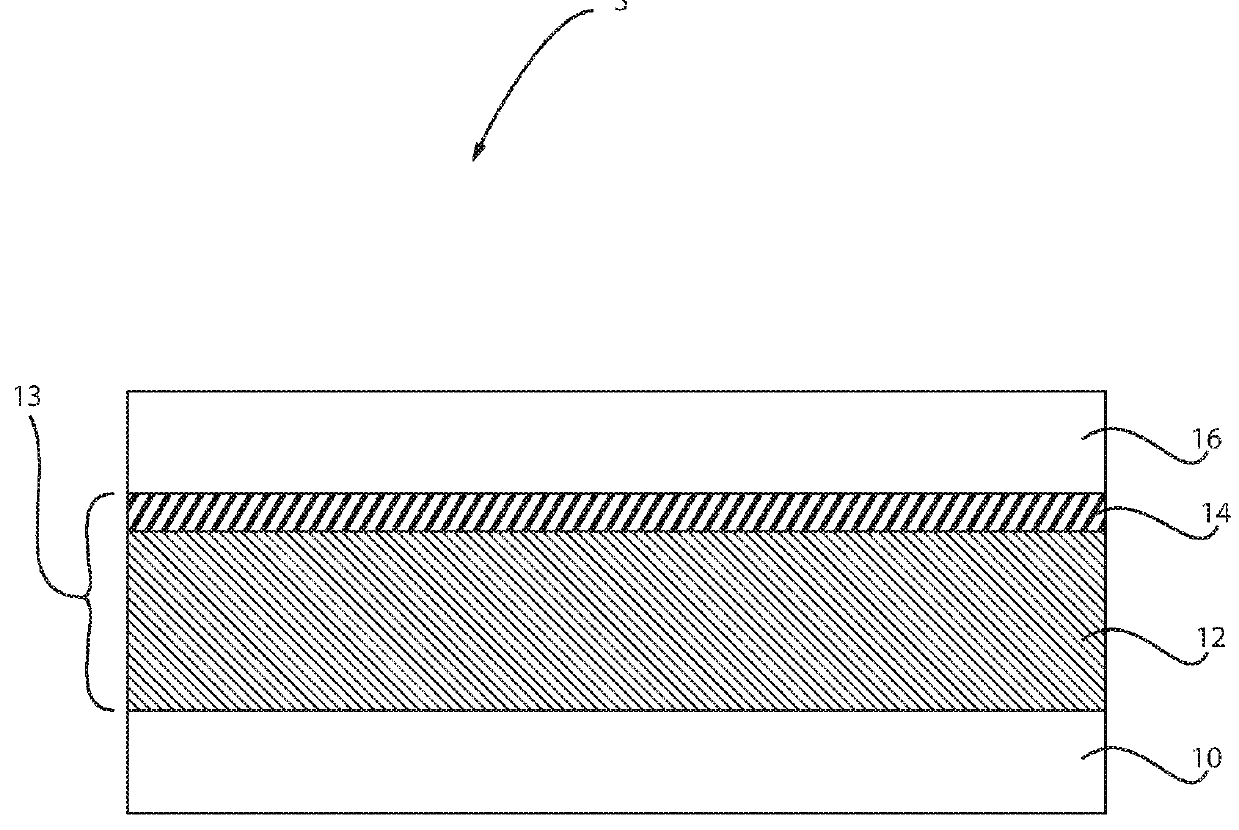

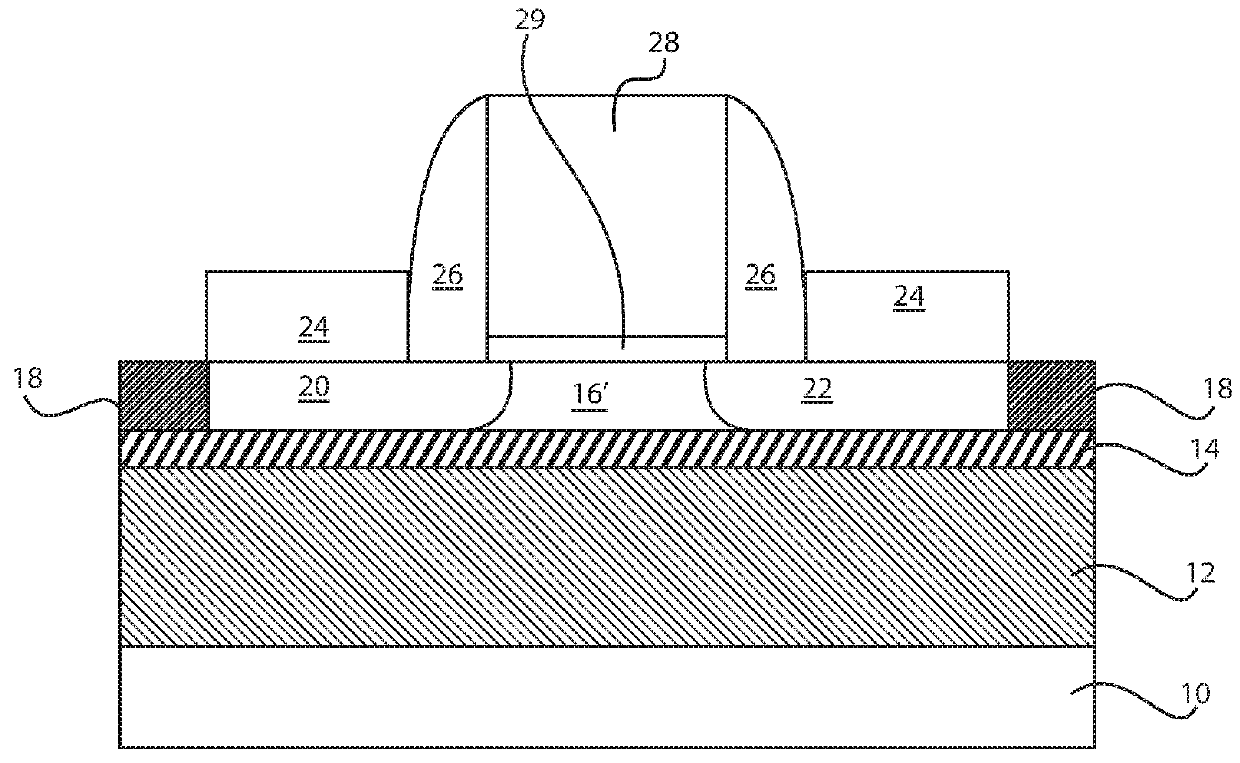

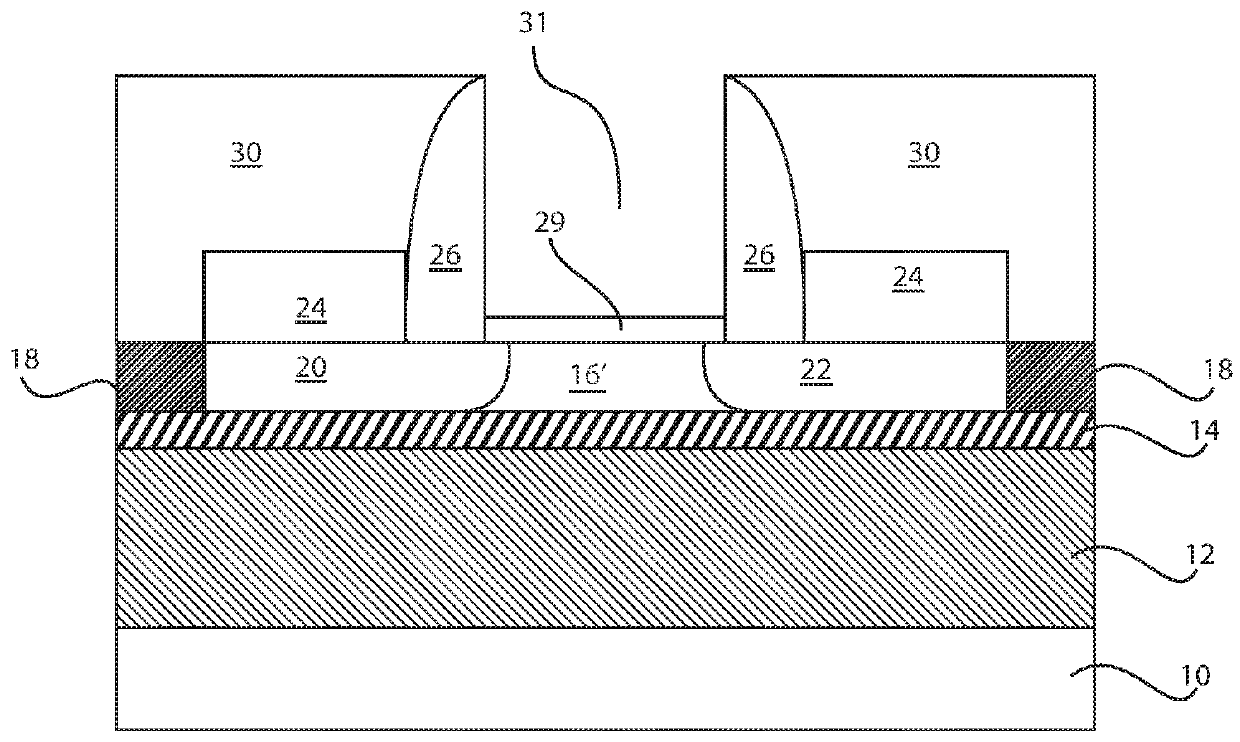

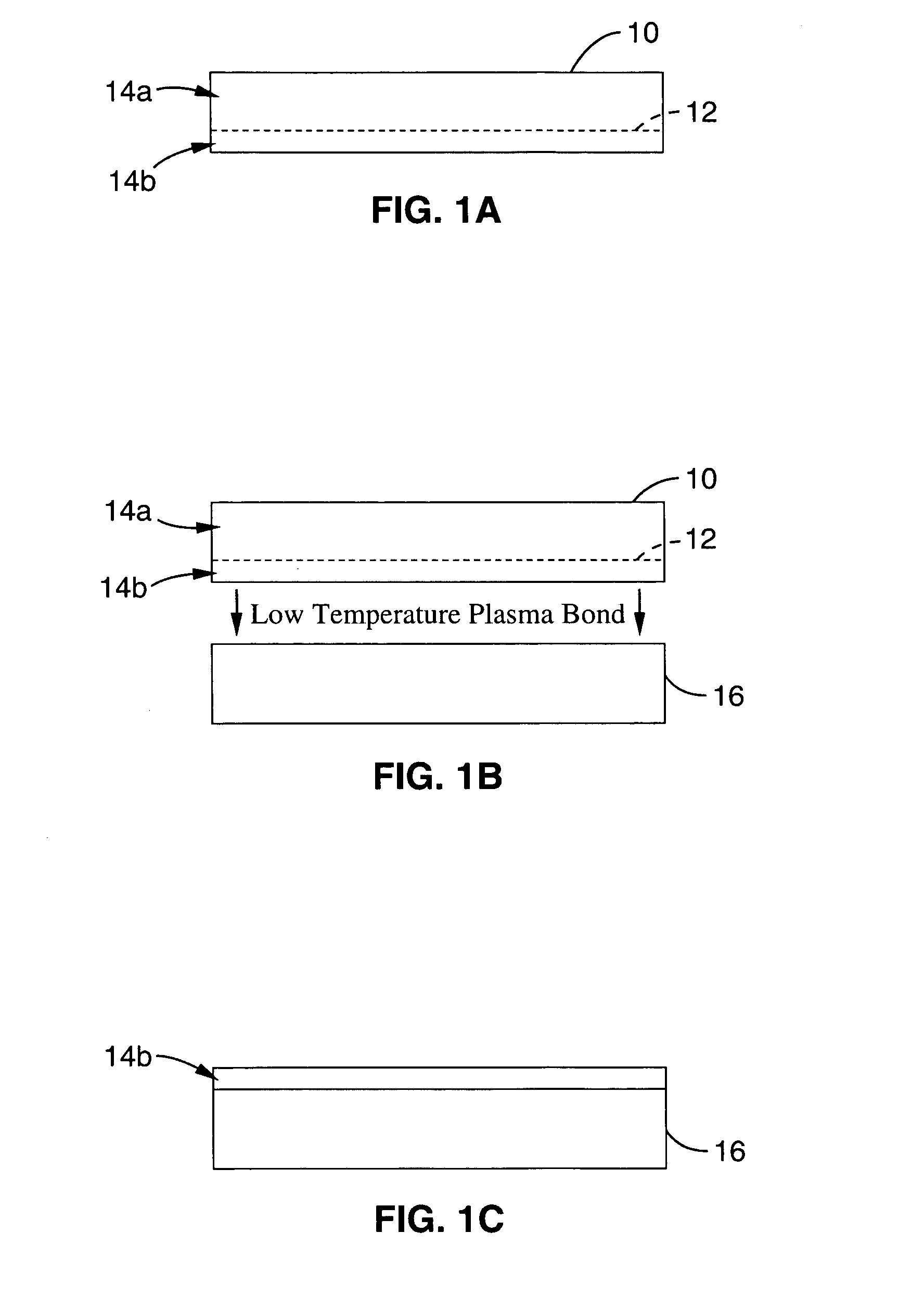

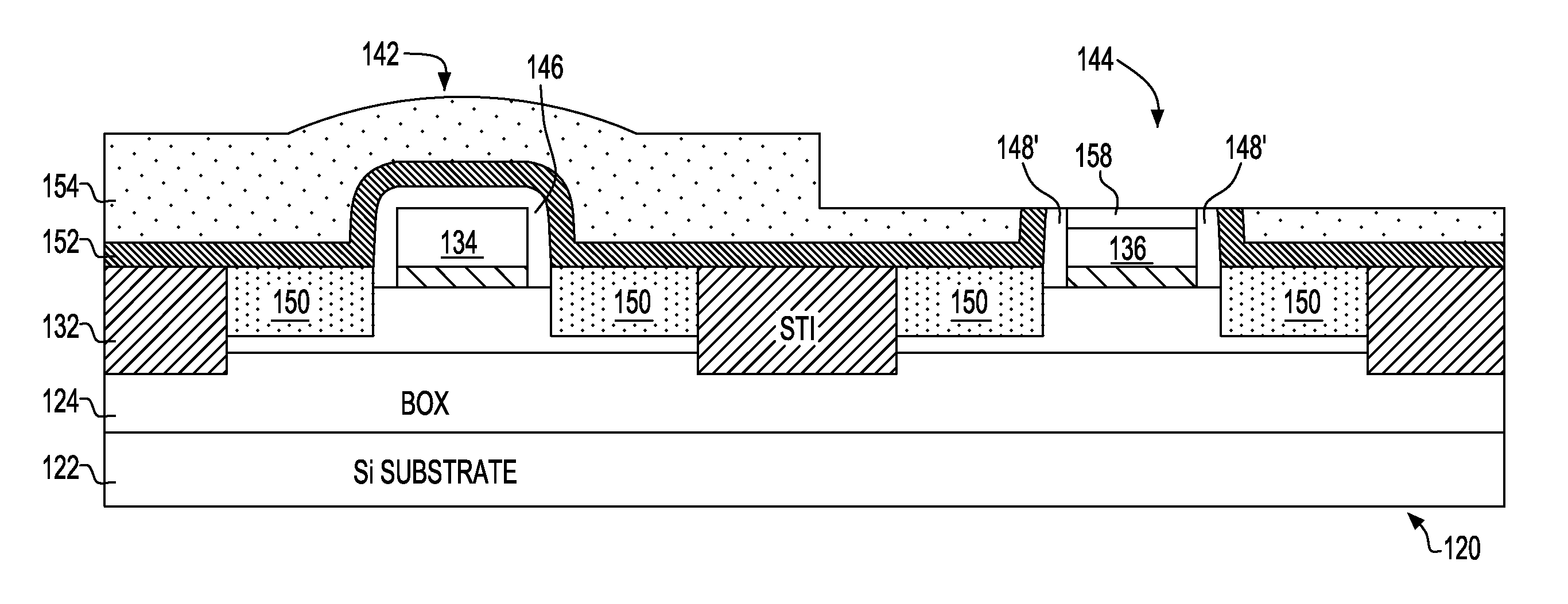

Integrated Circuit (IC) Chip Having Both Metal and Silicon Gate Field Effect Transistors (FETs) and Method of Manufacture

InactiveUS20120292664A1Suppression of short channel effectsWithout impairing performanceTransistorSemiconductor/solid-state device detailsField-effect transistorPolysilicon gate

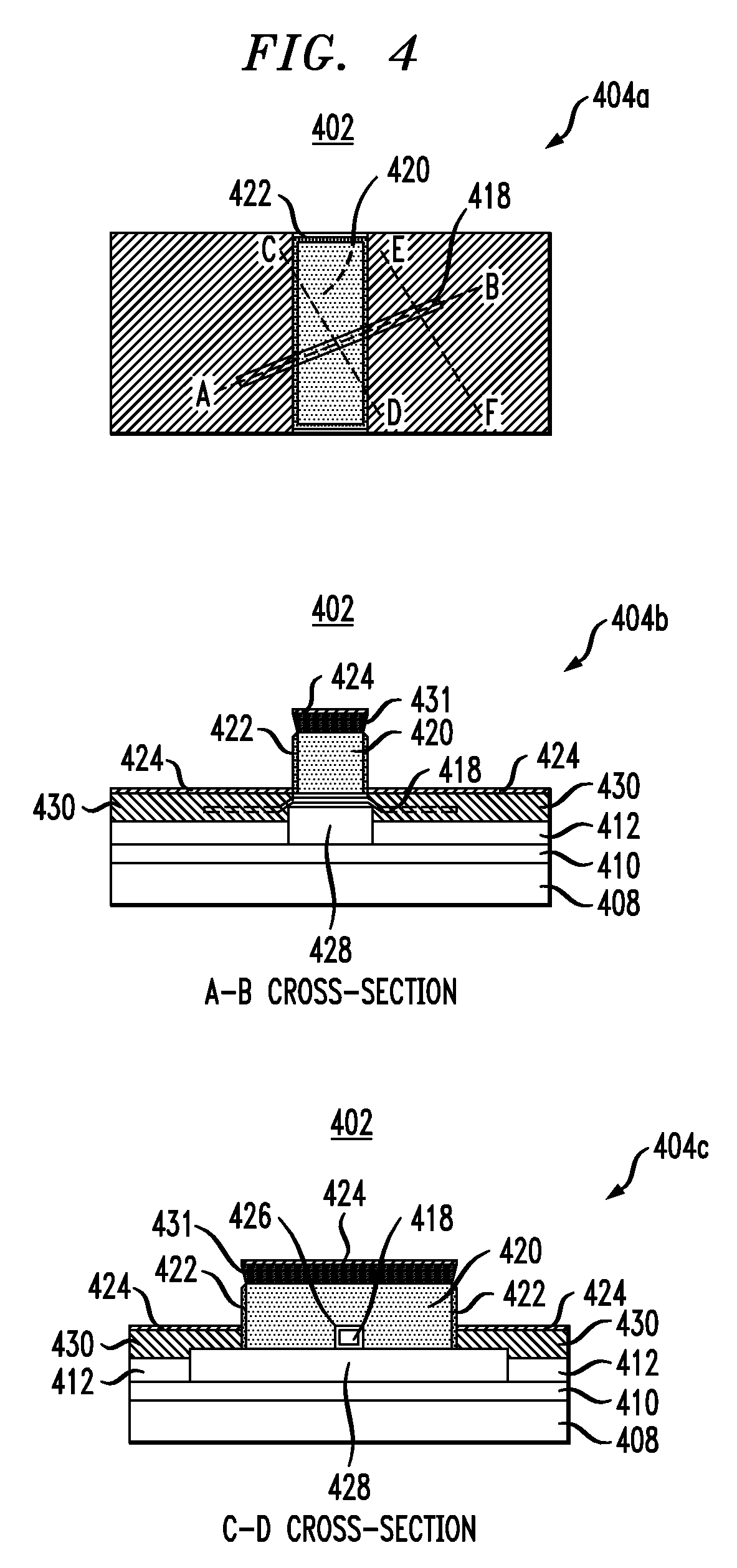

Field Effect Transistors (FETs), Integrated Circuit (IC) chips including the FETs, and a method of forming the FETs on ICs. FET locations are defined on a layered semiconductor wafer, preferably a Silicon On Insulator (SOI) wafer. One or more FET locations are defined as silicon gate locations and remaining as Replacement Metal Gate (RMG) FET locations with at least one of each on the IC. Polysilicon gates are formed in all FET locations. Gates in silicon gate locations are tailored, e.g., doped and silicided. Remaining polysilicon gates are replaced with metal in RMG FET locations. FETs are connected together into circuits with RMG FETs being connected to silicon gate FETs.

Owner:GLOBALFOUNDRIES INC

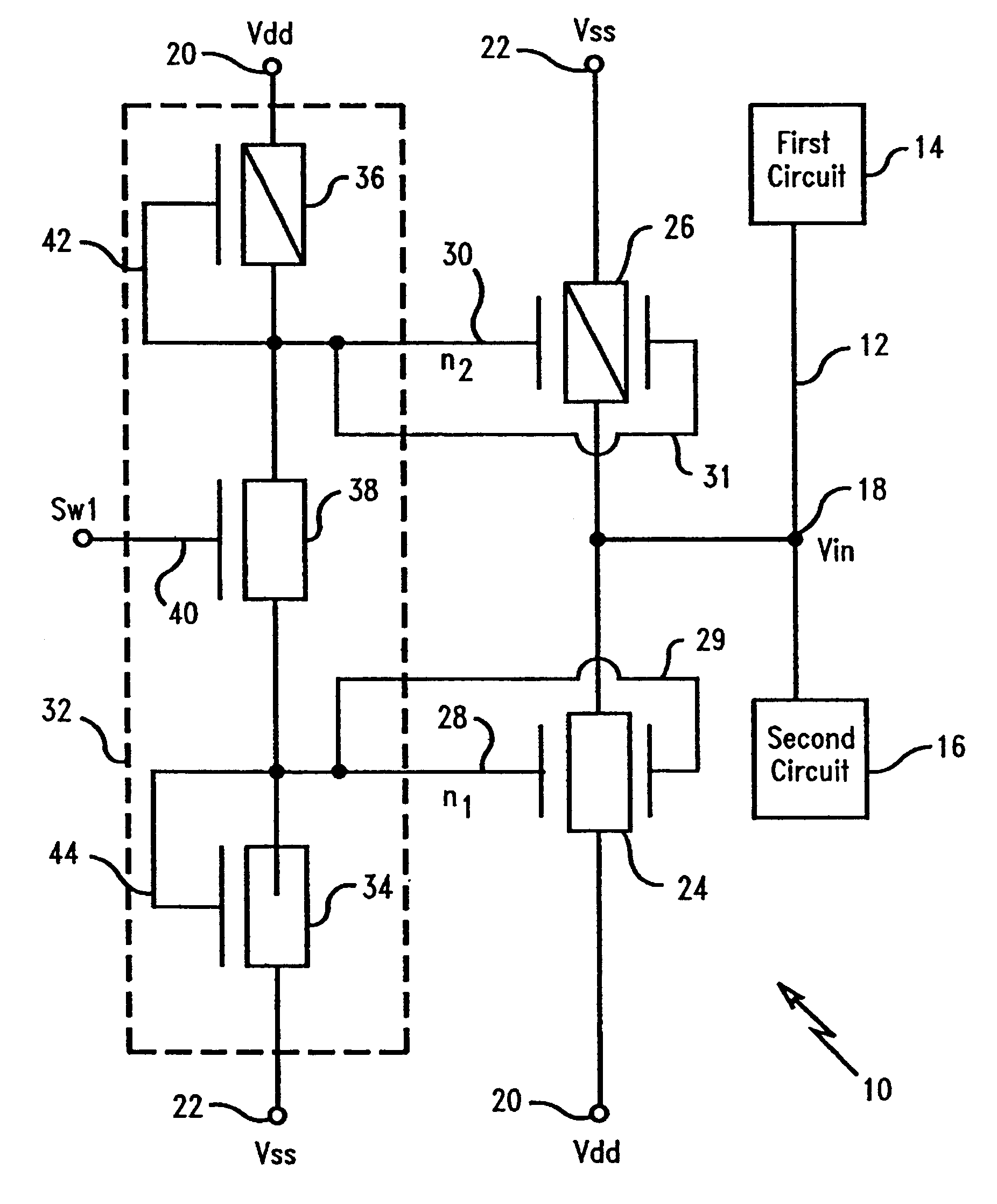

Double-gate low power SOI active clamp network for single power supply and multiple power supply applications

InactiveUS6433609B1Improve performanceReduce power consumptionTransistorPulse automatic controlActive clampLow voltage

A double-gated low power active clamp circuit for digital circuits includes a first double-gated MOSFET serially connected between an upper power supply voltage and an input terminal to be clamped, and a second double-gated MOSFET serially connected between a lower voltage power supply and the input terminal. The voltages at the gates of the first and second double-gated MOSFETs are held at constant reference voltages by a single or double reference circuits. The clamping action can be switched on or off. The double-gated active clamping network can be implemented with a single power supply voltage, or with multiple power supply voltages. The use of the back gates of the double-gated active clamping network enables additional clamping and ESD protection for smaller generations of transistors, such as, those having dimensions below 0.1 micron. The device is particularly suited for use with dynamic threshold double-gated silicon-on-insulator, FINFET, and bulk triple well technologies.

Owner:GLOBALFOUNDRIES US INC

Silicon-on-insulator (SOI) substrate and method of fabricating the same

InactiveUS6211041B1Solid-state devicesSemiconductor/solid-state device manufacturingHydrogenSilicon oxide

There is provided a method of fabricating a silicon-on-insulator substrate, including the steps of (a) forming a silicon substrate at a surface thereof with an oxygen-containing region containing oxygen at such a concentration that oxygen is not precipitated in the oxygen-containing region in later mentioned heat treatment, (b) forming a silicon oxide film at a surface of the silicon substrate, (c) implanting hydrogen ions into the silicon substrate through the silicon oxide film, (d) overlapping the silicon substrate and a support substrate each other so that the silicon oxide film makes contact with the support substrate, and (e) applying heat treatment to the thus overlapped silicon substrate and support substrate to thereby separate the silicon substrate into two pieces at a region into which the hydrogen ions have been implanted, one of the two pieces remaining on the silicon oxide film as a silicon-on-insulator active layer. The support substrate, the silicon oxide film located on the support substrate, and the silicon-on-insulator active layer formed on the silicon oxide film defines a silicon-on-insulator structure. The method makes it possible to significantly reduce crystal defect density in the silicon-on-insulator active layer, which ensures that a substrate made in accordance with the method can be used for fabricating electronic devices thereon.

Owner:NEC CORP

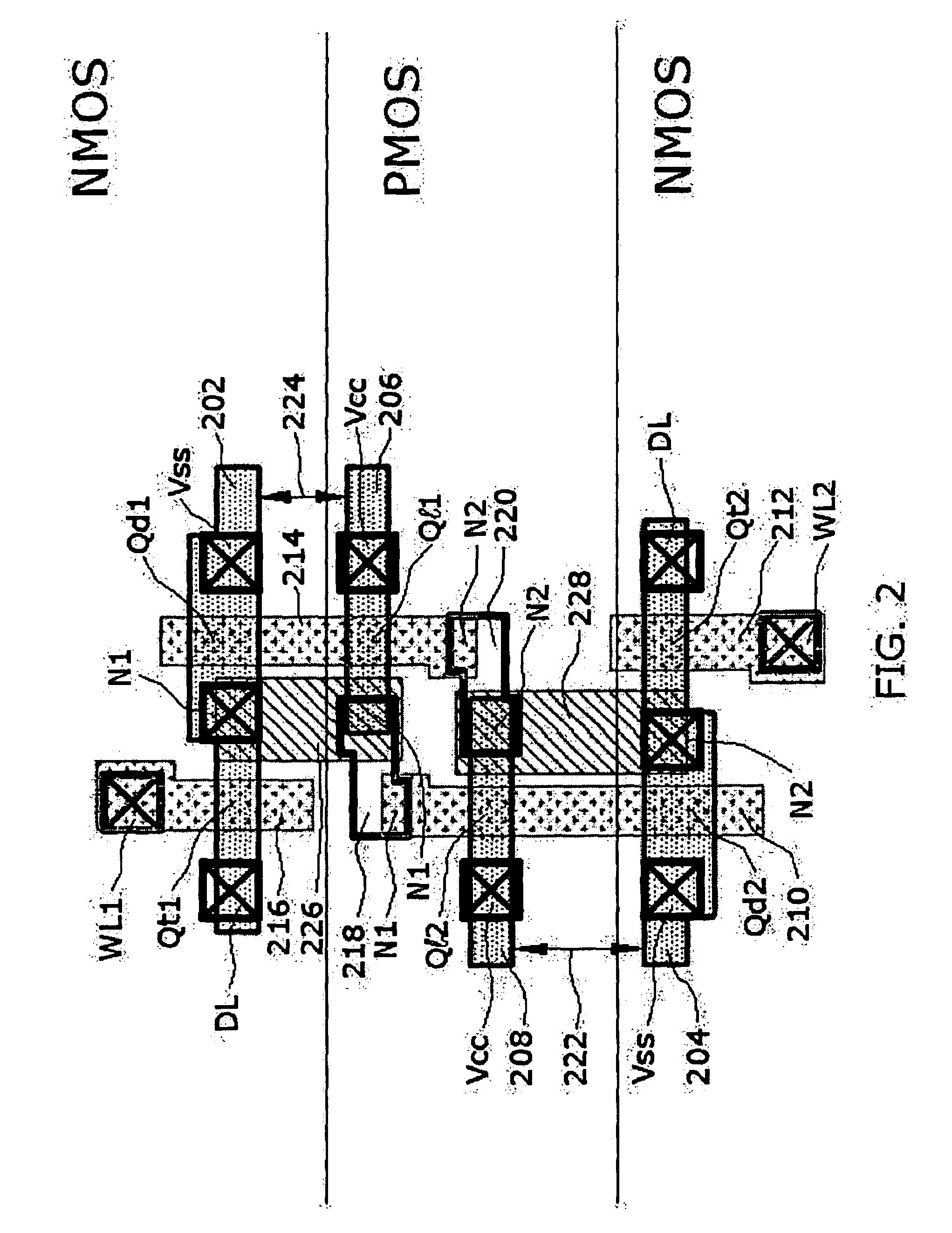

Compact SRAM cell with FinFET

InactiveUS6924560B2Distance minimizationTransistorSolid-state devicesElectrical conductorSemiconductor package

A method and system is disclosed for an SRAM device cell having at least one device of a first semiconductor type and at lease one device of a second semiconductor type. The cell has a first device of the first type constructed as a part of a first FinFET having one or more devices of the first type, a first device of the second type whose poly region is an extension of a poly region of the first device of the first type with no contact needed to connect therebetween, wherein the two devices are constructed using a silicon-on-insulator (SOI) technology so that they are separated by an insulator region therebetween so as to minimize the distance between the two devices.

Owner:TAIWAN SEMICON MFG CO LTD

Symmetrically and asymmetrically stacked transistor grouping RF switch

InactiveUS20060194567A1Reduce areaImprove area efficiencyTransistorDc-dc conversionMOSFETEngineering

A silicon-on-insulator (SOI) RF switch adapted for improved power handling capability using a reduced number of transistors is described. In one embodiment, an RF switch includes pairs of switching and shunting stacked transistor groupings to selectively couple RF signals between a plurality of input / output nodes and a common RF node. The switching and shunting stacked transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. In one embodiment, the transistor groupings are “symmetrically” stacked in the RF switch (i.e., the transistor groupings all comprise an identical number of transistors). In another embodiment, the transistor groupings are “asymmetrically” stacked in the RF switch (i.e., at least one transistor grouping comprises a number of transistors that is unequal to the number of transistors comprising at least one other transistor grouping). The stacked configuration of the transistor groupings enable the RF switch to withstand RF signals of varying and increased power levels. The asymmetrically stacked transistor grouping RF switch facilitates area-efficient implementation of the RF switch in an integrated circuit. Maximum input and output signal power levels can be withstood using a reduced number of stacked transistors.

Owner:PSEMI CORP

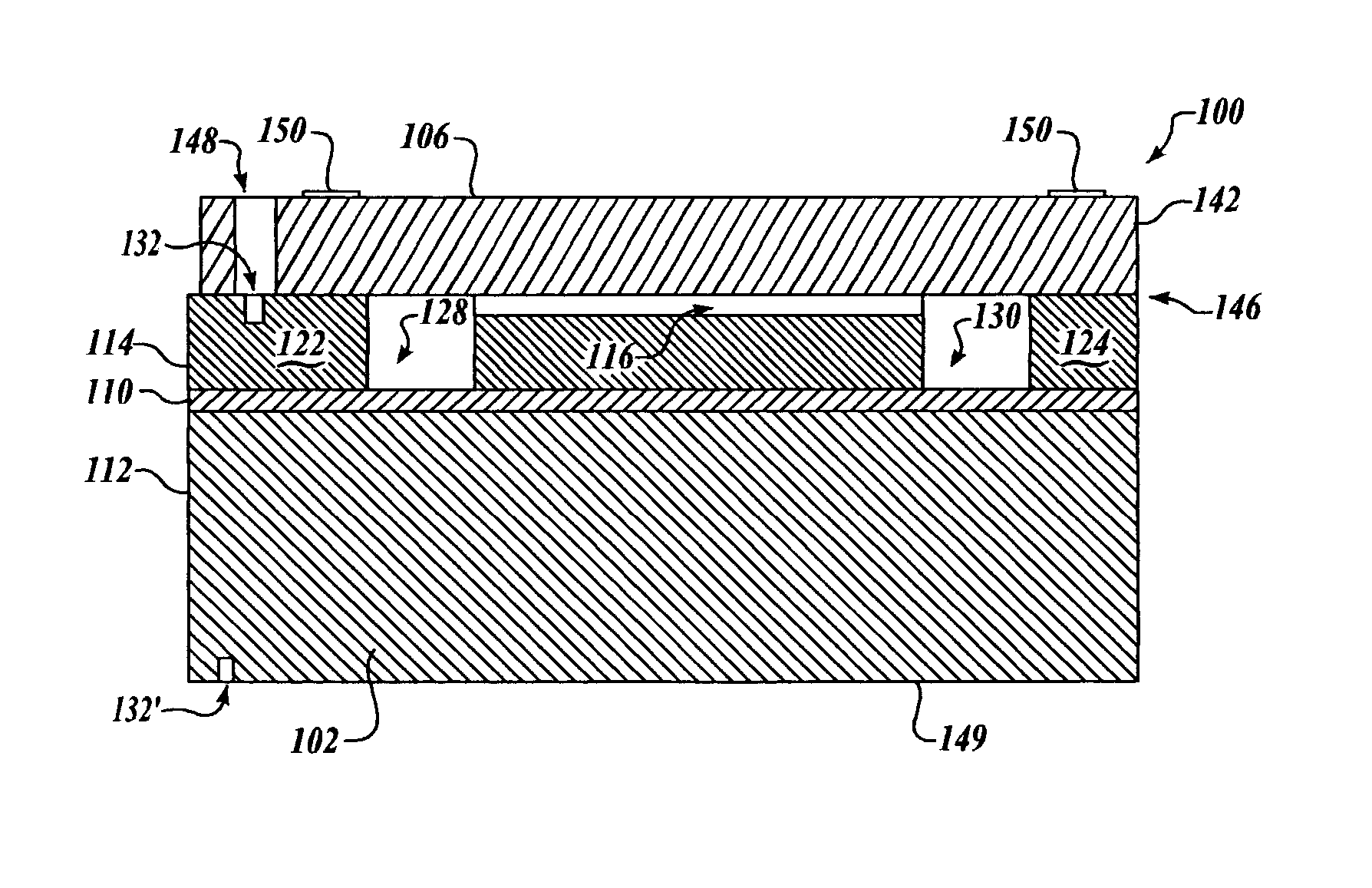

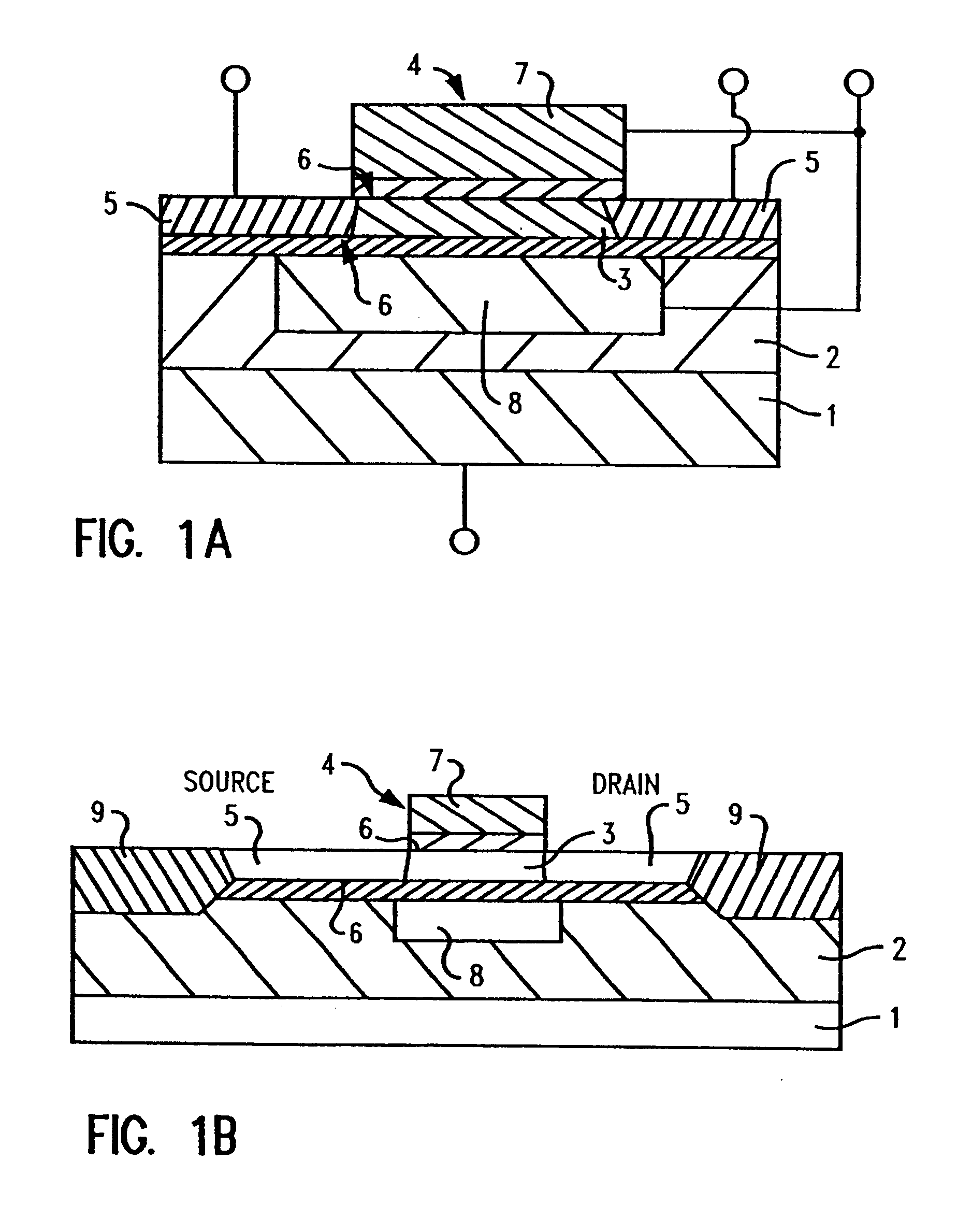

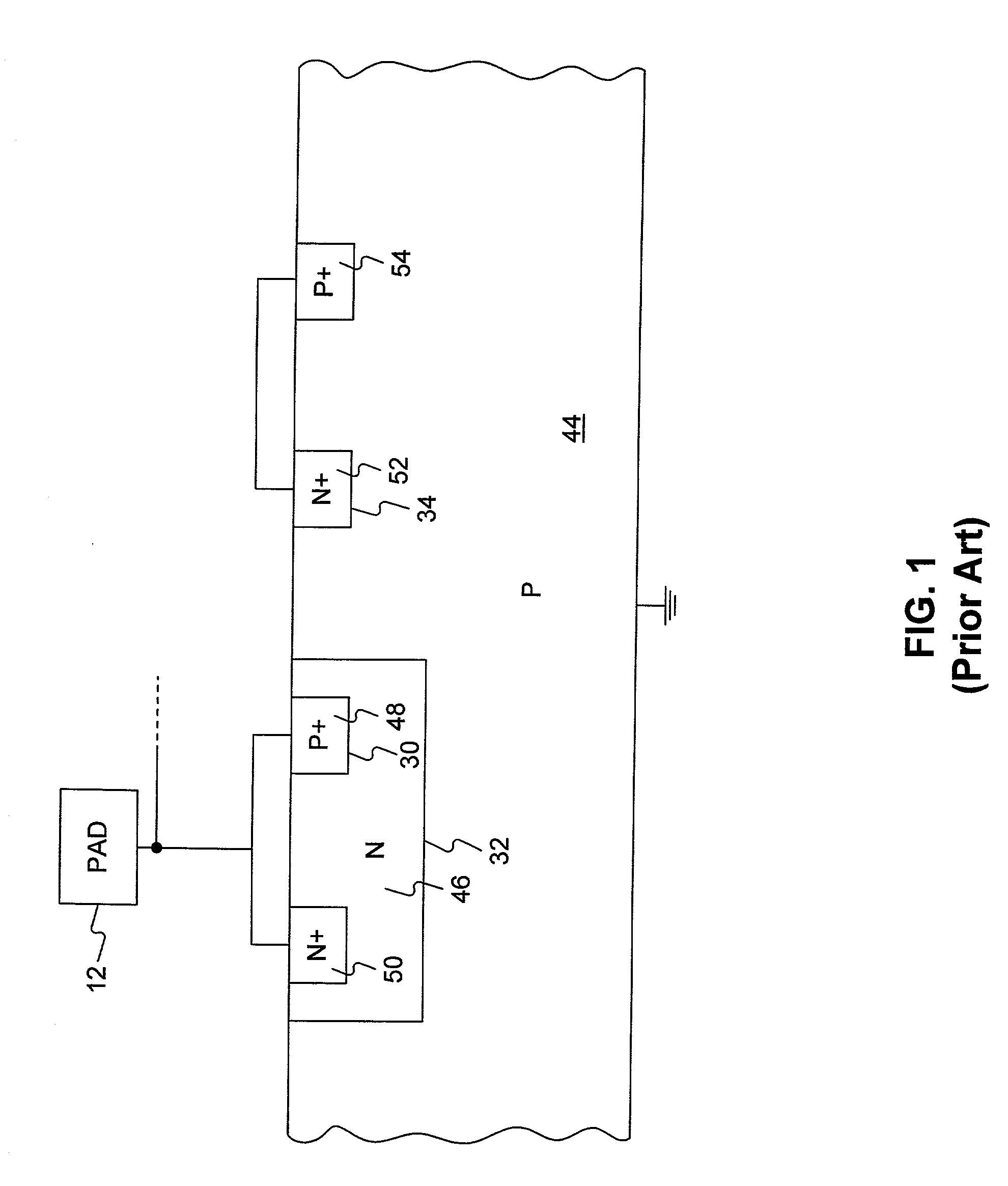

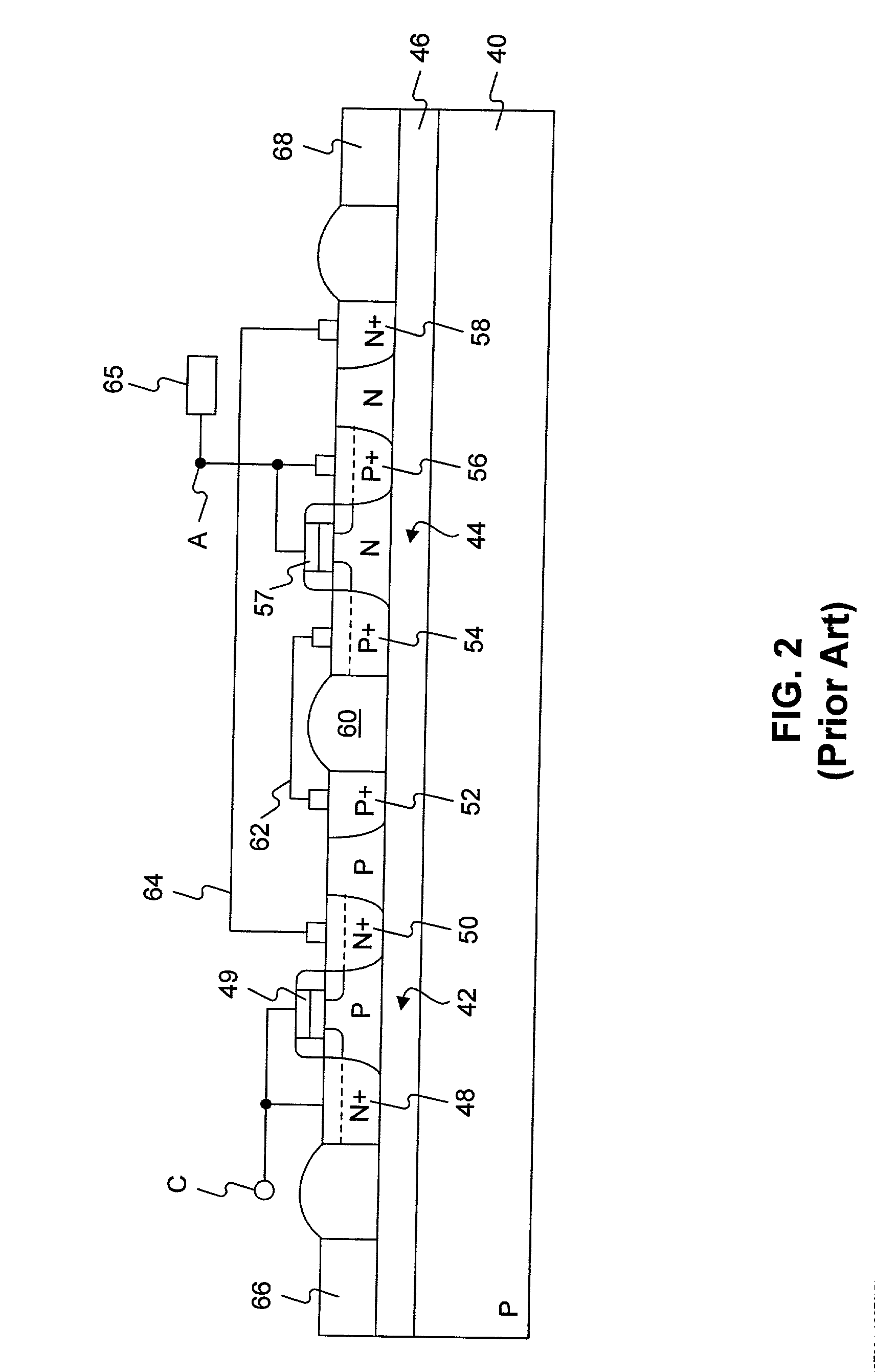

Semiconductor diode with reduced leakage

InactiveUS20050035410A1Reduce reverse leakage currentReduce leakage currentTransistorThyristorGate dielectricPermittivity

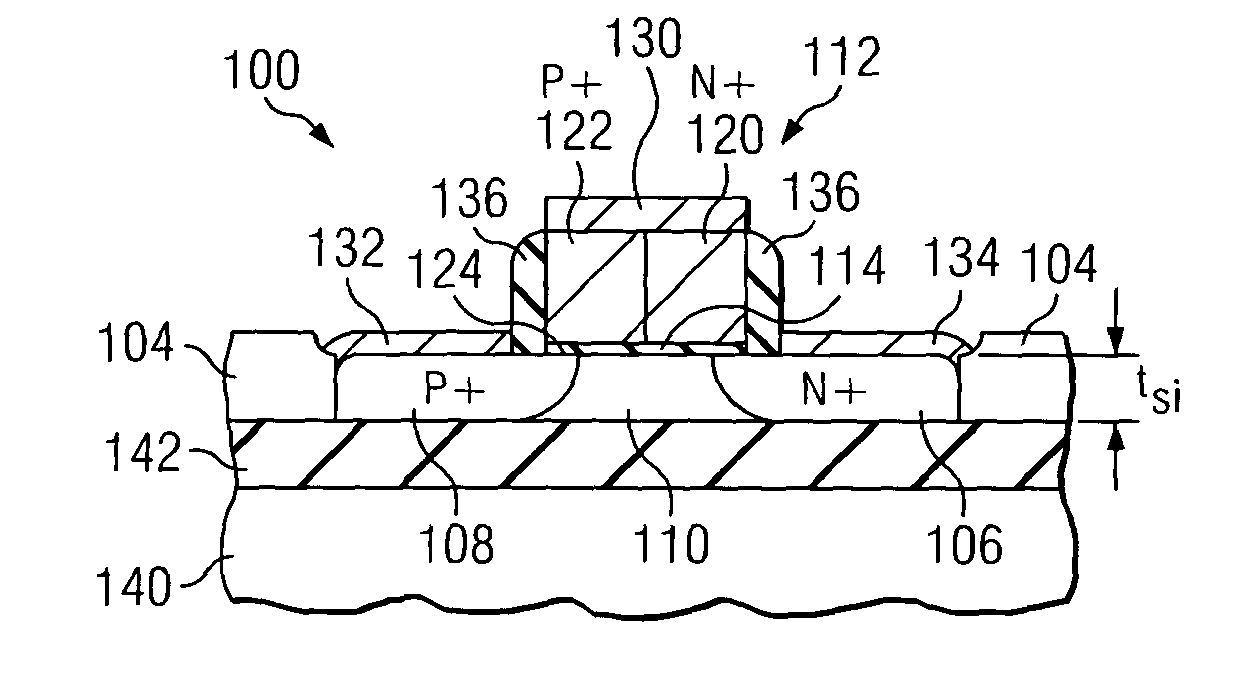

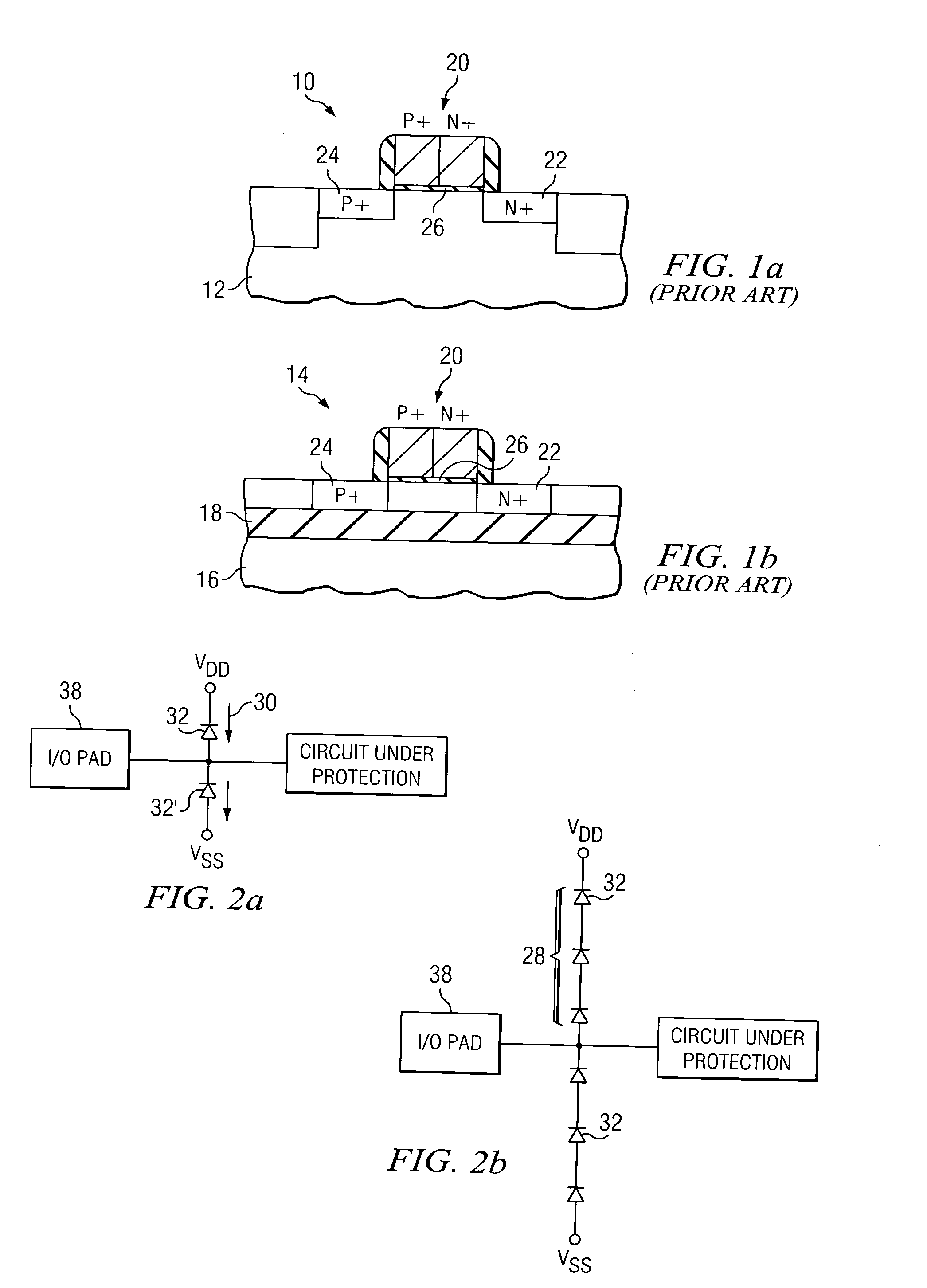

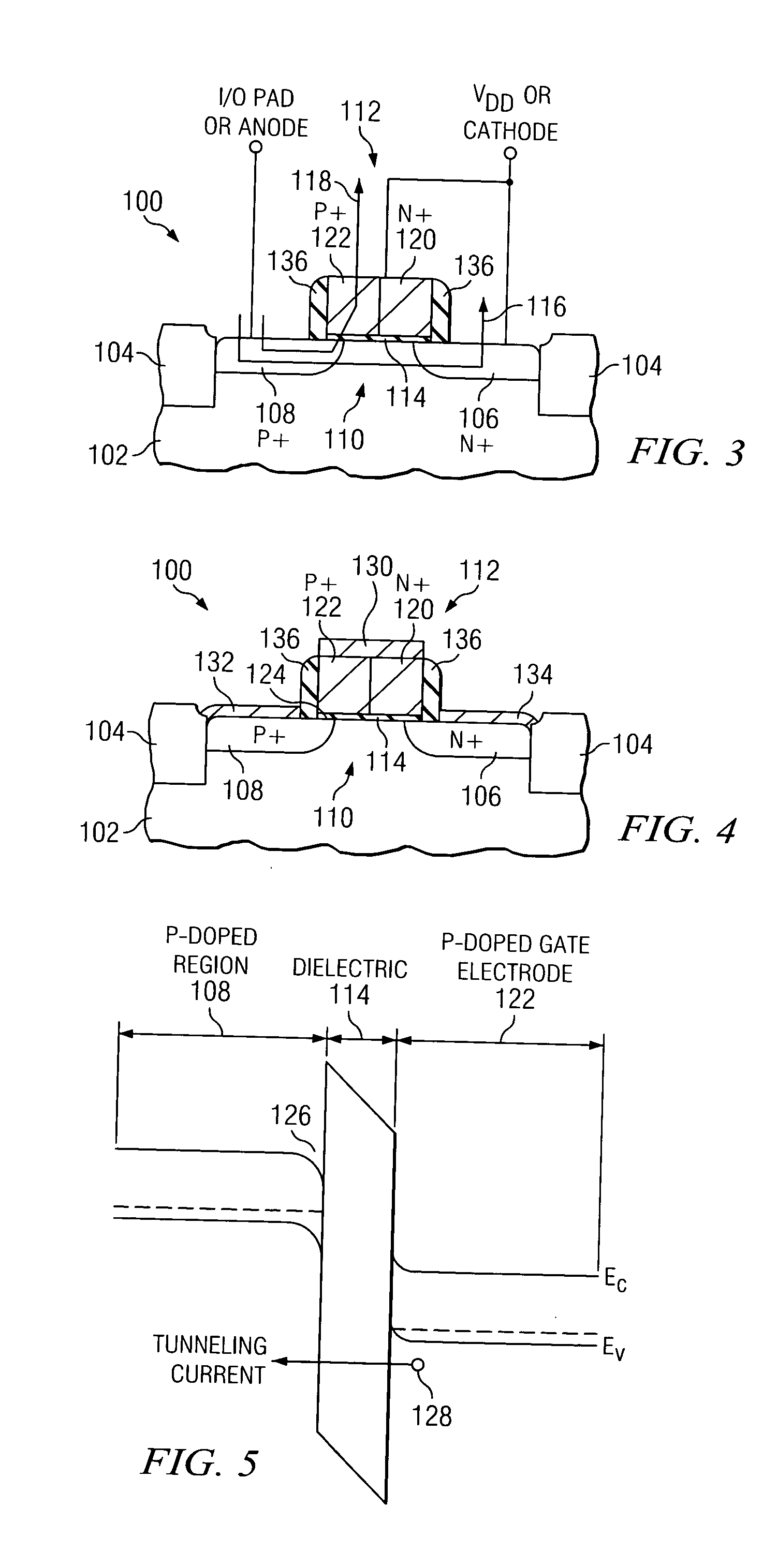

A diode 100 is formed on a silicon-on-insulator substrate that includes a silicon layer overlying an insulator layer 142. An active region is formed in the silicon layer and includes a p-doped region 108 and an n-doped region 106 separated by a body region 110. A high permittivity gate dielectric 114 overlies the body region 110 and a gate electrode 112 overlies the gate dielectric 114. As an example, the diode can be used for ESD protection.

Owner:TAIWAN SEMICON MFG CO LTD

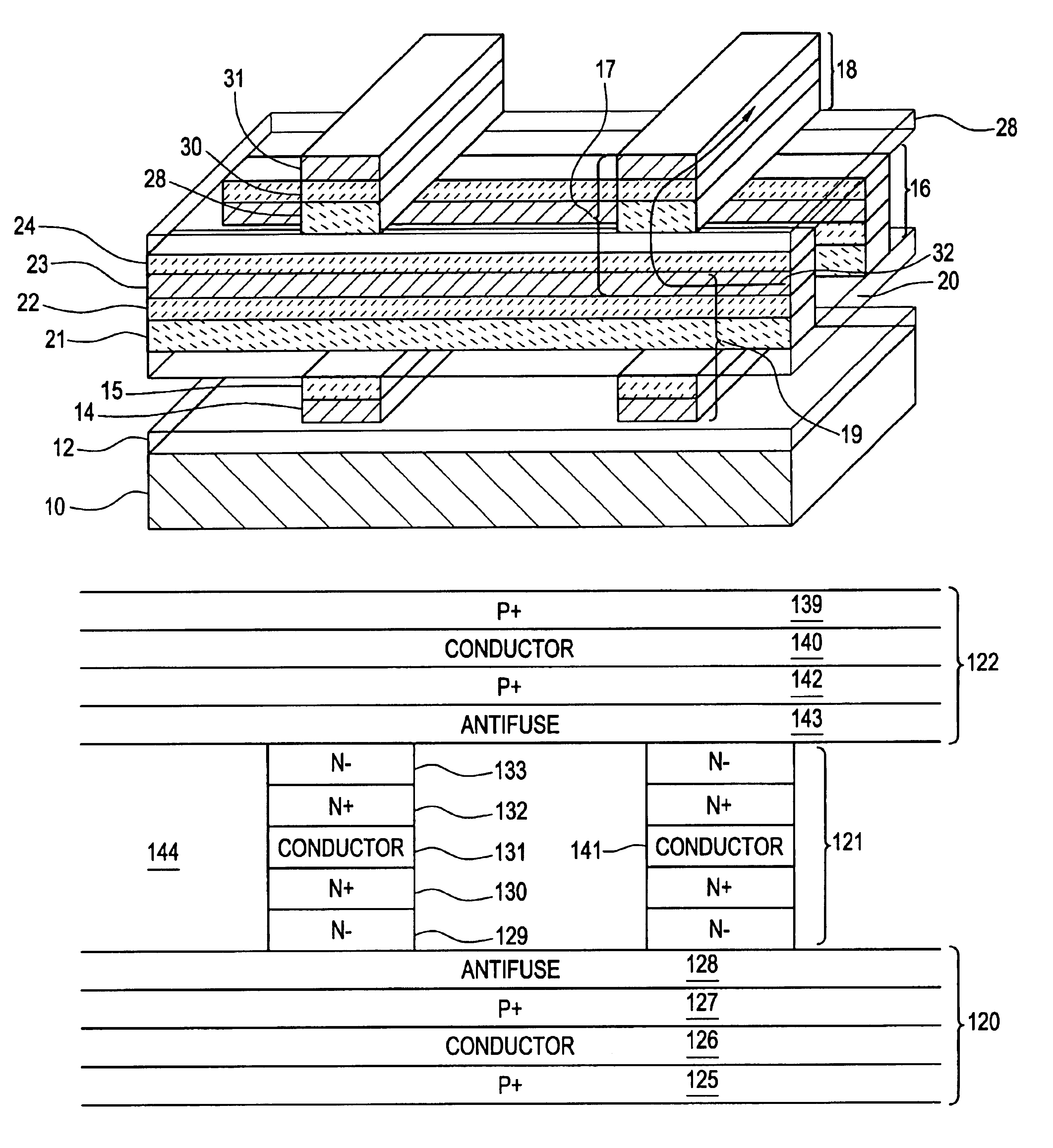

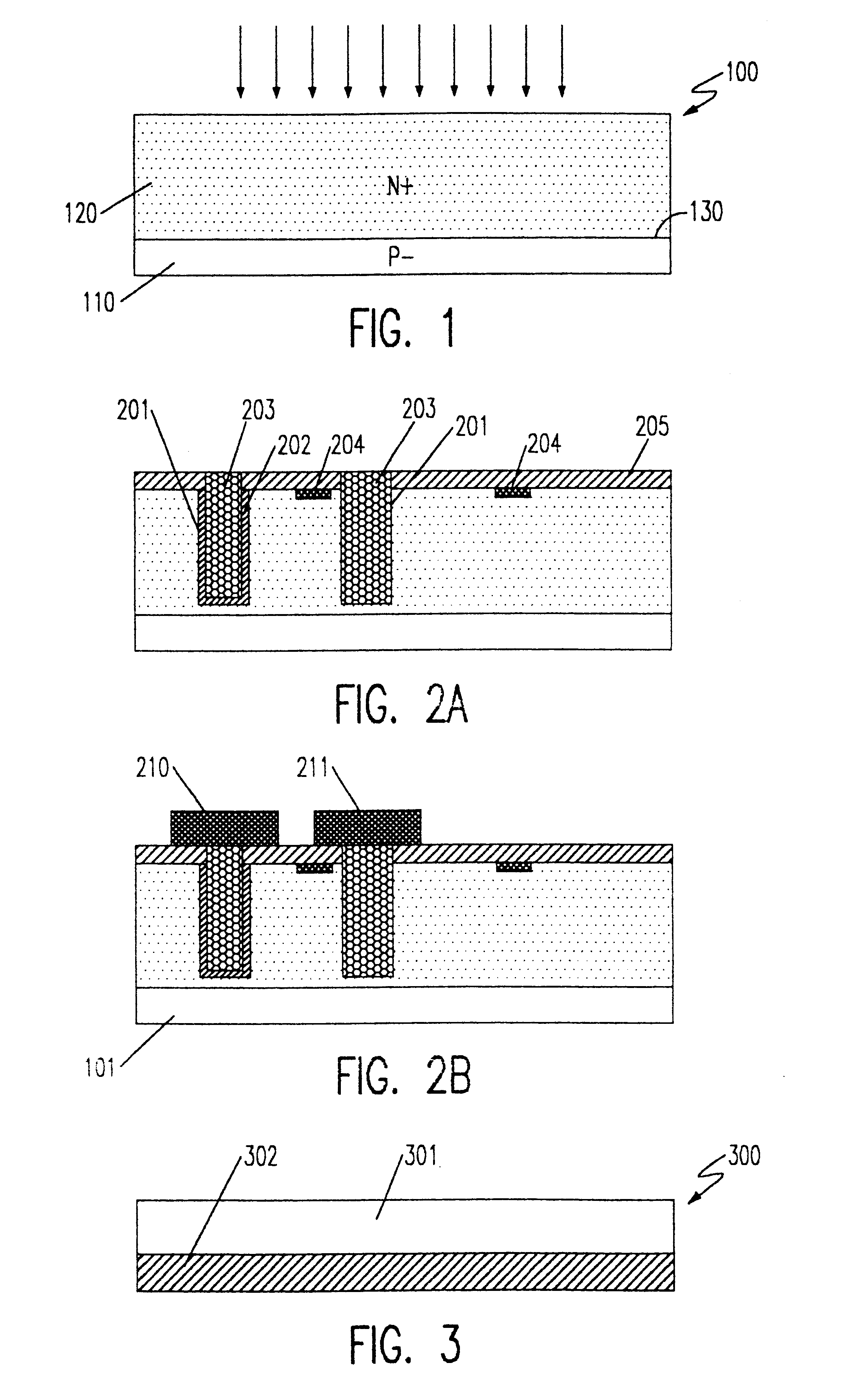

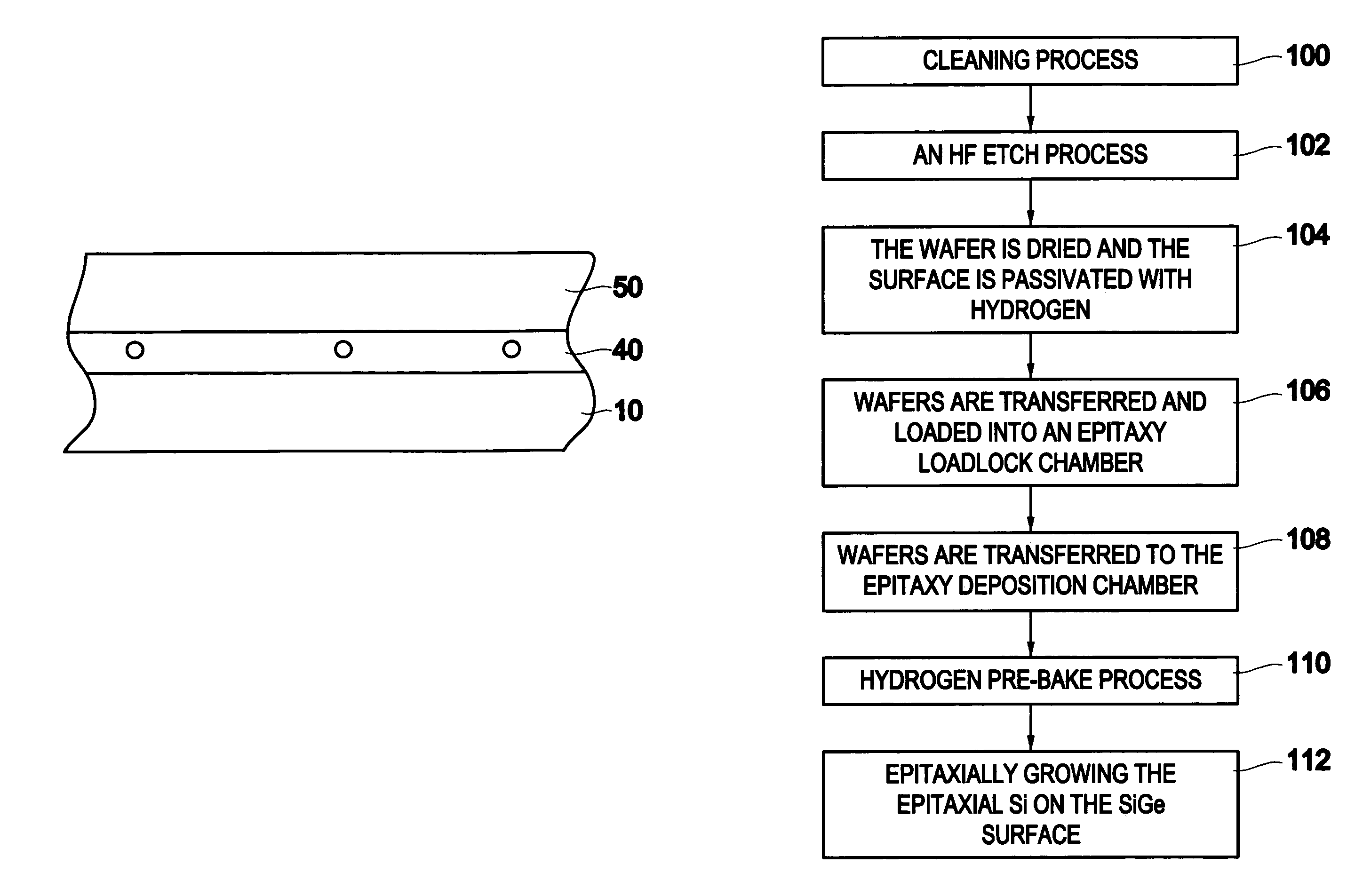

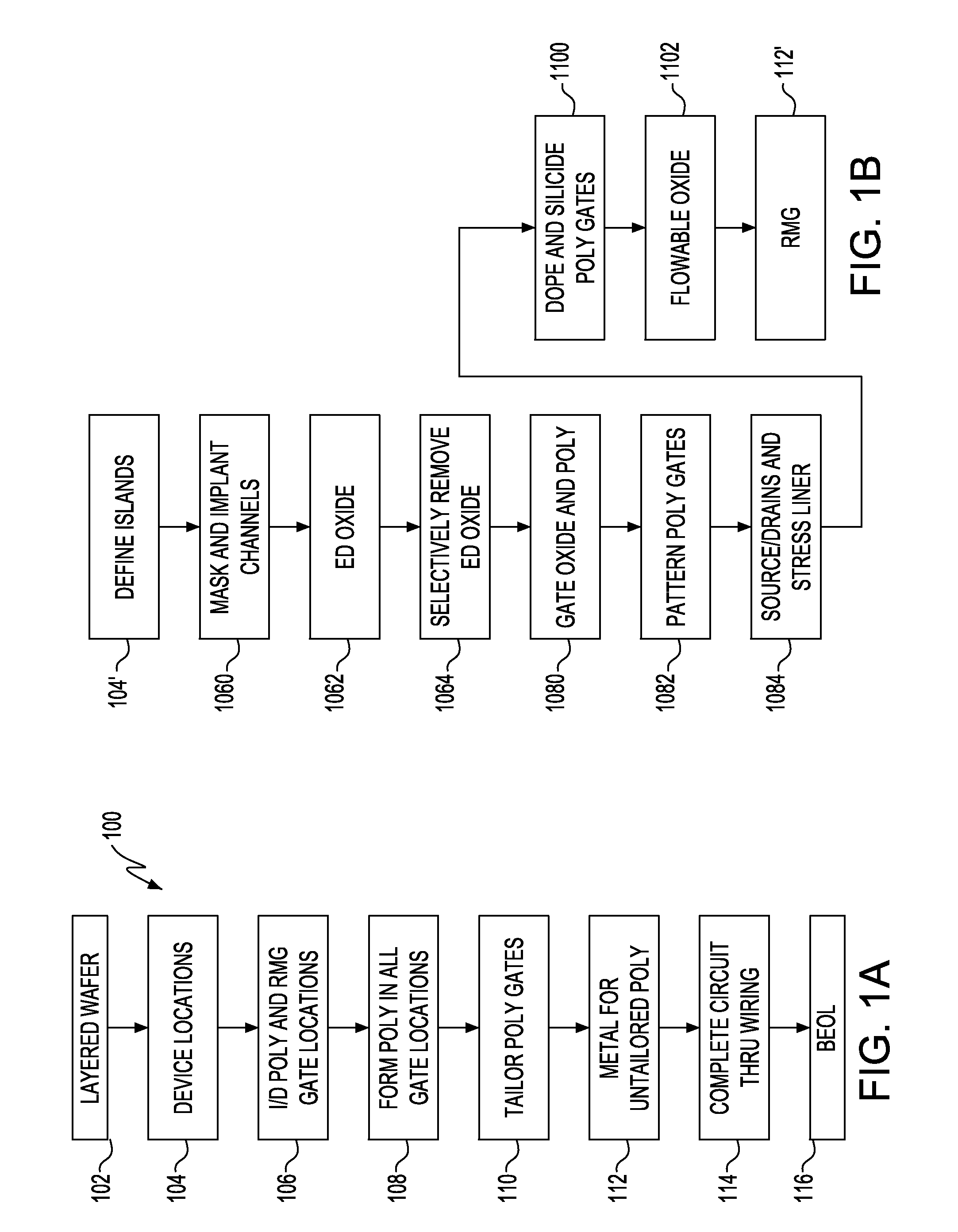

High mobility heterojunction complementary field effect transistors and methods thereof

InactiveUS7057216B2High hole mobilitySimilar current carrying capabilityTransistorSolid-state devicesHeterojunctionPresent day

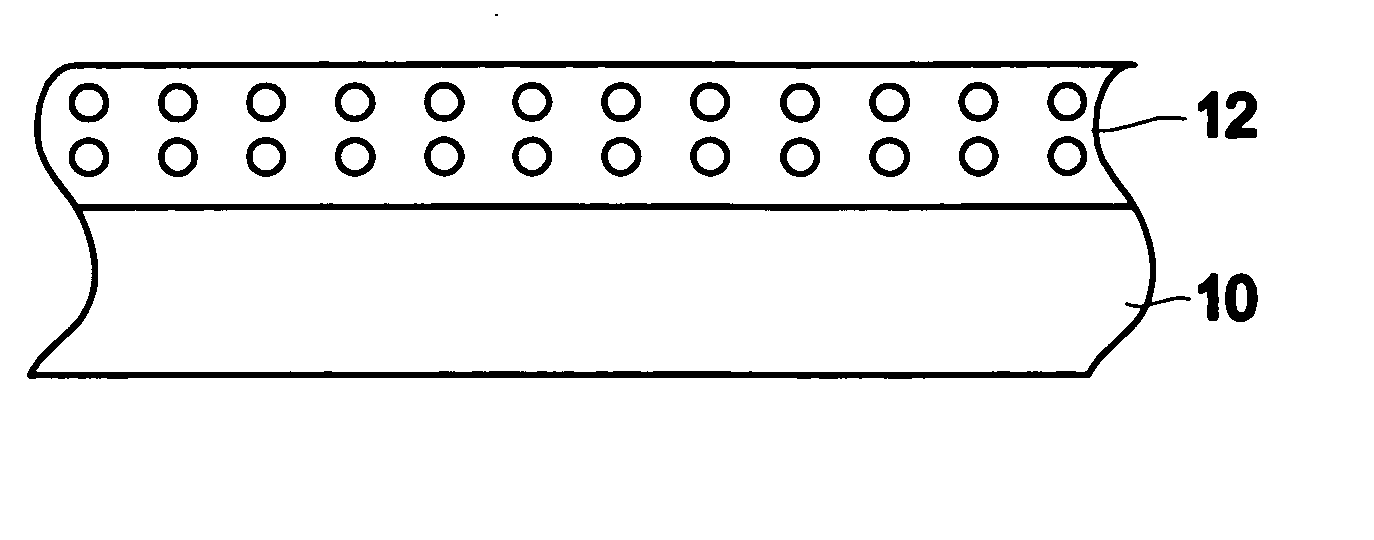

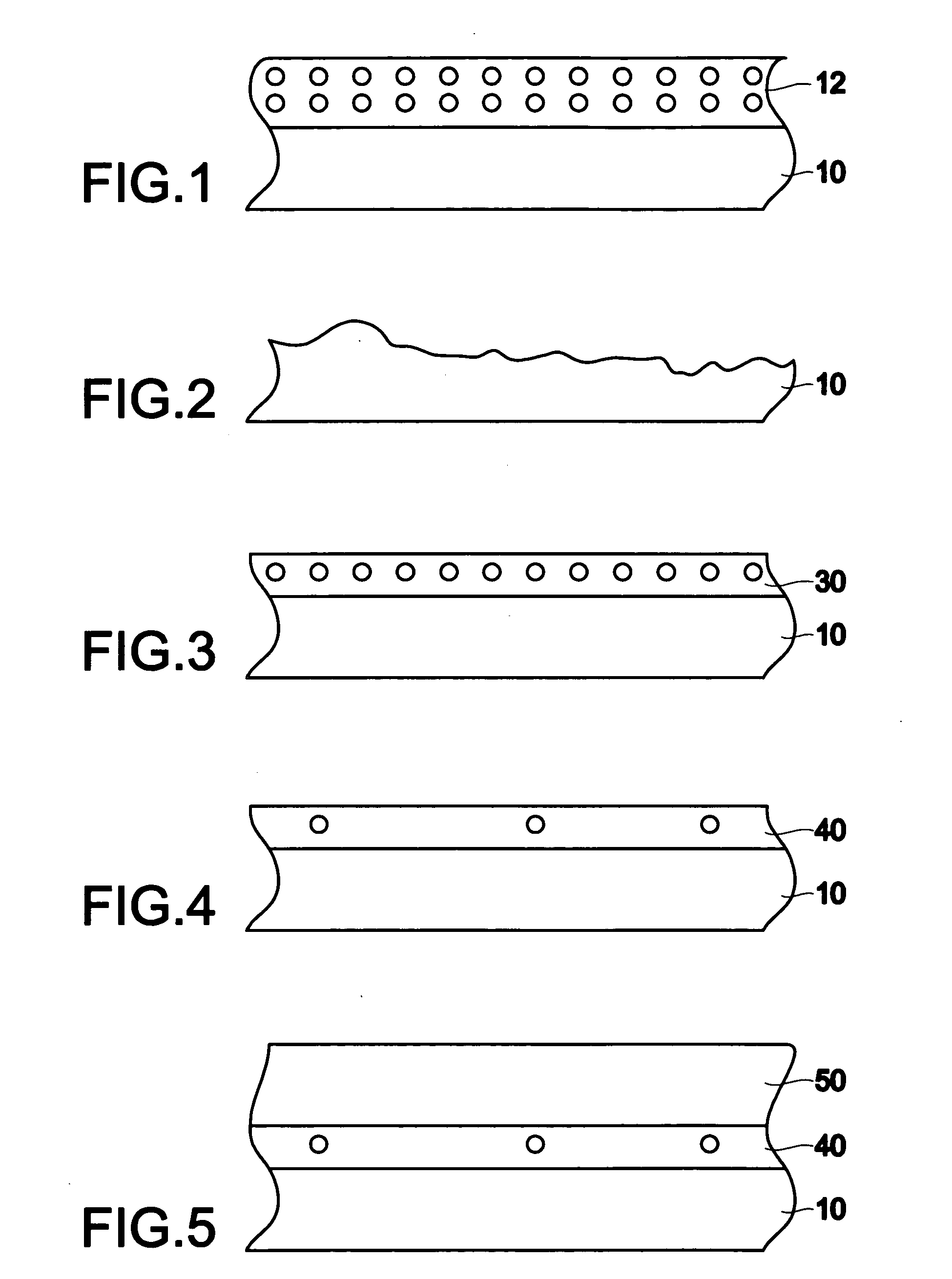

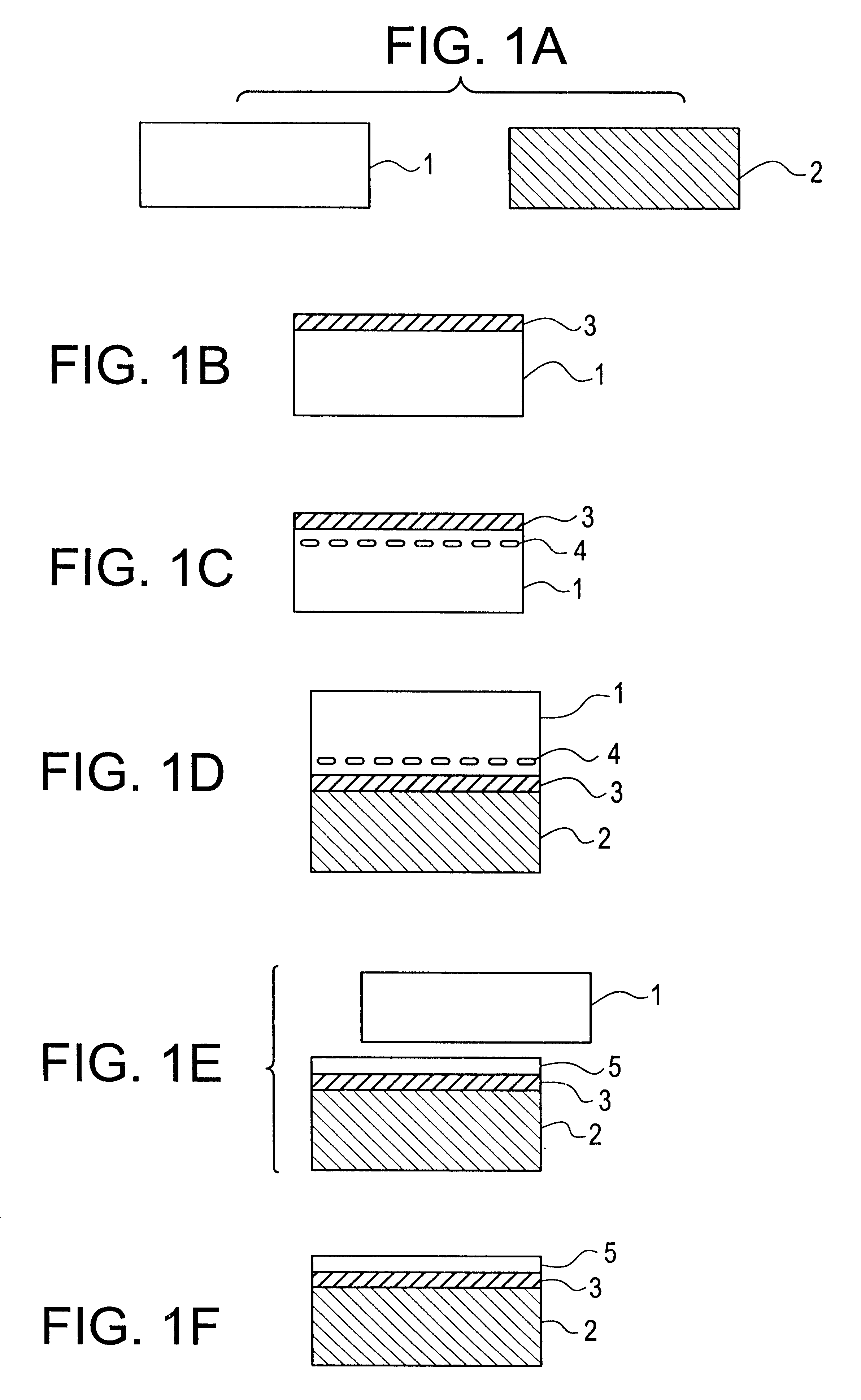

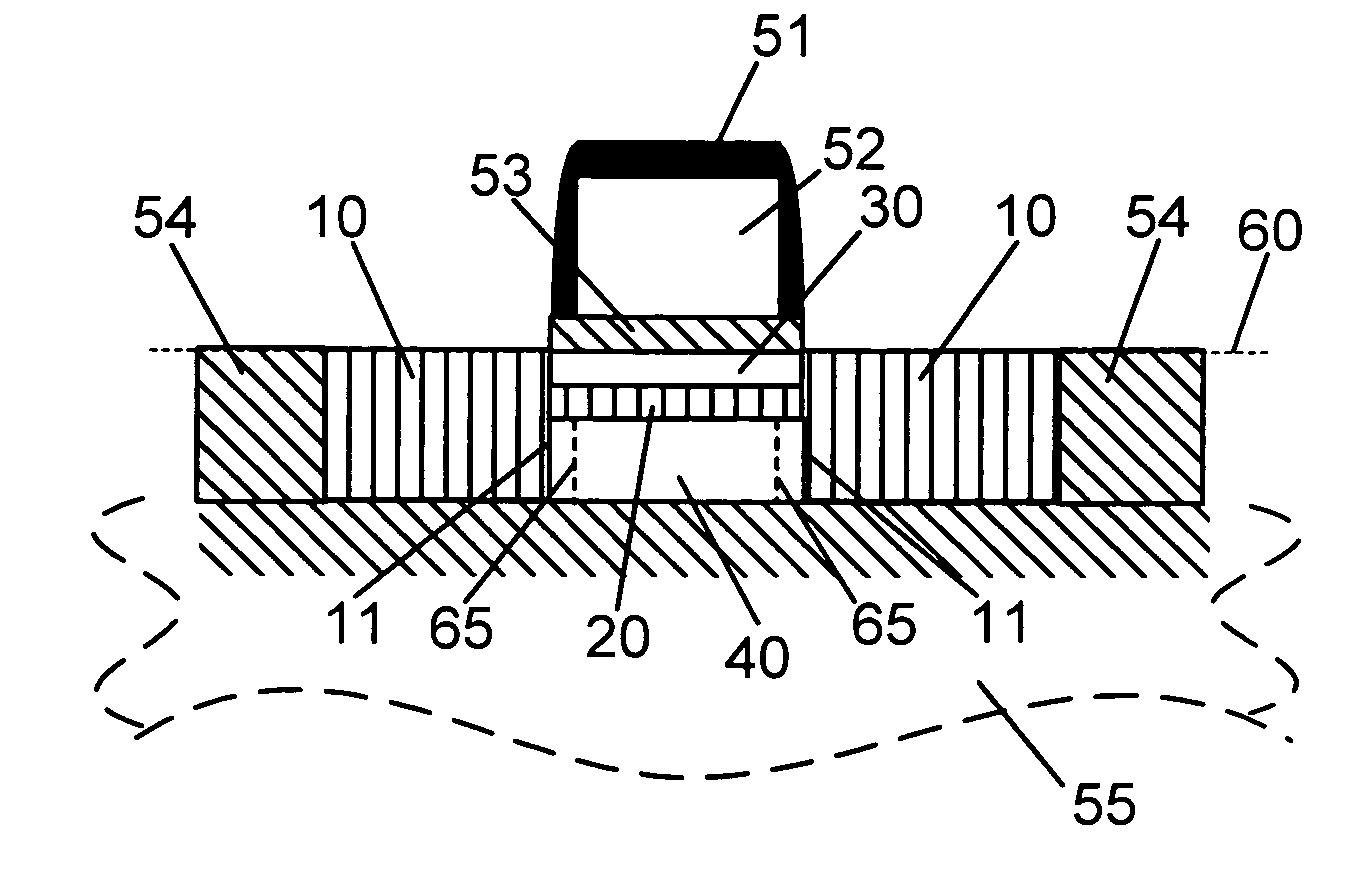

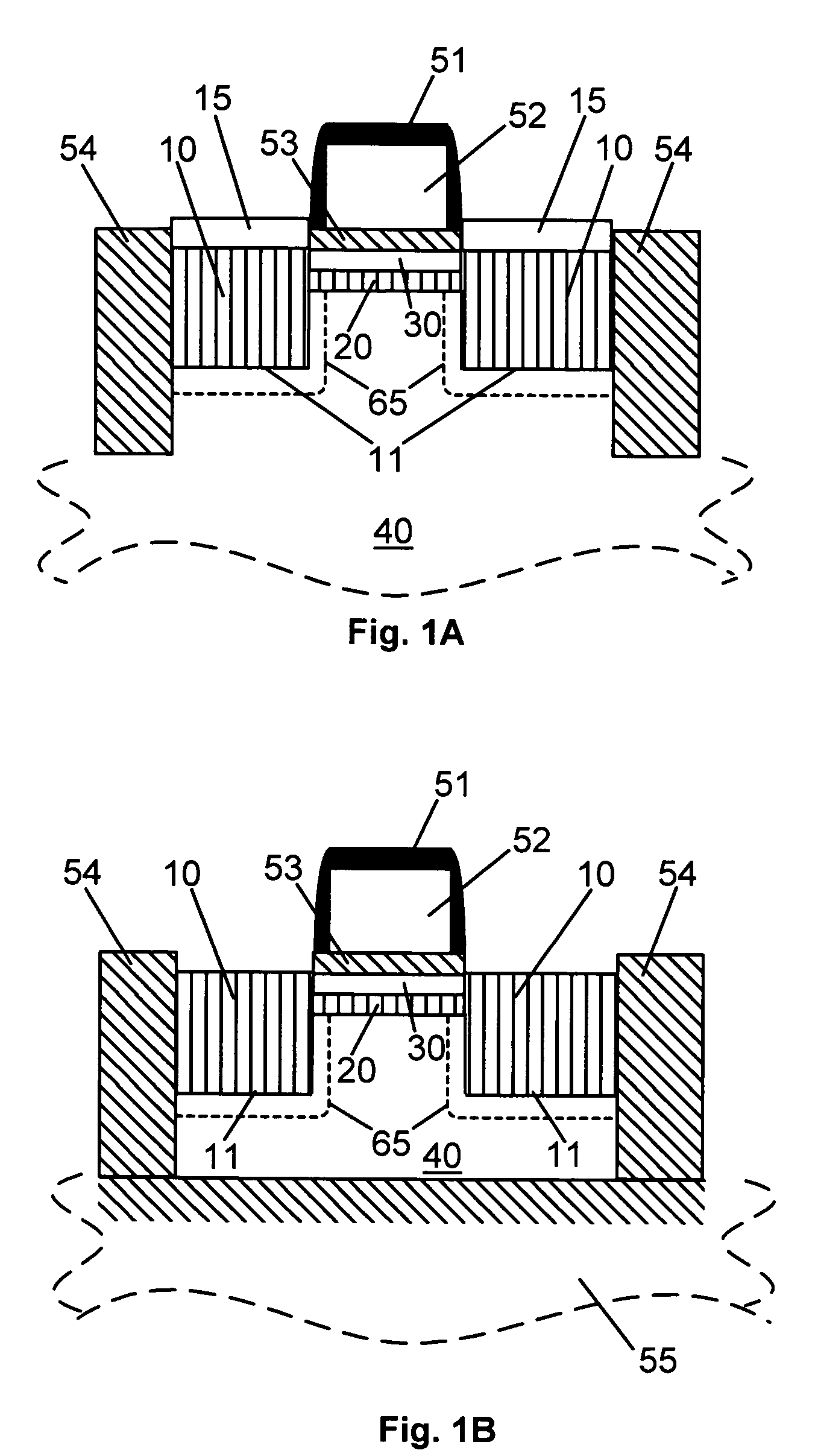

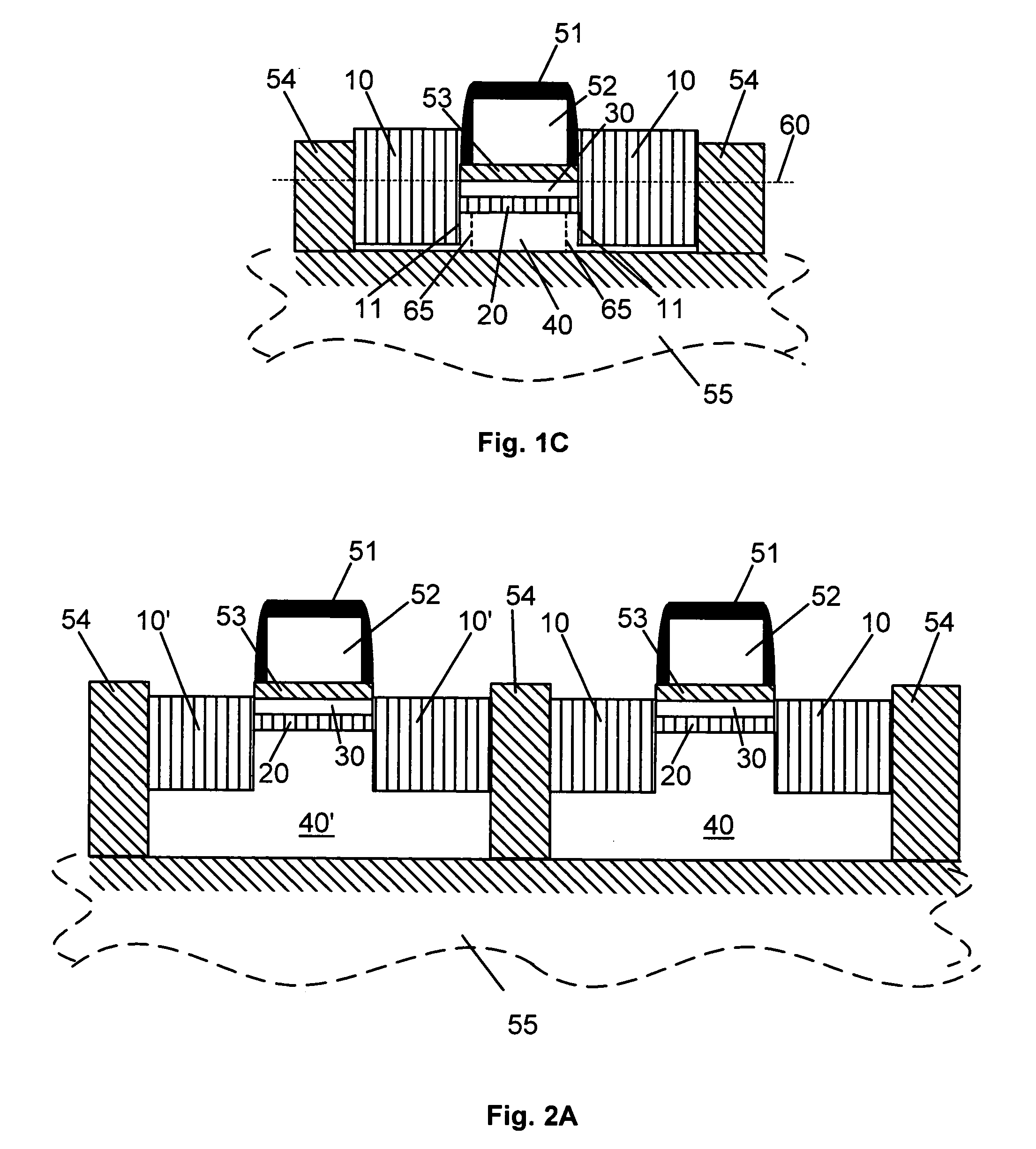

In all representative embodiments presented, the Ge concentration in the source and drain 10 and the SiGe epitaxial channel layer 20 is in the 15% to 50% range, preferably between about 20% to 40%. The SiGe thicknesses in the source / drain 10 are staying below the critical thickness for the given Ge concentration. The critical thickness is defined such that above it the SiGe will relax and defects and dislocations will form. The thickness of the SiGe epitaxial layer 20 typically is between about 5nm and 15nm. The thickness of the epitaxial Si layer 30 is typically between about 5nm and 15nm. FIG. 1A shows an embodiment where the body is bulk Si. These type of devices are the most common devices in present day microelectronics. FIGS. 1B and 1C show representative embodiment of the heterojunction source / drain FET device when the Si body 40 is disposed on top of an insulating material 55. This type of technology is commonly referred to as silicon on insulator (SOI) technology. The insulator material 55 usually, and preferably, is SiO2. FIG. 1B shows an SOI embodiment where the body 40 has enough volume to contain mobile charges. Such SOI devices are called partially depleted devices. FIG. 1C shows an SOI embodiment where the volume of the body 40 is insufficient to contain mobile charges. Such SOI devices are called fully depleted devices. For devices shown in FIG. 1B and 1C there is, at least a thin, layer of body underneath the source and drain 10. This body material serves as the seed material onto which the epitaxial SiGe source and drain 10 are grown. In an alternate embodiment, shown in FIG. 1D. for extremely thin fully depleted SOI devices, one could grow the source and drain 10 laterally, from a lateral seeding, in which case the source and drain 10 would penetrate all the way down to the insulating layer 55.

Owner:GLOBALFOUNDRIES US INC

Nanowire field-effect transistors

Field-effect transistors (FETs) having nanowire channels are provided. In one aspect, a FET is provided. The FET comprises a substrate having a silicon-on-insulator (SOI) layer which is divided into at least two sections electrically isolated from one another, one section included in a source region and the other section included in a drain region; a channel region connecting the source region and the drain region and including at least one nanowire; an epitaxial semiconductor material, grown from the SOI layer, covering the nanowire and attaching the nanowire to each section of the SOI layer; and a gate over the channel region.

Owner:GLOBALFOUNDRIES US INC

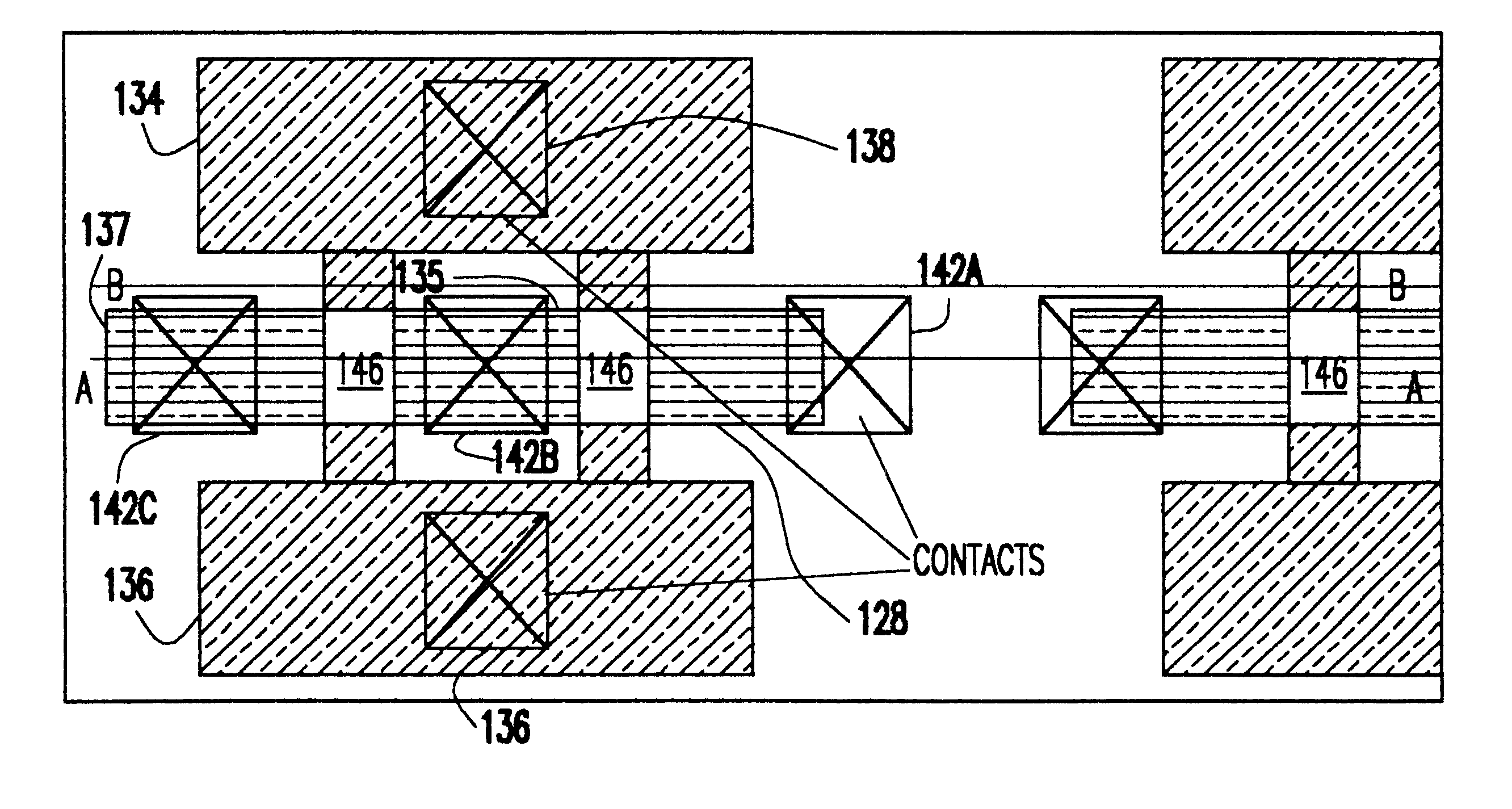

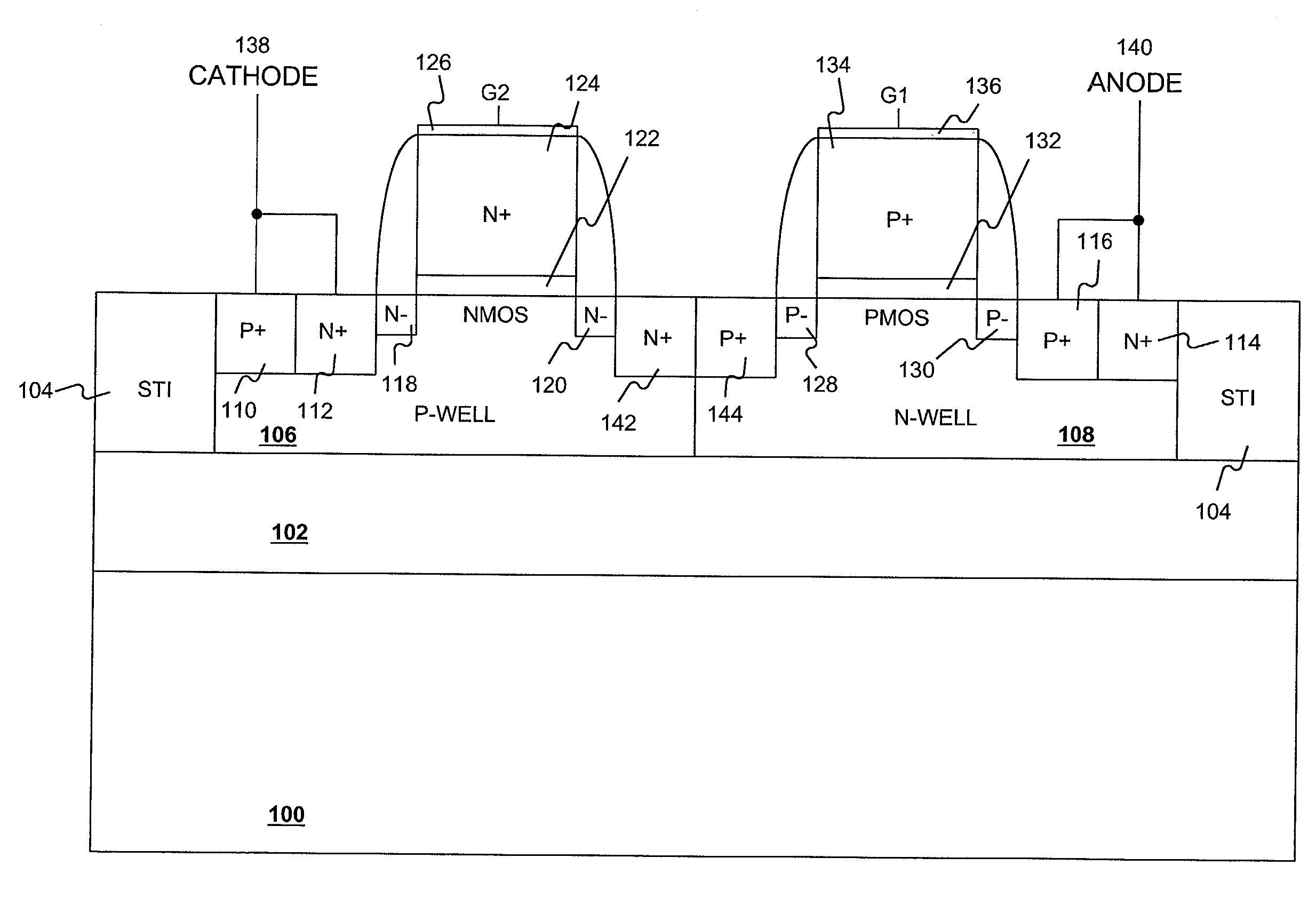

SCR devices in silicon-on-insulator CMOS process for on-chip ESD protection

InactiveUS20030146474A1TransistorSemiconductor/solid-state device detailsSilicon-controlled rectifierSilicon on insulator

A silicon-on-isolator CMOS integrated circuit device includes a semiconductor substrate, an isolation layer formed over the semiconductor substrate, an n-type MOS transistor having a gate, a drain region, and a source region formed over the isolation layer, and a p-type MOS transistor having a gate, a drain region, and a source region formed over the isolation layer and contiguous with the n-type MOS transistor, wherein the n-type MOS transistor and the p-type MOS transistor form a silicon controlled rectifier to provide electrostatic discharge protection.

Owner:TRANSPACIFIC IP LTD

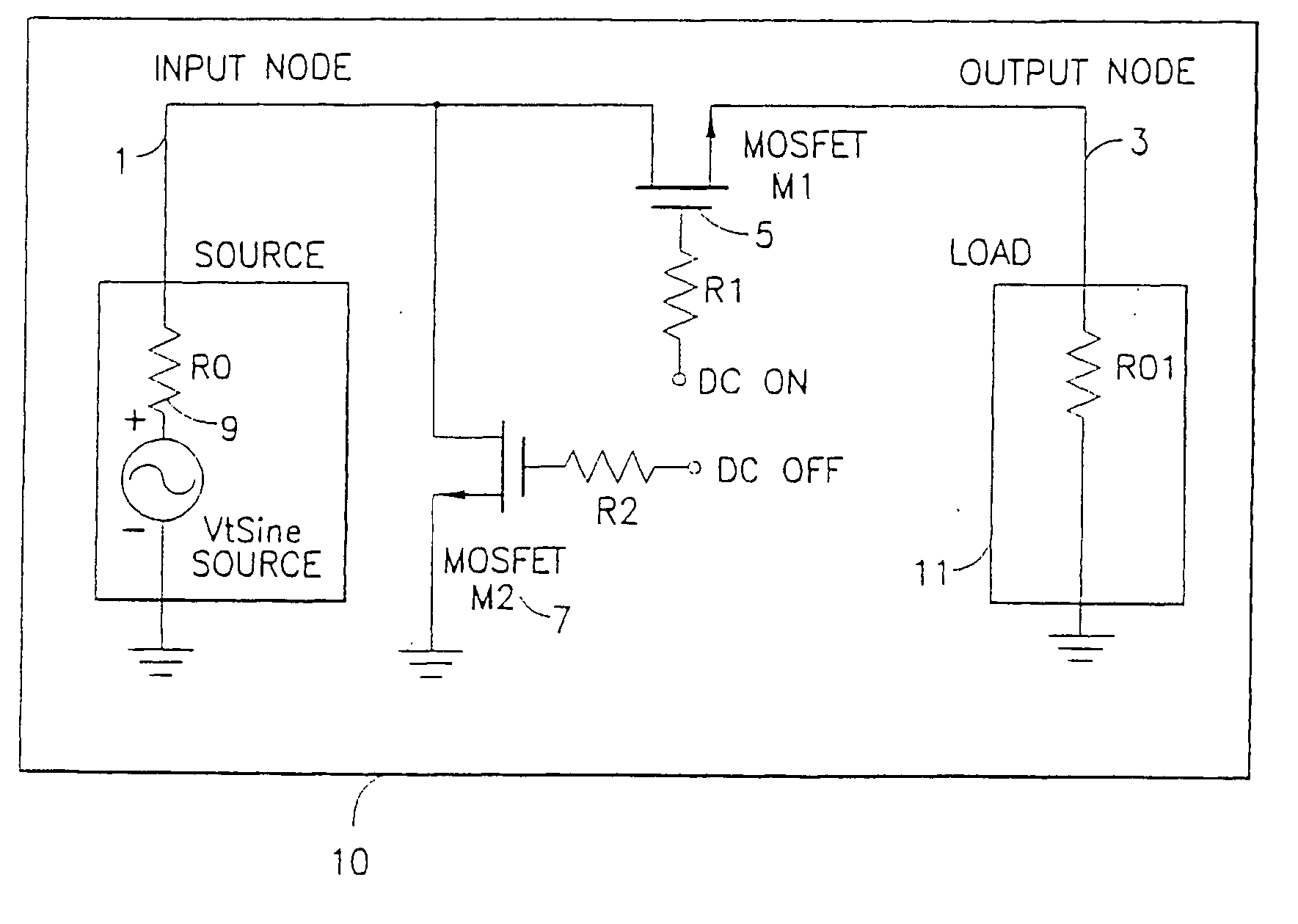

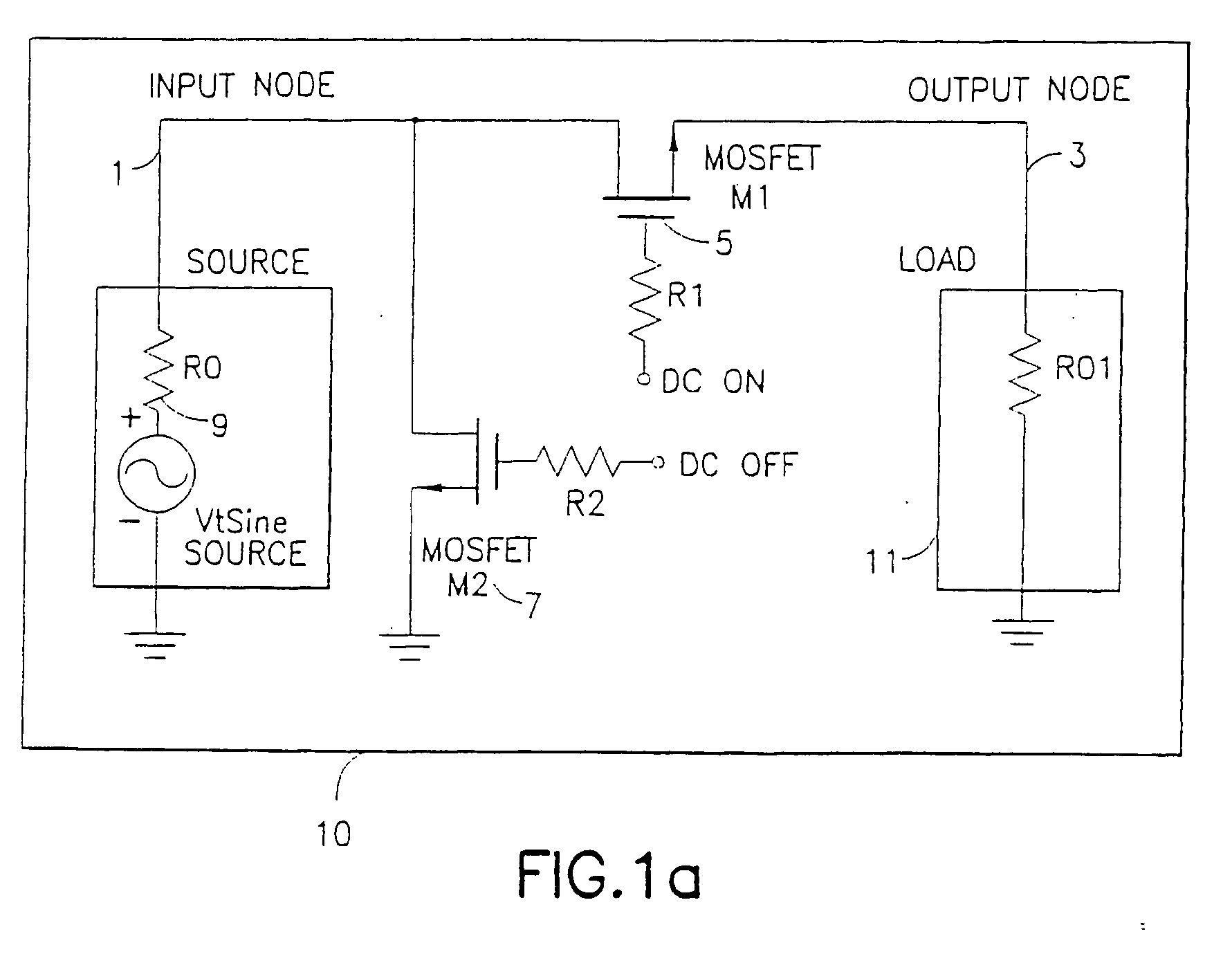

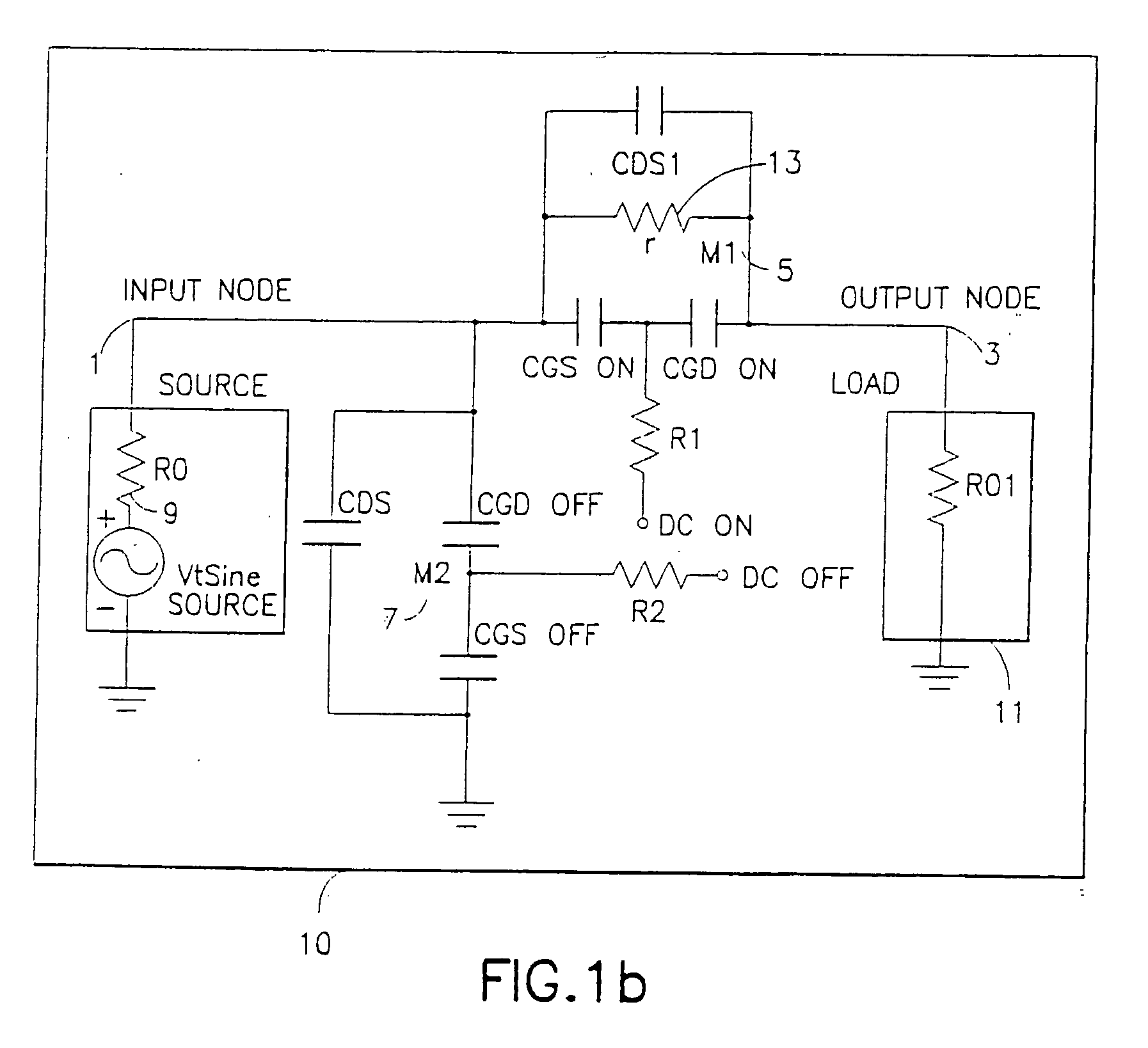

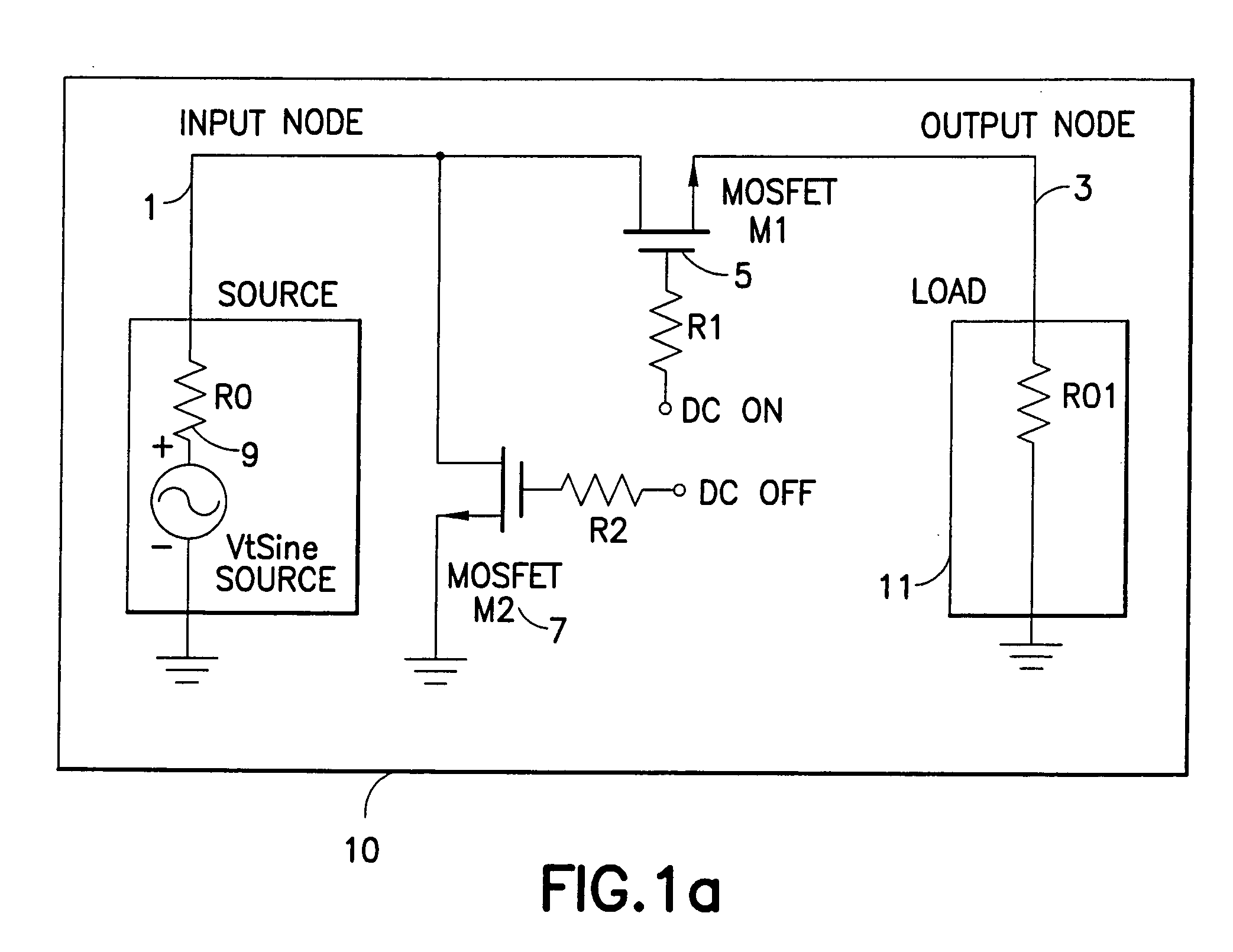

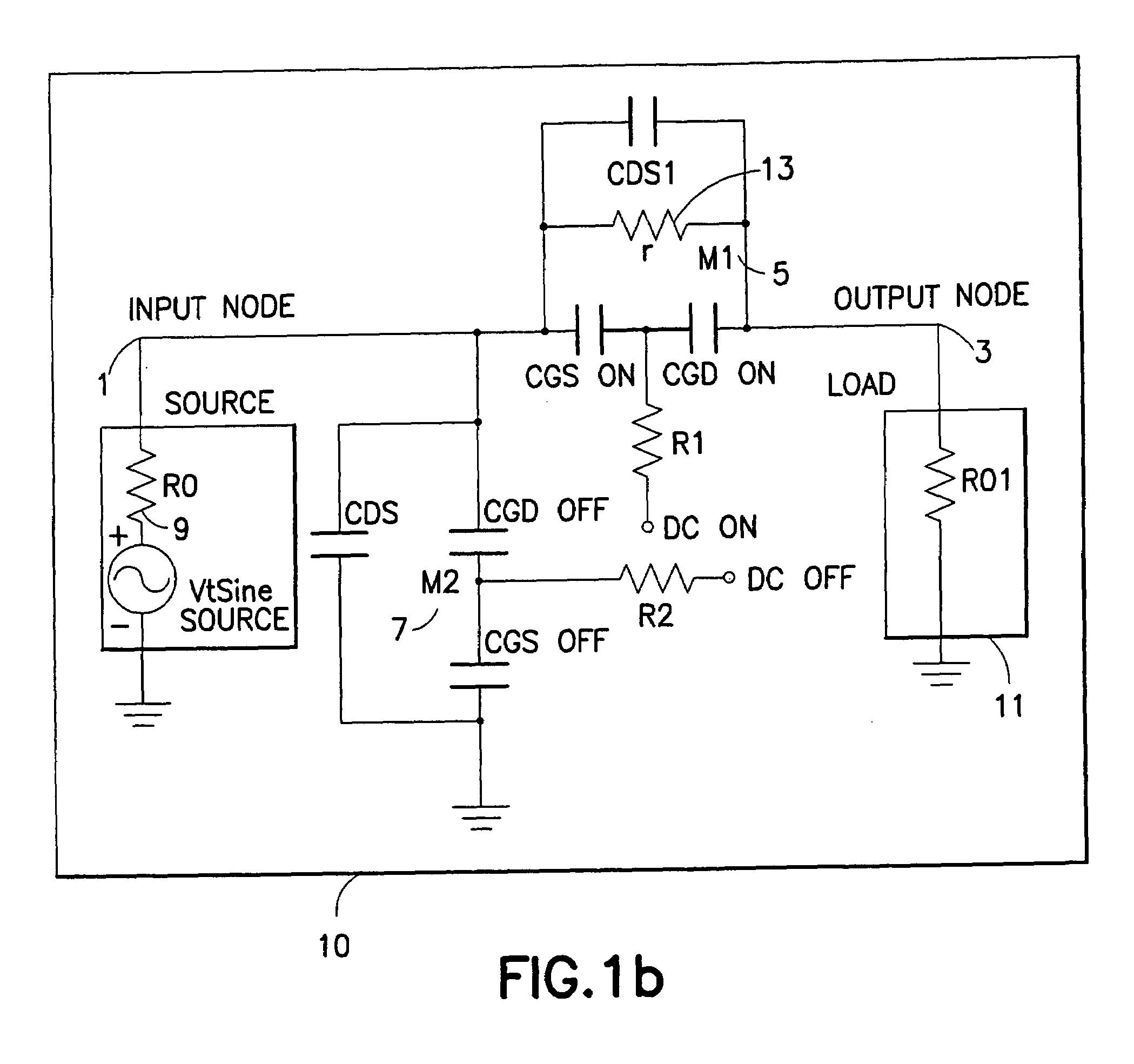

Switch circuit and method of switching radio frequency signals

InactiveUS7123898B2Easy to switchImprove reliabilityTransistorSolid-state devicesMOSFETDigital control

A novel RF buffer circuit adapted for use with an RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. The switching and shunting transistor grouping pairs are controlled by a switching control voltage (SW) and its inverse (SW_). The switching and shunting transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. The stacking of transistor grouping devices, and associated gate resistors, increase the breakdown voltage across the series connected switch transistors and operate to improve RF switch compression. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The inventive RF switch provides improvements in insertion loss, switch isolation, and switch compression.

Owner:PSEMI CORP

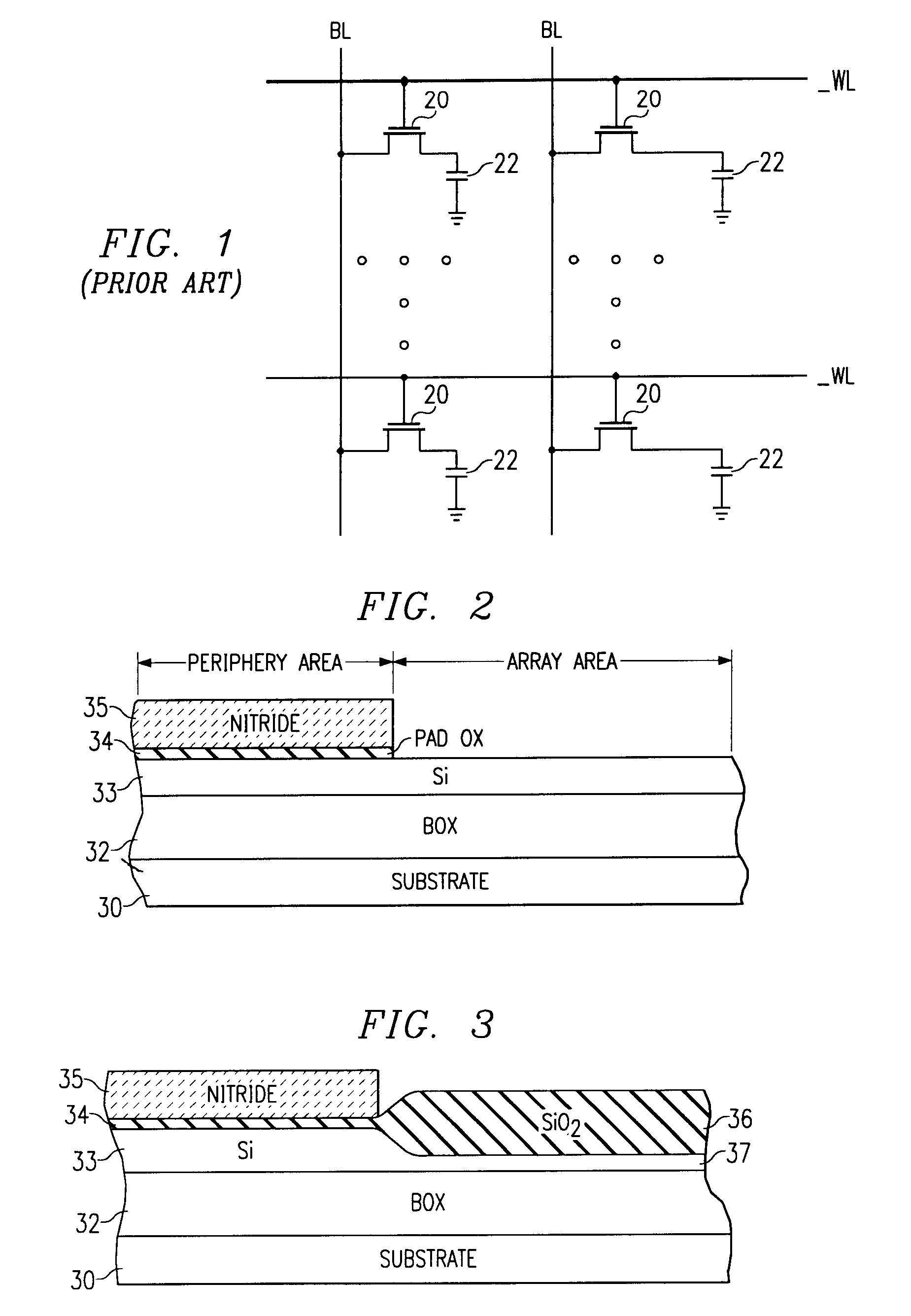

SOI DRAM having P-doped poly gate for a memory pass transistor

An integrated circuit including a DRAM is disclosed, wherein the DRAM includes a memory array including a plurality of pass gate transistors and a plurality of memory elements. The pass gate transistors include a gate material selected to provide a substantially near mid-gap work function or greater. The DRAM also includes a peripheral area including a plurality of logic transistors. In a preferred embodiment the pass gate transistors are silicon-on-insulator transistors.

Owner:TEXAS INSTR INC

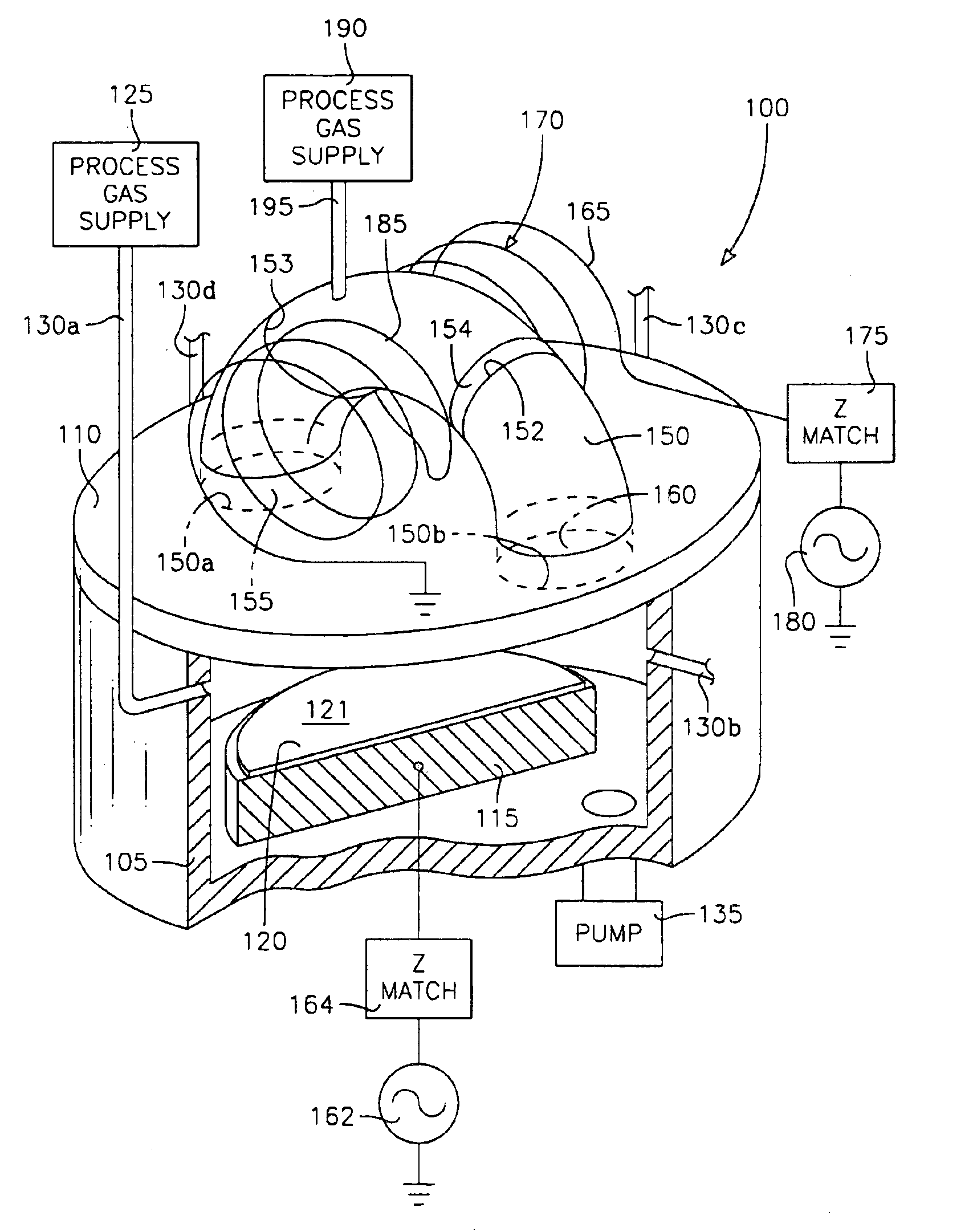

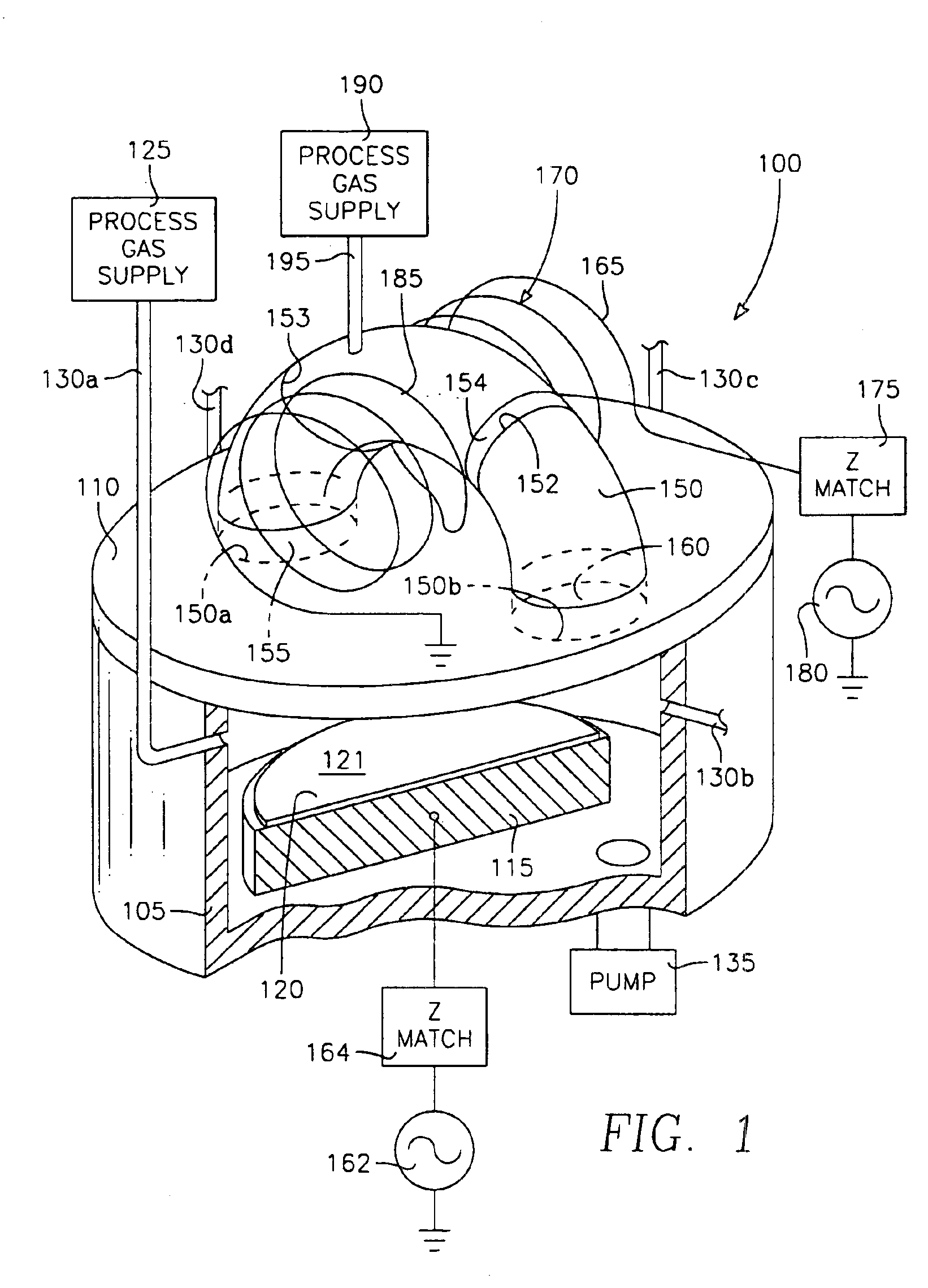

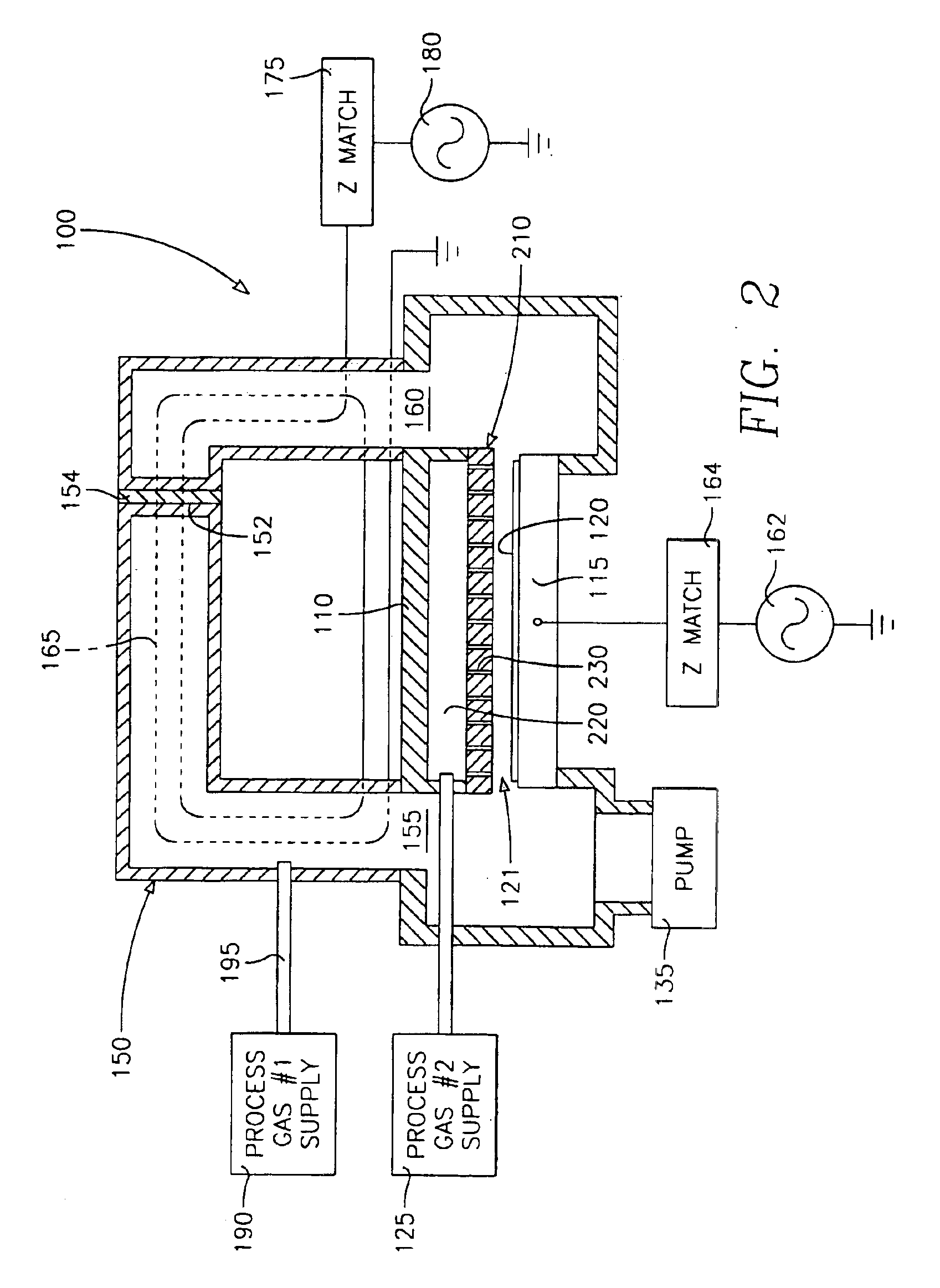

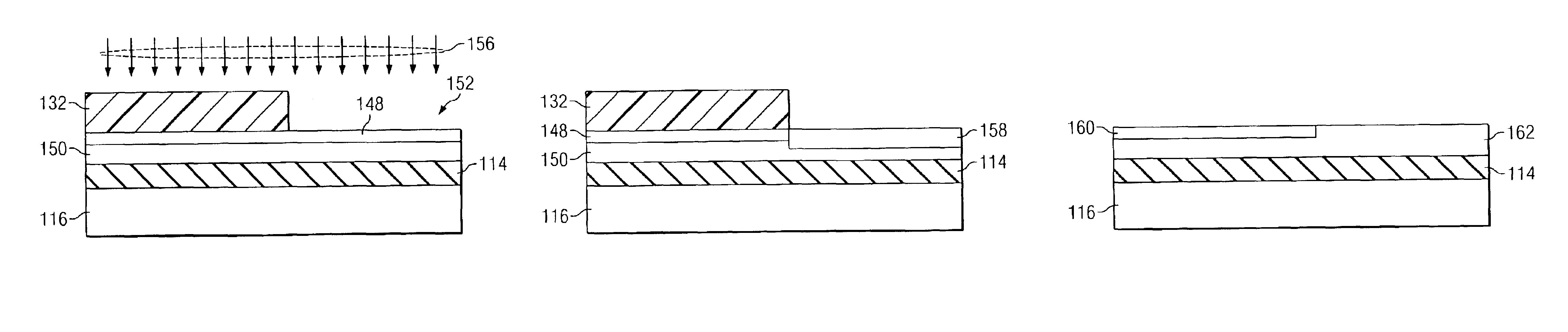

Fabrication of silicon-on-insulator structure using plasma immersion ion implantation

InactiveUS6893907B2Reduce oxygen concentrationElectric discharge tubesSemiconductor/solid-state device manufacturingSurface layerPlasma-immersion ion implantation

A method of fabricating a silicon-on-insulator structure having a silicon surface layer in a semiconductor workpiece, is carried out by maintaining the workpiece at an elevated temperature and producing an oxygen-containing plasma in the chamber while applying a bias to the workpiece and setting the bias to a level corresponding to an implant depth in the workpiece below the silicon surface layer to which oxygen atoms are to be implanted, whereby to form an oxygen-implanted layer in the workpiece having an oxygen concentration distribution generally centered at the implant depth and having a finite oxygen concentration in the silicon surface layer. The oxygen concentration in the silicon surface layer is then reduced to permit epitaxial silicon deposition.

Owner:APPLIED MATERIALS INC

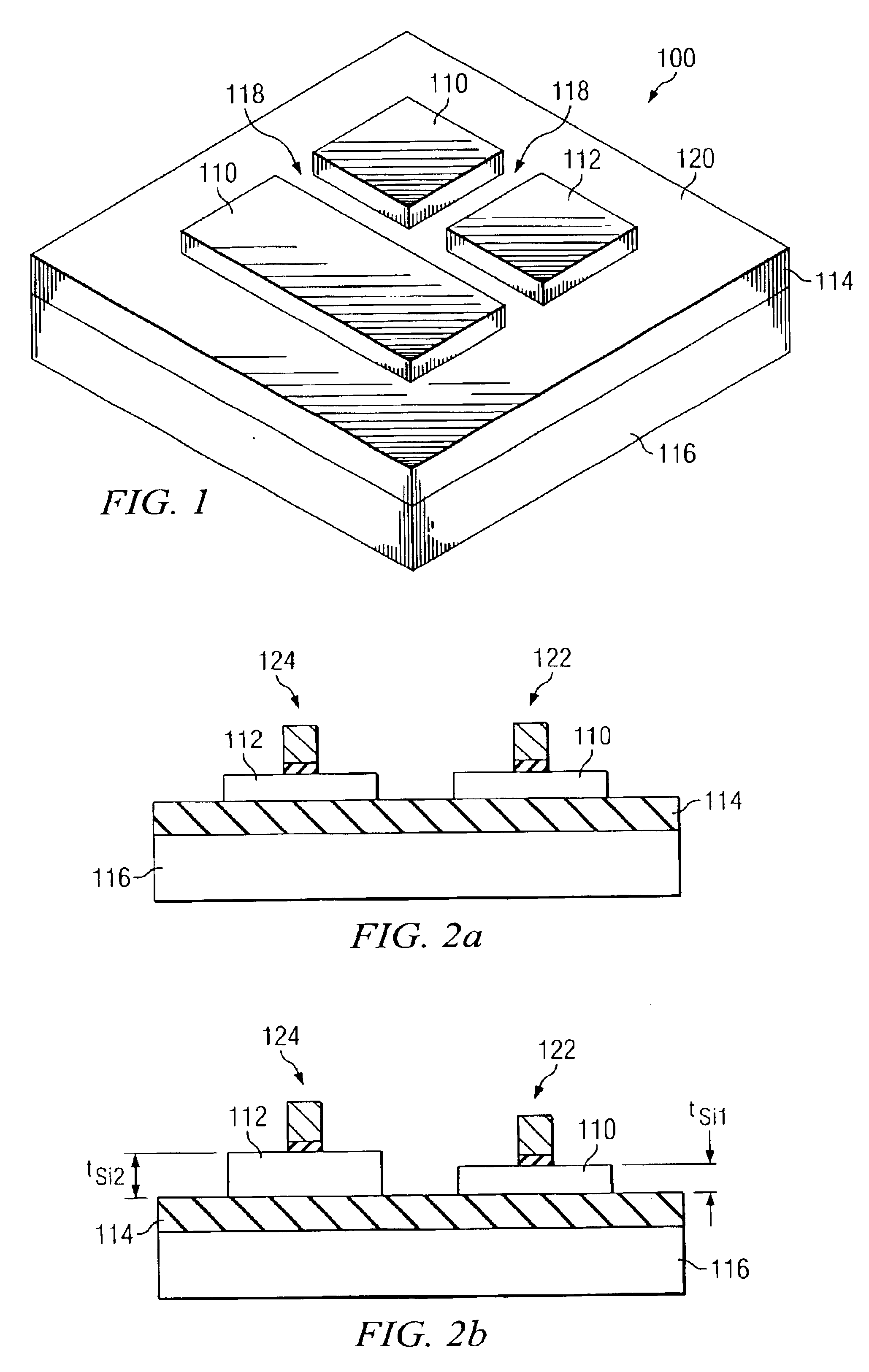

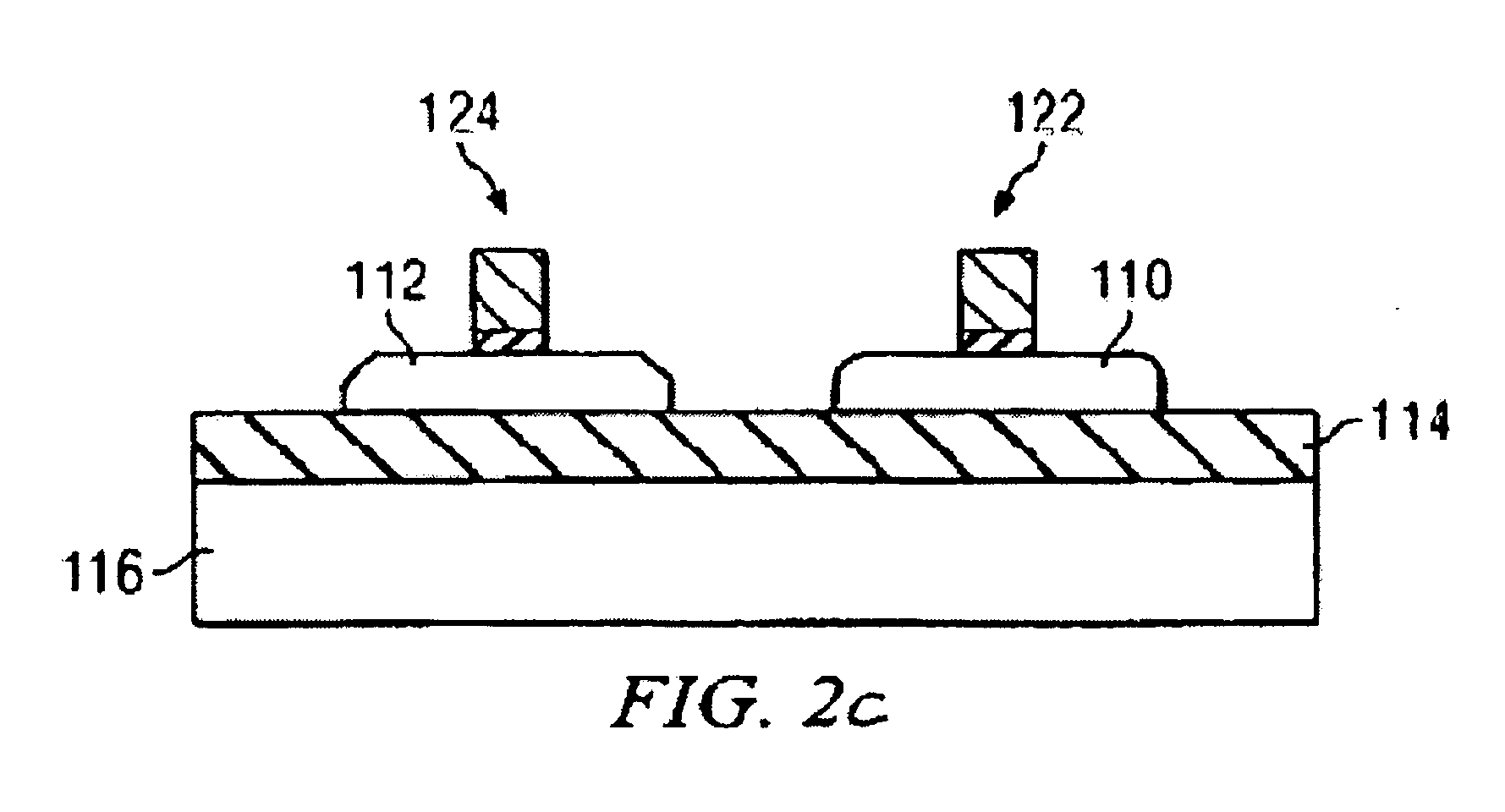

Silicon-on-insulator chip with multiple crystal orientations

A silicon-on-insulator chip includes an insulator layer, typically formed over a substrate. A first silicon island with a surface of a first crystal orientation overlies the insulator layer and a second silicon island with a surface of a second crystal orientation also overlies the insulator layer. In one embodiment, the silicon-on-insulator chip also includes a first transistor of a first conduction type formed on the first silicon island, and a second transistor of a second conduction type formed on the second silicon island. For example, the first crystal orientation can be (110) while the first transistor is a p-channel transistor, and the second crystal orientation can be (100) while the second transistor is an n-channel transistor.

Owner:TAIWAN SEMICON MFG CO LTD