Patents

Literature

164 results about "Three dimensional integration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

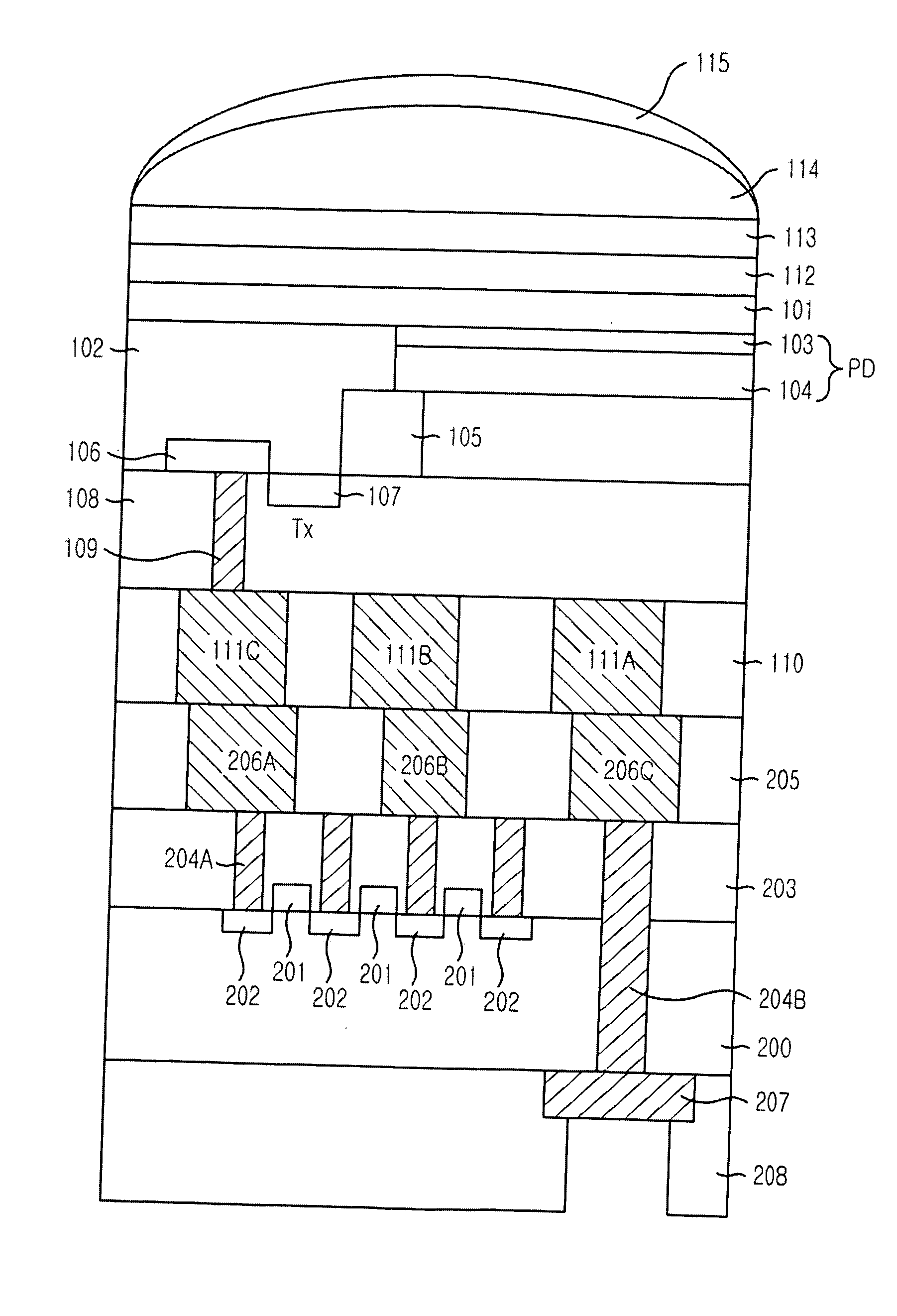

Three-dimensional integrated semiconductor devices

InactiveUS6943067B2Semiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

The present invention describes a process for three-dimensional integration of semiconductor devices and a resulting device. The process combines low temperature wafer bonding methods with backside / substrate contact processing methods, preferably with silicon on insulator devices. The present invention utilizes, in an inventive fashion, low temperature bonding processes used for bonded silicon on insulator (SOI) wafer technology. This low temperature bonding technology is adopted for stacking several silicon layers on top of each other and building active transistors and other circuit elements in each one. The back-side / substrate contact processing methods allow the interconnection of the bonded SOI layers.

Owner:ADVANCED MICRO DEVICES INC

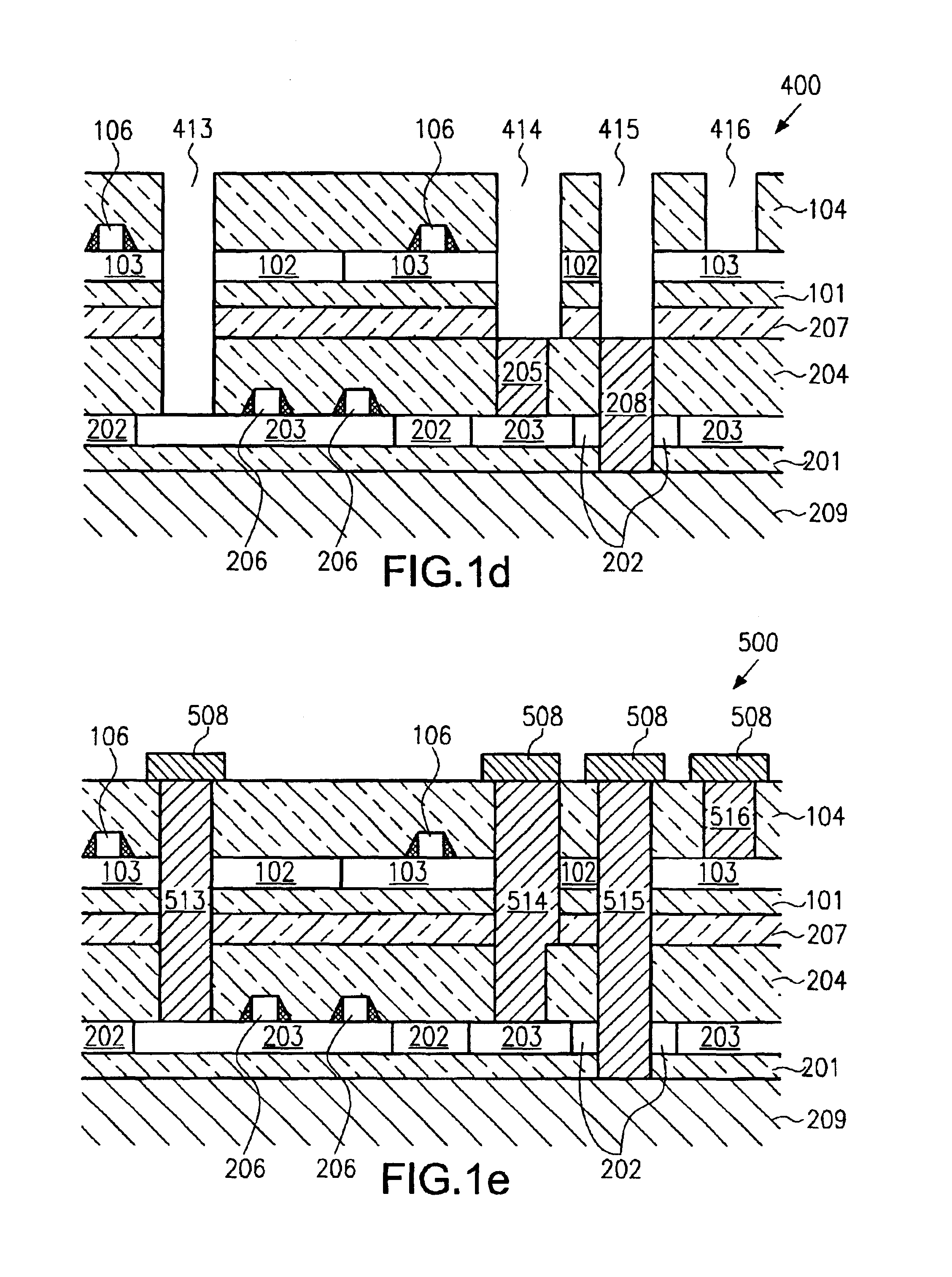

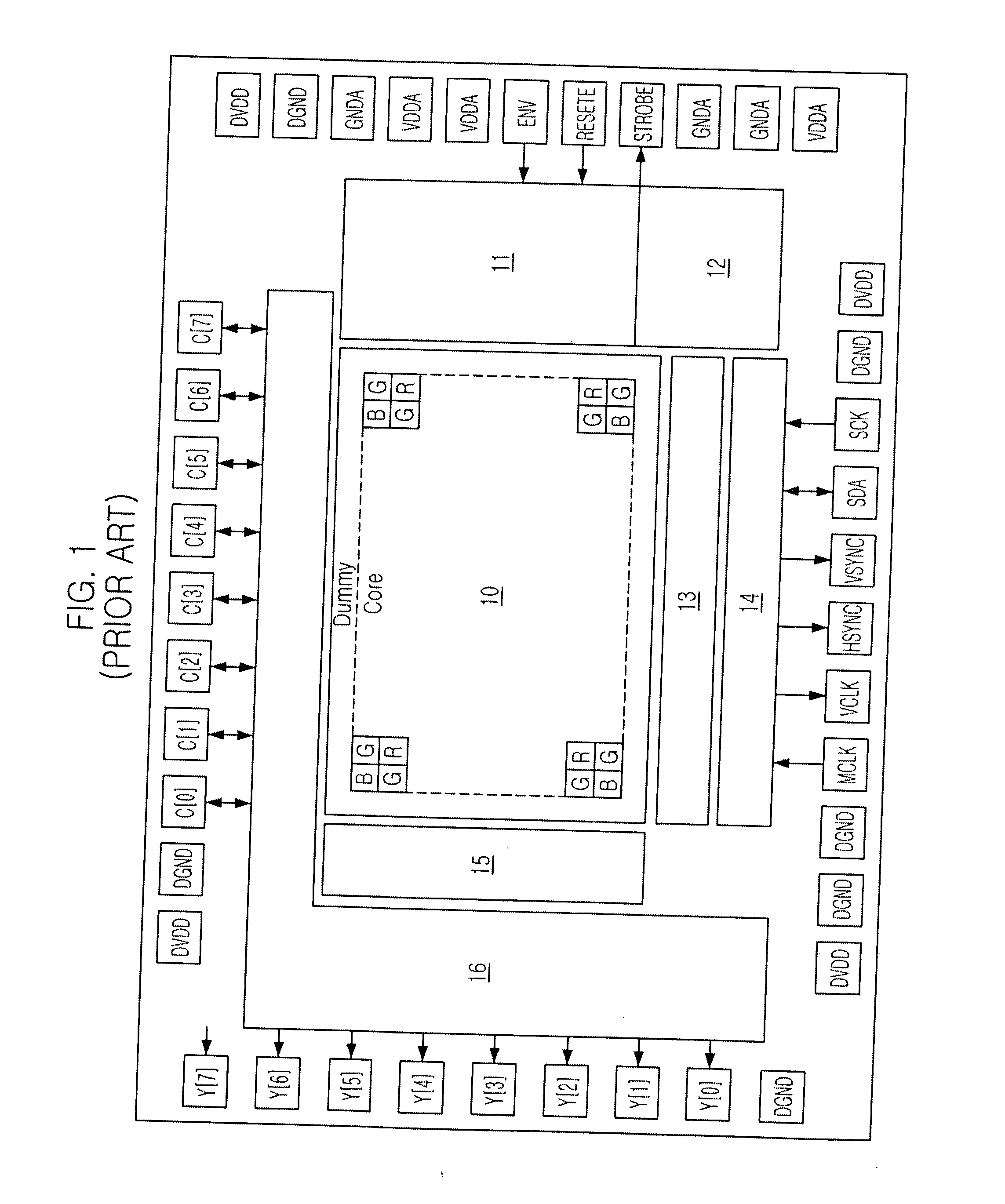

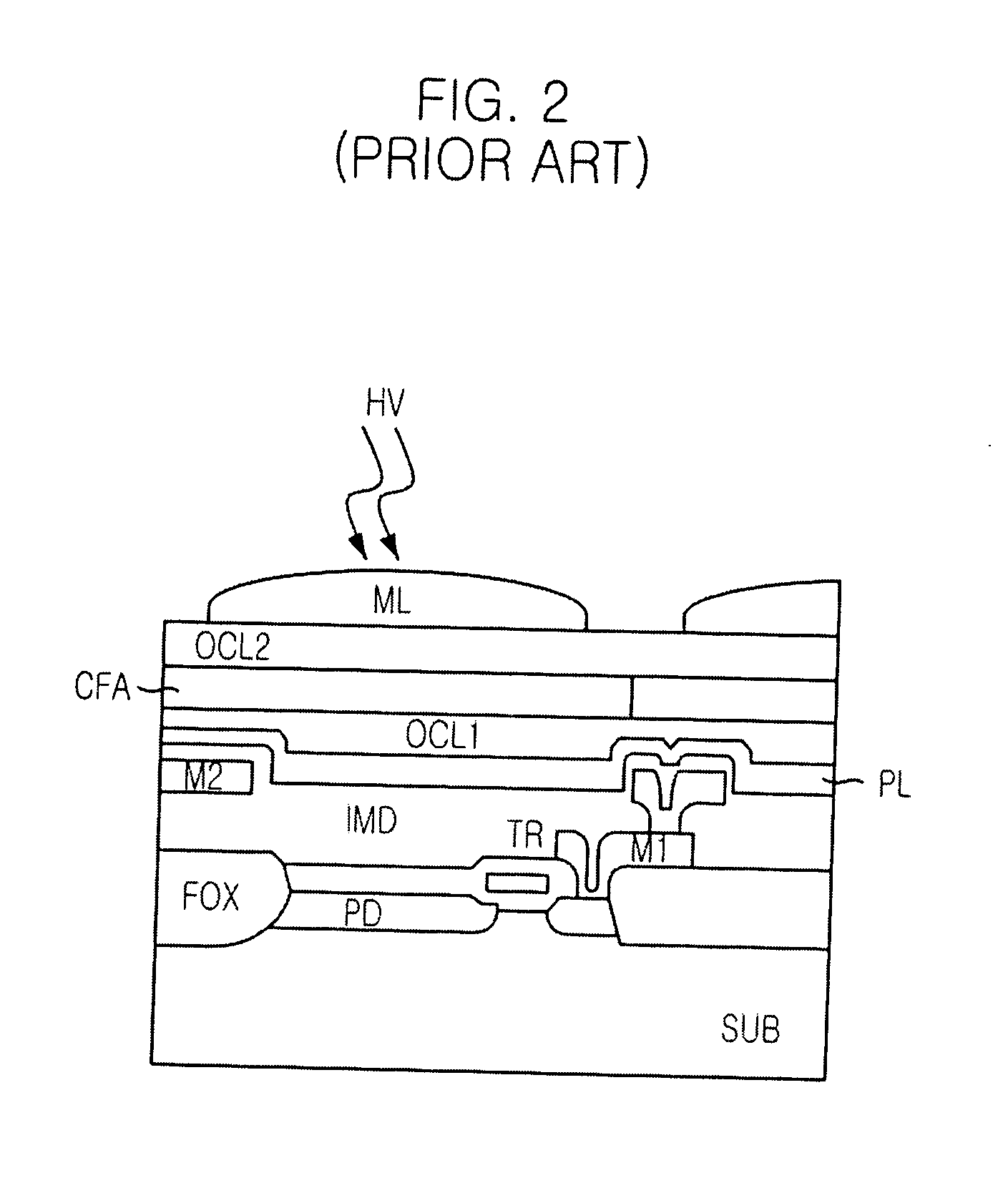

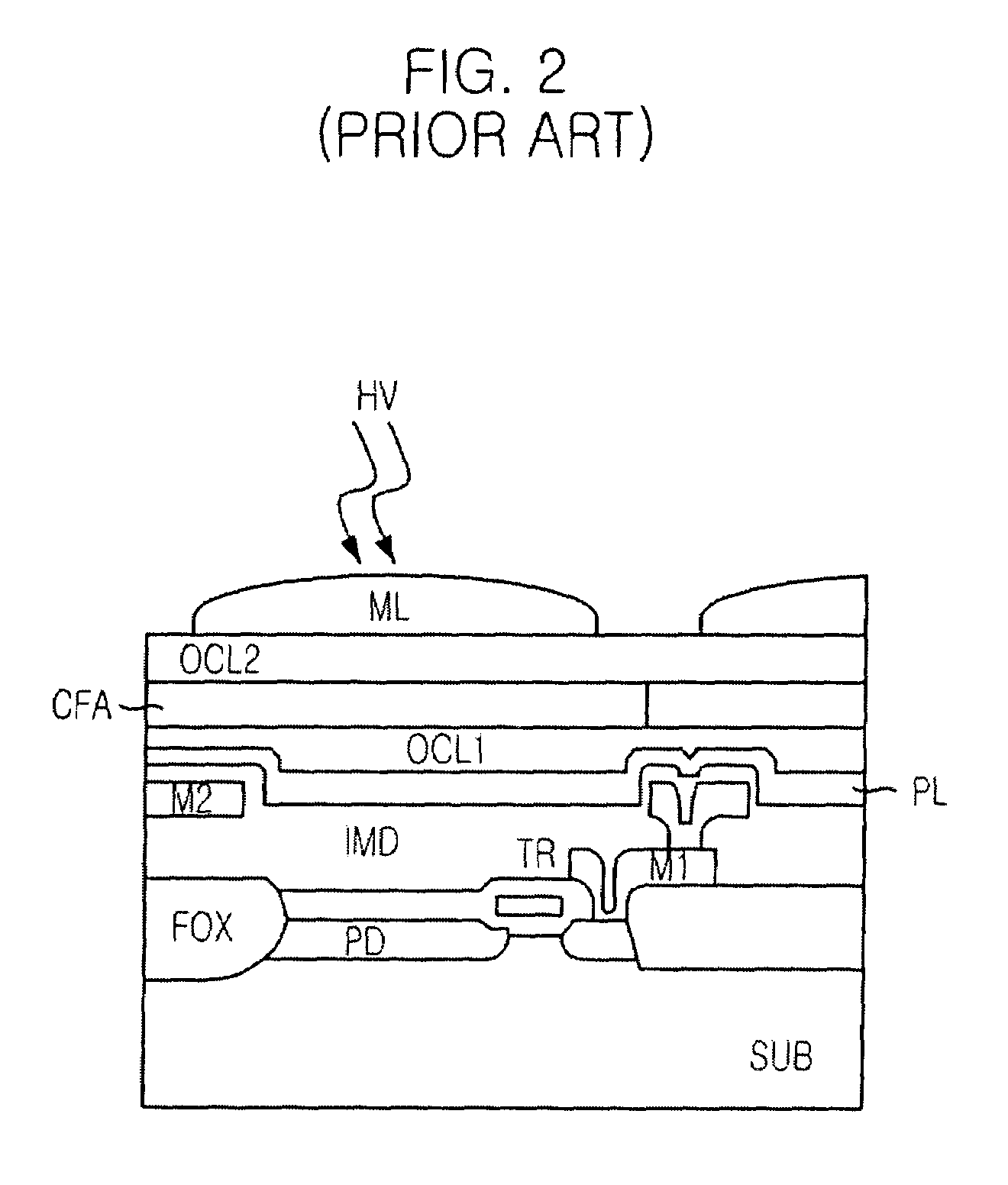

Image sensor with enlarged photo detection area and method for fabricating the same

ActiveUS20060146233A1Maximizing detection regionSolid-state devicesSemiconductor/solid-state device manufacturingCMOSThree dimensional integration

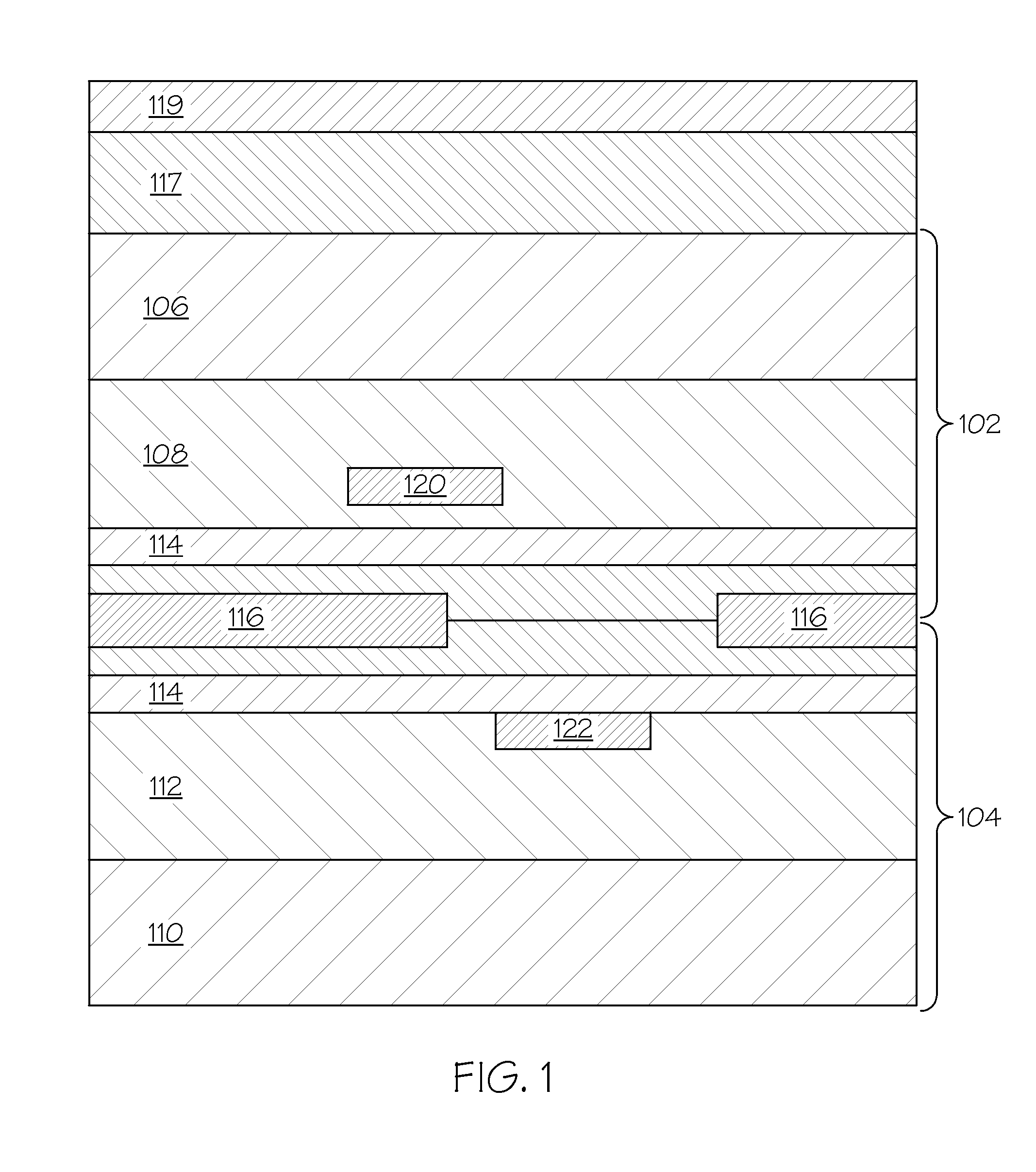

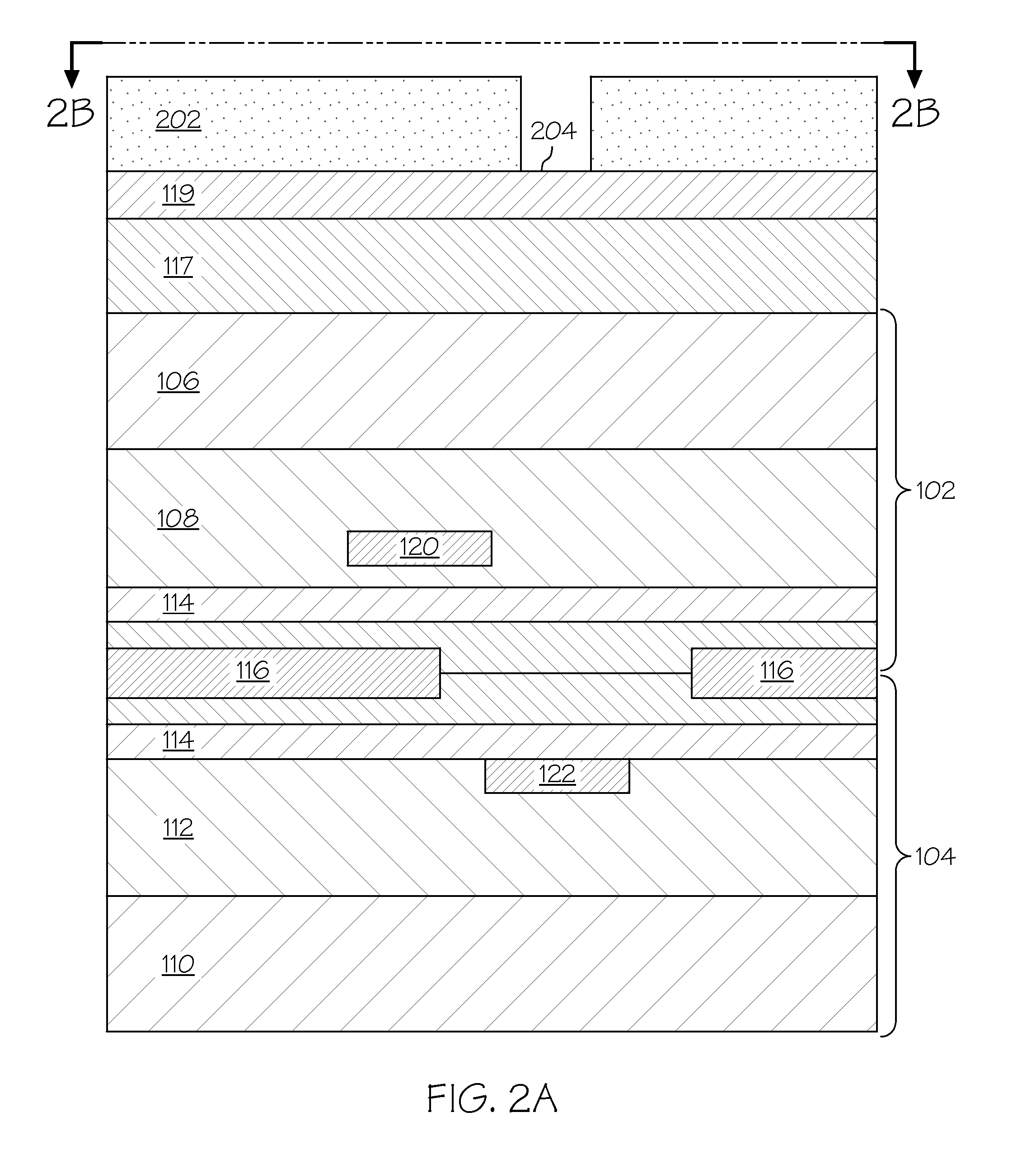

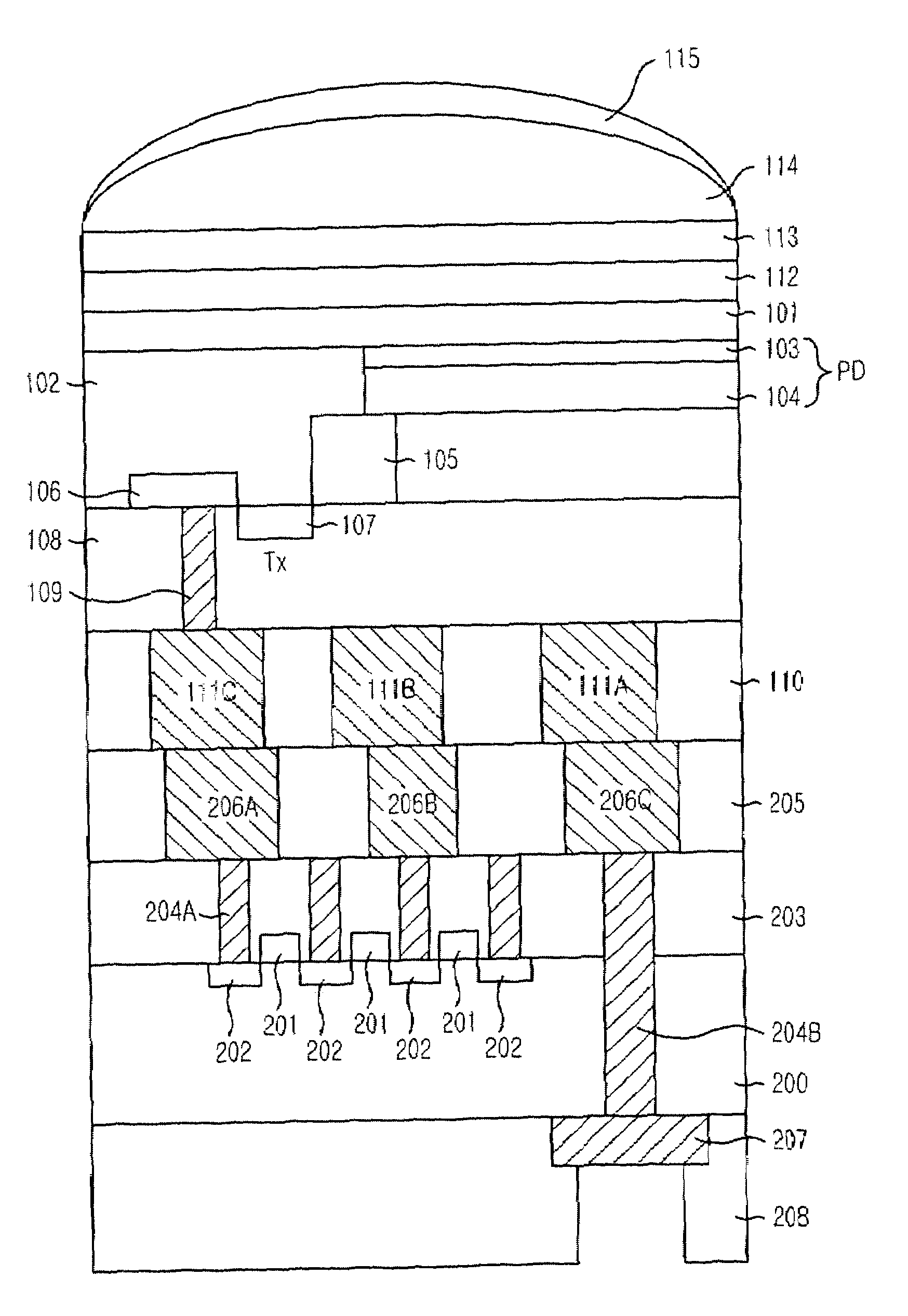

A complementary metal oxide semiconductor (CMOS) device with a three dimensional integration structure and a method for fabricating the same are provided. An image sensor includes a first substrate in which a photo detection device is formed; a second substrate in which a peripheral circuit is formed, wherein the first substrate and the second substrate are bonded through a plurality of bonding pads formed on both the first substrate and the second substrate, and a back side of the first substrate is turned upside down; and a microlens formed on a top portion of the back side of the first substrate.

Owner:INTELLECTUAL VENTURES II

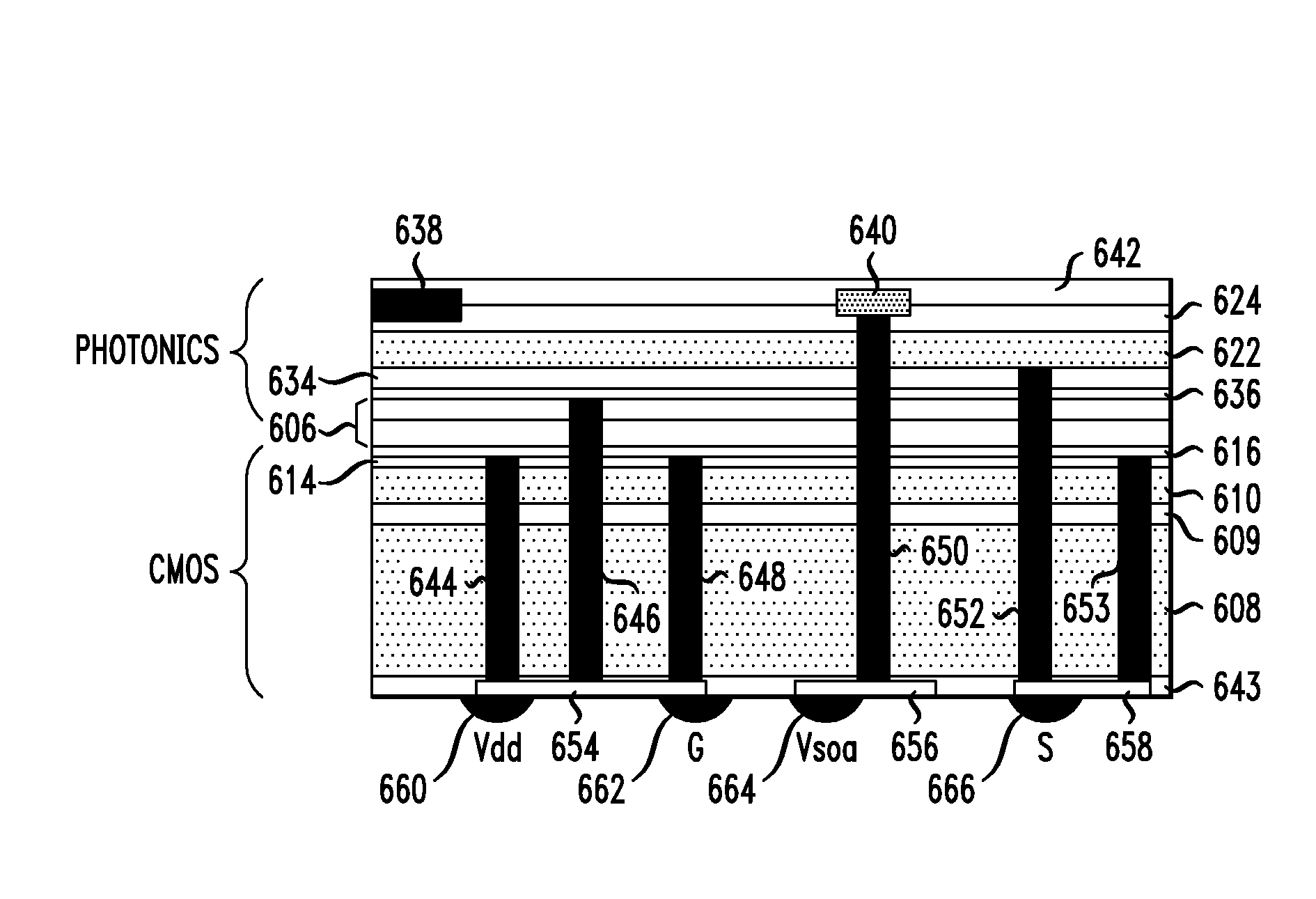

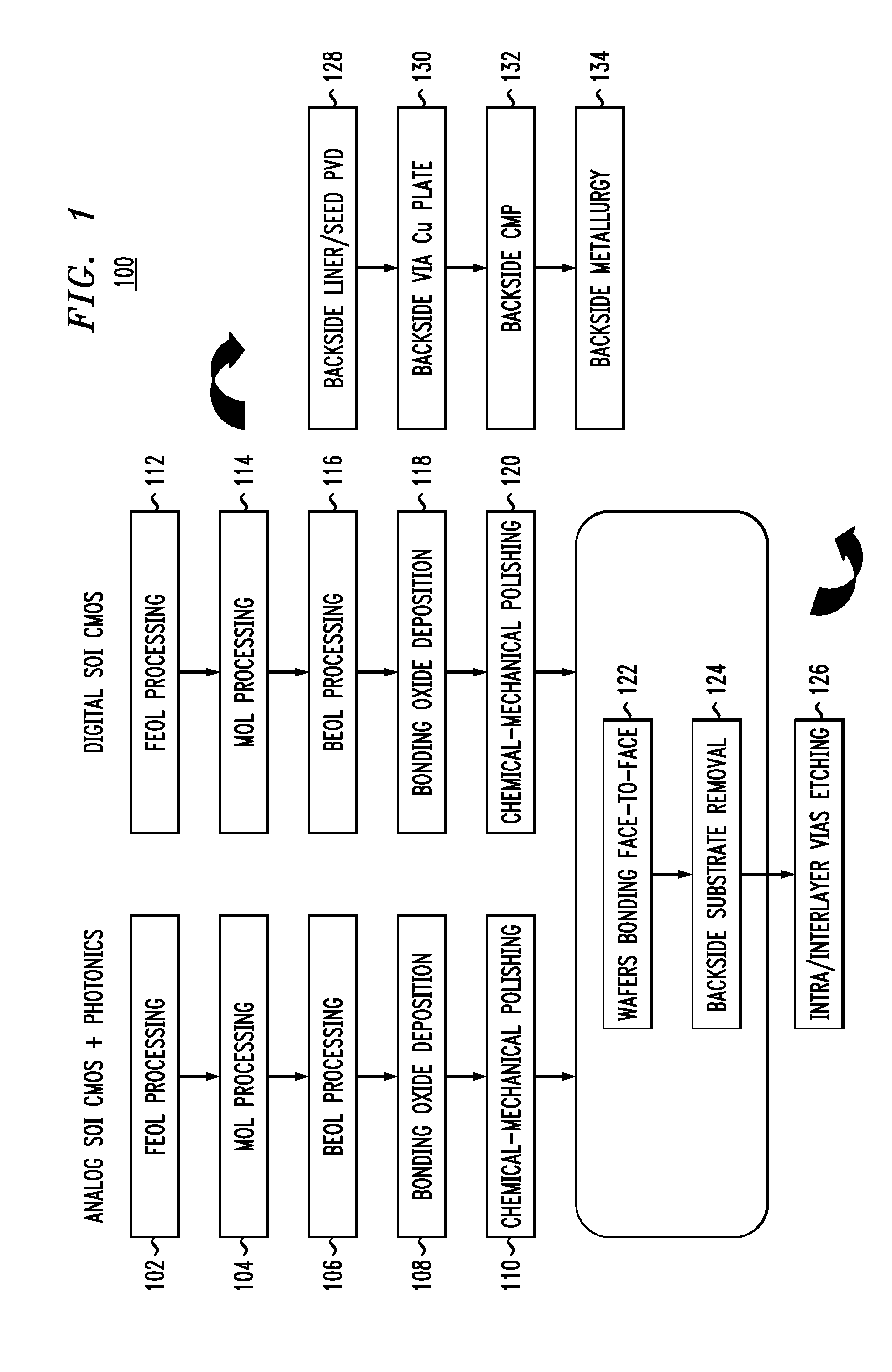

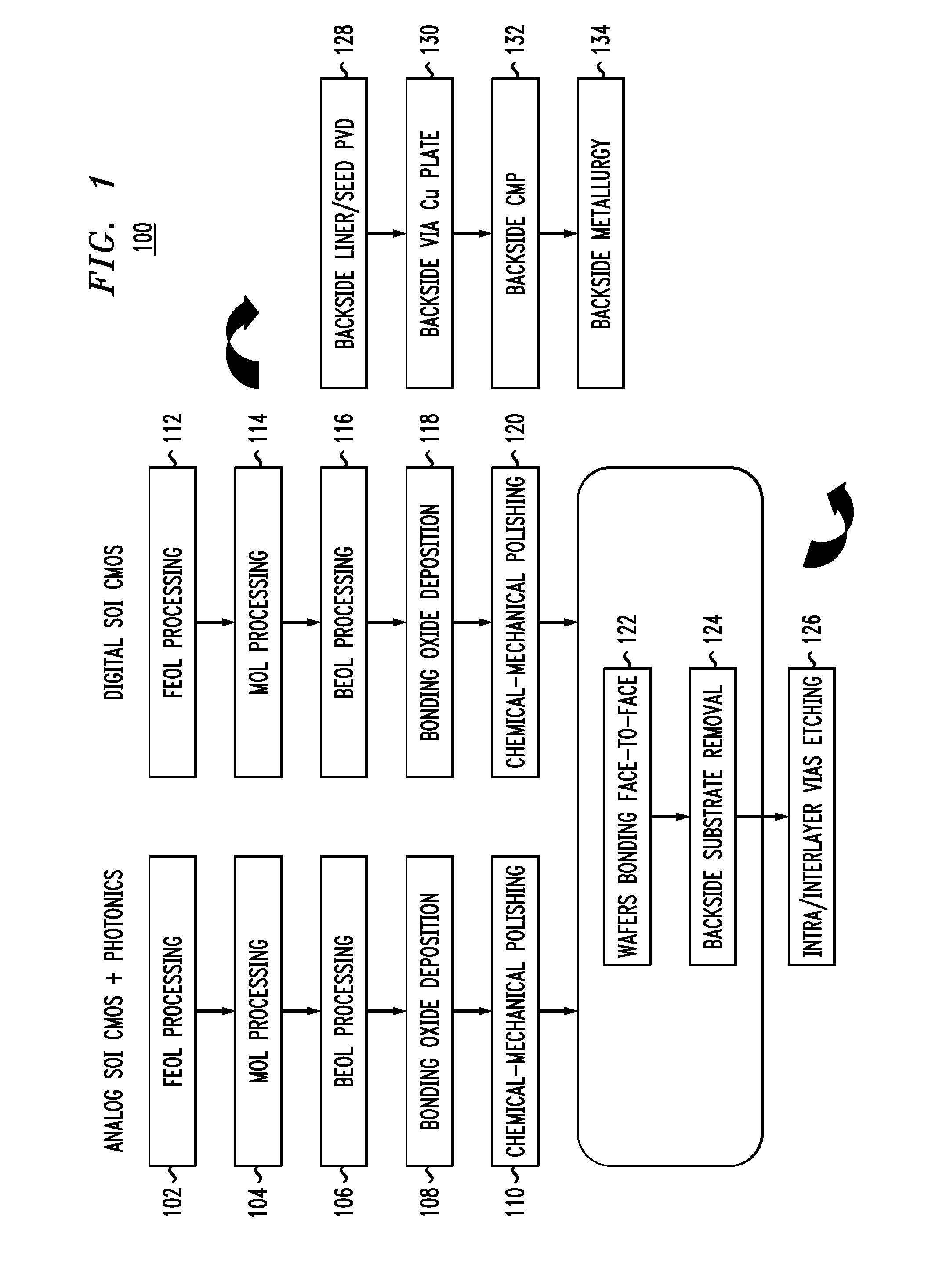

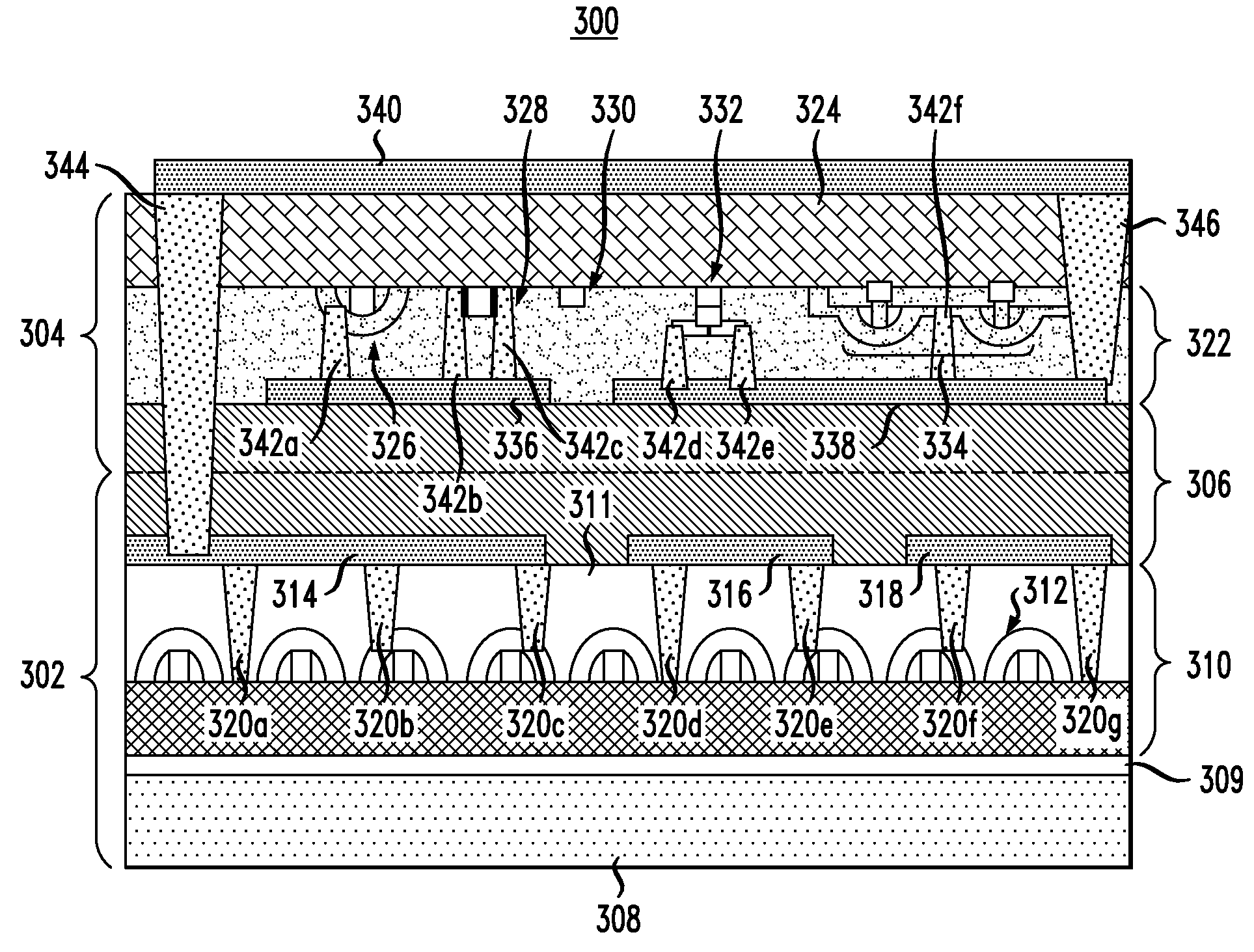

Three-Dimensional Integrated Circuits and Techniques for Fabrication Thereof

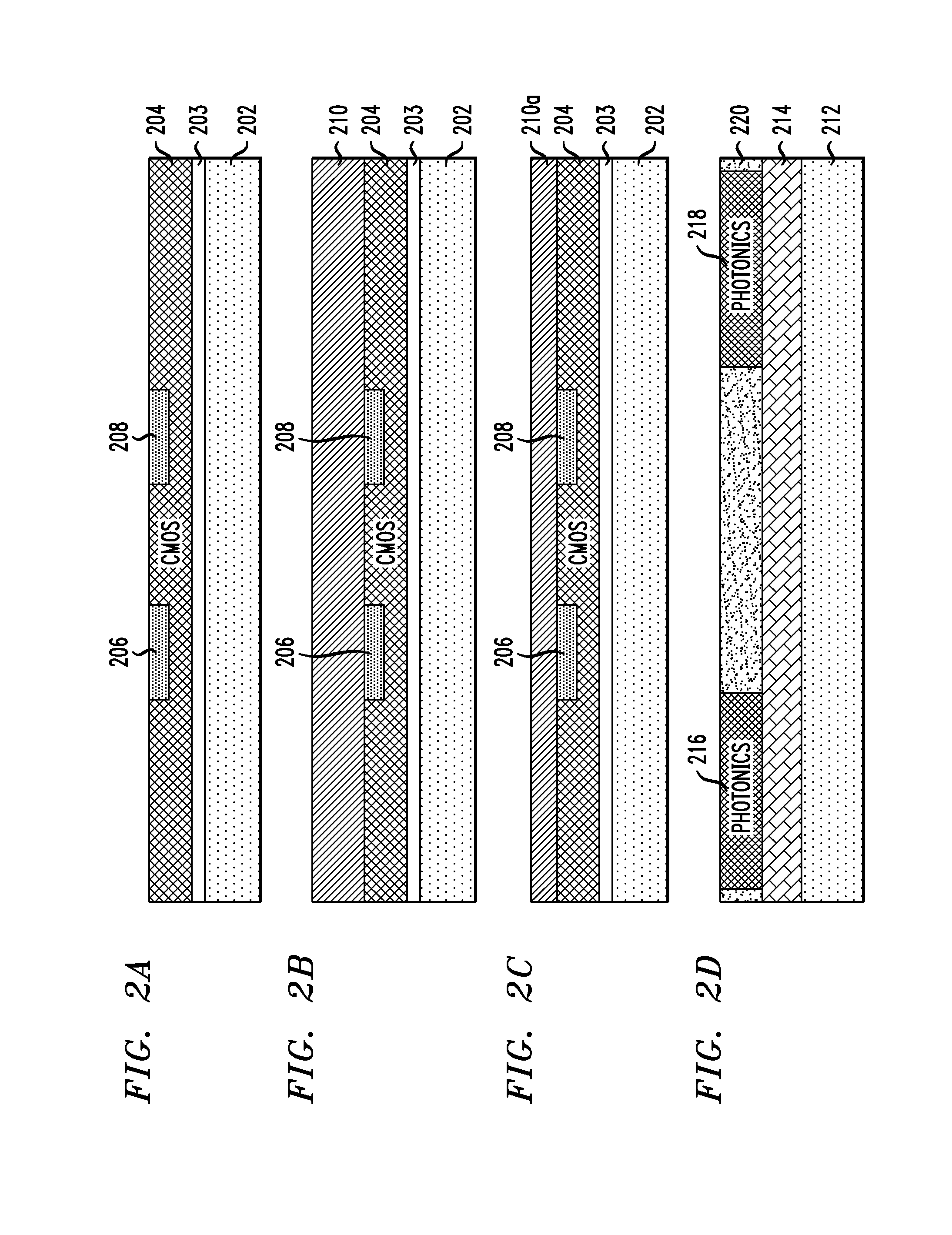

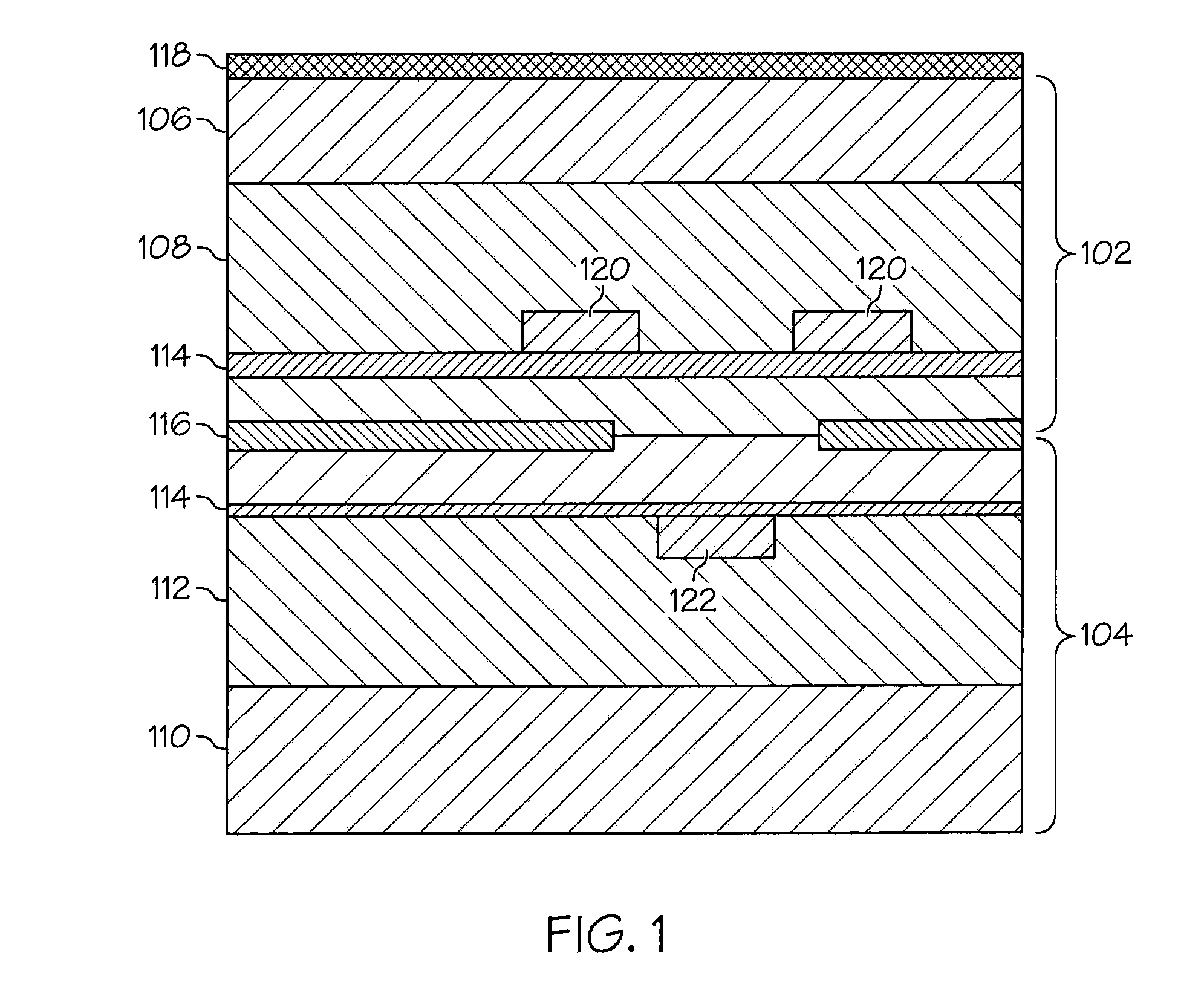

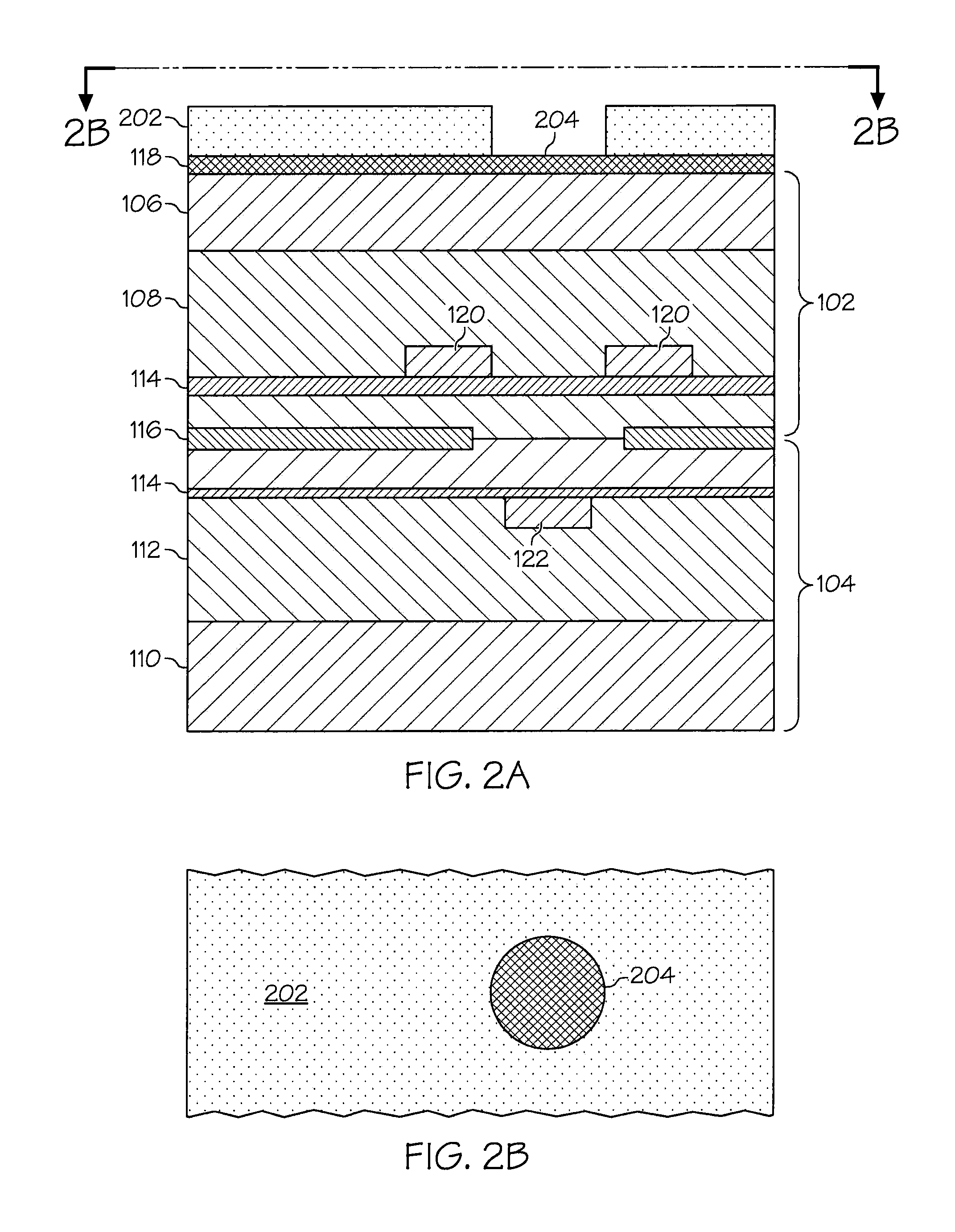

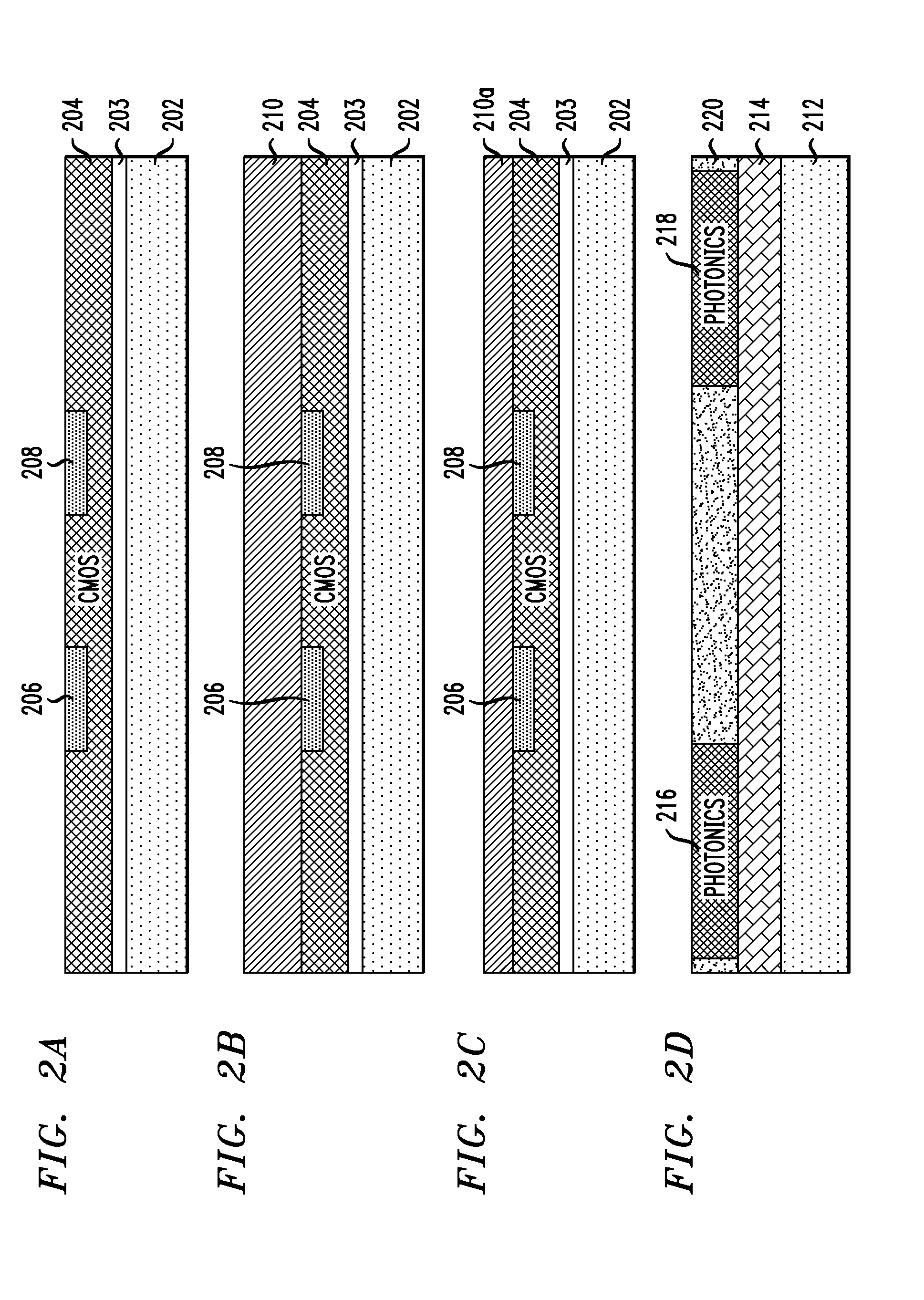

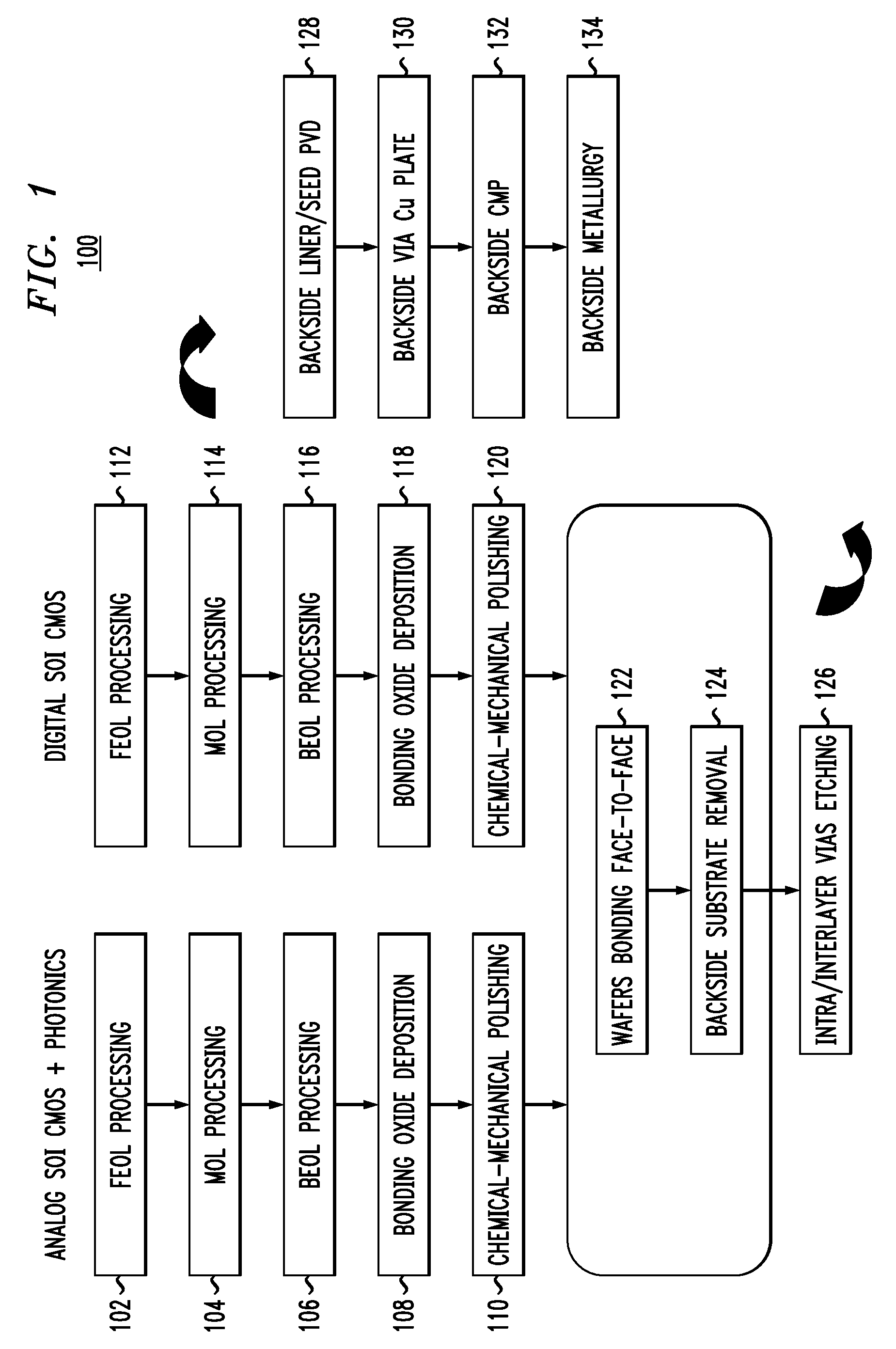

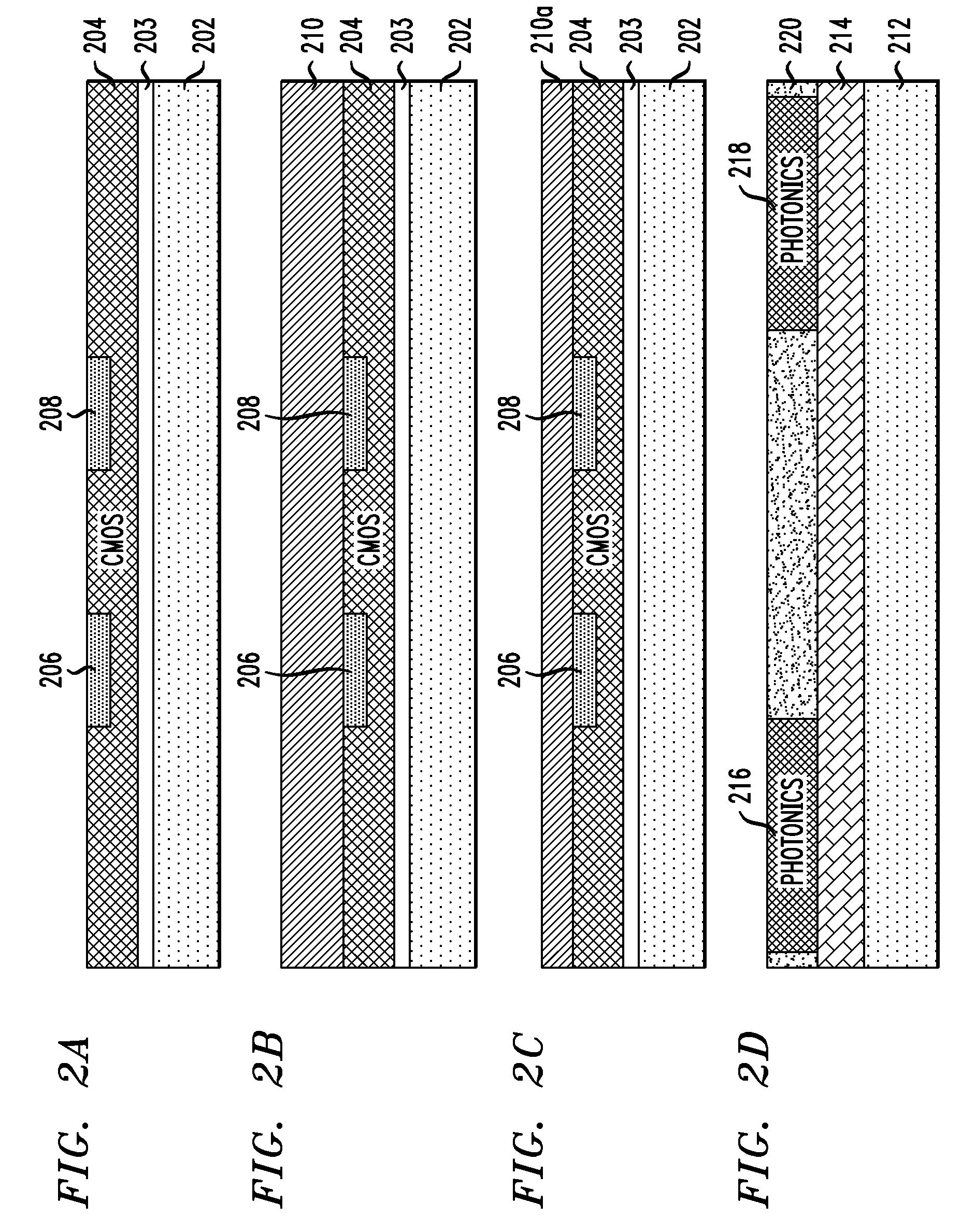

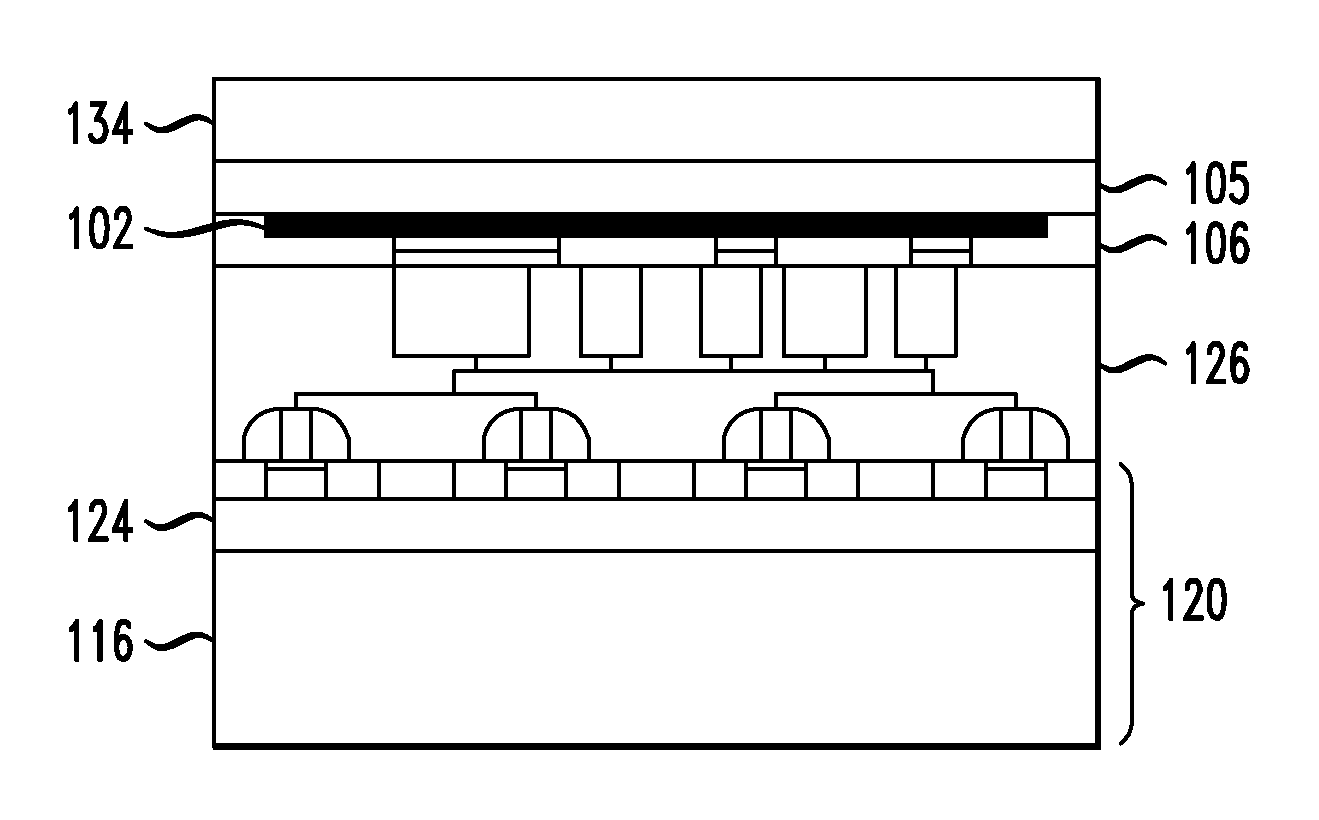

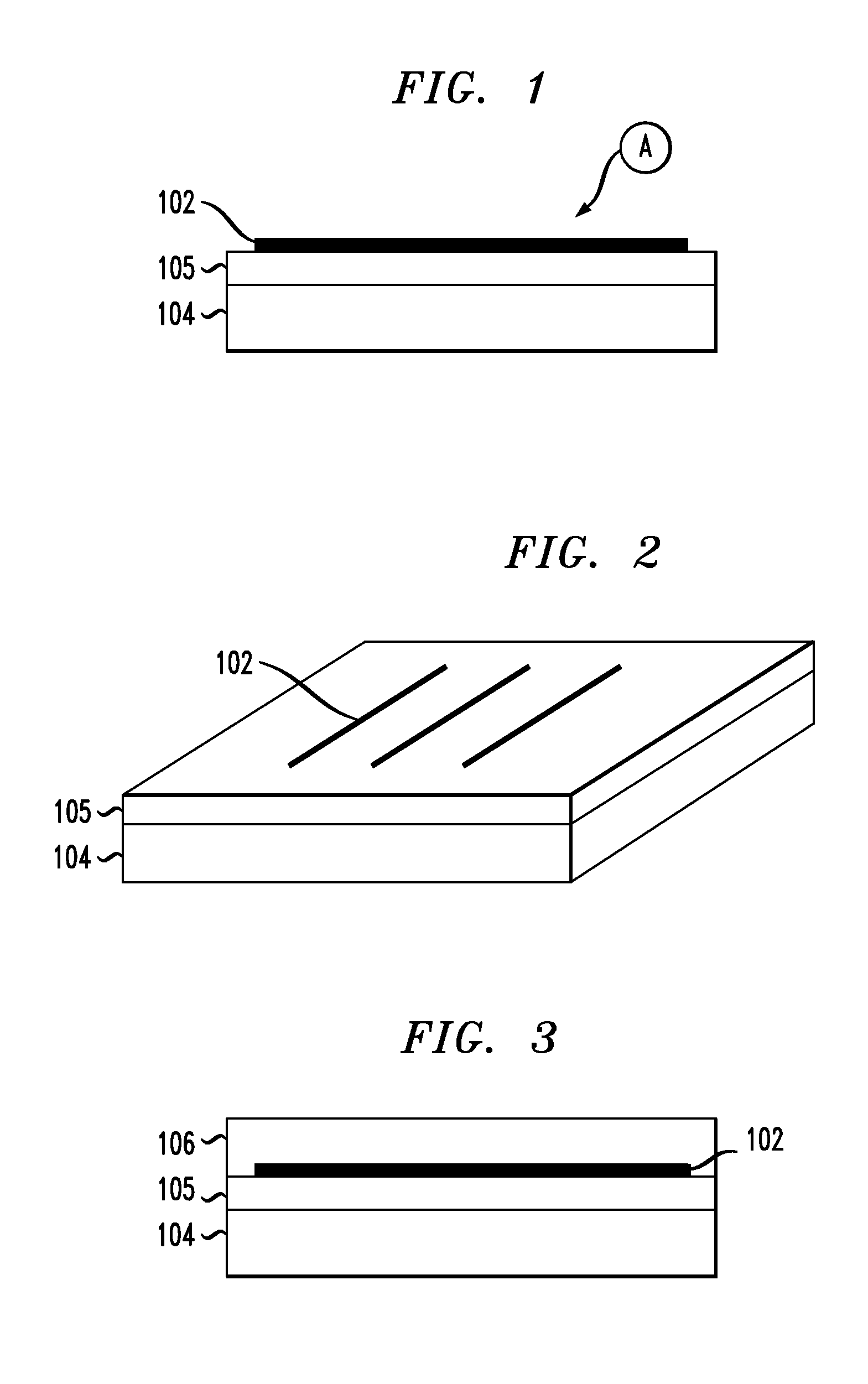

ActiveUS20090294814A1Solid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologyPhotonics

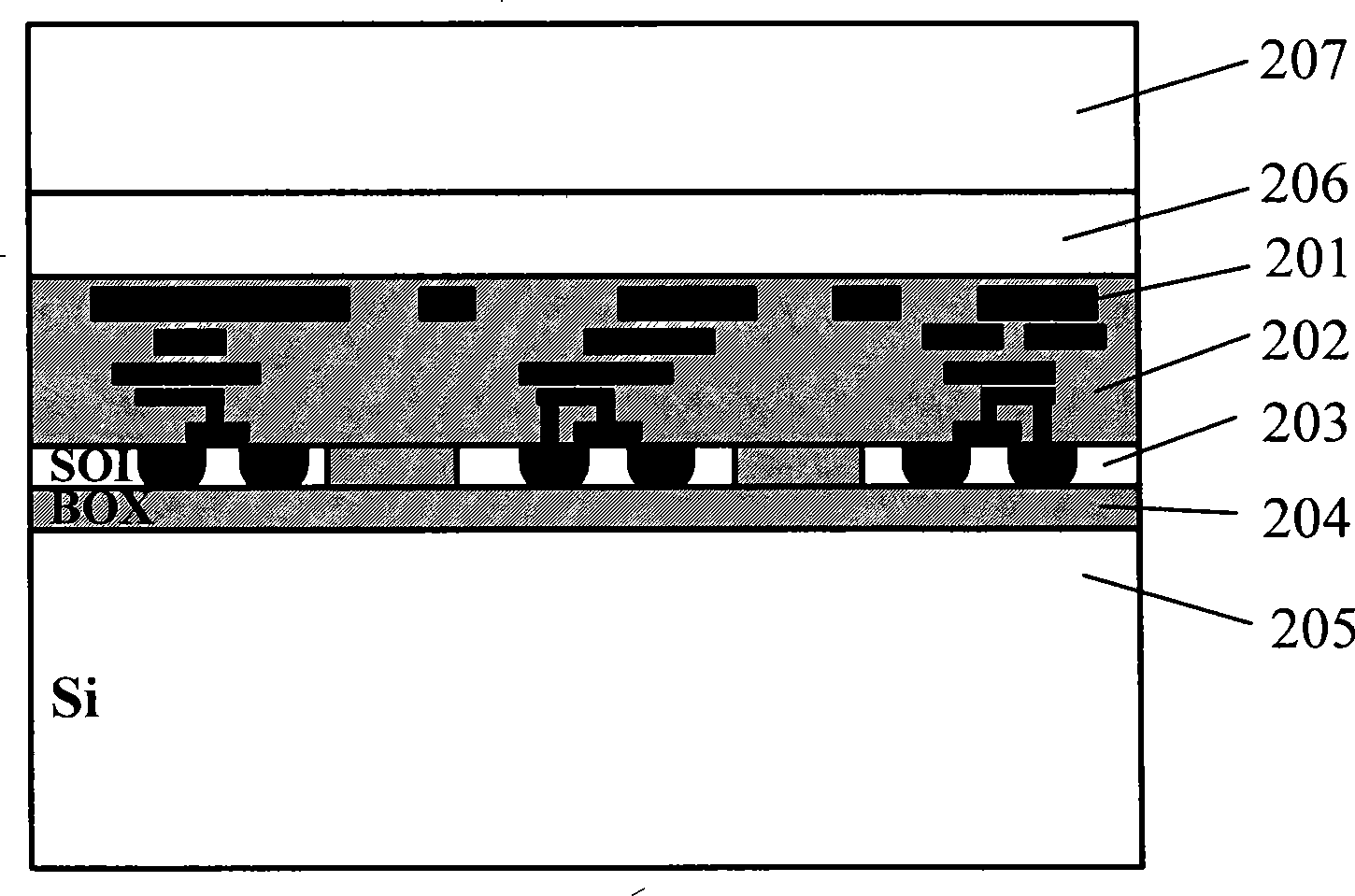

Integrated circuits having complementary metal-oxide semiconductor (CMOS) and photonics circuitry and techniques for three-dimensional integration thereof are provided. In one aspect, a three-dimensional integrated circuit comprises a bottom device layer and a top device layer. The bottom device layer comprises a substrate; a digital CMOS circuitry layer adjacent to the substrate; and a first bonding oxide layer adjacent to a side of the digital CMOS circuitry layer opposite the substrate. The top device layer comprises an analog CMOS and photonics circuitry layer formed in a silicon-on-insulator (SOI) layer having a buried oxide (BOX) with a thickness of greater than or equal to about 0.5 micrometers; and a second bonding oxide layer adjacent to the analog CMOS and photonics circuitry layer. The bottom device layer is bonded to the top device layer by an oxide-to-oxide bond between the first bonding oxide layer and the second bonding oxide layer.

Owner:GLOBALFOUNDRIES US INC

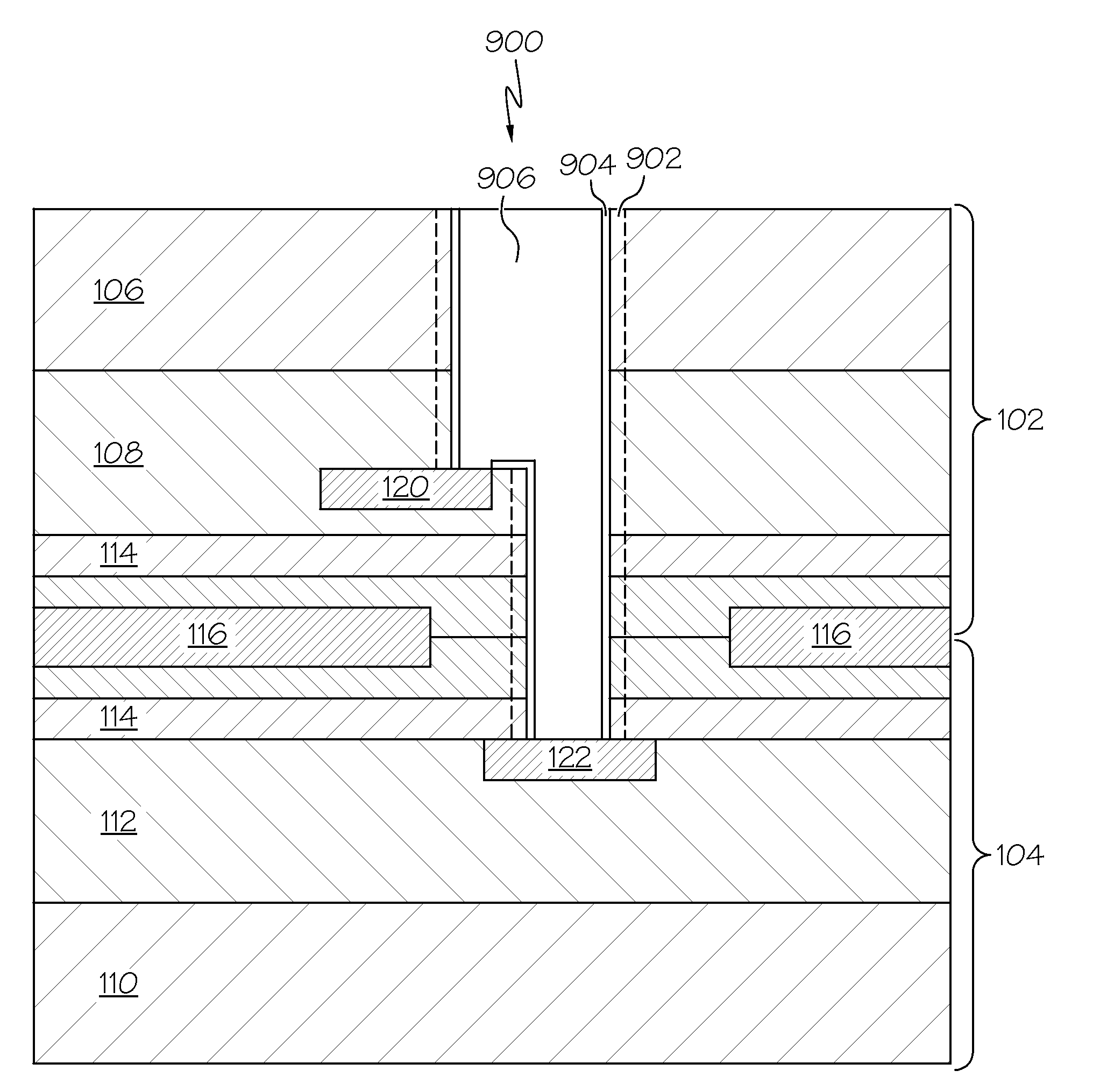

Three Dimensional Integration With Through Silicon Vias Having Multiple Diameters

ActiveUS20110171582A1Add depthSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorComputational physics

A method is disclosed which includes patterning a photoresist layer on a substrate of a structure, removing a first portion of the photoresist layer to expose a first area of the substrate, etching the first area to form a cavity having a first depth, removing a second portion of the photoresist to expose an additional area of the substrate, and etching the cavity to expose a first conductor in the structure and the additional area to expose a second conductor in the structure.

Owner:IBM CORP

Three Dimensional Integration and Methods of Through Silicon Via Creation

InactiveUS20110171827A1Increase the areaAdd depthSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorPhotoresist

A method includes patterning a photoresist layer on a structure to define an opening and expose a first planar area on a substrate layer, etching the exposed planar area to form a cavity having a first depth in the structure, removing a second portion of the photoresist to expose a second planar area on the substrate layer, forming a doped portion in the second planar area, and etching the cavity to expose a first conductor in the structure and the doped portion to expose a second conductor in the structure.

Owner:ELPIS TECH INC

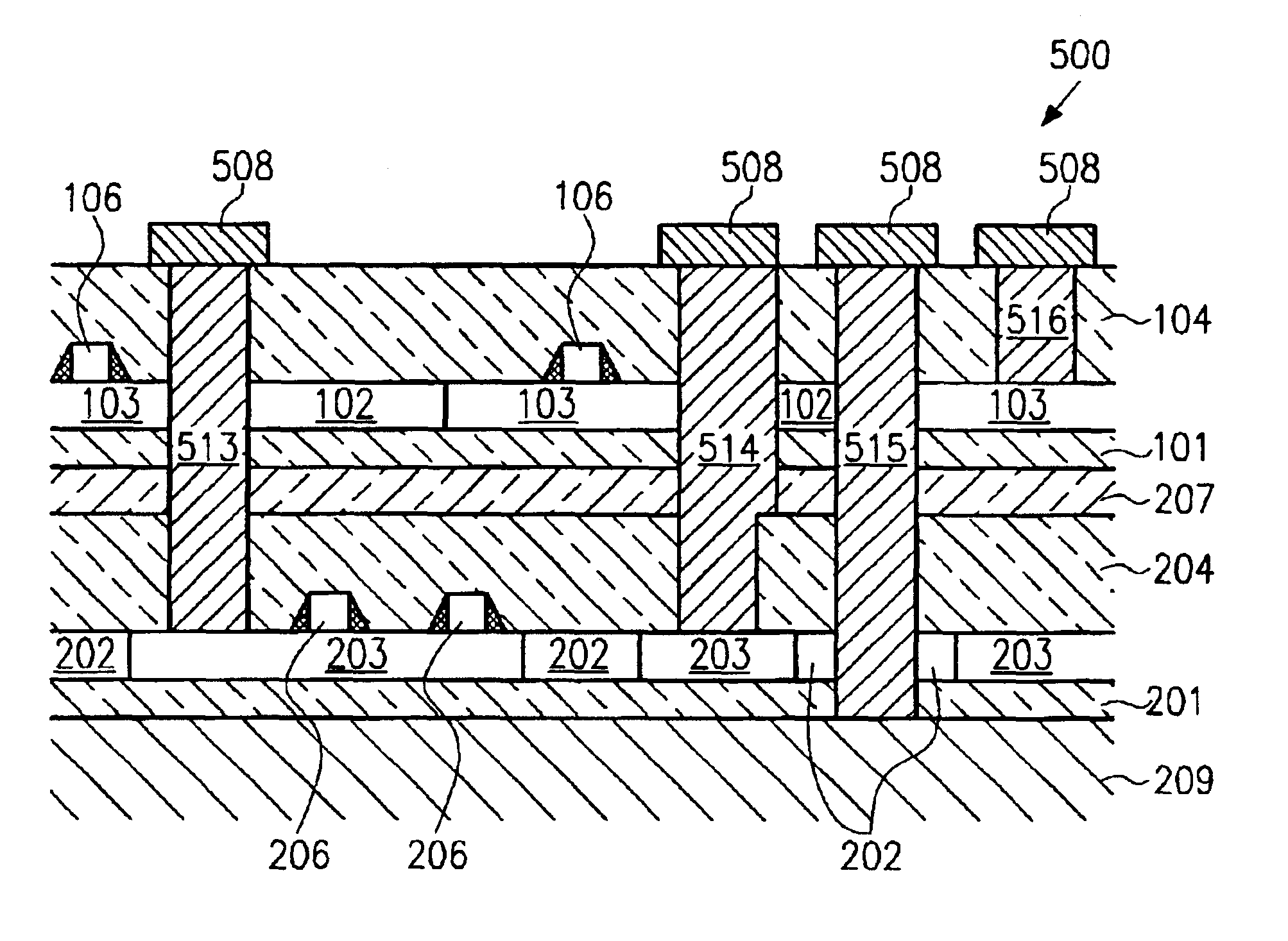

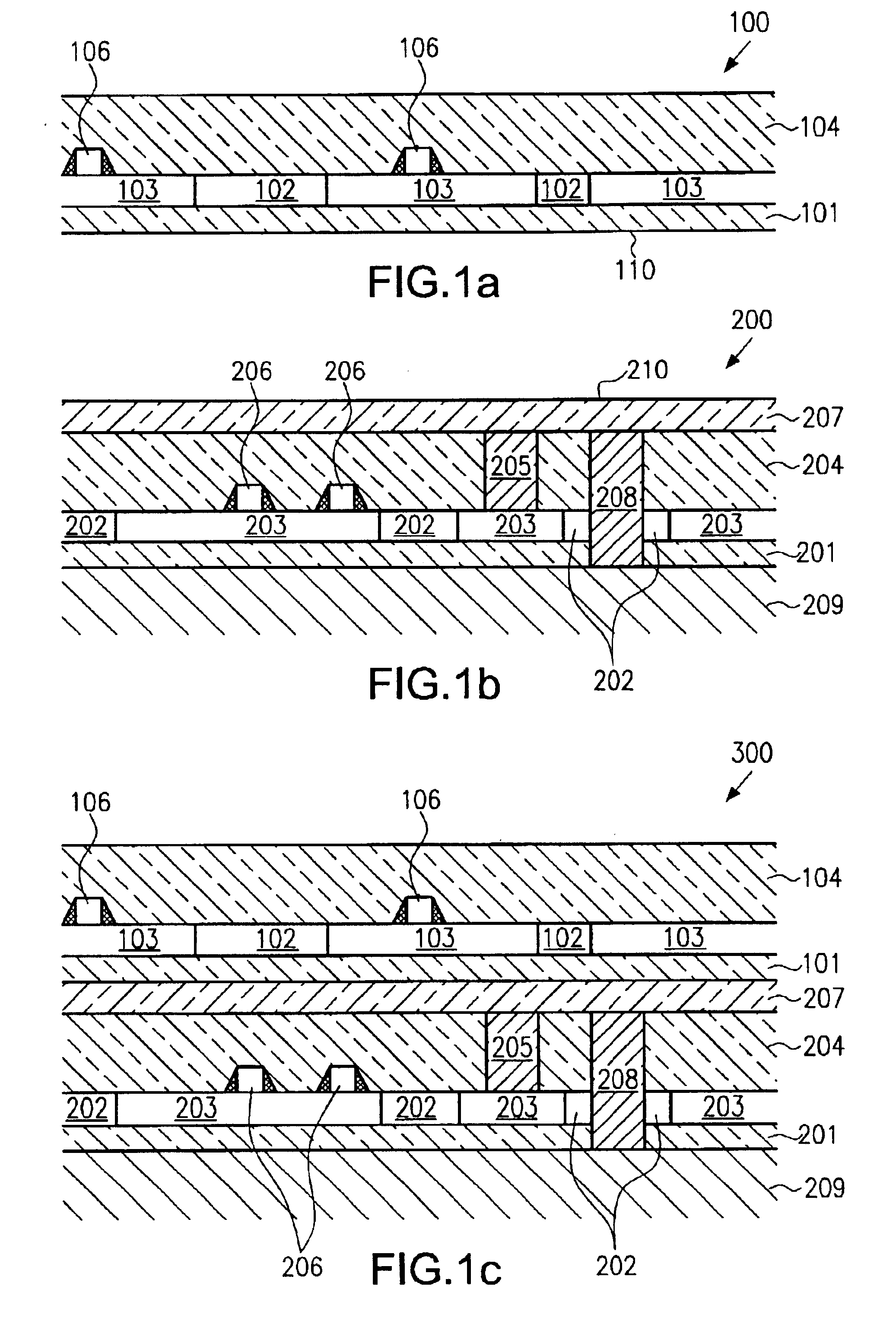

Image sensor with stacked and bonded photo detection and peripheral circuit substrates

ActiveUS7495206B2Maximizing detection regionSolid-state devicesMaterial analysis by optical meansCMOSEngineering

A complementary metal oxide semiconductor (CMOS) device with a three dimensional integration structure and a method for fabricating the same are provided. An image sensor includes a first substrate in which a photo detection device is formed; a second substrate in which a peripheral circuit is formed, wherein the first substrate and the second substrate are bonded through a plurality of bonding pads formed on both the first substrate and the second substrate, and a back side of the first substrate is turned upside down; and a microlens formed on a top portion of the back side of the first substrate.

Owner:INTELLECTUAL VENTURES II

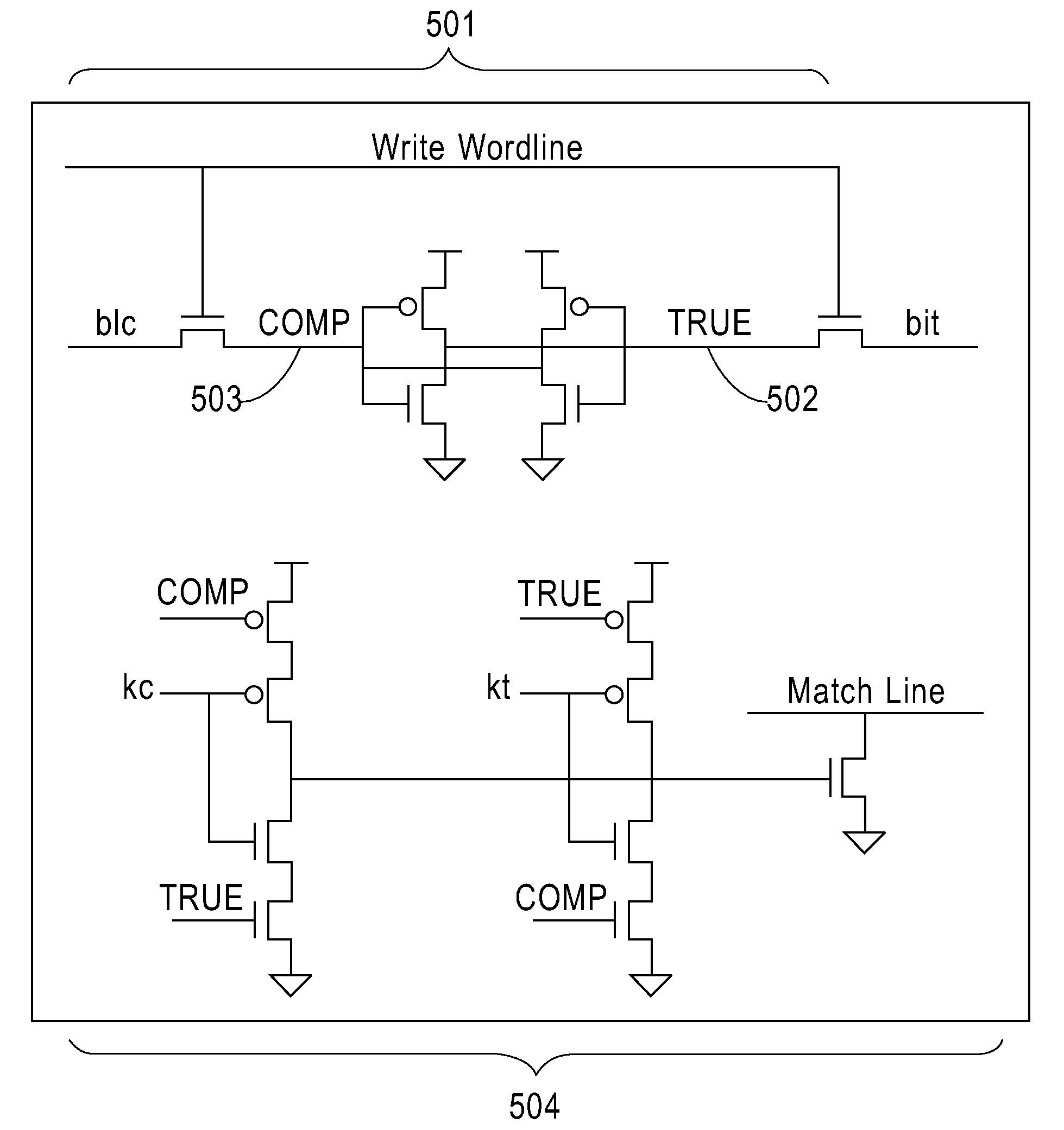

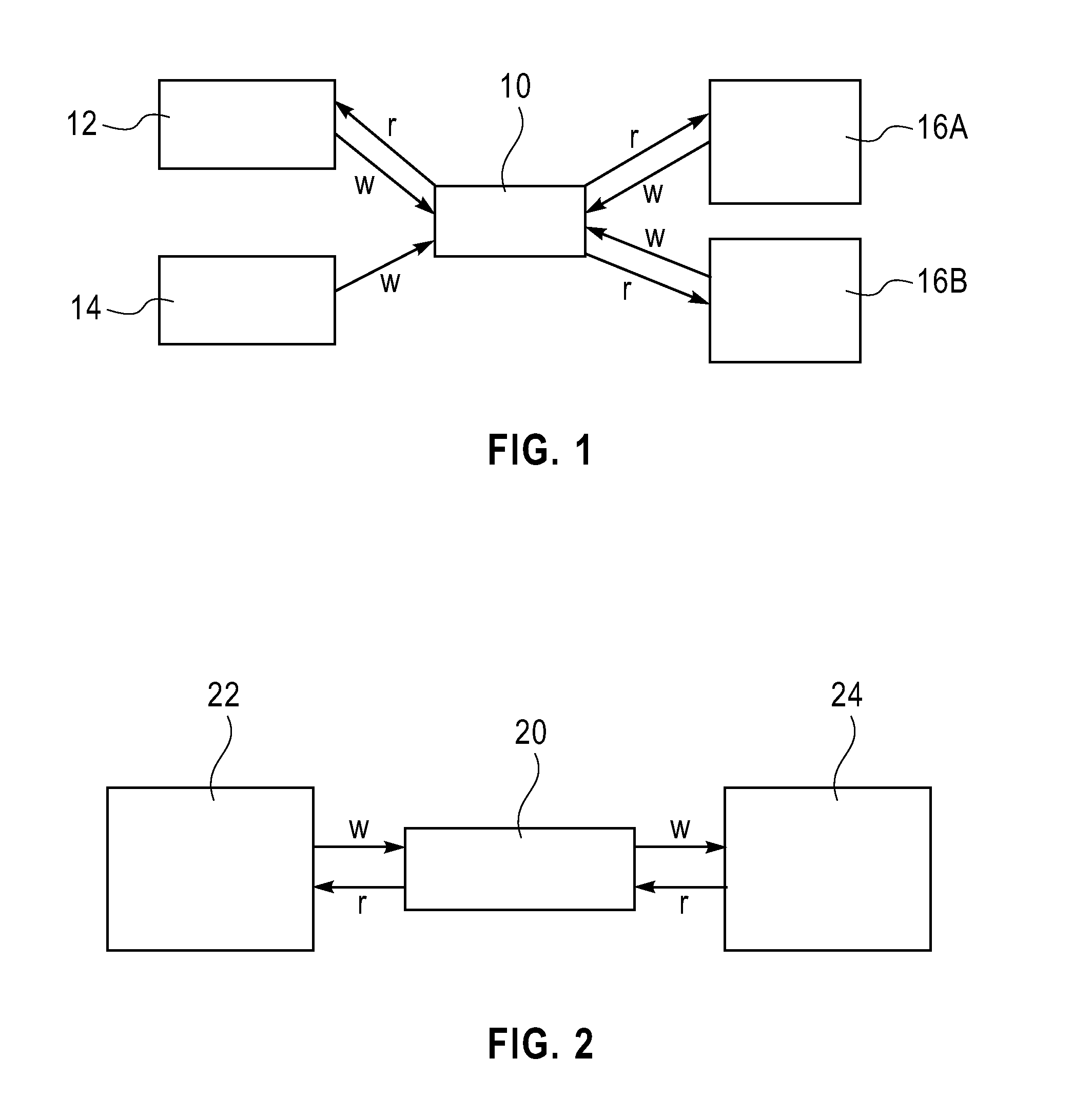

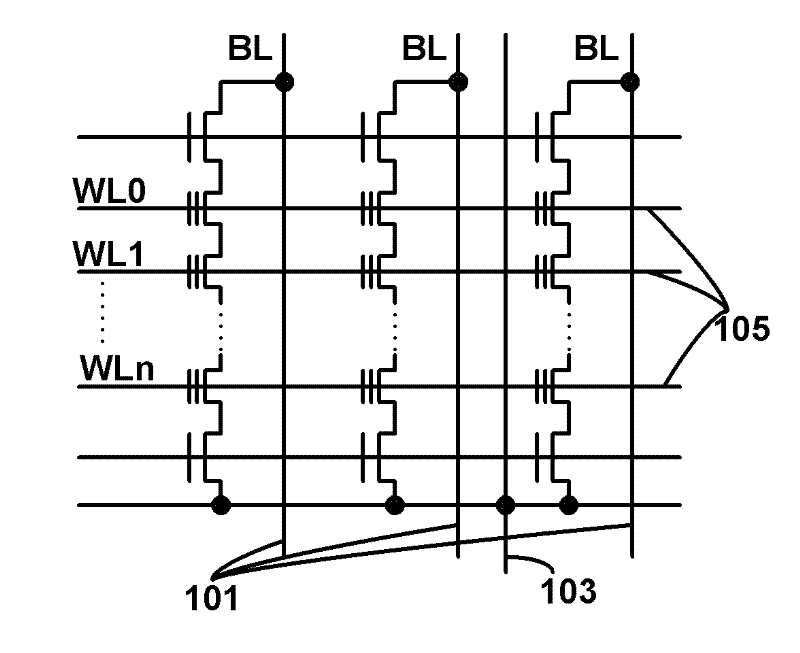

Multi-wafer 3D cam cell

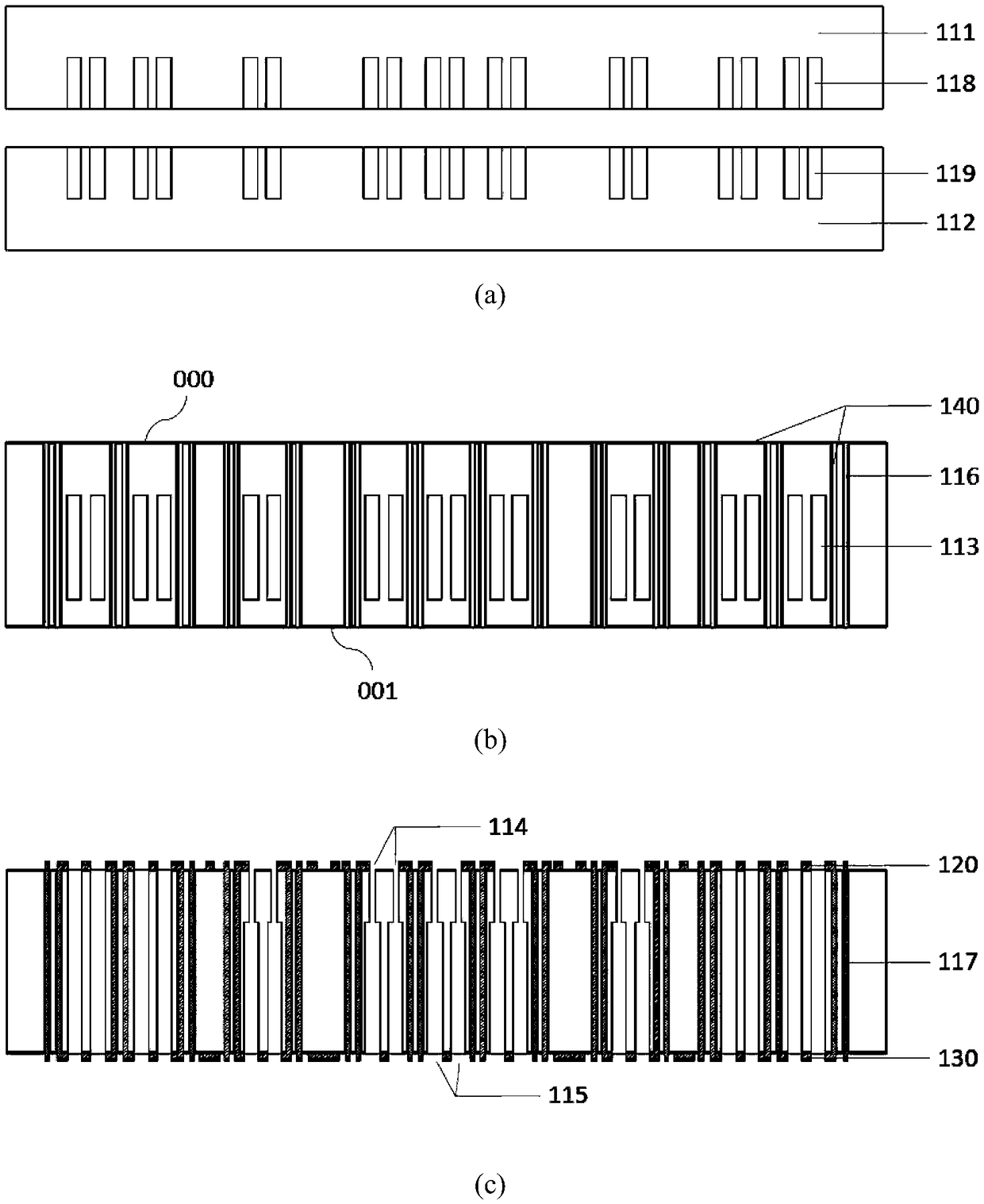

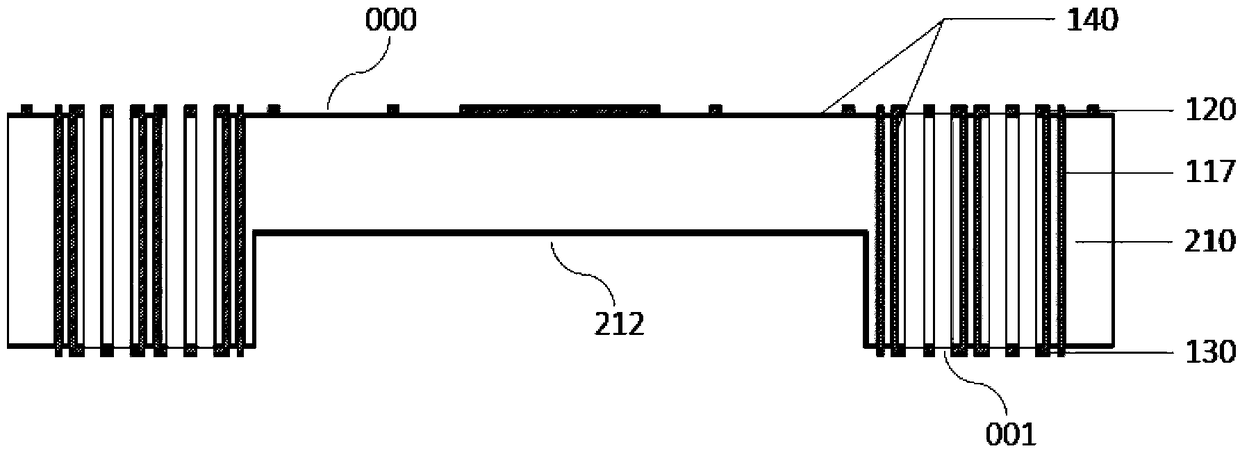

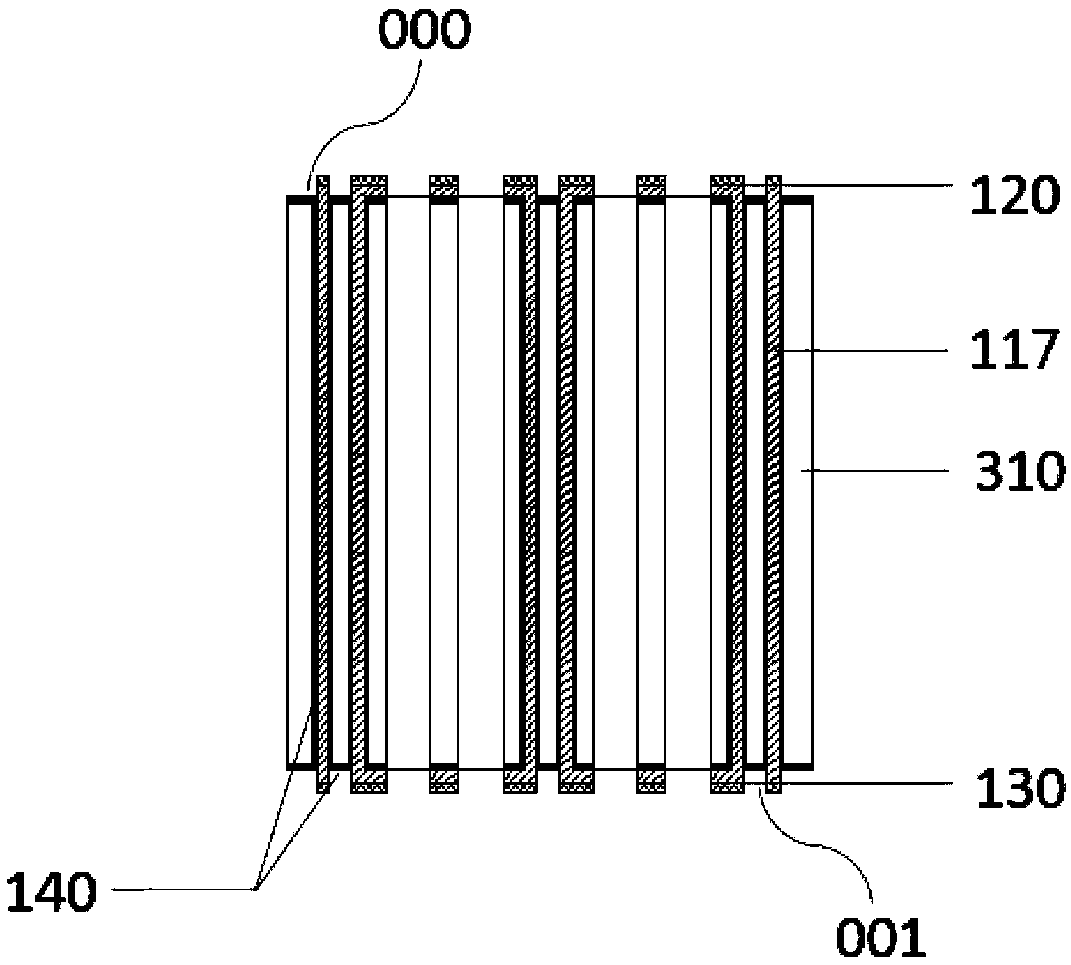

InactiveUS20080288720A1Reduce negative impactMinimizing accessSolid-state devicesSemiconductor/solid-state device manufacturingRandom access memoryData access

A multi-wafer CAM cell in which the negative effects of increased travel distance have been substantially reduced is provided. The multi-wafer CAM cell is achieved in the present invention by utilizing three-dimensional integration in which multiple active circuit layers are vertically stack and vertically aligned interconnects are employed to connect a device from one of the stacked layers to another device in another stack layer. By vertically stacking multiple active circuit layers with vertically aligned interconnects, each compare port of the inventive CAM cell can be implemented on a separate layer above or below the primary data storage cell. This allows the multi-wafer CAM structure to be implemented within the same area footprint as a standard Random Access Memory (RAM) cell, minimizing data access and match compare delays.

Owner:GLOBALFOUNDRIES INC

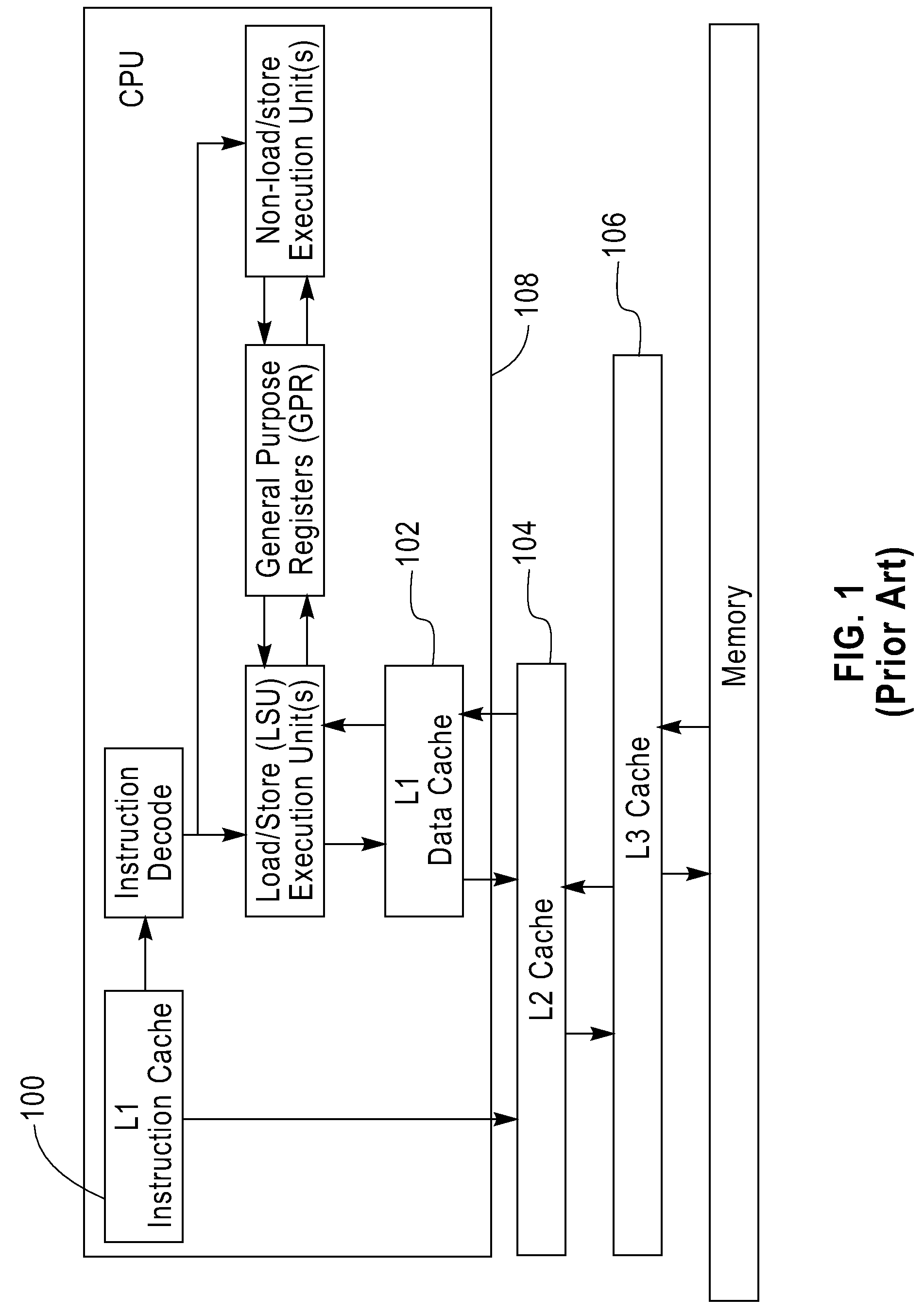

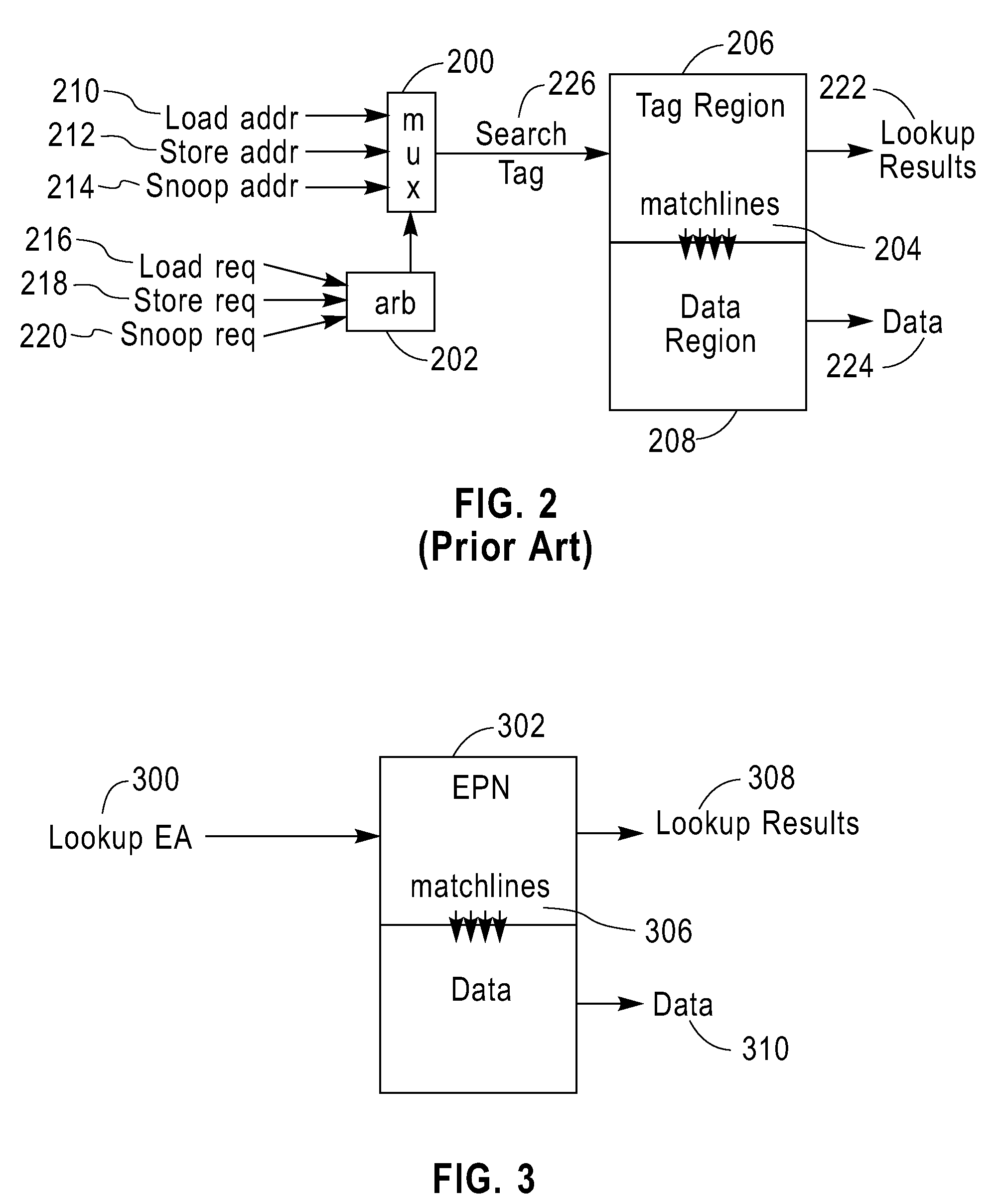

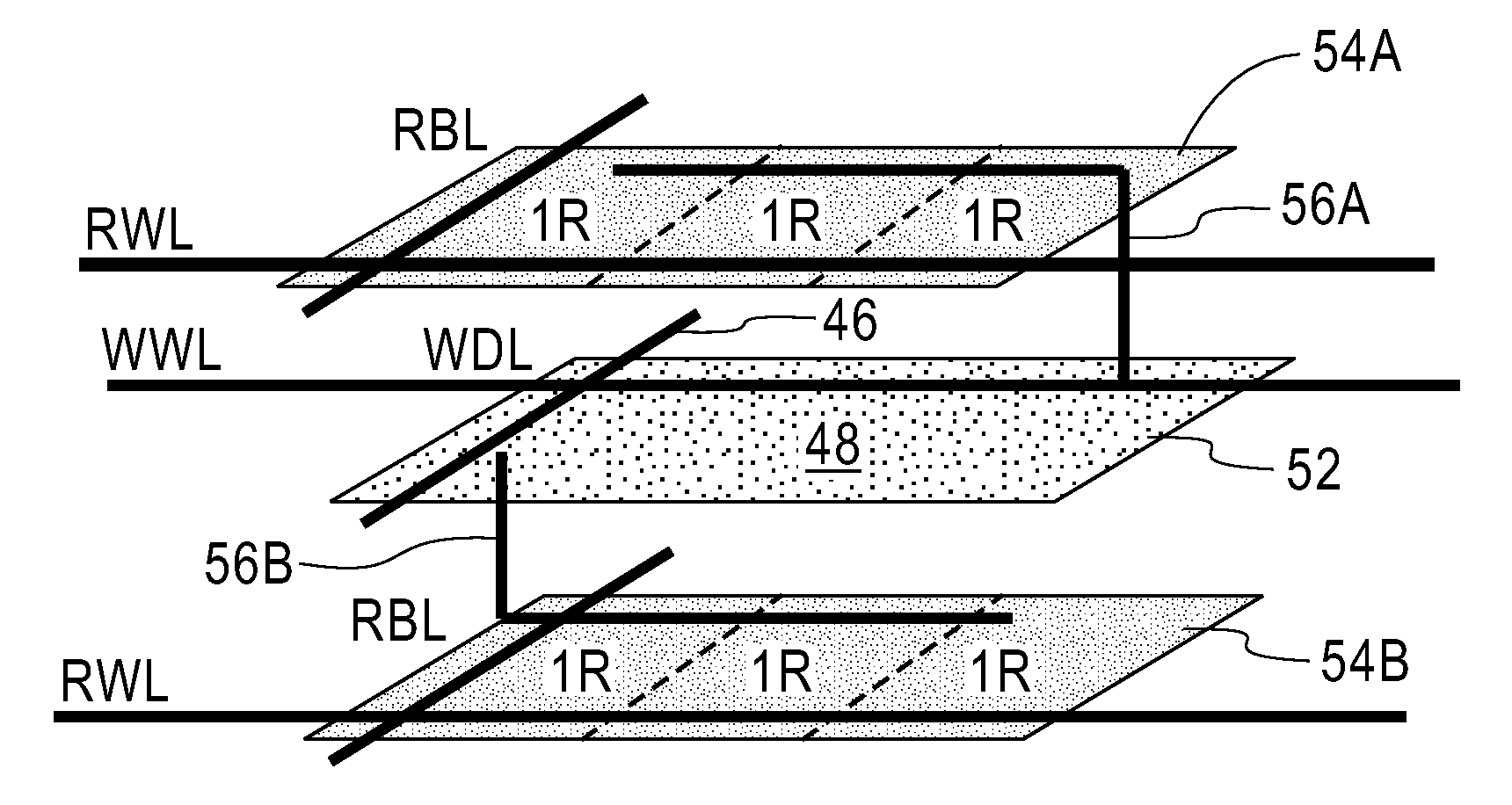

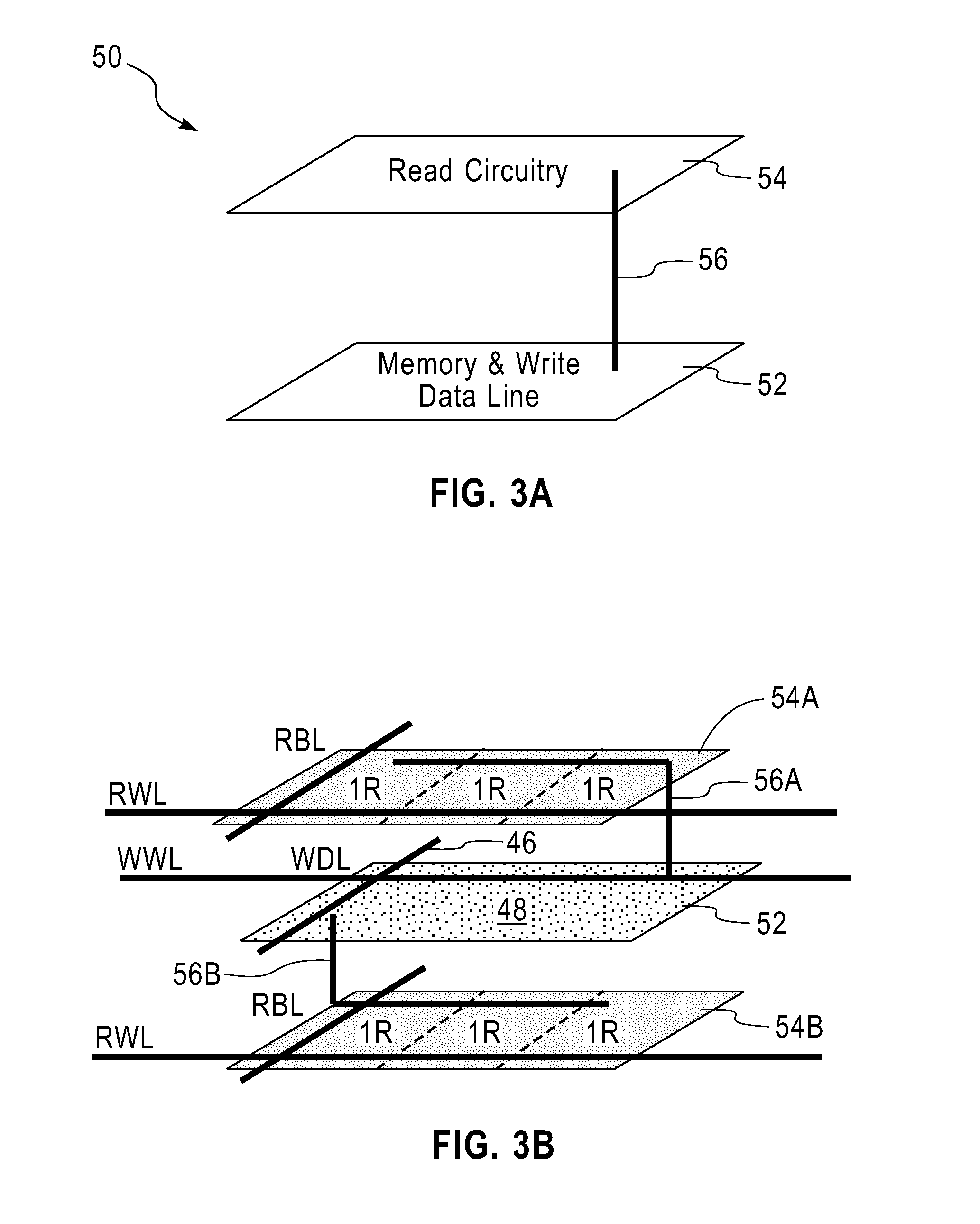

Multiple wafer level multiple port register file cell

InactiveUS20080291767A1Reduce loadMinimizing dataSolid-state devicesSemiconductor/solid-state device manufacturingProcessor registerMulti port

A multi-port register file (e.g., memory element) is provided in which each read port of the register file is located in a separate wafer above and / or below the primary data storage element. This is achieved in the present invention by utilizing three-dimensional integration in which multiple active circuit layers are vertically stacked and vertically aligned interconnects are employed to connect a device from one of the stacked layers to another device in another stacked layer.

Owner:IBM CORP

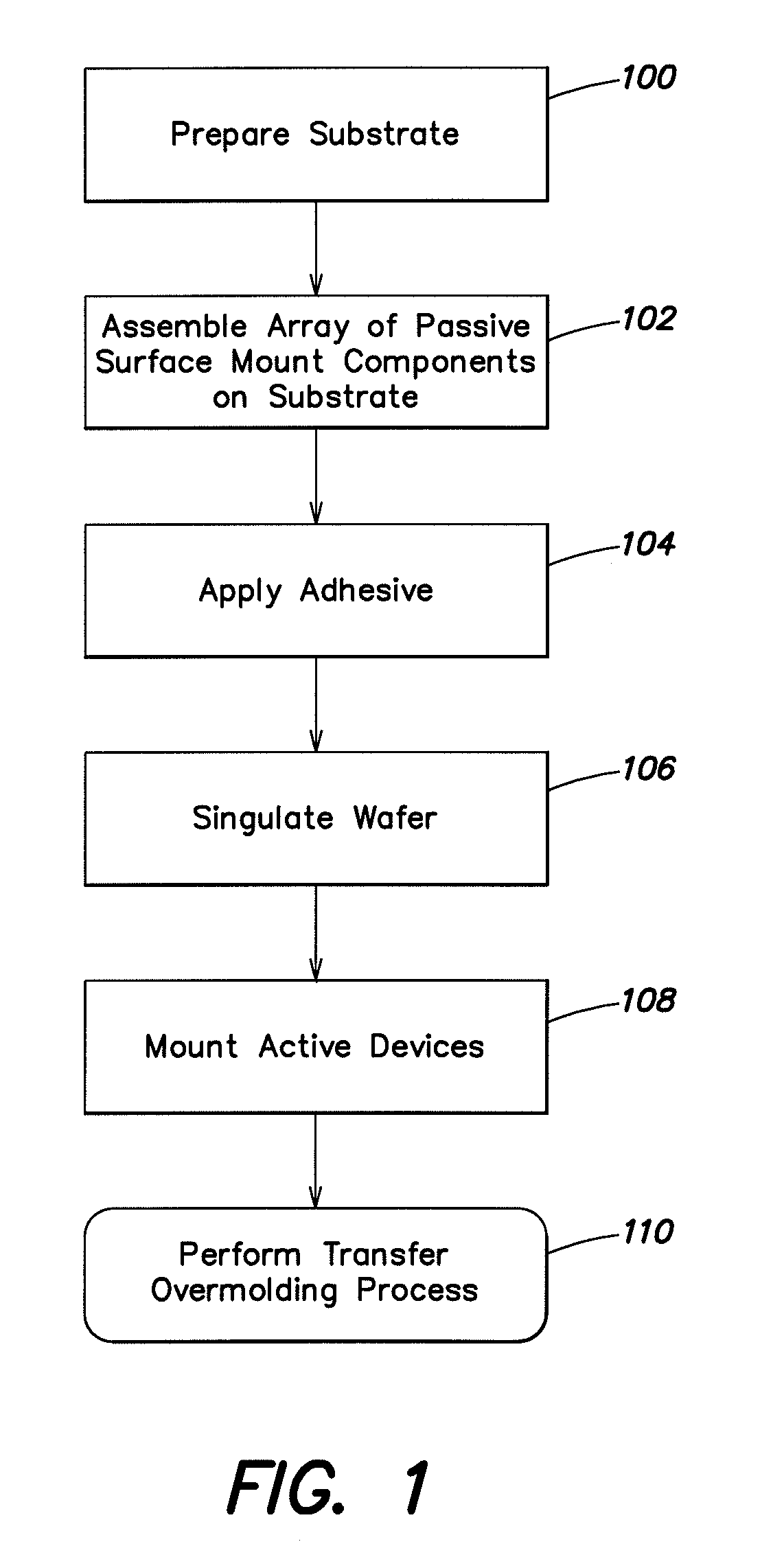

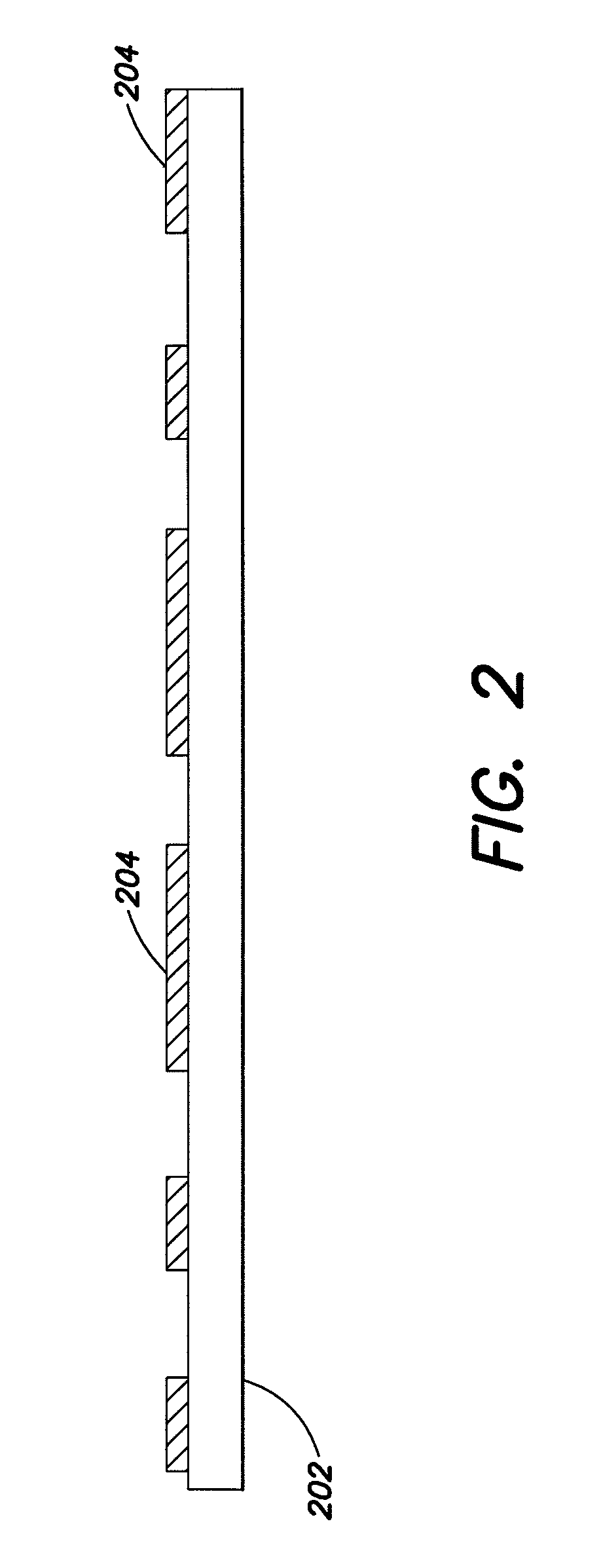

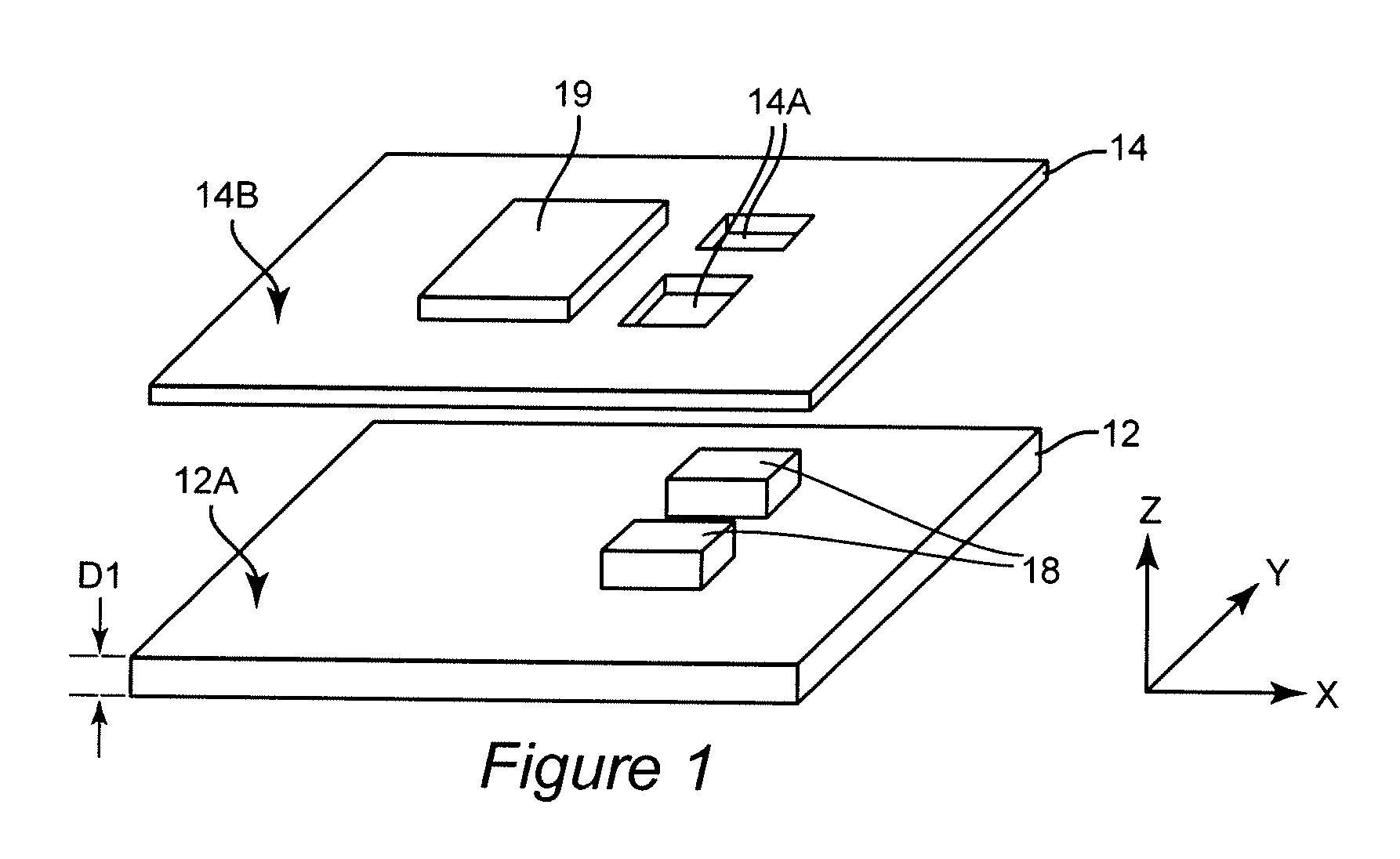

3-d stacking of active devices over passive devices

ActiveUS20090267220A1Increase in board densitySize of substrate can be reducedFinal product manufactureSemiconductor/solid-state device detailsAdhesiveSurface mounting

Single-die or multi-die packaged modules that incorporate three-dimensional integration of active devices with discrete passive devices to create a package structure that allows active devices (such as, silicon or gallium-arsenide devices) to share the same footprint area as an array of passive surface mount components. In one example, a module includes at least one active device stacked on top of an array of passive surface mount components on a substrate. A conductive or non-conductive adhesive can be used to adhere the active device to the array of passive devices.

Owner:SKYWORKS SOLUTIONS INC

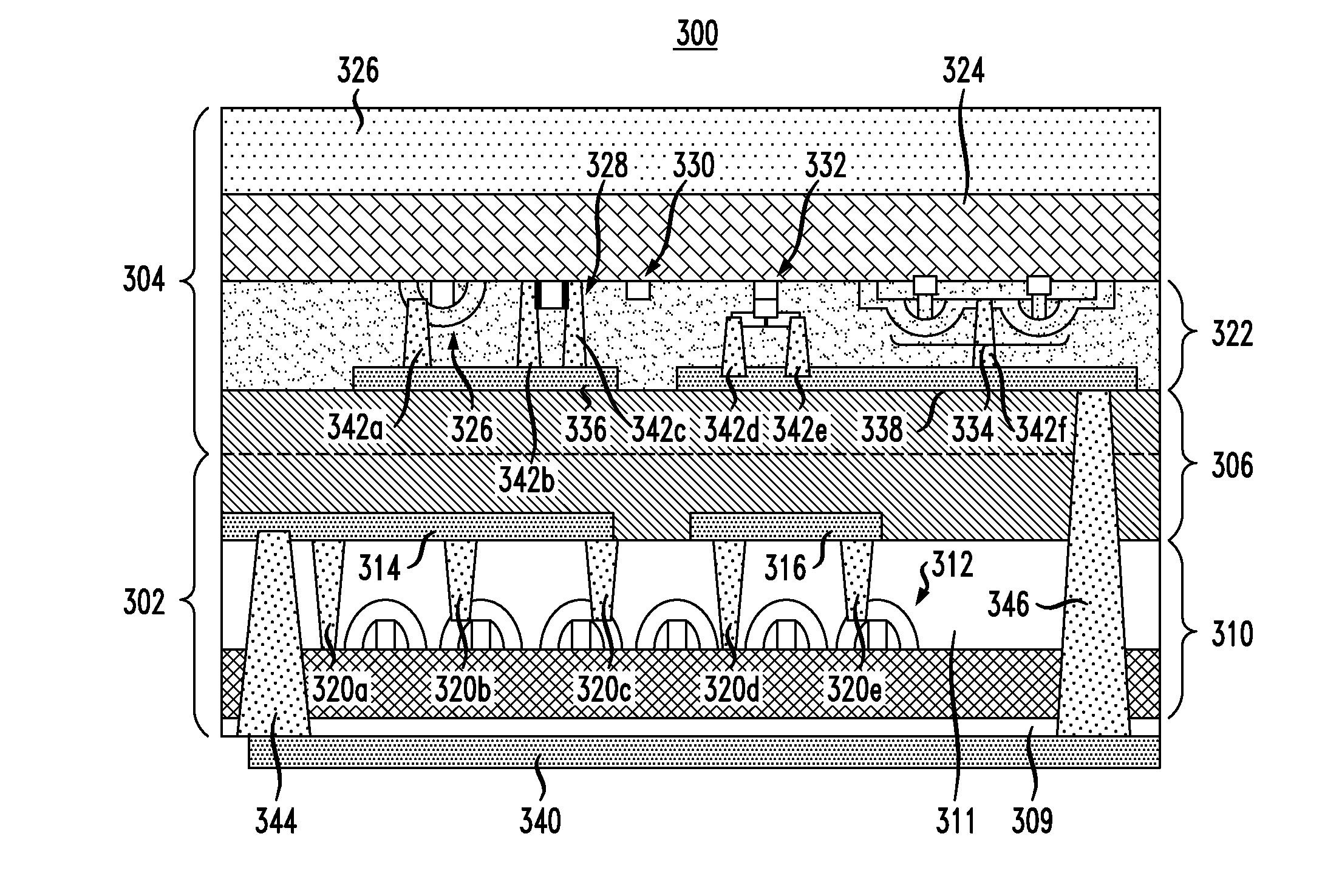

Techniques for Three-Dimensional Circuit Integration

InactiveUS20090297091A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSMicrometer

Integrated circuits having complementary metal-oxide semiconductor (CMOS) and photonics circuitry and techniques for three-dimensional integration thereof are provided. In one aspect, a three-dimensional integrated circuit comprises a bottom device layer and a top device layer. The bottom device layer comprises a digital CMOS circuitry layer; and a first bonding oxide layer adjacent to the digital CMOS circuitry layer. The top device layer comprises a substrate; an analog CMOS and photonics circuitry layer formed in a silicon-on-insulator (SOI) layer adjacent to the substrate, the SOI layer having a buried oxide (BOX) with a thickness of greater than or equal to about one micrometer; and a second bonding oxide layer adjacent to a side of the analog CMOS and photonics circuitry layer opposite the substrate. The bottom device layer is bonded to the top device layer by an oxide-to-oxide bond between the first bonding oxide layer and the second bonding oxide layer.

Owner:GLOBALFOUNDRIES INC

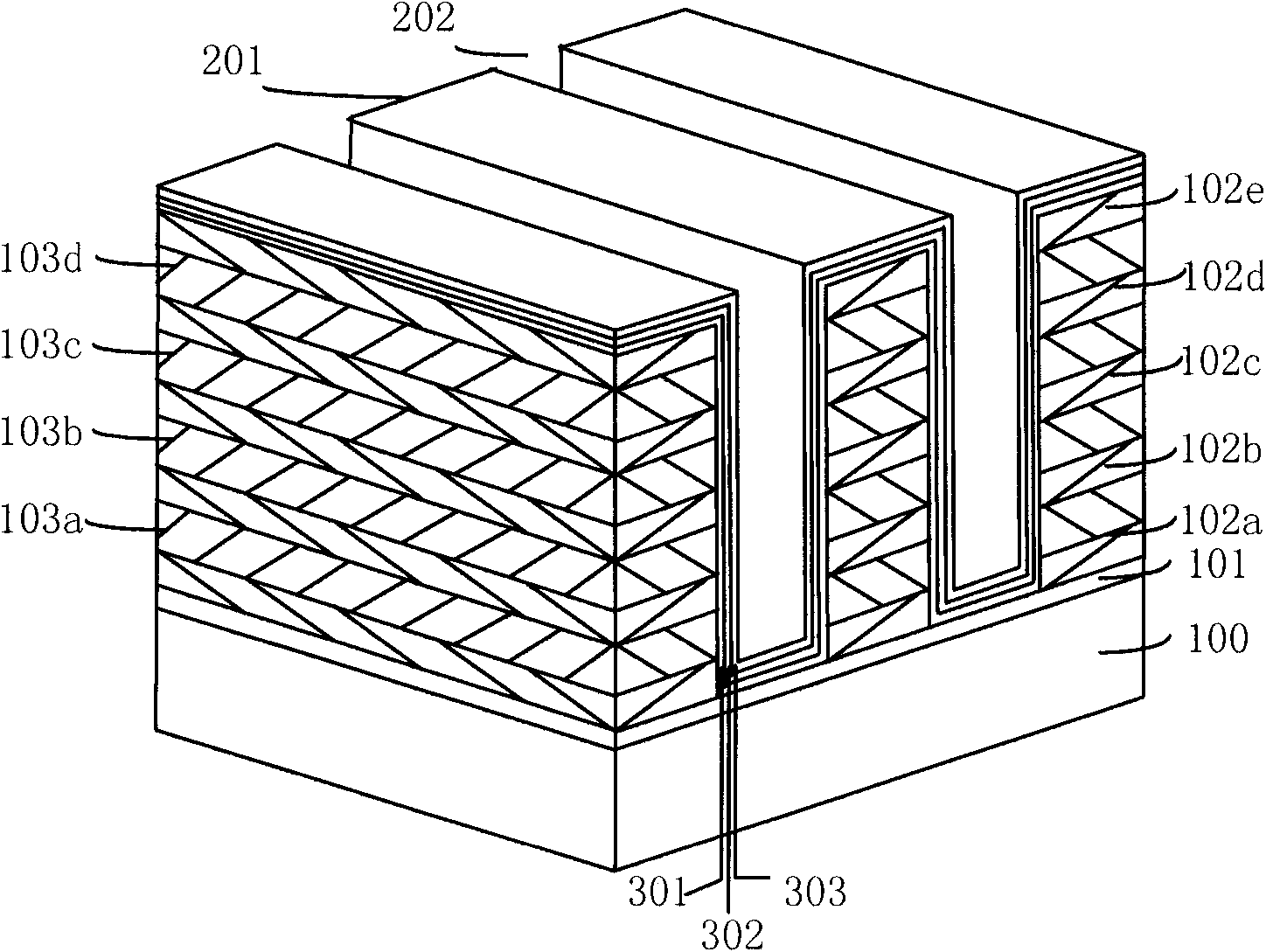

Packaging method of three-dimensional heterostructure for realizing heat dissipation of high power GaN device layer

ActiveCN108766897AOvercoming Existence Shunt DesignOvercoming traditional three-dimensional microfluidicsSolid-state devicesSemiconductor/solid-state device manufacturingRadio frequencyThree dimensional integration

The invention proposes a packaging method of a three-dimensional heterostructure for realizing heat dissipation of a high power GaN device layer for the integrated requirements of three-dimensional heterostructure integration of a high power GaN device and the heat dissipation of a device layer. A three-dimensional folding micro-channel design is realized by utilizing a plurality of laminated substrates such as a GaN chip body-TSV radio frequency adapter plate-silicon supporting block; a microfluid flows in from the bottom layer of a packaging shell and then steps up to cool a GaN device layer hot spot and then steps down and flows out, therefore, the problems in a traditional TSV three-dimensional integration technology that when an embedded micro-channel extends from the TSV adapter plate to the high power GaN chip body, a shunt design exists, a traditional three-dimensional micro-channel and a packaging body-chip are integrated and manufactured in a compatible way are solved, and the three-dimensional radio frequency heterogeneous integration application with high manufacturability, high heat dissipation efficiency and high stability is further achieved, thus the packaging method is of great significance.

Owner:XIAMEN UNIV

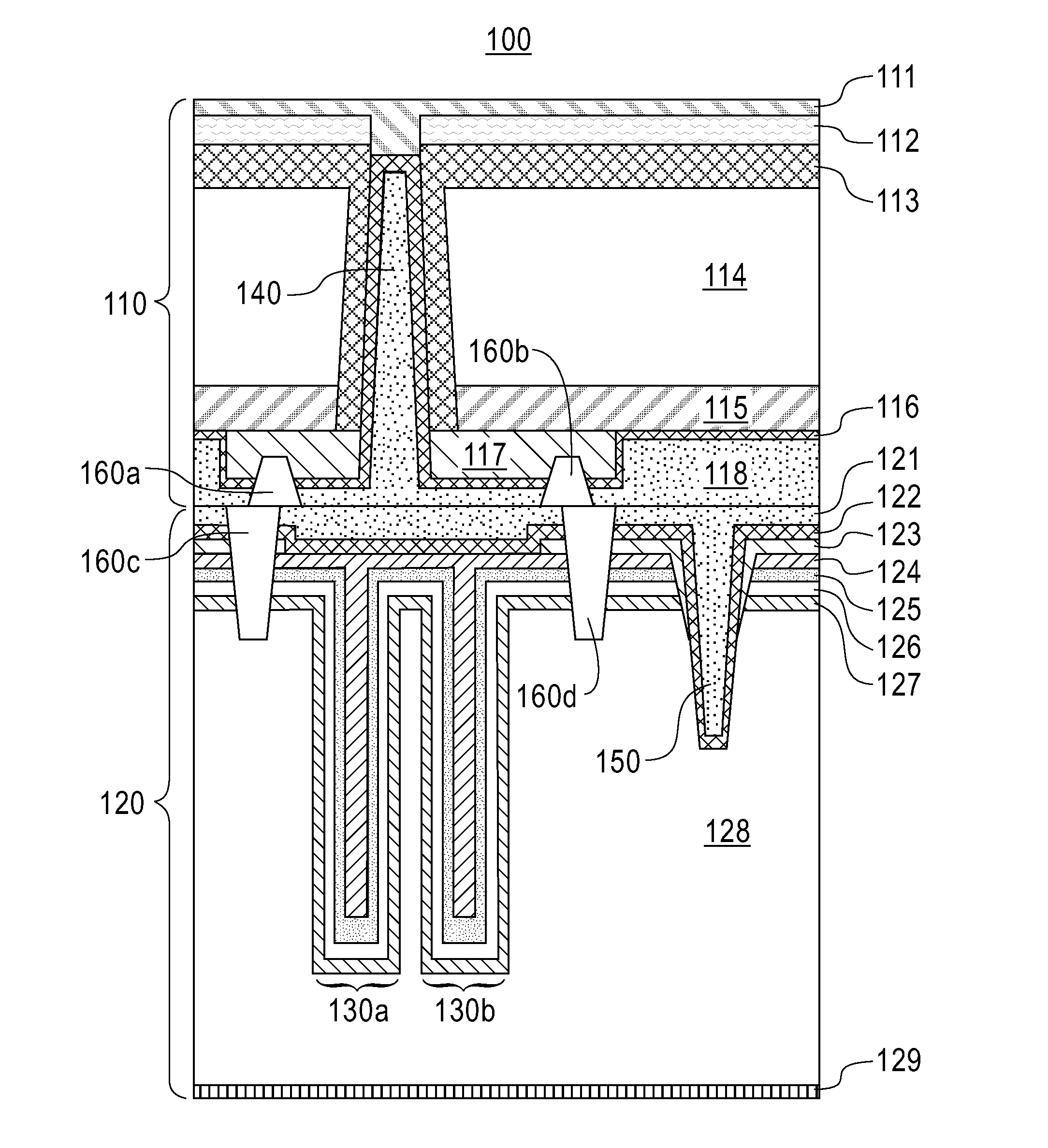

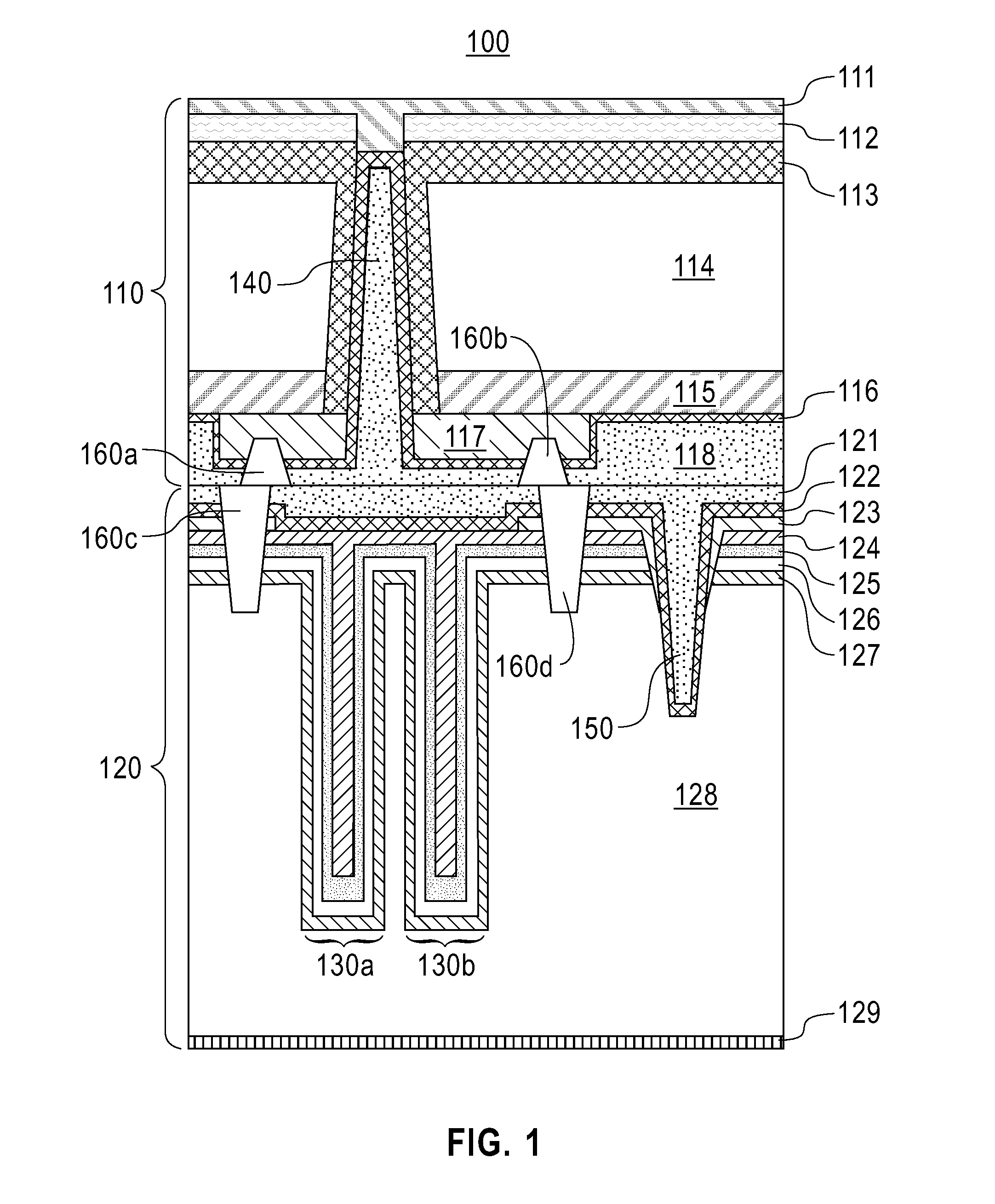

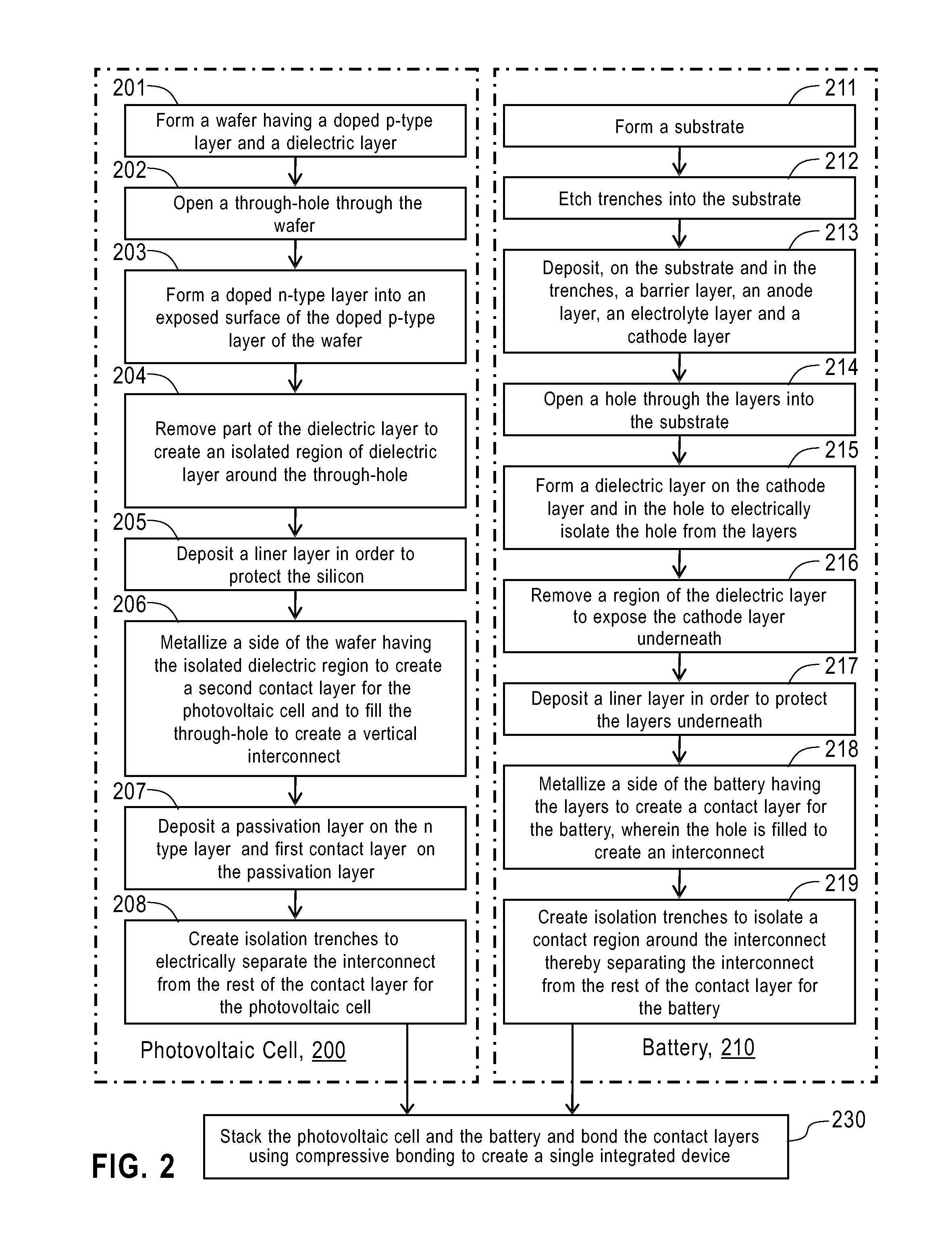

Solar cell and battery 3D integration

An integrated photovoltaic cell and battery device, a method of manufacturing the same and a photovoltaic power system incorporating the integrated photovoltaic cell and battery device. The integrated photovoltaic cell and battery device includes a photovoltaic cell, a battery, and interconnects providing three-dimensional integration of the photovoltaic cell and the battery into an integrated device for capturing and storing solar energy. Also provided is a design structure readable by a machine to simulate, design, or manufacture the above integrated photovoltaic cell and battery device.

Owner:IBM CORP

Three-dimensional integrated method of sensor array and signal processing circuits

InactiveCN102689874ARealize floatingSimplify the manufacturing processDecorative surface effectsChemical vapor deposition coatingSensor arraySignal processing circuits

The invention discloses a three-dimensional integrated method of a sensor array and signal processing circuits in the technical field of semiconductor three-dimensional integration. The three-dimensional integrated method comprises the following steps of: (1) manufacturing sensors on a top layer single crystal material of an insulating substrate device; (2) manufacturing the signal processing circuits and metal interconnection lines on the surface of a signal processing circuit substrate and manufacturing metal salient points on the metal interconnection lines; (3) carrying out a bonding process or a three-dimensional interconnection process; (4) carrying out metal thermocompression bonding on bonding metal salient points and the salient points; (5) removing a temporary bonding polymer layer and auxiliary wafers; and (6) manufacturing plane interconnection lines. By utilizing the three-dimensional integrated method, integration of the sensors and the signal processing circuits is realized, hovering of the sensors is realized, electric signal connection of the sensors and the signal processing circuits is realized by utilizing three-dimensional interconnection lines, the manufacture process is simple, the sensors can be suspended, and excellent consistency of the sensors and large-scale array structure can be obtained.

Owner:TSINGHUA UNIV

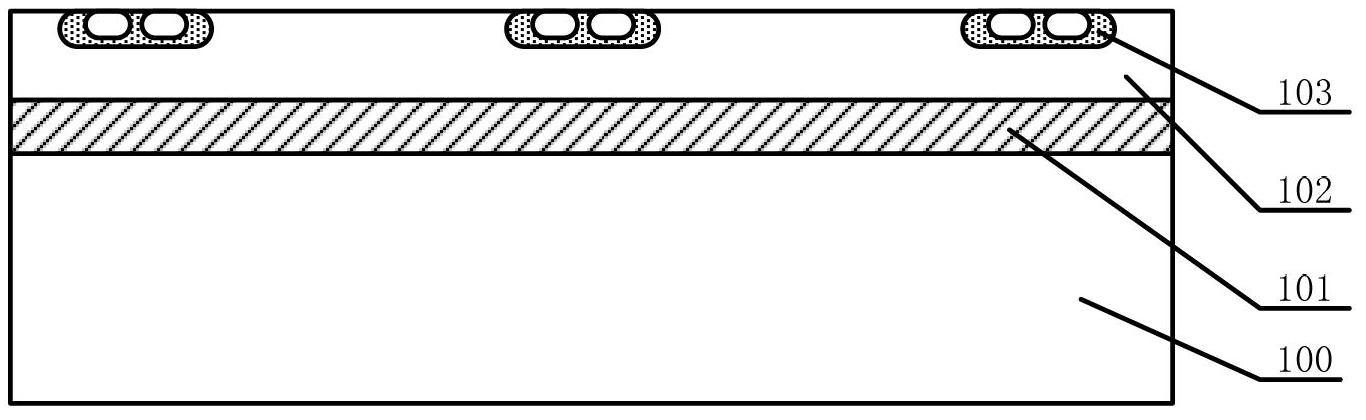

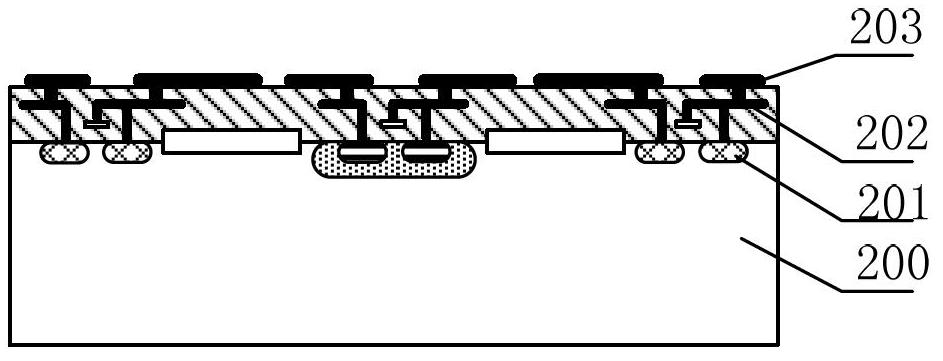

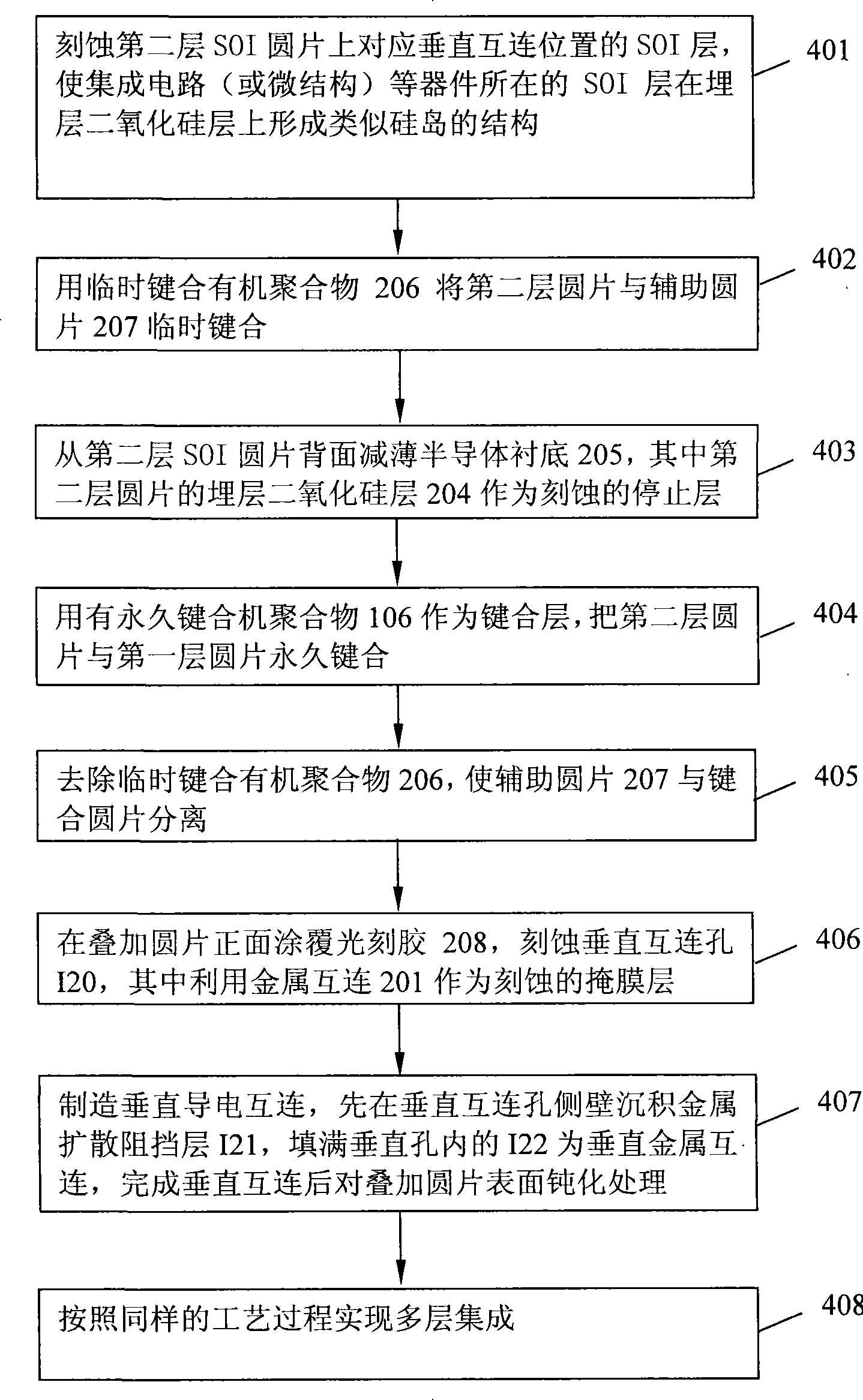

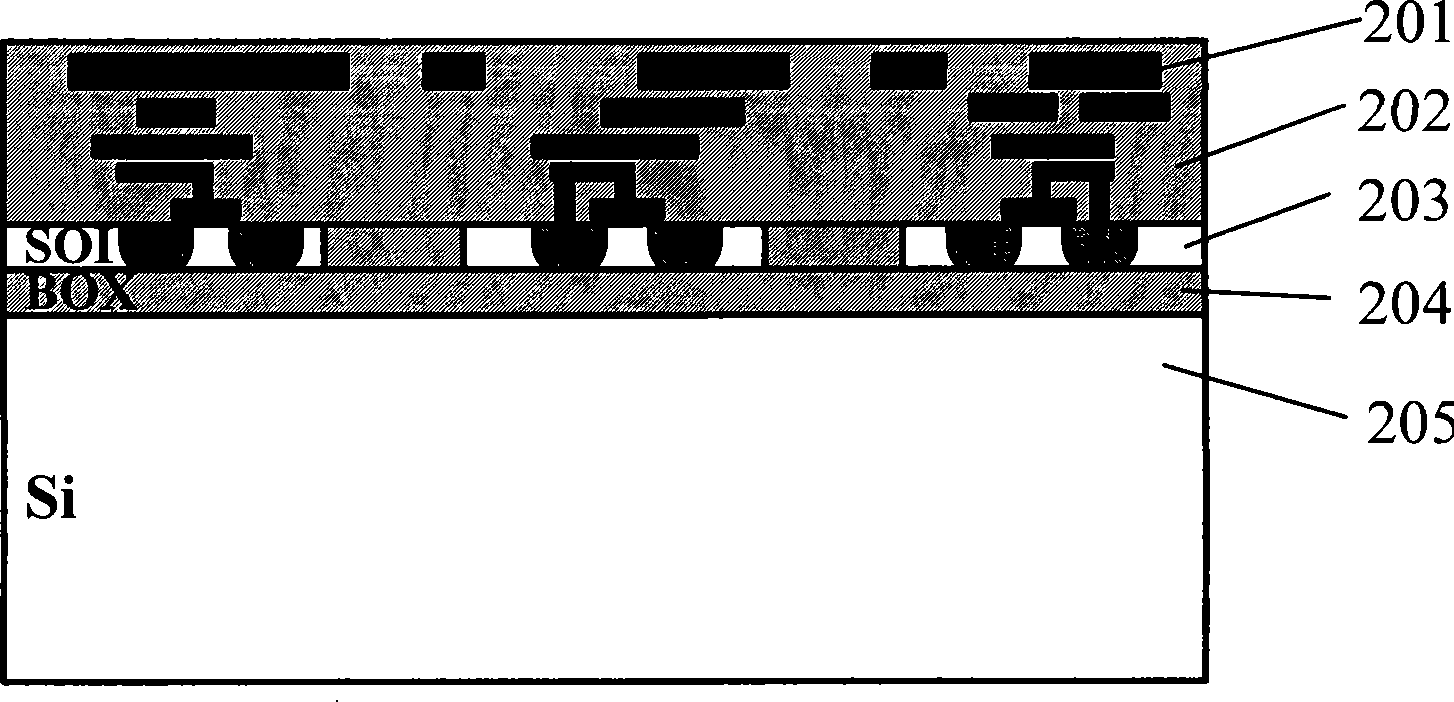

Realization method for 3-D integrated circuit based on SOI round slice

ActiveCN101241882AAchieve integrationRealize temporary transferSemiconductor/solid-state device manufacturingInterconnectionSilicon dioxide

The invention discloses an implementation method of three-dimensional integrated circuit based on SOI disk. The method includes: etching removing the SOI device layer which perpendicularly interconnects with the silicon (SOI) disk on the insulator manufacturing the integrated circuit; utilizing the organic polymer to temporarily bond the SOI disk on the supplementary disk so as to remove the displacing the SOI layer to the supplementary disk by the SOI disk substrate; utilizing the organic polymer to implement the back to front permanent bonding of temporary displacing the SOI disk with another bottom disk manufacturing the integrated circuit so as to form the stack disks; front etching the silicon dioxide layer and the permanent bonding layer form the stack disks and filling metal for implementing the perpendicular interconnection of the SOI layer disk with the bottom disk. The invention manufactures the perpendicular interconnection on the insulating position so as to solve the problem that the lateral wall of the deep hole is insulating, and reduces the manufacturing degree of difficulty of the three-dimensional integration. The method can be used in integrated circuit and micro sensor field for implementing three-dimensional integration of the back to front bonding of the multilayer chip.

Owner:TSINGHUA UNIV

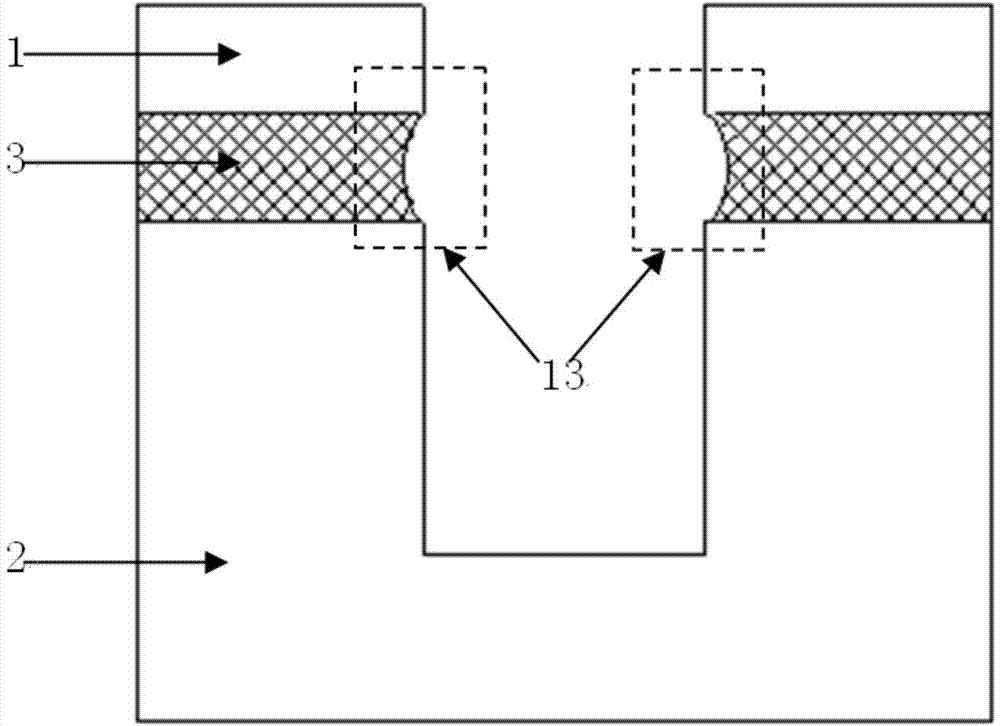

Through silicon var wafer interconnection process

InactiveCN104377164AReduce complexityAvoid short circuitSemiconductor/solid-state device manufacturingInterconnectionThree dimensional integration

The invention relates to the technical field of semi-conductor manufacturing, in particular to a through silicon var wafer interconnection process. First, a first wafer and a second wafer are bonded together, a first silicon substrate layer which is thinned through etching process carried out for the first time is opened, a film on the upper side of a first metal layer is opened through the etching process carried out for the second time, and a film on the upper side of a second metal layer is opened with the first metal layer as a blocking layer, so that a groove which allows the first metal layer and the second metal layer to be both exposed is formed; the groove and openings are filled with metal, the upper surface of the metal and the upper surface of the first silicon substrate layer are covered with protective layers, and accordingly three-dimensional integration of the wafers is achieved. The through silicon var wafer interconnection process overcomes the defect that the etching process needs to be carried out three times in a traditional wafer three-dimensional integration method before circuits on different wafers on the same area are led out for circuit interconnection.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Through silicon via process

ActiveCN104319258AReduce volumePrevent proliferationSemiconductor/solid-state device manufacturingEtchingThree dimensional integration

The invention belongs to the semiconductor manufacturing technical field and relates to a through silicon via process. The through silicon via process includes the following steps that: traditional wafer three-dimensional integration is performed on a part of a second metal layer contained in a first BEOL dielectric layer and a third metal layer contained in a second BEOL dielectric layer, so that the size of a wafer can be reduced greatly with the properties of the wafer unchanged; and a part of a first metal layer contained in the first BEOL dielectric layer is not connected with any circuit, and therefore, accumulation of a large number of charges in first wafer metal which is caused by long-term bombardment of charged particles to metal in the first BEOL dielectric layer in secondary etching in a traditional process can be avoided, and damage to a semiconductor device in the first BEOL dielectric layer can be avoided.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Three-dimensional integrated circuits and techniques for fabrication thereof

Integrated circuits having complementary metal-oxide semiconductor (CMOS) and photonics circuitry and techniques for three-dimensional integration thereof are provided. In one aspect, a three-dimensional integrated circuit comprises a bottom device layer and a top device layer. The bottom device layer comprises a substrate; a digital CMOS circuitry layer adjacent to the substrate; and a first bonding oxide layer adjacent to a side of the digital CMOS circuitry layer opposite the substrate. The top device layer comprises an analog CMOS and photonics circuitry layer formed in a silicon-on-insulator (SOI) layer having a buried oxide (BOX) with a thickness of greater than or equal to about 0.5 micrometers; and a second bonding oxide layer adjacent to the analog CMOS and photonics circuitry layer. The bottom device layer is bonded to the top device layer by an oxide-to-oxide bond between the first bonding oxide layer and the second bonding oxide layer.

Owner:GLOBALFOUNDRIES US INC

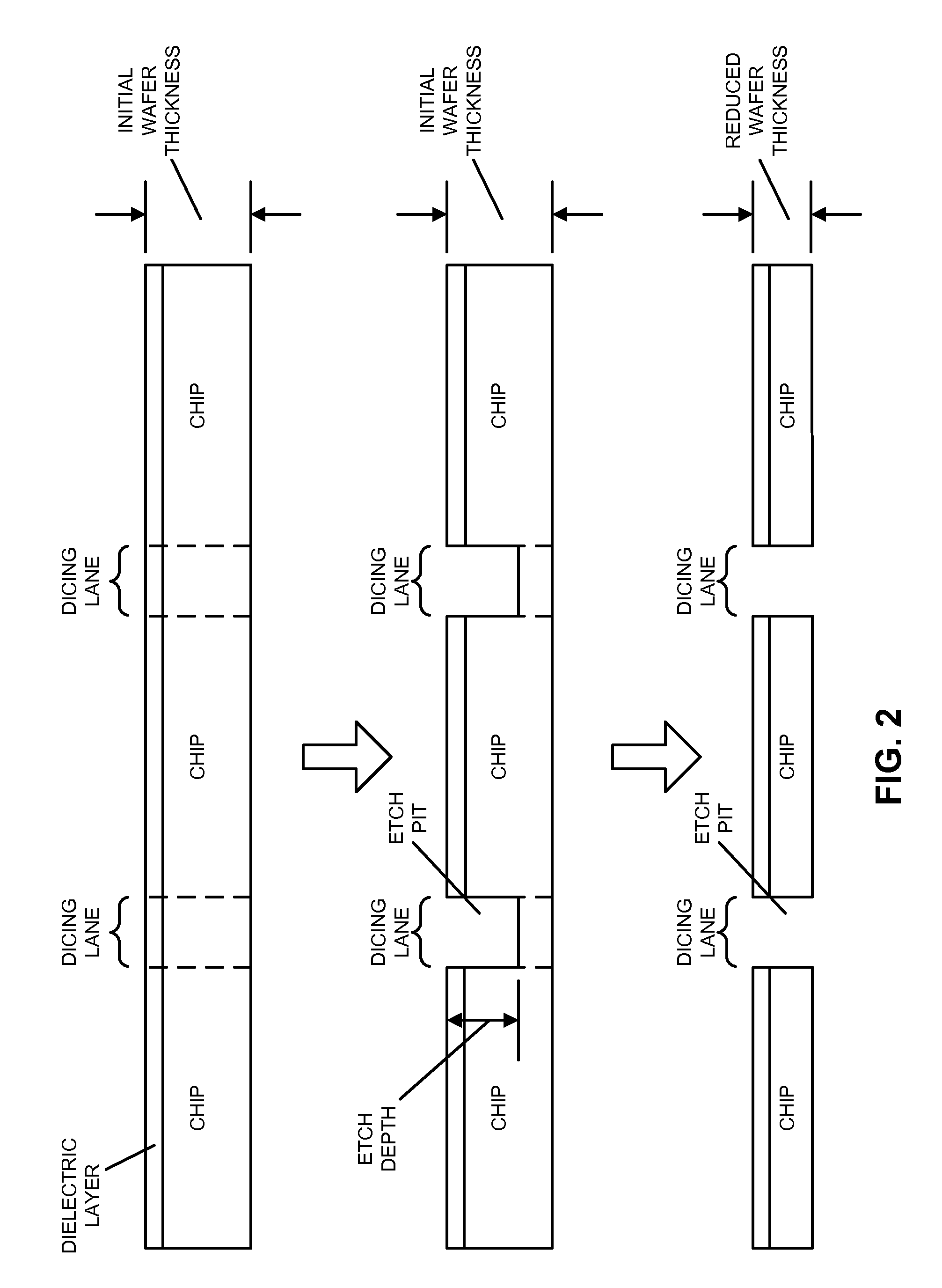

Batch process for three-dimensional integration

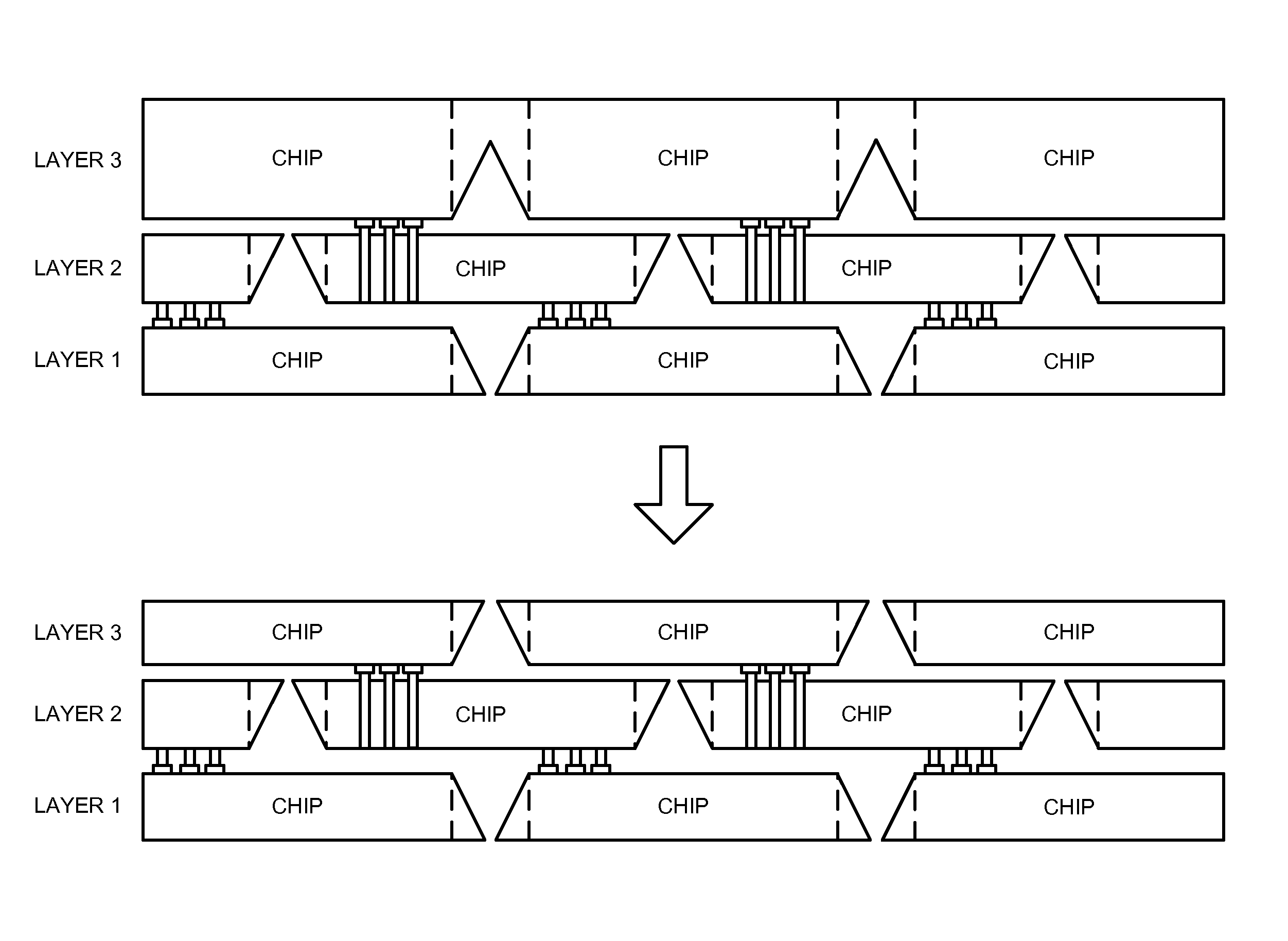

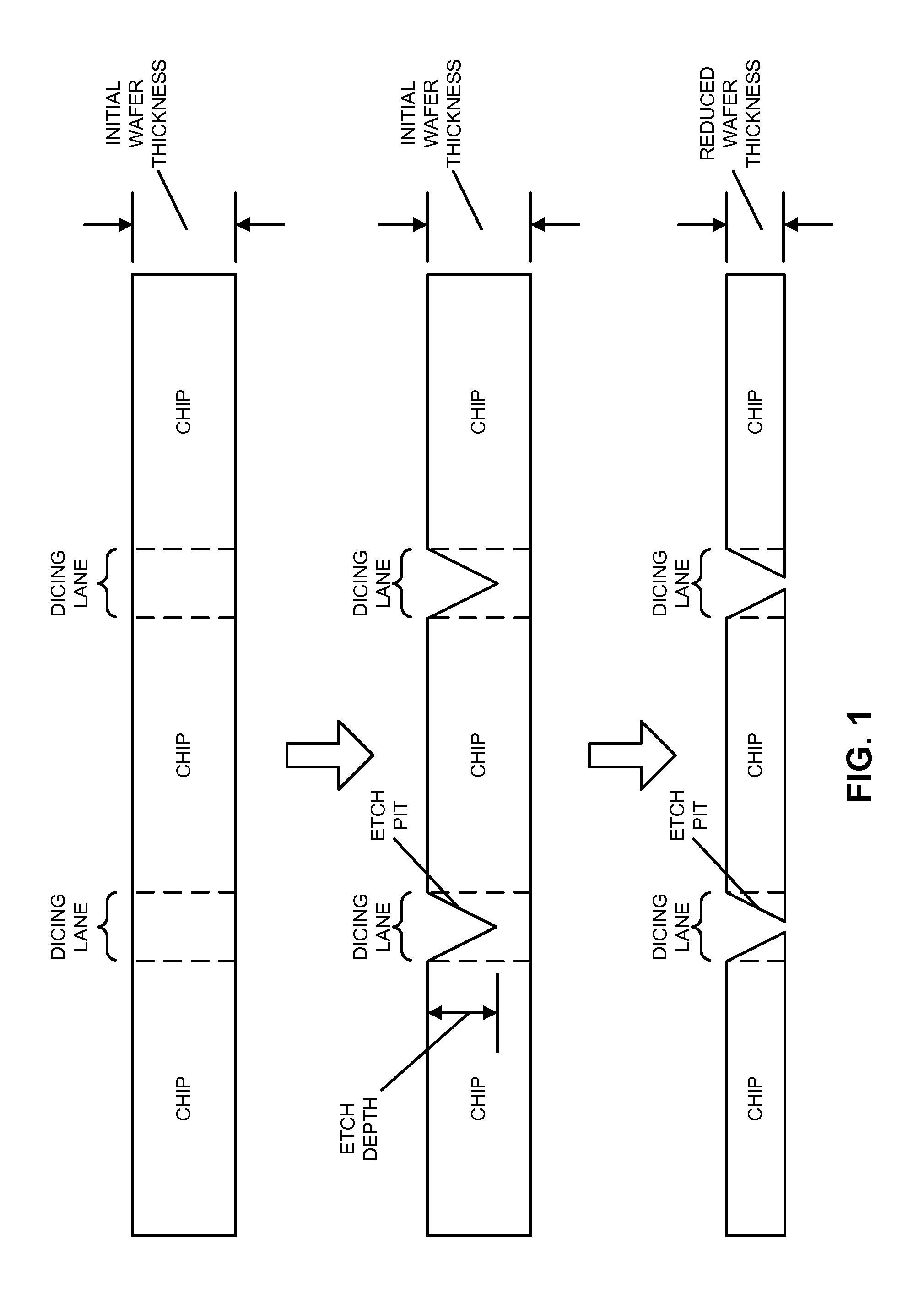

ActiveUS20130320567A1Eliminate damageReduce harmSemiconductor/solid-state device detailsSolid-state devicesEngineeringThree dimensional integration

A chip package is described which includes a first chip having a first surface and first sides having a first side-wall angle, and a second chip having a second surface and second sides having a second side-wall angle, which faces and is mechanically coupled to the first chip. The chip package is fabricated using a batch process, and the chips in the chip package were singulated from their respective wafers after the chip package is assembled. This is accomplished by etching the first and second side-wall angles and thinning the wafer thicknesses prior to assembling the chip package. For example, the first and / or the second side walls can be fabricated using wet etching or dry etching. Therefore, the first and / or the second side-wall angles may be other than vertical or approximately vertical.

Owner:ORACLE INT CORP

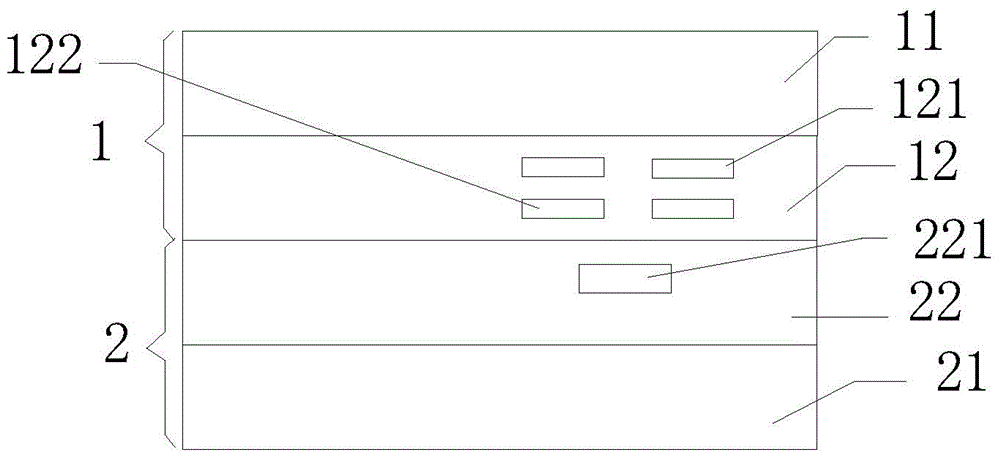

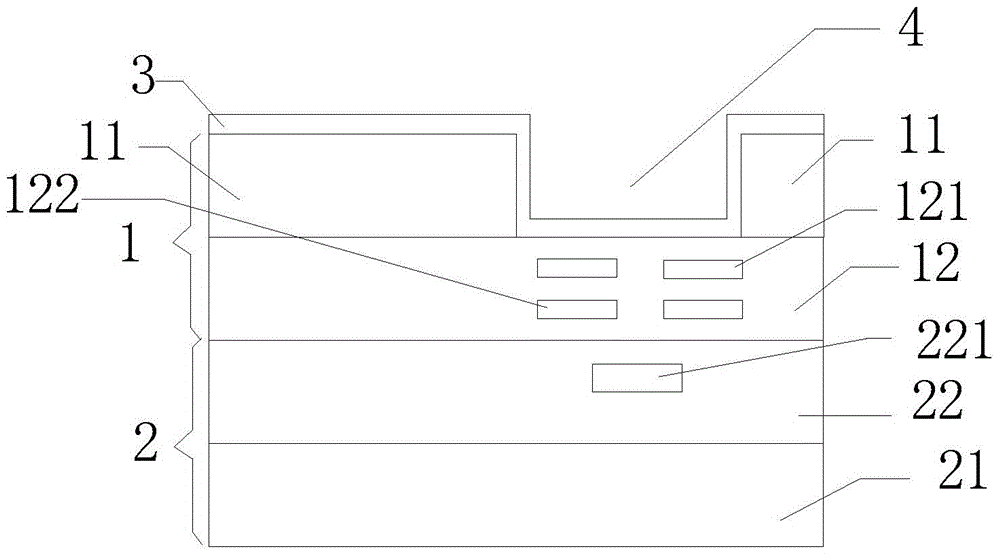

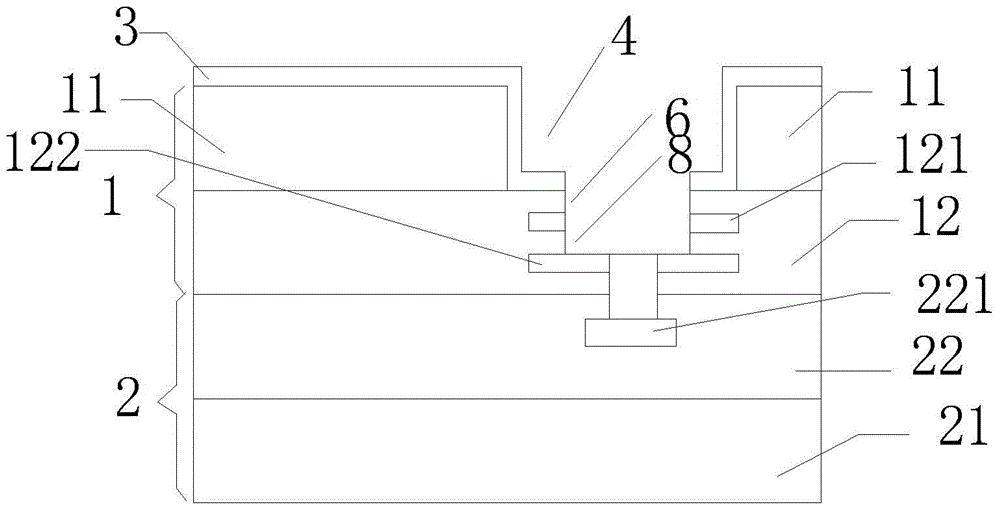

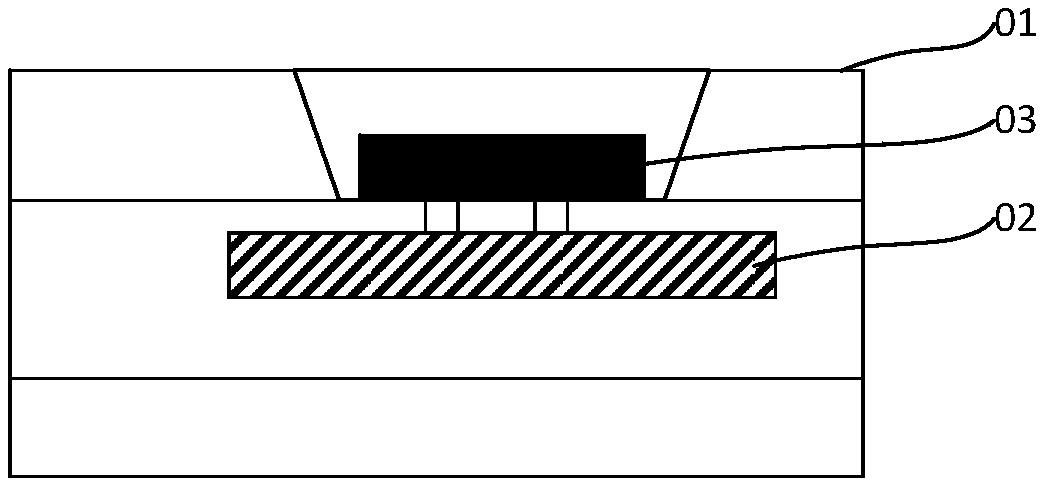

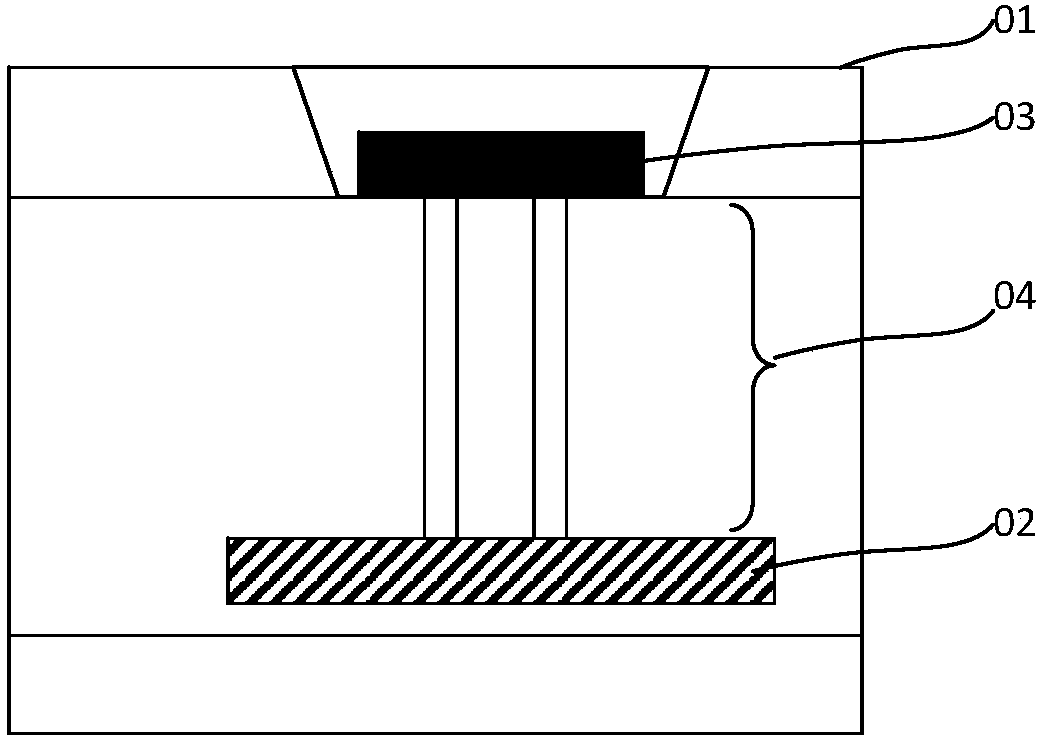

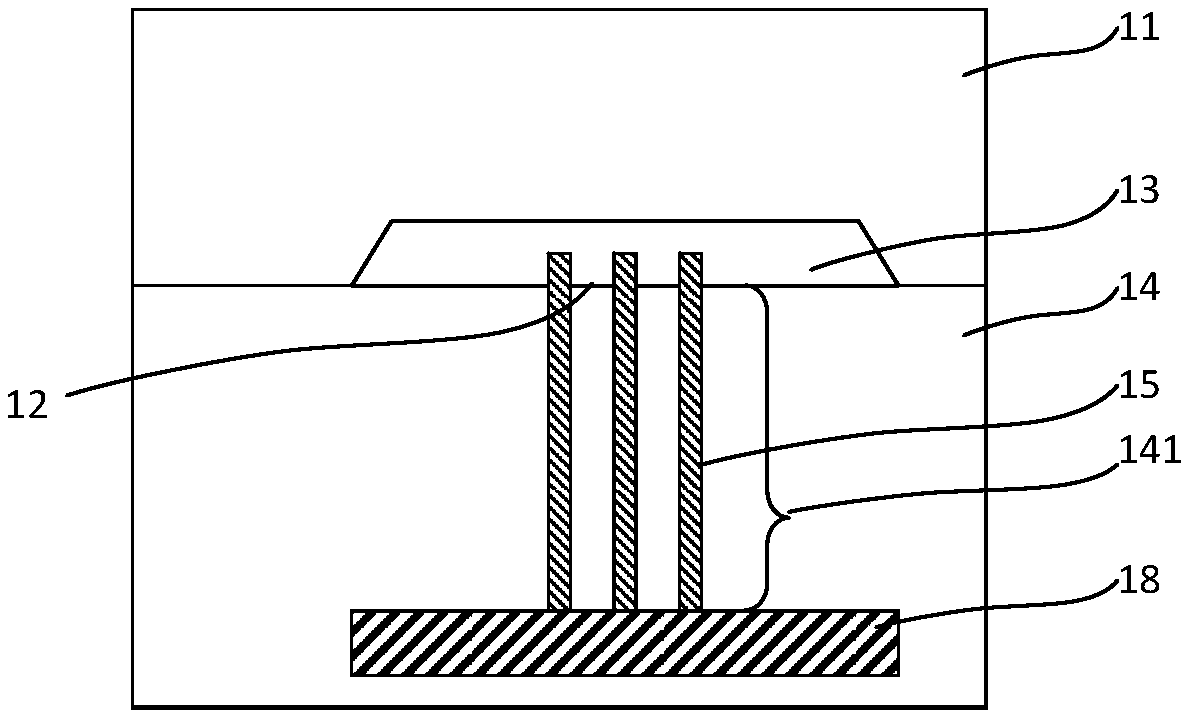

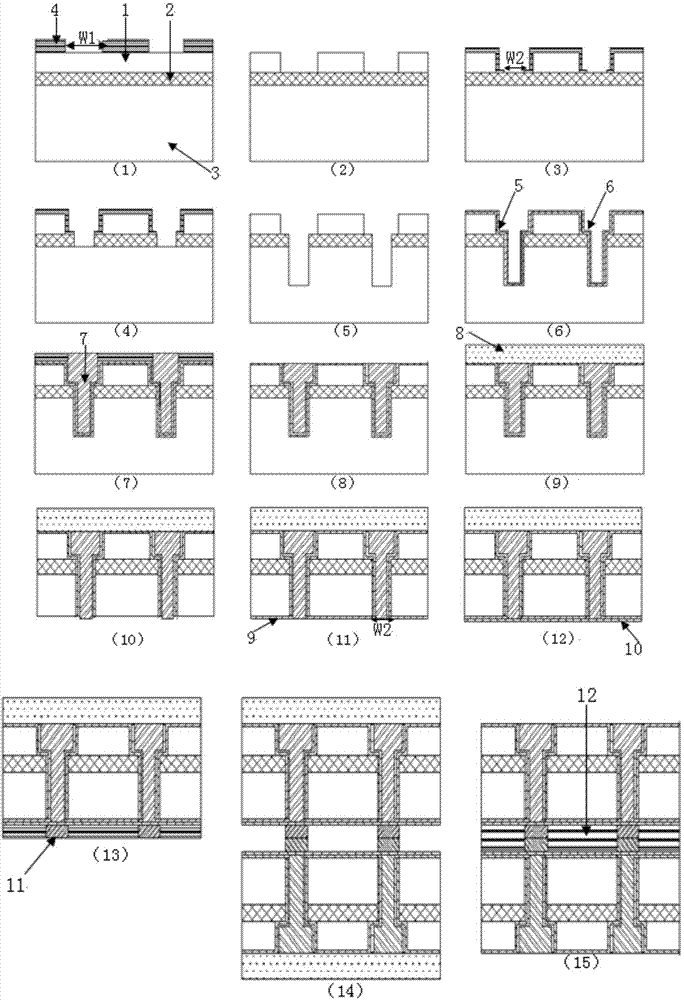

Wafer three-dimensional integrated lead wire process for three-dimensional memory and structure thereof

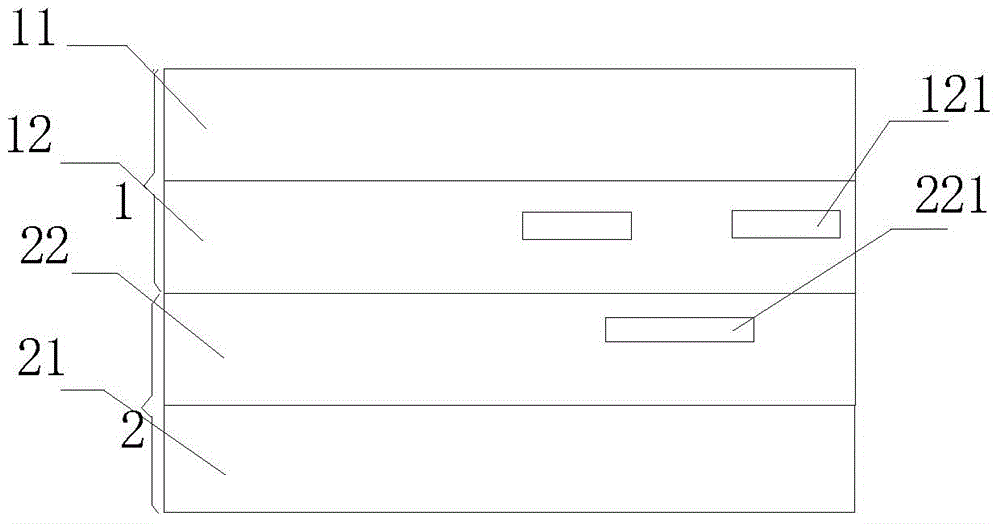

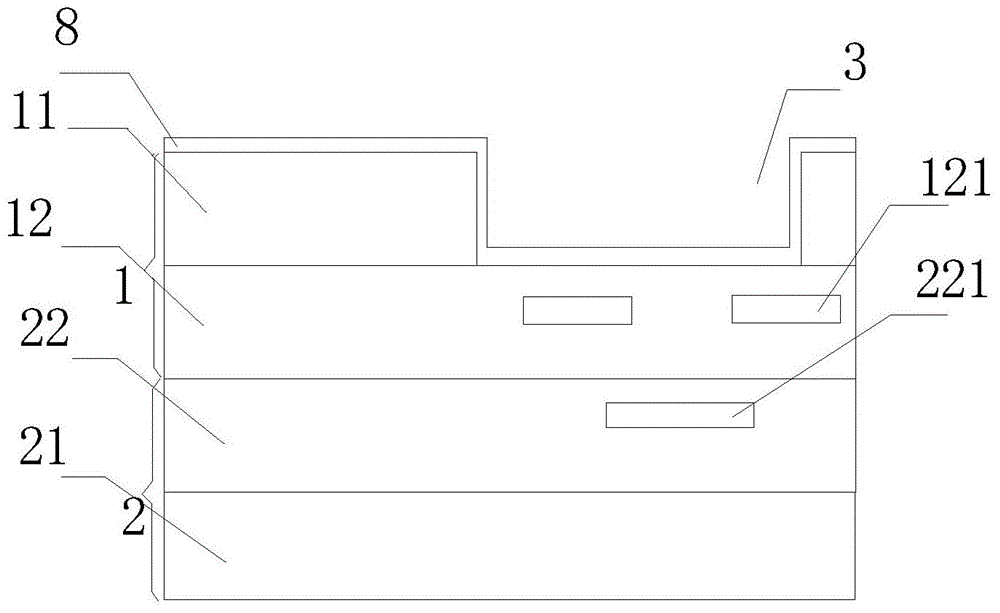

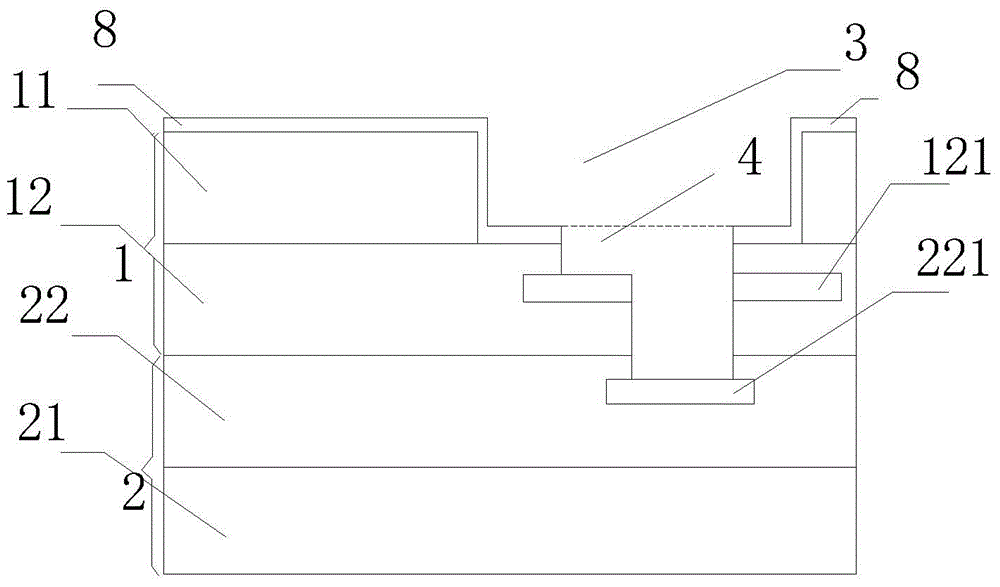

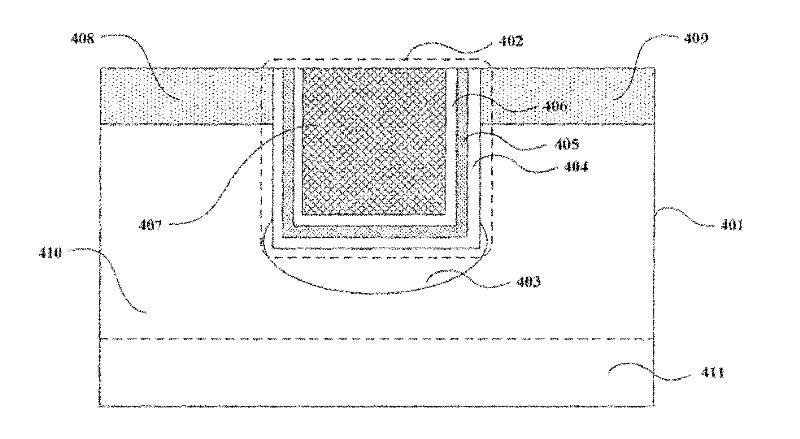

ActiveCN107644837AReduce manufacturing costImprove yieldSemiconductor/solid-state device detailsSolid-state devicesInterconnectionThree dimensional integration

The invention provides a wafer three-dimensional integrated lead wire process and a structure thereof. The process can be applied to a wafer three-dimensional integration process for the wafers of a three-dimensional memory. A dielectric layer 13 is arranged between a first wafer 11 and a three-dimensional memory device 14 and a contact hole 15 for metal interconnection is configured to be in contact with the dielectric layer 13. The invention provides a new lead wire process, making it possible to pass through a thick device layer for wire leading on a backside.

Owner:YANGTZE MEMORY TECH CO LTD

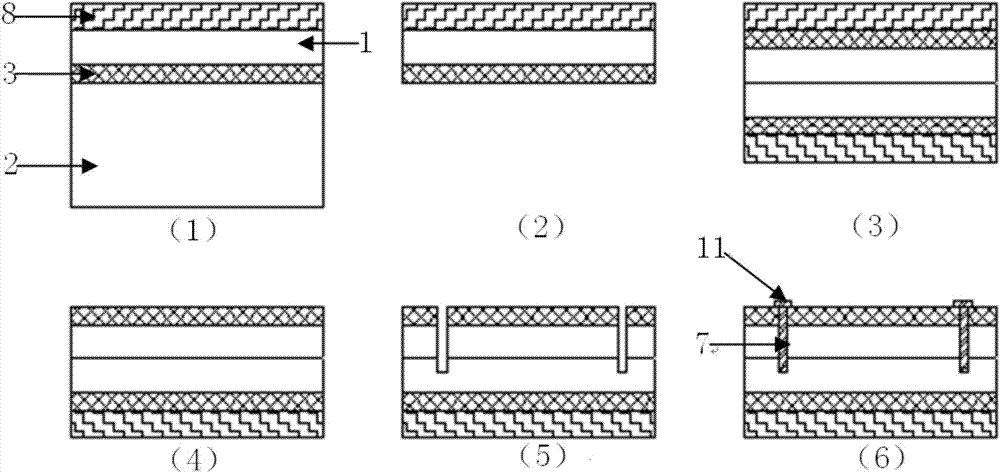

High-reliability TSV (Through Silicon Via) technique based on SOI (Silicon-On-Insulator) substrate

ActiveCN103700617AReduce leakageImprove reliabilitySemiconductor/solid-state device manufacturingLayer interfaceSoi substrate

The invention provides a high-reliability TSV technique based on a SOI substrate. According the technique, the existing silicon-silicon dioxide-silicon sandwich structure of the SOI substrate is not damaged, but three-dimensional integration of the SOI substrate is directly performed, so that each layer of the formed three-dimensional integrated device is provided with a buried oxide layer. The three-step etching technology is adopted to replace the existing single-step etching technology in the traditional SOI TSV technique. The method comprises the following steps: firstly etching top layer silicon, secondly etching the buried oxide layers, and at last etching bottom layer silicon, wherein the etching window of the top layer silicon is larger than that of the buried layers and the bottom layer silicon to form a horizontal etching margin on the buried oxide layer interface. The high-reliability TSV technique can avoid potential safety hazards such as the increase of electric leakage possibility and the reduction of withstand voltage, increase the possibility of the three-dimensional integrated device, greatly improve the performance of the SOI three-dimensional integrated device, and is high in the reliability.

Owner:珠海天成先进半导体科技有限公司

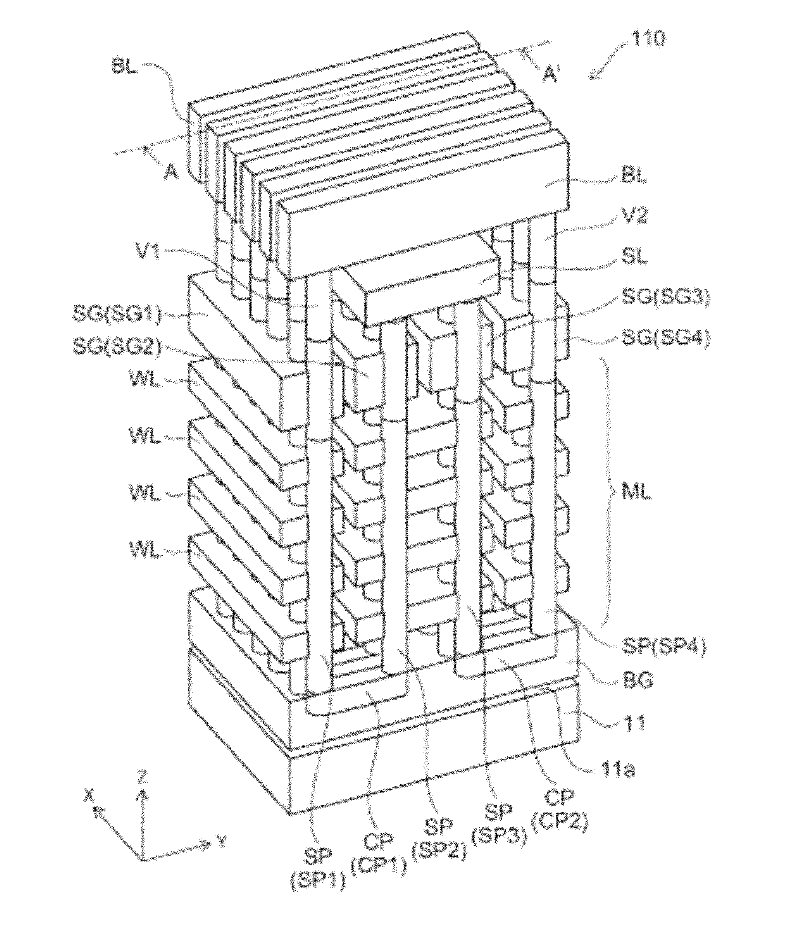

Vertical foldaway memory array structure

InactiveCN102184740ASimple structureImprove high-density mass storage capabilitiesSolid-state devicesRead-only memoriesBit lineHigh density

Owner:TSINGHUA UNIV

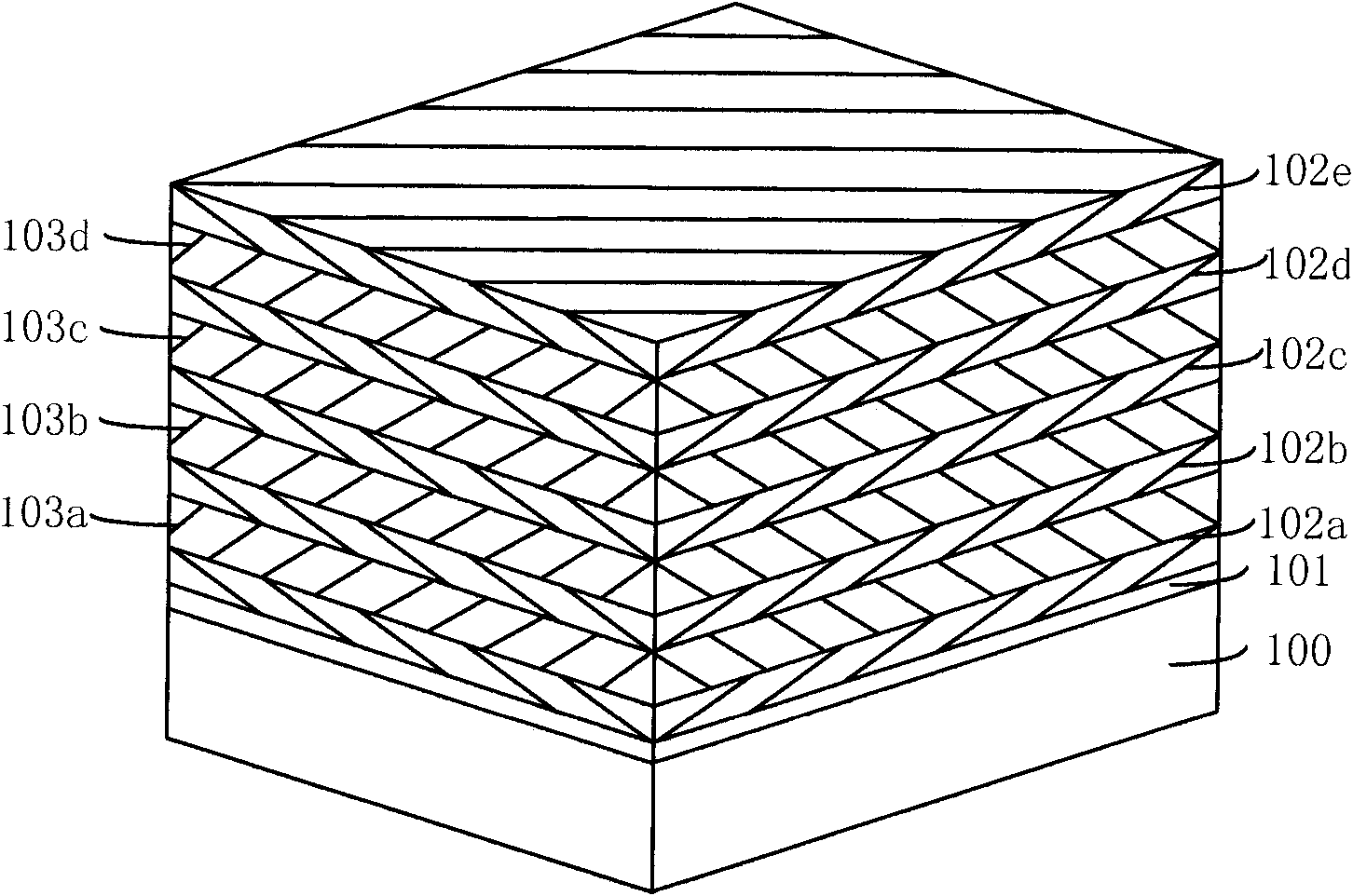

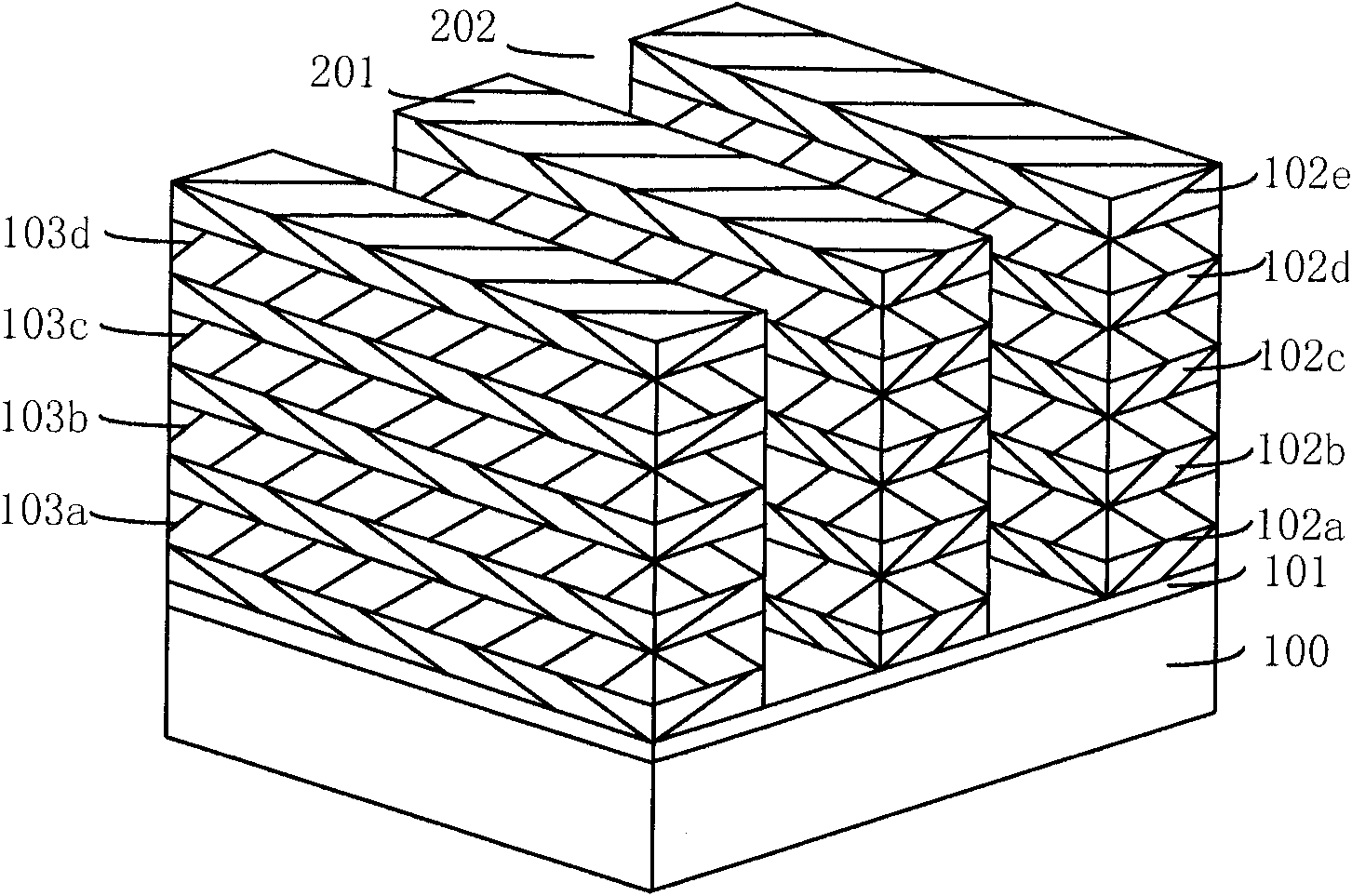

Method for preparing three-dimensional multivalue nonvolatile memory

InactiveCN102315173AExcellent programmingExcellent erasureSemiconductor/solid-state device manufacturingCMOSMedia layer

The invention discloses a method for preparing a three-dimensional multivalue nonvolatile memory. The method comprises the following steps of: A, forming a grid lamination structure on a semiconductor substrate; B, forming a grid medium layer; C, forming a channel region and a source / drain doped region; and D, leading a bit line and a word line out of the source / drain doped region and a grid region so as to form three-dimensional integration of the nonvolatile memory. In the method, a plurality of physical storage points are obtained from a single device by comprehensively using a charge local storage property in a charge capture layer and a space characteristic of a vertical stack structure, so that multivalue storage is realized and the three-dimensional integration is formed on a storage device array; therefore, the storage density is increased basically. Meanwhile, the memory prepared by the method has higher device performance, namely programming, erasing, retaining and the like. The process for preparing the three-dimensional multivalue nonvolatile memory is compatible with the conventional silicon plane complementary metal oxide semiconductor (CMOS) process; the conventional storage device array structure integration can be adopted; and the method can be applied widely.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

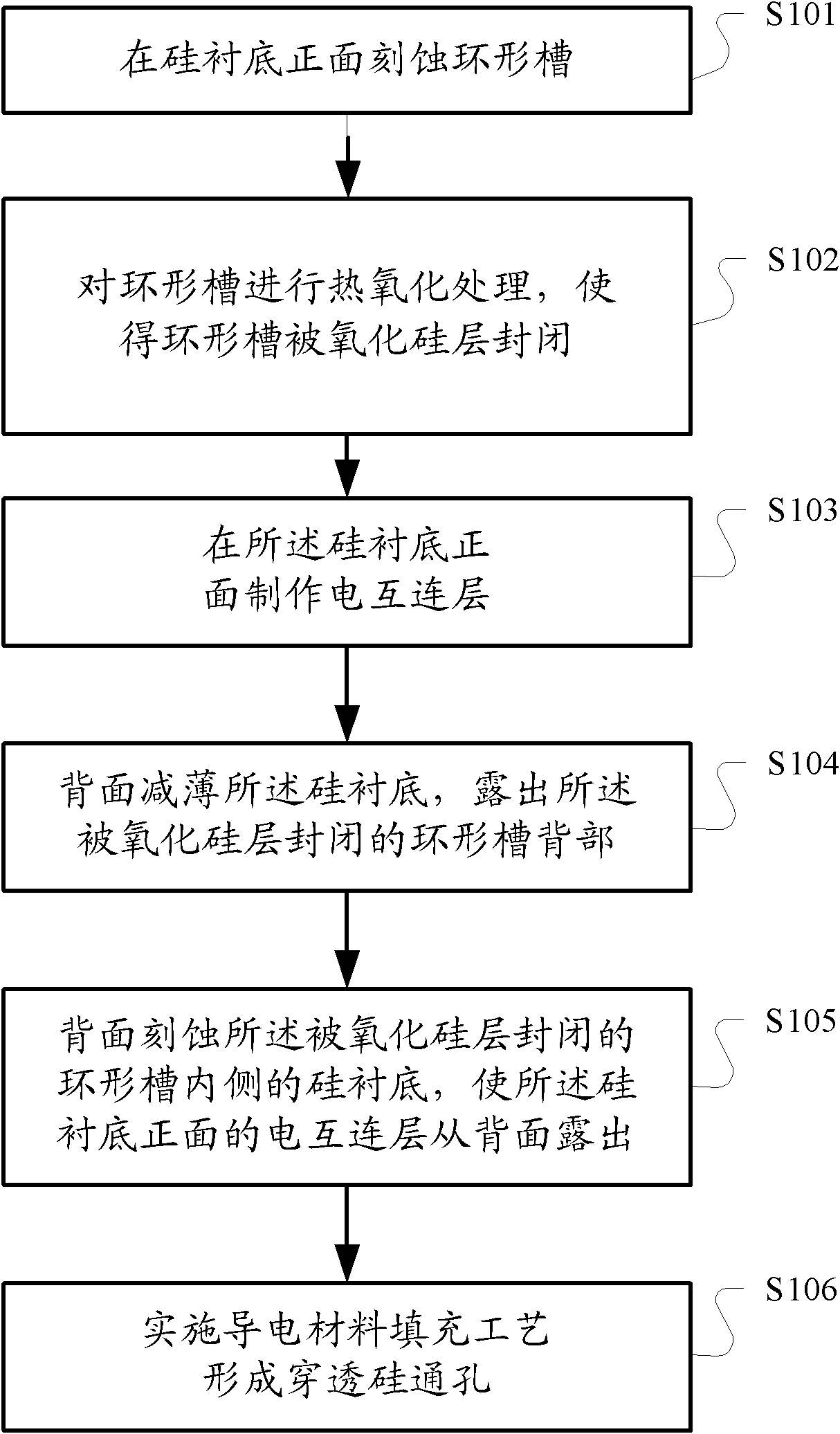

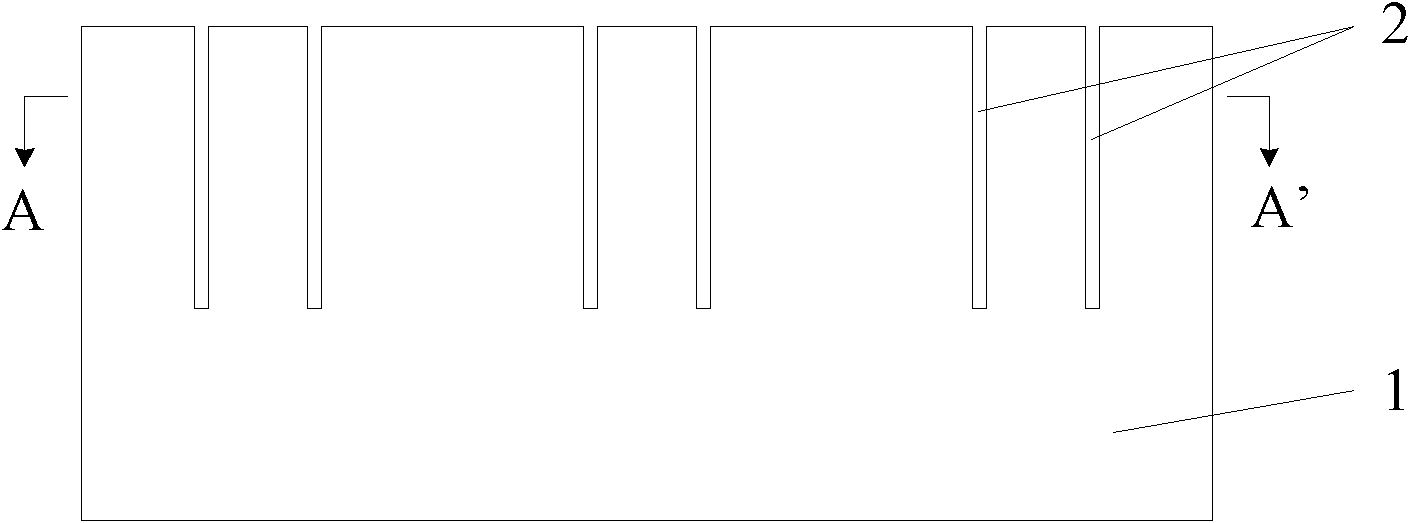

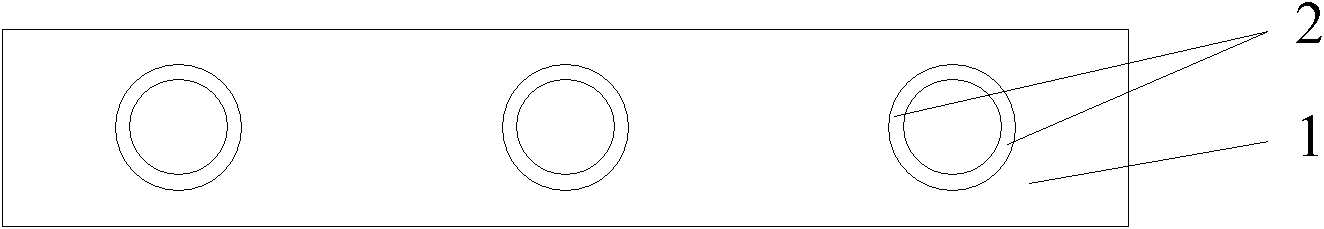

Method for forming through silicon vias (TSV)

InactiveCN102208363AImprove reliabilityImprove electrical performanceSemiconductor/solid-state device manufacturingConductive materialsInterconnection

The invention discloses a method for forming through silicon vias (TSV), belonging to the semiconductor device manufacture, microelectronic packaging and three dimensional integration field. The method comprises the following steps: (1) etching annular grooves on the right side of a silicon substrate; (2) carrying out a thermal oxidation treatment on the annular grooves; (3) making an electrical interconnection layer on the right side of the silicon substrate; (4) thinning the silicon substrate from the back side of the silicon substrate; (5) etching the silicon substrate in the annular grooves which are sealed by an oxygen ambient silica layer to remove the oxygen ambient silica layer totally and forming deep holes in the inner side of the annular grooves; and filling conductive material in the deep holes to form the through silicon vias (TSV). By using the method provided in the invention, the through silicon vias (TSV) using high quality thick oxygen ambient silica layer, metallic sidewall isolation and conductive filling material can be obtained, and the reliability and electricity performance of the through silicon vias (TSV) are improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

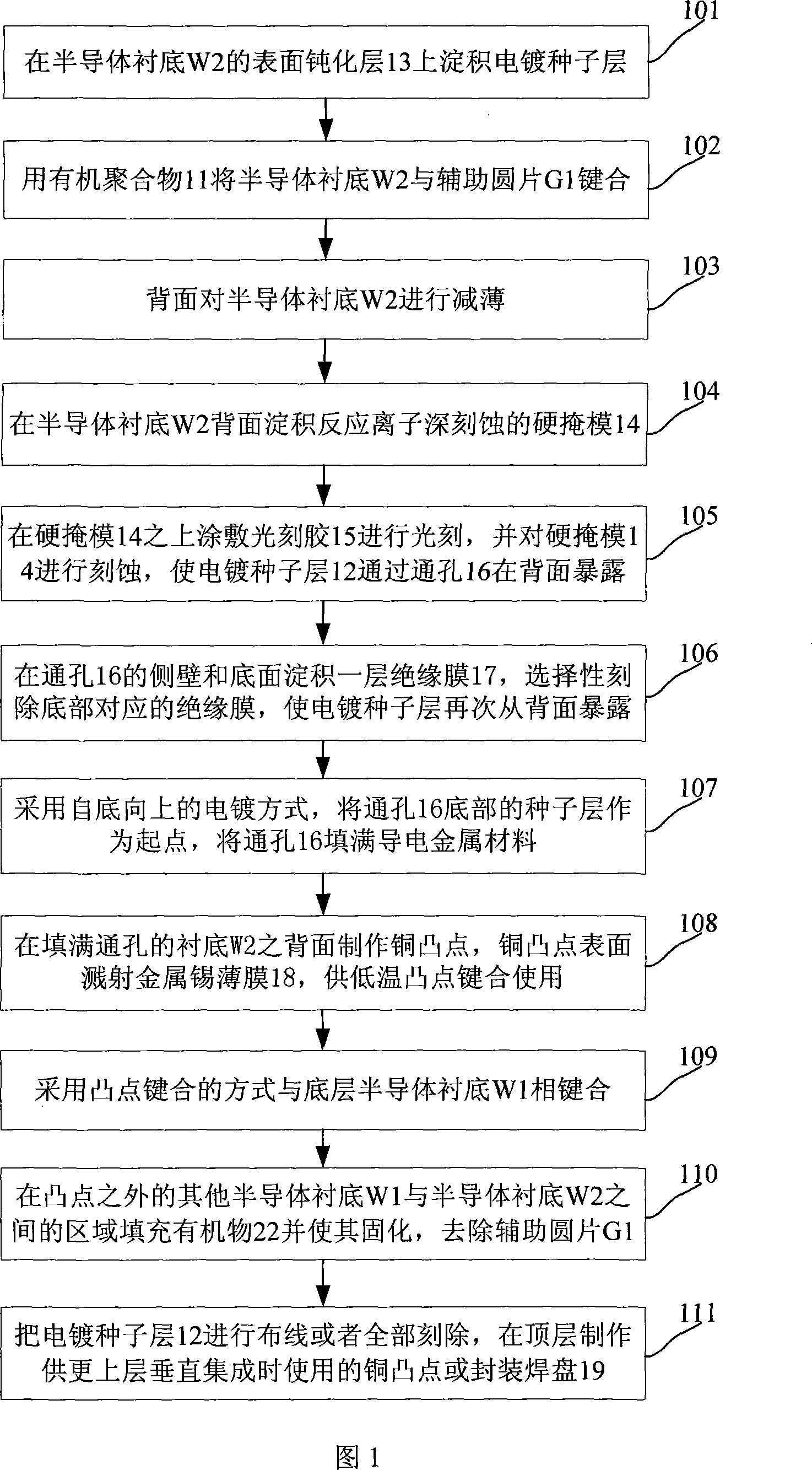

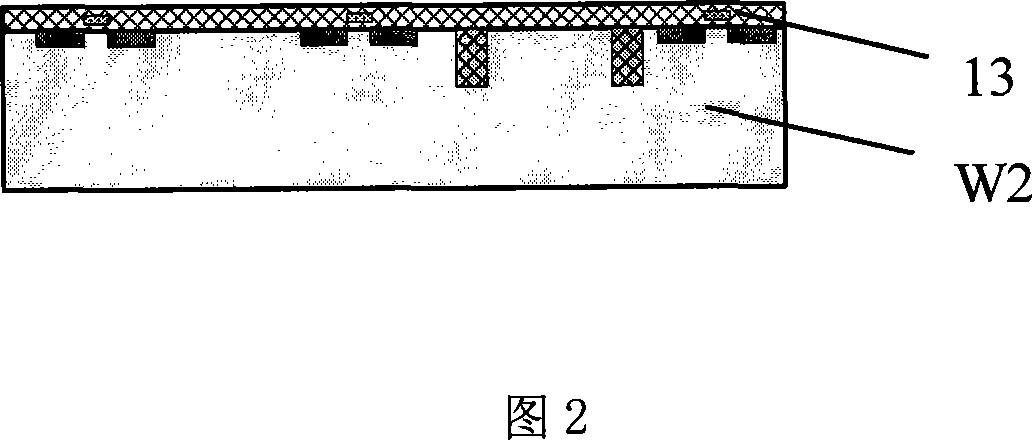

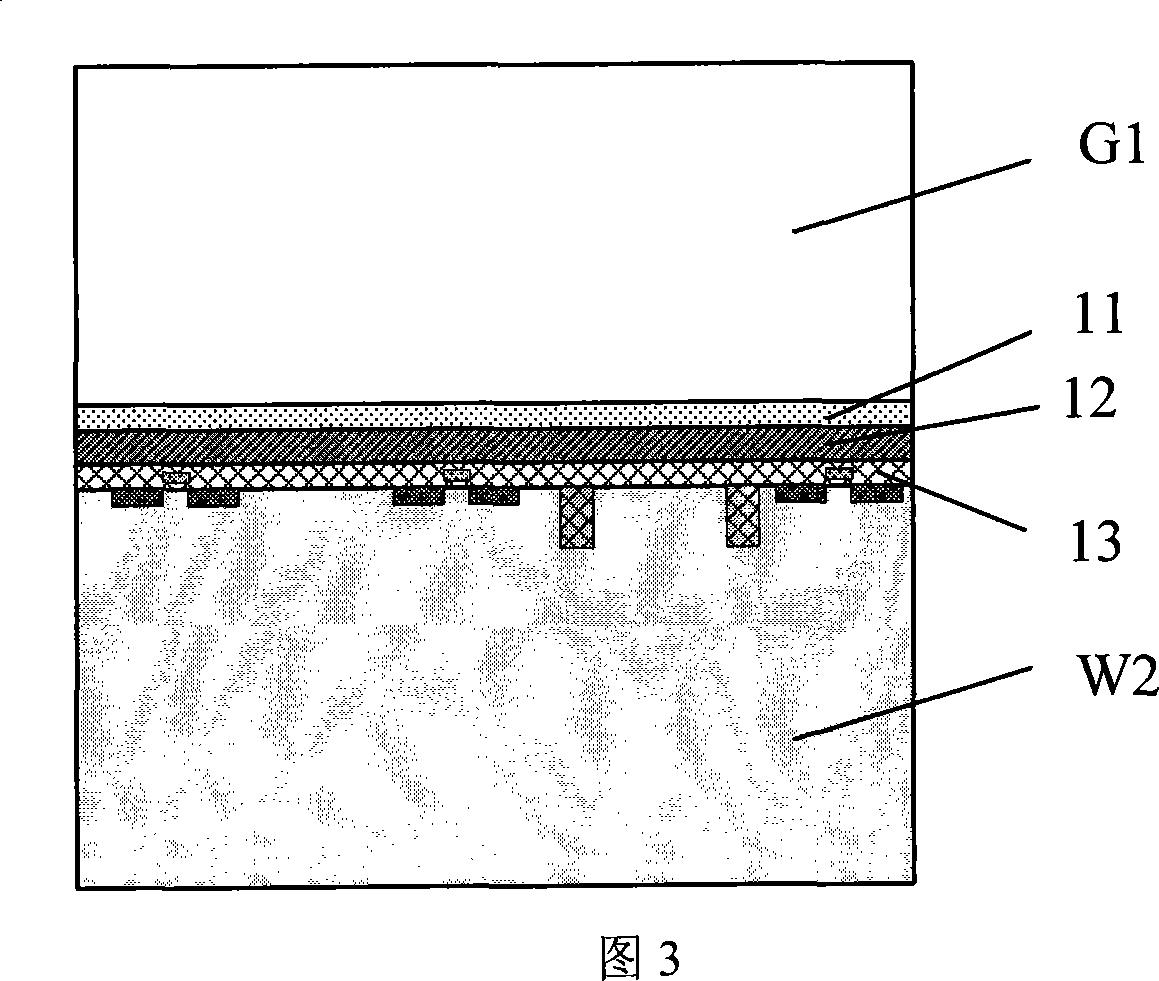

Implementation method for 3D integrated circuit

InactiveCN101079386AReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitEngineering

The invention discloses a realizng method of three-dimensional integrated circuit in the semiconductor making technique and three-dimensional integrated technical domain, which comprises the following steps: sedimenting plating seed layer on the bonding face of the first circuit disc or auxiliary disc; making the auxiliary disc as the through-hole to reduce the back to support the first layer of circuit disc and etch the disc; exposing the plating seed layer through the through-hole; using plating technique from bottom to top; adopting the plating seed layer as original; plating to fill the through-hole; making projection on the filled through-hole; adopting bonding pattern to connect the first layer of circuit disc and the second layer of circuit disc. The invention reduces the technical difficulty to realize three-dimensional integration on the silicon substrate, which has good versatility.

Owner:TSINGHUA UNIV

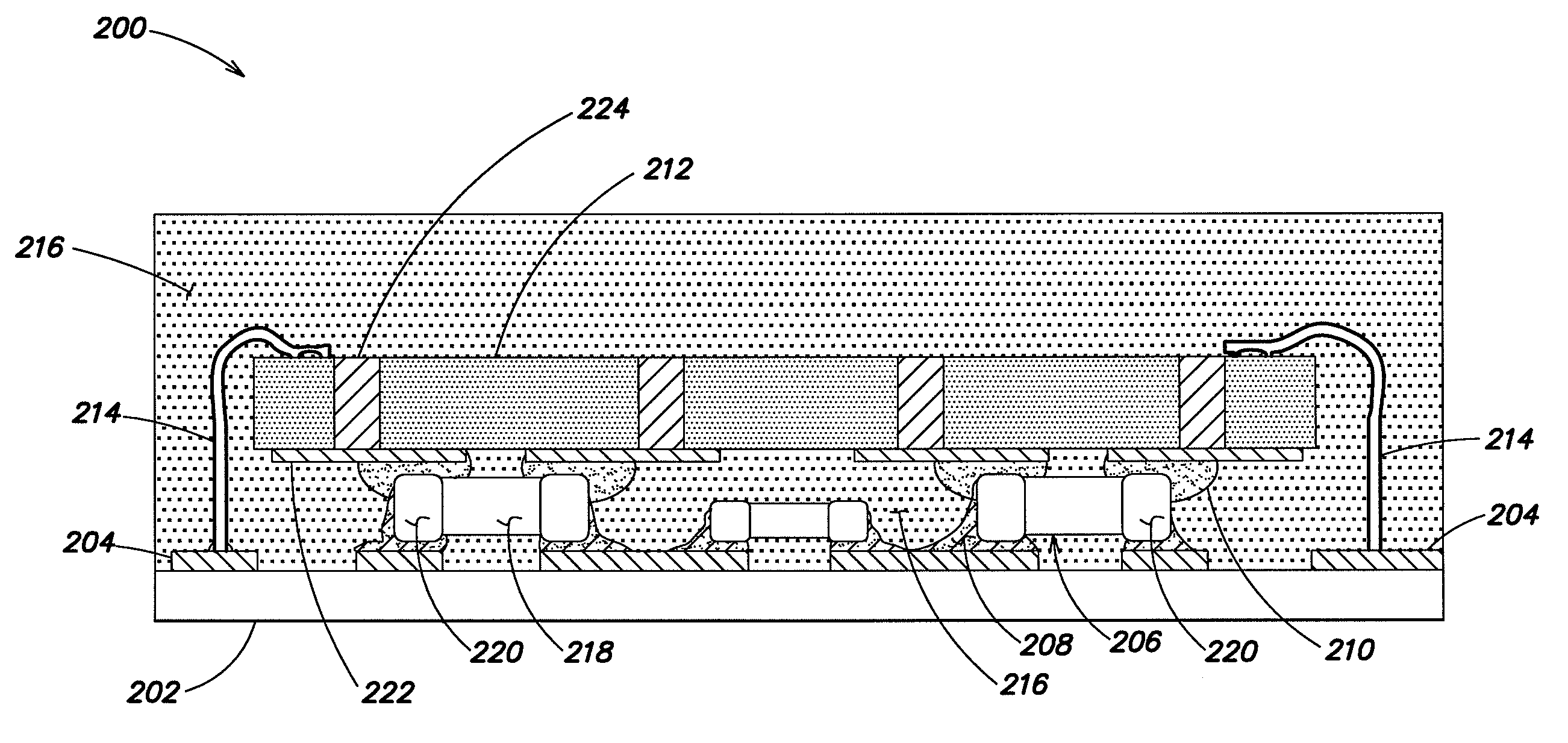

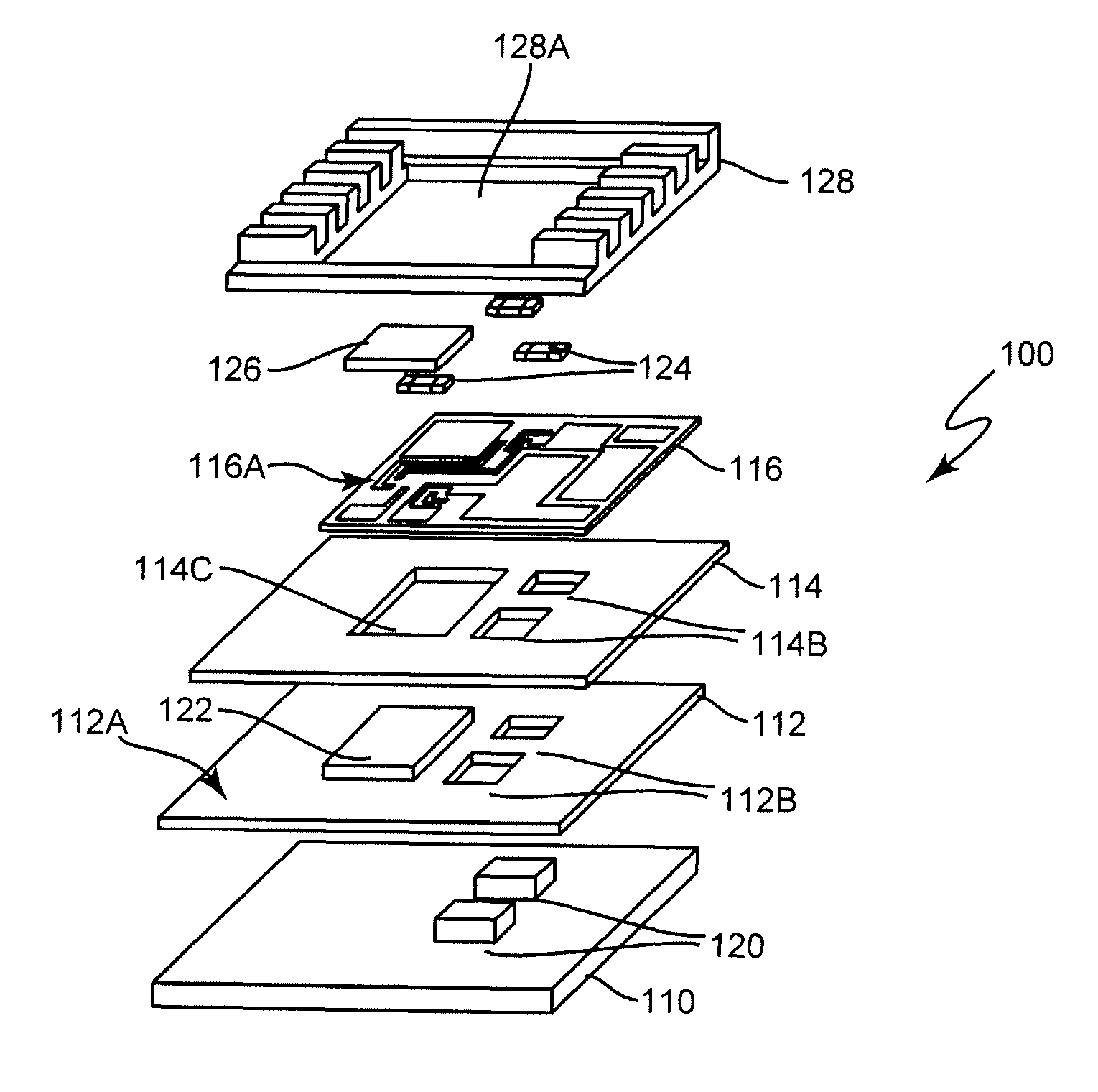

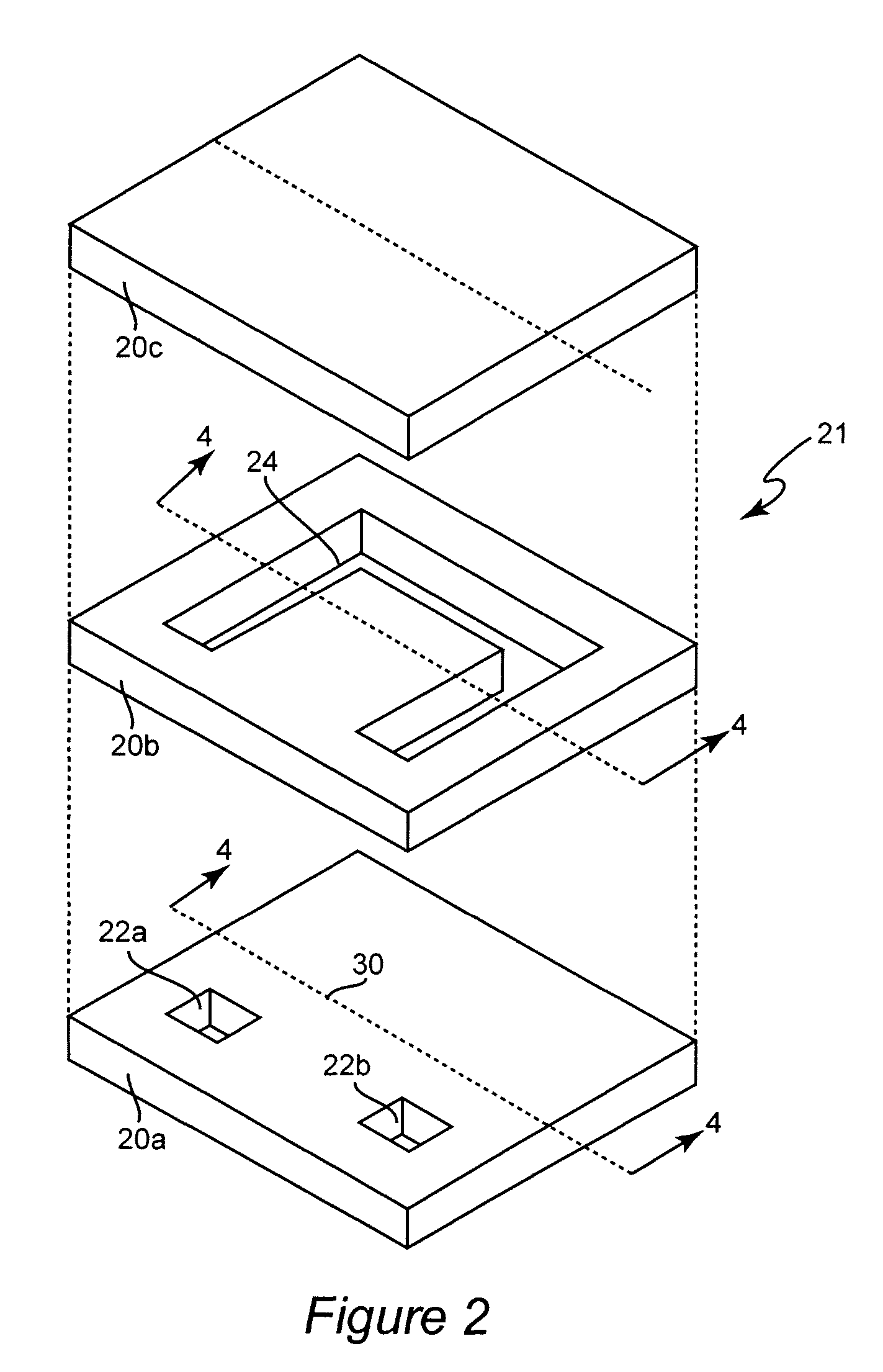

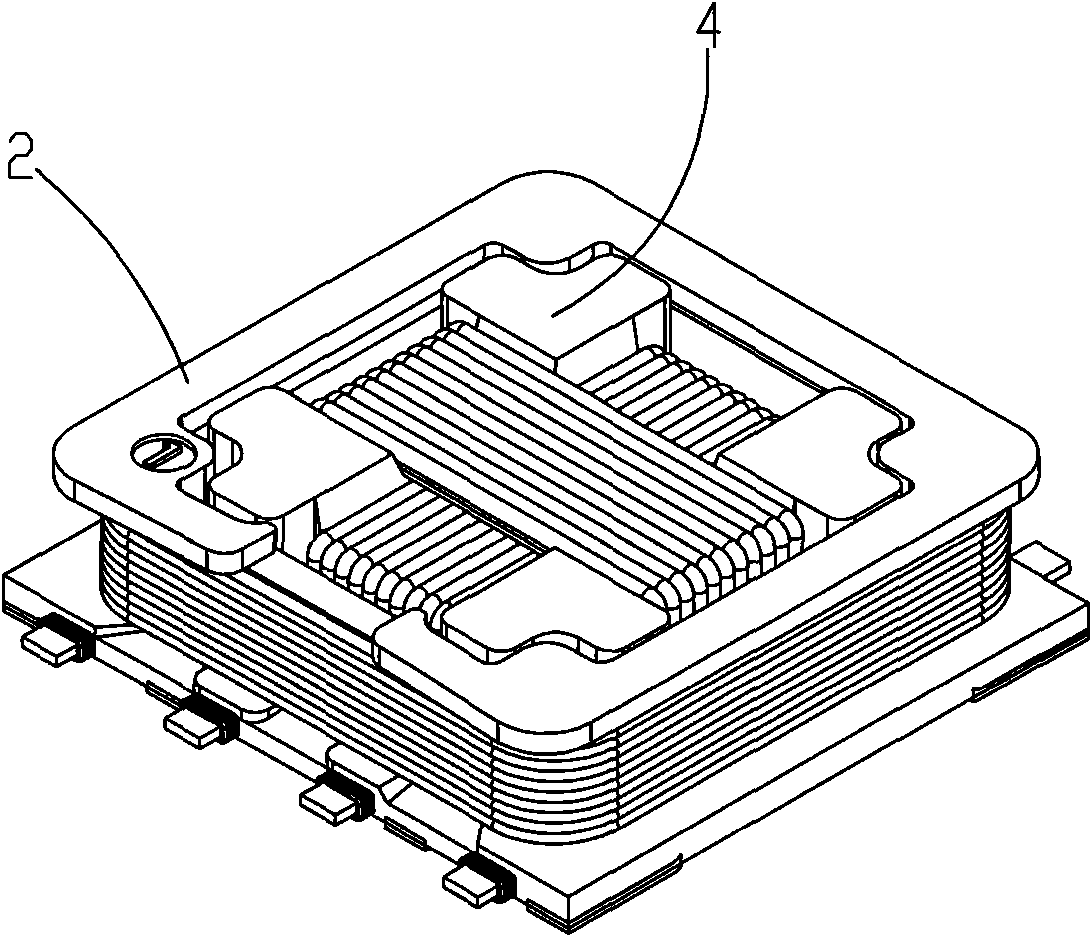

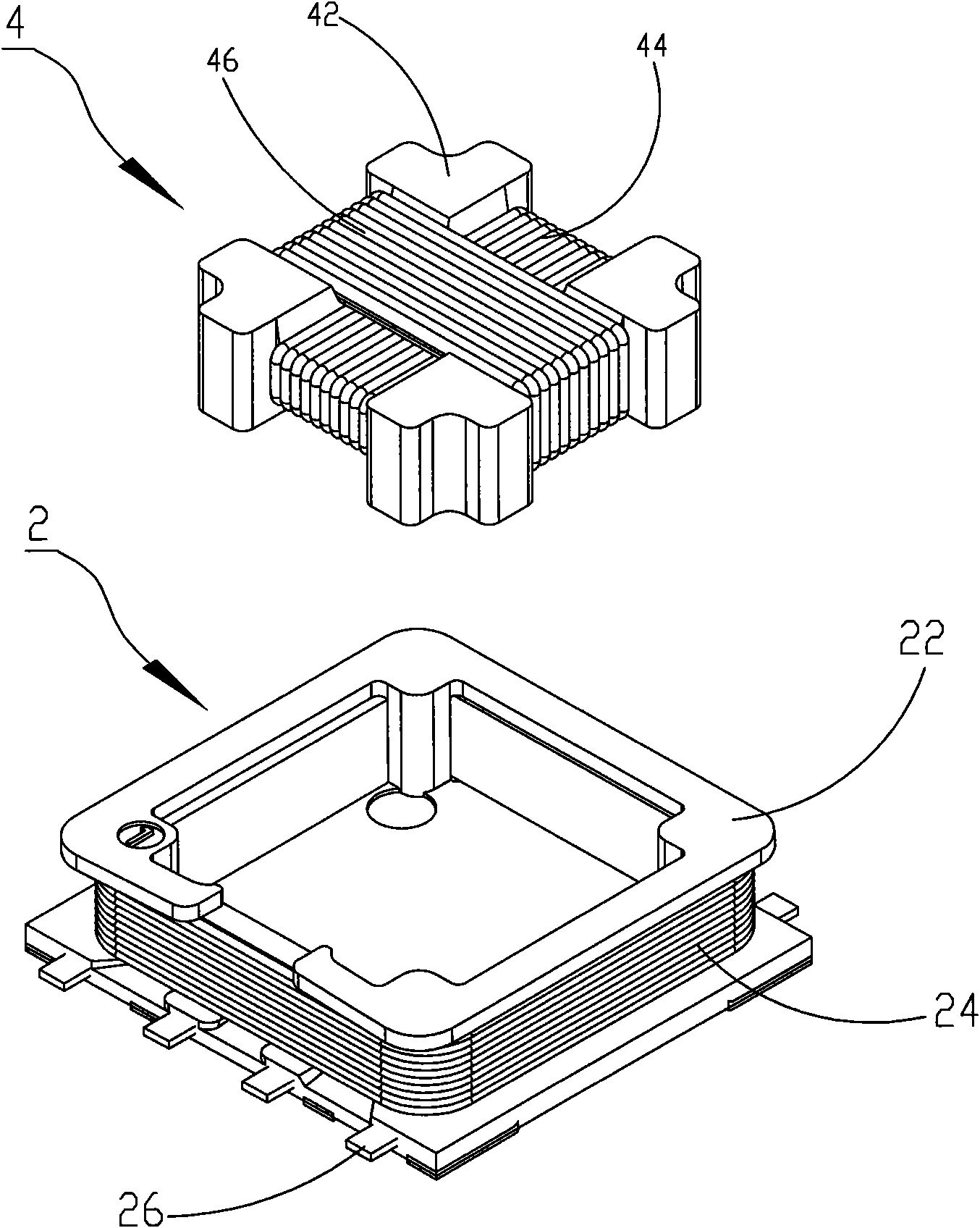

Method and apparatus for three-dimensional integration of embedded power module

InactiveUS7932800B2High conductanceImprove abilitiesTransformers/inductances coolingTransformers/inductances coils/windings/connectionsElectrical conductorElectrical connection

A modified planar Low Temperature Co-Fired Ceramic (LTCC) high conductance inductor, embedding a large cross section conductor, supports a stacked arrangement of heat spreader, inductor and active device layers. Interlayer electrical connections connect the layers. Optionally, a DC-DC converter includes the modified planar LTCC high conductance inductor, embedding a large cross section conductor, supporting a stacked arrangement of heat spreader, capacitor and active device layers, the active devices layer including the switching transistors. The active devices layer may include semiconductor dies embedded in a substrate.

Owner:VIRGINIA TECH INTPROP INC

Three-dimensional low-frequency antenna coil

InactiveCN101635387ASimple structureReduce volumeLoop antennas with ferromagnetic coreCores/yokesMiniaturizationThree dimensional integration

The invention relates to a three-dimensional low-frequency antenna coil which comprises a base and a magnetic body sleeved in the base, wherein the base comprises a body, a first coil wound at the lateral surface of the body and a plurality of metal terminals arranged on the body; the magnetic body comprises a magnetic core, a second coil and a third coil which are wound on the magnetic core; and the first coil, the second coil and the third coil are orthogonally vertical relatively to the central position of the magnetic core and respectively connected with the metal terminals. The invention realizes the three-dimensional integration by the combination of the independent magnetic core and the base, and the independent magnetic core and the base are simple in structure and easy to manufacture and can effectively reduce the production cost; in addition, and the magnetic core is made of materials with high magnetic conductivity and can effective reduce the volume of the coils, thereby being good for the miniaturization of the coils.

Owner:嵊州市兰花电器科技有限公司

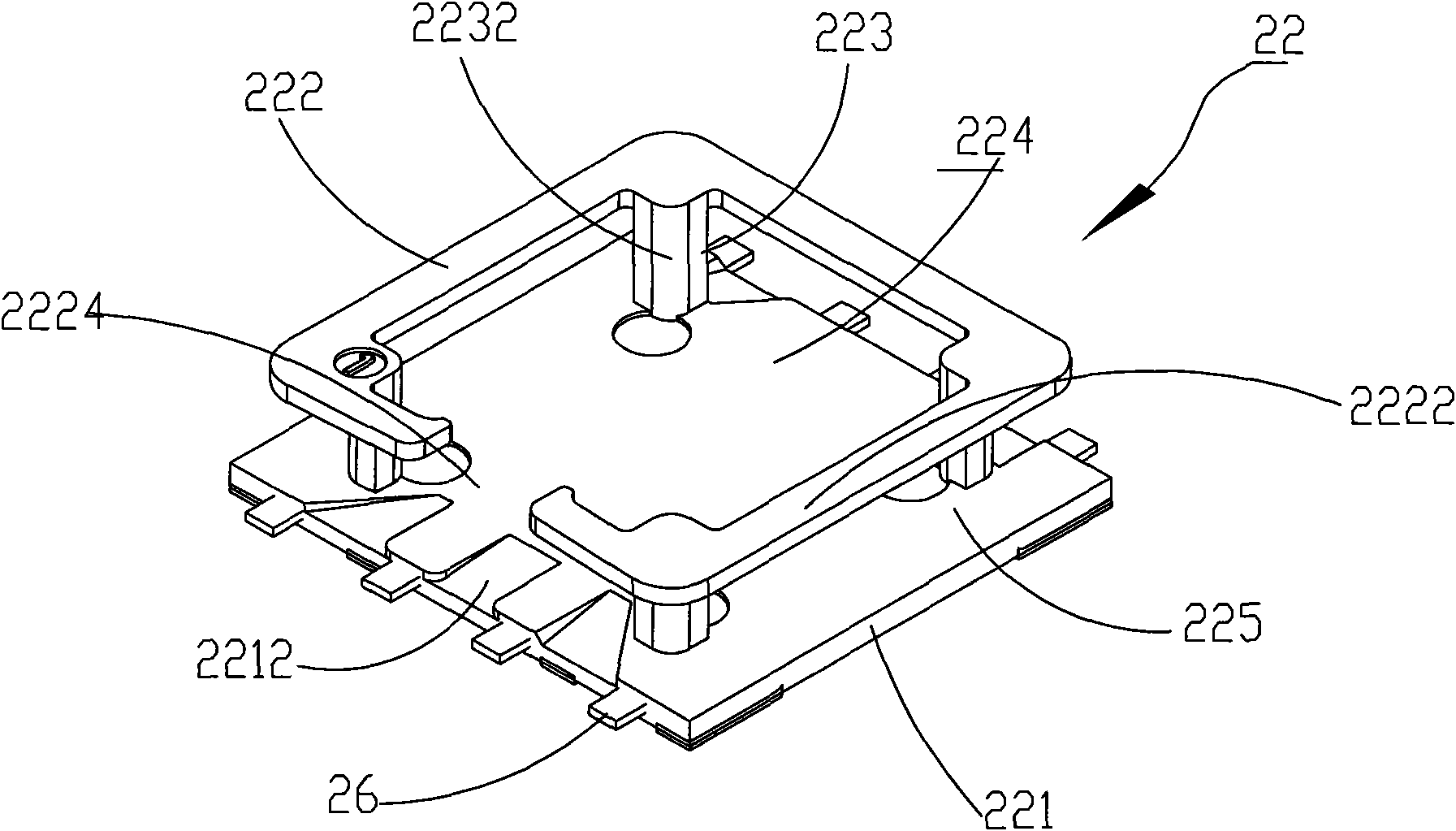

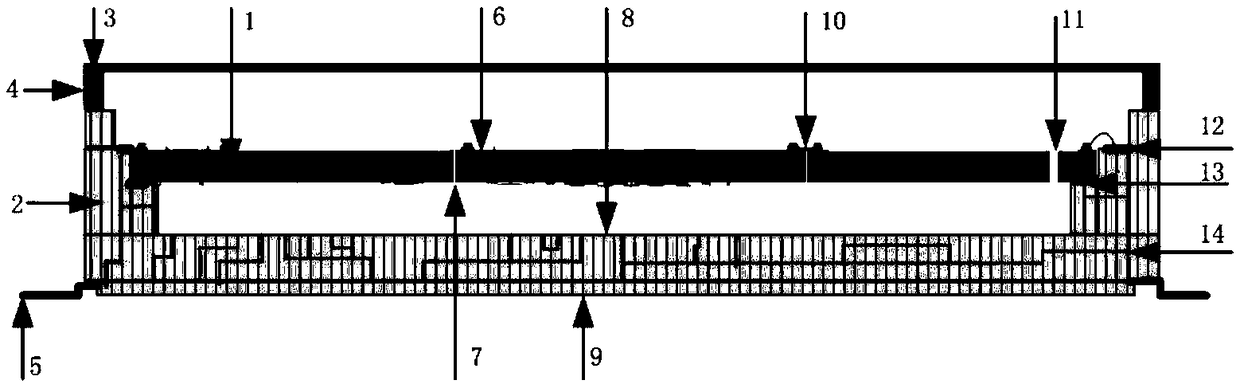

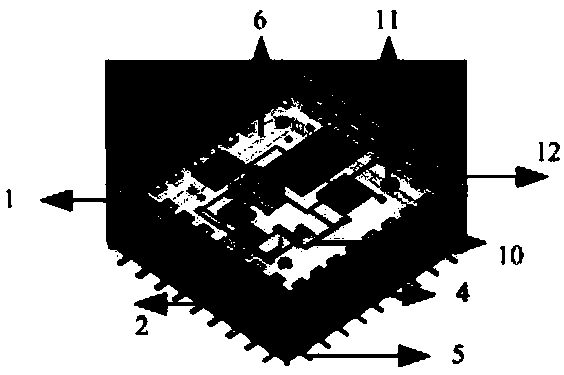

3D stereoscopic package structure and package method of I/F conversion system

PendingCN109256373AHigh precisionReliable integrationSemiconductor/solid-state device detailsSolid-state devicesMiniaturizationInterconnection

A 3-D stereoscopic package structure and a package method of an I / F conversion system can solve that technical problem that the prior art is large in volume and heavy in weight, and cannot be appliedto the field of high precision. The structure comprises an LTCC double panel and an HTCC package main body, wherein the HTCC package main body comprises a ceramic cavity, a metal ring frame, an outerlead and a cover plate, wherein the metal ring frame is arranged on the top of the ceramic cavity, and the cover plate is arranged on the metal ring frame; The LTCC double panel is horizontally arranged inside the ceramic cavity, the LTCC double panel is a multi-layer metallized ceramic substrate, metallized pads are respectively arranged on both sides of the LTCC double panel and the inner bottomsurface of the ceramic cavity, and the outer leads are horizontally arranged on the outer side surface of the ceramic cavity bottom plate. The invention realizes the three-dimensional integration ofthe system by adopting the stacking structure of the double-panel and the AlN integrated packaging main body and the vertical interconnection technology. The invention has strong universality and canbe widely applied to the integration of the high-precision, high-reliability and miniaturization inertial navigation system.

Owner:NO 43 INST OF CHINA ELECTRONICS TECH GRP CETC

Method to fabricate high performance carbon nanotube transistor integrated circuits by three-dimensional integration technology

ActiveUS20130119548A1Semiconductor/solid-state device detailsNanoinformaticsCarbon nanotubeTechnology/technique

Techniques for fabricating carbon nanotube-based devices are provided. In one aspect, a method for fabricating a carbon nanotube-based integrated circuit is provided. The method comprises the following steps. A first wafer comprising carbon nanotubes is provided. A second wafer comprising one or more device elements is provided. One or more of the carbon nanotubes are connected with one or more of the device elements by bonding the first wafer and the second wafer together. A carbon nanotube-based integrated circuit is also provided.

Owner:GLOBALFOUNDRIES US INC

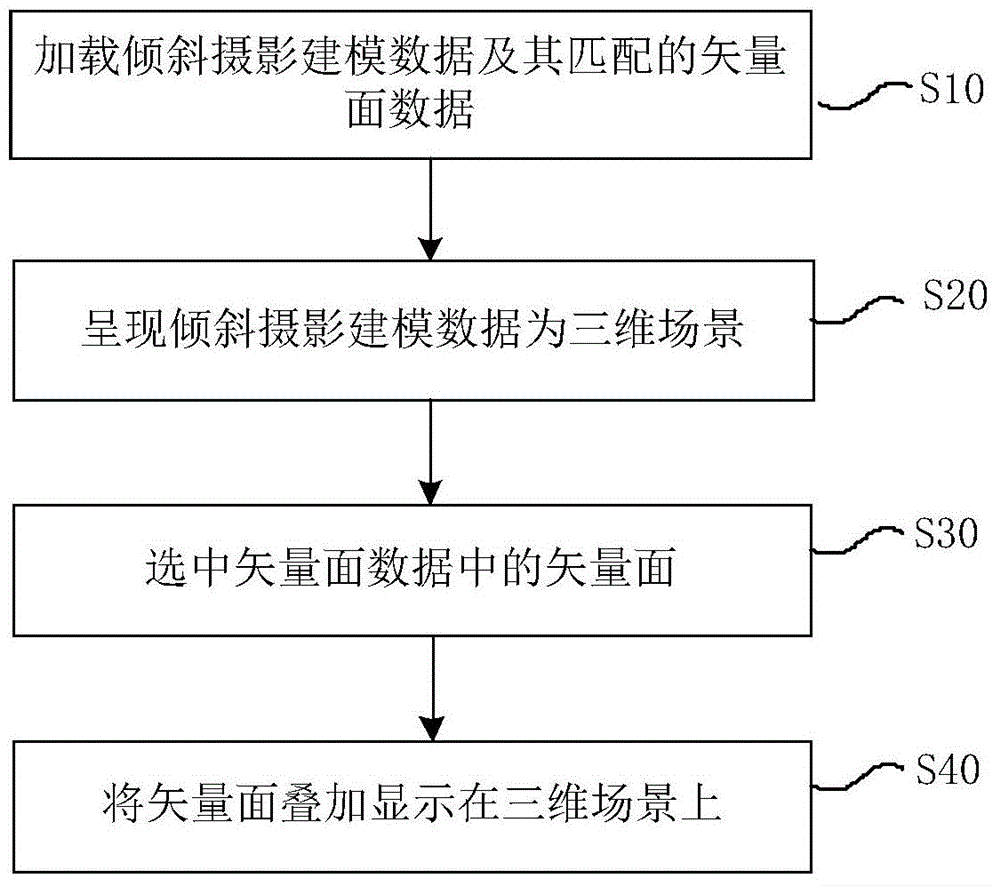

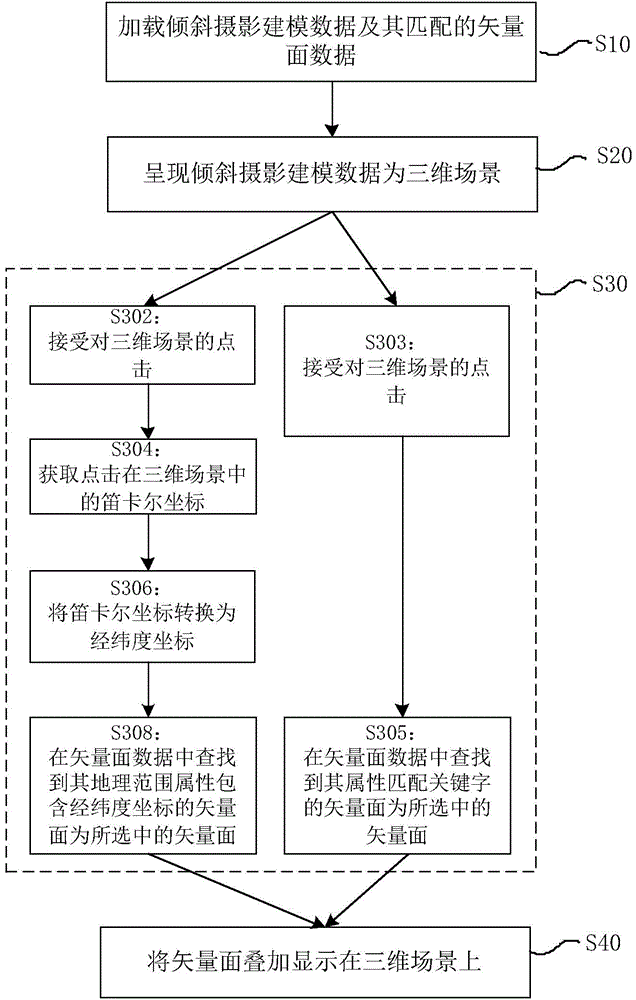

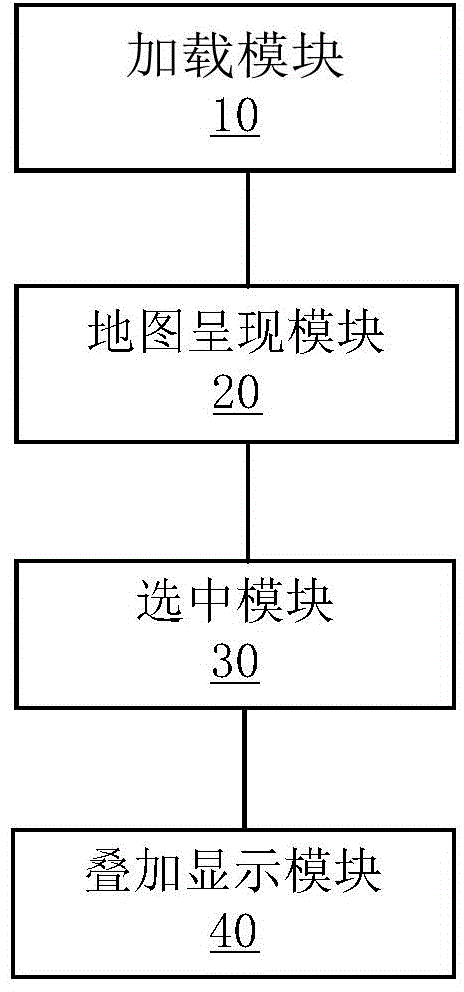

Oblique modeling data based two and three dimensional integration method and system

InactiveCN104537043ASolve the problem that cannot be singled outTo achieve singleGeographical information databasesSpecial data processing applicationsComputer graphics (images)Three dimensional integration

The invention provides an oblique modeling data based two and three dimensional integration method and system. The oblique modeling data based two and three dimensional integration method comprises the steps of loading oblique photograph modeling data and vector face data matched with the oblique photograph modeling data, showing the oblique photograph modeling data as a three dimensional scene, selecting a vector face in the vector face data and displaying the vector face on the three dimensional scene in a superposed mode. By means of the oblique modeling data based two and three dimensional integration method and system, the oblique photograph modeling data are permitted to be highlighted and subjected to other protruded display through vector face and three dimensional scene superposed two and three dimensional integration, monomerization is achieved, and the problem that a GIS established according to the oblique photograph modeling data by means of correlation techniques cannot be monomerized is solved.

Owner:BEIJING SUPERMAP SOFTWARE CO LTD

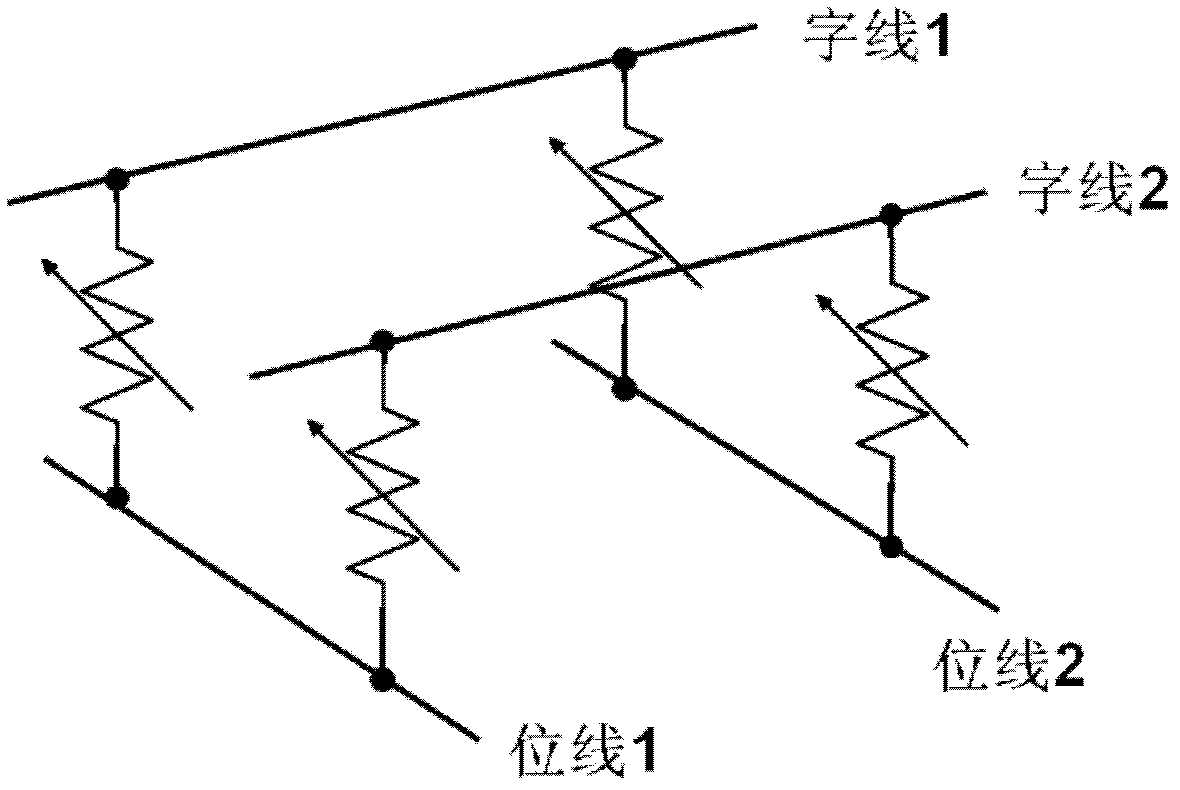

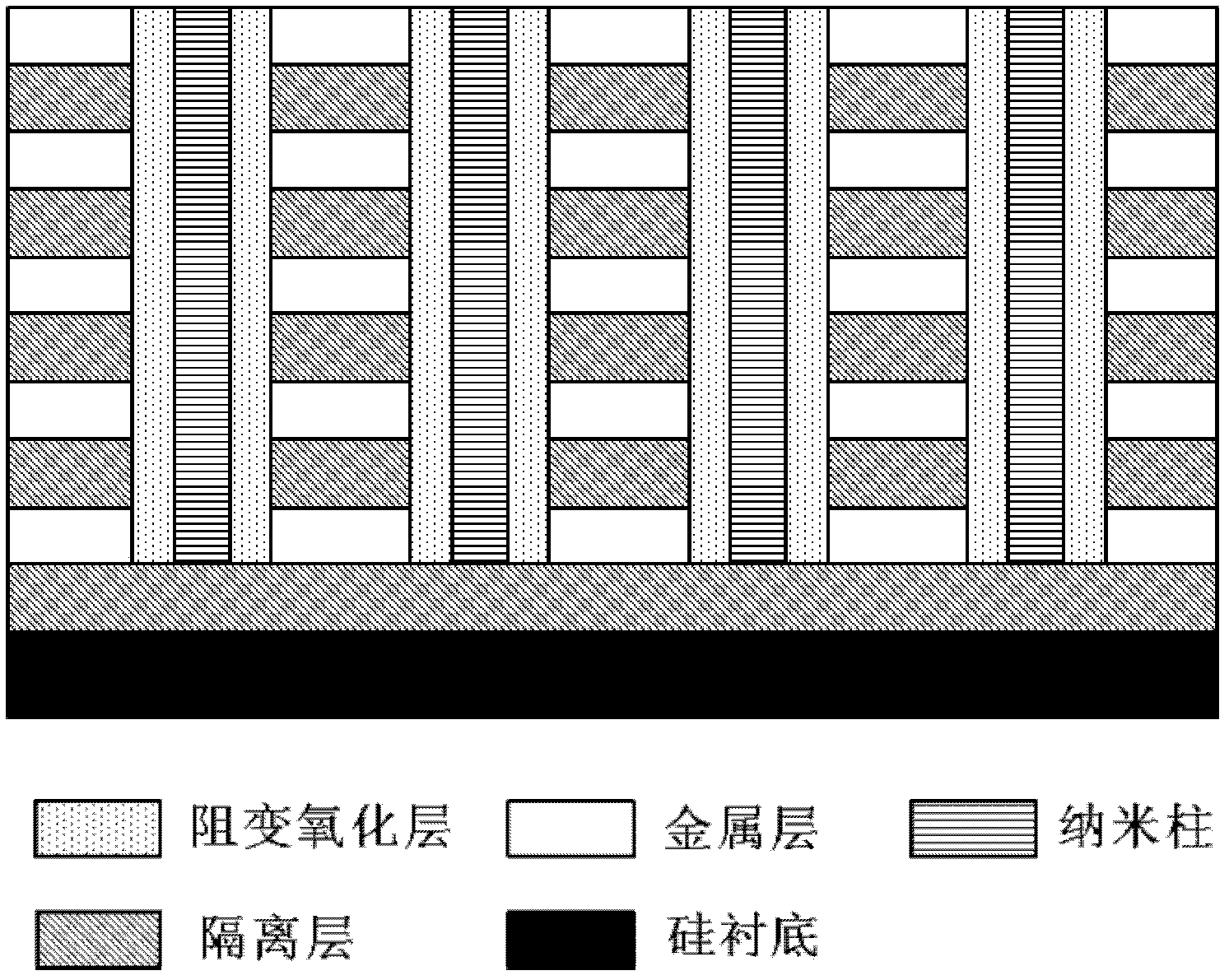

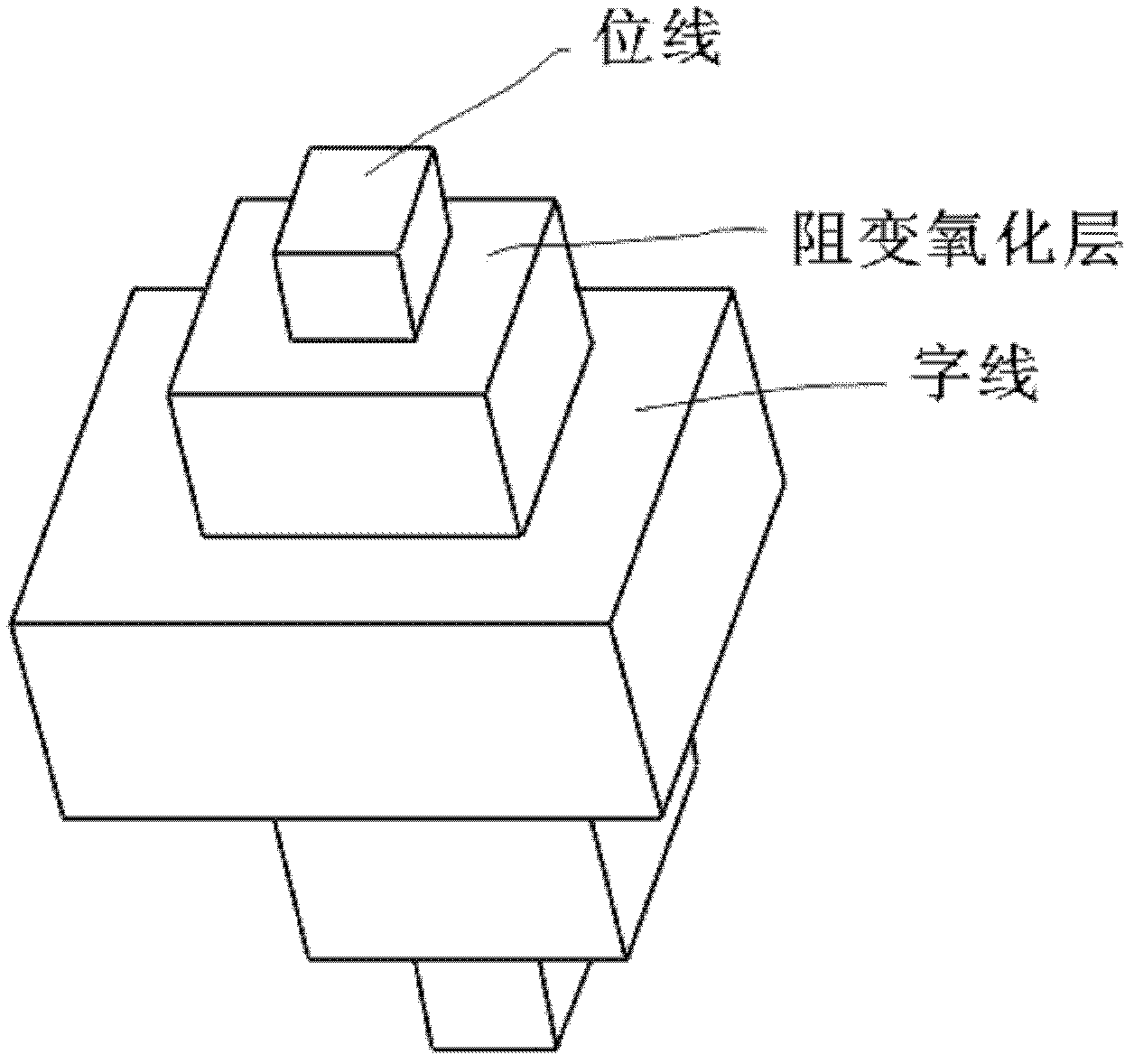

Resistance random access memory with cross array structure and preparation method

InactiveCN102522501AReduce process complexitySolid-state devicesDigital storageManufacturing technologyStatic random-access memory

The invention discloses a resistance random access memory with a cross array structure and a preparation method and relates to the technical field of a semiconductor integrated circuit and manufacturing thereof. The memory comprises a silicon substrate. A first isolation layer is arranged on the silicon substrate. At least one nano column vertical to the first isolation layer is arranged on the first isolation layer. A resistive oxide layer is arranged around the side wall of the nano column by a circle. A metal layer and a second isolation layer are arranged around the outer side wall of the resistive oxide layer by a circle at intervals from bottom to top. The nano column is made of metal. According to a certain structure setting, the aim of providing the memory which is suitable for three-dimensional integration under the condition that the process complexity is not increased is fulfilled.

Owner:PEKING UNIV