Method for forming through silicon vias (TSV)

A technology of TSV and deep via, which is applied in the manufacturing of electrical components, circuits, semiconductor/solid-state devices, etc., can solve the problem of limited high frequency performance of TSV, and it is difficult to ensure the side of TSV at the same time. Wall isolation performance and electrical conduction performance and other issues, to achieve the effect of improving reliability and electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

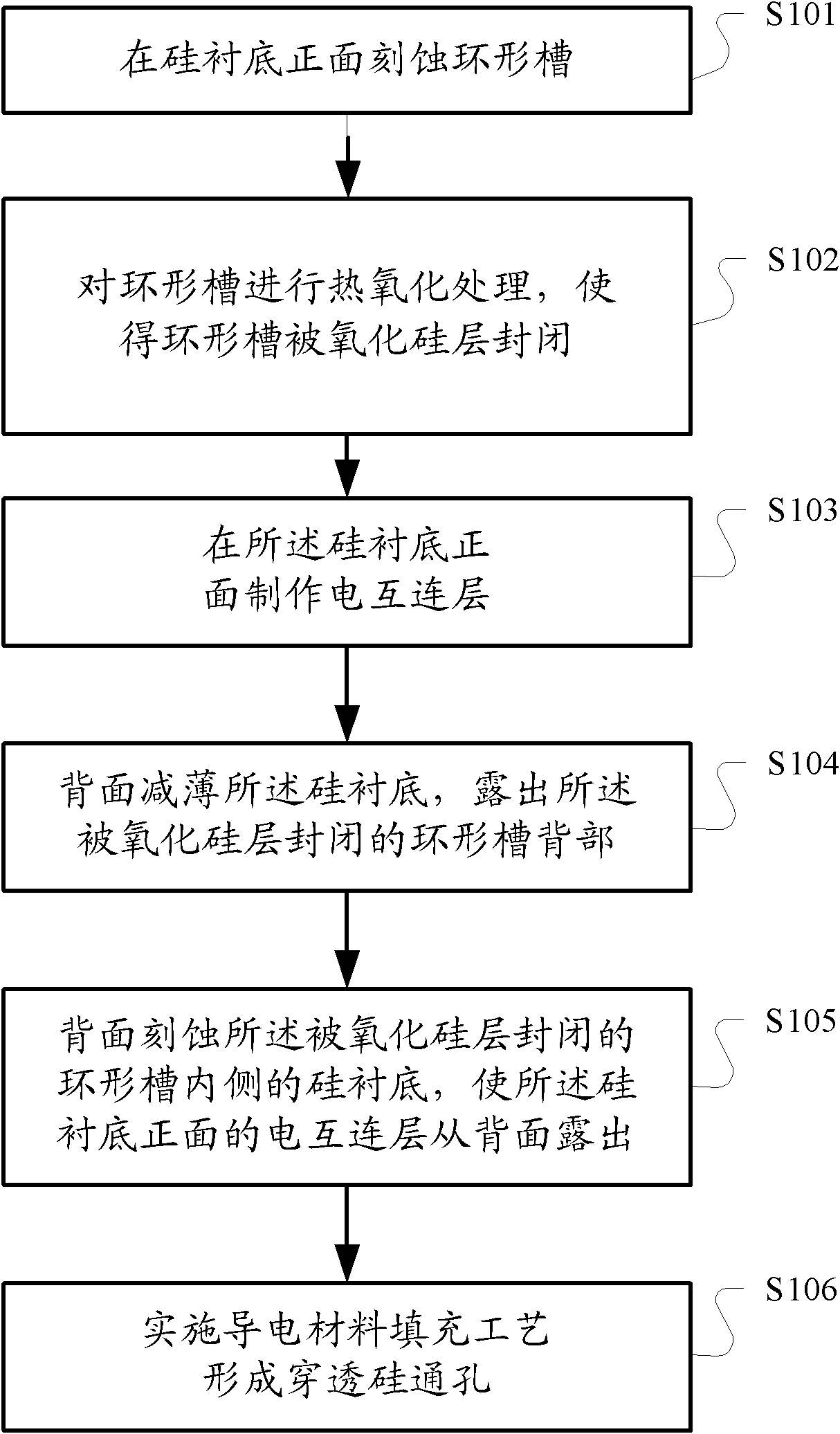

[0039] like figure 1 As shown, the method for forming TSVs provided by the present invention comprises the following steps:

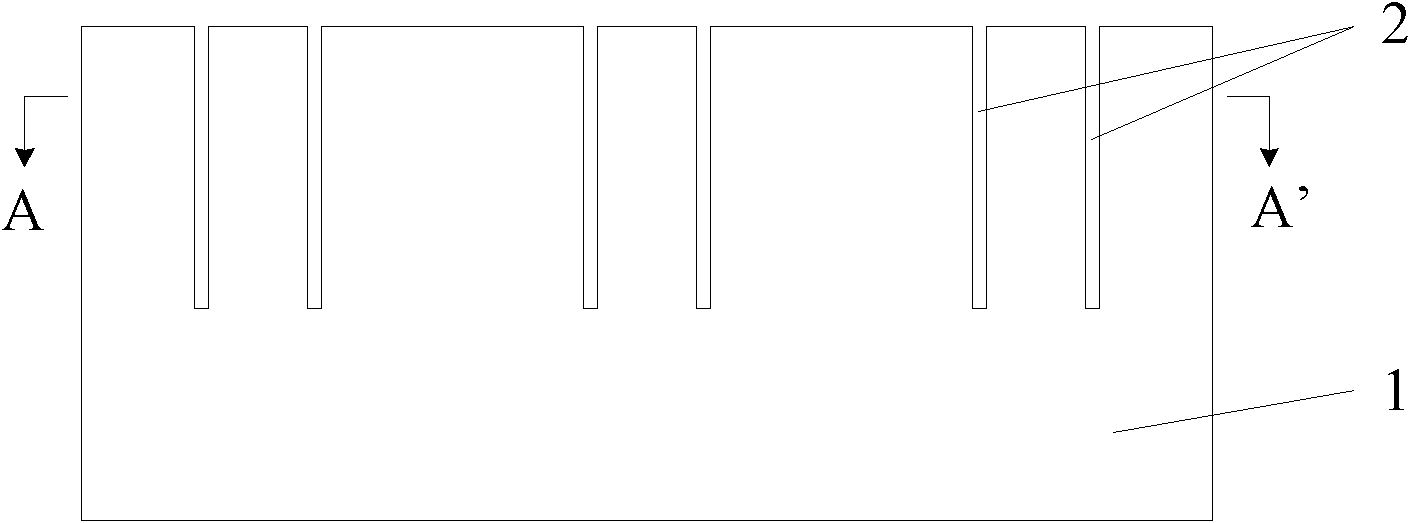

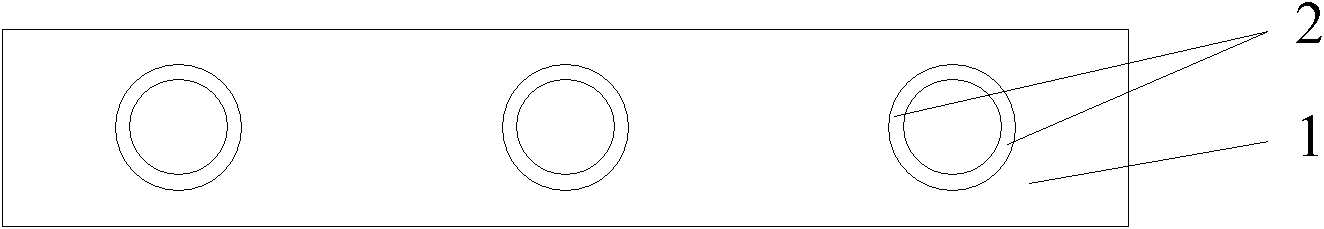

[0040] first step, such as figure 2 and image 3 As shown, an annular groove 2 is etched on the front surface of a silicon substrate 1 .

[0041] The width of the annular groove 2 can range from 0.5 μm to 3 μm, and the depth of the annular groove 2 is equal to or greater than the length of the TSV to be obtained, so as to ensure the processing feasibility and the smooth progress of subsequent steps; the annular groove 2 is in the The width at the opening is equal to or greater than the width of the annular groove 2 at its depth, wherein the difference between the width of the annular groove 2 at the opening and the width of the annular groove 2 at its depth is in the range of 0 to 2 μm to facilitate subsequent processing The silicon oxide layer 3 closes the annular groove 2 . In this embodiment, the method used to etch the annular groove 2 is a dee...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width range | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More