Patents

Literature

1067 results about "Chip stacking" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

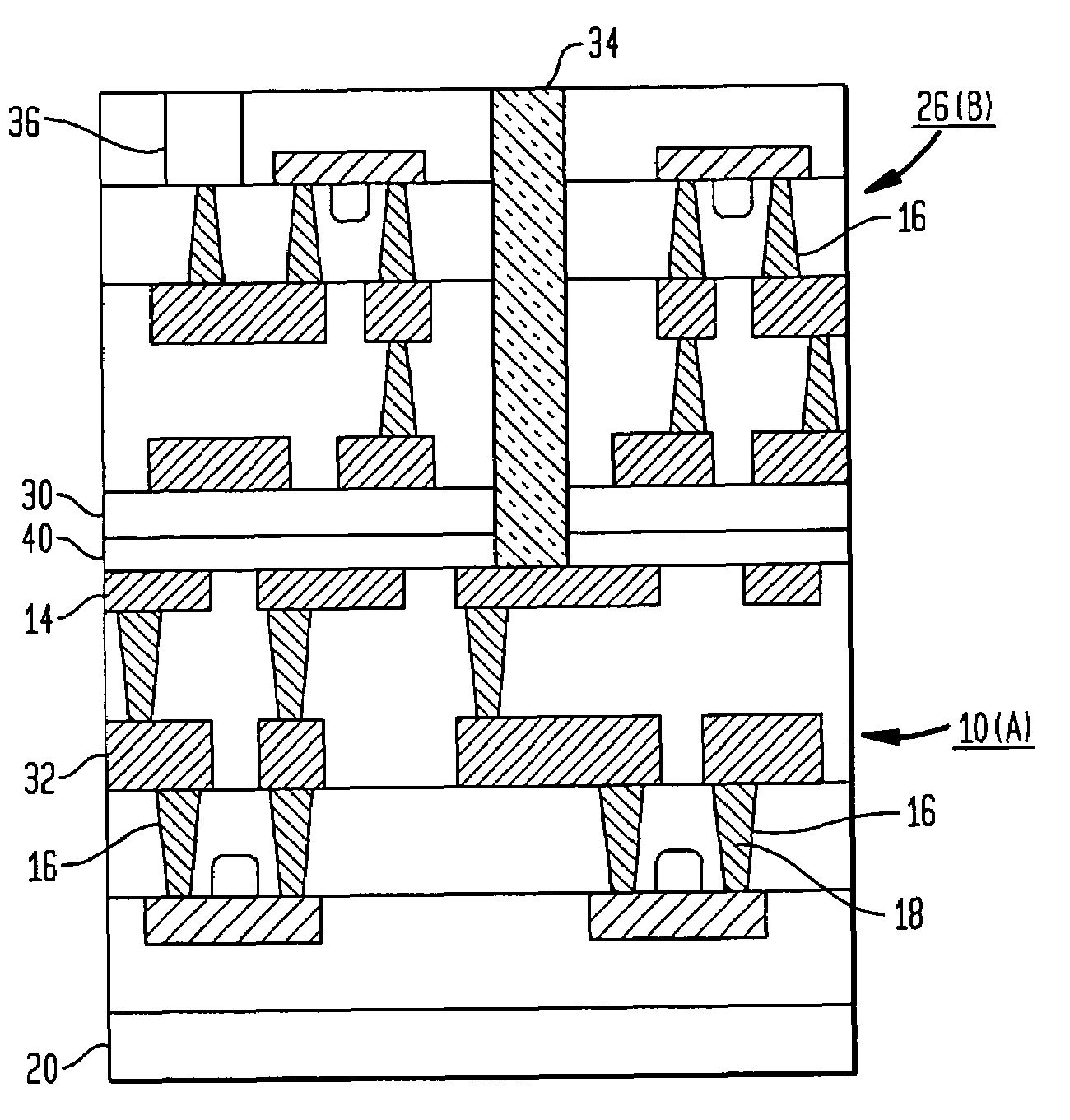

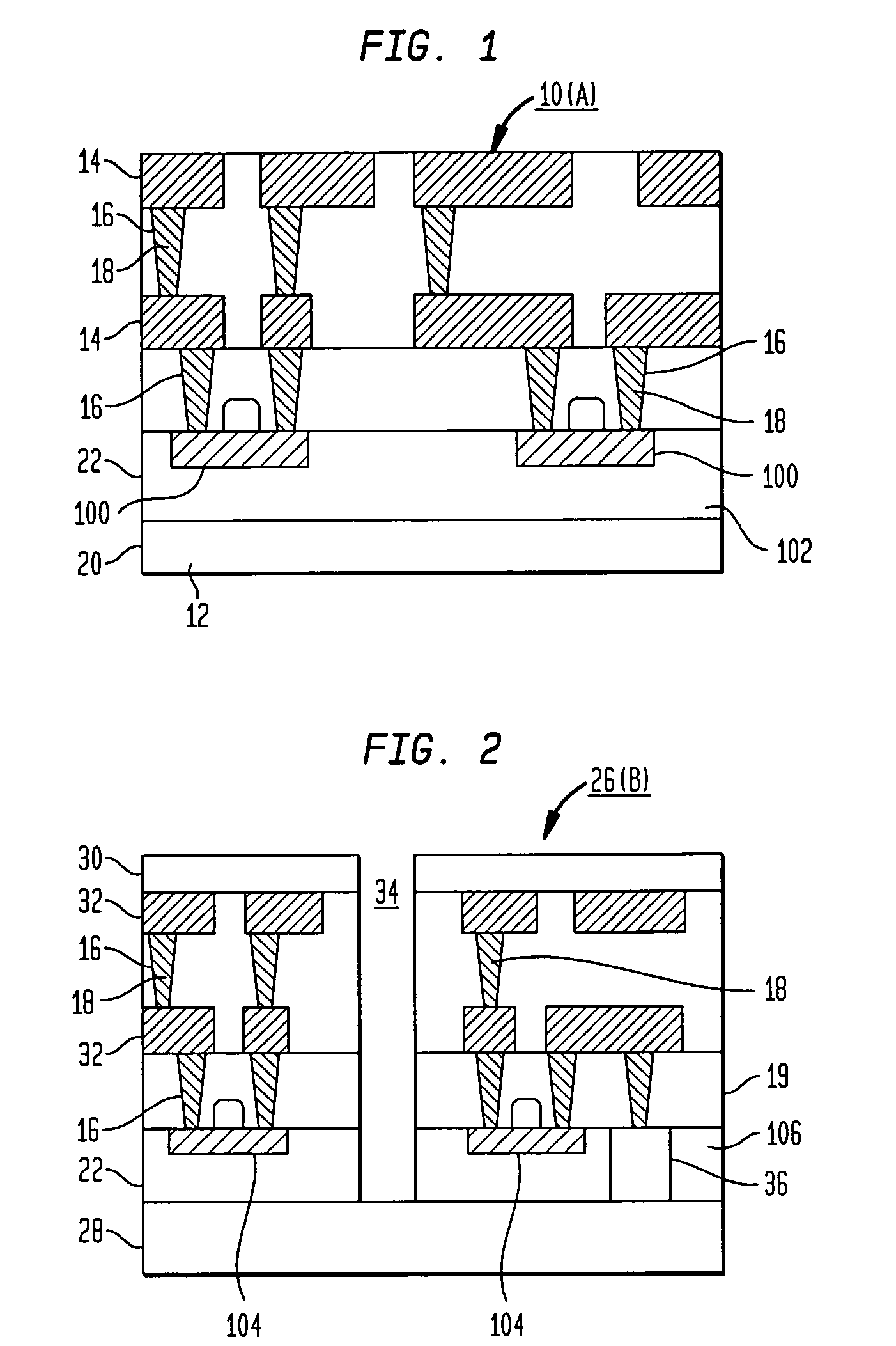

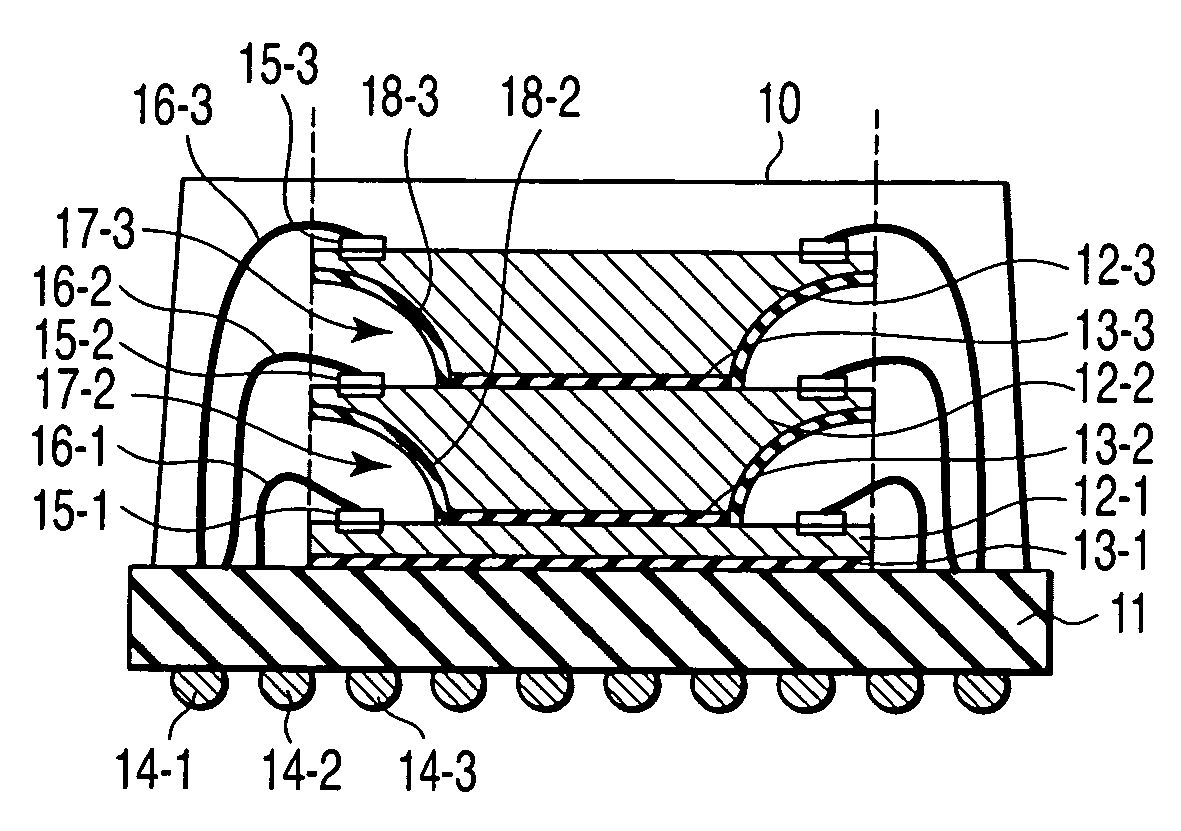

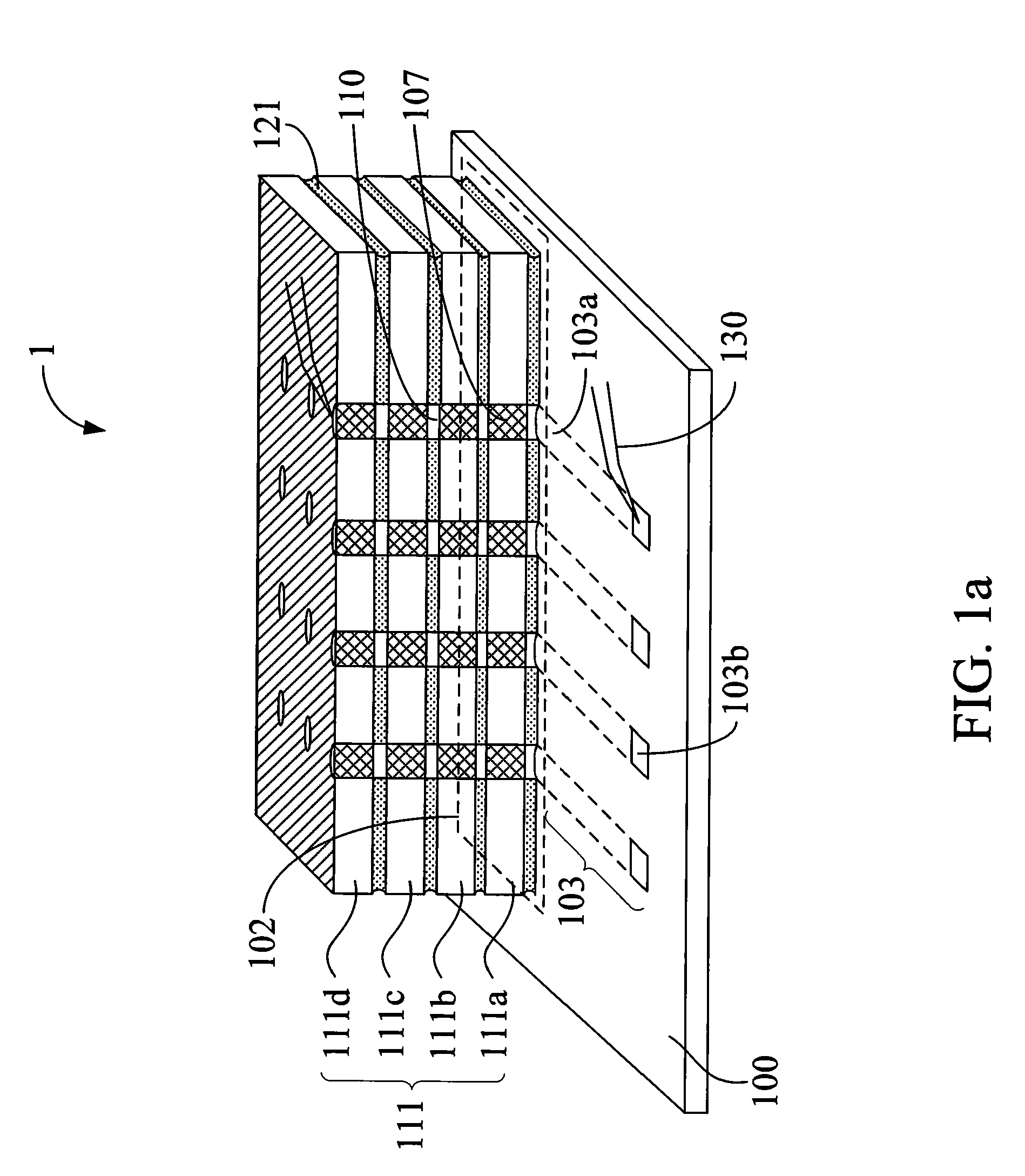

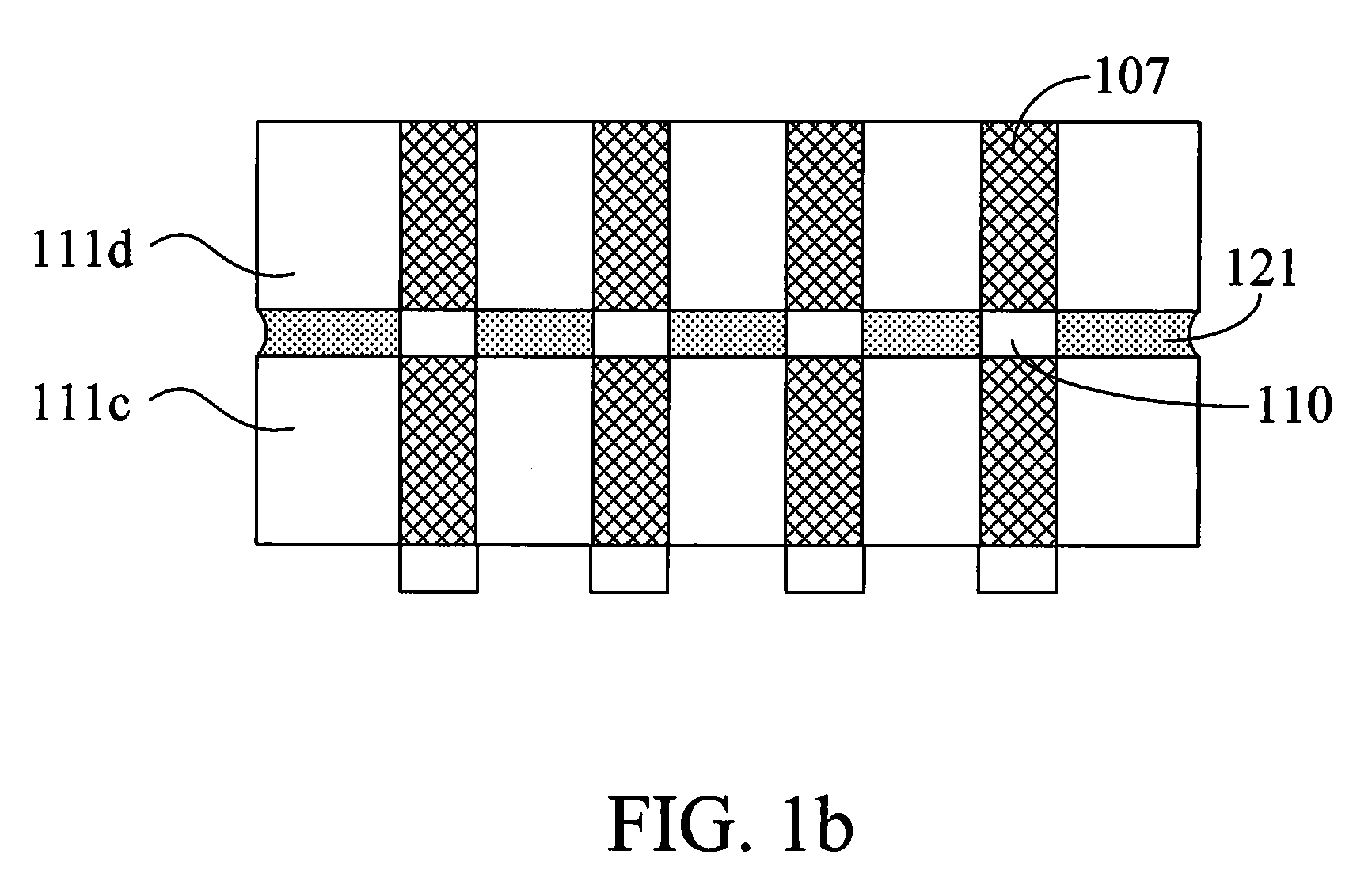

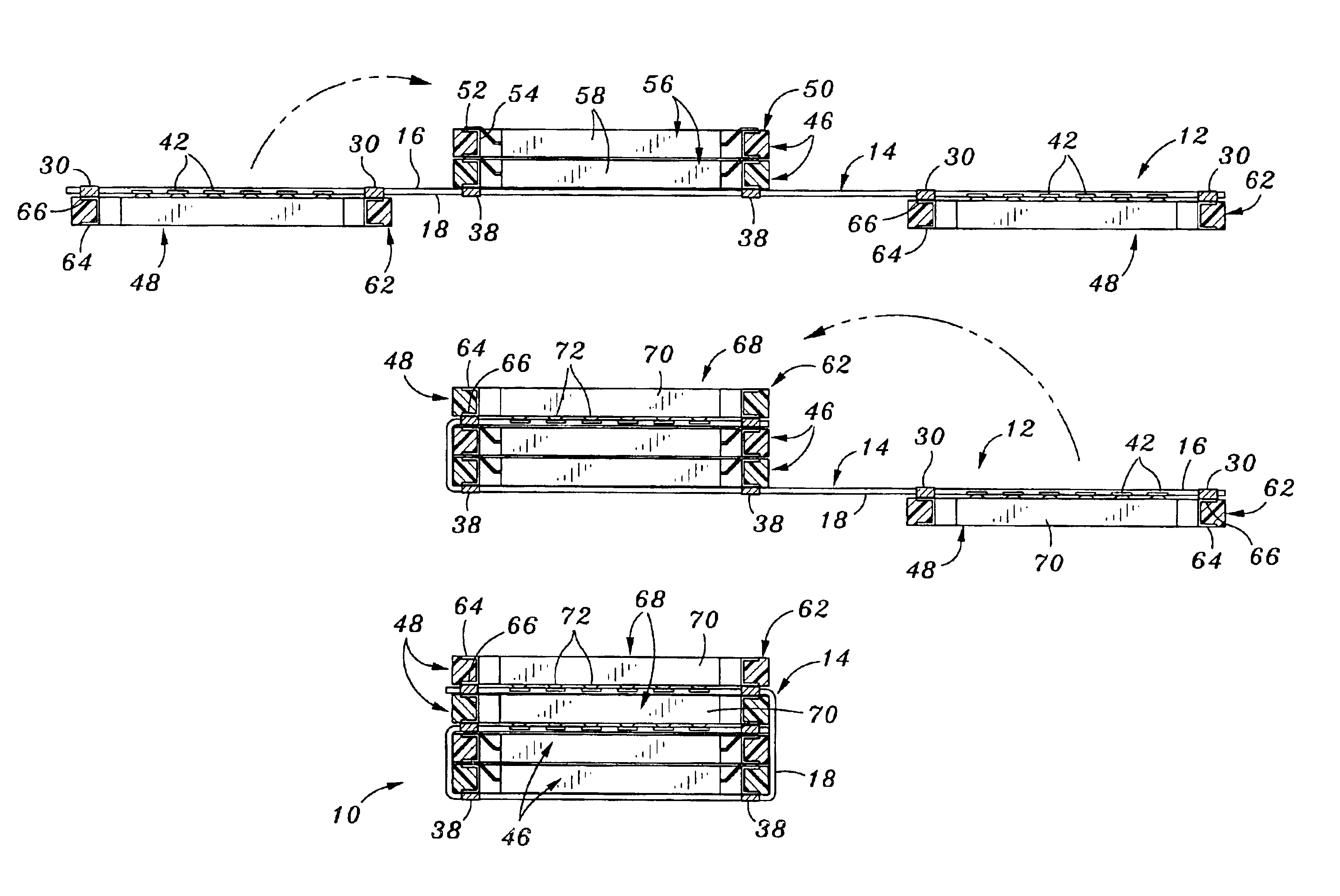

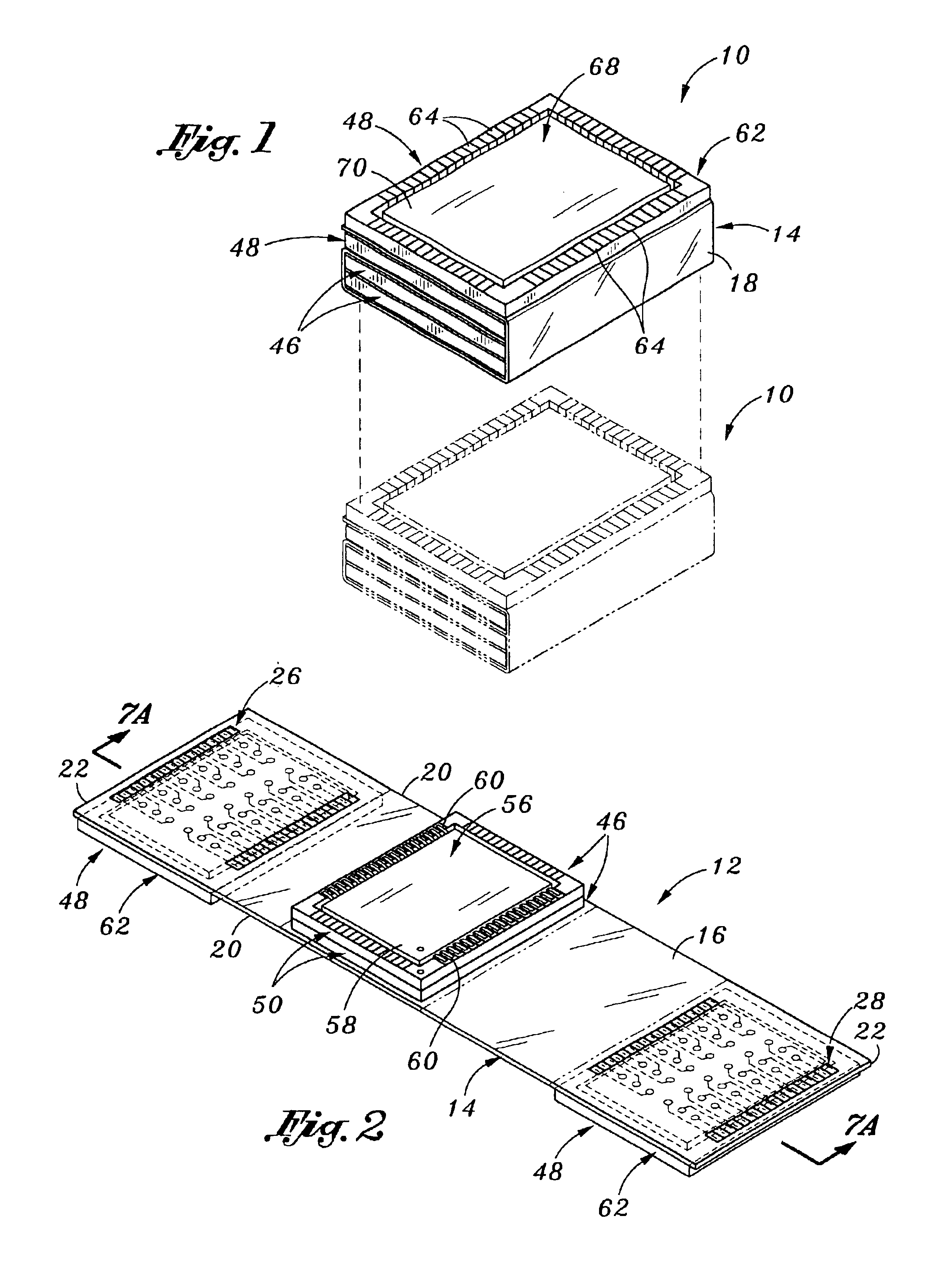

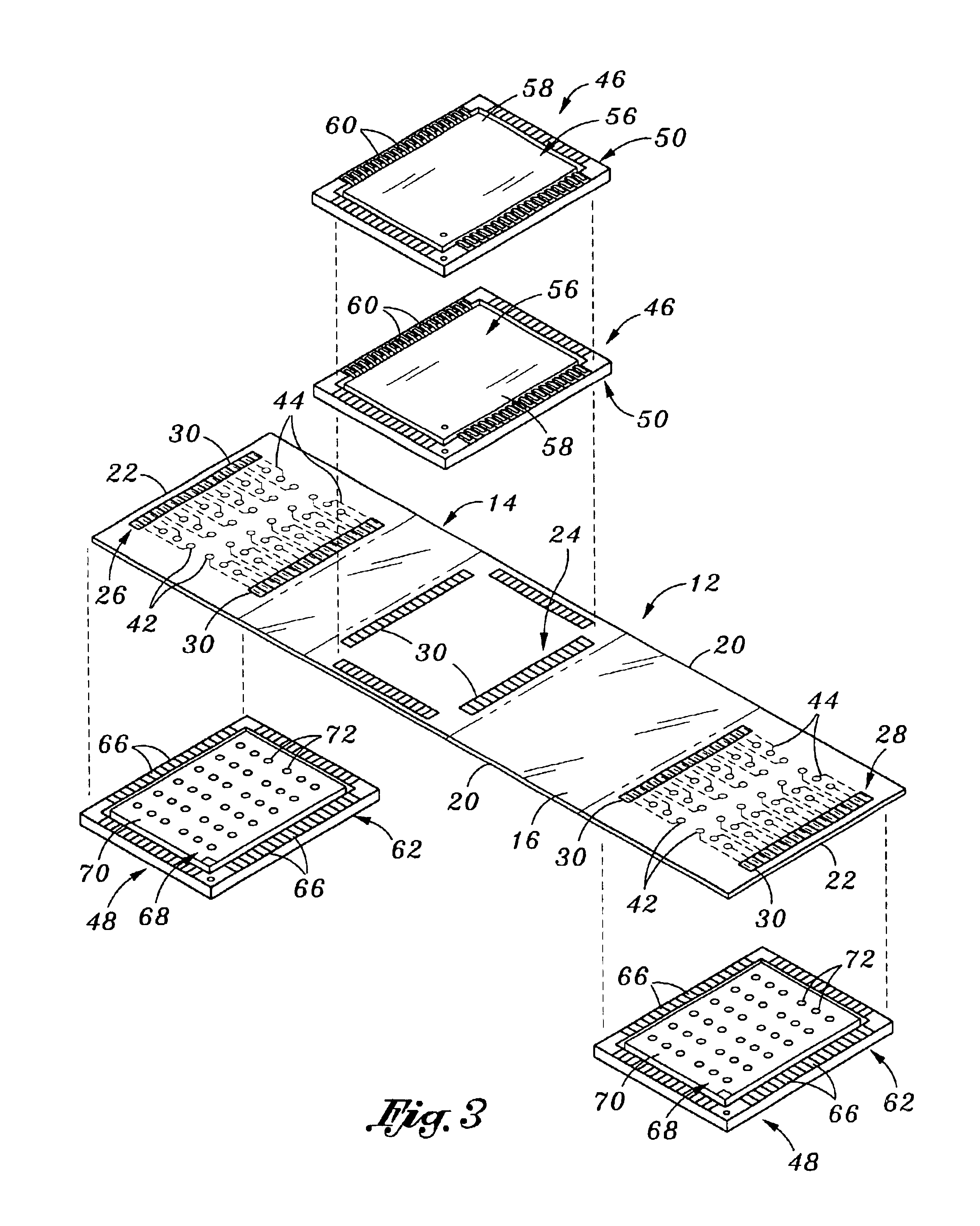

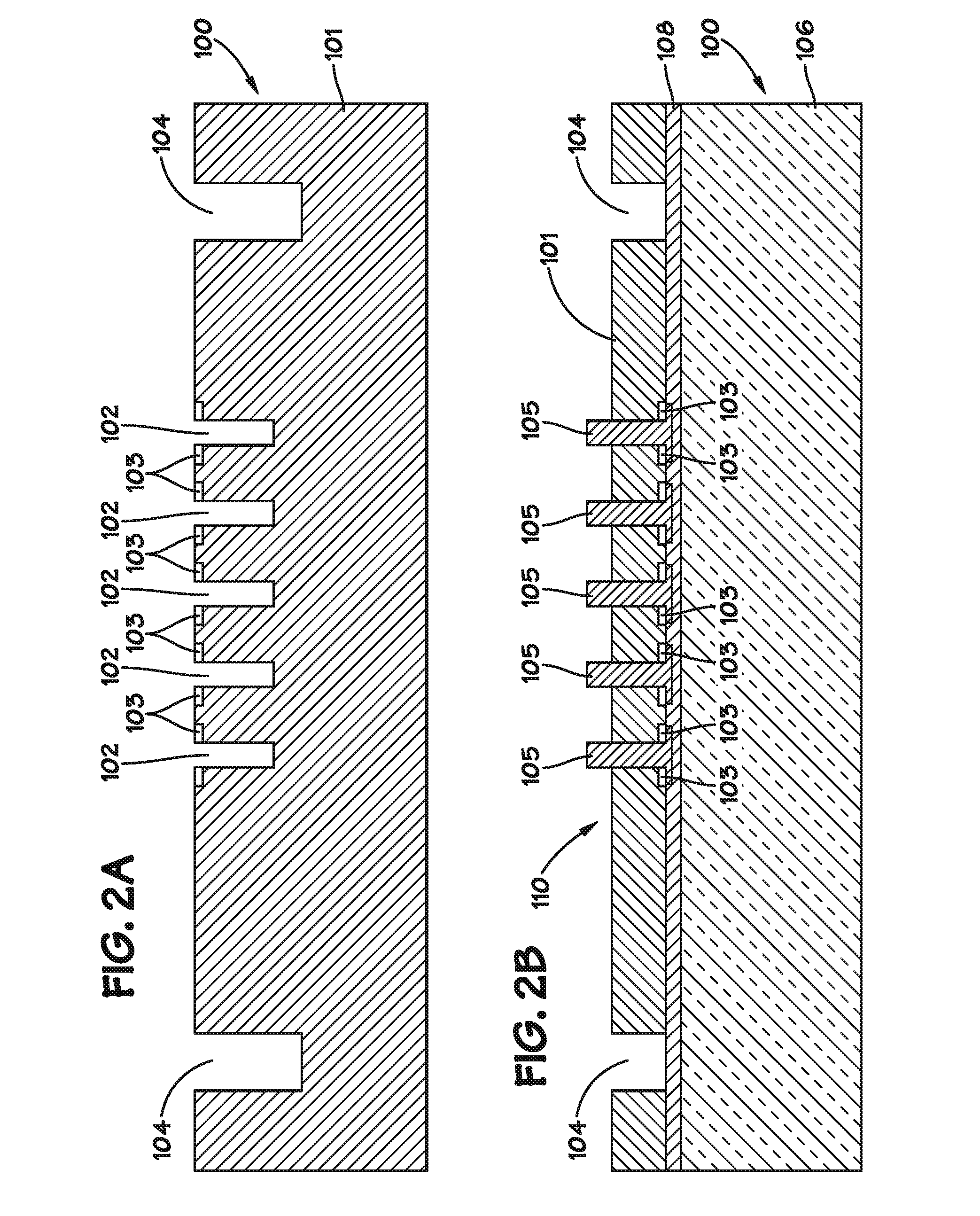

Three-dimensional chip stacking assembly

InactiveUS6355501B1Precise alignmentGood mechanical integritySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringThree-dimensional integrated circuit

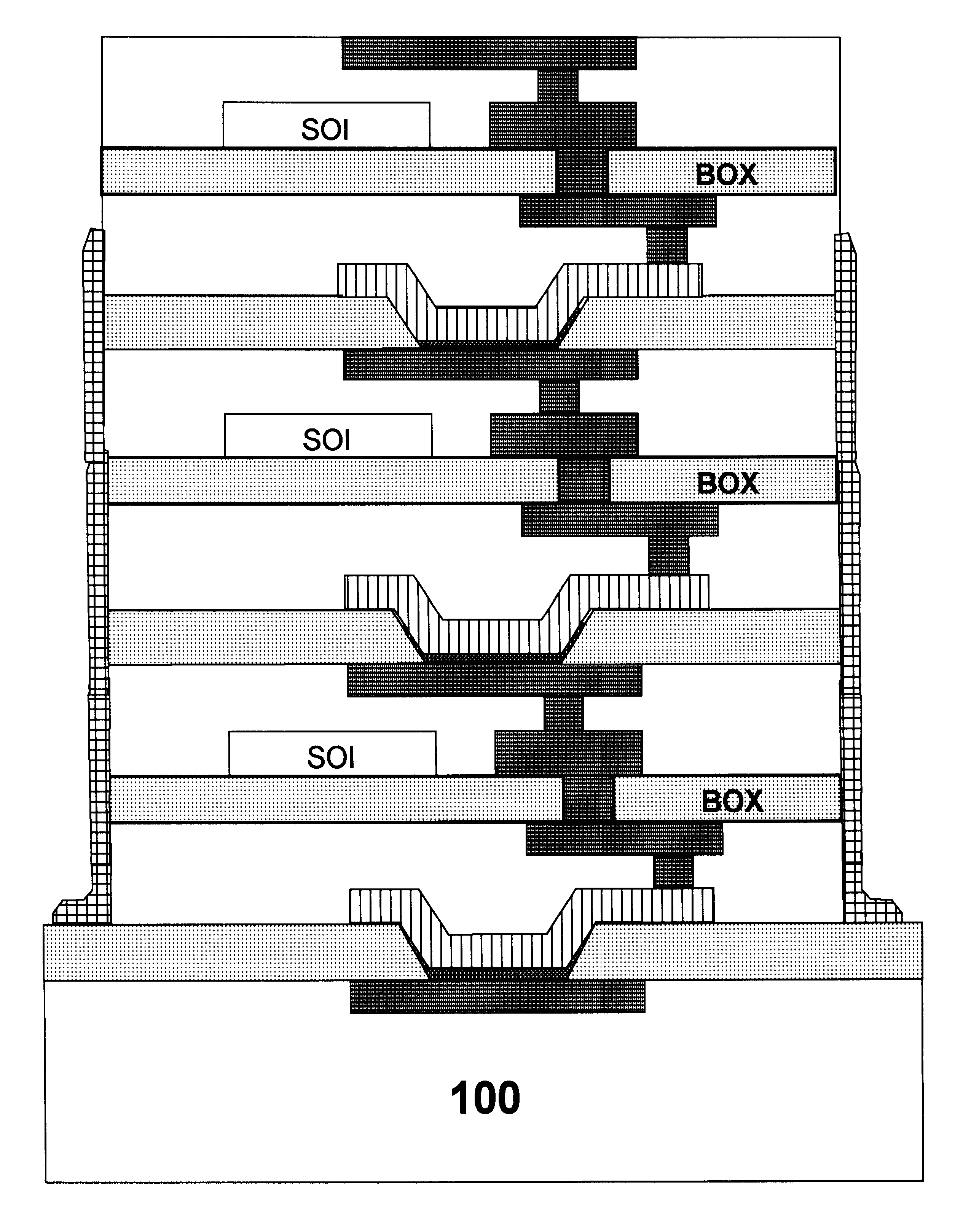

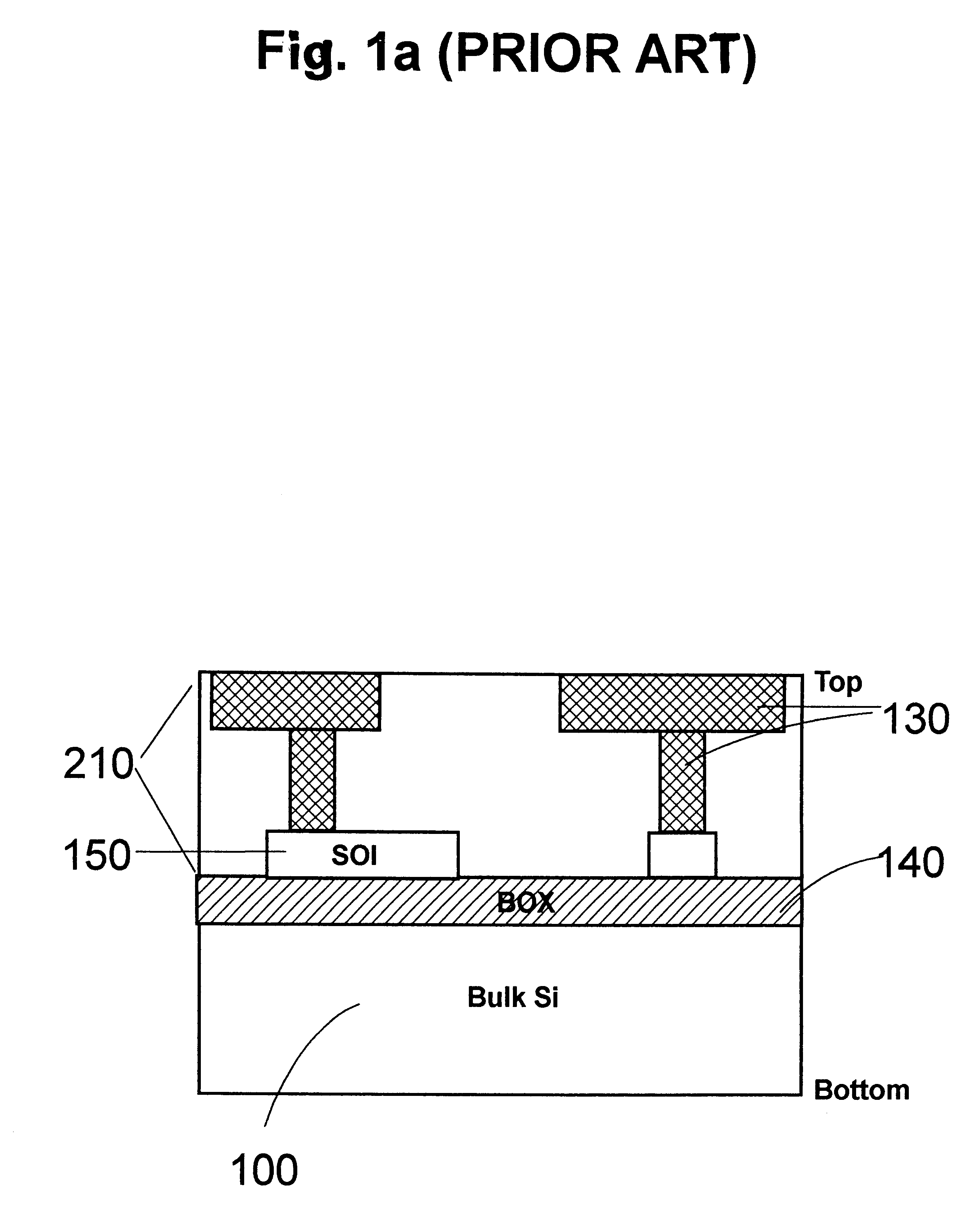

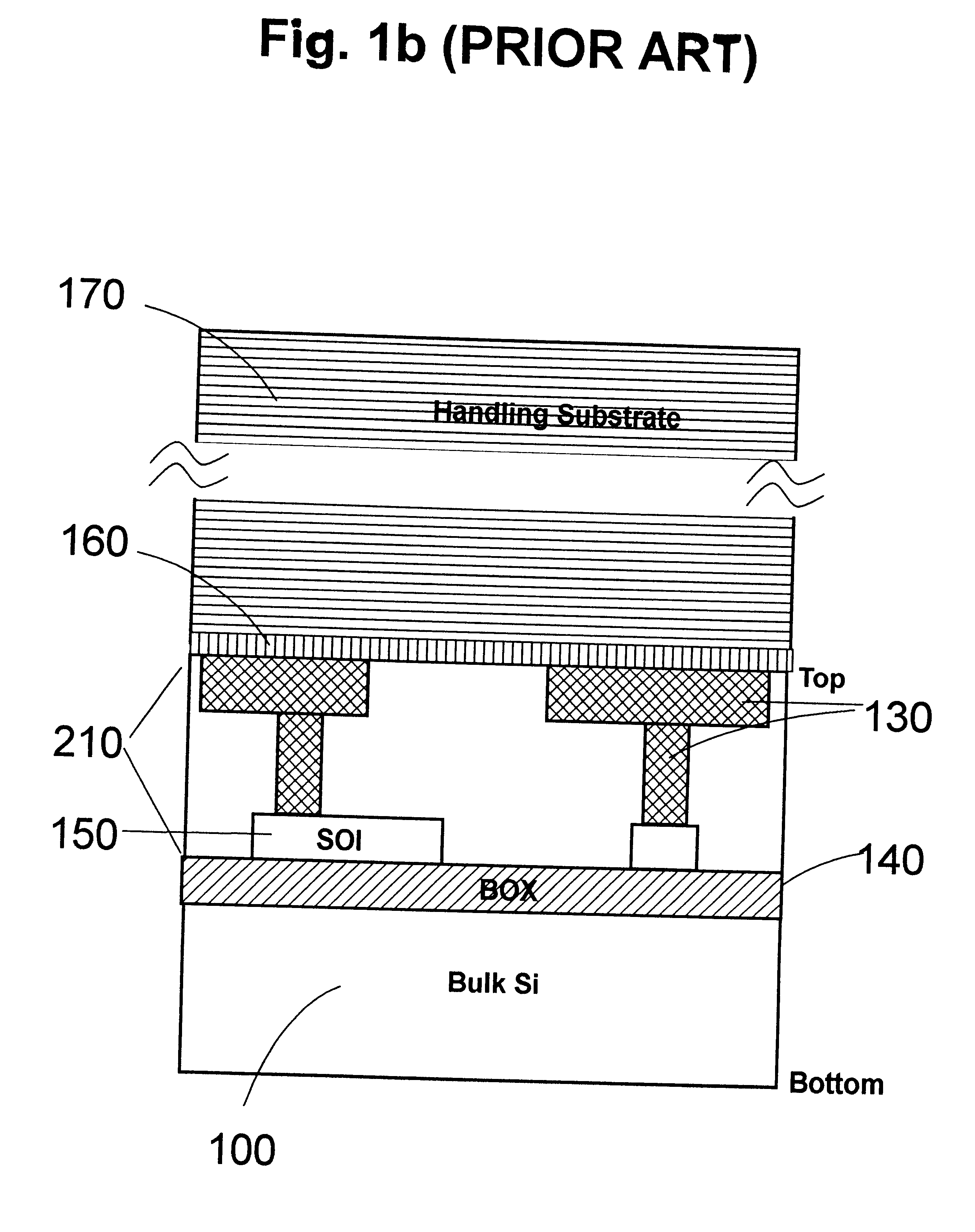

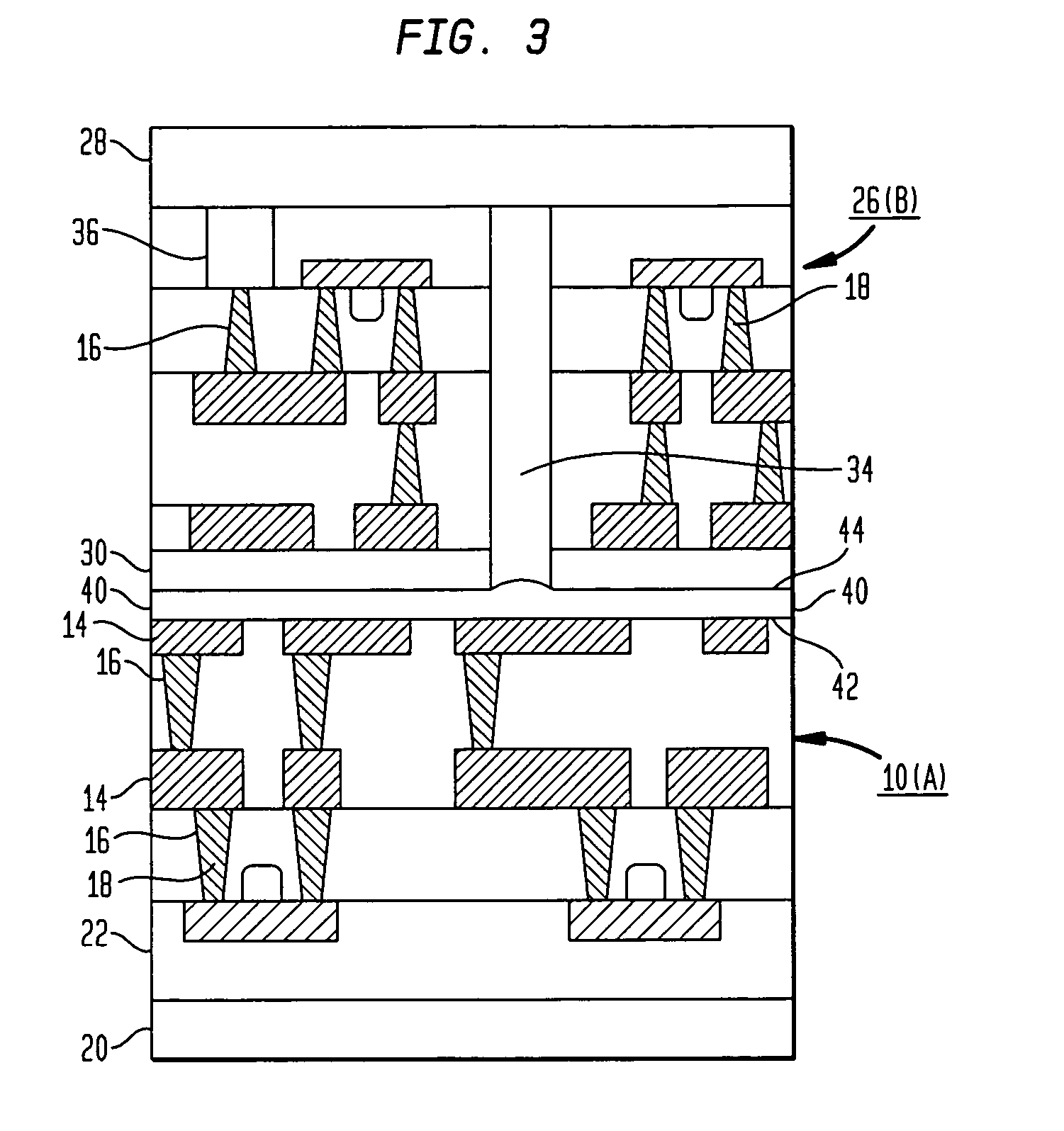

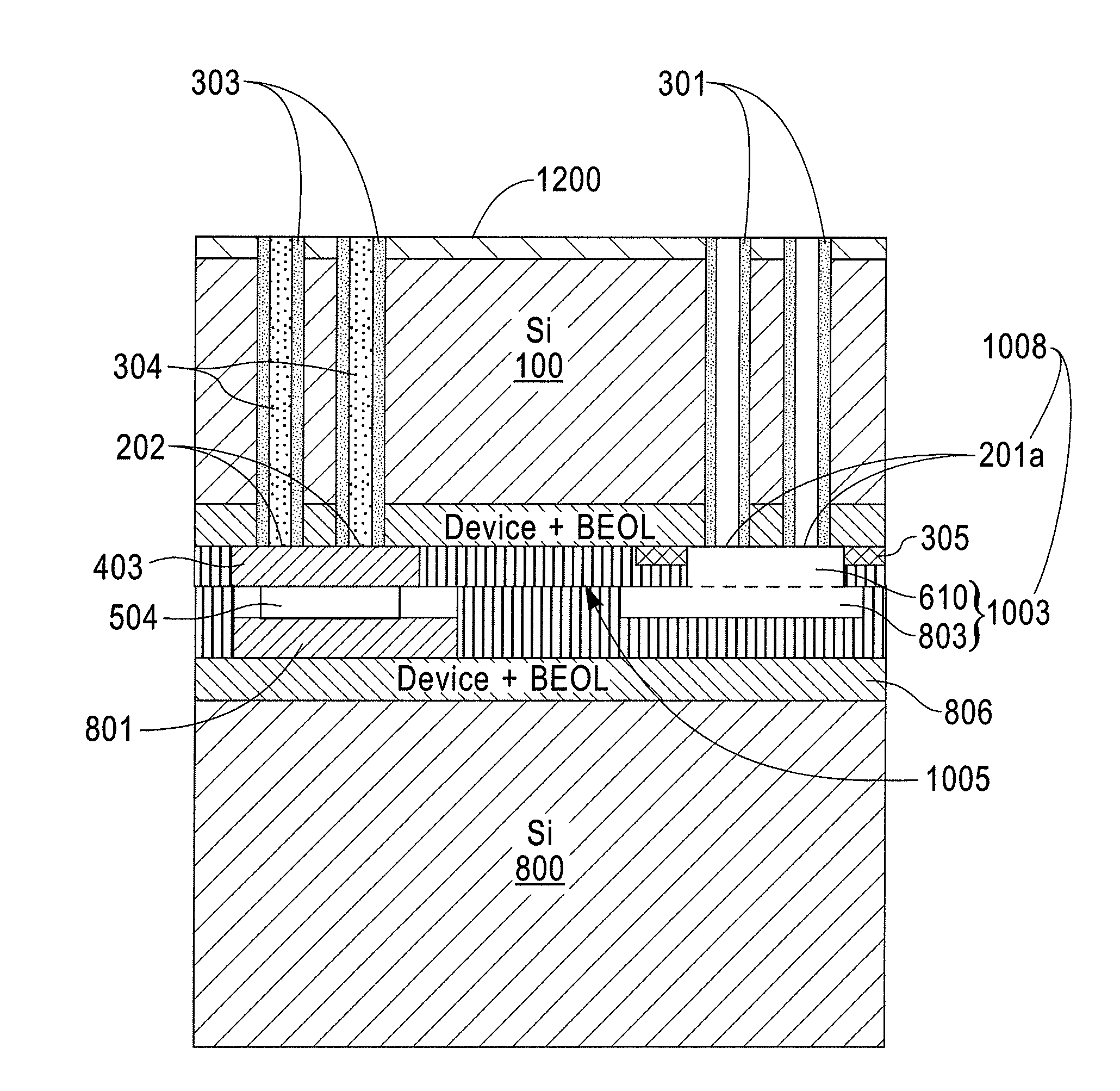

An assembly consisting of three dimensional stacked SOI chips, and a method of forming such integrated circuit assembly, each of the SOI chips including a handler making mechanical contact to a first metallization pattern making electrical contact to a semiconductor device. The metalized pattern, in turn, contacts a second metallization pattern positioned on an opposite surface of the semiconductor device. The method of fabricating the three-dimensional IC assembly includes the steps of: a) providing a substrate having a third metalized pattern on a first surface of the substrate; b) aligning one of the SOI chips on the first surface of the substrate, by having the second metallization pattern of the SOI chip make electrical contact with the third metalized pattern of the substrate; c) removing the handler from the SOI chip, exposing the first metallization pattern of the SOI chip; d) aligning a second one of the SOI chips with the first SOI chip, having the second metallization pattern of the second SOI chip make electrical contact to the exposed first metallization pattern of the first SOI chip; and e) repeating steps c) and d) for mounting subsequent SOI chips one on top of the other.

Owner:IBM CORP

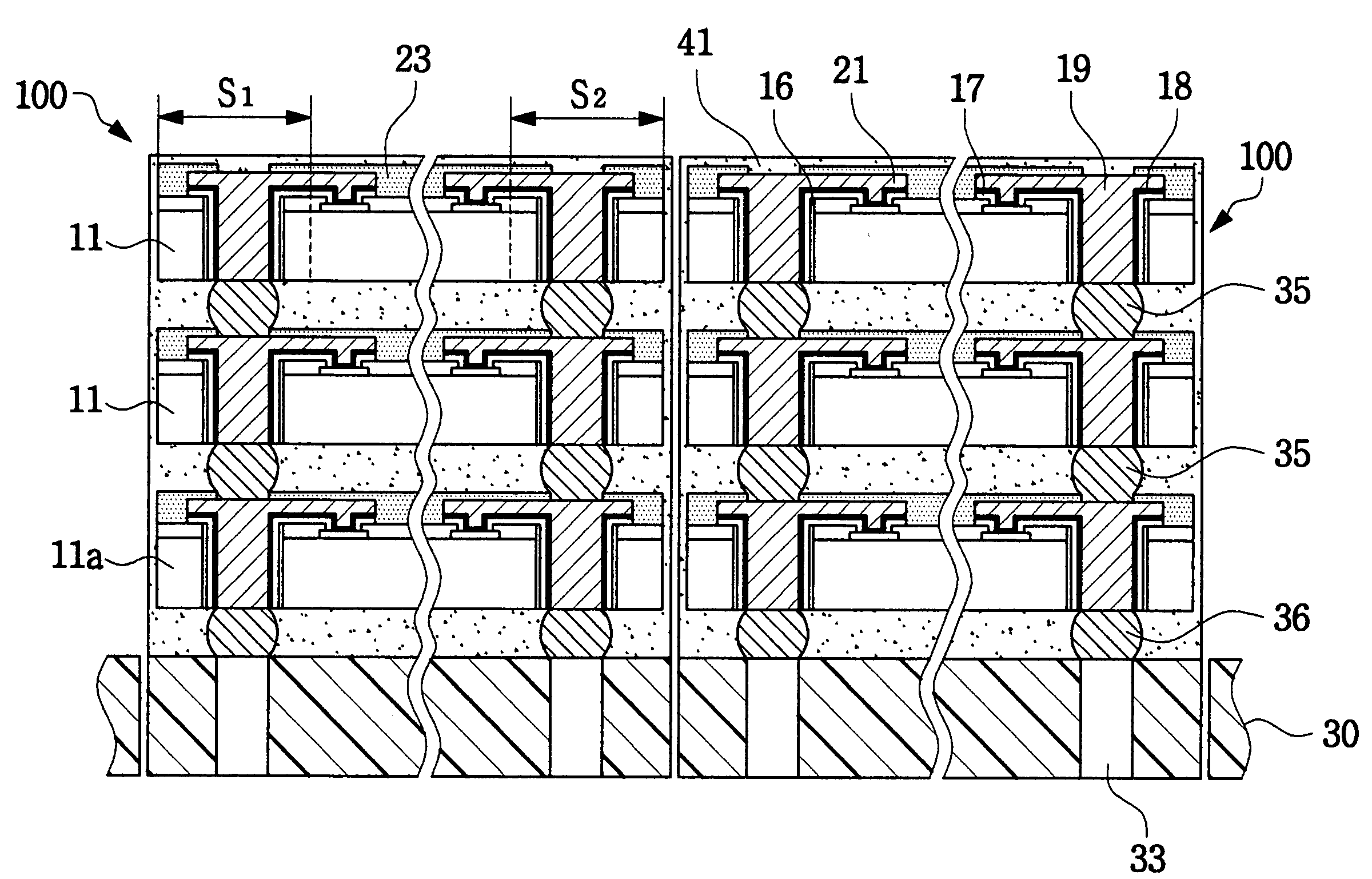

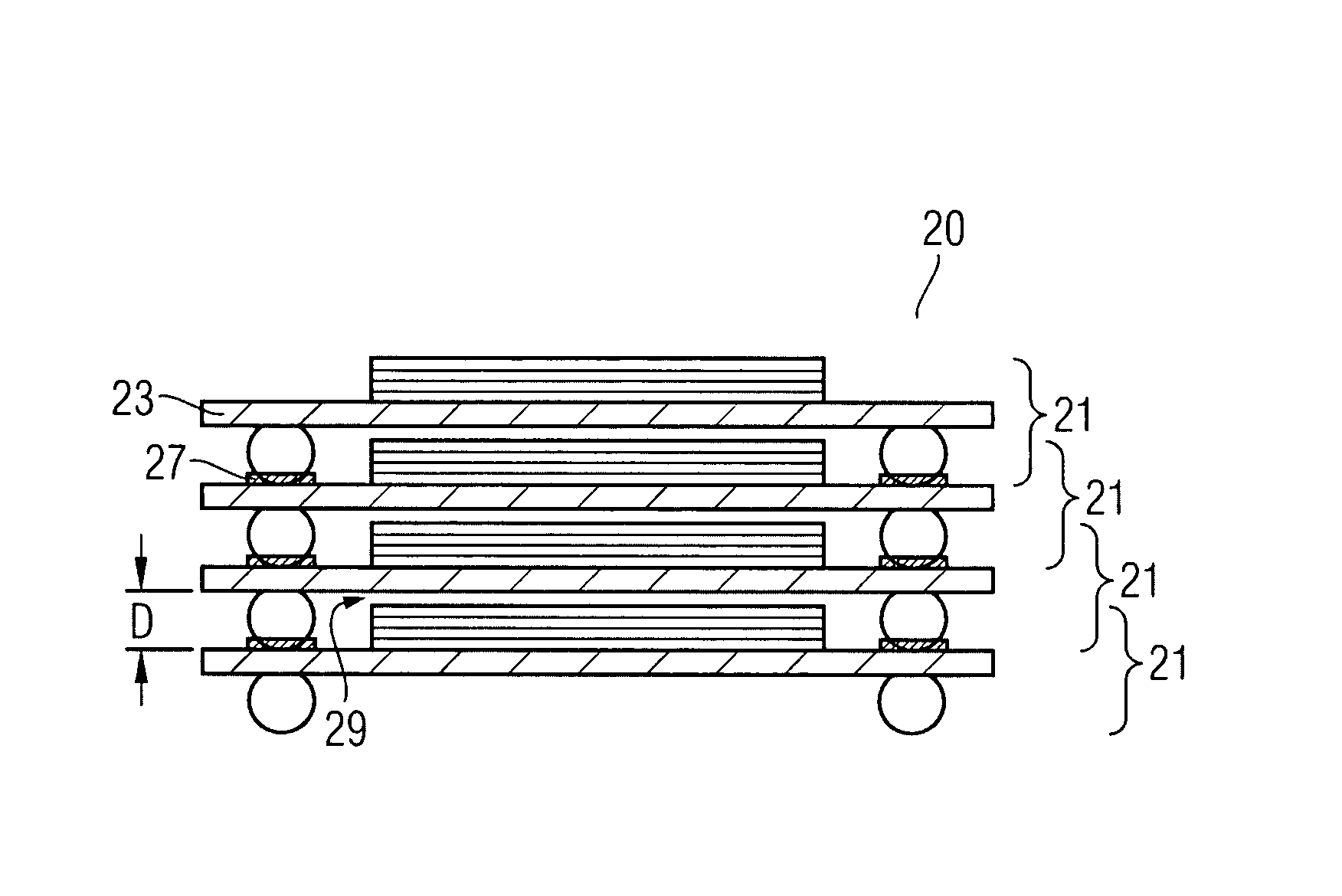

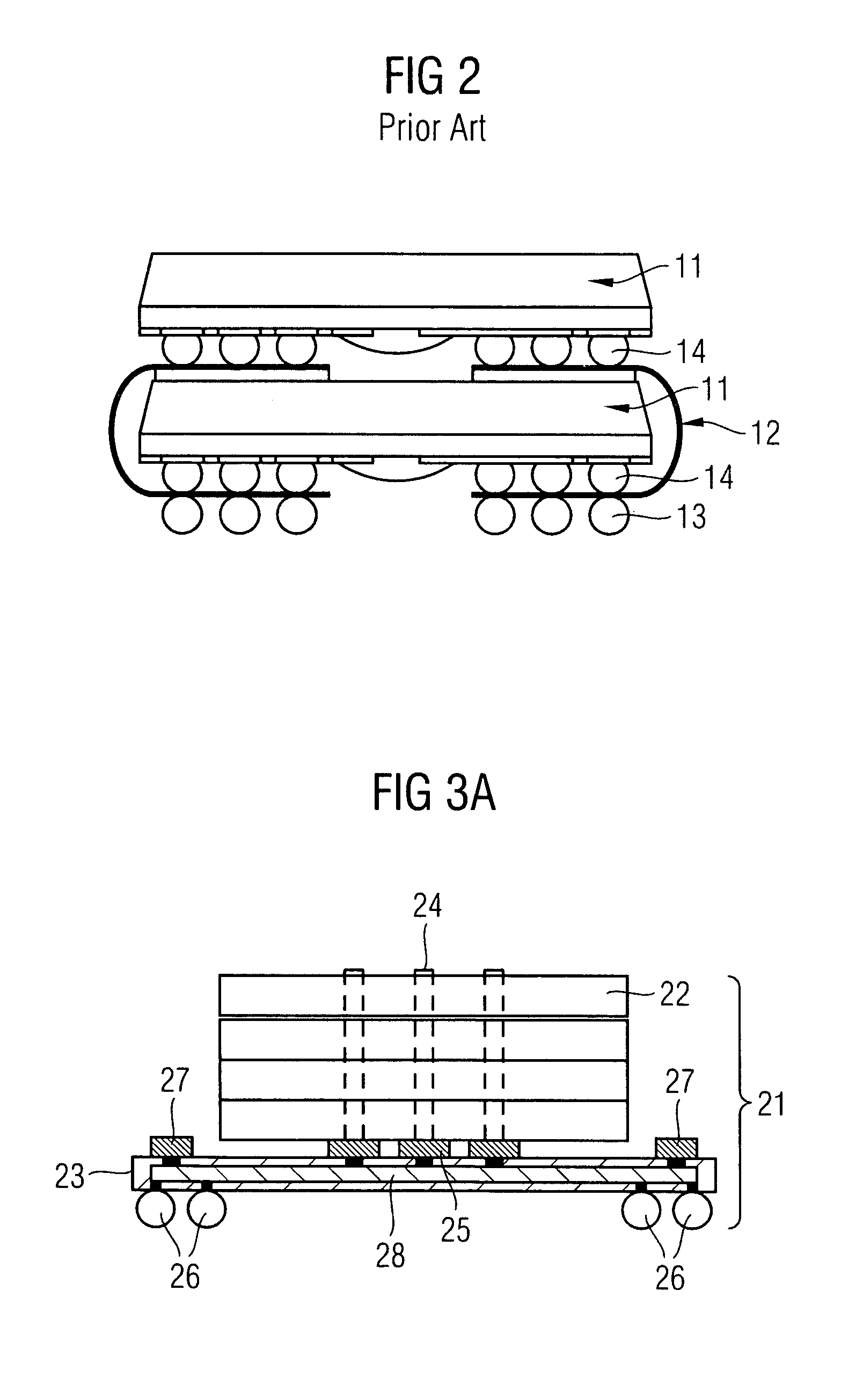

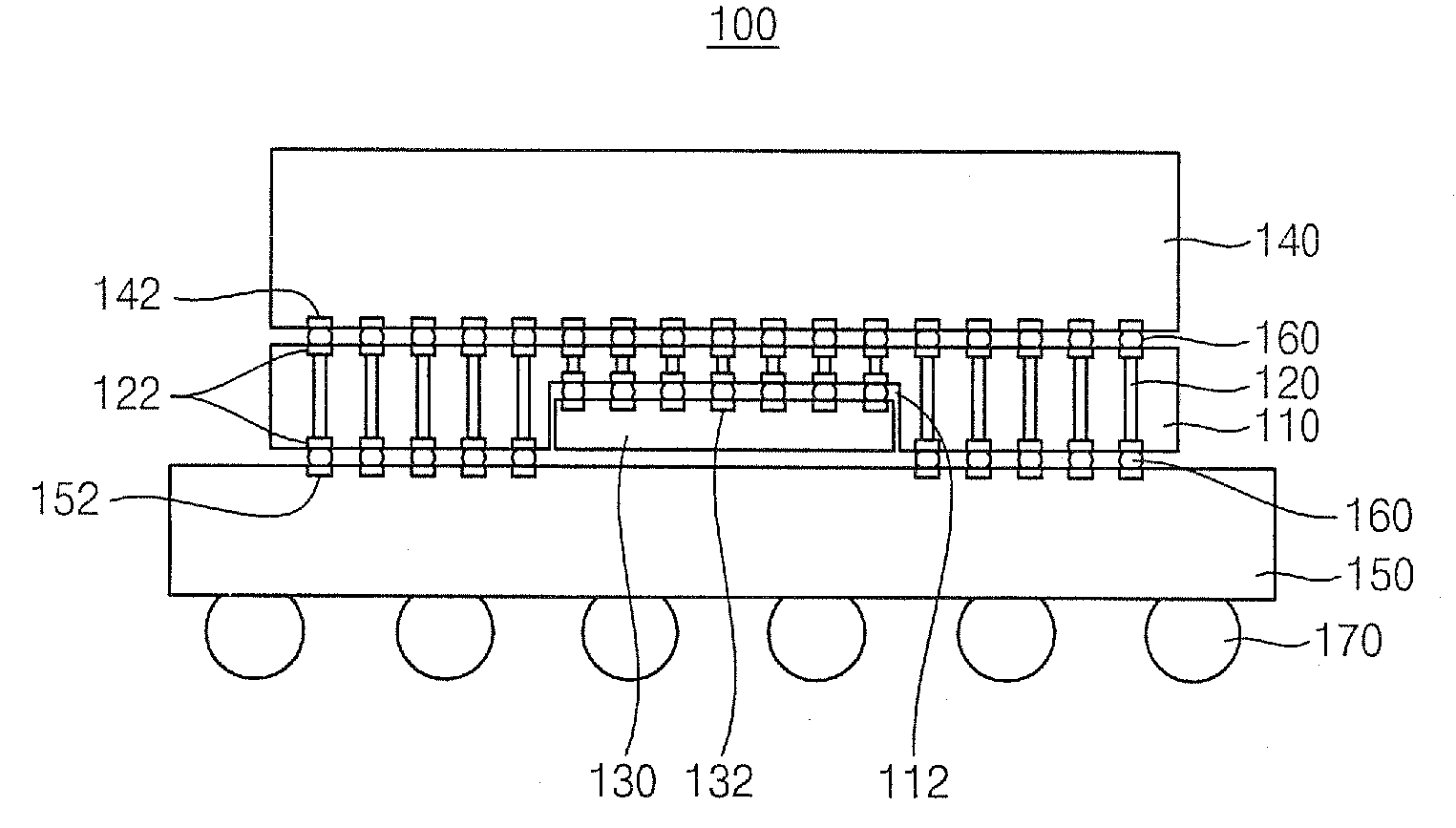

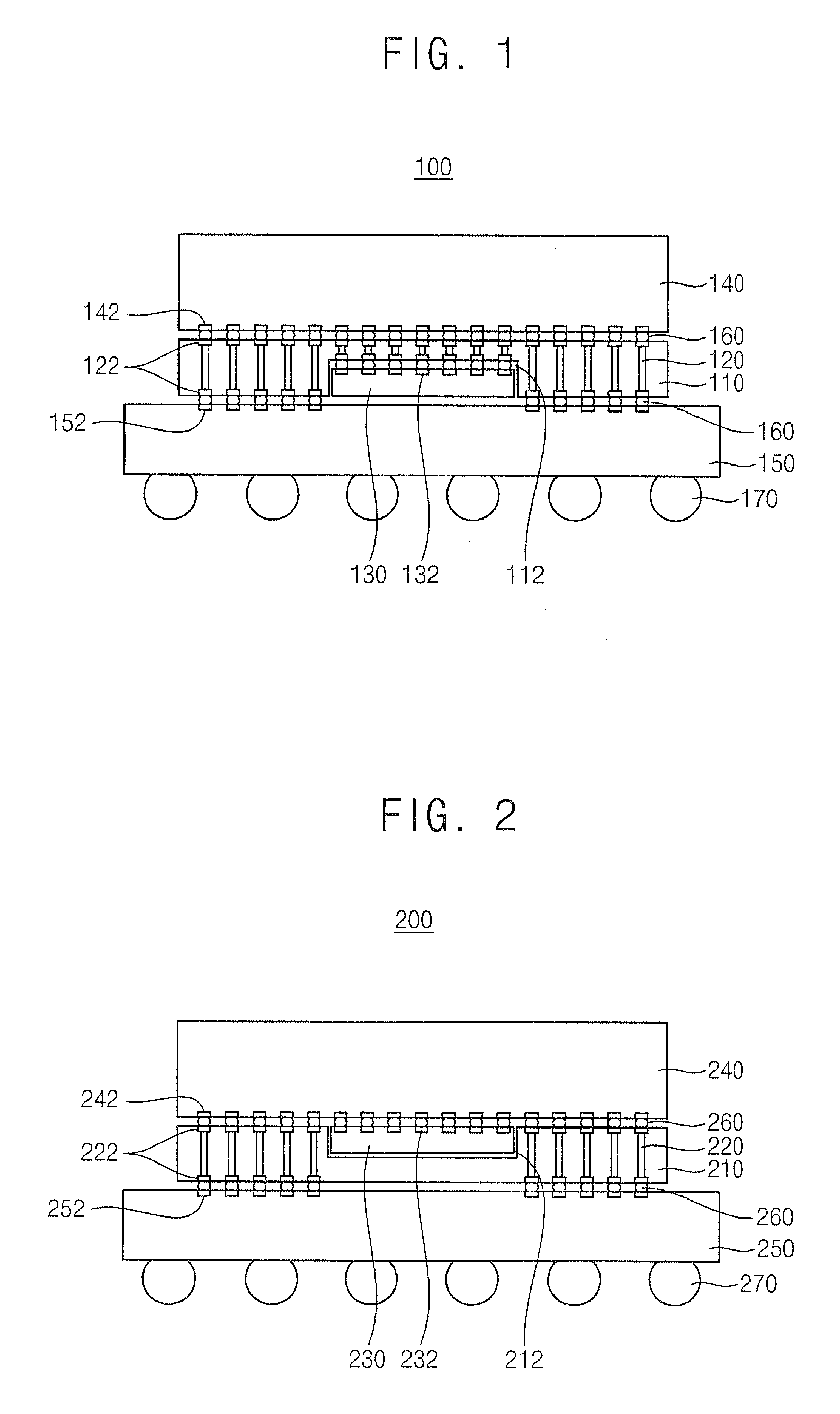

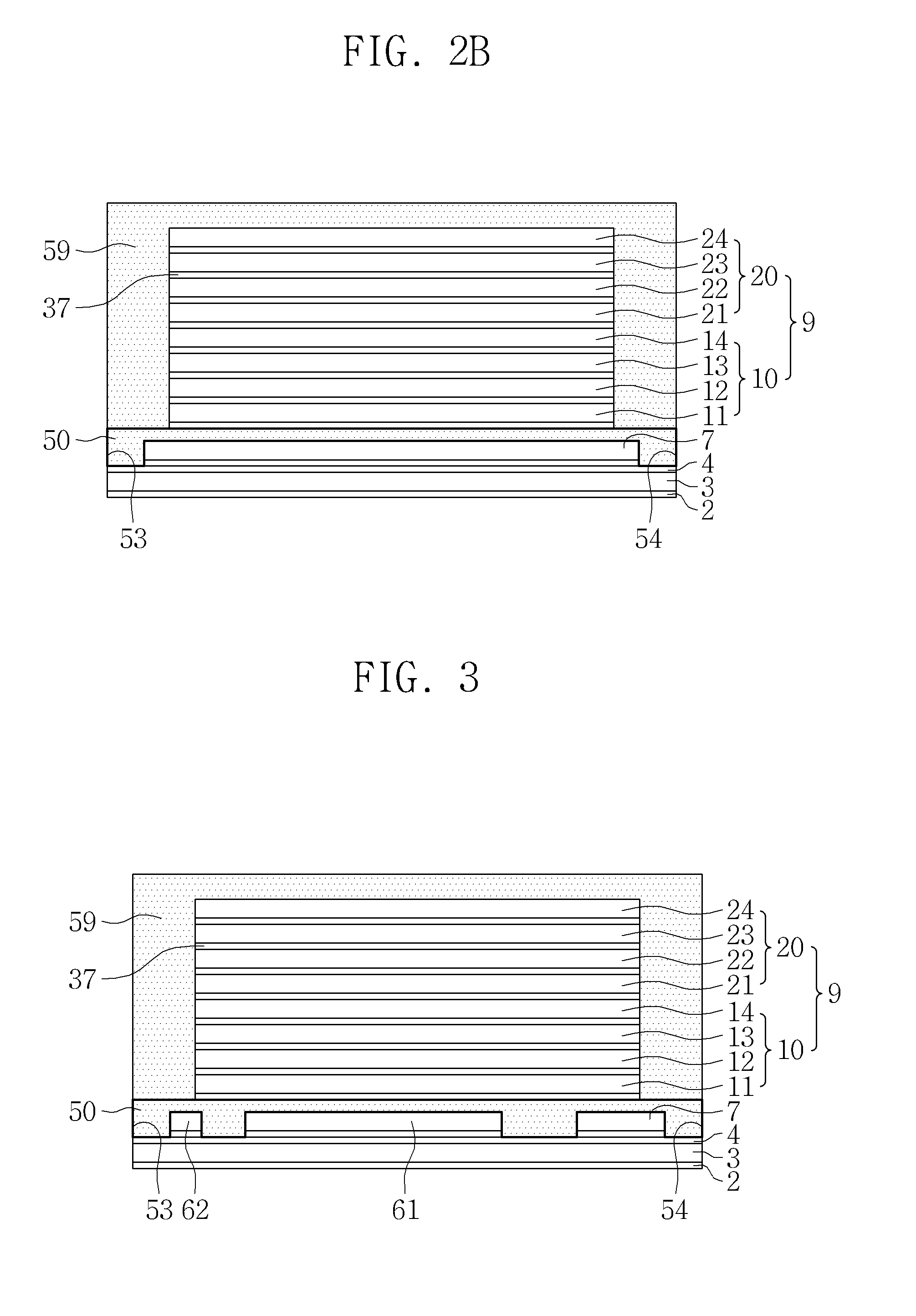

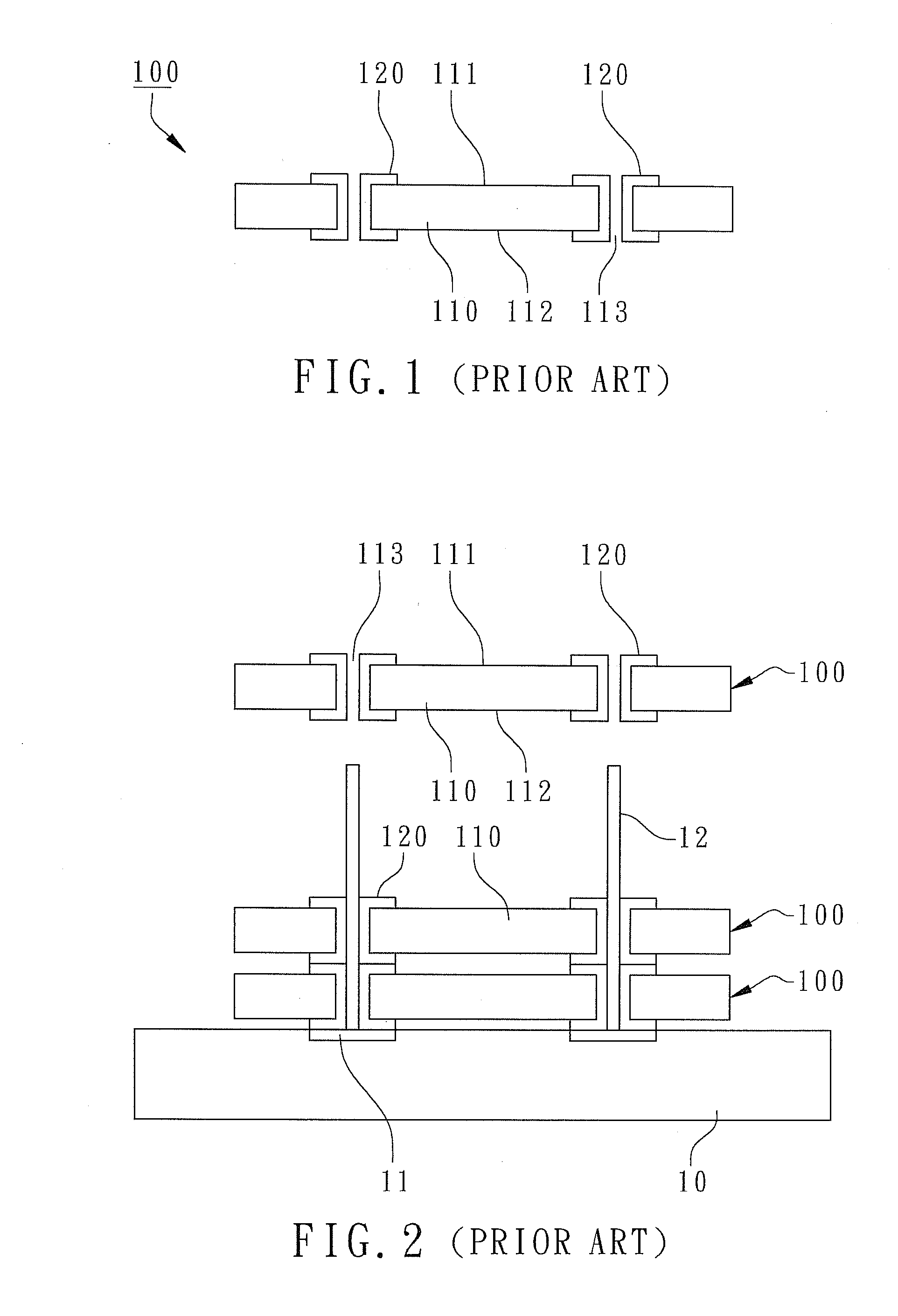

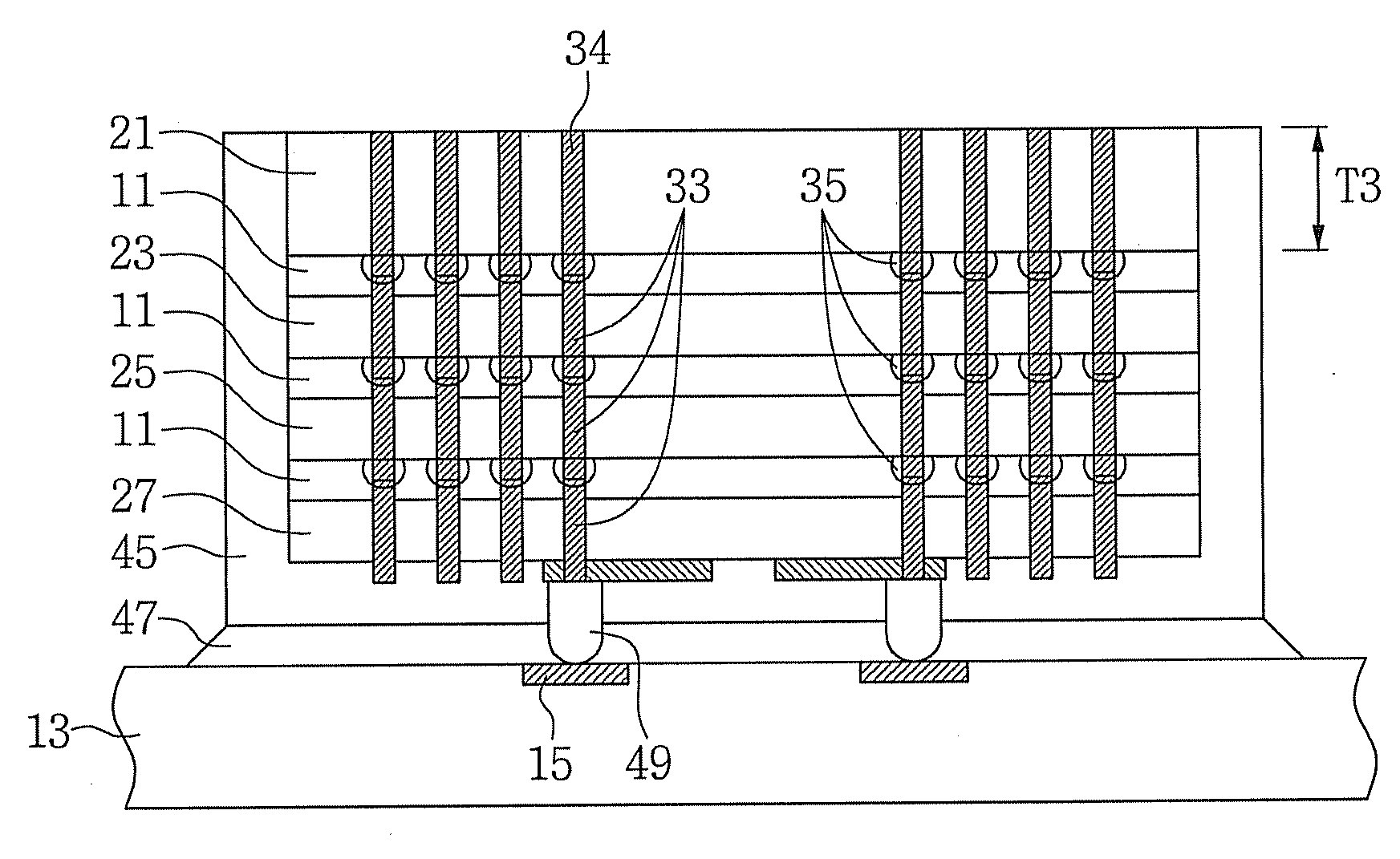

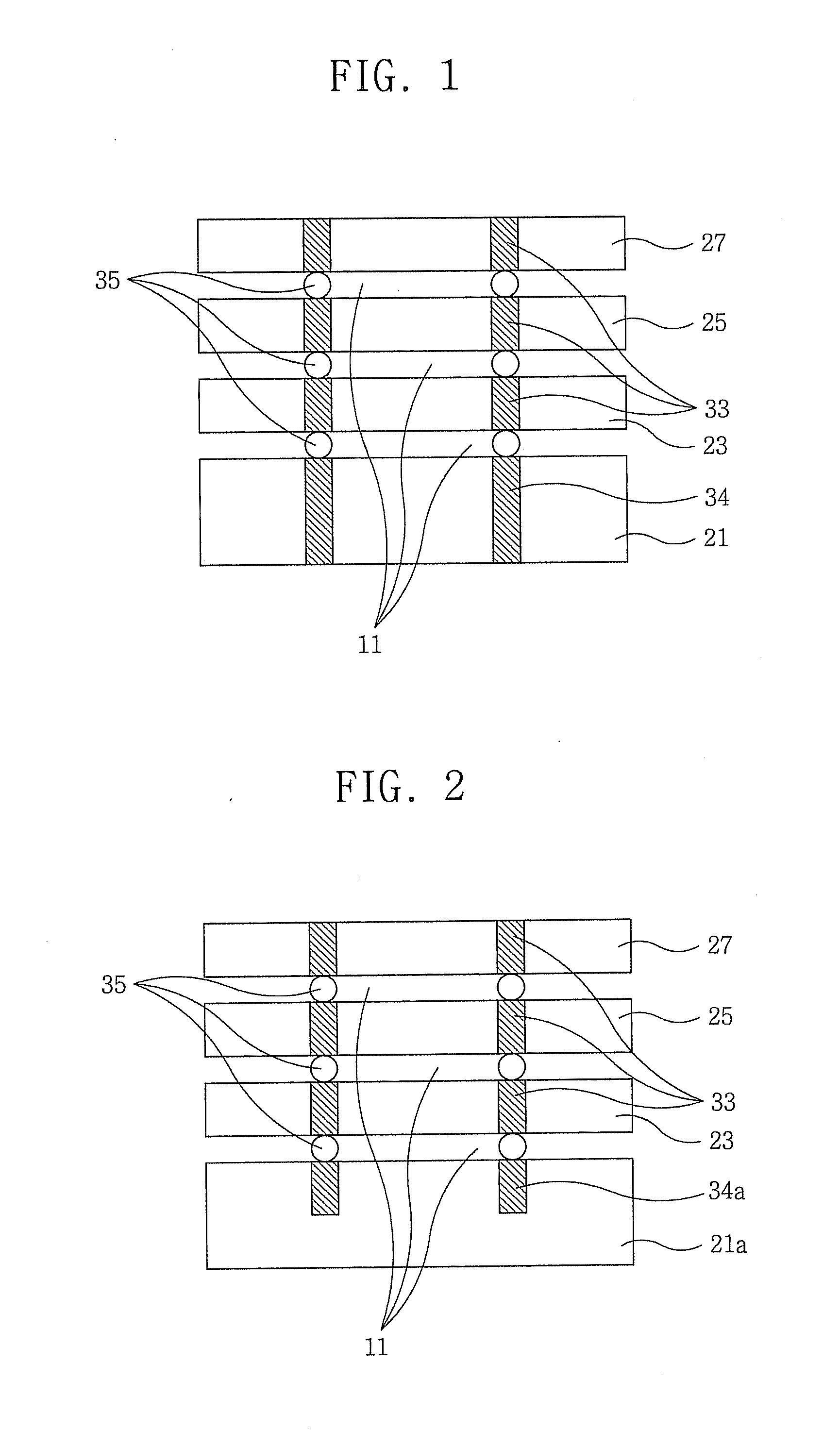

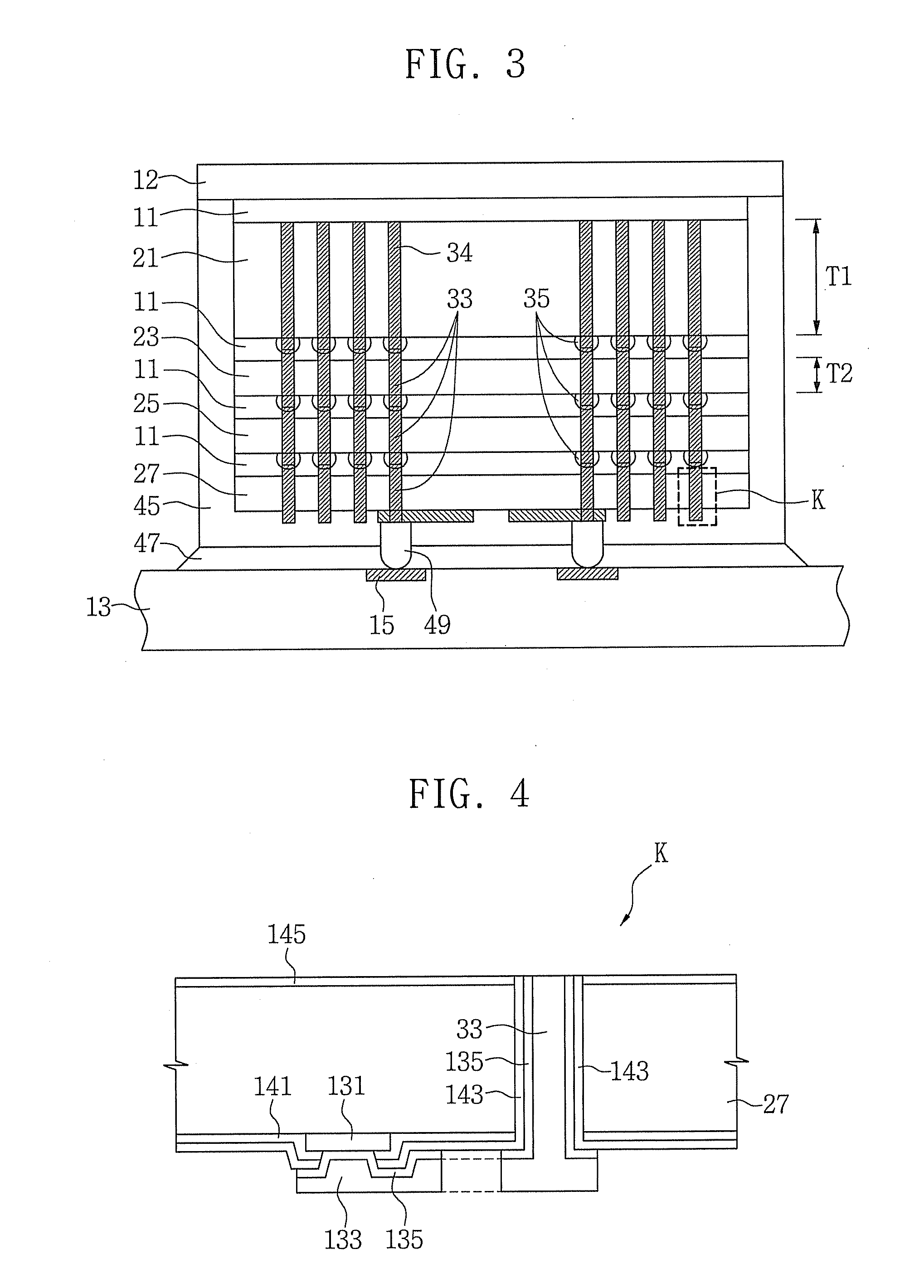

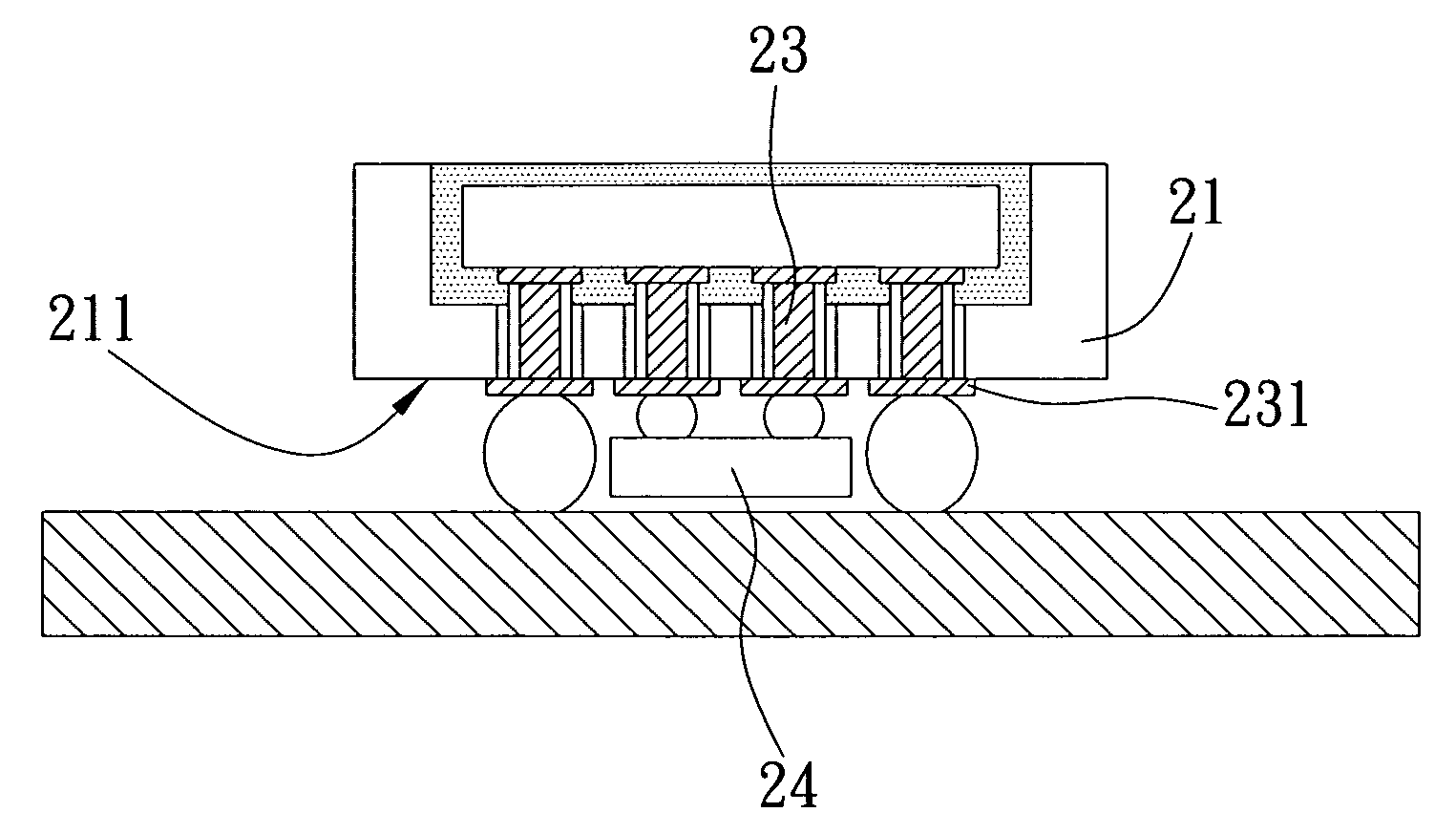

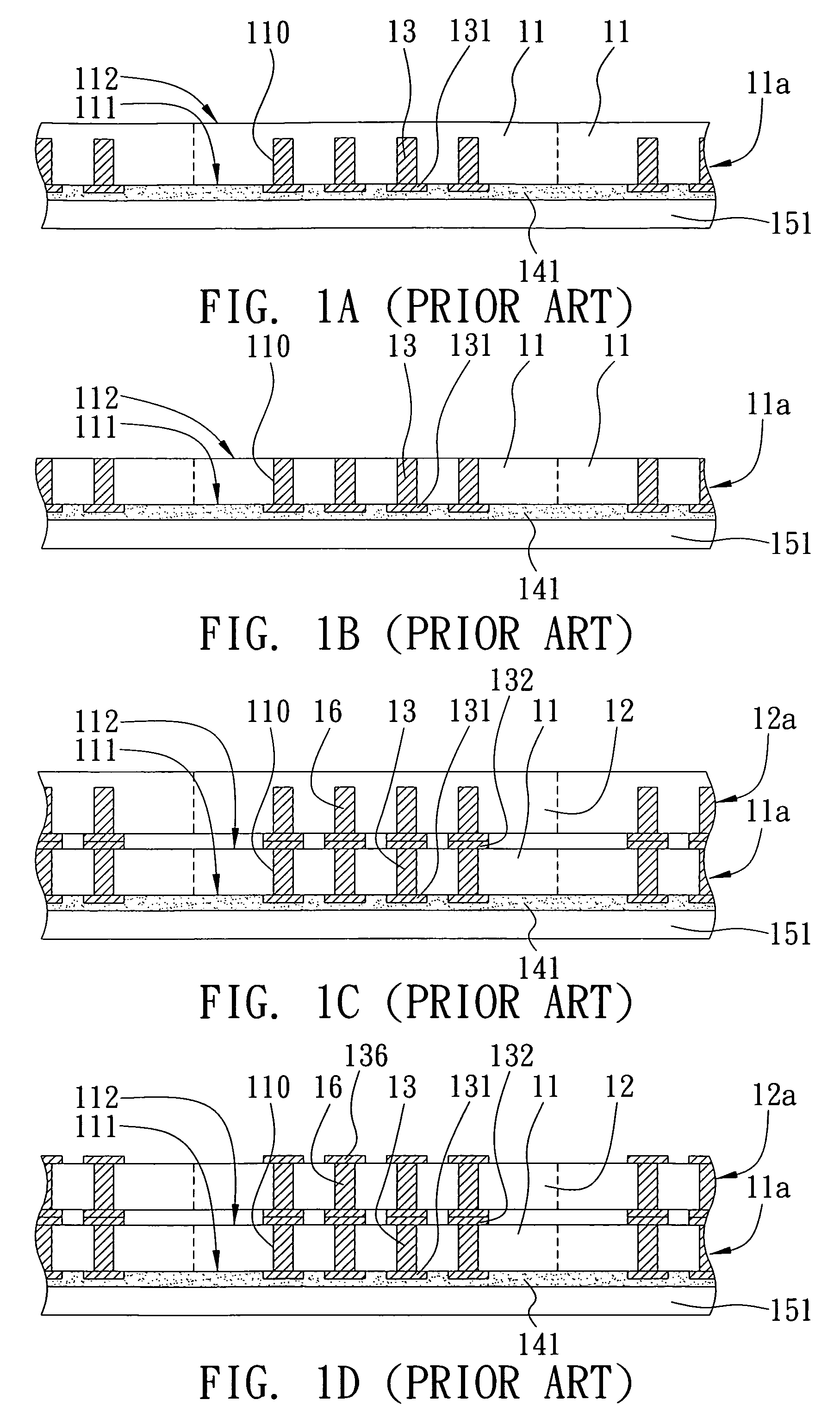

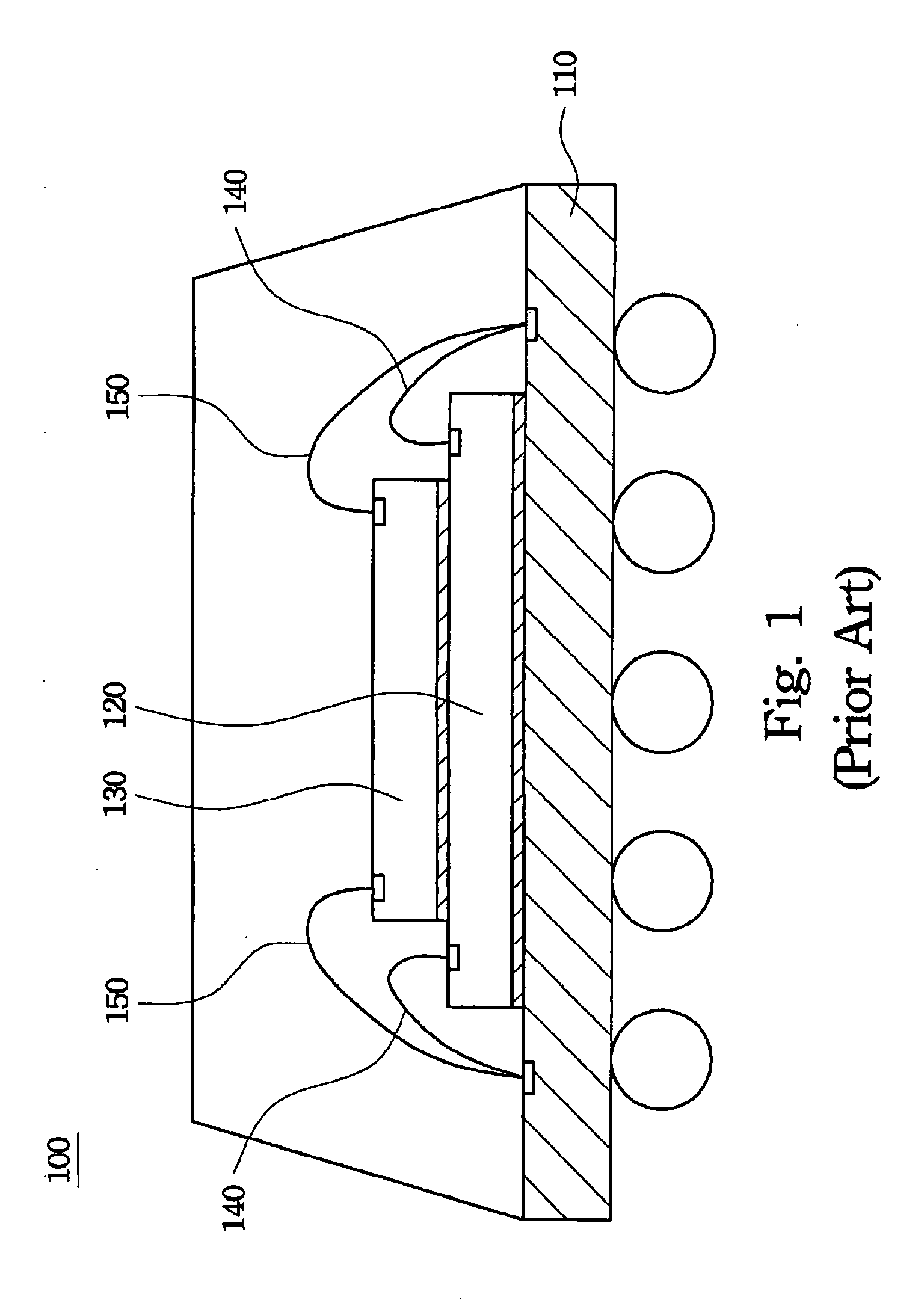

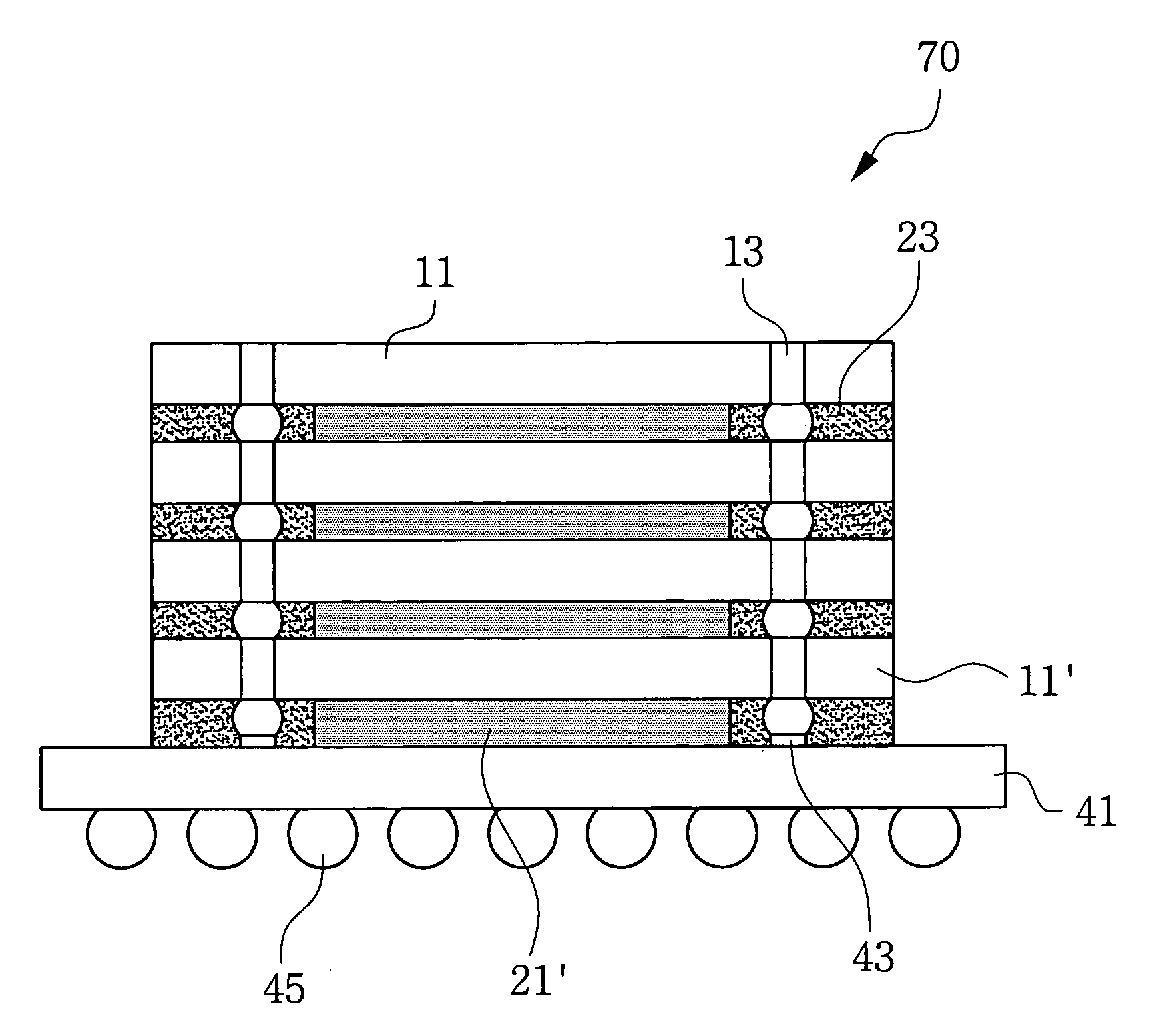

Chip stack package and manufacturing method thereof

ActiveUS20050046002A1Reduce manufacturing costReduce time costSemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical connection

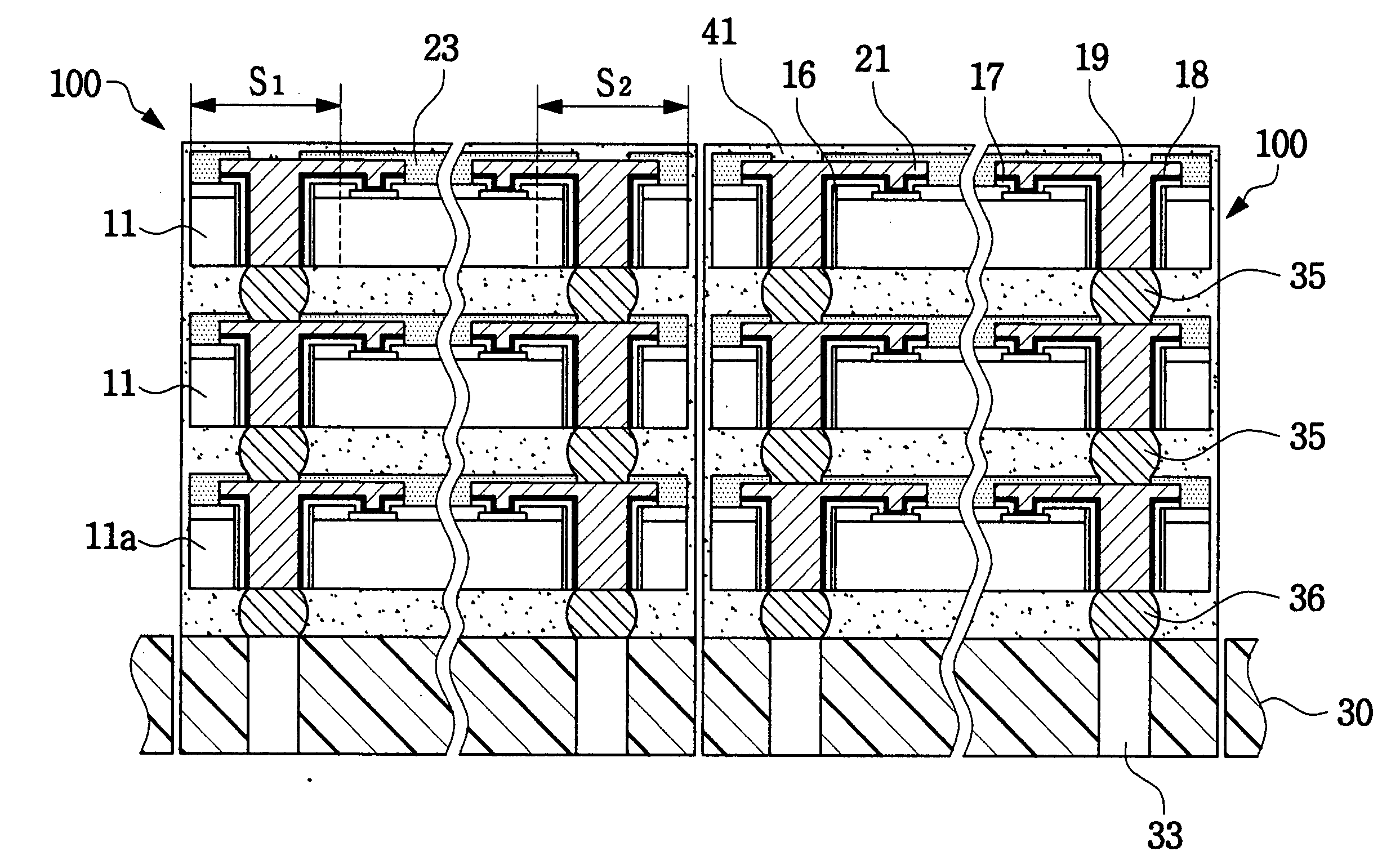

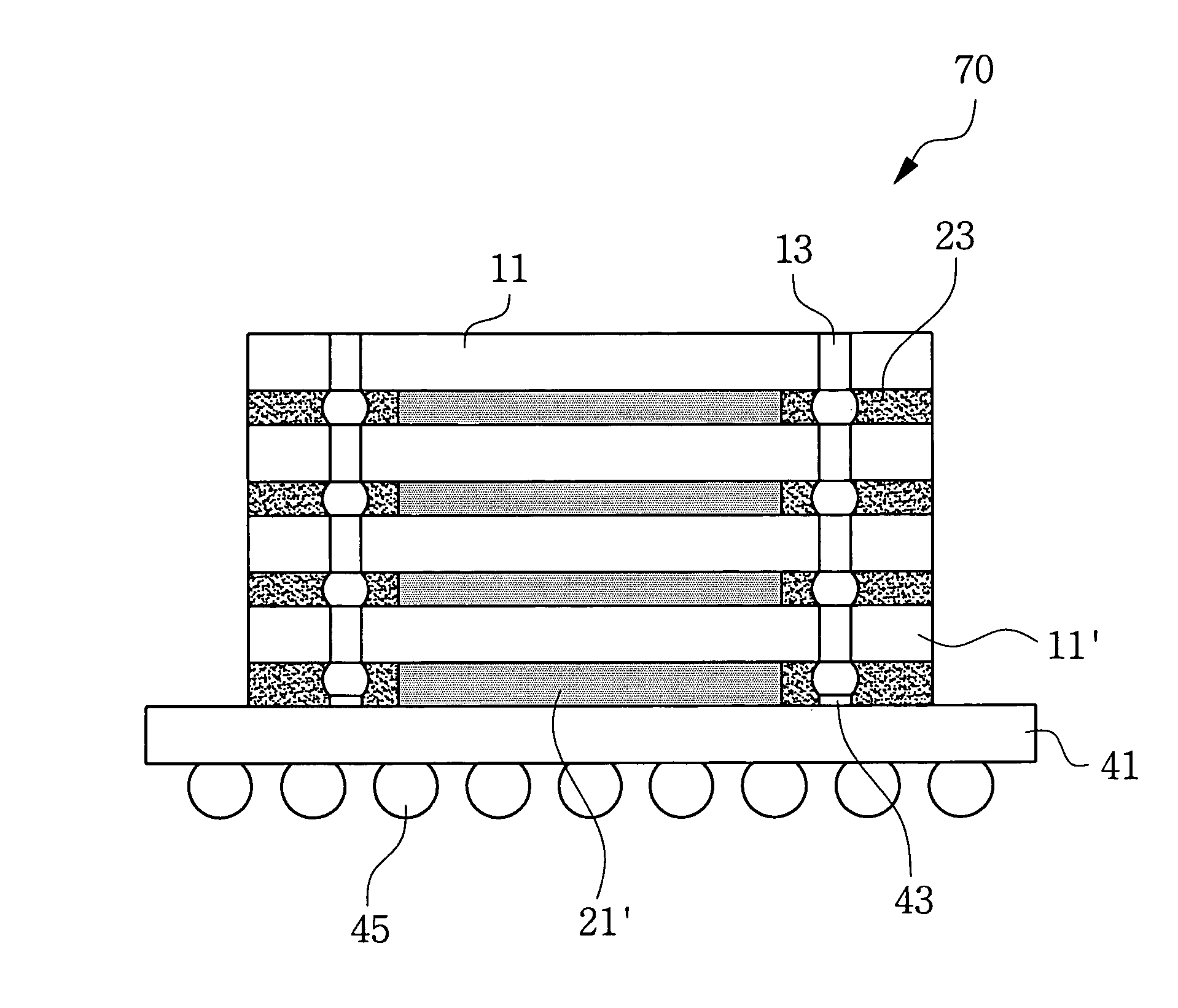

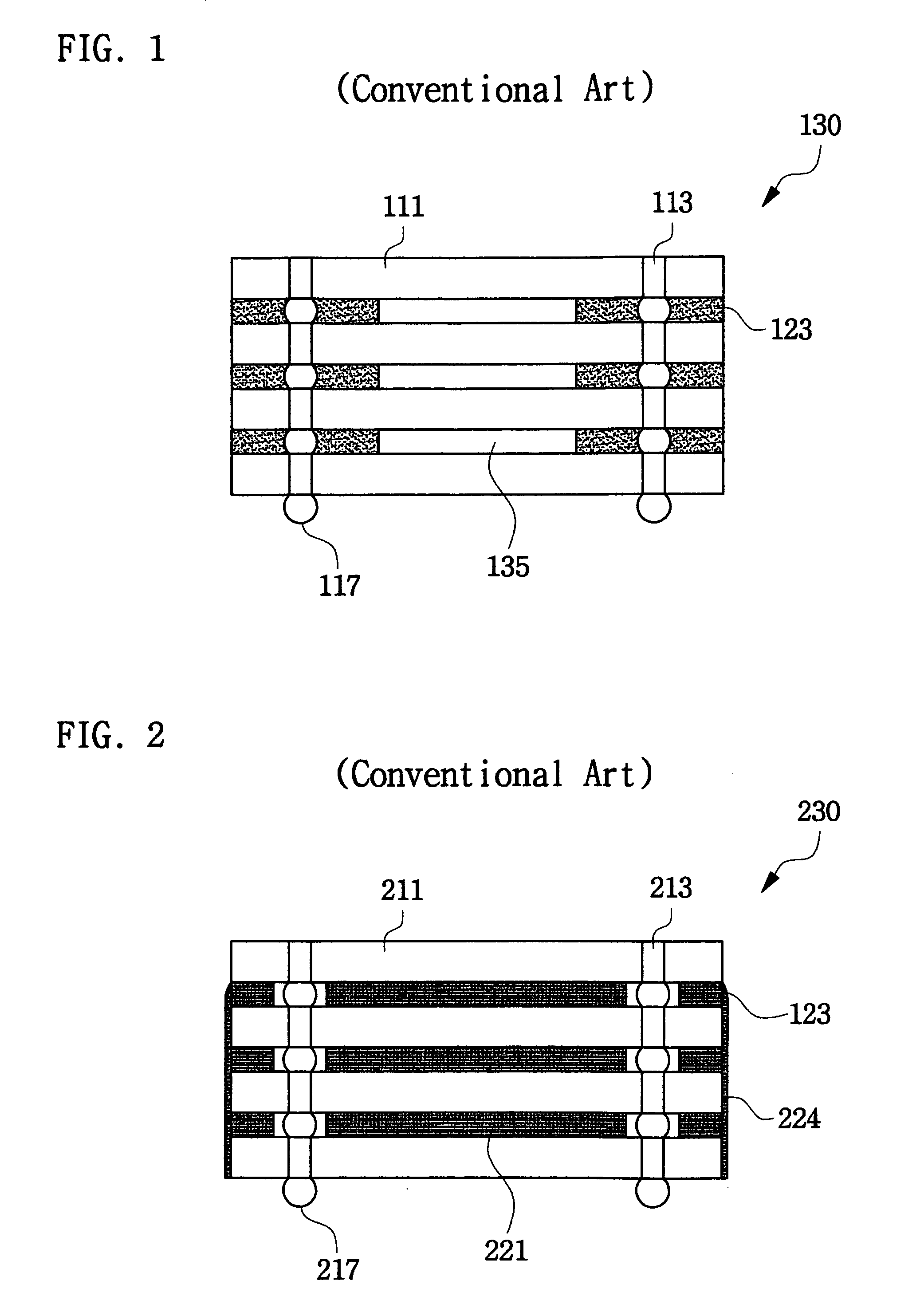

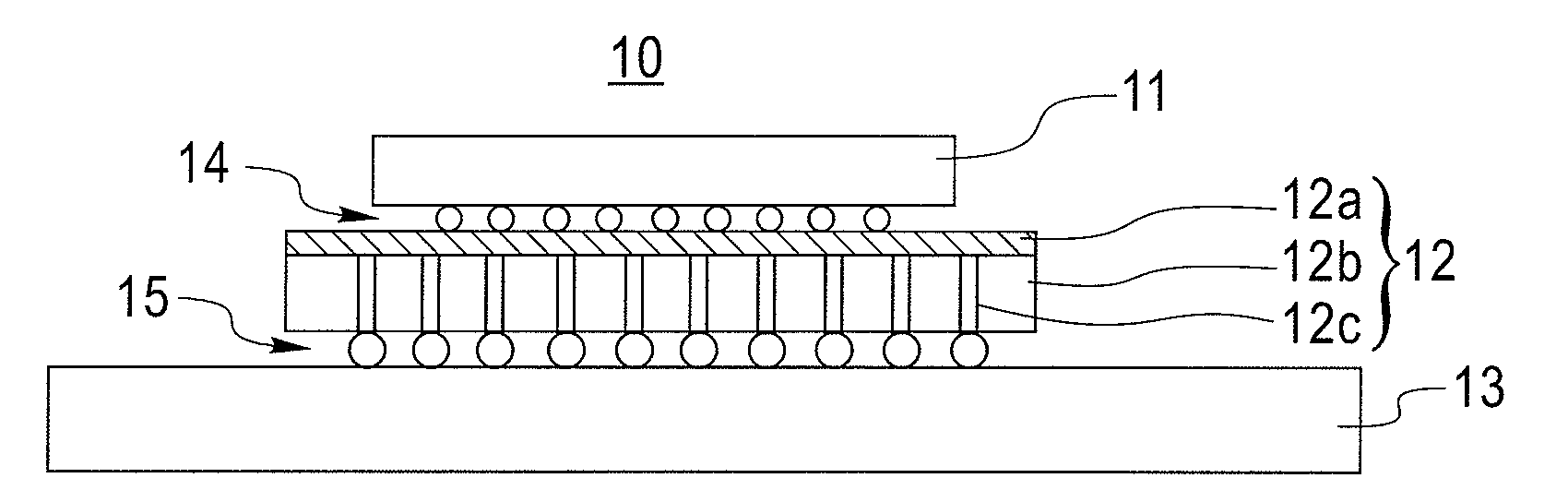

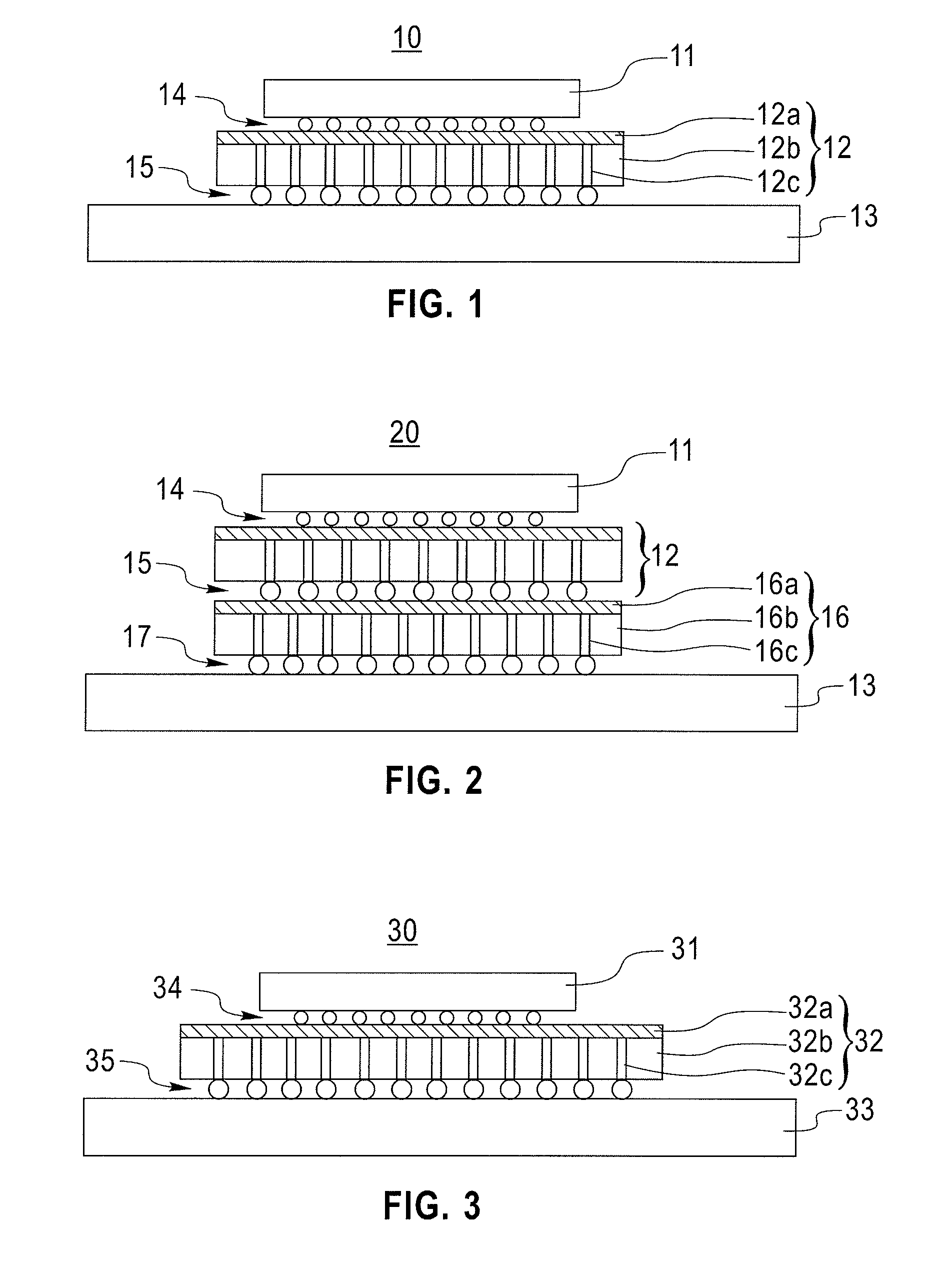

A chip stack package is manufactured at a wafer level by forming connection vias in the scribe lanes adjacent the chips and connecting the device chip pads to the connection vias using rerouting lines. A lower chip is then attached and connected to a substrate, which may be a test wafer, and an upper chip is attached and connected to the lower chip, the electrical connections being achieved through their respective connection vias. In addition to the connection vias, the chip stack package may include connection bumps formed between vertically adjacent chips and / or the lower chip and the substrate. The preferred substrate is a test wafer that allows the attached chips to be tested, and replaced if faulty, thereby ensuring that each layer of stacked chips includes only “known-good die” before the next layer of chips is attached thereby increasing the production rate and improving the yield.

Owner:SAMSUNG ELECTRONICS CO LTD

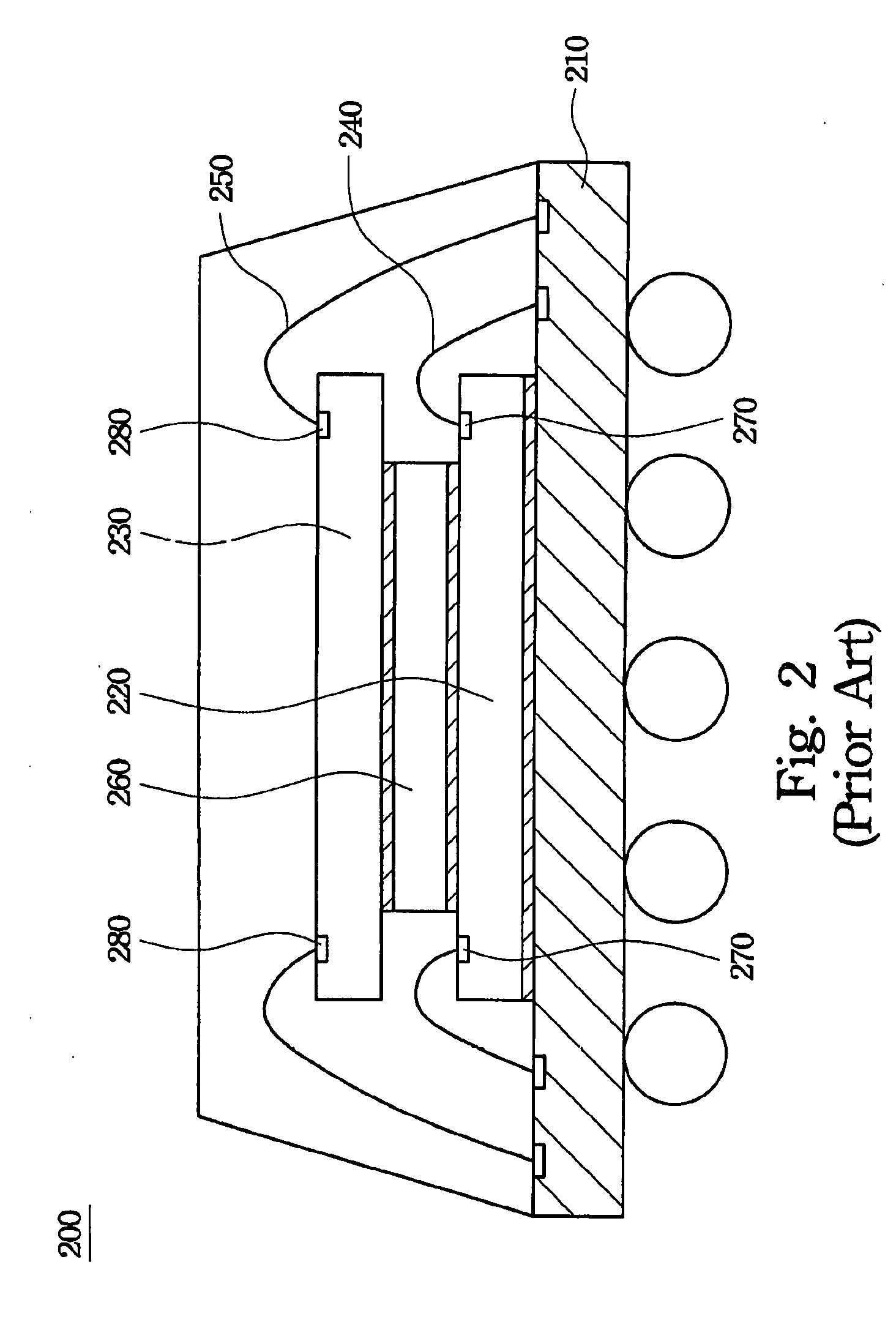

Chip stack package and manufacturing method thereof

ActiveUS7276799B2Low costShorten the timeSemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical connection

A chip stack package is manufactured at a wafer level by forming connection vias in the scribe lanes adjacent the chips and connecting the device chip pads to the connection vias using rerouting lines. A lower chip is then attached and connected to a substrate, which may be a test wafer, and an upper chip is attached and connected to the lower chip, the electrical connections being achieved through their respective connection vias. In addition to the connection vias, the chip stack package may include connection bumps formed between vertically adjacent chips and / or the lower chip and the substrate. The preferred substrate is a test wafer that allows the attached chips to be tested, and replaced if faulty, thereby ensuring that each layer of stacked chips includes only “known-good die” before the next layer of chips is attached thereby increasing the production rate and improving the yield.

Owner:SAMSUNG ELECTRONICS CO LTD

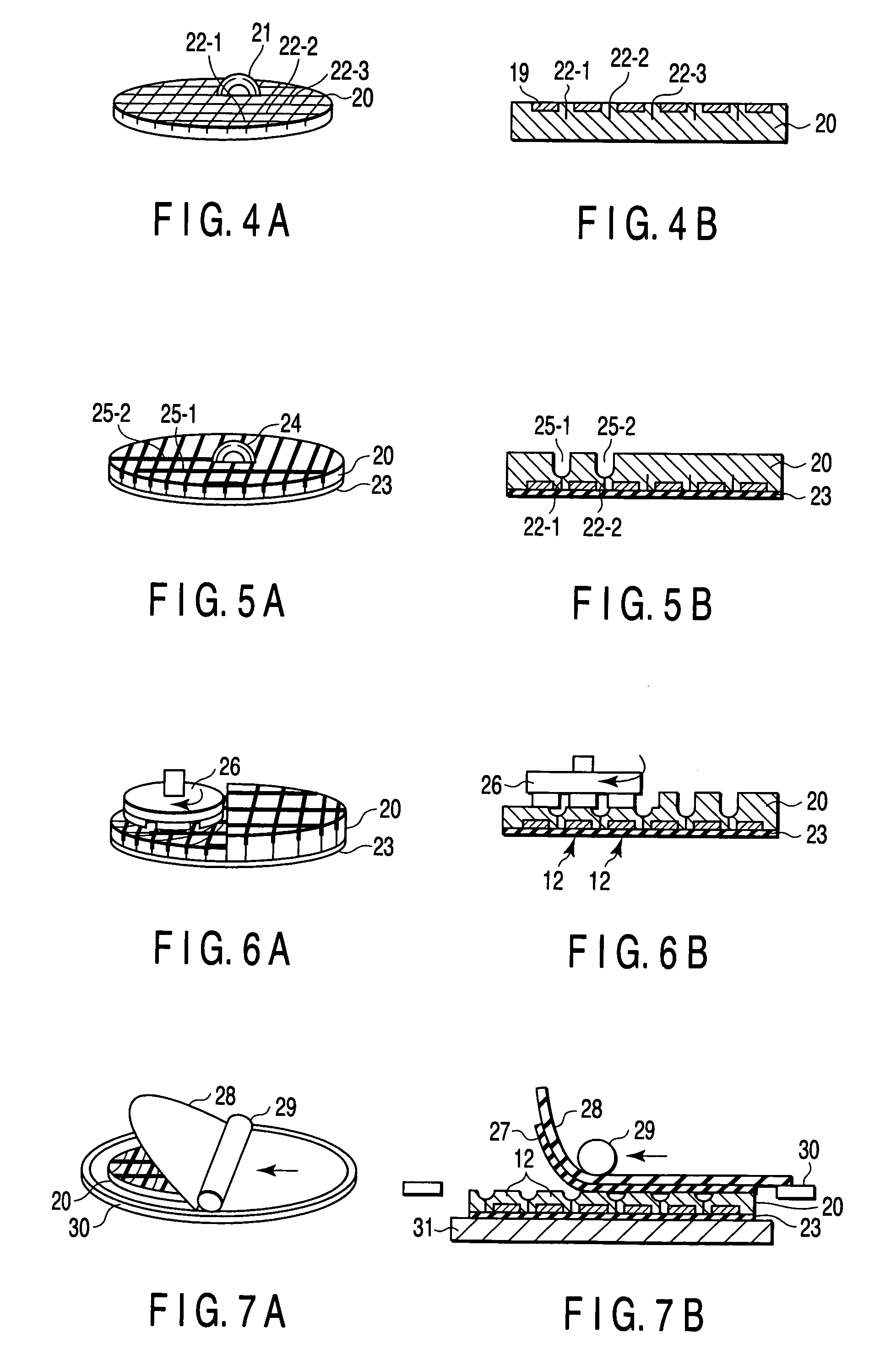

Method for manufacturing wafer level chip stack package

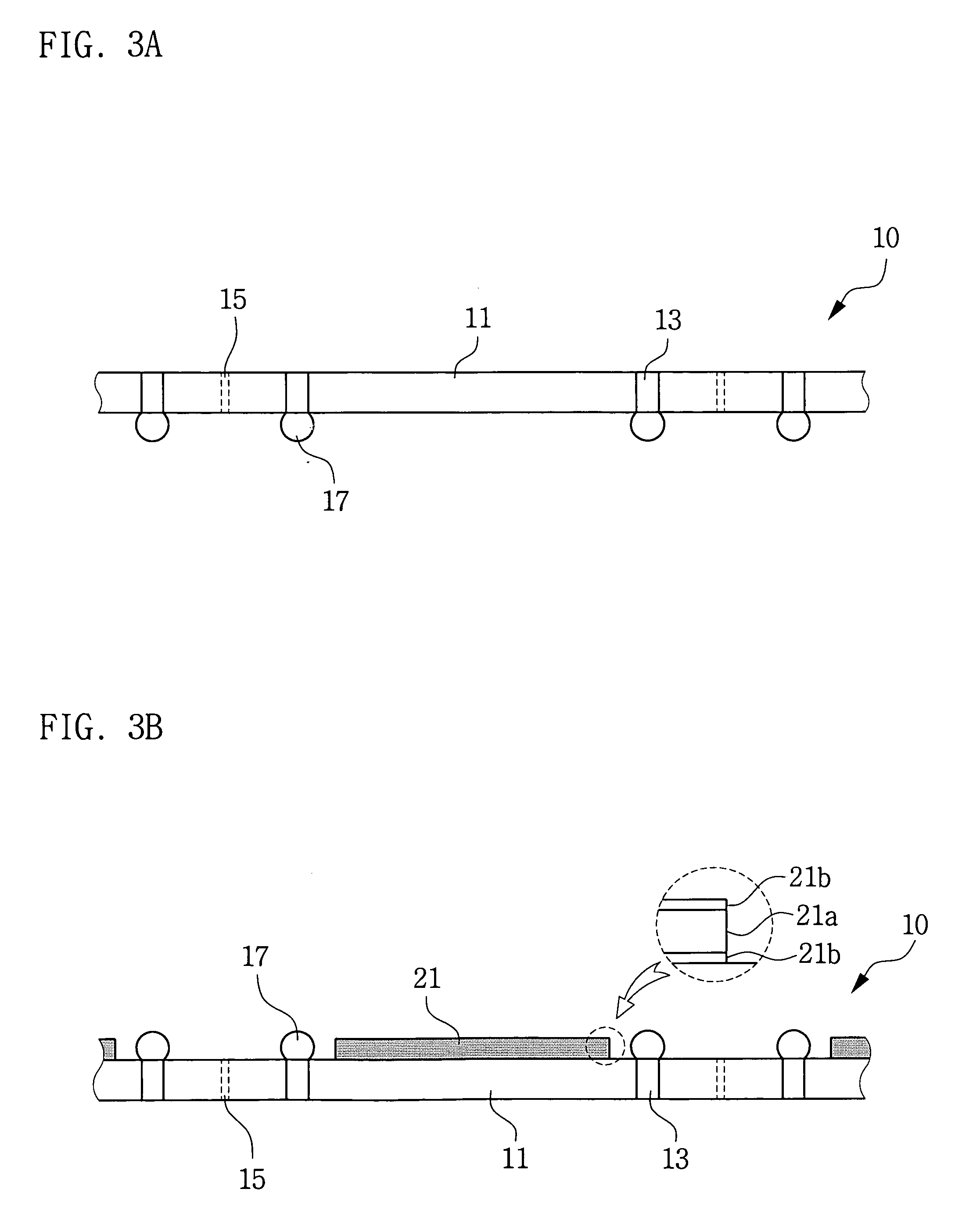

ActiveUS7151009B2Improve reliabilityHigh strengthSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

Provided is a method for manufacturing WLCSP devices that includes preparing at least two wafers, each wafer having a plurality of corresponding semiconductor chips, each semiconductor chip having through electrodes formed in the peripheral surface region, forming or applying a solid adhesive region to a central surface region, stacking a plurality of wafers and attaching corresponding chips provided on adjacent wafers with the solid adhesive region and connecting corresponding through electrodes of adjacent semiconductor chips, dividing the stacked wafers into individual chip stack packages, and injecting a liquid adhesive into a space remaining between adjacent semiconductor chips incorporated in the resulting chip stack package. By reducing the likelihood of void regions between adjacent semiconductor chips, it is expected that a method according to the exemplary embodiments of the present invention exhibit improved mechanical stability and reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

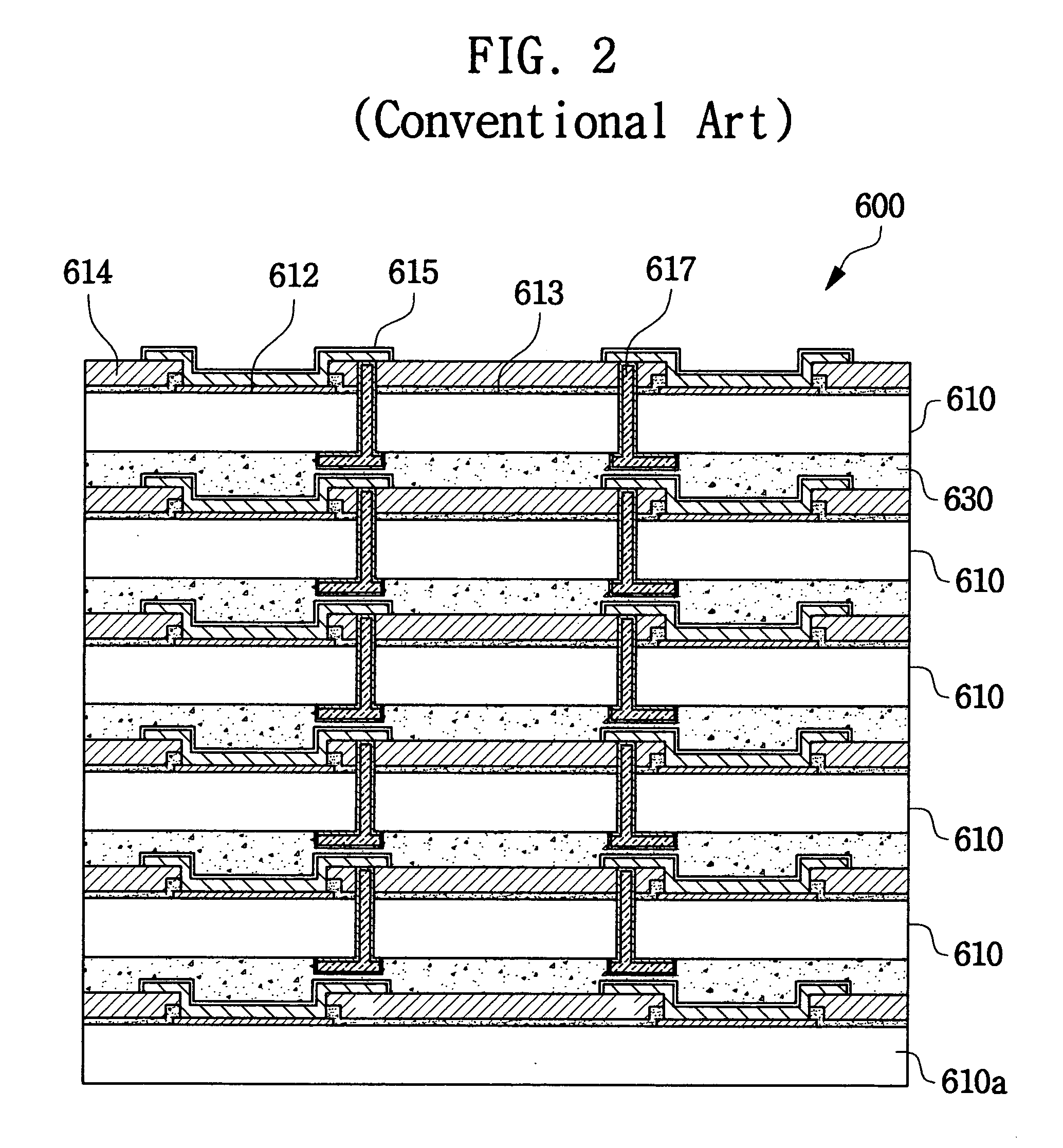

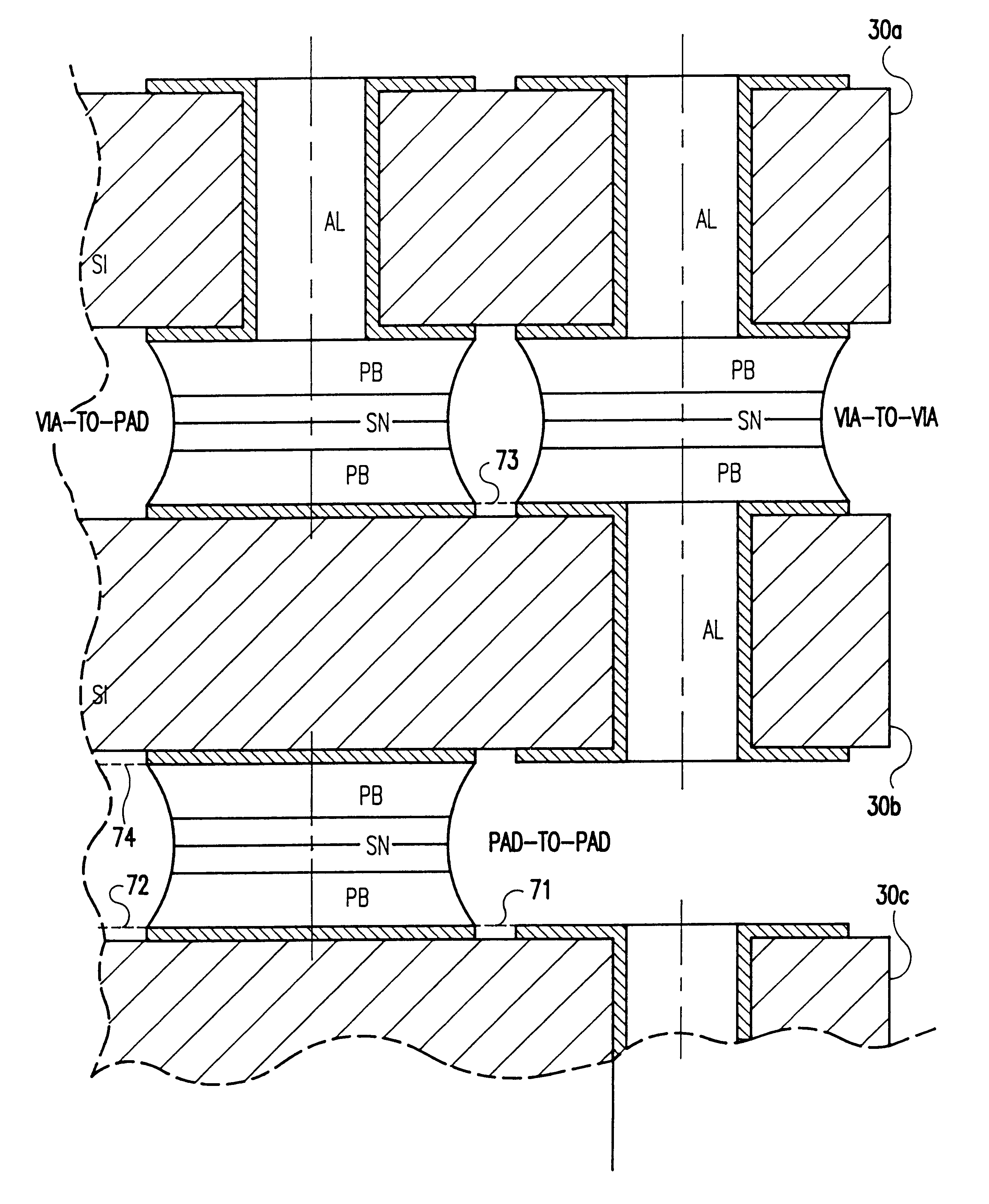

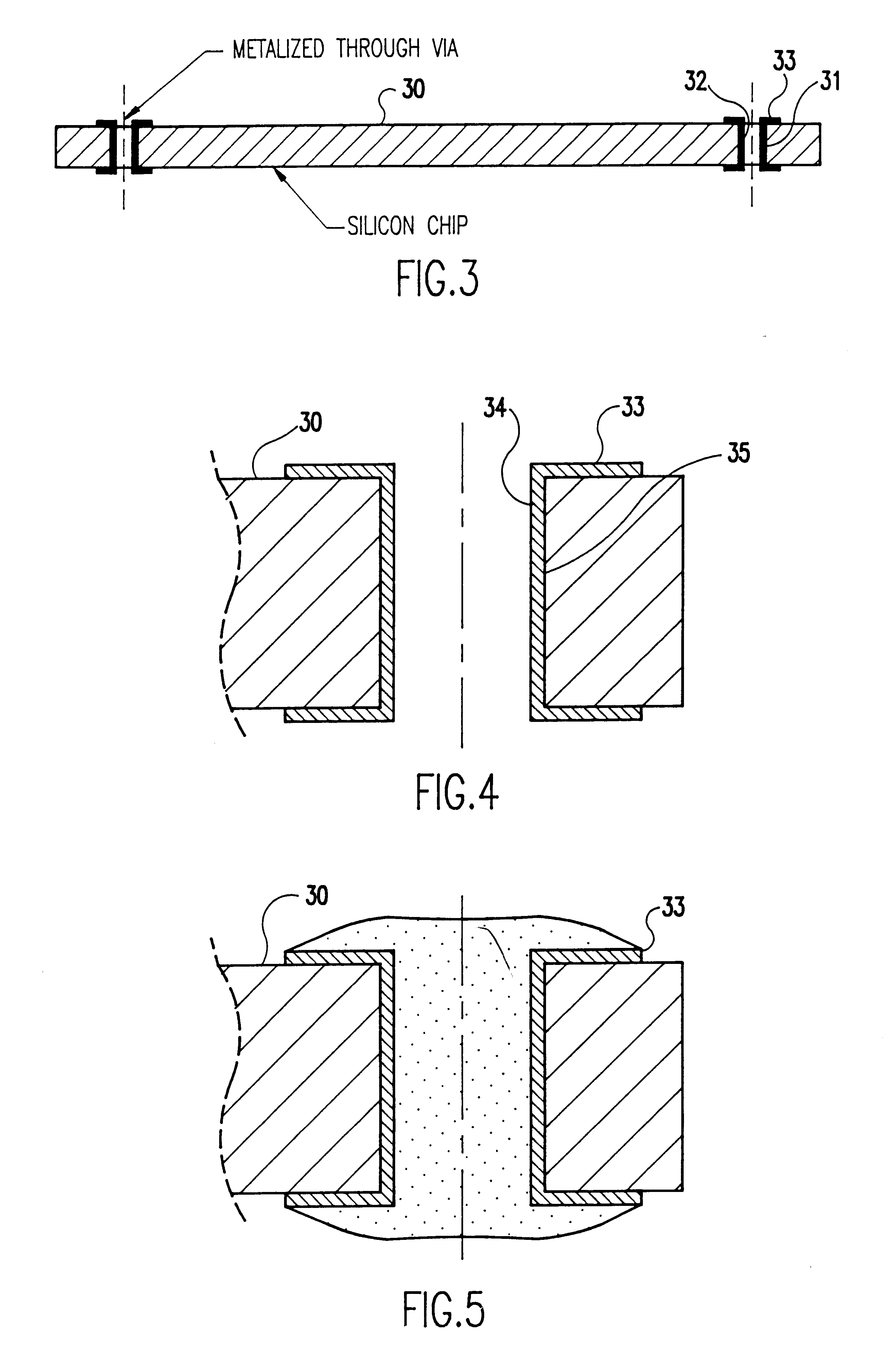

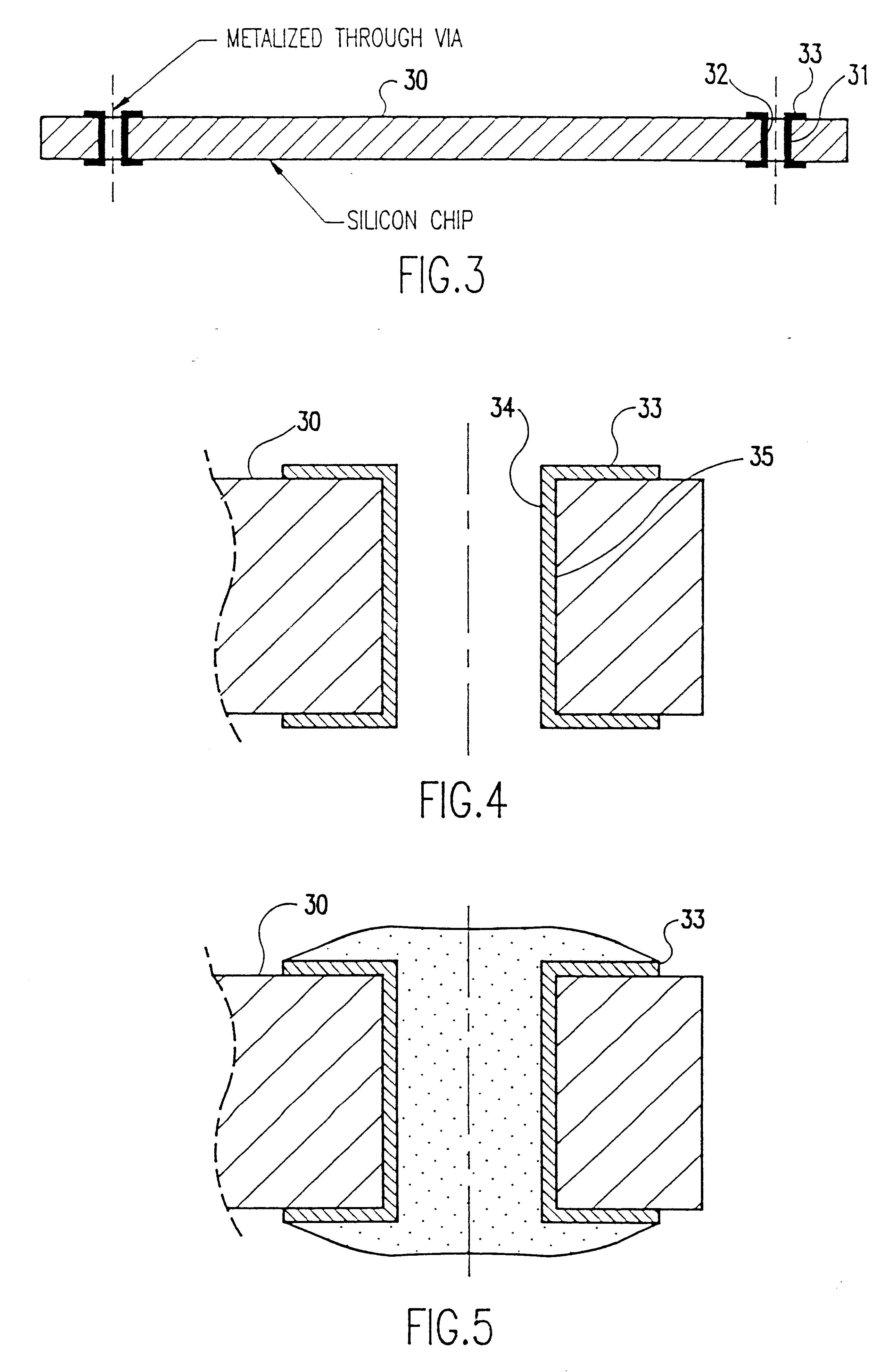

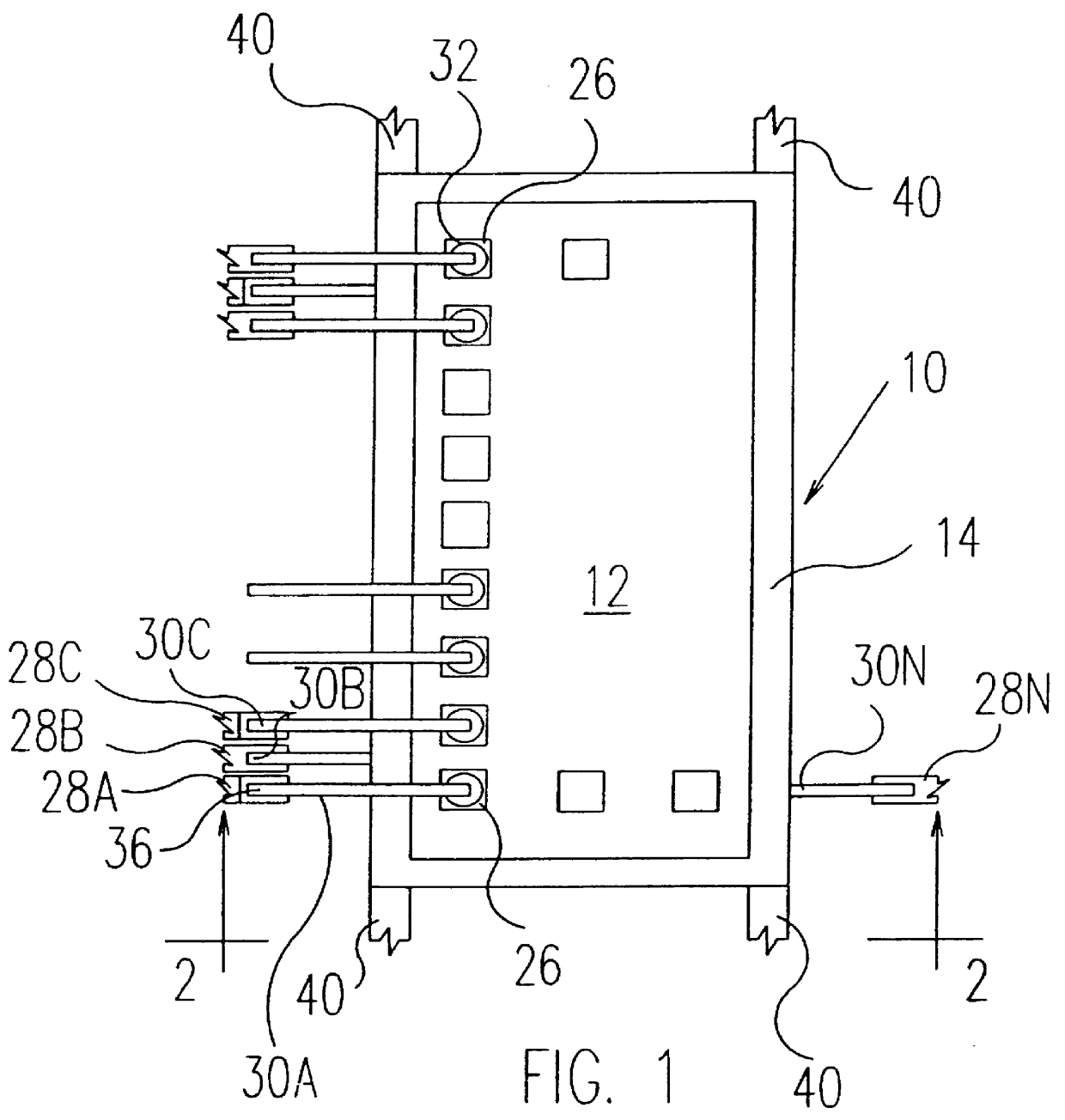

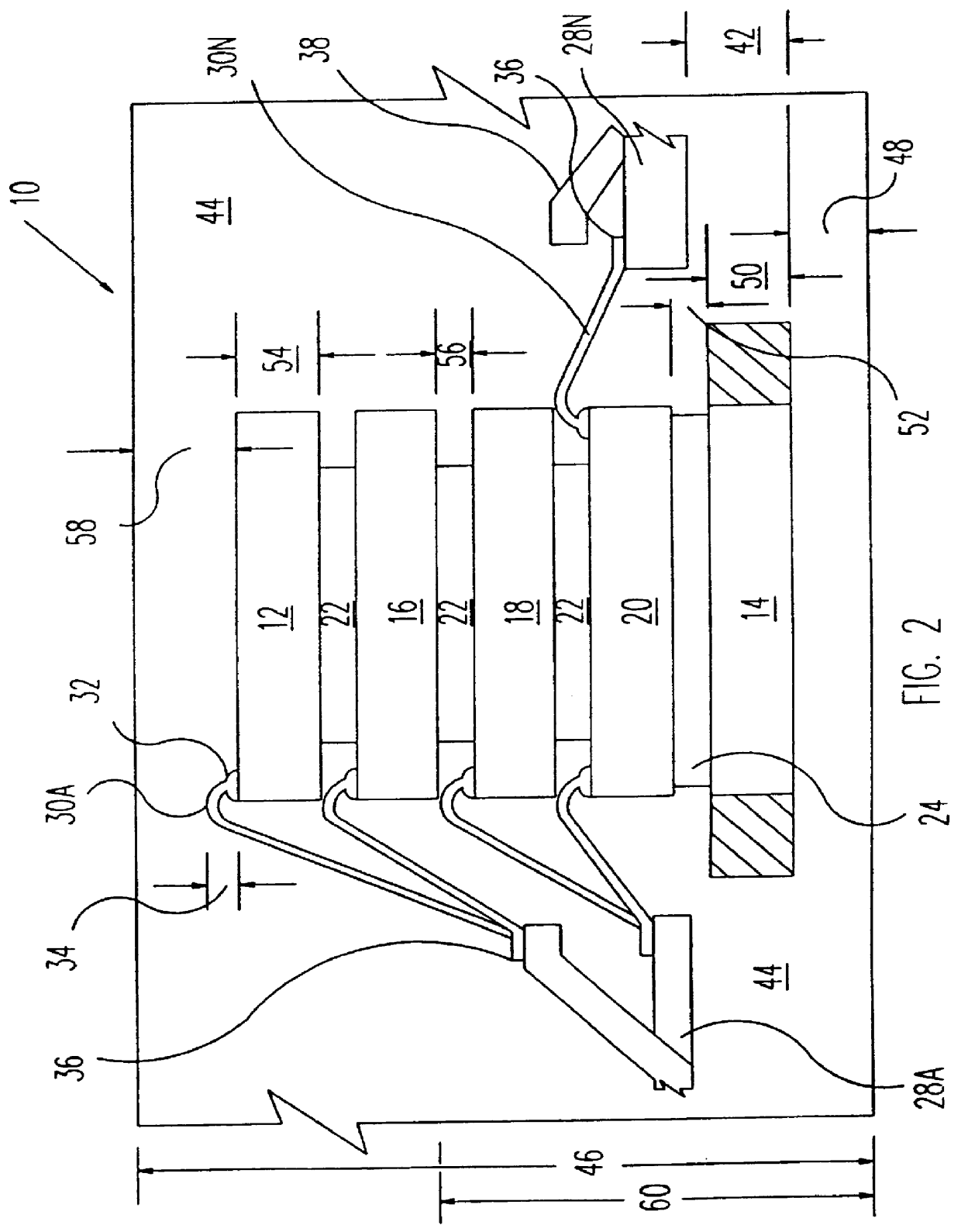

High density integrated circuit packaging with chip stacking and via interconnections

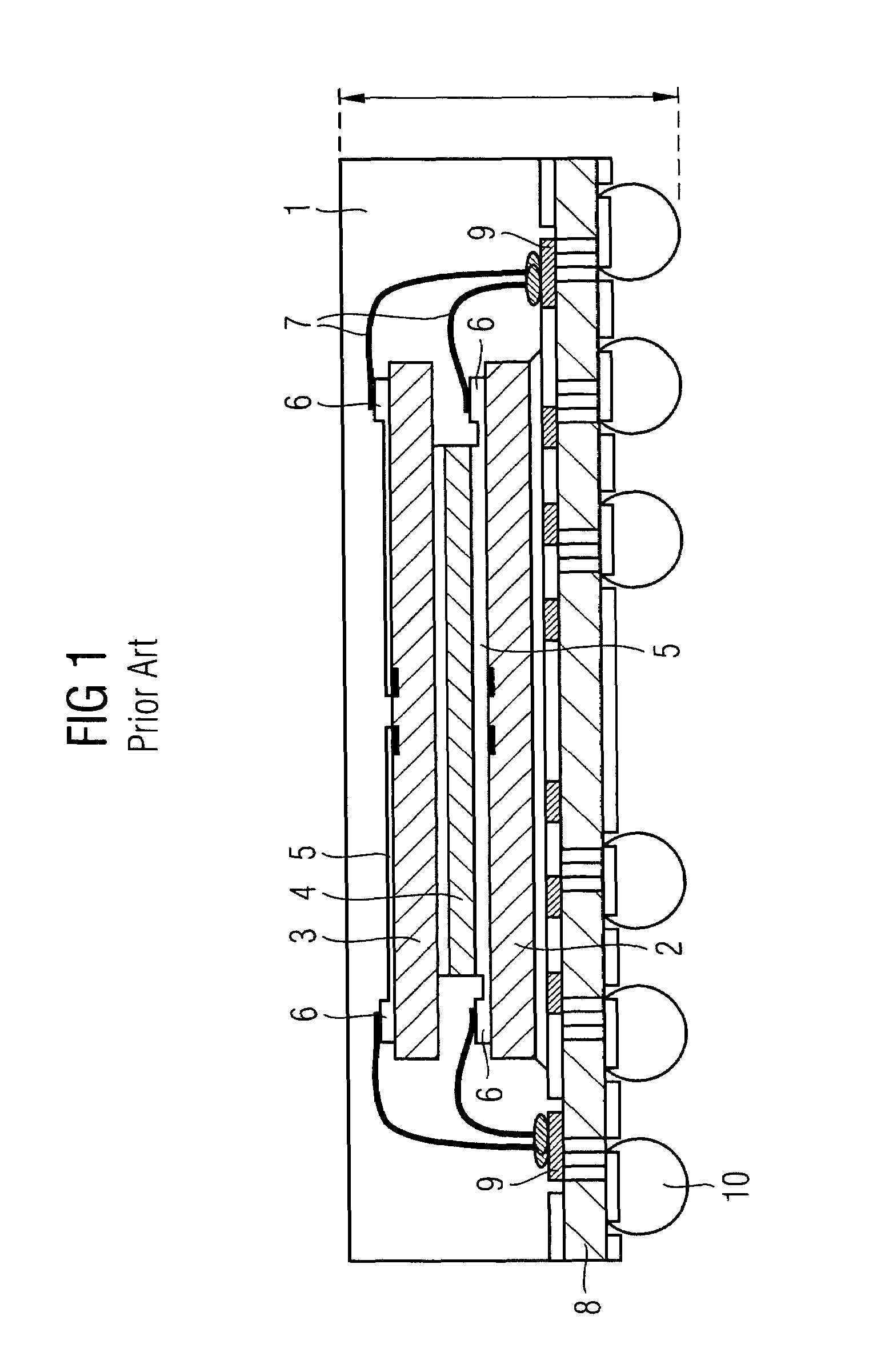

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

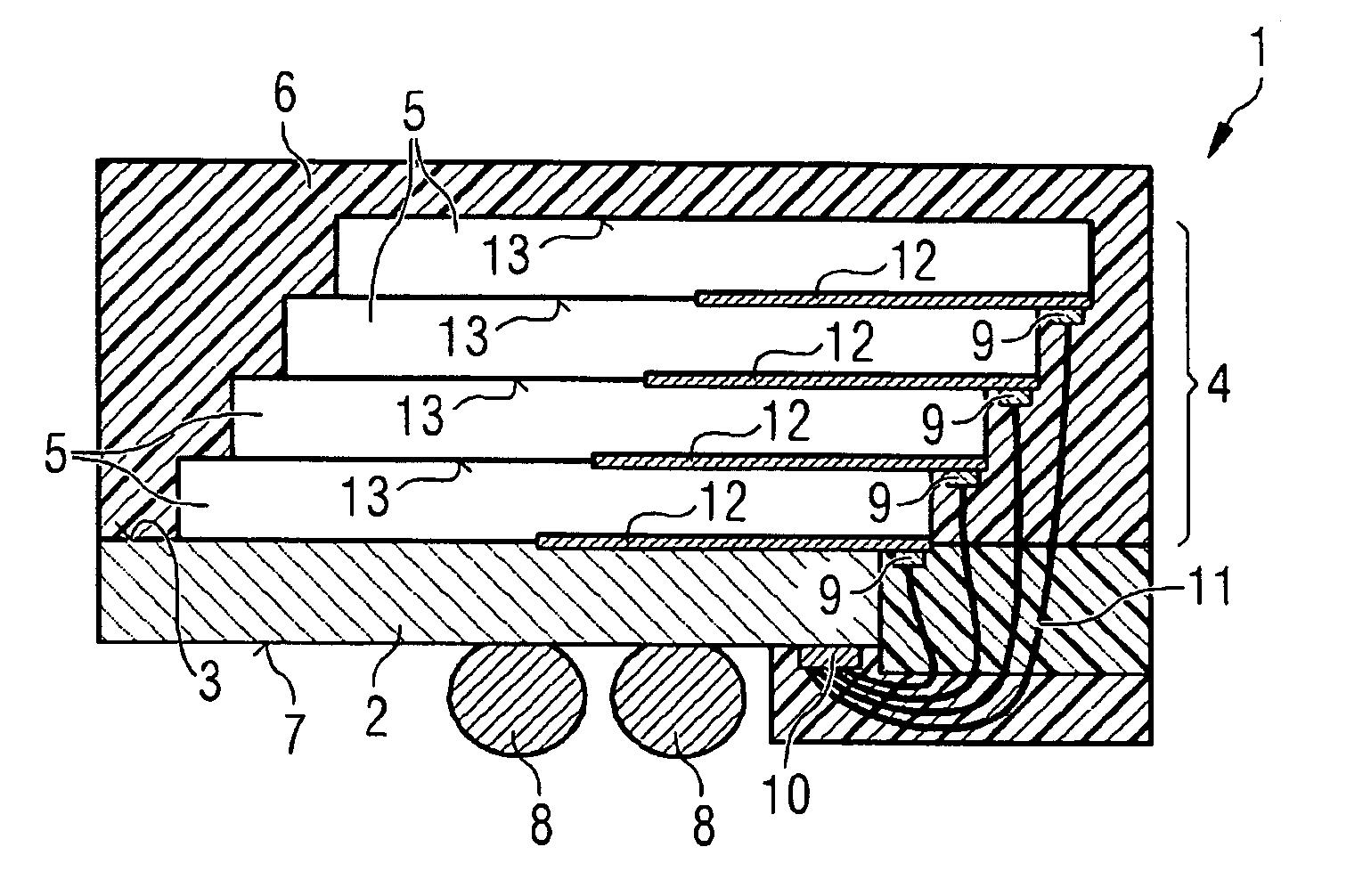

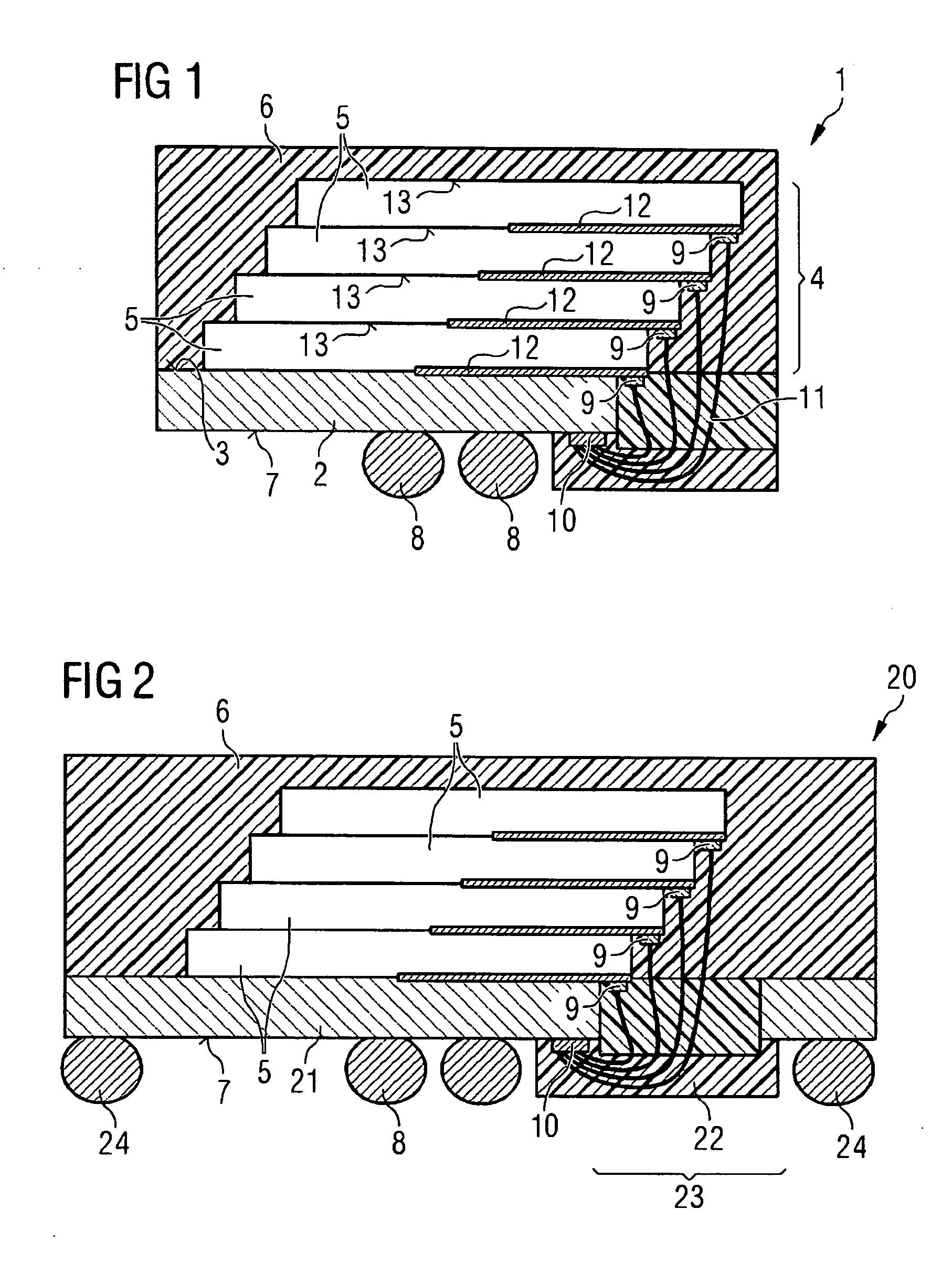

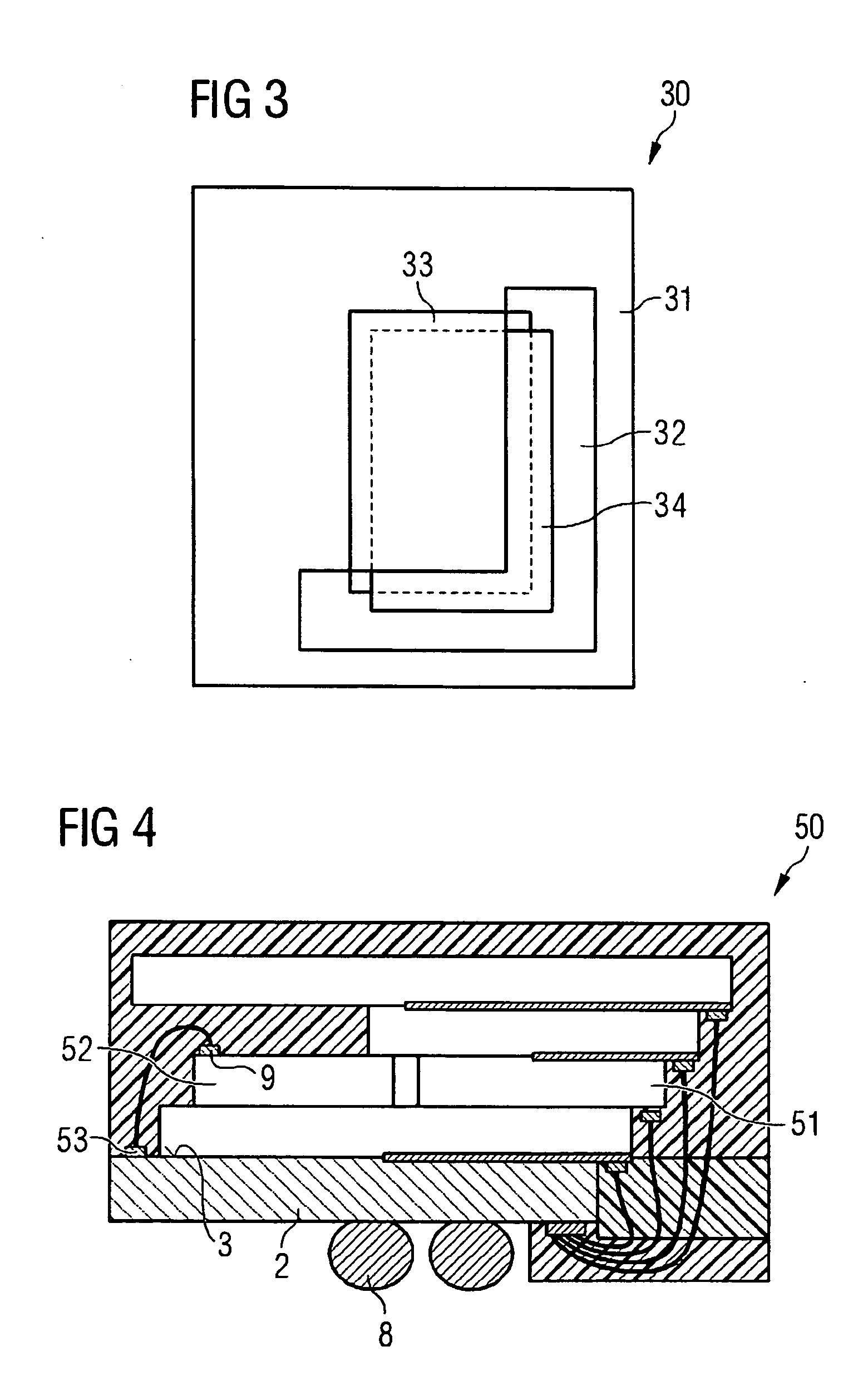

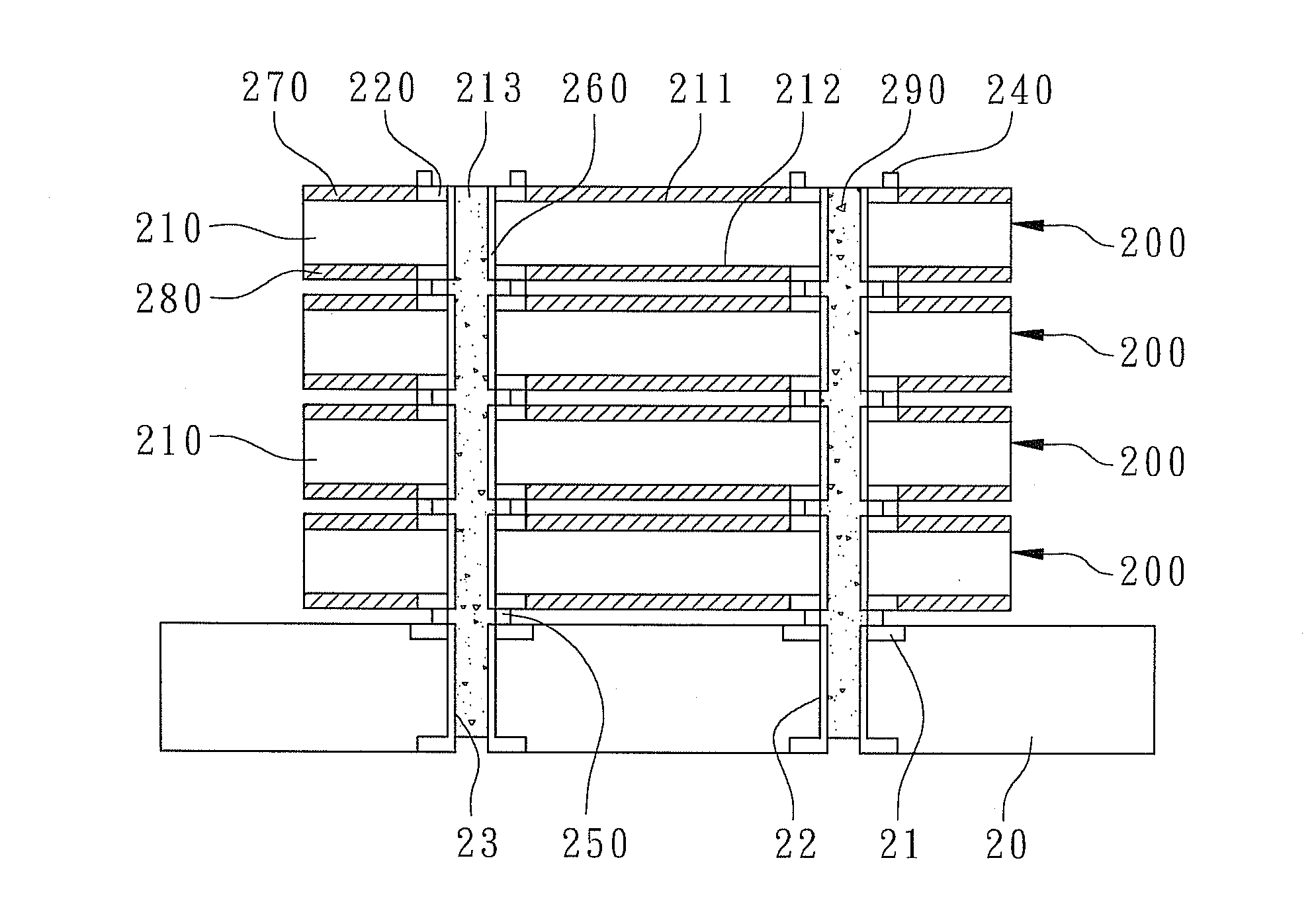

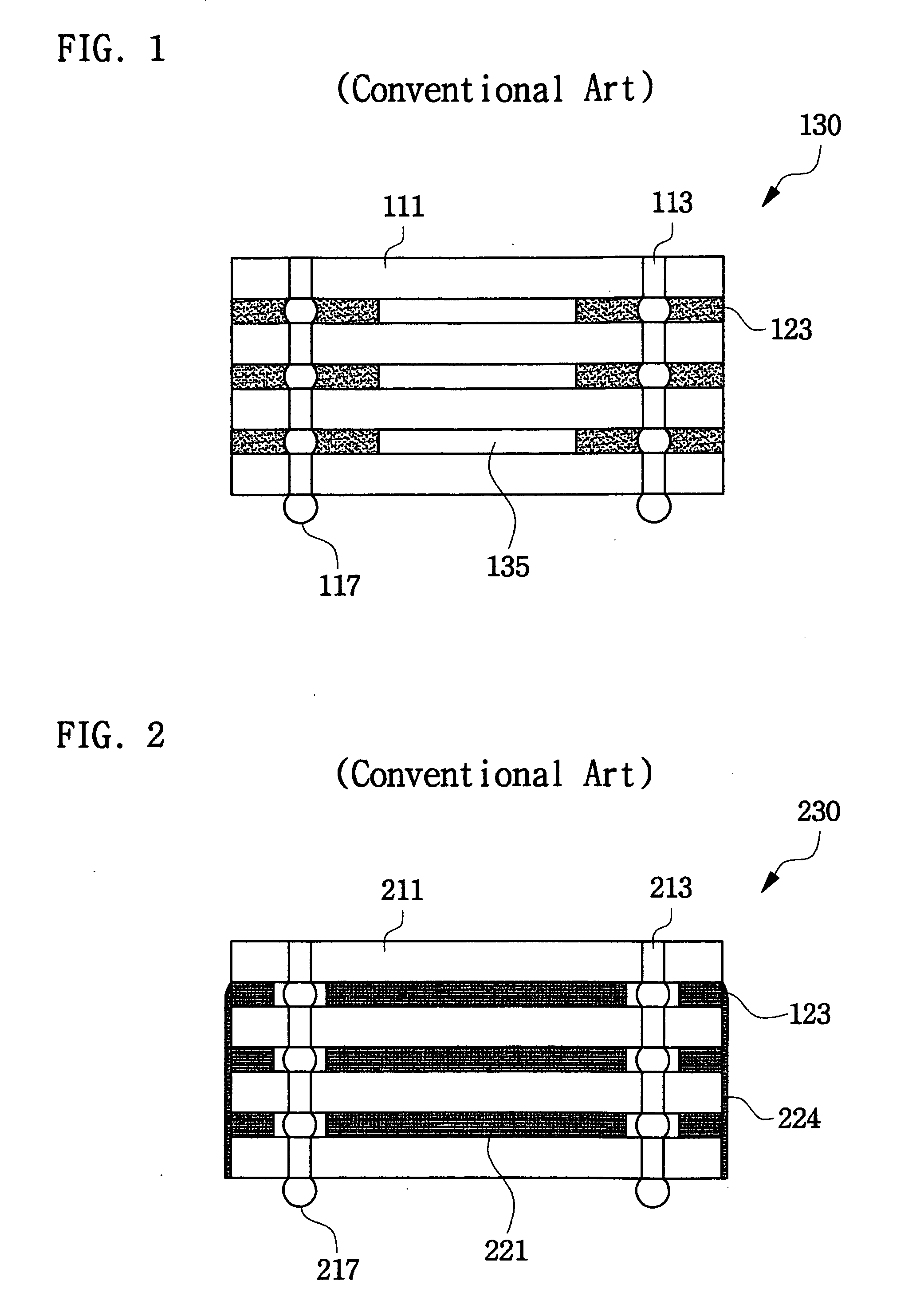

Multi-chip device and method for producing a multi-chip device

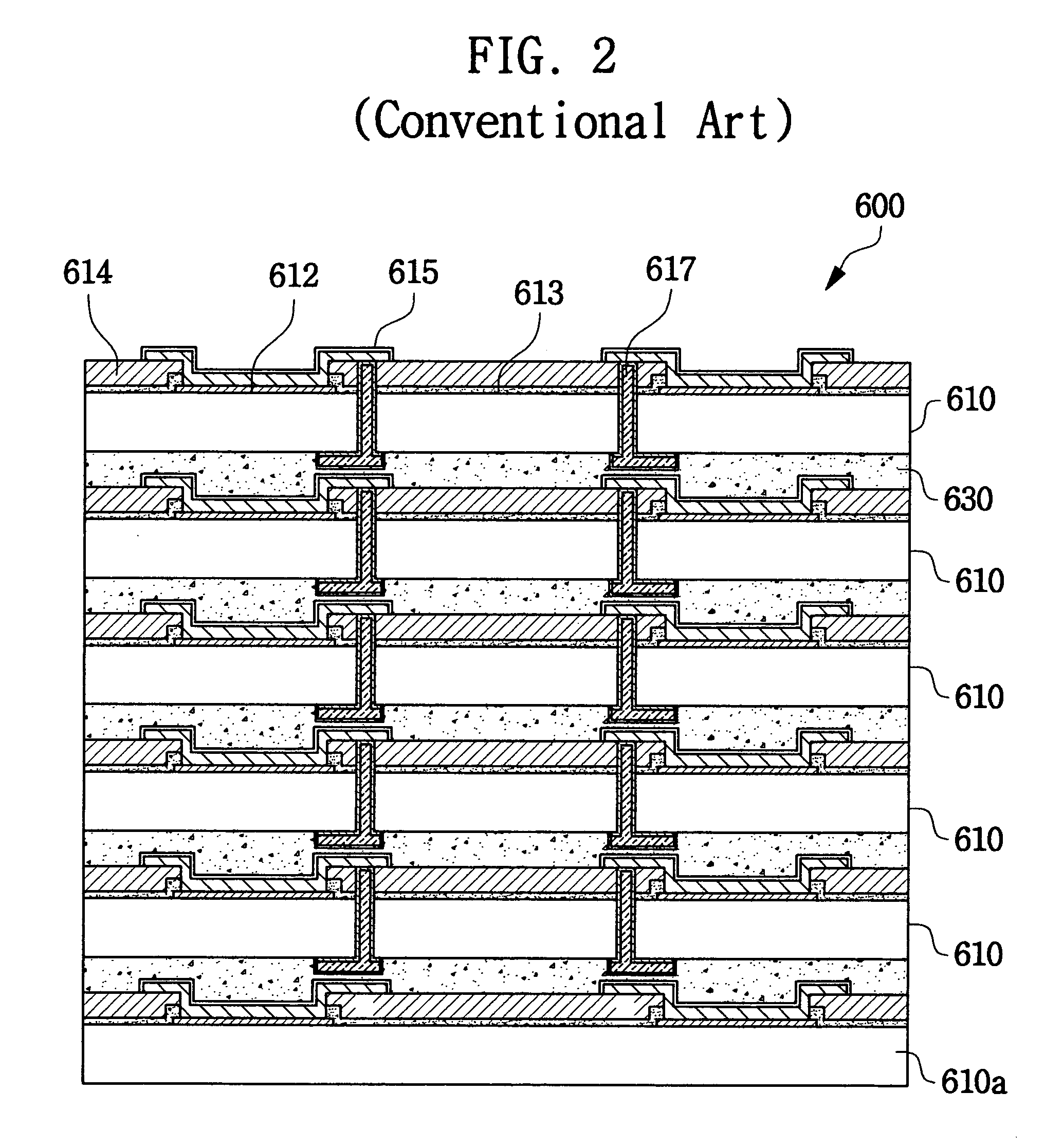

InactiveUS7297574B2Increase productionIncrease memory capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringContact element

The present invention relates to a multi-chip device comprising a plurality of chip stacks each including a plurality of single chips stacked on each other, wherein the stacked single chips are electrically interconnected by one or more through-chip-connection extending through at least one of the single chips and a substrate providing one or more first contact elements each of which is in contact with one of the through-chip-connections and providing one or more second contact elements being in electrical contact with the first contact elements, wherein the plurality of chip stacks are stacked onto each other and wherein the second contact elements of one of the chip stacks each being arranged to be in contact to one or more third contact elements of an adjacent one of the chip stacks.

Owner:POLARIS INNOVATIONS LTD

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

Multi-chip stacked devices

InactiveUSRE36613E1Semiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

A multiple stacked die device is disclosed that contains up to four dies and does not exceed the height of current single die packages. Close-tolerance stacking is made possible by a low-loop-profile wire-bonding operation and thin-adhesive layer between the stacked dies.

Owner:ROUND ROCK RES LLC

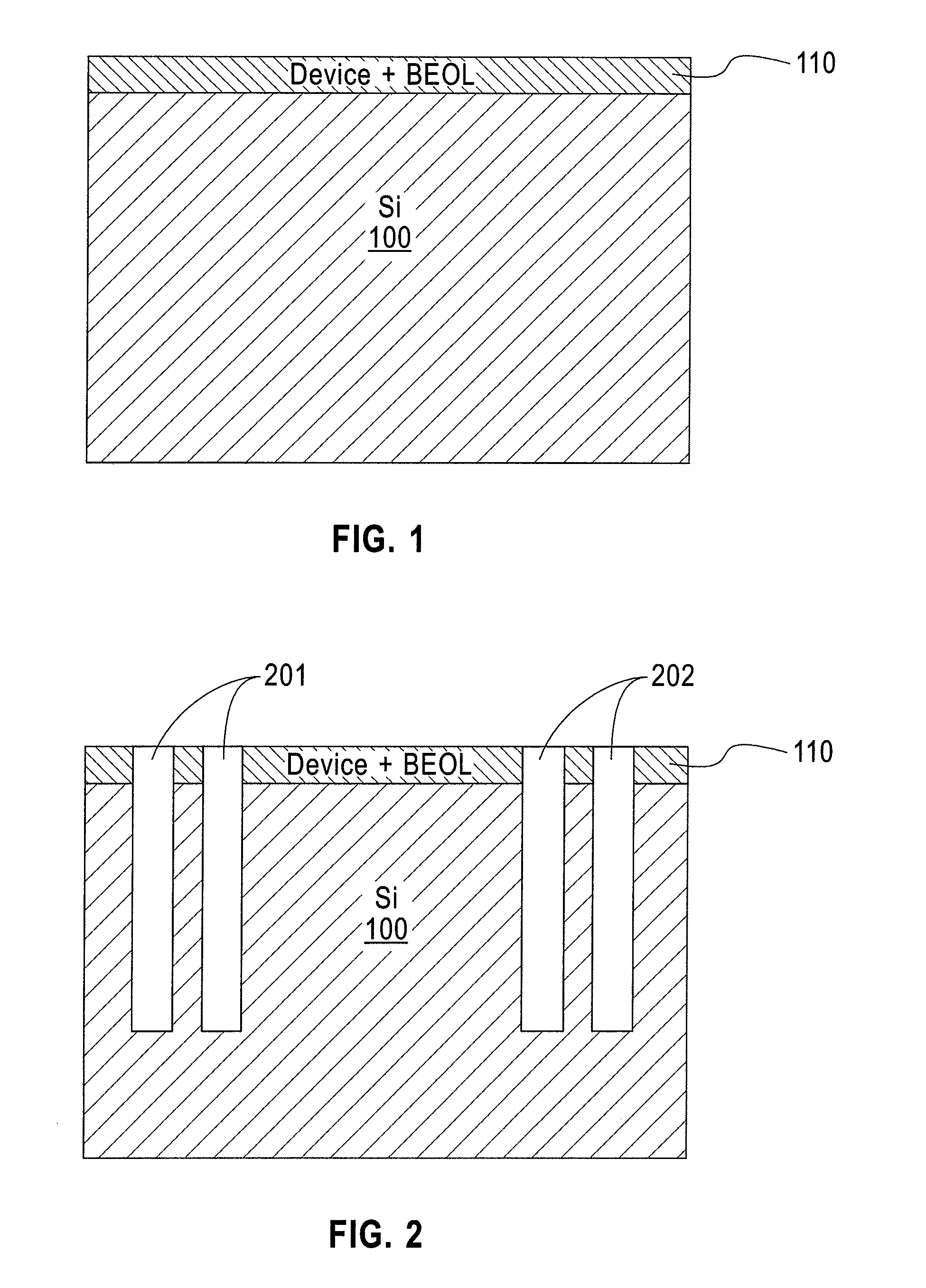

Accessible chip stack and process of manufacturing thereof

InactiveUS7528494B2Readily capable being thinnedYield maximizationSemiconductor/solid-state device detailsSolid-state devicesEngineeringThree-dimensional integrated circuit

A process of manufacturing a three-dimensional integrated circuit chip or wafer assembly and, more particularly, a processing of chips while arranged on a wafer prior to orienting the chips into stacks. Also disclosed is the manufacture of the three-dimensional integrated circuit wherein the chip density can be very high and processed while the wafers are still intact and generally of planar constructions.

Owner:ALSEPHINA INNOVATIONS INC

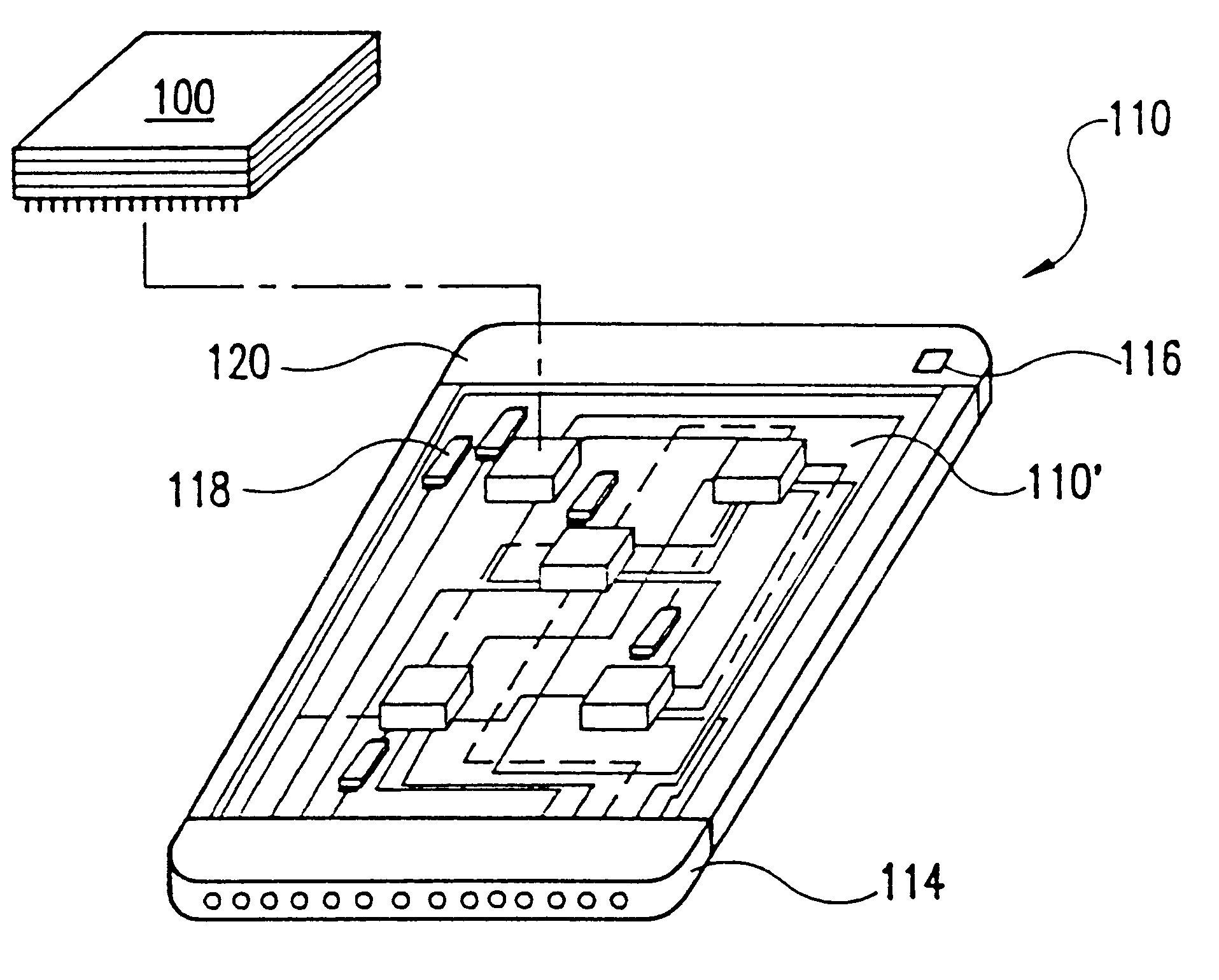

Apparatus and Methods for Constructing Semiconductor Chip Packages with Silicon Space Transformer Carriers

InactiveUS20080284037A1Cost assemblyCost handlingSemiconductor/solid-state device detailsSolid-state devicesHigh densityTransformer

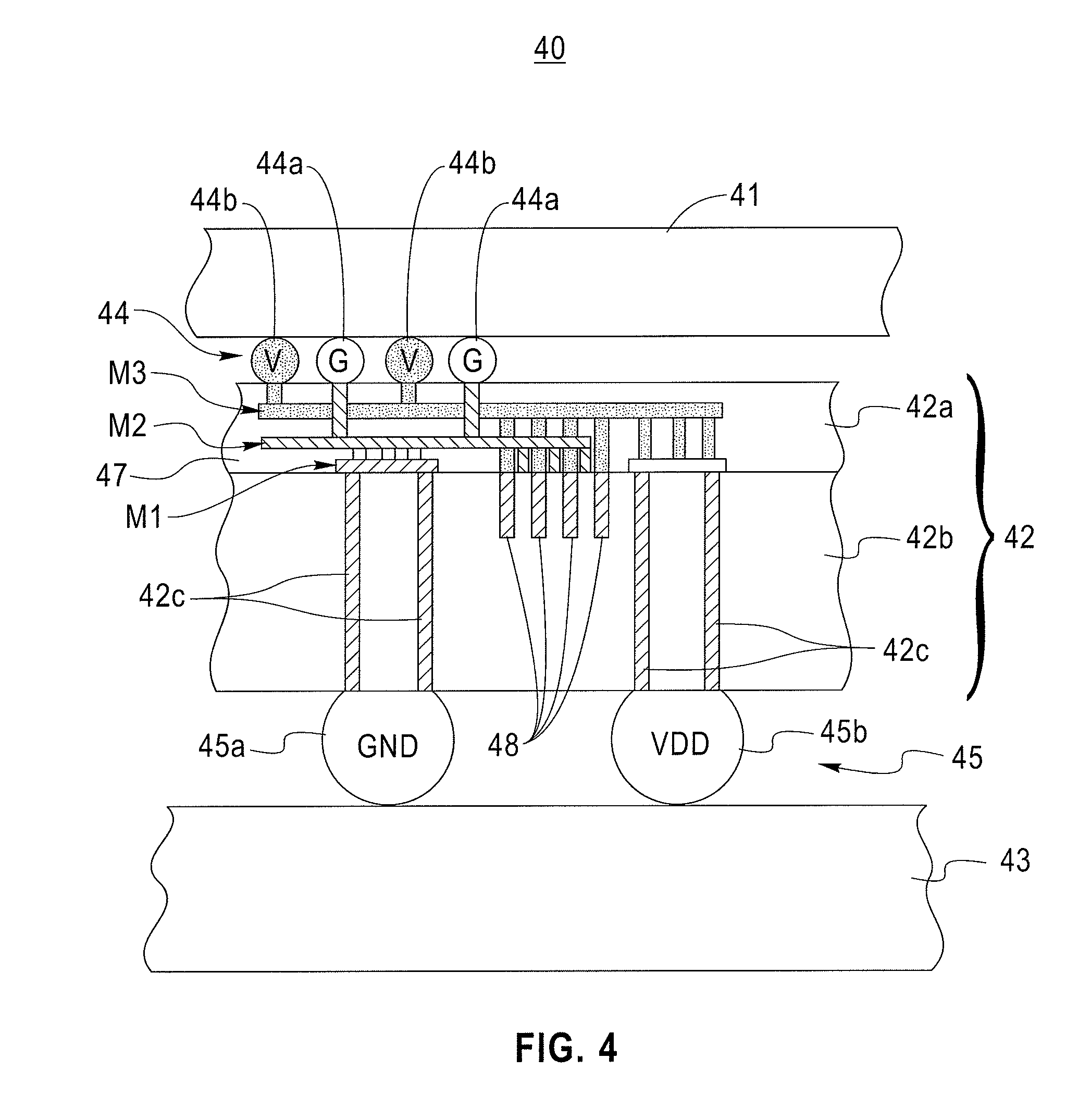

Apparatus and methods are provided for high density packaging of semiconductor chips using silicon space transformer chip level package structures, which allow high density chip interconnection and / or integration of multiple chips or chip stacks high I / O interconnection and heterogeneous chip or function integration.

Owner:IBM CORP

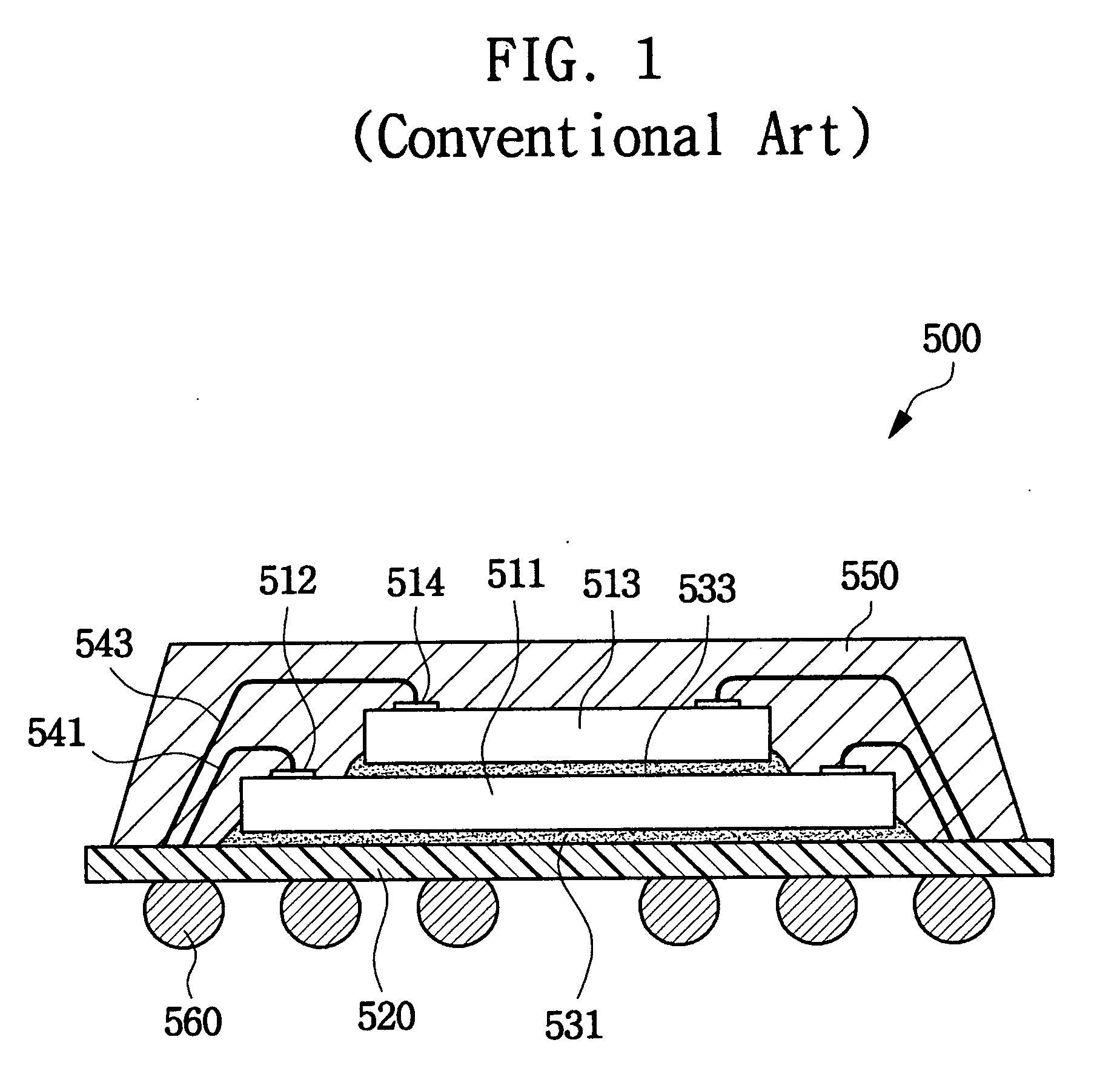

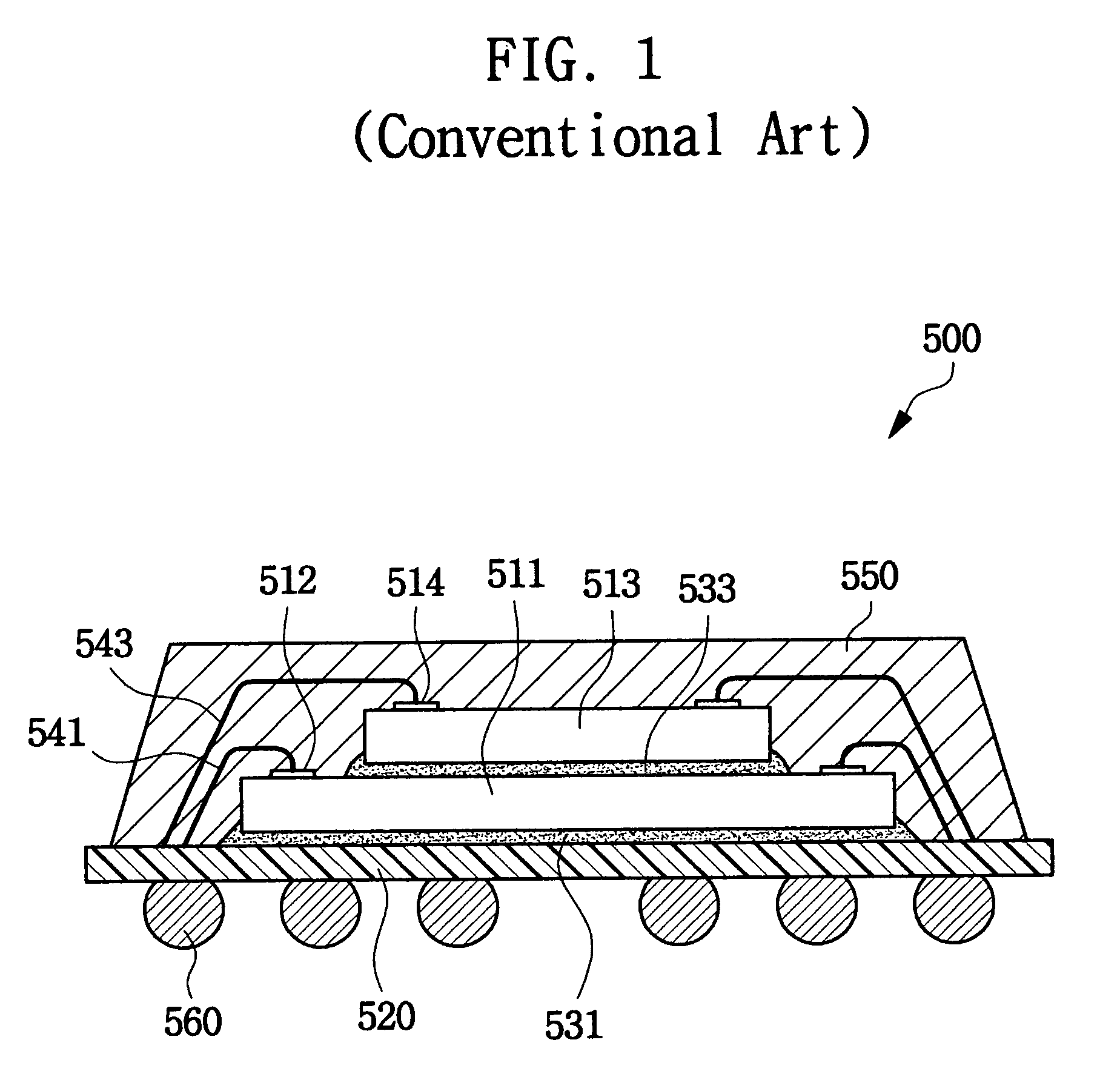

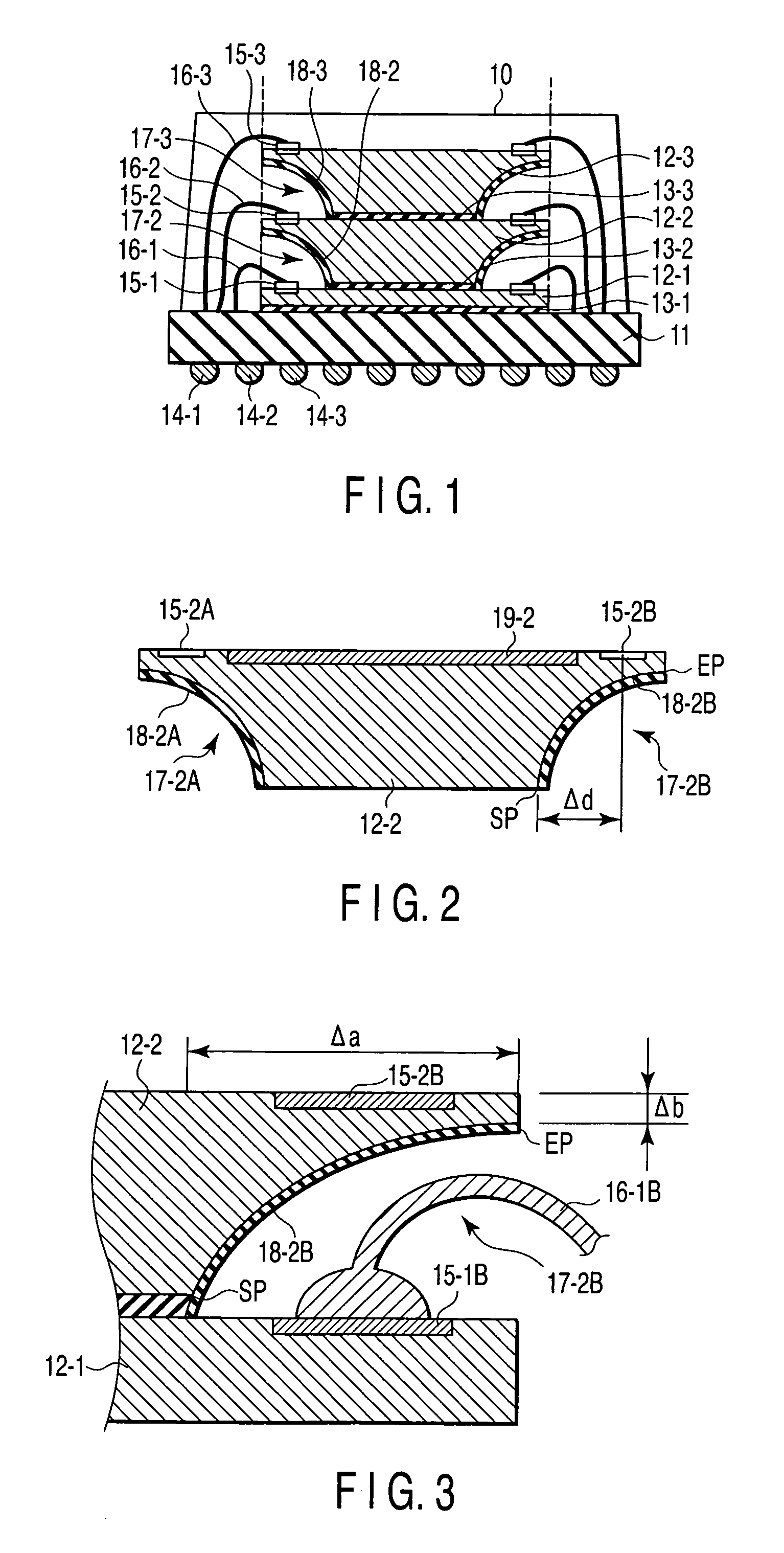

Semiconductor device having semiconductor chips stacked and mounted thereon and manufacturing method thereof

ActiveUS20060175697A1Semiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor chip

Chips are stacked and mounted on a circuit board having external connection electrodes and mounted thereon by wire bonding. At least one of the chips stacked on the chip includes overhung portions each of which has a start point inside bonding pads, is made thinner in a direction towards the outer periphery to an end point reaching the side wall and forms a space used to accommodate ball bonding portions between the overhung portion and the main surface of the chip arranged in the lower stage on a backside corresponding in position to the bonding pads, and insulating members formed to cover the overhung portions and prevent bonding wires of the chip arranged in the lower stage from being brought into contact with the upper-stage chip.

Owner:KIOXIA CORP

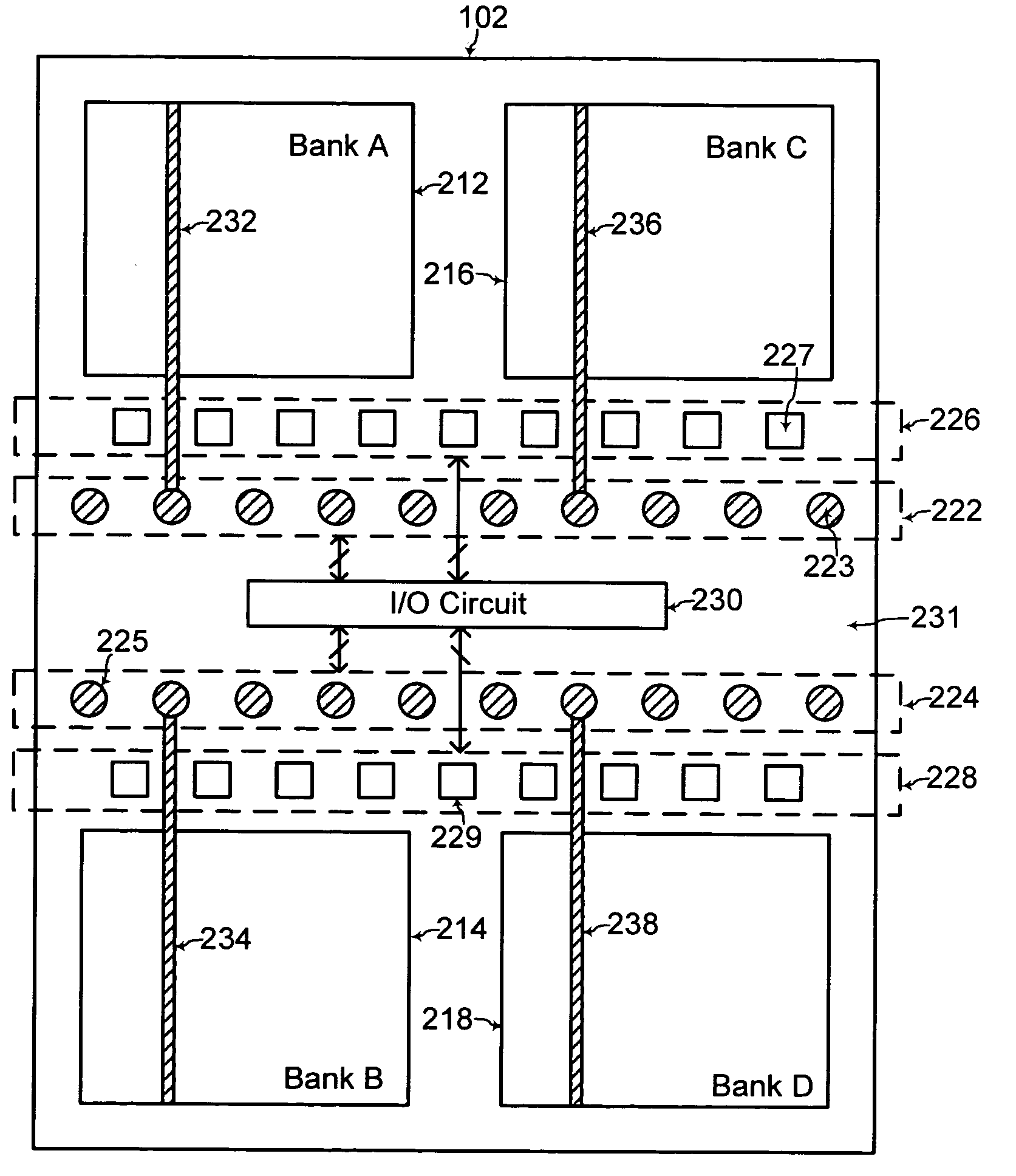

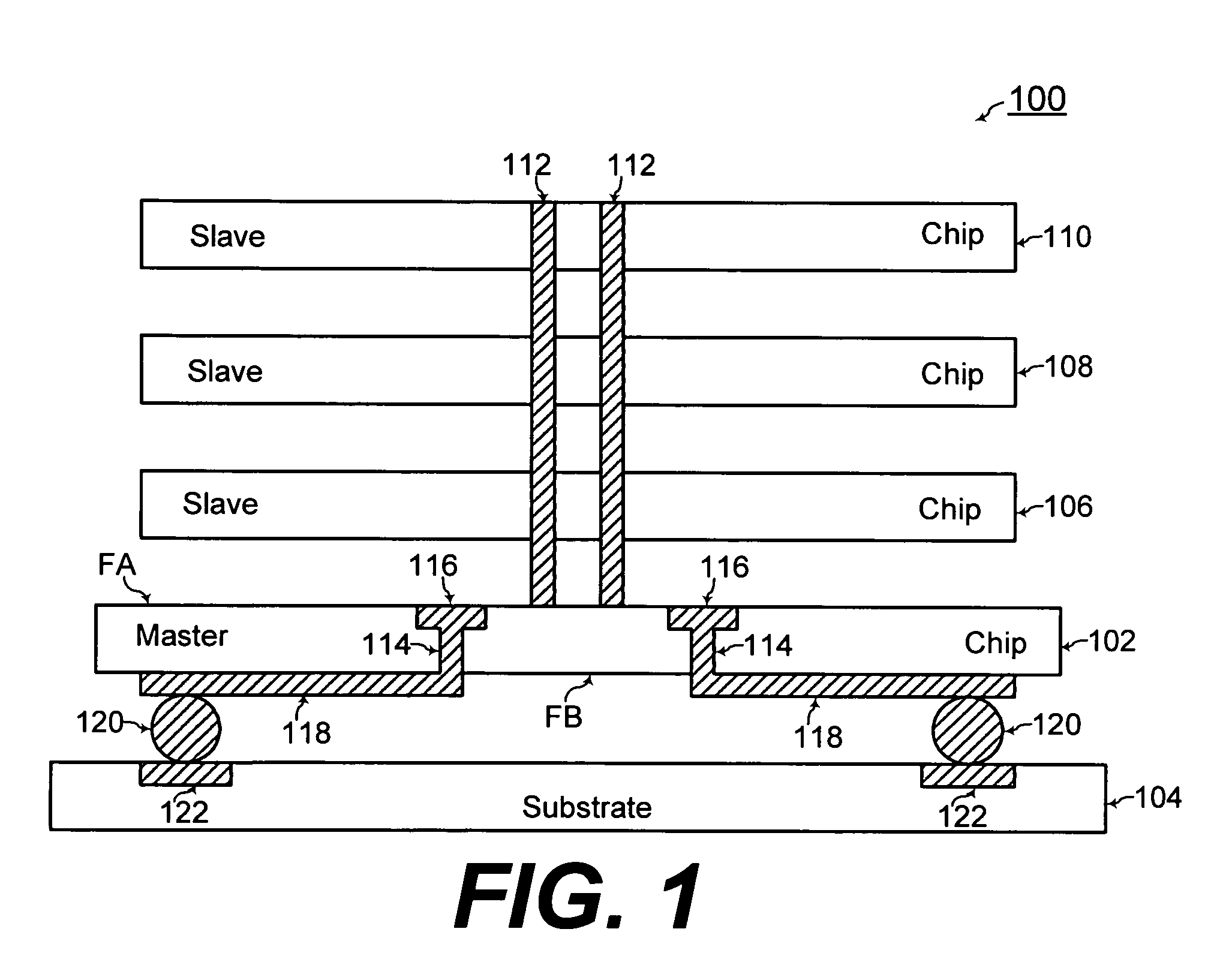

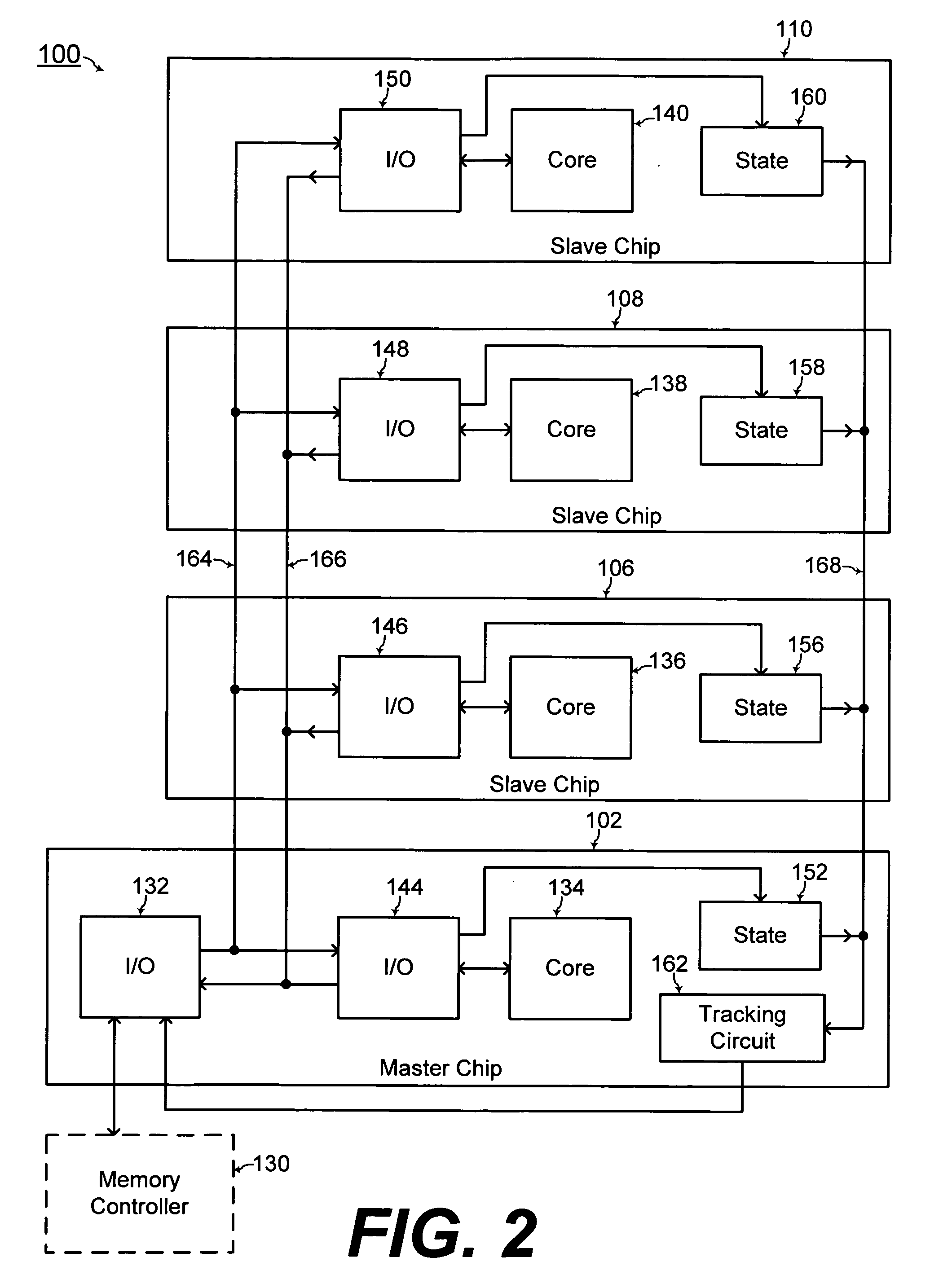

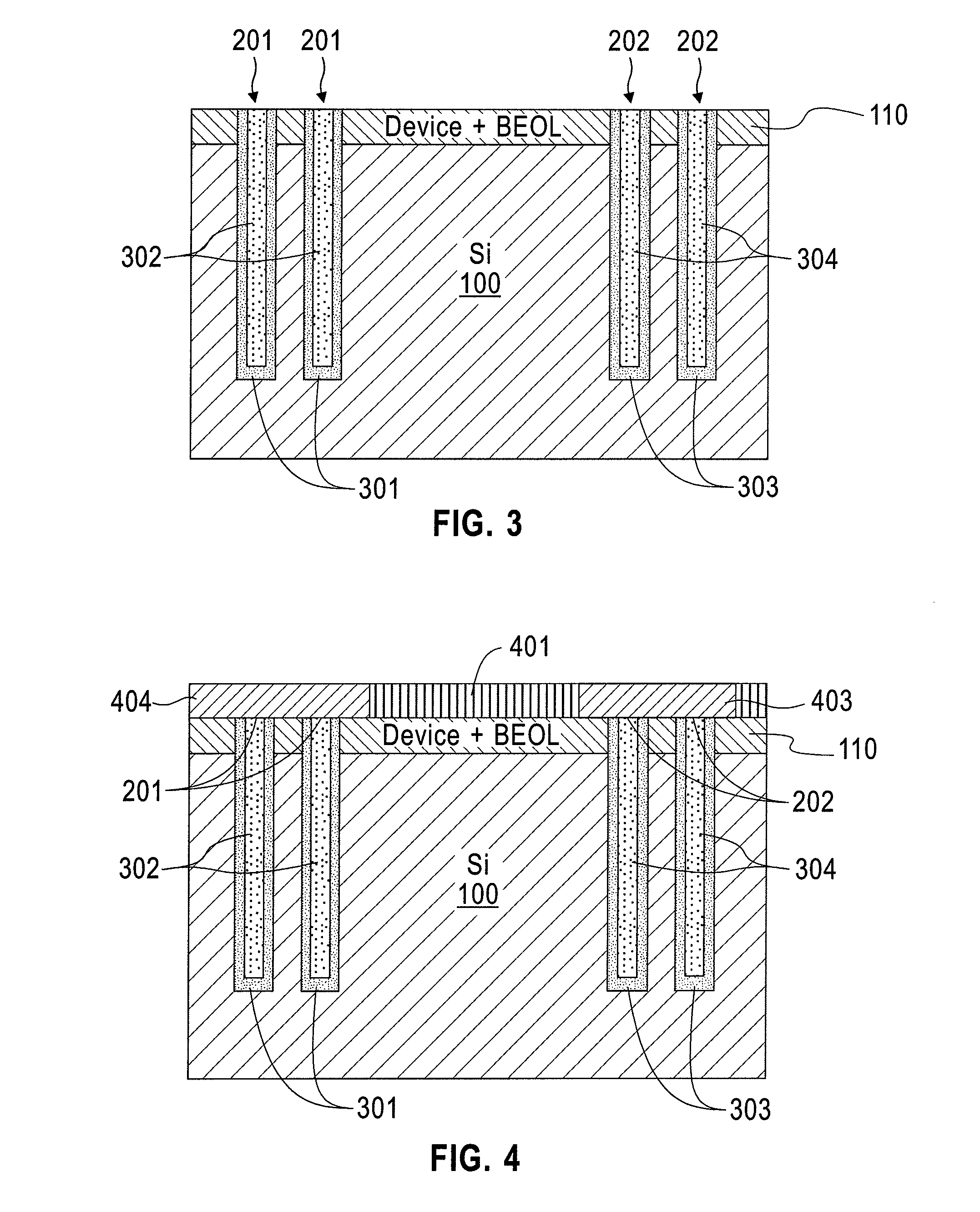

Stacked memory module and system

ActiveUS20100020583A1Increase memory capacityEfficient wiring and capacity organizationSemiconductor/solid-state device detailsSolid-state devicesMemory bankComputer module

A three dimensional memory module and system are formed with at least one slave chip stacked over a master chip. Through semiconductor vias (TSVs) are formed through at least one of the master and slave chips. The master chip includes a memory core for increased capacity of the memory module / system. In addition, capacity organizations of the three dimensional memory module / system resulting in efficient wiring is disclosed for forming multiple memory banks, multiple bank groups, and / or multiple ranks of the three dimensional memory module / system.

Owner:SAMSUNG ELECTRONICS CO LTD

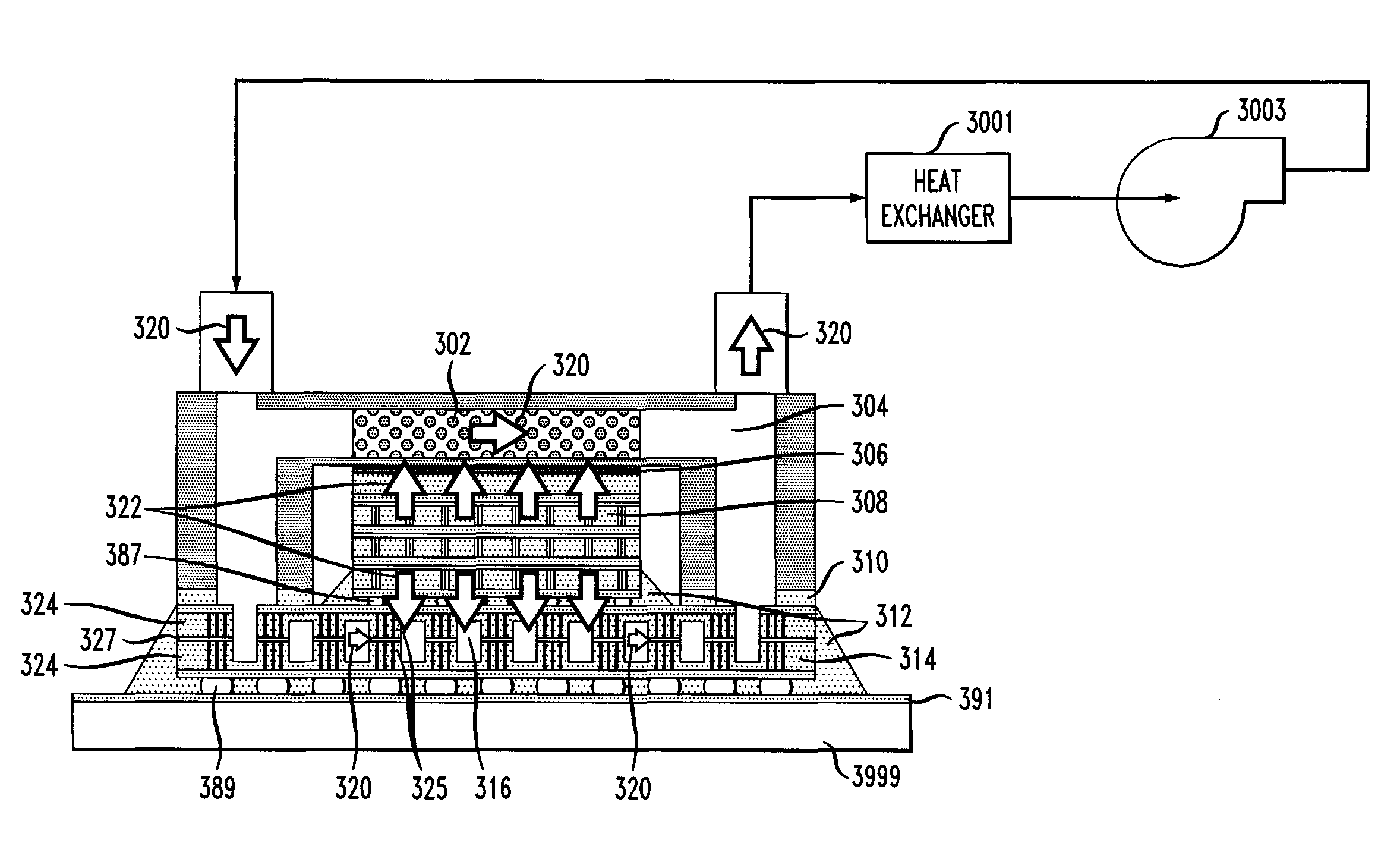

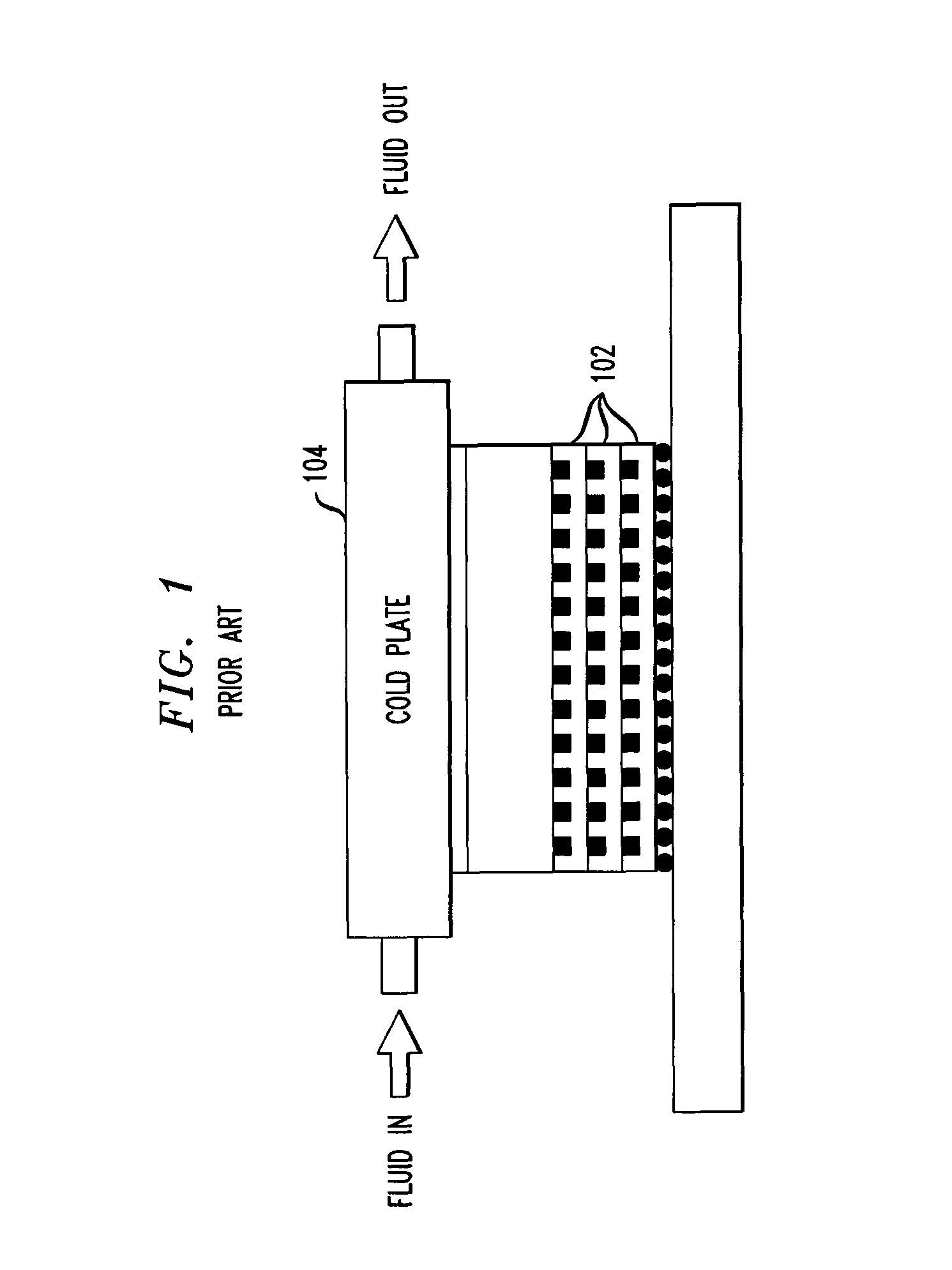

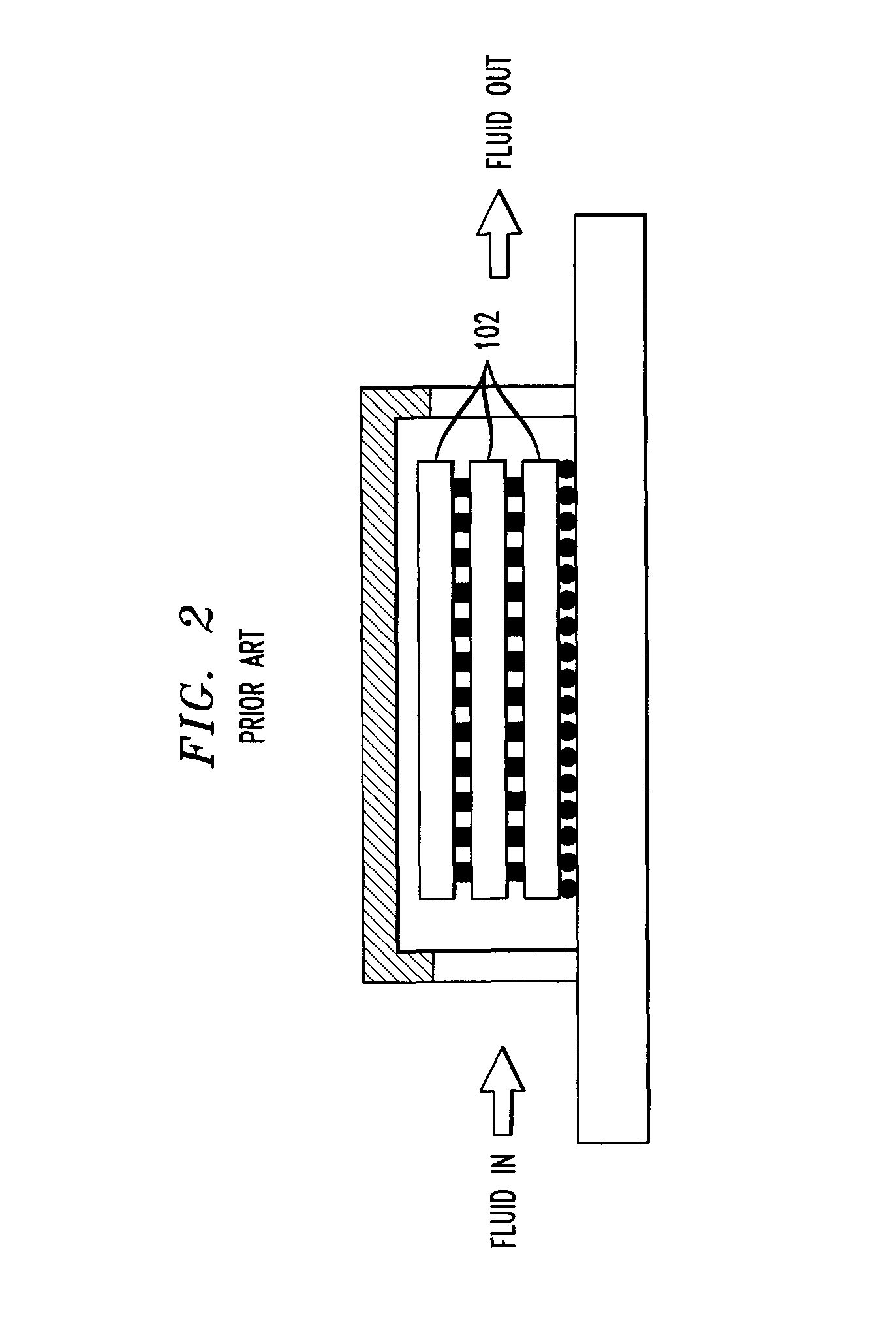

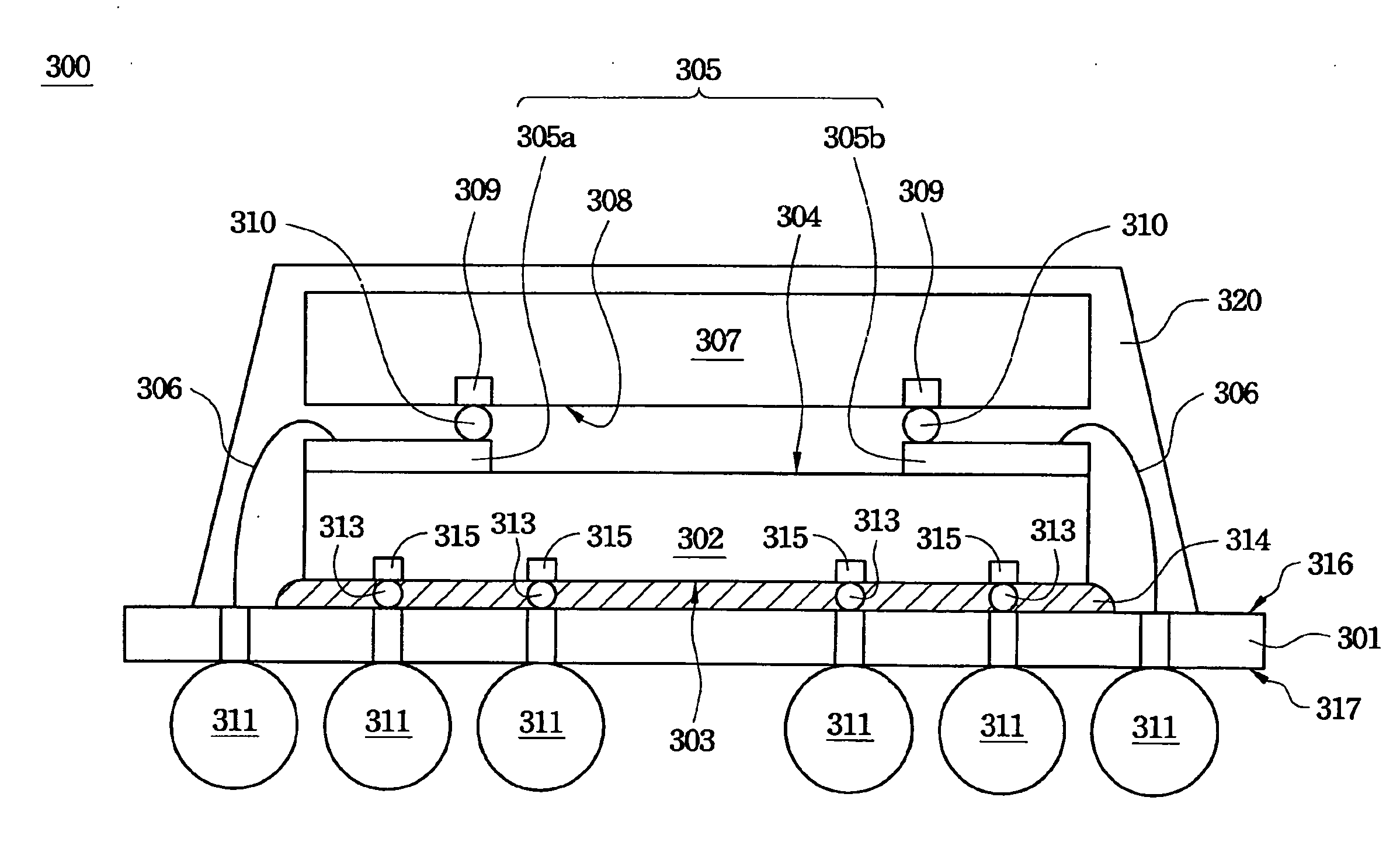

Double-face heat removal of vertically integrated chip-stacks utilizing combined symmetric silicon carrier fluid cavity and micro-channel cold plate

ActiveUS7990711B1Simple actionSemiconductor/solid-state device detailsSolid-state devicesElectricityCarrier fluid

A plurality of heat-dissipating electronic chips are arranged in a vertical chip stack. The electronic chips have electronic components thereon. A cold plate is secured to a back side of the chip stack. A silicon carrier sandwich, defining a fluid cavity, is secured to a front side of the chip stack. An inlet manifold is configured to supply cooling fluid to the cold plate and the fluid cavity of the silicon carrier sandwich. An outlet manifold is configured to receive the cooling fluid from the cold plate and the fluid cavity of the silicon carrier sandwich. The cold plate, the silicon carrier sandwich, the inlet manifold, and the outlet manifold are configured and dimensioned to electrically isolate the cooling fluid from the electronic components. A method of operating an electronic apparatus and a method of manufacturing an electronic apparatus are also disclosed. Single-sided heat removal with double-sided electrical input-output and double-sided heat removal with double-sided electrical input-output are also disclosed.

Owner:GLOBALFOUNDRIES US INC

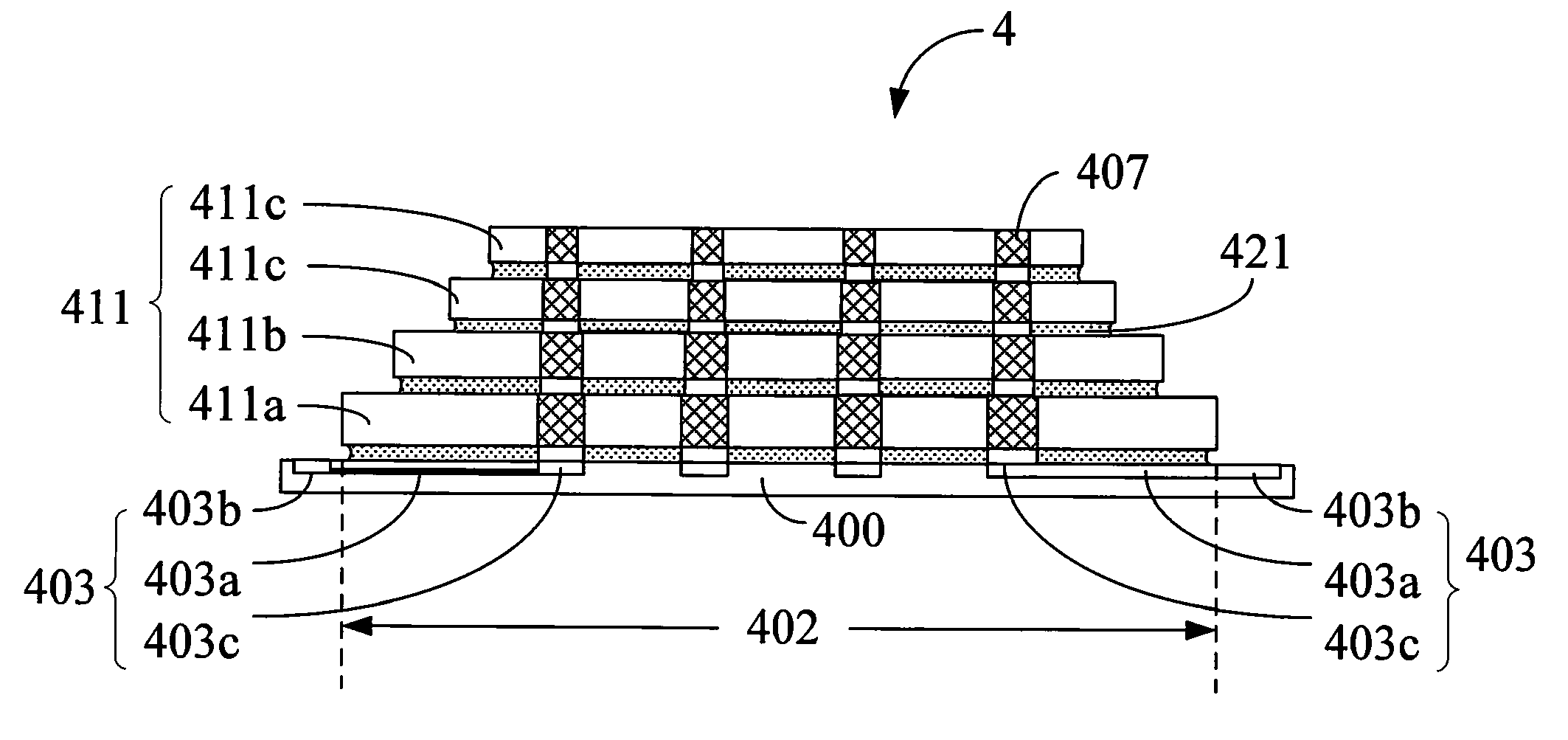

Multi-chip device and method for producing a multi-chip device

InactiveUS20060290005A1Semiconductor/solid-state device detailsSolid-state devicesContact elementChip stacking

The present invention relates to a multi-chip device comprising a substrate having a first surface on which a number of first contact elements is provided, a plurality of integrated circuit chips arranged in a chip stack which is arranged on a second surface of the substrate opposing the first surface, wherein each of the chips having a surface on which a number of second contact elements are provided, wherein a first one of the chips and the second contact elements thereon is arranged such that its second contact elements are uncovered by any of the chips or by the substrate and face towards the second surface of the substrate; and connecting elements which are arranged such as to connect at least one of the first contact elements of the substrate and at least one of the second contact elements of the first chip.

Owner:POLARIS INNOVATIONS LTD

Semiconductor package structure and method for manufacturing the same

ActiveUS20100007001A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor chipSemiconductor package

Semiconductor package structures and methods for manufacturing the same are provided. The semiconductor package structure comprises a substrate unit and a first chip stack structure. The substrate unit comprises a circuit structure having test pads. The first chip stack structure comprises chips, and each of the chips has a plurality of through silicon plugs. The through silicon plugs of two adjacent chips are electrically connected and further electrically connected to the test pads of the substrate unit for electrical testing. Another semiconductor package structure provided by the present invention comprises a first semiconductor chip and a second semiconductor chip. Each of the semiconductor chips has test pads for electrical testing and a plurality of through silicon plugs connecting to the test pads. The second semiconductor chip is mounted on the first semiconductor chip, and a portion of the through silicon plugs of two semiconductor chips are electrically connected with each other.

Owner:ZAWASHIRO DIGITAL INNOVATIONS

Chip stack package and method of manufacturing the same

InactiveUS20080128882A1Small sizeAccelerated dissipationSemiconductor/solid-state device detailsSolid-state devicesEngineeringChip stacking

A chip stack package comprising an intermediate substrate having a recess, a first chip mounted in the recess, a second chip over the intermediate substrate, a package substrate formed under the intermediate substrate and first plugs through the intermediate substrate is disclosed. The second chip is configured to be electrically connected to the first chip. The first plugs are configured to electrically connect the second chip and the package substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor package having plural semiconductor chips and method of forming the same

ActiveUS20130049221A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package includes a first semiconductor chip mounted to a substrate, a first encapsulant covering the first semiconductor chip and have first to fourth sidewall surfaces, and a chip stack mounted to the substrate and disposed on the first encapsulant. The chip stack includes a plurality of second semiconductor chips. A second encapsulant covers the chip stack. The second encapsulant may cover the first sidewall surface of the first encapsulant and expose the third sidewall surface of the first encapsulant.

Owner:SAMSUNG ELECTRONICS CO LTD

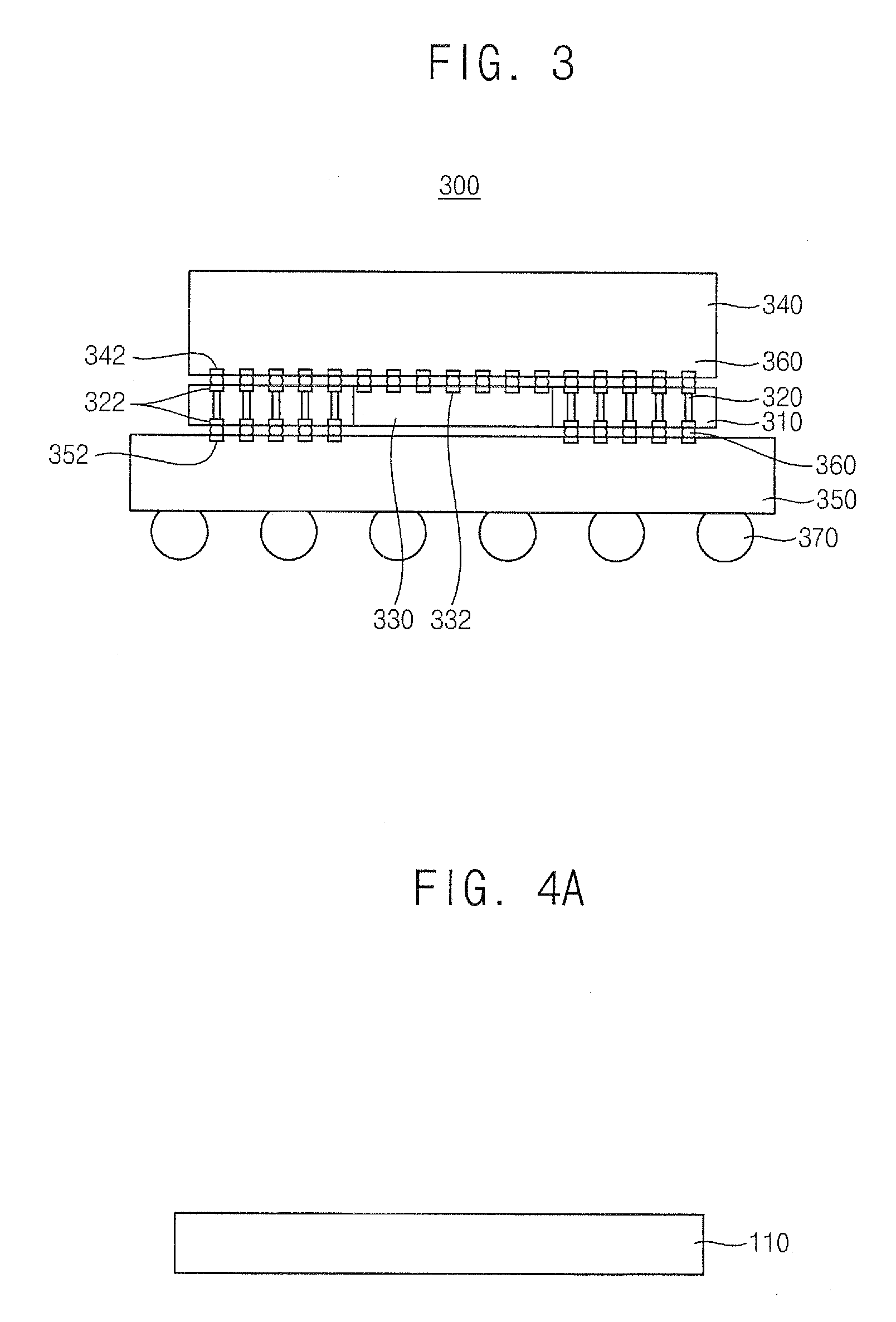

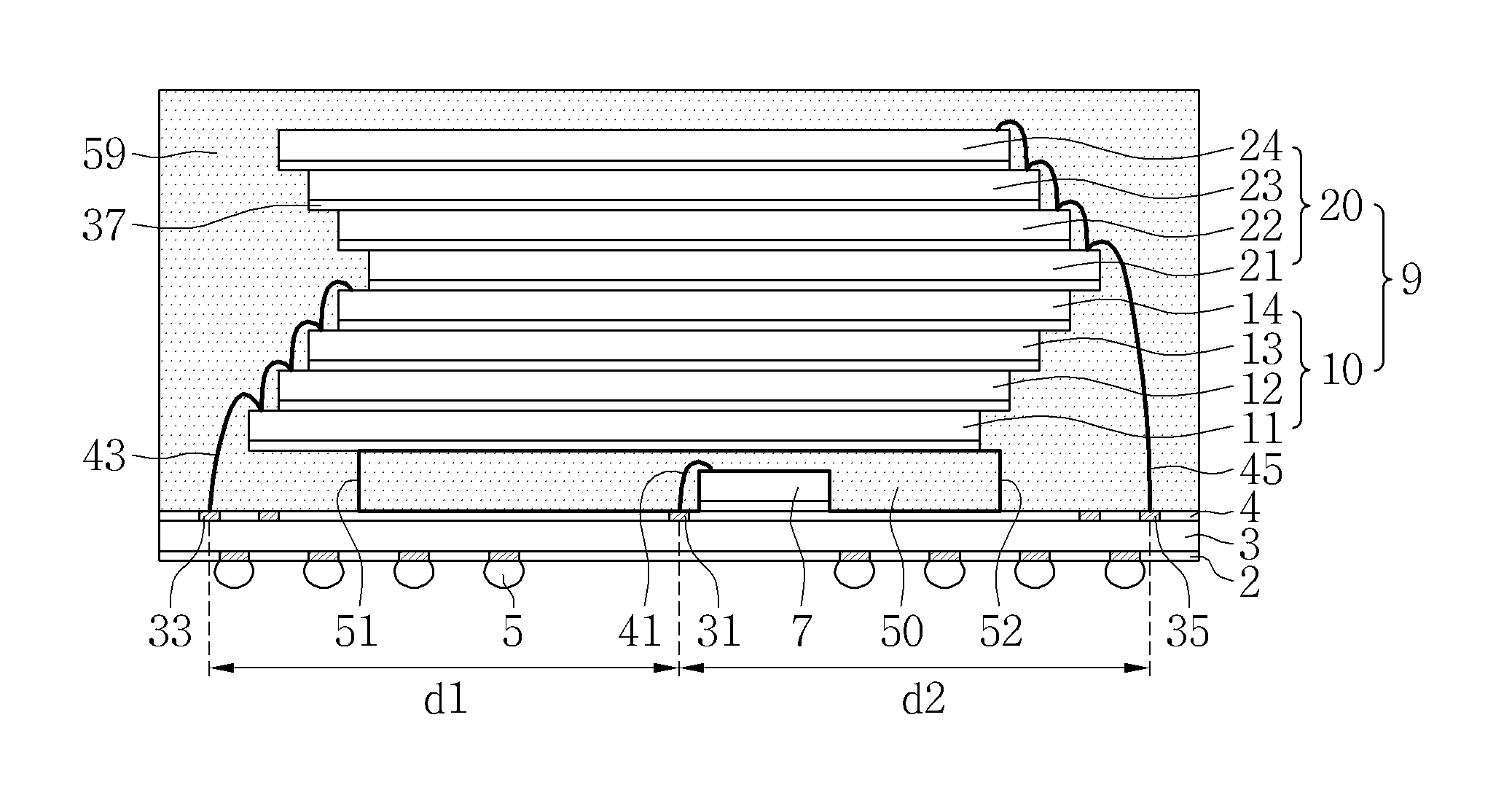

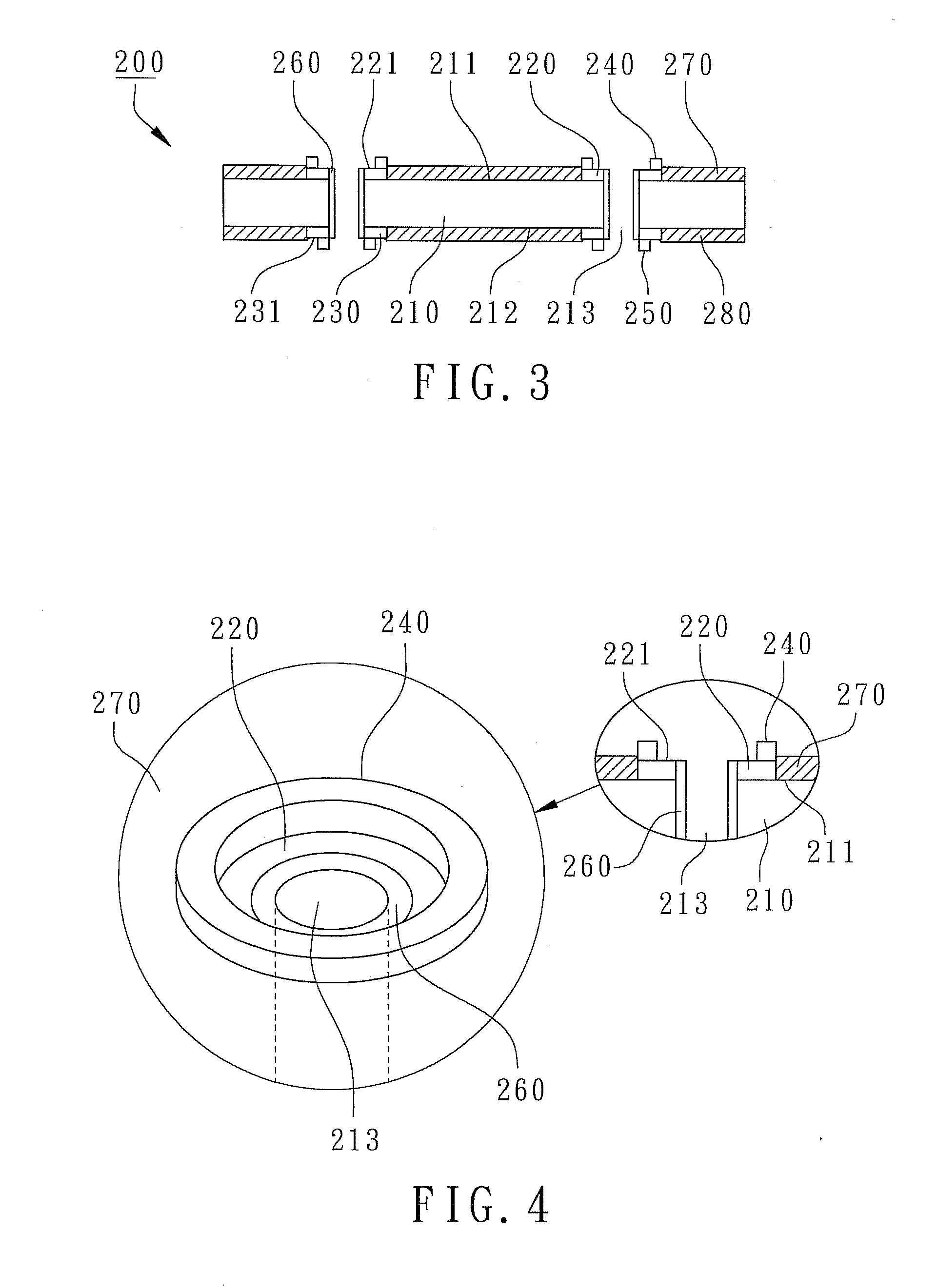

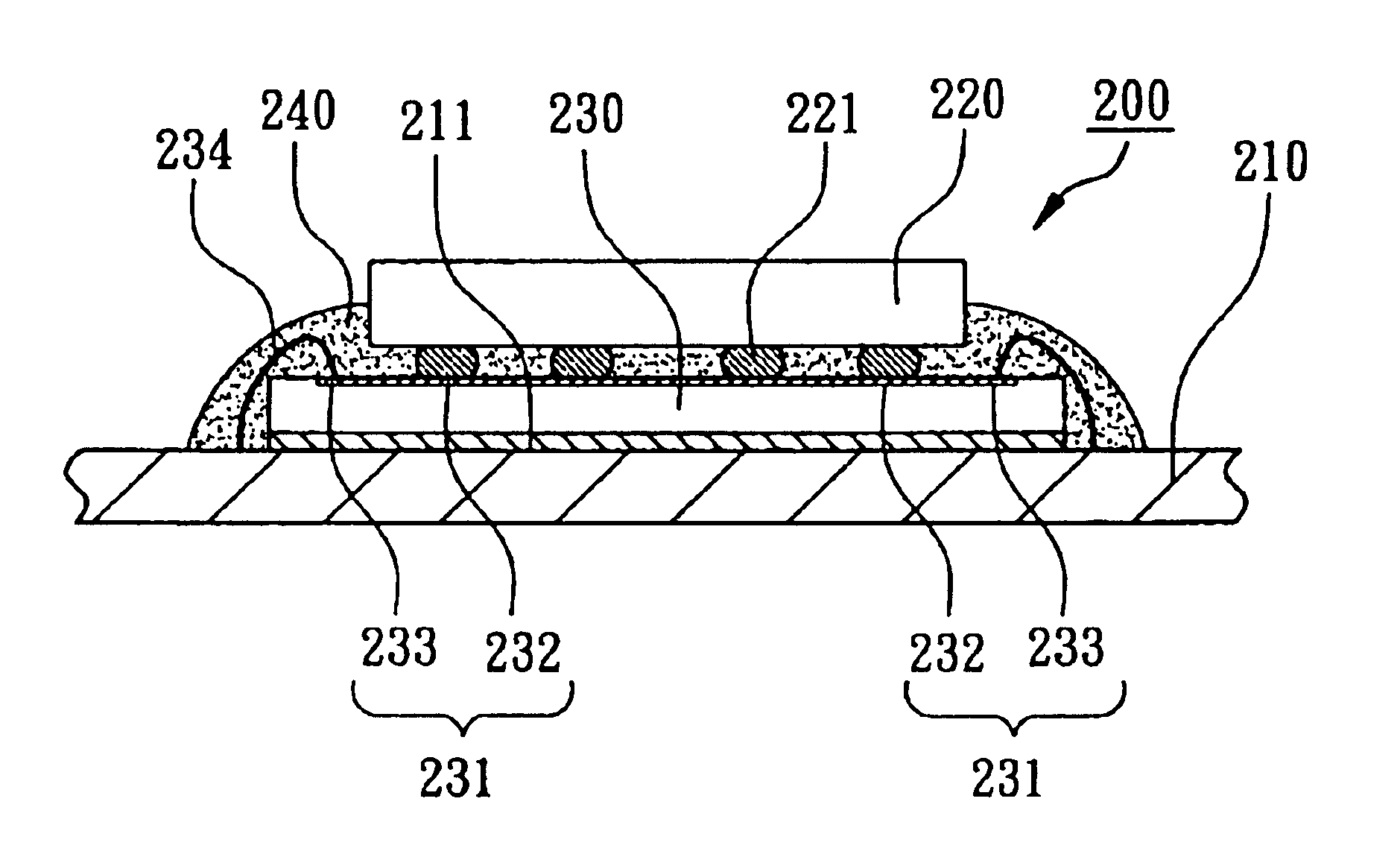

Semiconductor chip having TSV (through silicon via) and stacked assembly including the chips

InactiveUS20090267194A1Precise alignmentReduce the overall heightSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip having through silicon vias (TSV) and a stacked assembly including the chip are revealed. The chip has a plurality of first and second bonding pads disposed on two opposing surfaces of a semiconductor substrate respectively. Through hole vertically penetrate through the semiconductor substrate and the first and second bonding pads. By forming first extruded ring, the first bonding pad has a first contact surface located between the first extruded ring and the through hole. By forming second extruded ring, the second bonding pad has a second contact surface located outside and adjacent to the second extruded rings to encircle the second extruded ring. The second extruded ring has a proper dimension to fit in the first extruded ring. Accordingly, a plurality of semiconductor chip can be stacked each other with accurate alignment without shifting to effectively reduce the stacked assembly height, moreover, chip stacking processes are accomplished by vertically stacking a plurality of chips first then filling conductive material into the through holes without electrical short between the adjacent bonding pads due to overflow of conductive material to meet the fine-pitch requirements of TSV. The process flow for the stacked assembly is simplified with higher production yields.

Owner:POWERTECH TECHNOLOGY

Stacked Semiconductor Device And Method Of Fabricating The Same

InactiveUS20120038045A1Easily emit heatDecrease fault rate of reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A stacked semiconductor device may have a plurality of chips stacked in three-dimension. The stacked semiconductor device may include a first semiconductor chip and at least one second semiconductor chip. The first semiconductor chip may include a plurality of first through silicon vias (TSVs). The at least one second semiconductor chip may include a plurality of second TSVs. The at least one second semiconductor chip may be stacked above the first semiconductor chip and may be thinner than the first semiconductor chip. Therefore, the stacked semiconductor device may have an improved reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

Multi-chip stack structure having through silicon via and method for fabrication the same

InactiveUS20090032928A1Simplify the manufacturing processReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesChip stackingContamination

The invention discloses a multi-chip stack structure having through silicon via and a method for fabricating the same. The method includes: providing a wafer having a plurality of first chips; forming a plurality of holes on a first surface of each of the first chips and forming metal posts and solder pads corresponding to the holes so as to form a through silicon via (TSV) structure; forming at least one groove on a second surface of each of the first chips to expose the metal posts of the TSV structure so as to allow at least one second chip to be stacked on the first chip, received in the groove and electrically connected to the metal posts exposed from the groove; filling the groove with an insulating material for encapsulating the second chip; mounting conductive elements on the solder pads of the first surface of each of the first chips and singulating the wafer; and mounting and electrically connecting the stacked first and second chips to a chip carrier via the conductive elements. The wafer, which is not totally thinned but includes a plurality of first chips, severs a carrying purpose during the fabrication process and thereby solves problems, namely a complicated process, high cost, and adhesive layer contamination, facing the prior art that entails repeated use of a carrier board and an adhesive layer for vertically stacking a plurality of chips and mounting the stacked chips on a chip carrier.

Owner:SILICONWARE PRECISION IND CO LTD

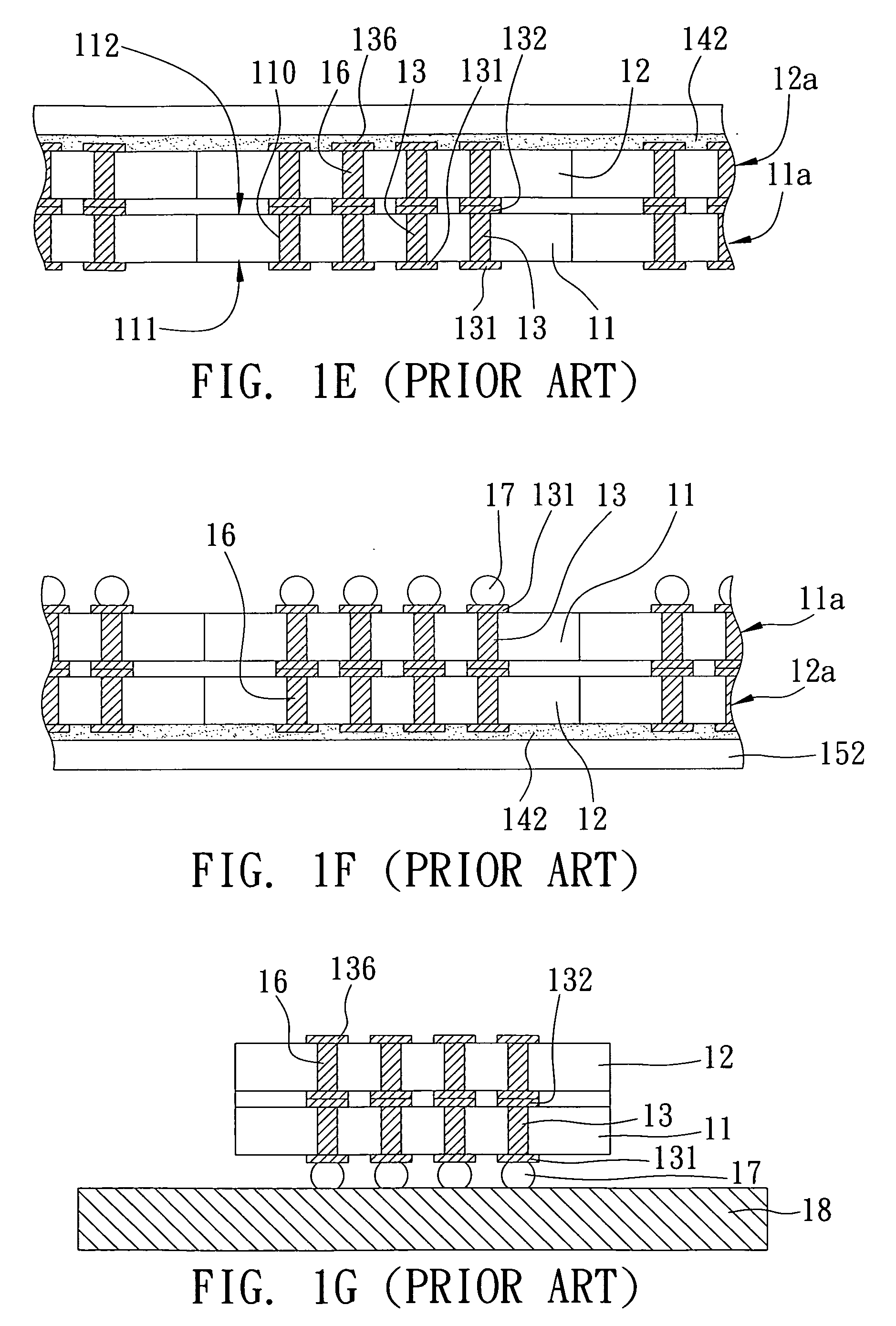

Method for joining lead frames in a package assembly, method for forming a chip stack package, and a chip stack package

InactiveUS20040014257A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

A method for joining lead frames in a chip stack package or a package stack, a chip stack package, and a method of forming a chip stack package. A joining mediator is formed on joining portions of at least one lead frame. The joining mediator has an anti-oxidation property and an inter-metallic diffusion property, and may be formed of gold wires, gold bumps, gold bars, solder bumps, solder, or solder bars. By clamping or compressing the lead frames under heat and pressure, the joining mediator forms an inter-metallic joint layer that reliably interconnects the lead frames at the joining portions.

Owner:SAMSUNG ELECTRONICS CO LTD

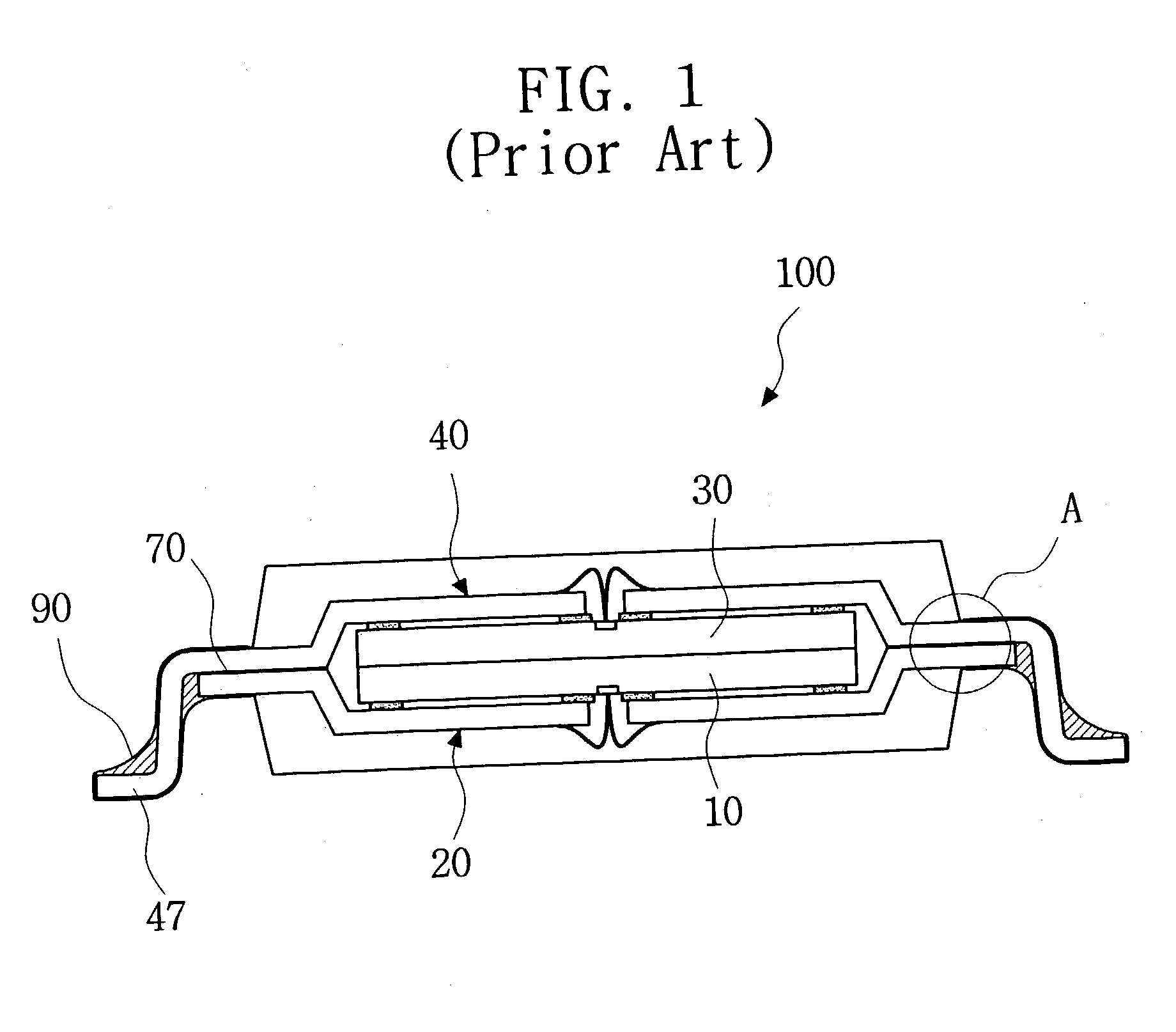

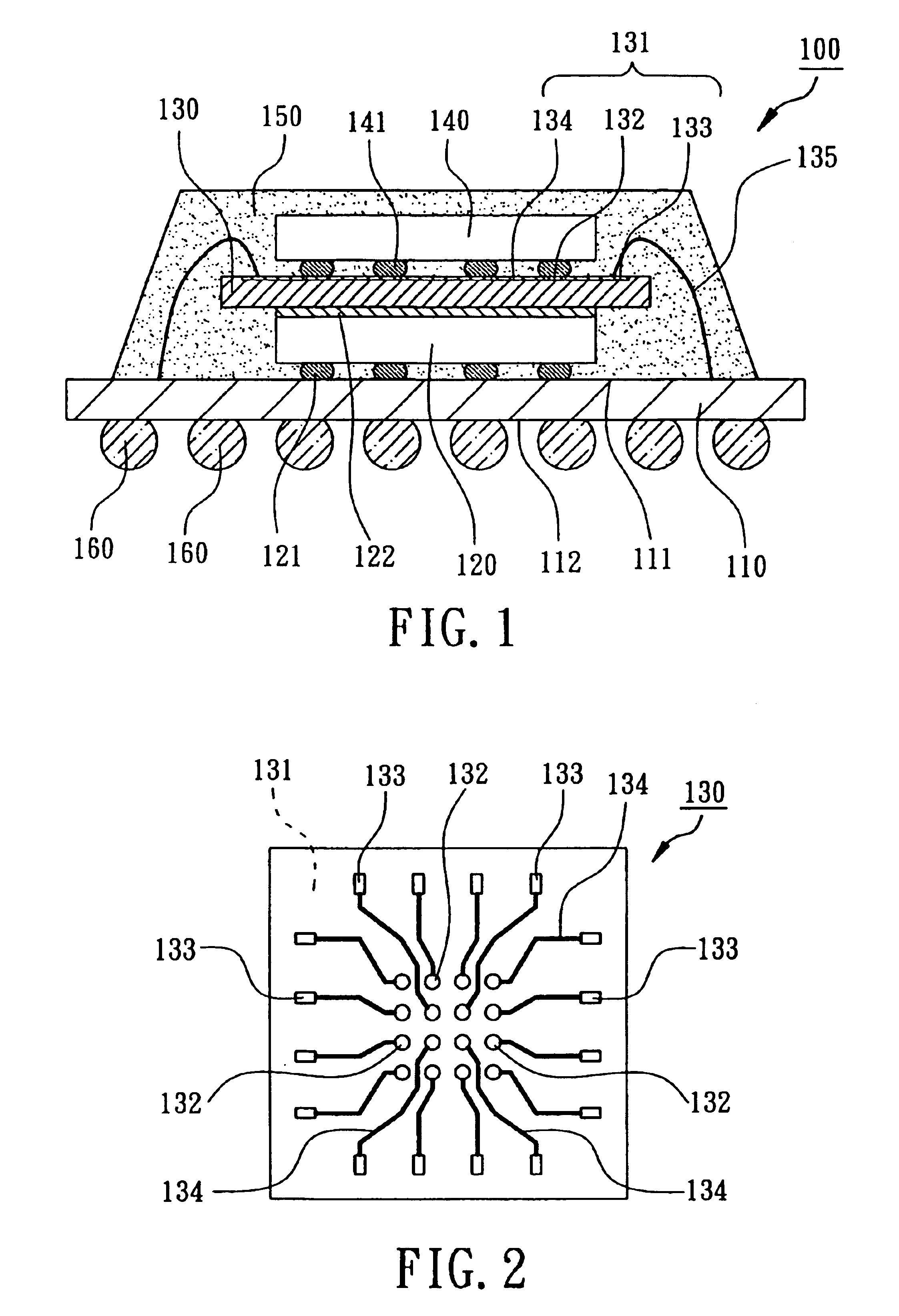

Chip-Stacked Package Structure

InactiveUS20080265397A1Extend length and radianSmall sizeSemiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

A chip stacked package structure and applications are provided, wherein the chip stacked package structure comprises a substrate, a first chip, a patterned circuit layer and a second chip. The substrate has a first surface and an opposite second surface. The first chip with a first active area and an opposite first rear surface is electrically connected to first surface of substrate by a flip chip bonding process. The patterned circuit layer set on the dielectric layer is electrically connected to the substrate via a bonding wire. The second chip set on the patterned circuit layer has a second active area and a plurality of second pads formed on the second active area, wherein the second bonding pad is electrically connected to the patterned circuit layer.

Owner:CHIPMOS TECH INC +1

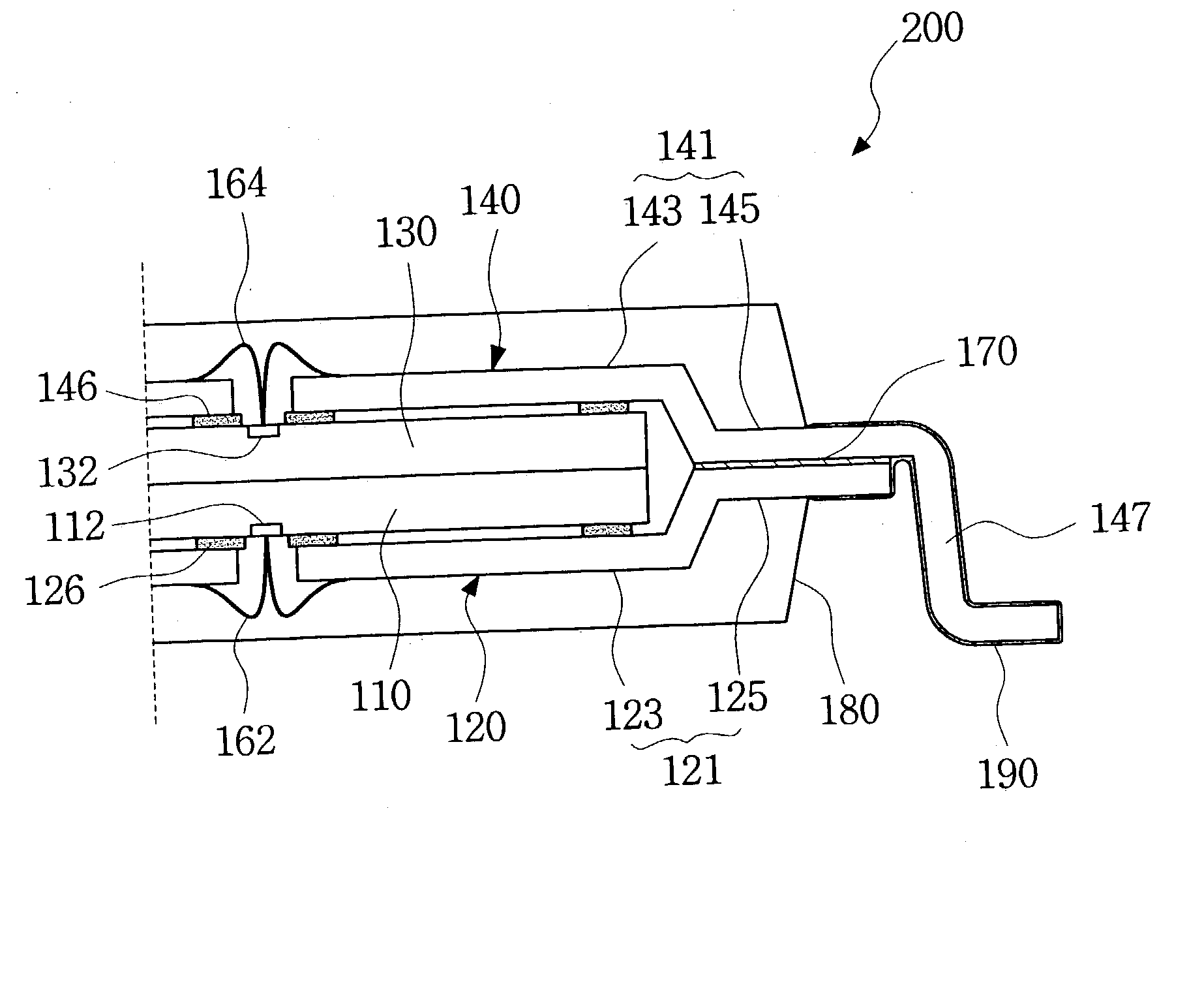

Chip stack with differing chip package types

InactiveUS6908792B2Semiconductor/solid-state device detailsSolid-state devicesChip stackingChip-scale package

A chip stack comprising a flex circuit which itself comprises a flexible substrate having opposed, generally planar top and bottom surfaces. Disposed on the top surface of the substrate in spaced relation to each other are at least first and second top conductive patterns. Similarly, disposed on the bottom surface of the substrate in spaced relation to each other are at least first and second bottom conductive patterns. The first top and bottom conductive patterns are electrically connected to each other, as are the second top and bottom conductive patterns. At least one top chip package including a first packaged chip is electrically connected to the first top conductive pattern, with at least one bottom chip package including a second packaged chip being electrically connected to the second bottom conductive pattern. The substrate is folded such that the second top conductive pattern is electrically connected to the top chip package.

Owner:M RED INC

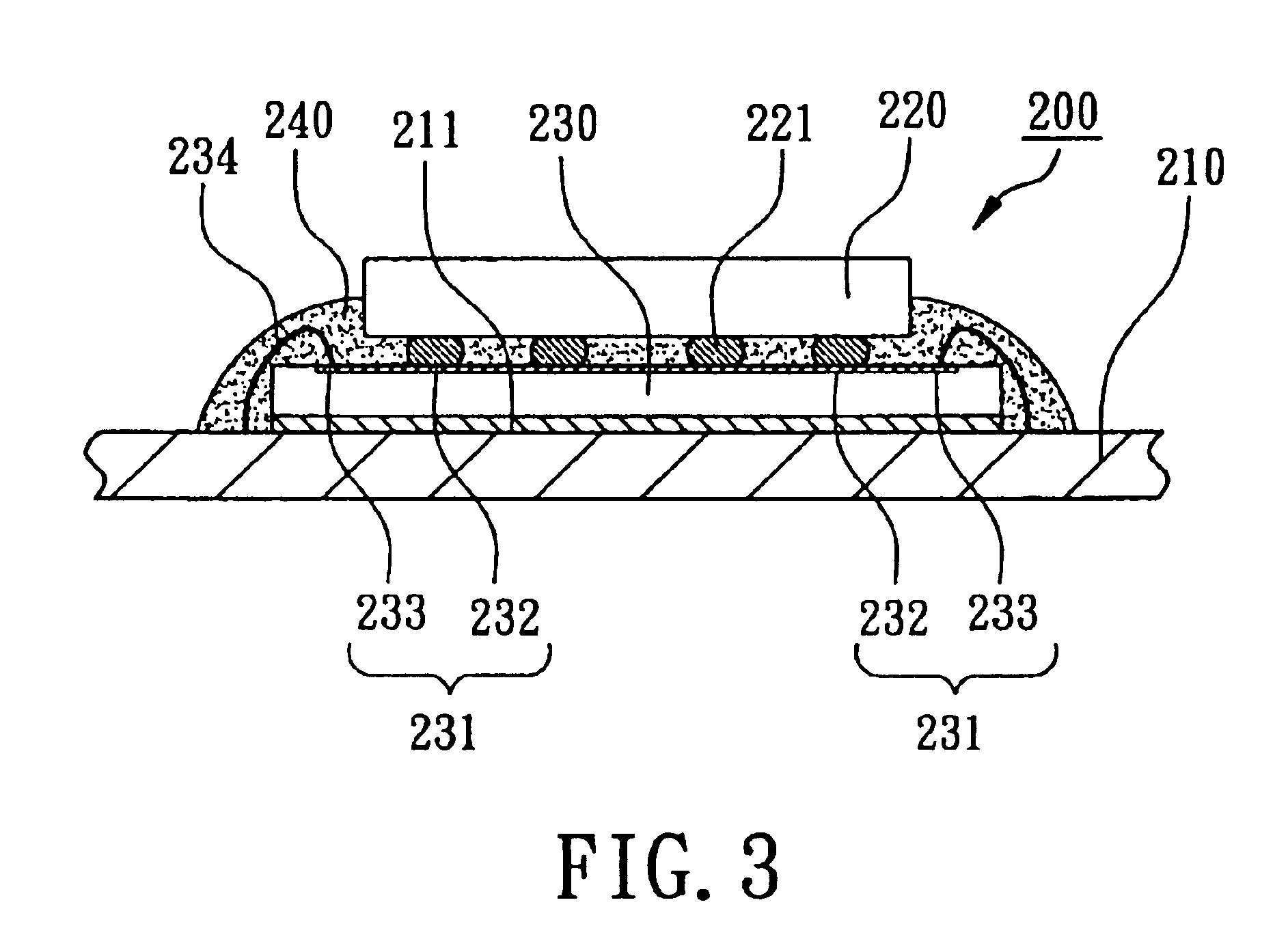

Multi-chip stack flip-chip package

ActiveUS6861761B2Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

A multi-chip stack flip-chip package comprises a substrate and a chip assembly on the substrate. The chip assembly includes a dummy chip and a flip chip. The dummy chip has a redistribution layer that has a plurality of bump pads for mounting the flip chip, a plurality of peripheral pads for electrically connecting to the substrate, and a plurality of integrated circuit traces connecting the bump pads with the peripheral pads. The dummy chip is disposed between the flip chip and the substrate as an electrically connecting interface between the flip chip and the substrate for multi-chip flip-chip stack and fine pitch flip-chip mounting.

Owner:ADVANCED SEMICON ENG INC

Method of Creating Alignment/Centering Guides for Small Diameter, High Density Through-Wafer Via Die Stacking

ActiveUS20090255705A1Line/current collector detailsSemiconductor/solid-state device detailsHigh densityElectrical and Electronics engineering

A method if provided for forming a die stack. The method includes forming a plurality of through-wafer vias and a first plurality of alignment features in a first die. A second plurality of alignment features is formed in a second die, and the first die is stacked on the second die such that the first plurality of alignment features engage the second plurality of alignment features. A method of manufacturing a die stack is also provided that includes forming a plurality of through-wafer vias on a first die, forming a plurality of recesses on a first die, and forming a plurality of protrusions on a second die. A die stack and a system are also provided.

Owner:MICRON TECH INC

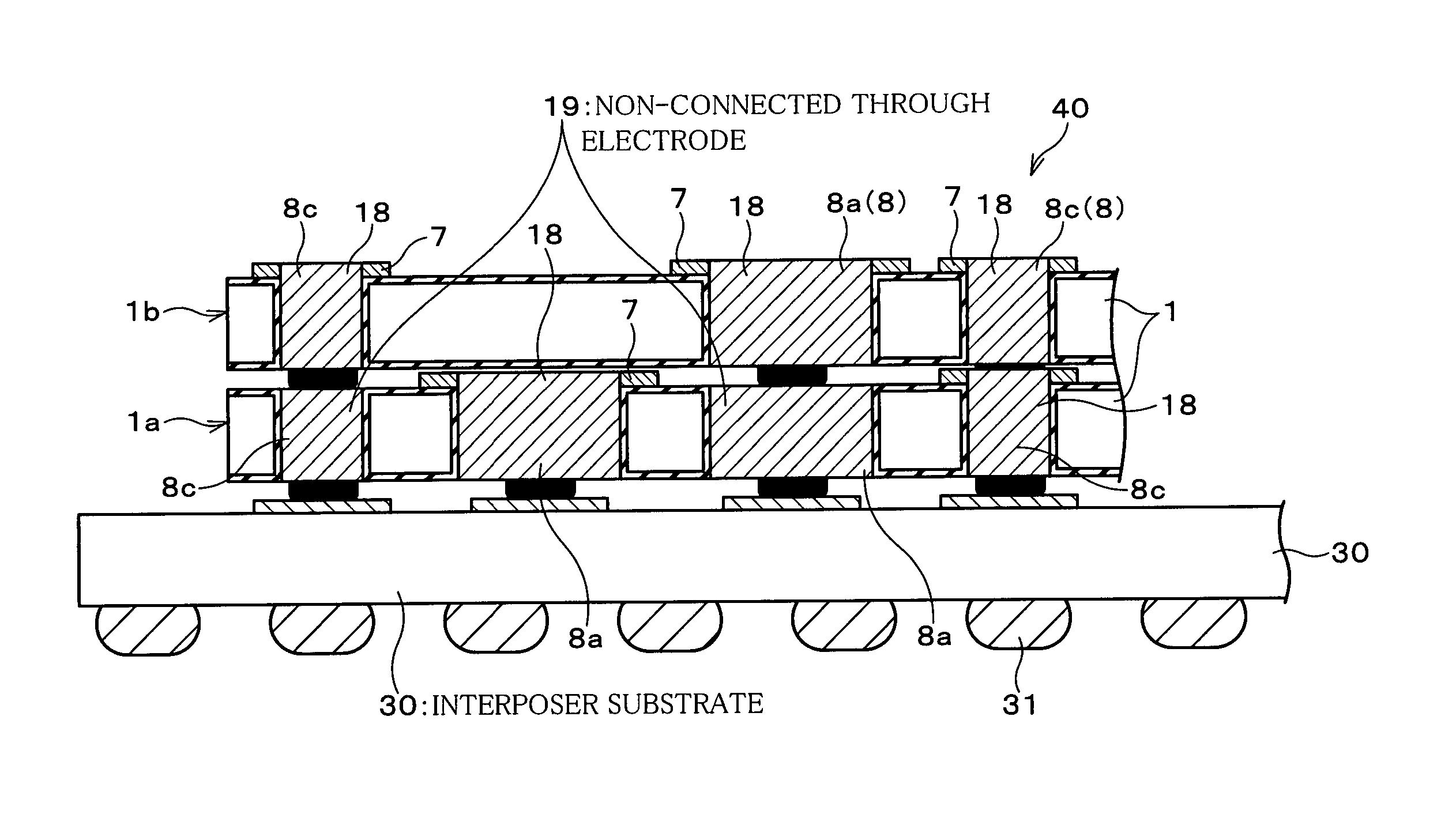

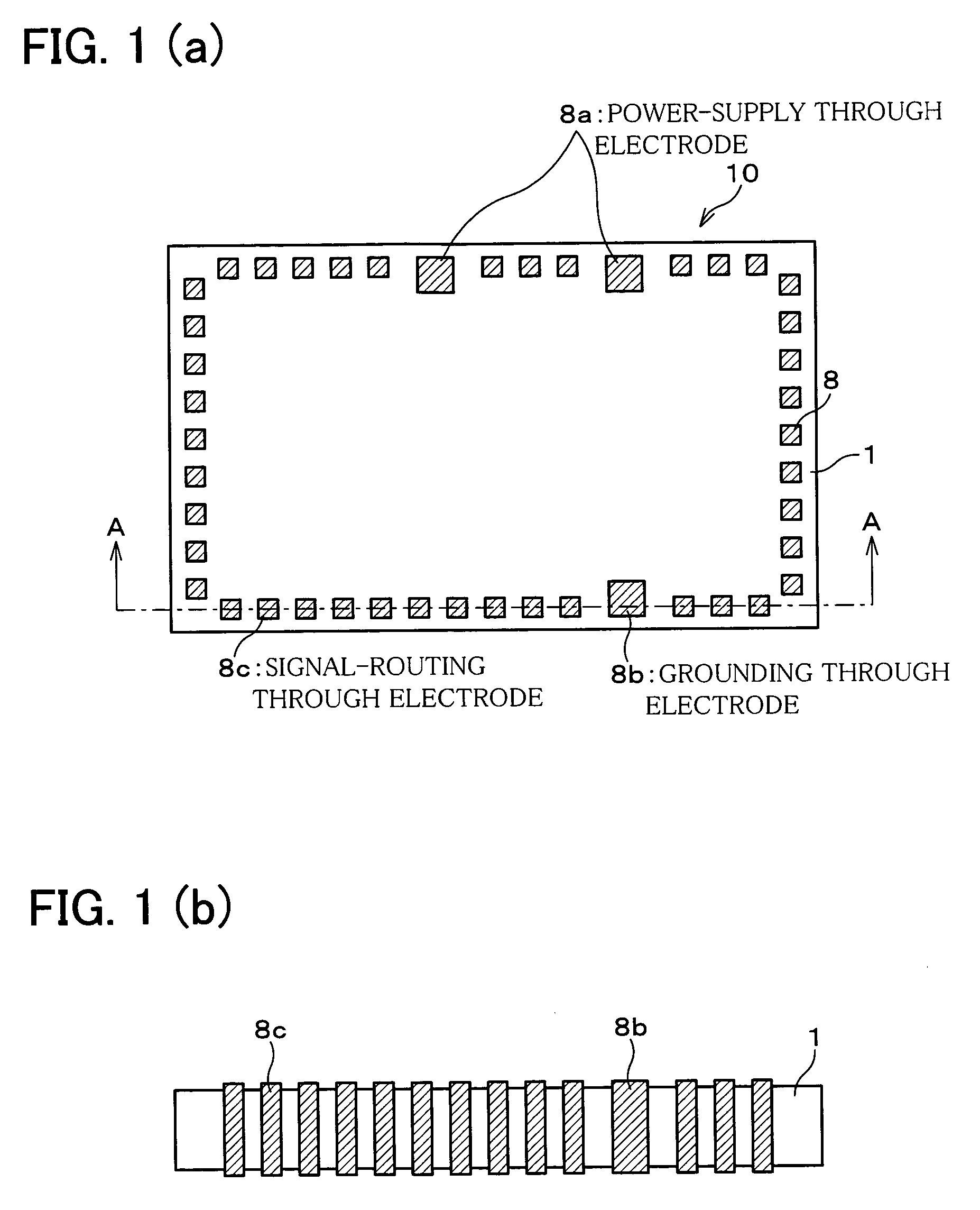

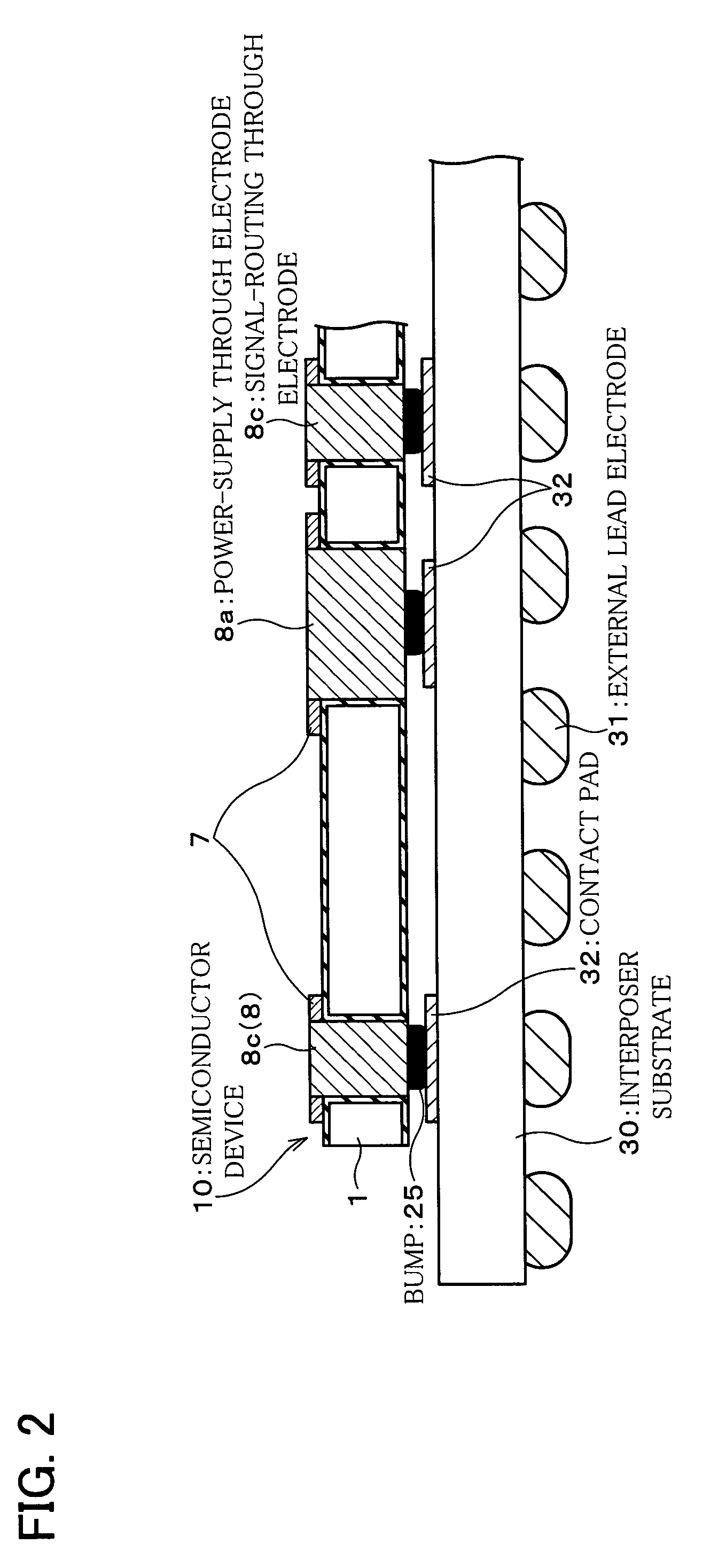

Semiconductor device and chip-stack semiconductor device

ActiveUS7115972B2Delayed deteriorationReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceSignal routing

A semiconductor device has multiple power-supply through electrodes, grounding through electrodes, and signal-routing through electrodes made through a semiconductor chip. The power-supply through electrodes, the grounding through electrodes, and the signal-routing through electrodes differ mutually in cross-sectional area. Hence, a semiconductor device and a chip-stack semiconductor device are provided which are capable of preventing the electrodes' resistance from developing excessive voltage drop, heat, delay, and loss, and also from varying from one electrode to the other.

Owner:SAMSUNG ELECTRONICS CO LTD

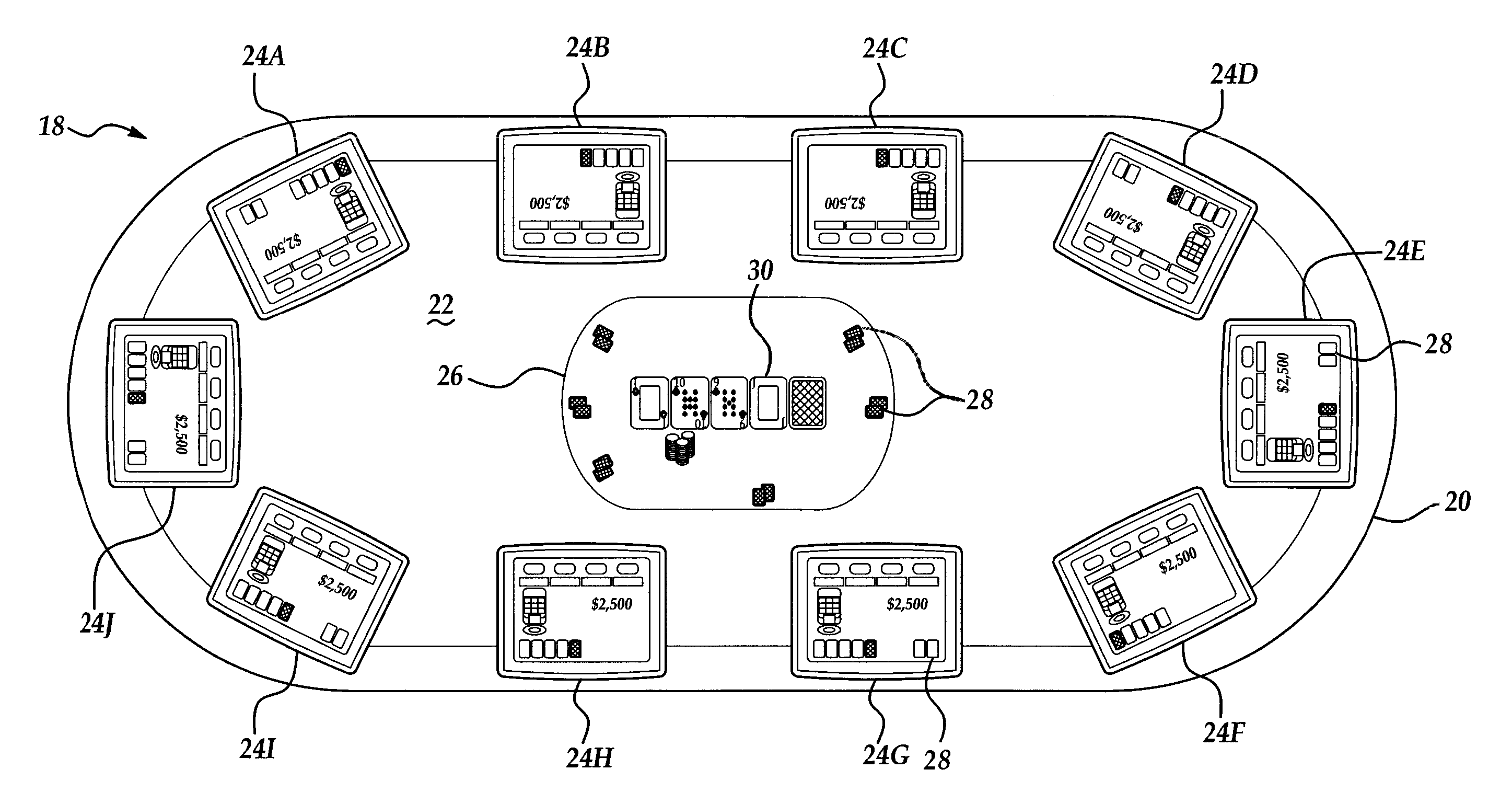

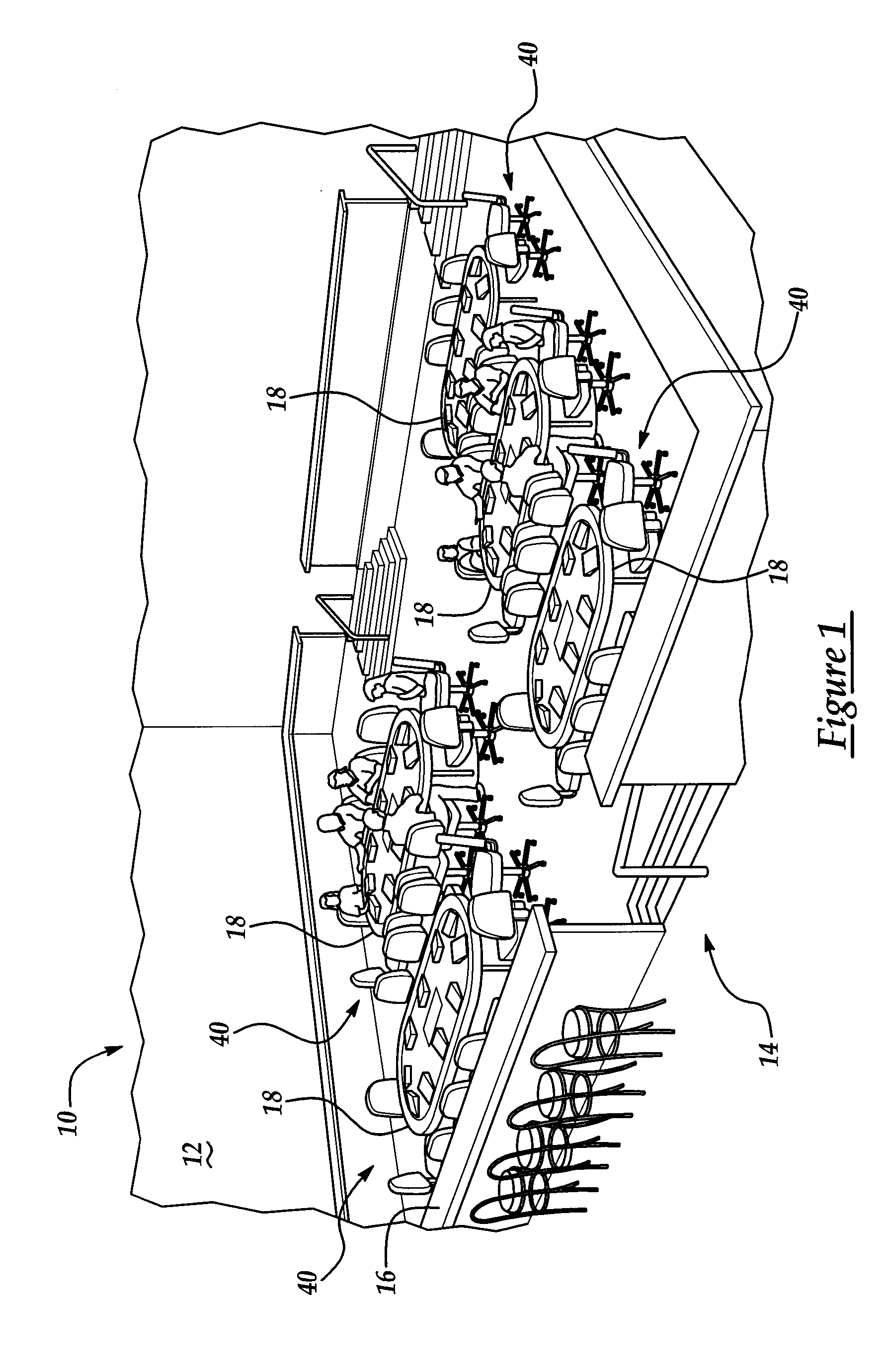

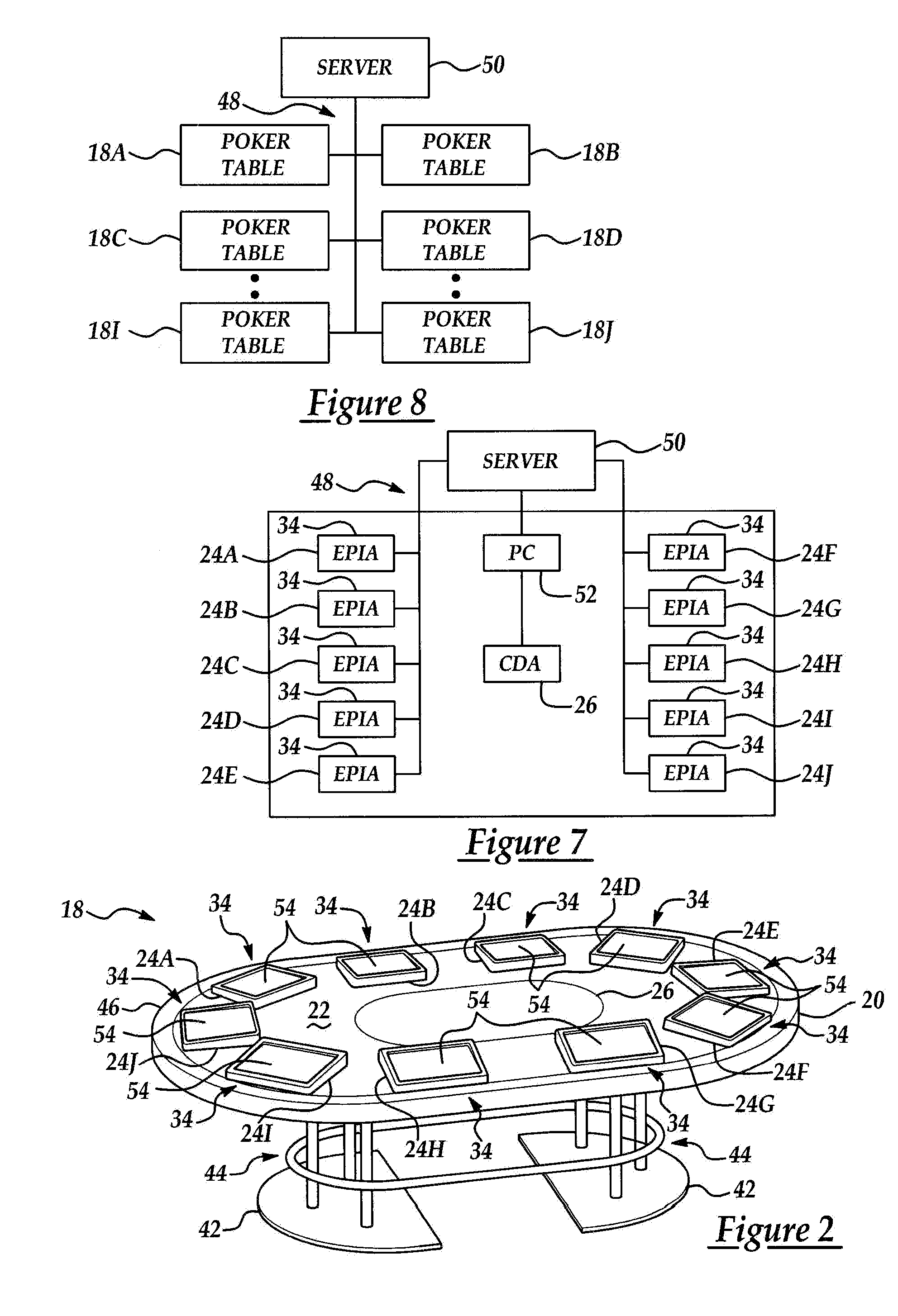

System and method for providing a host console for adjust a pot or chip stack of a player of an electronic card game

InactiveUS20060287066A1Apparatus for meter-controlled dispensingVideo gamesComputer hardwareDisplay device

A host console and method for use with an electronic card table is disclosed. The electronic card table has plurality of electronic player interaction areas located around a periphery of the table and a game computer. The game computer administers the electronic card table and is coupled to the plurality of electronic player interaction areas. The host console is connected to the game computer. The host console includes a host display, a host interface, and a host controller. The host controller is coupled to the host display and the host interface and allows the host to replay a previous hand of an electronic card game.

Owner:POKERTEK

Air channel interconnects for 3-d integration

ActiveUS20110031633A1Remove heatSemiconductor/solid-state device detailsSolid-state devicesBond interfaceWafer bonding

A three-dimensional (3D) chip stack structure and method of fabricating the structure thereof are provided. The 3D chip stack structure includes a plurality of vertically stacked chips which are interconnected and bonded together, wherein each of the vertically stacked chips include one or more IC device strata. The 3D chip stack structure further includes an air channel interconnect network embedded within the chip stack structure, and wherein the air channel interconnect network is formed in between at least two wafers bonded to each other of the vertically stacked wafers and in between at least two bonded wafers of the vertically stacked wafers at a bonding interface thereof. In addition, the 3D chip stack structure further includes one or more openings in a peripheral region of the chip stack structure that lead into and out of the air channel interconnect network, so that air can flow into and out of the air channel interconnect network through the one or more openings to remove heat from the chip stack structure.

Owner:GLOBALFOUNDRIES US INC

Method for manufacturing wafer level chip stack package

ActiveUS20050280160A1High mechanical strengthImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

Provided is a method for manufacturing WLCSP devices that includes preparing at least two wafers, each wafer having a plurality of corresponding semiconductor chips, each semiconductor chip having through electrodes formed in the peripheral surface region, forming or applying a solid adhesive region to a central surface region, stacking a plurality of wafers and attaching corresponding chips provided on adjacent wafers with the solid adhesive region and connecting corresponding through electrodes of adjacent semiconductor chips, dividing the stacked wafers into individual chip stack packages, and injecting a liquid adhesive into a space remaining between adjacent semiconductor chips incorporated in the resulting chip stack package. By reducing the likelihood of void regions between adjacent semiconductor chips, it is expected that a method according to the exemplary embodiments of the present invention exhibit improved mechanical stability and reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

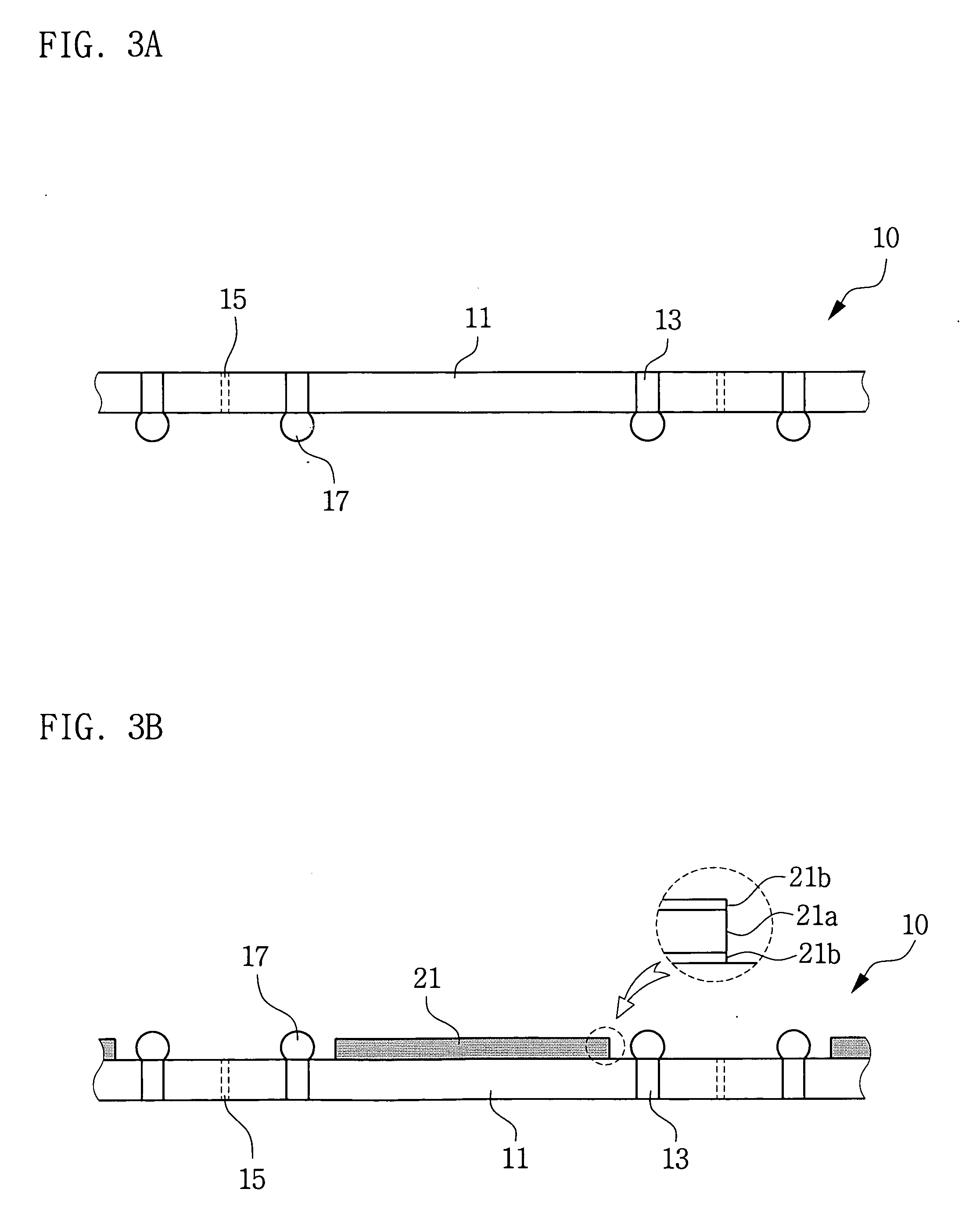

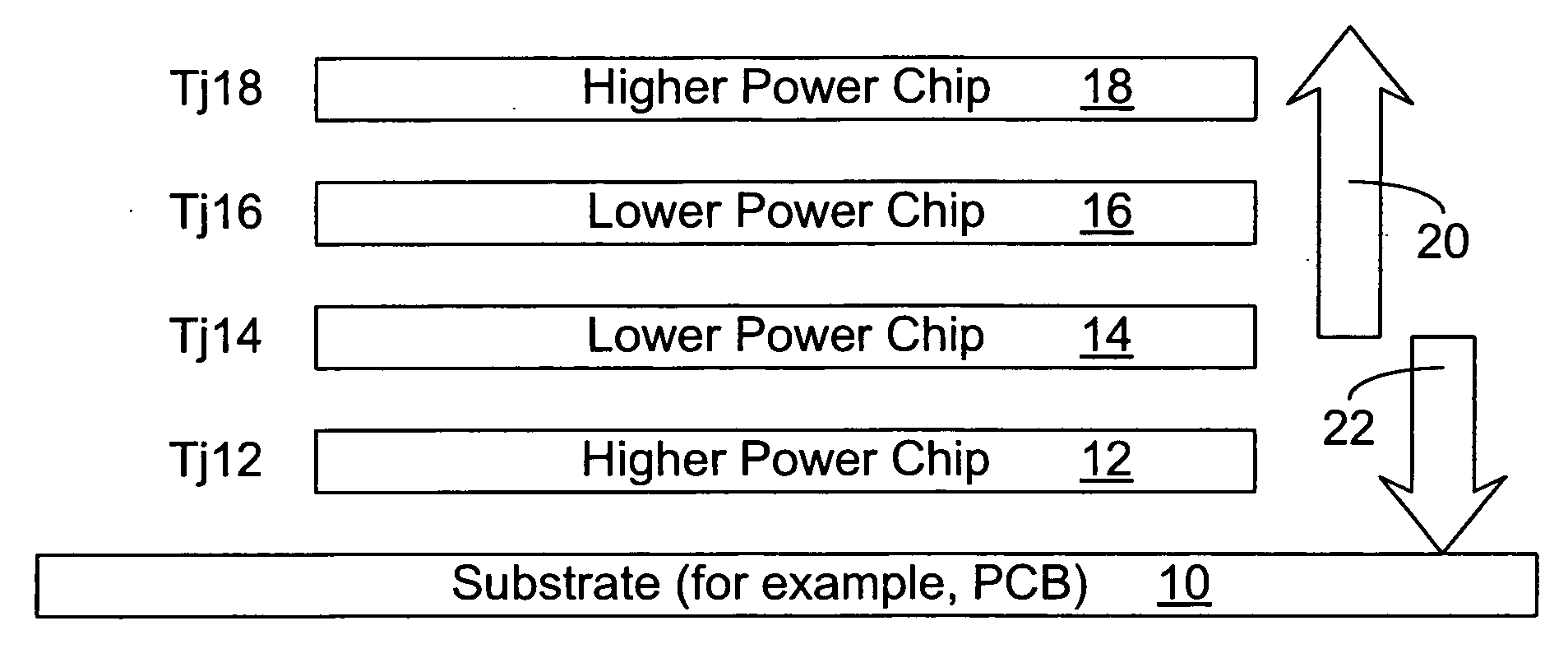

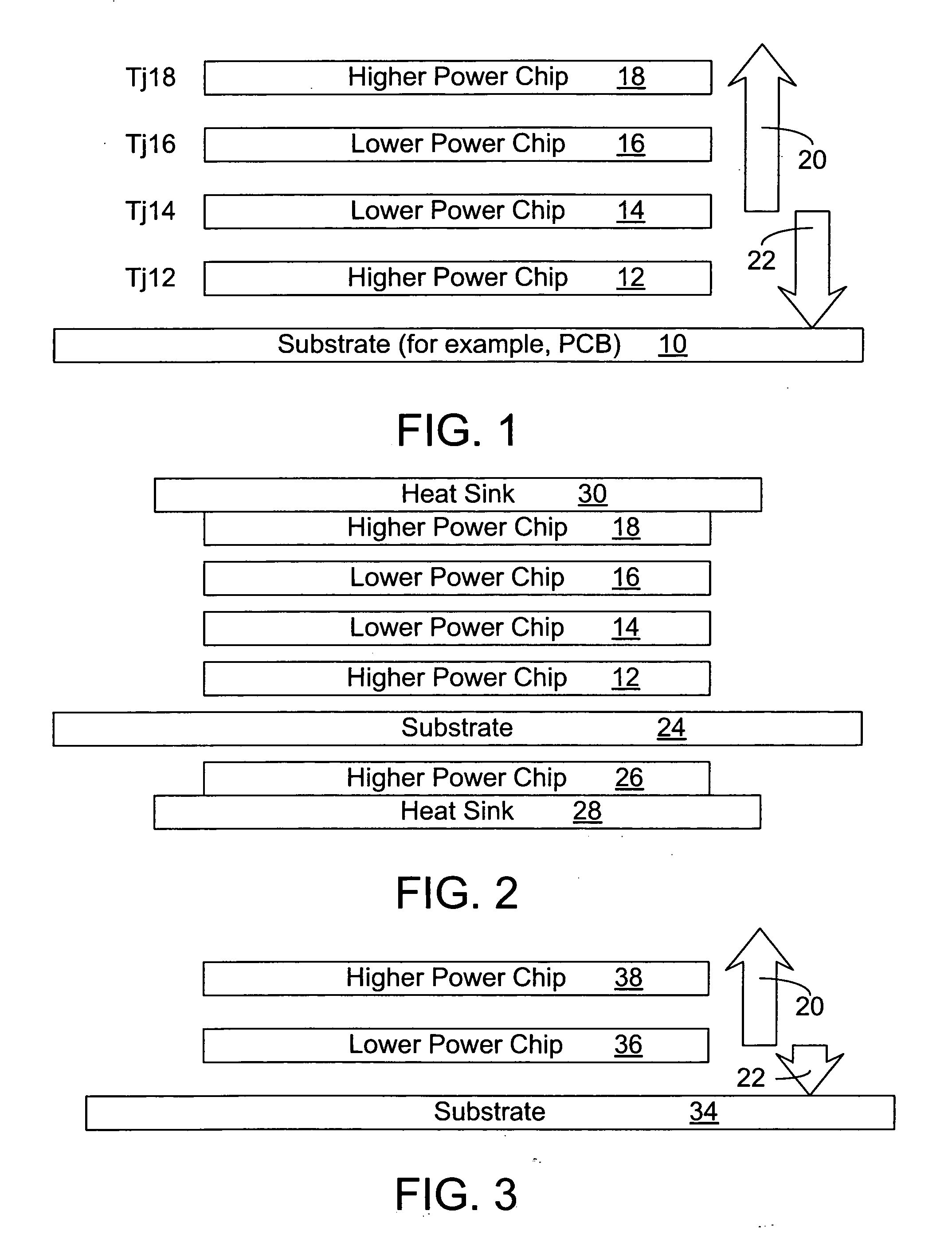

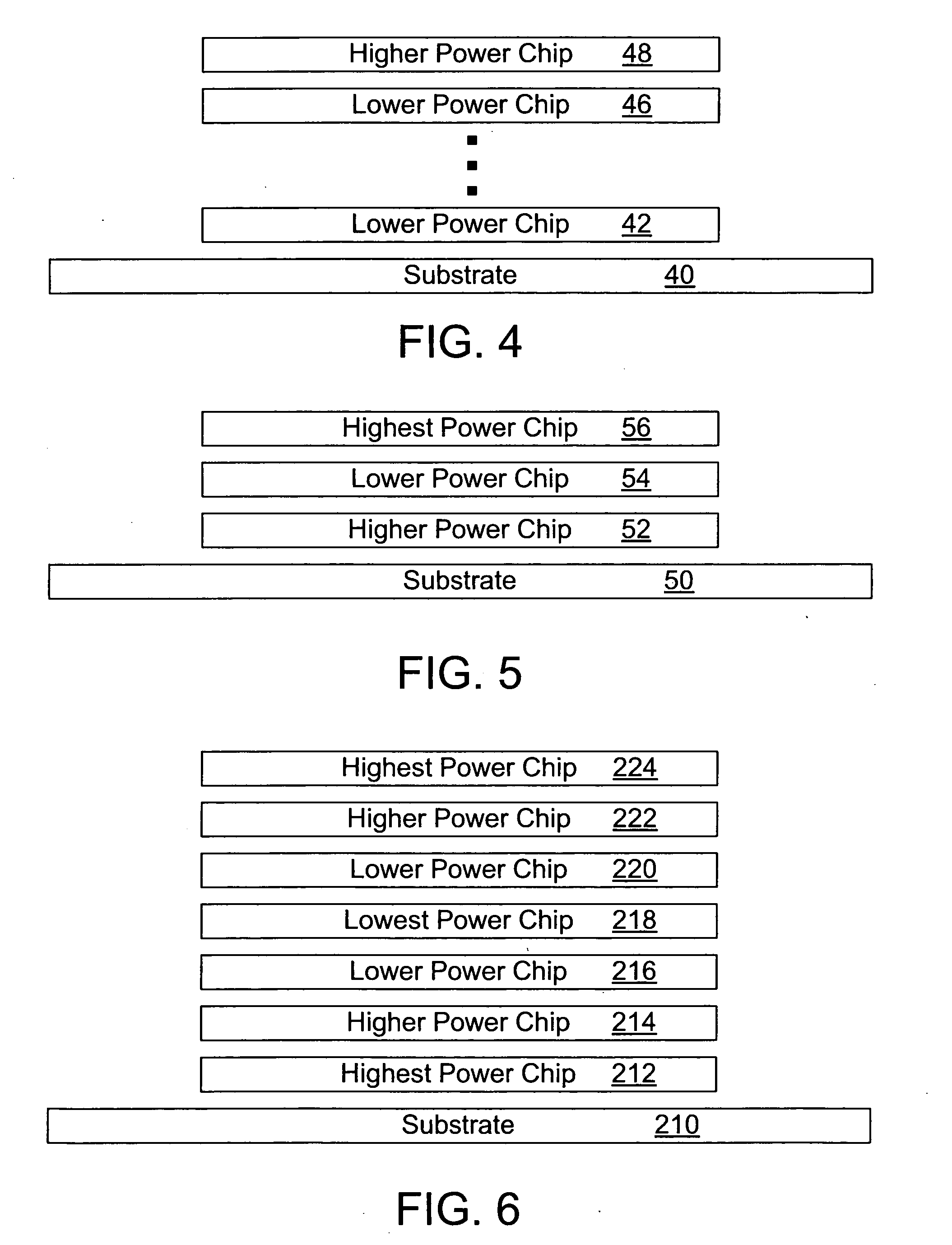

Chip stack with a higher power chip on the outside of the stack

InactiveUS20070290333A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringChip stacking

In some embodiments, a system includes a circuit board, a first chip, and a second chip stacked on the first chip. The first chip is coupled between the circuit board and the second chip, and the first chip includes circuitry to repeats commands the first chip receives to the second chip. Other embodiments are described.

Owner:INTEL CORP