Apparatus and Methods for Constructing Semiconductor Chip Packages with Silicon Space Transformer Carriers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

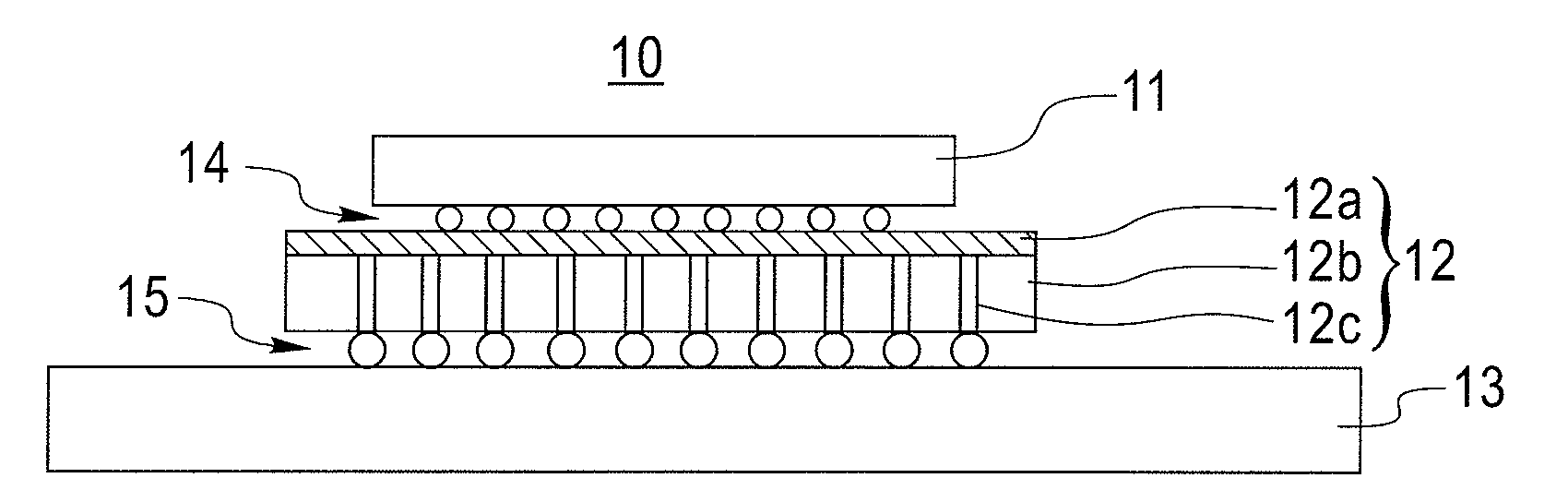

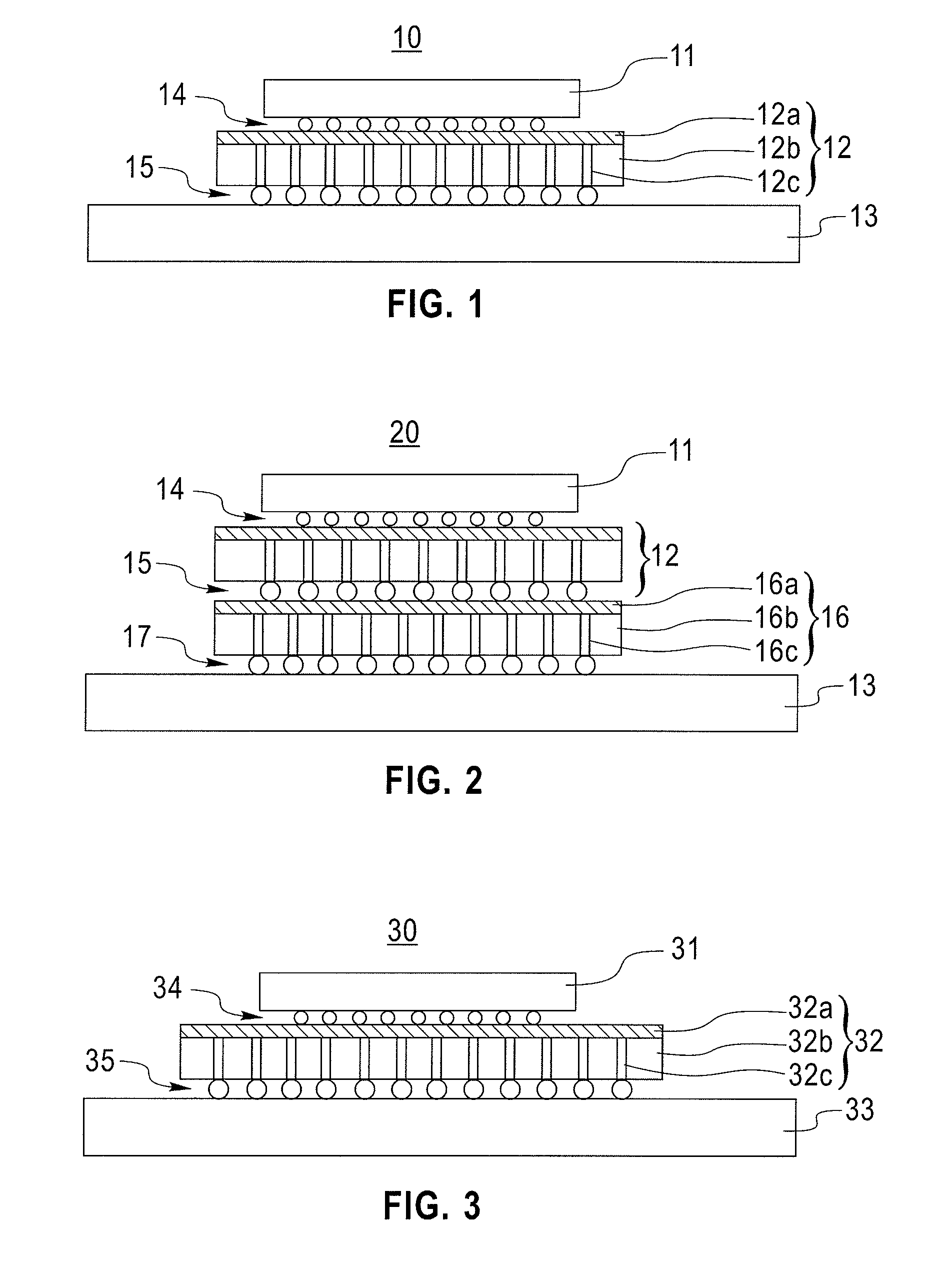

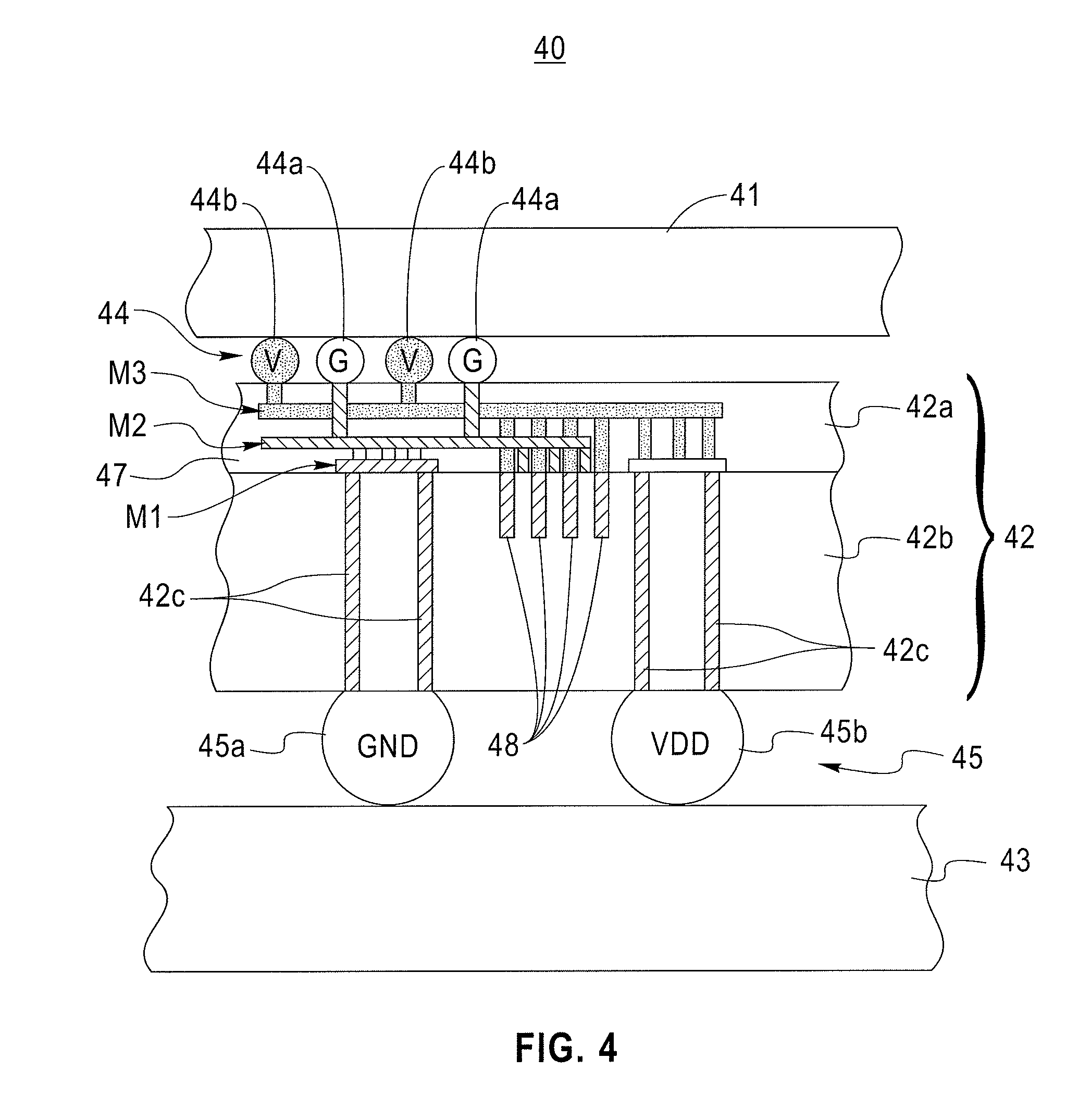

[0025]Exemplary embodiments of the invention as discussed herein generally include apparatus and methods for high density packaging of semiconductor chips using silicon space transformer chip level package structures. For instance, FIGS. 1˜4 and 5A˜5C are high-level schematic illustrations of various chip package structures in which high-density chip level packaging may be realized using one or more thinned silicon space transformer substrate layers. As explained in further detail below, silicon space transformer package structures according to exemplary embodiments of the invention may utilize state of the art silicon manufacturing techniques which follow CMOS back-end-of line design rules to realize low-cost fabrication of silicon space transformer package structures having high density wiring and conductive through-via interconnects which provide space transformation using one or more thinned silicon space transformer substrate layers for high I / O density packaging of one or more...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More