Multi-chip stacked devices

a technology of multi-chips and devices, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problem of primarily limited density of ic packages

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

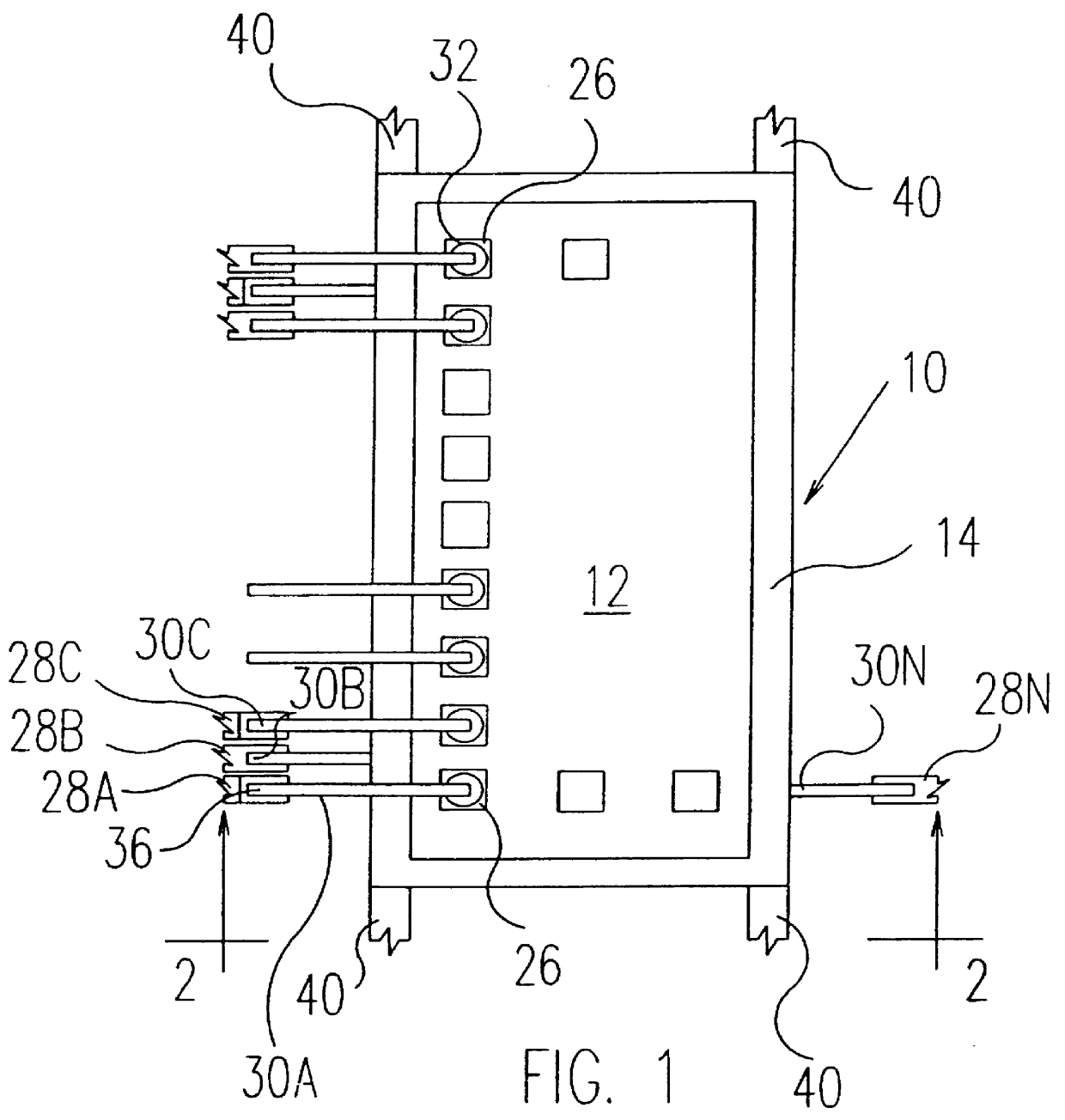

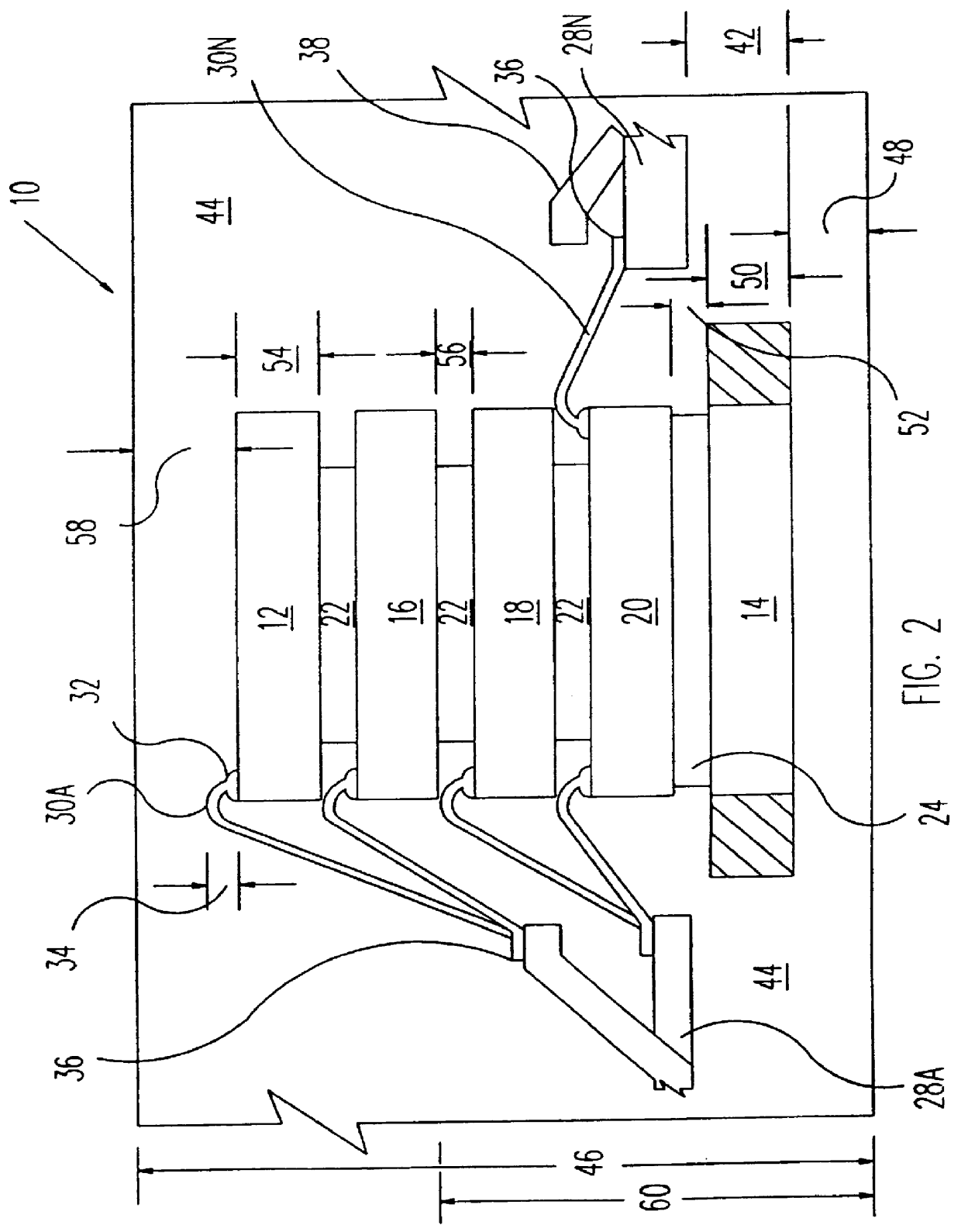

Referring to FIG. 1, the stacked die device 10 is shown prior to encapsulation disclosing the top die 12 mounted the paddle 14 and other dies 16, 18, and 20 (FIG. 2) which are adhesively connected to each other by a controlled-thickness thermoplastic-adhesive layer at 22. Thermoplastic indicating the adhesive sets at an elevated temperature. The group of four dies are attached to the paddle 14 by a controlled thin-adhesive layer 24.

Each of the die bonding pads 26 in double rows are electrically connected to multiple lead fingers 28A, 28B, 28C . . . 28N by thin (0.001 inch) gold or aluminum wires 30A, 30B, 30C . . . 30N; gold being the preferred metal. For clarity, only part of the 18 bonding pads, wires, and fingers are shown. The critical bonding method used at the die end pad 26 is ultrasonic ball bond as named by the shape of the bond as at 32. This first-installed bond and formed gold wire are low-loop wire bonds as seen at critical dimension 34, as will be described later.

The o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More