Patents

Literature

2563 results about "Die bonding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Die bonding. Die bonding (die attach) is the process of attaching a die (or chip) to a substrate, package, or another die. Palomar machines enable two levels of attachment: in situ eutectic die attach and epoxy die attach, and en masse void-free die attach.

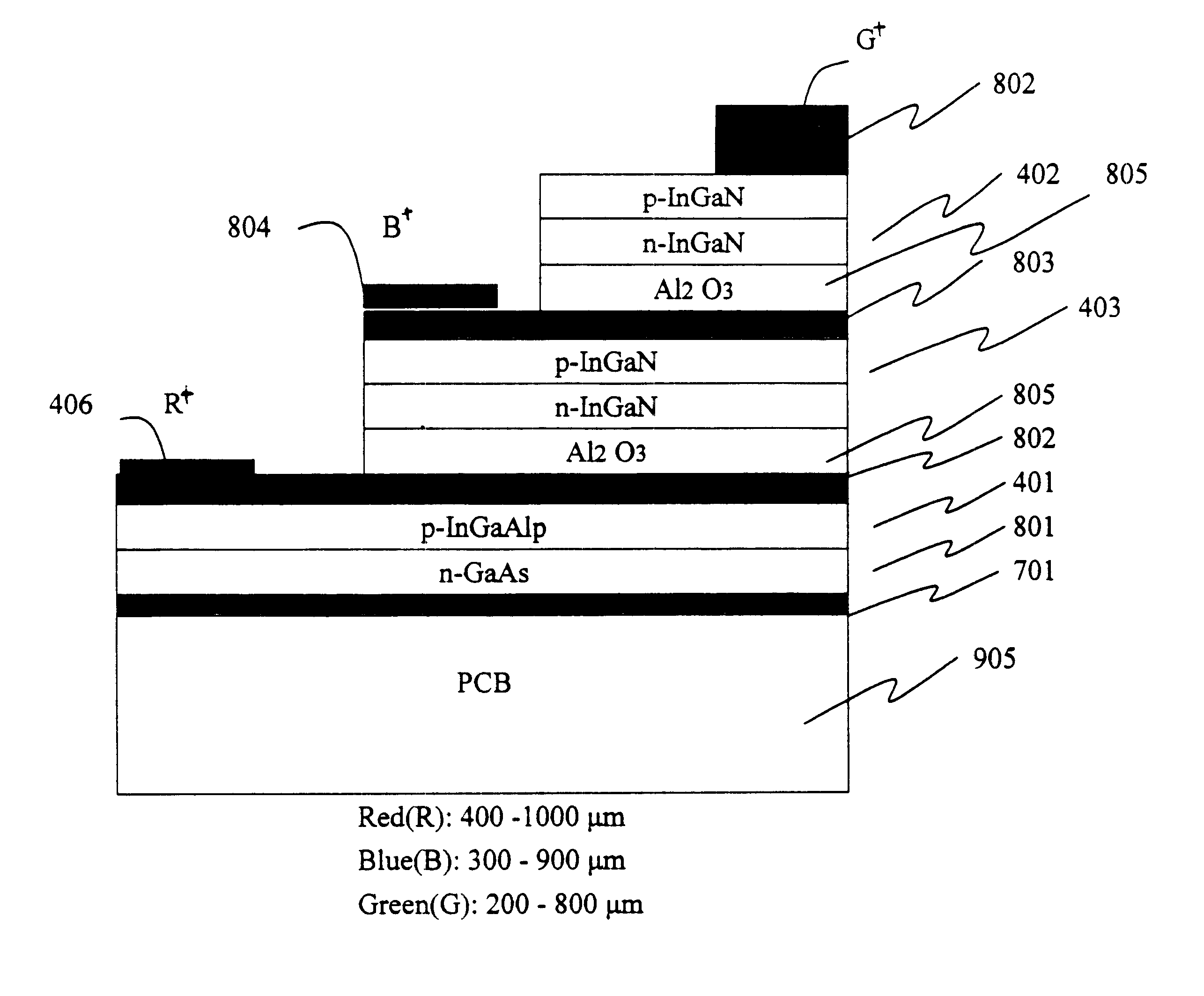

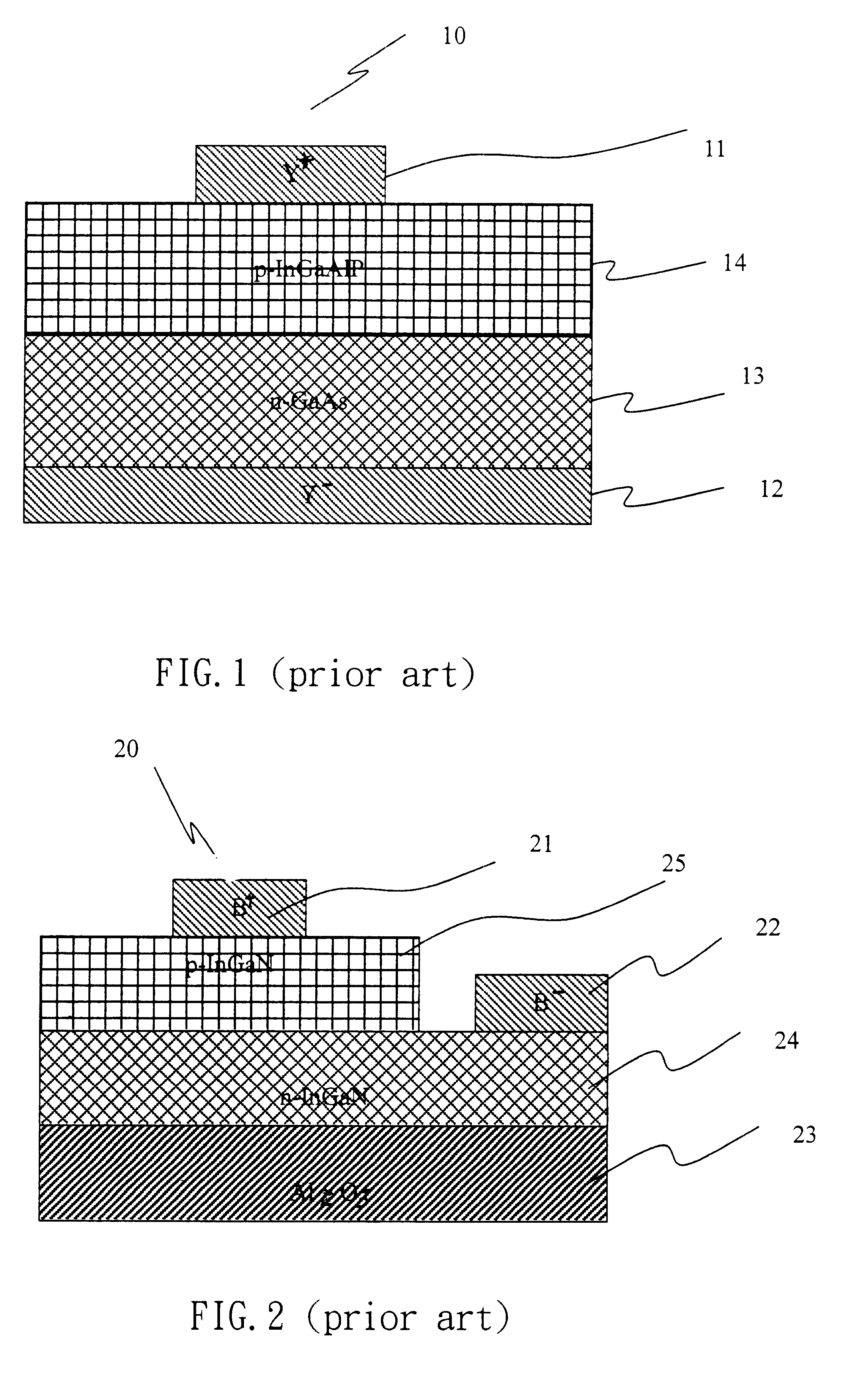

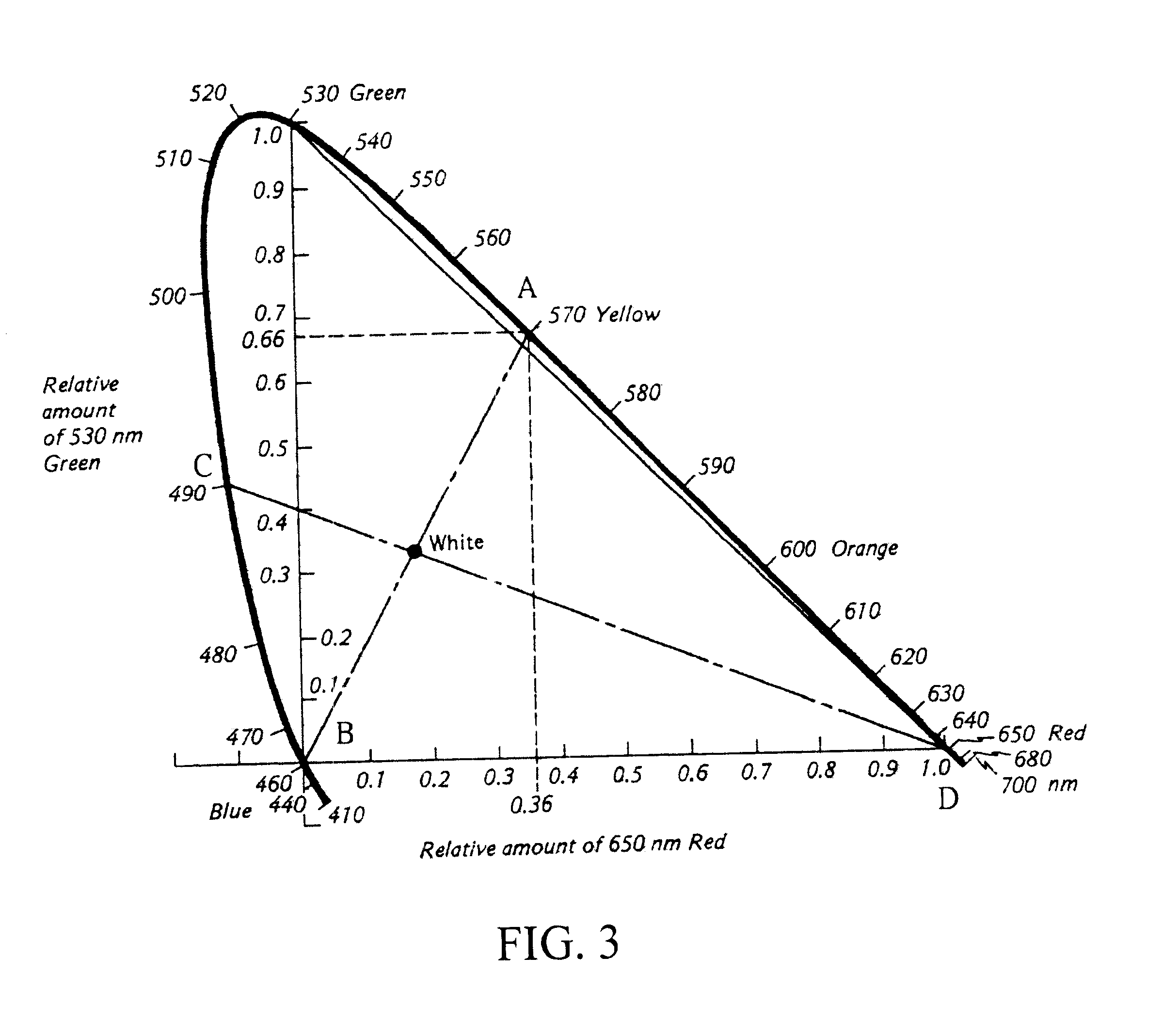

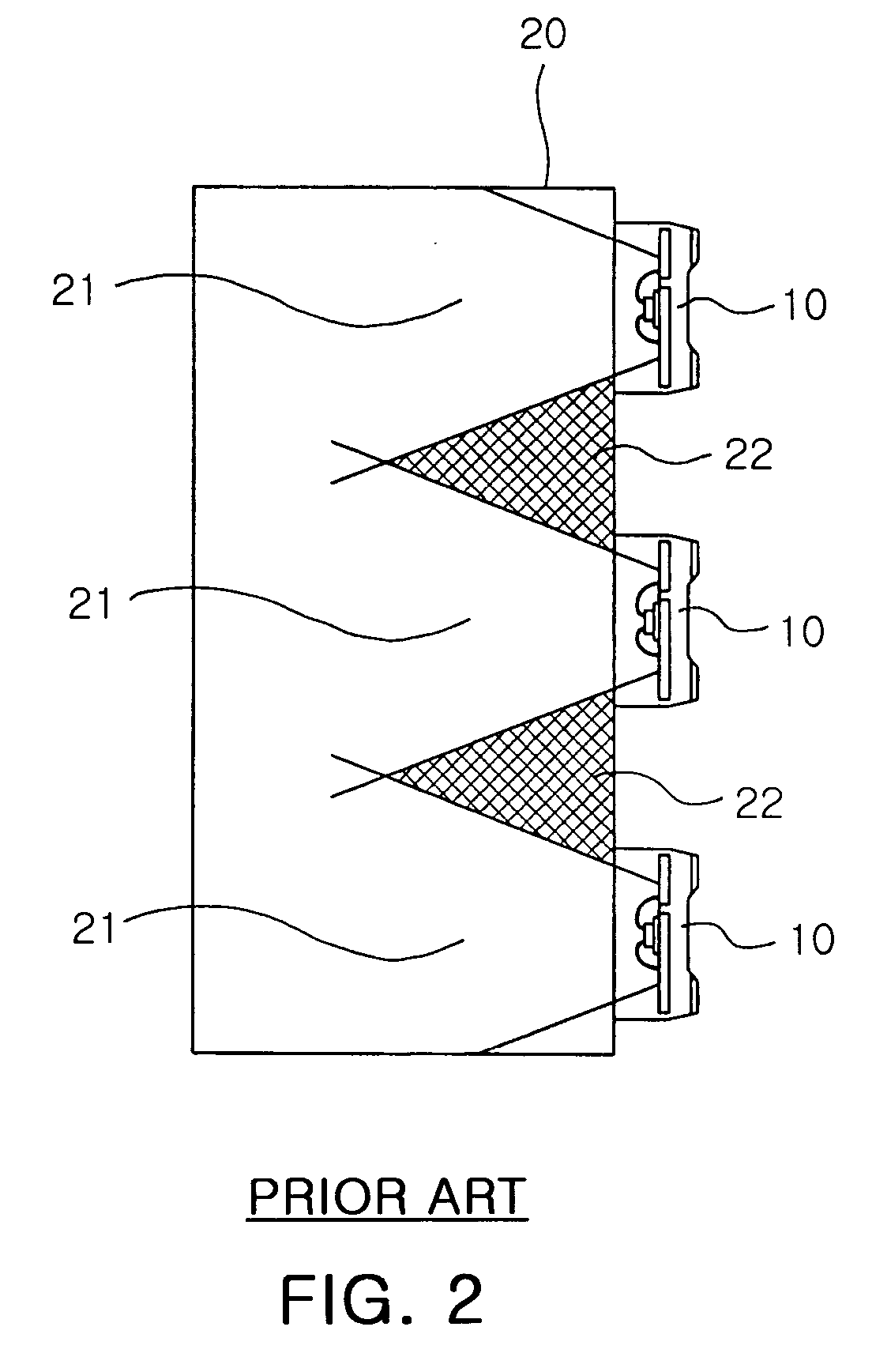

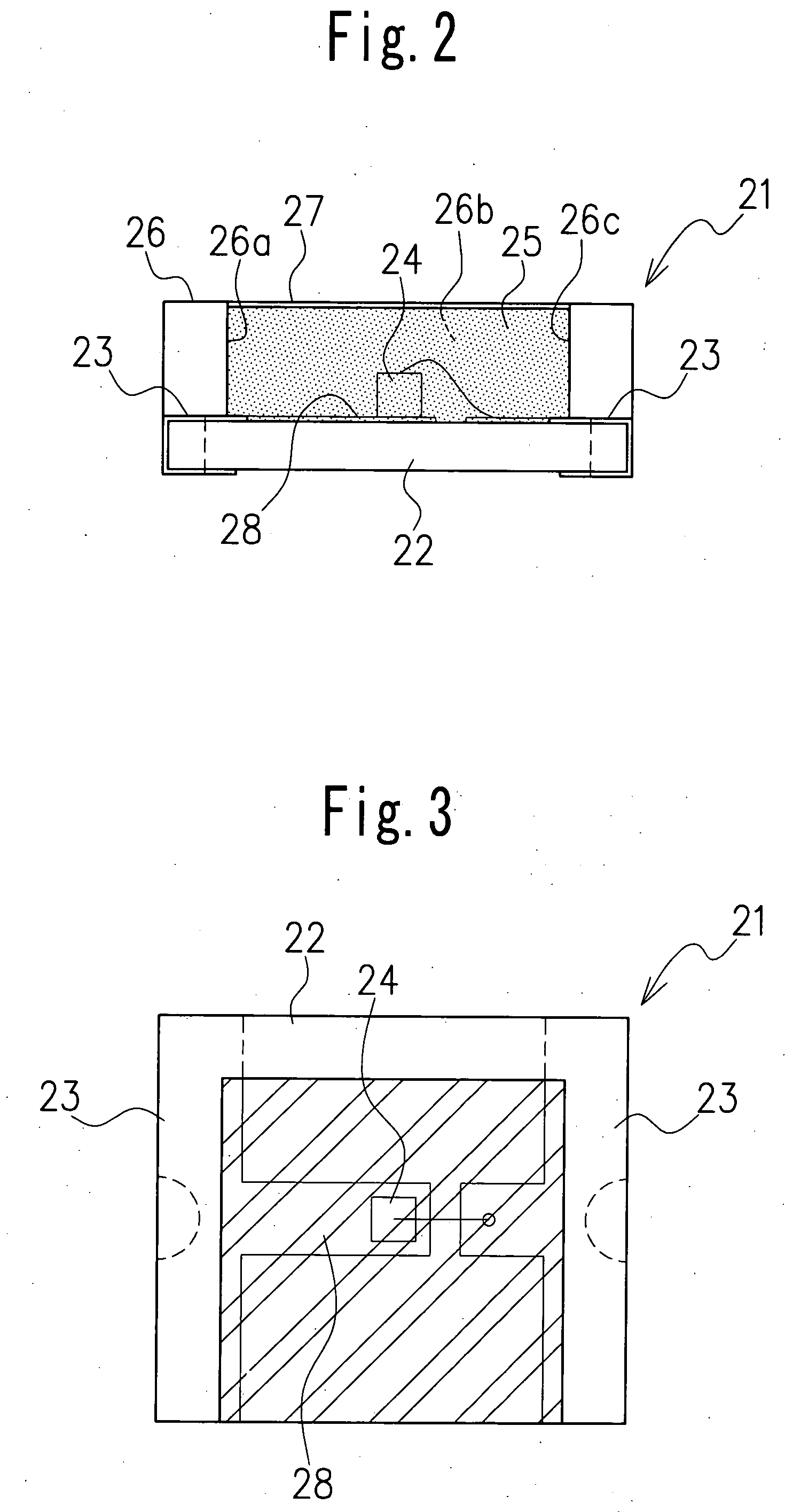

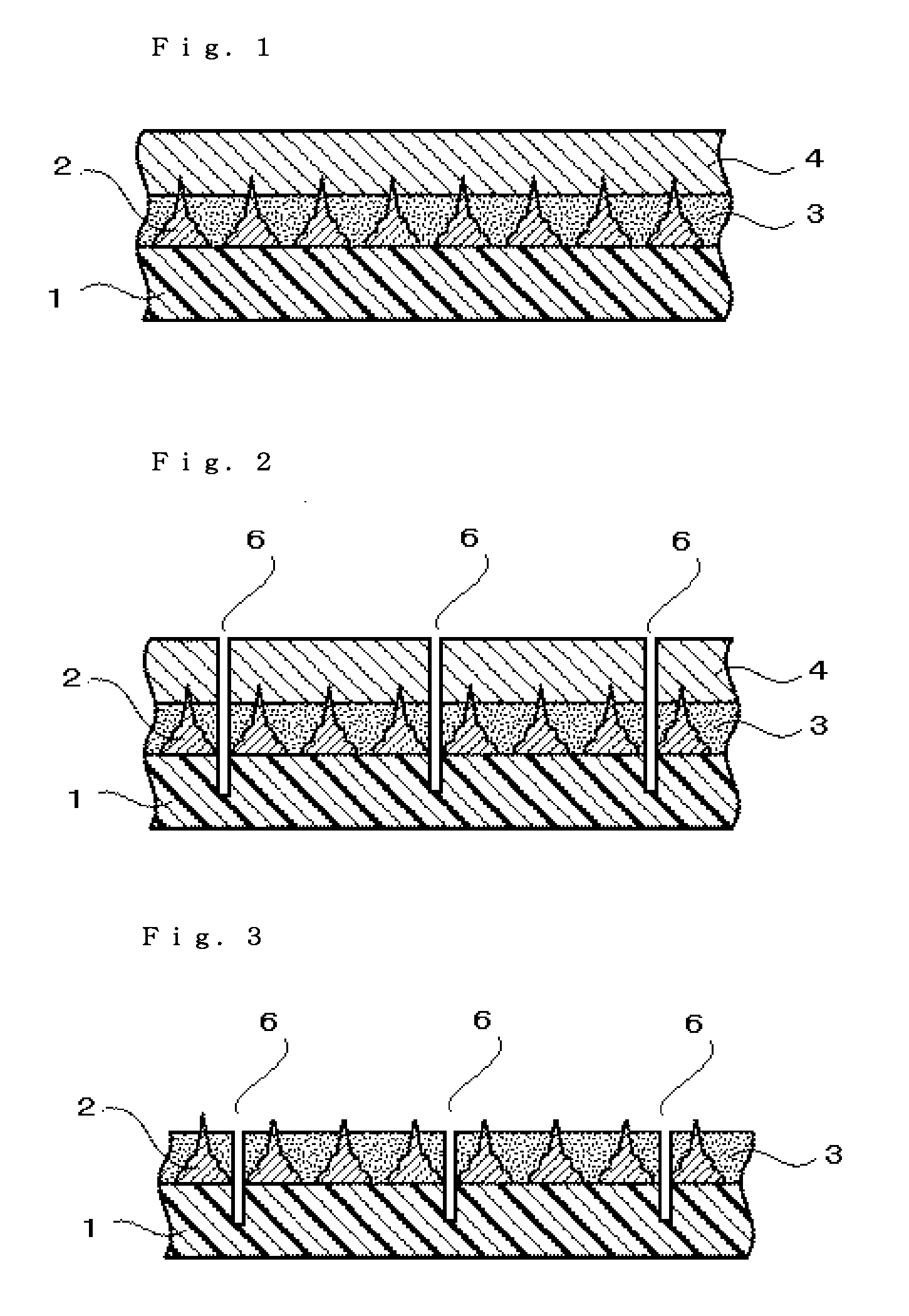

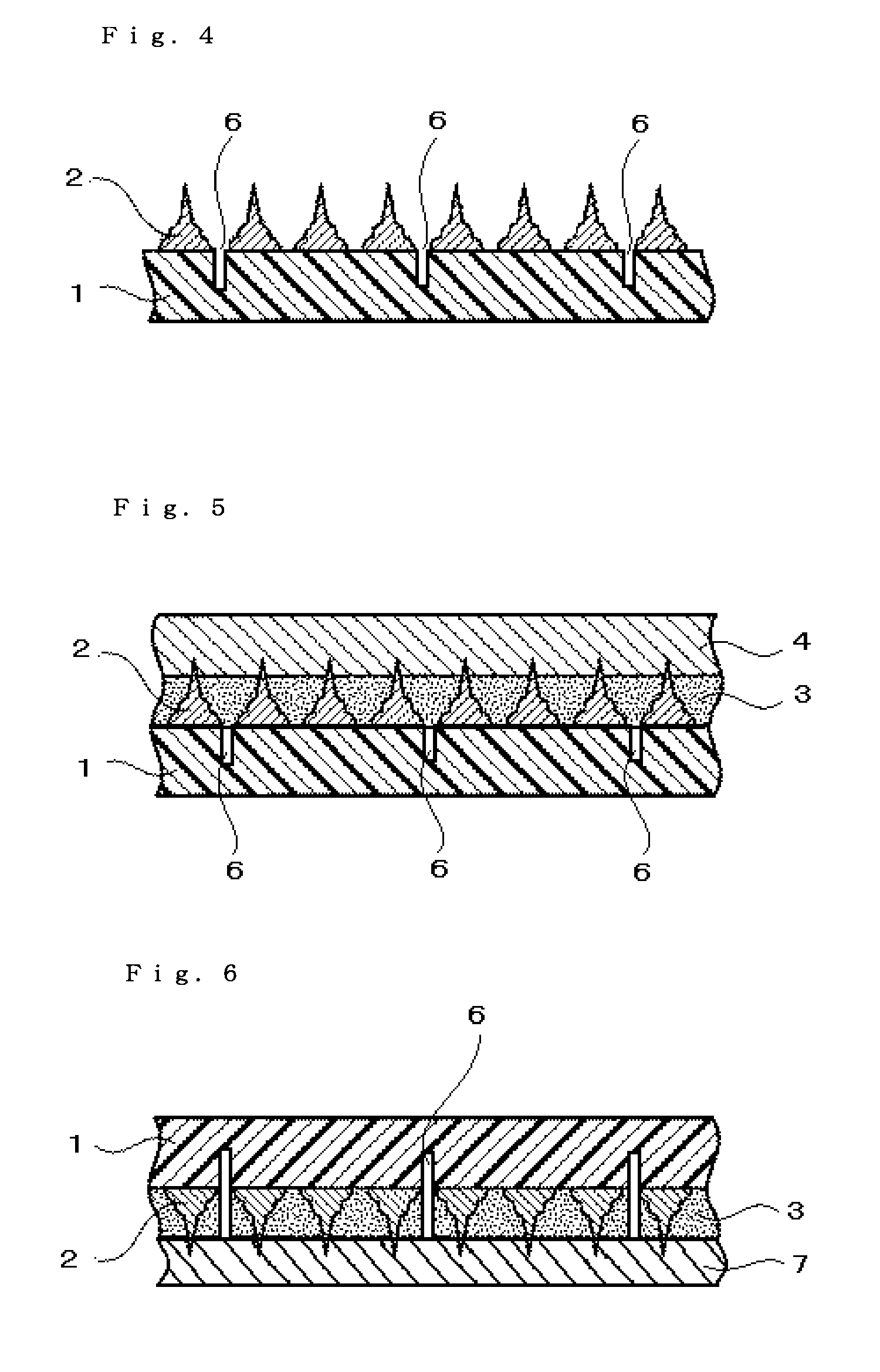

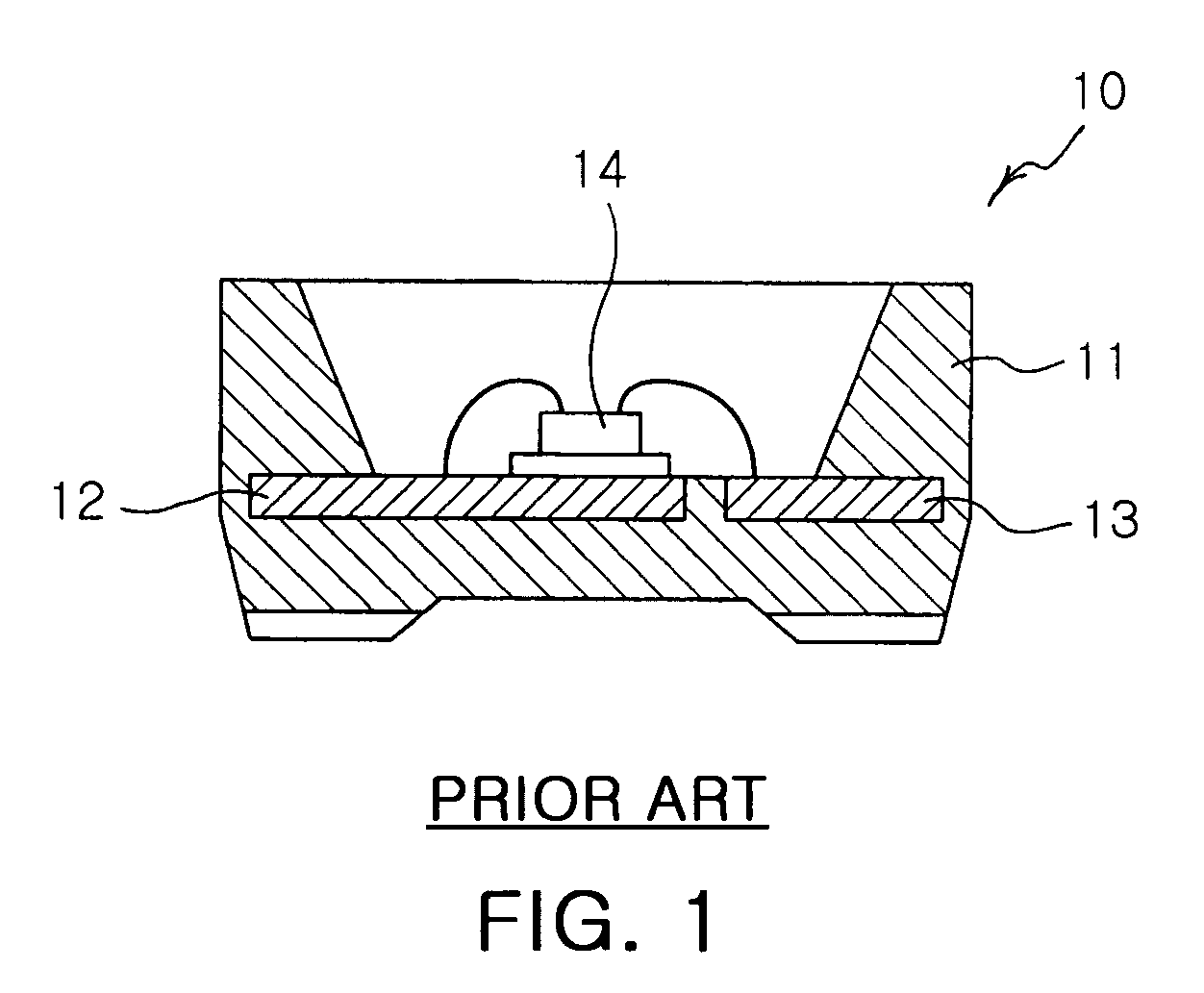

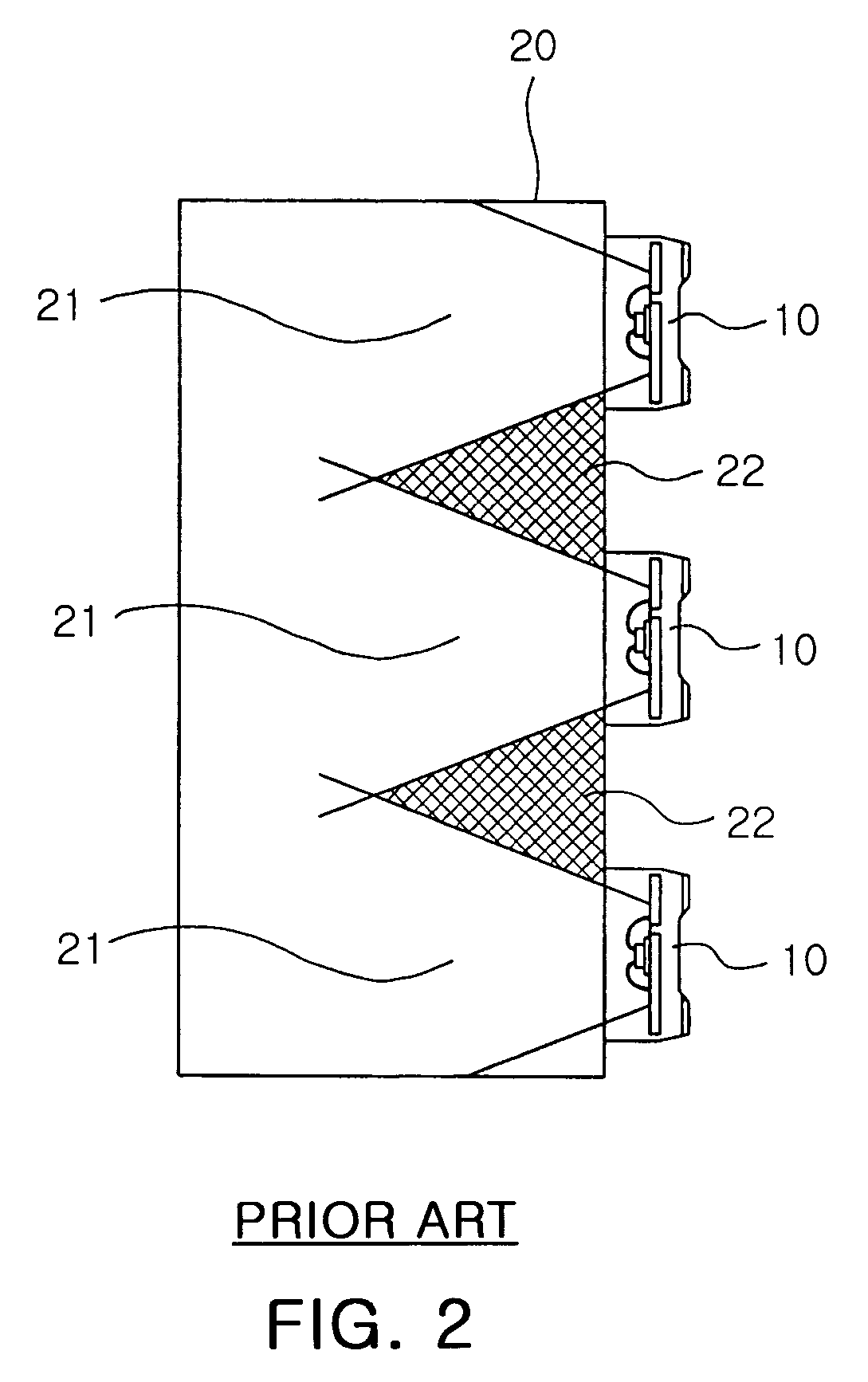

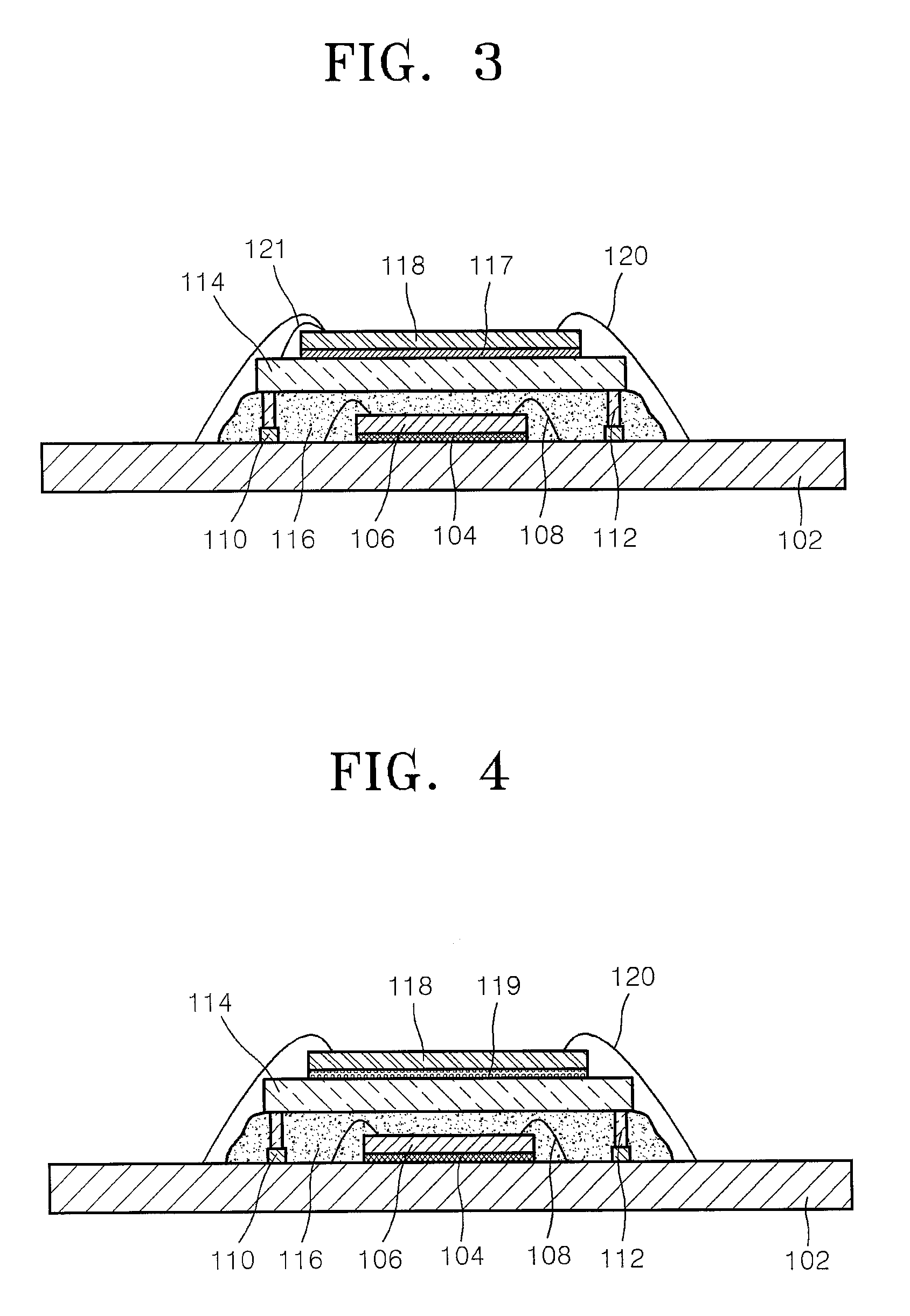

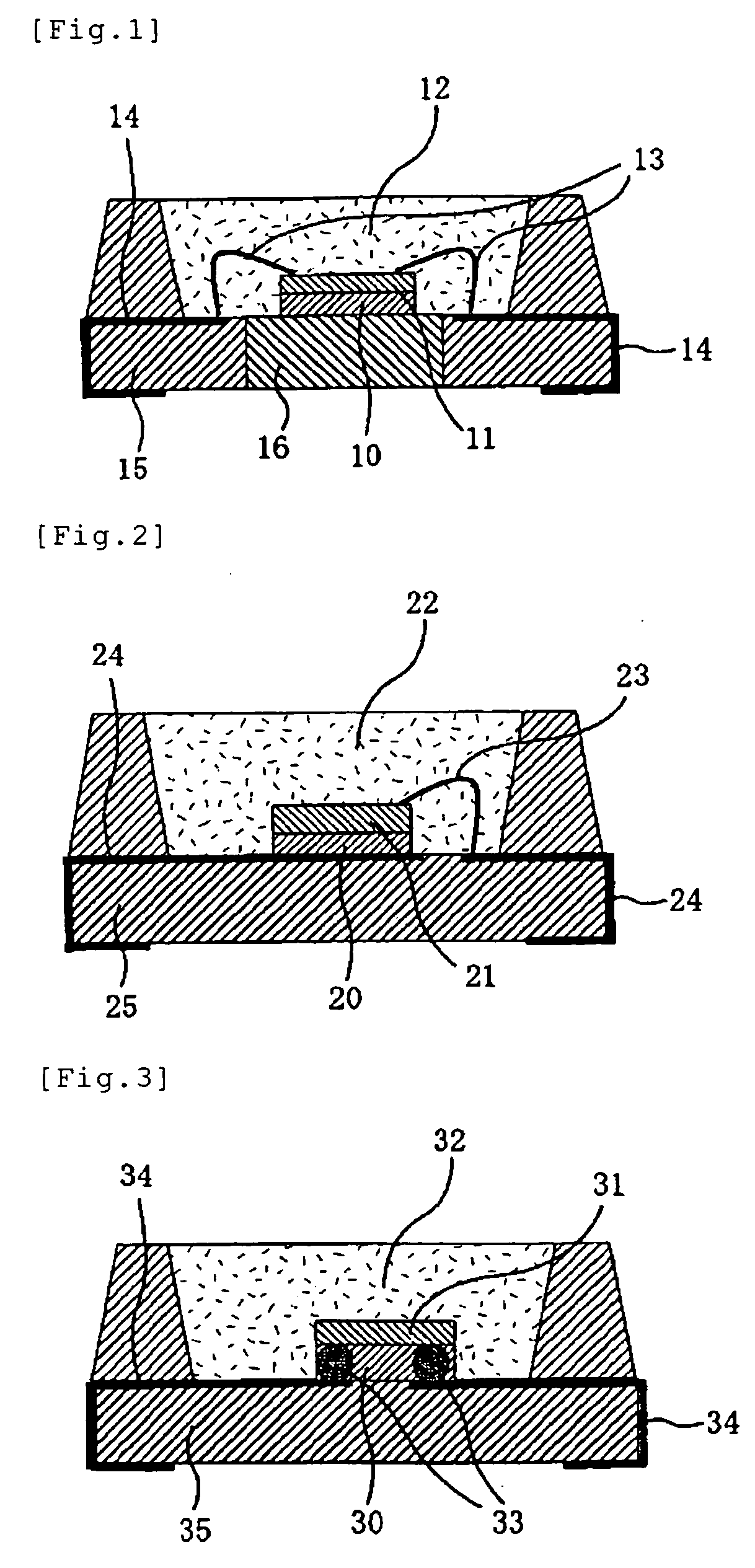

Package structure of full color LED form by overlap cascaded die bonding

InactiveUS6563139B2High strengthHigh resolutionSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGreen led

The present invention discloses a light source of full color LED (light emitted diode) by using die bond and packaging technology. A first mono-color LED chip with reflective metal on the bottom and transparent metal-oxide on the top of the chip is bonded on the PC board by thermal or ultrasonic die bond. A second mono-color LED chip with reflective metal on both sides is bonded in cascade on the first LED chip by thermal or ultrasonic die bond. The first LED chip emits light through the transparent metal-oxide to mix with the second LED light such that a different color light will obtain. The reflective metal reflects all the light to enforce the light intensity. In near field application, a red, a blue and a green LED are die bond in cascade to get a white light or full color light. In far field application, a yellow and a blue LED are die bond in cascade on the PC board, in its side is another cascaded die bond of a red and a green LED to get a white light or full color light.

Owner:HEN CHANG HSIU

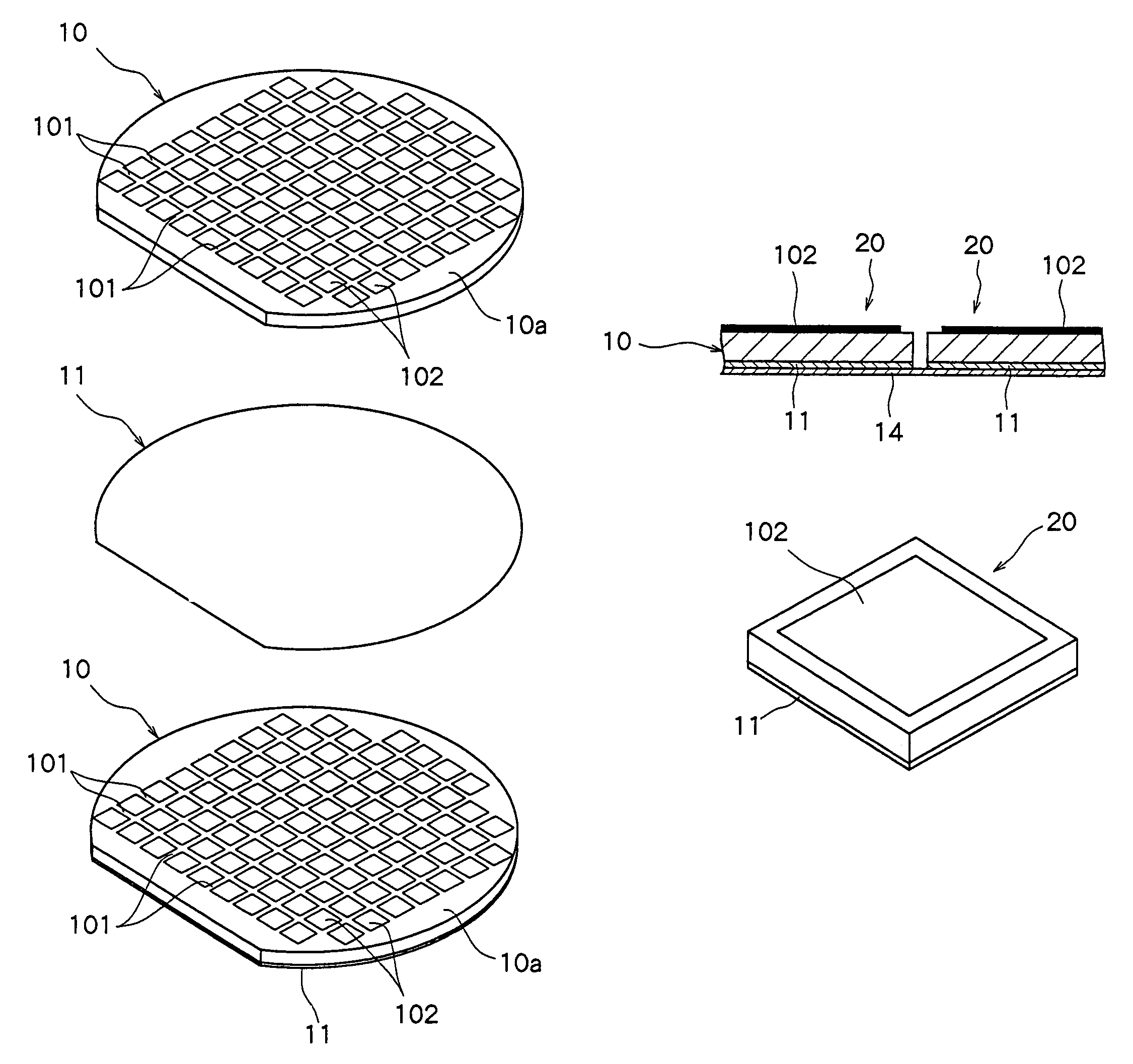

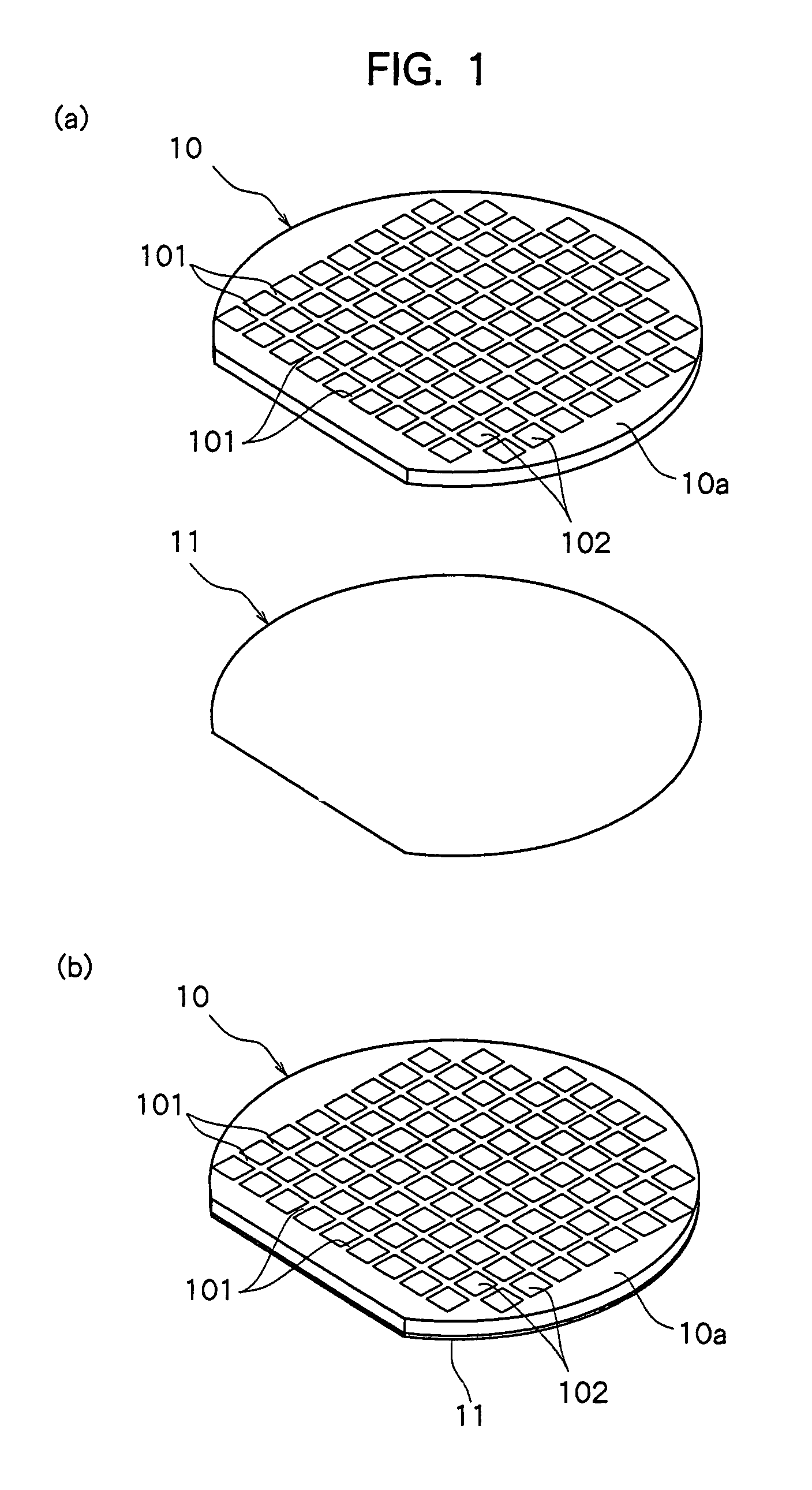

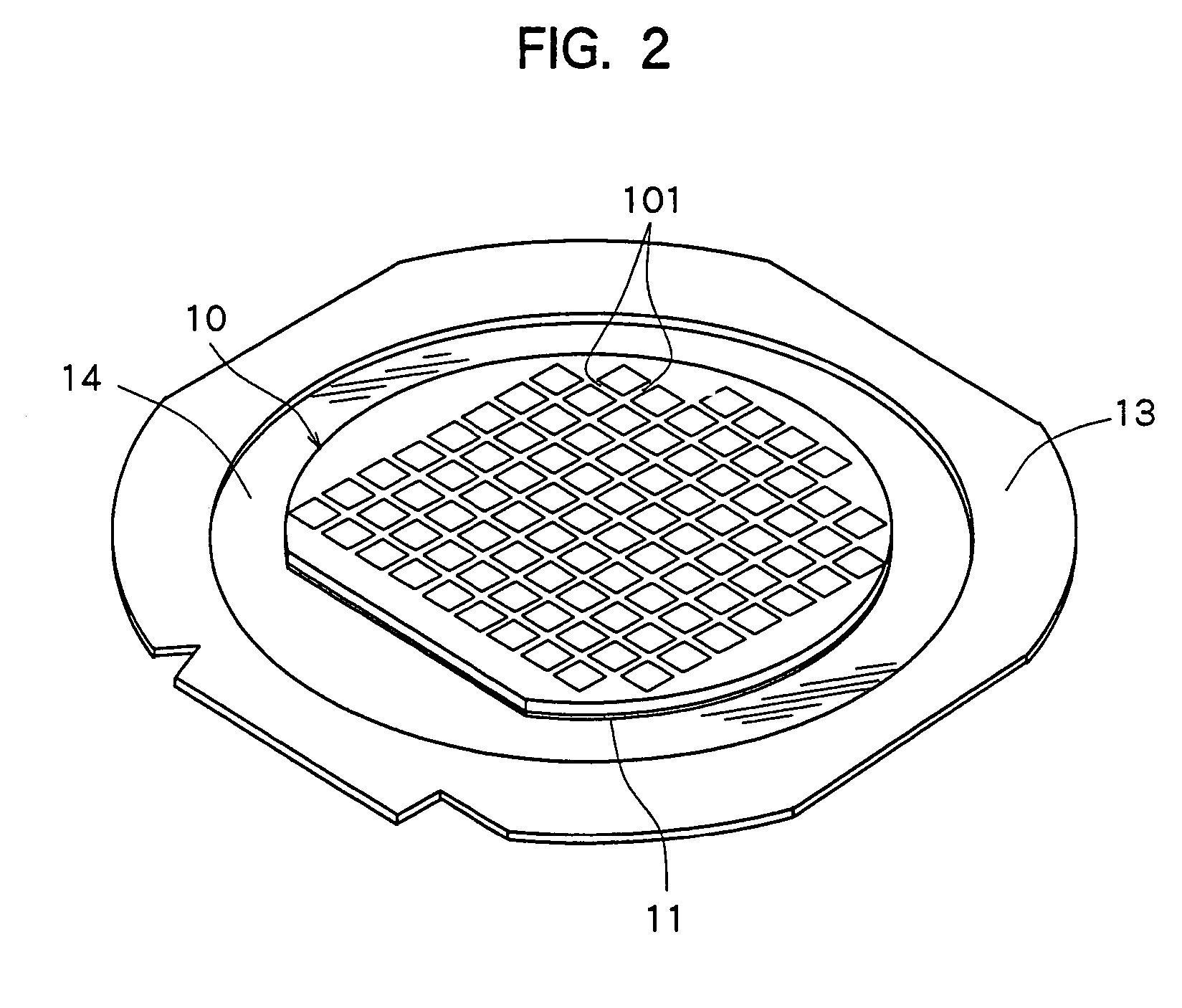

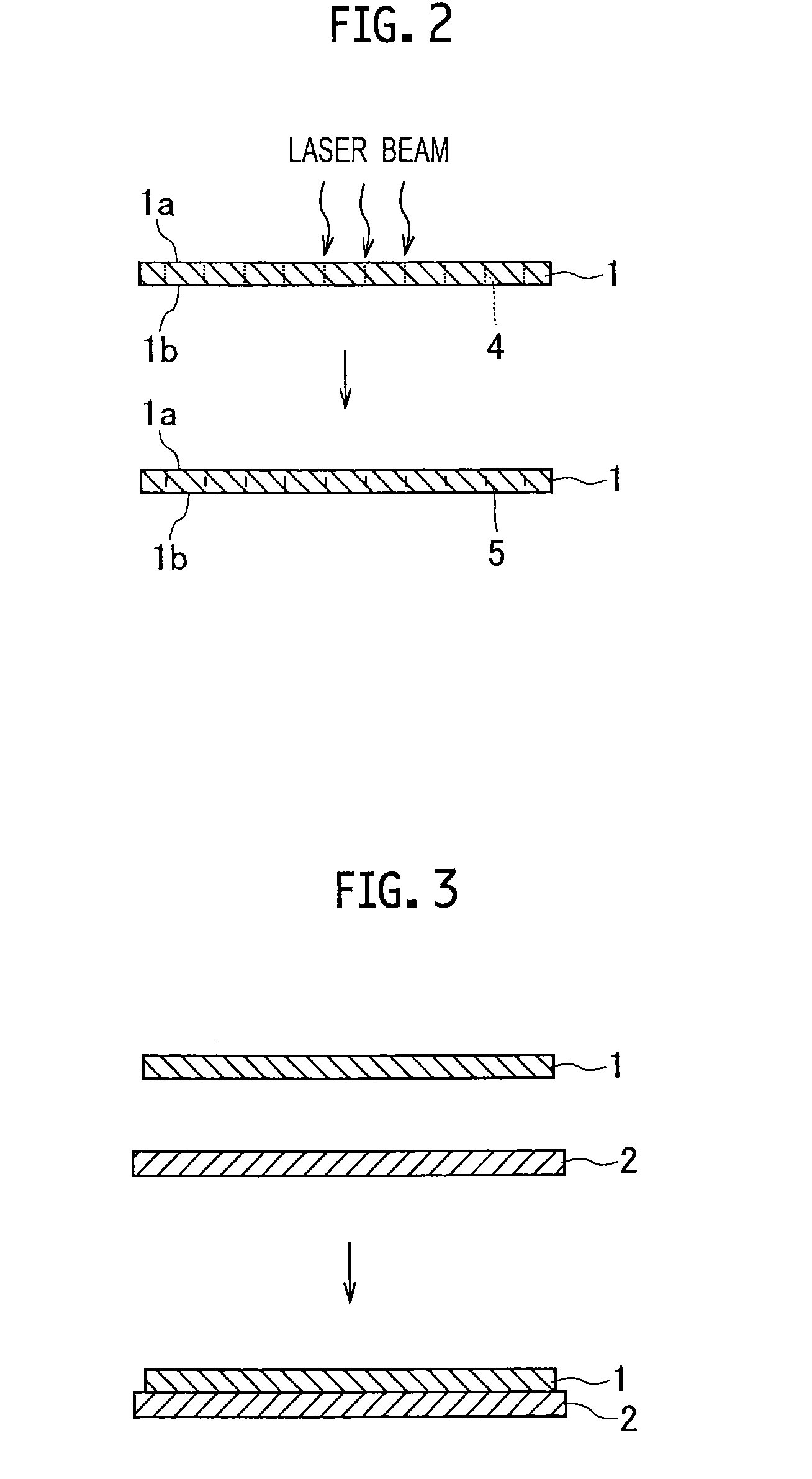

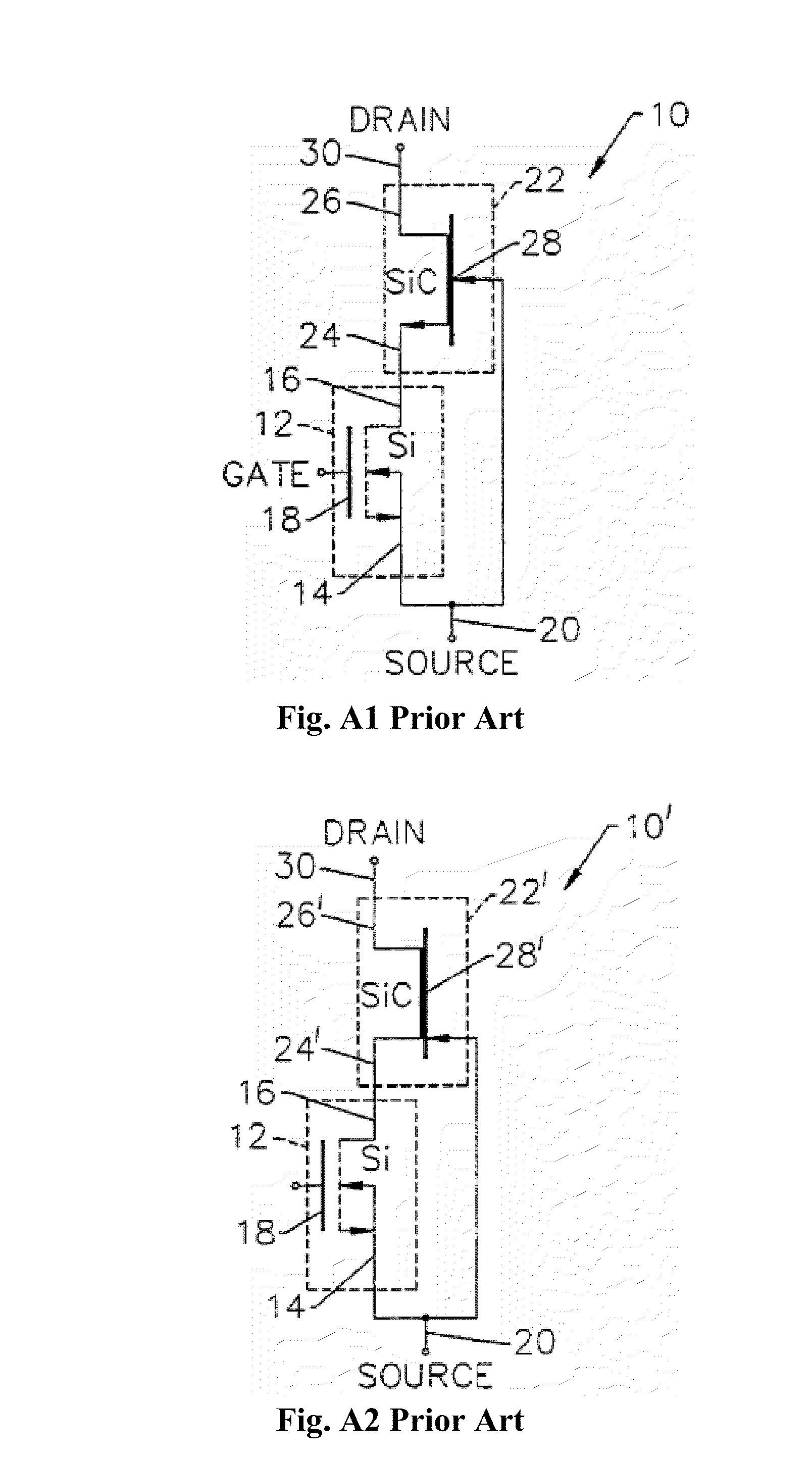

Method of dividing a semiconductor wafer

ActiveUS7129150B2Solid-state devicesSemiconductor/solid-state device manufacturingAdhesive beltSemiconductor chip

A method of dividing a semiconductor wafer comprising:a bonding film adhering step of adhering a bonding film for die bonding to the back surface of the semiconductor wafer;a protective adhesive tape affixing step of affixing an extensible protective adhesive tape to the bonding film side of the semiconductor wafer having the bonding film on the back surface;a dividing step of dividing the semiconductor wafer affixed to the protective adhesive tape into individual semiconductor chips by applying a laser beam along the streets;a bonding film breaking step of breaking the bonding film for every semiconductor chip by extending the protective adhesive tape so as to give tensile force to the bonding film; anda semiconductor chip removing step of removing the semiconductor chips having the broken bonding film from the protective adhesive tape.

Owner:DISCO CORP

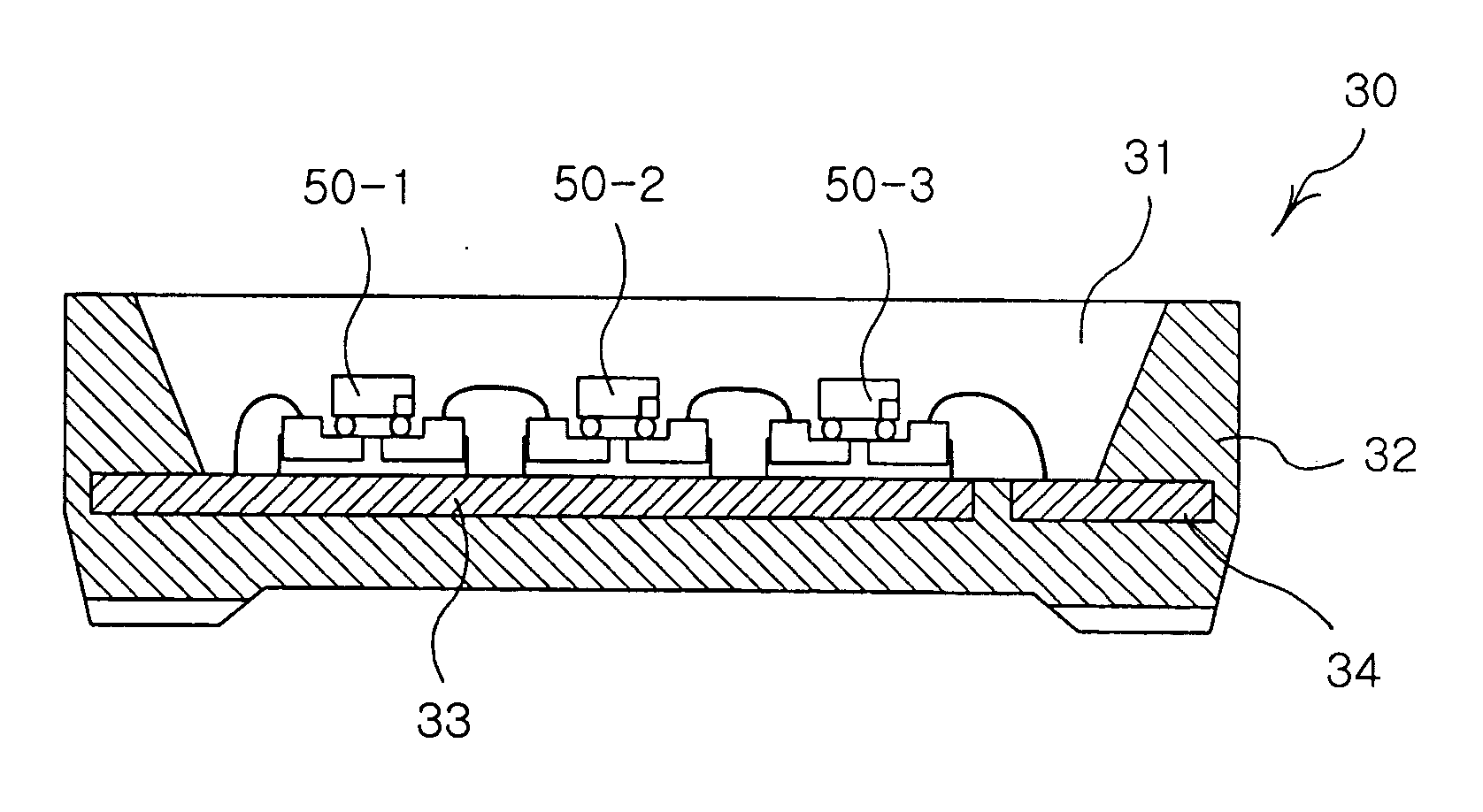

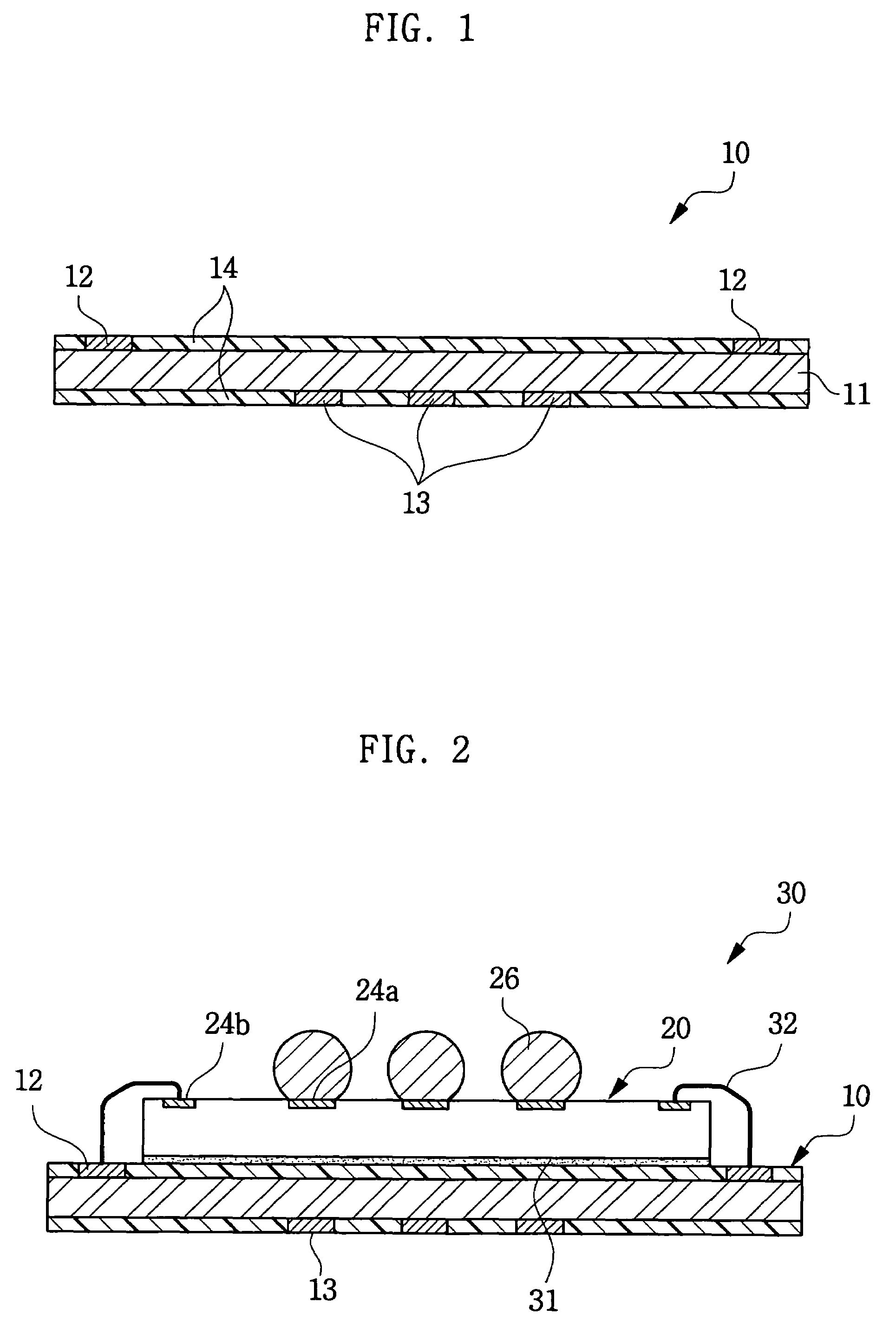

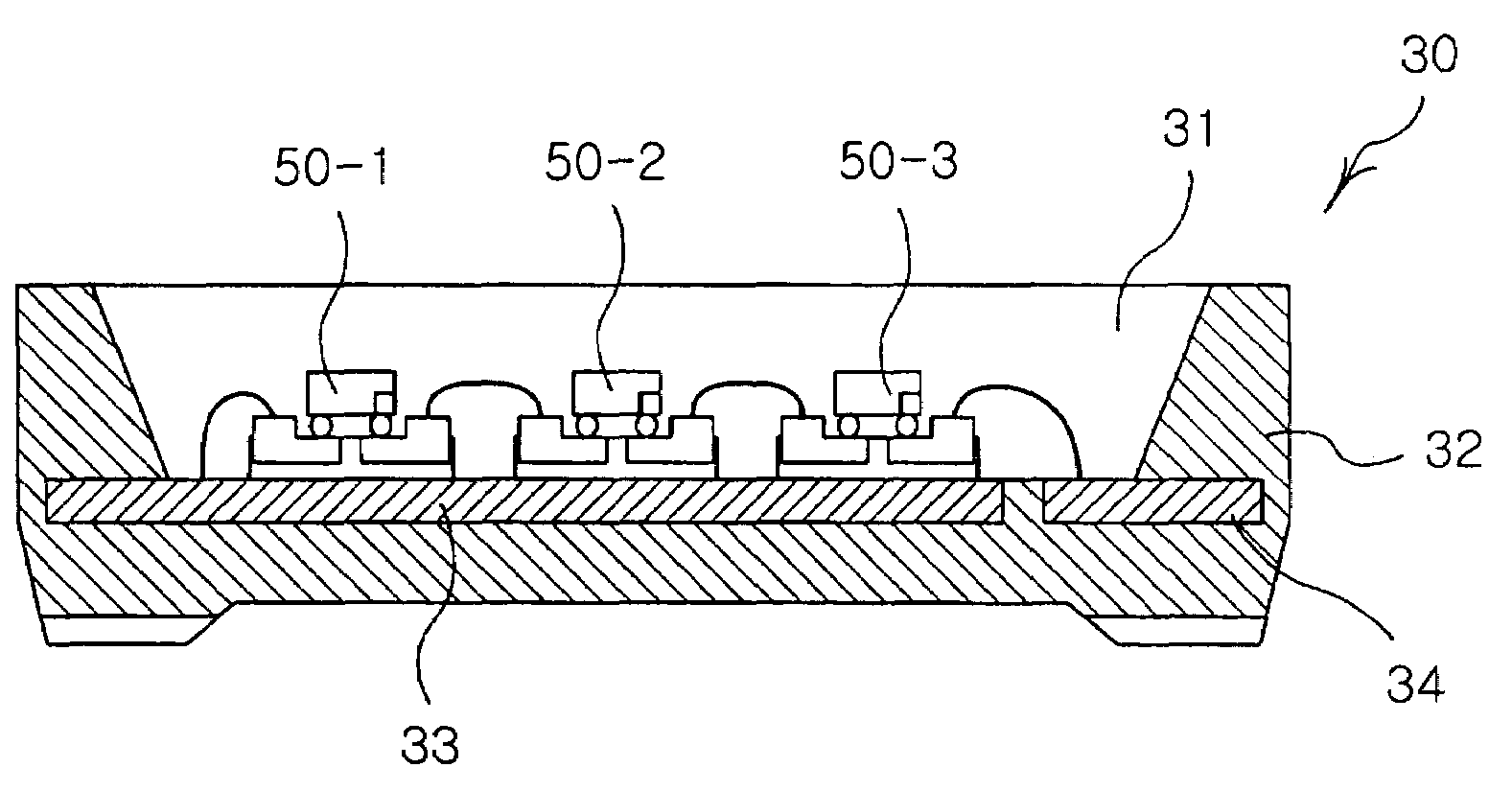

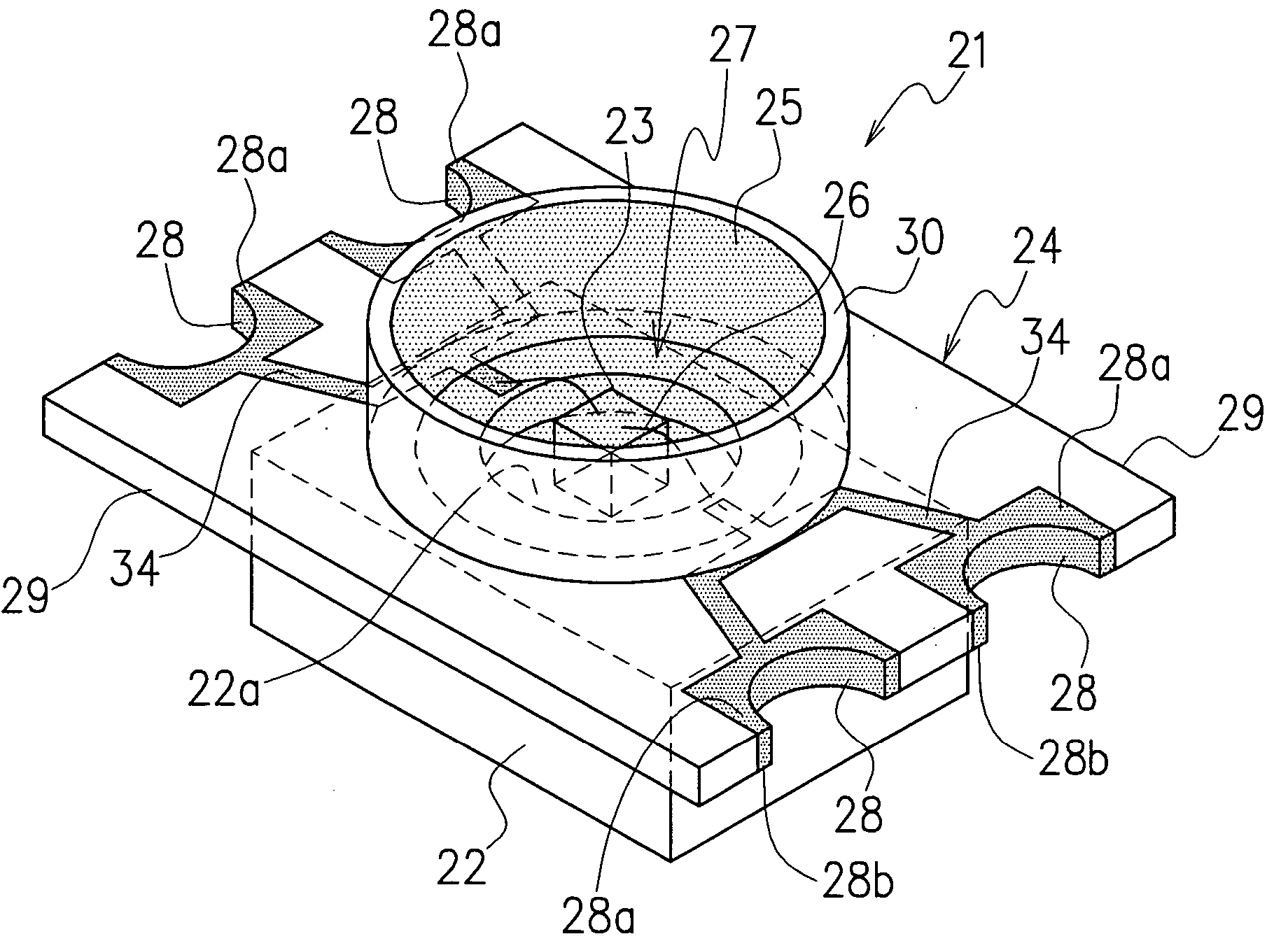

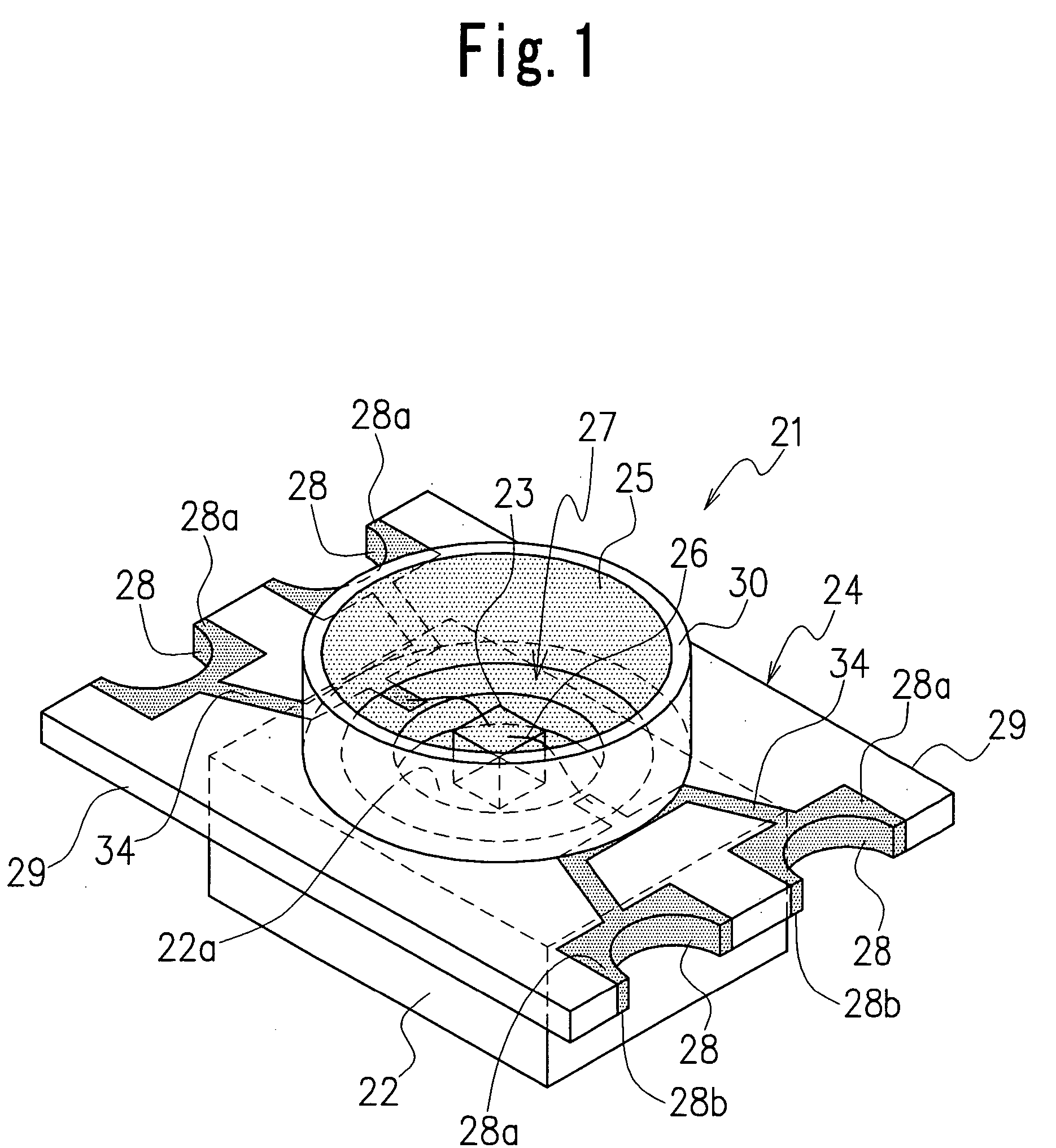

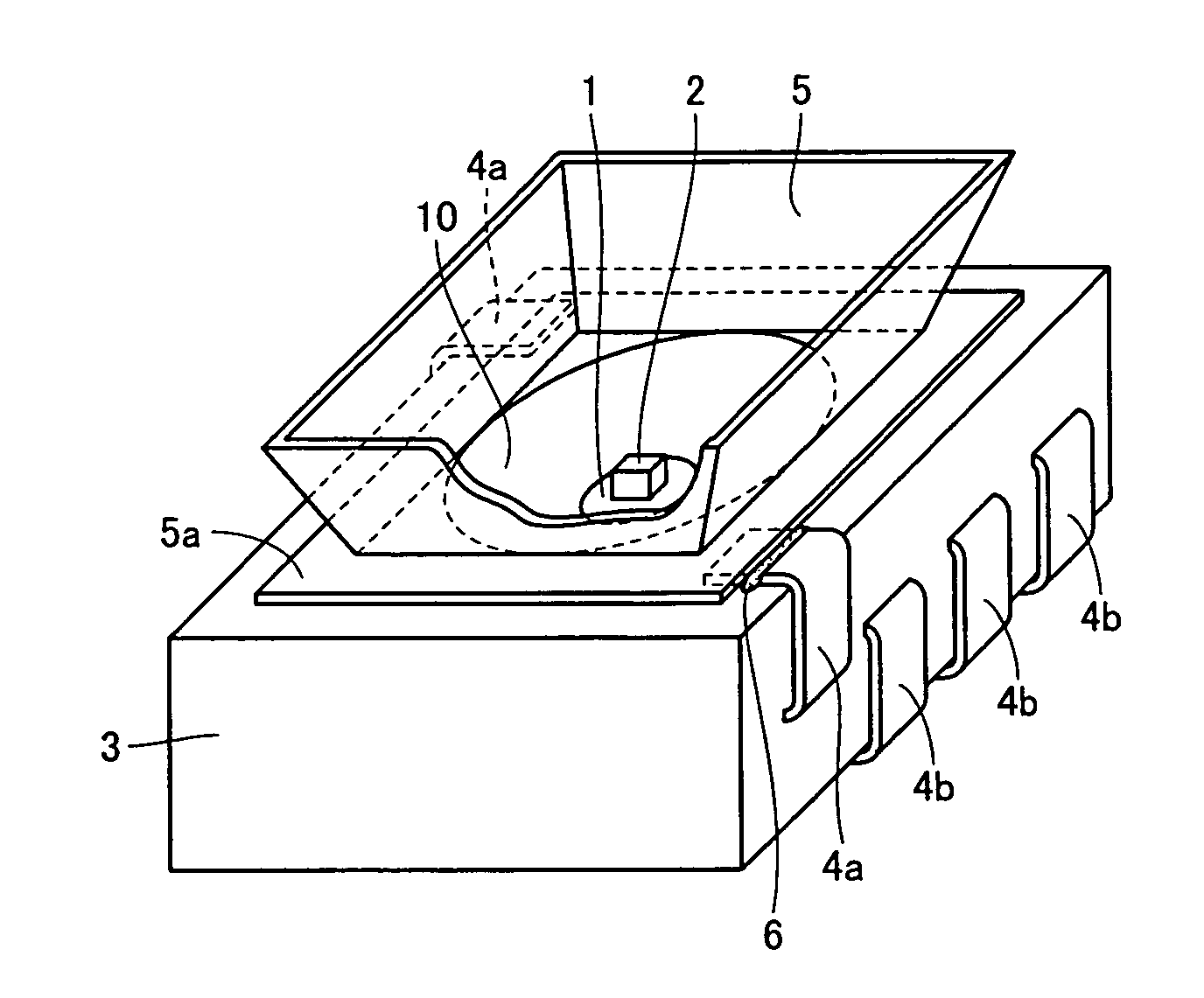

LED package for backlight unit

ActiveUS20060023451A1Avoid deformationImprove image qualityLighting support devicesGlass furnace apparatusEngineeringDie bonding

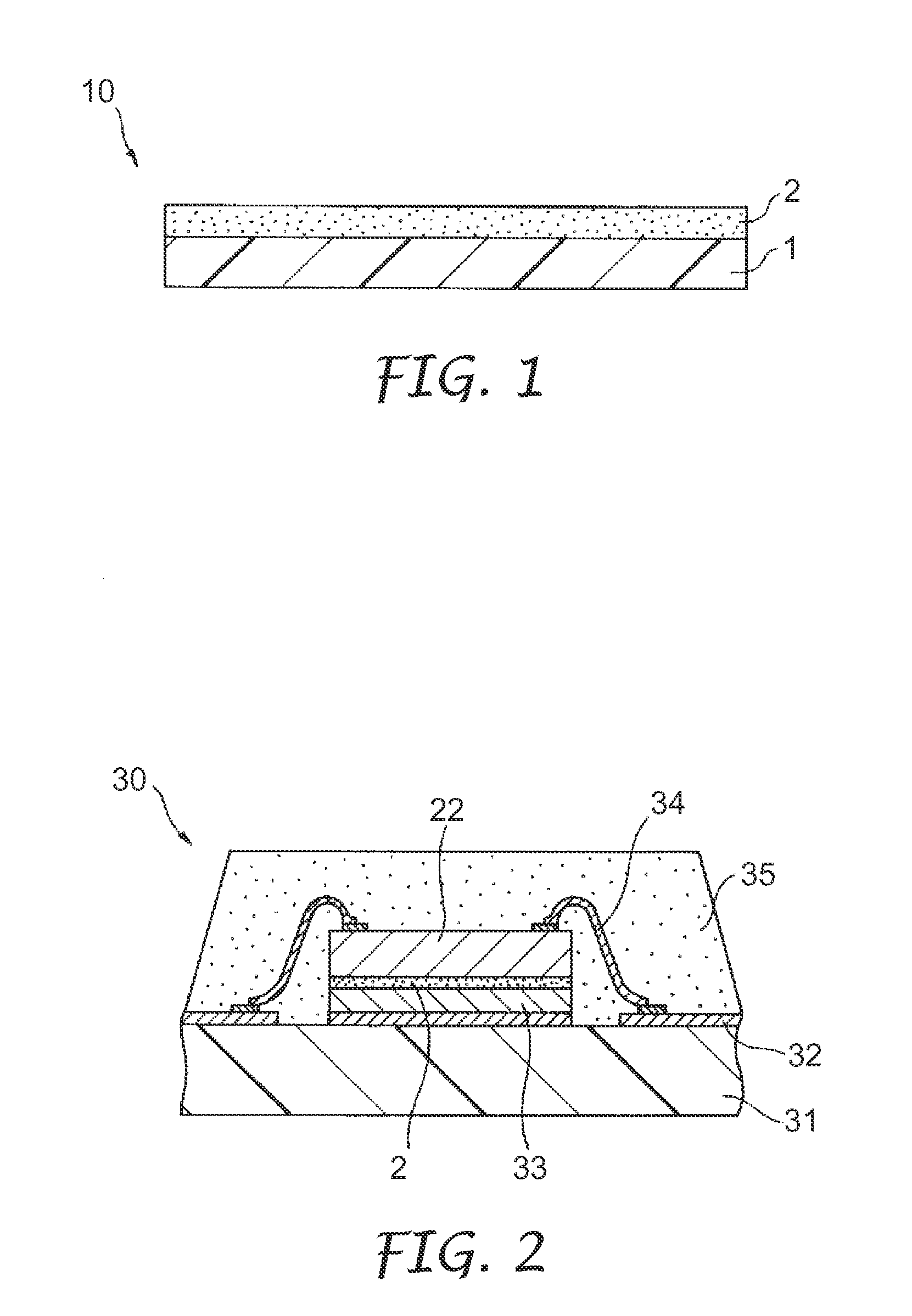

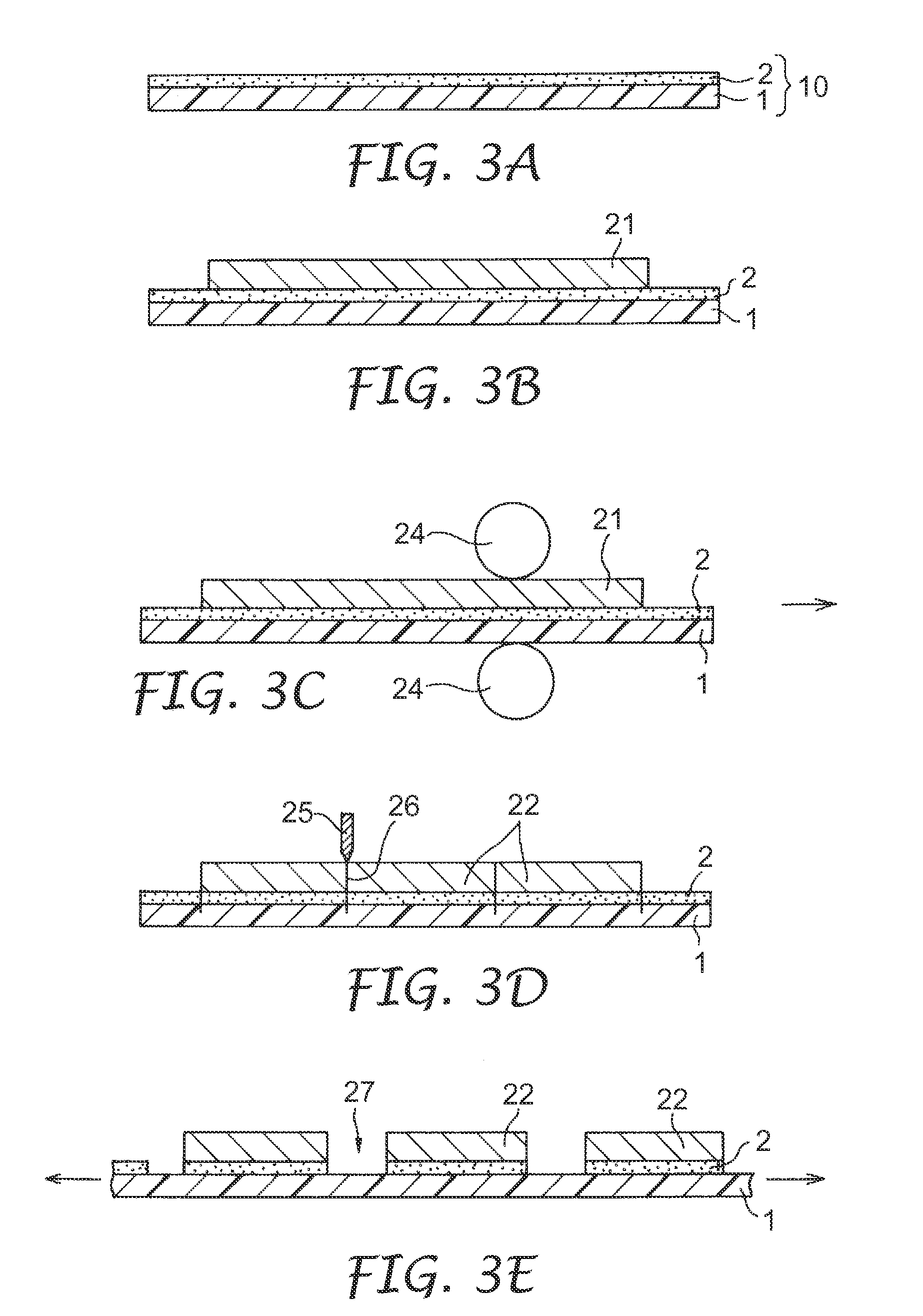

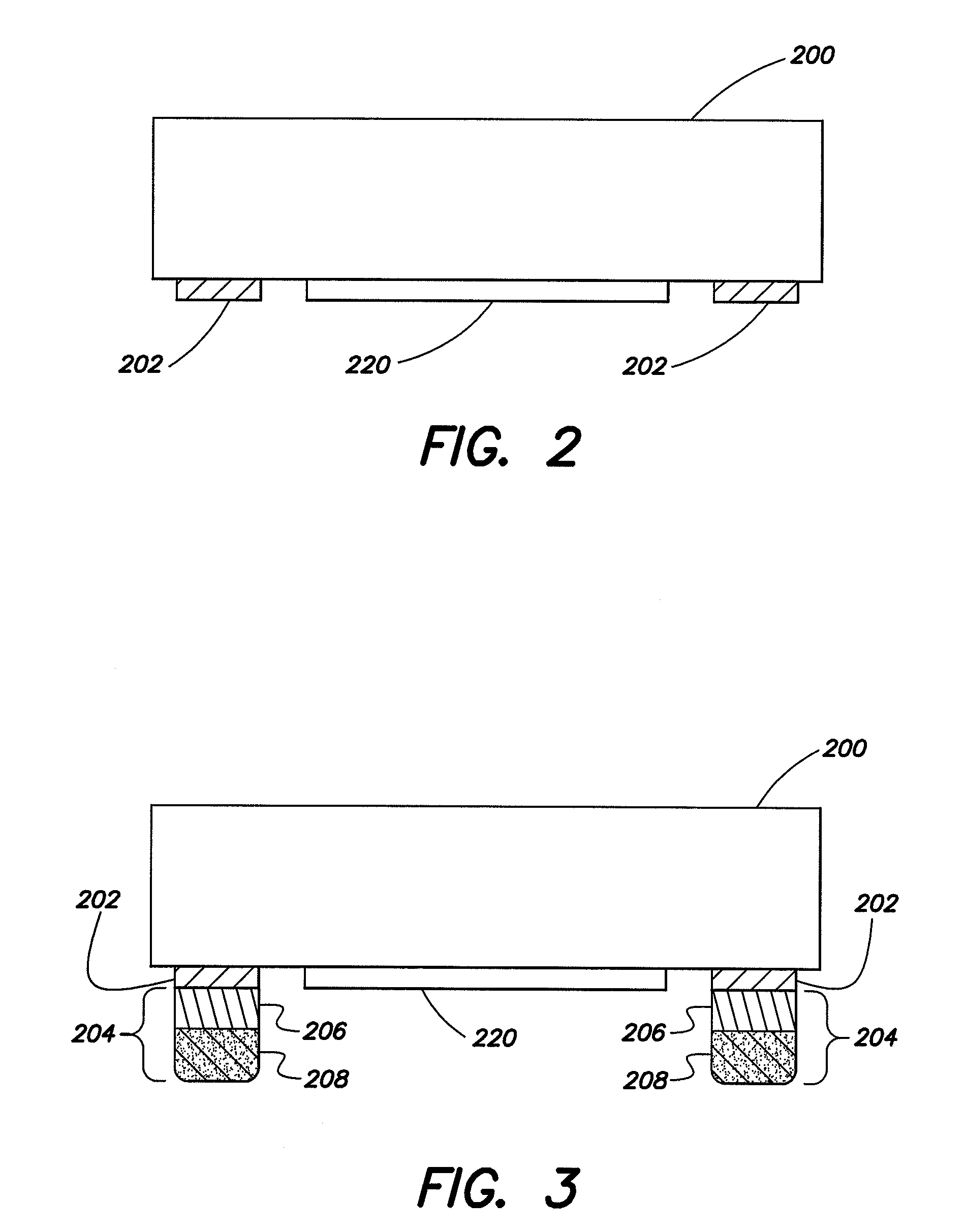

Disclosed herein is an LED package for a backlight unit. The LED package includes a plurality of LEDs, a die bonding part, a wire bonding part and a body. The die bonding part, on which the plurality of LEDs is arranged, allows the first electrodes of the LEDs to be electrically connected to an external circuit. The wire bonding part is spaced apart from the die bonding part by a predetermined distance to be insulated from the die bonding part and allows the second electrodes of the LEDs to be electrically connected to the external circuit so that the LEDs are operated. The body has a molding cup which is used to fill a space above the LEDs with transparent resin and a base on which the die bonding part and the wire bonding part are arranged.

Owner:SAMSUNG ELECTRONICS CO LTD

Chip bonding process

ActiveUS20050266670A1Avoid pollutionImprove productivitySemiconductor/solid-state device detailsSolid-state devicesInsulation layerBonding process

A bonding process includes the following process. A bump is formed on a first electric device. A patterned insulation layer is formed on a second electric device, wherein the patterned insulation layer has a thickness between 5 μm and 400 μm, and an opening is in the patterned insulation layer and exposes the second electric device. The bump is joined to the second electric device exposed by the opening in the patterned insulation layer.

Owner:QUALCOMM INC

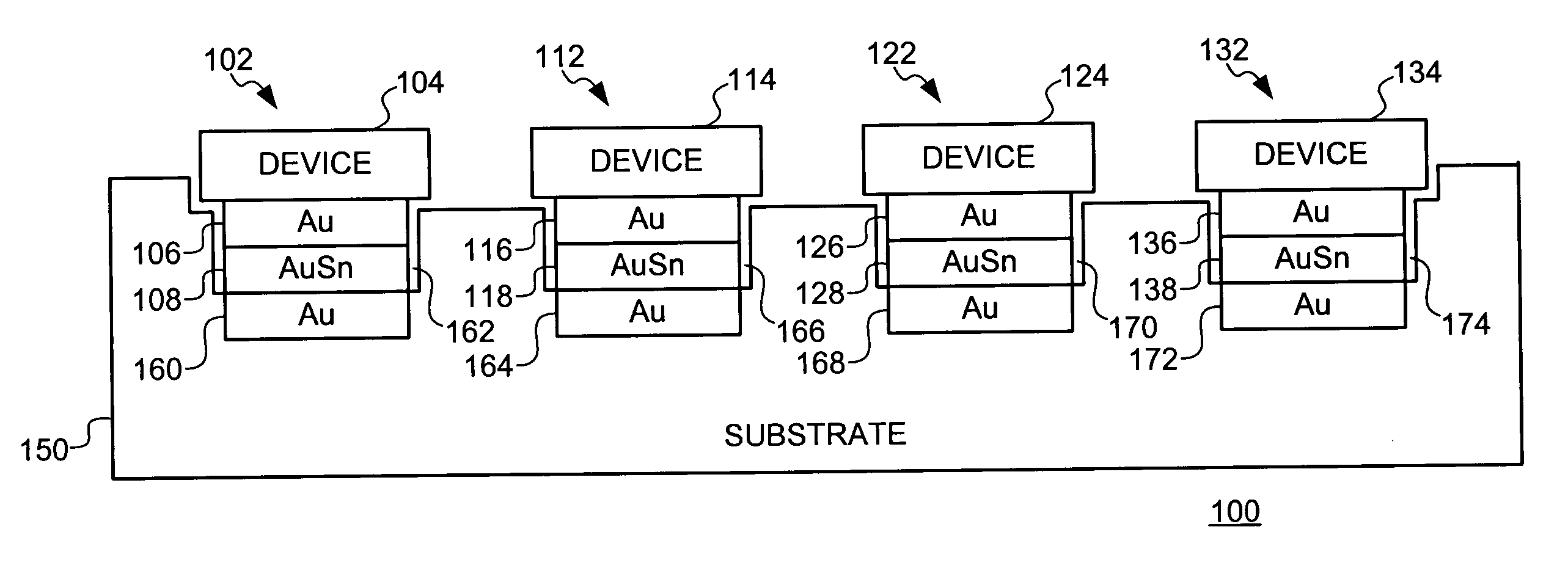

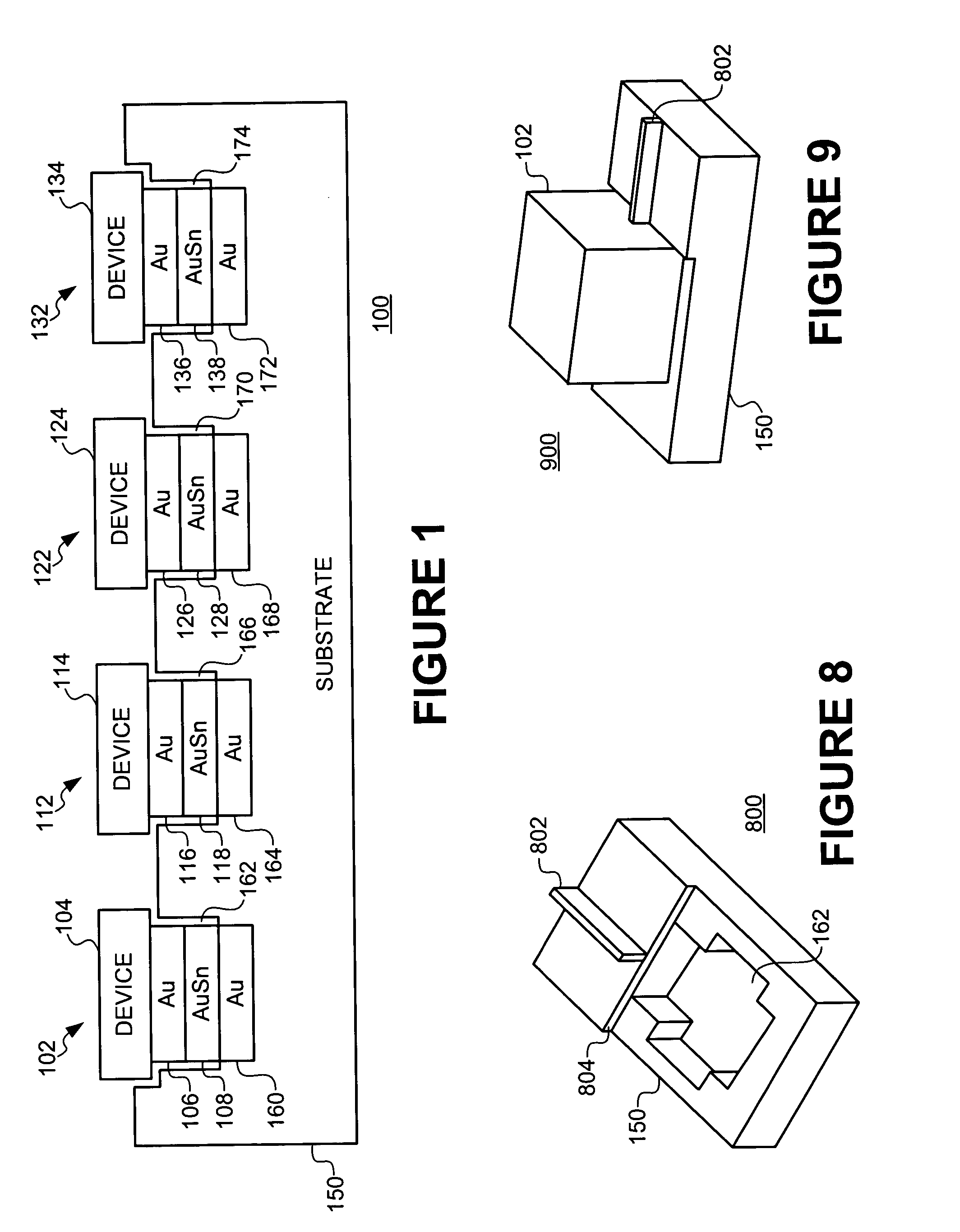

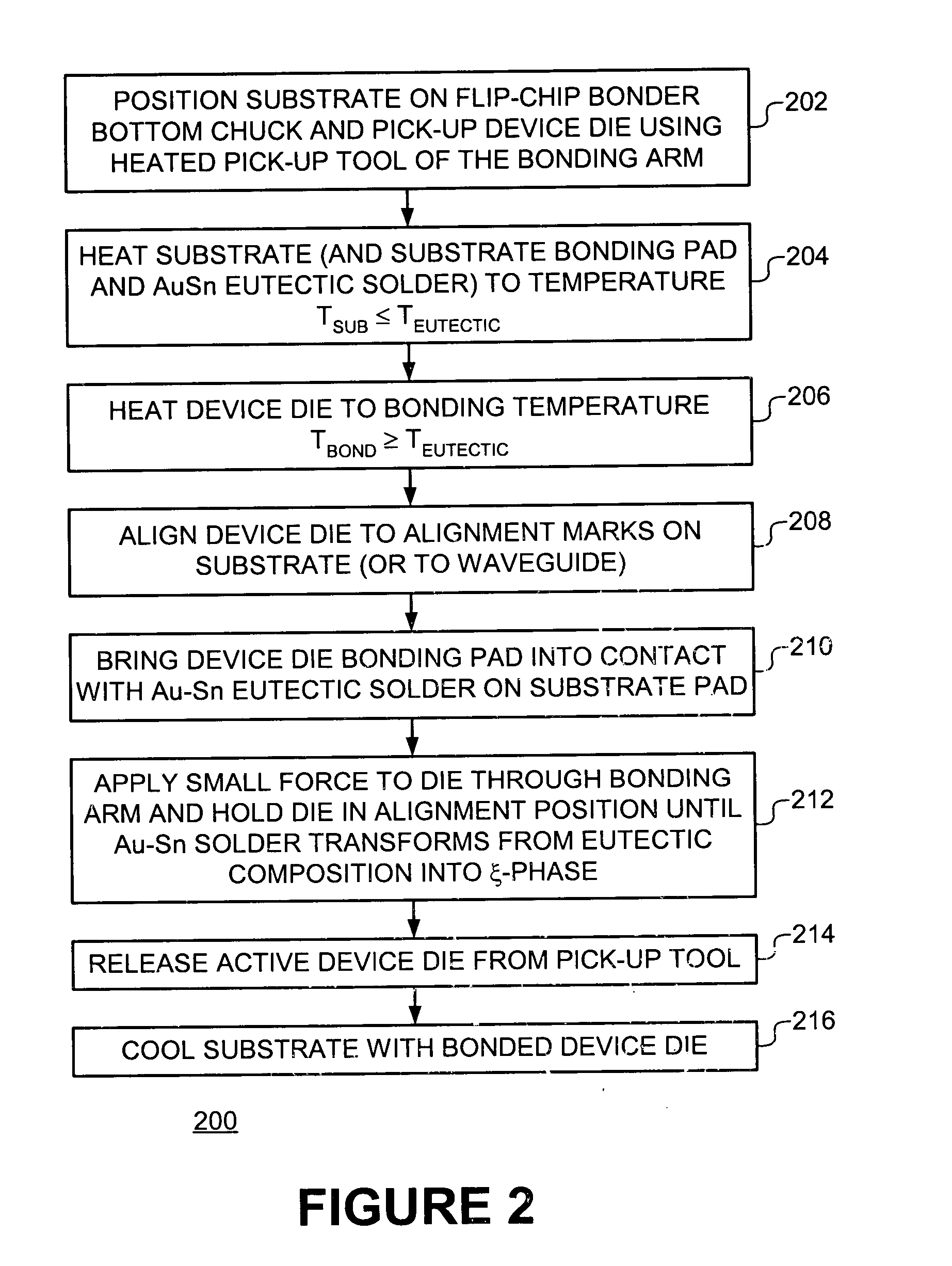

Packaging of multiple active optical devices

InactiveUS20040029304A1Printed circuit assemblingSemiconductor/solid-state device manufacturingEngineeringElectron

A cost effective method is provided for assembly of hybrid optoelectronic circuits requiring flip-chip bonding of multiple active optoelectronic devices onto common substrate or optical bench platform with fine pitch and high accuracy "after-bonding" alignment to the alignment features on substrate and / or to other elements of the hybrid circuit. A Flip-Chip Bonder equipped with high precision Bonding Arm and optical and mechanical system, heated substrate chuck and heated pick-up tool may be used both for alignment and thermal bonding of active component dies to corresponding bonding pads on the common substrate using gold-tin (Au-Sn) solder disposed between die bonding pad and the corresponding substrate bonding pad. During bonding of the first die, tin (Sn) diffuses from a eutectic composition of gold-tin (Au-Sn) solder to (gold (Au) on) the die-bonding pad and / or (gold (Au) on) the substrate bonding-pad resulting in transformation of the Au-Sn eutectic composition to a zeta-phase composition having much higher melting temperature as compared to that of a eutectic composition. As bonding of one or more subsequent dies is performed at temperatures equal to or slightly higher than the melting temperature of a eutectic composition and significantly lower than the melting temperature of a zeta-phase composition, the gold-tin (Au-Sn) solder at the bond of previously attached die does not melt and, consequently, the alignment is not compromised.

Owner:INTEL CORP

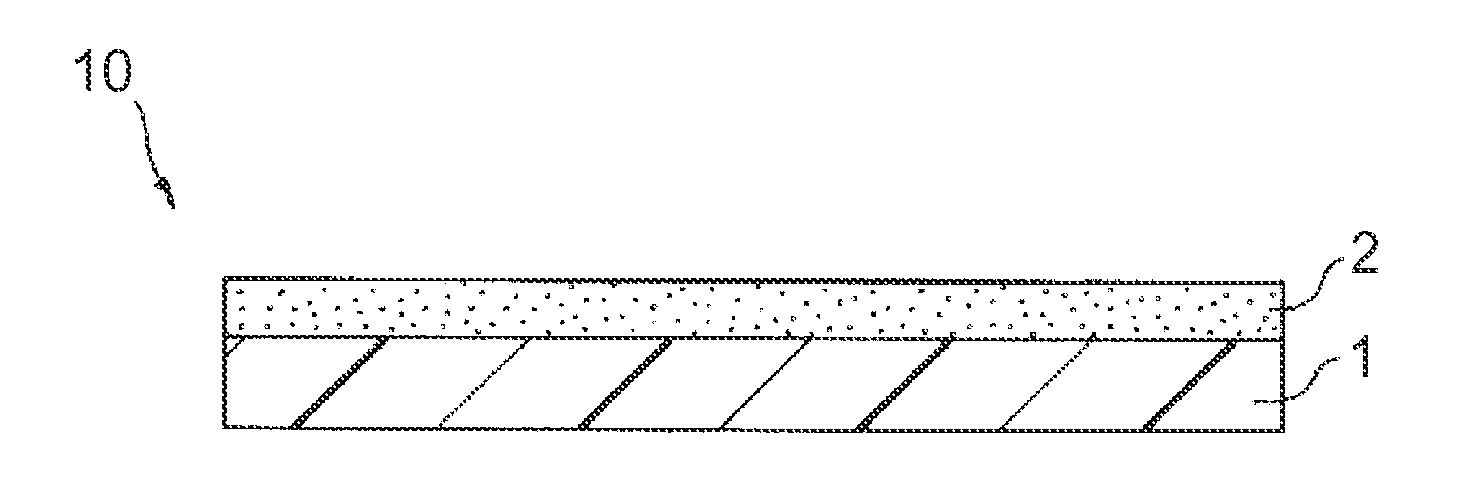

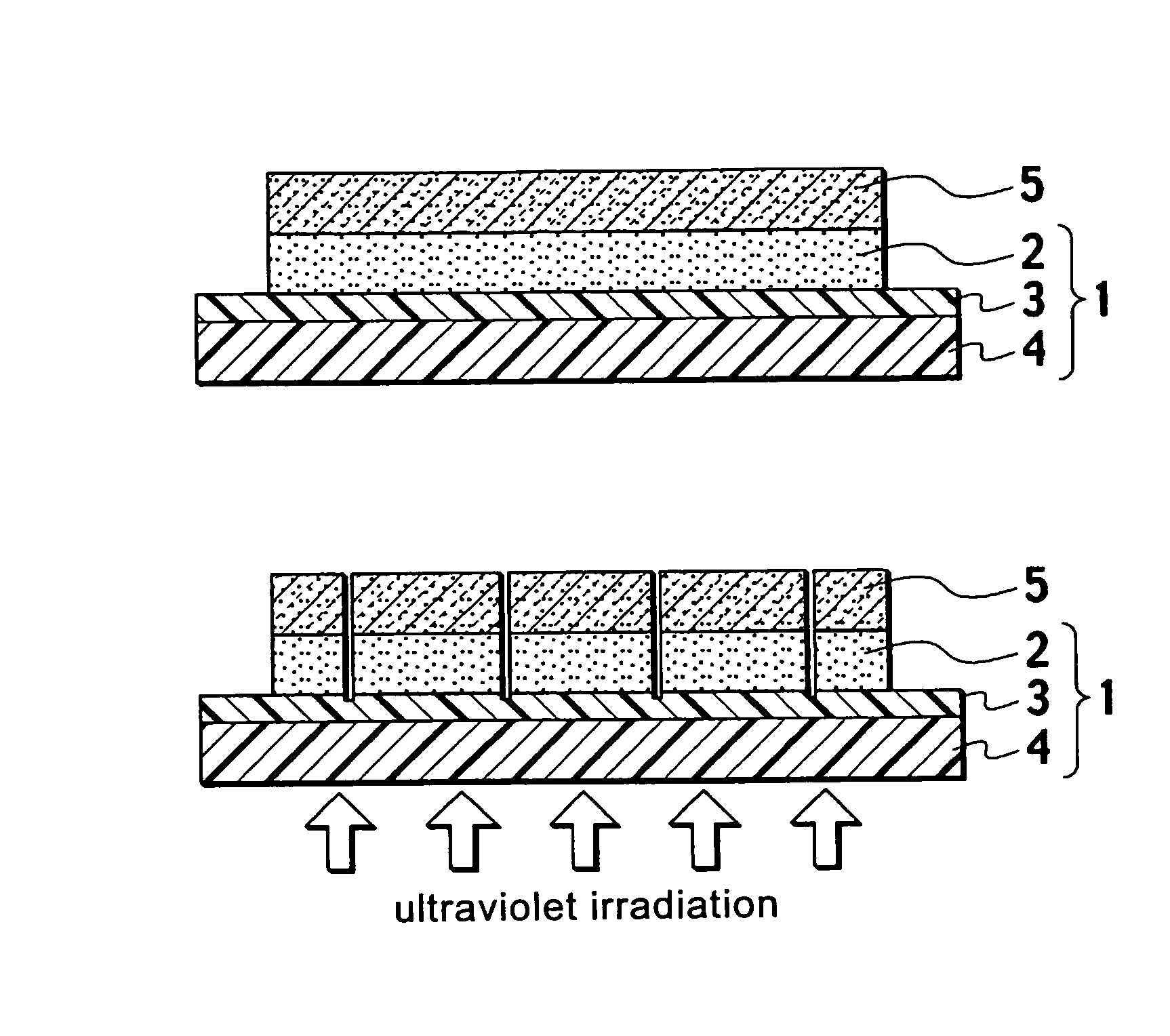

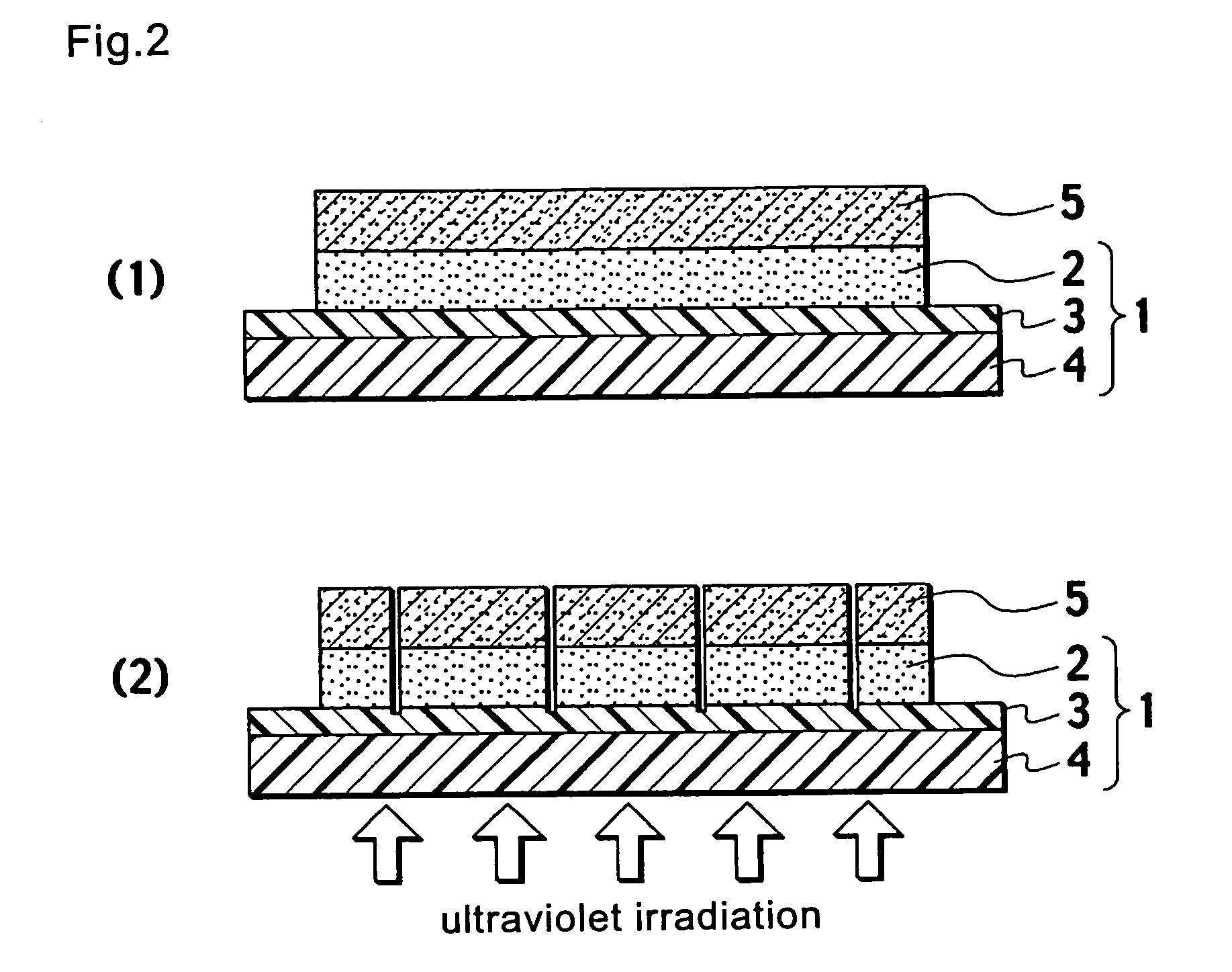

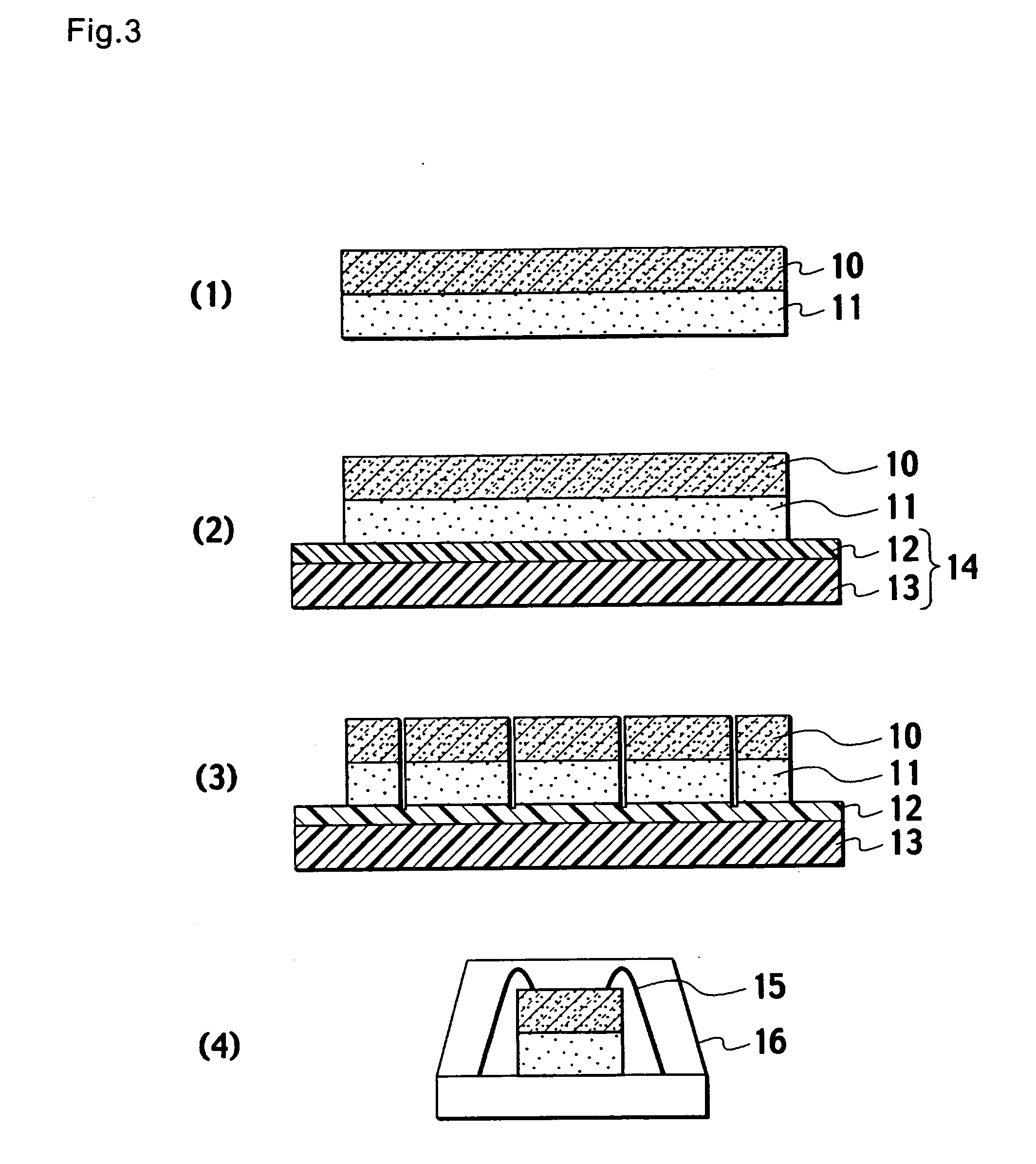

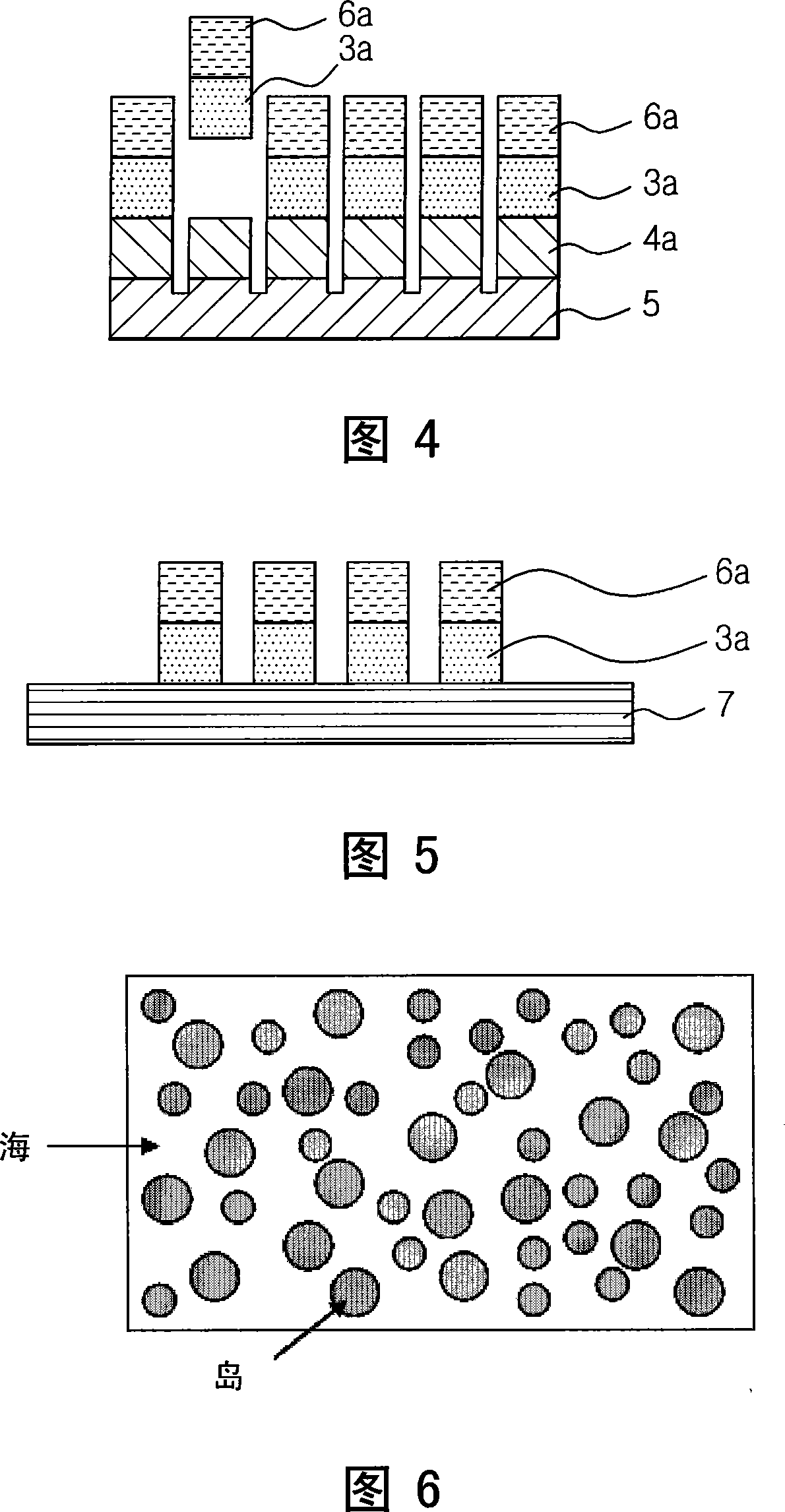

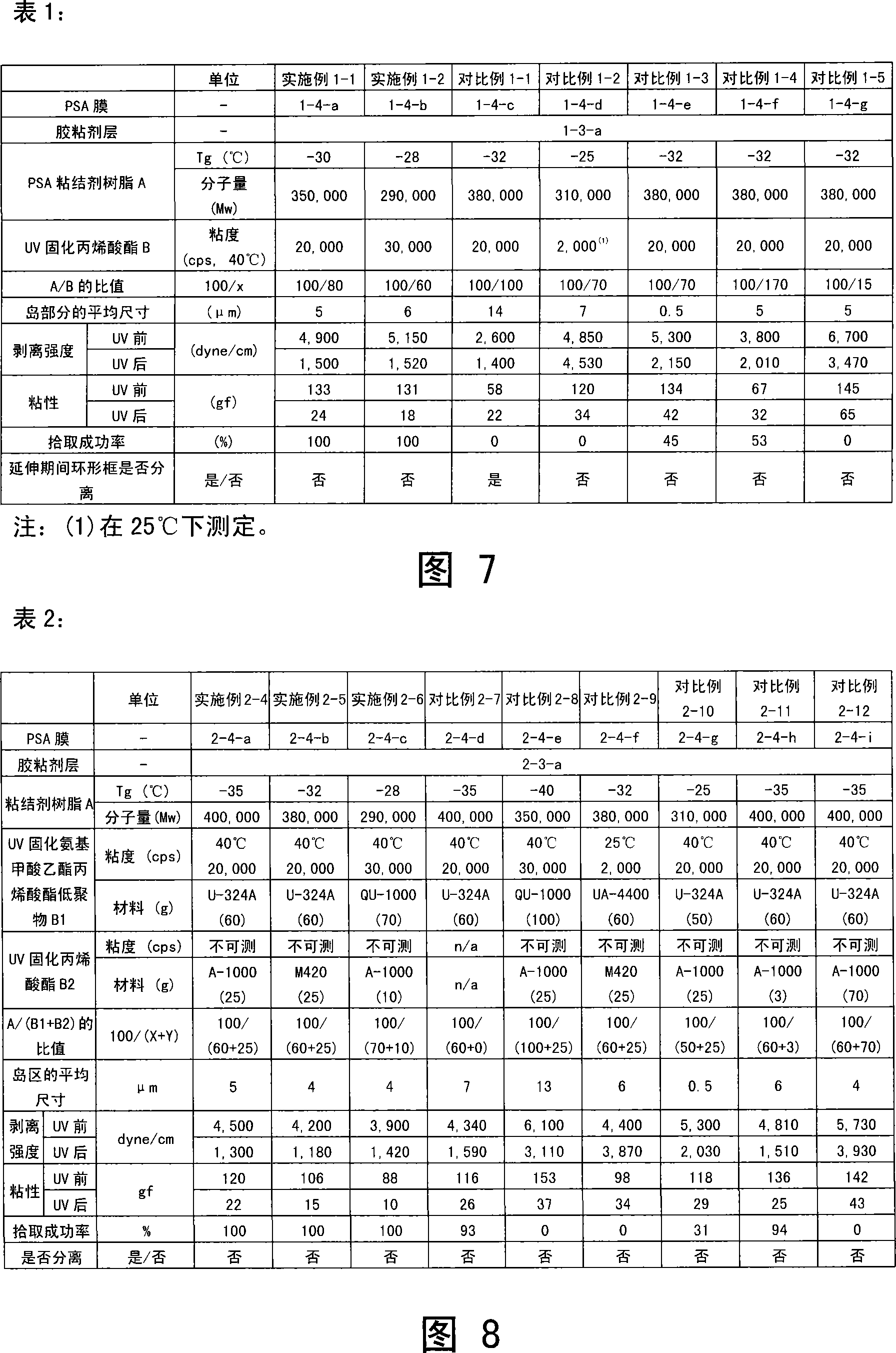

Composition for pressure sensitive adhesive film, pressure sensitive adhesive film, and dicing die bonding film including the same

A composition, including a polymer binder resin A, a UV-curing acrylate B, a heat curing agent C, and a photopolymerization initiator D. The composition includes about 20 to about 150 parts by weight of the UV-curing acrylate B per 100 parts by weight of the polymer binder resin A, and the UV-curing acrylate B is a solid or near-solid at room temperature and has a viscosity of about 10,000 cps or more at 40° C.

Owner:CHEIL IND INC

Light emitting diode

ActiveUS20050167682A1Reduce thicknessImprove efficiencySolid-state devicesOptical light guidesSurface mountingEngineering

An LED comprises: a chip substrate formed with a die bond pattern and electrode terminals; an LED chip mounted on the chip substrate; a reflective frame arranged on the chip substrate to enclose a circumference of the LED chip and having an opening at a part of its side walls and on an upper surface; reflecting surfaces formed on inner circumferential surfaces of the side walls of the reflective frame; a light transmissive resin body formed in the reflective frame and using the opening in the side wall as a light emission face; and a reflecting film covering an upper surface of the light transmissive resin body exposed on an upper surface side of the reflective frame; wherein light produced by the LED chip is reflected by a reflecting surface of the refractive frame and by the reflecting film and is emitted outward from the light emission face. The side emission type LED of this construction can be reduced in thickness for surface mounting and can illuminate a small-width side surface of a liquid crystal panel with high efficiency.

Owner:CITIZEN ELECTRONICS CO LTD

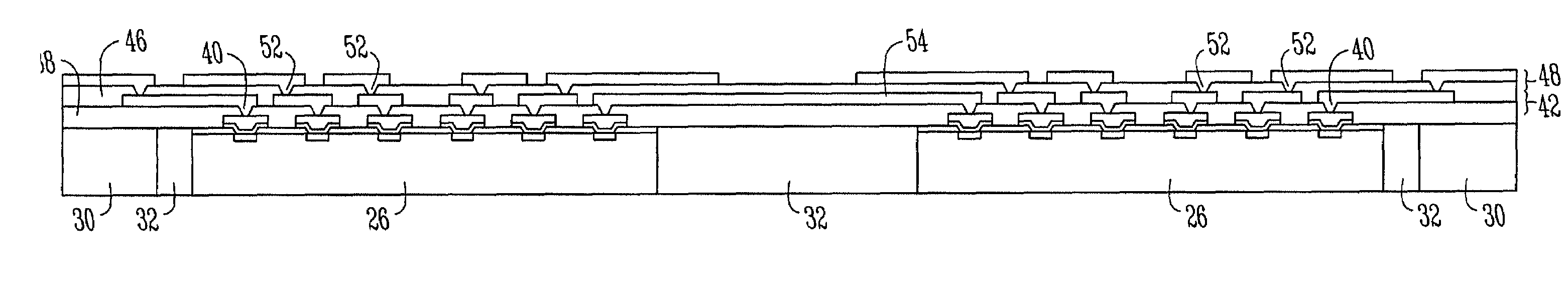

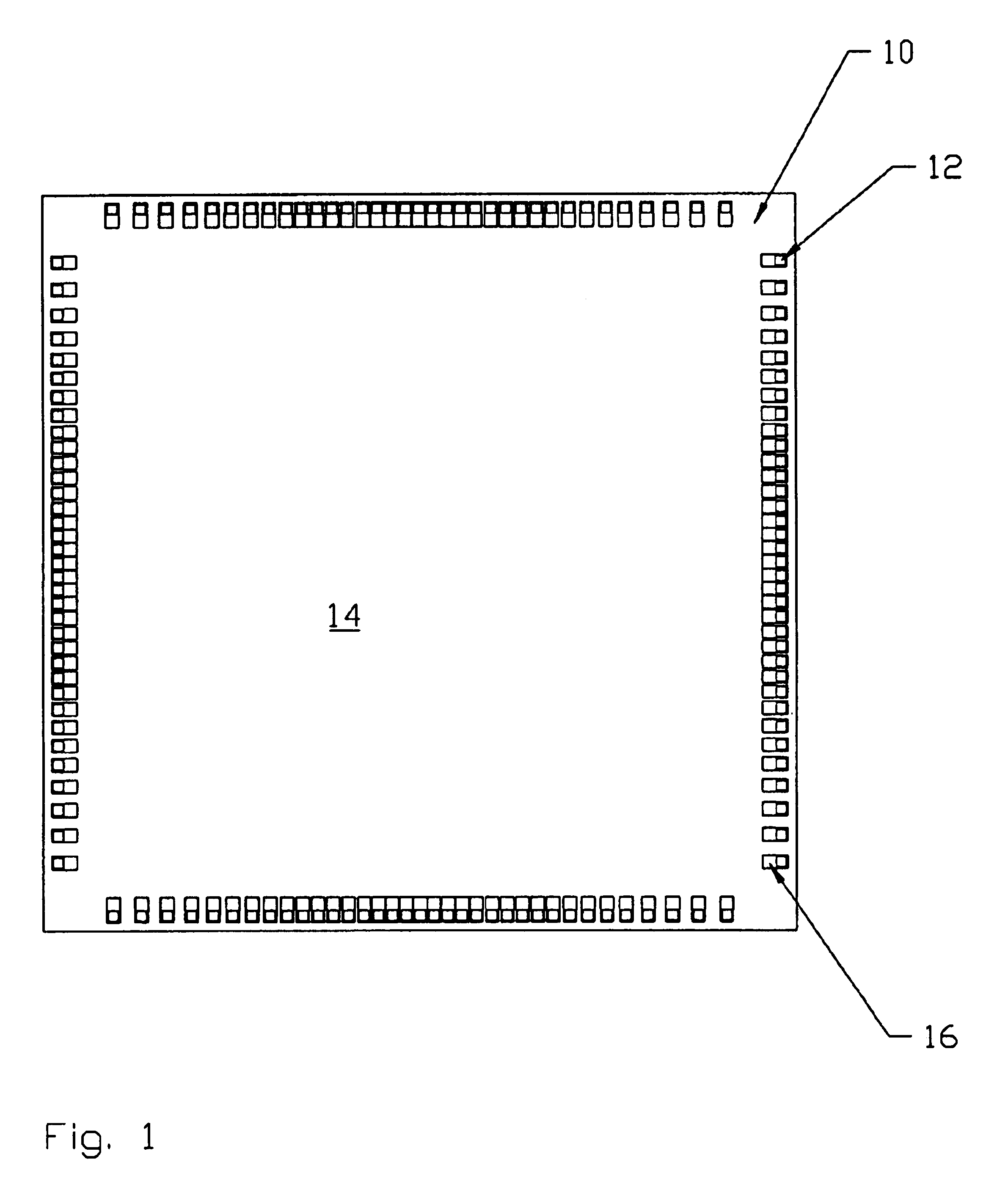

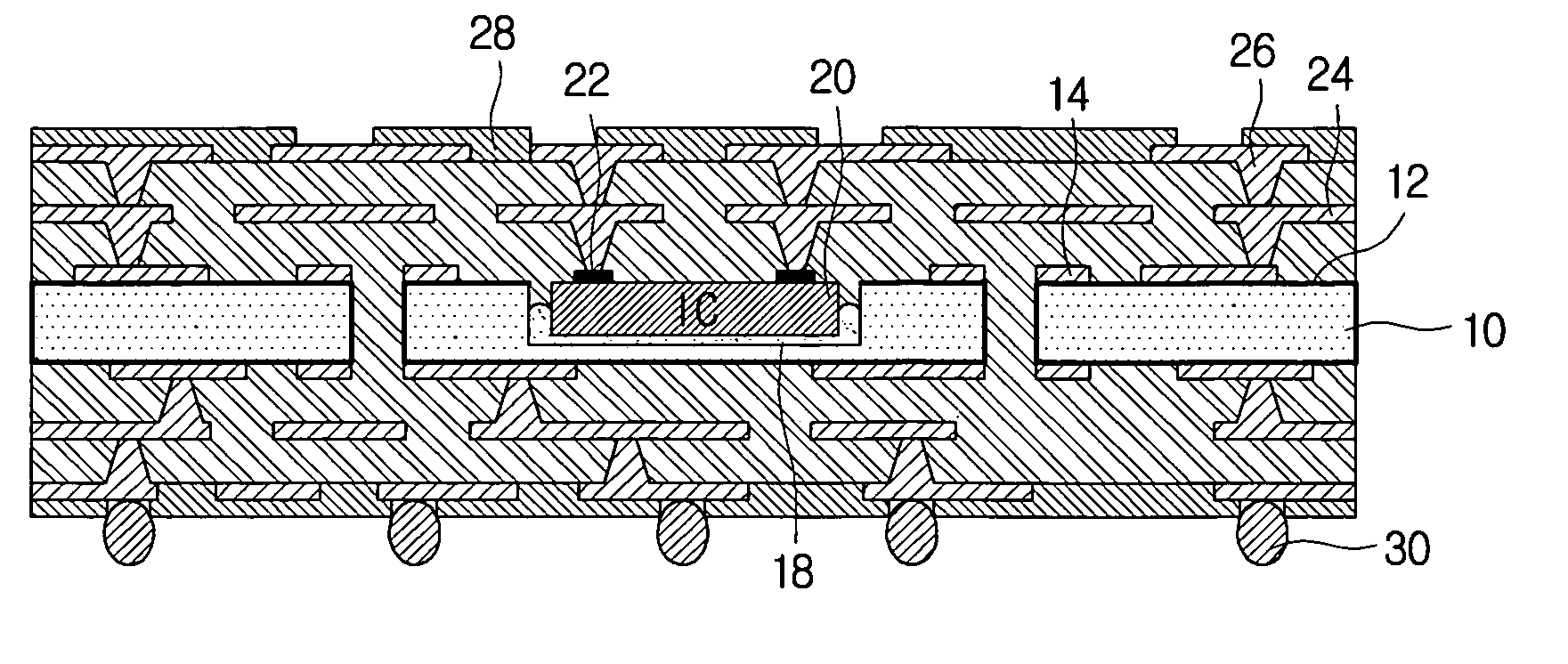

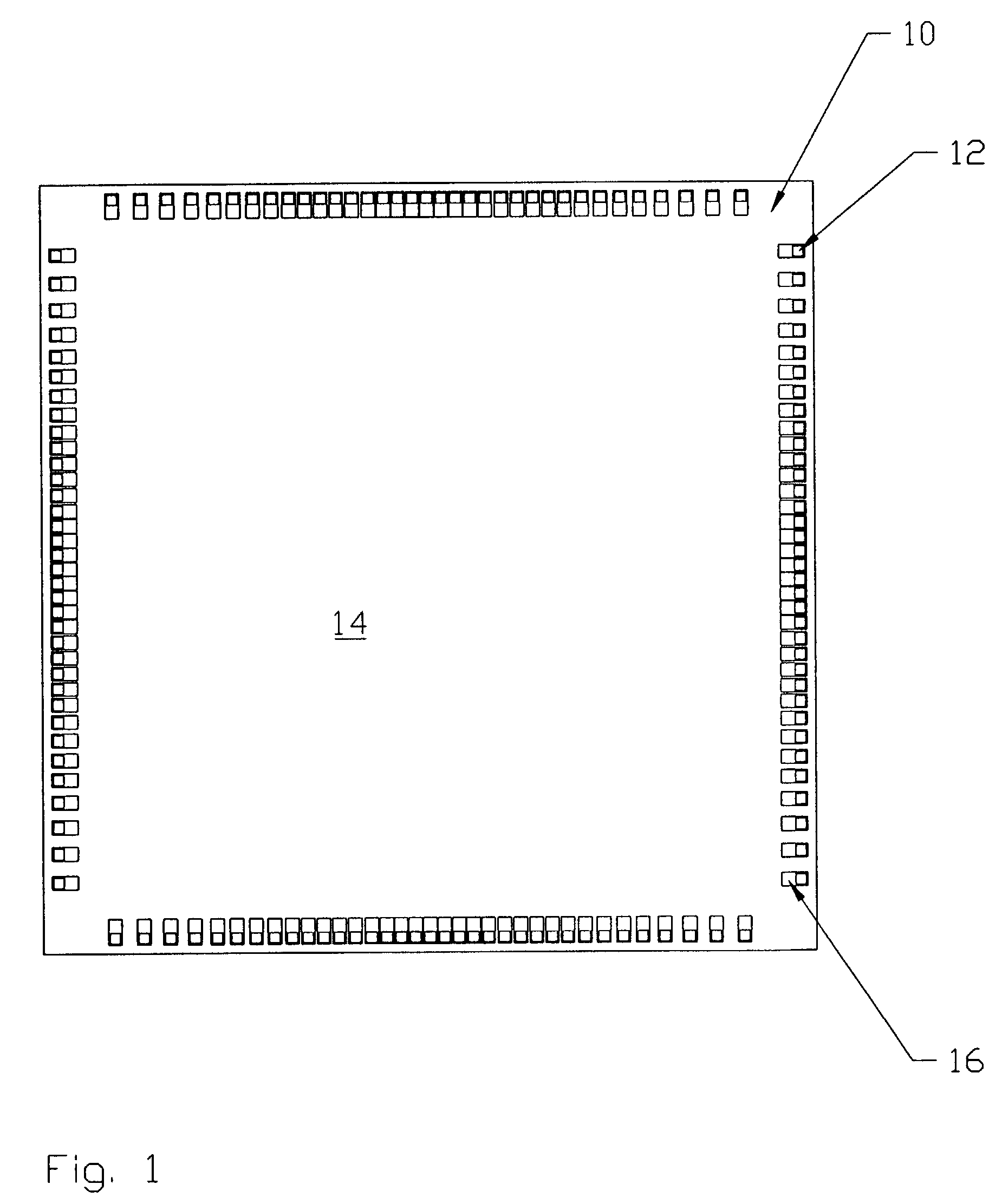

Method for packaging a microelectronic device using on-die bond pad expansion

InactiveUS7071024B2Semiconductor/solid-state device detailsSolid-state devicesWafer dicingDie bonding

Expanded bond pads are formed over a passivation layer on a semiconductor wafer before the wafer is diced into individual circuit chips. After dicing, the individual chips are packaged by fixing each chip within a package core and building up one or more metallization layers on the resulting assembly. In at least one embodiment, a high melting temperature (lead free) alternative bump metallurgy (ABM) form of controlled collapse chip connect (C4) processing is used to form relatively wide conducting platforms over the bond pads on the wafer.

Owner:INTEL CORP

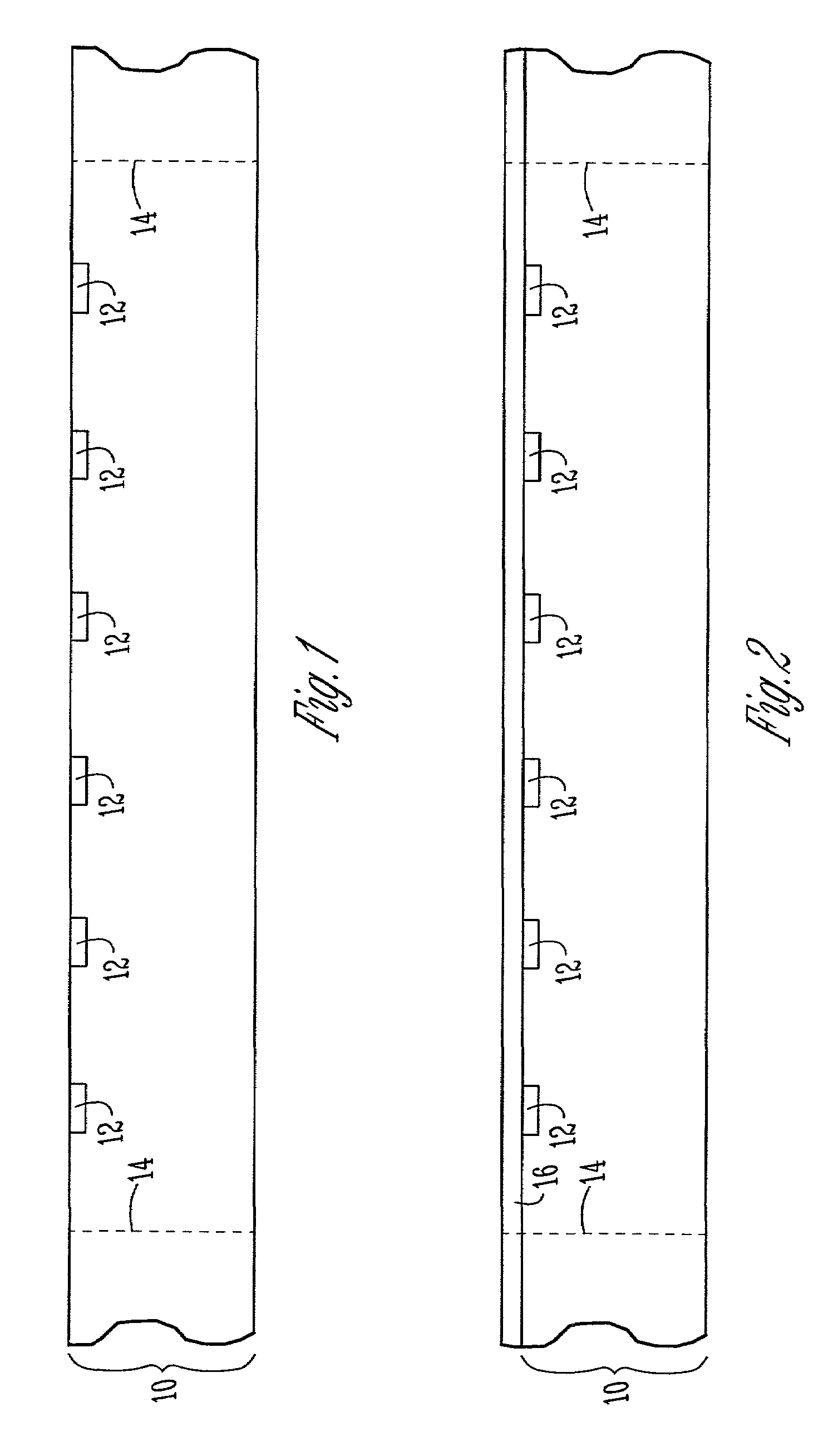

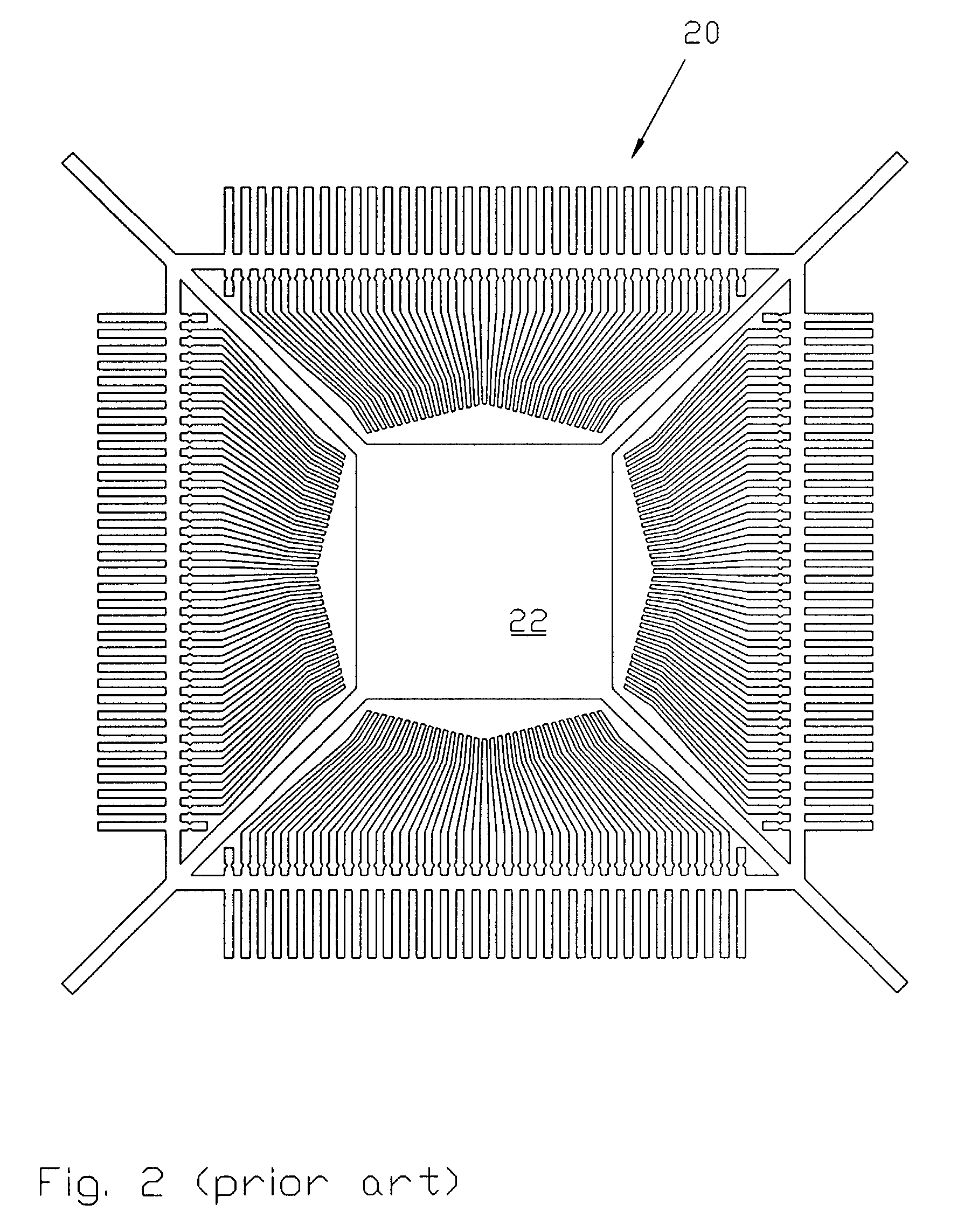

Multilayer laser trim interconnect method

InactiveUS6756252B2Semiconductor/solid-state device detailsSolid-state devicesContact padEngineering

A method for creating electrical interconnects between a semiconductor die and package. In the preferred embodiment, an insulating material is applied over the die and extends to the substrate contact pads, leaving a portion of each contact pad exposed. Holes are then trimmed through the insulating material, exposing at least a portion of each die bond pad. A conductive material is then applied over the die, flowing into the holes, contacting the die bond pads, and extending out to contact at least a portion of each substrate contact pad. In another preferred embodiment, an electrically conductive bump may be formed on each die bond pad, protruding through said non-conductive material and at least partially through said conductive material. The conductive layer is then laser trimmed, forming conductive patches that serve as electrical interconnects between the die and package substrate.

Owner:TEXAS INSTR INC

Manufacturing Method of Semiconductor Device

ActiveUS20100190293A1Improve reliabilitySimple manufacturing processSolid-state devicesSemiconductor/solid-state device manufacturingAmbient pressureEngineering

The present invention has been achieved reflecting such situation, and its object is to provide a manufacturing method of a semiconductor device capable of continuously performing the mounting process which applies a so-called DBG process and a flip chip bonding method, and can contribute to simplify the manufacturing process and to improve the reliability with no void in the product. The manufacturing method of a semiconductor device according to the present invention comprises:laminating a surface protective sheet to a circuit surface side of a wafer formed with grooves which divide each circuit wherein an adhesive film is adhered on the circuit surface of the wafer;reducing the thickness of the wafer and finally dividing the wafer into individual chips by grinding a back face of the wafer;picking up individual chips together with the adhesive film;die-bonding said individual chip to predetermined position of a chip mounting substrate via said adhesive film;fixing the chip to the chip mounting substrate by heating the die-bonded chip having the adhesive film; andapplying a static pressure larger than an ambient pressure by 0.05 MPa or more to a stacked body including the adhesive film one or more times, at any point between adhering the wafer to the adhesive film and fixing the chip to the chip mounting substrate.

Owner:LINTEC CORP

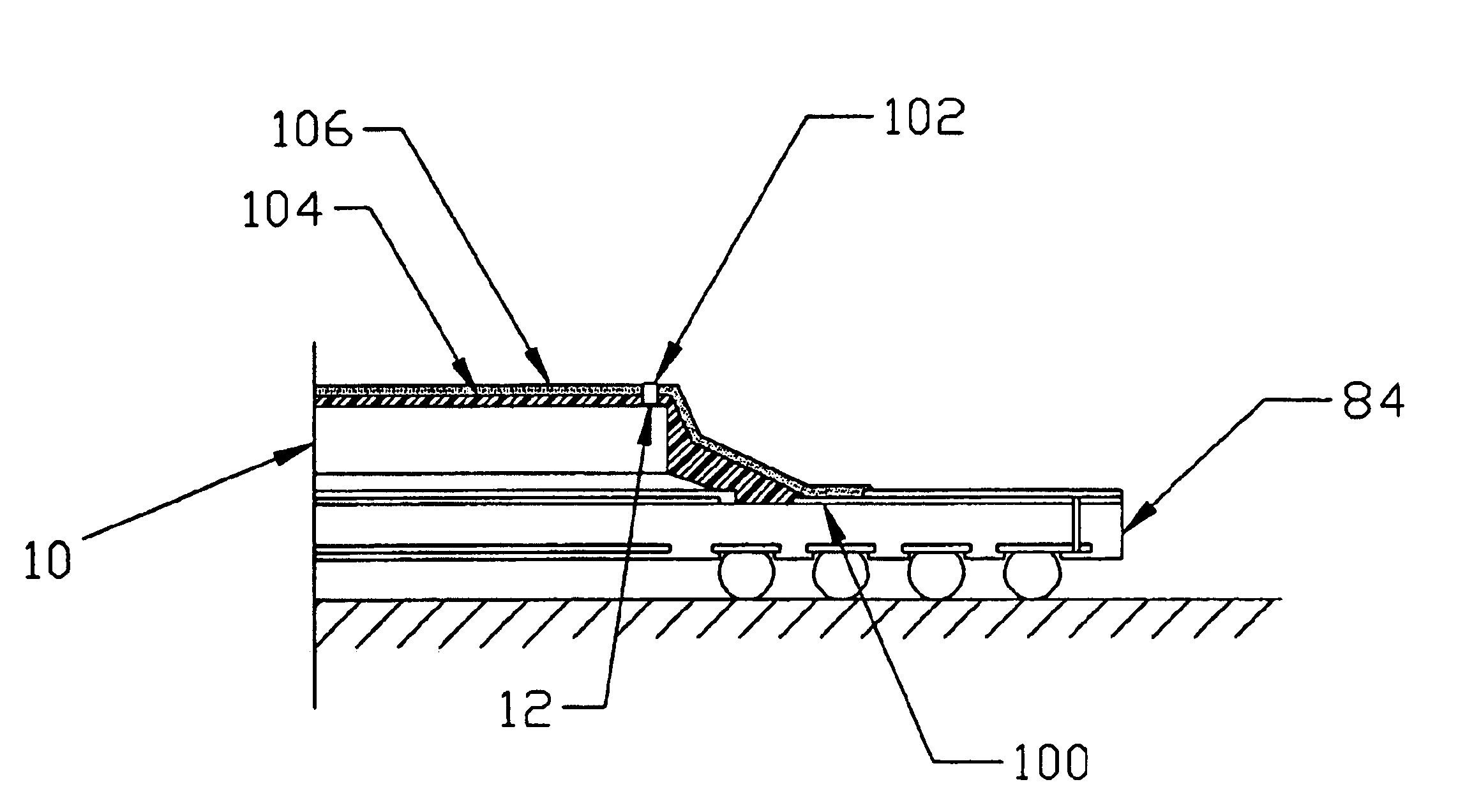

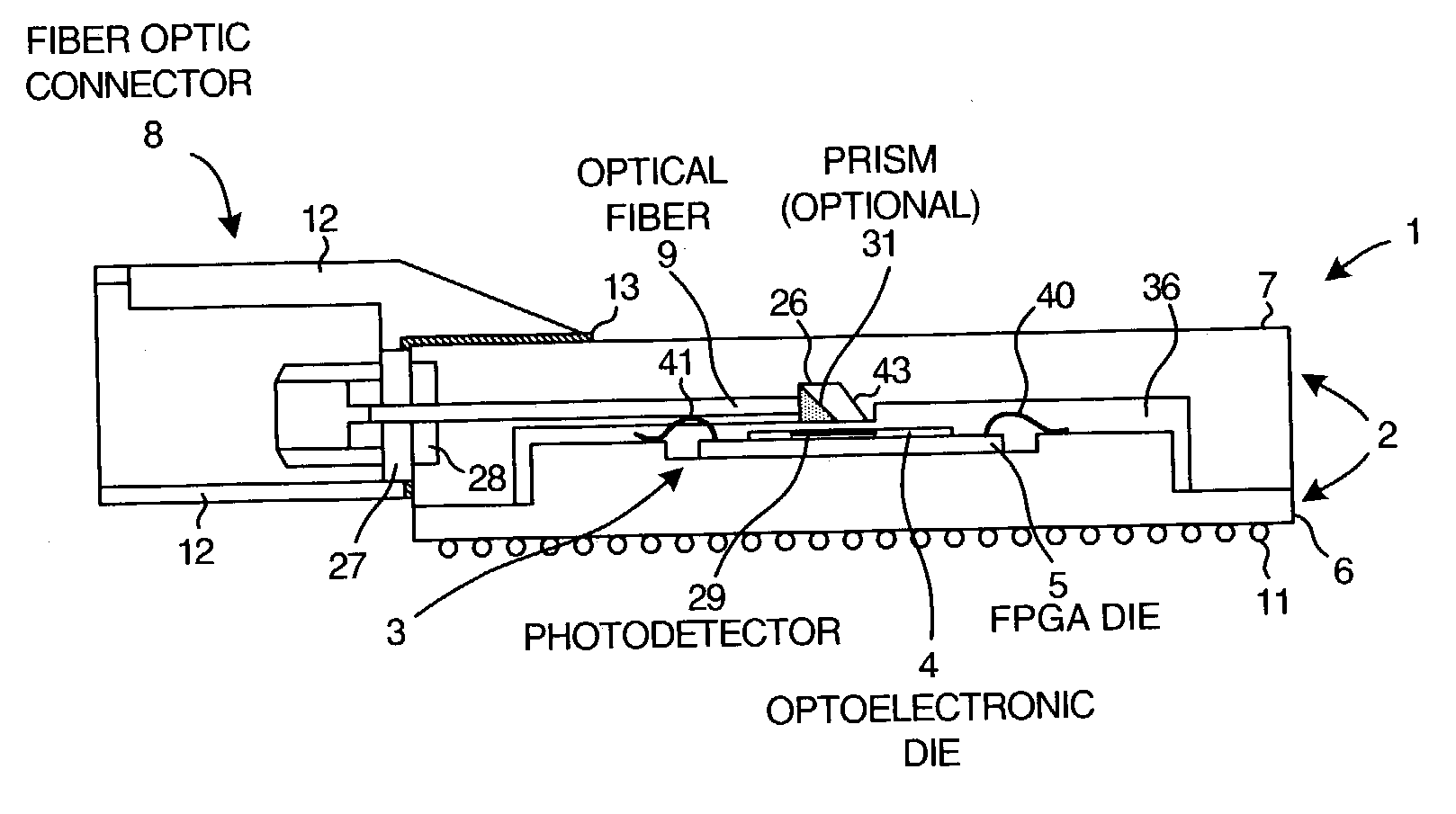

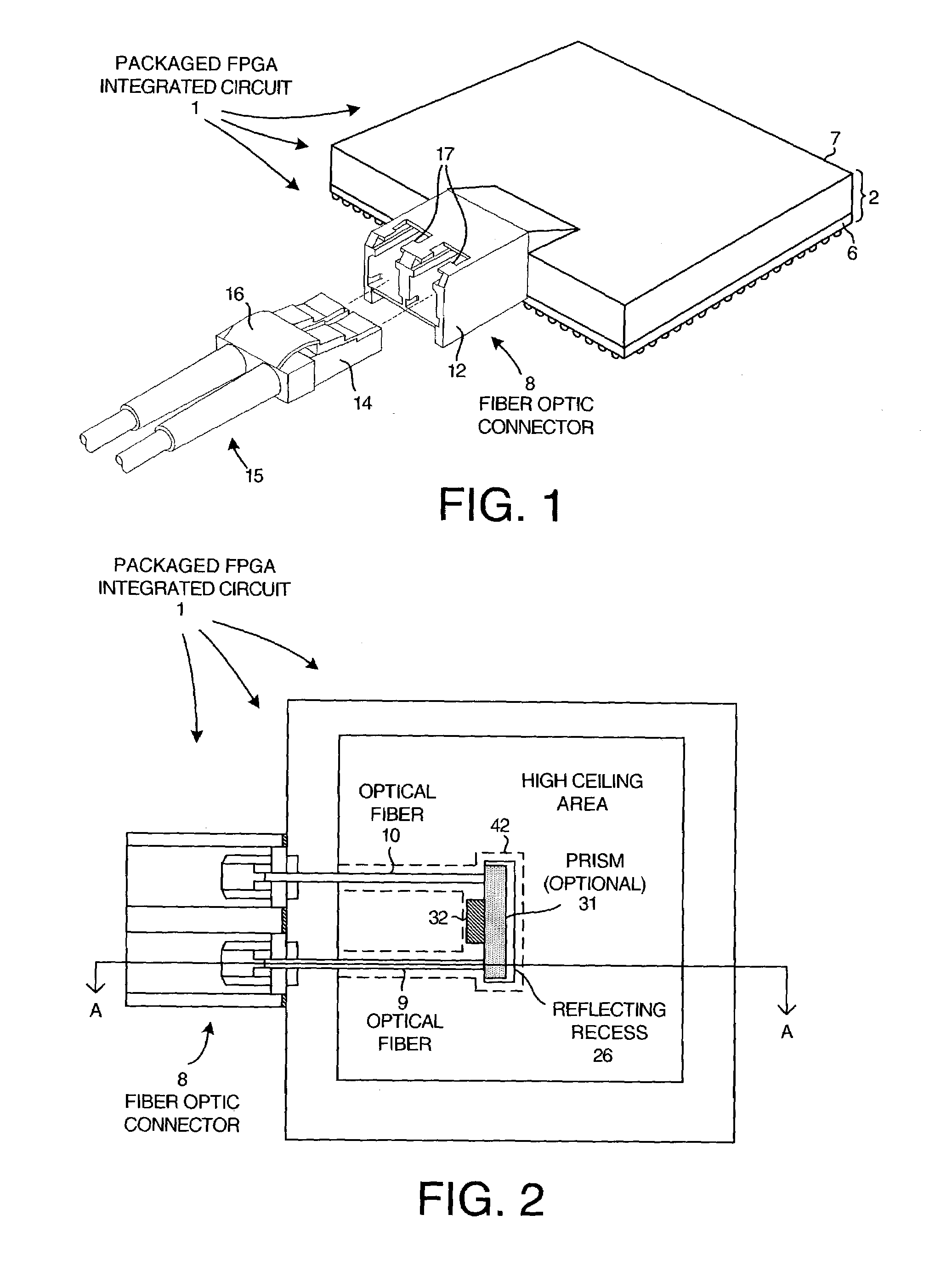

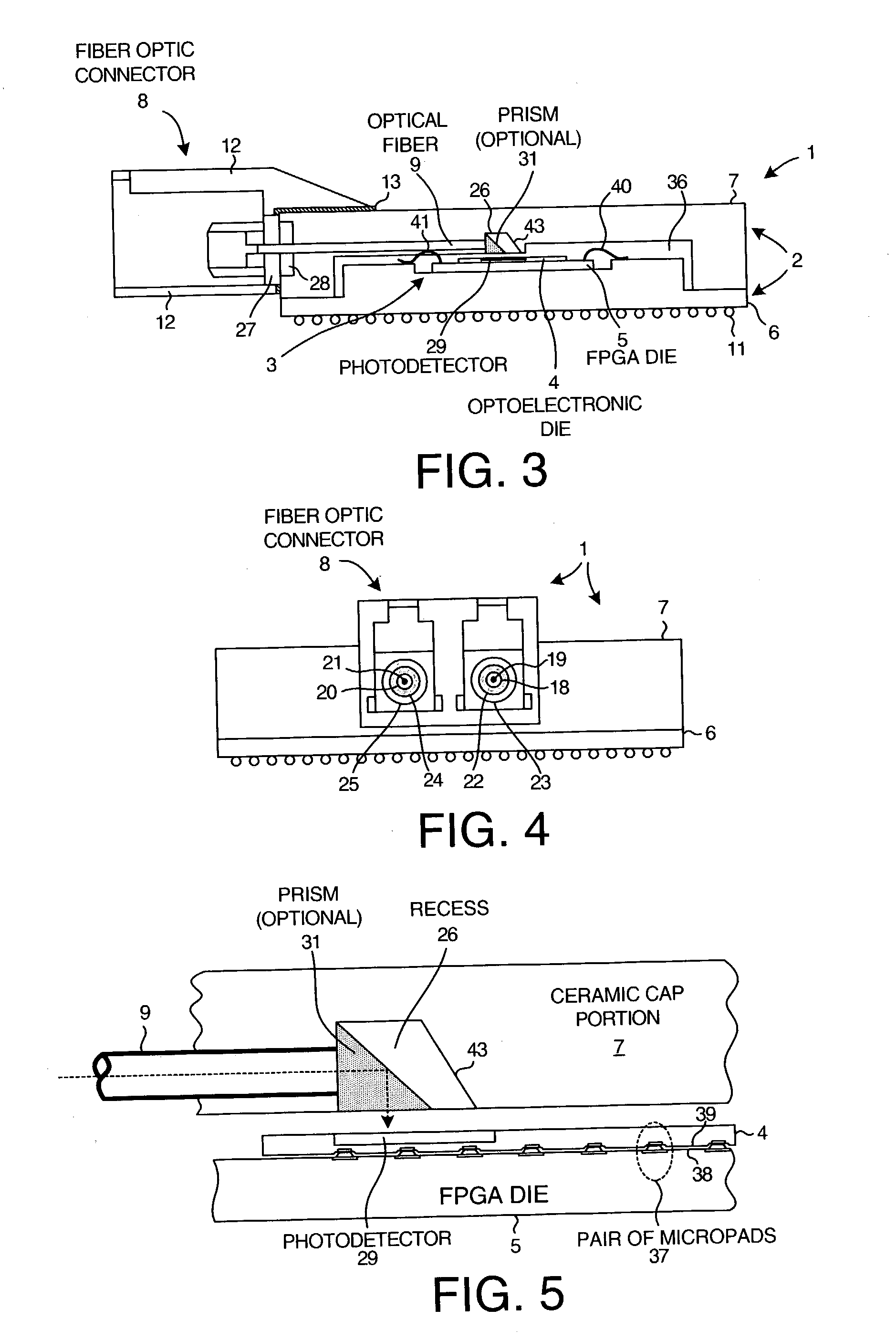

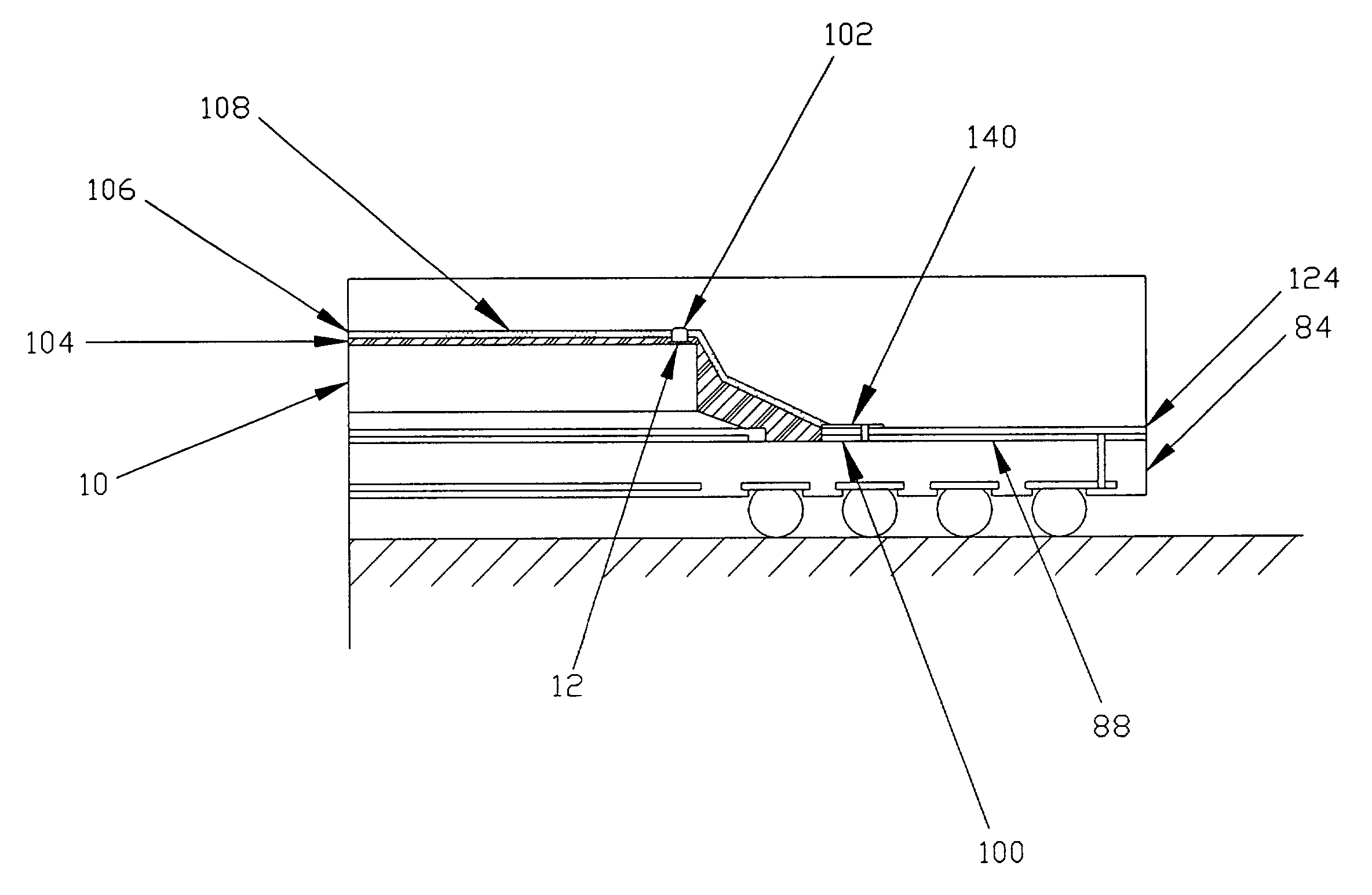

Fiber optic field programmable gate array integrated circuit packaging

ActiveUS6945712B1Thin profileReduce power consumptionSolid-state devicesCoupling light guidesFiberPhotodetector

An FPGA is readily connectable to a high-speed fiber optic link by snap fitting an external fiber optic cable into an accommodating duplex fiber optic connector of a low-profile packaged FPGA integrated circuit. The low-profile packaged FPGA integrated circuit includes a die-bonded assembly disposed within a co-fired multilayer ceramic integrated circuit package. The die-bonded assembly includes the optoelectronic die, the bottom surface of which is die-bonded and electrically interconnected by micropads to the upper surface of the core of an FPGA integrated circuit die. A first optical fiber communicates light from the connector, through the package, and to a photodetector on the optoelectronic die. A second optical fiber communicates light from a laser diode on the optoelectronic die, through the package, and to the connector. In some embodiments, a micromirror device is disposed within the package to redirect light between the optoelectronic die and the optical fibers.

Owner:XILINX INC

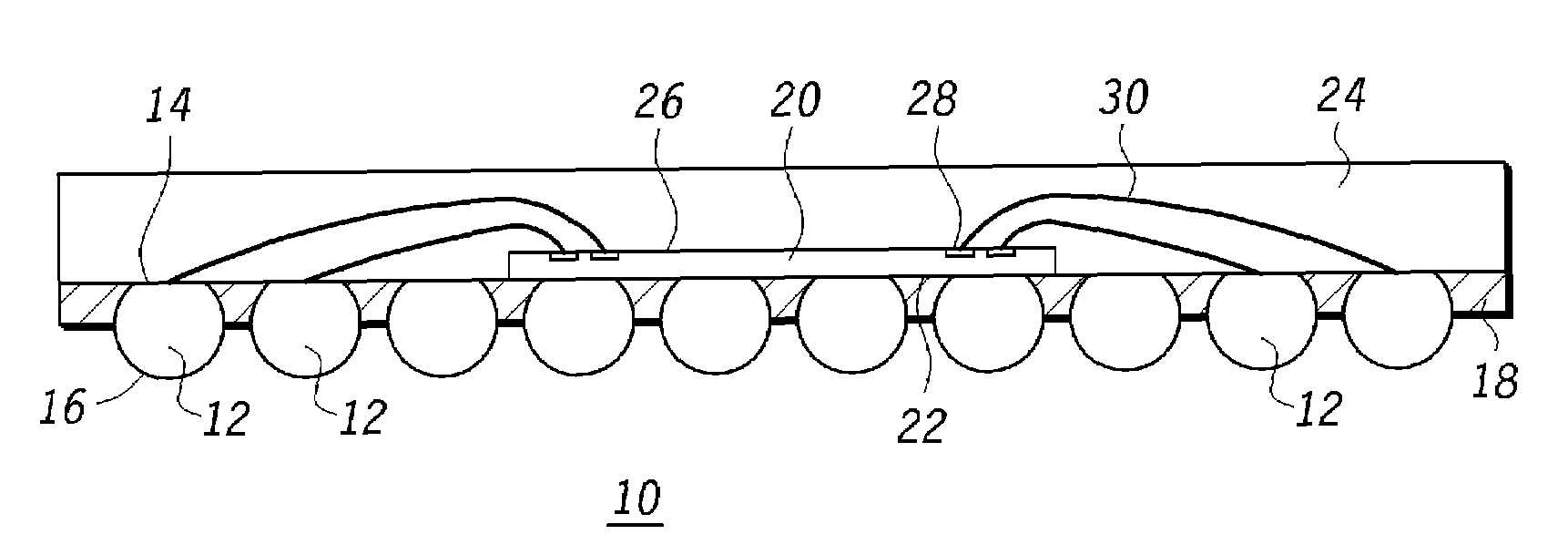

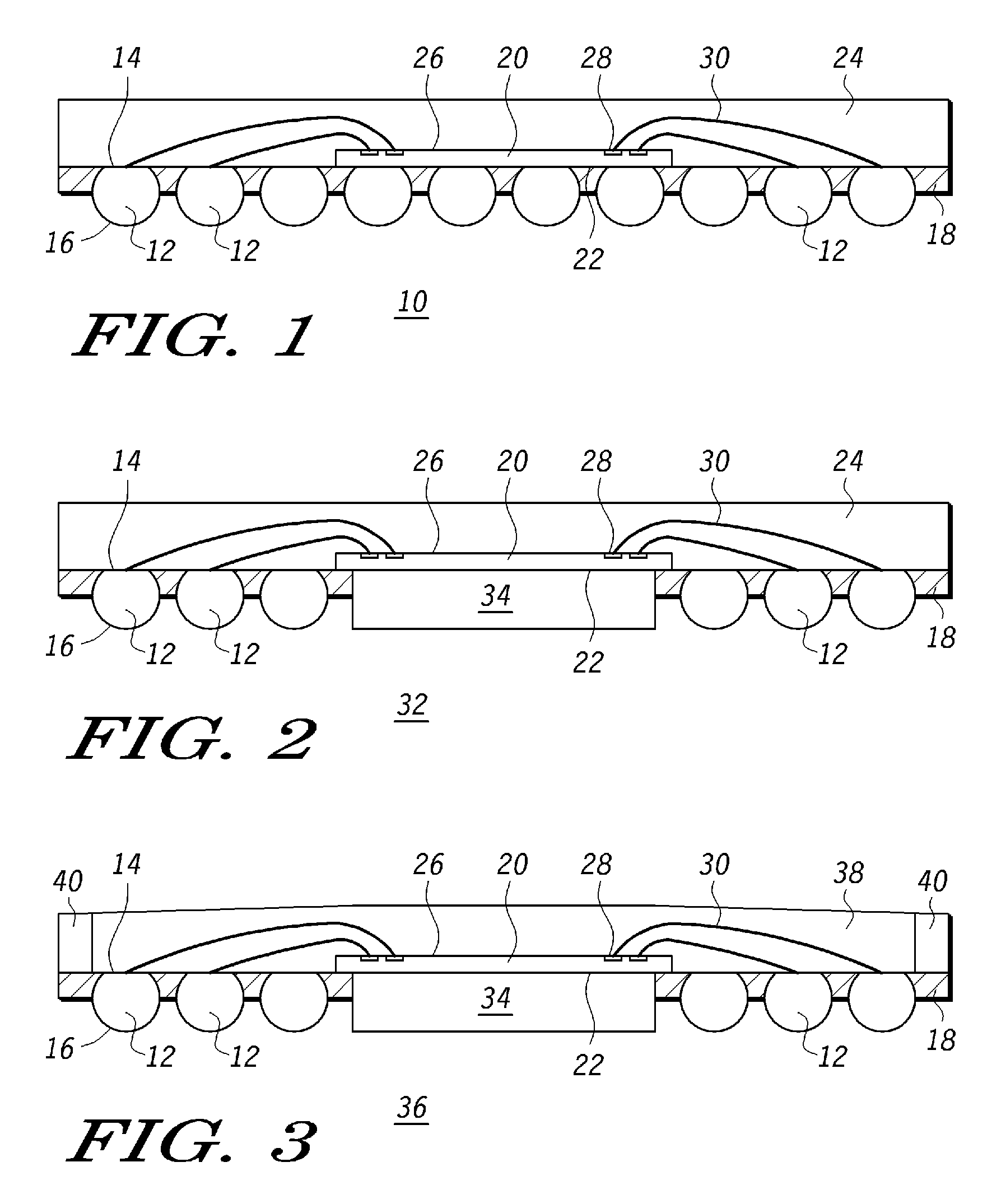

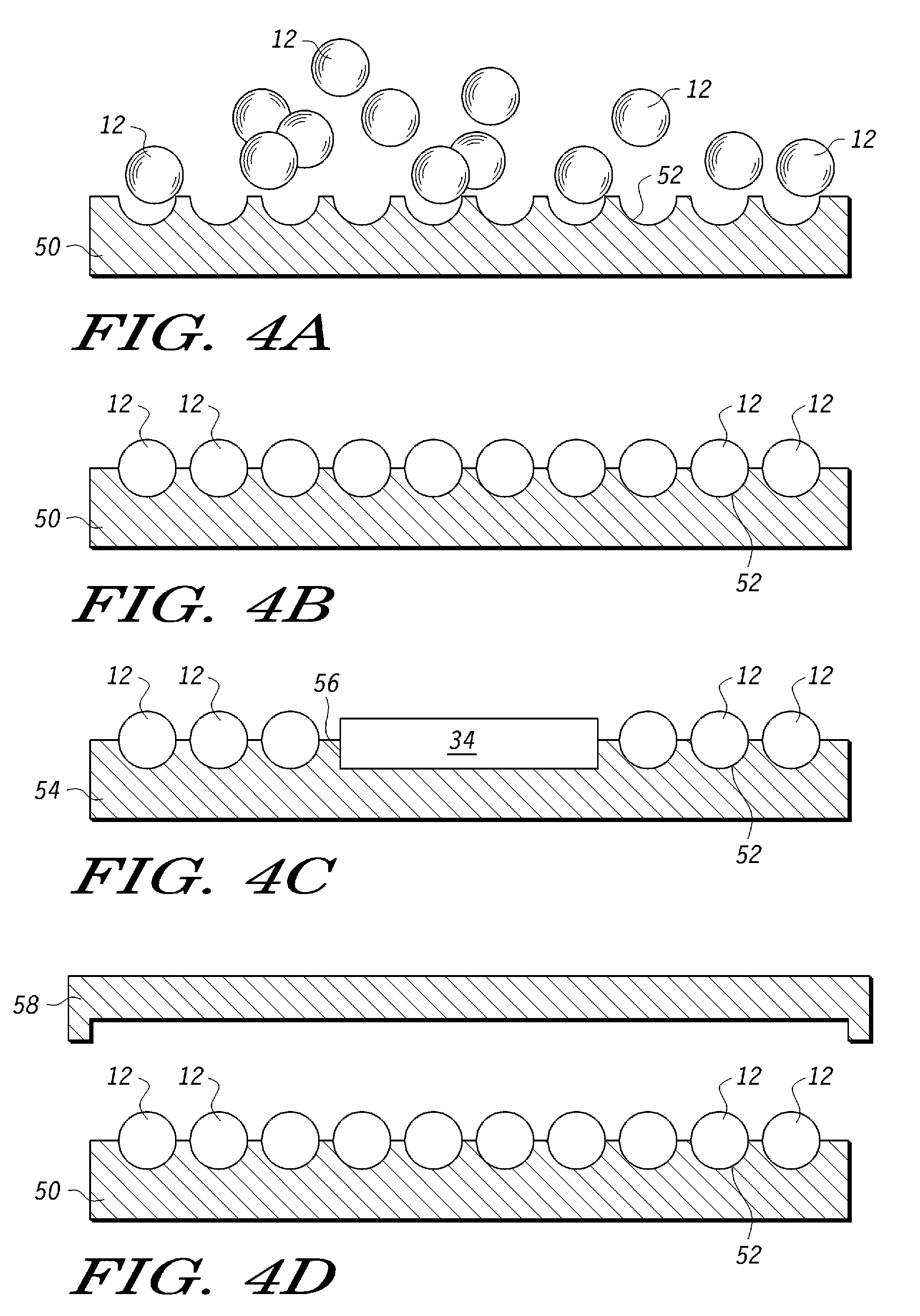

Packaged device and method of forming same

InactiveUS7285855B2Semiconductor/solid-state device detailsSolid-state devicesShell moldingElectrical connection

Owner:TAIWAN SEMICON MFG CO LTD

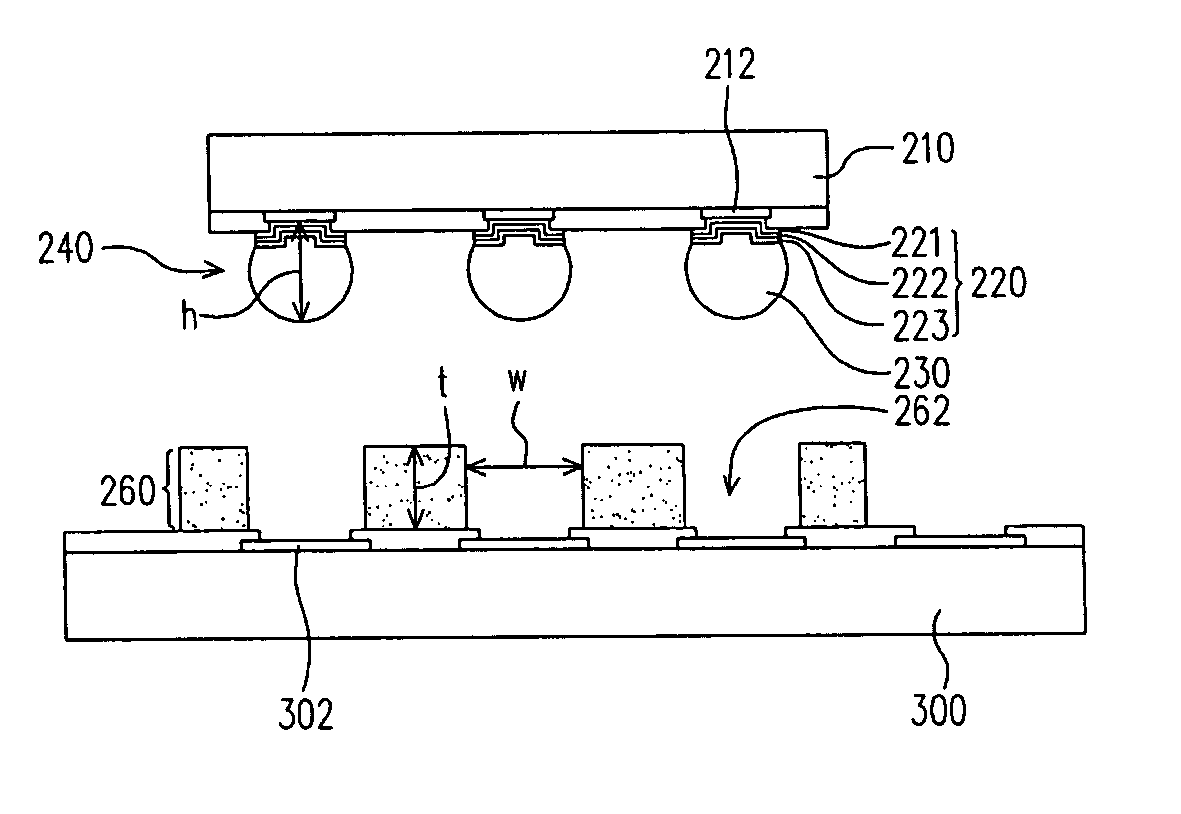

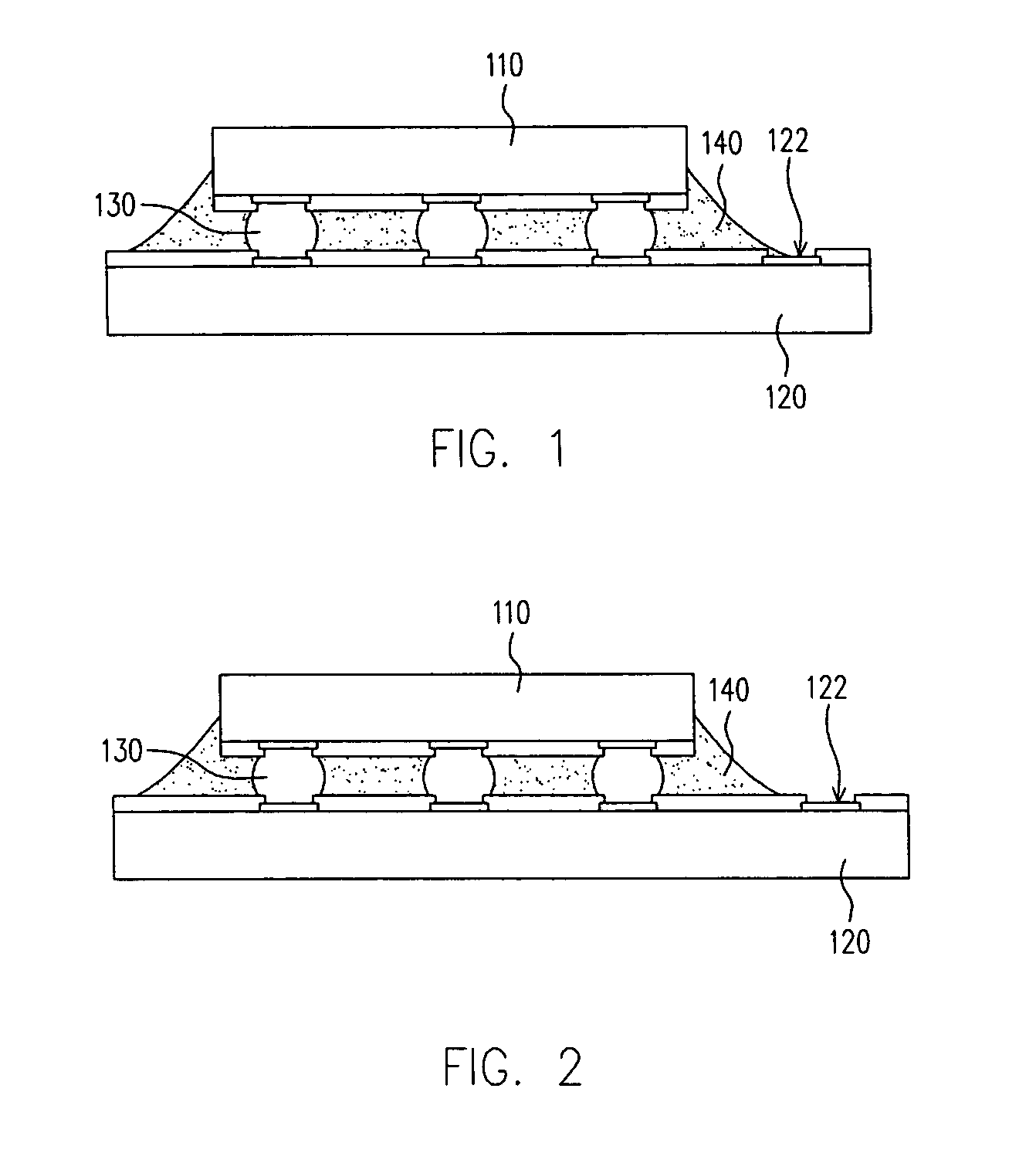

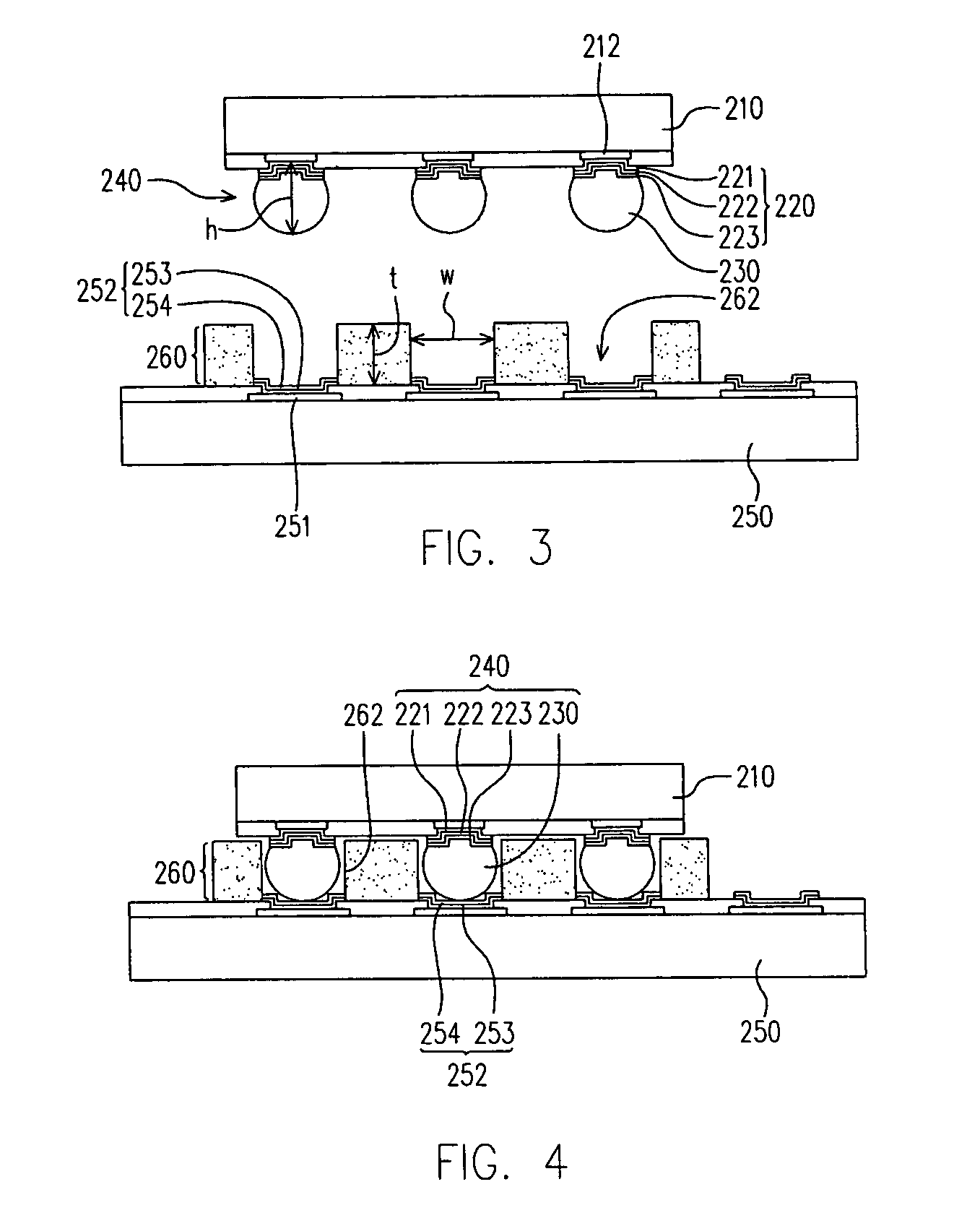

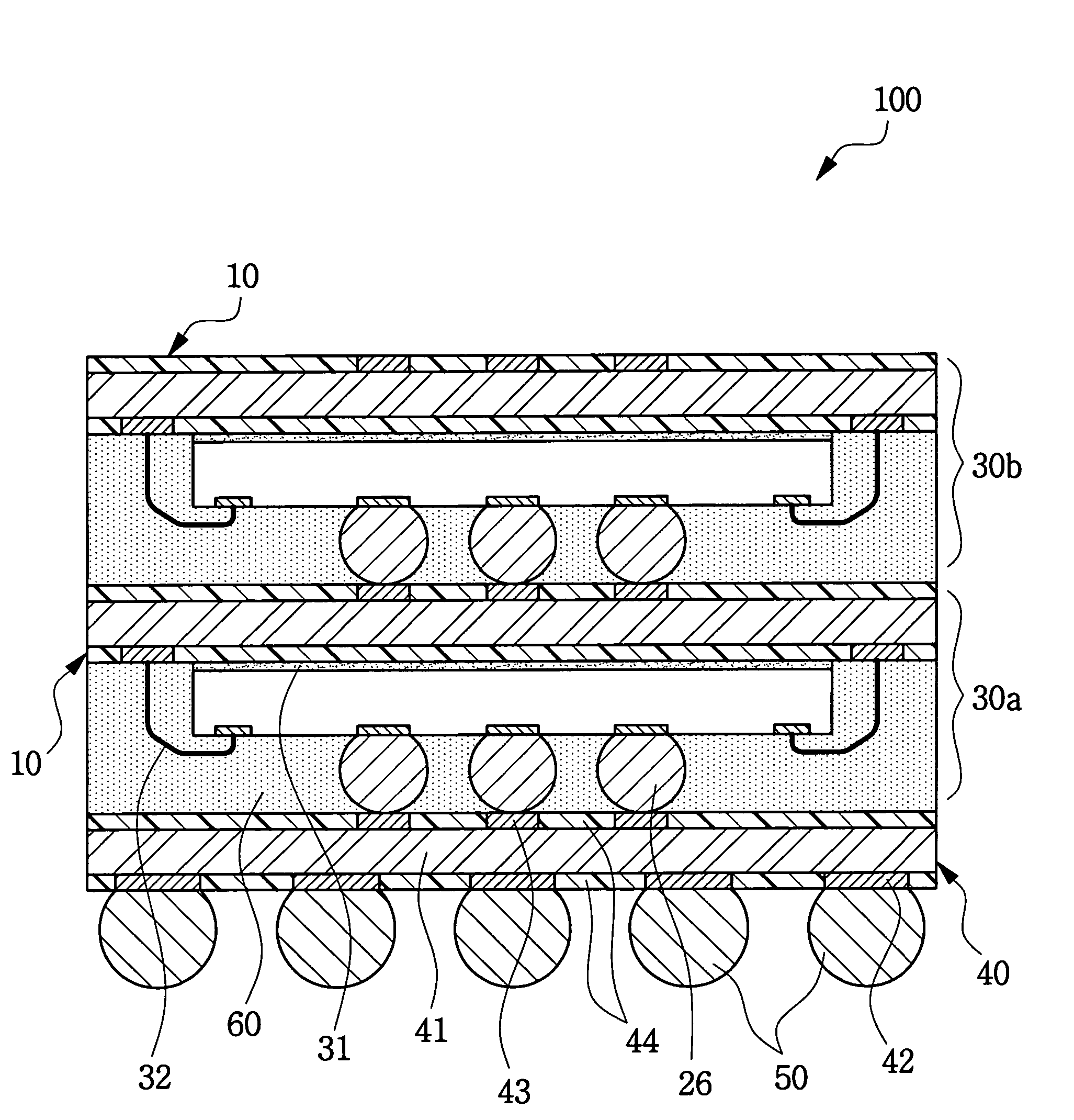

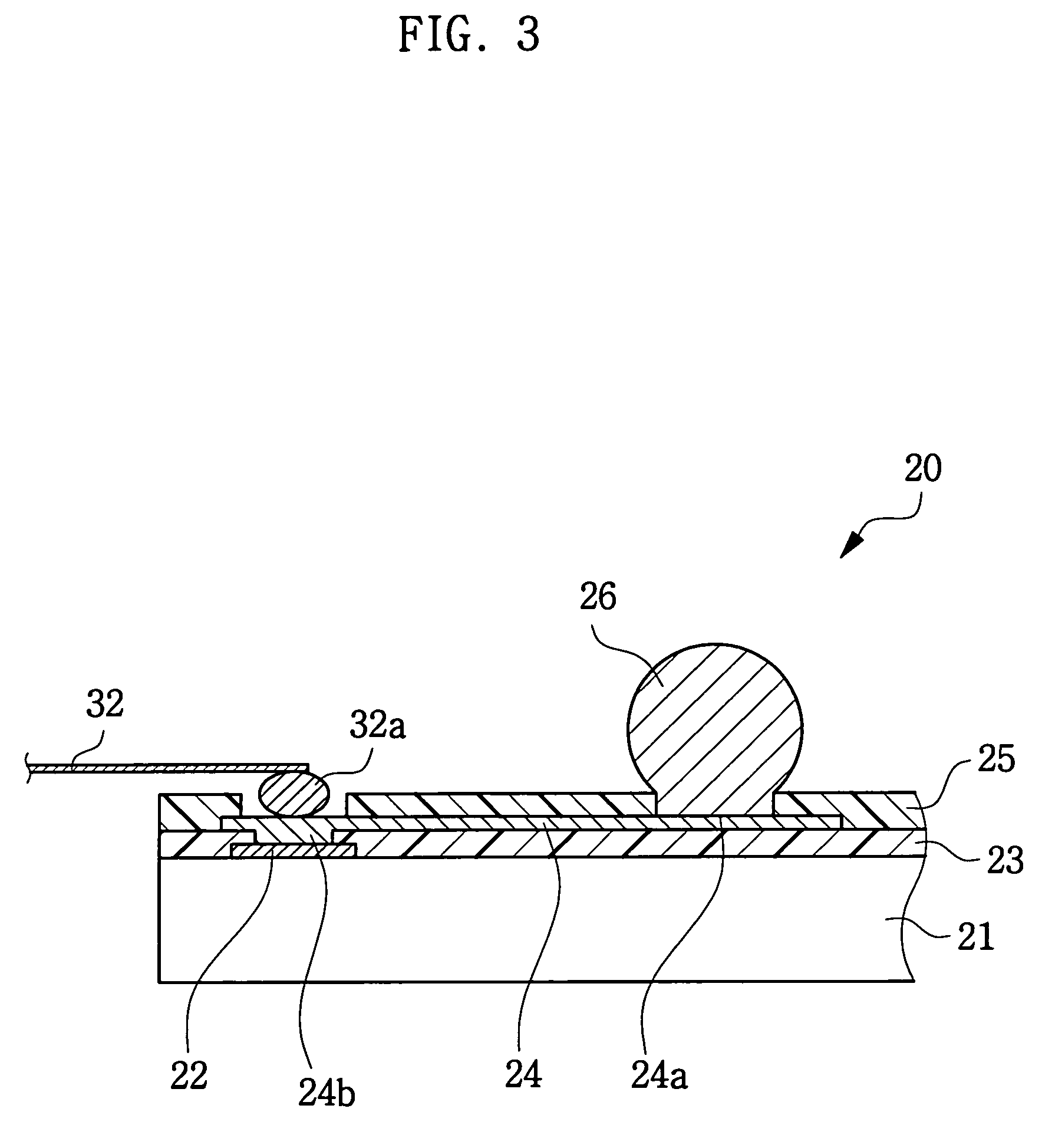

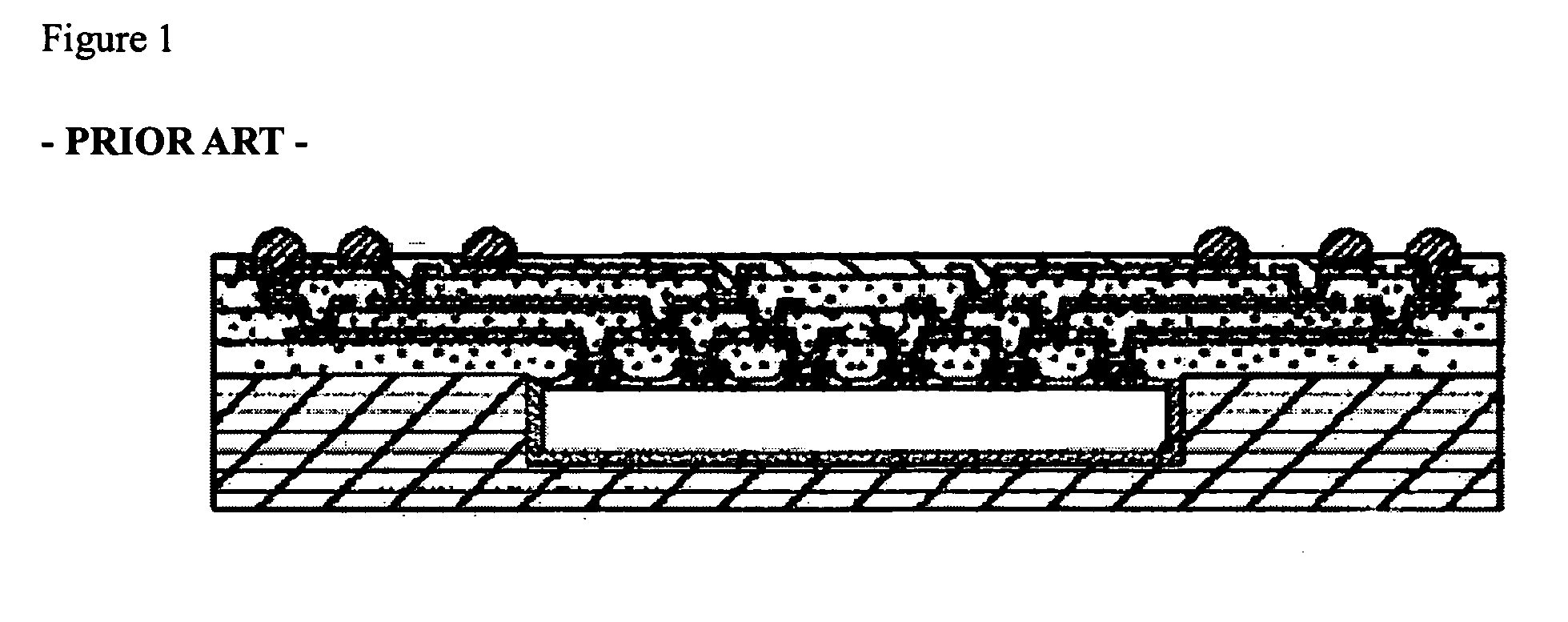

Semiconductor package, manufacturing method thereof and IC chip

ActiveUS7355274B2Semiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor package

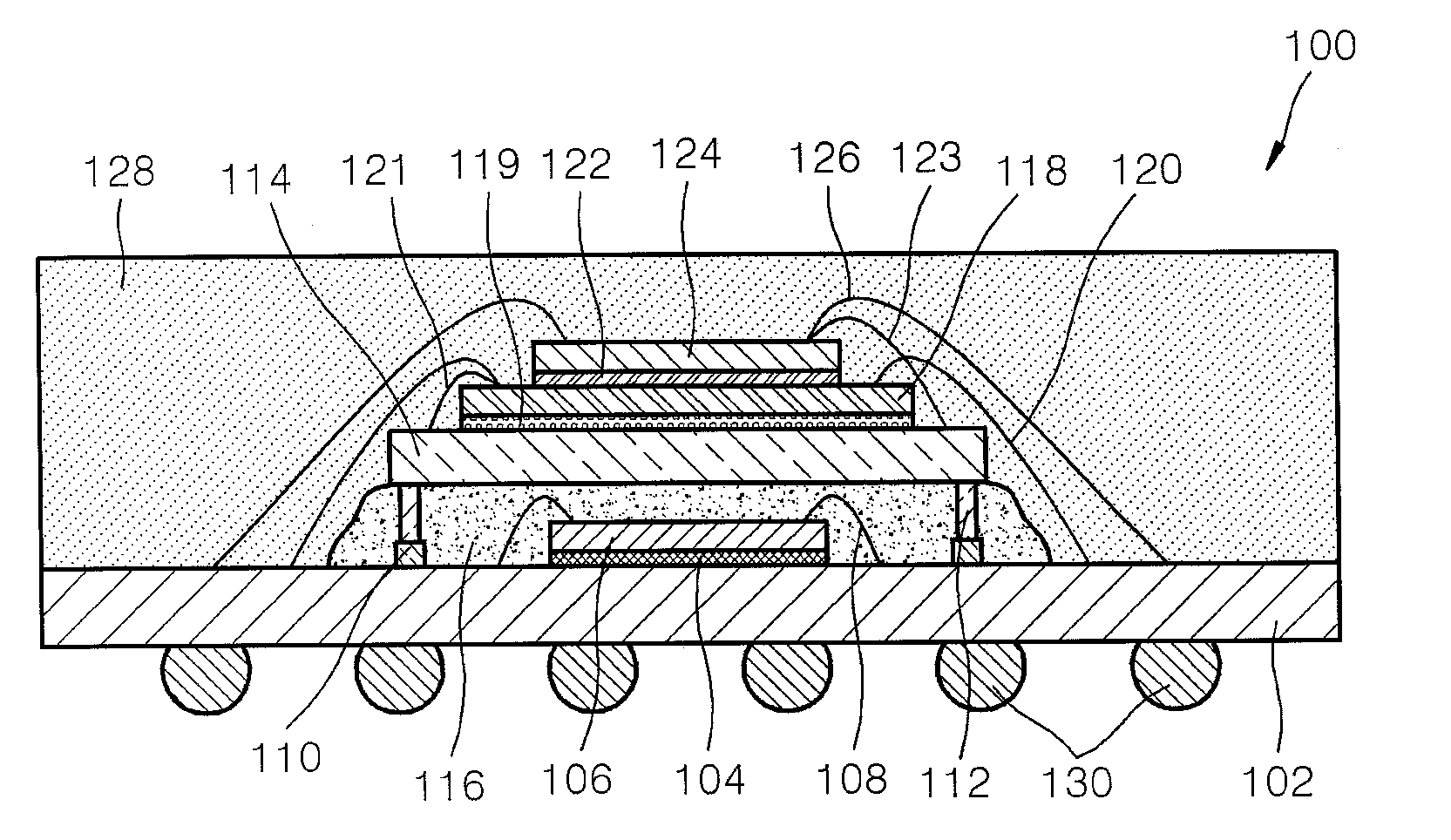

A package may include a lower unit package and an upper unit package. Each of the unit packages may include a circuit substrate having a lower surface and an upper surface. Wire bonding pads may be provided of the lower surface of the circuit substrate, and chip bonding pads may be provided on the upper surface of the circuit substrate. An IC chip may be provided on the lower surface of the circuit substrate. The IC chip may have an active surface with wire lands and bump lands. Chip bumps may be provided on the bump land. The wire bonding pads of the circuit substrate may be connected to the wire lands of the IC chip using bonding wires. The chip bumps of the upper unit package may be connected to the chip bonding pads of the lower unit package. An IC chip may include a substrate. A conductive layer may be provided on the substrate. The conductive layer may define a bump land for supporting a chip bump and a wire land for connecting to a bonding wire. The bump land and the wire land may be spaced apart from each other on an active surface of the IC chip.

Owner:SAMSUNG ELECTRONICS CO LTD

Heat curable adhesive composition, article, semiconductor apparatus and method

InactiveUS20080090085A1Lose resistanceLose strengthSemiconductor/solid-state device detailsSynthetic resin layered productsEpoxySemiconductor chip

Provided are a heat curable adhesive composition and an adhesive article suited for dicing of a semiconductor and die-bonding of the diced semiconductor chip, and a semiconductor apparatus and a process for preparing a semiconductor apparatus using the adhesive composition and article. In one embodiment, the present invention provides a heat curable adhesive composition comprising a caprolactone-modified epoxy resin and a tack reducing component. Another embodiment of the present invention provides an adhesive article comprising a heat curable adhesive layer of a heat curable adhesive composition comprising a caprolactone-modified epoxy resin, a tack reducing component, and a backing layer carrying said adhesive layer on at least a portion of the backing layer.

Owner:3M INNOVATIVE PROPERTIES CO

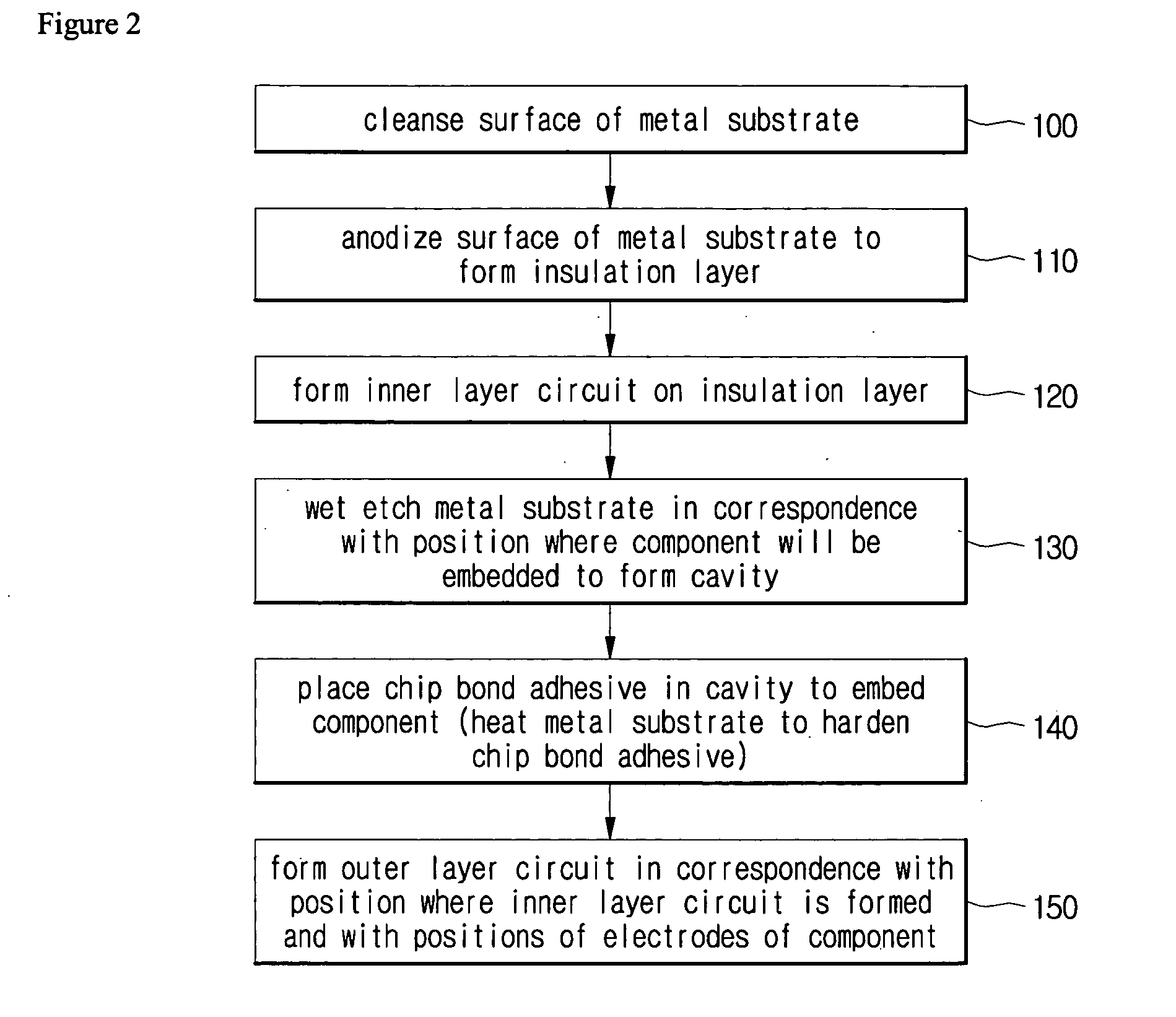

Printed circuit board and manufacturing method thereof

InactiveUS20070074900A1Increase stiffnessImprove heat-releasing propertyPrinted circuit assemblingPrinted electric component incorporationManufacturing cost reductionEtching

A printed circuit board and manufacturing method thereof are disclosed. By use of a method of manufacturing a printed circuit board, which uses a metal substrate as a core member and has an electronic component embedded in the metal substrate, mainly comprising: (a) anodizing at least one surface of the metal substrate to form at least one insulation layer, (b) forming an inner layer circuit on the at least one insulation layer, (d) placing chip bond adhesive in correspondence with a position where the electronic component is to be embedded and mounting the electronic component, and (e) forming an outer layer circuit in correspondence with a position where the inner layer circuit is formed and with positions of the electrodes of the electronic component, and which may further comprise an operation (c) of etching the metal substrate to form a cavity in correspondence with a position where the electronic component is to be embedded between the operations (b) and (d), a metal substrate, such as that of aluminum, etc., is rendered electrically insulating by applying an anodizing process and is used as a core member in a printed circuit board, so that bending stiffness and heat-releasing property are improved; wet etching can be applied, so that manufacturing costs are reduced; and a chip bond adhesive, die attach film, or nonconductive paste, etc., that is high in thixotropy is used in embedding the electronic component, so that the degree of precision may be increased for the position and height of the electronic component when embedding the electronic component.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

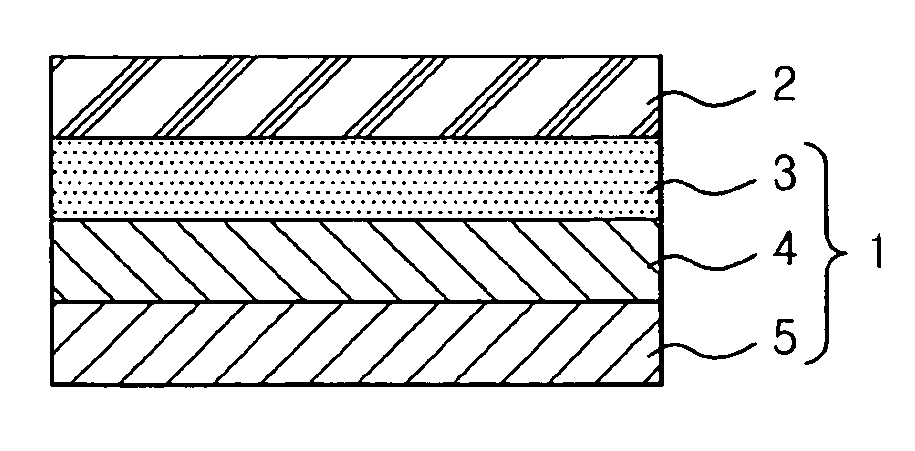

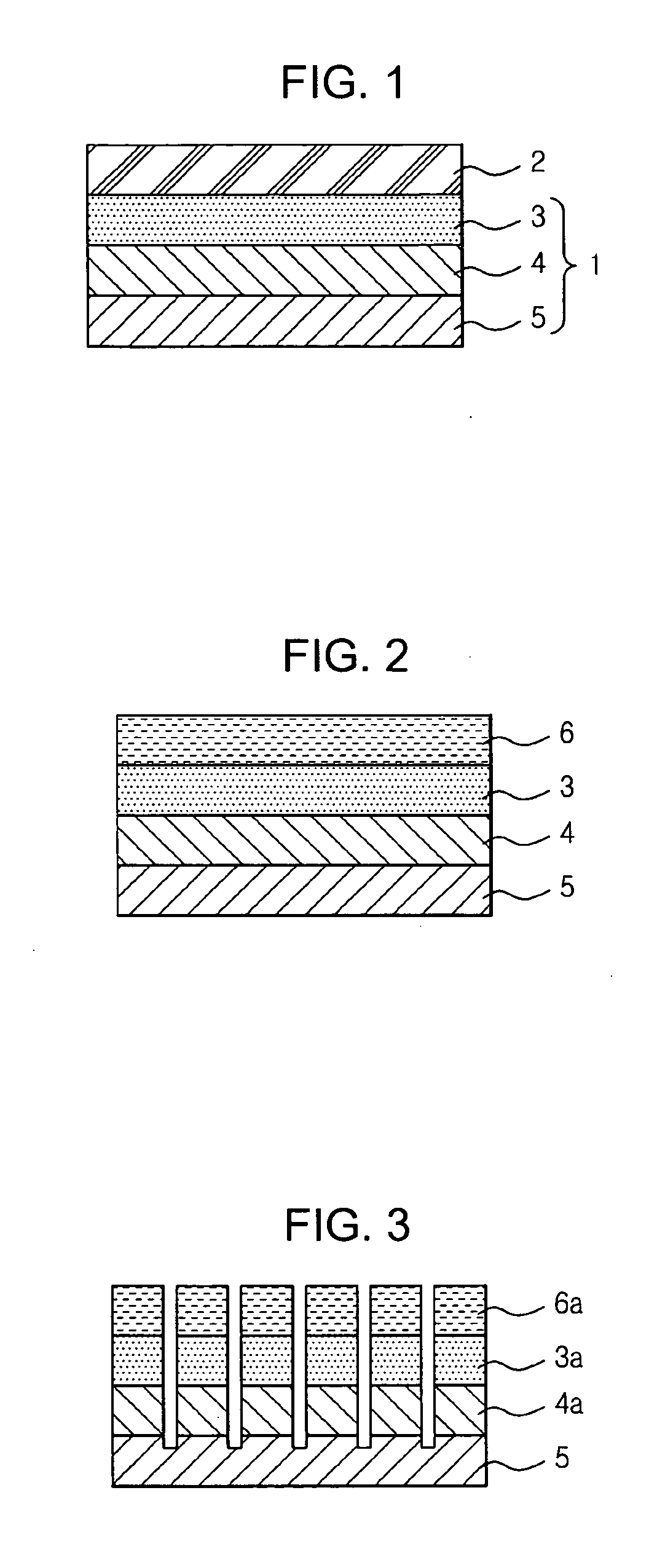

Dicing/die bonding sheet

ActiveUS20070026572A1Satisfactory adhesivenessEasy to separatePolyureas/polyurethane adhesivesSynthetic resin layered productsEpoxyDicing tape

The present invention provides a dicing / die bonding sheet which can be used as a dicing tape during dicing, enables ready separation of the semiconductor element and the adhesive layer from the pressure-sensitive adhesive layer during pickup, and in which the adhesive layer has satisfactory adhesiveness as a die bonding material. A dicing / die bonding sheet in which the pressure-sensitive adhesive layer comprises a compound (A), containing intramolecular, radiation curable carbon-carbon double bonds with an iodine value of 0.5 to 20, and at least one compound (B) selected from a group consisting of polyisocyanates, melamine-formaldehyde resins, and epoxy resins, and the adhesive layer comprises an epoxy resin (a), a phenolic resin (b) with a hydroxyl equivalent of at least 150 g / eq., an epoxy group-containing acrylic copolymer (c), comprising from 0.5 to 6% by weight of glycidyl acrylate or glycidyl methacrylate, and with a weight average molecular weight of at least 100,000, a filler (d), and a curing accelerator (e).

Owner:RESONAC CORP +1

LED package for backlight unit

ActiveUS7156538B2Improve image qualityImprove luminous efficiencyLighting support devicesGlass furnace apparatusEngineeringDie bonding

Owner:SAMSUNG ELECTRONICS CO LTD

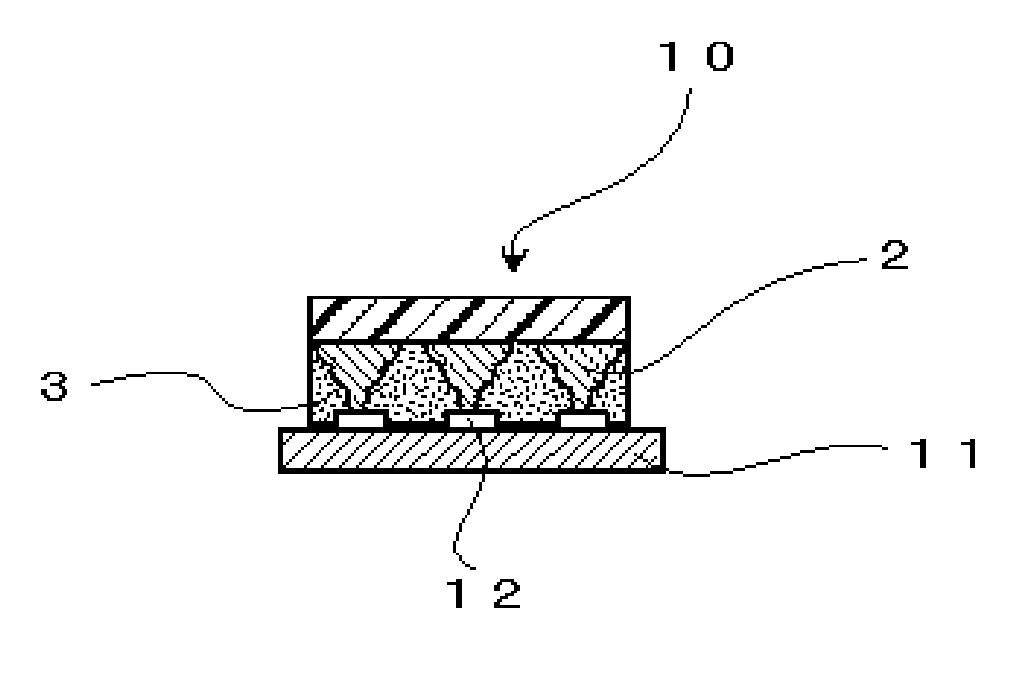

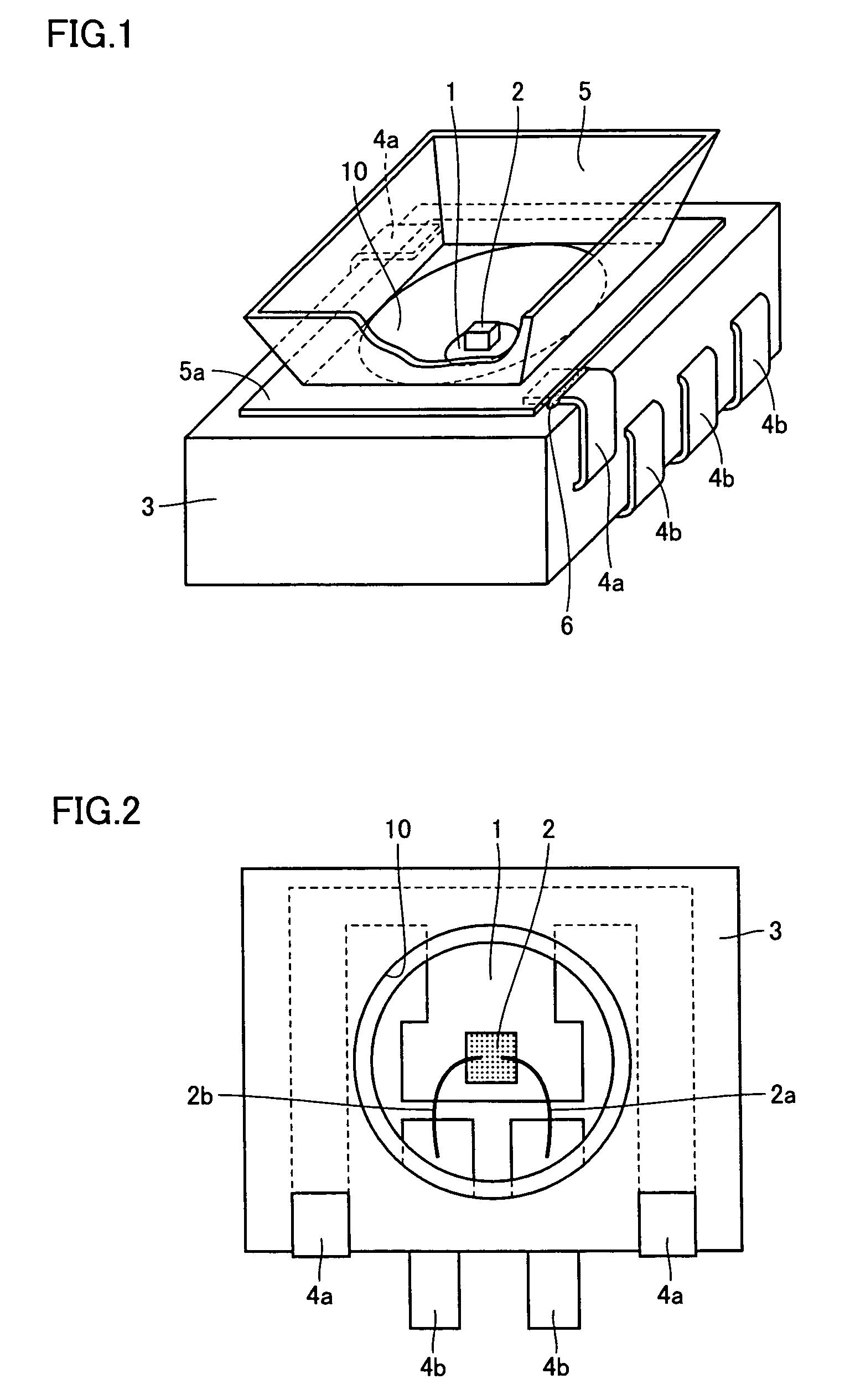

Semiconductor device using semiconductor chip

InactiveUS20050156187A1Reduce positional deviationSmall sizeSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

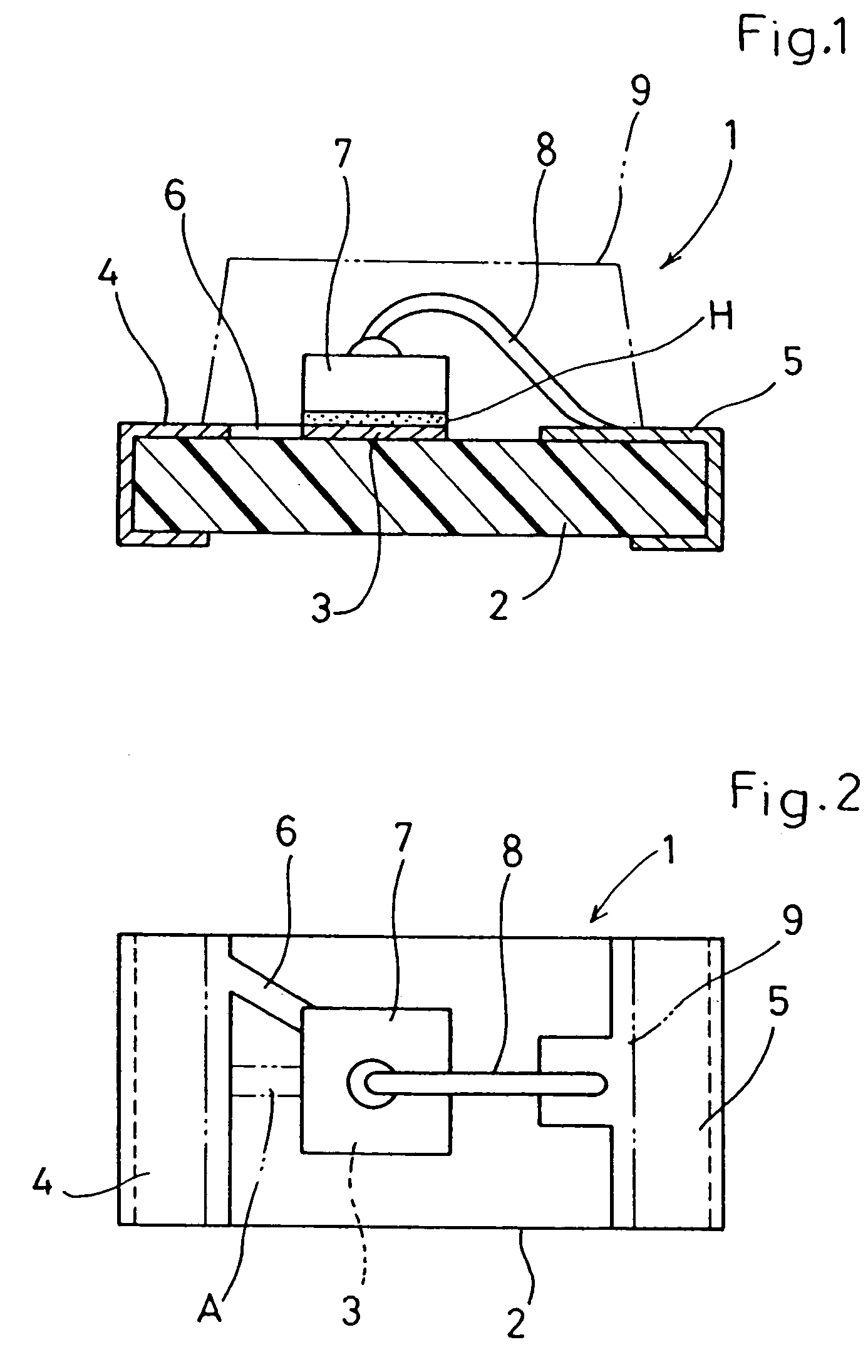

A semiconductor device includes an insulating substrate 2 having an obverse surface formed with a die pad 3, a rectangular semiconductor chip 7 such as an LED chip bonded to the die pad with a die bonding material 10, and a molded portion 9 made of a synthetic resin for packaging the semiconductor chip. The die pad 3 may be rectangular with dimensions close to those of the semiconductor chip or circular with a diameter close to the diagonal dimension of the semiconductor chip, whereby the positioning and orienting of the semiconductor chip can be accurately performed in bonding the semiconductor chip.

Owner:ROHM CO LTD

Vertical stack type multi-chip package having improved grounding performance and lower semiconductor chip reliability

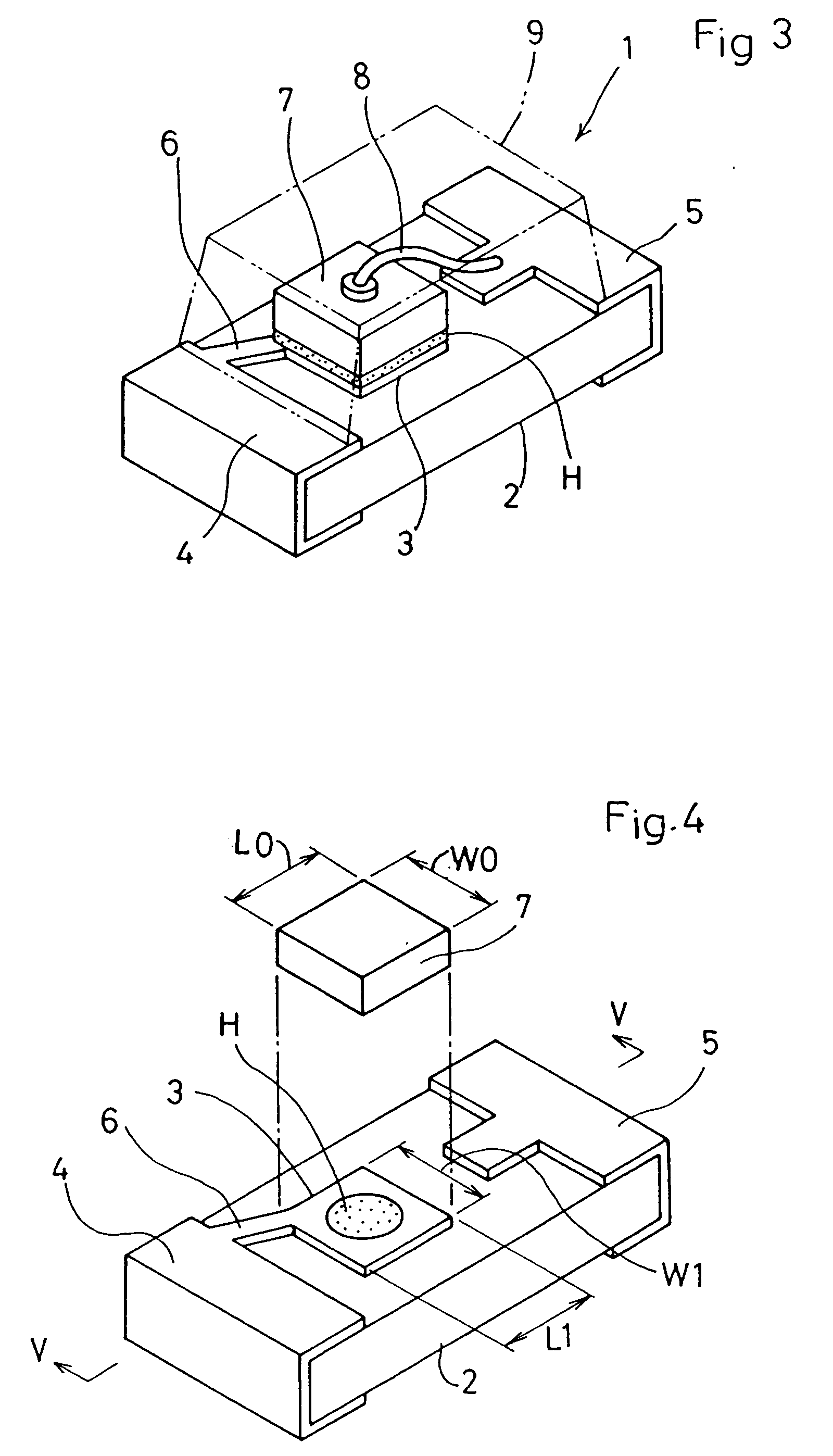

ActiveUS20080029869A1Good grounding effectSmall sizeSemiconductor/solid-state device detailsSolid-state devicesMoisture penetrationSolder ball

A vertical stack type multi-chip package is provided having improved reliability by increasing the grounding performance and preventing the decrease in reliability of the multi-chip package from moisture penetration into a lower semiconductor chip. The vertical stack type multi-chip package comprises an organic substrate having a printed circuit pattern on which a semiconductor chip is mounted. A first semiconductor chip is mounted on a die bonding region of the organic substrate and is electrically connected to the organic substrate through a first wire. A metal stiffener is formed on the first semiconductor chip and connected to the organic substrate by a first ground unit around the first semiconductor chip. An encapsulant is used to seal the first semiconductor chip below the metal stiffener. A second semiconductor chip, which is larger in size than that the first semiconductor chip, is mounted on the metal stiffener and connected by a second ground unit. The second semiconductor chip is connected to the organic substrate by a second wire. A mold resin seals the second semiconductor chip and a solder ball is bonded to a solder ball pad below the organic substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

Hardenable pressure sensitive adhesive sheet for dicing/die-bonding and method for manufacturing semiconductor device

InactiveUS20060252234A1Reduce production efficiencyGood embedding effectLamination ancillary operationsPaper/cardboard articlesDevice materialEngineering

A dicing and die bonding pressure-sensitive adhesive sheet having a pressure-sensitive adhesive layer that exhibits excellent embedding properties in die bonding to thereby prevent formation of voids between die pads and the pressure-sensitive adhesive layer even when chips are mounted on die pads exhibiting great differences in height. The dicing and die bonding pressure-sensitive adhesive sheet comprises a base material and a pressure-sensitive adhesive layer disposed thereon, the pressure-sensitive adhesive layer having a ratio (M100 / M70) of a modulus of elasticity at 100° C. (M100) to a modulus of elasticity at 70° C. (M70) of 0.5 or less.

Owner:LINTEC CORP

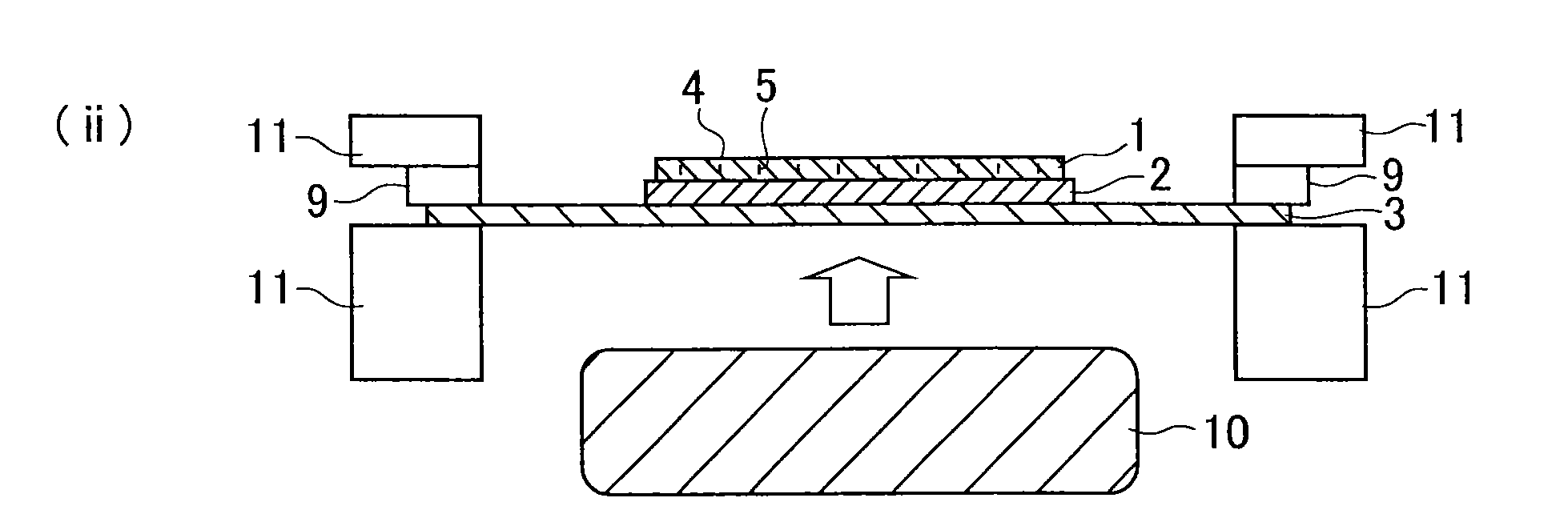

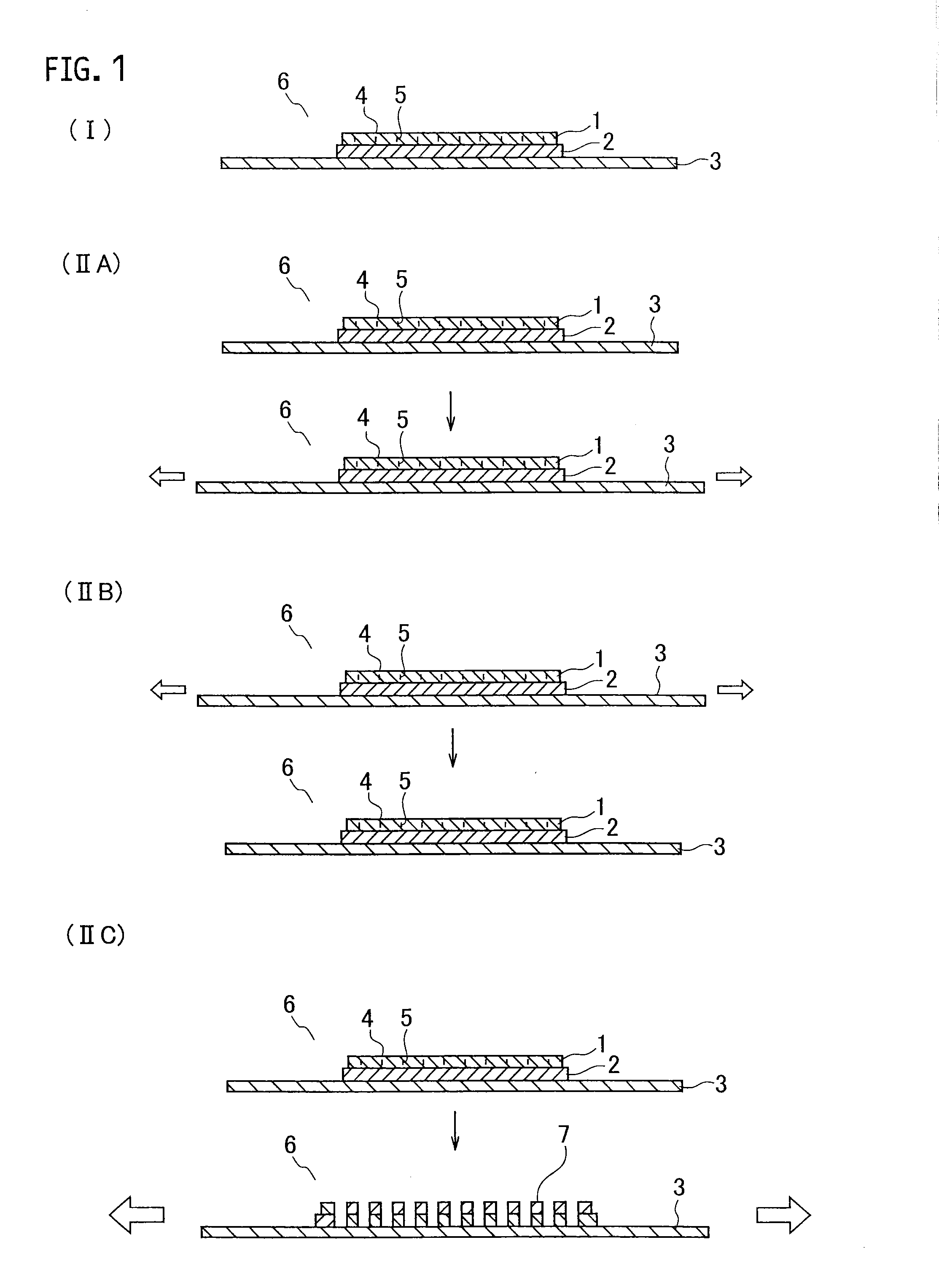

Expansion method, method for manufacturing semiconductor device, and semiconductor device

ActiveUS20150348821A1Efficient preparationEasy to cutSemiconductor/solid-state device detailsSolid-state devicesDicing tapeEngineering

An embodiment of the present invention relates to an expansion method comprising: a step (I) of preparing a laminate having a semiconductor wafer in which modified sections have been formed along intended cutting lines, a die bonding film and a dicing tape, a step (IIA) of expanding the dicing tape with the laminate in a cooled state, a step (IIB) of loosening the expanded dicing tape, and a step (IIC) of expanding the dicing tape with the laminate in a cooled state, dividing the semiconductor wafer and the die bonding film into chips along the intended cutting lines, and widening the spaces between the chips.

Owner:RESONAC CORP

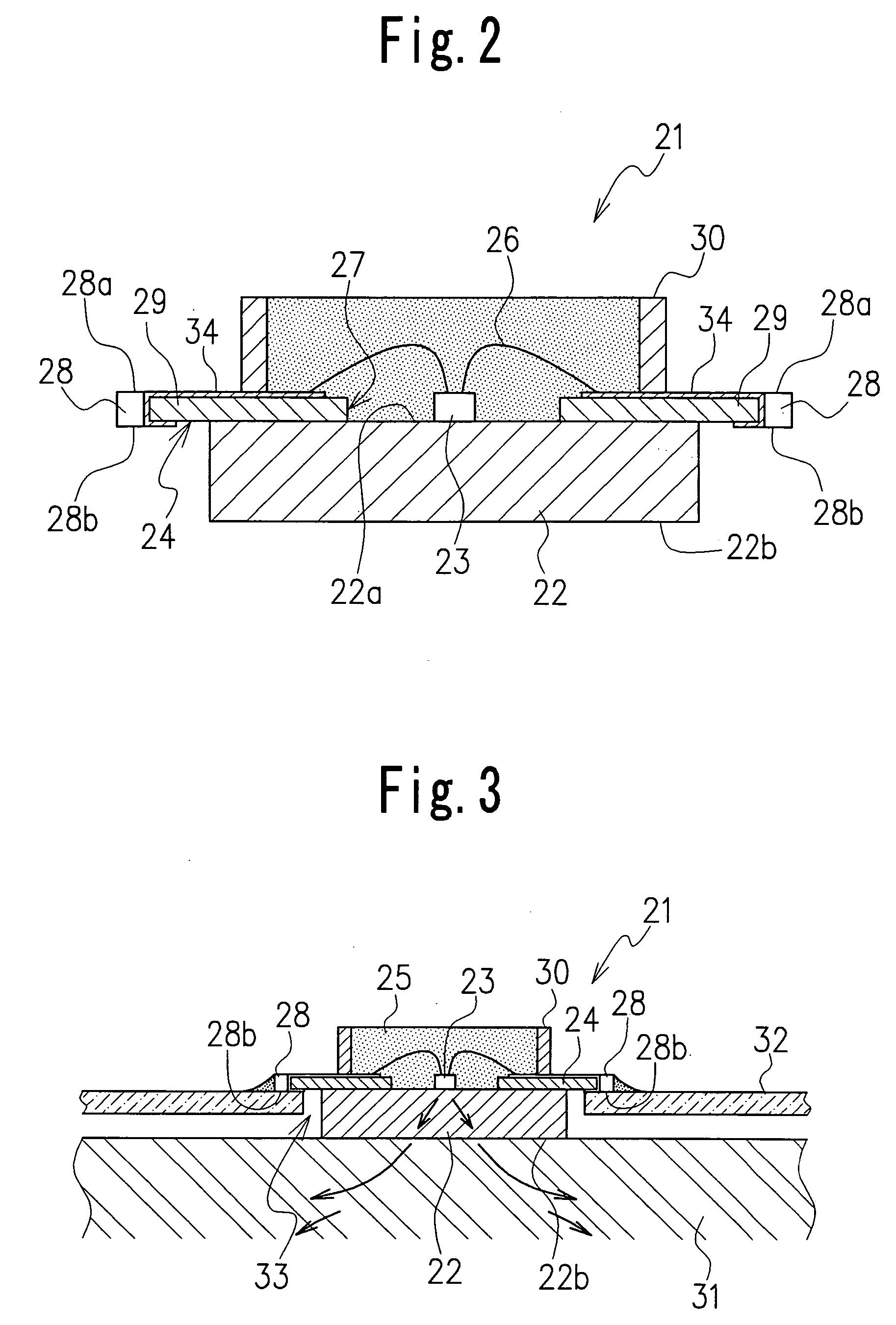

Light-emitting diode

ActiveUS20060001361A1Power Loss MinimizationMinimize power consumptionPrinted circuit assemblingDischarge tube luminescnet screensEngineeringDie bonding

The LED comprises: a base having high thermal conductivity and having a mounting surface for die bonding; a printed circuit board mounted on the base and having a hole to expose a part of the mounting surface of the base and having a protruding portion projecting horizontally outward on the outer periphery of the base; an LED element mounted on the mounting surface of the base exposed in the hole of the printed circuit board; and a resin material sealing the LED element from above; wherein through-holes electrically connected to the LED element are formed at the outer periphery of the protruding portion and an external connection electrode is provided to the upper and lower surfaces of the through-holes. This LED enhances the heat dissipating effect to enable generation of high-luminance light and can also be mounted on either the upper or lower surface of a motherboard.

Owner:CITIZEN ELECTRONICS CO LTD

Multilayer laser trim interconnect method

InactiveUS20040014309A1Avoid problemsMore assembledSemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

A method for creating electrical interconnects between a semiconductor die and package. In the preferred embodiment, an insulating material is applied over the die and extends to the substrate contact pads, leaving a portion of each contact pad exposed. Holes are then trimmed through the insulating material, exposing at least a portion of each die bond pad. A conductive material is then applied over the die, flowing into the holes, contacting the die bond pads, and extending out to contact at least a portion of each substrate contact pad. In another preferred embodiment, an electrically conductive bump may be formed on each die bond pad, protruding through said non-conductive material and at least partially through said conductive material. The conductive layer is then laser trimmed, forming conductive patches that serve as electrical interconnects between the die and package substrate.

Owner:TEXAS INSTR INC

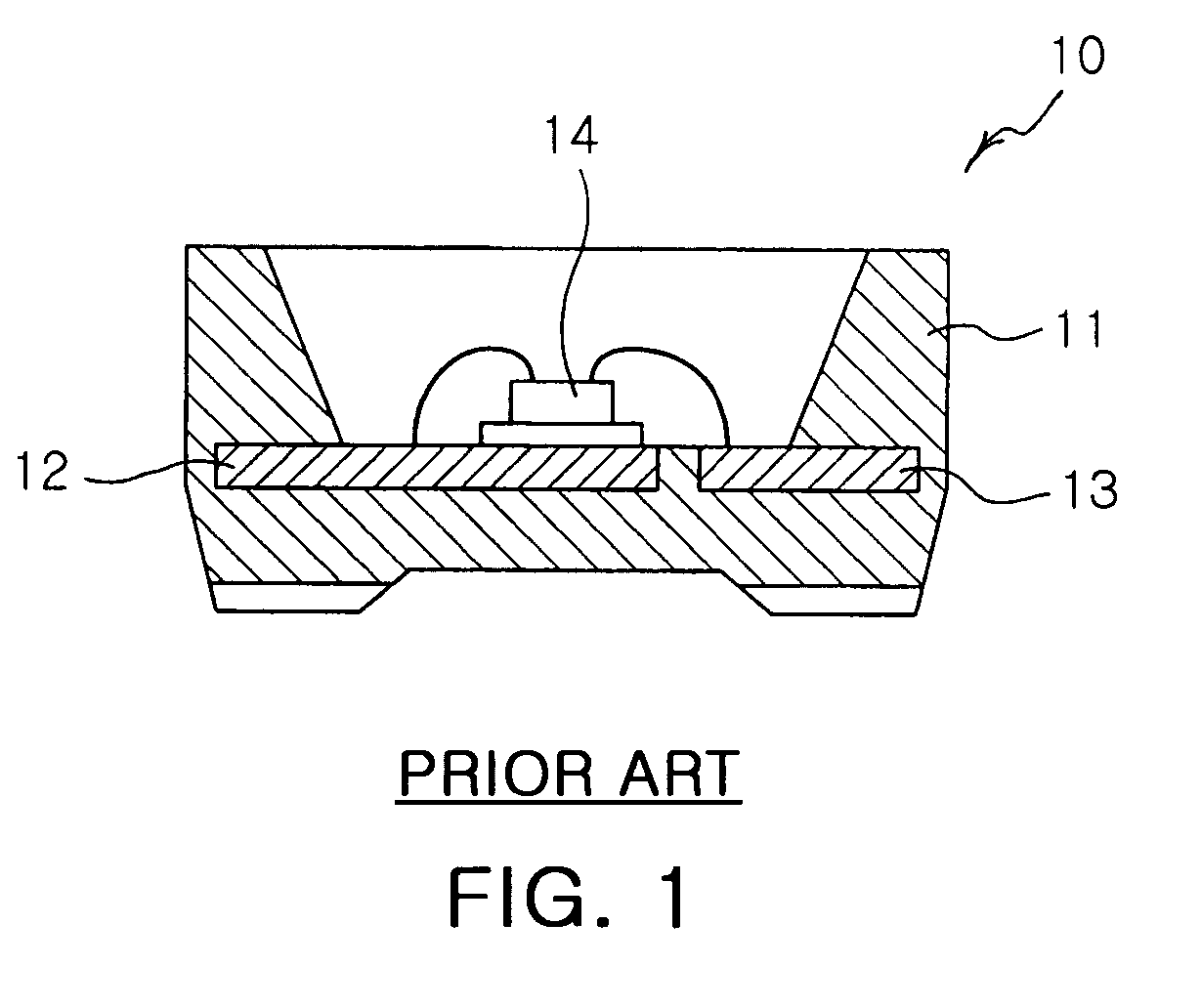

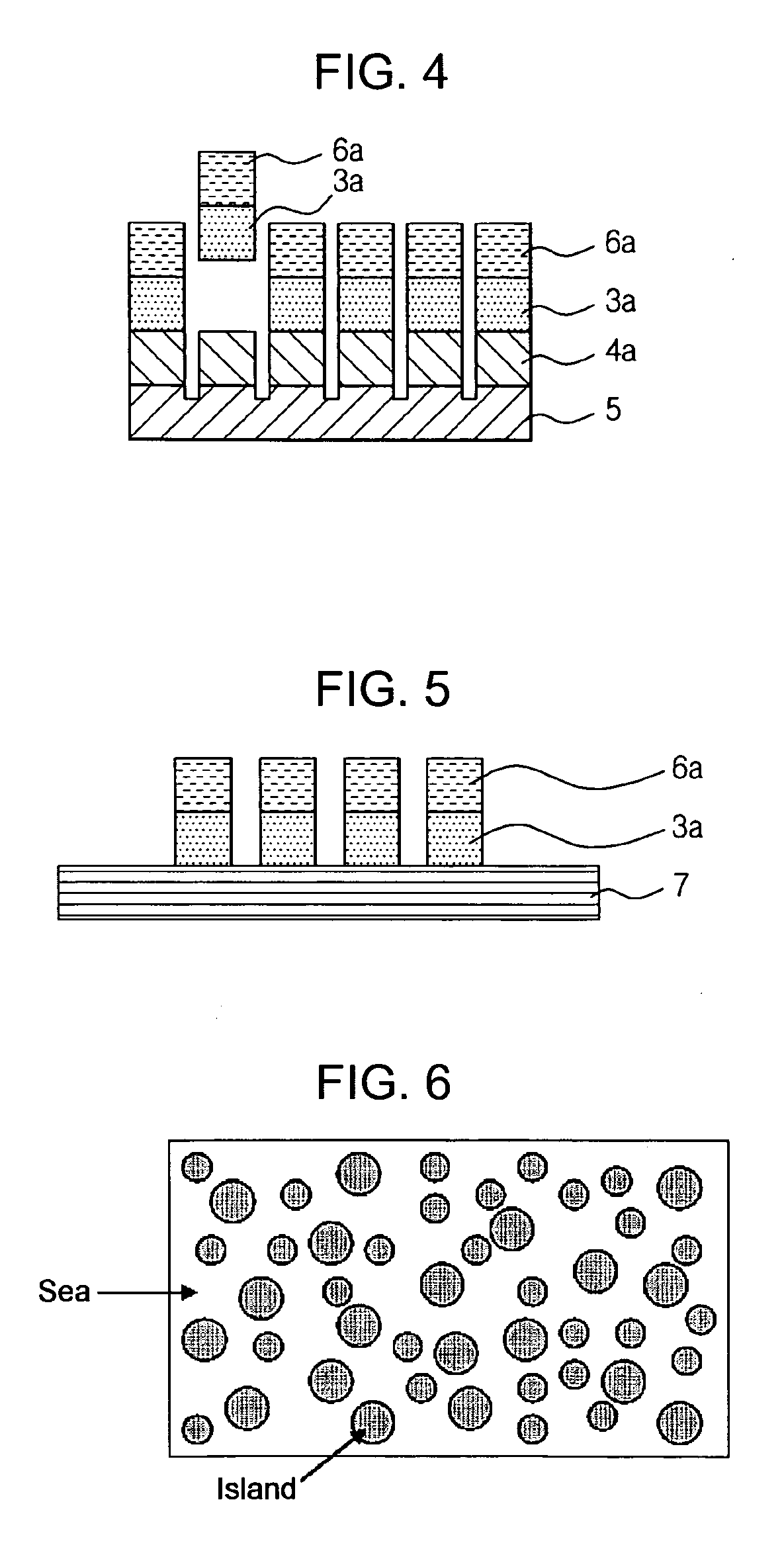

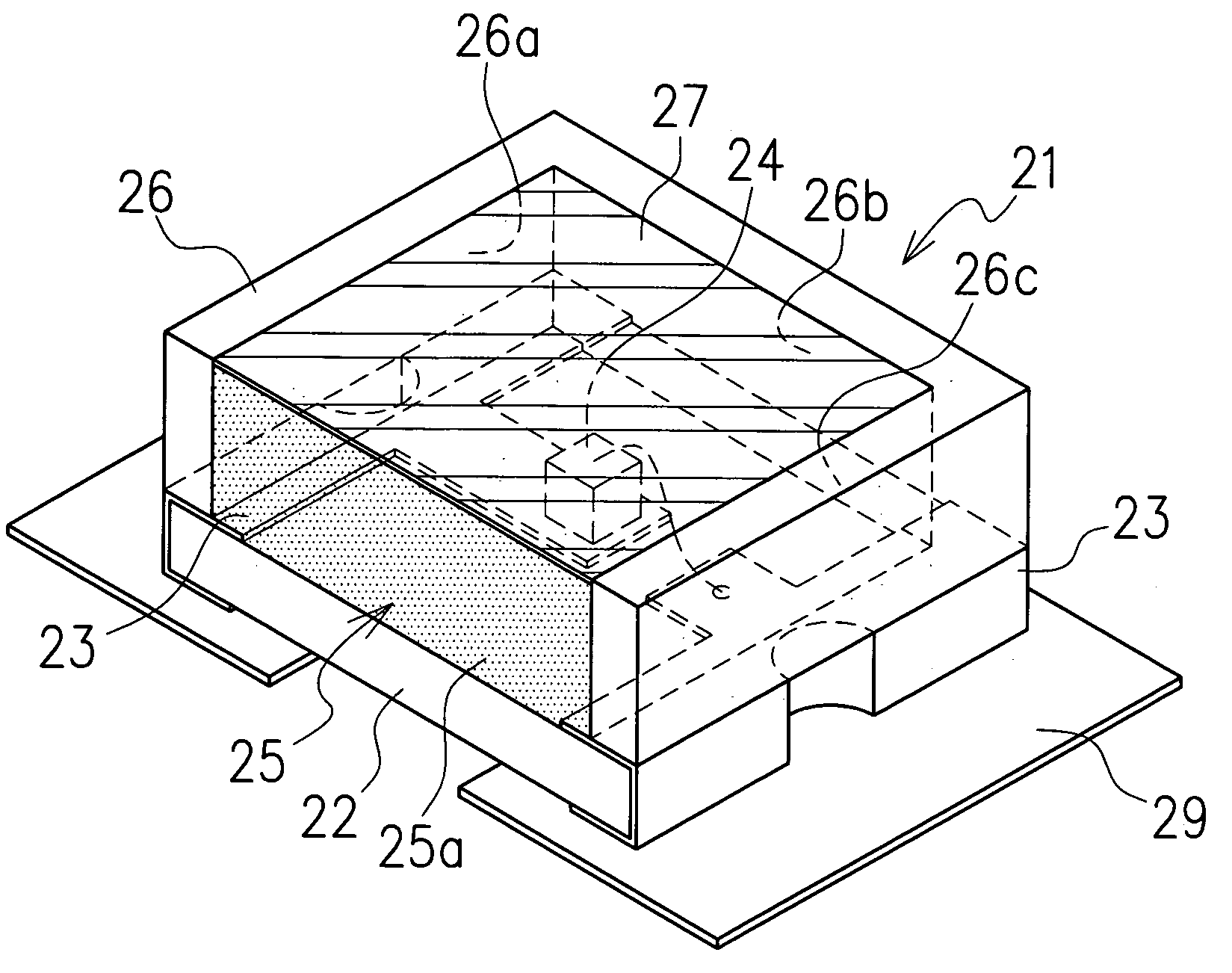

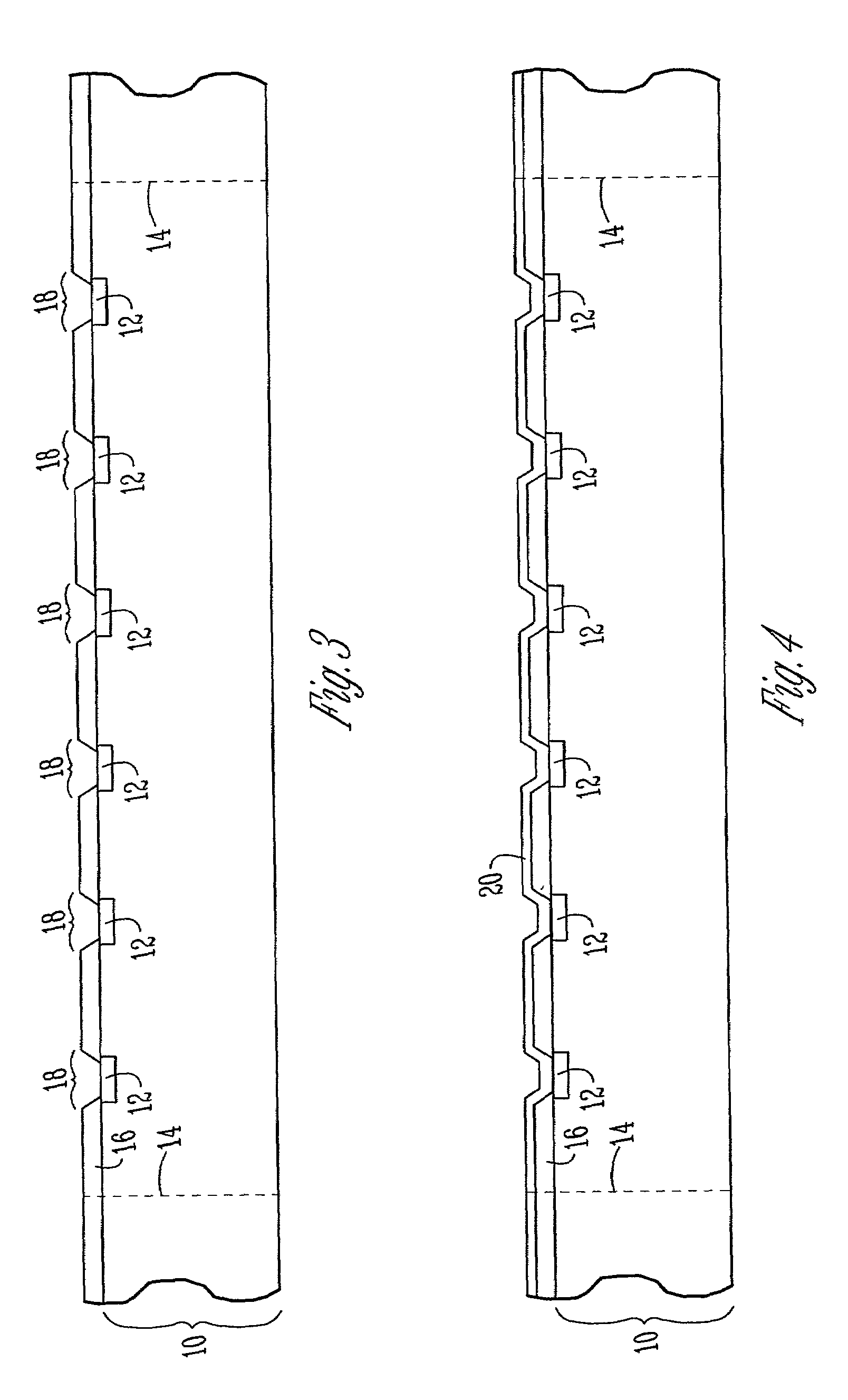

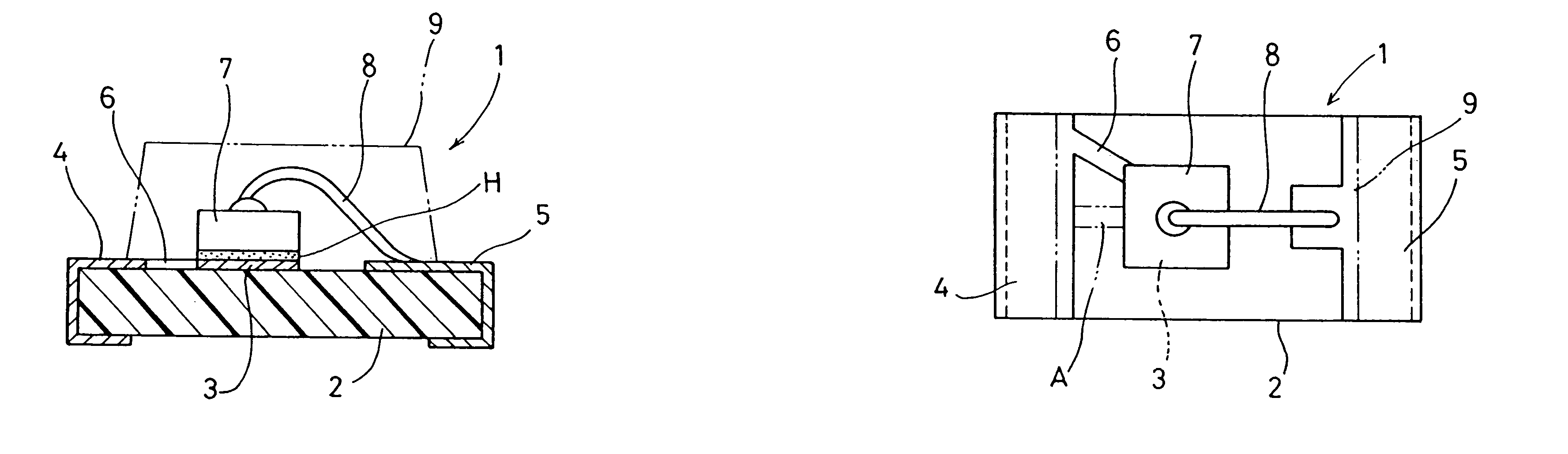

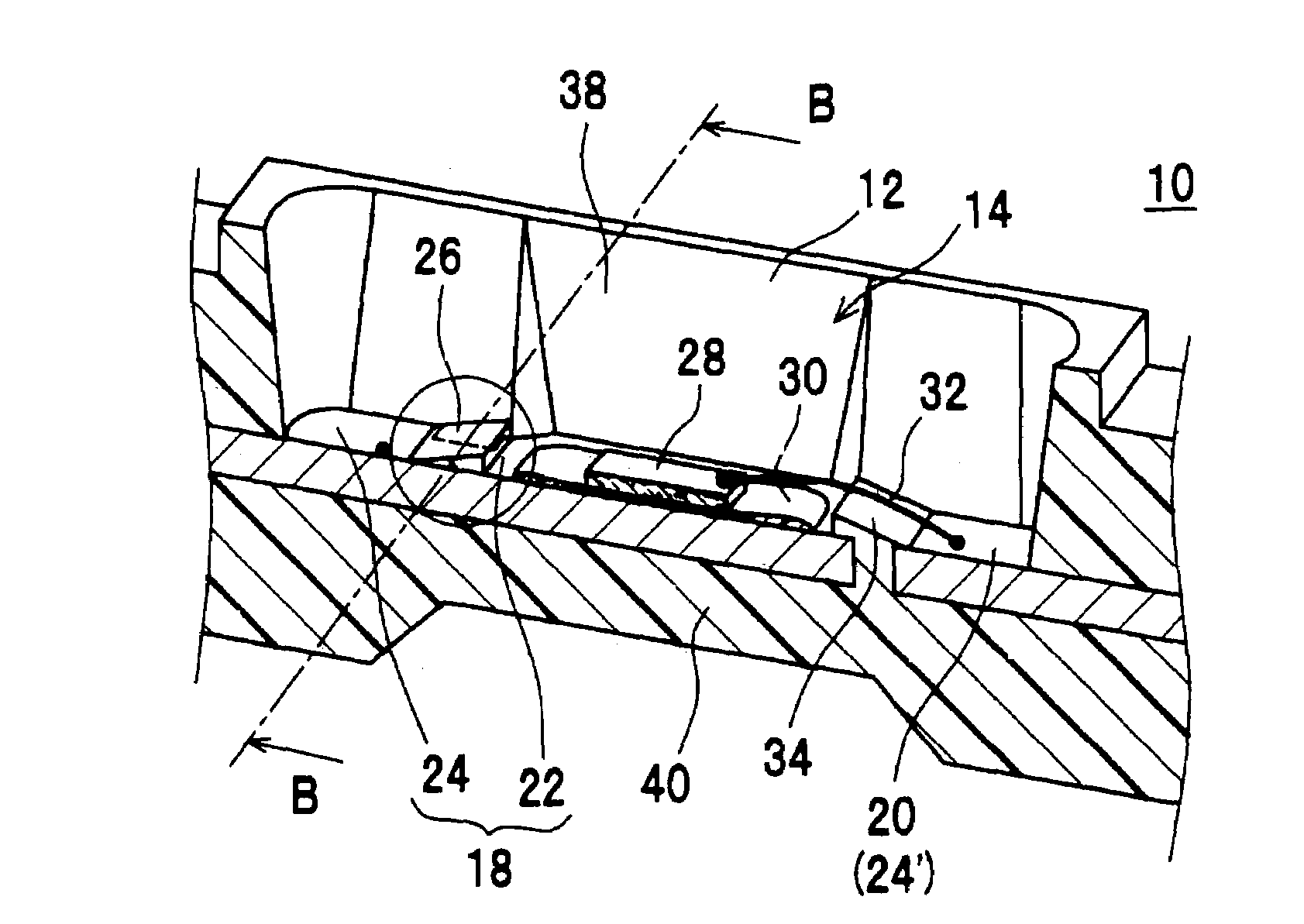

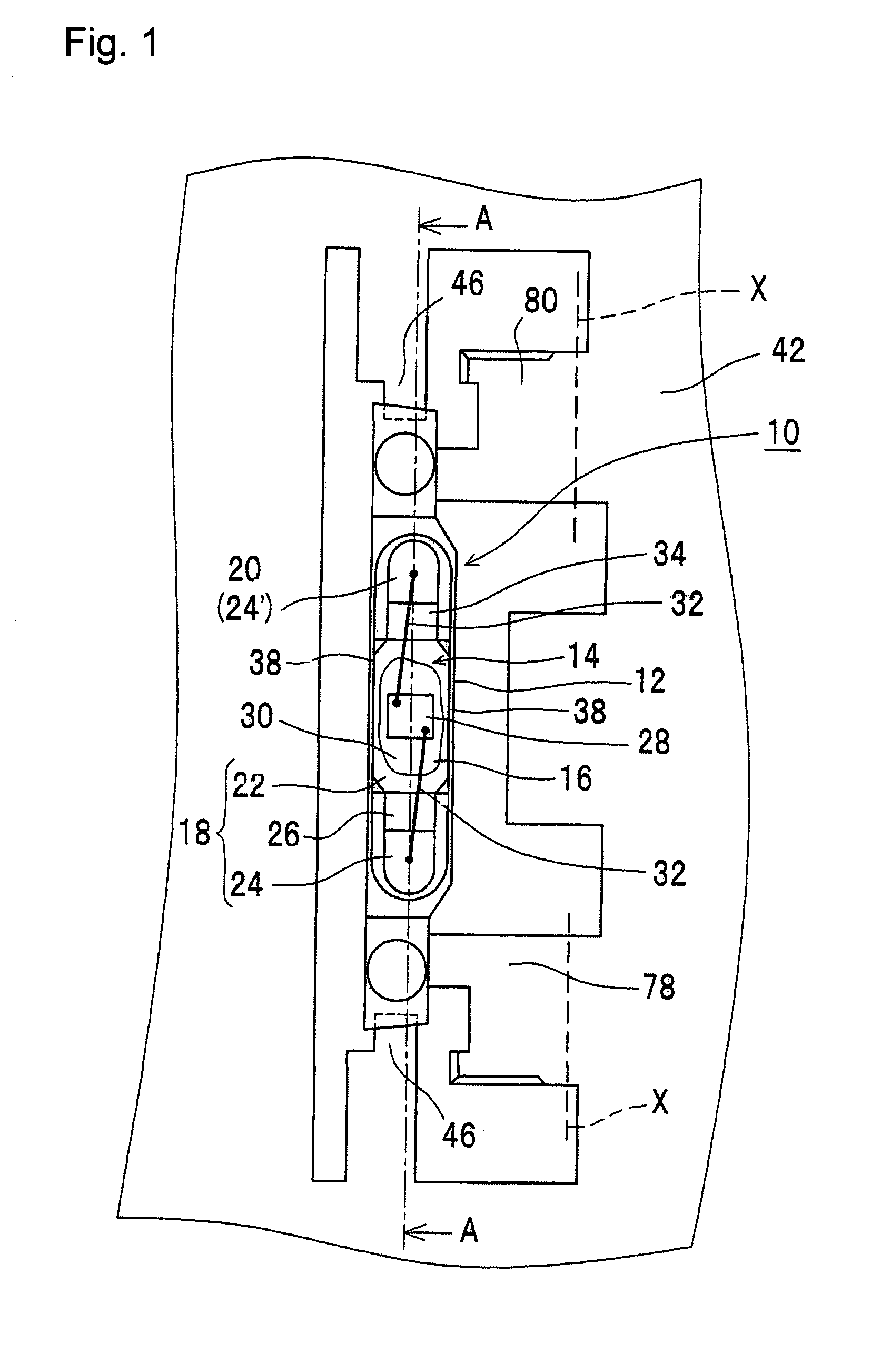

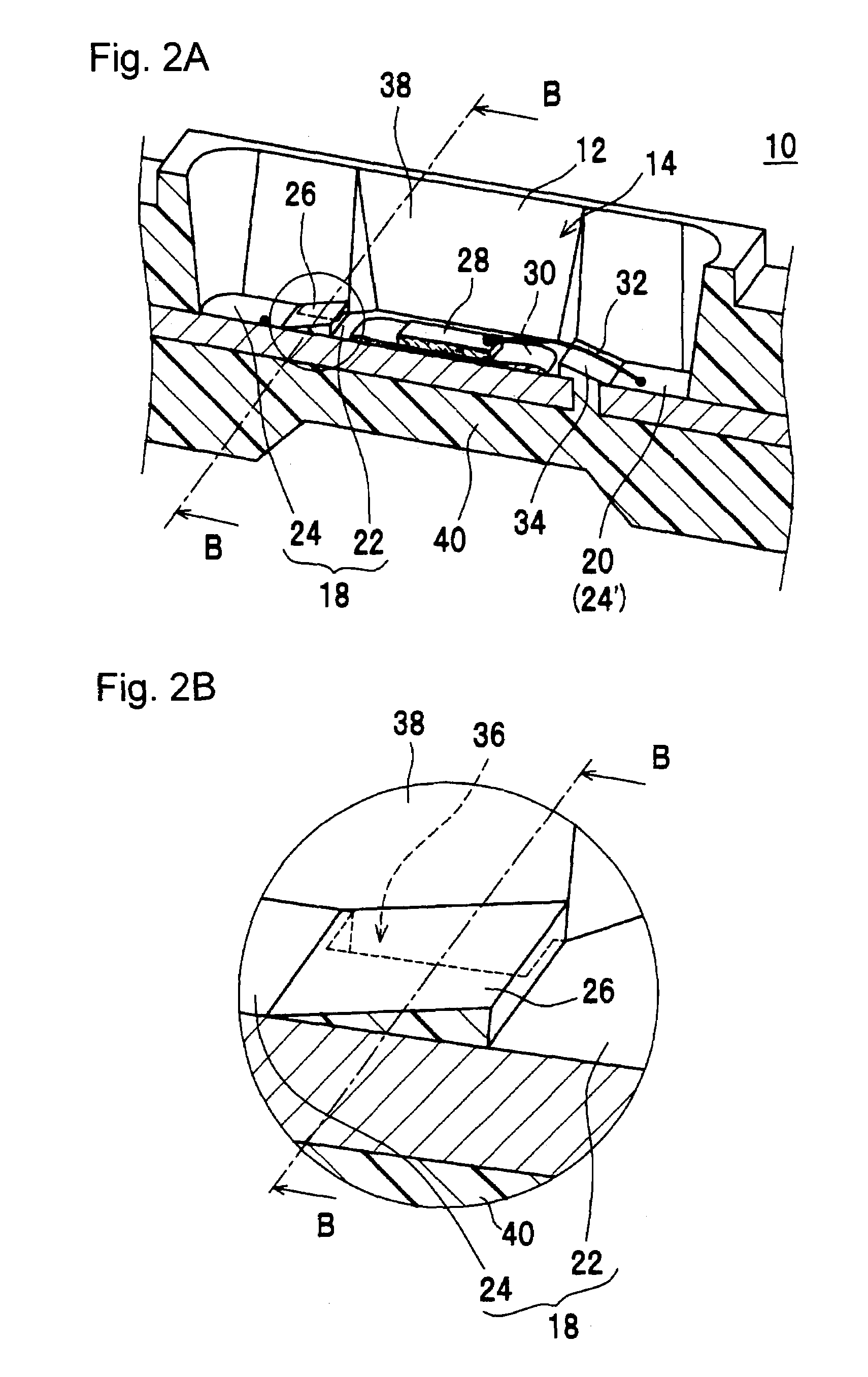

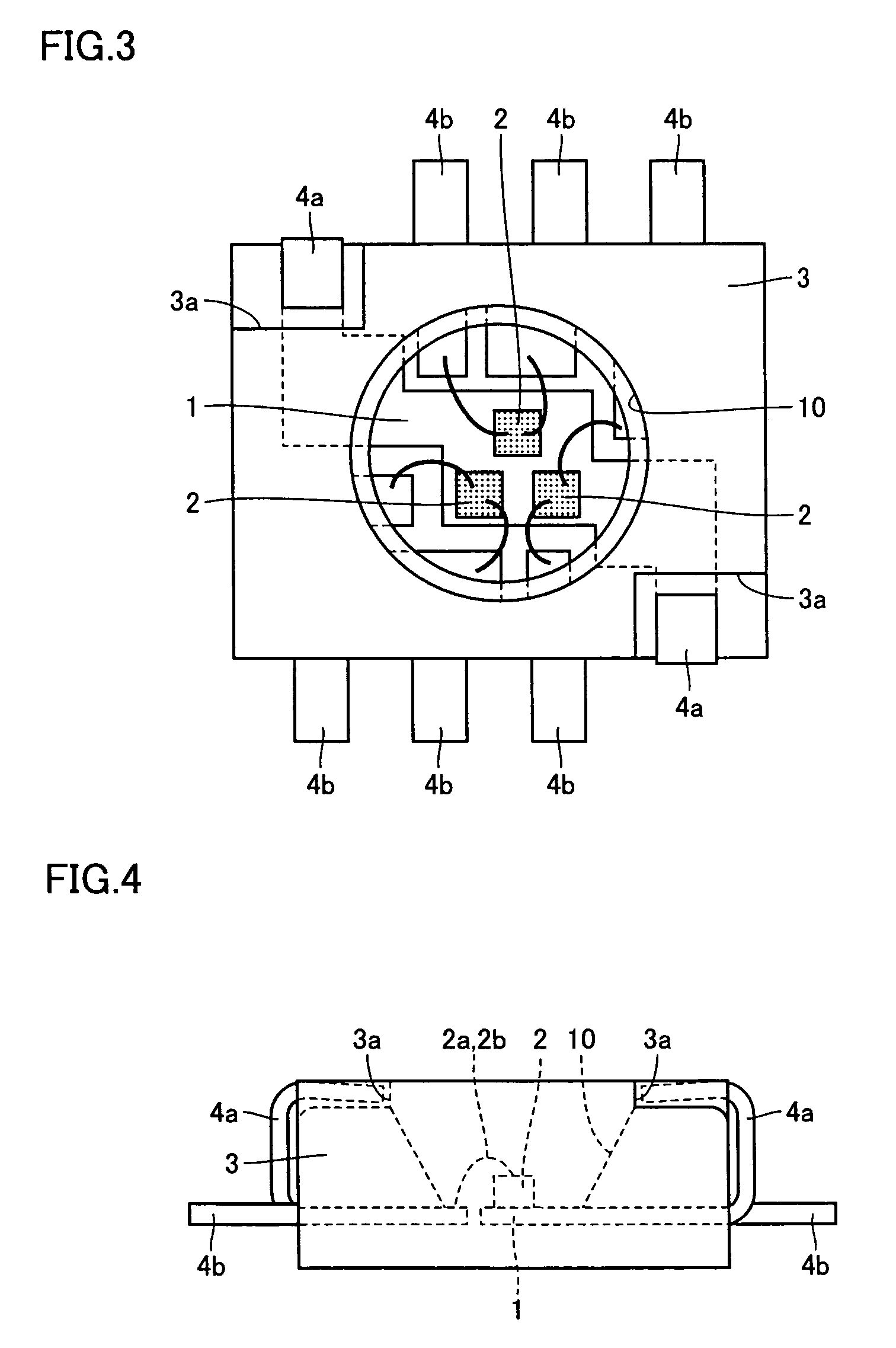

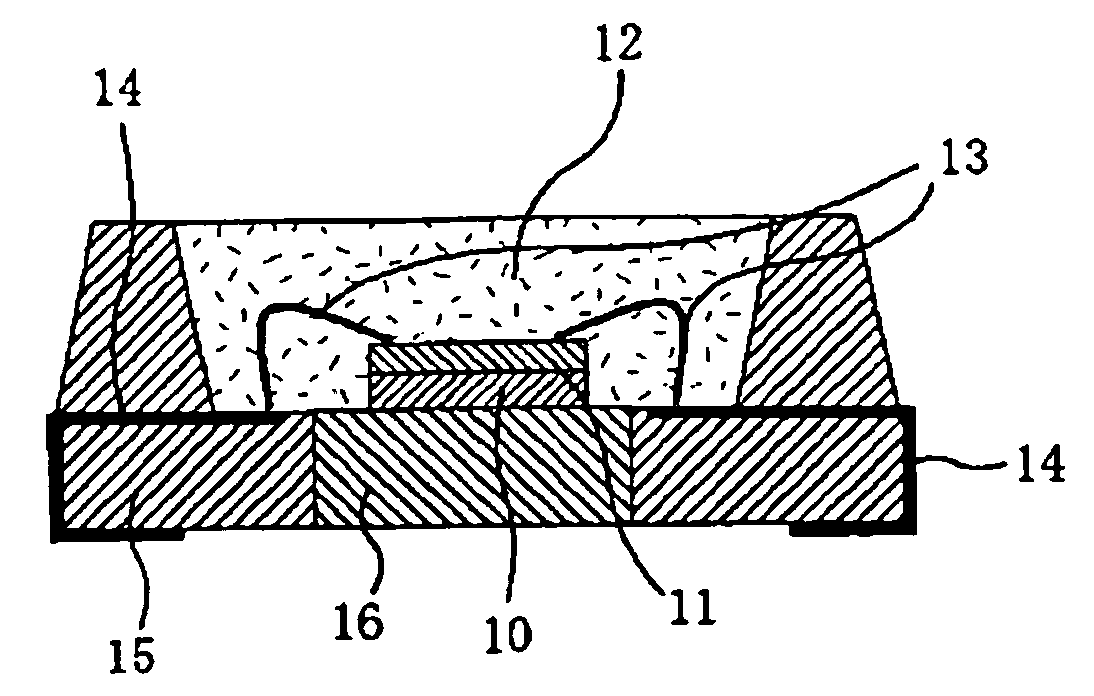

Semiconductor device

The present invention provides a semiconductor device capable of preventing an adhesive for die bonding from flowing to wire bonding area.The semiconductor device of the present invention comprises a semiconductor element 28 having a pair of electrodes, a housing 12 having the recess 14 for accommodating the semiconductor element 28, a first lead electrode 18 and the second lead electrode 20 which are exposed on the bottom of the recess 14, an adhesive layer 30 for die bonding between the semiconductor element 28 and the first lead electrode 18, and electrically conductive wires 32 for wire bonding between one electrode of the pair of electrodes of the semiconductor element and the first lead electrode 18 and between the other electrode and the second lead electrode 20, wherein the housing 12 has the wall 26 formed to extend across the bottom surface of the recess 14 so as to divide the surface of the first lead electrode 18 into a die bonding area 22 and a wire bonding area 24, and the first lead electrode 18 has the notch 36 which is formed by cutting off a portion of an edge of the first lead electrode 18 and located at least just below the wall 26, while the wall 26 and the bottom portion 40 of the housing 12 are connected to each other through the notch 36.

Owner:NICHIA CORP

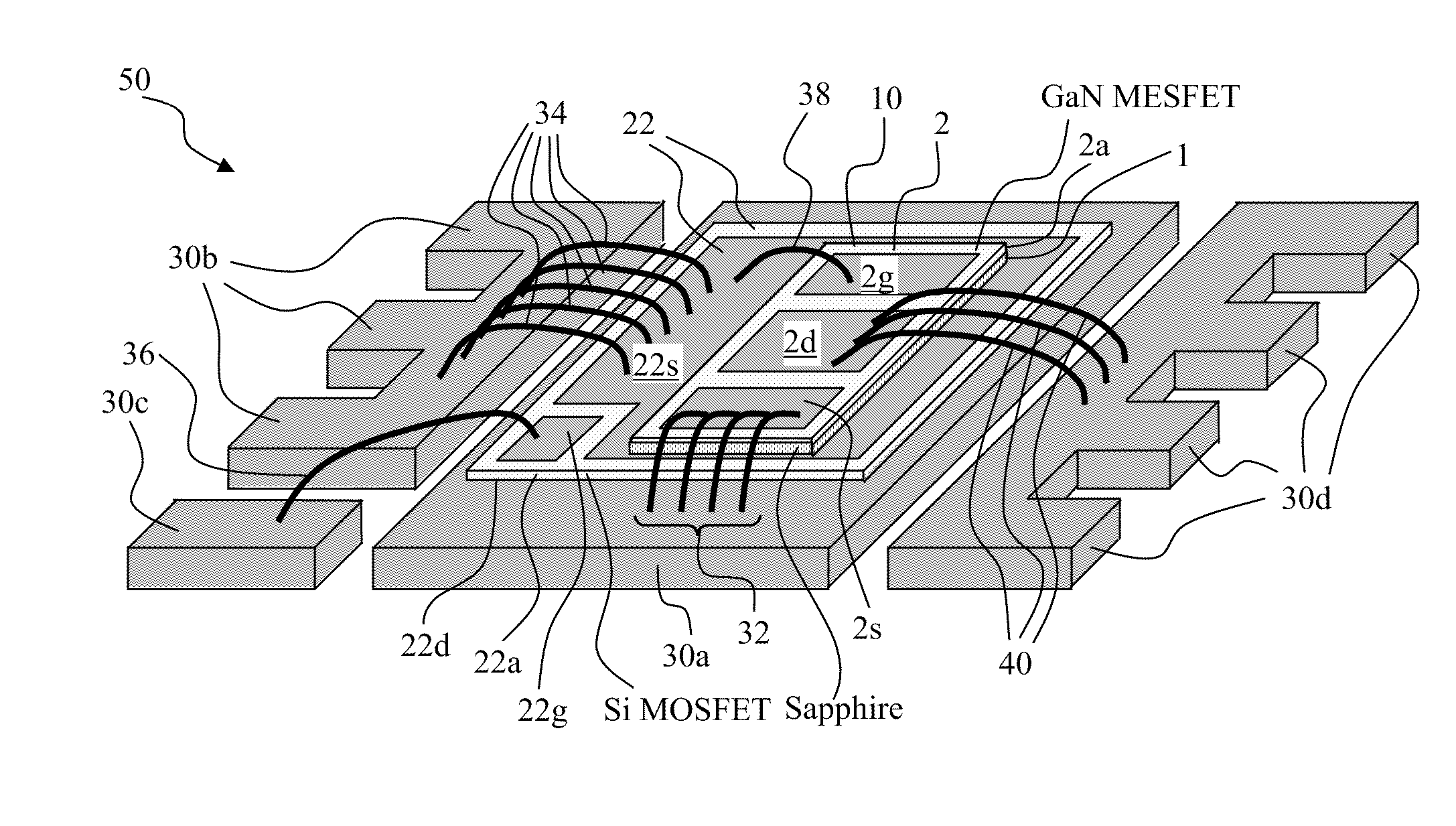

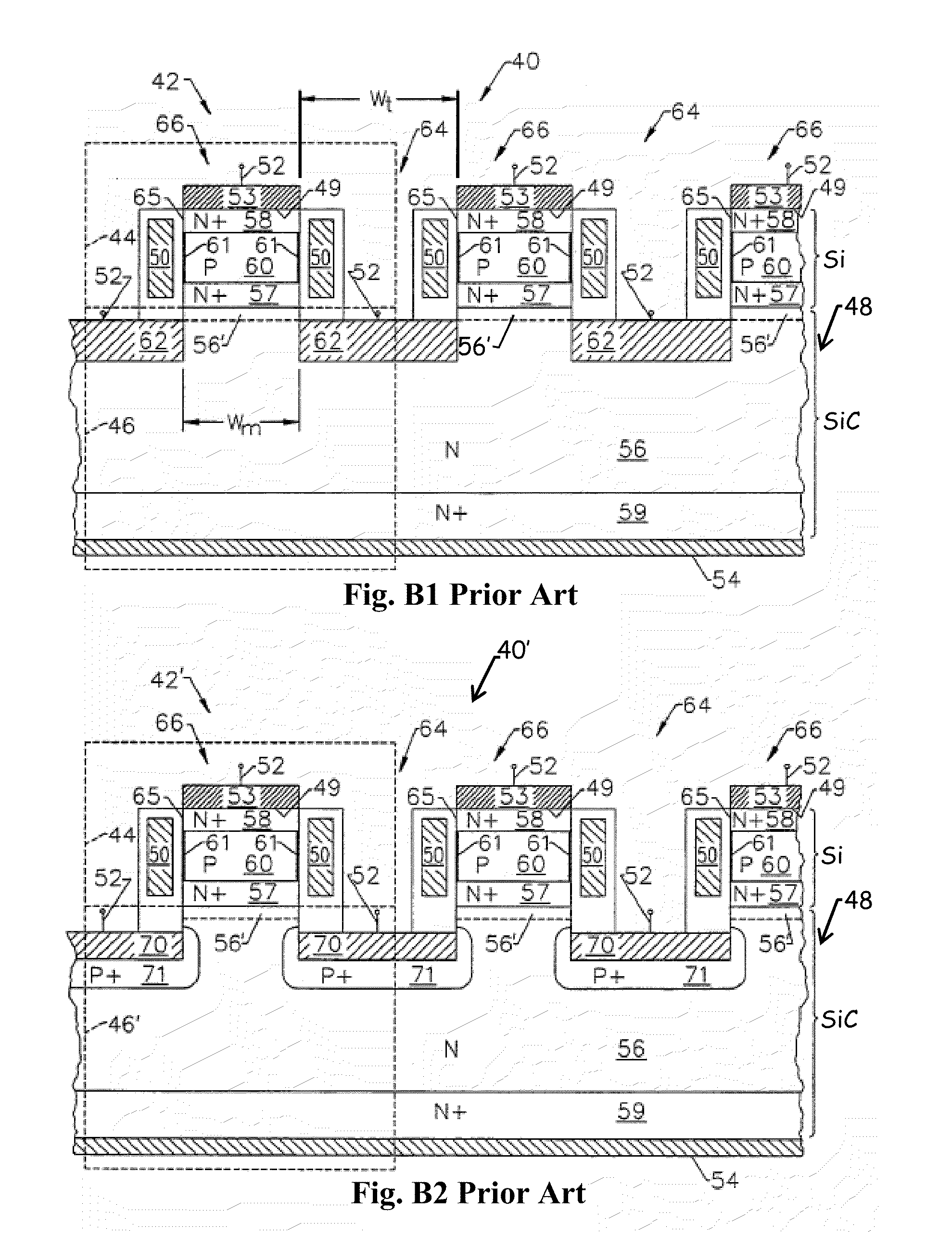

Hybrid Packaged Gate Controlled Semiconductor Switching Device Using GaN MESFET

InactiveUS20110049580A1Reduced footprintIncrease in sizeTransistorSemiconductor/solid-state device detailsDie bondingSemiconductor

A hybrid packaged gate controlled semiconductor switching device (HPSD) has an insulated-gate transistor (IGT) made of a first semiconductor die and a rectifying-gate transistor (RGT) made of a second semiconductor die. The RGT gate and source are electrically connected to the IGT source and drain respectively. The HPSD includes a package base with package terminals for interconnecting the HPSD to external environment. The IGT is die bonded atop the package base. The second semiconductor die is formed upon a composite semiconductor epi layer overlaying an electrically insulating substrate (EIS) thus creating a RGT die. The RGT die is stacked and bonded atop the IGT die via the EIS. The IGT, RGT die and package terminals are interconnected with bonding wires. Thus, the HPSD is a stacked package of IGT die and RGT die with reduced package footprint while allowing flexible placements of device terminal electrodes on the IGT.

Owner:ALPHA & OMEGA SEMICON INC

Semiconductor light emitting device

ActiveUS7282740B2Reliable heat conductionEfficient heat dissipationNon-electric lightingPoint-like light sourceEngineeringLead frame

A light emitting element is die-bonded to a portion of a lead frame exposed at the bottom of an opening formed at a top face of a resin package. A reflector to direct light emitted from the light emitting element towards a predetermined direction is attached to the top face of the resin package. Lead terminals are arranged so as to protrude from two opposite side regions of the resin package. A predetermined lead terminal among the plurality of lead terminals, connected to a portion where the light emitting element is die-bonded, is bent upwards, and soldered to the reflector by solder paste.

Owner:SHARP KK

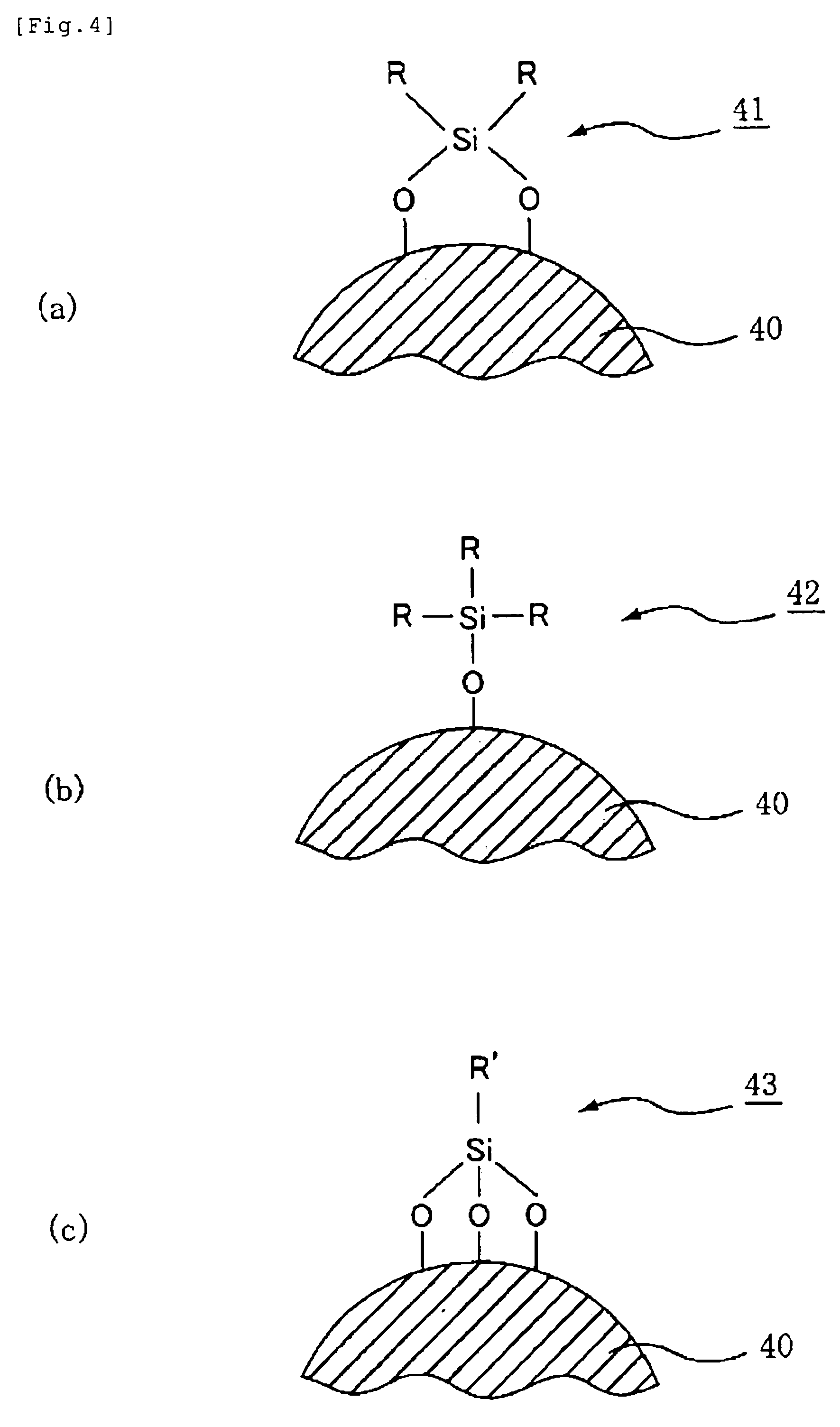

Themosetting Composition for Optical Semiconductor, Die Bond Material for Optical Semiconductor Device, Underfill Material for Optical Semiconductor Device, Sealing Agent for Optical Semiconductor Device, and Optical Semiconductor Device

InactiveUS20090091045A1Free-from decrease in thicknessFree-from decrease in discolorationSemiconductor/solid-state device detailsSolid-state devicesFilling materialsCyclic ether

A thermosetting composition for an optical semiconductor containing a silicone resin having a cyclic ether-containing groups and a thermosetting agent capable of reacting with said cyclic ether-containing group, wherein the silicone resin has, as the principal components, a structural unit expressed by the following formula (1) and a structural unit expressed by the following formula (2). The content of the structural unit expressed by the formula (1) is 0.6 to 0.95 (on a molar basis) and the content of the structural unit expressed by the formula (2) is 0.05 to 0.4 (on a molar basis) when total number of the structural units contained is taken as 1, and the content of the cyclic ether-containing group is 5 to 40 mol %:[formula 1](R1R2SiO2 / 2) (1)and[formula 2](R3SiO3 / 2) (2)at least one of R1, R2 and R3 represents a cyclic ether-containing group, R1, R2 and R3 other than the cyclic ether-containing group represent hydrocarbon having 1 to 8 carbon atoms or fluoride thereof.

Owner:SEKISUI CHEM CO LTD

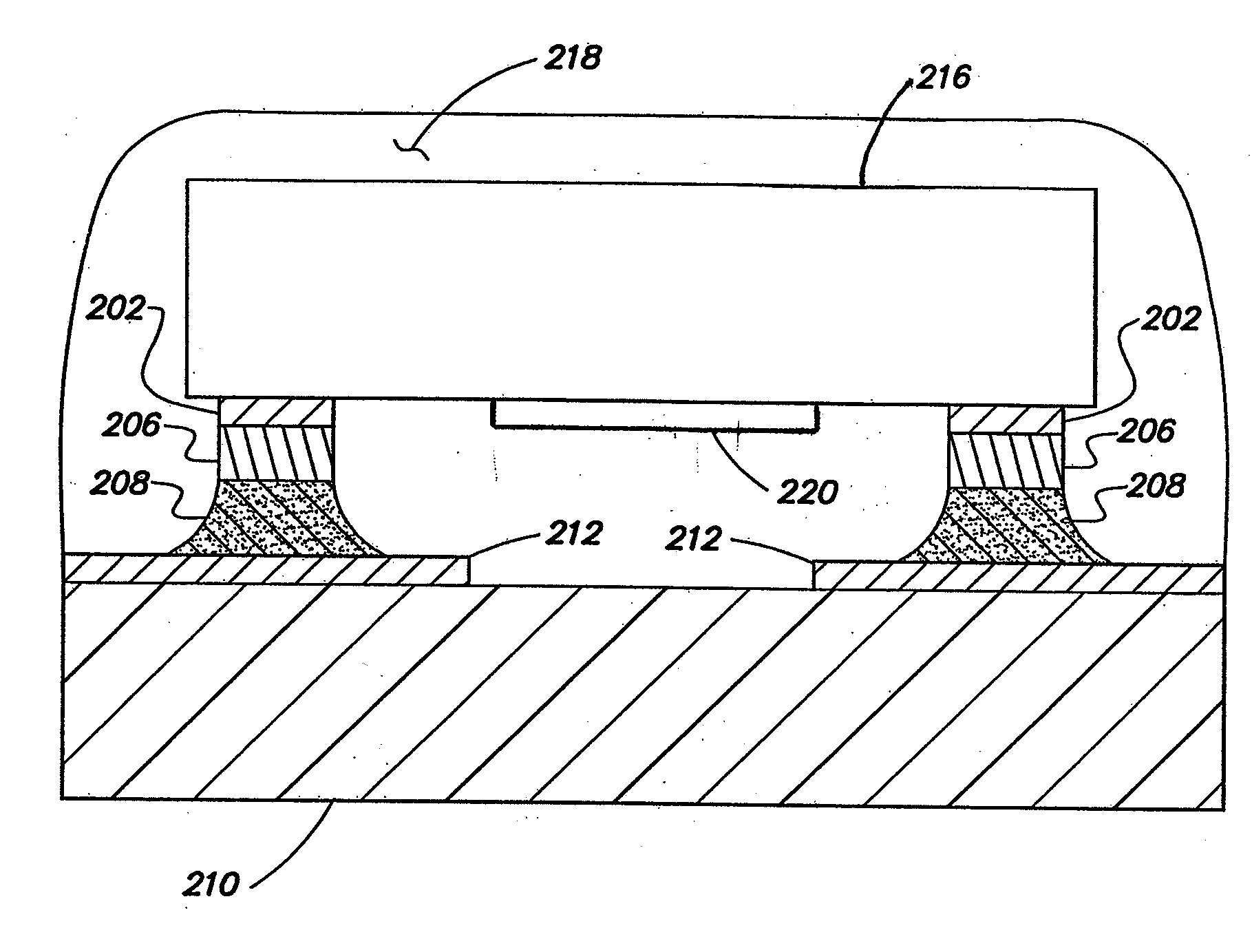

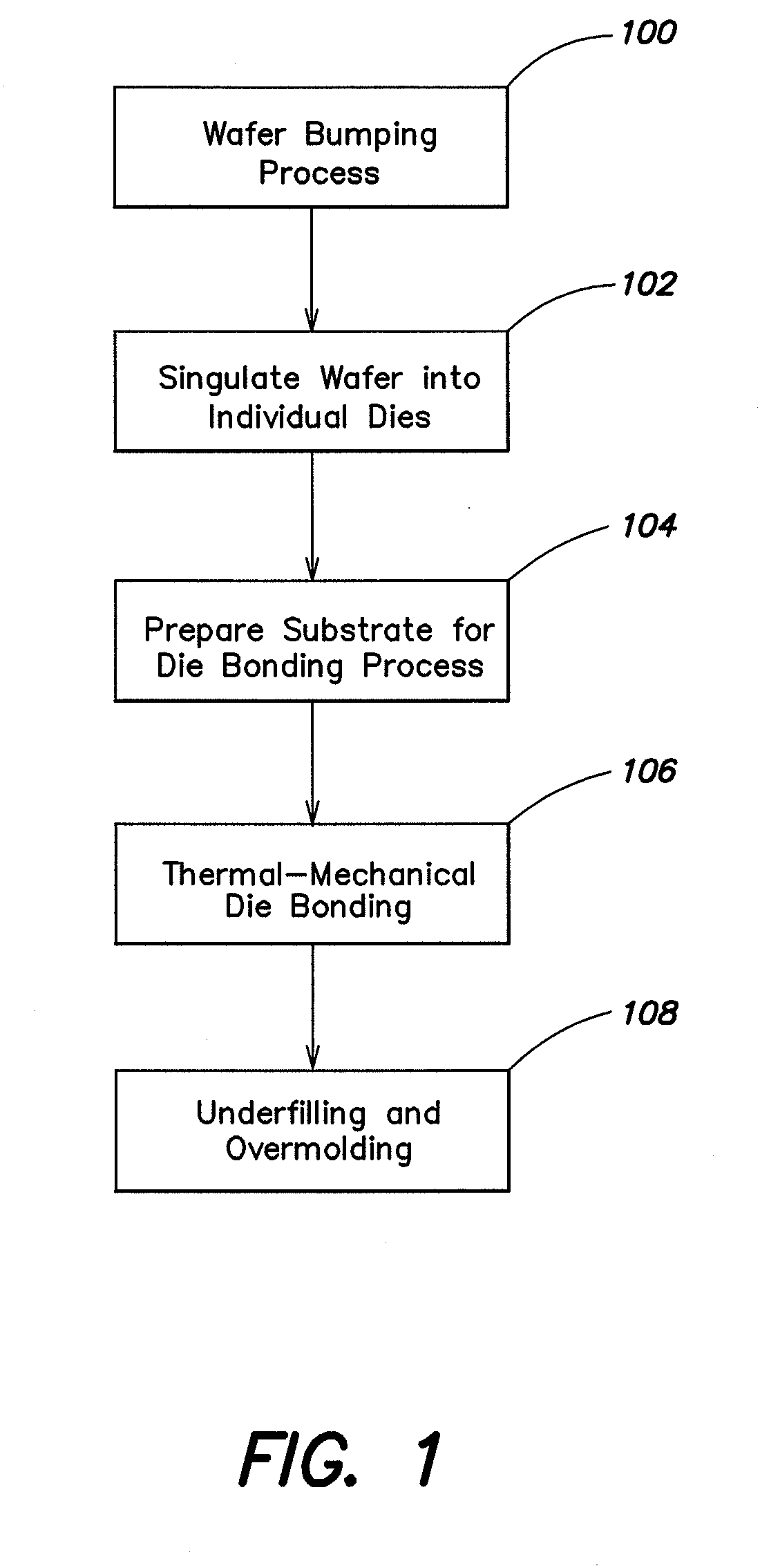

Thermal mechanical flip chip die bonding

ActiveUS20090155955A1High bonding strengthImprove electrical performanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringCopper

A thermal mechanical process for bonding a flip chip die to a substrate. The flip chip die includes a plurality of copper pillar bumps, each copper pillar bump of the plurality of copper pillar bumps having a copper portion attached to the die and a bonding cap attached to the copper portion. The process includes positioning the die on the substrate such that the bonding cap of each copper pillar bump of the plurality of copper pillar bumps contacts a corresponding respective one of a plurality of bonding pads on the substrate, and thermosonically bonding the die to the substrate.

Owner:SKYWORKS SOLUTIONS INC

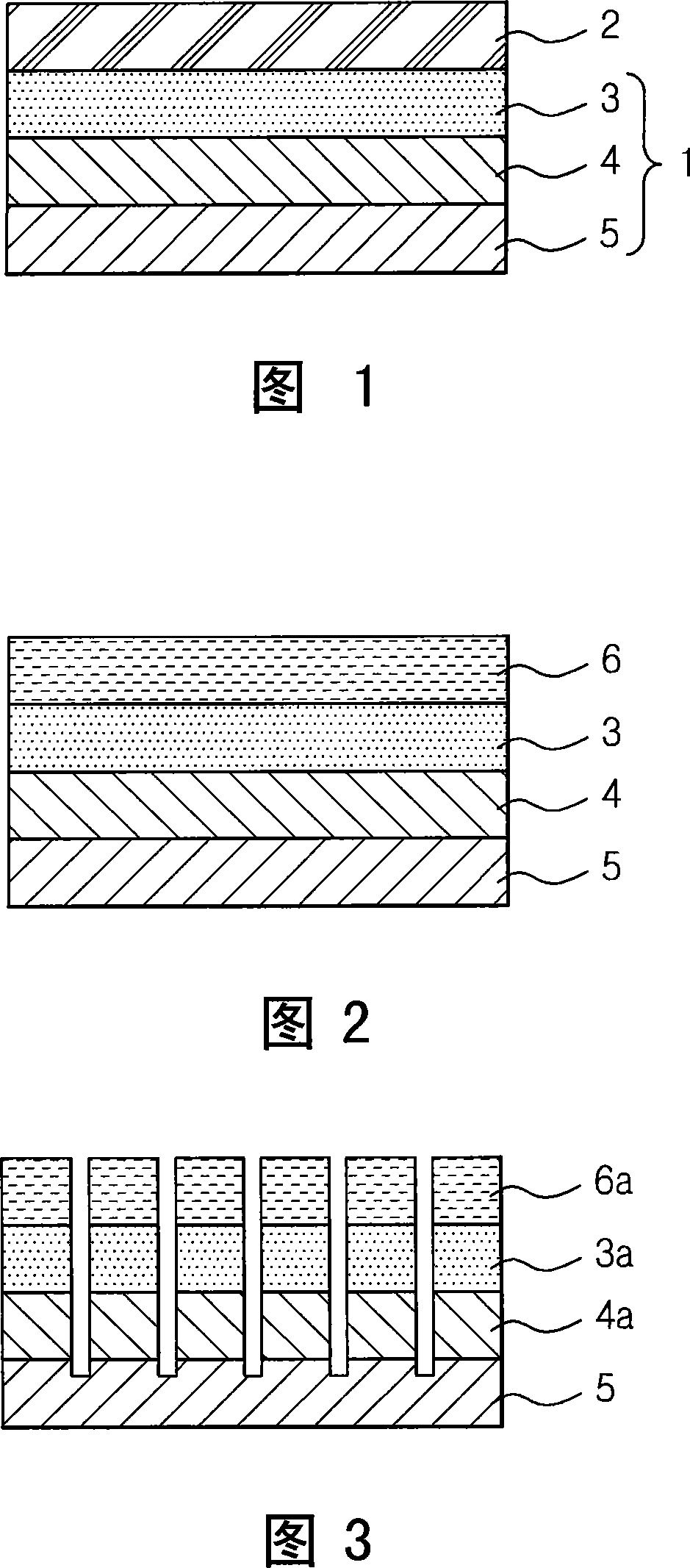

Dicing/die-bonding film, method of fixing chipped work and semiconductor device

InactiveUS20050046042A1Improve balanceInferior dicingAdhesive processesFilm/foil adhesivesDevice materialEngineering

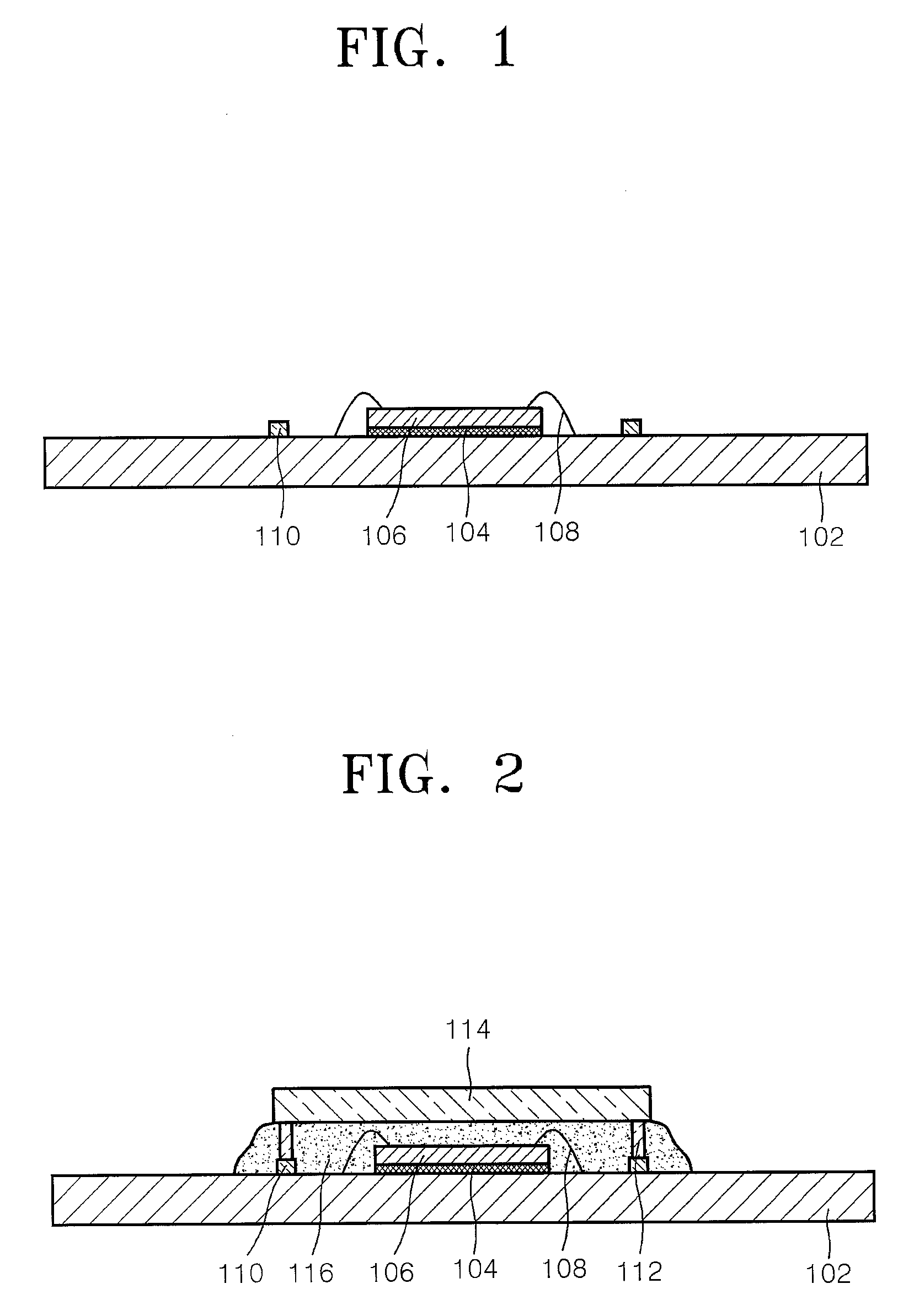

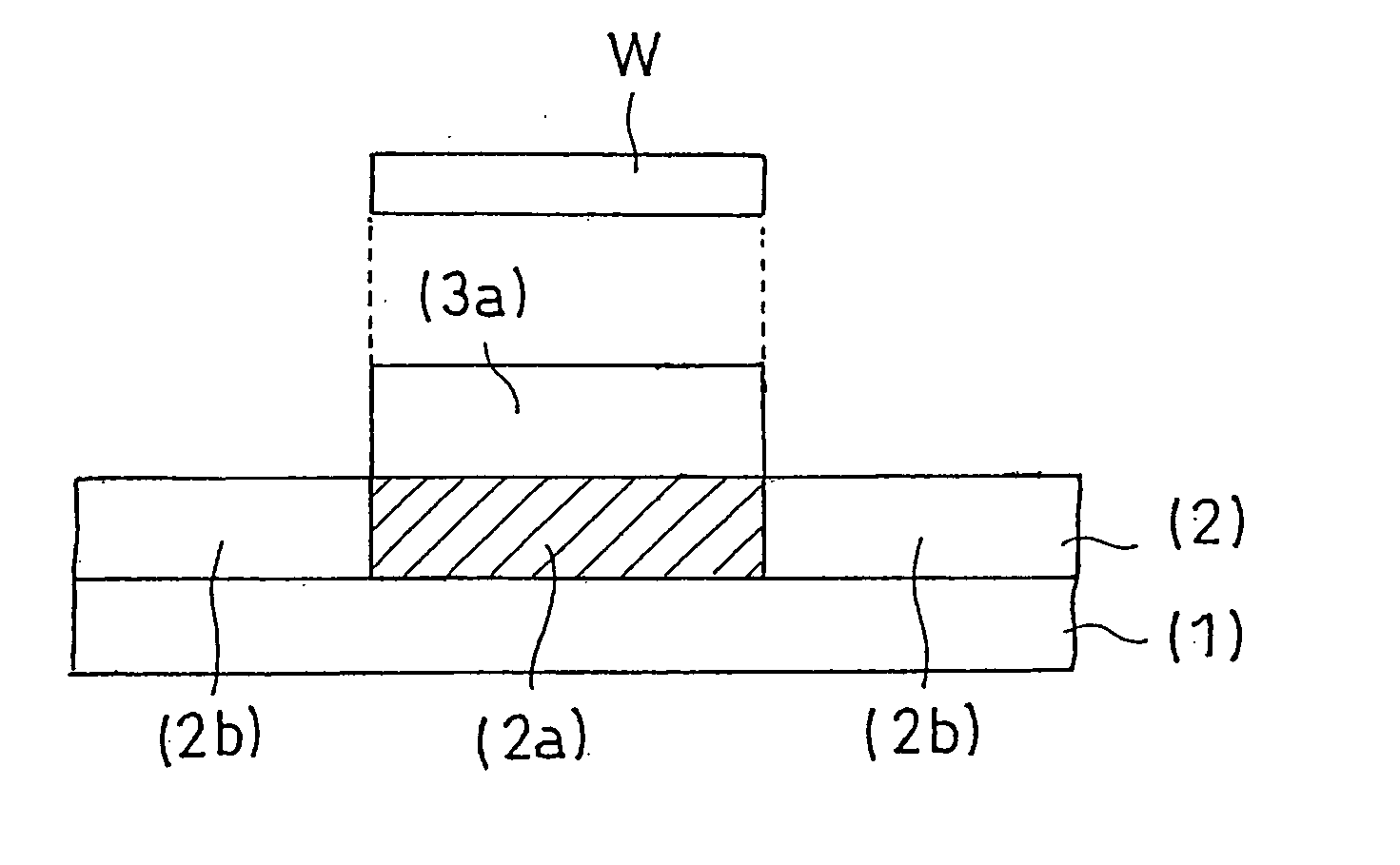

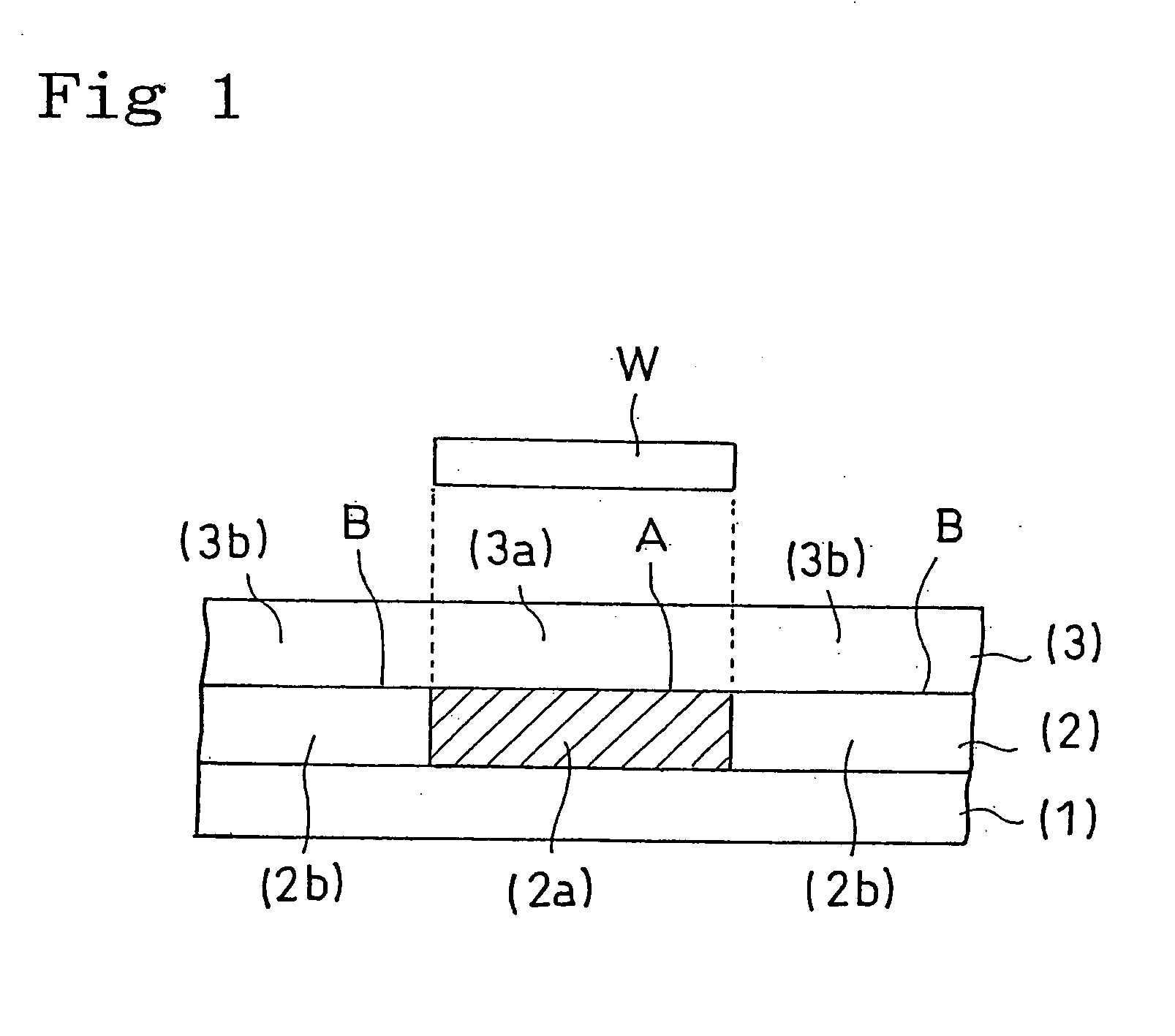

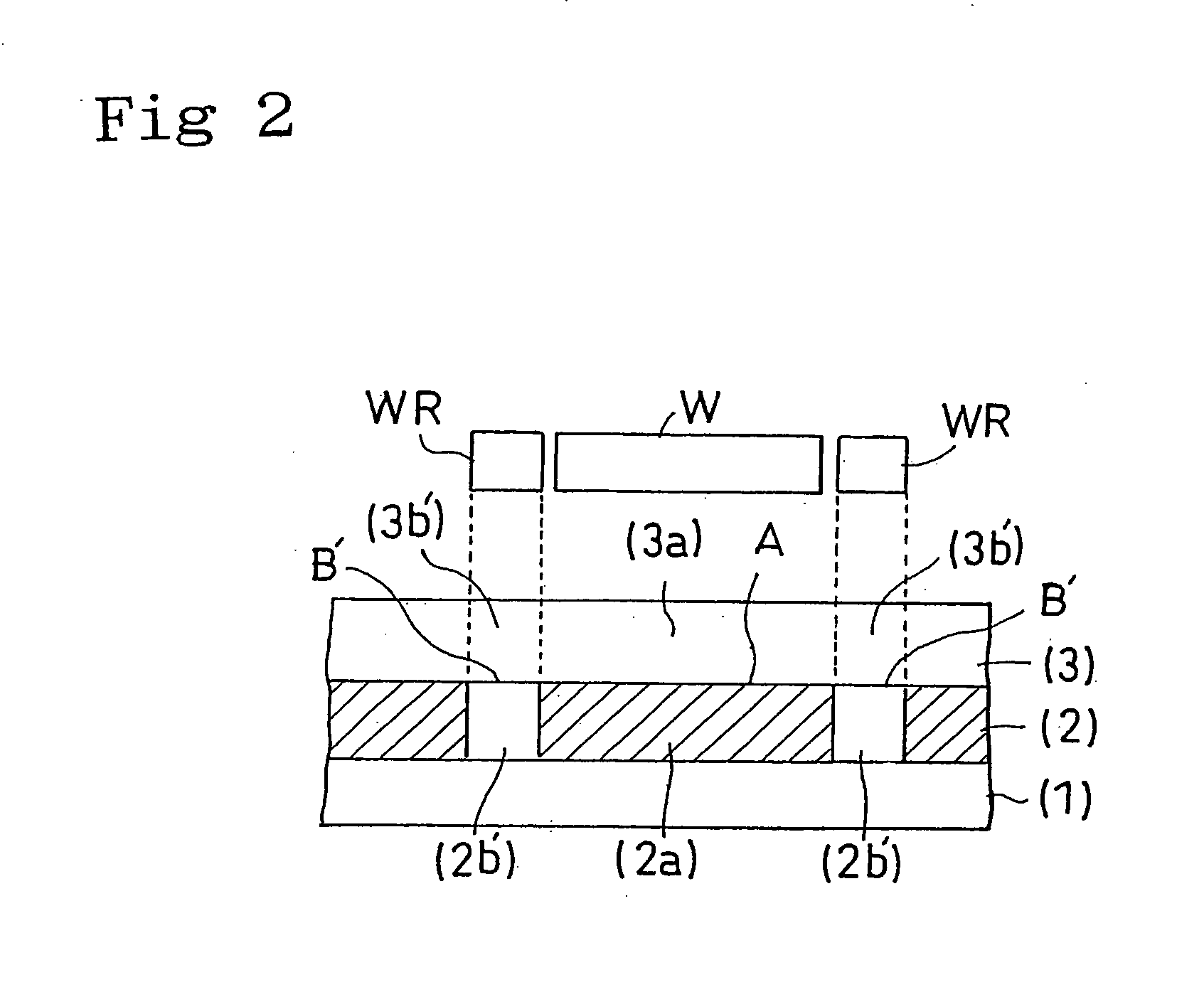

A dicing / die-bonding film including a pressure-sensitive adhesive layer (2) on a supporting base material (1) and a die-bonding adhesive layer (3) on the pressure-sensitive adhesive layer (2), wherein a releasability in an interface between the pressure-sensitive adhesive layer (2) and the die-bonding adhesive layer (3) is different between an interface (A) corresponding to a work-attaching region (3a) in the die-bonding adhesive layer (3) and an interface (B) corresponding to a part or a whole of the other region (3b), and the releasability of the interface (A) is higher than the releasability of the interface (B). The dicing / die-bonding film is excellent in balance between retention in dicing a work and releasability in releasing its diced chipped work together with the die-bonding adhesive layer.

Owner:NITTO DENKO CORP

Composition for pressure sensitive adhesive film, pressure sensitive adhesive film, and dicing die bonding film including the same

A composition for forming an adhesive film is provided to prevent an acrylic adhesive binder and UV curable acrylate from being transferred to an adhesive layer when used in a dicing die bonding film, and to realize high pick-up property even in large chips greater than 10 mm X 10 mm after UV irradiation. A composition for forming an adhesive film comprises: (A) 100 parts by weight of a polymer binder resin; (B) 20-150 parts by weight of a low-molecular weight UV curable acrylate; (C) 0.1-10 parts by weight of a thermal curing agent; and (D) 0.1-5 parts by weight of a photopolymerization initiator based on 100 parts by weight of the UV curable acrylate. The adhesive film formed by the composition has a sea-island surface structure, wherein the island region has an average size of 1-10 micrometers.

Owner:CHEIL IND INC