Patents

Literature

795 results about "Fine pitch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

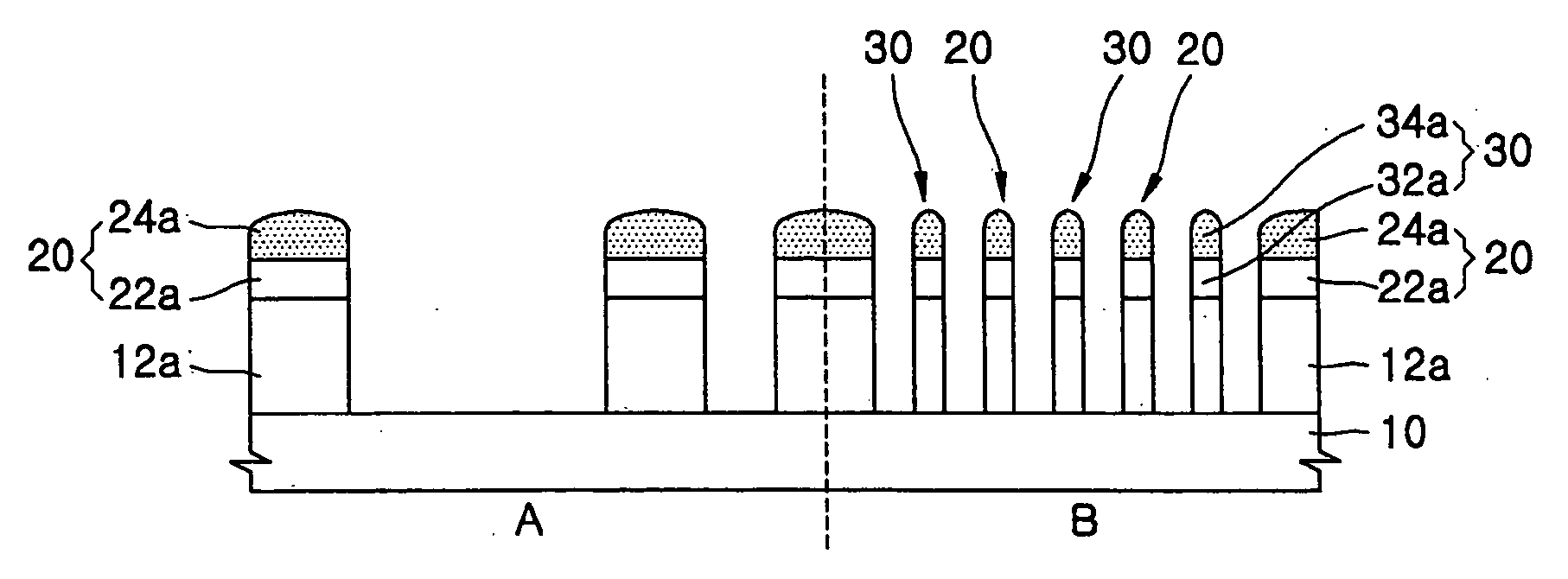

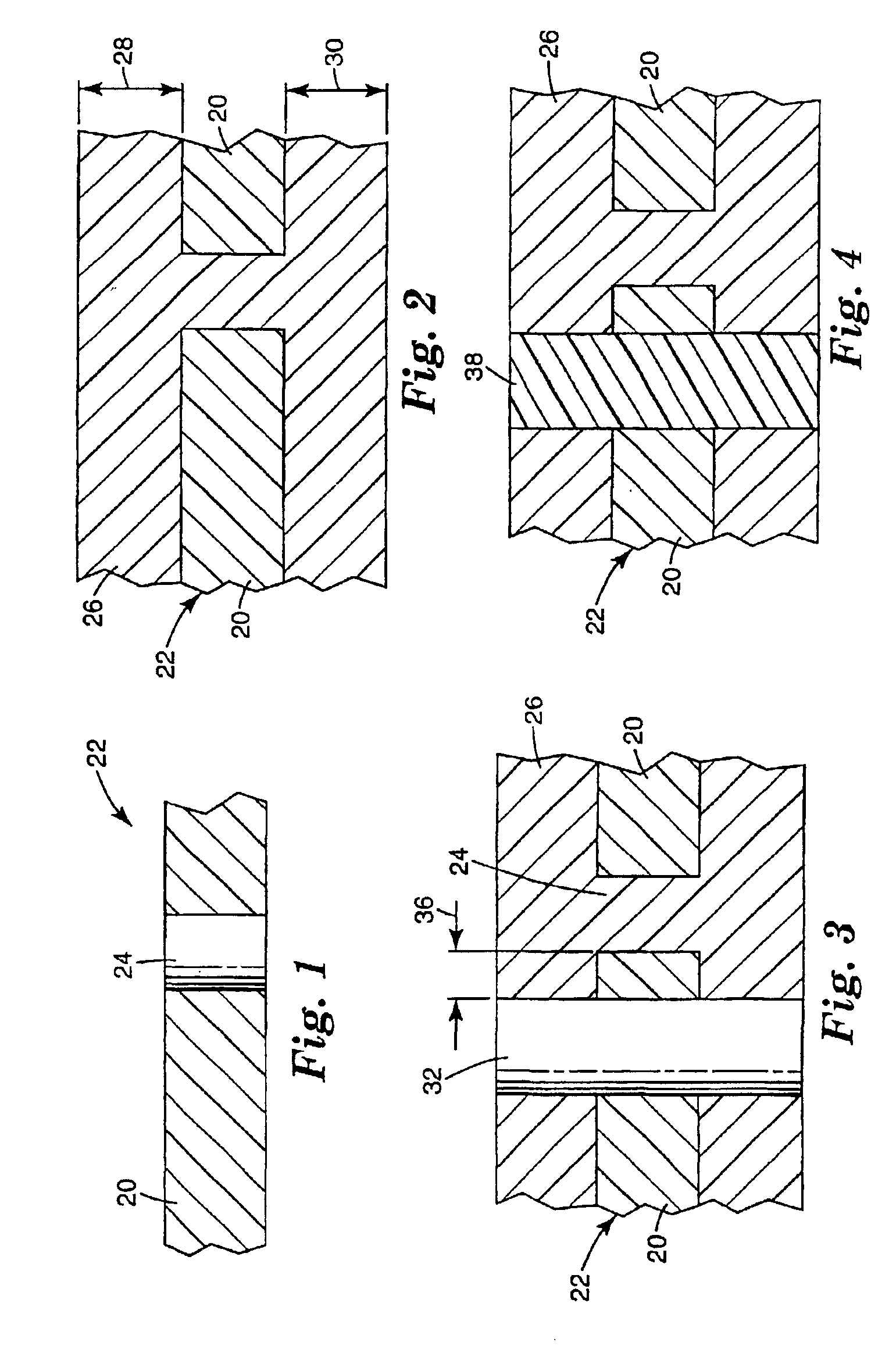

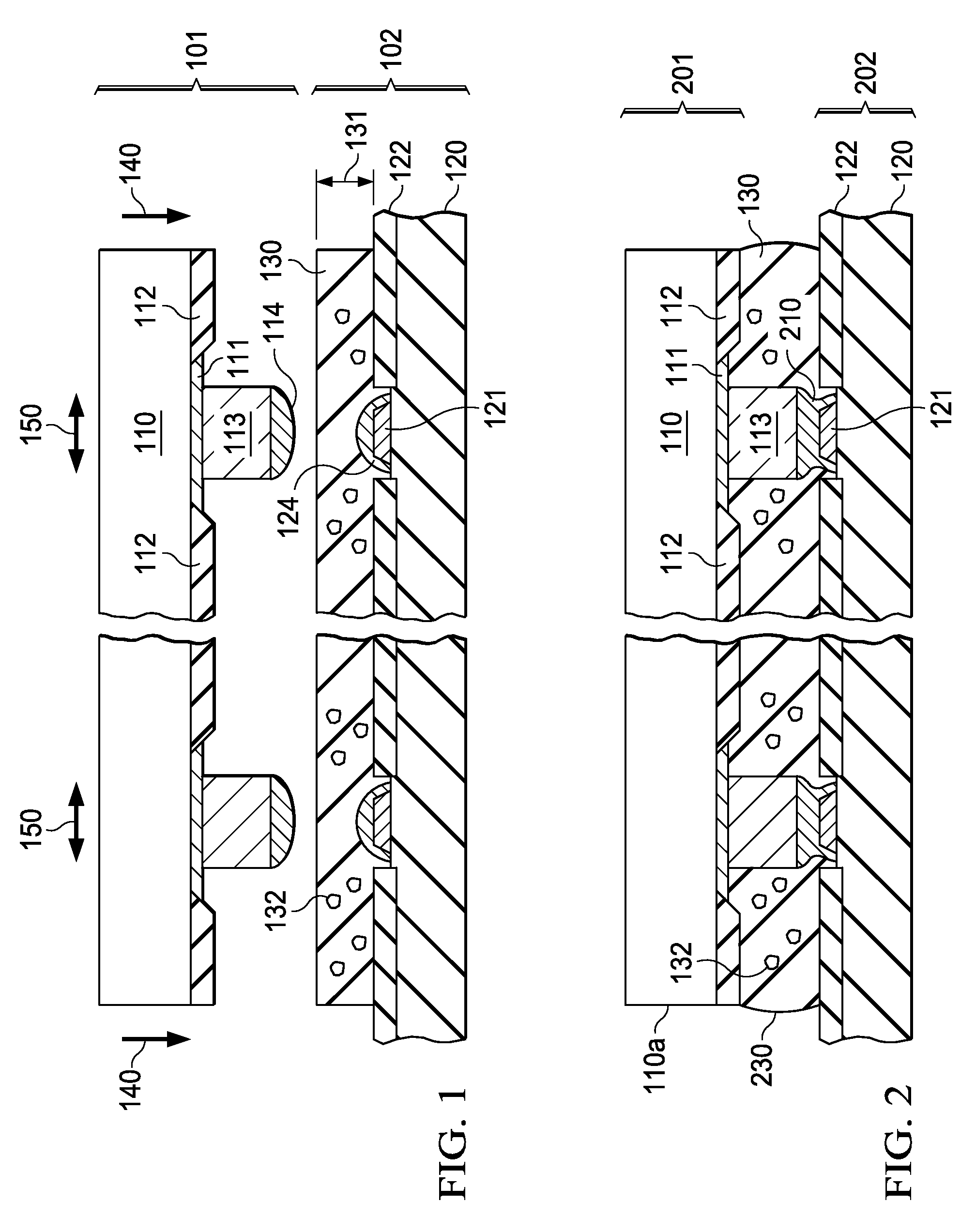

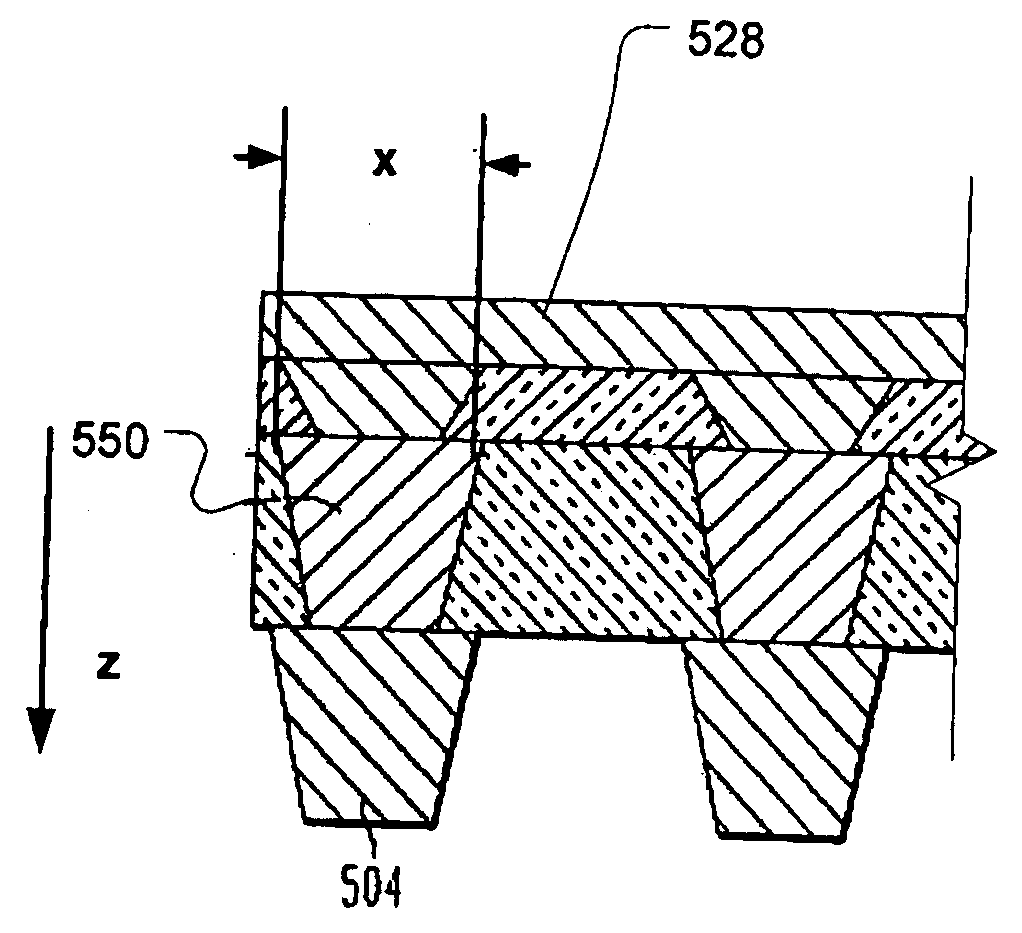

Method of forming pattern using fine pitch hard mask

A method of forming a first hard mask pattern including a plurality of first line patterns formed on the etch target layer in a first direction and having a first pitch. A third layer is formed on sidewalls and an upper surface of the first hard mask pattern, such that the third layer includes a top surface having a recess formed between two adjacent first line patterns. A second hard mask pattern including a plurality of second line patterns each extending in the first direction within the recess is formed. Then, the third layer is anisotropically etched to selectively expose an etch target layer between the first line patterns and the second line patterns. Then, the etch target layer is anisotropically etched using the first hard mask pattern and the second hard mask pattern as an etch mask.

Owner:SAMSUNG ELECTRONICS CO LTD

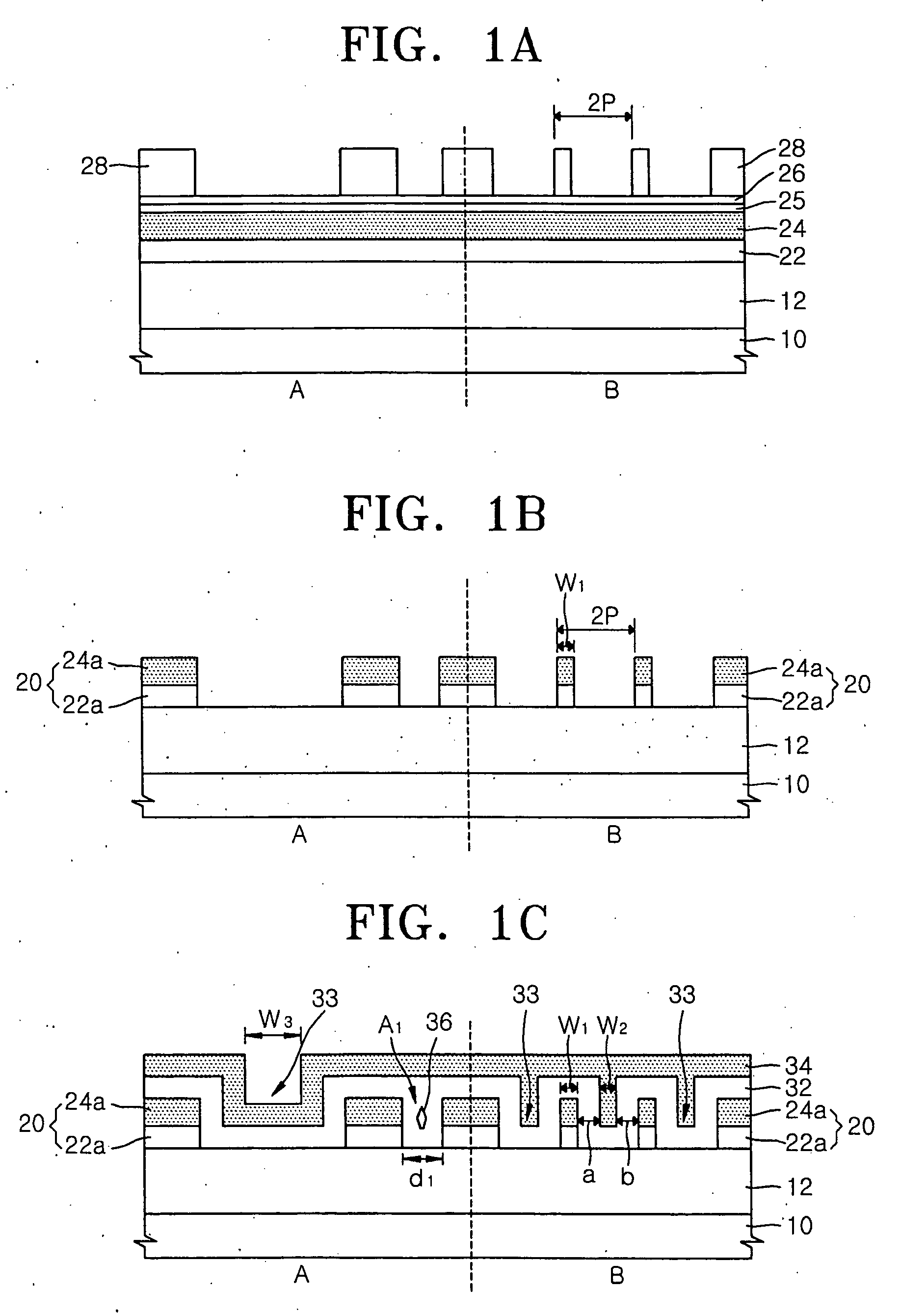

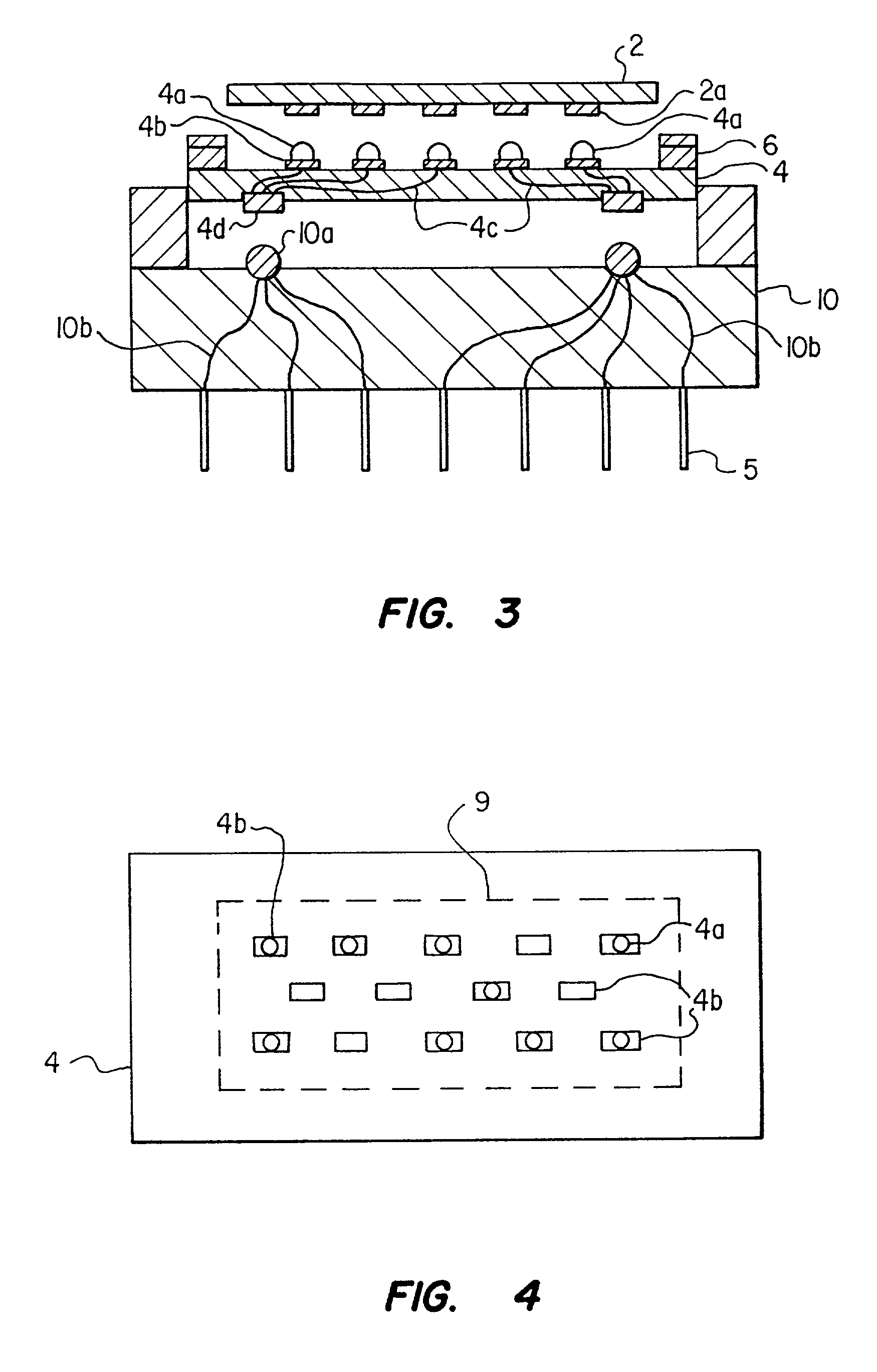

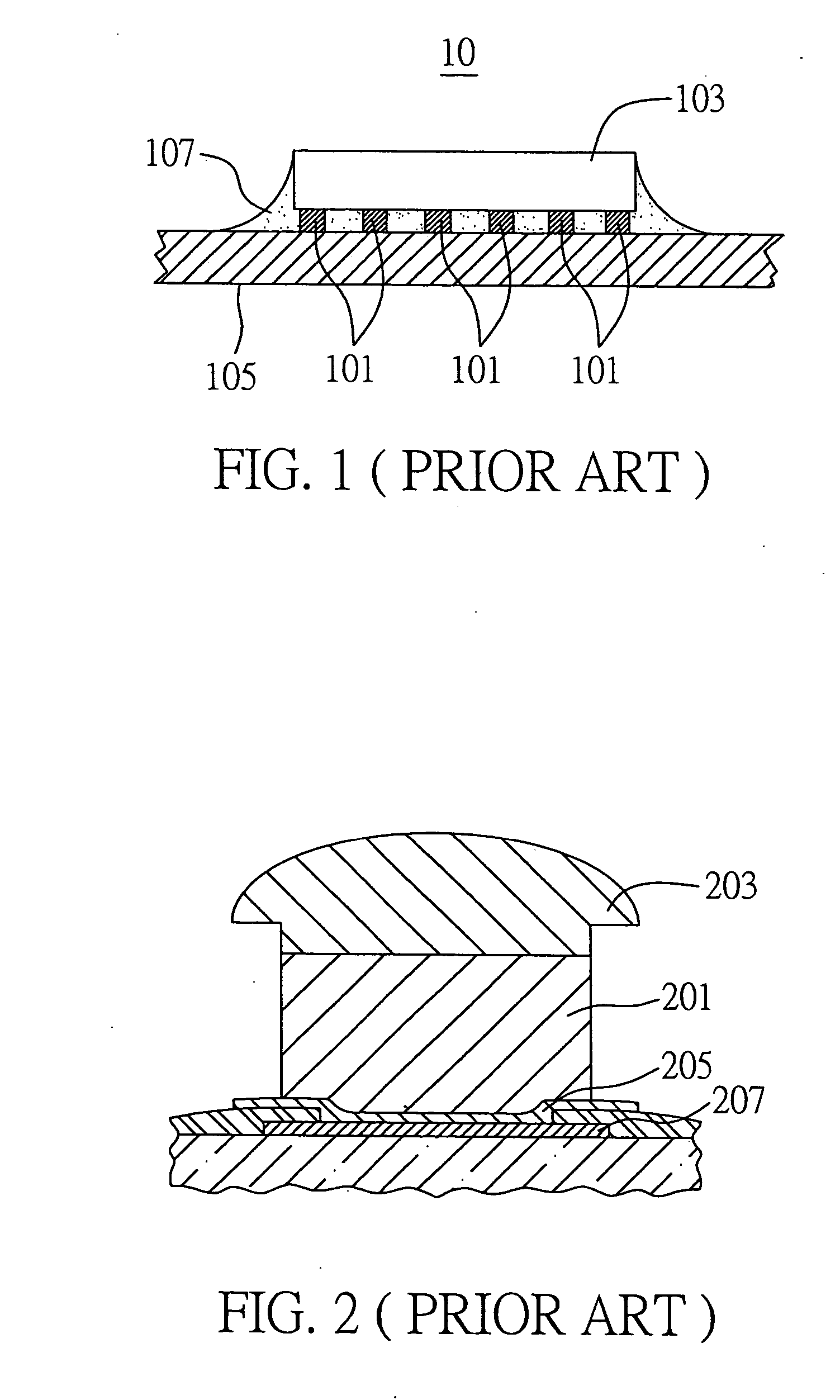

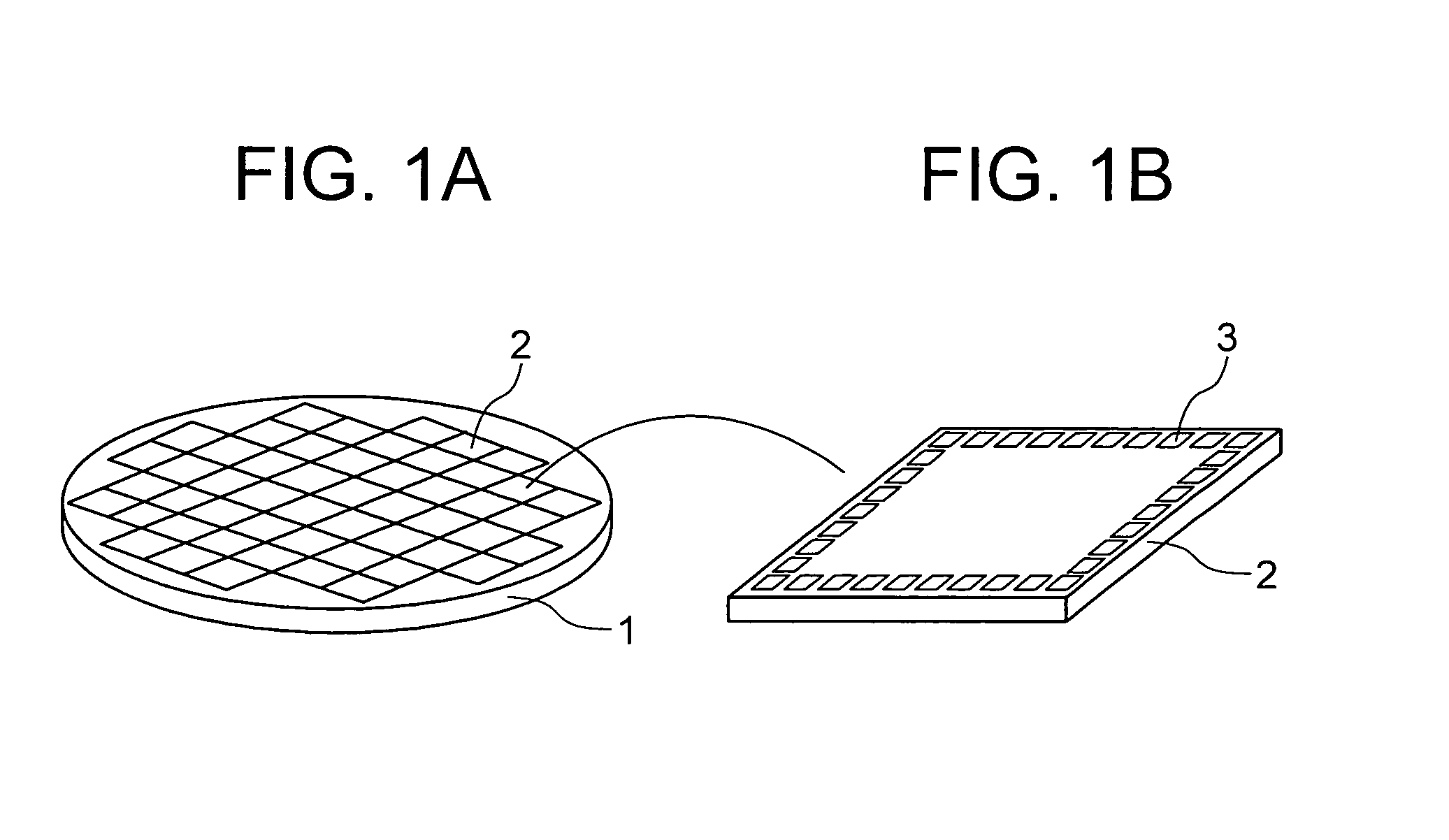

Method for forming conductive bumps for the purpose of contrructing a fine pitch test device

InactiveUS20020011859A1Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityEngineering

A system is described for using with fine pitch devices including singulated bare die, semiconductor wafers, chip sized packages, printed circuit boards, and the like to determine that the fine pitch device is not faulty. The system is also usable for transfer of data, energy, for collecting data measurements or measurement-related data between two pieces, and for effecting at least part of an identification process. The disclosed embodiment includes a substrate having a circuit pad pattern in the mirror image of the pattern of contact points, usually bond pads of the fine pitch device to be connected. A conductive elastomeric probe is permanently formed on the circuit pads of the substrate such that the probe is malleable and allows repetitive electrical contact. The system may also contain an alignment template for orienting the fine pitch device onto the elastomeric probes of the contact point pattern of the substrate.

Owner:EPITECH +1

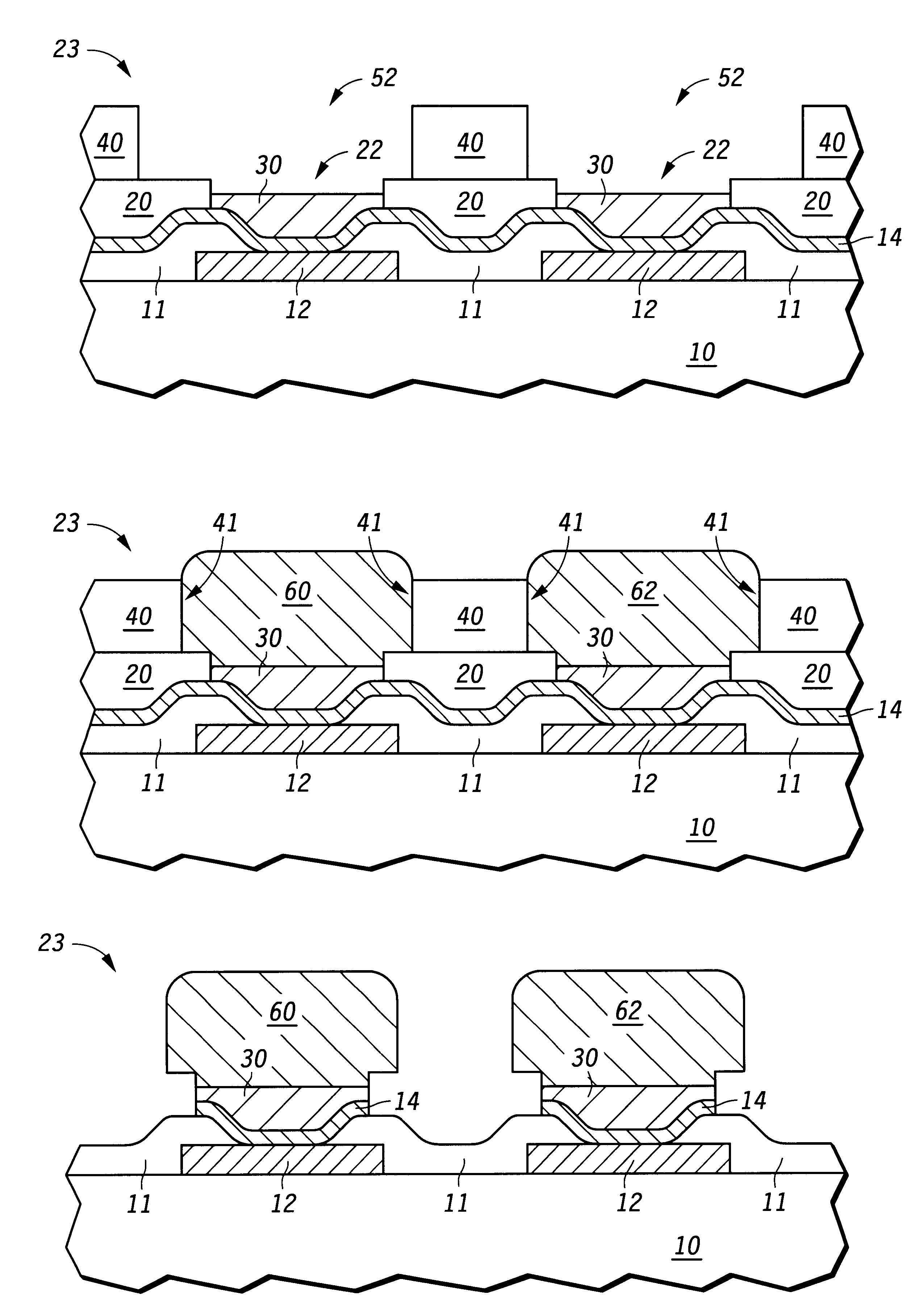

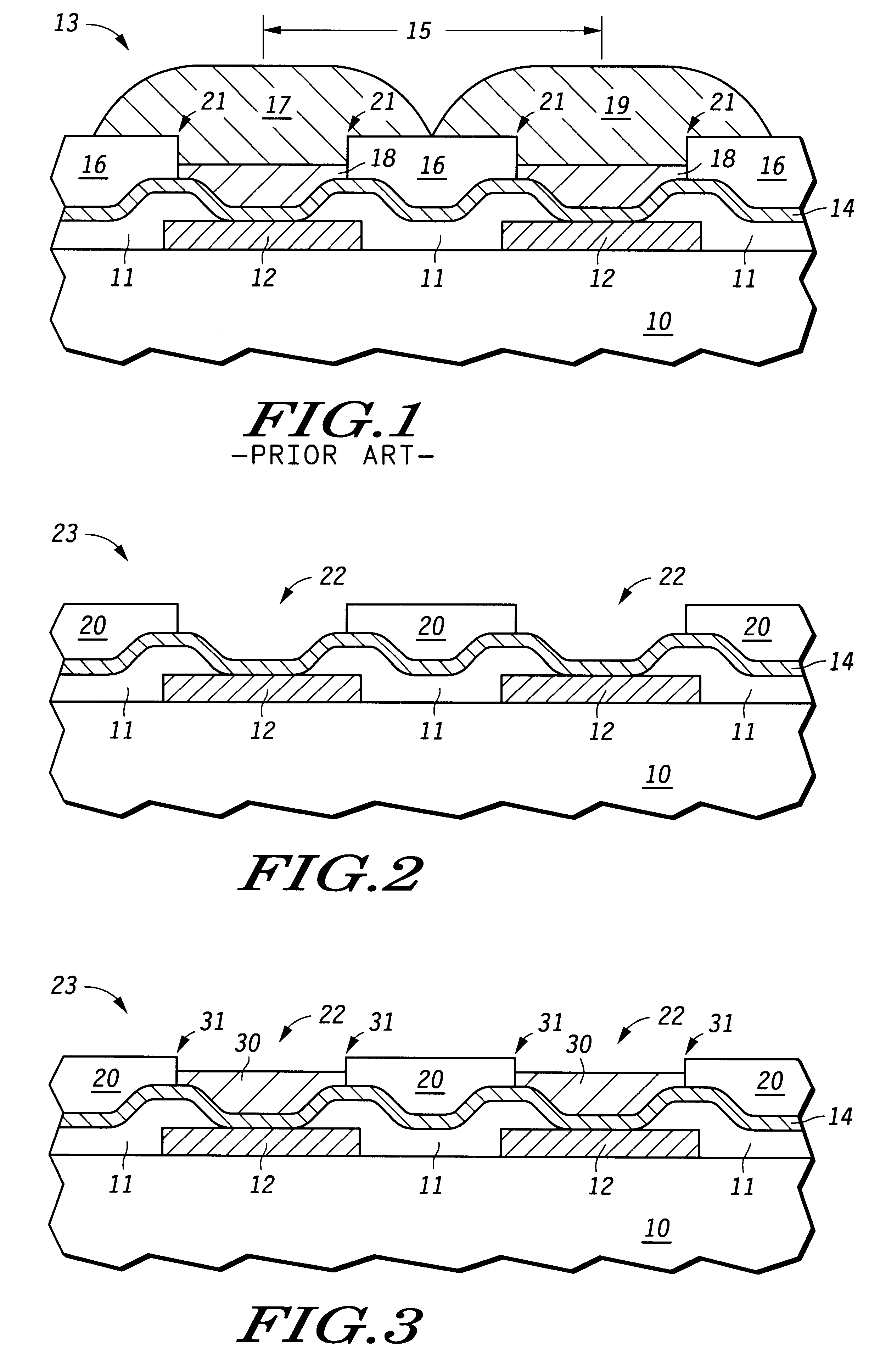

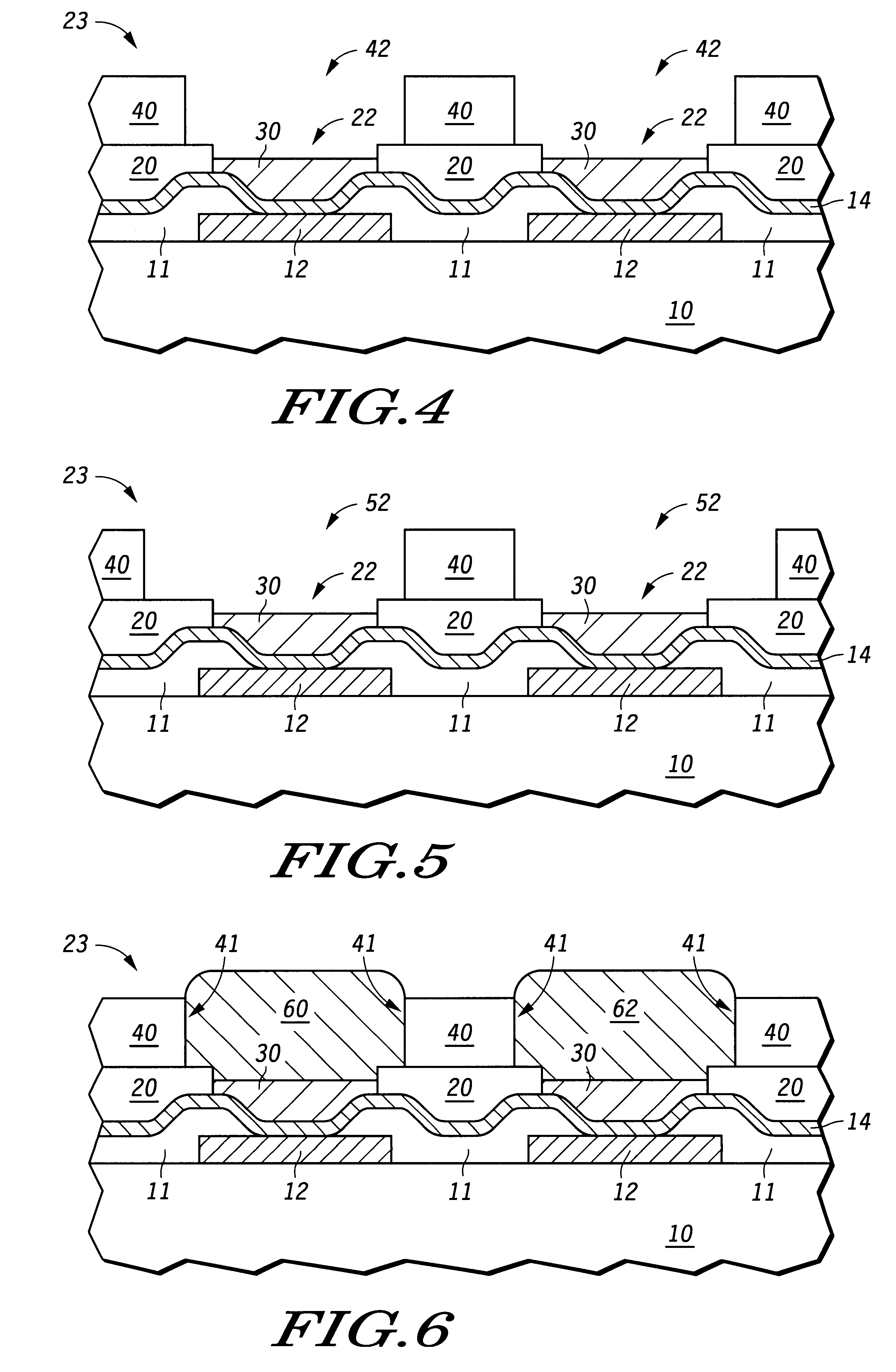

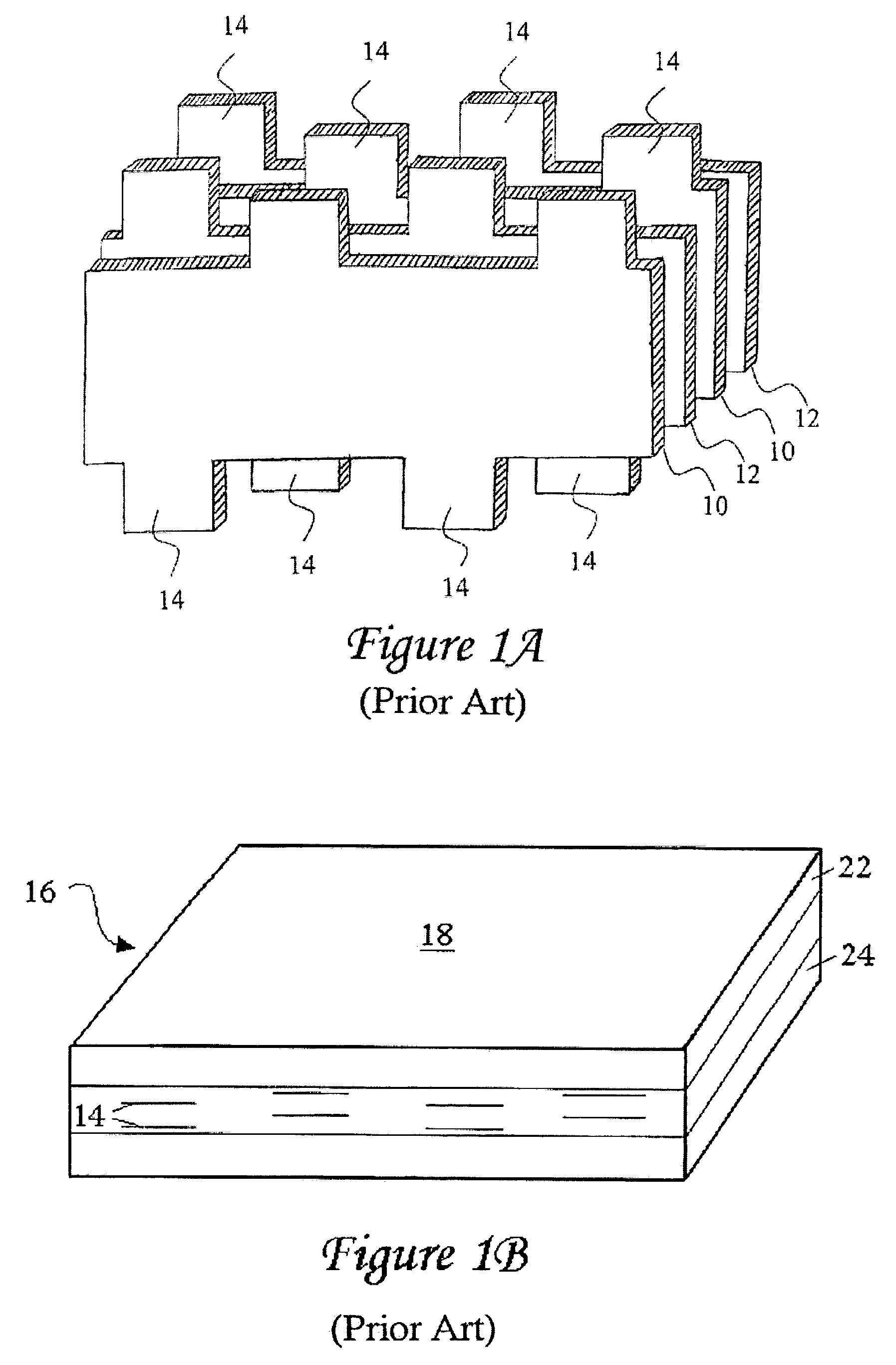

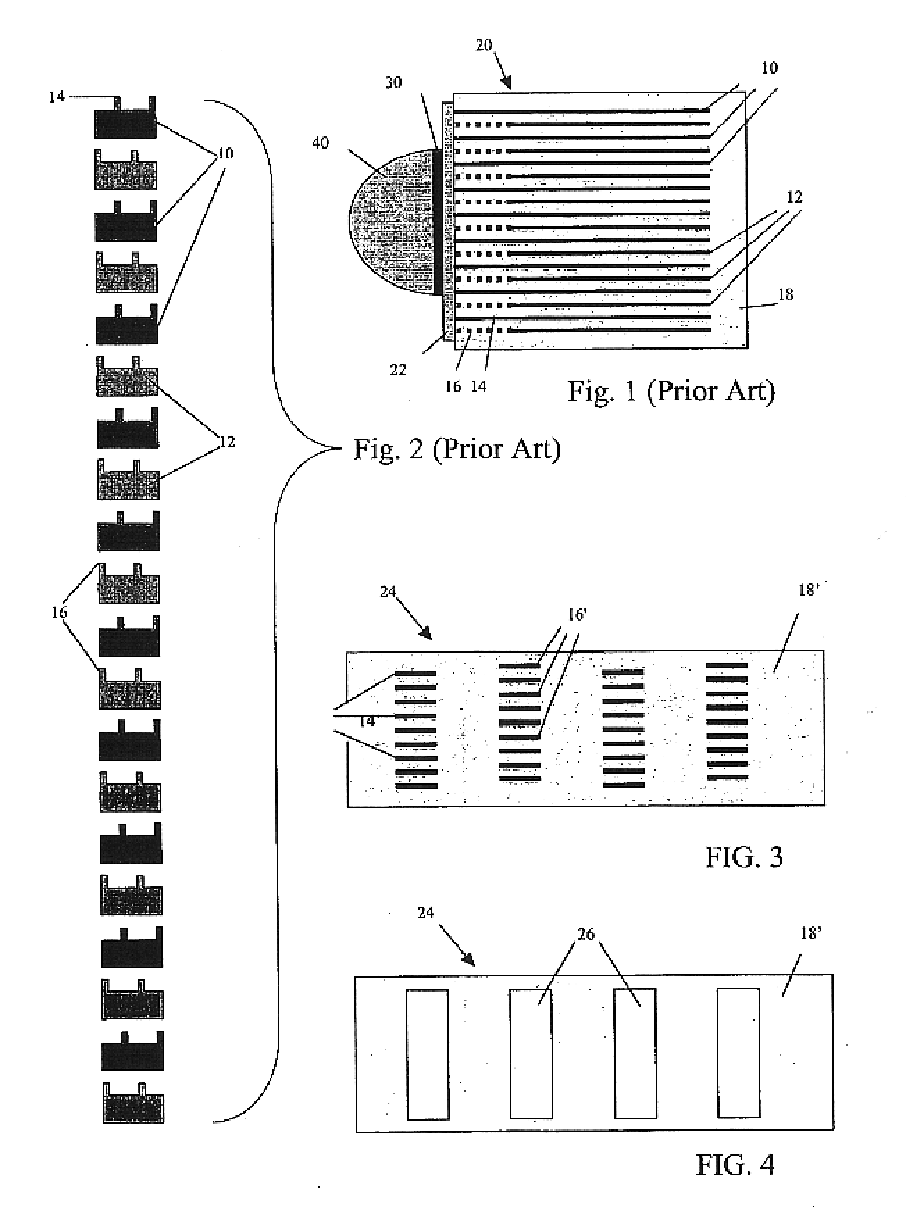

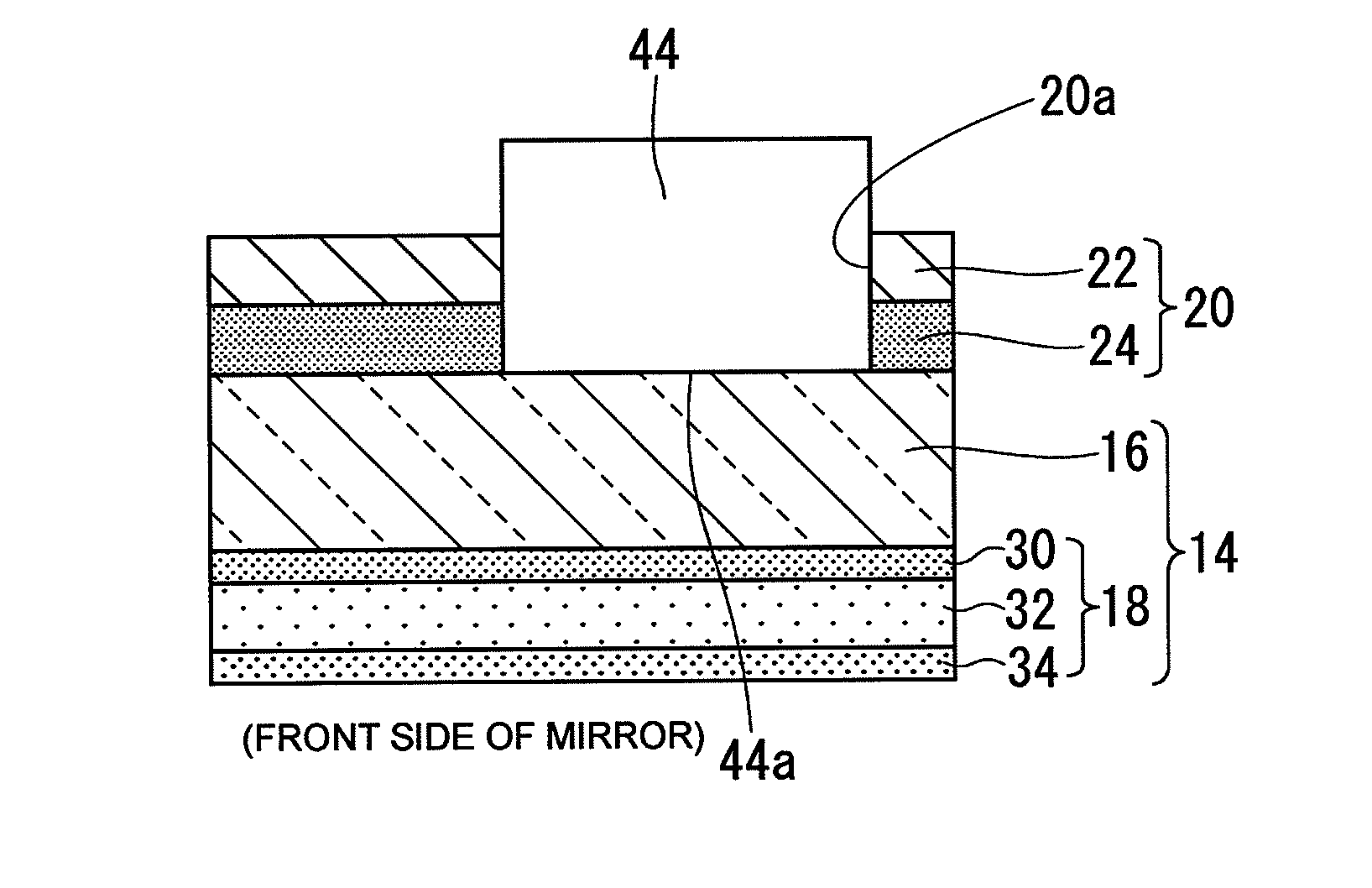

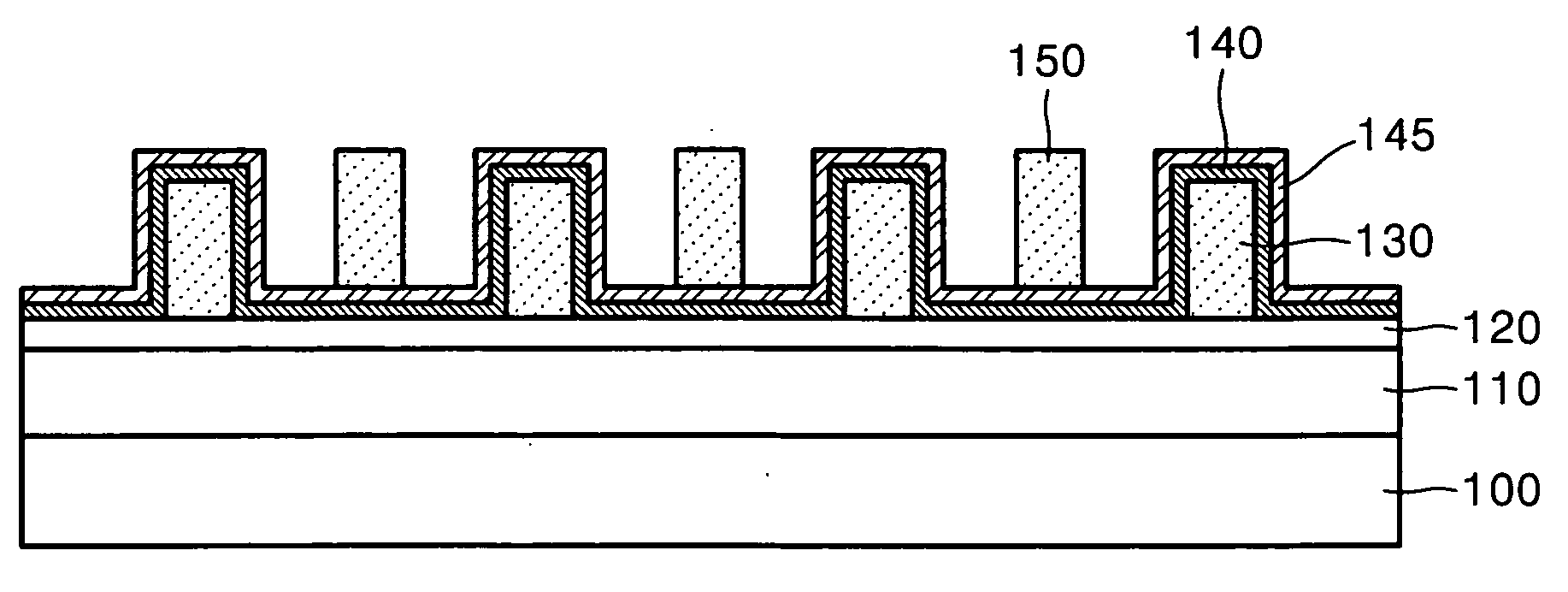

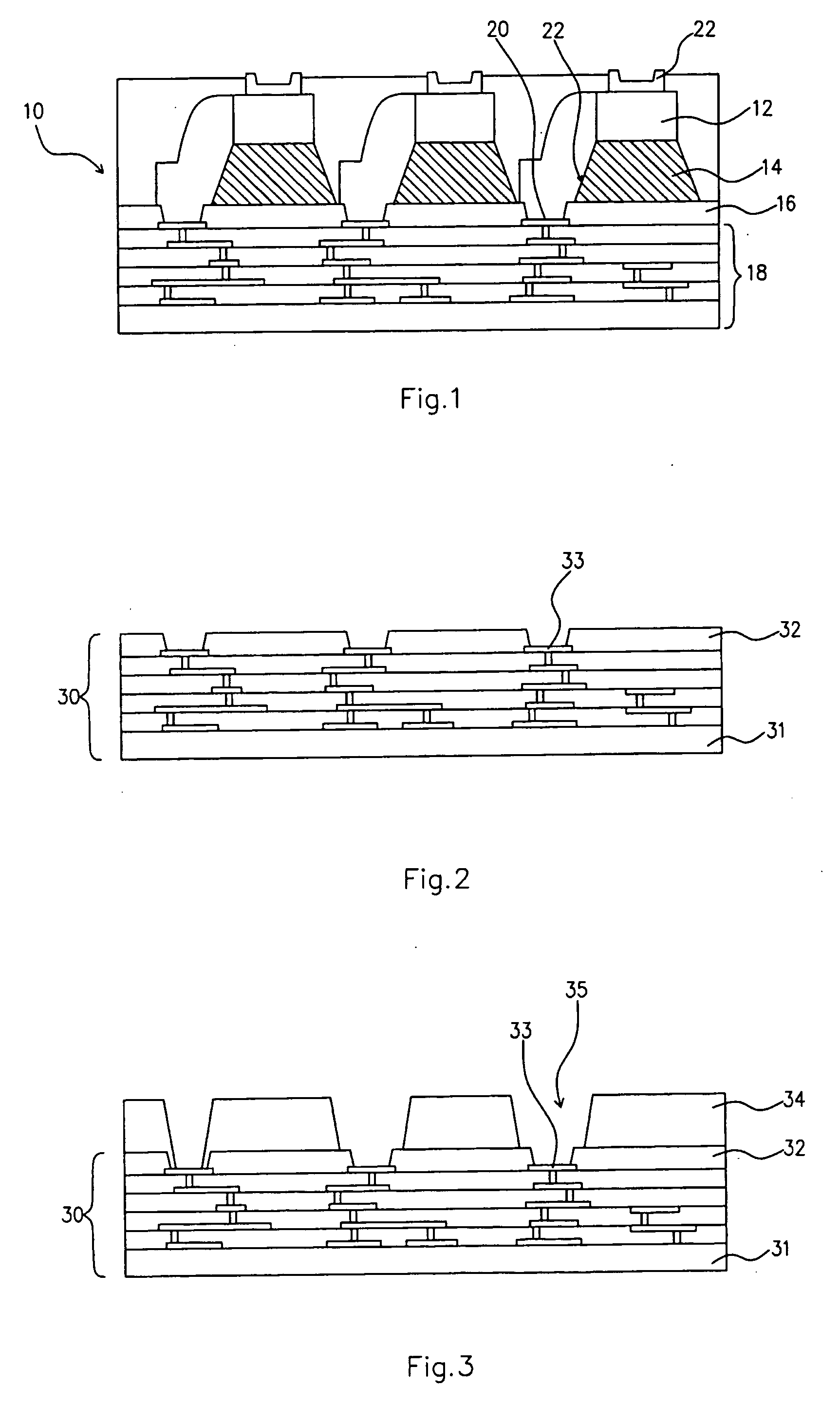

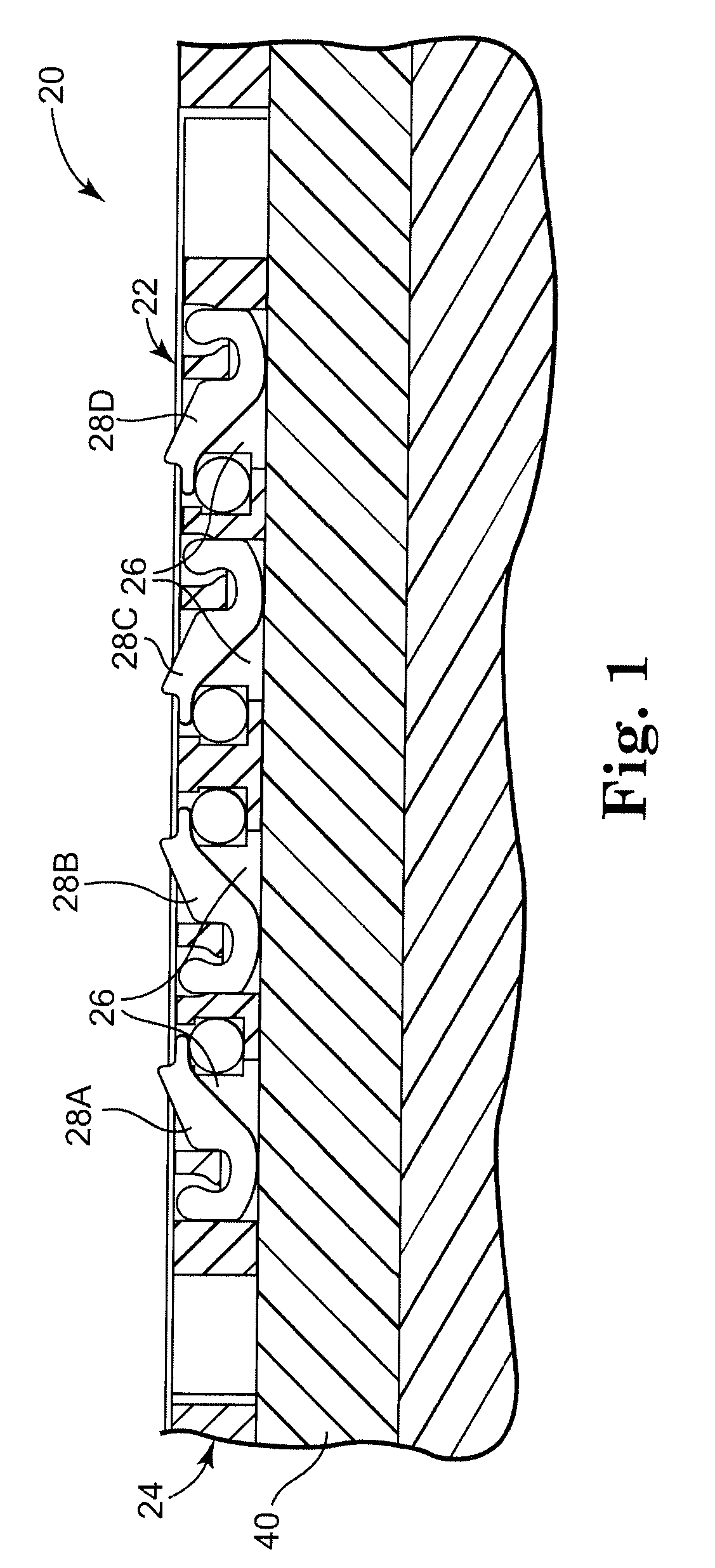

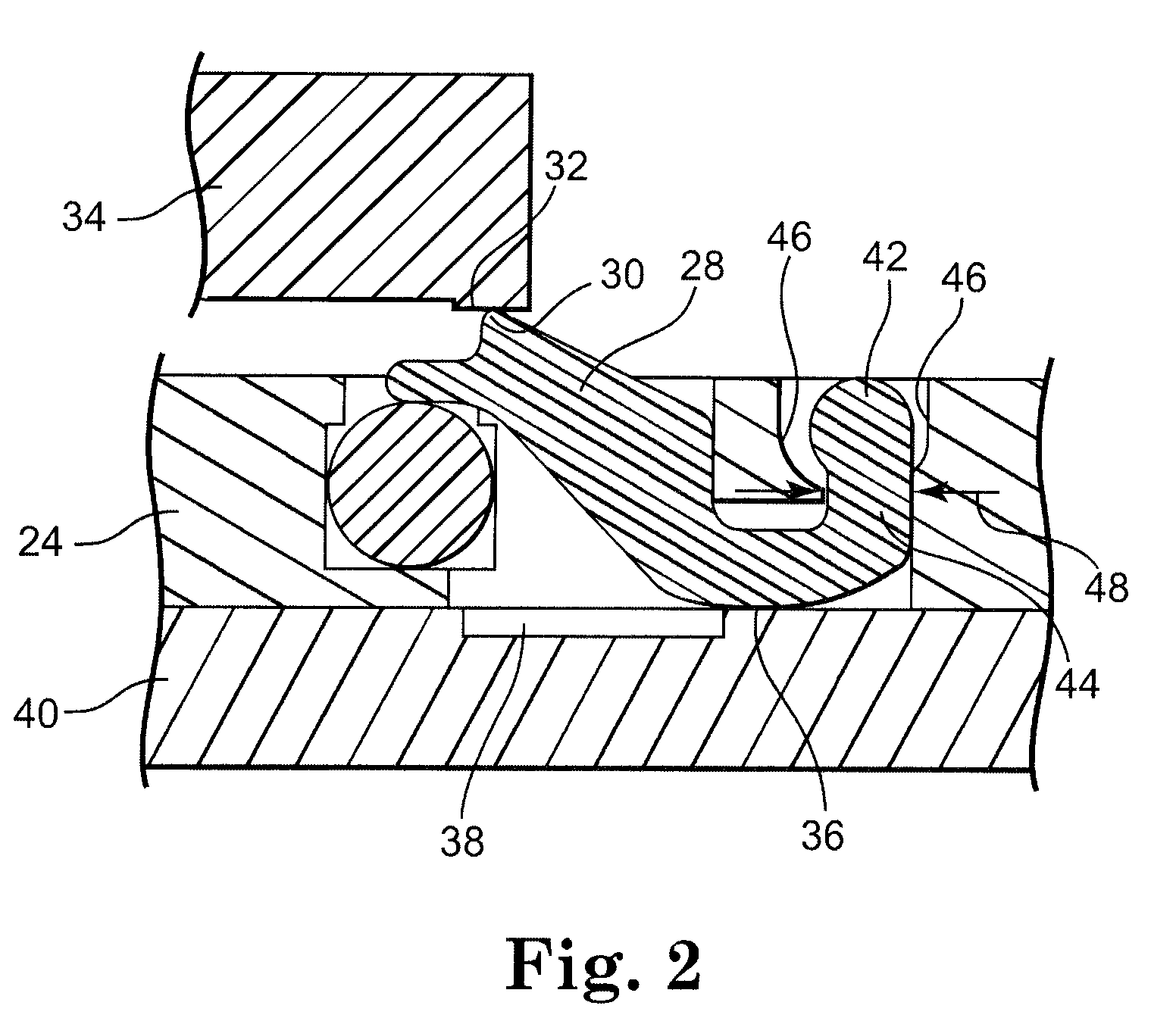

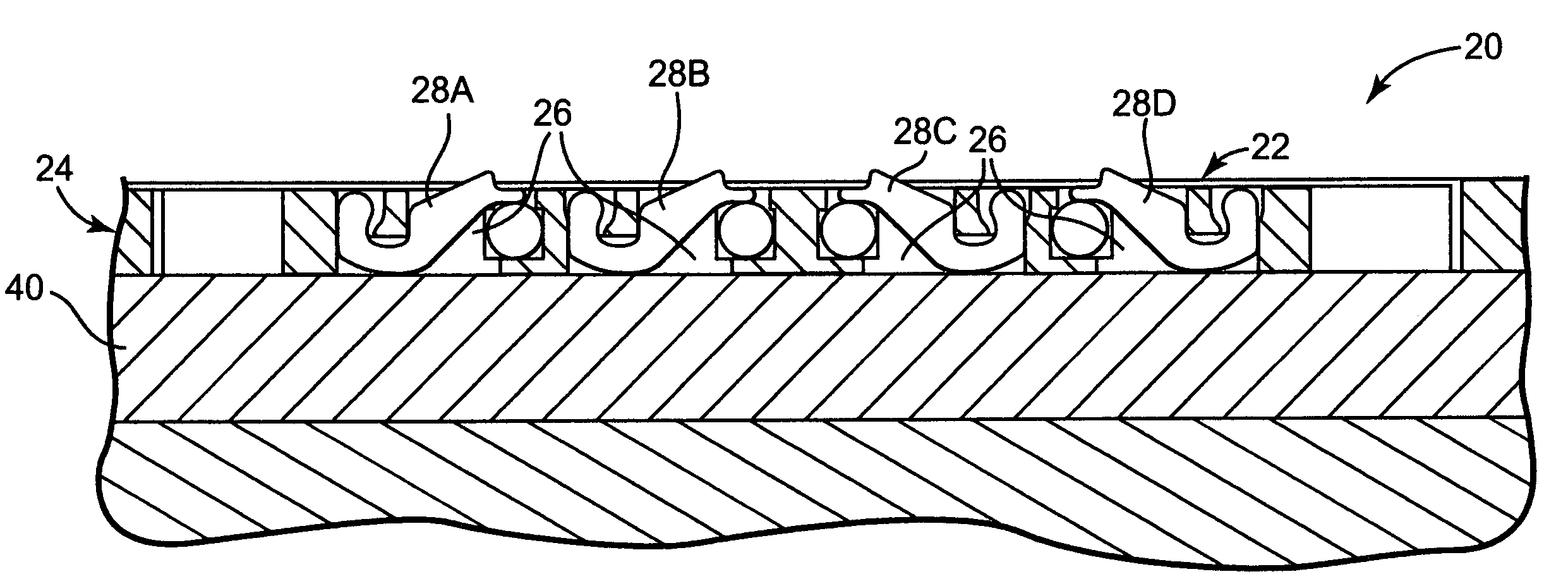

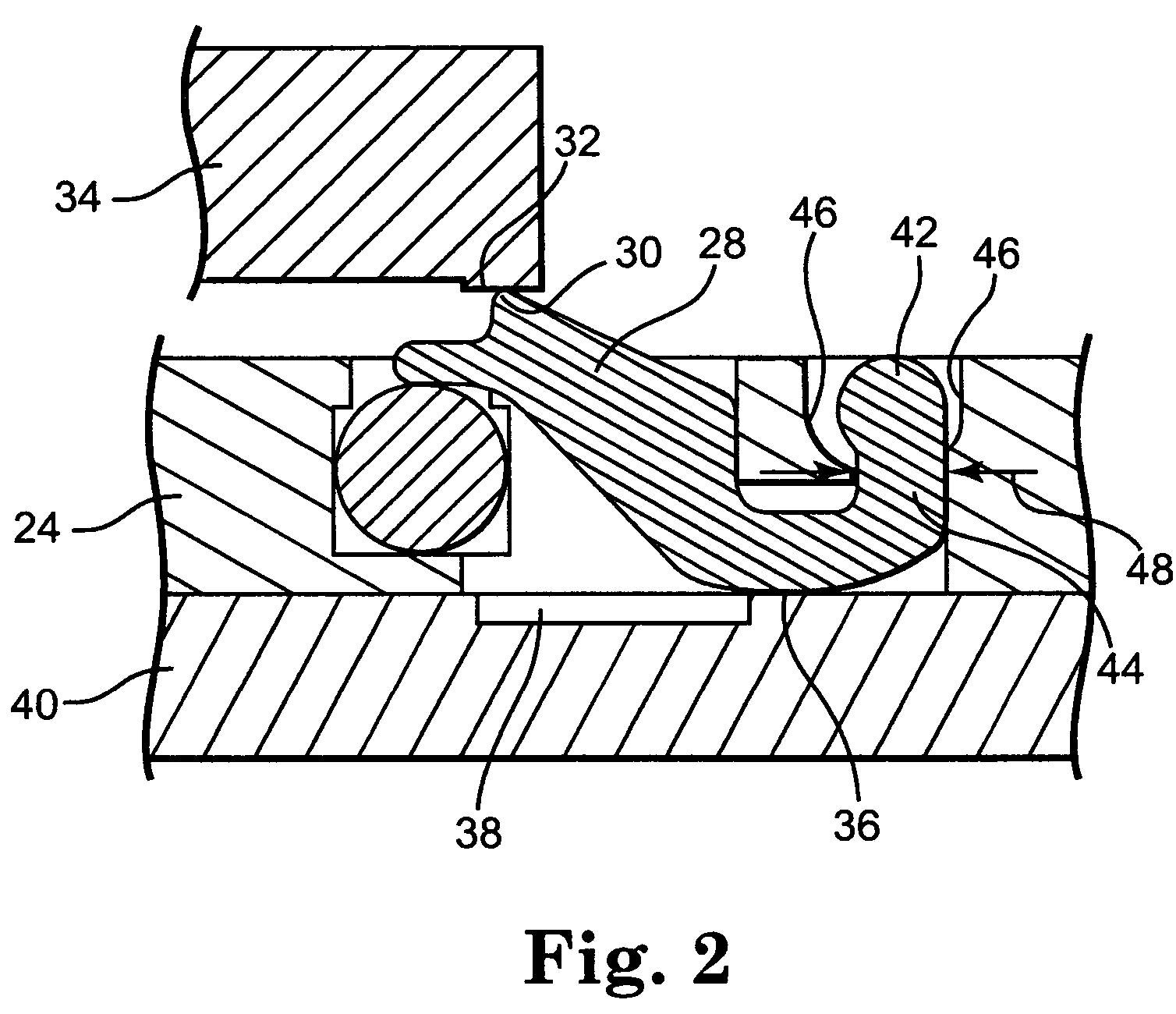

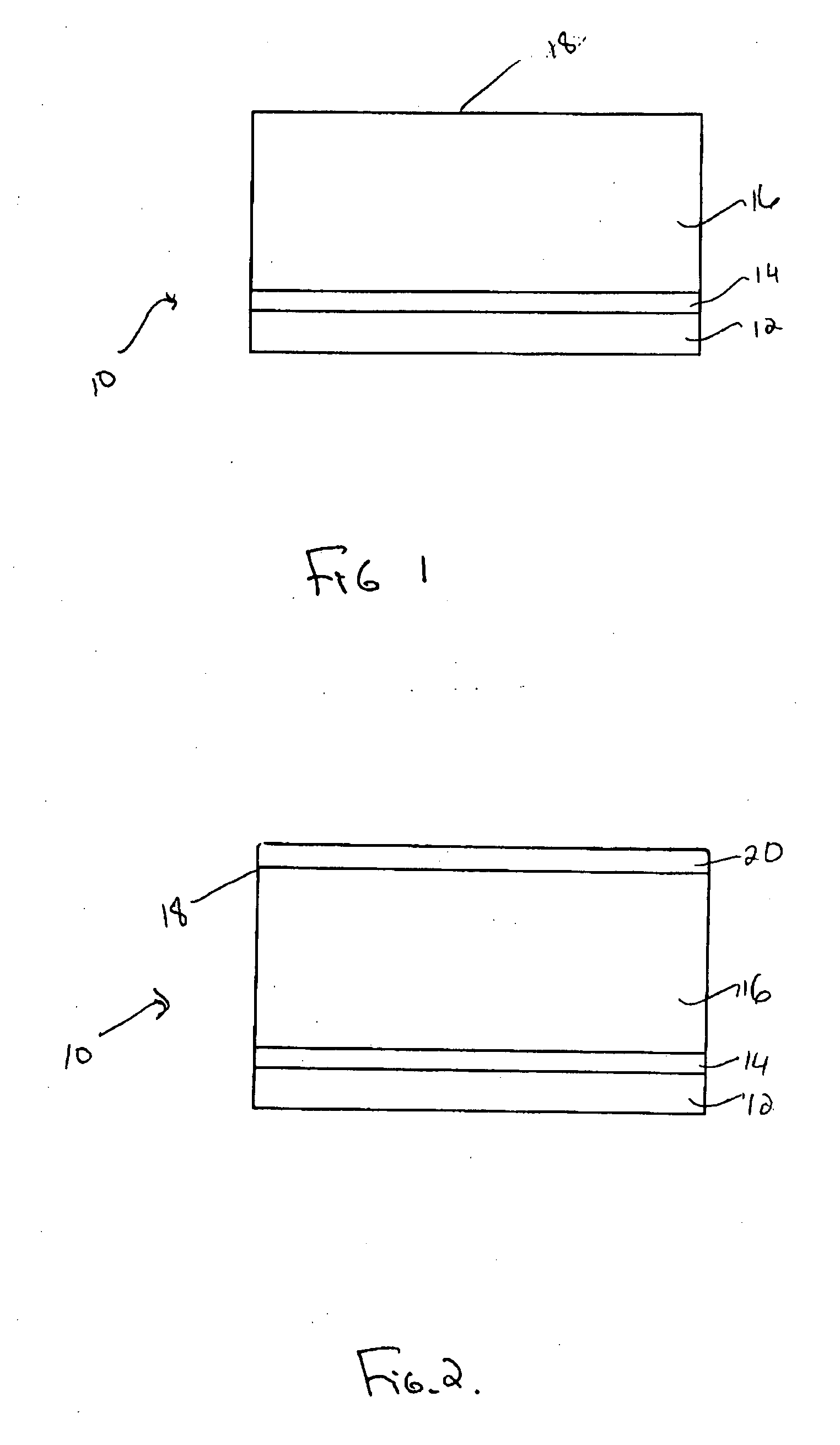

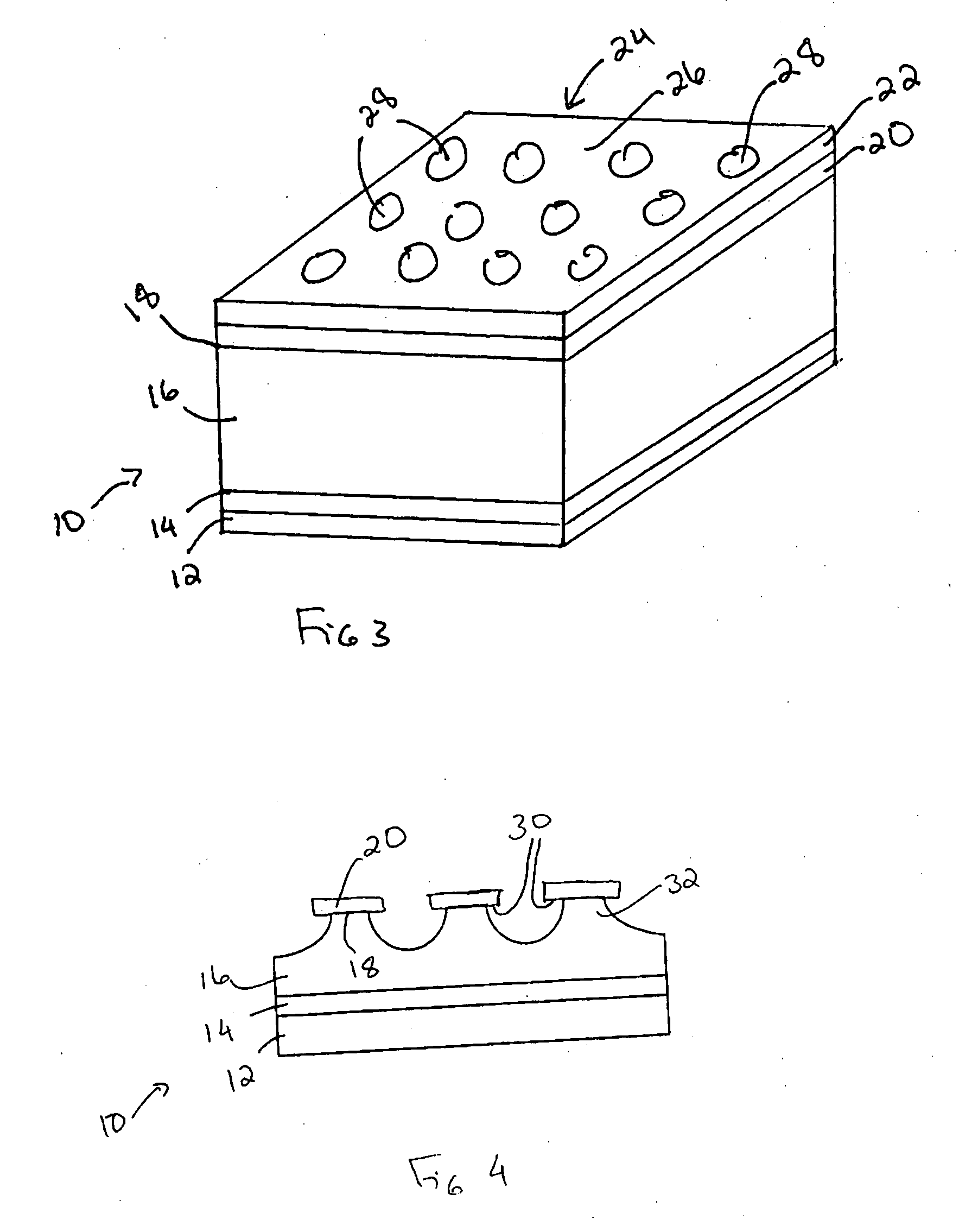

Fine pitch bumping with improved device standoff and bump volume

Embodiments of the present invention relate generally to solder bump formation and semiconductor device assemblies. One embodiment related to a method for forming a bump structure includes providing a semiconductor device (10) having a bond pad (12), and forming a first masking layer (20) overlying the bond pad (12). The first masking layer (20) is patterned to form a first opening (22) overlying at least a portion of the bond pad (12). A second masking layer (40) is formed overlying the first masking layer (20), and the second masking layer (40) is patterned to form a second opening (42) overlying at least a portion of the first opening (22). The method further includes forming a stud (30) at least within the first opening (22) and a solder bump (60) at least within the second opening (42).

Owner:NORTH STAR INNOVATIONS

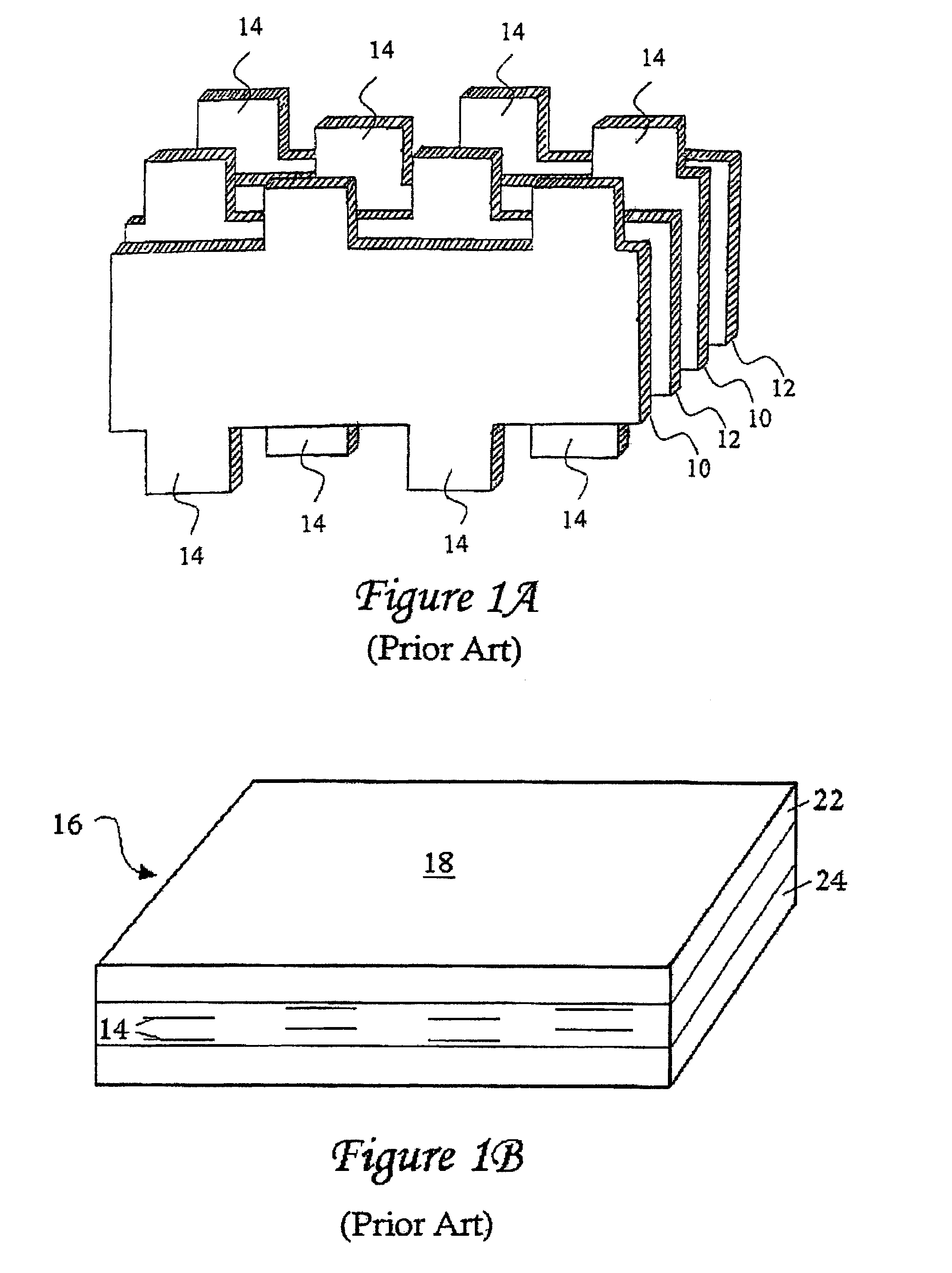

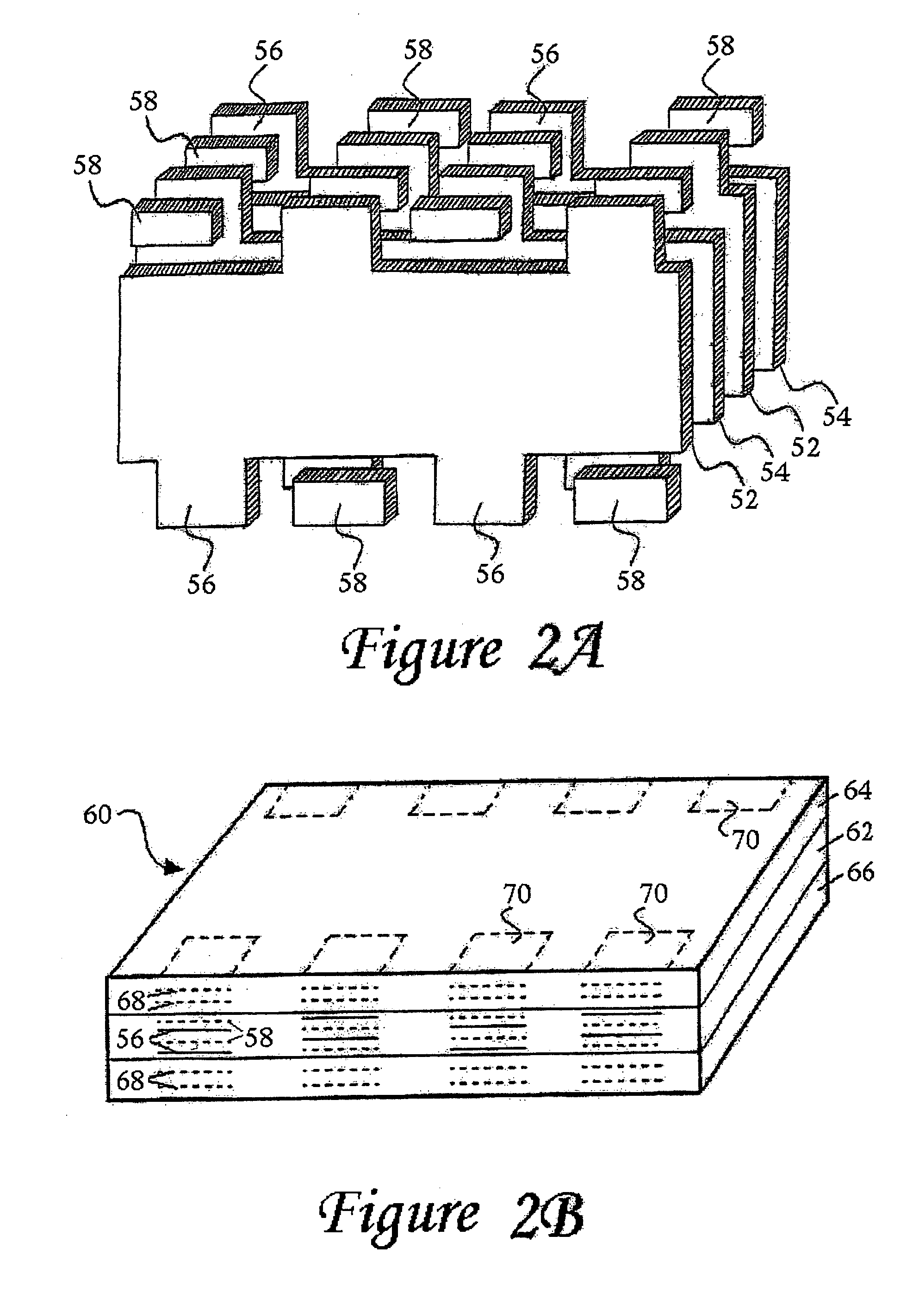

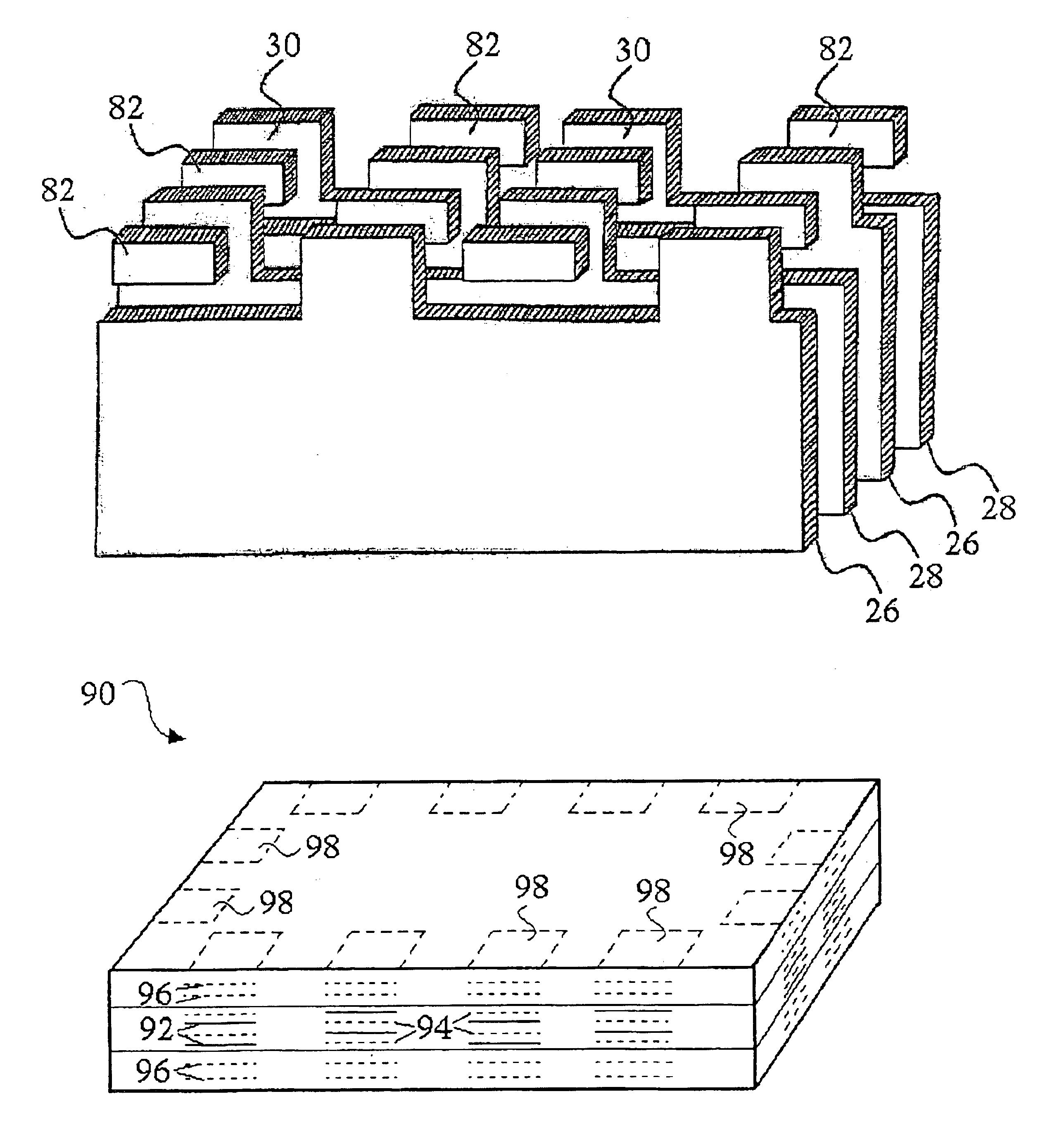

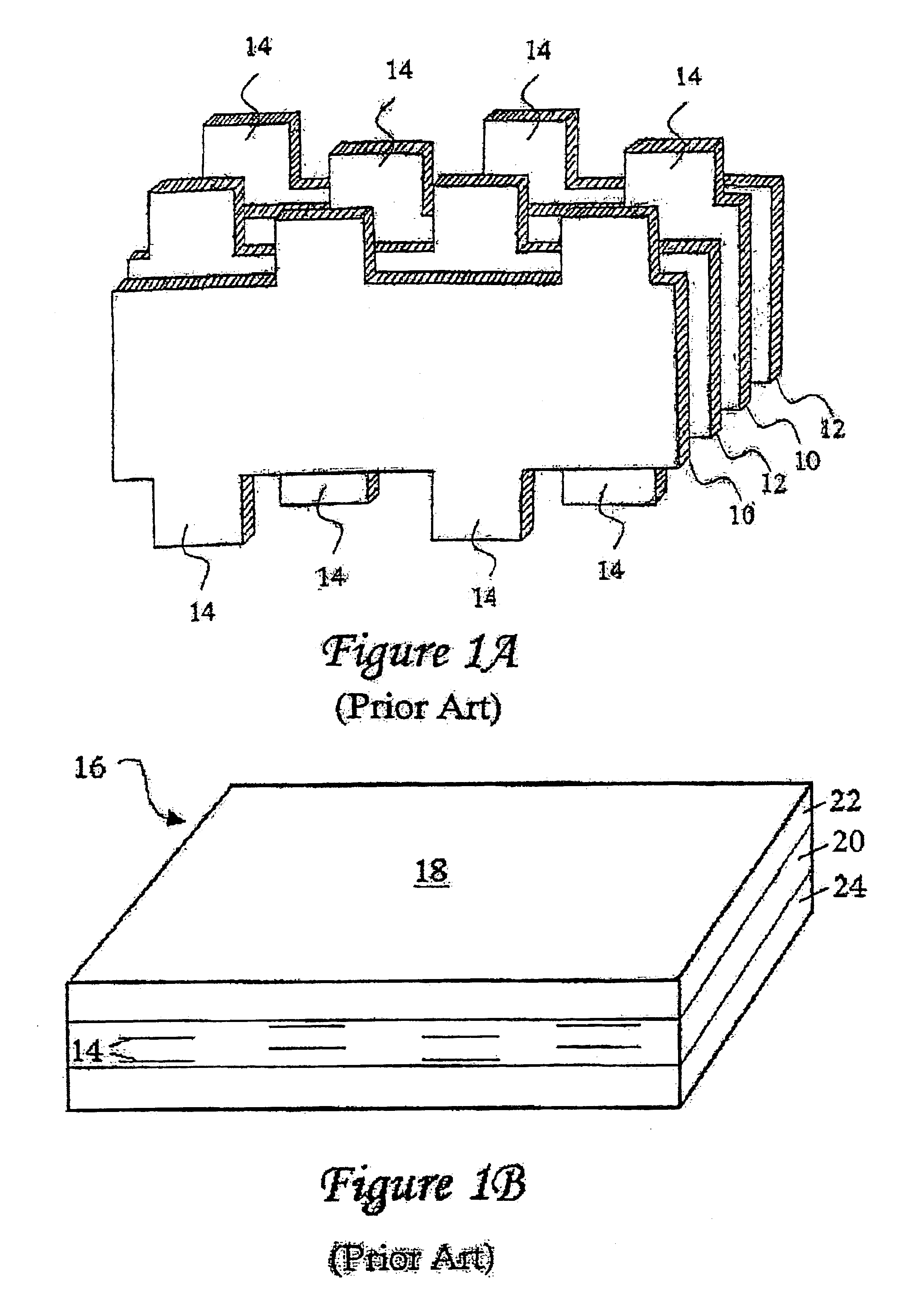

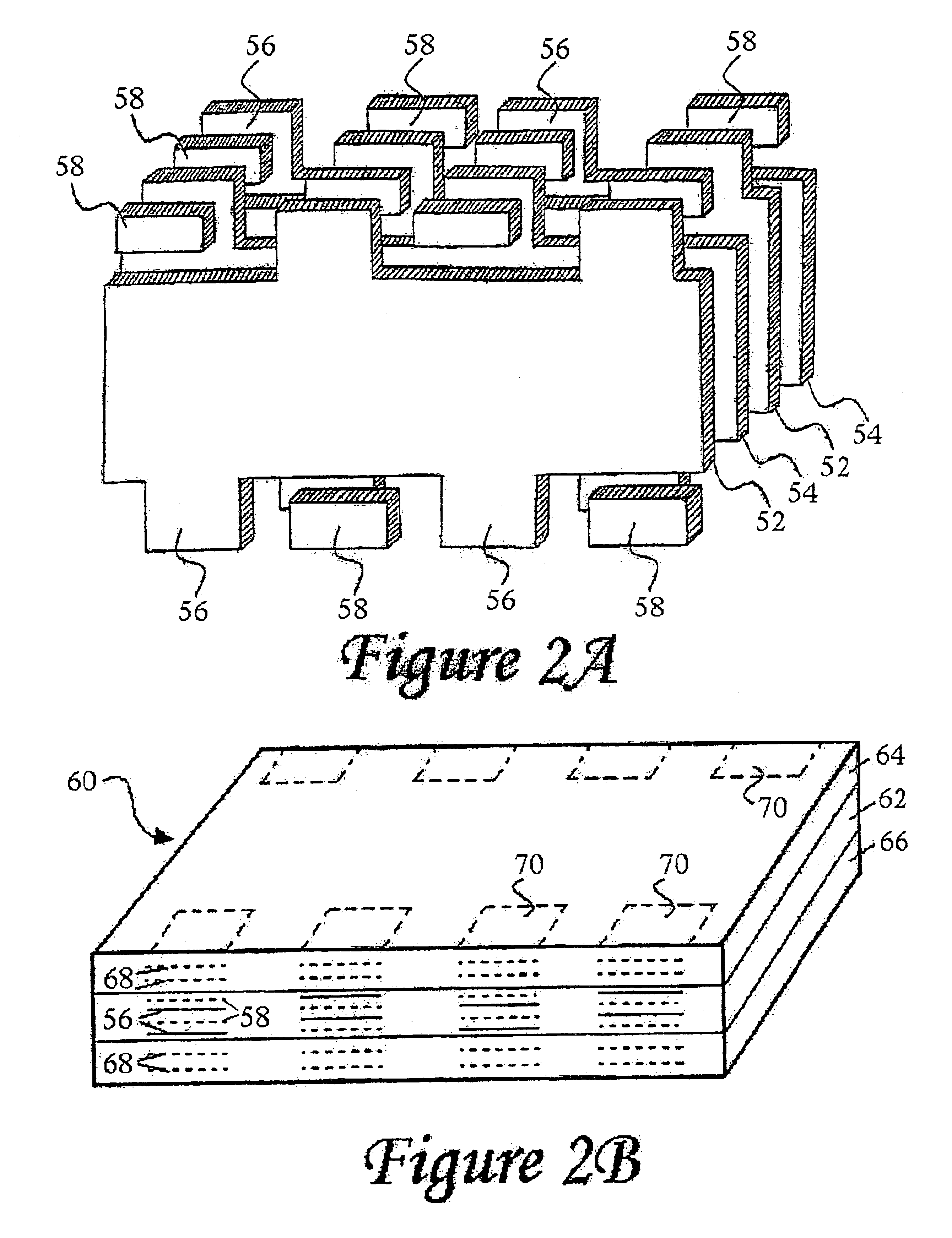

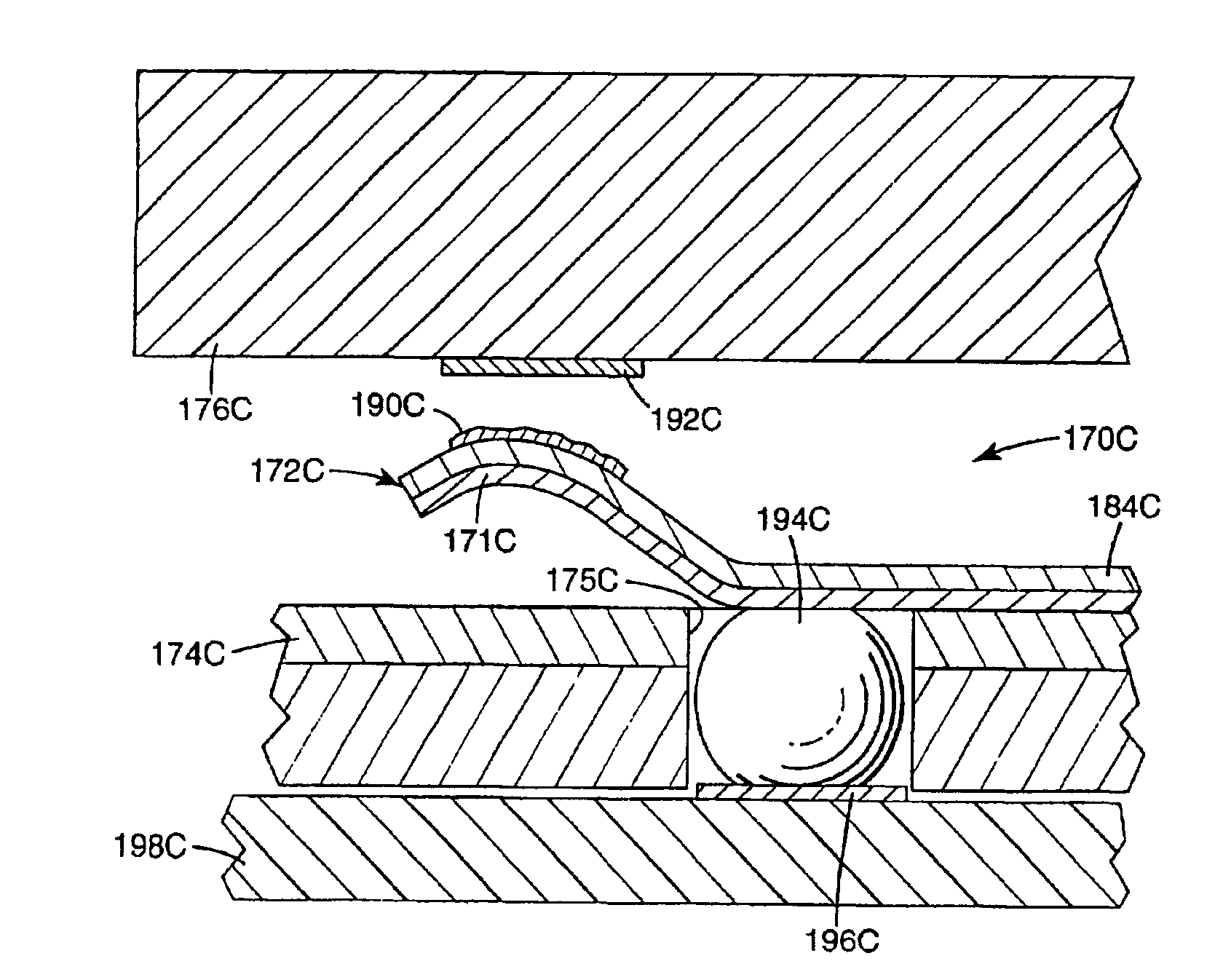

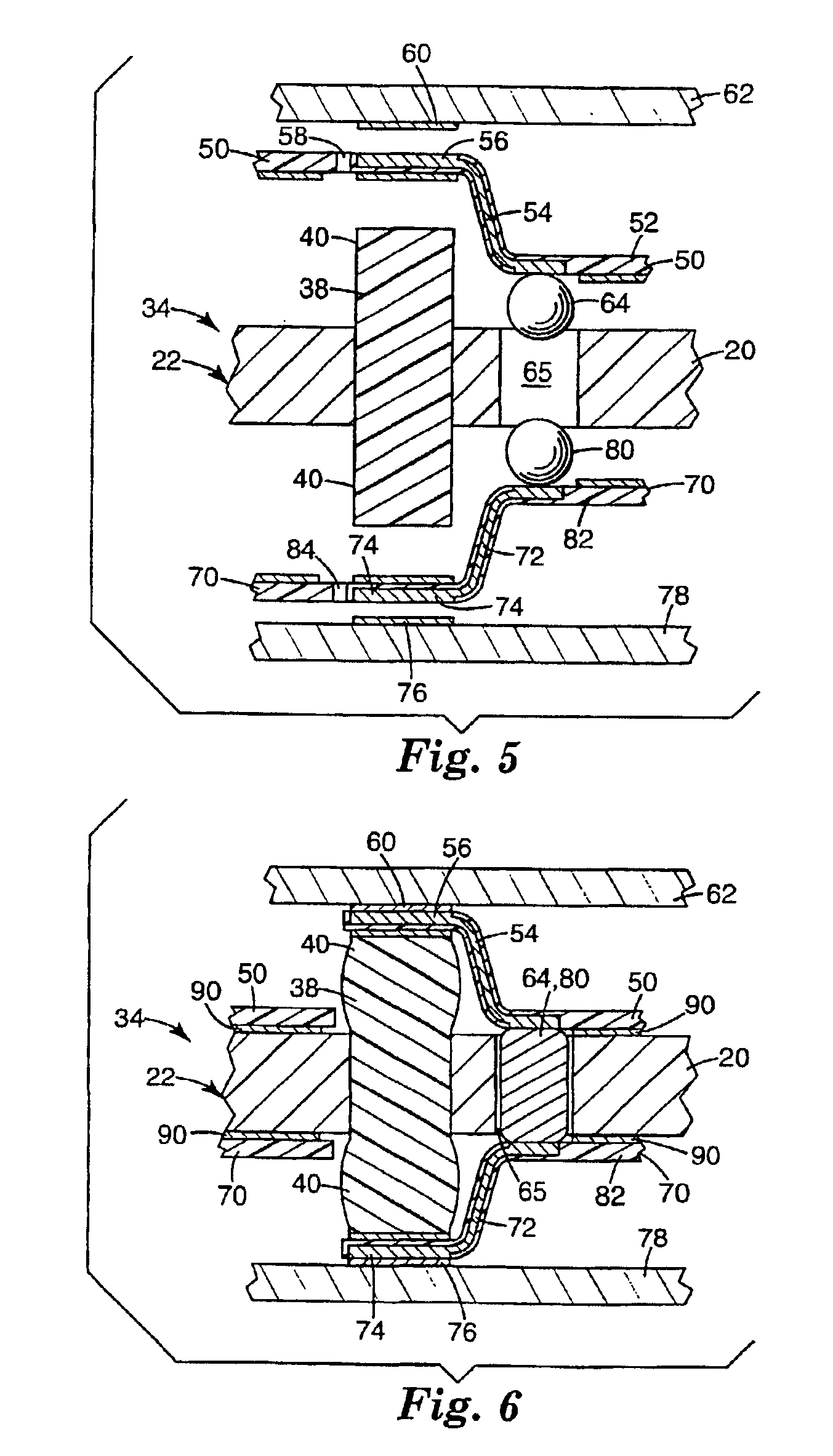

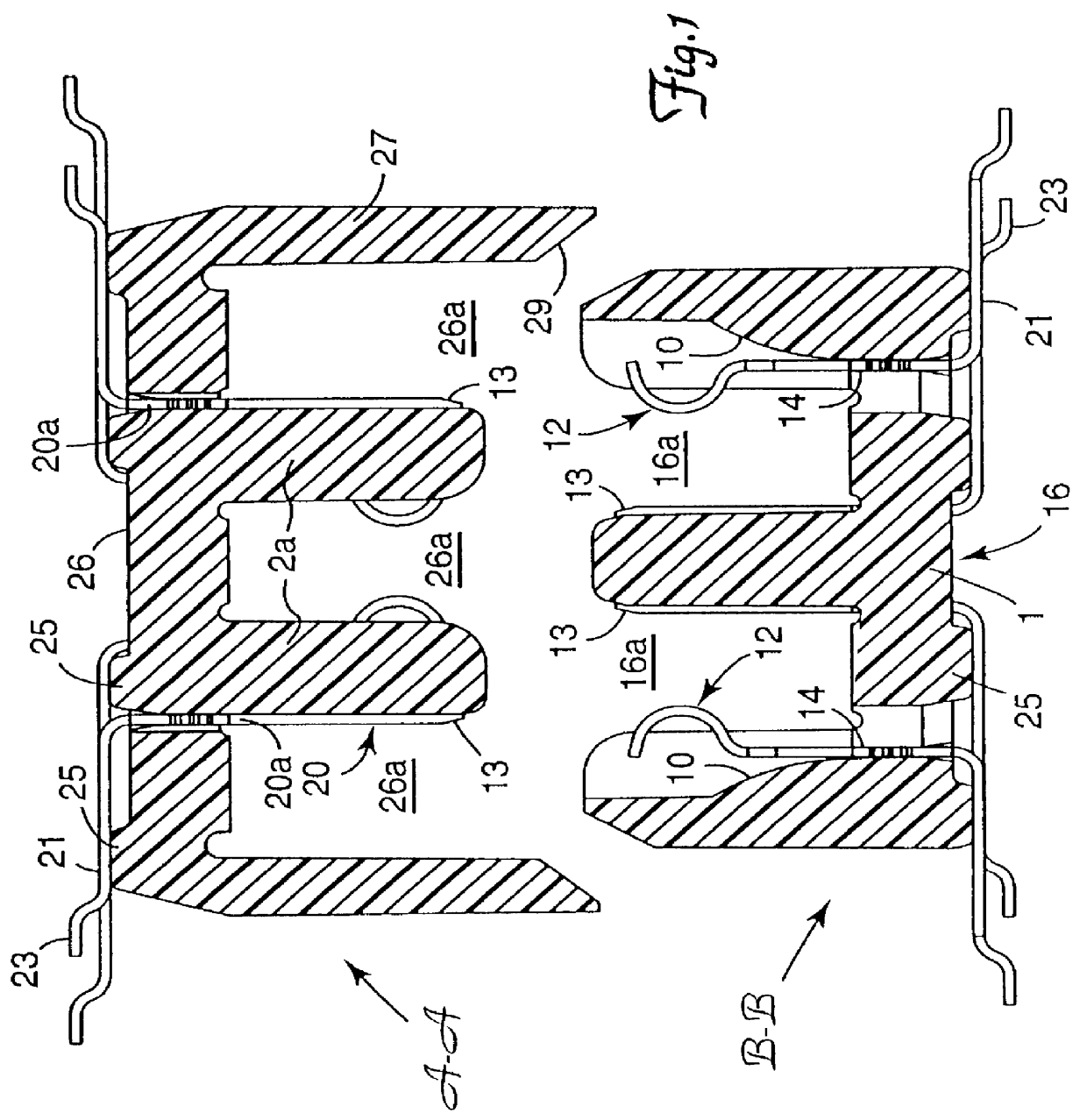

Plated terminations

InactiveUS6960366B2Improved termination featureEliminate and greatly simplifyResistor terminals/electrodesFinal product manufactureTermination problemEngineering

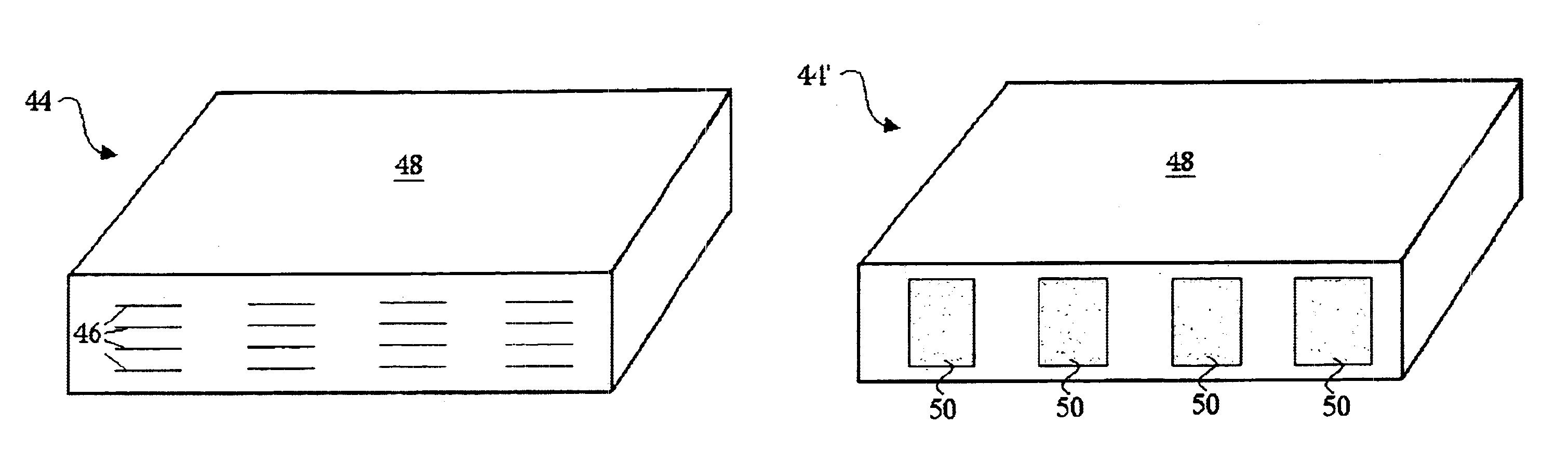

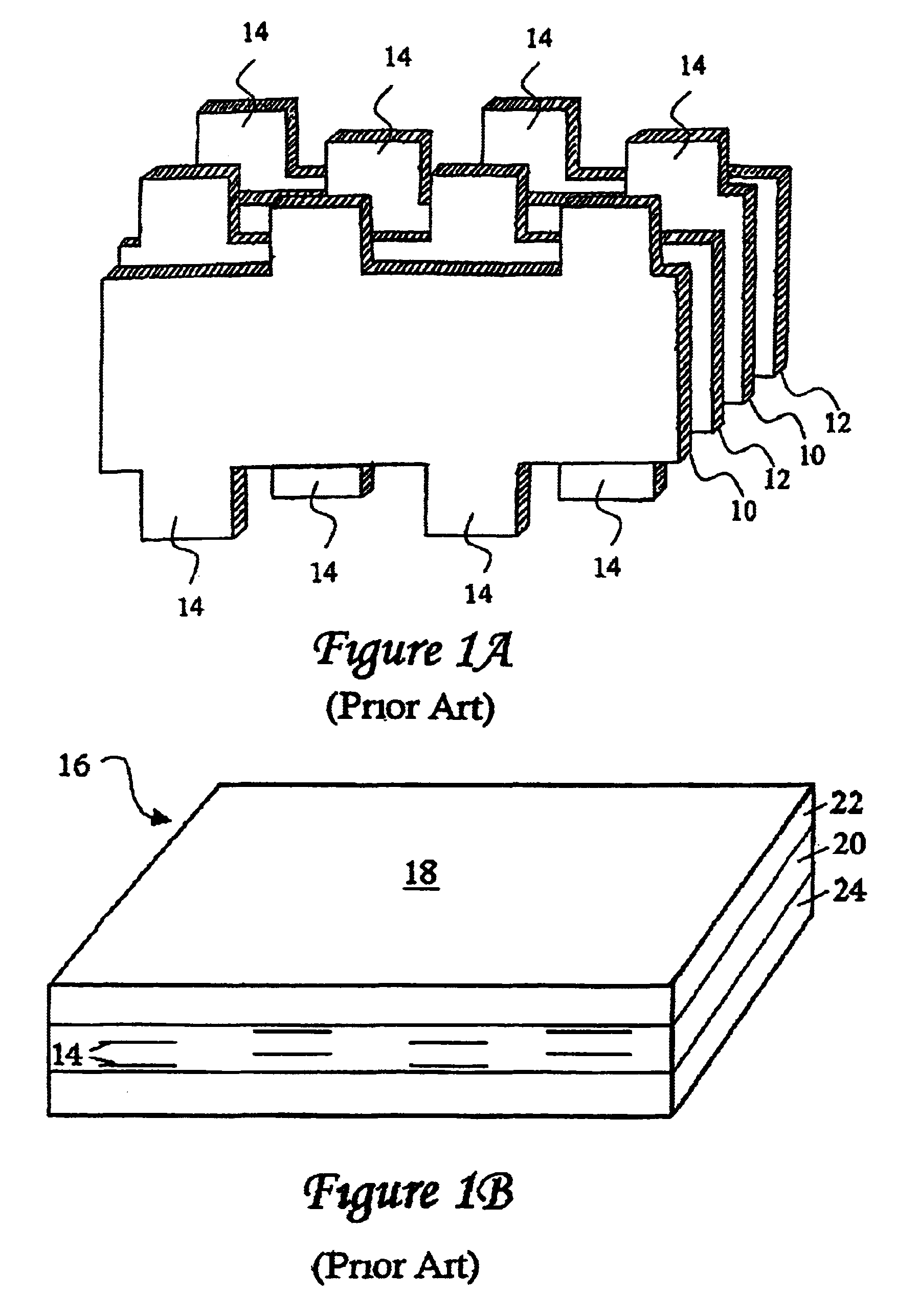

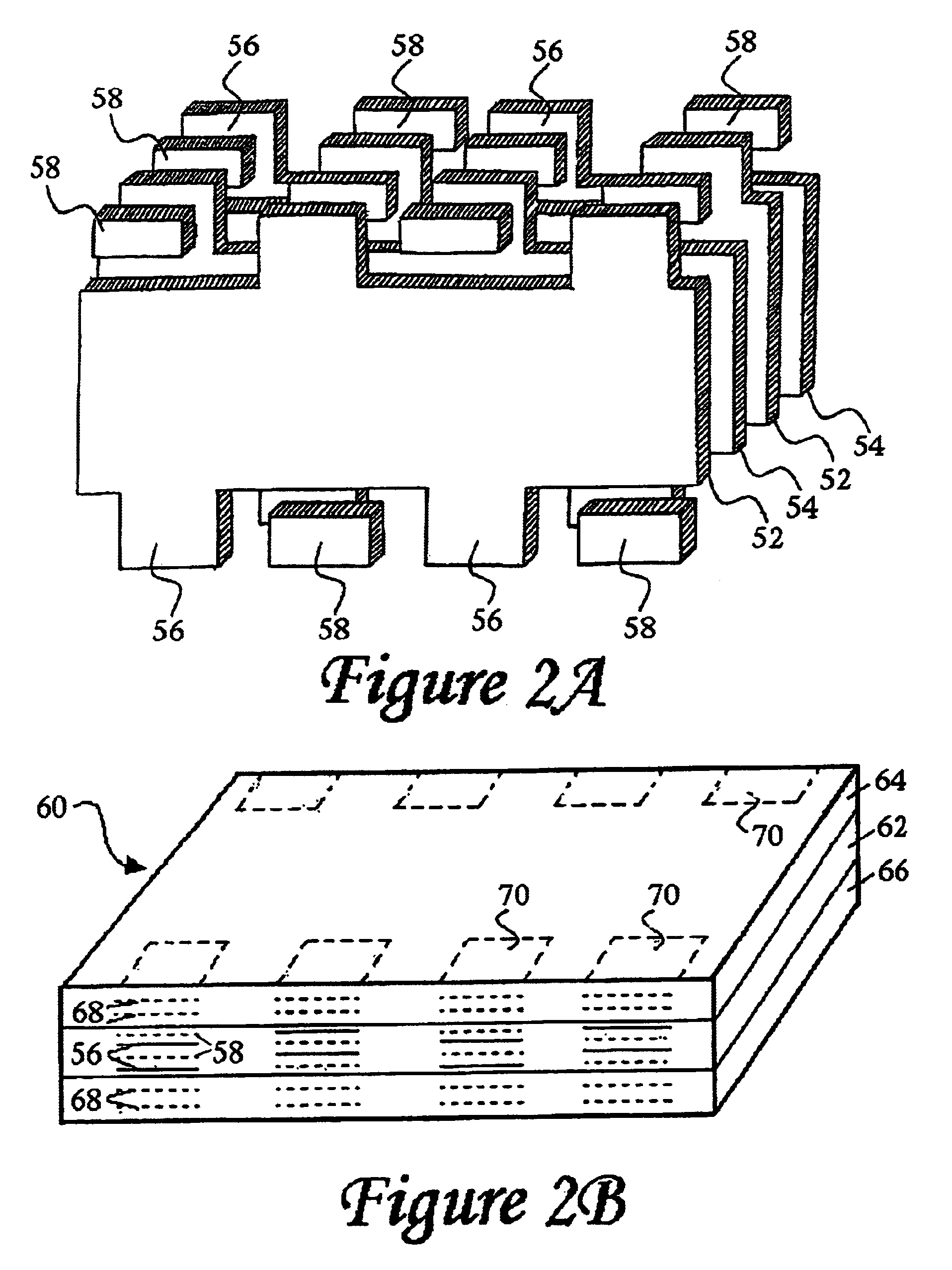

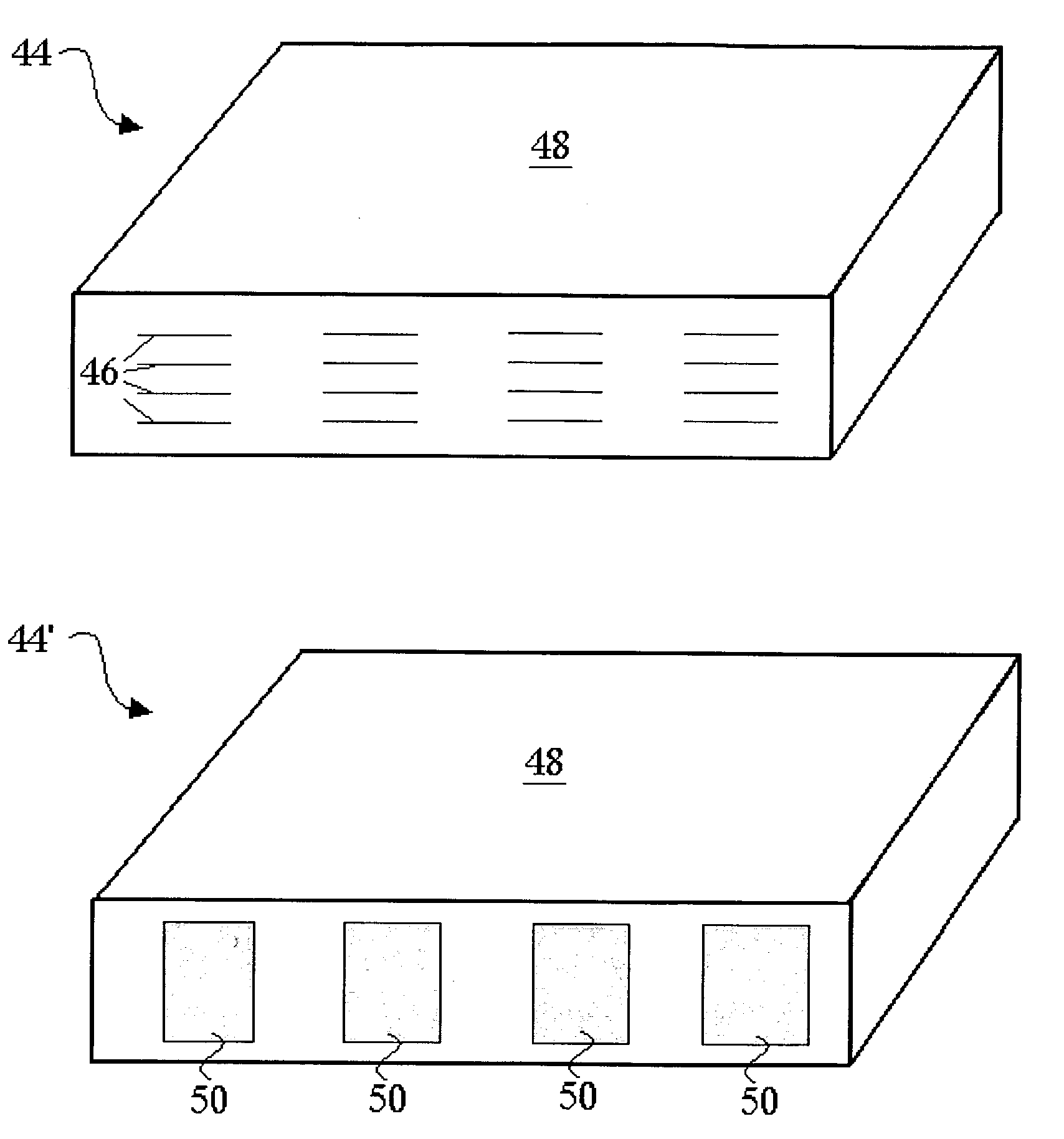

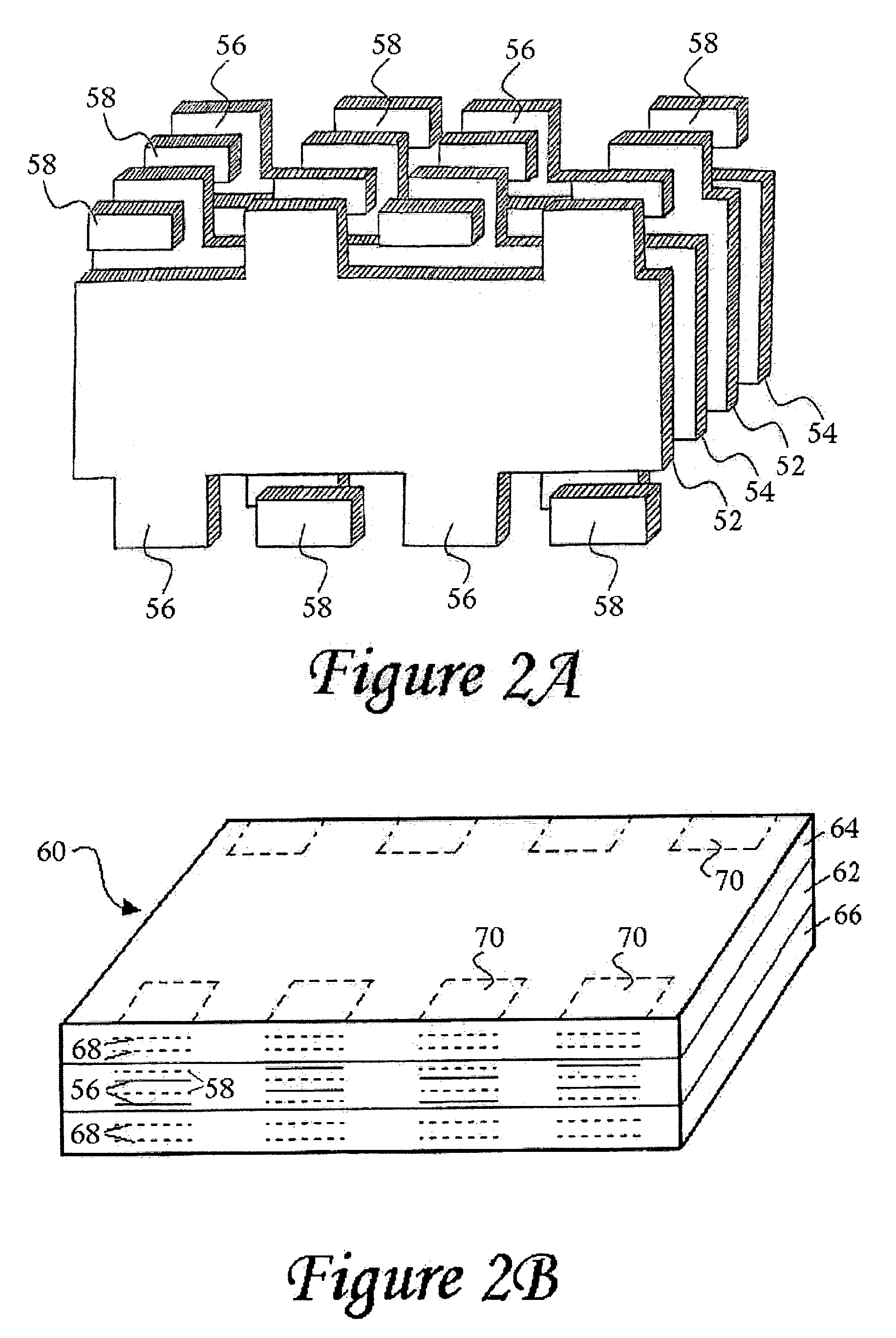

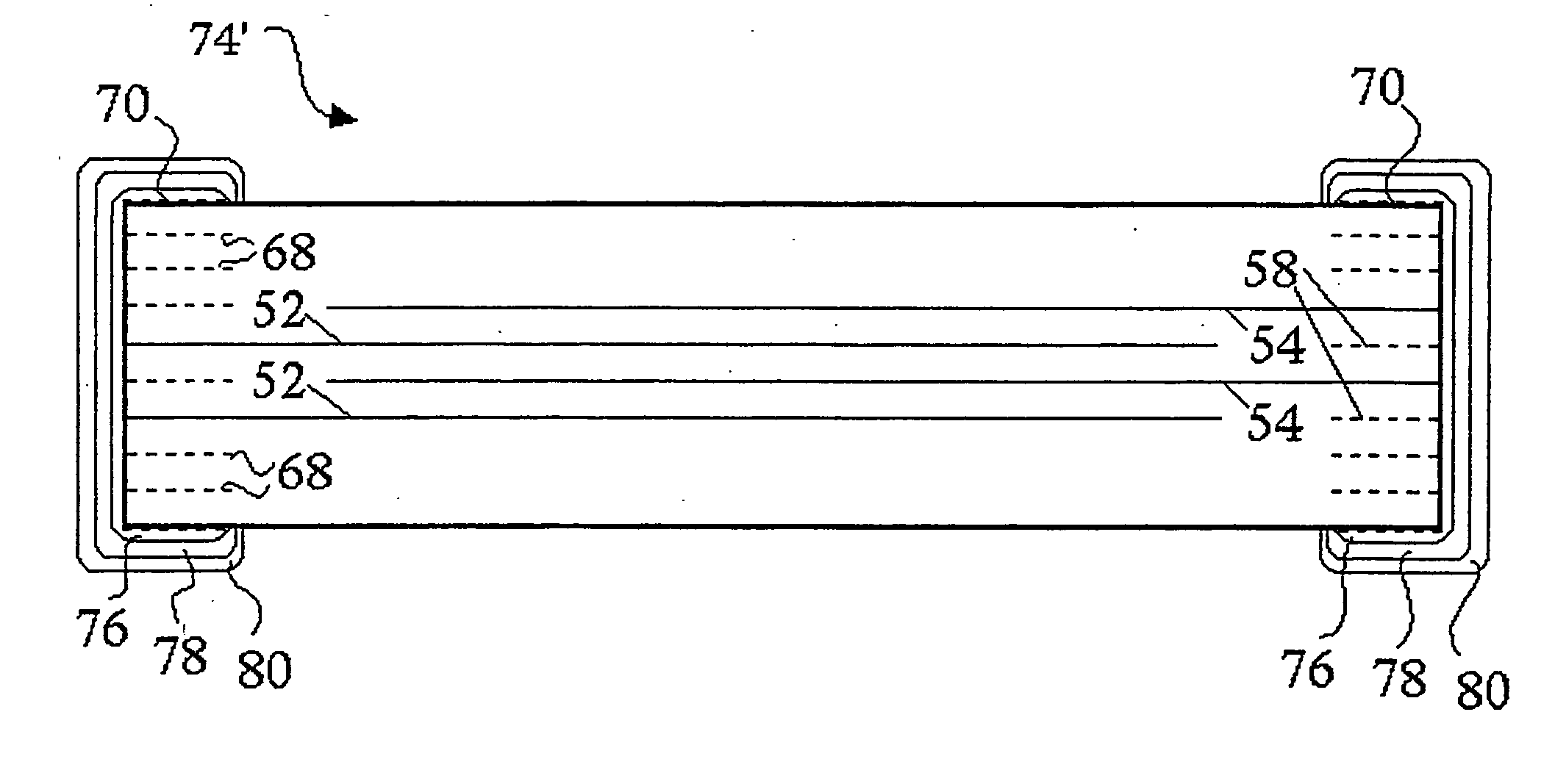

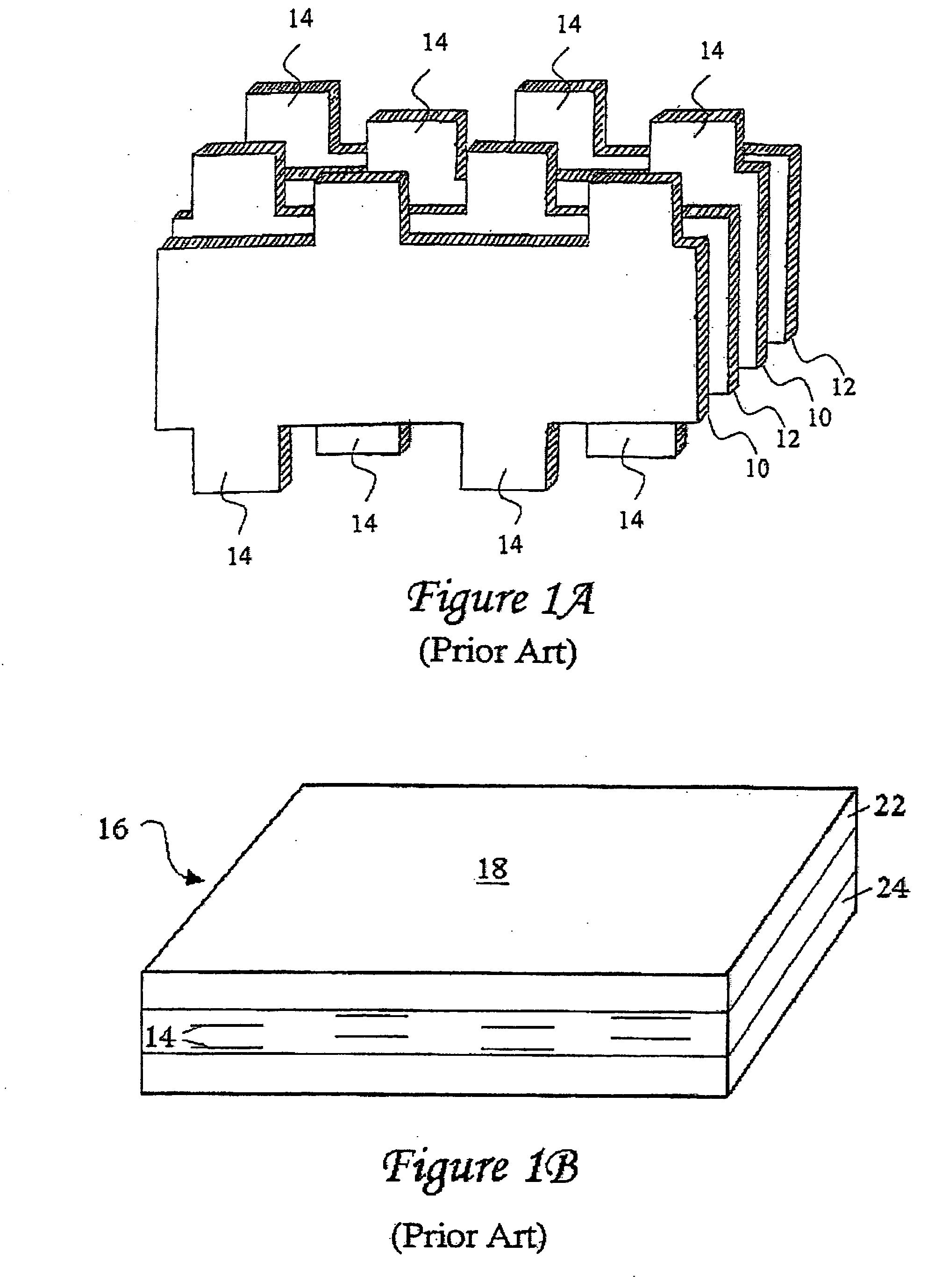

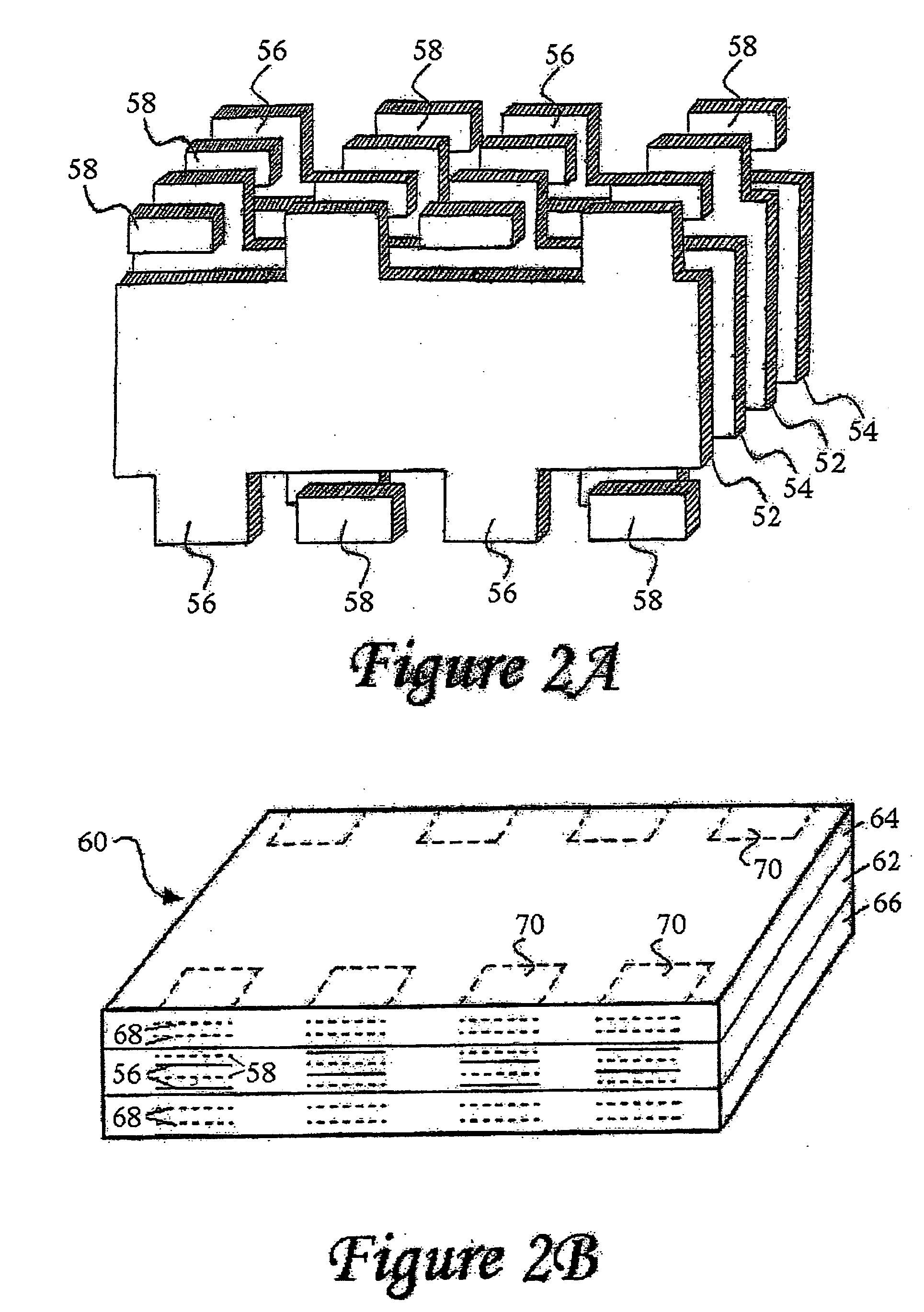

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on one or both of top and bottom surfaces of a monolithic structure can facilitate the formation of selective wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

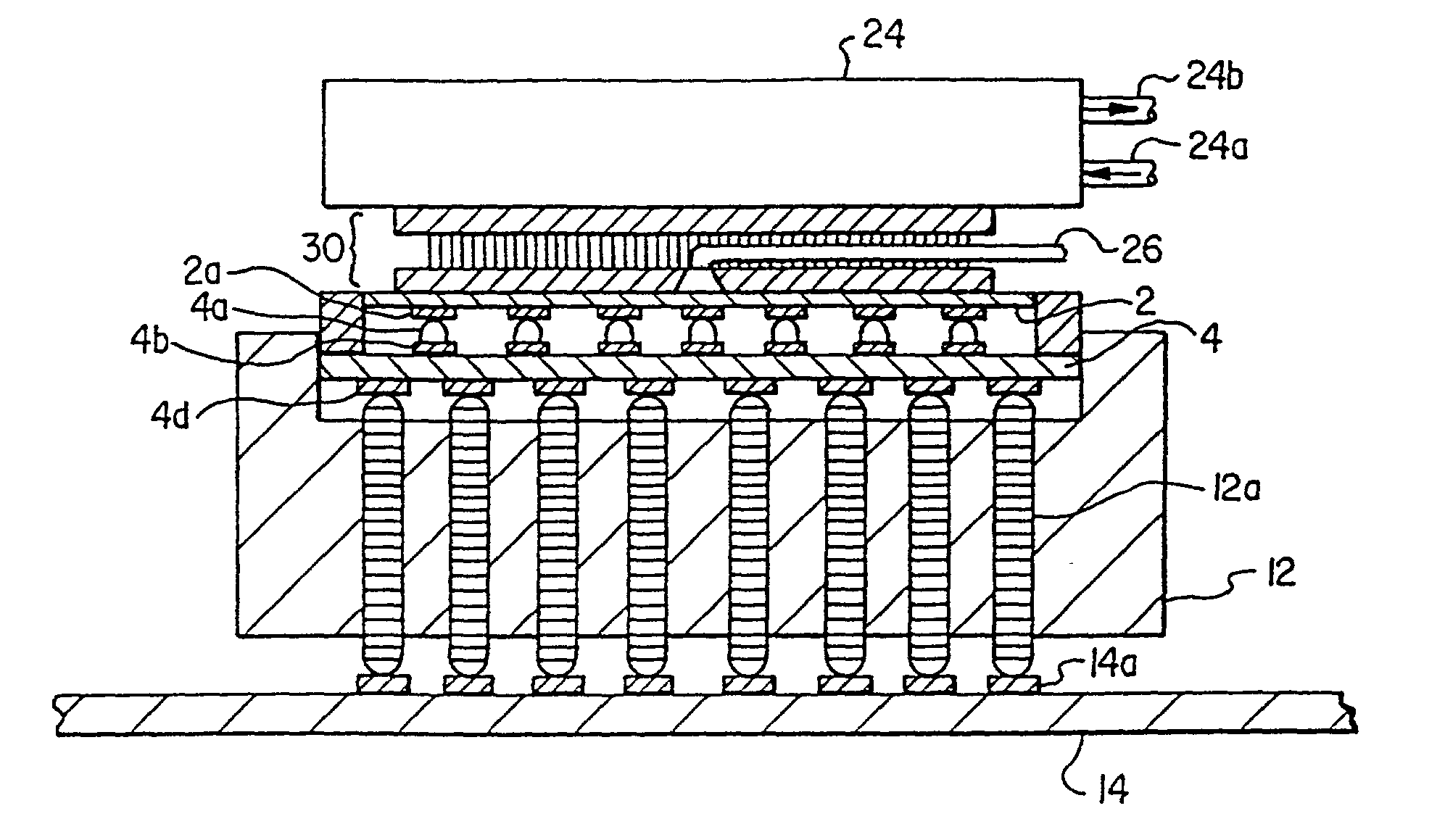

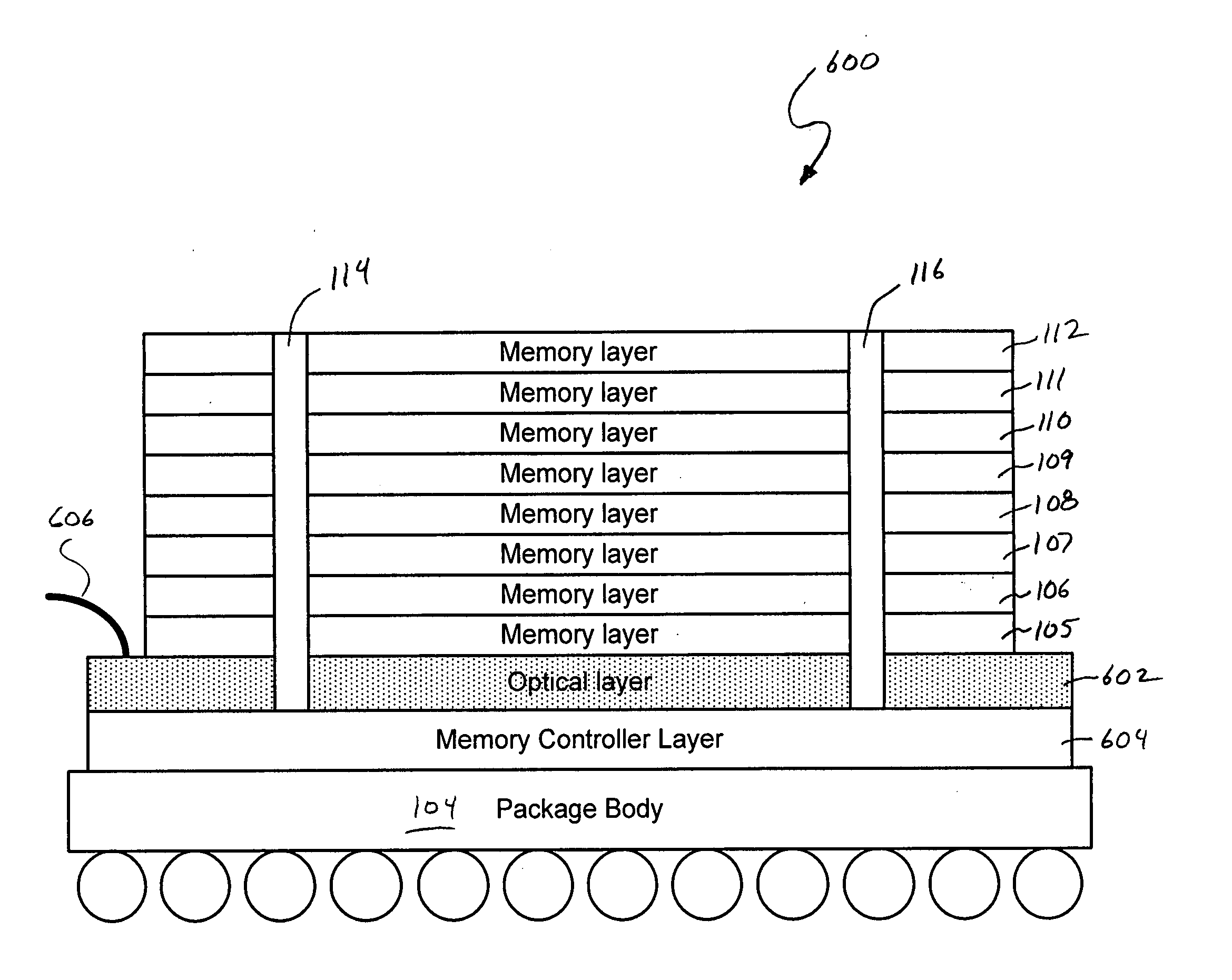

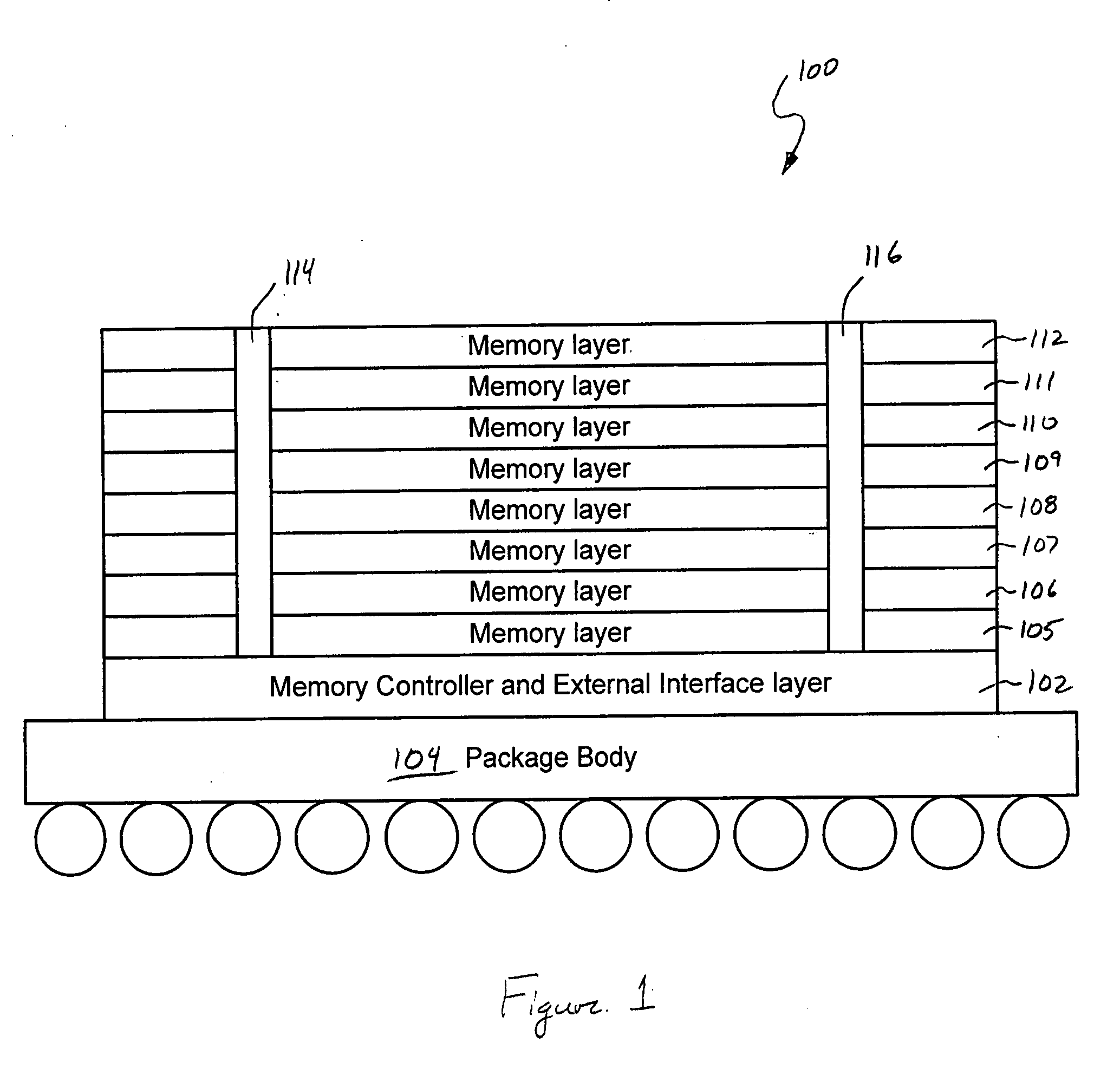

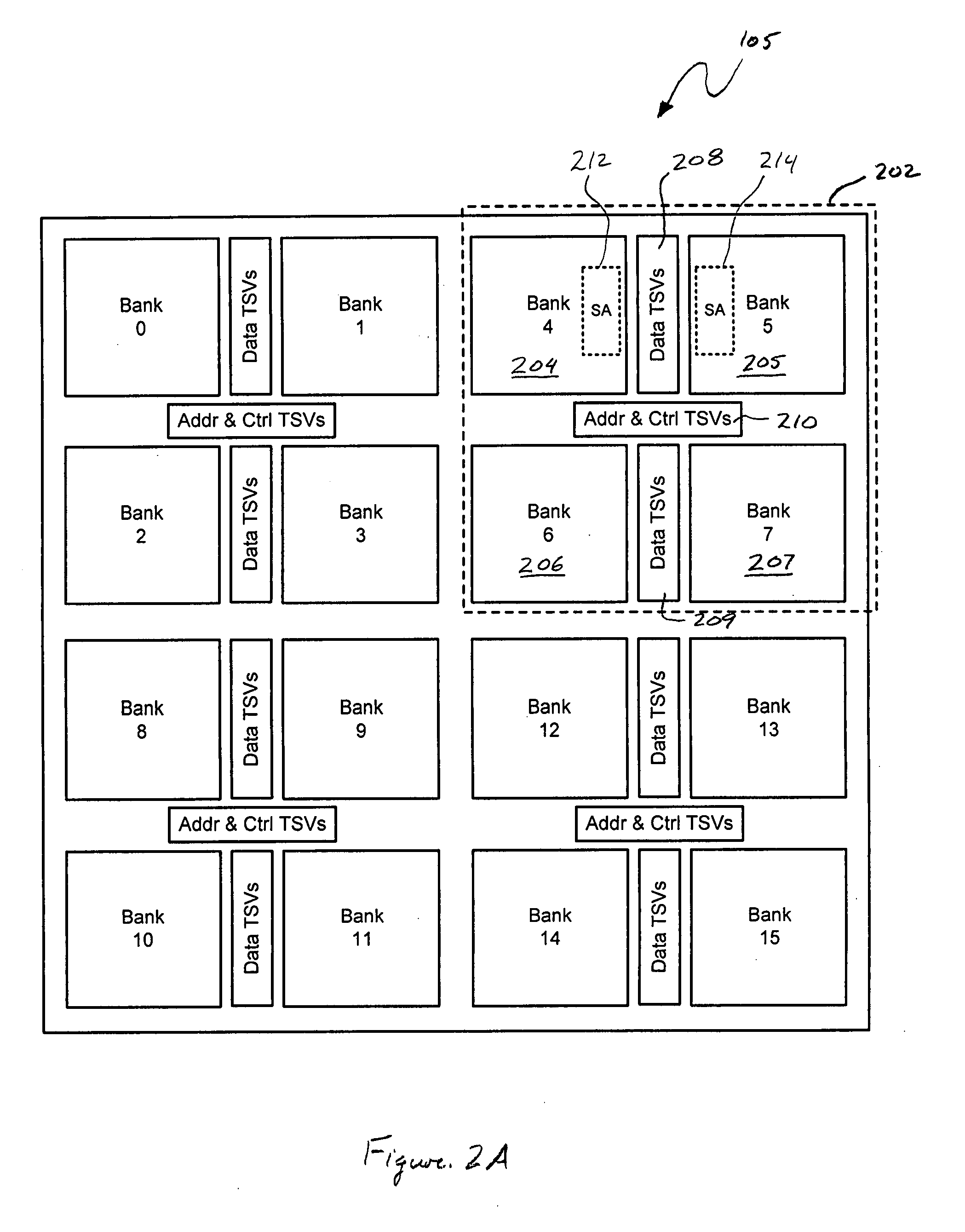

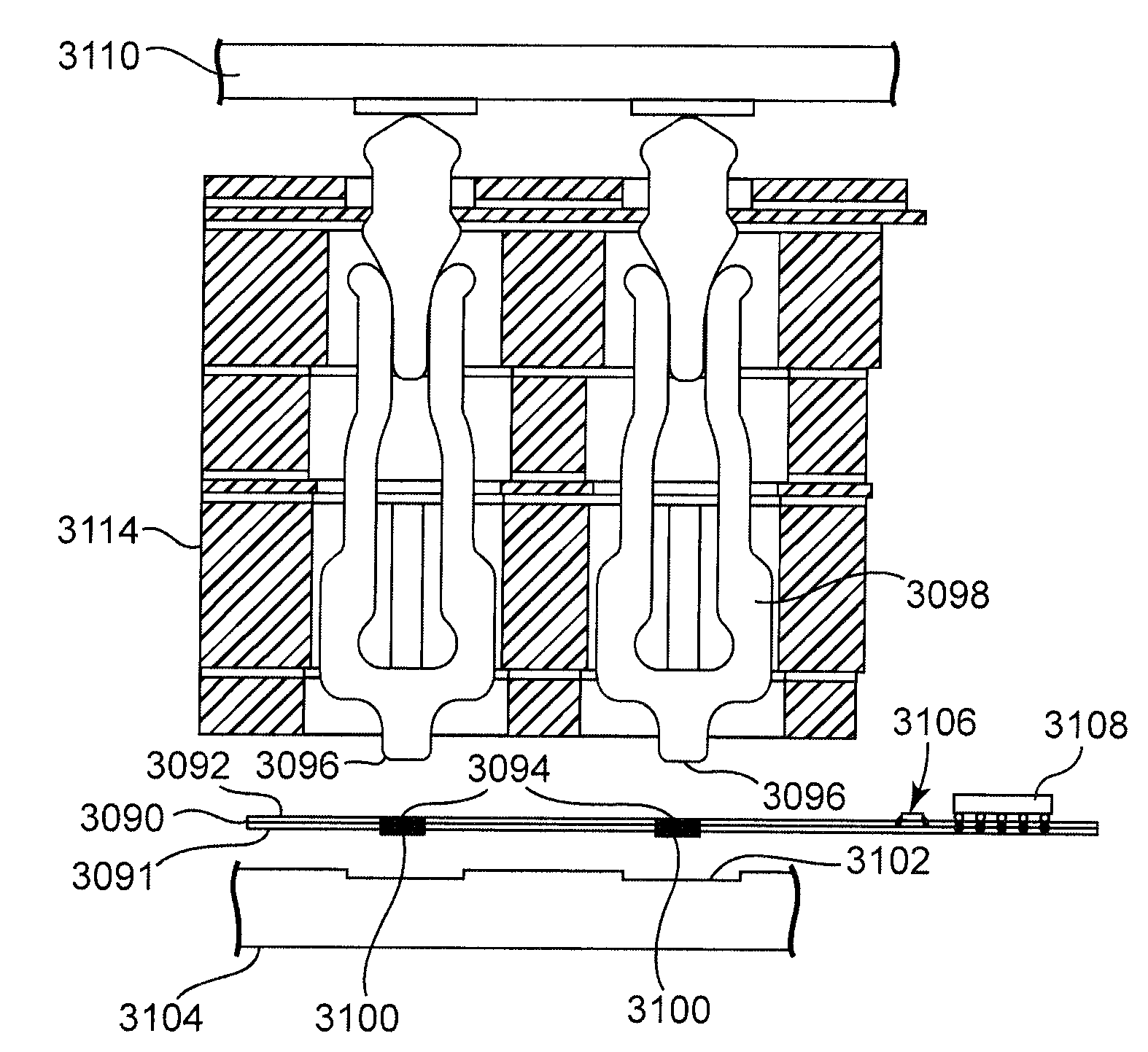

Three-dimensional memory module architectures

Various embodiments of the present invention are directed to stacked memory modules. In one embodiment of the present invention, a memory module comprises at least one memory-controller layer stacked with at least one memory layer. Fine pitched through vias (e.g., through silicon vias) extend approximately perpendicular to a surface of the at least one memory controller through the stack providing electronic communication between the at least one memory controller and the at least one memory layers. Additionally, the memory-controller layer includes at least one external interface configured to transmit data to and from the memory module. Furthermore, the memory module can include an optical layer. The optical layer can be included in the stack and has a bus waveguide to transmit data to and from the at least one memory controller. The external interface can be an optical external interface which interfaces with the optical layer.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Method for forming plated terminations

InactiveUS7152291B2Improved termination featureEliminate or greatly simplify thick-film stripesElectrolytic capacitorsSemiconductor/solid-state device detailsTermination problemEngineering

Improved method steps for terminating multilayer electronic components are disclosed. Monolithic components are formed with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. Electrode and dielectric layers are provided in an interleaved arrangement and selected portions of the electrode layers are exposed. Electrically isolated anchor tabs may optionally be provided and exposed in some embodiments. Termination material is then plated to the exposed portions of the electrode layers until exposed portions of selected such portions thereof are connected. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

Plated terminations

InactiveUS20050046536A1Improved termination featureEliminate and greatly simplifyWave amplification devicesResistor terminals/electrodesTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on top and bottom sides of a monolithic structure can facilitate the formation of wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

Plated terminations

InactiveUS7154374B2Improved termination featureEliminate or greatly simplify thick-film stripesResistor terminals/electrodesSemiconductor/solid-state device detailsTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on top and bottom sides of a monolithic structure can facilitate the formation of wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

Plated terminations

InactiveUS6972942B2Improved termination featureEliminate or greatly simplify thick-film stripesFixed capacitor dielectricSolid-state devicesTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on one or both of top and bottom surfaces of a monolithic structure can facilitate the formation of selective wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

Component formation via plating technology

InactiveUS6982863B2Improved termination featureEliminate or greatly simplify thick-film stripesStacked capacitorsWound capacitorsTermination problemSolder ball

Improved terminations, interconnection techniques, and inductive element features for multilayer electronic components are formed in accordance with disclosed plating techniques. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such plated termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed varying width internal electrode tabs and additional anchor tab portions. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. The combination of electrode tabs and anchor tabs may be exposed in respective arrangements to form generally discoidal portions of plated material. Such plated material may ultimately form generally round portions of ball limiting metallurgy (BLM) to which solder balls may be reflowed. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and materials may be employed in the formation of the subject self-determining plated terminations and inductive components.

Owner:KYOCERA AVX COMPONENTS CORP

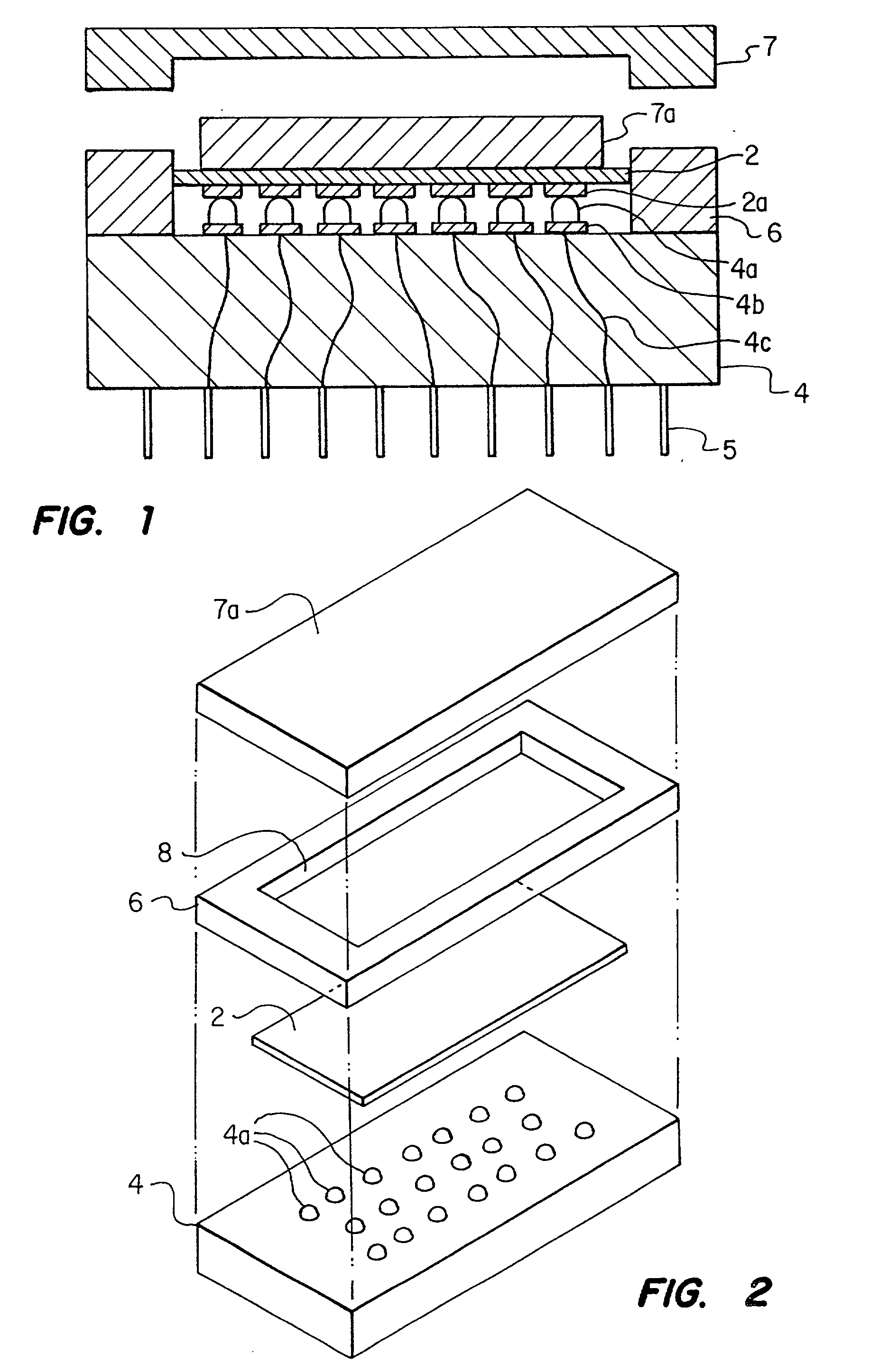

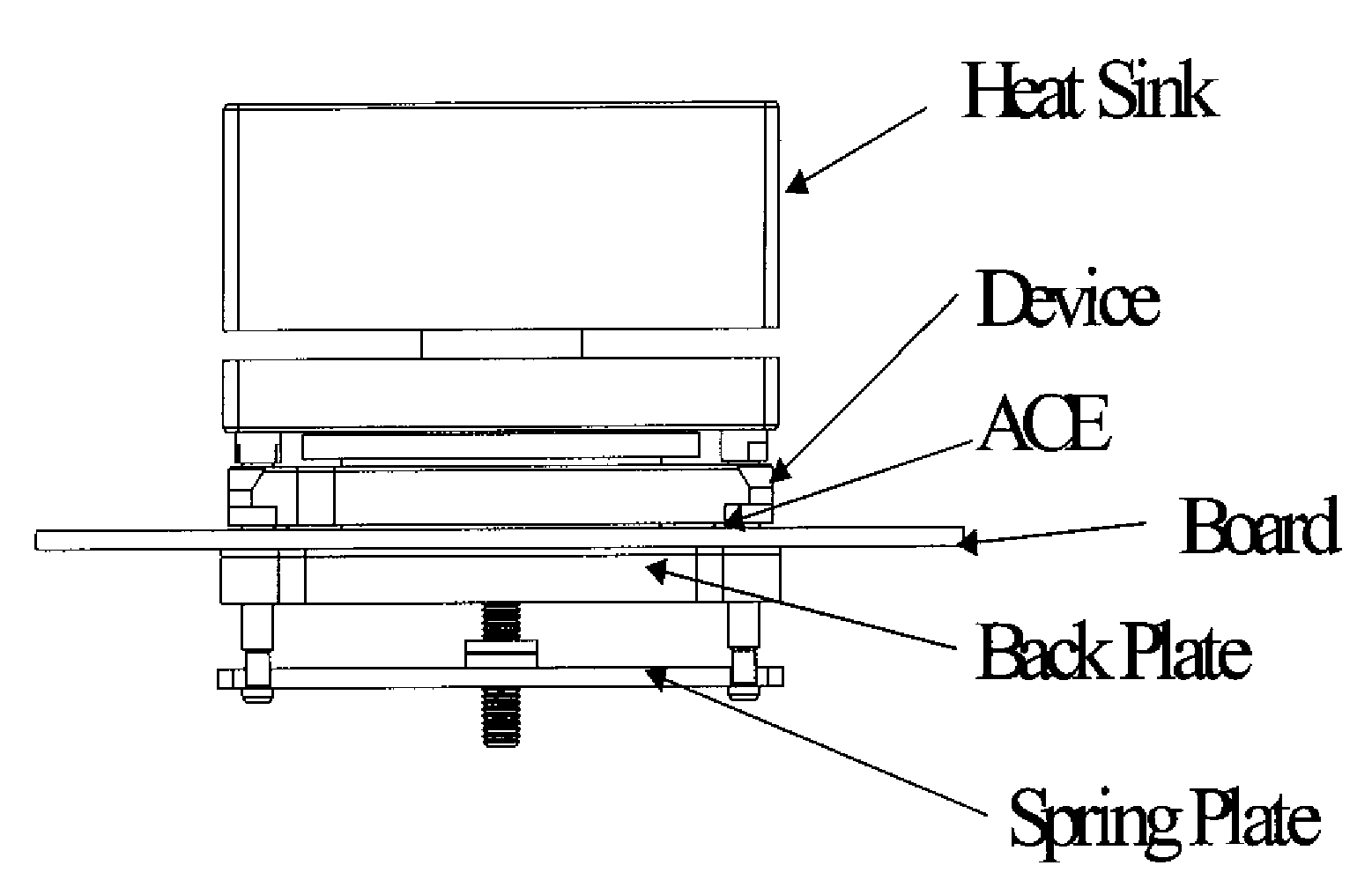

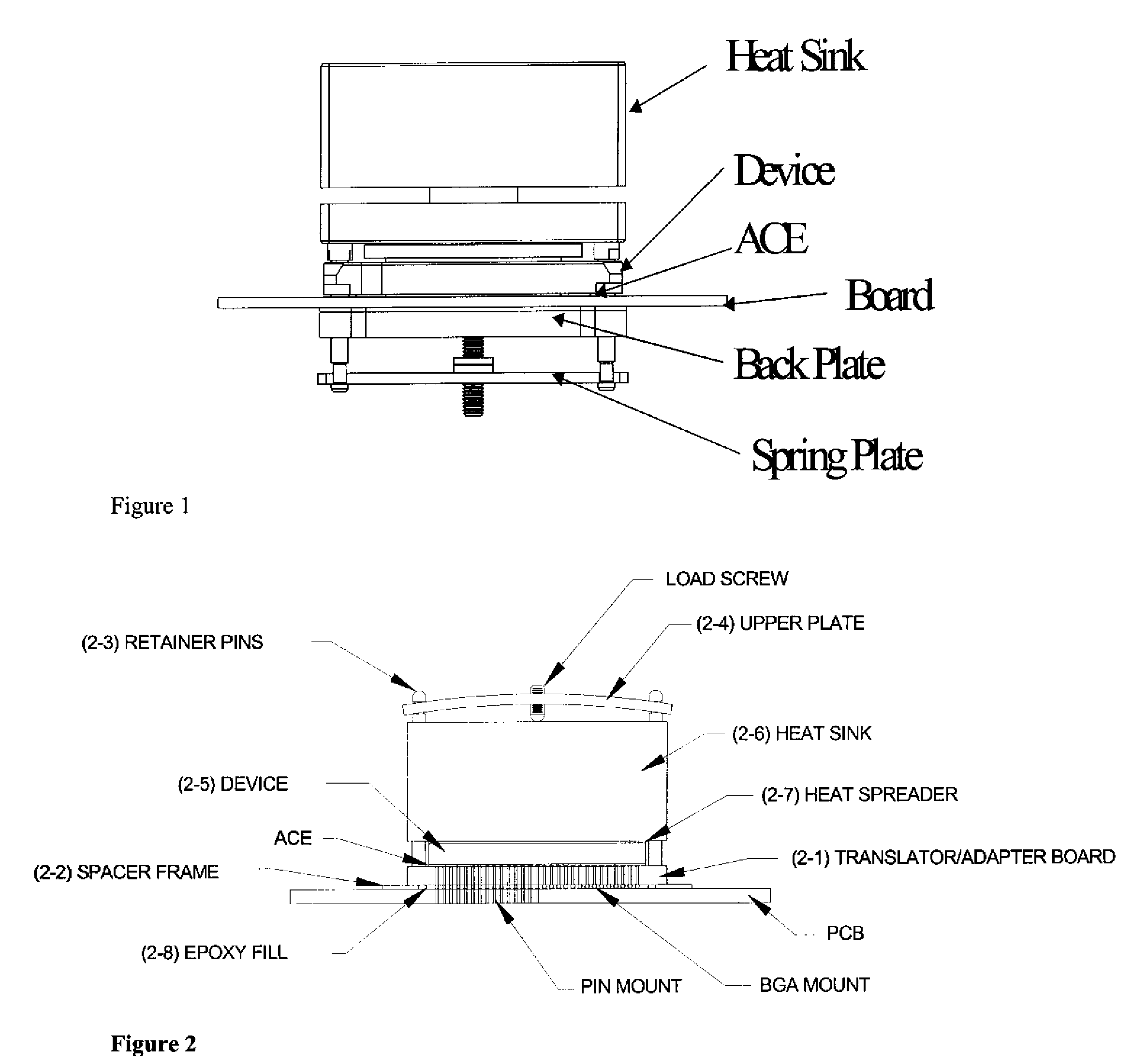

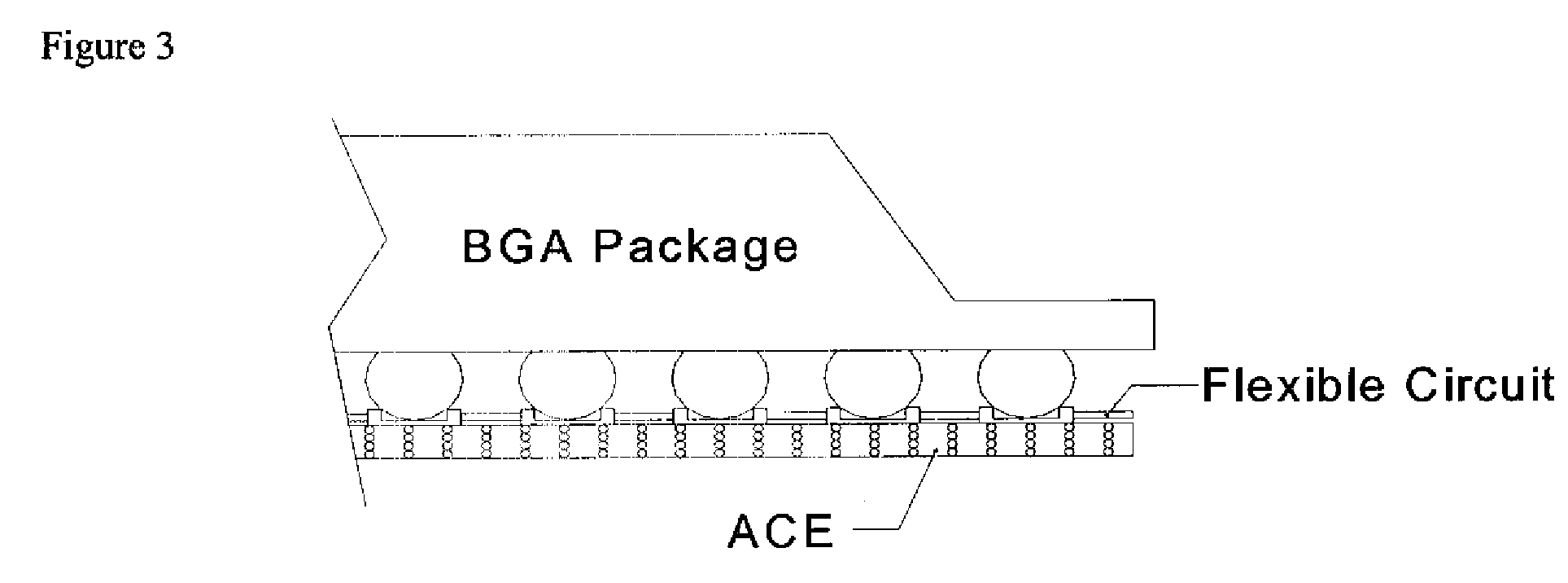

Separable electrical interconnect with anisotropic conductive elastomer for translating footprint

InactiveUS7249954B2Increase stiffnessPrinted circuit aspectsCoupling device detailsElastomerEngineering

A separable electrical connector for electrically interconnecting an electrical device to a substrate. In one embodiment, the connector includes an adapter board electrically connected to the substrate, the adapter board having electrical contacts on both sides, and a layer of ACE between the electrical device and the adapter board. A mechanical structure is used to apply a compressive force on the ACE through the adapter board and the electrical device. In another embodiment, the connector includes a translator board having electrical contacts on both sides and electrical circuits within to expand the footprint of the fine pitch electrical device to the coarser pitch of the substrate. The connector further includes a layer of ACE between the translator board and the substrate.

Owner:PARICON TECH

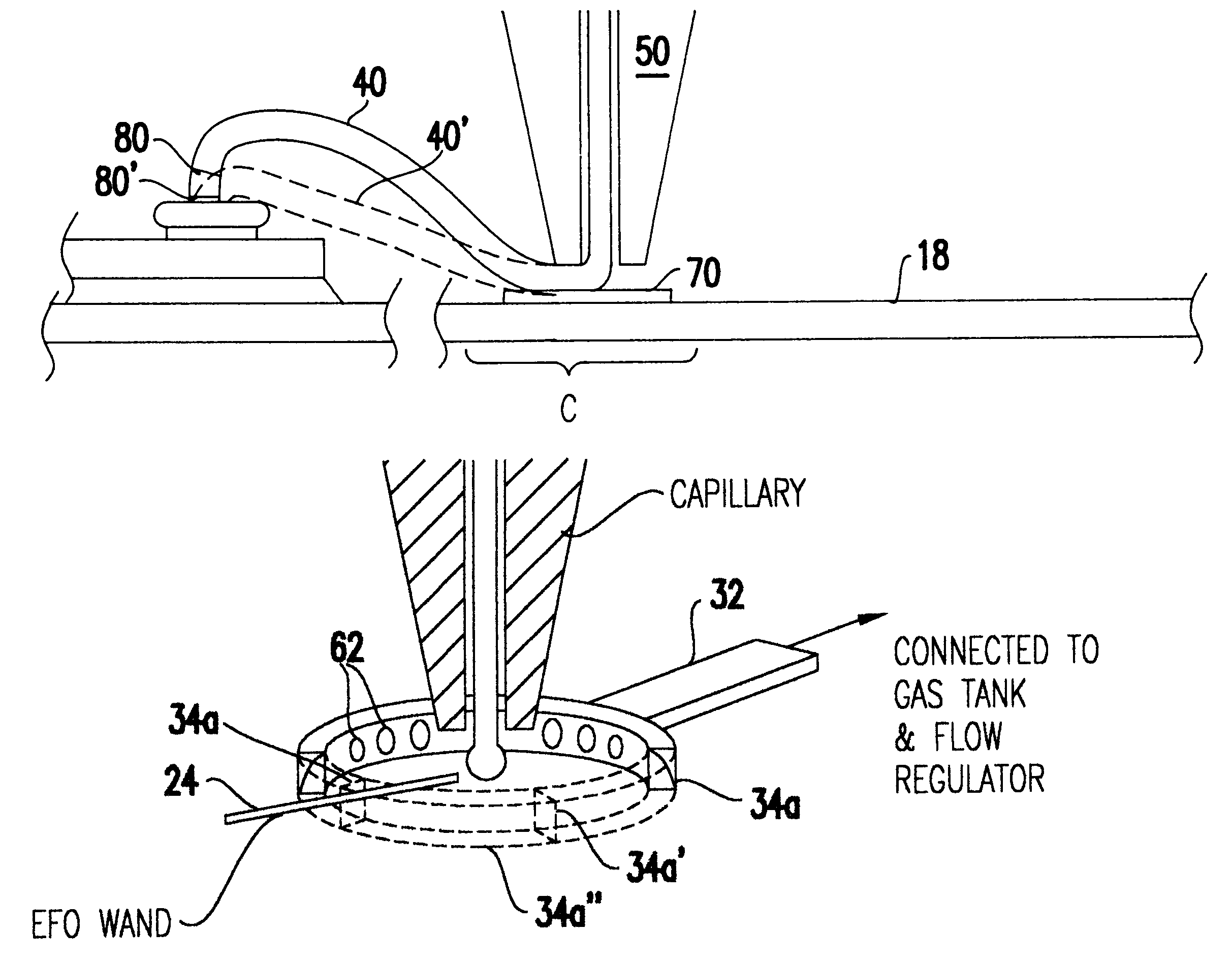

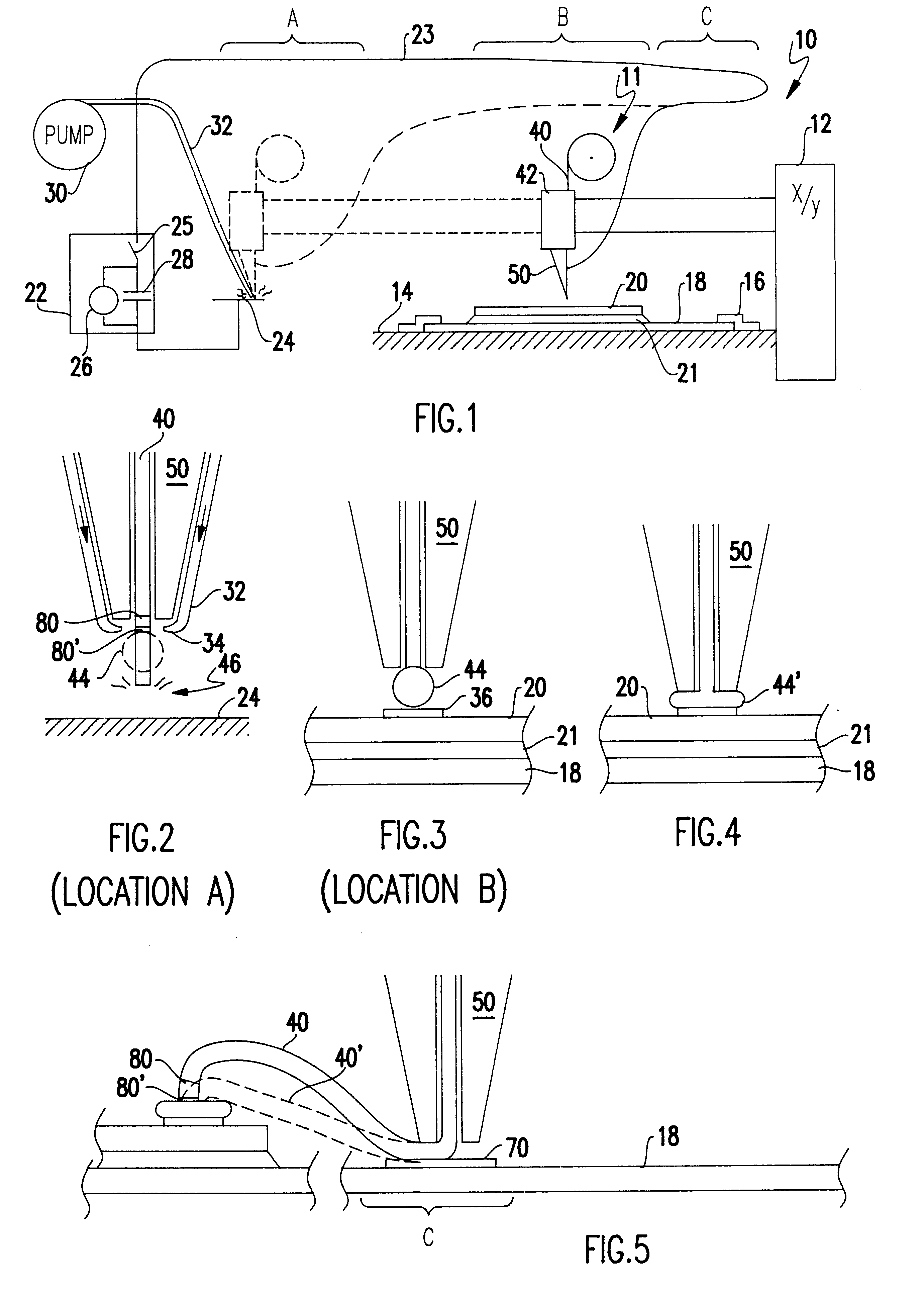

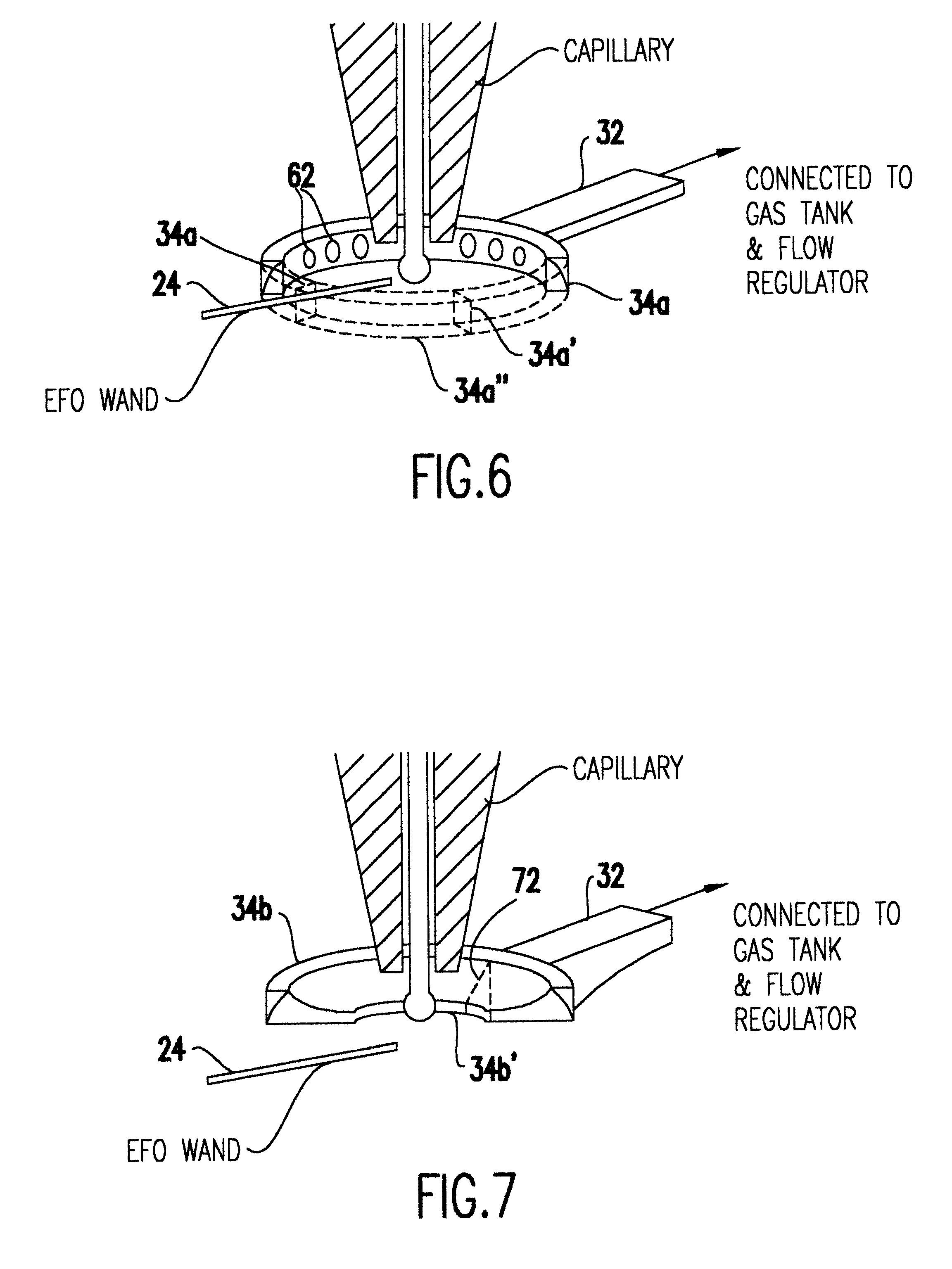

Control of size and heat affected zone for fine pitch wire bonding

InactiveUS6180891B1Electrically conductive connectionsSemiconductor/solid-state device detailsHeat-affected zoneLead bonding

The amount of melting of the bonding wire is closely regulated, and reduction of size and improvement of uniformity of the free air ball is obtained for ball bonding at pitches of less than ninety mils even when bonding wire of reduced diameter is employed. Quenching of the bonding wire adjacent to the free air ball also limits the temperature rise in the bonding wire and the extent of a heat affected zone having less tensile strength and stiffness to less than one micron and with reduced grain enlargement. The present invention provides such a bond for electronic packaging of increased reliability, potential functionality, increased manufacturing yield and reduced process complexity.

Owner:IBM CORP

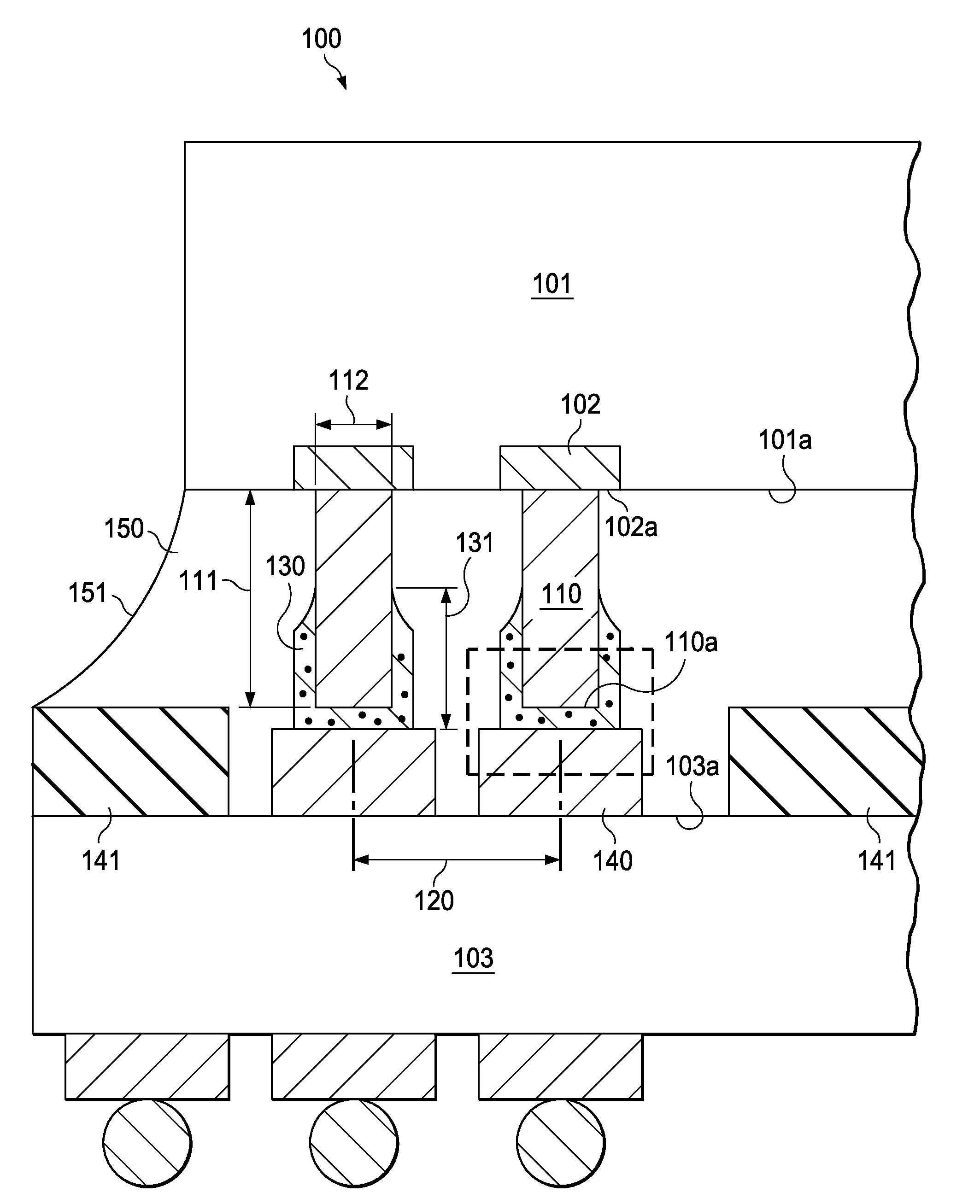

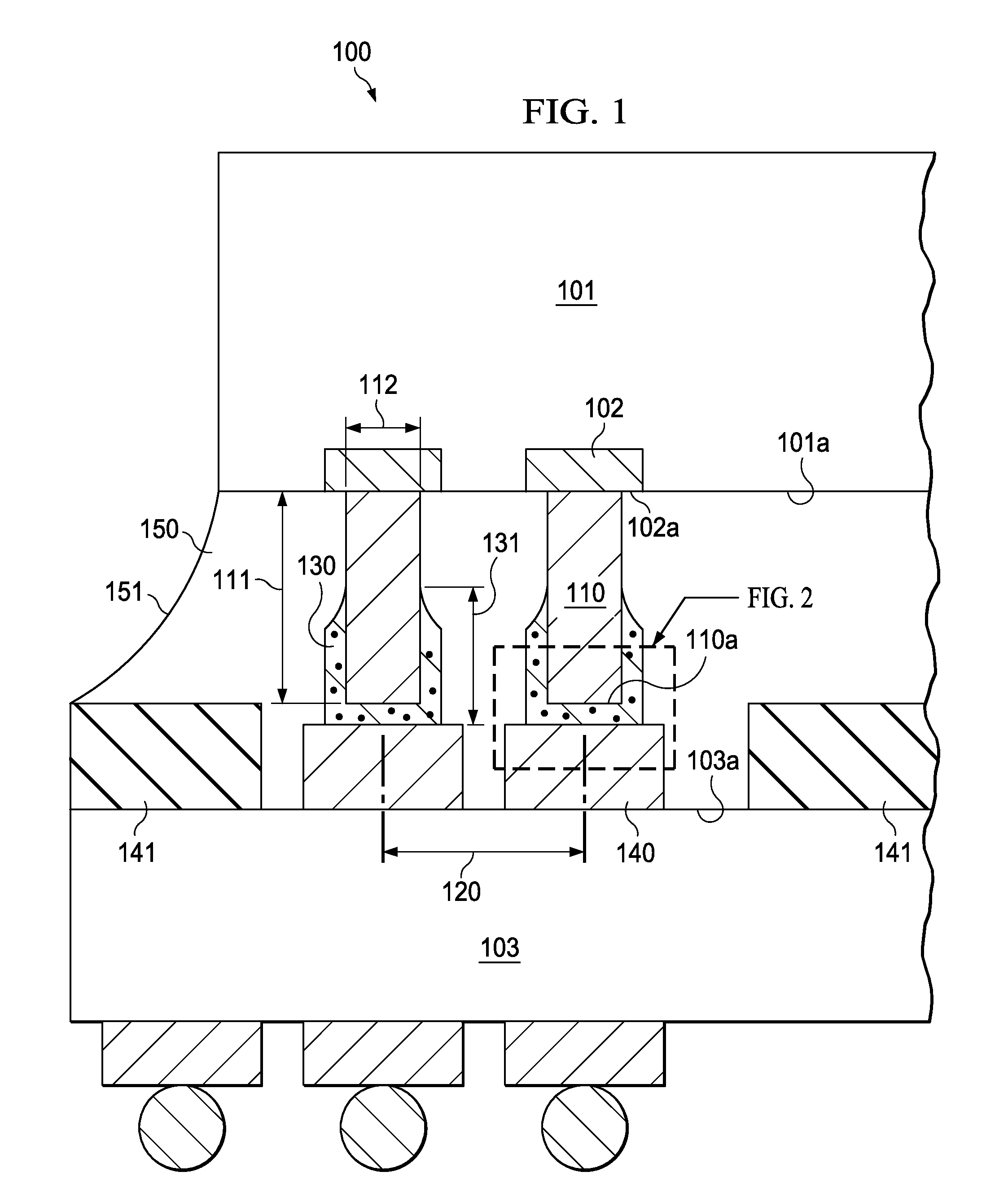

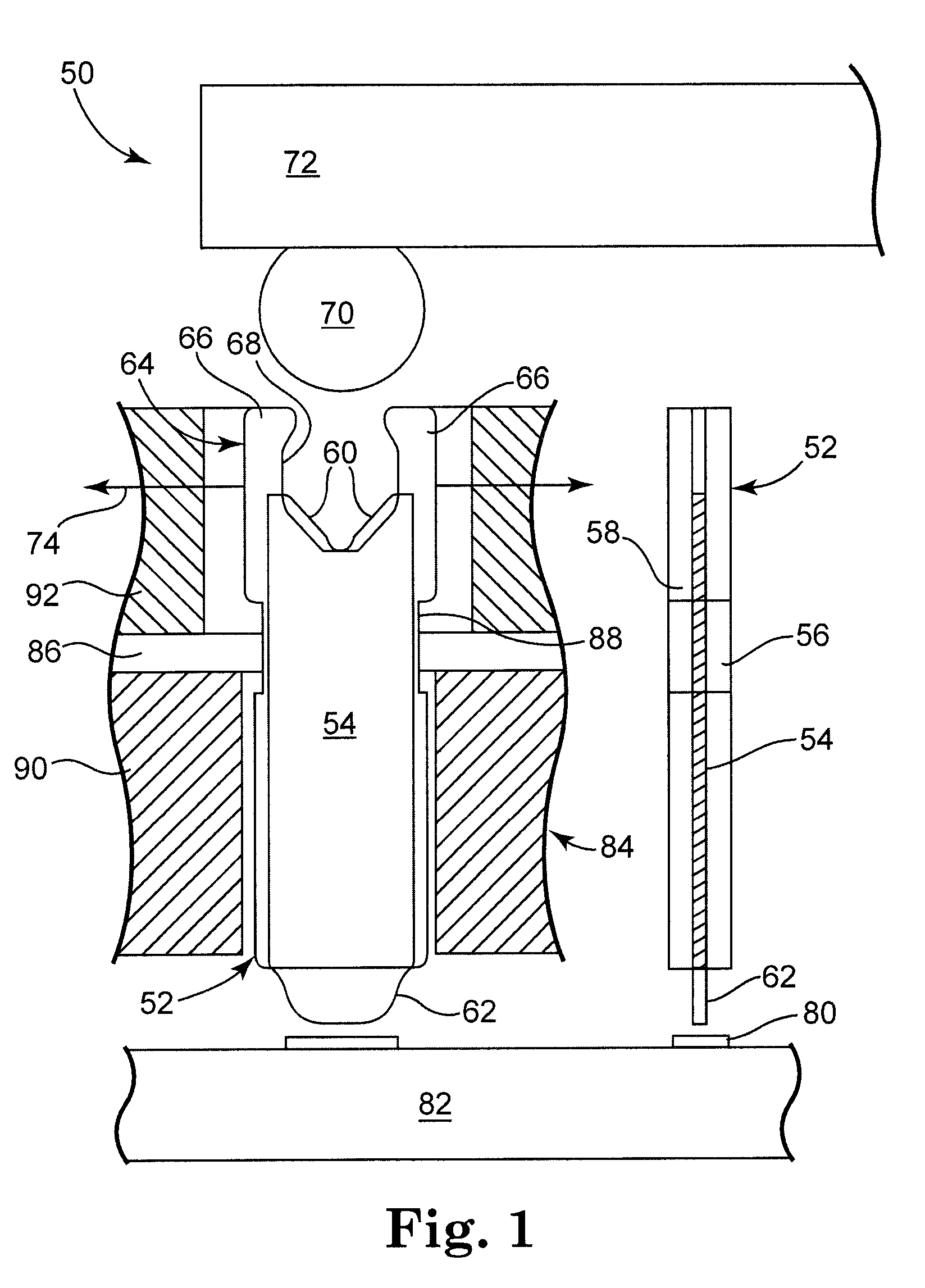

Method for low stress flip-chip assembly of fine-pitch semiconductor devices

ActiveUS7898083B2Short turnaround timeReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesMatrix embeddingFine pitch

A device including a first body (101) with terminals (102) on a surface (101a), each terminal having a metallic connector (110), which is shaped as a column substantially perpendicular to the surface. Preferably, the connectors have an aspect ratio of height to diameter of 2 to 1 or greater, and a fine pitch center-to-center. The connector end (110a) remote from the terminal is covered by a film (130) of a sintered paste including a metallic matrix embedded in a first polymeric compound. Further a second body (103) having metallic pads (140) facing the respective terminals (102). Each connector film (130) is in contact with the respective pad (140), whereby the first body (101) is spaced from the second body (103) with the connector columns (110) as standoff. A second polymeric compound (150) is filling the space of the standoff.

Owner:TEXAS INSTR INC

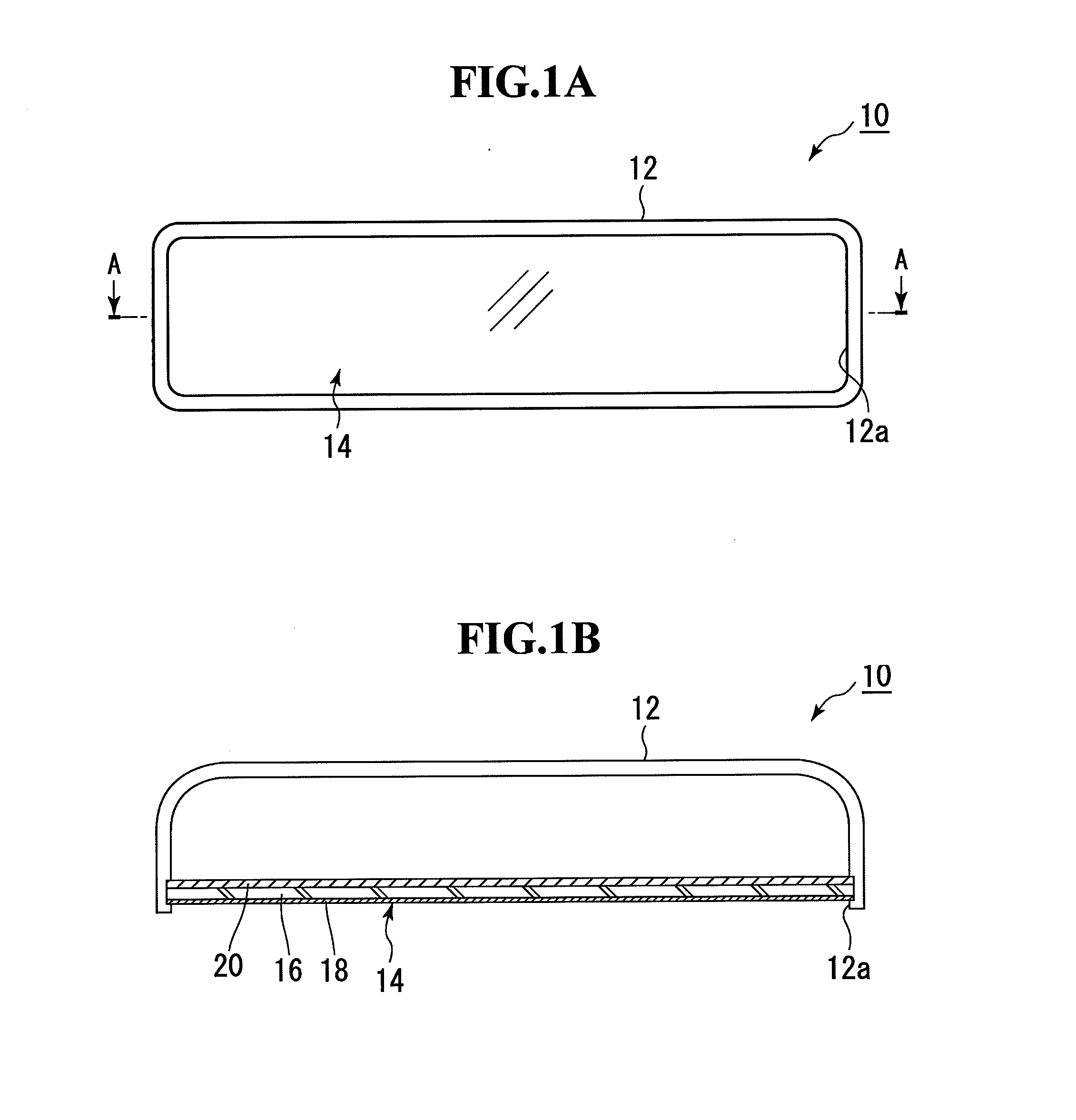

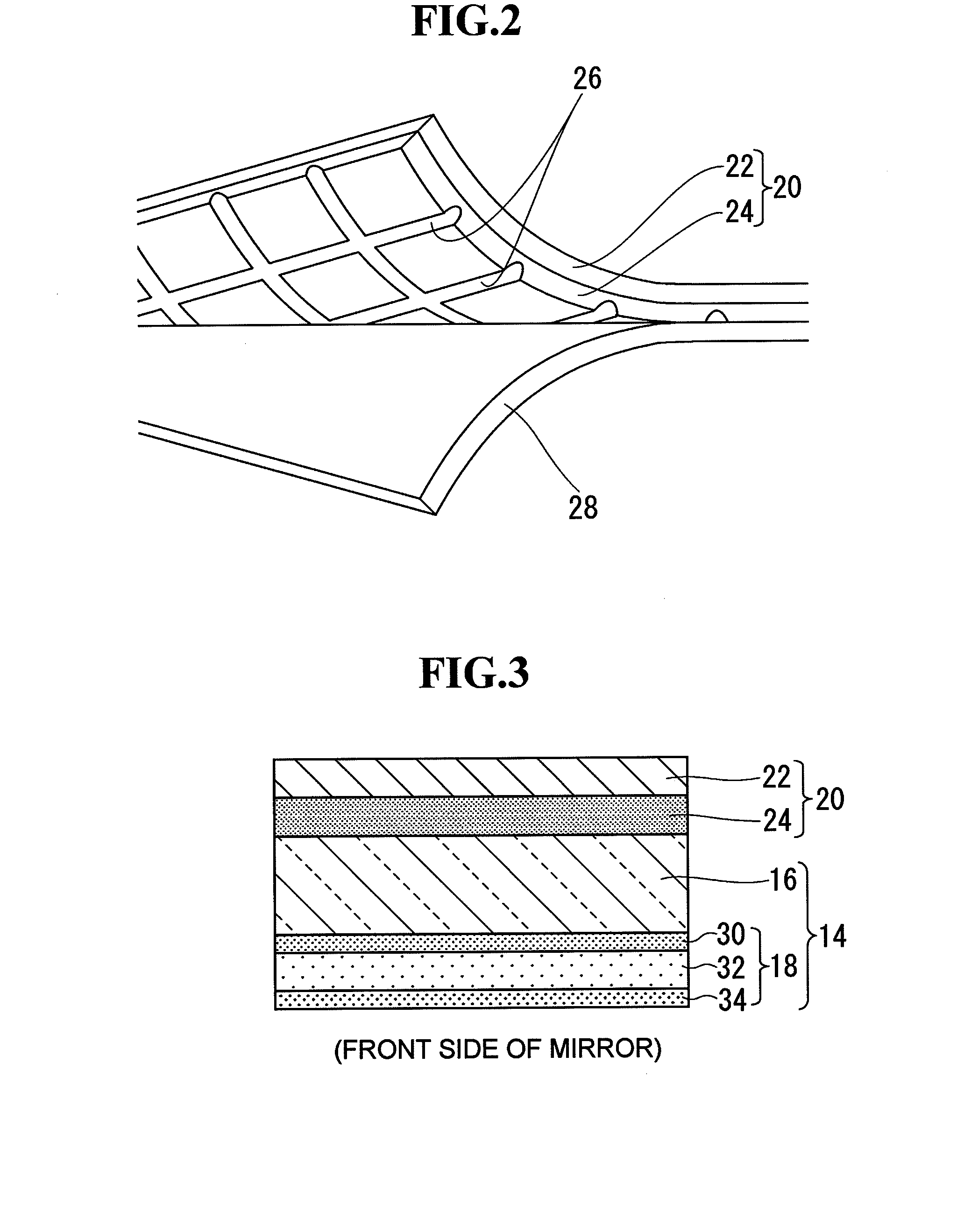

Vehicle mirror and manufacturing method therefor

ActiveUS20100214662A1Reduce the number of partsAvoid lightMirrorsLaminationEngineeringRear-view mirror

The present invention provides a vehicle mirror and a manufacturing method therefor which allow the rear face side of a mirror element to be dark-colored without using a color plate or color coating. A mirror element is configured by forming a semitransparent reflective film made of a dielectric multilayer film on the front face of a flat transparent substrate. A dark-colored self-adhesive film is attached to the rear face of the mirror element. The dark-colored self-adhesive film is configured by forming an adhesive layer on the rear face of a dark-colored film layer by means of application. Grid-like air release channels are formed at fine pitches with minimal depth on an entire surface of the adhesive layer. After the dark-colored self-adhesive film is attached to the rear face of the mirror element, the grid-like air release channels visible from a front side of the mirror element are eliminated by heating and / or pressurizing.

Owner:MURAKAMI CORP

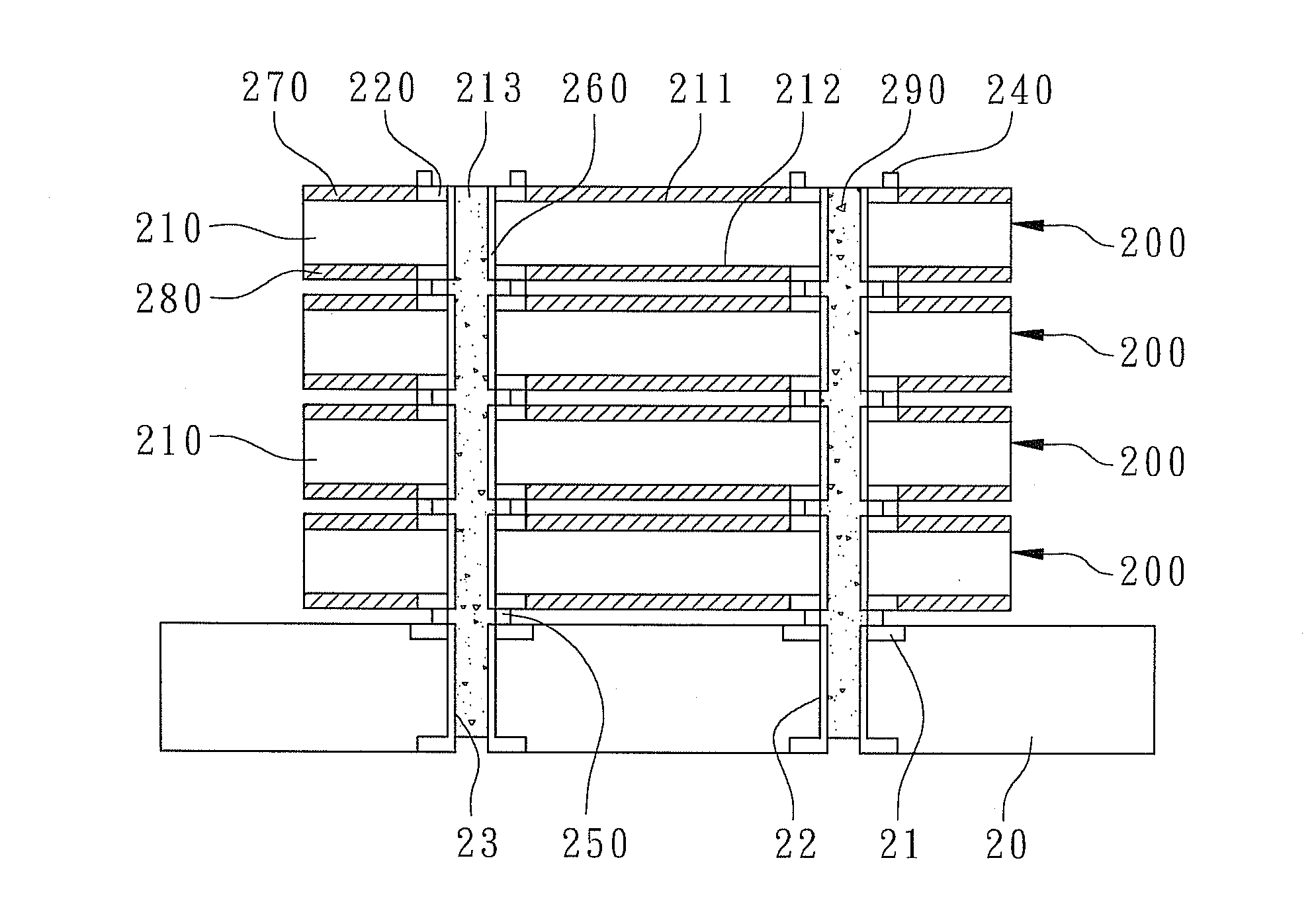

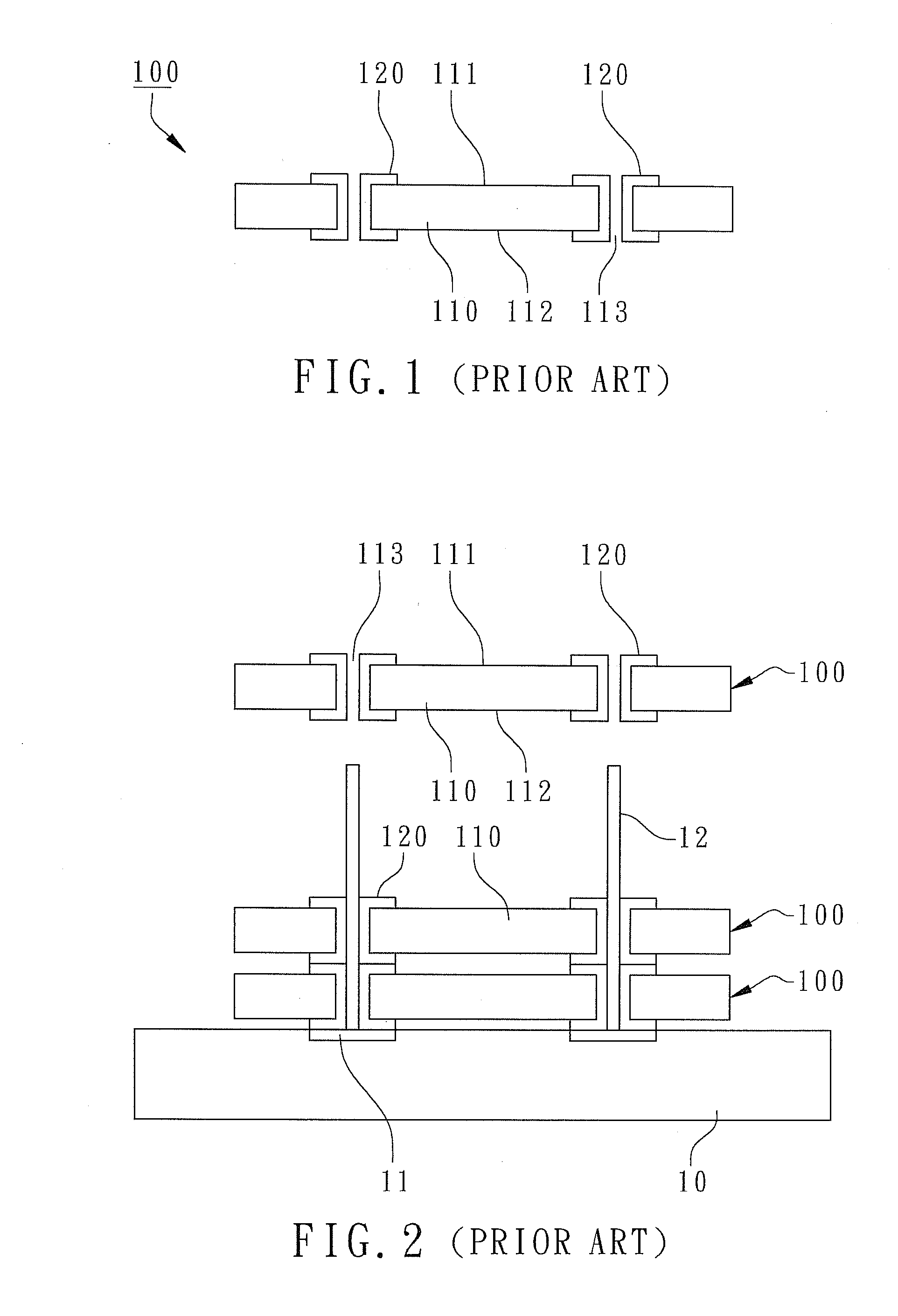

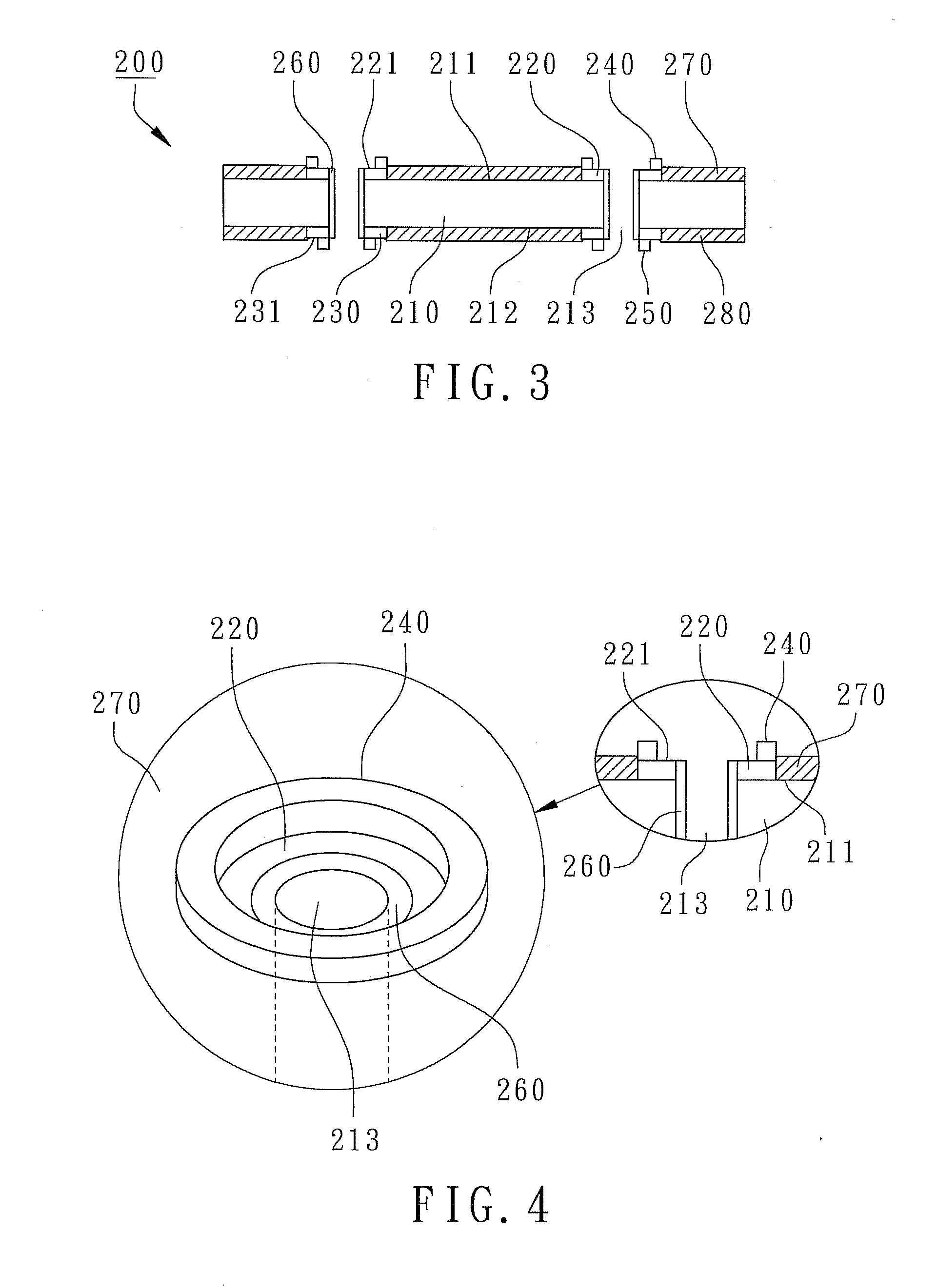

Semiconductor chip having TSV (through silicon via) and stacked assembly including the chips

InactiveUS20090267194A1Precise alignmentReduce the overall heightSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip having through silicon vias (TSV) and a stacked assembly including the chip are revealed. The chip has a plurality of first and second bonding pads disposed on two opposing surfaces of a semiconductor substrate respectively. Through hole vertically penetrate through the semiconductor substrate and the first and second bonding pads. By forming first extruded ring, the first bonding pad has a first contact surface located between the first extruded ring and the through hole. By forming second extruded ring, the second bonding pad has a second contact surface located outside and adjacent to the second extruded rings to encircle the second extruded ring. The second extruded ring has a proper dimension to fit in the first extruded ring. Accordingly, a plurality of semiconductor chip can be stacked each other with accurate alignment without shifting to effectively reduce the stacked assembly height, moreover, chip stacking processes are accomplished by vertically stacking a plurality of chips first then filling conductive material into the through holes without electrical short between the adjacent bonding pads due to overflow of conductive material to meet the fine-pitch requirements of TSV. The process flow for the stacked assembly is simplified with higher production yields.

Owner:POWERTECH TECHNOLOGY

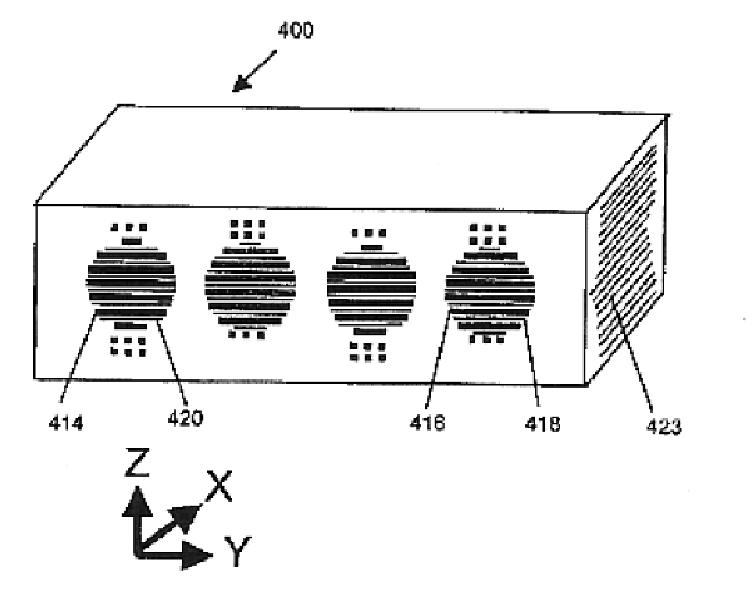

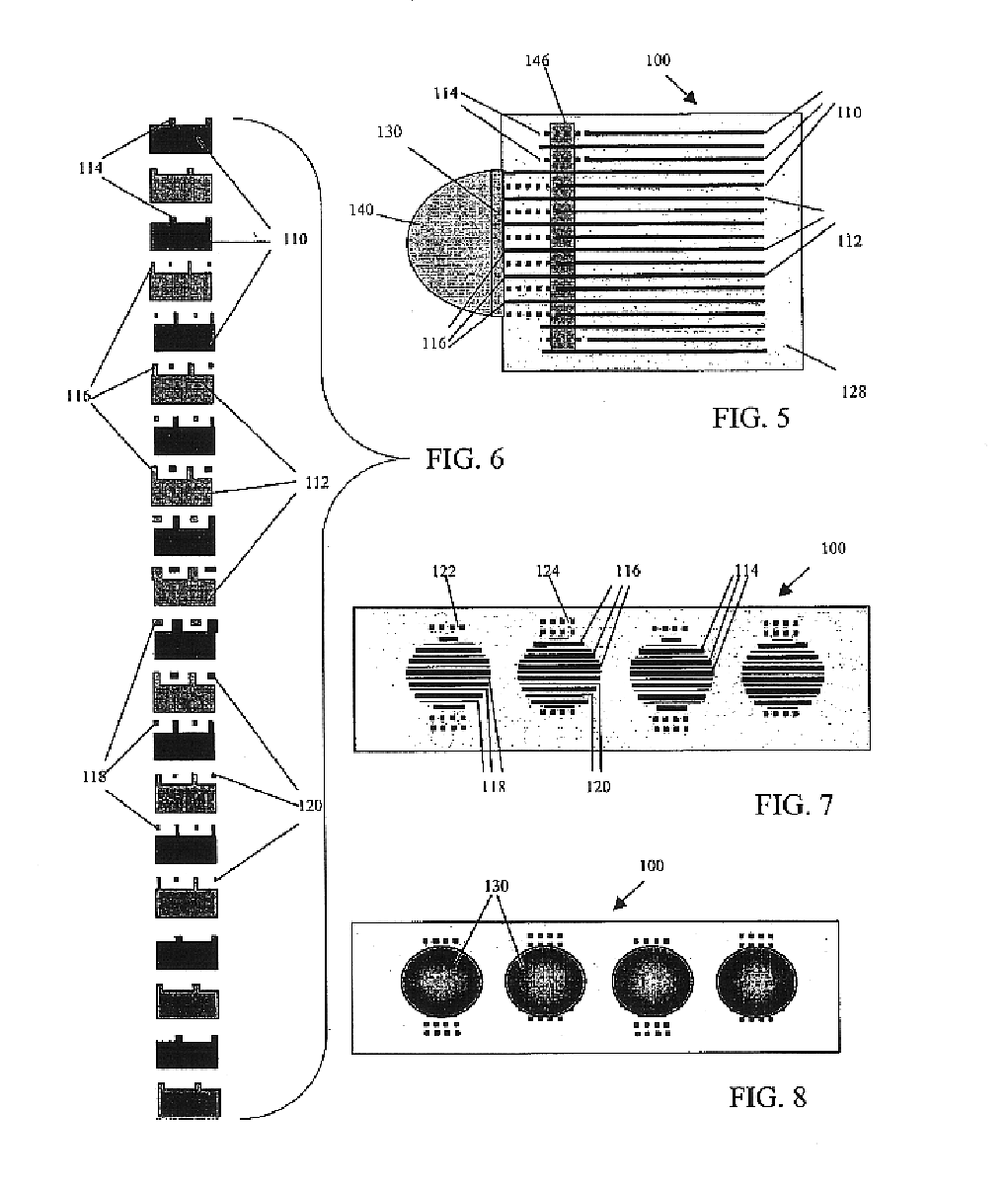

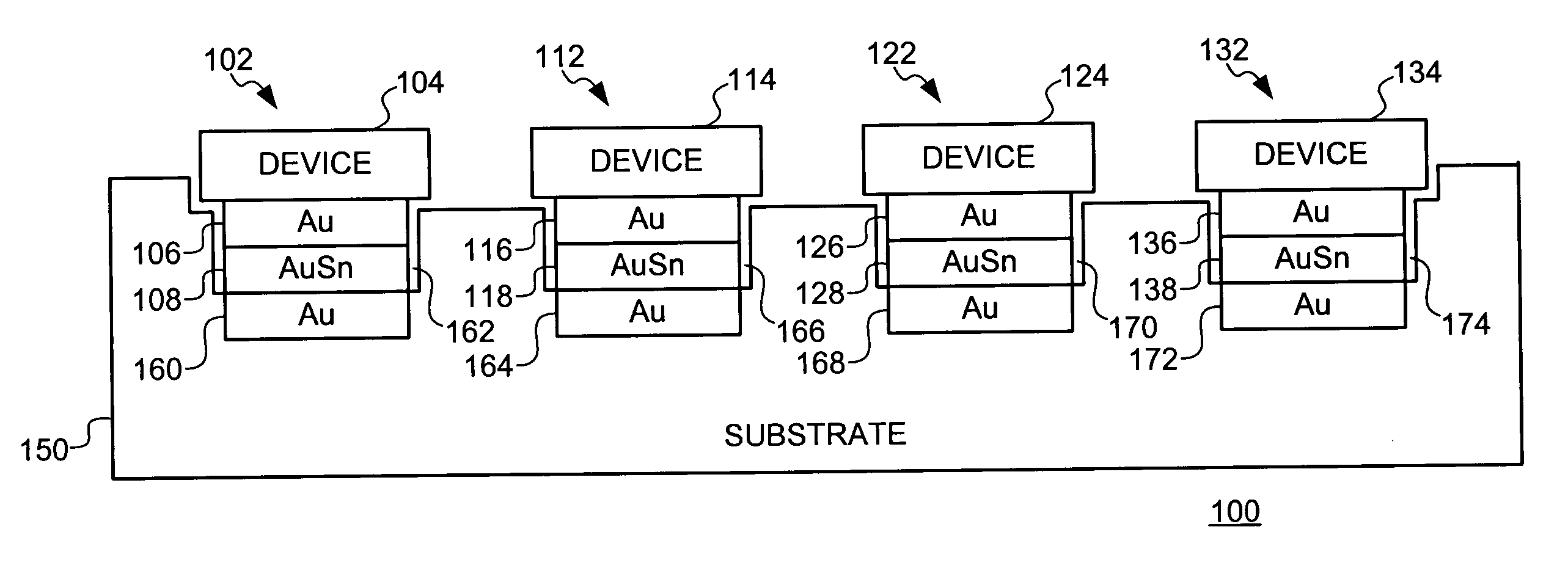

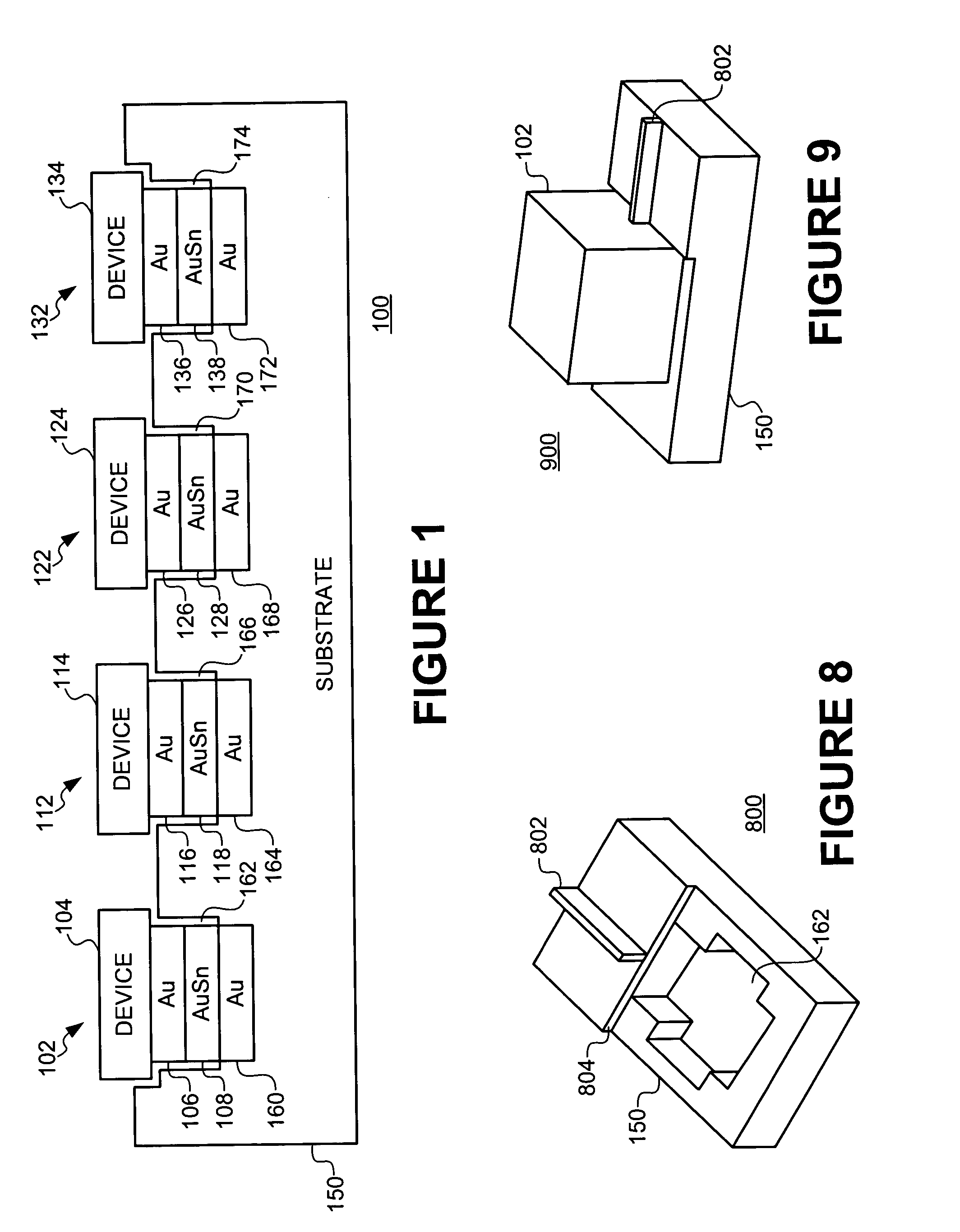

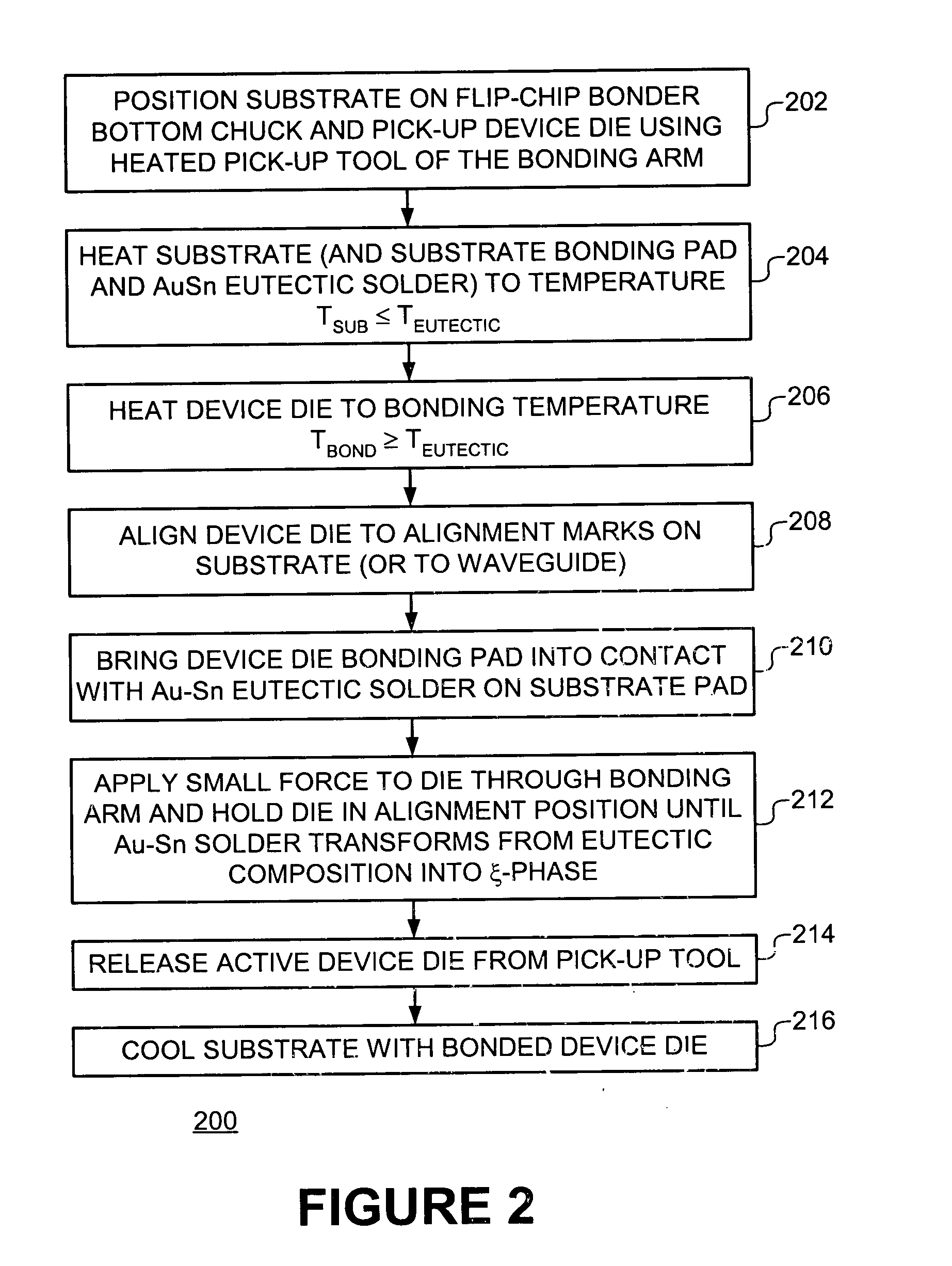

Packaging of multiple active optical devices

InactiveUS20040029304A1Printed circuit assemblingSemiconductor/solid-state device manufacturingEngineeringElectron

A cost effective method is provided for assembly of hybrid optoelectronic circuits requiring flip-chip bonding of multiple active optoelectronic devices onto common substrate or optical bench platform with fine pitch and high accuracy "after-bonding" alignment to the alignment features on substrate and / or to other elements of the hybrid circuit. A Flip-Chip Bonder equipped with high precision Bonding Arm and optical and mechanical system, heated substrate chuck and heated pick-up tool may be used both for alignment and thermal bonding of active component dies to corresponding bonding pads on the common substrate using gold-tin (Au-Sn) solder disposed between die bonding pad and the corresponding substrate bonding pad. During bonding of the first die, tin (Sn) diffuses from a eutectic composition of gold-tin (Au-Sn) solder to (gold (Au) on) the die-bonding pad and / or (gold (Au) on) the substrate bonding-pad resulting in transformation of the Au-Sn eutectic composition to a zeta-phase composition having much higher melting temperature as compared to that of a eutectic composition. As bonding of one or more subsequent dies is performed at temperatures equal to or slightly higher than the melting temperature of a eutectic composition and significantly lower than the melting temperature of a zeta-phase composition, the gold-tin (Au-Sn) solder at the bond of previously attached die does not melt and, consequently, the alignment is not compromised.

Owner:INTEL CORP

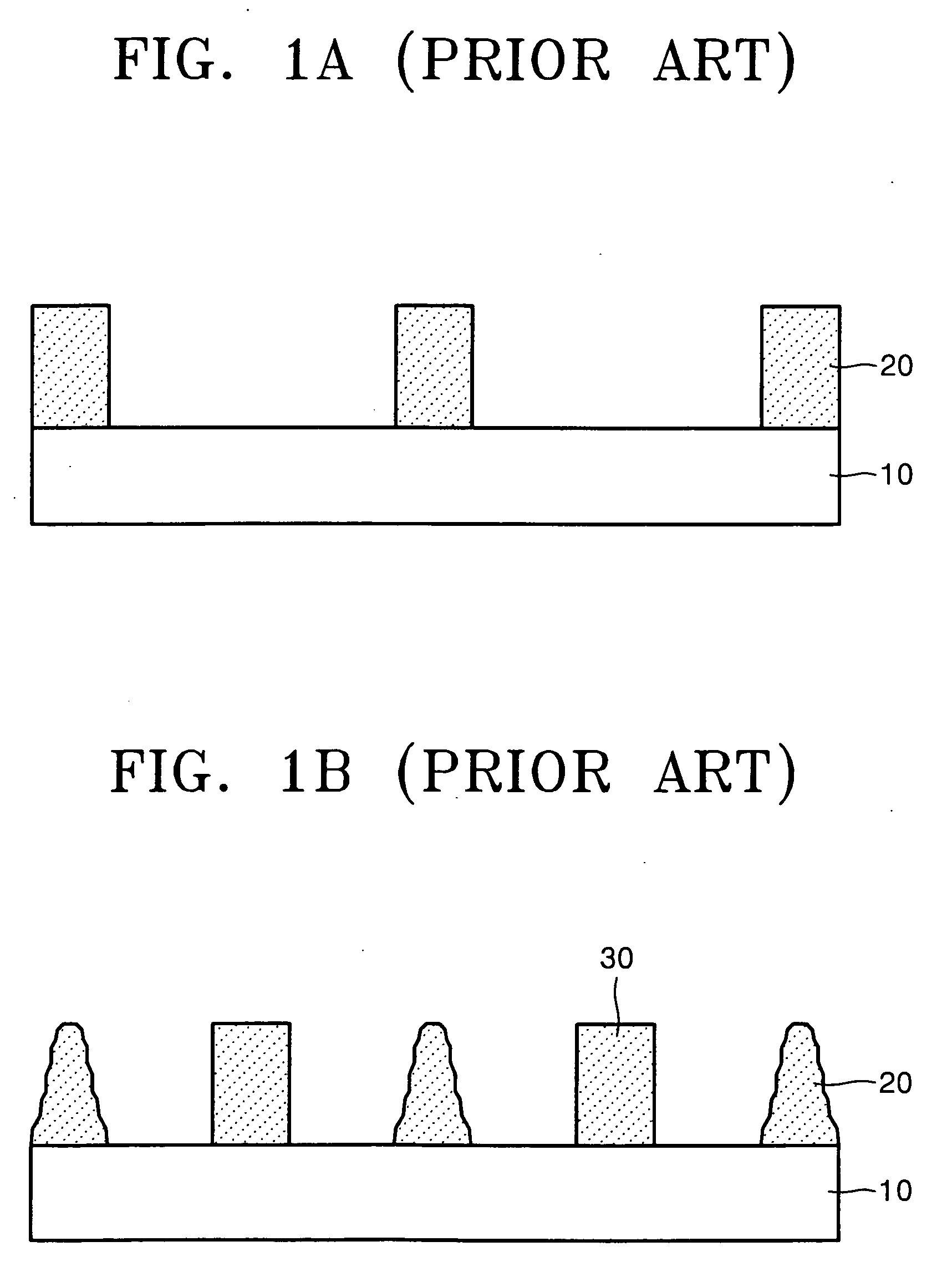

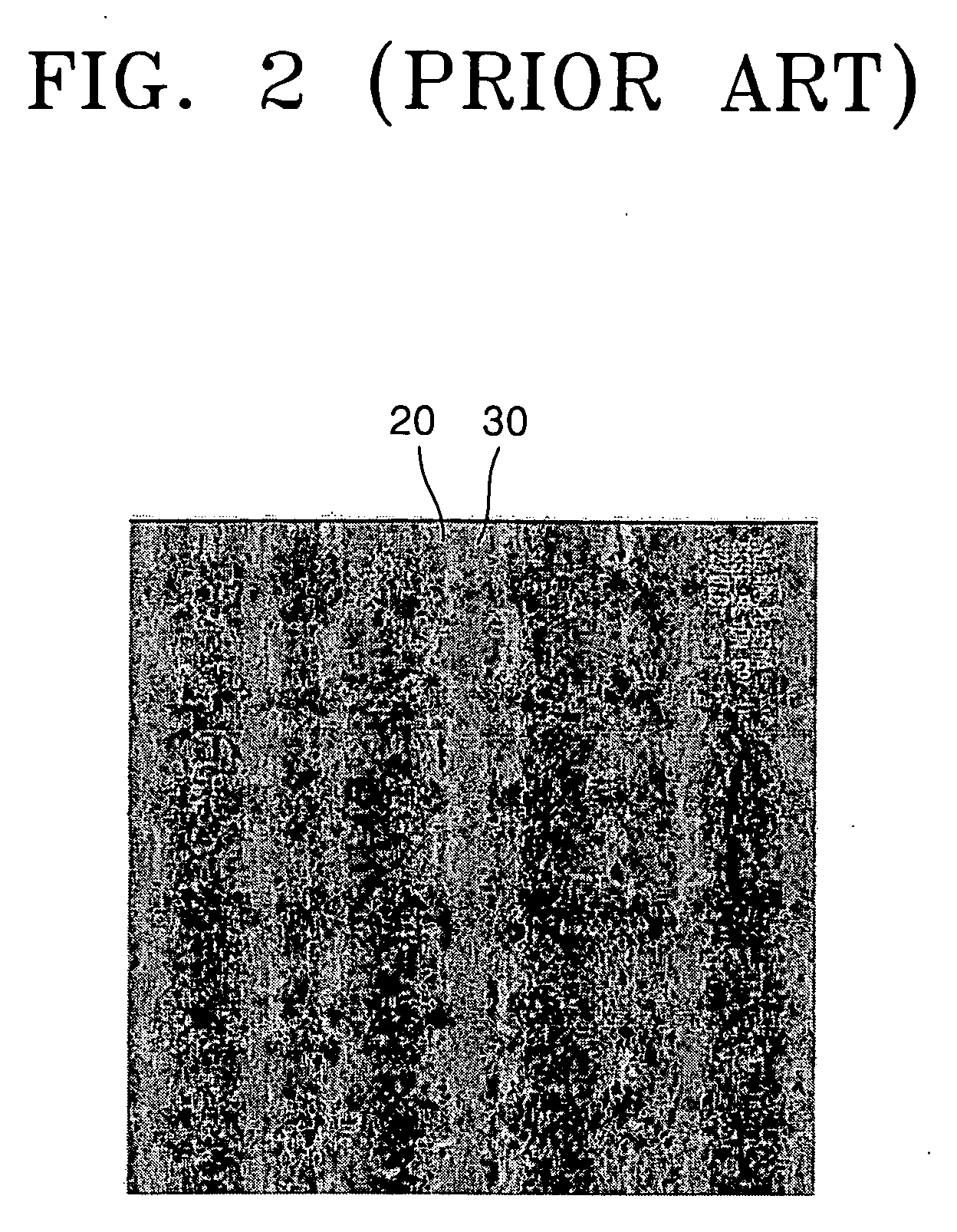

Method of forming fine pitch photoresist patterns using double patterning technique

InactiveUS20060228895A1Electric circuit arrangementsLighting heating/cooling arrangementsHydrogen bromidePhotoresist

A method of forming a photoresist pattern comprises providing a semiconductor substrate on which a layer to be etched is formed. The method further comprises forming a first photoresist pattern on the layer to be etched, processing the first photoresist pattern with hydrogen bromide (HBr) plasma, and forming a second photoresist pattern on the semiconductor substrate between the first photoresist patterns

Owner:SAMSUNG ELECTRONICS CO LTD

Post passivation structure for a semiconductor device and packaging process for same

ActiveUS20060291029A1Reduce lateral displacementRelieve pressureSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A post passivation rerouting support structure comprises a relatively thin support layer above the passivation layer to support the RDL, and a relatively thick support layer for fine pitch interconnects extending from the RDL and terminating as contact structures at the surface of the thick support layer, for a next level packaging structure. The thick support layer is planarized before defining the contact structures. The thick support layer may be formed after the conducting posts have been formed, or the thick support layer is formed before forming the conducting posts in vias formed in the thick support layer. An encapsulating layer may be provided above the thick support layer, which top surface is planarized before defining the contact structures. The encapsulating layer and the further support layer may be the same layer.

Owner:QUALCOMM INC

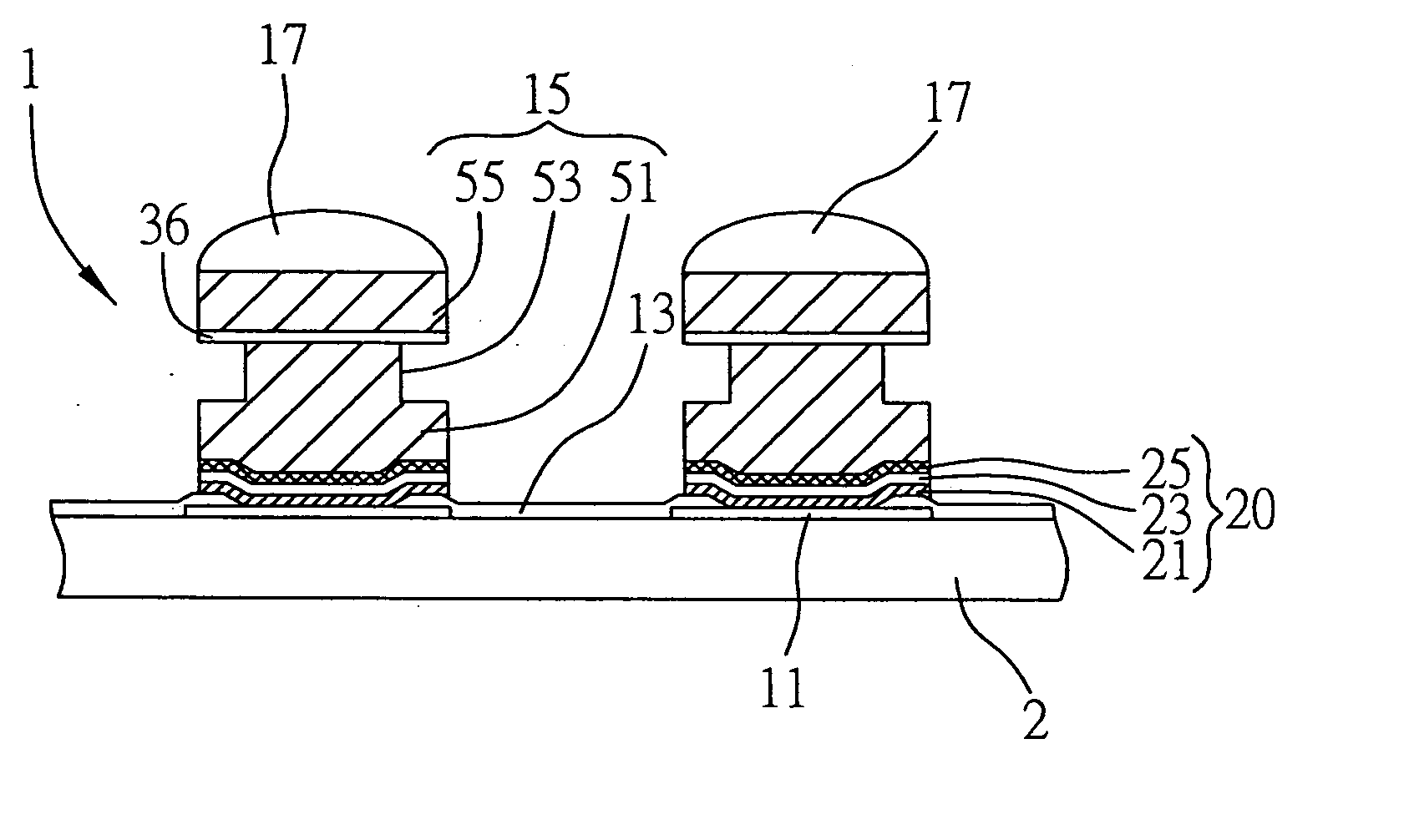

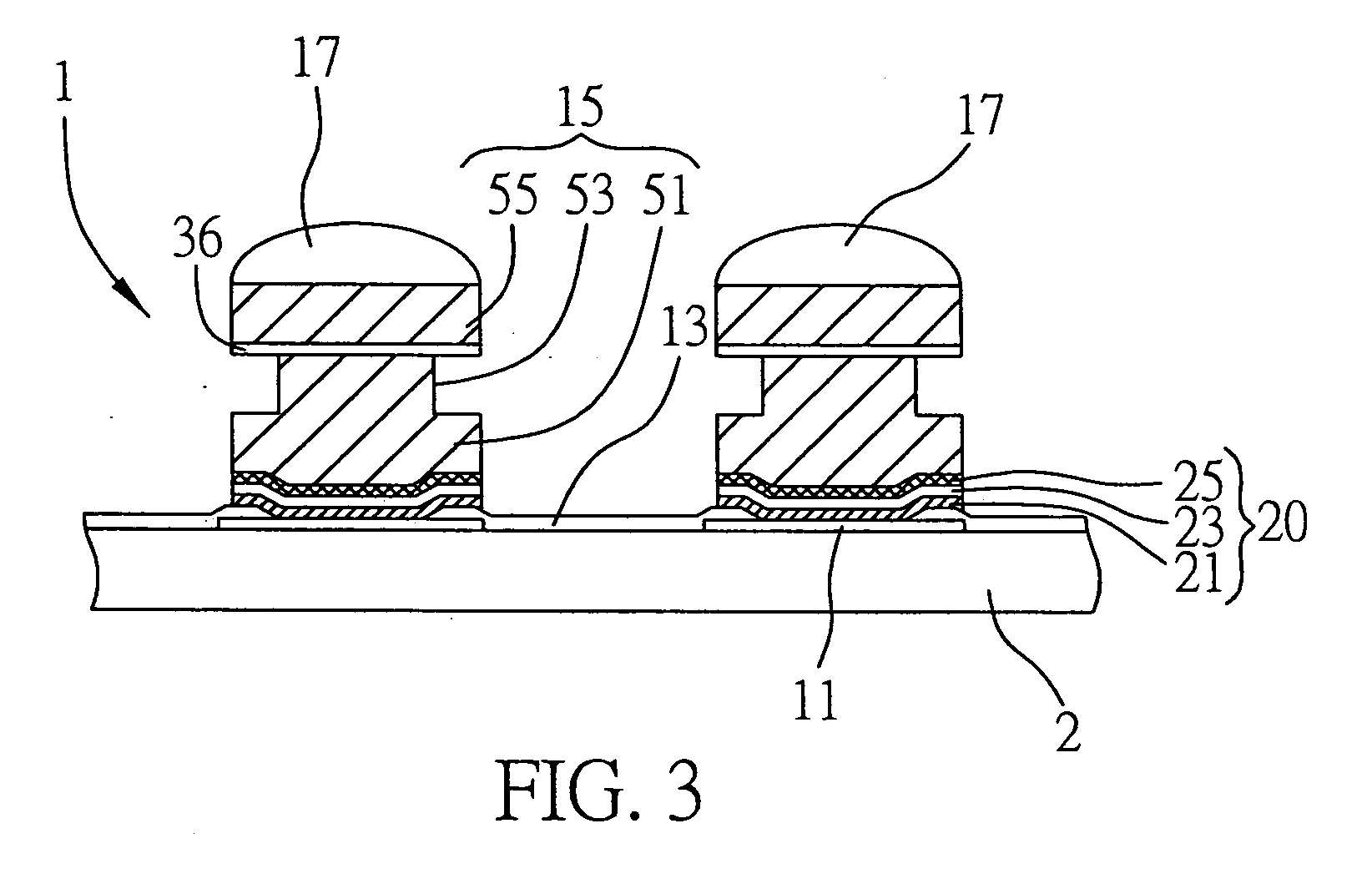

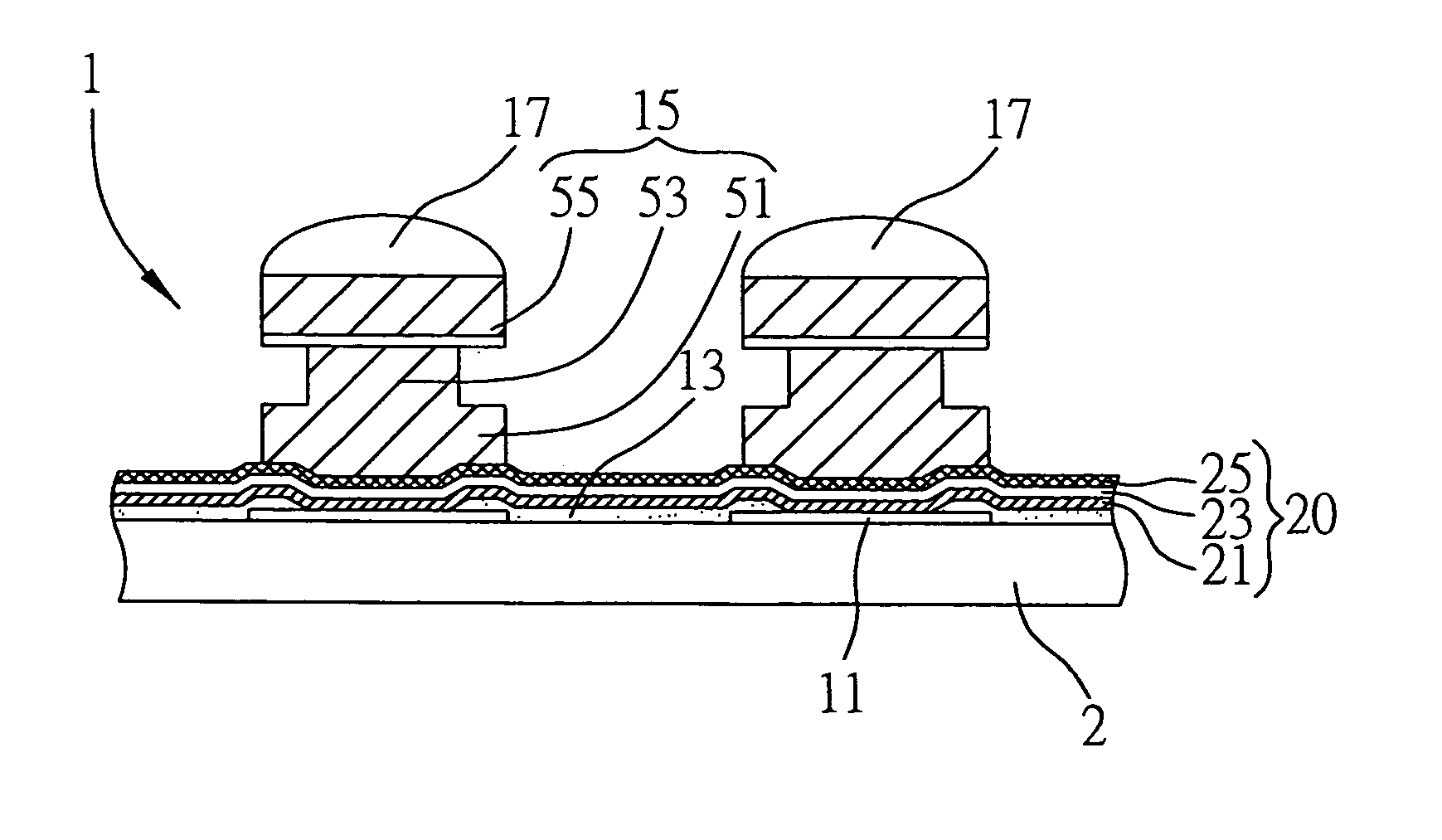

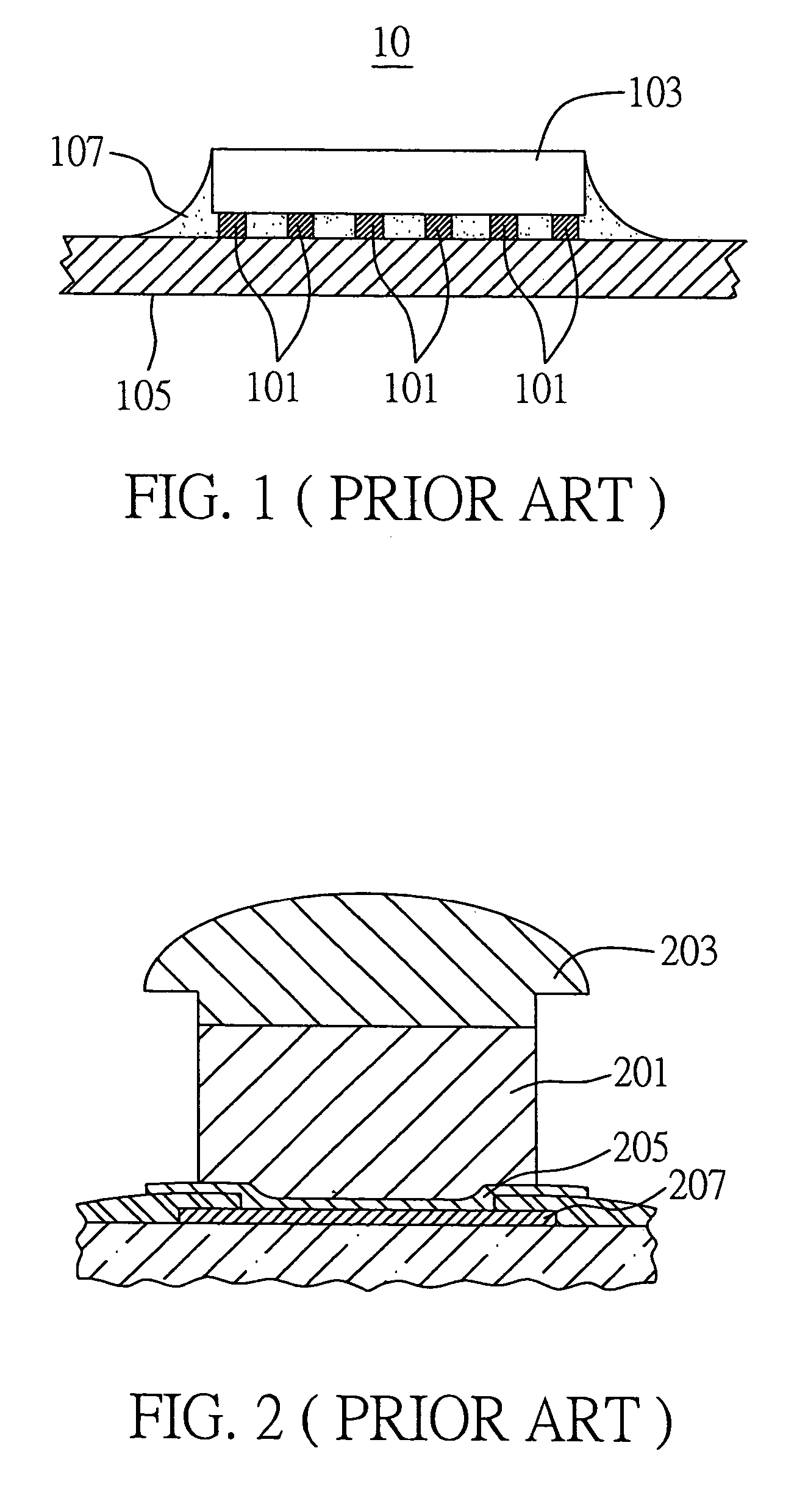

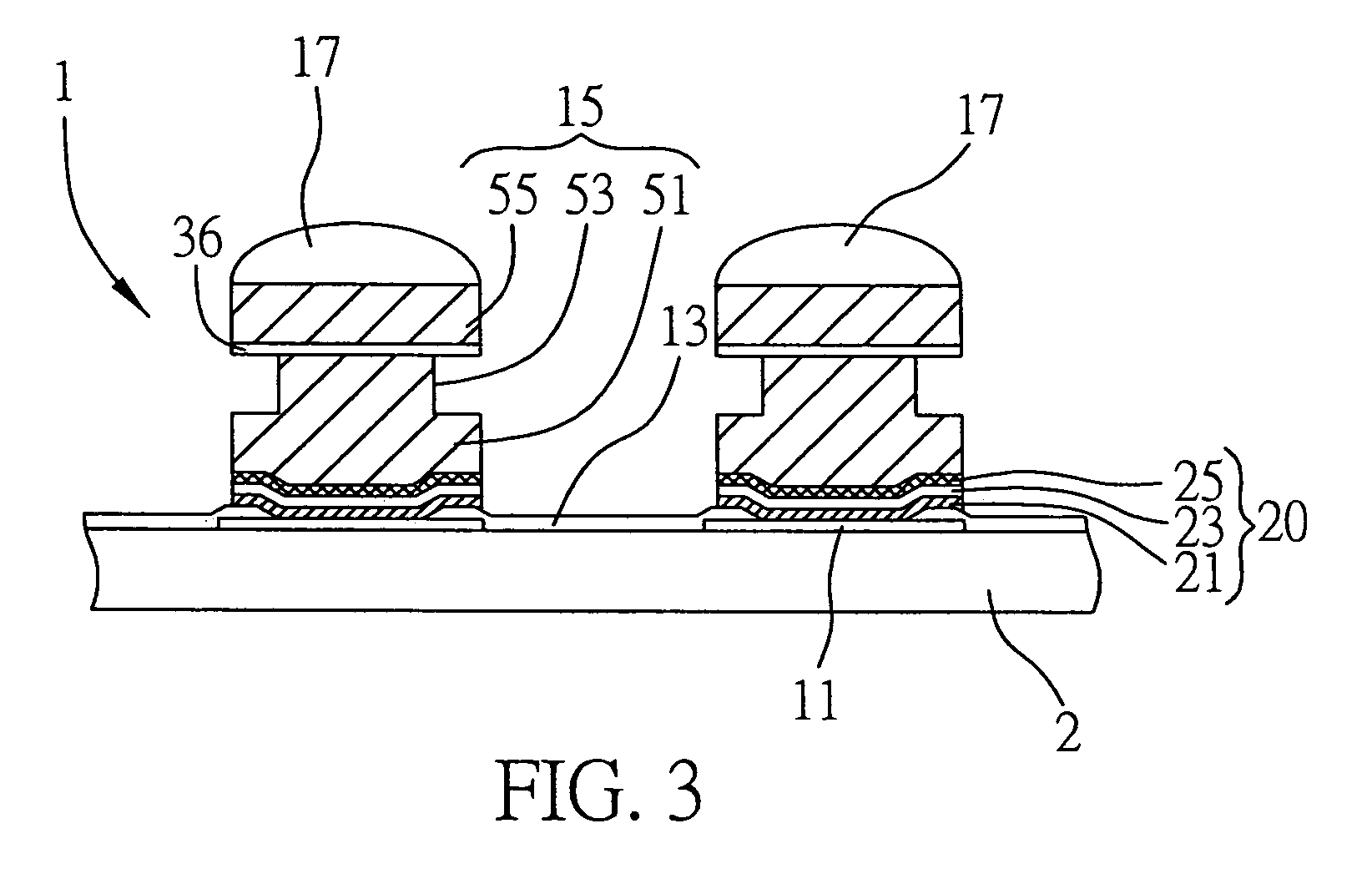

Bump structure of semiconductor package and method for fabricating the same

InactiveUS20060051954A1Increase spacingReduces the formation of voidsSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical connectionSemiconductor package

A bump structure of a semiconductor package and a method for fabricating the same are provided. The bump structure is used to connect a semiconductor element to a carrier of the semiconductor package. The fabrication method primarily employs an electroplating process to form the bump structure including an under bump metallurgy (UBM) layer, at least one I-shaped conductive pillar, and a solder material. This allows fine-pitch electrical connection pads to be arranged in the semiconductor package, and also provides an enhanced support structure and a sufficient height between the semiconductor element and the carrier.

Owner:SILICONWARE PRECISION IND CO LTD

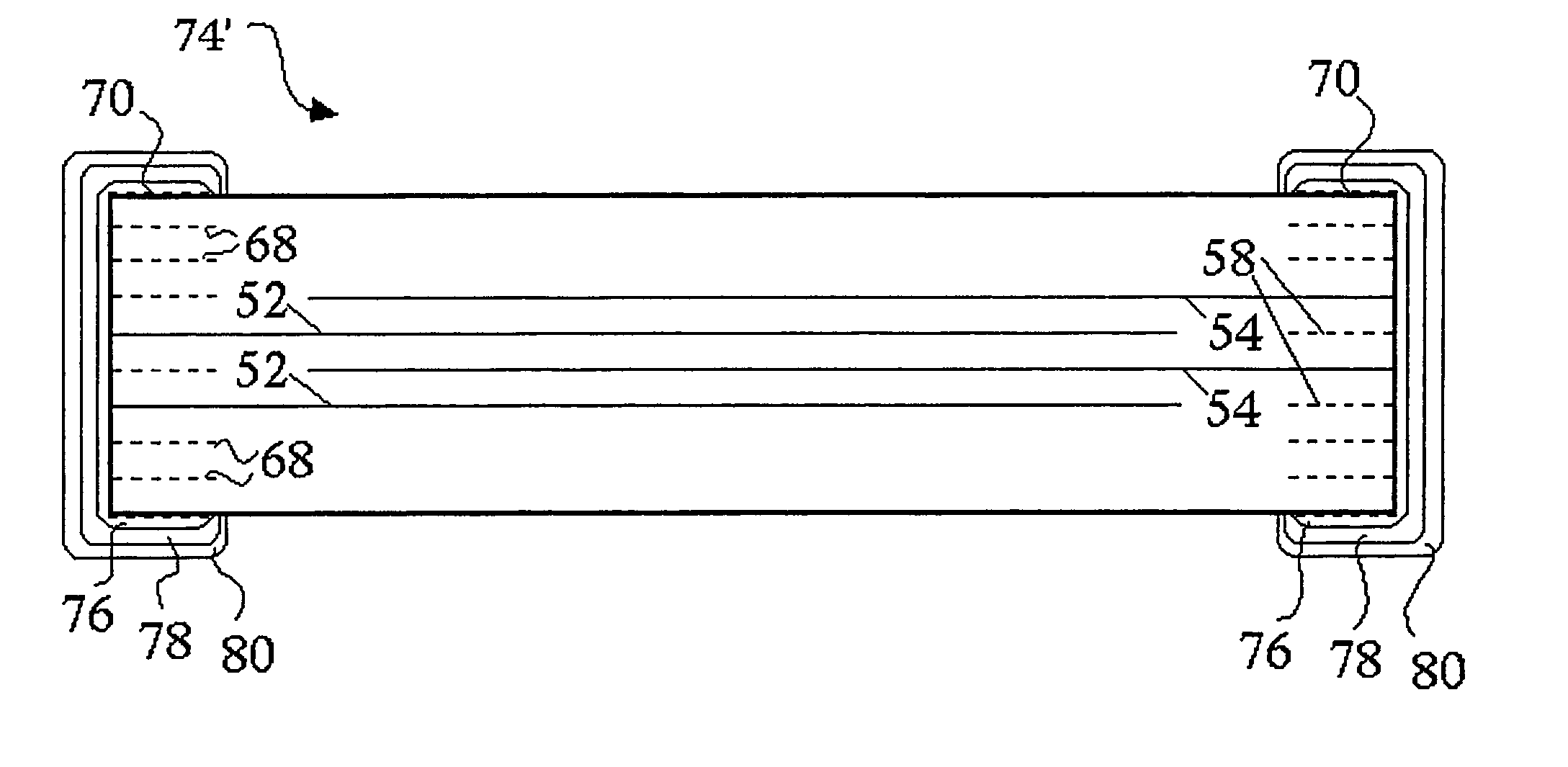

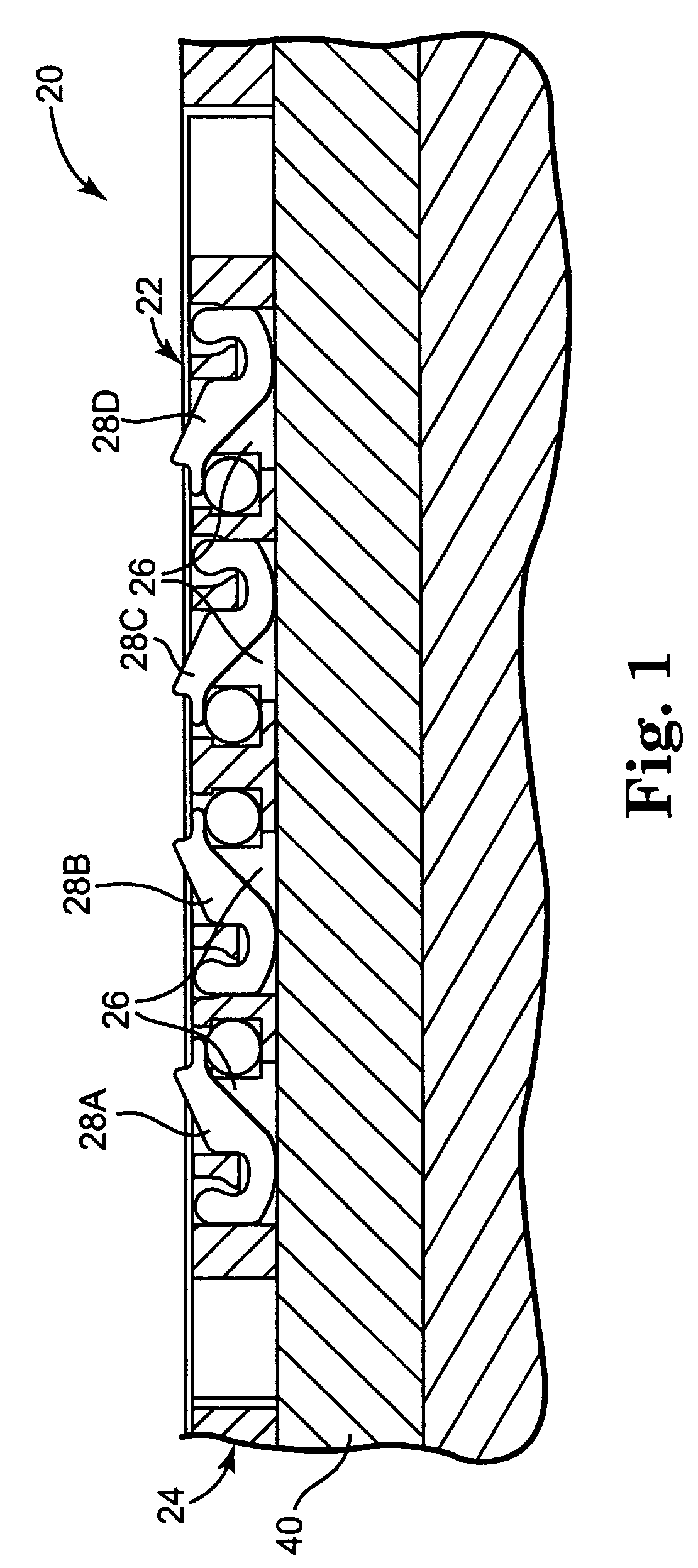

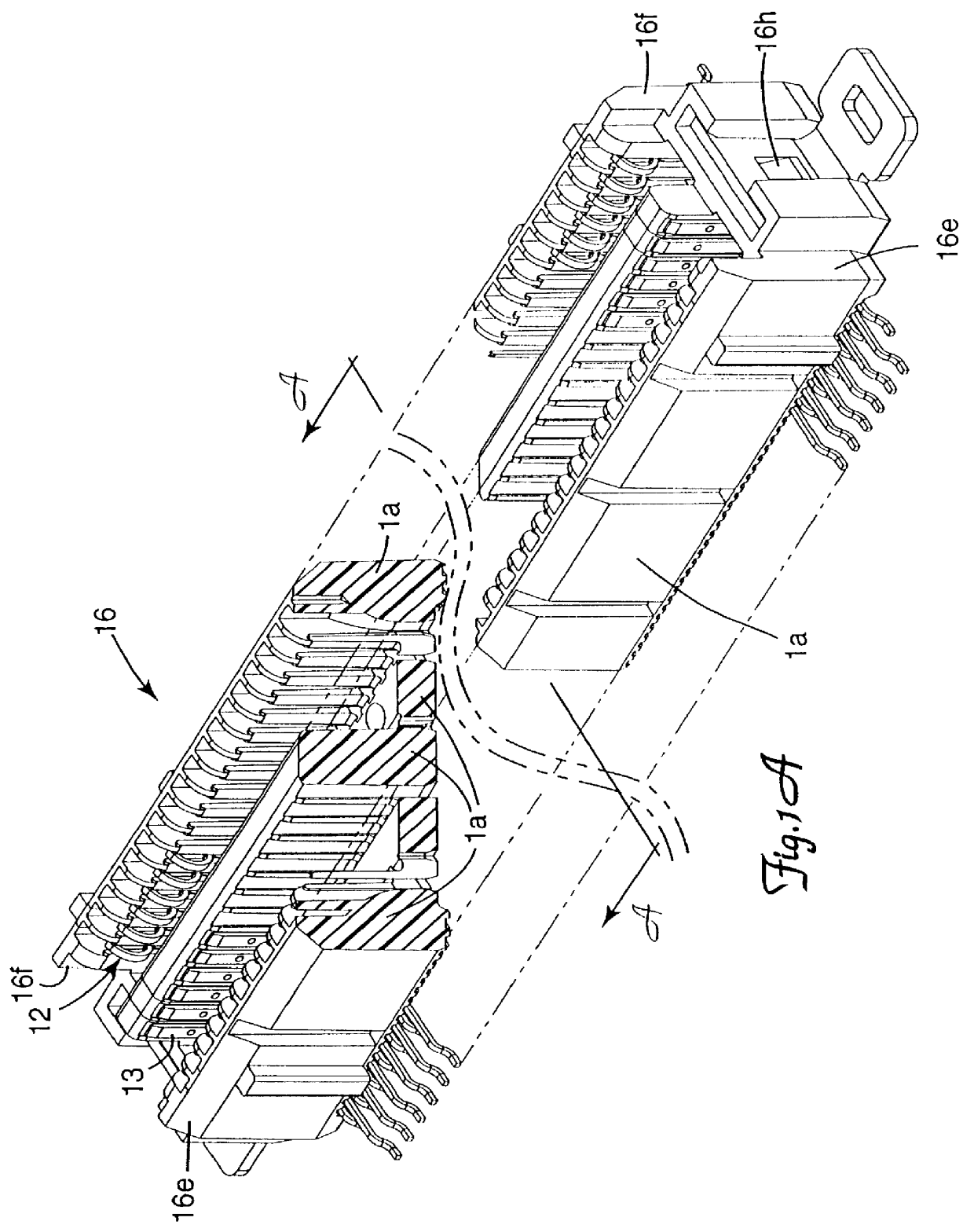

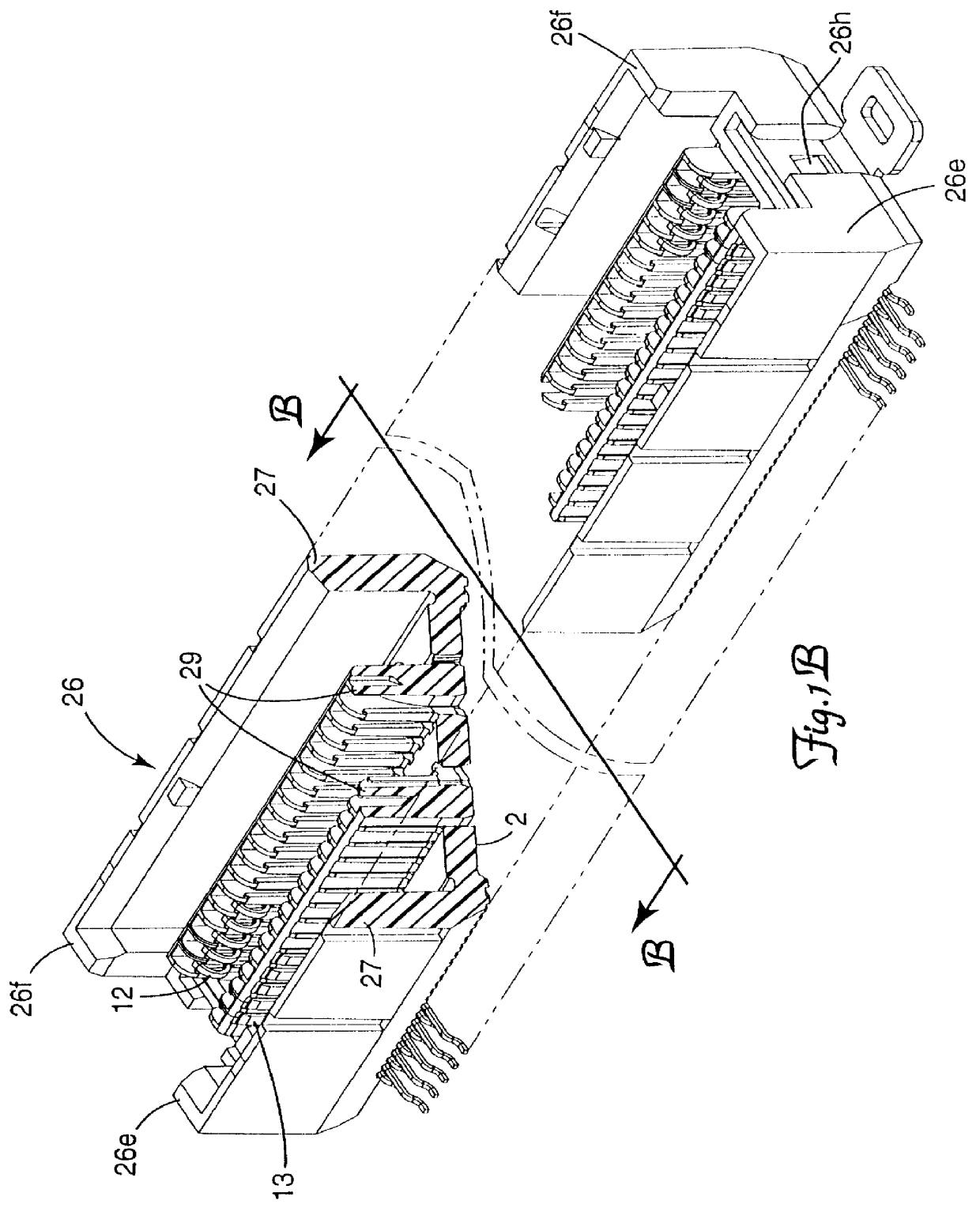

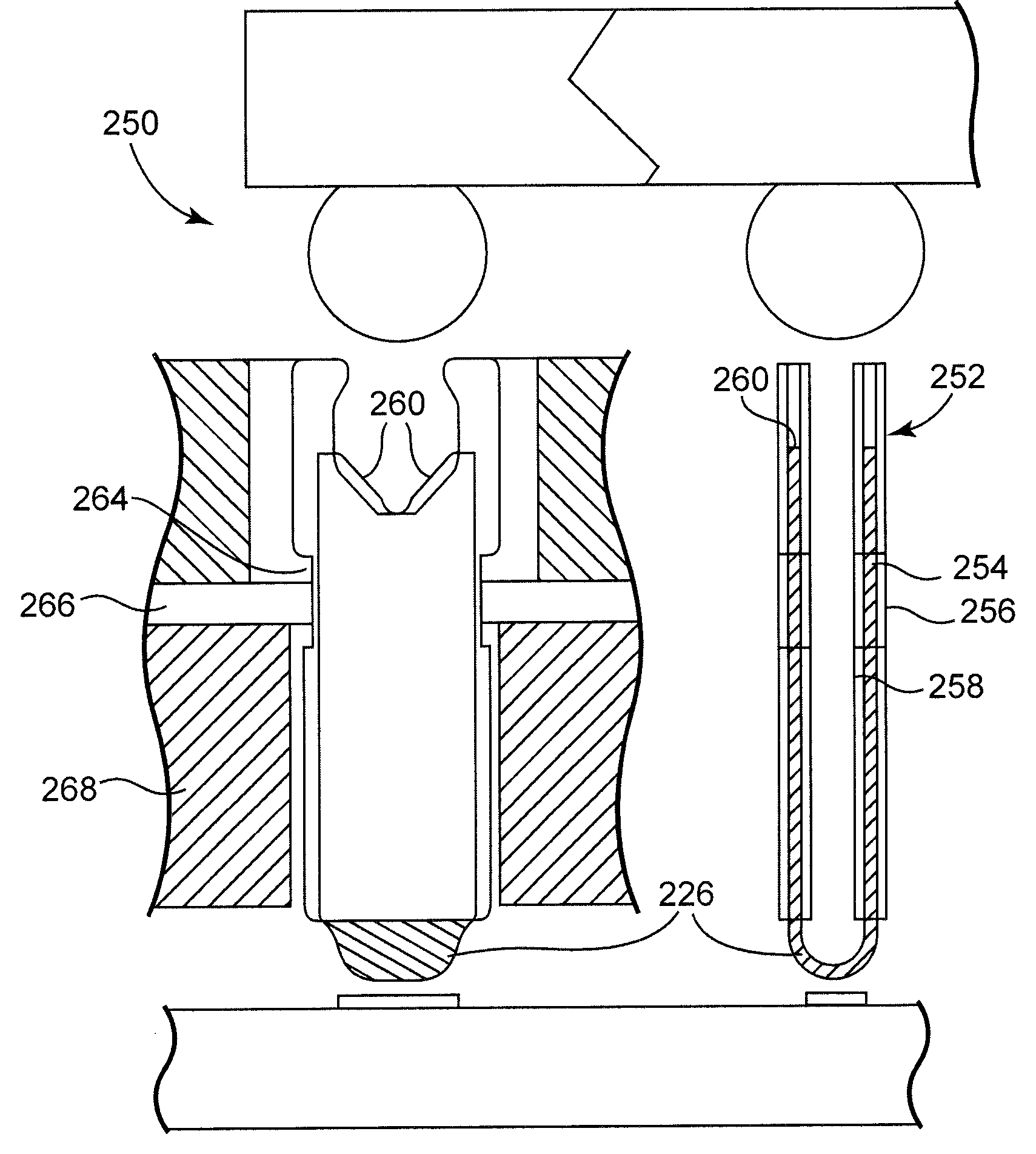

Fine pitch electrical interconnect assembly

ActiveUS7537461B2Low costLarge spacingElectrically conductive connectionsFinal product manufactureFlexible circuitsFine pitch

An electrical assembly including a socket assembly, a first circuit member electrically coupled to contact members along a first side of a socket assembly, and a second circuit member electrically coupled to the contact members along a second side of the socket assembly. A flexible circuit member is interposed between the socket assembly and the second circuit member. The flexible circuit member comprises a plurality of electrical traces electrically coupled with the contact members on the socket assembly. In one embodiment the flexible circuit member comprises a distal portion extending the electrical traces beyond the socket assembly.

Owner:R&D SOCKETS INC

Fine pitch electrical interconnect assembly

InactiveUS7326064B2High densityImprove reliabilitySecuring/insulating coupling contact membersCoupling contact membersFine pitchElectrical interconnect

An electrical interconnect assembly for electrically interconnecting terminals on a first circuit member with terminals on a second circuit member. The electrical interconnect assembly includes a housing having a plurality of through openings extending between a first surface and a second surface. A plurality of electrical contact member are positioned in a plurality of the through openings. The contact members have at least one engagement feature forming a snap-fit relationship with the housing. A stabilizing structure on the housing limits deflection of the contact members in at least one direction.

Owner:R&D SOCKETS INC

Flexible compliant interconnect assembly

InactiveUS6939143B2Wide rangeEngagement/disengagement of coupling partsPrinted circuit assemblingContact padFlexible circuits

A method and apparatus for achieving a fine pitch interconnect between a flexible circuit member and another circuit member with co-planar electrical contacts that have a large range of compliance. The interconnect assembly includes a substrate with one or more compliant raised portions. At least one flexible circuit member having a first surface with a plurality of contact pads and a second surface is provided. The substrate is located along the second surface of the flexible circuit member with the compliant raised portions aligned with the contact pads so that the compliant raised portions bias the contact pads with corresponding contact pads on the first circuit member when in a compressive relationship.

Owner:R&D SOCKETS INC

Bump structure of semiconductor package and method for fabricating the same

InactiveUS7271483B2Increase spacingReduce formationSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageElectrical connection

A bump structure of a semiconductor package and a method for fabricating the same are provided. The bump structure is used to connect a semiconductor element to a carrier of the semiconductor package. The fabrication method primarily employs an electroplating process to form the bump structure including an under bump metallurgy (UBM) layer, at least one I-shaped conductive pillar, and a solder material. This allows fine-pitch electrical connection pads to be arranged in the semiconductor package, and also provides an enhanced support structure and a sufficient height between the semiconductor element and the carrier.

Owner:SILICONWARE PRECISION IND CO LTD

Electrical interconnection system and device

InactiveUS6135781AReduce the amount requiredReduce partElectrically conductive connectionsIncorrect coupling preventionElectricityEngineering

An interconnection providing multiple electrical interconnections at a fine pitch can be formed in a pluggable and unpluggable form using multiple connector channels and rows of contact elements in each of a plug and socket. The contacts may be a mixture of active and passive contacts. Furthermore, a contact support structure may provide improve spring characteristics in the contacts. The contacts may be formed in a number of configurations including vertical staggering, alternating or offset patterns, mulit-level tail exit designs, rotated contacts, staggered or nonalign retention features and dedicated power contacts. Anchors or permanent latches, separable latches, and polarization keys may also be utilized. Alternative embodiments may include straddlemount and attachment clip embodiments.

Owner:3M CO

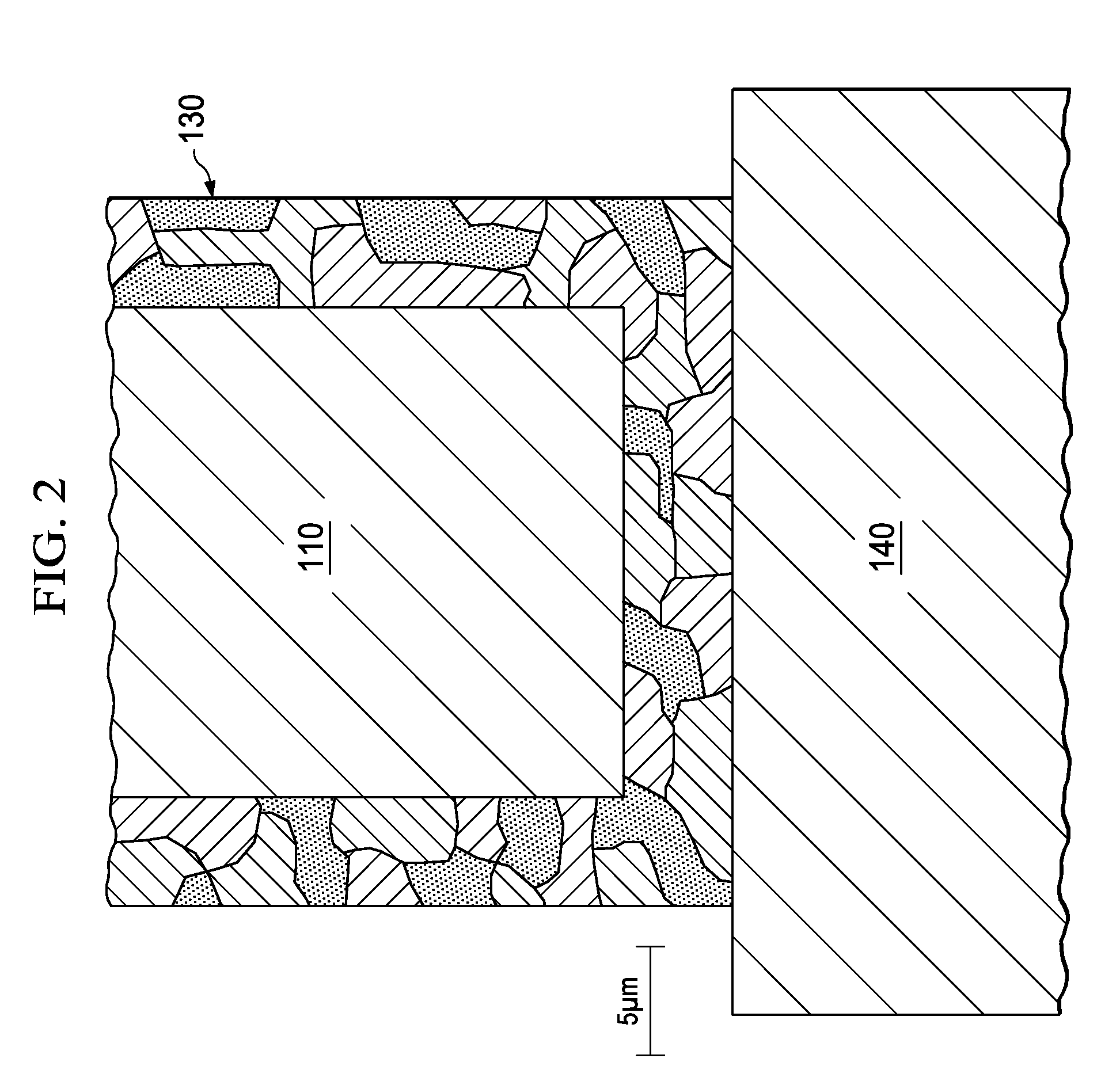

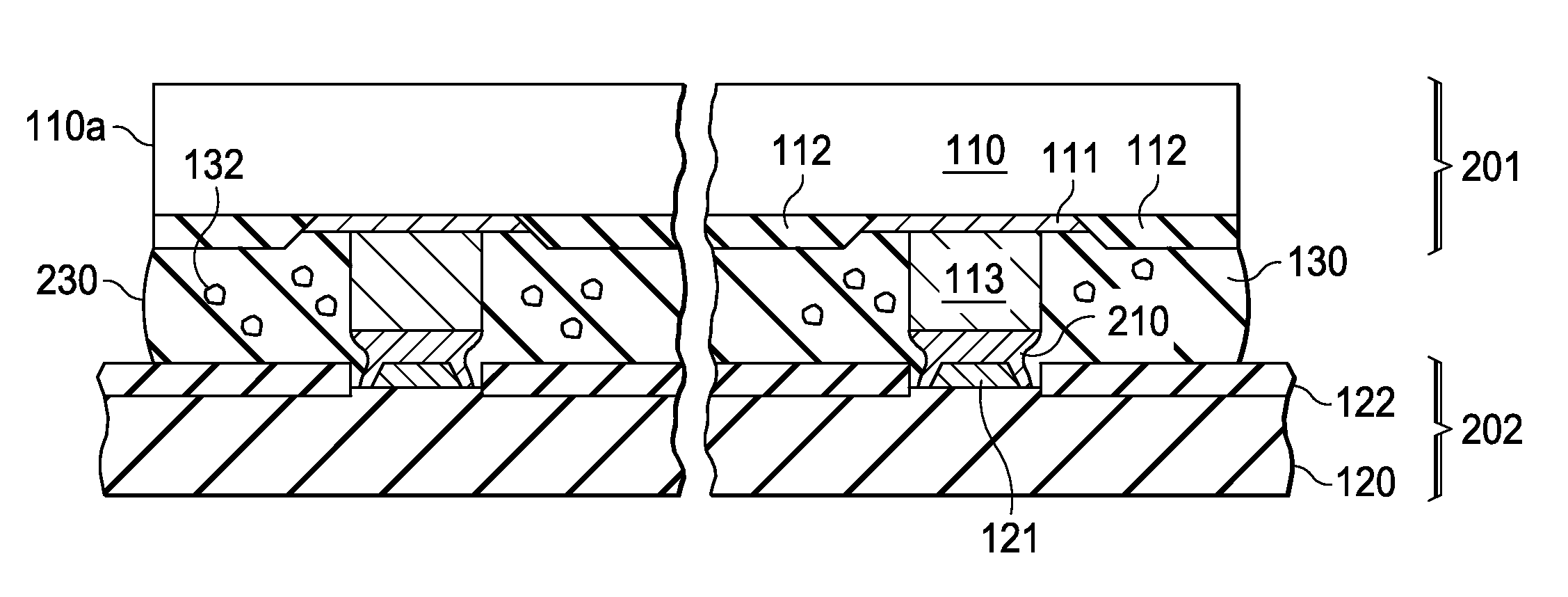

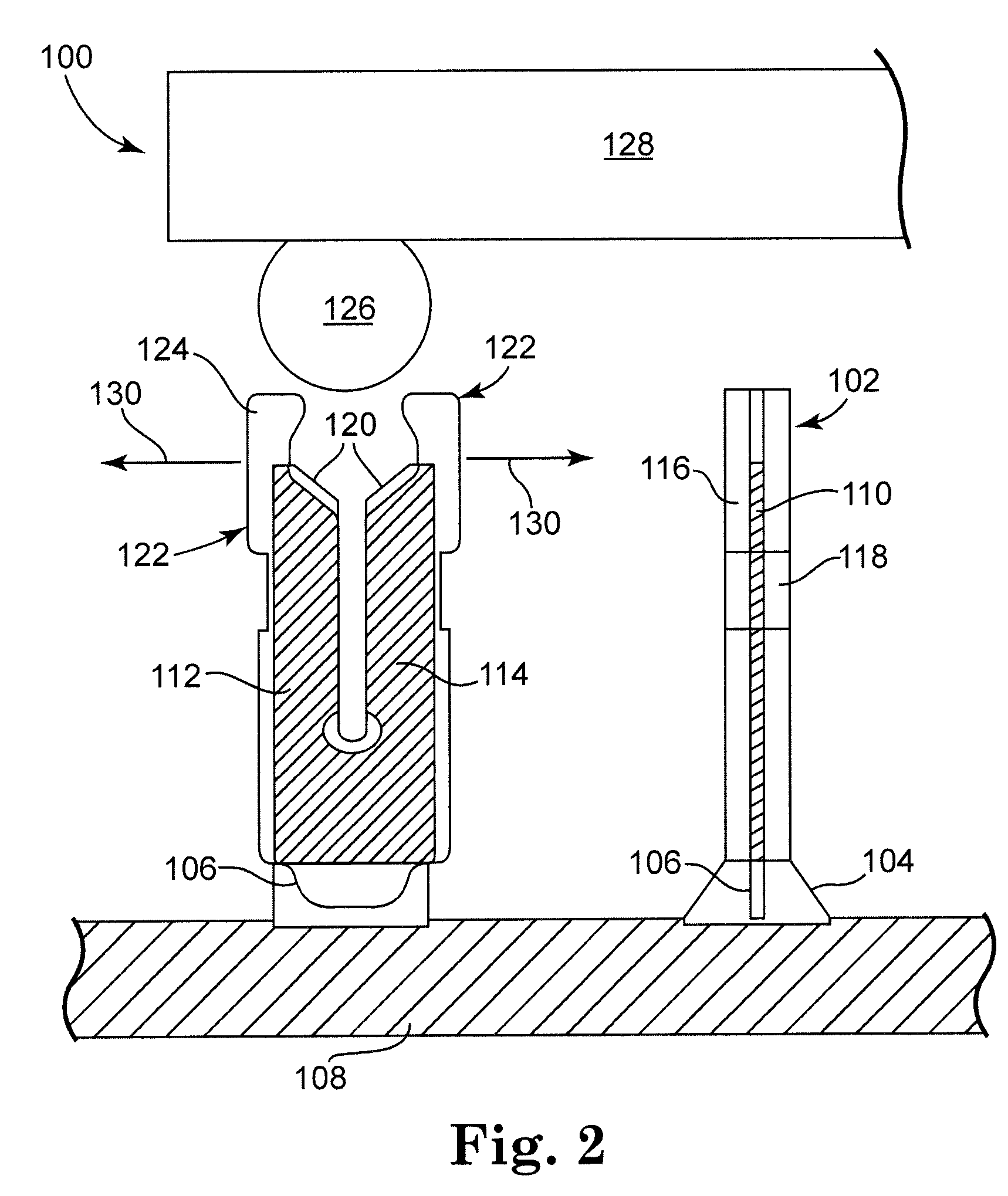

Method for fine-pitch, low stress flip-chip interconnect

ActiveUS7790509B2Easy to separateSolid-state devicesSemiconductor/solid-state device manufacturingFlip chip interconnectSemiconductor chip

Attaching a semiconductor chip to a substrate by applying mechanical vibrations (150) to a polymeric compound (130) and the contacting areas (114, 124) of a first (113) and a second (121) metallic member immersed in the compound, while the two metallic members approach (140) each other until they touch. The mechanical vibration causes displacements of the first member relative to the second member, and the vibration includes displacements (150) oriented at right angles to the direction (140) of the approach. The polymeric compound (130) includes a non-conductive adhesive resin paste (NCP) and filler particles; the paste is deposited before the attaching step. The first member (113) is affixed to the chip and the second member (121) to the substrate.

Owner:TEXAS INSTR INC

Composite contact for fine pitch electrical interconnect assembly

InactiveUS20090127698A1High dielectric constantImprove electrical performanceSemiconductor/solid-state device detailsCoupling device detailsCouplingEngineering

An electrical interconnect assembly for electrically interconnecting terminals on a first circuit member with terminals on a second circuit member. The electrical interconnect includes a housing having a plurality of through openings extending between a first surface and a second surface. A plurality of composite contacts are positioned in a plurality of the through openings. The composite contacts include a conductive member having a central portion and at least first and second interface portions. One or more polymeric layers extend along at least the central portion conductive member. One or more coupling features on the composite contacts engage with the housing. At least one engagement feature formed in the polymeric layers proximate the first interface portion mechanically couples with the terminals on the first circuit member.

Owner:R&D SOCKETS INC

Fine pitch microcontacts and method for forming thereof

ActiveUS20080003402A1Increase widthDecorative surface effectsLayered productsFine pitchMaterials science

A method includes applying a final etch-resistant material to an in-process substrate so that the final etch-resistant material at least partially covers first microcontact portions integral with the substrate and projecting upwardly from a surface of the substrate, and etching the surface of the substrate so as to leave second microcontact portions below the first microcontact portions and integral therewith, the final etch-resistant material at least partially protecting the first microcontact portions from etching during the further etching step. A microelectronic unit includes a substrate, and a plurality of microcontacts projecting in a vertical direction from the substrate, each microcontact including a base region adjacent the substrate and a tip region remote from the substrate, each microcontact having a horizontal dimension which is a first function of vertical location in the base region and which is a second function of vertical location in the tip region.

Owner:TESSERA INC

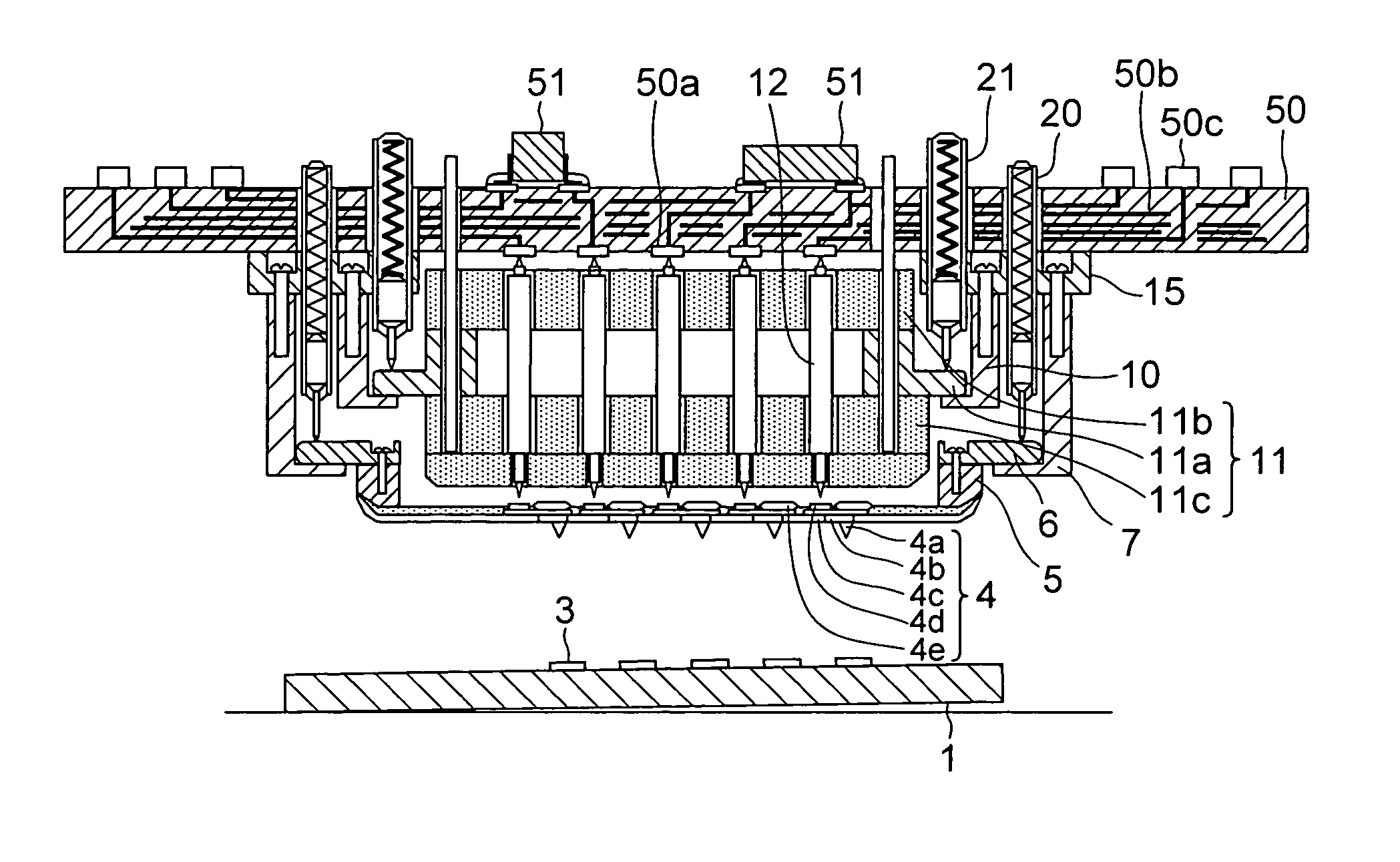

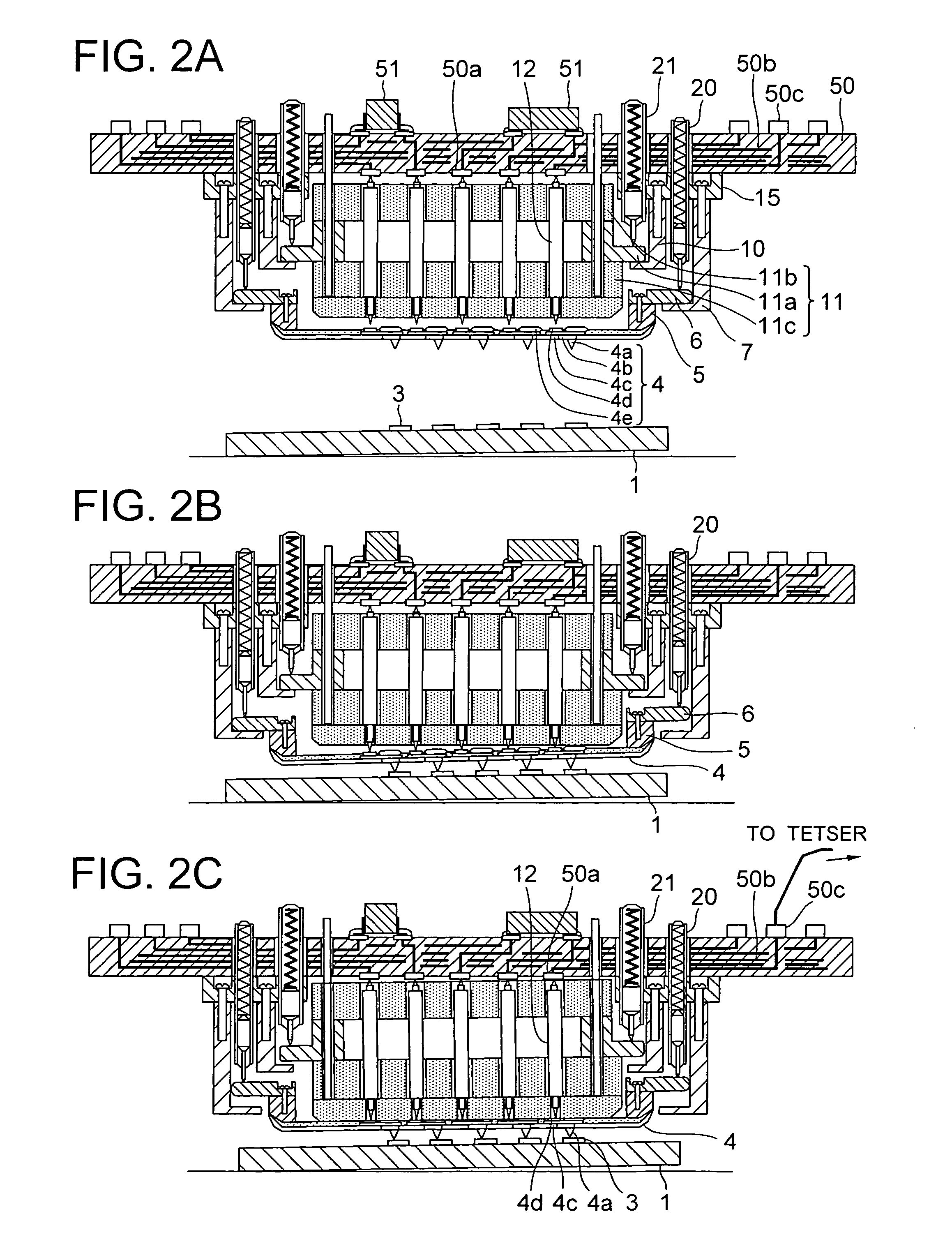

Probe sheet, probe card, semiconductor test equipment and semiconductor device fabrication method

InactiveUS7049837B2Reduce manufacturing costLow costSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityProbe card

Owner:RENESAS ELECTRONICS CORP

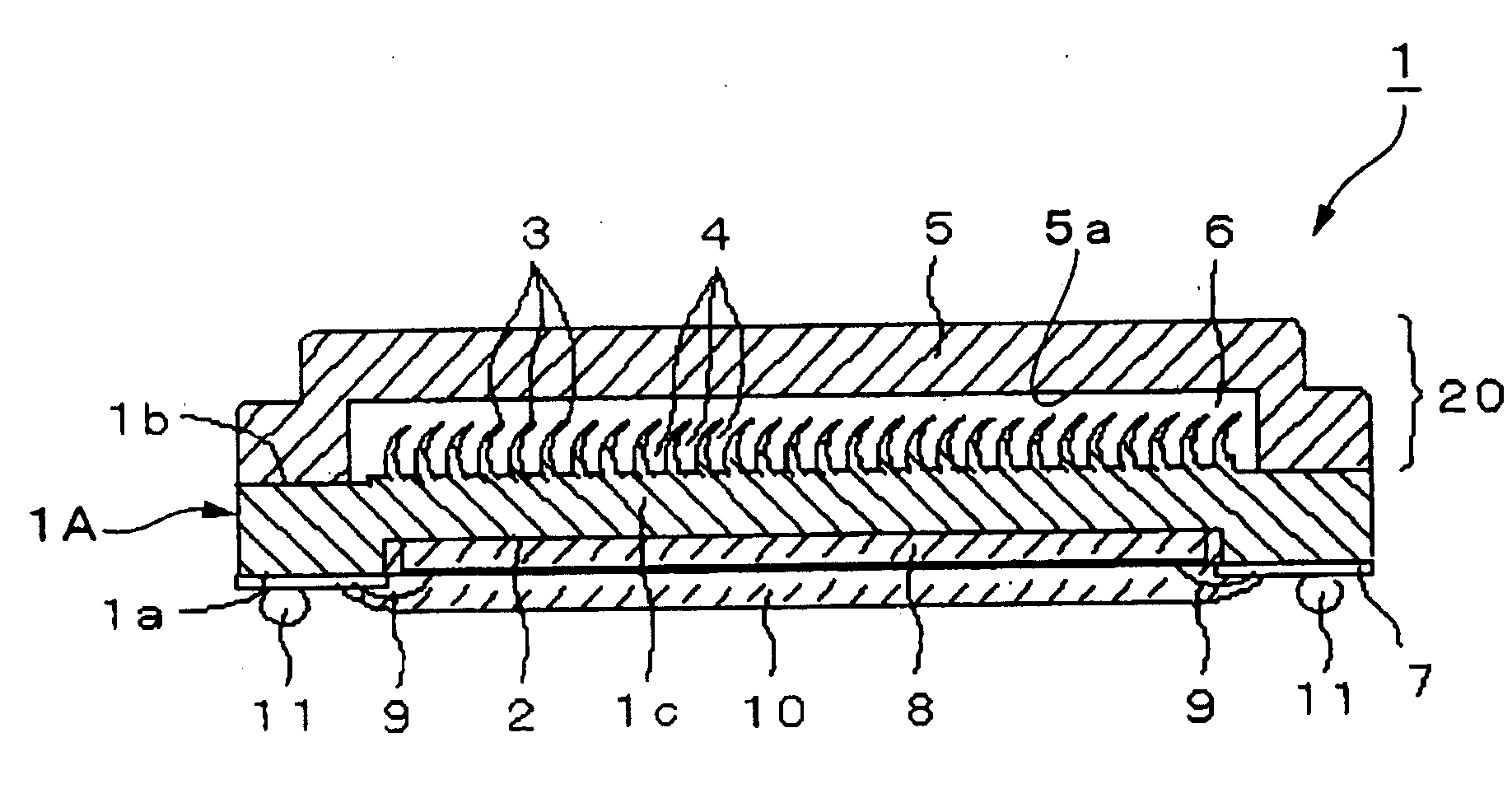

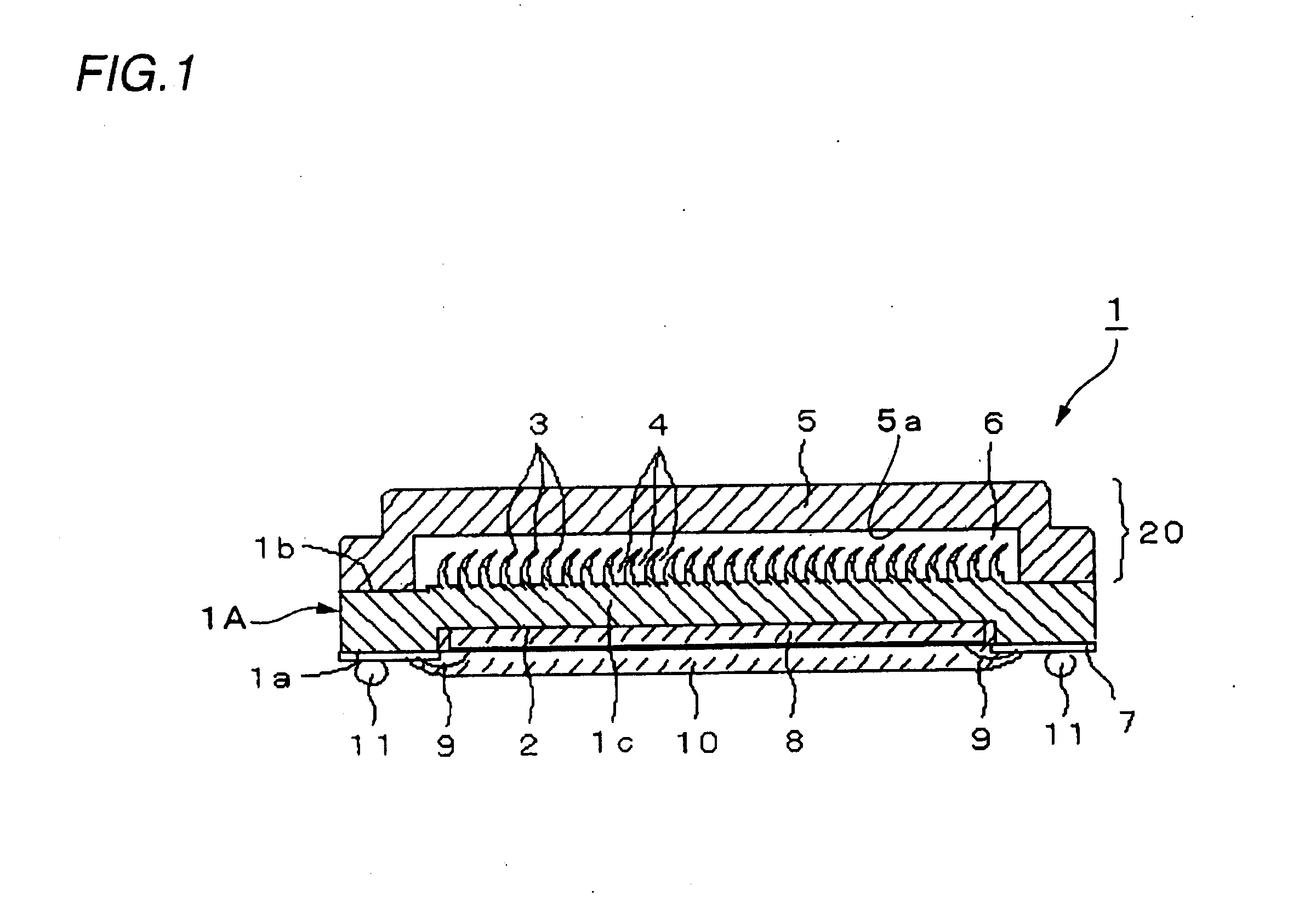

Component package having heat exchanger

InactiveUS20070163749A1Good cooling functionEfficient executionSemiconductor/solid-state device detailsSolid-state devicesWorking fluidCarve out

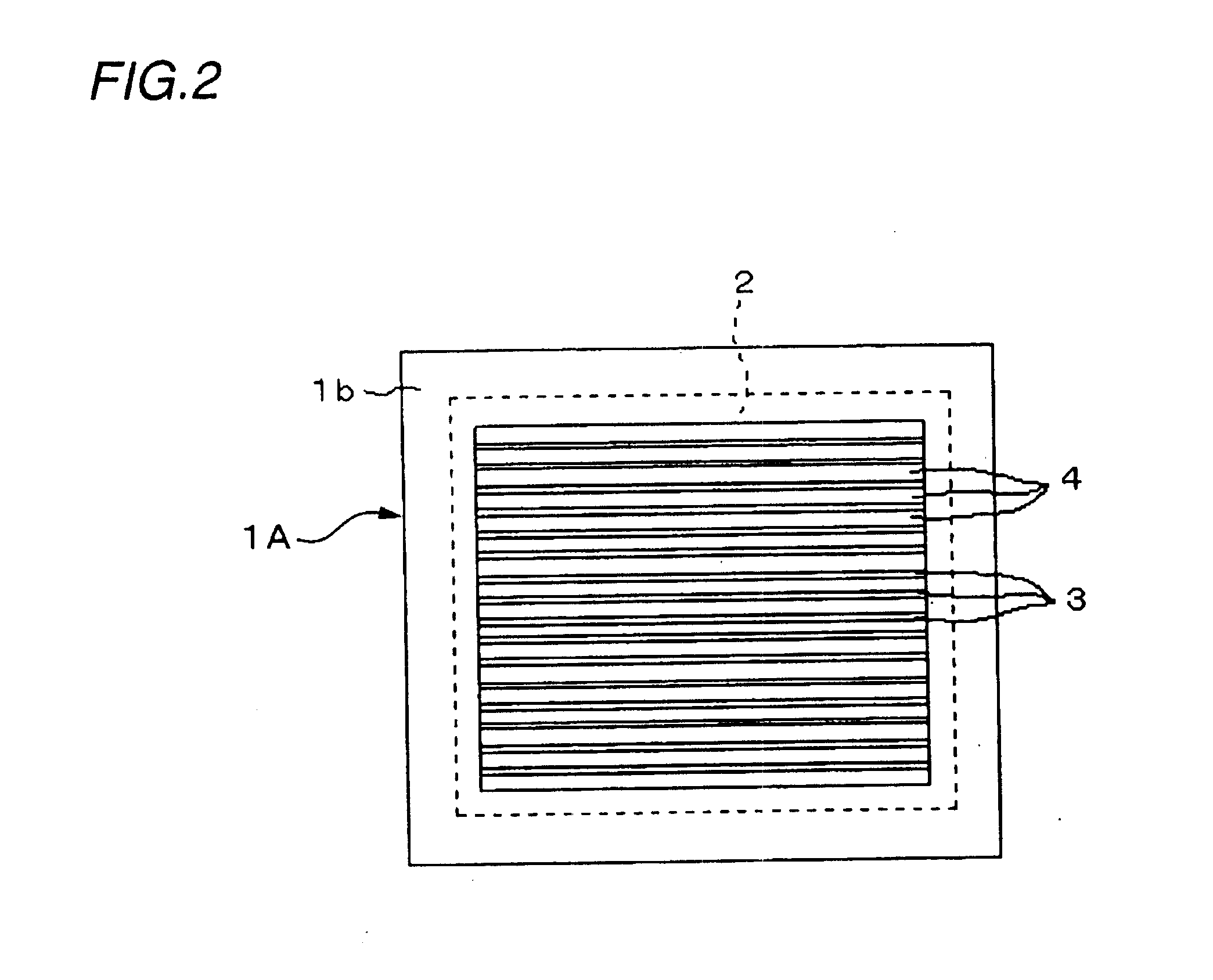

In an electrical component package (1) provided with a liquid-cooled heat exchanger (20), a main-body plate (1A) of the package and a crowning member (5) that are composed of metal plates are joined together, forming a hollow part (6) therebetween for use as a liquid-cooled heat exchanger in which a working fluid is sealed. A concavity (2) for use in mounting an electrical component (8) to be cooled is formed on the outer surface portion of the main-body plate (1A) of the package disposed opposite to the hollow part (6). An inner surface portion (5a) that faces into the hollow part (6) of the main-body plate (1A) of the package is carved out using a carving tool, whereby fins (3) are formed at a fine pitch on the inner surface portion. Minute channels (4) for moving the working fluid are formed between the fins. A flat electrical component package can [therefore] be provided with a liquid-cooled heat exchanger that has excellent heat-radiating functionality.

Owner:NAKAMURA IND MFG CO LTD

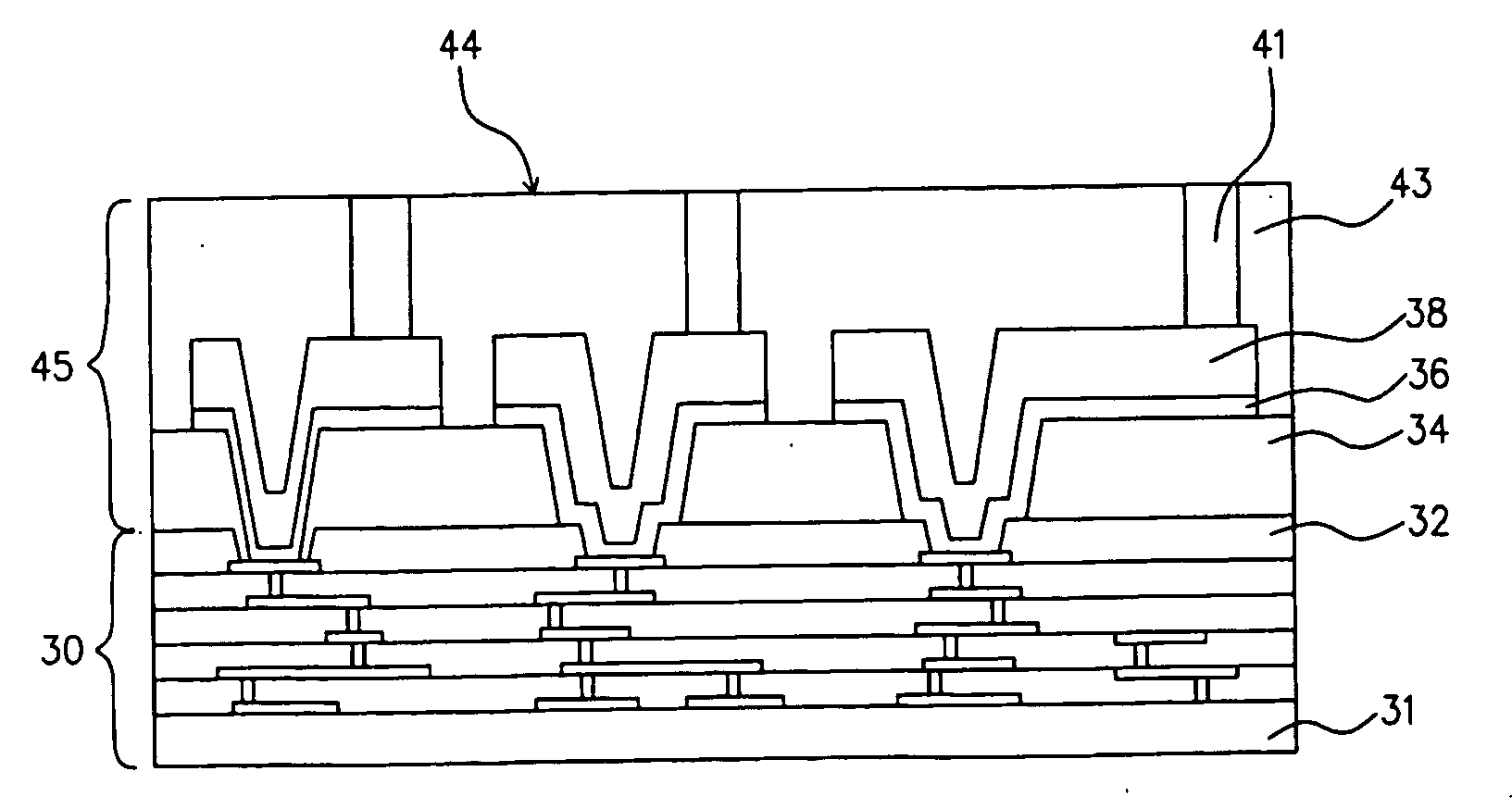

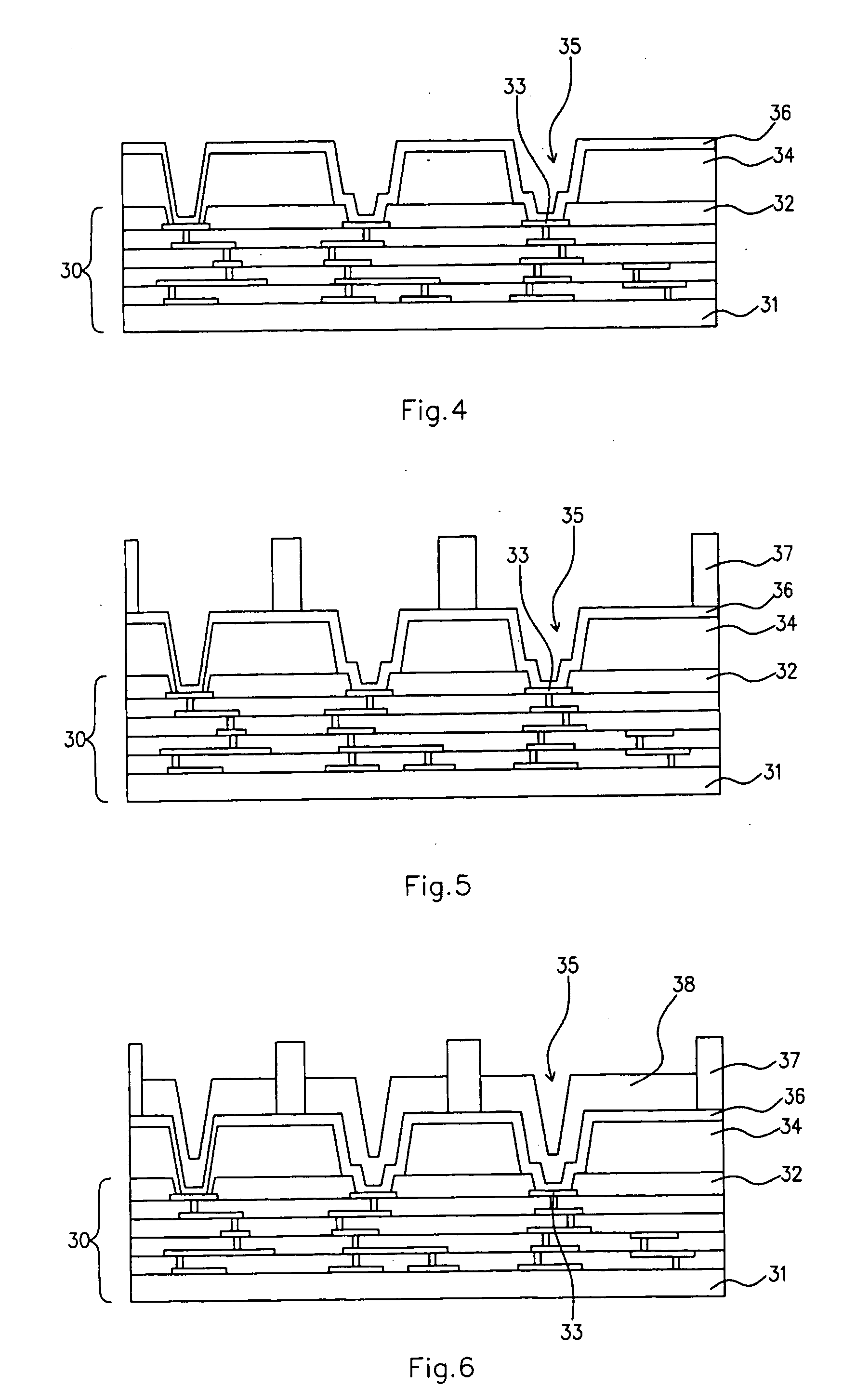

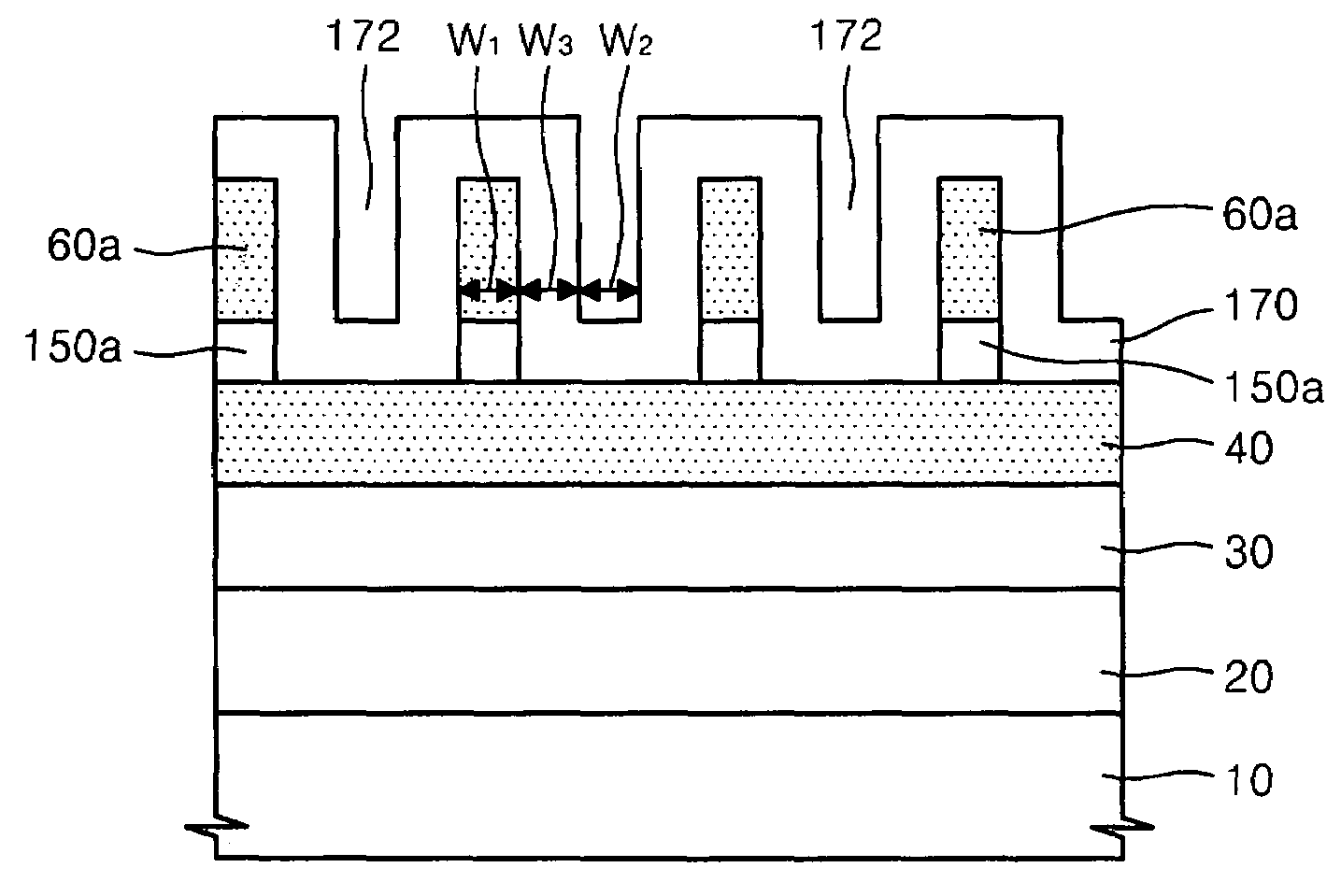

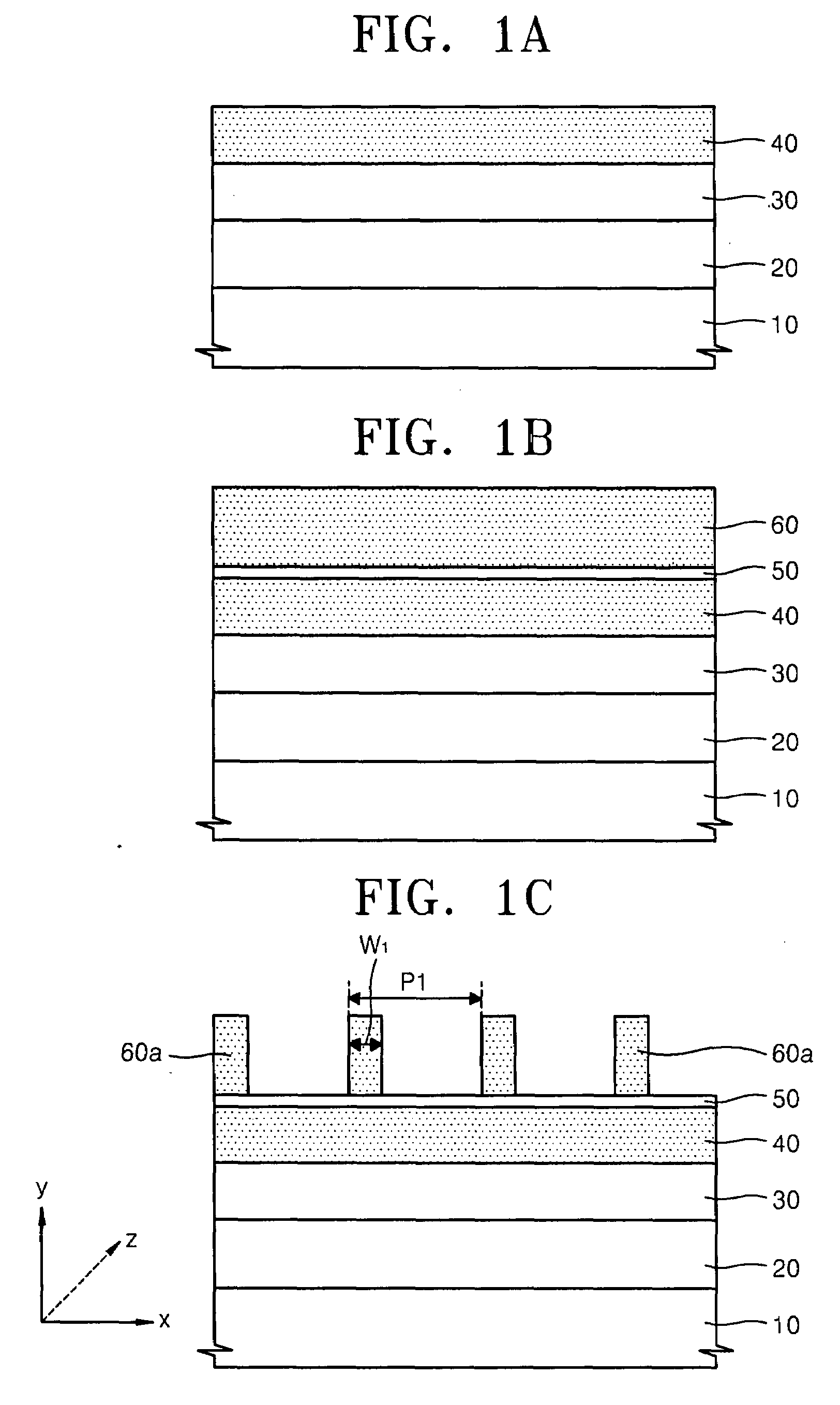

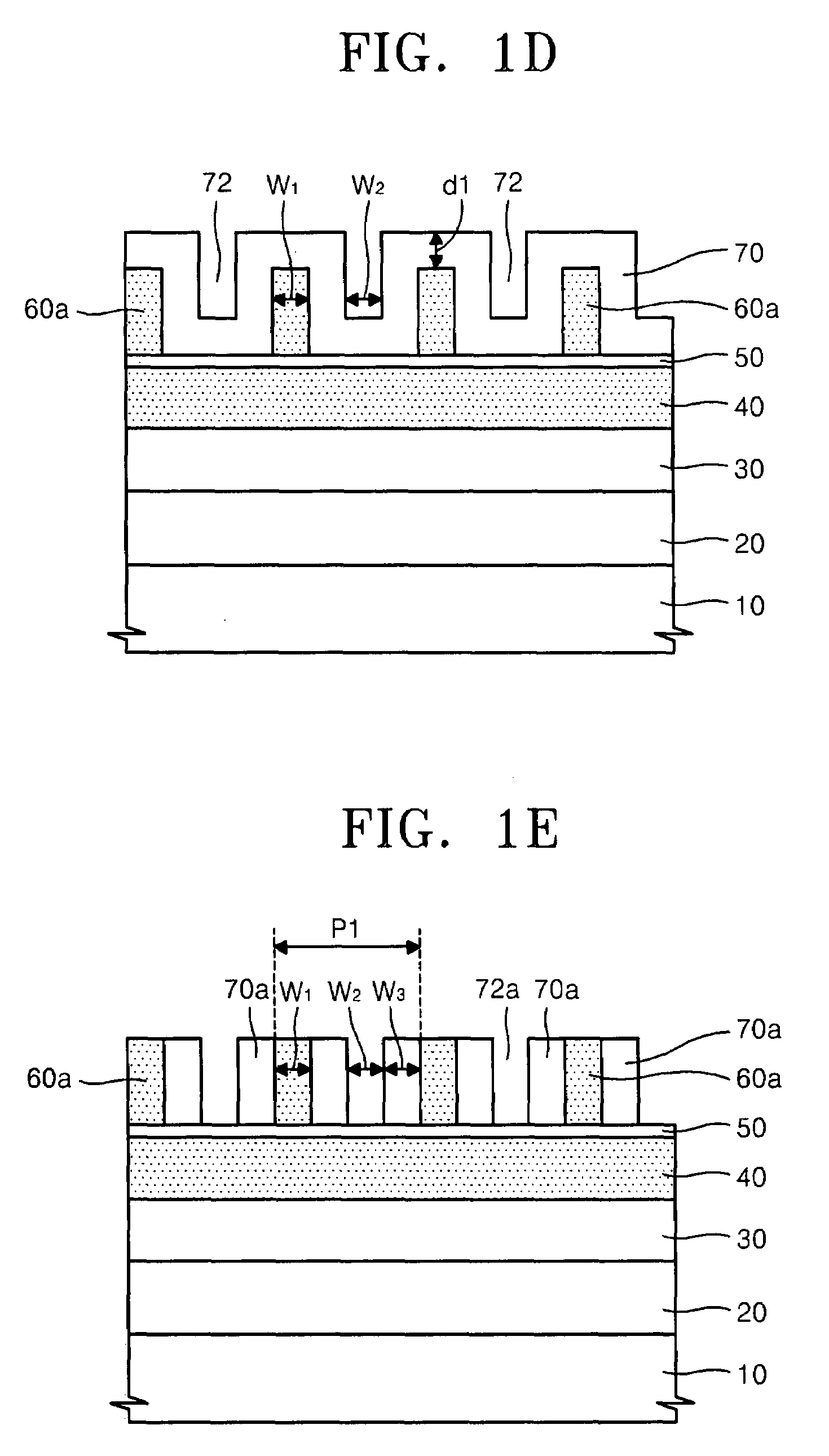

Method for forming hard mask patterns having a fine pitch and method for forming a semiconductor device using the same

ActiveUS20080131793A1Overcome disadvantagesDecorative surface effectsSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A method for forming hard mask patterns includes, sequentially forming first, second, and third hard mask layers formed of materials having different etching selectivities on a substrate, forming first sacrificial patterns having a first pitch therebetween on the third hard mask layer, forming fourth hard mask patterns with a second pitch between the first sacrificial patterns, the second pitch being substantially equal to about ½ of the first pitch, patterning the third hard mask layer to form third hard mask patterns using the fourth hard mask patterns as an etch mask, patterning the second hard mask layer to form second hard mask patterns using the third and fourth hard mask patterns as an etch mask, and patterning the first hard mask layer to form first hard mask patterns with the second pitch therebetween using the second and third hard mask patterns as an etch mask.

Owner:SAMSUNG ELECTRONICS CO LTD