Patents

Literature

55 results about "Flip chip interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

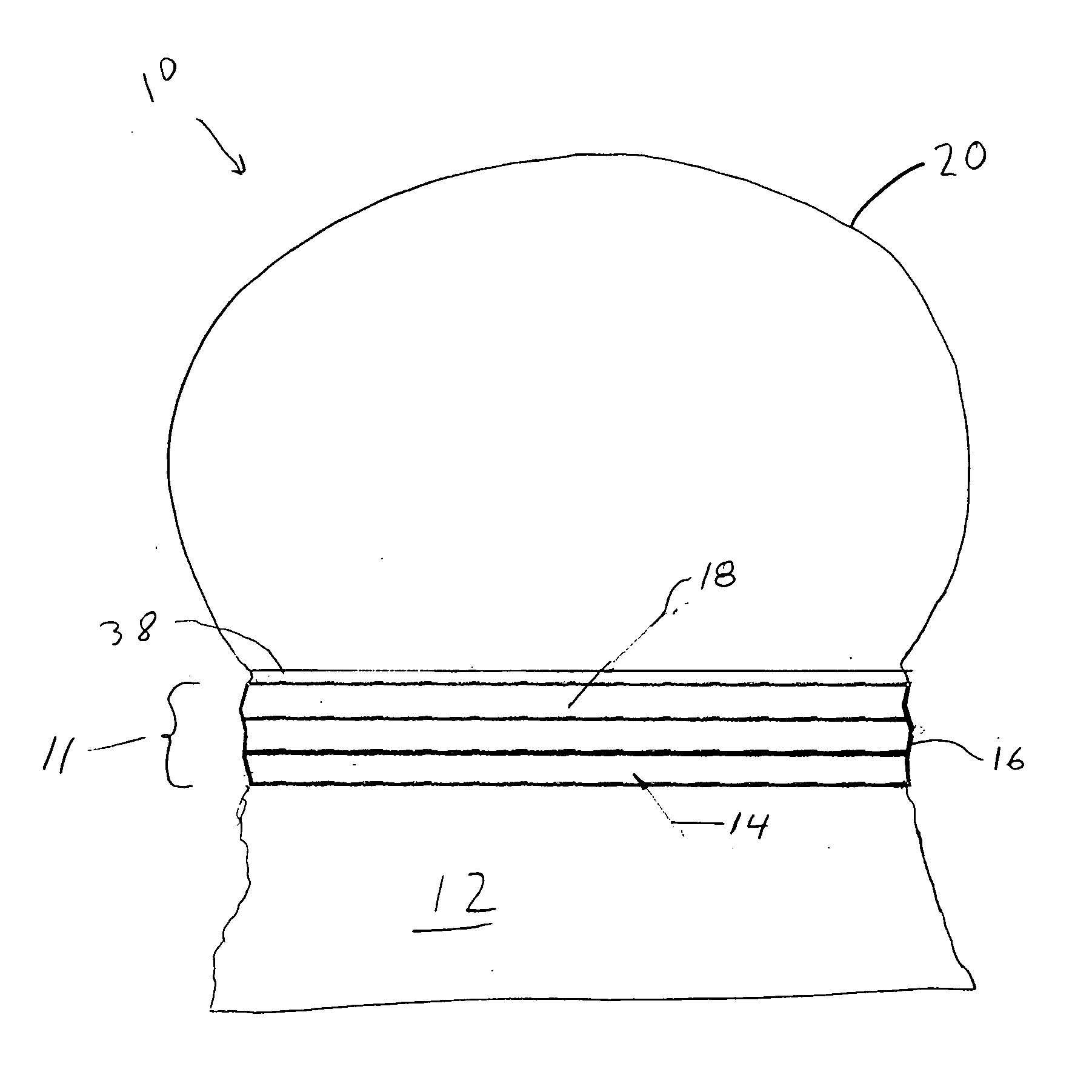

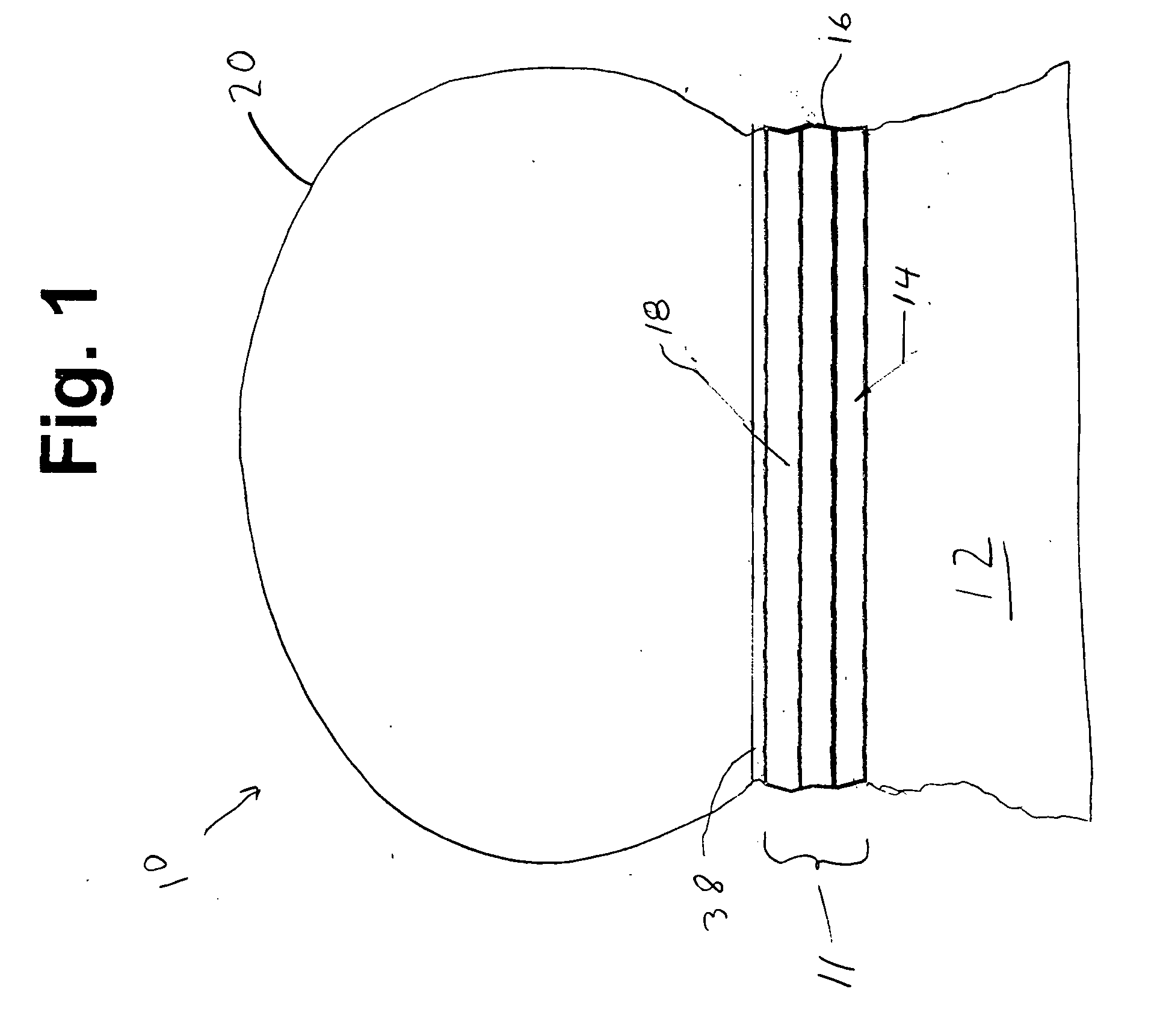

Pillar connections for semiconductor chips and method of manufacture

InactiveUS6578754B1Reduce chanceInduced in connectionSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor chip

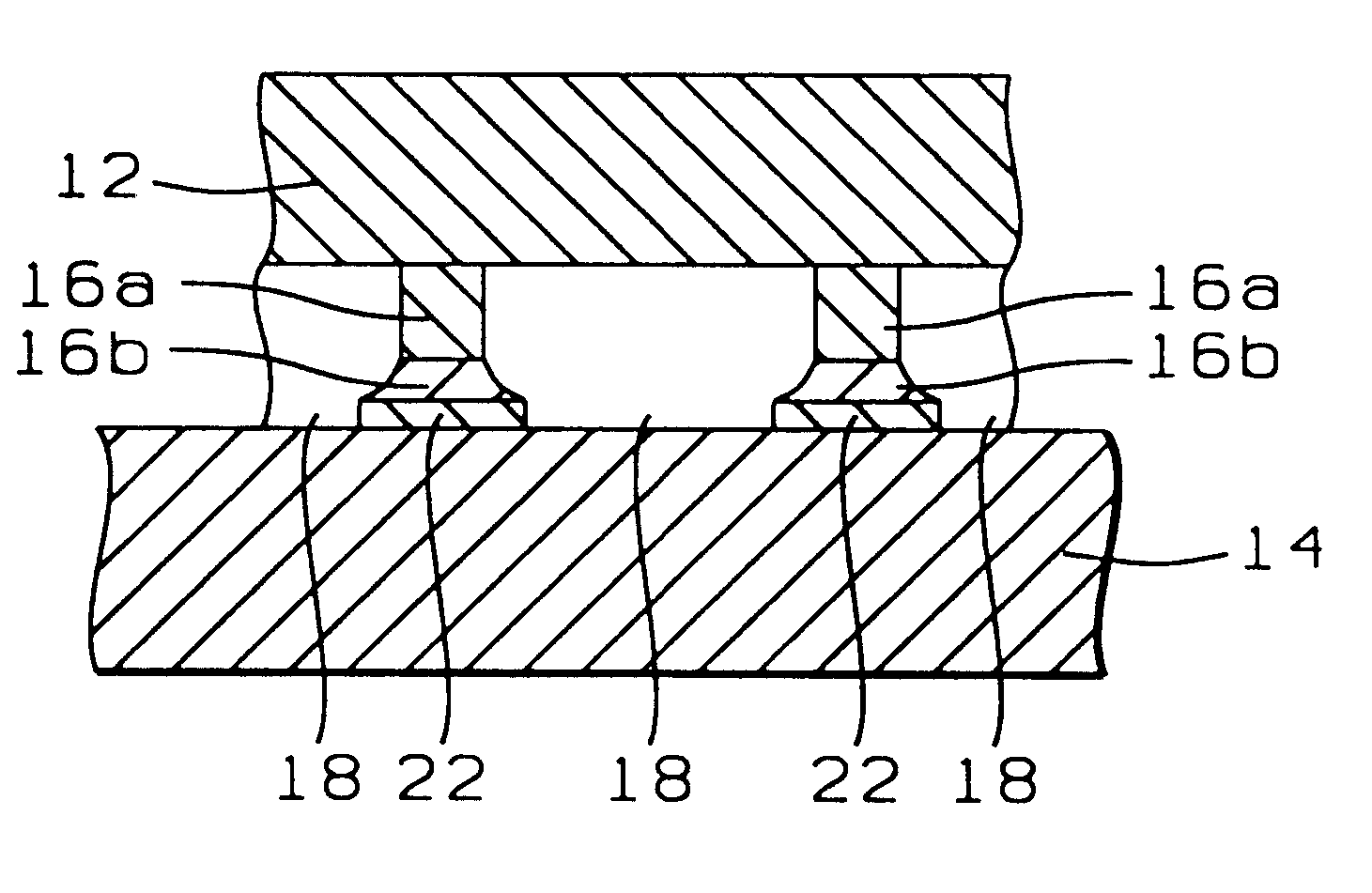

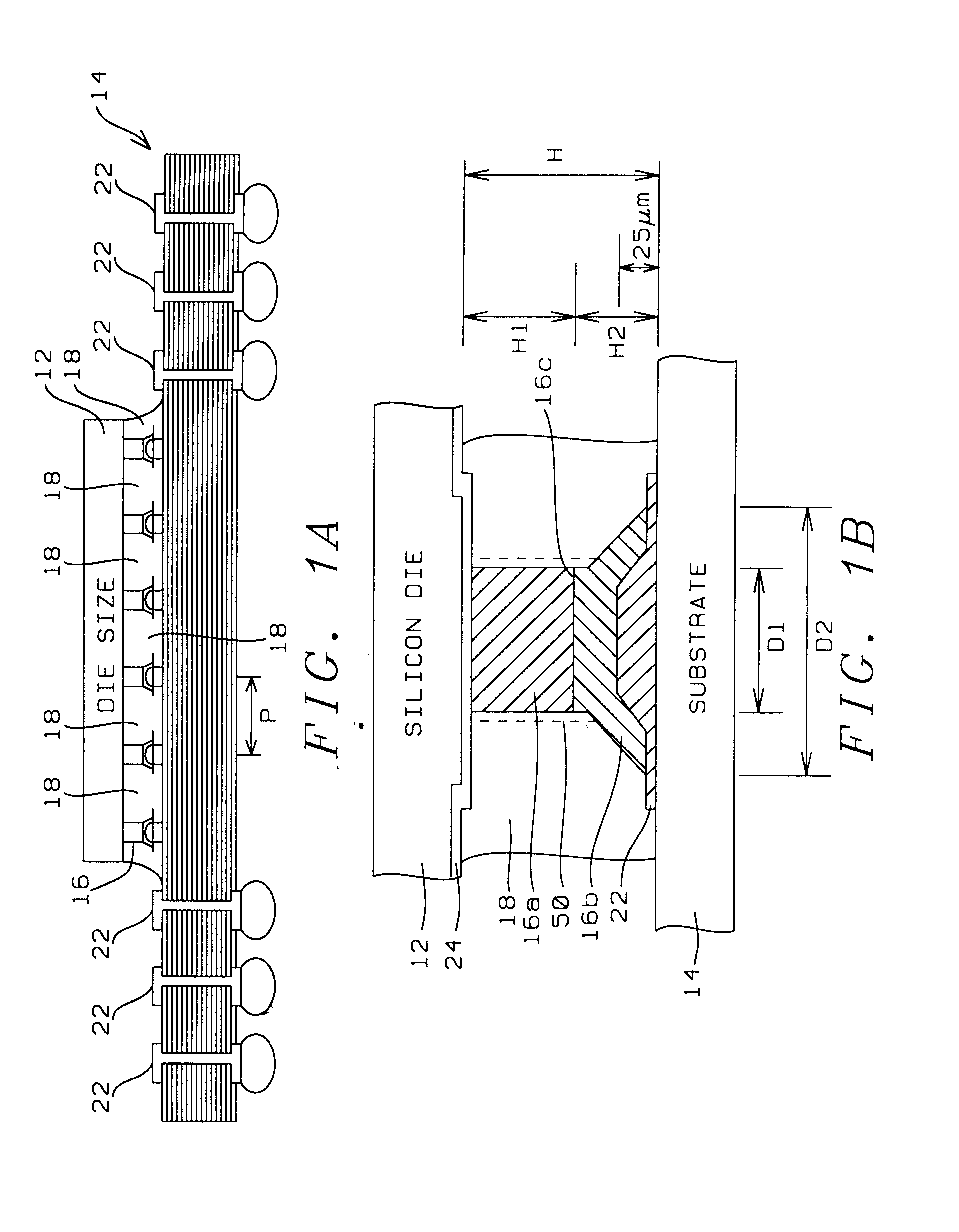

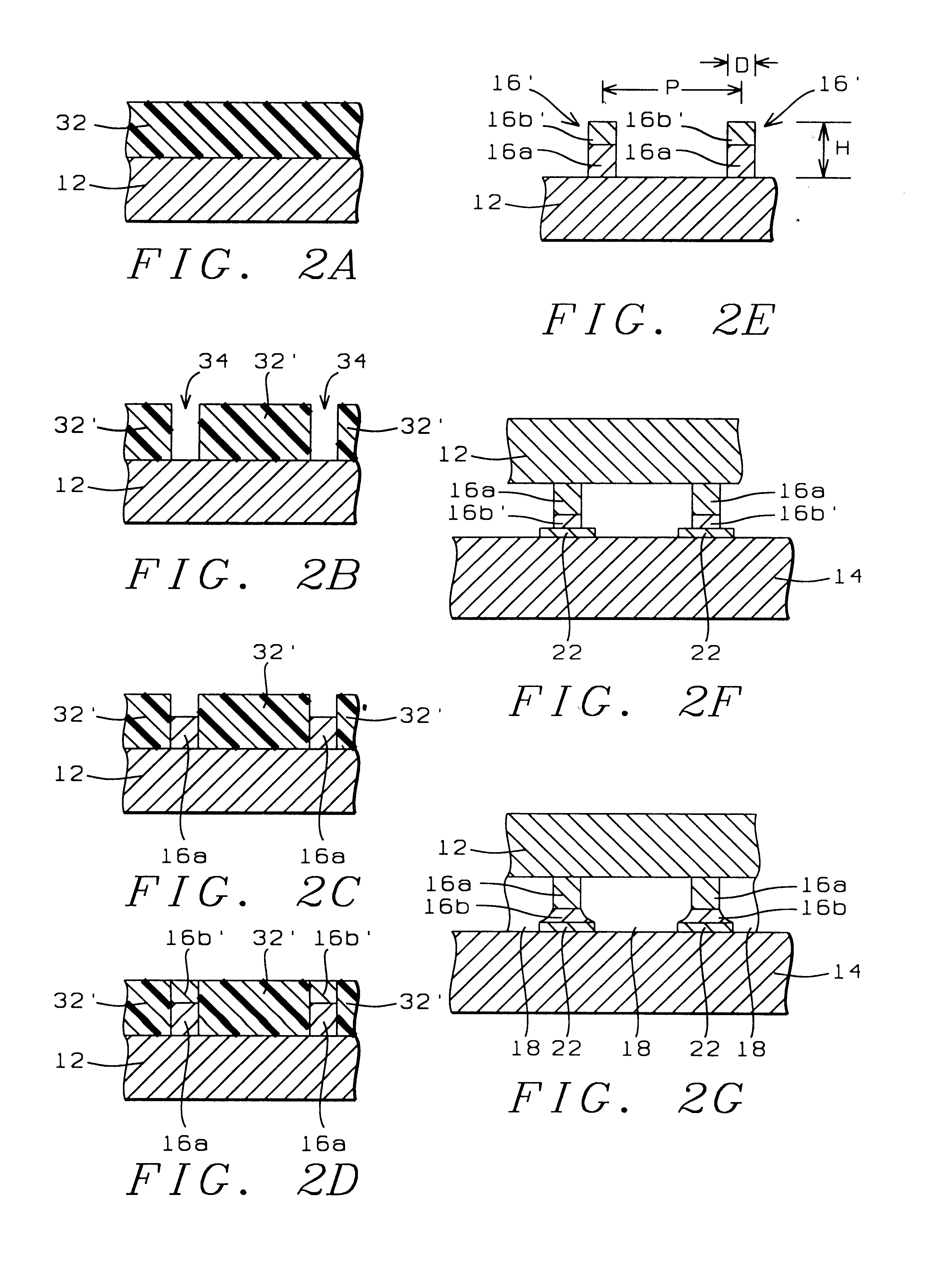

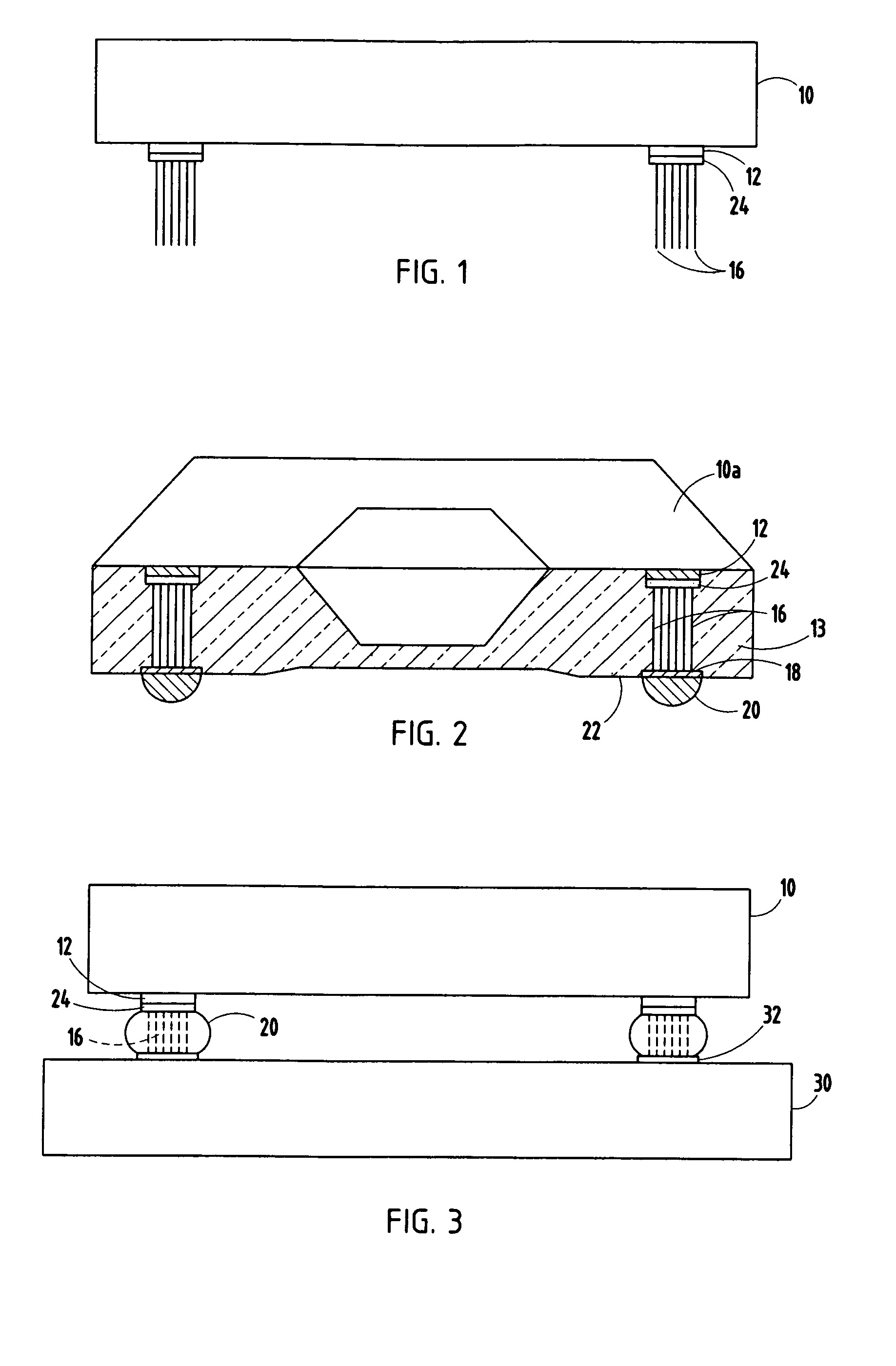

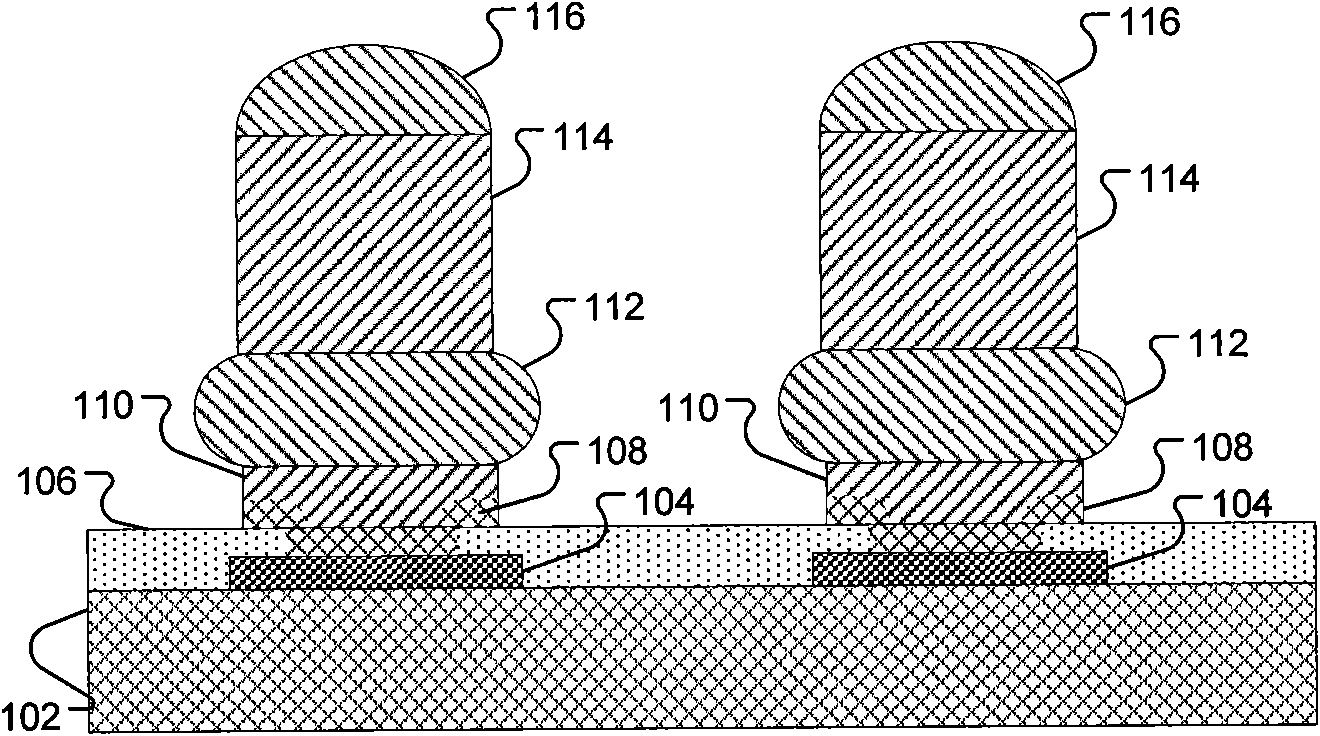

A flip chip interconnect system comprises and elongated pillar comprising two elongated portions, one portion including copper and another portion including solder. The portion including copper is in contact with the semiconductor chip and has a length preferably of more than 55 microns to reduce the effect of .alpha. particles from the solder from affecting electronic devices on the chip. The total length of the pillar is preferably in the range of 80 to 120 microns.

Owner:ADVANPAK SOLUTIONS PTE

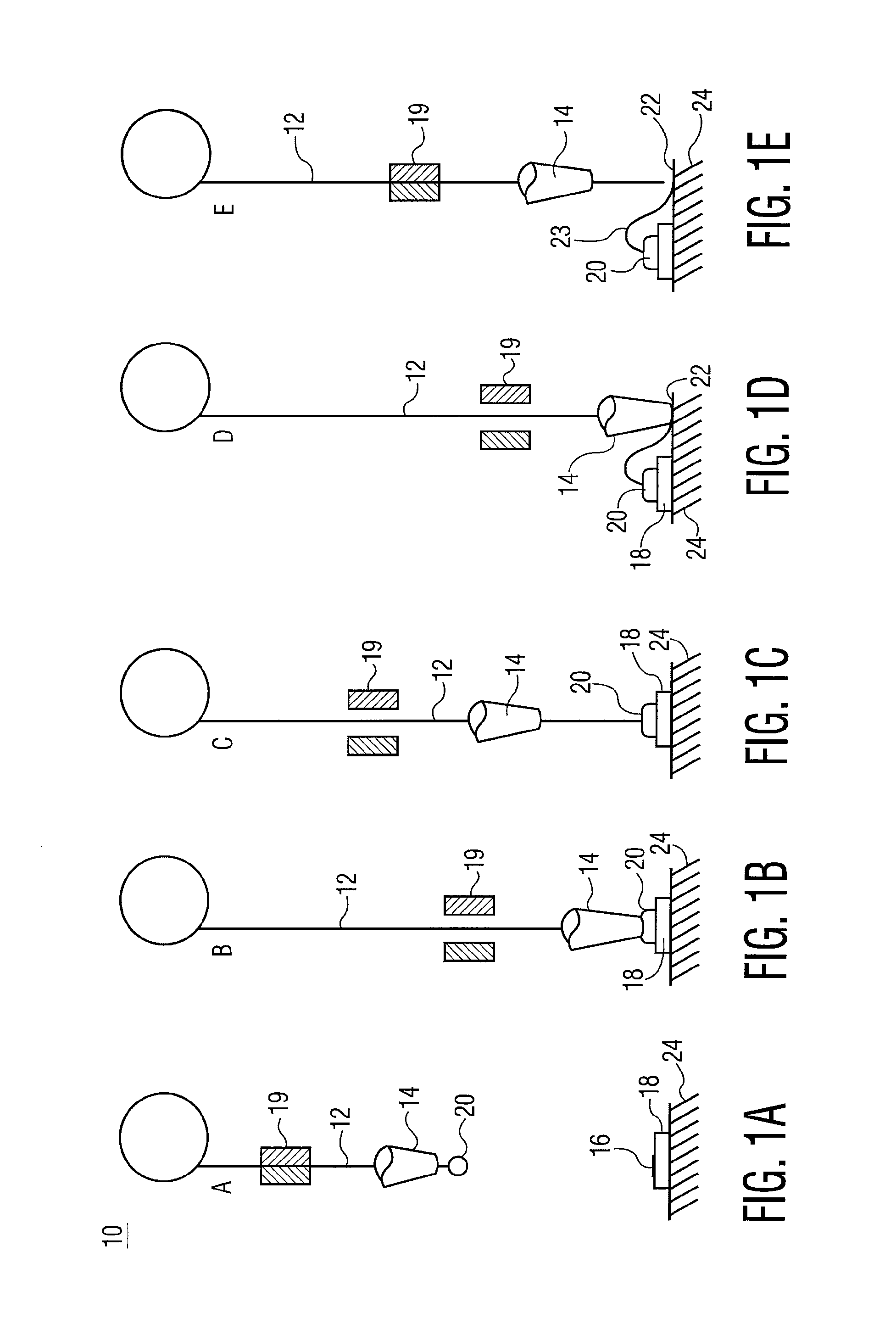

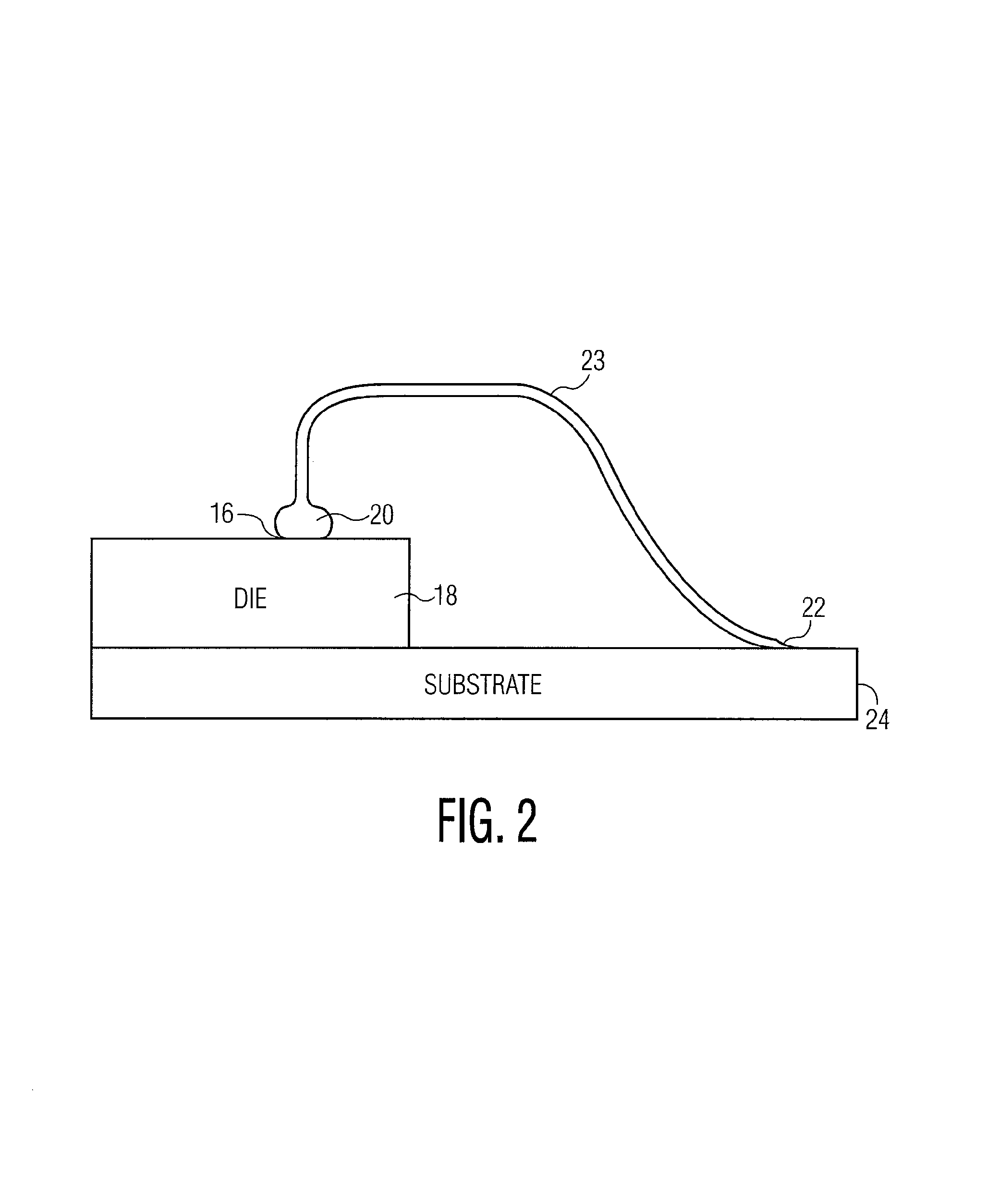

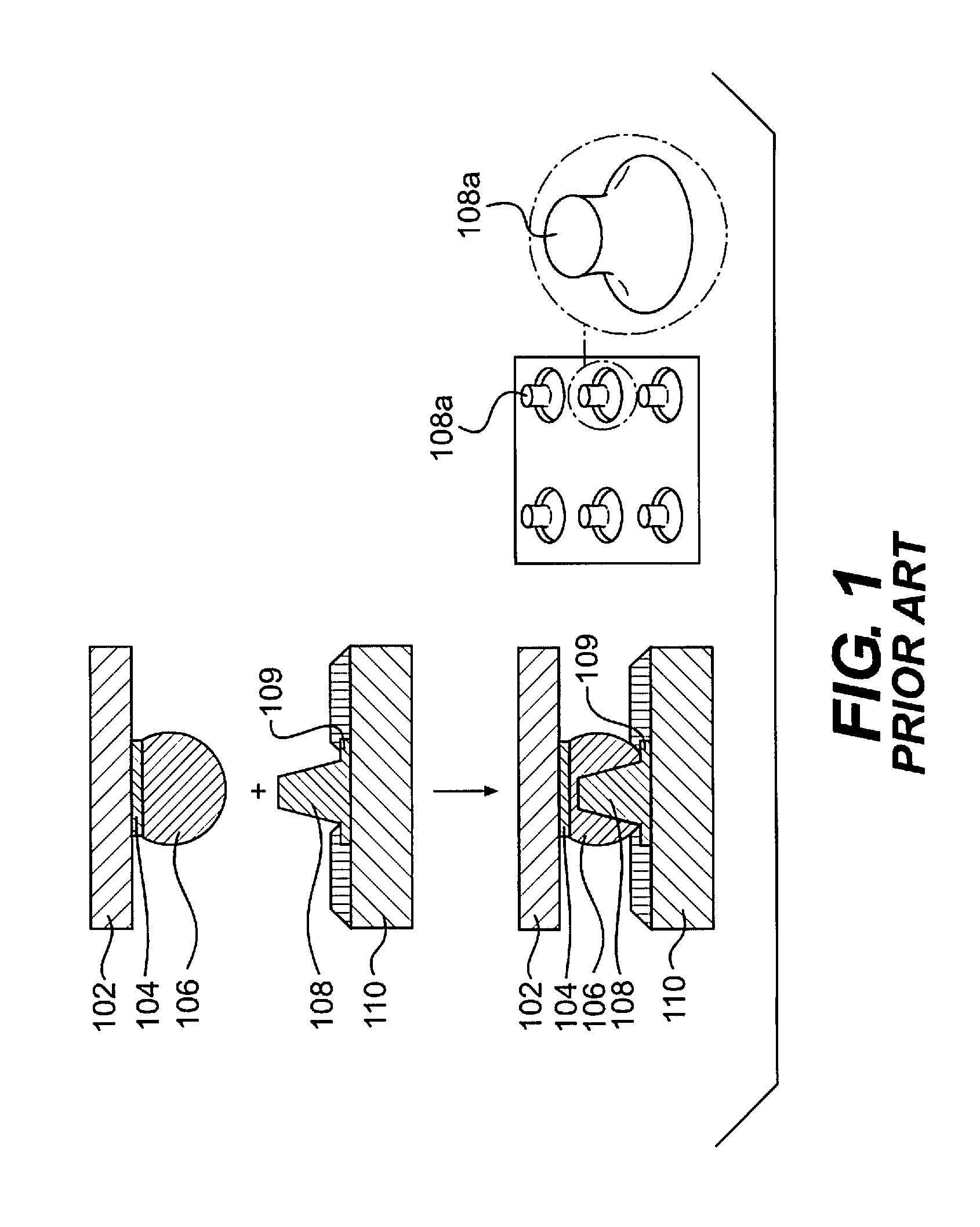

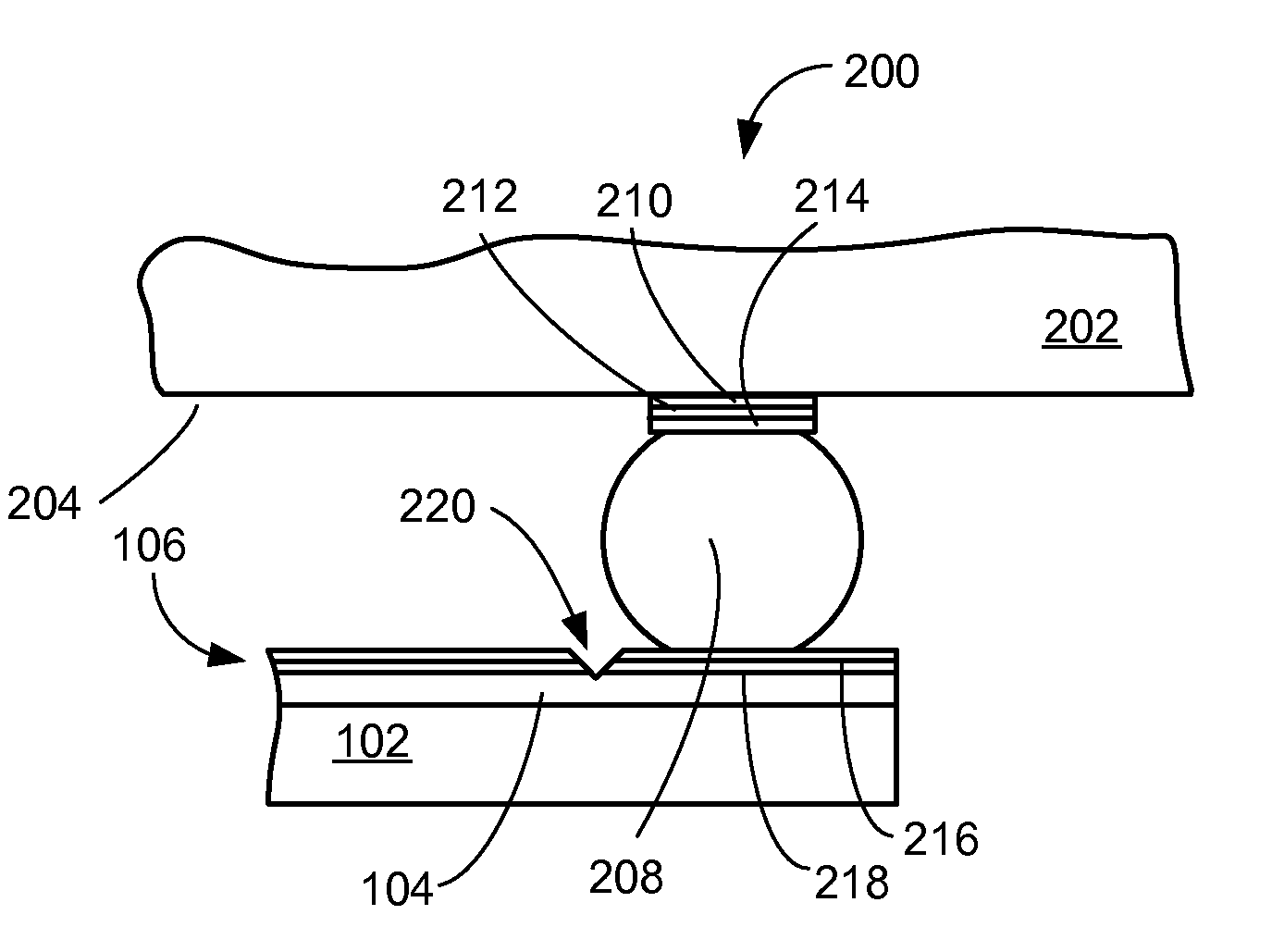

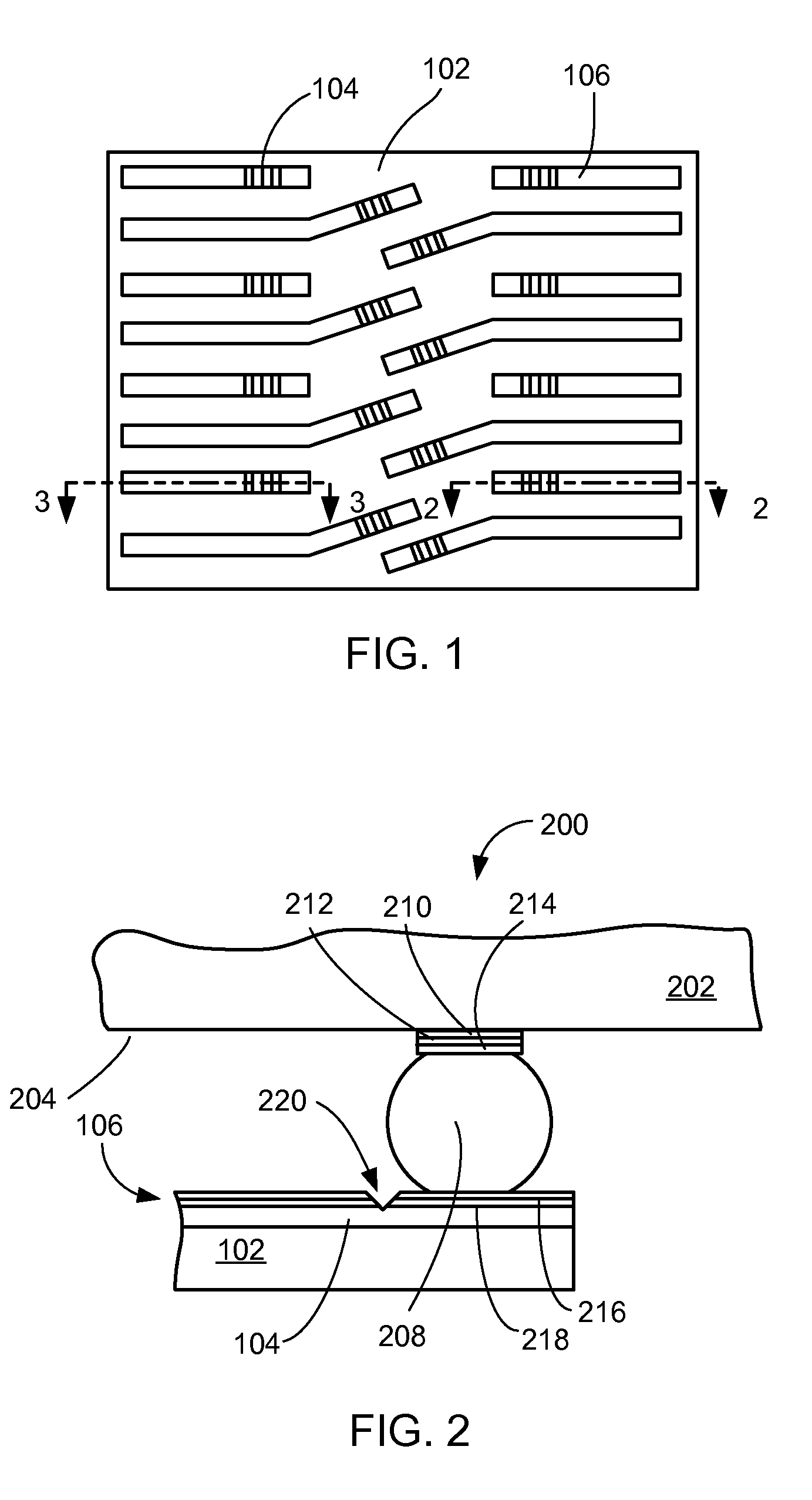

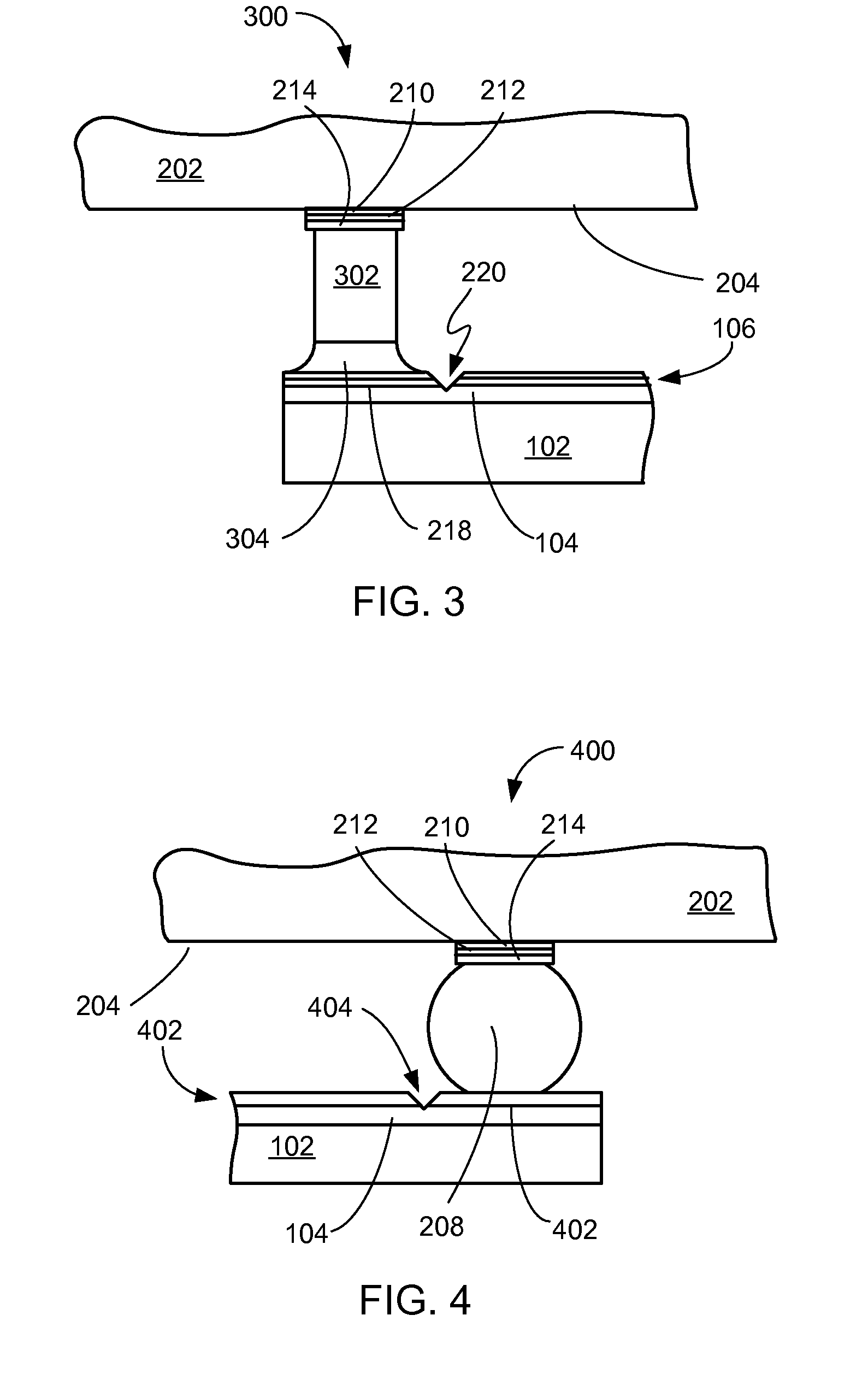

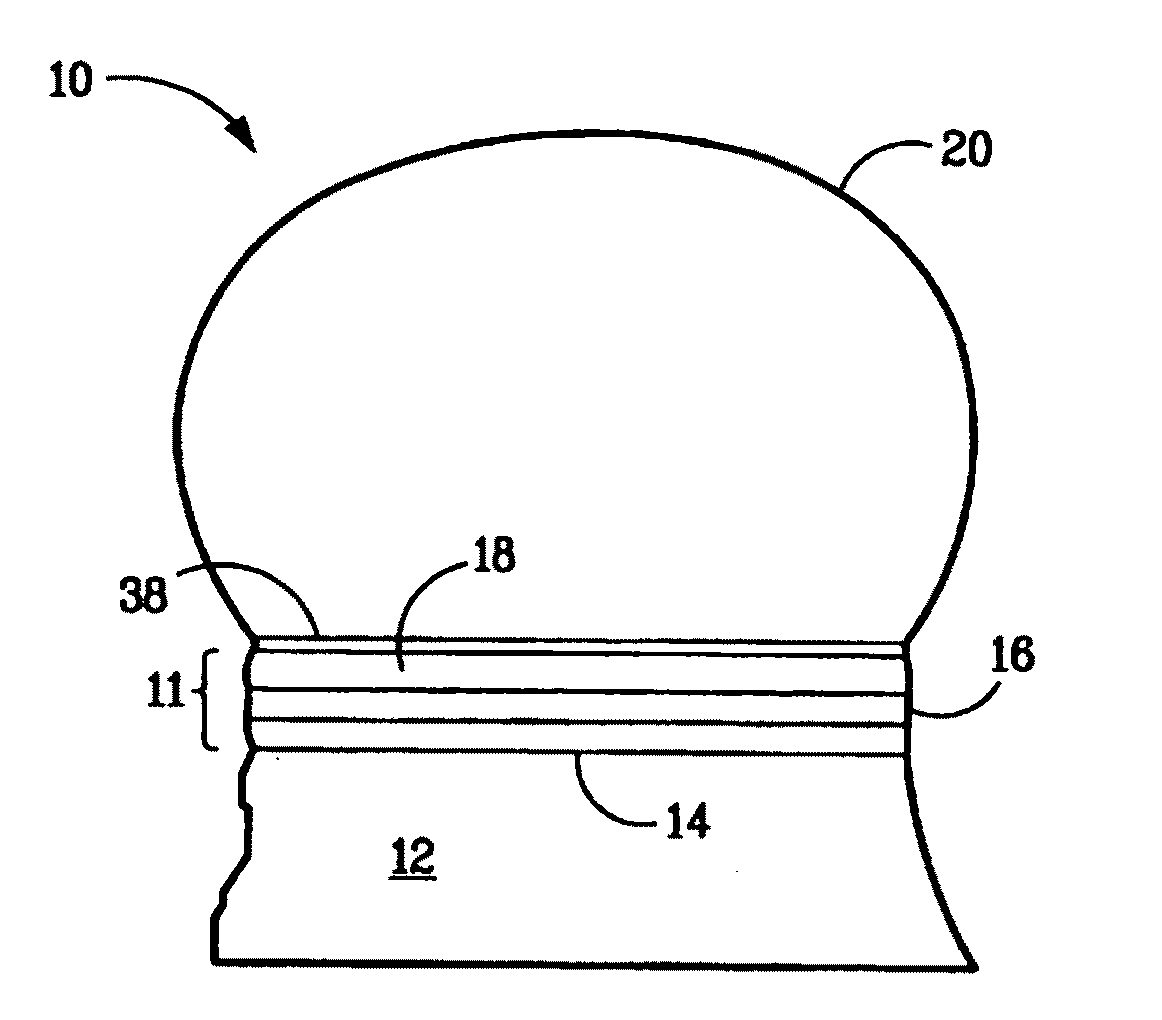

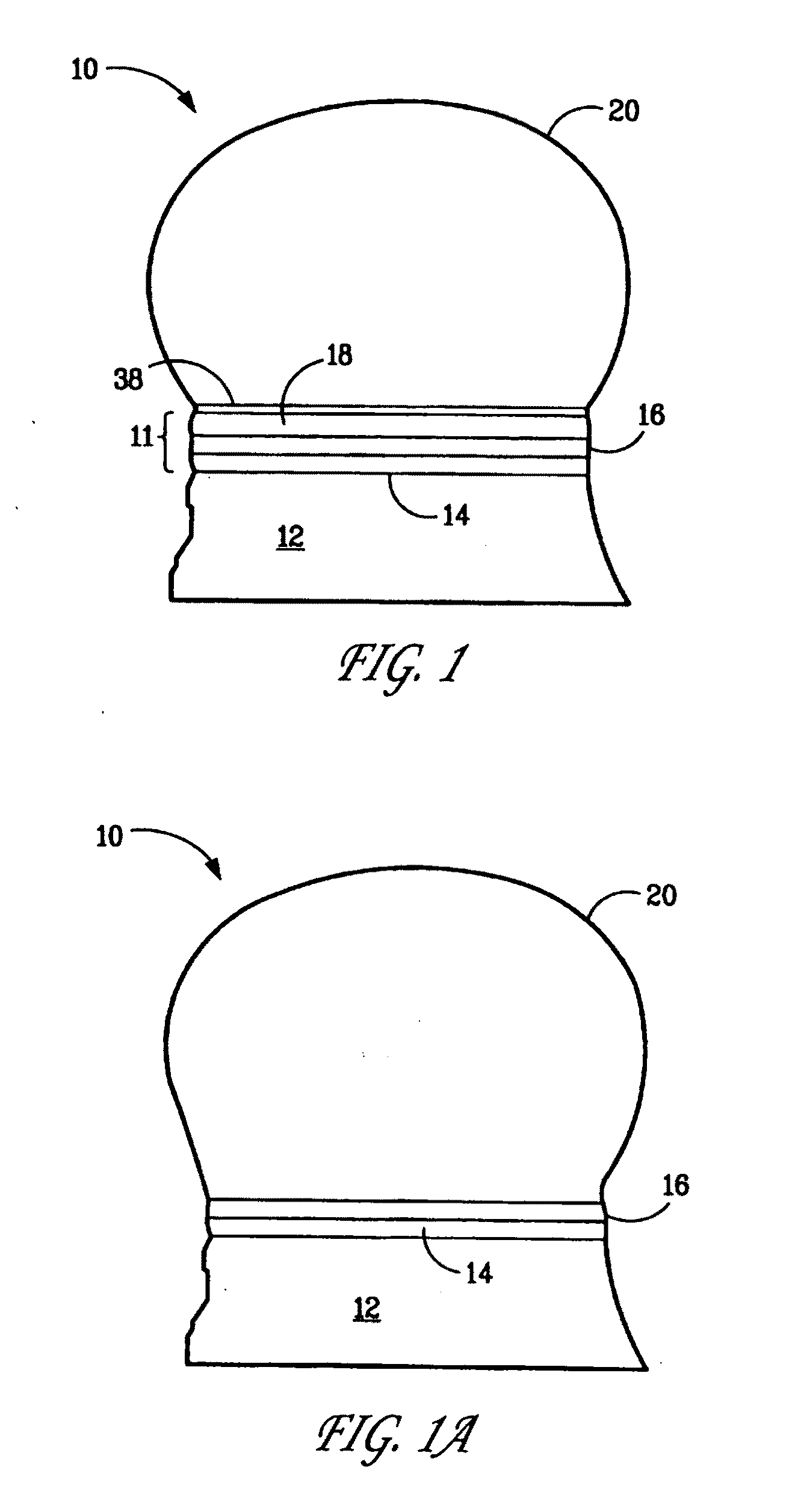

Method and apparatus for forming bumps for semiconductor interconnections using a wire bonding machine

InactiveUS7229906B2Increase the gapMinimizes wire sagSolid-state devicesSemiconductor/solid-state device manufacturingFlip chip interconnectWire loop

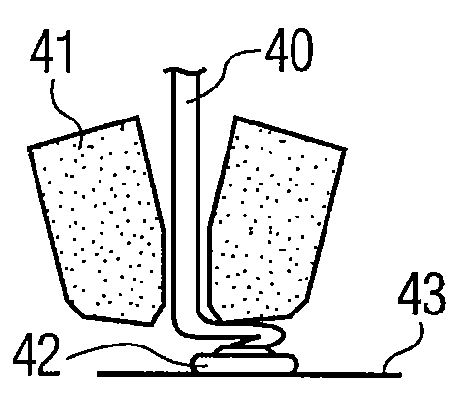

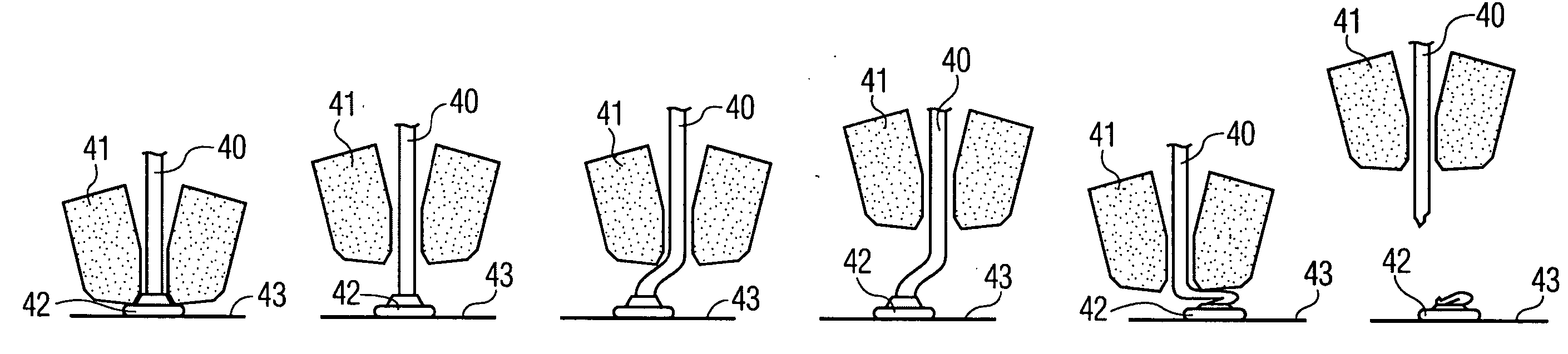

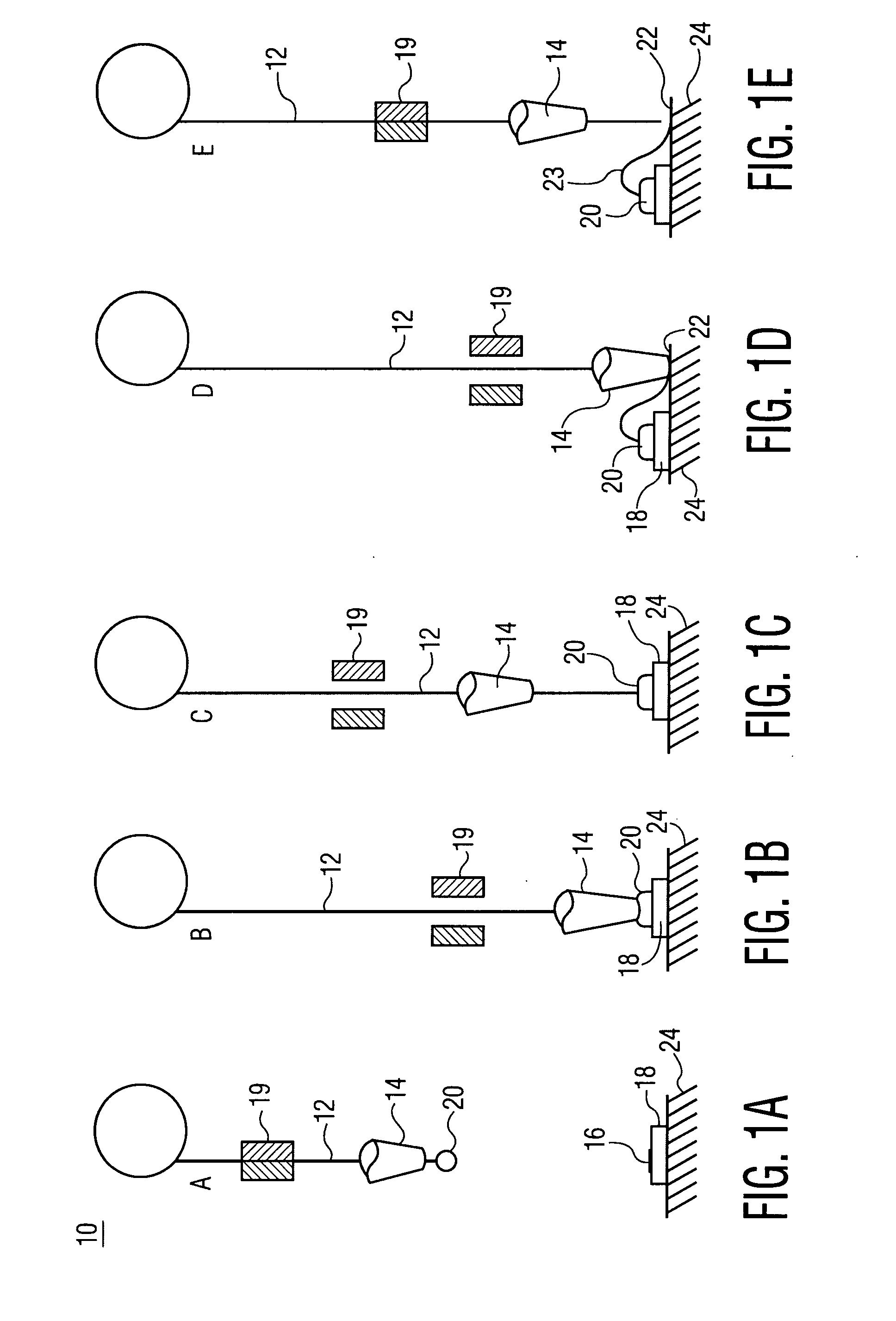

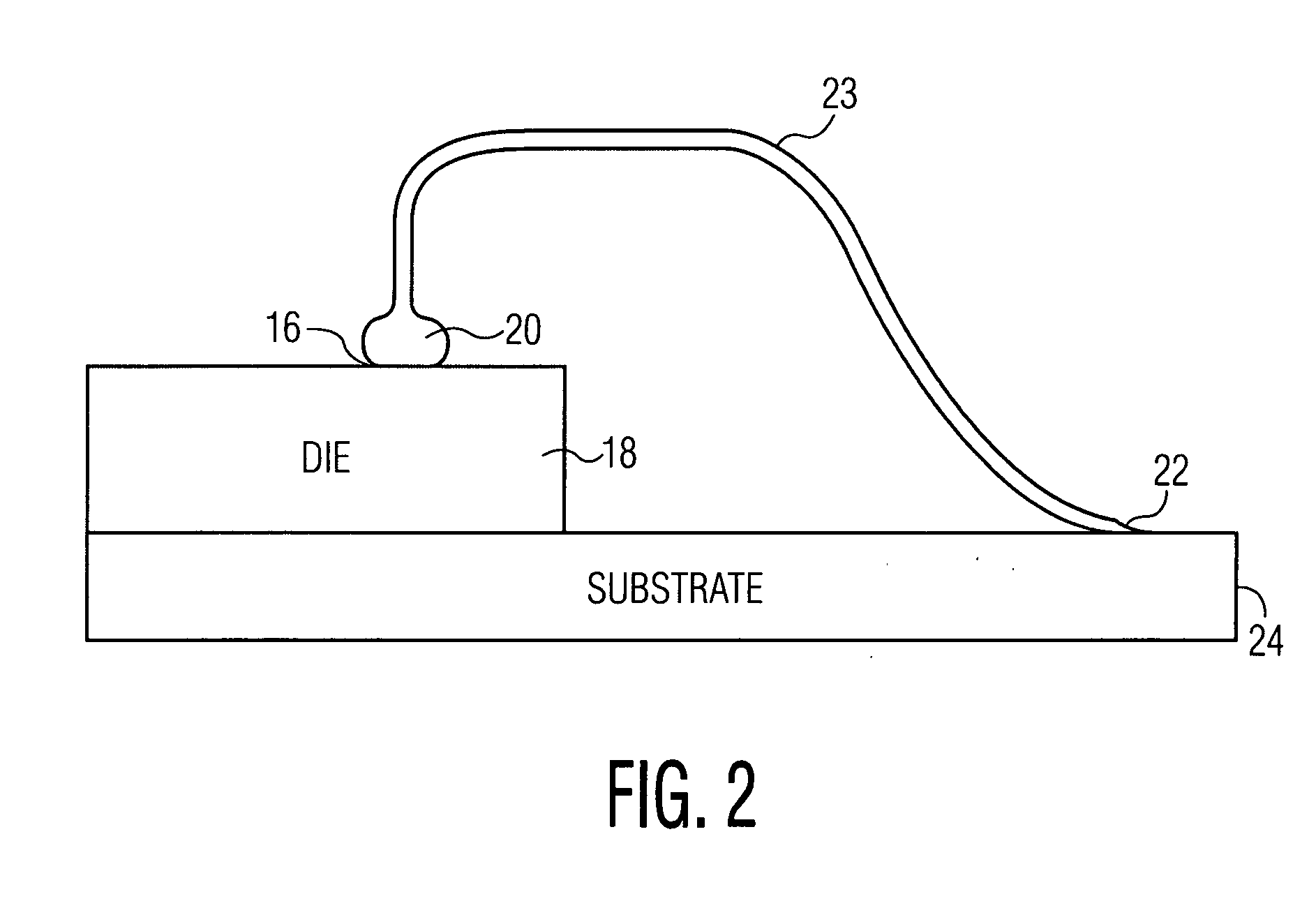

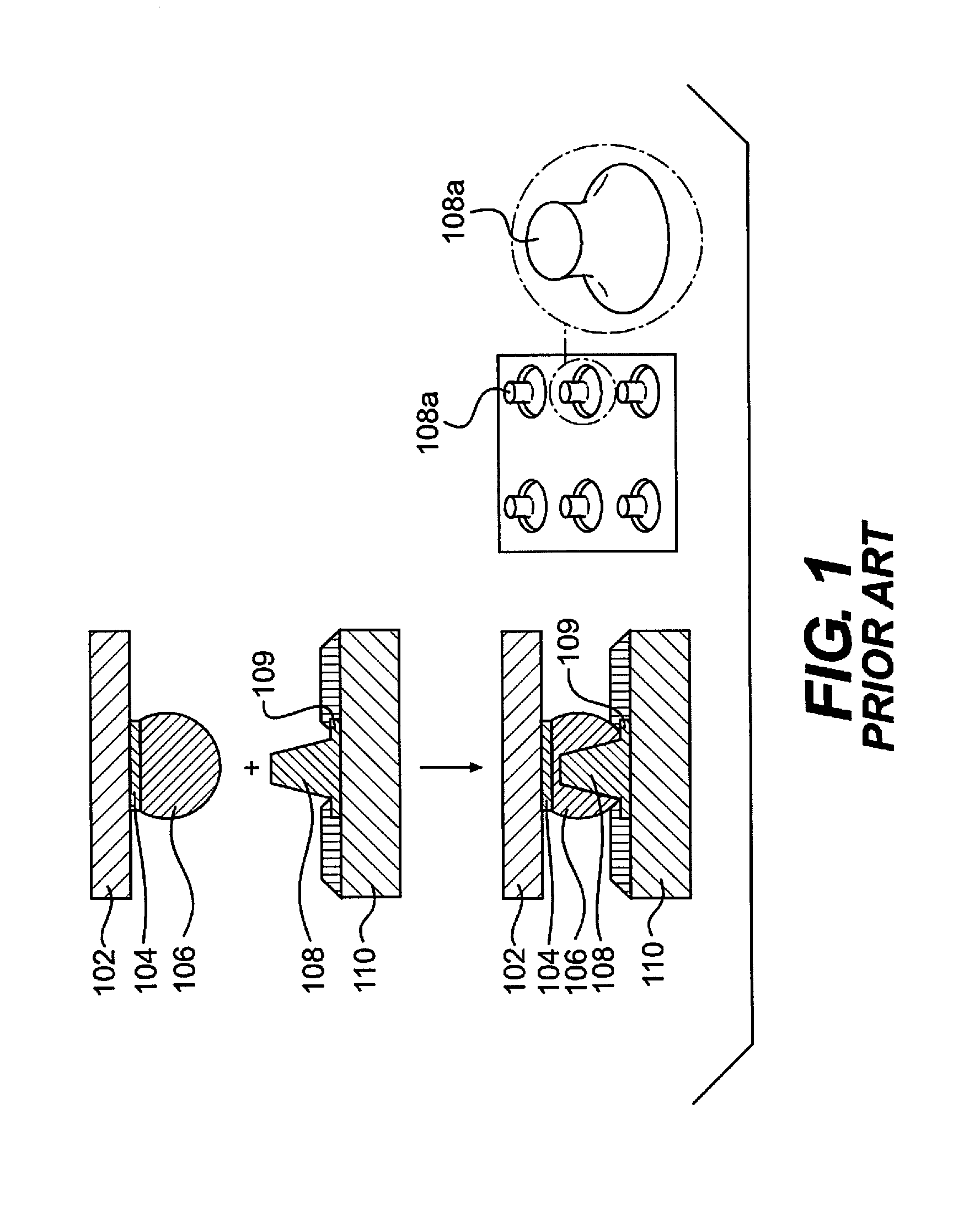

The present invention is a method and apparatus for forming a bump for semiconductor interconnect applications, such as reverse wire bonding or stud bumping for flip chip interconnections. The bump is formed by (1) ball bonding at the bump site, (2) raising the capillary a predetermined height after forming the ball bond with the wire paying out of the capillary tip, (3) moving the capillary laterally a predetermined distance, preferably in a direction toward the site of other end of the wire loop, if the bump is to be used as the platform for a stitch bond of a wire loop, (4) raising the capillary further, and (5) moving the capillary diagonally downwardly and in the opposite direction of the first lateral motion. The wire is then severed by raising the capillary, closing the clamps and raising the capillary again to snap the wire pigtail off at the bump.

Owner:KULICKE & SOFFA IND INC

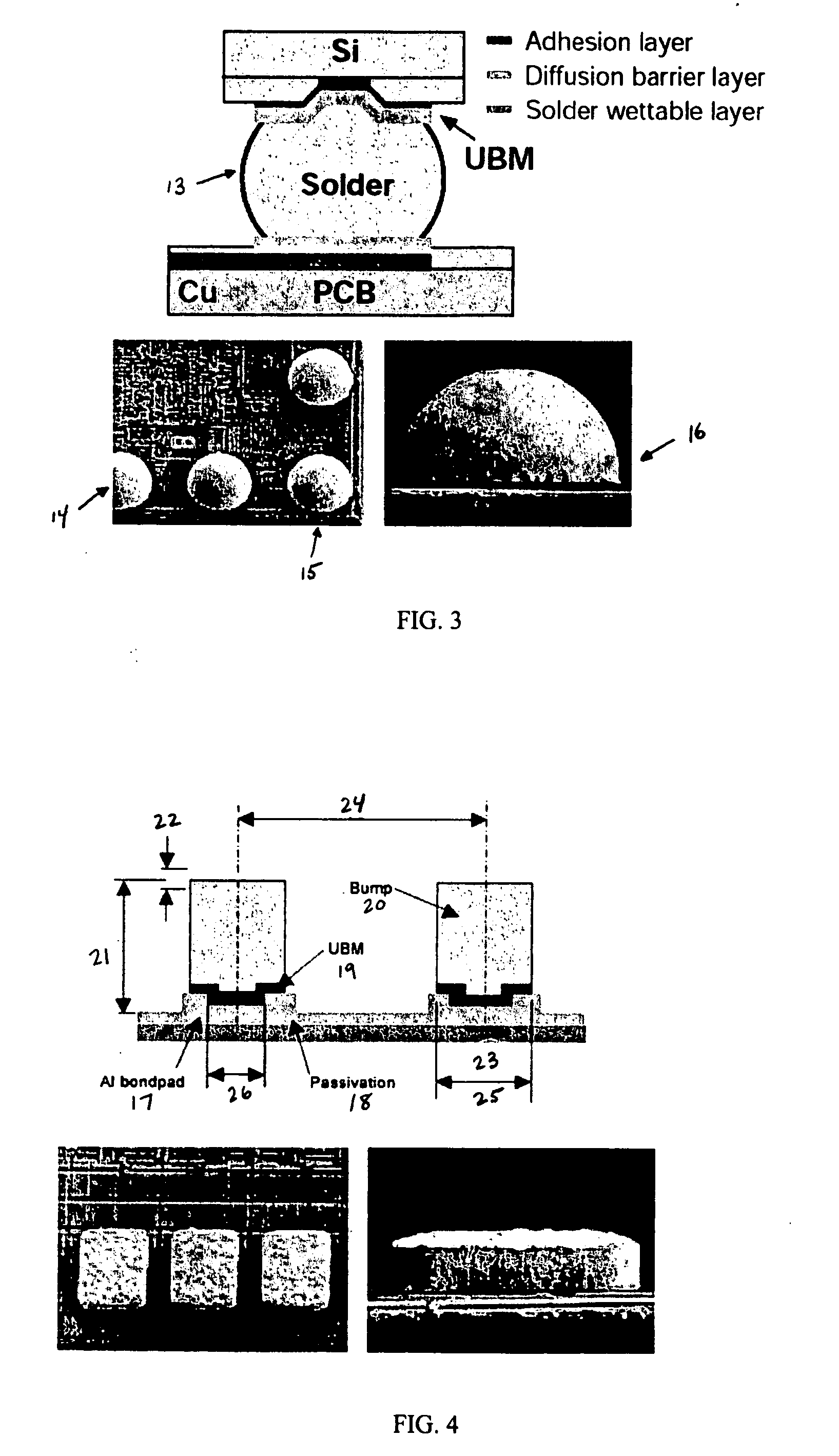

Interconnections for flip-chip using lead-free solders and having reaction barrier layers

InactiveUS20050224966A1Soft errorCost-effectivePrinted circuit assemblingSemiconductor/solid-state device detailsFlip chip interconnectSolder ball

An interconnection structure suitable for flip-chip attachment of microelectronic device chips to packages, comprising a two, three or four layer ball-limiting composition including an adhesion / reaction barrier layer, and having a solder wettable layer reactive with components of a tin-containing lead free solder, so that the solderable layer can be totally consumed during soldering, but a barrier layer remains after being placed in contact with the lead free solder during soldering. One or more lead-free solder balls is selectively situated on the solder wetting layer, the lead-free solder balls comprising tin as a predominant component and one or more alloying components.

Owner:ULTRATECH INT INC

Flip chip interconnection structure

InactiveUS7033859B2Lower yield strengthHigh elongation at breakPrinted circuit assemblingSemiconductor/solid-state device detailsFlip chip interconnectInterconnection

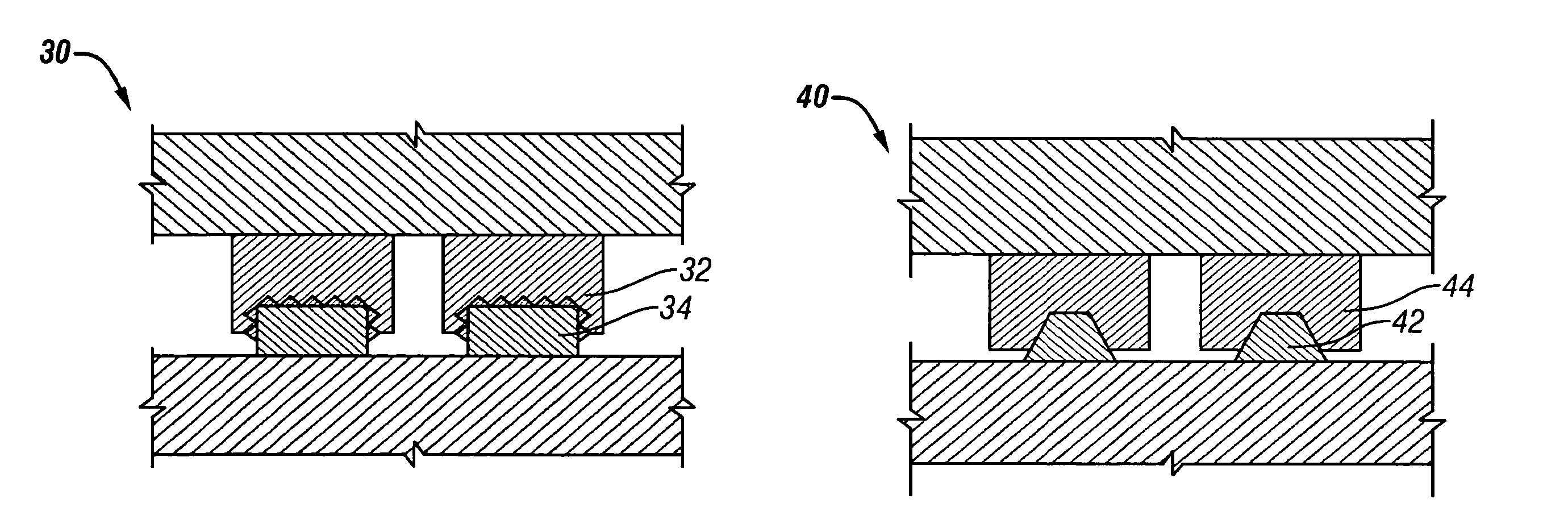

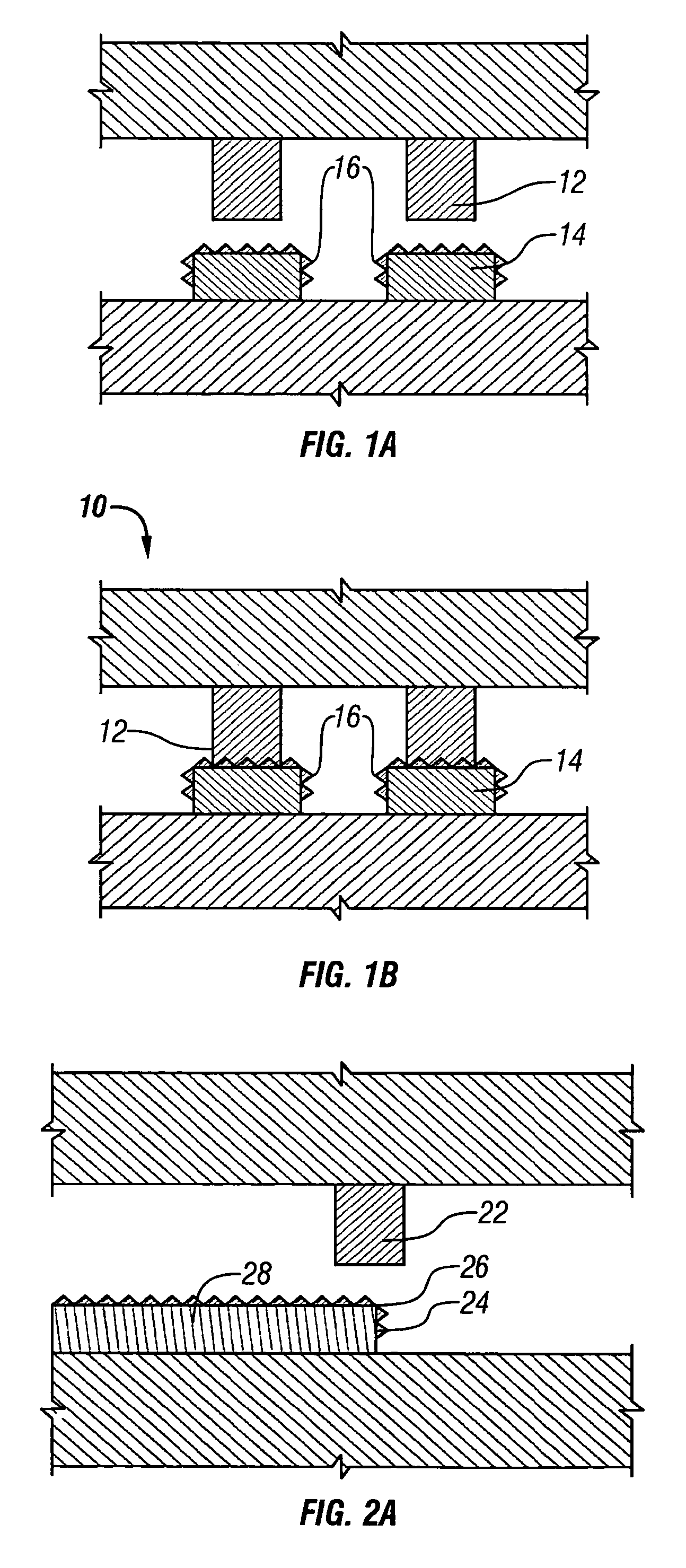

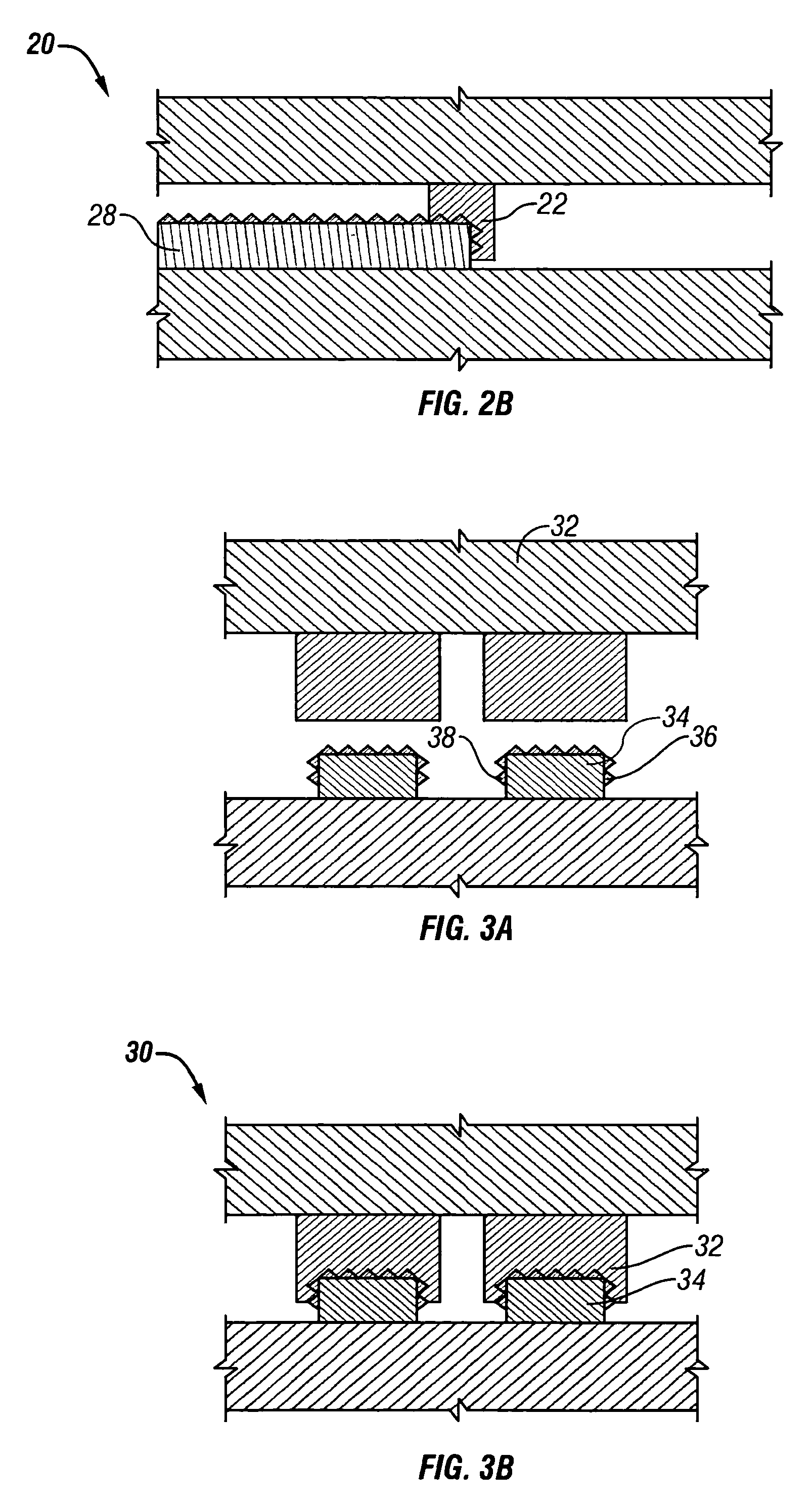

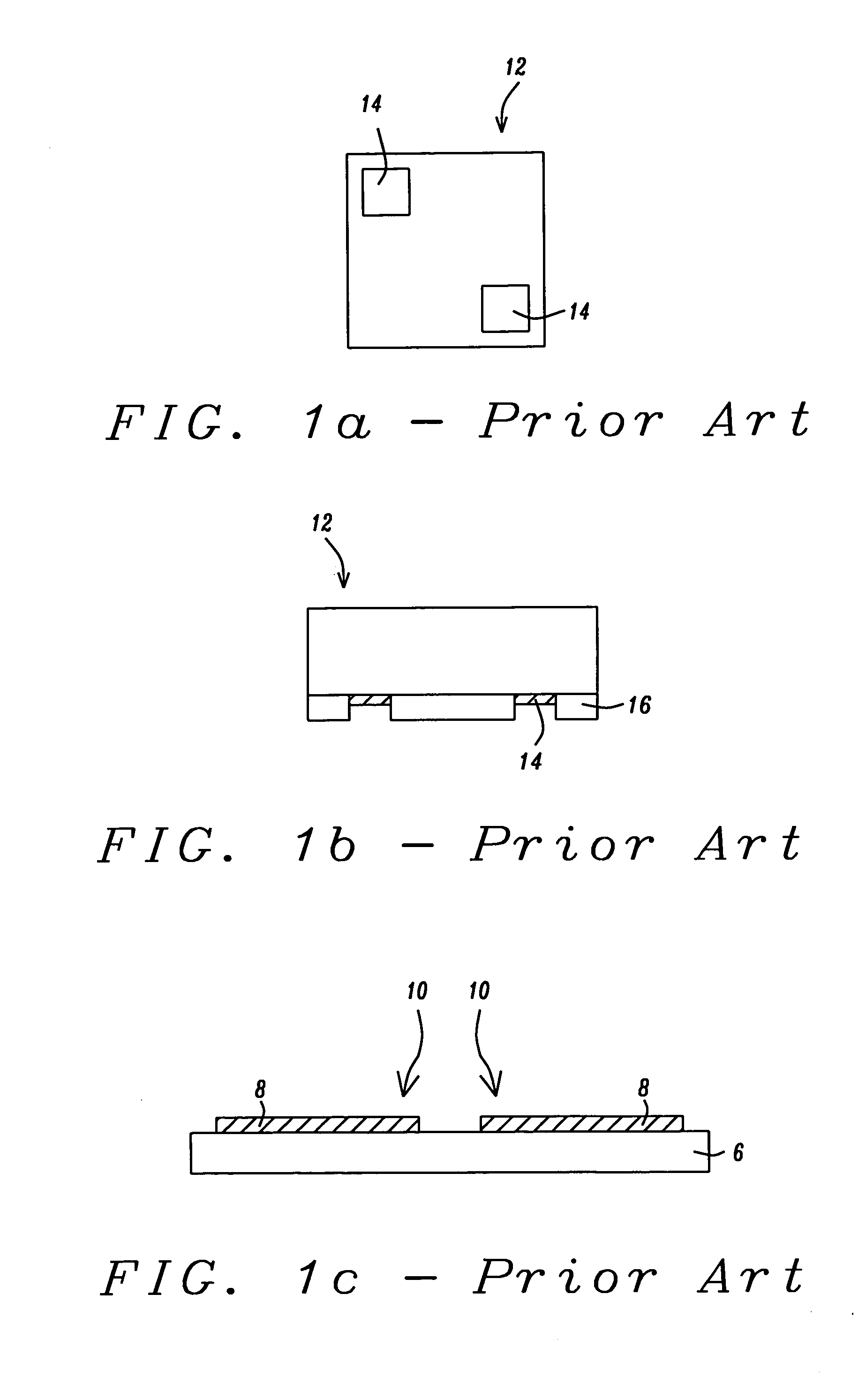

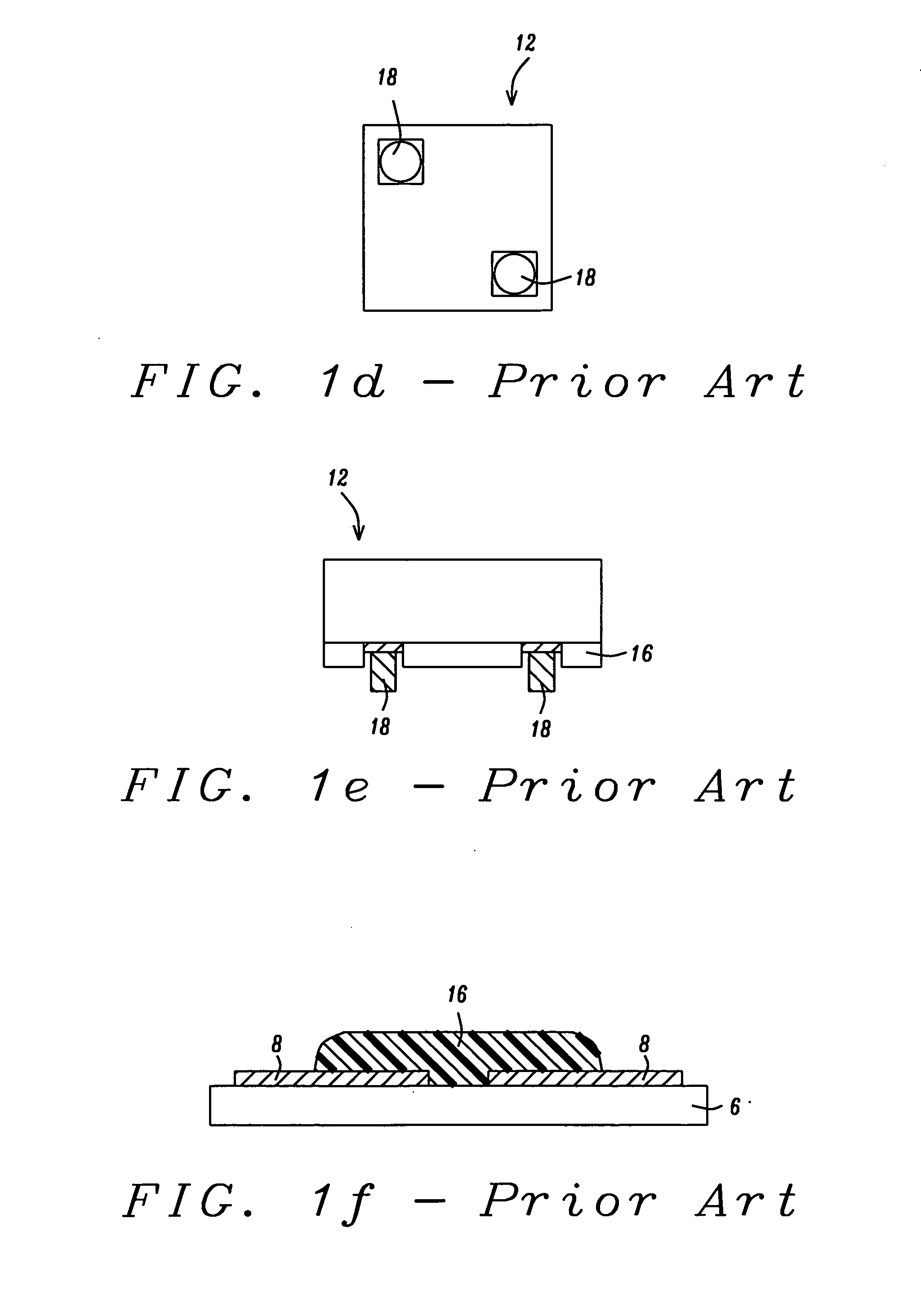

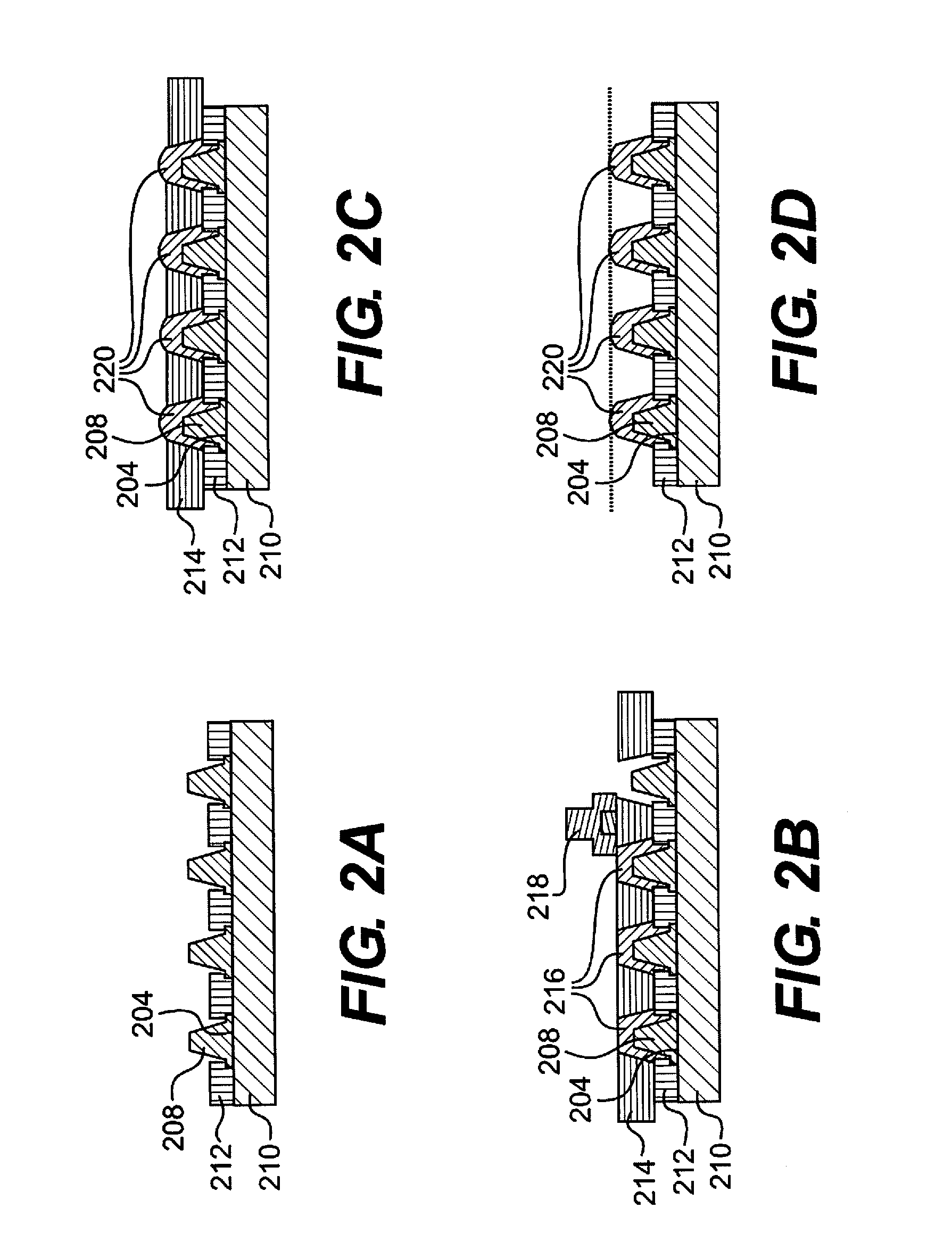

A flip chip interconnection structure is formed by mechanically interlocking joining surfaces of a first and second element. The first element, which may be a bump on an integrated circuit chip, includes a soft, deformable material with a low yield strength and high elongation to failure. The surface of the second element, which may for example be a substrate pad, is provided with asperities into which the first element deforms plastically under pressure to form the mechanical interlock.

Owner:STATS CHIPPAC LTD

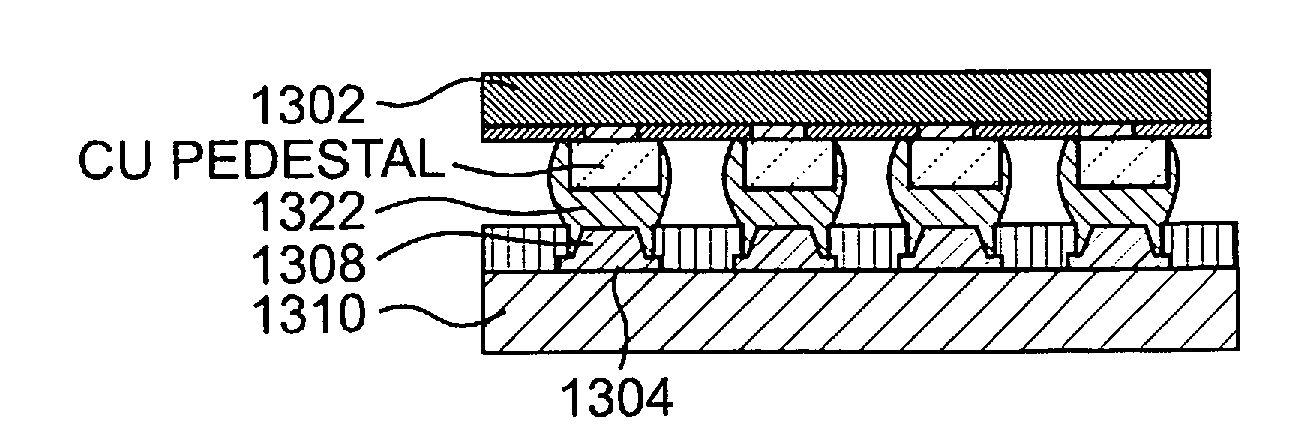

Copper Post Solder Bumps on Substrate

ActiveUS20120252168A1Relieve pressureEasy to cleanSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectEngineering

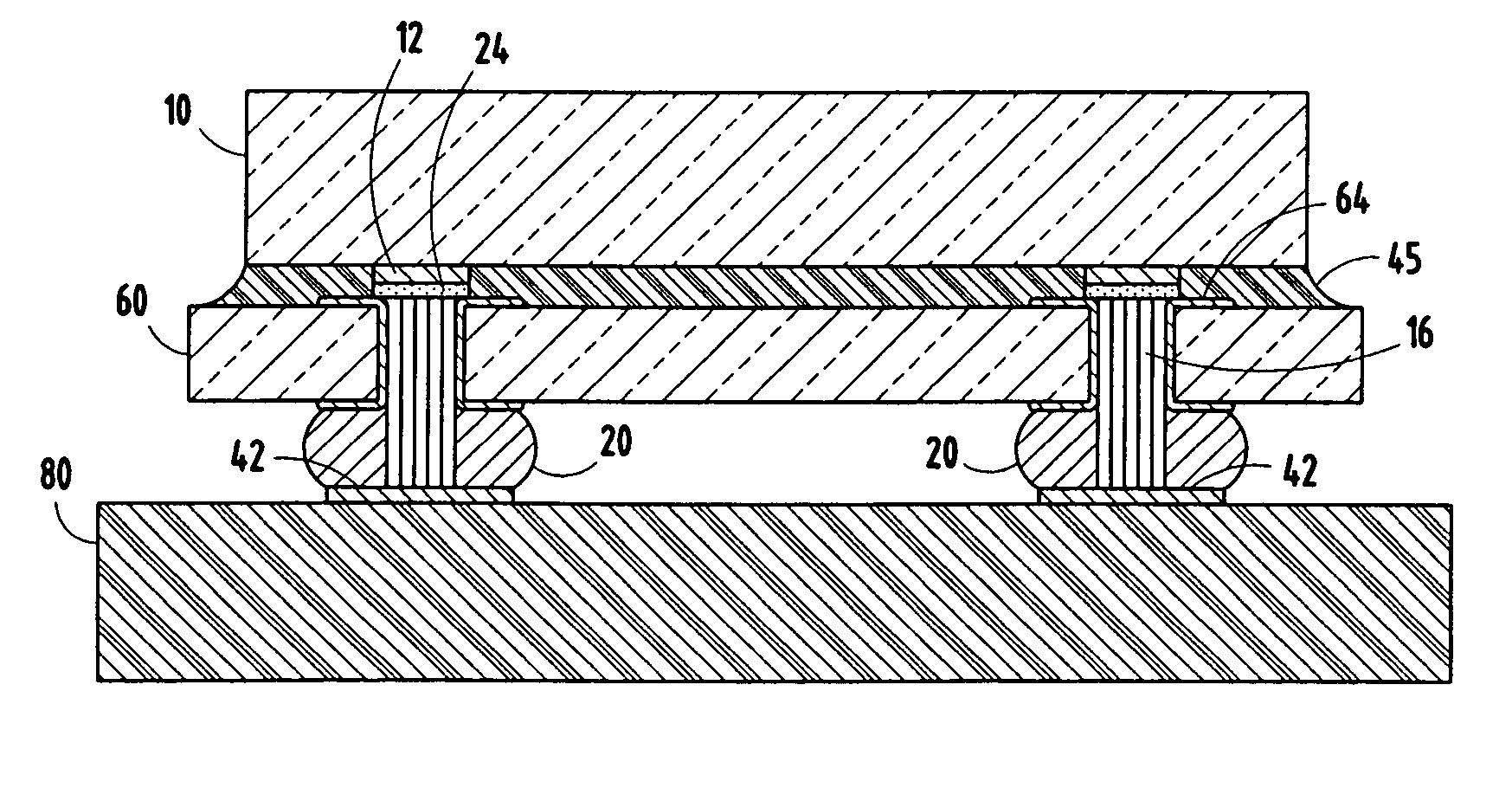

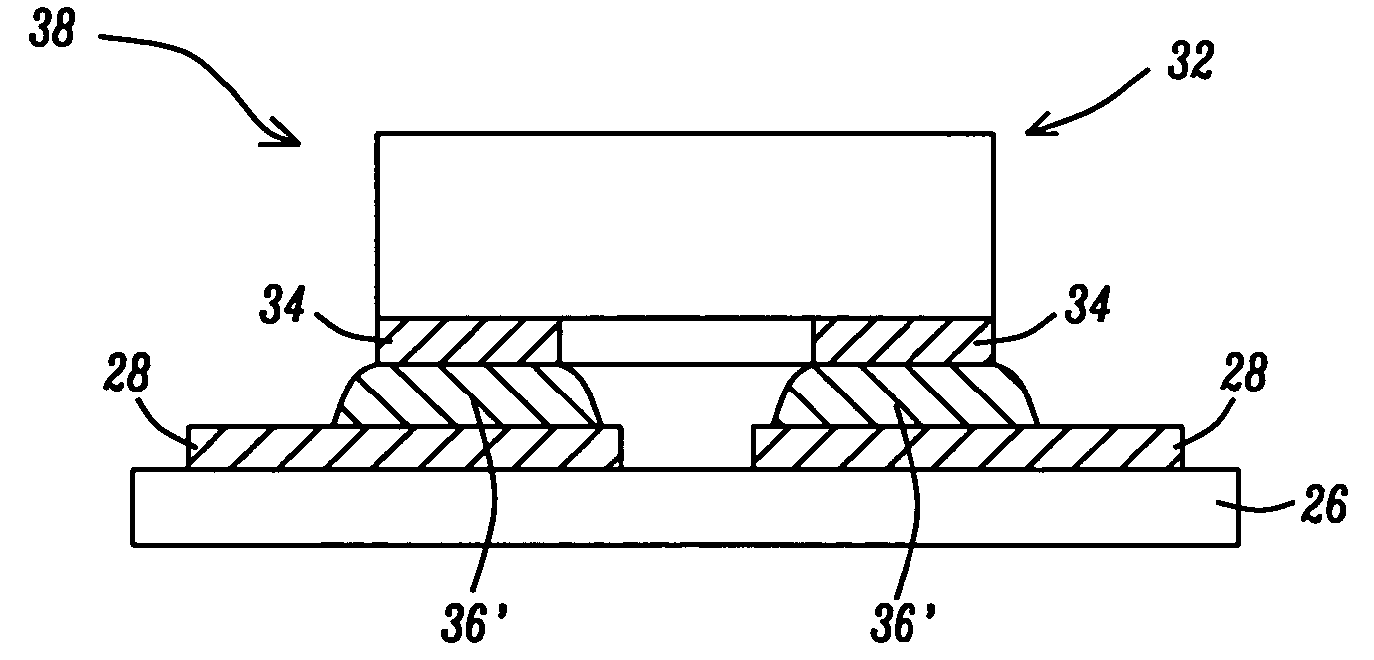

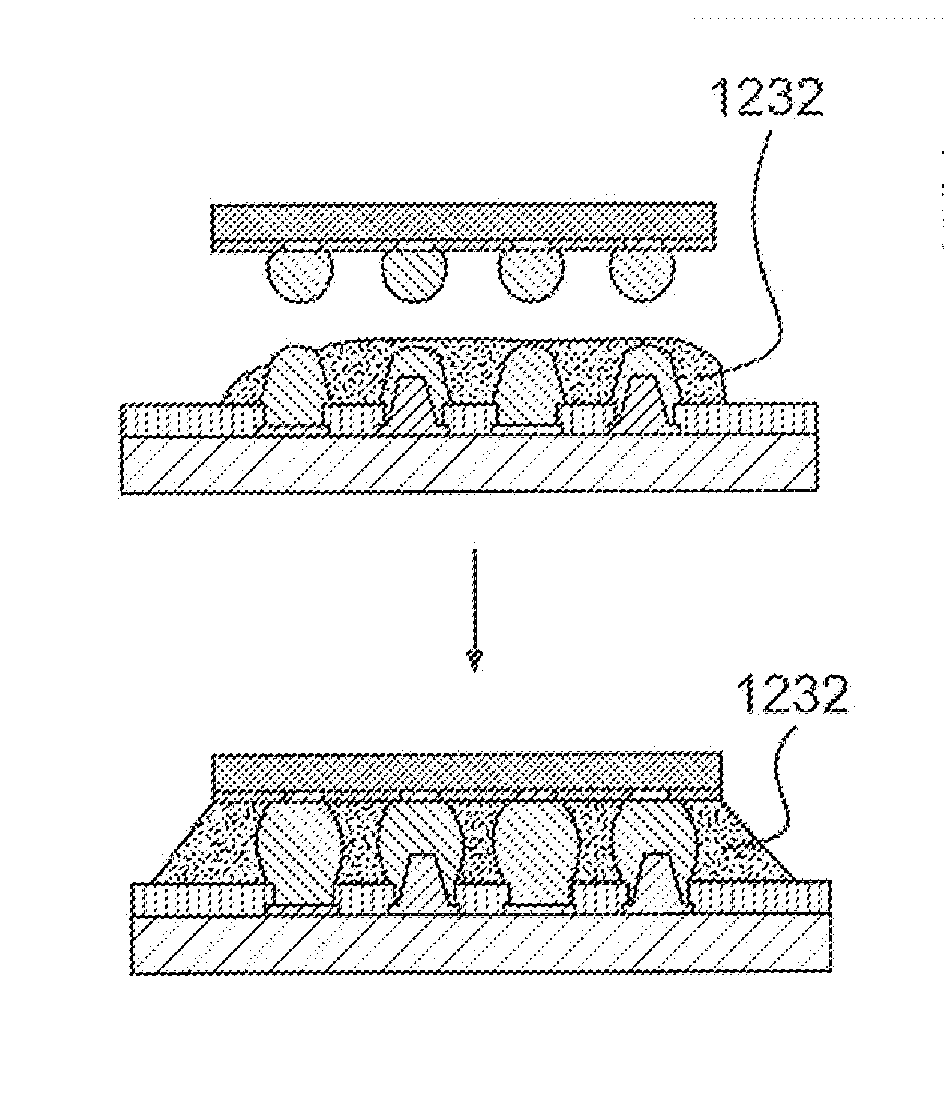

A method comprises forming semiconductor flip chip interconnects where the flip chip comprises a wafer and a substrate having electrical connecting pads and electrically conductive posts operatively associated with the pads and extending away from the pads to terminate in distal ends. Solder bumping the distal ends by injection molding solder onto the distal ends produces a solder bumped substrate. Another embodiment comprises providing the substrate having the posts on the pads with a mask having a plurality of through hole reservoirs and aligning the reservoirs in the mask to be substantially concentric with the distal ends. This is followed by injecting liquid solder into the reservoirs to provide a volume of liquid solder on the distal ends, cooling the liquid solder in the reservoirs to solidify the solder, removing the mask to expose the solidified solder after the cooling and thereby provide a solder bumped substrate. This is followed by positioning the solder bumped substrate on a wafer in a manner that leaves a gap between the wafer and the substrate. The wafer has electrically conductive sites on the surface for soldering to the posts. Abutting the sites and the solder bumped posts followed by heating the solder to its liquidus temperature joins the wafer and substrate, after which, the gap is optionally filled with a material comprising an underfill.

Owner:IBM CORP

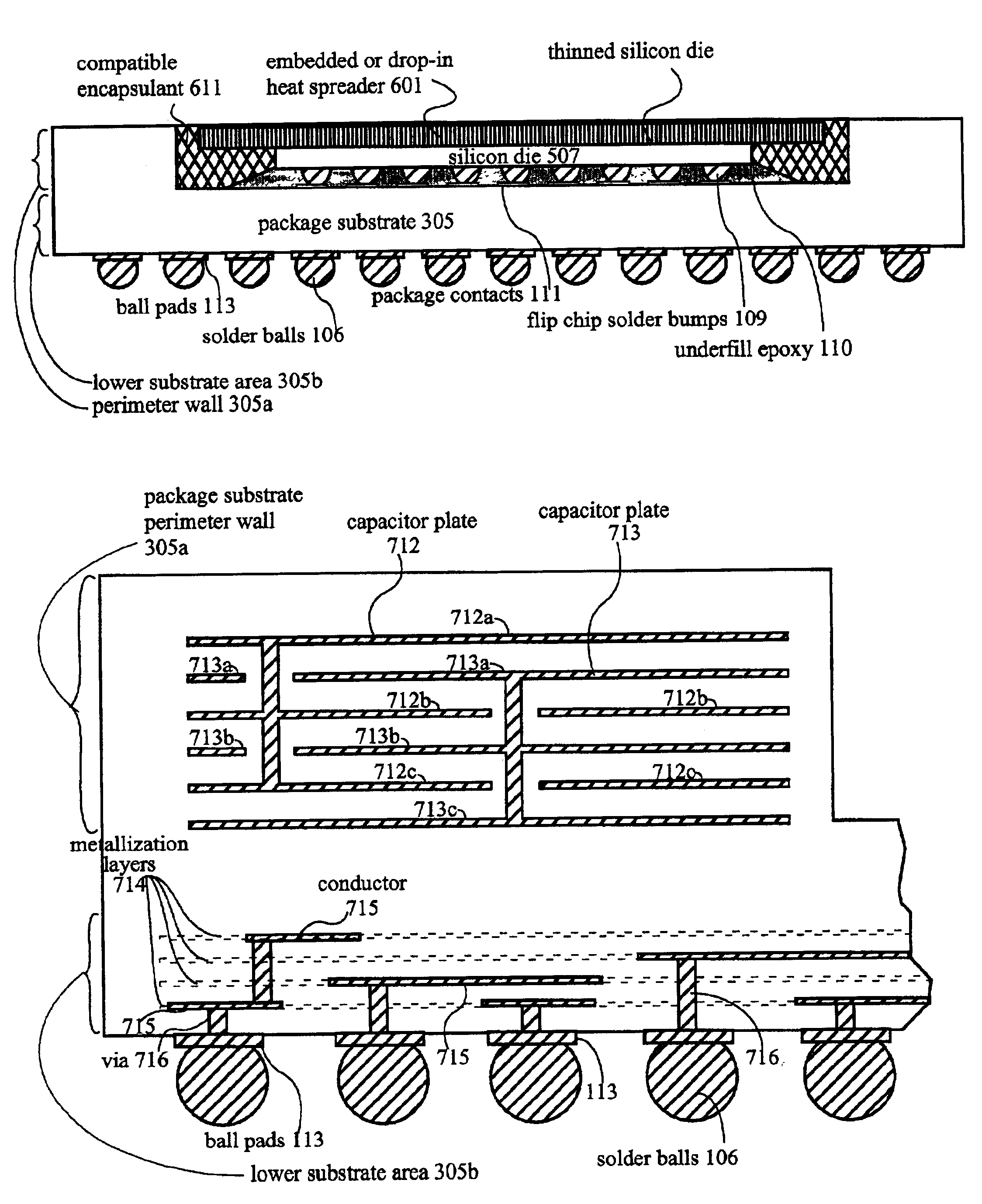

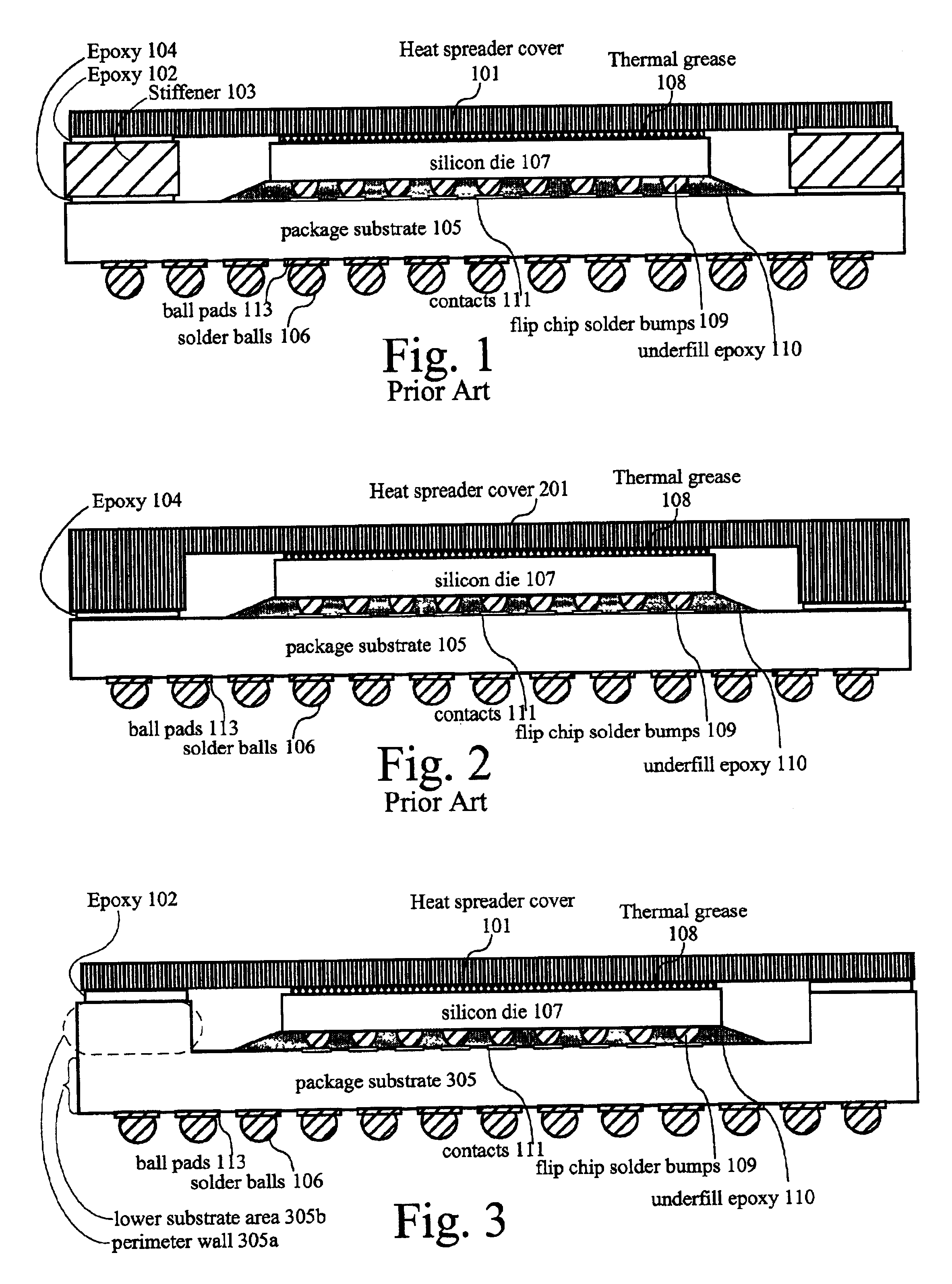

High performance flipchip package that incorporates heat removal with minimal thermal mismatch

InactiveUS7061102B2Reduce warpageMinimize interfacial stressSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor package

A semiconductor flipchip package includes a central cavity area on the first major side for receiving a flipchip die therein. The package substrate is substantially made from a single material that serves as the support and stiffener and provides within the cavity floor all the connecting points for flipchip interconnection to the silicon die. The integral cavity wall serves as a stiffener member of the package and provides the required mechanical stability of the whole arrangement without the need for a separate stiffener material to be adhesively attached. The cavity walls may contain extra routing metallization to create bypass capacitors to enhance electrical performance. Optional methods to cover the silicon die enhance thermal performance of the package.

Owner:XILINX INC

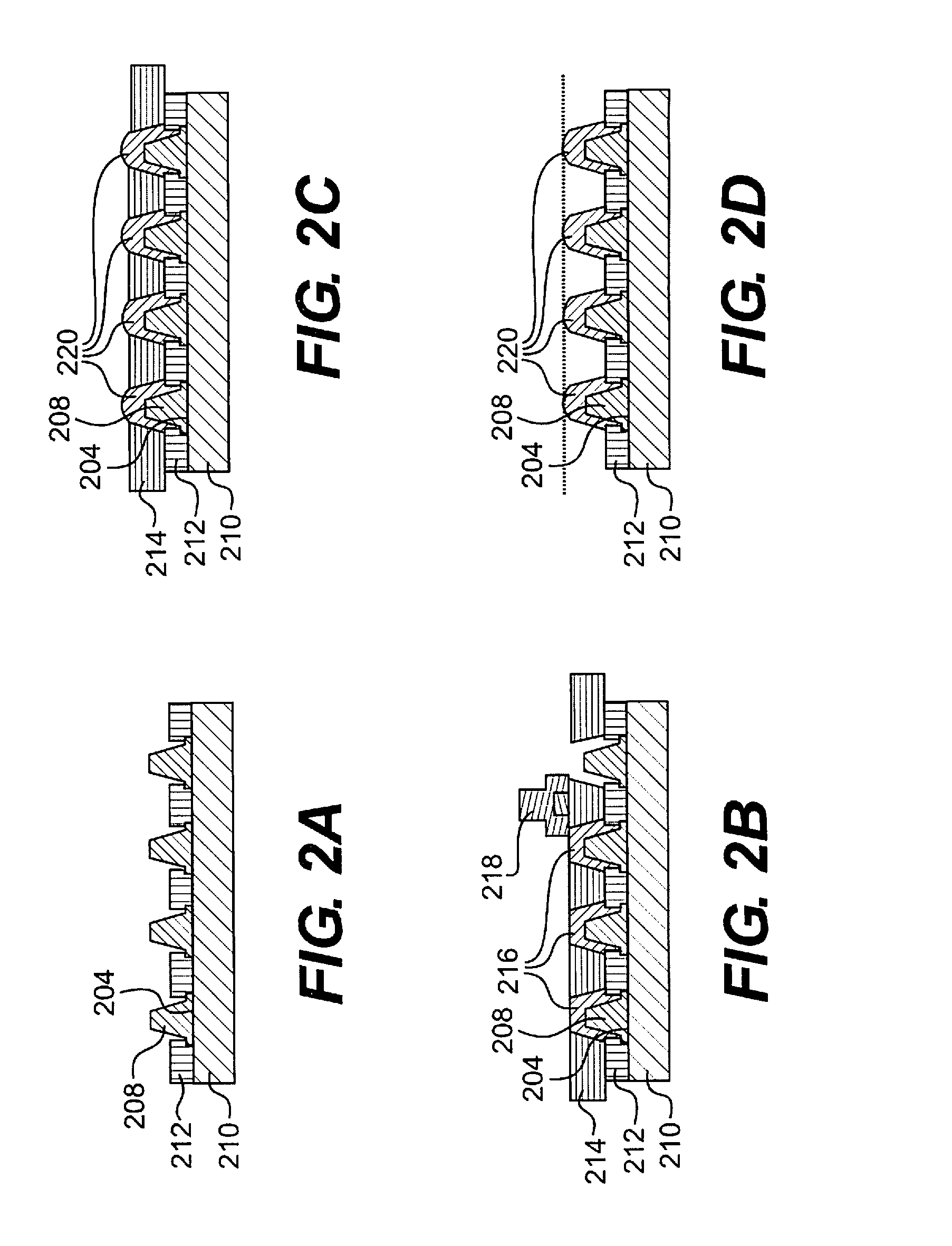

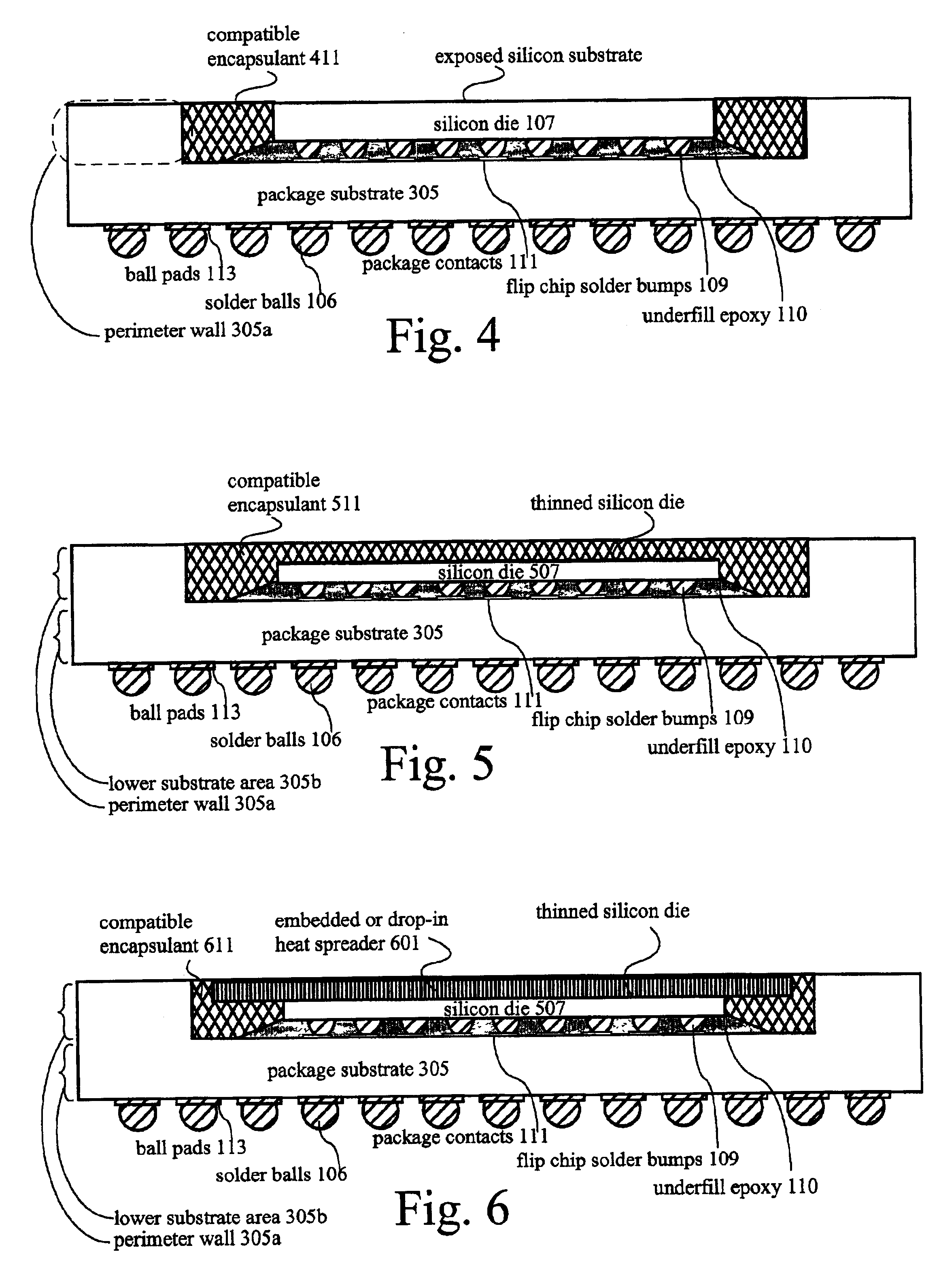

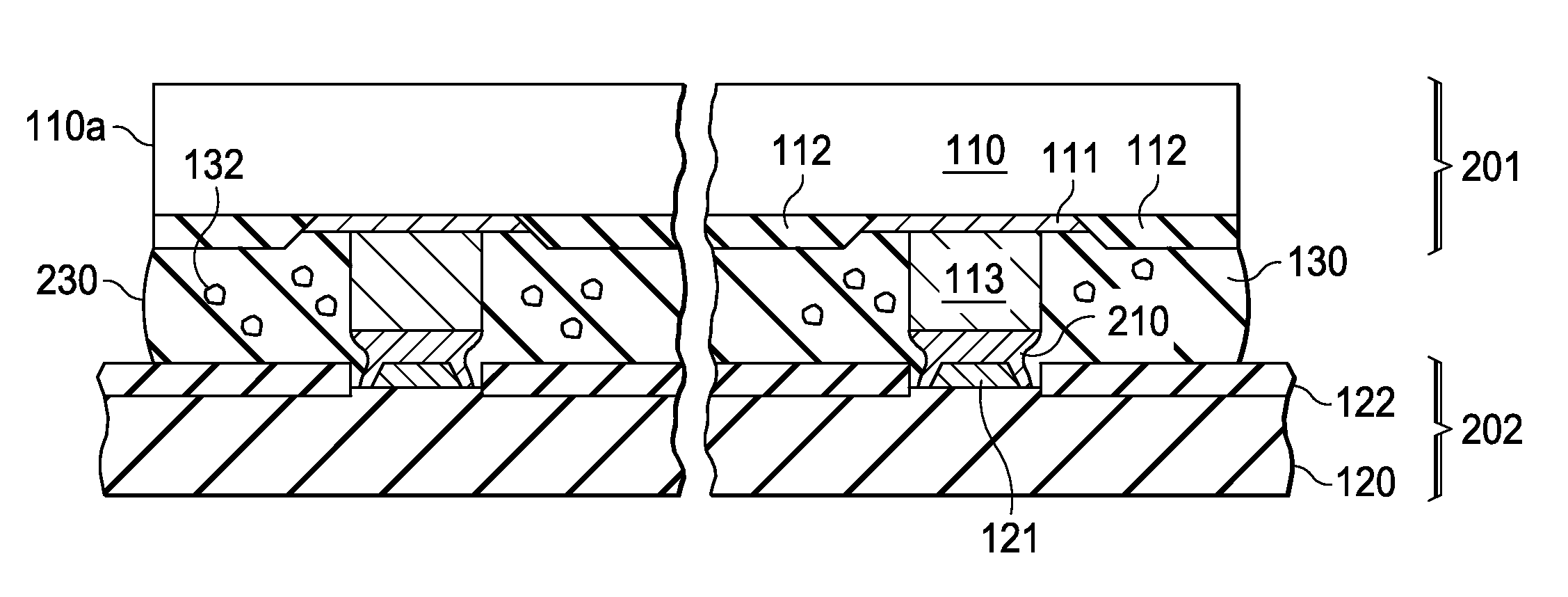

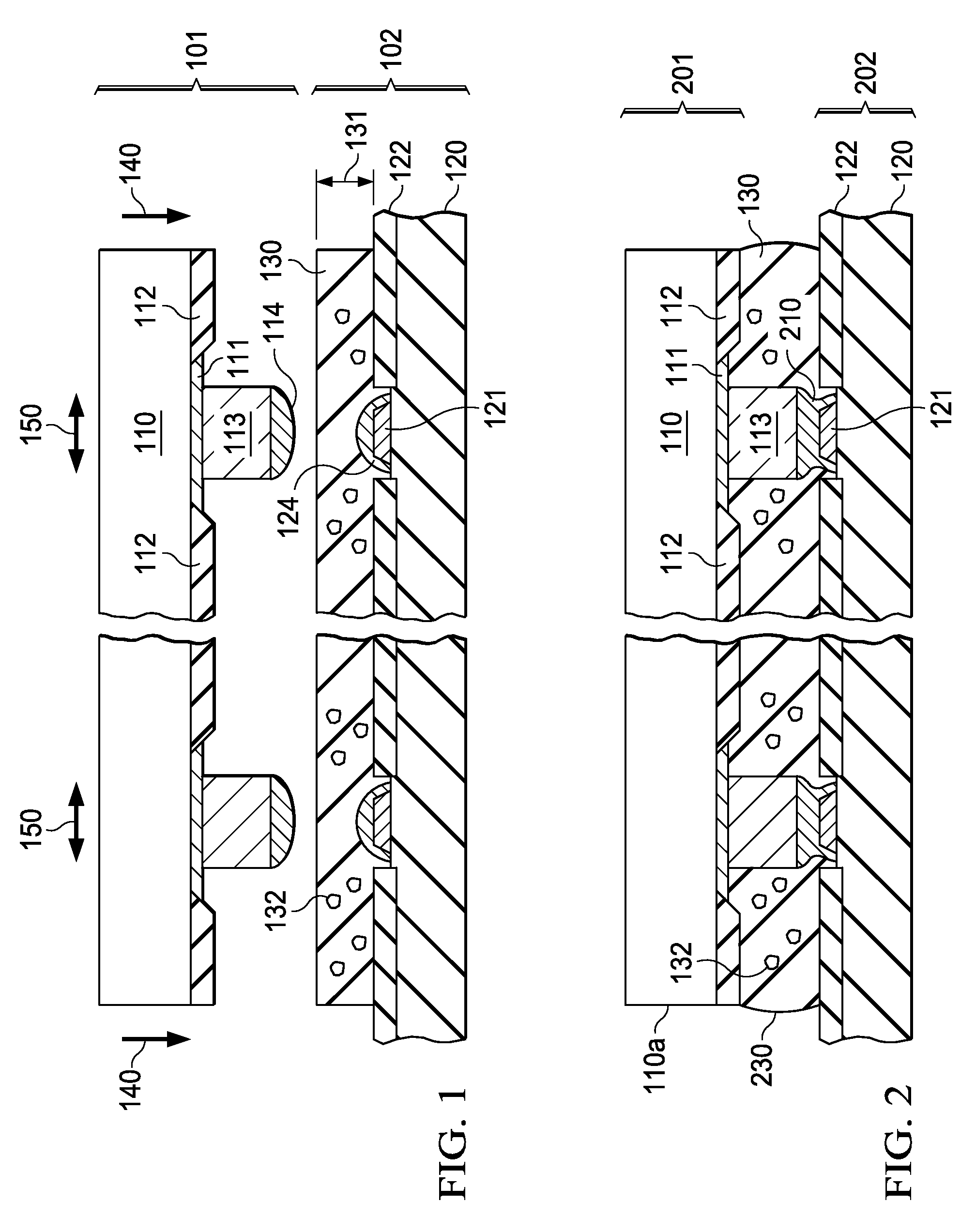

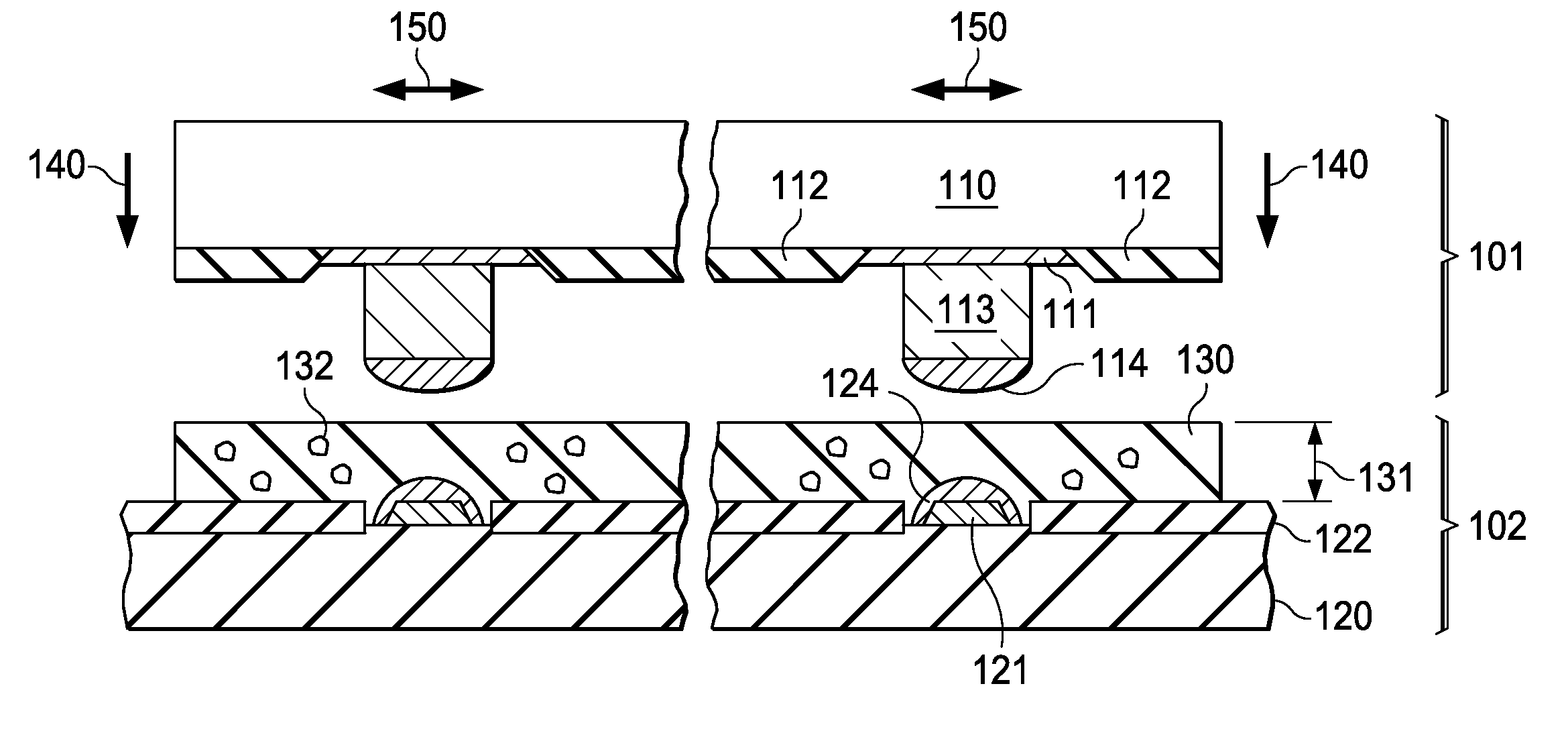

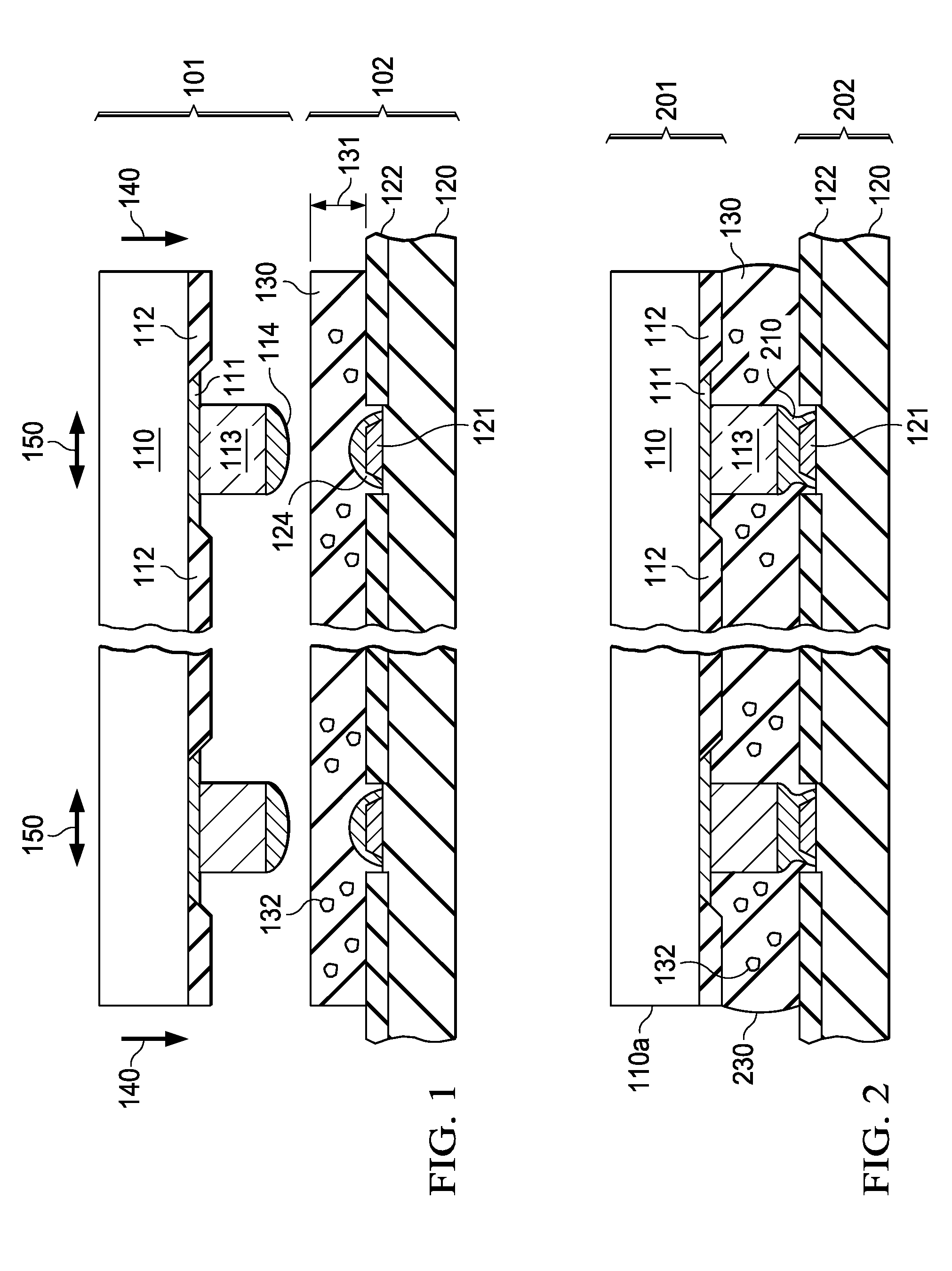

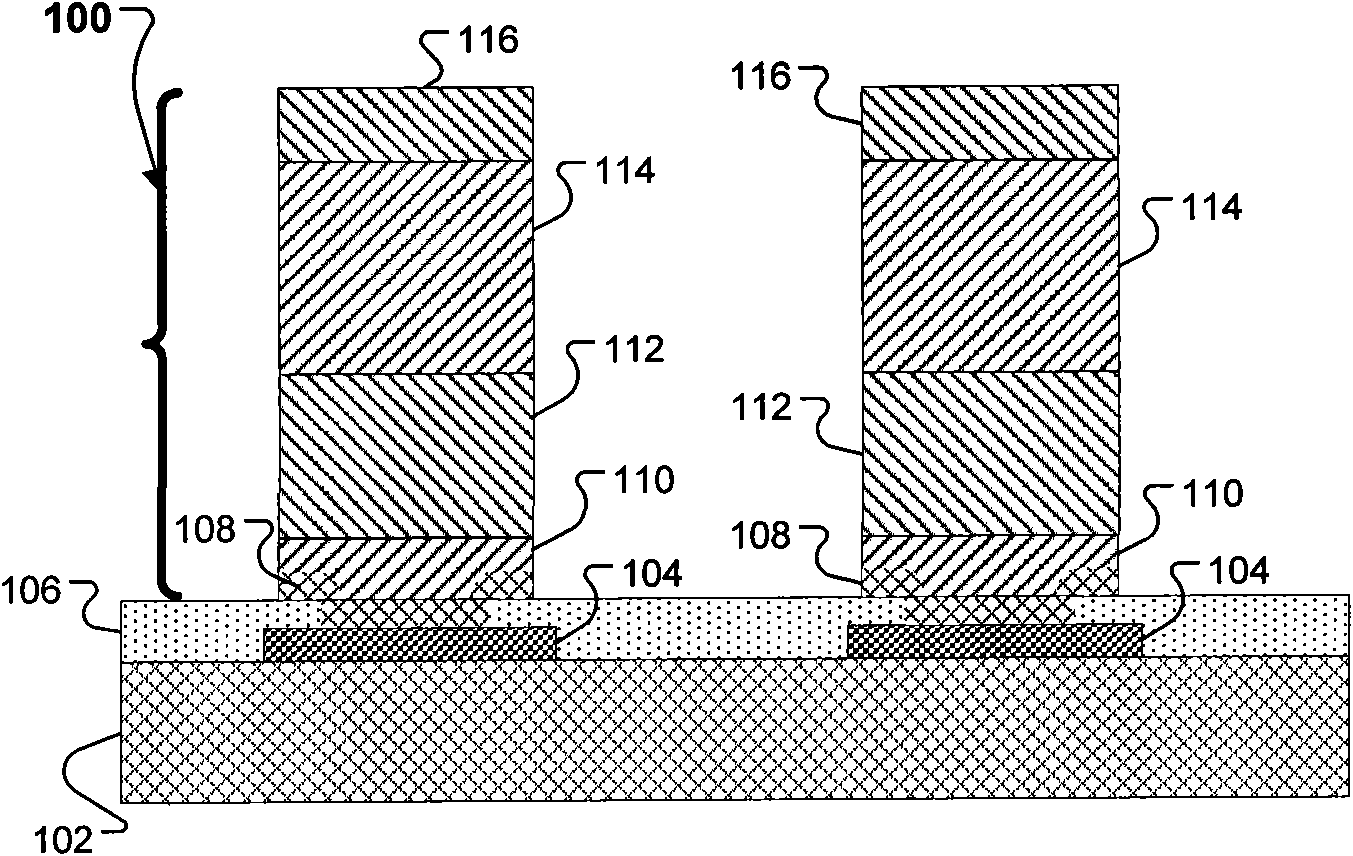

Method for fine-pitch, low stress flip-chip interconnect

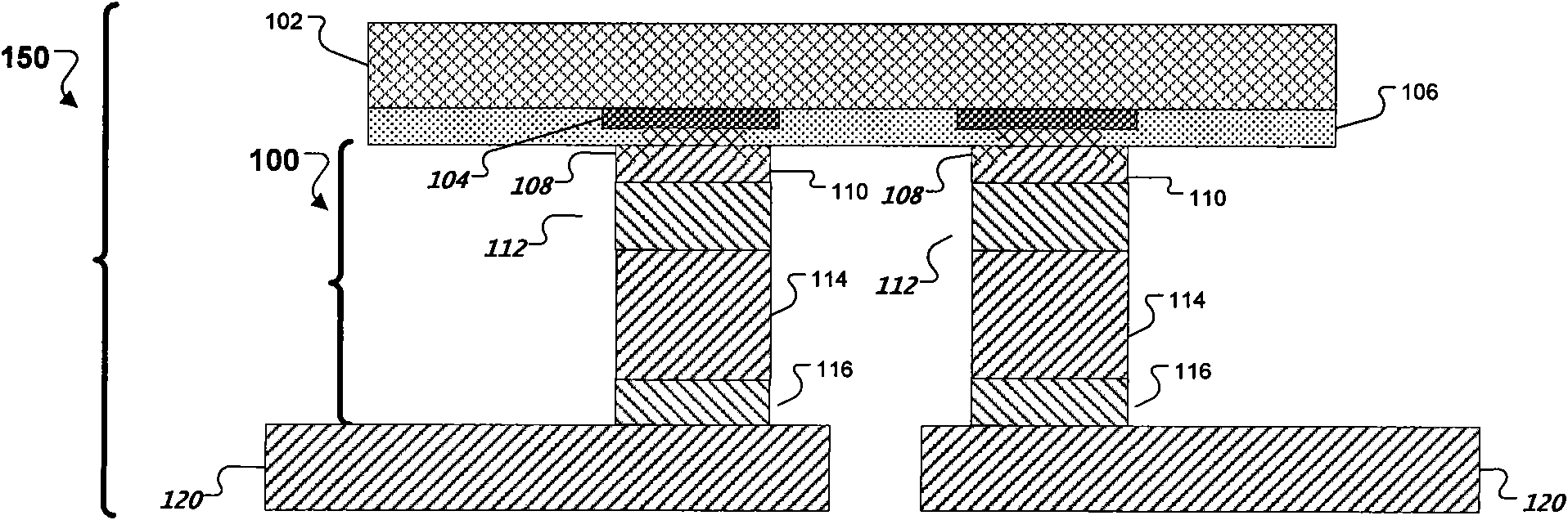

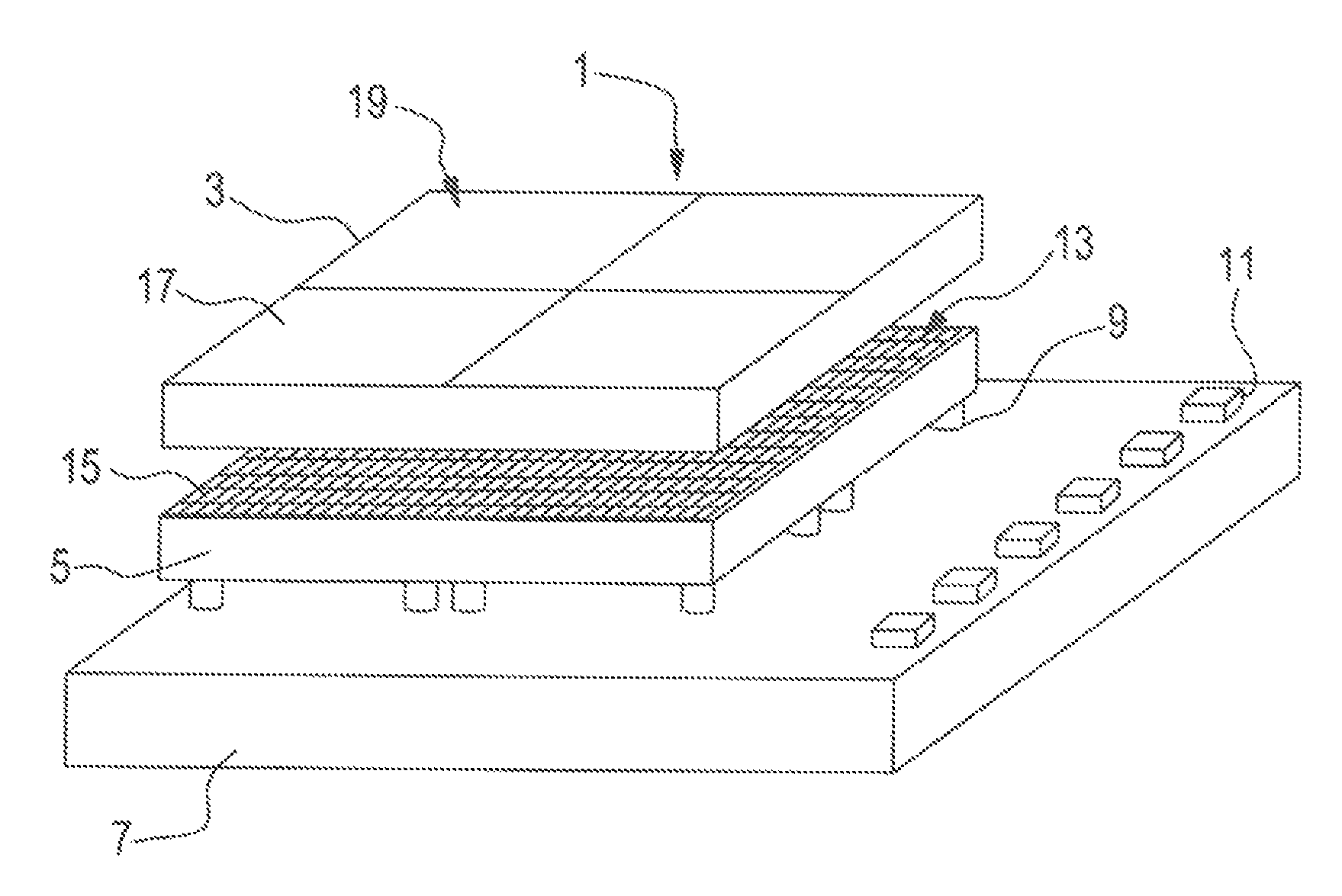

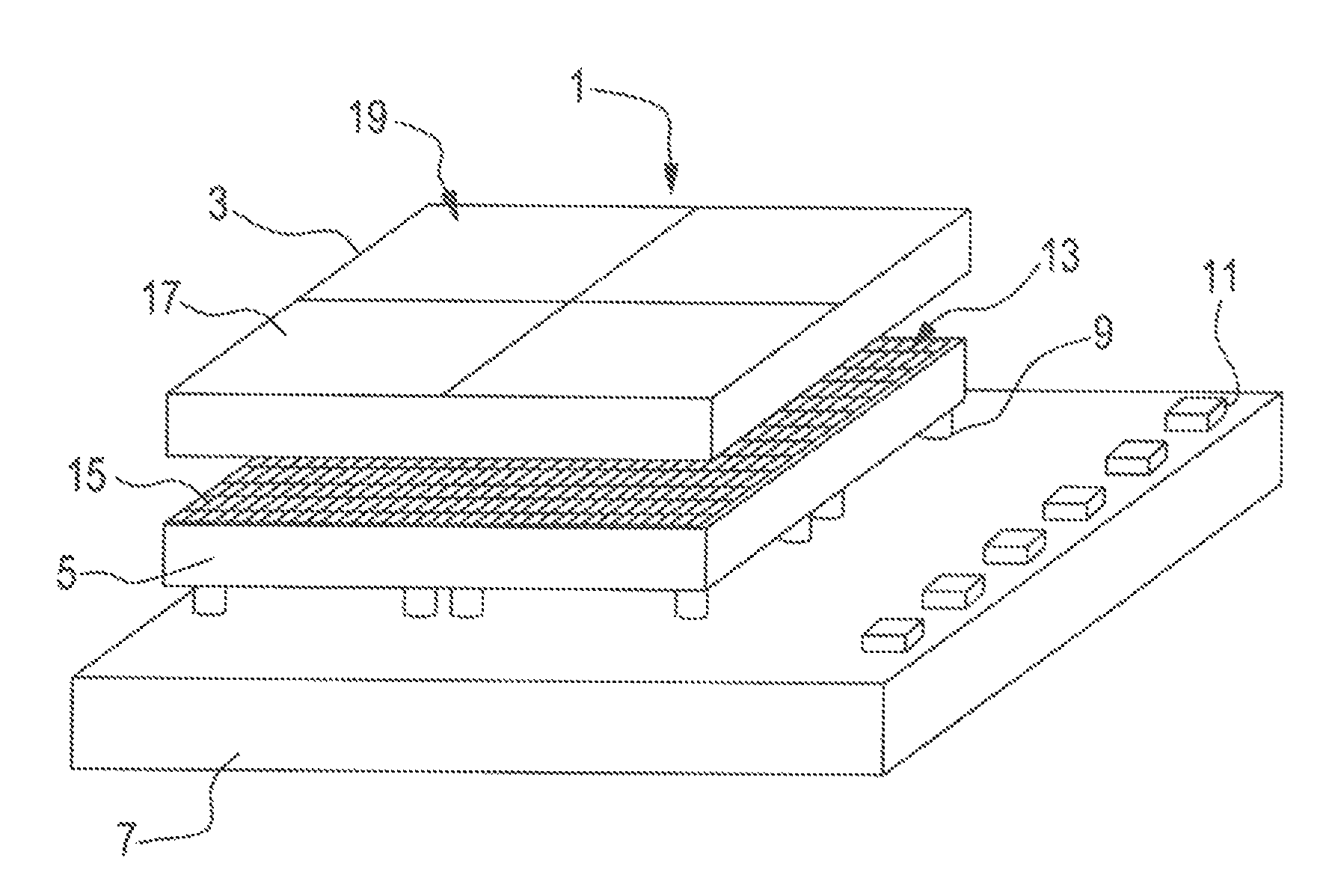

ActiveUS7790509B2Easy to separateSolid-state devicesSemiconductor/solid-state device manufacturingFlip chip interconnectSemiconductor chip

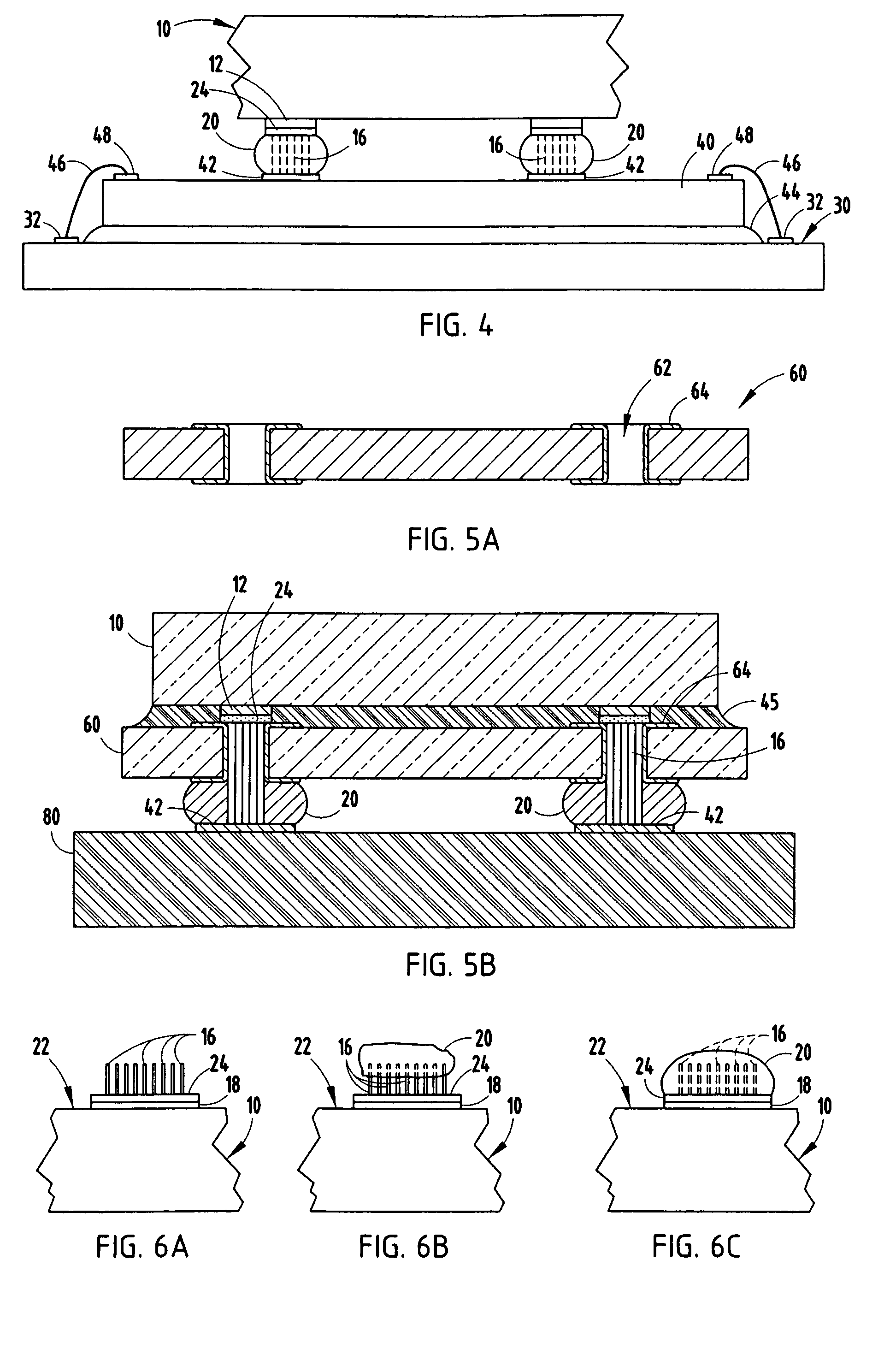

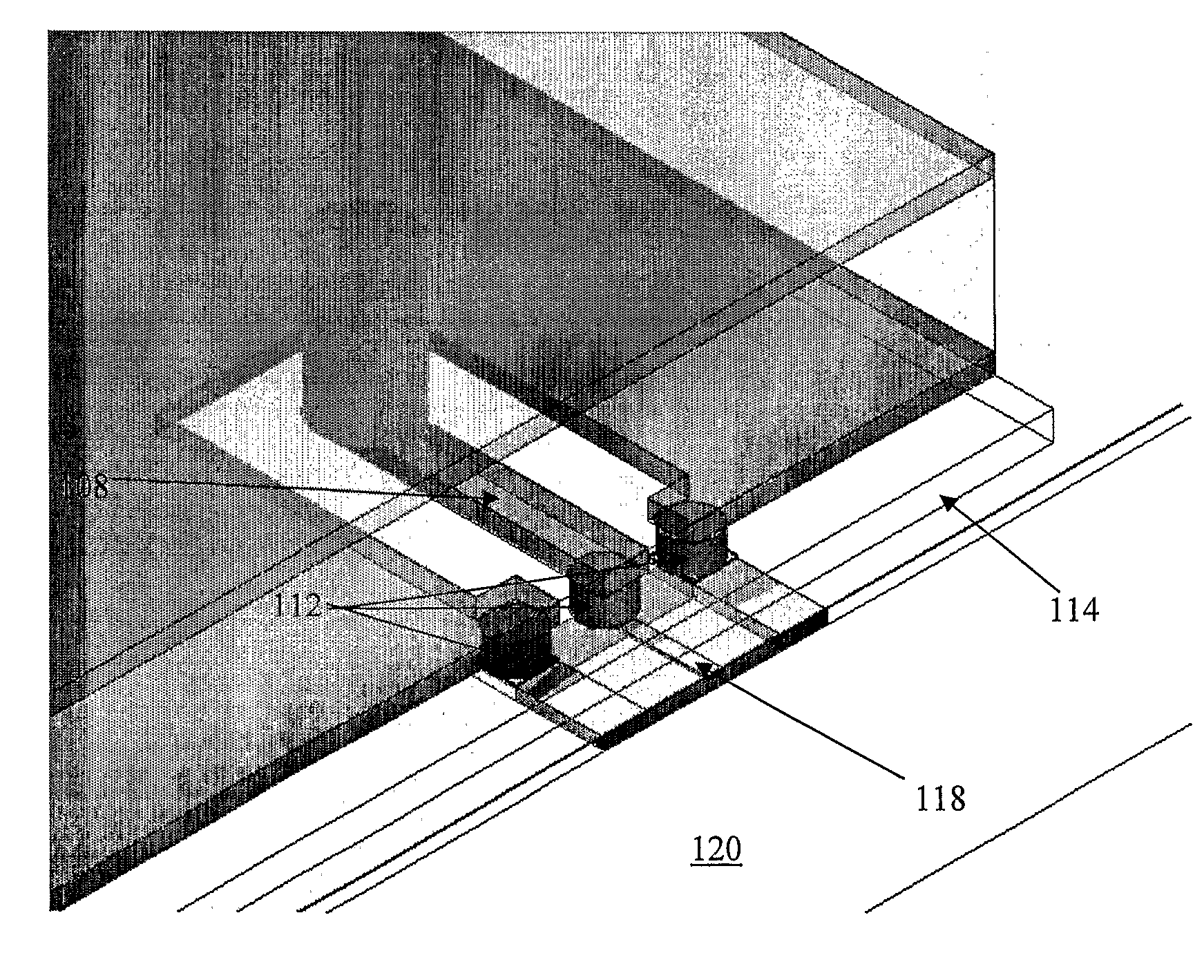

Attaching a semiconductor chip to a substrate by applying mechanical vibrations (150) to a polymeric compound (130) and the contacting areas (114, 124) of a first (113) and a second (121) metallic member immersed in the compound, while the two metallic members approach (140) each other until they touch. The mechanical vibration causes displacements of the first member relative to the second member, and the vibration includes displacements (150) oriented at right angles to the direction (140) of the approach. The polymeric compound (130) includes a non-conductive adhesive resin paste (NCP) and filler particles; the paste is deposited before the attaching step. The first member (113) is affixed to the chip and the second member (121) to the substrate.

Owner:TEXAS INSTR INC

Flip chip interconnection system

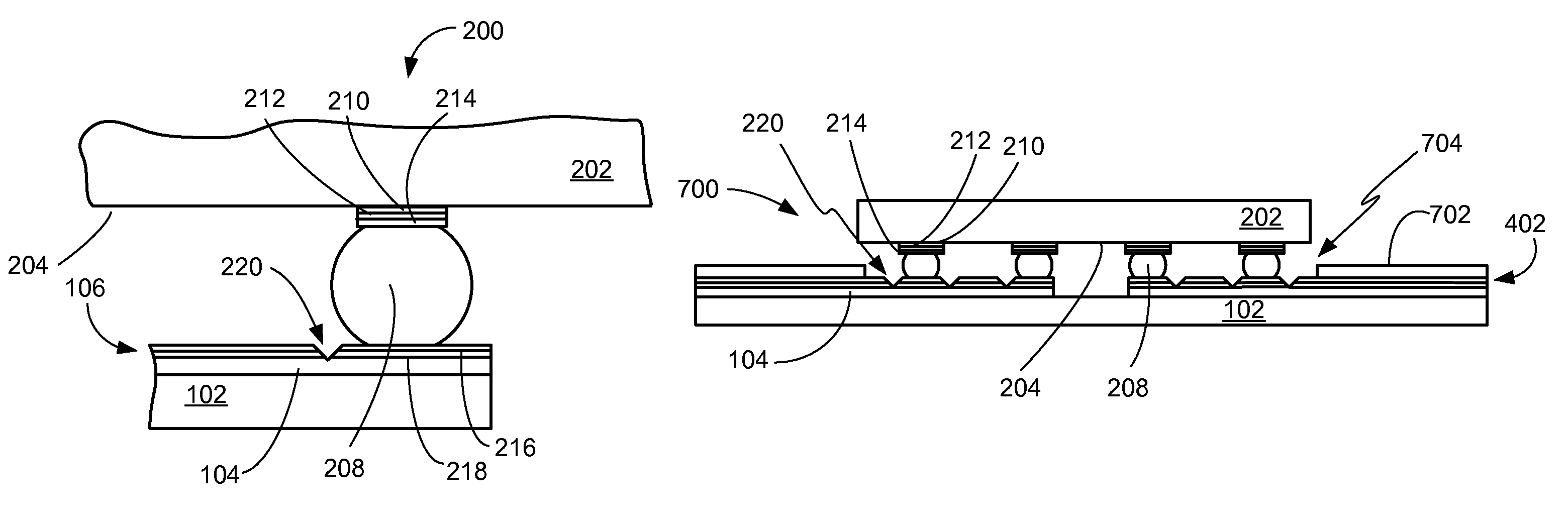

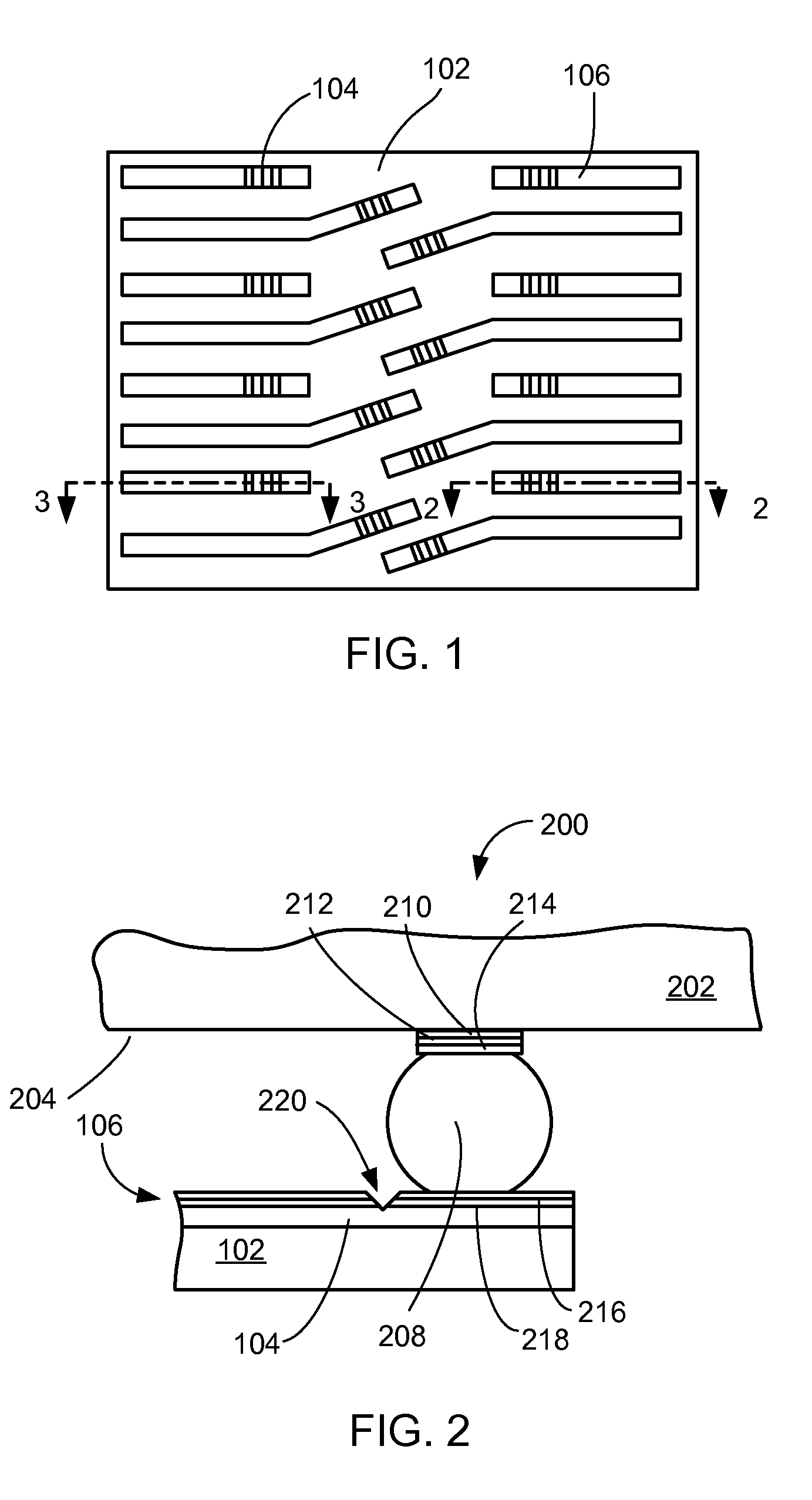

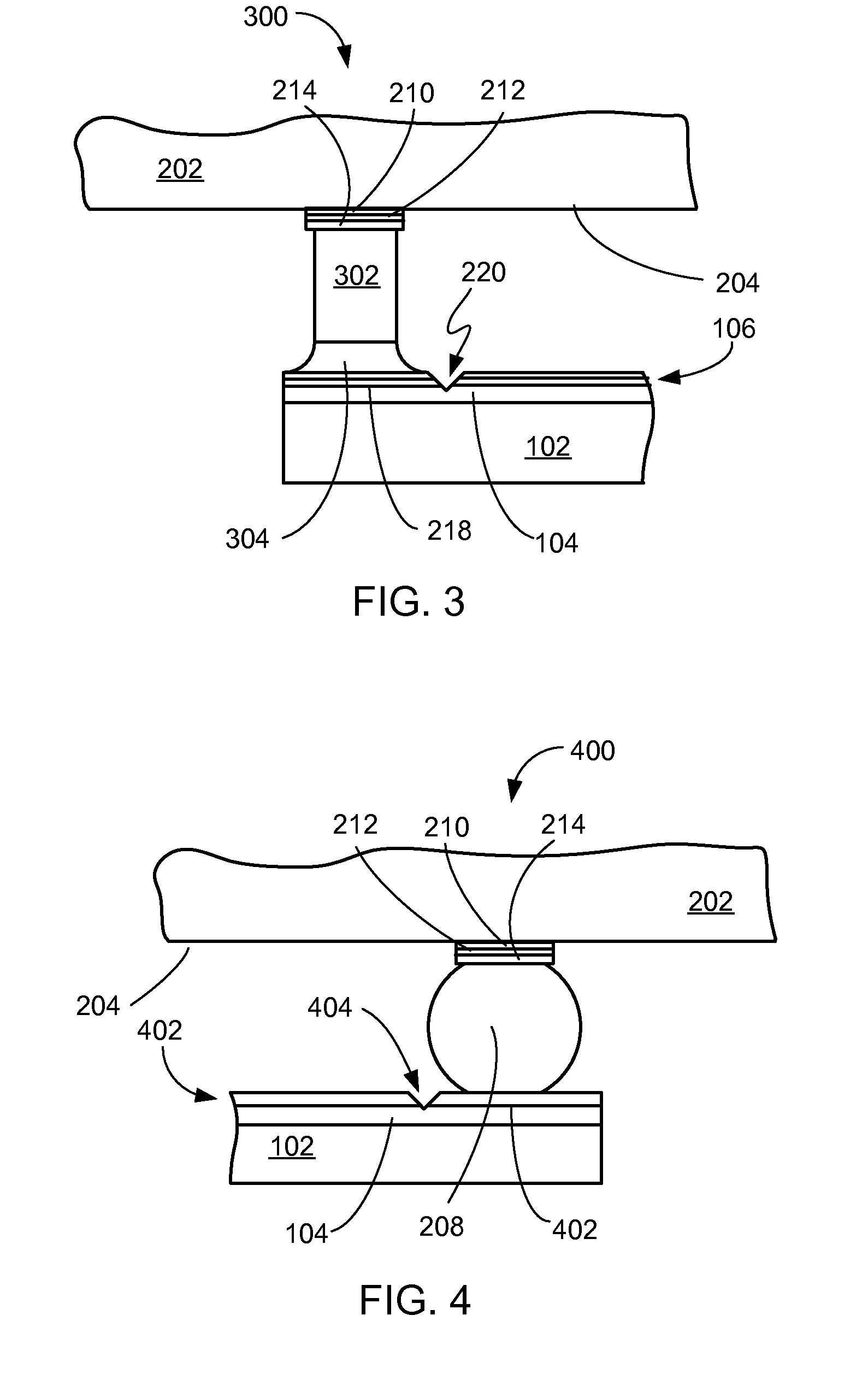

ActiveUS20090236756A1Semiconductor/solid-state device detailsPrinted circuit aspectsFlip chip interconnectInterconnection

A flip chip interconnection system includes: providing a conductive lead coated with a protective coating; forming a groove through the protective coating to the conductive lead for controlling solder position on a portion of the conductive lead; and attaching a flip chip having a solderable conductive interconnect to the portion of the conductive lead.

Owner:STATS CHIPPAC LTD

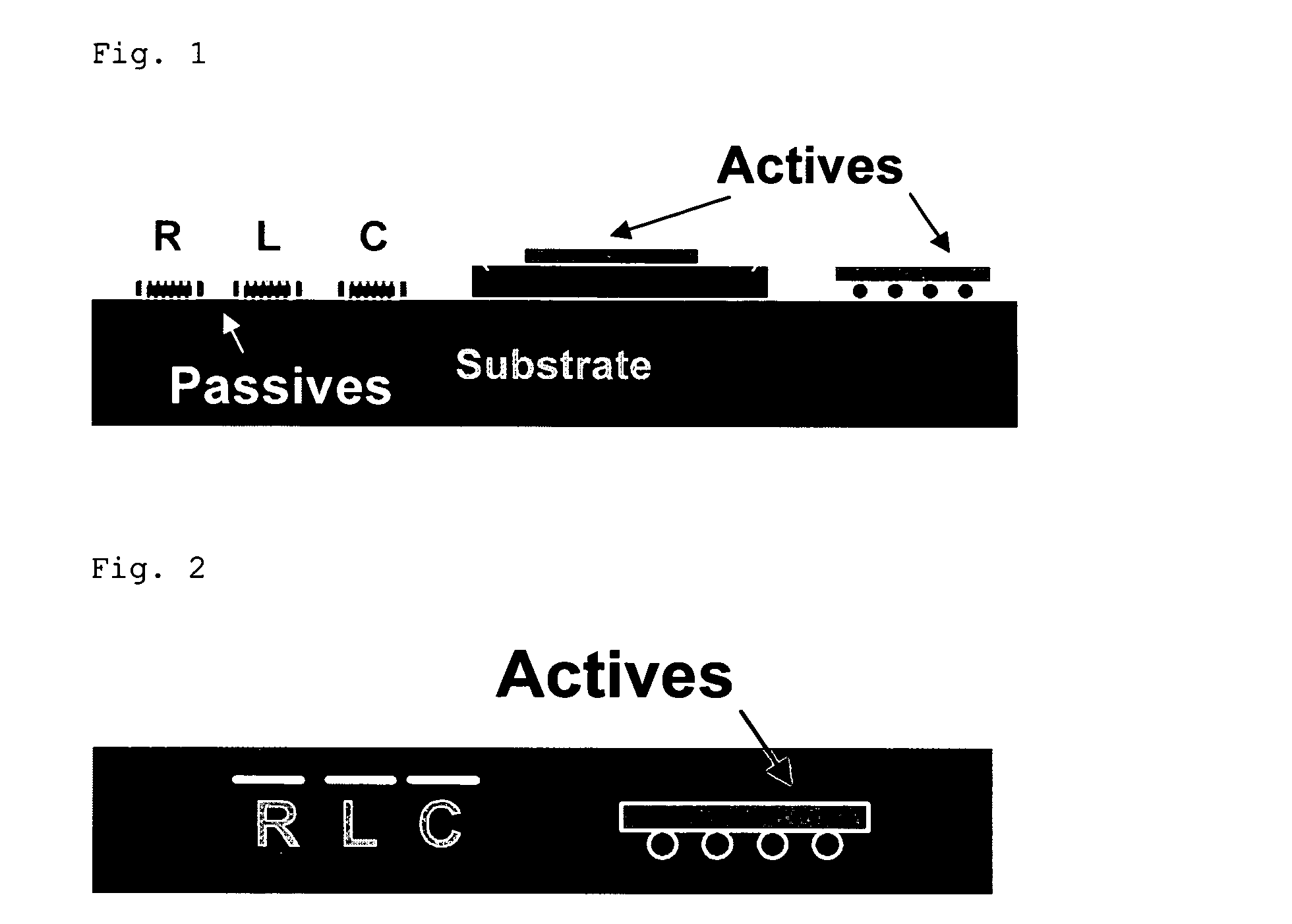

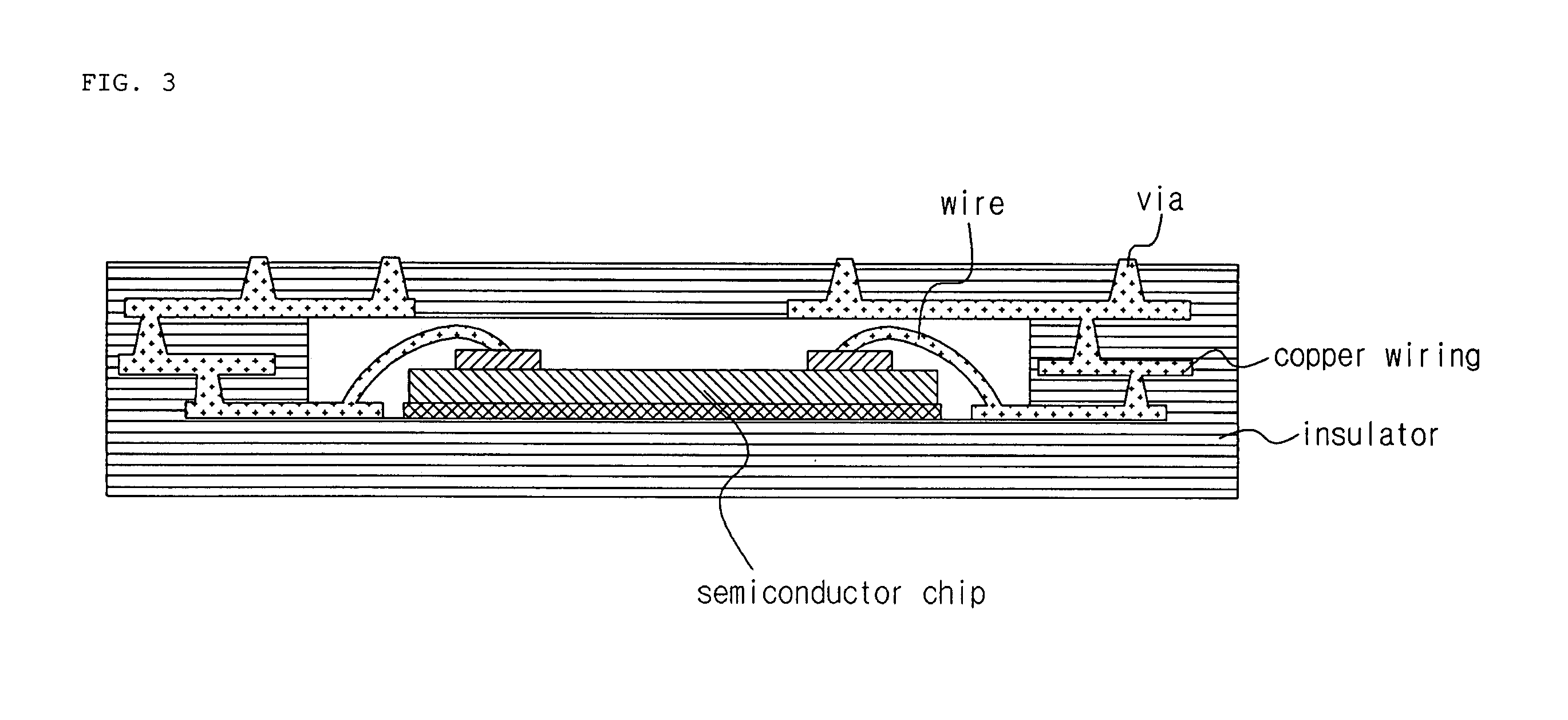

Fabrication method of an organic substrate having embedded active-chips

InactiveUS20090042336A1Large capacityImprove package reliabilitySemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectAdhesive

The fabrication method of an organic substrate having embedded active-chips such as semiconductor chips is disclosed. The present invention previously applies the conductive adhesives in a wafer state, makes them in a B-stage state, obtains individual semiconductor chips through dicing, and positions the individual semiconductor chips previously applied with the conductive adhesives in the cavities, making it possible to simultaneously obtain an electrical connection and a physical adhesion of the substrate and the semiconductor chips by means of a method of applying heat and pressure and stack the copper clad laminates on the upper portion of the substrate to which the semiconductor chips are connected. The present invention has advantages in processes such as a lead-free process, an environmental-friendly fluxless process, a low temperature process, ultra-fine pitch applications, etc., by mounting the active-chips through the flip chip interconnection using the non-solder bumps and the conductive adhesives.

Owner:KOREA ADVANCED INST OF SCI & TECH

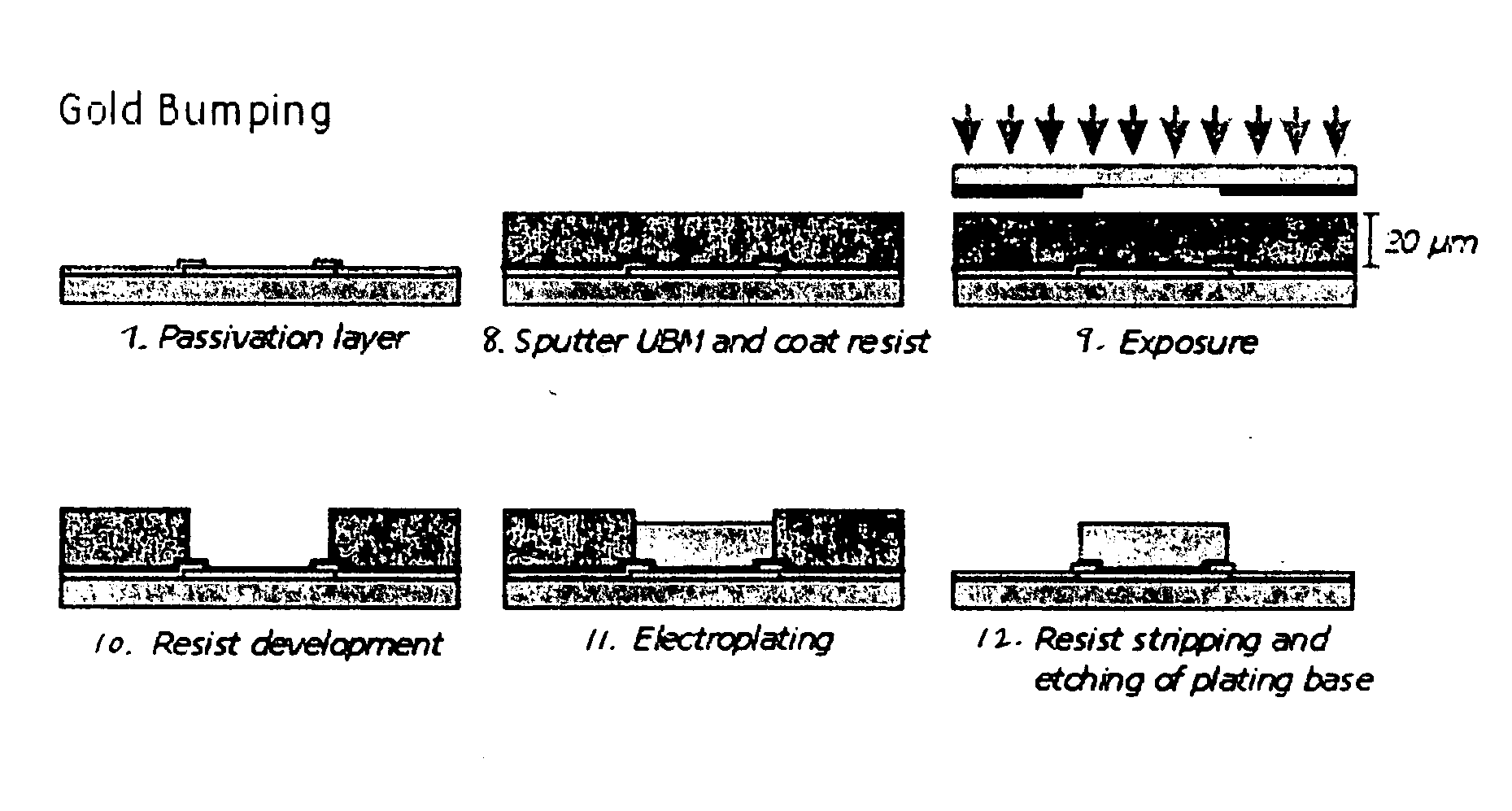

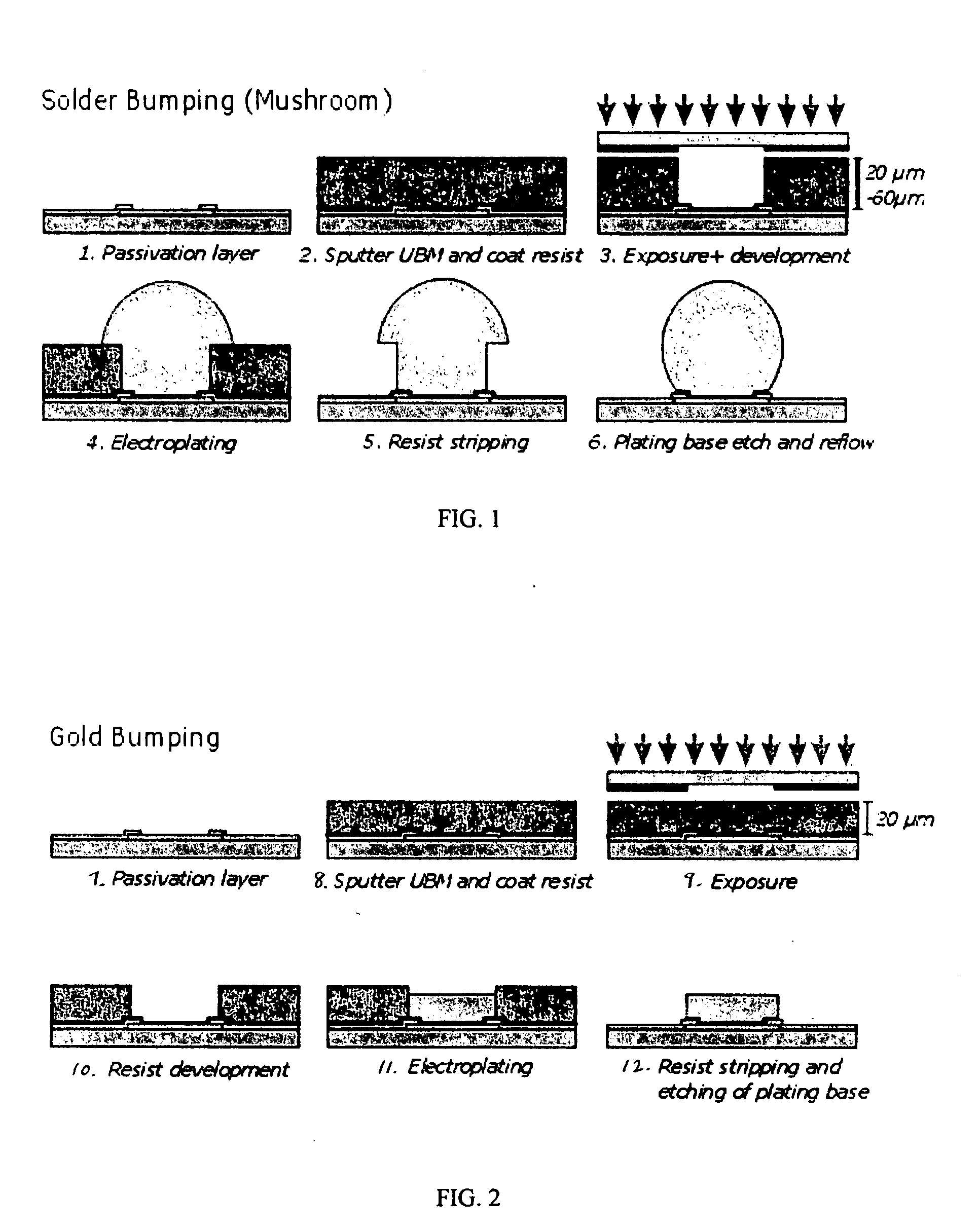

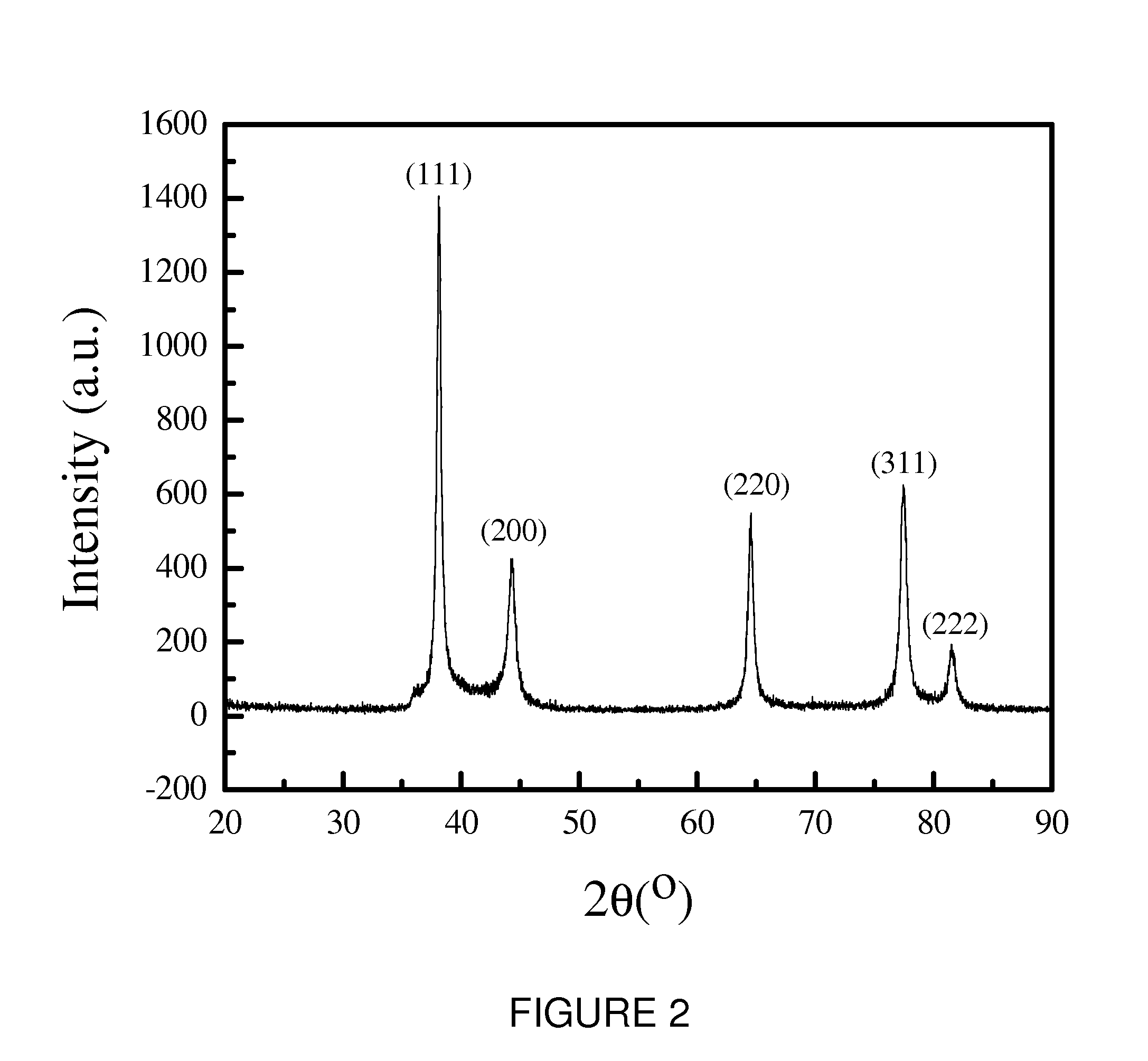

Alloys for flip chip interconnects and bumps

InactiveUS20070114663A1Improve corrosion resistanceLess expensiveSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectDevice material

The present invention provides alloys for forming sputtered under bump metallization seed layers and electroplated or otherwise deposited bump metallurgy. The alloys of the present invention are comprised of silver with gold or palladium, copper with gold, or gold with nickel or palladium which provide suitable sputtering and electrical characteristics and resistance to corrosion and tarnishing. The invention further provides for semiconductor devices made from metal alloys for UBM and bump metallurgy, and for a method of making such semiconductor devices.

Owner:WILLIAMS ADVANCED MATERIALS

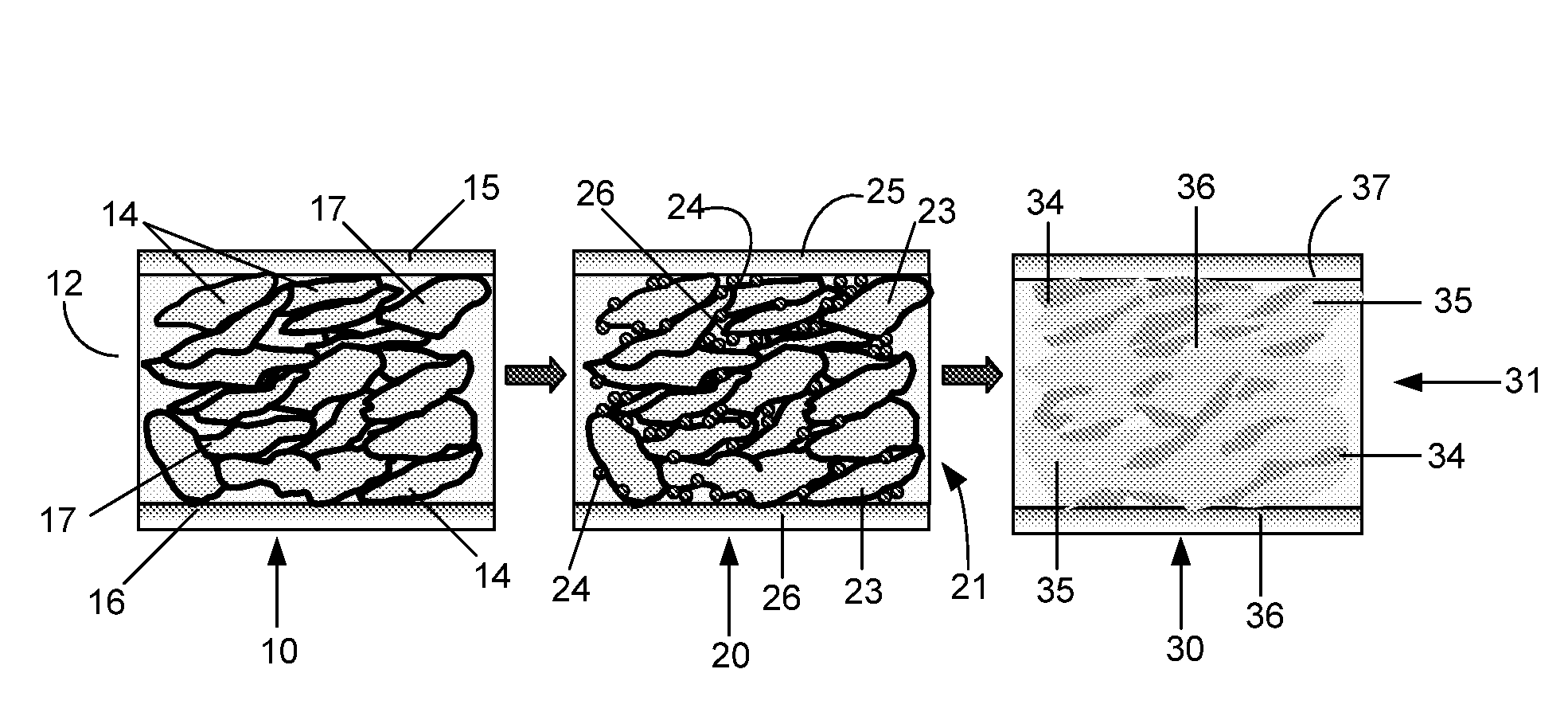

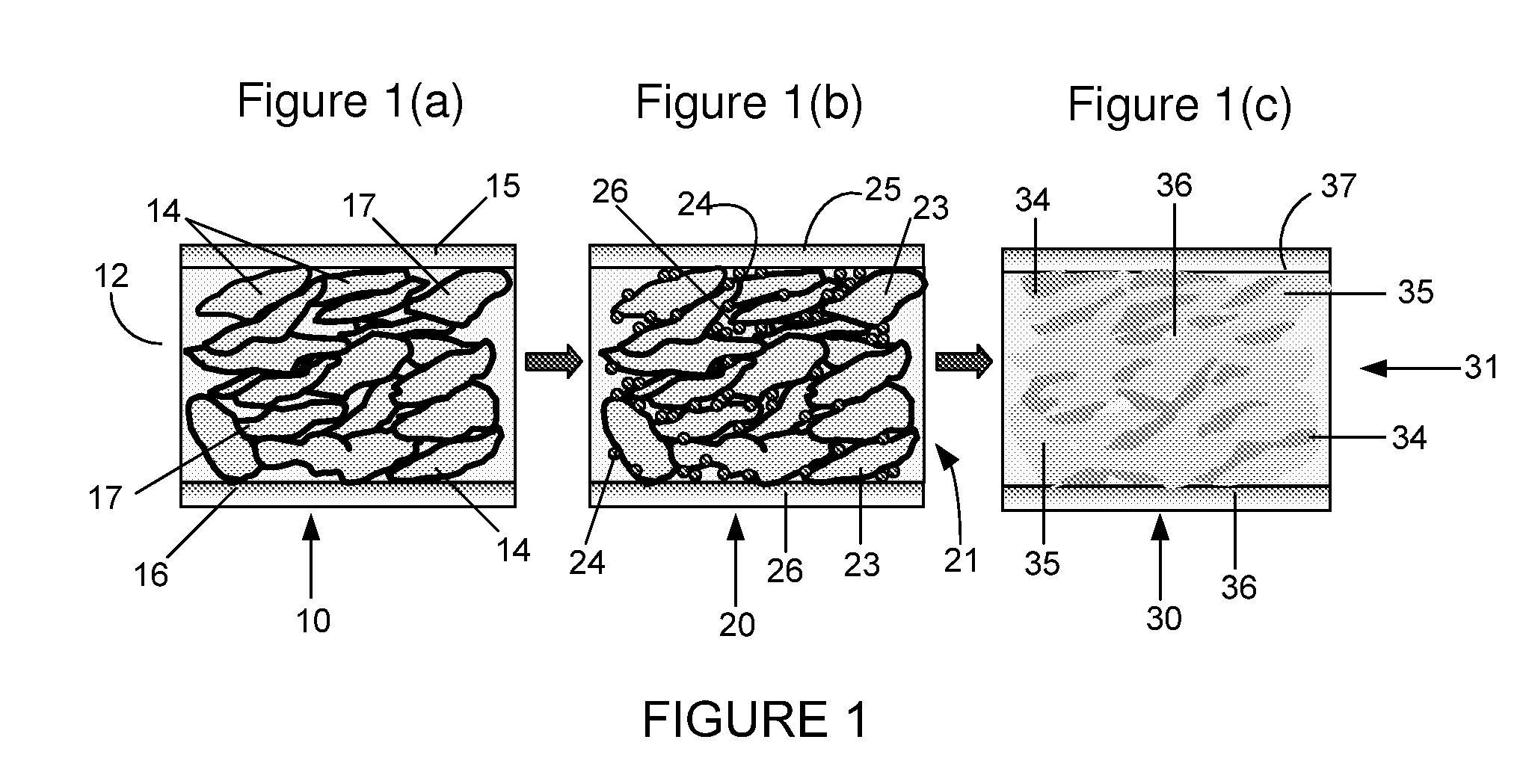

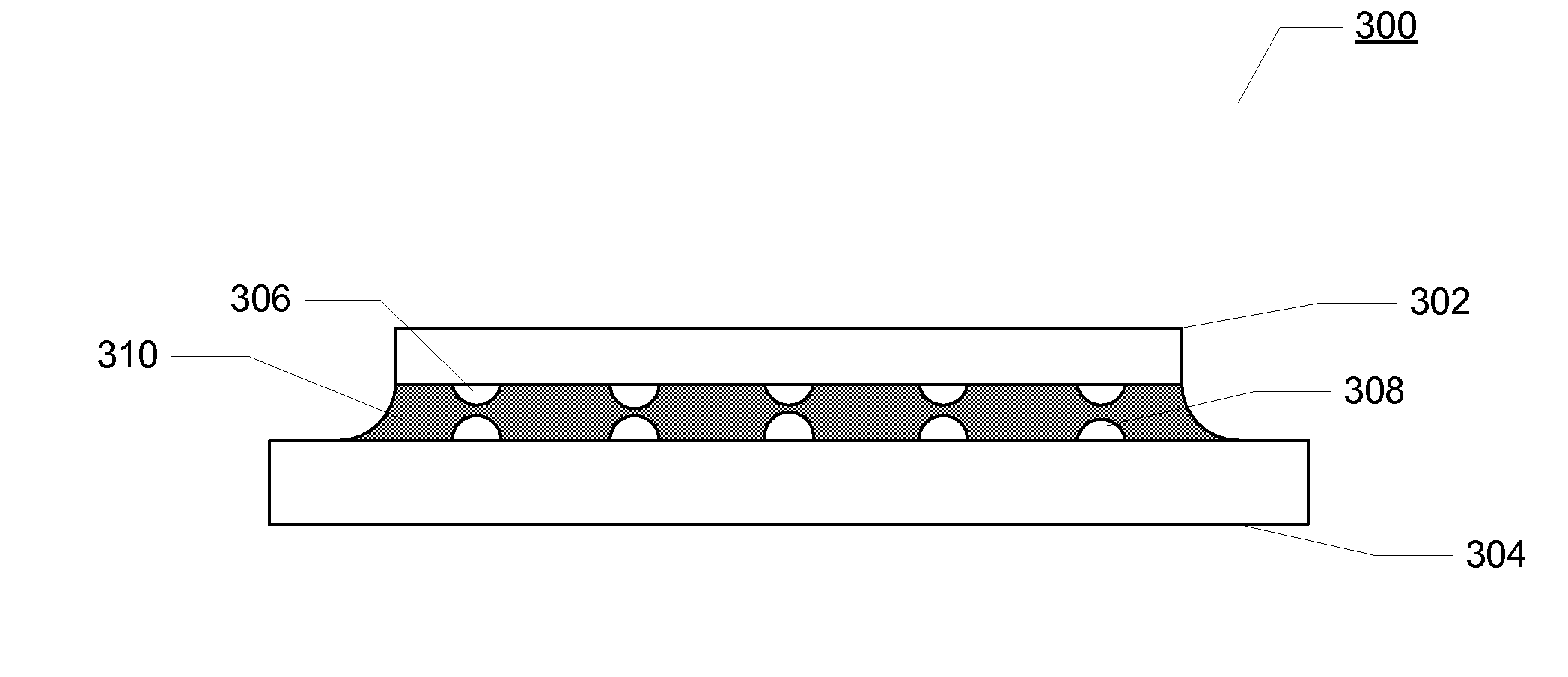

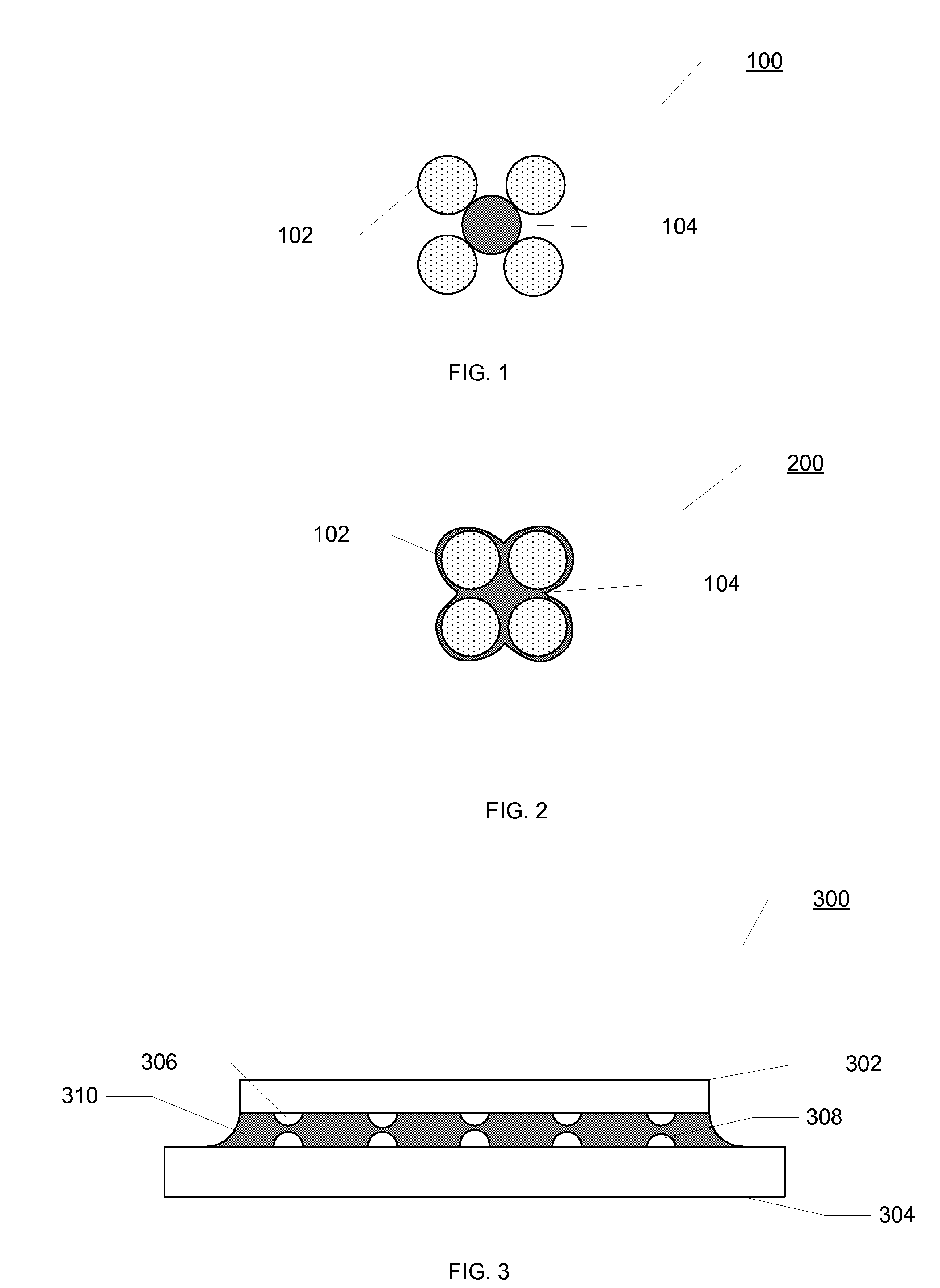

Conductive polymer composites

InactiveUS20080272344A1Printed circuit aspectsConductive materialConductive polymer compositeFlip chip interconnect

The present invention relates generally to conductive polymer composites, electrically conductive adhesives, and methods of producing the same. The conductive polymer composites and electrically conductive adhesives may be used for electronic component interconnects, flip chip interconnections, electrical connections to circuit boards, jumper connections, or similar uses. The method of forming a conductive polymer composite includes mixing conductive metal flakes, functionalized conductive metal nanoparticles, and a polymer precursor and curing the polymer precursor to form a composite. In one embodiment, the conductive polymer composites may be composed of microparticles of silver flake and sintered silver nanoparticles between the silver flakes. The polymer composites have an electrical conductivity of less than 10−5 Ω·cm.

Owner:GEORGIA TECH RES CORP

Method and apparatus for forming bumps for semiconductor interconnections using a wire bonding machine

InactiveUS20070199974A1Increase the gapMinimizes wire sagSemiconductor/solid-state device detailsSoldering apparatusFlip chip interconnectLead bonding

The present invention is a method and apparatus for forming a bump for semiconductor interconnect applications, such as reverse wire bonding or stud bumping for flip chip interconnections. The bump is formed by (1) ball bonding at the bump site, (2) raising the capillary a predetermined height after forming the ball bond with the wire paying out of the capillary tip, (3) moving the capillary laterally a predetermined distance, preferably in a direction toward the site of other end of the wire loop, if the bump is to be used as the platform for a stitch bond of a wire loop, (4) raising the capillary further, and (5) moving the capillary diagonally downwardly and in the opposite direction of the first lateral motion. The wire is then severed by raising the capillary, closing the clamps and raising the capillary again to snap the wire pigtail off at the bump.

Owner:KULICKE & SOFFA IND INC

Carbon nanotube via interconnect

ActiveUS7453154B2Improved performance characteristicsImprove performanceDischarge tube luminescnet screensFinal product manufactureFlip chip interconnectCarbon nanotube

An electronic device that facilitates improved electrical and thermal performance and / or allows fabrication of smaller electronic devices exhibiting excellent performance characteristics, especially for devices operating at microwave frequencies, includes an input / output pad, and a carbon nanotube extending from the input / output pad to provide wafer-level nano-interconnect for flip chip interconnections and die stacking on a substrate.

Owner:DELPHI TECH IP LTD

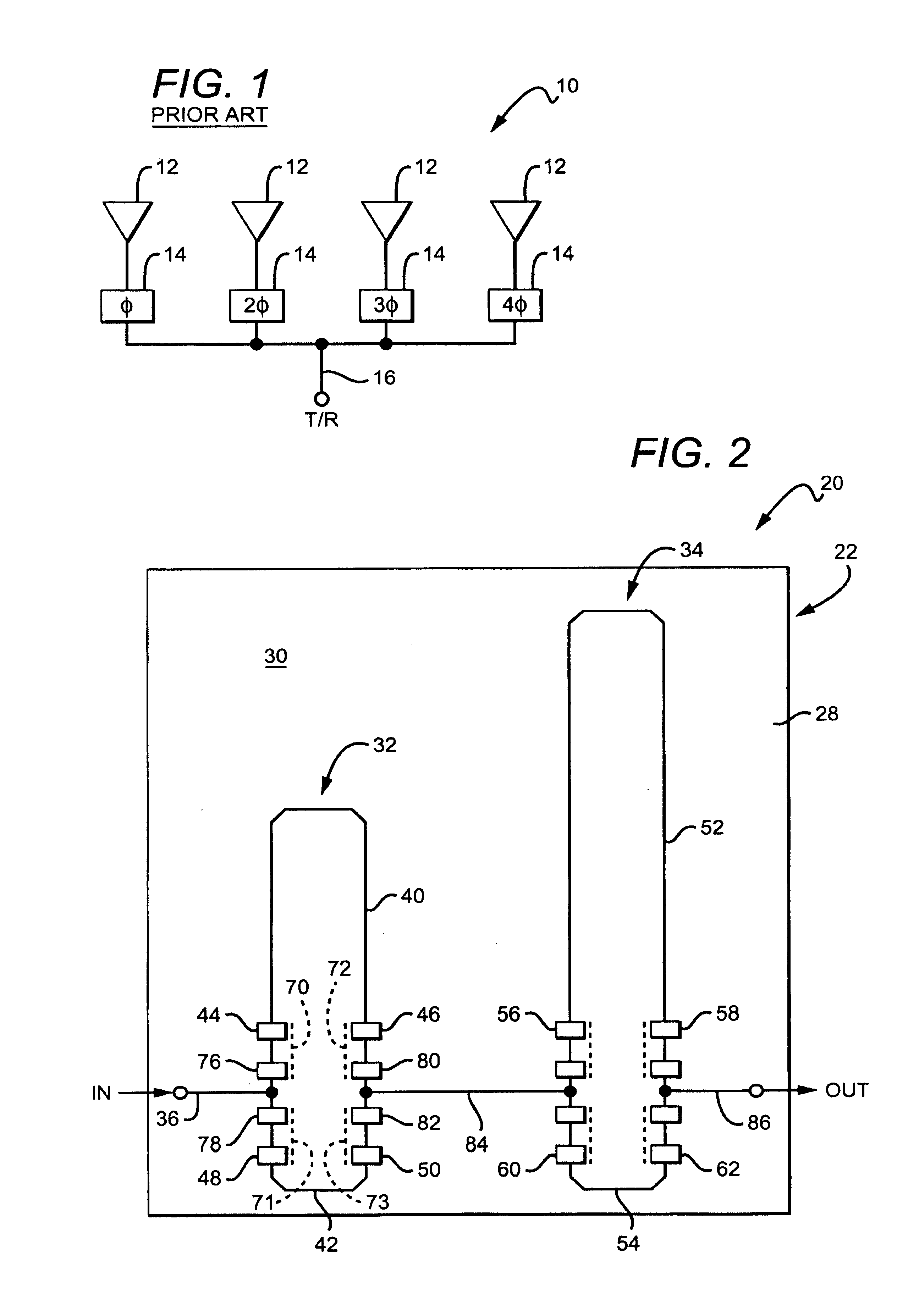

Low loss RF phase shifter with flip-chip mounted MEMS interconnection

ActiveUS7068220B2Reduce lossAvoid incompatibilitiesDelay linesWaveguidesFlip chip interconnectComputer module

Owner:TELEDYNE SCI & IMAGING

Method of forming a surface mountable IC and its assembly

InactiveUS20060057763A1Wide alignment toleranceIncrease production capacityFinal product manufacturePrinted circuit aspectsProduction rateFlip chip interconnect

A flip-chip interconnect structure for a RFID tag is described which permits the use of an isotropic electrically conductive adhesive (ECA) without requirement of critical alignment of the chip terminal pads to antenna terminals on the substrate. The interconnect foot print utilizes design principles of standard discrete SMD terminal footprint, which does not require alignment accuracy of a NCA / ACA flip chip bonder. The use of an ECA also eliminates the need for curing the adhesive while under heat and pressure on the chip placement machine. Because of the wide placement tolerance the chips can be placed with a low cost highly productive SMT placement machine. After placement, the assemblies leave the placement machine and are cured in an oven, thereby further improving the productivity of the placement machine. Further productivity improvement is realized by the elimination of bumping which is no longer required. The overall cost reduction of the final assembly by the process of the invention is estimated at about 60 to 85 percent.

Owner:AGENCY FOR SCI TECH & RES

Method for fine-pitch, low stress flip-chip interconnect

ActiveUS20090325348A1Reliability problemEasy to separateSolid-state devicesSemiconductor/solid-state device manufacturingFlip chip interconnectSemiconductor chip

Attaching a semiconductor chip to a substrate by applying mechanical vibrations (150) to a polymeric compound (130) and the contacting areas (114, 124) of a first (113) and a second (121) metallic member immersed in the compound, while the two metallic members approach (140) each other until they touch. The mechanical vibration causes displacements of the first member relative to the second member, and the vibration includes displacements (150) oriented at right angles to the direction (140) of the approach. The polymeric compound (130) includes a non-conductive adhesive resin paste (NCP) and filler particles; the paste is deposited before the attaching step. The first member (113) is affixed to the chip and the second member (121) to the substrate.

Owner:TEXAS INSTR INC

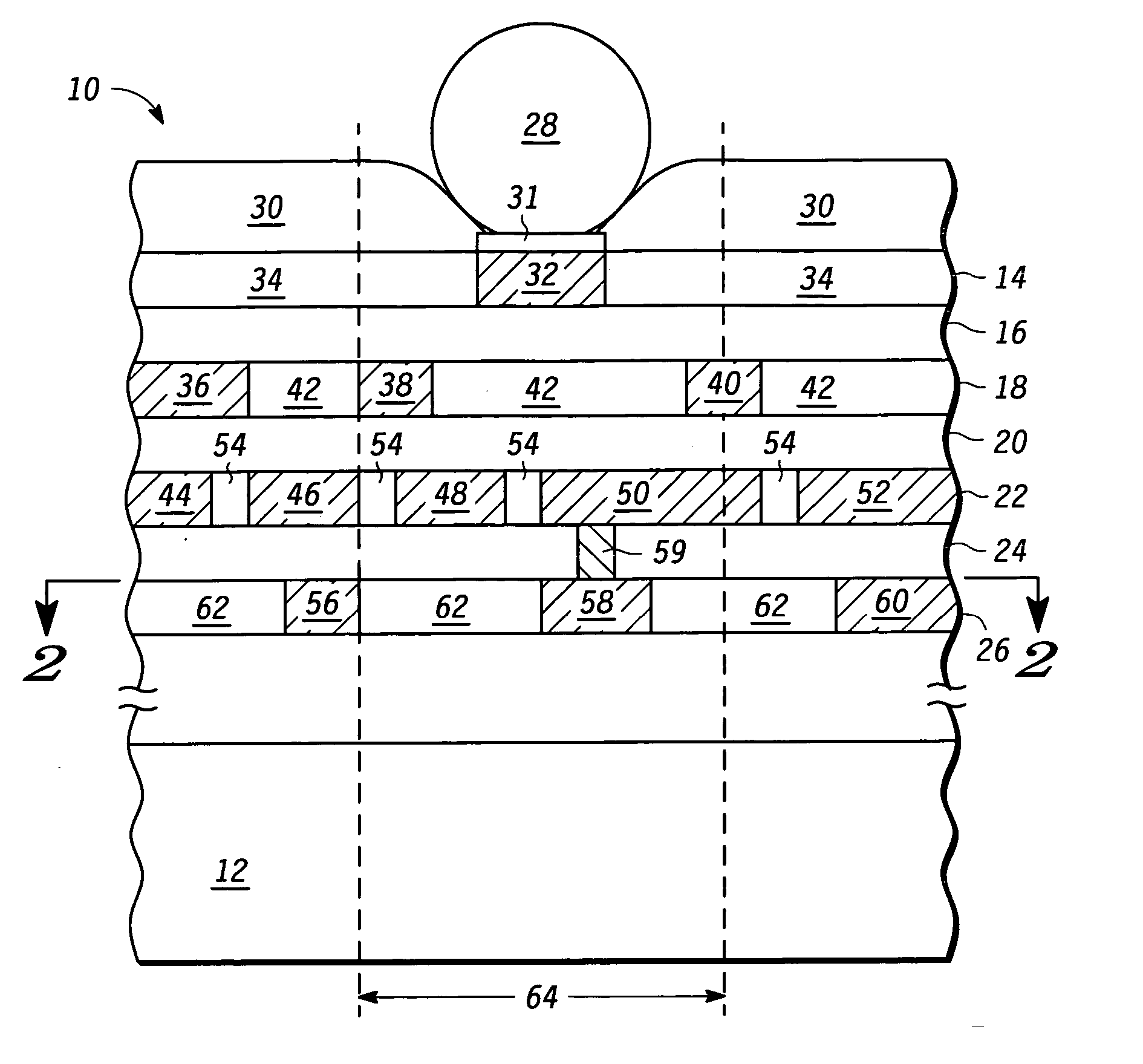

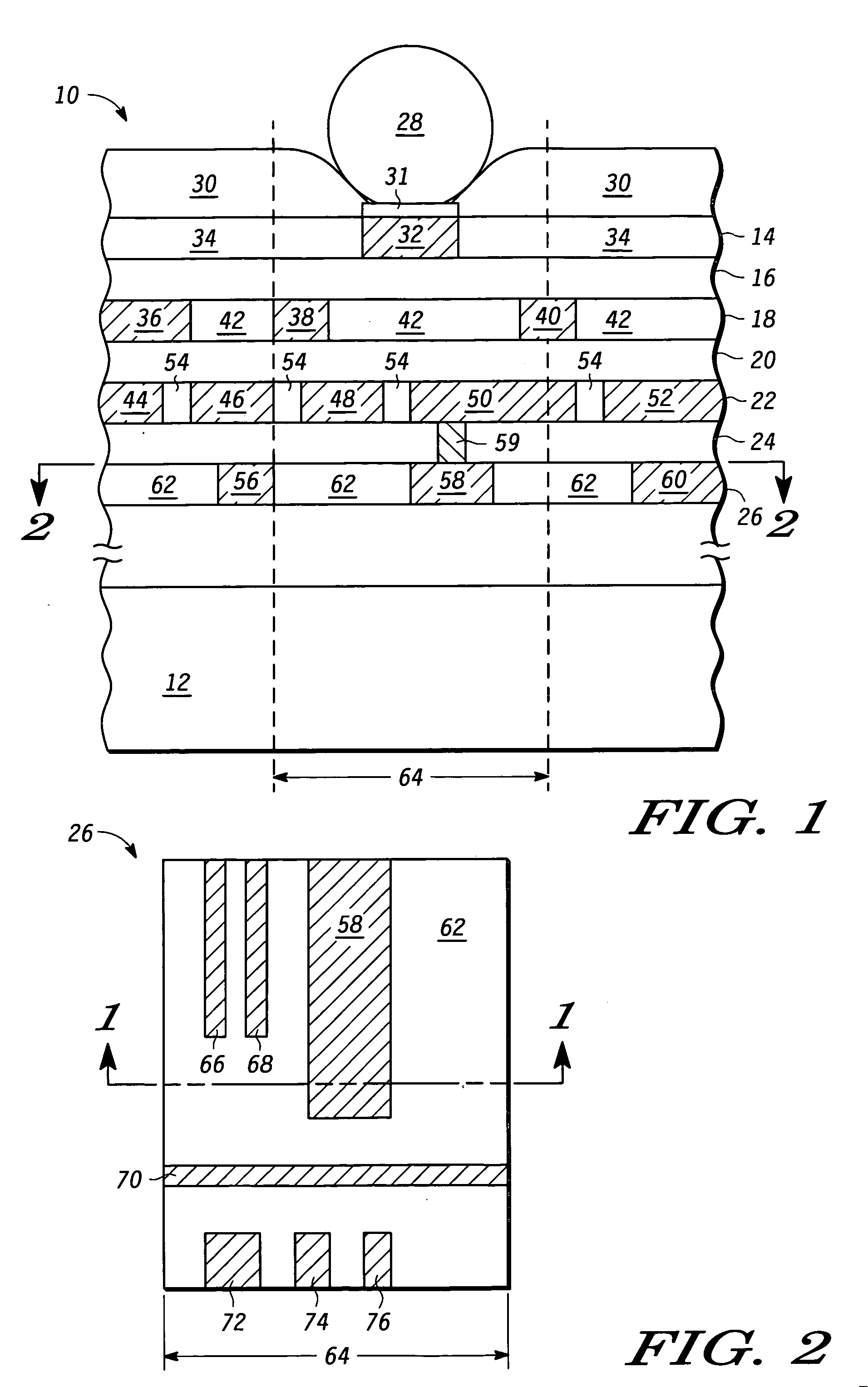

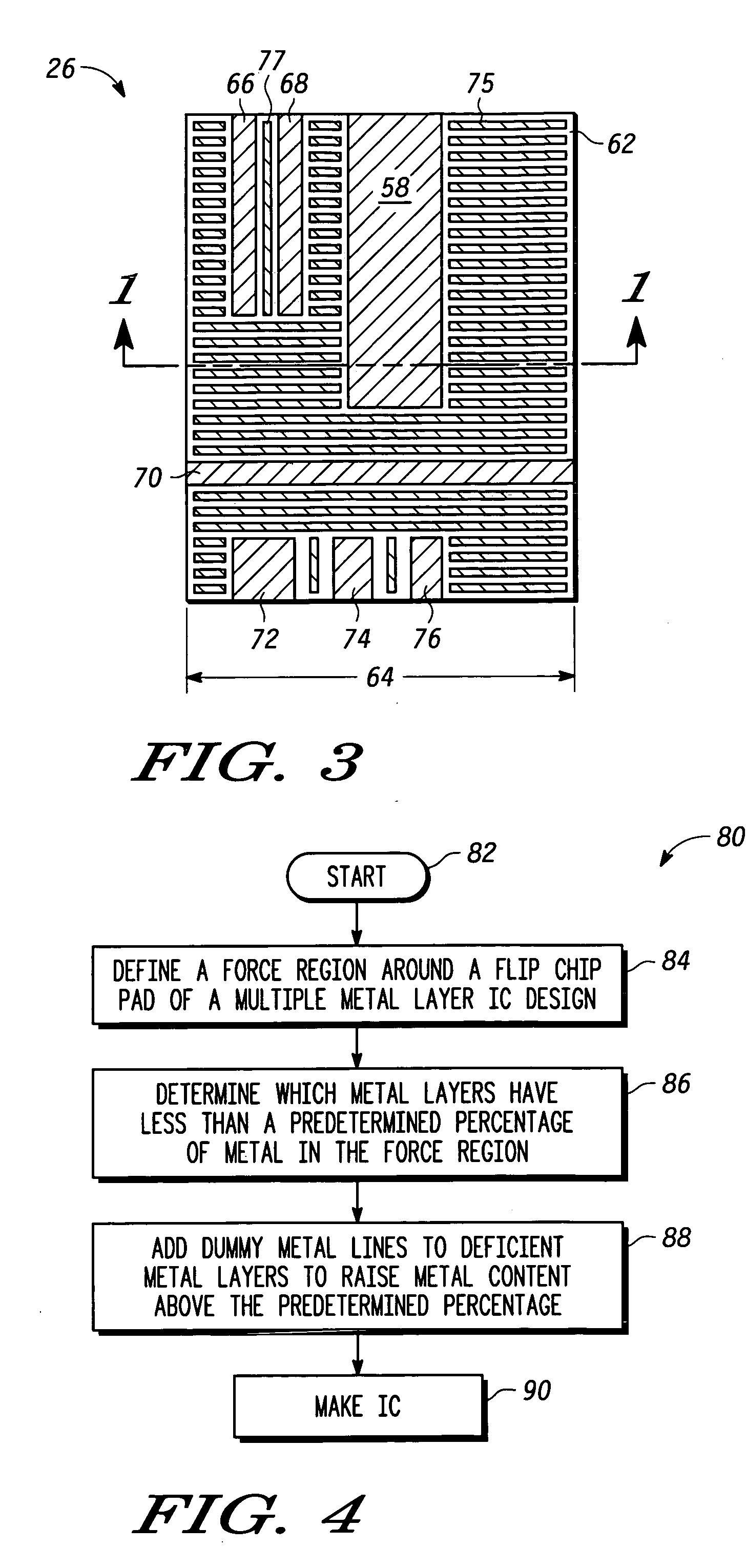

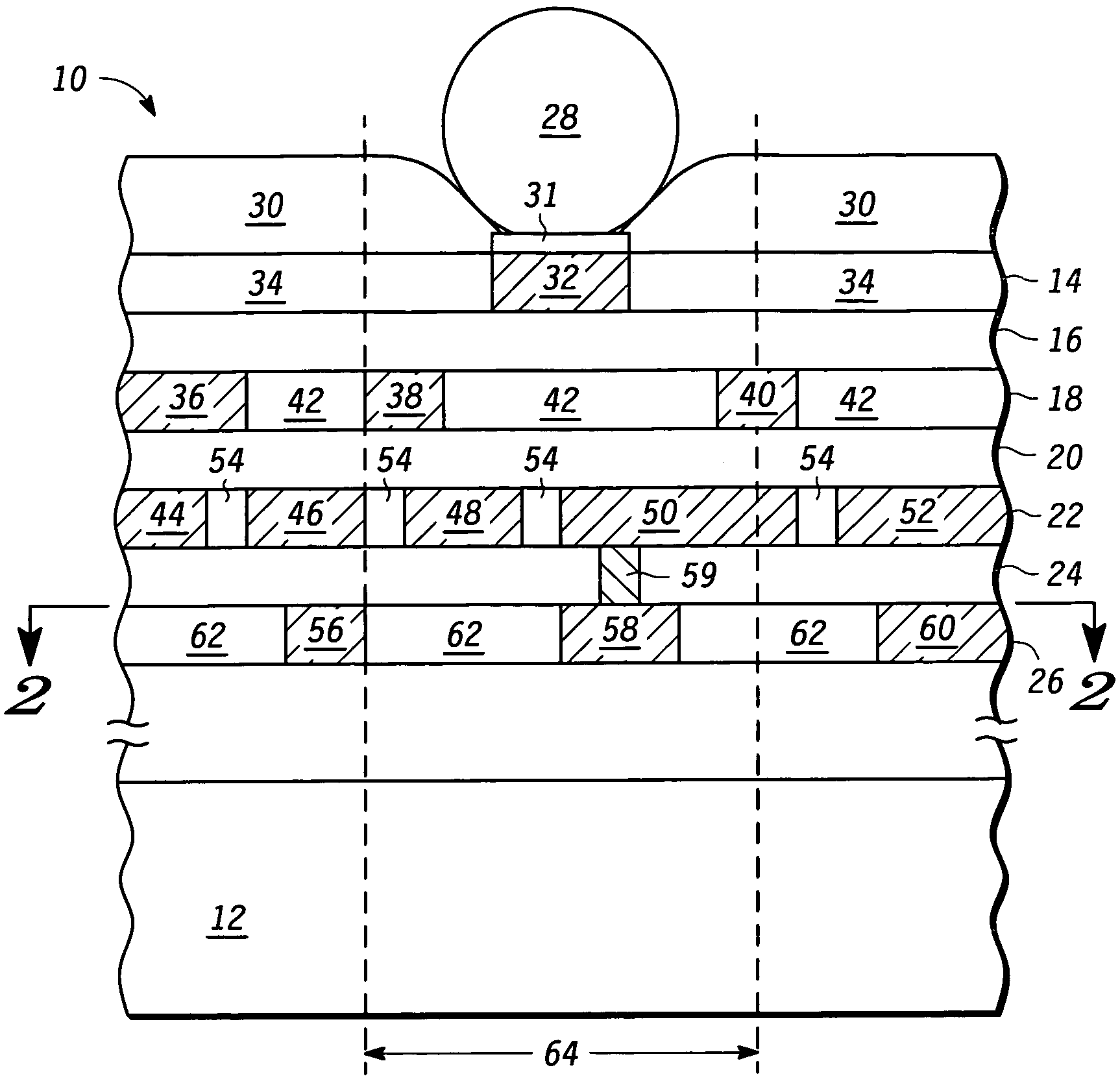

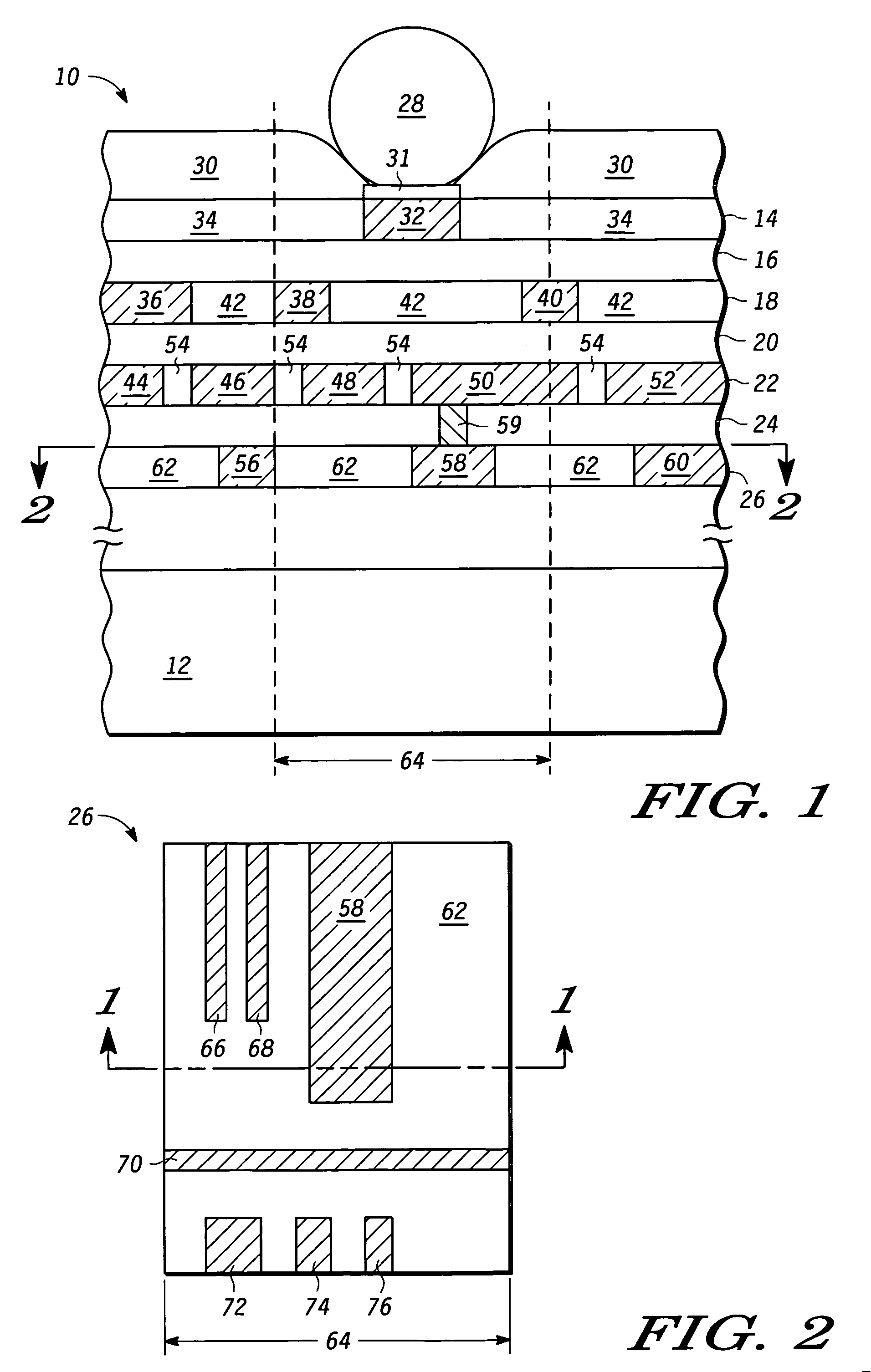

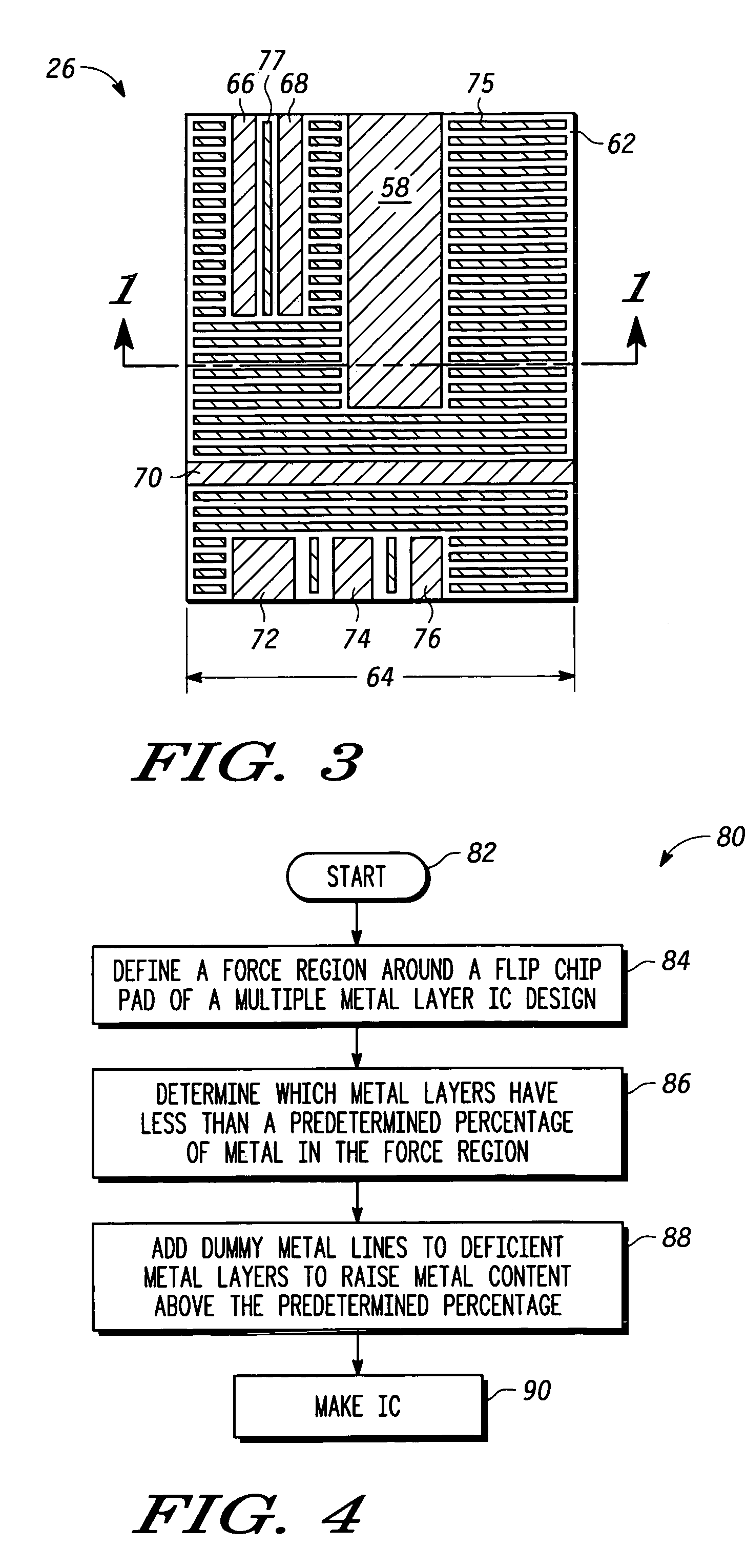

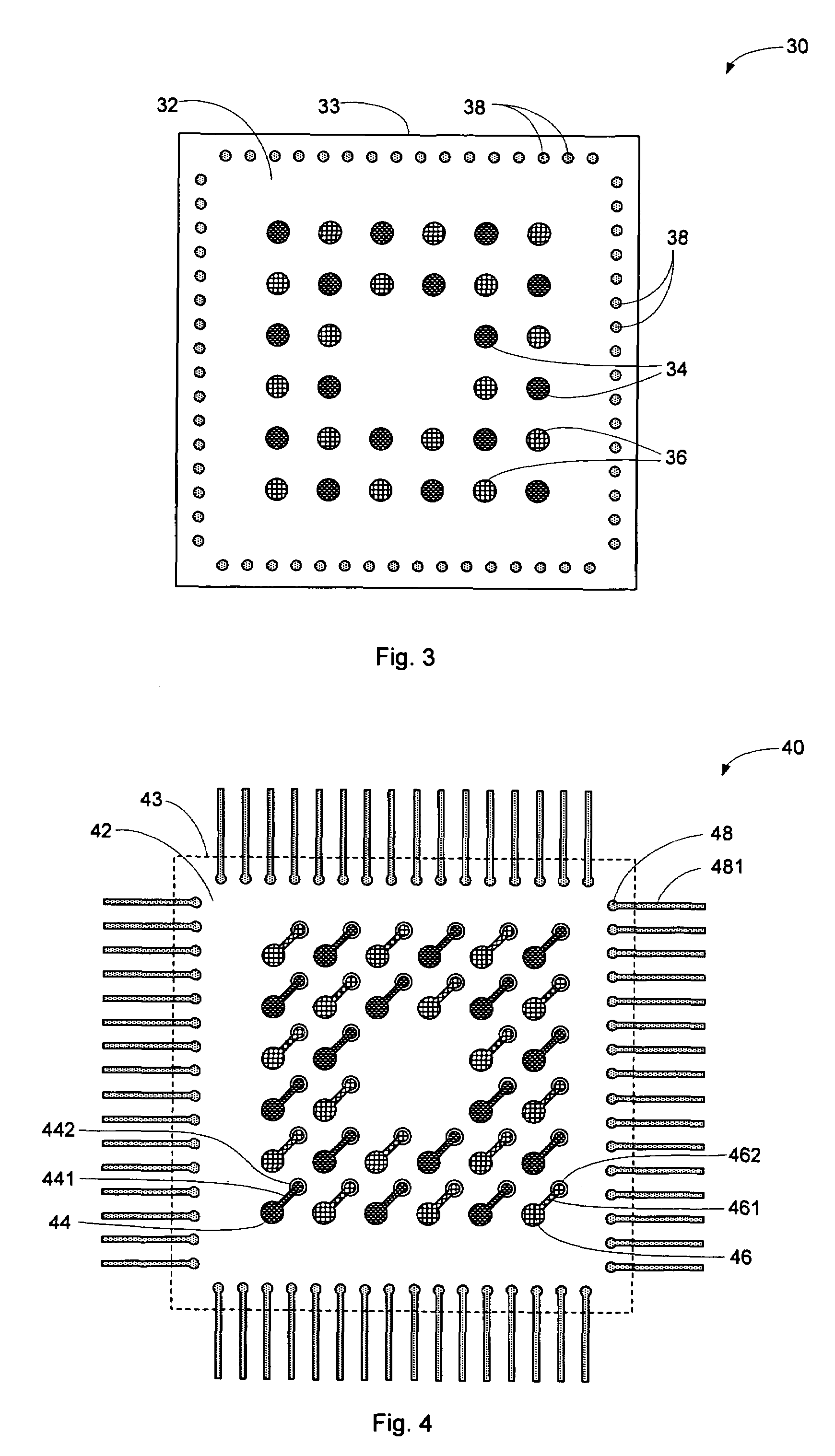

Integrated circuit having structural support for a flip-chip interconnect pad and method therefor

ActiveUS20060154470A1Semiconductor/solid-state device detailsSolid-state devicesDielectricFlip chip interconnect

A technique for alleviating the problems of defects caused by stress applied to bond pads (32) includes, prior to actually making an integrated circuit (10), adding dummy metal lines (74, 76) to interconnect layers (18, 22, 26) to increase the metal density of the interconnect layers. These problems are more likely when the interlayer dielectrics (16, 20, 24) between the interconnect layers are of a low-k material. A critical area or force area (64) around and under each bond pad defines an area in which a defect may occur due to a contact made to that bond pad. Any interconnect layer in such a critical area that has a metal density below a certain percentage can be the cause of a defect in the interconnect layers. Any interconnect layer that has a metal density below that percentage in the critical area has dummy metal lines added to it.

Owner:VLSI TECH LLC

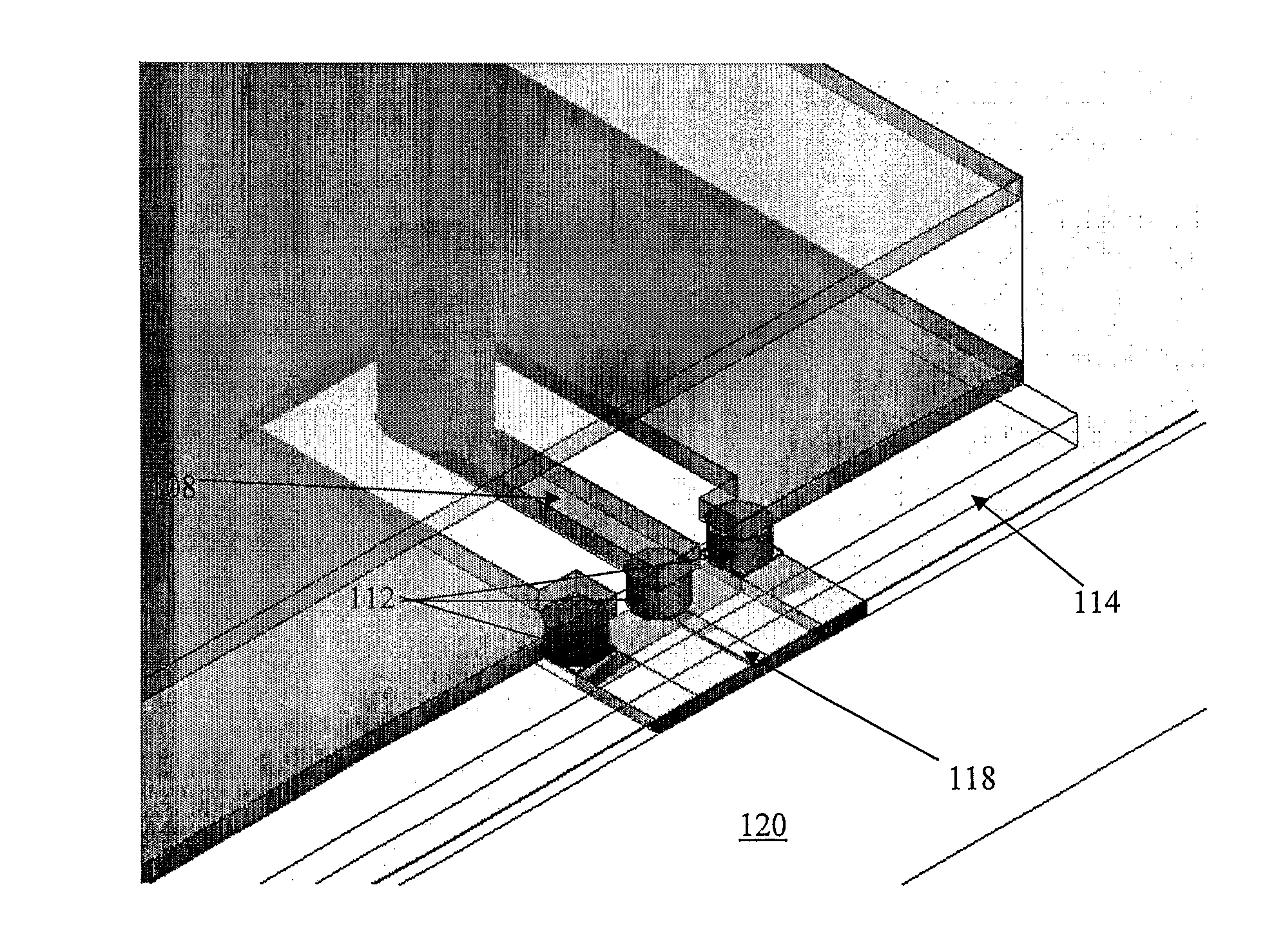

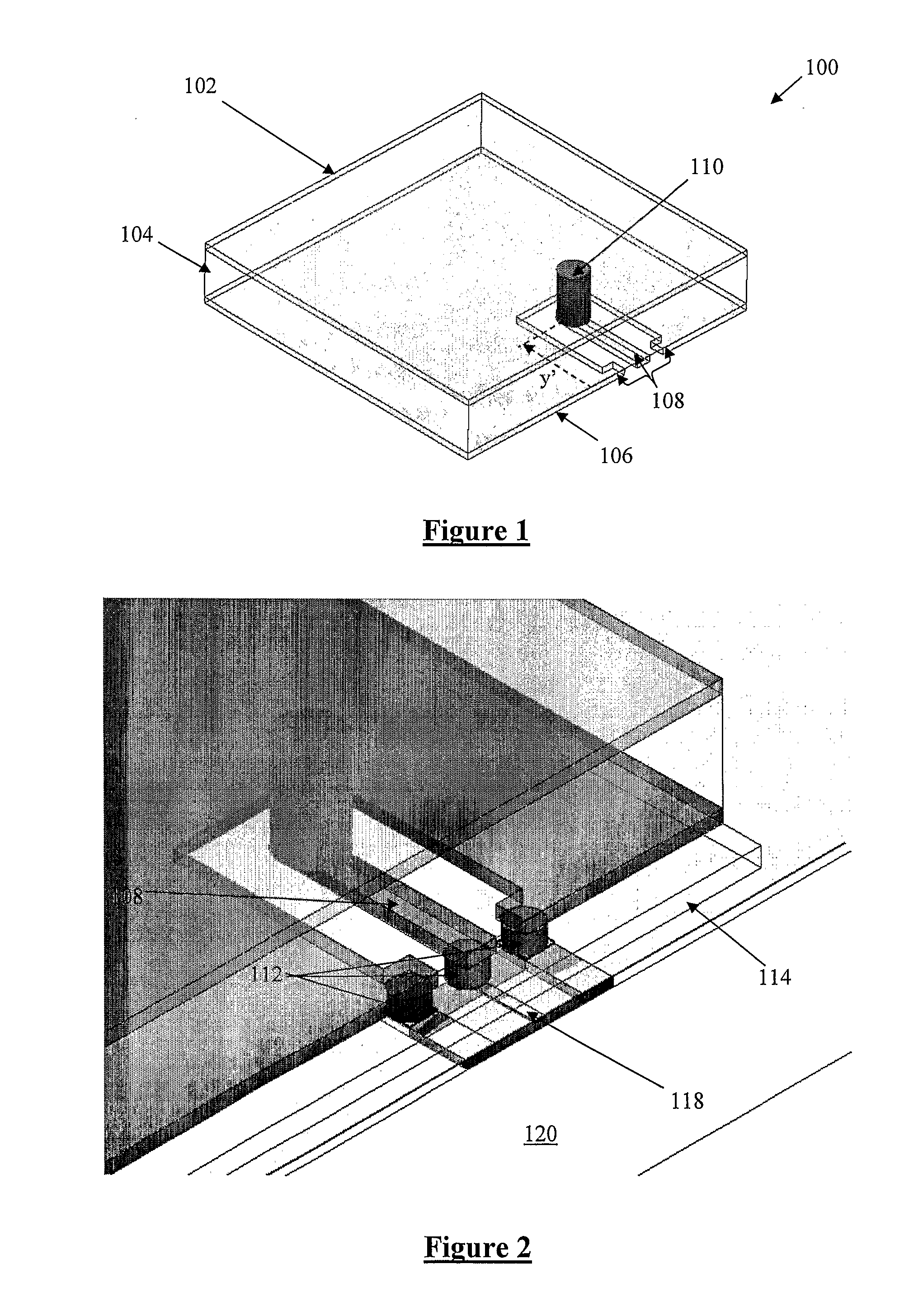

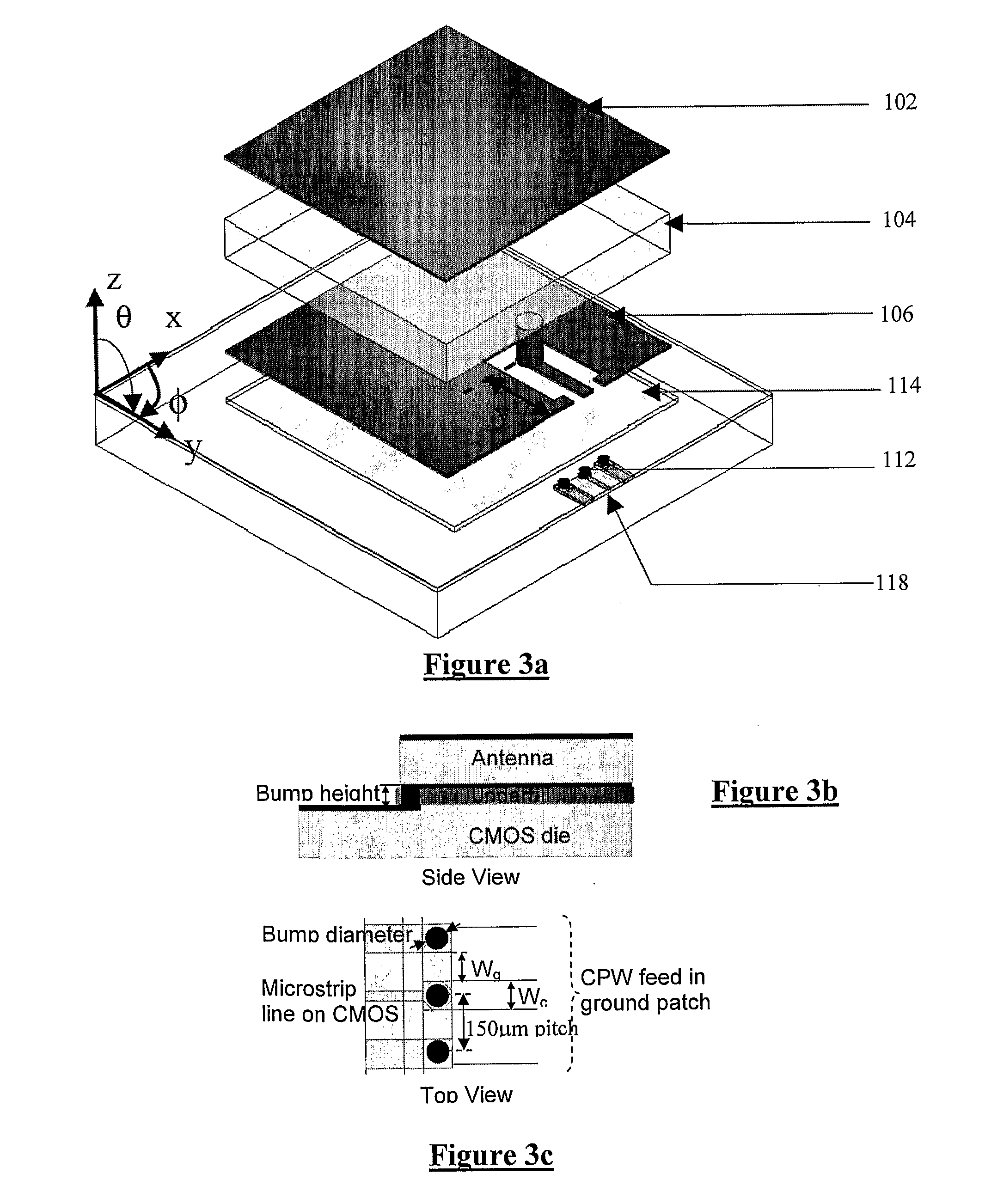

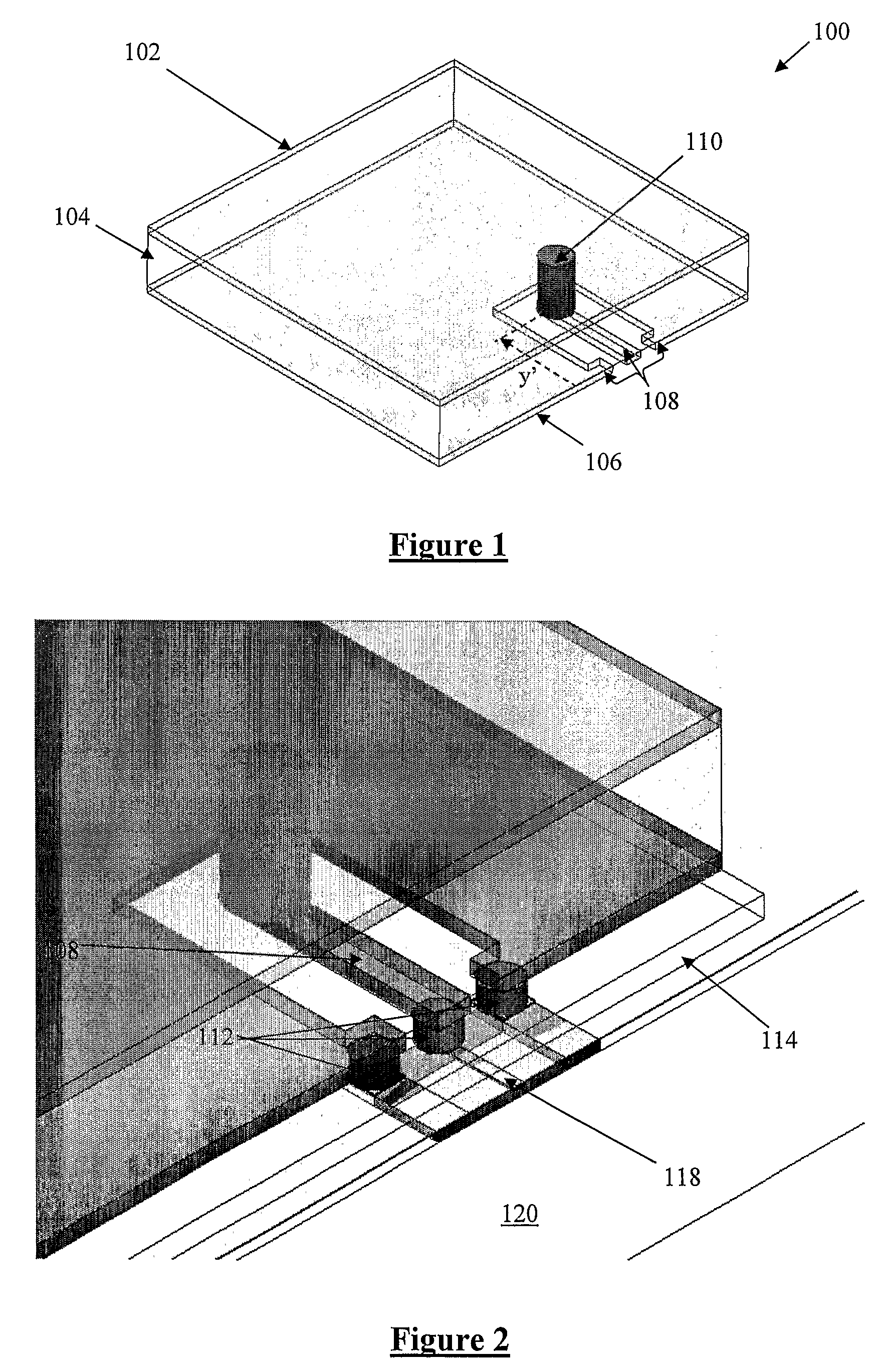

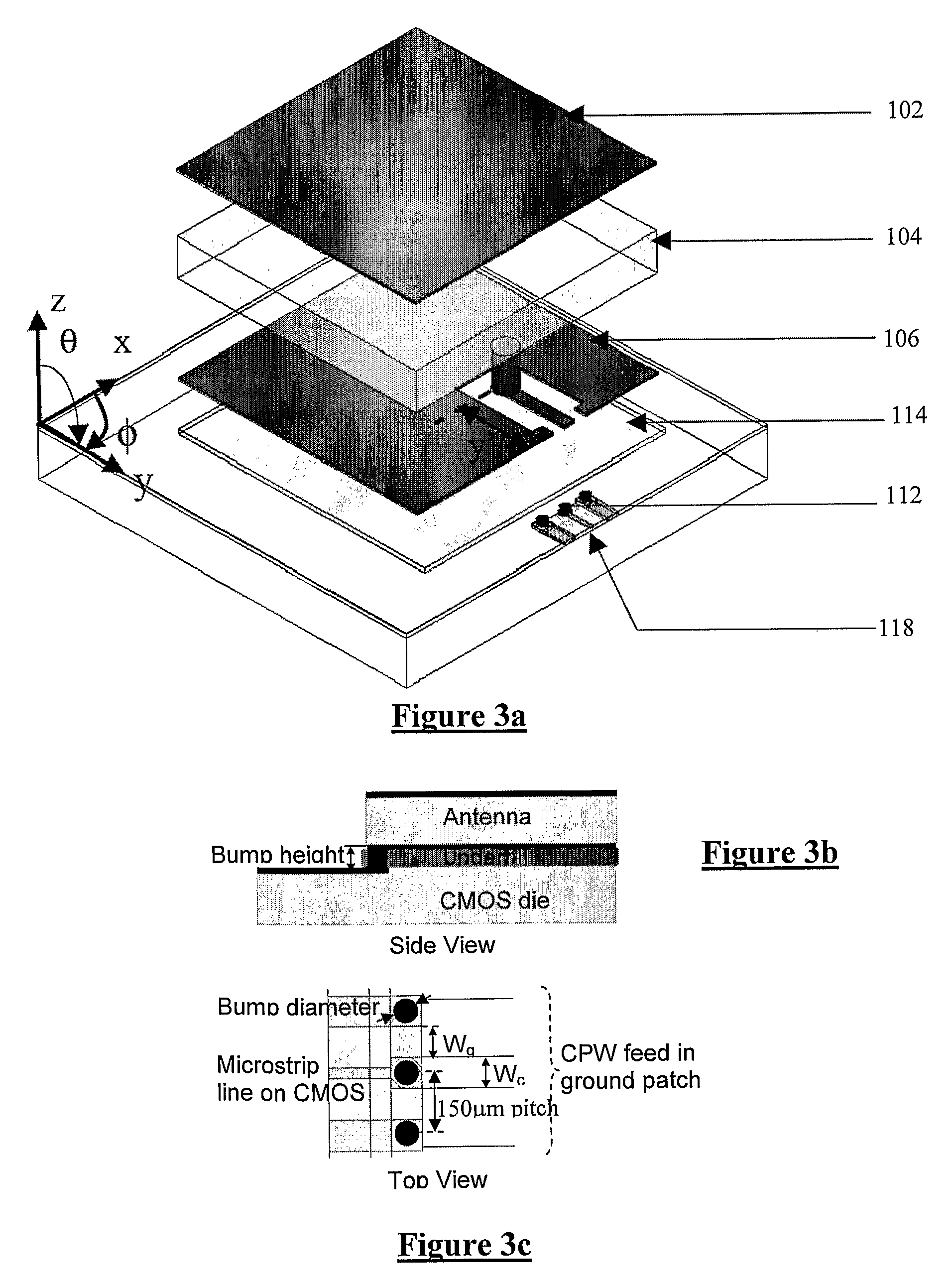

Integration of microstrip antenna with CMOS transceiver

ActiveUS20110260943A1Low costLow interconnectionSimultaneous aerial operationsRadiating elements structural formsMicrostrip patch antennaCMOS

A monolithic antenna element comprises a microstrip patch antenna and a ground plane, with a substrate between the patch antenna and the ground plane. A feeding via extends from the ground plane layer through the substrate to the patch antenna, connecting to the antenna distal from lateral edges of the antenna. A coplanar waveguide (CPW) feed line is formed in the ground plane layer, and interrupts and is electrically distinct from the ground plane. The CPW extends from a lateral edge of the ground layer to the feeding via. The antenna can be flip chip bonded to a CMOS die, reducing cost of millimetre wave transceivers, e.g. 57-64 GHz. The antenna is fabricated using standard PCB technology and a single substrate for the antenna. Antenna arrays can be fabricated. Appropriately designed antenna feeds, flip chip interconnects and antenna shape provide suitably broad antenna bandwidth, with relatively high efficiency.

Owner:ADVANCED MICRO DEVICES INC +1

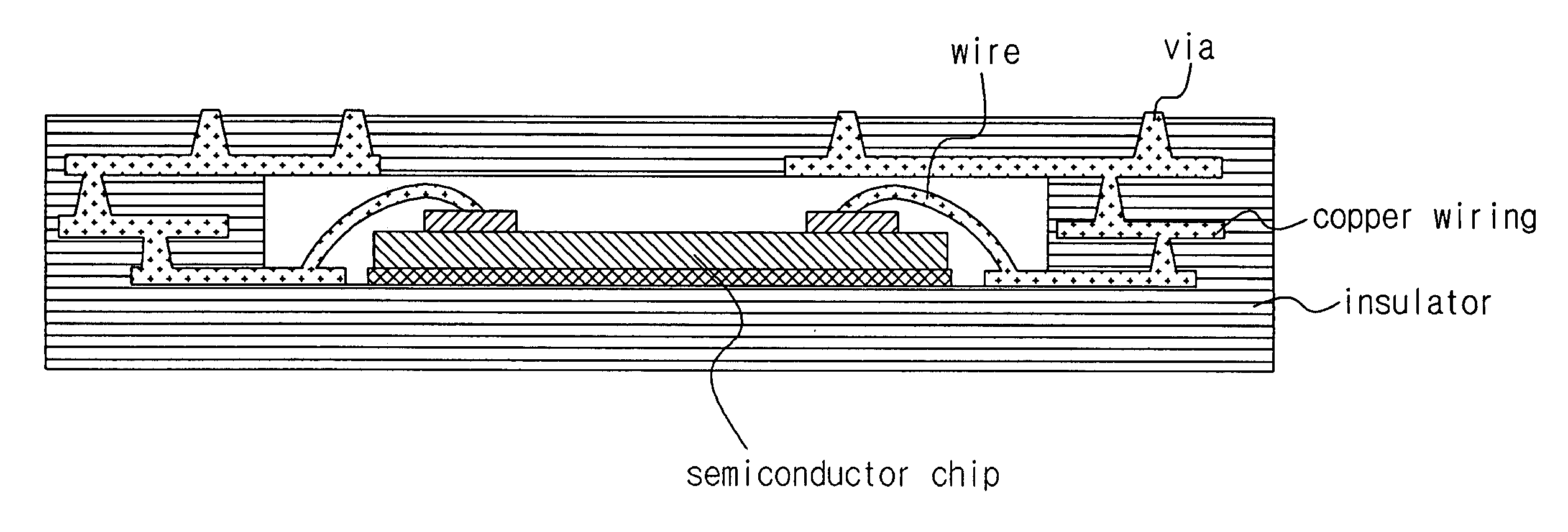

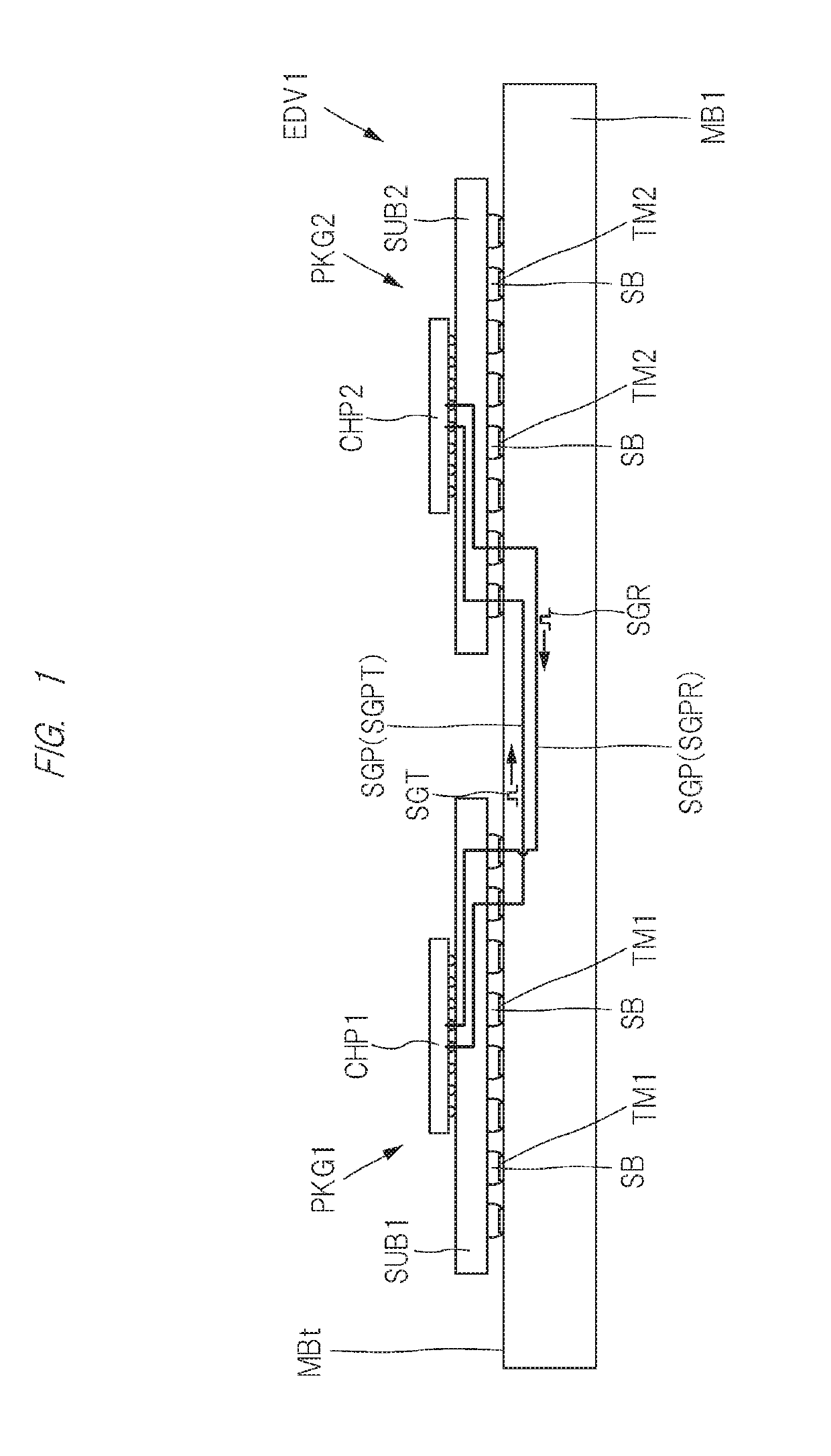

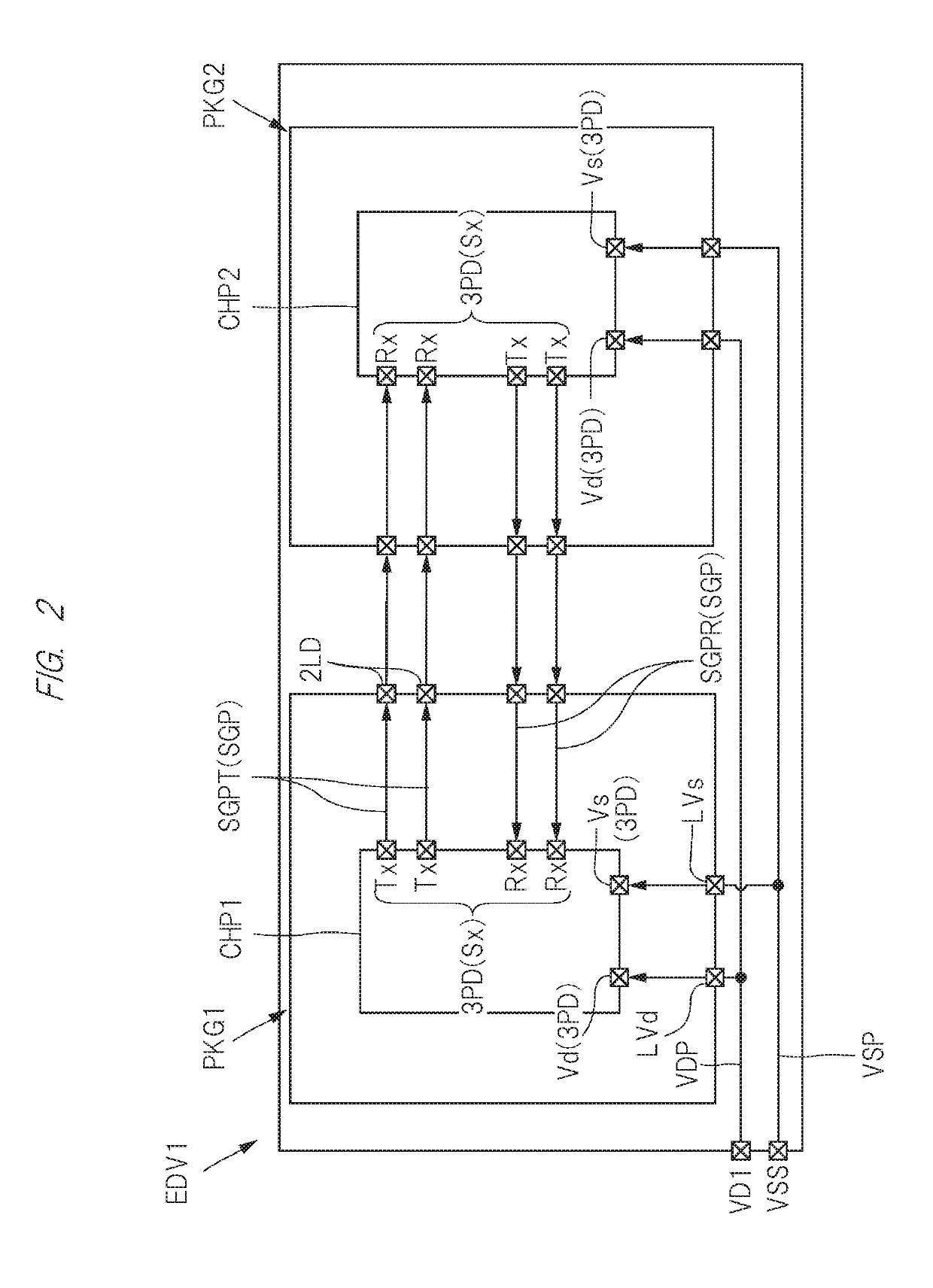

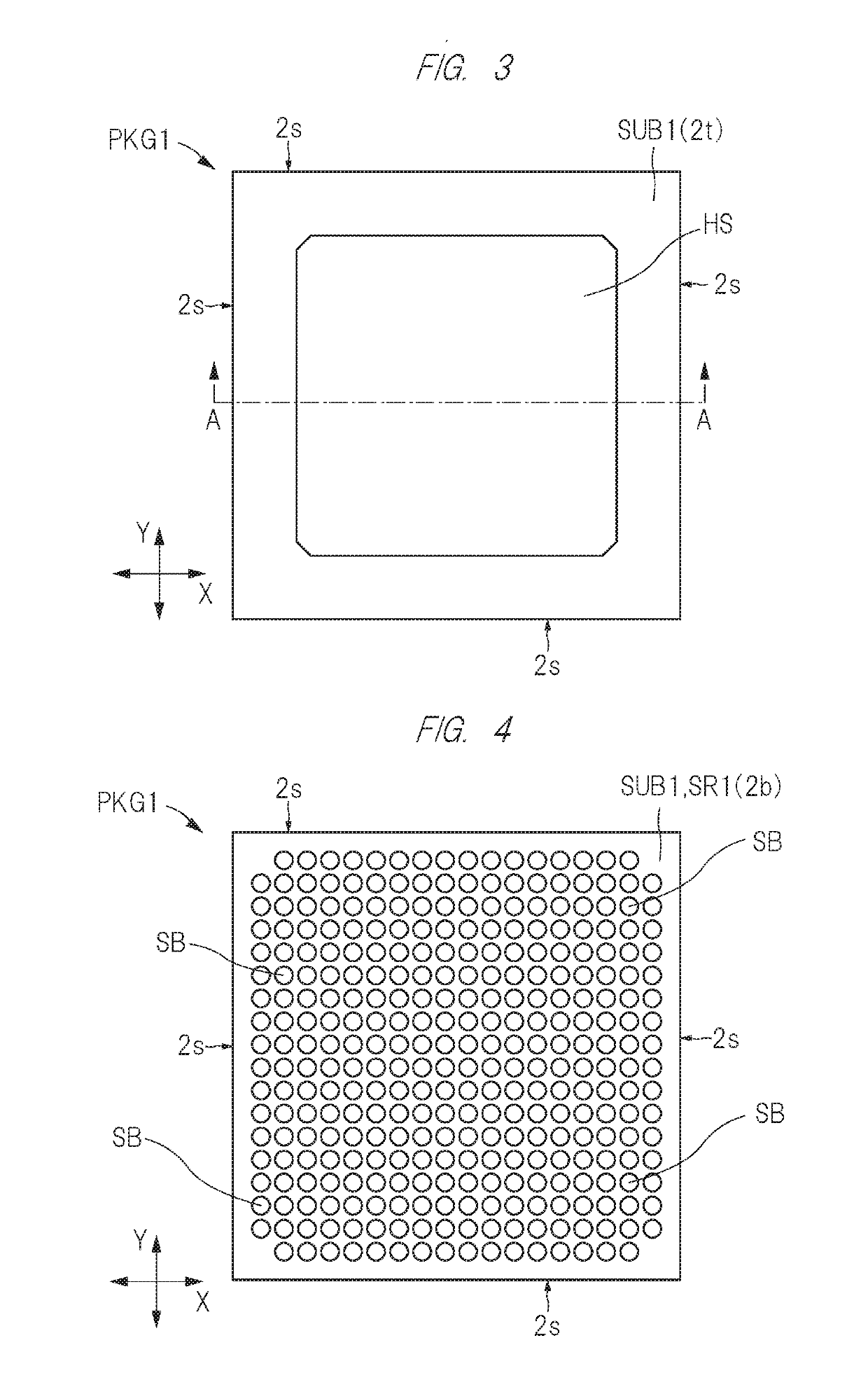

Semiconductor device

ActiveUS20190318990A1Improve semiconductor device performanceSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceFlip chip interconnect

A semiconductor device includes a wiring substrate provided with a plurality of pads electrically connected to a semiconductor chip in a flip-chip interconnection. The wiring substrate includes a pad forming layer in which a signal pad configured to receive transmission of a first signal and a second pad configured to receive transmission of a second signal different from the first signal are formed and a first wiring layer located at a position closest to the pad forming layer. In the wiring layer, a via land overlapping with the signal pad, a wiring connected to the via land, and a wiring connected to the second pad and extending in an X direction are formed. In a Y direction intersecting the X direction, a width of the via land is larger than a width of the wiring. A wiring is adjacent to the via land and overlaps with the signal pad.

Owner:RENESAS ELECTRONICS CORP

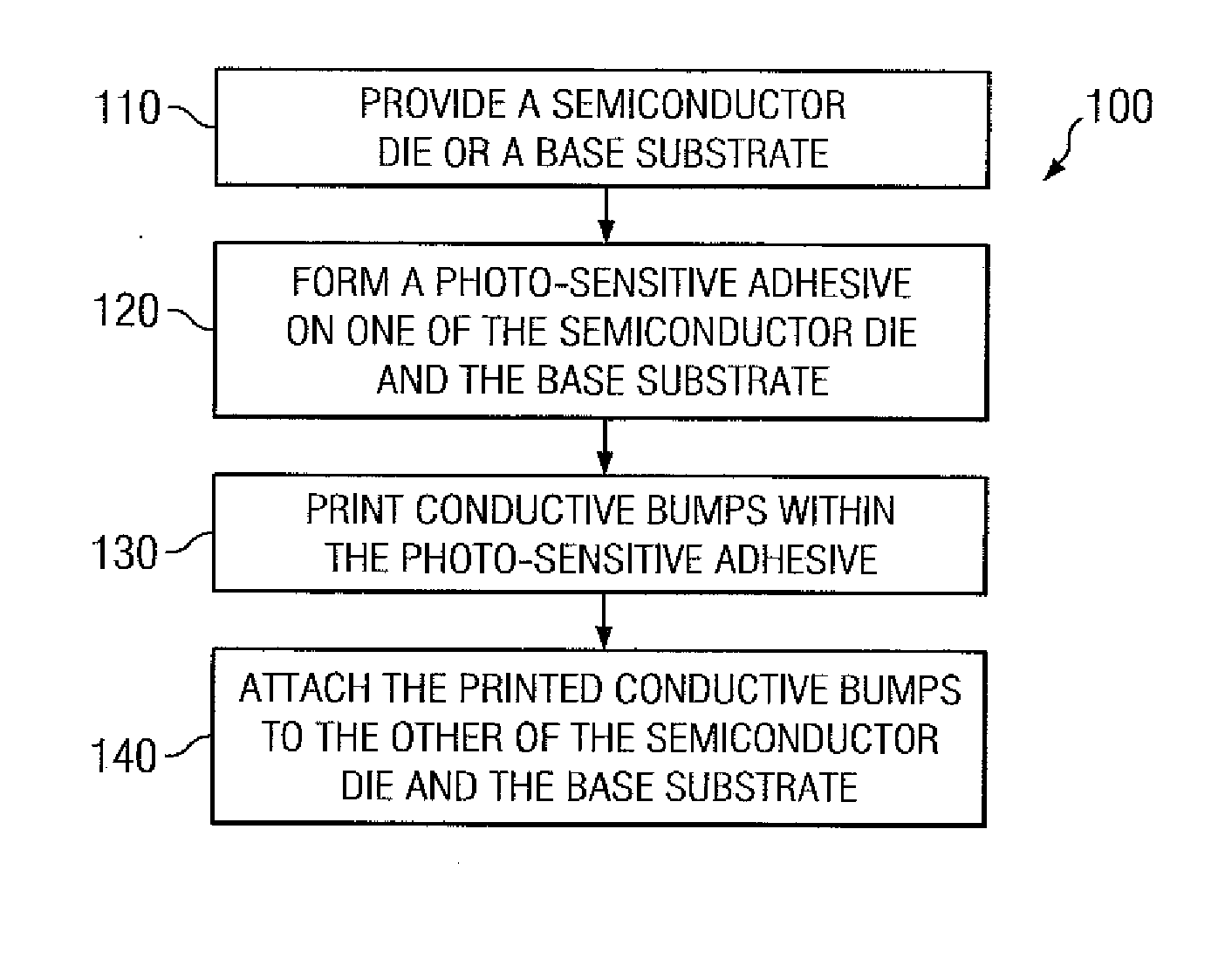

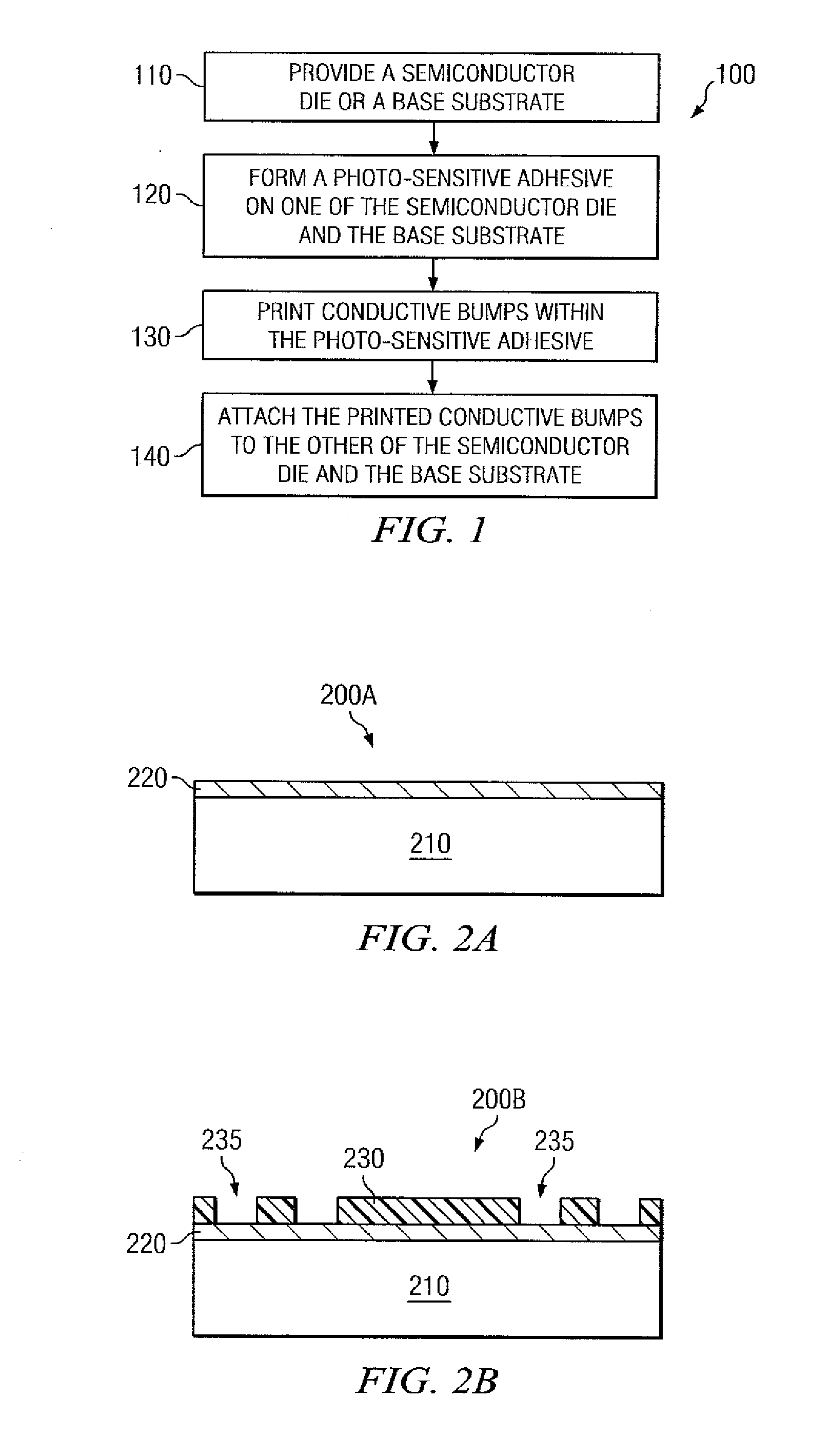

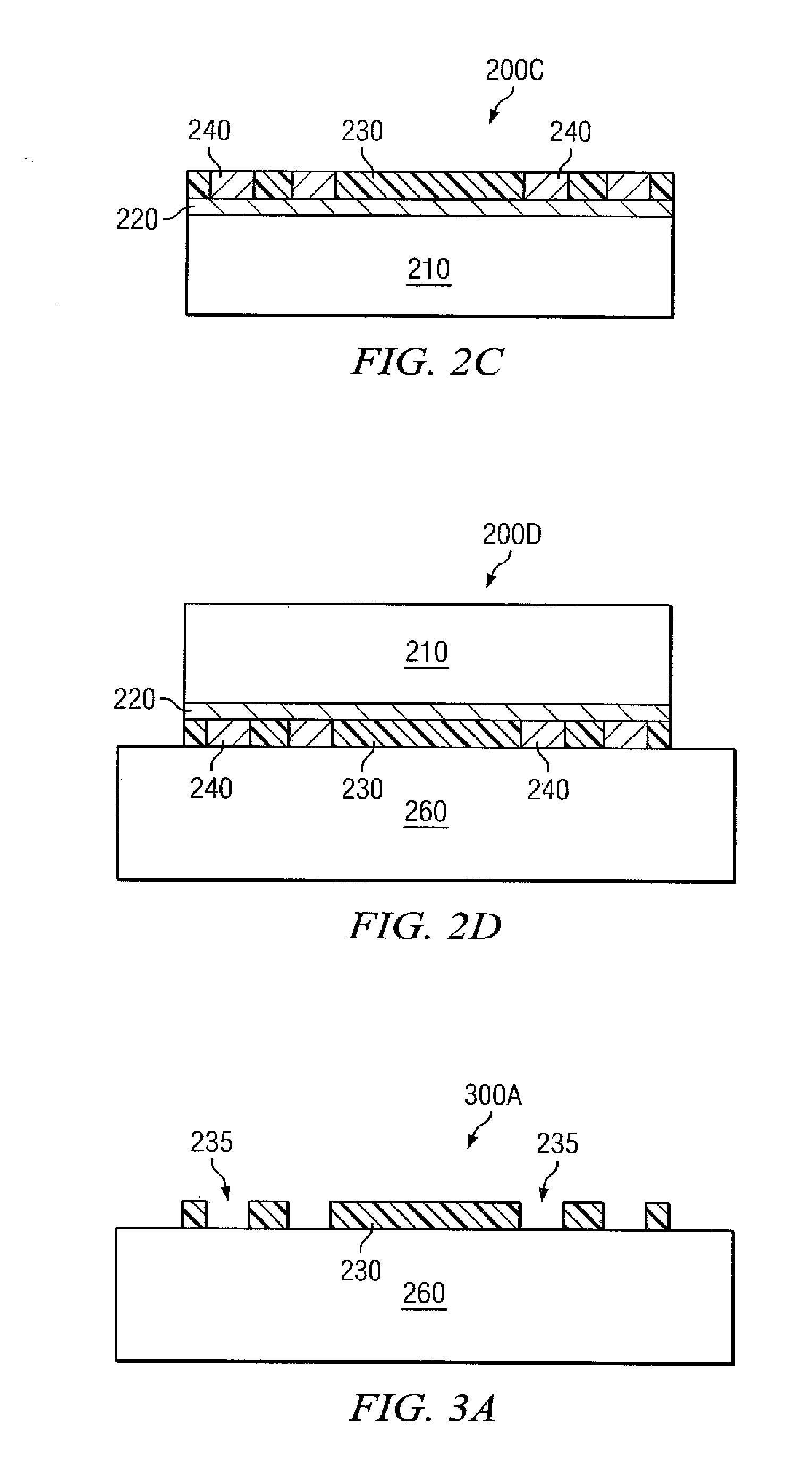

Low-cost flip-chip interconnect with an integrated wafer-applied photo-sensitive adhesive and metal-loaded epoxy paste system

InactiveUS20100159644A1Simple process flowReduce equipmentSemiconductor/solid-state device detailsSolid-state devicesEpoxyFlip chip interconnect

Various exemplary embodiments provide materials and methods for flip-chip packaging technology. The disclosed flip-chip packaging technology can use a single B-stage wafer-applied photo-sensitive adhesive along with printed interconnects, which does not include conventional underfill materials and processes. In one embodiment, a photo-sensitive adhesive can be applied on a semiconductor die or a base substrate with conductive bumps printed in through-openings of the photo-sensitive adhesive. One or more semiconductor dies can be laterally packaged or vertically stacked on the base substrate using the printed conductive bumps as interconnects there-between.

Owner:TEXAS INSTR INC

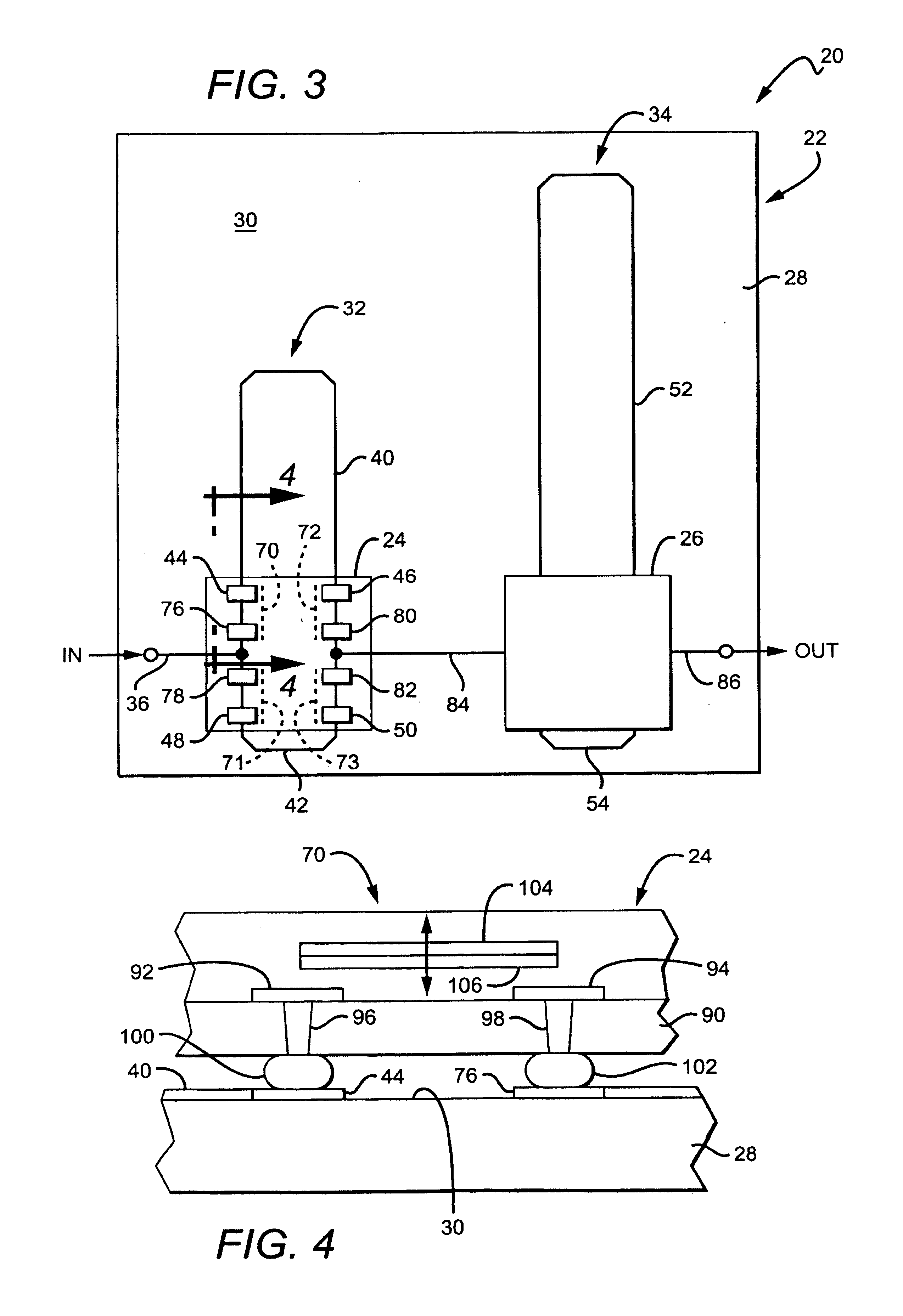

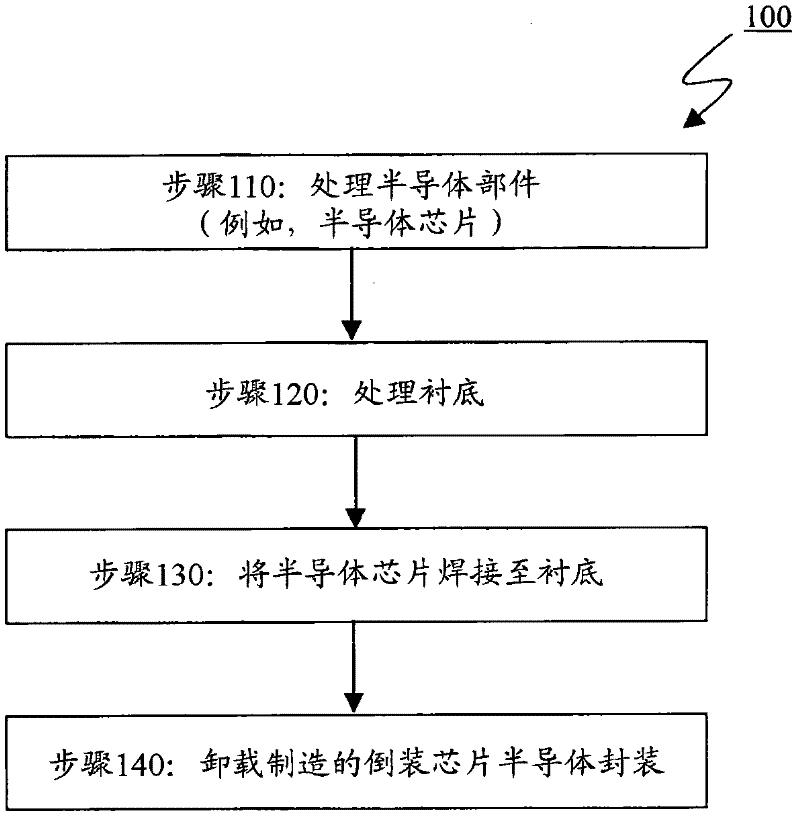

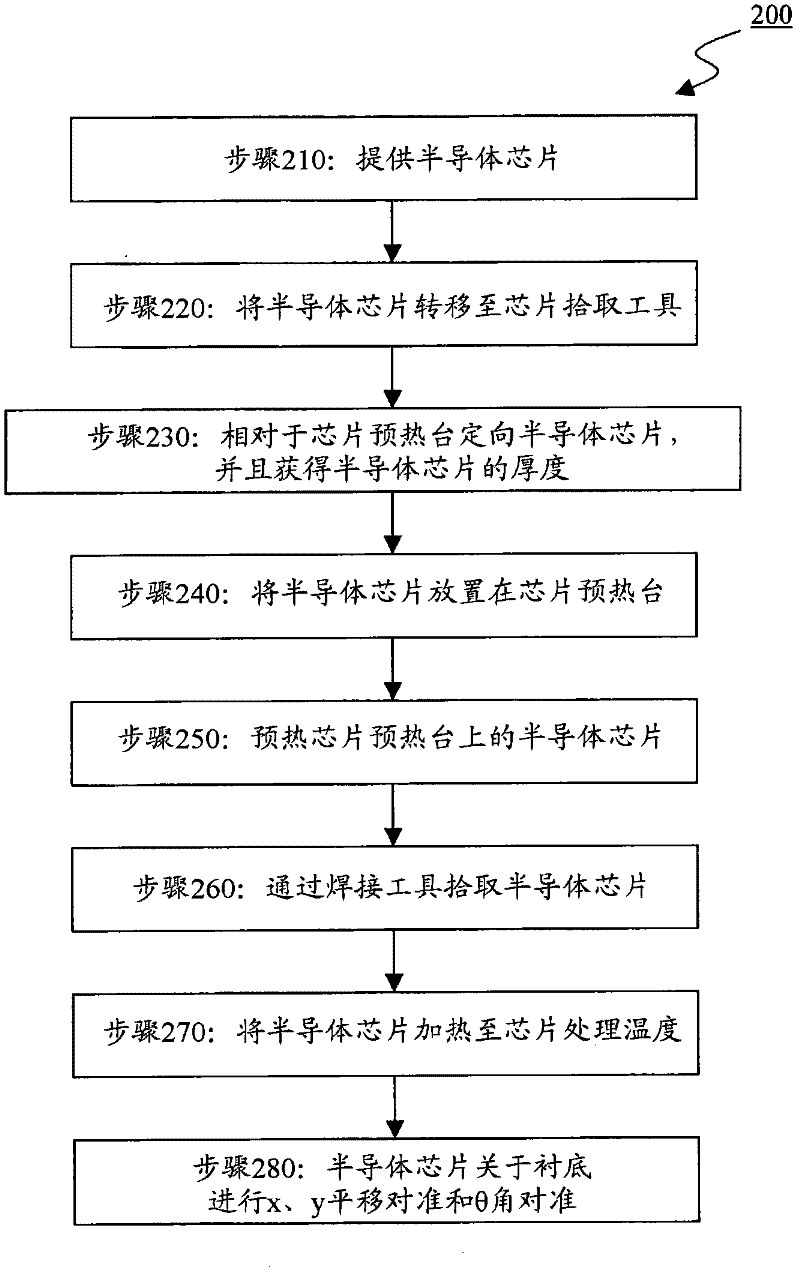

In-situ melting and reflow process and system for forming flip-chip interconnects

A method for fabricating a flip-chip semiconductor package comprising processing a semiconductor device, for example a semiconductor chip and processing a device carrier, for example a substrate. The semiconductor device comprises bump structures formed on a surface thereof. The substrate comprises bond pads formed on a surface thereof. The semiconductor chip is heated to a chip process temperature. The chip process temperature melts solder portions on the bump structures. The substrate is heated to a substrate process temperature, wherein said substrate process temperature may be different to the chip process temperature. The semiconductor chip is spatially aligned in relation to the substrate to correspondingly align the bump structures in relation to the bond pads. The semiconductor chip is displaced towards the substrate to abut the bump structures with the bond pads to thereby form bonds there between. A system for performing the above method is also disclosed.

Owner:ORION SYST INTEGRATION

Integrated circuit having structural support for a flip-chip interconnect pad and method therefor

ActiveUS7247552B2Semiconductor/solid-state device detailsSolid-state devicesDielectricFlip chip interconnect

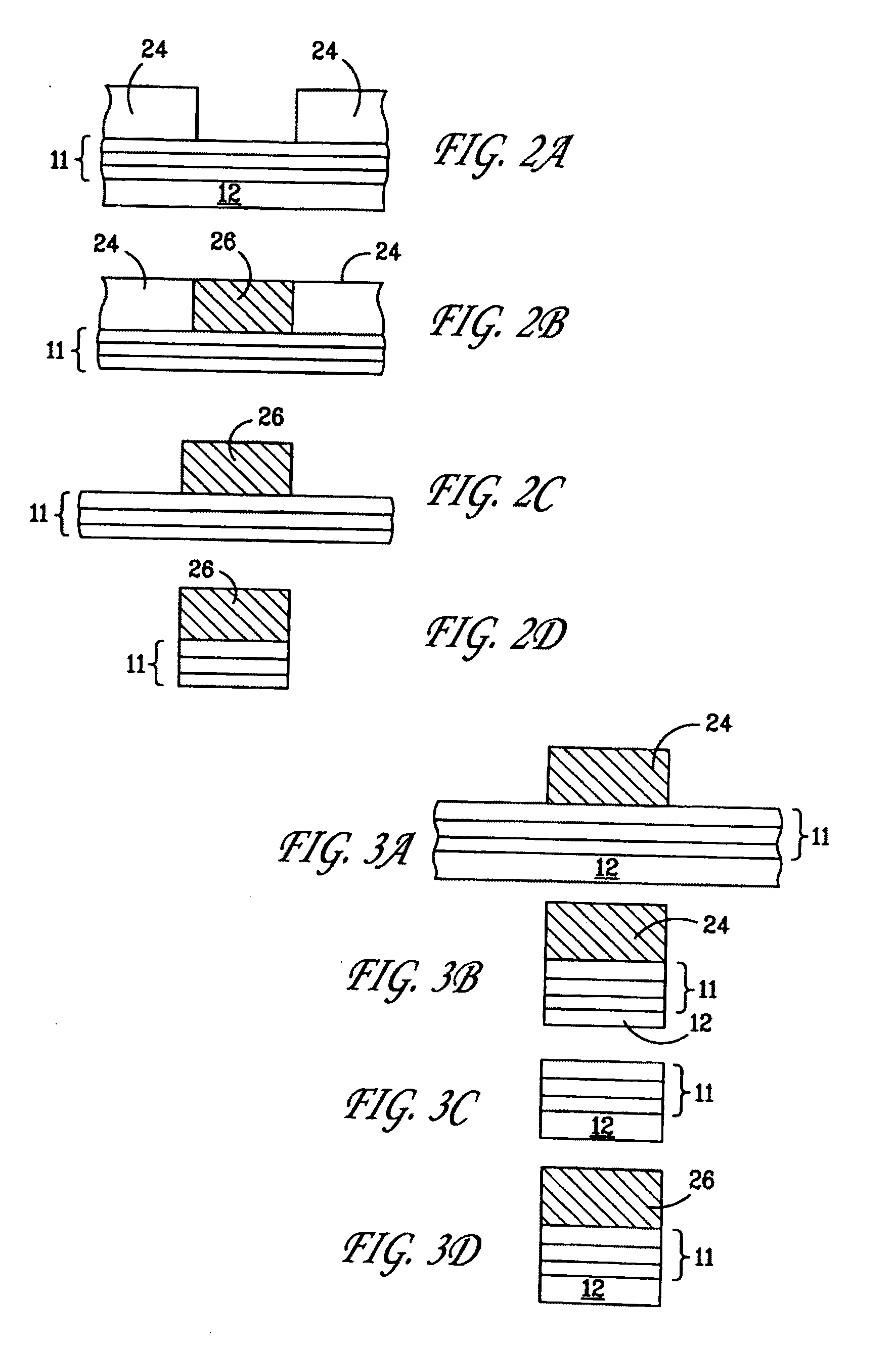

A technique for alleviating the problems of defects caused by stress applied to bond pads (32) includes, prior to actually making an integrated circuit (10), adding dummy metal lines (74, 76) to interconnect layers (18, 22, 26) to increase the metal density of the interconnect layers. These problems are more likely when the interlayer dielectrics (16, 20, 24) between the interconnect layers are of a low-k material. A critical area or force area (64) around and under each bond pad defines an area in which a defect may occur due to a contact made to that bond pad. Any interconnect layer in such a critical area that has a metal density below a certain percentage can be the cause of a defect in the interconnect layers. Any interconnect layer that has a metal density below that percentage in the critical area has dummy metal lines added to it.

Owner:VLSI TECH LLC

Copper Post Solder Bumps on Substrates

InactiveUS20140057392A1Small sizeReduce volumeSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectEngineering

Owner:INT BUSINESS MASCH CORP

Integration of microstrip antenna with CMOS transceiver

ActiveUS9257751B2Low costLow interconnectionAntennas earthing switches associationWaveguide type devicesMicrostrip patch antennaCMOS

A monolithic antenna element comprises a microstrip patch antenna and a ground plane, with a substrate between the patch antenna and the ground plane. A feeding via extends from the ground plane layer through the substrate to the patch antenna, connecting to the antenna distal from lateral edges of the antenna. A coplanar waveguide (CPW) feed line is formed in the ground plane layer, and interrupts and is electrically distinct from the ground plane. The CPW extends from a lateral edge of the ground layer to the feeding via. The antenna can be flip chip bonded to a CMOS die, reducing cost of millimeter wave transceivers, e.g. 57-64 GHz. The antenna is fabricated using standard PCB technology and a single substrate for the antenna. Antenna arrays can be fabricated. Appropriately designed antenna feeds, flip chip interconnects and antenna shape provide suitably broad antenna bandwidth, with relatively high efficiency.

Owner:ADVANCED MICRO DEVICES INC +1

Interconnection for flip-chip using lead-free solders and having improved reaction barrier layers

InactiveUS20100062597A1Soft errorCost-effectiveSemiconductor/solid-state device detailsSolid-state devicesSolder ballSolder wetting

An interconnection structure suitable for flip-chip attachment of microelectronic device chips to packages, comprising a two, three or four layer ball-limiting metallurgy including an adhesion / reaction barrier layer, and having a solder wettable layer reactive with components of a tin-containing lead free solder, so that the solderable layer can be totally consumed during soldering, but a barrier layer remains after being placed in contact with the lead free solder during soldering. One or more lead-free solder balls is selectively situated on the solder wetting layer, the lead-free solder balls comprising tin as a predominant component and one or more alloying components.

Owner:ULTRATECH INT INC

Flip chip interconnection system having solder position control mechanism

ActiveUS8604624B2Semiconductor/solid-state device detailsPrinted circuit aspectsFlip chip interconnectInterconnection

A flip chip interconnection system includes: providing a conductive lead coated with a protective coating; forming a groove through the protective coating to the conductive lead for controlling solder position on a portion of the conductive lead; and attaching a flip chip having a solderable conductive interconnect to the portion of the conductive lead.

Owner:STATS CHIPPAC LTD

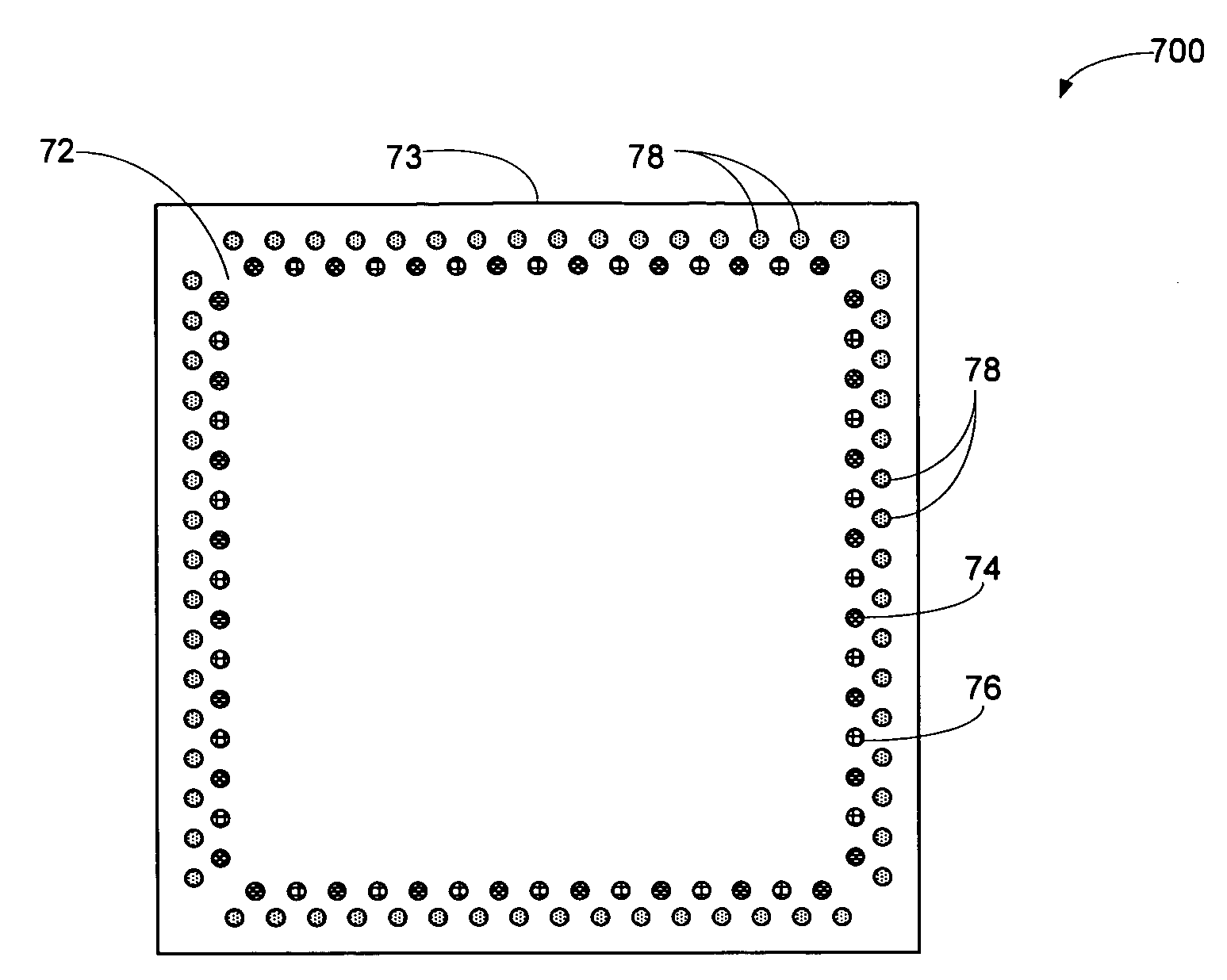

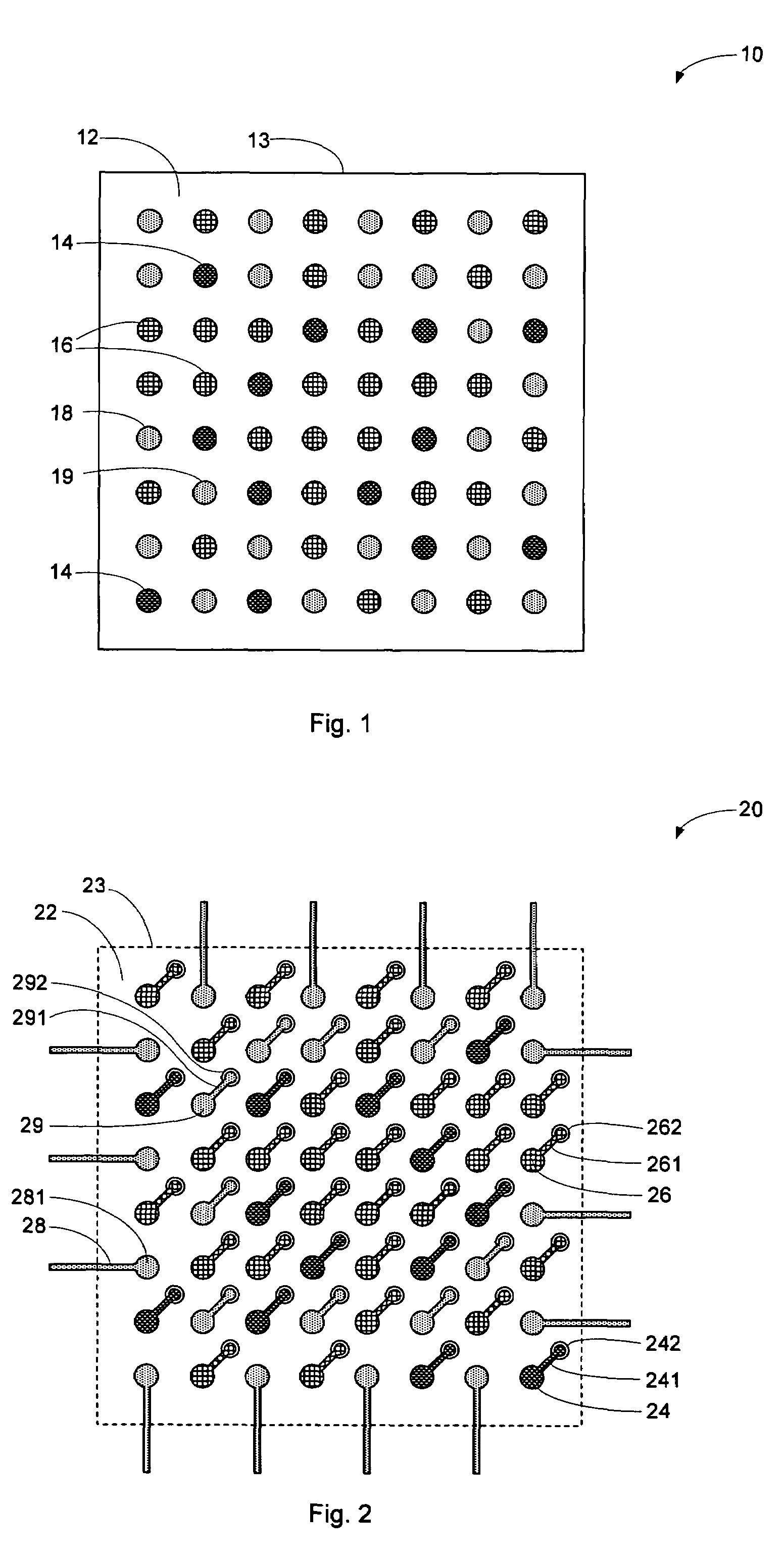

Flip chip interconnection pad layout

ActiveUS7372170B2High signal trace escape routing densityLow costSemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor package

A flip chip interconnect pad layout has the die signal pads are arranged on the die surface near the perimeter of the die, and the die power and ground pads arranged on the die surface inboard from the signal pads; and has the signal pads on the corresponding package substrate arranged in a manner complementary to the die pad layout and the signal lines routed from the signal pads beneath the die edge away from the die footprint, and has the power and ground lines routed to vias beneath the die footprint. Also, a flip chip semiconductor package in which the flip chip interconnect pad layouts have the die signal pads situated in the marginal part of the die and the die power and ground pads arranged on the die surface inboard from the signal pads, and the corresponding package substrates have signal pads arranged in a manner complementary to the die pad layout and signal lines routed from the signal pads beneath the die edge away from the die footprint.

Owner:STATS CHIPPAC LTD

Flip-chip assembly and manufacture method thereof

InactiveCN101567349ARelieve mechanical stressIncrease production capacitySemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectSemiconductor chip

The invention discloses a flip-chip assembly and manufacture method thereof. Various aspects can be implemented for providing flip-chip interconnect structures for connecting or mounting semiconductor chips to supporting substrates, such as cards, circuit boards, carriers, lead frames, and the like. In general, one aspect can be a method of providing a flip-chip interconnect structure that includes providing a semiconductor work piece that includes one or more bond pads. The method also includes depositing a first non-reflowable layer that has a first melting temperature higher than a predetermined first reflow temperature. The method further includes depositing a reflowable stress relief layer that reflows at the predetermined first reflow temperature. The method additionally includes depositing a second non-reflowable layer that has a second melting temperature higher than the predetermined first reflow temperature such that the deposited reflowable stress relief layer is between the first and the second non-reflowable layers.

Owner:CHENGDU MONOLITHIC POWER SYST

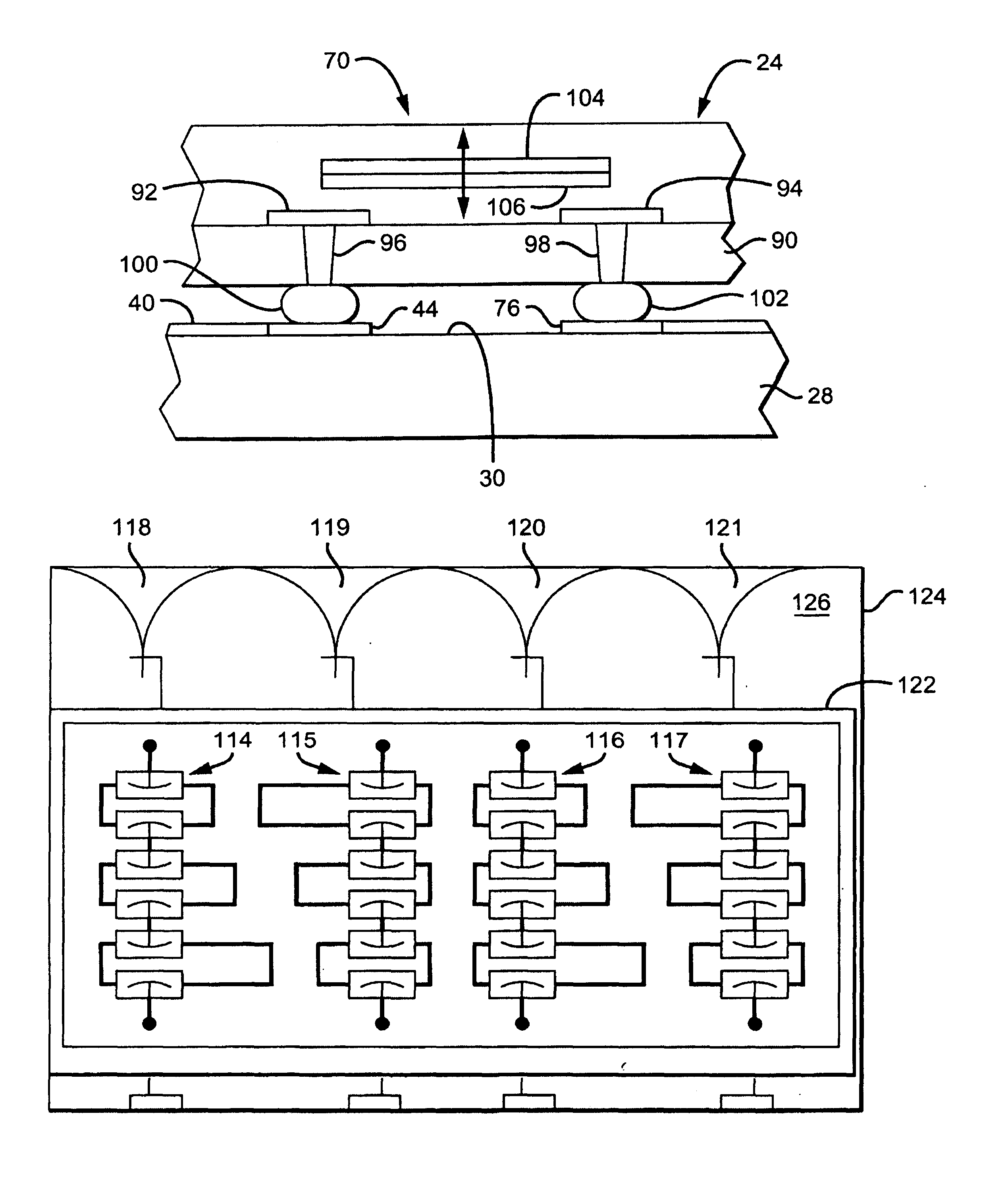

Dual color/dual function focal plane

ActiveUS8153978B1Accurate trackingEliminate needRadiation pyrometryDirection controllersWavelengthSpatial calibration

A single focal plane integrated circuit hybrid replaces multiple focal plane circuits and associated off-focal plane signal processing electronics. A dual function, dual color focal plane PSD sensor chip assembly includes a PSD array, a traditional pixelized camera array, a signal processing chip, and flip-chip interconnects and wirebond pads to support electronics on the signal processing chip. The camera array is made of a material sensitive to wavelengths longer than the PSD array material is sensitive to. The PSD array is disposed in the same substrate as the camera array. The PSD array tracks object locations and directs the camera array to window and zoom while capturing images. Inherent registration of PSD cells to the pixelized camera array makes responsivity map testing and spatial calibration unnecessary. Reduction in power dissipation is achieved by powering on the camera array only when the PSD detects a change in scene.

Owner:OCEANIT LAB

Low stress, low-temperature metal-metal composite flip chip interconnect

In some embodiments, a low stress, low-temperature metal-metal composite flip chip interconnect is presented. In this regard, a method is introduced consisting of combining a powder of substantially pure tin with a powder of tin alloy having a lower melting point than pure tin and depositing the combination of metals between an integrated circuit device and a package substrate. Other embodiments are also disclosed and claimed.

Owner:INTEL CORP