Patents

Literature

5136 results about "Flip chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

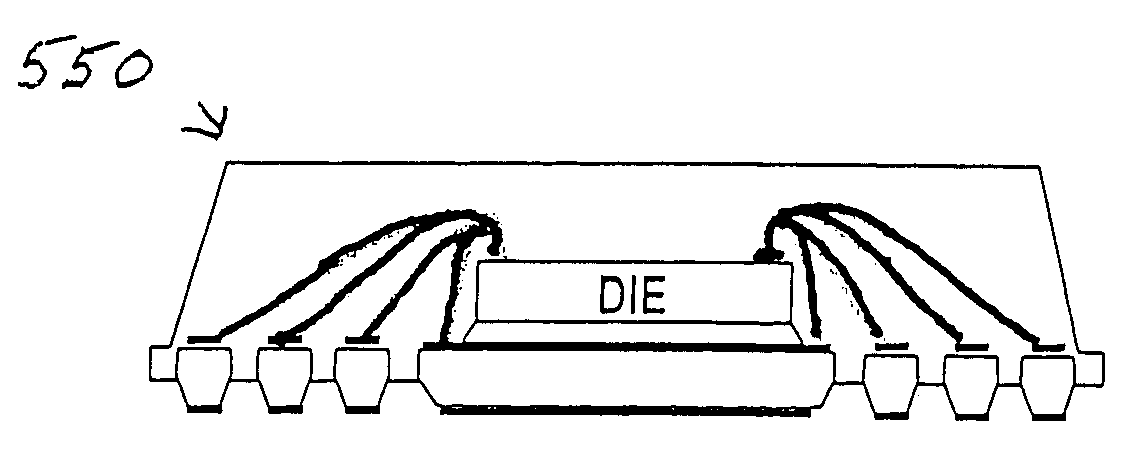

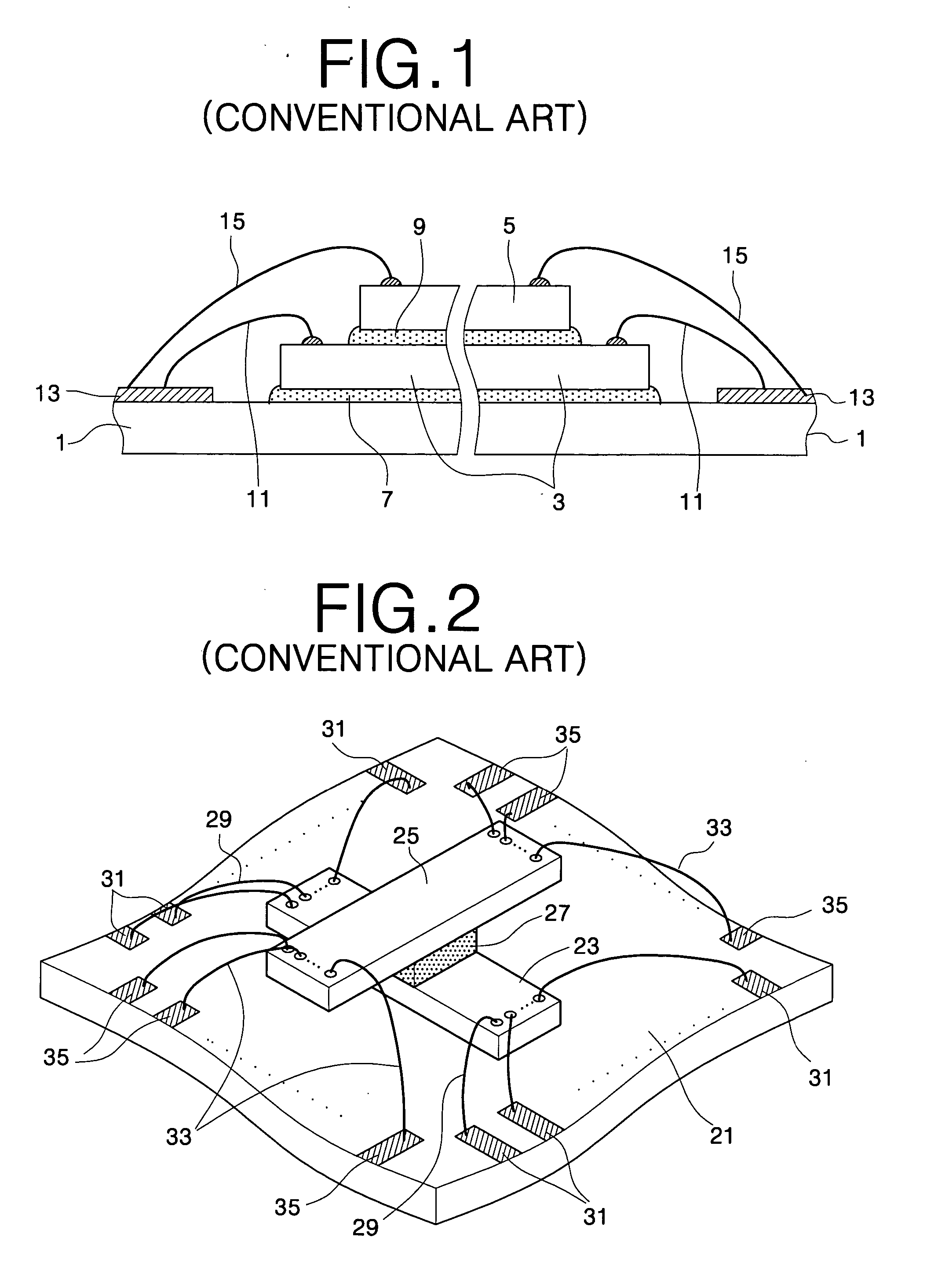

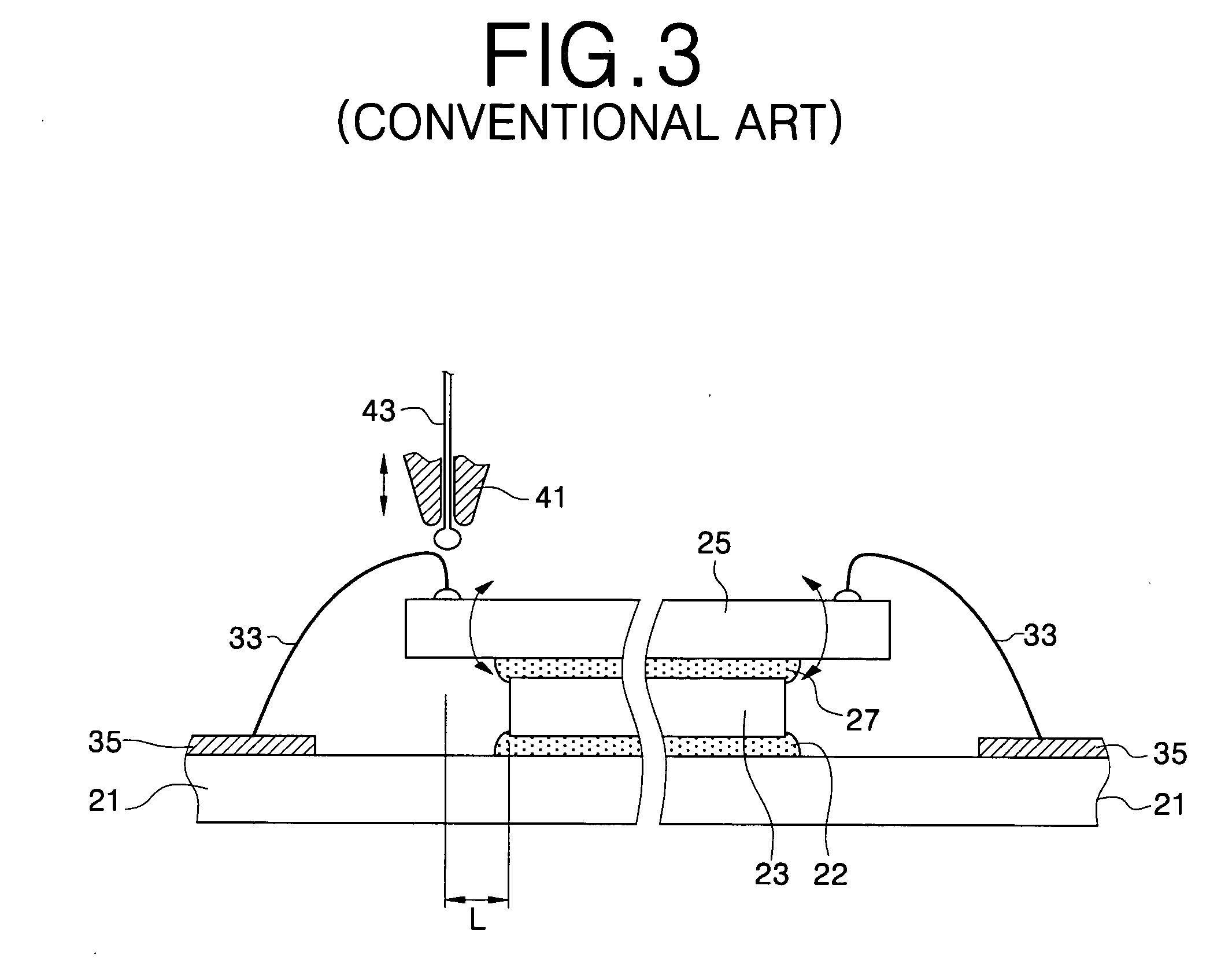

Flip chip, also known as controlled collapse chip connection or its abbreviation, C4, is a method for interconnecting semiconductor devices, such as IC chips and microelectromechanical systems (MEMS), to external circuitry with solder bumps that have been deposited onto the chip pads. The technique was developed by General Electric's Light Military Electronics Dept., Utica, N.Y. The solder bumps are deposited on the chip pads on the top side of the wafer during the final wafer processing step. In order to mount the chip to external circuitry (e.g., a circuit board or another chip or wafer), it is flipped over so that its top side faces down, and aligned so that its pads align with matching pads on the external circuit, and then the solder is reflowed to complete the interconnect. This is in contrast to wire bonding, in which the chip is mounted upright and wires are used to interconnect the chip pads to external circuitry.

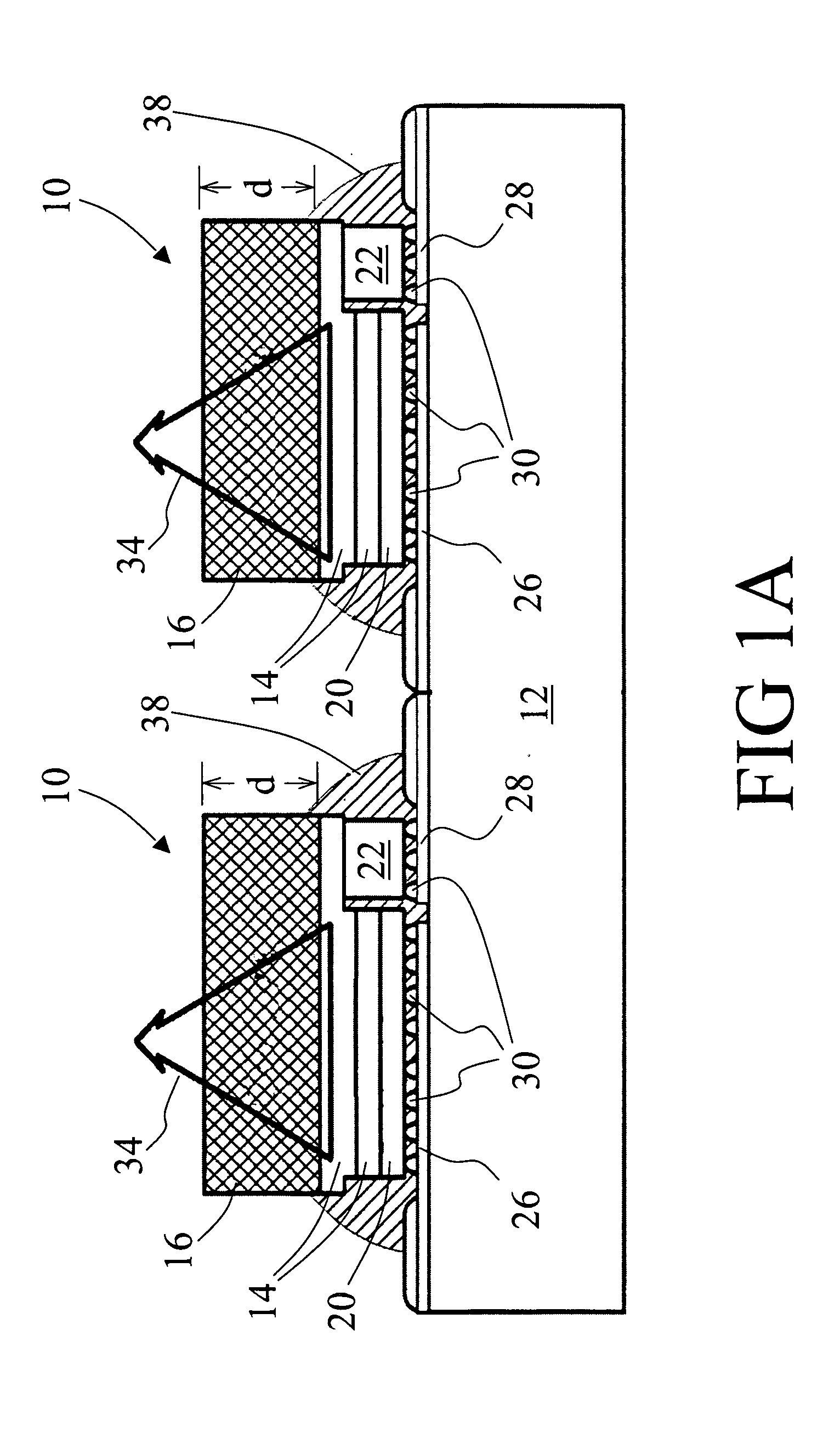

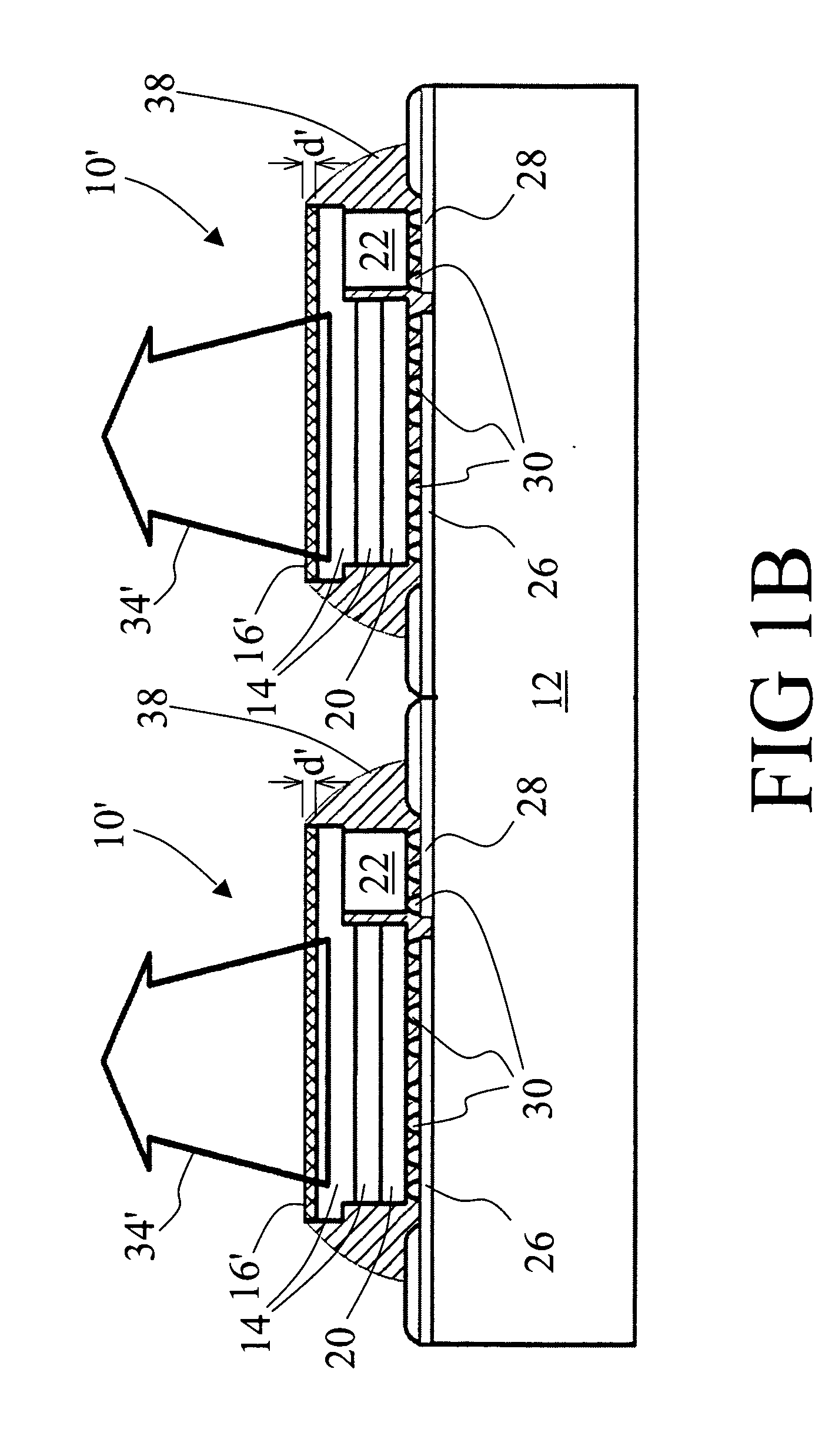

Wafer level phosphor coating method and devices fabricated utilizing method

ActiveUS20080179611A1Solid-state devicesSemiconductor/solid-state device manufacturingPhosphorLight-emitting diode

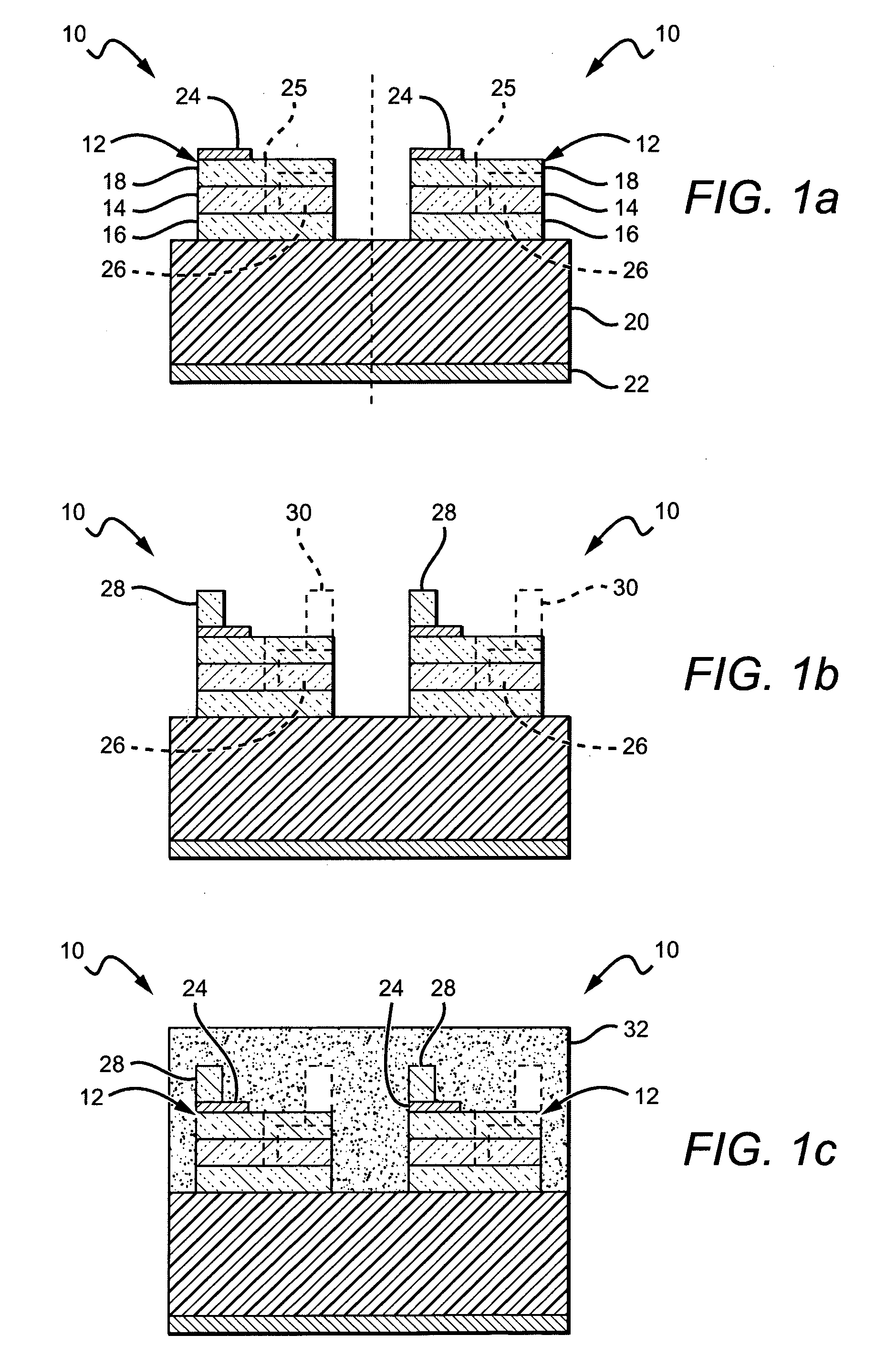

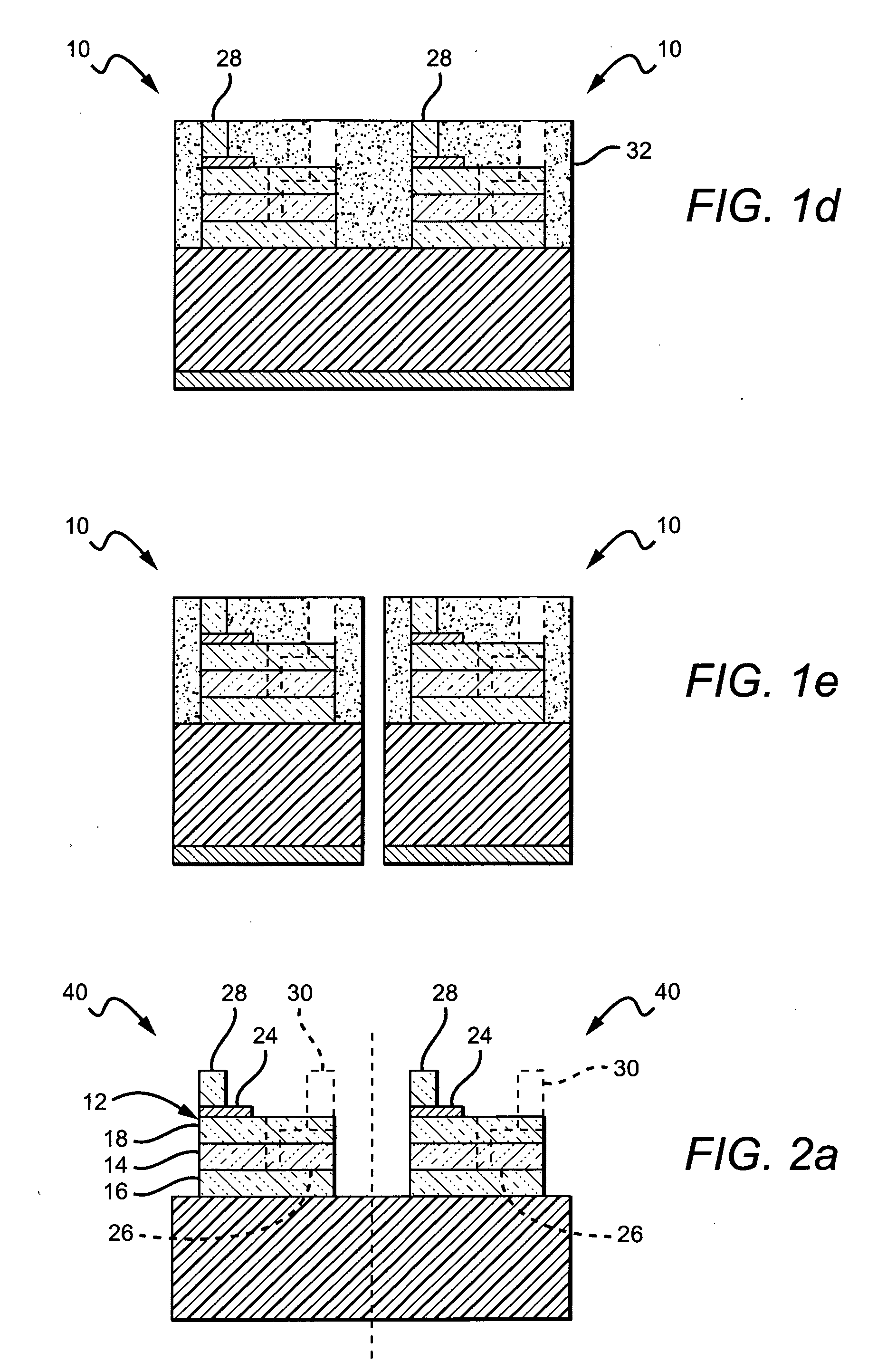

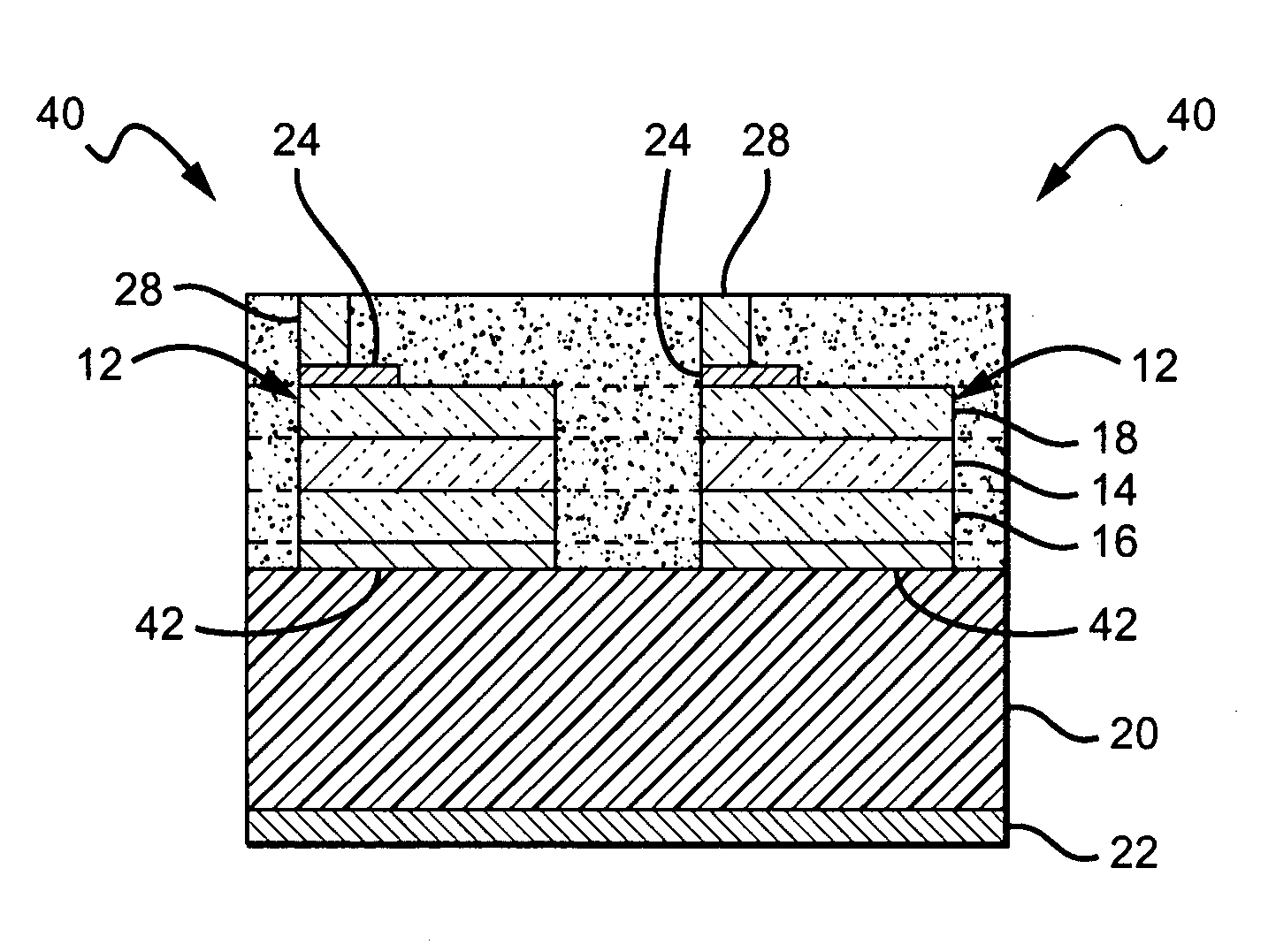

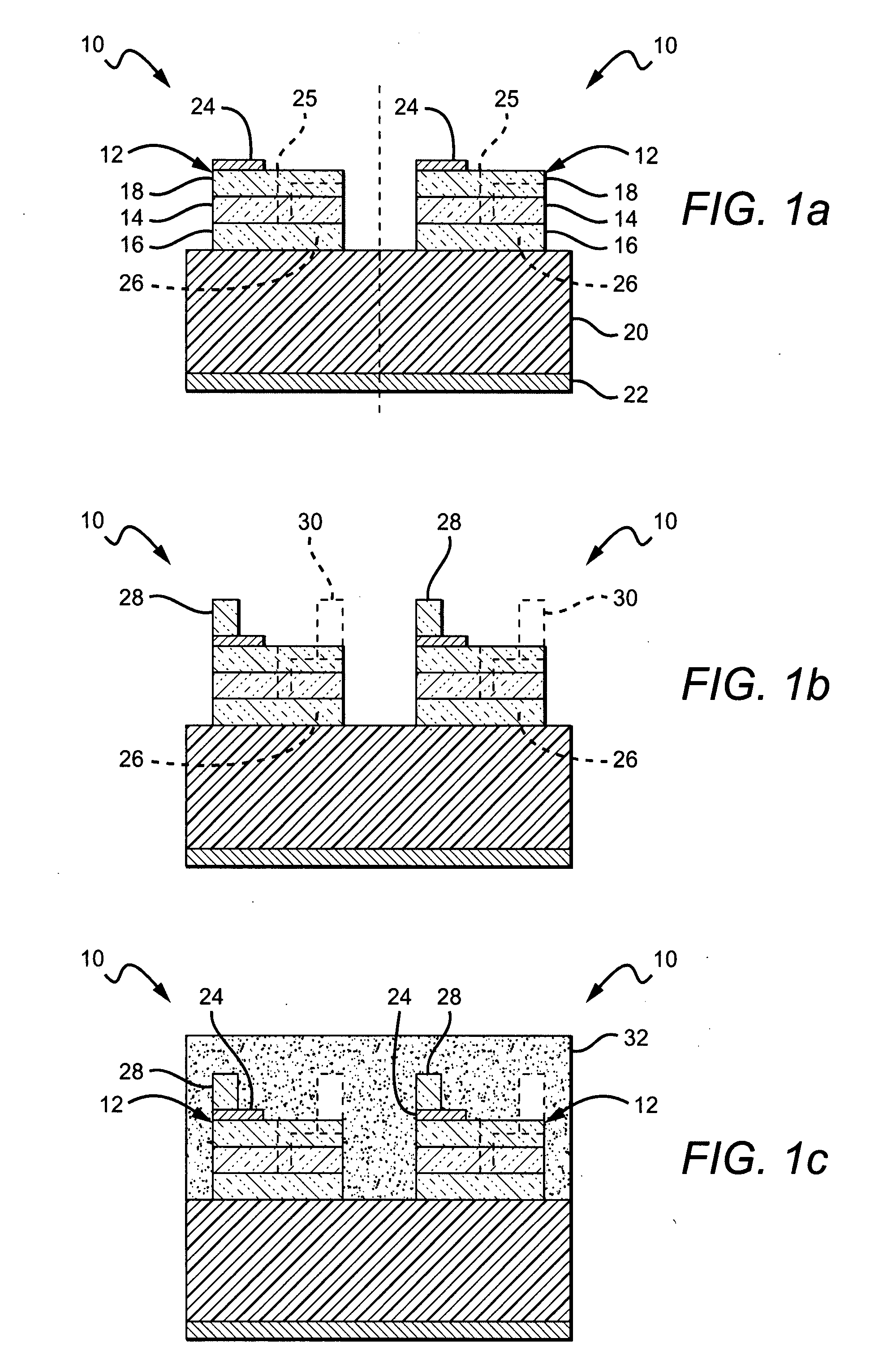

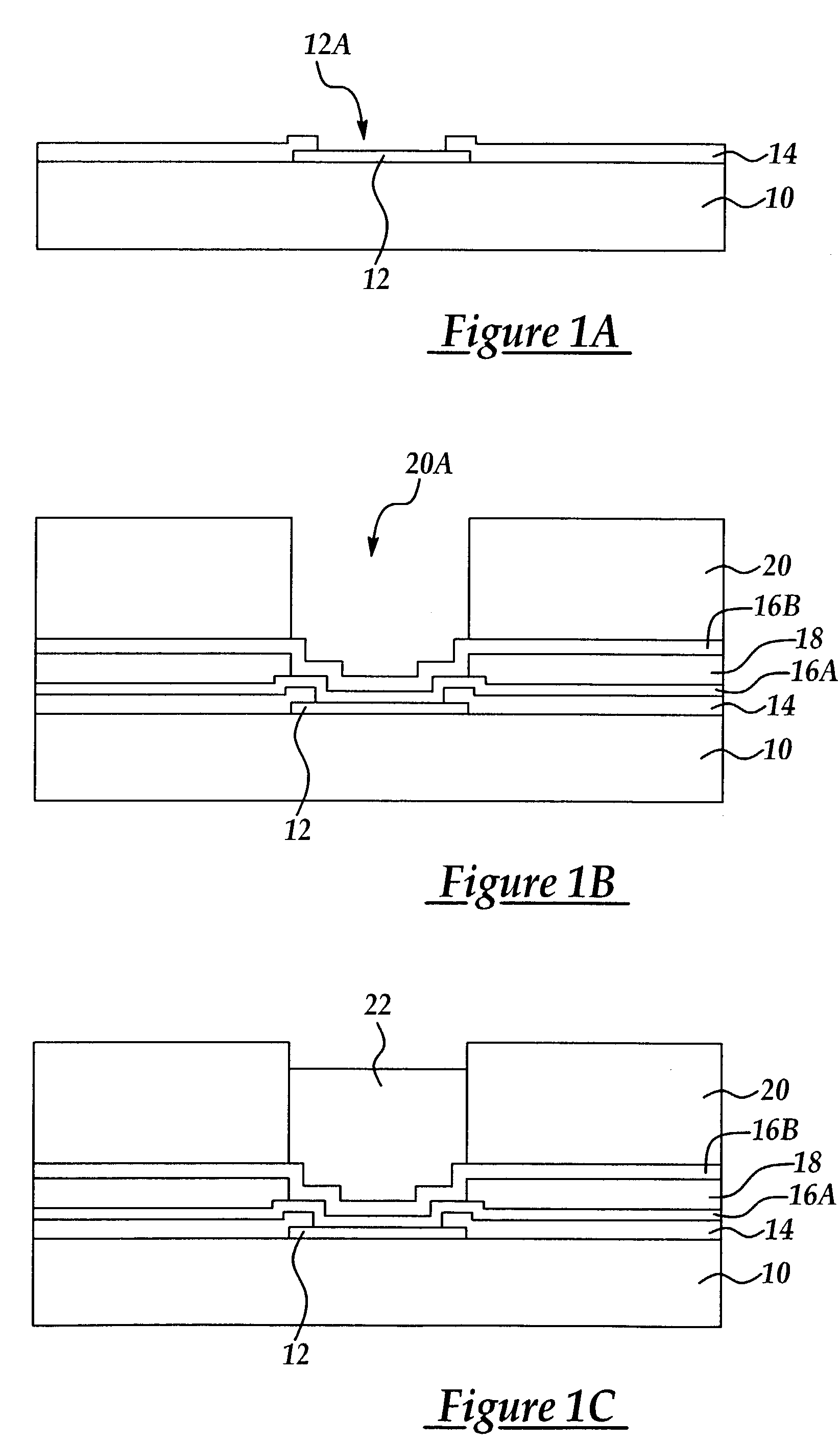

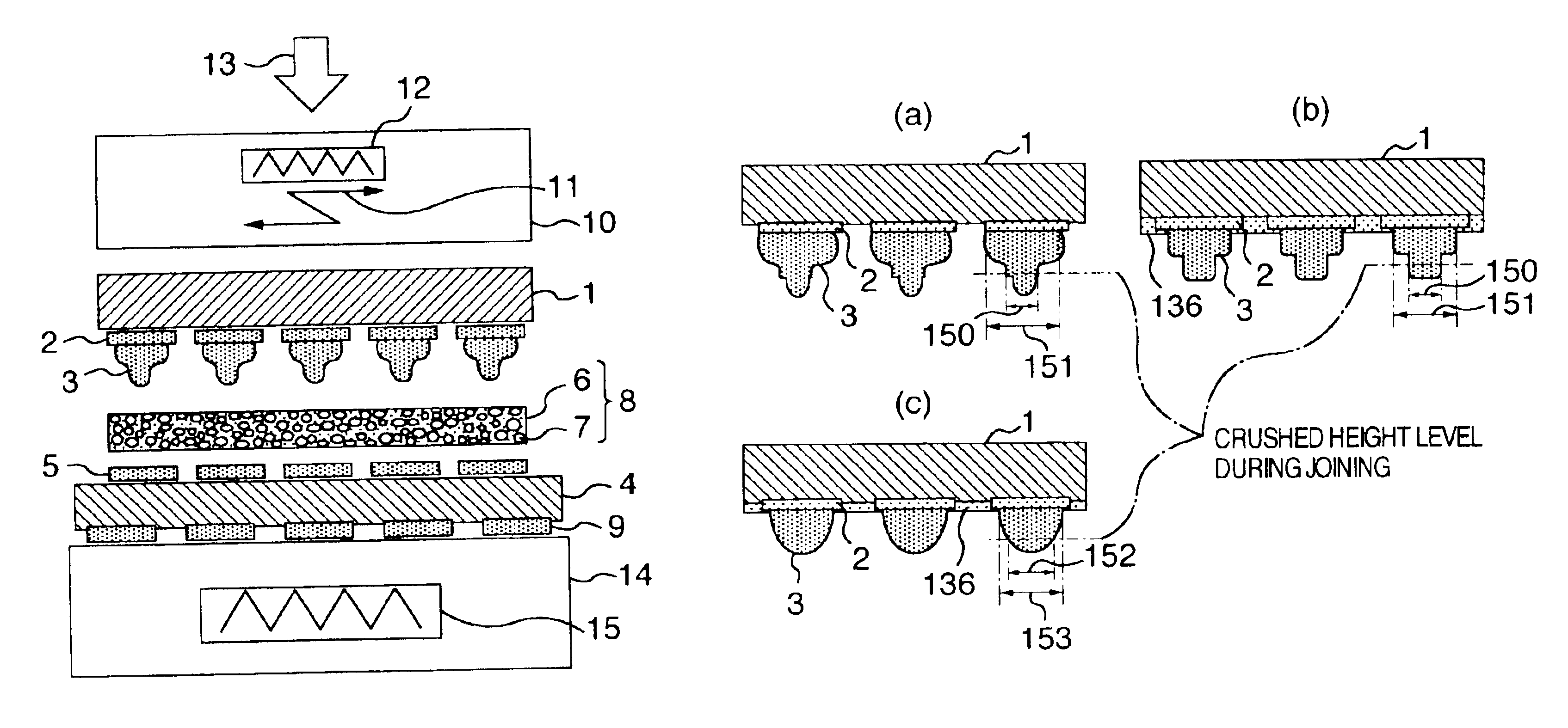

Methods for fabricating light emitting diode (LED) chips comprising providing a plurality of LEDs typically on a substrate. Pedestals are deposited on the LEDs with each of the pedestals in electrical contact with one of the LEDs. A coating is formed over the LEDs with the coating burying at least some of the pedestals. The coating is then planarized to expose at least some of the buried pedestals while leaving at least some of said coating on said LEDs. The exposed pedestals can then be contacted such as by wire bonds. The present invention discloses similar methods used for fabricating LED chips having LEDs that are flip-chip bonded on a carrier substrate and for fabricating other semiconductor devices. LED chip wafers and LED chips are also disclosed that are fabricated using the disclosed methods.

Owner:CREELED INC

Wafer level phosphor coating method and devices fabricated utilizing method

ActiveUS20080173884A1Semiconductor/solid-state device detailsSolid-state devicesPhosphorLight-emitting diode

Methods for fabricating light emitting diode (LED) chips comprising providing a plurality of LEDs typically on a substrate. Pedestals are deposited on the LEDs with each of the pedestals in electrical contact with one of the LEDs. A coating is formed over the LEDs with the coating burying at least some of the pedestals. The coating is then planarized to expose at least some of the buried pedestals while leaving at least some of said coating on said LEDs. The exposed pedestals can then be contacted such as by wire bonds. The present invention discloses similar methods used for fabricating LED chips having LEDs that are flip-chip bonded on a carrier substrate and for fabricating other semiconductor devices. LED chip wafers and LED chips are also disclosed that are fabricated using the disclosed methods.

Owner:CREELED INC

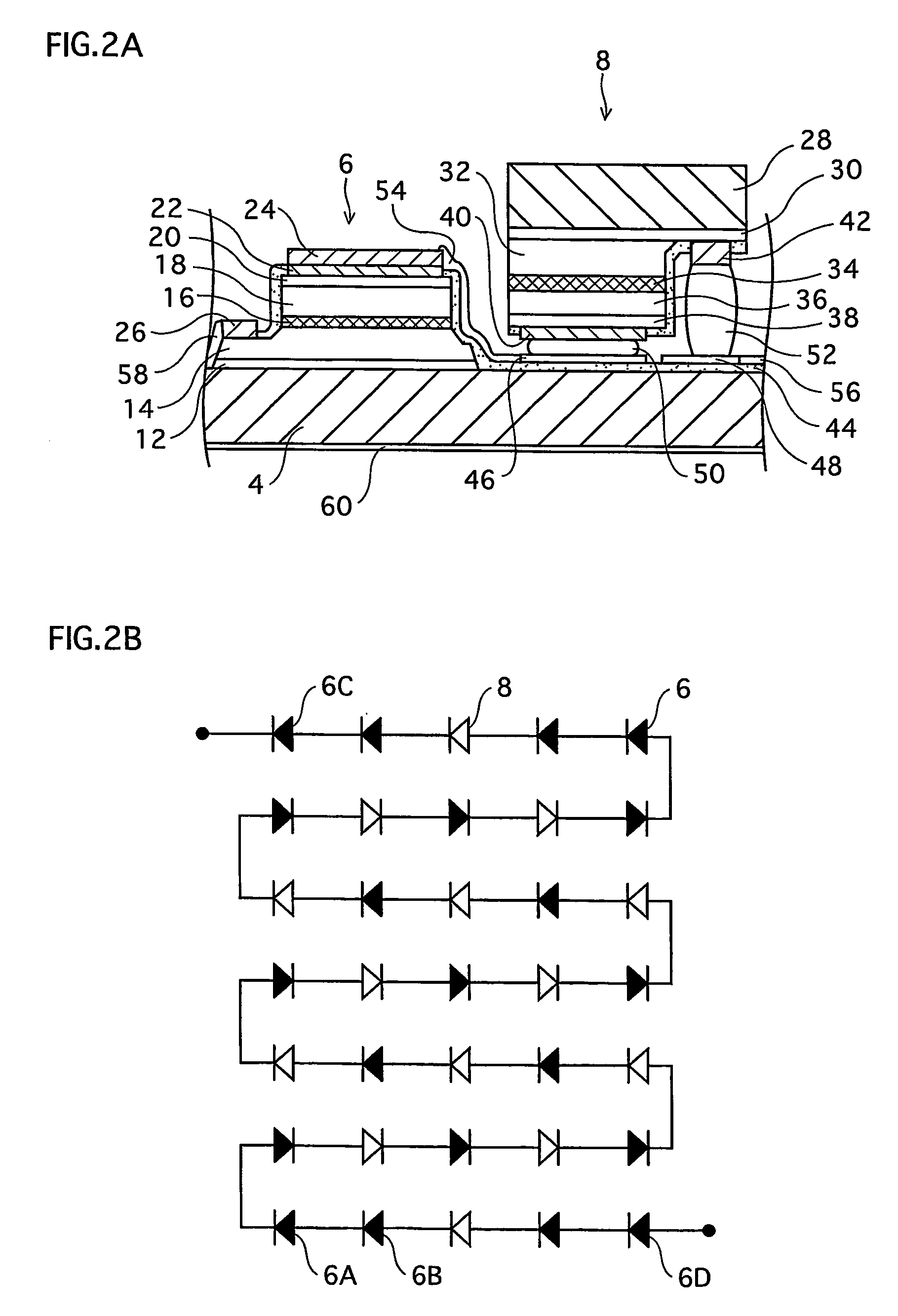

Electronic devices having a header and antiparallel connected light emitting diodes for producing light from AC current

InactiveUS7009199B2Improve light outputEliminate needSolid-state devicesElectric light circuit arrangementEngineeringLight-emitting diode

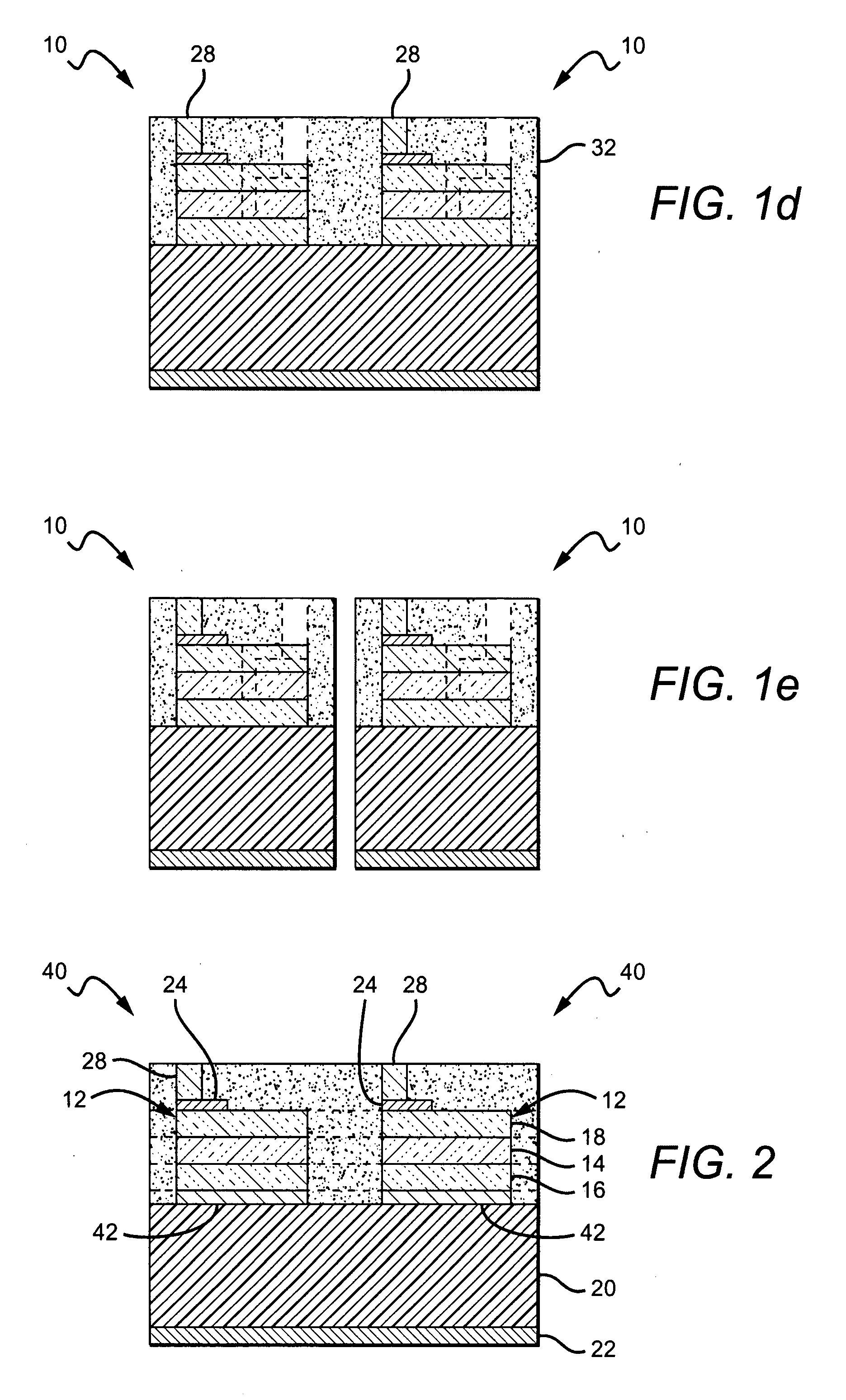

A light engine comprises a pair of LED active elements mounted on a common header having first and second terminals. The first terminal is connected to the cathode of the first LED active element and the anode of the second LED active element, while the second terminal is connected to the anode of the first LED active element and the cathode of the second LED active element, thereby connecting the LEDs in an anti-parallel arrangement. A light engine having a single insulating or semi-insulating substrate having formed thereon plural LED active elements with associated p- and n-type contacts forming cathode and anode contacts, respectively, for each LED active element is also provided. The LED active elements may be mounted in a flip-chip configuration on a header having a plurality of leads. The header may include a pair of leads adapted such that two LEDs may be flip-mounted thereon with the anode of the first LED and the cathode of the second LED contacting one lead, while the cathode of the first LED and the anode of the second LED contact the other lead. In addition, the header may be adapted to permit a substrate having multiple active elements to be mounted thereon.

Owner:IDEAL IND LIGHTING LLC

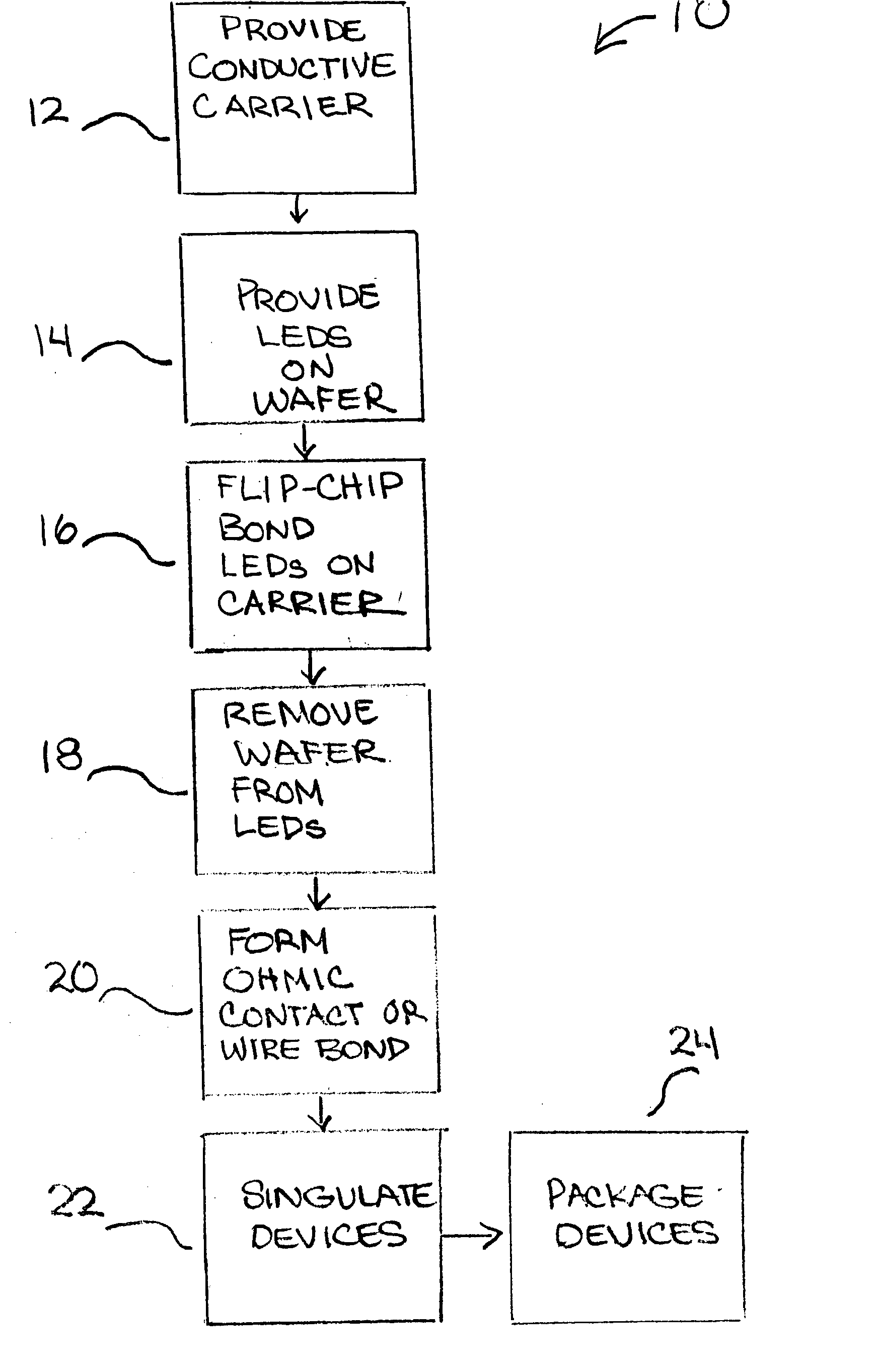

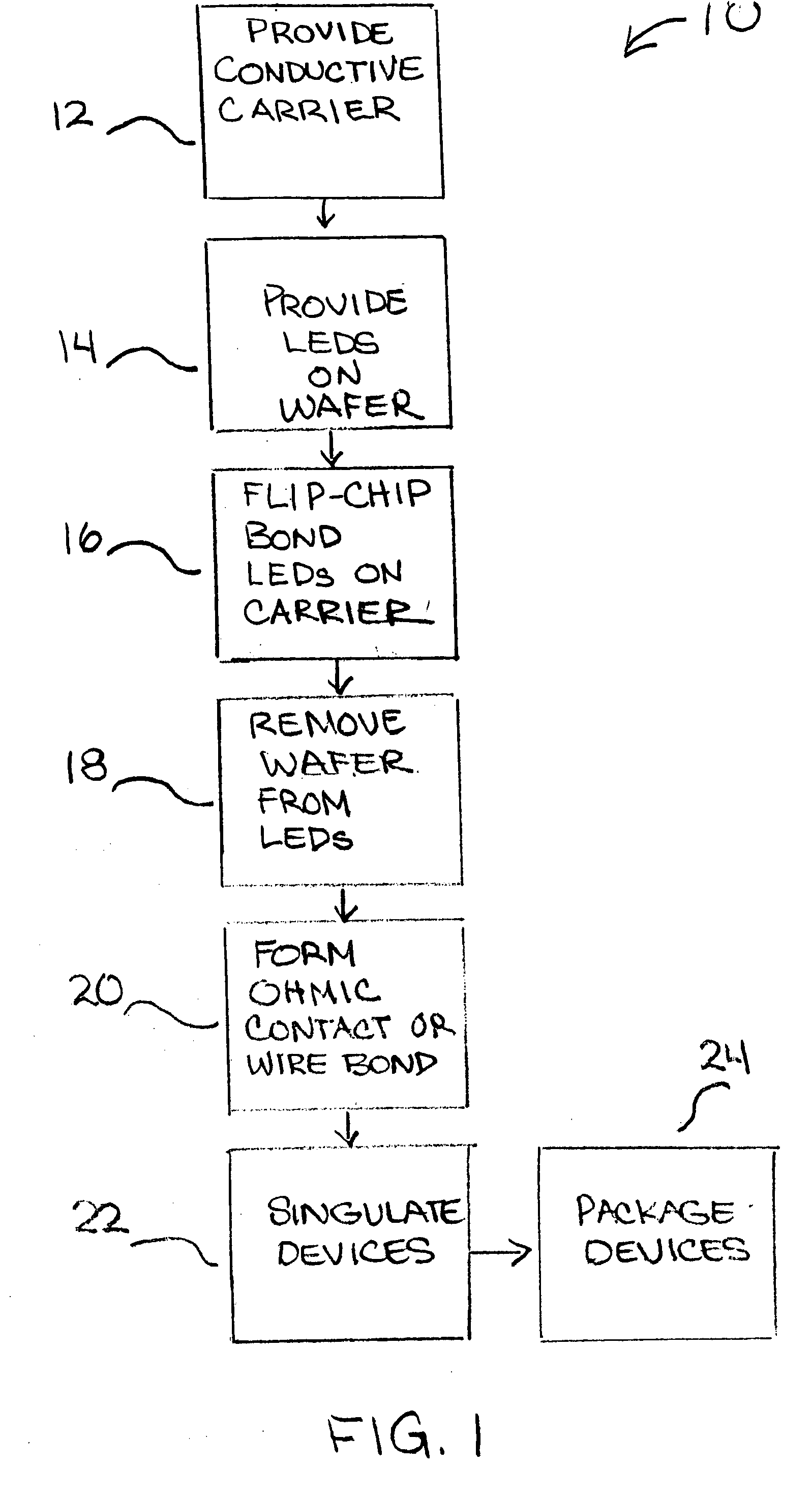

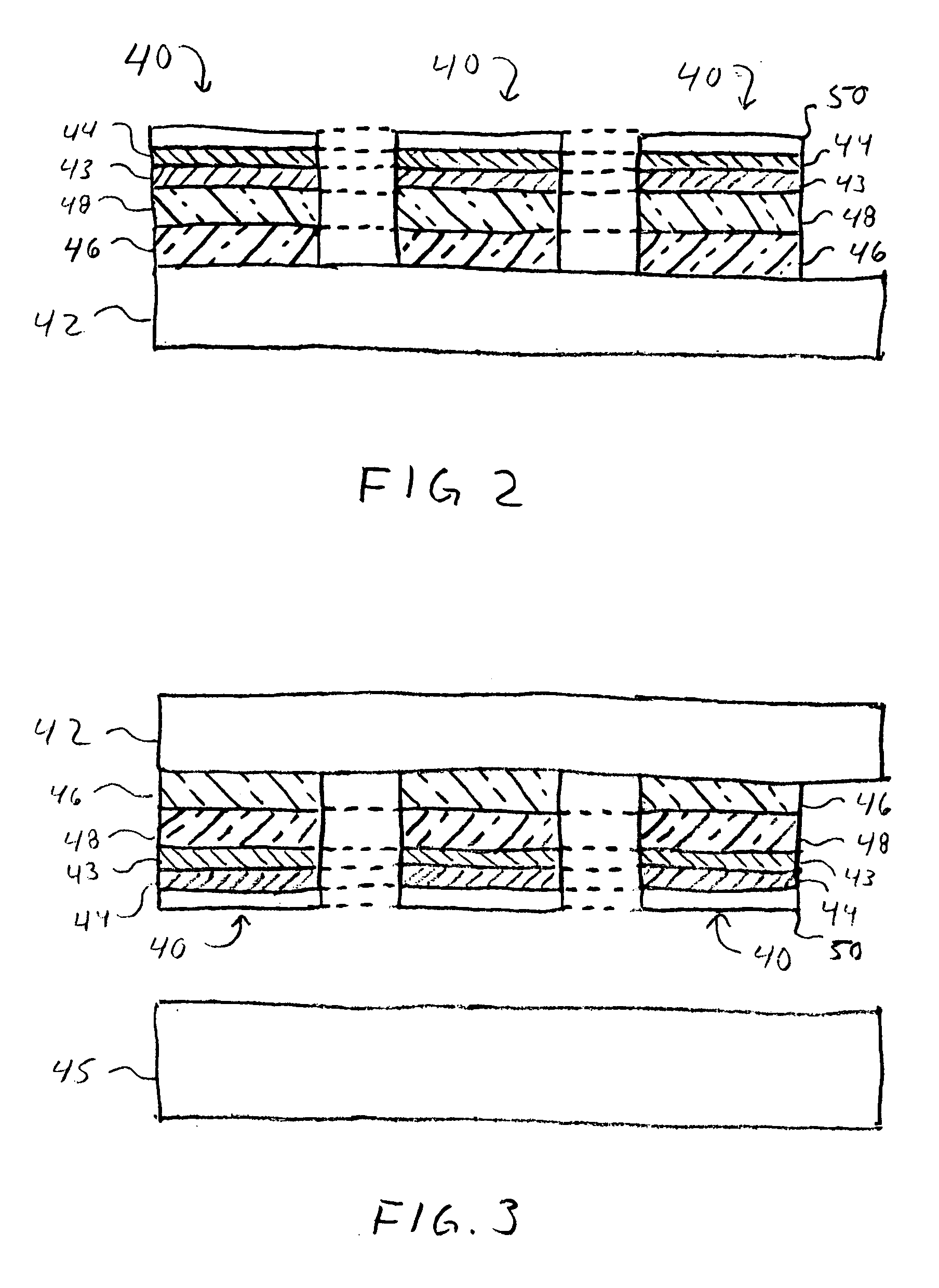

Substrate removal process for high light extraction LEDs

ActiveUS20060189098A1Index matchingImprove light extractionSemiconductor/solid-state device manufacturingSemiconductor devicesNitrideLight-emitting diode

A method for fabricating light emitting diode (LEDs) comprises providing a plurality of LEDs on a substrate wafer, each of which has an n-type and p-type layer of Group-III nitride material formed on a SiC substrate with the n-type layer sandwiched between the substrate and p-type layer. A conductive carrier is provided having a lateral surface to hold the LEDs. The LEDs are flip-chip mounted on the lateral surface of the conductive carrier. The SiC substrate is removed from the LEDs such that the n-type layer is the top-most layer. A respective contact is deposited on the n-type layer of each of the LEDs and the carrier is separated into portions such that each of the LEDs is separated from the others, with each of the LEDs mounted to a respective portion of said carrier.

Owner:CREELED INC

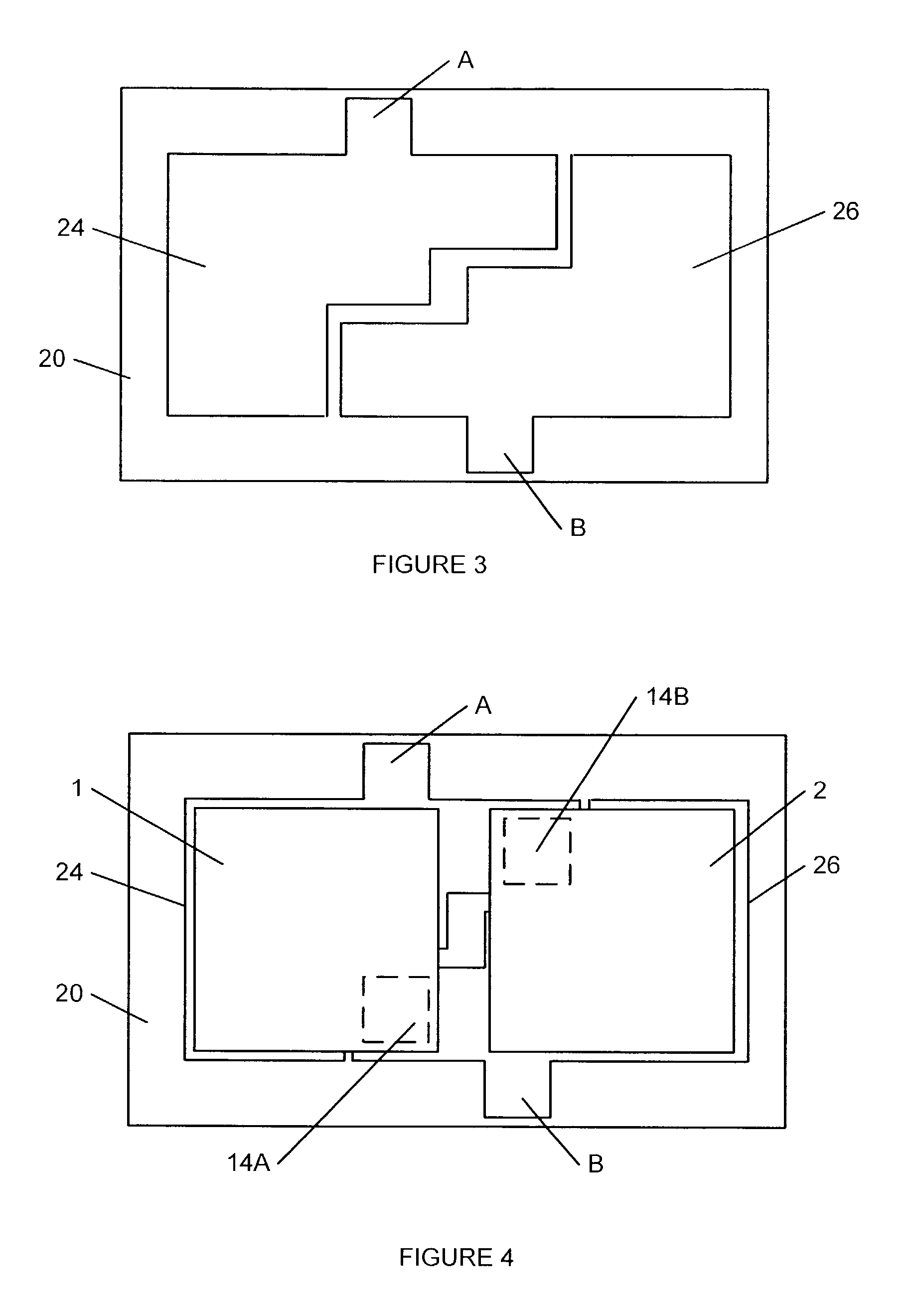

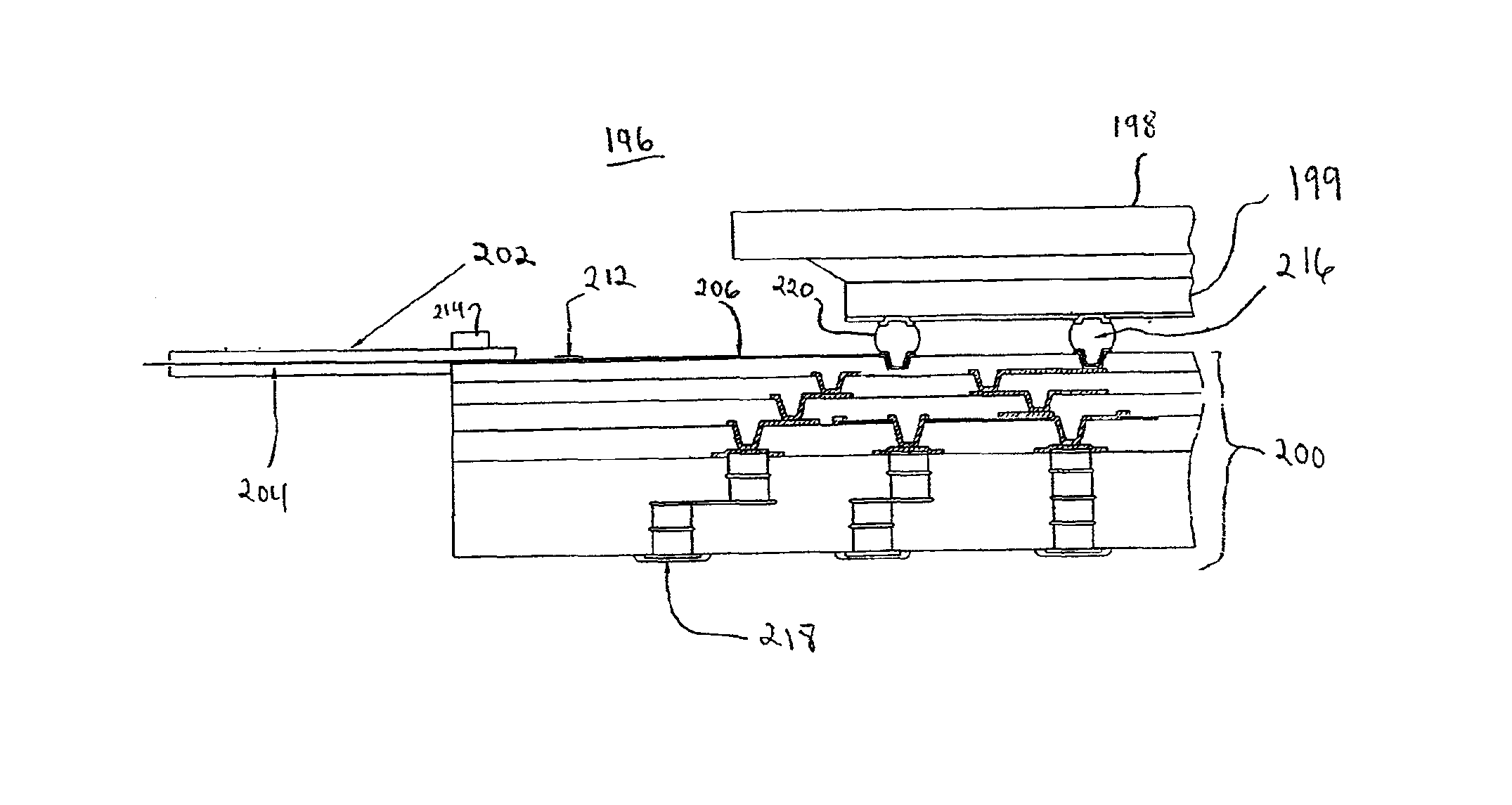

Panel Array

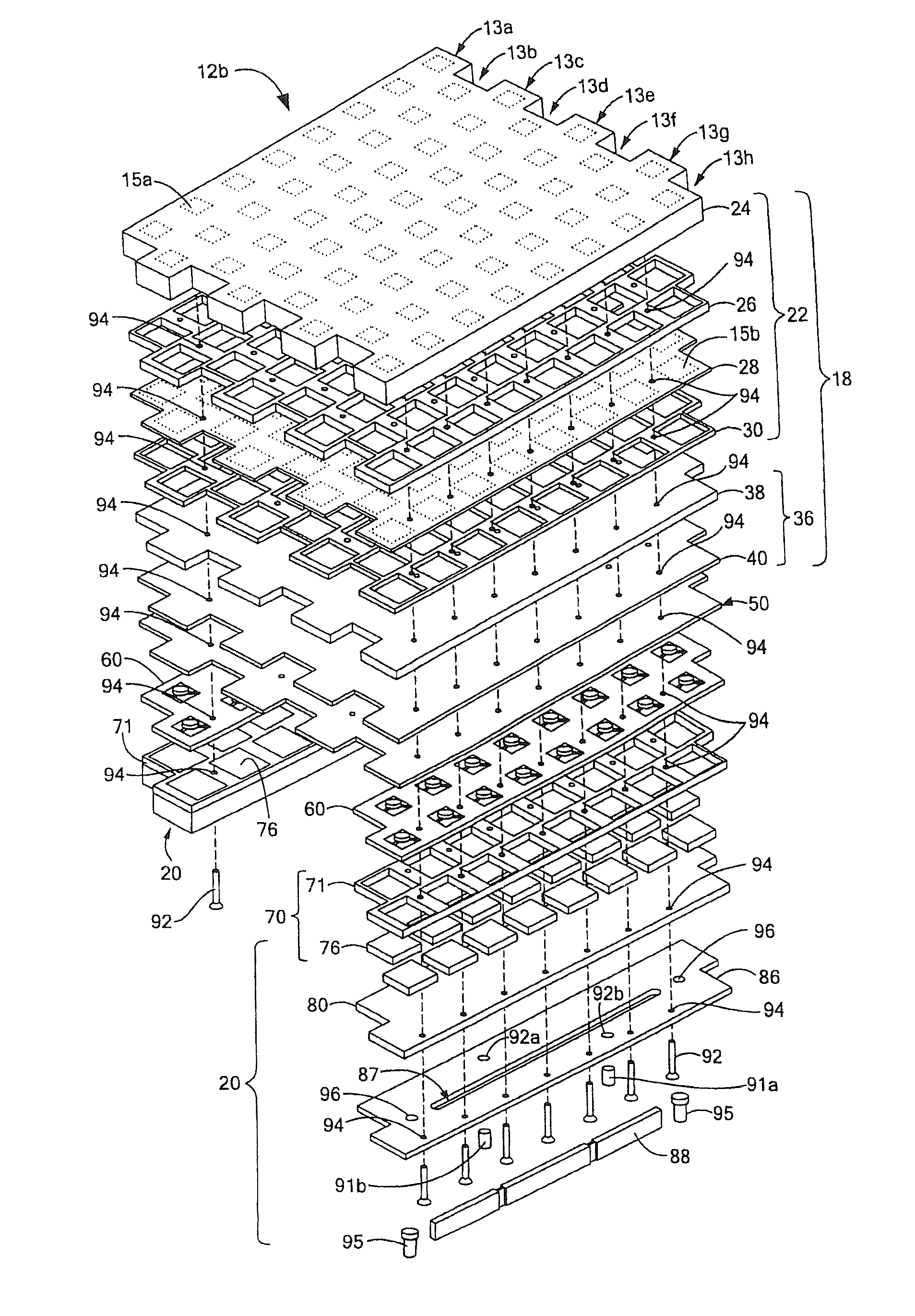

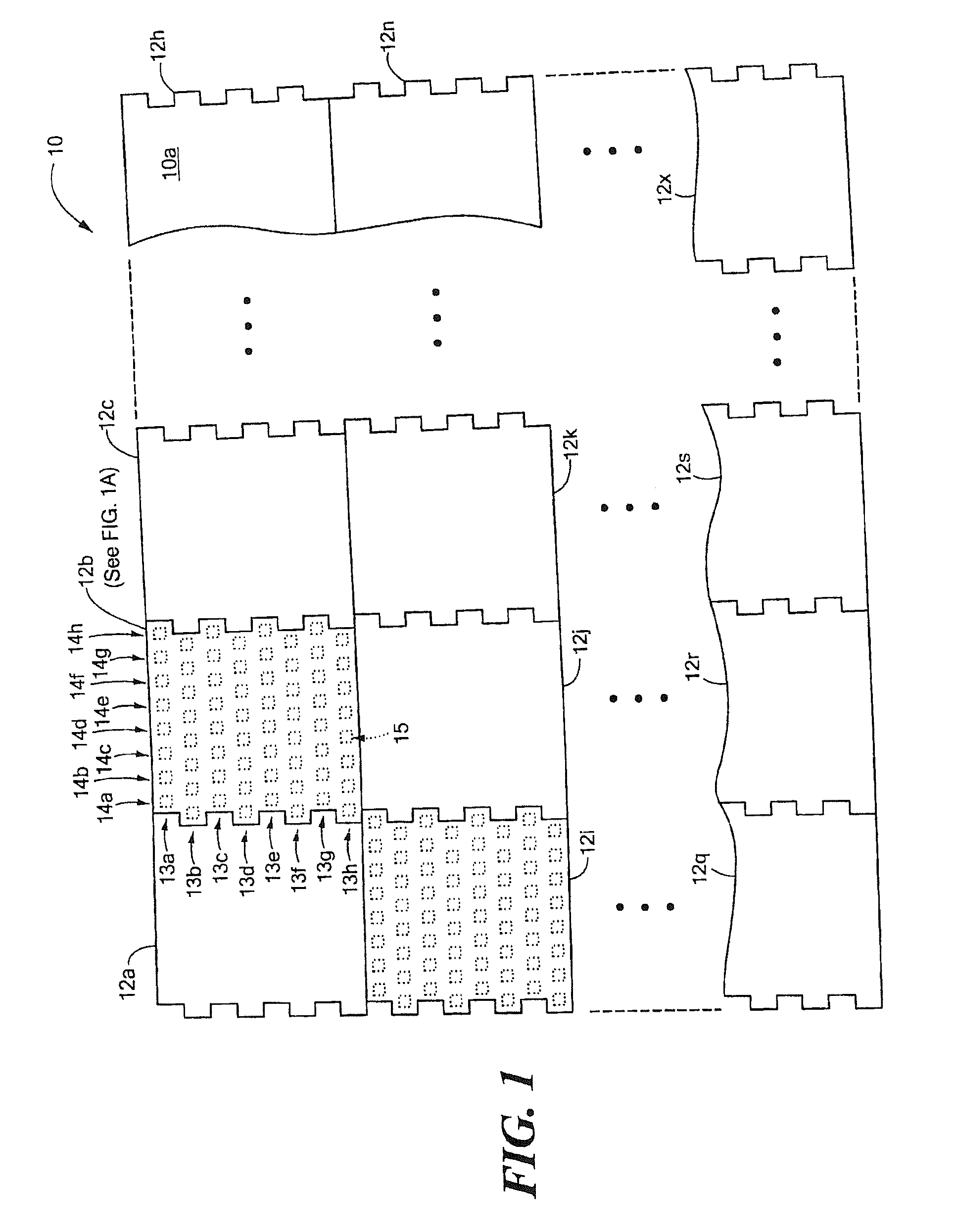

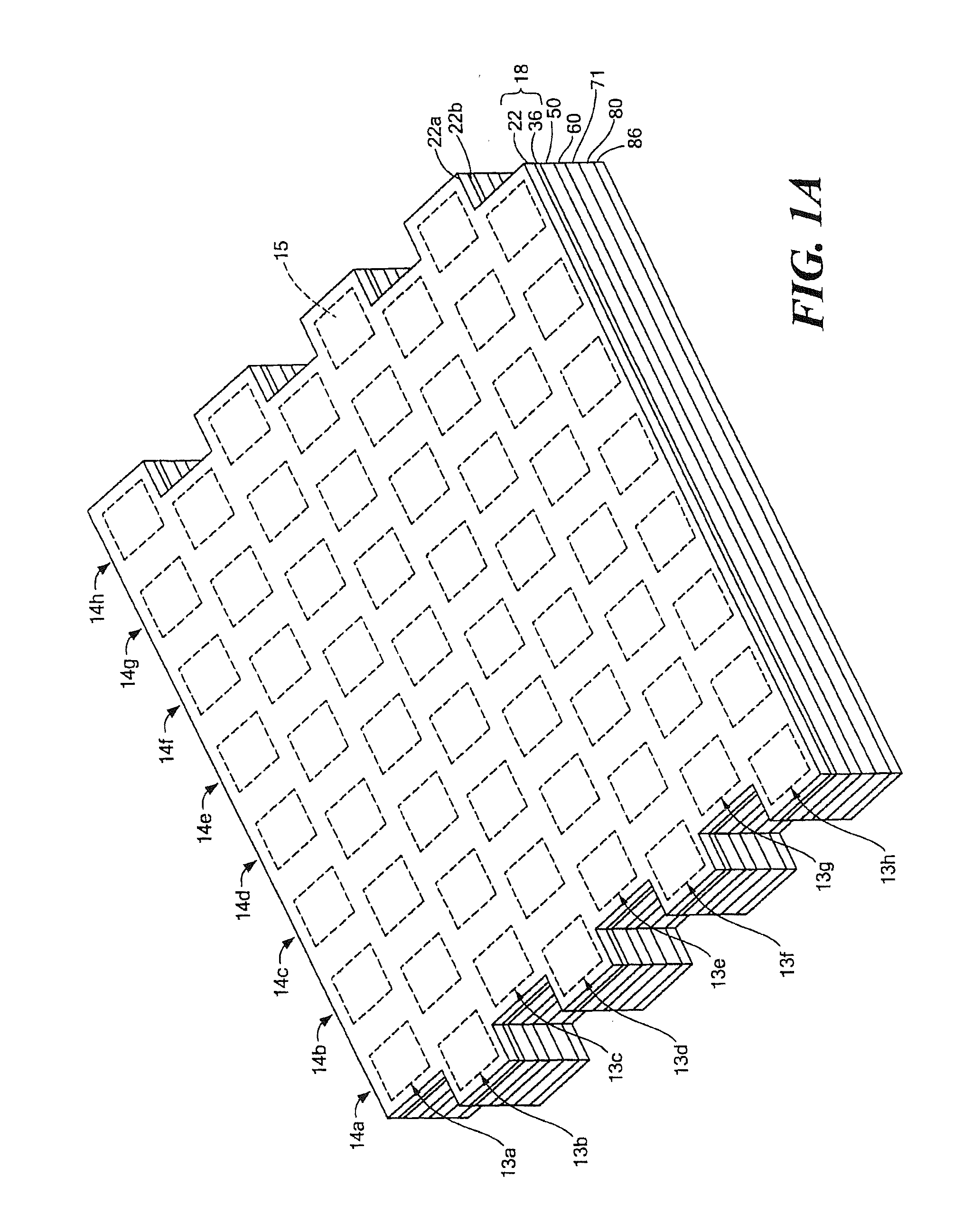

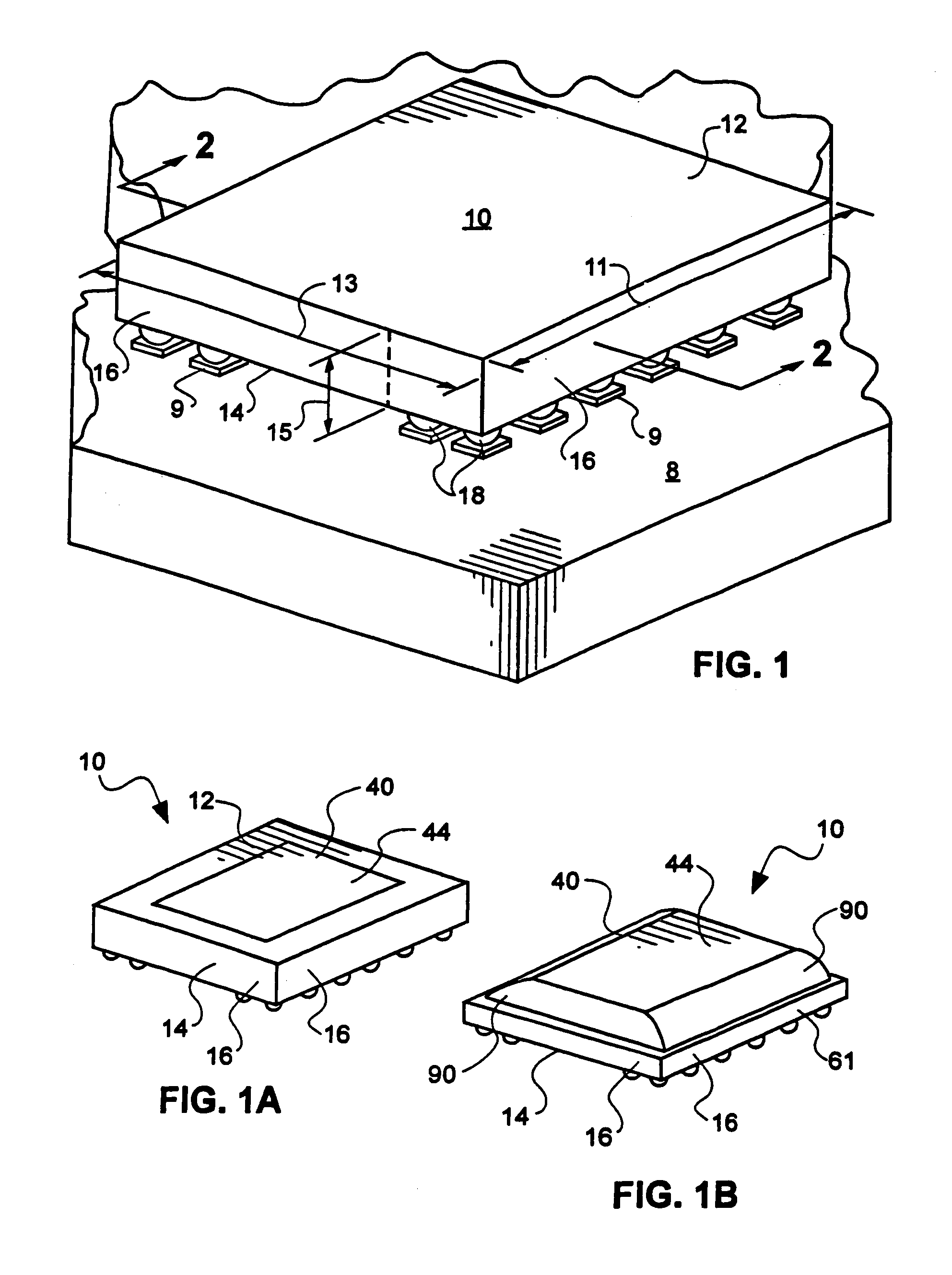

ActiveUS20100066631A1Low insertion lossEliminate needAntenna arrays manufactureModular arraysHemt circuitsChipset

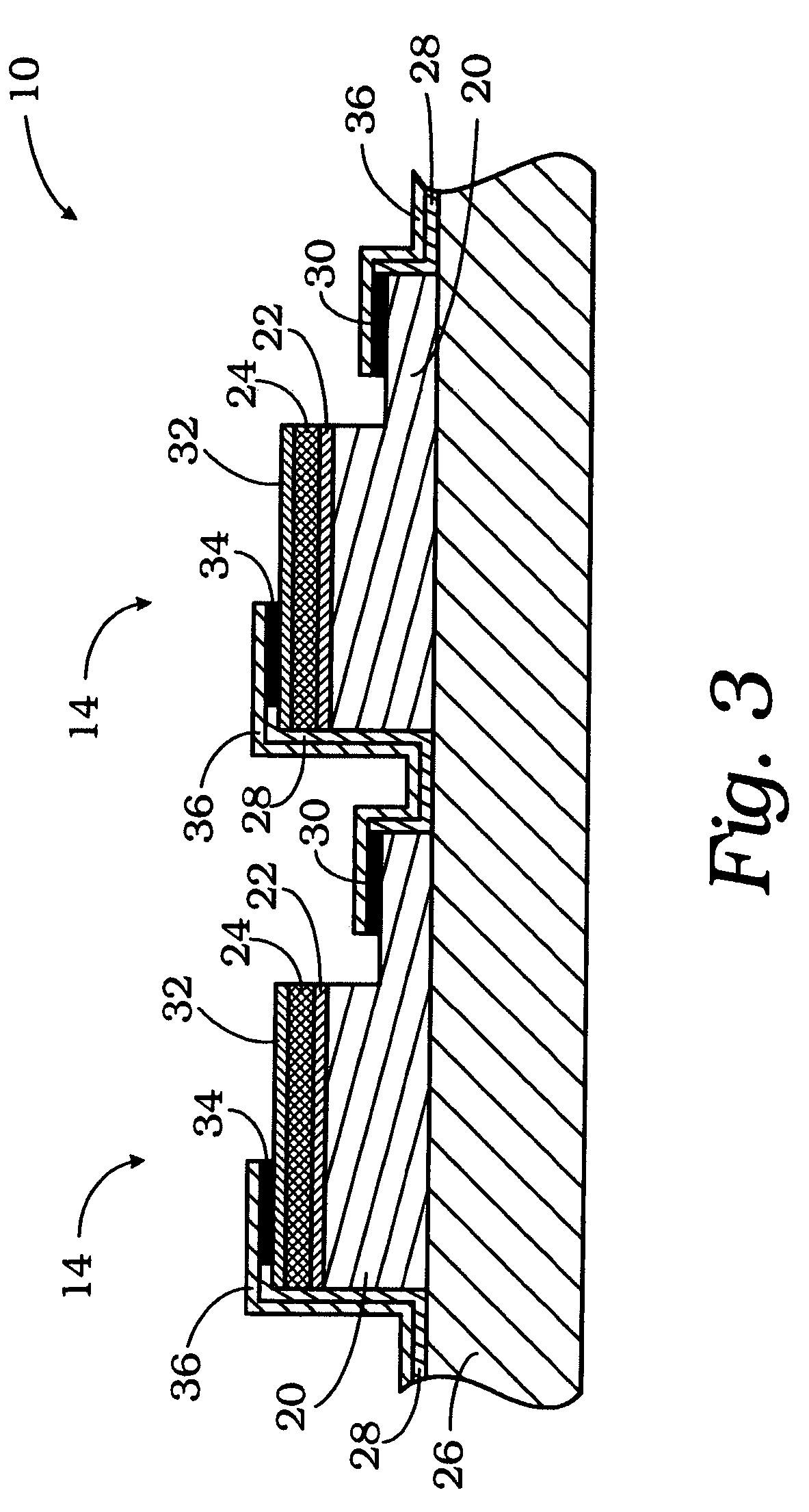

A mixed-signal, multilayer printed wiring board fabricated in a single lamination step is described. The PWB includes one or more radio frequency (RF) interconnects between different circuit layers on different circuit boards which make up the PWB. The PWB includes a number of unit cells with radiating elements and an RF cage disposed around each unit cell to isolate the unit cell. A plurality of flip-chip circuits are disposed on an external surface of the PWB and a heat sink can be disposed over the flip chip components.

Owner:RAYTHEON CO

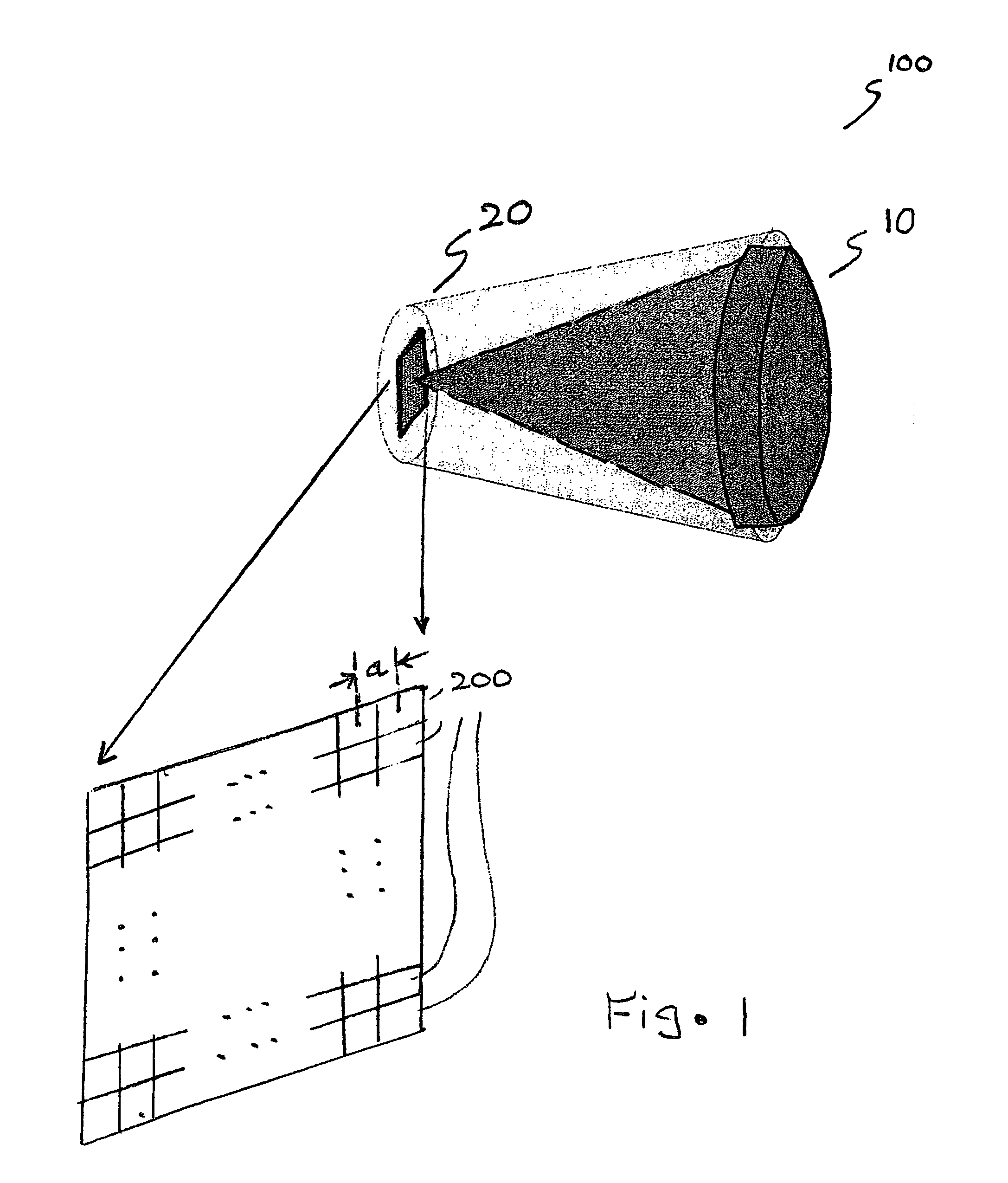

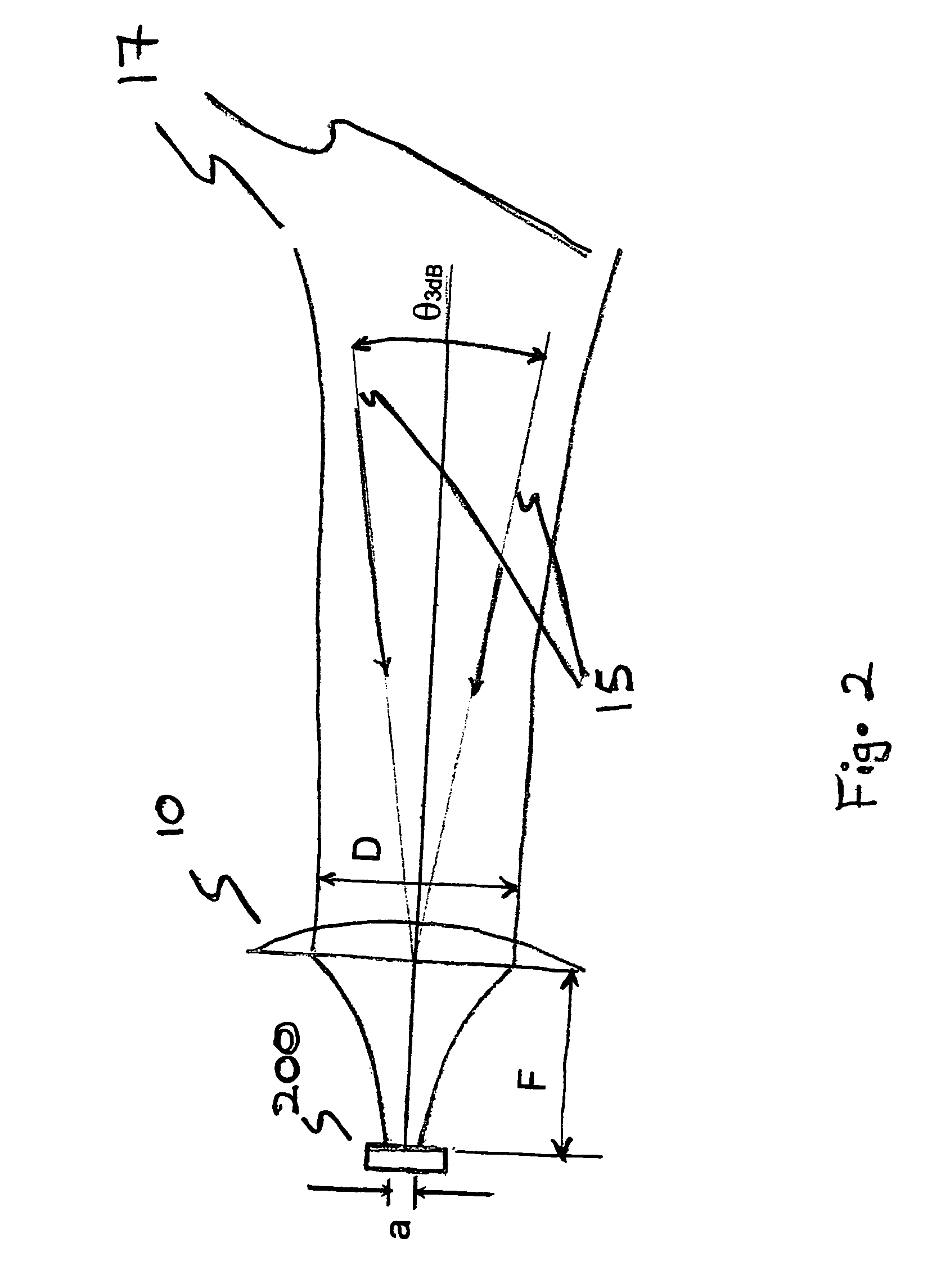

Low cost millimeter wave imager

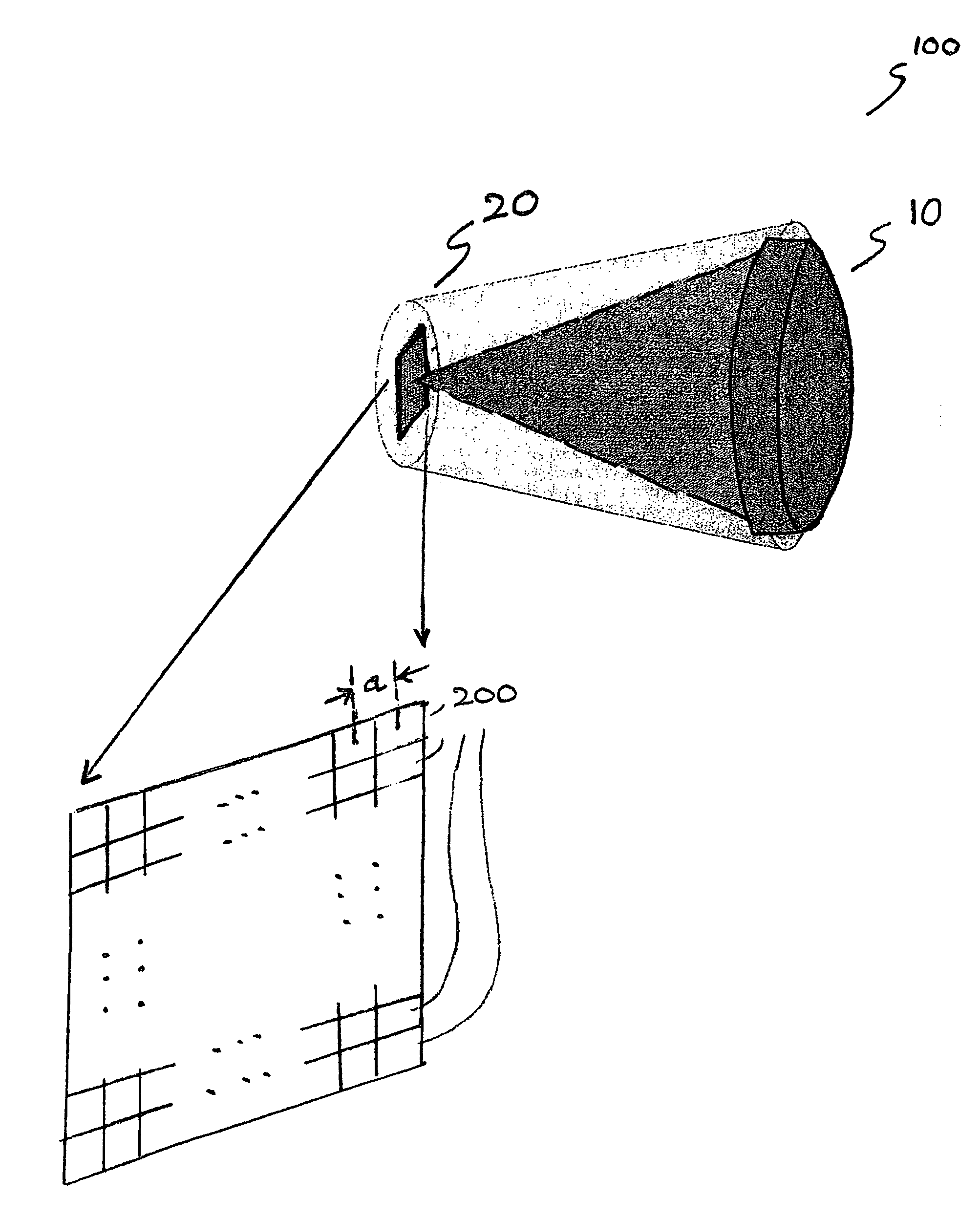

InactiveUS7583074B1Low costUseful sensitivity levelMeasurement using dc-ac conversionMeasurement using ac-dc conversionLow noiseTunnel diode

Low cost millimeter wave imagers using two-dimensional focal plane arrays based on backward tunneling diode (BTD) detectors. Two-dimensional focal arrays of BTD detectors are used as focal plane arrays in imagers. High responsivity of BTD detectors near zero bias results in low noise detectors that alleviate the need for expensive and heat generating low noise amplifiers or Dicke switches in the imager. BTD detectors are installed on a printed circuit board using flip chip packaging technology and horn antennas direct the waves toward the flip chip including the BTD detectors. The assembly of the horn antennas, flip chips, printed circuit board substrate, and interconnects together work as an imaging sensor. Corrugated surfaces of the components prevent re-radiation of the incident waves.

Owner:HRL LAB

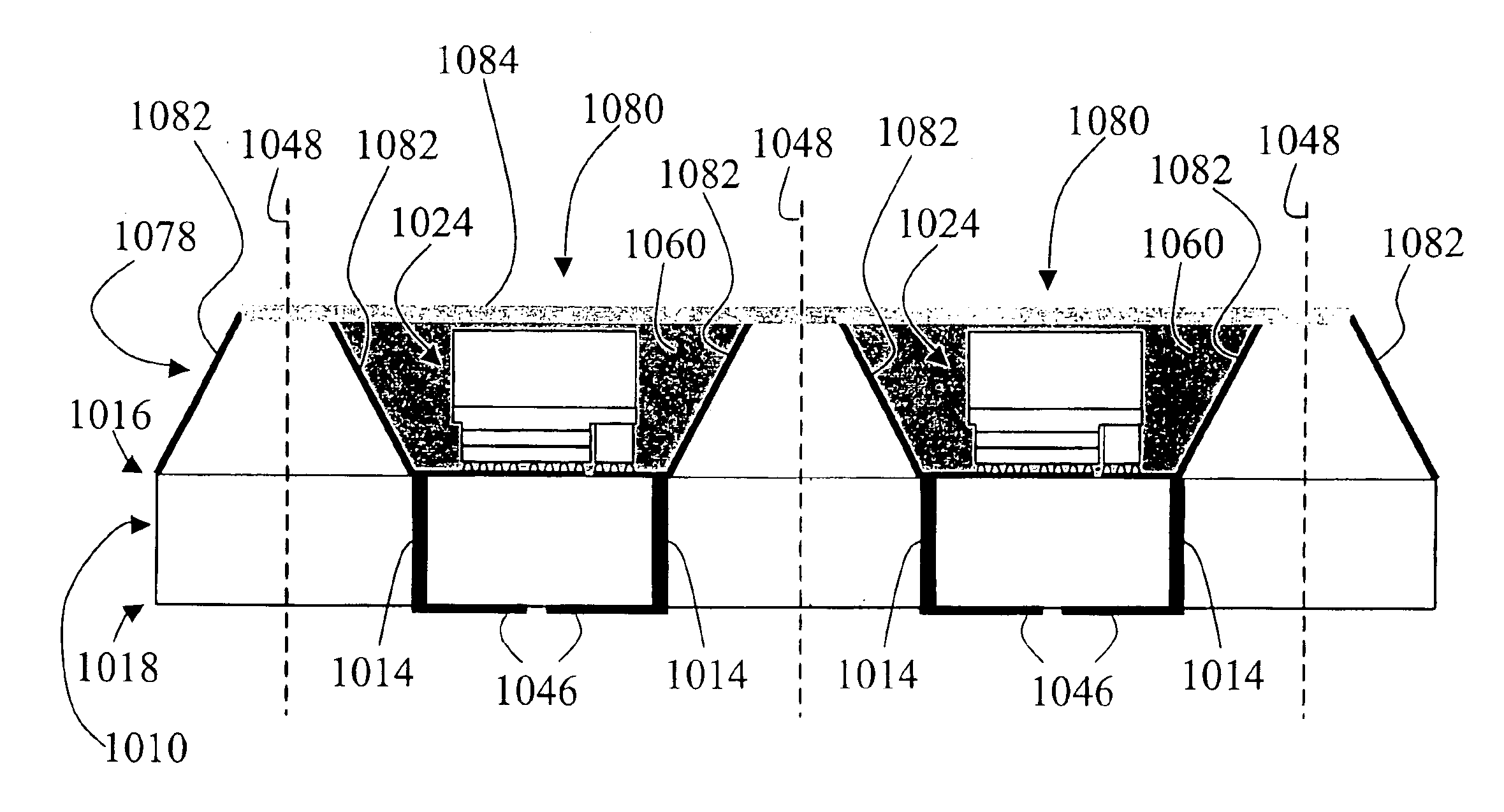

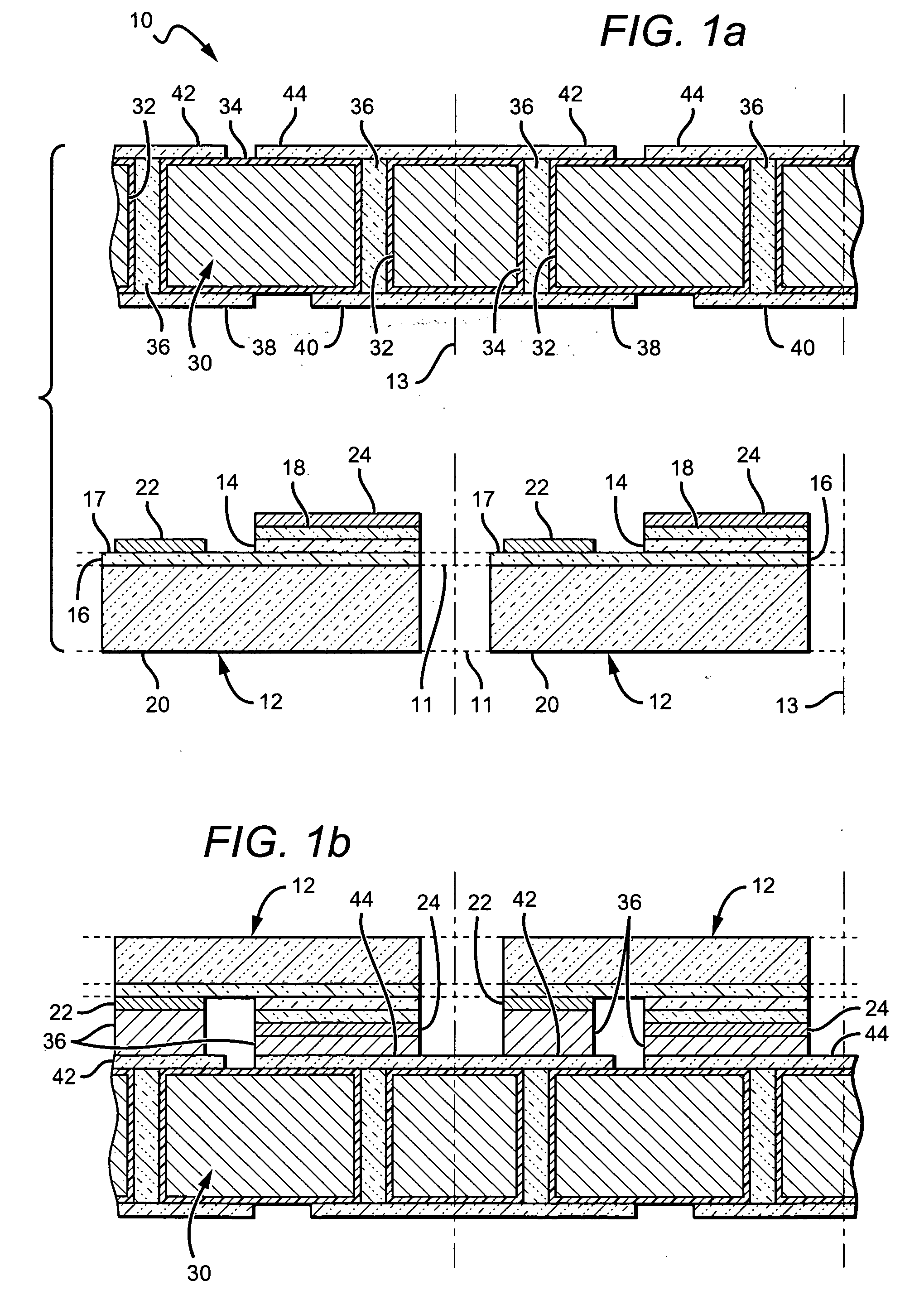

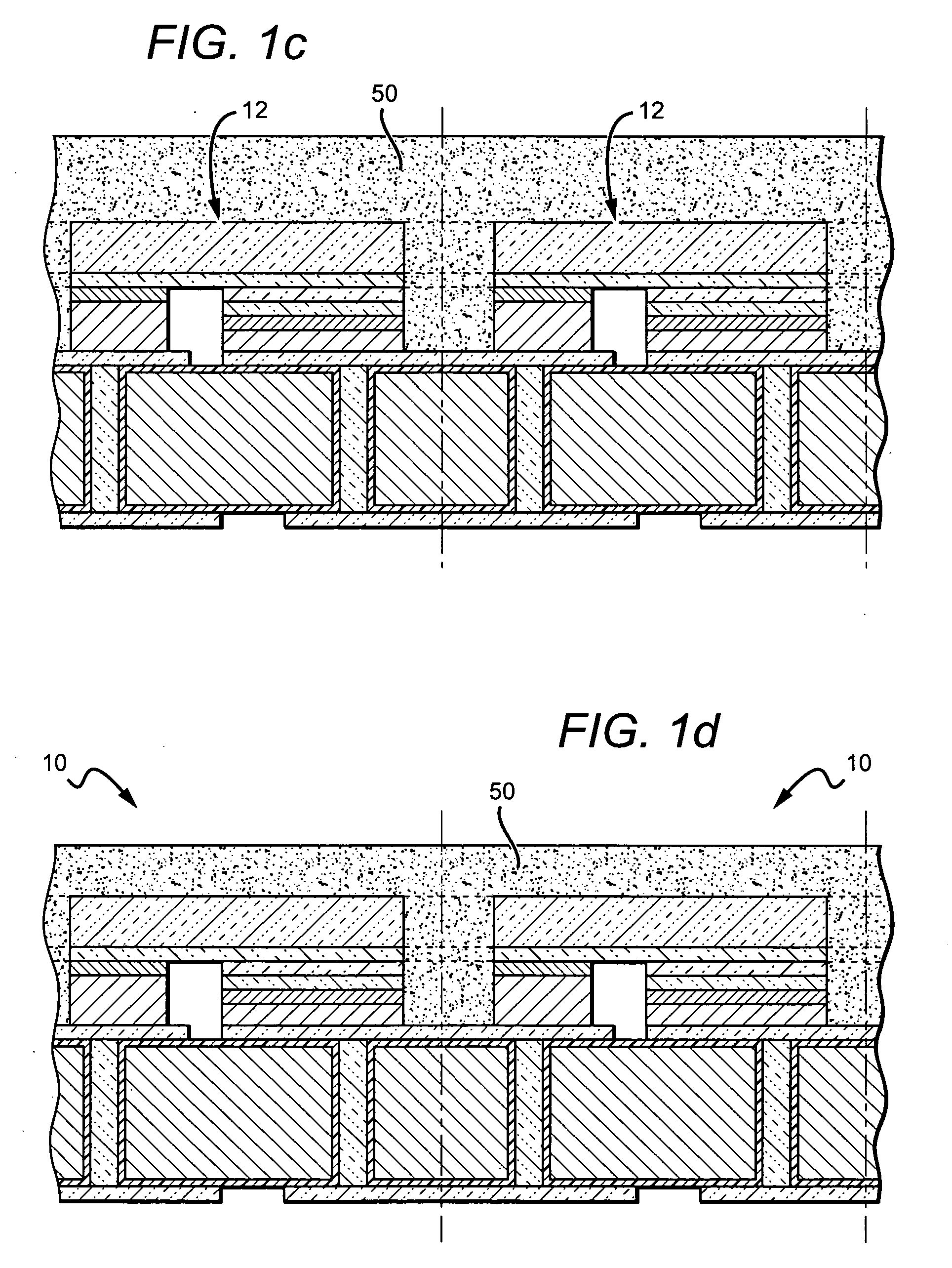

LED power package

InactiveUS6964877B2Solid-state devicesSemiconductor/solid-state device manufacturingSurface mountingEngineering

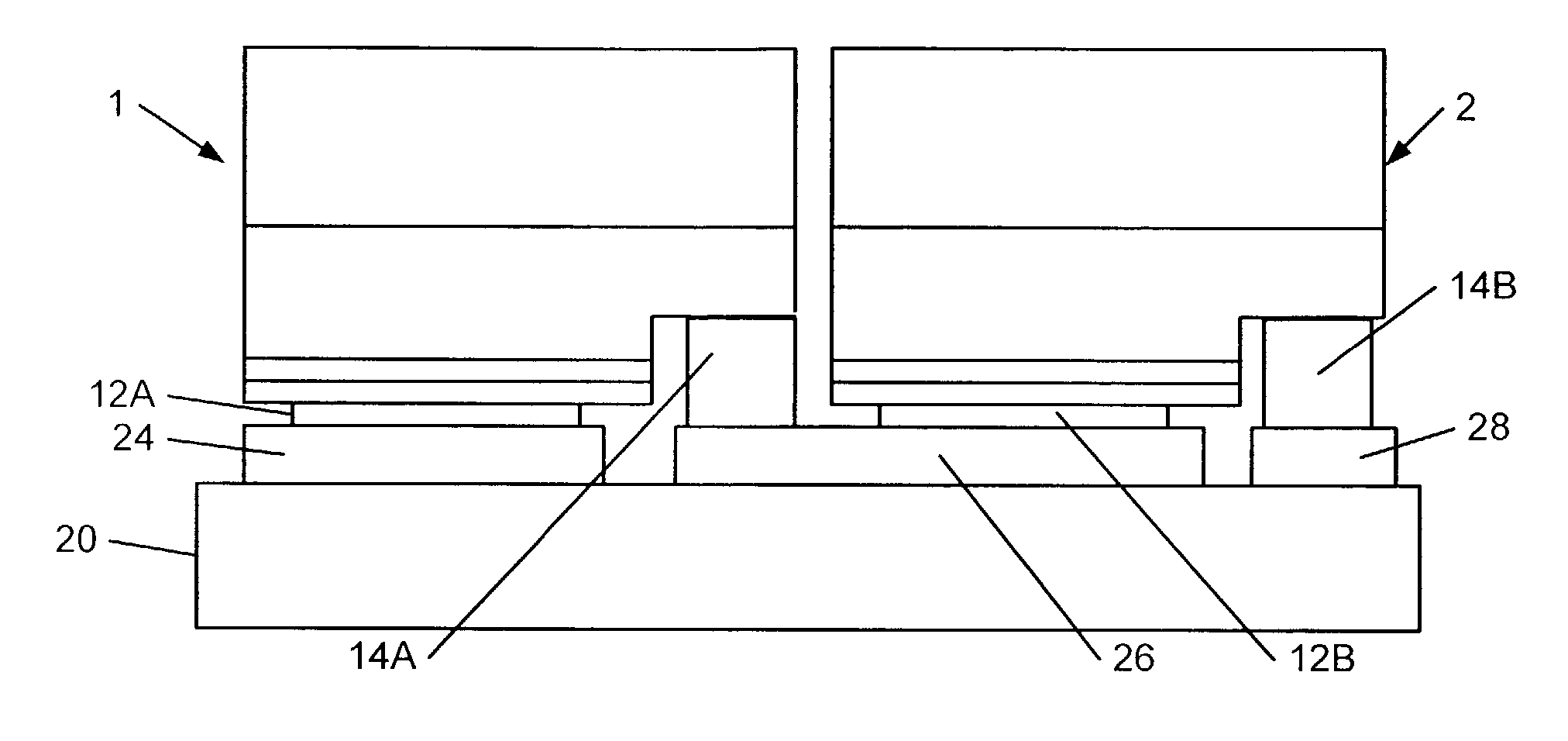

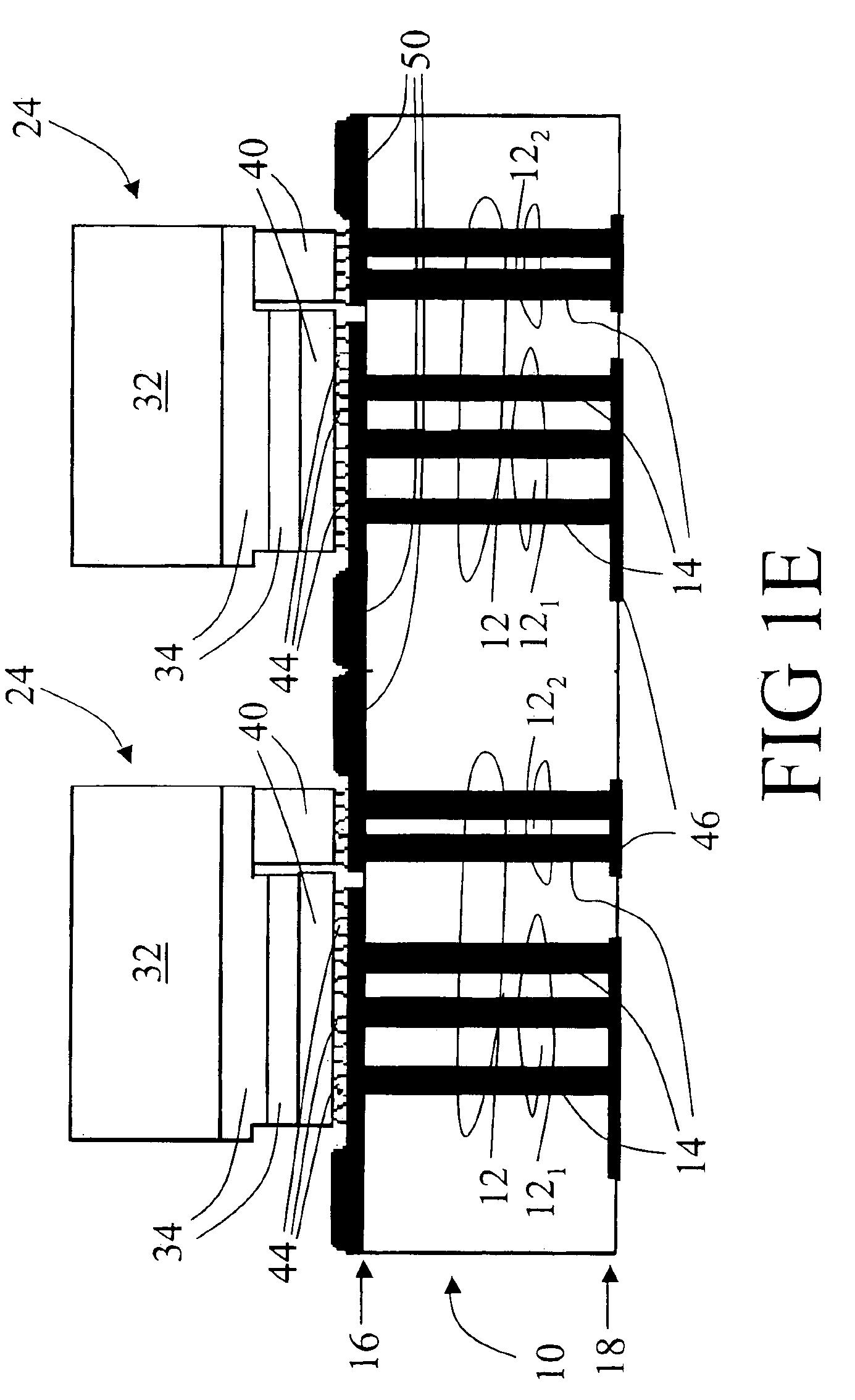

Surface mount light emitting diode (LED) packages each contain a light emitting diode (LED) die (24). A plurality of arrays of openings are drilled into an electrically insulating sub-mount wafer (10). A metal is applied to the drilled openings to produce a plurality of via arrays (12). The LED dice (24) are flip-chip bonded onto a frontside (16) of the sub-mount wafer (10). The p-type and n-type contacts of each flip-chip bonded LED (24) electrically communicate with a solderable backside (18) of the sub-mount wafer (10) through a via array (12). A thermal conduction path (10, 12) is provided for thermally conducting heat from the flip-chip bonded LED dice (24) to the solderable backside (18) of the sub-mount wafer (10). Subsequent to the flip-chip bonding, the sub-mount wafer (10) is separated to produce the surface mount LED packages.

Owner:PROLIGHT OPTO TECH

Flip Chip Interconnection with double post

ActiveUS20090146303A1Semiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

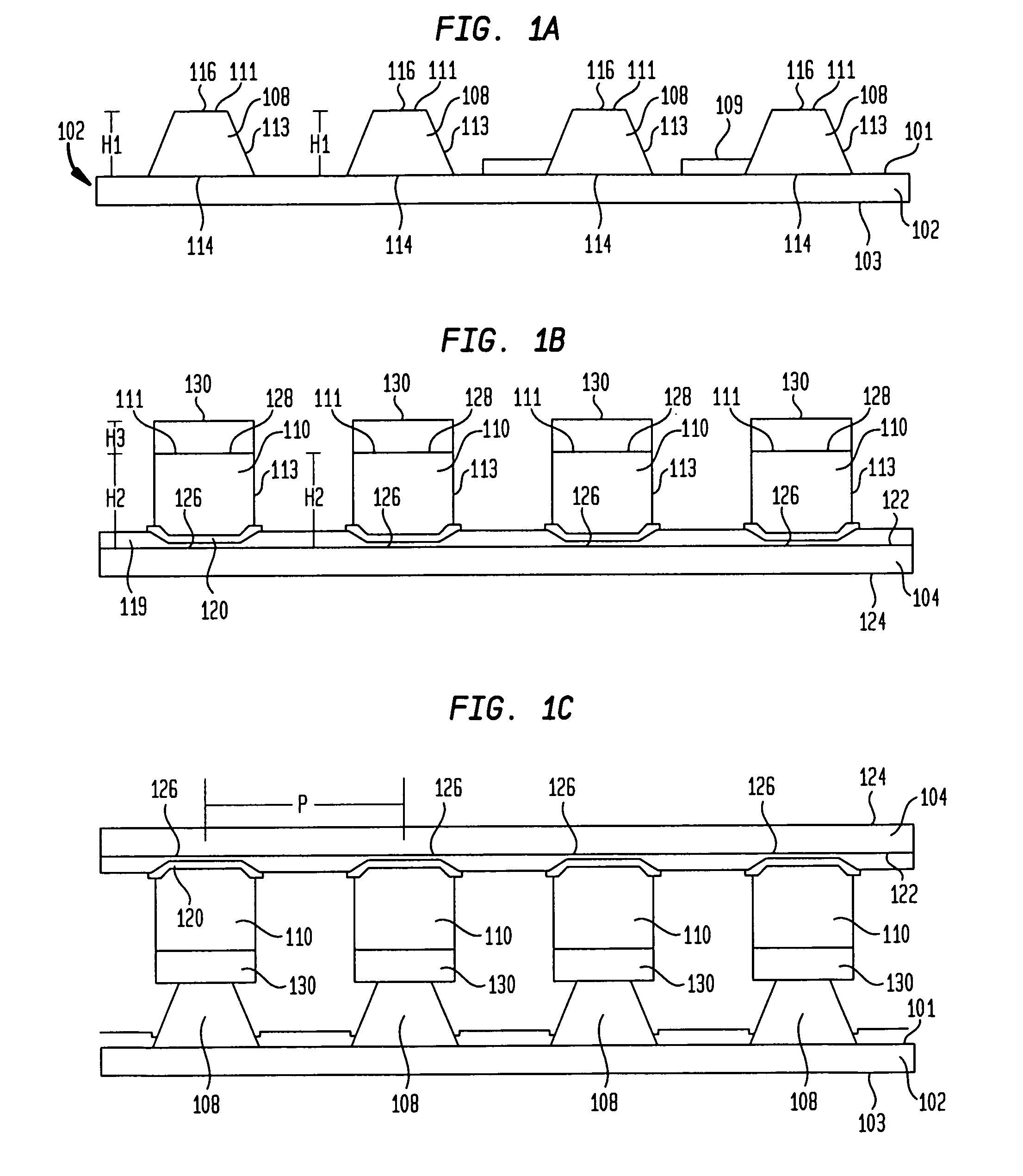

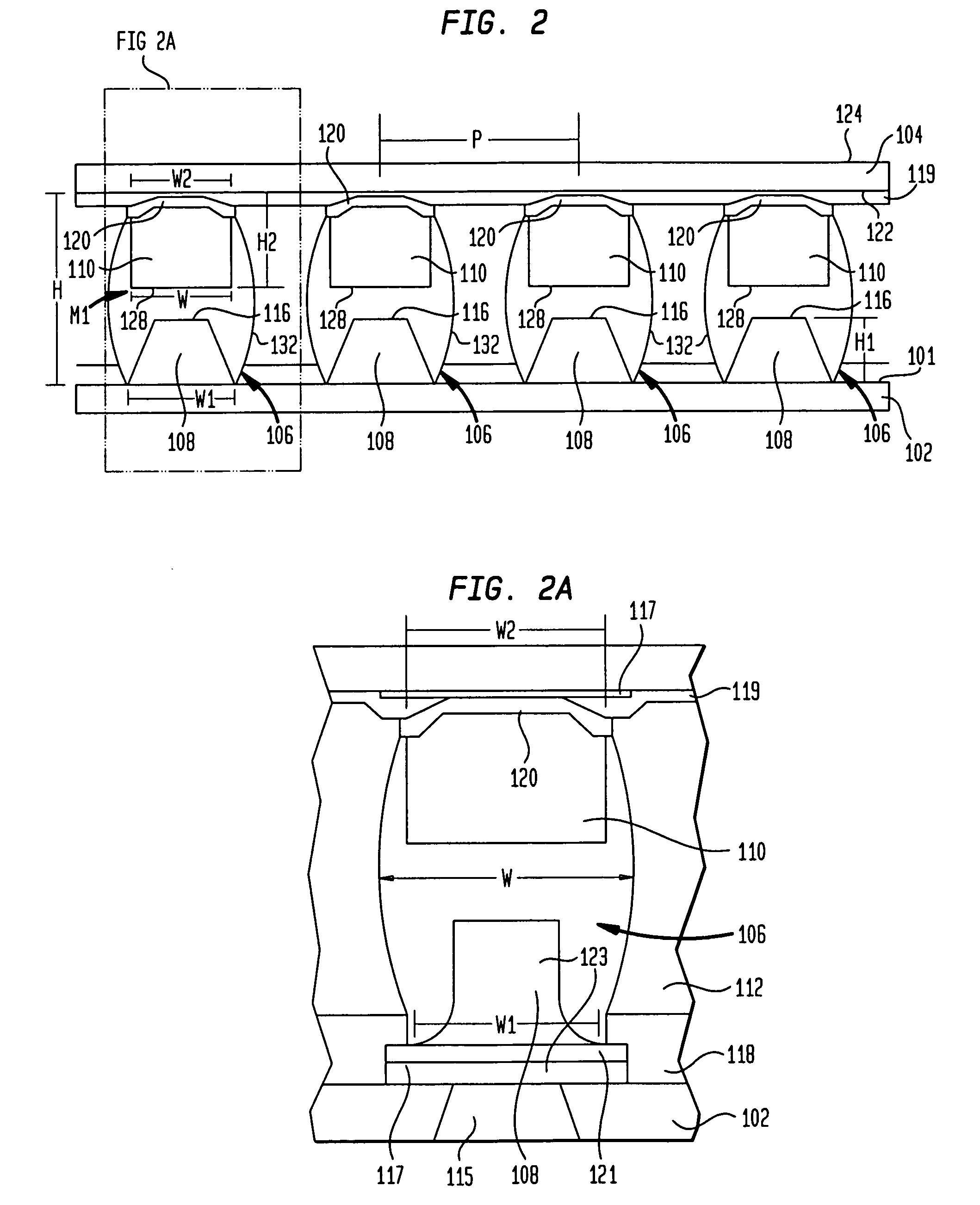

A packaged microelectronic assembly includes a microelectronic element having a front surface and a plurality of first solid metal posts extending away from the front surface. Each of the first posts has a width in a direction of the front surface and a height extending from the front surface, wherein the height is at least half of the width. There is also a substrate having a top surface and a plurality of second solid metal posts extending from the top surface and joined to the first solid metal posts.

Owner:TESSERA INC

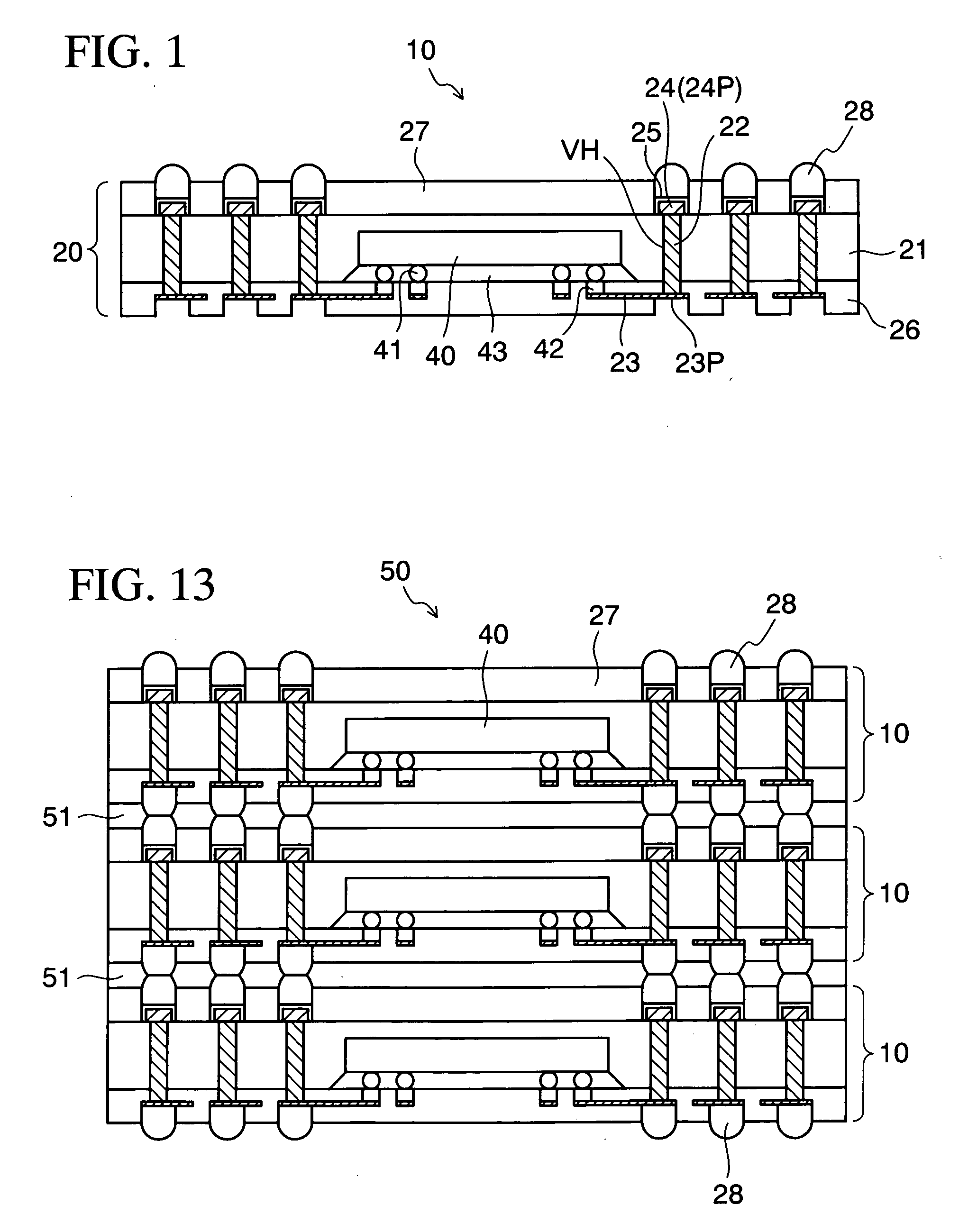

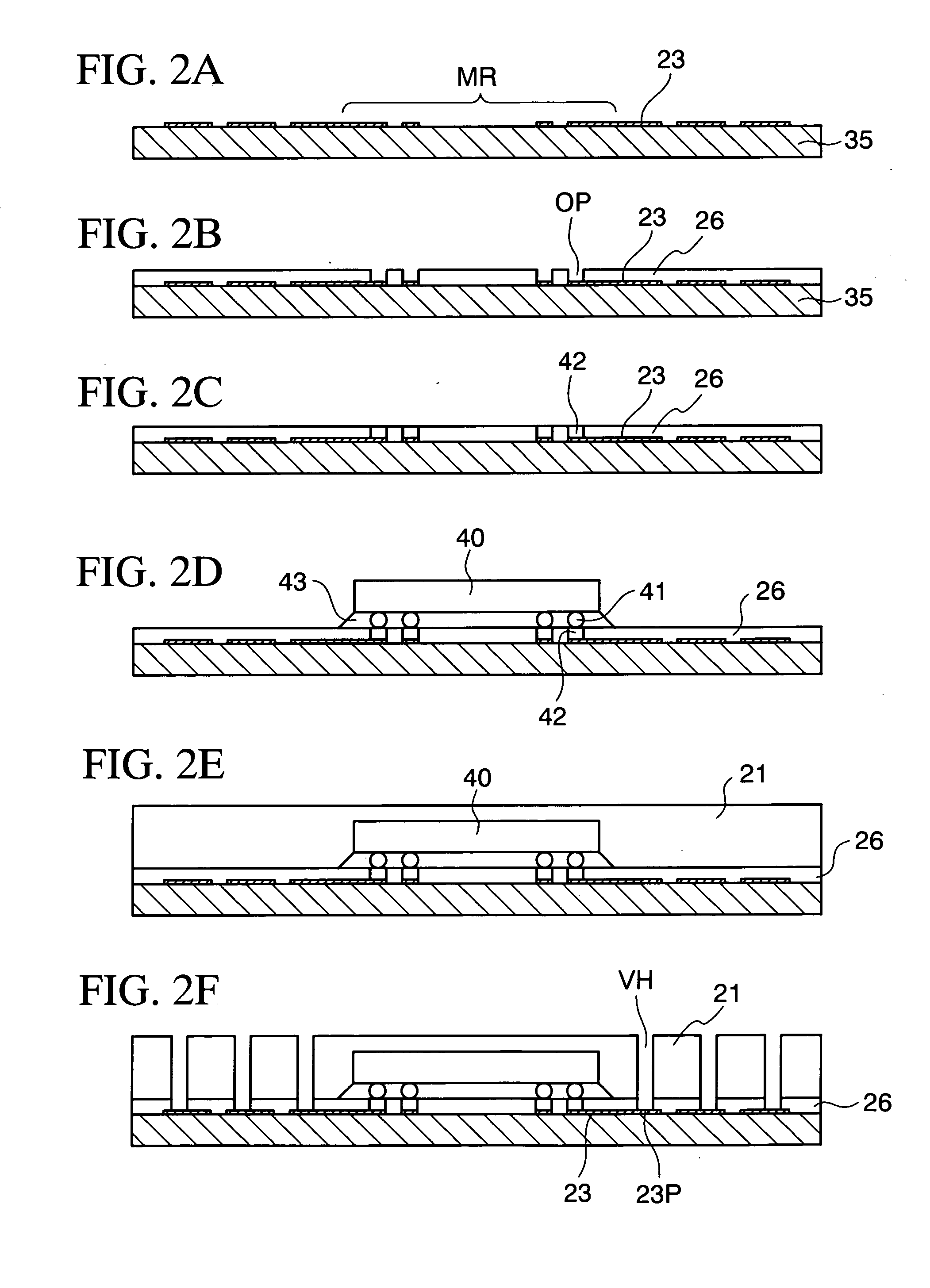

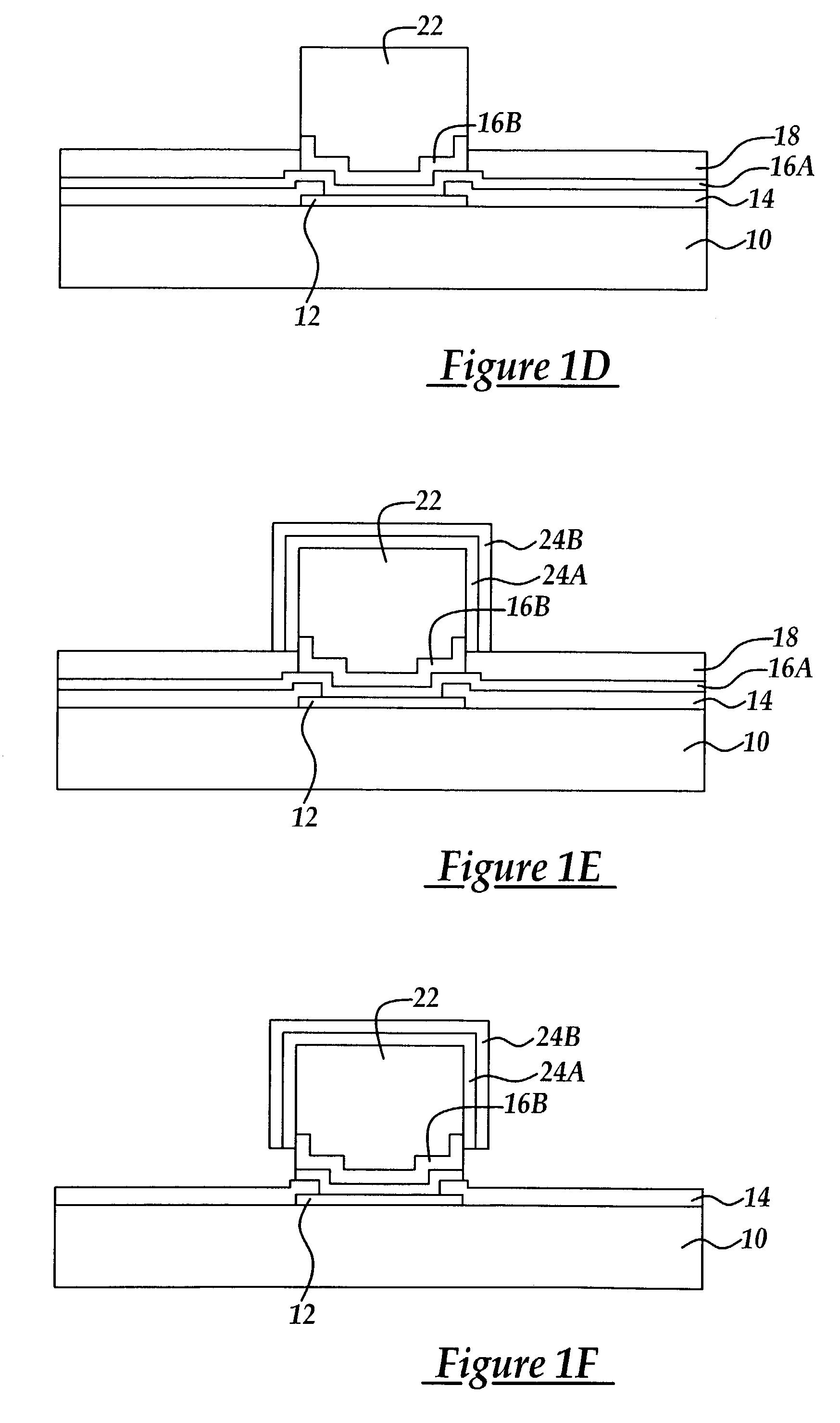

Semiconductor device and method of manufacturing the same

InactiveUS20050184377A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, and conductor layers are respectively formed to be connected to one end and another end of the conductor filled in the individual via hole. Portions (pad portions) of the conductor layers which correspond to the conductors are exposed from protective films, or external connection terminals are bonded to the pad portions. The chip is mounted with flip-chip technology so that at least some of electrode terminals thereof are electrically connected to the conductor layers.

Owner:SHINKO ELECTRIC IND CO LTD

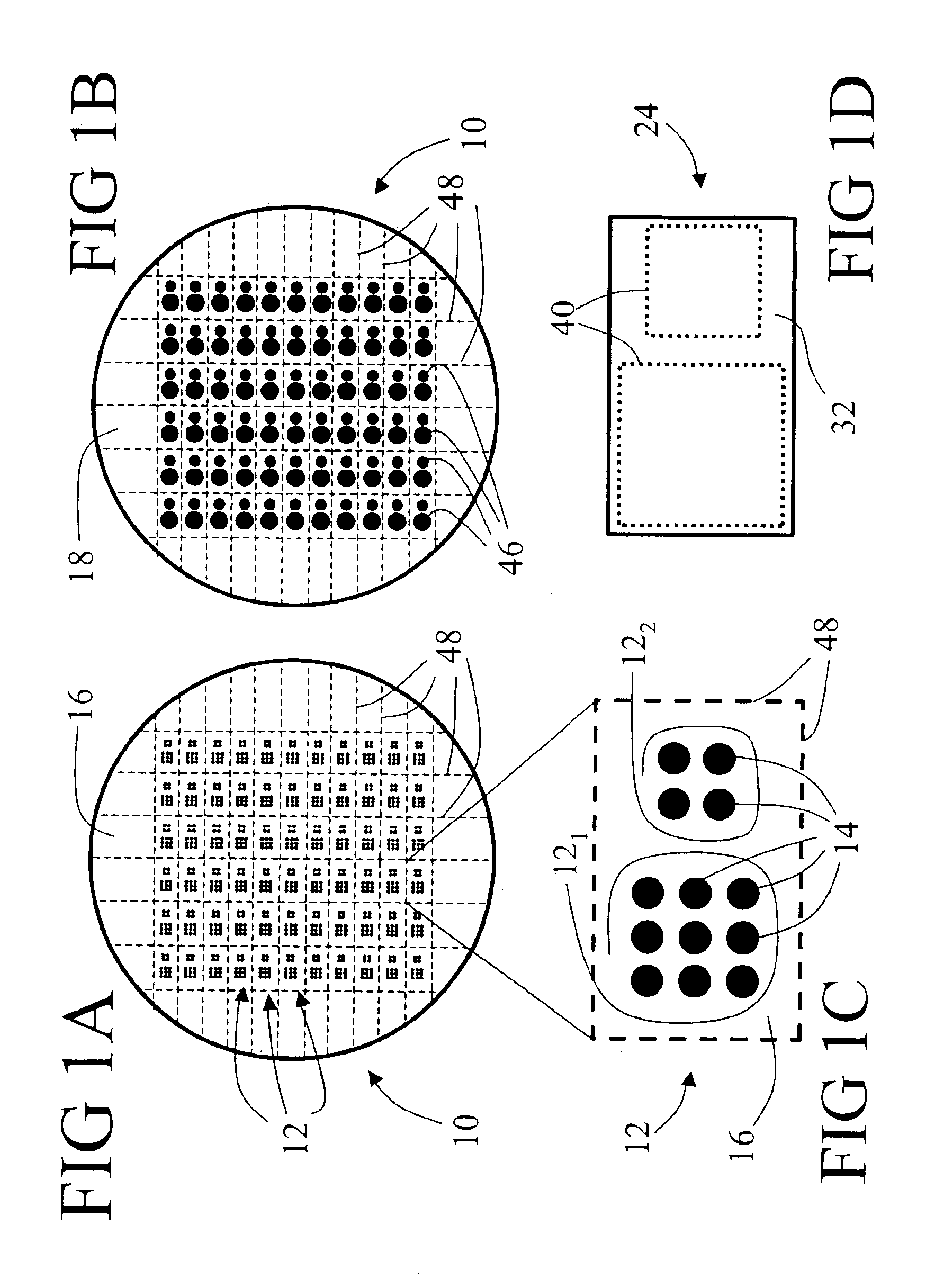

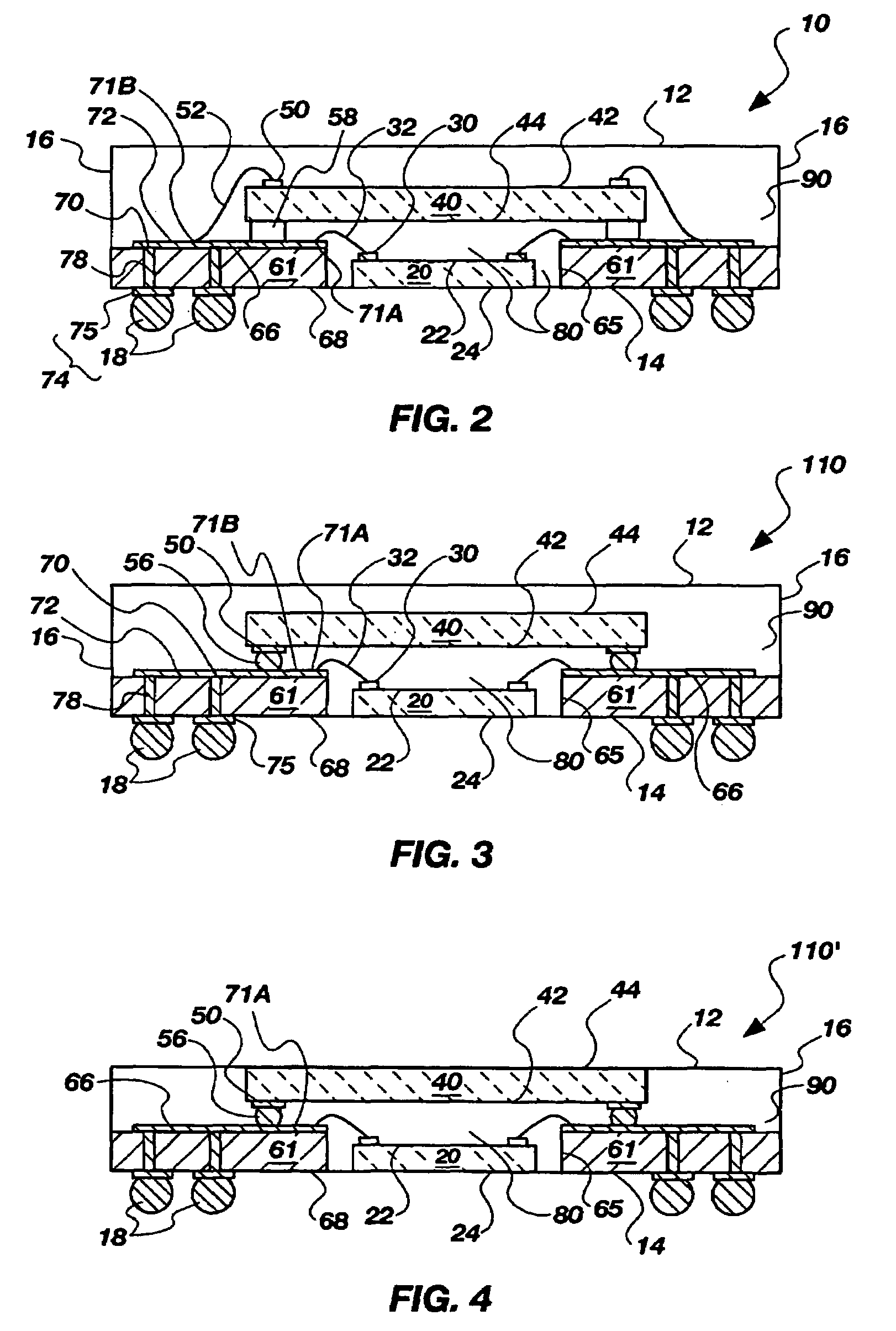

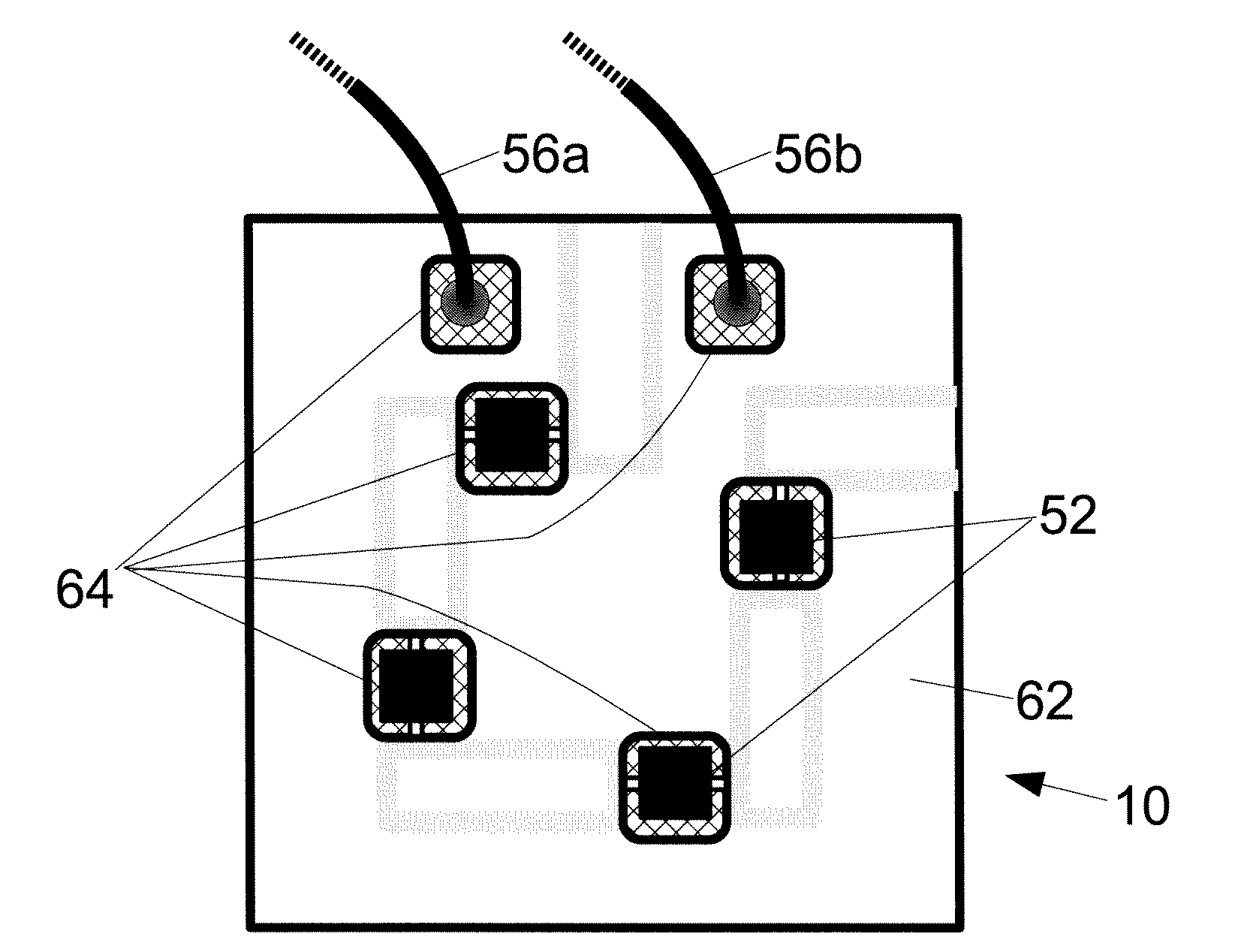

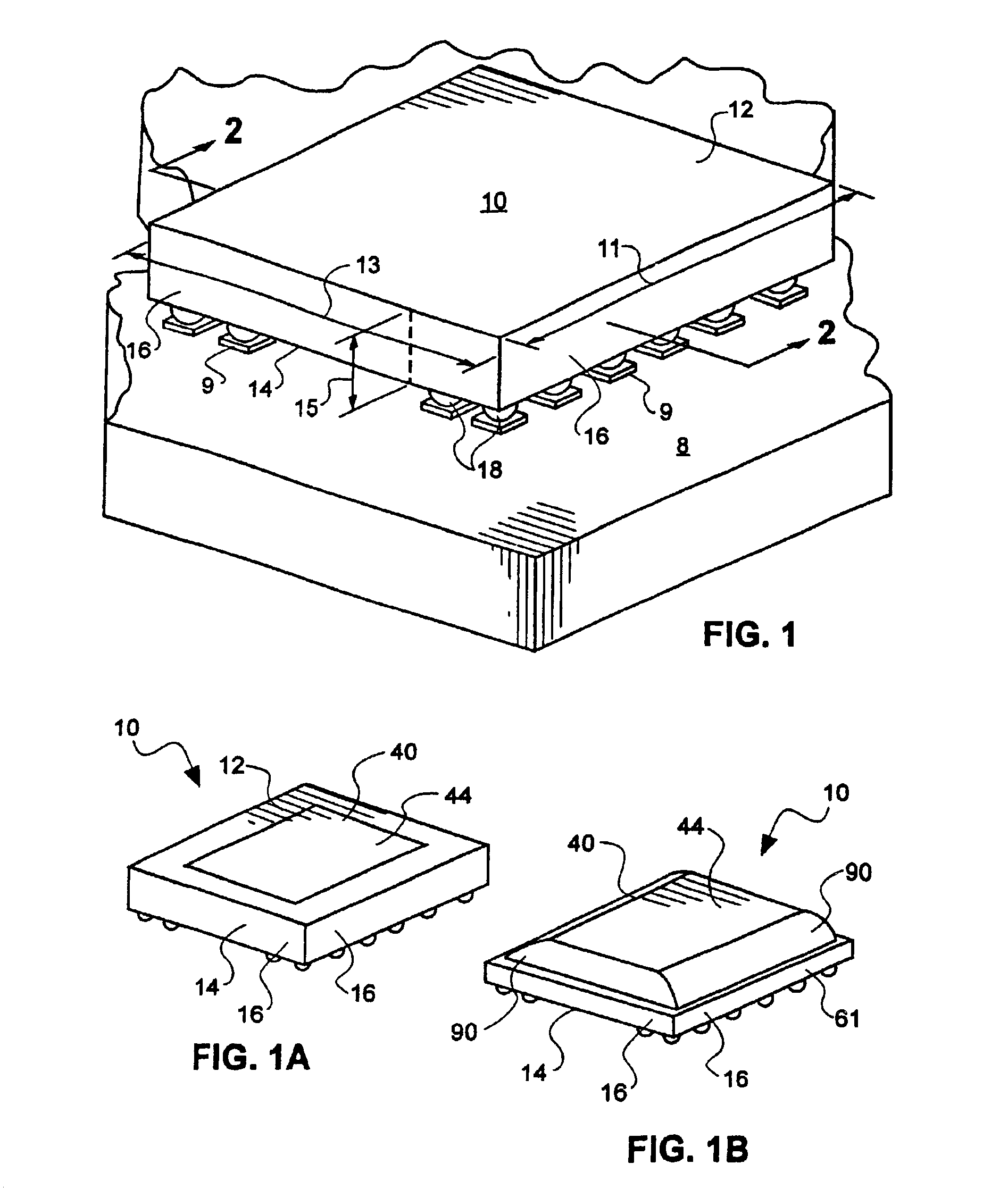

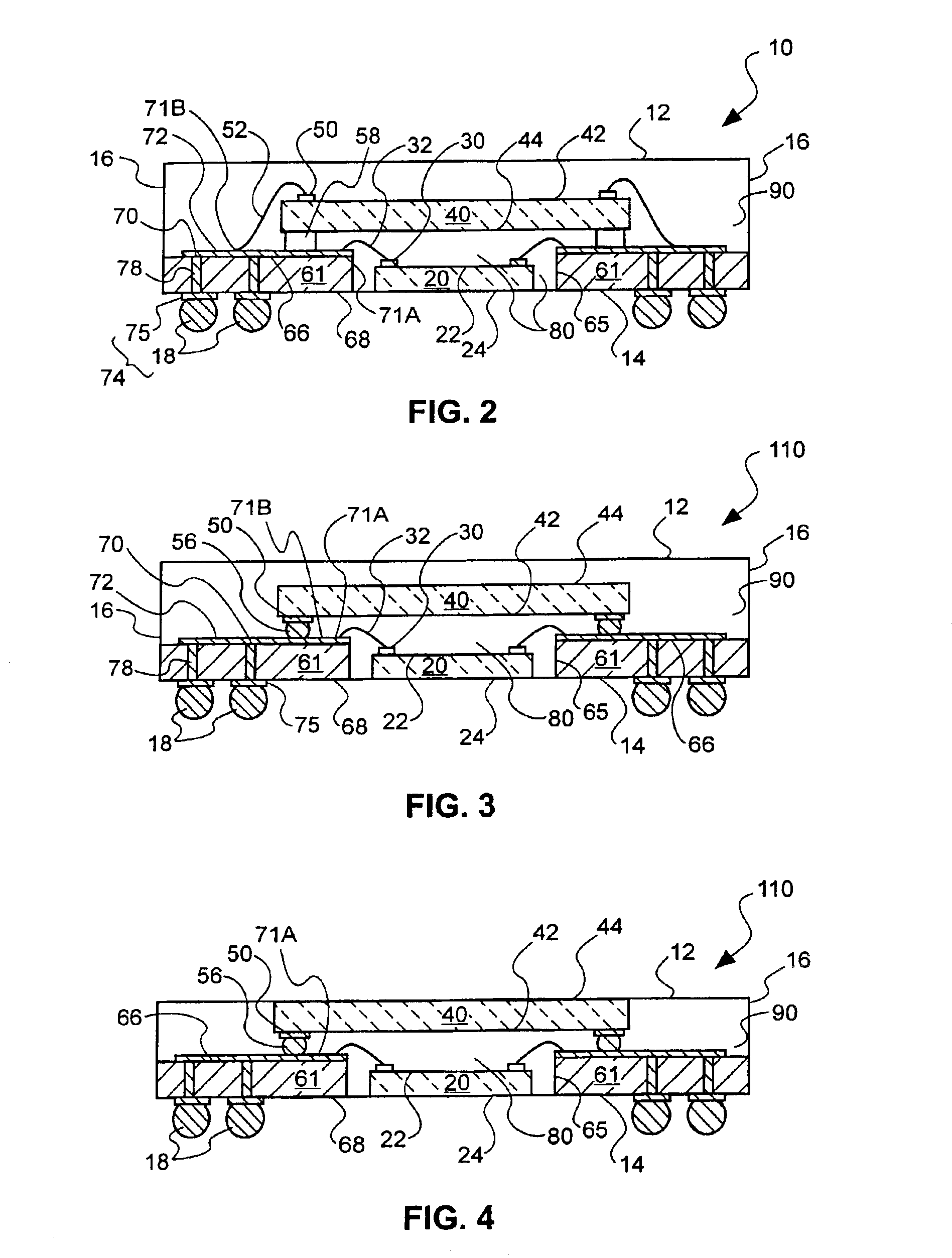

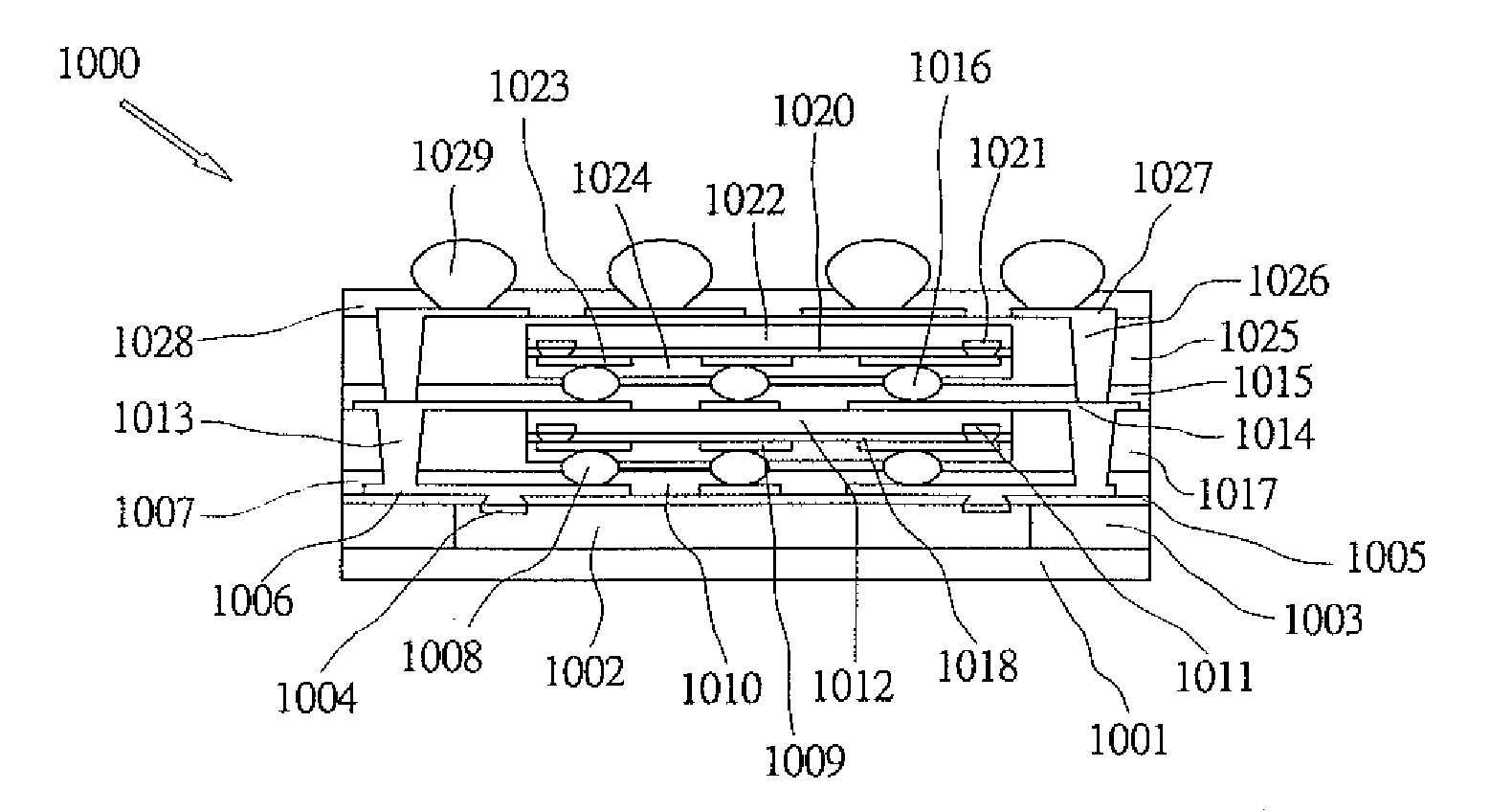

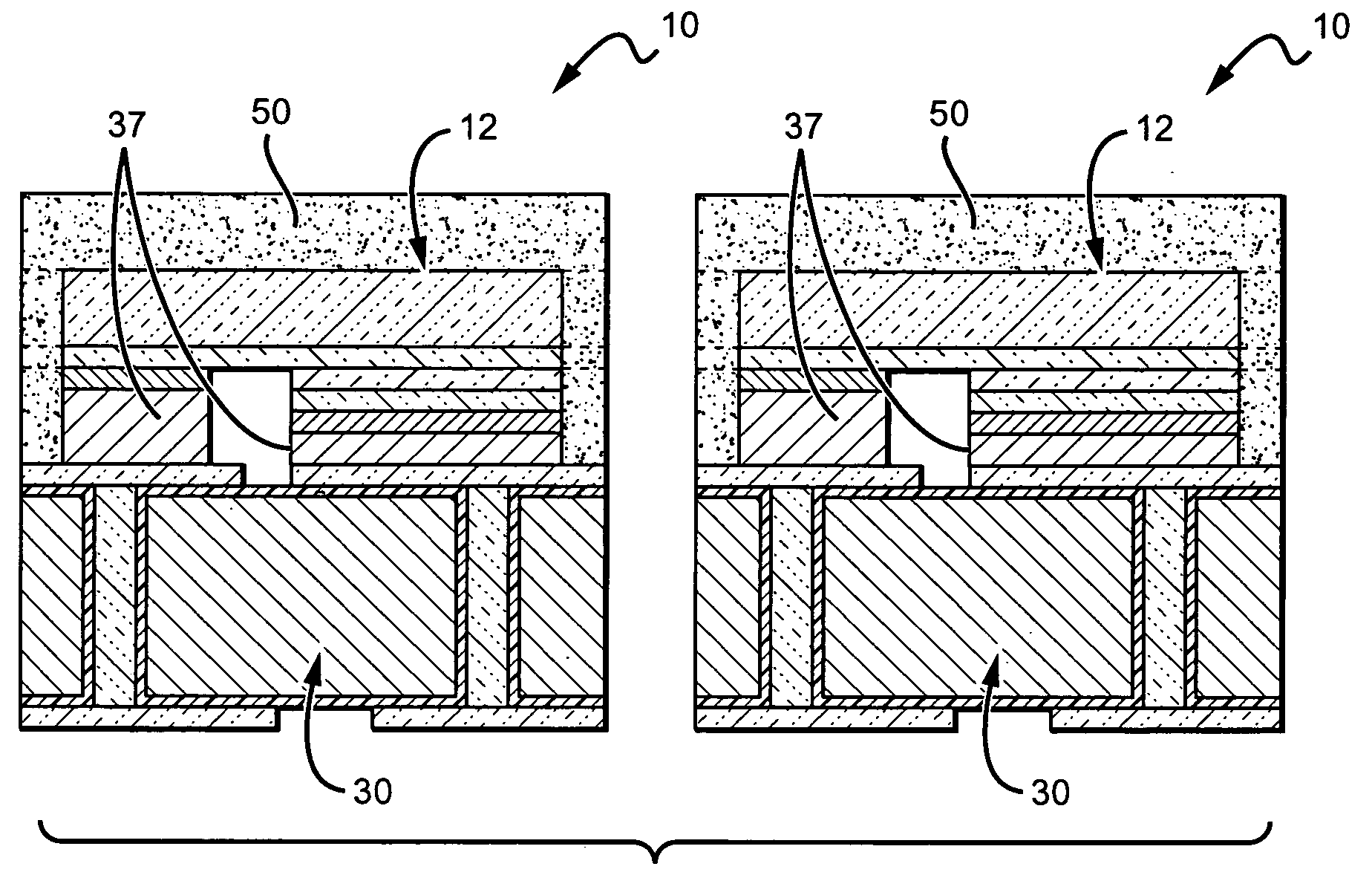

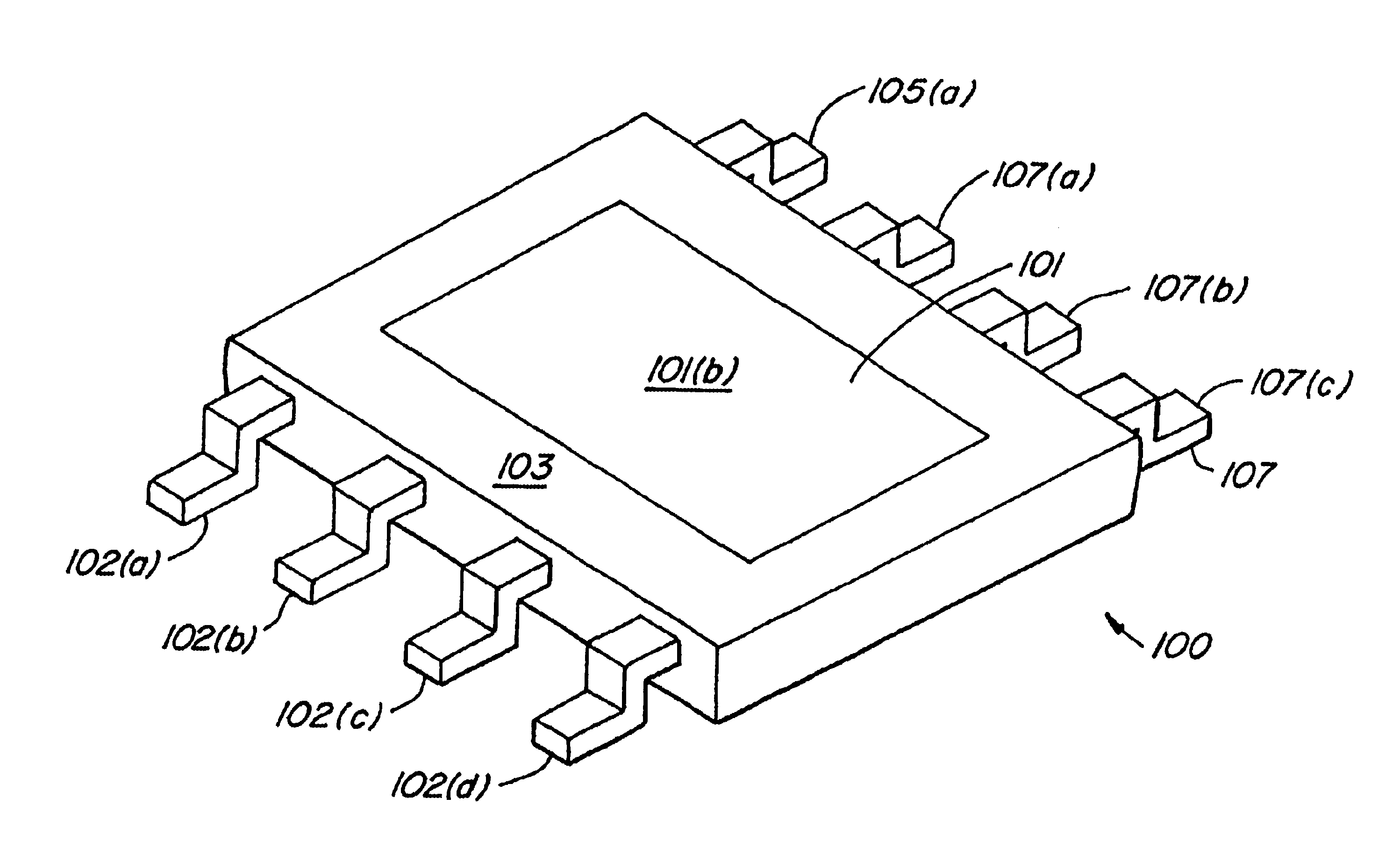

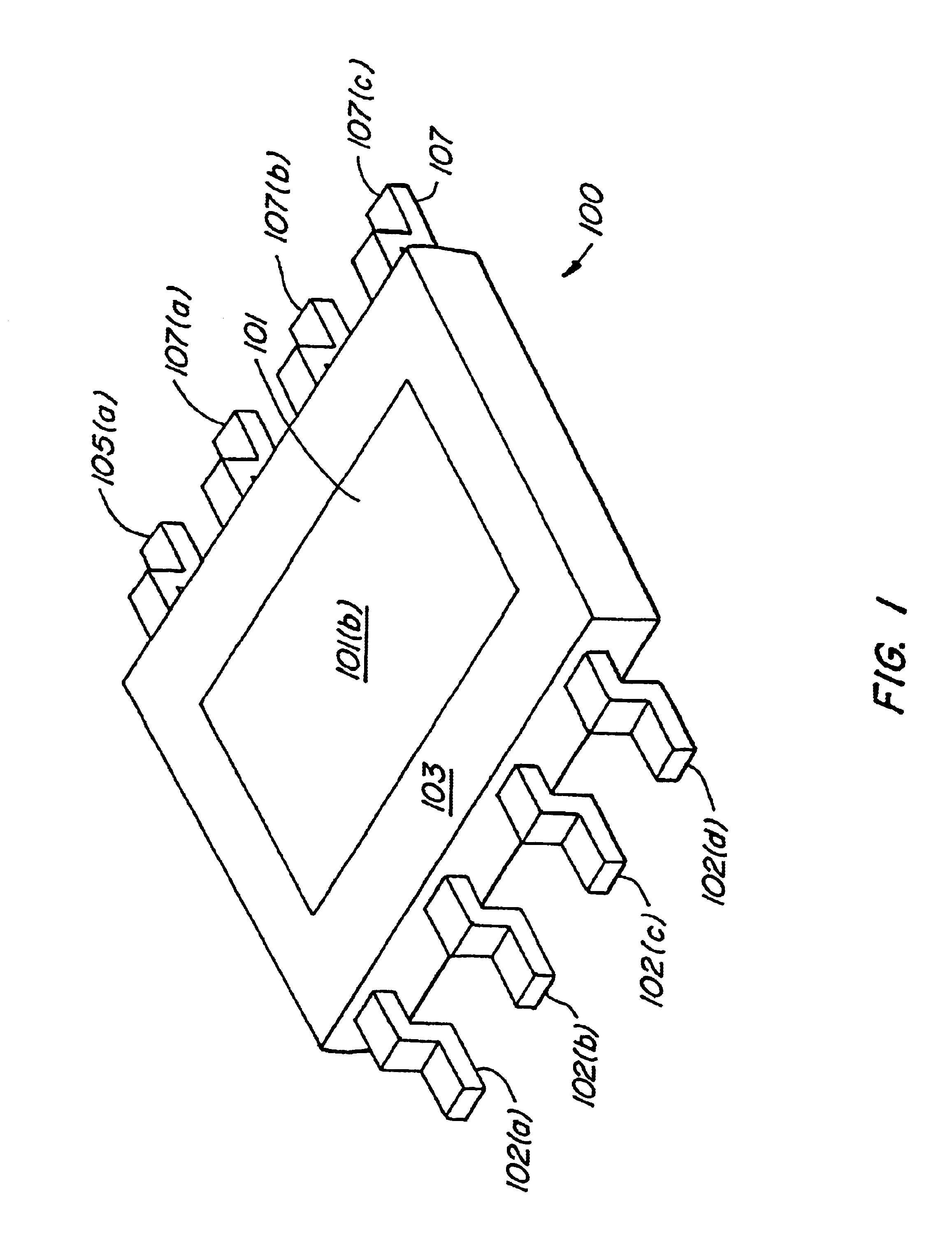

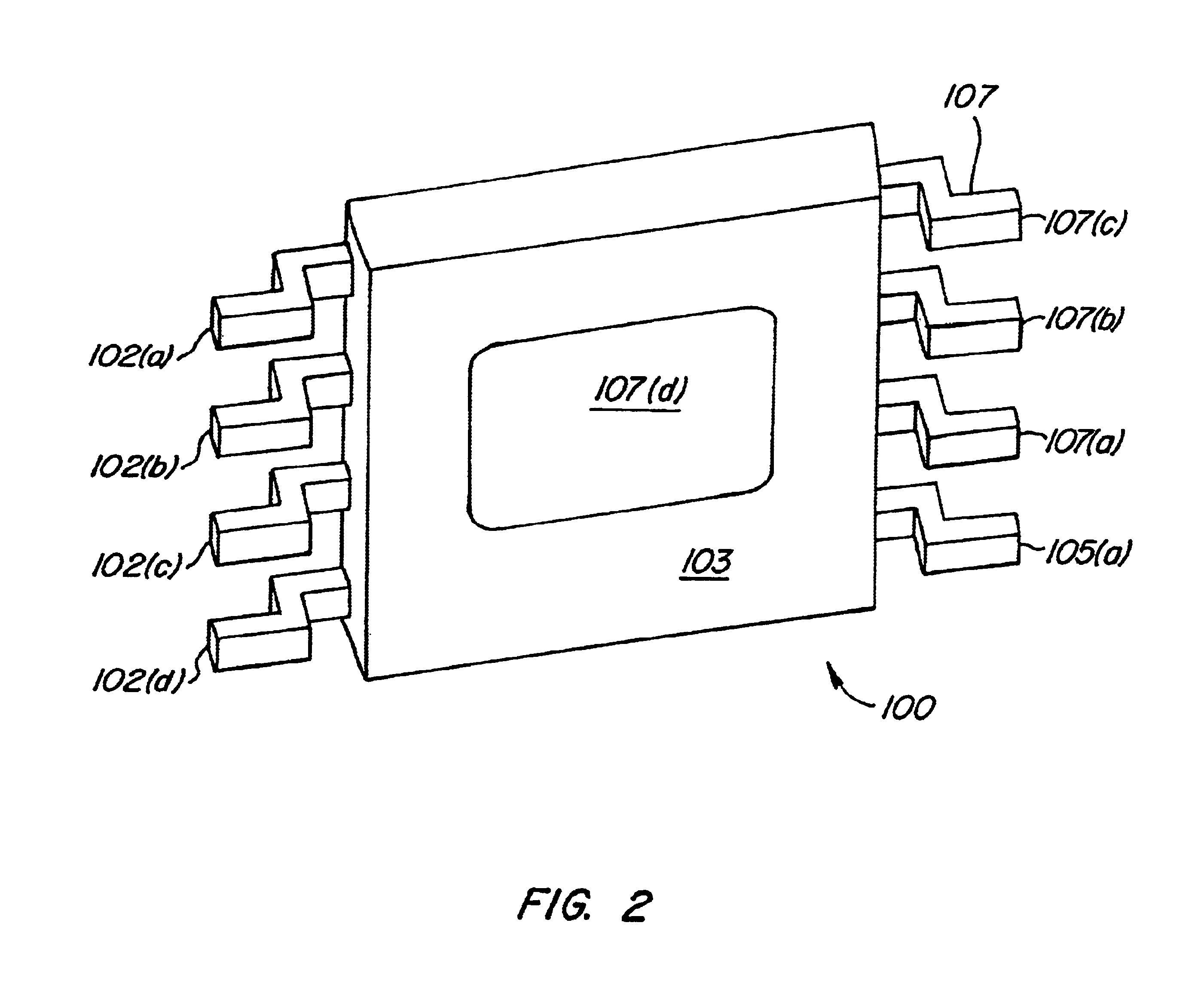

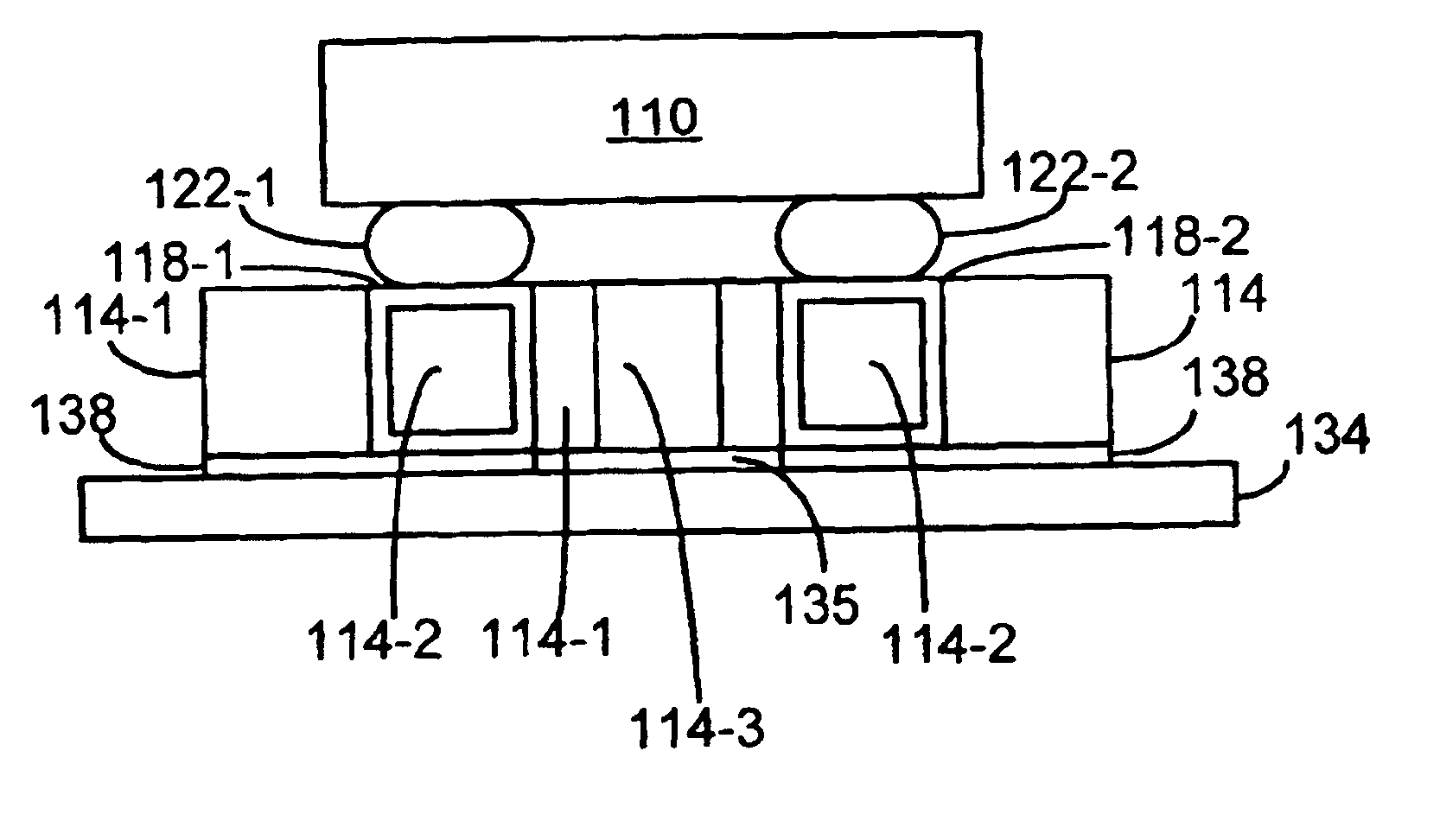

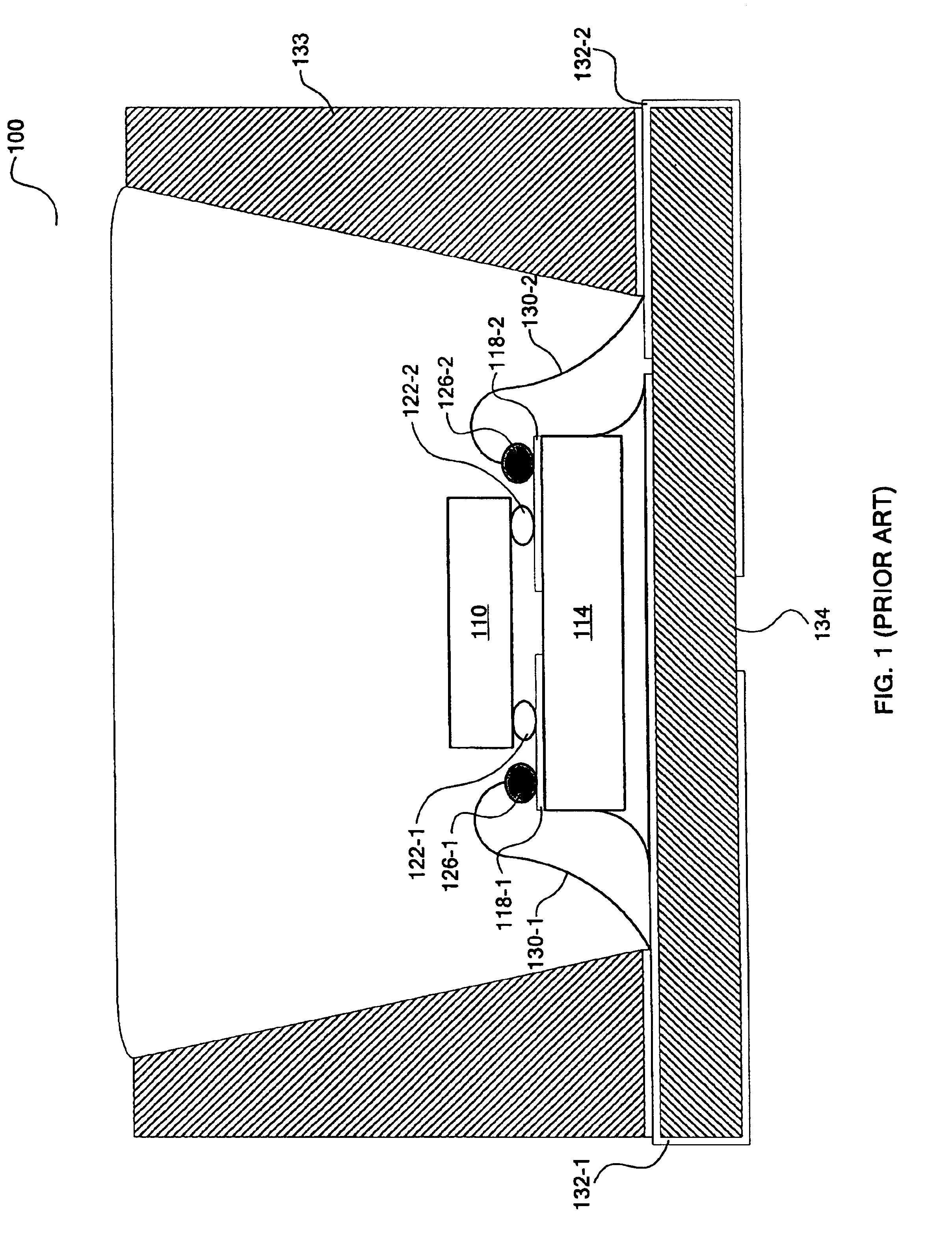

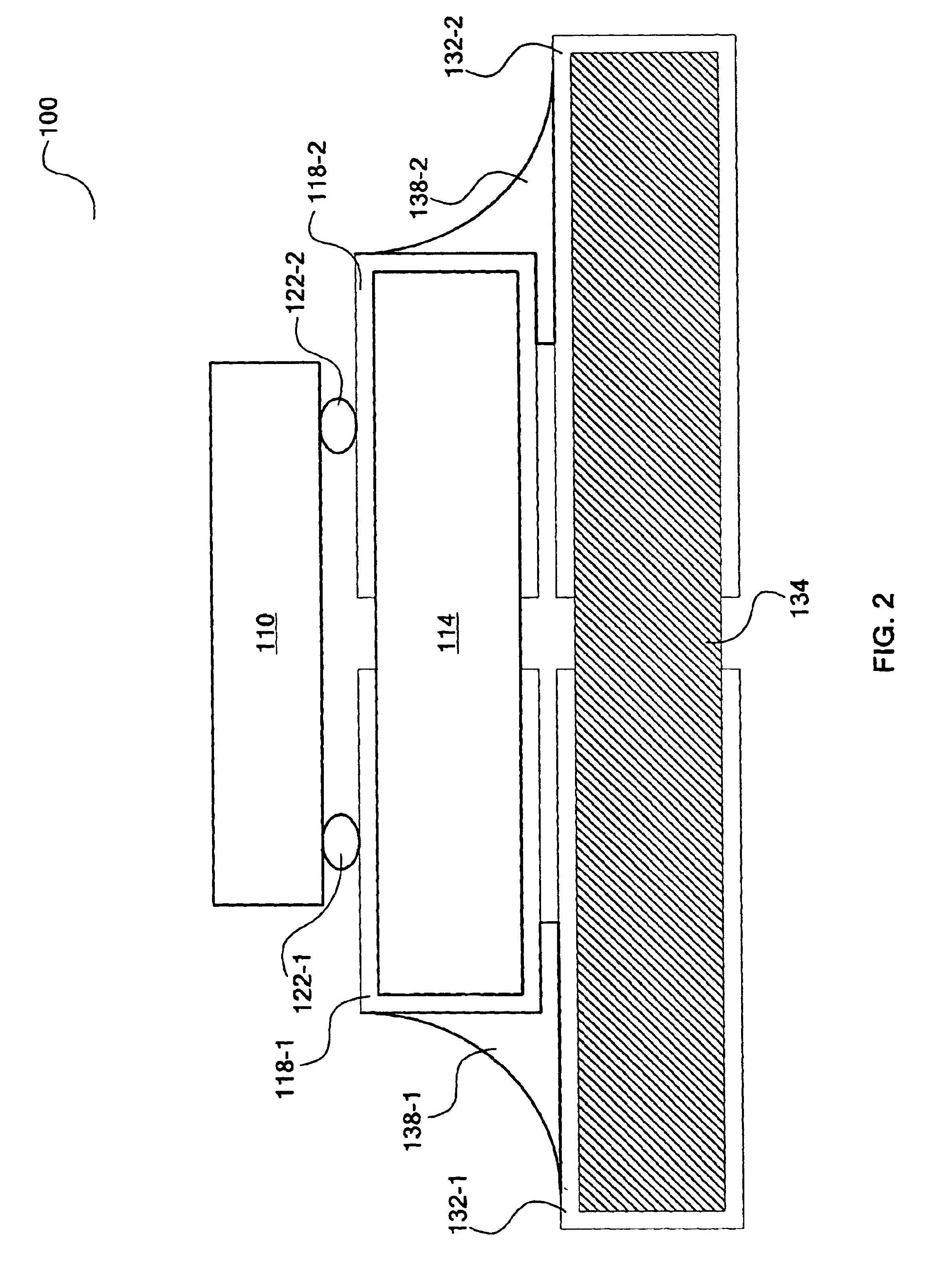

Methods for assembling multiple semiconductor devices

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

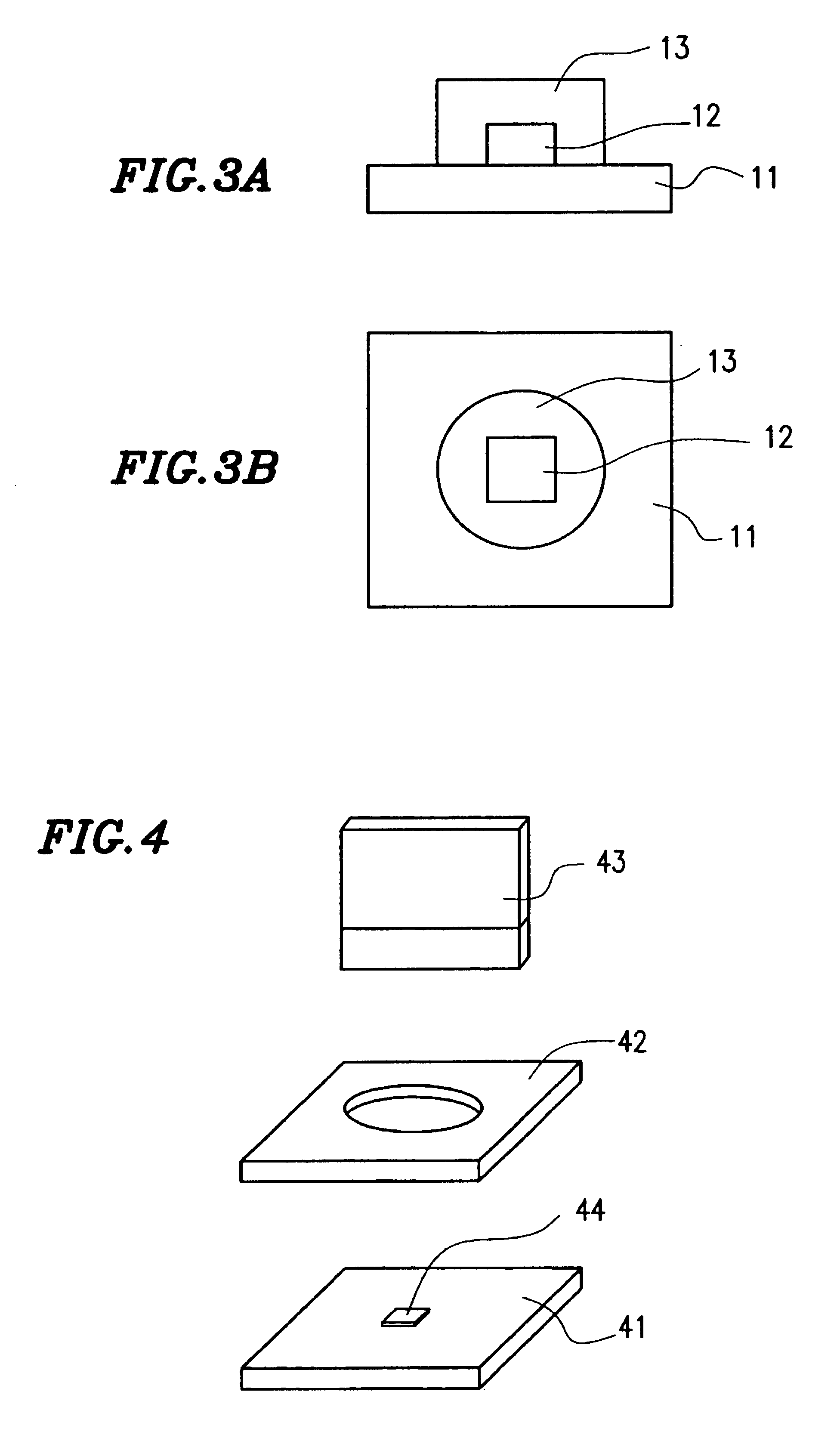

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

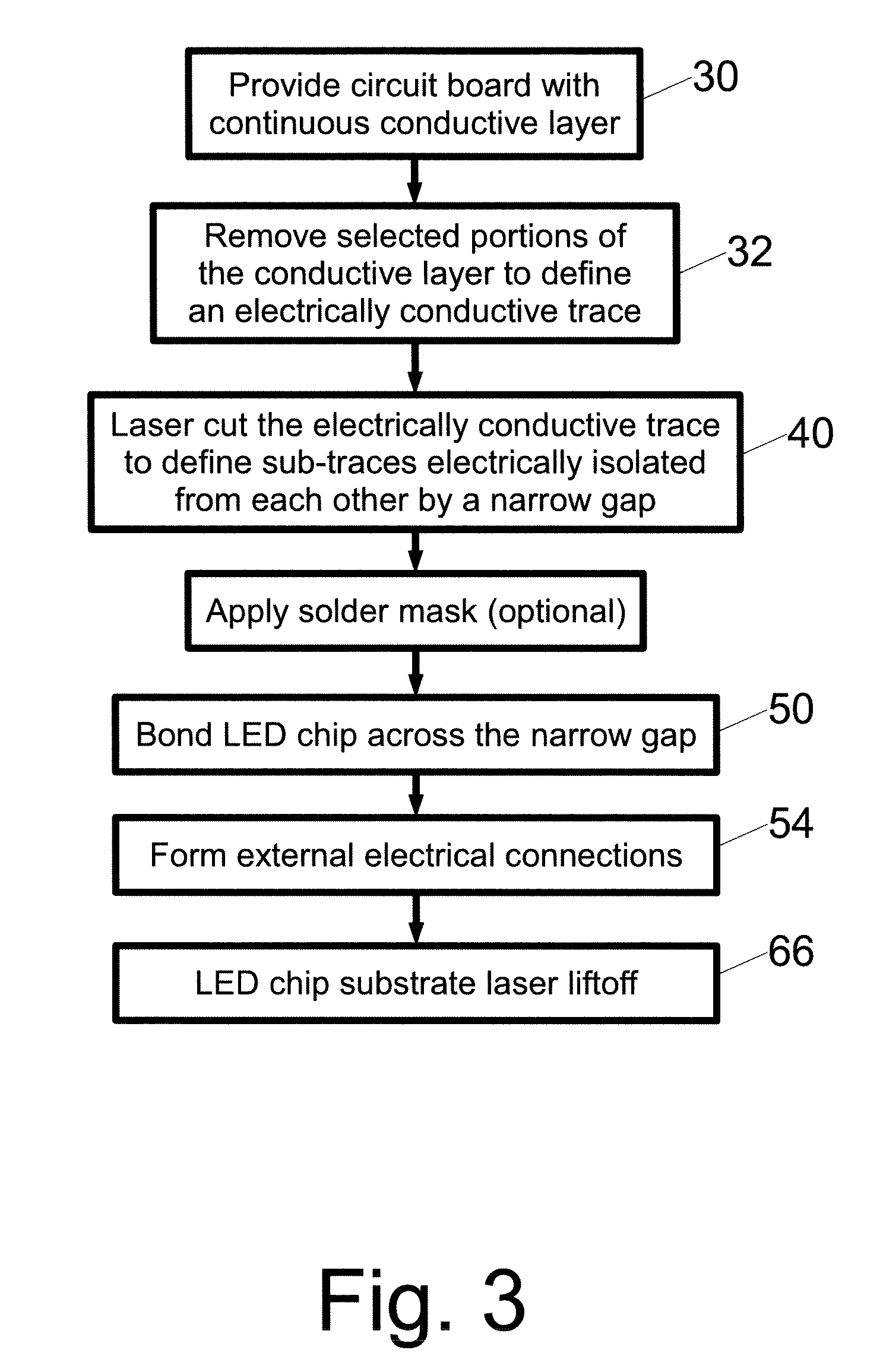

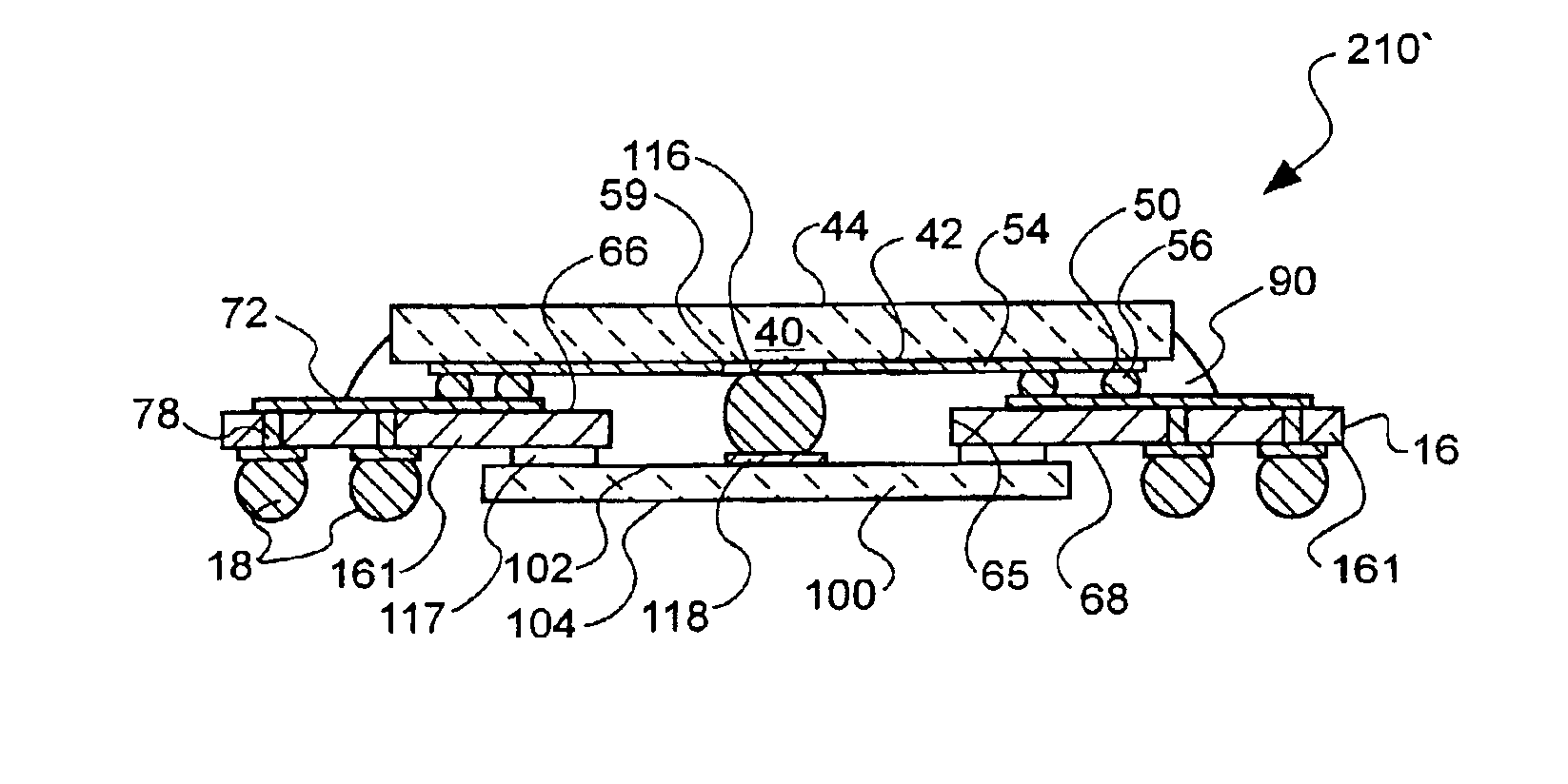

Circuit board for direct flip chip attachment

InactiveUS20090212317A1Semiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageLaser cutting

A packaging method comprises: forming a circuit board by forming a substantially continuous conductive layer on an insulating board and removing selected portions of the continuous conductive layer to define an electrically conductive trace; laser cutting the electrically conductive trace to define sub-traces electrically isolated from each other by a laser-cut gap formed by the laser cutting; and bonding a light emitting diode (LED) chip to the circuit board across or adjacent to the laser-cut gap, the bonding including operatively electrically connecting an electrode of the LED chip to one of the sub-traces without using an interposed submount. A semiconductor package comprises an LED chip flip-chip bonded to sub-traces of an electrically conductive trace of a circuit board, the sub-traces being electrically isolated from each other by a narrow gap of less than or about 100 microns.

Owner:LUMINATION

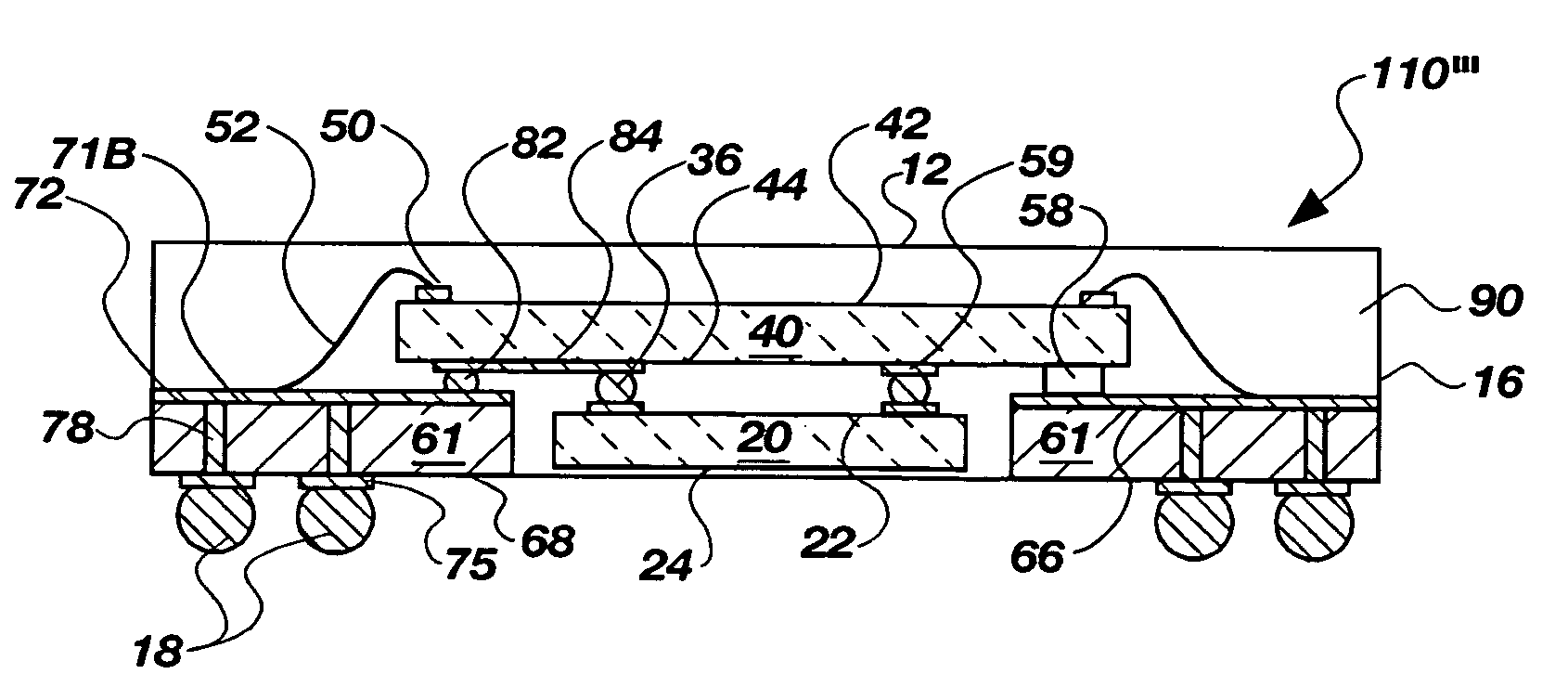

Semiconductor device assemblies and packages including multiple semiconductor devices and methods

InactiveUS6906415B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

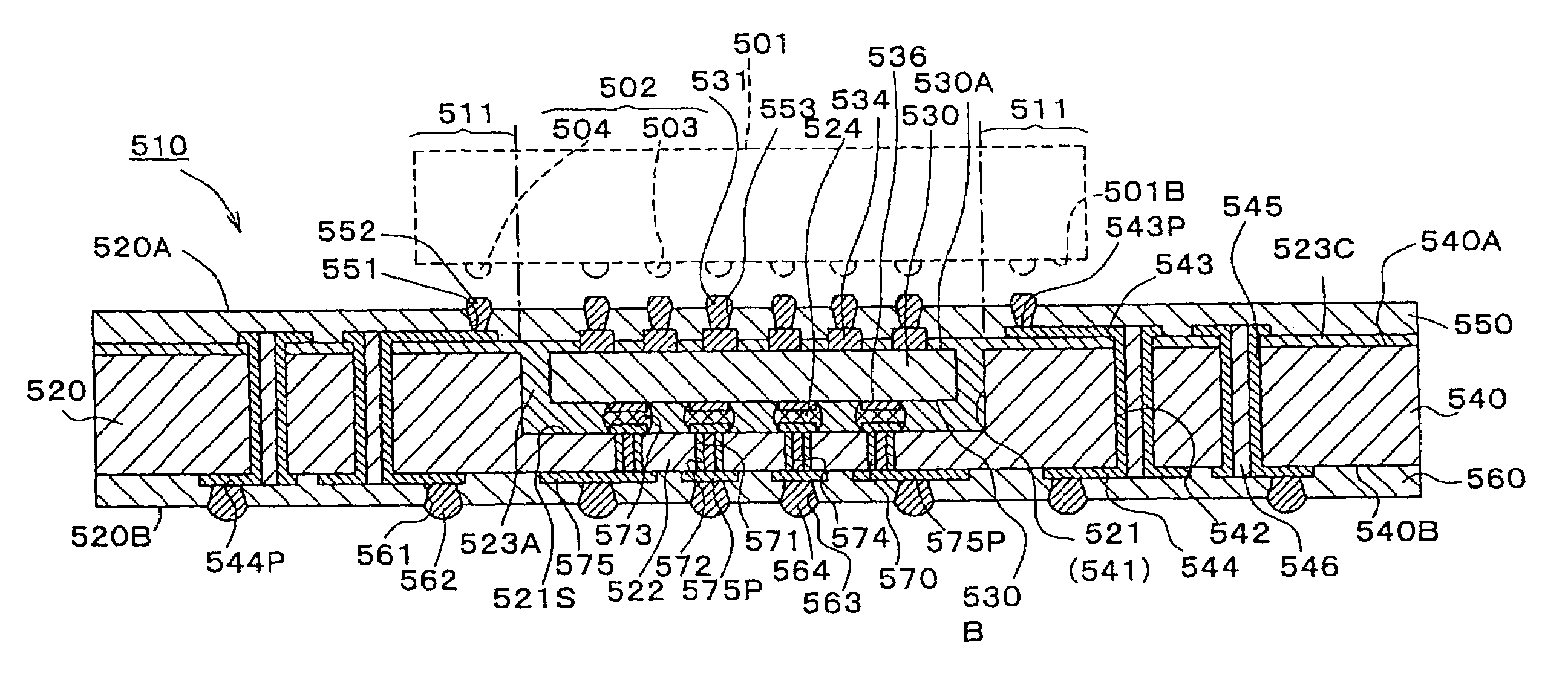

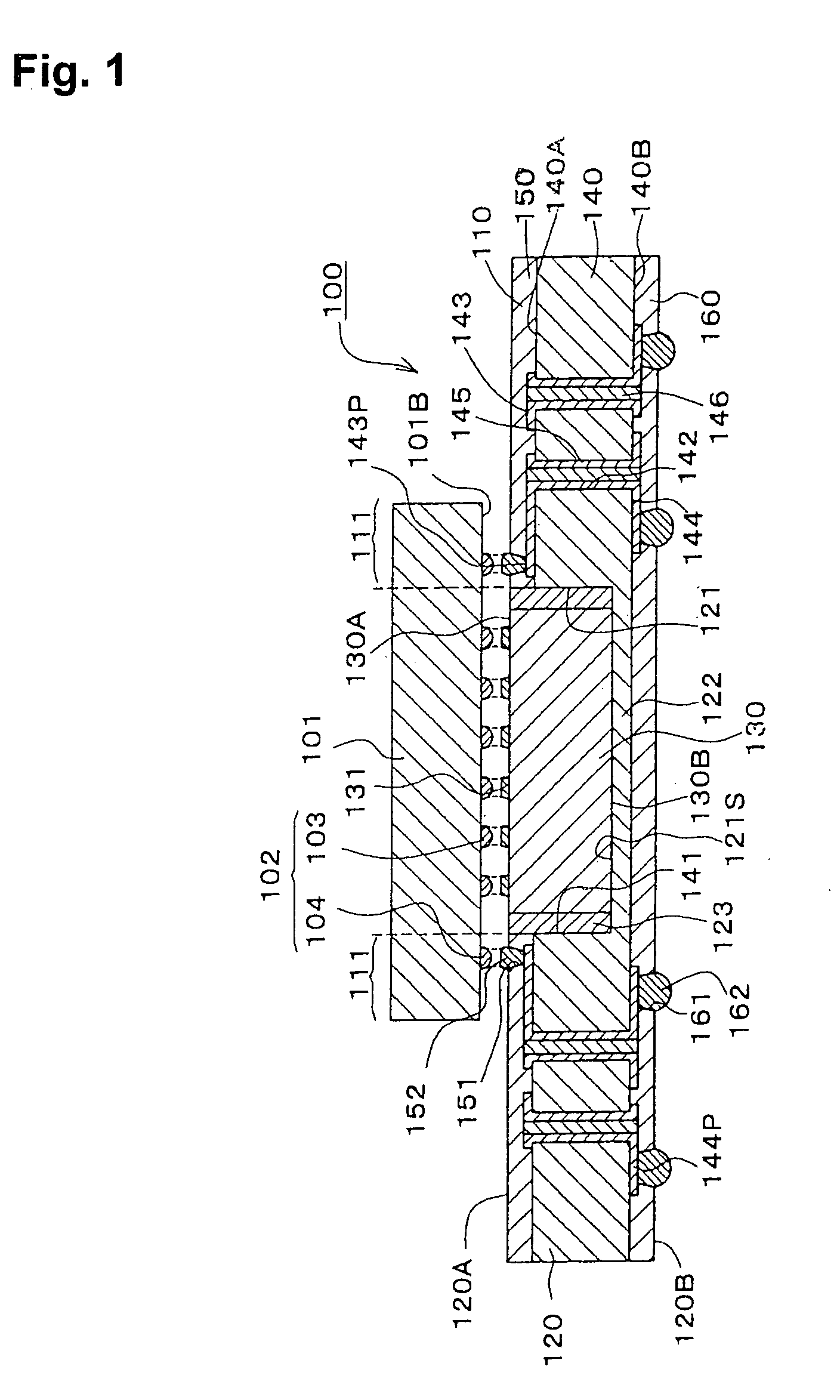

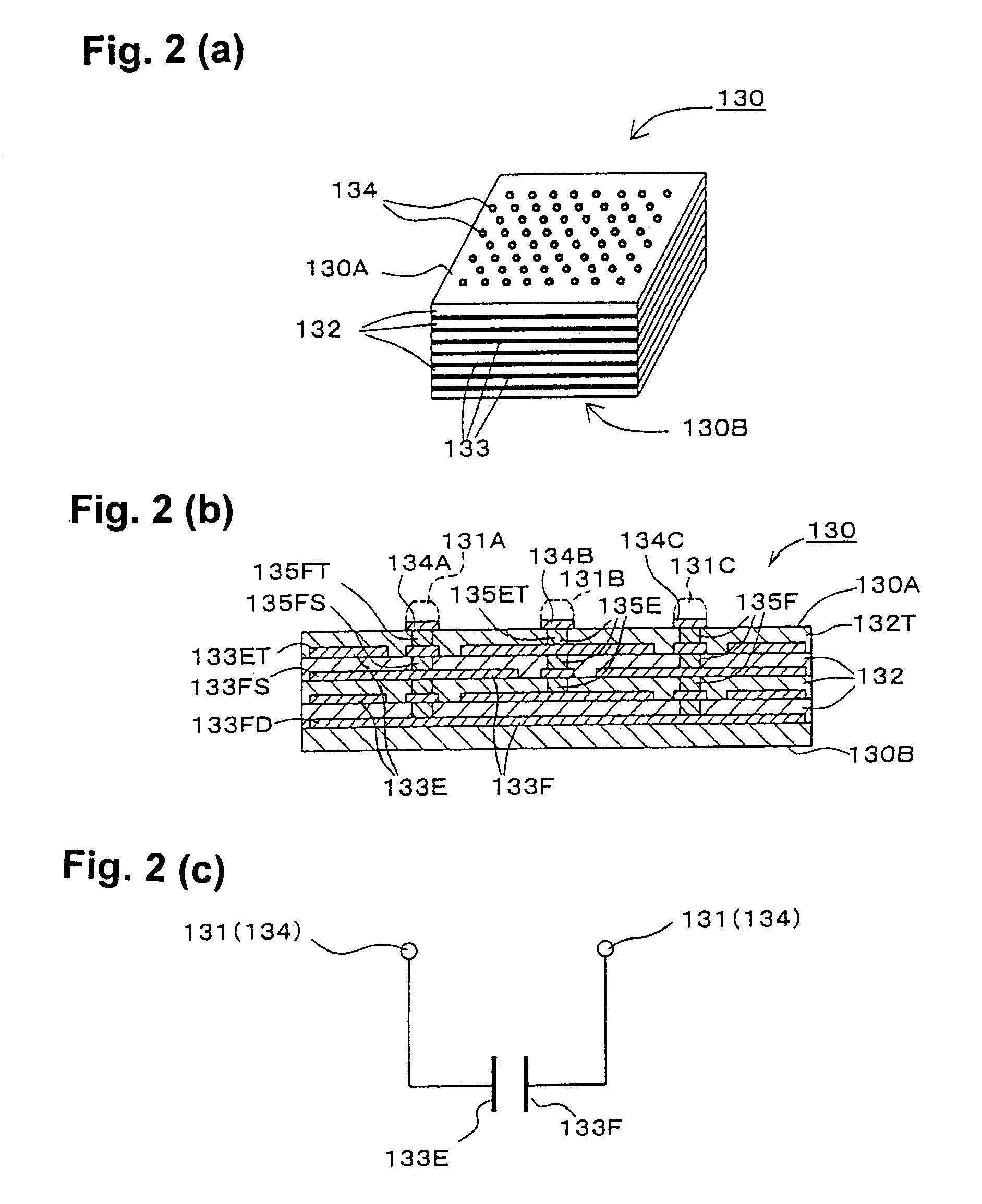

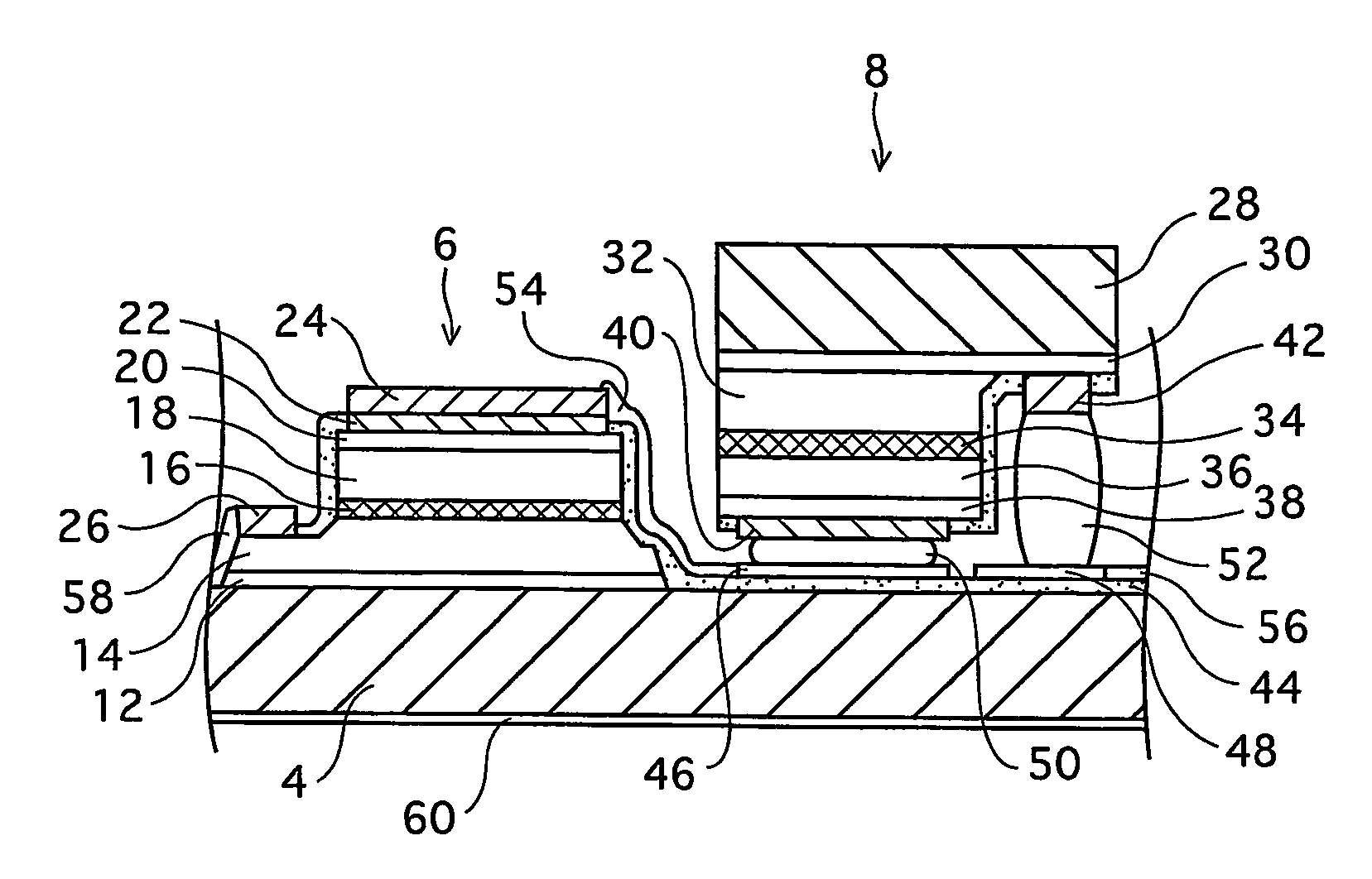

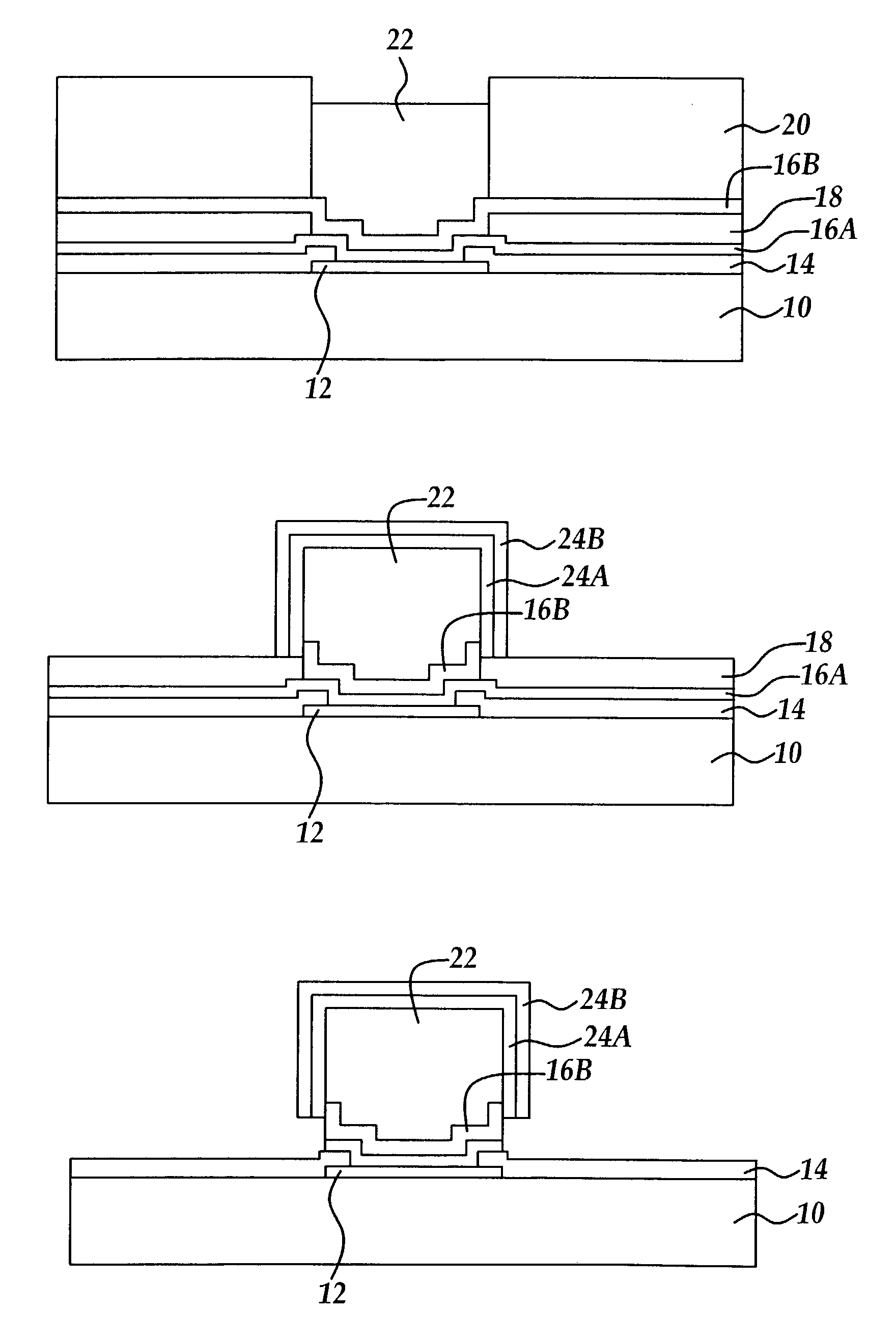

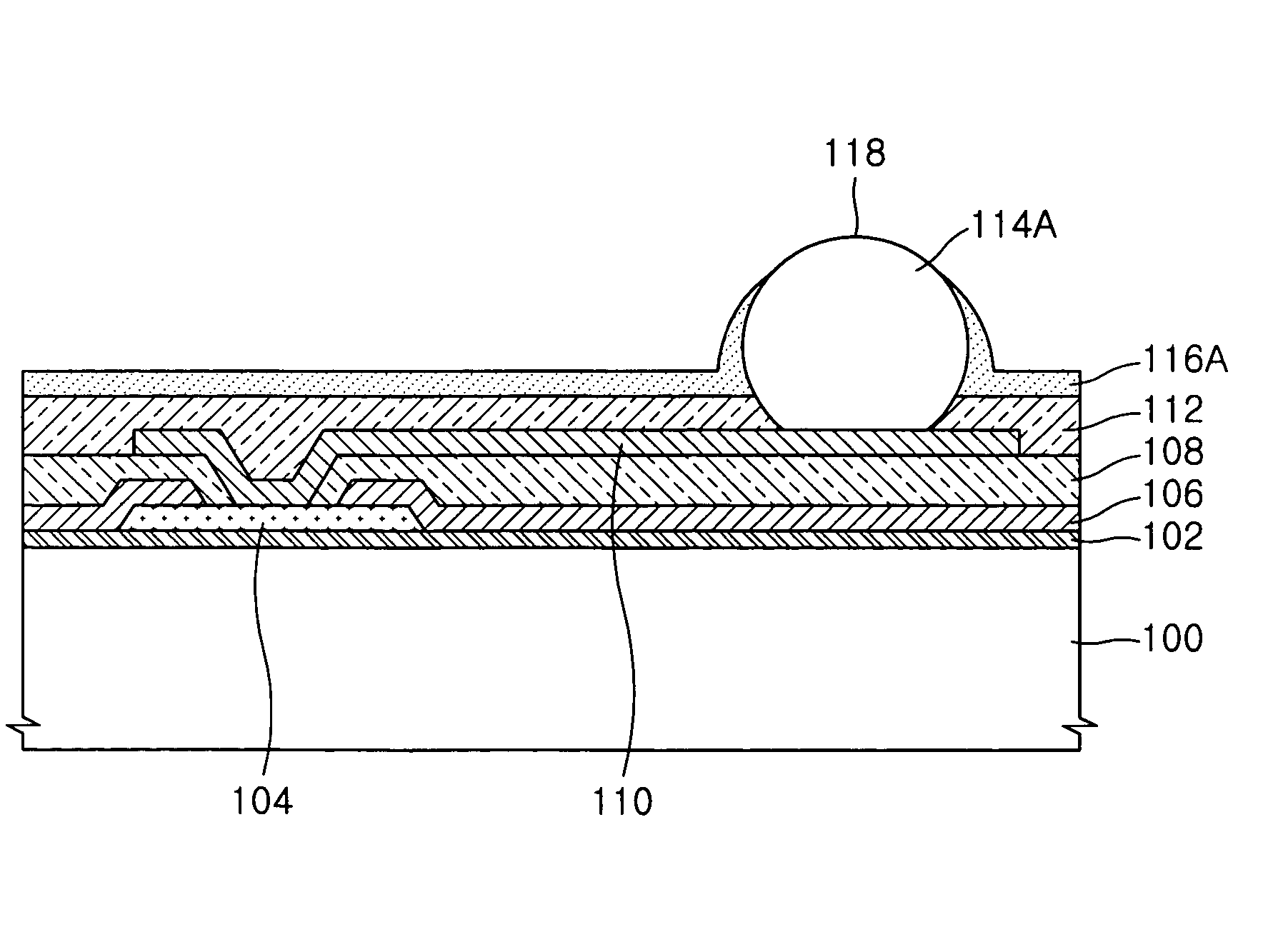

Capacitor-built-in type printed wiring substrate, printed wiring substrate, and capacitor

InactiveUS6952049B1Firmly connectedReliably eliminate noiseCross-talk/noise/interference reductionSemiconductor/solid-state device detailsLow inductanceEngineering

A capacitor-built-in-type printed wiring substrate which can reliably eliminate noise and attain extremely low resistance and low inductance in connections between an IC chip and the capacitor, and a printed wiring substrate and capacitor for use in the same. A capacitor-built-in-type printed wiring substrate 100 on which an IC chip is mounted includes a capacitor-built-in-type printed wiring substrate 110 and an IC chip 101 mounted on the capacitor-built-in-type printed wiring substrate 110. A printed wiring substrate 120 includes a number of connection-to-IC substrate bumps 152 and a closed-bottomed capacitor accommodation cavity 121 formed therein. A capacitor 130 is disposed in the cavity 121 and includes a pair of electrode groups 133E and 133F and a number of connection-to-IC capacitor bumps 131 connected to either one of the paired electrode groups 133E and 133F. The connection-to-IC capacitor bumps 131 are flip-chip-bonded to corresponding connection-to-capacitor bumps 103 on the IC chip 101. The connection-to-IC substrate bumps 152 are flip-chip-bonded to corresponding connection-to-substrate bumps 104 on the IC chip 101.

Owner:NGK SPARK PLUG CO LTD

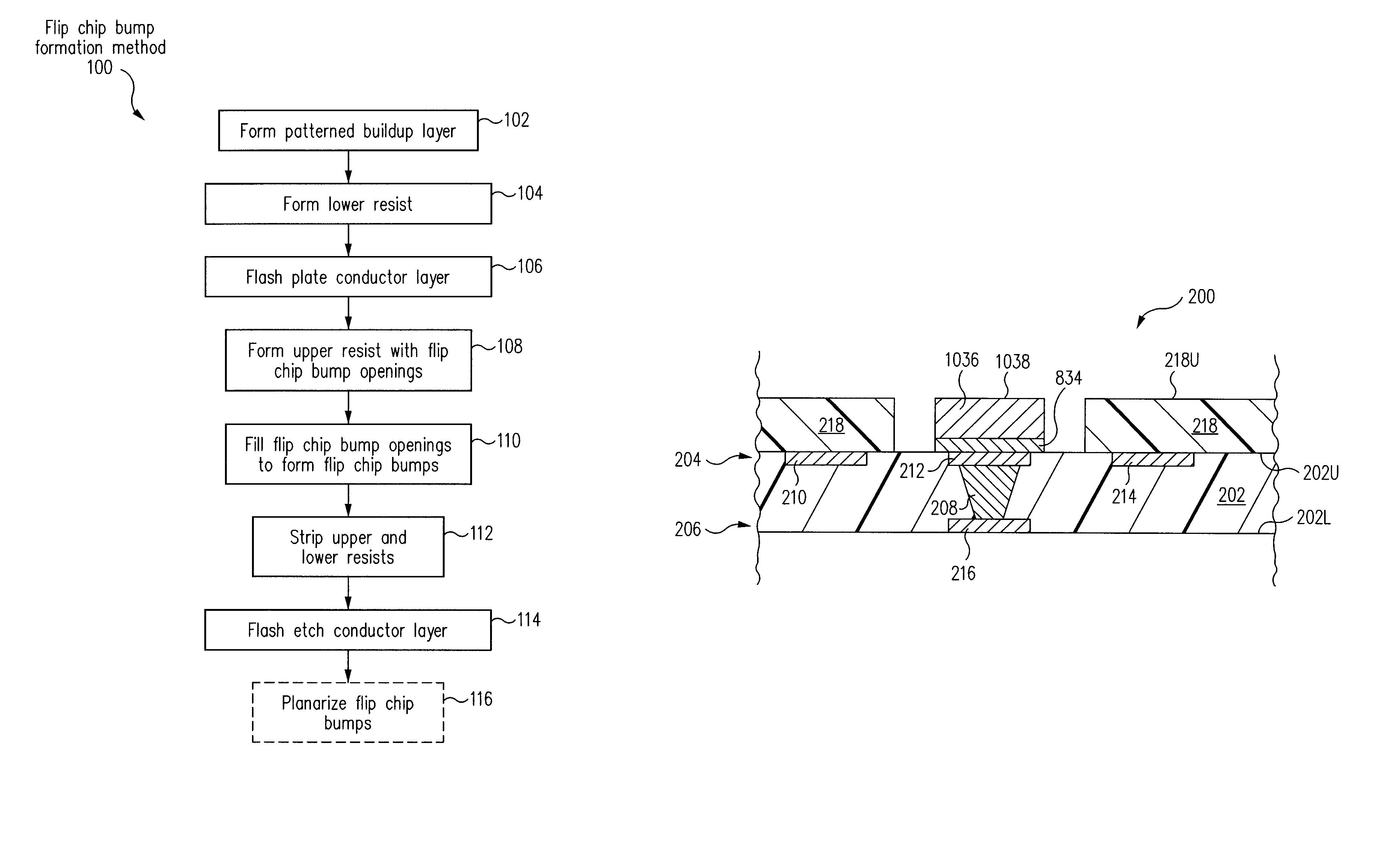

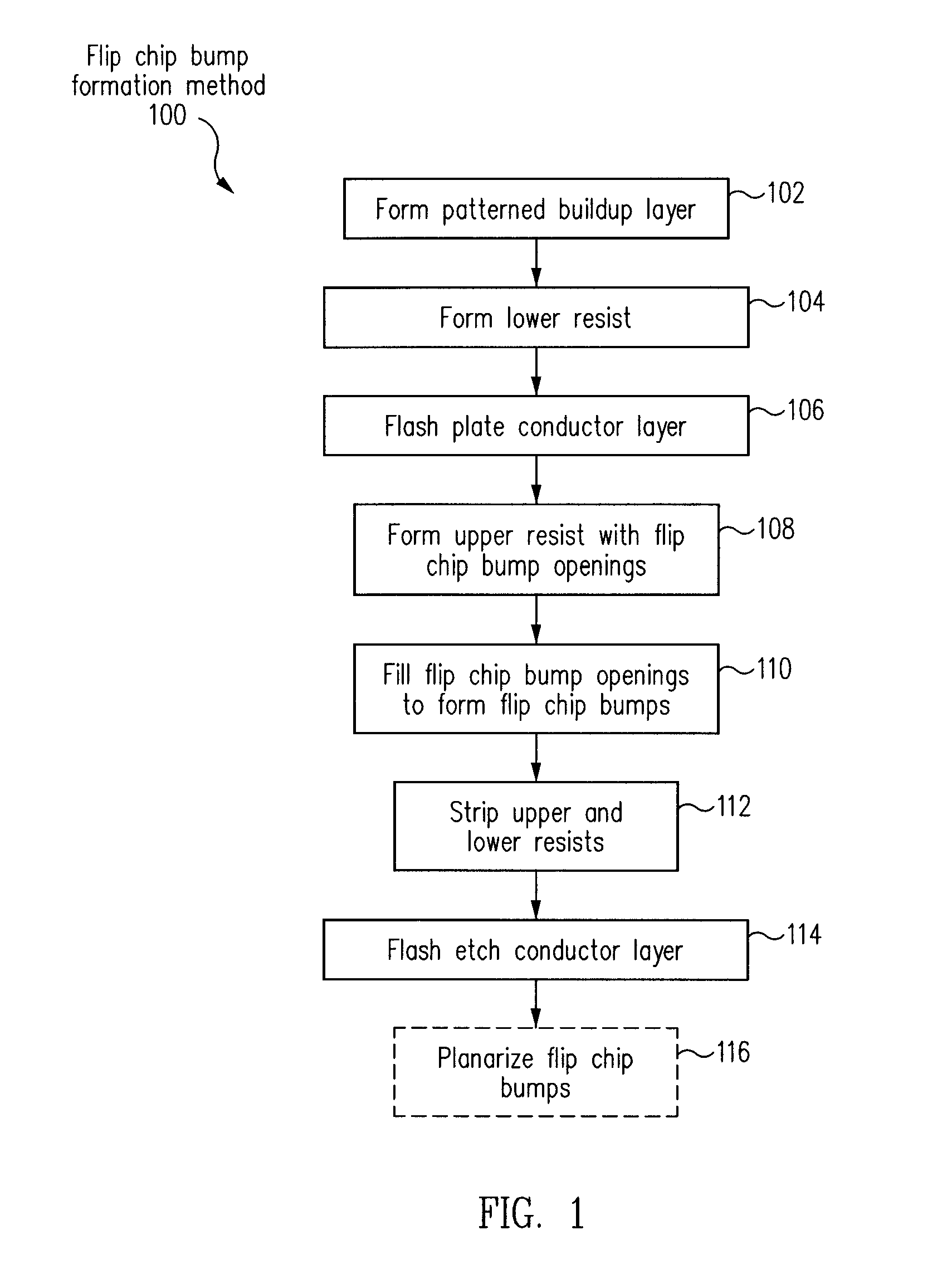

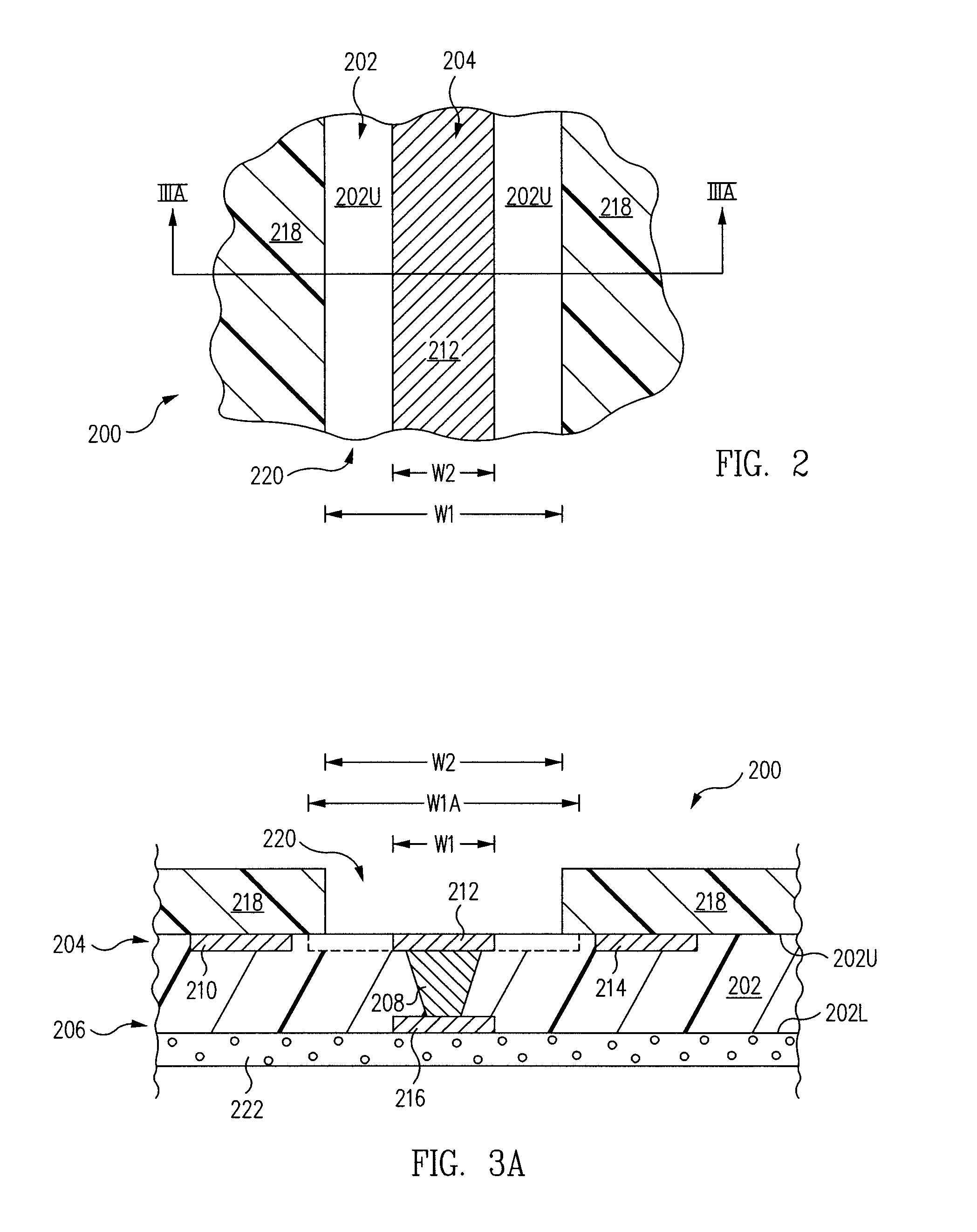

Flip chip bump structure and fabrication method

ActiveUS7932170B1Small spacingSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorOptoelectronics

A method includes forming a patterned buildup layer on a first surface of a dielectric layer, the patterned buildup layer including a patterned buildup layer opening exposing a trace coupled to the dielectric layer. A conductor layer is flash plated on the patterned buildup layer and within the patterned buildup layer opening. The patterned buildup layer opening is filled with a blanket conductive filler layer. The blanket conductive filler layer and the conductor layer are planarized to form a flip chip bump.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

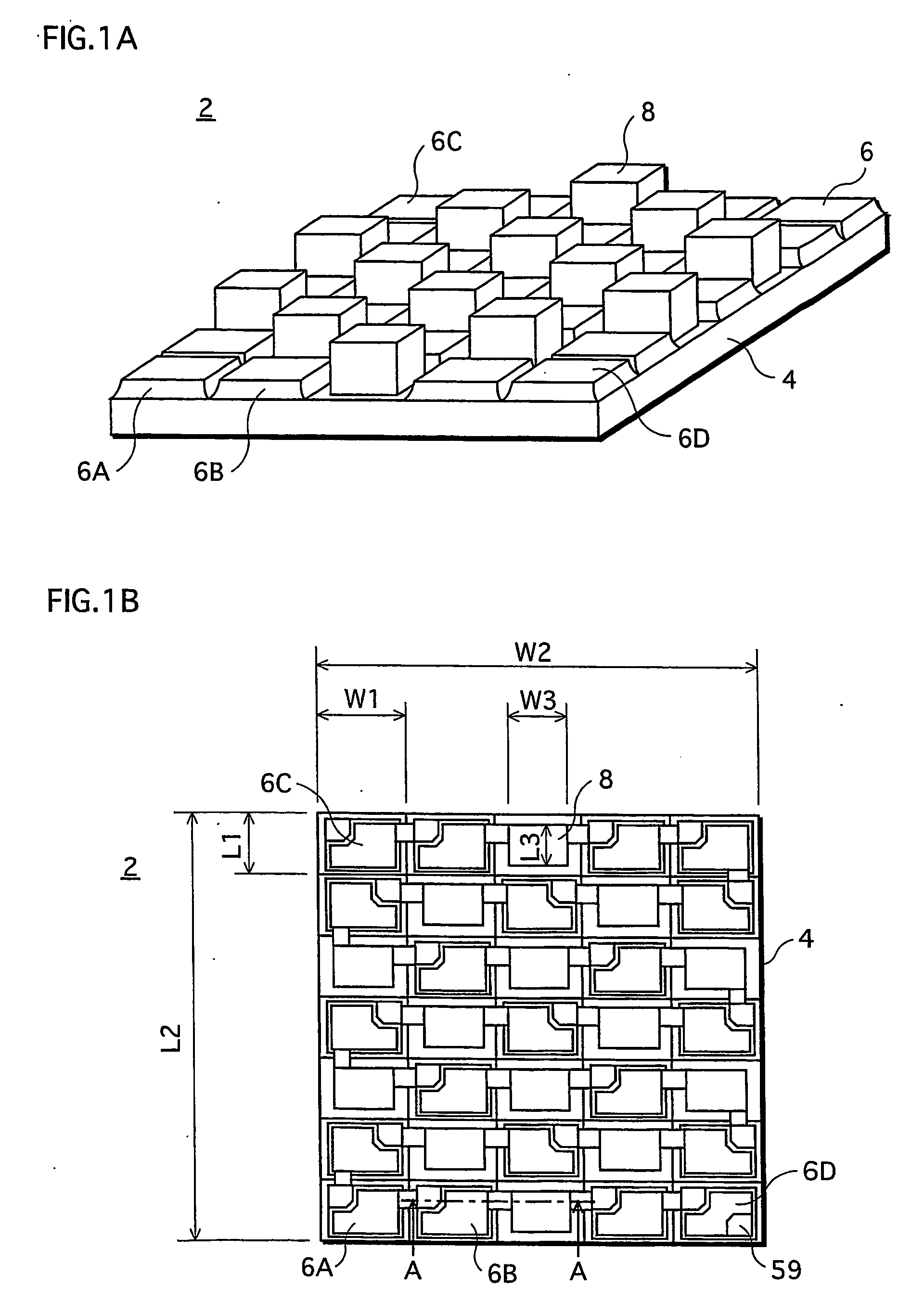

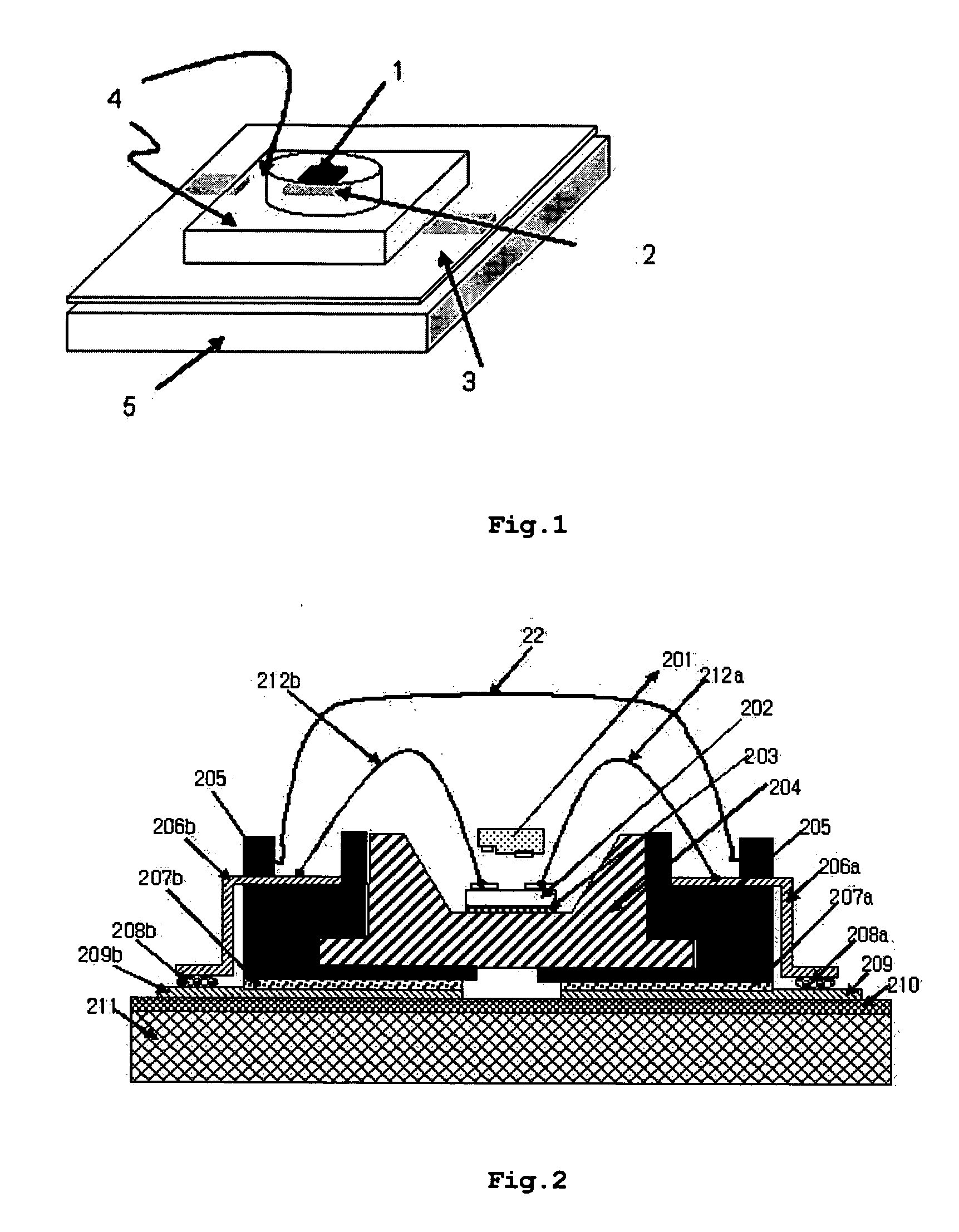

Semiconductor light emitting device, light emitting module and lighting apparatus

ActiveUS20060180818A1Reduce color unevennessImprove manufacturing productivityPlanar light sourcesLight source combinationsLight equipmentLed array

An LED array chip (2) includes blue LEDs (6) and red LEDs (8). The blue LEDs (6) are formed by epitaxial growth on an SiC substrate (4). Bonding pads (46 and 48) are formed on the SiC substrate (4) in a wafer fabrication process. The red LEDs (8) are separately manufactured from the blue LEDs (6), and flip-chip mounted on the bonding pads (46 and 48) formed on the SiC substrate.

Owner:PANASONIC CORP

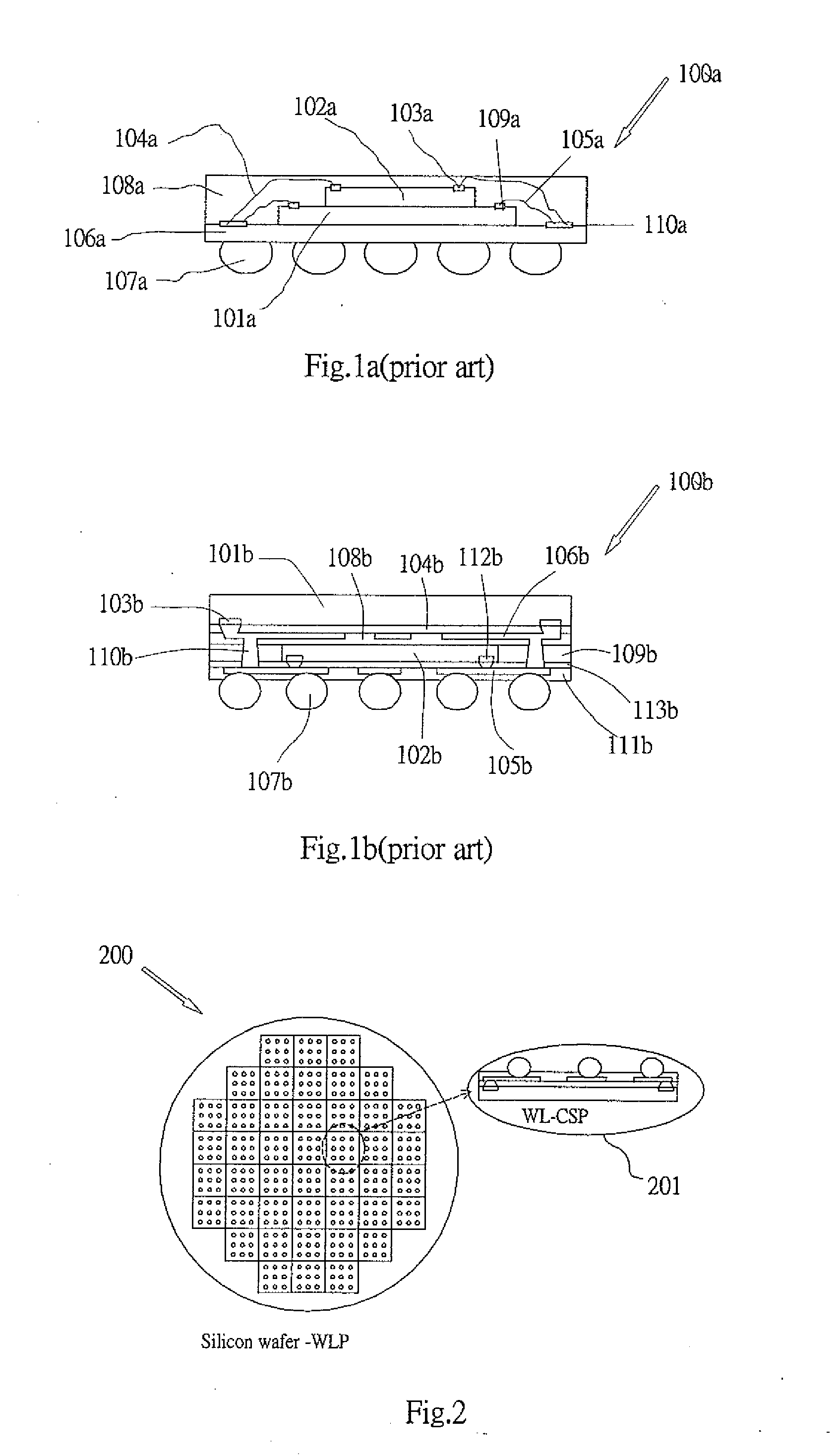

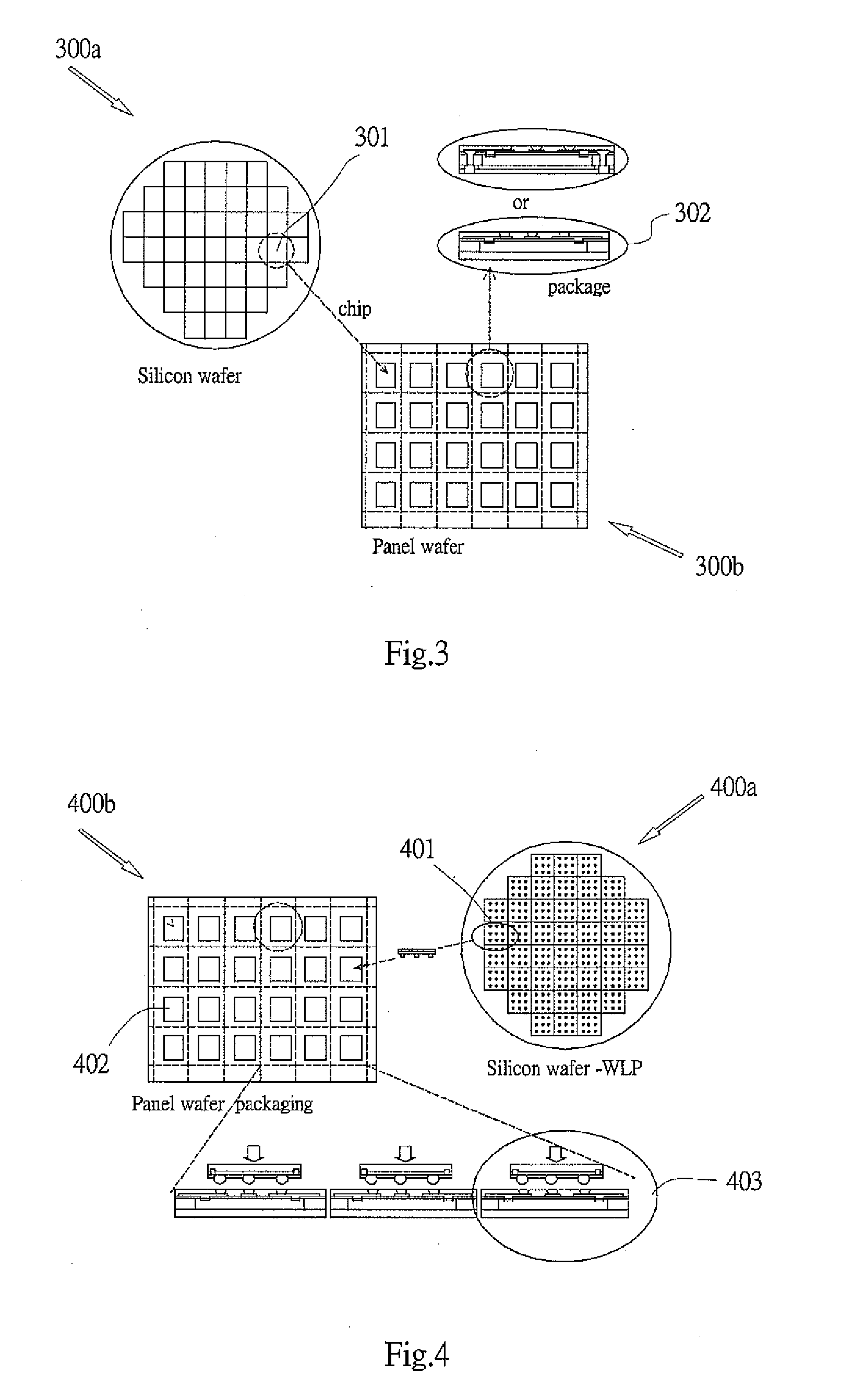

Multi-chip package structure and method of forming the same

InactiveUS20080136004A1Avoid problemsIncrease productionSemiconductor/solid-state device detailsSolid-state devicesChip sizeChip-scale package

To pick and place standard first chip size package on a base with a second chip for obtaining an appropriate stacking chip size package than the original chip size package. The package structure has a larger chip size package than the size of the traditional stacking package. Moreover, the terminal pins of the flip chip package may be located on peripheral of LGA package or on array of BGA package.

Owner:ADVANCED CHIP ENG TECH

Flip-chip electrode light-emitting element formed by multilayer coatings

InactiveUS20060081869A1High reflective functionLuminous efficiencySolid-state devicesSemiconductor devicesInter layerOhmic contact

A flip-chip electrode light-emitting element formed by multilayer coatings where a translucent conducting layer and a highly reflective metal layer acts as flip-chip electrode for enhancing the LED luminous efficiency. The flip-chip electrode light-emitting element includes a translucent substrate, a semiconductor die structure attached on the translucent substrate and made of group III nitride compounds, and an intermediate layer adapted to support the inverted semiconductor die structure on a submount. The flip-chip electrode formed by multiplayer coatings includes a current-spreading transparent conducting layer formed on a top side of the second type semiconductor layer, a highly reflective metal layer formed on a top side of the transparent conducting layer, a metallic diffusion barrier layer formed on a top side of the highly reflective metal layer, and a bonding layer electrically coupled to the intermediate layer and formed on a top side of the barrier layer. Moreover, an ohmic contact layer is formed on the transparent conducting layer. And a passivation layer encloses the die structure for insulating p / n interface and for avoiding the creation of the leakage current.

Owner:ARIMA OPTOELECTRONICS

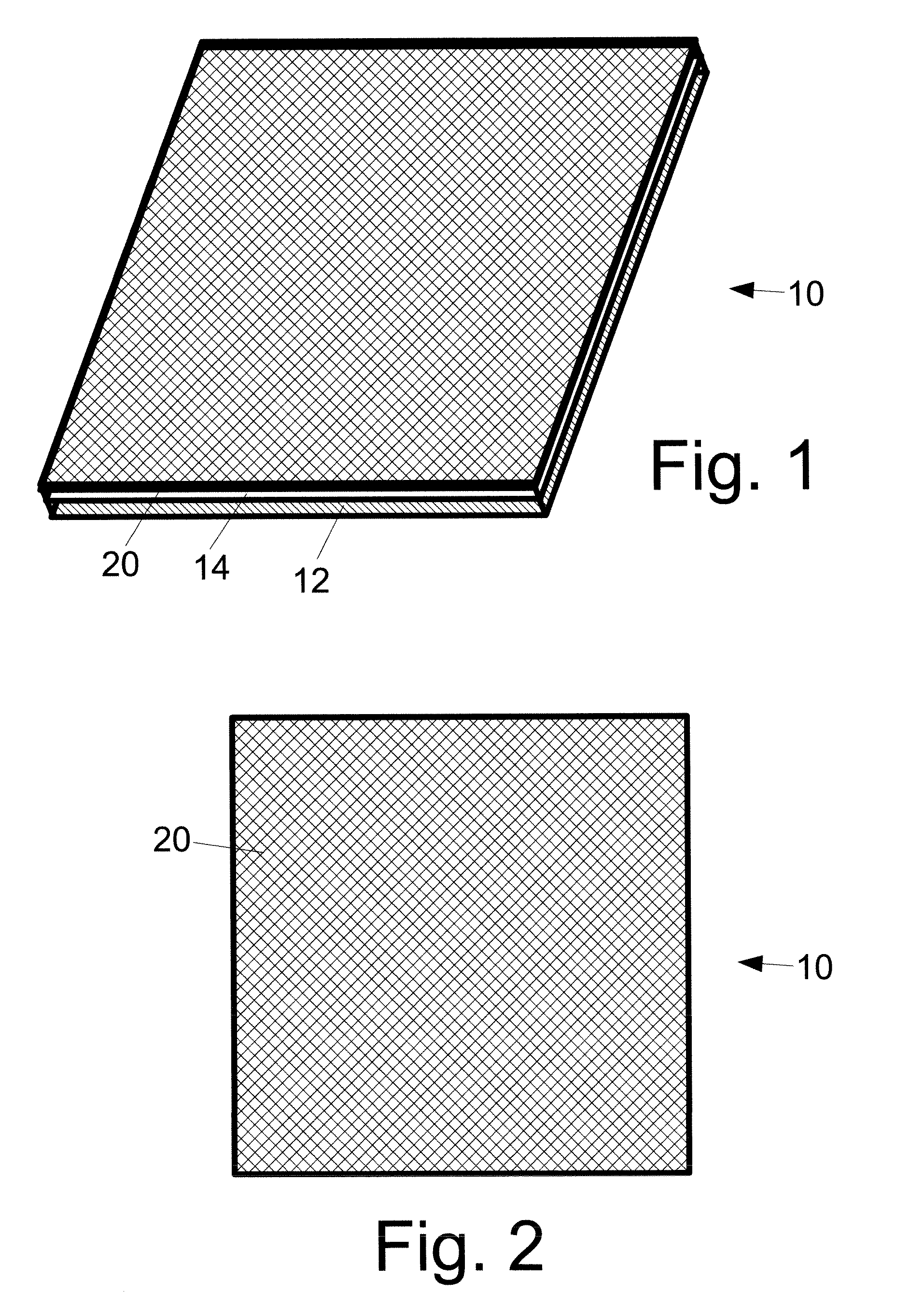

Method for forming copper bump antioxidation surface

InactiveUS7008867B2Improve oxidation resistanceImprove thermal stabilitySemiconductor/solid-state device detailsSolid-state devicesTitaniumDeposition process

A method for forming a copper bump for flip chip bonding having improved oxidation resistance and thermal stability including providing a copper column having a thickness of at least about 40 microns overlying a metallurgy including an uppermost copper metal layer and a lowermost titanium layer the lowermost titanium layer in contact with an exposed copper bonding pad portion surrounded by a passivation layer; and, selectively depositing at least one protective metal layer over the copper column according to an electrolytic deposition process.

Owner:HON HAI PRECISION IND CO LTD

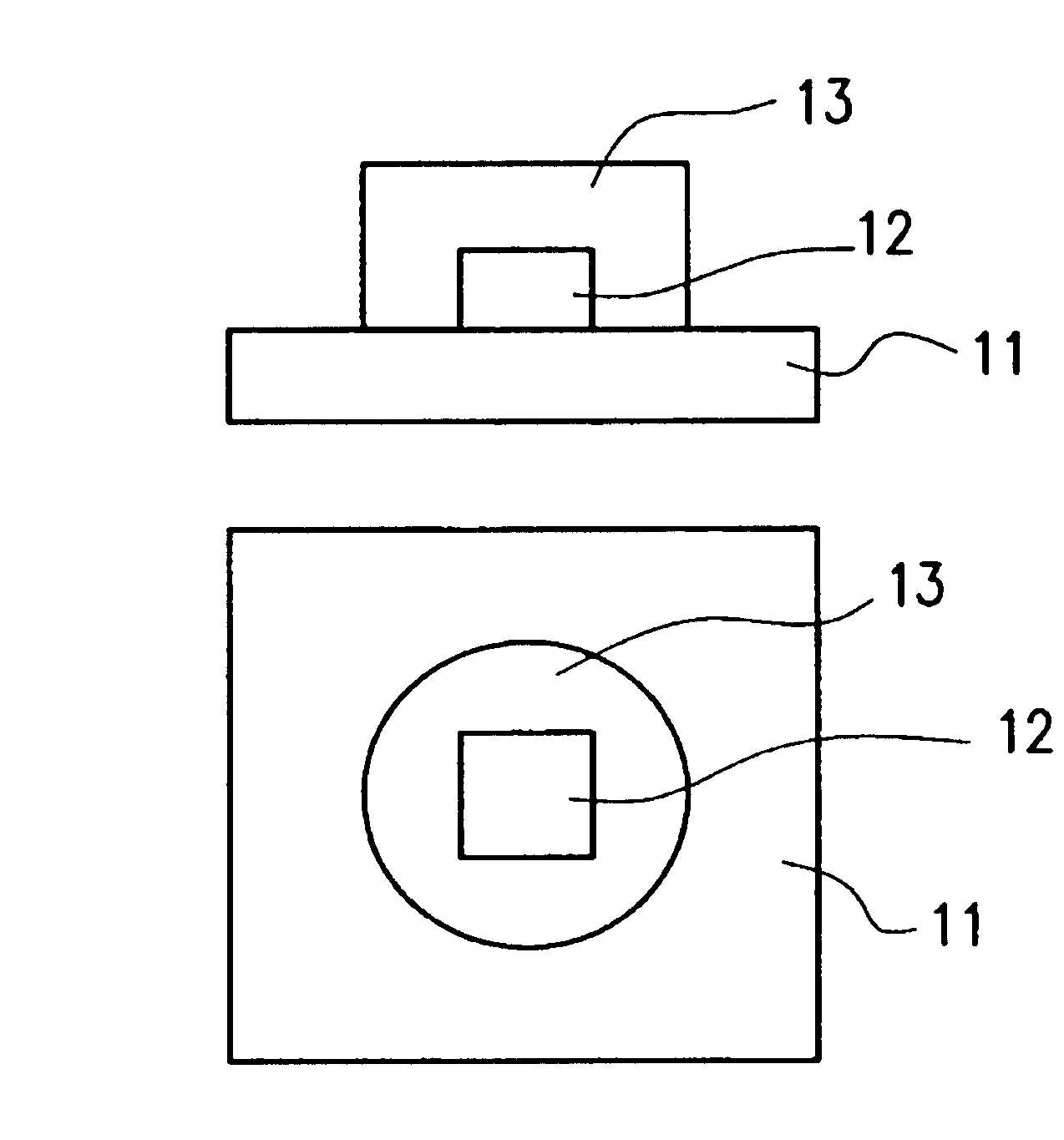

LED lamp

ActiveUS6963166B2Reduce color unevennessDischarge tube luminescnet screensLamp detailsPhosphorEngineering

An LED lamp includes a substrate, an LED chip, and a resin portion. The LED chip is flip-chip bonded to the substrate. The resin portion covers the LED chip and includes at least one type of phosphor that transforms the emission of the LED chip into light having a longer wavelength than the emission. In this LED lamp, the resin portion has at least one side surface. The side surface is separated from another surface that can reflect the outgoing light of the resin portion, surrounds the side surfaces of the LED chip and is curved at least partially.

Owner:SOVEREIGN PEAK VENTURES LLC

Electrode structure of a semiconductor device and method of manufacturing the same

InactiveUS20060038291A1Electrically conductive connectionsFinal product manufactureDevice materialEngineering

In the manufacture of a semiconductor device, a photosensitive layer is deposited to cover an exposed portion of an electrode with the photosensitive layer. The photosensitive layer is then subjected to a photolithography process to partially remove the photosensitive layer covering the electrode. The electrode may be a ball electrode or a bump electrode, and the semiconductor device may be contained in a wafer level package (WLP) or flip-chip package.

Owner:SAMSUNG ELECTRONICS CO LTD

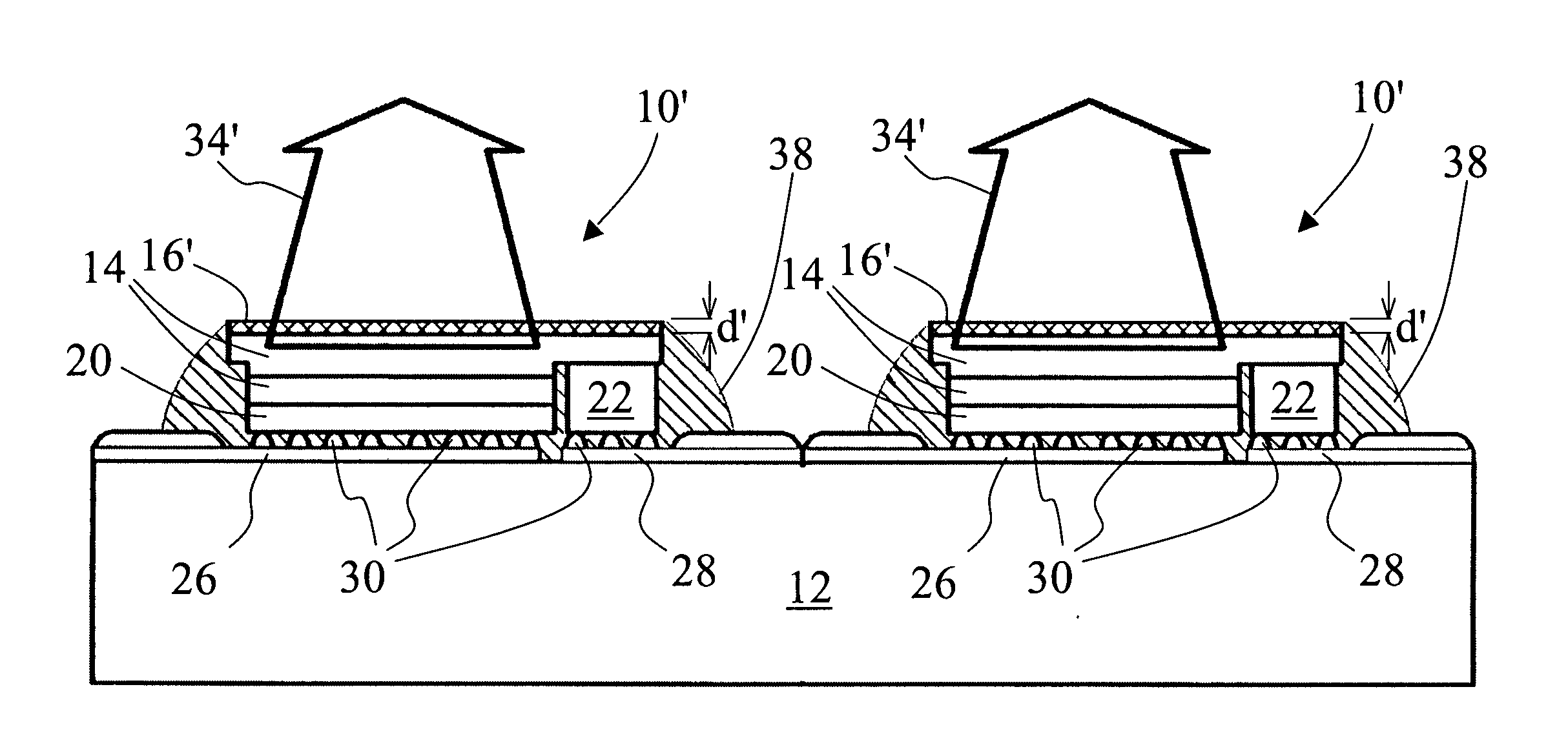

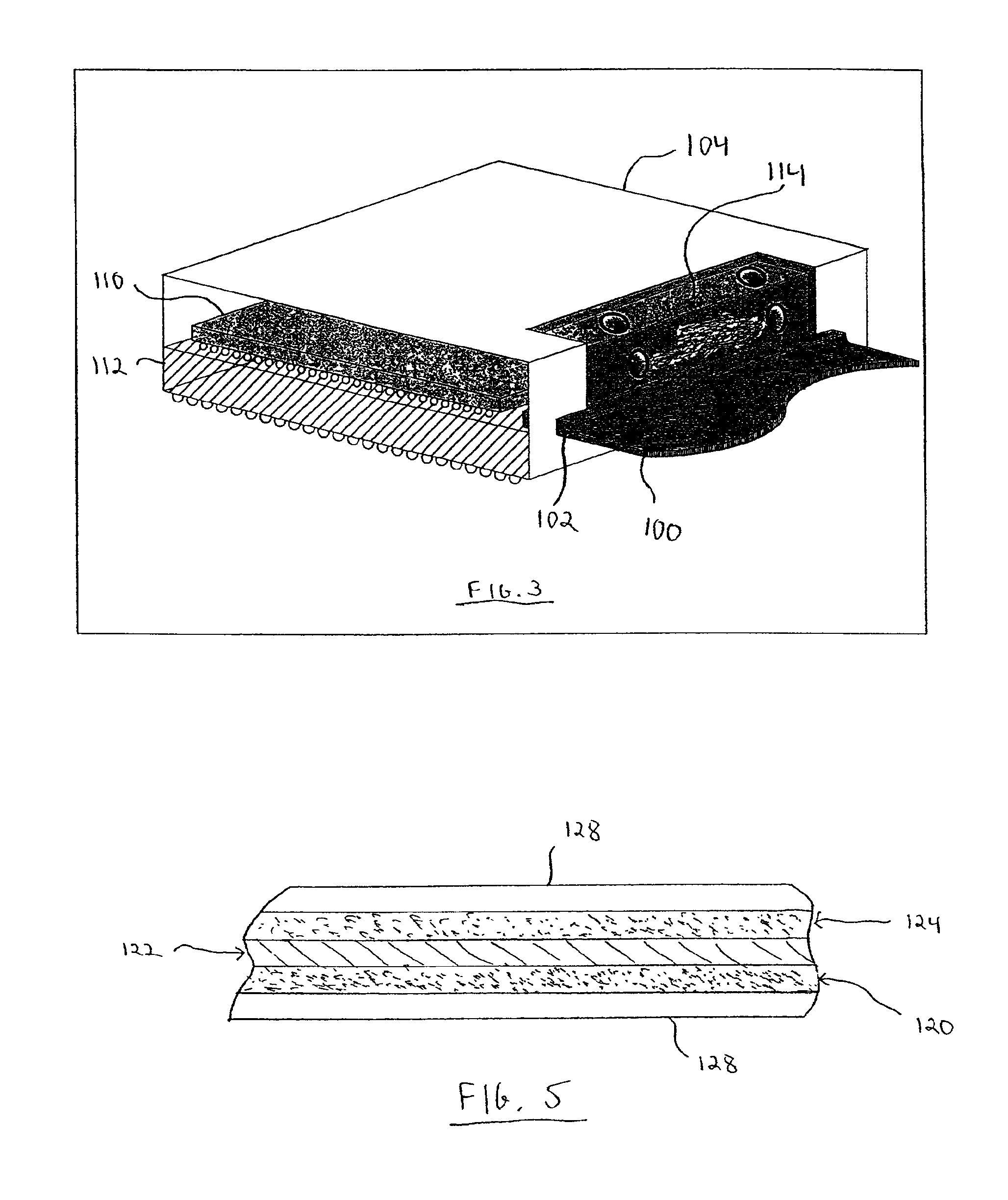

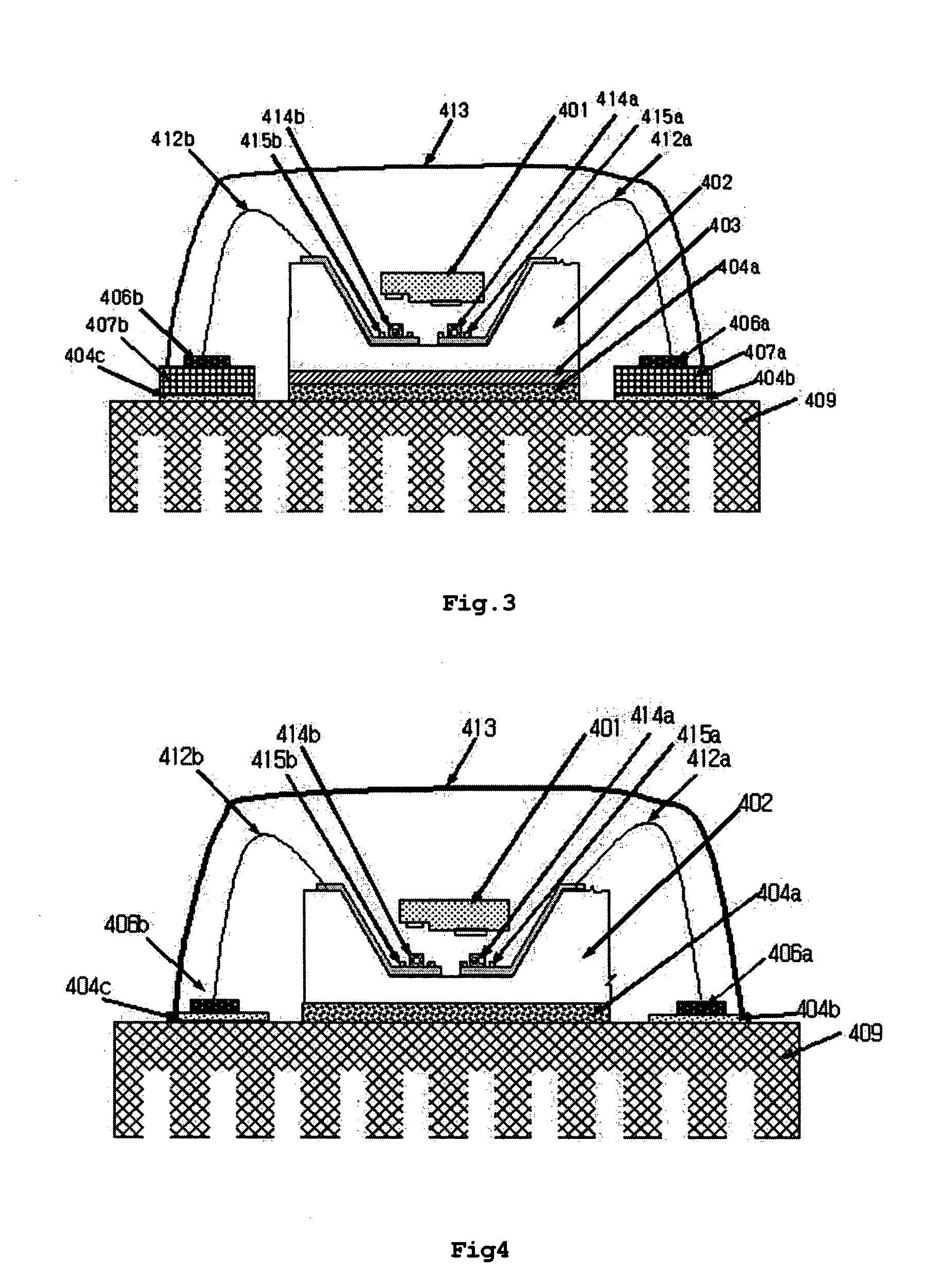

Flip-chip phosphor coating method and devices fabricated utilizing method

ActiveUS20090179207A1Solid-state devicesSemiconductor/solid-state device manufacturingPhosphorEngineering

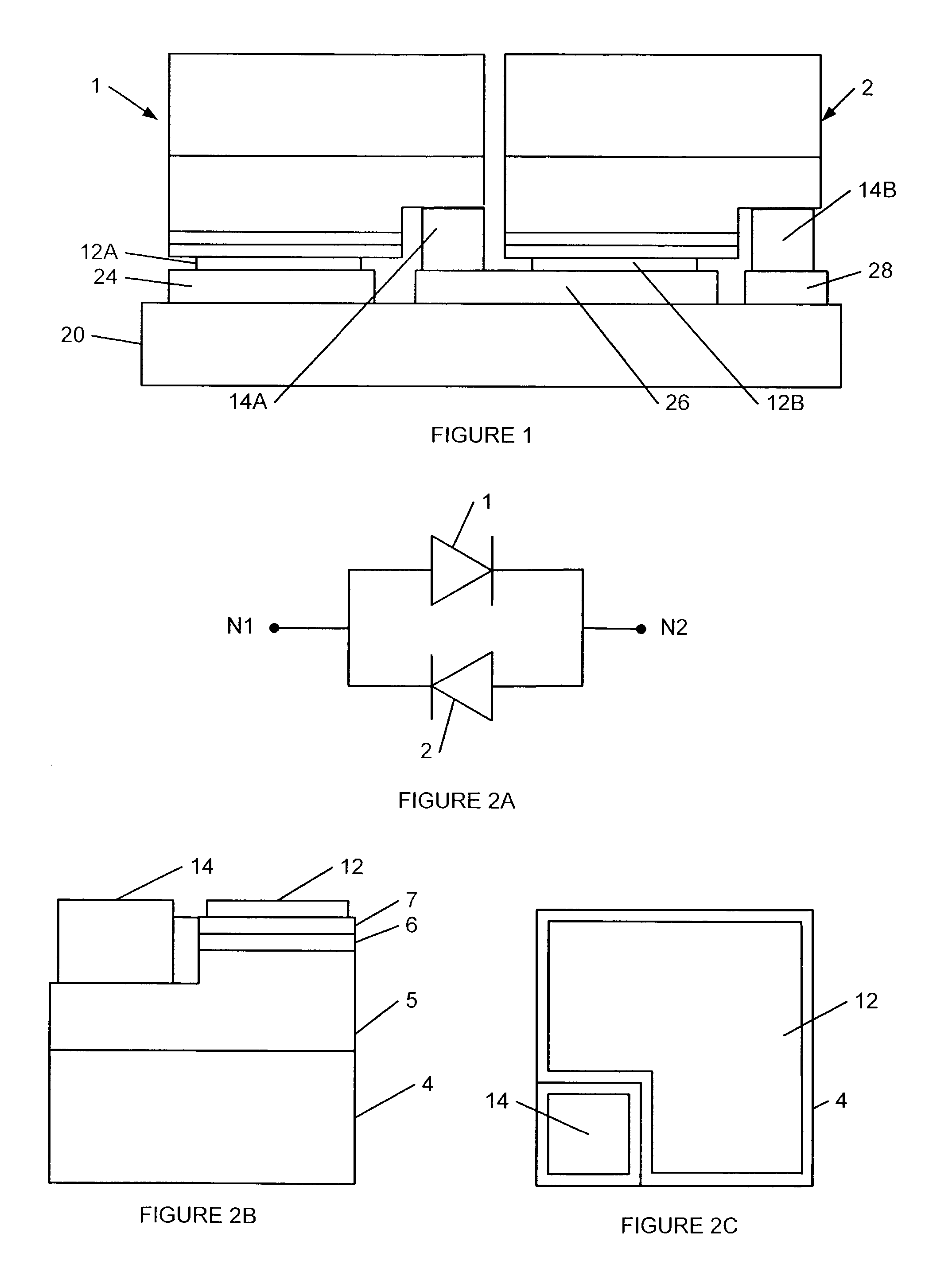

Methods for fabricating light emitting diode (LED) chips one of which comprises flip-chip mounting a plurality of LEDs on a surface of a submount wafer and forming a coating over said LEDs. The coating comprising a conversion material at least partially covering the LEDs. The coating is planarized to the desired thickness with the coating being continuous and unobstructed on the top surface of the LEDs. The LEDs chips are then singulated from the submount wafer. An LED chip comprising a lateral geometry LED having first and second contacts, with the LED flip-chip mounted to a submount by a conductive bonding material. A phosphor loaded binder coats and at least partially covers the LED. The binder provides a substantially continuous and unobstructed coating over the LED. The phosphor within the coating absorbs and converts the wavelength of at least some of the LED light with the coating planarized to achieve the desired emission color point of the LED chip.

Owner:CREELED INC

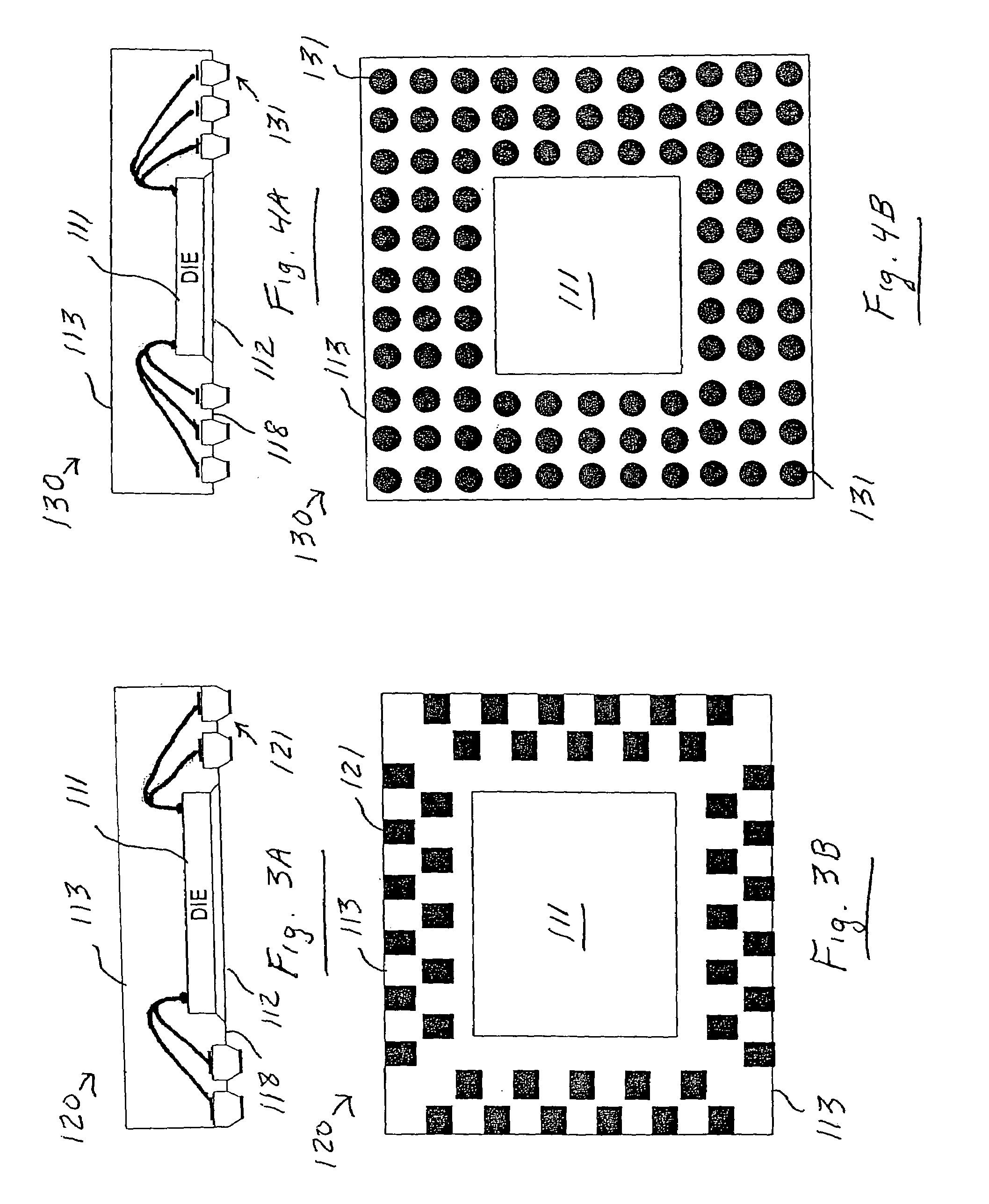

Flat no-lead semiconductor die package including stud terminals

ActiveUS7060535B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipMetal sheet

A flat no-lead semiconductor die package contains a plurality of studs that protrude from the bottom surface of the capsule and act as electrical contacts, allowing the package to be mounted on a flat surface such as a printed circuit board, while permitting external circuit to be located on the flat surface directly beneath the package. The package may or may not contain a die-attach pad. The die may be mounted flip-chip style on the stud contacts and die-attach pad. A method of fabricating the package includes etching an upper portion of a metal sheet through a mask layer, attaching dice at locations on the surface of the metal sheet, forming a layer of molding compound over the dice, etching the lower portion of the metal sheet through a second mask layer, and separating the packages with a dicing saw or punch tool.

Owner:UTAC HEADQUARTERS PTE LTD

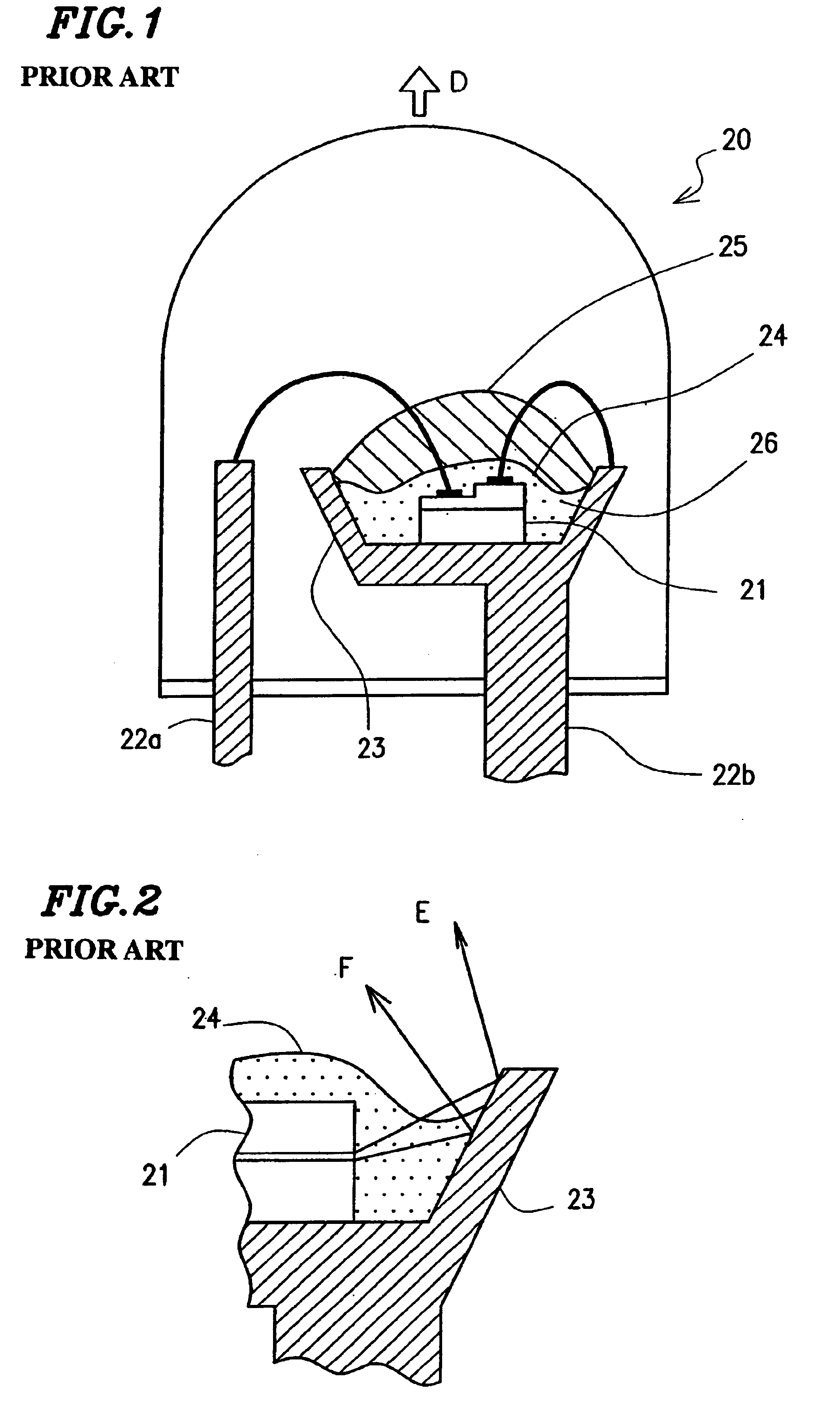

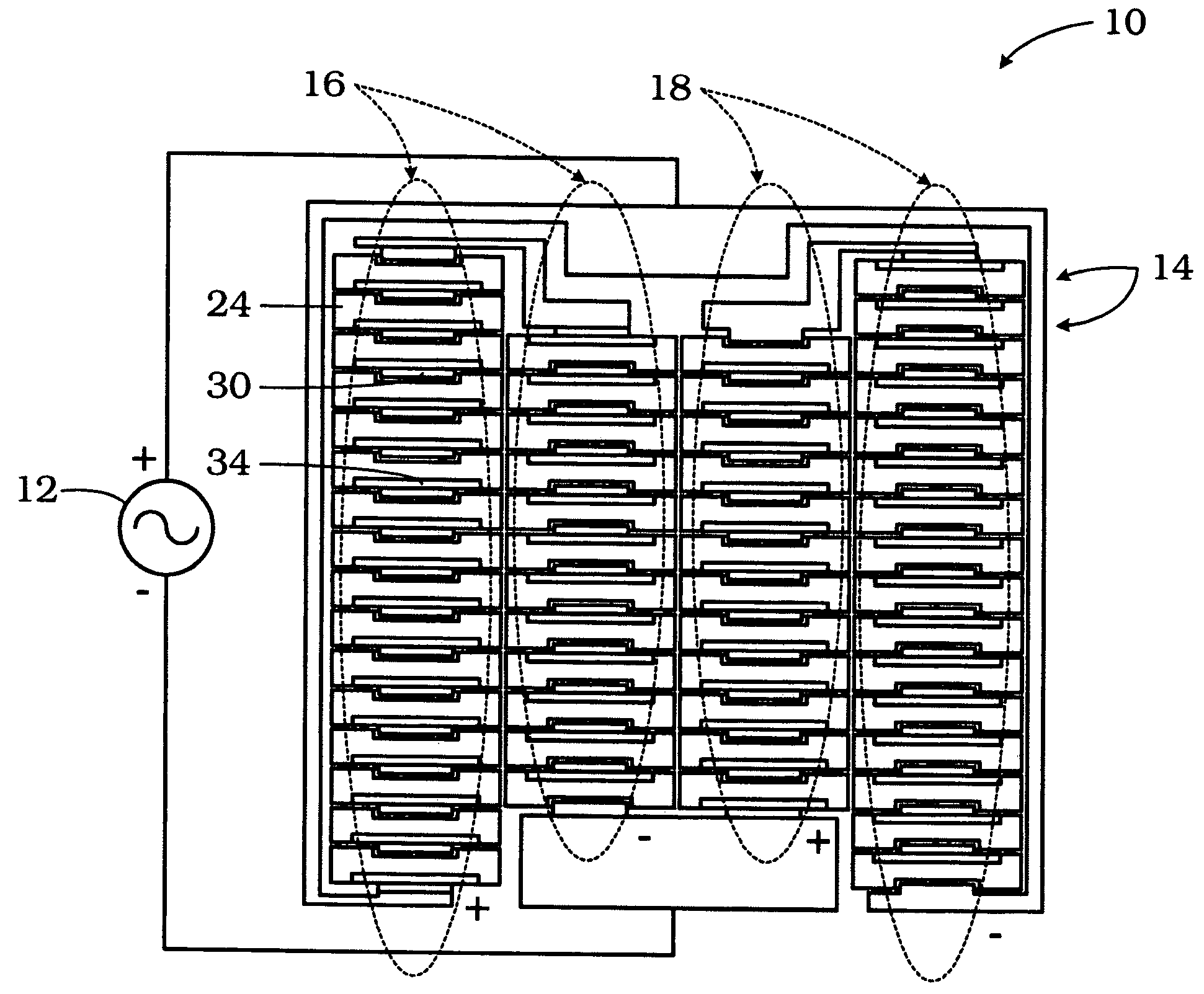

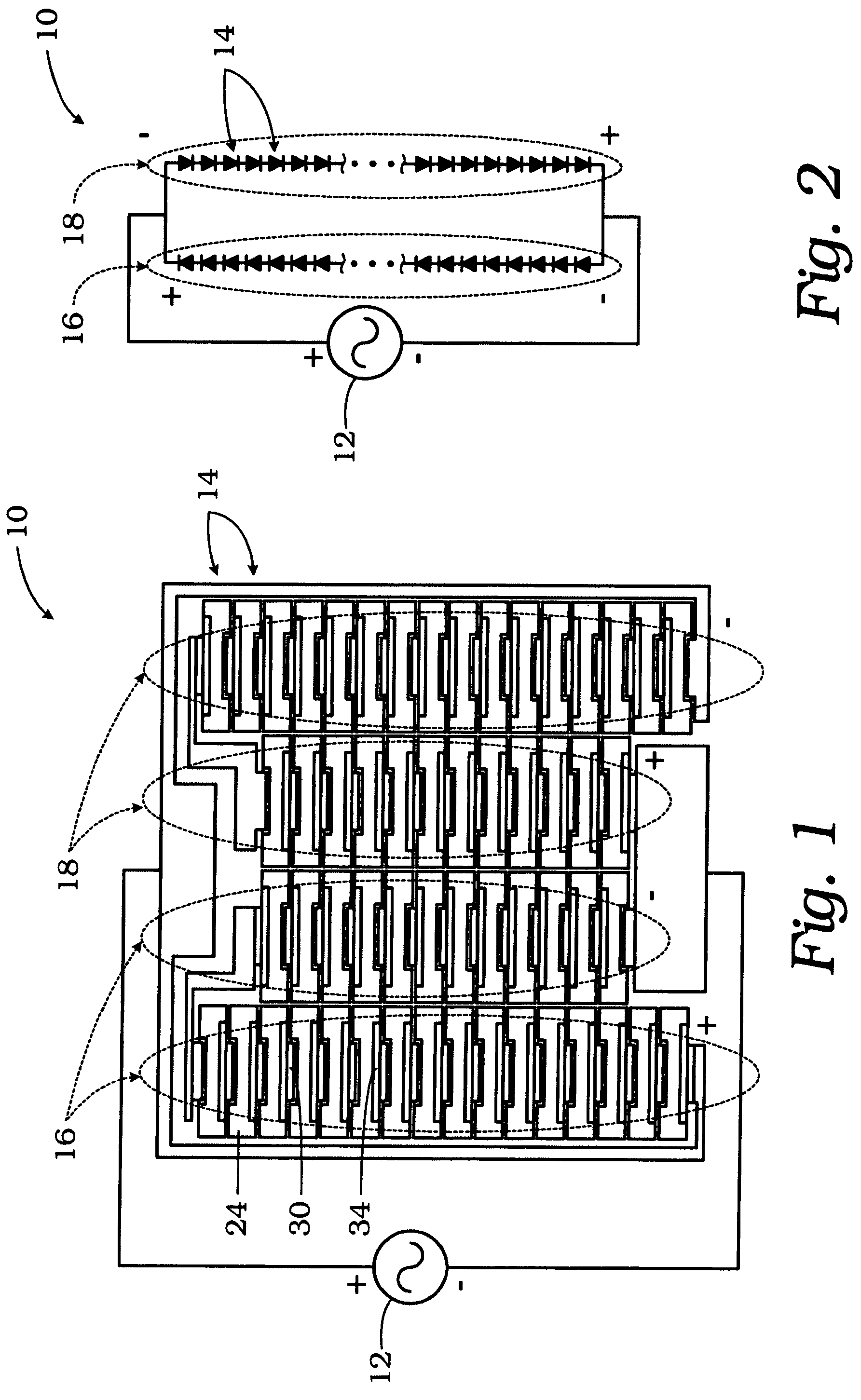

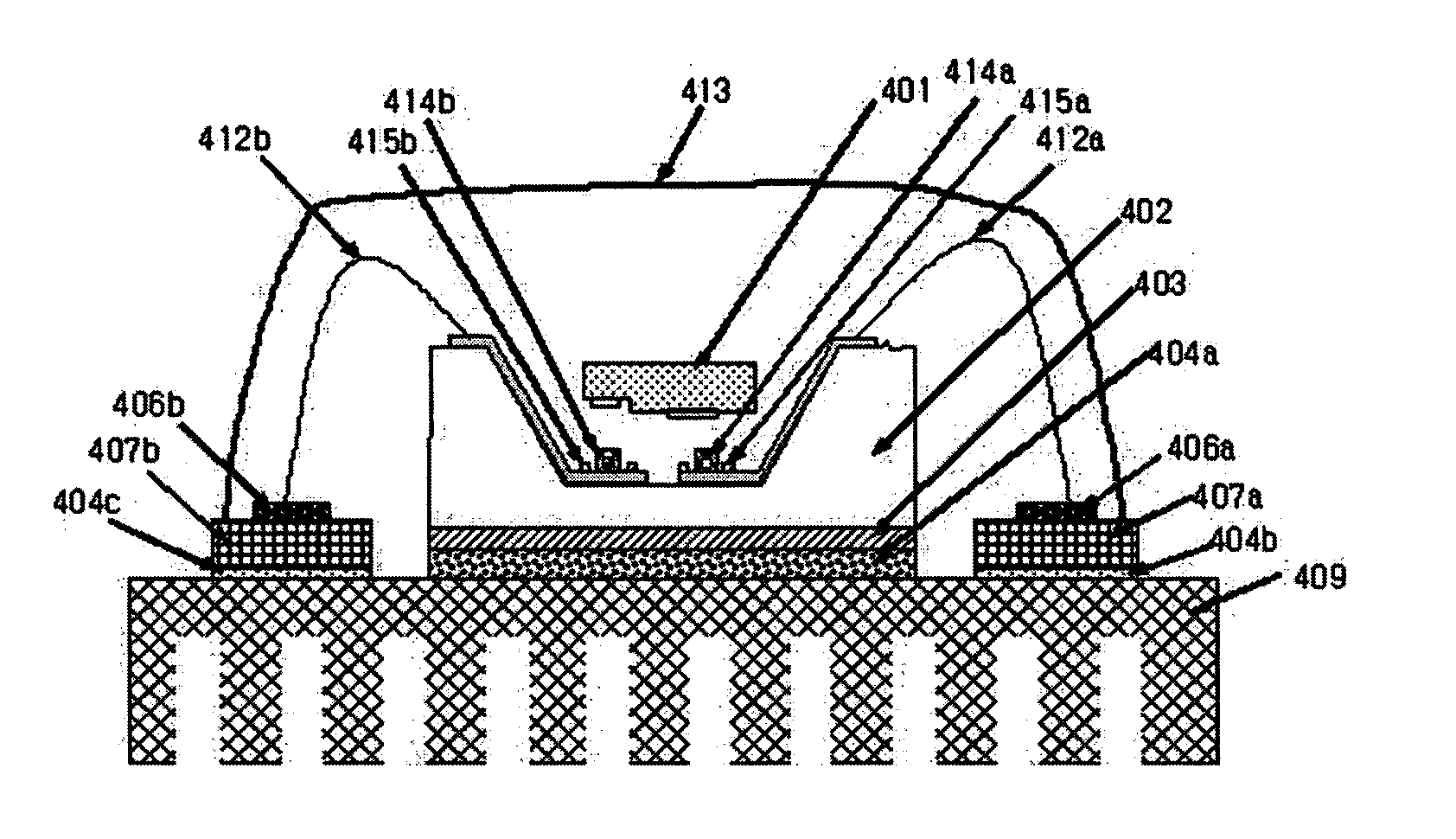

Light emitting diodes for high AC voltage operation and general lighting

InactiveUS7213942B2Improve heat transfer performanceLighting support devicesPoint-like light sourceLed arrayEffect light

A single-chip integrated LED particularly adapted for direct use with a high voltage AC power comprises a plurality of series-connected LEDs arranged in two arrays and flip chip bonded to a transparent substrate. The opposite polarities of the arrays are connected together and then connected to the AC power source. During the positive half of the AC cycle, one array of LEDs is forward biased and energized, while the other array is reverse biased. During the negative half of the AC cycle, the other array of LEDs is forward biased and thus energized, while the first array is reverse biased and thus not energized. The arrays are alternately energized and de-energized at the frequency of the AC power source, and thus the single-chip integrated LED always appears to be energized.

Owner:SEOUL SEMICONDUCTOR

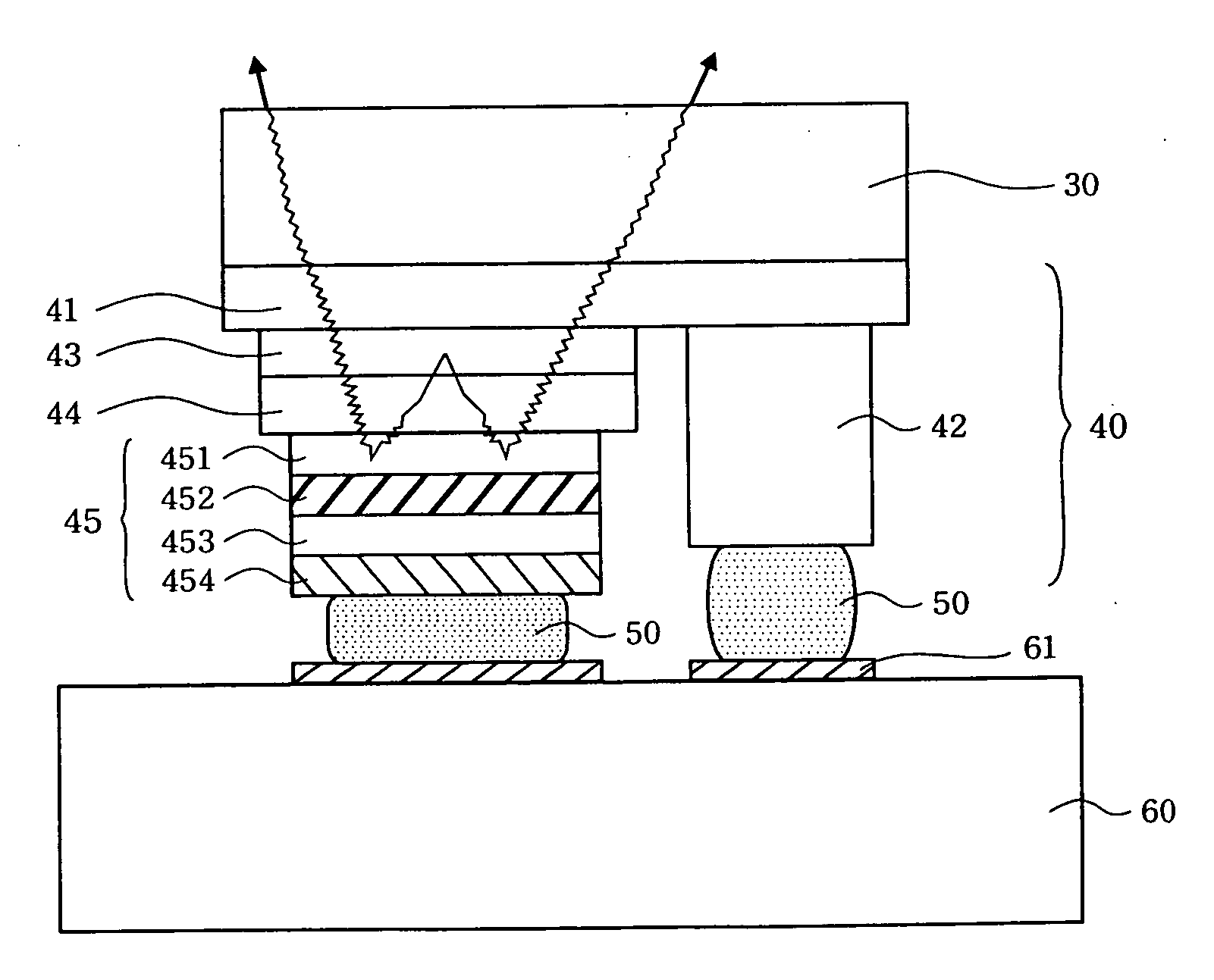

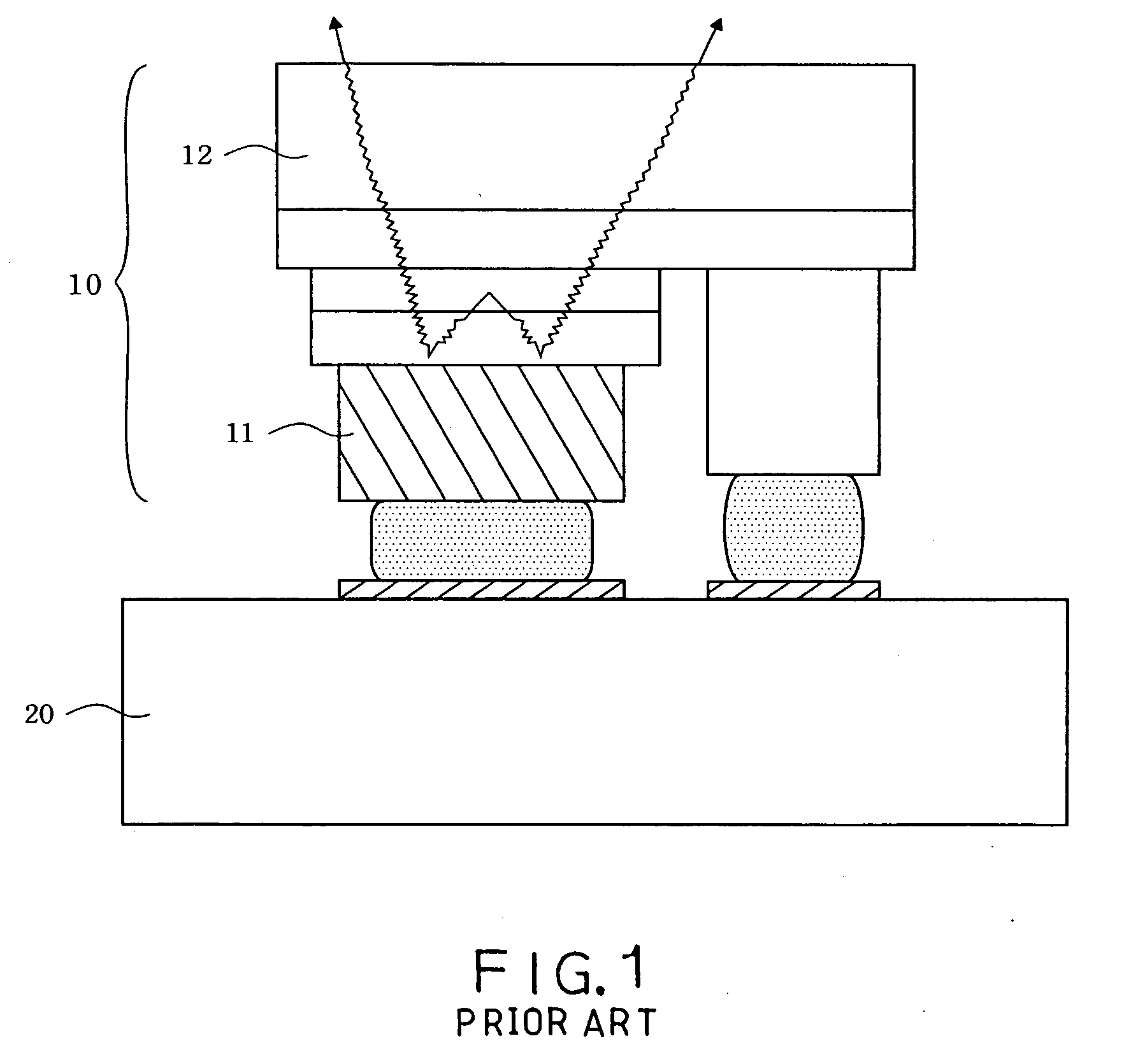

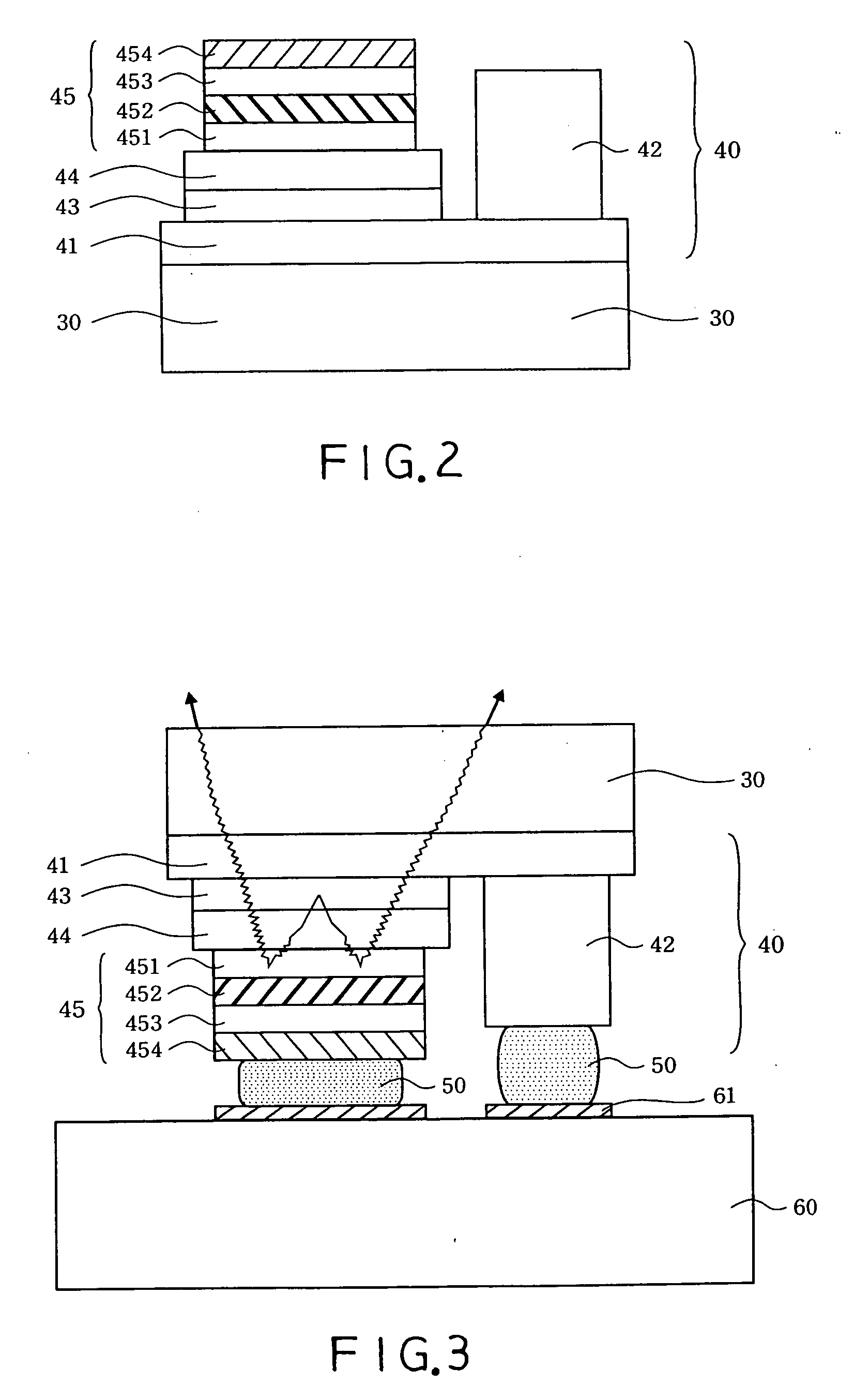

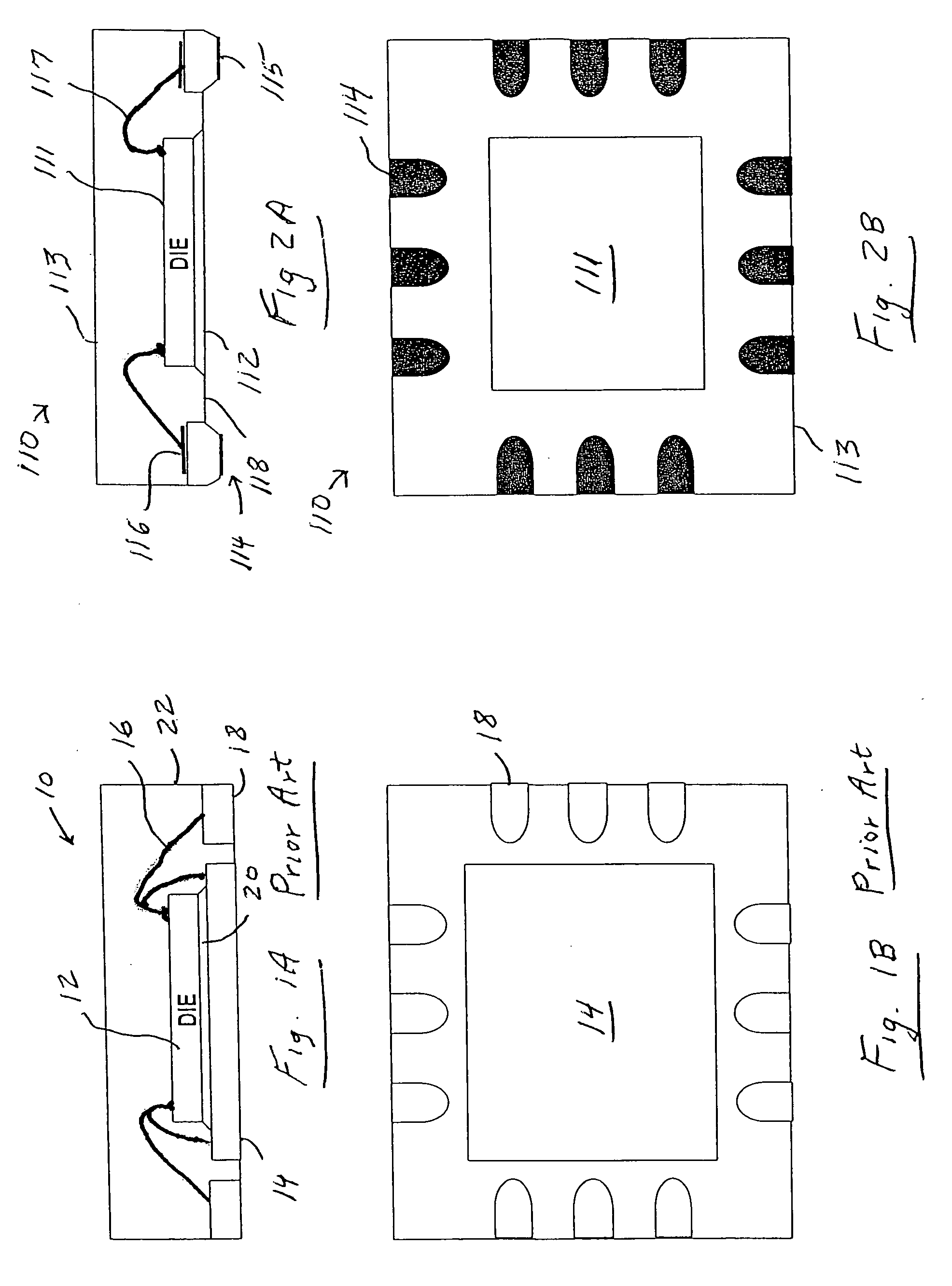

Thin, thermally enhanced flip chip in a leaded molded package

InactiveUS6891256B2Low profileThin profileSemiconductor/solid-state device detailsSolid-state devicesEngineeringLead structure

Embodiments of the invention are directed to semiconductor die packages. One embodiment of the invention is directed to a semiconductor die package including, (a) a semiconductor die including a first surface and a second surface, (b) a source lead structure including protruding region having a major surface, the source lead structure being coupled to the first surface, (c) a gate lead structure being coupled to the first surface, and (d) a molding material around the source lead structure and the semiconductor die, where the molding material exposes the second surface of the semiconductor die and the major surface of the source lead structure.

Owner:SEMICON COMPONENTS IND LLC

Flip chip light emitting diode devices having thinned or removed substrates

ActiveUS20050023550A1Reduce thicknessSemiconductor/solid-state device detailsSolid-state devicesLight-emitting diodePhysics

Owner:GE LIGHTING SOLUTIONS LLC

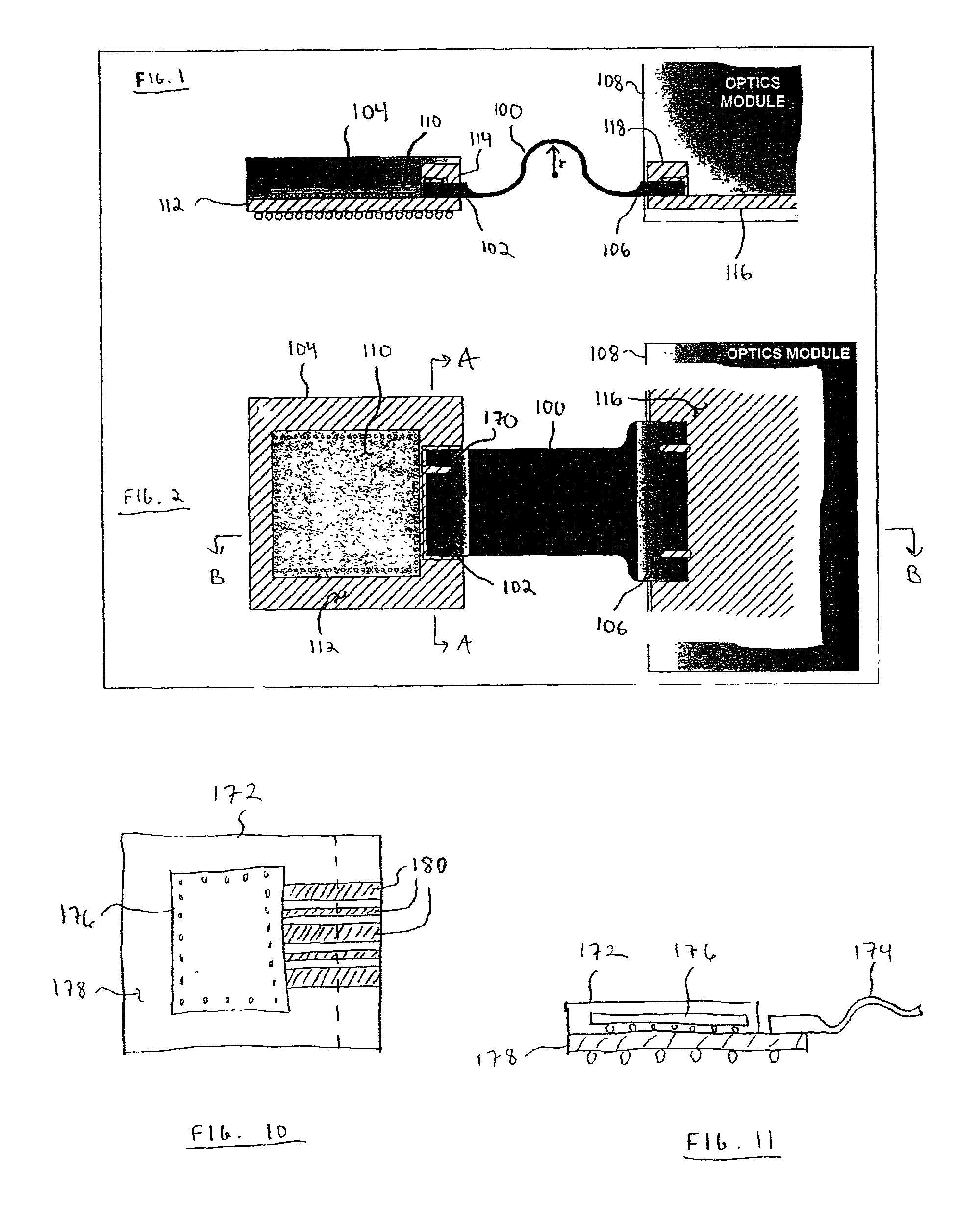

High frequency signal transmission from the surface of a circuit substrate to a flexible interconnect cable

InactiveUS6867668B1Facilitates high speed signal transmissionLow costPrinted circuit assemblingCross-talk/noise/interference reductionElectricityCoplanar waveguide

A high speed flexible interconnect cable includes a number of conductive layers and a number of dielectric layers. Conductive signal traces, located on the conductive layers, combine with the dielectric layers to form one or more high speed electrical transmission line structures. The transmission line structure may be realized as a grounded coplanar waveguide structure, a microstrip structure, a stripline structure, or the like. The cable can be coupled to destination components using a variety of connection techniques, e.g., direct bonding to a circuit substrate, direct soldering to a flip chip, mechanical attachment to a component, or integration with a circuit substrate. The cable can also be terminated with any number of known or standardized connector packages, e.g., SMA, GPPO, or V connectors.

Owner:QUALCOMM INC

High power LED package

InactiveUS20050274959A1Heat radiation property can be improvedIncrease powerSolid-state devicesSemiconductor devicesLiquid-crystal displayEngineering

Disclosed is a high power LED package, including an LED; a silicon submount to which the LED is flip chip bonded; a reflective film formed on the silicon submount and electrically connected to the LED to increase light emitting efficiency of the LED; electrical wires connected to the reflective film to connect the LED to an external circuit; an insulating body formed below the silicon submount; a heat sink formed below the insulating body; an insulating substrate formed on the heat sink; and metal lines formed on the insulating substrate and connected to the electrical wires. In the LED package, since the silicon submount having the LED flip chip bonded thereto is directly attached to the heat sink, heat generated upon operation of the LED can be effectively radiated. Also, the LED package has a simple structure, thus having drastically decreased manufacturing costs. The high power LED can be applied to backlight units of LCDs or general illumination fixtures, and as well, to backlight units of conventional PCS phones or LED packages for key pads, therefore increasing the light properties of the LED. In particular, the LED package has an array of two or more submounts each having an LED flip chip bonded thereto, and thus, it can be applied to a module of a backlight unit for LCDs, thus having remarkably reduced manufacturing costs.

Owner:LG ELECTRONICS INC

Mount for semiconductor light emitting device

Owner:LUMILEDS

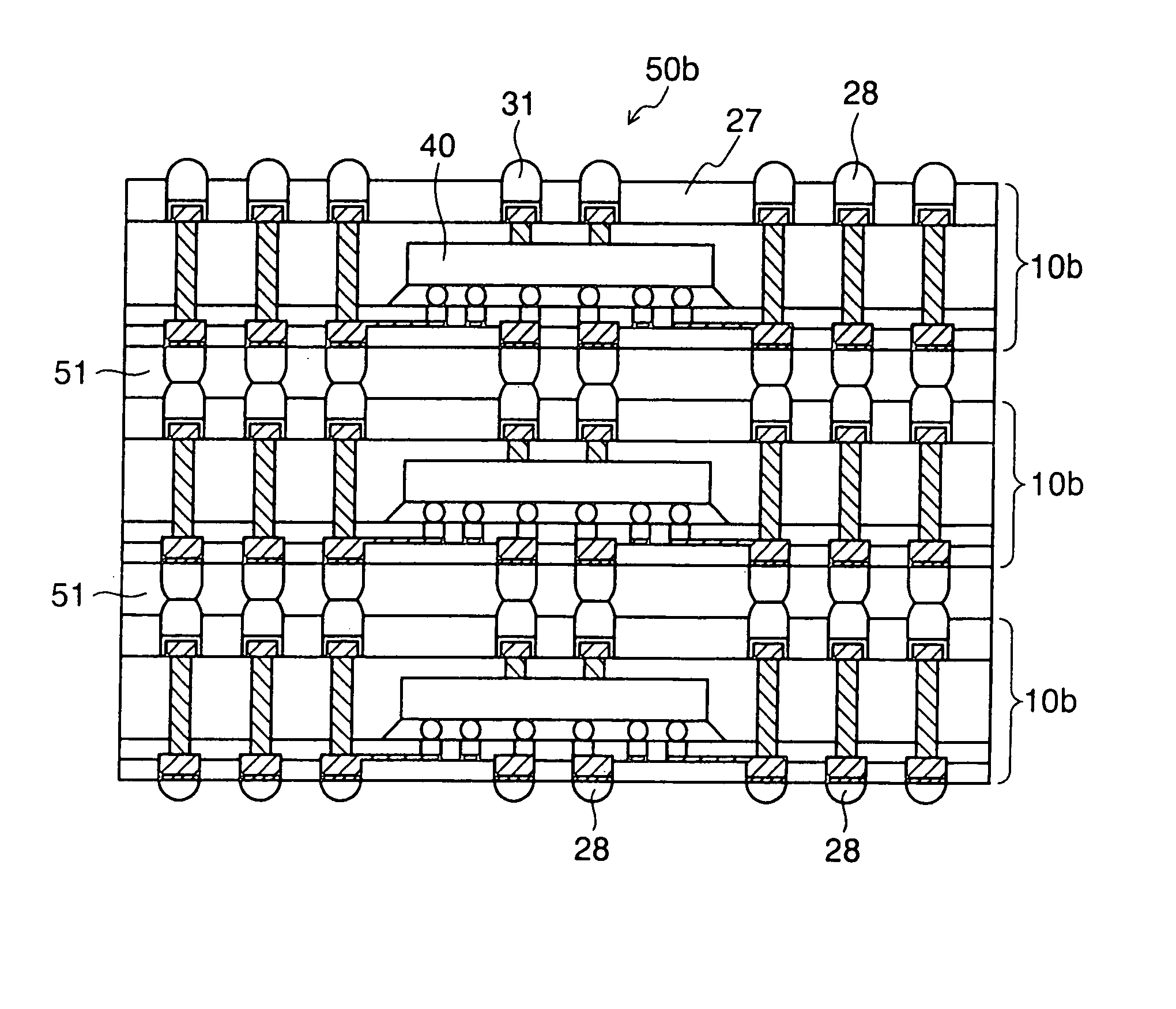

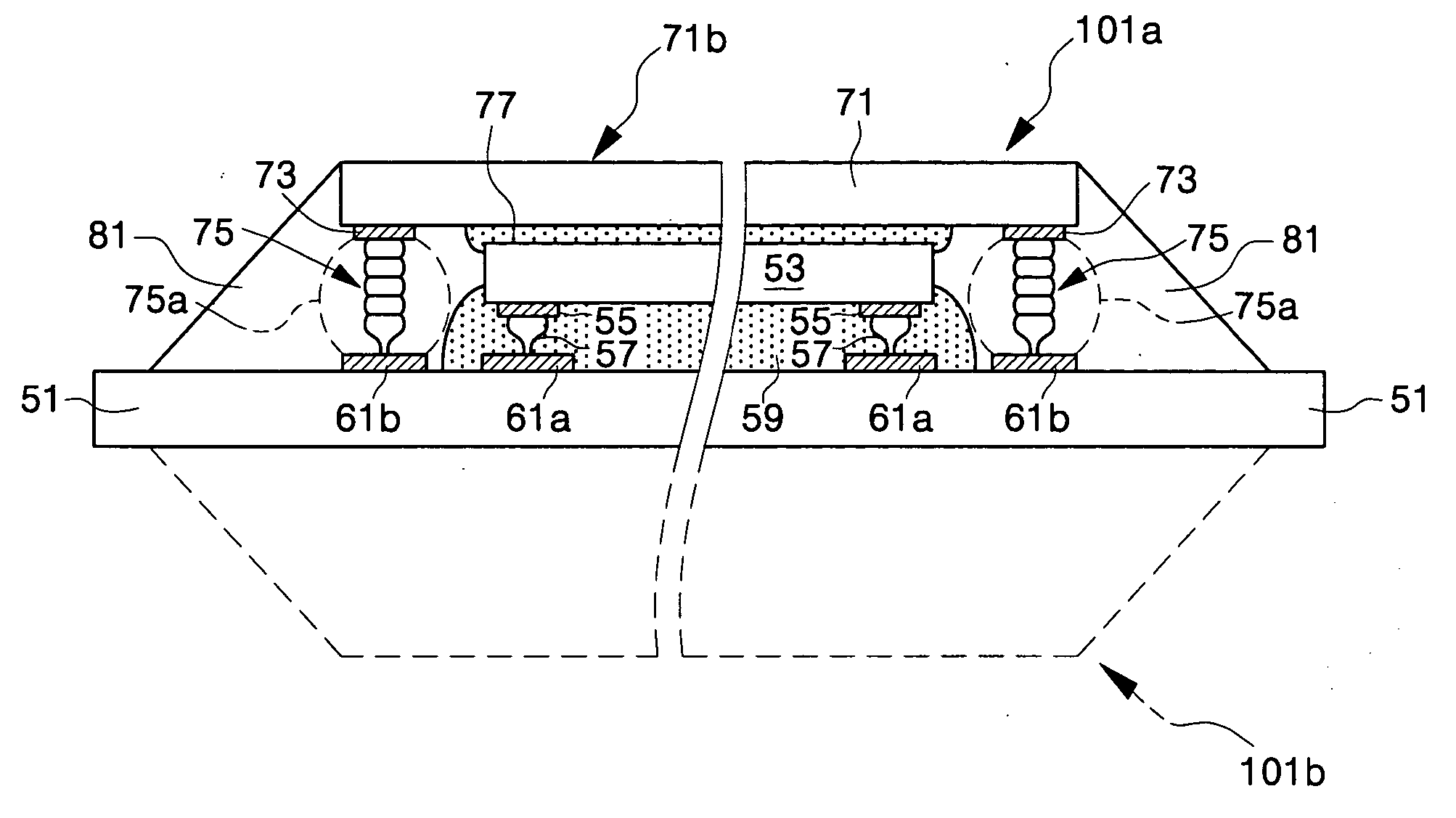

Multi-chip packages having a plurality of flip chips and methods of manufacturing the same

InactiveUS20040262774A1Semiconductor/solid-state device detailsSolid-state devicesInterconnectionPrinted circuit board

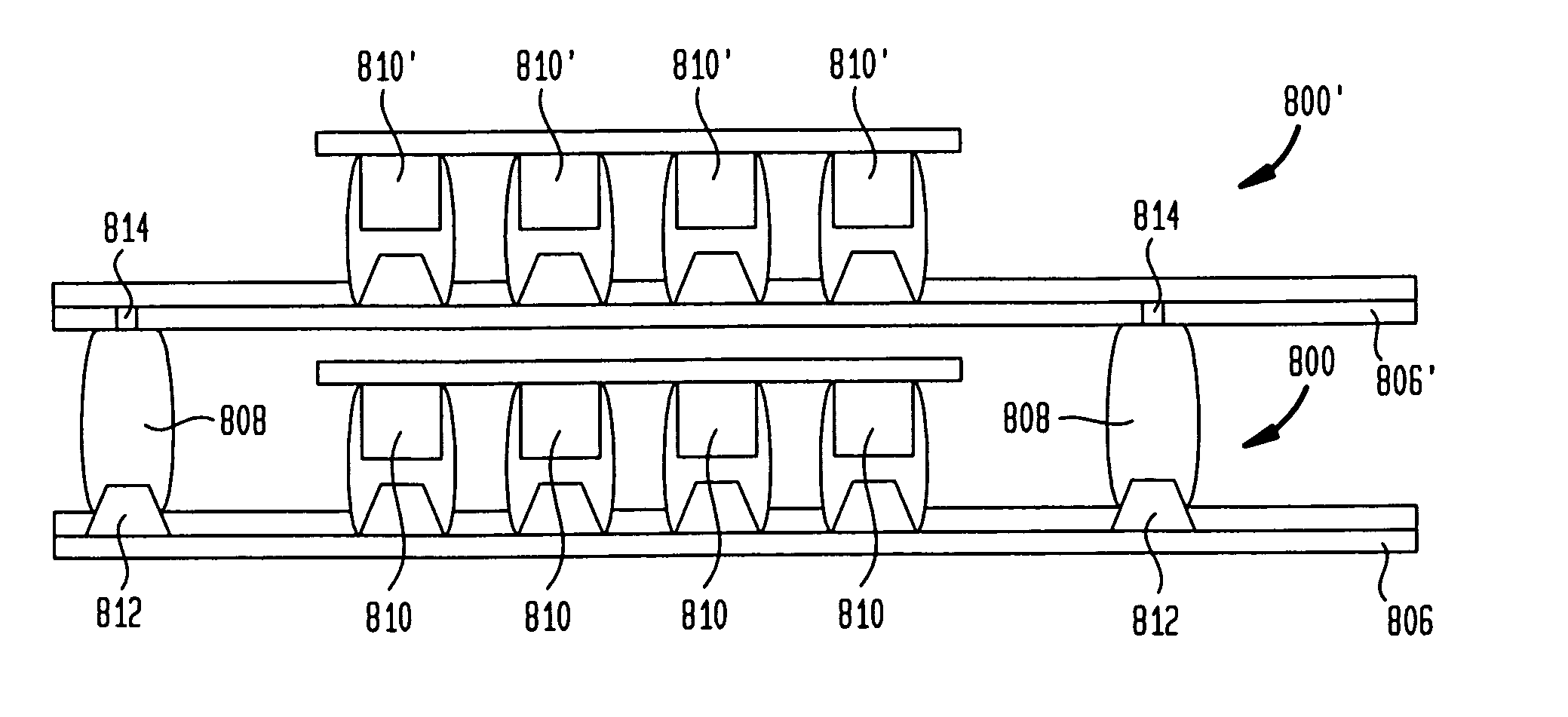

Multi-chip packages having at least two flip chips and methods of manufacturing the same are provided. The multi-chip packages may include a printed circuit board having a substrate and a plurality of interconnection lines formed on a front surface of the substrate. The at least two flip chips may be stacked on the front surface of the substrate. The flip chips may be stacked so that pads of the flip chips face the printed circuit board. A first group of bumps may be interposed between the pads of the first flip chip and a first group of interconnection lines of the plurality of lines. Further, a second group of bumps may be interposed between the pads of the at least one upper flip chip and a second group of interconnection lines of the plurality of lines.

Owner:SAMSUNG ELECTRONICS CO LTD

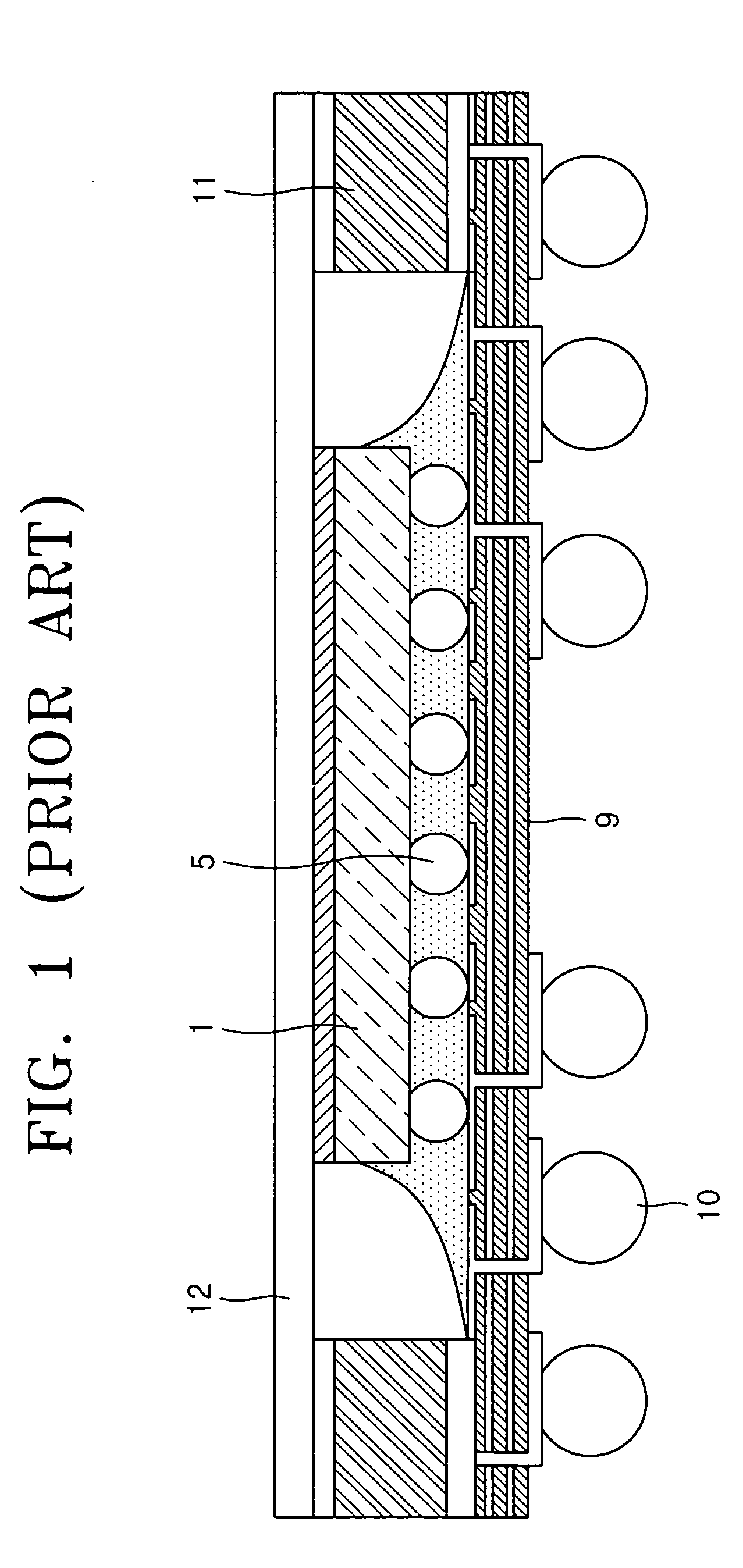

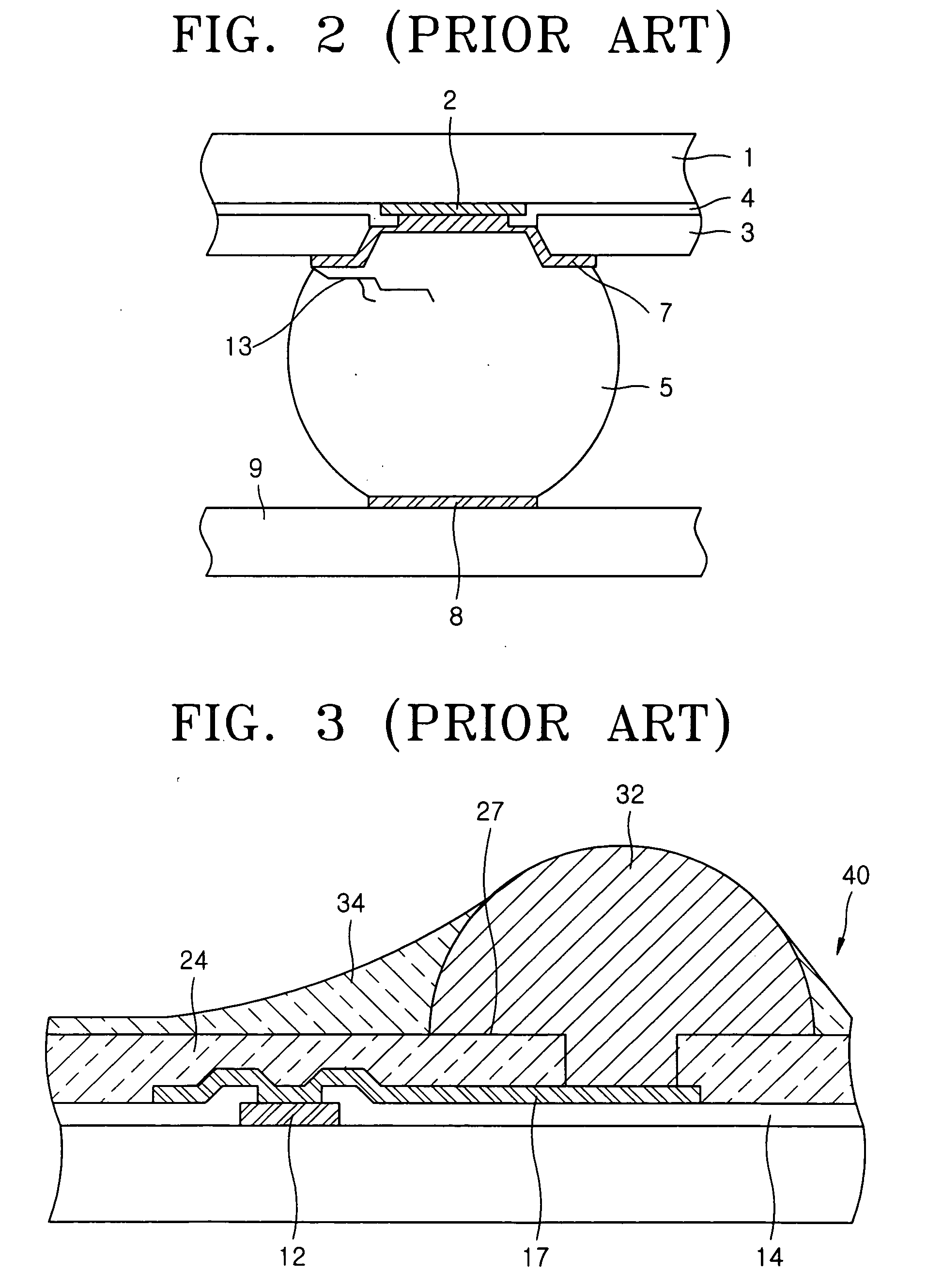

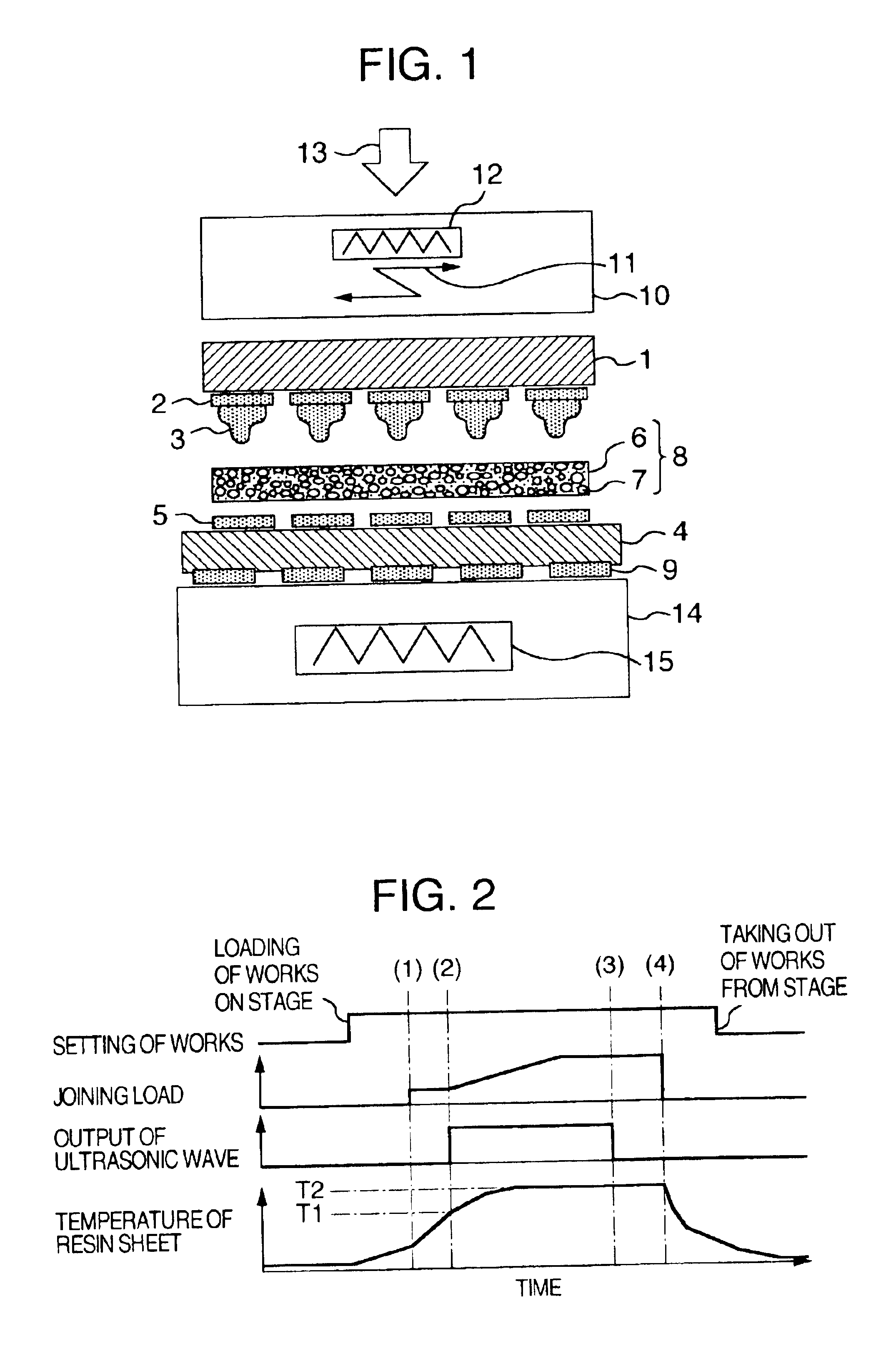

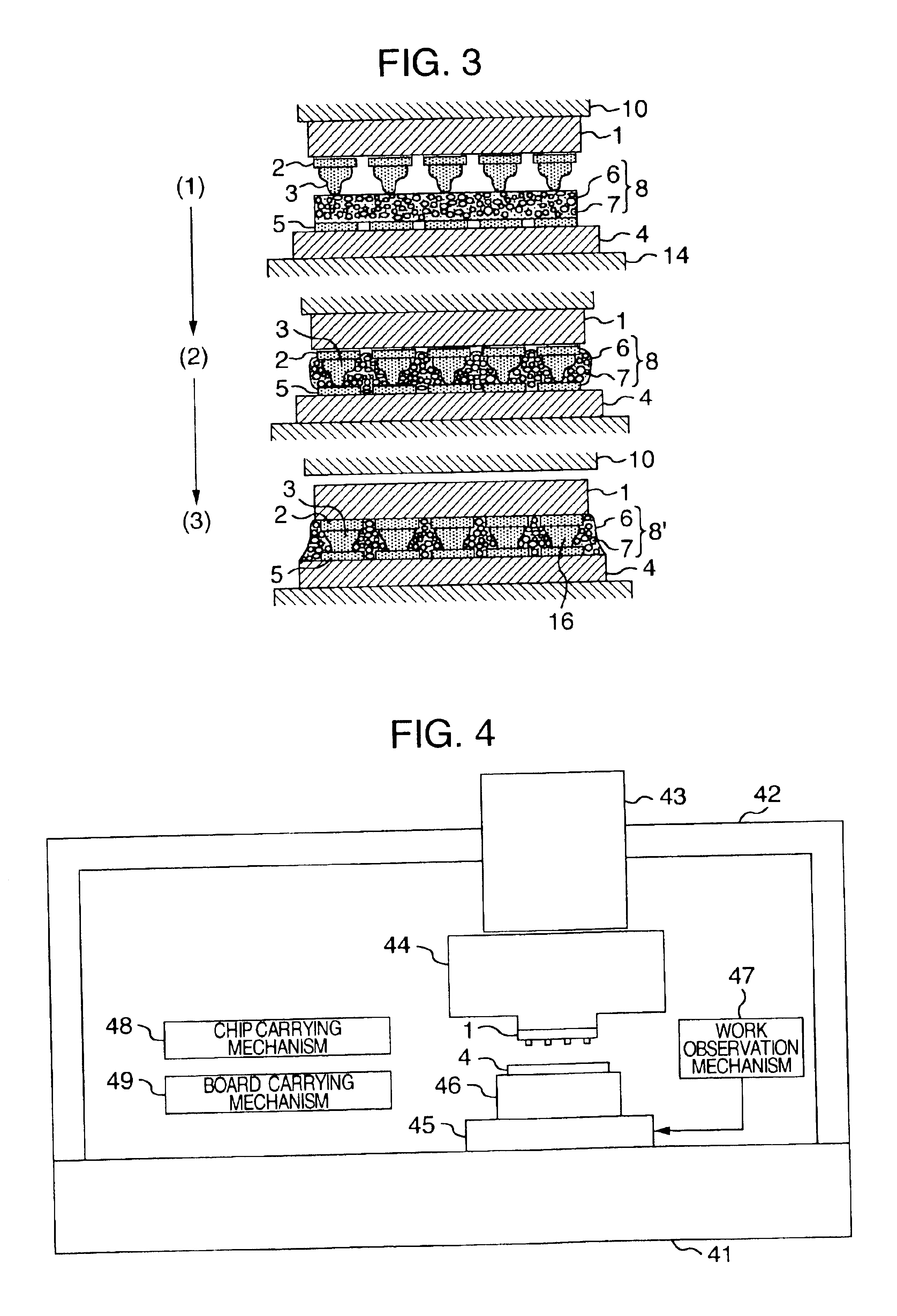

Flip chip assembly structure for semiconductor device and method of assembling therefor

InactiveUS6798072B2Improve productivityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialMetallic materials

A semiconductor device includes a semiconductor chip and a printed circuit board. Metal electrodes of the semiconductor chip and the internal connection terminals of the printed circuit board are electrically connected through the metallic joining via precious metal bumps. A melting point of a metal material constituting each of the metallic joining parts is equal to or higher than 275 degrees, and a space defined between the chip and the board is filled with resin (under fill) containing 50 vol % or more inorganic fillers.

Owner:HITACHI LTD