Patents

Literature

1248 results about "Chip-scale package" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A chip scale package or chip-scale package (CSP) is a type of integrated circuit package. Originally, CSP was the acronym for chip-size packaging. Since only a few packages are chip size, the meaning of the acronym was adapted to chip-scale packaging. According to IPC's standard J-STD-012, Implementation of Flip Chip and Chip Scale Technology, in order to qualify as chip scale, the package must have an area no greater than 1.2 times that of the die and it must be a single-die, direct surface mountable package. Another criterion that is often applied to qualify these packages as CSPs is their ball pitch should be no more than 1 mm.

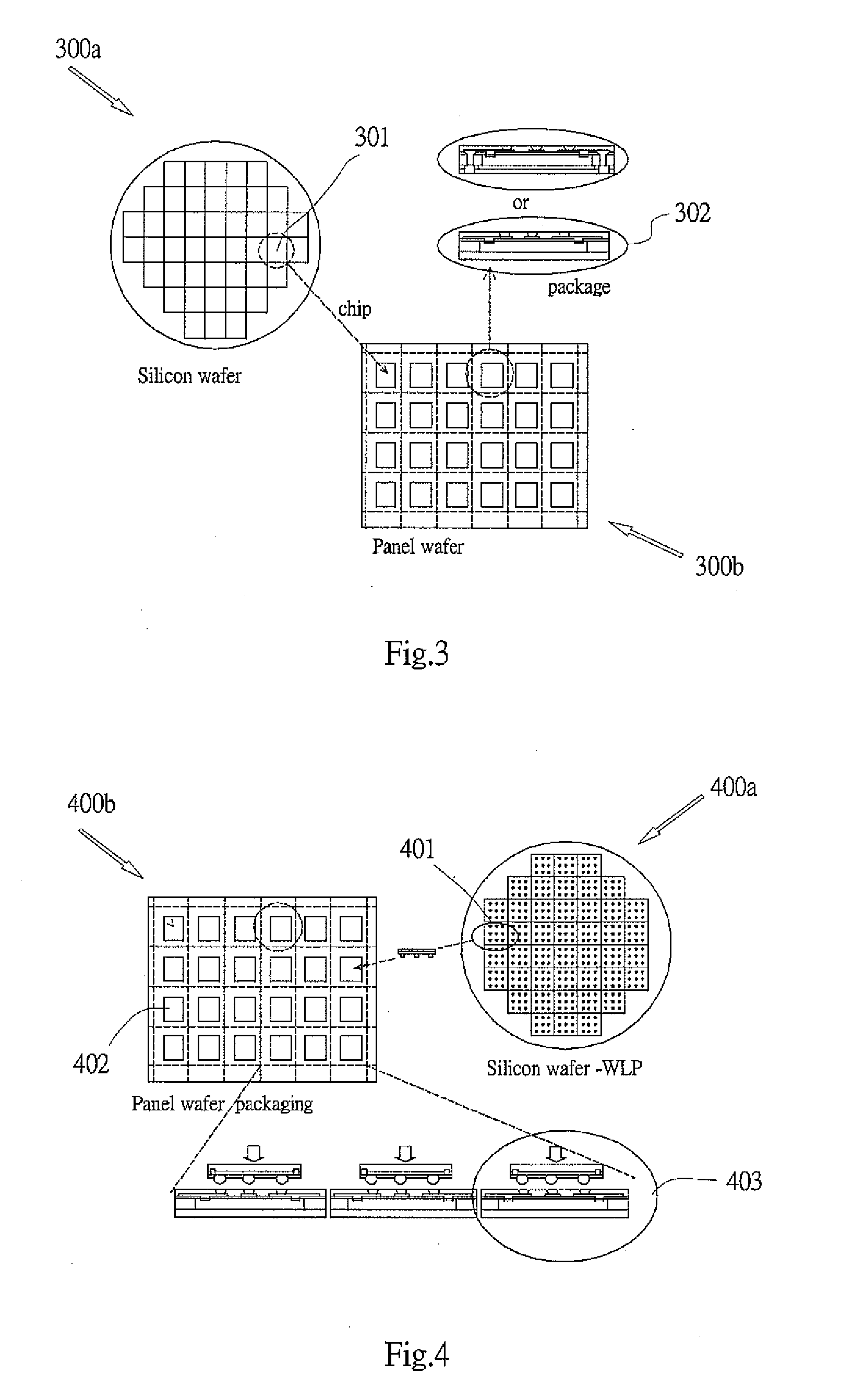

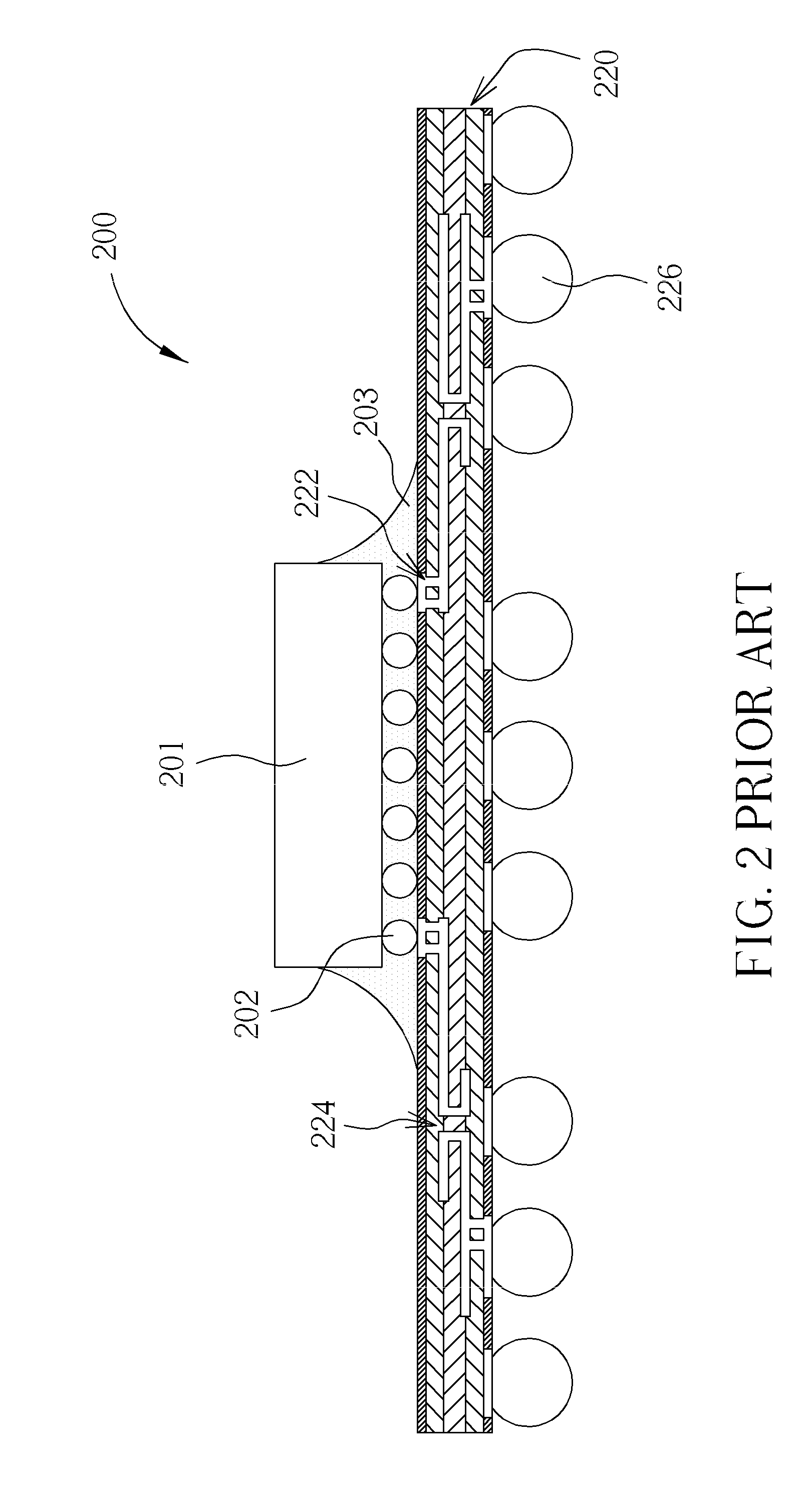

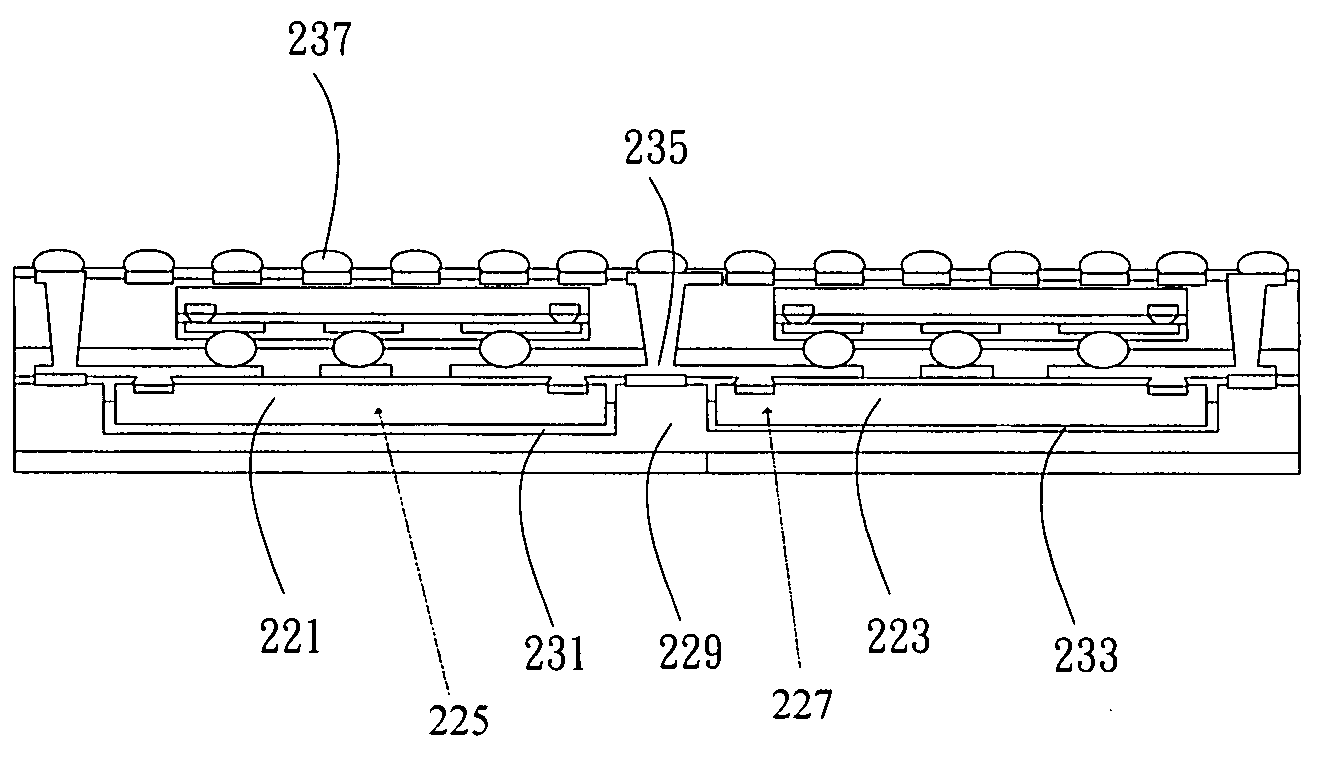

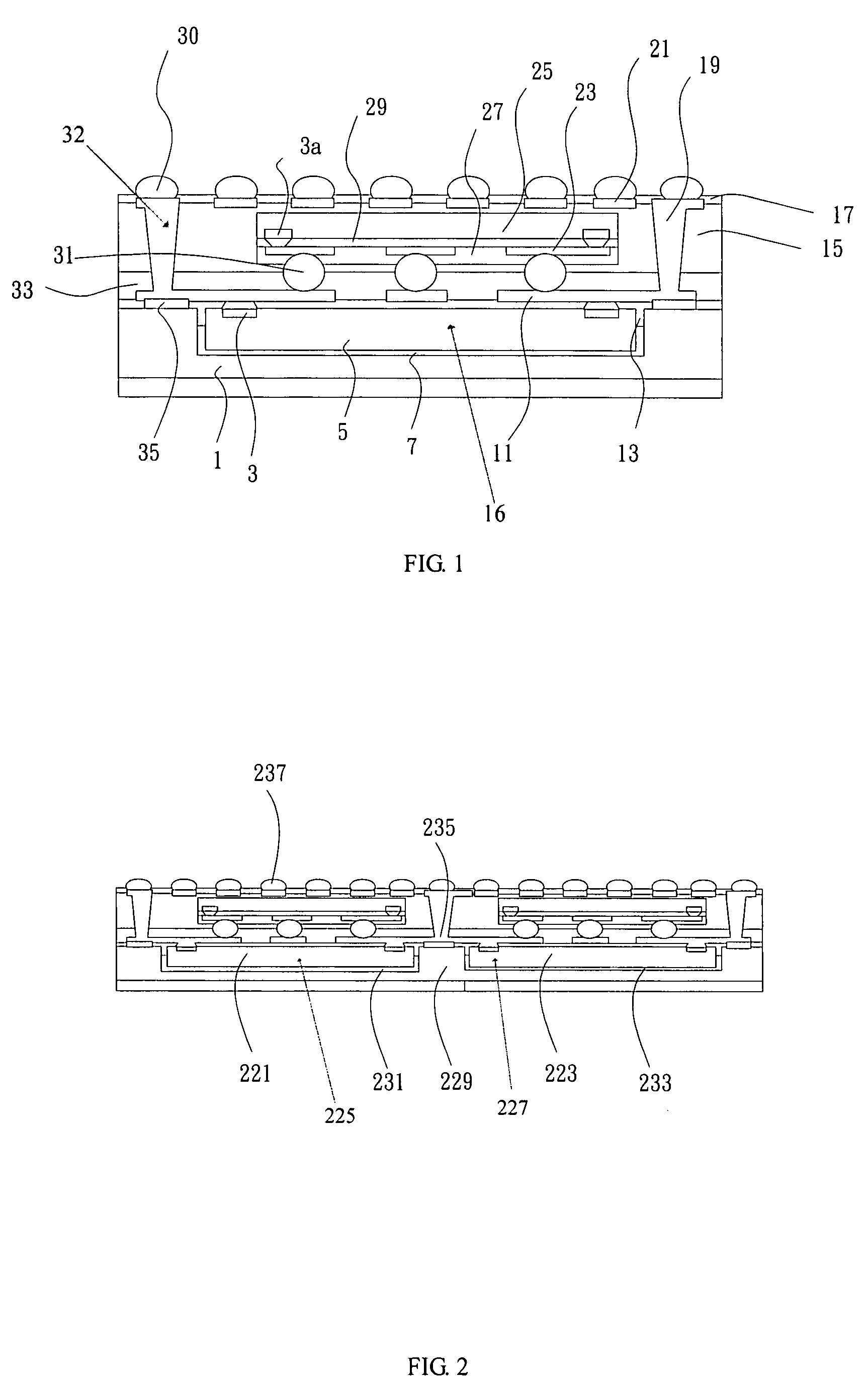

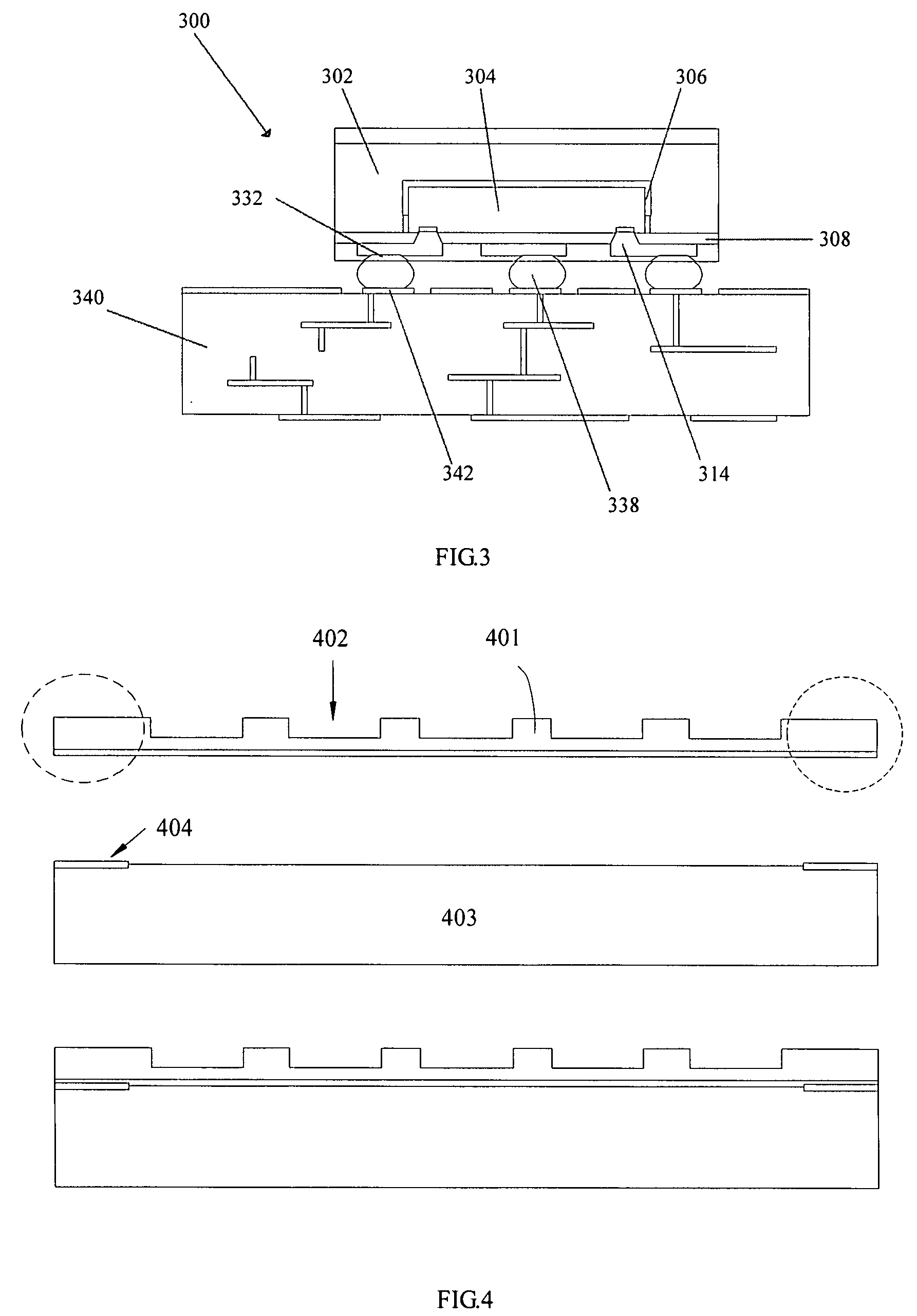

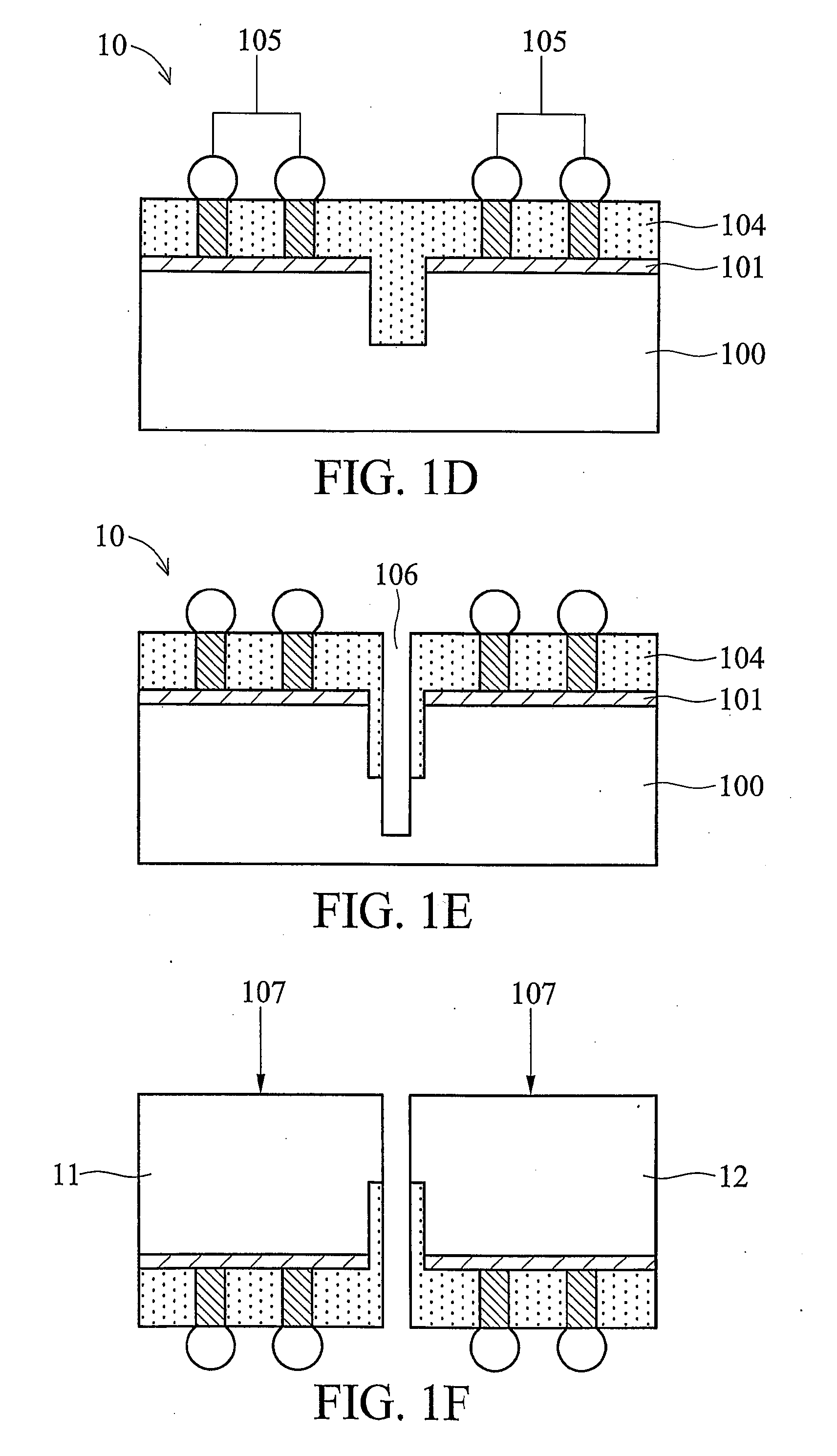

Chip stack package and manufacturing method thereof

ActiveUS7276799B2Low costShorten the timeSemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical connection

A chip stack package is manufactured at a wafer level by forming connection vias in the scribe lanes adjacent the chips and connecting the device chip pads to the connection vias using rerouting lines. A lower chip is then attached and connected to a substrate, which may be a test wafer, and an upper chip is attached and connected to the lower chip, the electrical connections being achieved through their respective connection vias. In addition to the connection vias, the chip stack package may include connection bumps formed between vertically adjacent chips and / or the lower chip and the substrate. The preferred substrate is a test wafer that allows the attached chips to be tested, and replaced if faulty, thereby ensuring that each layer of stacked chips includes only “known-good die” before the next layer of chips is attached thereby increasing the production rate and improving the yield.

Owner:SAMSUNG ELECTRONICS CO LTD

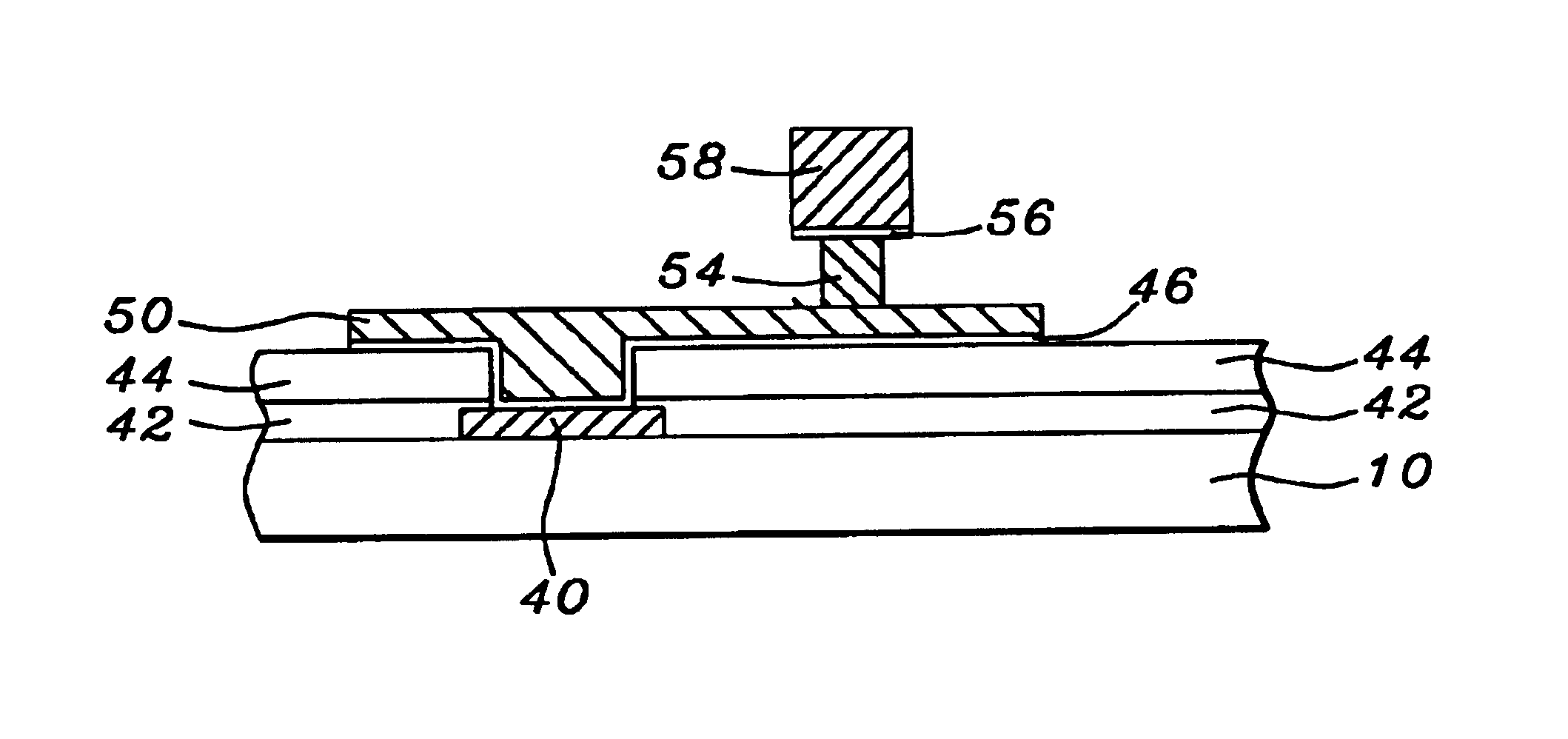

Method for forming conductive bumps for the purpose of contrructing a fine pitch test device

InactiveUS20020011859A1Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityEngineering

A system is described for using with fine pitch devices including singulated bare die, semiconductor wafers, chip sized packages, printed circuit boards, and the like to determine that the fine pitch device is not faulty. The system is also usable for transfer of data, energy, for collecting data measurements or measurement-related data between two pieces, and for effecting at least part of an identification process. The disclosed embodiment includes a substrate having a circuit pad pattern in the mirror image of the pattern of contact points, usually bond pads of the fine pitch device to be connected. A conductive elastomeric probe is permanently formed on the circuit pads of the substrate such that the probe is malleable and allows repetitive electrical contact. The system may also contain an alignment template for orienting the fine pitch device onto the elastomeric probes of the contact point pattern of the substrate.

Owner:EPITECH +1

Multi-chip package structure and method of forming the same

InactiveUS20080136004A1Avoid problemsIncrease productionSemiconductor/solid-state device detailsSolid-state devicesChip sizeChip-scale package

To pick and place standard first chip size package on a base with a second chip for obtaining an appropriate stacking chip size package than the original chip size package. The package structure has a larger chip size package than the size of the traditional stacking package. Moreover, the terminal pins of the flip chip package may be located on peripheral of LGA package or on array of BGA package.

Owner:ADVANCED CHIP ENG TECH

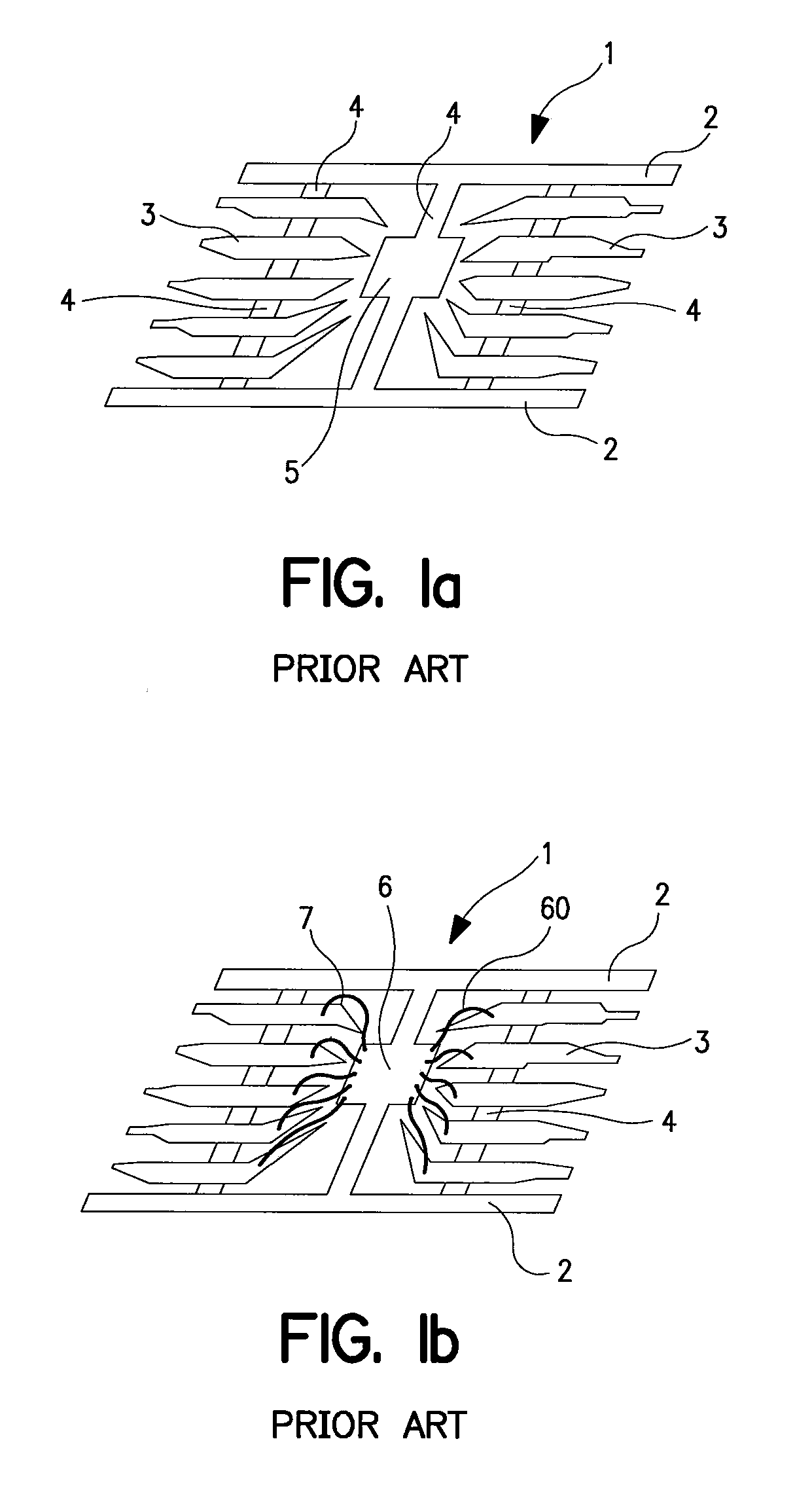

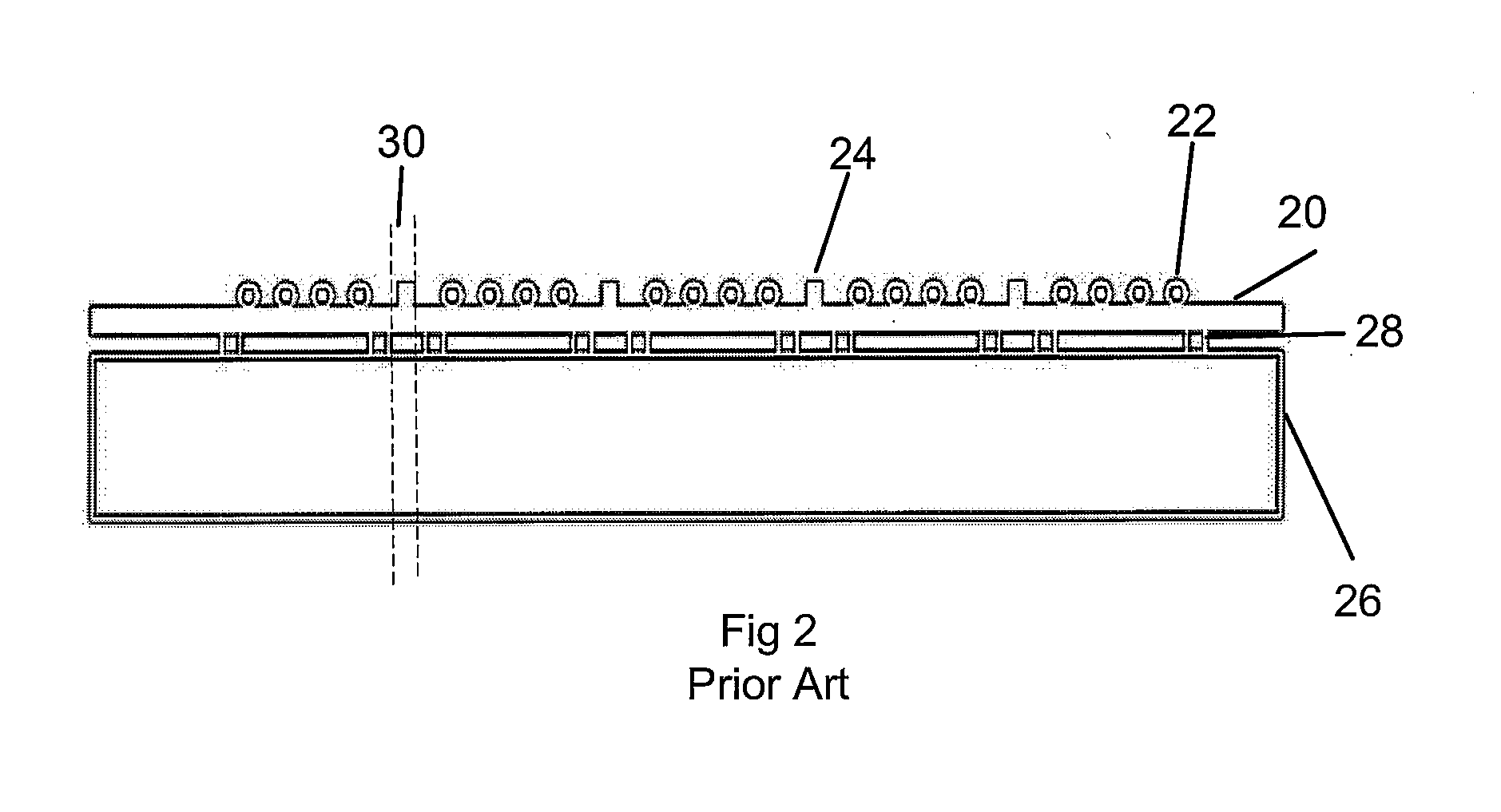

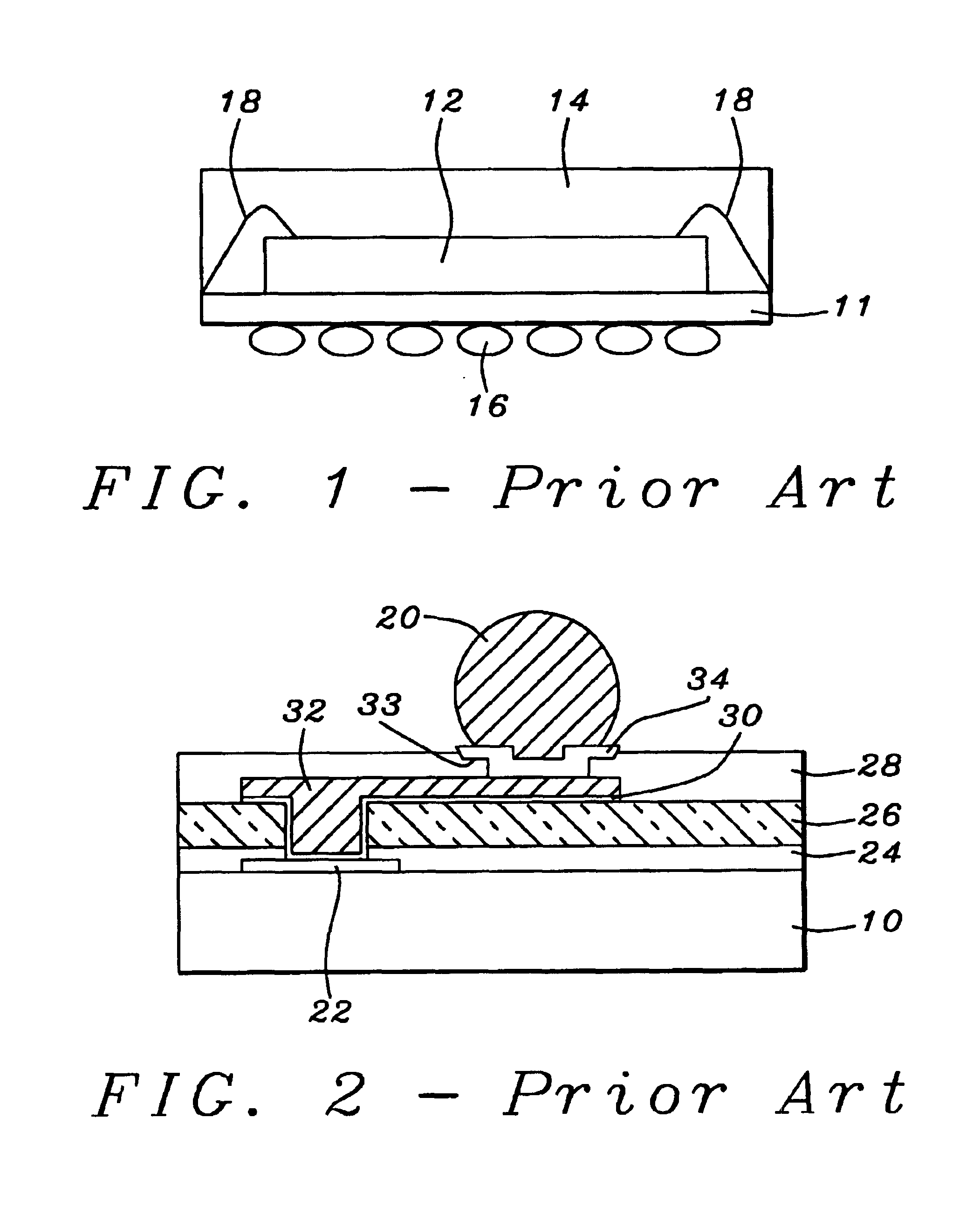

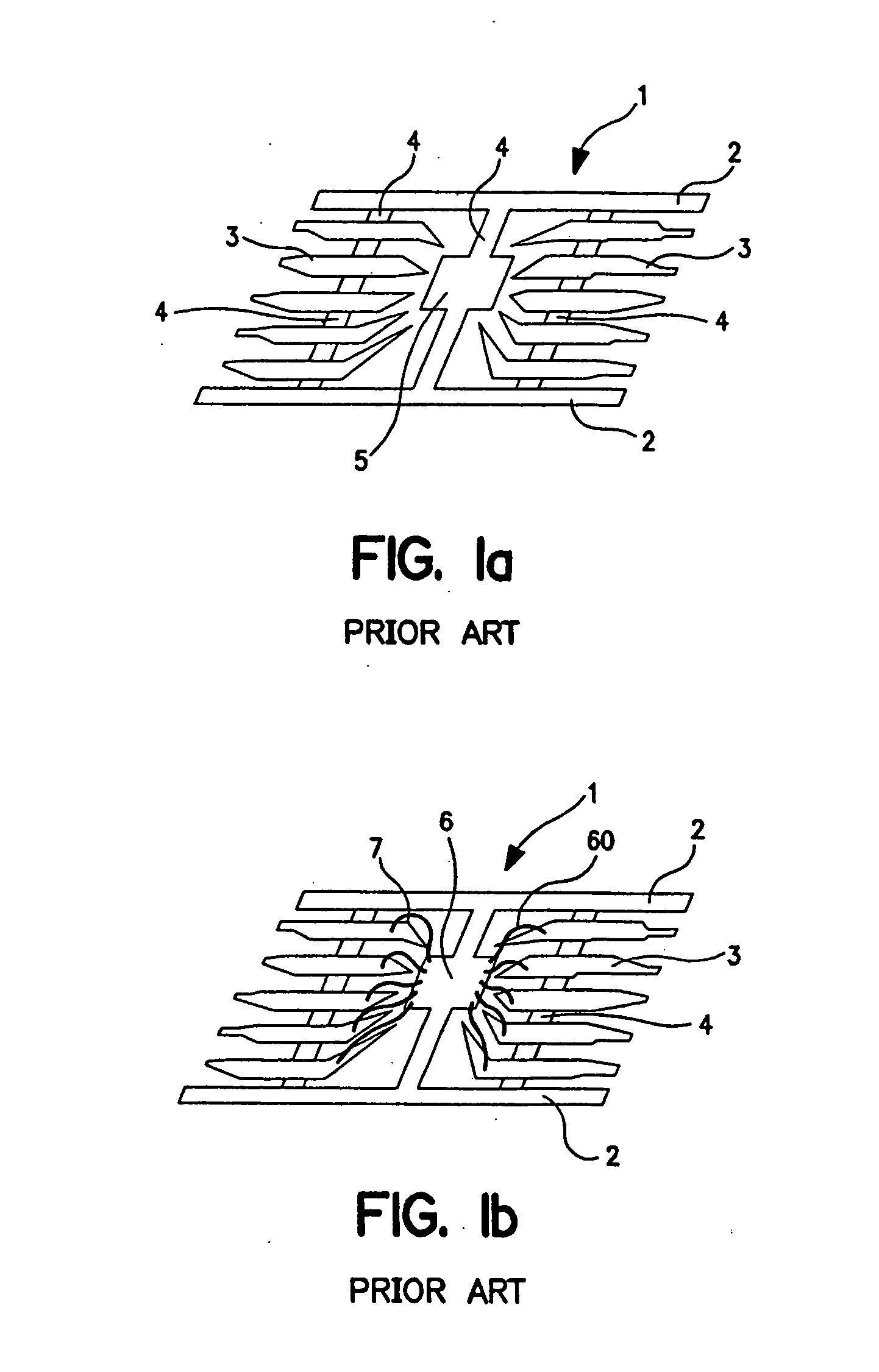

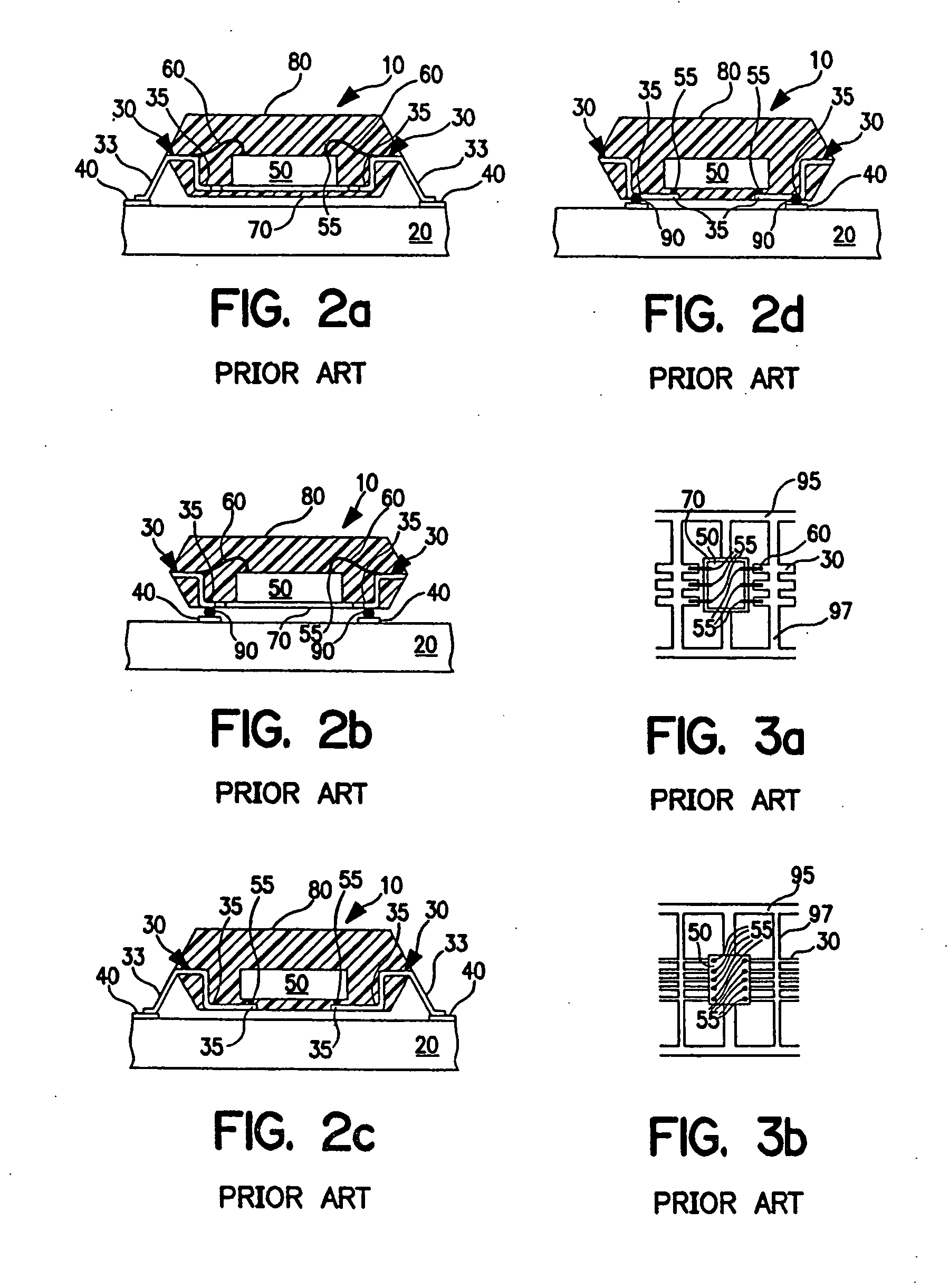

Partially patterned lead frames and methods of making and using the same in semiconductor packaging

InactiveUS20080258278A1Reduce thicknessImprove structural rigiditySemiconductor/solid-state device detailsSolid-state devicesLead bondingBonding process

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging lead-count, wherein the method lends itself to better automation of the manufacturing line and improved quality and reliability of the packages produced therefrom. A major portion of the manufacturing process steps is performed with a partially patterned strip of metal formed into a web-like lead frame on one side so that the web-like lead frame is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation.

Owner:UNISEM M BERHAD

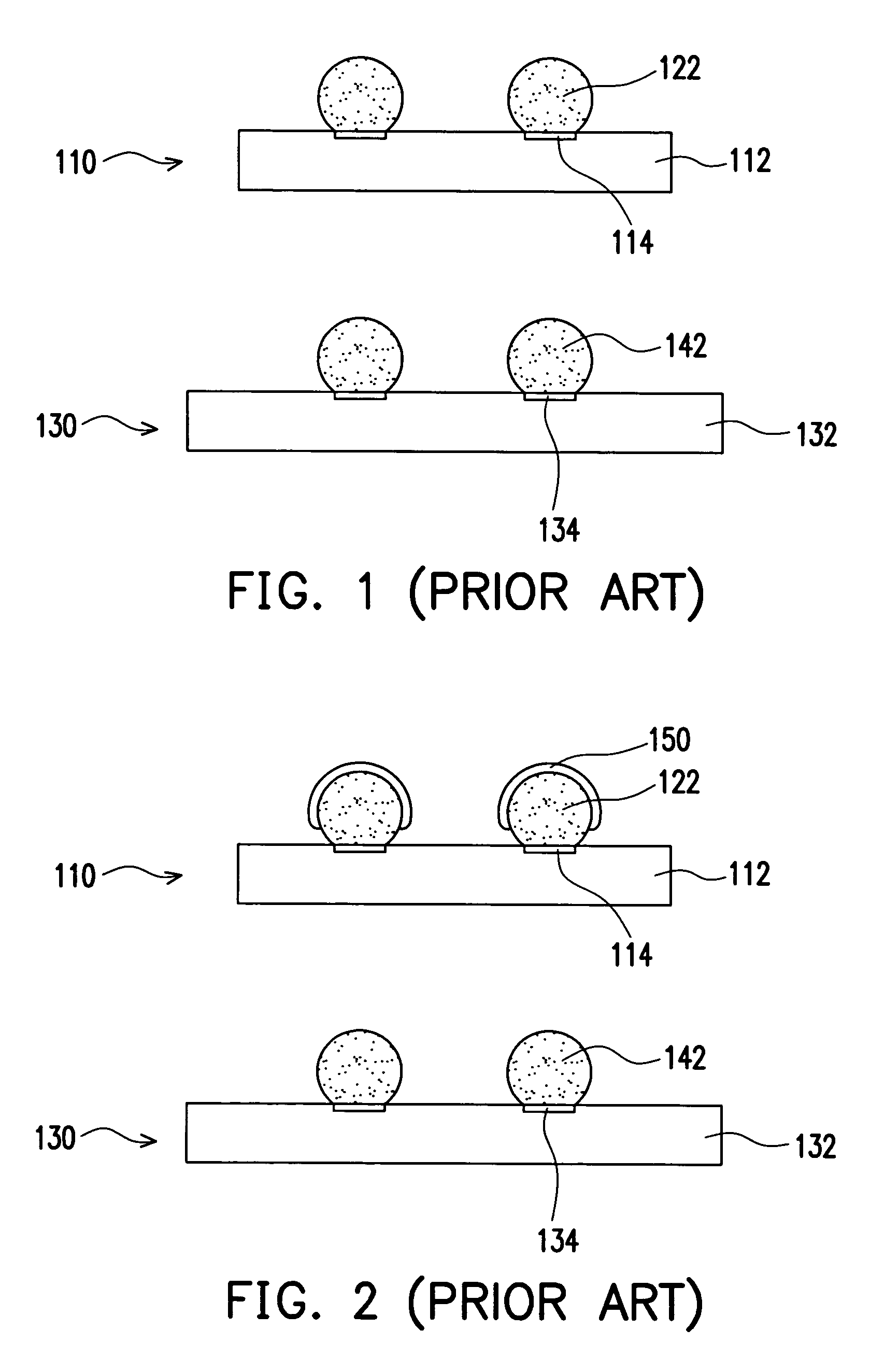

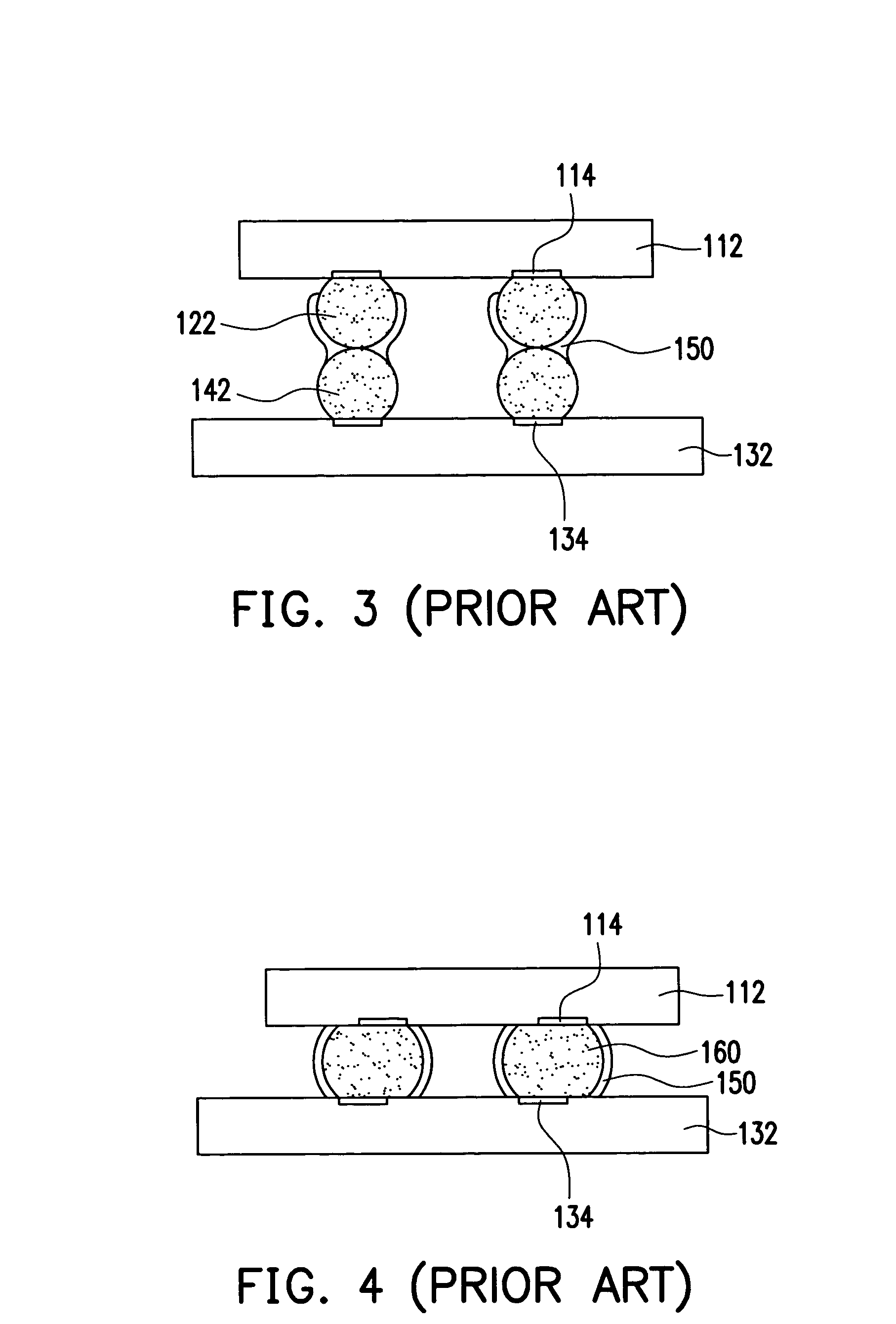

Chip package with multiple chips connected by bumps

InactiveUS7242099B2Improve assembly reliabilityPrecise alignmentPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringChip-scale package

A method of assembling chips. A first chip and a second chip are provided. At least one conductive pillar is formed on the first chip, and a conductive connecting material is formed on the conductive pillar. The second chip also comprises at least one conductive pillar. The first chip is connected to the second chip via the conductive pillars and the conductive connecting material.

Owner:QUALCOMM INC

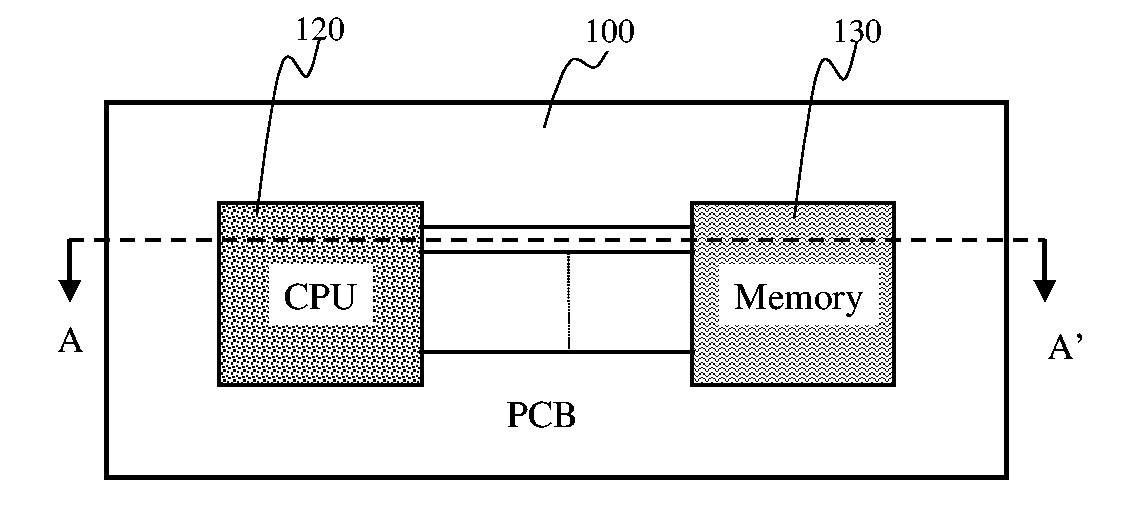

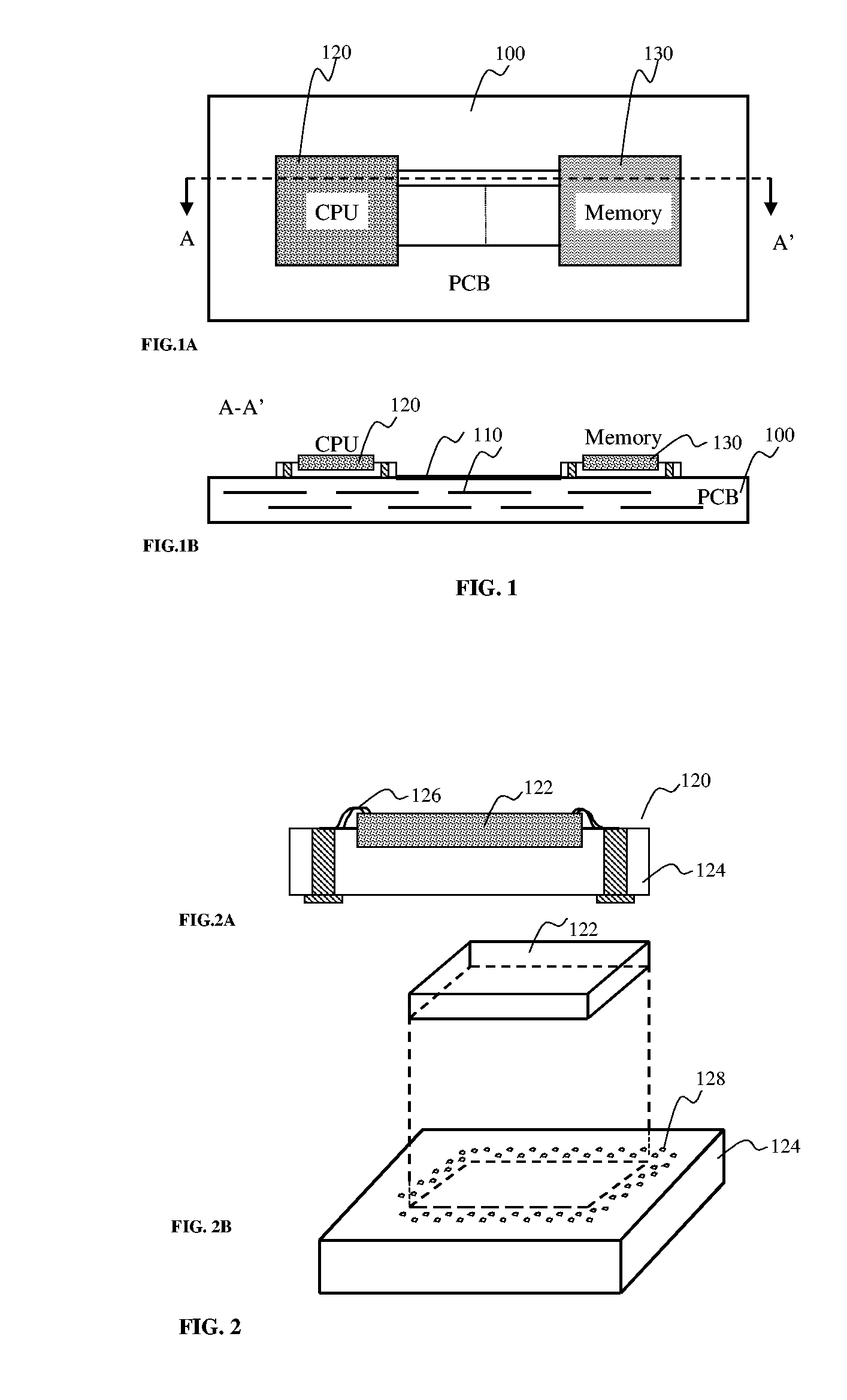

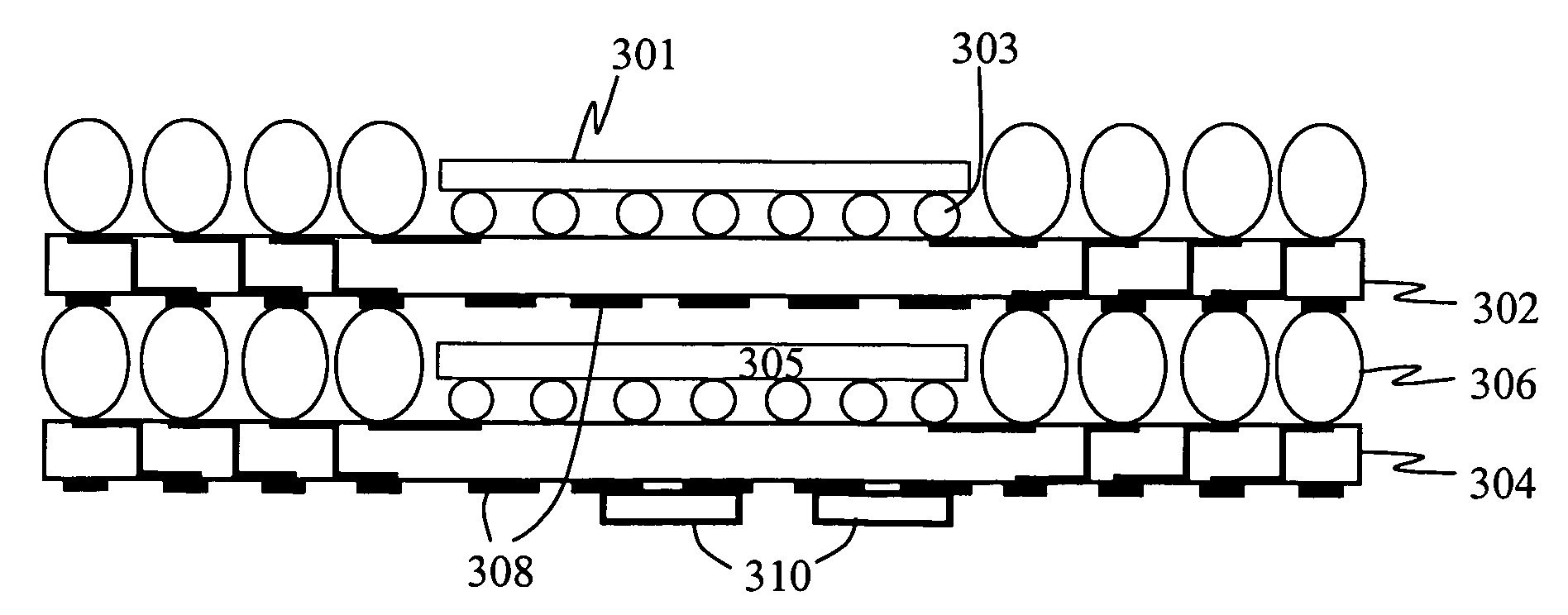

Stackable optoelectronics chip-to-chip interconnects and method of manufacturing

ActiveUS20050224946A1Minimize skewEasily stackable/mountableCircuit optical detailsSemiconductor/solid-state device detailsElectrical conductorEngineering

An optoelectronics chip-to-chip interconnects system is provided, including packaged chips to be connected on printed-circuit-board (PCB), multiple-packaged chip, optical-electrical(O-E) conversion means, waveguide-board, and PCB. Single to multiple chips interconnects can be possible using this technique. The packaged-chip includes semiconductor-die and its package based on the ball-grid array or chip-scale-package. The O-E board includes the optoelectronics components and multiple electrical contacts. The waveguide board includes electrical conductors transferring signal from O-E board to PCB and the flex optical waveguide easily stackable onto the PCB, to guide optical signal from one chip-to-other chip. The chip-to-chip interconnects system is pin-free and compatible with the PCB. The main advantages are that standard packaged-chip and conventional PCB technology can be used for low speed electrical signal connection. Also, the part of the heat from the packaged chip can be transmitted to PCB through conductors, so that complex cooling system can be avoided.

Owner:BANPIL PHOTONICS

Method for Laser Singulation of Chip Scale Packages on Glass Substrates

InactiveUS20100248451A1Preclude creationMinimized in sizeSemiconductor/solid-state device manufacturingWelding/soldering/cutting articlesLaser processingOptoelectronics

An improved method for singulation of compound electronic devices is presented. Compound electronic devices are manufactured by combining two or more substrates into an assembly containing multiple devices. Presented are methods for singulation of compound electronic devices using laser processing. The methods presented provide fewer defects such as cracking or chipping of the substrates while minimizing the width of the kerf and maintaining system throughput.

Owner:ELECTRO SCI IND INC

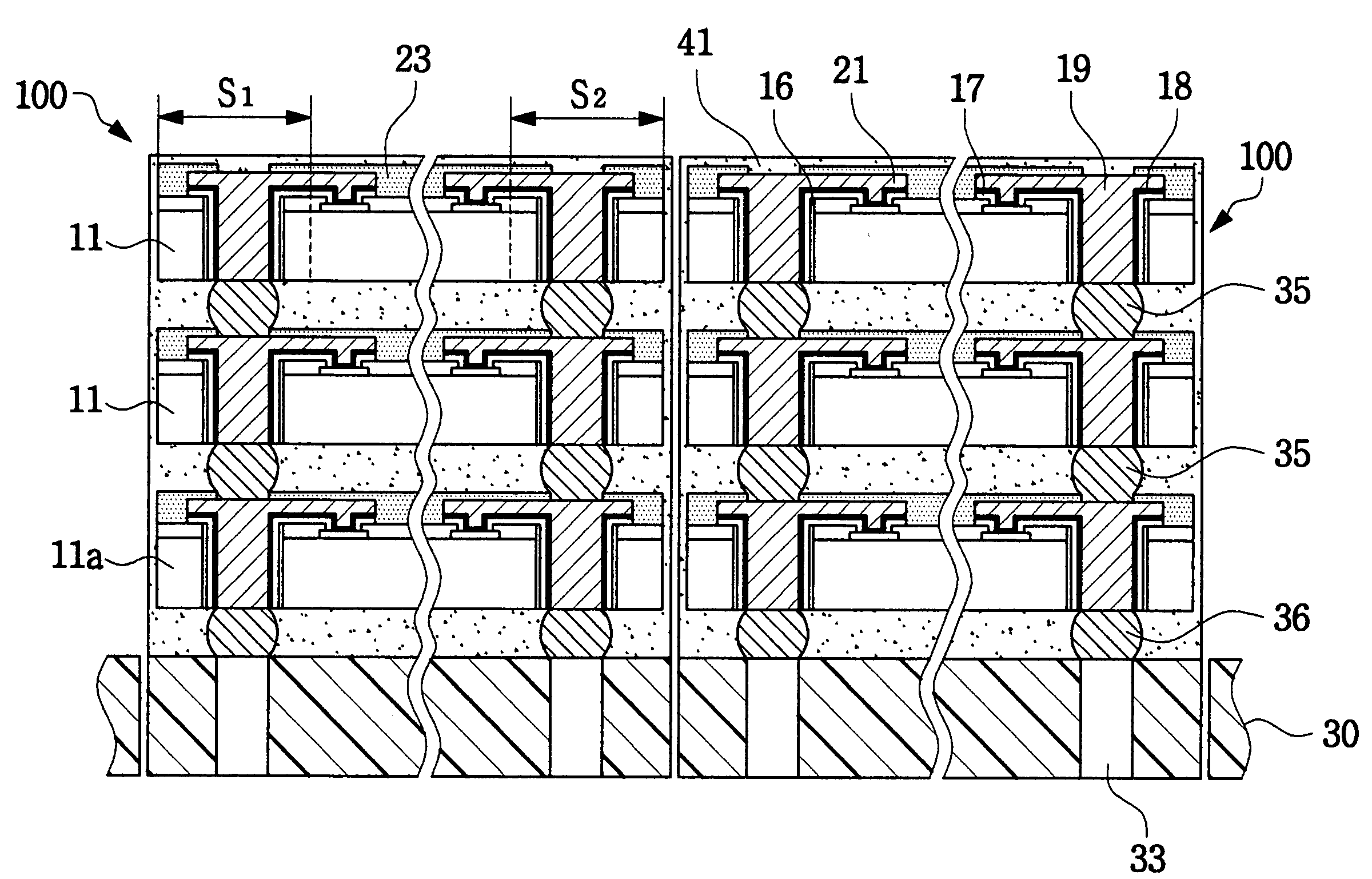

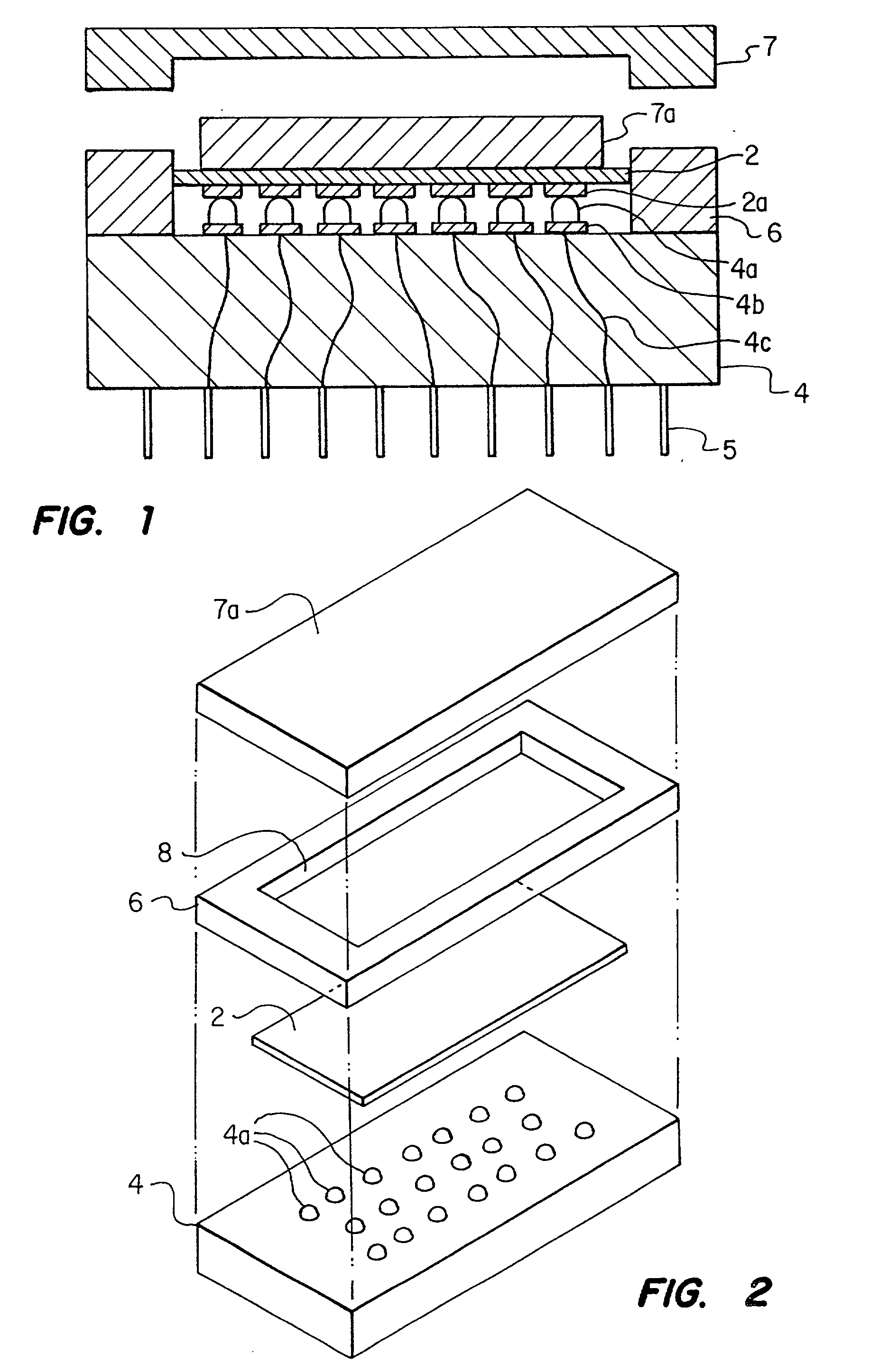

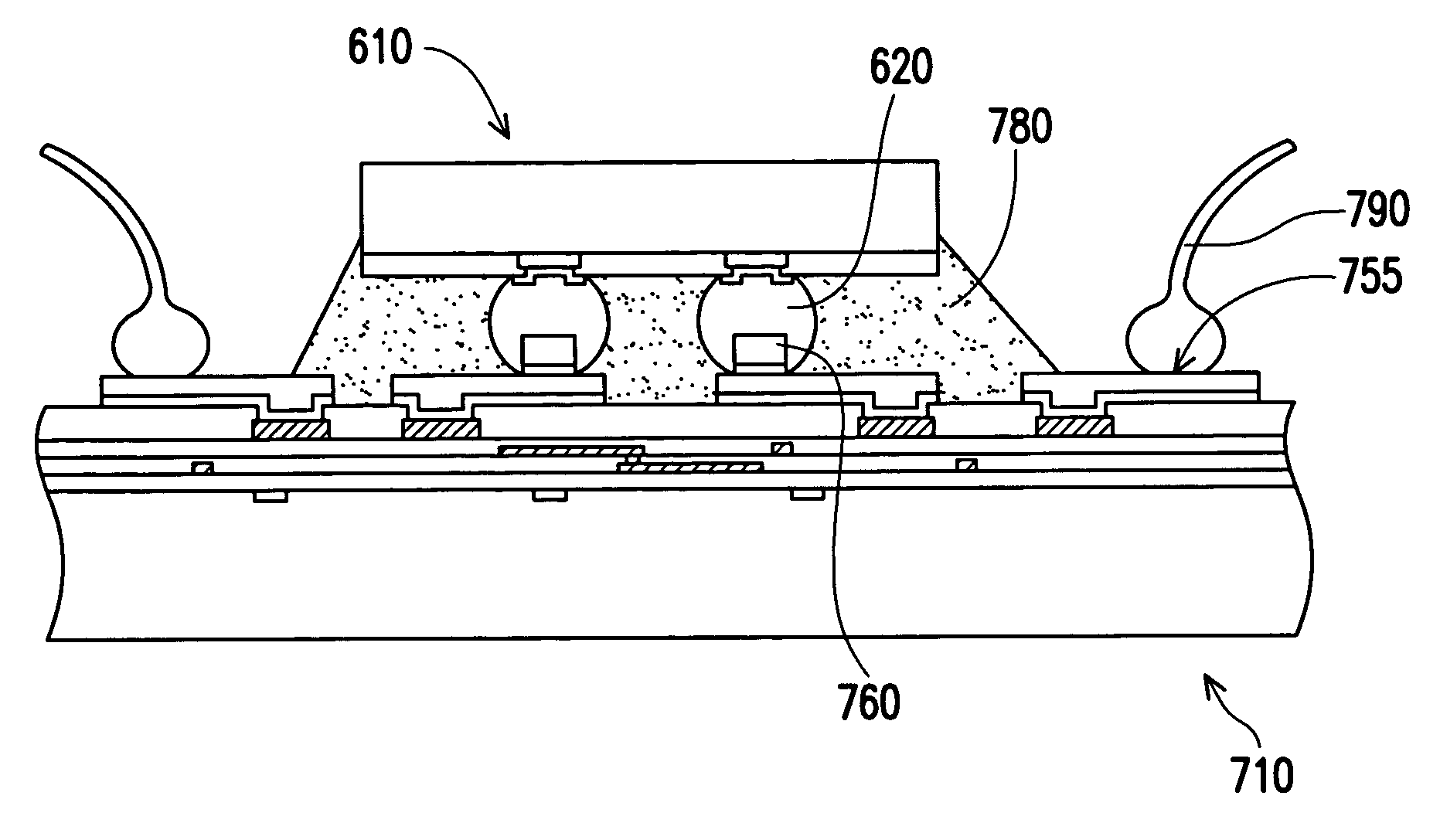

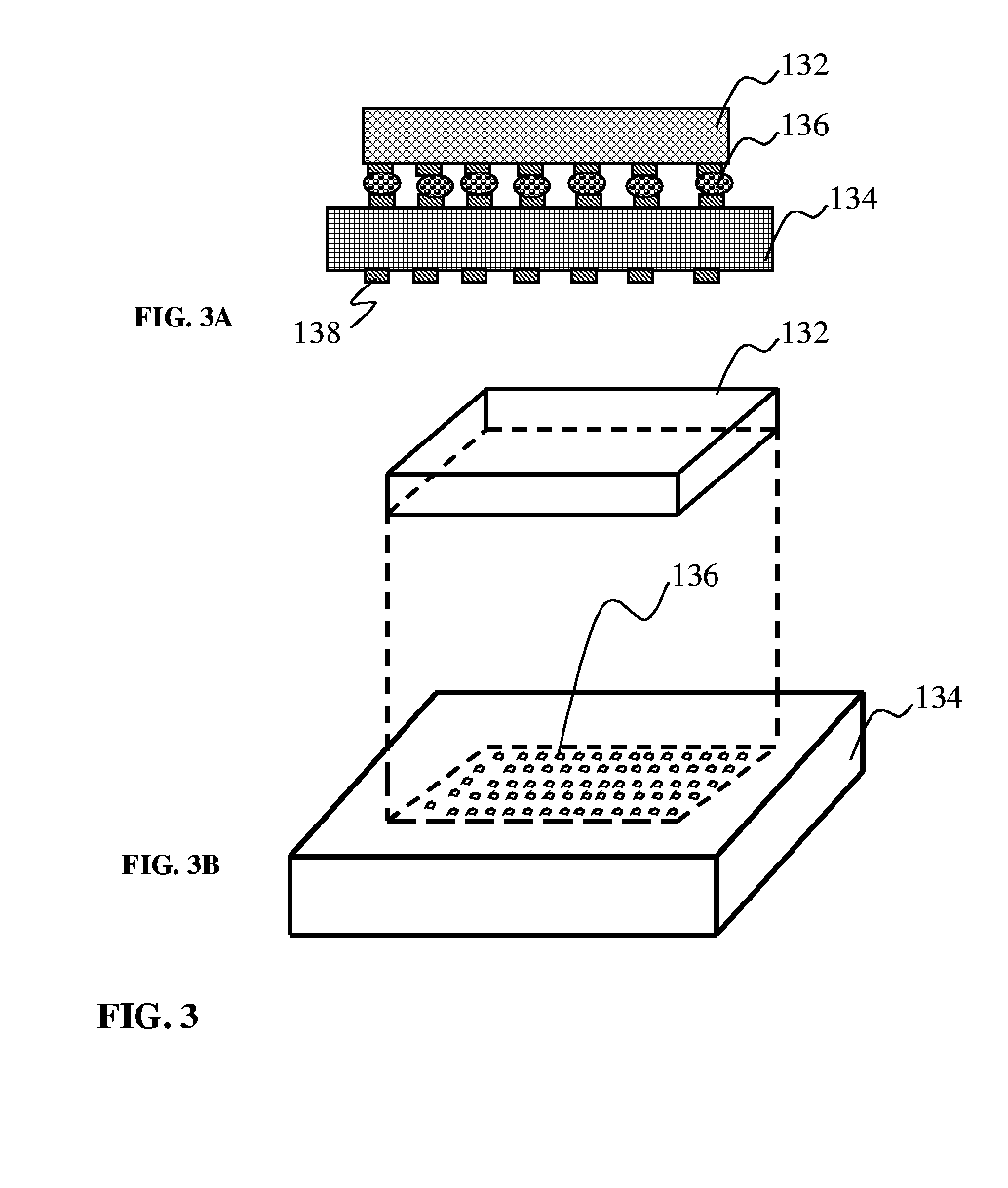

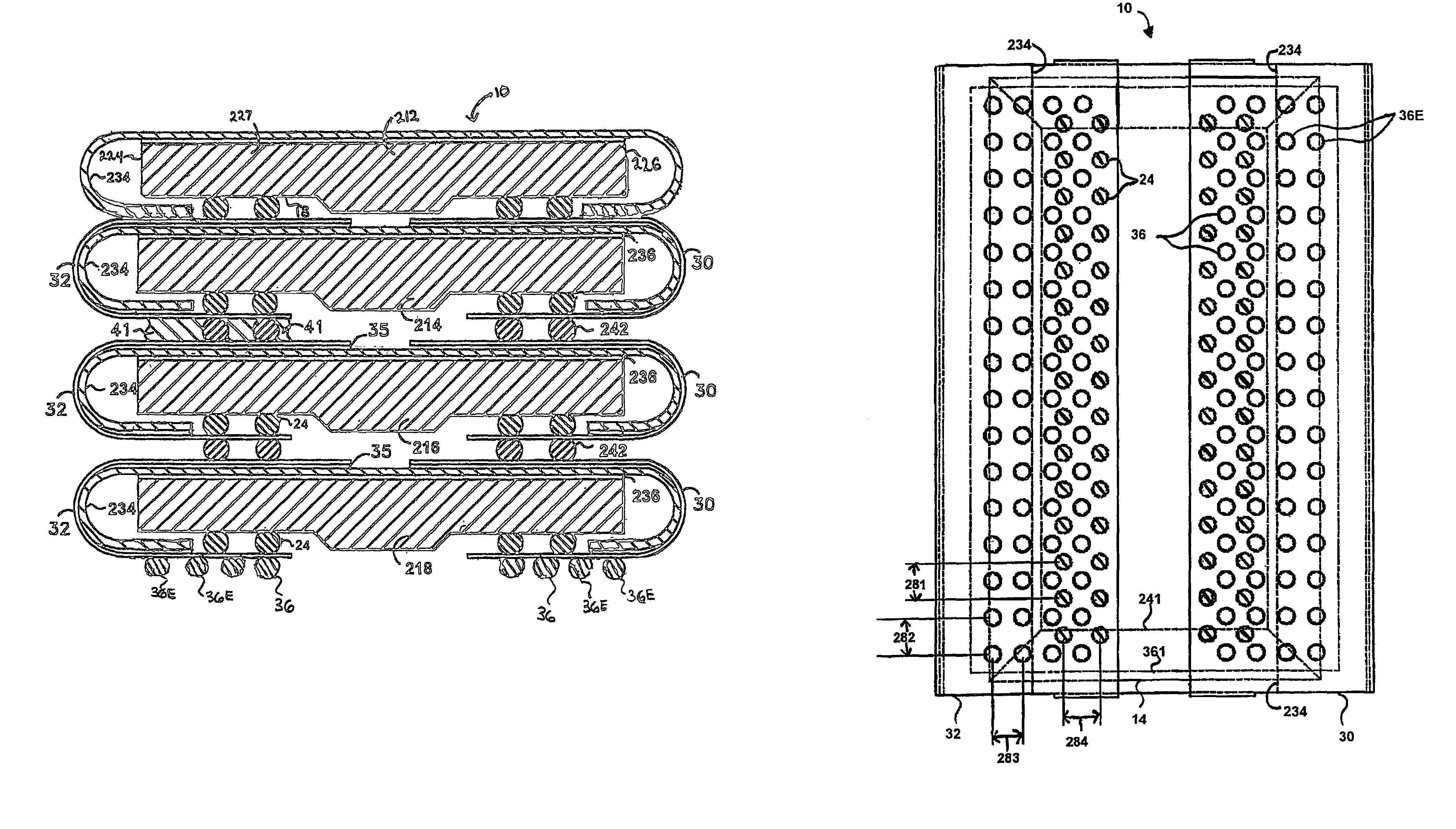

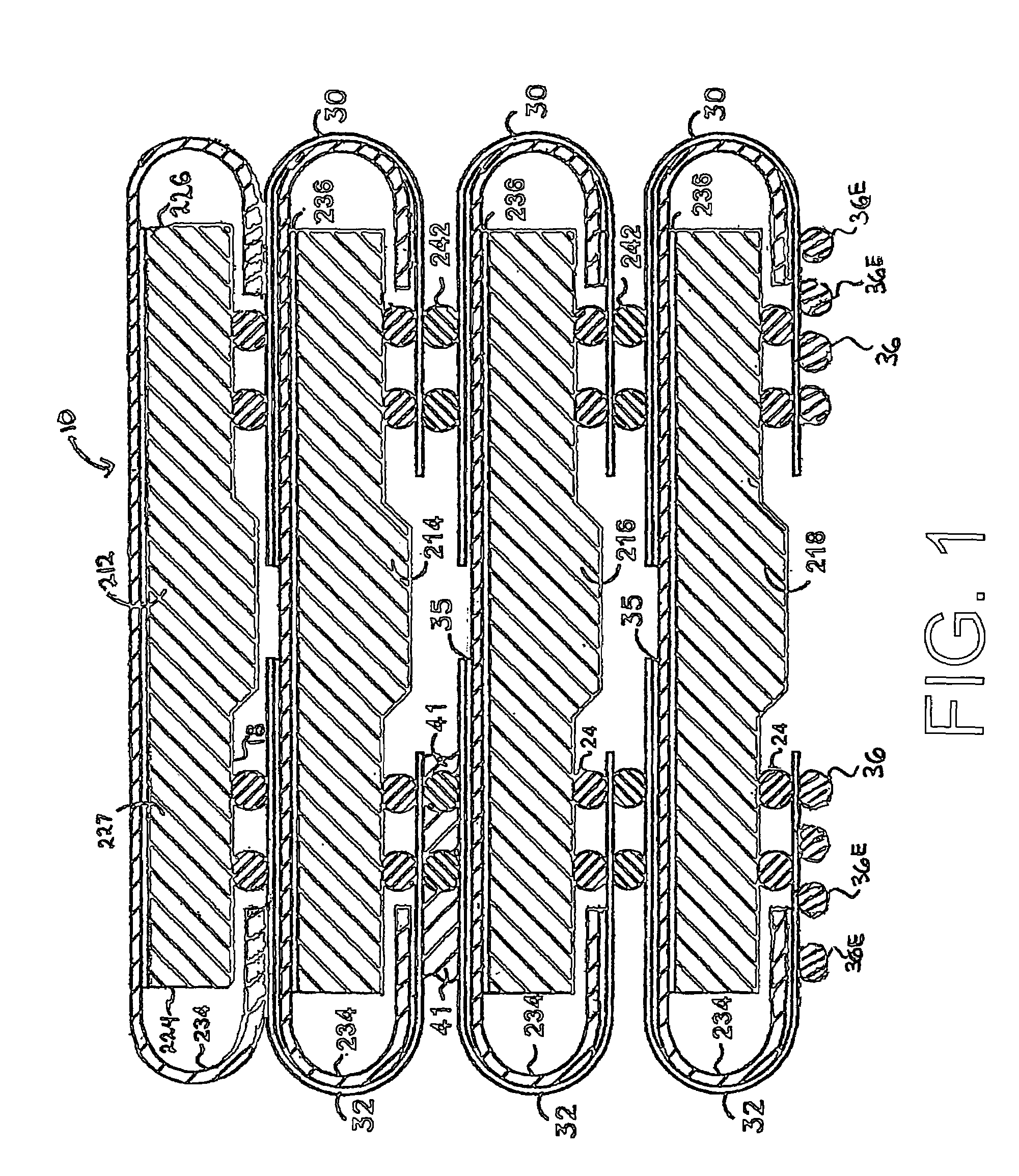

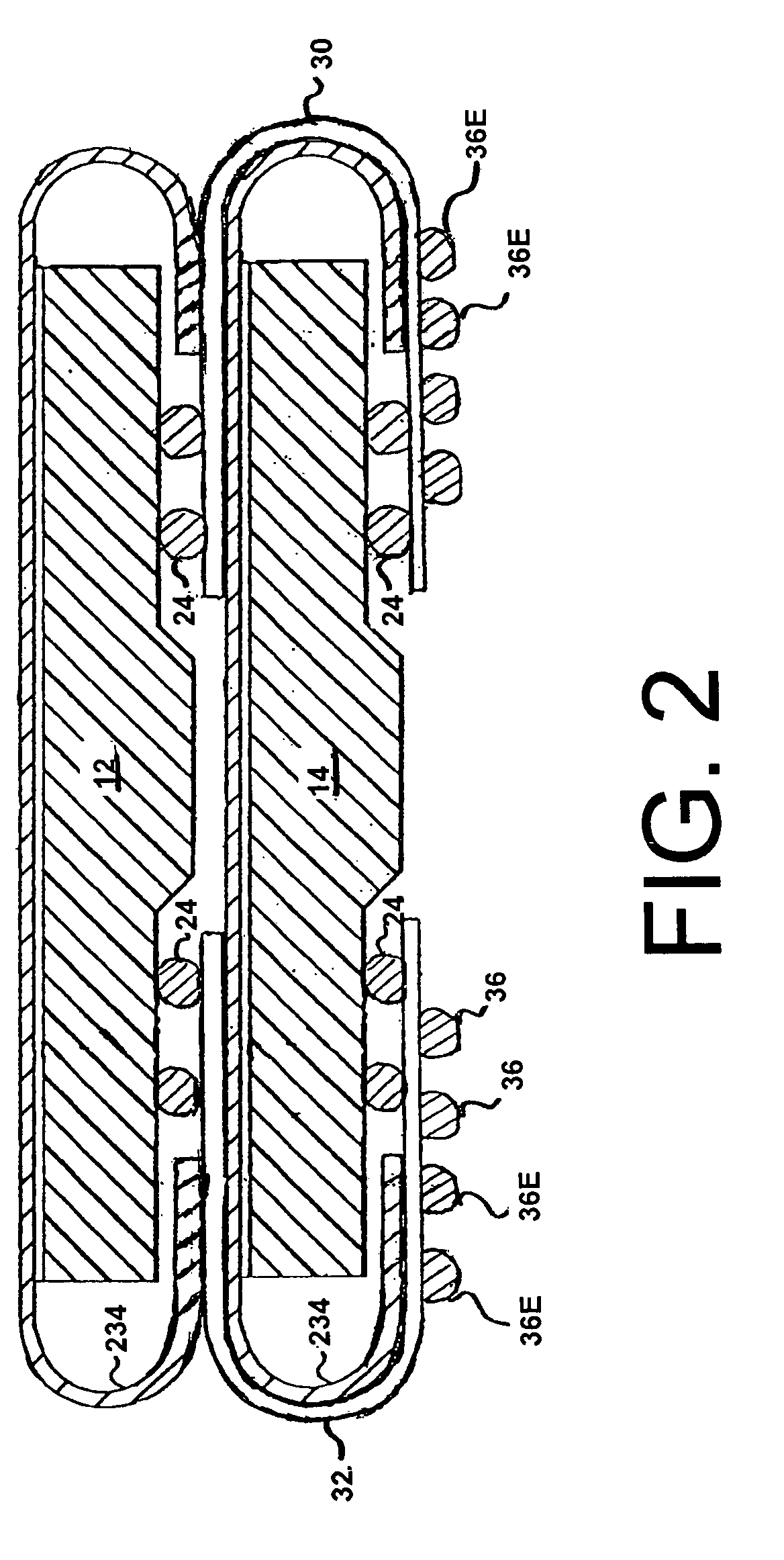

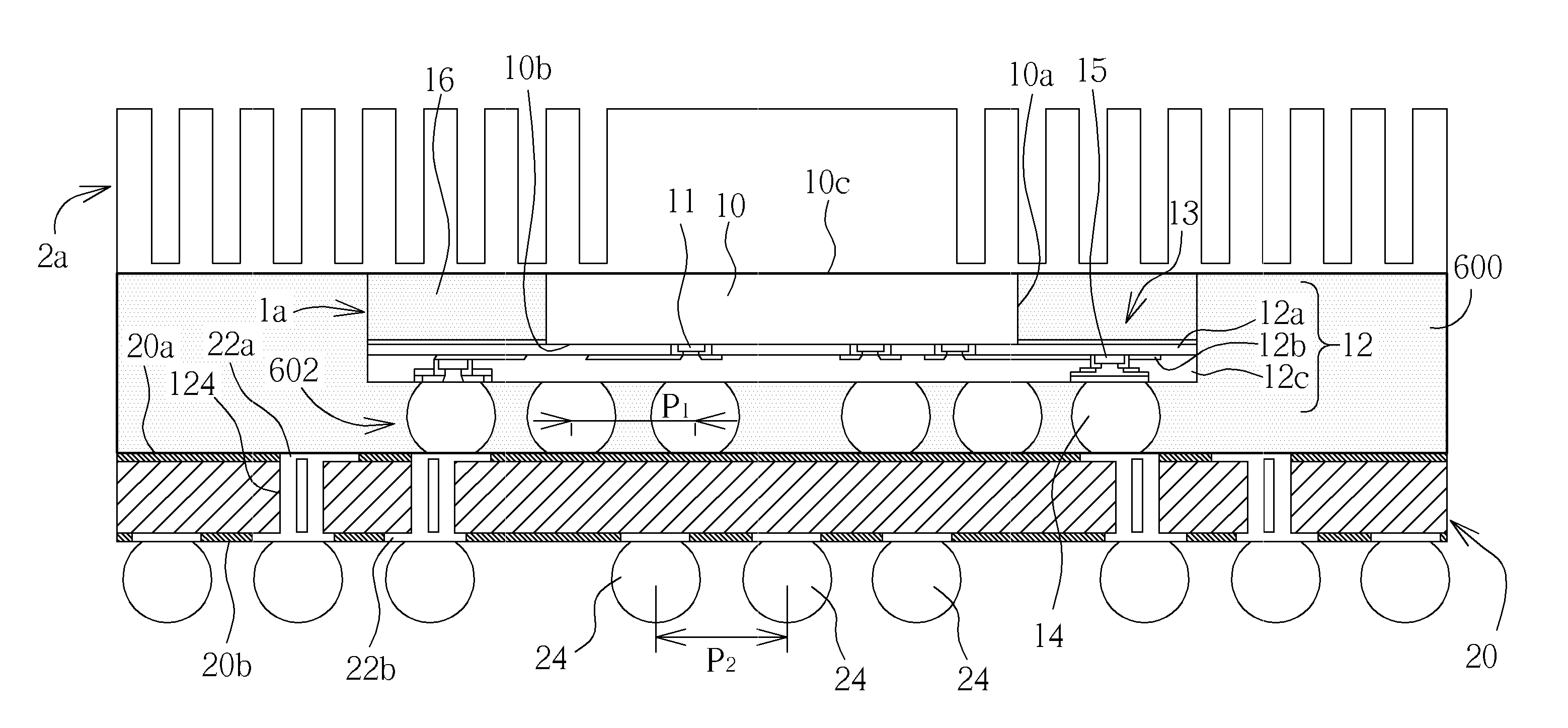

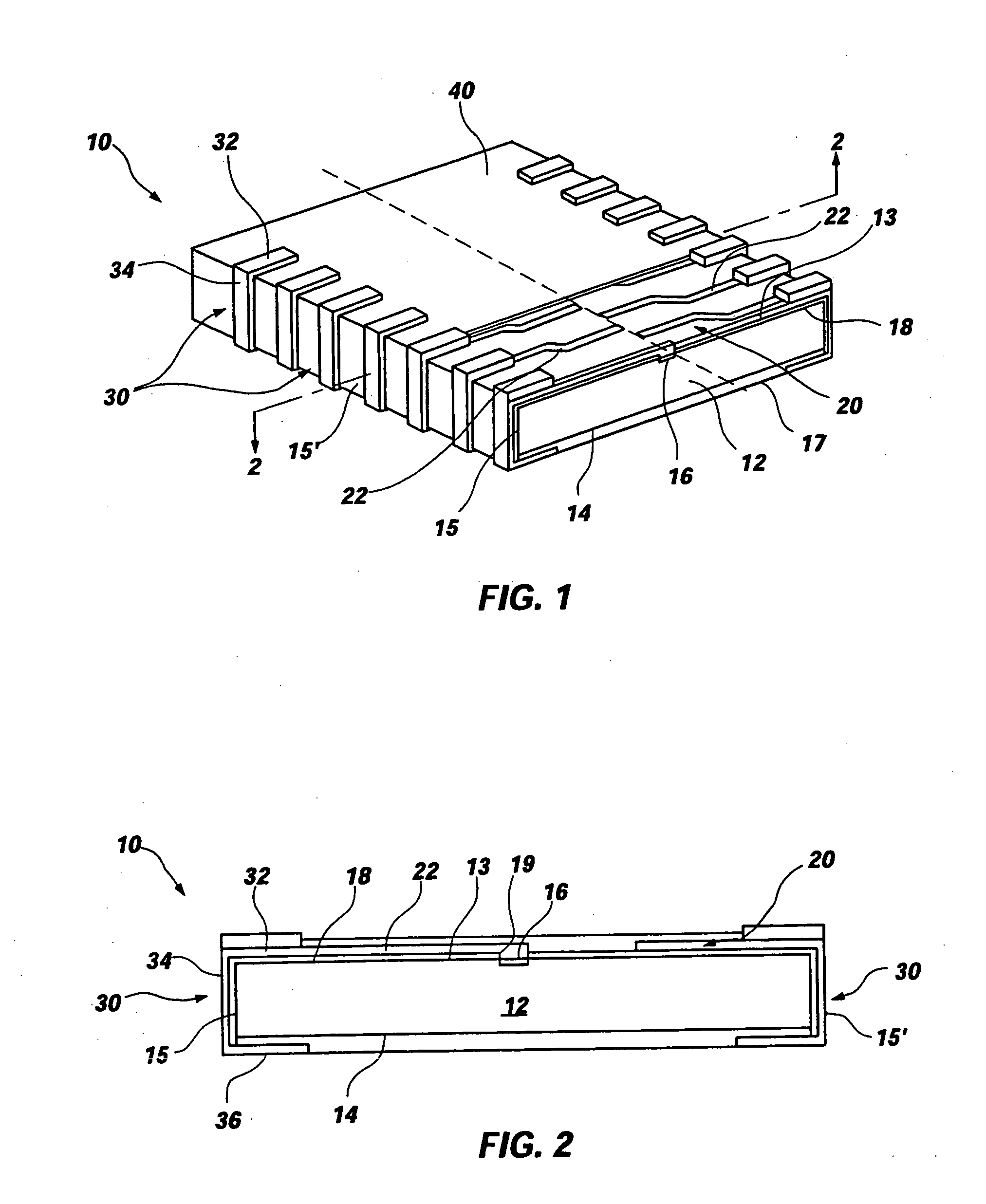

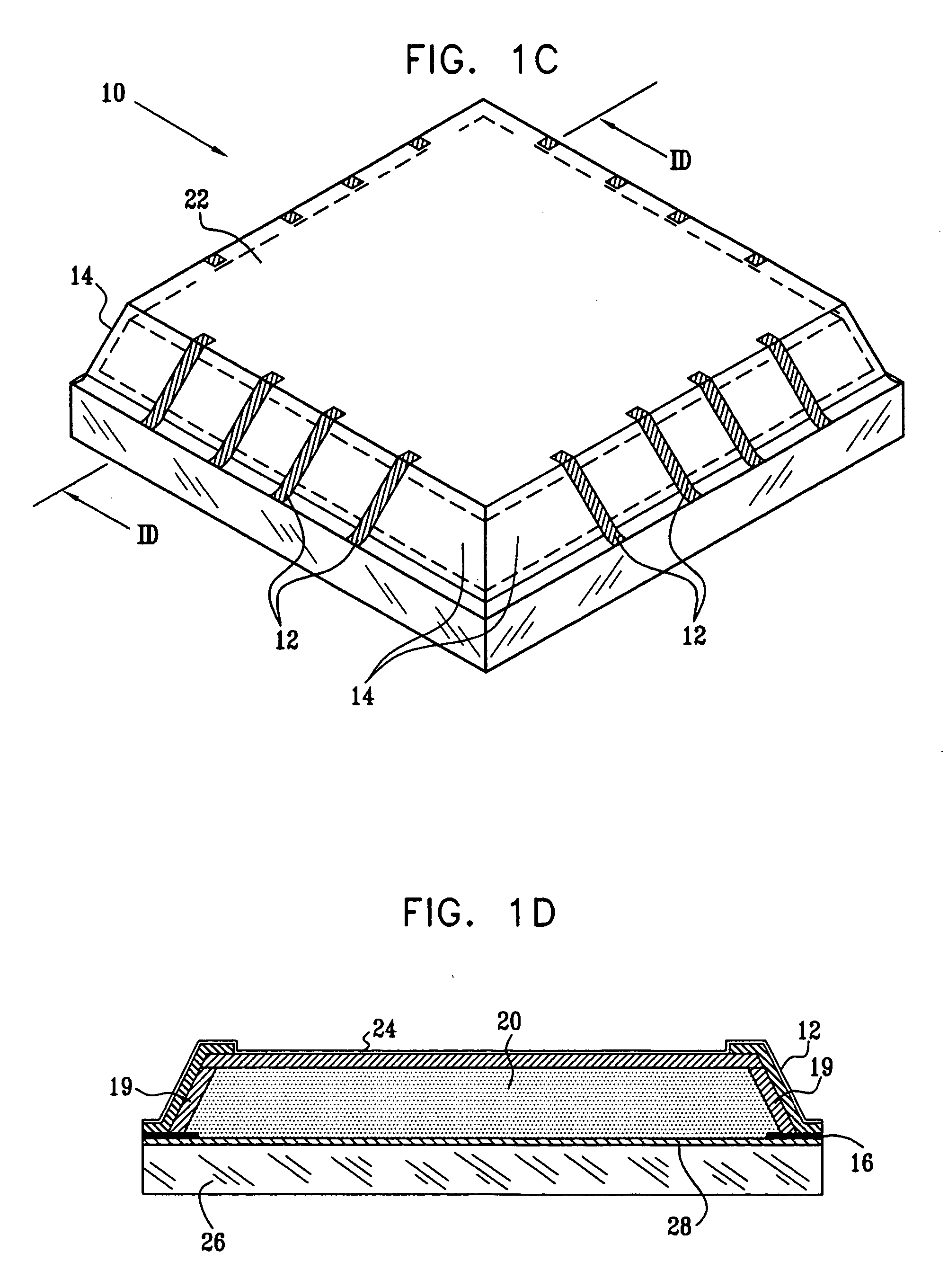

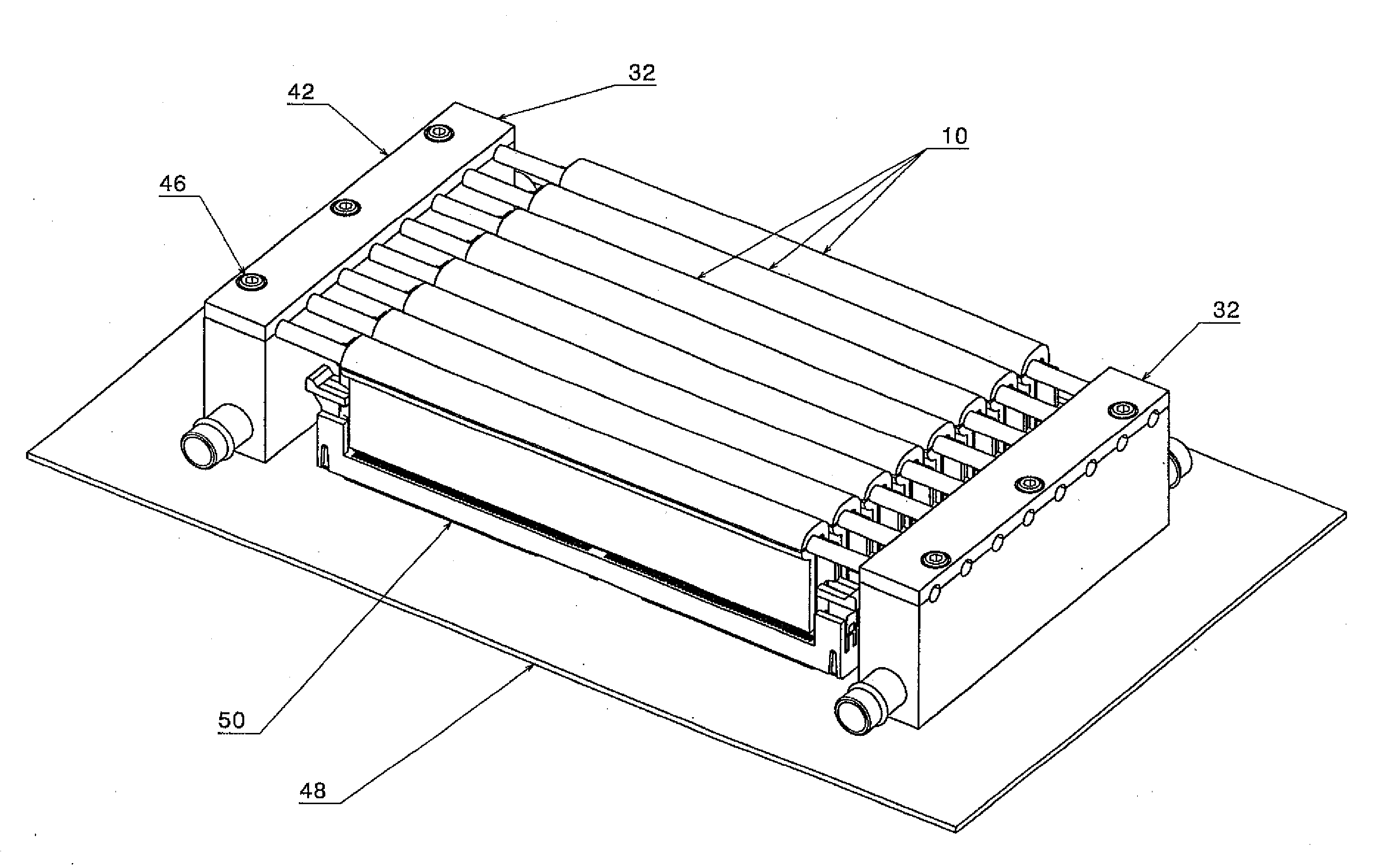

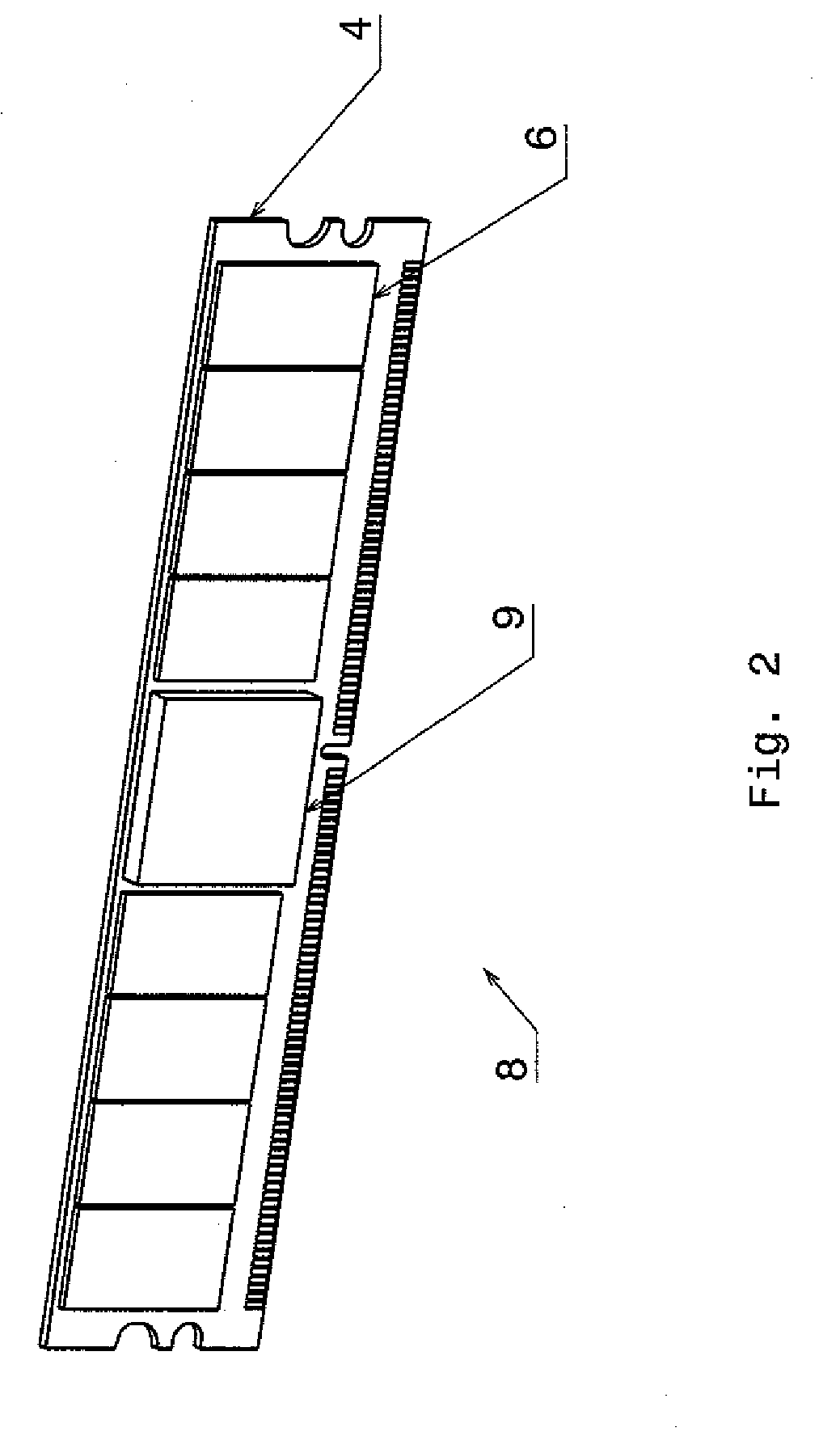

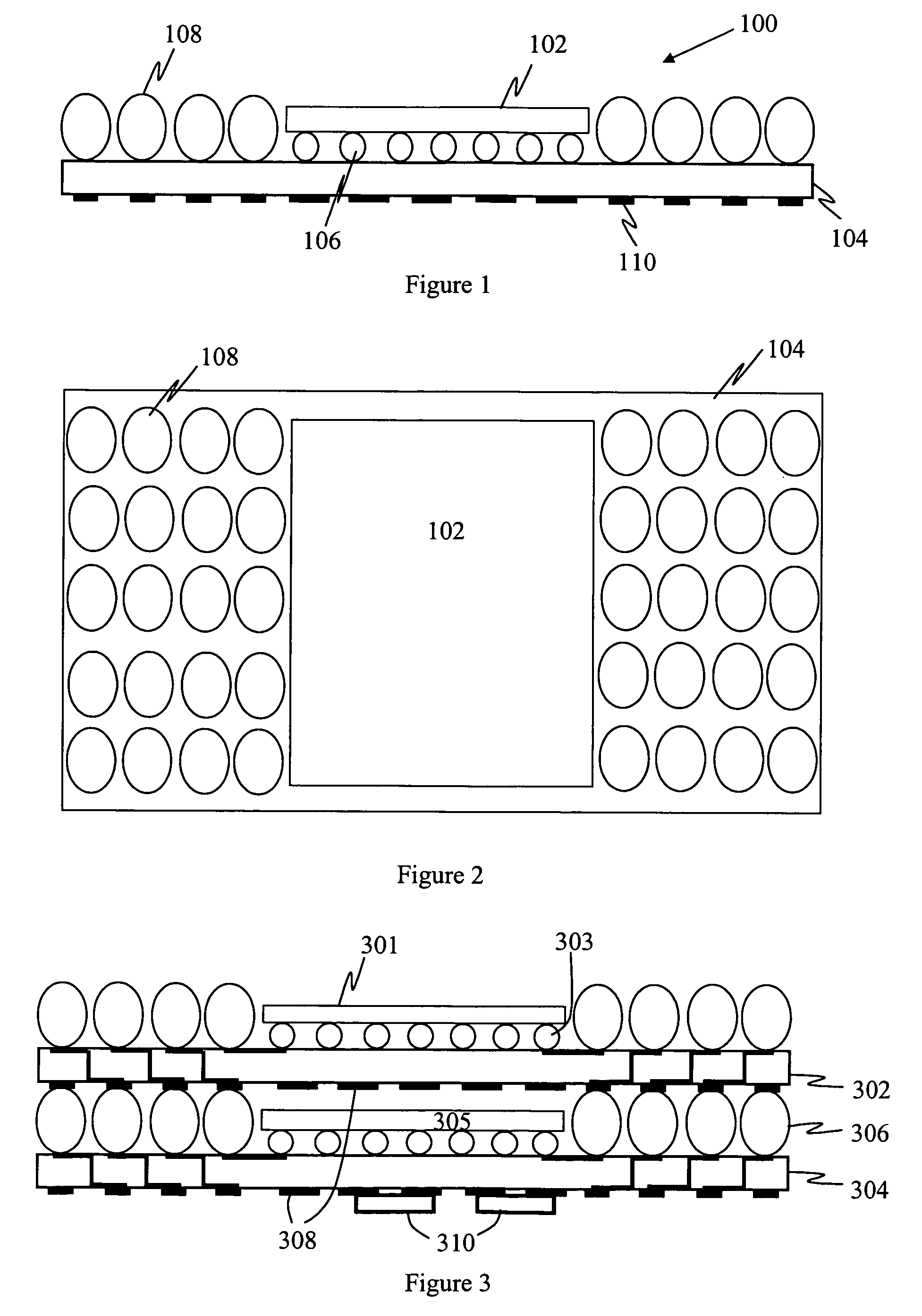

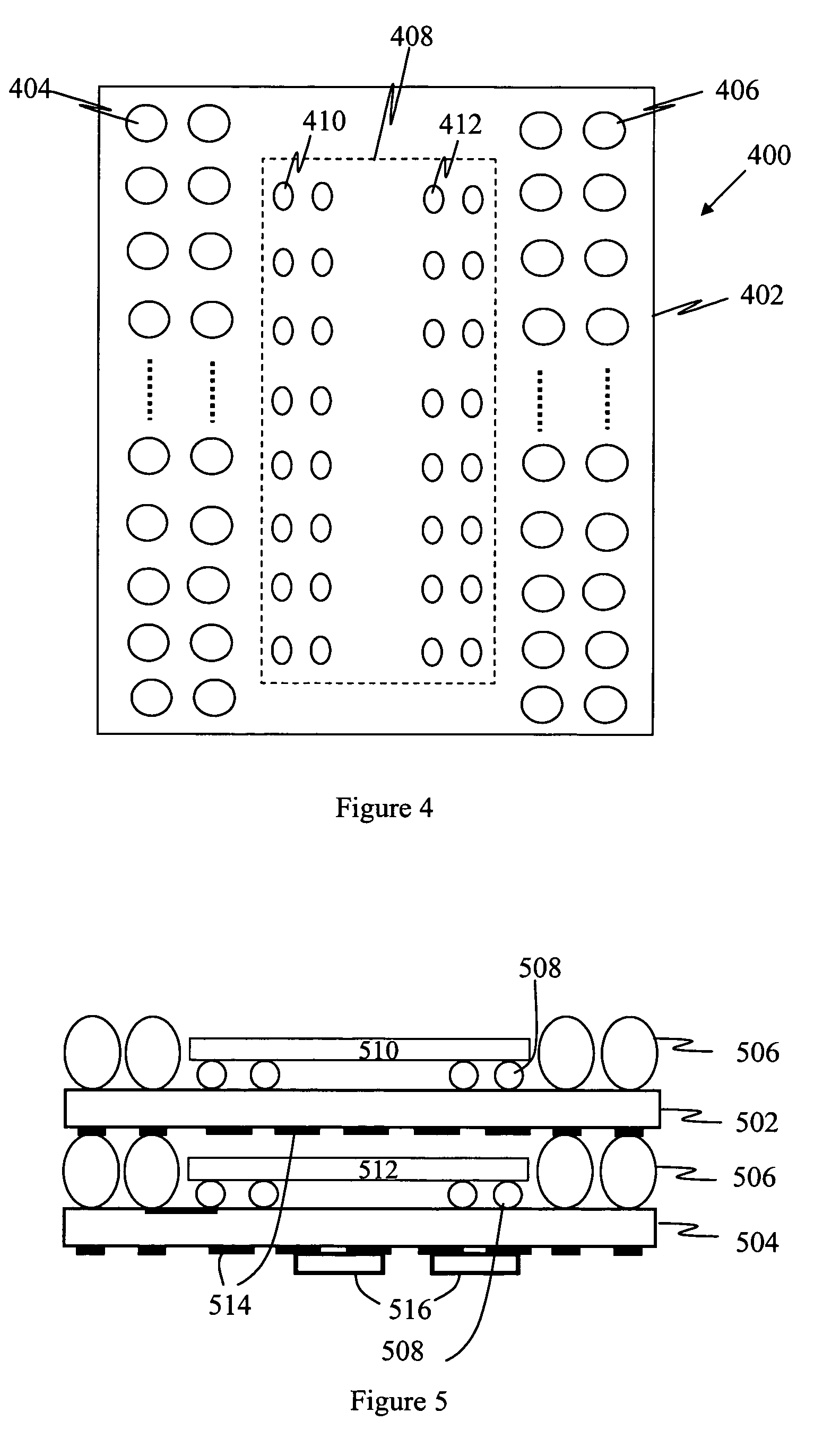

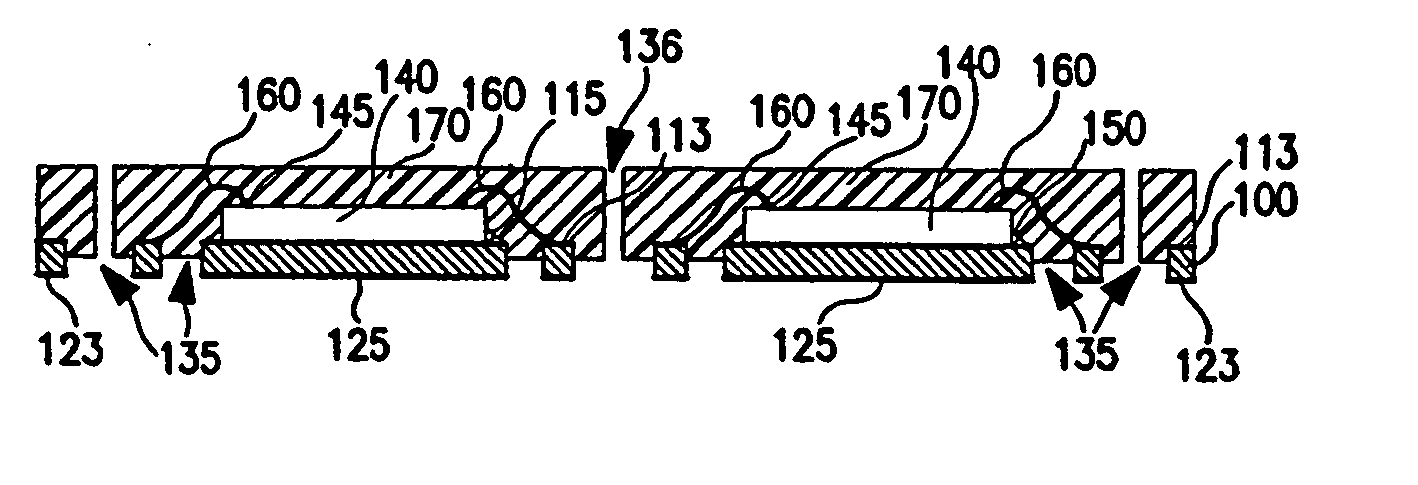

Pitch change and chip scale stacking system

InactiveUS7053478B2Printed circuit assemblingSemiconductor/solid-state device detailsHigh densityFlexible circuits

The present invention stacks integrated circuits into modules that conserve board surface area. In a two-high stack or module devised in accordance with a preferred embodiment of the present invention, a pair of integrated circuits is stacked, with one integrated circuit above the other. The two integrated circuits are connected with a pair of flexible circuit structures. Each of the pair of flexible circuit structures is partially wrapped about a respective opposite lateral edge of the lower integrated circuit of the module. The flex circuit pair connects the upper and lower integrated circuits and provides a thermal and electrical path connection path between the module and its application environment. The module has a ballout pattern with a different pitch and / or supplemental module contacts devised to allow combined signaling to the integrated circuits through contacts having a desired ballout footprint. The present invention may be employed to advantage in numerous configurations and combinations of integrated circuits in modules provided for high-density memories or high capacity computing.

Owner:TAMIRAS PER PTE LTD LLC

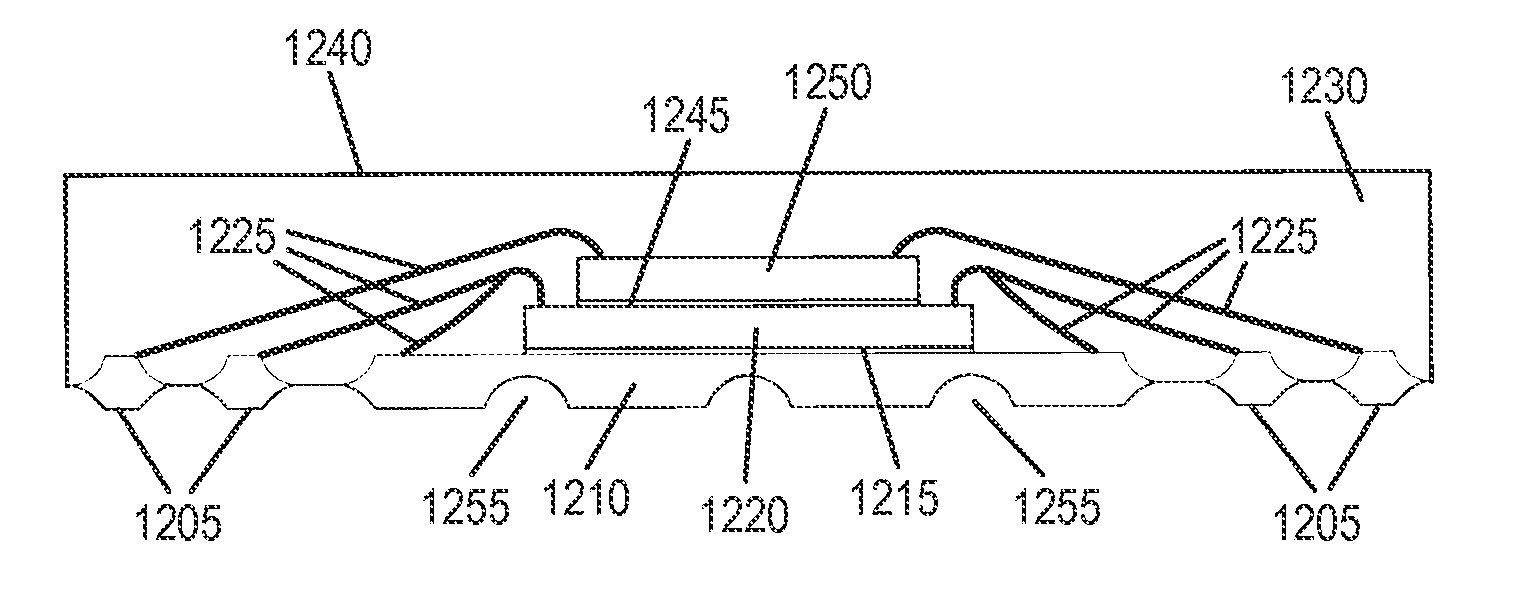

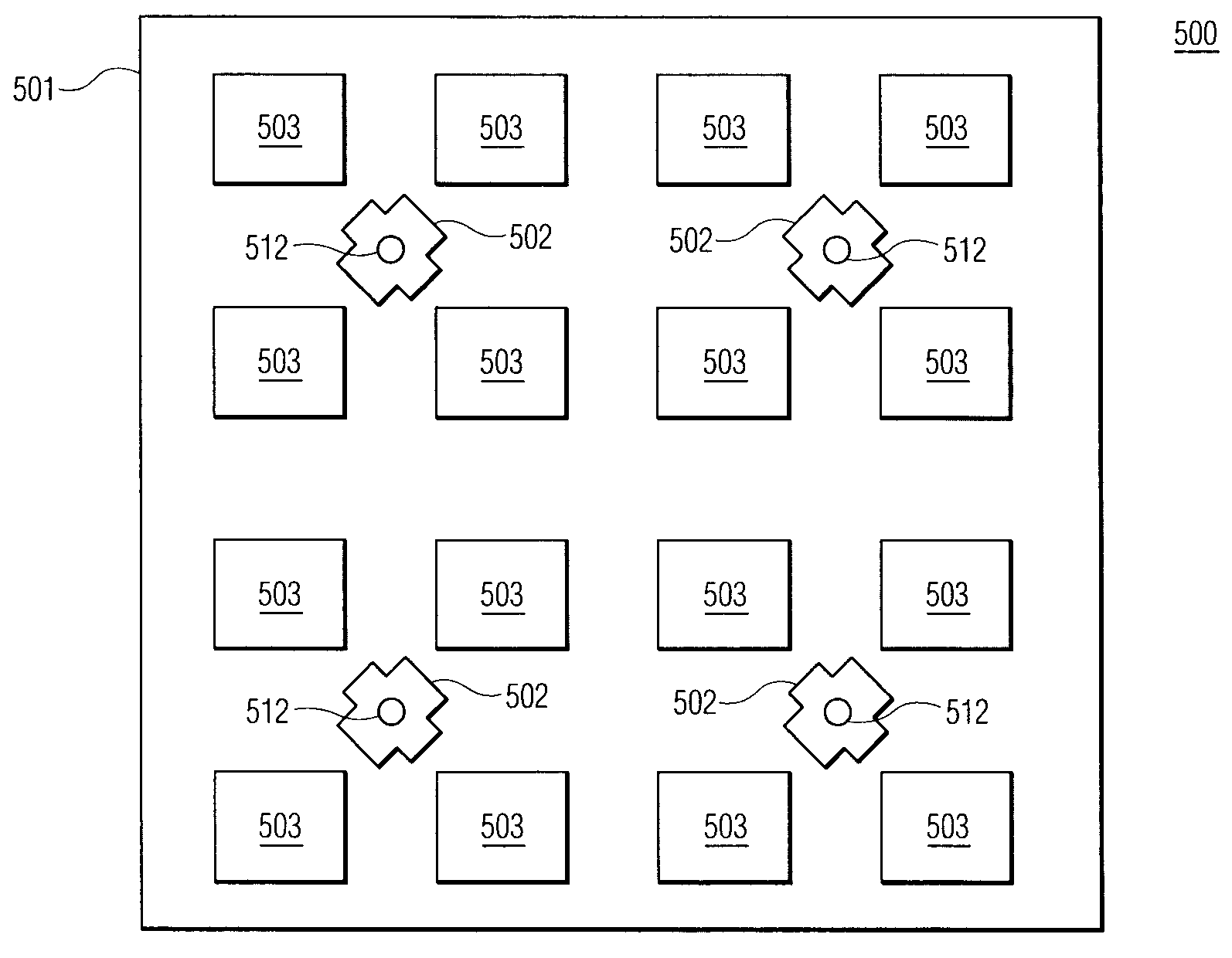

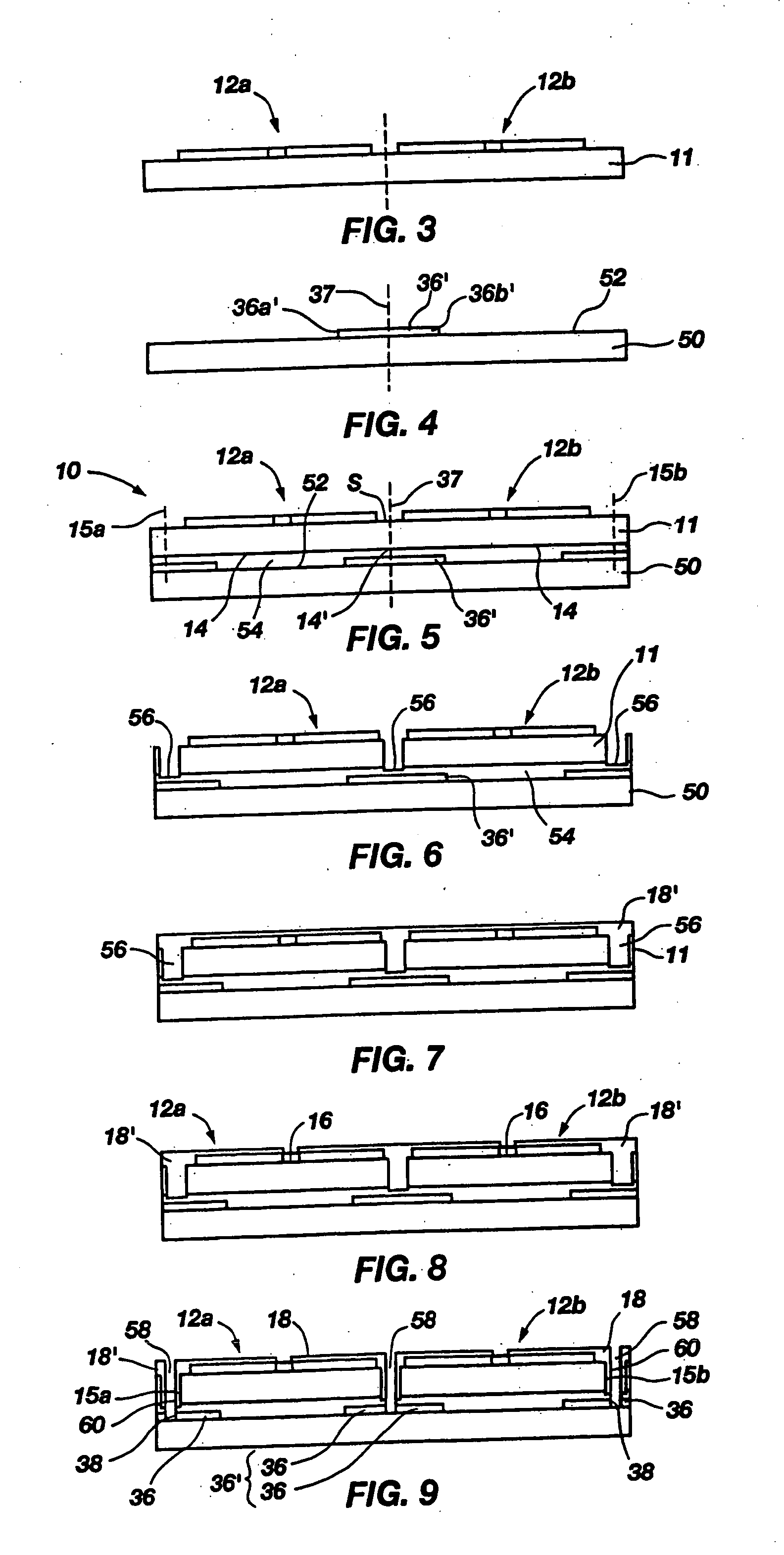

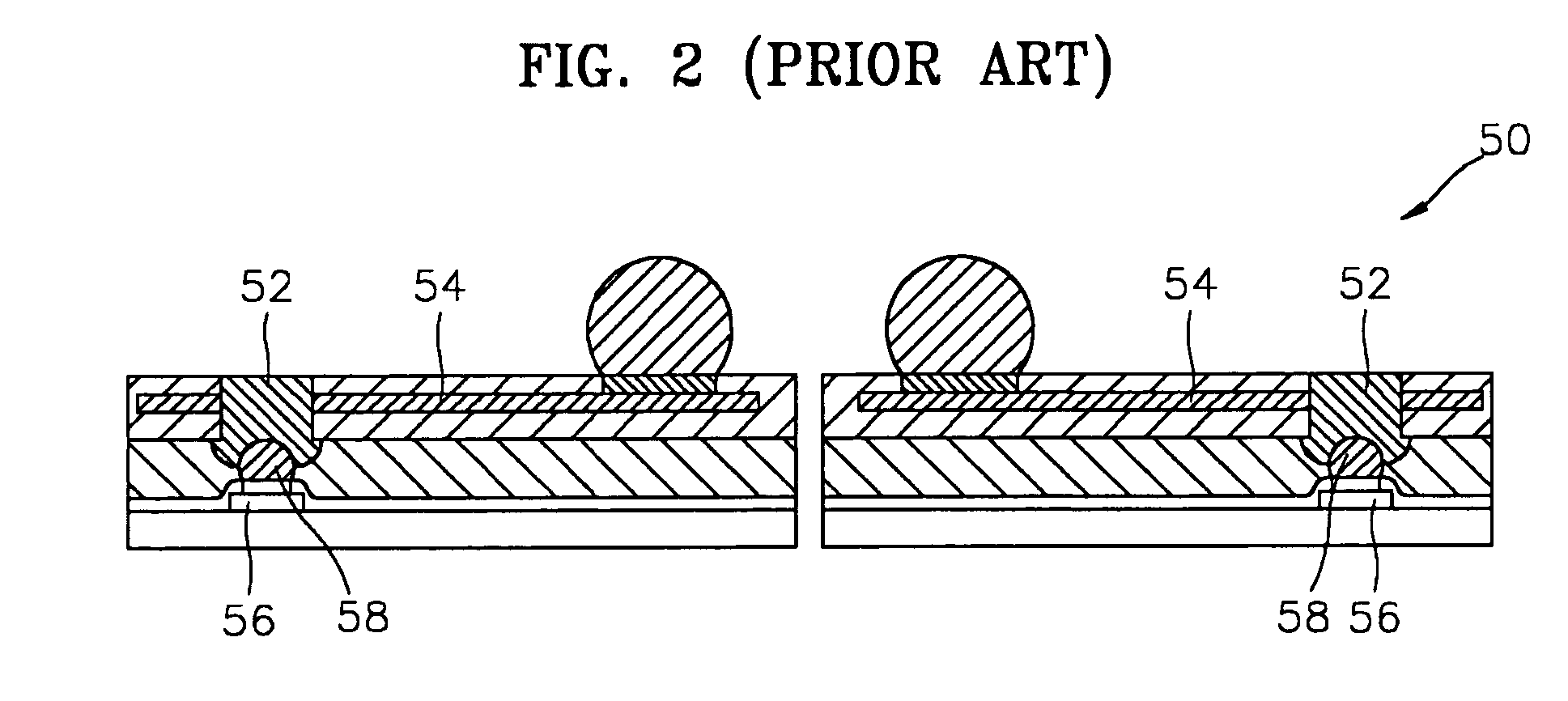

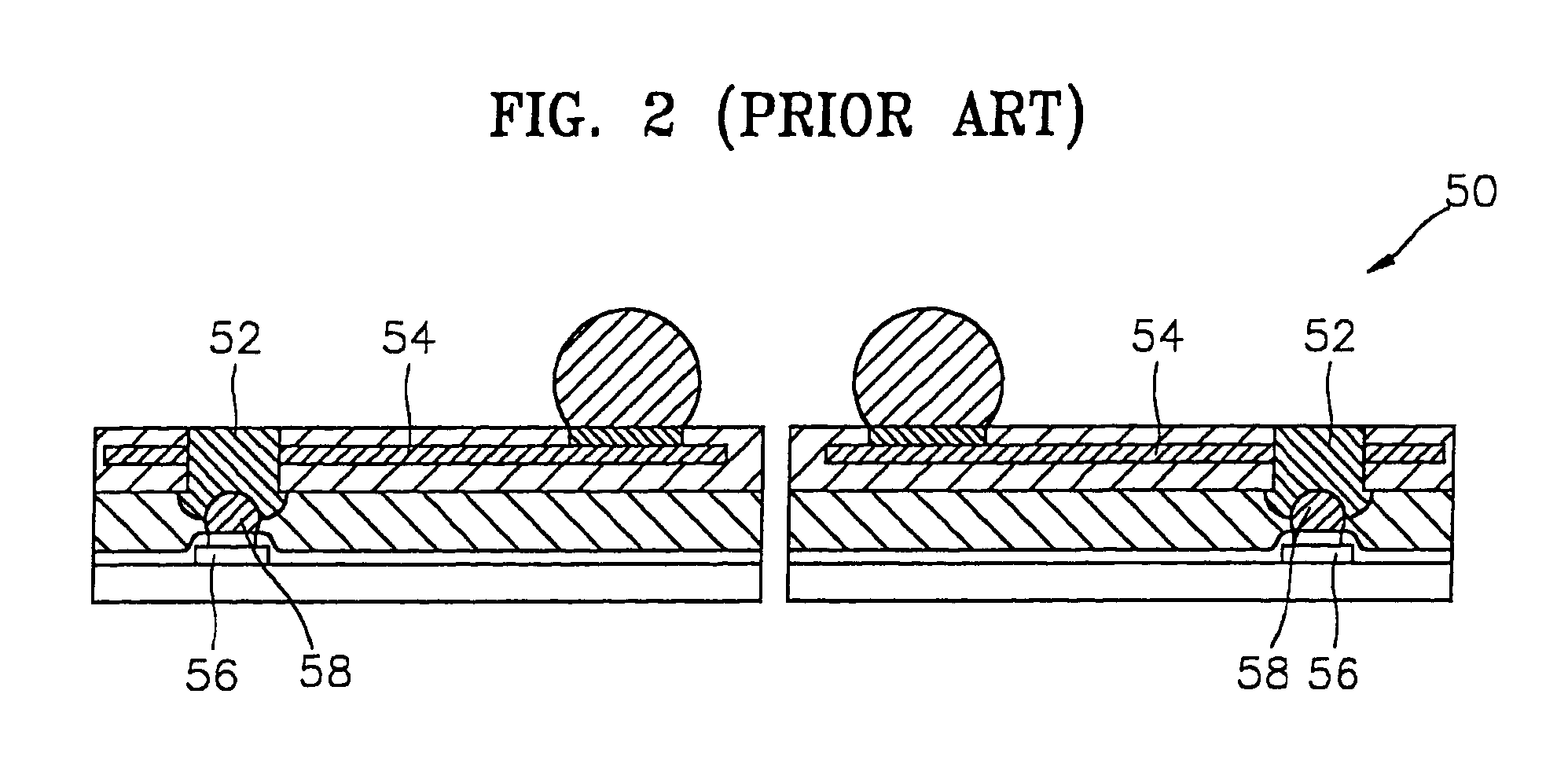

Method for manufacturing wafer level chip scale package using redistribution substrate

InactiveUS20060079019A1Increase widthIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringChip-scale package

The present invention provides a method for manufacturing a wafer level chip scale package using a redistribution substrate, which has patterned bump pairs connected by redistribution lines and formed on a transparent insulating substrate. The redistribution substrate is produced separately from a wafer and then bonded to the wafer. One part of each bump pair is in contact with a chip pad on the active surface of the wafer, and the other part coincides with one of holes formed in the wafer. Conductive lines are formed in the holes and on the non-active surface of the wafer. External connection terminals are formed on the conductive lines at the non-active surface.

Owner:EPWORKS

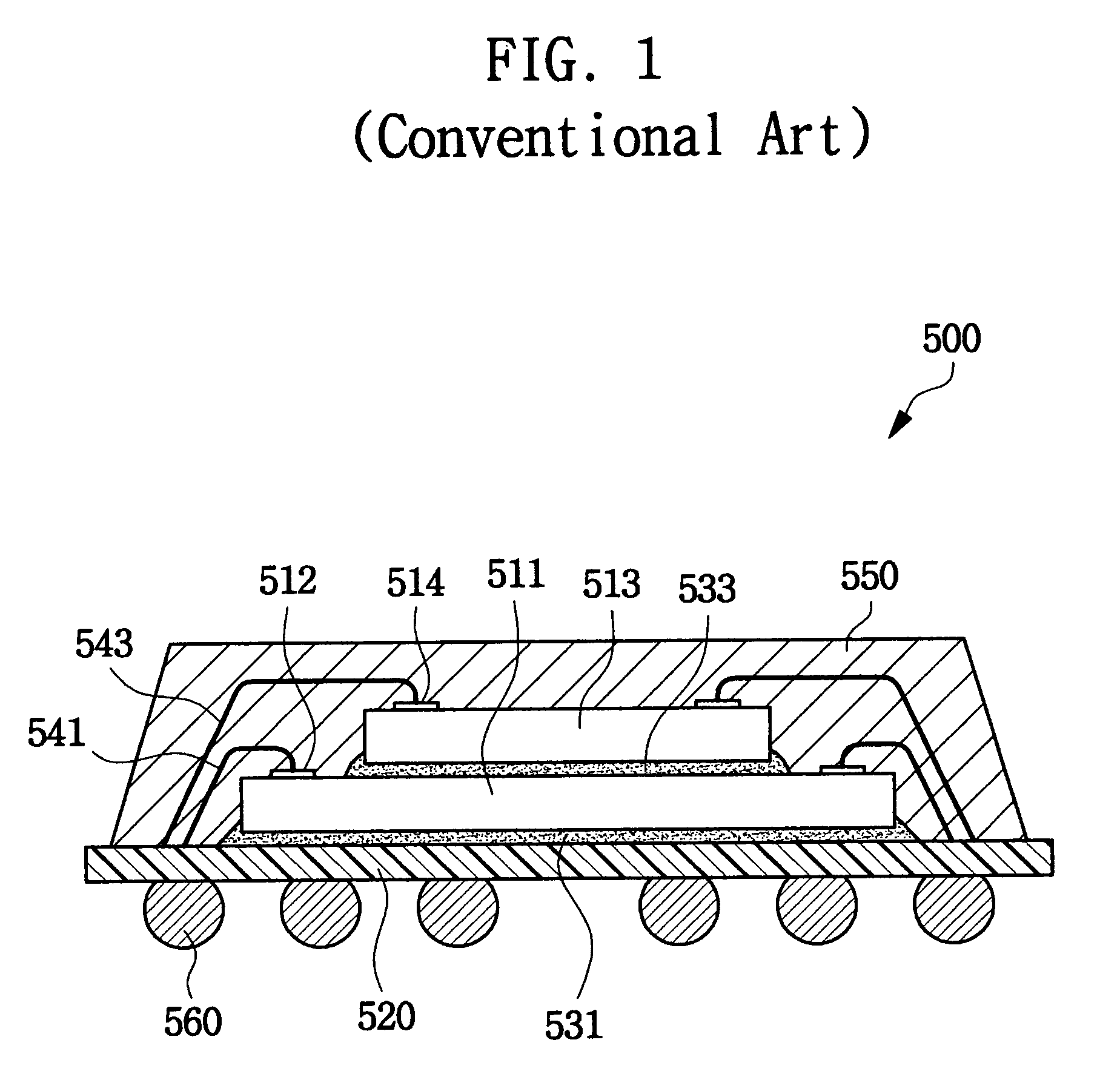

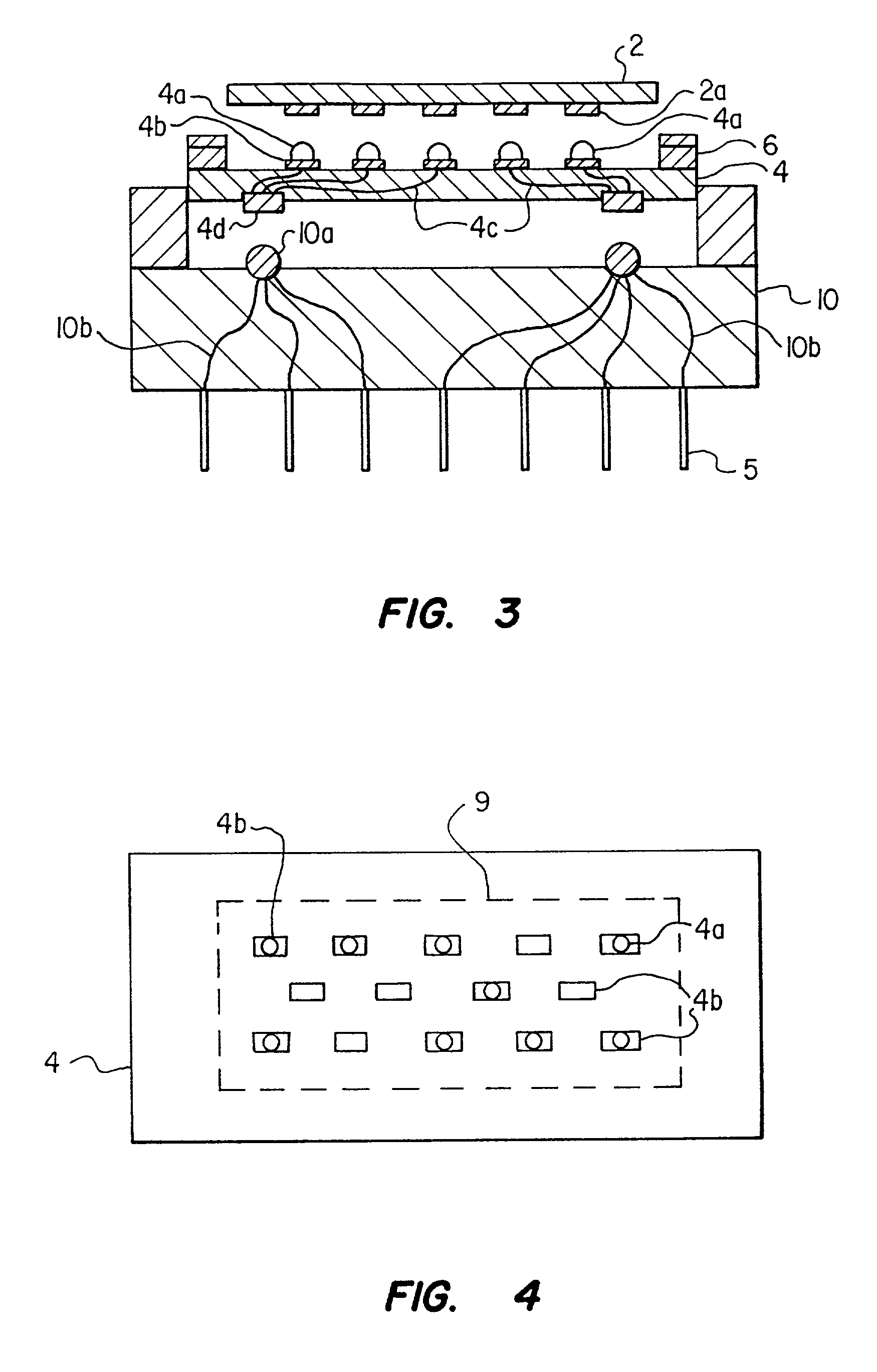

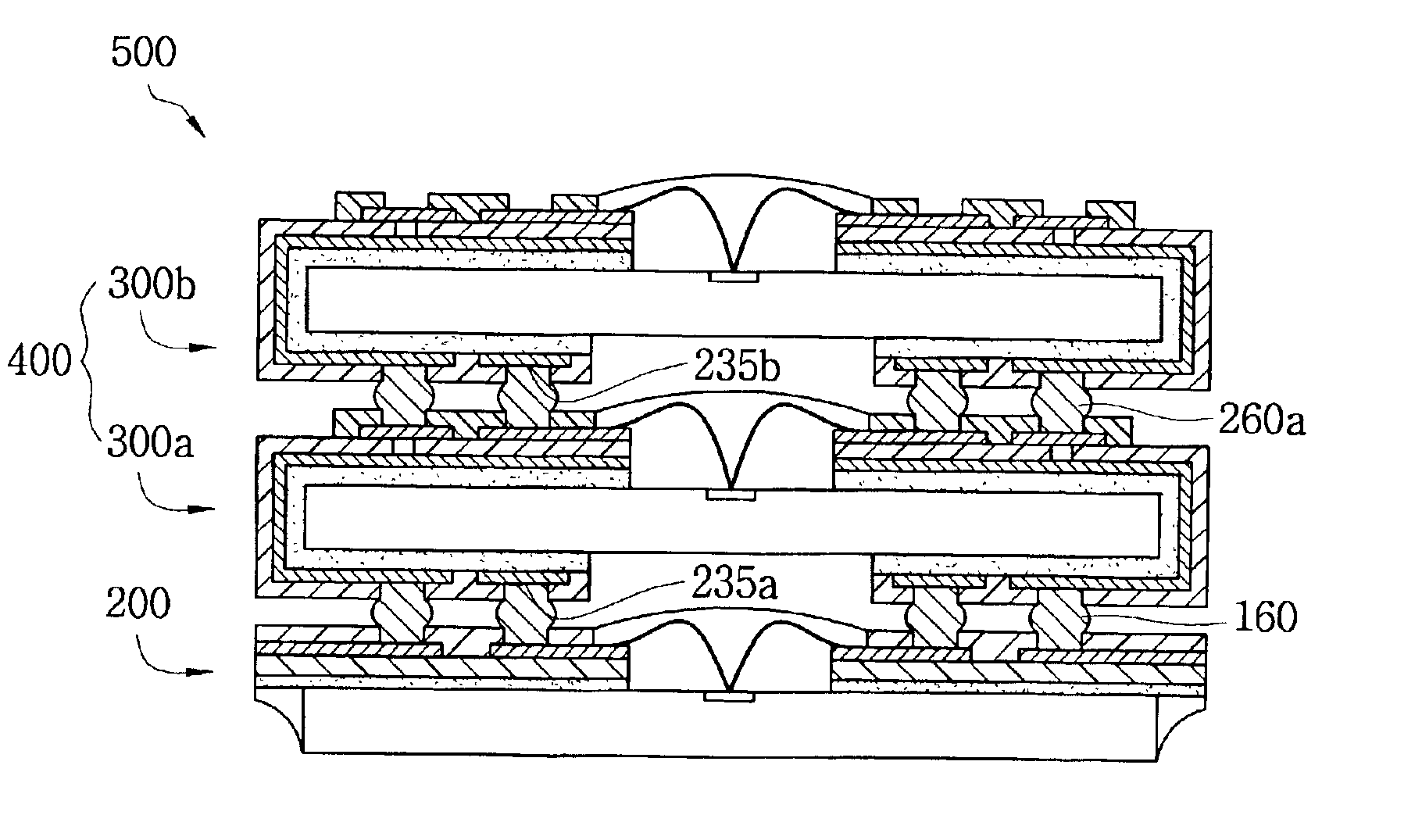

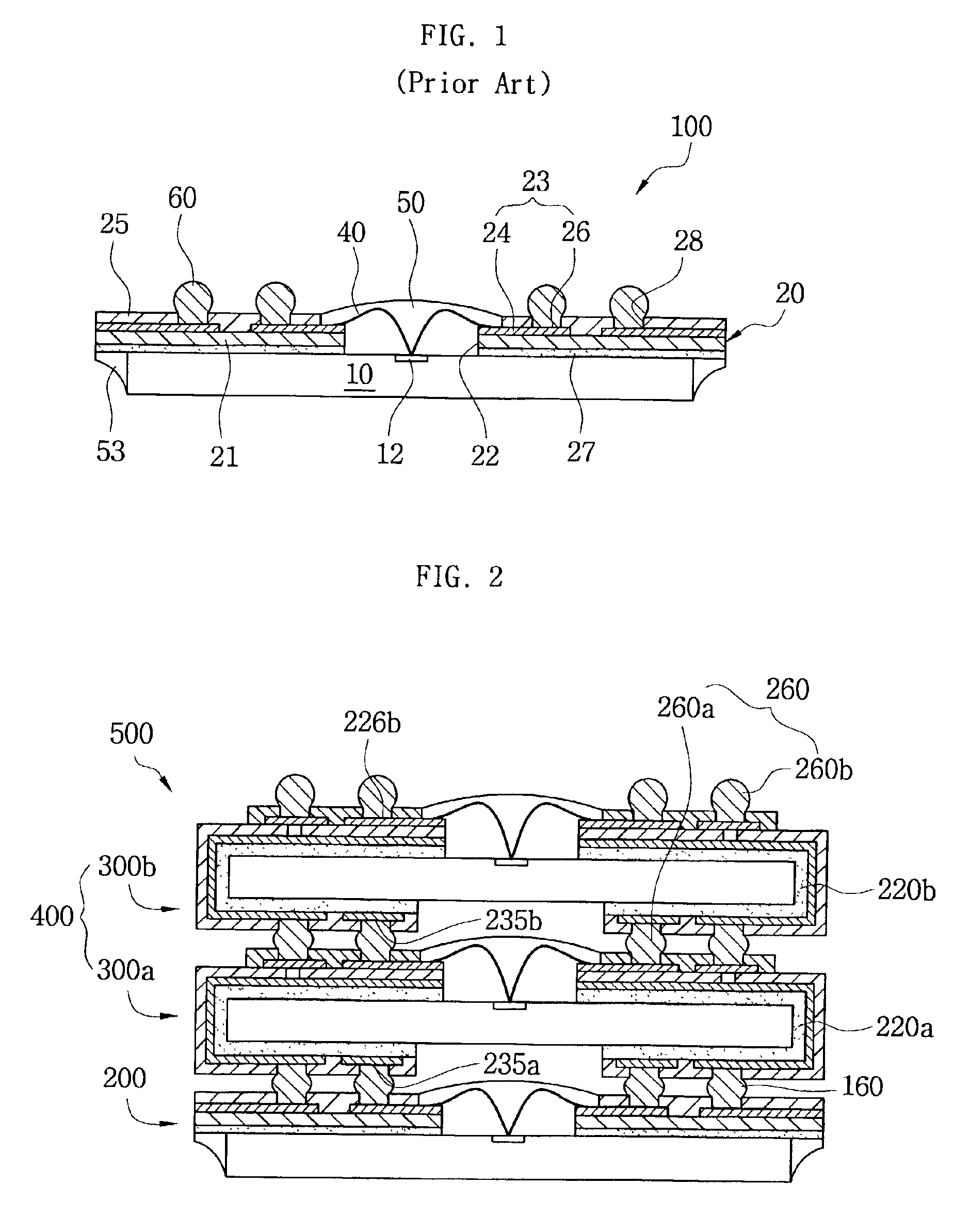

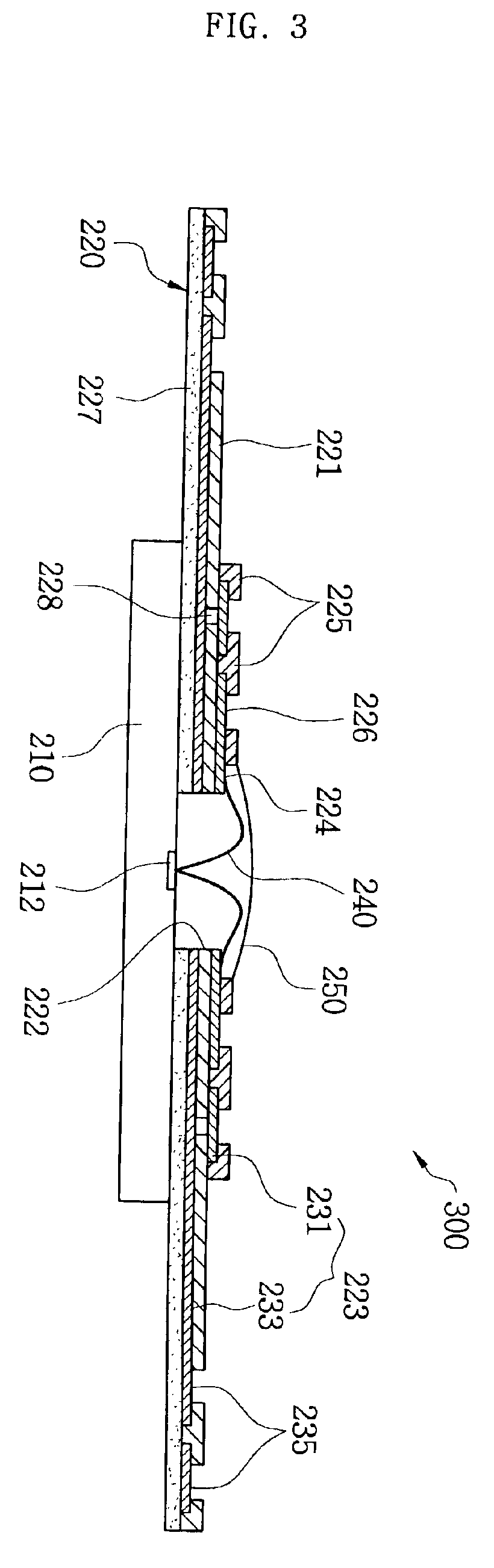

Stack package using flexible double wiring substrate

InactiveUS6876074B2Semiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

A Chip Scale Package (CSP) type unit package including a semiconductor chip and a double wiring substrate, the double wiring substrate including an adhesive and a flexible tape having an upper surface with a first wiring pattern, a lower surface with a second wiring pattern and a plurality of vias electrically connecting portions of the first and second wiring patterns. Additionally, the unit package may be stacked on a conventional base package or on another unit package, where stacked packages are electrically interconnected.

Owner:SAMSUNG ELECTRONICS CO LTD

Flip-chip package with fan-out wlcsp

ActiveUS20090294938A1Overcome limitationsCost-effectiveSemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

A flip-chip package includes a package carrier; a semiconductor die having a die face and a die edge, the semiconductor die being assembled face-down to a chip side of the package carrier, and contact pads are situated on the die face; a rewiring laminate structure between the semiconductor die and the package carrier, the rewiring laminate structure including a re-routed metal layer, and at least a portion of the re-routed metal layer projects beyond the die edge; and bumps arranged on the rewiring laminate structure for electrically connecting the semiconductor die with the package carrier.

Owner:MEDIATEK INC

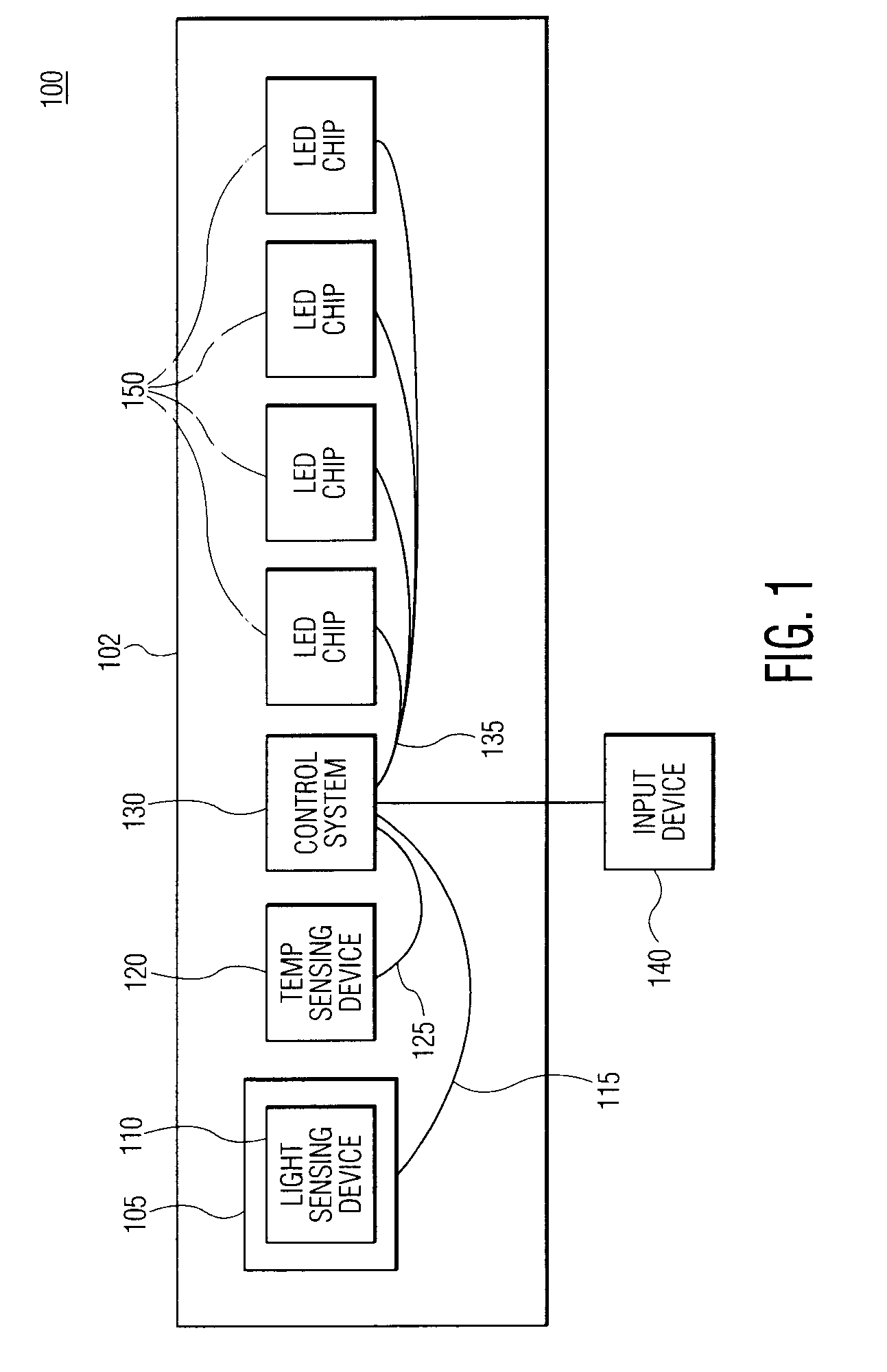

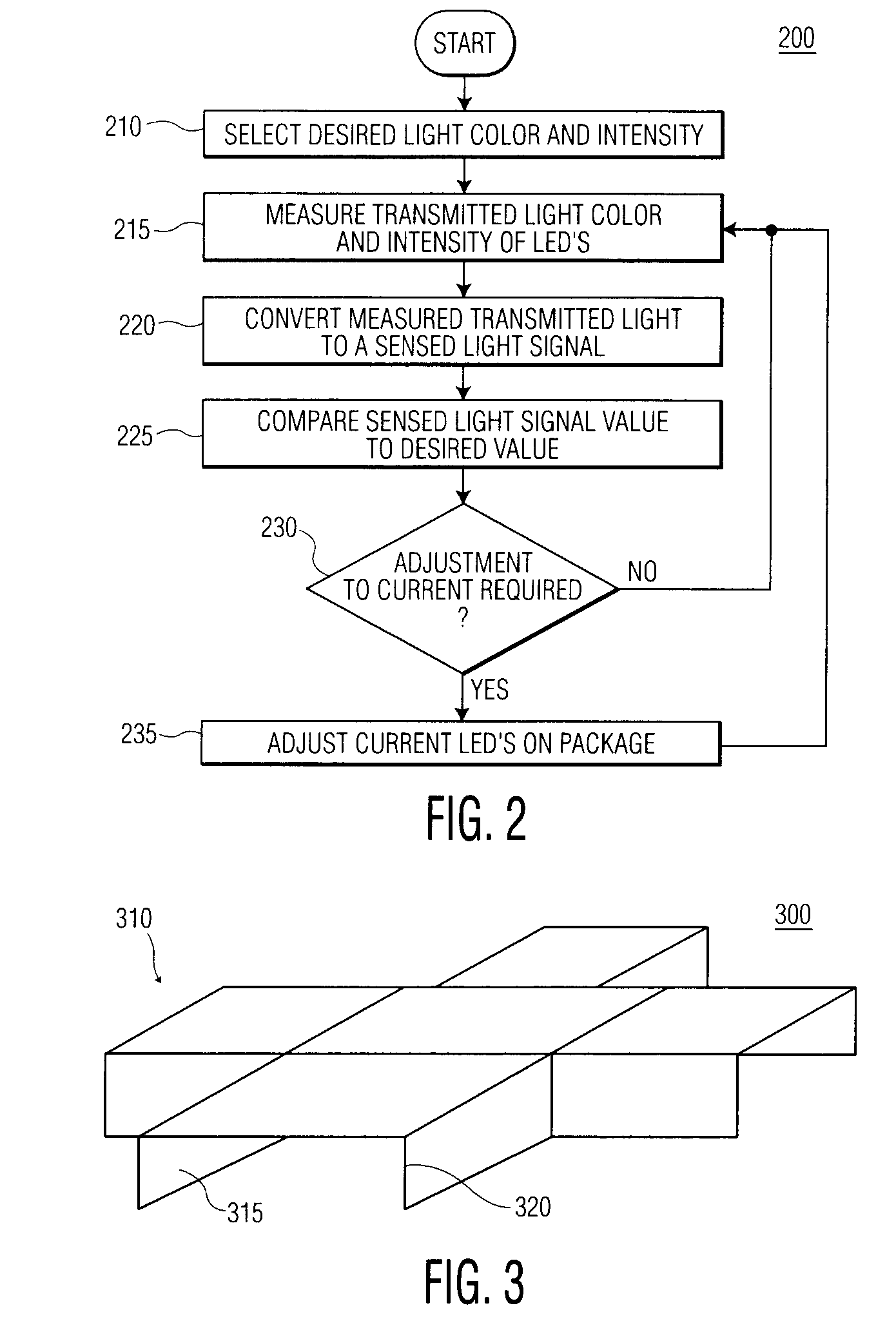

Method for maintaining light characteristics from a multi-chip LED package

InactiveUS6998594B2Maintaining light characteristicNon-electric lightingPhotometry using reference valueLight-emitting diodeChip-scale package

The present invention provides a method, system and structure for maintaining light characteristics from a multi-chip LED package. This may be done by selecting a desired light output and restricting light from a plurality of light emitting diodes in the multi-chip LED package. It may also be done by measuring the restricted light, comparing the measured output light to the desired light and by adjusting current to LEDs in the multi-chip LED package based on the measured light.

Owner:SIGNIFY HLDG BV

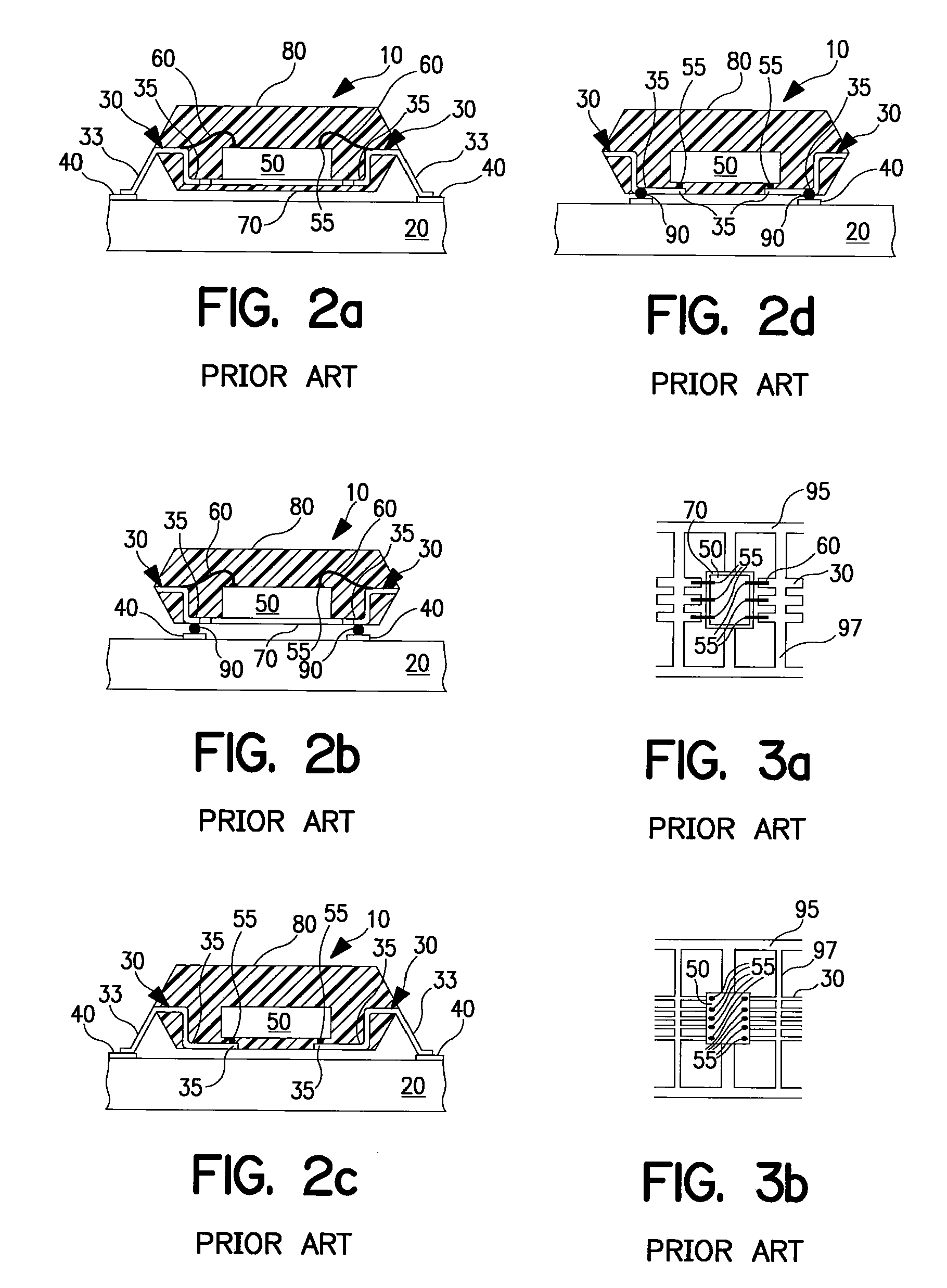

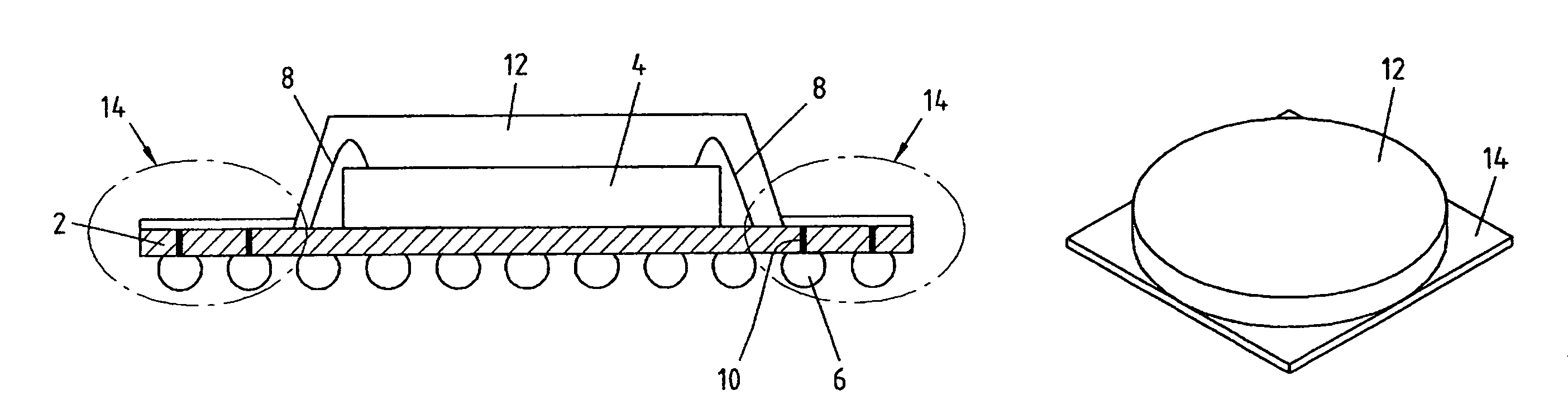

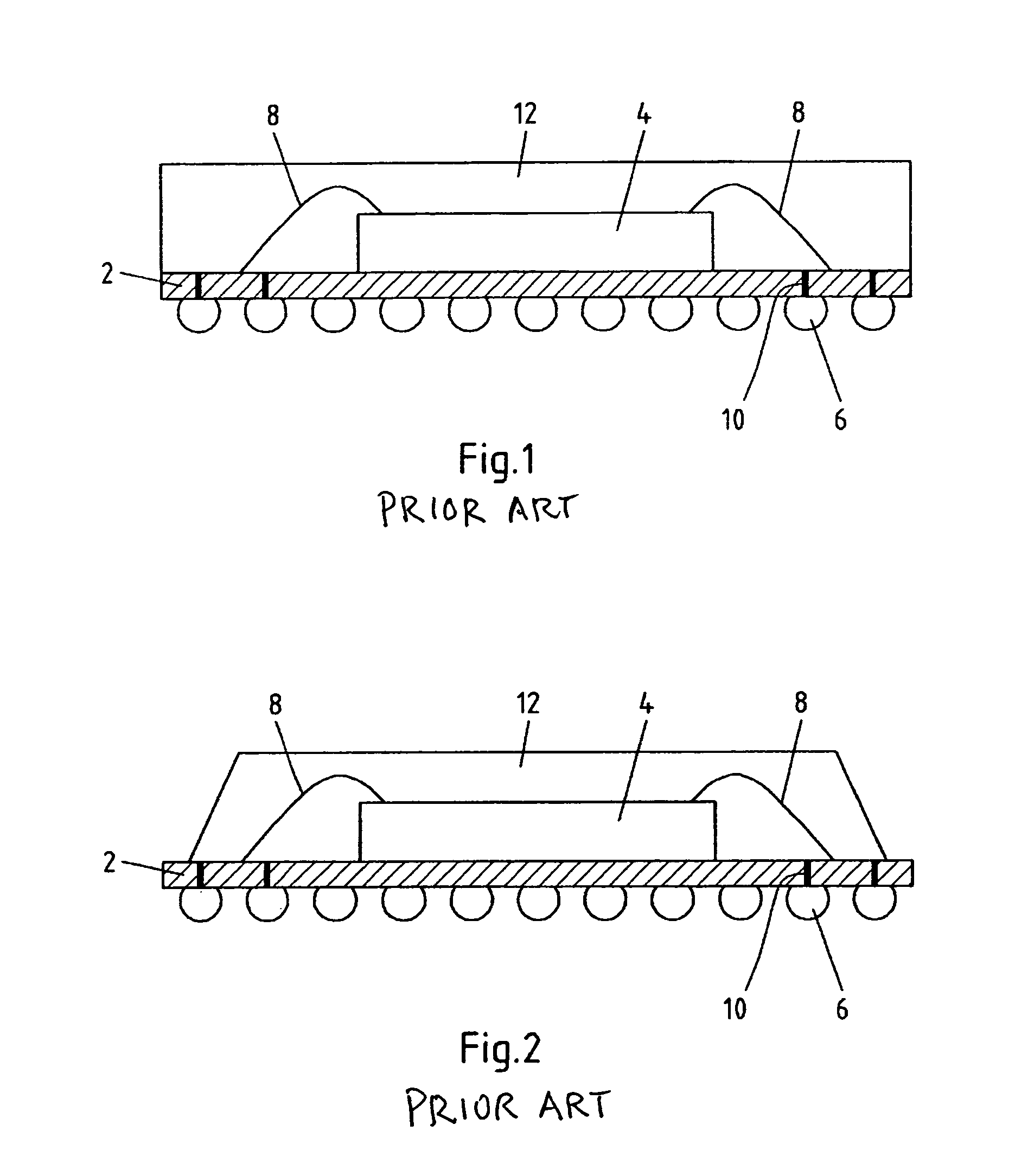

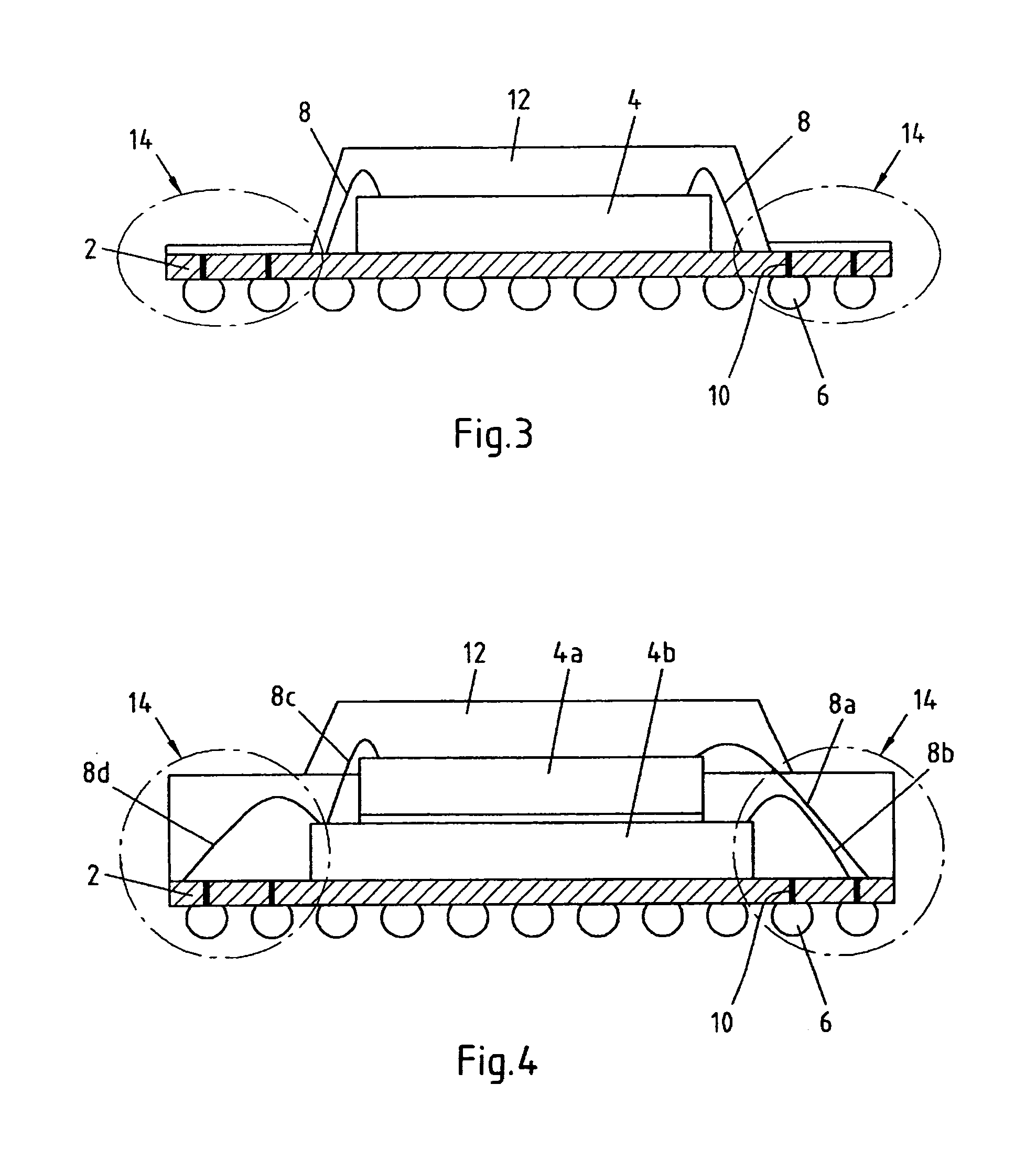

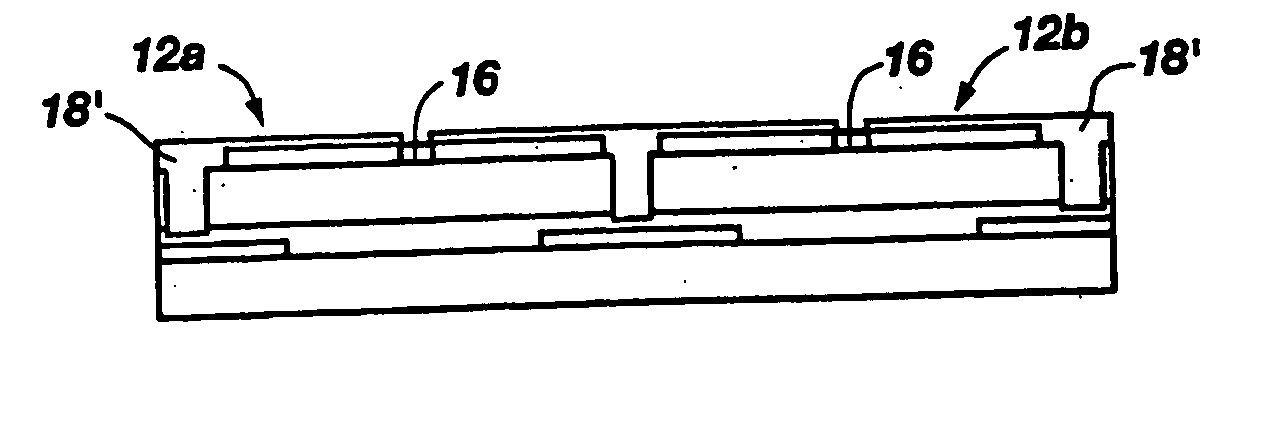

Integrated circuit package with optimized mold shape

InactiveUS7233057B2Reduce stiffnessIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesChip sizeInterconnection

The invention relates to an integrated circuit package, in particular an integrated chip size package or an integrated chip scale package, comprising a substrate carrying a die, and connection elements, interconnection elements, connecting pins of said die with said connection elements, and a mold encapsulating said die on said substrate. To increase reliability and to reduce failure due to deformation stress, the invention provides said mold with reduced stiffness at areas located substantially at one of said interconnection elements providing increased flexibility of said package at said areas compared to other areas of said package.

Owner:NOKIA CORP

Castellated chip-scale packages and methods for fabricating the same

ActiveUS20050067680A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A method for fabricating a chip-scale package includes securing a device substrate that carries at least two adjacent semiconductor devices to a sacrificial substrate. The sacrificial substrate may include conductive elements on a surface thereof, which are located so as to align along a street between each adjacent pair of semiconductor devices on the device substrate. The device substrate is then severed along each street and the newly formed peripheral edge of each semiconductor device coated with dielectric material. If the sacrificial substrate includes conductive elements, they may be exposed between adjacent semiconductor devices and subsequently serve as lower sections of contacts. Peripheral sections of contacts are formed on the peripheral edge. Upper sections of the contacts may also be formed over the active surfaces of the semiconductor devices. Once the contacts are formed, the sacrificial substrate is substantially removed from the back sides of the semiconductor devices.

Owner:MICRON TECH INC

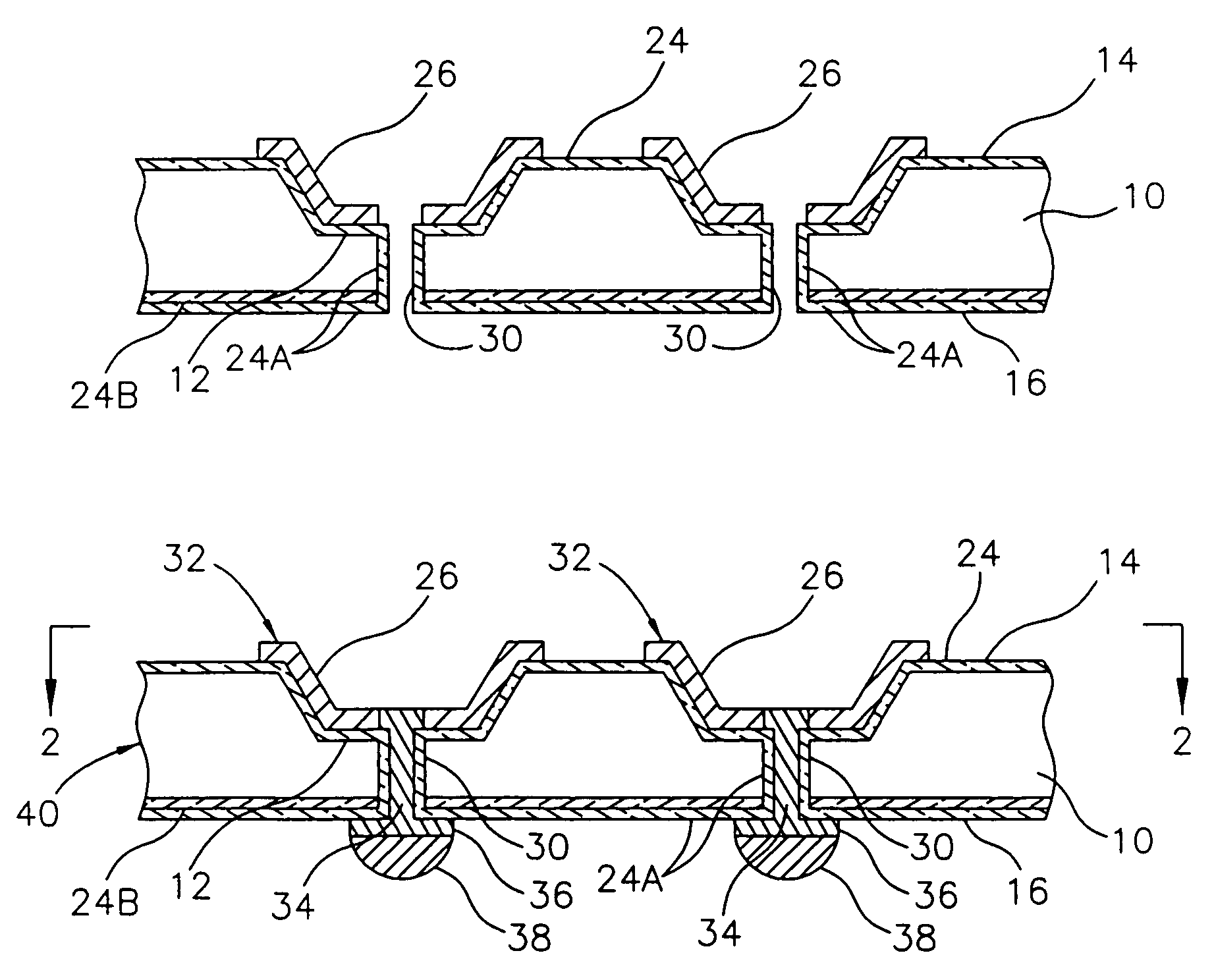

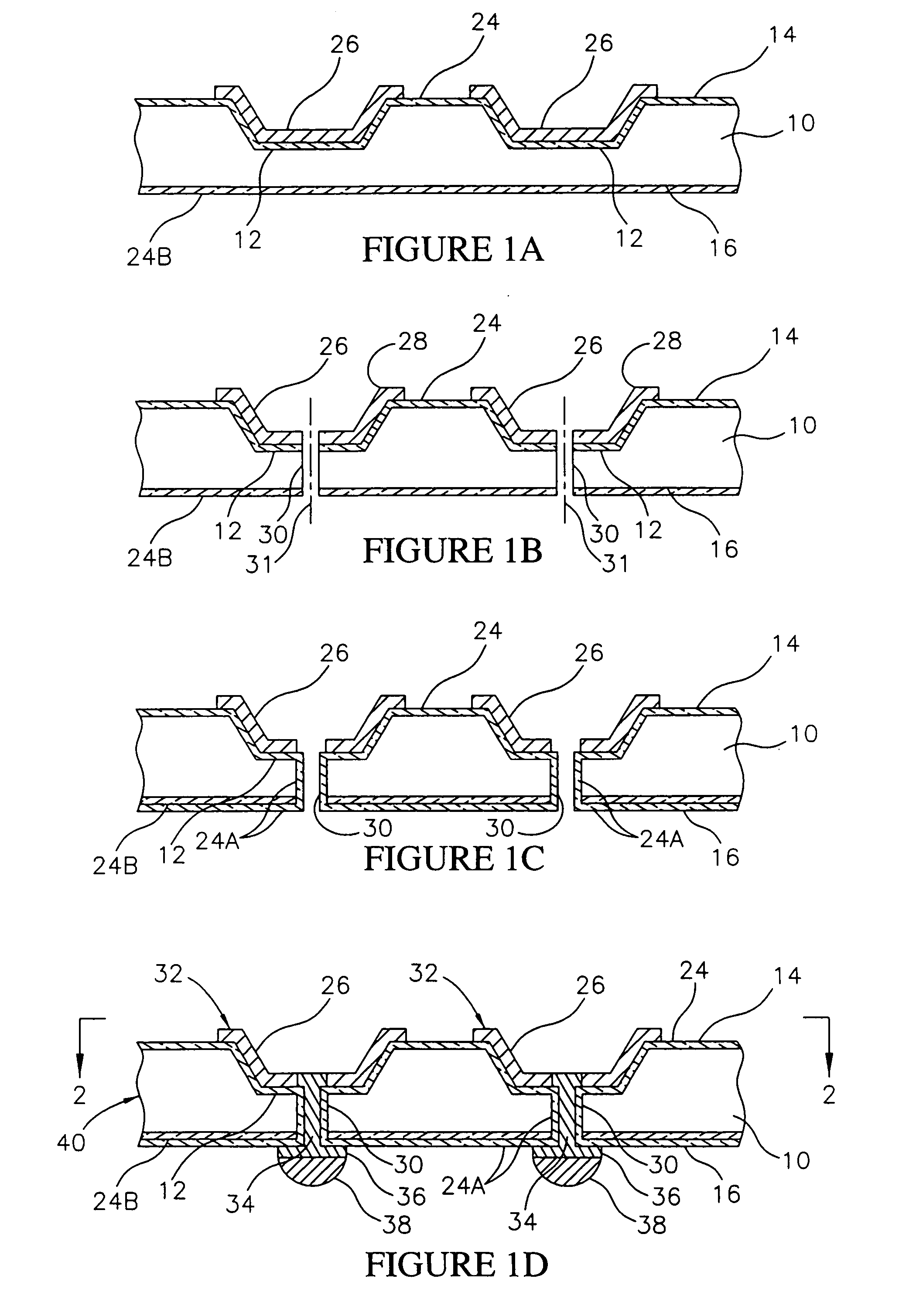

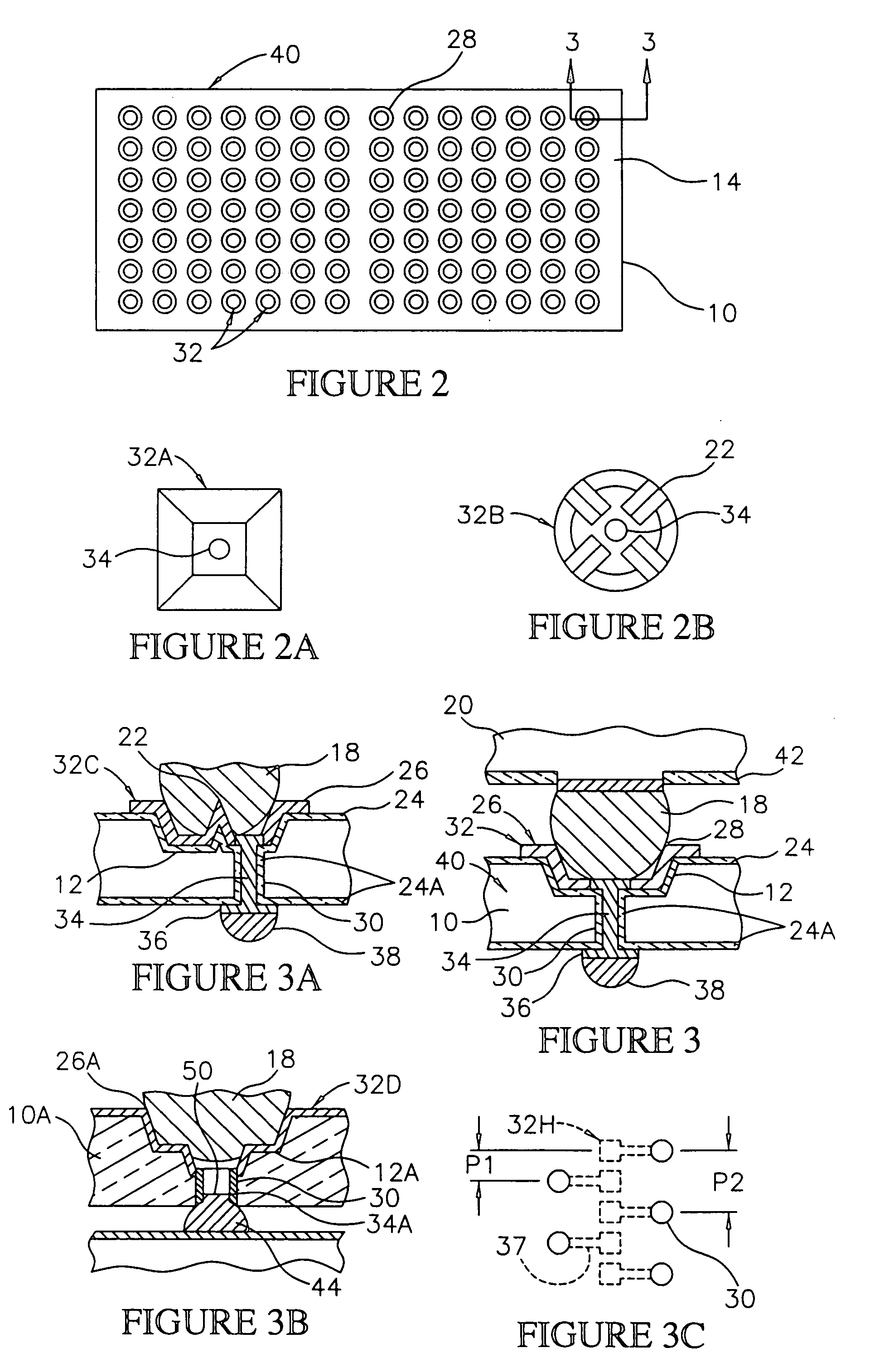

Methods and apparatus for packaging integrated circuit devices

ActiveUS20050104179A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorInsulation layer

An integrally packaged integrated circuit device including an integrated circuit die including a crystalline substrate having first and second generally planar surfaces and edge surfaces and semiconductor circuitry formed over the first generally planar surface, at least one chip scale packaging layer formed over the semiconductor circuitry and the first generally planar surface, an insulation layer formed over the second generally planar surface and the edge surfaces and at least one electrical conductor formed directly on the insulation layer overlying the second generally planar surface, the at least one electrical conductor being connected to the circuitry by at least one pad formed directly on the first generally planar surface.

Owner:TESSERA TECH HUNGARY KFT +1

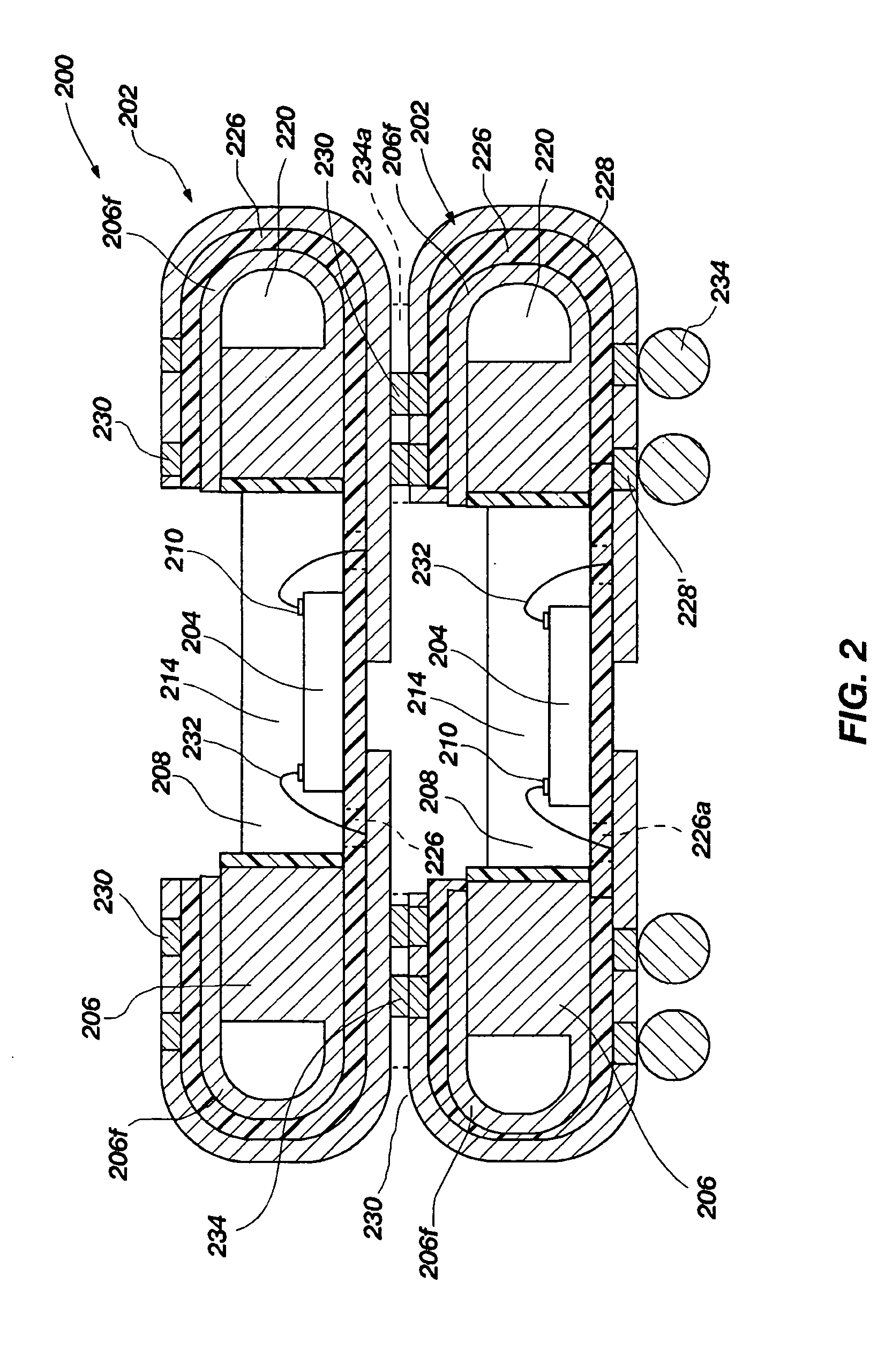

Metal core foldover package structures, systems including same and methods of fabrication

ActiveUS20080048309A1Additive manufacturing apparatusSemiconductor/solid-state device detailsOn boardAlloy

Chip scale packages and assemblies thereof and methods of fabricating such packages including Chip-On-Board, Board-On-Chip, and vertically stacked Package-On-Package modules are disclosed. The chip scale package includes a core member of a metal or alloy having a recess for at least partially receiving a die therein and includes at least one flange member partially folded over another portion of the core member. Conductive traces extend from one side of the package over the at least one flange member to an opposing side of the package. Systems including the chip scale packages and assemblies are also disclosed.

Owner:MICRON TECH INC

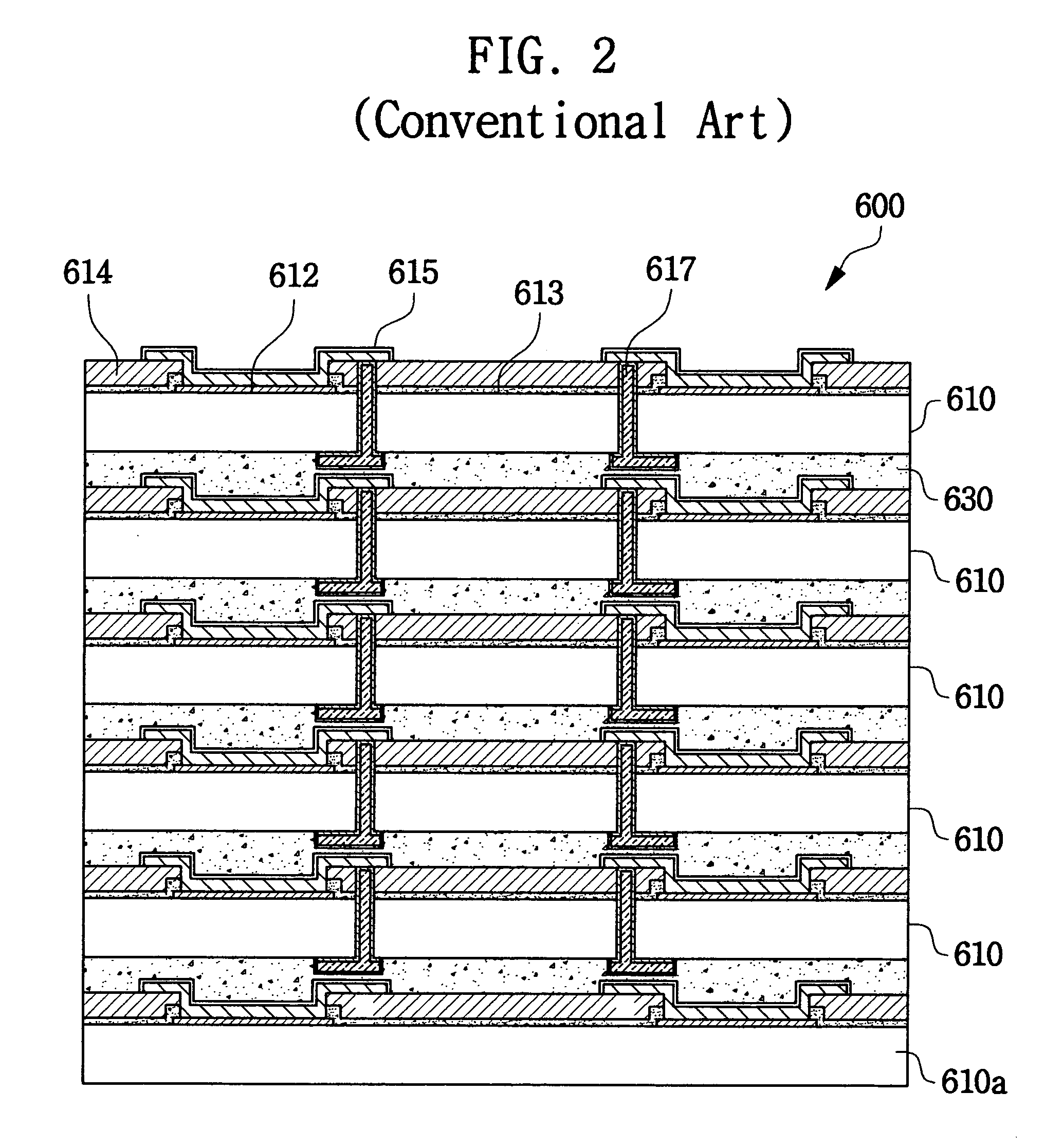

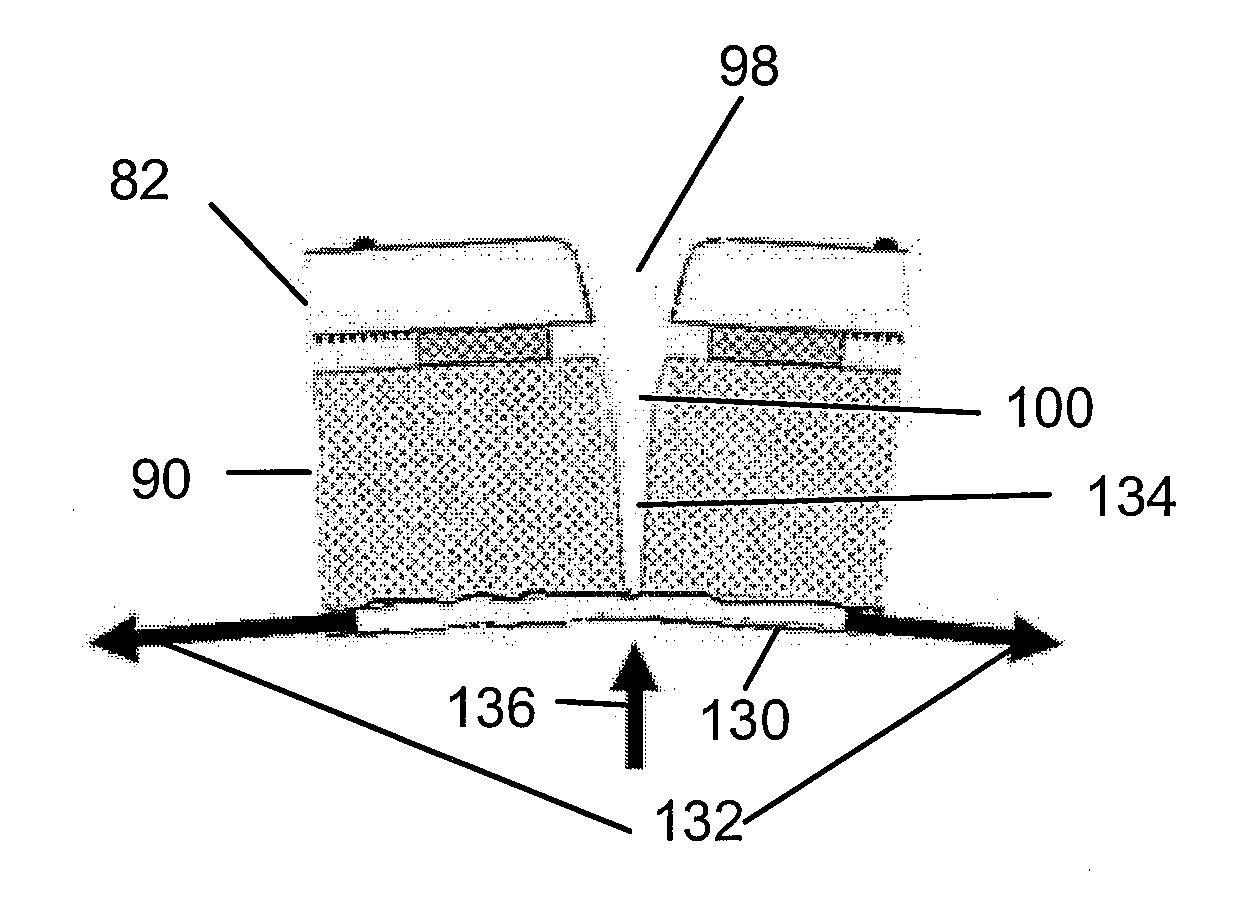

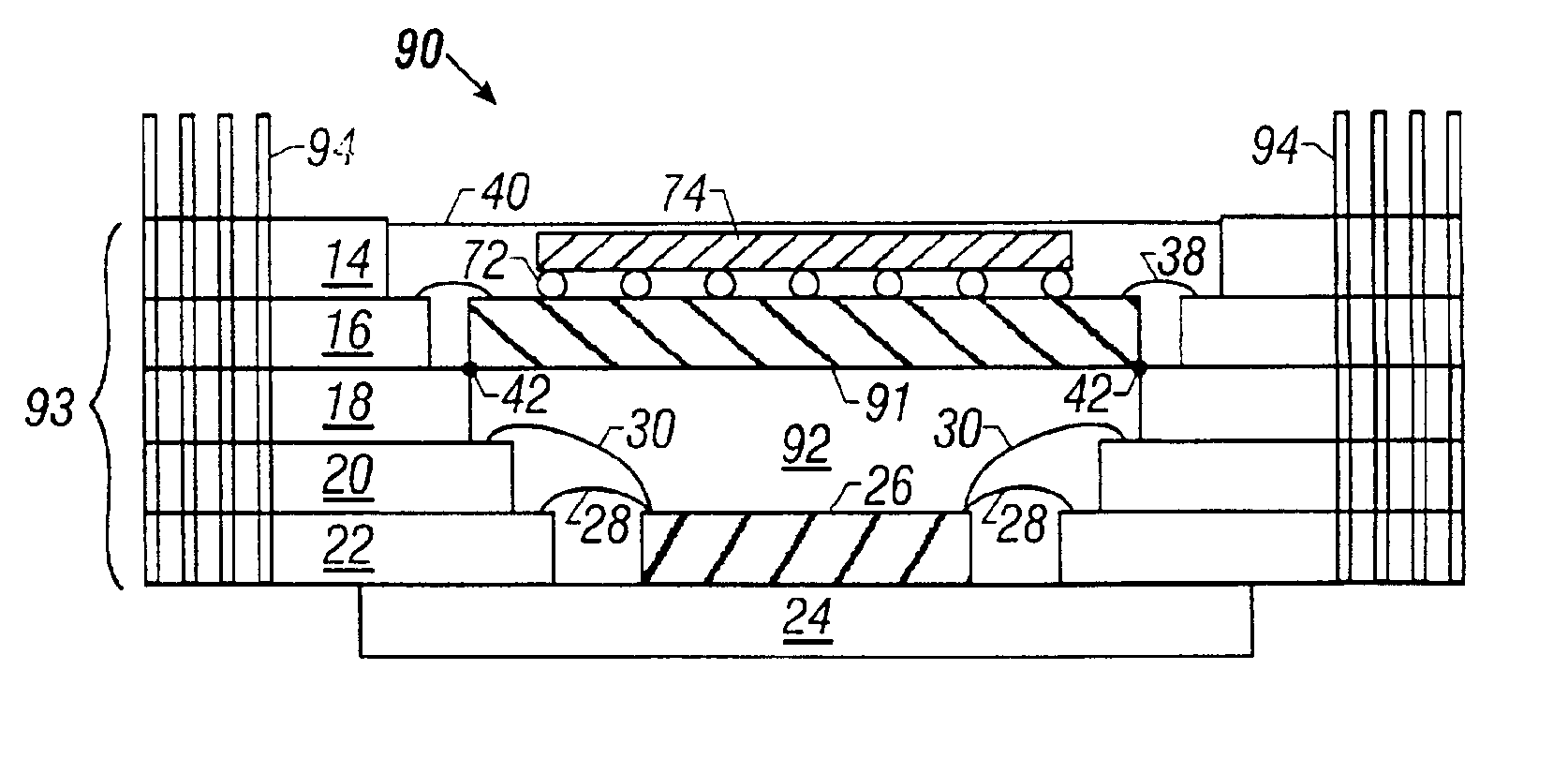

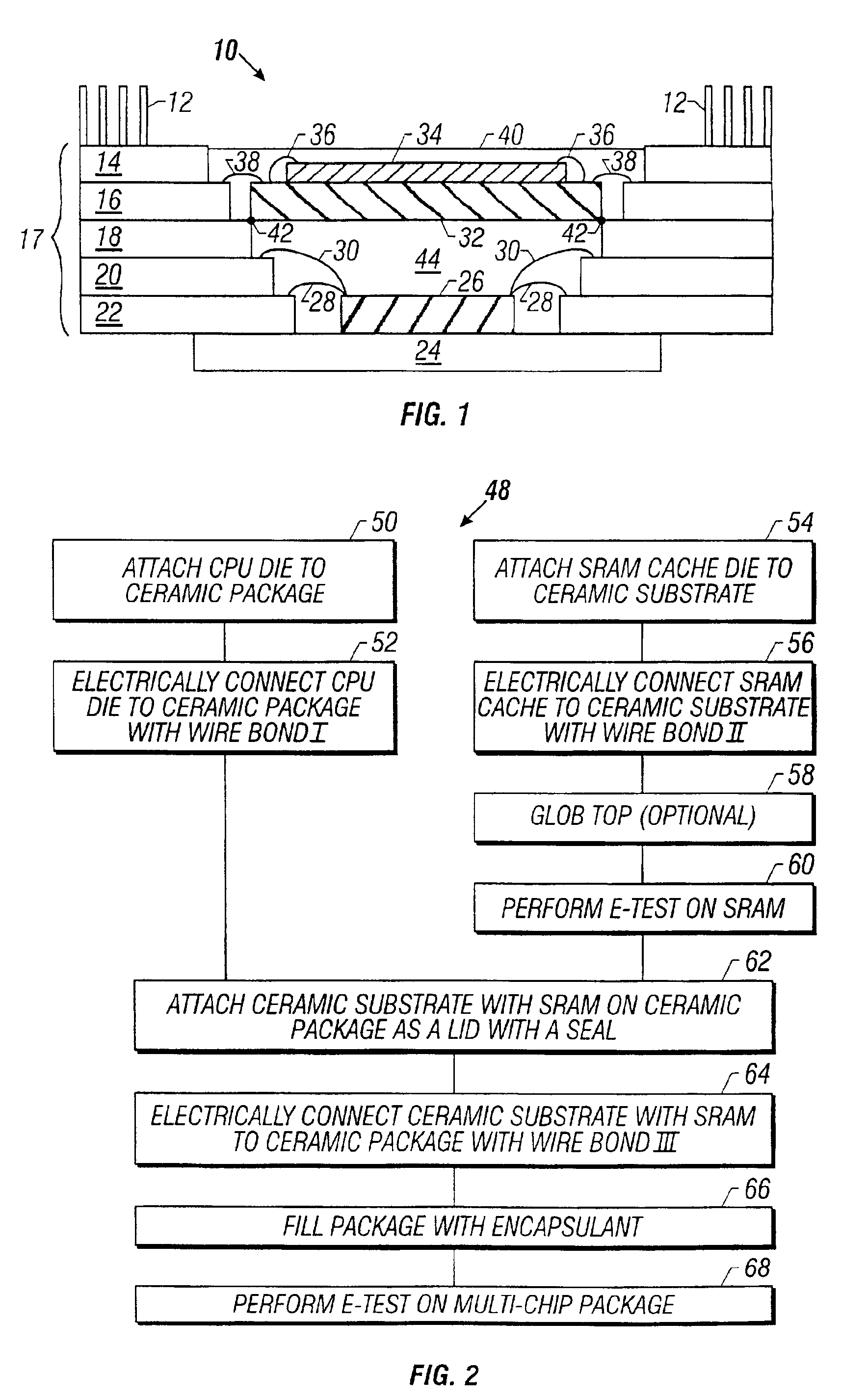

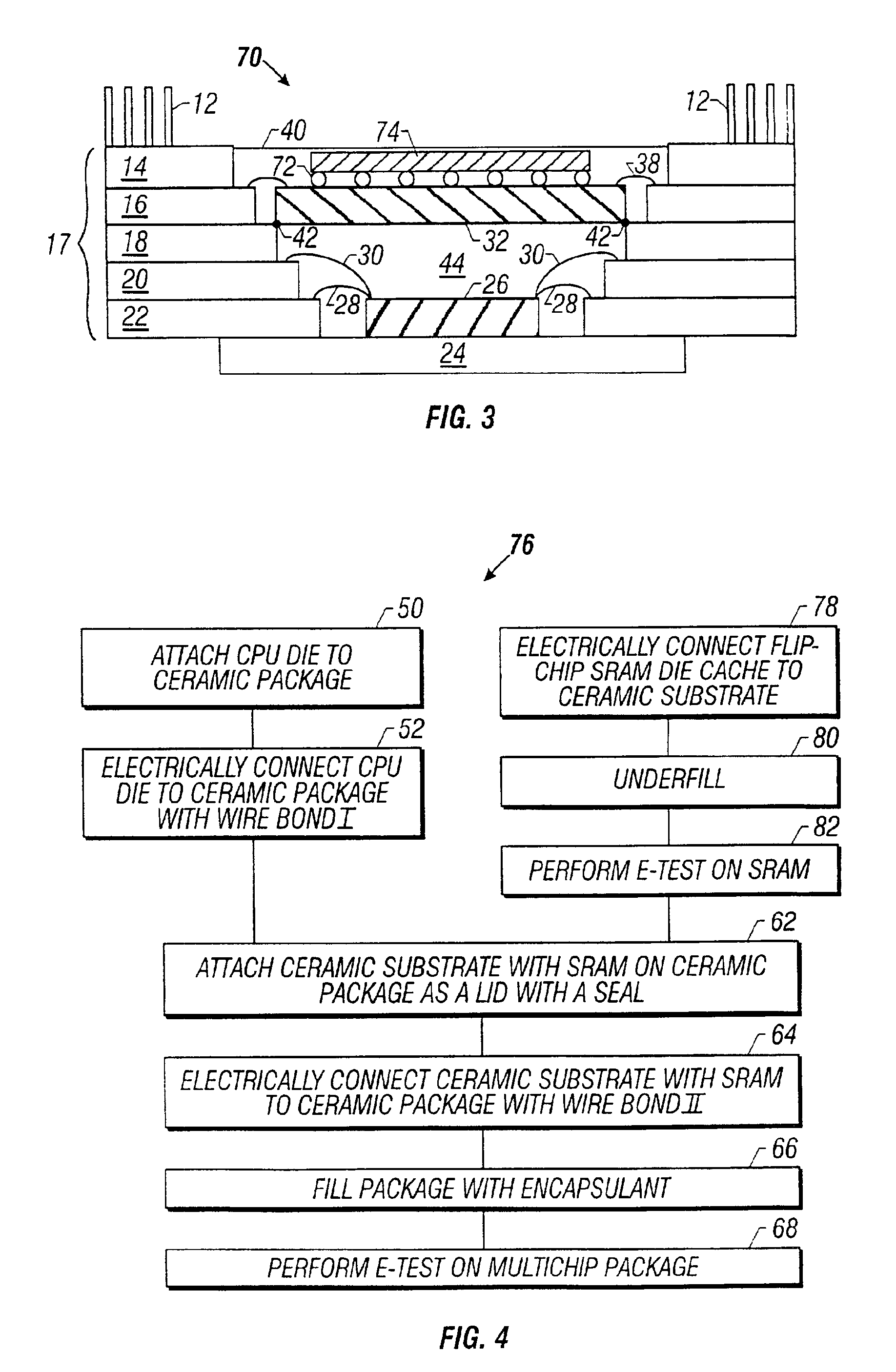

Stacked chip packaging

InactiveUS6890798B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

A multi-chip package and a method of manufacturing the same. The multi-chip package of the present invention has a plurality of shelves. A first semiconductor is electrically coupled to at least one of the package's shelves. A second semiconductor die is electrically coupled to at least one of the package's shelves, wherein the second semiconductor die is above said first semiconductor die.

Owner:INTEL CORP

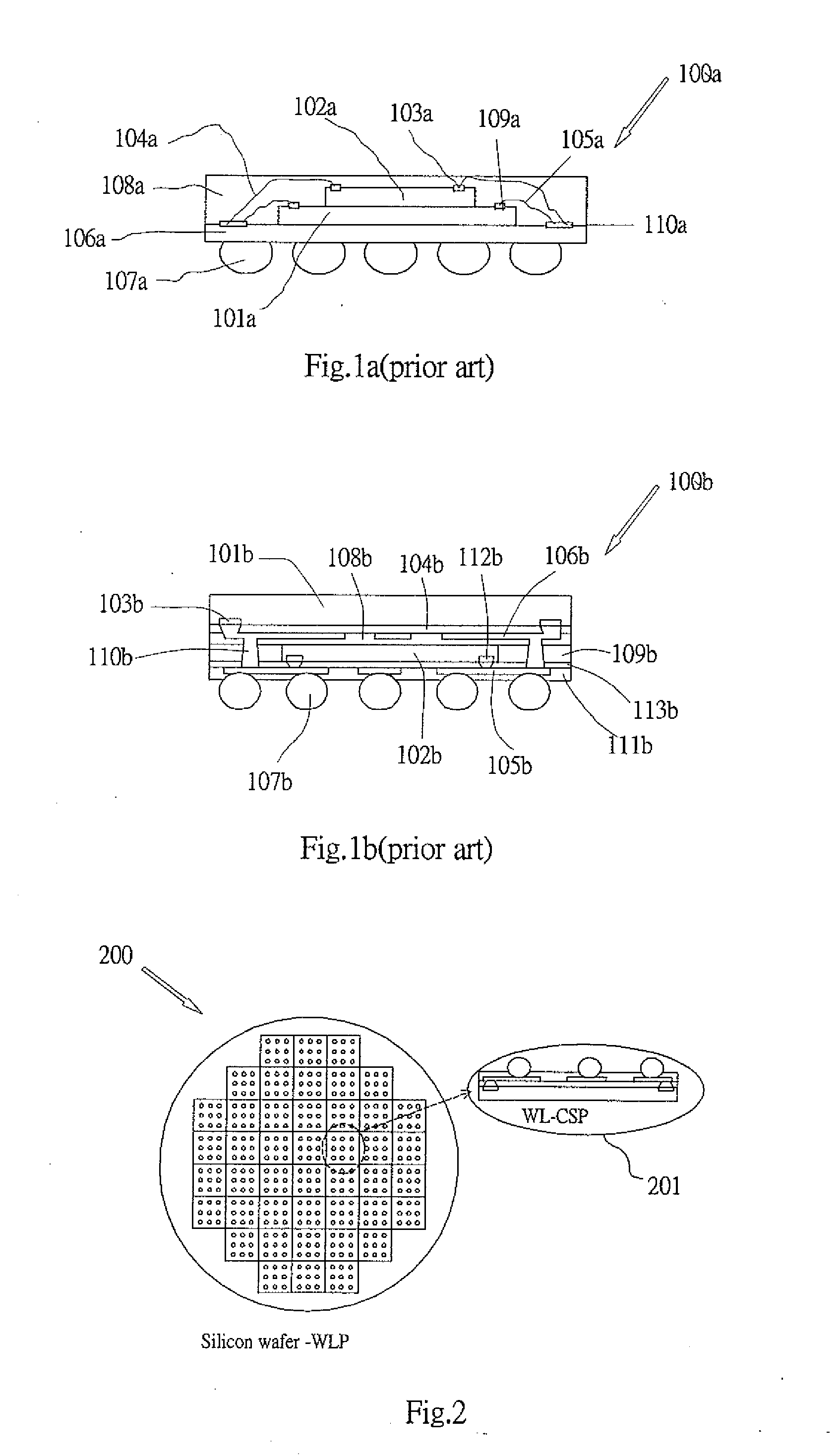

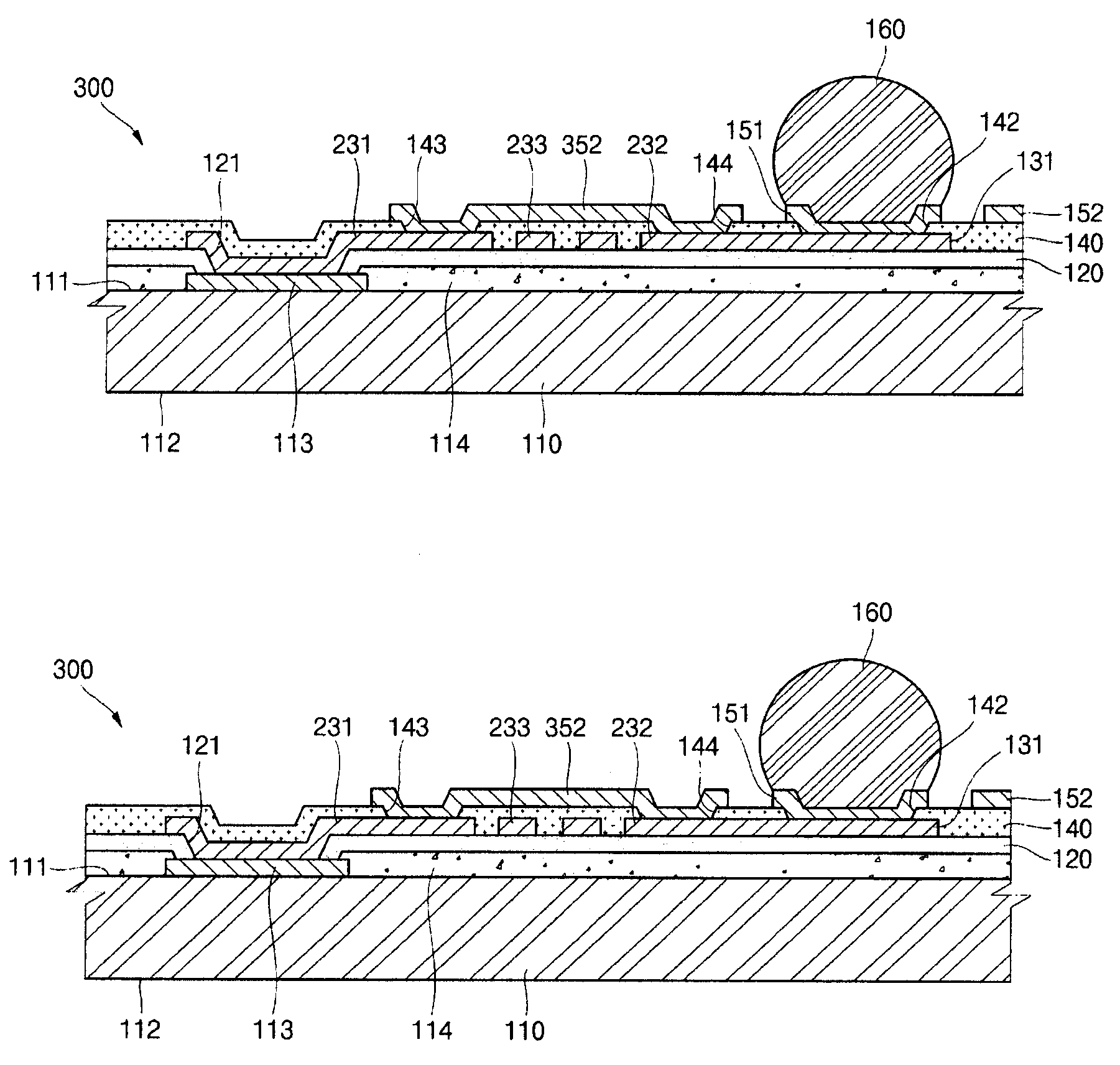

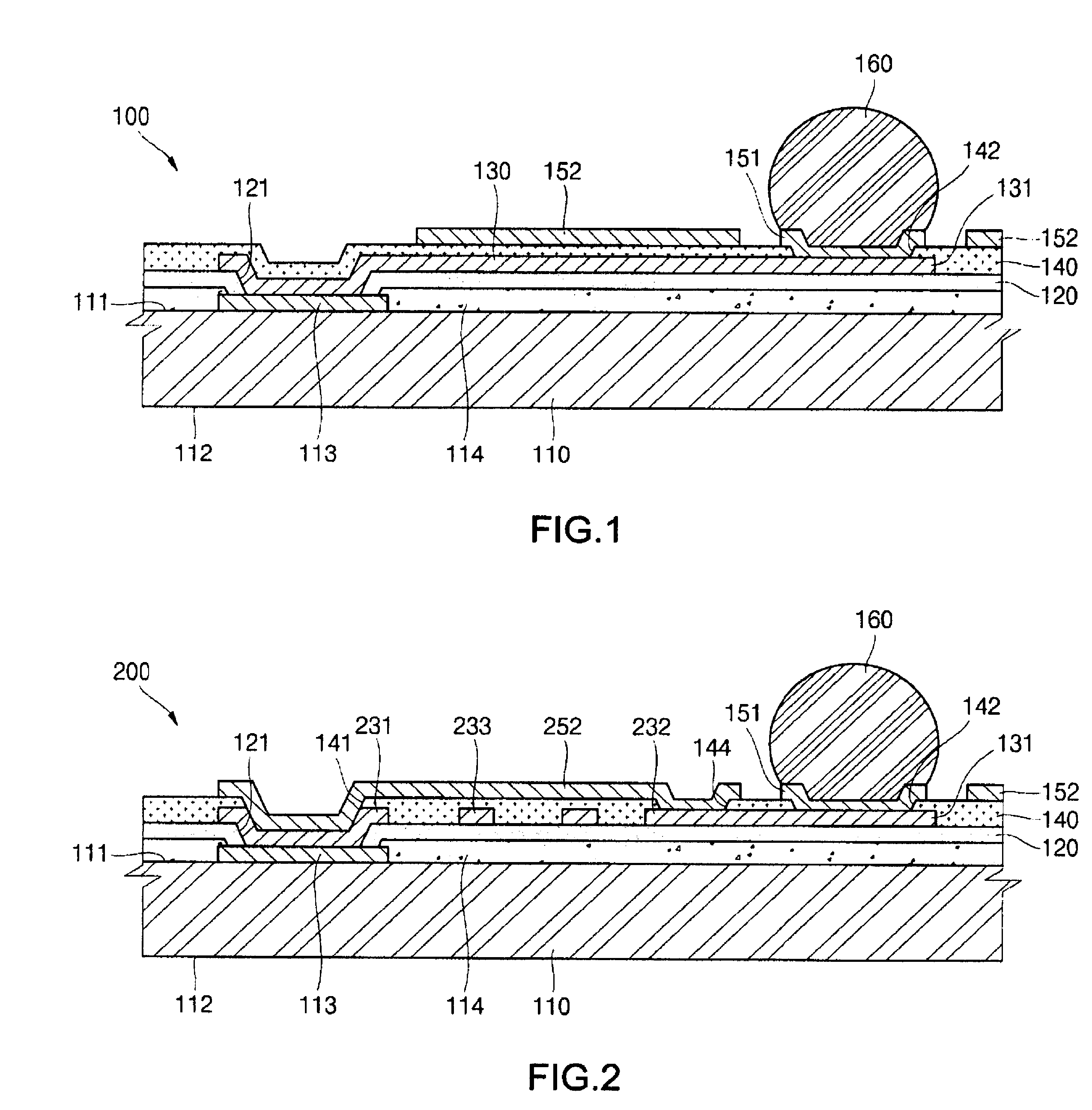

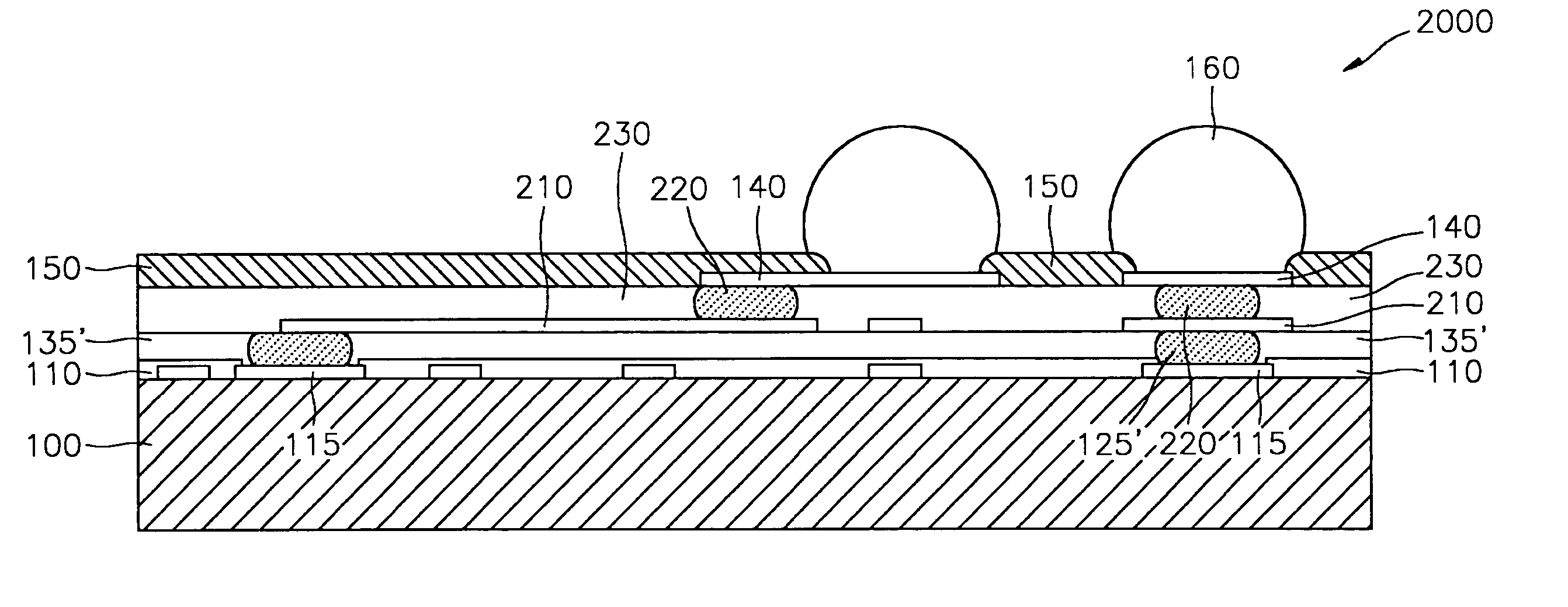

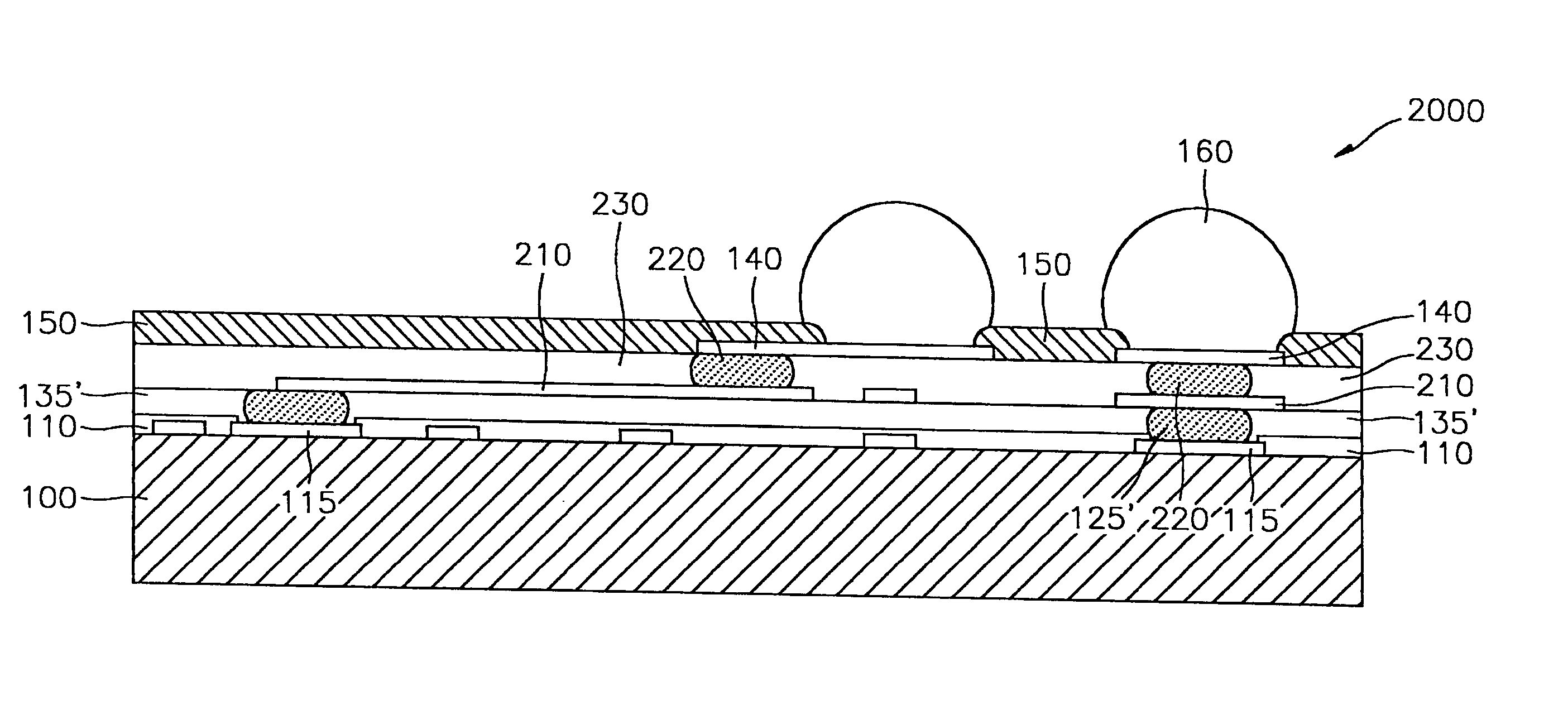

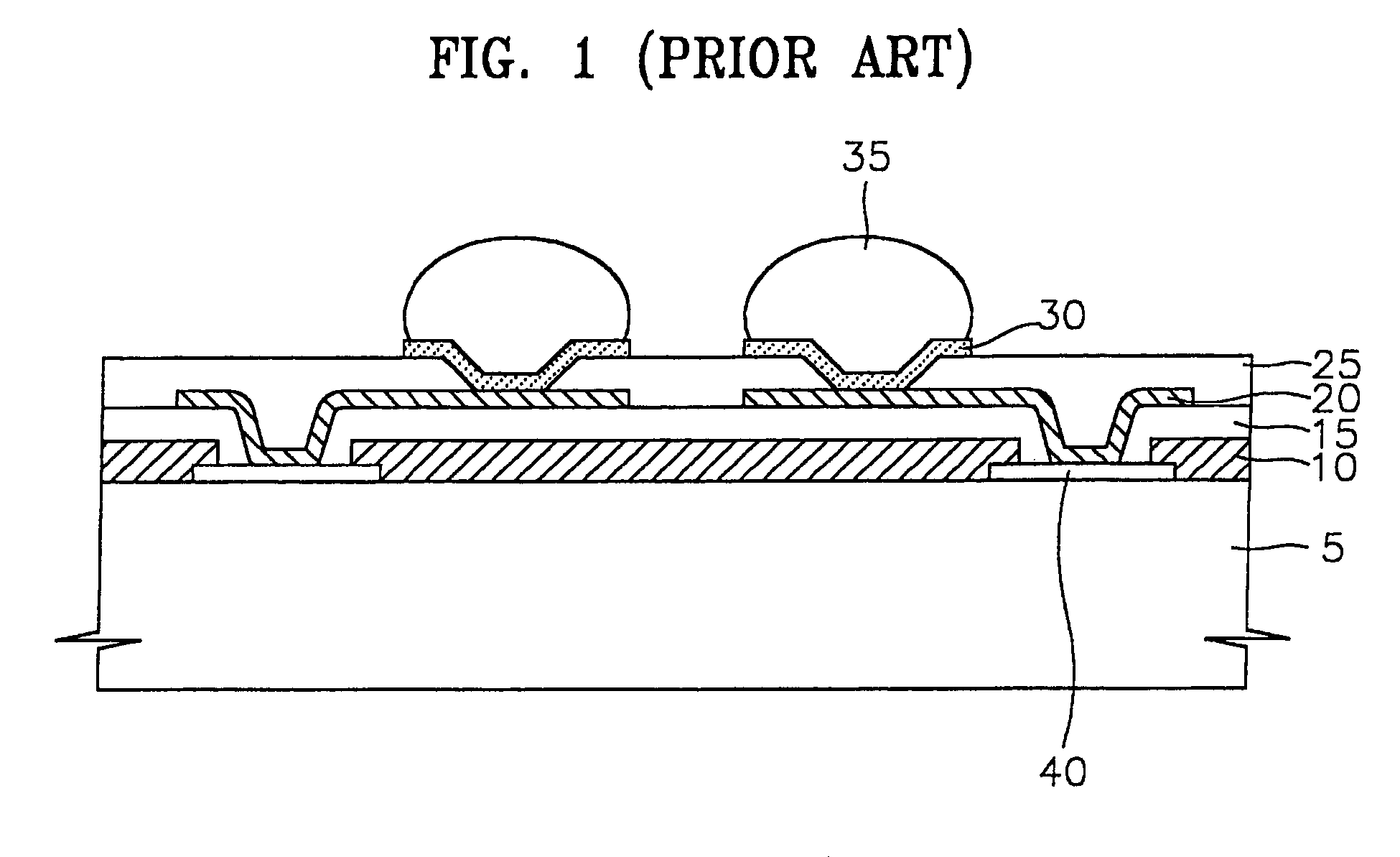

Wafer level chip size package having redistribution layers

ActiveUS7977783B1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A wafer level chip size package (WLCSP) and a method of manufacturing the same are disclosed. Lands are formed at the ends of redistribution layers. The redistribution layers excluding the lands and a first dielectric layer are covered with a second dielectric layer. After forming a first under bump metallurgy (UBM) layer on the land, a solder ball is reflowed to the first UBM layer. A second UBM layer is widely formed on the entire second dielectric layer that is the outer circumference of the first UBM layer and is connected to the redistribution layer through a via-hole. Therefore, the second UBM layer having a large area can be used as a ground plane or a power plane. In addition, the second UBM layer can electrically connect the redistribution layers physically separated from each other. Therefore, the plurality of redistribution layers can cross each other without being electrically shorted with each other.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

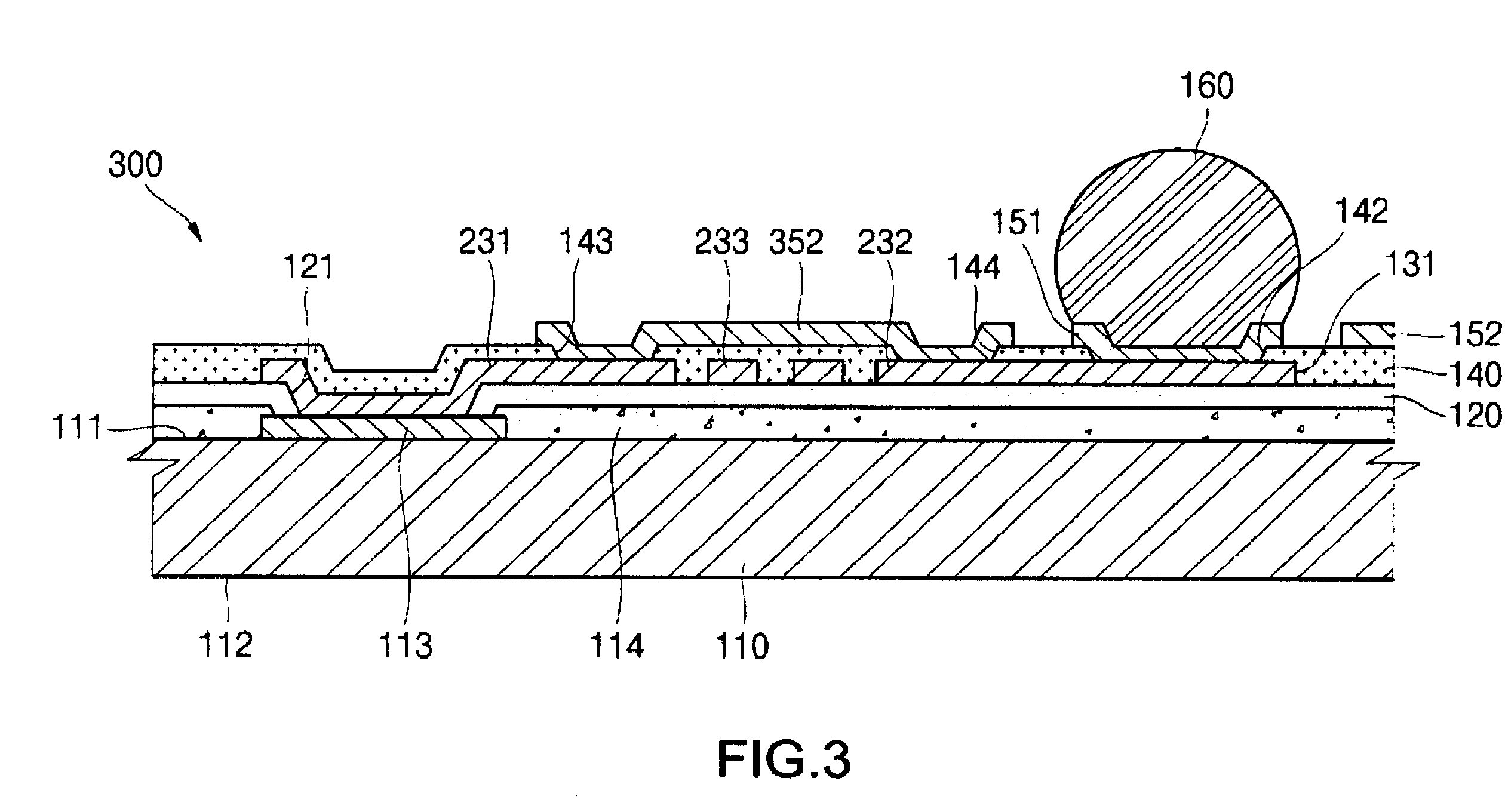

Method and apparatus of water cooling several parallel circuit cards each containing several chip packages

InactiveUS20090277616A1Digital data processing detailsSemiconductor/solid-state device detailsEngineeringChip-scale package

A cooling or heat transfer apparatus and method is disclosed for cooling an electronic device. The apparatus includes a heat producing electronic device which may include an electronic circuit card with many heat sources. A heat transfer device is connected to the heat producing electronic device which is thermally communicating with the heat producing device for transferring heat from the heat producing device to the heat transfer device. A heat conduit is connected to the heat transfer device and thermally communicating with the heat transfer device for transferring heat to the heat conduit from the heat transfer device. A cooling housing is connected to the heat conduit and the cooling housing thermally communicating with the heat conduit for transferring heat to the cooling housing from the heat conduit. The apparatus enables the replacement of circuit cards in the field because it eliminates the need to apply thermal-interface materials.

Owner:GLOBALFOUNDRIES INC

Wafer-level chip scale package and method for fabricating and using the same

InactiveUS20050012225A1Address rising pricesSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A packaged semiconductor device (a wafer-level chip scale package) containing a conductive adhesive material as an electrical interconnect route between the semiconductor die and a patterned conductive substrate is described. The patterned conductive substrate acts not only as a substrate, but also as a redistribution layer that converts the dense pad layout of the die to a larger array configuration of the solder balls in the circuit board. Using the invention allows the formation of a lower priced chip scale package that also overcomes the restriction of the die size used in die-sized chip packages and the input-output pattern that can be required by the printed circuit board. Thus, the invention can provide a familiar pitch (i.e.,interface) to the printed circuit board for any small die.

Owner:SEMICON COMPONENTS IND LLC

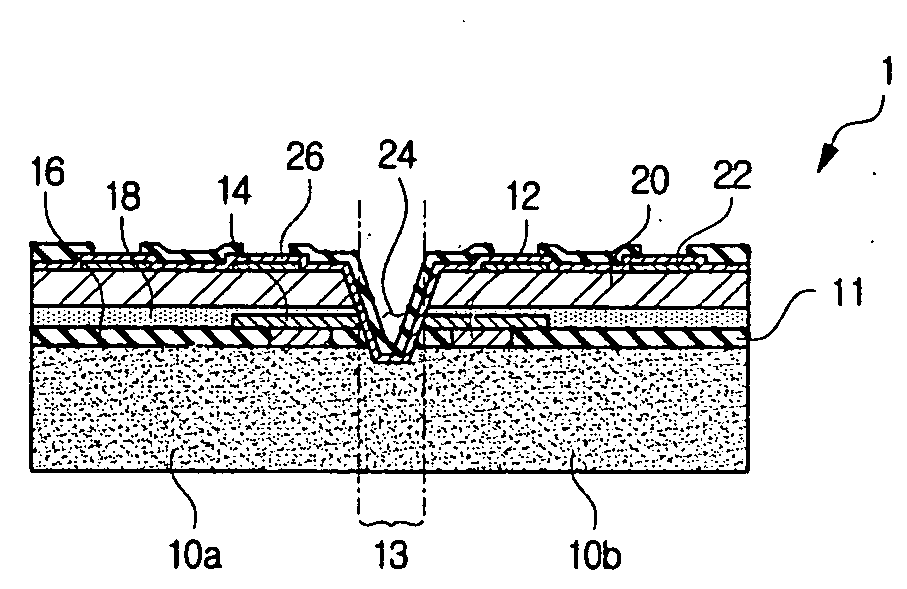

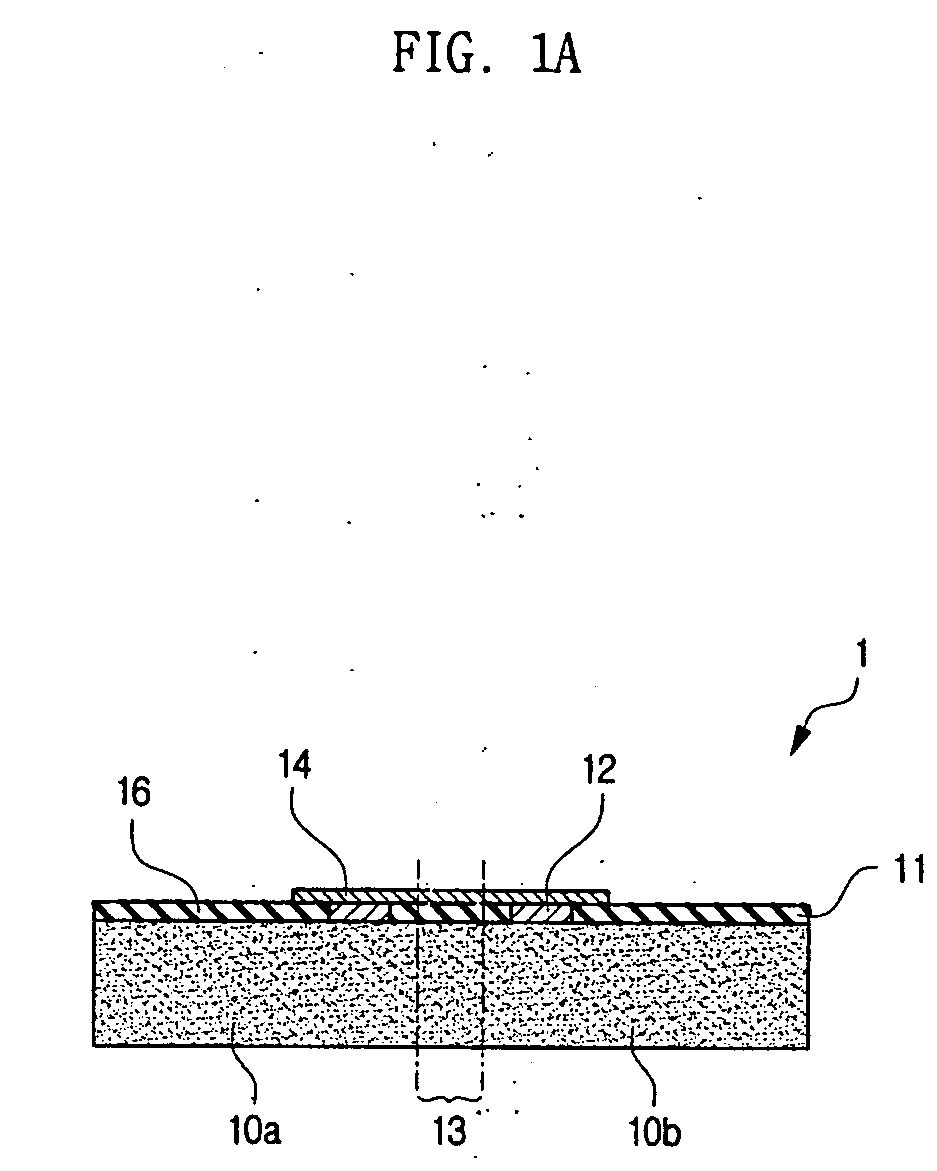

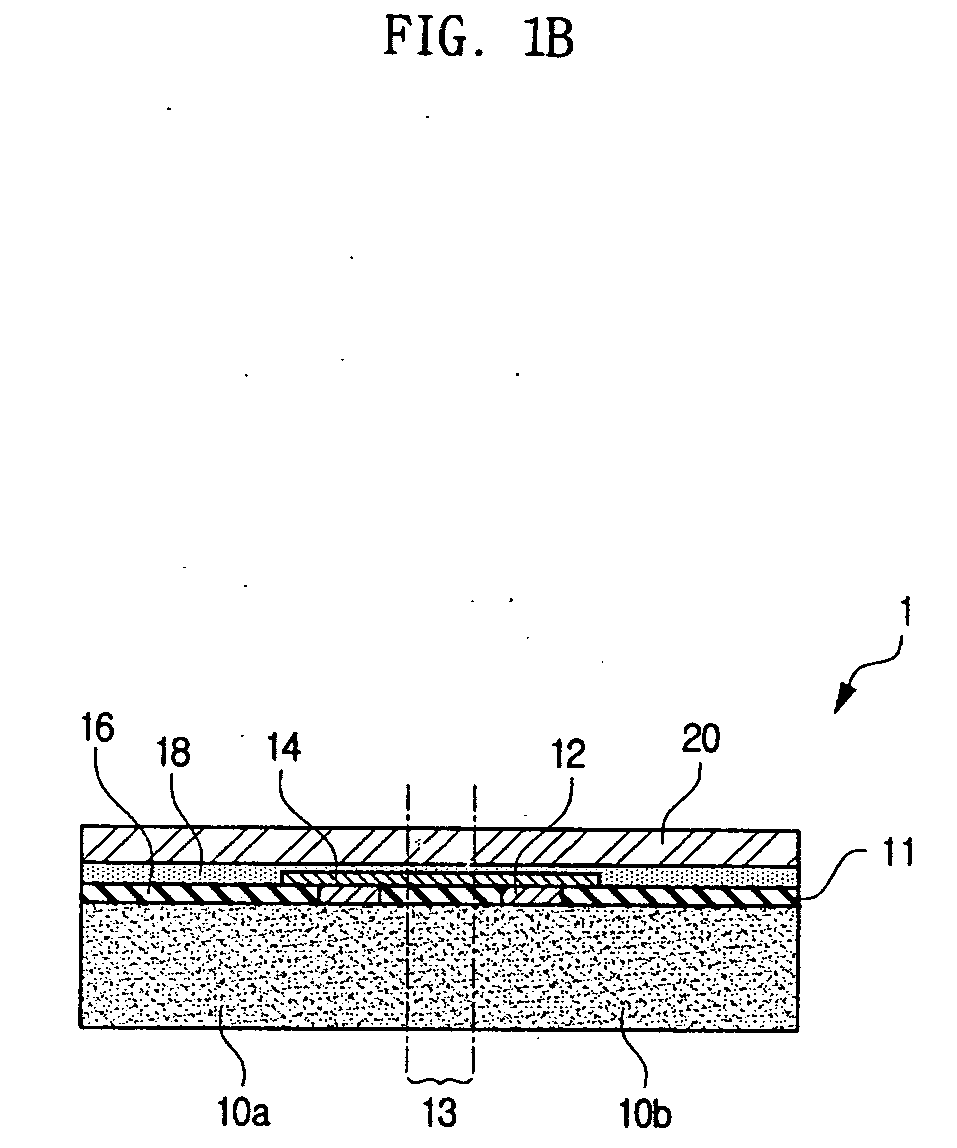

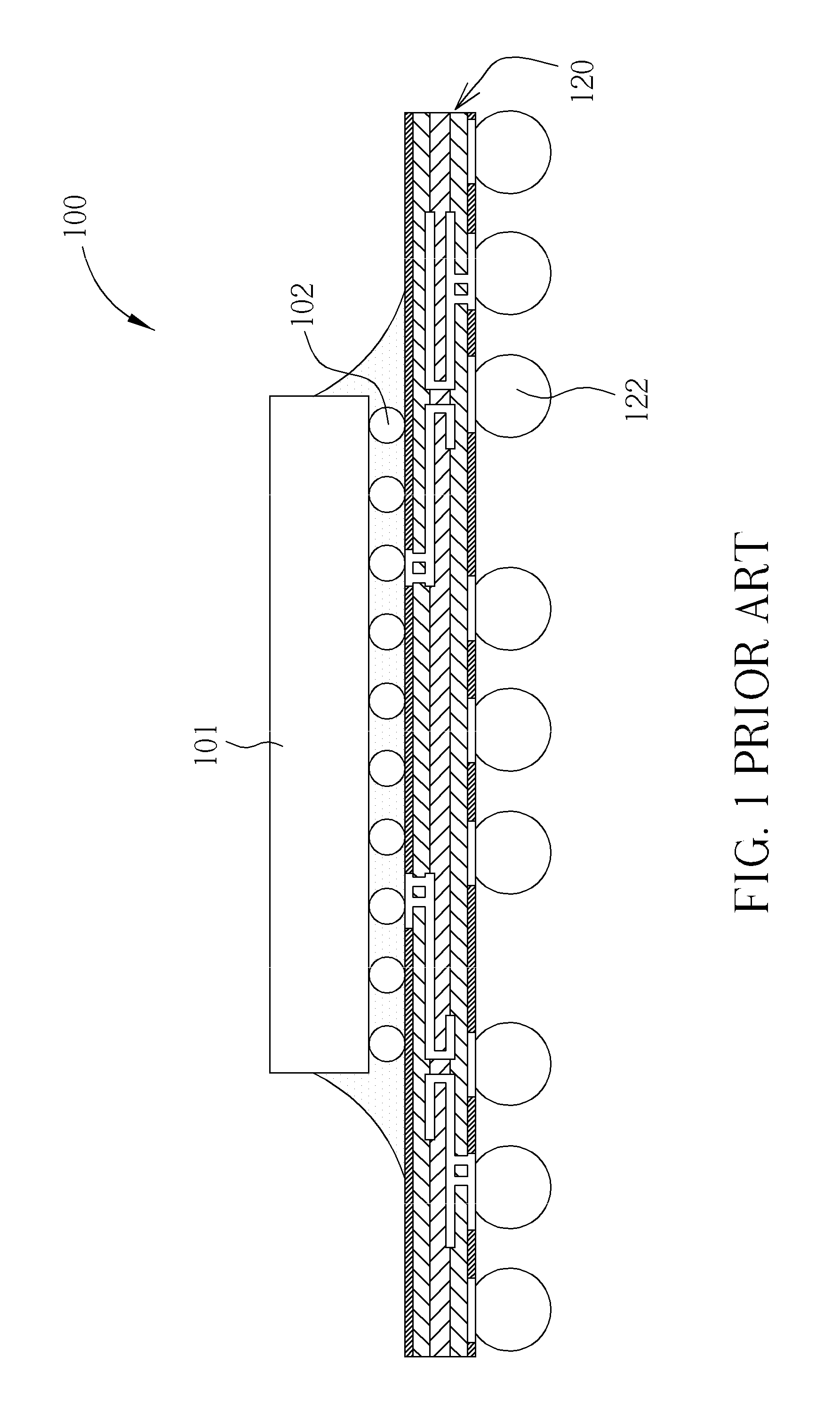

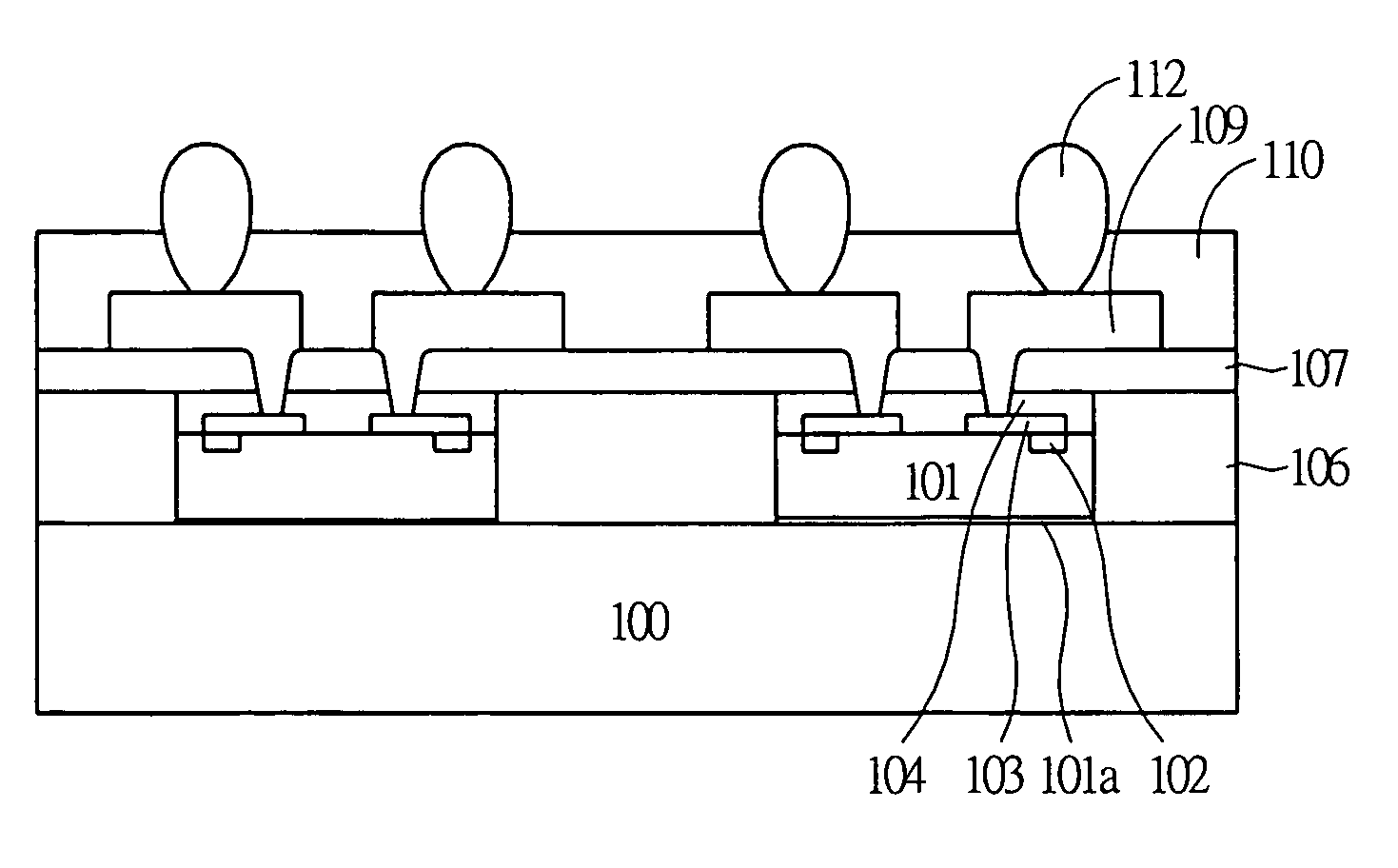

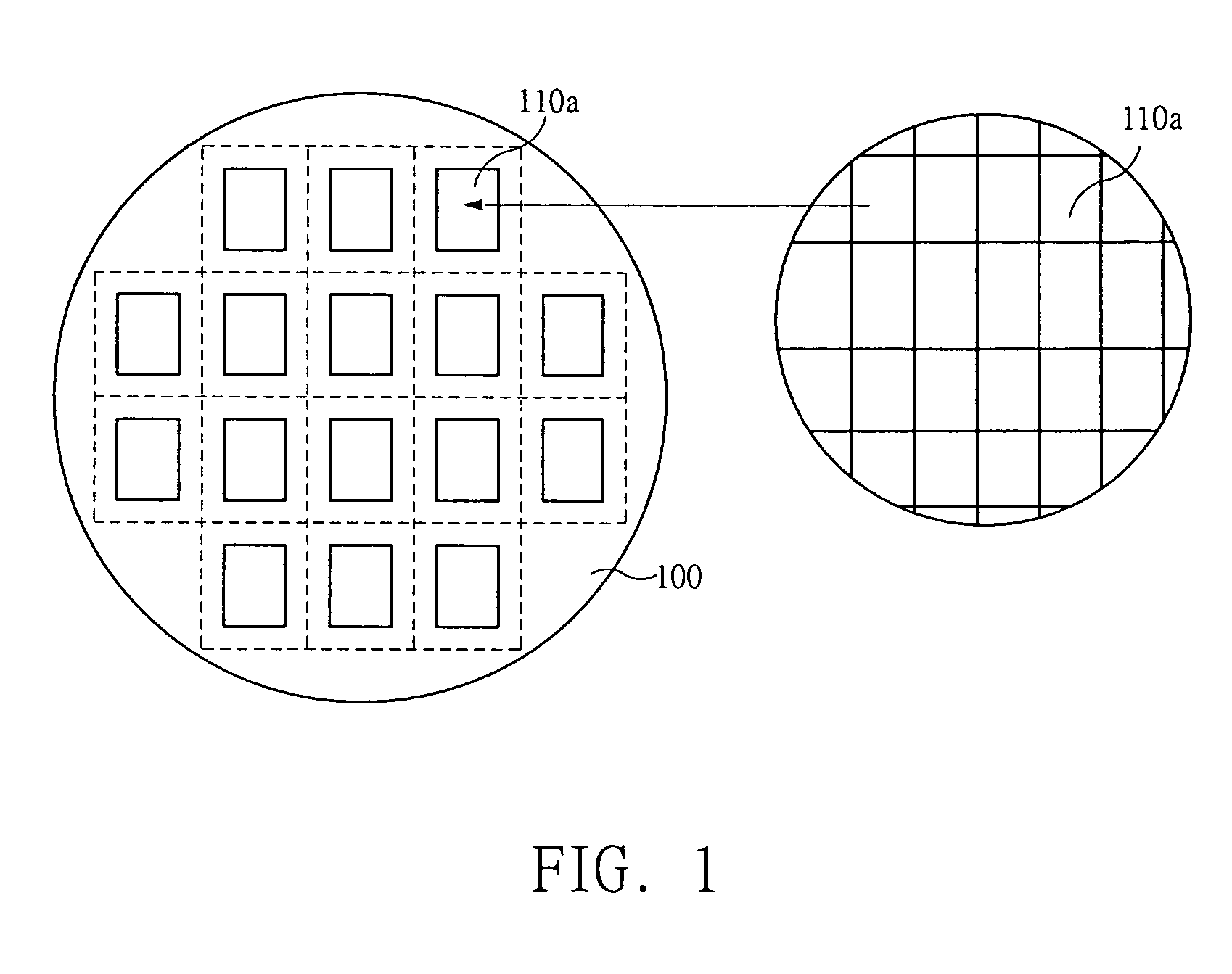

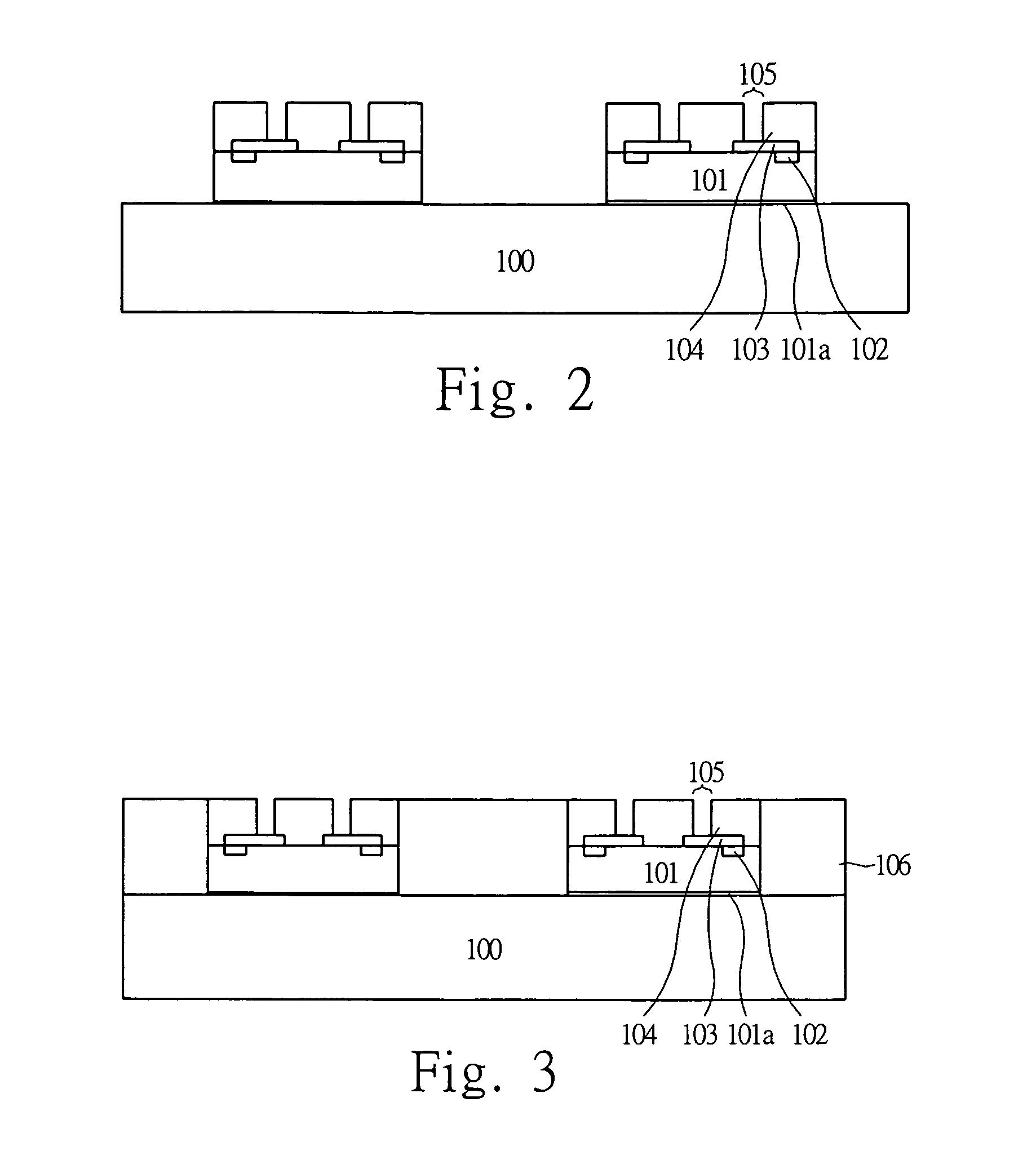

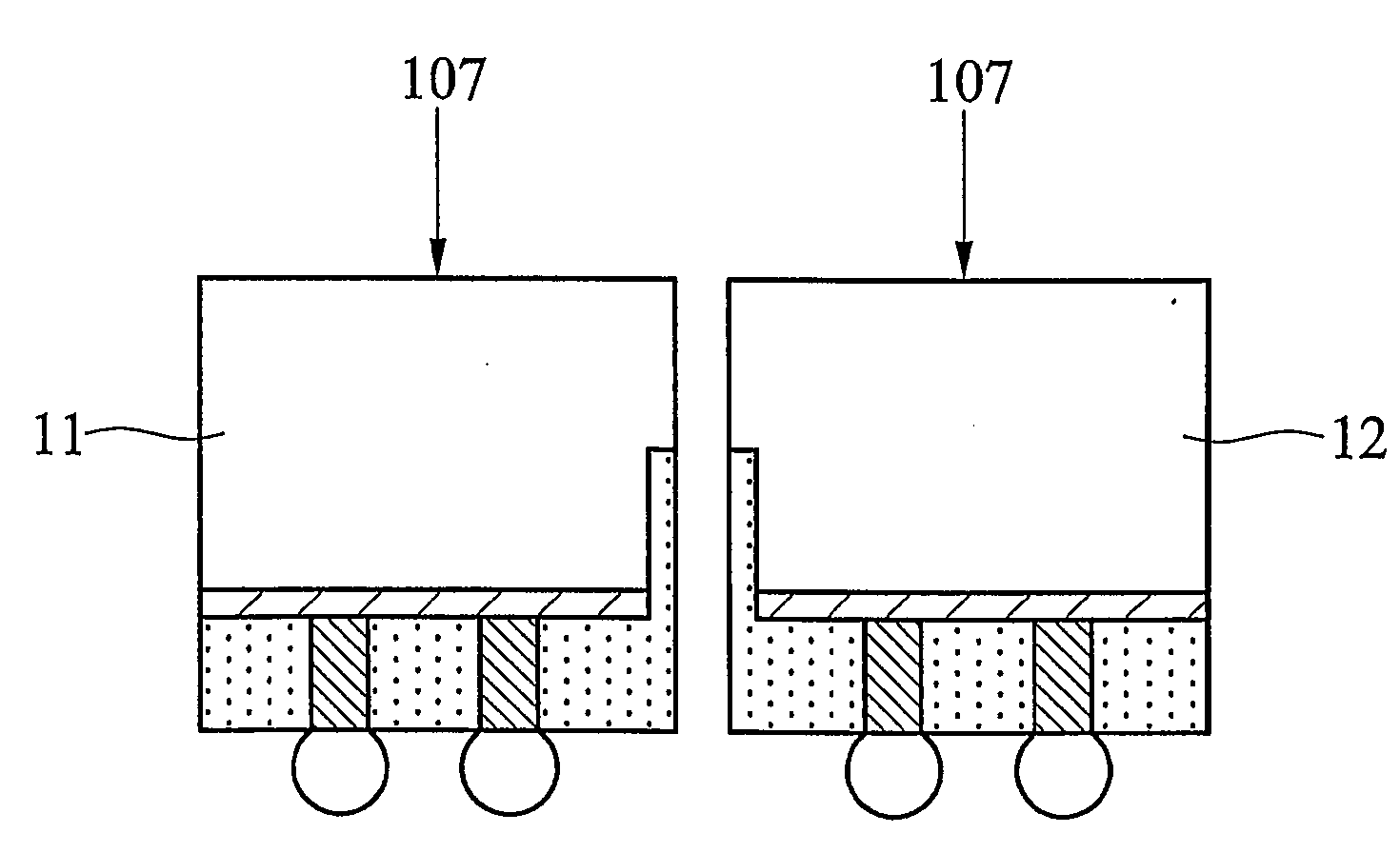

Chip-size package structure and method of the same

ActiveUS7238602B2Reduce contact resistanceLow costSemiconductor/solid-state device detailsSolid-state devicesChip sizeSolder ball

Owner:ADL ENERGY CORP

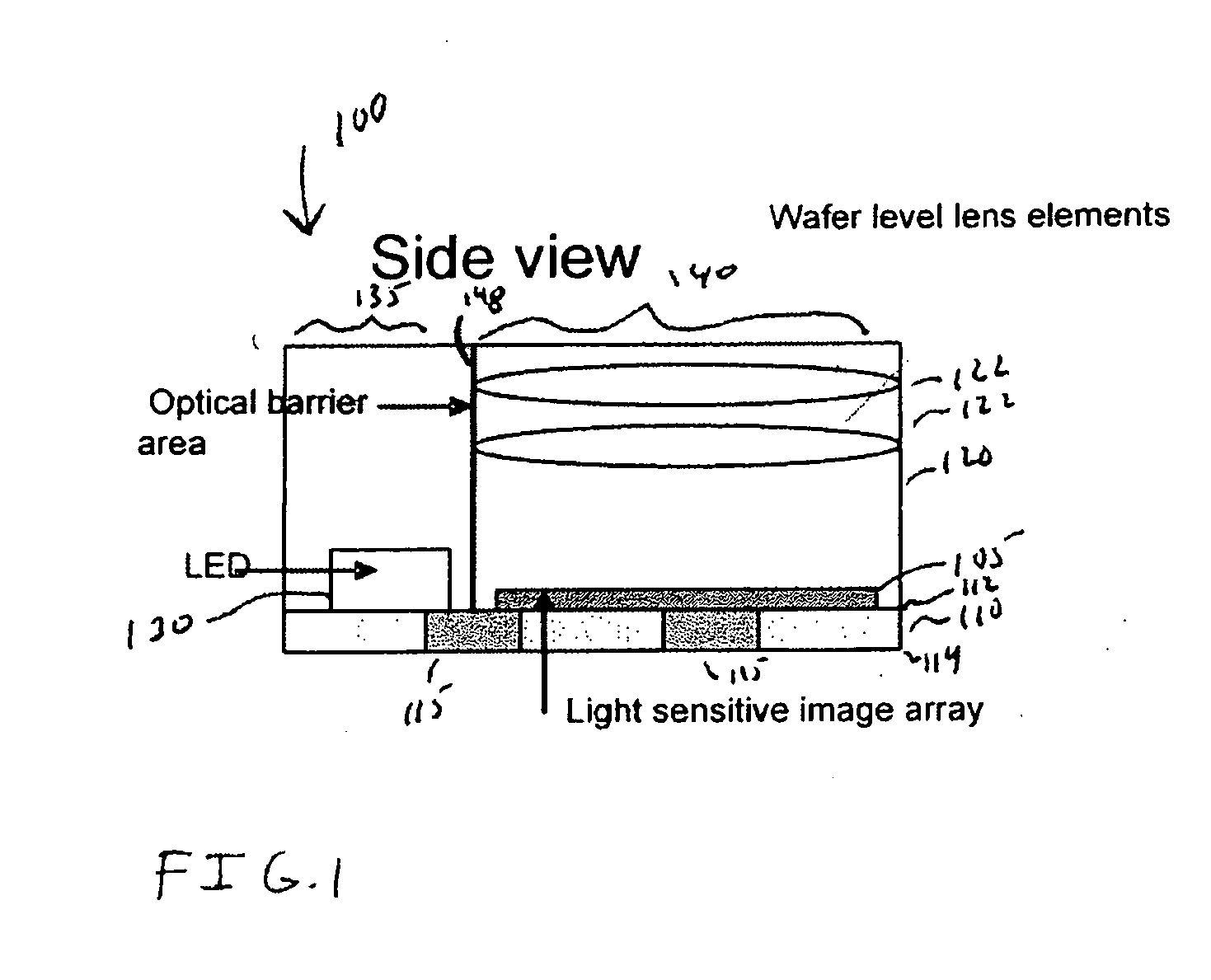

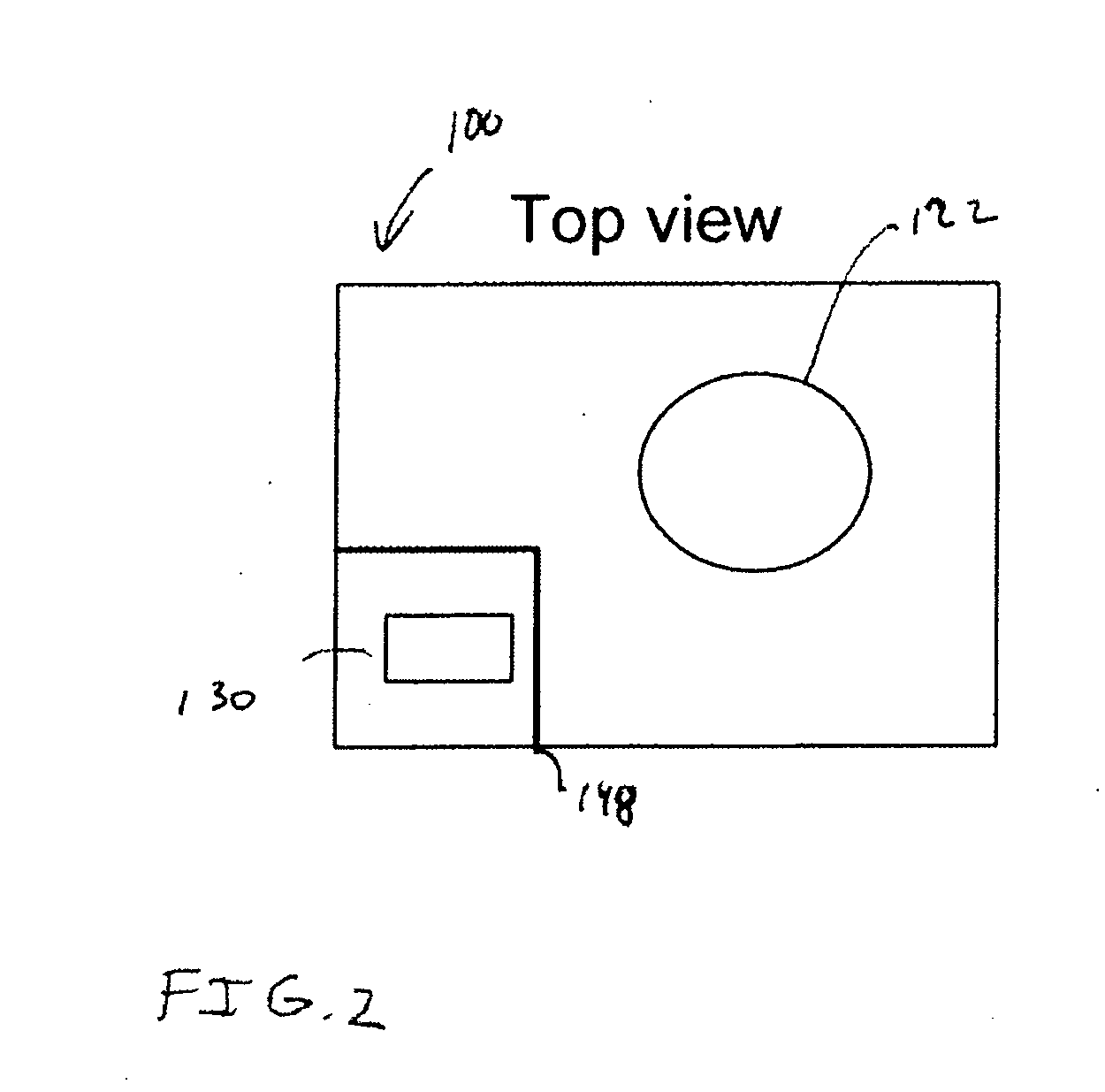

Reflowable Camera Module With Integrated Flash

ActiveUS20090153729A1Avoid strayTelevision system detailsSemiconductor/solid-state device manufacturingImaging qualityComputer module

A reflowable camera module is implemented using a Chip Scale Package (CSP). An image sensor is formed on one portion of the carrier. A light emitting diode (LED) is formed on another portion of the carrier. The LED serves as an integrated camera flash. Additional optical isolation is provided within the camera module to prevent stray light generated by the LED from degrading image quality.

Owner:OMNIVISION TECH INC

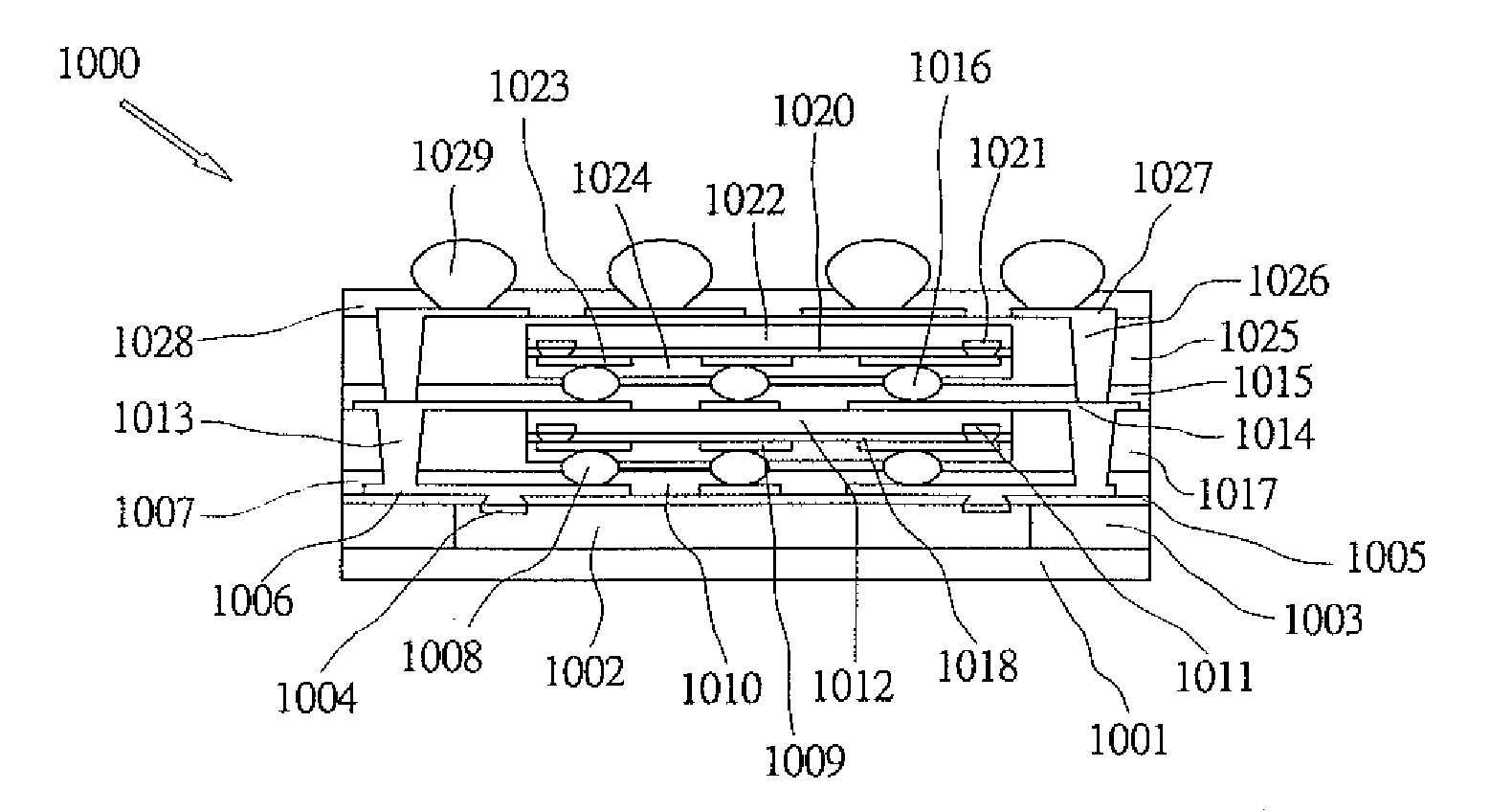

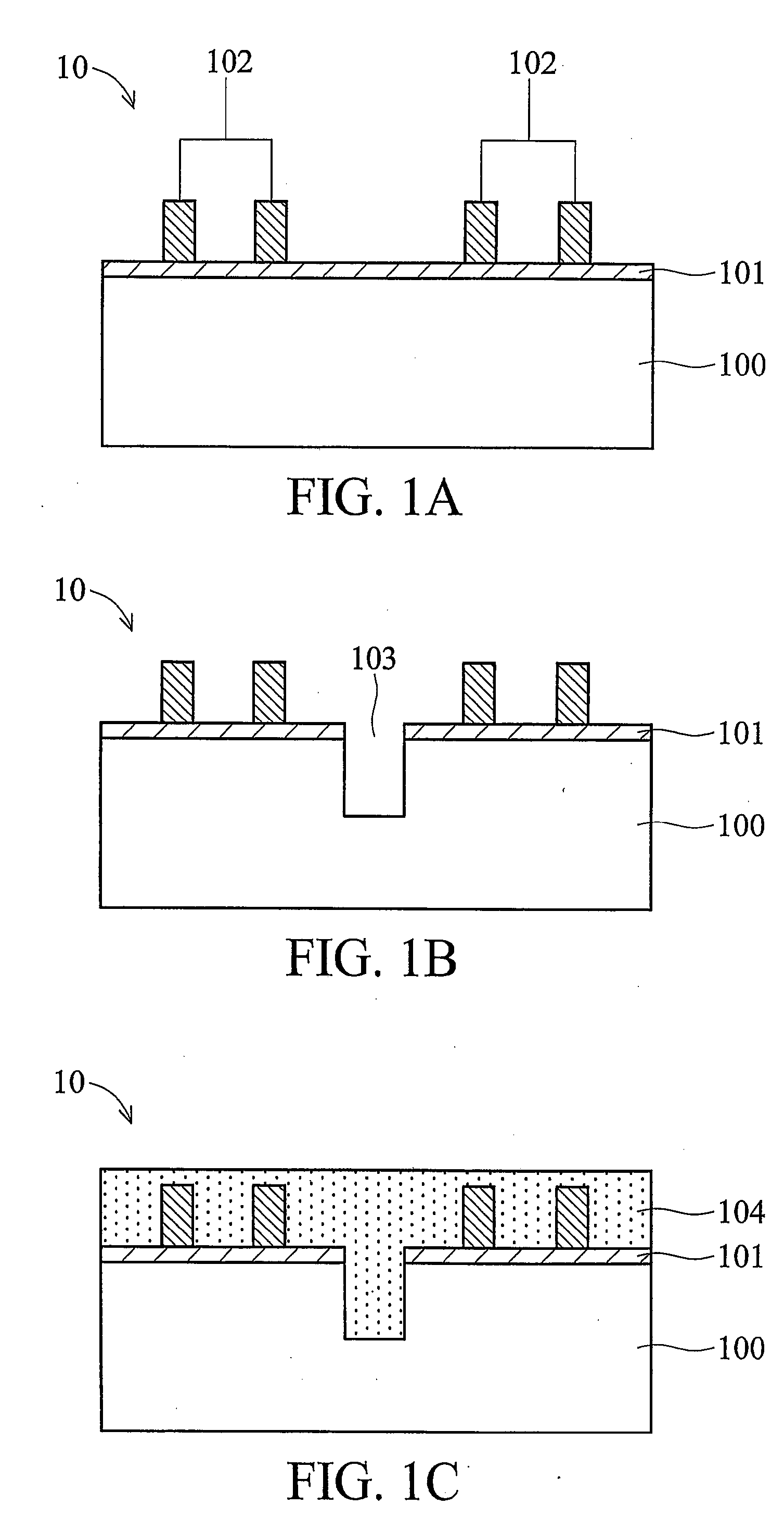

Multi-chips package with reduced structure and method for forming the same

InactiveUS20080197469A1Improve reliabilityReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

The present invention provides a structure of multi-chips package and Method of the same comprising a substrate with a pre-formed die receiving cavity formed within an upper surface of the substrate. A die is disposed within the die receiving cavity by adhesion and an elastic dielectric layer filled into a gap between the die and the substrate to absorb thermal mechanical stress; therefore the thickness of the package is reduced and the CTE mismatch of the structure is reduced. The present invention also provides a structure for SIP with higher reliability and lower manufacturing cost. the process is simpler and it is easy to form the multi-chips package than the traditional one. Therefore, the present invention discloses a fan-out WLP with reduced thickness and good CTE matching performance.

Owner:ADVANCED CHIP ENG TECH

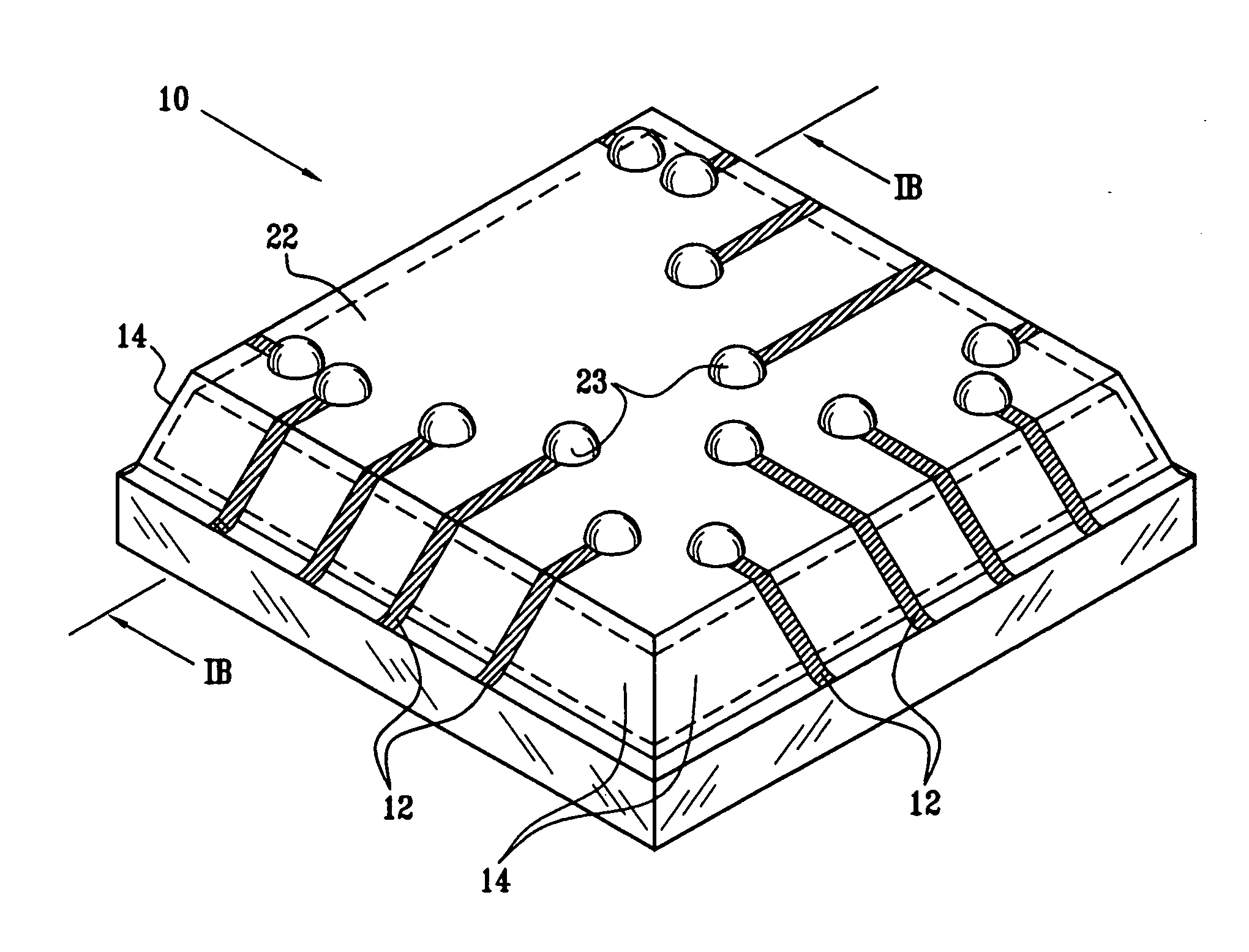

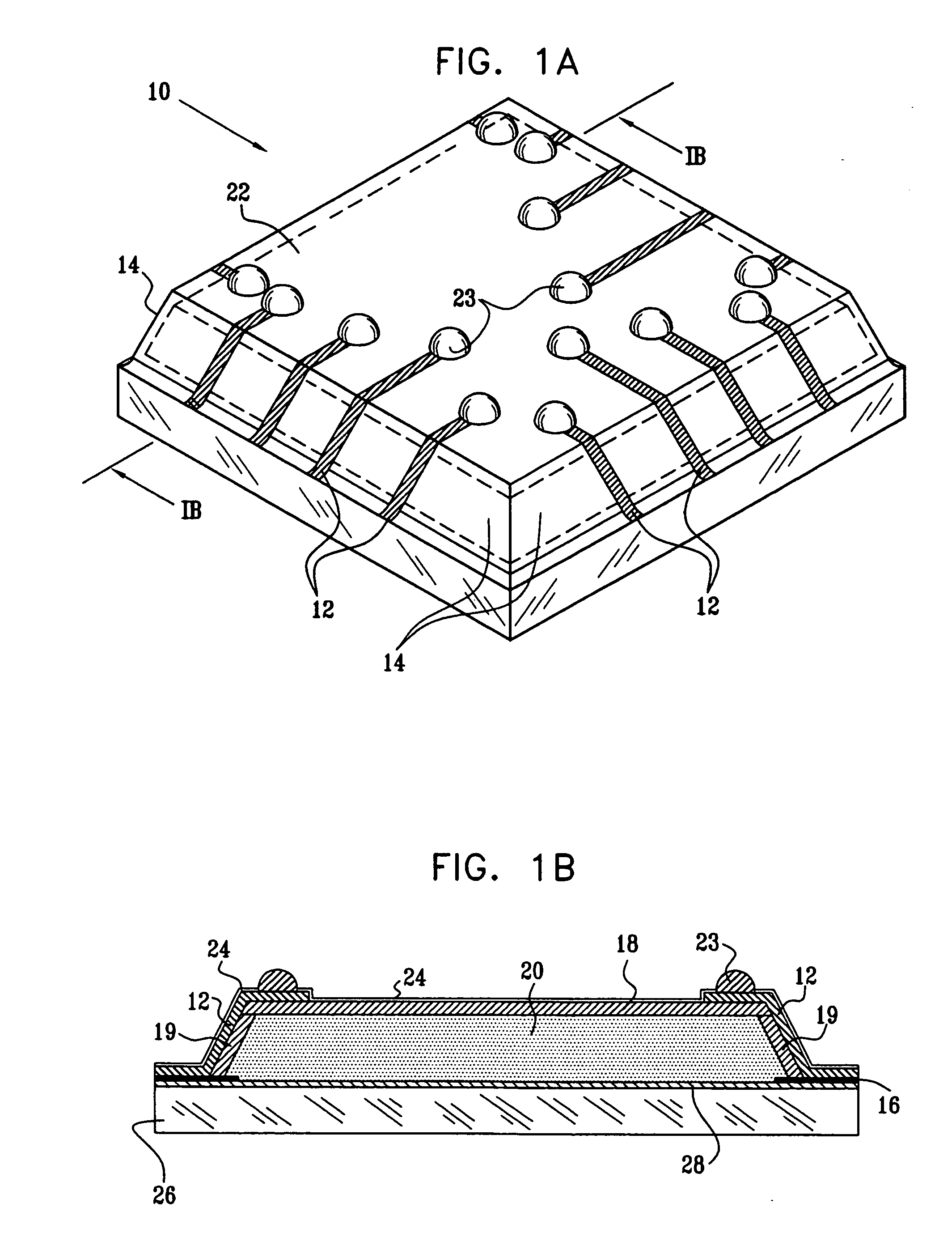

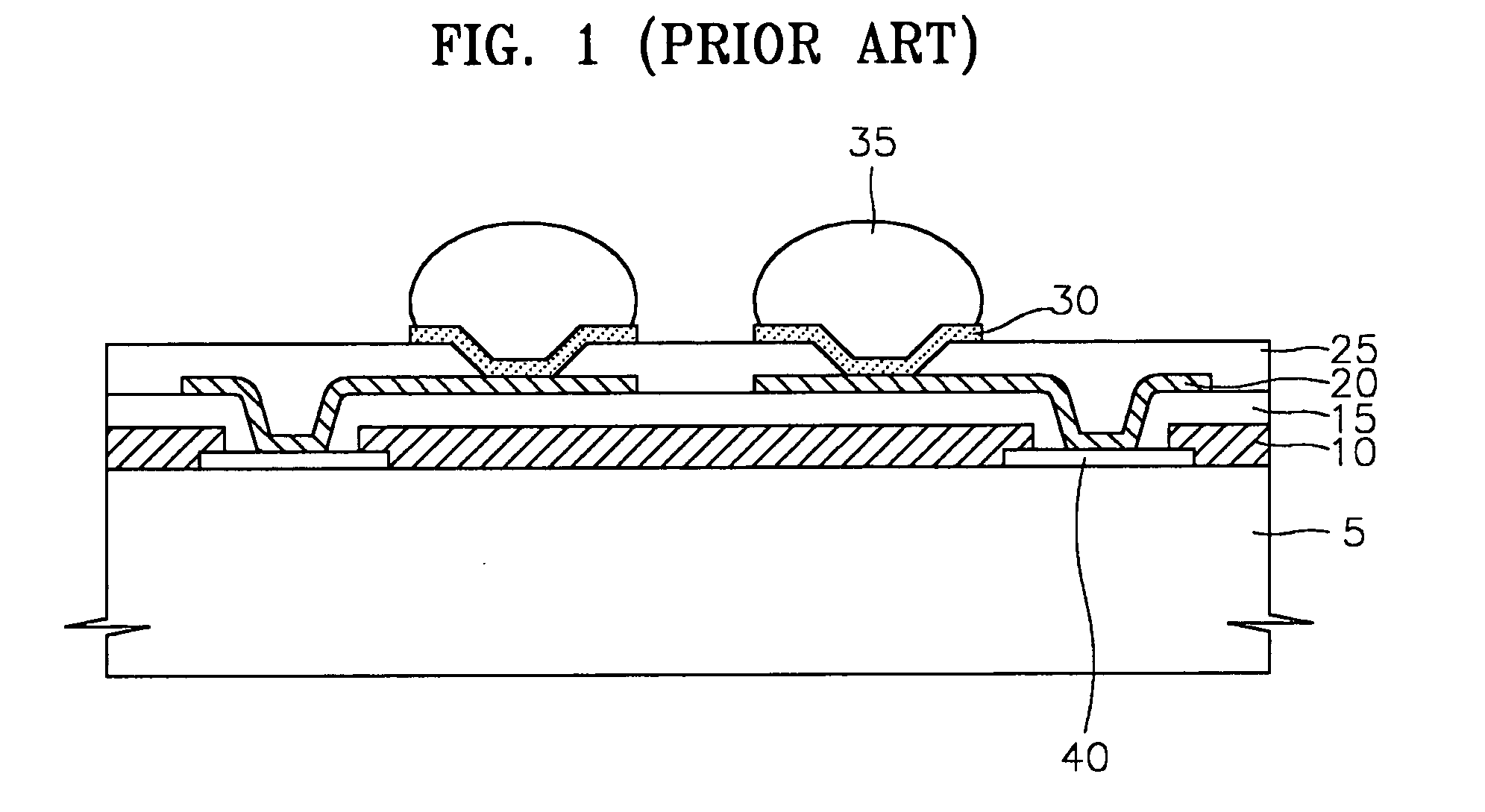

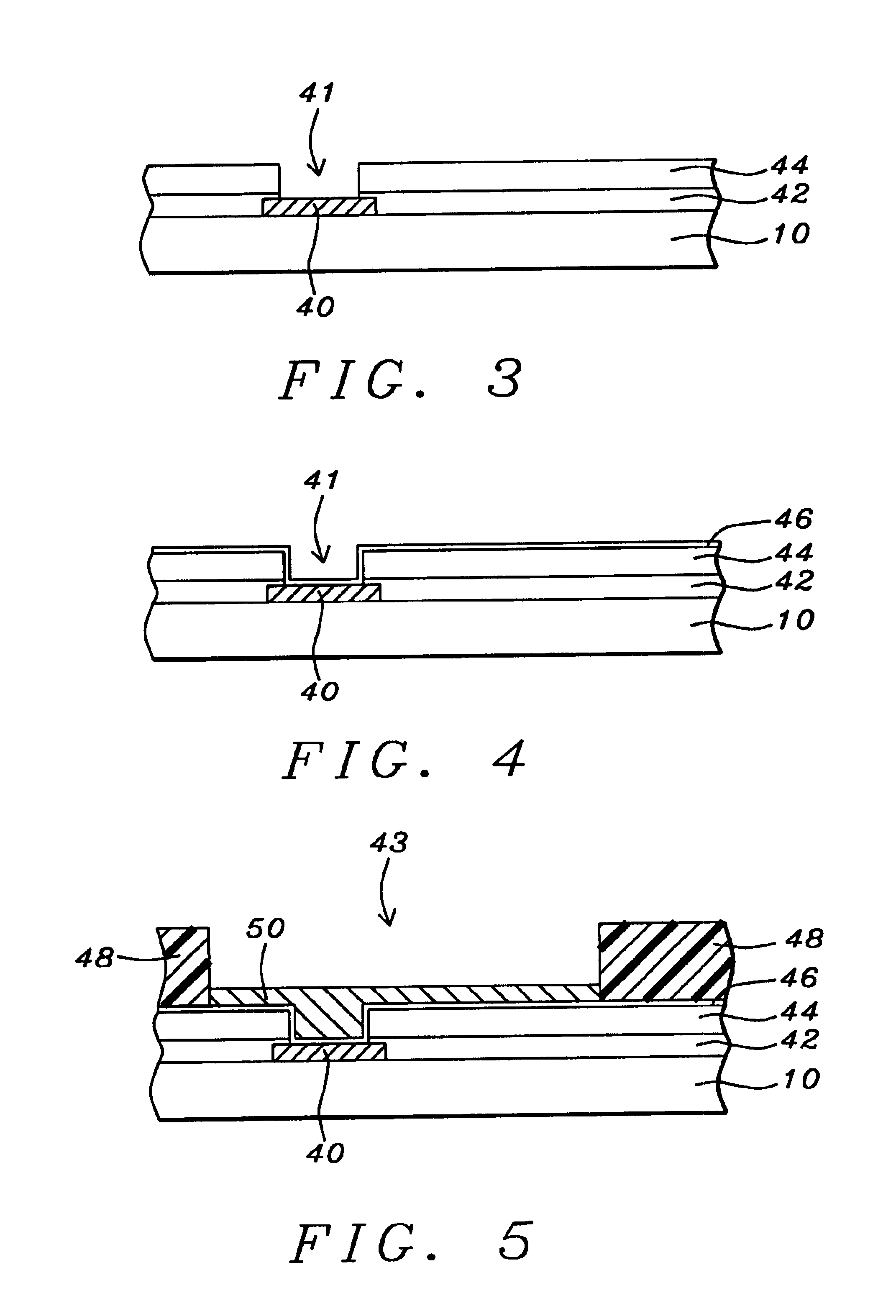

Low fabrication cost, high performance, high reliability chip scale package

InactiveUS6917119B2Minimize damageImprove reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsElastomerContact pad

The invention provides a new method and chip scale package is provided. The inventions starts with a substrate over which a contact point is provided, the contact point is exposed through an opening created in the layer of passivation and a layer of polymer or elastomer. A barrier / seed layer is deposited, a first photoresist mask is created exposing the barrier / seed layer where this layer overlies the contact pad and, contiguous therewith, over a surface area that is adjacent to the contact pad and emanating in one direction from the contact pad. The exposed surface of the barrier / seed layer is electroplated for the creation of interconnect traces. The first photoresist mask is removed from the surface of the barrier / seed layer. A second photoresist mask, defining the solder bump, is created exposing the surface area of the barrier / seed layer that is adjacent to the contact pad and emanating in one direction from the contact pad. The solder bump is created in accordance with the second photoresist mask, the second photoresist mask is removed from the surface of the barrier / seed layer, exposing the electroplating and the barrier / seed layer with the metal plating overlying the barrier / seed layer. The exposed barrier / seed layer is etched in accordance with the pattern formed by the electroplating, reflow of the solder bump is optionally performed.

Owner:QUALCOMM INC

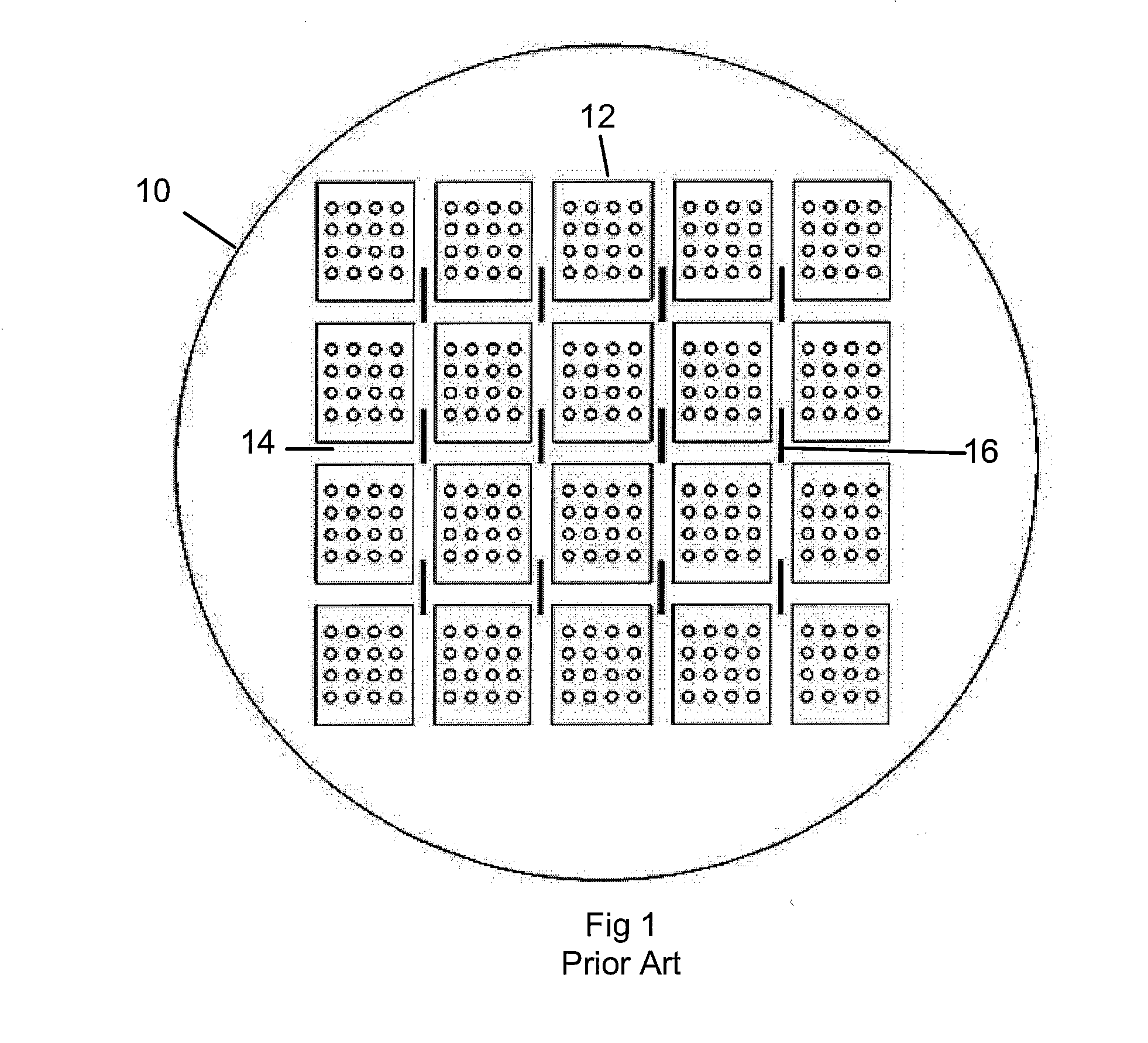

Method for fabricating semiconductor components by forming conductive members using solder

InactiveUS6998344B2Semiconductor/solid-state device detailsPrinted circuit aspectsConductive polymerConductive materials

An interconnect for semiconductor components such as dice, wafers and chip scale packages is provided. The interconnect includes a substrate, and patterns of contacts formed on a face side of the substrate adapted to electrically engage external contacts (e.g., bond pads, solder bumps) on the components. The interconnect also includes insulated conductive members through the substrate, which provide direct electrical paths from the interconnect contacts to a backside of the substrate. The conductive members can be formed by laser machining openings in the substrate, and then filling the openings with a conductive material (e.g., metal, conductive polymer). The conductive members can also include pads with contact balls, configured for electrical interface with a test apparatus, such as test carrier or wafer handler. The interconnect can be used to construct test systems for testing semiconductor components, or to construct chip scale packages and multi chip modules.

Owner:ROUND ROCK RES LLC

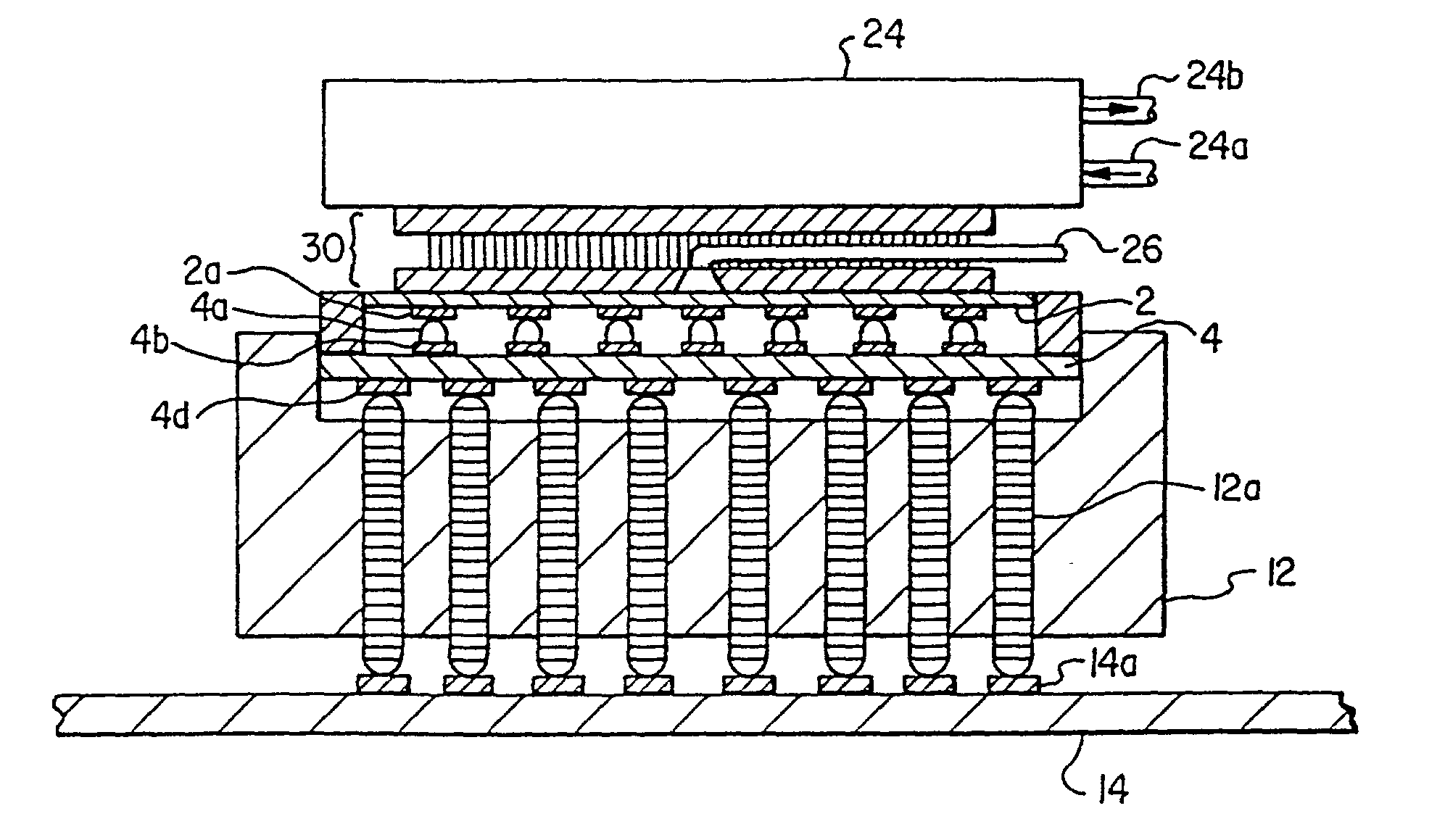

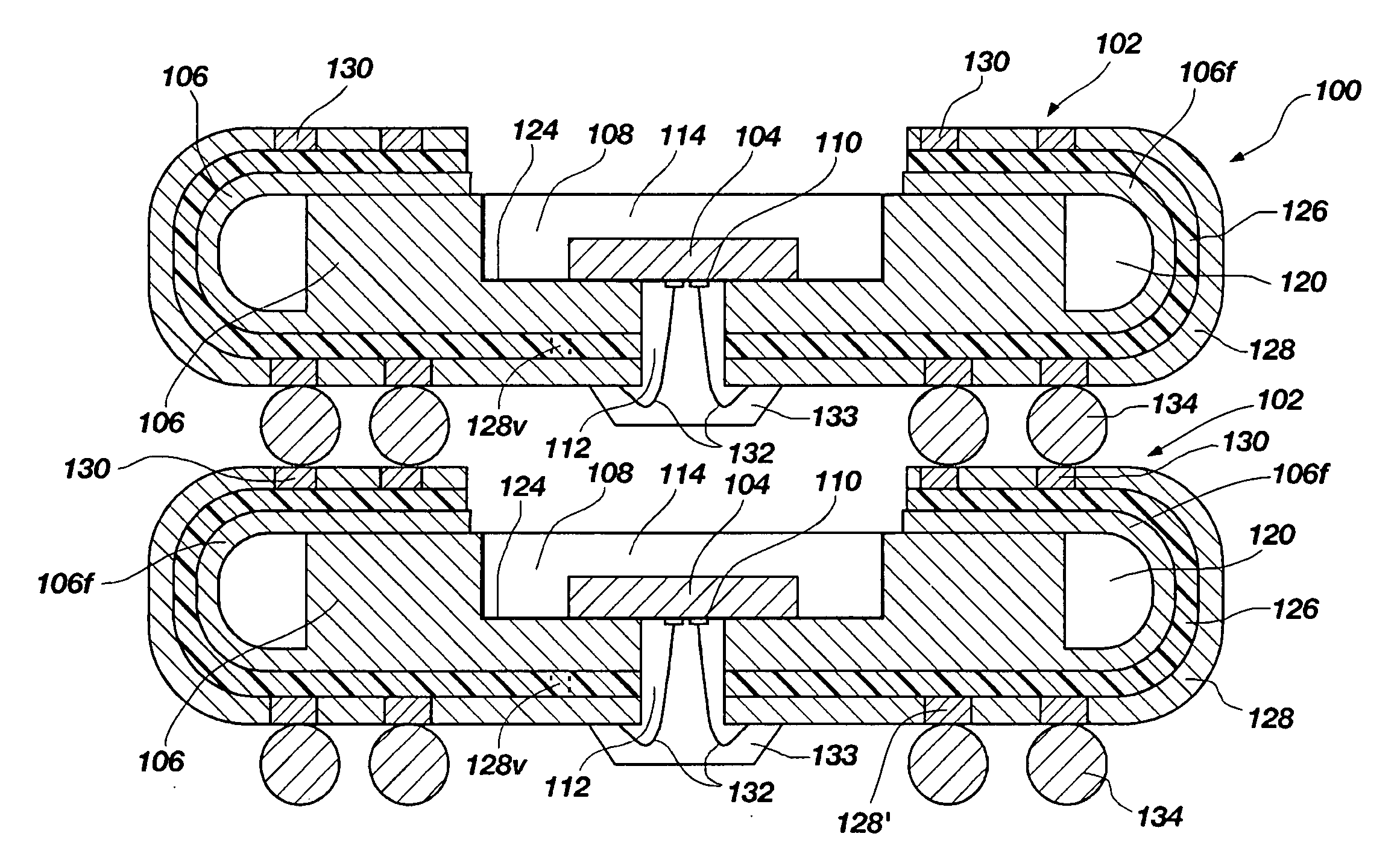

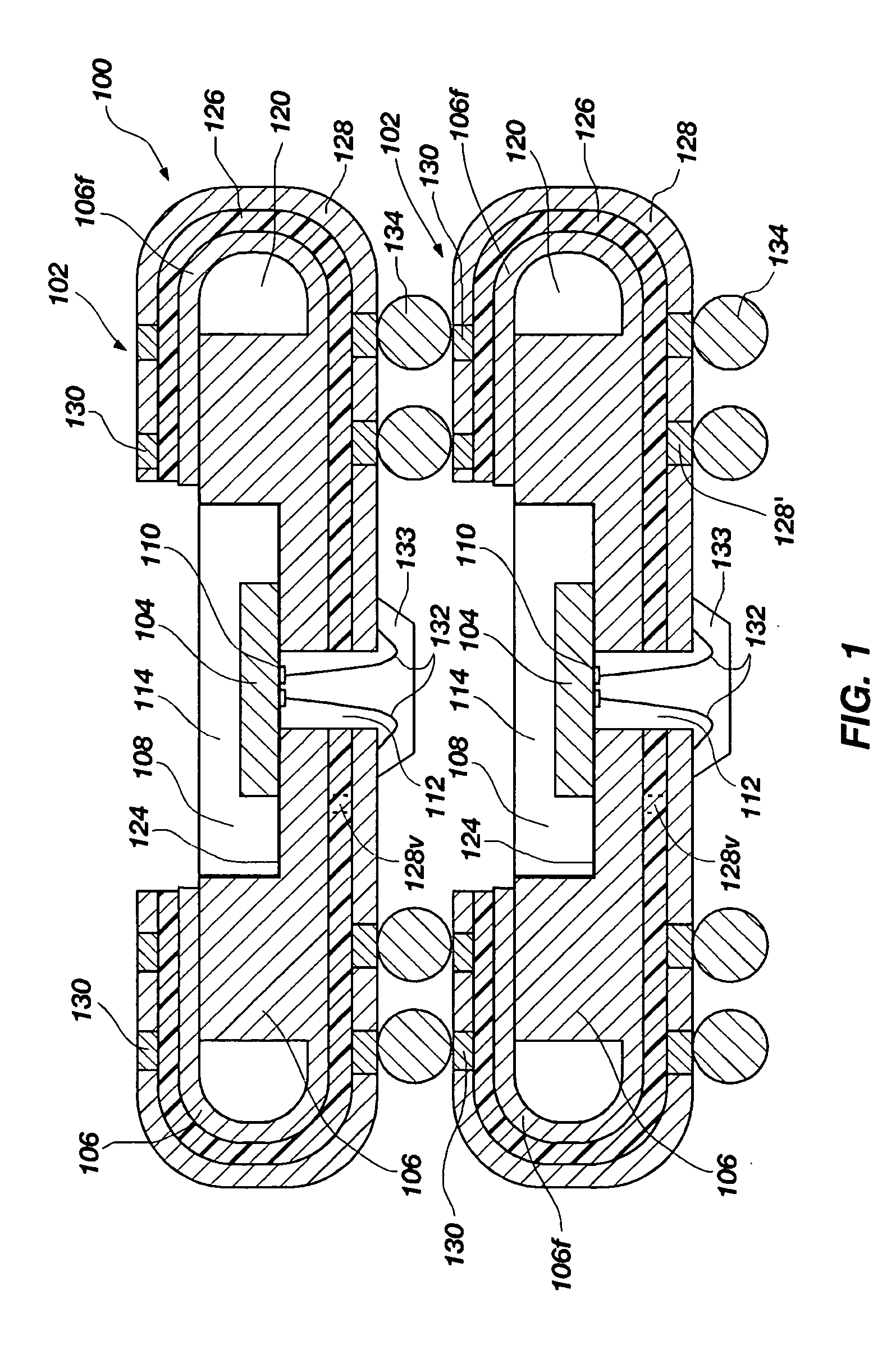

Stackable electronic assembly

InactiveUS7180165B2Reduce crackingImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesCombined useEngineering

On implementation of the invention provides a stackable chip-scale package for improving memory density that may be mounted within a limited area or module. A novel staggered routing scheme enables the use of the same trace routing at every level of the stacked architecture for efficiently accessing individual memory devices in a chip-scale package stack. The use of a ball grid array chip-scale package architecture in combination with thermally compatible materials decreases the risk of thermal cracking while improving heat dissipation. Moreover, this architecture permits mounting support components, such as capacitors and resistors, on the chip-scale package.

Owner:SANMINA-SCI CORPORATION

Enhanced Reliability of Wafer-Level Chip-Scale Packaging (WLCSP) Die Separation Using Dry Etching

ActiveUS20090011543A1Improve reliabilityReduce riskSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsEngineering

An improved Wafer-Level Chip-Scale Packaging (WLCSP) process is described that includes forming a plurality of conductive pillars on a first surface of a semiconductor wafer. One or more grooves are dry etched into the first surface of the semiconductor wafer, where the grooves define at least one boundary between each of a plurality of die within the semiconductor wafer. A layer of encapsulating material is deposited over the first surface. A recess is then cut in each of the grooves through the encapsulating material, where the cutting leaves a piece of semiconductor material on the second surface of the semiconductor wafer. The second surface is then ground to remove the piece of semiconductor material, where the removal of this material separates the plurality of die.

Owner:TAIWAN SEMICON MFG CO LTD

Partially patterned lead frames and methods of making and using the same in semiconductor packaging

InactiveUS20050263864A1Improve structural rigidityProcess stabilityLine/current collector detailsSemiconductor/solid-state device detailsLead bondingBonding process

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging (CSP) lead-counts is disclosed, wherein the method lends itself to better automation of the manufacturing line as well as to improving the quality and reliability of the packages produced therefrom. This is accomplished by performing a major portion of the manufacturing process steps with a partially patterned strip of metal formed into a web-like lead frame on one side, in contrast with the conventional fully etched stencil-like lead frames, so that the web-like lead frame, which is solid and flat on the other side is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation without having to cut into any additional metal. The use of the instant partially patterned lead frame in making ELP, ELPF and ELGA-type CSPs is also disclosed.

Owner:UNISEM M BERHAD

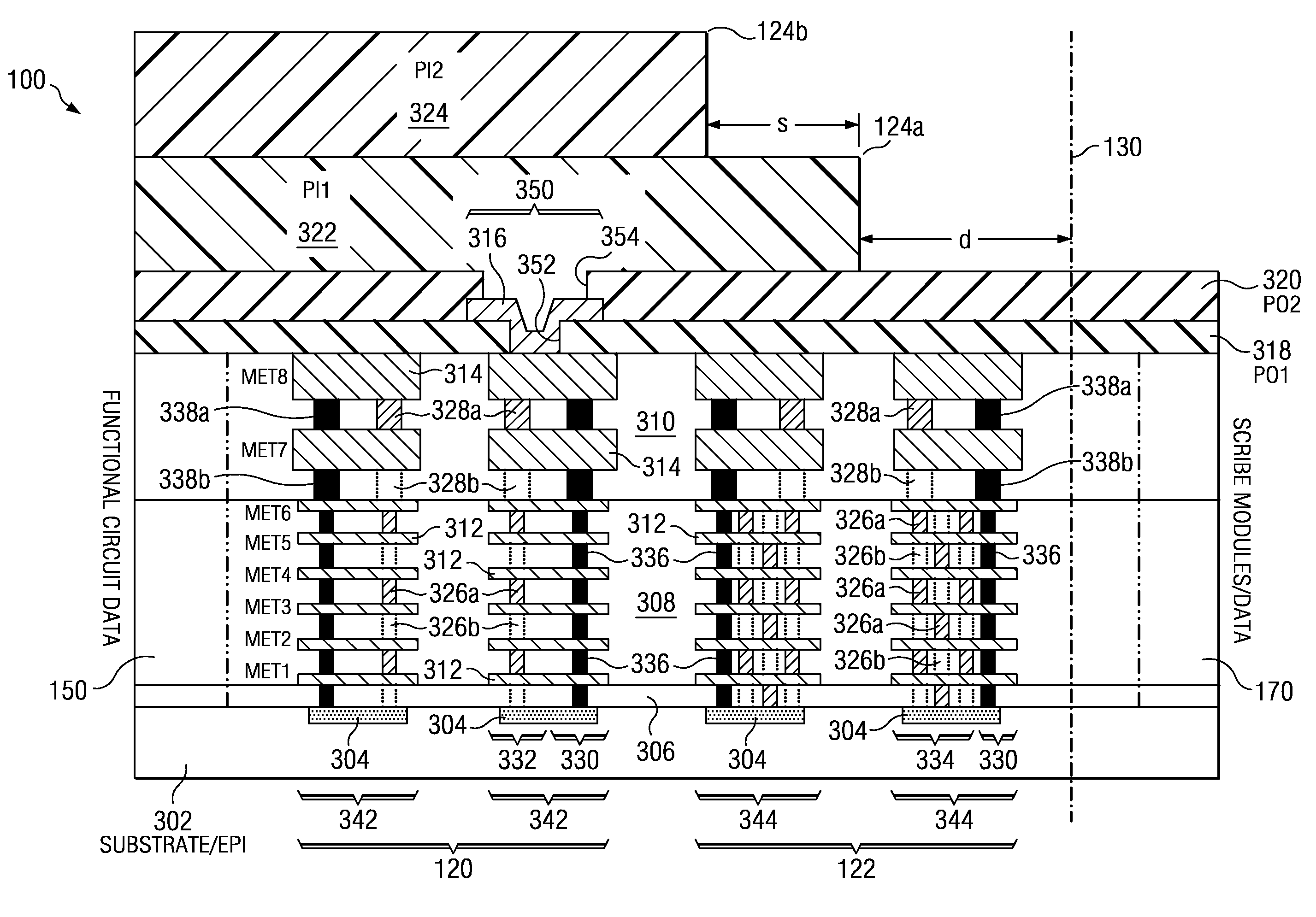

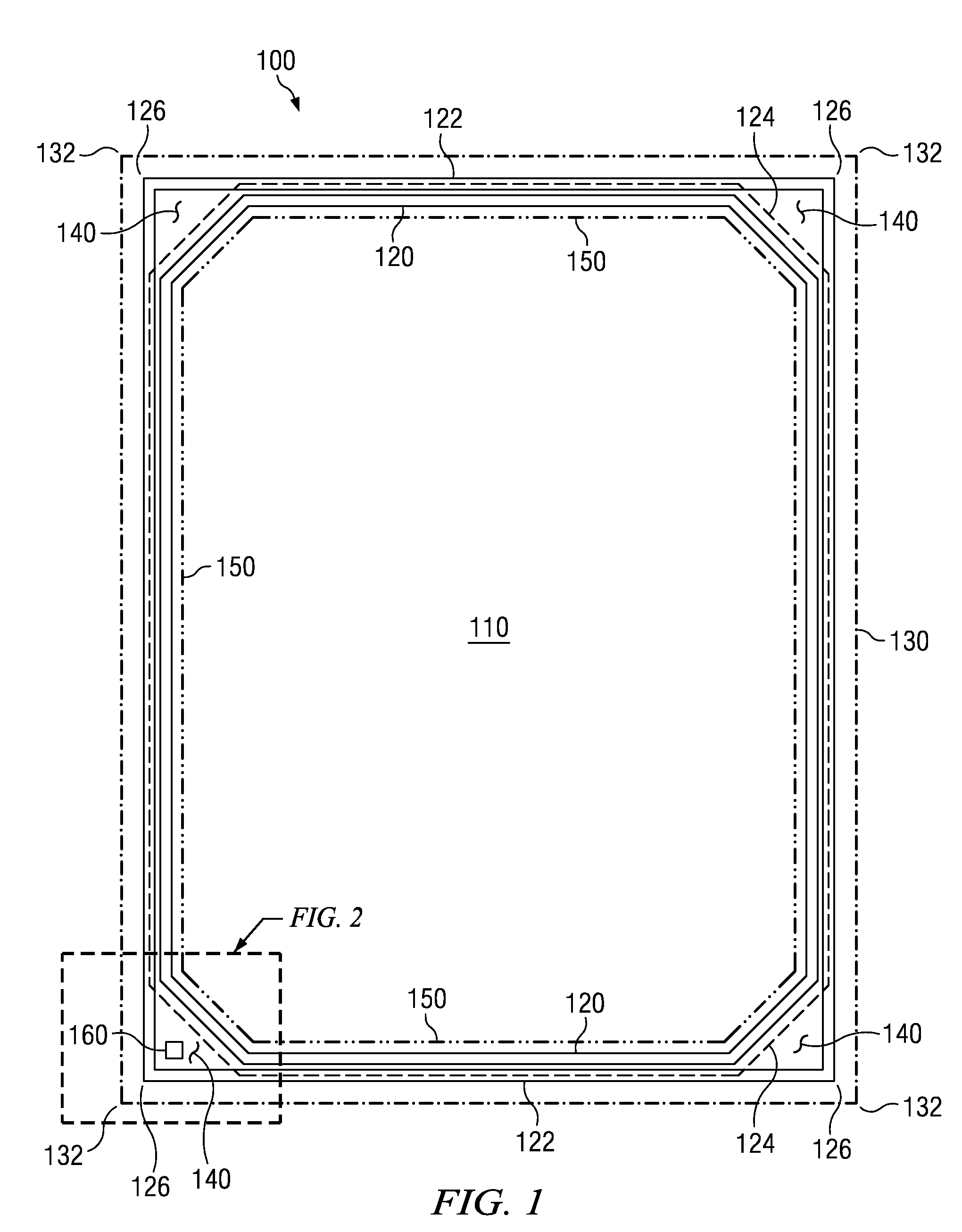

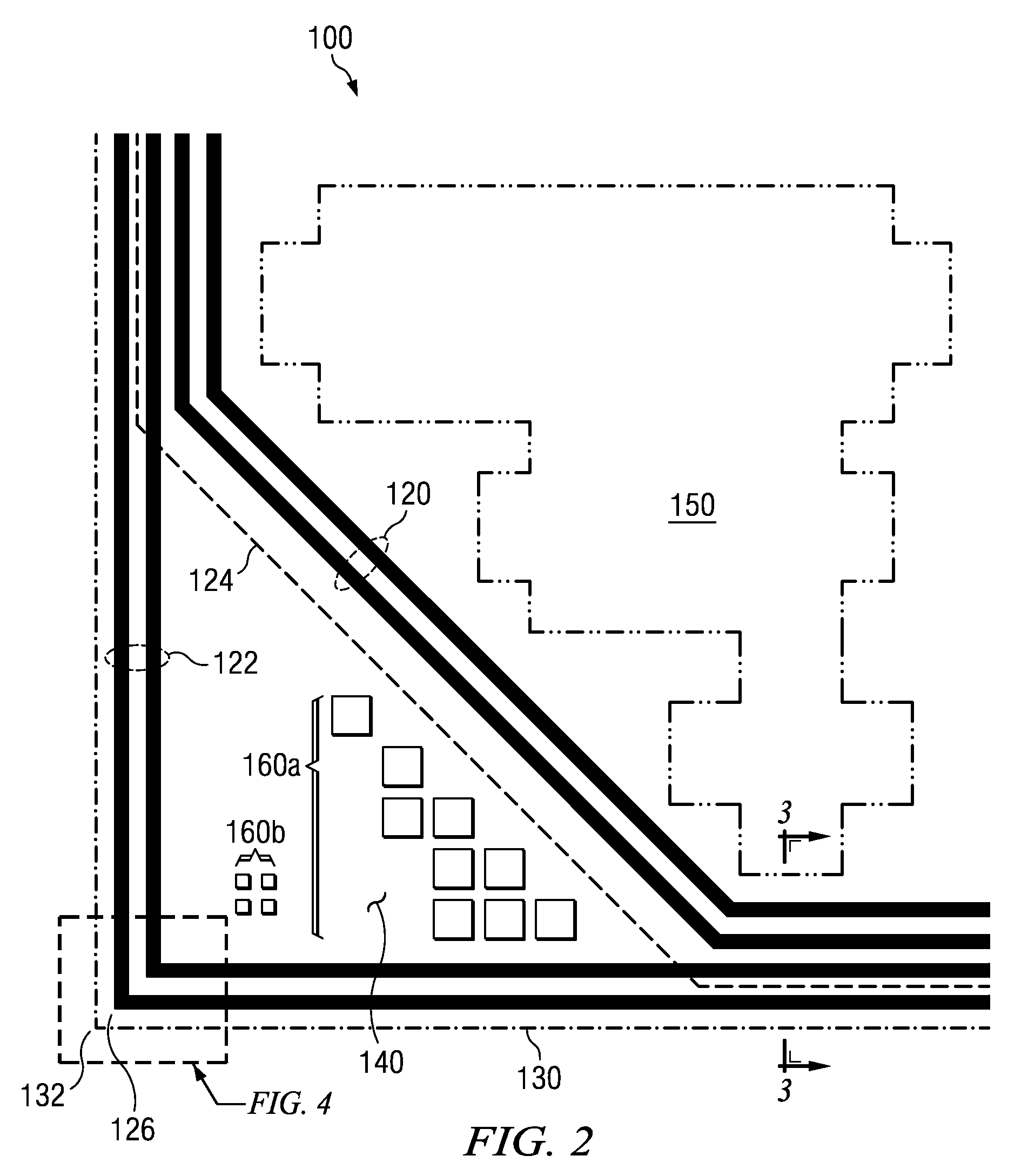

Environmental die seal enhancement for wafer level chip scale packages

ActiveUS20100078769A1Improve barrier propertiesImprove strength propertiesSemiconductor/solid-state device detailsSolid-state devicesMoisture penetrationEngineering

In a semiconductor device for use in a wafer level chip scale package (WLCSP) and a method for fabrication, an inner scribe seal is formed around a functional circuit area that does not extend all the way into the corners of the rectangular die, and an outer scribe seal follows the perimeter of the die and into the corners, with the outer scribe seal having a continuous barrier wall towards the die edges so that moisture penetration in dielectric layers of the die is minimized, and cracks and delamination are stopped near the die edges. Limiting the extent of the insulating layer or layers in the WLCSP to cover the functional circuit area also reduces the stresses caused by these layers near the die corners. Other features further enhance the strength and barrier properties of the scribe seals and the layers near the die corners, terminate cracks and delamination at various levels within the dielectric stack of the die and the die protective overcoat, and prevent damage during the WLCSP assembly process.

Owner:TEXAS INSTR INC

Wafer-level chip scale package and method for fabricating and using the same

InactiveUS20050176233A1Reduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesManufacturing cost reductionInsulation layer

A packaged semiconductor device (a wafer-level chip scale package) containing no UBM between a chip pad and an RDL pattern is described. As well, the device contains only a single non-polymeric insulation layer between the RDL pattern and the solder bump. The single non-polymeric insulation layer does not need high temperature curing processes and so does not induce thermal stresses into the device. As well, manufacturing costs are diminished by eliminating the UBM between the chip pad and the RDL pattern.

Owner:SEMICON COMPONENTS IND LLC